ARM® Compiler V5.06 For µVision® Armcc User Guide DUI0375G 02 Mdk

User Manual:

Open the PDF directly: View PDF ![]() .

.

Page Count: 863 [warning: Documents this large are best viewed by clicking the View PDF Link!]

- ARM® Compiler v5.06 for µVision® armcc User Guide

- Contents

- List of Figures

- List of Tables

- Preface

- 1 : Overview of the Compiler

- 2 : Getting Started with the Compiler

- 2.1 : Compiler command-line syntax

- 2.2 : Compiler command-line options listed by group

- 2.3 : Default compiler behavior

- 2.4 : Order of compiler command-line options

- 2.5 : Using stdin to input source code to the compiler

- 2.6 : Directing output to stdout

- 2.7 : Filename suffixes recognized by the compiler

- 2.8 : Compiler output files

- 2.9 : Factors influencing how the compiler searches for header files

- 2.10 : Compiler command-line options and search paths

- 2.11 : Compiler search rules and the current place

- 2.12 : The ARMCC5INC environment variable

- 2.13 : Code compatibility between separately compiled and assembled modules

- 2.14 : Linker feedback during compilation

- 2.15 : Unused function code

- 2.16 : Minimizing code size by eliminating unused functions during compilation

- 2.17 : Compilation build time

- 2.17.1 : Compilation build time

- 2.17.2 : Minimizing compilation build time

- 2.17.3 : Minimizing compilation build time with a single armcc invocation

- 2.17.4 : Effect of --multifile on compilation build time

- 2.17.5 : Minimizing compilation build time with parallel make

- 2.17.6 : Compilation build time on Windows

- 3 : Compiler Features

- 3.1 : Compiler intrinsics

- 3.2 : Performance benefits of compiler intrinsics

- 3.3 : ARM assembler instruction intrinsics

- 3.4 : Generic intrinsics

- 3.5 : Compiler intrinsics for controlling IRQ and FIQ interrupts

- 3.6 : Compiler intrinsics for inserting optimization barriers

- 3.7 : Compiler intrinsics for inserting native instructions

- 3.8 : Compiler intrinsics for Digital Signal Processing (DSP)

- 3.9 : Compiler support for European Telecommunications Standards Institute (ETSI) basic operations

- 3.10 : Overflow and carry status flags for C and C++ code

- 3.11 : Texas Instruments (TI) C55x intrinsics for optimizing C code

- 3.12 : Compiler support for accessing registers using named register variables

- 3.13 : Pragmas recognized by the compiler

- 3.14 : Compiler and processor support for bit-banding

- 3.15 : Compiler type attribute, __attribute__((bitband))

- 3.16 : --bitband compiler command-line option

- 3.17 : How the compiler handles bit-band objects placed outside bit-band regions

- 3.18 : Compiler support for thread-local storage

- 3.19 : Compiler support for literal pools

- 3.20 : Compiler eight-byte alignment features

- 3.21 : Precompiled Header (PCH) files

- 3.22 : Automatic Precompiled Header (PCH) file processing

- 3.23 : Precompiled Header (PCH) file processing and the header stop point

- 3.24 : Precompiled Header (PCH) file creation requirements

- 3.25 : Compilation with multiple Precompiled Header (PCH) files

- 3.26 : Obsolete Precompiled Header (PCH) files

- 3.27 : Manually specifying the filename and location of a Precompiled Header (PCH) file

- 3.28 : Selectively applying Precompiled Header (PCH) file processing

- 3.29 : Suppressing Precompiled Header (PCH) file processing

- 3.30 : Message output during Precompiled Header (PCH) processing

- 3.31 : Performance issues with Precompiled Header (PCH) files

- 3.32 : Default compiler options that are affected by optimization level

- 4 : Compiler Coding Practices

- 4.1 : The compiler as an optimizing compiler

- 4.2 : Compiler optimization for code size versus speed

- 4.3 : Compiler optimization levels and the debug view

- 4.4 : Selecting the target processor at compile time

- 4.5 : Enabling FPU for bare-metal

- 4.6 : Optimization of loop termination in C code

- 4.7 : Loop unrolling in C code

- 4.8 : Compiler optimization and the volatile keyword

- 4.9 : Code metrics

- 4.10 : Code metrics for measurement of code size and data size

- 4.11 : Stack use in C and C++

- 4.12 : Benefits of reducing debug information in objects and libraries

- 4.13 : Methods of reducing debug information in objects and libraries

- 4.14 : Guarding against multiple inclusion of header files

- 4.15 : Methods of minimizing function parameter passing overhead

- 4.16 : Returning structures from functions through registers

- 4.17 : Functions that return the same result when called with the same arguments

- 4.18 : Comparison of pure and impure functions

- 4.19 : Recommendation of postfix syntax when qualifying functions with ARM function modifiers

- 4.20 : Inline functions

- 4.21 : Compiler decisions on function inlining

- 4.22 : Automatic function inlining and static functions

- 4.23 : Inline functions and removal of unused out-of-line functions at link time

- 4.24 : Automatic function inlining and multifile compilation

- 4.25 : Restriction on overriding compiler decisions about function inlining

- 4.26 : Compiler modes and inline functions

- 4.27 : Inline functions in C++ and C90 mode

- 4.28 : Inline functions in C99 mode

- 4.29 : Inline functions and debugging

- 4.30 : Types of data alignment

- 4.31 : Advantages of natural data alignment

- 4.32 : Compiler storage of data objects by natural byte alignment

- 4.33 : Relevance of natural data alignment at compile time

- 4.34 : Unaligned data access in C and C++ code

- 4.35 : The __packed qualifier and unaligned data access in C and C++ code

- 4.36 : Unaligned fields in structures

- 4.37 : Performance penalty associated with marking whole structures as packed

- 4.38 : Unaligned pointers in C and C++ code

- 4.39 : Unaligned Load Register (LDR) instructions generated by the compiler

- 4.40 : Comparisons of an unpacked struct, a __packed struct, and a struct with individually __packed fields, and of a __packed struct and a #pragma packed struct

- 4.41 : Compiler support for floating-point arithmetic

- 4.42 : Default selection of hardware or software floating-point support

- 4.43 : Example of hardware and software support differences for floating-point arithmetic

- 4.44 : Vector Floating-Point (VFP) architectures

- 4.45 : Limitations on hardware handling of floating-point arithmetic

- 4.46 : Implementation of Vector Floating-Point (VFP) support code

- 4.47 : Compiler and library support for half-precision floating-point numbers

- 4.48 : Half-precision floating-point number format

- 4.49 : Compiler support for floating-point computations and linkage

- 4.50 : Types of floating-point linkage

- 4.51 : Compiler options for floating-point linkage and computations

- 4.52 : Floating-point linkage and computational requirements of compiler options

- 4.53 : Processors and their implicit Floating-Point Units (FPUs)

- 4.54 : Integer division-by-zero errors in C code

- 4.55 : Software floating-point division-by-zero errors in C code

- 4.56 : About trapping software floating-point division-by-zero errors

- 4.57 : Identification of software floating-point division-by-zero errors

- 4.58 : Software floating-point division-by-zero debugging

- 4.59 : New language features of C99

- 4.60 : New library features of C99

- 4.61 : // comments in C99 and C90

- 4.62 : Compound literals in C99

- 4.63 : Designated initializers in C99

- 4.64 : Hexadecimal floating-point numbers in C99

- 4.65 : Flexible array members in C99

- 4.66 : __func__ predefined identifier in C99

- 4.67 : inline functions in C99

- 4.68 : long long data type in C99 and C90

- 4.69 : Macros with a variable number of arguments in C99

- 4.70 : Mixed declarations and statements in C99

- 4.71 : New block scopes for selection and iteration statements in C99

- 4.72 : _Pragma preprocessing operator in C99

- 4.73 : Restricted pointers in C99

- 4.74 : Additional <math.h> library functions in C99

- 4.75 : Complex numbers in C99

- 4.76 : Boolean type and <stdbool.h> in C99

- 4.77 : Extended integer types and functions in <inttypes.h> and <stdint.h> in C99

- 4.78 : <fenv.h> floating-point environment access in C99

- 4.79 : <stdio.h> snprintf family of functions in C99

- 4.80 : <tgmath.h> type-generic math macros in C99

- 4.81 : <wchar.h> wide character I/O functions in C99

- 4.82 : How to prevent uninitialized data from being initialized to zero

- 5 : Compiler Diagnostic Messages

- 5.1 : Severity of compiler diagnostic messages

- 5.2 : Options that change the severity of compiler diagnostic messages

- 5.3 : Controlling compiler diagnostic messages with pragmas

- 5.4 : Prefix letters in compiler diagnostic messages

- 5.5 : Compiler exit status codes and termination messages

- 5.6 : Compiler data flow warnings

- 6 : Using the Inline and Embedded Assemblers of the ARM Compiler

- 6.1 : Compiler support for inline assembly language

- 6.2 : Inline assembler support in the compiler

- 6.3 : Restrictions on inline assembler support in the compiler

- 6.4 : Inline assembly language syntax with the __asm keyword in C and C++

- 6.5 : Inline assembly language syntax with the asm keyword in C++

- 6.6 : Inline assembler rules for compiler keywords __asm and asm

- 6.7 : Restrictions on inline assembly operations in C and C++ code

- 6.8 : Inline assembler register restrictions in C and C++ code

- 6.9 : Inline assembler processor mode restrictions in C and C++ code

- 6.10 : Inline assembler Thumb instruction set restrictions in C and C++ code

- 6.11 : Inline assembler Vector Floating-Point (VFP) restrictions in C and C++ code

- 6.12 : Inline assembler instruction restrictions in C and C++ code

- 6.13 : Miscellaneous inline assembler restrictions in C and C++ code

- 6.14 : Inline assembler and register access in C and C++ code

- 6.15 : Inline assembler and the # constant expression specifier in C and C++ code

- 6.16 : Inline assembler and instruction expansion in C and C++ code

- 6.17 : Expansion of inline assembler instructions that use constants

- 6.18 : Expansion of inline assembler load and store instructions

- 6.19 : Inline assembler effect on processor condition flags in C and C++ code

- 6.20 : Inline assembler expression operands in C and C++ code

- 6.21 : Inline assembler register list operands in C and C++ code

- 6.22 : Inline assembler intermediate operands in C and C++ code

- 6.23 : Inline assembler function calls and branches in C and C++ code

- 6.24 : Inline assembler branches and labels in C and C++ code

- 6.25 : Inline assembler and virtual registers

- 6.26 : Embedded assembler support in the compiler

- 6.27 : Embedded assembler syntax in C and C++

- 6.28 : Effect of compiler ARM and Thumb states on embedded assembler

- 6.29 : Restrictions on embedded assembly language functions in C and C++ code

- 6.30 : Compiler generation of embedded assembly language functions

- 6.31 : Access to C and C++ compile-time constant expressions from embedded assembler

- 6.32 : Differences between expressions in embedded assembler and C or C++

- 6.33 : Manual overload resolution in embedded assembler

- 6.34 : __offsetof_base keyword for related base classes in embedded assembler

- 6.35 : Compiler-supported keywords for calling class member functions in embedded assembler

- 6.36 : __mcall_is_virtual(D, f)

- 6.37 : __mcall_is_in_vbase(D, f)

- 6.38 : __mcall_offsetof_vbase(D, f)

- 6.39 : __mcall_this_offset(D, f)

- 6.40 : __vcall_offsetof_vfunc(D, f)

- 6.41 : Calling nonstatic member functions in embedded assembler

- 6.42 : Calling a nonvirtual member function

- 6.43 : Calling a virtual member function

- 6.44 : Accessing sp (r13), lr (r14), and pc (r15)

- 6.45 : Differences in compiler support for inline and embedded assembly code

- 7 : Compiler Command-line Options

- 7.1 : -Aopt

- 7.2 : --allow_fpreg_for_nonfpdata, --no_allow_fpreg_for_nonfpdata

- 7.3 : --allow_null_this, --no_allow_null_this

- 7.4 : --alternative_tokens, --no_alternative_tokens

- 7.5 : --anachronisms, --no_anachronisms

- 7.6 : --apcs=qualifier...qualifier

- 7.7 : --arm

- 7.8 : --arm_only

- 7.9 : --asm

- 7.10 : --asm_dir=directory_name

- 7.11 : --autoinline, --no_autoinline

- 7.12 : --bigend

- 7.13 : --bitband

- 7.14 : --branch_tables, --no_branch_tables

- 7.15 : --brief_diagnostics, --no_brief_diagnostics

- 7.16 : --bss_threshold=num

- 7.17 : -c

- 7.18 : -C

- 7.19 : --c90

- 7.20 : --c99

- 7.21 : --code_gen, --no_code_gen

- 7.22 : --compatible=name

- 7.23 : --compile_all_input, --no_compile_all_input

- 7.24 : --conditionalize, --no_conditionalize

- 7.25 : --cpp

- 7.26 : --cpp11

- 7.27 : --cpp_compat

- 7.28 : --cpu=list

- 7.29 : --cpu=name compiler option

- 7.30 : --create_pch=filename

- 7.31 : -Dname[(parm-list)][=def]

- 7.32 : --data_reorder, --no_data_reorder

- 7.33 : --debug, --no_debug

- 7.34 : --debug_macros, --no_debug_macros

- 7.35 : --default_extension=ext

- 7.36 : --dep_name, --no_dep_name

- 7.37 : --depend=filename

- 7.38 : --depend_dir=directory_name

- 7.39 : --depend_format=string

- 7.40 : --depend_single_line, --no_depend_single_line

- 7.41 : --depend_system_headers, --no_depend_system_headers

- 7.42 : --depend_target=target

- 7.43 : --diag_error=tag[,tag,...]

- 7.44 : --diag_remark=tag[,tag,...]

- 7.45 : --diag_style=arm|ide|gnu compiler option

- 7.46 : --diag_suppress=tag[,tag,...]

- 7.47 : --diag_suppress=optimizations

- 7.48 : --diag_warning=tag[,tag,...]

- 7.49 : --diag_warning=optimizations

- 7.50 : --dollar, --no_dollar

- 7.51 : --dwarf2

- 7.52 : --dwarf3

- 7.53 : -E

- 7.54 : --echo

- 7.55 : --emit_frame_directives, --no_emit_frame_directives

- 7.56 : --enum_is_int

- 7.57 : --errors=filename

- 7.58 : --exceptions, --no_exceptions

- 7.59 : --exceptions_unwind, --no_exceptions_unwind

- 7.60 : --execute_only

- 7.61 : --extended_initializers, --no_extended_initializers

- 7.62 : --feedback=filename

- 7.63 : --float_literal_pools, --no_float_literal_pools

- 7.64 : --force_new_nothrow, --no_force_new_nothrow

- 7.65 : --forceinline

- 7.66 : --fp16_format=format

- 7.67 : --fpmode=model

- 7.68 : --fpu=list

- 7.69 : --fpu=name compiler option

- 7.70 : --friend_injection, --no_friend_injection

- 7.71 : -g

- 7.72 : --global_reg=reg_name[,reg_name,...]

- 7.73 : --gnu

- 7.74 : --gnu_defaults

- 7.75 : --gnu_instrument, --no_gnu_instrument

- 7.76 : --gnu_version=version

- 7.77 : --guiding_decls, --no_guiding_decls

- 7.78 : --help

- 7.79 : -Idir[,dir,...]

- 7.80 : --ignore_missing_headers

- 7.81 : --implicit_include, --no_implicit_include

- 7.82 : --implicit_include_searches, --no_implicit_include_searches

- 7.83 : --implicit_key_function, --no_implicit_key_function

- 7.84 : --implicit_typename, --no_implicit_typename

- 7.85 : --info=totals

- 7.86 : --inline, --no_inline

- 7.87 : --integer_literal_pools, --no_integer_literal_pools

- 7.88 : --interface_enums_are_32_bit

- 7.89 : --interleave

- 7.90 : -Jdir[,dir,...]

- 7.91 : --kandr_include

- 7.92 : -Lopt

- 7.93 : --library_interface=lib

- 7.94 : --library_type=lib

- 7.95 : --liclinger=seconds

- 7.96 : --licretry

- 7.97 : --link_all_input, --no_link_all_input

- 7.98 : --list

- 7.99 : --list_dir=directory_name

- 7.100 : --list_macros

- 7.101 : --littleend

- 7.102 : --locale=lang_country

- 7.103 : --long_long

- 7.104 : --loop_optimization_level=opt

- 7.105 : --loose_implicit_cast

- 7.106 : --lower_ropi, --no_lower_ropi

- 7.107 : --lower_rwpi, --no_lower_rwpi

- 7.108 : -M

- 7.109 : --md

- 7.110 : --message_locale=lang_country[.codepage]

- 7.111 : --min_array_alignment=opt

- 7.112 : --mm

- 7.113 : --multibyte_chars, --no_multibyte_chars

- 7.114 : --multifile, --no_multifile

- 7.115 : --multiply_latency=cycles

- 7.116 : --narrow_volatile_bitfields

- 7.117 : --nonstd_qualifier_deduction, --no_nonstd_qualifier_deduction

- 7.118 : -o filename

- 7.119 : -Onum

- 7.120 : --old_specializations, --no_old_specializations

- 7.121 : --old_style_preprocessing

- 7.122 : --omf_browse

- 7.123 : --ool_section_name, --no_ool_section_name

- 7.124 : -Ospace

- 7.125 : -Otime

- 7.126 : --output_dir=directory_name

- 7.127 : -P

- 7.128 : --parse_templates, --no_parse_templates

- 7.129 : --pch

- 7.130 : --pch_dir=dir

- 7.131 : --pch_messages, --no_pch_messages

- 7.132 : --pch_verbose, --no_pch_verbose

- 7.133 : --pending_instantiations=n

- 7.134 : --phony_targets

- 7.135 : --pointer_alignment=num

- 7.136 : --preinclude=filename

- 7.137 : --preprocess_assembly

- 7.138 : --preprocessed

- 7.139 : --protect_stack, --no_protect_stack

- 7.140 : --reassociate_saturation, --no_reassociate_saturation

- 7.141 : --reduce_paths, --no_reduce_paths

- 7.142 : --relaxed_ref_def, --no_relaxed_ref_def

- 7.143 : --remarks

- 7.144 : --remove_unneeded_entities, --no_remove_unneeded_entities

- 7.145 : --restrict, --no_restrict

- 7.146 : --retain=option

- 7.147 : --rtti, --no_rtti

- 7.148 : --rtti_data, --no_rtti_data

- 7.149 : -S

- 7.150 : --share_inlineable_strings, --no_share_inlineable_strings

- 7.151 : --show_cmdline

- 7.152 : --signed_bitfields, --unsigned_bitfields

- 7.153 : --signed_chars, --unsigned_chars

- 7.154 : --split_ldm

- 7.155 : --split_sections

- 7.156 : --strict, --no_strict

- 7.157 : --strict_warnings

- 7.158 : --string_literal_pools, --no_string_literal_pools

- 7.159 : --sys_include

- 7.160 : --thumb

- 7.161 : --trigraphs, --no_trigraphs

- 7.162 : --type_traits_helpers, --no_type_traits_helpers

- 7.163 : -Uname

- 7.164 : --unaligned_access, --no_unaligned_access

- 7.165 : --use_frame_pointer, --no_use_frame_pointer

- 7.166 : --use_pch=filename

- 7.167 : --using_std, --no_using_std

- 7.168 : --version_number

- 7.169 : --vfe, --no_vfe

- 7.170 : --via=filename

- 7.171 : --vla, --no_vla

- 7.172 : --vsn

- 7.173 : -W

- 7.174 : --wchar, --no_wchar

- 7.175 : --wchar16

- 7.176 : --wchar32

- 7.177 : --whole_program

- 7.178 : --wrap_diagnostics, --no_wrap_diagnostics

- 8 : Language Extensions

- 8.1 : Preprocessor extensions

- 8.2 : #assert

- 8.3 : #include_next

- 8.4 : #unassert

- 8.5 : #warning

- 8.6 : C99 language features available in C90

- 8.7 : // comments

- 8.8 : Subscripting struct

- 8.9 : Flexible array members

- 8.10 : C99 language features available in C++ and C90

- 8.11 : Variadic macros

- 8.12 : long long

- 8.13 : restrict

- 8.14 : Hexadecimal floats

- 8.15 : Standard C language extensions

- 8.16 : Constant expressions

- 8.17 : Array and pointer extensions

- 8.18 : Block scope function declarations

- 8.19 : Dollar signs in identifiers

- 8.20 : Top-level declarations

- 8.21 : Benign redeclarations

- 8.22 : External entities

- 8.23 : Function prototypes

- 8.24 : Standard C++ language extensions

- 8.25 : ? operator

- 8.26 : Declaration of a class member

- 8.27 : friend

- 8.28 : Read/write constants

- 8.29 : Scalar type constants

- 8.30 : Specialization of nonmember function templates

- 8.31 : Type conversions

- 8.32 : Standard C and Standard C++ language extensions

- 8.33 : Address of a register variable

- 8.34 : Arguments to functions

- 8.35 : Anonymous classes, structures and unions

- 8.36 : Assembler labels

- 8.37 : Empty declaration

- 8.38 : Hexadecimal floating-point constants

- 8.39 : Incomplete enums

- 8.40 : Integral type extensions

- 8.41 : Label definitions

- 8.42 : Long float

- 8.43 : Nonstatic local variables

- 8.44 : Structure, union, enum, and bitfield extensions

- 8.45 : GNU extensions to the C and C++ languages

- 9 : Compiler-specific Features

- 9.1 : Keywords and operators

- 9.2 : __align

- 9.3 : __ALIGNOF__

- 9.4 : __alignof__

- 9.5 : __asm

- 9.6 : __forceinline

- 9.7 : __global_reg

- 9.8 : __inline

- 9.9 : __int64

- 9.10 : __INTADDR__

- 9.11 : __irq

- 9.12 : __packed

- 9.13 : __pure

- 9.14 : __smc

- 9.15 : __softfp

- 9.16 : __svc

- 9.17 : __svc_indirect

- 9.18 : __svc_indirect_r7

- 9.19 : __value_in_regs

- 9.20 : __weak

- 9.21 : __writeonly

- 9.22 : __declspec attributes

- 9.23 : __declspec(noinline)

- 9.24 : __declspec(noreturn)

- 9.25 : __declspec(nothrow)

- 9.26 : __declspec(notshared)

- 9.27 : __declspec(thread)

- 9.28 : Function attributes

- 9.29 : __attribute__((alias)) function attribute

- 9.30 : __attribute__((always_inline)) function attribute

- 9.31 : __attribute__((const)) function attribute

- 9.32 : __attribute__((constructor[(priority)])) function attribute

- 9.33 : __attribute__((deprecated)) function attribute

- 9.34 : __attribute__((destructor[(priority)])) function attribute

- 9.35 : __attribute__((format)) function attribute

- 9.36 : __attribute__((format_arg(string-index))) function attribute

- 9.37 : __attribute__((malloc)) function attribute

- 9.38 : __attribute__((noinline)) function attribute

- 9.39 : __attribute__((no_instrument_function)) function attribute

- 9.40 : __attribute__((nomerge)) function attribute

- 9.41 : __attribute__((nonnull)) function attribute

- 9.42 : __attribute__((noreturn)) function attribute

- 9.43 : __attribute__((notailcall)) function attribute

- 9.44 : __attribute__((nothrow)) function attribute

- 9.45 : __attribute__((pcs("calling_convention"))) function attribute

- 9.46 : __attribute__((pure)) function attribute

- 9.47 : __attribute__((section("name"))) function attribute

- 9.48 : __attribute__((sentinel)) function attribute

- 9.49 : __attribute__((unused)) function attribute

- 9.50 : __attribute__((used)) function attribute

- 9.51 : __attribute__((visibility("visibility_type"))) function attribute

- 9.52 : __attribute__((warn_unused_result))

- 9.53 : __attribute__((weak)) function attribute

- 9.54 : __attribute__((weakref("target"))) function attribute

- 9.55 : Type attributes

- 9.56 : __attribute__((bitband)) type attribute

- 9.57 : __attribute__((aligned)) type attribute

- 9.58 : __attribute__((packed)) type attribute

- 9.59 : __attribute__((transparent_union)) type attribute

- 9.60 : Variable attributes

- 9.61 : __attribute__((alias)) variable attribute

- 9.62 : __attribute__((at(address))) variable attribute

- 9.63 : __attribute__((aligned)) variable attribute

- 9.64 : __attribute__((deprecated)) variable attribute

- 9.65 : __attribute__((noinline)) constant variable attribute

- 9.66 : __attribute__((packed)) variable attribute

- 9.67 : __attribute__((section("name"))) variable attribute

- 9.68 : __attribute__((unused)) variable attribute

- 9.69 : __attribute__((used)) variable attribute

- 9.70 : __attribute__((visibility("visibility_type"))) variable attribute

- 9.71 : __attribute__((weak)) variable attribute

- 9.72 : __attribute__((weakref("target"))) variable attribute

- 9.73 : __attribute__((zero_init)) variable attribute

- 9.74 : Pragmas

- 9.75 : #pragma anon_unions, #pragma no_anon_unions

- 9.76 : #pragma arm

- 9.77 : #pragma arm section [section_type_list]

- 9.78 : #pragma diag_default tag[,tag,...]

- 9.79 : #pragma diag_error tag[,tag,...]

- 9.80 : #pragma diag_remark tag[,tag,...]

- 9.81 : #pragma diag_suppress tag[,tag,...]

- 9.82 : #pragma diag_warning tag[, tag, ...]

- 9.83 : #pragma exceptions_unwind, #pragma no_exceptions_unwind

- 9.84 : #pragma GCC system_header

- 9.85 : #pragma hdrstop

- 9.86 : #pragma import symbol_name

- 9.87 : #pragma import(__use_full_stdio)

- 9.88 : #pragma import(__use_smaller_memcpy)

- 9.89 : #pragma inline, #pragma no_inline

- 9.90 : #pragma no_pch

- 9.91 : #pragma Onum

- 9.92 : #pragma once

- 9.93 : #pragma Ospace

- 9.94 : #pragma Otime

- 9.95 : #pragma pack(n)

- 9.96 : #pragma pop

- 9.97 : #pragma push

- 9.98 : #pragma softfp_linkage, #pragma no_softfp_linkage

- 9.99 : #pragma thumb

- 9.100 : #pragma unroll [(n)]

- 9.101 : #pragma unroll_completely

- 9.102 : #pragma weak symbol, #pragma weak symbol1 = symbol2

- 9.103 : Instruction intrinsics

- 9.104 : __breakpoint intrinsic

- 9.105 : __cdp intrinsic

- 9.106 : __clrex intrinsic

- 9.107 : __clz intrinsic

- 9.108 : __current_pc intrinsic

- 9.109 : __current_sp intrinsic

- 9.110 : __disable_fiq intrinsic

- 9.111 : __disable_irq intrinsic

- 9.112 : __dmb intrinsic

- 9.113 : __dsb intrinsic

- 9.114 : __enable_fiq intrinsic

- 9.115 : __enable_irq intrinsic

- 9.116 : __fabs intrinsic

- 9.117 : __fabsf intrinsic

- 9.118 : __force_loads intrinsic

- 9.119 : __force_stores intrinsic

- 9.120 : __isb intrinsic

- 9.121 : __ldrex intrinsic

- 9.122 : __ldrexd intrinsic

- 9.123 : __ldrt intrinsic

- 9.124 : __memory_changed intrinsic

- 9.125 : __nop intrinsic

- 9.126 : __pld intrinsic

- 9.127 : __pli intrinsic

- 9.128 : __promise intrinsic

- 9.129 : __qadd intrinsic

- 9.130 : __qdbl intrinsic

- 9.131 : __qsub intrinsic

- 9.132 : __rbit intrinsic

- 9.133 : __rev intrinsic

- 9.134 : __return_address intrinsic

- 9.135 : __ror intrinsic

- 9.136 : __schedule_barrier intrinsic

- 9.137 : __semihost intrinsic

- 9.138 : __sev intrinsic

- 9.139 : __sqrt intrinsic

- 9.140 : __sqrtf intrinsic

- 9.141 : __ssat intrinsic

- 9.142 : __strex intrinsic

- 9.143 : __strexd intrinsic

- 9.144 : __strt intrinsic

- 9.145 : __swp intrinsic

- 9.146 : __usat intrinsic

- 9.147 : __wfe intrinsic

- 9.148 : __wfi intrinsic

- 9.149 : __yield intrinsic

- 9.150 : ARMv6 SIMD intrinsics

- 9.151 : ETSI basic operations

- 9.152 : C55x intrinsics

- 9.153 : VFP status intrinsic

- 9.154 : __vfp_status intrinsic

- 9.155 : Fused Multiply Add (FMA) intrinsics

- 9.156 : Named register variables

- 9.157 : GNU built-in functions

- 9.158 : Predefined macros

- 9.159 : Built-in function name variables

- 10 : C and C++ Implementation Details

- 10.1 : Character sets and identifiers in ARM C and C++

- 10.2 : Basic data types in ARM C and C++

- 10.3 : Operations on basic data types ARM C and C++

- 10.4 : Structures, unions, enumerations, and bitfields in ARM C and C++

- 10.5 : Using the ::operator new function in ARM C++

- 10.6 : Tentative arrays in ARM C++

- 10.7 : Old-style C parameters in ARM C++ functions

- 10.8 : Anachronisms in ARM C++

- 10.9 : Template instantiation in ARM C++

- 10.10 : Namespaces in ARM C++

- 10.11 : C++ exception handling in ARM C++

- 10.12 : Extern inline functions in ARM C++

- 10.13 : C++11 supported features

- 11 : What is Semihosting?

- 11.1 : What is semihosting?

- 11.2 : The semihosting interface

- 11.3 : Can I change the semihosting operation numbers?

- 11.4 : Debug agent interaction SVCs

- 11.5 : angel_SWIreason_EnterSVC (0x17)

- 11.6 : angel_SWIreason_ReportException (0x18)

- 11.7 : SYS_CLOSE (0x02)

- 11.8 : SYS_CLOCK (0x10)

- 11.9 : SYS_ELAPSED (0x30)

- 11.10 : SYS_ERRNO (0x13)

- 11.11 : SYS_FLEN (0x0C)

- 11.12 : SYS_GET_CMDLINE (0x15)

- 11.13 : SYS_HEAPINFO (0x16)

- 11.14 : SYS_ISERROR (0x08)

- 11.15 : SYS_ISTTY (0x09)

- 11.16 : SYS_OPEN (0x01)

- 11.17 : SYS_READ (0x06)

- 11.18 : SYS_READC (0x07)

- 11.19 : SYS_REMOVE (0x0E)

- 11.20 : SYS_RENAME (0x0F)

- 11.21 : SYS_SEEK (0x0A)

- 11.22 : SYS_SYSTEM (0x12)

- 11.23 : SYS_TICKFREQ (0x31)

- 11.24 : SYS_TIME (0x11)

- 11.25 : SYS_TMPNAM (0x0D)

- 11.26 : SYS_WRITE (0x05)

- 11.27 : SYS_WRITEC (0x03)

- 11.28 : SYS_WRITE0 (0x04)

- 12 : ARMv6 SIMD Instruction Intrinsics

- 12.1 : ARMv6 SIMD intrinsics by prefix

- 12.2 : ARMv6 SIMD intrinsics, summary descriptions, byte lanes, affected flags

- 12.3 : ARMv6 SIMD intrinsics, compatible processors and architectures

- 12.4 : ARMv6 SIMD instruction intrinsics and APSR GE flags

- 12.5 : __qadd16 intrinsic

- 12.6 : __qadd8 intrinsic

- 12.7 : __qasx intrinsic

- 12.8 : __qsax intrinsic

- 12.9 : __qsub16 intrinsic

- 12.10 : __qsub8 intrinsic

- 12.11 : __sadd16 intrinsic

- 12.12 : __sadd8 intrinsic

- 12.13 : __sasx intrinsic

- 12.14 : __sel intrinsic

- 12.15 : __shadd16 intrinsic

- 12.16 : __shadd8 intrinsic

- 12.17 : __shasx intrinsic

- 12.18 : __shsax intrinsic

- 12.19 : __shsub16 intrinsic

- 12.20 : __shsub8 intrinsic

- 12.21 : __smlad intrinsic

- 12.22 : __smladx intrinsic

- 12.23 : __smlald intrinsic

- 12.24 : __smlaldx intrinsic

- 12.25 : __smlsd intrinsic

- 12.26 : __smlsdx intrinsic

- 12.27 : __smlsld intrinsic

- 12.28 : __smlsldx intrinsic

- 12.29 : __smuad intrinsic

- 12.30 : __smuadx intrinsic

- 12.31 : __smusd intrinsic

- 12.32 : __smusdx intrinsic

- 12.33 : __ssat16 intrinsic

- 12.34 : __ssax intrinsic

- 12.35 : __ssub16 intrinsic

- 12.36 : __ssub8 intrinsic

- 12.37 : __sxtab16 intrinsic

- 12.38 : __sxtb16 intrinsic

- 12.39 : __uadd16 intrinsic

- 12.40 : __uadd8 intrinsic

- 12.41 : __uasx intrinsic

- 12.42 : __uhadd16 intrinsic

- 12.43 : __uhadd8 intrinsic

- 12.44 : __uhasx intrinsic

- 12.45 : __uhsax intrinsic

- 12.46 : __uhsub16 intrinsic

- 12.47 : __uhsub8 intrinsic

- 12.48 : __uqadd16 intrinsic

- 12.49 : __uqadd8 intrinsic

- 12.50 : __uqasx intrinsic

- 12.51 : __uqsax intrinsic

- 12.52 : __uqsub16 intrinsic

- 12.53 : __uqsub8 intrinsic

- 12.54 : __usad8 intrinsic

- 12.55 : __usada8 intrinsic

- 12.56 : __usat16 intrinsic

- 12.57 : __usax intrinsic

- 12.58 : __usub16 intrinsic

- 12.59 : __usub8 intrinsic

- 12.60 : __uxtab16 intrinsic

- 12.61 : __uxtb16 intrinsic

- 13 : Via File Syntax

- 14 : Summary Table of GNU Language Extensions

- 15 : Standard C Implementation Definition

- 15.1 : Implementation definition

- 15.2 : Translation

- 15.3 : Environment

- 15.4 : Identifiers

- 15.5 : Characters

- 15.6 : Integers

- 15.7 : Floating-point

- 15.8 : Arrays and pointers

- 15.9 : Registers

- 15.10 : Structures, unions, enumerations, and bitfields

- 15.11 : Qualifiers

- 15.12 : Expression evaluation

- 15.13 : Preprocessing directives

- 15.14 : Library functions

- 15.15 : Behaviors considered undefined by the ISO C Standard

- 16 : Standard C++ Implementation Definition

- 17 : C and C++ Compiler Implementation Limits

ARM® Compiler v5.06 for µVision®

Version 5

armcc User Guide

Confidential - Draft - Beta

Copyright © 2007, 2008, 2011, 2012, 2014, 2015 ARM. All rights reserved.

ARM DUI0375G_02

ARM® Compiler v5.06 for µVision®

armcc User Guide

Copyright © 2007, 2008, 2011, 2012, 2014, 2015 ARM. All rights reserved.

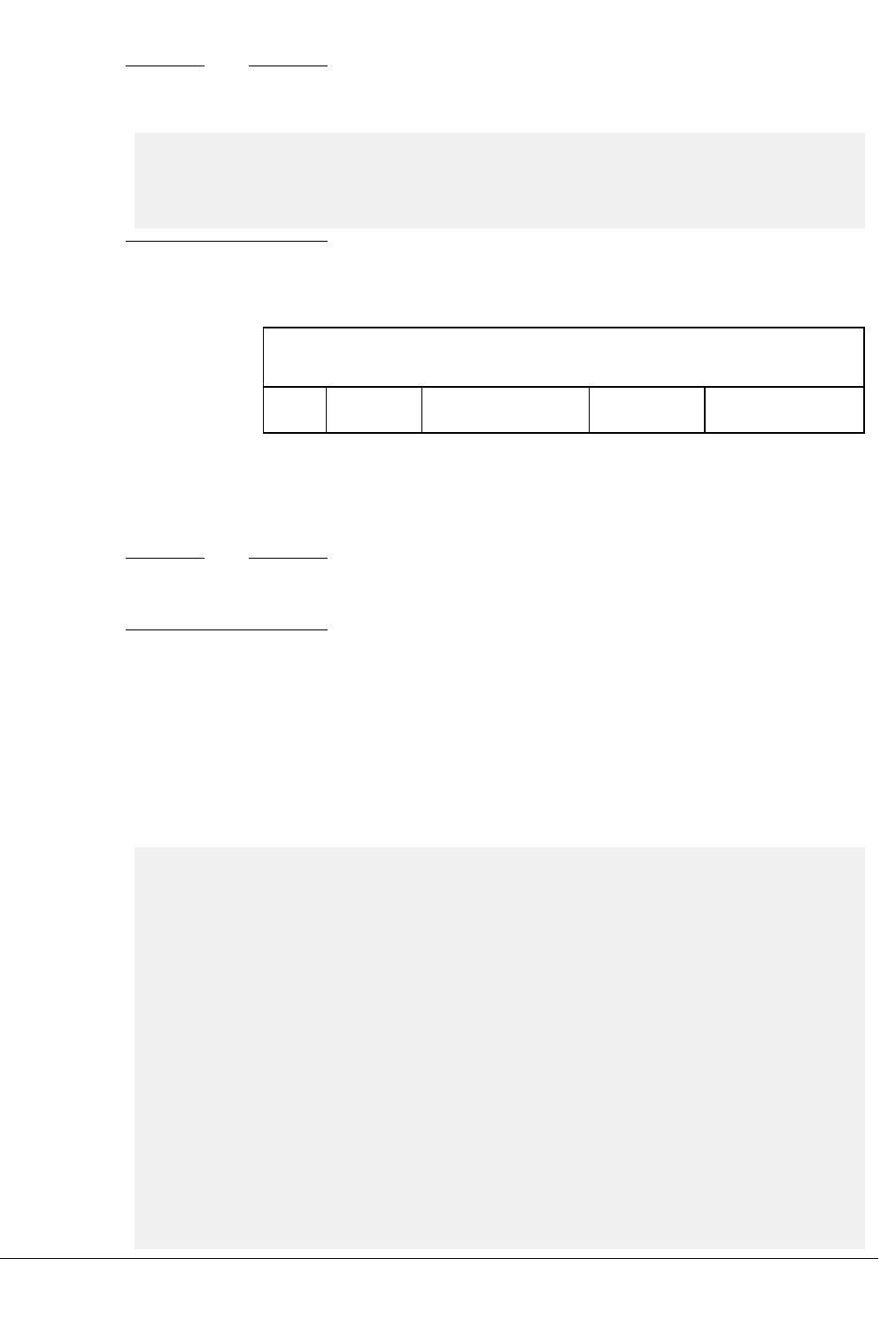

Release Information

Document History

Issue Date Confidentiality Change

A May 2007 Non-Confidential Release for RVCT v3.1 Release for µVision

B December 2008 Non-Confidential Release for RVCT v4.0 Release for µVision

C June 2011 Non-Confidential Release for ARM Compiler v4.1 for µVision

D July 2012 Non-Confidential Release for ARM Compiler v5.02 for µVision

E 30 May 2014 Non-Confidential Release for ARM Compiler v5.04 for µVision

F 12 December 2014 Non-Confidential Release for ARM Compiler v5.05 for µVision

G-02 15 August 2015 Confidential - Draft Release for ARM Compiler v5.06 for µVision

Confidential Proprietary Notice

This document is CONFIDENTIAL and any use by you is subject to the terms of the agreement between you and ARM or the

terms of the agreement between you and the party authorised by ARM to disclose this document to you.

This document is protected by copyright and other related rights and the practice or implementation of the information contained in

this document may be protected by one or more patents or pending patent applications. No part of this document may be

reproduced in any form by any means without the express prior written permission of ARM. No license, express or implied, by

estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use

the information: (i) for the purposes of determining whether implementations infringe any third party patents; (ii) for developing

technology or products which avoid any of ARM’s intellectual property; or (iii) as a reference for modifying existing patents or

patent applications or creating any continuation, continuation in part, or extension of existing patents or patent applications; or (iv)

for generating data for publication or disclosure to third parties, which compares the performance or functionality of the ARM

technology described in this document with any other products created by you or a third party, without obtaining ARM’s prior

written consent.

THIS DOCUMENT IS PROVIDED “AS IS”. ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES,

EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF

MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE

WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, ARM makes no representation with respect to, and has

undertaken no analysis to identify or understand the scope and content of, third party patents, copyrights, trade secrets, or other

rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES,

INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR

CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING

OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH

DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of

this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is

not exported, directly or indirectly, in violation of such export laws. Use of the word “partner” in reference to ARM’s customers is

not intended to create or refer to any partnership relationship with any other company. ARM may make changes to this document at

any time and without notice.

If any of the provisions contained in these terms conflict with any of the provisions of any signed written agreement covering this

document with ARM, then the signed written agreement prevails over and supersedes the conflicting provisions of these terms.

ARM® Compiler v5.06 for µVision®

ARM DUI0375G_02 Copyright © 2007, 2008, 2011, 2012, 2014, 2015 ARM. All rights

reserved.

2

Confidential - Draft - Beta

This document may be translated into other languages for convenience, and you agree that if there is any conflict between the

English version of this document and any translation, the terms of the English version of the Agreement shall prevail.

Words and logos marked with ® or ™ are registered trademarks or trademarks of ARM Limited or its affiliates in the EU and/or

elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective

owners. Please follow ARM’s trademark usage guidelines at http://www.arm.com/about/trademarks/guidelines/index.php

Copyright © [2007, 2008, 2011, 2012, 2014, 2015], ARM Limited or its affiliates. All rights reserved.

ARM Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

LES-PRE-20348

Additional Notices

Some material in this document is based on IEEE 754-1985 IEEE Standard for Binary Floating-Point Arithmetic. The IEEE

disclaims any responsibility or liability resulting from the placement and use in the described manner.

Confidentiality Status

This document is Confidential. This document may only be used and distributed in accordance with the terms of the agreement

entered into by ARM and the party that ARM delivered this document to.

Product Status

The information in this document is for a Beta product, that is a product under development.

Web Address

http://www.arm.com

ARM® Compiler v5.06 for µVision®

ARM DUI0375G_02 Copyright © 2007, 2008, 2011, 2012, 2014, 2015 ARM. All rights

reserved.

3

Confidential - Draft - Beta

Contents

ARM® Compiler v5.06 for µVision® armcc User

Guide

Preface

About this book ..................................................... ..................................................... 24

Chapter 1 Overview of the Compiler

1.1 The compiler ............................................................................................................ 1-28

1.2 Source language modes of the compiler ................................ ................................ 1-29

1.3 Language extensions .............................................................................................. 1-31

1.4 Language compliance .............................................. .............................................. 1-32

1.5 The C and C++ libraries .......................................................................................... 1-33

Chapter 2 Getting Started with the Compiler

2.1 Compiler command-line syntax ....................................... ....................................... 2-35

2.2 Compiler command-line options listed by group ...................................................... 2-36

2.3 Default compiler behavior ........................................................................................ 2-42

2.4 Order of compiler command-line options ................................ ................................ 2-43

2.5 Using stdin to input source code to the compiler .......................... .......................... 2-44

2.6 Directing output to stdout ............................................ ............................................ 2-46

2.7 Filename suffixes recognized by the compiler ............................ ............................ 2-47

2.8 Compiler output files ................................................................................................ 2-49

2.9 Factors influencing how the compiler searches for header files .............................. 2-50

2.10 Compiler command-line options and search paths ........................ ........................ 2-51

2.11 Compiler search rules and the current place ............................. ............................. 2-52

ARM DUI0375G_02 Copyright © 2007, 2008, 2011, 2012, 2014, 2015 ARM. All rights

reserved.

4

Confidential - Draft - Beta

2.12 The ARMCC5INC environment variable .................................................................. 2-53

2.13 Code compatibility between separately compiled and assembled modules ............ 2-54

2.14 Linker feedback during compilation .................................... .................................... 2-55

2.15 Unused function code .............................................................................................. 2-56

2.16 Minimizing code size by eliminating unused functions during compilation .............. 2-57

2.17 Compilation build time .............................................. .............................................. 2-58

Chapter 3 Compiler Features

3.1 Compiler intrinsics ................................................. ................................................. 3-64

3.2 Performance benefits of compiler intrinsics .............................. .............................. 3-65

3.3 ARM assembler instruction intrinsics ................................... ................................... 3-66

3.4 Generic intrinsics .................................................. .................................................. 3-67

3.5 Compiler intrinsics for controlling IRQ and FIQ interrupts ................... ................... 3-68

3.6 Compiler intrinsics for inserting optimization barriers .............................................. 3-69

3.7 Compiler intrinsics for inserting native instructions .................................................. 3-70

3.8 Compiler intrinsics for Digital Signal Processing (DSP) ..................... ..................... 3-71

3.9 Compiler support for European Telecommunications Standards Institute (ETSI) basic

operations ................................................................................................................ 3-72

3.10 Overflow and carry status flags for C and C++ code ....................... ....................... 3-74

3.11 Texas Instruments (TI) C55x intrinsics for optimizing C code .................................. 3-75

3.12 Compiler support for accessing registers using named register variables .............. 3-76

3.13 Pragmas recognized by the compiler ...................................................................... 3-79

3.14 Compiler and processor support for bit-banding .......................... .......................... 3-81

3.15 Compiler type attribute, __attribute__((bitband)) .......................... .......................... 3-82

3.16 --bitband compiler command-line option ................................ ................................ 3-83

3.17 How the compiler handles bit-band objects placed outside bit-band regions .......... 3-84

3.18 Compiler support for thread-local storage ............................... ............................... 3-85

3.19 Compiler support for literal pools ...................................... ...................................... 3-86

3.20 Compiler eight-byte alignment features ................................. ................................. 3-87

3.21 Precompiled Header (PCH) files ...................................... ...................................... 3-88

3.22 Automatic Precompiled Header (PCH) file processing ............................................ 3-90

3.23 Precompiled Header (PCH) file processing and the header stop point ......... ......... 3-91

3.24 Precompiled Header (PCH) file creation requirements ..................... ..................... 3-93

3.25 Compilation with multiple Precompiled Header (PCH) files .................. .................. 3-95

3.26 Obsolete Precompiled Header (PCH) files .............................................................. 3-96

3.27 Manually specifying the filename and location of a Precompiled Header (PCH) file ....

.................................................................................................................................. 3-97

3.28 Selectively applying Precompiled Header (PCH) file processing ............................ 3-98

3.29 Suppressing Precompiled Header (PCH) file processing ........................................ 3-99

3.30 Message output during Precompiled Header (PCH) processing ............. ............. 3-100

3.31 Performance issues with Precompiled Header (PCH) files ................. ................. 3-101

3.32 Default compiler options that are affected by optimization level ............................ 3-102

Chapter 4 Compiler Coding Practices

4.1 The compiler as an optimizing compiler ................................................................ 4-106

4.2 Compiler optimization for code size versus speed ................................................ 4-107

4.3 Compiler optimization levels and the debug view .................................................. 4-108

4.4 Selecting the target processor at compile time ...................................................... 4-111

4.5 Enabling FPU for bare-metal ........................................ ........................................ 4-112

4.6 Optimization of loop termination in C code ............................................................ 4-113

ARM DUI0375G_02 Copyright © 2007, 2008, 2011, 2012, 2014, 2015 ARM. All rights

reserved.

5

Confidential - Draft - Beta

4.7 Loop unrolling in C code ........................................................................................ 4-115

4.8 Compiler optimization and the volatile keyword .......................... .......................... 4-117

4.9 Code metrics .......................................................................................................... 4-119

4.10 Code metrics for measurement of code size and data size ................. ................. 4-120

4.11 Stack use in C and C++ ............................................ ............................................ 4-121

4.12 Benefits of reducing debug information in objects and libraries ............................ 4-123

4.13 Methods of reducing debug information in objects and libraries ............. ............. 4-124

4.14 Guarding against multiple inclusion of header files ....................... ....................... 4-125

4.15 Methods of minimizing function parameter passing overhead ............... ............... 4-126

4.16 Returning structures from functions through registers ..................... ..................... 4-127

4.17 Functions that return the same result when called with the same arguments ... ... 4-128

4.18 Comparison of pure and impure functions .............................. .............................. 4-129

4.19 Recommendation of postfix syntax when qualifying functions with ARM function

modifiers ................................................................................................................ 4-130

4.20 Inline functions ................................................... ................................................... 4-131

4.21 Compiler decisions on function inlining ................................ ................................ 4-132

4.22 Automatic function inlining and static functions .......................... .......................... 4-133

4.23 Inline functions and removal of unused out-of-line functions at link time ....... ....... 4-134

4.24 Automatic function inlining and multifile compilation ...................... ...................... 4-135

4.25 Restriction on overriding compiler decisions about function inlining .......... .......... 4-136

4.26 Compiler modes and inline functions .................................. .................................. 4-137

4.27 Inline functions in C++ and C90 mode .................................................................. 4-138

4.28 Inline functions in C99 mode ........................................ ........................................ 4-139

4.29 Inline functions and debugging .............................................................................. 4-141

4.30 Types of data alignment ............................................ ............................................ 4-142

4.31 Advantages of natural data alignment ................................. ................................. 4-143

4.32 Compiler storage of data objects by natural byte alignment .................................. 4-144

4.33 Relevance of natural data alignment at compile time ............................................ 4-145

4.34 Unaligned data access in C and C++ code ............................. ............................. 4-146

4.35 The __packed qualifier and unaligned data access in C and C++ code ....... ....... 4-147

4.36 Unaligned fields in structures ........................................ ........................................ 4-148

4.37 Performance penalty associated with marking whole structures as packed .... .... 4-149

4.38 Unaligned pointers in C and C++ code .................................................................. 4-150

4.39 Unaligned Load Register (LDR) instructions generated by the compiler ....... ....... 4-151

4.40 Comparisons of an unpacked struct, a __packed struct, and a struct with individually

__packed fields, and of a __packed struct and a #pragma packed struct ...... ...... 4-152

4.41 Compiler support for floating-point arithmetic ........................................................ 4-154

4.42 Default selection of hardware or software floating-point support ............. ............. 4-156

4.43 Example of hardware and software support differences for floating-point arithmetic ....

................................................................................................................................ 4-157

4.44 Vector Floating-Point (VFP) architectures .............................. .............................. 4-159

4.45 Limitations on hardware handling of floating-point arithmetic ................................ 4-160

4.46 Implementation of Vector Floating-Point (VFP) support code ............... ............... 4-161

4.47 Compiler and library support for half-precision floating-point numbers ........ ........ 4-163

4.48 Half-precision floating-point number format ............................. ............................. 4-164

4.49 Compiler support for floating-point computations and linkage ............... ............... 4-165

4.50 Types of floating-point linkage ....................................... ....................................... 4-166

4.51 Compiler options for floating-point linkage and computations ............... ............... 4-167

4.52 Floating-point linkage and computational requirements of compiler options .... .... 4-169

4.53 Processors and their implicit Floating-Point Units (FPUs) .................. .................. 4-171

ARM DUI0375G_02 Copyright © 2007, 2008, 2011, 2012, 2014, 2015 ARM. All rights

reserved.

6

Confidential - Draft - Beta

4.54 Integer division-by-zero errors in C code ............................... ............................... 4-173

4.55 Software floating-point division-by-zero errors in C code ...................................... 4-175

4.56 About trapping software floating-point division-by-zero errors ............... ............... 4-176

4.57 Identification of software floating-point division-by-zero errors .............................. 4-177

4.58 Software floating-point division-by-zero debugging ....................... ....................... 4-179

4.59 New language features of C99 .............................................................................. 4-180

4.60 New library features of C99 ......................................... ......................................... 4-182

4.61 // comments in C99 and C90 ........................................ ........................................ 4-183

4.62 Compound literals in C99 ...................................................................................... 4-184

4.63 Designated initializers in C99 ................................................................................ 4-185

4.64 Hexadecimal floating-point numbers in C99 .......................................................... 4-186

4.65 Flexible array members in C99 .............................................................................. 4-187

4.66 __func__ predefined identifier in C99 .................................................................... 4-188

4.67 inline functions in C99 ............................................. ............................................. 4-189

4.68 long long data type in C99 and C90 ...................................................................... 4-190

4.69 Macros with a variable number of arguments in C99 ............................................ 4-191

4.70 Mixed declarations and statements in C99 ............................................................ 4-192

4.71 New block scopes for selection and iteration statements in C99 ............. ............. 4-193

4.72 _Pragma preprocessing operator in C99 ............................... ............................... 4-194

4.73 Restricted pointers in C99 .......................................... .......................................... 4-195

4.74 Additional <math.h> library functions in C99 ............................ ............................ 4-196

4.75 Complex numbers in C99 ...................................................................................... 4-197

4.76 Boolean type and <stdbool.h> in C99 ................................. ................................. 4-198

4.77 Extended integer types and functions in <inttypes.h> and <stdint.h> in C99 ........ 4-199

4.78 <fenv.h> floating-point environment access in C99 ....................... ....................... 4-200

4.79 <stdio.h> snprintf family of functions in C99 .......................................................... 4-201

4.80 <tgmath.h> type-generic math macros in C99 ........................... ........................... 4-202

4.81 <wchar.h> wide character I/O functions in C99 .......................... .......................... 4-203

4.82 How to prevent uninitialized data from being initialized to zero .............. .............. 4-204

Chapter 5 Compiler Diagnostic Messages

5.1 Severity of compiler diagnostic messages .............................. .............................. 5-206

5.2 Options that change the severity of compiler diagnostic messages ...................... 5-207

5.3 Controlling compiler diagnostic messages with pragmas ...................................... 5-209

5.4 Prefix letters in compiler diagnostic messages ...................................................... 5-211

5.5 Compiler exit status codes and termination messages .................... .................... 5-212

5.6 Compiler data flow warnings ........................................ ........................................ 5-213

Chapter 6 Using the Inline and Embedded Assemblers of the ARM Compiler

6.1 Compiler support for inline assembly language .......................... .......................... 6-216

6.2 Inline assembler support in the compiler ............................... ............................... 6-217

6.3 Restrictions on inline assembler support in the compiler ................... ................... 6-218

6.4 Inline assembly language syntax with the __asm keyword in C and C++ ...... ...... 6-219

6.5 Inline assembly language syntax with the asm keyword in C++ ............. ............. 6-220

6.6 Inline assembler rules for compiler keywords __asm and asm .............. .............. 6-221

6.7 Restrictions on inline assembly operations in C and C++ code .............. .............. 6-222

6.8 Inline assembler register restrictions in C and C++ code ...................................... 6-223

6.9 Inline assembler processor mode restrictions in C and C++ code ........................ 6-224

6.10 Inline assembler Thumb instruction set restrictions in C and C++ code ................ 6-225

6.11 Inline assembler Vector Floating-Point (VFP) restrictions in C and C++ code ...... 6-226

ARM DUI0375G_02 Copyright © 2007, 2008, 2011, 2012, 2014, 2015 ARM. All rights

reserved.

7

Confidential - Draft - Beta

6.12 Inline assembler instruction restrictions in C and C++ code .................................. 6-227

6.13 Miscellaneous inline assembler restrictions in C and C++ code ............. ............. 6-228

6.14 Inline assembler and register access in C and C++ code .................. .................. 6-229

6.15 Inline assembler and the # constant expression specifier in C and C++ code ...... 6-231

6.16 Inline assembler and instruction expansion in C and C++ code ............................ 6-232

6.17 Expansion of inline assembler instructions that use constants .............. .............. 6-233

6.18 Expansion of inline assembler load and store instructions .................................... 6-234

6.19 Inline assembler effect on processor condition flags in C and C++ code .............. 6-235

6.20 Inline assembler expression operands in C and C++ code ................. ................. 6-236

6.21 Inline assembler register list operands in C and C++ code ................. ................. 6-237

6.22 Inline assembler intermediate operands in C and C++ code ................ ................ 6-238

6.23 Inline assembler function calls and branches in C and C++ code ............ ............ 6-239

6.24 Inline assembler branches and labels in C and C++ code .................................... 6-241

6.25 Inline assembler and virtual registers .................................................................... 6-242

6.26 Embedded assembler support in the compiler ...................................................... 6-243

6.27 Embedded assembler syntax in C and C++ .......................................................... 6-244

6.28 Effect of compiler ARM and Thumb states on embedded assembler ......... ......... 6-245

6.29 Restrictions on embedded assembly language functions in C and C++ code ... ... 6-246

6.30 Compiler generation of embedded assembly language functions ............ ............ 6-247

6.31 Access to C and C++ compile-time constant expressions from embedded assembler ...

................................................................................................................................ 6-249

6.32 Differences between expressions in embedded assembler and C or C++ ............ 6-250

6.33 Manual overload resolution in embedded assembler ............................................ 6-251

6.34 __offsetof_base keyword for related base classes in embedded assembler ........ 6-252

6.35 Compiler-supported keywords for calling class member functions in embedded

assembler .............................................................................................................. 6-253

6.36 __mcall_is_virtual(D, f) .......................................................................................... 6-254

6.37 __mcall_is_in_vbase(D, f) .......................................... .......................................... 6-255

6.38 __mcall_offsetof_vbase(D, f) ........................................ ........................................ 6-256

6.39 __mcall_this_offset(D, f) ........................................................................................ 6-257

6.40 __vcall_offsetof_vfunc(D, f) ......................................... ......................................... 6-258

6.41 Calling nonstatic member functions in embedded assembler ............... ............... 6-259

6.42 Calling a nonvirtual member function .................................................................... 6-260

6.43 Calling a virtual member function .......................................................................... 6-261

6.44 Accessing sp (r13), lr (r14), and pc (r15) ............................... ............................... 6-262

6.45 Differences in compiler support for inline and embedded assembly code ...... ...... 6-263

Chapter 7 Compiler Command-line Options

7.1 -Aopt ...................................................................................................................... 7-268

7.2 --allow_fpreg_for_nonfpdata, --no_allow_fpreg_for_nonfpdata .............. .............. 7-269

7.3 --allow_null_this, --no_allow_null_this ................................. ................................. 7-270

7.4 --alternative_tokens, --no_alternative_tokens ........................... ........................... 7-271

7.5 --anachronisms, --no_anachronisms .................................. .................................. 7-272

7.6 --apcs=qualifier...qualifier ........................................... ........................................... 7-273

7.7 --arm ...................................................................................................................... 7-277

7.8 --arm_only ...................................................... ...................................................... 7-278

7.9 --asm .......................................................... .......................................................... 7-279

7.10 --asm_dir=directory_name .......................................... .......................................... 7-280

7.11 --autoinline, --no_autoinline ......................................... ......................................... 7-281

7.12 --bigend ........................................................ ........................................................ 7-282

ARM DUI0375G_02 Copyright © 2007, 2008, 2011, 2012, 2014, 2015 ARM. All rights

reserved.

8

Confidential - Draft - Beta

7.13 --bitband ................................................................................................................ 7-283

7.14 --branch_tables, --no_branch_tables .................................. .................................. 7-284

7.15 --brief_diagnostics, --no_brief_diagnostics ............................................................ 7-286

7.16 --bss_threshold=num .............................................. .............................................. 7-287

7.17 -c ............................................................................................................................ 7-288

7.18 -C ............................................................. ............................................................. 7-289

7.19 --c90 ...................................................................................................................... 7-290

7.20 --c99 ...................................................................................................................... 7-291

7.21 --code_gen, --no_code_gen .................................................................................. 7-292

7.22 --compatible=name ................................................................................................ 7-293

7.23 --compile_all_input, --no_compile_all_input .......................................................... 7-295

7.24 --conditionalize, --no_conditionalize ...................................................................... 7-296

7.25 --cpp ...................................................................................................................... 7-297

7.26 --cpp11 ......................................................... ......................................................... 7-298

7.27 --cpp_compat .................................................... .................................................... 7-299

7.28 --cpu=list ................................................................................................................ 7-301

7.29 --cpu=name compiler option .................................................................................. 7-302

7.30 --create_pch=filename ............................................. ............................................. 7-304

7.31 -Dname[(parm-list)][=def] ........................................... ........................................... 7-305

7.32 --data_reorder, --no_data_reorder .................................... .................................... 7-306

7.33 --debug, --no_debug .............................................................................................. 7-307

7.34 --debug_macros, --no_debug_macros .................................................................. 7-308

7.35 --default_extension=ext ............................................ ............................................ 7-309

7.36 --dep_name, --no_dep_name ................................................................................ 7-310

7.37 --depend=filename ................................................ ................................................ 7-311

7.38 --depend_dir=directory_name ....................................... ....................................... 7-312

7.39 --depend_format=string ............................................ ............................................ 7-313

7.40 --depend_single_line, --no_depend_single_line .................................................... 7-314

7.41 --depend_system_headers, --no_depend_system_headers ................ ................ 7-315

7.42 --depend_target=target .......................................................................................... 7-316

7.43 --diag_error=tag[,tag,...] ............................................ ............................................ 7-317

7.44 --diag_remark=tag[,tag,...] .......................................... .......................................... 7-318

7.45 --diag_style=arm|ide|gnu compiler option .............................................................. 7-319

7.46 --diag_suppress=tag[,tag,...] .................................................................................. 7-320

7.47 --diag_suppress=optimizations .............................................................................. 7-321

7.48 --diag_warning=tag[,tag,...] .................................................................................... 7-322

7.49 --diag_warning=optimizations ................................................................................ 7-323

7.50 --dollar, --no_dollar ................................................................................................ 7-324

7.51 --dwarf2 ........................................................ ........................................................ 7-325

7.52 --dwarf3 ........................................................ ........................................................ 7-326

7.53 -E ............................................................. ............................................................. 7-327

7.54 --echo .................................................................................................................... 7-328

7.55 --emit_frame_directives, --no_emit_frame_directives ..................... ..................... 7-329

7.56 --enum_is_int .................................................... .................................................... 7-330

7.57 --errors=filename ................................................. ................................................. 7-331

7.58 --exceptions, --no_exceptions ....................................... ....................................... 7-332

7.59 --exceptions_unwind, --no_exceptions_unwind .......................... .......................... 7-333

7.60 --execute_only ................................................... ................................................... 7-334

7.61 --extended_initializers, --no_extended_initializers ........................ ........................ 7-335

7.62 --feedback=filename .............................................................................................. 7-336

ARM DUI0375G_02 Copyright © 2007, 2008, 2011, 2012, 2014, 2015 ARM. All rights

reserved.

9

Confidential - Draft - Beta

7.63 --float_literal_pools, --no_float_literal_pools .......................................................... 7-337

7.64 --force_new_nothrow, --no_force_new_nothrow ......................... ......................... 7-338

7.65 --forceinline ............................................................................................................ 7-339

7.66 --fp16_format=format .............................................. .............................................. 7-340

7.67 --fpmode=model .................................................................................................... 7-341

7.68 --fpu=list ........................................................ ........................................................ 7-343

7.69 --fpu=name compiler option ......................................... ......................................... 7-344

7.70 --friend_injection, --no_friend_injection ................................ ................................ 7-347

7.71 -g ............................................................. ............................................................. 7-348

7.72 --global_reg=reg_name[,reg_name,...] .................................................................. 7-349

7.73 --gnu ...................................................................................................................... 7-350

7.74 --gnu_defaults ........................................................................................................ 7-351

7.75 --gnu_instrument, --no_gnu_instrument ................................................................ 7-352

7.76 --gnu_version=version ............................................. ............................................. 7-353

7.77 --guiding_decls, --no_guiding_decls ...................................................................... 7-354

7.78 --help .......................................................... .......................................................... 7-355

7.79 -Idir[,dir,...] .............................................................................................................. 7-356

7.80 --ignore_missing_headers .......................................... .......................................... 7-357

7.81 --implicit_include, --no_implicit_include ................................ ................................ 7-358

7.82 --implicit_include_searches, --no_implicit_include_searches ................................ 7-359

7.83 --implicit_key_function, --no_implicit_key_function ....................... ....................... 7-360

7.84 --implicit_typename, --no_implicit_typename ........................................................ 7-361

7.85 --info=totals ............................................................................................................ 7-362

7.86 --inline, --no_inline ................................................ ................................................ 7-363

7.87 --integer_literal_pools, --no_integer_literal_pools ........................ ........................ 7-364

7.88 --interface_enums_are_32_bit ....................................... ....................................... 7-365

7.89 --interleave ...................................................... ...................................................... 7-366

7.90 -Jdir[,dir,...] ...................................................... ...................................................... 7-367

7.91 --kandr_include ...................................................................................................... 7-368

7.92 -Lopt ...................................................................................................................... 7-369

7.93 --library_interface=lib .............................................. .............................................. 7-370

7.94 --library_type=lib .................................................................................................... 7-372

7.95 --liclinger=seconds ................................................ ................................................ 7-373

7.96 --licretry .................................................................................................................. 7-374

7.97 --link_all_input, --no_link_all_input ........................................................................ 7-375

7.98 --list ........................................................................................................................ 7-376

7.99 --list_dir=directory_name ........................................... ........................................... 7-378

7.100 --list_macros .......................................................................................................... 7-379

7.101 --littleend ................................................................................................................ 7-380

7.102 --locale=lang_country ............................................................................................ 7-381

7.103 --long_long ...................................................... ...................................................... 7-382

7.104 --loop_optimization_level=opt ................................................................................ 7-383

7.105 --loose_implicit_cast .............................................................................................. 7-384

7.106 --lower_ropi, --no_lower_ropi ........................................ ........................................ 7-385

7.107 --lower_rwpi, --no_lower_rwpi ....................................... ....................................... 7-386

7.108 -M .......................................................................................................................... 7-387

7.109 --md ........................................................... ........................................................... 7-388

7.110 --message_locale=lang_country[.codepage] ............................ ............................ 7-389

7.111 --min_array_alignment=opt ......................................... ......................................... 7-390

7.112 --mm ...................................................................................................................... 7-391

ARM DUI0375G_02 Copyright © 2007, 2008, 2011, 2012, 2014, 2015 ARM. All rights

reserved.

10

Confidential - Draft - Beta

7.113 --multibyte_chars, --no_multibyte_chars ............................... ............................... 7-392

7.114 --multifile, --no_multifile ............................................ ............................................ 7-393

7.115 --multiply_latency=cycles ........................................... ........................................... 7-394

7.116 --narrow_volatile_bitfields ...................................................................................... 7-395

7.117 --nonstd_qualifier_deduction, --no_nonstd_qualifier_deduction ............................ 7-396

7.118 -o filename ...................................................... ...................................................... 7-397

7.119 -Onum .................................................................................................................... 7-399

7.120 --old_specializations, --no_old_specializations .......................... .......................... 7-402

7.121 --old_style_preprocessing .......................................... .......................................... 7-403

7.122 --omf_browse .................................................... .................................................... 7-404