00 ERA770

User Manual: ERA770

Open the PDF directly: View PDF ![]() .

.

Page Count: 94

MODEL ER-A770

(For "V" version)

CHAPTER 1. SPECIFICATIONS ................................................................1 - 1

CHAPTER 2. OPTIONS ..............................................................................2 - 1

CHAPTER 3. SERVICE PRECAUTION......................................................3 - 1

CHAPTER 4. SRV RESET (Program Loop Reset) and switch to SRV mode...4 - 1

CHAPTER 5. MASTER RESET ..................................................................5 - 1

CHAPTER 6. DIAGNOSTICS SPECIFICATIONS.......................................6 - 1

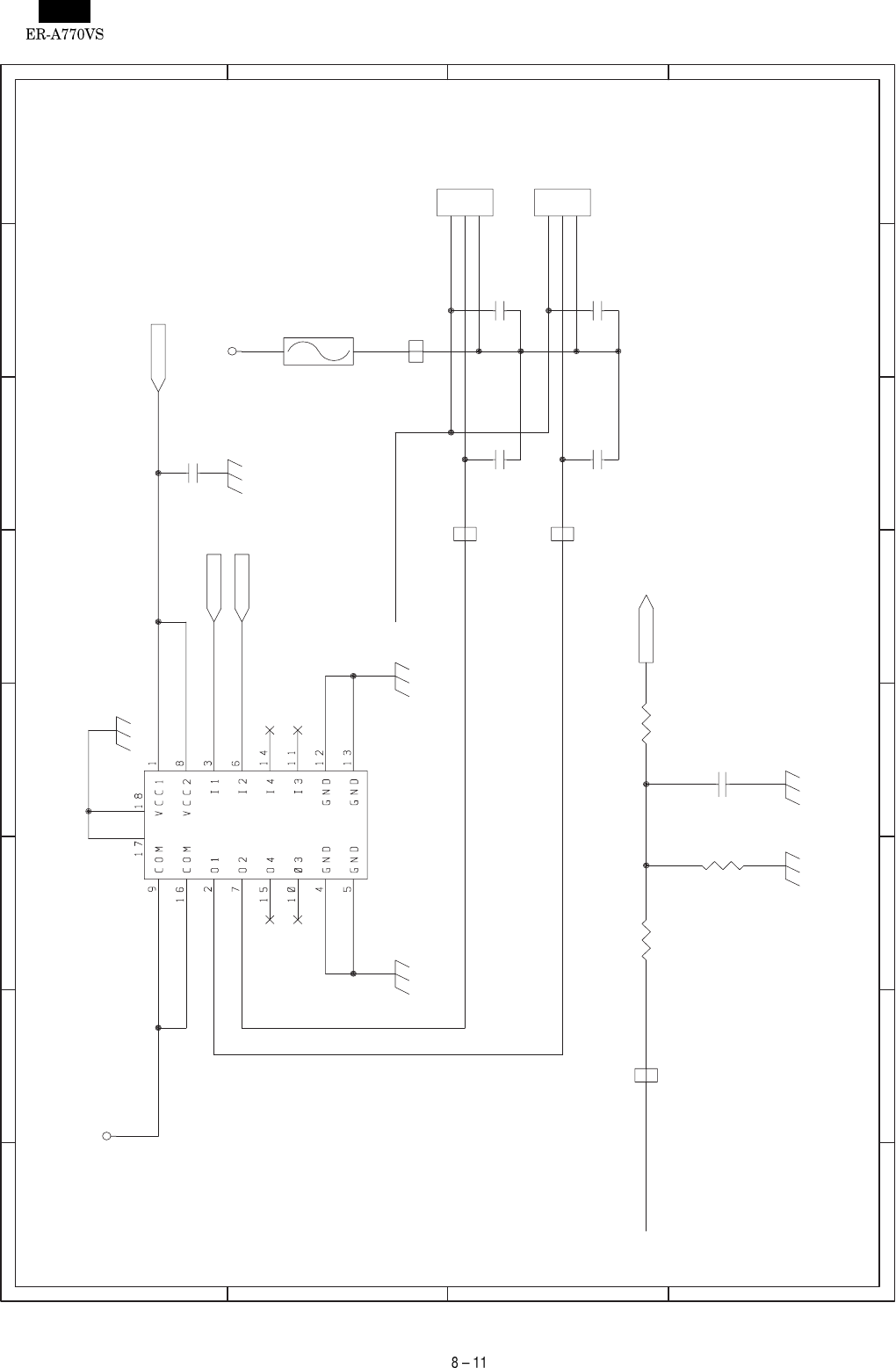

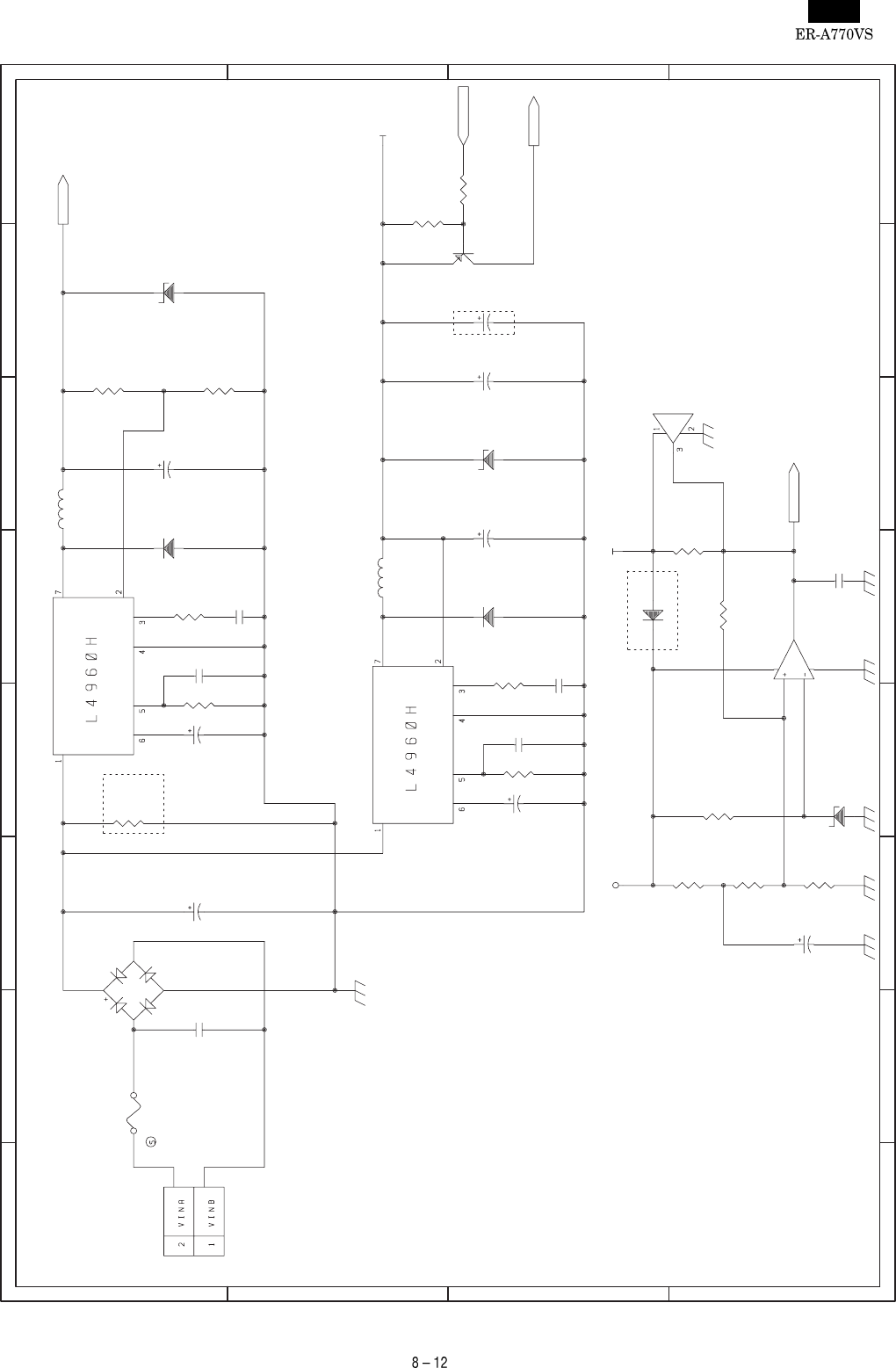

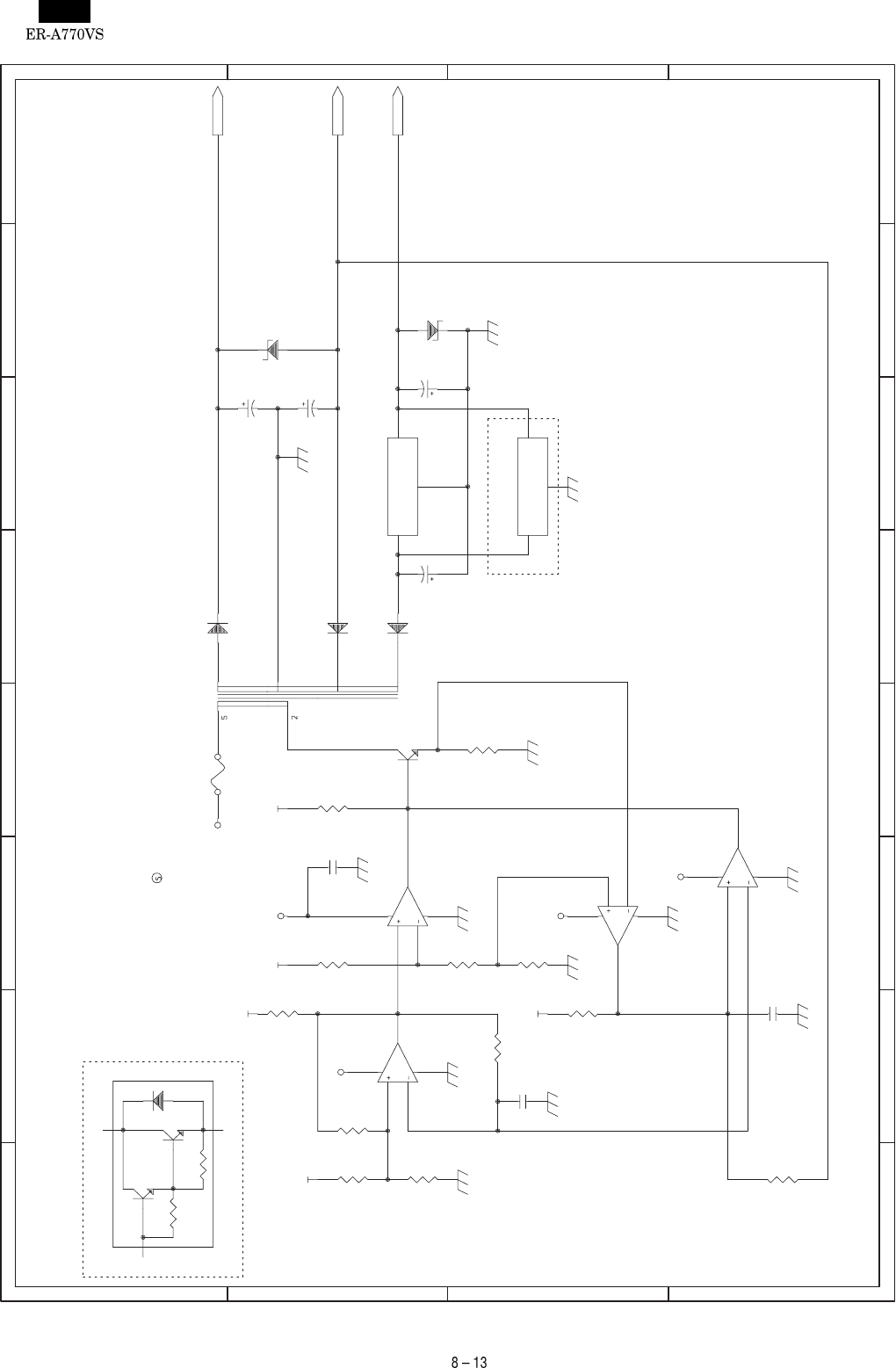

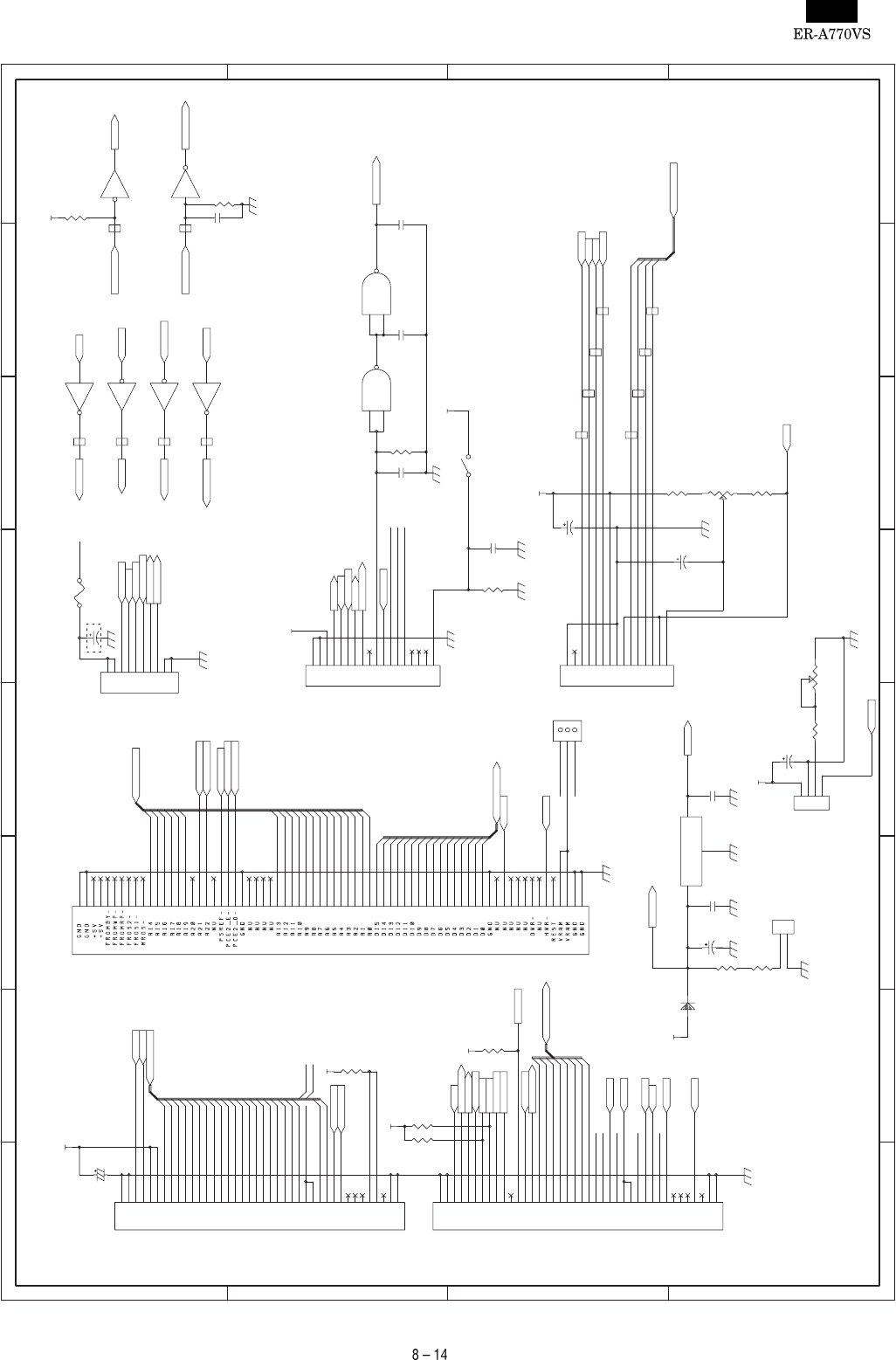

CHAPTER 7. CIRCUIT DESCRIPTION ......................................................7 - 1

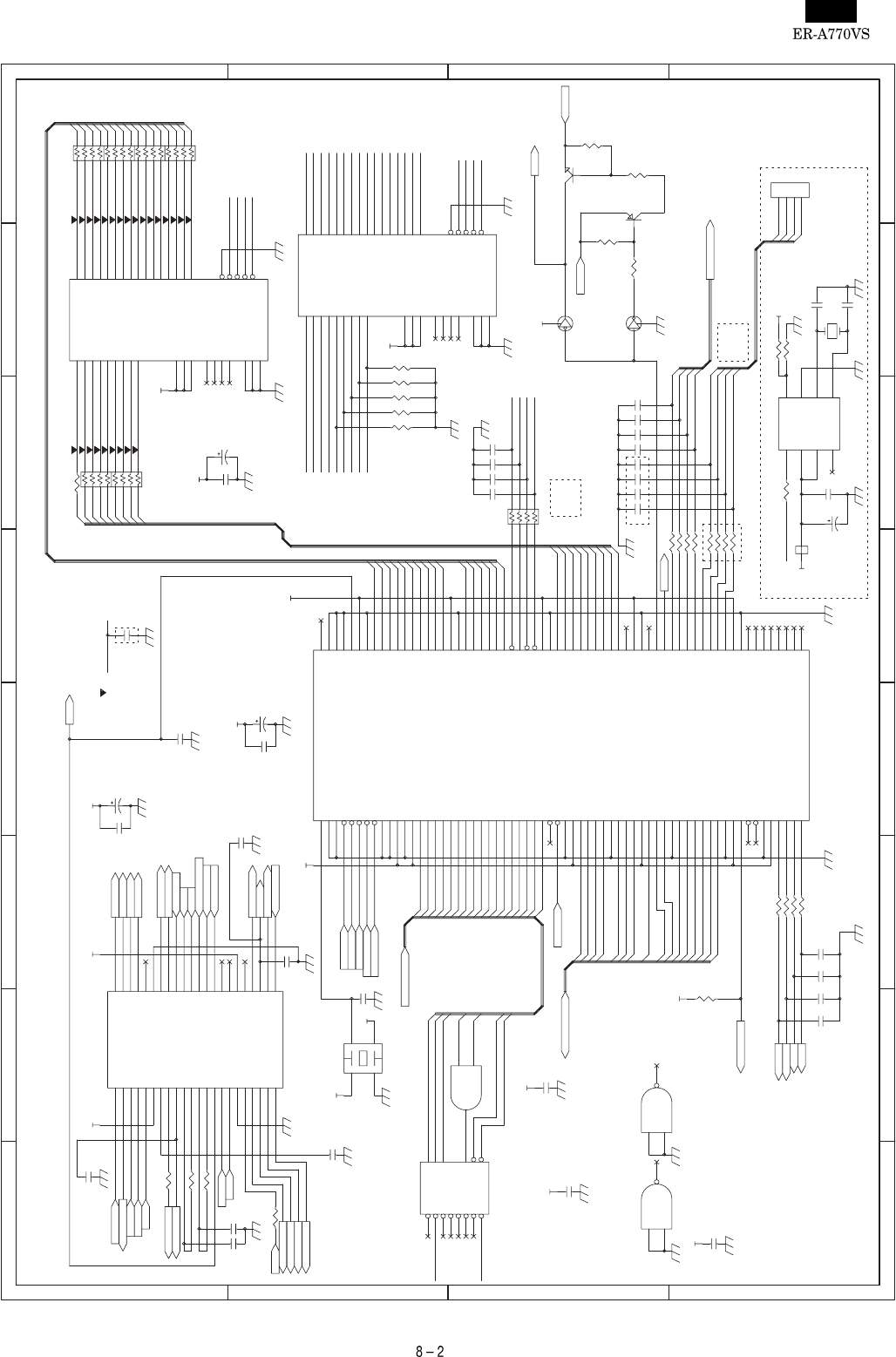

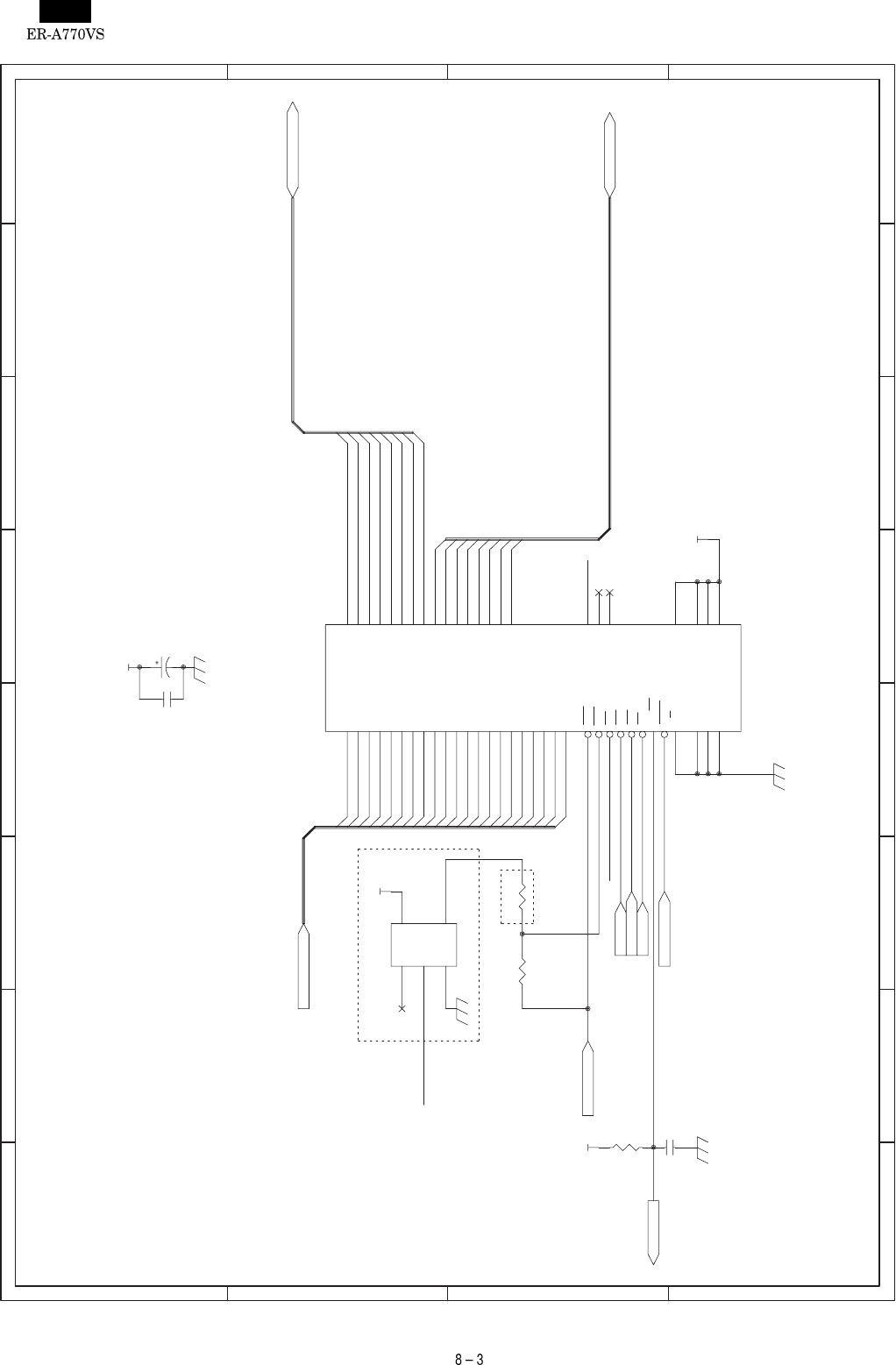

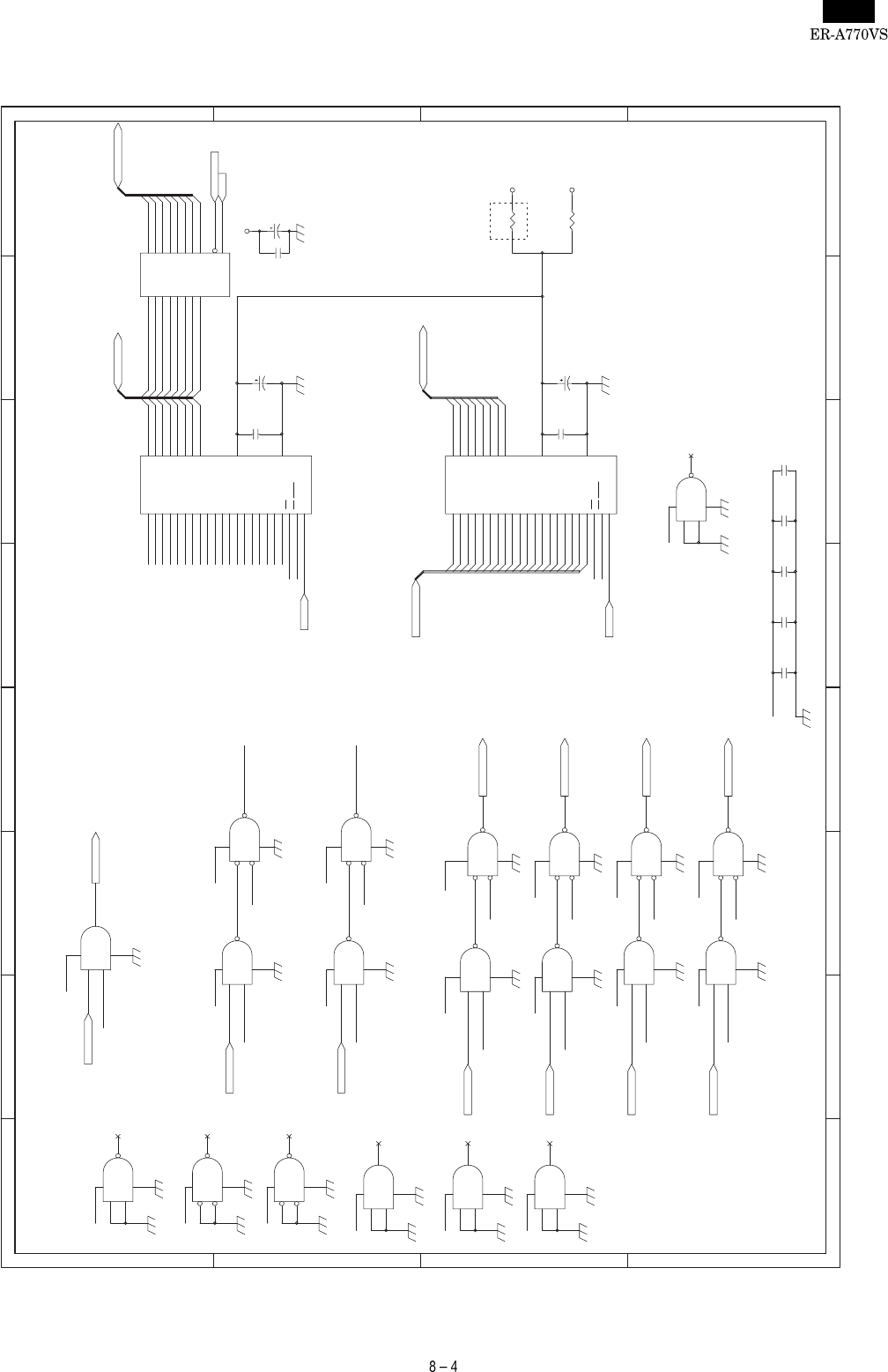

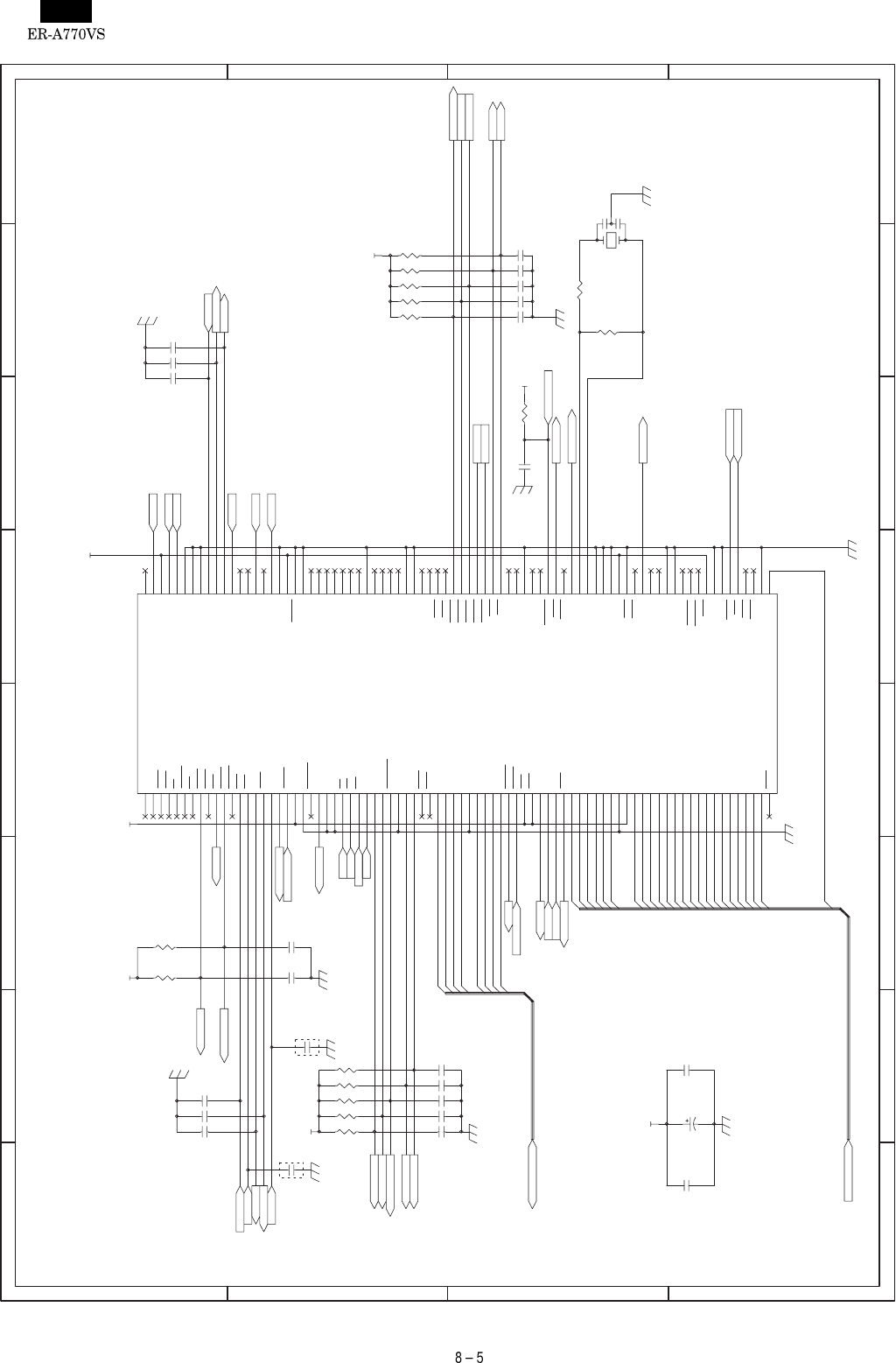

CHAPTER 8. CIRCUIT DIAGRAM..............................................................8 - 1

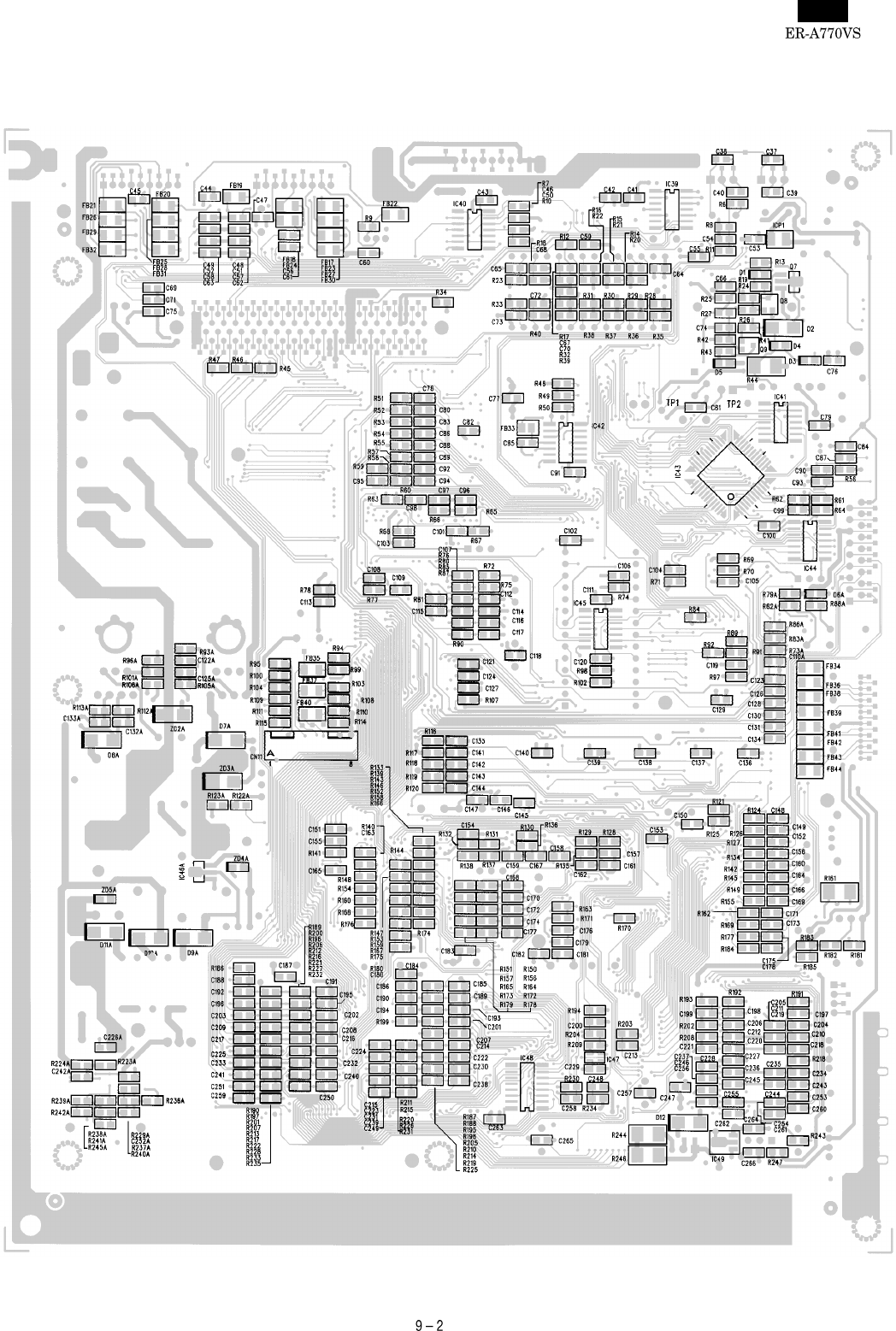

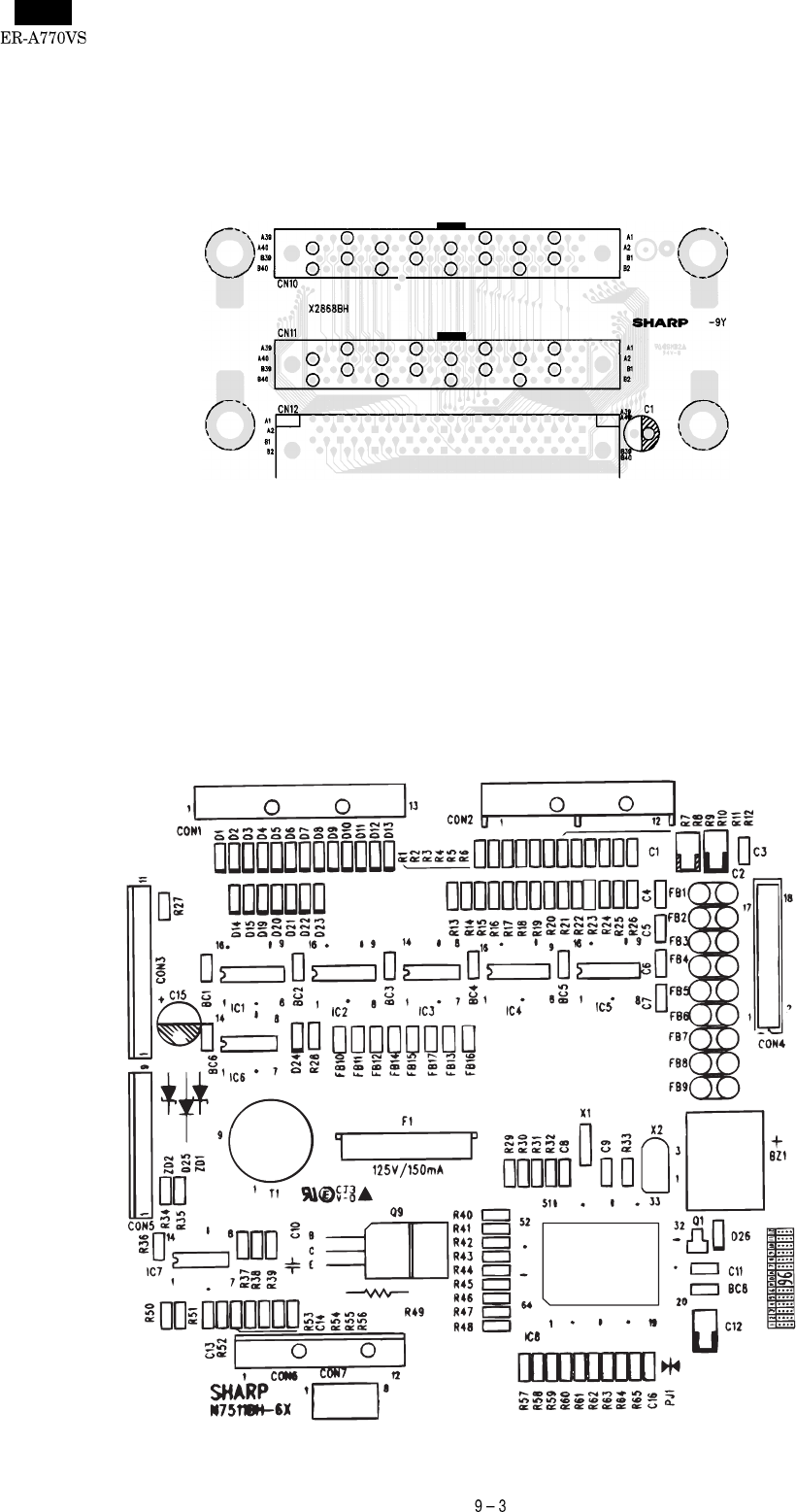

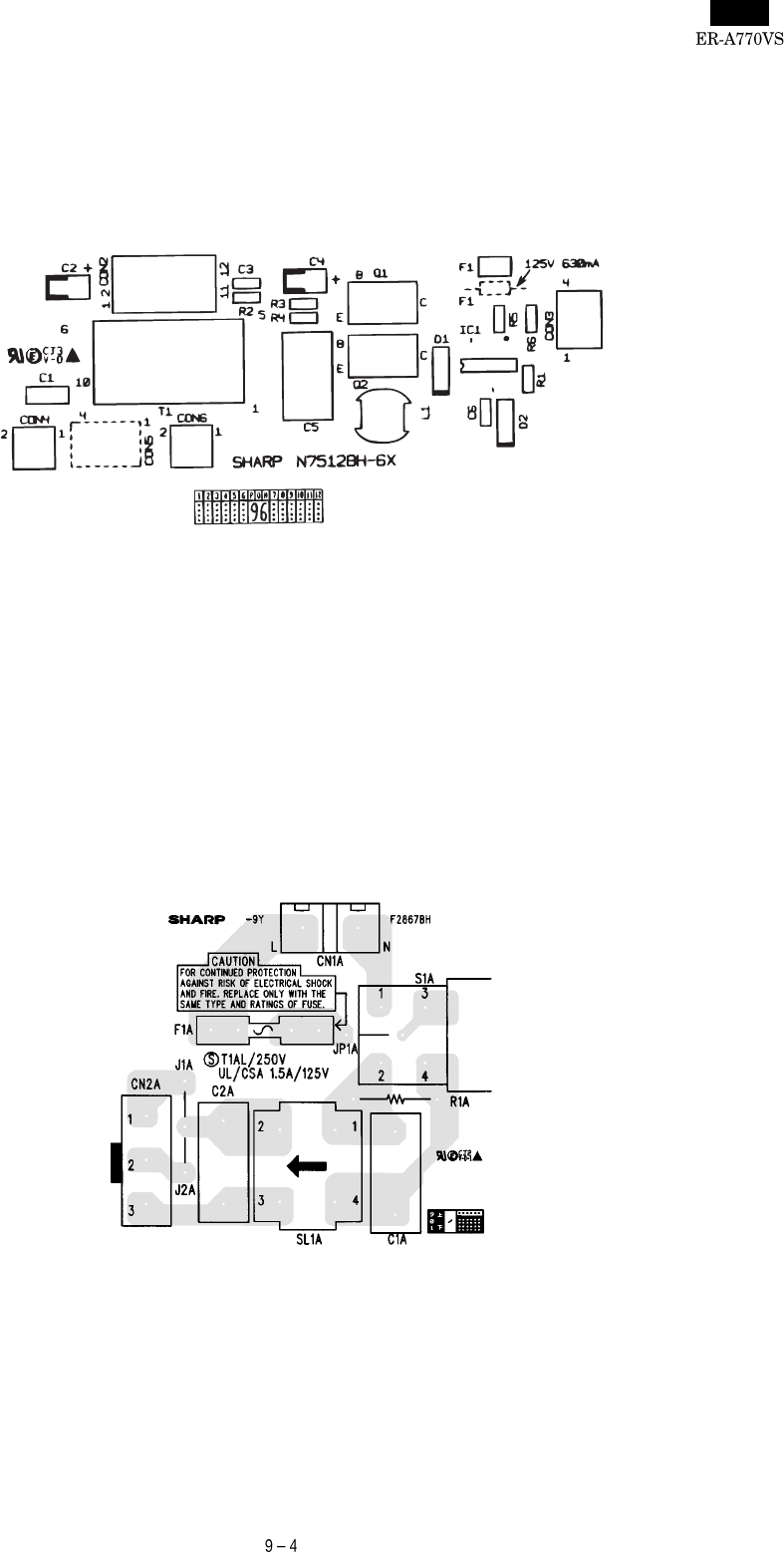

CHAPTER 9. PWB LAYOUT.......................................................................9 - 1

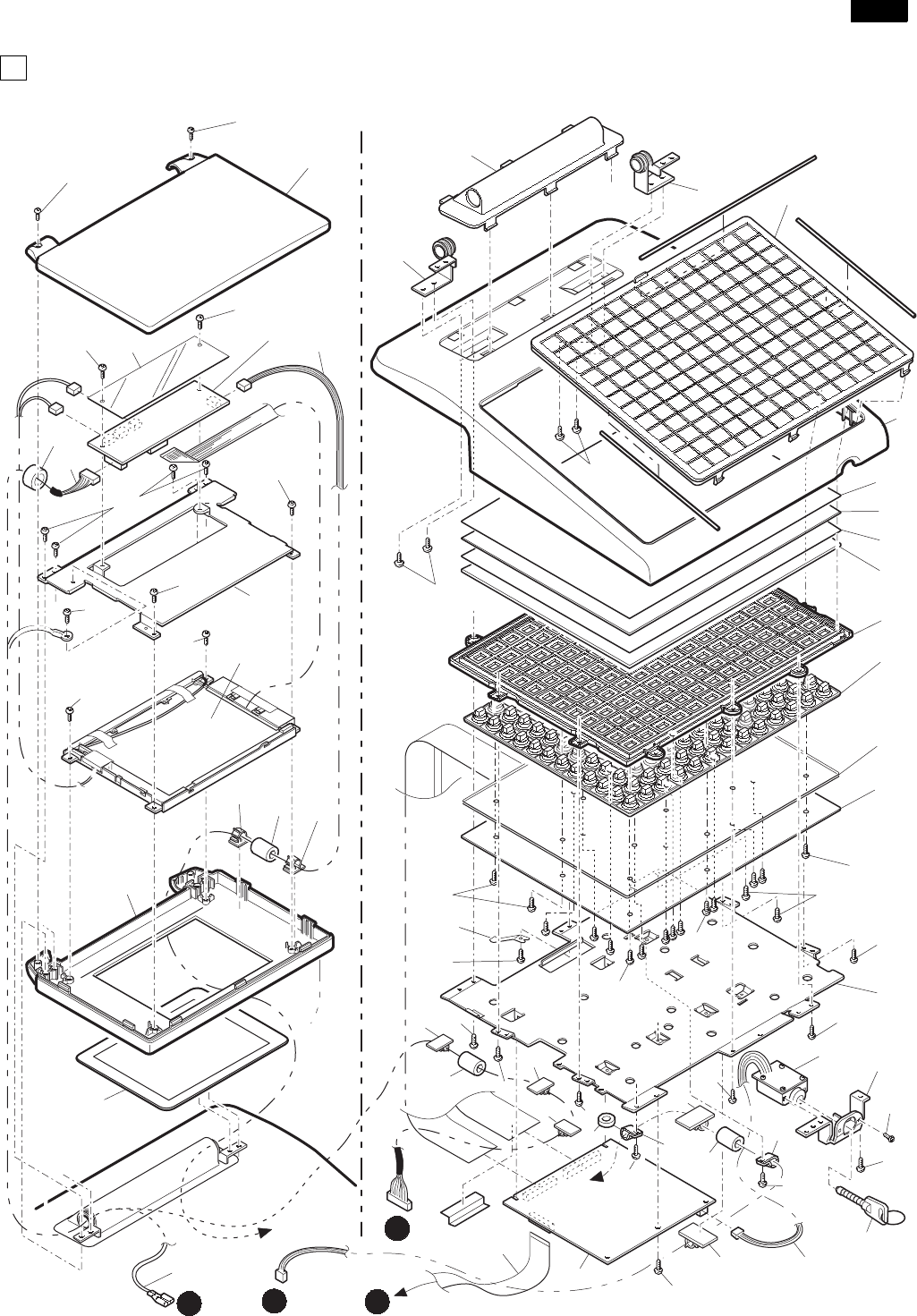

PARTS GUIDE

CONTENTS

Parts marked with " " are important for maintaining the safety of the set. Be sure to replace these parts with specified

ones for maintaining the safety and performance of the set.

SHARP CORPORATION This document has been published to be used

for after sales service only.

The contents are subject to change without notice.

SERVICE MANUAL

CHAPTER 1. SPECIFICATION

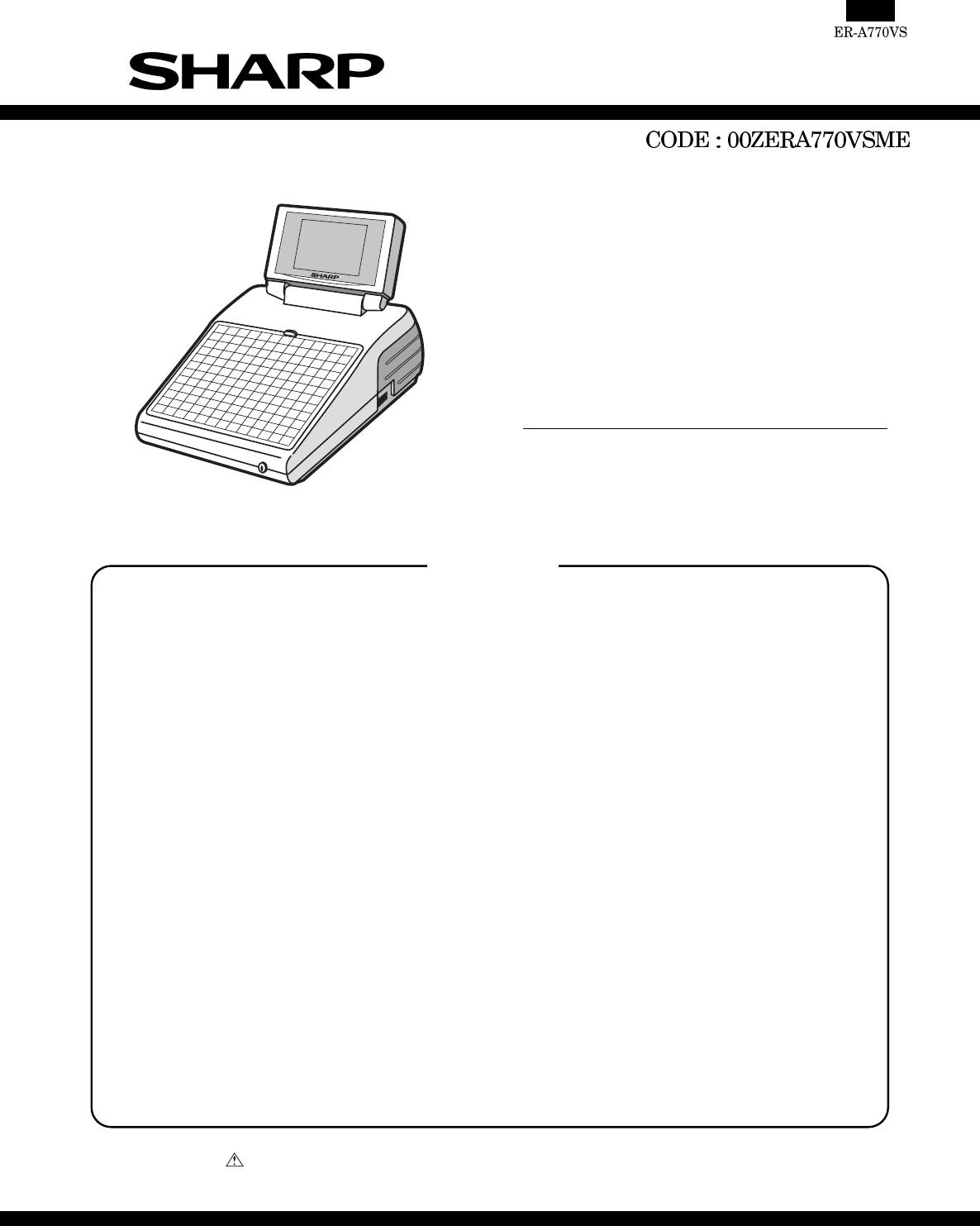

1. Apearance

External view

Front view

Rear view

2. Rating

External dimensions 290 (W) 365 (D) 282 (H) mm

Weight 5.5 kg

Power source Official voltage and frequency

Power consumption Stand-by: 26W

Operating: 32W (max.)

Working temperatures 0 to 40 °C

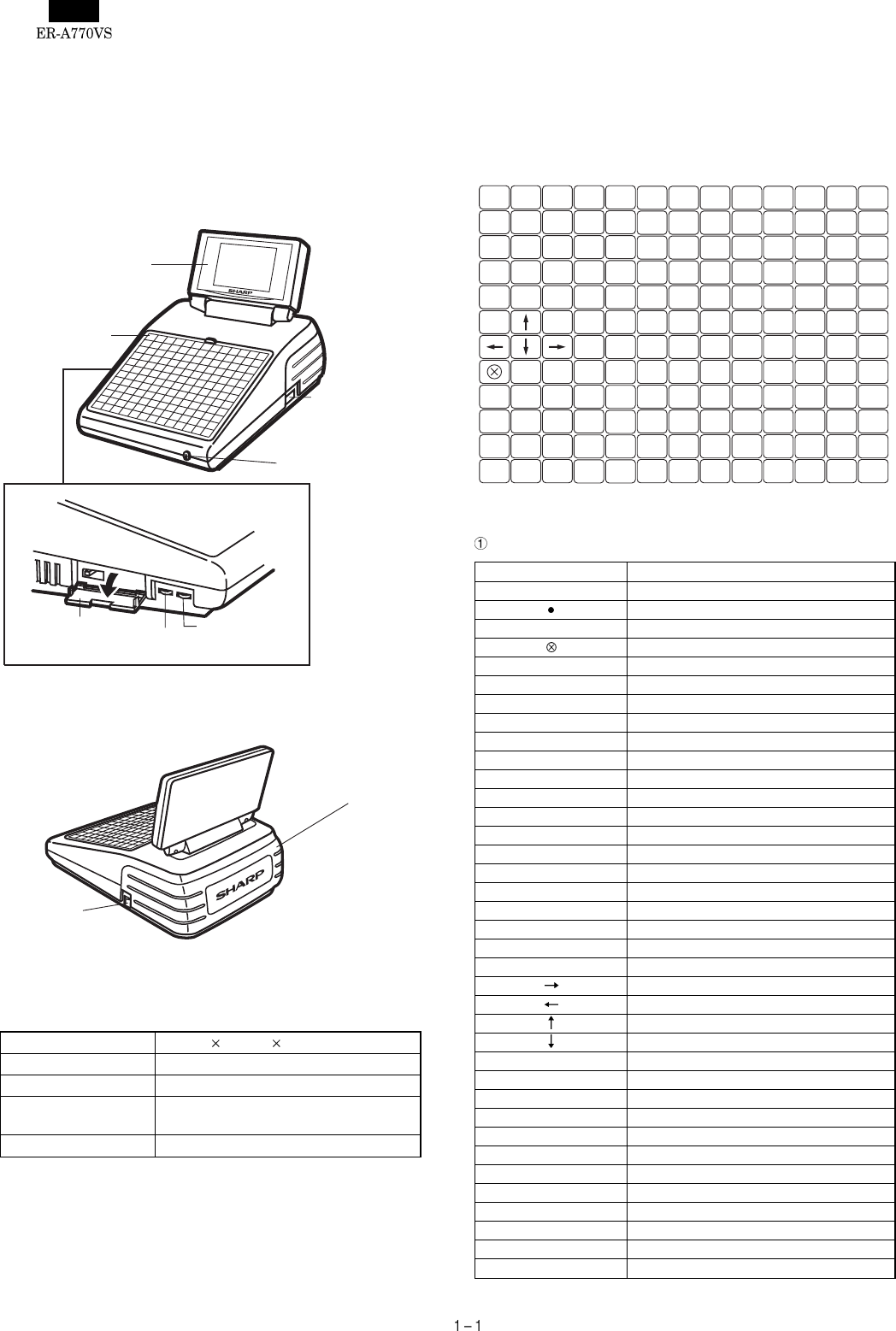

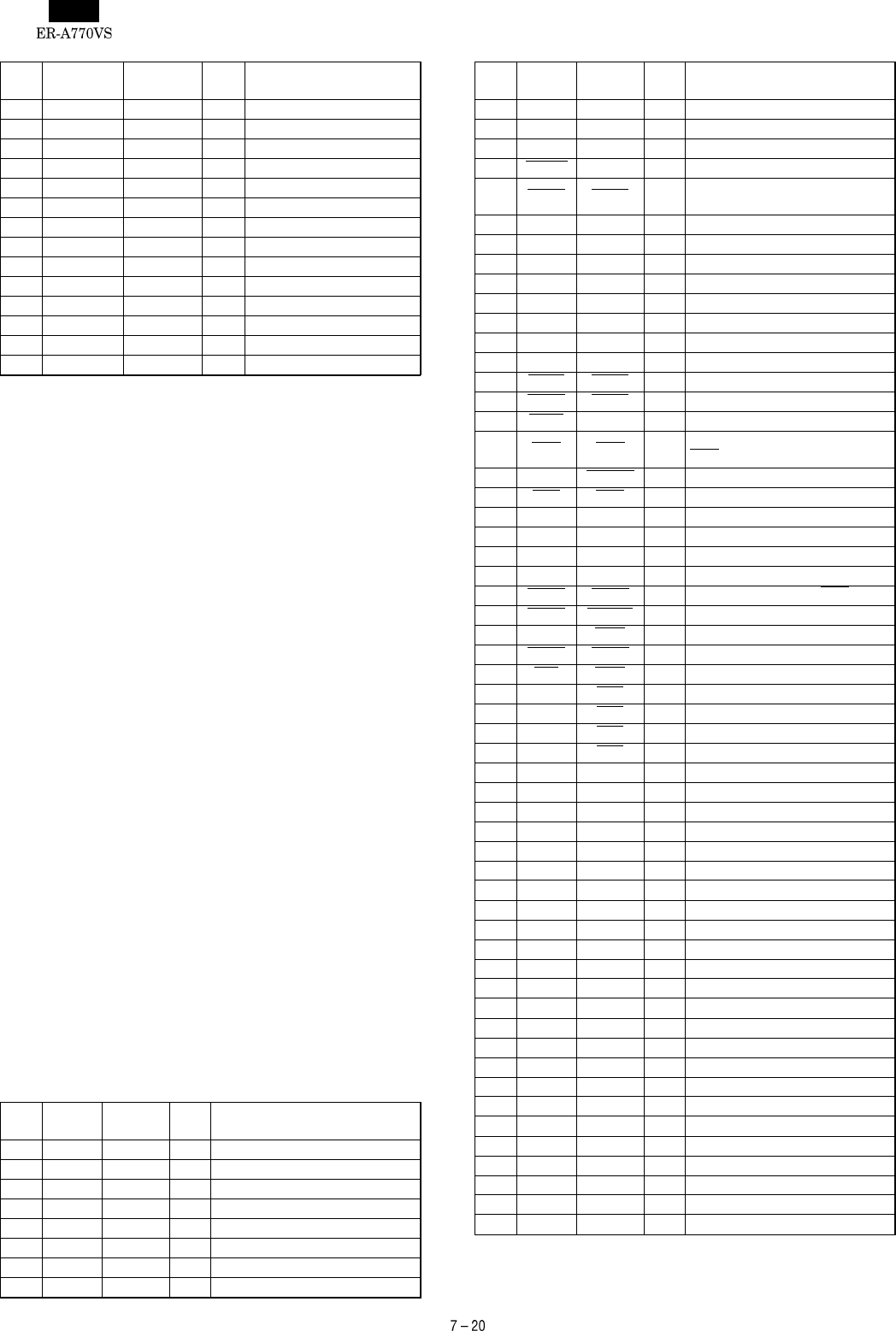

3. Keyboard

1) Standard keyboard layout

2) Key top name

Standard key top

KEY TOP DESCRIPTION

0 ~ 9,000,00 Numeric keys

Decimal point key

CL Clear key

Multiplication key

VAT SHIFT Value-added tax shift key

RF Refund key

VOID Void key

PLU / SUB Price lookup / Subdepartment key

1 ~ 96 Direct price look up key

L1 ~ L3 PLU level shift 1 ~ 3 keys

FINAL Tentative finalization key

MISC FUNC Miscellaneous function key

MODE Mode menu key

ENTER Enter key

AUTO1,2 Automatic sequencing 1 and 2 keys

CR# Credit menu key

CH# Check menu key

ST Subtotal key

TL Total key

PAGE UP Page up key

PAGE DOWN Page down key

Cursor right key

Cursor left key

Cursor up key

Cursor down key

CANCEL Cancel key

WITH With key

WITH OUT Without key

TEXT1 ~ 6 Direct text 1 ~ 6 keys

PRICE SHIFT 1 ~ 3 Price level shit 1 ~ 3 keys

GC RCPT Guest check receipt key

GUEST # Guest number entry key

OPENED GLU Opened GLU list key

GLU Guest lookup key

NBAL New balance key

TRANS OUT Transfer out key

TRANS IN Transfer in key

Operator display

Keyboard

Switch cover Contrast control

Clerk switch

Left side

of the

machine

Power switch

Insure that the power

switch is placed in the

OFF position prior to

connecting AC power.

Brightness

control

Power switch

Rear cover

12

11

10

9

8

7

6

5

4

3

2

1

24

23

22

21

20

19

18

17

16

15

14

13

36

35

34

33

32

31

30

29

28

27

26

25

48

47

46

45

44

43

42

41

40

39

38

37

60

59

58

57

56

55

54

53

52

51

50

49

72

71

70

69

68

67

66

65

64

63

62

61

84

83

82

81

80

79

78

77

76

75

74

73

96

95

94

93

92

91

90

89

88

87

86

85

TEXT

1TEXT

2TEXT

3

TEXT

4TEXT

5TEXT

6

MISC

FUNC

GC

RCPT

TRANS

OUT TRANS

IN

VAT

SHIFT

WITH

OUT

PRICE

SHIFT3

PRICE

SHIFT2

PRICE

SHIFT1

ENTER

CANCEL

ST TL

BS BT

VOID RF

GLU

WITH

L1

L2

L3

SLIP

FINAL

NBAL

GUEST

#

CR

#

CH

#

PAGE

UP PAGE

DOWN

PLU/

SUB

AUTO

1

AUTO

2

MODE

•

00 0 000

CL

789

456

123

OPENED

GLU

KEY TOP DESCRIPTION

SLIP Slip print key

BS Bill separation key

BT Bill totalize / Bill transfer key

Optional key top

KEY TOP DESCRIPTION

97 ~ 135 Direct price look up keys

1 ~ 99 Department keys

%1 ~ %9 Percent 1 ~ 9 keys

1 ~ 9 keys Discount 1 ~ 9 keys

CR1 ~ CR8 Credit 1 ~ 8 keys

CA2 Cash total 2 key

RA1,RA2 Received on account 1 and 2 keys

PO1,PO2 Paid out 1 and 2 keys

AUTO3 ~ AUTO25 Automatic sequencing 3 ~ 25 keys

CH1 ~ CH4 Check 1 ~ 4 keys

CASH TIP Cash tip key

TIP PAID Tip paid key

# Non-add code entry key

NS No-sale key

MGR# Manager code entry key

OPEN TARE Tare entry Key

REPEAT Repeat entry key

PERSON# Person number entry key

IND. PAYMENT Individual payment key

RCP. SW Receipt ON / OFF key

SCALE Scale entry key

TEXT 7 ~ 40 Text 7 ~ 40 keys

EX1 ~ 9 Foreign currency exchange 1 ~ 9 keys

AMT Amount entry key

DRV NC New check 2 key (For drive-thruogh)

DRV GLU Guest look up 2 key (For drive-through)

VAT Value-added tax key

NON-CASH TIP Non-cash tip key

1/2 1/2 key

CLERK# Clerk code entry key

RCPT Receipt print key

PINT Pint key

DEPO(+) Deposit plus entry key

DEPO(–) Deposit minus entry key

TEXT# Text number key

EMP# Employee key

TIME IN Time in key

SBTL VOID Subtotal void key

TIME OUT Time out key

BREAK IN/OUT Break in/out key

VP Validation print key

RTN Return key

DEPT SHIFT 1 ~ 4 Department shift 1 ~ 4 keys

DIFFER ST Difference subtotal key

C.BILL Cumulated bill key

GC COPY Guest check copy key

EX# Foreign currency exchange menu key

VIP VIP sale key

H.T. Hotel transfer key

CLK1 ~ 10 Clerk entry 1 ~ 10 keys

CHECK PRINT Check print key

BACK SPACE Back space key

DEL Delete key

L4 ~ L10 PLU level shift 4 through 10 keys

KEY TOP DESCRIPTION

PRICE SHIFT 4 ~

PRICE SHIFT 7

Price level shift 4 through 7 keys

PLU MENU 01 ~

PLU MENU 50

PLU menu 1 through 50 keys

WASTE WASTE mode key

WAIT WAIT mode key (for drive-thru)

RECALL Re-call key (for drive thru)

C_NEXT Condiments next key

D_DISP Drive-thru menu key

E. BILL Entertainment bill key

RC TTL Recall TOTAL STATUS key

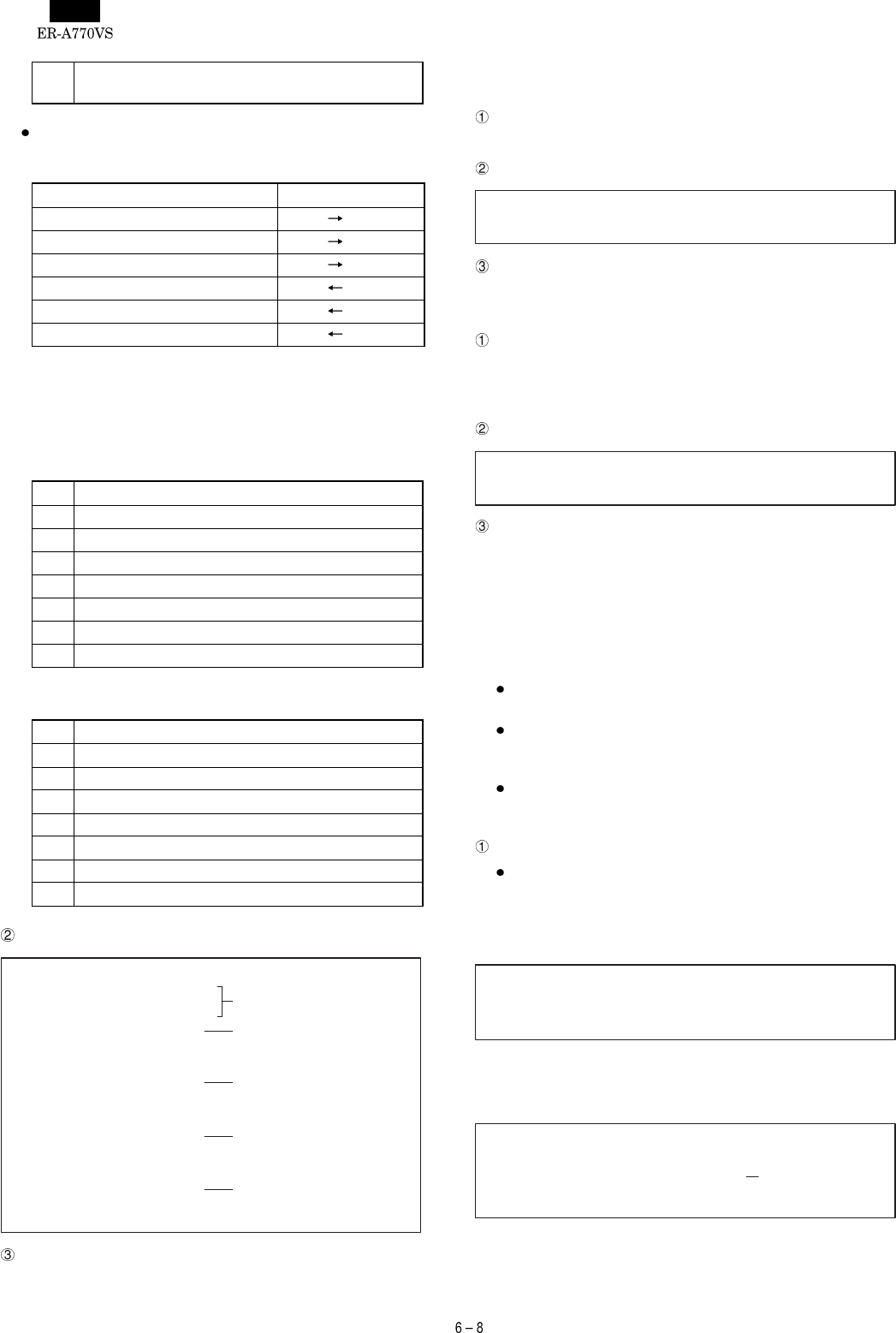

3) Text programming key sheet layout

: The shaded area contains the character keys which are

used for programming characters.

KEY TOP DESCRIPTION

SHIFT Used for programming characters. For more

information about programming characters,

see the section "How to Enter Alphanumeric

Characters."

DC

INS

DEL

BACK SPACE

[], [ ], [ ], [ ] Used to move the cursor.

ENTER Used to program each setting.

TL Used to finalize programming.

CANCEL Used to cancel programming and to get back

to the previous screen.

MODE Used for changing the operating mode.

PREV RECORD

Used to go back to the previous record, e.g.,

from the department 2 programming window

back to the department 1 programming window.

NEXT RECORD

Used to go to the next record, for example, in

order to program unit prices for sequential

departments.

PAGE DOWN Used to scroll the window to go to the next

page.

PAGE UP Used to scroll the window to go back to the

previous page.

CL Used to clear the last setting you have

programmed or clear the error state.

Used to toggle between two or more options.

ST Used to list those options which you can toggle

by the key.

RECALL Used to call up a desired code.

Numeric keys Used for entering figures.

BACK

SPACE

Prev.

Record

Next

Record

(CANCEL)

(SHIFT) (SHIFT)

(SPACE) (SPACE) (SPACE) (SPACE) (SPACE) (SPACE)

(ENTER)

PAGE

DOWN

PAGE

UP

(MODE)

(INS)

(DEL)

(RECALL)

(DC)

•

A

Ä Ö Ü ß

HJKL

ERTY

â à á ê è é

Ñ Ø

_

–

-

¿

1 2 3

1/2 1/4 3/4 Æ û

>> <<

ù ú Ç Å £

3

2

1

4 5 6 7 8 9 0

©

®

ï ÿ

?

”

¤

´

ˆ

OP

/

!

][

#

$&=

÷

ZM

CL

00 0 000 ST TL

∂

{}

ìí

789

456

123

XCV

SDFG

BN

;:

WQUI

()

,.

+

%@

<>

>>>>> USE FONT <<<<<

Helvetica/ Helvetica-Condensed/ Century-Schoolbook/ Symbol & OriginalFonts: (RingWorld2/RingFont2/Pa

Symbol/PartsCod)

- - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -

4) Blank key sheet layout

3. Display

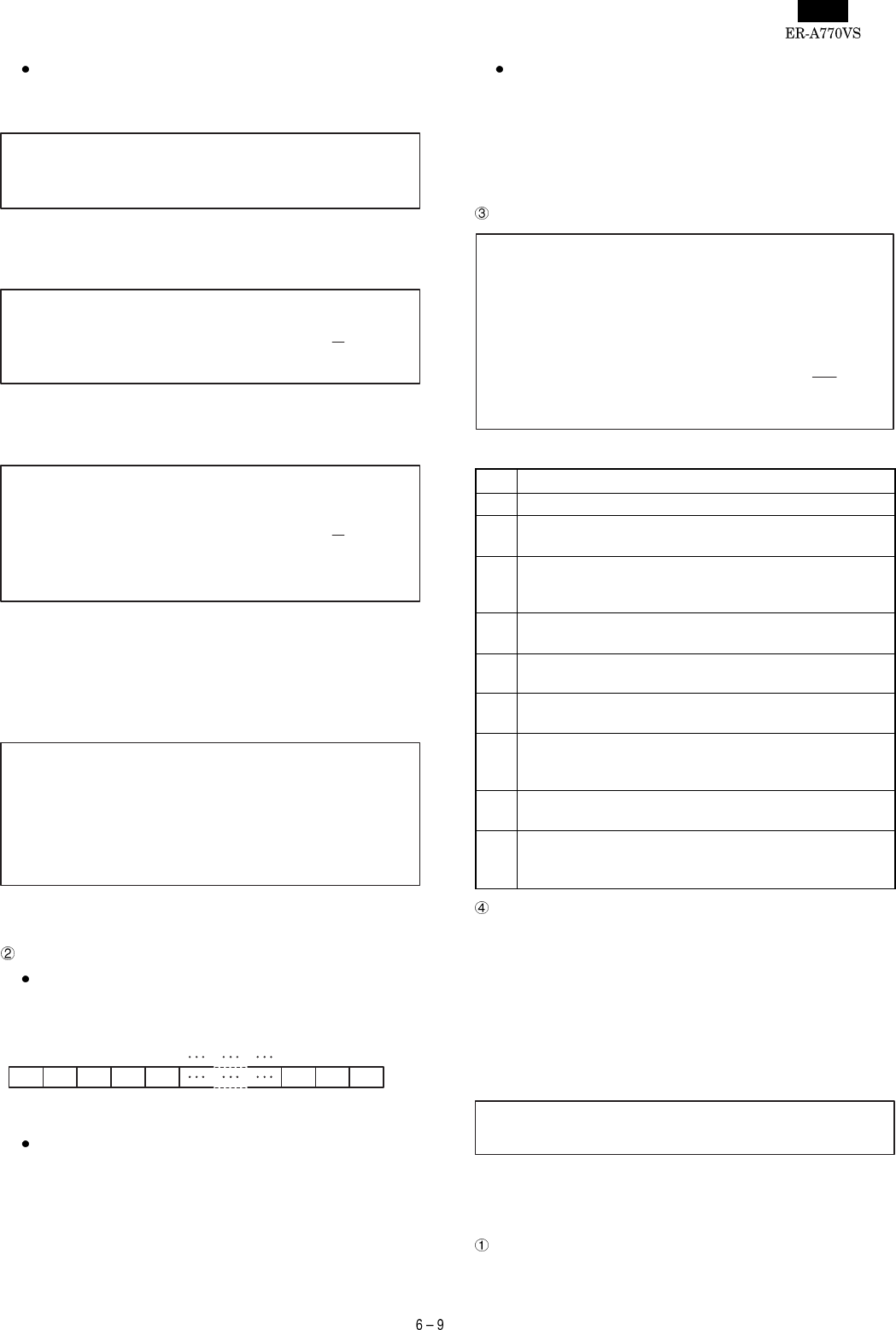

1) Operator display

Screen example 1 (REG mode)

Prive level shift indica-

tor (P1-P7) : Shows the PLU price level currently

selected.

PLU level shift indicator

(L01-L10) : Shows the PLU level currently se-

lected.

Stock alarm indicator

(!) : Appears when the stock of the PLU

which you entered is zero or negative.

Department shift status

indicator (D1-D4) : Shows the department shift status cur-

rently selected.

VAT shift status indica-

tor (V) : Appears when the VAT status is

shifted.

Receipt ON/OFF status

indicator (R) : Appears when the receipt ON-OFF

function signs OFF.

Sentinel mark (X) : Appears in the lower right corner of

the screen when the cash in drawer

exceeds a programmed sentinel

amount.

The sentinel check is performed for

the total cash in drawer.

Screen example 2 (PGM mode)

Screen save mode

When you want to save the electric power or save the display’s

life, use the screen save function. This function can turn the LCD

backlight off when any server does not operate the POS terminal

for an extended period of time. You can program the time for

which your POS terminal should keep the normal status (in which

the backlight is "ON") before it goes into the screen save mode.

To go back to the normal mode, press any key.

Device type LCD display

Dot format 320(W) 240(H) Full dot

Dot size 0.33 0.33 mm

Dot space 0.03 mm

Dot color White

Back color Dark blue

Weight 180 g

2) Display adjustment

You can adjust the brightness and contrast of the display by using the

corresponding controls.

Mode name

Clerk code

Time

Numeric entry:

Entered figures appear at

the cursor position.

Window:

In the REG mode, the window shows sales information you have

just entered such as items and media types.

Received media type

Sales amount including taxes

Clerk code

Mode name

Time

Double-size character mode indicator (W):

Appears when the double-size character

mode is selected during text programming.

Window

In the PGM mode,

programmable items are listed.

Caps lock indicator (A/a):

The upper-case letter "A" appears when

Caps Lock is on, and the lower-case

letter "a" appears when Caps Lock is off

during text programming.

Contrast control

Turning the control backwards

darkens the display and turning

it forwards lightens the display.

Brightness control

Turning the control backwards

darkens the display and turning it

forwards brightens the display.

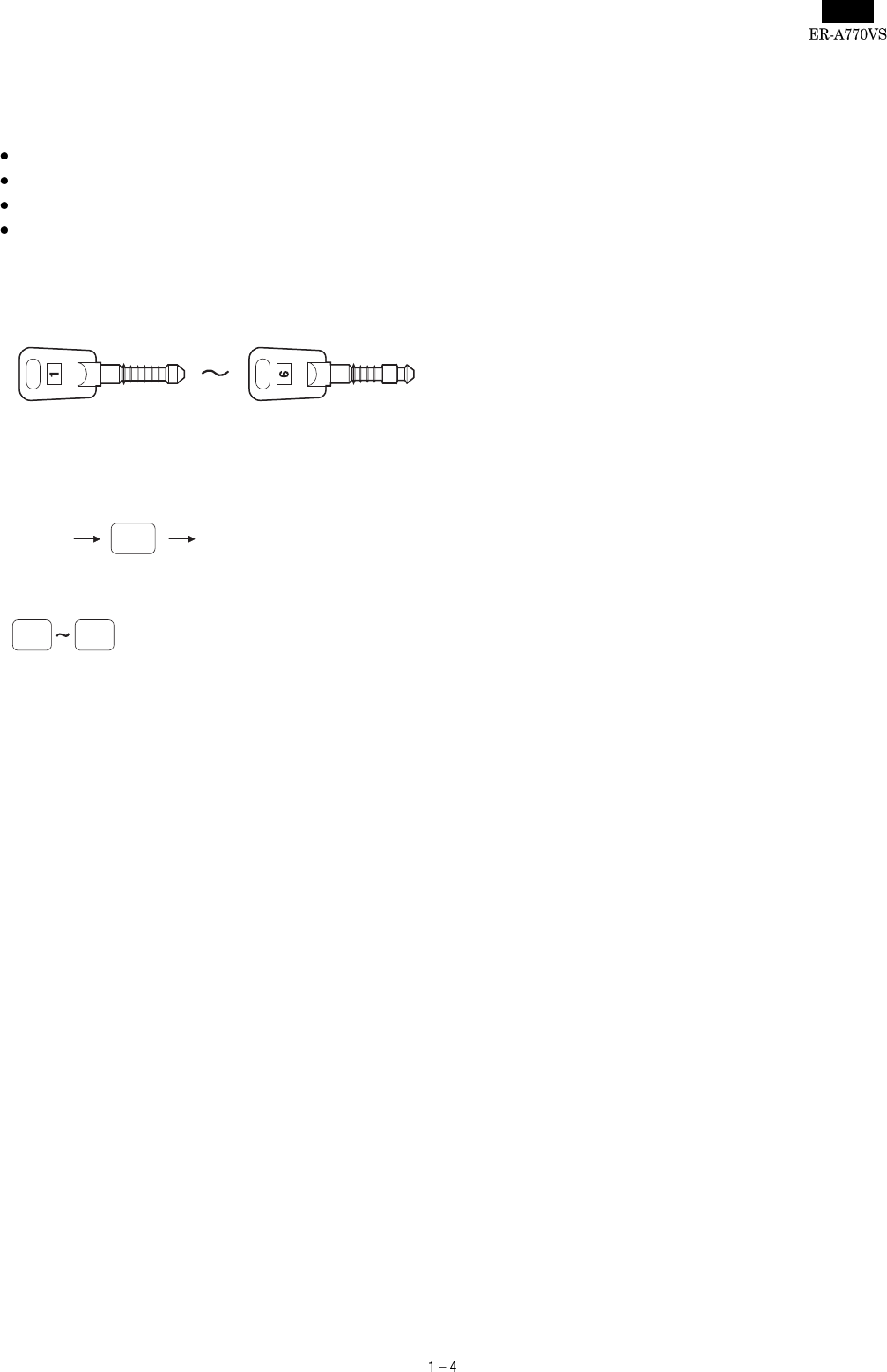

4. Clerk Keys

This POS terminal allows the operator to use the following four clerk

identification systems :

Real clerk keys (standard 6 clerks / max. 126 clerks)

Clerk code entry (max. 255 clerks)

Clerk entry keys (max. 10 clerks)

WMF clerk keys (max. 127 clerks)

The standard POS terminal has been shipped with the real clerk key

system being programmed. If you want to change the clerk identifica-

tion system, contact your authorized SHARP dealer

Real clerk keys (1, 2, 3, 4, 5, and 6)

These keys serve to identify clerks. Put one of the 1 through 6 keys in

the clerk switch.

Clerk code entry (1 through 9999)

Enter the clerk code by using the following procedure :

Clerk entry keys

These keys identify clerks. Press any one of these keys.

WMF clerk keys

Put one of the WMF clerk keys in the WMF clerk switch.

XXXX

Clerk code

CLERK

#

CLK

1CLK

10

INLINE Communication

Expansion

memory

board

<Option>

UP-P02MB2

PC

<Local purchase>

EFT Terminal

<Local purchase>

Satelite

(RS-232)

(SRN)

Mastermachine

Remote

Drawer

<Option>

ER-03DW/

04DW/05DW

MCR

<Option>

UP-E12MR

Pole Display

<Option>

UP-P16DP

R/J Printer

<Option>

ER-01PU

RS-232 Communication

RS-232 Board

<Option>

ER-A7RS

EFT VF Board

<Option>

ER-02EF

Remote Printer

<Option>

ER-04RP/03RP

PC

<Local purchase>

Customer Display

<Option>

UP-I16DP

Drink Dispenser

<Local purchase>

Scale

<Local purchase>

CAT

<Local purchase>

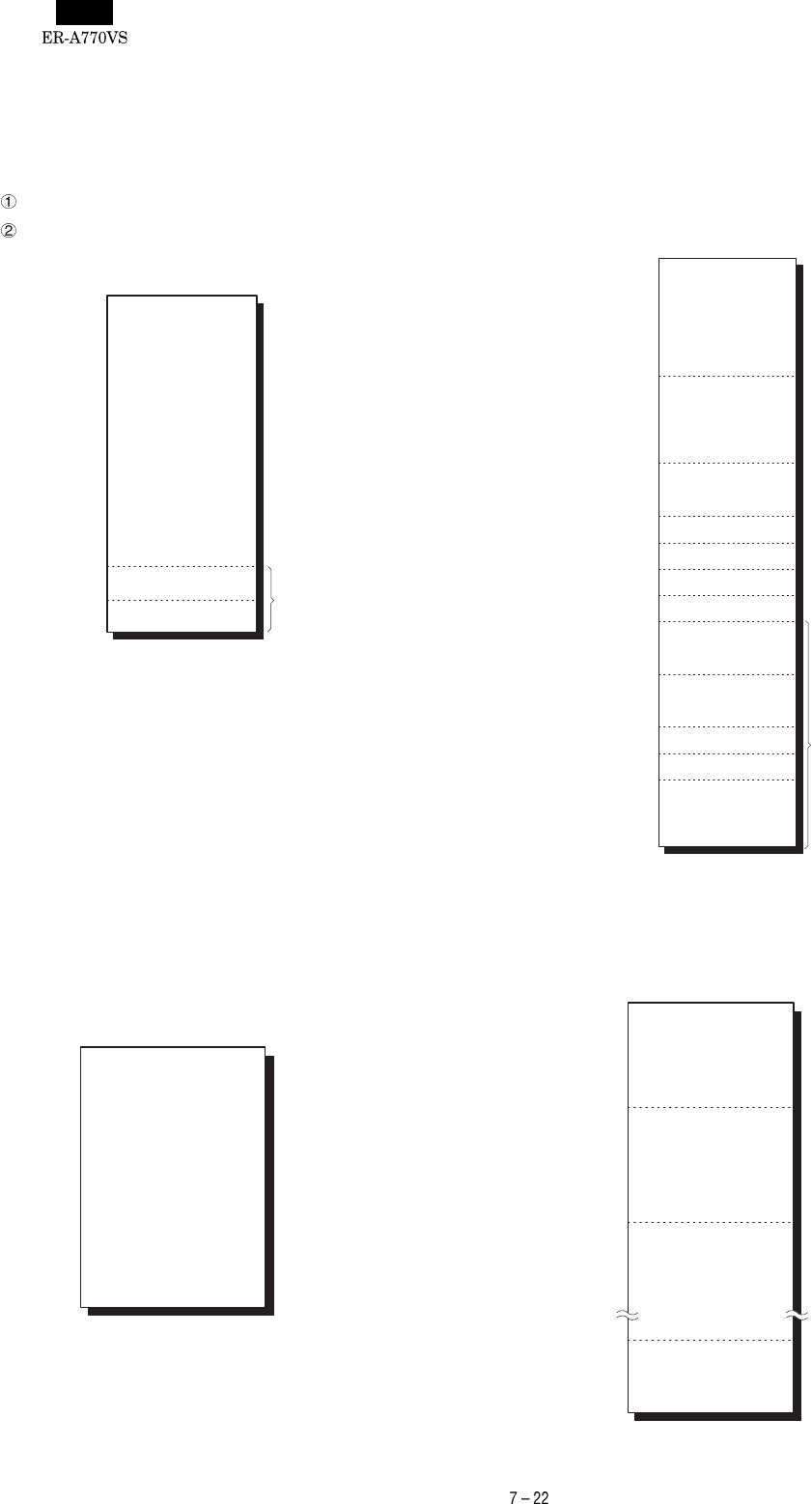

CHAPTER 2. OPTIONS

1. System configuration

2. Sales Options

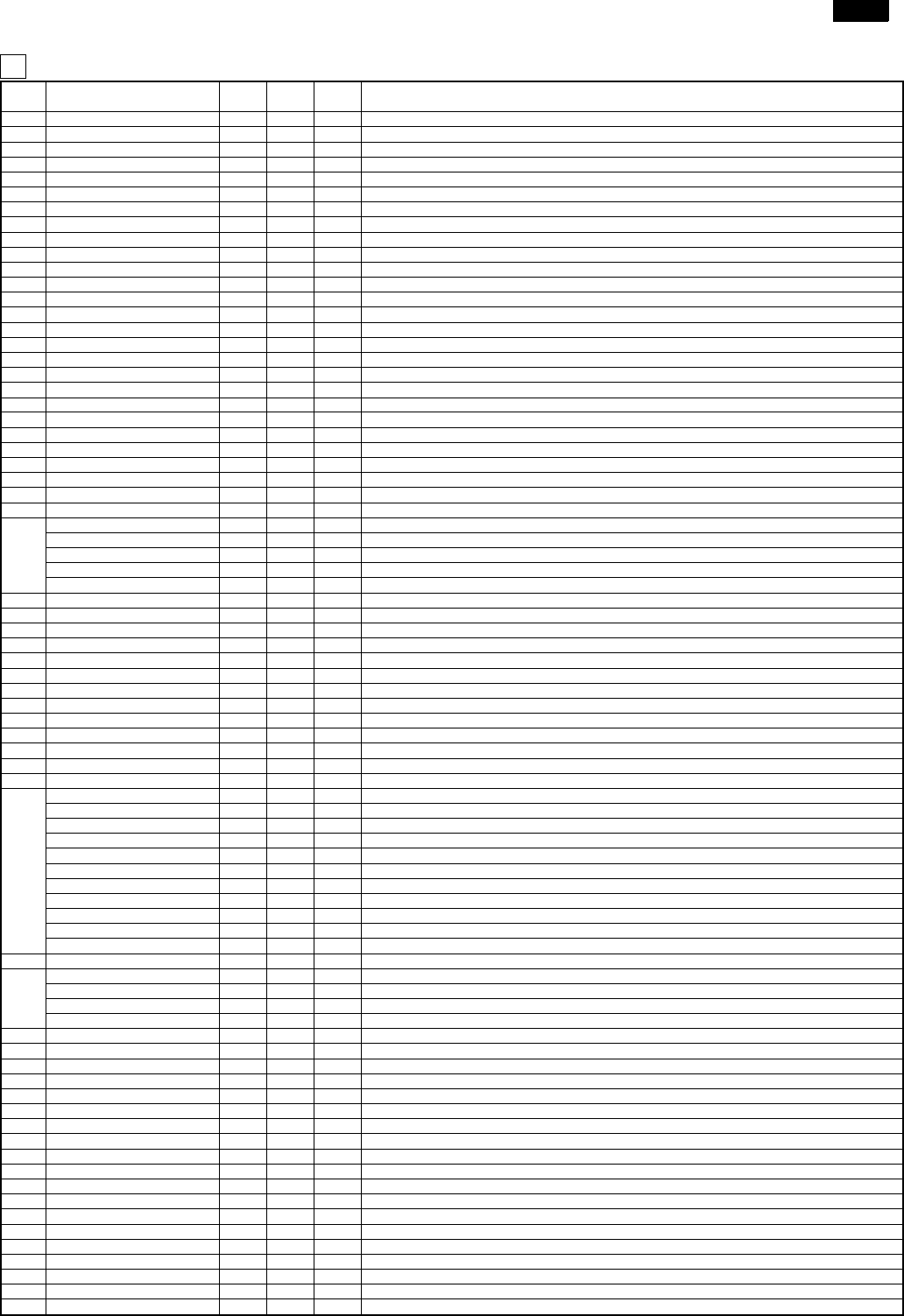

No. CLASSIFICATION COMPONENT NAME MODEL NAME REMARK

1

Printer External R/J printer ER-01PU Via RS-232 I/F

Remote printer ER-03RP Via SRN I/F

ER-04RP

2Display Remote display (Pole type) UP-P16DP 11-Dig. 7-Seg. +16-Dig. Dot

Customer display UP-I16DP 11-Dig. 7-Seg. +16-Dig. Dot

3

Drawer Remote drawer ER-03DW

ER-04DW

ER-05DW

Coin case ER-48CC2 4B/8C

ER-48CC3 4B/8C

ER-58CC2 5B/8C

Coin case cover ER-01CV1-5

ER-02CV1-5

ER-03CV

4 Memory Expansion RAM disk board UP-P02MB2 2M bytes PS-RAM board

5 On-line function RS232 I/F board ER-A7RS 2 ports RS232 I/F

6OTHER MCR (Magnetic Card Reader) UP-E12MR for ISO 1 & 2 stripe card

EFT terminal I/F ER-02EF

3. Local purchase options

No. COMPONENT NAME MODEL NAME

1External printer TM-T85/T88

TM-U210

2Slip printer TM-U295

TM-H5000

3Scale I/F

4 Drink Dispensor

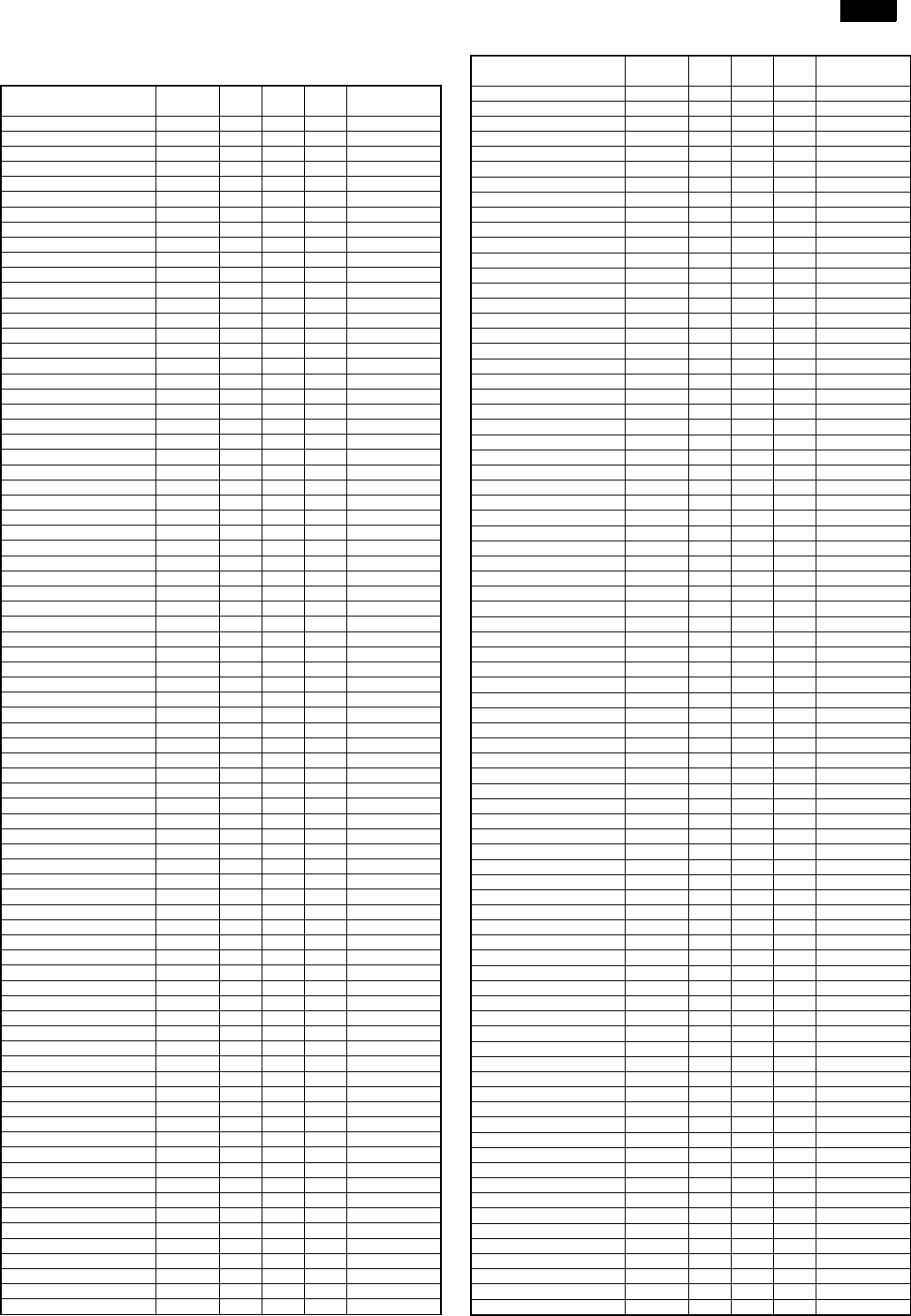

4. Service options

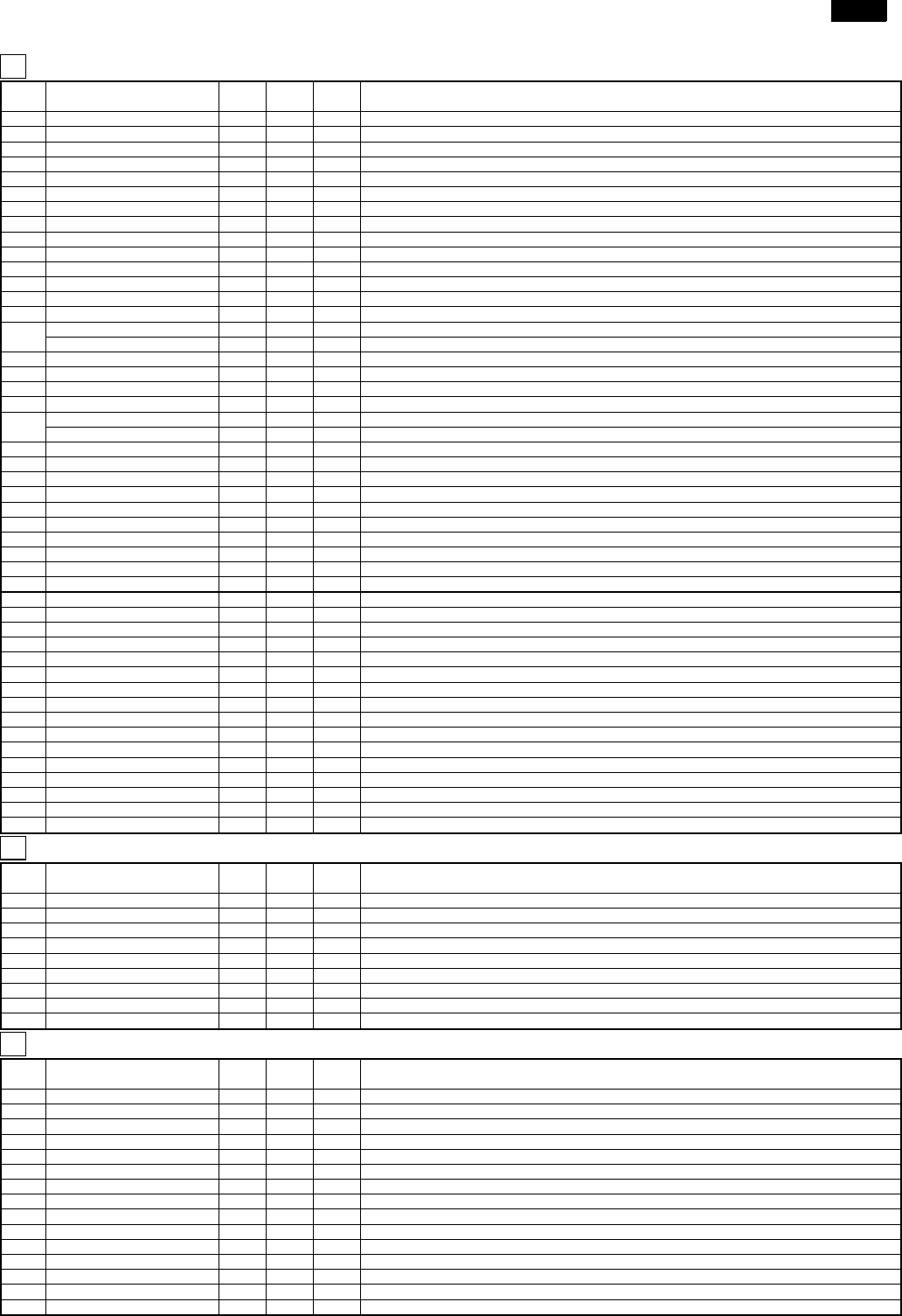

No. NAME PARTS CODE DESCRIPTION

1 1 hole clerk key

The key No.1 to No.6 ore supplied together with ER-A770.

Key No. 7

Key No. 8

Key No. 9

Key No. 10

Key No. 11

Key No. 12

Key No. 13

Key No. 14

Key No. 15

Key No. 16

Key No. 17

Key No. 18

Key No. 19

Key No. 20

Key No. 21

Key No. 22

Key No. 23

Key No. 24

Key No. 25

Key No. 26

Key No. 27

Key No. 28

>>>>> USE FONT <<<<<

Helvetica/ Helvetica-Condensed/ Century-Schoolbook/ Symbol & OriginalFonts: (RingWorld2/RingFont2/Pa

Symbol/PartsCod)

- - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -

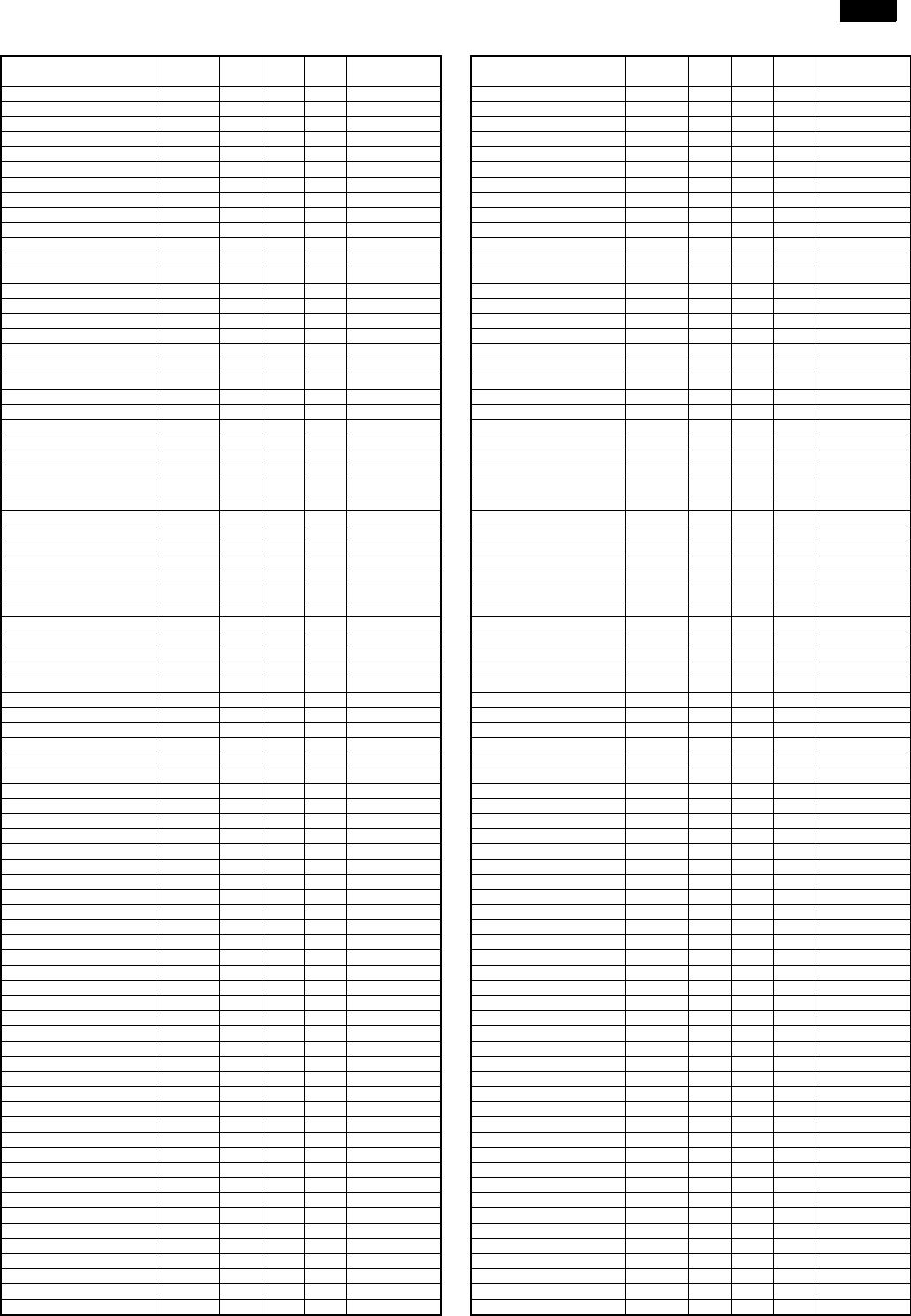

No. NAME PARTS CODE DESCRIPTION

1 1 hole clerk key

The key No.1 to No.6 ore supplied together with ER-A770.

Key No. 29

Key No. 30

Key No. 31

Key No. 32

Key No. 33

Key No. 34

Key No. 35

Key No. 36

Key No. 37

Key No. 38

Key No. 39

Key No. 40

Key No. 41

Key No. 42

Key No. 43

Key No. 44

Key No. 45

Key No. 46

Key No. 47

Key No. 48

Key No. 49

Key No. 50

Key No. 51

Key No. 52

Key No. 53

Key No. 54

Key No. 55

Key No. 56

Key No. 57

Key No. 58

Key No. 59

Key No. 60

Key No. 61

Key No. 62

Key No. 63

Key No. 64

Key No. 65

Key No. 66

Key No. 67

Key No. 68

Key No. 69

Key No. 70

Key No. 71

Key No. 72

Key No. 73

Key No. 74

Key No. 75

Key No. 76

Key No. 77

Key No. 78

Key No. 79

Key No. 80

Key No. 81

Key No. 82

Key No. 83

Key No. 84

Key No. 85

Key No. 86

Key No. 87

Key No. 88

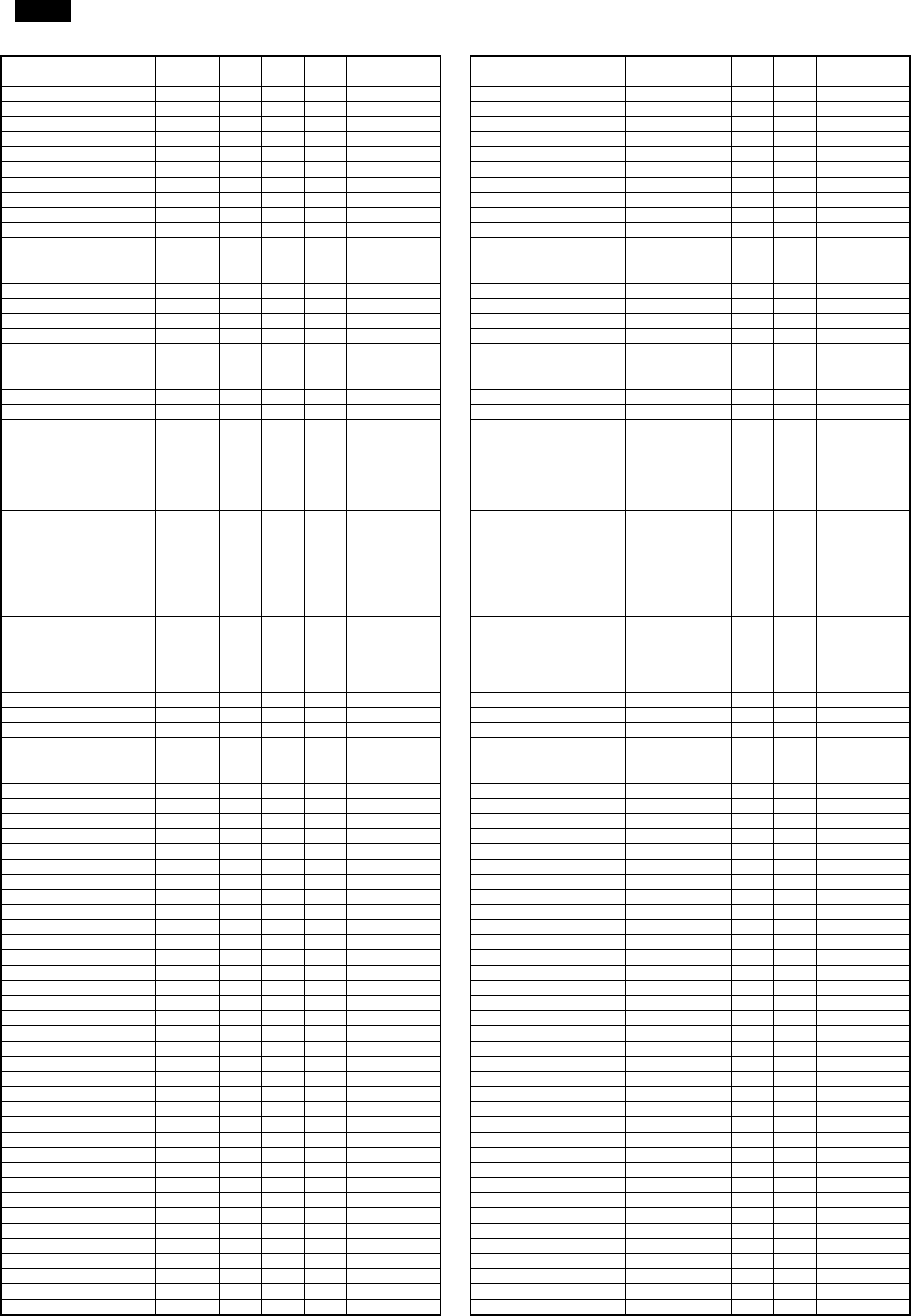

No. NAME PARTS CODE DESCRIPTION

1 1 hole clerk key

The key No.1 to No.6 ore supplied together with ER-A770.

Key No. 89

Key No. 90

Key No. 91

Key No. 92

Key No. 93

Key No. 94

Key No. 95

Key No. 96

Key No. 97

Key No. 98

Key No. 99

Key No. 100

Key No. 101

Key No. 102

Key No. 103

Key No. 104

Key No. 105

Key No. 106

Key No. 107

Key No. 108

Key No. 109

Key No. 110

Key No. 111

Key No. 112

Key No. 113

Key No. 114

Key No. 115

Key No. 116

Key No. 117

Key No. 118

Key No. 119

Key No. 120

Key No. 121

Key No. 122

Key No. 123

Key No. 124

Key No. 125

Key No. 126

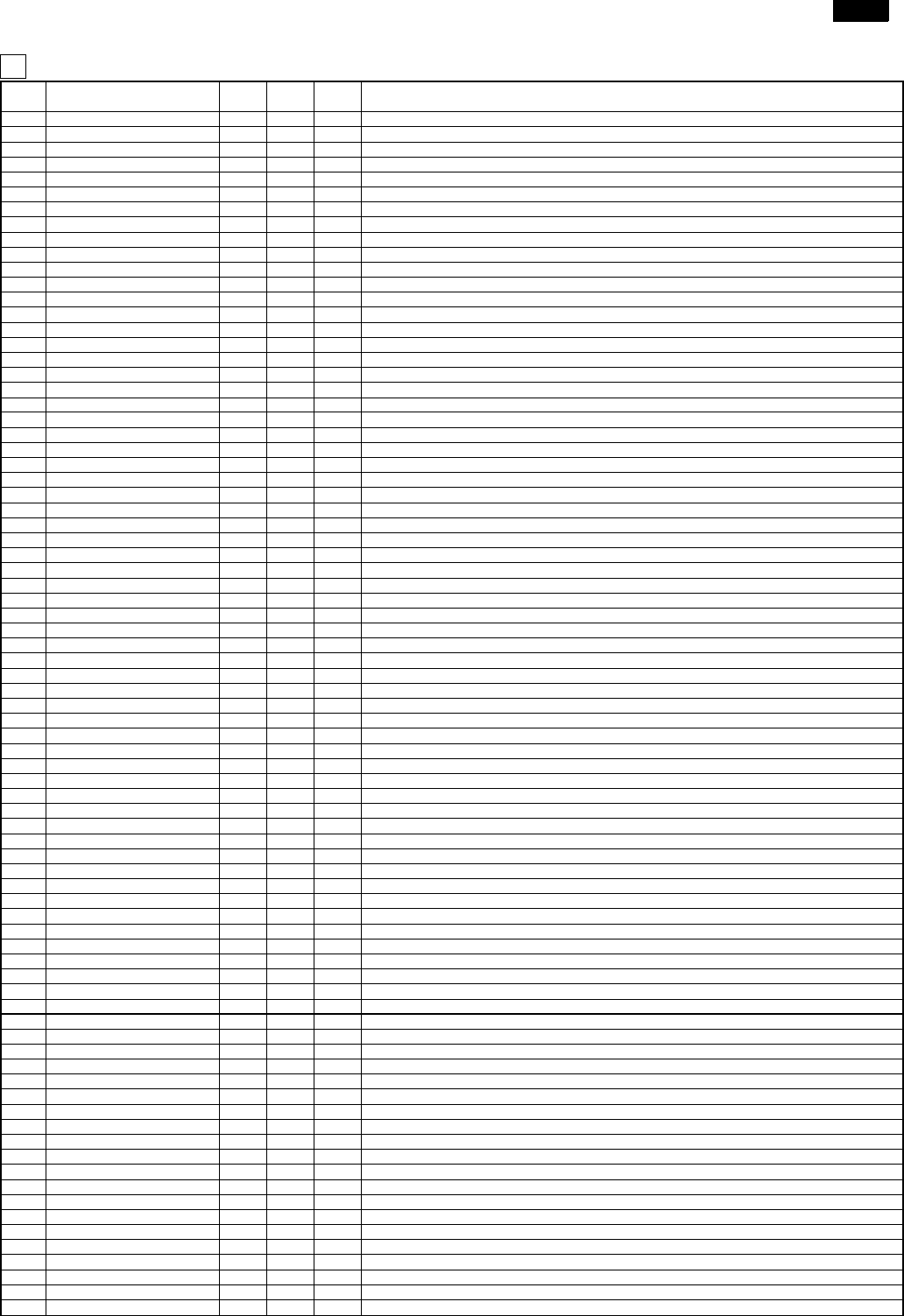

5. Service tools

No. NAME PARTS CODE PRICE DESCRIPTION

1 Terminator(50 )AZ for SRN in-line system

2 MCR test card BE for UP-E12MR

3 RS232 loop back connector BC for RS232 connector

4 Expansion PWB BX

6. Supplies : None

No. NAME PARTS CODE PRICE

1 Blank key sheet AQ

7. How to use service tools

7-1. Expansion PWB : CKOG-6724BHZZ

Extrenal view

Plain view

Connection diagram

7-2. MCR test card: UKOG-6718RCZZ

Used when executing the diagnostics of the UP-E12MR.

External view

Test pins : Used to check the bus signals.

Bus connector : Used to check the bus signals.

Connected to the UP-3300 Mother PWB.

ER-A770 bus connector

ER-A7RS

CHAPTER 3. SERVICE PRECAUTION

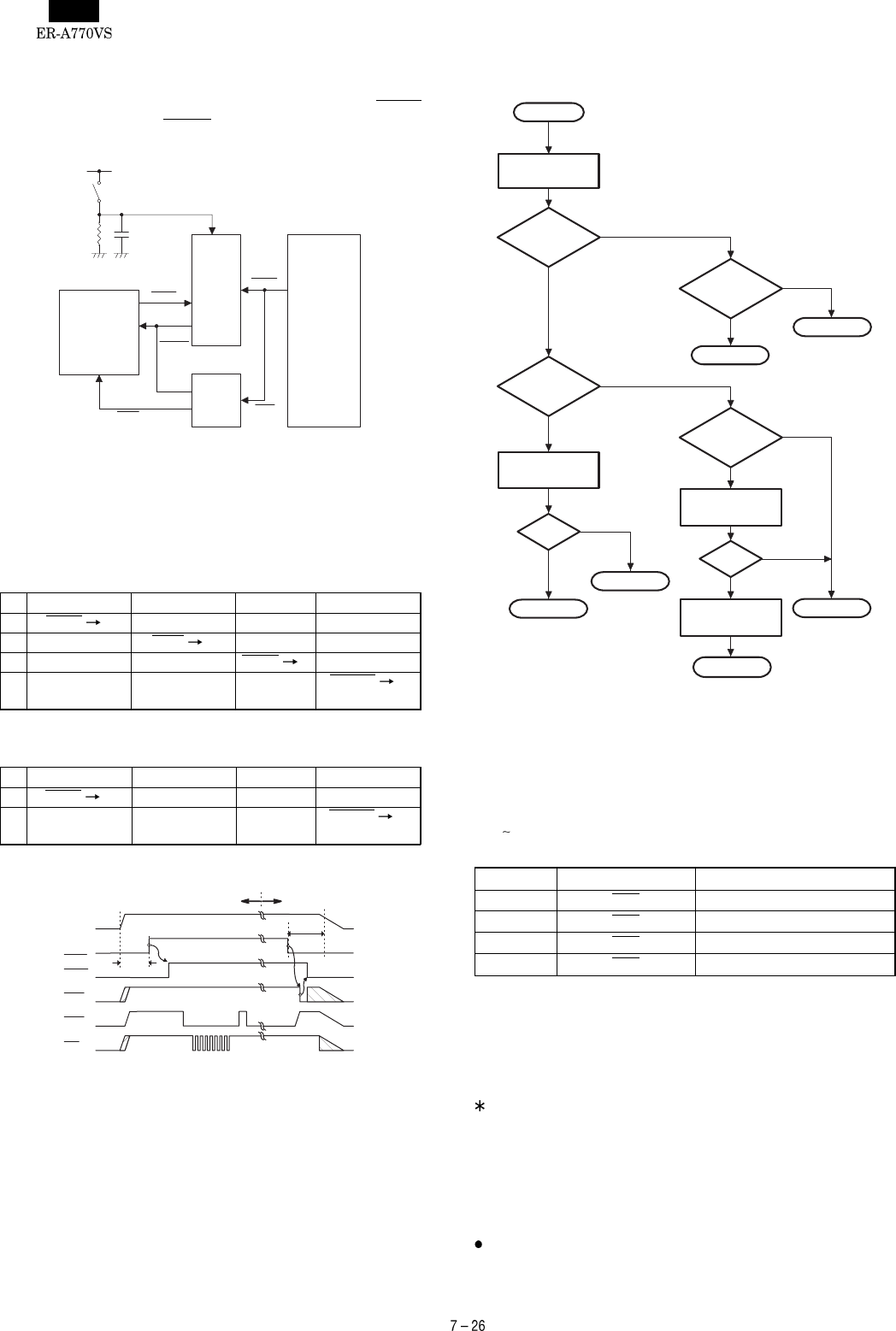

1. Adjustment for SRN (IN-LINE) interface

circuit

If transistor Q9 in the transmitter/receiver section has been replaced

or if the SRN level requires readjustment, the following alignment is

required:

1) Tools and Instruments Required

Oscilloscope (50MHz or better)............................................1

ER-A770 ..............................................................................1

2) Dummy Network Specifications

The oscillator should be connected to the points indicated by and

.

: Connect the positive side of the oscillator.

: Connect the negative side of the oscillator.

3) Connections

Attach the BNC connector to the SRN connector (CN7) on the main

PWB.

4) Alignment Procedure

When Using an Oscillator

a) Checking the 1MHz oscillator output

Using an oscilloscope check the 1MHz oscillator’s output waveform.

NOTE: The oscillator used should have an output impedance of

50 .

b) Connecting the oscillator and its adjustment

Connect a dummy network or branch-trunk network to the output of

the SRN connector (CN7), and connect the oscillator to the dummy or

branch-trunk network.

Waveform adjustment

Adjust VR1 until the signal waveform as shown in Fig. 4 is obtained

across TP1 and TP2 (GND).

Turning VR1 clockwise extends the interval of T1.

2. IPL (Initial program Loading) function

1) Introduction

The application software of the ER-A770 written in the flash ROM.

In the following cases, writing procedure of the application software

into the flash ROM is required

When the flash ROM is replaced with new one. The service part

flash ROM does not include the application software in it.

When IPL writing is required because of change in the software.

The service part ofthe main PWB unit includes the flash ROM with

the application software written in it, and there is no need for

writing the application software when replacing the main PWB unit.

2) IPL procedure

There are two ways of IPL procedures.

IPL from P-ROM via ER-A7RS

IPL from PC communication (Please refer the next section)

The detailed descriptions on the above procedures are given below.

R2

R1

C1

R1 100ΩJ (1/4W carbon)

R2 150ΩJ (1/4W carbon)

C1 0.01µF(mylar firm)

Fig. 1 Dummy network

BNC connector

Main PWB

Fig. 2

5V

0V

0.5µS 0.5µS

Fig. 3 1MHz oscillator output waveform

T1=580 to 620ms

T2=380 to 420ms

T1 T2

VOH

VOL

Fig. 4 Receiver regeneration waveform (with dummy network)

TP1TP2

Fig. 5 Board location

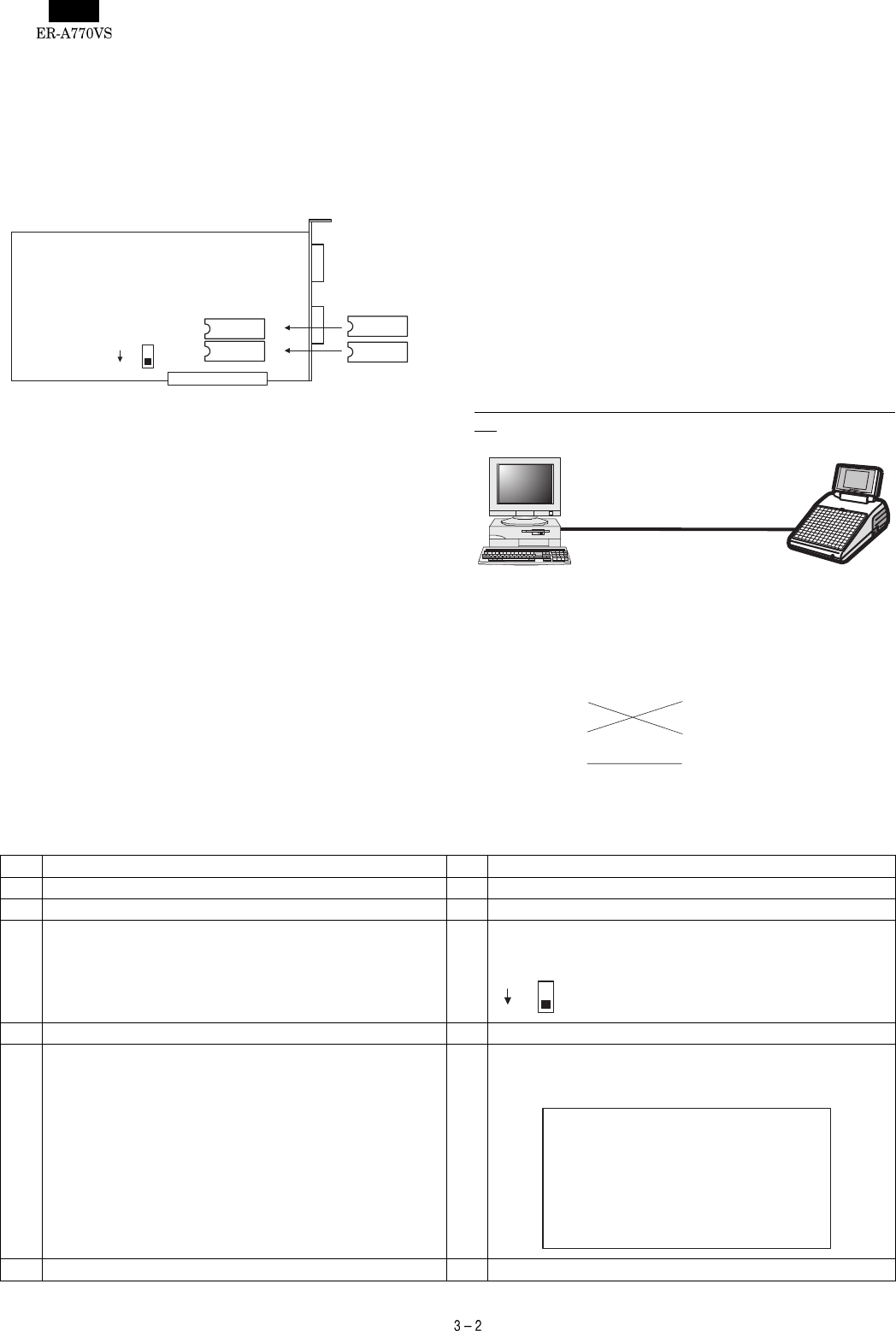

3) IPL from P-ROM via ER-A7RS

(1) Install the two master ROMs to the IC socket (IC12 , IC13) on the

ER-A7RS.

Master ROM -1 : VHI27801RAHxx

Master ROM -2 : VHI27801RAIxx

(2) IPL sitch on the ER-A7RS : Set the IPL SW to ON position.

(3) Install the ER-A7RS to the ER-A770. (The ER-A770 power should

be turned OFF.)

(4) Turned on the power of the ER-A770.

(5) The buzzer sounds intermittently during the running of IPL and the

program finishes after the buzzer gives five beeps at short inter-

vals.

(6) Turn OFF the power of the ER-A770.

(7) Remove the ER-A7RS from the ER-A770.

(8) Perform the Master reset.

3. ER-A770 Utility tools

1. Outline

This Specification document describes the explanation about "POSU-

TILITYTOOL.EXEhand "02FD.EXE".

"POSUTILITYTOOL.EXE"and "02FD.EXE" works on Windows 95/98

of PC and they have the following

Functions by connecting ER-A770 with RS232.

POSUTILITYTOOL.EXE : IPL of ER-A770 Program Object

02FD.EXE : All RAM Data Upload/Download

(PC software tool instead of the current

ER-02FD.)

2. Environment

PC and ER-A770 are connected by RS232.

Connect the CH2 port of the ER-A770 to the RS-232 interface of the

PC.

RS232 Cable Connecting:

3. Procedure

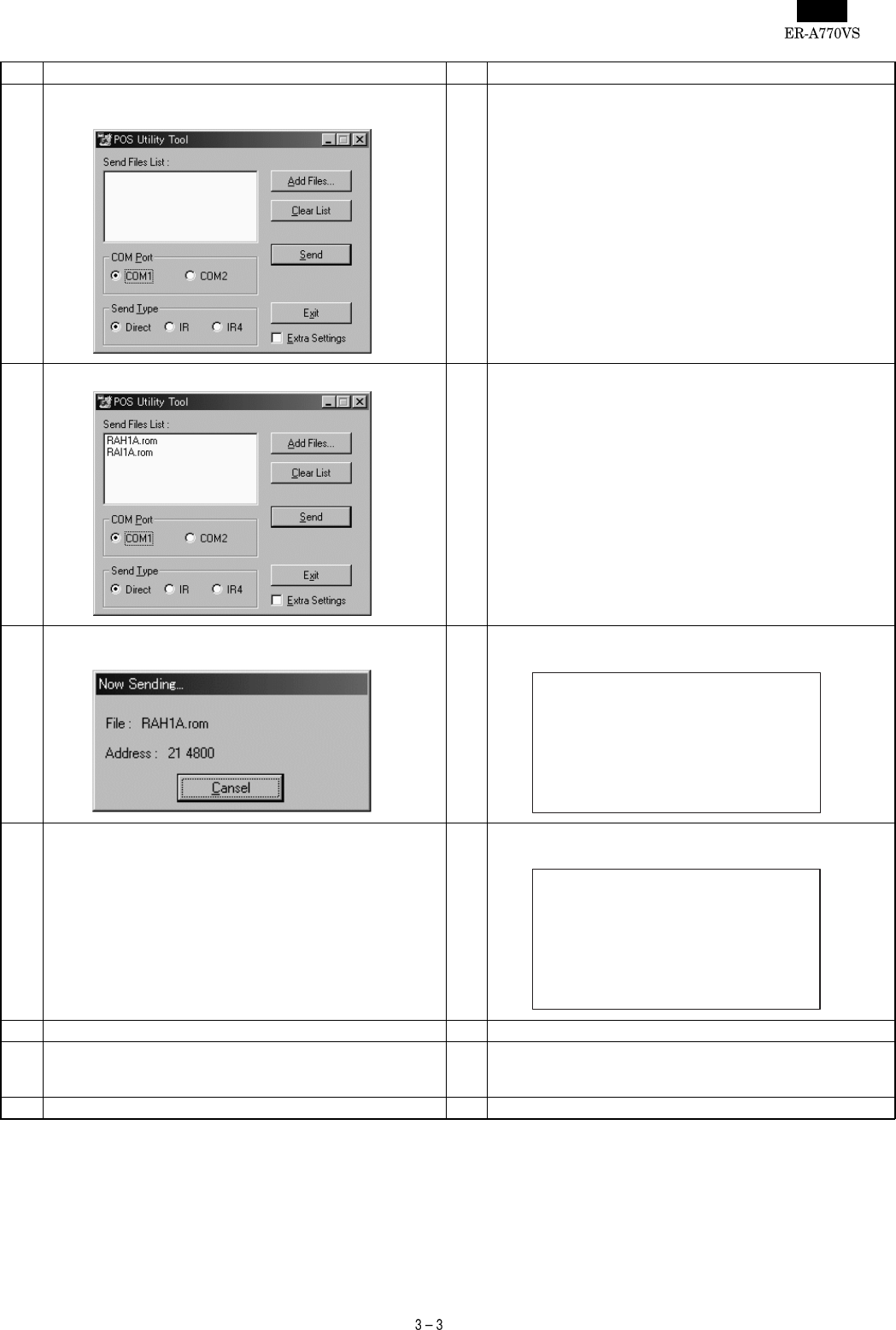

3.1 POS UTILITY TOOL

No Procedure on P.C. side No Procedure on ER-A770 side

1 Install "POSUTILITYTOOL.EXE" on the P.C.

2 Turn OFF the power.

3 Select "IPL Mode".

Set "IPL Switch" of ER-A770 to "ON".

4 Turn ON the power.

5 Starting of "IPL Mode".

ER-A770 shows

"IPL from Serial I/O"

6 Connect P.C. and ER-A770 (CH2) via RS232. (Fig 1)

IPL SW

OFF

ON

IC13 ROM2

IC12 ROM1

MASTER

P-ROM -2

MASTER

P-ROM -1

RS-232

PC POS

CH2

Fig. 1 Connection between PC and ER-A770

[PC]

3 TXD 3 TXD

2 RXD 2 RXD

5 S.G. 5 S.G.

[ER-A770]

IPL SW

OFF

ON

IPL from Serial I/O

>>>>> USE FONT <<<<<

Helvetica/ Helvetica-Condensed/ Century-Schoolbook/ Symbol & OriginalFonts: (RingWorld2/RingFont2/Pa

Symbol/PartsCod)

- - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -

No Procedure on P.C. side No Procedure on ER-A770 side

7 Execute "POSUTILITUTOOL.EXE" on P.C.

*Don’t execute the other Software at the same time.

8 Select the ROM object Files by "Add Files.." button.

9 Push "SEND" button.

Program data is sent to ER-A770 automatically. 9Program data is received from P.C. automatically.

ER-A770 shows

10 When sending is completed,

the initial Window is shown after "Complete" window. 10 ER-A770 shows

"Completed."

11 Turn OFF the power.

12

Select "Normal Mode".

Set "IPL switch" to "OFF".

(Ref. Hardware manual)

13 Execute "Service Reset" on ER-A770.

IPL from IR

Connected IRDA 115200

21 22 23 24 25 26 27 28

IPL from Serial I/O

Connected IRDA 115200

21 22 23 24 25 26 27 28

29 2A 2B 2C 2D 2E 2F

Completed.

IPL from Serial I/O

Connected IRDA 115200

30 31 32 33 34 35 36 37

38 39 3A 3B 3C 3D 3E 3F

Completed.

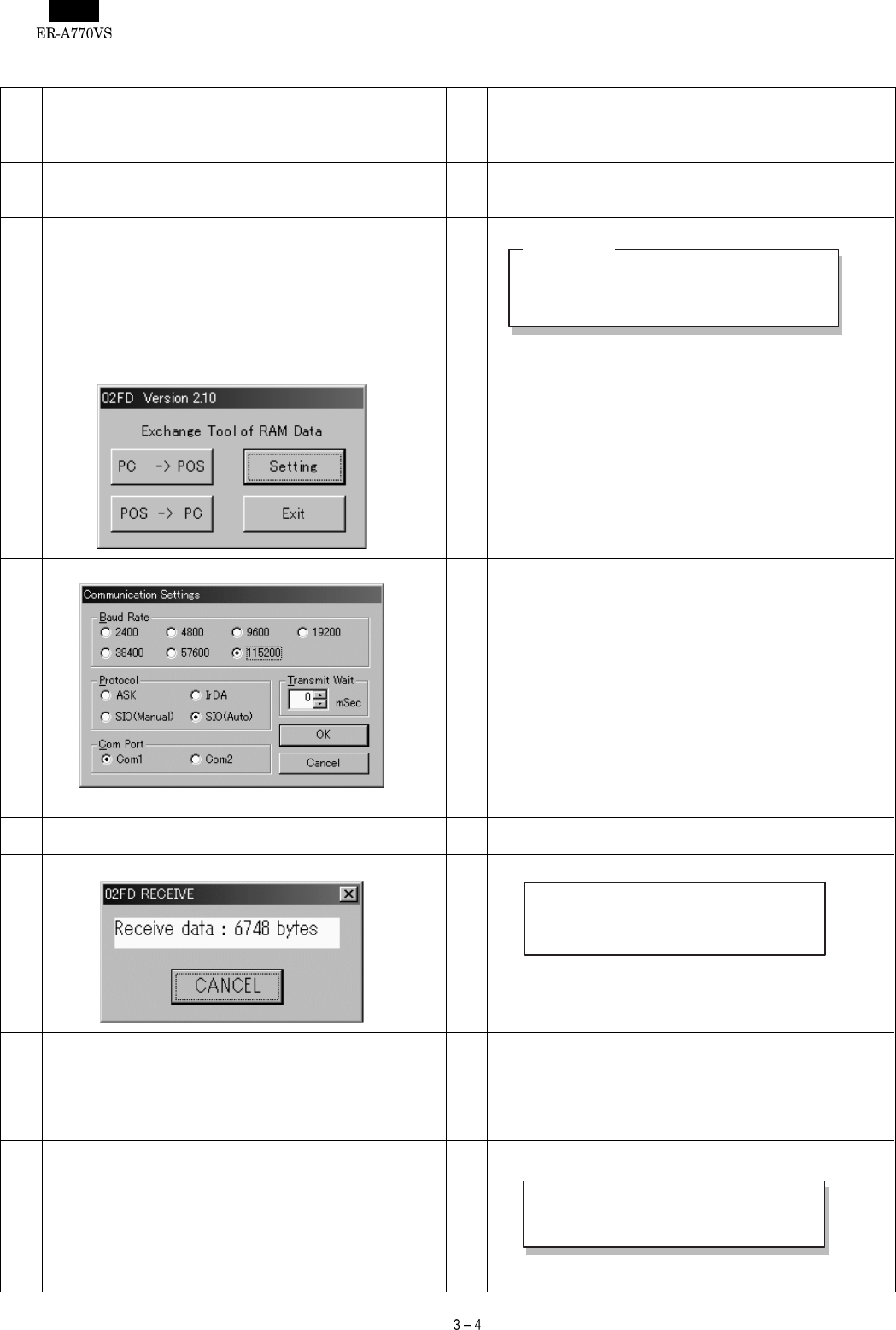

3.2 02FD

No Procedure on P.C. side No Procedure on ER-A770 side

1 Install "02FD.EXE" on the P.C.

ALL RAM Data UpLoad : Go to "2"

ALL RAM Data DownLoad : Go to "9"

2 ALL RAM Data UpLoad

Connect P.C. and ER-A770 (CH2) via RS232. (Fig 1) 2

Enter the SRV mode.

Select " 2 SETTING ".

Select " 14 BACKUP SEND"

3 ER-A770 shows

4 Execute "02FD.EXE" on P.C.

*Don’t execute the other Software at the same time.

5 Set the Communication method by "Setting" Button.

Push "OK" Button.

6 Push "Receive Start" Button.

And Select the Receiving File.

7 Communication starts. 7 Push TL key. ER-A770 shows

8 UpLoad is completed.

The initial Window is shown.

Push "Exit" Button.

8 UpLoad is completed.

The SETTING menu is shown.

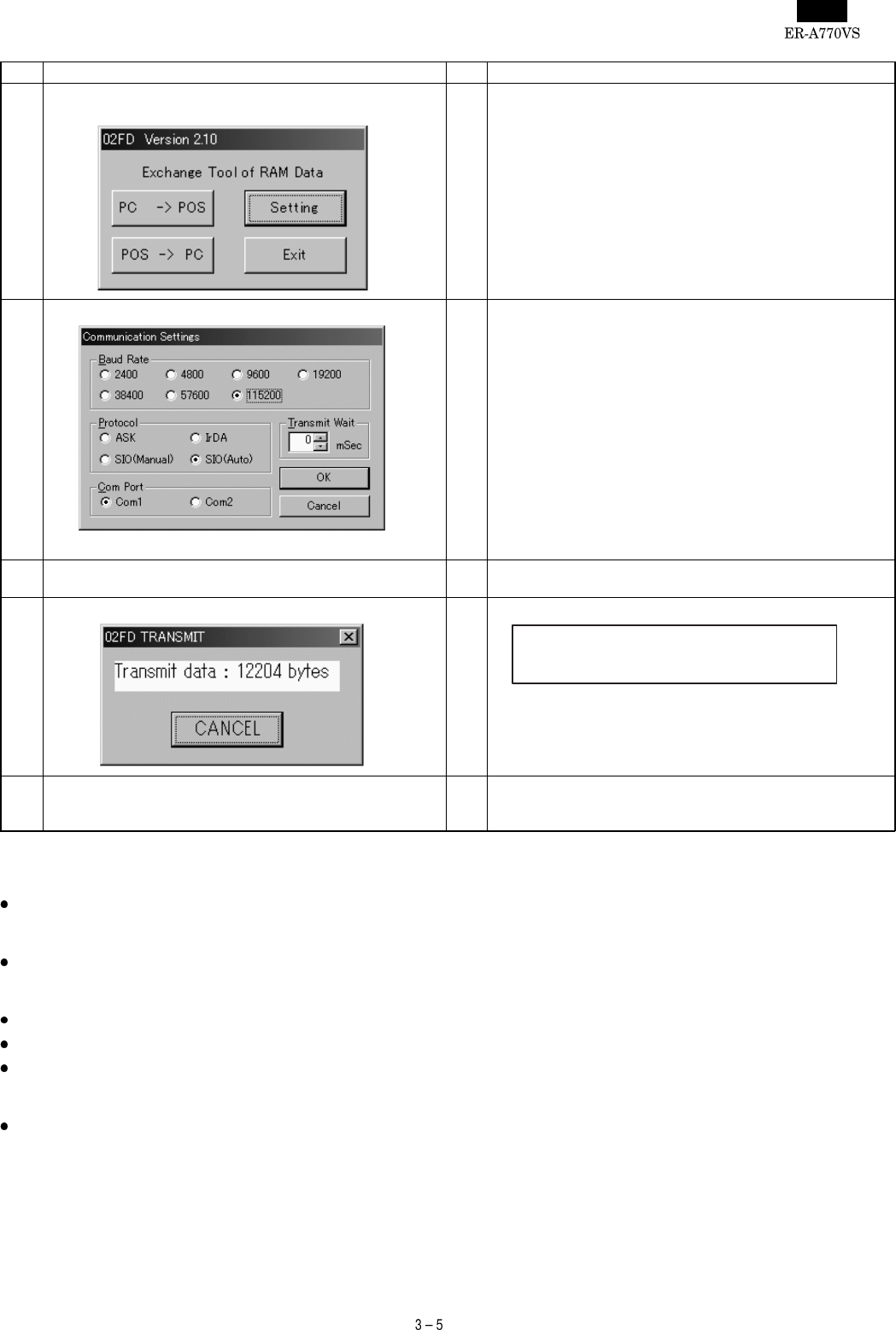

9 ALL RAM Data UpLoad

Connect P.C. and ER-A770 (CH2) via RS232. (Fig 1)

9 Enter the SRV mode.

Select " 2 SETTING".

Select " 15 BACKUP RECEIVE"

10 ER-A770 shows

Push TL key.

SEND DATA ALL RAM

SPEED PROGRAMMED SPEED

BACKUP SEND

SENDING 00000

BACKUP RECEIVE

SPEED PROGRAMMED SPEED

No Procedure on P.C. side No Procedure on ER-A770 side

11 Execute "02FD.EXE" on P.C.

*Don’t execute the other Software at the same time.

12 Set the Communication method by "Setting" Button.

Push "OK" Button.

13 Push "Transmit Start" Button.

And Select the Sending File.

14 Communication starts. 14 ER-A770 shows

15 DownLoad is completed.

The initial Window is shown.

Push "Exit" Button.

15 DownLoad is completed.

The SETTING menu is shown.

4. Note for handling of LCD

The LCD elements are made of glass. BE careful not to give them

strong mechanical shock, or they may be broken. Use extreme

care not to break them.

If the LCD element is broken and the liquid is leaked, do not lick it.

If the liquid is attached to your skin or cloth, immediately clean with

soap.

Use the unit under the rated conditions to prevent against damage.

Be careful not to drop water or other liquid on the display surface.

The reflection plate and the polarizing plate are easily scratched.

BE careful not to touch them with a hard thing such as glass,

tweezers. Never hit, push, or rub the surface with hard things.

When installing the unit, be careful not to apply stress to the LCD

module. If an excessive stress is applied, abnormal display or

uneven color may result.

RECEIVING 00000

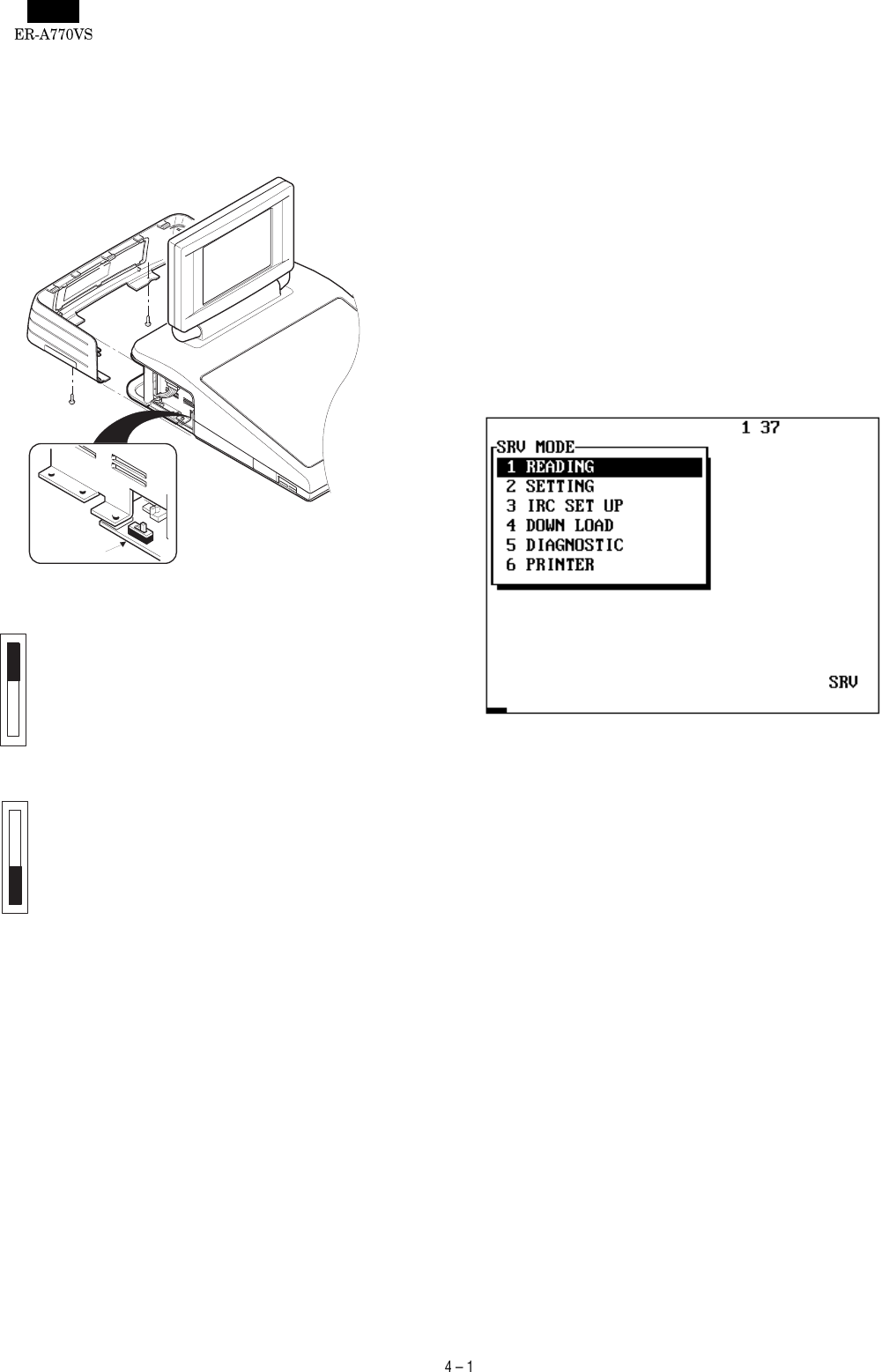

CHAPTER4. SRV RESET (Program Loop Reset) and switch to SRV mode

In the ER-A770, the following reset switch (location No. : SW1) is

used to switch to the service (SRV) mode and to reset. SRV. reset

Used to return the machine back to its operation state after a lock up

has occurred.

PROCEDURE

1) Turn off the AC switch.

2) Set the reset switch to "ON" position

3) Turn on the AC switch. (Wait one second)

4) Turn to "OFF" the reset switch.

5) The SRV mode is displayed as shown below.

DISPLAY:

Reset

switch

Rear side :"ON" position(Reset state)

ONOFF

Front side :"OFF" position(Run state)

ONOFF

RESET SW

RESET SW

SW1

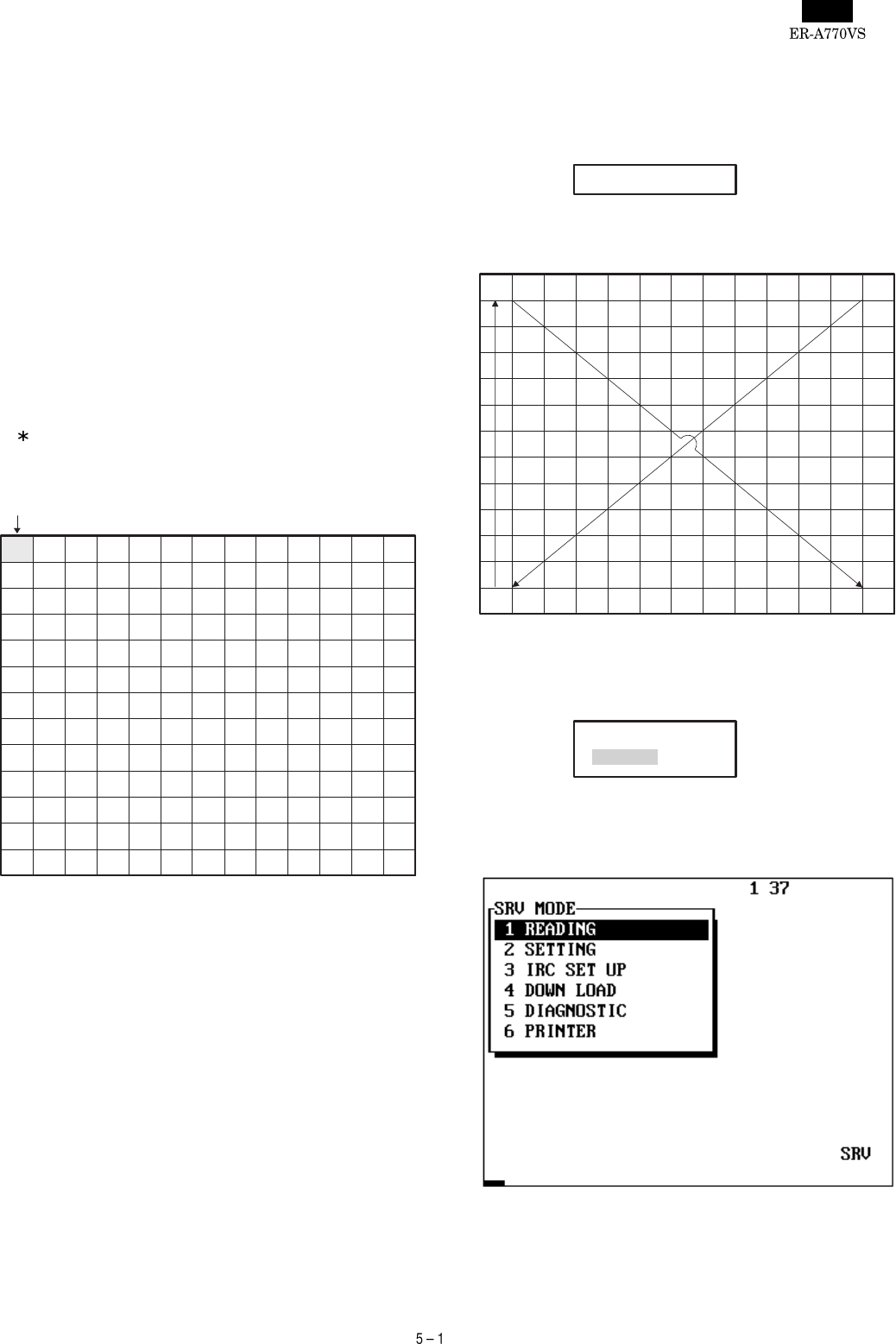

CHAPTER 5. MASTER RESET (All Memory Clear)

There are two possible methods to perform a master reset.

MRS-1 (Master resetting 1)

Used to clear all memory contents and return machine back to its

initial settings.

Return keyboard back to default for default kyeboard layout.

PROCEDURE

1) Turn off the AC switch.

2) Set the reset switch to "ON" position

3) Turn on the AC switch. (Wait one second)

4) While holding down MRS-1 key , turn to "OFF" the reset switch.

MRS-1 key : The key located on Left upper corner of the key-

board.

5) Enter the password key operation

DISPLAY:

Password input procedure:Press the four corners of the key-board

in the sequence of a, b, c, and d.

6) Master reset is started.

DISPLAY:

7) After completion of the master reset, the buzzer sounds three

times and the following SRV mode display is shown.

DISPLAY:

MRS-1 Key

keyboard layout

ENTER PASSWOPRD

ac

db

keyboard layout

MASTER RESET

MRS-2 (Master resetting 2)

Used to clear all memory and keyboard contents. This reset returns

all programming back to defaults.

The keyboard must be entered by hand. This reset is used if an

application needs different keyboard layout other than that supplied

by a normal MRS-1.

PROCEDURE

1) Turn off the AC switch.

2) Set the reset switch to "ON" position

3) Turn on the AC switch. (Wait one second)

4) While holding down MRS-2 key , turn to "OFF" the reset switch.

MRS-2 key: The key located on Right upper corner of the

keyboard.

5) Enter the password key operation

DISPLAY:

Password input procedure:Press the four corners of the key-board

in the sequence of a, b, c, and d.

6) Set the fixed keys in the table below. (Start from the zero "0" key,

The keys are displayed sequentially.)

DISPLAY:

[Key setup procedure]

NOTES:

1: When the 0 key is pressed, the key of the key number on

display is disabled.

2: Push the key on the position to be assigned. With this, the

key of the key number on display is assigned to that key

position.

3: When relocating the keyboard, the PGM 1/2 mode use

standard key layout.

Key

No.

Key

name

Key

No. Key name Key

No. Key name

001 "0" key 011 "00" key 021 RIGHT " " key

002 "1" key 012 "000" key 022 "CANCEL" key

003 "2" key 013 Decimal point " " key 023 "ENTER" key

004 "3" key 014 "CL" key 024 "TL" key

005 "4" key 015 " " key

006 "5" key 016 "SBTL" key

007 "6" key 017 "MODE" key

008 "7" key 018 UP " " key

009 "8" key 019 DOWN " " key

010 "9" key 020 LEFT " " key

7) Master reset is started.

DISPLAY:

8) After completion of the master reset, the buzzer sounds three

times and the following SRV mode display is shown.

DISPLAY:

MRS-2 Key

keyboard layout

ENTER PASSWOPRD

ac

db

keyboard layout

ENTER 0 KEY

0 Free key

0

Disable

MRS-2

executed Key

position set Setup

complete

MASTER RESET

>>>>> USE FONT <<<<<

Helvetica/ Helvetica-Condensed/ Century-Schoolbook/ Symbol & OriginalFonts: (RingWorld2/RingFont2/Pa

Symbol/PartsCod)

- - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -

CHAPTER 6. DIAGNOSTICS SPECIFICATIONS

CONTENTS

1. General ........................................................................................ 1

2. System configuration ................................................................... 1

2-1. Test system ....................................................................... 1

3. Diagnostics .................................................................................. 1

1) Master reset procedure ............................................... 1

2) Program reset (service reset) procedure ..................... 1

3-1. Execution of diagnostics ................................................... 1

3-2. RAM Diagnostics .............................................................. 2

1) Standard RAM Check ................................................. 2

2) UP-P02MB2 Check .................................................... 2

3-3. ROM & SSP Diagnostics .................................................. 3

1) Standard ROM Check ................................................. 3

2) SERVICE ROM Check ................................................ 3

3) SSP Check ................................................................. 4

3-4. Timer & Keyboard & Clerk Switch Diagnostics ................. 4

1) Timer Check ................................................................ 4

2) Keyboard Check .......................................................... 4

3) Clerk SW Check .......................................................... 4

3-5. RS232 I/F Diagnostics ...................................................... 4

1) CHANNEL Check ........................................................ 4

2) CH1 Check .................................................................. 5

3) CH2 Check .................................................................. 5

4) CH3 Check .................................................................. 5

5) CH4 Check .................................................................. 5

6) CH5 Check .................................................................. 5

7) CH6 Check .................................................................. 5

8) CH7 Check .................................................................. 6

9) CH8 Check .................................................................. 6

3-6. Liquid Crystal Display Diagnostics .................................... 6

1) Liquid Crystal Display Check ...................................... 6

3-7. Rear & Pole Display Diagnostics ...................................... 7

1) Rear & Pole Display Check ......................................... 7

3-8. SHARP Retail Network Diagnostics .................................. 7

1) SRN Self Check ........................................................... 7

2) SRN Flag Send Check ................................................ 8

3) SRN Data Send Check ................................................ 8

4) Data Transmission Check ........................................... 8

3-9. EFT Diagnostics ................................................................ 9

1) EFT Check ................................................................... 9

3-10. Magnetic Card Reader Diagnostics ................................ 10

1) Magnetic Card Reader Check ................................... 10

3-11. Drawer Diagnostics ......................................................... 10

1) Drawer 1 Check ......................................................... 10

2) Drawer 2 Check ......................................................... 10

1. General

This diagnostics program is used for simplified check of the ER-A770

series operations in servicing.

The diagnostics program is built in the standard ROM.

2. System configuration

2-1. Test system

ER-A770 only

3. Diagnostics

Starting the diagnostics

This diagnostics program is written in the external ROM and executed

by the CPU (H8/510). To operate this program, the following condi-

tions must be satisfied.

The power for the logic system is proper.

(+5V, VRAM, VCKDC, POFF, +20V)

The input/output pins and the internal logic of the CPU are normal.

In addition, CKDC9, MPCA8, the system bus, and the standard

ROM/RAM are normal.

To start the machine for the first time, perform the master reset.

In order to add an option unit when the machine is normally operat-

ing, perform the program reset.

1) Master reset procedure

Turn off the power.

Set the CKDC reset switch to RESET position.

Turn on the power.

While pressing the specified key, set the CKDC reset switch to the

normal position.

2) Program reset (service reset) procedure

Turn off the power.

Set the CKDC reset switch to RESET position.

Turn on the power.

Set the CKDC reset switch to the normal position. (Do not pres-

sany key.)

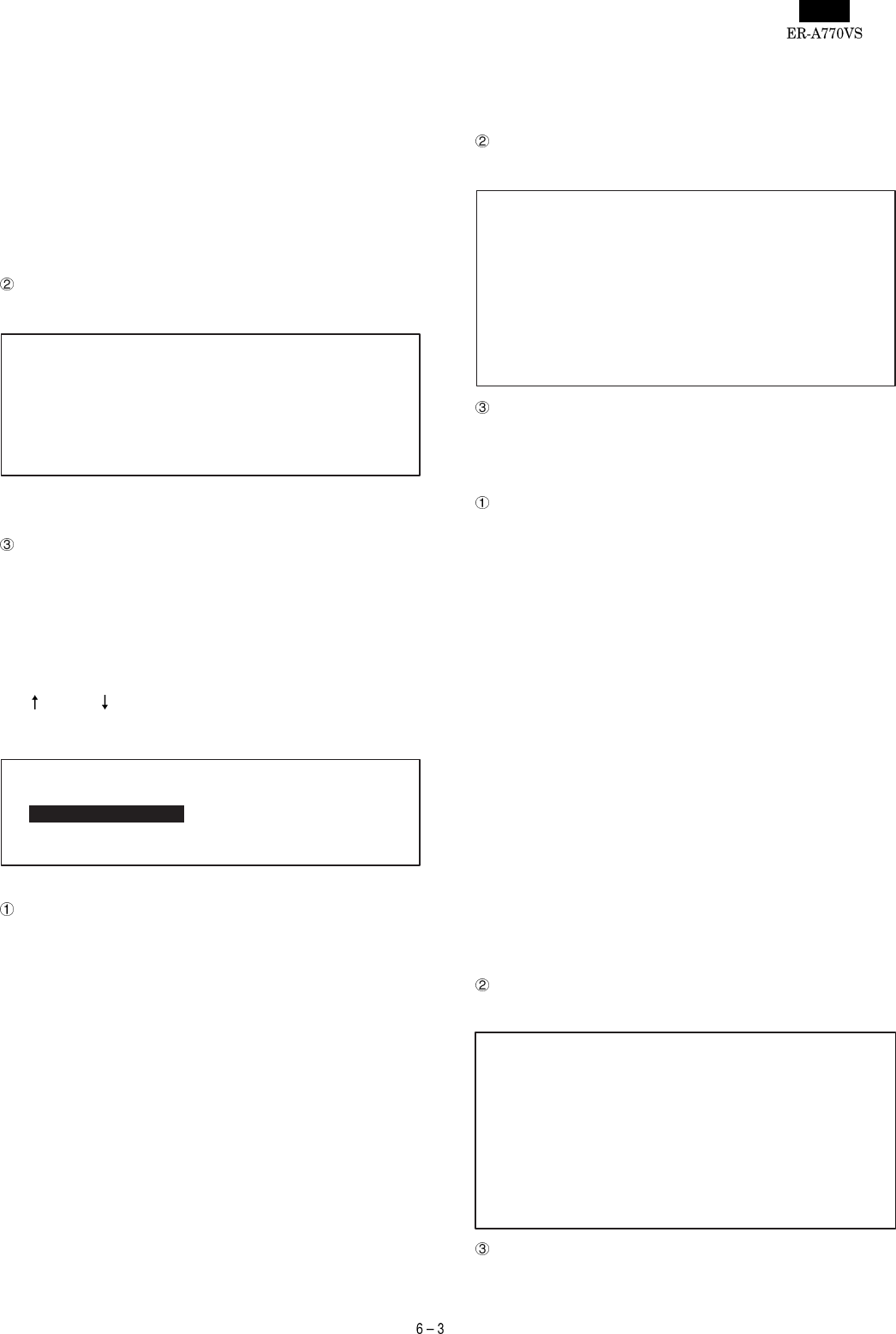

3-1. Execution of diagnostics

To start the diagnostics, select "DIAGNOSTICS" with the cursor in the

menu selection in SRV mode, and press the enter key.

The DIAG MAIN MENU is started and the following menu screen is

display. The cursor position is highlighted. Use key and key to

move the cursor. Move the cursor to the process you desire and

press the enter key. The selected individual diagnostics program is

executed. When the individual diagnostics program is completed, the

display returns to the menu screen. To terminate the diagnostics,

press the CANCEL key. Then the display returns to the SRV mode

menu screen.

ER-A770

"Product & Test Diagnostics" is used only in the production

process, and must be not used in servicing.

3-2. RAM Diagnostics

This diagnostics is used to test the standard RAM and the expansion

RAM.

The following menu is displayed. The cursor position is highlighted.

Use key and key to move the cursor. Move the cursor to the

process you desire and press the enter key. The selected individual

diagnostics program is executed.

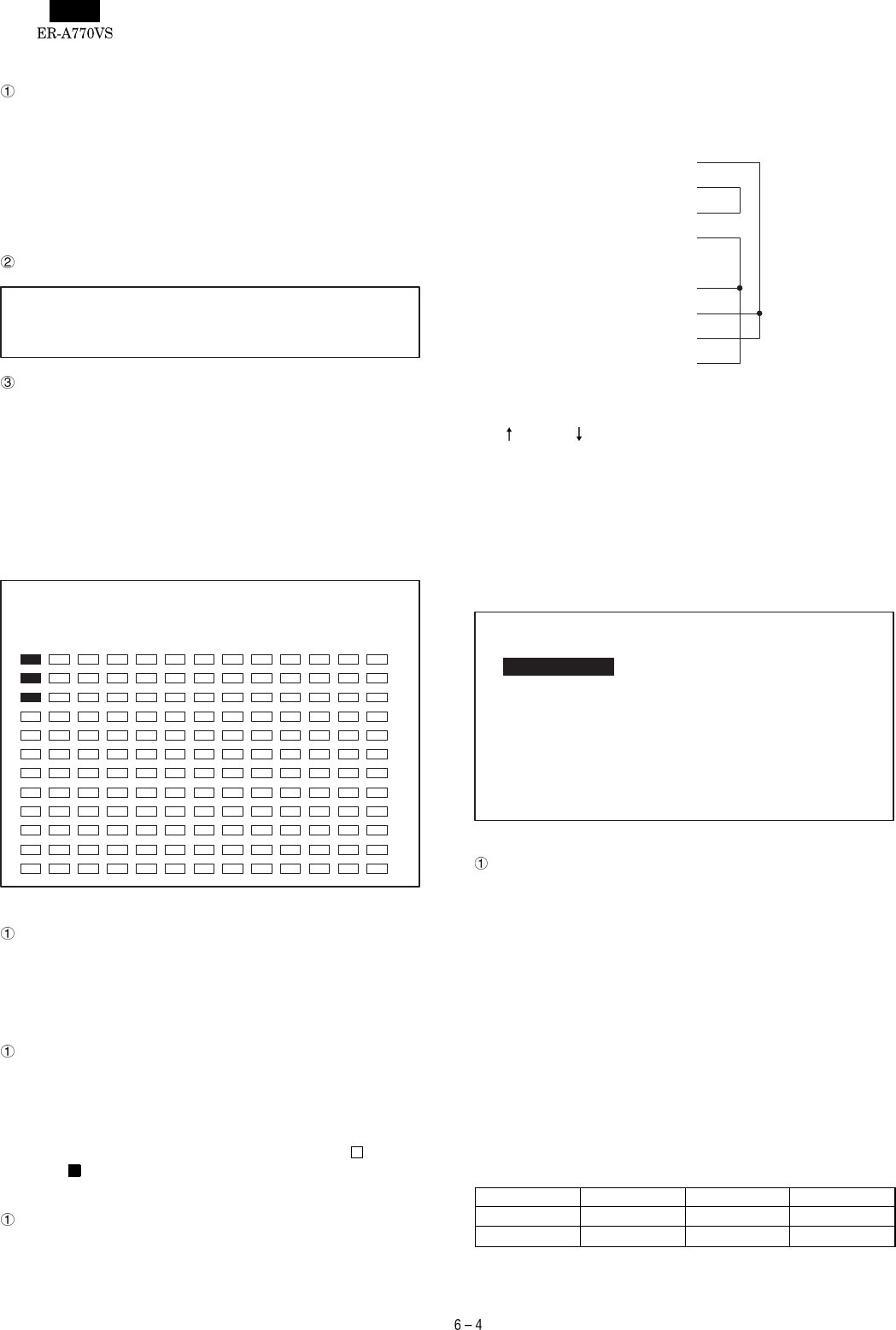

1) Standard RAM Check

Check content

For the pseudo SRAM of the standard RAM 1MB, the following

check is performed. The memory contents will not be changed by

this check.

The following processes are performed for the memory address

(700000H ~ 7FFFFFH) to be checked.

PASS1: Memory data save

PASS2: Data "0000H" write

PASS3: Data "0000H" read/compare, data "5555H" write

PASS4: Data "5555H" read/compare, data "AAAAH" write

PASS5: Data "AAAAH" read/compare

PASS6: Memory data writed the saved data

In case of a compare error in the check sequences of PASS1 ~

PASS6, an error display is made. If there is no error at all, the

check is normally terminated.

In addition, the following address check is performed.

In case of an error, an error display is made and read/write of the

address where the error occurred is repeated.

Check point address = 700000H, 700001H

700002H, 700004H

700008H, 700010H

700020H, 700040H

700080H, 700100H

700200H, 700400H

700800H, 701000H

702000H, 704000H

708000H, 710000H

720000H, 740000H

780000H

Display

The screen displays the capacity of RAM in the unit of 64 KB.

The error address and the bit are displayed only when the error

occurs. (If the error does not occur, they are not displayed.)

Terminating procedure

After completion of check, press the CANCEL key.

2) UP-P02MB2 Check

Check content

The UP-P02MB2 presence check is performed in the following

procedure. The memory contents must not be changed by this

check.

55AAH is written into 9FFFFEH.

9FFFFEH is read and compared with 55AAH. If the both data

are correct, the following procedure is performed. The system

reads 9FFFFEH and compares it with 55AAH. If both data are

correct, the following tests will be performed. If not, the screen

displays the message "Extended RAM size : 0KB", and ends

the test.

For the UP-P02MB2, the following check is performed.

The following processes are performed for the check address

(800000H ~ 9FFFFFH).

PASS1: Memory data save

PASS2: Data "0000H" write

PASS3: Data "0000H" read/compare, data "5555H" write

PASS4: Data "5555H" read/compare, data "AAAAH" write

PASS5: Data "AAAAH" read/compare

PASS6: Memory data writed the saved data

In case of a compare error in the check sequences of PASS1 ~

PASS6, an error display is made. If there is no error at all, the

check is normally terminated.

In addition, the following address check is performed in the above

check sequence.

In case of an error, an error display is made and read/write of the

address where the error occurred is repeated without performing

the check.

RAM Diagnostics

ROM & SSP Diagnostics

Clock & Keyboard & Clerk Diagnostics

Serial I/O Diagnostics

LCD Diagnostics

Rear & Pole Display Diagnostics

SRN Diagnostics

EFT Diagnostics

MCR Diagnostics

Drawer Diagnostics

Diagnostics End

ER-A770 Diagnostics V 1.0A

Product & Test Diagnostics

RAM Diagnostics

UP-P02MB2 Check

Standard RAM Check

Standard RAM Check

Standard memory size : 1024KB PASS!!(or ERROR!!)

Error Address xxxxxxH

Write Data xxxxH

Read Data xxxxH

Check point address = 800000H,800001H

800002H,800004H

800008H,800010H

800020H,800040H

800080H,800100H

800200H,800400H

800800H,801000H

802000H,804000H

808000H,810000H

820000H,840000H

880000H,900000H

Display

The screen displays the capacity of RAM in the unit of 64 KB.

The error address and the bit are displayed only when the error

occurs. (If the error does not occur, they are not displayed.)

Terminating procedure

After completion of check, press the CANCEL key.

3-3. ROM & SSP Diagnostics

The standard ROM and the service ROM are checked. The SSP

circuit is also checked.

The following menu is displayed. The cursor position is highlighted.

Use key and key to move the cursor. Move the cursor to the

process you desire and press the enter key. The selected individual

diagnostics program is executed.

1) Standard ROM Check

Check contents

The standard ROM area (200000H ~ 3FFFFFH) is added in the

unit of byte. If the lower two digits of the result is 20H, it is normal.

The ROM version and the model name code which are stored in

address 31FFE0H ~ 31FFEFH where the ROM version and the

check sum correction data are stored are displayed. The format of

data (ASCII) to be stored is as follows:

31FFE0H ~ 31FFEFH: Model name code (example: ER-A770.

Display is made up to 00H of data.)

31FFF0H ~ 31FFF9H: 27801R****(****=PROGRAM VERSION)

31FFFAH ~ 31FFFBH: BLOCK NO. ("20" ~ "3F")

31FFFCH: TERMINATOR ("=")

31FFFDH ~ 31FFFEH: BLOCK VERSION (example "00")

31FFFFH: CHECK SUM CORRECTION DATA

The flash ROM used as the standard ROM has rewriting block of

64KB as the unit. To control the version in each block, the compo-

sition is the same as the above 31FFF0H or later and arranged in

each 64KByte. At that time, correction is made so that the sum of

each block becomes 01H, and the total of 2MByte is 20H.

The program version of the IPL is displayed so that 0PAGE

(BLOCK) where the IPL is stored is individually controlled.

Display

The screen displays the capacity of RAM in the unit of 64 KB.

Terminating procedure

After displaying the check result, press the CANCEL key to termi-

nate the check.

2) SERVICE ROM Check

Check content

For the SERVICE ROM area (D00000H ~ EFFFFFH) consisting of

two EPROMs, addition is made in the unit of byte for each chip.

The lower two digits of the result are 10H, it is regarded as normal.

The ROM version and the model name code which are stored in

address D1FFE0H ~ D1FFFFH where the ROM version and the

check sum correction data are stored are displayed. The format of

data (ASCII) to be stored is as follows:

D1FFE0H ~ D1FFEFH: Model name code (example: ER-A770.

Display is made up to 00H of data.)

D1FFF0H ~ D1FFF9H: 27801R****(****=PROGRAM VERSION)

D1FFFAH ~ D1FFFBH: BLOCK NO. ("20" ~ "2F")

D1FFFCH: TERMINATOR ("=")

D1FFFDH ~ D1FFFEH: BLOCK VERSION (example "00")

D1FFFFH: CHECK SUM CORRECTION DATA

This SERVICE ROM allows to write into the FLASH ROM when

re-execution is impossible because of an abnormality during re-

writing into the FLASH ROM. The composition is the same as the

standard ROM.

The program version of the IPL is displayed so that 0PAGE

(BLOCK) where the IPL is stored is individually controlled.

Display

The screen displays the capacity of RAM in the unit of 64 KB.

Terminating procedure

After displaying the check result, press the CANCEL key to termi-

nate the check.

UP-P02MB2 Check

Extended RAM size : 2048KB PASS!!(or ERROR!!)

Error Address xxxxxxH

Write Data xxxxH

Read Data xxxxH

ROM & SSP Check

Service ROM Check

SSP Check

Standard ROM Check

Standard ROM Sum Check : PASS!!(or ERROR!!)

IPL PROGRAM Version

**

APL PROGRAM Version

← Displays the version.

27801R**** ER-A770

27801R**** ER-A770

BLOCK Version

20=**,21=**,22=**,23=**,24=**,25=**,26=**,27=**

28=**,29=**,2A=**,2B=**,2C=**,2D=**,2E=**,2F=**

:

Standard ROM Sum Check : PASS!!(or ERROR!!)

IPL PROGRAM Version

**

APL PROGRAM Version

← Displays the version.

27801R**** ER-A770

27801R**** ER-A770

BLOCK Version

20=**,21=**,22=**,23=**,24=**,25=**,26=**,27=**

28=**,29=**,2A=**,2B=**,2C=**,2D=**,2E=**,2F=**

:

3) SSP Check

Check content

By starting this check program, the SSP setting for checking is

automatically performed and the SSP check is executed and the

result is displayed.

The SSP check sets data for check in the vacant space in the

SSP entry register, and deletes the data for check after comple-

tion of checking. Therefore, the already set data are not changed

by this check.

Display

Terminating procedure

After displaying the check result, press the CANCEL key to termi-

nate the check.

3-4. Timer & Keyboard & Clerk Switch Diagnostics

The operation of the clock crystal of CKDC, the keyboard, and the

clerk switch are tested.

When the CANCEL key is pressed, the display returns to the diagnos

tics menu.

1) Timer Check

Check content

The operation of the clock crystal of CKDC9 is checked.

The screen displays "YY/MM/DD & MM:HH:SS". Make sure that

the time displayed is updated.

2) Keyboard Check

Check content

The A770 main body keyboard input test is performed. The posi-

tion code corresponding to the inputted key is displayed in three

digits. The key layout corresponding to the input is displayed on

the LCD screen. Press the corresponding key to input. The display

of the inputted key is changed from white square to black

square and a catch sound is generated.

3) Clerk SW Check

Check content

The code of the key which is inserted into the clerk key switch is

displayed in a decimal number.

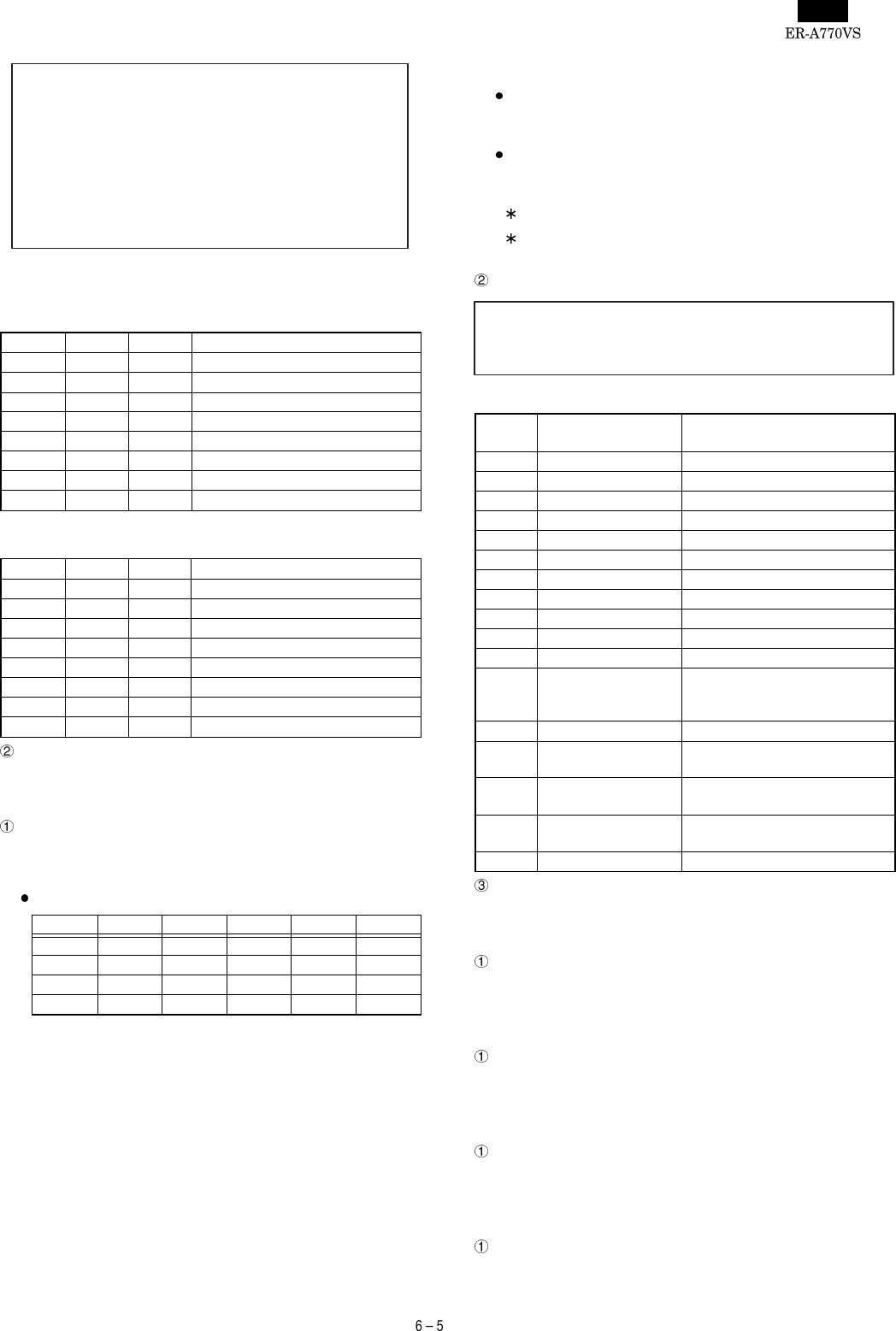

3-5. RS232 I/F Diagnostics

The main PWB and the option PWB (RS232 interface of ER-A7RS)

are checked. Attach the 9-pin D-Sub loop back connector (UKOG-

6717RCZZ) of wiring in Fig. 3-11.

Fig. 3-11. Wiring diagram of loop back connector (UKOG-6717RCZZ)

The following menu is displayed. The cursor position is highlighted.

Use key and key to move the cursor. Move the cursor to the

process you desire and press the enter key. The selected individual

diagnostics program is executed. When the CANCEL key is pressed,

the display returns to the diagnostics menu.

When setting channels of RS232, do not set two or more ports to

one channel. In the ER-A770, max. two units of ER-A7RS can be

installed. In each PWB, do not set two or more ports to the same

channel. If two or more ports should be set to one channel, the

hardware would be destroyed.

1) CHANNEL Check

Check content

The CHANNEL setting of the connected RS232 is displayed. The

display content and the setting of DIP SW for CHANNEL setting

on the RS232 I/F PWB are compared.

Since the RS232 on the main PWB of the ER-A770 is fixed to

CH1 and CH8, that in the ER-A7RS must be set to CH2 ~ CH7.

Relationship between the physical channel and logical

channel of the ER-A770’s RS232.

The ER-A770 comes equipped with 2 channels of the RS232C inter-

face as standard.

These two channels are expressed as physical channels "CH1" and

"CH2" on the cabinet and application. On hardware, however, the

"CH2" is defined as a logical channel "CH8" because it has a different

circuit configuration.

Therefore, the relationship of channel definitions between the cabinet

indication and the RS232 I/F Diag is as shown in the table below.

Cabinet indication Logical channel Definition in Diag. Application

CH1 CH1 CH1 CH1

CH2 CH8 CH8 CH2

SSP Check

SSP (NMI) Check : PASS!!(ERROR!!)

Timer & Keyboard & Clerk SW Diagnostics

DATA & TIME = YY/MM/DD & HH:MM:SS

KEY CODE = *** CLERK CODE = ***

CD 1pin

2pin

3pin

4pin

5pin

6pin

7pin

8pin

9pin

RD

SD

ER

GND

DR

RS

CS

CI

RS232 I/F Diagnostics

CH1 Check

CH2 Check

CH3 Check

CH4 Check

CH5 Check

CH6 Check

CH7 Check

CH8 Check

CHANNEL Check

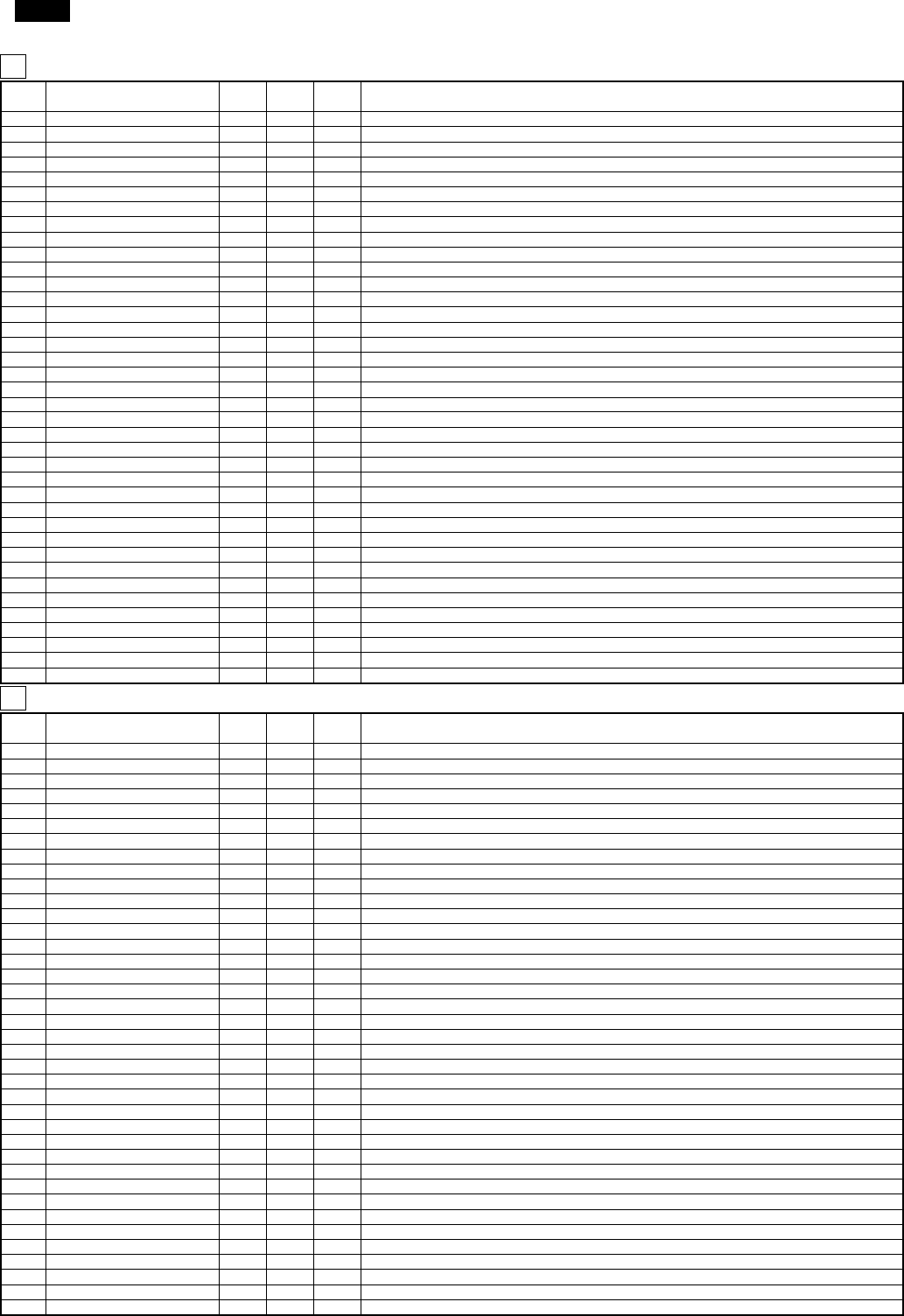

(Reference) ER-A7RS CHANNEL setting (In the table below, "1" =

SW OFF, "0" = SW ON.)

ER-A7RS CON3

S1-1 S1-2 S1-3 LOGICAL CHANNEL

0 0 0 Invalid

0 0 1 CHANNEL 1: Impossible to set

0 1 0 CHANNEL 2:

0 1 1 CHANNEL 3

1 0 0 CHANNEL 4

1 0 1 CHANNEL 5

1 1 0 CHANNEL 6

1 1 1 CHANNEL 7

ER-A7RS CON3

S1-4 S1-5 S1-6 LOGICAL CHANNEL

0 0 0 Invalid

0 0 1 CHANNEL 1: Impossible to set

0 1 0 CHANNEL 2

0 1 1 CHANNEL 3

1 0 0 CHANNEL 4

1 0 1 CHANNEL 5

1 1 0 CHANNEL 6

1 1 1 CHANNEL 7

Terminating procedure

Press the CANCEL key to terminate the check.

2) CH1 Check

Check content

When the channel is not set, an error display is made (ER-

ROR:CH1). When the channel is set, the following check is performed.

Control signal check

ERn RSn DRn CIn CDn CSn

OFF OFF OFF OFF OFF OFF

OFF ON OFF OFF ON ON

ON OFF ON ON OFF OFF

ON ON ON ON ON ON

The read check of the above inputs and the interruption check of

CS, CI, and CD are performed.

In the read check, ER and RS are changed over in the above

sequence and the logic states of DR, CI, CD, and CS are

checked.

If the logic differs from that in the table, an error display is made.

"ON" in the table means Active LOW, and "OFF" means Active

HIGH.

In the interruption check, an interruption of CS, CI, or CD is

allowed one by one. (MASK is canceled.)

If an interruption is not made when each signal is active, or if an

interruption is made when each signal is not active, an error

display is made.

The above check is repeated four cycles.

Data transfer check

The loop back data (256 bytes) of 00H ~ 0FFH are used for

data transfer check. The baud rate is set to 38400BPS.

Timer check (RS232 on board timer)

Before performing the check, set the timer to RCVDT start and

5ms. Then perform the following procedure.

During execution of the check, TRQ- must not be generated.

After 5ms from completion of the check, TRQ- must be gener-

ated.

Display

All the contents of an error must be displayed.

ERROR

No. ERROR display ERROR content

1 ER-DR:ERROR ER-DR LOOP ERROR

2 ER-CI:ERROR ER-CI LOOP ERROR

3 RS-CD:ERROR RS-CD LOOP ERROR

4 RS-CS:ERROR RS-CS LOOP ERROR

5 CI INT:ERROR CI interruption is not made.

6 CD INT:ERROR CD interruption is not made.

7 CS INT:ERROR CS interruption is not made.

8 TXEMP:ERROR TXEMP is not set.

9 TXEMP INT:ERROR TXEMP interruption is not made.

10 TXRDY:ERROR TXRDY interruption is not made.

11 TXRDY INT:ERROR TXRDY interruption is not made.

12 RCVRDY:ERROR RCVRDY is not set.

(Reception enabled. TR-Q is

generated during check)

13 RCVRDY INT:ERROR RCVRDY interruption is not made.

14 SD-RD:ERROR SD-RD LOOP ERROR

(DATA ERROR)

15 SD-RD:ERROR SD-RD LOOP ERROR (DATA

ERROR

16 TIMER:ERROR TIMER ERROR (TMRQ is not set

after completion of check.)

17 TIMER INT:ERROR TRQ-1 interruption is not made.

Terminating procedure

Press the CANCEL key to terminate the check.

3) CH2 Check

Check content

The check procedure, the display, and the terminating procedure

are the same as CH1 Check.

4) CH3 Check

Check content

The check procedure, the display, and the terminating procedure

are the same as CH1 Check.

5) CH4 Check

Check content

The check procedure, the display, and the terminating procedure

are the same as CH1 Check.

6) CH5 Check

Check content

The check procedure, the display, and the terminating procedure

are the same as CH1 Check.

RS232 I/F Diagnostics

CHANNEL Check

CH1 = exist!

←

Display when channel present

CH2 = exist!

CH3 = none!

←

Display when no channel

CH4 = none!

CH5 = none!

CH6 = none!

CH7 = none!

RS232 CH1 Check

ER-DR : ERROR!!

7) CH6 Check

Check content

The check procedure, the display, and the terminating procedure

are the same as CH1 Check.

8) CH7 Check

Check content

The check procedure, the display, and the terminating procedure

are the same as CH1 Check.

9) CH8 Check

Check content

When the channel is set, the following check is performed.

Control signal check

Ern RSn DRn Cin CDn CSn

OFF OFF OFF OFF OFF OFF

OFF ON OFF OFF ON ON

ON OFF ON ON OFF OFF

ON ON ON ON ON ON

The read check of the above inputs.

In the read check, ER and RS are changed over in the above

sequence and the logic states of DR, CI, CD, and CS are

checked.

If the logic differs from that in the table, an error display is made.

"ON" in the table means Active LOW, and "OFF" means Active

HIGH.

The above check is repeated four cycles.

Data transfer check

The loop back data (256 bytes) of 00H ~ 0FFH are used for

data transfer check. The baud rate is set to 115200BPS.

Display

All the contents of an error must be displayed.

ERROR

No. ERROR display ERROR content

1 ER-DR:ERROR ER-DR LOOP ERROR

2 ER-CI:ERROR ER-CI LOOP ERROR

3 RS-CD:ERROR RS-CD LOOP ERROR

4 RS-CS:ERROR RS-CS LOOP ERROR

5

6

7

8 TXEMP:ERROR TXEMP is not set.

9 TXEMP INT:ERROR TXEMP interruption is not made.

10 TXRDY:ERROR TXRDY interruption is not made.

11 TXRDY INT:ERROR TXRDY interruption is not made.

12

RCVRDY:ERROR RCVRDY is not set.

(Reception enabled. TR-Q is

generated during check)

13 RCVRDY INT:ERROR RCVRDY interruption is not made.

14 SD-RD:ERROR SD-RD LOOP ERROR (DATA

ERROR)

15

SD-RD:ERROR SD-RD LOOP ERROR

(DATA ERROR, FRAMING

ERROR, etc.)

16

17

Terminating procedure

Press the CANCEL key to terminate the check.

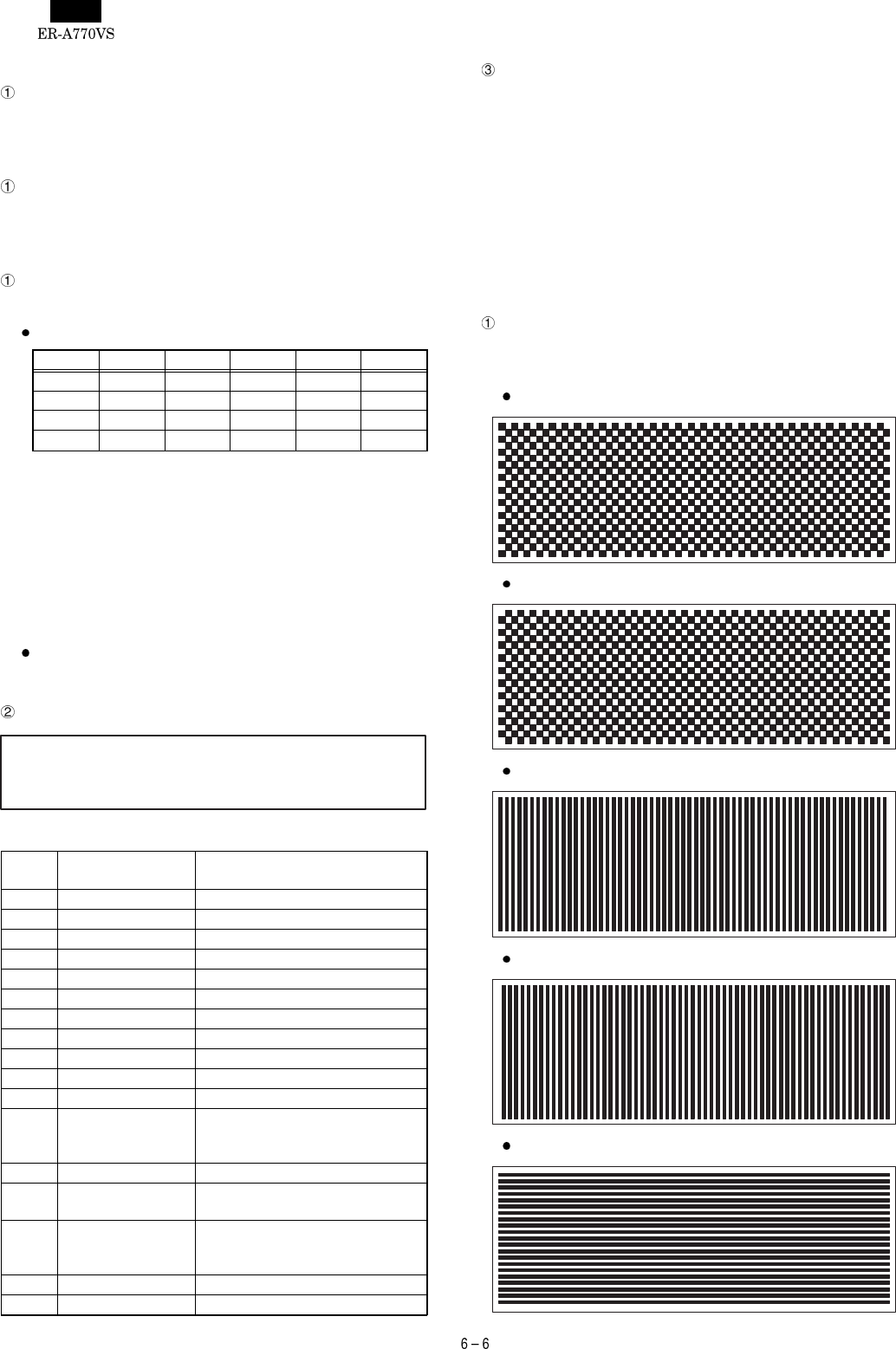

3-6. Liquid Crystal Display Diagnostics

The ER-A770 LCD display is checked.

The test program displays the patterns in the following sequence.

Every time when the ENTER key is pressed, the next pattern is

displayed. When the ENTER key is pressed at the final pattern, or

when the CANCEL key is pressed at the midst of the check, the

display returns to the menu screen.

1) Liquid Crystal Display Check

Check content

The test patterns are displayed in the following sequence. When

the ENTER key is pressed, the next pattern is displayed.

Black and white pattern at 1 dot pitch

Reversed pattern of the above

Vertical stripe pattern at 1 dot pitch

Reversed pattern of the above

Horizontal stripe pattern at 1 dot pitch

RS232 CH1 Check

ER-DR : ERROR!!

Reversed pattern of the above

The outermost peripheral of the LCD’s active area is displayed

in one-dot line.

"H" pattern. "H" is displayed in 40 digits and 15 lines. The 15th

line only has 39 digits of "H."

Terminating procedure

Press the ENTER key at the final pattern, or press the CANCEL

key to terminate the check.

3-7. Rear & Pole Display Diagnostics

The rear display is checked.

The test program displays the following patterns. When the CANCEL

key is pressed, the display returns to the diagnostics menu.

1) Rear & Pole Display Check

Check content

The test patterns are displayed in the following sequence. When

the ENTER key is pressed, the next pattern is displayed.

(i) The test pattern below is displayed.

(ii) The screen displays a test pattern showing that all digits are lit.

Display

Terminating procedure

Press the CANCEL key to turn off all the elements of the rear

display.

3-8. SHARP Retail Network Diagnostics

The SRN test is performed.

To perform this test, the following composition is required.

ER-A770

Terminal resistor

Branch (trunk) cable (only for data transfer test)

The following menu is displayed. The cursor position is highlighted.

Use key and key to move the cursor. Move the cursor to the

process you desire and press the enter key. The selected individual

diagnostics program is executed. When the individual diagnostics

program is completed, the display returns to this menu screen. When

the CANCEL key is pressed, the display returns to the diagnostics

menu.

1) SRN Self Check

Check content

The ROM and RAM for SRN are checked, and CTC interruption and

carrier sense are checked. Also ADLC function and transmission/re-

ception DMA check is made by using the self loop function of ADLC

(MC6854). In addition, the other signals are checked. The check

procedure is as follows:

Execute diagnostics command 2. The number of resending is

displayed.

Execute diagnostics command 0. The error status is displayed.

The error status is as shown in the table below. When an error

occurs in this test, the following tests are not performed.

b7 An error occurs. (The error print is always 1.)

b6 An unexpected interruption is made.

b5 A collision is generated.

b4 An interruption of send complete cannot be made.

(DMAC TC UP interruption)

b3 An interruption of carrier OFF cannot be made. The

mirror image of carrier OFF shows carrier ON.

b2 An interruption of CTC CH2 or CH3 cannot be made.

(Timer interruption)

b1 ROM sum check error

b0 RAM error

Execute diagnostics command 1. The error status is displayed.

The error status is as shown in the table below.

b7 An error is generated. (The error print is always 1.)

b6 An unexpected interruption is generated.

b5 DMA sent data and received data are different.

b4 The number of data received in DMA is abnormal.

b3 The number of data transmitted in DMA is abnormal.

b2 An overrun error is generated.

b1 An underrun error is generated.

DOT DISPLAY :

7SEG DISPLAY :

0 1 2 3 4 5 6 7 8 9 ; A a B b C

0. 1. 2. 3. 4. 5. 6. 7. 8. 9. -.

Rear Display Check

SRN Diagnostics

Flag Send Check

Data Send Check

Data Check (Satellite Machine)

Data Check (Master Machine)

Self Check

b0 An interruption of send complete cannot be made.

(DMAC TC UP interruption)

Execute diagnostics command 5. The error status is displayed.

The names and the directions of the signals which are subject

to diagnostics 5 command are as shown in the table below.

Signal name Direction

Power interruption notice Host Controller

Power interruption ON initialization Host Controller

Power interruption ON continuation Host Controller

Power interruption process complete Host Controller

CH1 reception data present. Host Controller

CH2 reception data present. Host Controller

Check that the target bit of two statuses obtained by diagnostics

5 command is "0" for ST1 and "1" for ST2. (The other bits must

be masked.) In the other cases, the error status is displayed with

the error occurrence bit as "1." The normal bit shows "0."

The error status from the host to the controller is as shown in the

table below.

b7 Not used. ("0" is always displayed.)

b6 Power interruption notice

b5 Not used. ("0" is always displayed.)

b4 Not used. ("0" is always displayed.)

b3 Not used. ("0" is always displayed.)

b2 Not used. ("0" is always displayed.)

b1 Power ON continuation

b0 Power ON initializing

The error status from the controller to the host is as shown in the

table below.

b7 Not used. ("0" is always displayed.)

b6 Power interruption notice

b5 Not used. ("0" is always displayed.)

b4 CH2 reception data exits.

b3 CH1 reception data exits.

b2 Power interruption process complete

b1 Not used. ("0" is always displayed.)

b0 Not used. ("0" is always displayed.)

Display

Terminating procedure

Press the CANCEL key to terminate the check. After terminating,

perform the service reset.

2) SRN Flag Send Check

Check content

Execute diagnostics 3 command to send Flag (7EH) continuously.

Display

Terminating procedure

Perform the service reset.

3) SRN Data Send Check

Check content

Execute diagnostics 4 command to send data of 00H ~ FFH

(256Byte) as one packet at 12.8msec packet interval at 1Mbps

continuously.

Display

Terminating procedure

Perform the service reset.

4) Data Transmission Check

Data transmission is checked in an actually composed system. The

system is composed of one master machine and max. 15 satellite

machines.

Note for starting the check

When checking the set in which the SRN setting has been

made, cancel the SRN setting before starting this check.

When checking the actually composed system, disconnect the

SRM cables of the sets which are not checked, or cancel the

SRN setting. If it is set to "SRN exits," data may be destroyed.

The transmission check setting must be performed after can-

celing the SRN setting of all the sets in the system. First, set

the satellite machines, then set the master machine.

Setting procedure

Satellite machine setting

In the menu screen, select "Data Transmission Check (Satel-

lite)."

The display is as follows:

Enter the terminal No. (000 ~ 254, 3 digits) of the machine to be

checked and press the ENTER key. The display is as shown

below.

SRN Self Check

DATA RETRY CNT.=xxx

ACK RETRY CNT.=xxx

DIAG 0

:xxxxxxxx

DIAG 1 :xxxxxxxx

DIAG 5 H

→

C :xxxxxxxx

DIAG 5 H

←

C :xxxxxxxx

The number of resending is displayed

in xxx with a decimal number.

In the sequence of b7, b6, ..., b0 from

the left. "1" is displayed in case of an

error, and "0" when normal.

In the sequence of b7, b6, ..., b0 from

the left. "1" is displayed in case of an

error, and "0" when normal.

In the sequence of b7, b6, ..., b0 from

the left. "1" is displayed in case of an

error, and "0" when normal.

In the sequence of b7, b6, ..., b0 from

the left. "1" is displayed in case of an

error, and "0" when normal.

SRN Flag Send Check

SRN Data Send Check

Data Transmission Check (Satellite)

Input Terminal Number :

Data Transmission Check (Satellite)

Input Terminal Number : xxx

Data Sequence Number : 0000

The entered

terminal No.

is displayed.

Master machine setting

In the menu screen, select "Data Transmission Check (Master

Machine)." The display is as shown below.

Enter the terminal No. (000 ~ 254, 3 digits) of the machine to be

checked and press the ENTER key. The display is as shown

below.

Enter the terminal No. (000 ~ 254, 3 digits) of the machine to be

connected to the machine to be checked and press the ENTER

key. The display is as shown below.

When checking with two or more satellite machines connected,

enter the terminal No. (000 ~ 254, 3 digits) and press the EN-

TER key similarly. To execute, press the ENTER key without

entering the terminal No. The display is as shown below. Do not

use the same terminal No. for different machines (master/satel-

lite).

With the above setting, data transmission between the master

machine and the satellite machine is started.

Check content

Data in the following format composed of 2byte sequence No.

and 254byte AAH data are transmitted from the master ma-

chine to the satellite machine. The master machine displays the

sequence No.

The satellite machine sends back the received data to the mas-

ter machine. The satellite machine displays the received se-

quence No.

The master machine receives the data, and checks the se-

quence No. and 256byte AAH data. In case of an error, the

master machine displays an error code and terminates the

check. If two or more satellite machines are used, the above

operation is repeated. If data transmission with all the satellite

machines are normally completed, the master machine incre

ments the sequence No.

The above operation is repeated.

Error display

The error codes are as shown below.

01 Command abnormality (except for during transmission)

02 No data received.

03 Received data present.

Received data remained.

04

Remote station not ready (in sending)

"NTDY" is sent back because the remote station is not

ready for reception.

05 Reception buffer full (in sending)

The controller reception buffer of the remote machine is full.

06 Resend error (in sending)

Retry over (5 times) when no response

07 Collision error (in sending)

When an collision occurred in data transmission

08

Line busy time out

Transmission cannot be made by multi-station

communication to cause time out in data send wait time.

09 Reception size over (in receiving)

The reception buffer size is insufficient.

0A

Hardware error

Interface abnormality (No SRN interface or abnormality in

SRN controller)

Terminating procedure

Press the CANCEL key to terminate the check. After terminating,

perform the service reset.

3-9. EFT Diagnostics

Perform EFT (ER-02EF) CHECK.

Select EFT Diag from the MENU and turn the Power OFF.

Press the CANCEL key to return to the Diag menu screen.

1) EFT Check

Set all DIPSW1 switches on the ER-02EF to OFF,turn the power of

the system ON. EFT CHECK will be automatically performed.

Details of the test

(1) For EFT CONNECTER,the LOOPBACK TEST is carried out

on ER-DR,ER-CI,RS-CS.

Data Transmission Check (Master)

Input Master Terminal Number :

Data Transmission Check (Master)

Input Master Terminal Number :xxx

Input Satellite Terminal Number:

The entered

terminal No.

is displayed.

Data Transmission Check (Master)

Input Master Terminal Number :xxx

Input Satellite Terminal Number:xxx

The entered

terminal No.

of satellite

machine is

displayed.

Data Transmission Check (Master)

Input Master Terminal Number : xxx

Input Satellite Terminal Number : xxx

xxx xxx xxx xxx xxx

Data Sequence Number : 0000

XX XX AA AA

AA

AA AA AA

256255254

5

4321

Byte

XXXX

AA

: Sequence No. (2byte: 4digits of binary decimal numbers)

: Transmission data (AAH) x 254 bytes

Data Transmission Check (Master)

Input Master Terminal Number : xxx

Input Satellite Terminal Number : xxx

xxx xxx xxx xxx xxx

Data Sequence Number : xxxx

IRC Error : xx

The

error

code is

displayed

EFT Diagnostics

(2) Check DIPSW1 by turning SWITCHES 1-8 ON one by one.

(3) When all switches are normal, SUM CHECK is carried out on

EFT ROM,while WRITE/READ CHECK is carried out on RAM.

Display (Normal end)

Display (Error end)

Exit the Diag program.

Press the CANCEL key to exit the program.

3-10. Magnetic Card Reader Diagnostics

Read check of the optional UP-E12MR is performed.

The test program reads the magnetic card of ISO 7811/1-5 standard

and displays the data. When the CANCEL key is pressed, the display

returns to the diagnostics menu.

1) Magnetic Card Reader Check

Check content

The test program reads tracks 1 and 2 of the magnetic card of

ISO 7811/1-5, and displays the data in ASCII code.

Display

XXXXX shows the data read by the MCR. Incase of an error, the

error code is displayed as shown below.

Terminating procedure

Press the CANCEL key to terminate the check.

3-11. Drawer Diagnostics

This diagnostics is used to check the drawer open and sensors.

The following menu is displayed. The cursor position is highlighted.

Use key and key to move the cursor. Move the cursor to the

process you desire and press the enter key. The selected individual

diagnostics program is executed. When the CANCEL key is pressed,

the display returns to the diagnostics menu.

1) Drawer 1 Check

Check content

The solenoid of drawer 1 is turned on, and the drawer open

sensor value is sensed at every 100ms, and the state is displayed.

Display

Terminating procedure

Press the CANCEL key to terminate the check.

2) Drawer 2 Check

Check content

The solenoid of drawer 2 is turned on, and the drawer open

sensor value is sensed at every 100ms, and the state is displayed.

The display and the terminating procedure are the same as

Drawer 1 Check.

DIAGO(SELF TEST) :OK

VHI27040R**1* :OK

256K SRAM :OK

In Loop Back Error

ER-DR LOOP ERROR

ER-CI LOOP ERROR

RS-CS LOOP ERROR

In Self Test Error

DIP SW ERROR

In Self Test Error

VHI27040R**1* :ERROR

256K SRAM :ERROR

MCR (Magnetic Card Reader) Check

TRACK1:

xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx

xxxxxxxxxx

xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx

TRACK2:

xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx

Magnetic Card Reader Check

TRACK1:BUFFER EMPTY

TRACK1:MCR ERROR

TRACK2:BUFFER EMPTY

TRACK2:MCR ERROR

Displayed when TRACK1 empty

code is sent back.

Displayed when TRACK1 empty

code is sent back.

Displayed when TRACK2 empty

code is sent back.

Displayed when TRACK2 empty

code is sent back.

Drawer Diagnostics

Drawer 2 Check

Drawer 1 Check

Drawer 1 Check

Drawer Open Sensor : OPEN (or CLOSE)

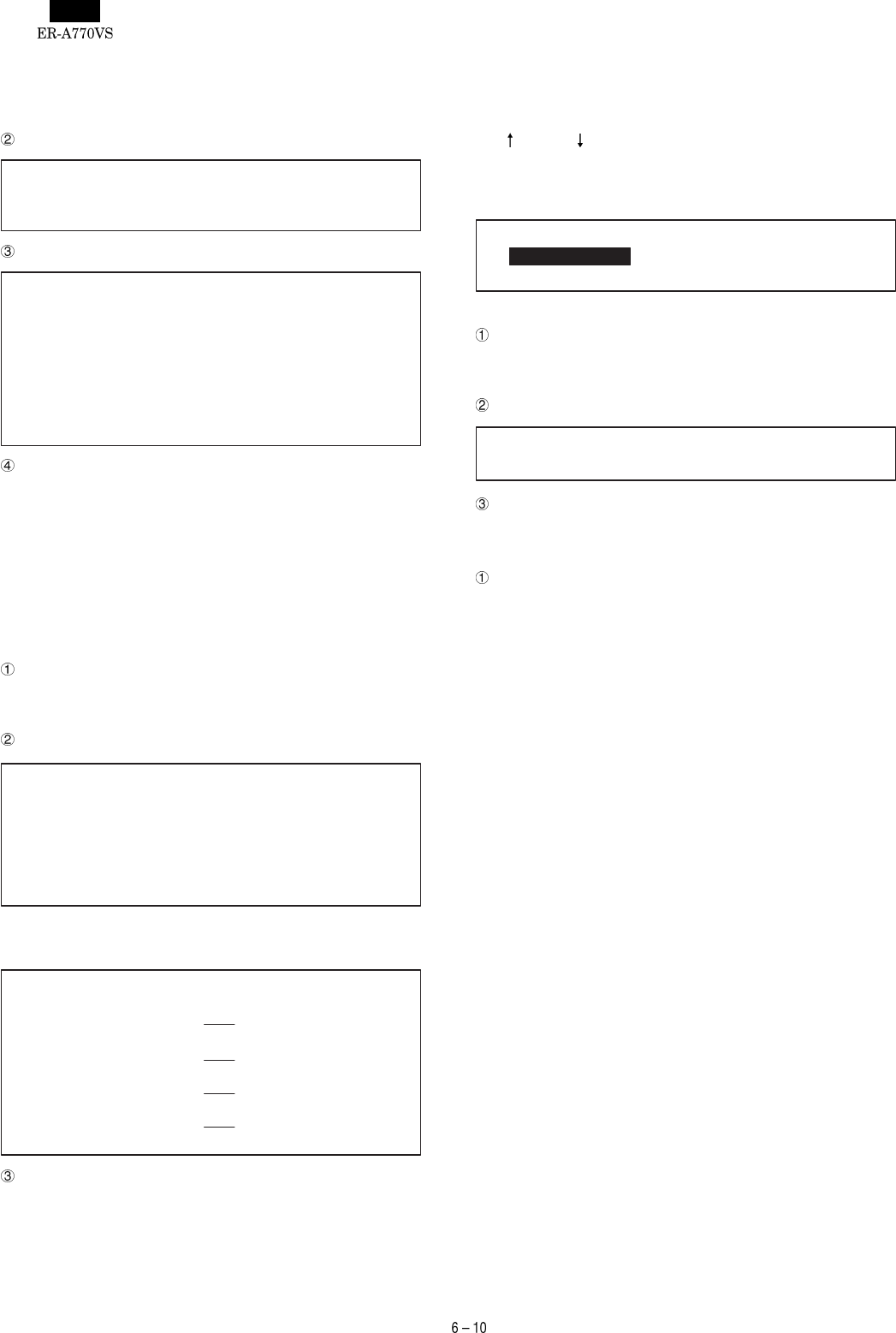

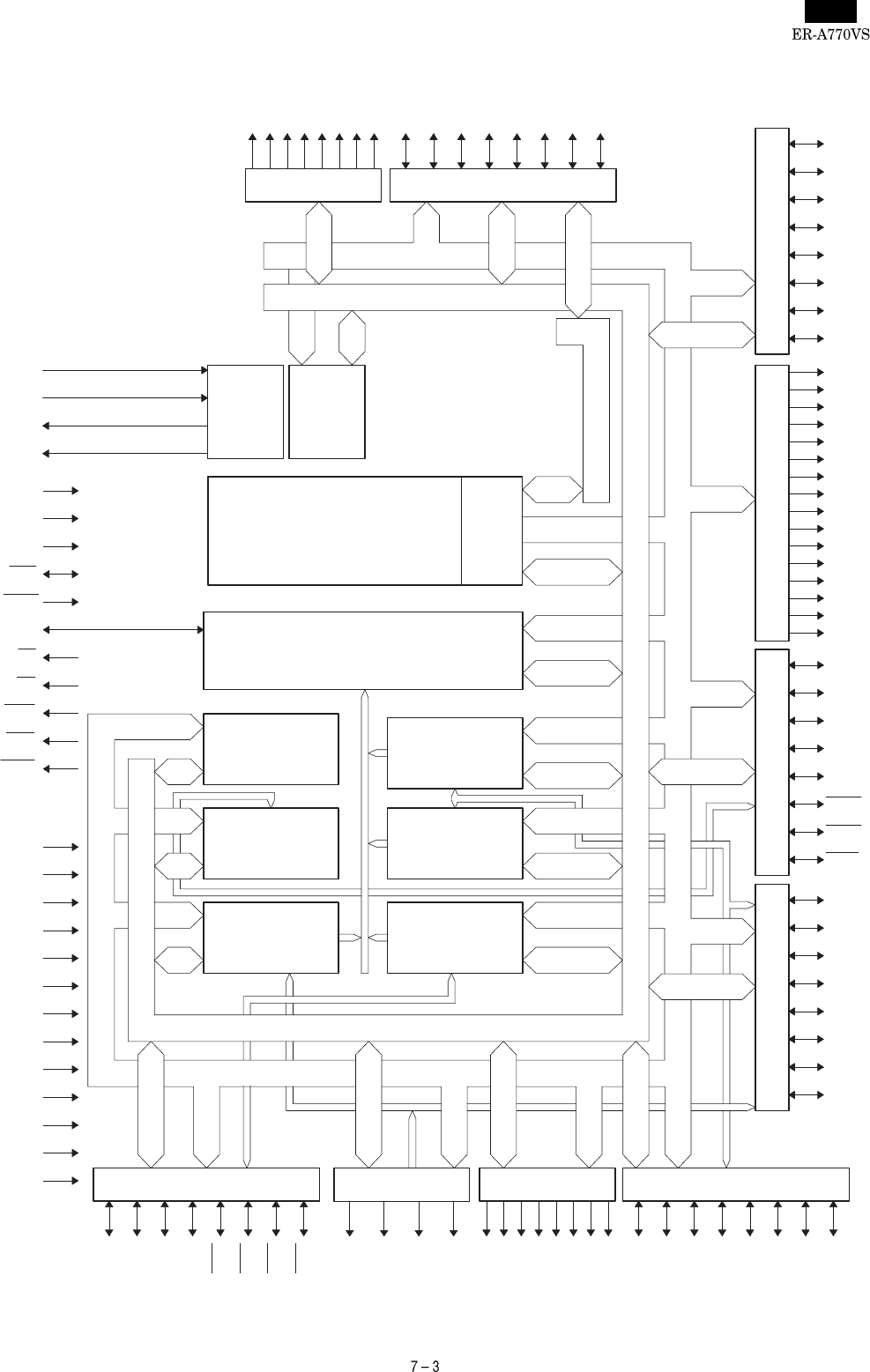

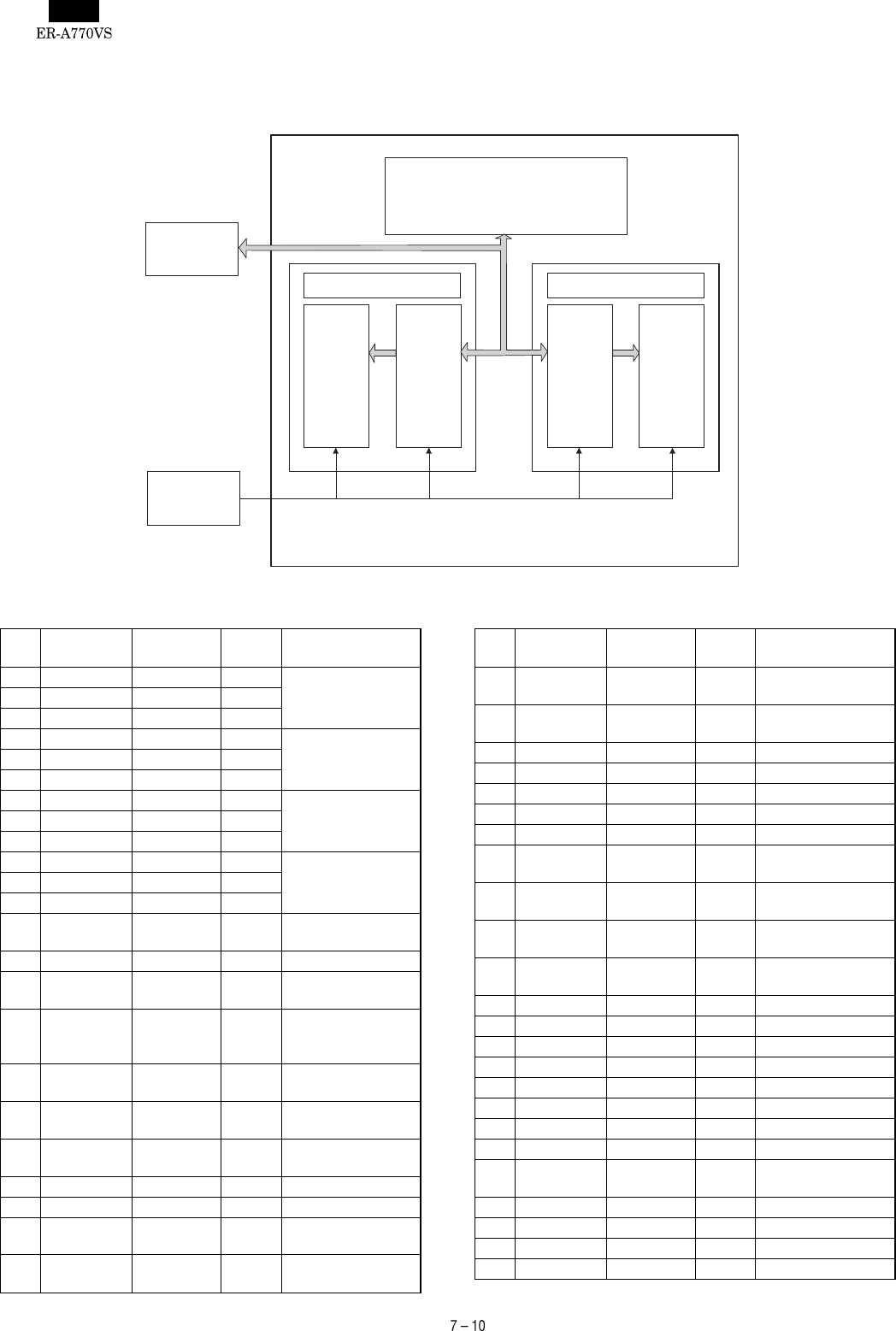

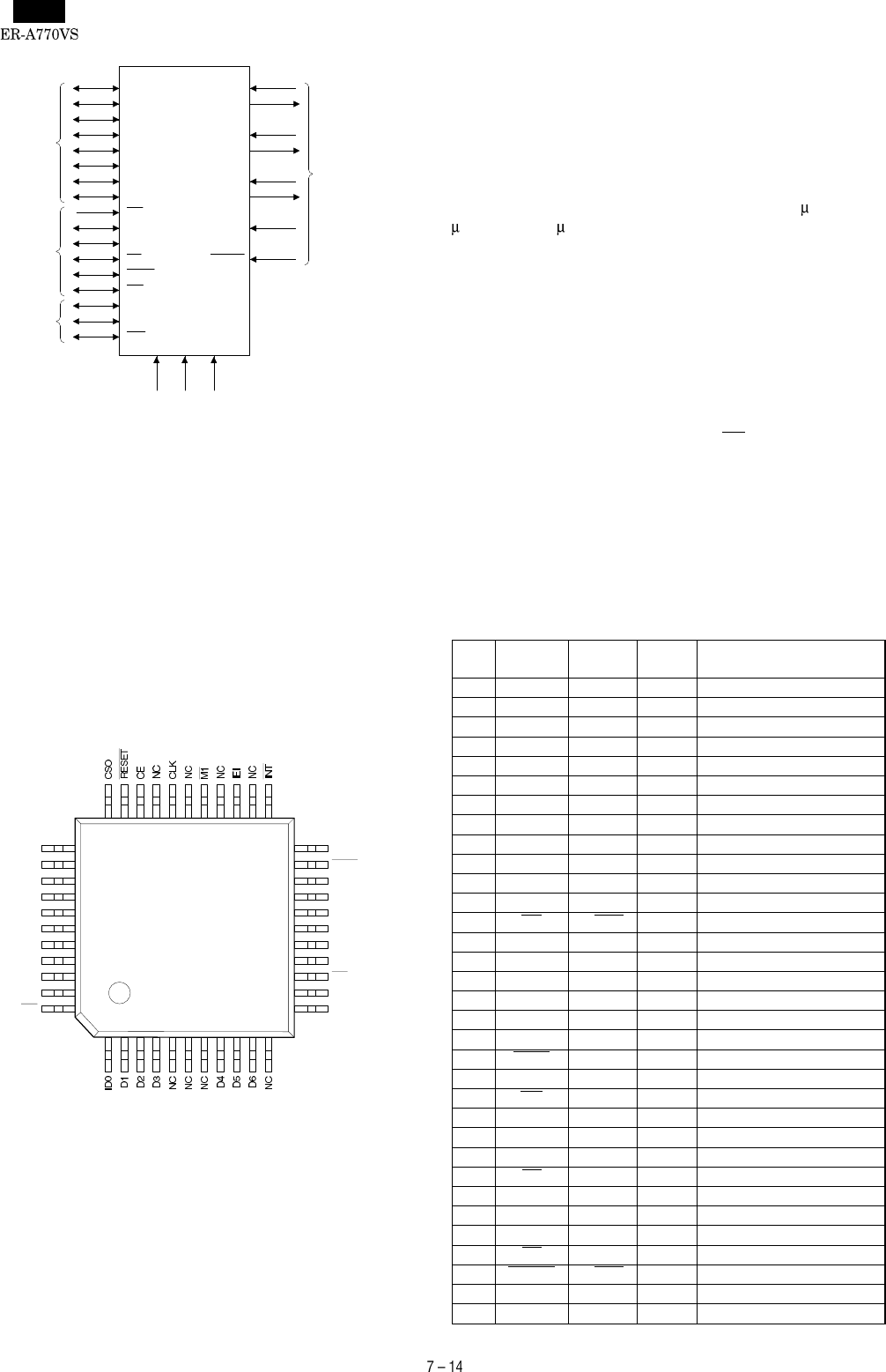

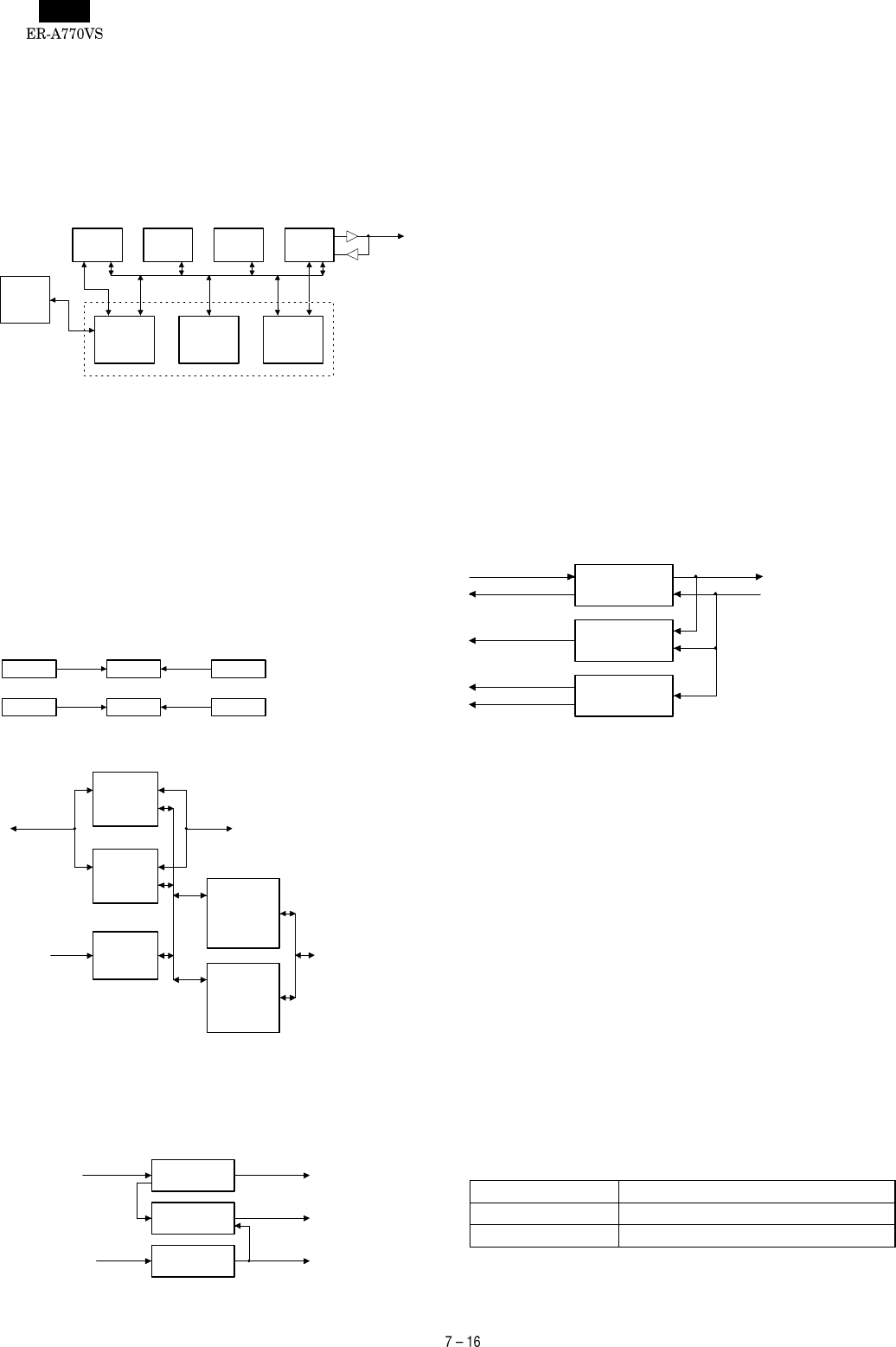

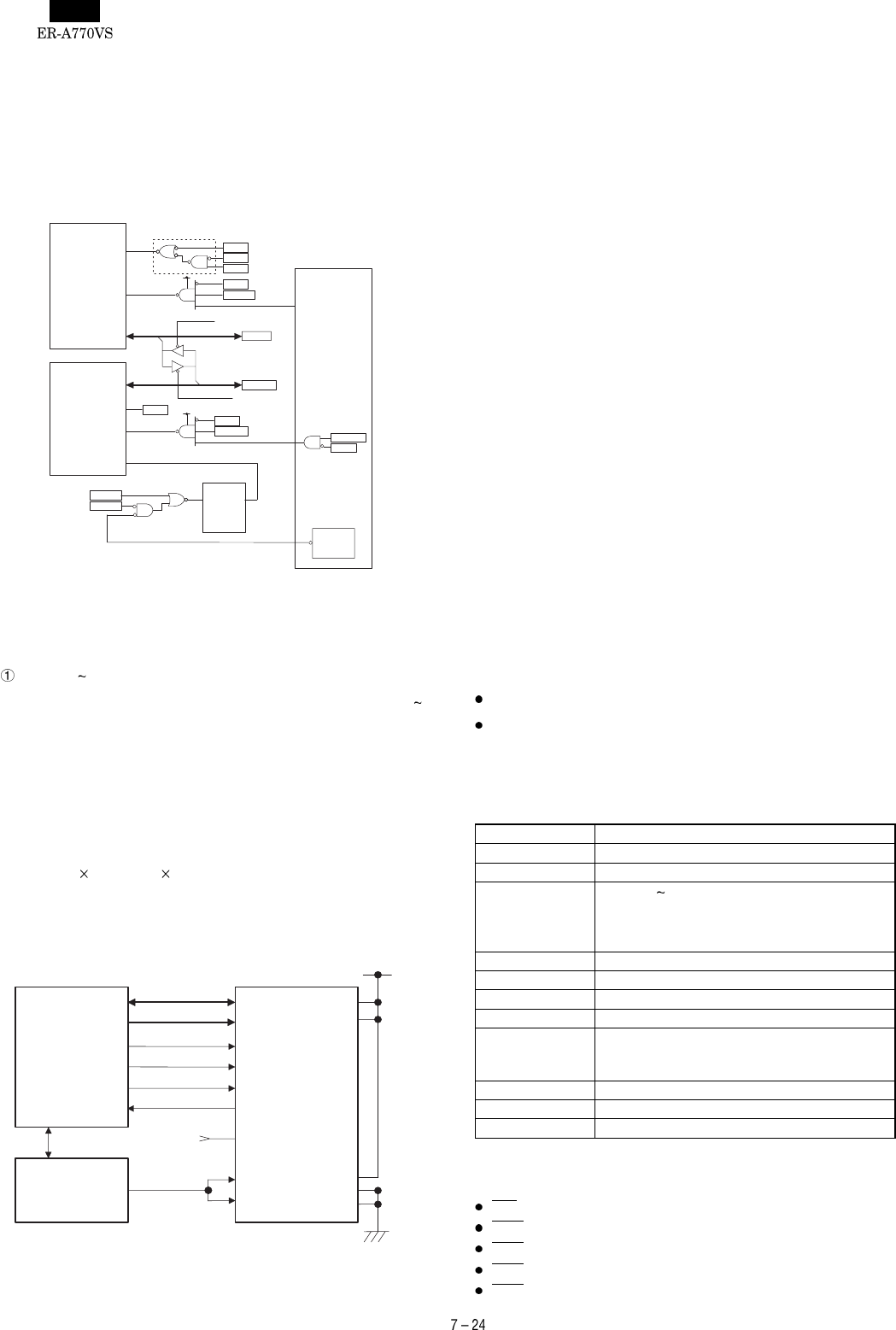

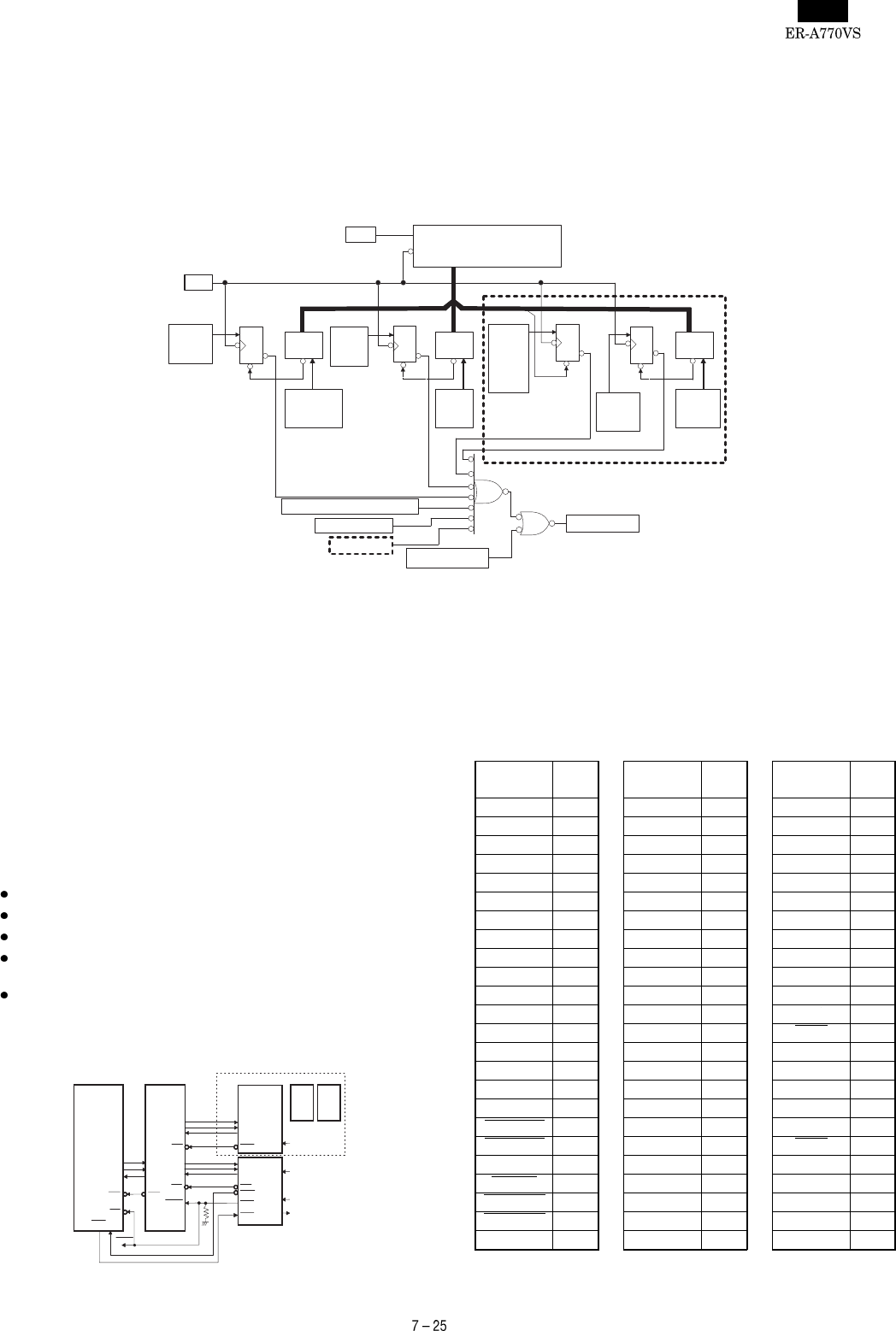

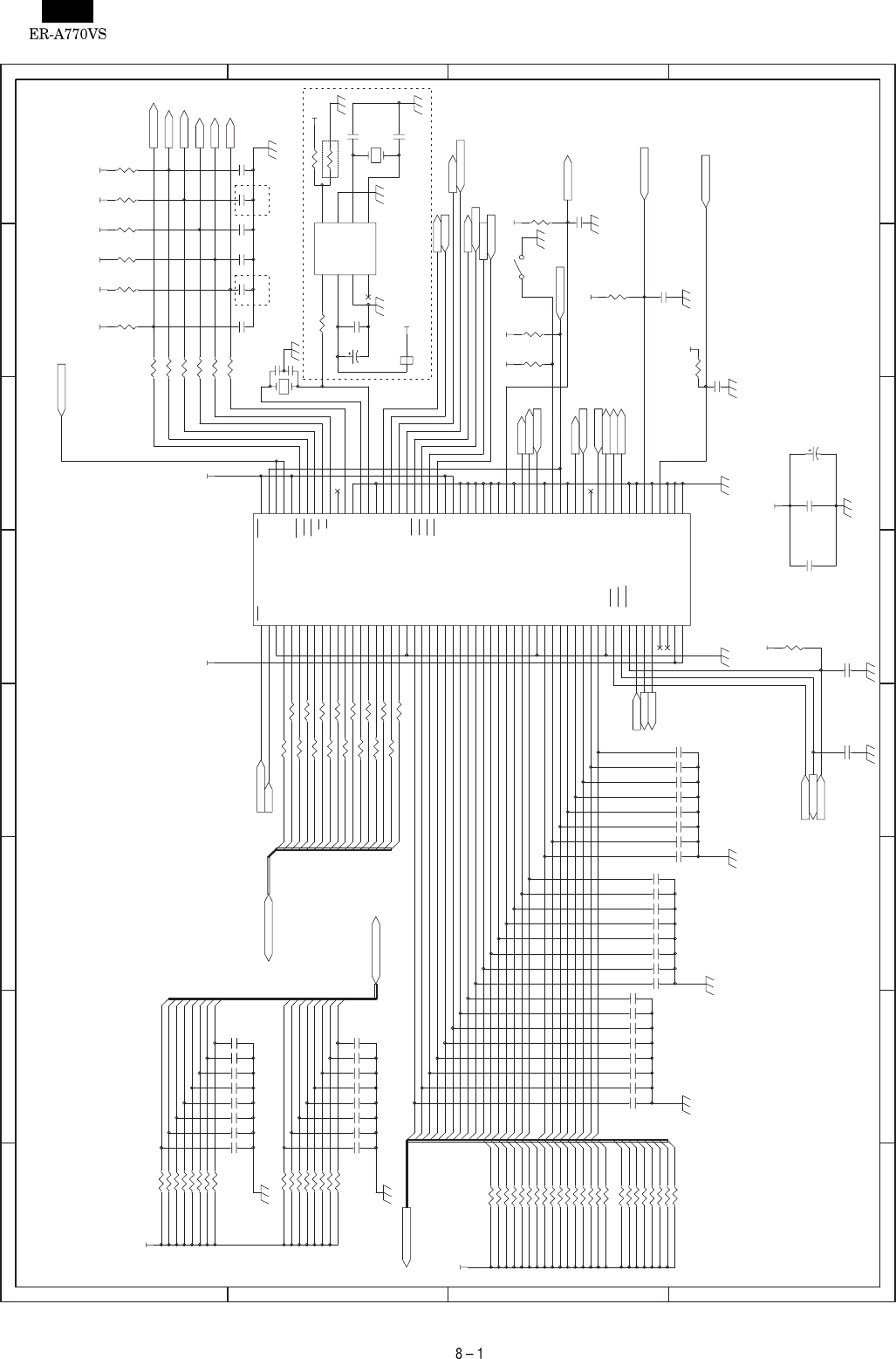

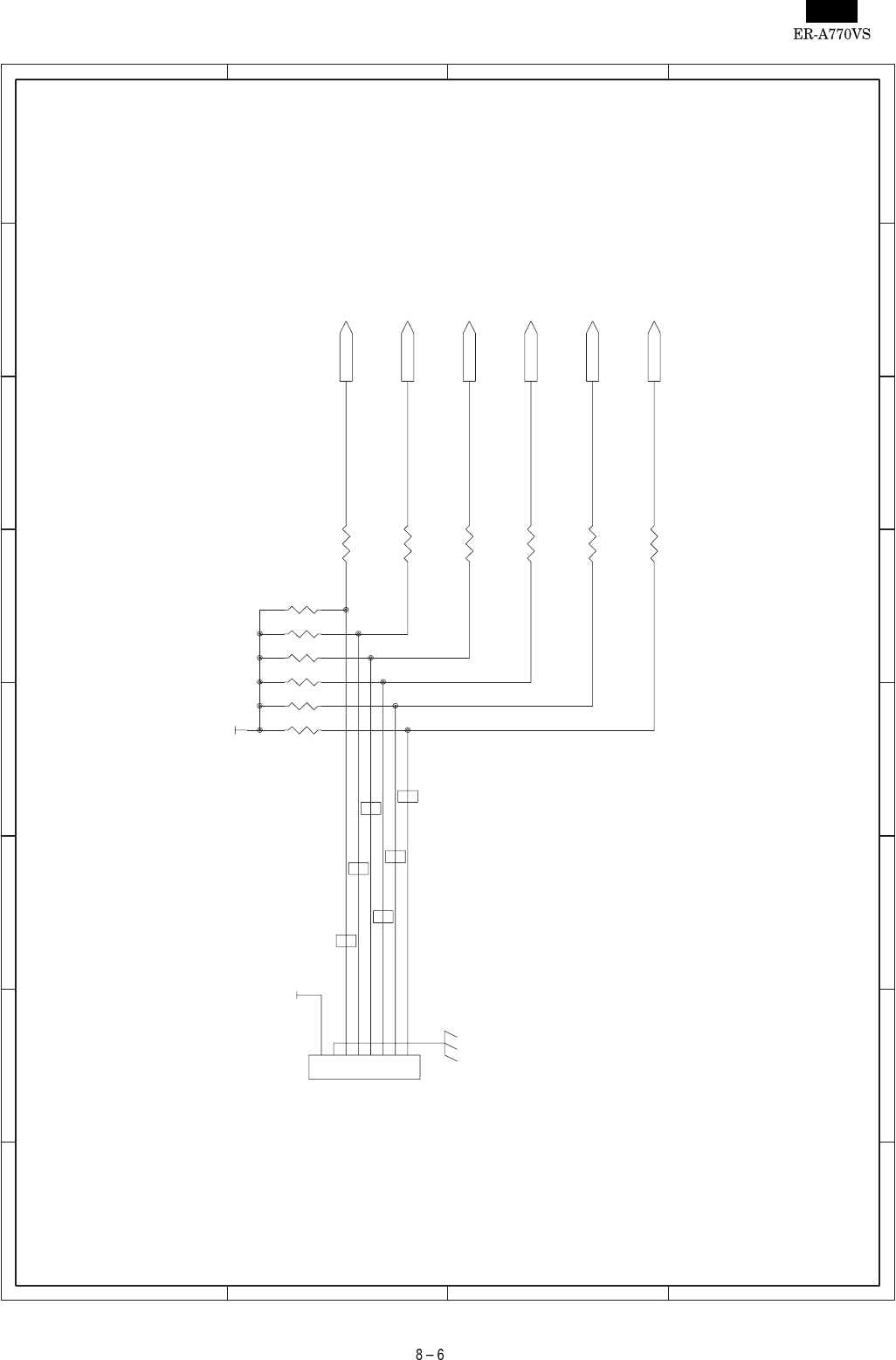

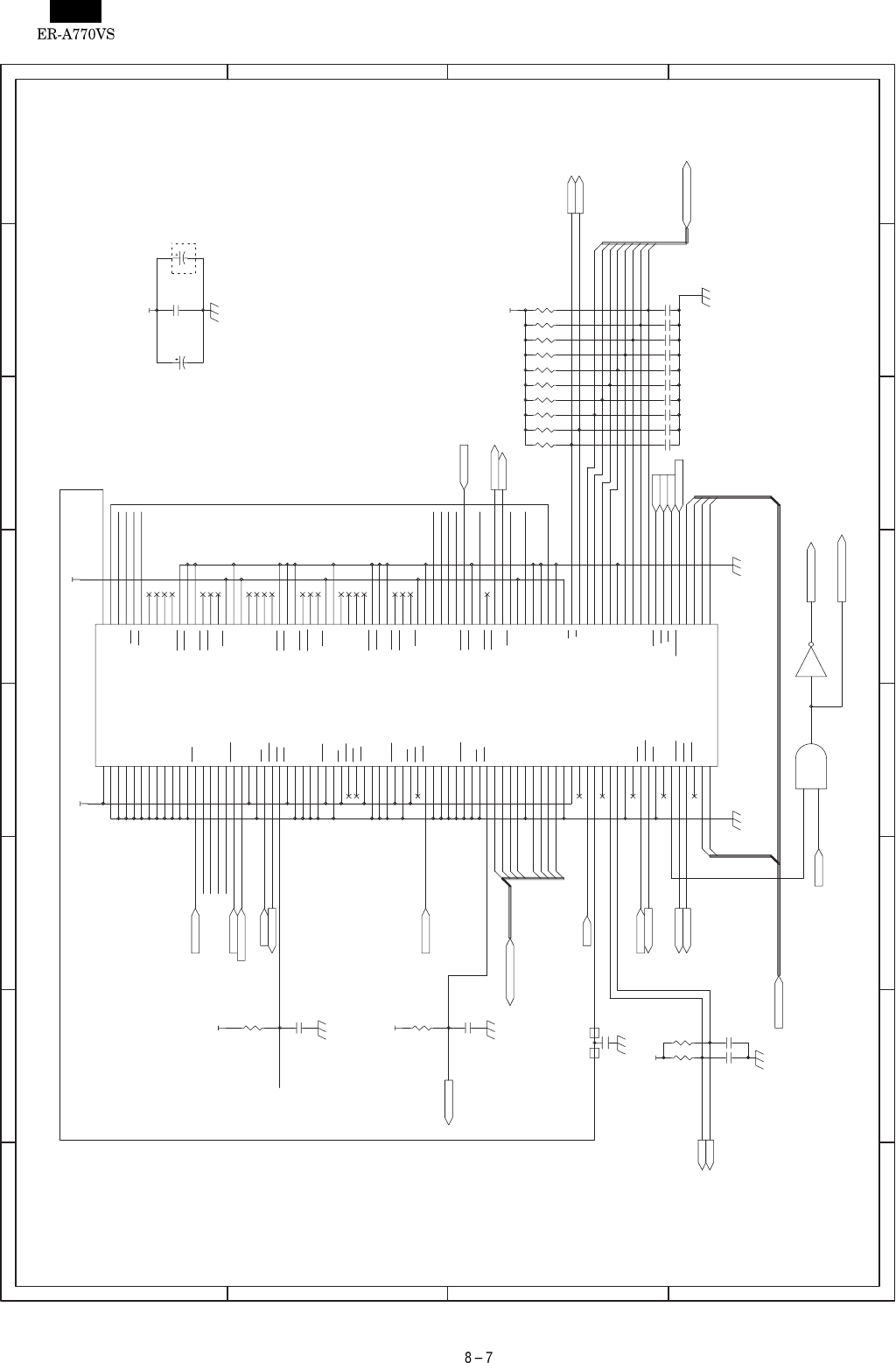

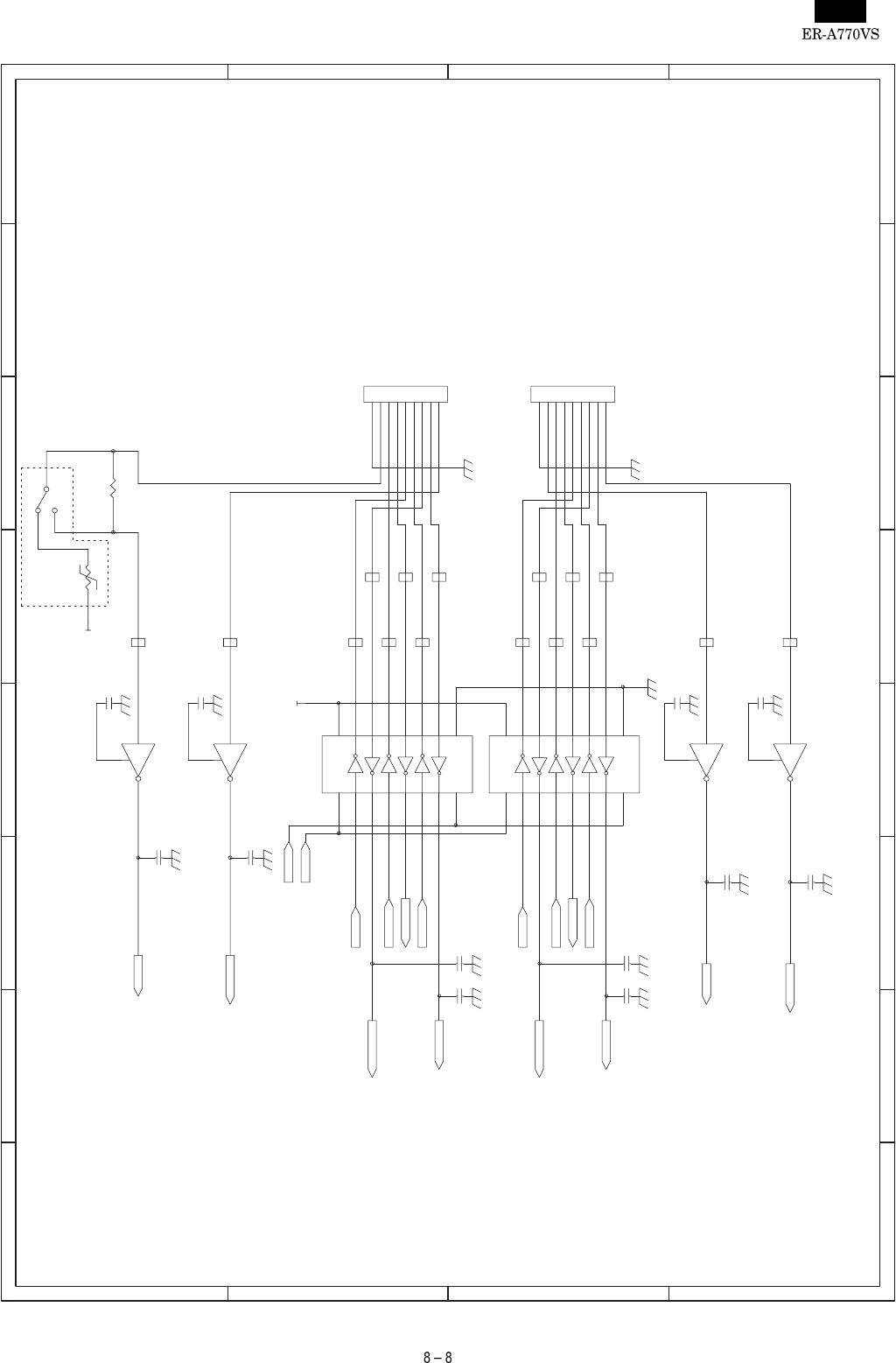

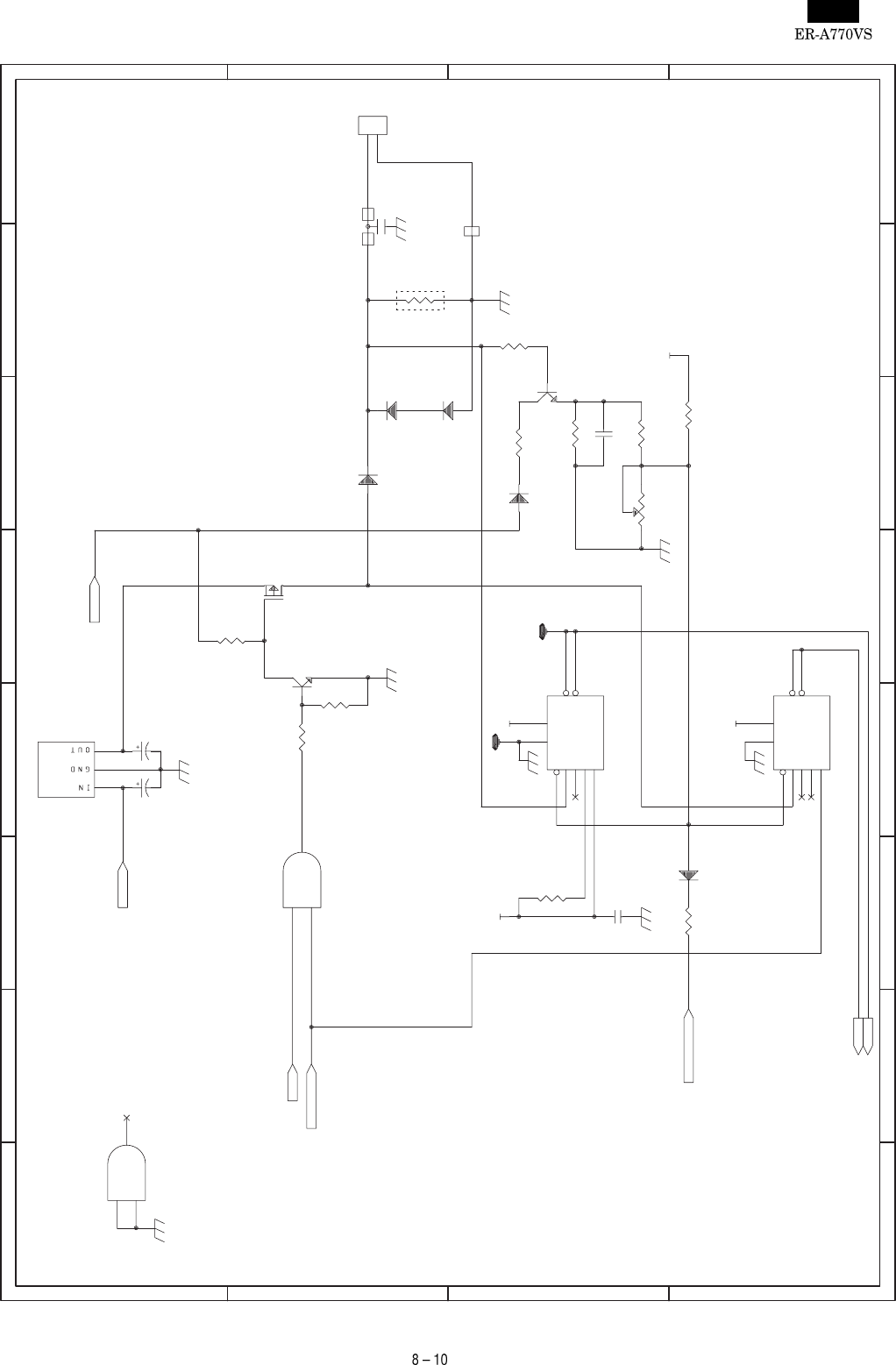

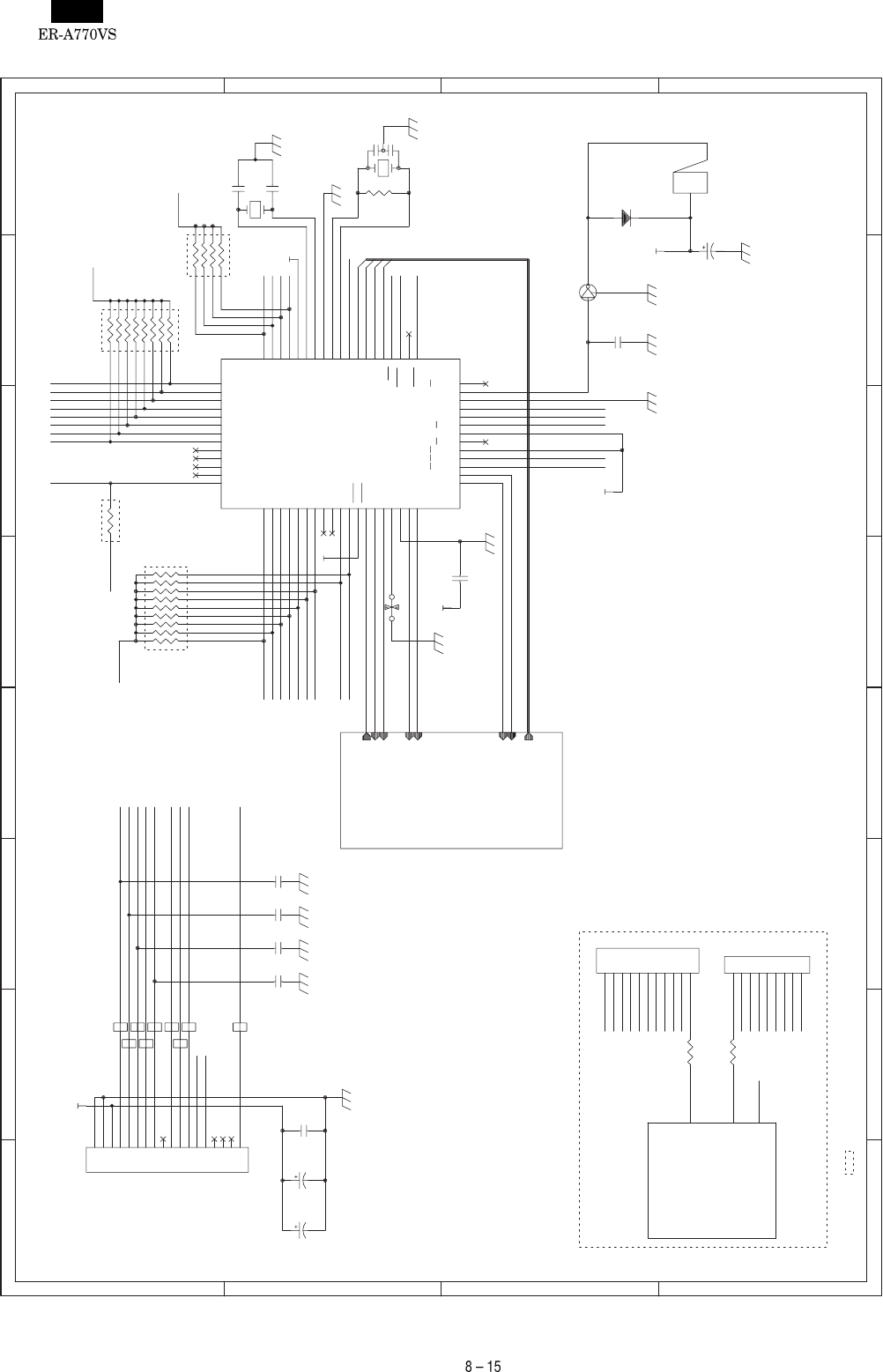

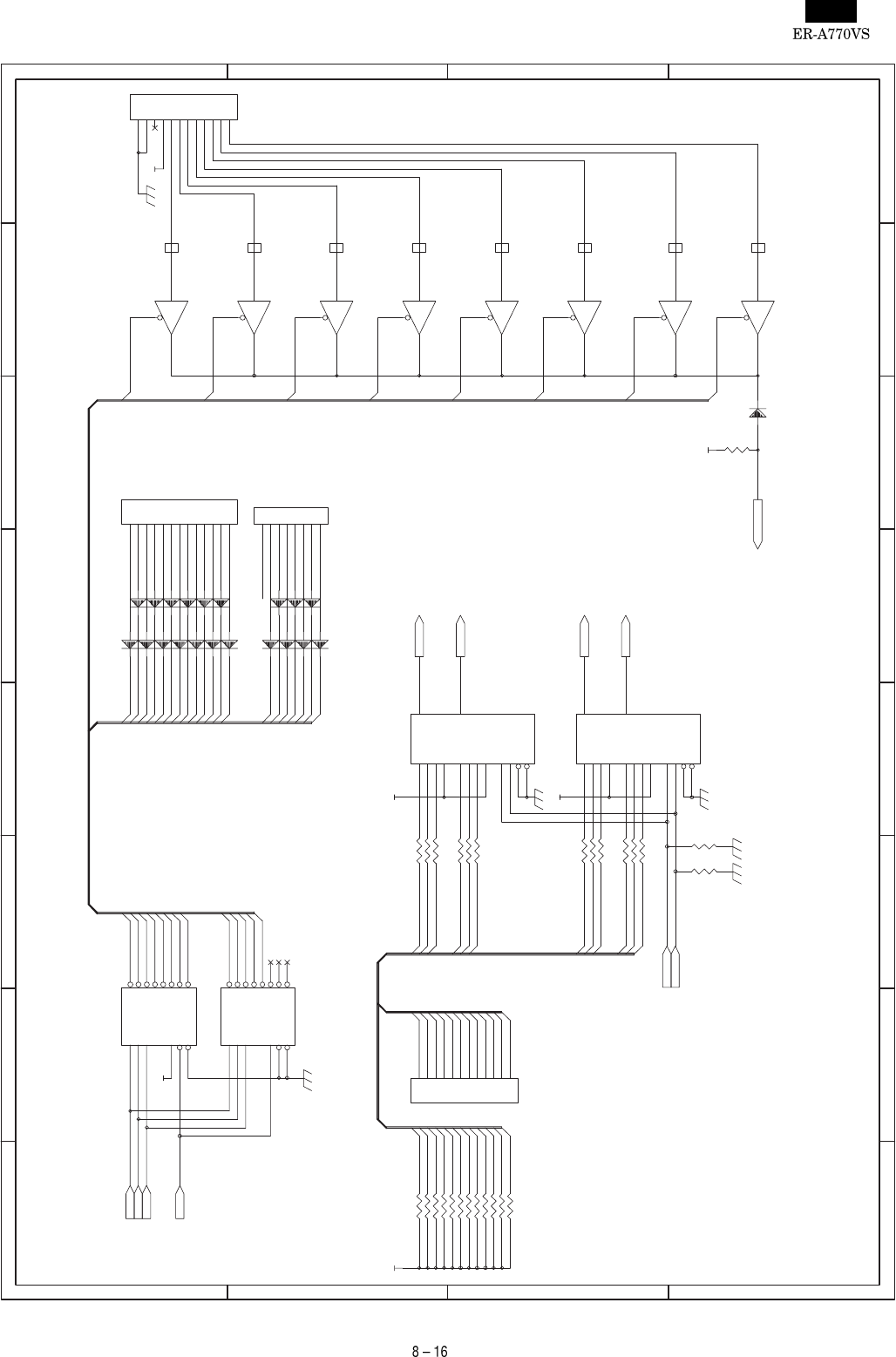

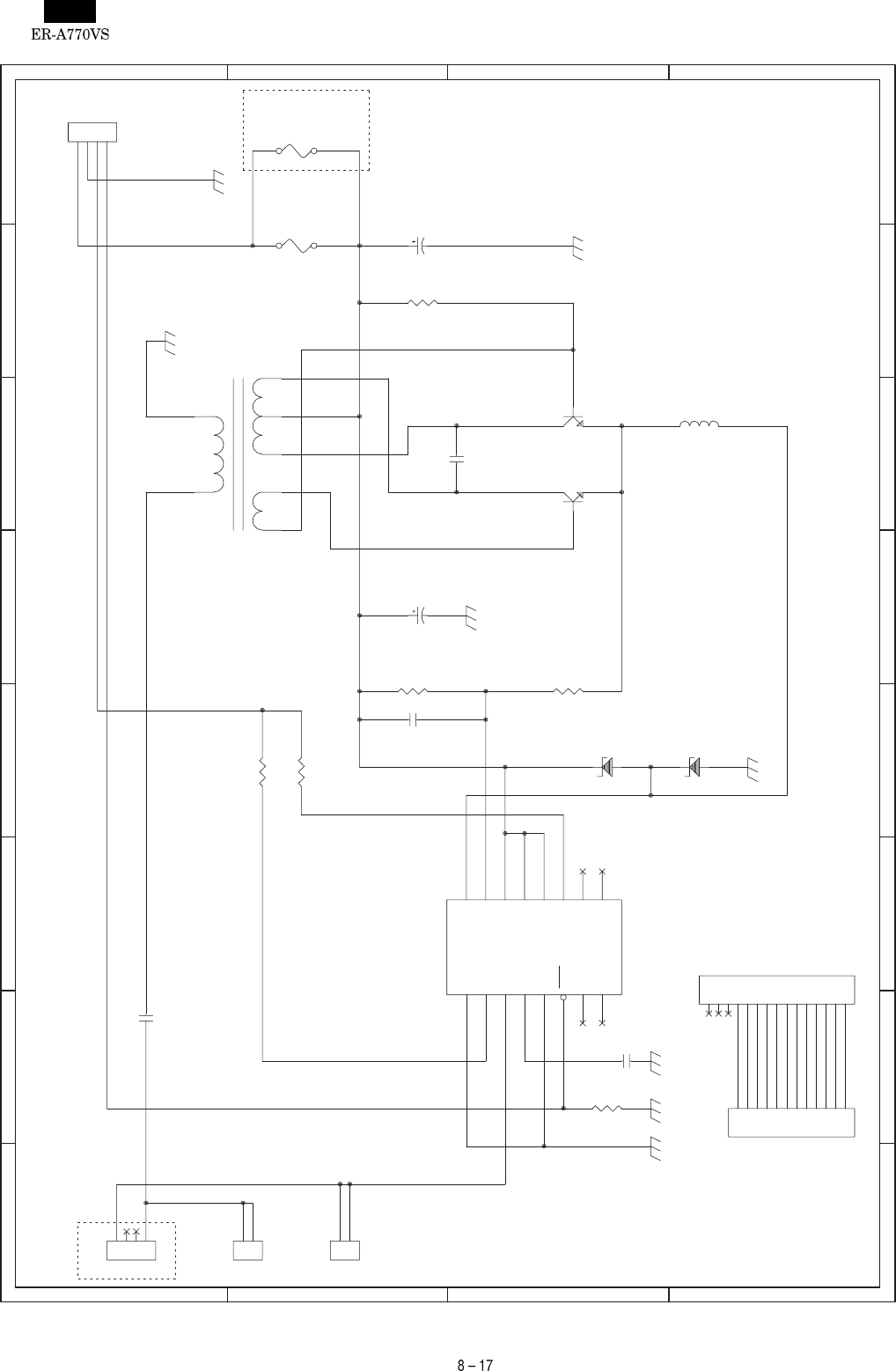

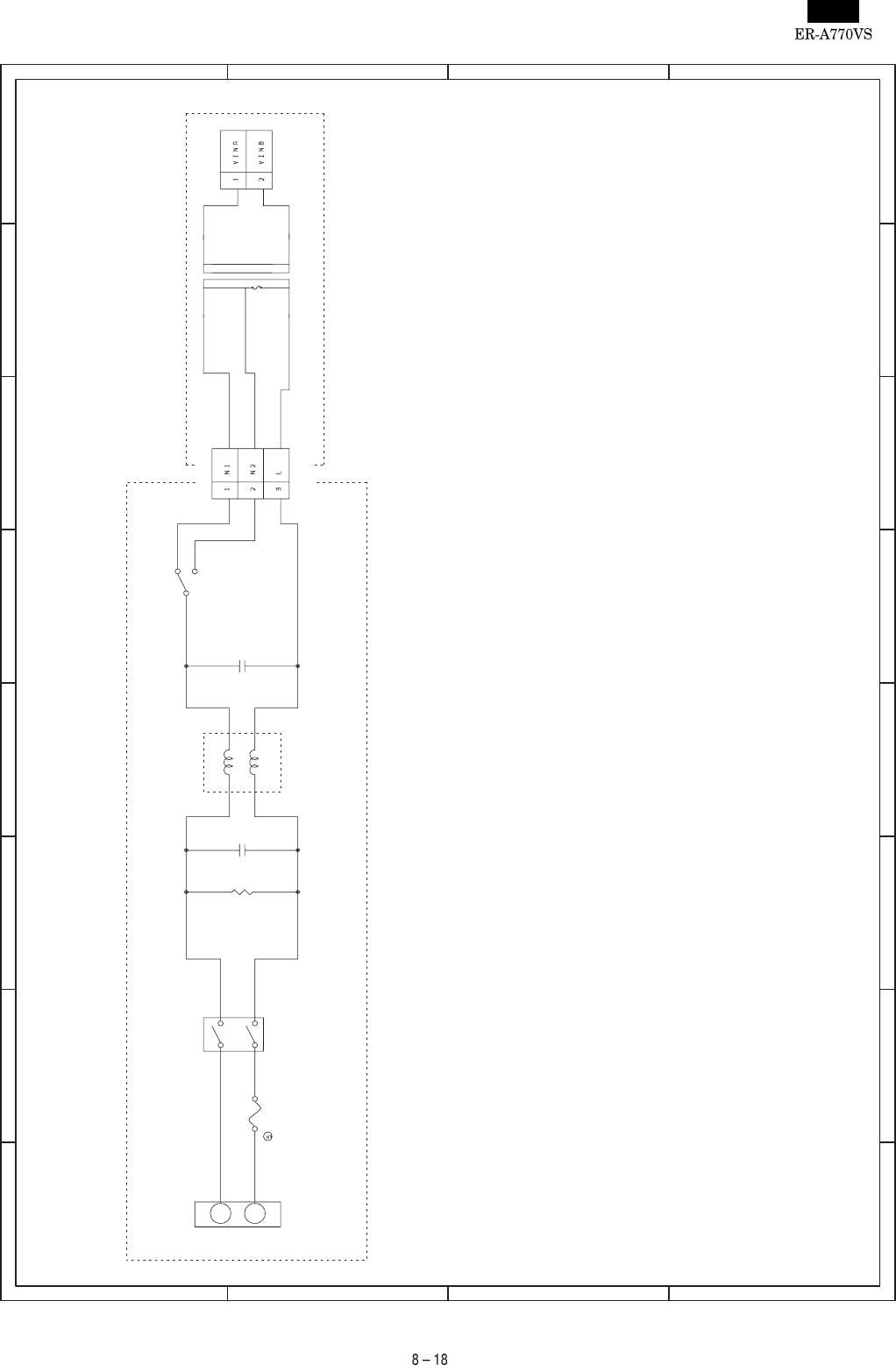

CHAPTER 7. CIRCUIT DESCRIPTION

1. Hardware block diagram

CPU

H8/510

G.A.

MPCA8

lsp2032

G.A.

OPC2

FLASH ROM

2MB

SRN

Logic

VGAC

MN89303A

Driver

+20V

Driver

/

Receiver CKDC9

LCD Module

QVGA (320 X 240)

Mono

Inverter

BIAS

and

Contrast

Power

supplay

Drawer X 2

Option Display

UP-P16DP or UP-I16DP

RAM Connector

SO-DIMM

72pin

PSEUDO SRAM

1MB

Clerk Switch

MCR

Keyboard

RS232 X 2

SRN

ER-A7RS

or

ER-02EF

VRAM

EDO-DRAM

512KB

ER-A7RS

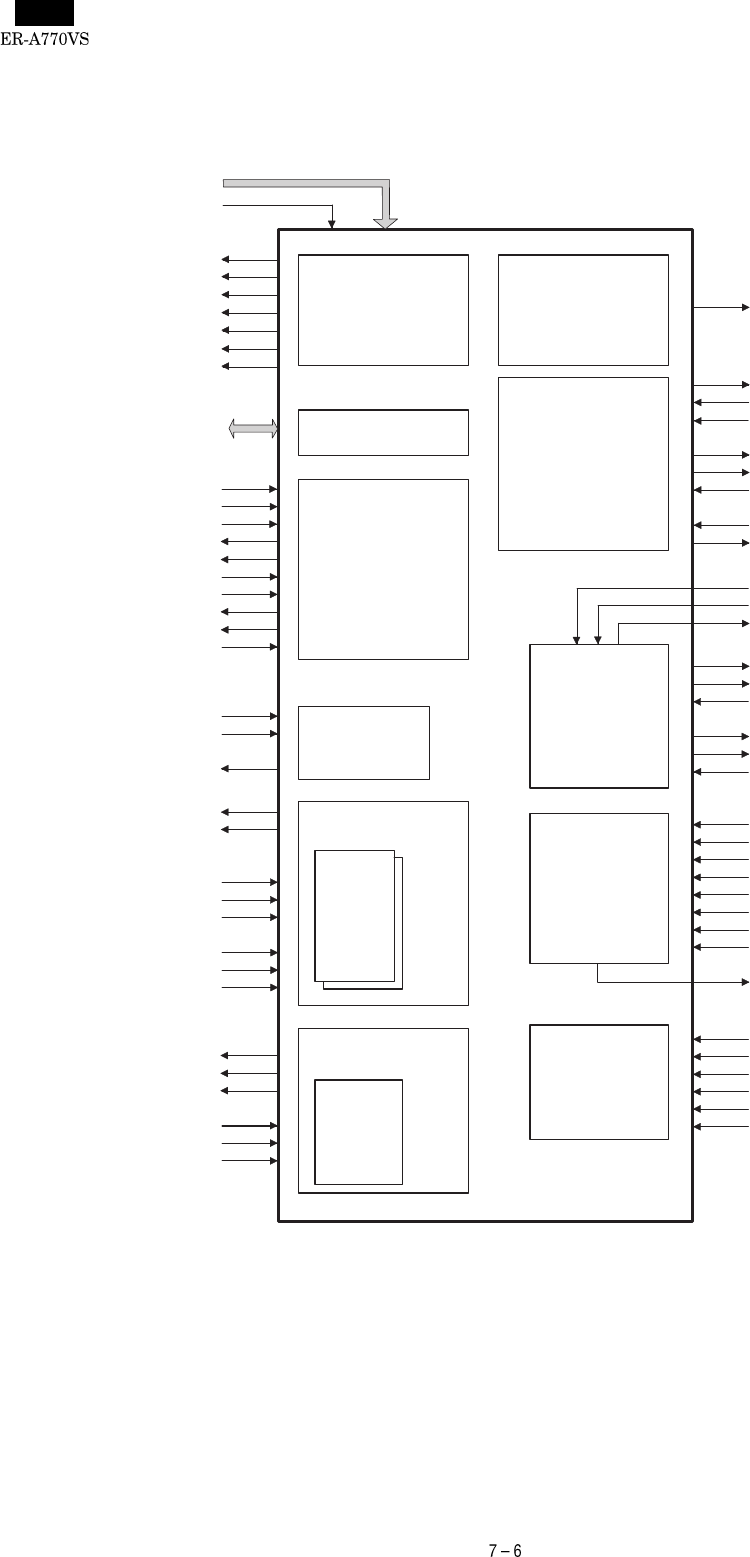

2. Description of main LSI’s

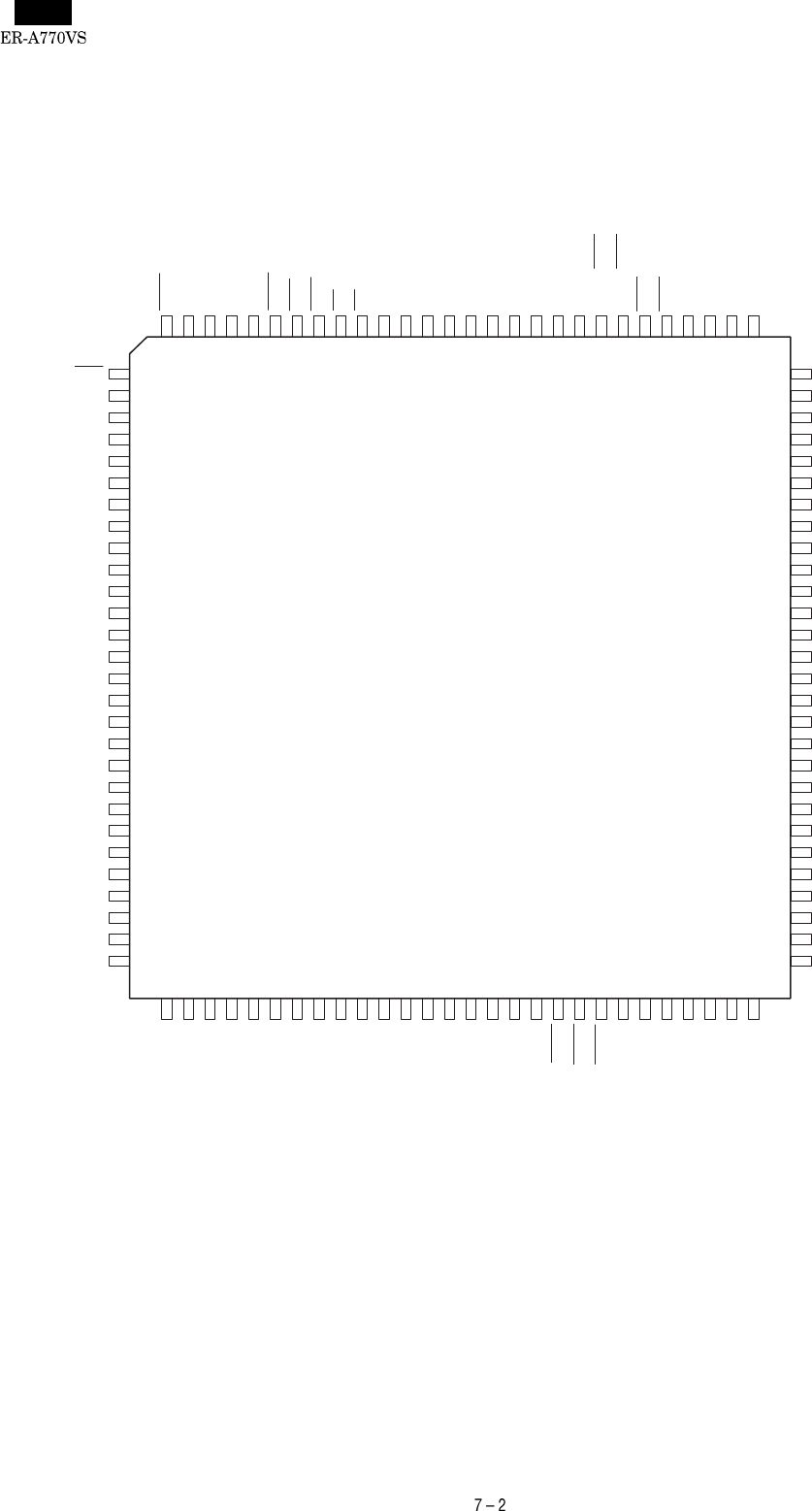

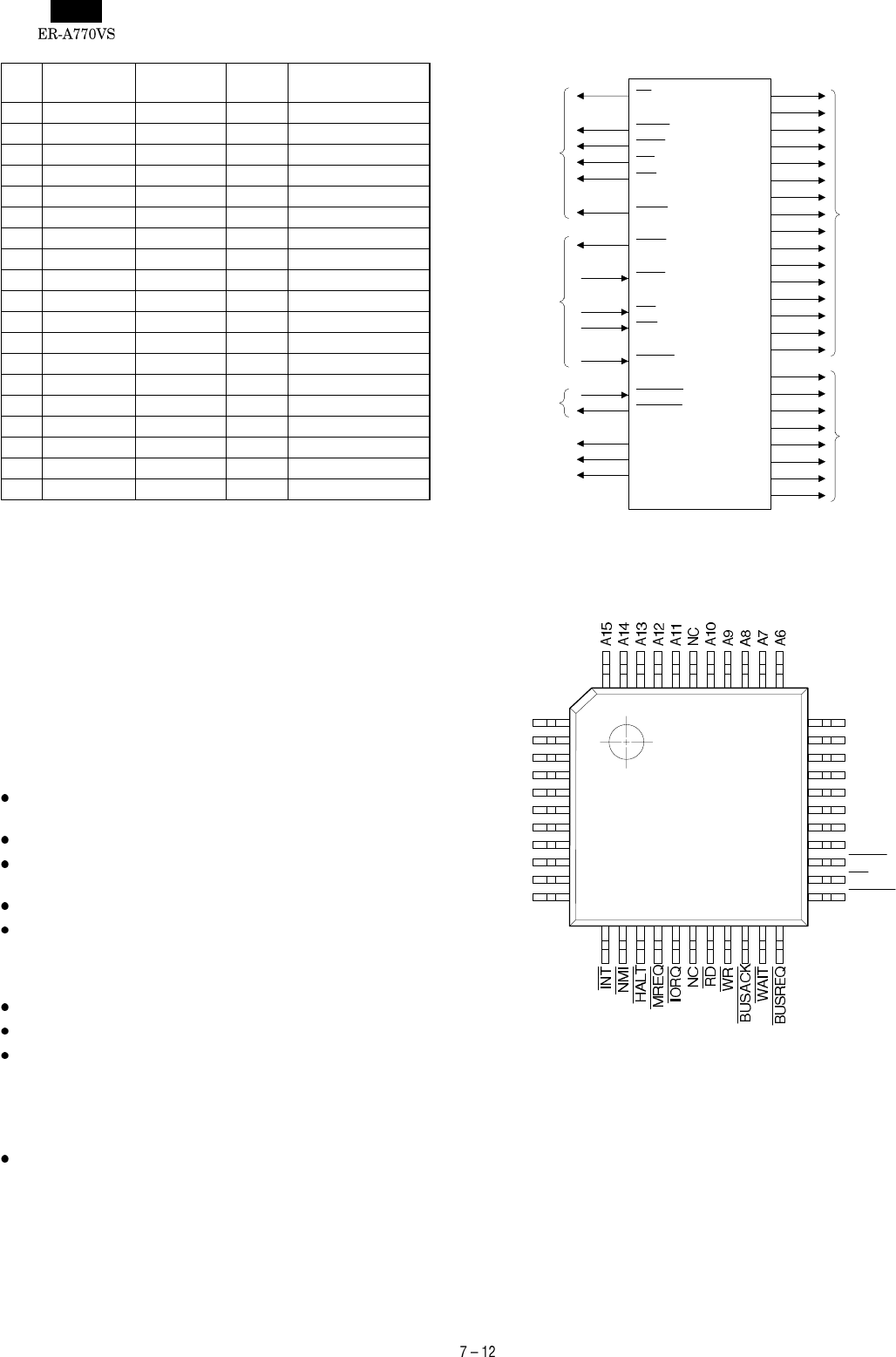

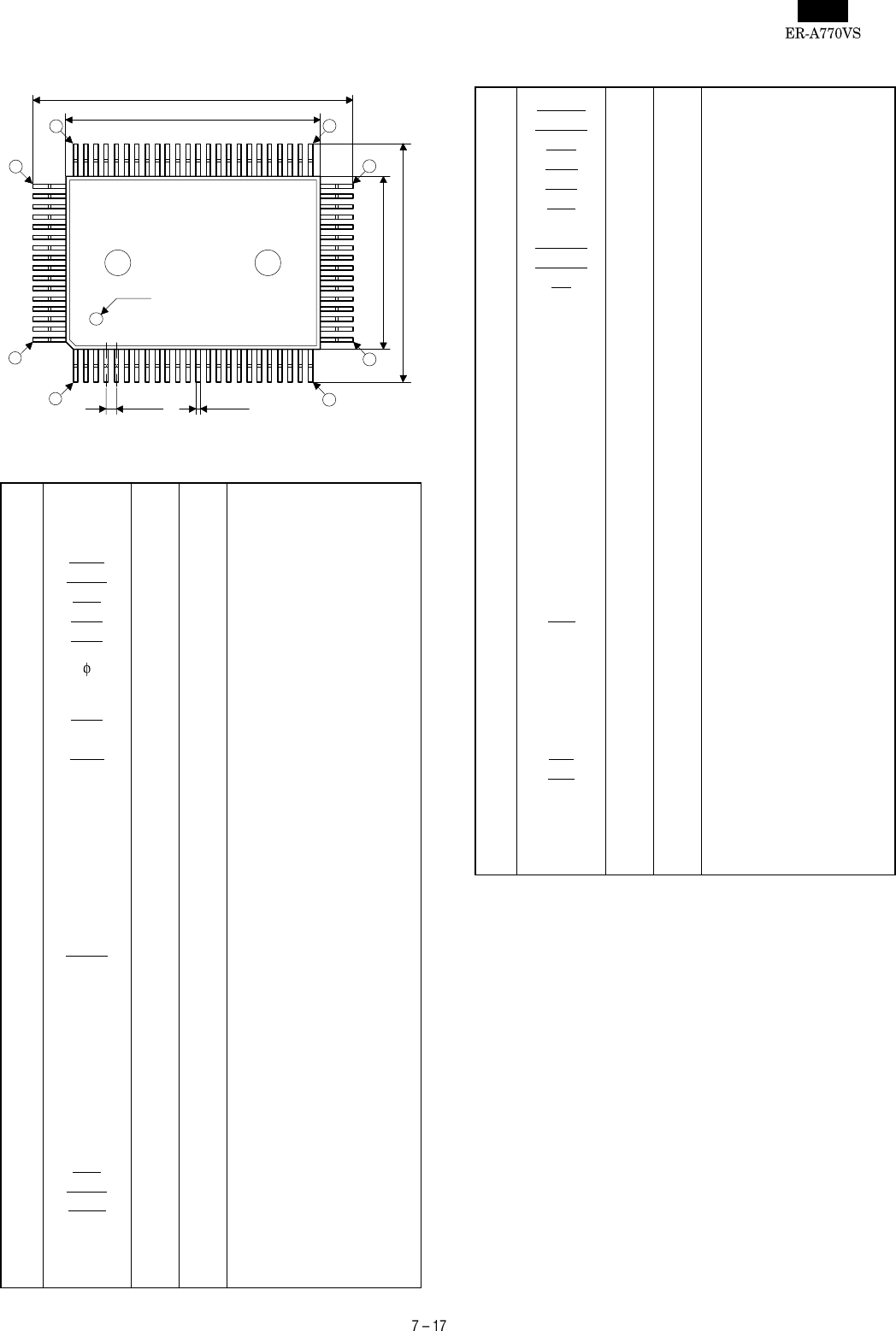

2-1. CPU (HD6415108FX)

1) Pin description

RES

NMI

VSS

P10

P11

P12

P13

P14

P15

P16

P17

D8

D9

D10

D11

D12

D13

D14

D15

VSS

A0

A1

A2

A3

A4

A5

A6

A7

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

STBY

MD2

MD1

MD0

VCC

RFSH

LWR

HWR

RD

AS

E

VSS

XTAL

EXTAL

VSS

TXD2

RXD2

TXD1

RXD1

SCK2/IRQ3

SCK1/IRQ2

IRQ1

IRQ0

VCC

AVCC

P73

P72

112

111

110

109

108

107

106

105

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

P41

P42

P43

P44

P45

P46

P47

VSS

P50

P51

P52

P53

P54

P56

P57

P60

P61

P62

P63

P64

P65

P66

P67

VSS

AVSS

P70

P71

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

78

80

81

82

83

84

A8

A9

A10

A11

A12

A13

A14

A15

VSS

A16

A17

A18

A19

A20

A21

A22

A23

VSS

P30/WAIT

P31/BACK

P32/BREQ

P33

P34

P35

P36

P37

VCC

P40

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

X

P55

>>>>> USE FONT <<<<<

Helvetica/ Helvetica-Condensed/ Century-Schoolbook/ Symbol & OriginalFonts: (RingWorld2/RingFont2/Pa

Symbol/PartsCod)

- - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -

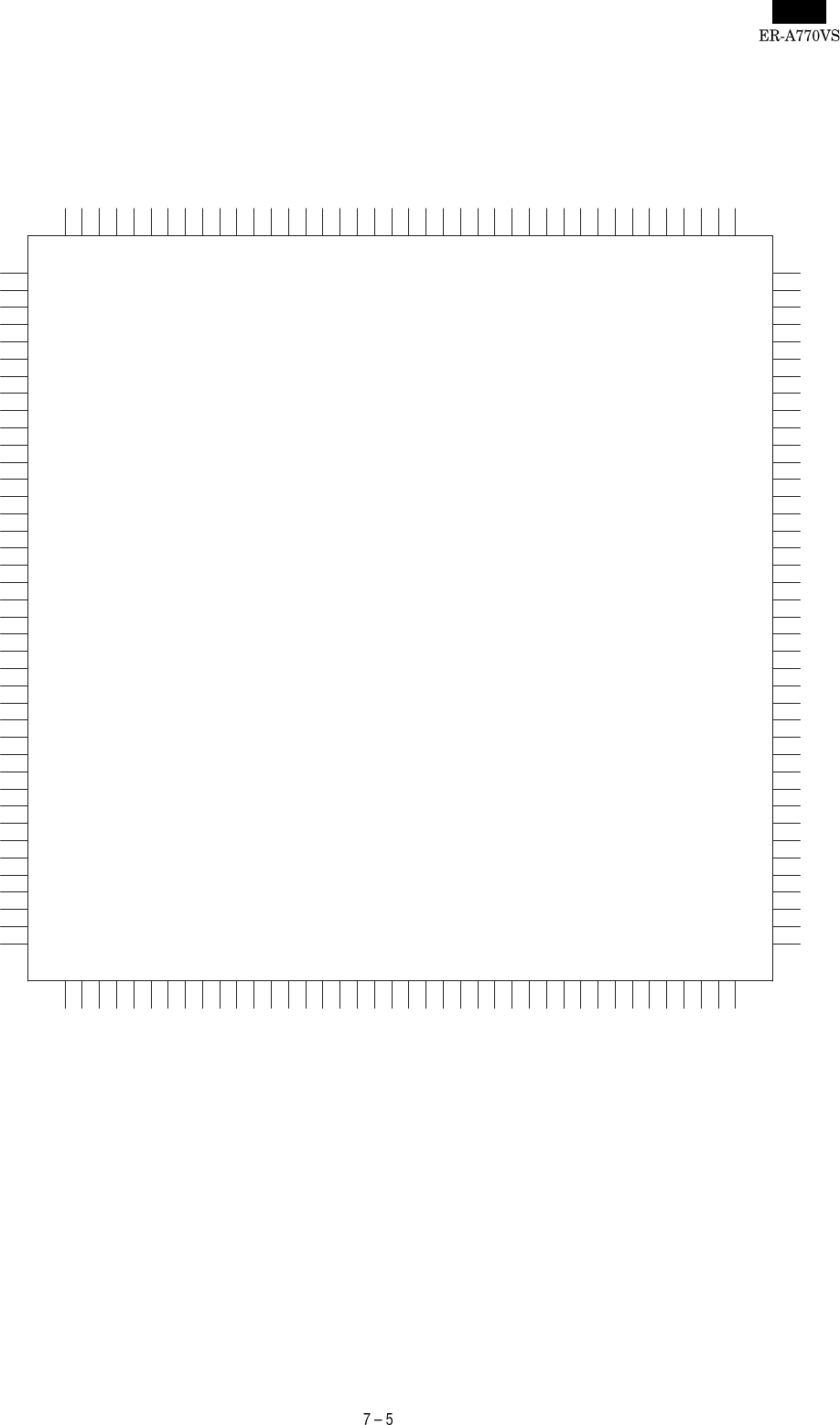

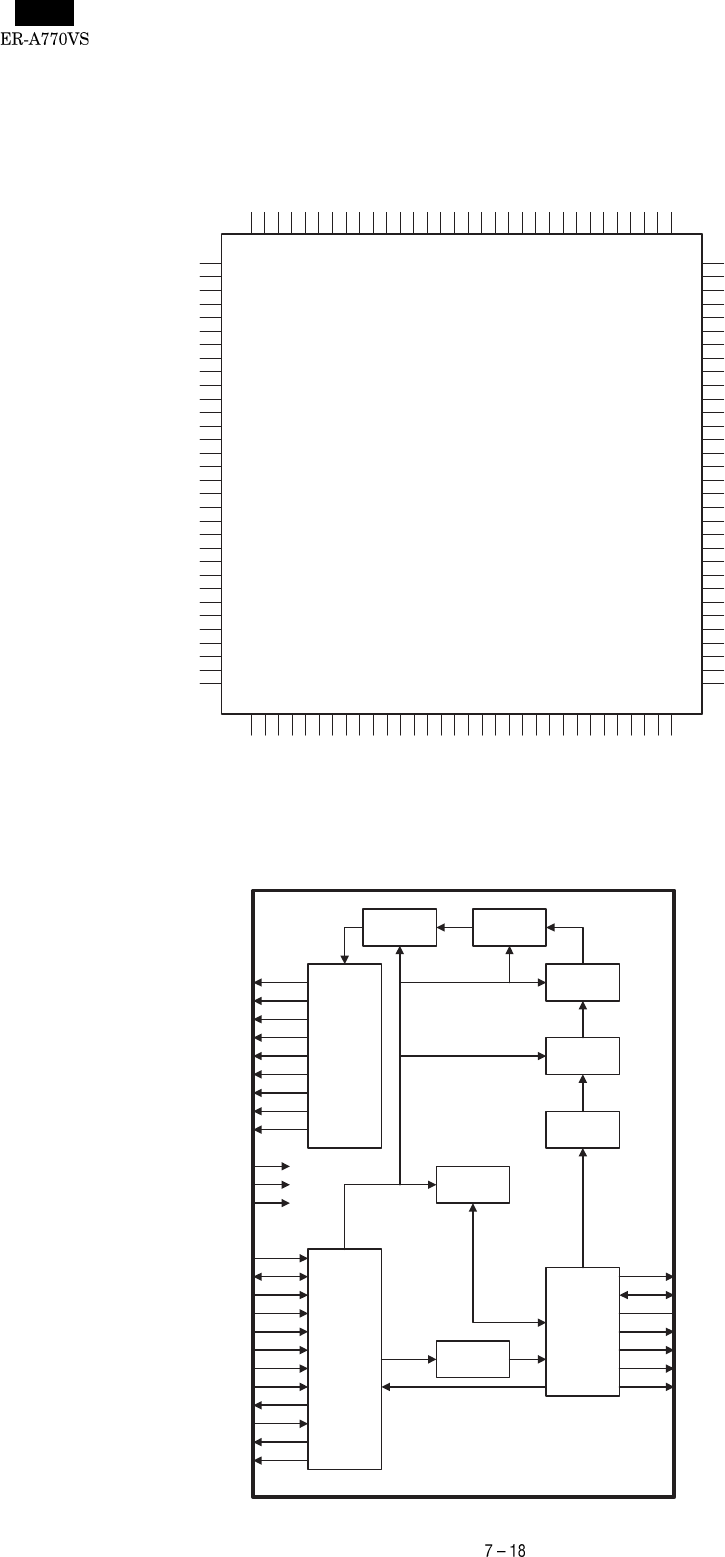

2) Block diagram

P47

P46

P45

P44

P43

P42

P41/TMCI

P40

P37

P36

P35

P34

P33

BREQ

BACK

WAIT

P27/A23

P26/A22

P25/A21

P24/A20

P23/A19

P22/A18

P21/A17

P20/A16

A15

A14

A13

A12

A11

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AVCC

AVSS

MD2

MD1

MD0

RES

STBY

NMI

AS

RD

HWR

LWR

RFSH

EXTAL

XTAL

E

P17

P16

P15

P14

P13

P12

P11

P10

D15

D14

D13

D12

D11

D10

D9

D8

P57

P56

P55

P54

P53

P52

P51

P50

P67

P66

P65

P64

P63

P62

P61

P60

P73

P72

P71

P70

TXD2

RXD2

TXD1

RXD1

SCK2/IRQ3

SCK1/IRQ2

IRQ1

IRQ0

H8/500 CPU DTC

Serial

communication

interface x 2ch

8bit timer

16bit free running

timer x 2ch

Refresh controller

Wait state

controller

A/D convertor

Interruption controller

Clock

oscillator Watch

dog timer

Data bus Port 1

Data bus (Lower)

Data bus (Upper)

Address bus

Port 2

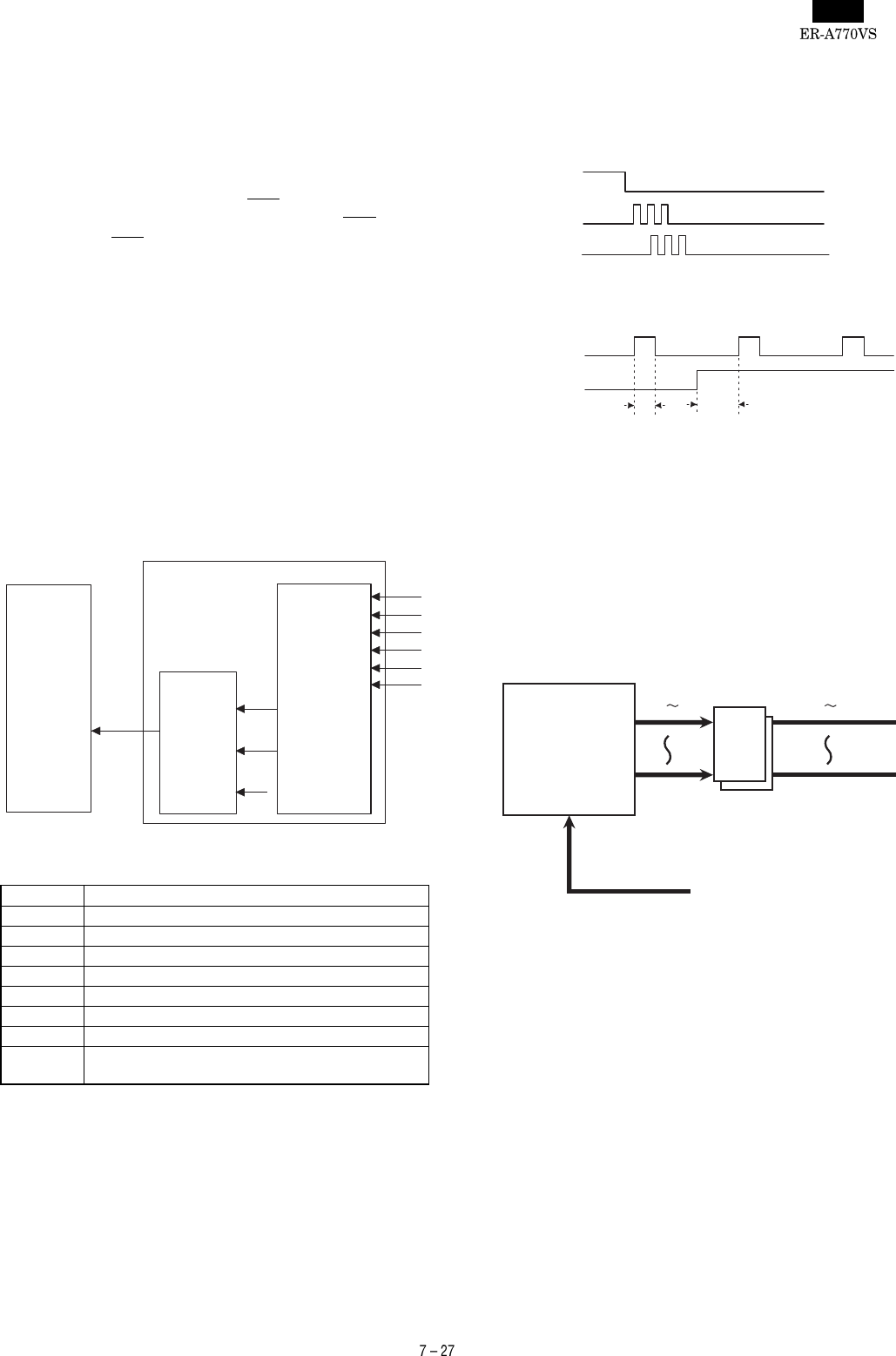

Port 3Port 4