GM Series/GM Series Detailed Service Manual 6864115B62 B

User Manual: -GM Series/GM Series Detailed service manual 6864115B62-B

Open the PDF directly: View PDF ![]() .

.

Page Count: 424 [warning: Documents this large are best viewed by clicking the View PDF Link!]

Professional Radio

GM Series

Detailed Service Manual

6864115B62-B

ii

WLS EMEA Publications Department, Jays Close, Viables Industrial Estate, Basingstoke, Hampshire, RG22 4PD, UK.

Issue : August 2002 iii

Professional Radio

GM Series

Detailed Service Manual

6864115B62-B

Contents

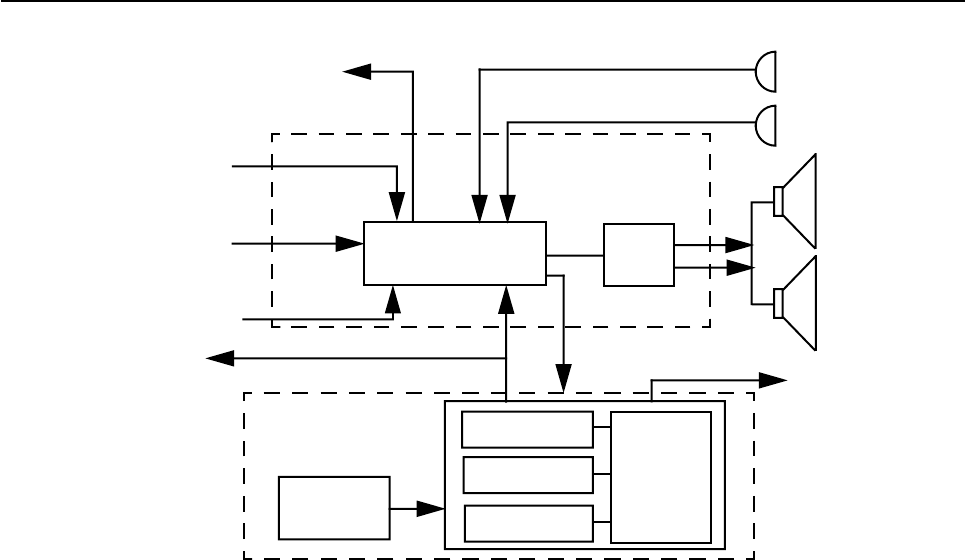

Section 1 Service Maintainability

Section 2 Controlhead Service Information

Section 3 Controller Service Information

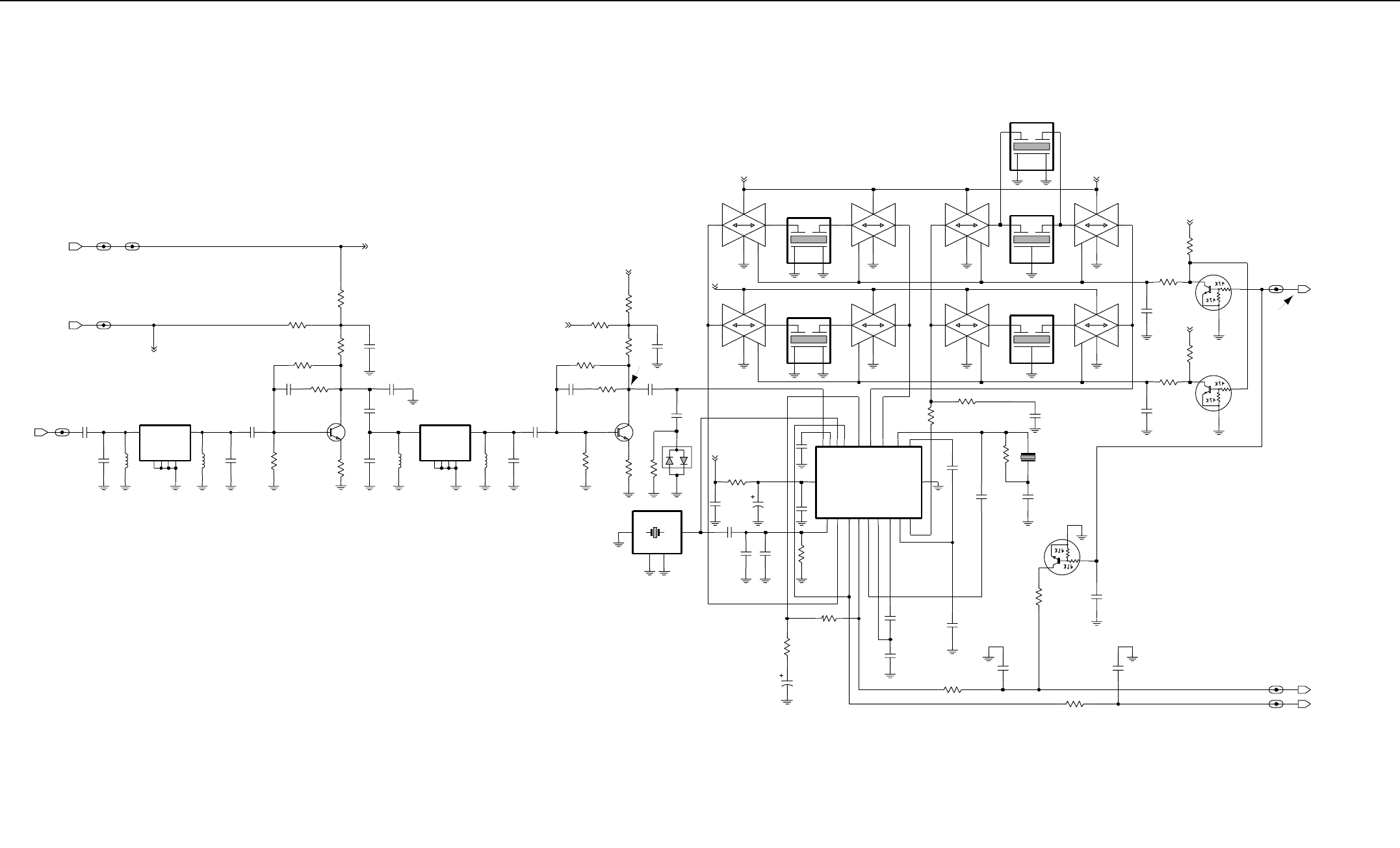

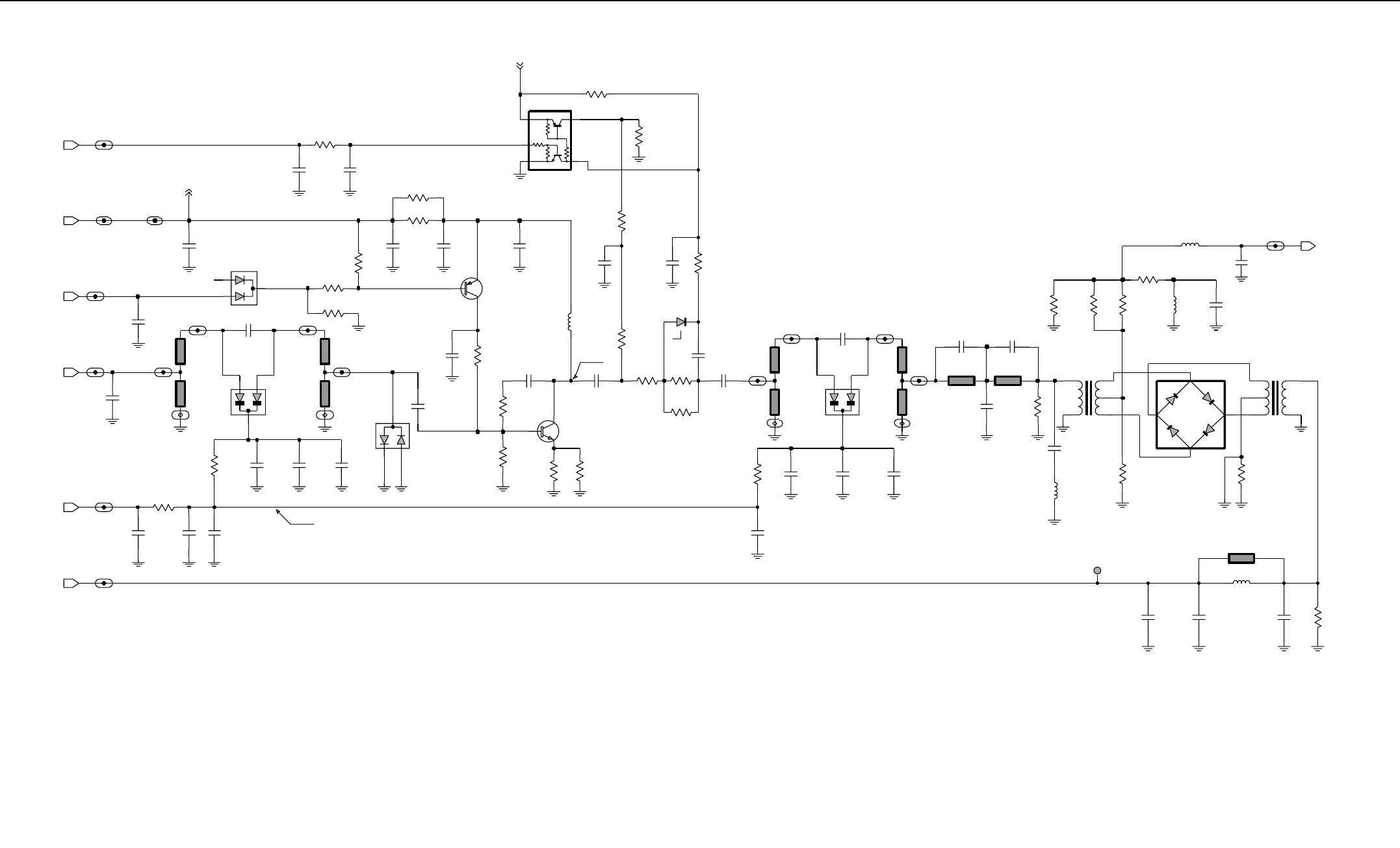

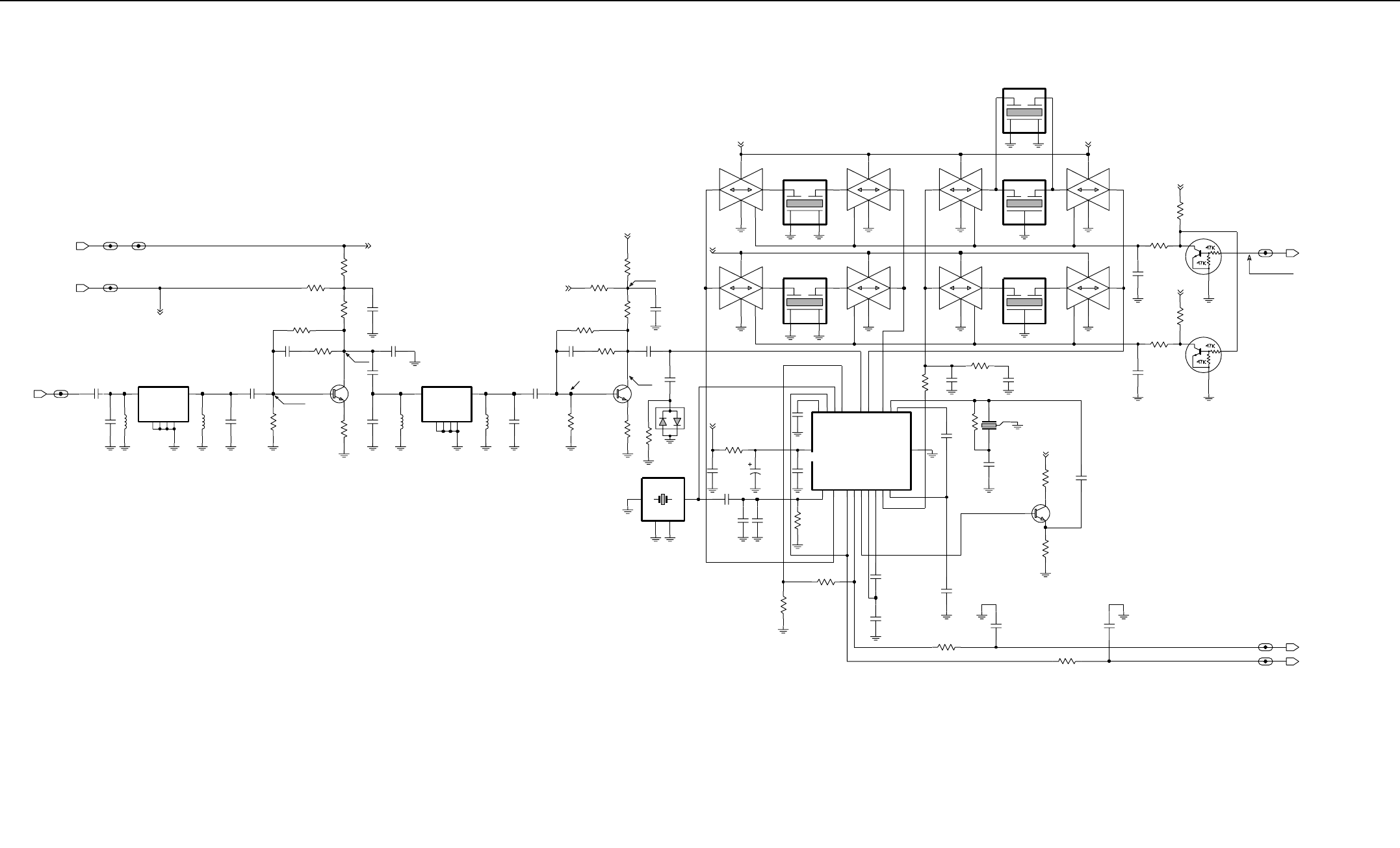

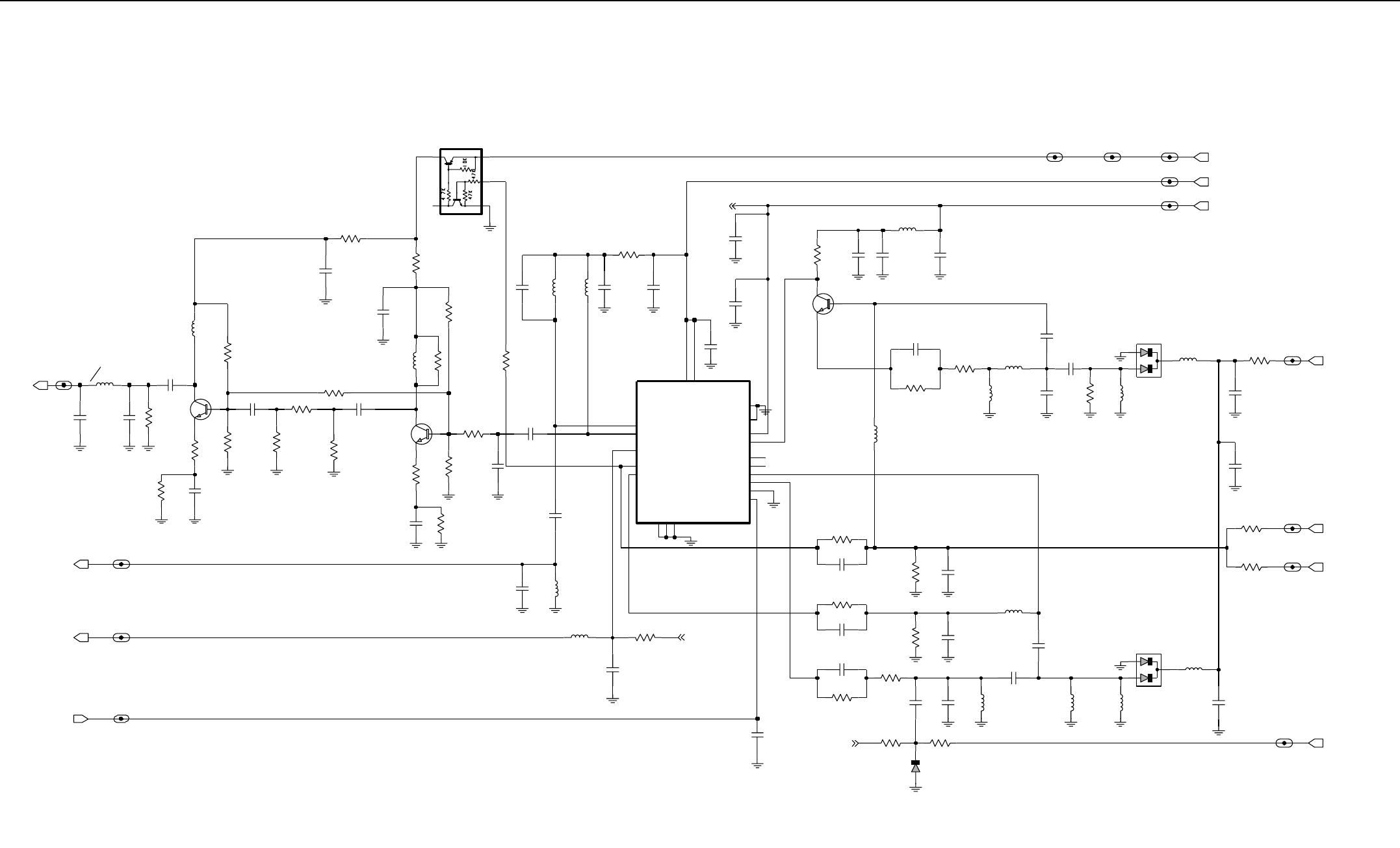

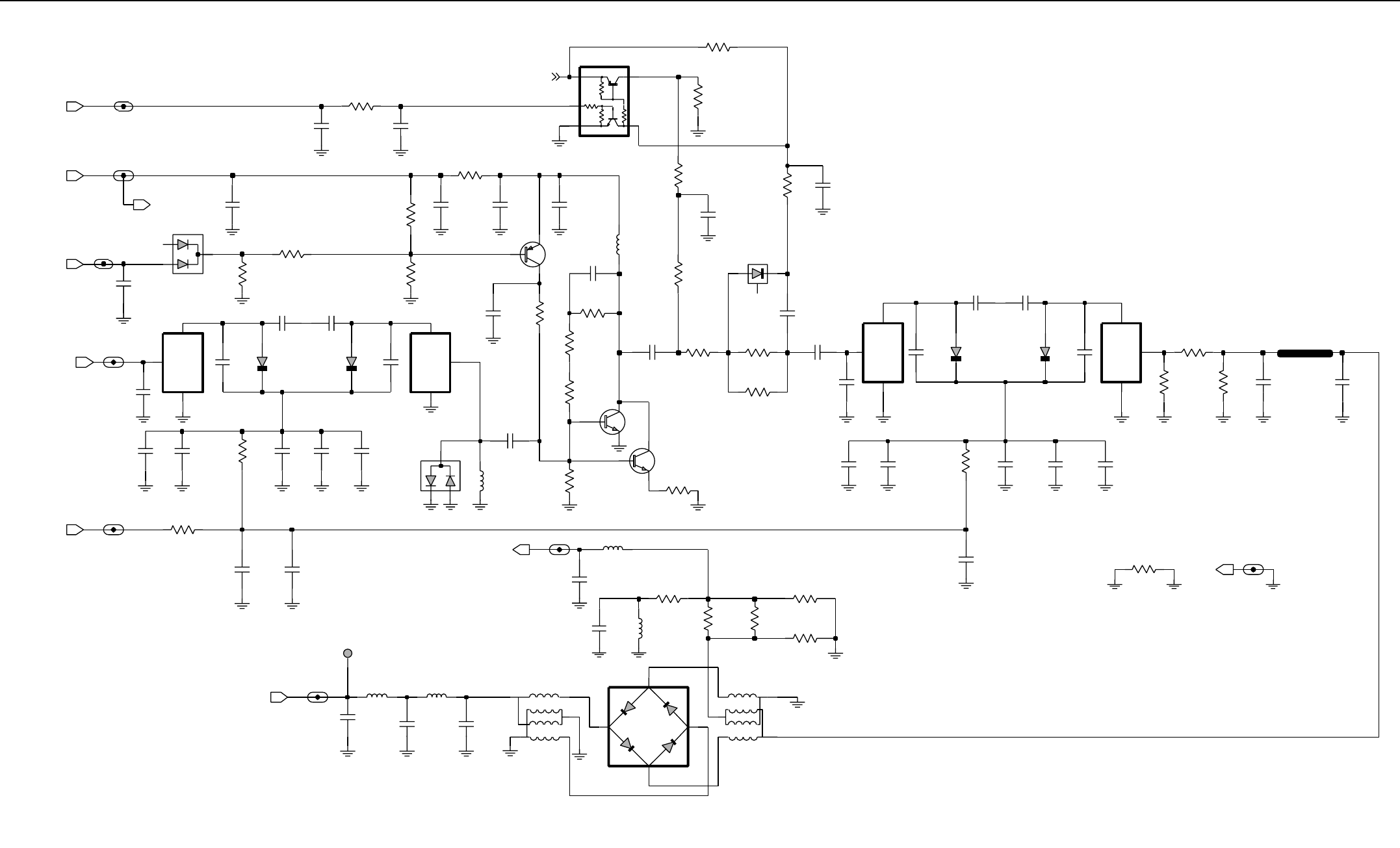

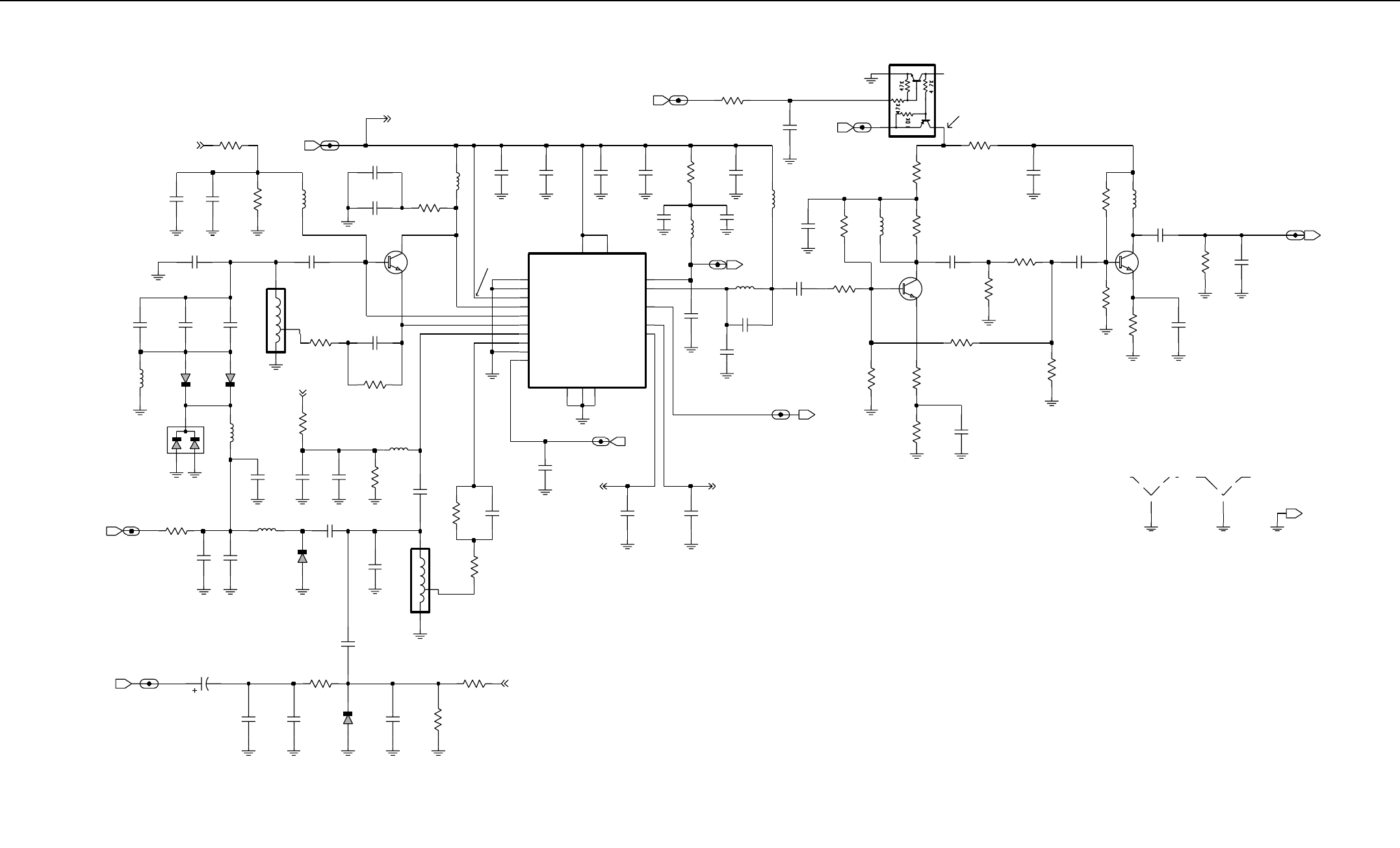

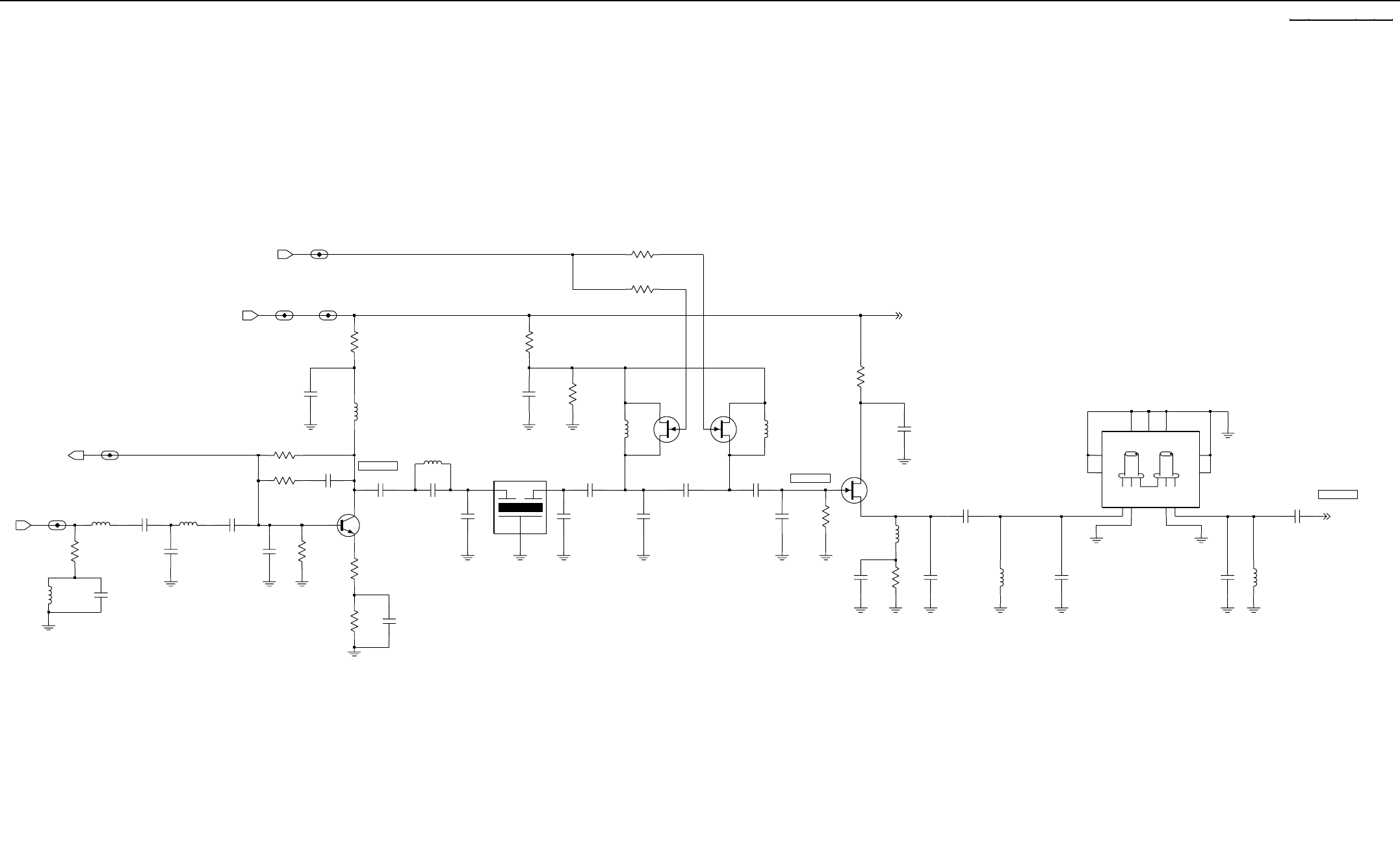

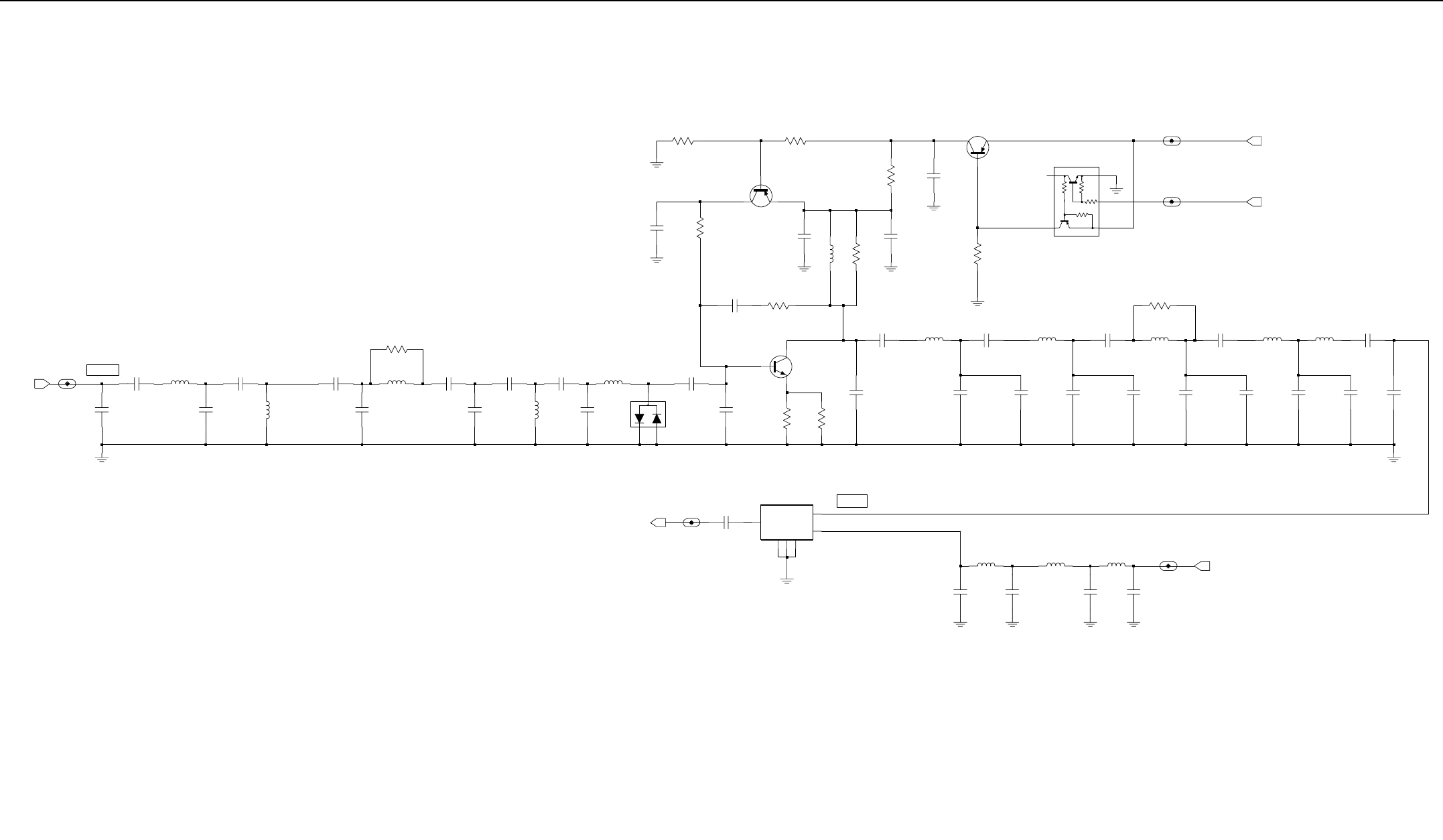

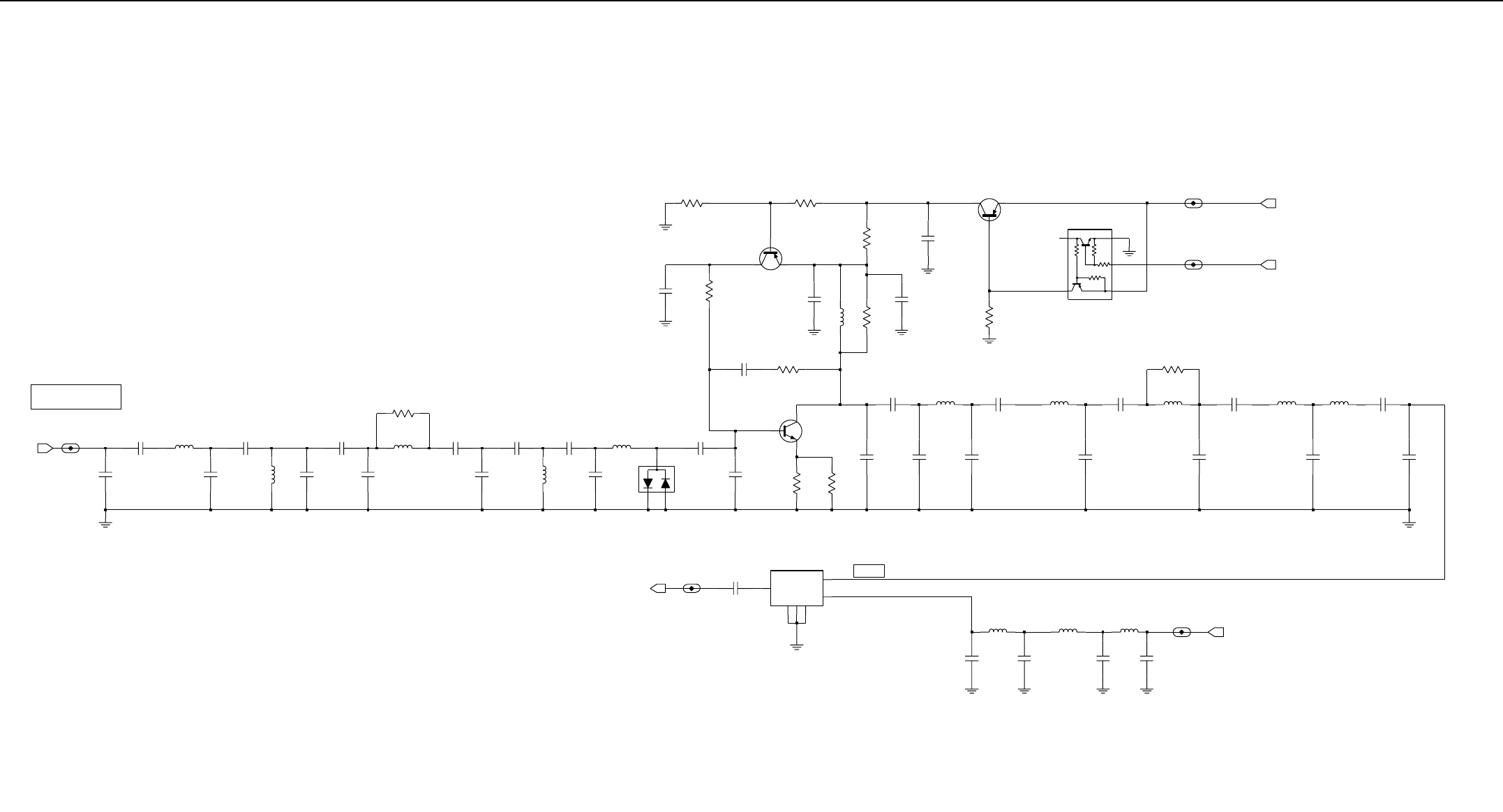

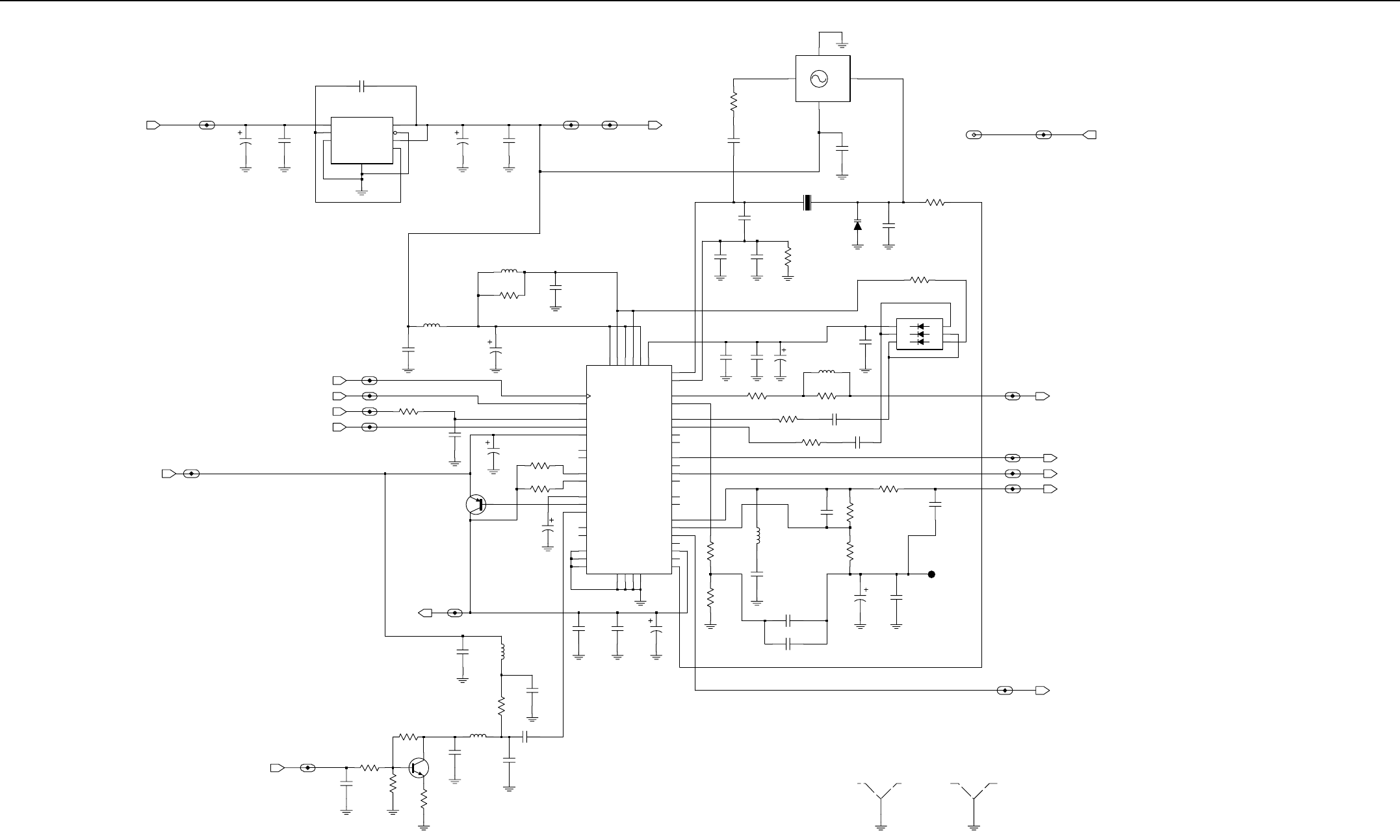

Section 4 VHF Service Information

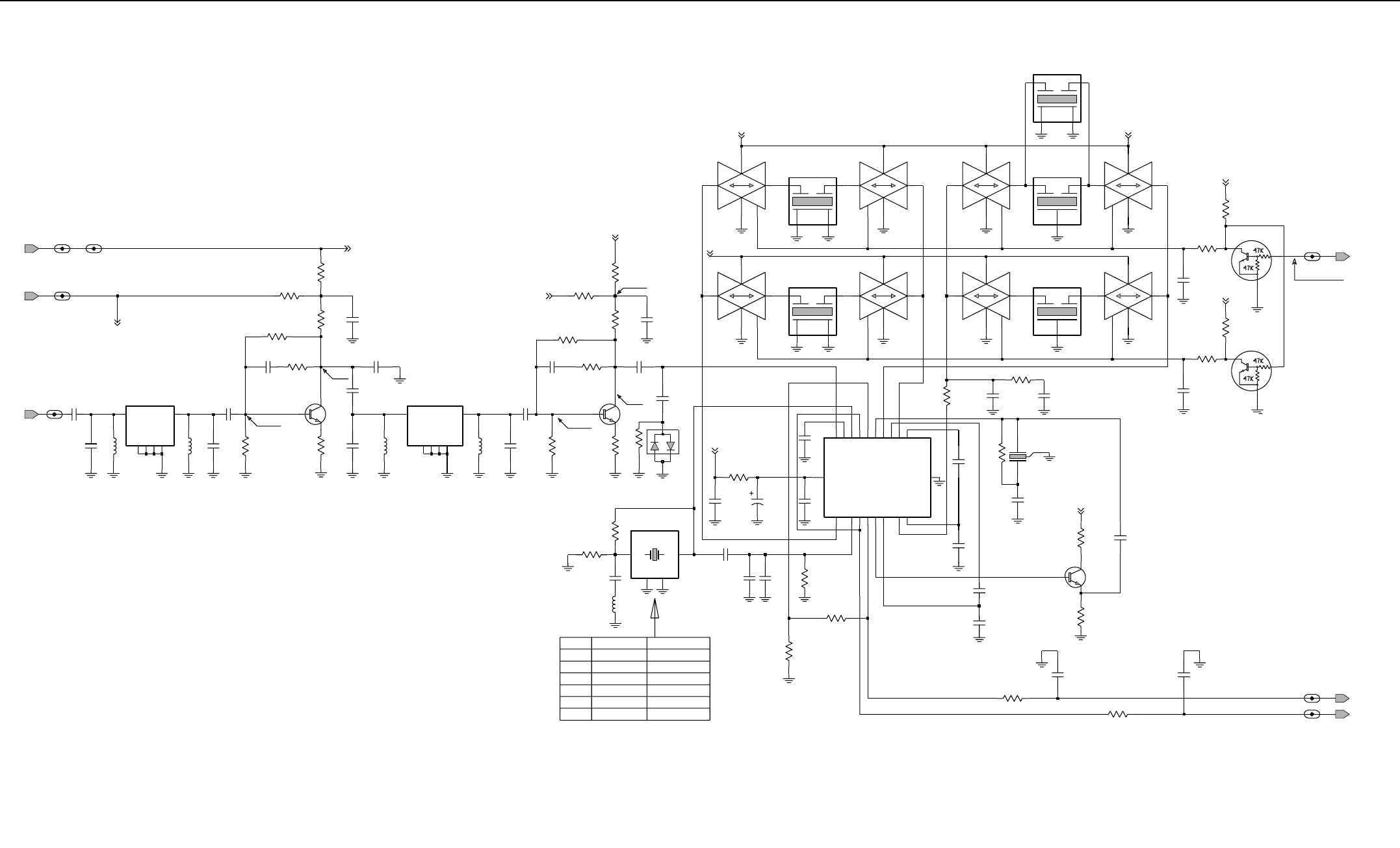

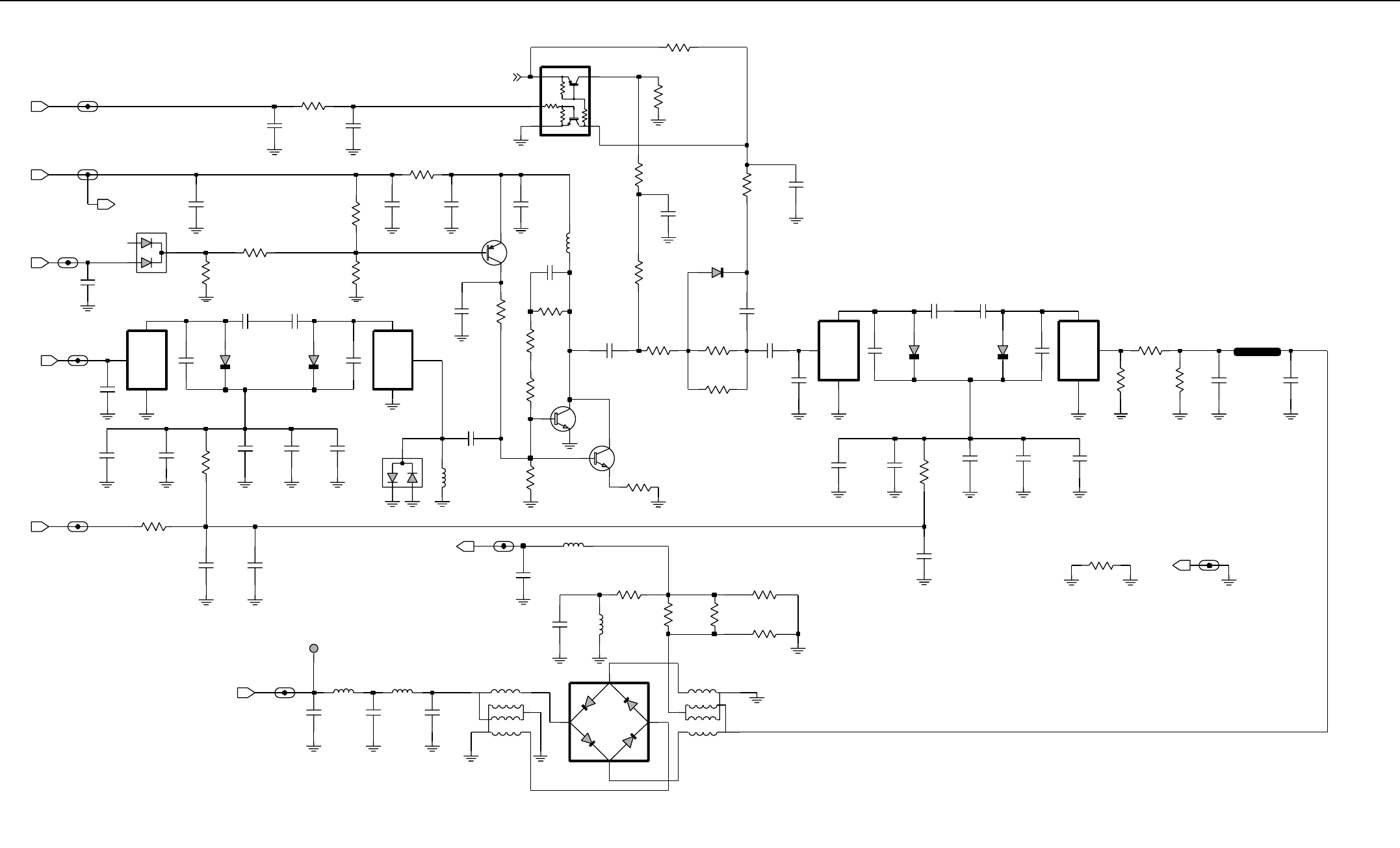

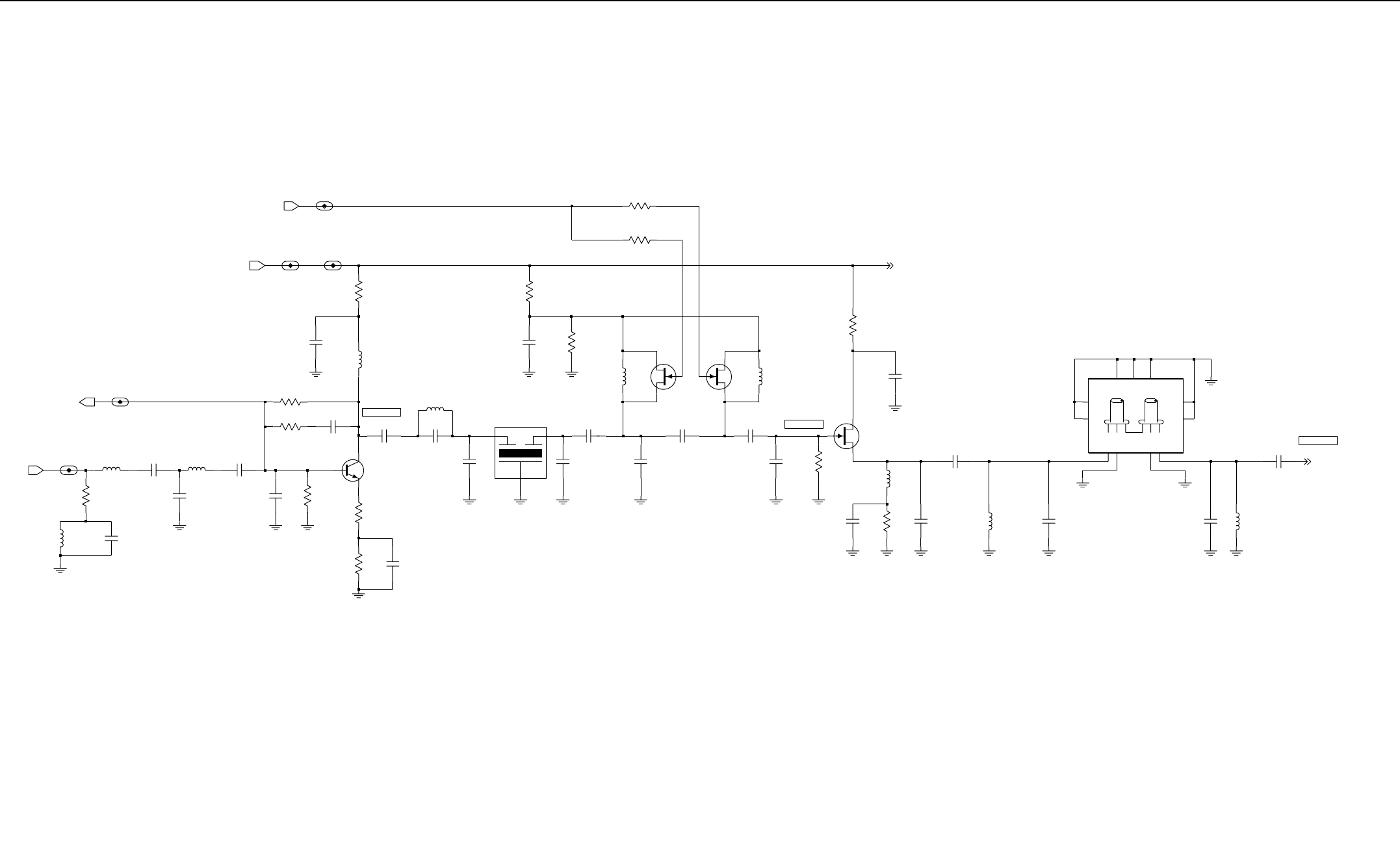

Section 5 UHF Service Information

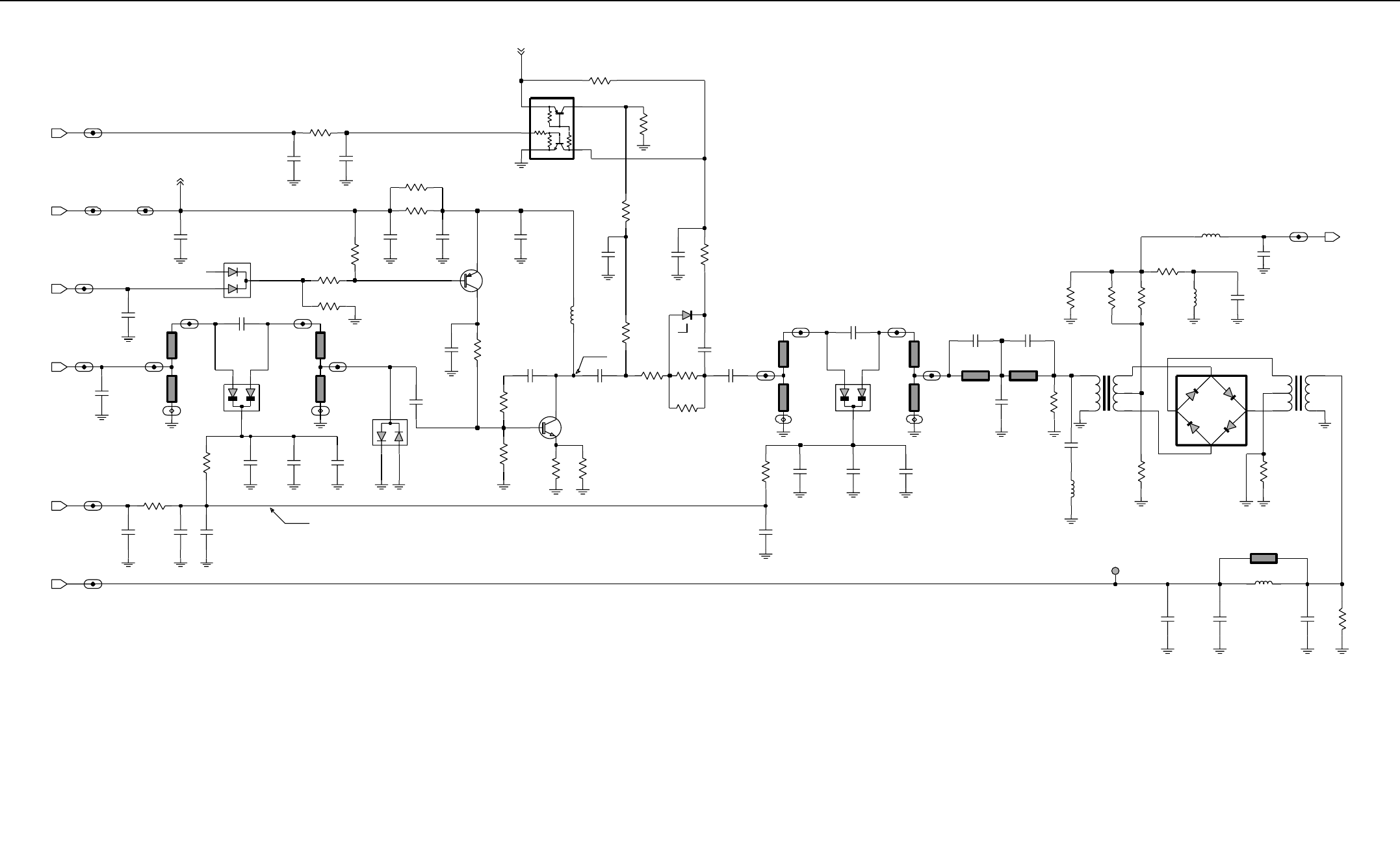

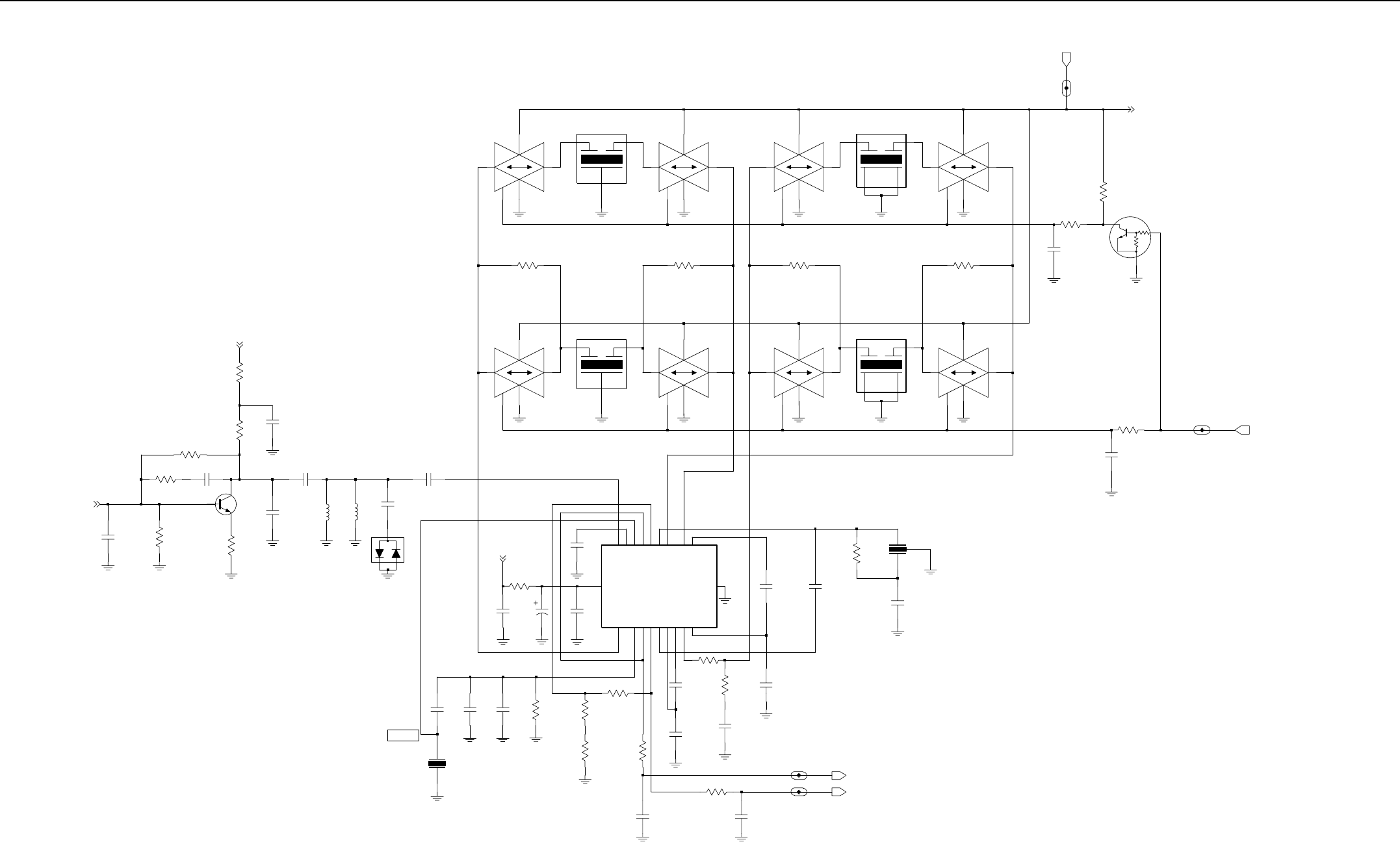

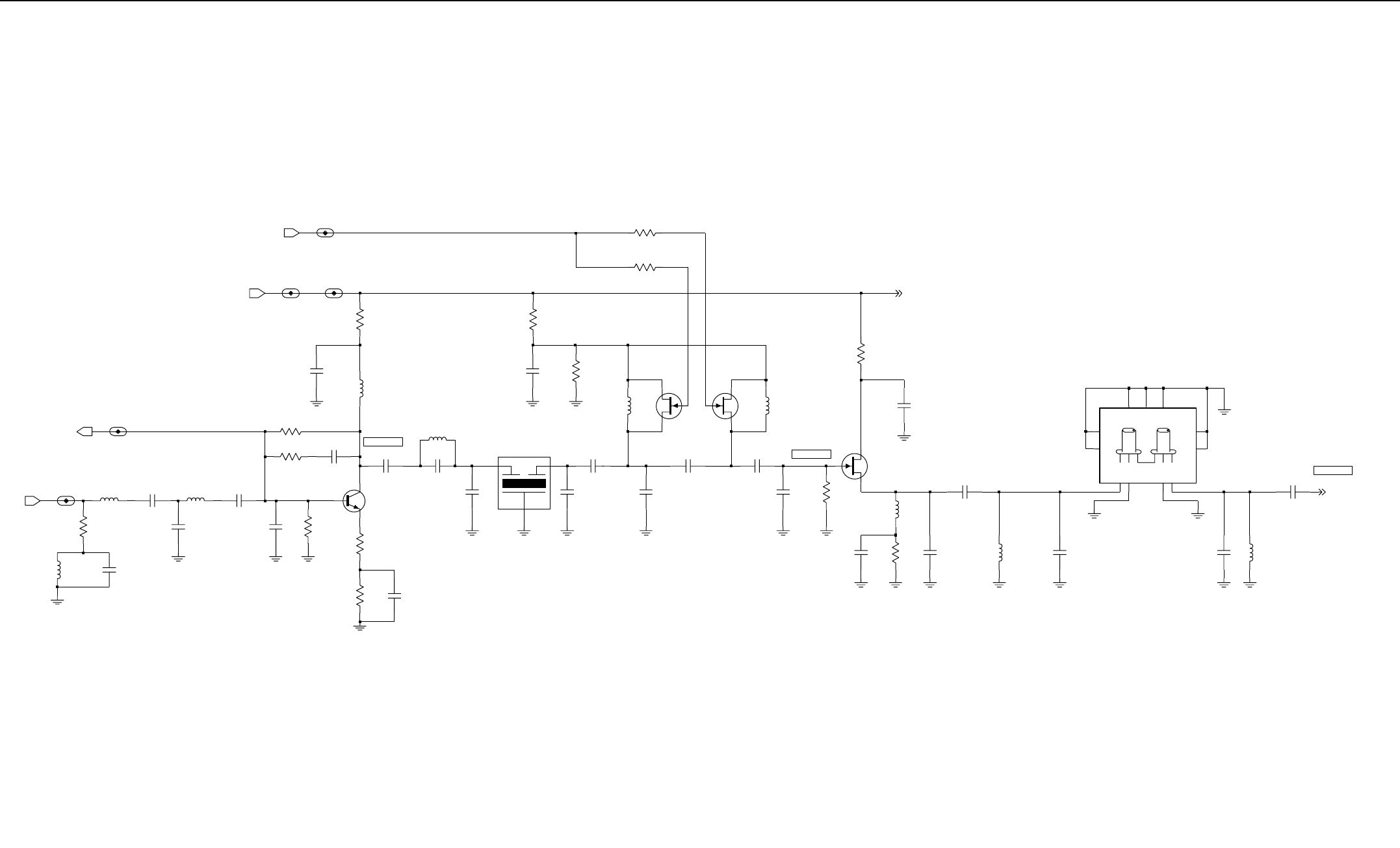

Section 6 Lowband Service Information

iv

Professional Radio

GM Series

Service Maintainability

Issue: August 2002

ii

Computer Software Copyrights

The Motorola products described in this manual may include copyrighted Motorola computer programs stored

in semiconductor memories or other media. Laws in the United States and other countries preserve for

Motorola certain exclusive rights for copyrighted computer programs, including the exclusive right to copy or

reproduce in any form, the copyrighted computer program. Accordingly, any copyrighted Motorola computer

programs contained in the Motorola products described in this manual may not be copied or reproduced in

any manner without the express written permission of Motorola. Furthermore, the purchase of Motorola

products shall not be deemed to grant, either directly or by implication, estoppel or otherwise, any license

under the copyrights, patents or patent applications of Motorola, except for the normal non-exclusive

royalty-free license to use that arises by operation of law in the sale of a product.

iii

Table of Contents

Chapter 1 INTRODUCTION

1.0 Scope of Manual ..................................................................................................1-1

2.0 Warranty and Service Support.............................................................................1-1

2.1 Warranty Period and Return Instructions .......................................................1-1

2.2 After Warranty Period .....................................................................................1-1

2.3 European Radio Support Centre (ERSC).......................................................1-2

2.4 Parts Identification and Ordering ....................................................................1-2

2.5 EMEA Test Equipment Support......................................................................1-2

2.6 Technical Support...........................................................................................1-3

2.7 Related Documents ........................................................................................1-3

3.0 Radio Model Information......................................................................................1-4

Chapter 2 MAINTENANCE

1.0 Introduction ..........................................................................................................2-1

2.0 Preventive Maintenance ......................................................................................2-1

2.1 Inspection .......................................................................................................2-1

2.2 Cleaning .........................................................................................................2-1

3.0 Safe Handling of CMOS and LDMOS..................................................................2-2

4.0 General Repair Procedures and Techniques.......................................................2-2

5.0 Notes For All Schematics and Circuit Boards ......................................................2-5

Chapter 3 SERVICE AIDS

1.0 Recommended Test Tools...................................................................................3-1

2.0 Test Equipment....................................................................................................3-2

iv

v

SAFETY AND GENERAL INFORMATION

IMPORTANT INFORMATION ON SAFE AND EFFICIENT OPERATION

Read this infomation before using your radio.

The information provided in this document supersedes the general safety information contained in user guides

published prior to July 2000. For information regarding radio use in a hazardous atmosphere please refer to the

Factory Mutual (FM) Approval Manual Supplement or Instruction Card, which is included with radio models that

offer this capability.

Radio Frequency (RF) Operational Characteristics

To transmit (talk) you must push the Push-To-Talk button; to receive (listen) you must release the Push-To-Talk

button. When the radio is transmitting, it generates radio frequency (RF) energy; when it is receiving, or when it

is off, it does not generate RF energy.

PORTABLE RADIO OPERATION AND EME EXPOSURE

Your Motorola radio is designed to comply with the following national and international standards and guidelines

regarding exposure of human beings to radio frequency electromagnetic energy:

●United States Federal Communications Commission, Code of Federal Regulations; 47 CFR part 2 sub-part J

●American National Standards Institute (ANSI) / Institute of Electrical and Electronic Engineers (IEEE)

C95. 1-1992

●Institute of Electrical and Electronic Engineers (IEEE) C95.1-1999 Edition

●National Council on Radiation Protection and Measurements (NCRP) of the United States, Report 86, 1986

●International Commission on Non-Ionizing Radiation Protection (ICNIRP) 1998

●Ministry of Health (Canada) Safety Code 6. Limits of Human Exposure to Radiofrequency Electromagnetic

Fields in the Frequency Range from 3 kHz to 300 GHz, 1999

●Australian Communications Authority Radiocommunications (Electromagnetic Radiation - Human Exposure)

Standard 1999 (applicable to wireless phones only)

To assure optimal radio performance and make sure human exposure to radio frequency electromagnetic energy

is within the guidelines set forth in the above standards, always adhere to the following procedures:

Phone operation

When placing or receiving a phone call, hold your phone as you would a wireline telephone. Speak directly into

the microphone.

Two-way radio operation

When using your radio hold the radio in a vertical position with the microphone 2.5 to 5 cm away from the lips.

Body-worn operation

To maintain compliance with FCC RF exposure guidelines, if you wear a radio on your body when transmitting,

always place the radio in a Motorola approved clip, holder, holster, case, or body harness for this product. Use of

non-Motorola-approved body worn accessories may exceed FCC RF exposure guidelines. If you do not use a

Motorola approved body-worn accessory and are not using the radio in the intended use positions along side of

the head in the phone mode or in front of the face in the two-way radio mode, then ensure the antenna and radio

is kept the following minimum distances from the body when transmitting:

●Phone or Two-way radio mode: 2.5 cm (one inch)

●Data operation using any data feature with or without an accessory cable: 2.5 cm (one inch) .

Antenna Care

Use only the supplied or an approved replacement antenna. Unauthorized antennas, modifications, or

attachments could damage the radio and may violate FCC regulations.

DO NOT hold the antenna when the radio is "IN USE". Holding the antenna affects call quality and may cause

the radio to operate at a higher power level than needed.

Approved Accessories

For a list of approved Motorola accessories please contact your dealer or local Motorola representative.

vi

ELECTROMAGNETIC INTERFERENCE/COMPATIBILITY

Facilities

To avoid electromagnetic interference and/or compatibility conflicts, turn off your radio in any facility where posted

notices instruct you to do so. Hospitals or health care facilities may be using equipment that is sensitive to

external RF energy.

Aircraft

When instructed to do so, turn off your radio when on board an aircraft. Any use of a radio must be in accordance

with applicable regulations per airline crew instructions.

Medical Devices

Pacemakers

The Health Industry Manufacturers Association recommends that a minimum separation of 15 cms

(6 inches) be maintained between a handheld wireless radio and a pacemaker.These recommendations are

consistent with those of the U.S. Food and Drug Administration.

Persons with pacemakers should:

●ALWAYS keep the radio more than 15 cms (6inches) from their pacemaker when the radio is turned ON.

●not carry the radio in the breast pocket.

●use the ear opposite the pacemaker to minimize the potential for interference.

●turn the radio OFF immediately if you have any reason to suspect that interference is taking place.

Hearing Aids

Some digital wireless radio products may interfere with some hearing aids. In the event of such interference, you

may want to consult your hearing aid manufacturer to discuss alternatives.

Other Medical Devices

If you use any other personal medical device, consult the manufacturer of your device to determine if it is

adequately shielded from RF energy. Your physician may be able to assist you in obtaining this information.

Safety and General

Use While Driving

Check the laws and regulations on the use of radios in the area where you drive. Always obey them.

When using your radio while driving, please:

●Give full attention to driving and to the road.

●Use hands-free operation, if available.

●Pull off the road and park before making or answering a call if driving conditions so require.

NOTE Nearly every electronic device is susceptible to electromagnetic interference (EMI) if

inadequately shielded, designed, or alternately configured for electromagnetic compatibility.

vii

OPERATIONAL WARNINGS

For Vehicles With An Air Bag

Potentially Explosive Atmospheres

Blasting Caps And Areas

OPERATIONAL CAUTIONS

Antennas

Do not use any portable radio that has a damaged antenna. If a damaged antenna comes into contact with your

skin, a minor burn can result.

Batteries

All batteries can cause property damage and/or bodily injury such as burns if a conductive material such as

jewellery, keys, or beaded chains touch exposed terminals. The conductive material may complete an electrical

circuit (short circuit) and become quite hot. Exercise care in handling any charged battery, particularly when

placing it inside a pocket, purse, or other container with metal objects.

MOBILE RADIO OPERATION AND EME EXPOSURE

To assure optimal radio performance and that human exposure to radio frequency electromagnetic energy is

within the guidelines referenced earlier in this document, transmit only when people outside the vehicle are at

least the minimum lateral distance away from a properly installed, externally-mounted antenna. Table 1 lists the

minimum distance for several different ranges of rated radio power.

WARNING: Do not place a portable radio in the area over an air bag or in the air bag

deployment area. Air bags inflate with great force. If a portable radio is placed in the air bag

deployment area and the air bag inflates, the radio product may be propelled with great force

and cause serious injury to occupants of vehicle.

NOTE The areas with potentially explosive atmospheres referred to above include fueling areas

such as below decks on boats, fuel or chemical transfer or storage facilities, areas where the

air contains chemicals or particles, such as grain, dust or metal powders, and any other

area where you would normally be advised to turn off your vehicle engine. Areas with poten-

tially explosive atmospheres are often but not always posted.

WARNING: Turn off your radio prior to entering any area with a potentially explosive

atmosphere, unless it is a radio type especially qualified for use in such areas as

"Intrinsically Safe" (for example, Factory Mutual, CSA, UL or CENELEC Approved). Do not

remove, install, or charge batteries in such areas. Sparks in a potentially explosive

atmosphere can cause an explosion or fire resulting in bodily injury or even death.

WARNING: To avoid possible interference with blasting operations, turn off your radio when

you are near electrical blasting caps, in a “blasting area” or in areas posted

“Turn off two-way radio”. Obey all signs and instructions.

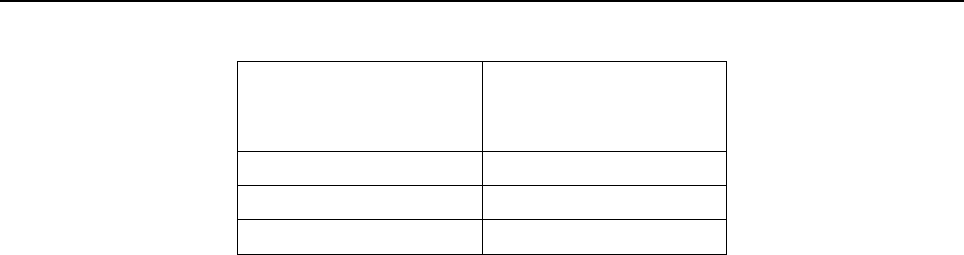

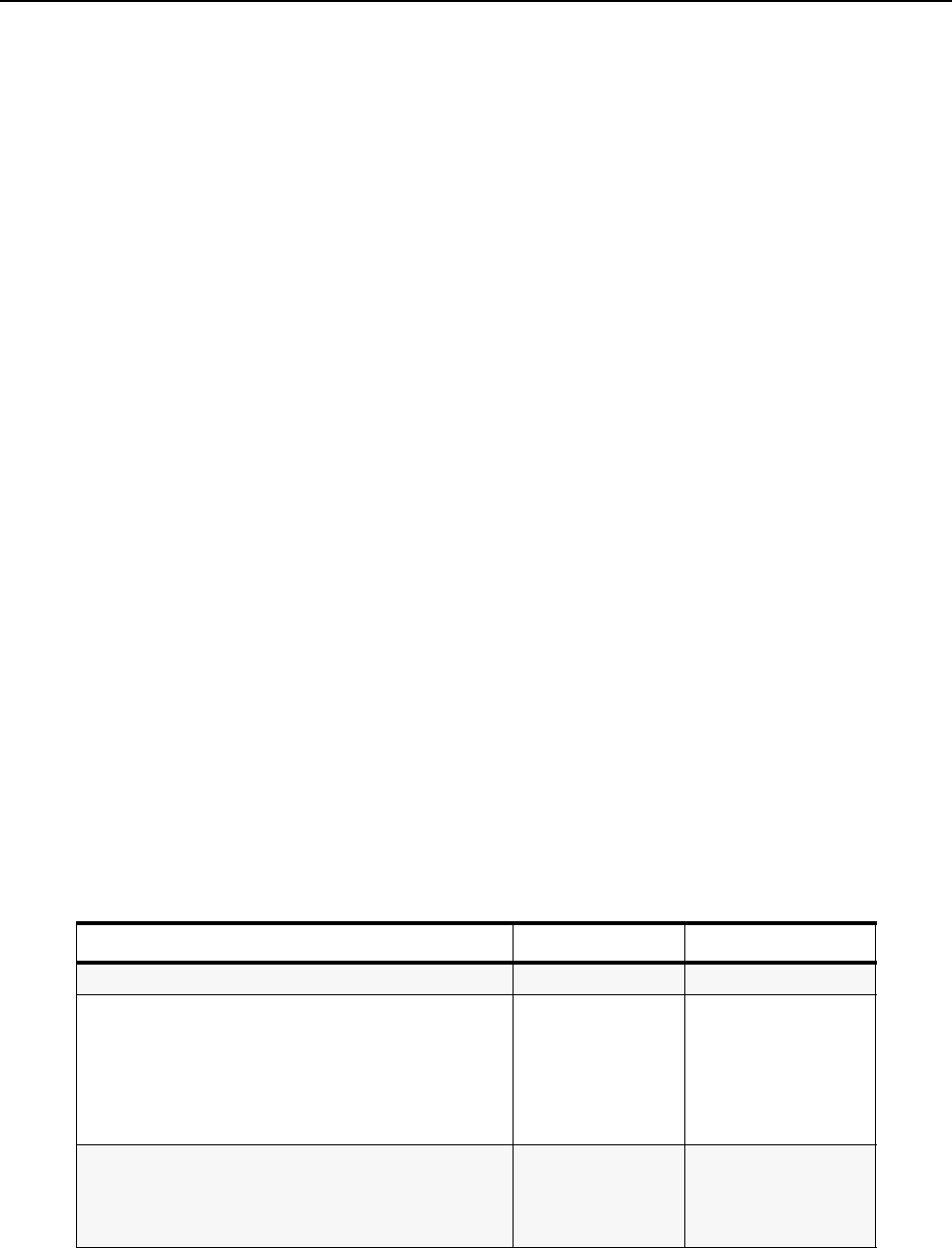

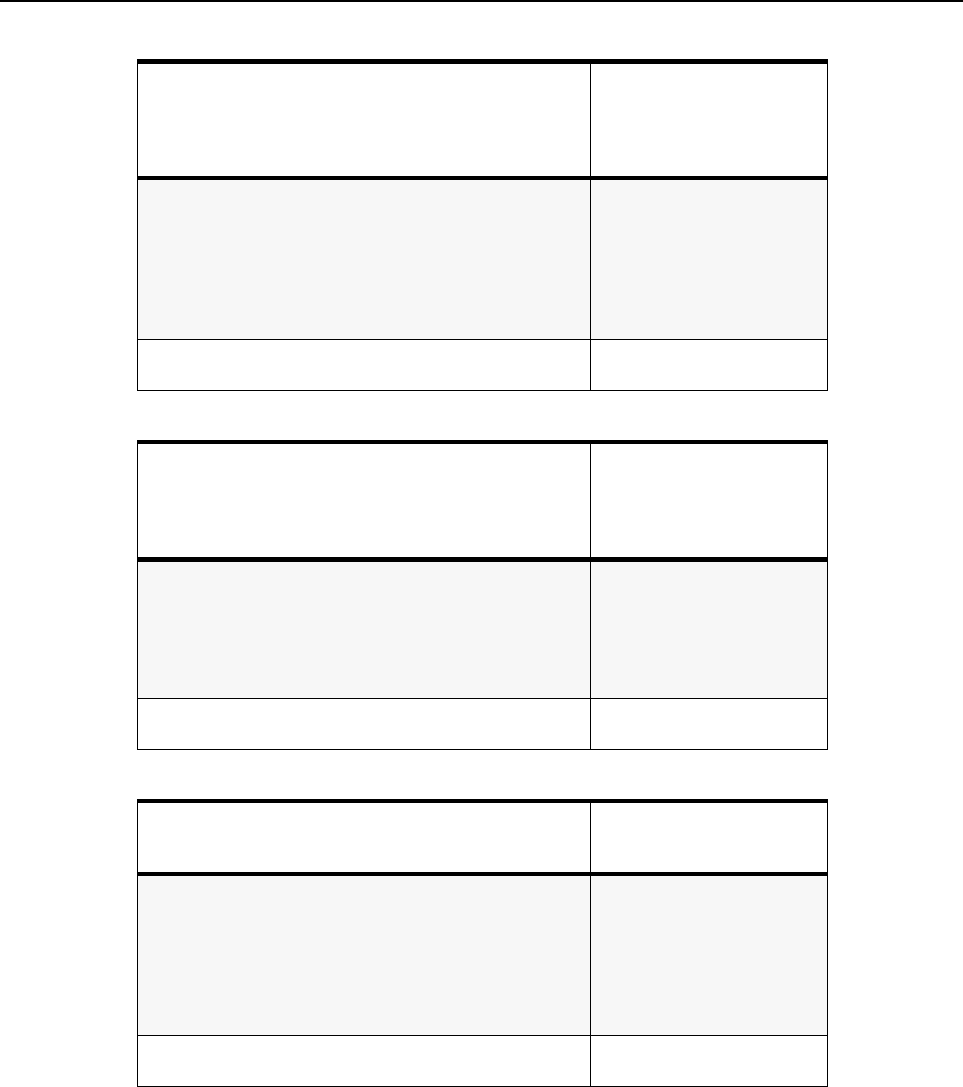

Ta b l e 1 : Table 1 Rated Power and Lateral Distance

Radiated Power of

Vehicle-installed

Mobile Two-way

Minimum Lateral

Distance From

Transmitting

Less than 7 Watts 20 cm (8 Inches)

!

!

!

viii

ANTENNA INSTALLATION

Mobile Antennas

Recommended mobile antenna installations are limited to metal body vehicles at the centre of the roof and centre

of the trunk deck locations.

The antenna installation must additionally be in accordance with:

a) The requirements of the antenna manufacturer/supplier

b) Instructions in the Radio Installation Manual

Fixed Site Antennas

Mobile radio equipment is sometimes installed at a fixed location and operated as a control station or as a fixed

unit. In such cases the antenna installation must comply with the following requirements in order to assure

optimal performance and make sure human exposure to radio frequency electromagnetic energy is within the

guidelines set forth in the above standards:

●The antenna must be mounted outside the building

●Mount the antenna on a tower if at all possible

●If the antenna is to be mounted on a building then it must be mounted on the roof.

As with all fixed site antenna installations, it is the responsibility of the licensee to manage the site in accordance

with applicable regulatory requirements and may require additional compliance actions such as site survey

measurements, signage, and site access restrictions in order to insure that exposure limits are not exceeded.

7 to 15 Watts 30 cm (1 Ft)

16 to 50 Watts 60 cm (2 Ft)

More than 50 Watts 90 cm (3 Ft)

Table 1: Table 1 Rated Power and Lateral Distance

Radiated Power of

Vehicle-installed

Mobile Two-way

Minimum Lateral

Distance From

Transmitting

Chapter 1

INTRODUCTION

1.0 Scope of Manual

This manual is intended for use by service technicians familiar with similar types of equipment. It

contains service information required for the equipment described and is current as of the printing

date. Changes which occur after the printing date may be incorporated by a complete Manual

revision or alternatively as additions.

2.0 Warranty and Service Support

Motorola offers long term support for its products. This support includes full exchange and/or repair

of the product during the warranty period, and service/ repair or spare parts support out of warranty.

Any "return for exchange" or "return for repair" by an authorised Motorola Dealer must be

accompanied by a Warranty Claim Form. Warranty Claim Forms are obtained by contacting an

Authorised Motorola Dealer.

2.1 Warranty Period and Return Instructions

The terms and conditions of warranty are defined fully in the Motorola Dealer or Distributor or

Reseller contract. These conditions may change from time to time and the following notes are for

guidance purposes only.

In instances where the product is covered under a "return for replacement" or "return for repair"

warranty, a check of the product should be performed prior to shipping the unit back to Motorola.

This is to ensure that the product has been correctly programmed or has not been subjected to

damage outside the terms of the warranty.

Prior to shipping any radio back to the appropriate Motorola warranty depot, please contact

Customer Resources (Please see page 2 and page 3 in this Chapter). All returns must be

accompanied by a Warranty Claim Form, available from your Customer Services representative.

Products should be shipped back in the original packaging, or correctly packaged to ensure no

damage occurs in transit.

2.2 After Warranty Period

After the Warranty period, Motorola continues to support its products in two ways.

1. Motorola's Radio Aftermarket and Accessory Division (AAD) offers a repair service to both

end users and dealers at competitive prices.

2. AAD supplies individual parts and modules that can be purchased by dealers who are techni-

cally capable of performing fault analysis and repair.

NOTE Before operating or testing these units, please read the Safety Information Section in the

front of this manual.

1-2 INTRODUCTION

2.3 European Radio Support Centre (ERSC)

The ERSC Customer Information Desk is available through the following service numbers:

Austria: 06 60 75 41 Italy: 16 78 77 387

Belgium: 08 00 72 471 Luxemburg: 08 00 23 27

Denmark: 80 01 55 72 Netherlands: 60 22 45 13

Finland: 08 00 11 49 10 Norway: 80 01 11 15

France: 05 90 30 90 Portugal: 05 05 49 35 70

Germany: 08 00 18 75 240 Spain: 90 09 84 902

Greece: 00 80 04 91 29 020 Sweden: 02 07 94 307

UK: 08 00 96 90 95 Switzerland: 1 55 30 82

Ireland: 18 00 55 50 21 Iceland: 80 08 147

Or dial Customer Care Centre:

Tel: +49 6128 70 2618

Please use these numbers for repair enquiries only.

2.4 Parts Identification and Ordering

Request for help in identification of non-referenced spare parts should be directed to the Customer

Care Organisation of Motorola’s local area representation. Orders for replacement parts, kits and

assemblies should be placed directly on Motorola’s local distribution organisation or via Motorola

Online (Extranet).

2.5 EMEA Test Equipment Support

Information related to support and service of Motorola Test Equipment is available via Motorola

Online (Extranet), through the Customer Care Organisation of Motorola’s local area representation

or by calling the Motorola switchboard in Germany on telephone number: +49 6128 700.

Warranty and Service Support 1-3

2.6 Technical Support

Motorola Product Services is available to assist the dealer/distributors in resolving any malfunctions

which may be encountered.

2.7 Related Documents

The following documents are directly related to the use and maintainability of this product.

UK/Ireland - Richard Russell

Telephone: +44 (0) 1256 488 082

Fax: +44 01256 488 080

Email: BRR001@email.mot.com

France - Lionel Lhermitte

Telephone: +33 1 6929 5722

Fax: +33 1 6929 5904

Email: TXE037@email.mot.com

East Europe, Turkey and Central Asia

Siggy Punzenberger

Telephone: +49 (0) 6128 70 2342

Fax: +49 (0) 6128 95 1096

Email: TFG003@email.mot.com

Russian Regional Repair Operations:

Telephone: +7 095 785 01 89

Italy - Ugo Gentile

Telephone: +39 0 2822 0325

Fax: +39 0 2822 0334

Email: C13864@email.mot.com

Scandinavia

Telephone: +46 8 735 9282

Fax: +46 8 735 9280

Email: TCW275X@email.mot.com

Middle East & Africa - Ralph Schubert

Telephone: +33 (0) 4 4230 5887

Fax: +33 (0) 4 4230 4784

Email: ralph.schubert@motorola.com

Central Europe (Germany, Benelux,

Austria & Switzerland) - Customer Connect

Telephone: +49 (0) 6128 70 2248

Fax: +49 (0) 6128 95 1082

Email: cgiss.emea@europe.mot.com

Motorola Support Centre South Africa:

Telephone: +27 11 254 4000

Title Language Part Number

GM100 Series Product Manual English ENLN4147

GM300 Series Product Manual English

German

French

Italian

Spanish

Russian

ENLN4137

ENLN4138

ENLN4139

ENLN4140

ENLN4141

ENLN4142

GM600/GM1200 Series Product Manual English

German

French

Russian

ENLN4143

ENLN4144

ENLN4145

ENLN4146

1-4 INTRODUCTION

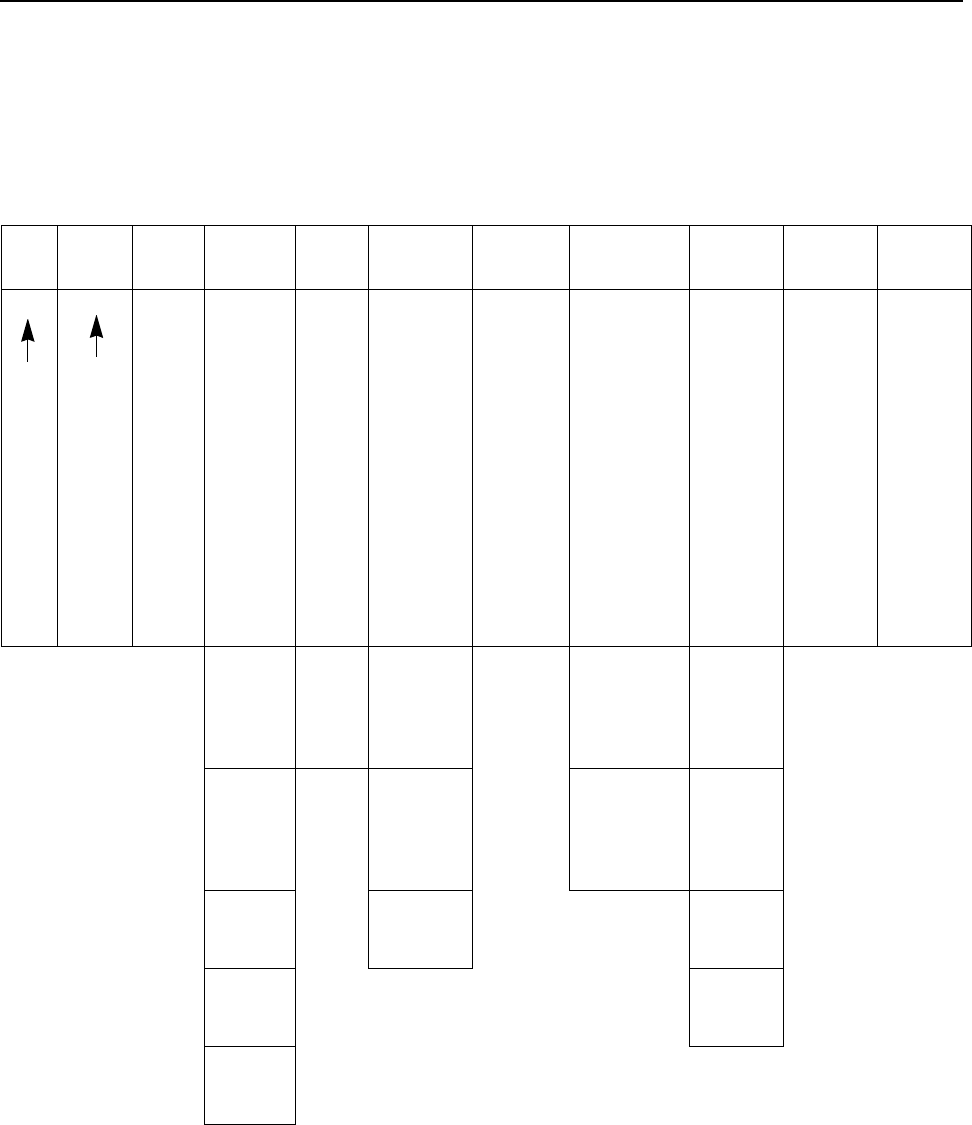

3.0 Radio Model Information

The model number and serial number are located on a label attached to the back of your radio. You

can determine the RF output power, frequency band, protocols, and physical packages. The

example below shows one mobile radio model number and its specific characteristics.

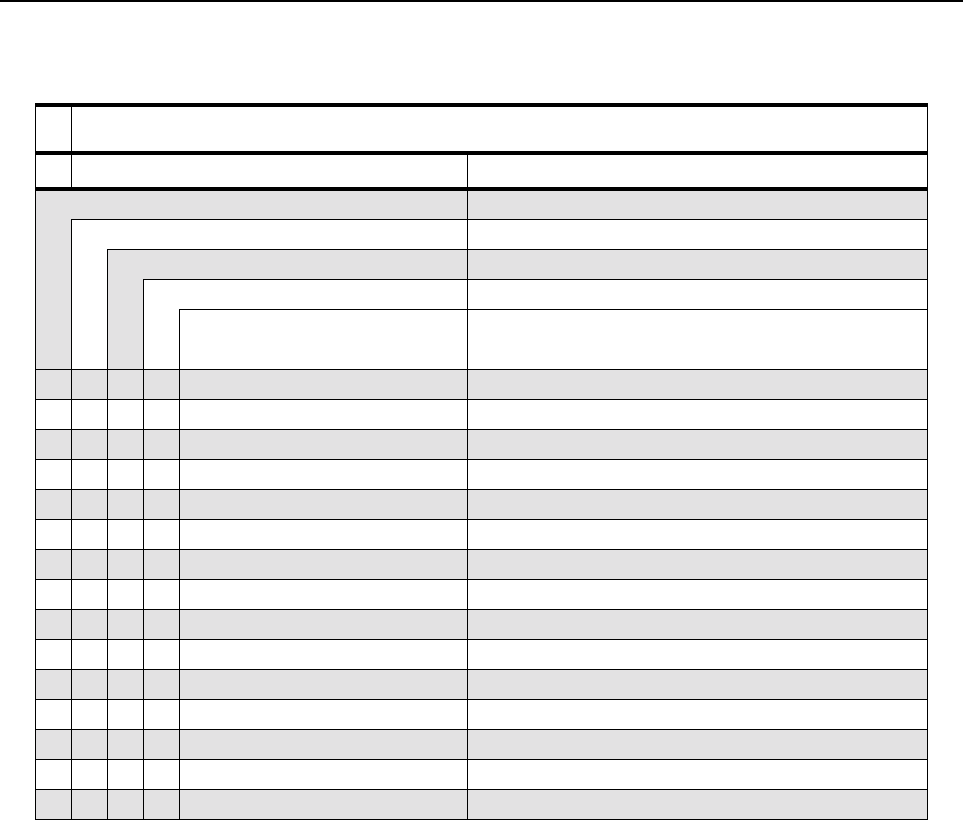

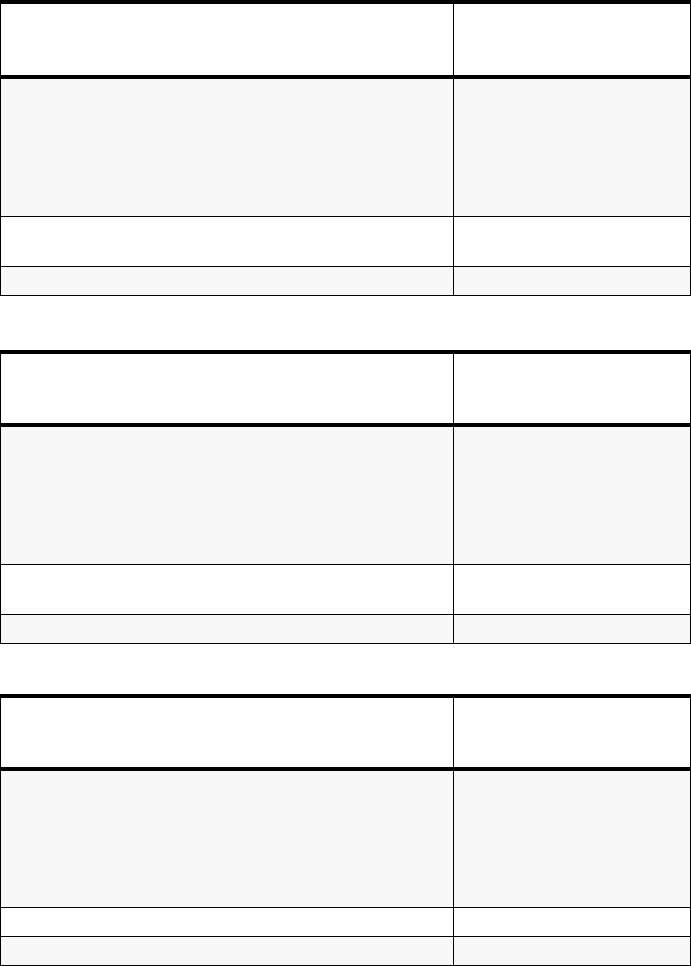

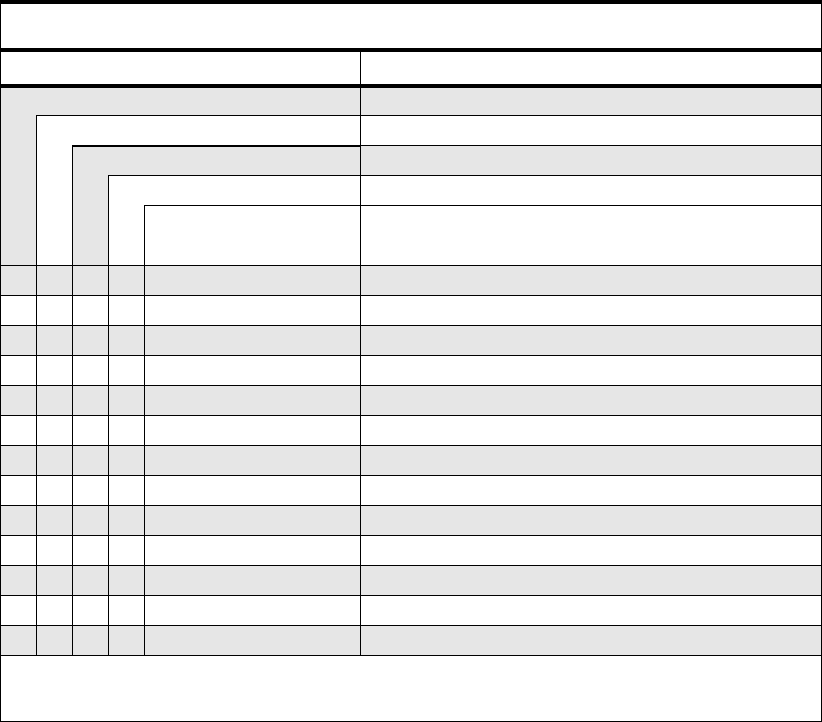

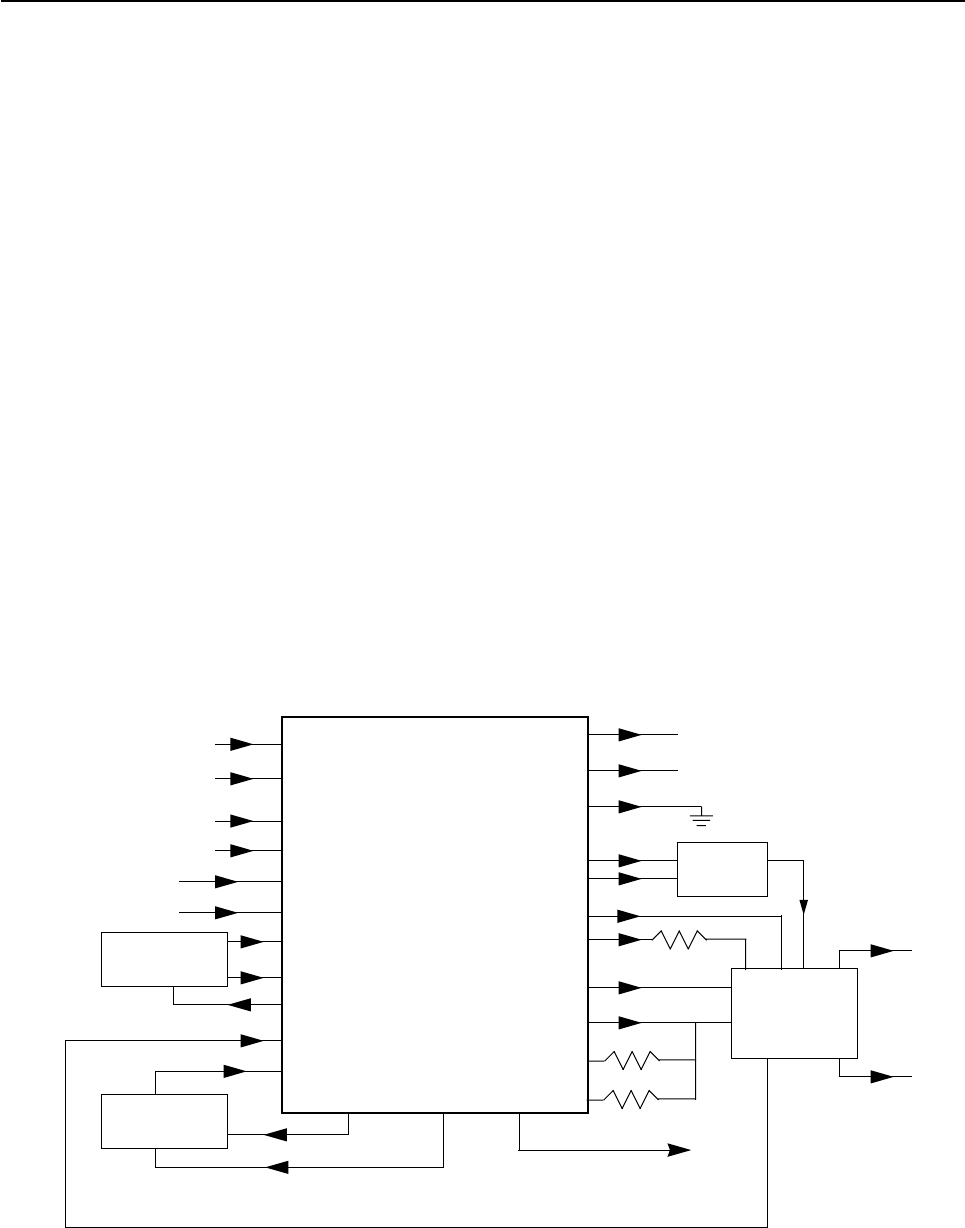

Table 1-1 Radio Model Number (Example: MDM25KHC9AN1AE)

Type of

Unit

Model

Series

Freq.

Band

Power

Level

Physical

Packages

Channel

Spacing Protocol Feature

Level

Model

Revision

Model

Package

MD M 25 K

VHF

(136-

174MHz)

H

1-25W

C

GM140,

GM340,

GM640

9

Program-

mable

AN

Conventional

5 Tone

1

GM140

GM340

GM640

AE

R

UHF 1

(403-

470MHz)

K

25-40W

40-60W

N

GM380,

GM1280

AA

Conventional

MDC

O

Databox

(5Tone)

S

UHF 2

(450-

527MHz)

F

GM160

GM360

GM660

CK

MPT

5

GM160

GM360

GM660

B

LB1

29-36MHz

A

Databox

8

GM380

GM1280

C

LB2

36-42MHz

7

Databox

(MPT)

D

LB3

42-50MHz

MD = Motorola Internal Use

M = Mobile

Chapter 2

MAINTENANCE

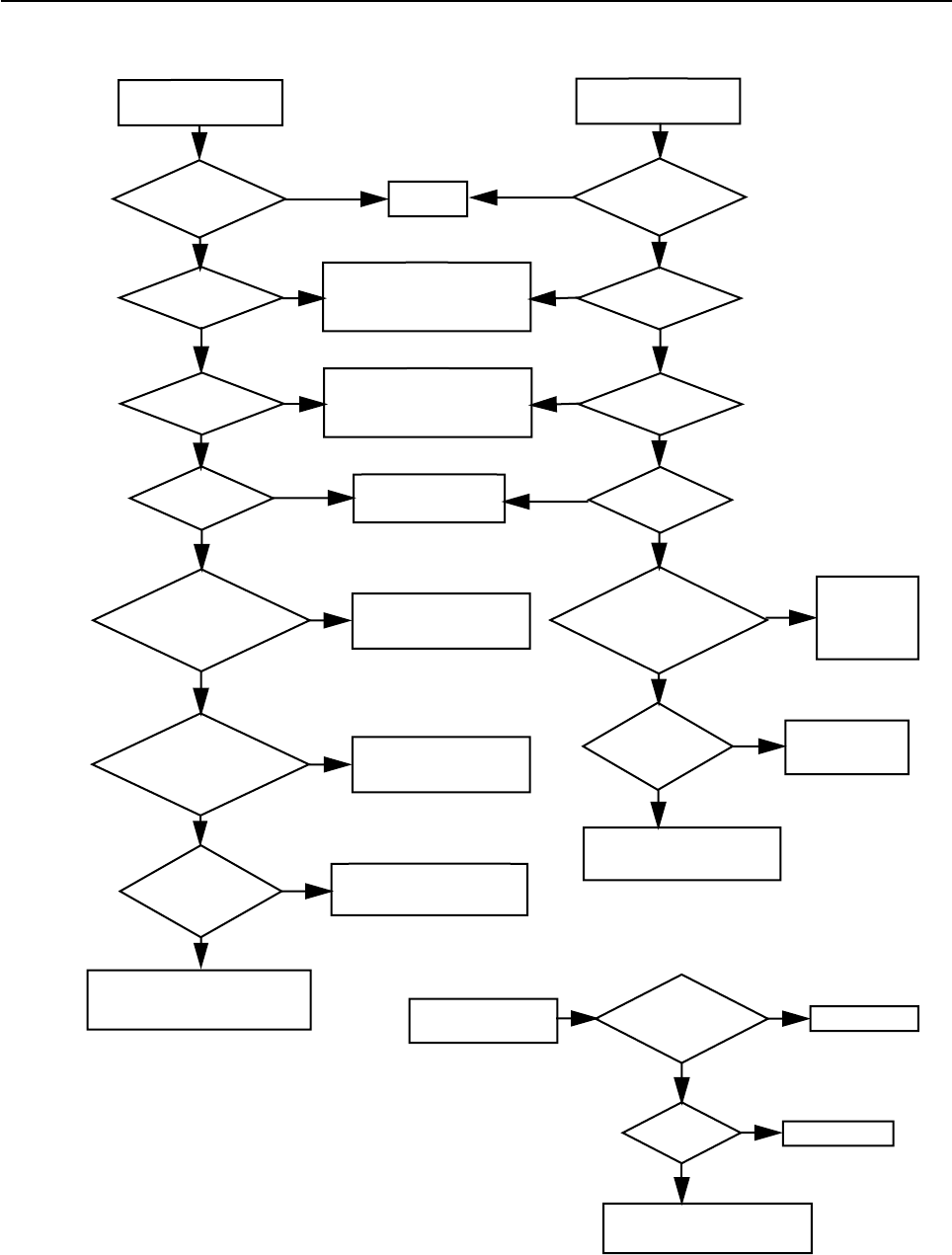

1.0 Introduction

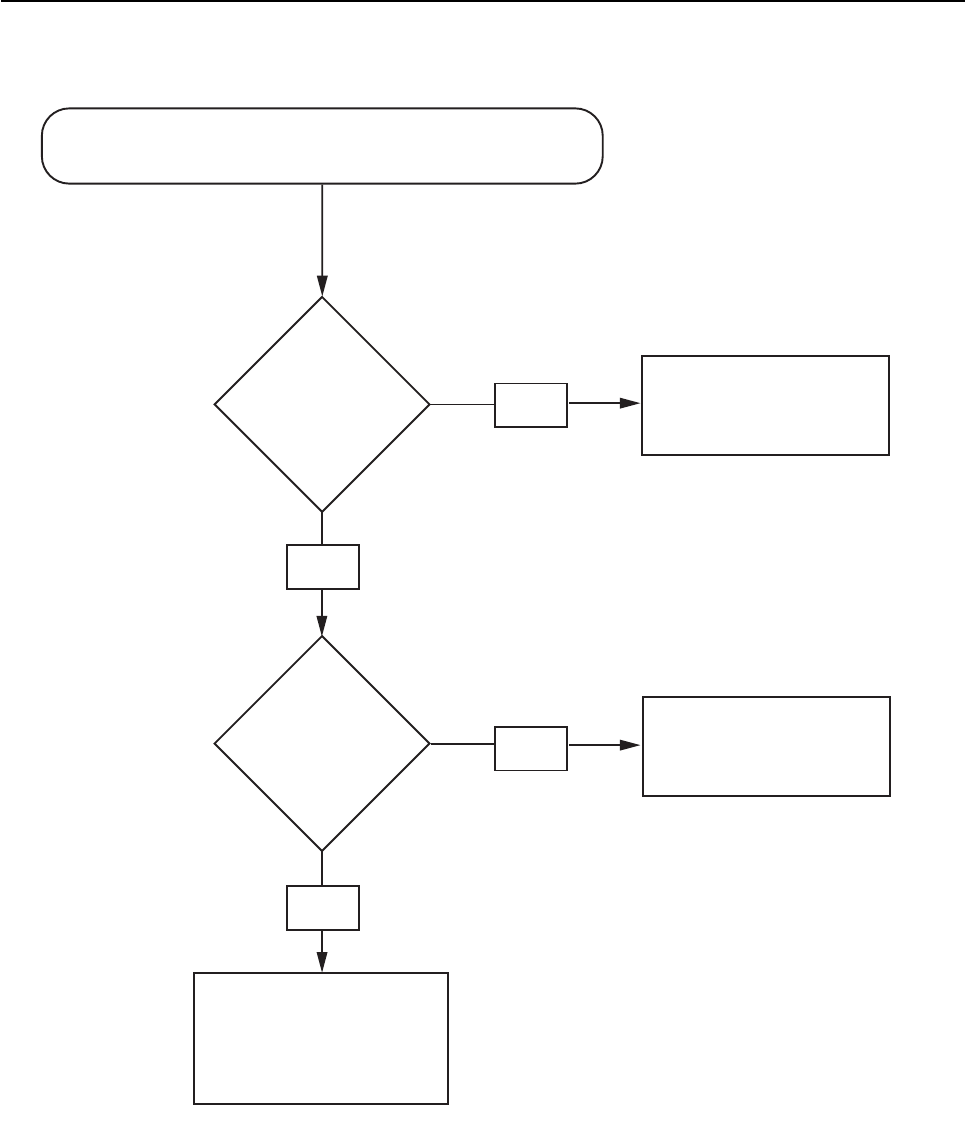

This chapter of the manual describes:

■■ preventive maintenance

■■ safe handling of CMOS devices

■■ repair procedures and techniques

2.0 Preventive Maintenance

The radios do not require a scheduled preventive maintenance program; however, periodic visual

inspection and cleaning is recommended.

2.1 Inspection

Check that the external surfaces of the radio are clean, and that all external controls and switches

are functional. It is not recommended to inspect the interior electronic circuitry.

2.2 Cleaning

The following procedures describe the recommended cleaning agents and the methods to be

used when cleaning the external and internal surfaces of the radio. External surfaces include the

front cover, housing assembly, and battery case. These surfaces should be cleaned whenever a

periodic visual inspection reveals the presence of smudges, grease, and/or grime.

The only recommended agent for cleaning the external radio surfaces is a 0.5% solution of a mild

dishwashing detergent in water. The only factory recommended liquid for cleaning the printed

circuit boards and their components is isopropyl alcohol (70% by volume).

1. Cleaning External Plastic Surfaces

The detergent-water solution should be applied sparingly with a stiff, non-metallic, short-

bristled brush to work all loose dirt away from the radio. A soft, absorbent, lintless cloth or

tissue should be used to remove the solution and dry the radio. Make sure that no water

remains entrapped near the connectors, cracks, or crevices.

2. Cleaning Internal Circuit Boards and Components

Isopropyl alcohol may be applied with a stiff, non-metallic, short-bristled brush to dislodge

embedded or caked materials located in hard-to-reach areas. The brush stroke should

direct the dislodged material out and away from the inside of the radio. Make sure that

controls or tunable components are not soaked with alcohol. Do not use high-pressure

air to hasten the drying process since this could cause the liquid to collect in unwanted

places. Upon completion of the cleaning process, use a soft, absorbent, lintless cloth to

dry the area. Do not brush or apply any isopropyl alcohol to the frame, front or back cover.

NOTE Internal surfaces should be cleaned only when the radio is disassembled for servicing or

repair.

CAUTION: The effects of certain chemicals and their vapors can have harmful results on

certain plastics. Aerosol sprays, tuner cleaners, and other chemicals should be avoided.

!

2-2 MAINTENANCE

3.0 Safe Handling of CMOS and LDMOS

Complementary metal-oxide semiconductor (CMOS) devices are used in this family of radios.

CMOS characteristics make them susceptible to damage by electrostatic or high voltage charges.

Damage can be latent, resulting in failures occurring weeks or months later. Therefore, special

precautions must be taken to prevent device damage during disassembly, troubleshooting, and

repair.

Handling precautions are mandatory for CMOS circuits and are especially important in low

humidity conditions. DO NOT attempt to disassemble the radio without first referring to the CMOS

CAUTION paragraph in the Disassembly and Reassembly section of the manual.

4.0 General Repair Procedures and Techniques

Parts Replacement and Substitution

When damaged parts are replaced, identical parts should be used. If the identical replacement

component is not locally available, check the parts list for the proper Motorola part number and

order the component from the nearest Motorola Communications parts center listed in the “Piece

Parts” section of this manual.

Rigid Circuit Boards

The family of radios uses bonded, multi-layer, printed circuit boards. Since the inner layers are not

accessible, some special considerations are required when soldering and unsoldering

components. The through-plated holes may interconnect multiple layers of the printed circuit.

Therefore, care should be exercised to avoid pulling the plated circuit out of the hole.

When soldering near the 18-pin and 40-pin connectors:

■■ avoid accidentally getting solder in the connector.

■■ be careful not to form solder bridges between the connector pins

■■ closely examine your work for shorts due to solder bridges.

NOTE Always use a fresh supply of alcohol and a clean container to prevent contamination by

dissolved material (from previous usage).

General Repair Procedures and Techniques 2-3

Chip Components

Use either the RLN4062 Hot-Air Repair Station or the Motorola 0180381B45 Repair Station for

chip component replacement. When using the 0180381B45 Repair Station, select the TJ-65 mini-

thermojet hand piece. On either unit, adjust the temperature control to 370 °C (700 °F), and

adjust the airflow to a minimum setting. Airflow can vary due to component density.

■

■To remove a chip component:

1. Use a hot-air hand piece and position the nozzle of the hand piece approximately 0.3 cm

(1/8") above the component to be removed.

2. Begin applying the hot air. Once the solder reflows, remove the component using a pair

of tweezers.

3. Using a solder wick and a soldering iron or a power desoldering station, remove the

excess solder from the pads.

■

■To replace a chip component using a soldering iron:

1. Select the appropriate micro-tipped soldering iron and apply fresh solder to one of the

solder pads.

2. Using a pair of tweezers, position the new chip component in place while heating the

fresh solder.

3. Once solder wicks onto the new component, remove the heat from the solder.

4. Heat the remaining pad with the soldering iron and apply solder until it wicks to the

component. If necessary, touch up the first side. All solder joints should be smooth and

shiny.

■

■To replace a chip component using hot air:

1. Use the hot-air hand piece and reflow the solder on the solder pads to smooth it.

2. Apply a drop of solder paste flux to each pad.

3. Using a pair of tweezers, position the new component in place.

4. Position the hot-air hand piece approximately 0.3 cm (1/8” ) above the component and

begin applying heat.

5. Once the solder wicks to the component, remove the heat and inspect the repair. All

joints should be smooth and shiny.

2-4 MAINTENANCE

Shields

Removing and replacing shields will be done with the R1070 station with the temperature control

set to approximately 215°C (415°F) [230°C (445°F) maximum].

■

■To remove the shield:

1. Place the circuit board in the R1070 circuit board holder.

2. Select the proper heat focus head and attach it to the heater chimney.

3. Add solder paste flux around the base of the shield.

4. Position the shield under the heat-focus head.

5. Lower the vacuum tip and attach it to the shield by turning on the vacuum pump.

6. Lower the focus head until it is approximately 0.3 cm (1/8”) above the shield.

7. Turn on the heater and wait until the shield lifts off the circuit board.

8. Once the shield is off, turn off the heat, grab the part with a pair of tweezers, and turn off

the vacuum pump.

9. Remove the circuit board from the R1070 circuit board holder.

■

■To replace the shield:

1. Add solder to the shield if necessary, using a micro-tipped soldering iron.

2. Next, rub the soldering iron tip along the edge of the shield to smooth out any excess

solder. Use solder wick and a soldering iron to remove excess solder from the solder

pads on the circuit board.

3. Place the circuit board back in the R1070 circuit board holder.

4. Place the shield on the circuit board using a pair of tweezers.

5. Position the heat-focus head over the shield and lower it to approximately 0.3 cm (1/8”)

above the shield.

6. Turn on the heater and wait for the solder to reflow.

7. Once complete, turn off the heat, raise the heat-focus head and wait approximately one

minute for the part to cool.

8. Remove the circuit board and inspect the repair. No cleaning should be necessary.

Notes For All Schematics and Circuit Boards 2-5

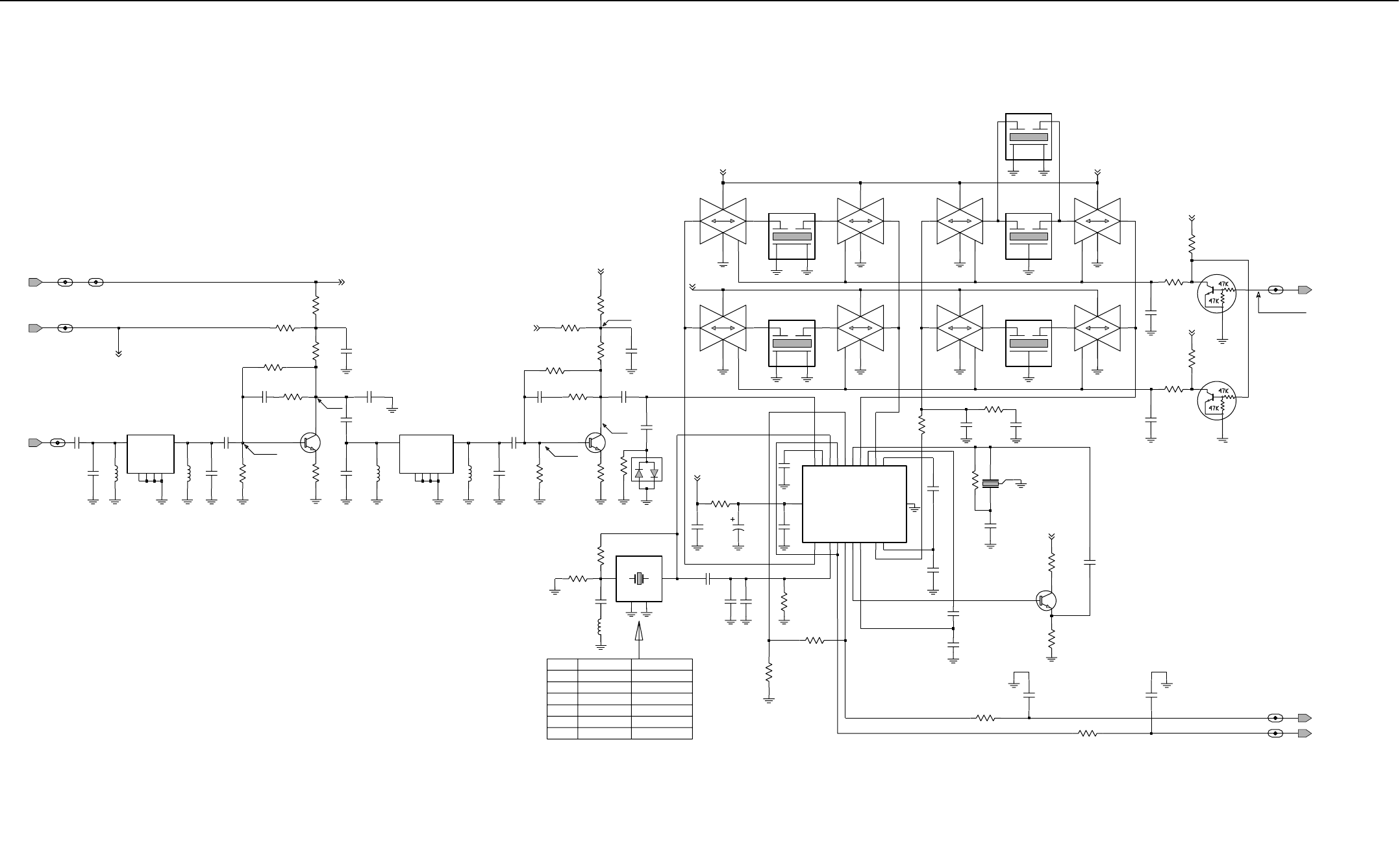

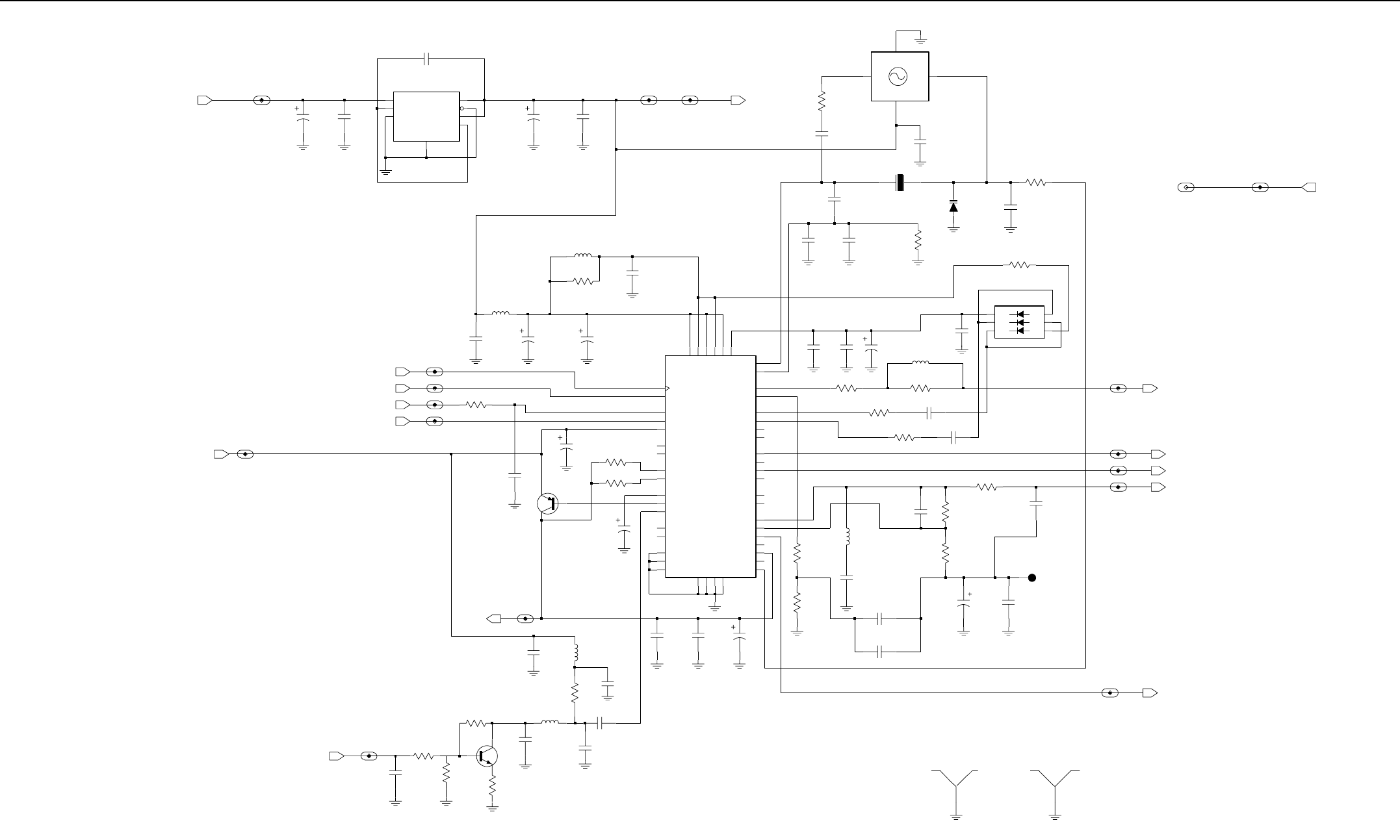

5.0 Notes For All Schematics and Circuit Boards

* Component is frequency sensitive. Refer to the Electrical Parts List for value and usage.

1. Unless otherwise stated, resistances are in Ohms (k = 1000), and capacitances are in picofarads

(pF) or microfarads (µF).

2. DC voltages are measured from point indicated to chassis ground using a Motorola DC

multimeter or equivalent. Transmitter measurements should be made with a 1.2 µH choke in

series with the voltage probe to prevent circuit loading.

3. Interconnect Tie Point Legend:

16_8MHz 16.8MHz Reference Frequency

3V3 Regulated 3.3V Supply Voltage for Voice Storage

5V Regulated 5V Supply Voltage for RF Circuitry

5V Regulated 5V Supply Voltage (Control Head)

5V RF Regulated 5V Supply Voltage for RF Circuitry

5V SOURCE 5V Signal to Switch On Control Head

5VD Regulated 5V Supply Voltage for Digital Circuitry

9V3 Regulated 9.3V Supply Voltage

9V3FLT Filtered 9.3V Supply Voltage

A+ 13.2V Supply Voltage

ADDR *P Address Lines

AN Analog Lines to Analog to Digital Converter

ANALOG INPUT 2 External Keypad Matrix Column Signal

ANALOG INPUT 3 External Keypad Matrix Row Signal

BATTERY VOLTAGE Battery Voltage Sense Line

BL A GREEN Back Light Anode Green

BL A RED Back Light Anode Red

BL GREEN Green Back Light Control

BL K GREEN Back Light Cathode Green

BL K RED Back Light Cathode Red

BL KP Green Green Keypad Back Light Control

BL KP RED Red Keypad Back Light Control

BL LCD GREEN Green Display Back Light Control

BL LCD RED Red Display Back Light Control

BL RED Red Back Light Control

BOOT CNTRL Bootstrap Mode Enable Signal

BOOT MODE Boot Mode Select

BOOT PWR ON Control Head Switch On Signal

BOOT SCI RX Serial Communication Interface Receive Line

BOOT SCI TX Serial Communication Interface Transmit Line

BOOT VPP Boot Mode Select

BUS+ Bi-directional Serial Communication Line

BWSELECT Signal to select between the Ceramic Filter Pairs

2-6 MAINTENANCE

CH ACT Channel Activity Indicator Signal (Fast Squelch)

CH KP ID Control Head Keypad ID (Data) Lines

CH REQUEST Control Head Request from Control Head *P

CLK Clock Signal

CNTLVLTG PA Power Control Voltage

CNTR AUDIO Audio Lines of the Controller

COL x Keypad Matrix Column x

CSX Chip Select Line PCIC / FRACN

DATA Data Signal

DC POWER ON Electronic Switching On or Off of the Radio's Voltage Regulators

DISCAUDIO Audio Output Signal from the Receiver IC

ECLK Clock (not used)

EE CS EEPROM Chip Select

EMERGENCY CONTROL Emergency Line to switch on the Radio's Voltage Regulators

EXP BD REQ Service Request Line from Expansion Board

EXP1 CS Expansion Board Chip Select 1

EXP2 CS Expansion Board Chip Select 2

EXT KP COL External Keypad Matrix Column Signal

EXT KP ROW External Keypad Matrix Row Signal

EXT MIC External (from Accessory Connector) Microphone Input

EXT SWB+ External Switched 13.2V Supply Voltage

F1200 Interrupt Line from ASFIC CMP

FECTRL 1 Control Voltage for Front End Filter

FECTRL 2 Control Voltage for Front End Attenuator Switch

FLASH CE Flash Chip Select

FLASH OE Flash Output Enable

FLAT RX SND Option Board Audio Output Signal

FLAT TX RTN Flat TX Input from Option Board and Accessory Connector

FLT A+ Filtered 13.2 V Supply Voltage

GP x IN General Purpose Input x

GP x IN ACC y General Purpose Input x from Accessory Connector Pin y

GP x IN OUT ACC y General Purpose Input /Output x from Accessory Connector Pin

y

GP x OUT General Purpose Output x

GP x OUT ACC y General Purpose Input x from Accessory Connector Pin y

GPIO General Purpose Input Output Lines

HANDSET AUDIO Handset Audio Output

HOOK Hang-up Switch Input

HSIO High Speed Clock In / Data Out

IF First Intermediate Frequency Signal

IGNITION CONTROL Ignition Line to switch on the Radio's Voltage Regulators

Notes For All Schematics and Circuit Boards 2-7

IN 5V RF REG Supply Voltage for 5V Regulator in RF Section

INT KP COL Internal Keypad Matrix Column Signal

INT KP ROW Internal Keypad Matrix Row Signal

INT MIC Internal (from Control Head) Microphone Input

INT SWB Internal Switched 13.2V Supply Voltage

INT SWB+ Internal Switched 13.2V Supply Voltage

IRQ Interrupt Request from Control Head

K9V1 9.1V in Transmit Mode

KEYPAD ID Keypad Identification Line

LCD A0 LCD Control / Display Data Select

LCD CS LCD Chip Select

LCD DATA LCD Data Lines

LCD E RD LCD Enable Read

LCD RW WR LCD Read Write Control

LED CNTRL LED Control Lines

LED GREEN Green LED Control

LED RED Red LED Control

LED YELLOW Yellow LED Control

LOCK Lock Detect Signal from Synthesizer

LSIO Low Speed Clock In / Data Out

LVZIF CS LVZIF Chip Select (not used)

MIC Microphone Input

MISO Serial Peripheral Interface Receive Line

MODIN Modulation Signal into the Synthesizer

MOSBIAS 2 PA Bias Voltage for second Stage

MOSBIAS 3 PA Bias Voltage for third Stage

NOISE BLNKR Noise Blanker Enable (Low Band only)

ON OFF CONTROL Service Request Line from Control Head / Manual Switching On

of the Radio's Voltage Regulators

ON OFF SENSE (Control Head)On Off Sense Line to Control Head *P

ON OFF SENSE (Controller) Service Request Line from Control Head

OPT CS Option Board Chip Select

OPT PTT PTT from Option Board

PA PWR SET ASFIC Output Voltage to set the Transmitter Power

PA SWB Switches Supply Voltage for PA Current Control Circuitry

PASUPVLTG 13.2 V Supply Voltage of the Transmitter PA

PCIC MOSBIAS 1 PA Bias Voltage for first Stage

PRESC Prescaler Signal from VCO to Synthesizer

PTT IRDEC Microphone PTT Input

PTT IRDECODER Microphone PTT Input

R W Read Write Signal for RAM / Flash

2-8 MAINTENANCE

RAM CS RAM Ship Select

RDY Service Request Line from Option Board

REF CS Reference Chip Select (not used)

RESET Reset Line

ROW x Keypad Matrix Row x

RSSI Received Signal Strength Indicator

RX ADAPT Flat TX Path Disable during Transmitter Key-up

RX AUD RTN Option Board Input / Output of Receiver Audio Path

RX FLAT FILTERED AUDIO Flat or Filtered Audio to Accessory Connector

RXIN RF Signal from Antenna Switch into the Receiver

RXINJ RF Signal from the VCO into the Mixer

SCI RX Serial Communication Interface Receive Line

SCI TX Serial Communication Interface Transmit Line

SPI Serial Peripheral Interface Bus

SPKR- Negative Audio PA Speaker Output

SPKR+ Positive Audio PA Speaker Output

SQ DET Squelch Detect Signal

SYN *P Clock Signal

TEMP SENSE Temperature Sense Line for LCD

TEMPSENSE Temperature Sense Line from PA to *P

TRB TX/RX VCO Switch Signal

TX AUD RTN Option Board Output to Transmit Audio Path

TX AUD SND Microphone Audio to Option Board

TXINJ RF Signal from the VCO into the Transmitter PA

U DRIVER Supply Voltage for PA Driver

U PREDRIVER Supply Voltage for PA Pre-driver

UNSW 5V Permanent 5V Supply

URX SND Filtered Audio Signal to Option Board

VAG 2.5V Reference Voltage for Analog Circuitry

VCOBIAS 1 Switch Signal from Synthesizer

VCOBIAS 2 Switch Signal from Synthesizer

VCOMOD Modulation Signal into VCO

VCTRL VCO Frequency Control Voltage

VDDA Regulated 5V for Digital Circuitry in RF Section

VOLTAGE SENSE Voltage Sense Line from LCD

VOLUME Volume Pot Output

VOX Voice Operated Transmit Level

VPP Boot Mode Select

VS AUDIOSEL Switch Signal to Enable Option Board Audio Output Signal

VS GAINSEL Voice Storage Gain Select Line

VS INT Voice Storage Interrupt Line

Notes For All Schematics and Circuit Boards 2-9

VS MIC Voice Storage Audio Signal into Microphone Path

VS RAC Voice Storage Row Address Clock Signal

VSF Voltage Super Filtered (5V)

VSTBY 5V Supply for *P when the Radio is switched off

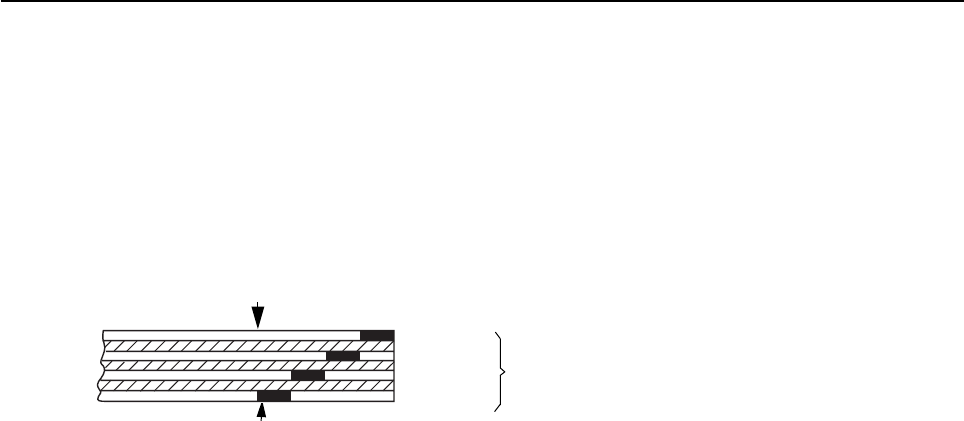

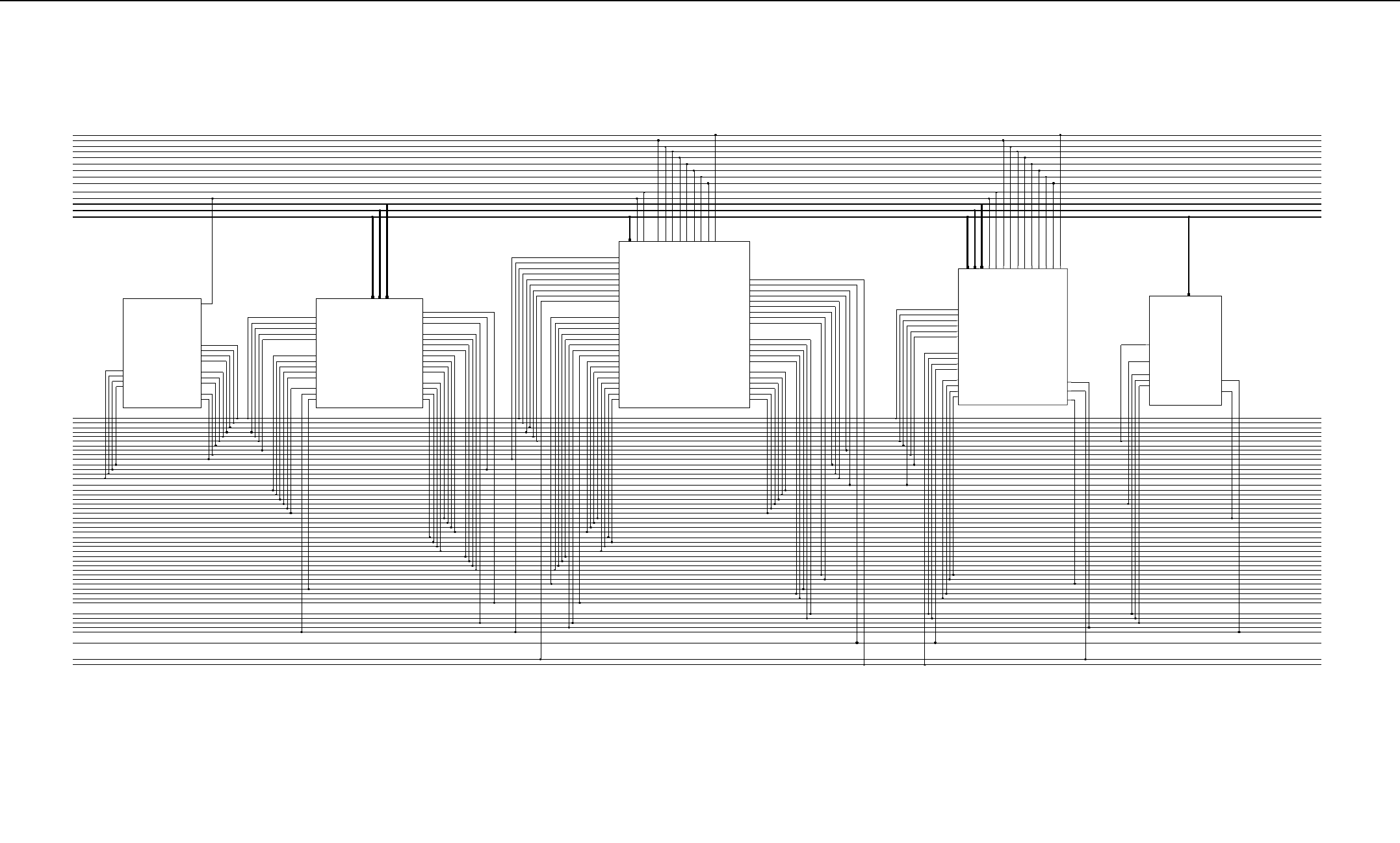

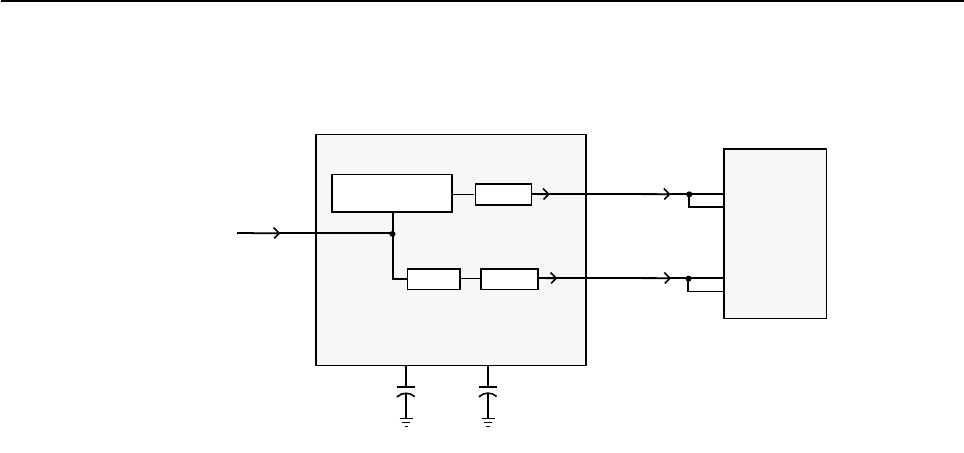

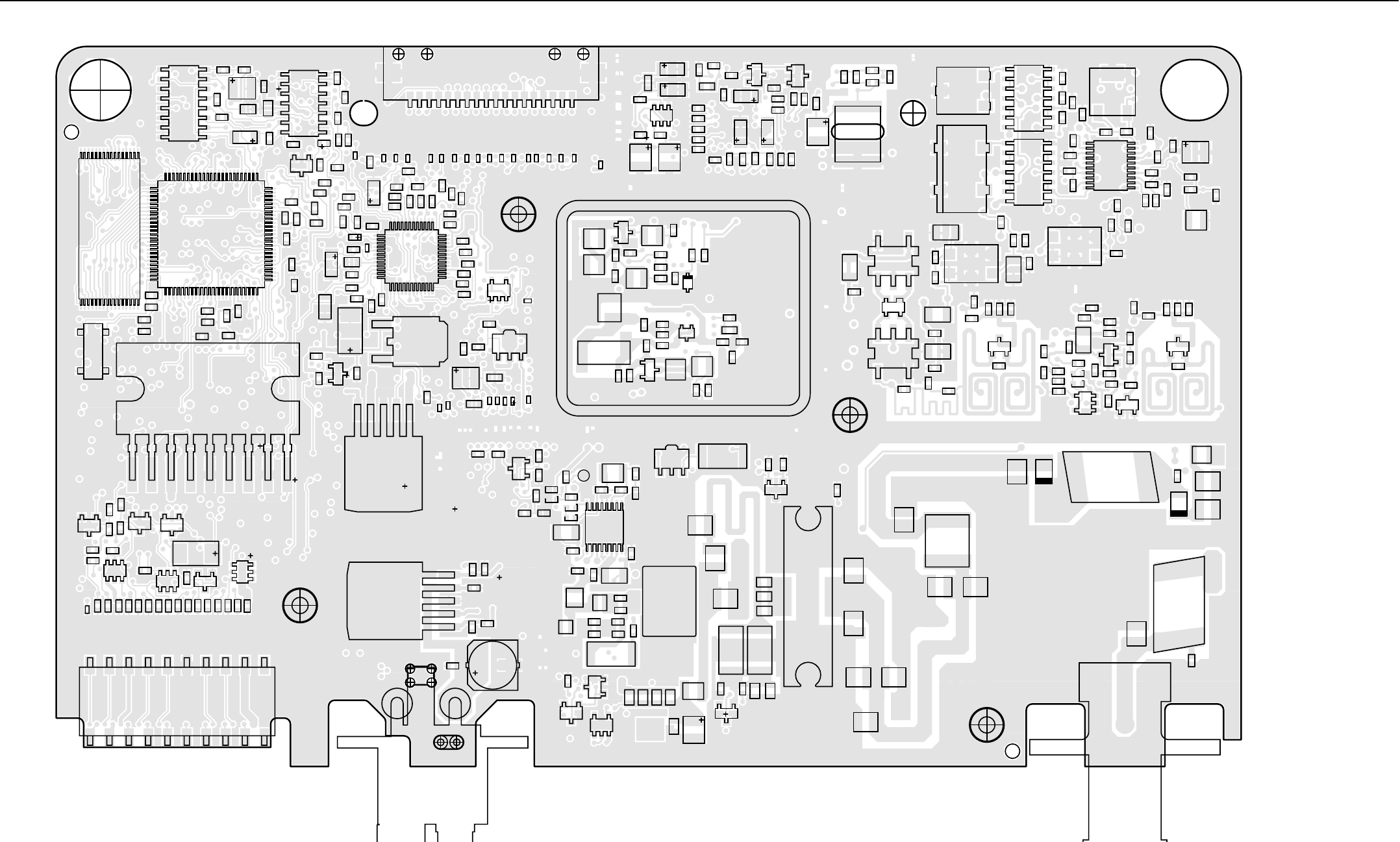

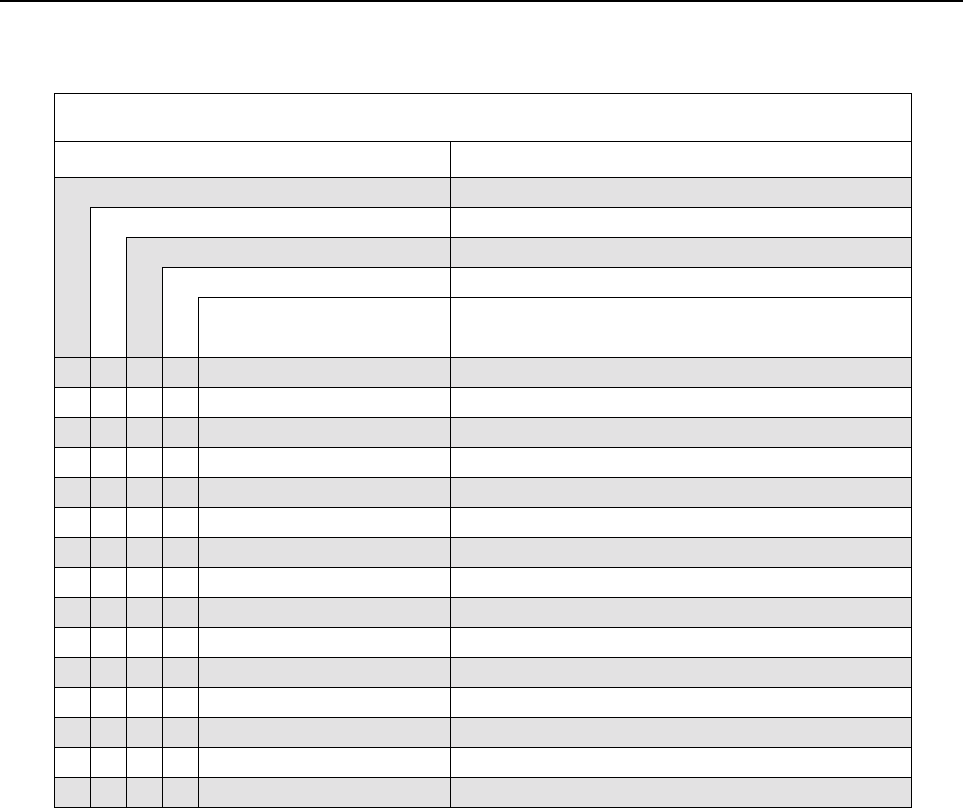

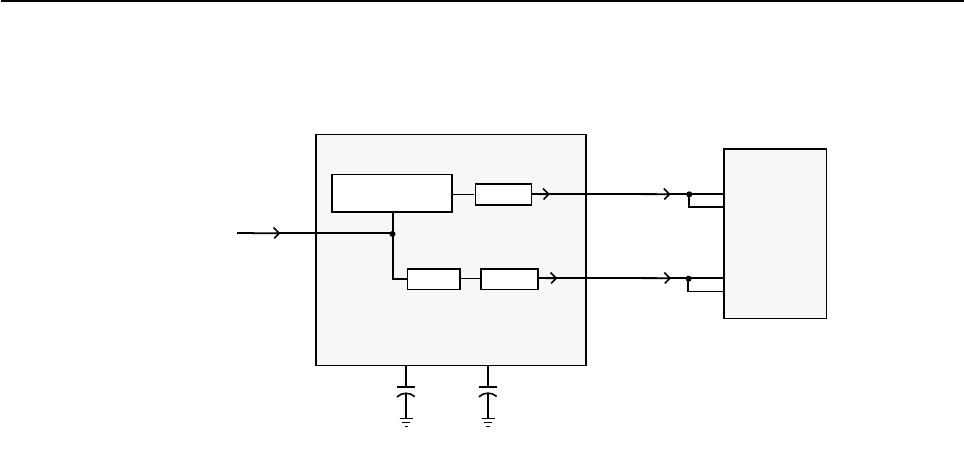

4-LAYER CIRCUIT BOARD DETAIL VIEWING

COPPER STEPS IN PROPER LAYER SEQUENCE

LAYER 1 (L1)

LAYER 2 (L2)

LAYER 3 (L3)

LAYER 4 (L4)

INNER LAYERS

SIDE 1

SIDE 2

2-10 MAINTENANCE

Chapter 3

SERVICE AIDS

1.0 Recommended Test Tools

Table 3-1 lists the service aids recommended for working on the radio. While all of these items are

available from Motorola, most are standard workshop equipment items, and any equivalent item

capable of the same performance may be substituted for the item listed.

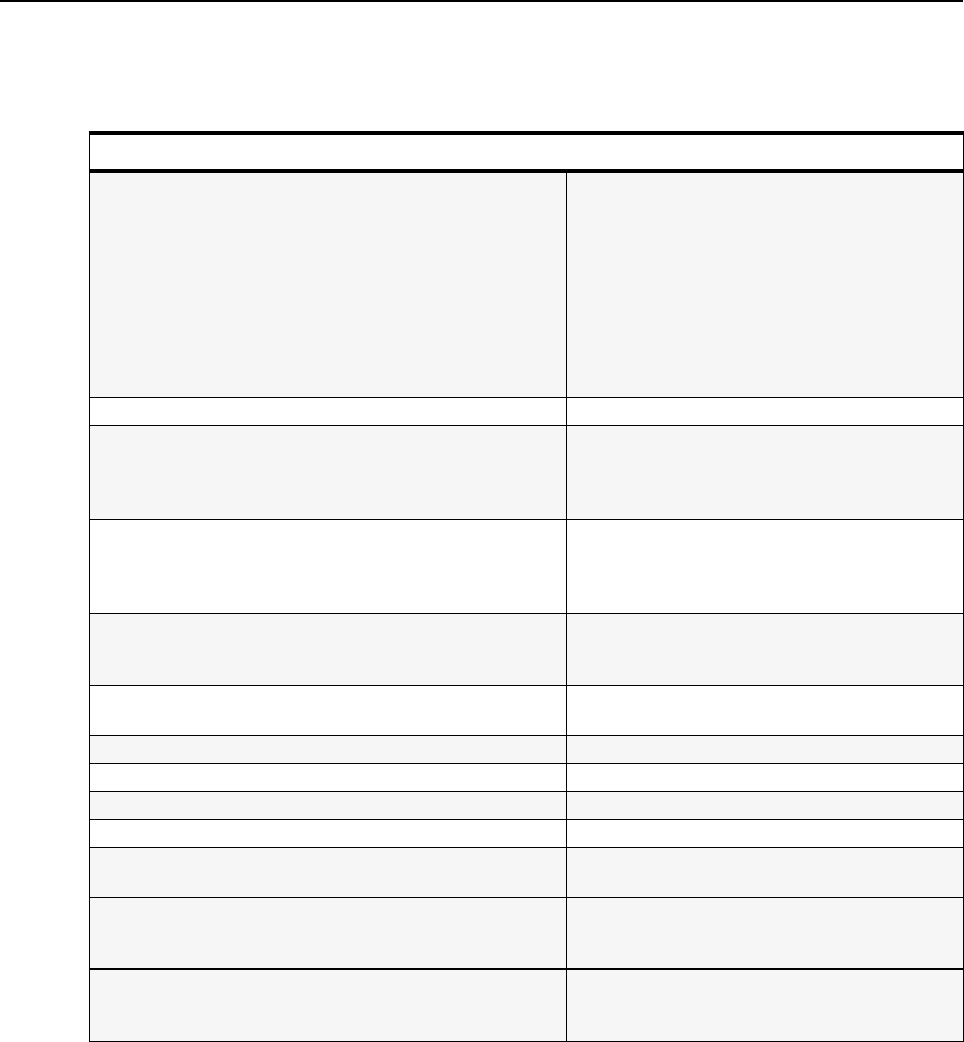

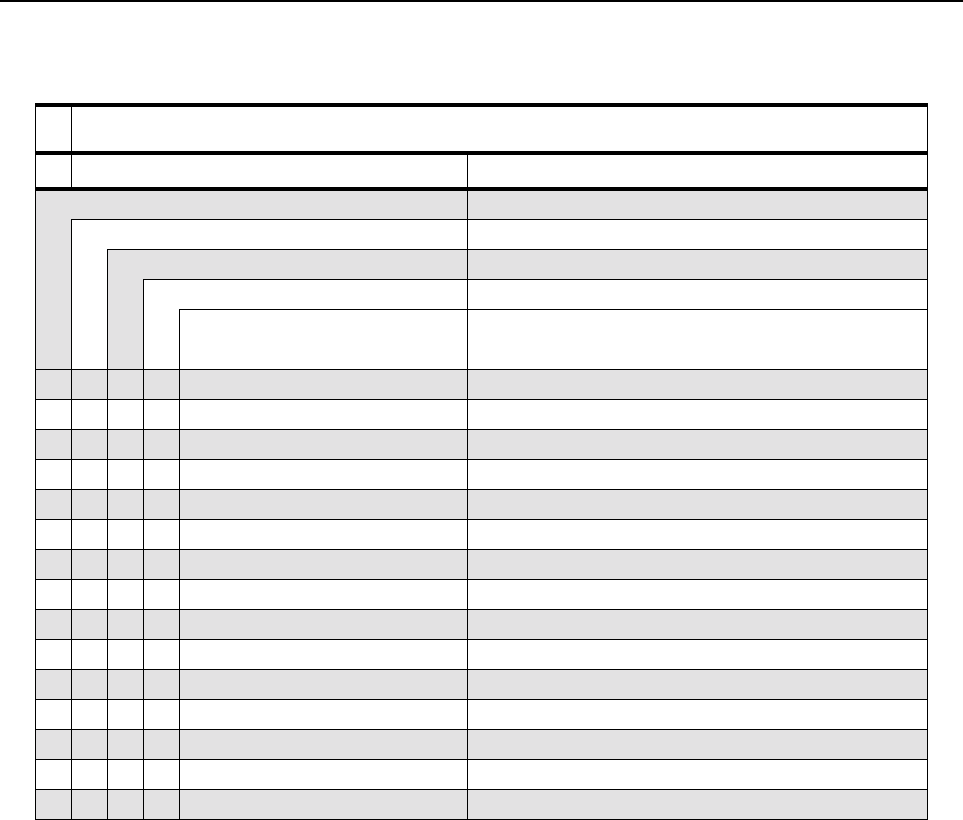

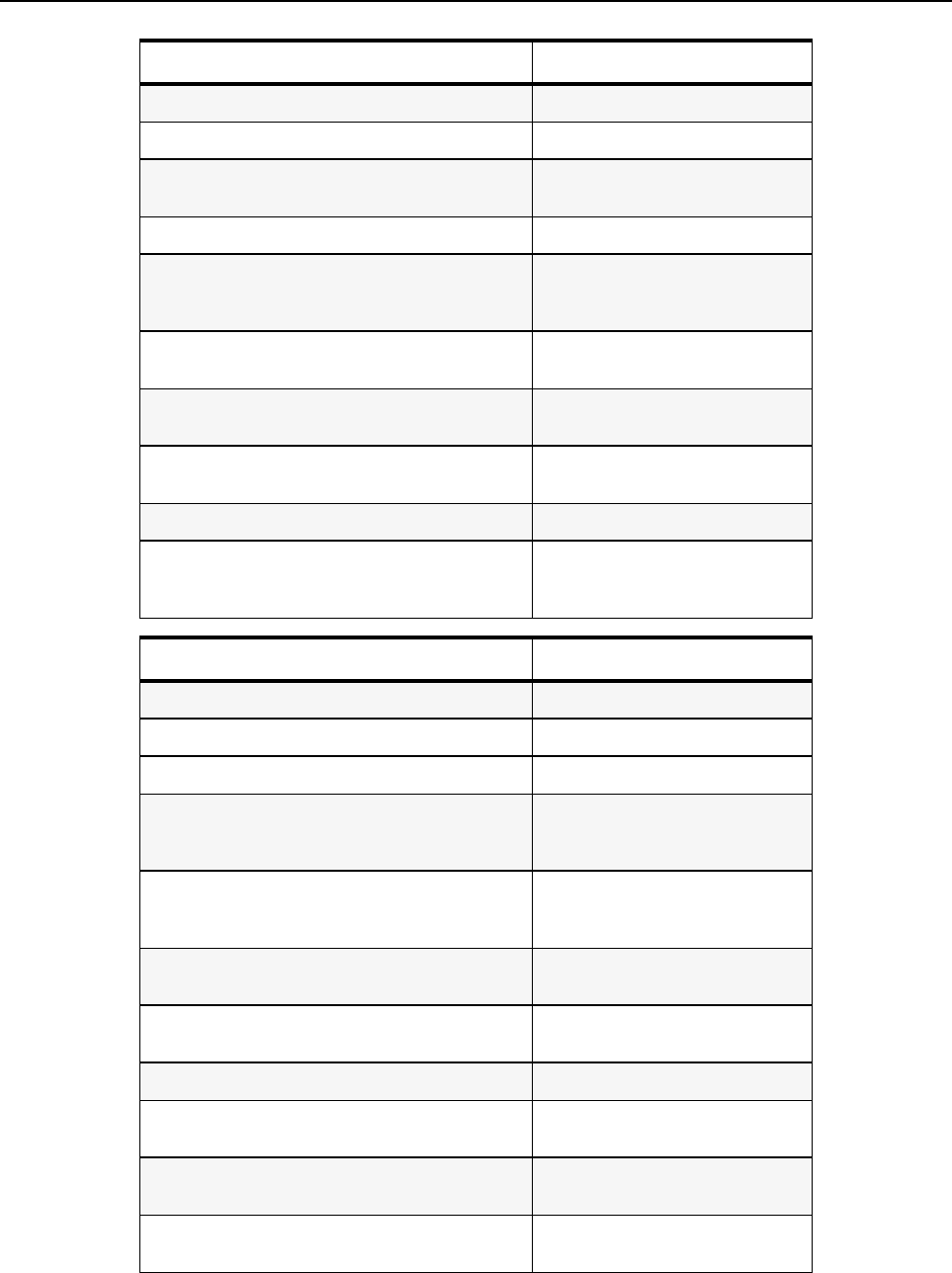

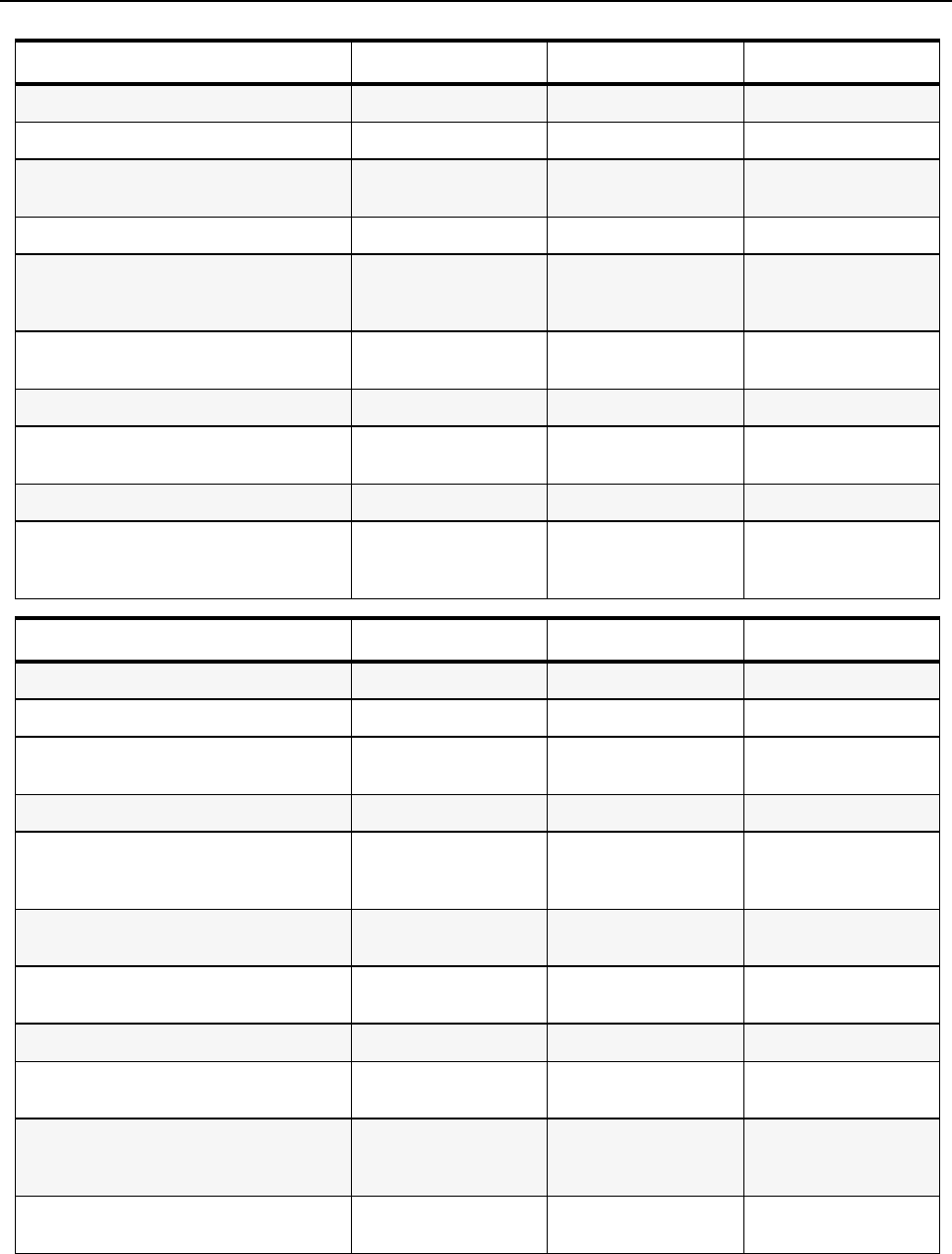

Table 3-1 Service Aids

Motorola Part

Number Description Application

RLN4460_ Portable Test Set Enables connection to audio/accessory jack.

Allows switching for radio testing.

RKN4081_ Programming Cable with

Internal RIB Includes radio interface box (RIB) capability.

RLN4853_ 10 to 20 Pin Adapter Connects RKN4081_ to the radio accessory

connector.

RKN4083_ Mobile Programming/Test

Cable Connects radio to RIB (RLN4008_).

GTF374_ Program Cable Connects RIB to Radio microphone input

RLN4008_ Radio Interface Box Enables communications between radio and

computer’s serial communications adapter.

HLN8027_ Mini UHF to BNC Adaptor Adapts radio antenna port to BNC cabling of

test equipment.

GPN6133_ Power Supply Provides the radio with power when bench

testing.

EPN4040_ Wall-Mounted Power Supply Used to supply power to the RIB (UK).

EPN4041_ Wall-Mounted Power Supply Used to supply power to the RIB (Euro)

8180384J59 Housing Eliminator (short) Test Fixture used to bench test the radio pcb

8180384L95 Housing Eliminator

(short + top) Test Fixture used to bench test the radio pcb.

(Radio using pressure pads to retain pcb)

8180384J60 Housing Eliminator

(medium) Test Fixture used to bench test the radio pcb

8180384J61 Housing Eliminator (long) Test Fixture used to bench test the radio pcb

3080369B71 Computer Interface Cable Connects the RIB to the Computer (25-pin)

3080369B72 Computer Interface Cable Connects the RIB to the Computer 9-pin

(Use for IBM PC AT - other IBM models use

the B71 cable above)

6686119B01 Removal Tool Assists in the removal of radio control head.

3-2 SERVICE AIDS

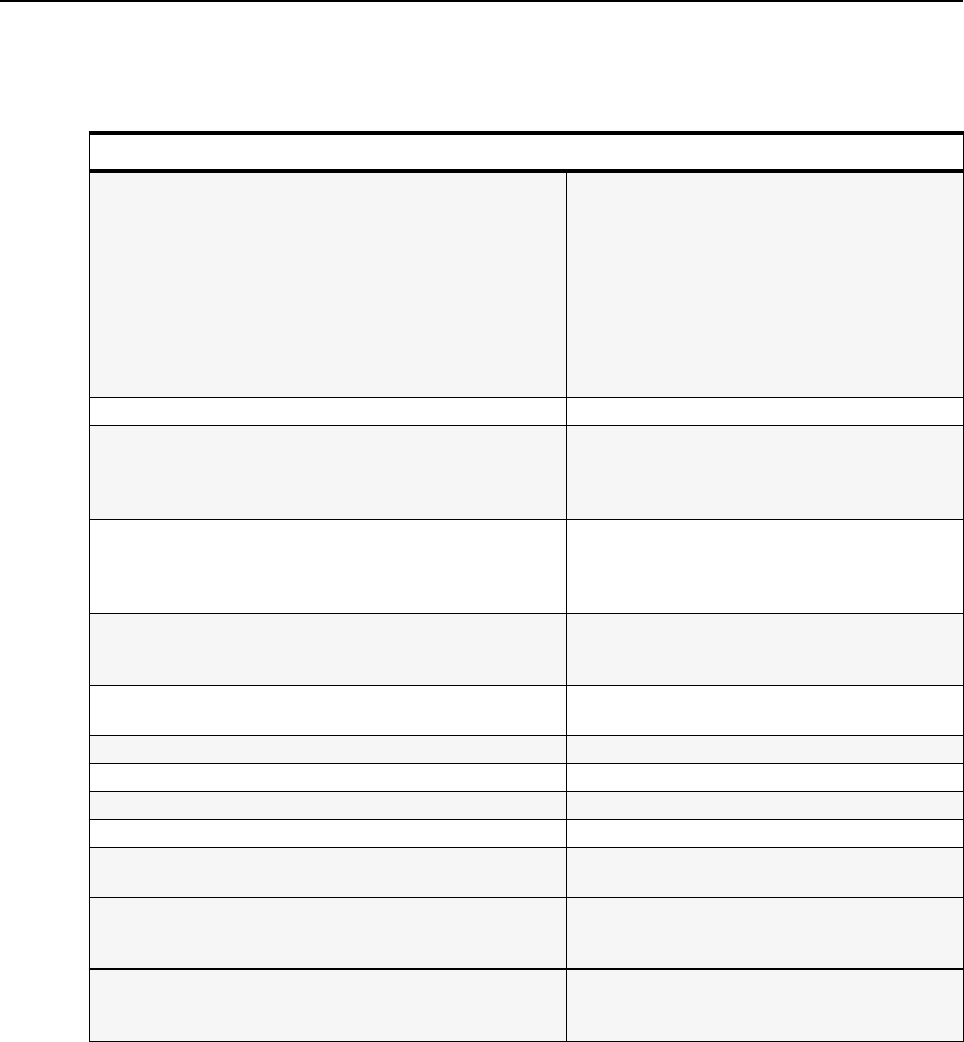

2.0 Test Equipment

Table 3-2 lists test equipment required to service the radio and other two-way radios.

Table 3-2 Recommended Test Equipment

Motorola Part

Number Description Characteristics Application

R2600_NT Comms System Analyzer

(non MPT) This monitor will

substitute for items

with an asterisk*

Frequency/deviation

meter and signal

generator for

widerange

troubleshooting and

alignment

R2680_NT Comms System Analyzer

( MPT1327) to be ordered

with

RLN1022_ (H/W)

RLN1023_ (S/W)

This monitor will

substitute for items

with an asterisk*.

Frequency/deviation

meter and signal

generator for

widerange

troubleshooting and

alignment

*R1072_ Digital Multimeter AC/DC voltage and

current

measurements

*R-1377_ AC Voltmeter 100µV to 300V, 5Hz -

1MHz, 10Megohm

input impedance

Audio voltage

measurements

WADN133 Delay Oscilloscope 2 Channel 40MHz

bandwidth,

5mV/cm - 20 V/cm

Waveform

measurements

R1440_

0180305F17

0180305F31

0180305F39

RLN4610

T1013_

Wattmeter,

Plug-in Elements

Plug-in Elements

Plug-in Elements

Carry case

RF Dummy Load

Thruline 50-Ohm,

±5% accuracy

100W, 25 - 60MHz

25W, 100-250MHz

10W, 200-250MHz

Wattmeter and

6 elements

Transmitter power

output

measurements

S1339_ RF Millivolt Meter 100mV to 3 VRF.

10kHz to 1.2GHz RF level

measurements

R1011_/220V 220V Power Supply 0 - 40V 0 - 40A Programmable

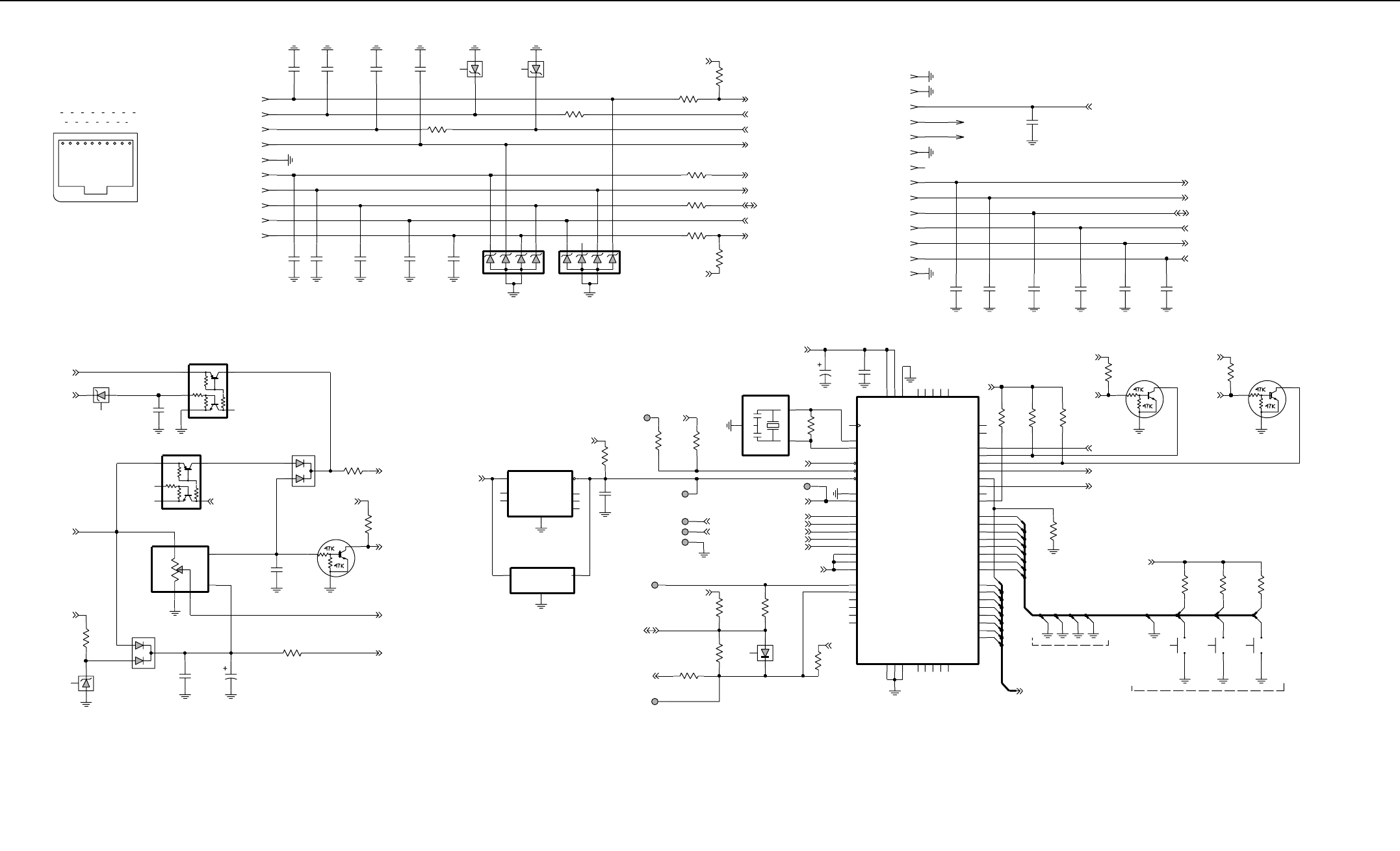

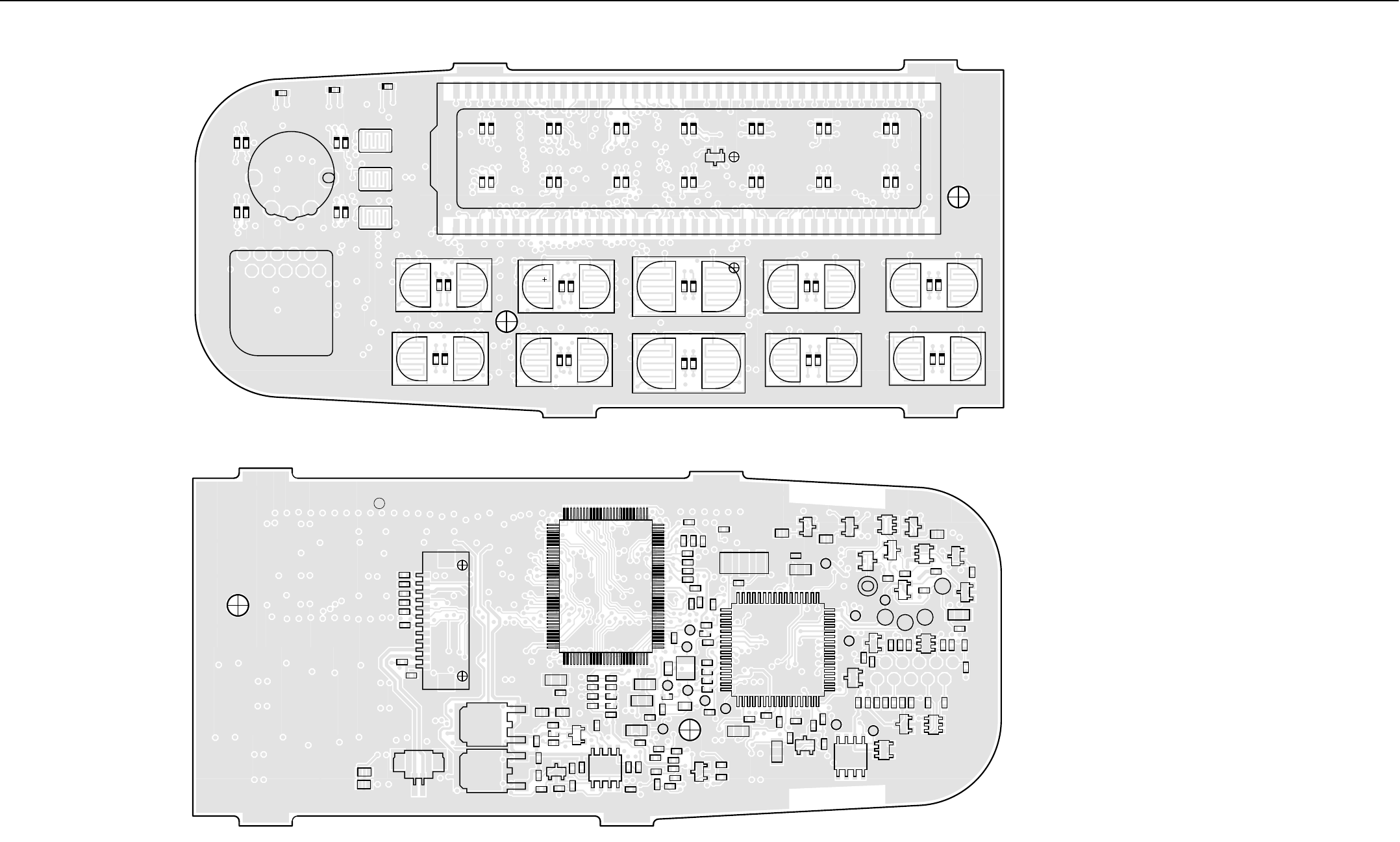

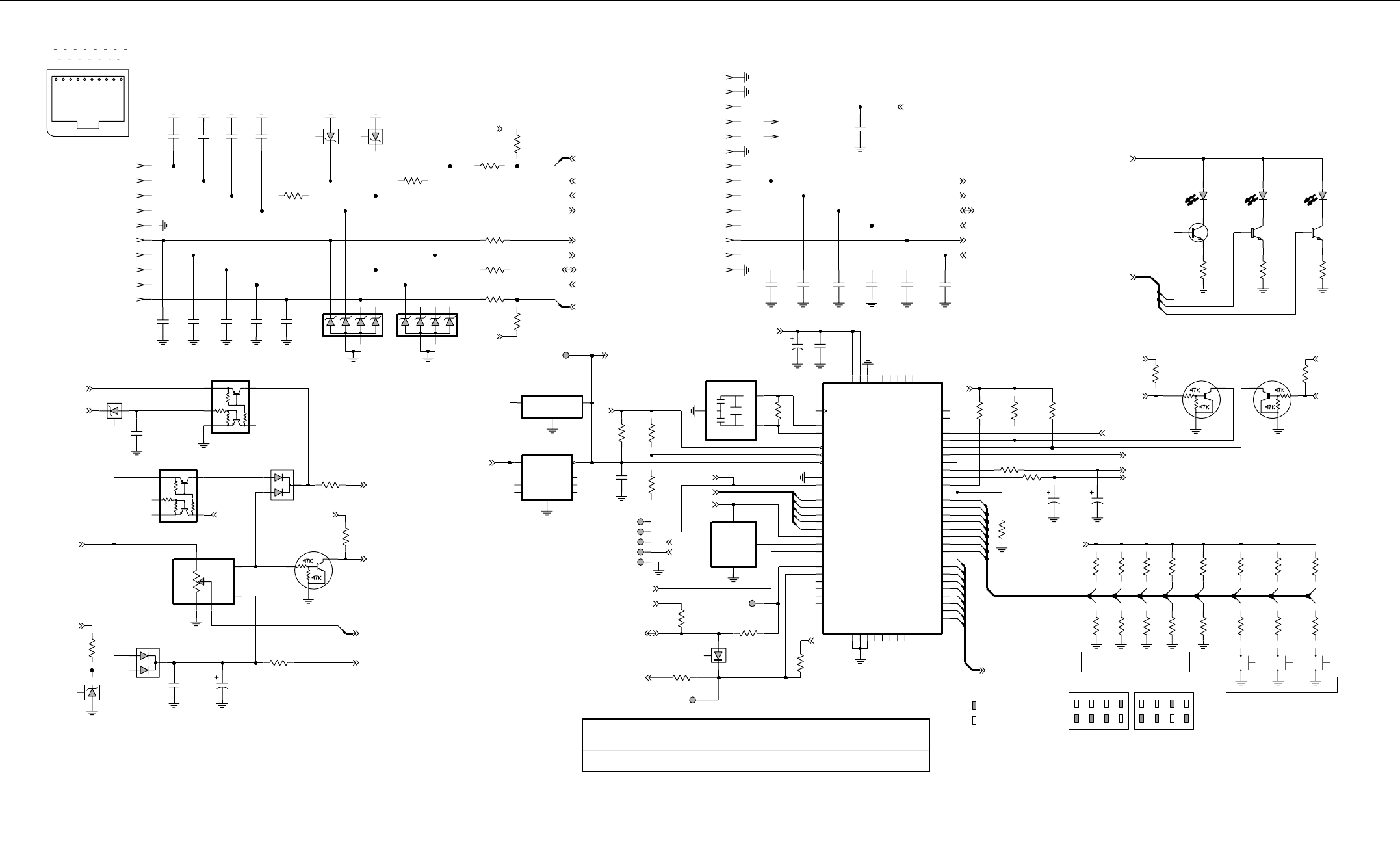

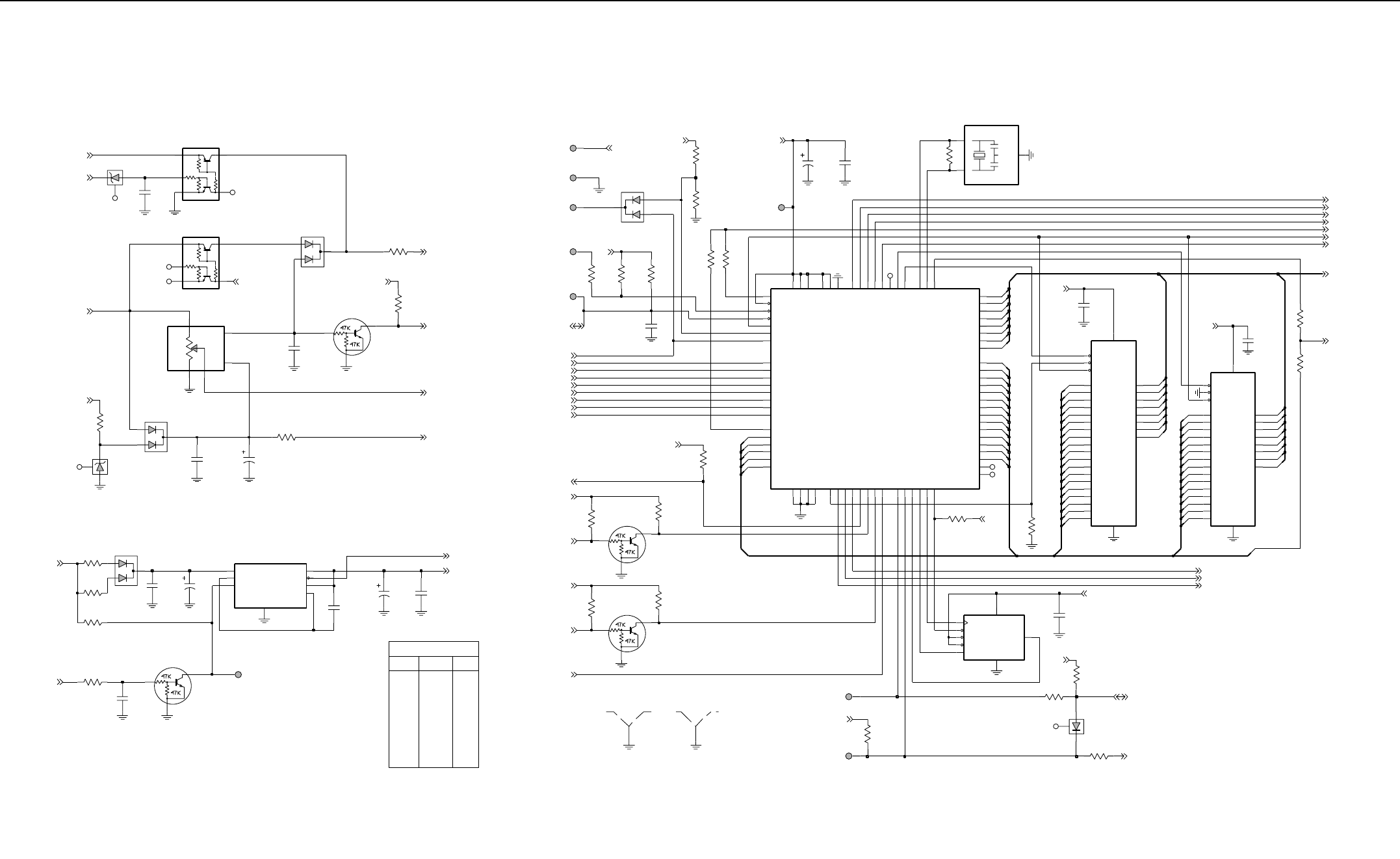

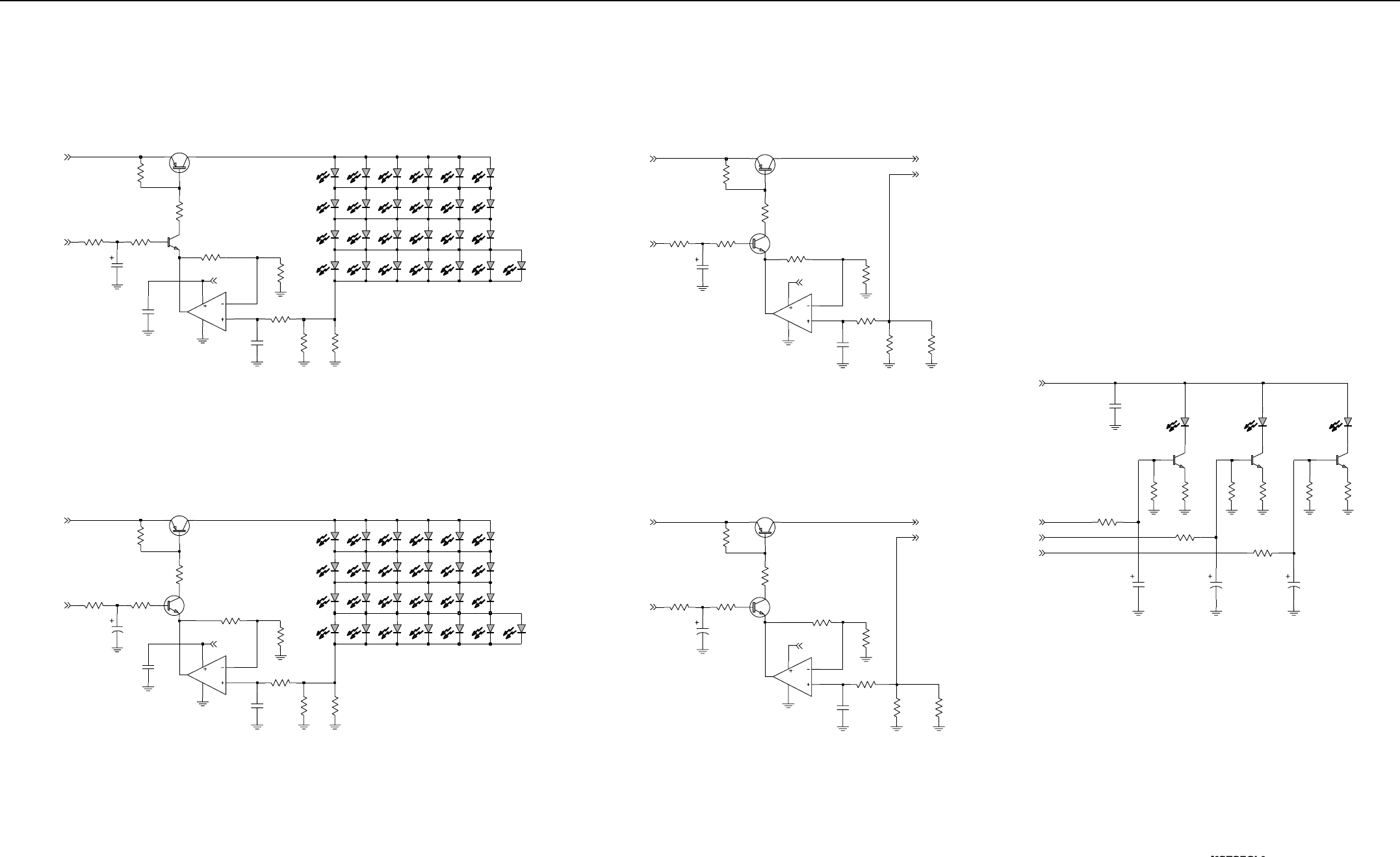

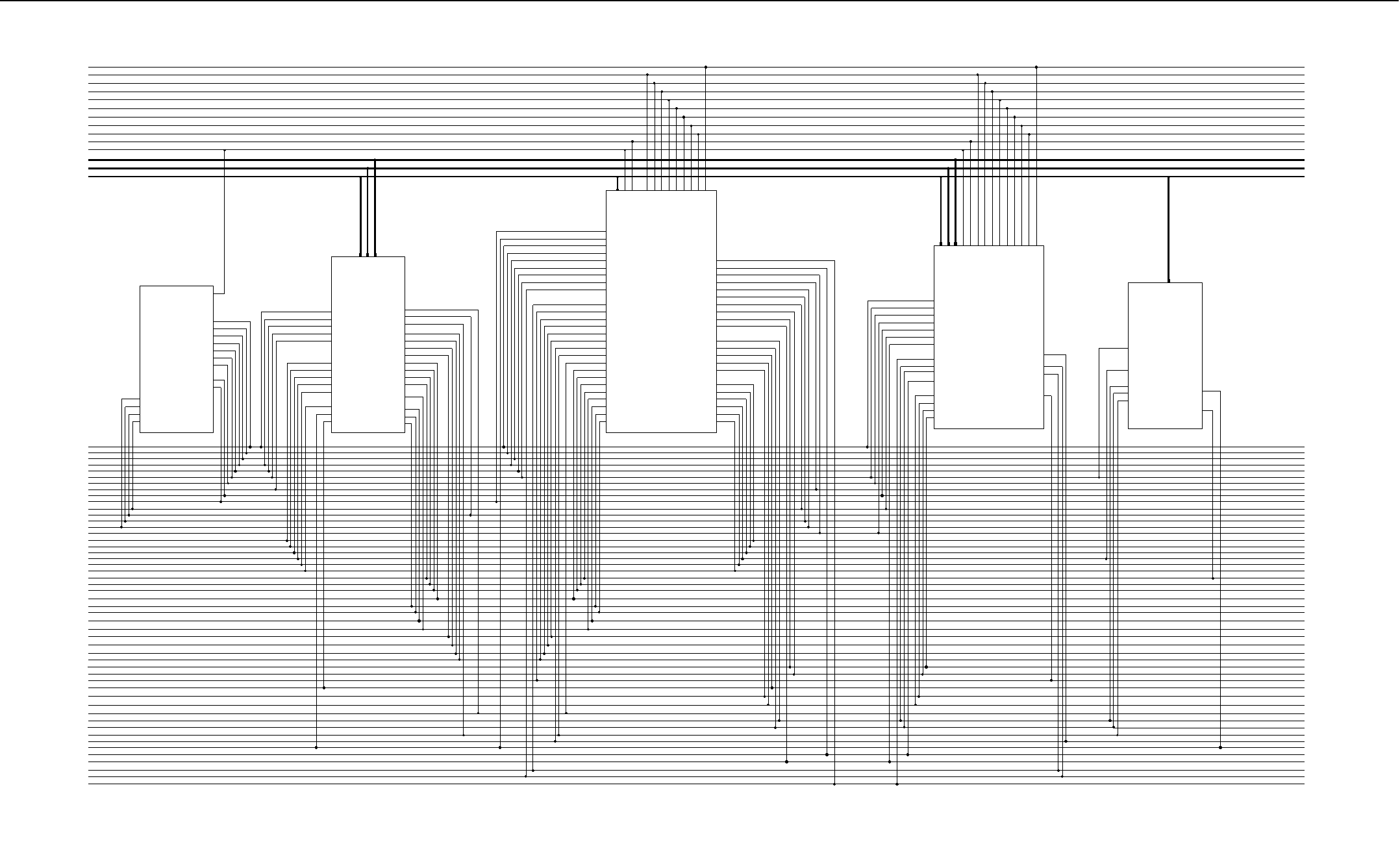

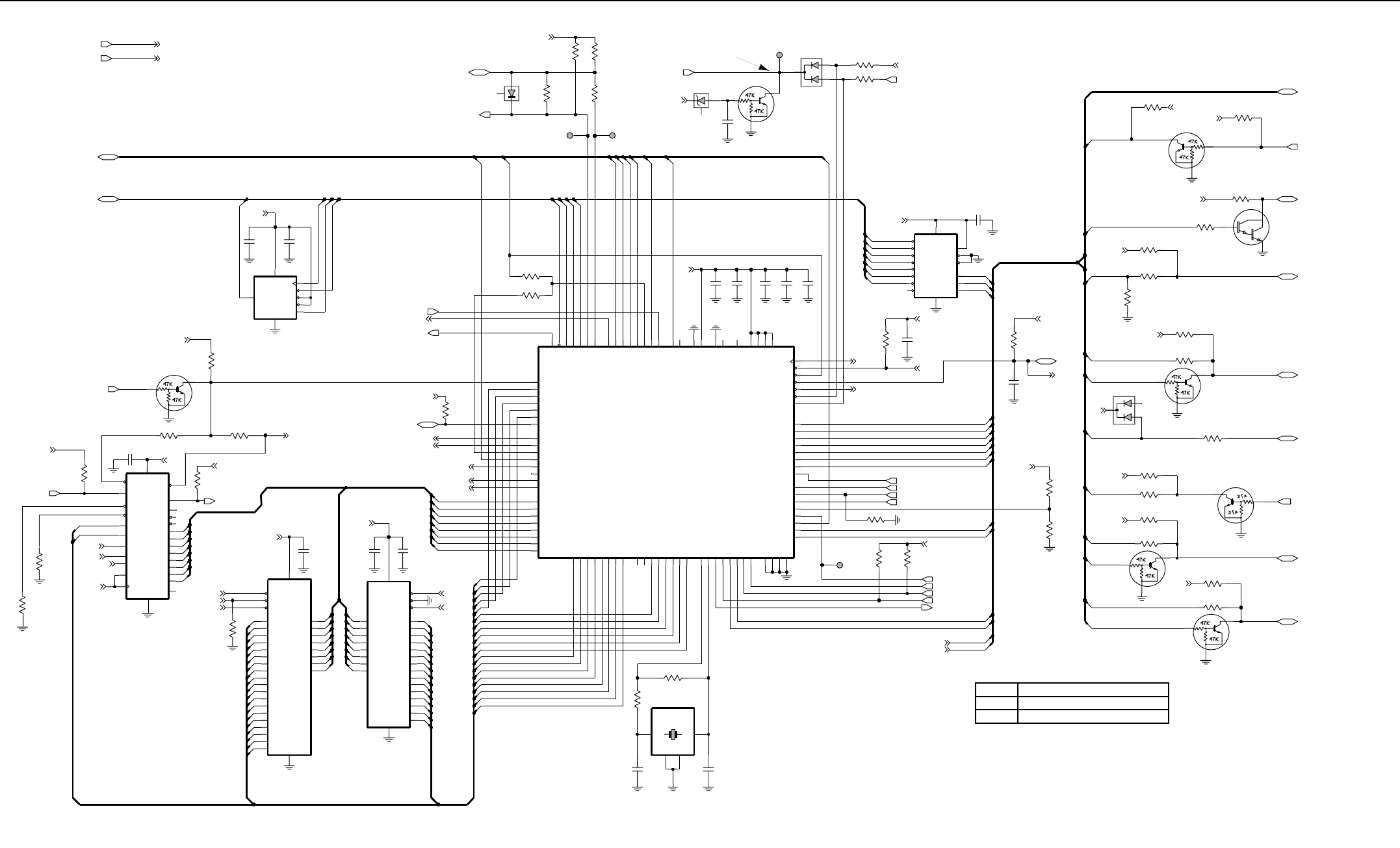

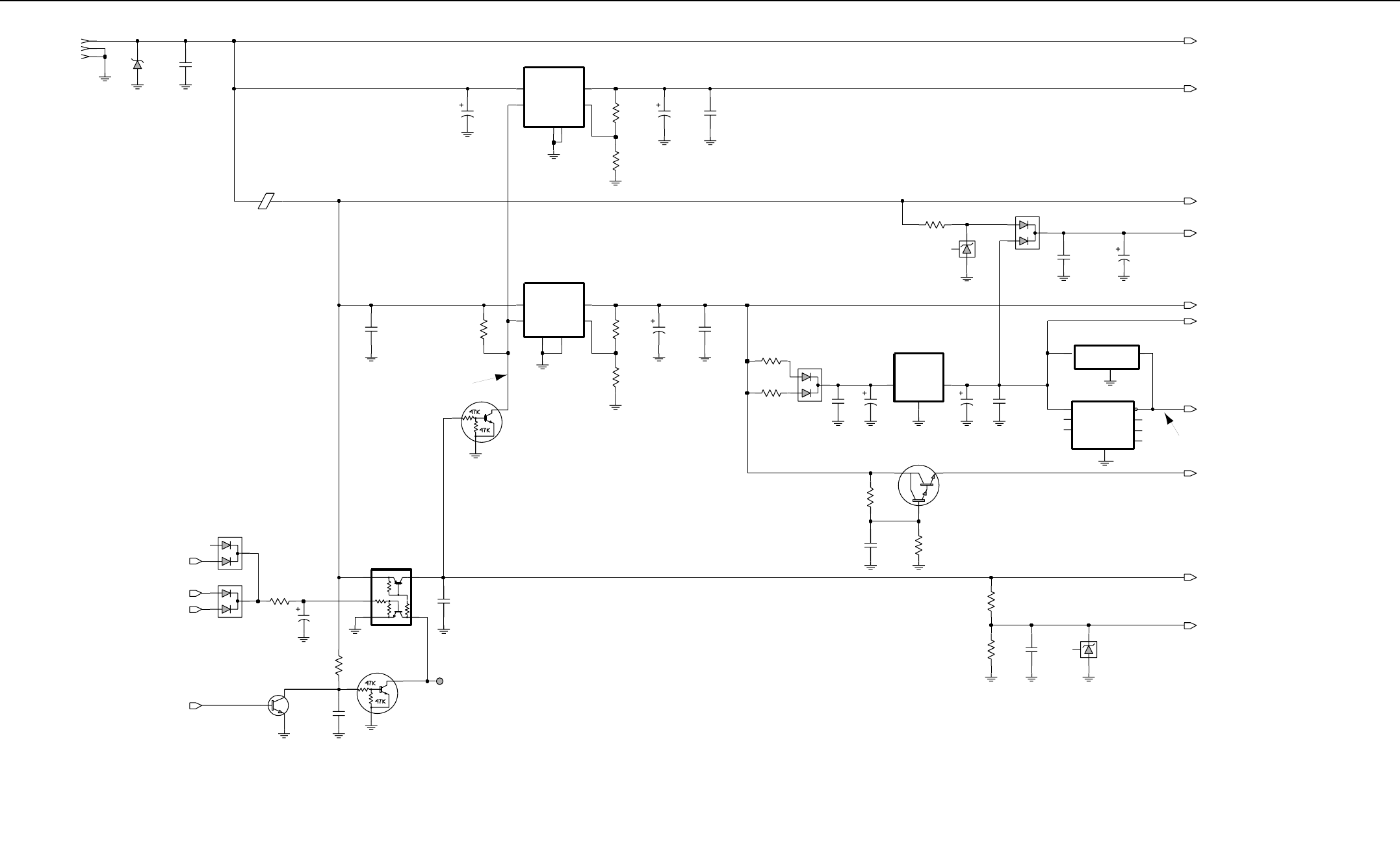

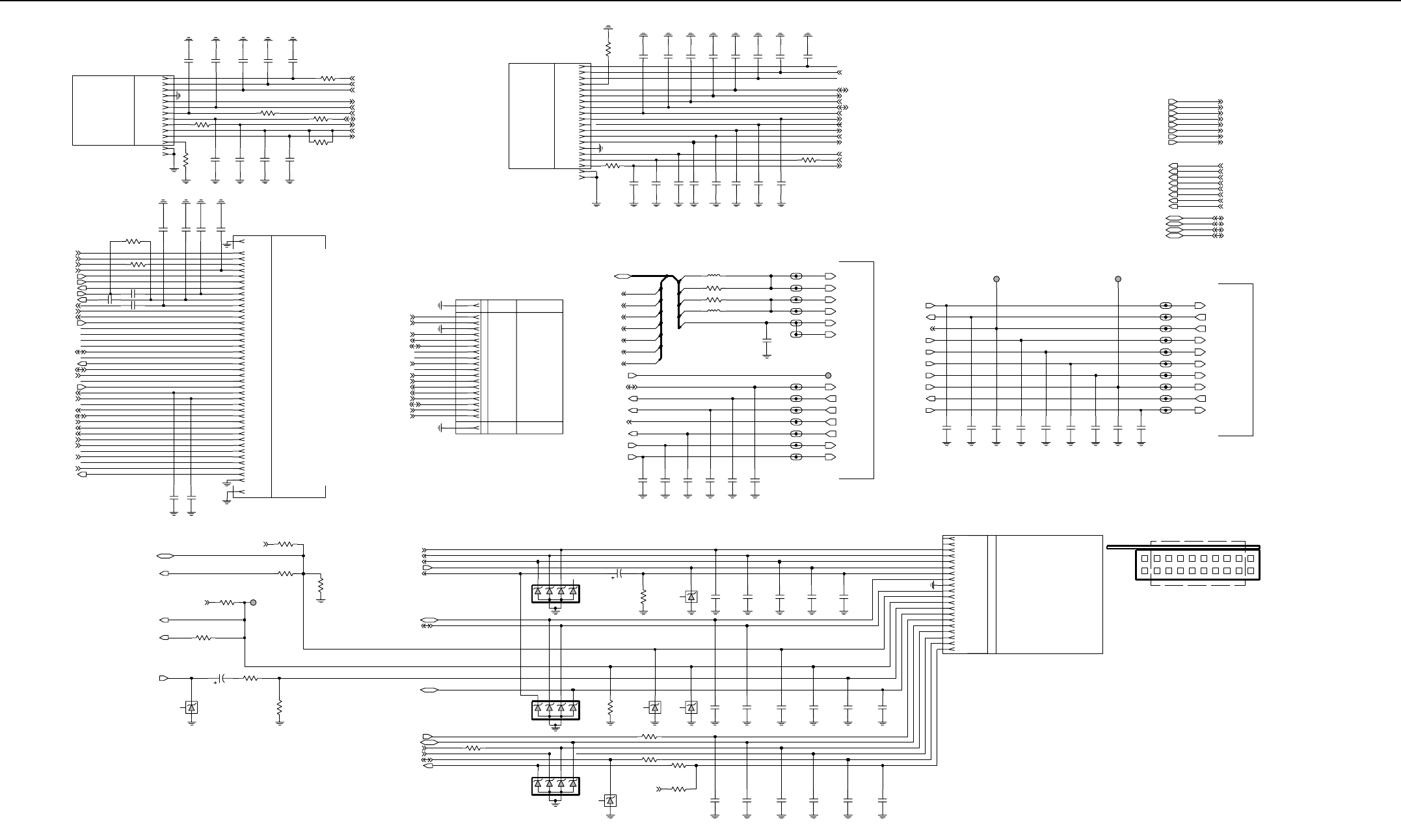

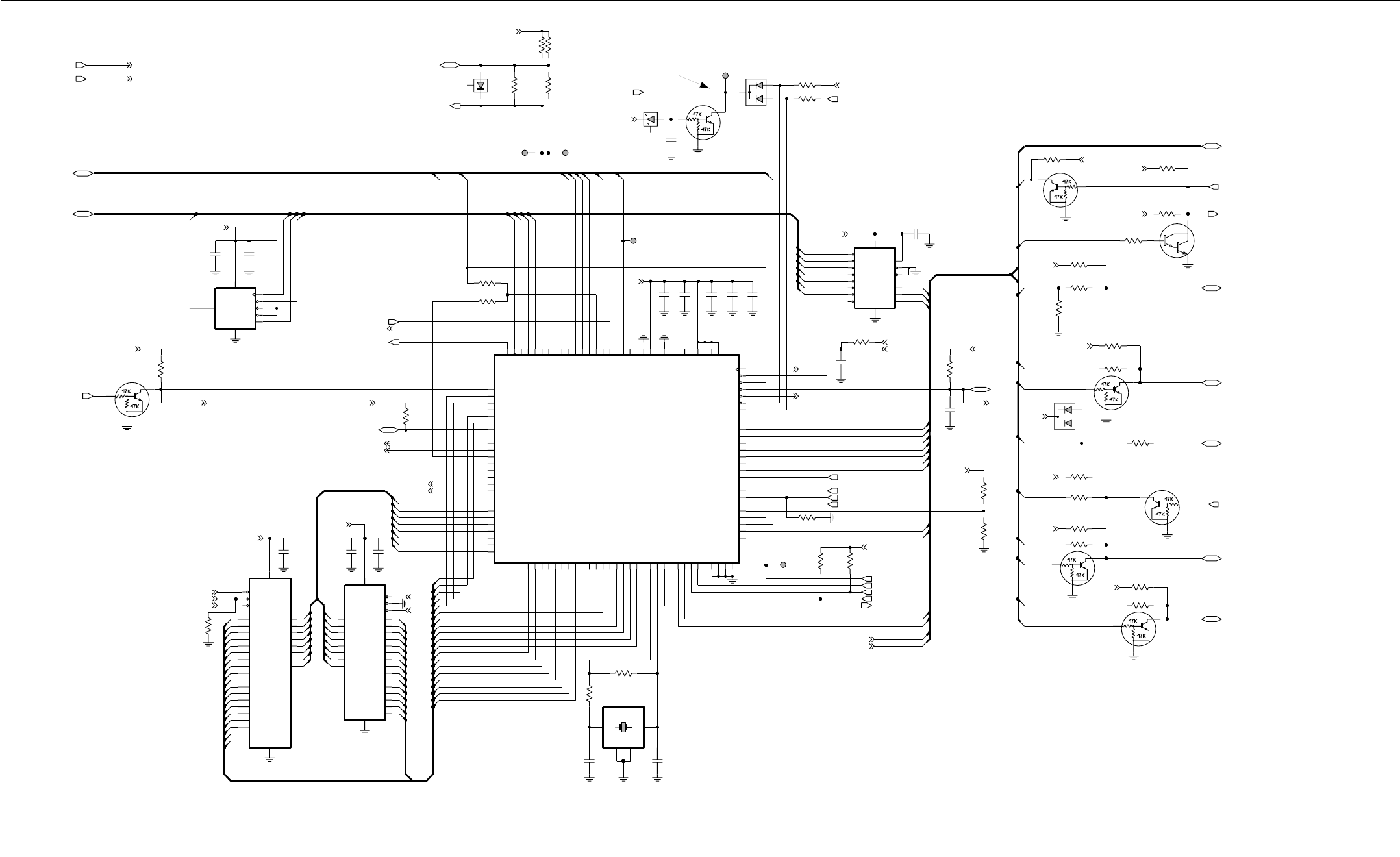

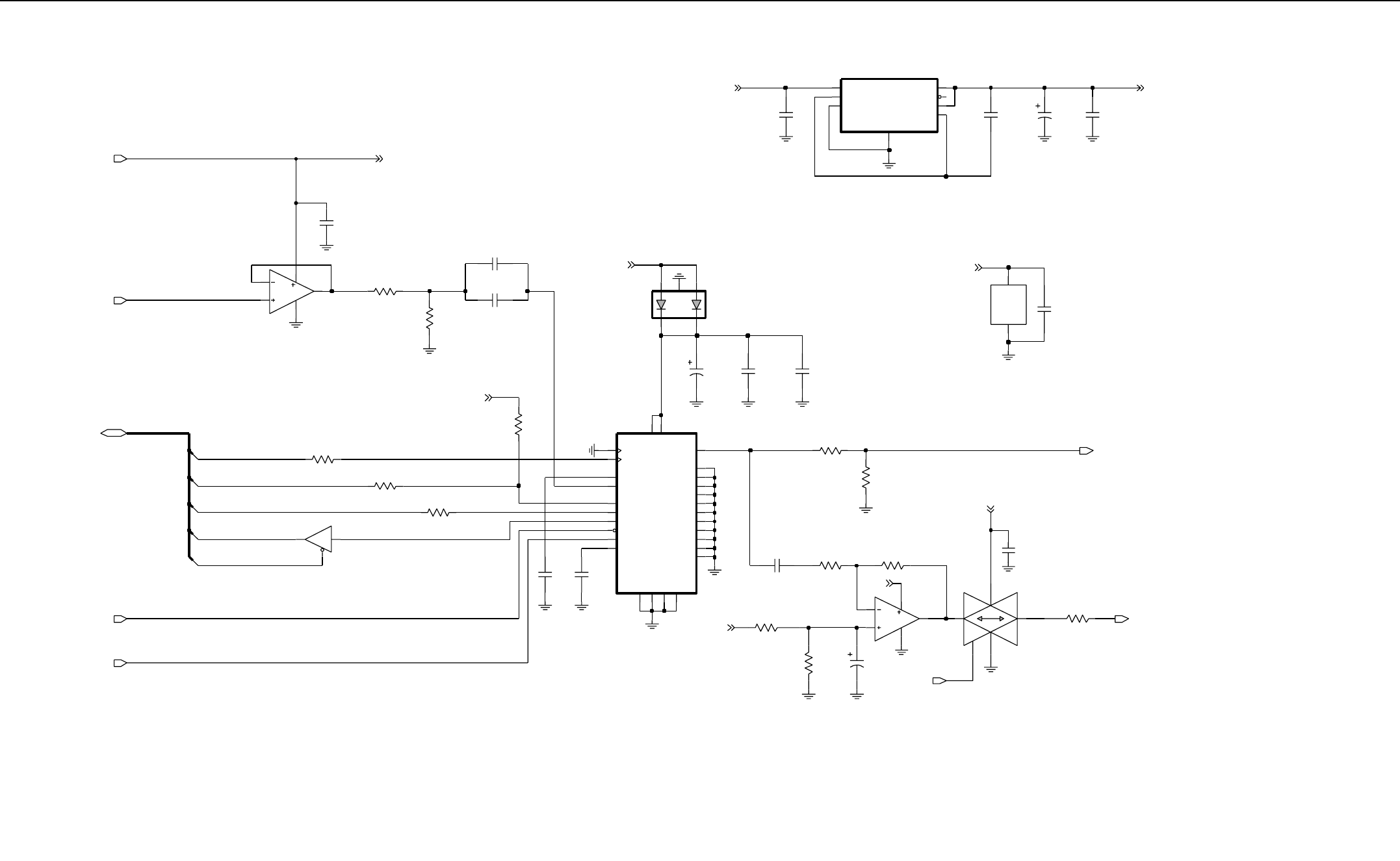

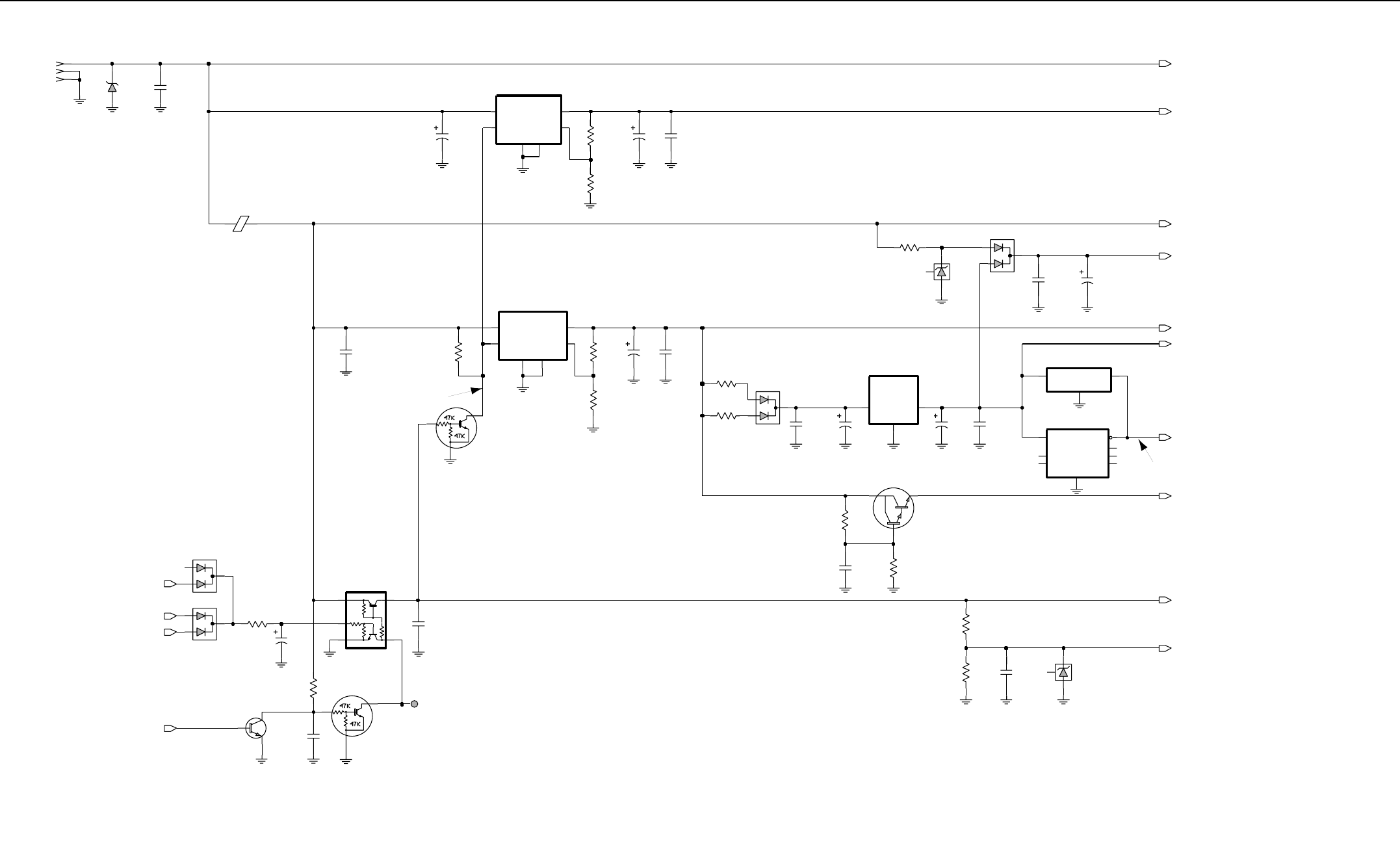

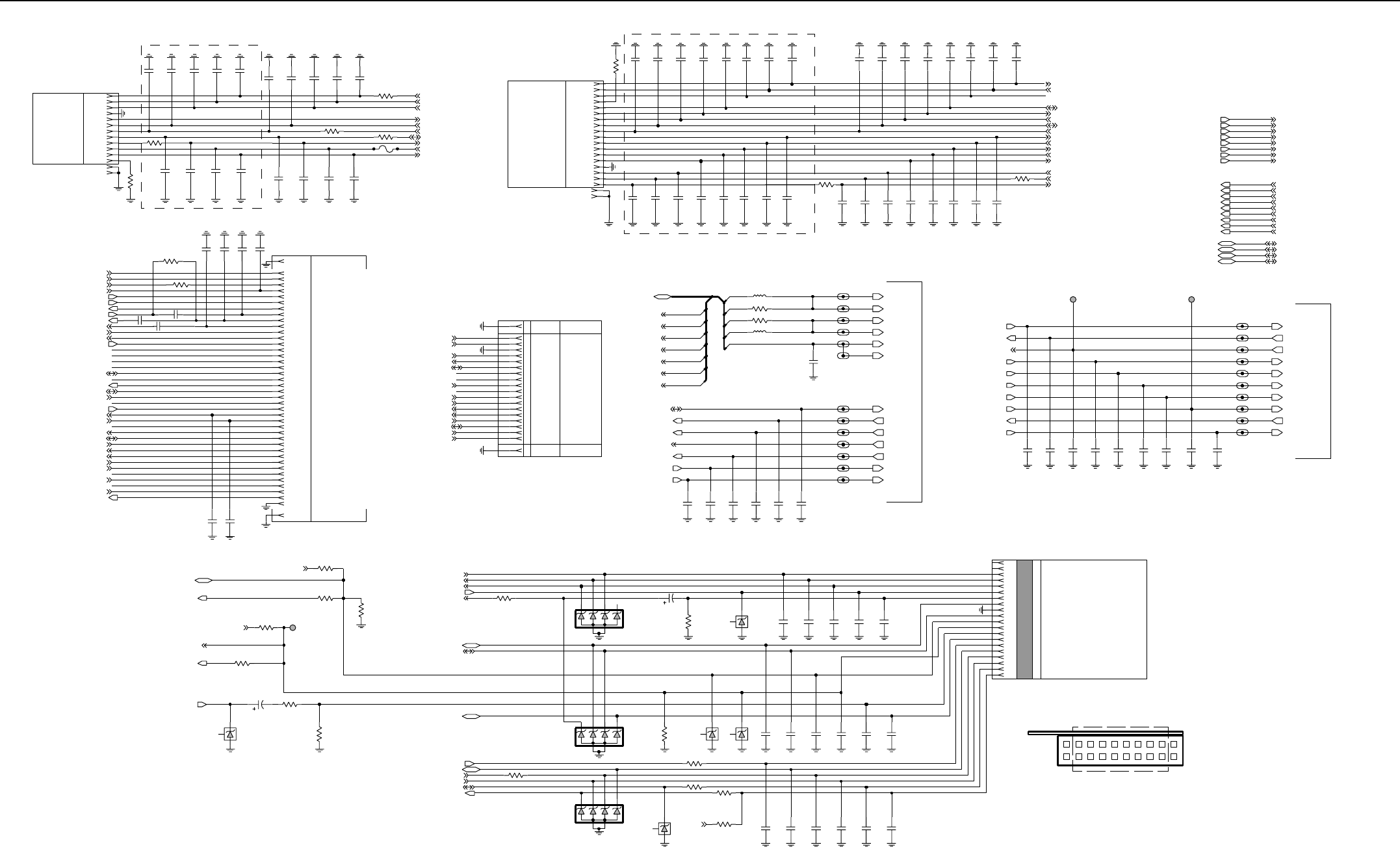

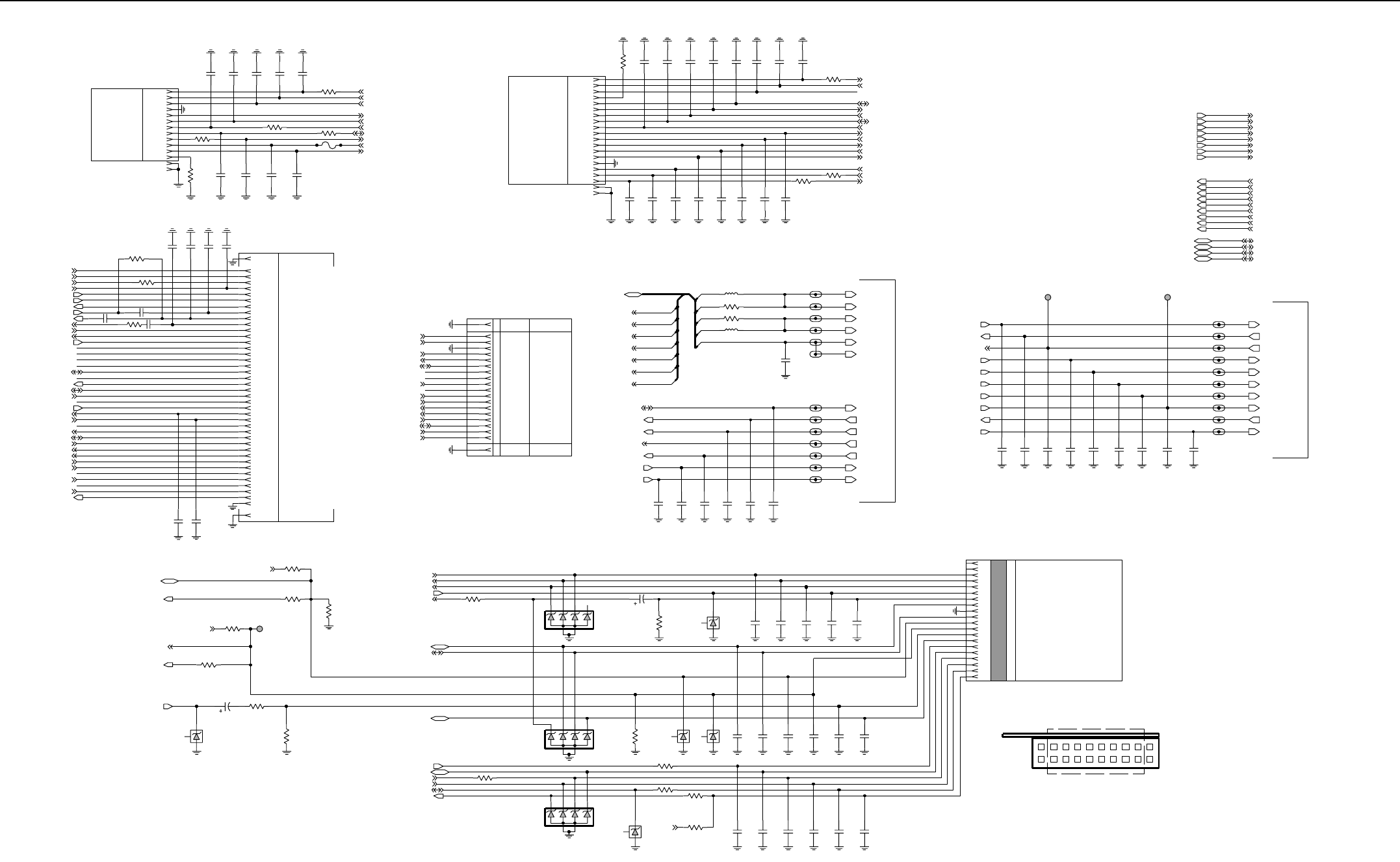

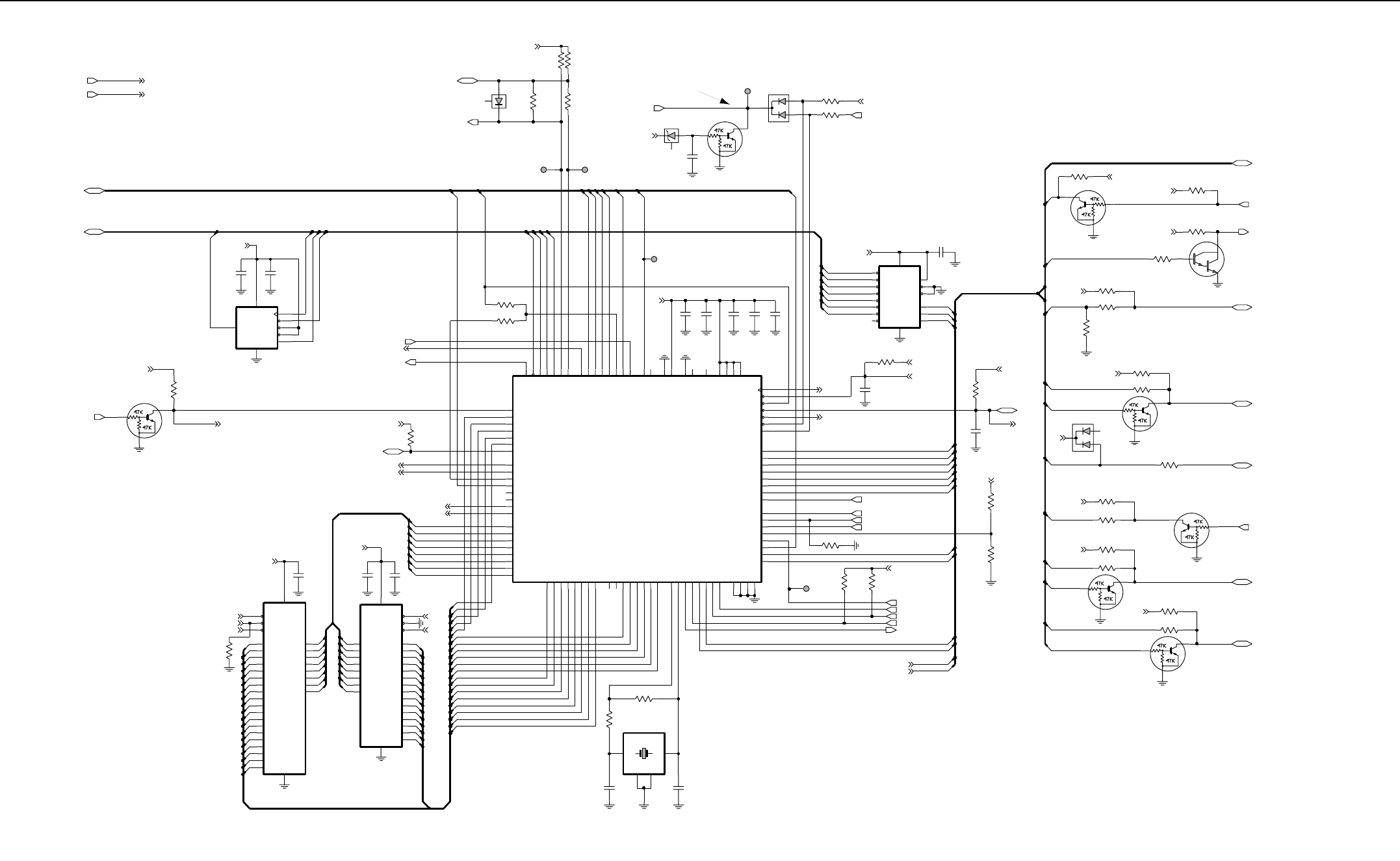

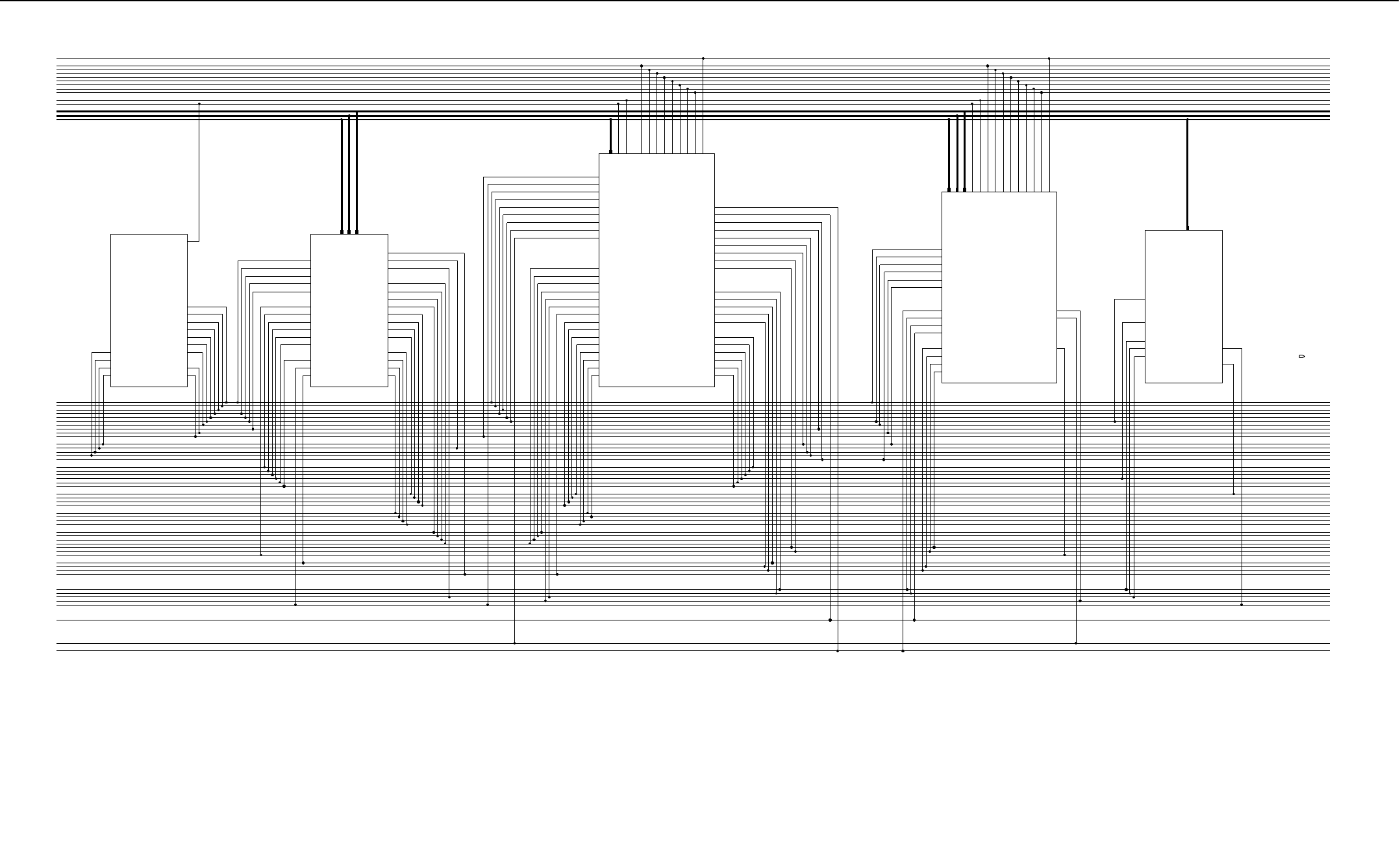

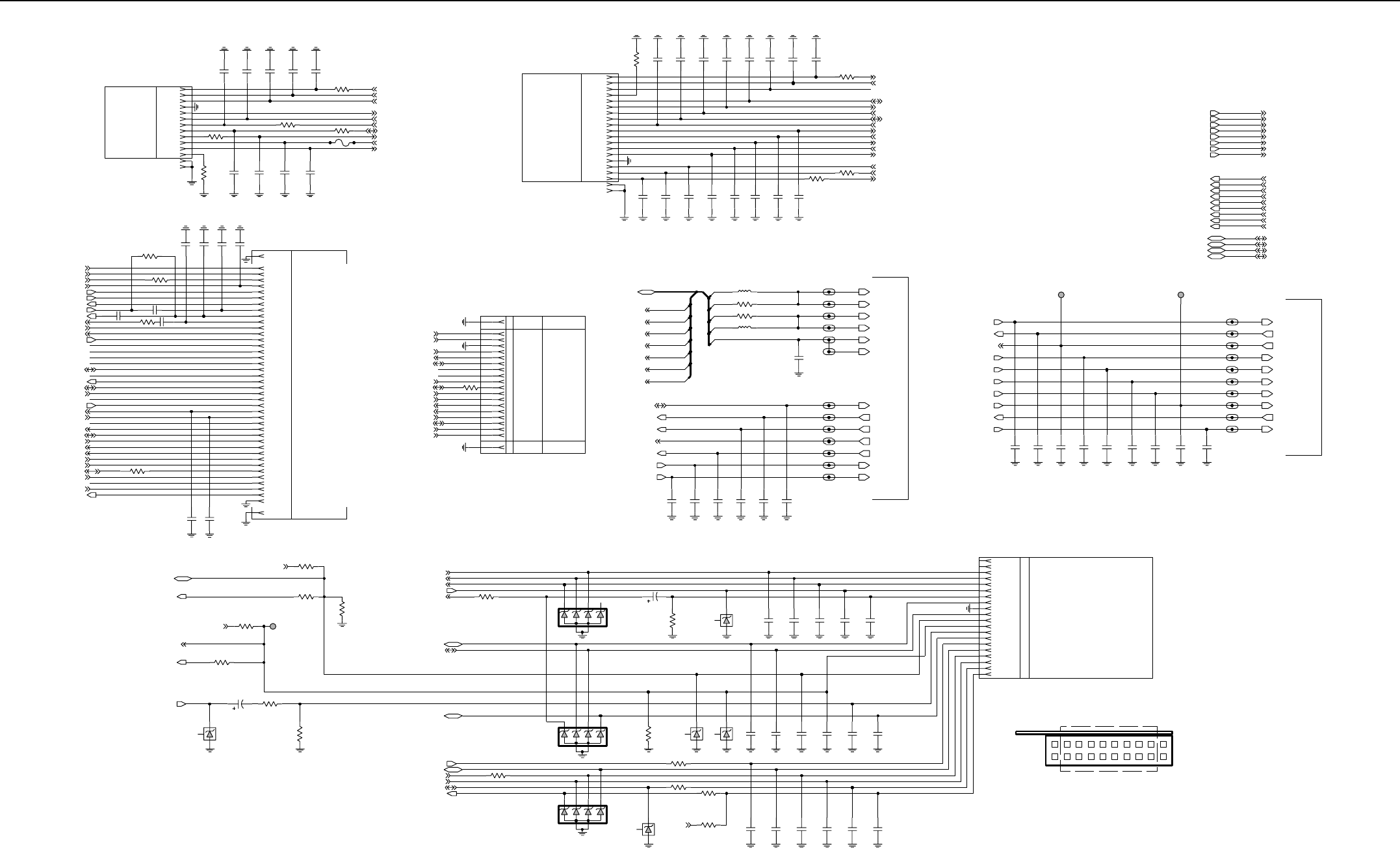

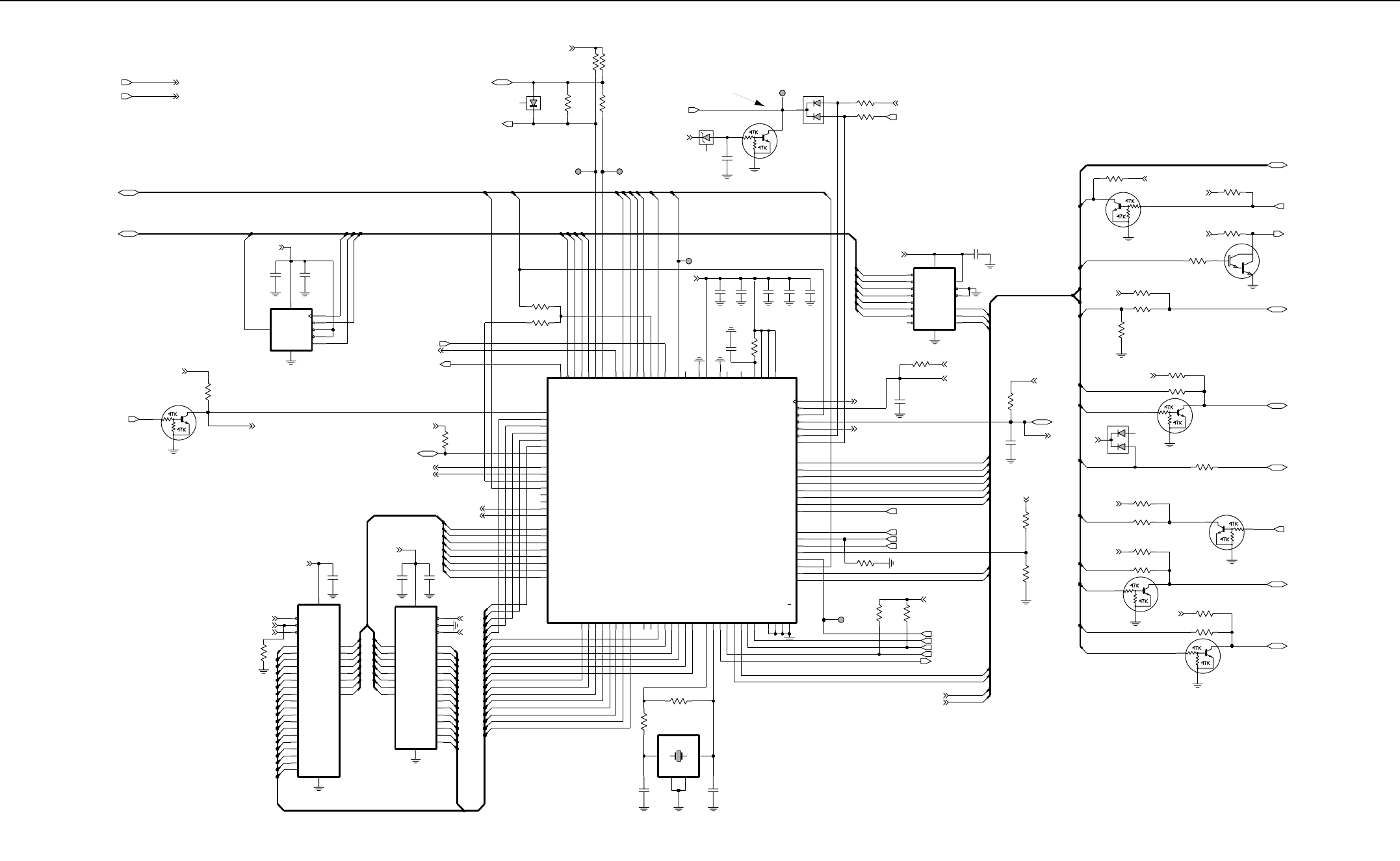

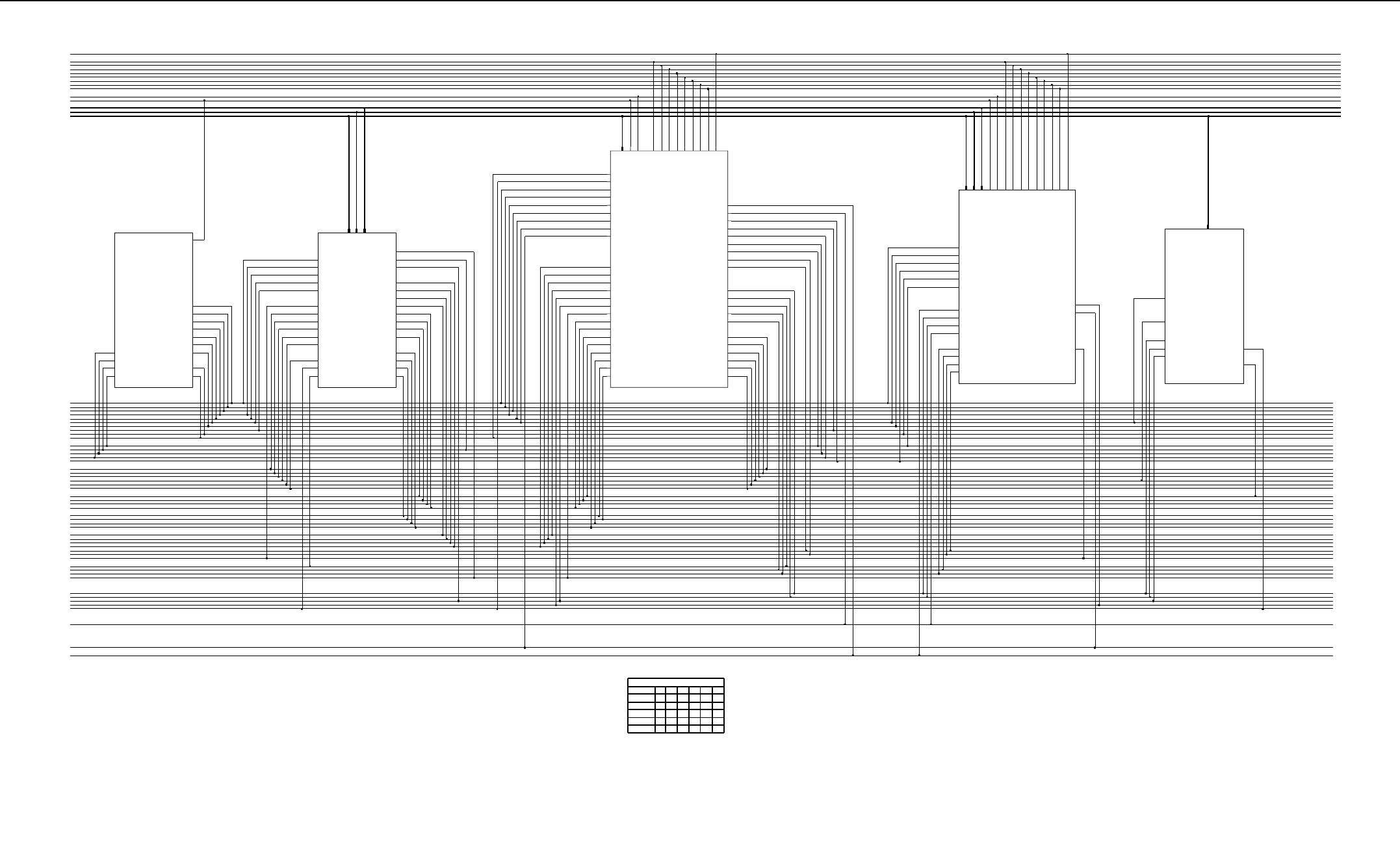

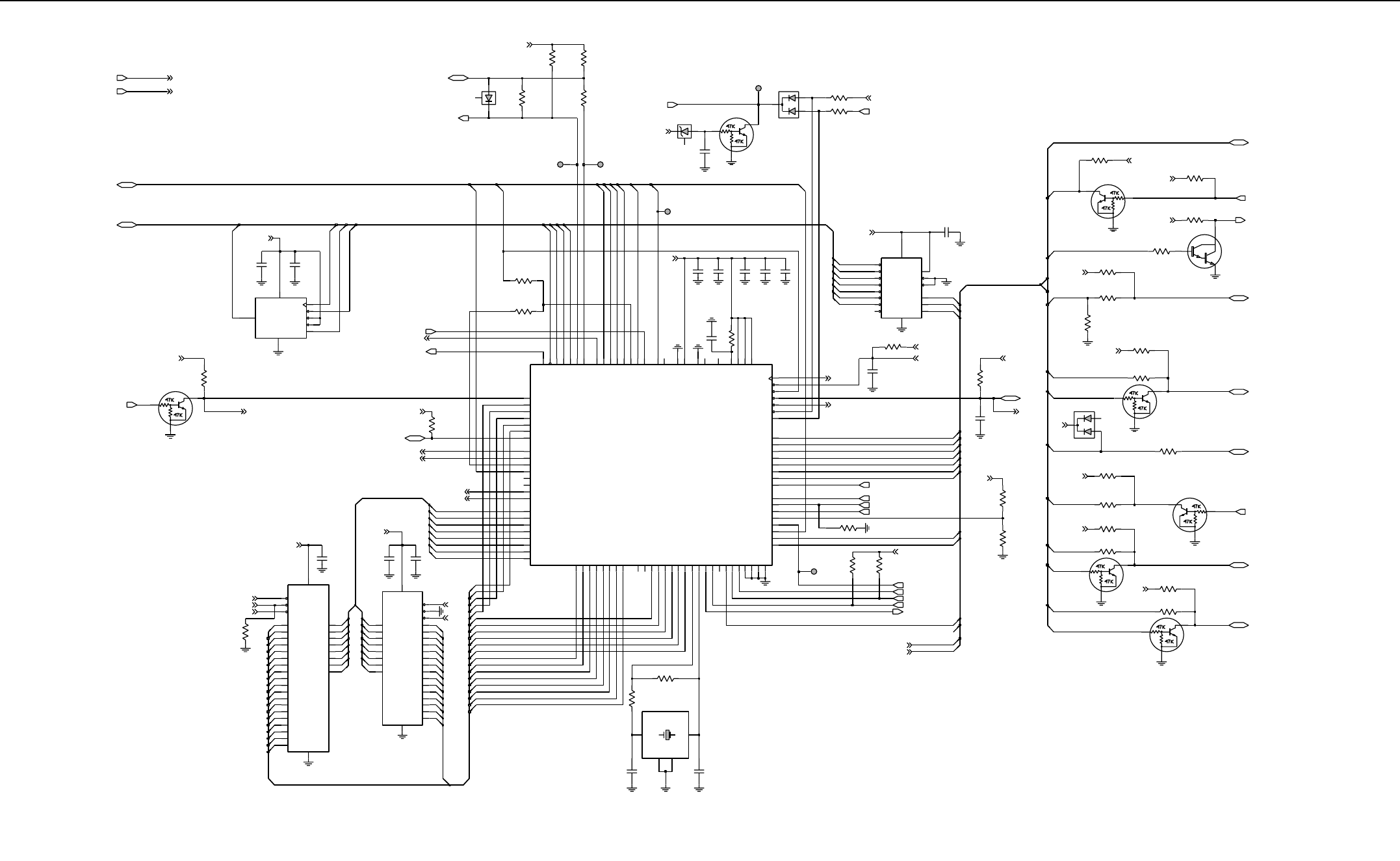

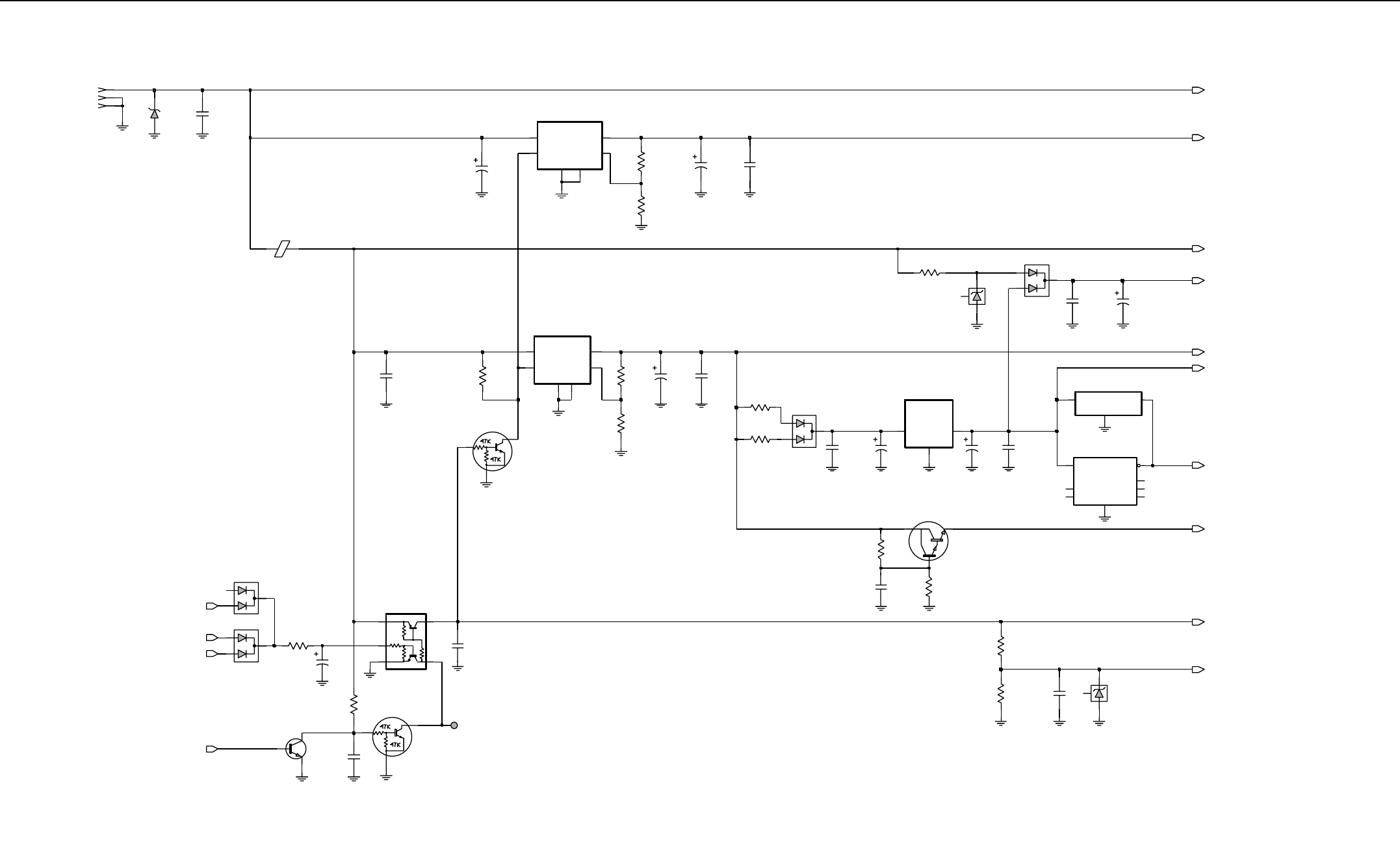

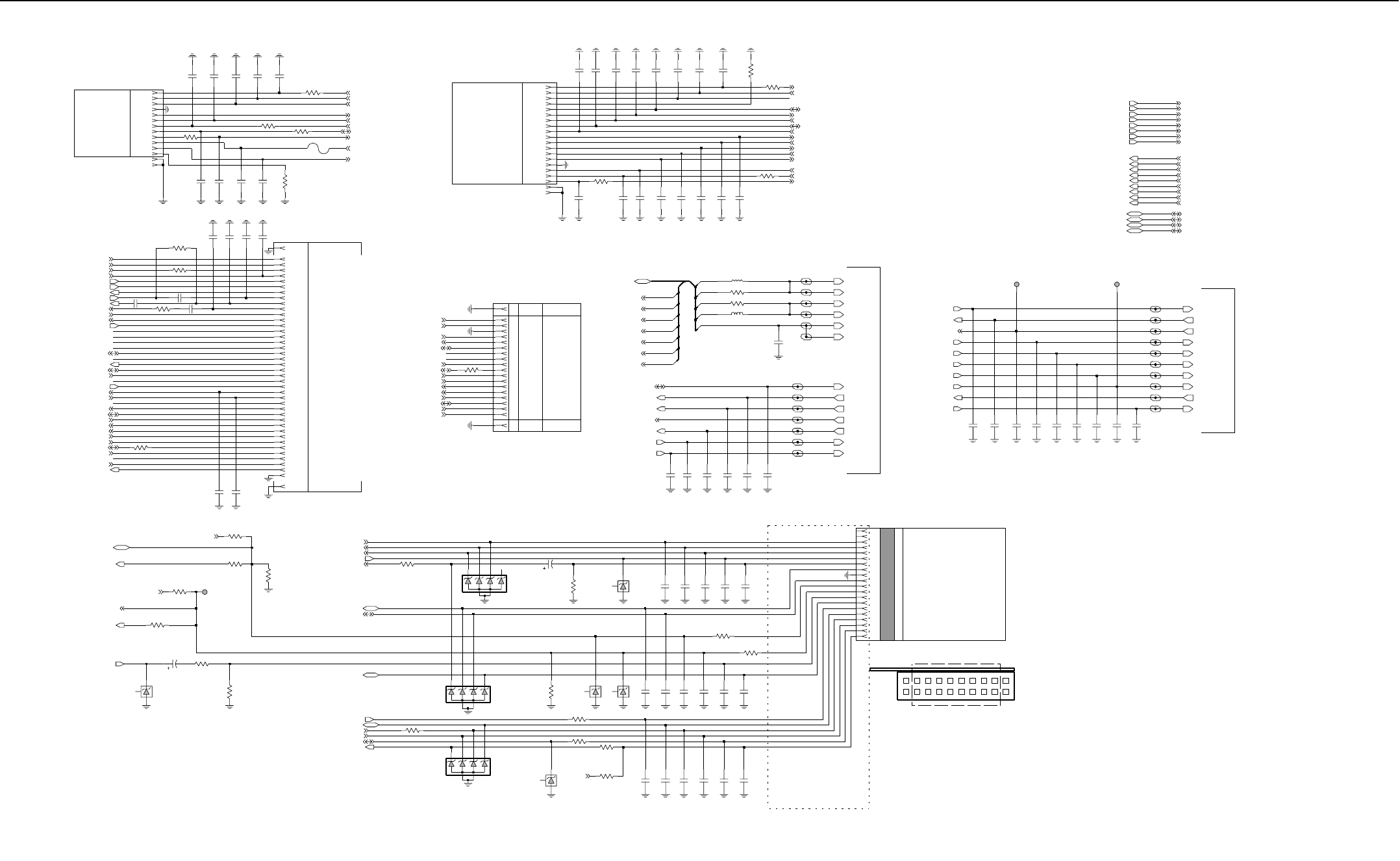

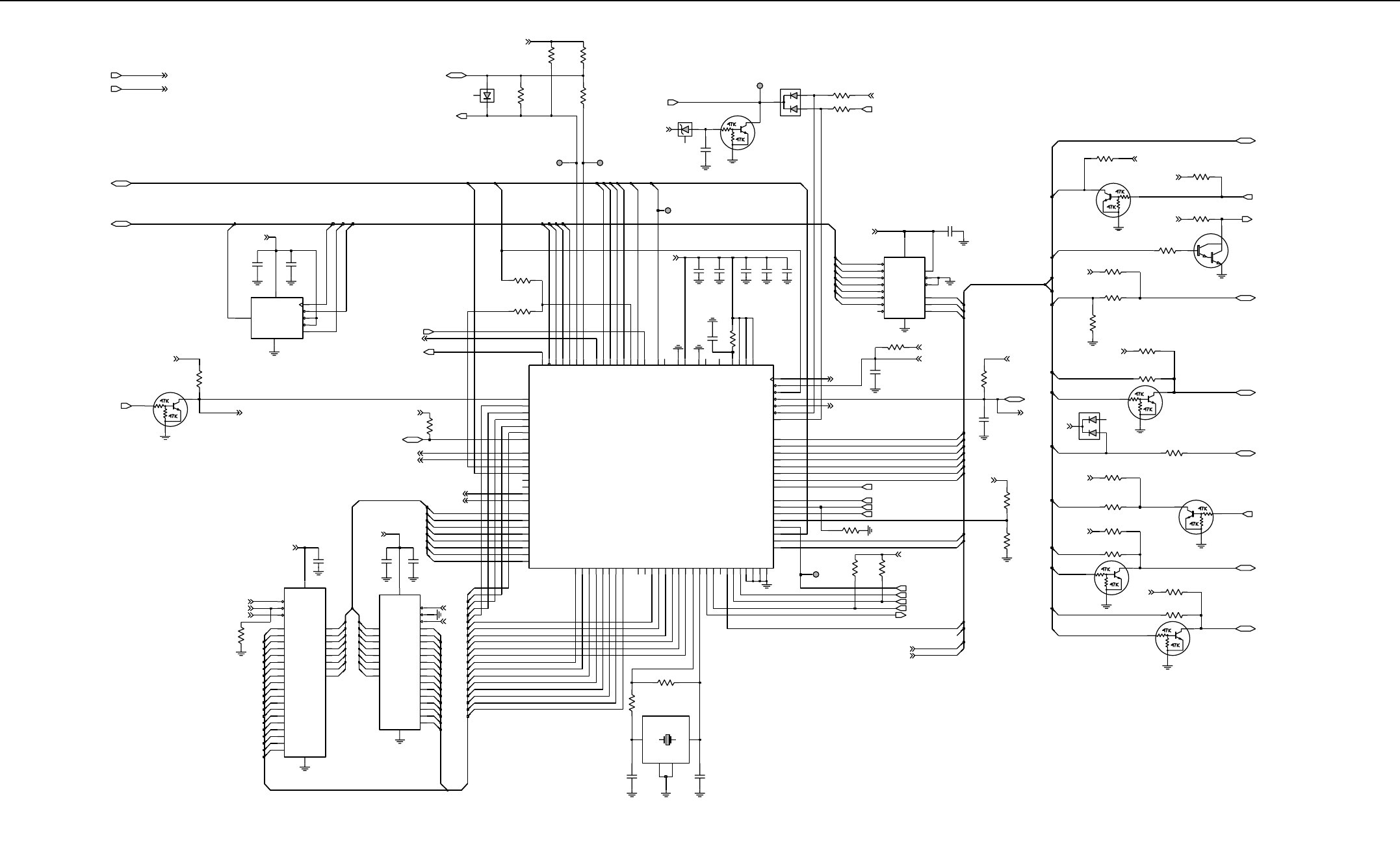

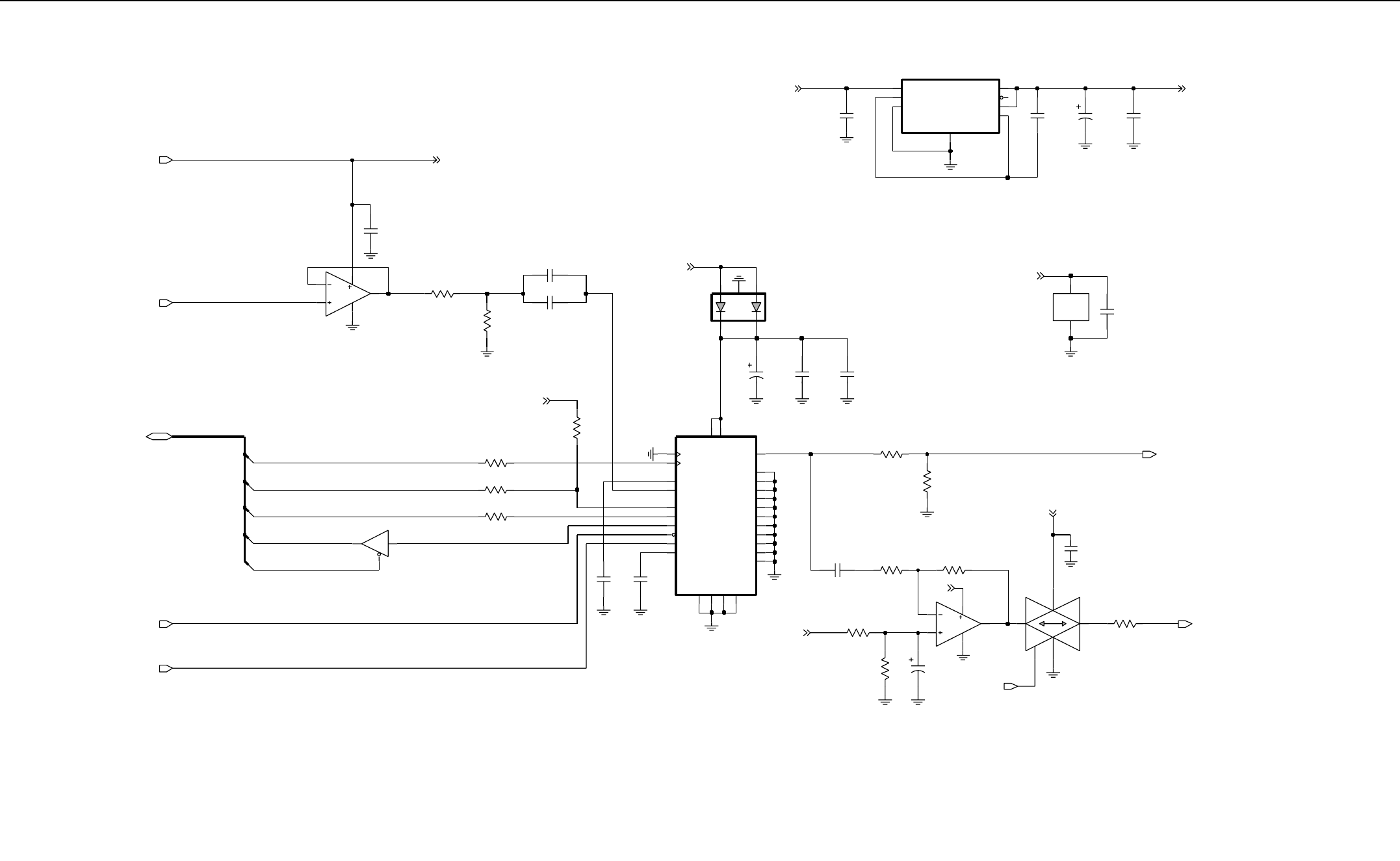

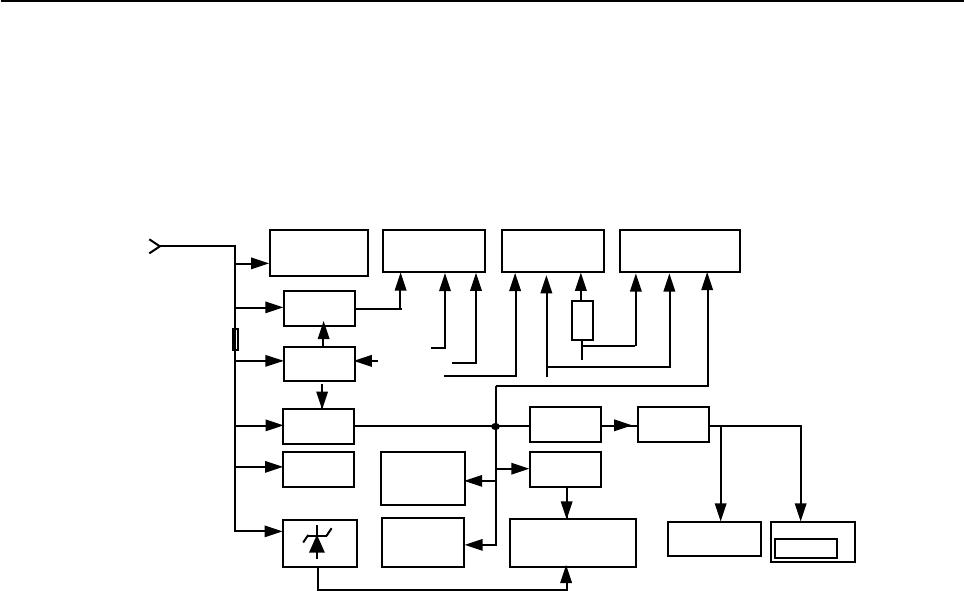

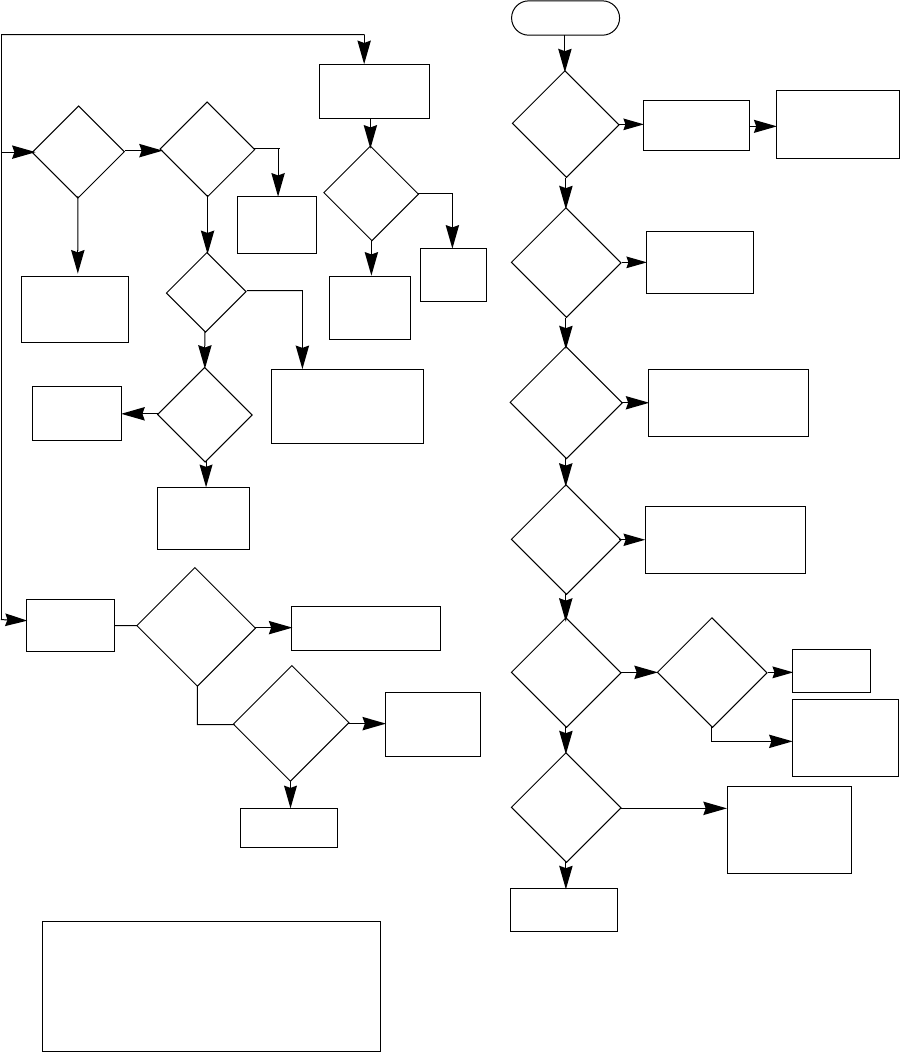

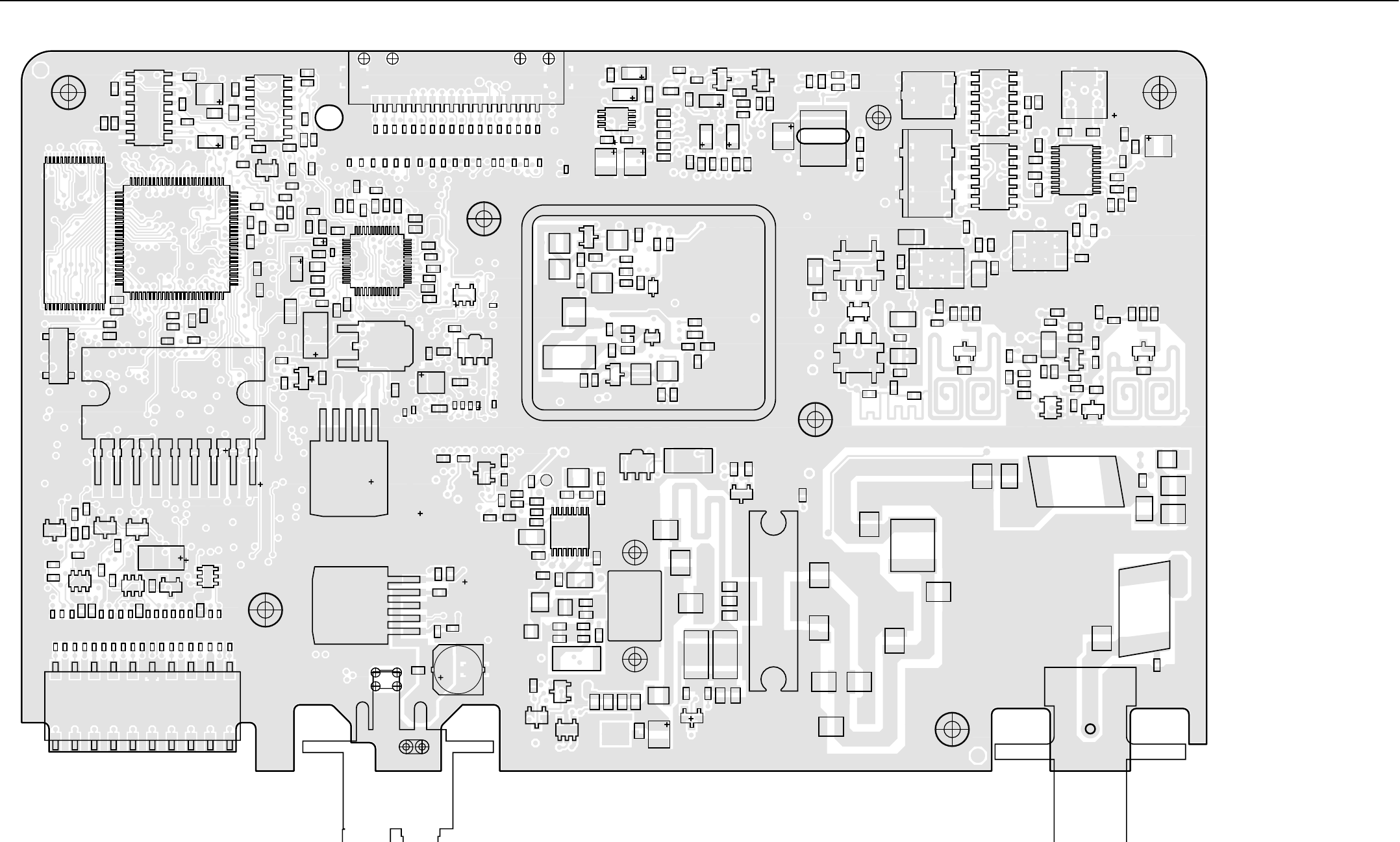

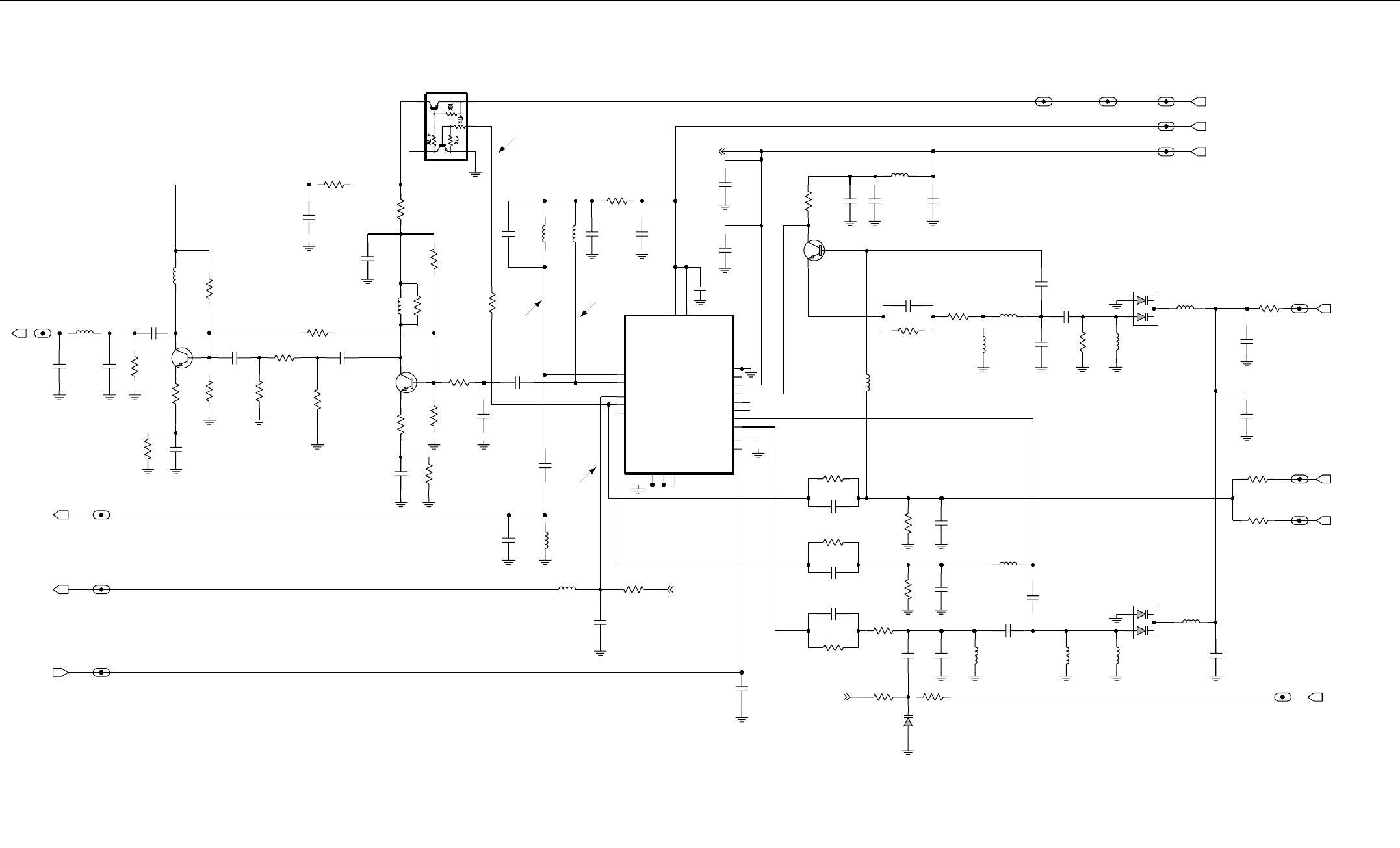

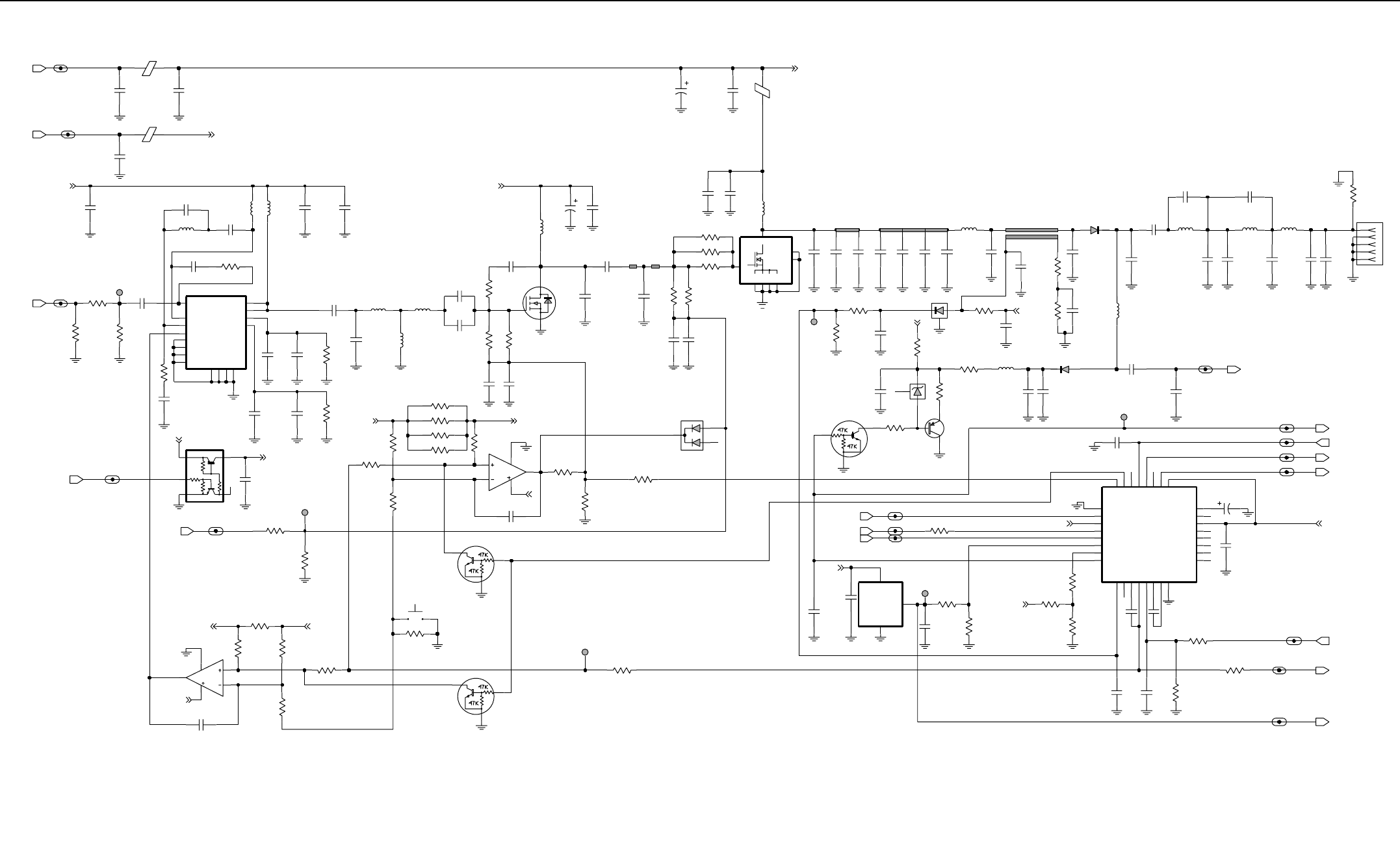

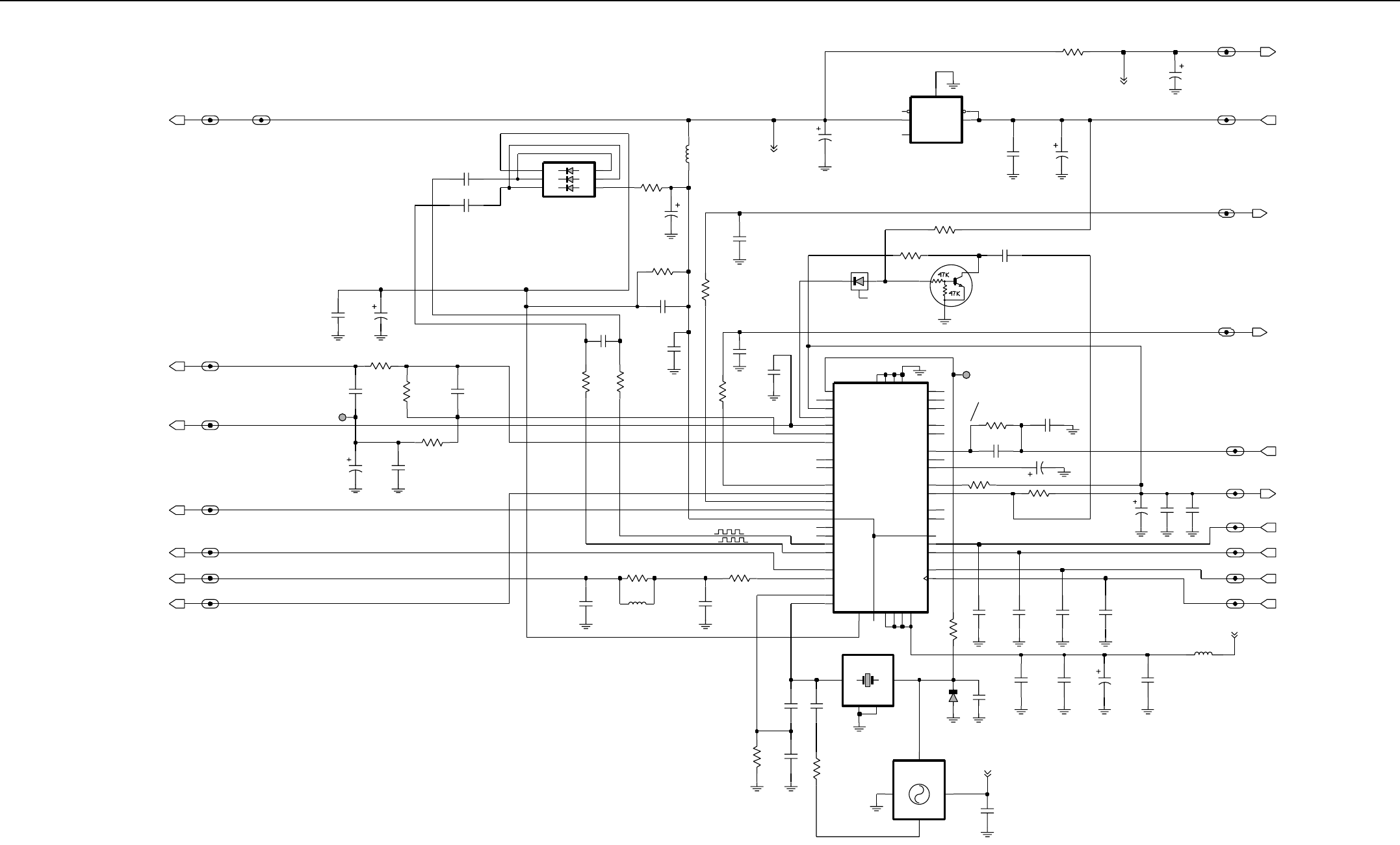

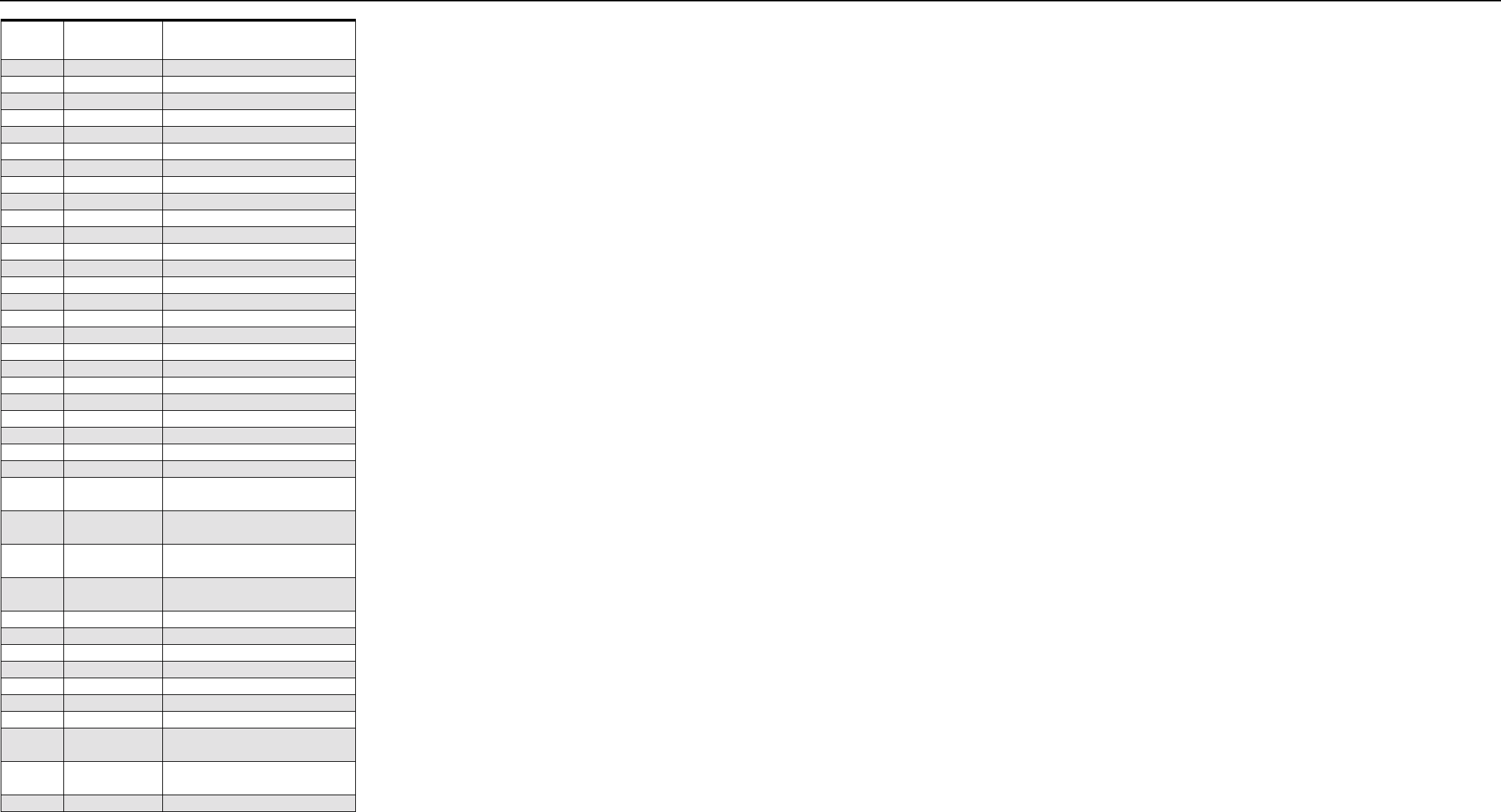

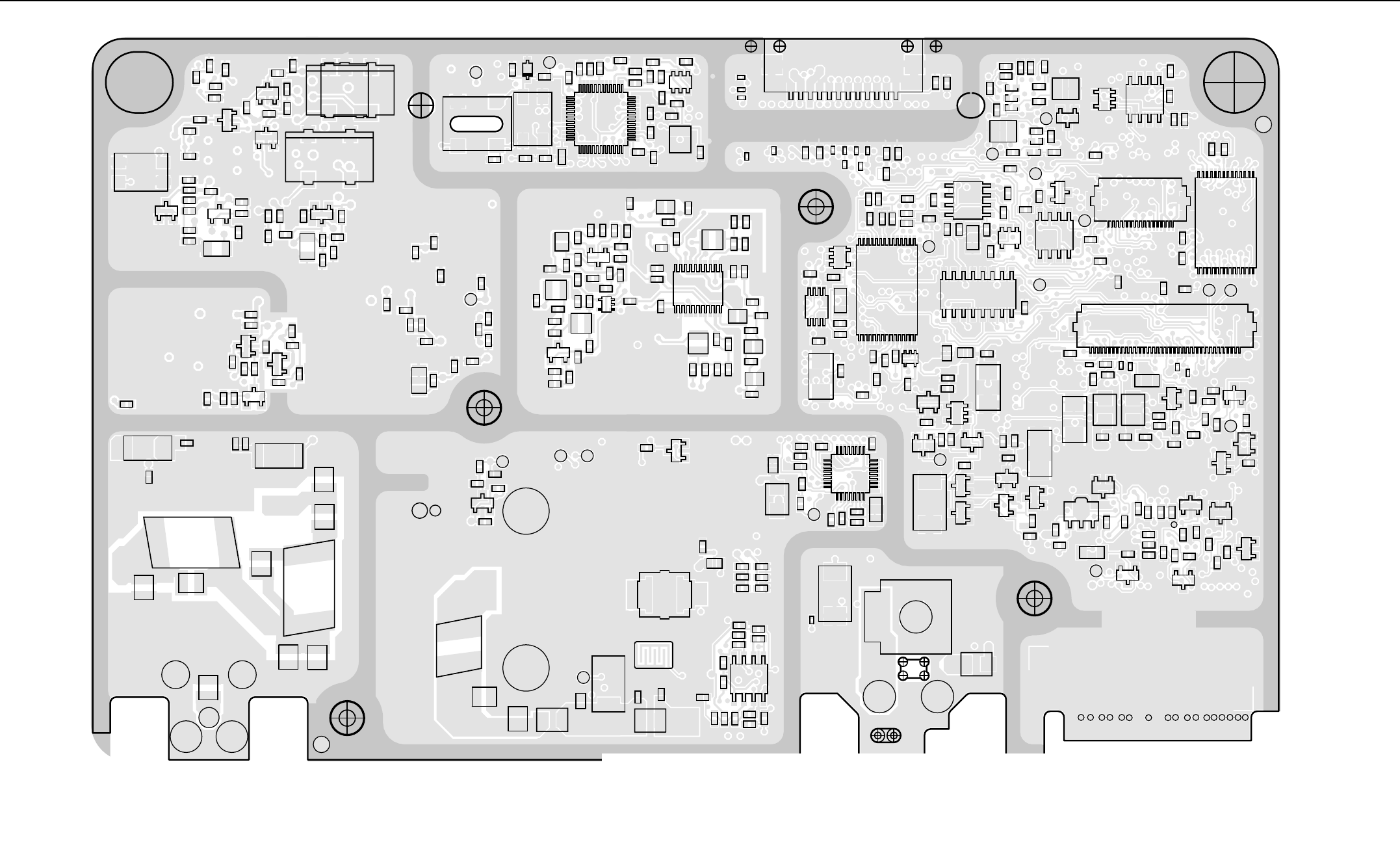

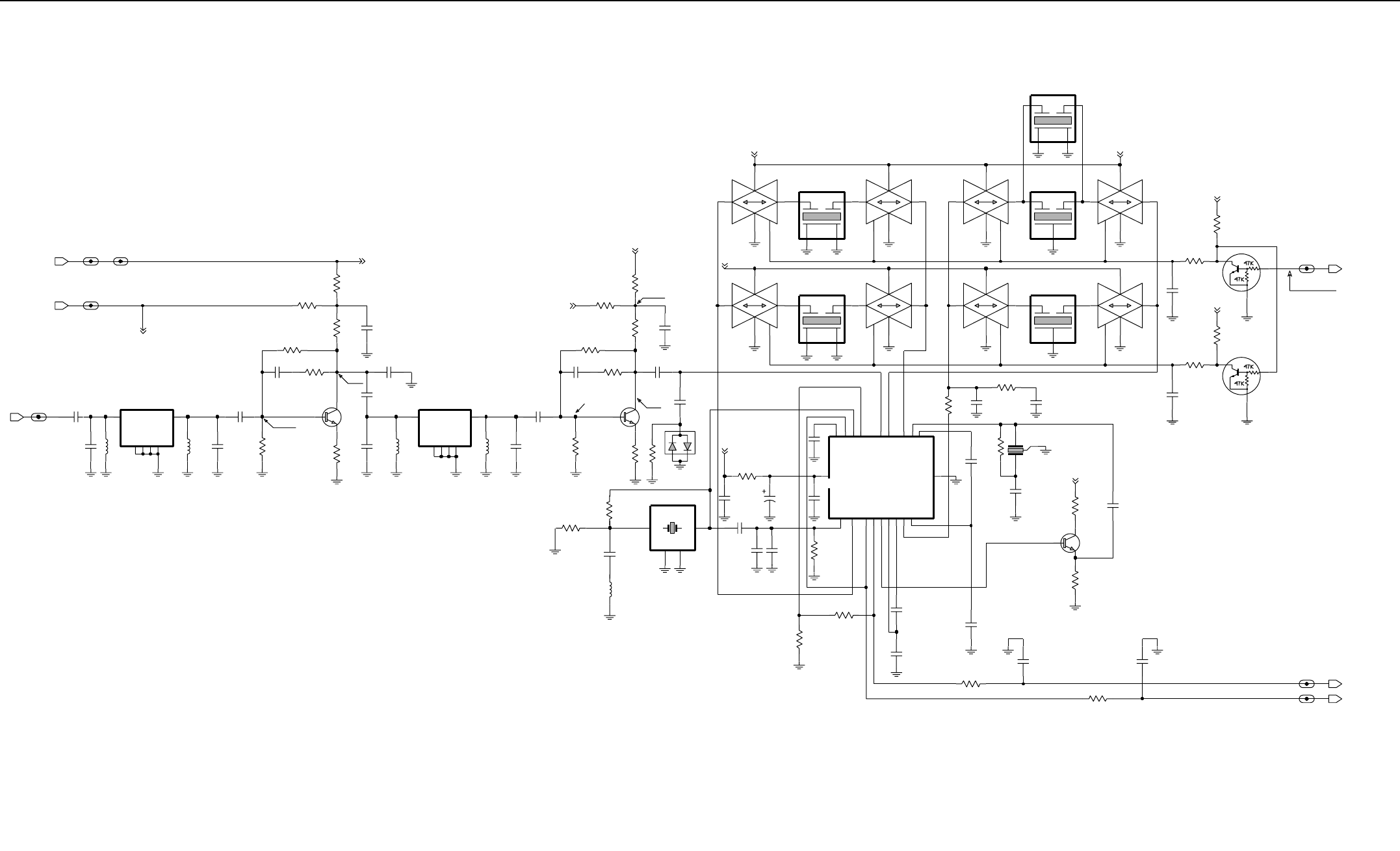

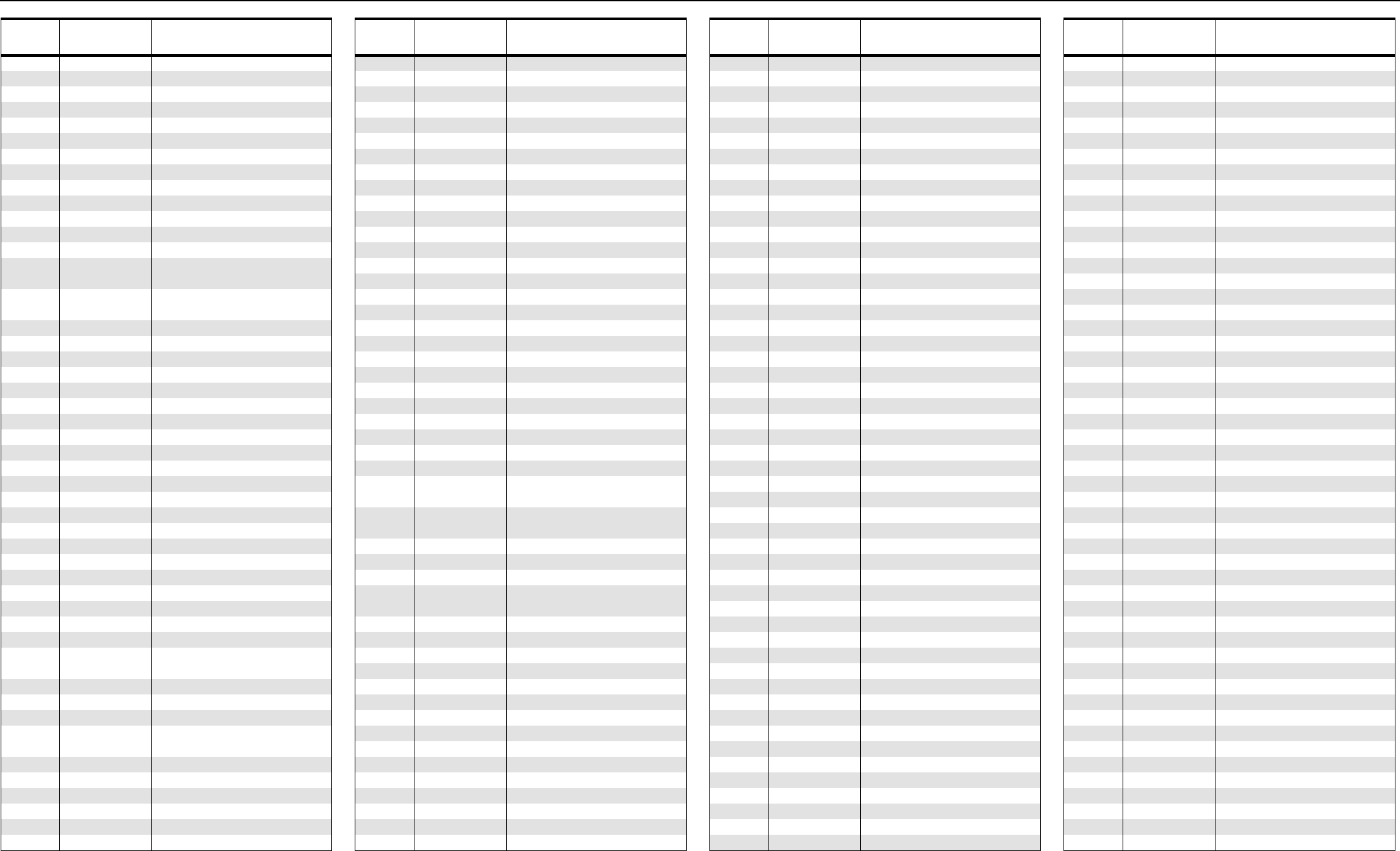

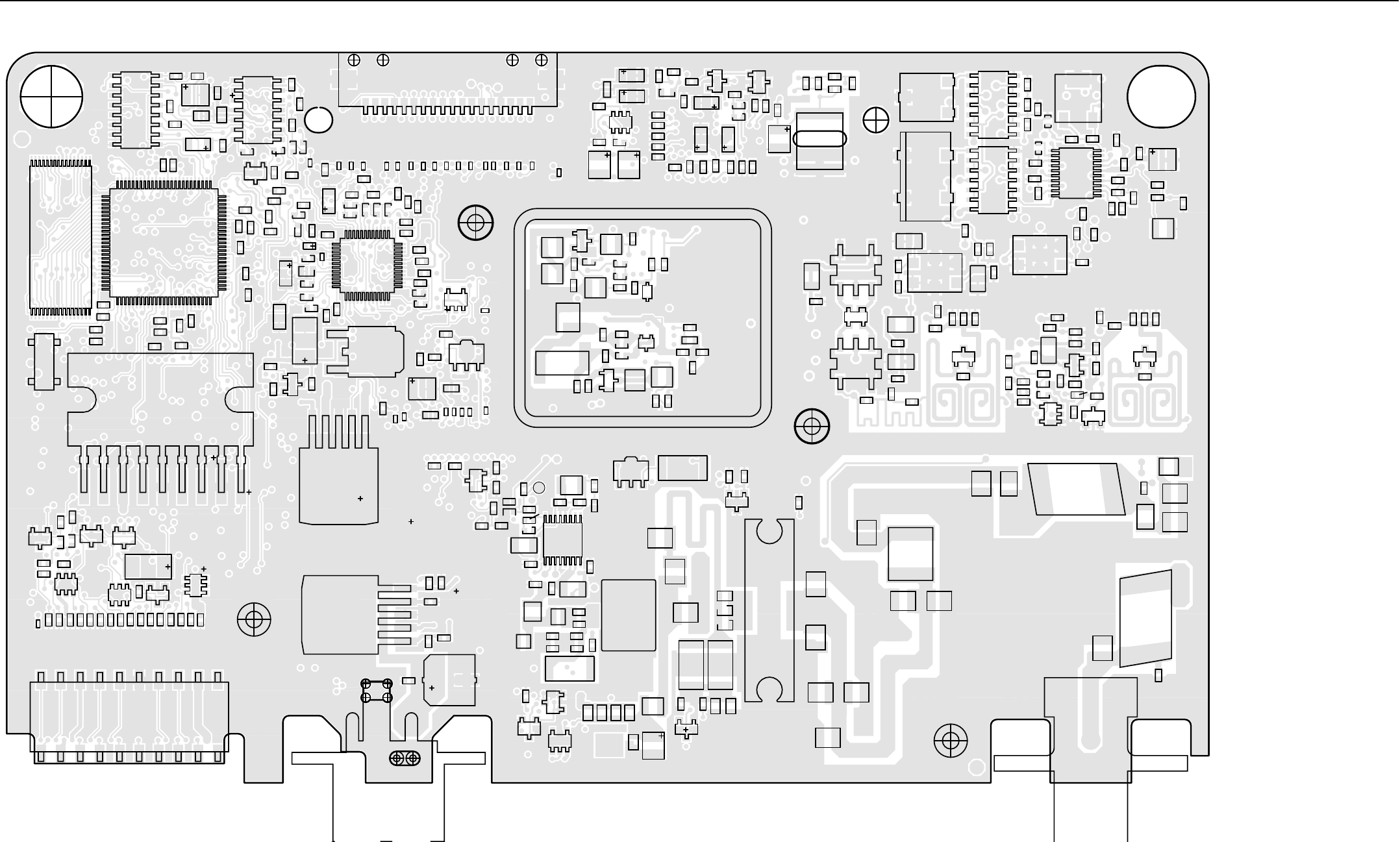

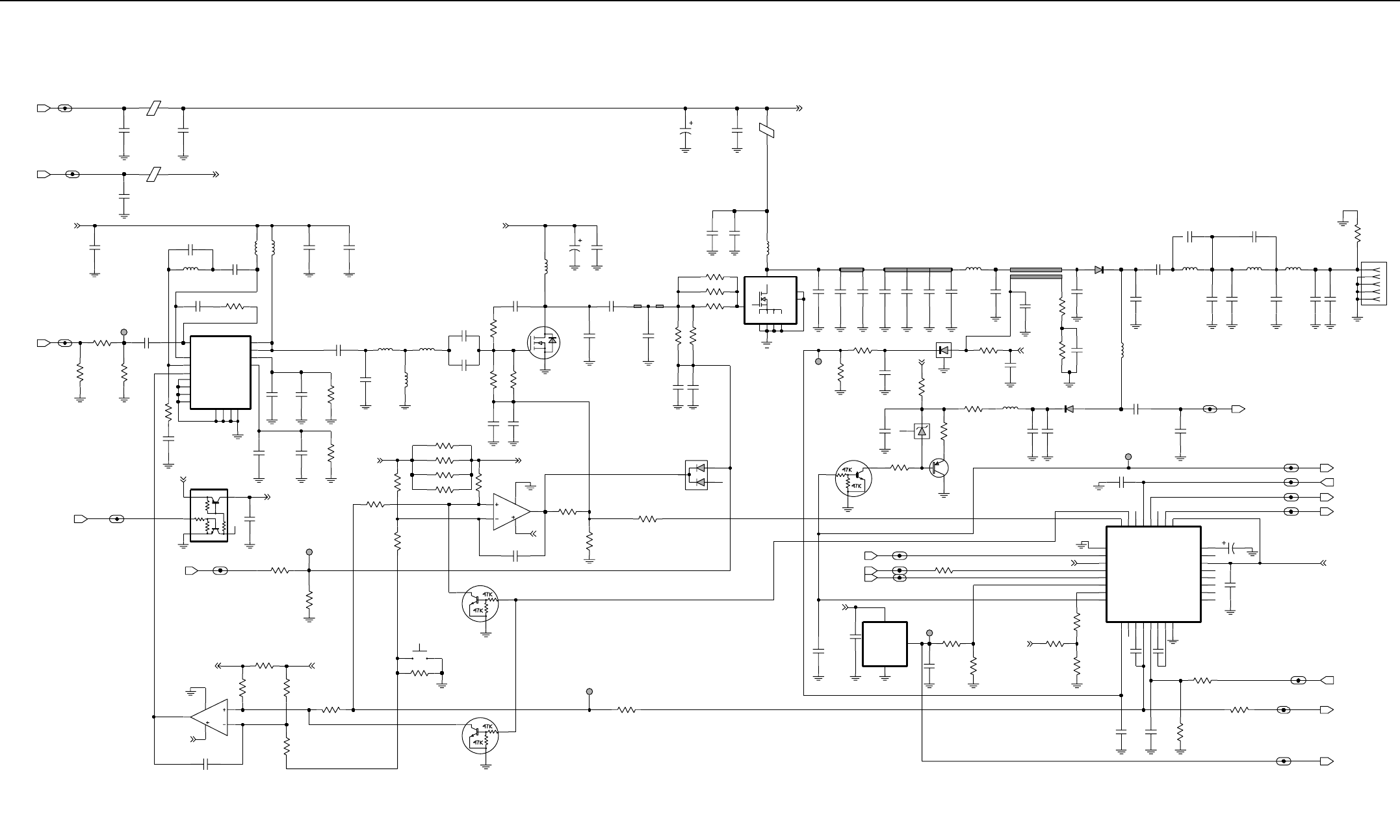

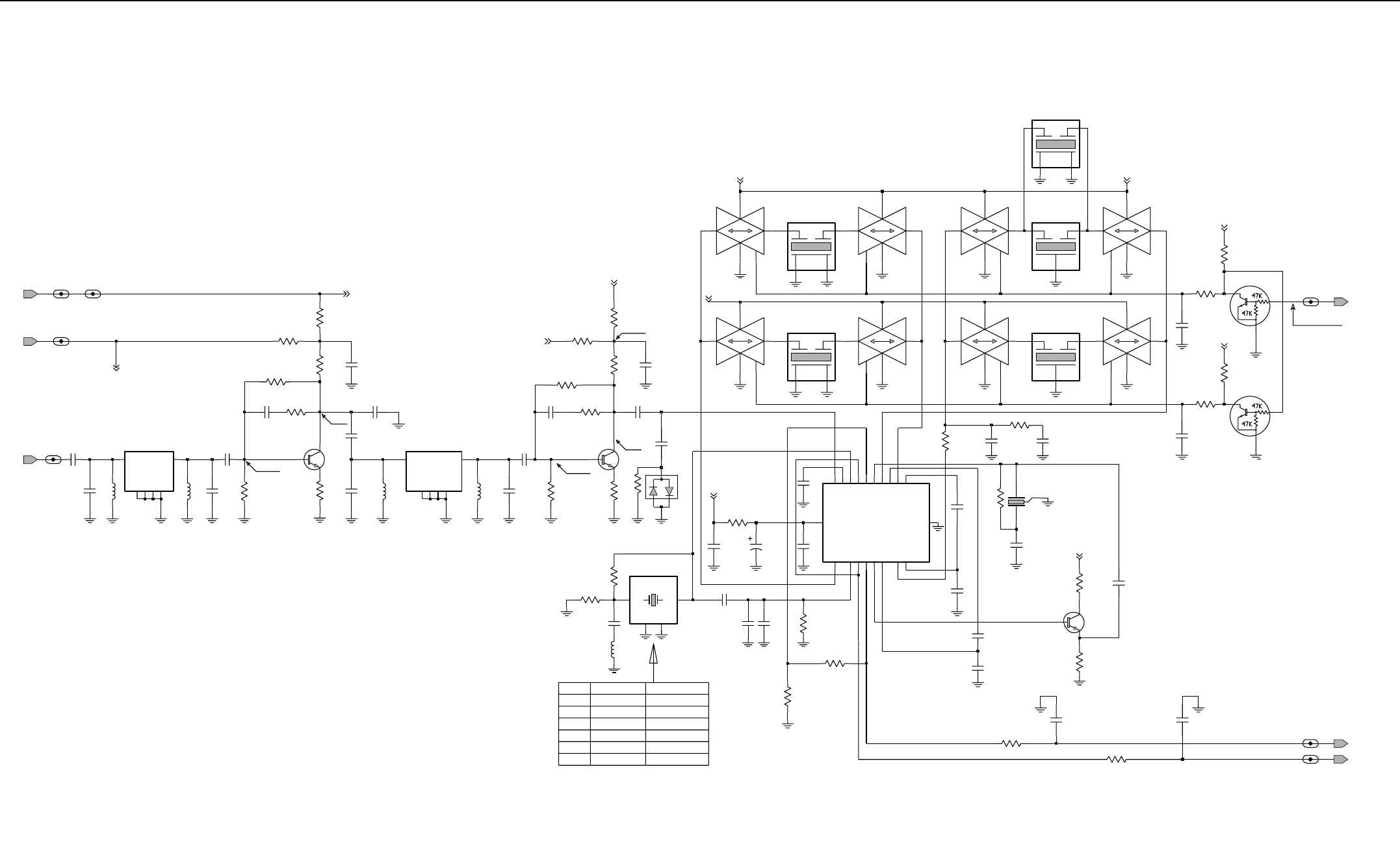

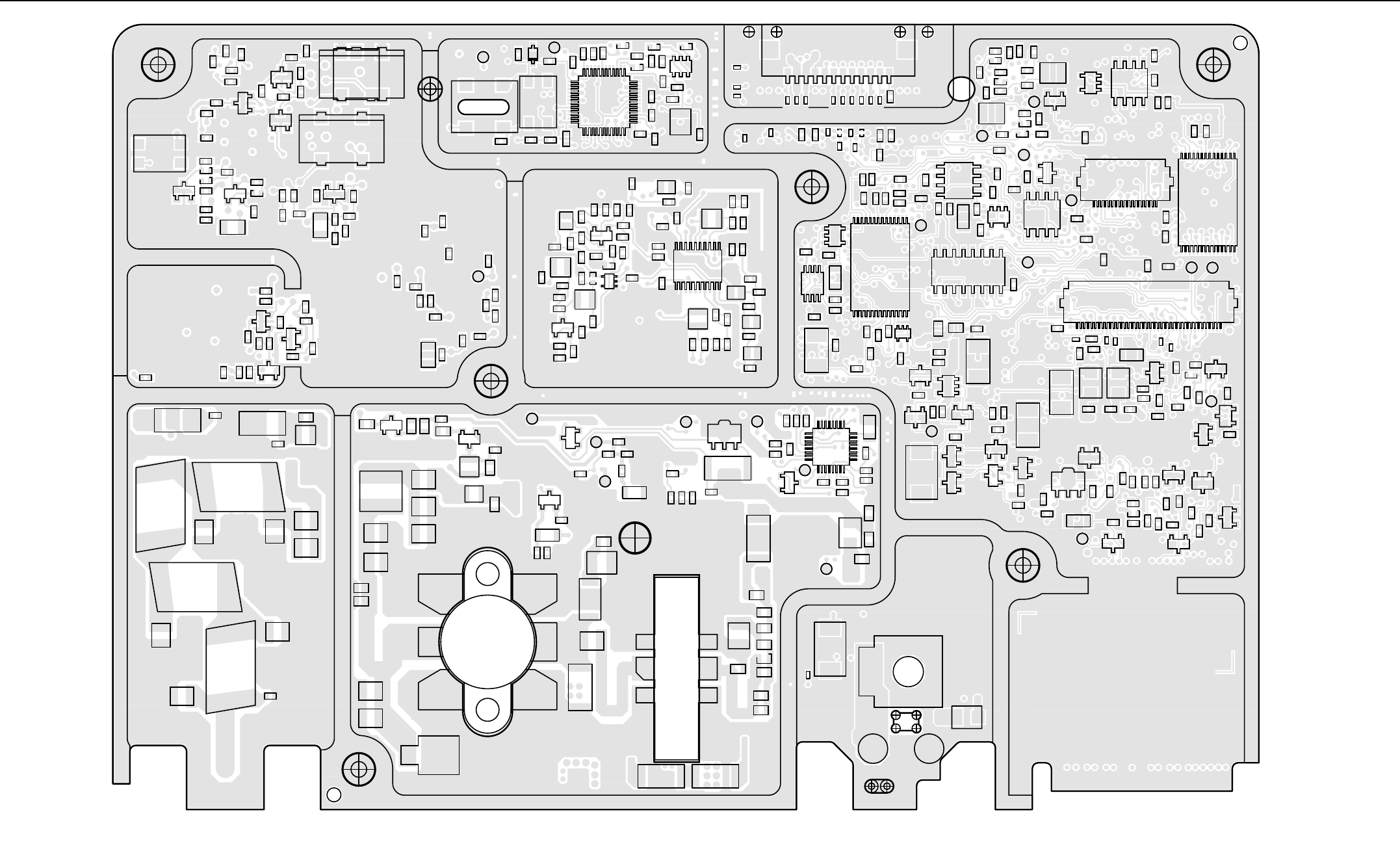

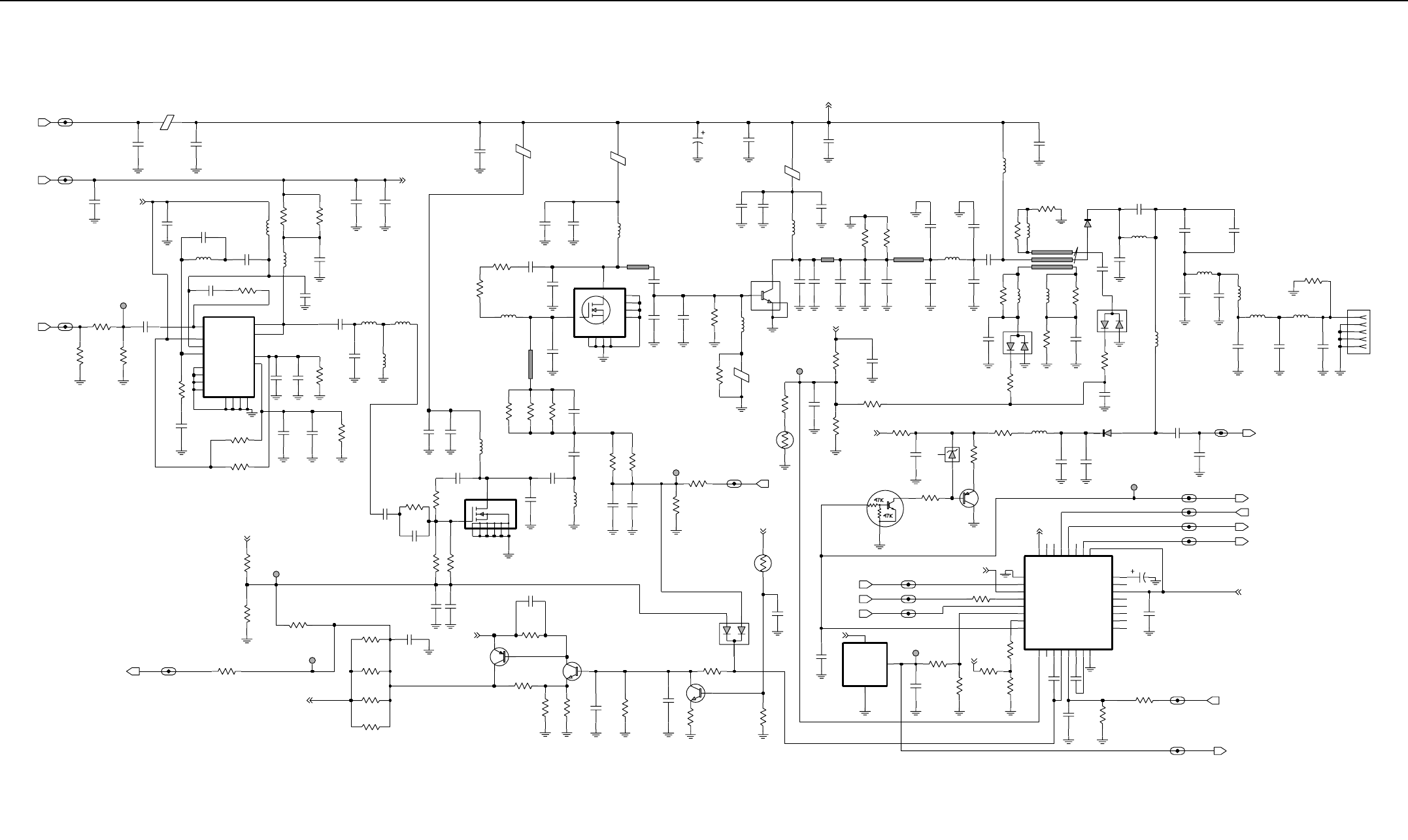

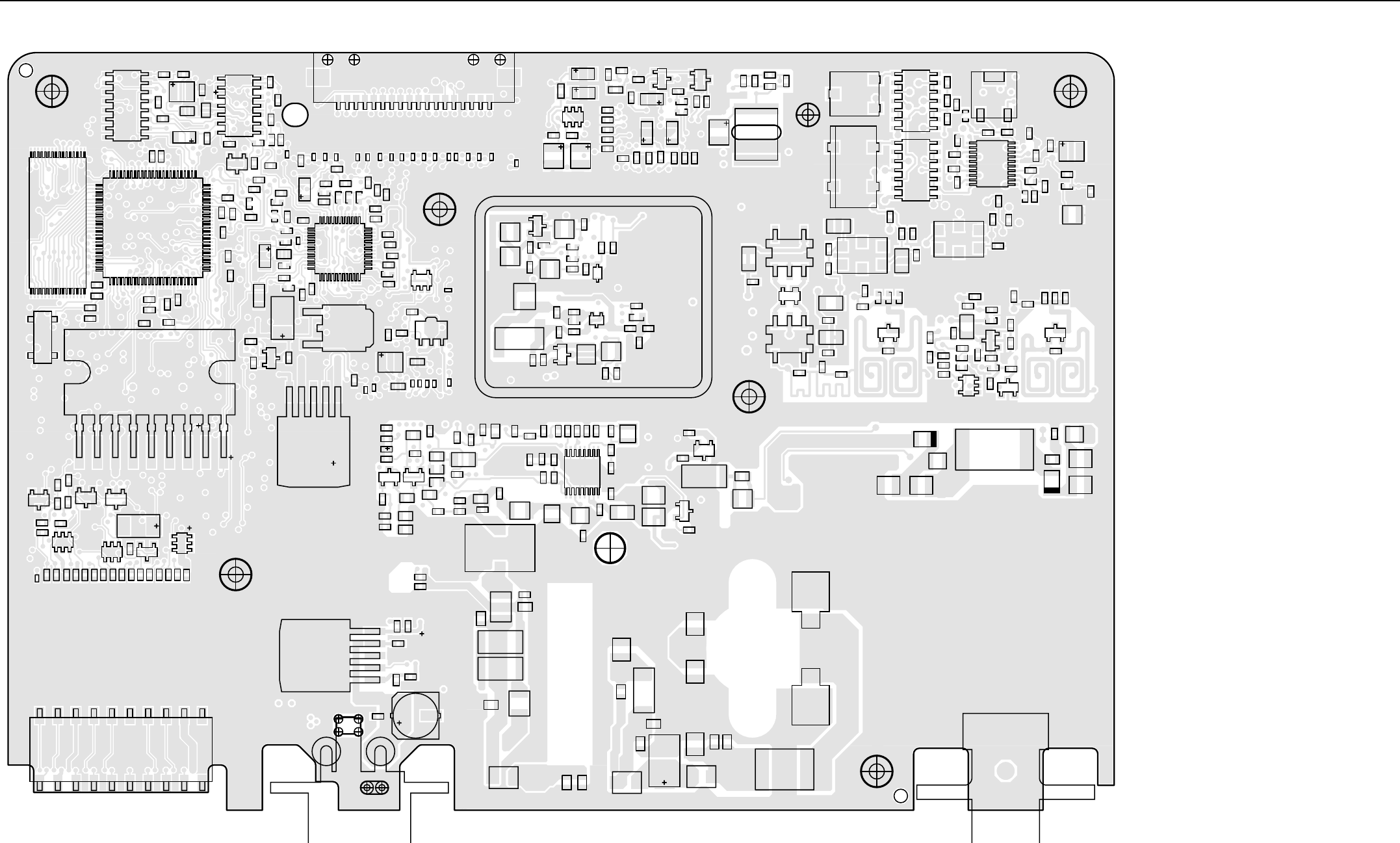

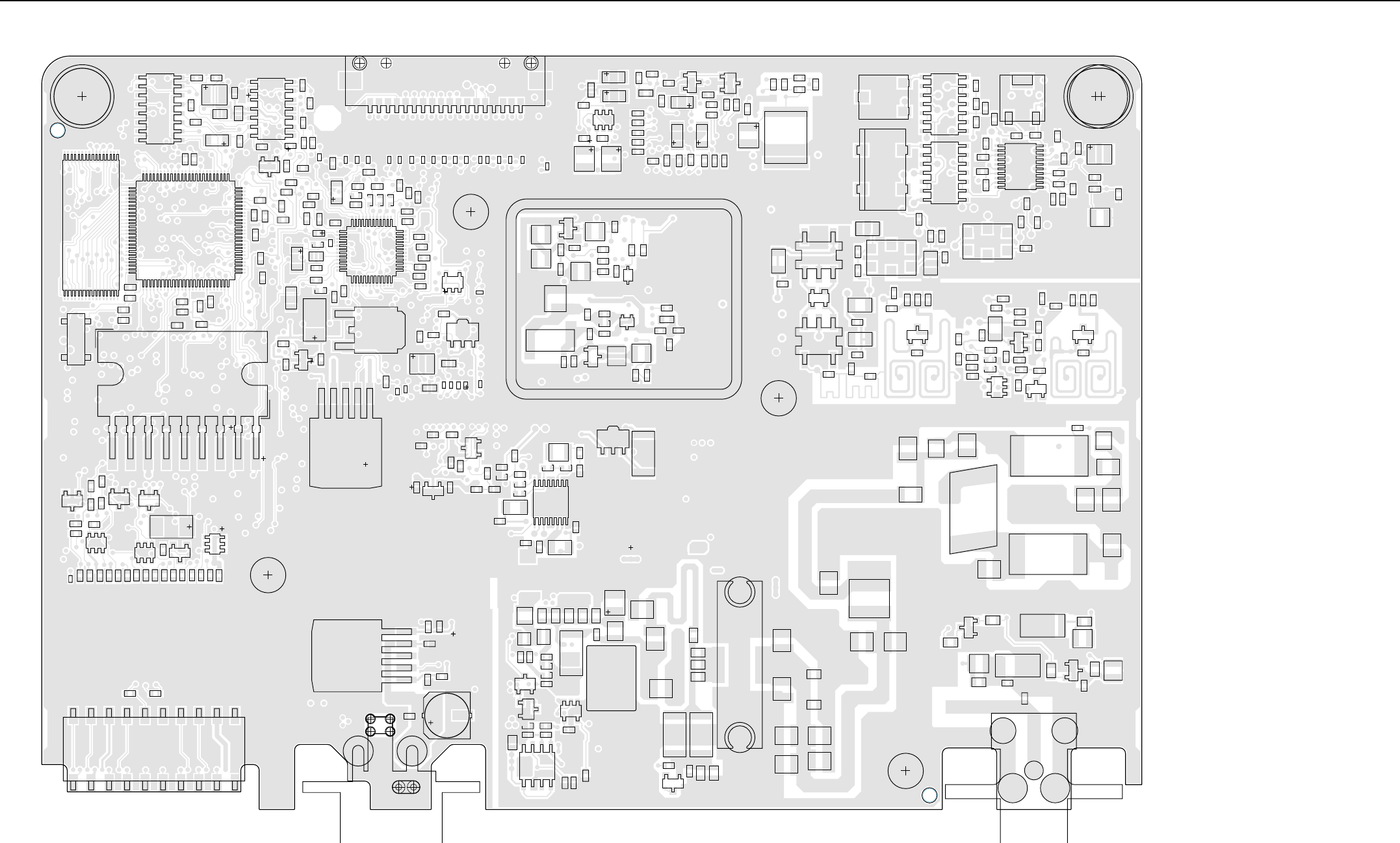

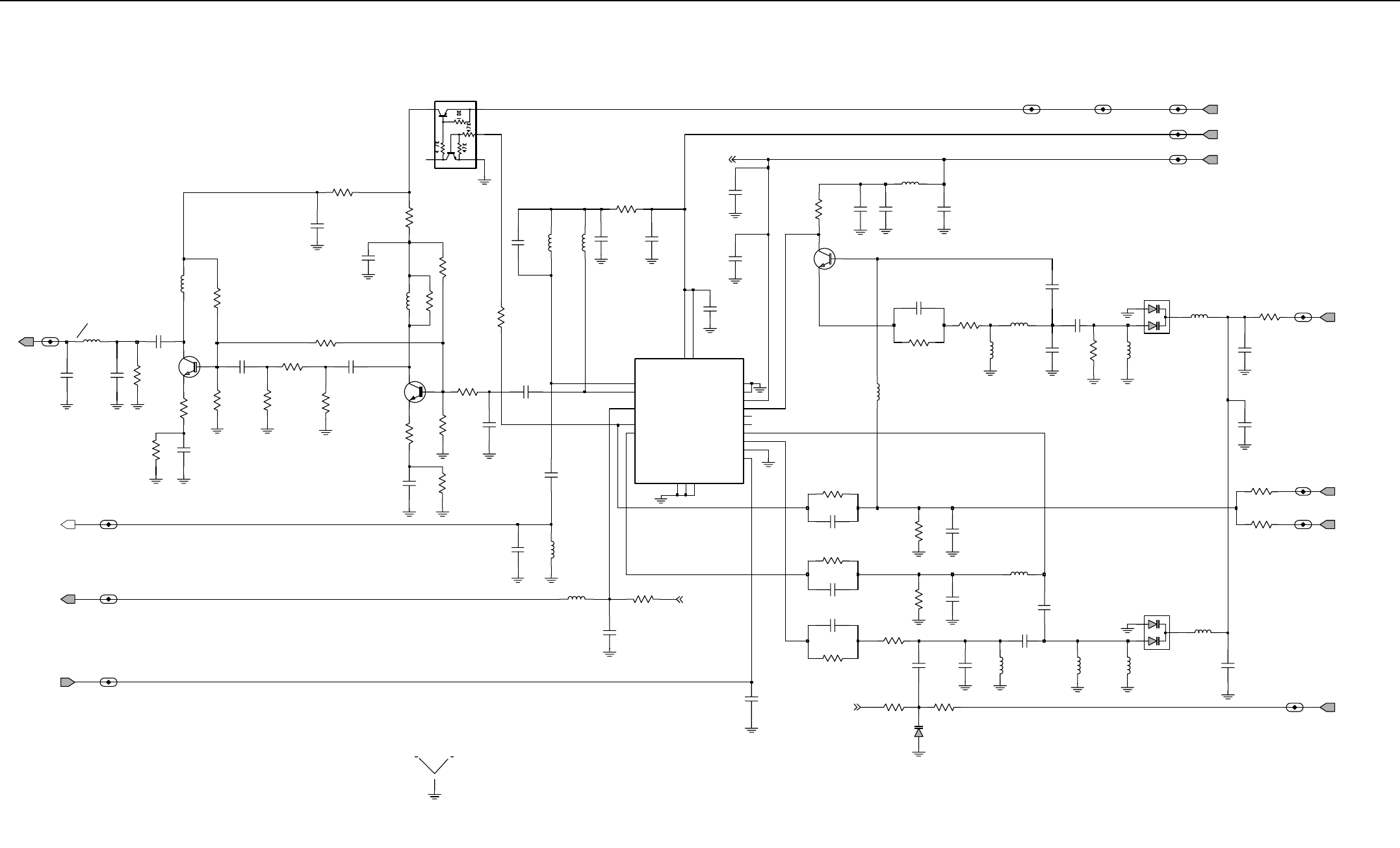

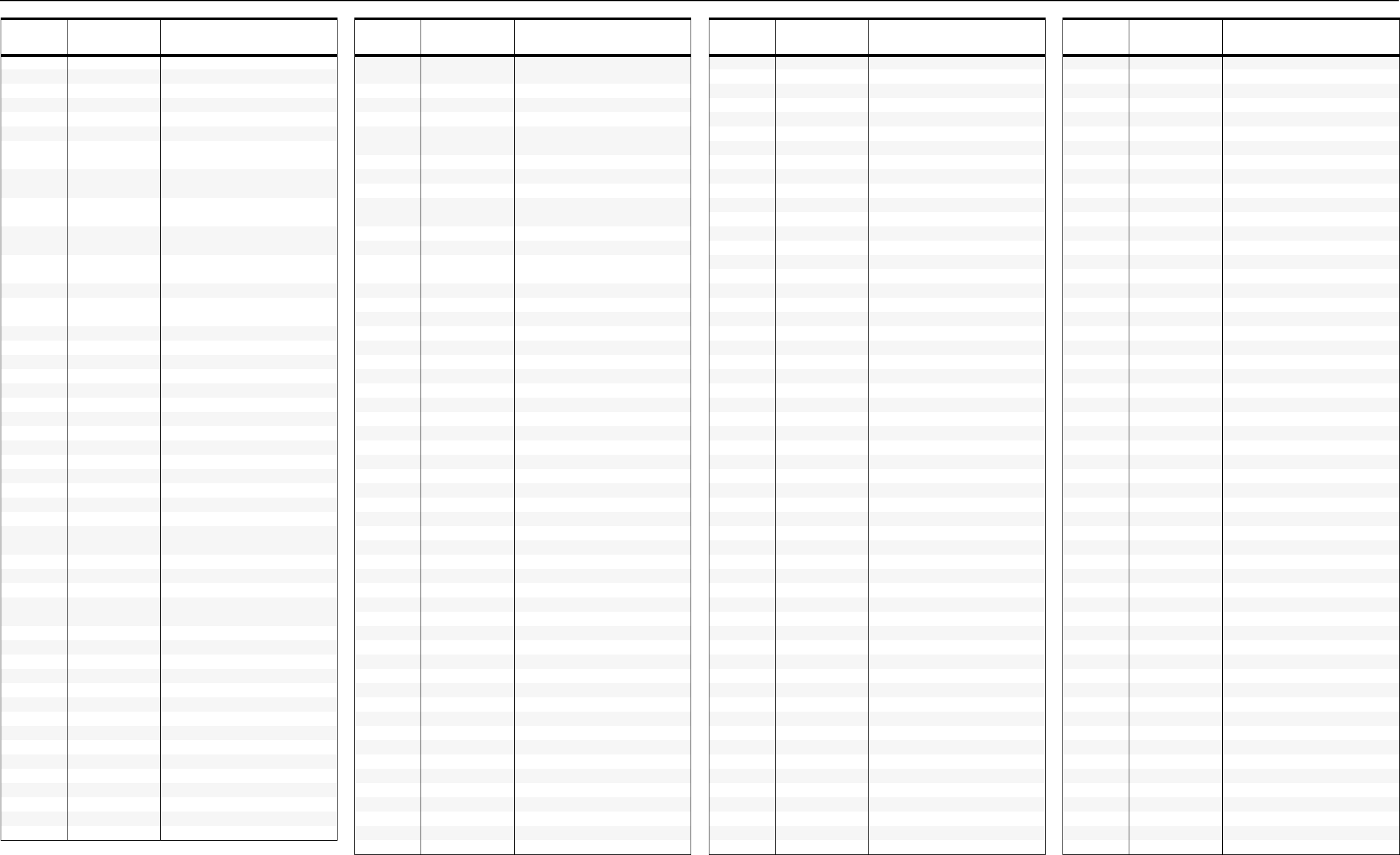

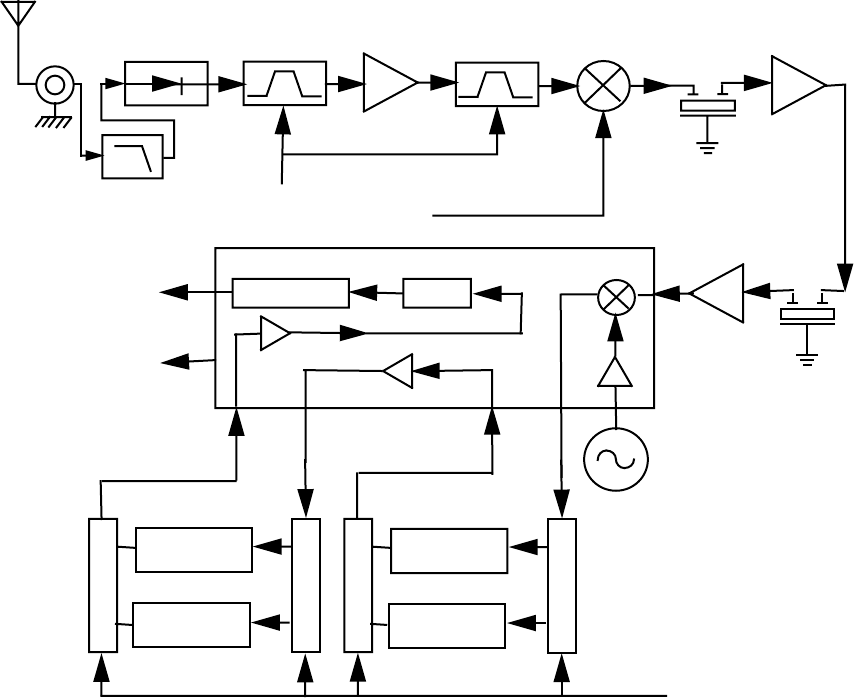

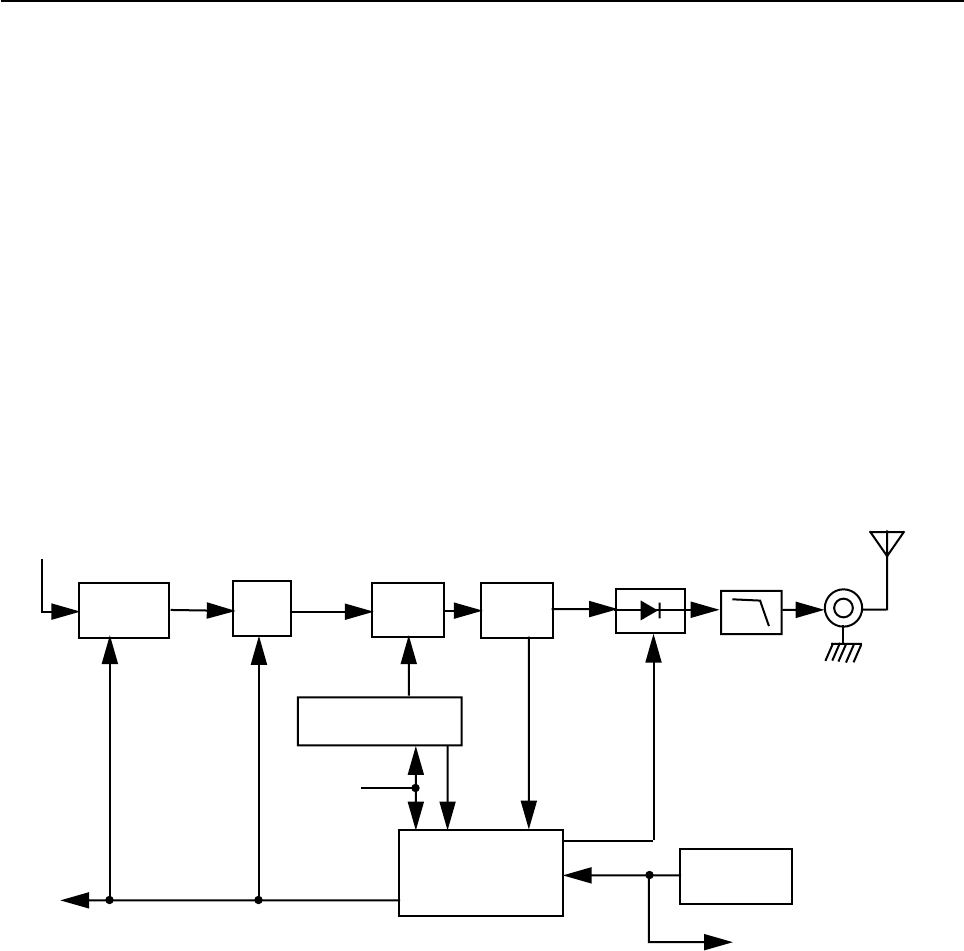

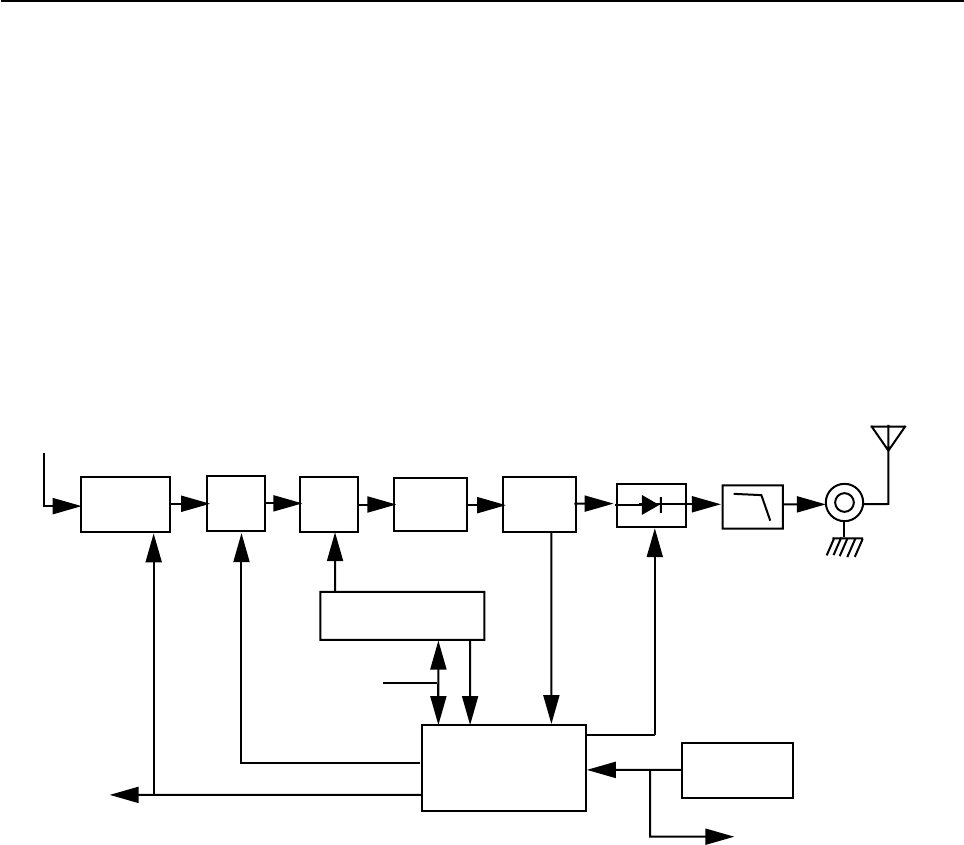

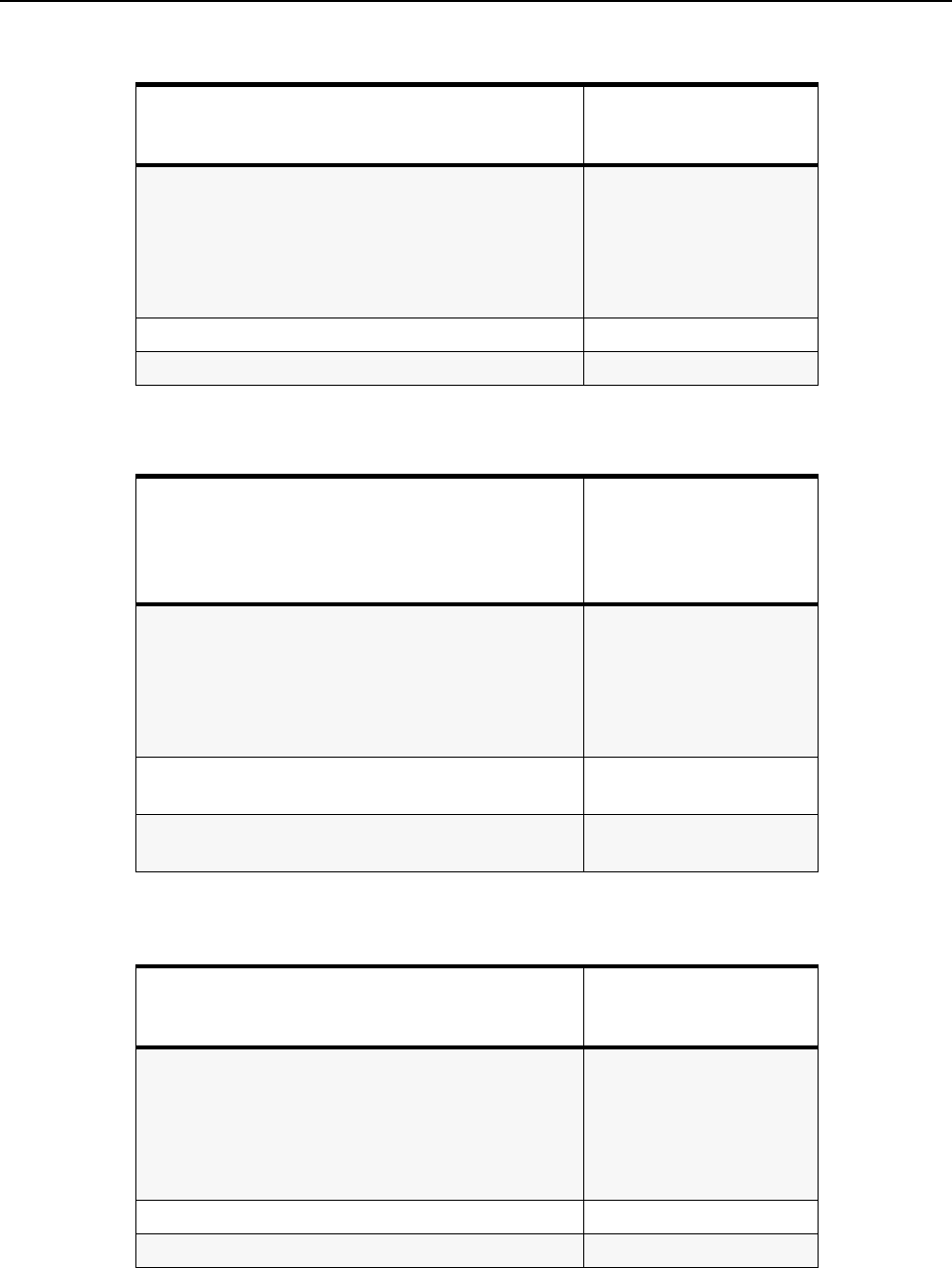

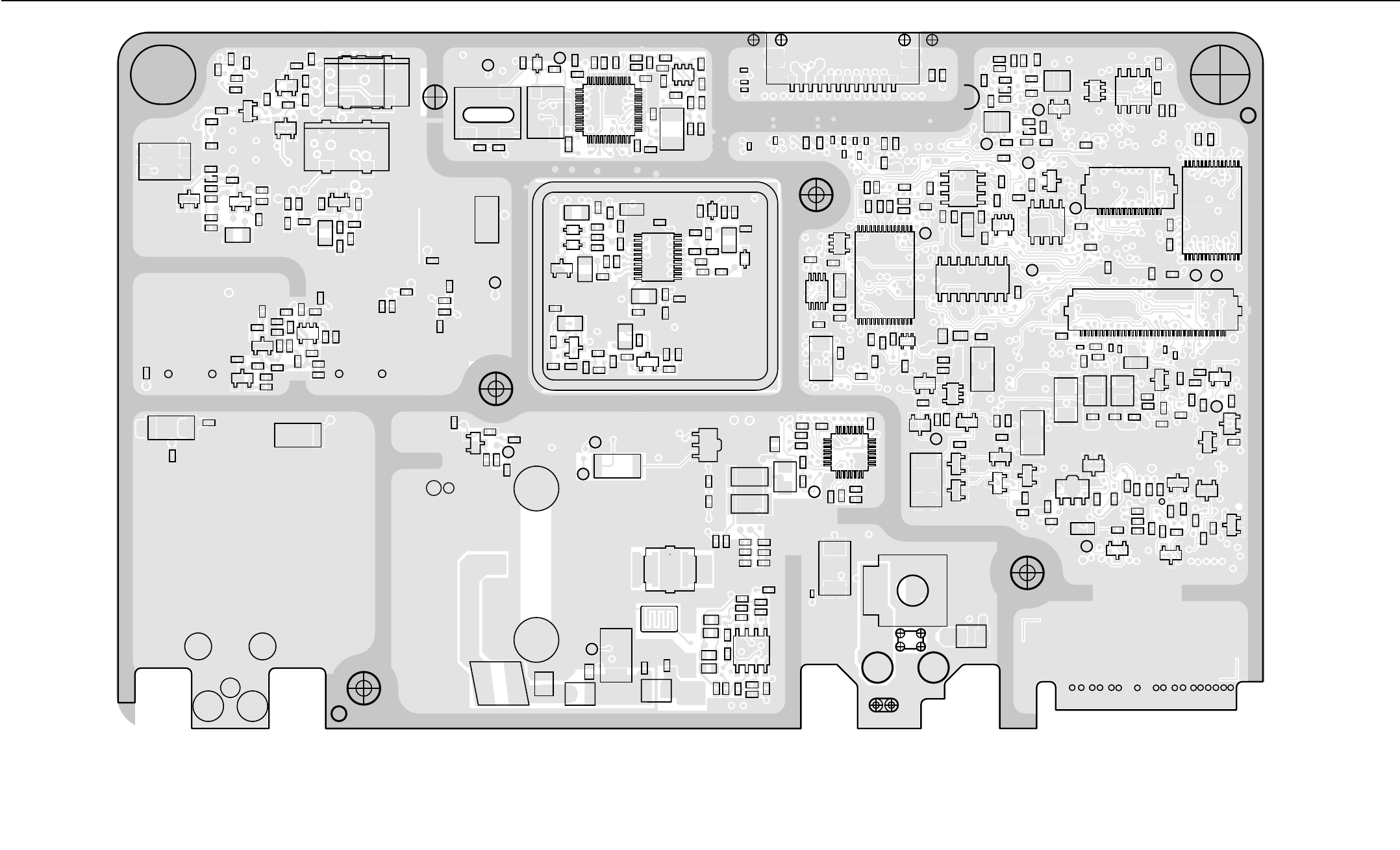

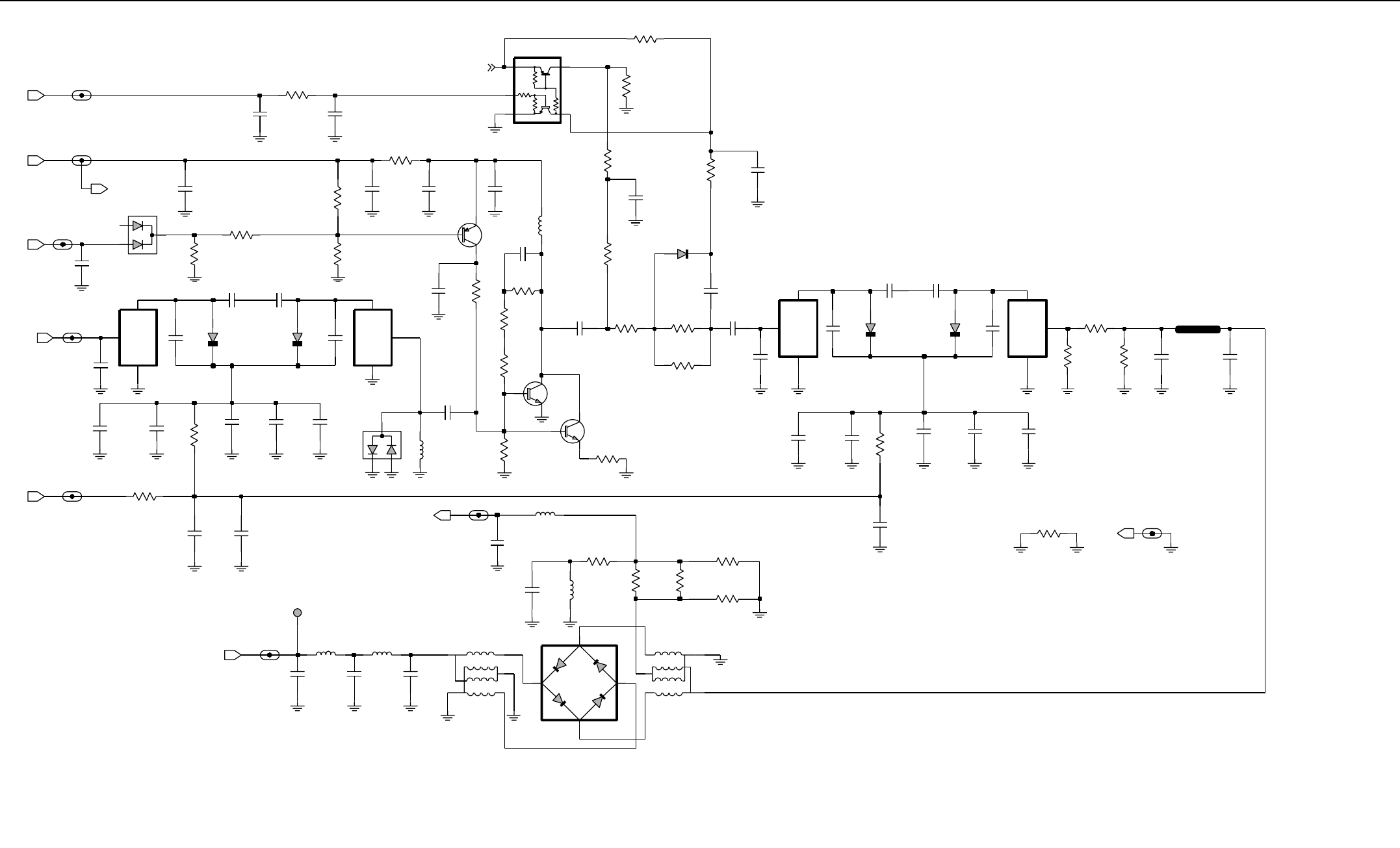

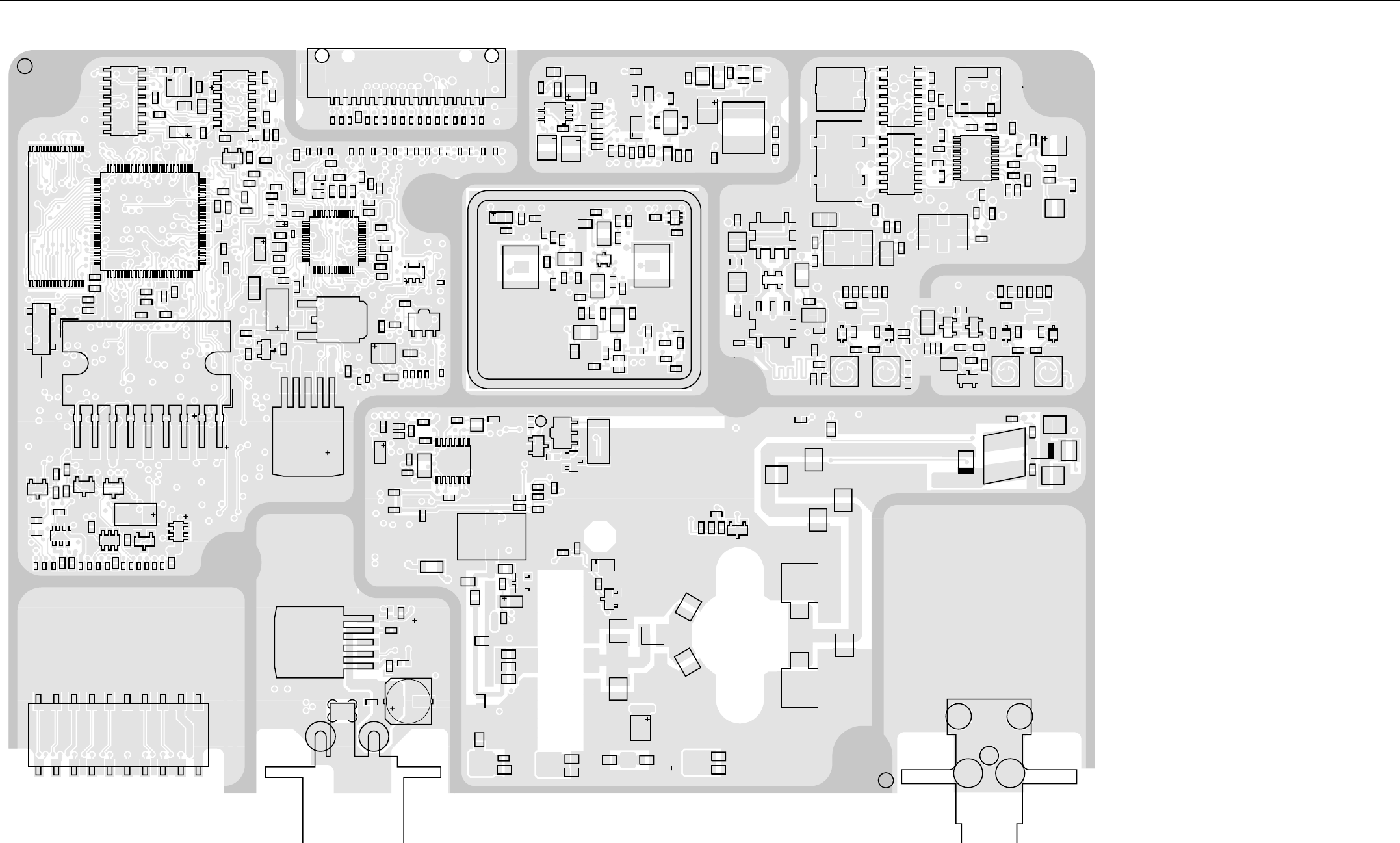

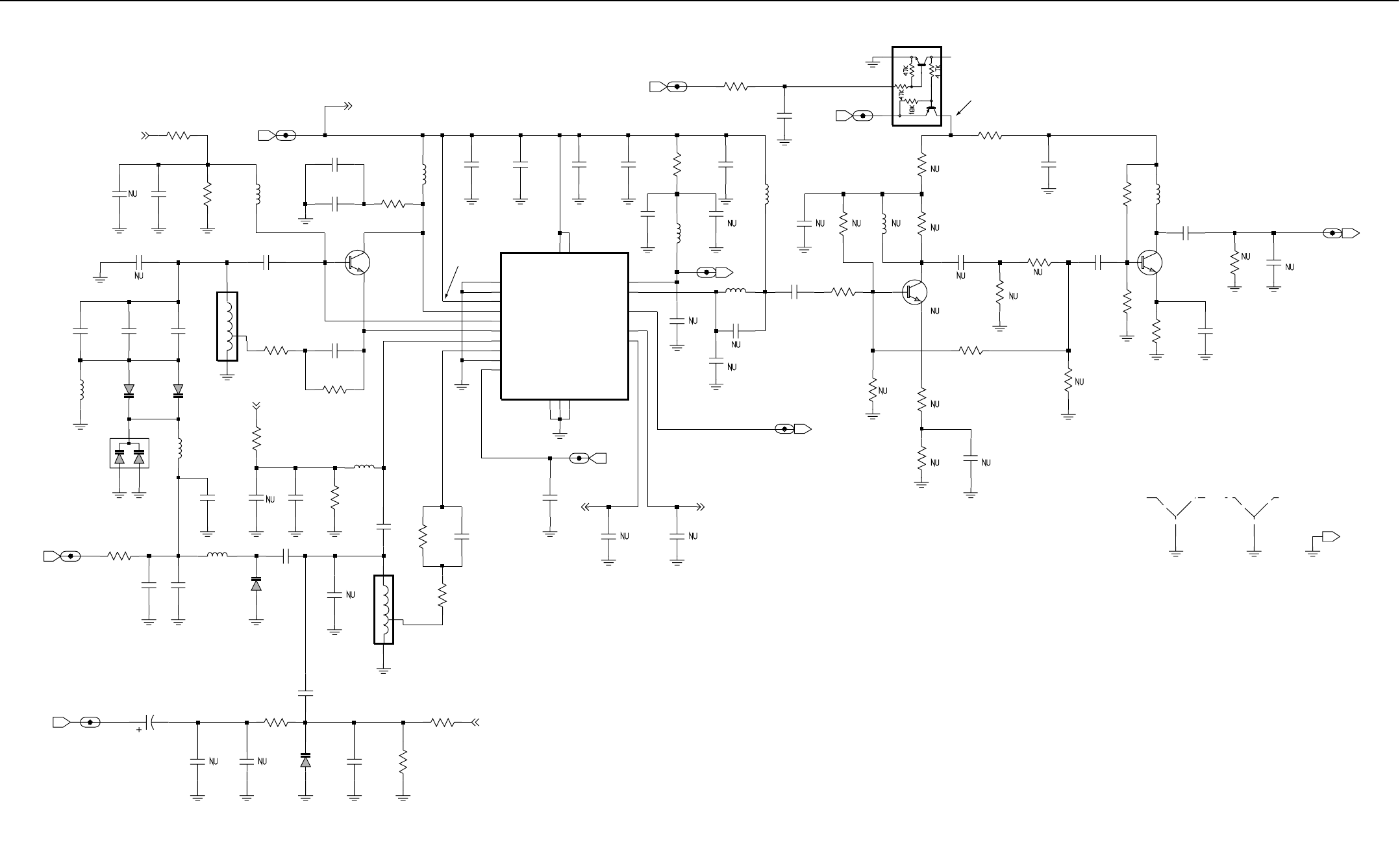

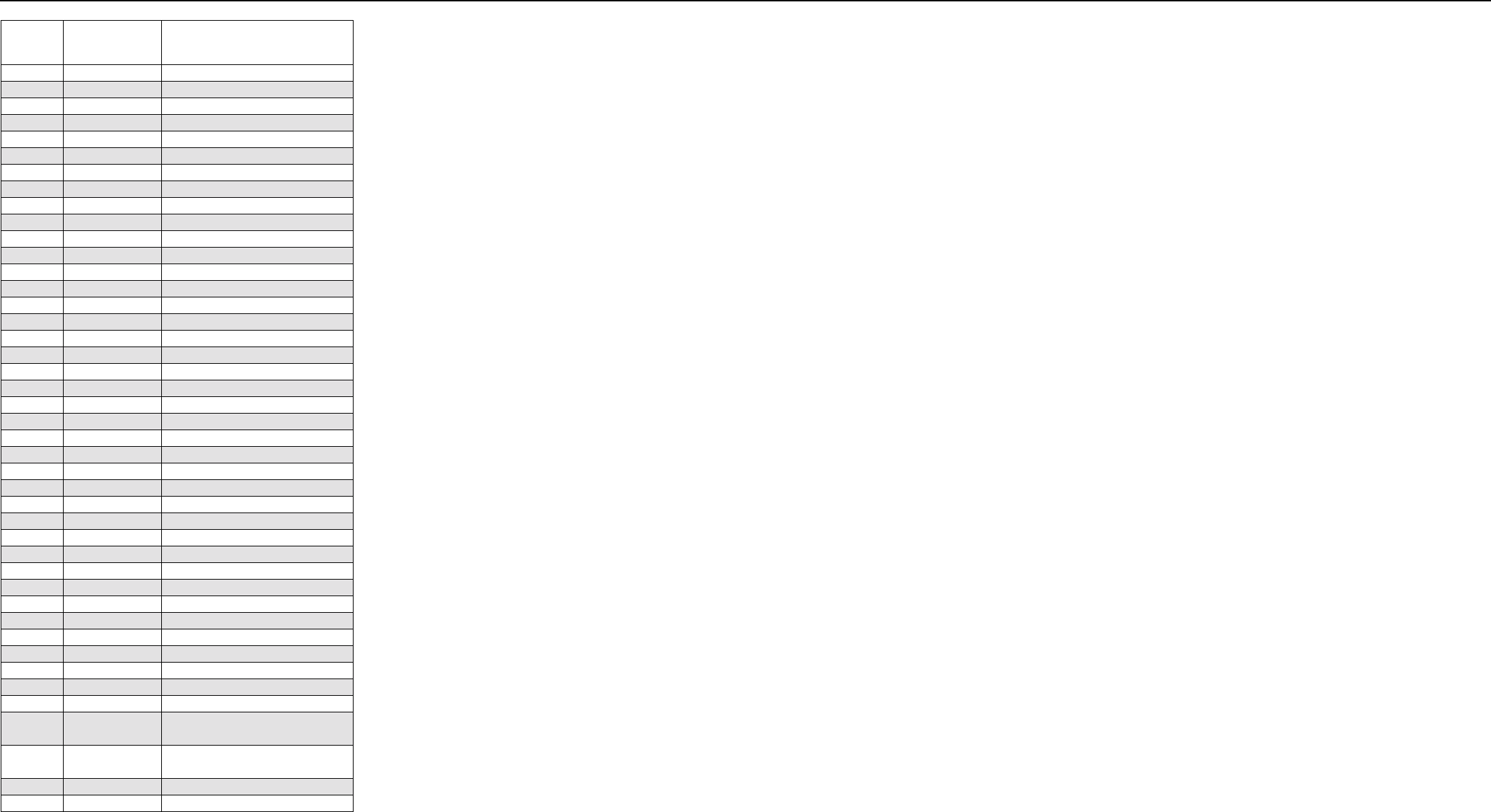

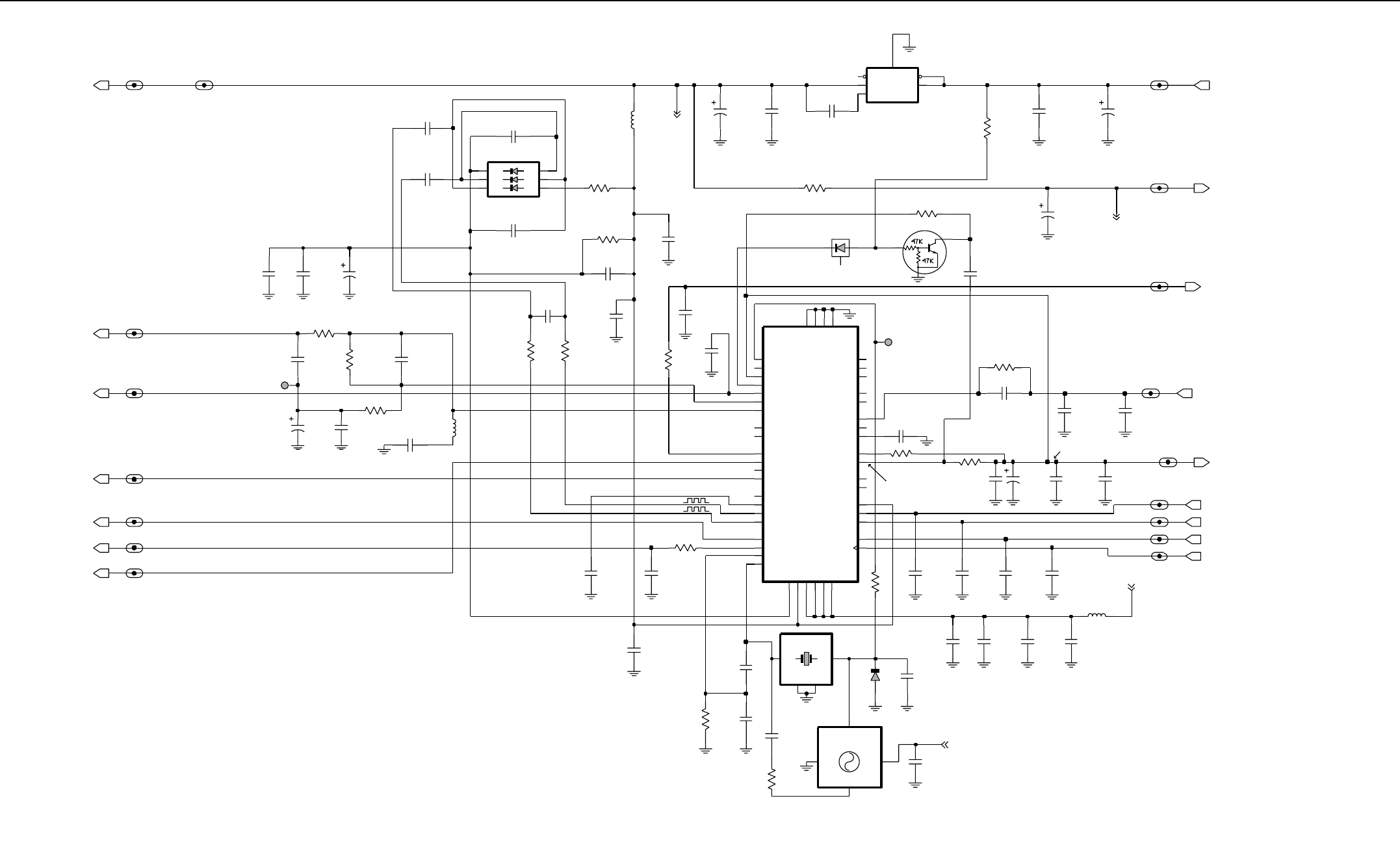

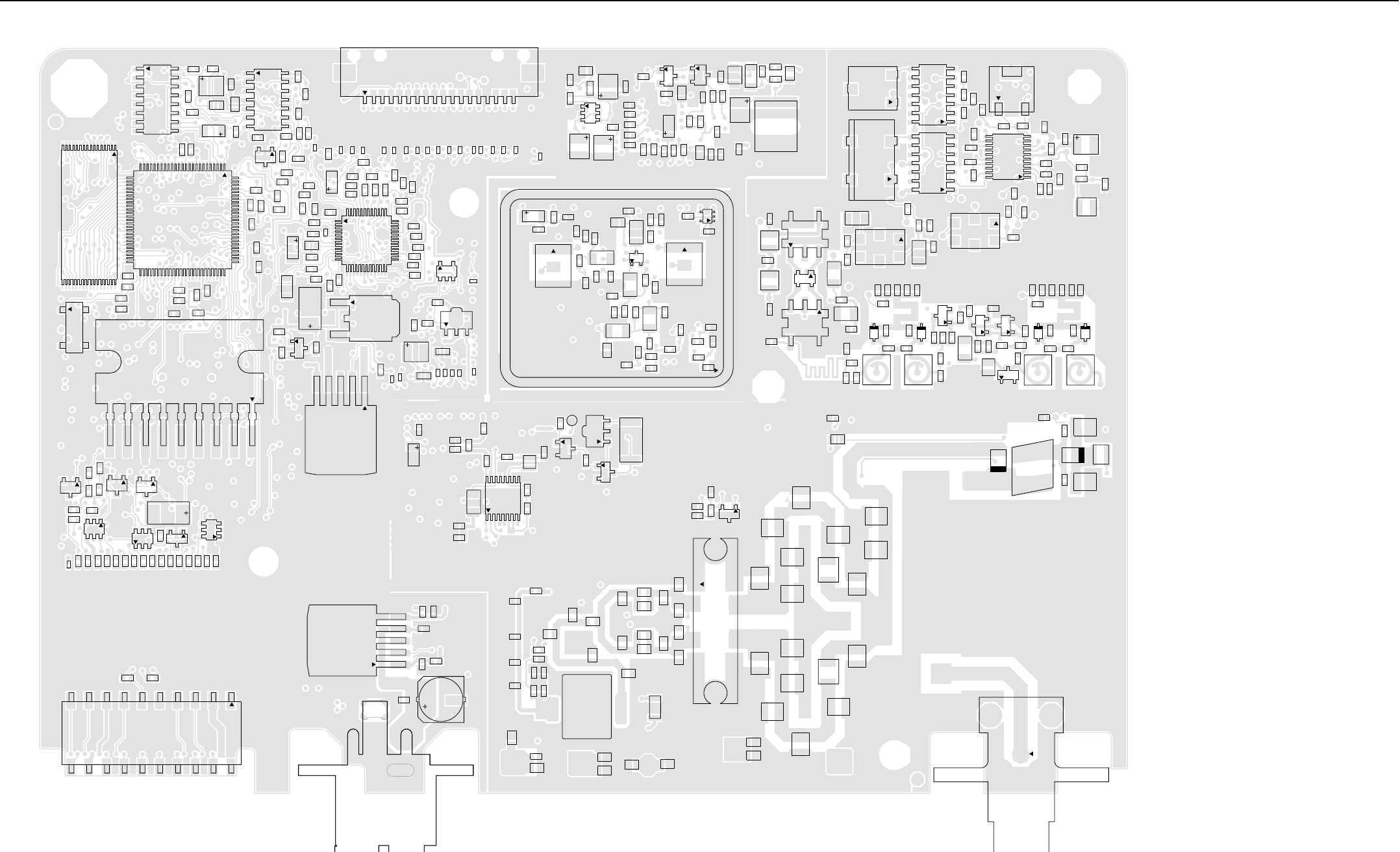

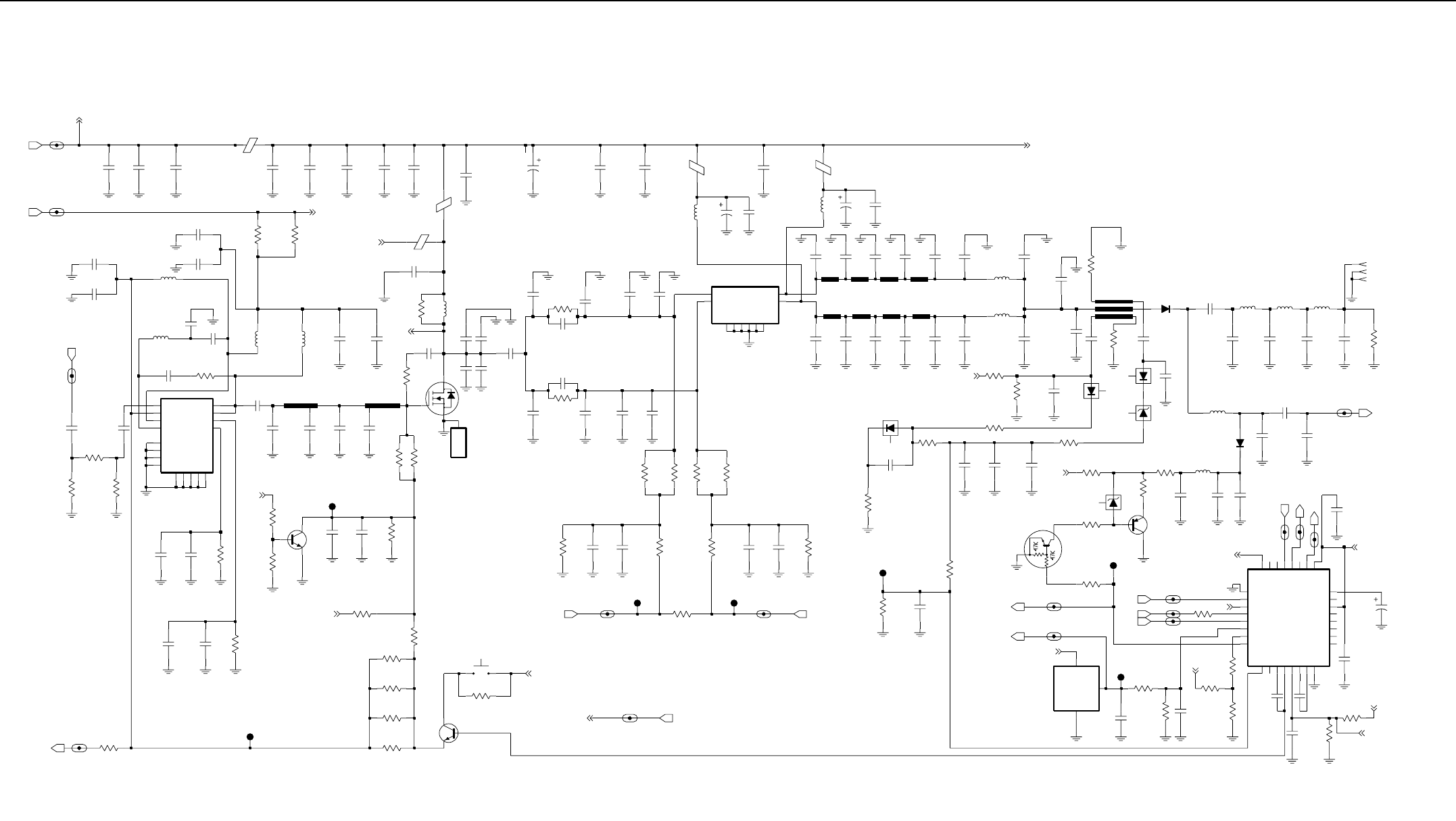

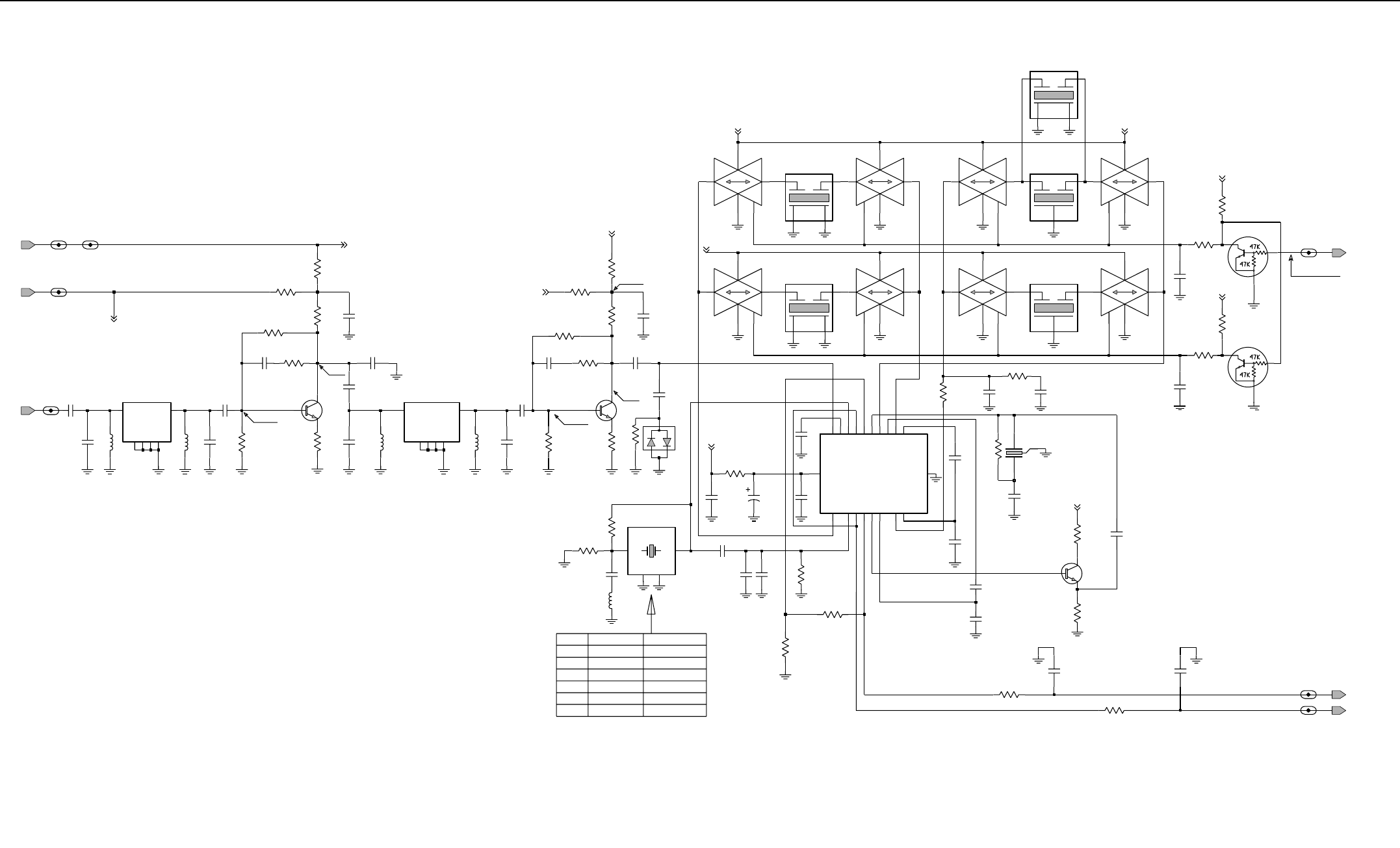

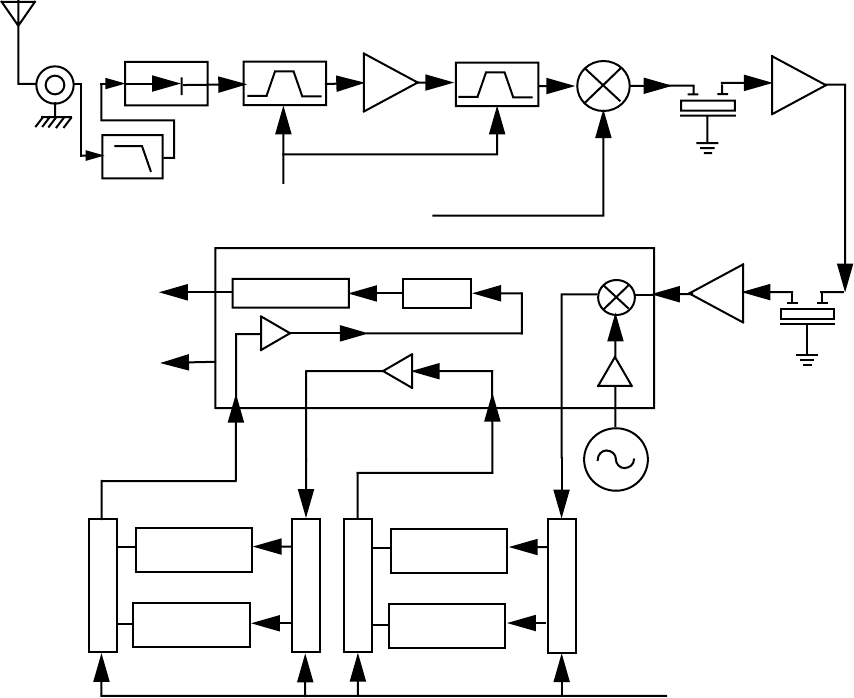

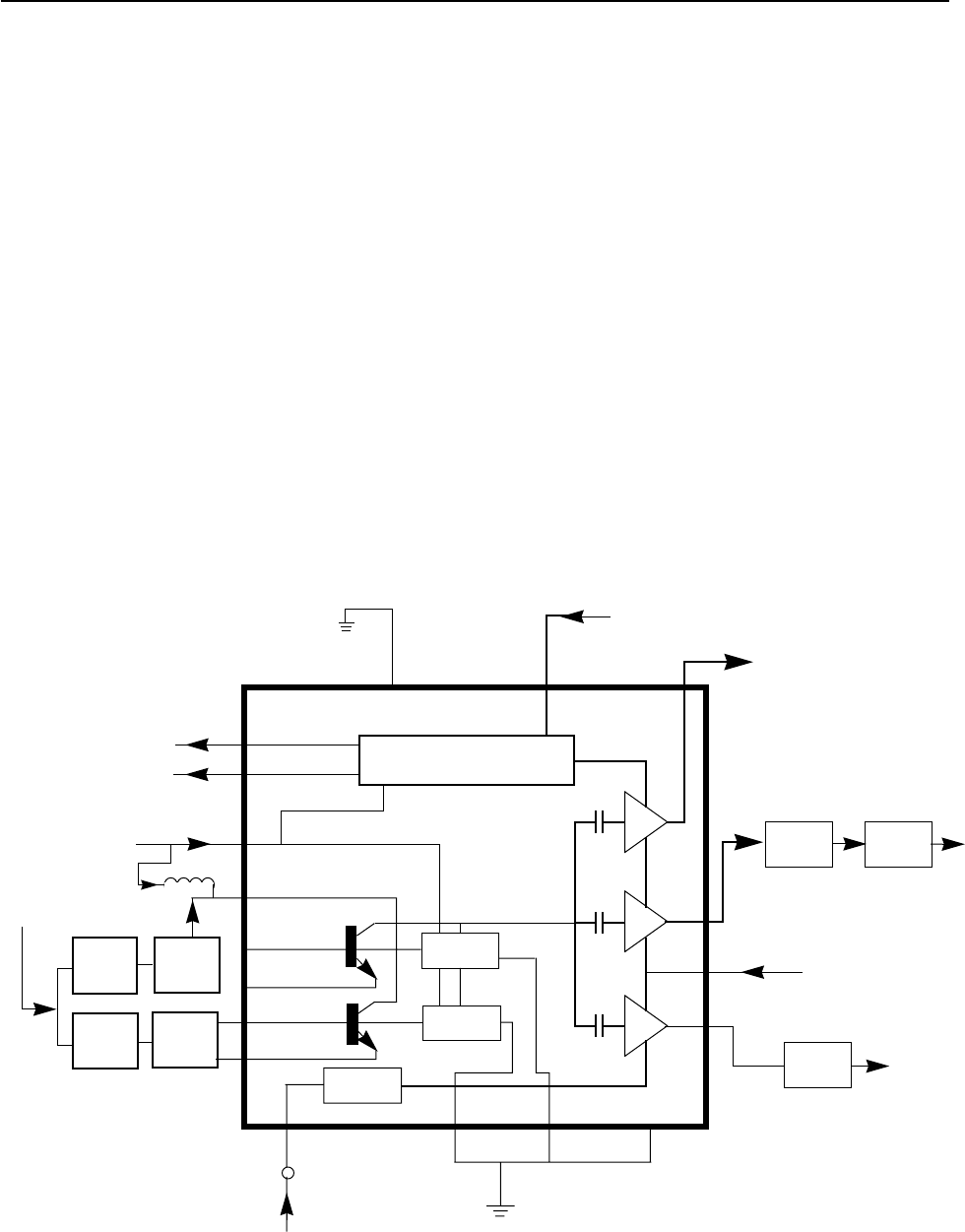

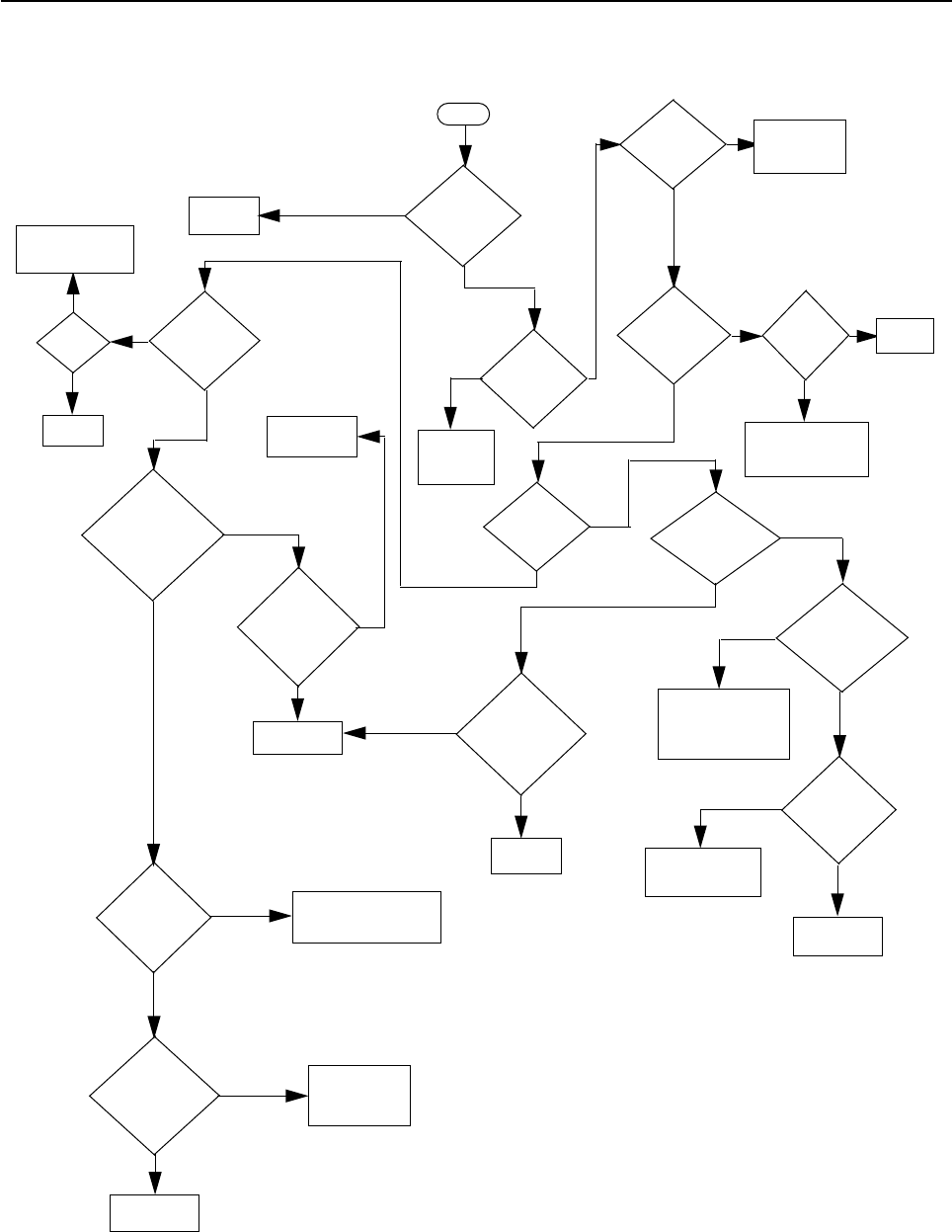

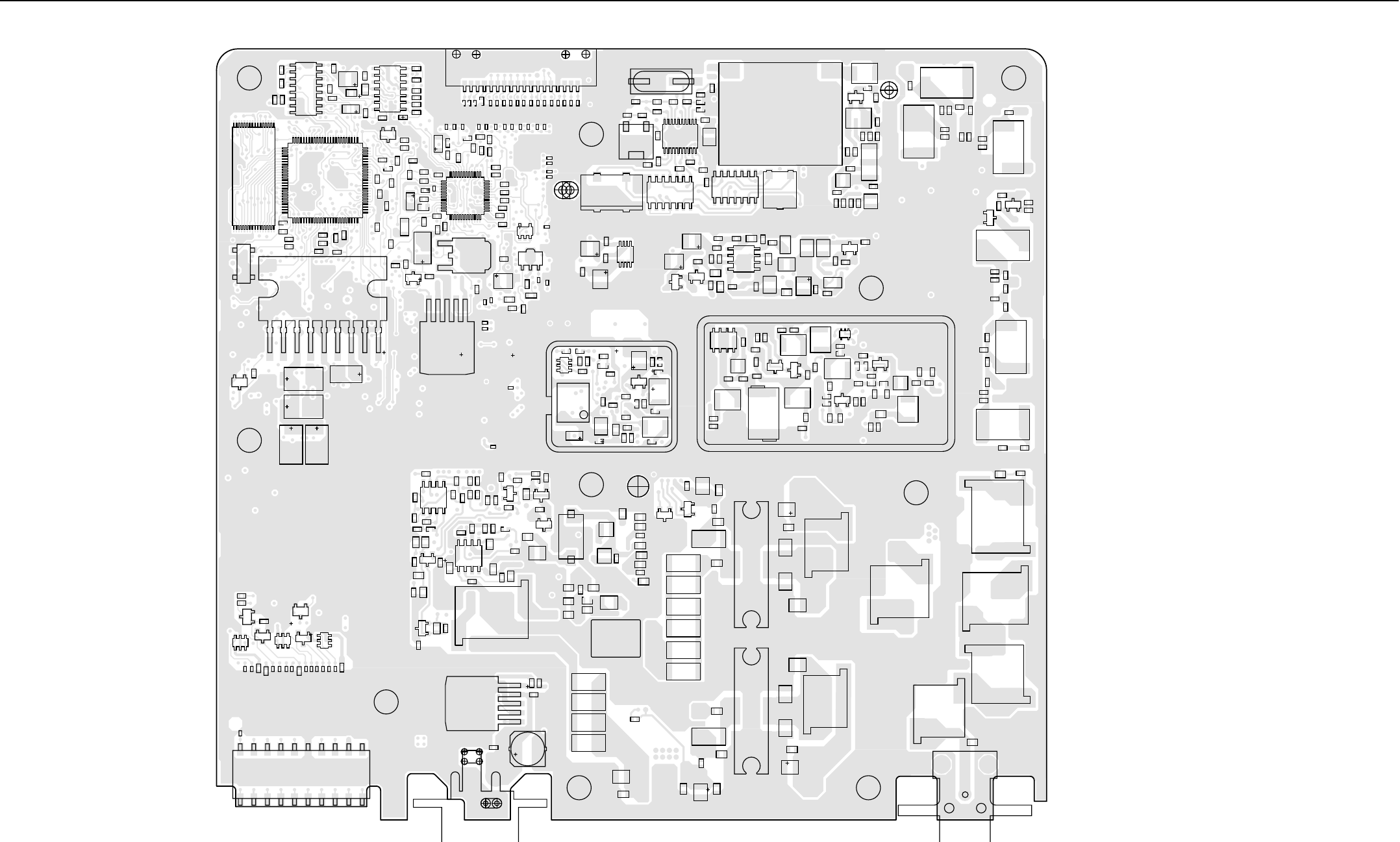

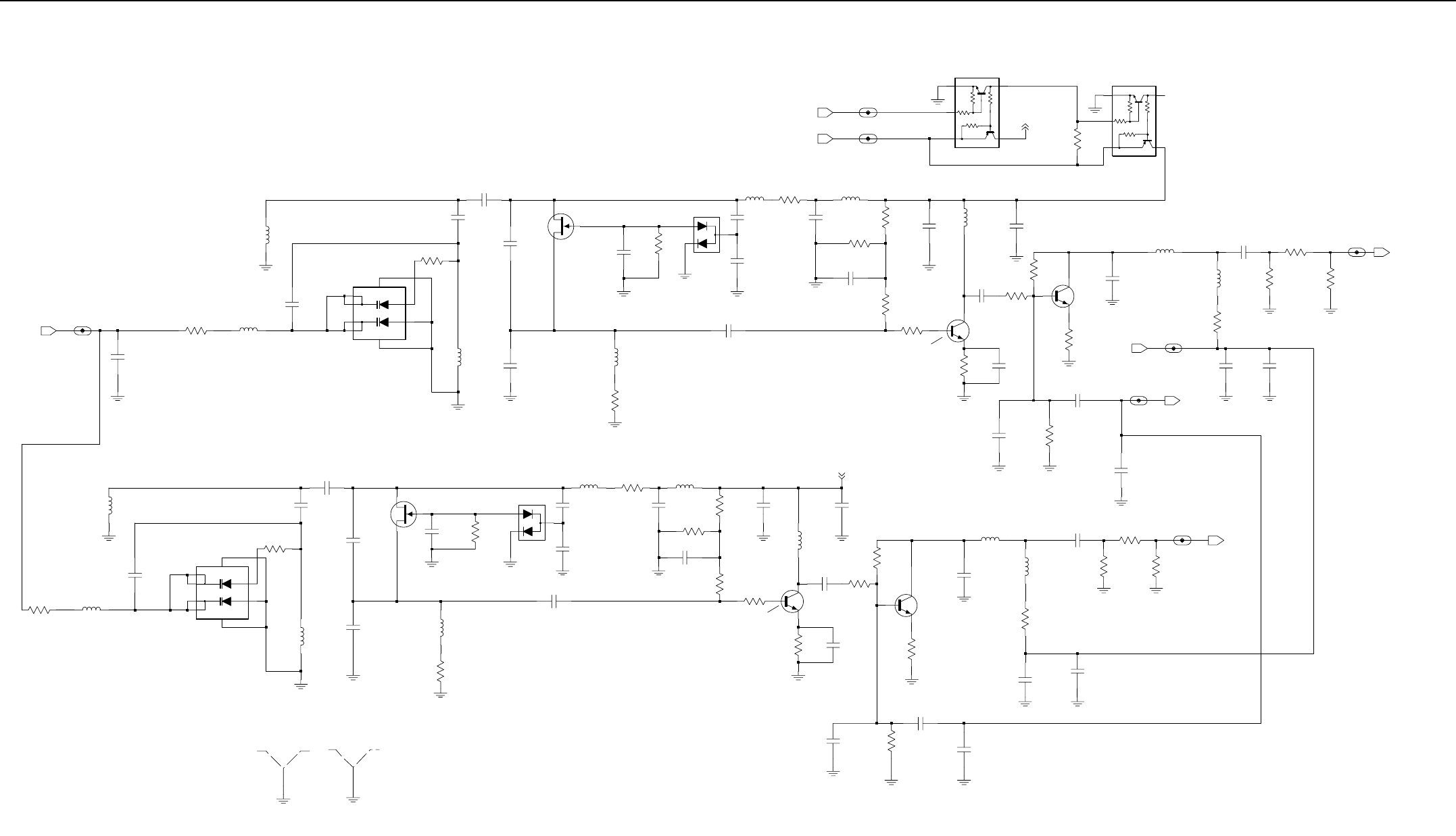

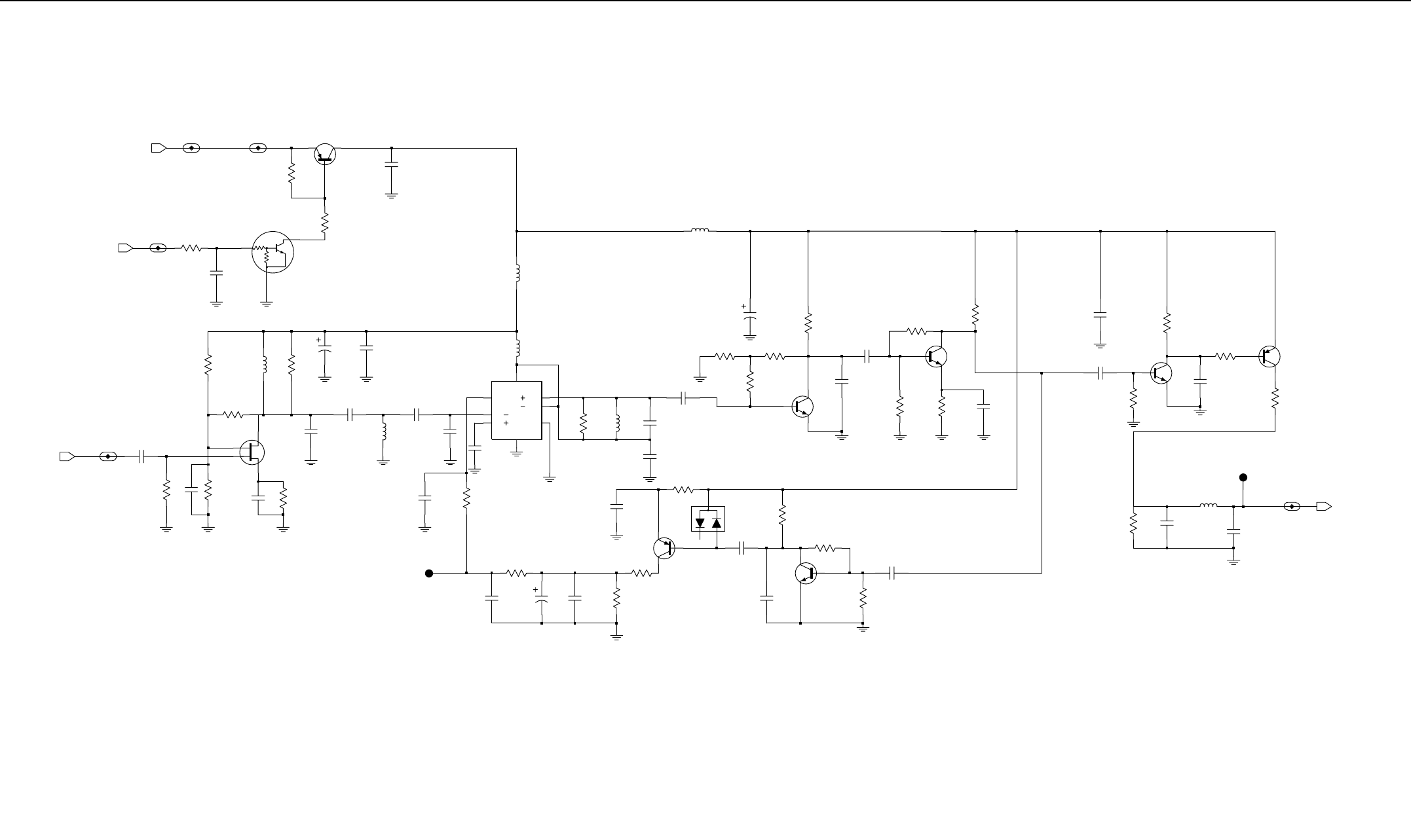

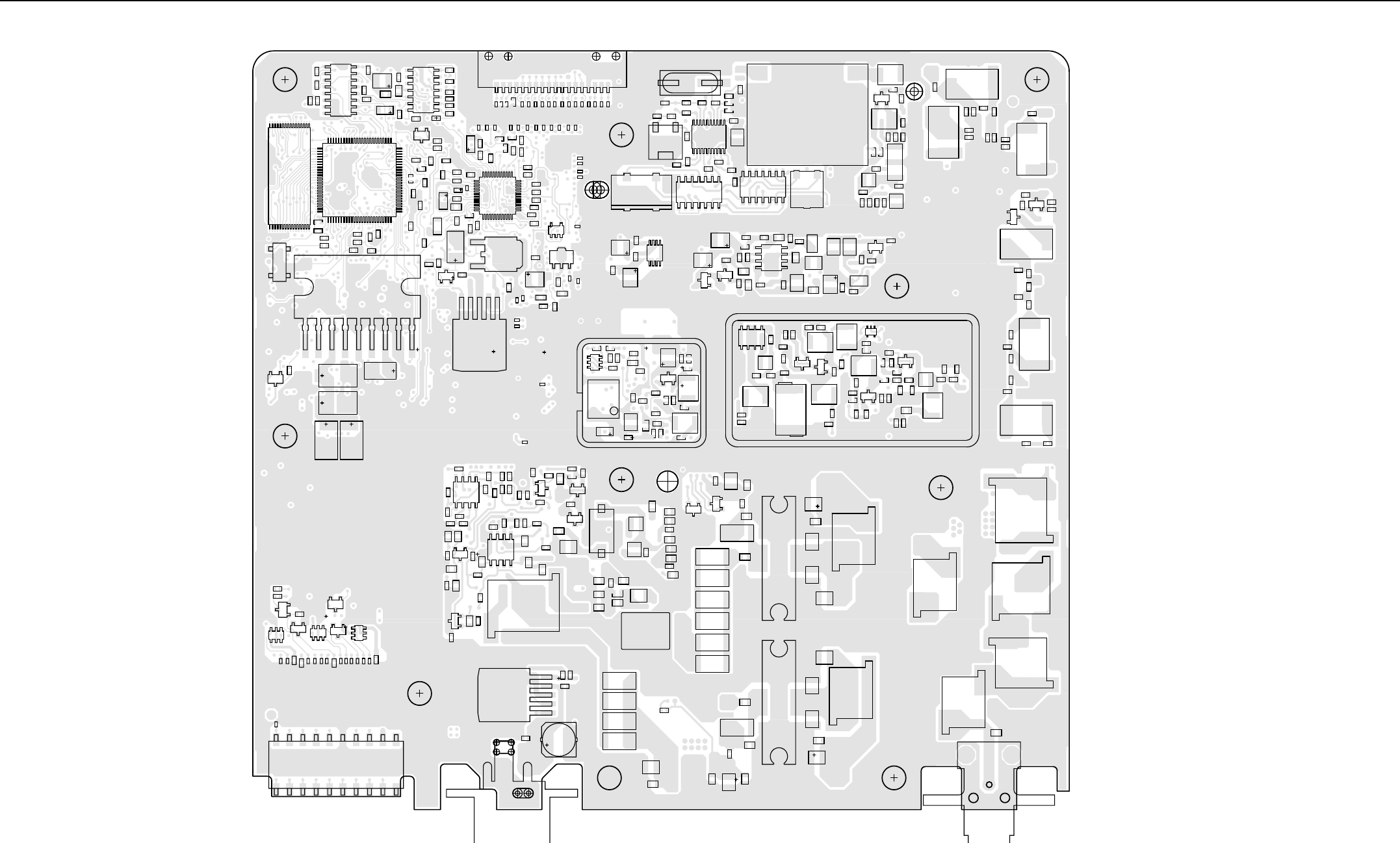

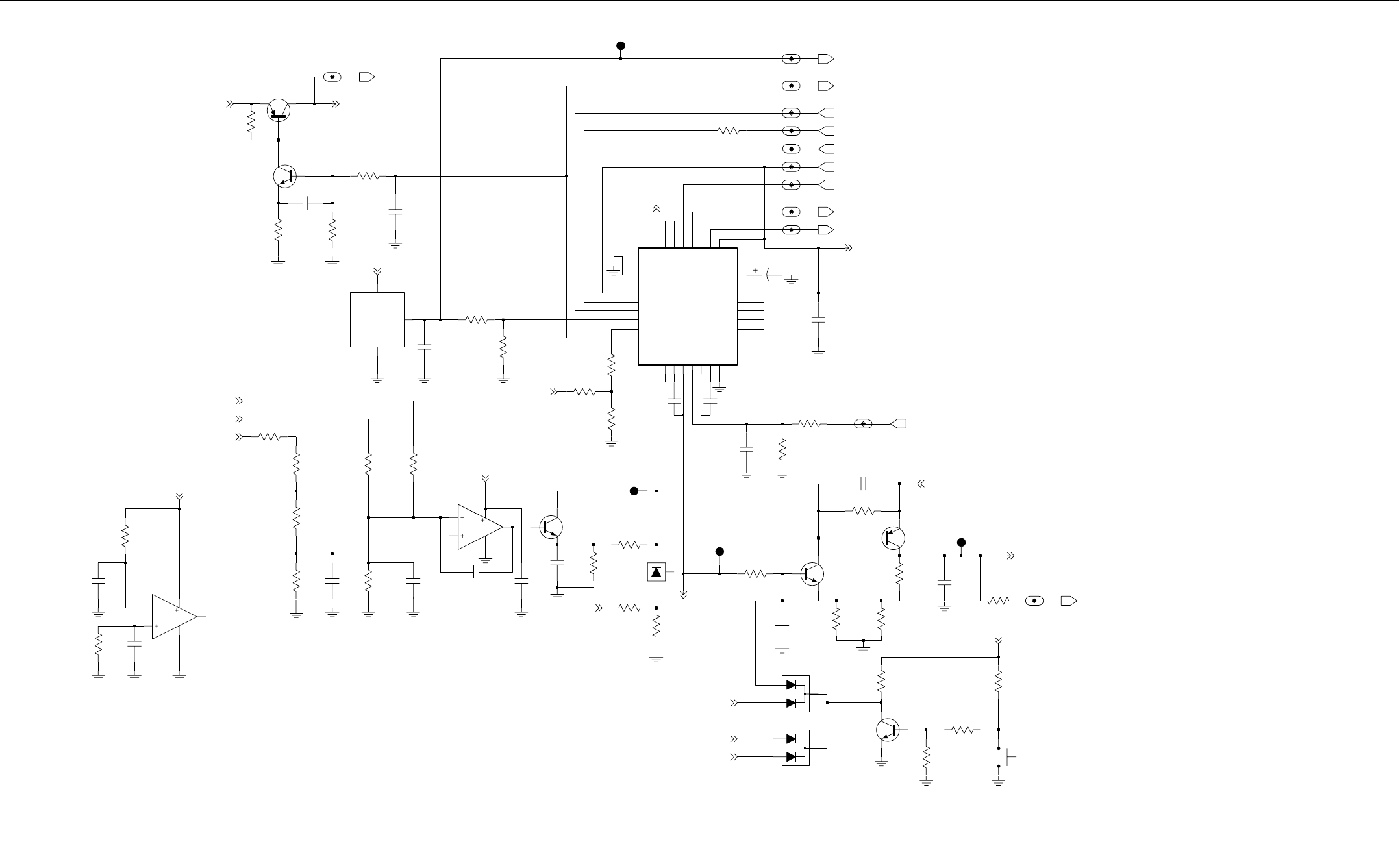

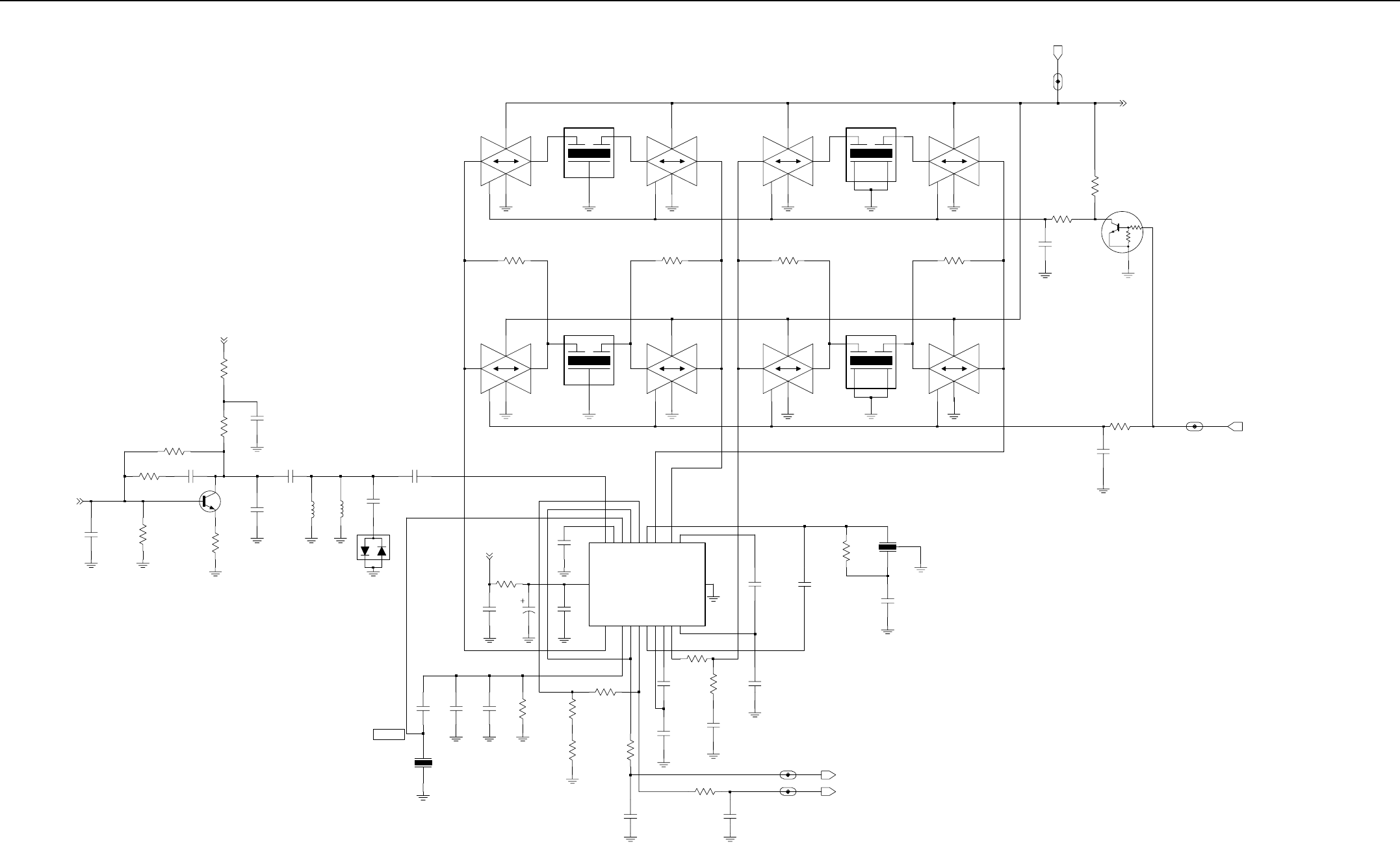

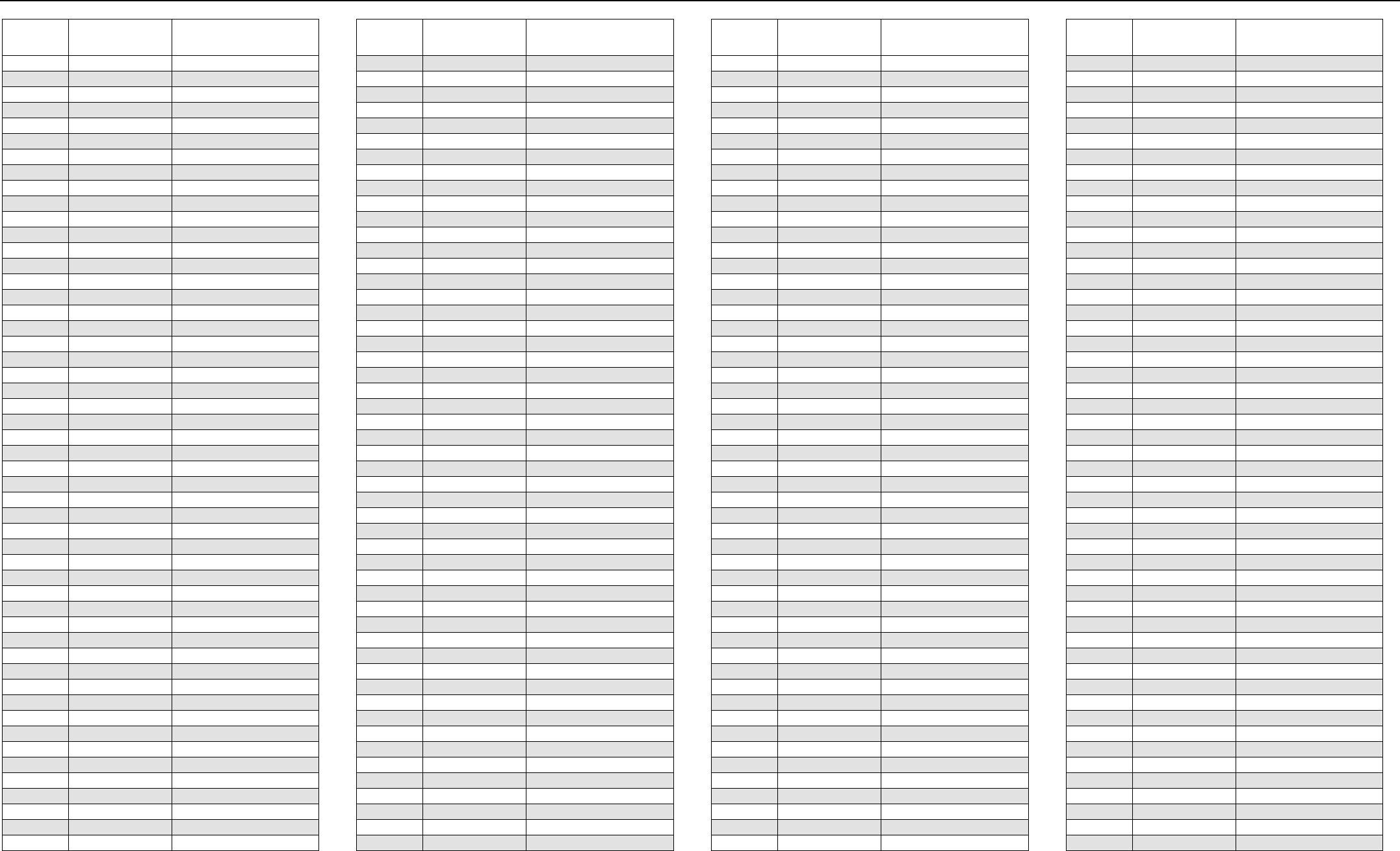

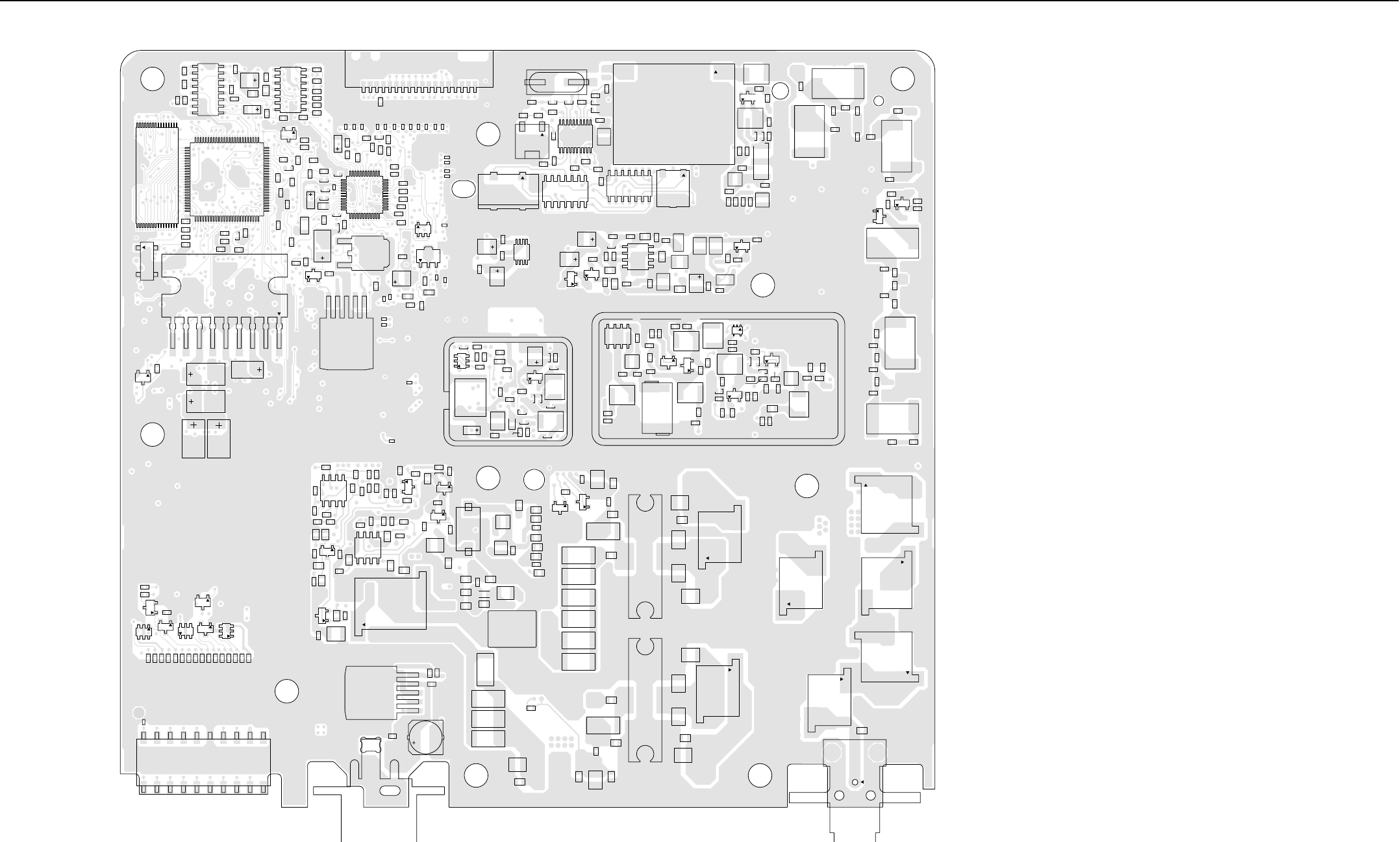

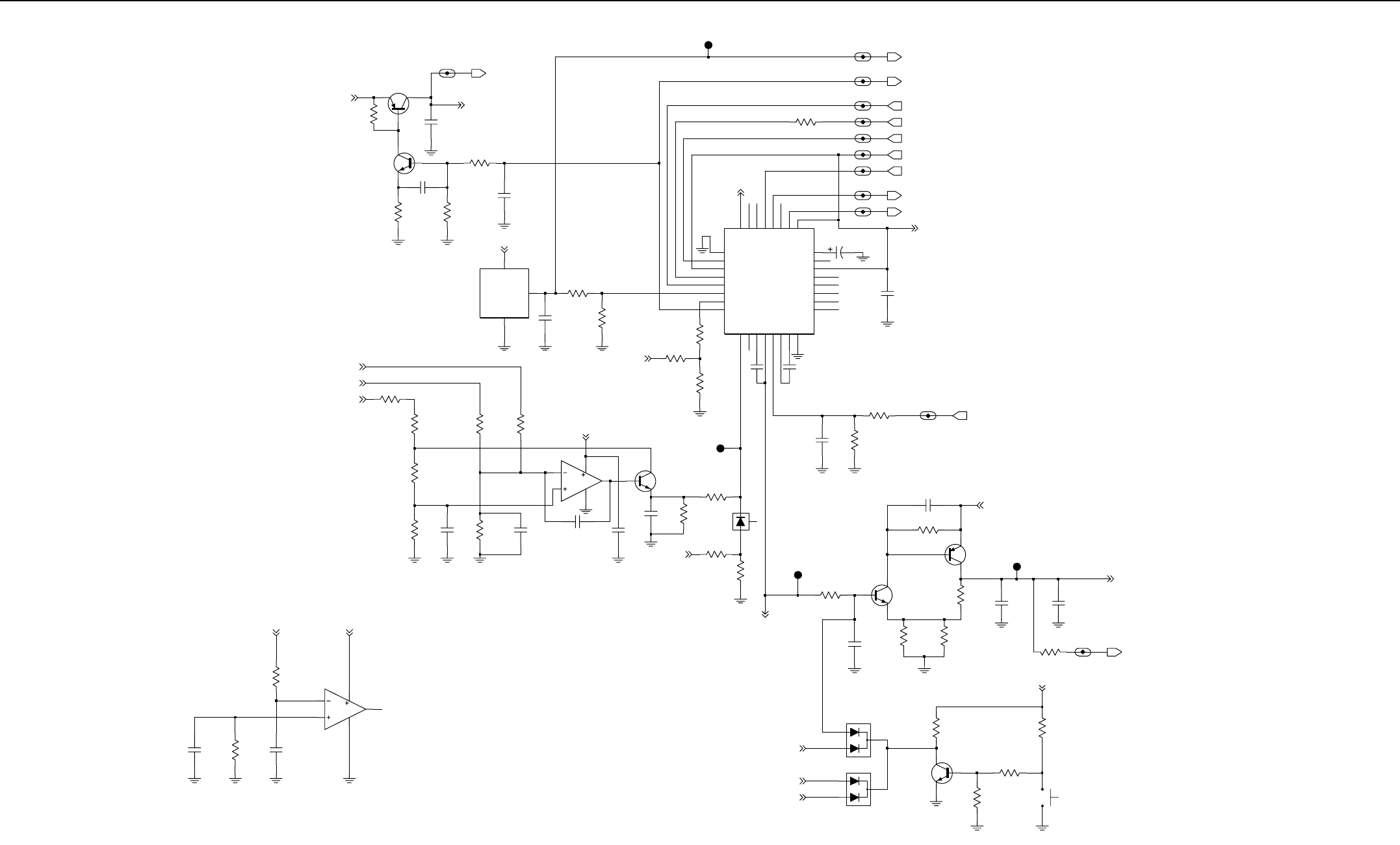

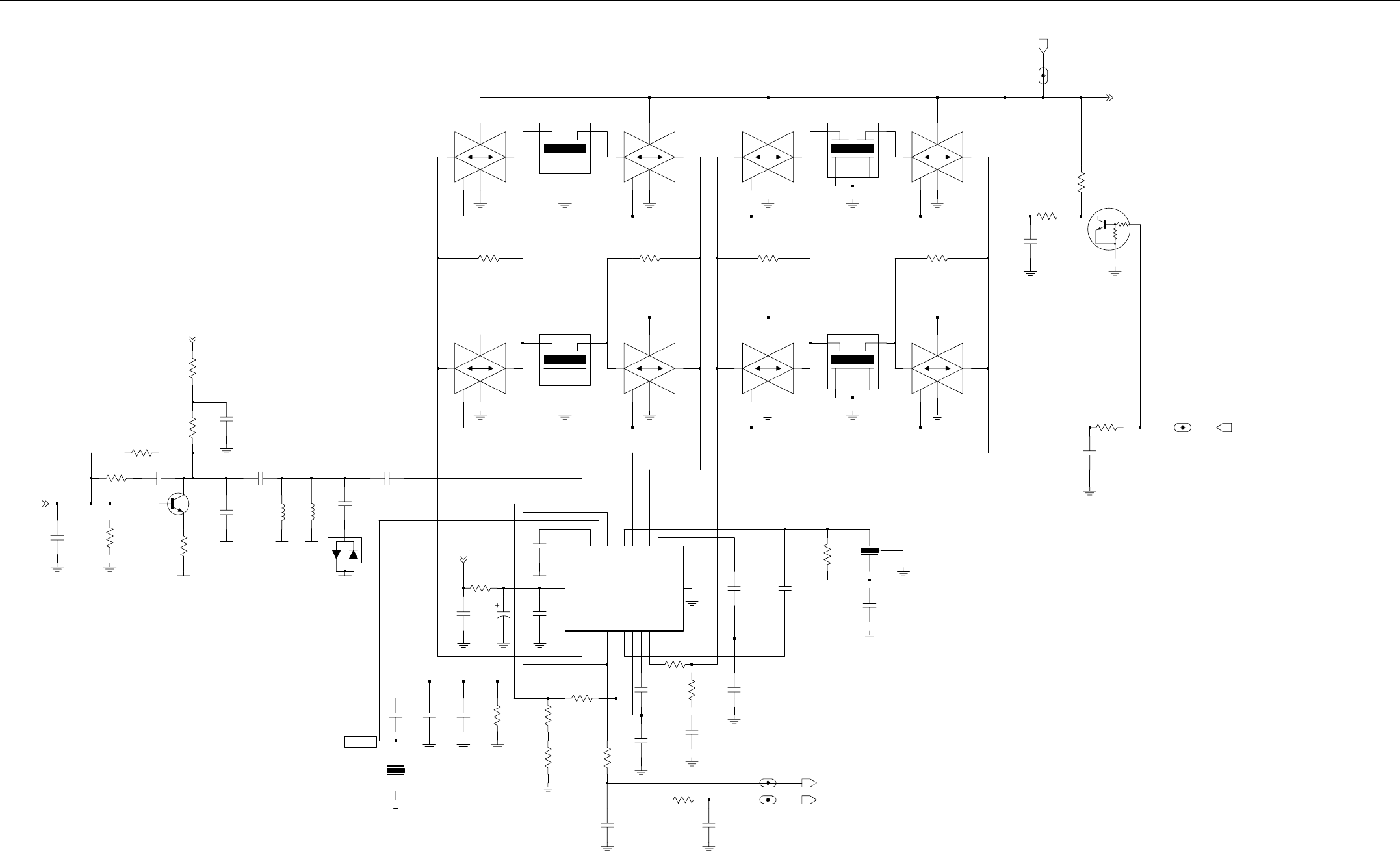

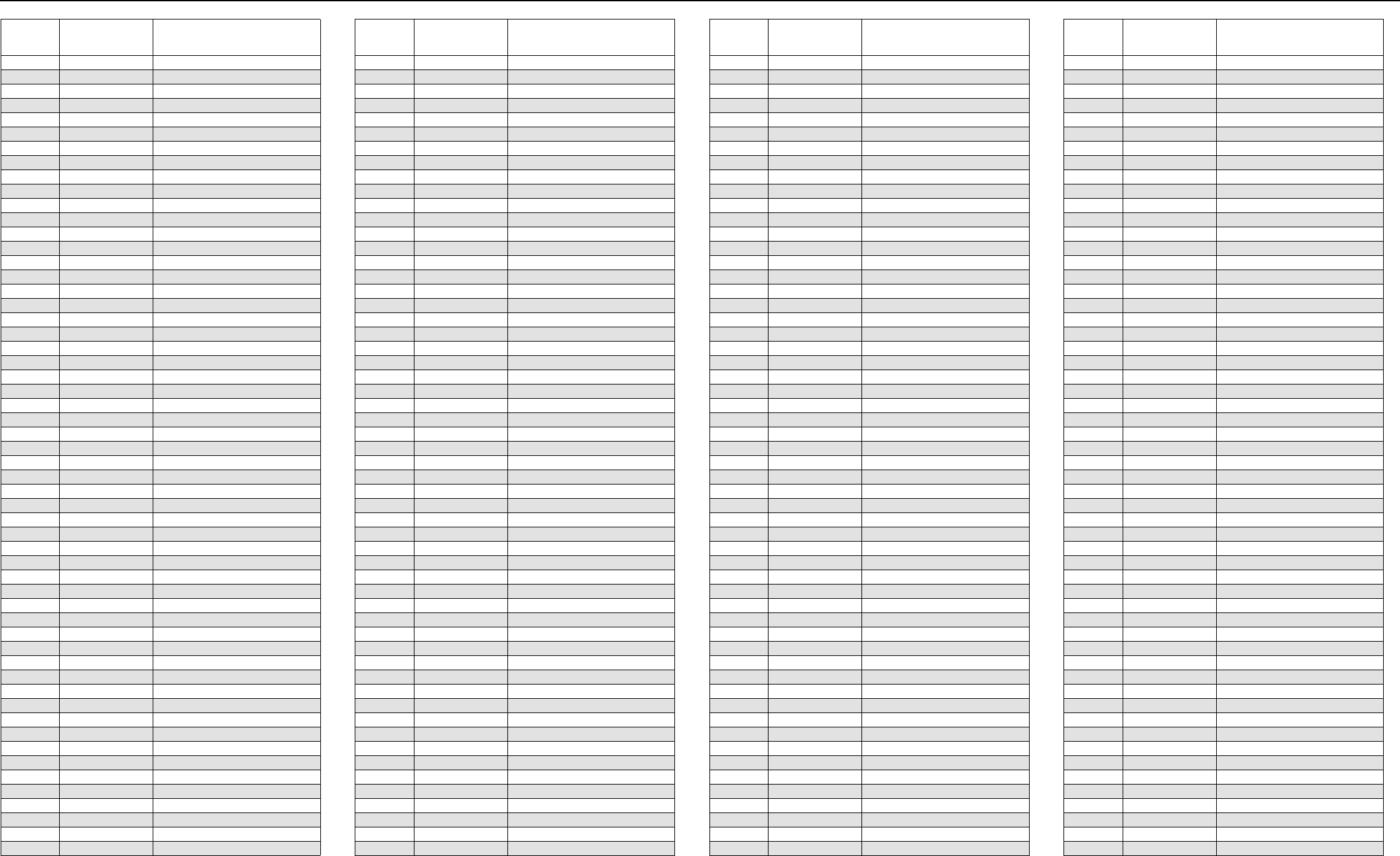

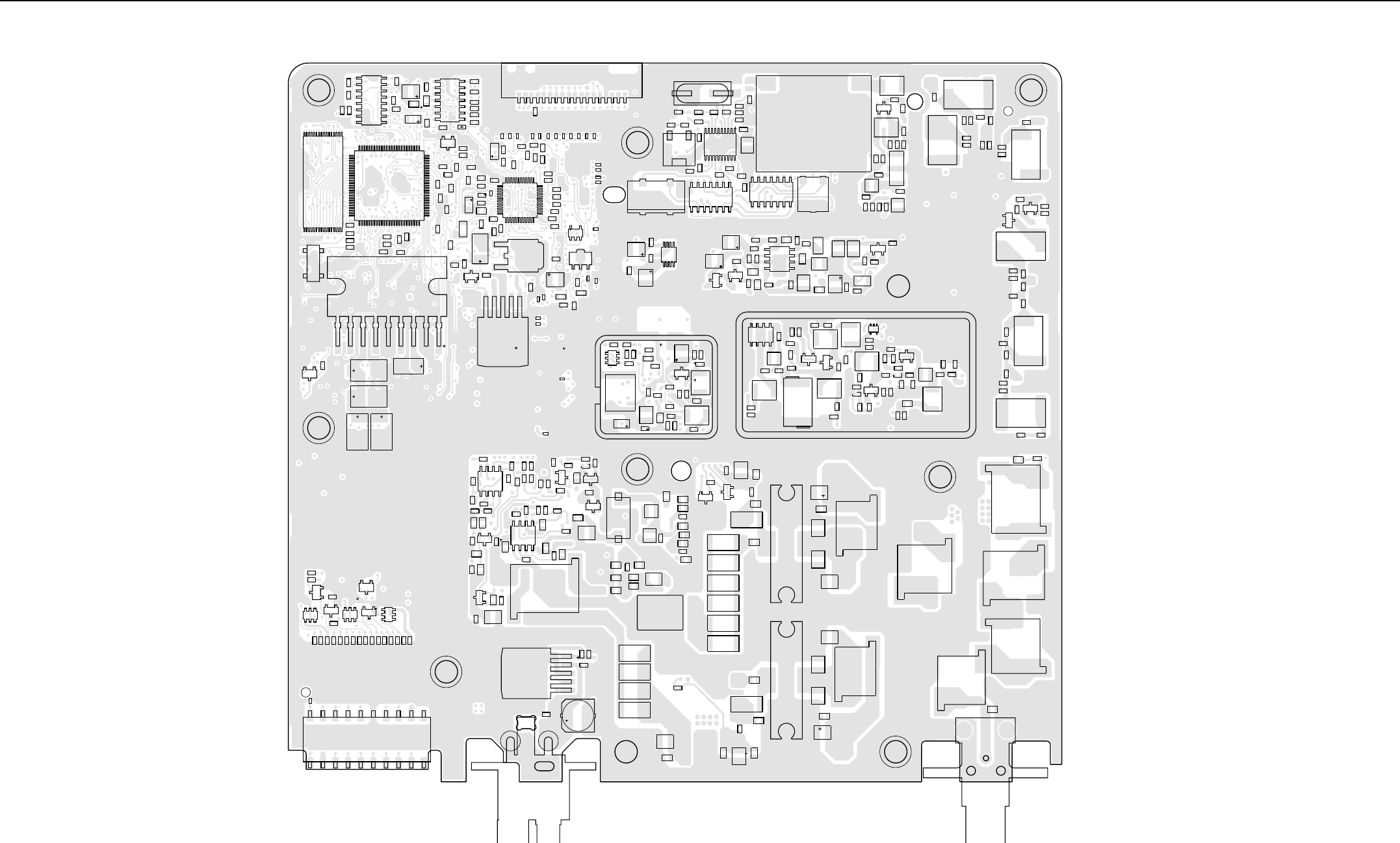

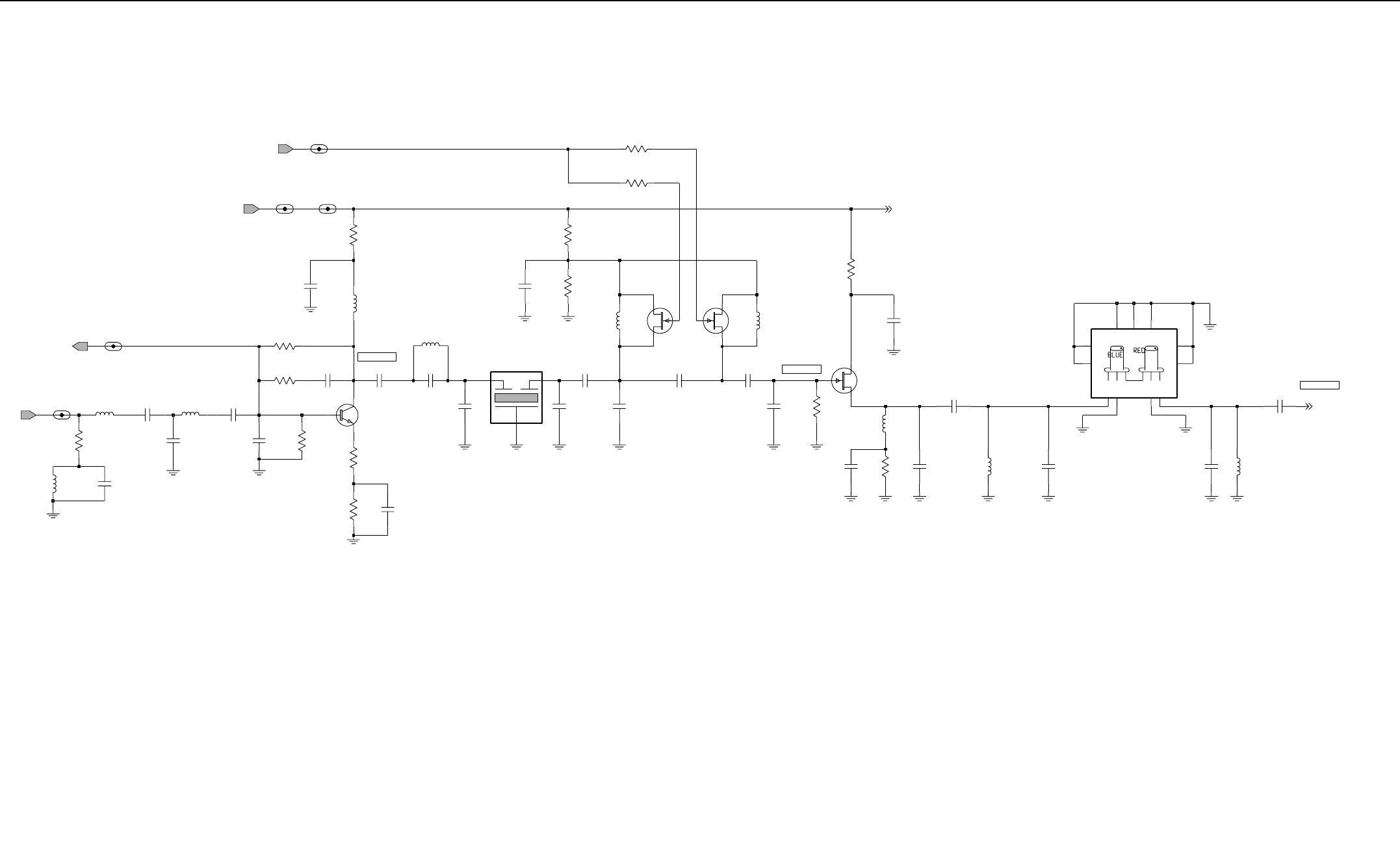

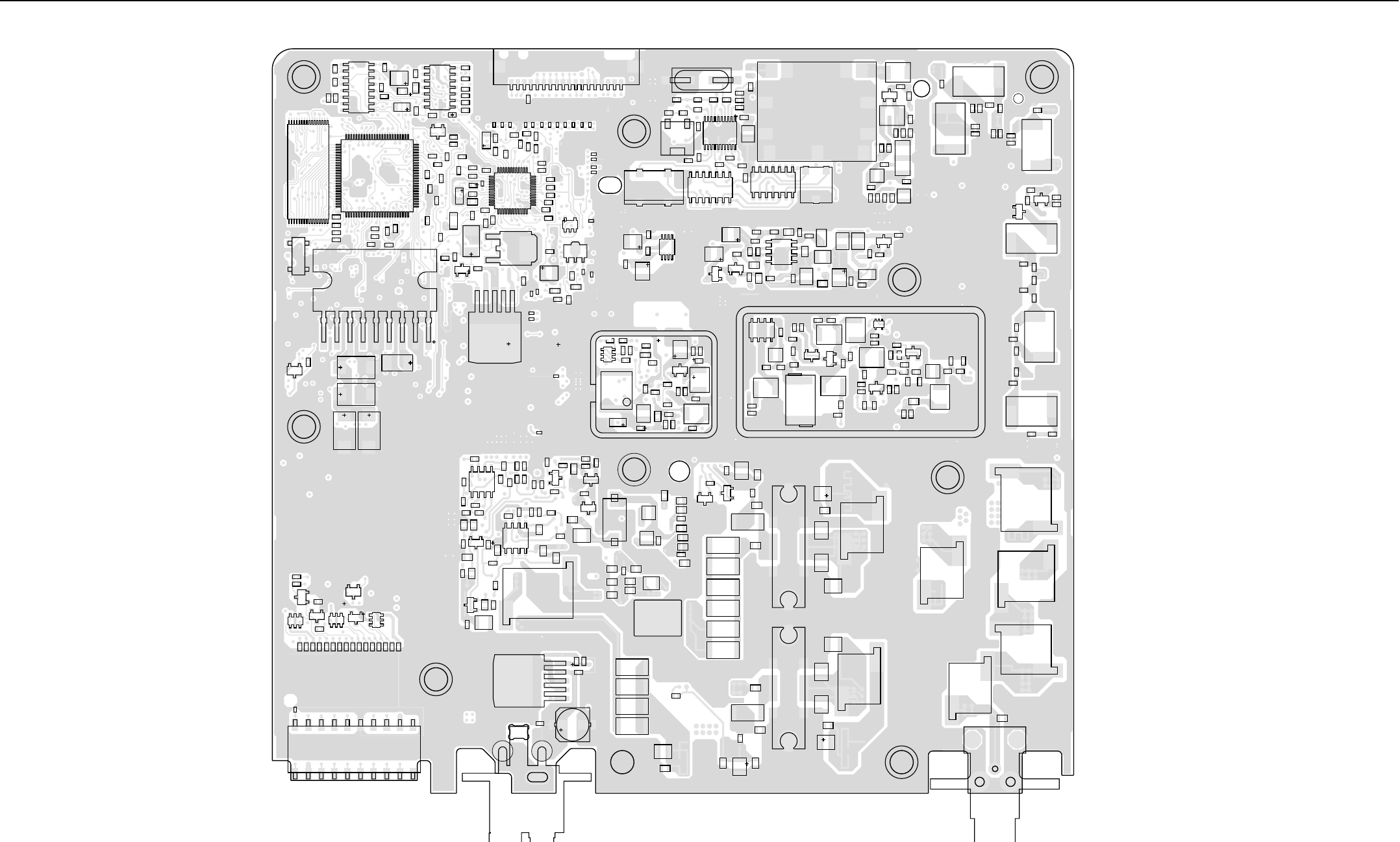

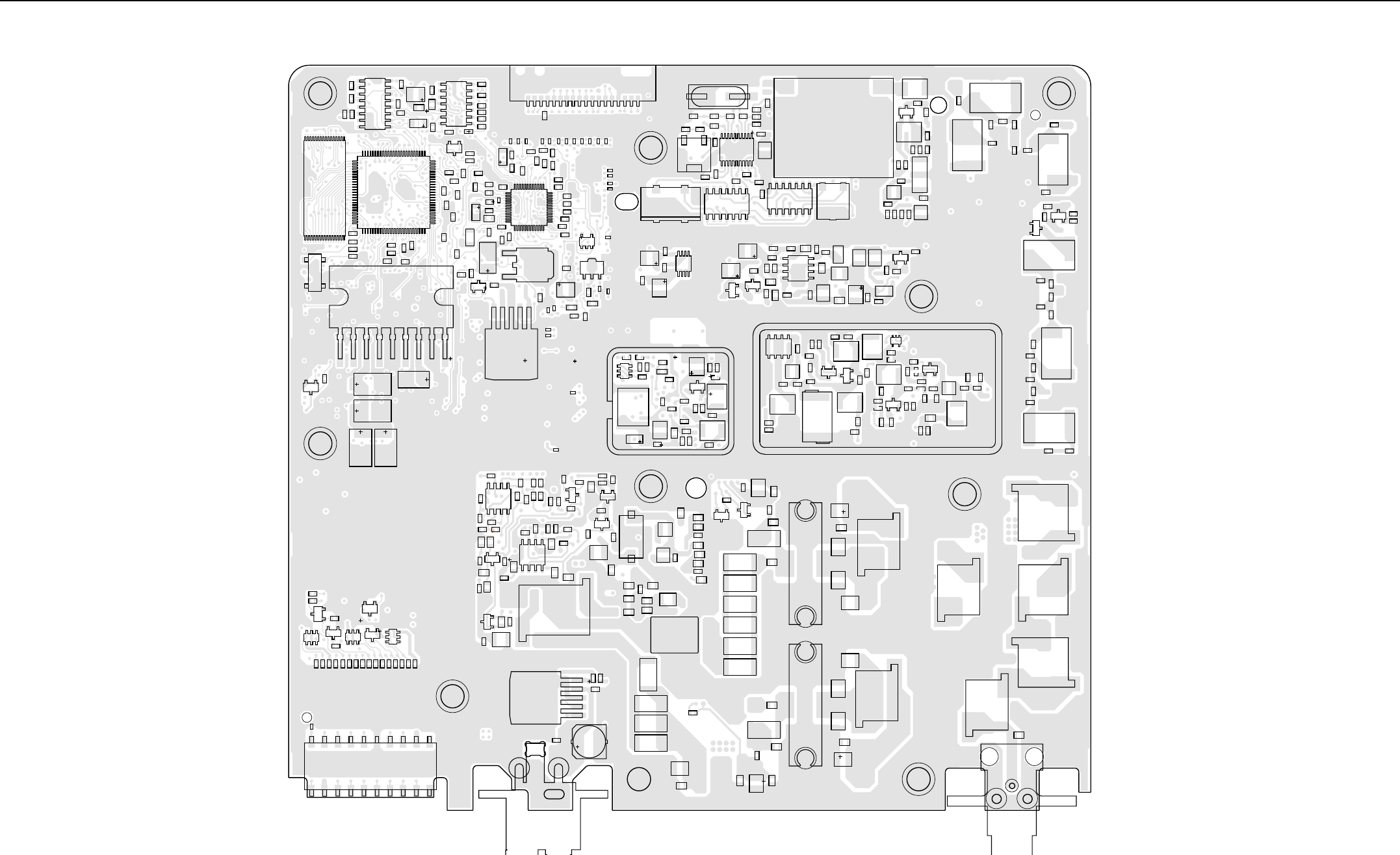

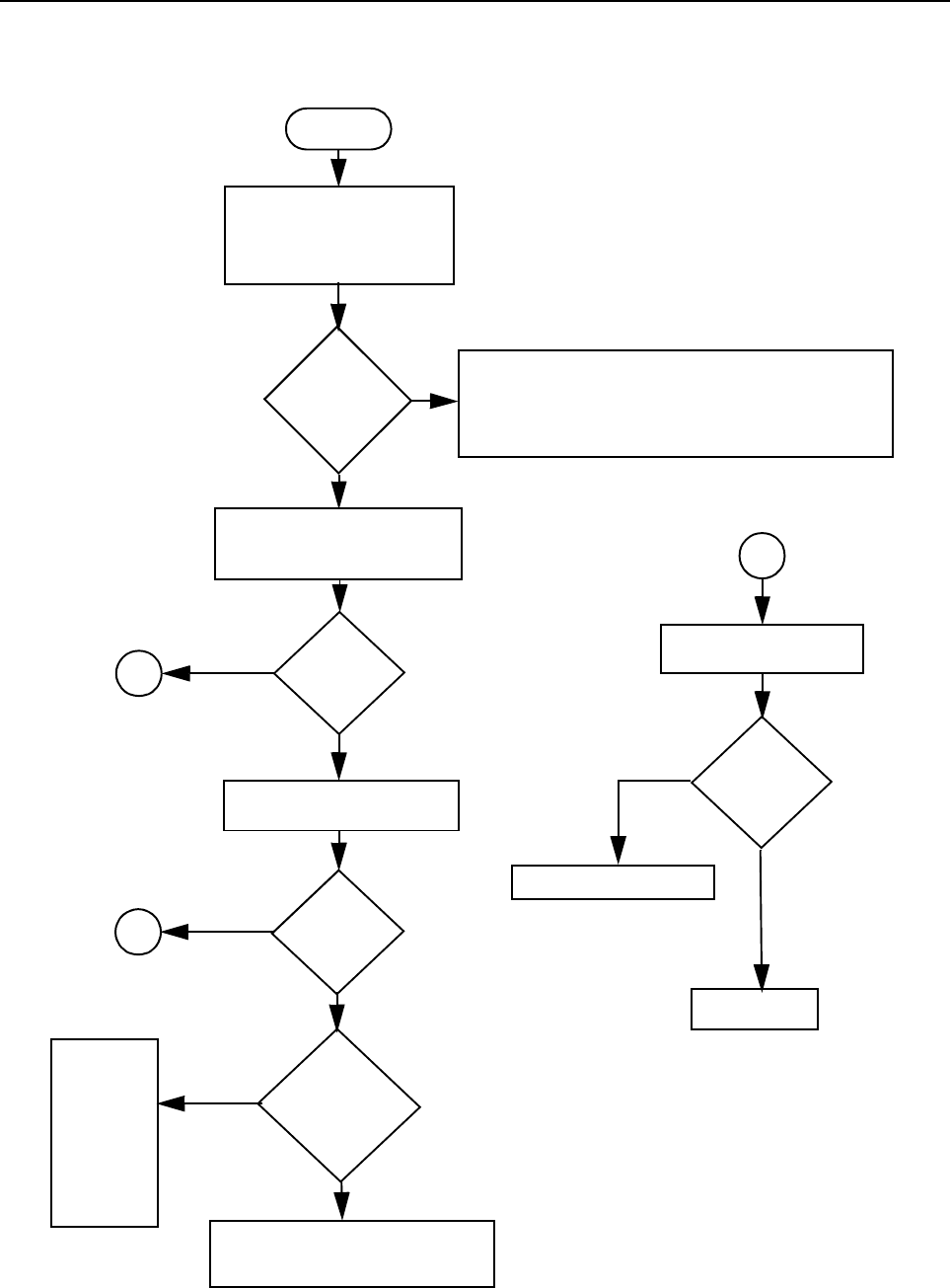

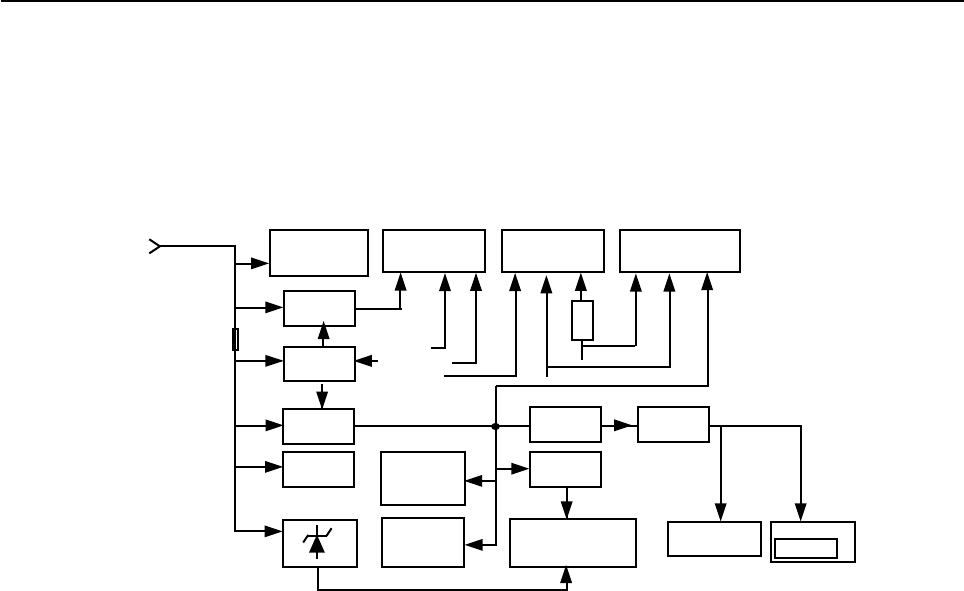

Controlhead GM140/340/640 - PCB 8486146B07 / Schematics 4-3

2.0 Controlhead GM140/340/640 - PCB 8486146B07 / Schematics

D0871

D0872

D0873

D0874 D0875 D0876

D0877 D0878 D0879

D0881

D0884

D0885

D0886

D0887 D0888

2

3579

864 10

J0811

JU0852

JU0853

JU0854

4

123

5

R0823

S0861

S0862

S0863

S0864

S0865

S0866

ZWG0130114-A

C0802

C0803

C0804

C0805

C0806

C0808

C0809

C0810

C0811

C0813

C0815

C0816

C0817

C0818

C0819

C0821

C0822

C0823

C0824

C0831

C0832

C0833

C0843

D0821

D0822

D0831

12

J0801

1

2

P0801

Q0821

Q0822

Q0823

Q0841

Q0843

Q0871

Q0872

Q0873

Q0874

Q0875

Q0876

Q0877

Q0878

Q0879

Q0881

Q0885

R0810

R0811

R0812

R0813

R0814

R0815

R0816

R0821

R0822

R0824

R0825

R0831

R0832

R0833

R0834

R0835

R0836

R0837

R0838

R0839

R0841

R0842R0843 R0844

R0845

R0847

R0849

R0852

R0853

R0854

R0861 R0862

R0864

R0866 R0867

R0871

R0872

R0873

R0874

R0875

R0876

R0877

R0878

R0879

R0880

R0881

R0885

TP0831

TP0832

TP0833

TP0834

TP0835

TP0836

TP0837

TP0838

1

49

17

33

U0831

1

45

8

U0832

3

U0833

U0835

VR0811

VR0816

VR0817

VR0821

VR0822

VR0823

64

1

1

MOTOROLA

c

8486146B07-0

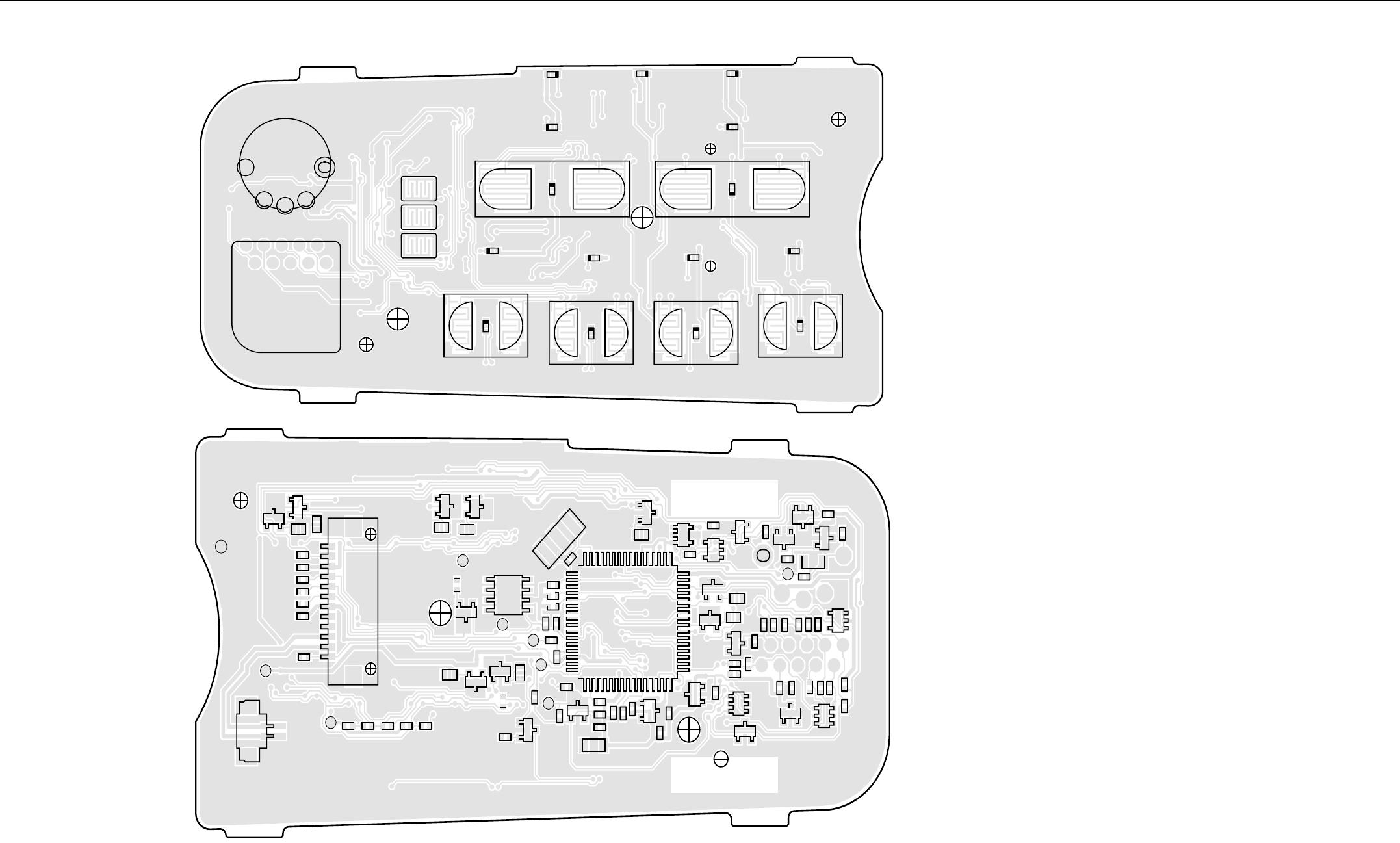

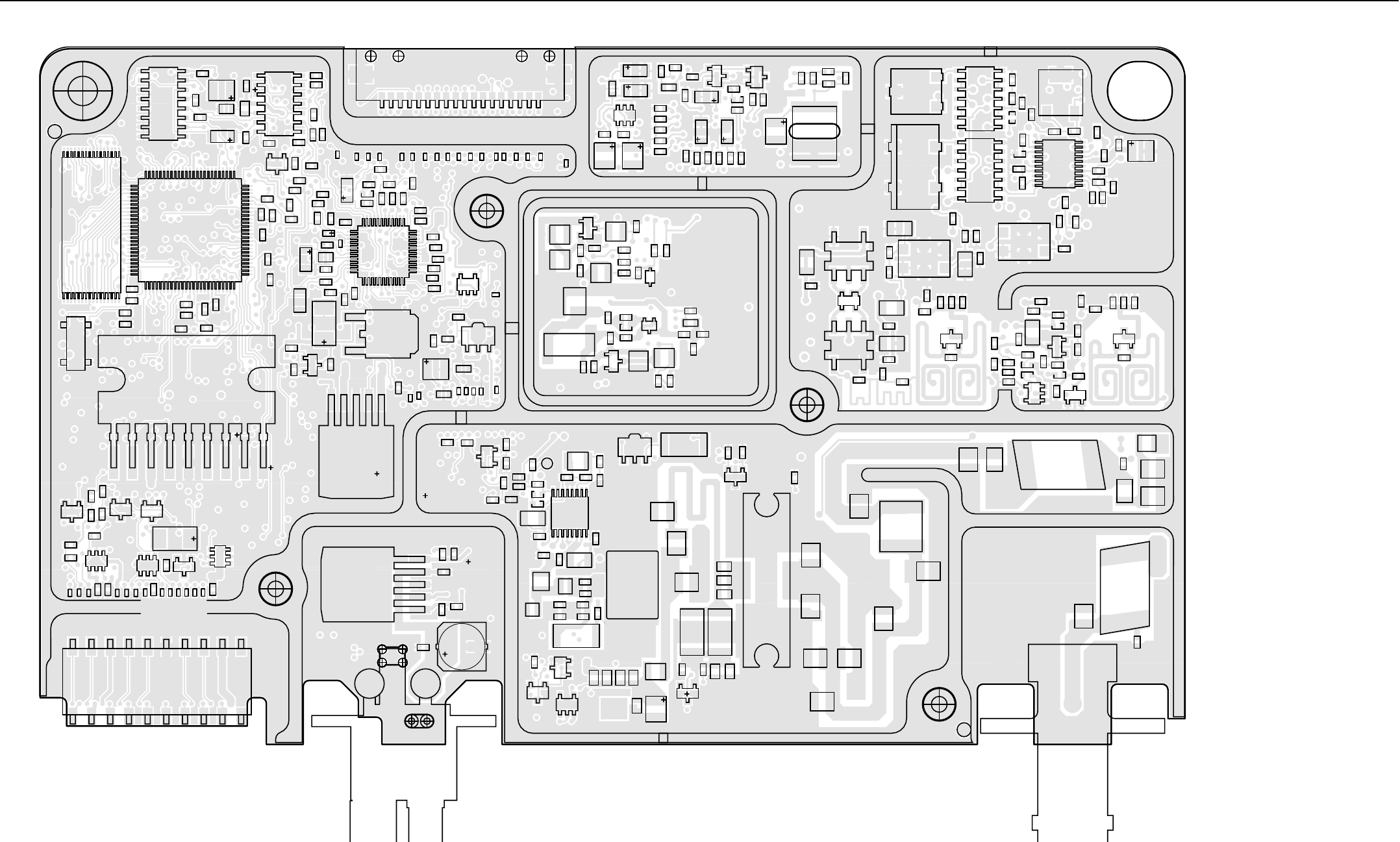

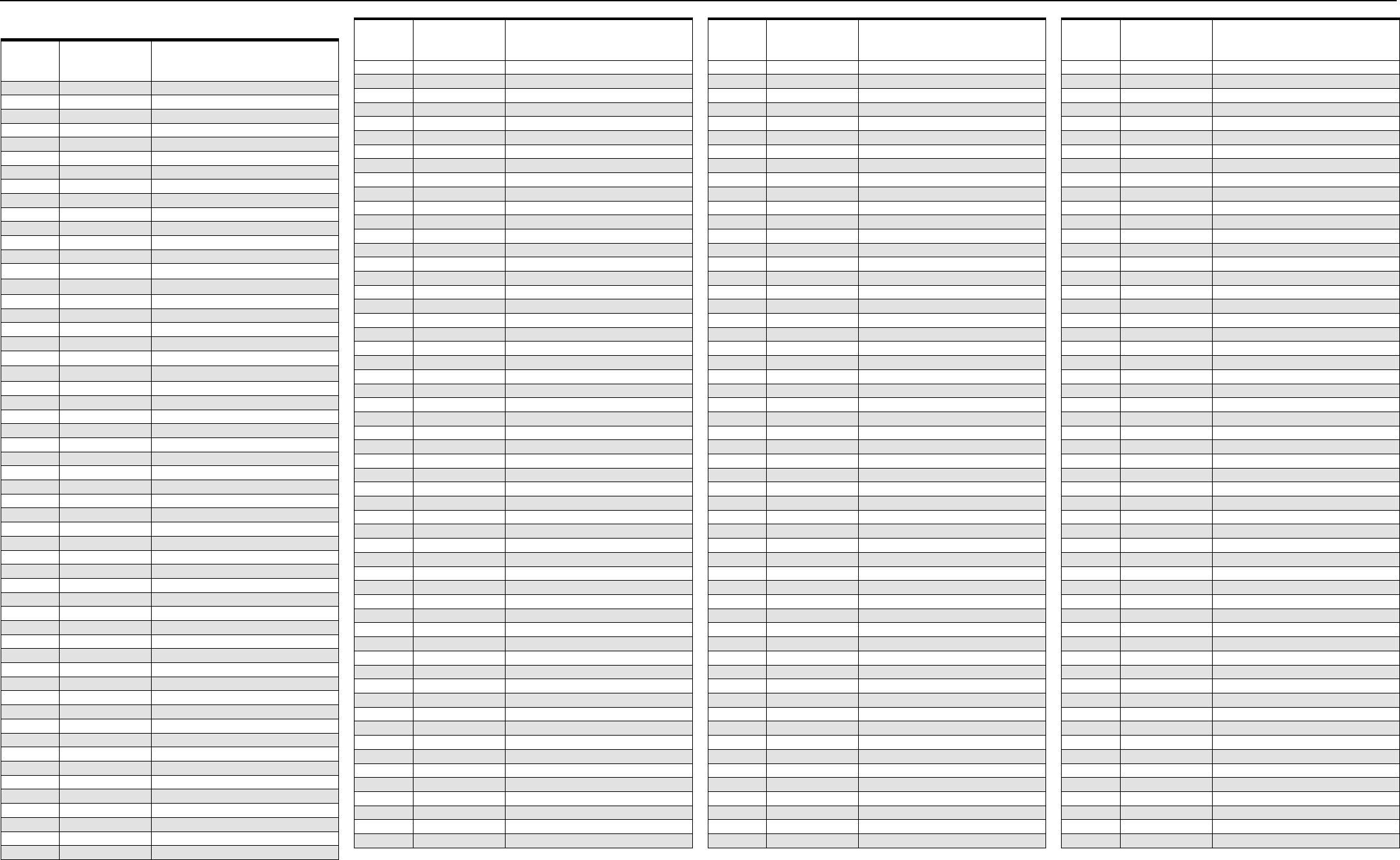

Controlhead GM140/340/640 - PCB8486146B07

ZWG0130114-A Top Side

ZWG0130113-B Bottom Side

4-4 Controlhead GM140/340/640 - PCB 8486146B07 / Schematics

HOOK

GROUND

MIC

10

GM300

CONTROL HEAD

PTT_IRDECODER

7

CONNECTOR

8

J0801

9

MICROPHONE

CONNECTOR

SCI_RX

BOOT_VPP

J0811

RESET BOOT_MODE

WARIS

HANDSET_AUDIO

1

CONTROLLER

KEYPAD ID

CONTROL HEAD ID

SCI_TX

EXT_KP_ROW

EXT_KP_COL

FLT_A+

456

BUS+

23 5V

VR0822

5.6V

R0843

2.2K

NU

GND

INPUT RESET_

7

U0835

MC33464N-45ATR

J0801-8

JU0853

SWITCH

C0833

R0833

0.1uF

2

47K

10K

R0844

55

VDD 22

VRH 21

VRL

23 VSS1

VSS2

24

49 VSS3

45 XIRQ

33 XTAL

PE3_AN3

19

PE4_AN4

14

16 PE5_AN5

PE6_AN6

18

PE7_AN7

20

43 RESET

28

STRA_AS 30

STRB_RW*

PD1_TXD

50

PD2_MISO

51

PD3_MOSI

52

53 PD4_SCK

PD5_SS*

54

PE0_AN0

13

PE1_AN1

15

PE2_AN2

17 PC1_AD1 36

PC2_AD2 37

PC3_AD3 38

PC4_AD4 39

40

PC5_AD5

PC6_AD6 41

PC7_AD7 42

PD0_RXD

47

PB1_A9 11

PB2_A10 10

PB3_A11 9

PB4_A12 8

7

PB5_A13

PB6_A14 6

PB7_A15 5

PC0_AD0 34

64

PA1_IC2 63

PA2_IC1 62

PA3_OC5_OC1 59

PA4_OC4_OC1 58

PA5_OC3_OC1 57

PA6_OC2_OC1 56

PA7_PA1_OC1

PB0_A8 12

NC3

4

NC4

26

NC5

32

35

NC6 44

NC7

NC8 48

60

NC9

1

PA0_IC3

29 CLK_E

31 EXTAL

46 IRQ

27 MODA_LIR*

25 MODB_VSTBY

NC1

2

NC10 61

3NC2

MC68HC711E9

U0831

7

J0801-11

J0801-7

3

TP0832

50K

NEG

POS

TAB

TAB1

VAR

R0823

4.7K

R0824

J0811-5

1

0

Q0843

NU

R0835

100

0

R0839

R0847

22

J0811-4

270

R0814

R0815

0.1uF

C0832

13K

C0831

3.3uF

J0811-1

1

C0823

.01uF

2

06

2

C0809

NU

82pF

Q0823

D0822

10

R0813

1

C1

3

C2

2

GND

4

R0812

CSTCC8.00MG

U0833

22

5.6V

5

VR0821

100K

R0853

8

5.6V

VR0823

J0811-10

0

P0801-2

5

4

J0801-9

TP0837

INPUT

2

NC1

3

NC2

5NC3 6

NC4 7

8

NC5

RESET 1

U0832

MC33064

GND

4

Q0821

J0811-6

J0801-10

J0801-6

JU0852 SWITCH

JU0854

6

1

SWITCH

C0804

470pF

0

R0852

100K

C0817

82pF

J0811-8

7

R0845

4.7K

NU

VR0811

33V

470pF

NU

470pF

C0818

C0816

33K

R0837

NU

C0808

470pF 470pF

C0806

10K

3

R0841

R0811

51K

J0811-3

J0811-2

1MEG

R0831

VR0816

20V

13K

J0811-9

R0810

4

TP0833

10K

R0821

47K

J0801-14

R0849

P0801-1

2.2K

R0832

J0801-3

J0801-5

TP0838

TP0834

NU

470pF

NU

C0810

470pF

32

C0819

100K

R0854

6

1

J0801-12

R0838

10K

J0811-7

R0834

270

20V

VR0817

2.2uF

J0801-4

C0822

470pF

NU

5

13K

C0821

R0816

R0822

51K

470pF

C0815

C0811

470pF

TP0831

R0836

10K

TP0836

J0801-13

J0801-1

NU

J0801-2

470pF

C0802

C0803

470pF

470pF

C0843 C0813

TP0835

470pF

NU

C0824

.01uF

R0825

1K

D0821

C0805

82pF

Q0822

R0842

47K

Q0841

INT_KP_ROW

INT_KP_COL

USW_5V

5V

5V

5V

5V

FLT_A+

BUS+

EXT_KP_ROW

MIC

EXT_KP_COL

FLT_A+

D0831

5V

CH_KP_ID(0:7)

LED_CNTRL(0:8)

CH_REQUEST

5V

CH_REQUEST

5V

5V

5V

5V

PTT_IRDEC

HOOK

ON_OFF_SENSE

ON_OFF_CONTROL

5V

USW_5V

VOLUME

VOLUME

EXT_KP_ROW

EXT_KP_COL

PTT_IRDEC

FLT_A+

FLT_A+

5V

5V

PTT_IRDEC

SCI_TX

SCI_TX

BUS+

5V

5V

BL_GREEN

ON_OFF_SENSE

5V

HOOK

5V

5V

HANDSET_AUDIO

ON_OFF_CONTROL

FLT_A+

MIC

BUS+

HANDSET_AUDIO

5V

Shown from Front Side

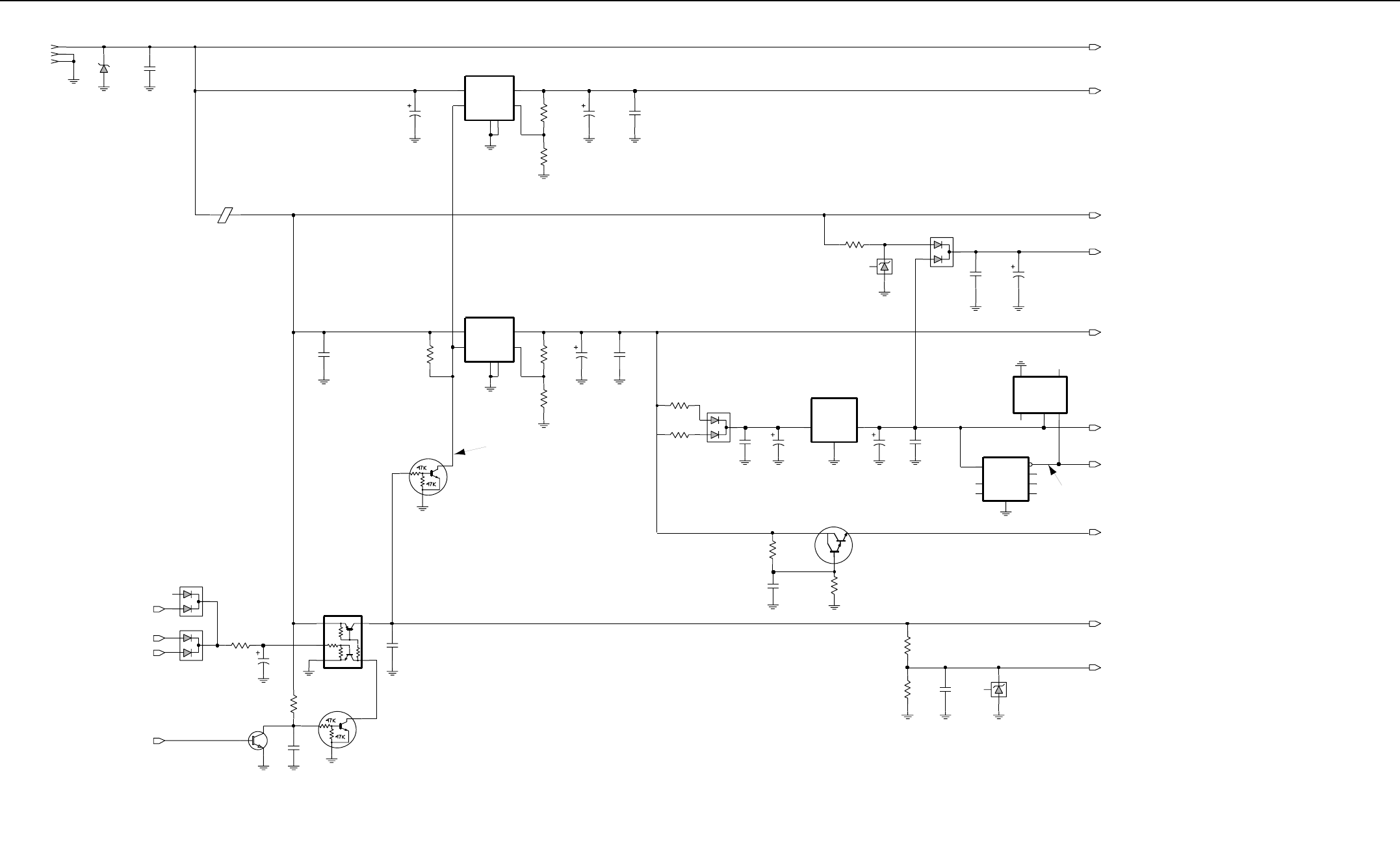

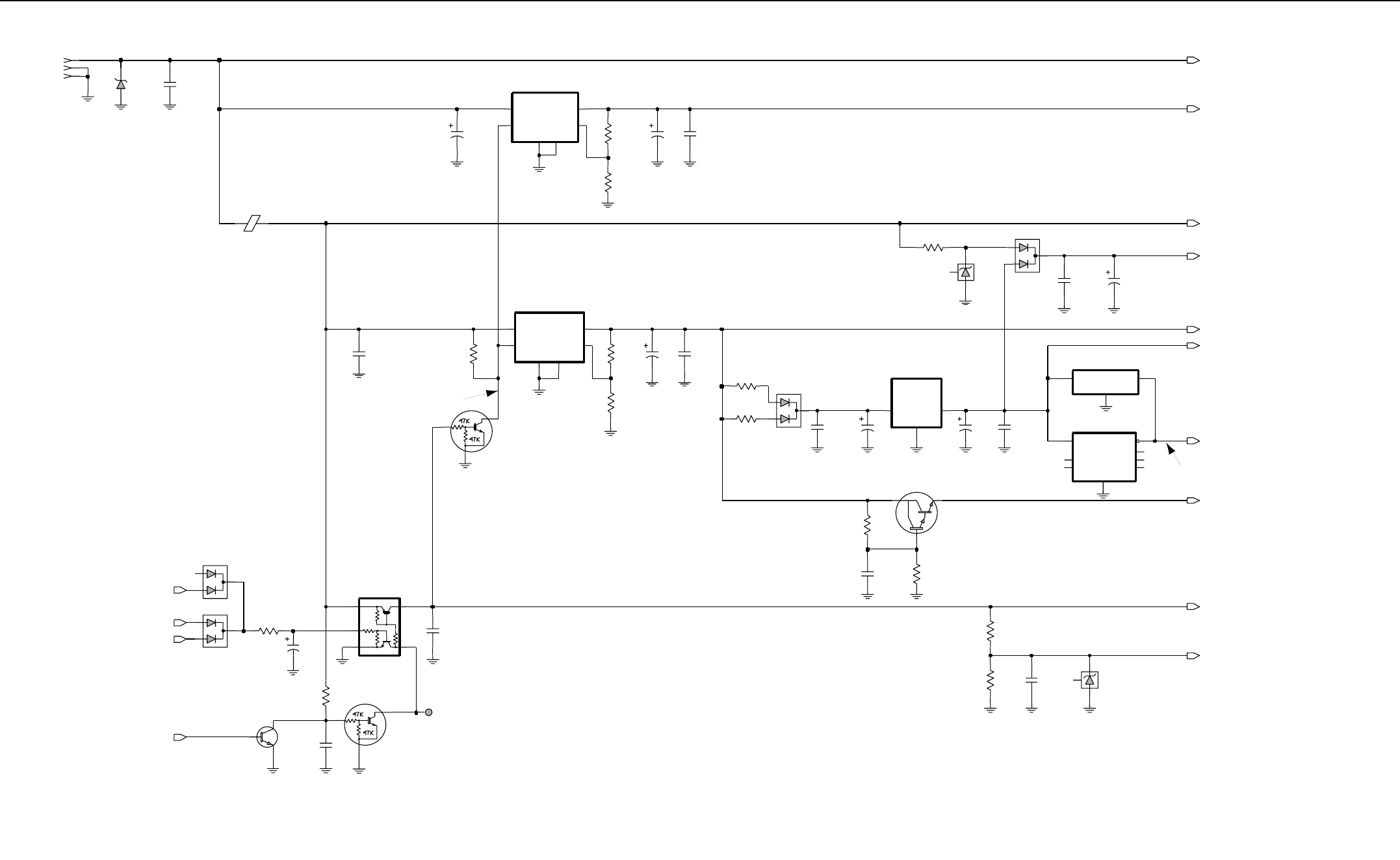

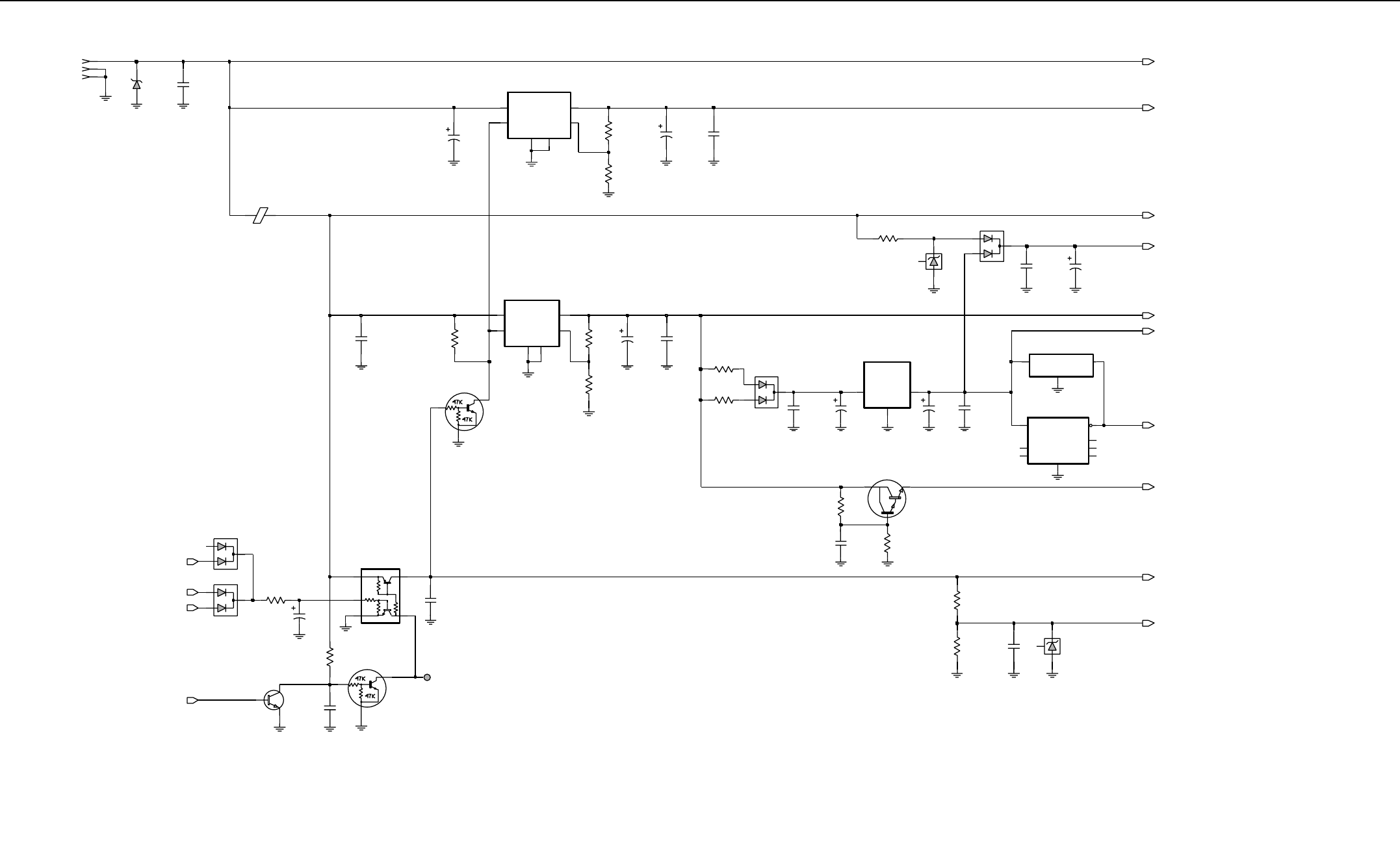

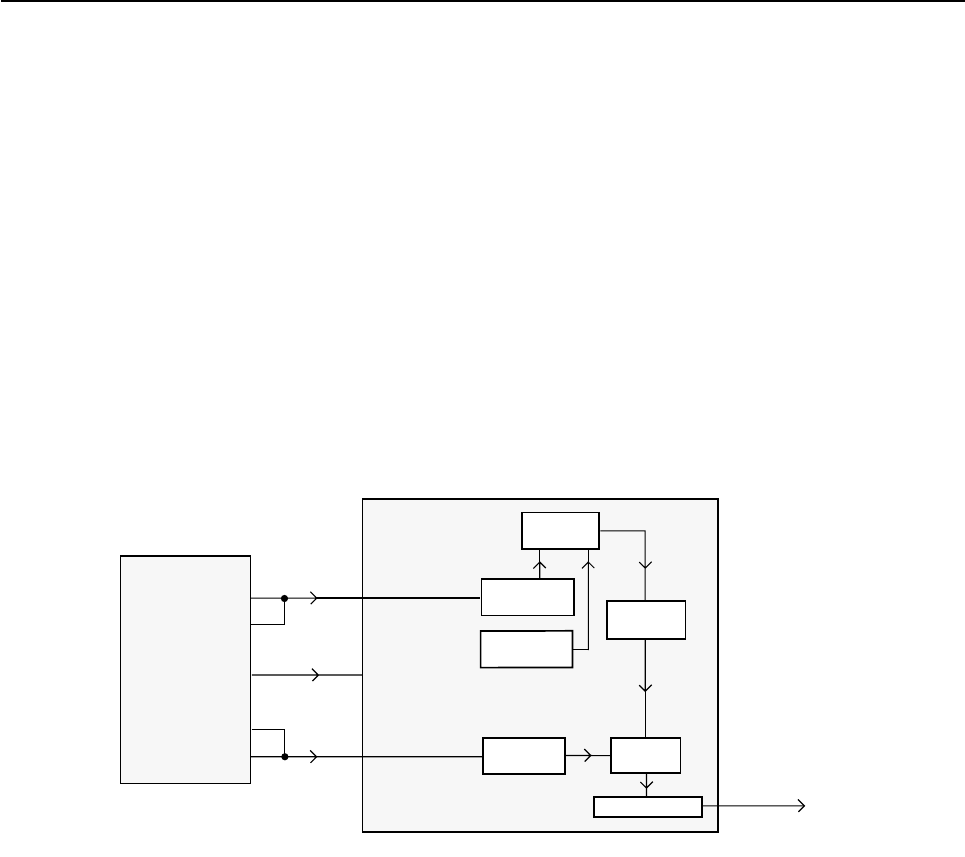

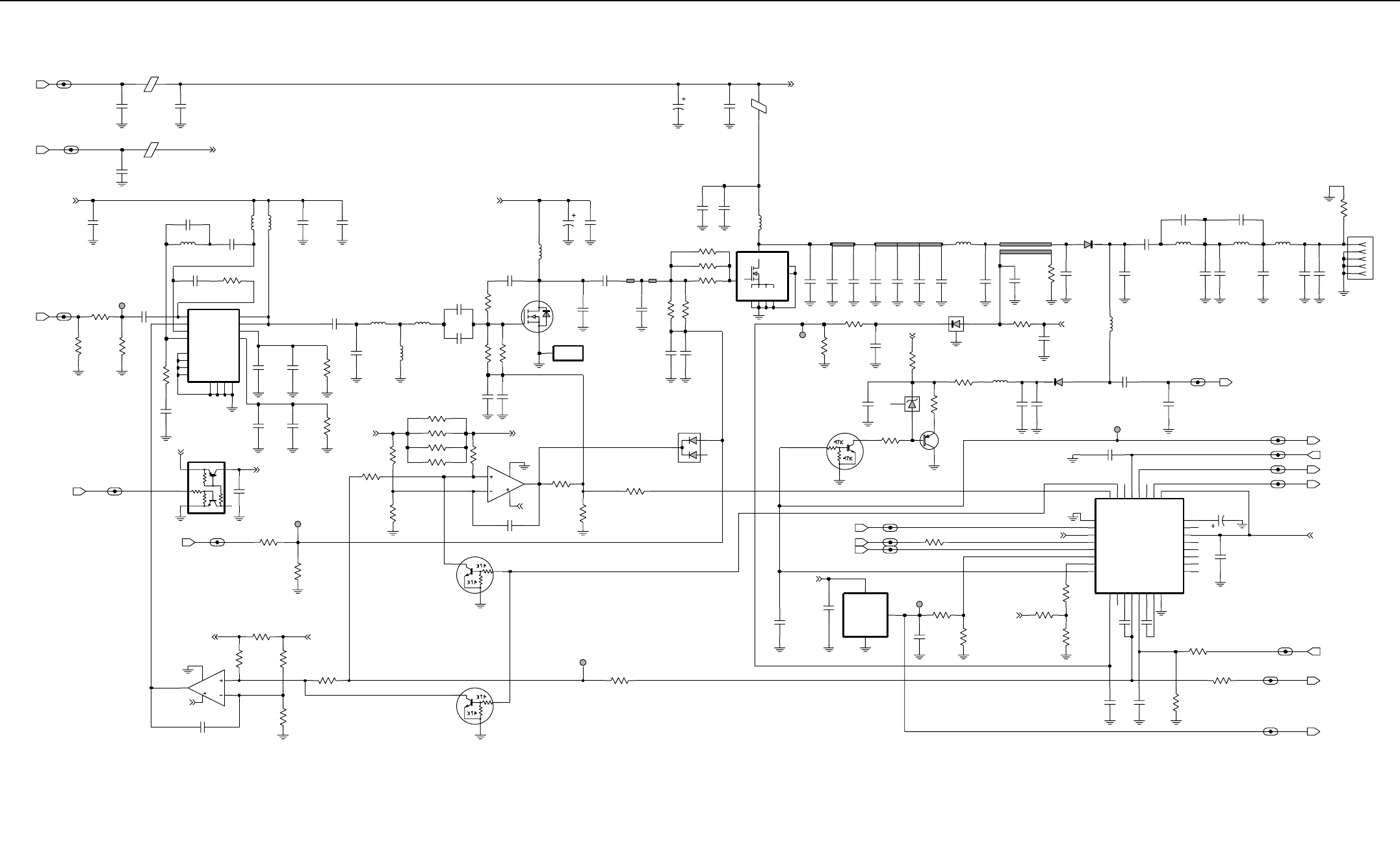

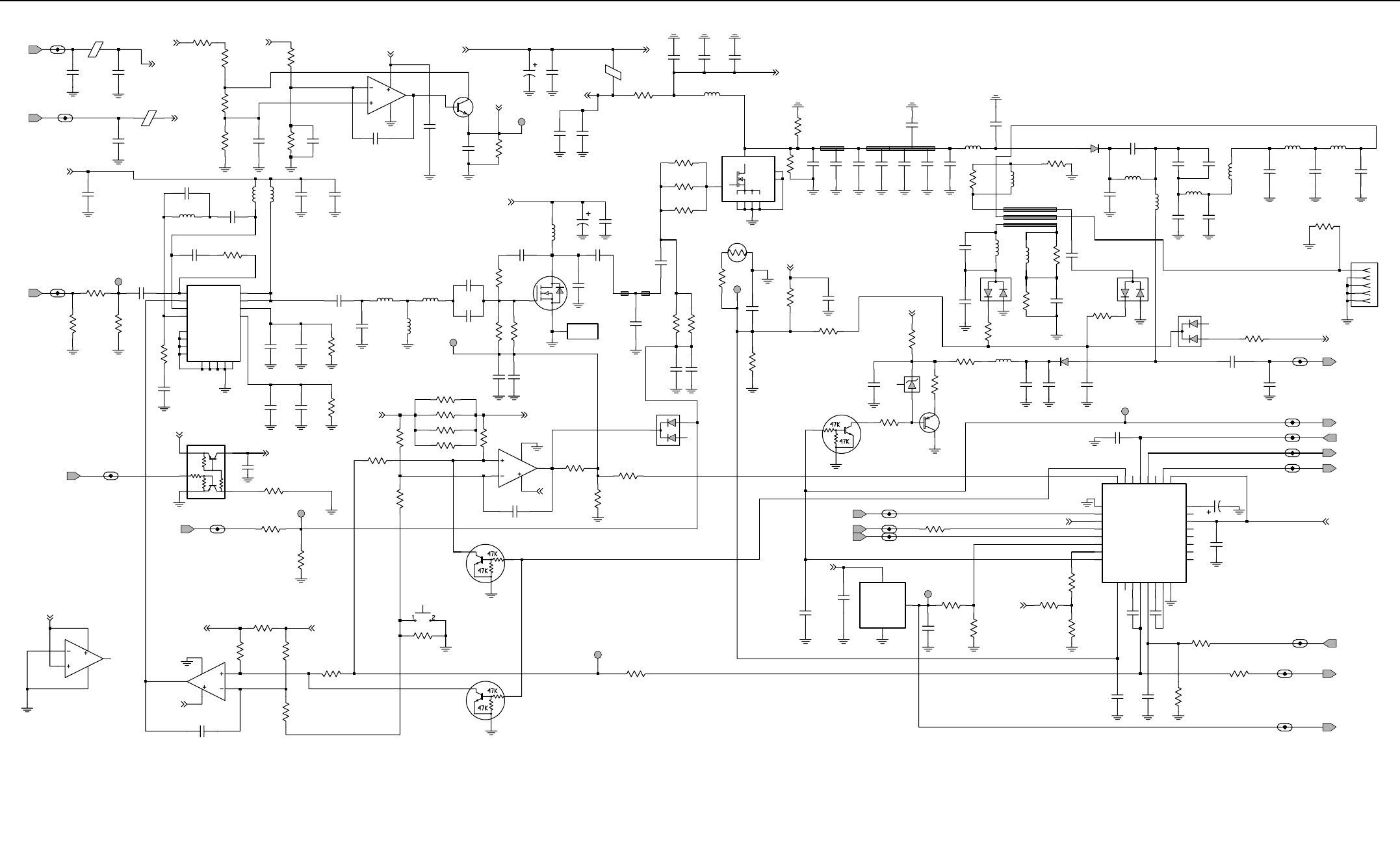

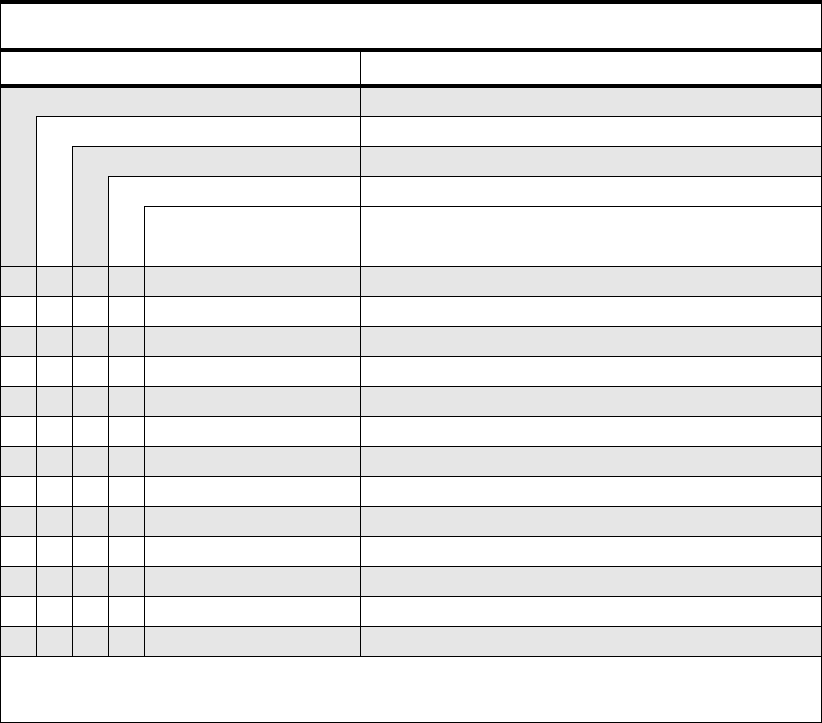

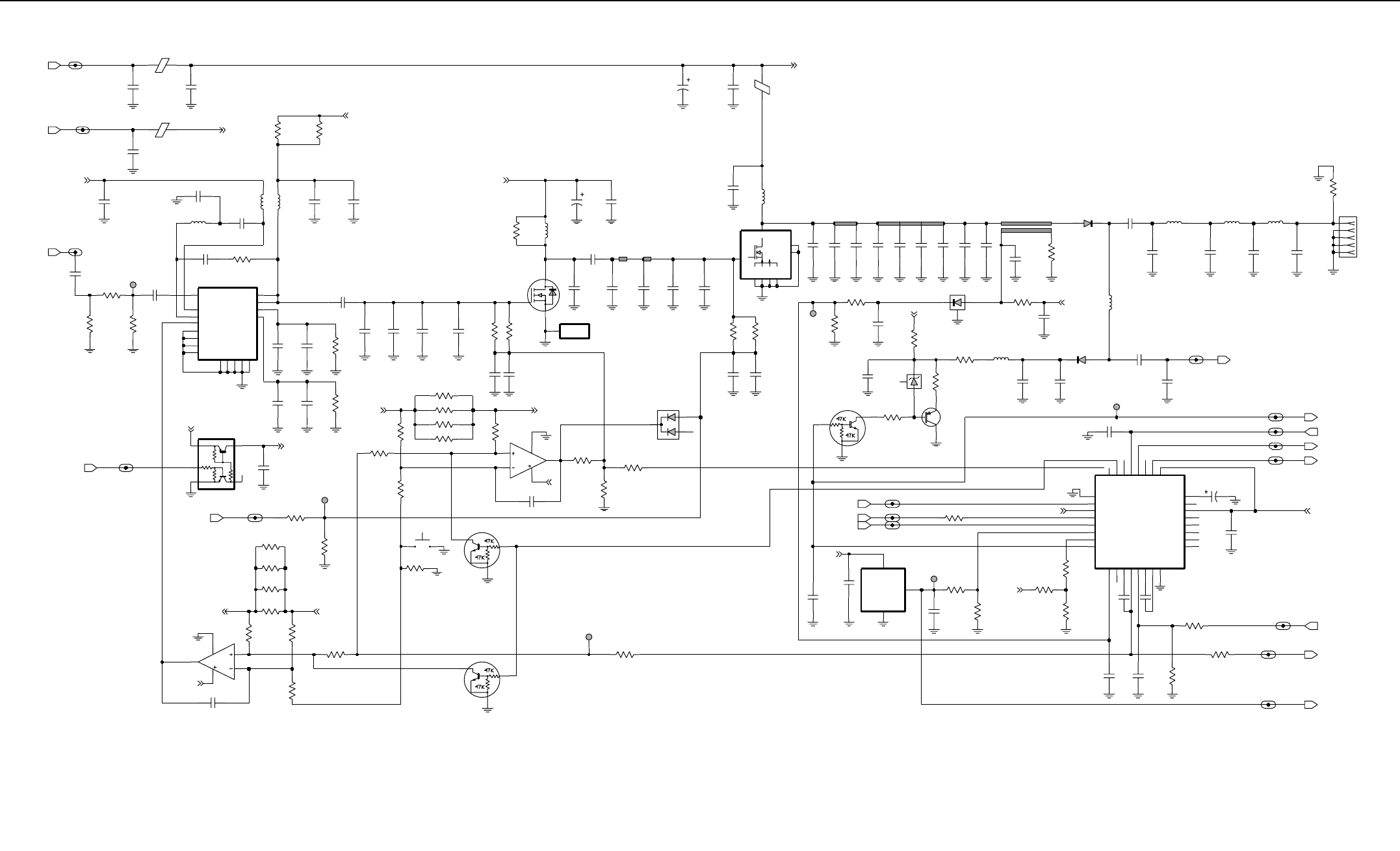

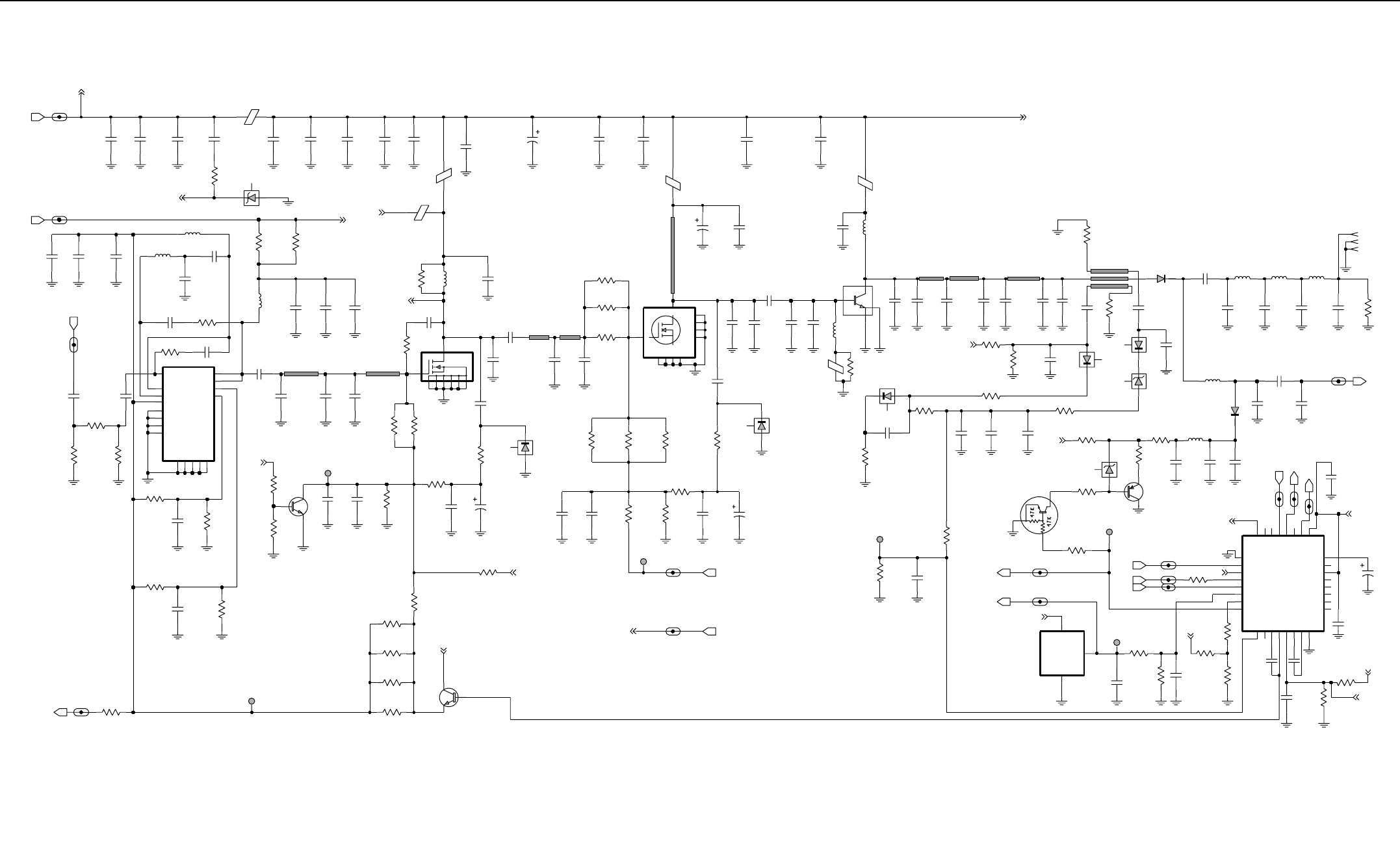

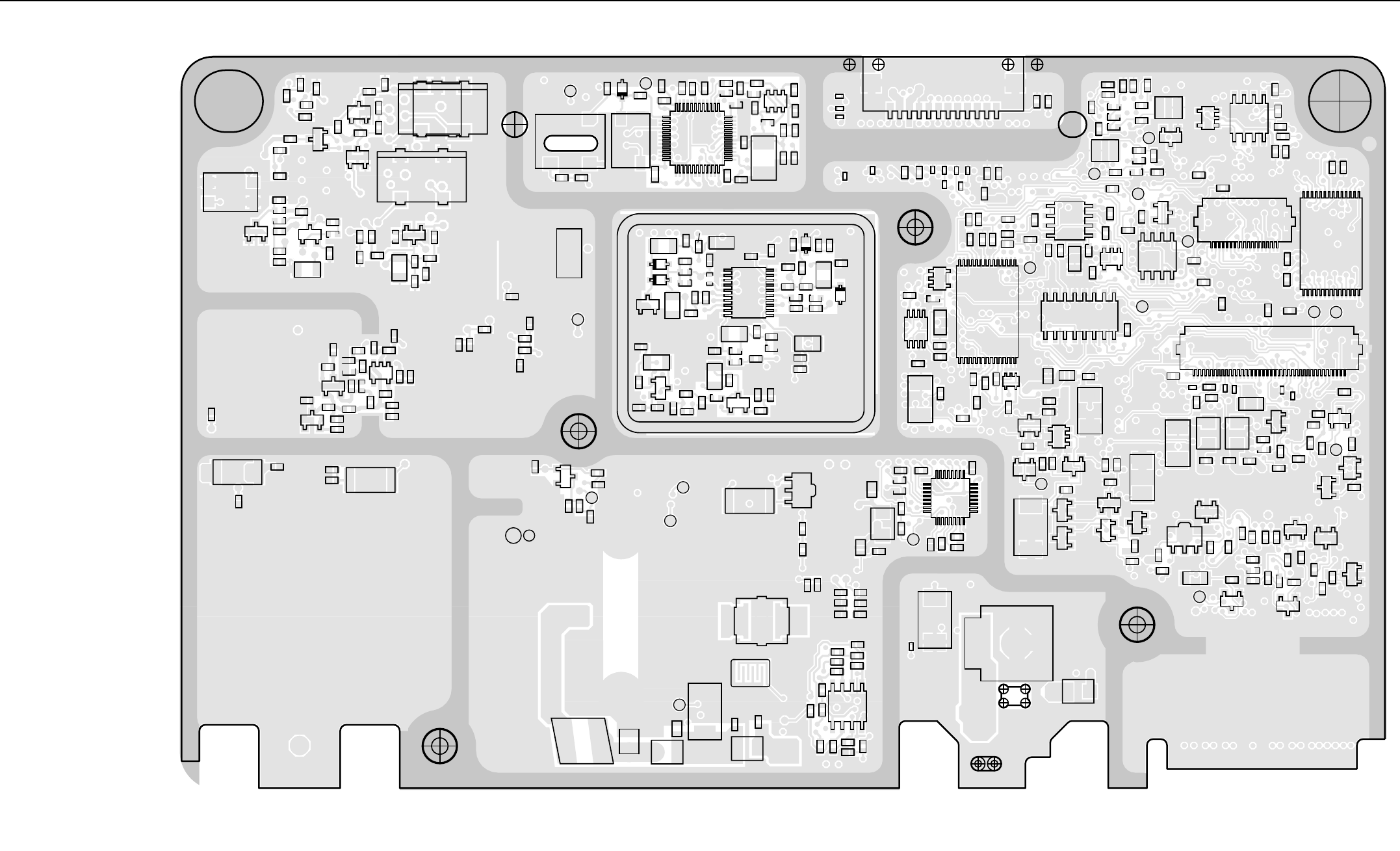

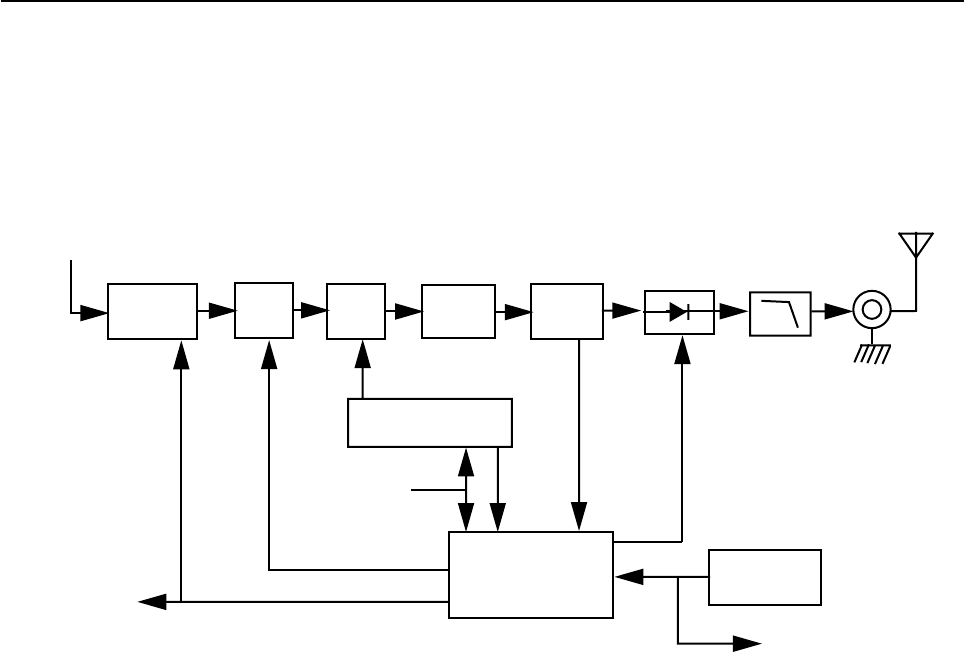

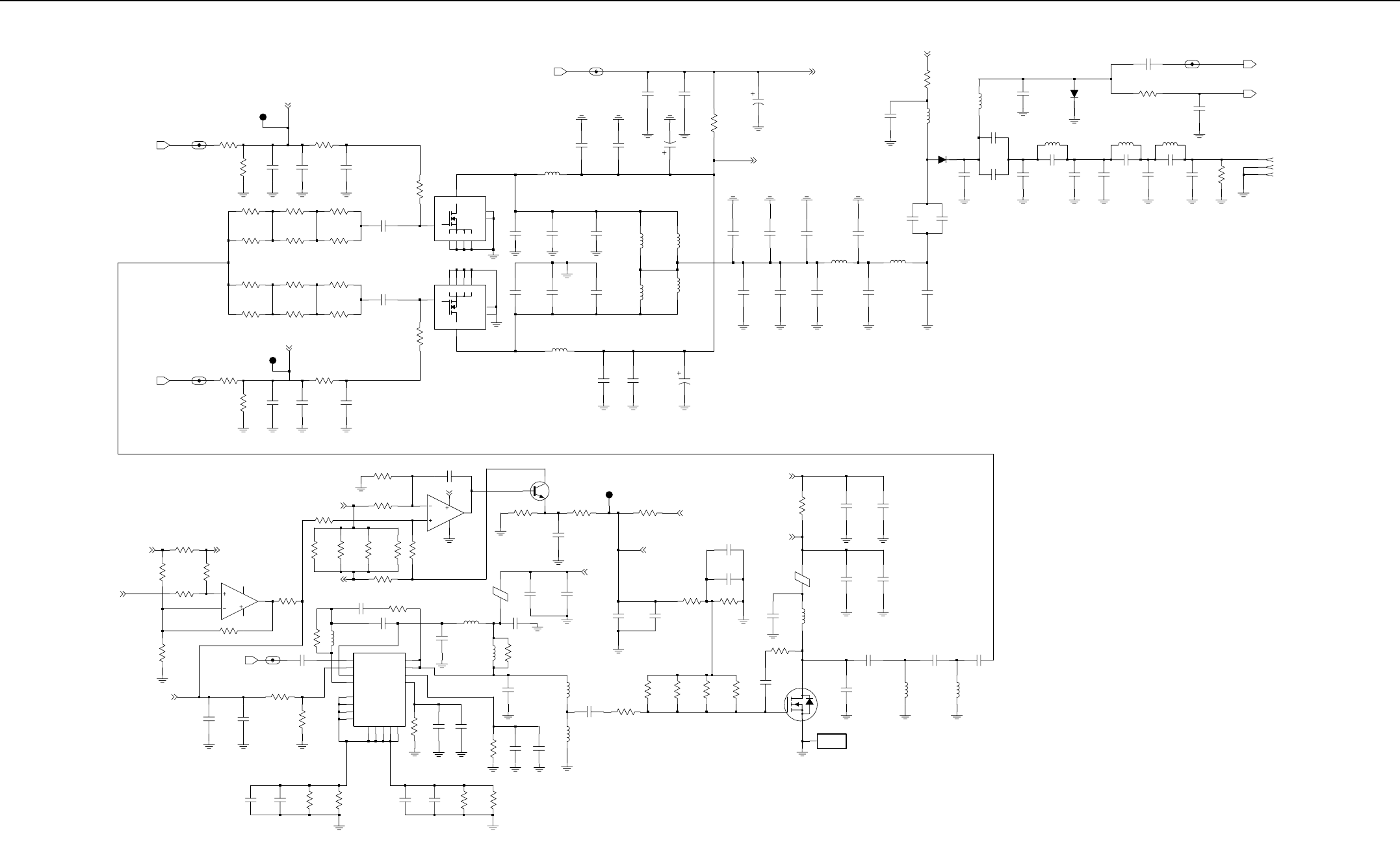

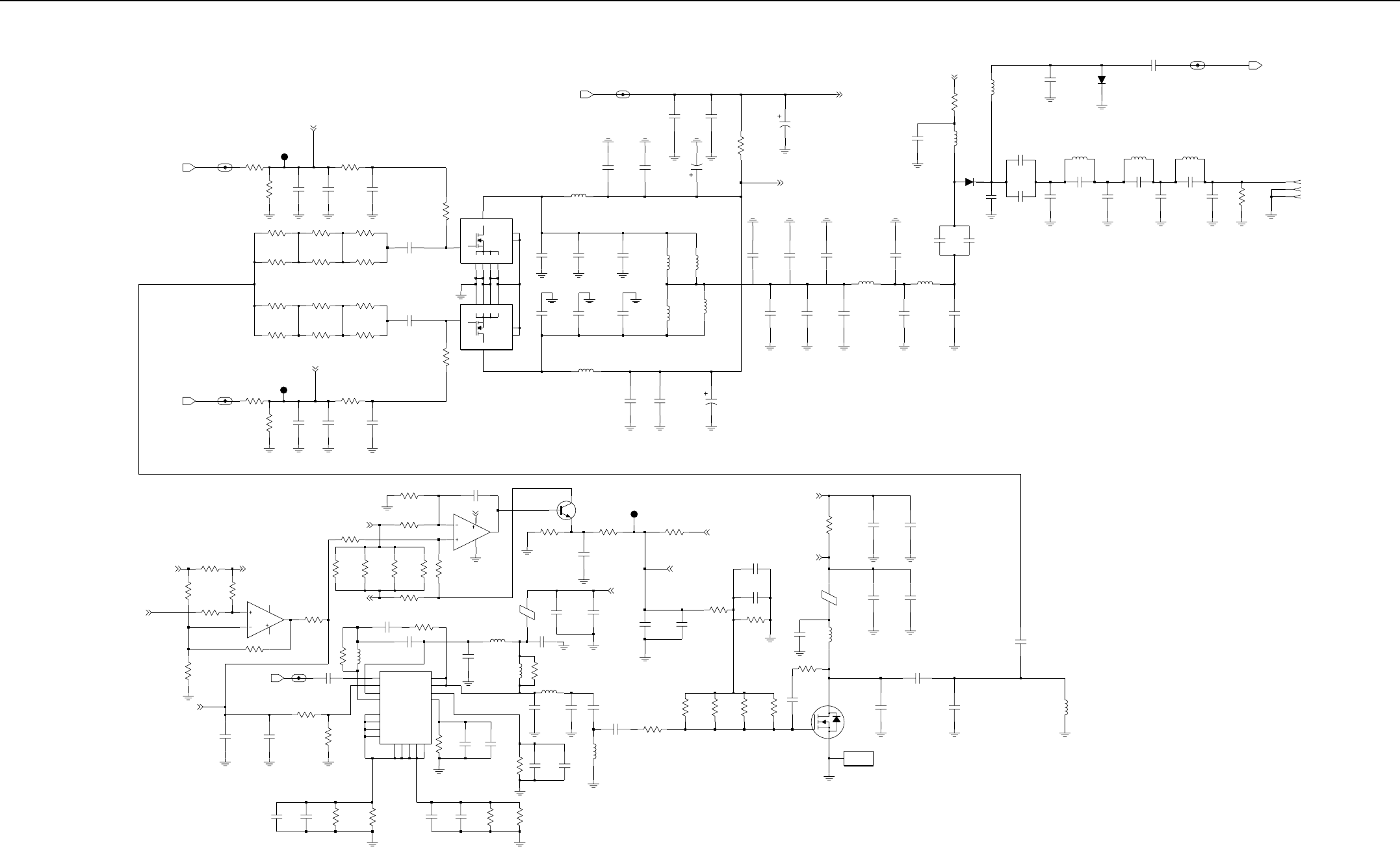

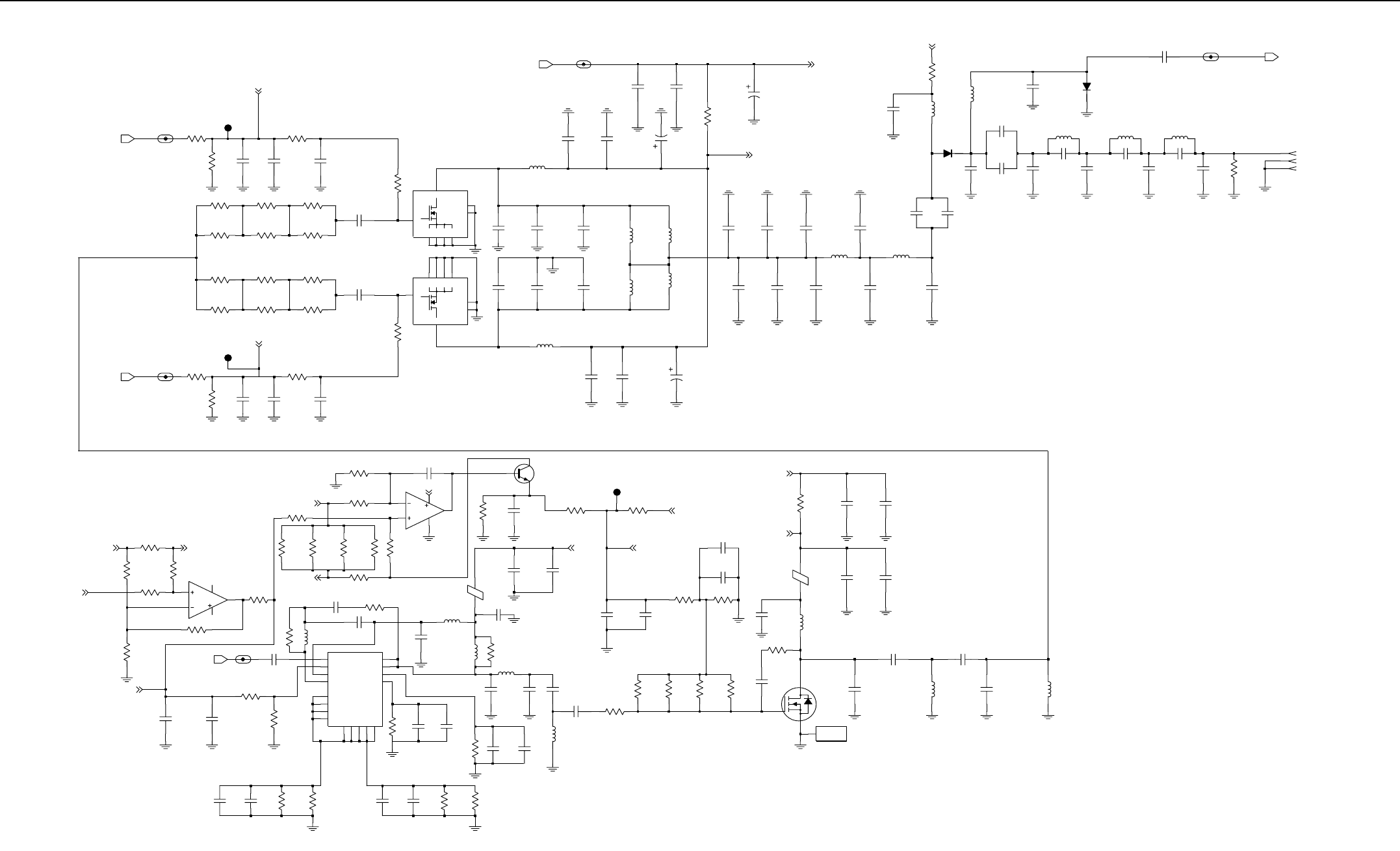

Controlhead GM140/340/640 - Schematic Sheet 1 of 2

ZWG01300239-B

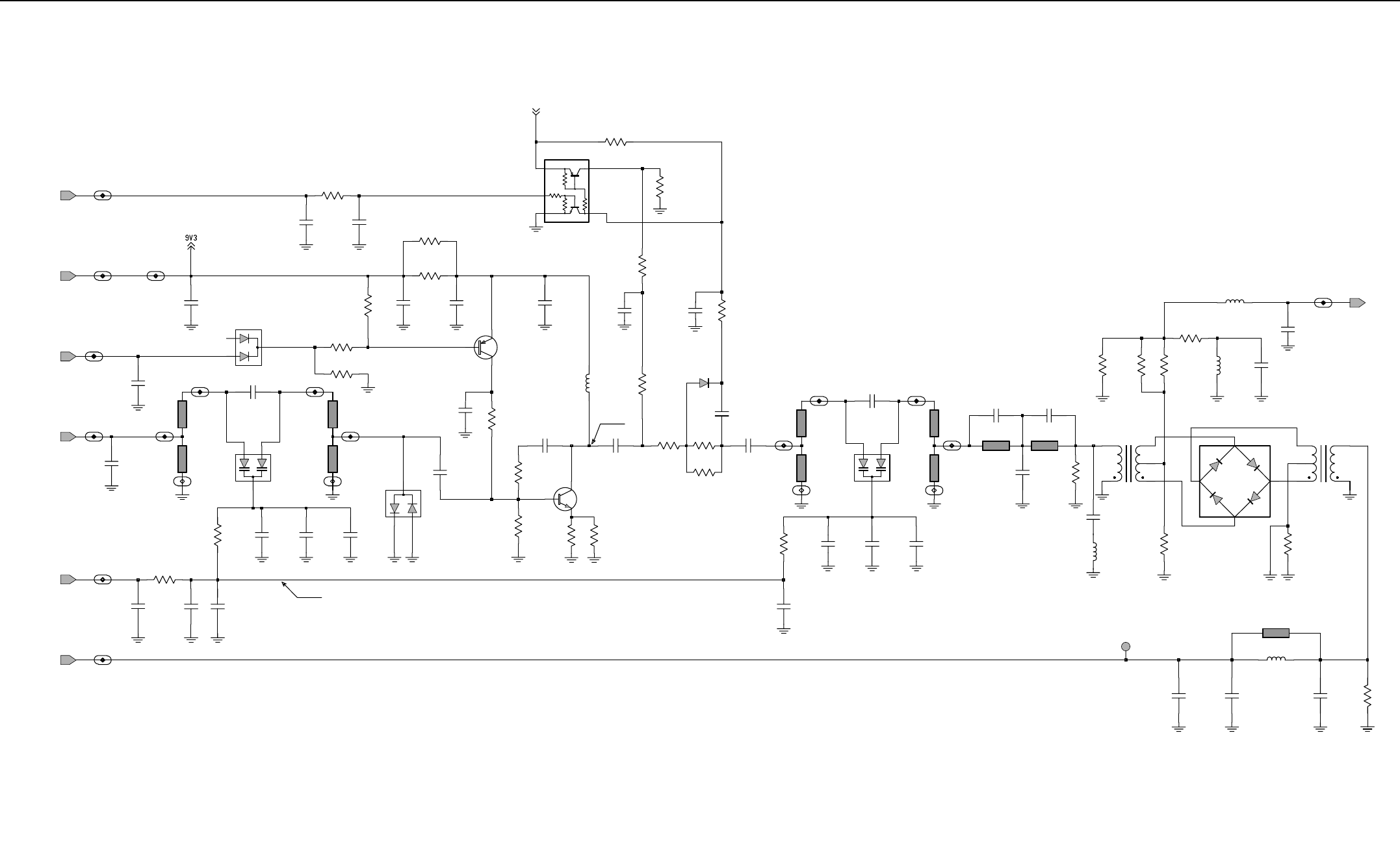

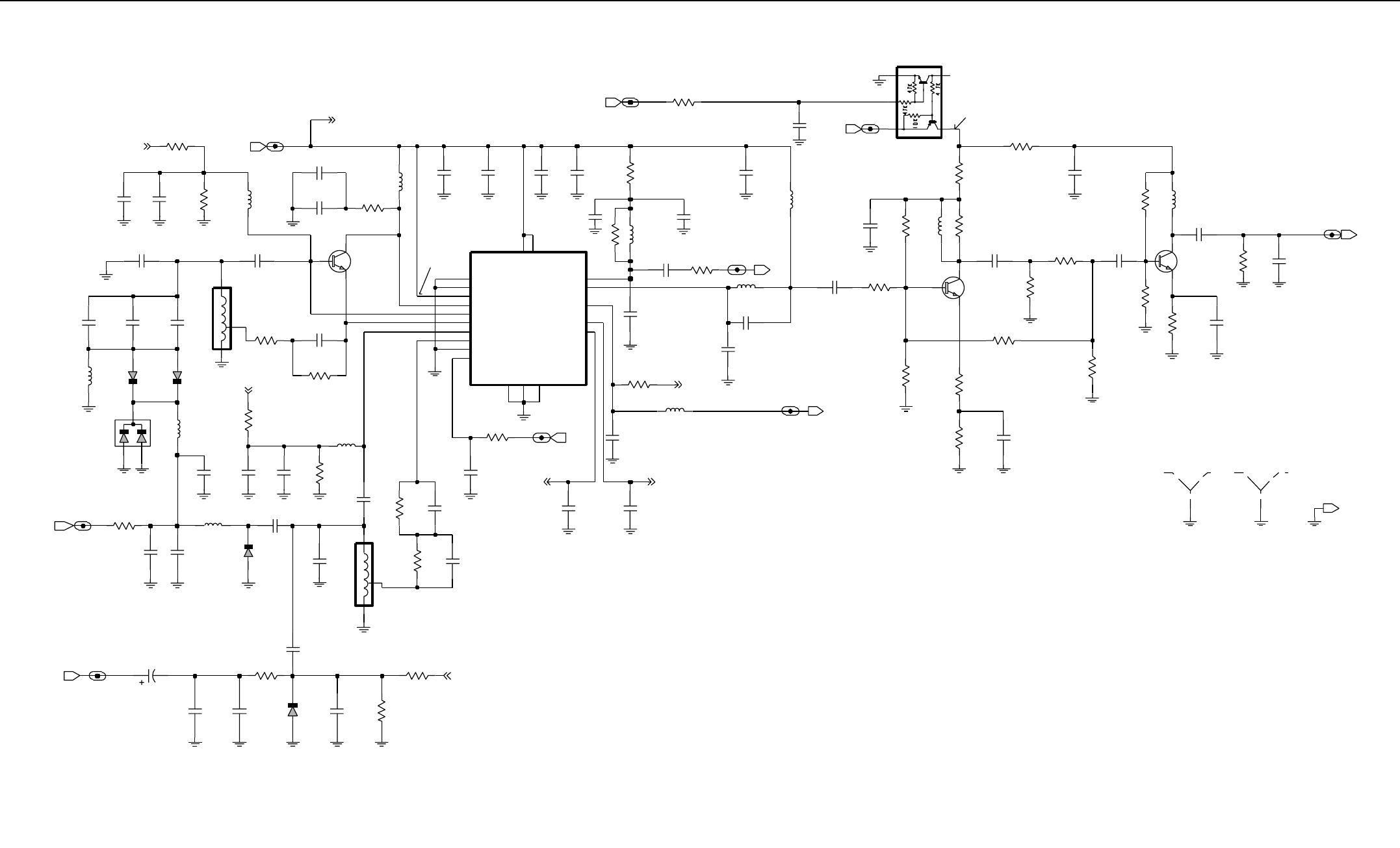

Controlhead GM140/340/640 - PCB 8486146B07 / Schematics 4-5

S0862

LED5LED4 LED6LED1 LED2 LED3

F4 P2

F3 P1

F2

F1

F1 F2 F3 F4

P1 P2

LED1 LED2 LED3

1V/1V

0V/0V

0V/1V

LED4

LED6 LED5

S0864 S0863 S0861

S0866 S0865

KEYPAD

red yellow green

0V/2V

0V/3V

1V/0V

R0867

green

D0885

13K green

D0888

D0886

green

green

D0887

green

D0884

green

D0881

270

R0885

270

R0881

Q0885

1P1

2P2

3P3

4P4

5P5

6P6

7P7

8P8

8P8

S0865

1P1

2P2

3P3

P4

4

5P5

6P6

7P7

R0864

S0861

43K

R0866

51K

R0861

51K

R0880

22K

7

P8

8

13K

R0862

P1

1

P2

2

P3

3

P4

4P5

5

P6

6

P7

6P6

7P7

8P8

S0864

1P1

2P2

3P3

P4

4

5P5

P5

5

P6

6

P7

7

P8

8

S0863

P1

1

P2

2

P3

3

P4

4P4

4P5

5

P6

6

7P7

P8

8

S0862 S0866

P1

1

P2

2

P3

3

270

green

R0877

D0877 D0879

Q0877

red

270

R0878

Q0879

Q0878

yellow

D0878

Q0873

R0879

270

R0871

270

Q0871 Q0872

82

red

D0876

7

D0875

red

red

D0874

R0876

270

R0875

270

R0874

Q0876

270

Q0875Q0874

6

CH_A

sheet 2

5

43

red

Q0881

D0872 D0873

red red

R0873

D0871

270

10

R0872

FLT_A+

LED_CNTRL(0:8)

BL_GREEN

FLT_A+

FLT_A+

LED_CNTRL(0:8)

5V

5V

INT_KP_COL

INT_KP_ROW

270

ZWG0130240-A

Controlhead GM140/340/640 - Schematic Sheet 2 of 2

4-6 Controlhead GM140/340/640 - PCB 8486146B07 / Schematics

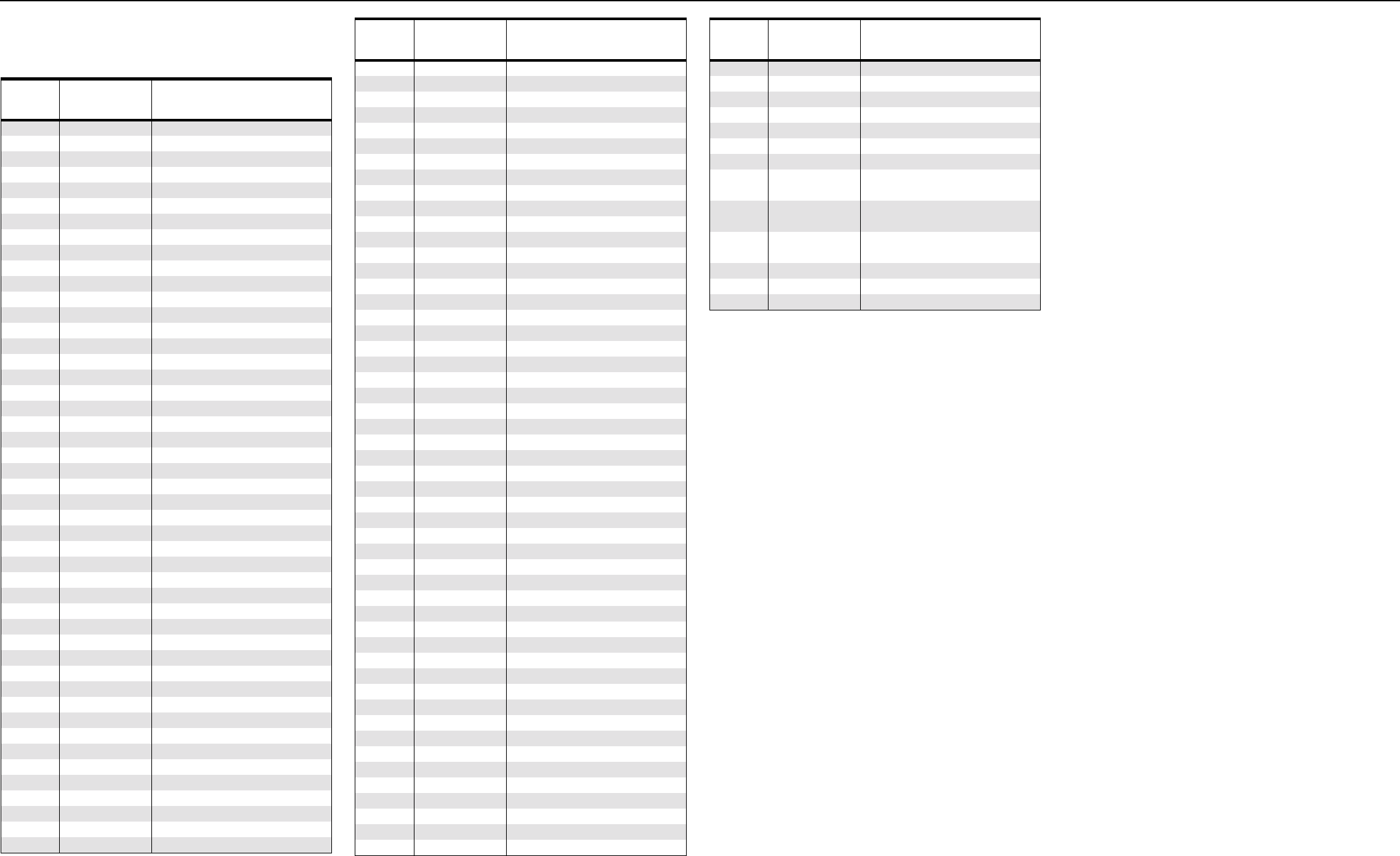

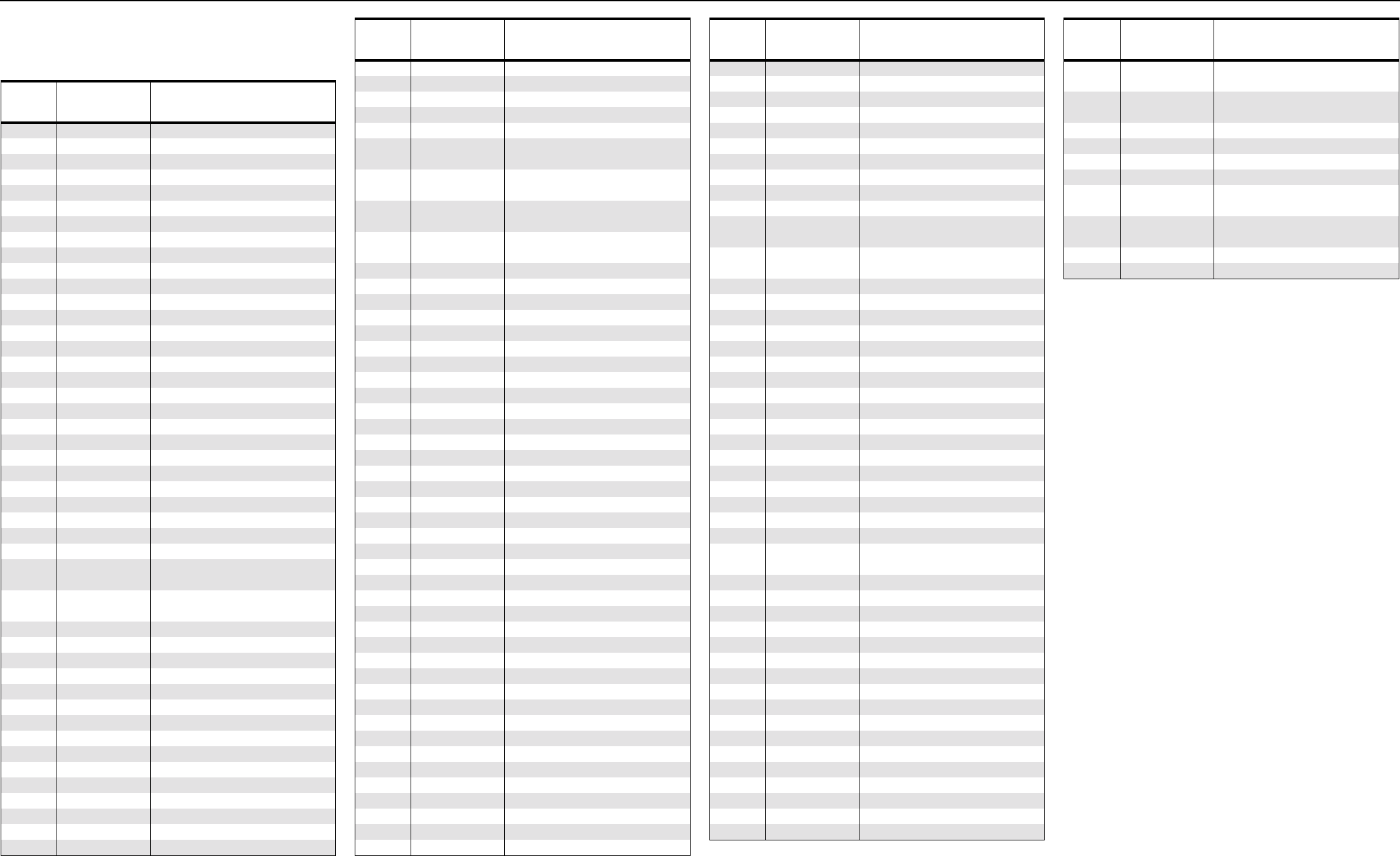

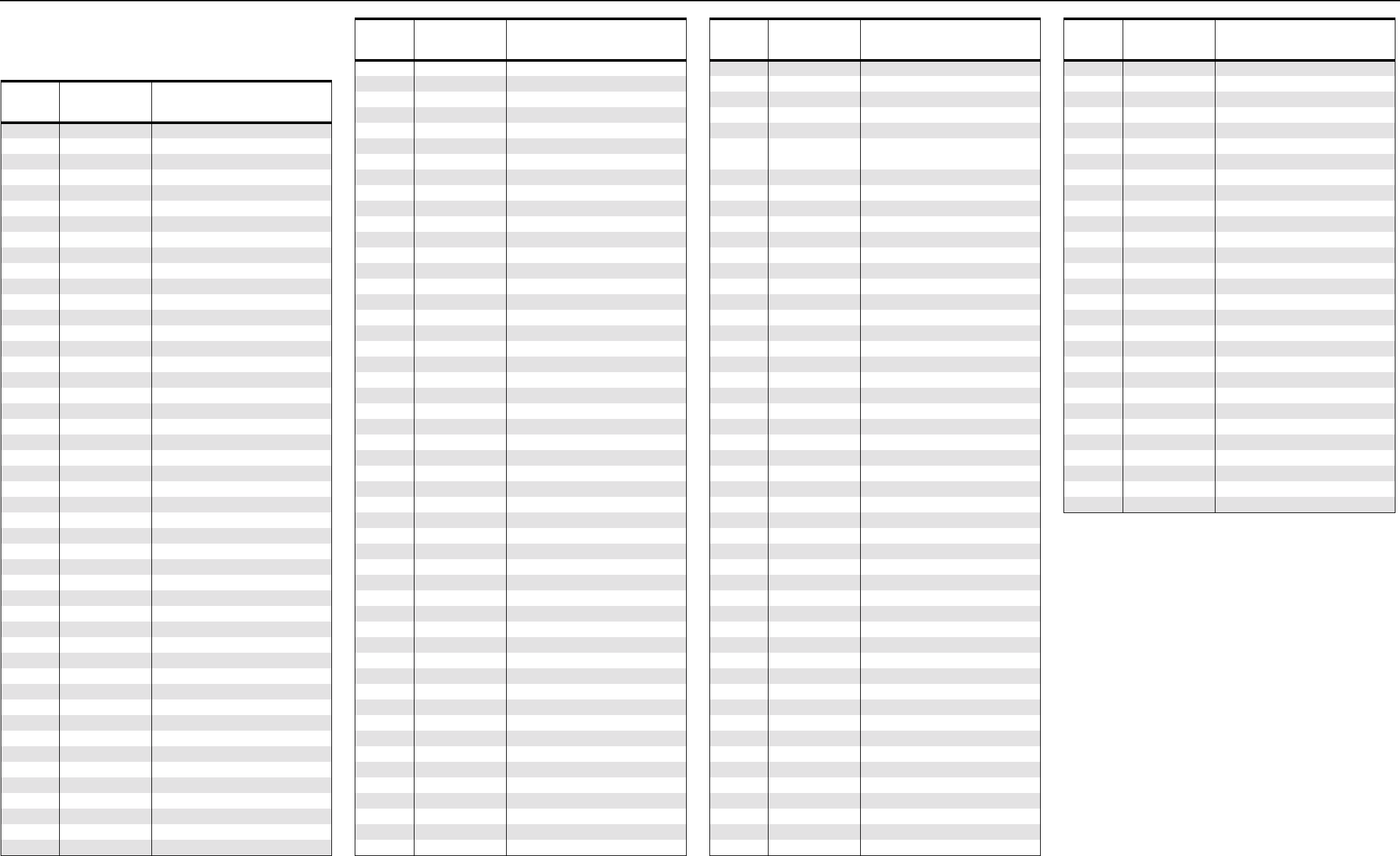

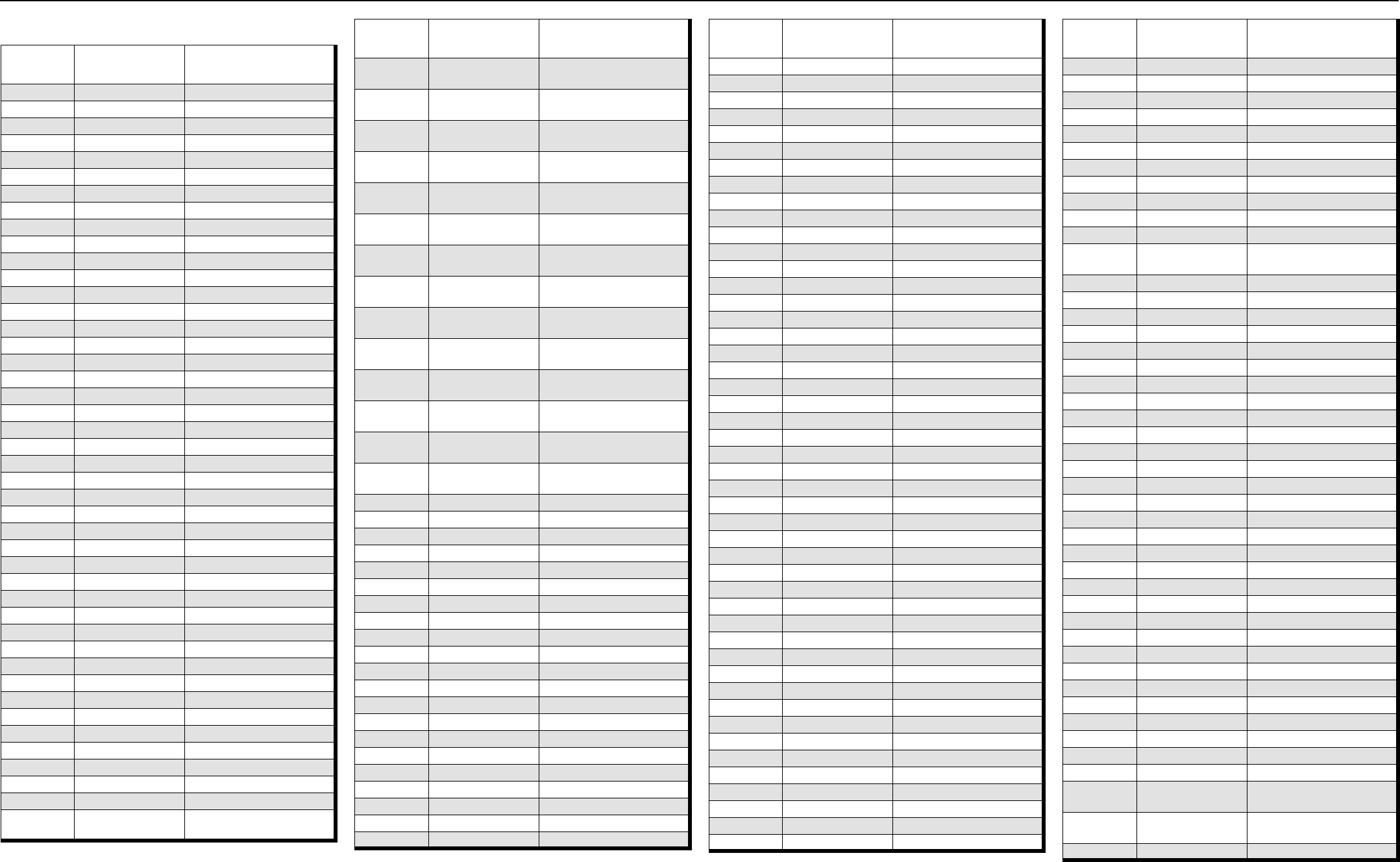

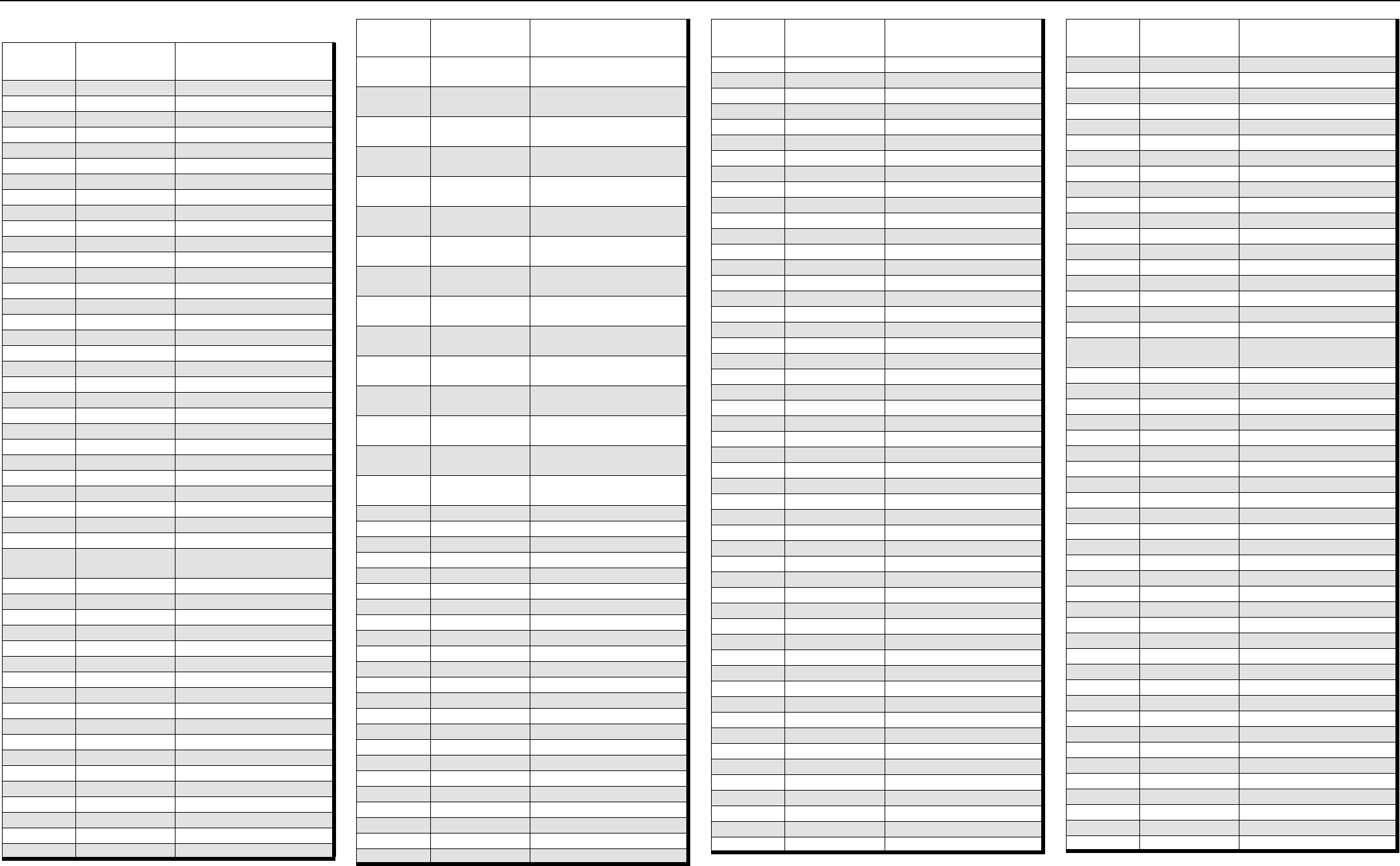

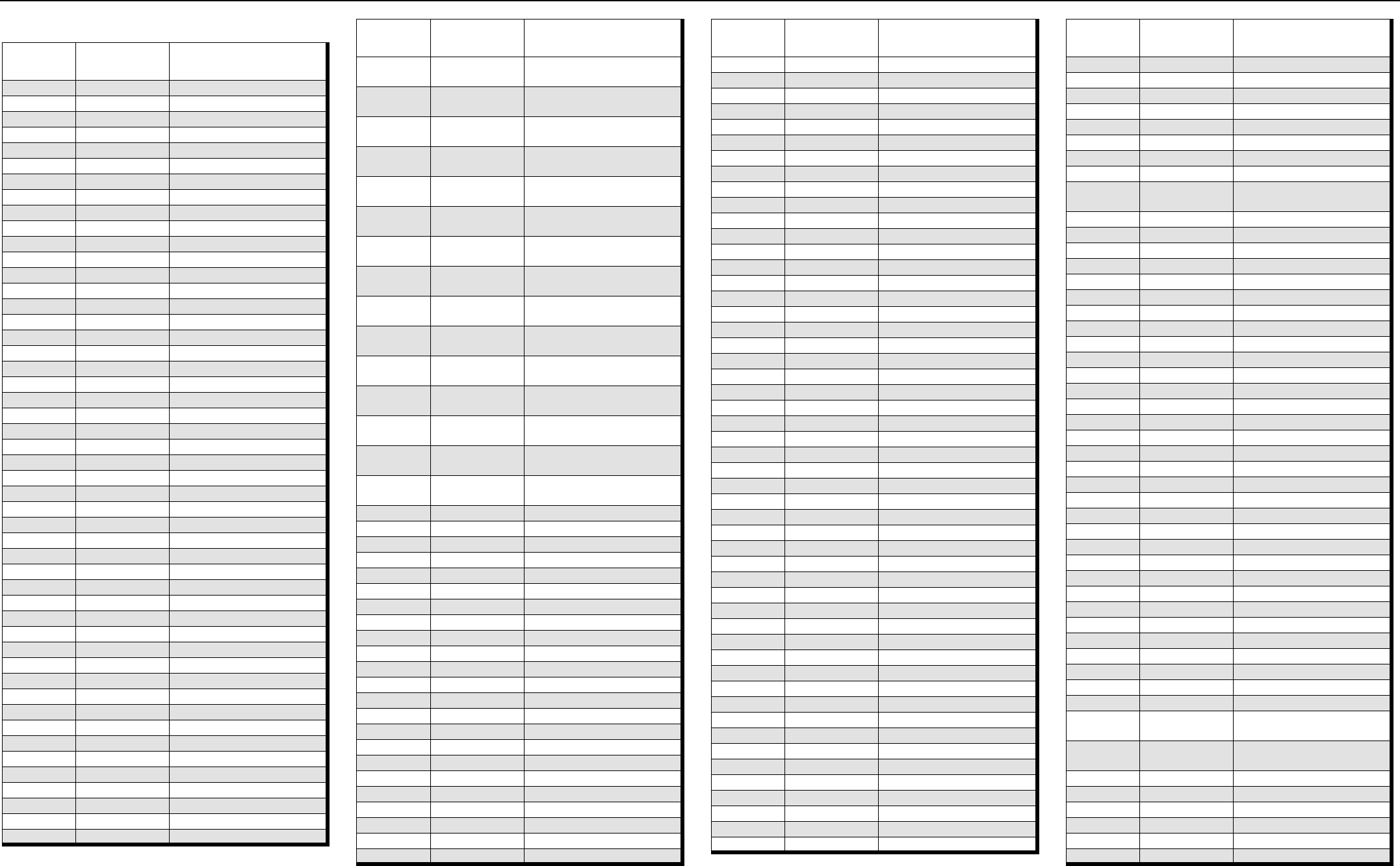

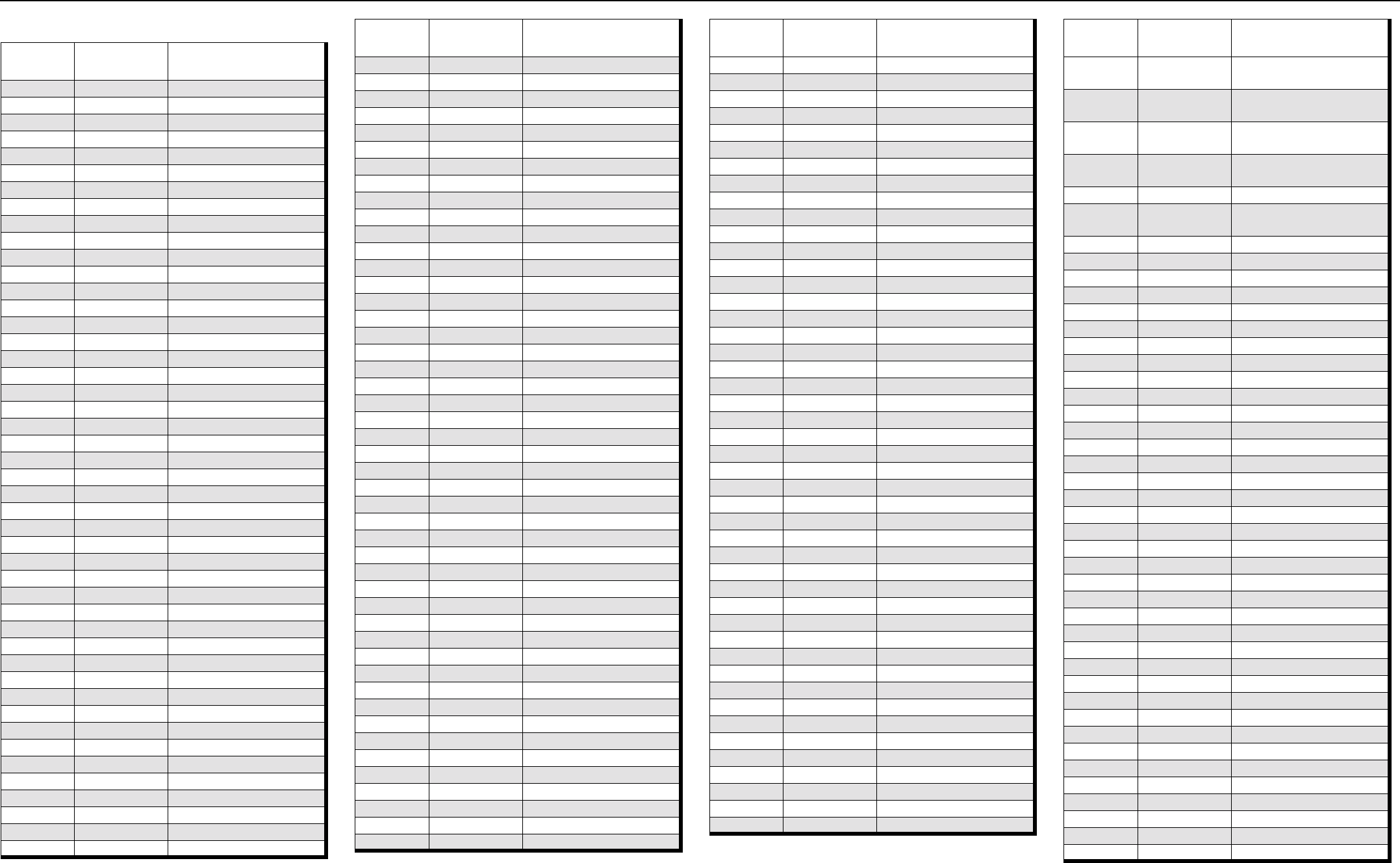

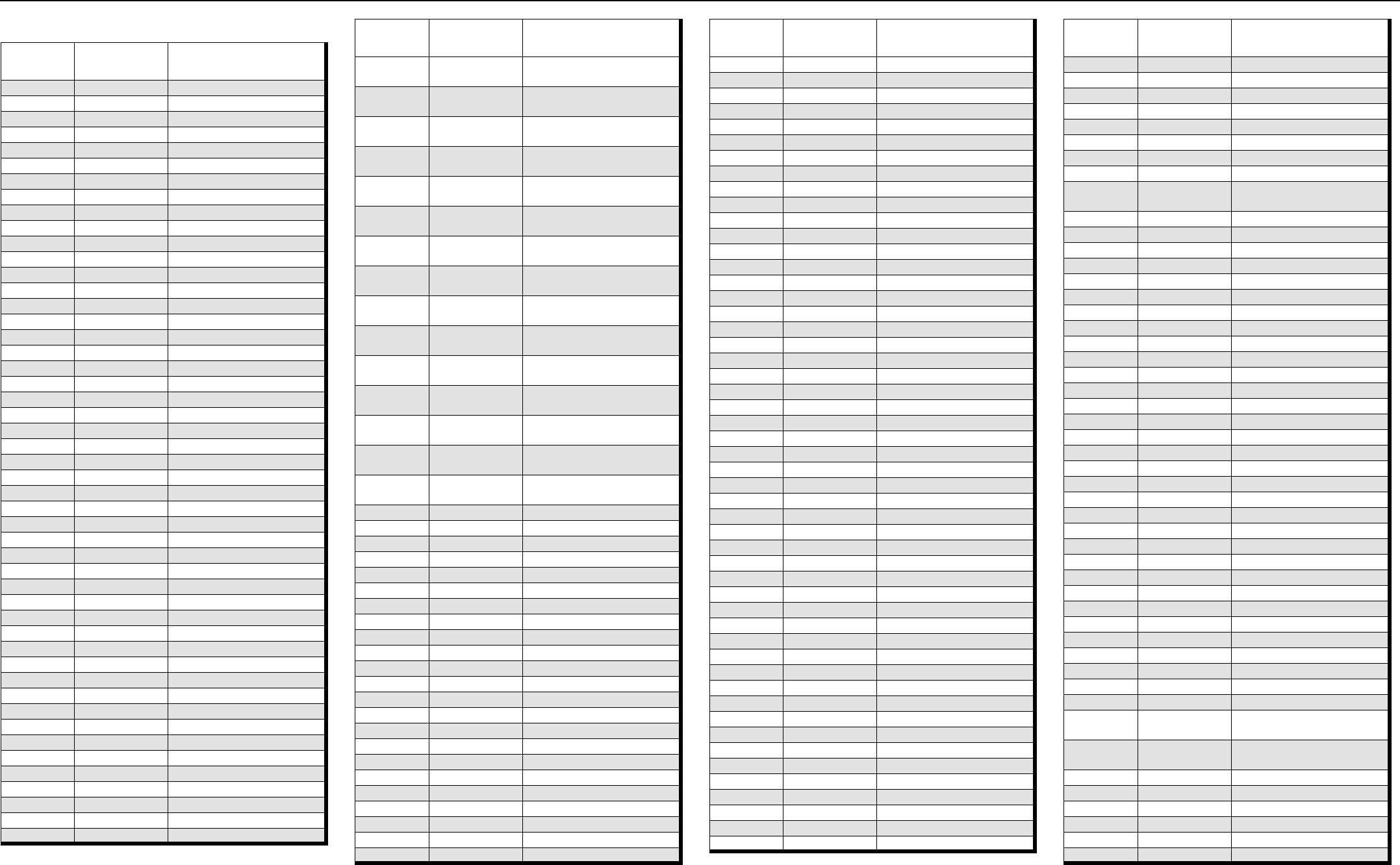

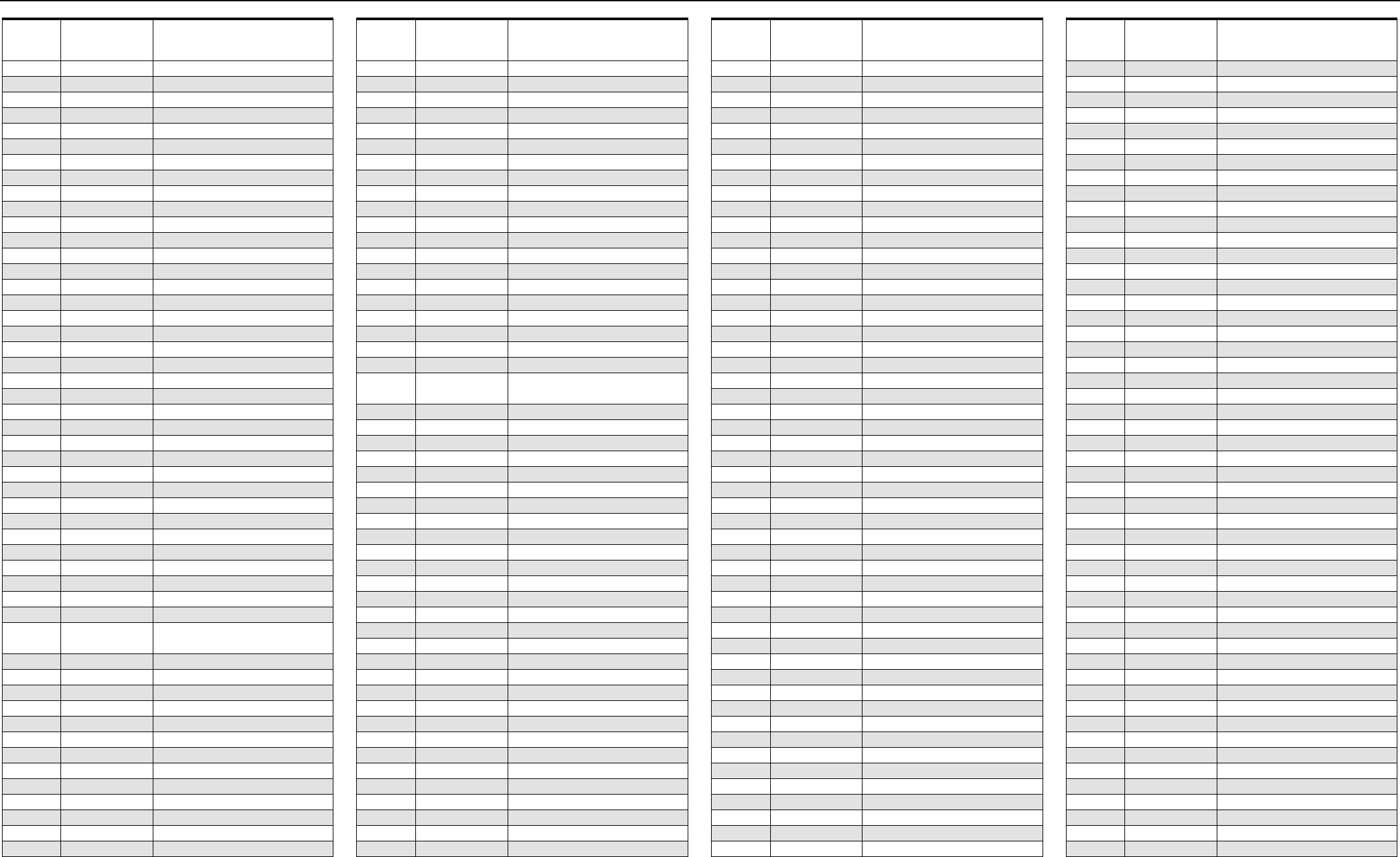

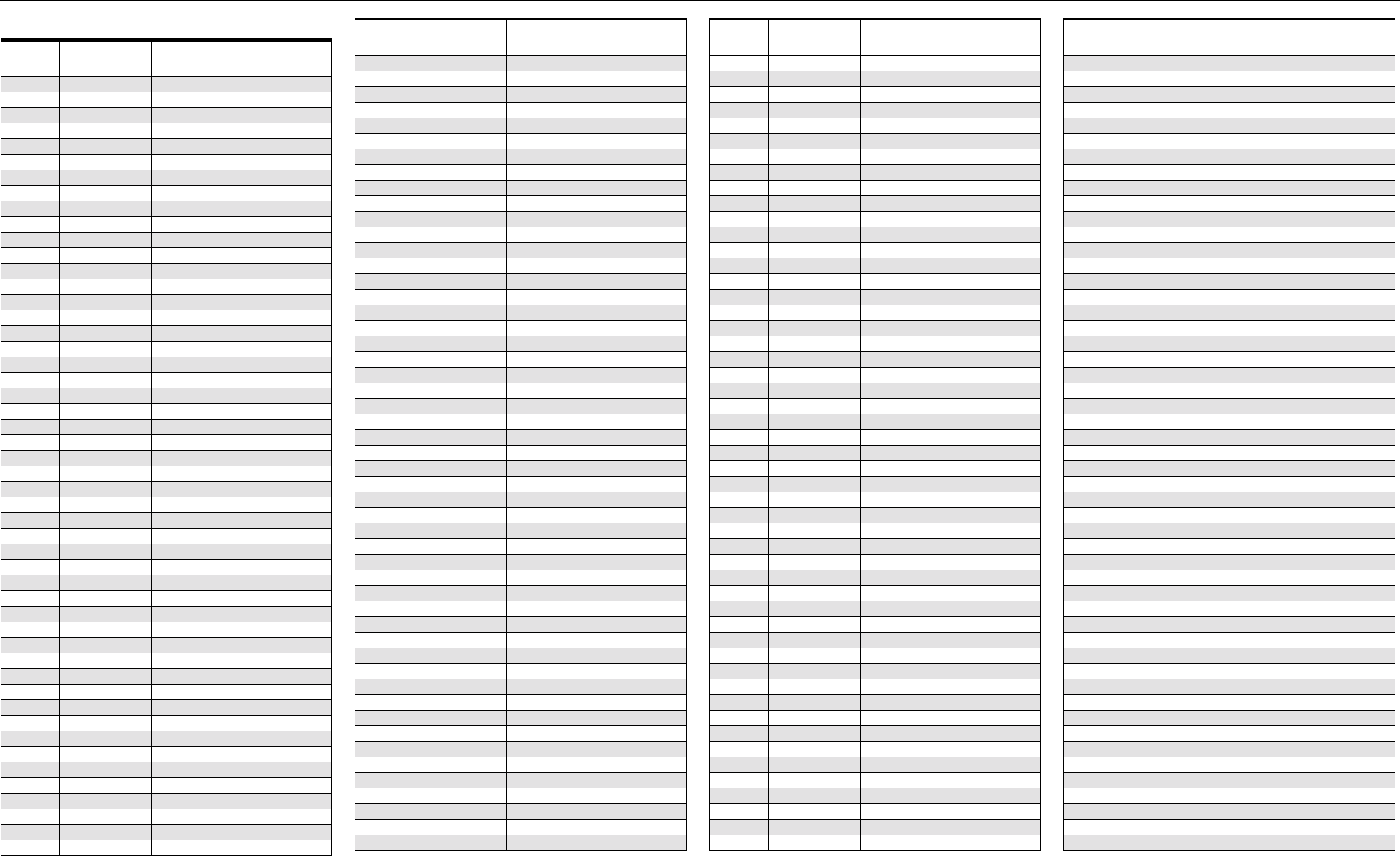

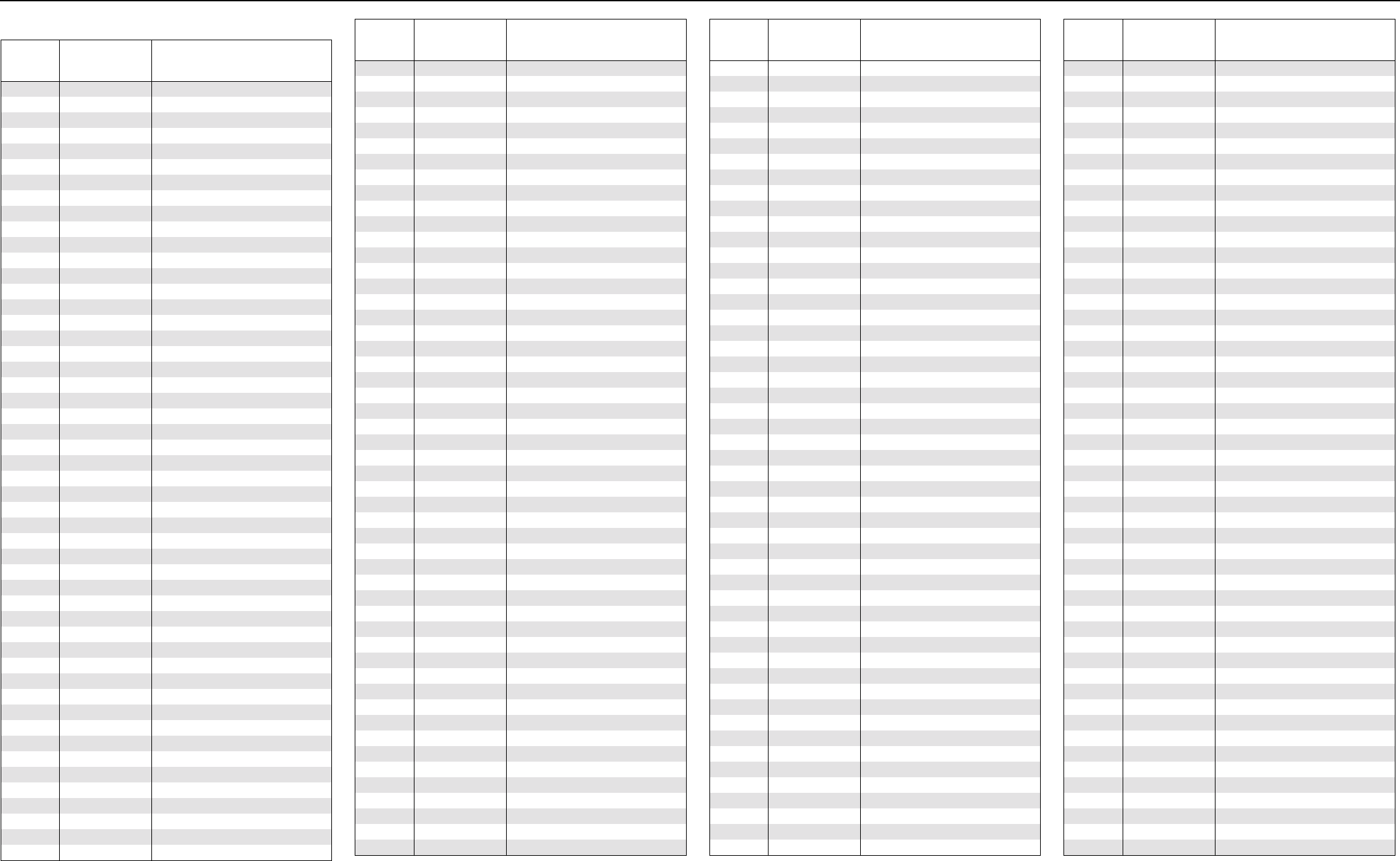

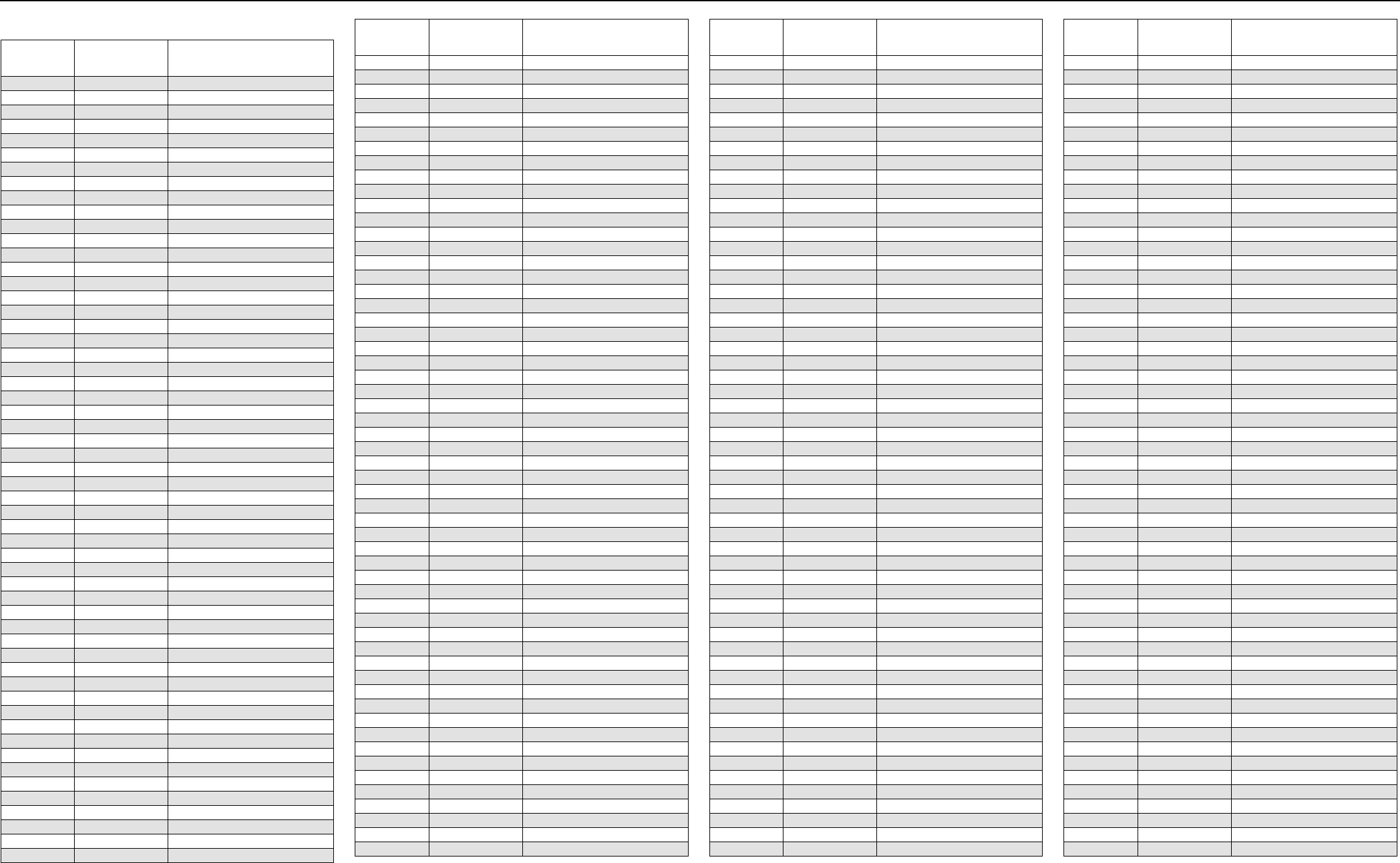

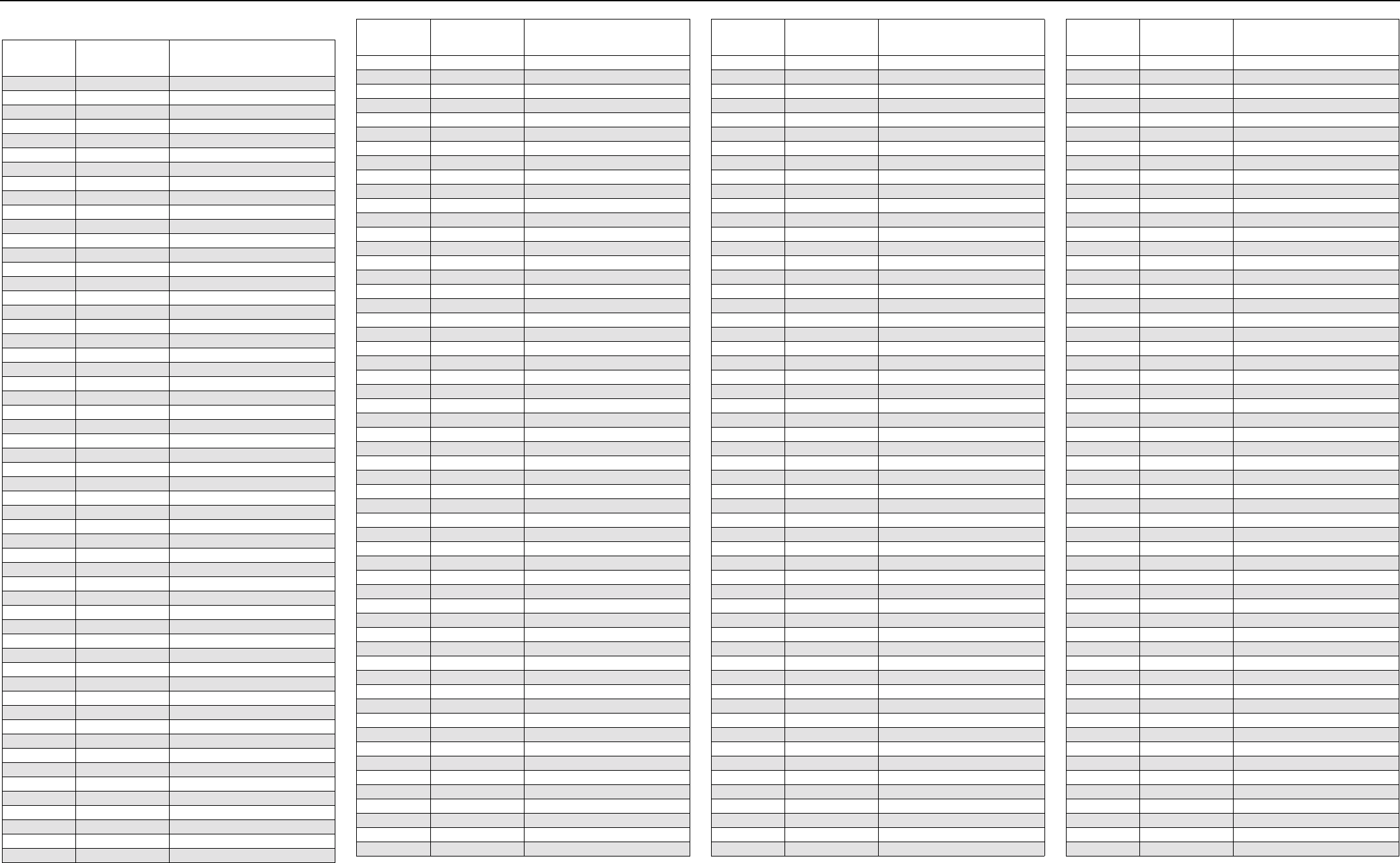

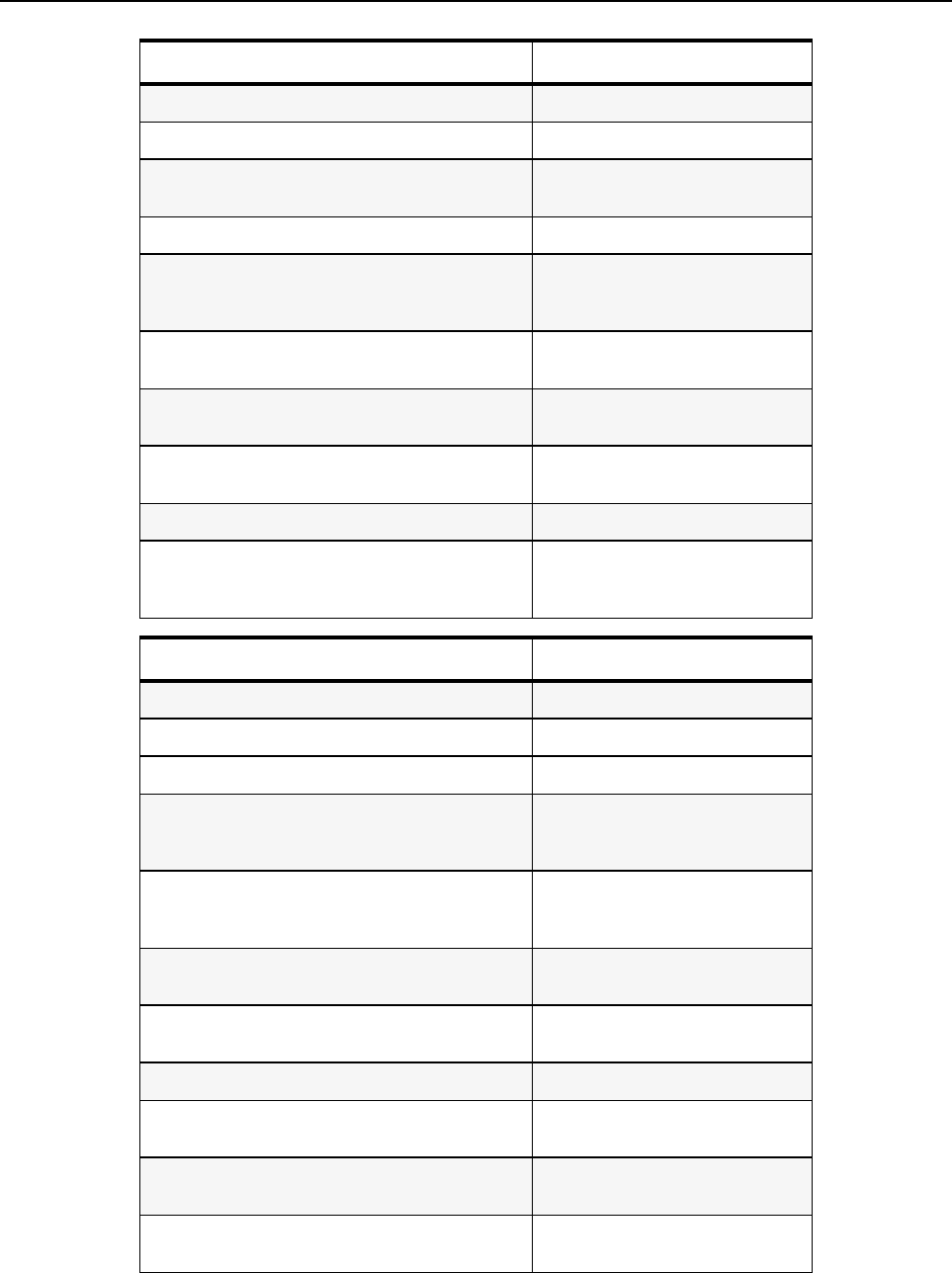

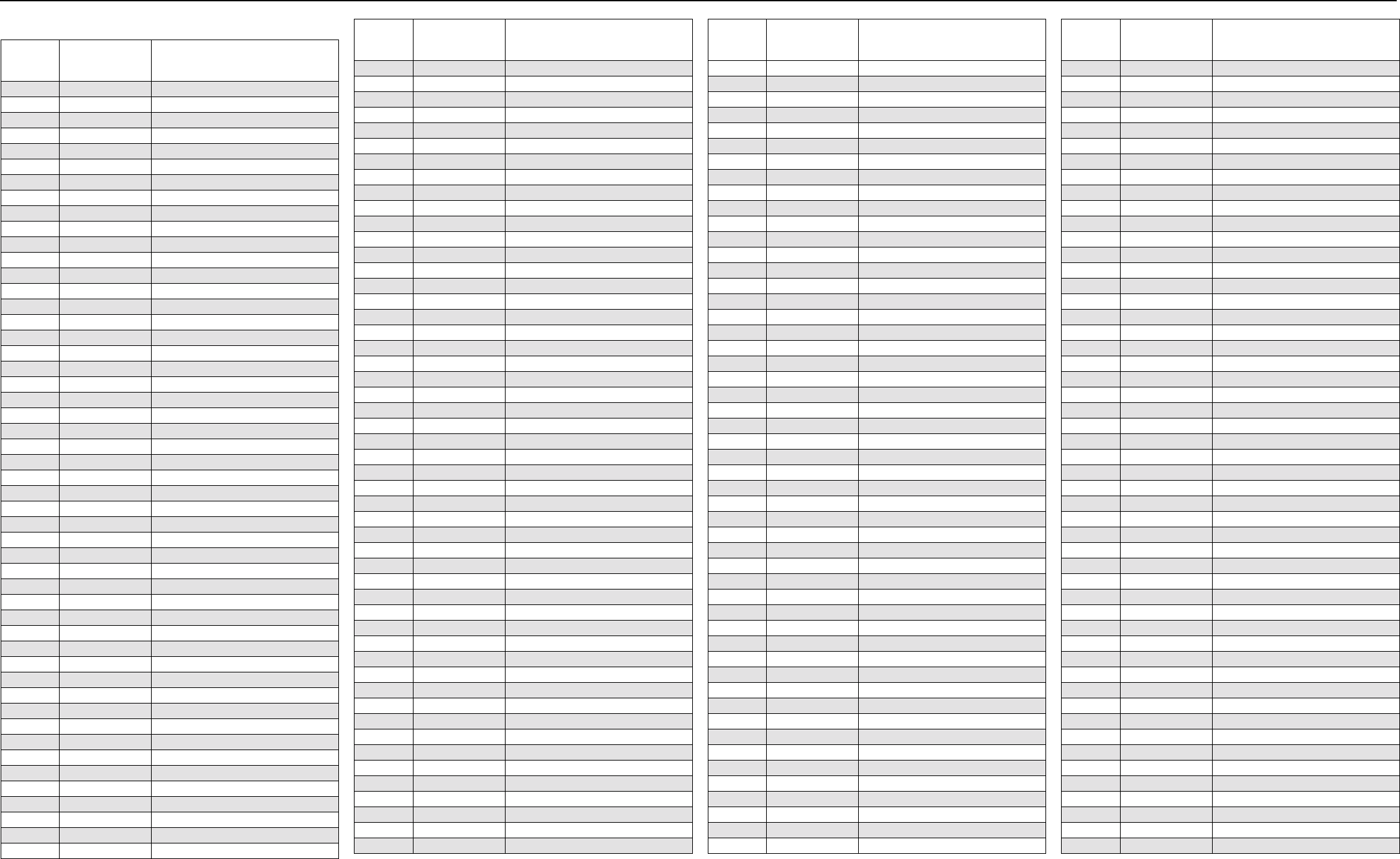

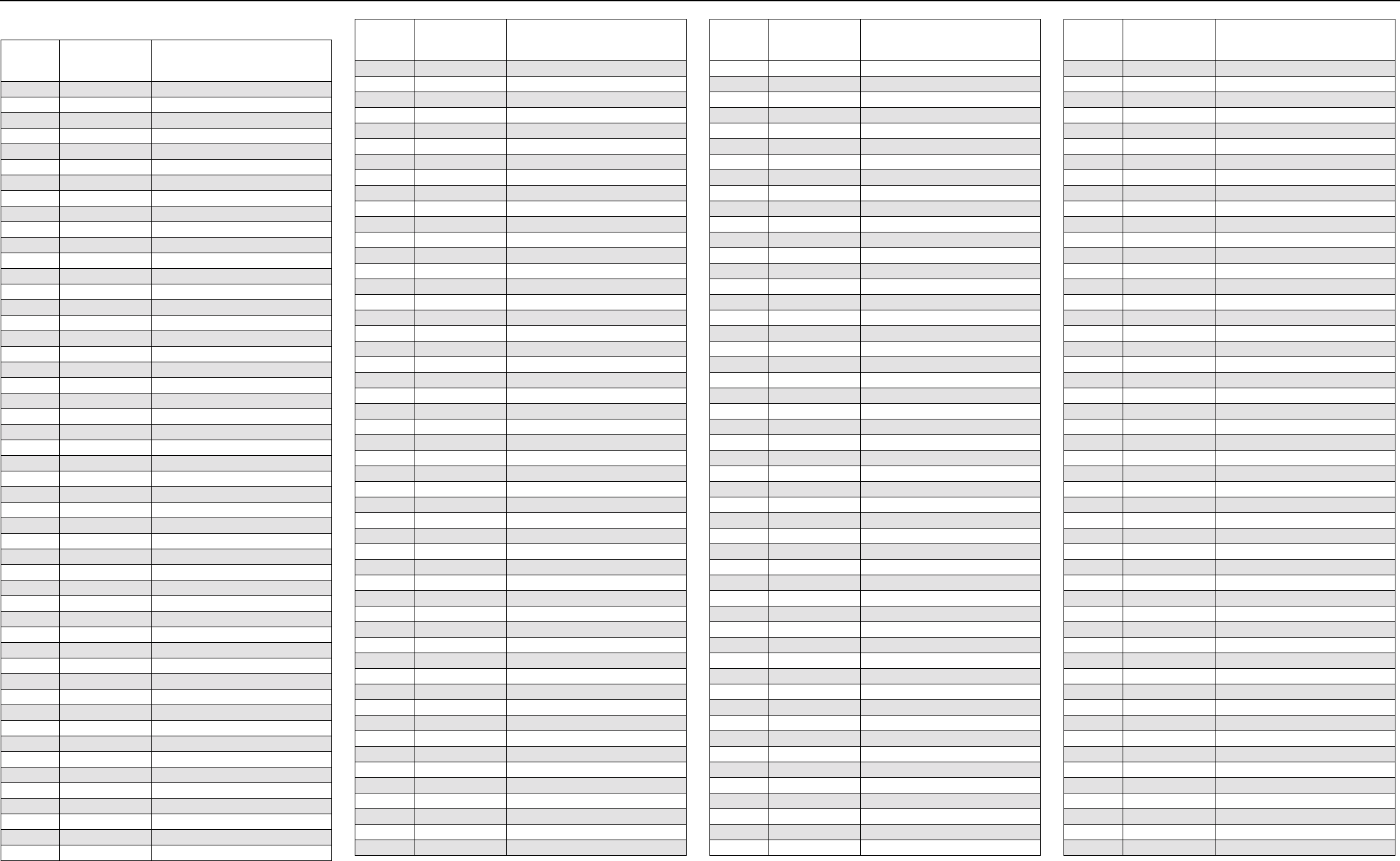

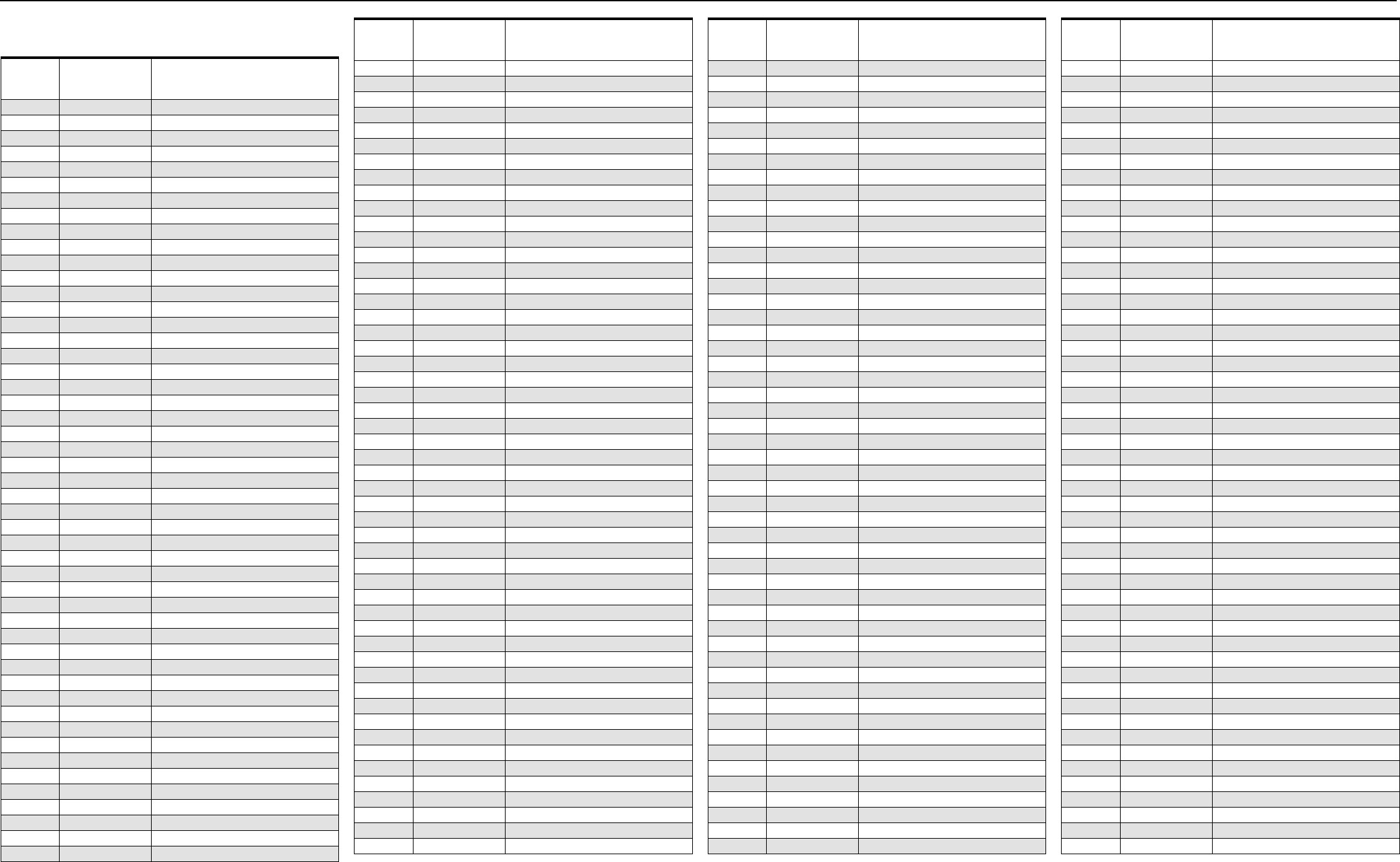

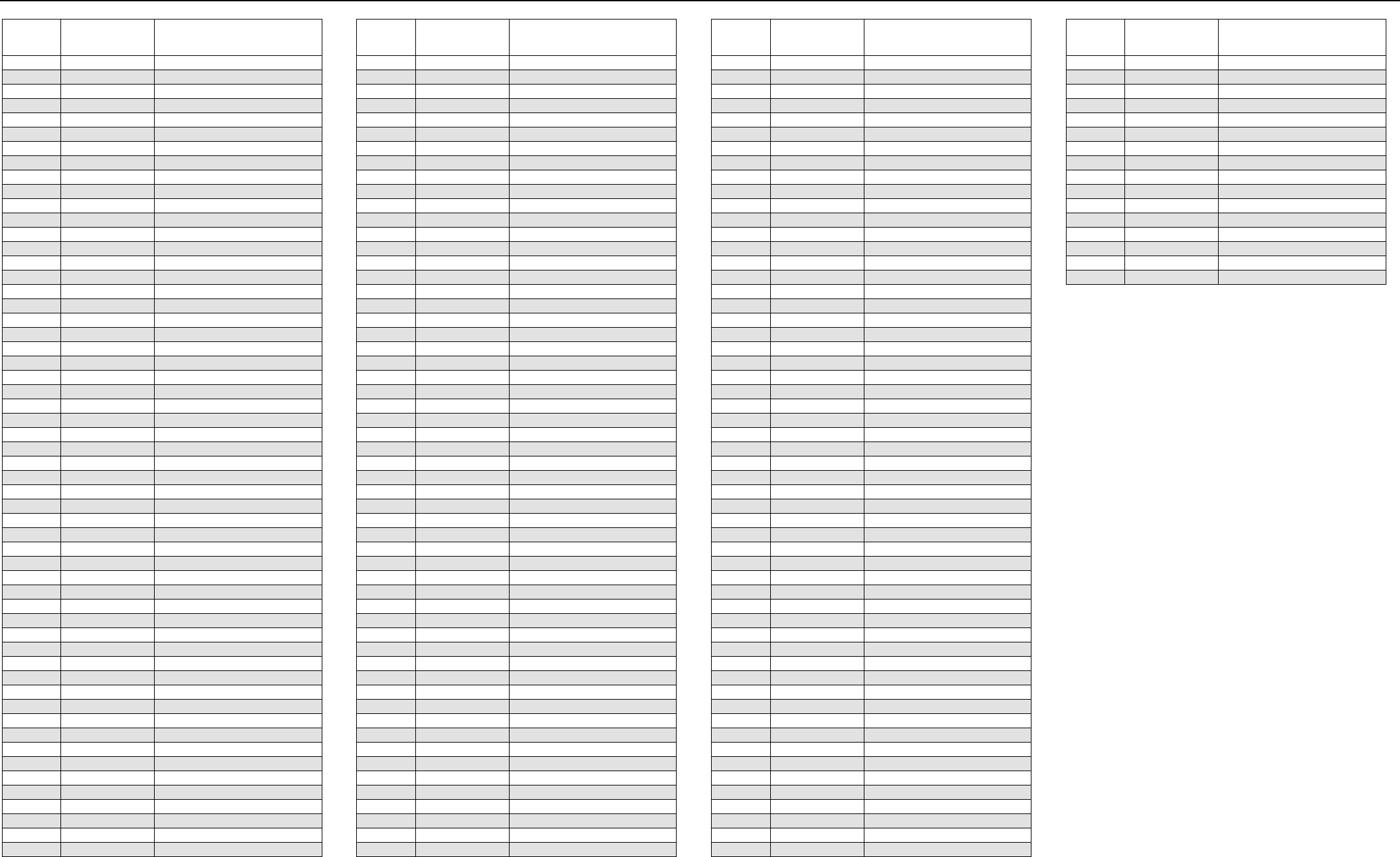

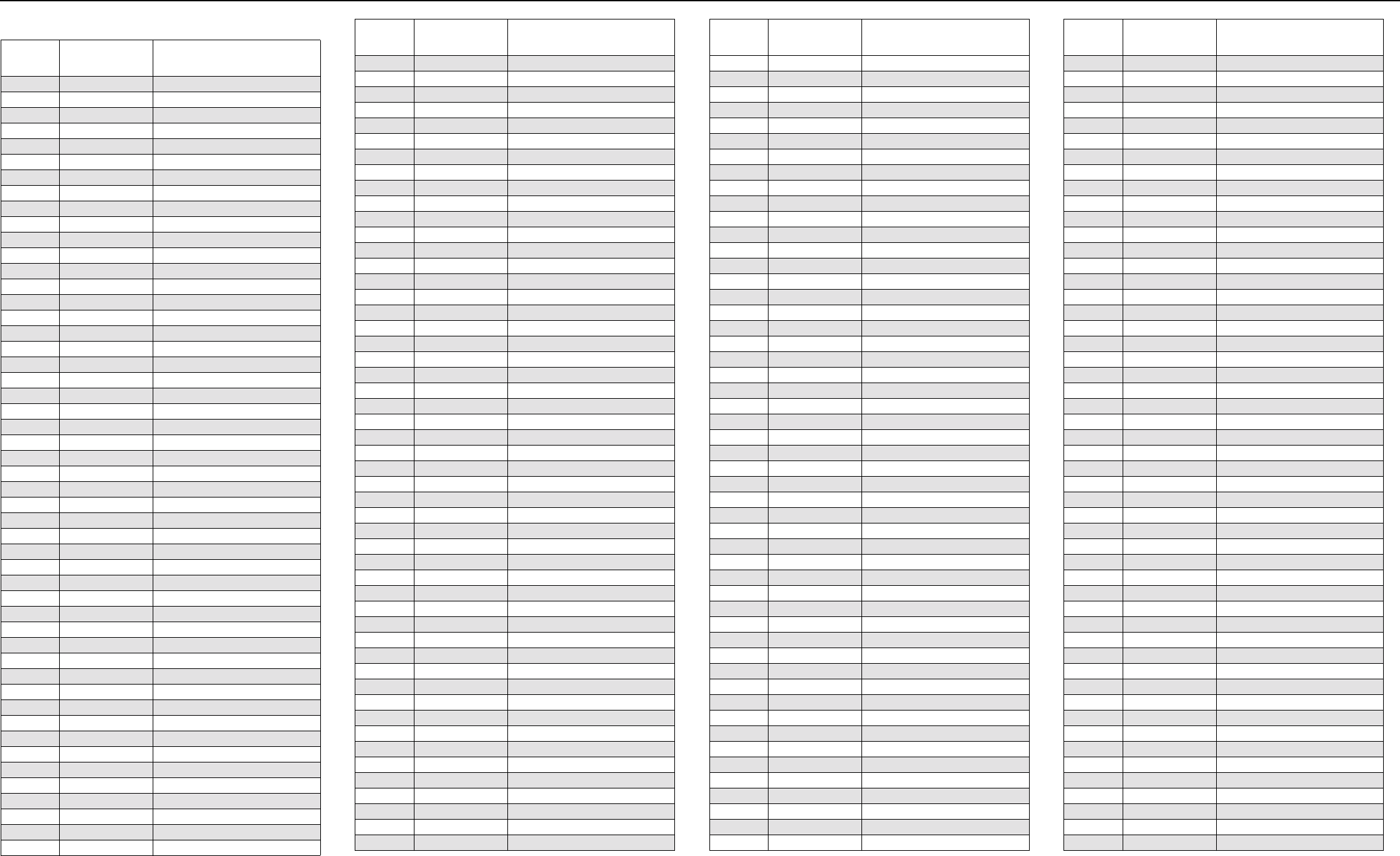

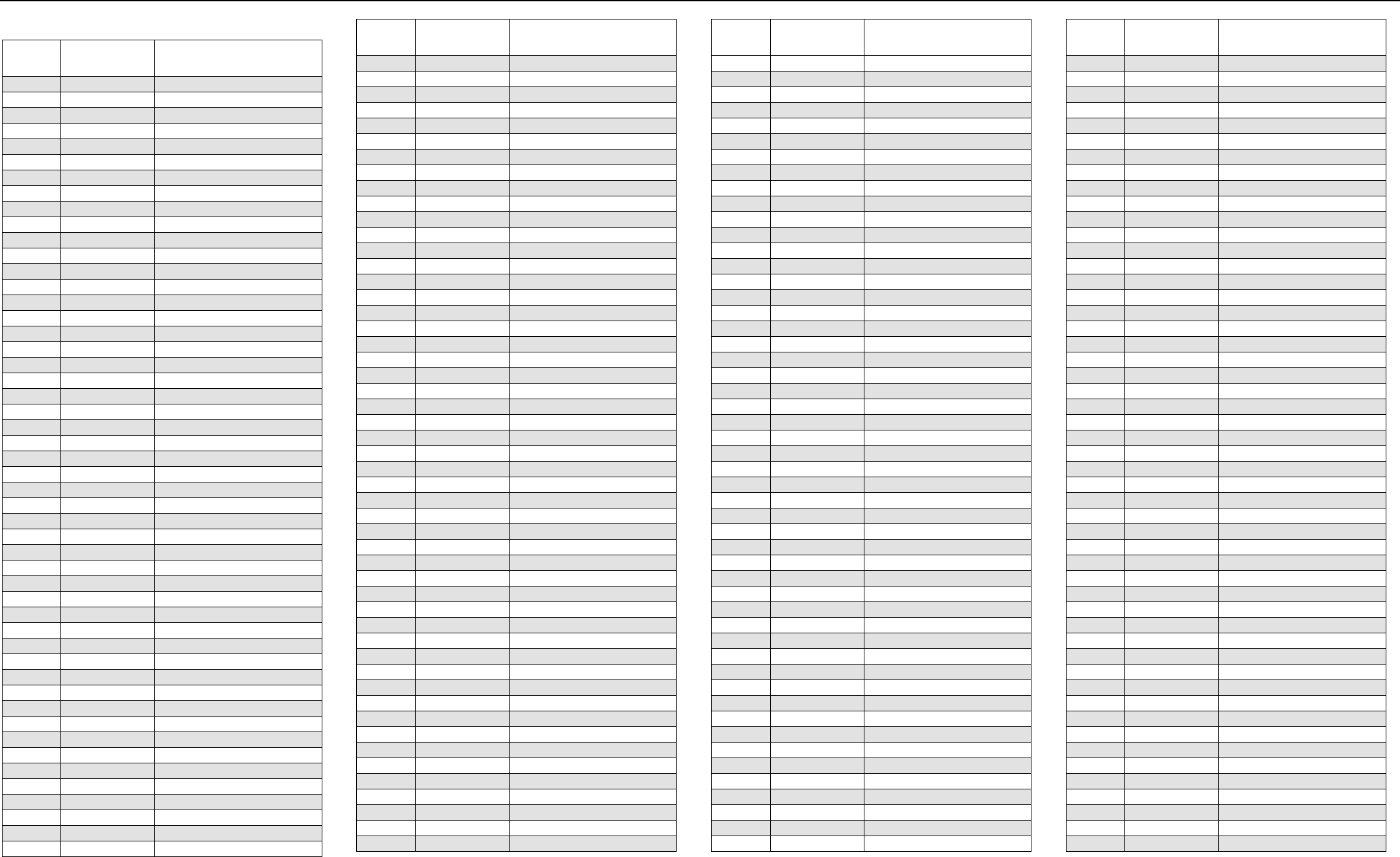

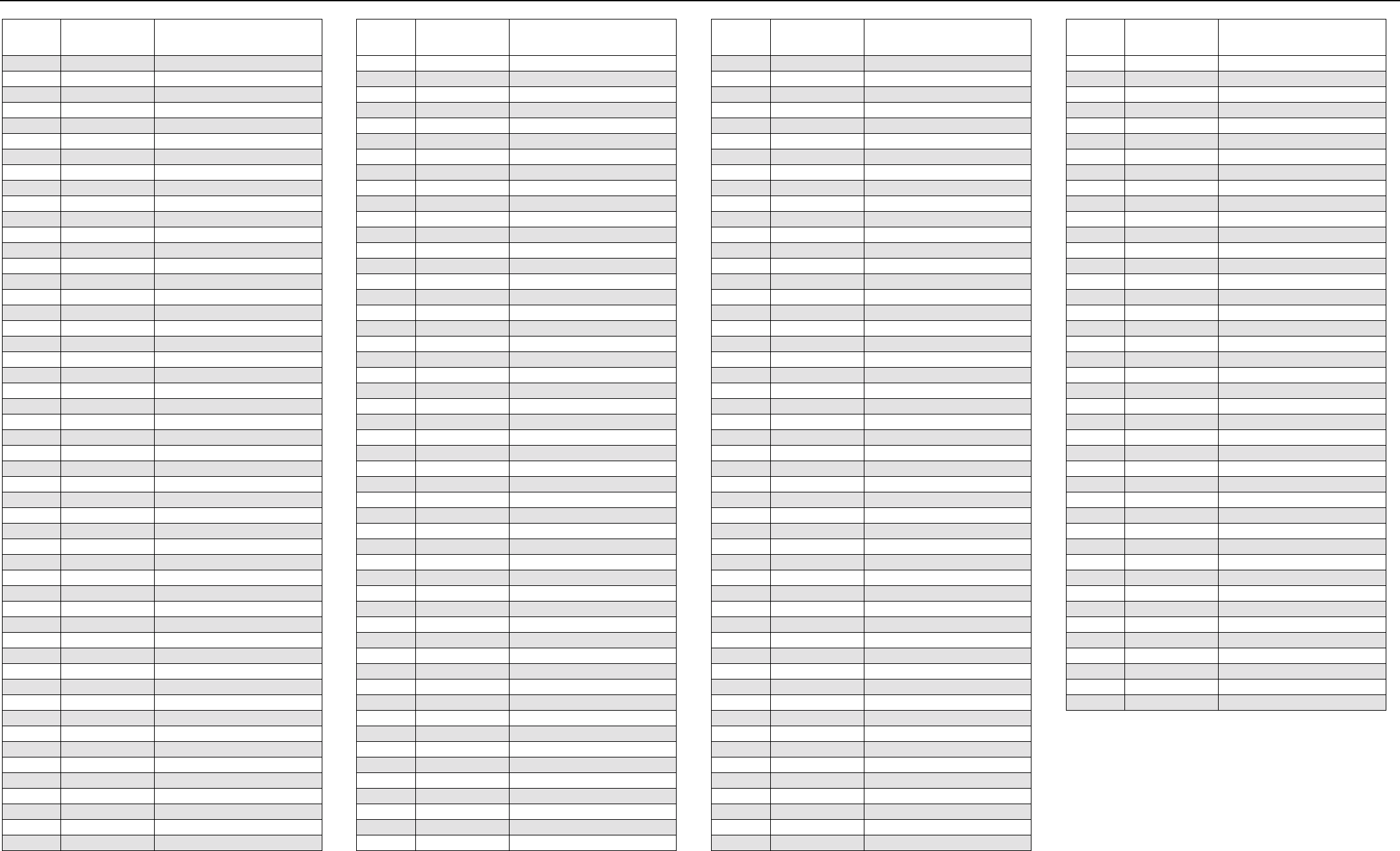

2.1 Controlhead PCB 8486146B07

Parts List

* Motorola Depot Servicing only

Reference designators with an asterisk indicate

components which are not fieldreplaceable

because they need to be calibrated with

specialized factory equipment after installation.

Radios in which these parts have been replaced in

the field will be off frequency at temperature

extremes.

Circuit

Ref Motorola

Part No Description

C0802 2113741F17 470pF 50V

C0803 2113741F17 470pF 50V

C0804 2113741F17 470pF 50V

C0805 2113740F49 82pF 5% 50V

C0806 2113741F17 470pF 50V

C0808 2113741F17 470pF 50V

C0810 2113741F17 470pF 50V

C0811 2113741F17 470pF 50V

C0813 2113741F17 470pF 50V

C0815 2113741F17 470pF 50V

C0816 2113741F17 470pF 50V

C0817 2113740F49 82pF 5% 50V

C0818 2113741F17 470pF 50V

C0821 2113741F17 470pF 50V

C0822 2311049A40 TANT CP 2.2uF 10% 10V

C0823 2113741F49 10nF 50V

C0824 2113741F49 10nF 50V

C0831 2311049A42 TANT CP 3.3uF 10% 6V

C0832 2113743E20 100nF 16V

C0833 2113743E20 100nF 16V

C0843 2113741F17 470pF 50V

D0821 4813833C02 DUAL SOT MMBD6100

D0822 4813833C02 DUAL SOT MMBD6100

D0831 4880236E05 DIODE CHIP SCHOTTKY

D0871 4886171B01 LED RED

D0872 4886171B01 LED RED

D0873 4886171B01 LED RED

D0874 4886171B01 LED RED

D0875 4886171B01 LED RED

D0876 4886171B01 LED RED

D0877 4886171B01 LED RED

D0878 4886171B03 LED YELLOW

D0879 4886171B04 LED GREEN

D0881 4886171B04 LED GREEN

D0884 4886171B04 LED GREEN

D0885 4886171B04 LED GREEN

D0886 4886171B04 LED GREEN

D0887 4886171B04 LED GREEN

D0888 4886171B04 LED GREEN

J0801 0902636Y02 CONNECTOR FLEX 12 PIN

J0811 2864287B01 CONN TELCO 10 PIN JACK

P0801 2809926G01 CONN 1.25MM 2PIN SURMT

Q0821 4805921T02 TSTR DUAL ROHM FMC2 RH

Q0822 4880048M01 TSTR NPN DIG 47k/47k

Q0823 4805921T02 TSTR DUAL ROHM FMC2 RH

Q0841 4880048M01 TSTR NPN DIG 47k/47k

Q0843 4880048M01 TSTR NPN DIG 47k/47k

Q0871 4813824A10 TSTR NPN 40V .2A B=50-150

Q0872 4813824A10 TSTR NPN 40V .2A B=50-150

Q0873 4813824A10 TSTR NPN 40V .2A B=50-150

Q0874 4813824A10 TSTR NPN 40V .2A B=50-150

Q0875 4813824A10 TSTR NPN 40V .2A B=50-150

Q0876 4813824A10 TSTR NPN 40V .2A B=50-150

Q0877 4813824A10 TSTR NPN 40V .2A B=50-150

Q0878 4813824A10 TSTR NPN 40V .2A B=50-150

Q0879 4813824A10 TSTR NPN 40V .2A B=50-150

Q0881 4813824A10 TSTR NPN 40V .2A B=50-150

Q0885 4813824A10 TSTR NPN 40V .2A B=50-150

R0810 0662057A76 13k 1/16W 5%

R0811 0662057A90 51k 1/16W 5%

R0812 0662057A09 22 1/16W 5%

R0813 0662057A01 10 1/16W 5%

R0814 0662057A35 270 1/16W 5%

R0815 0662057A76 13k 1/16W 5%

R0816 0662057A90 51k 1/16W 5%

R0821 0662057A73 10k 1/16W 5%

R0822 0662057A76 13K 1/16W 5%

R0823 1805911V02 POT VOL

R0824 0662057A65 4k7 1/16W 5%

R0825 0662057A49 1k 1/16W 5%

R0831 0662057B22 1M 1/16W 5%

R0832 0662057A57 2k2 1/16W 5%

R0833 0662057A89 47k 1/16W 5%

R0834 0662057A35 270 1/16W 5%

R0835 0662057A25 100 1/16W 5%

R0836 0662057A73 10k 1/16W 5%

R0837 0662057A85 33k 1/16W 5%

R0838 0662057A73 10k 1/16W 5%

R0841 0662057A73 10k 1/16W 5%

R0842 0662057A89 47k 1/16W 5%

R0843 0662057A57 2.2k 1/16W 5%

R0844 0662057A73 10k 1/16W 5%

R0845 0662057A65 4k7 1/16W 5%

R0847 0662057A09 22 1/16W 5%

R0849 0662057A89 47k 1/16W 5%

R0852 0662057A97 100k 1/16W

R0853 0662057A97 100k 1/16W

R0854 0662057A97 100k 1/16W

R0861 0662057A90 51k 1/16W 5%

R0862 0662057A76 13k 1/16W 5%

R0864 0662057A88 43k 1/16W 5%

R0866 0662057A90 51k 1/16W 5%

R0867 0662057A76 13k 1/16W 5%

R0873 0660076A35 270 5 1/8

R0874 0660076A35 270 5 1/8

R0875 0660076A35 270 5 1/8

R0876 0660076A35 270 5 1/8

R0877 0660076A35 270 5 1/8

Circuit

Ref Motorola

Part No Description

R0878 0660076A35 270 5 1/8

R0879 0660076A35 270 5 1/8

R0880 0662057A81 22k 1/16W 5%

R0881 0662057A35 270 1/16W 5%

R0885 0662057A35 270 1/16W 5%

*U0831 5113802A24 IC 68HC11 W/SCI,SPI,A/D

U0832 5113815A02 IC

U0833 4886061B01 CER RESONATOR 8MHZ

CSTCC8.00MG

VR0816 4805656W09 DIODE ZENER QUAD

MMQA20VT1

VR0817 4805656W09 DIODE ZENER QUAD

MMQA20VT1

VR0821 4813830A15 DIODE 5.6V 5% 225mW

VR0822 4813830A15 DIODE 5.6V 5% 225mW

VR0823 4813830A15 DIODE 5.6V 5% 225mW

Circuit

Ref Motorola

Part No Description

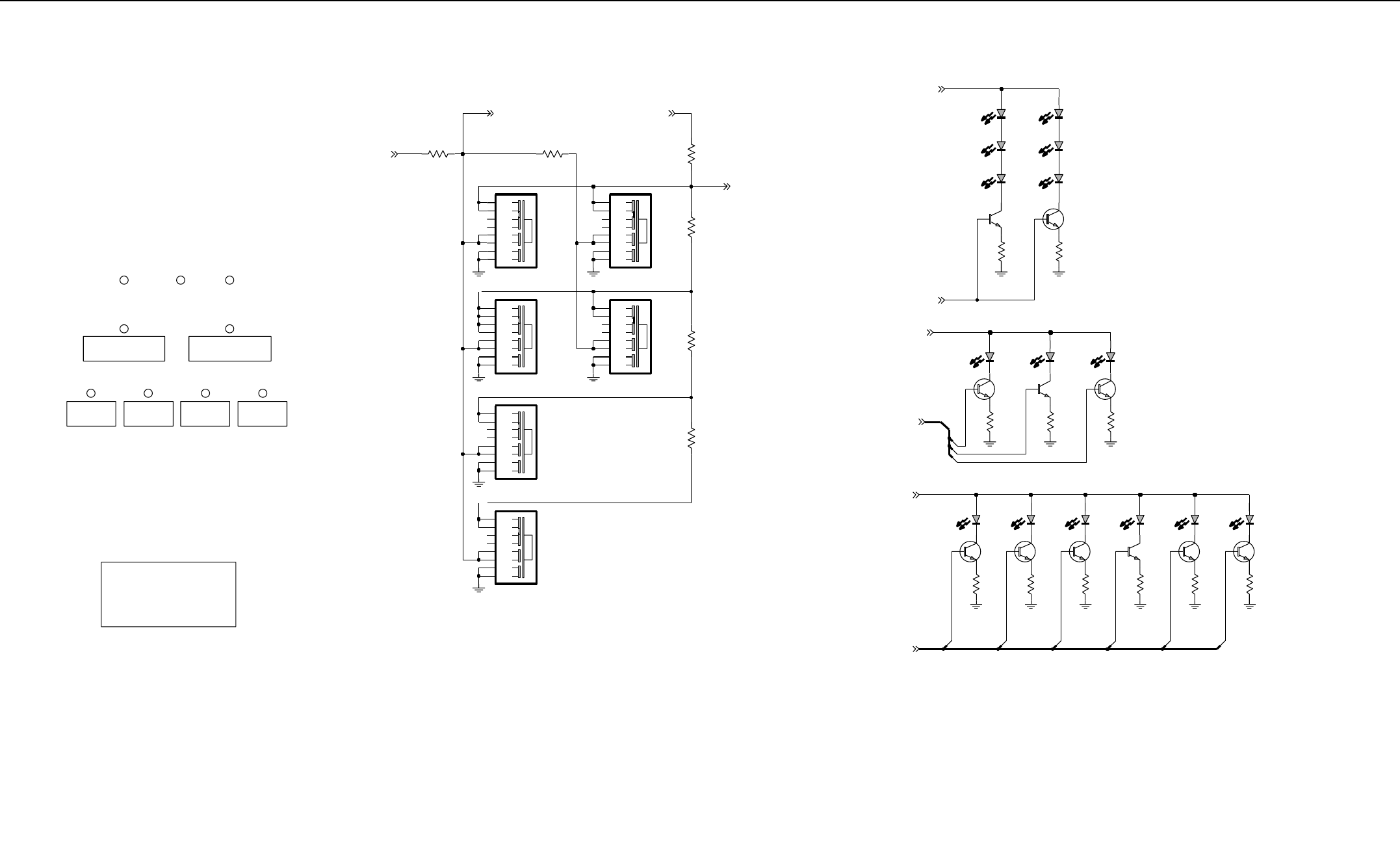

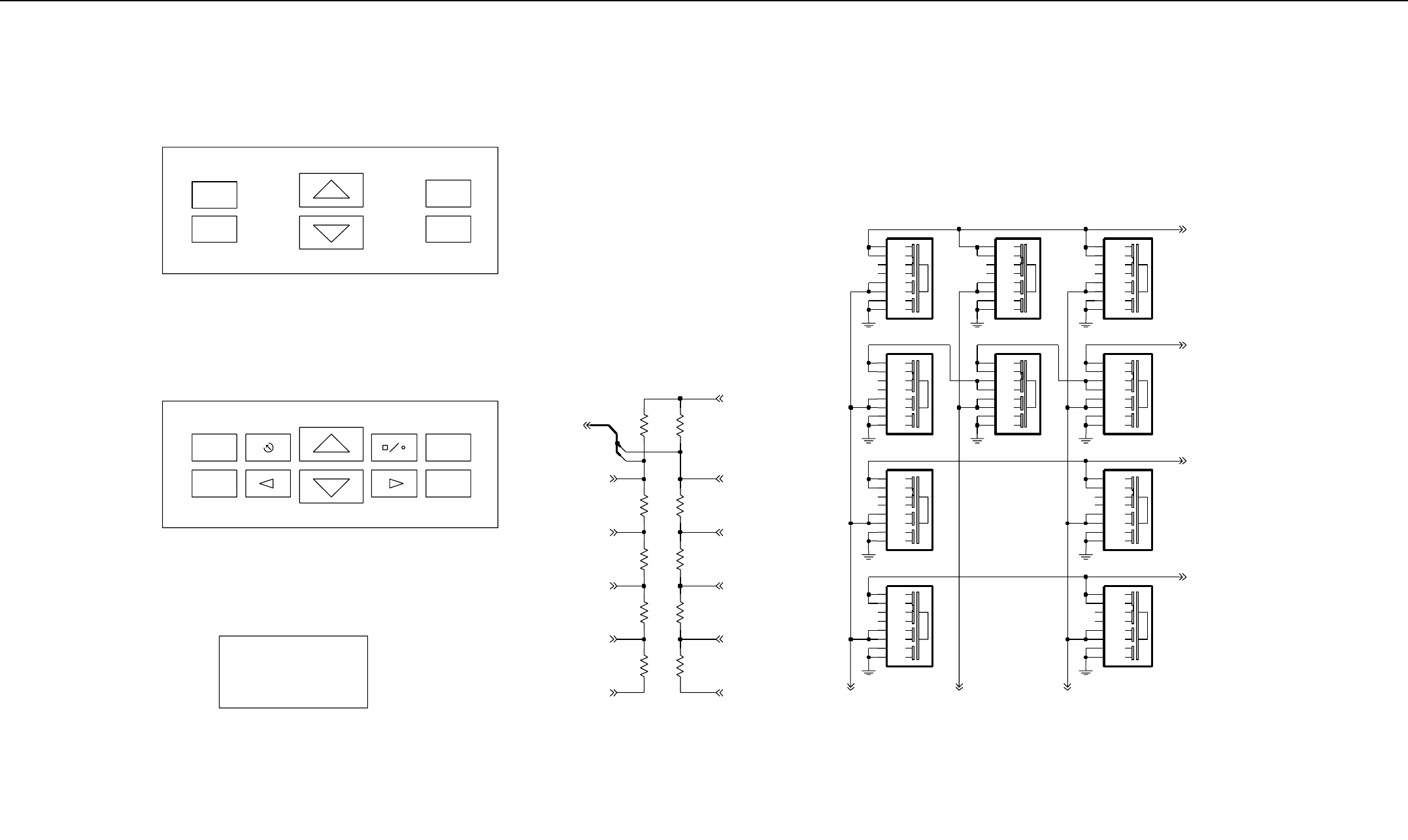

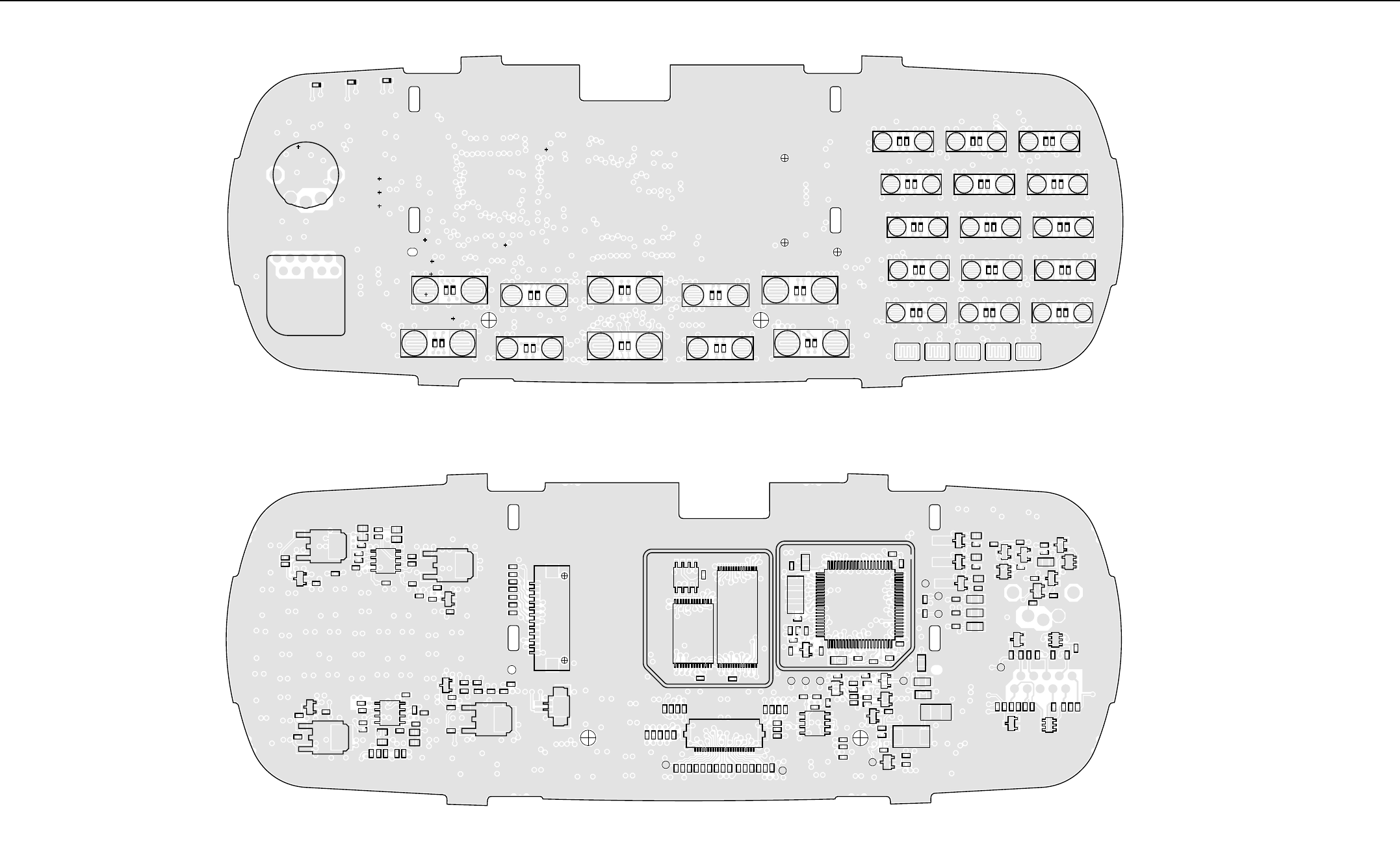

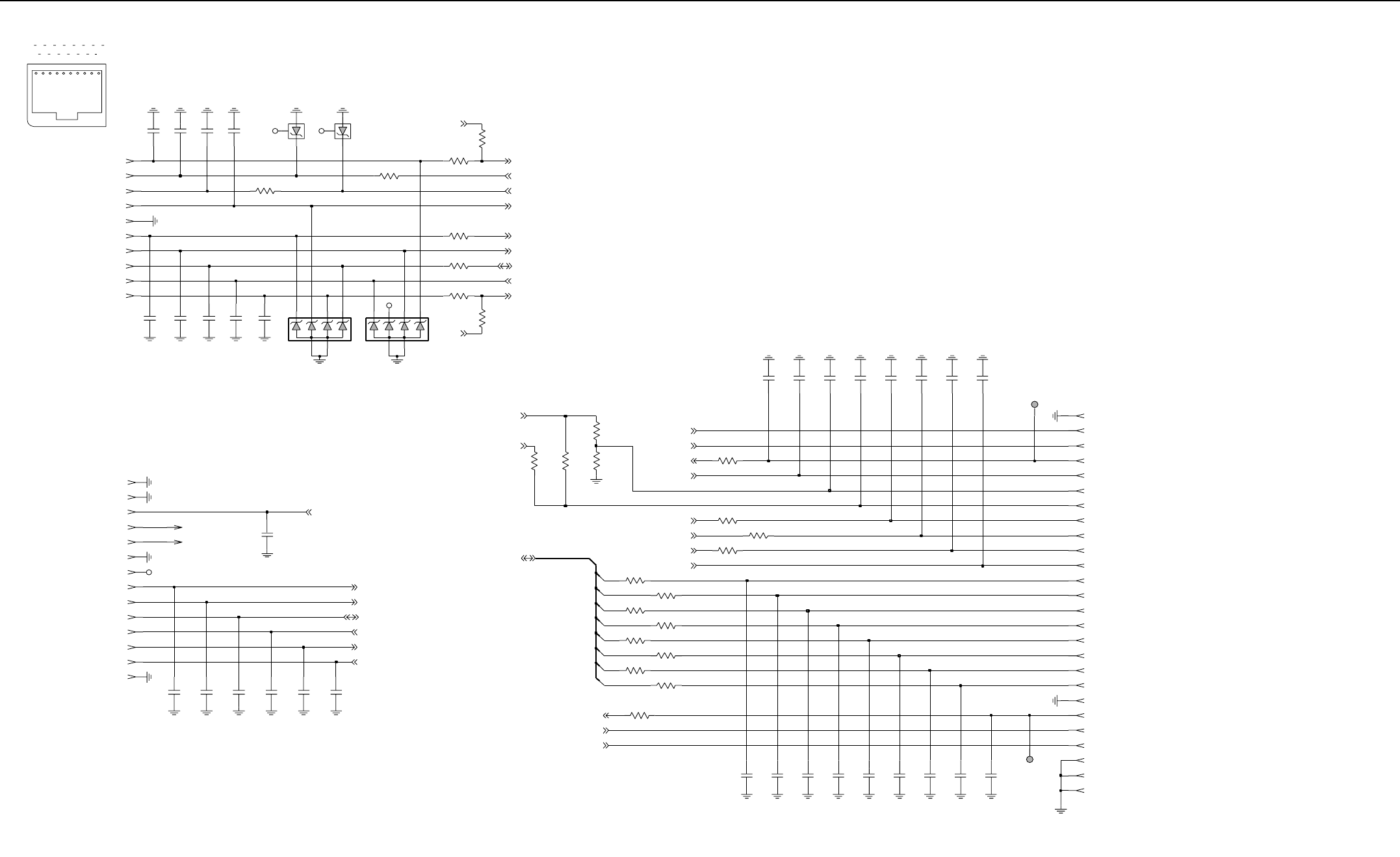

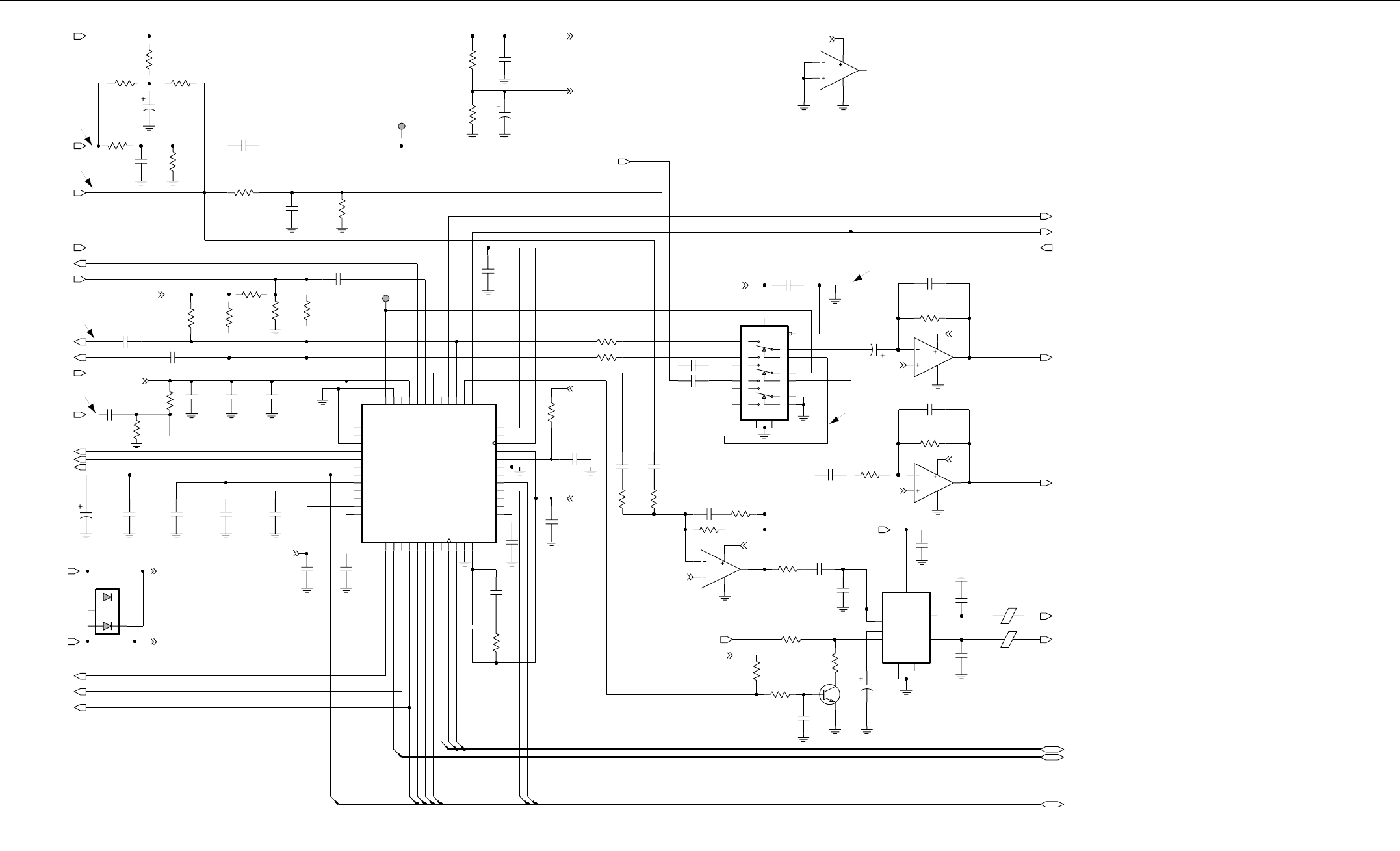

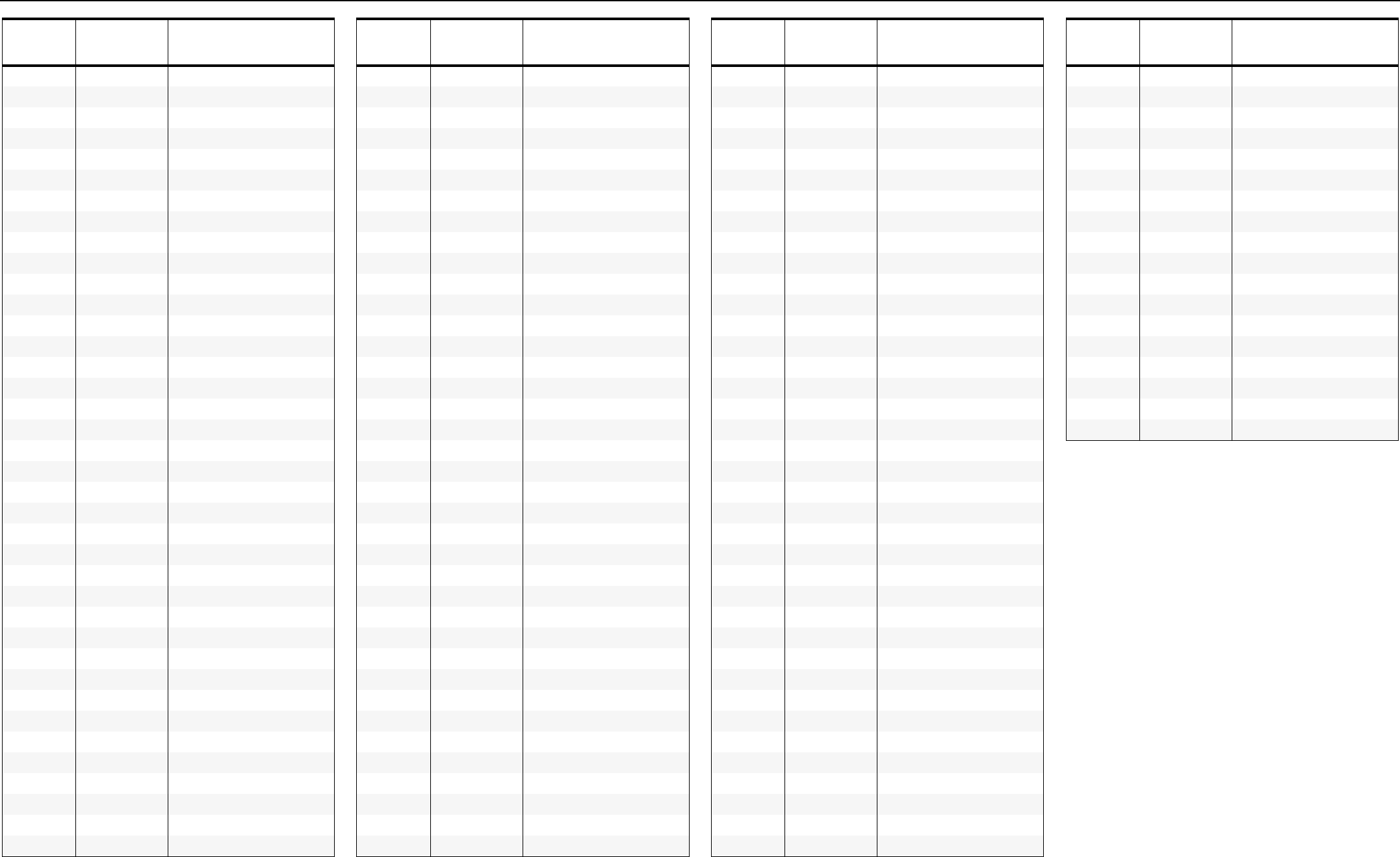

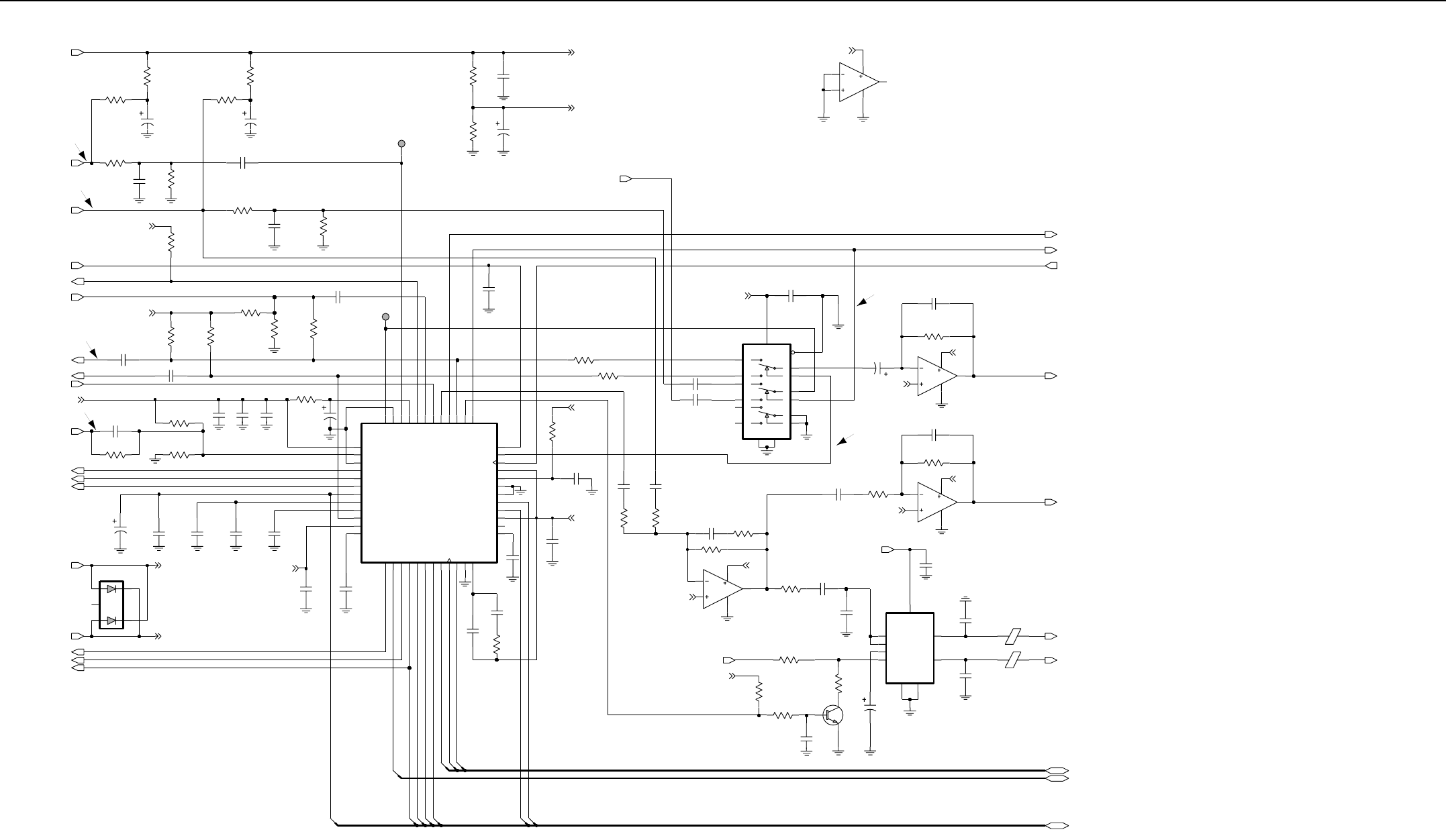

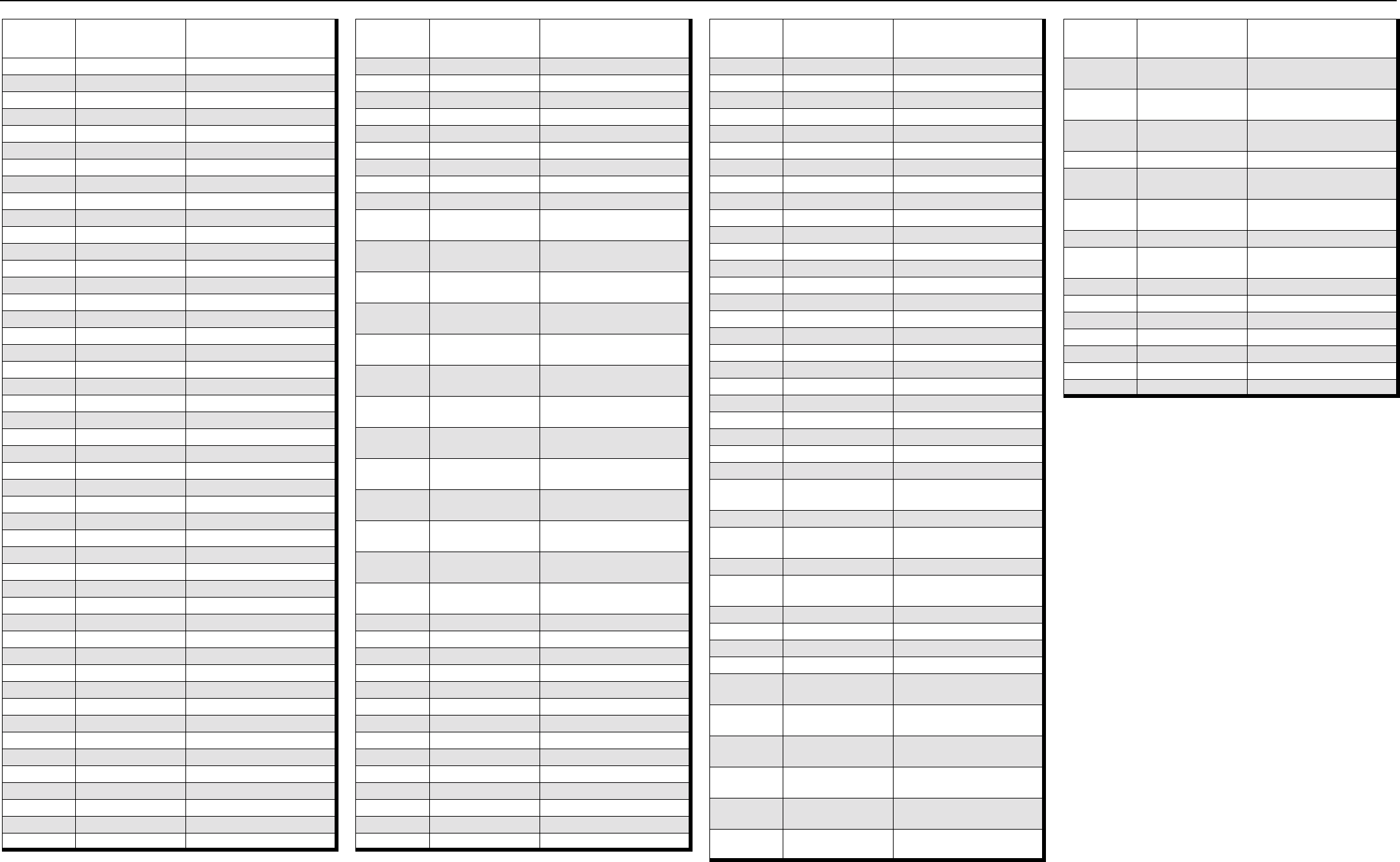

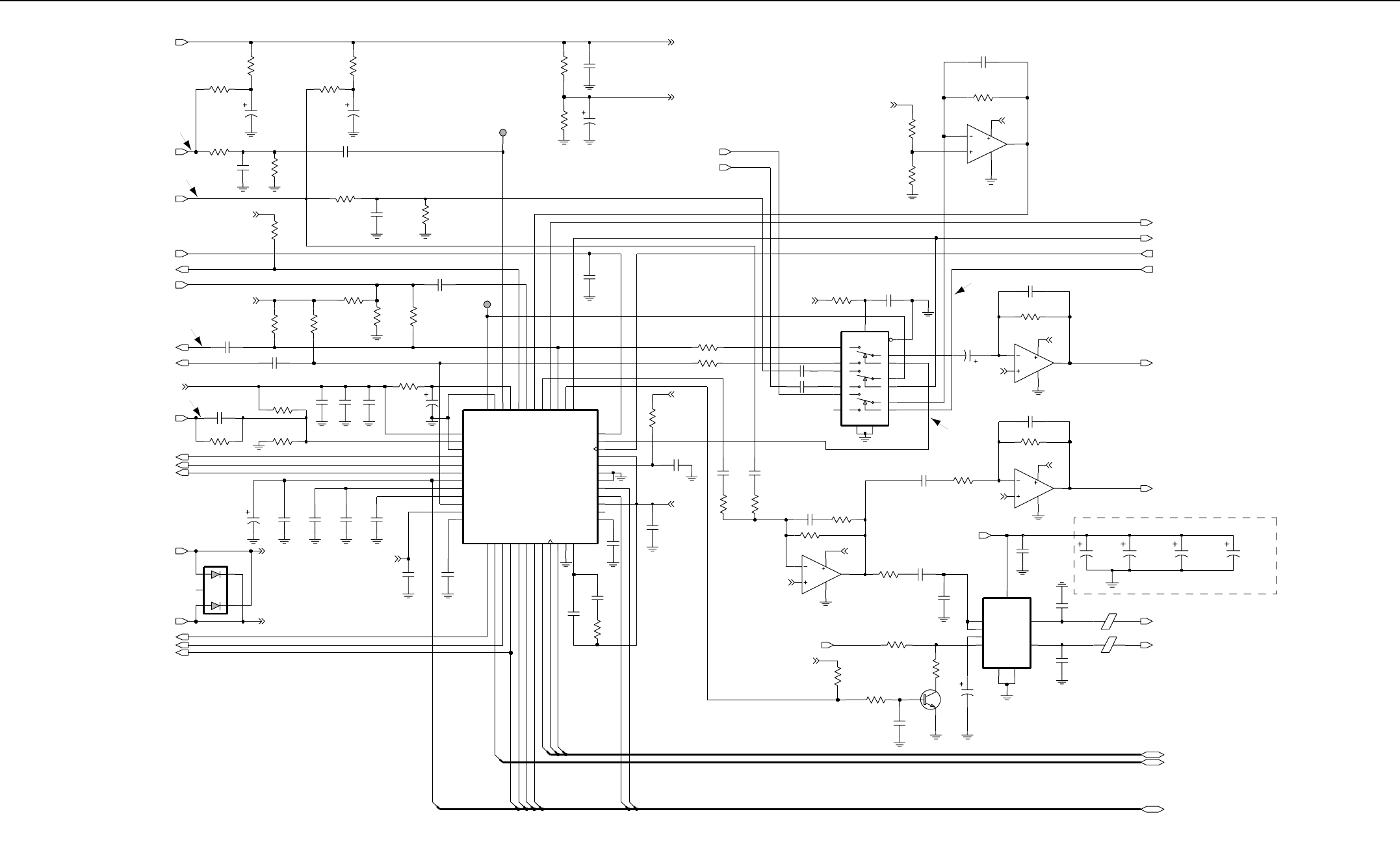

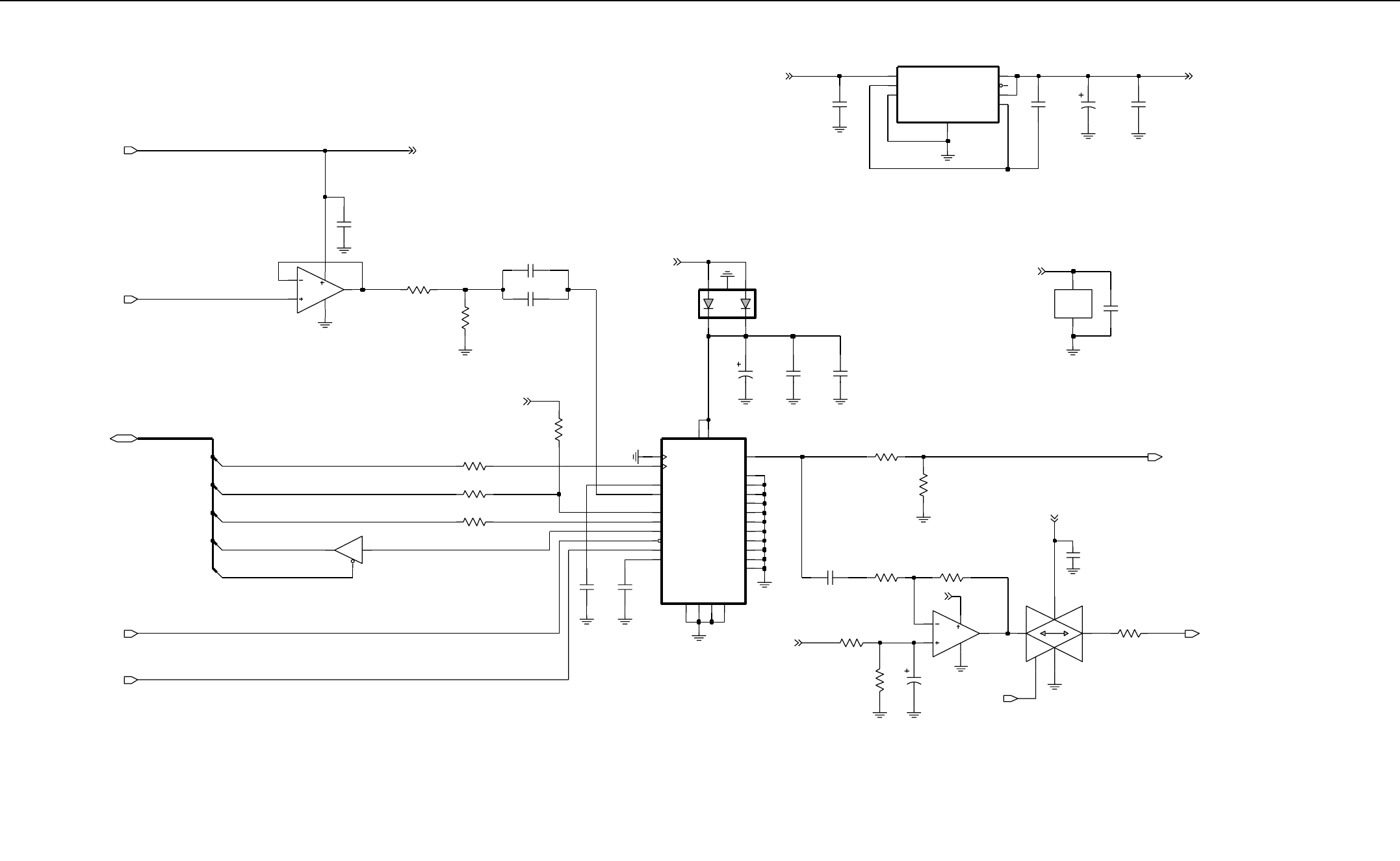

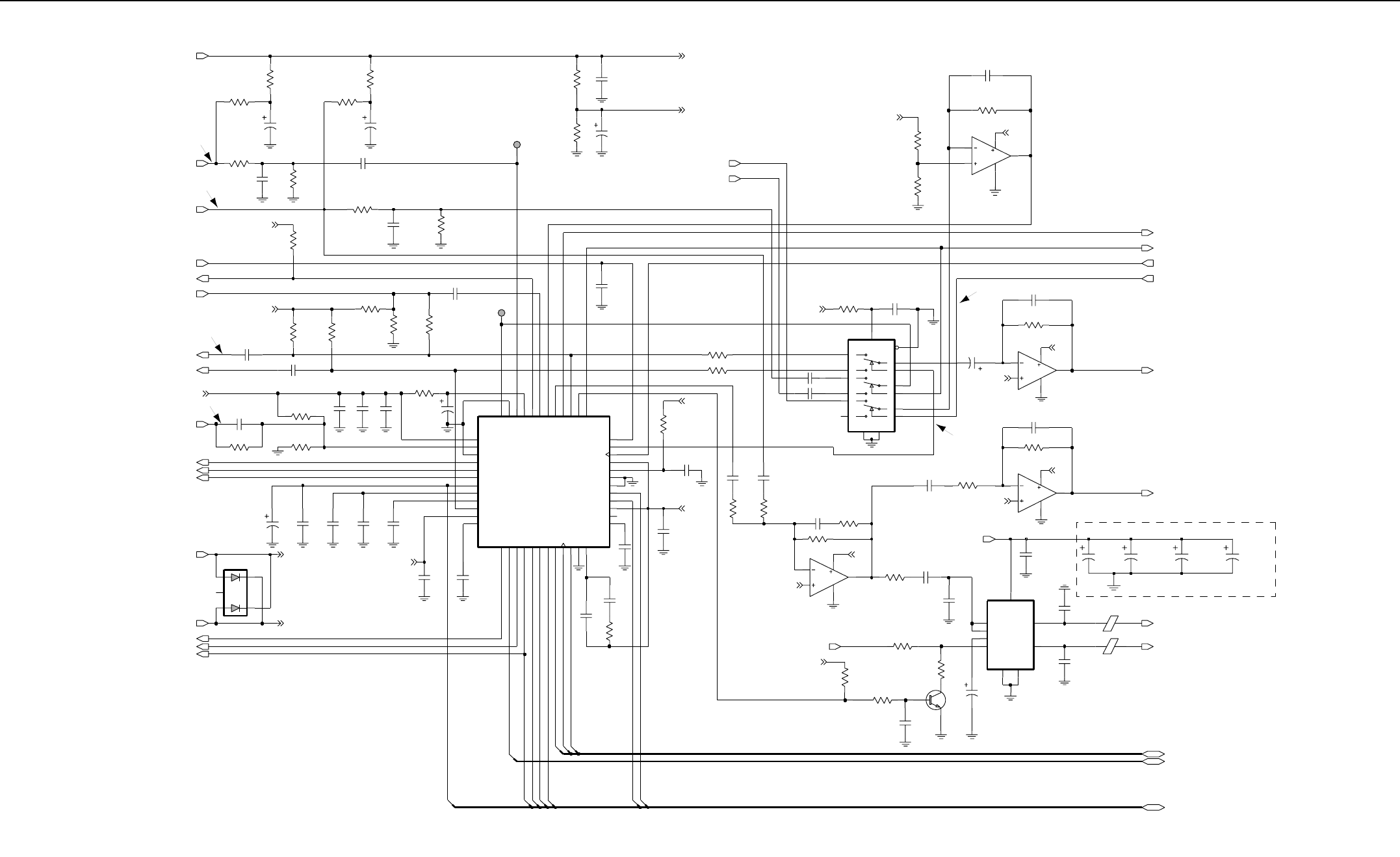

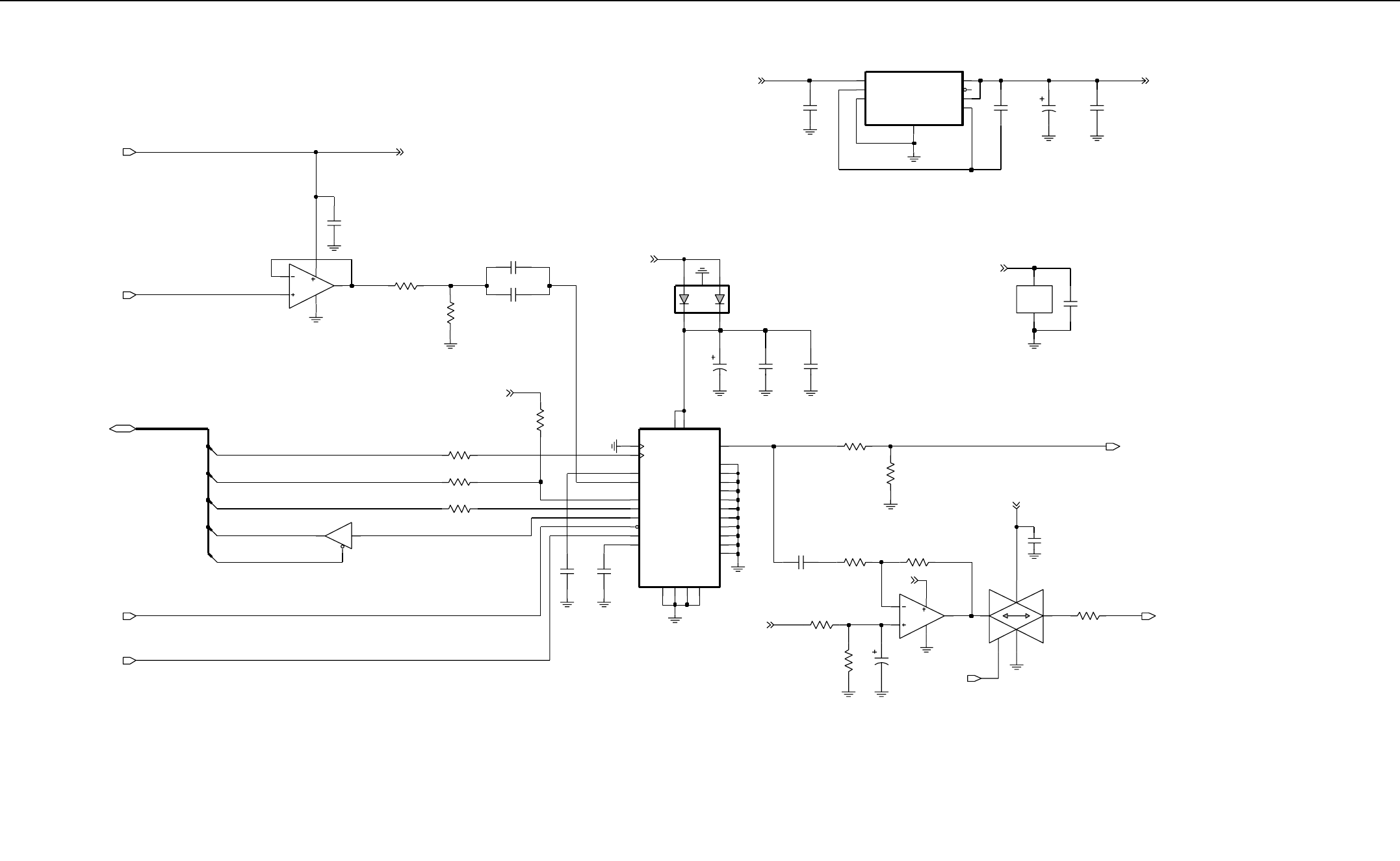

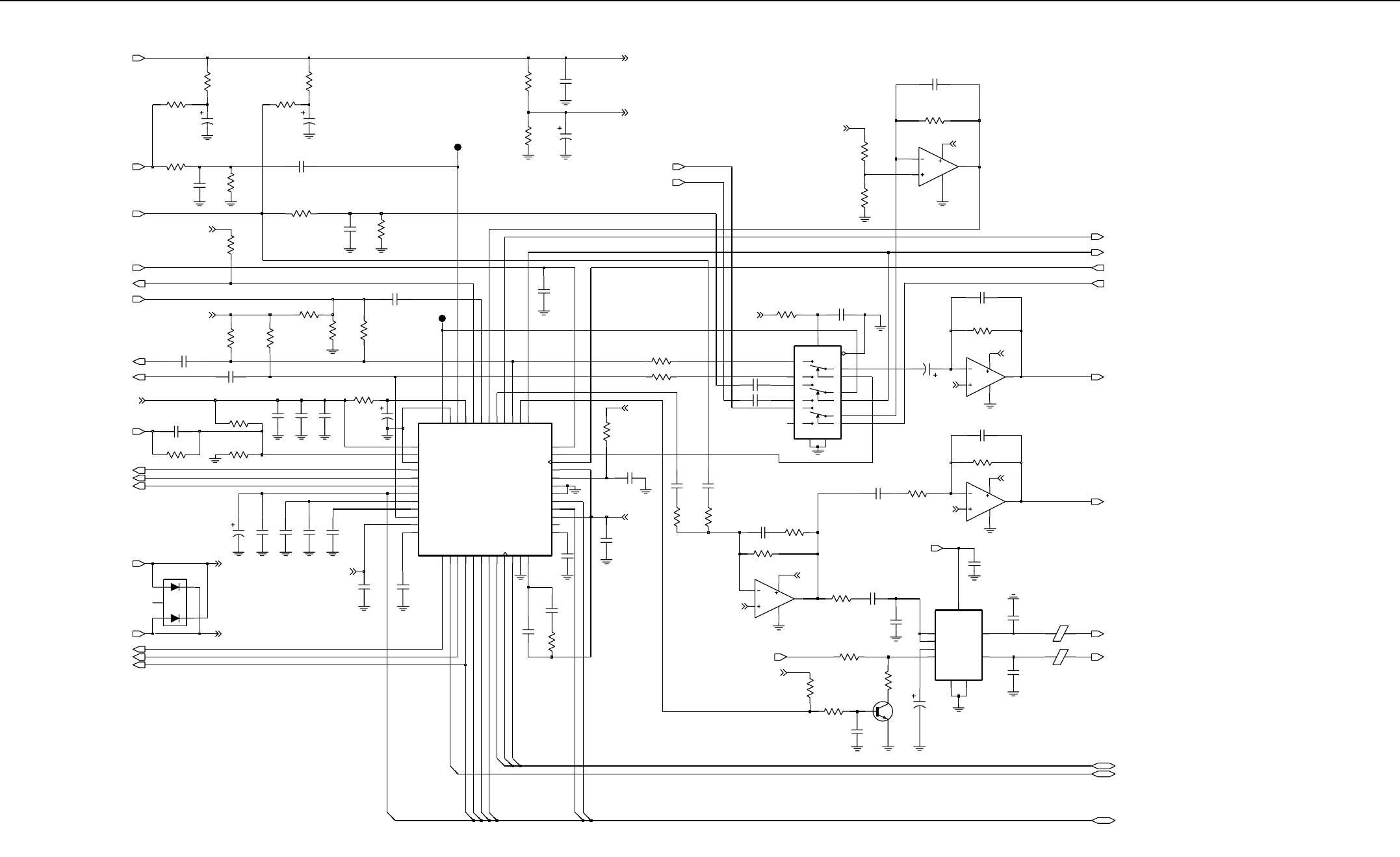

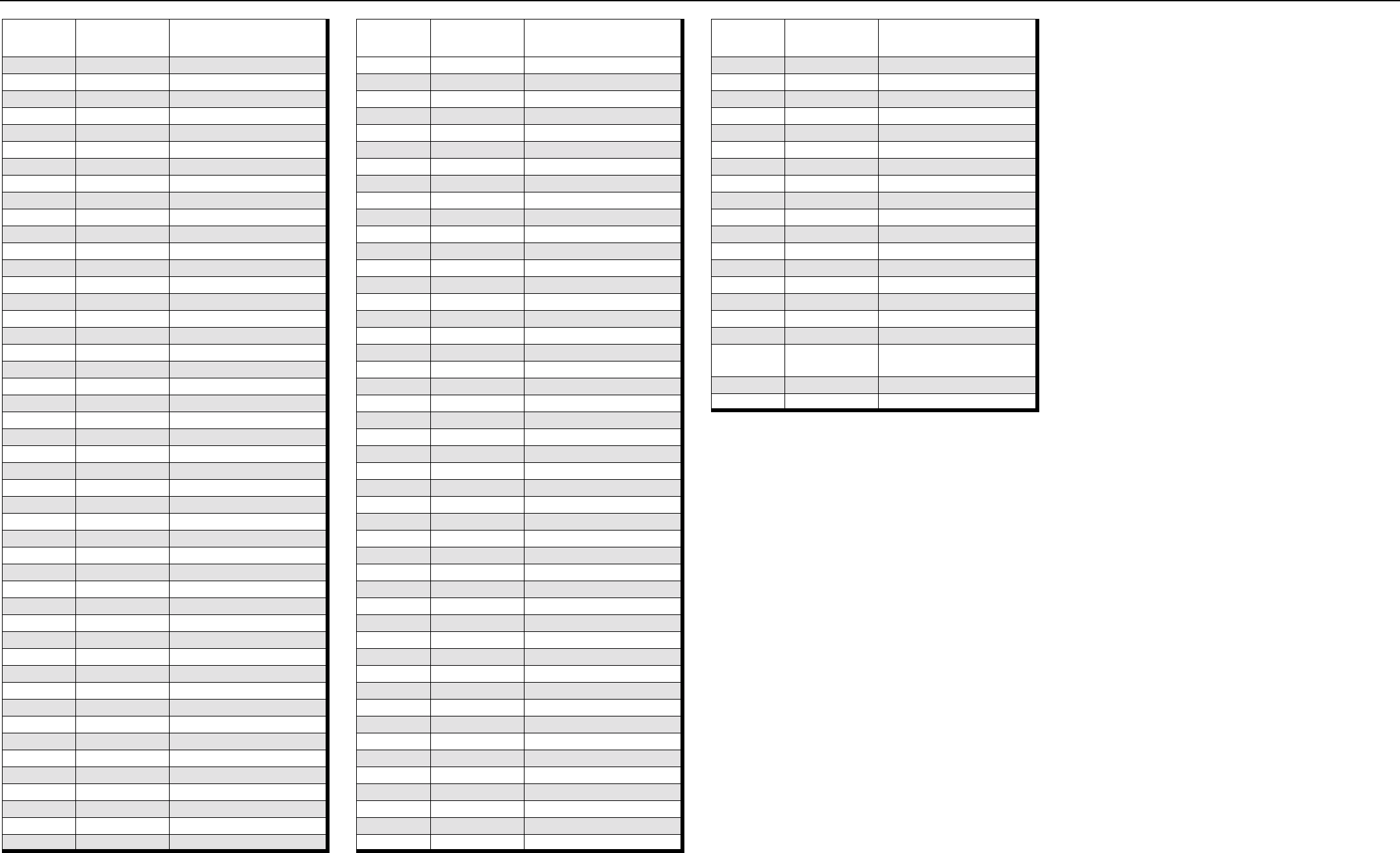

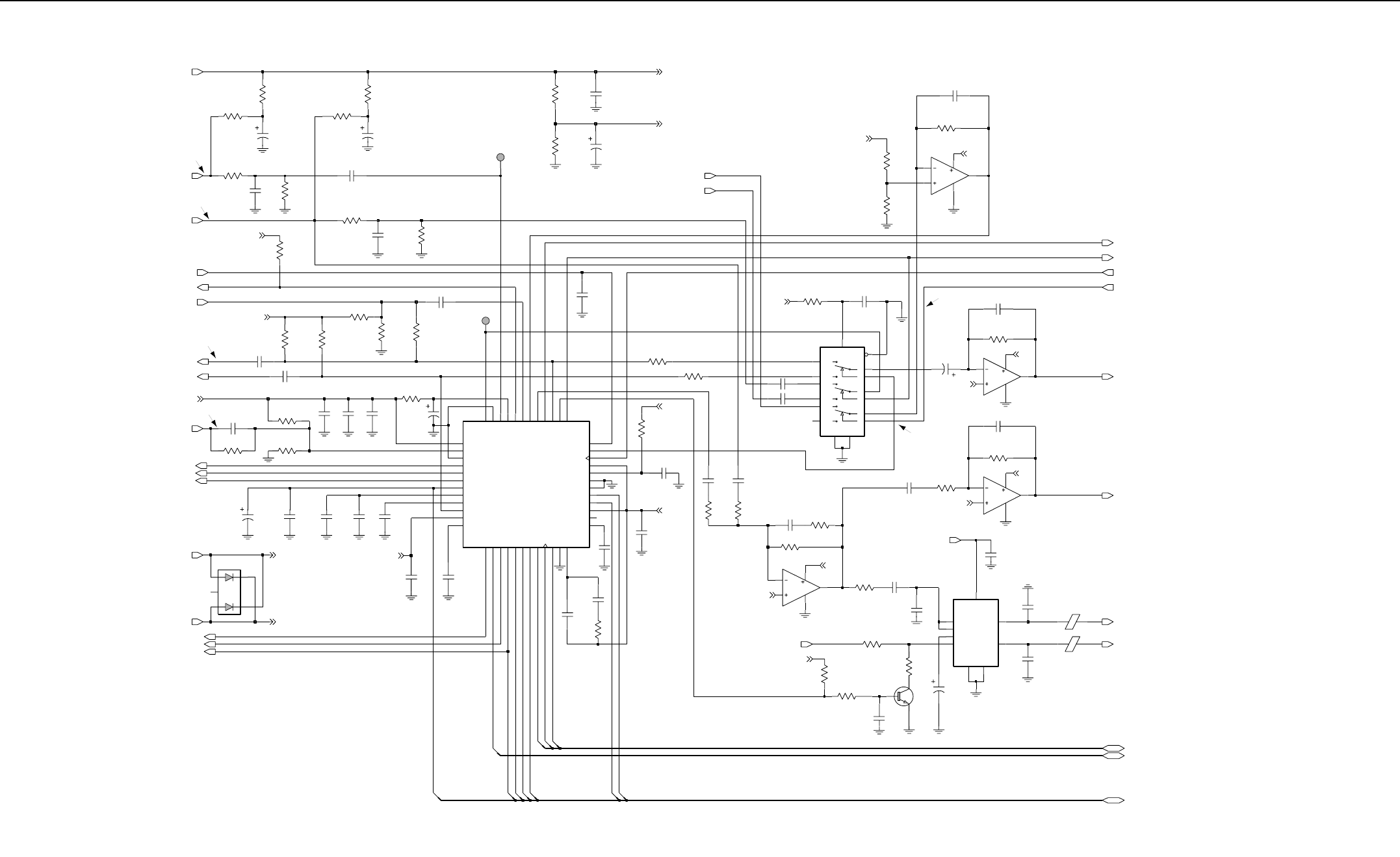

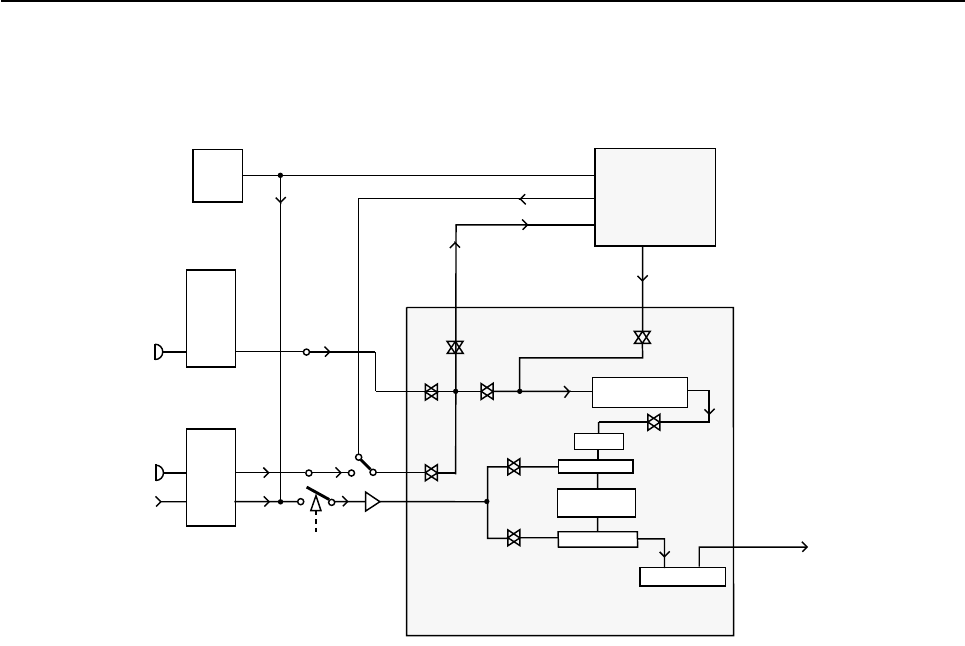

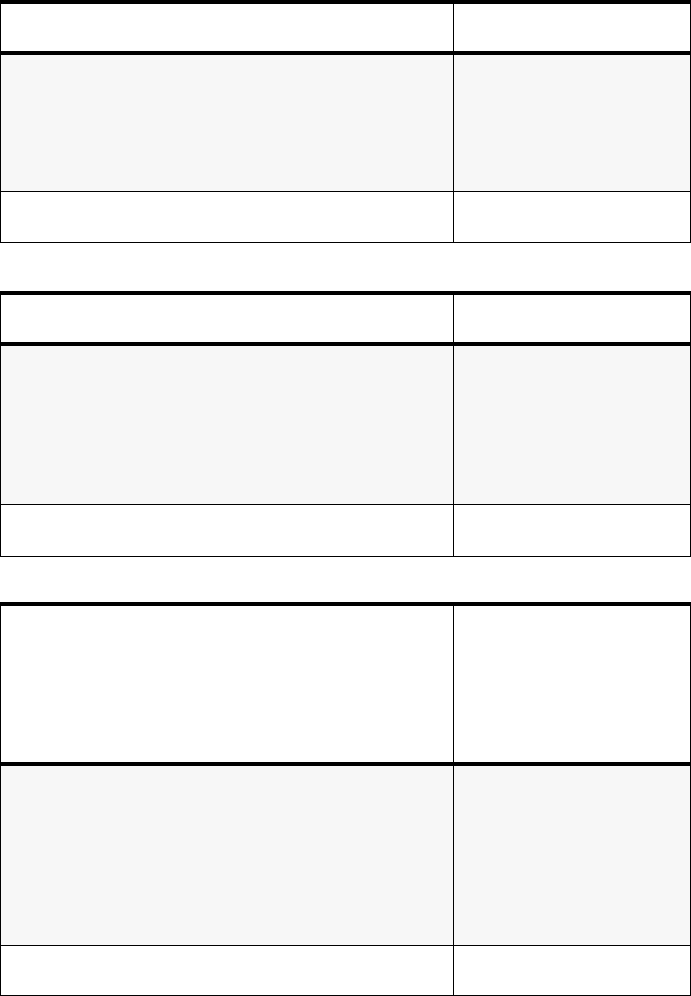

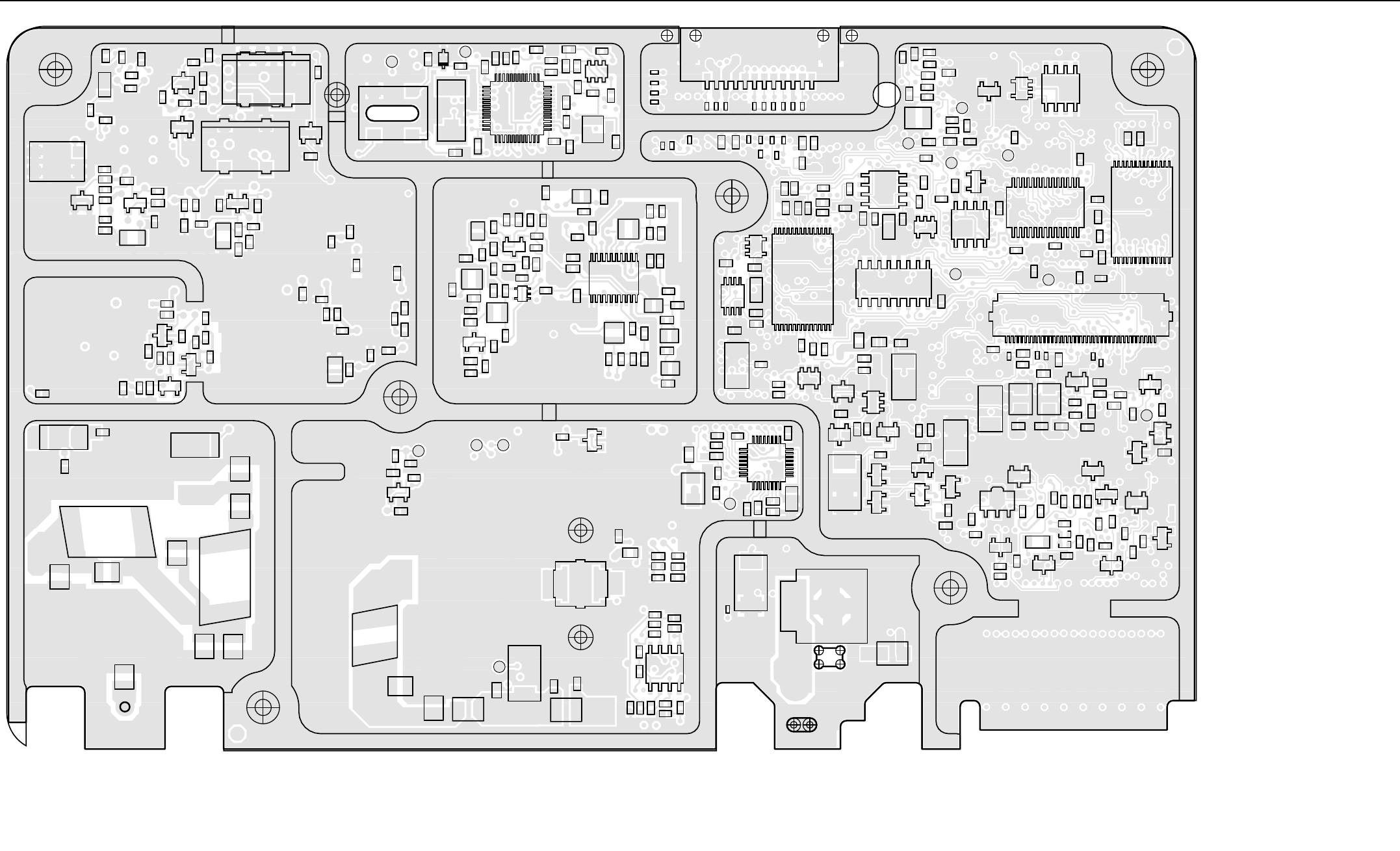

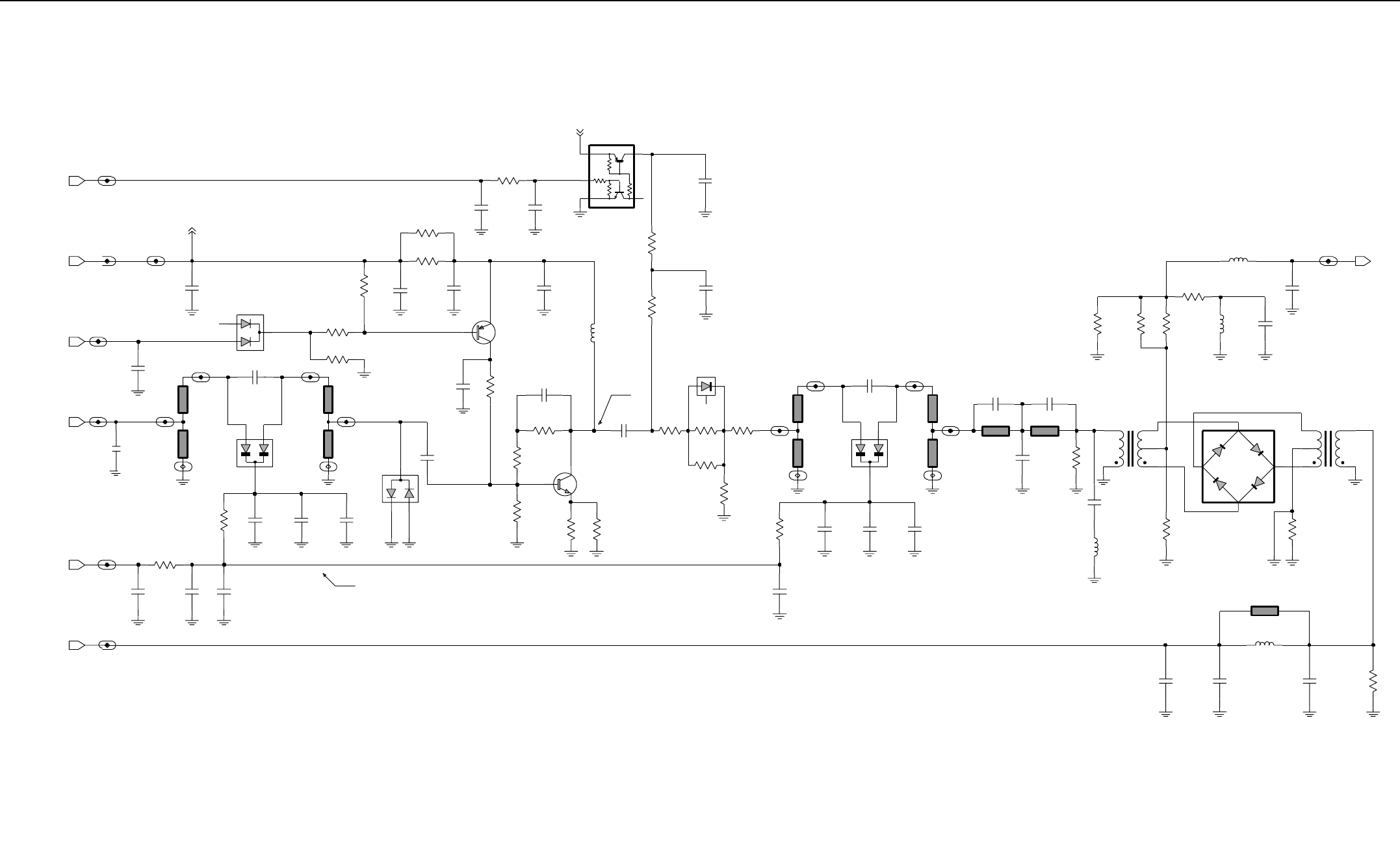

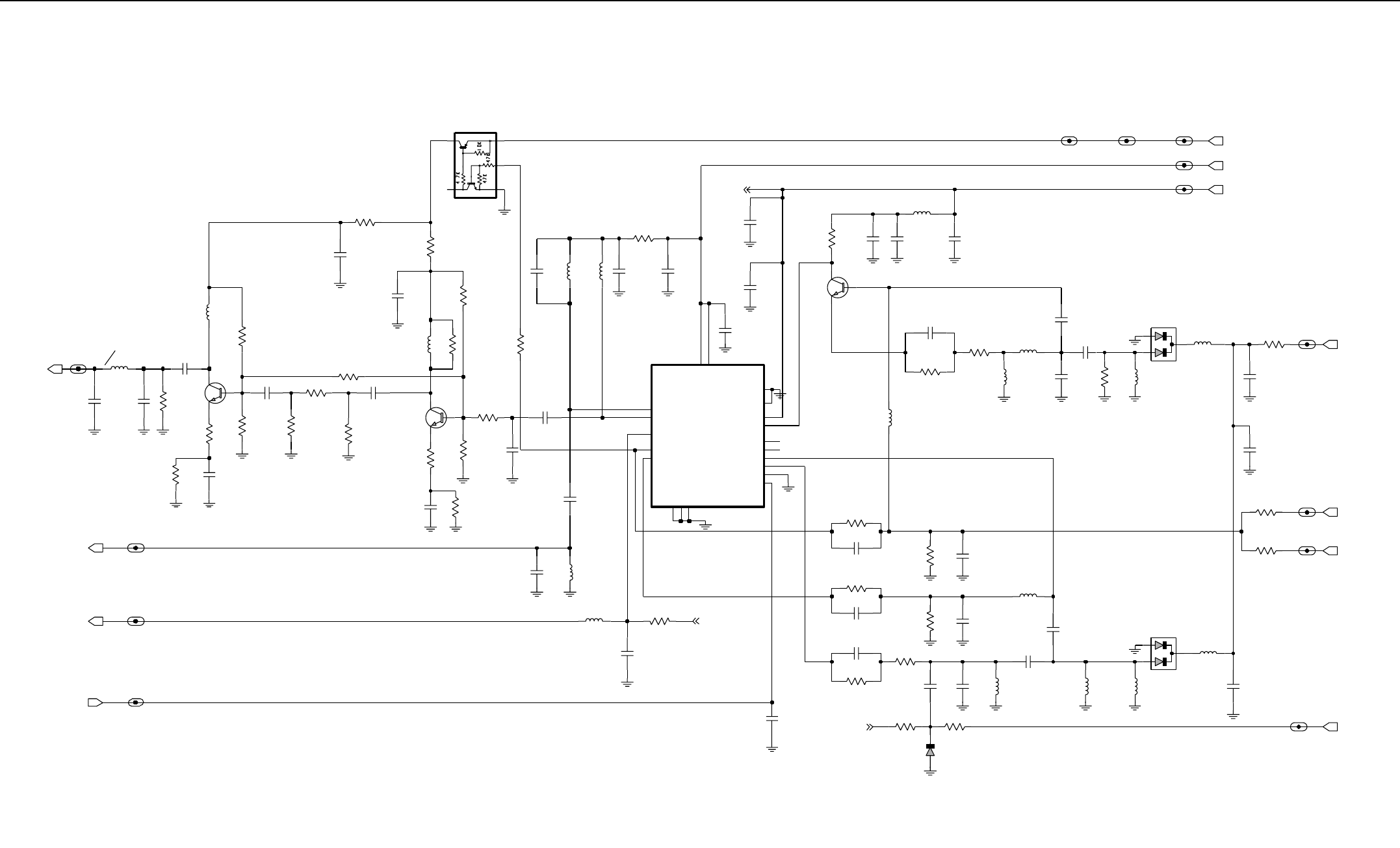

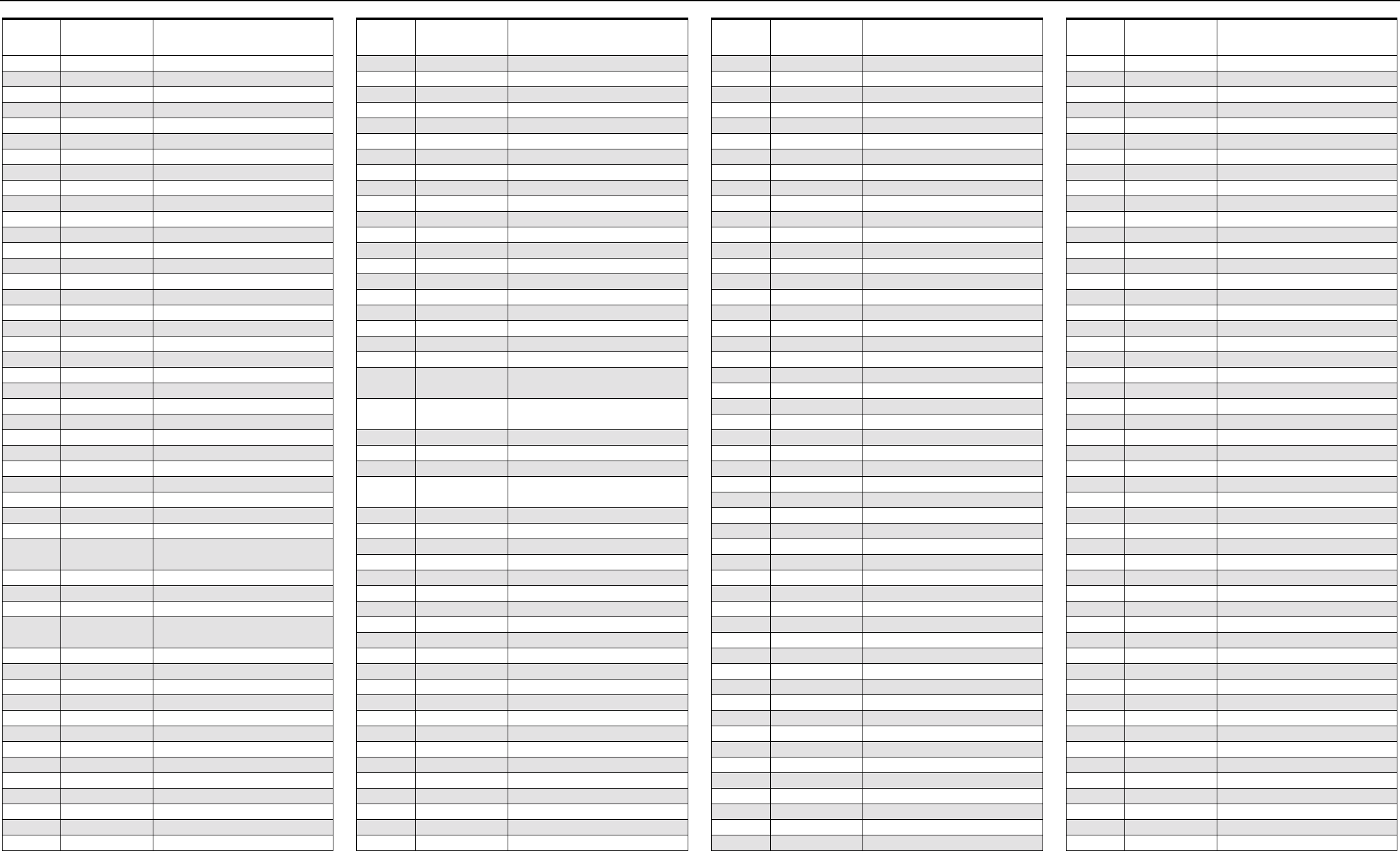

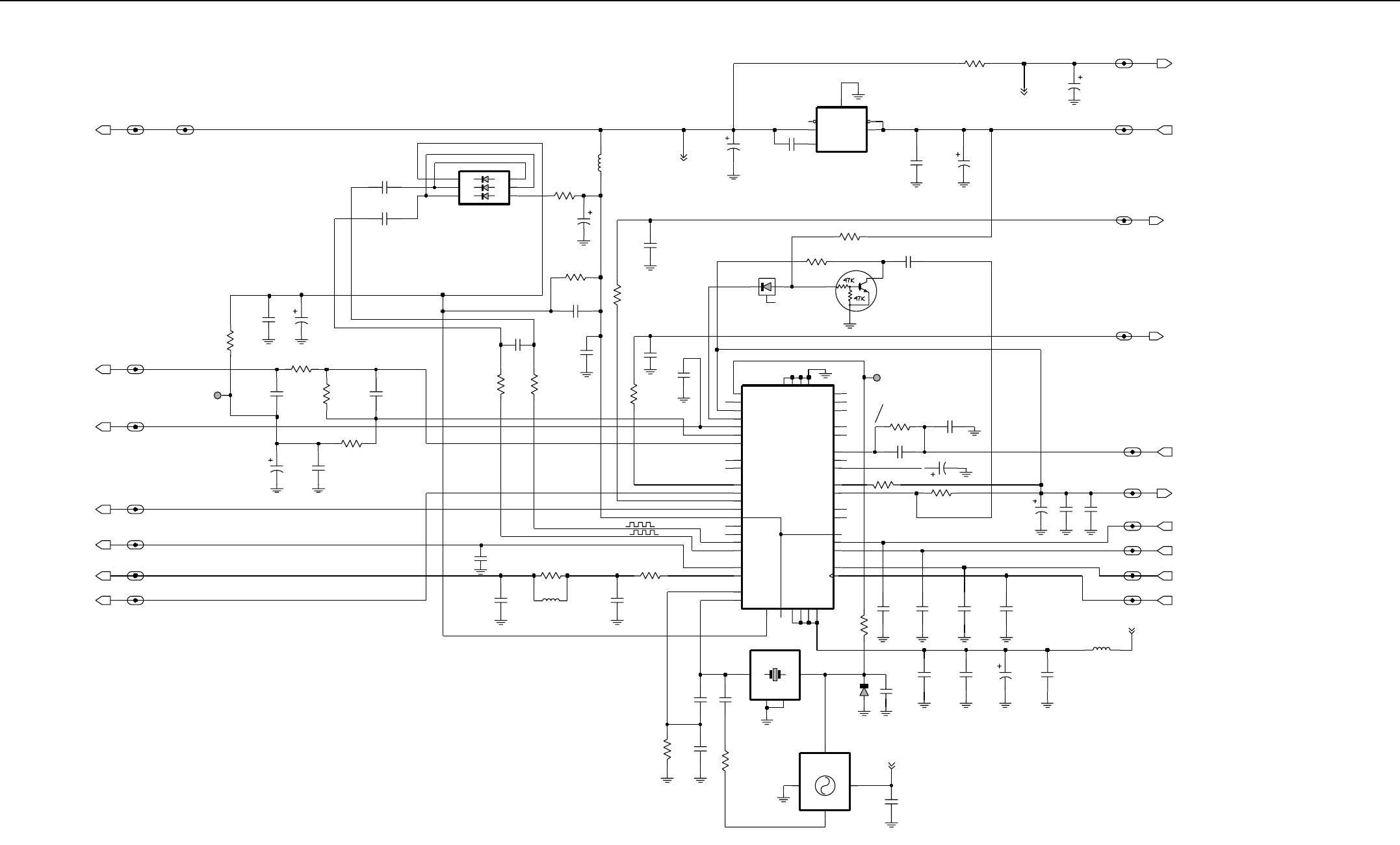

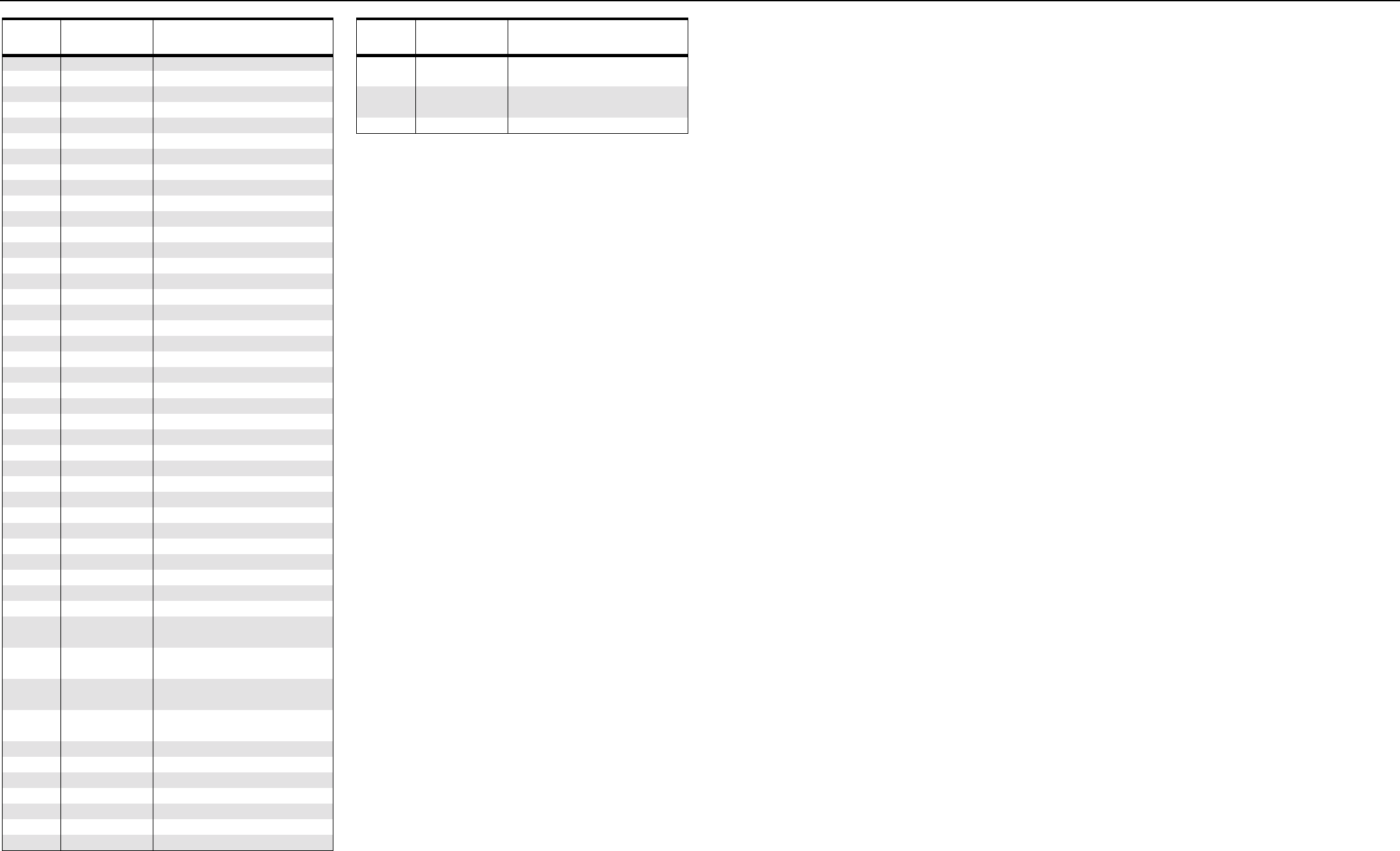

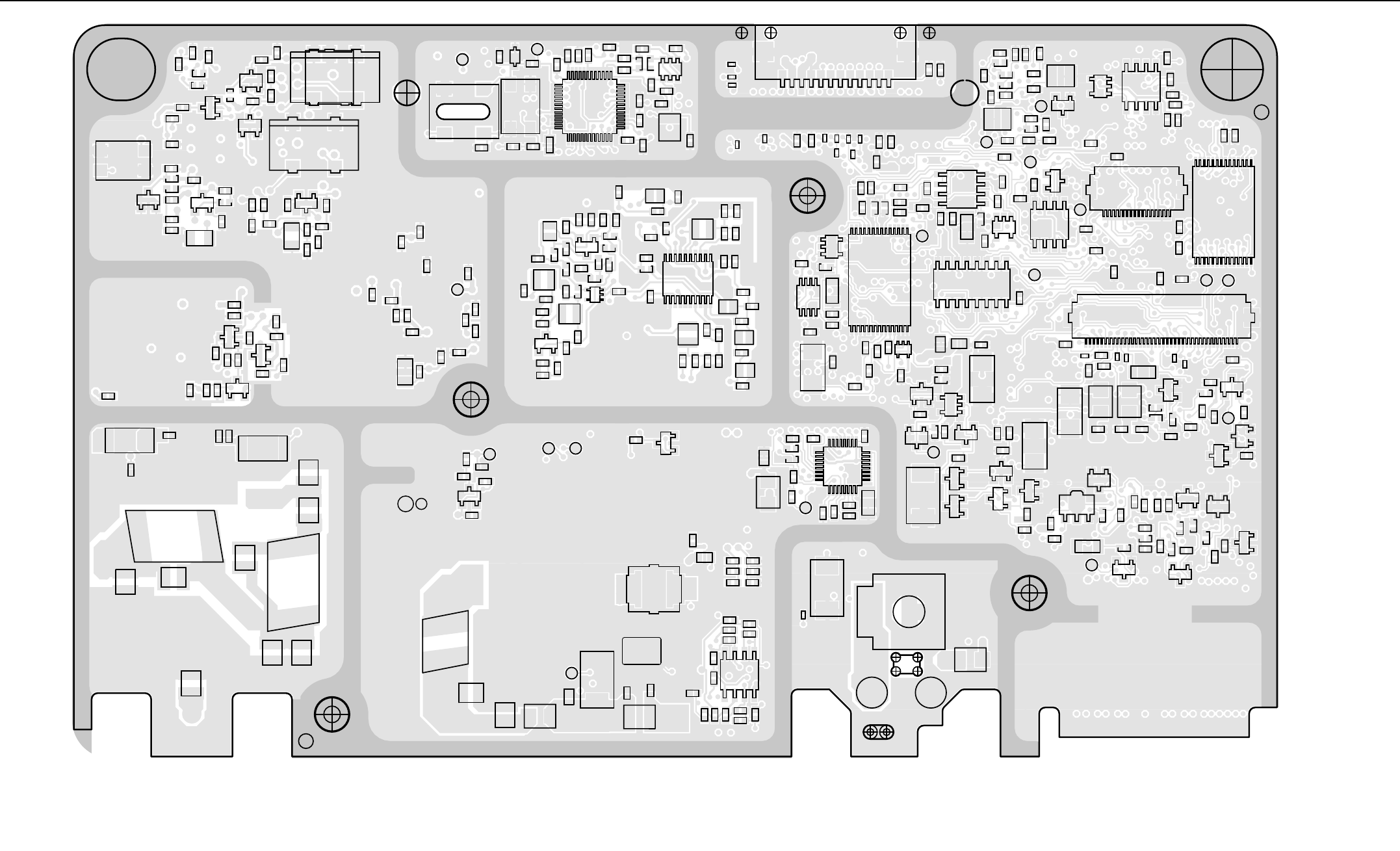

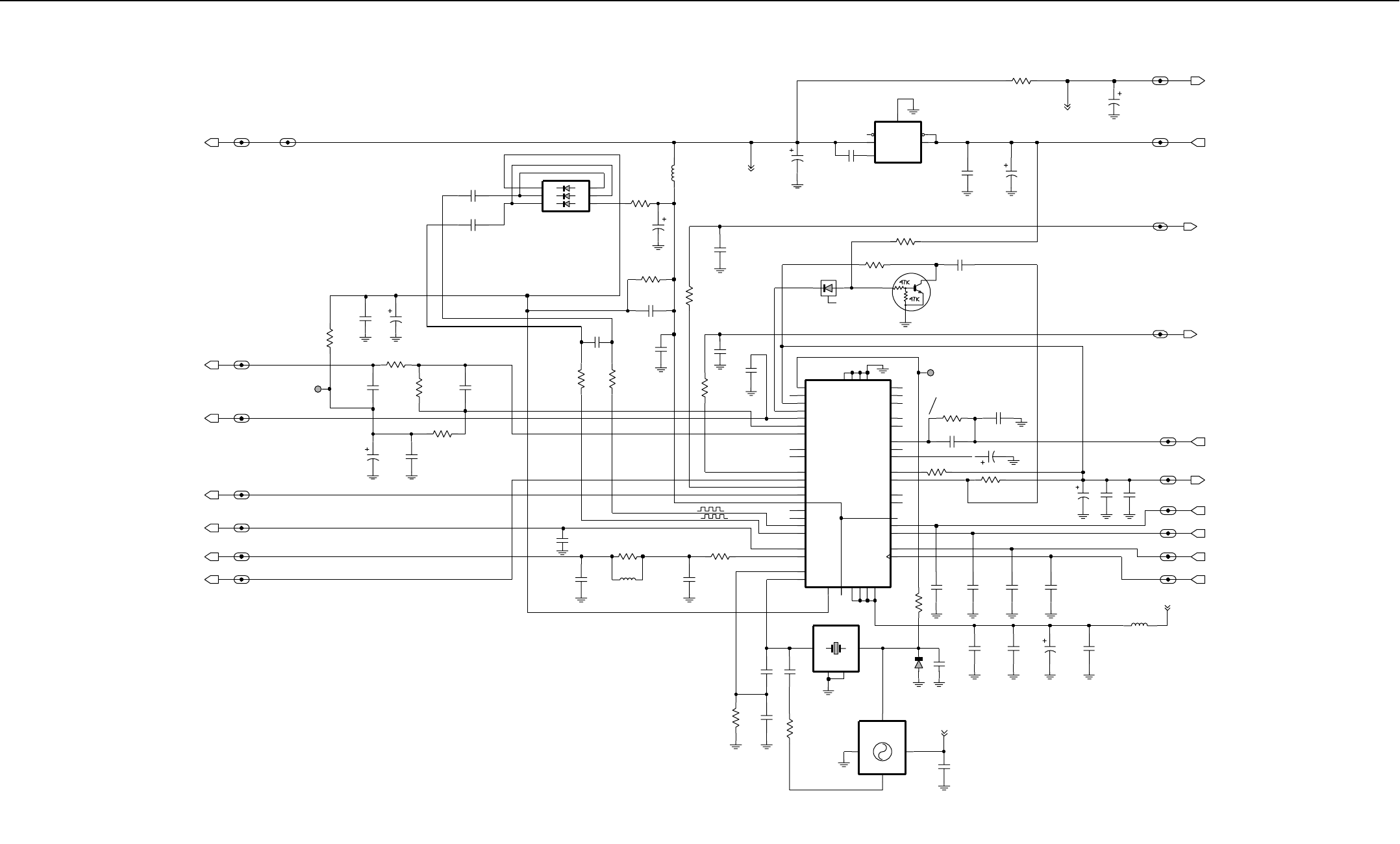

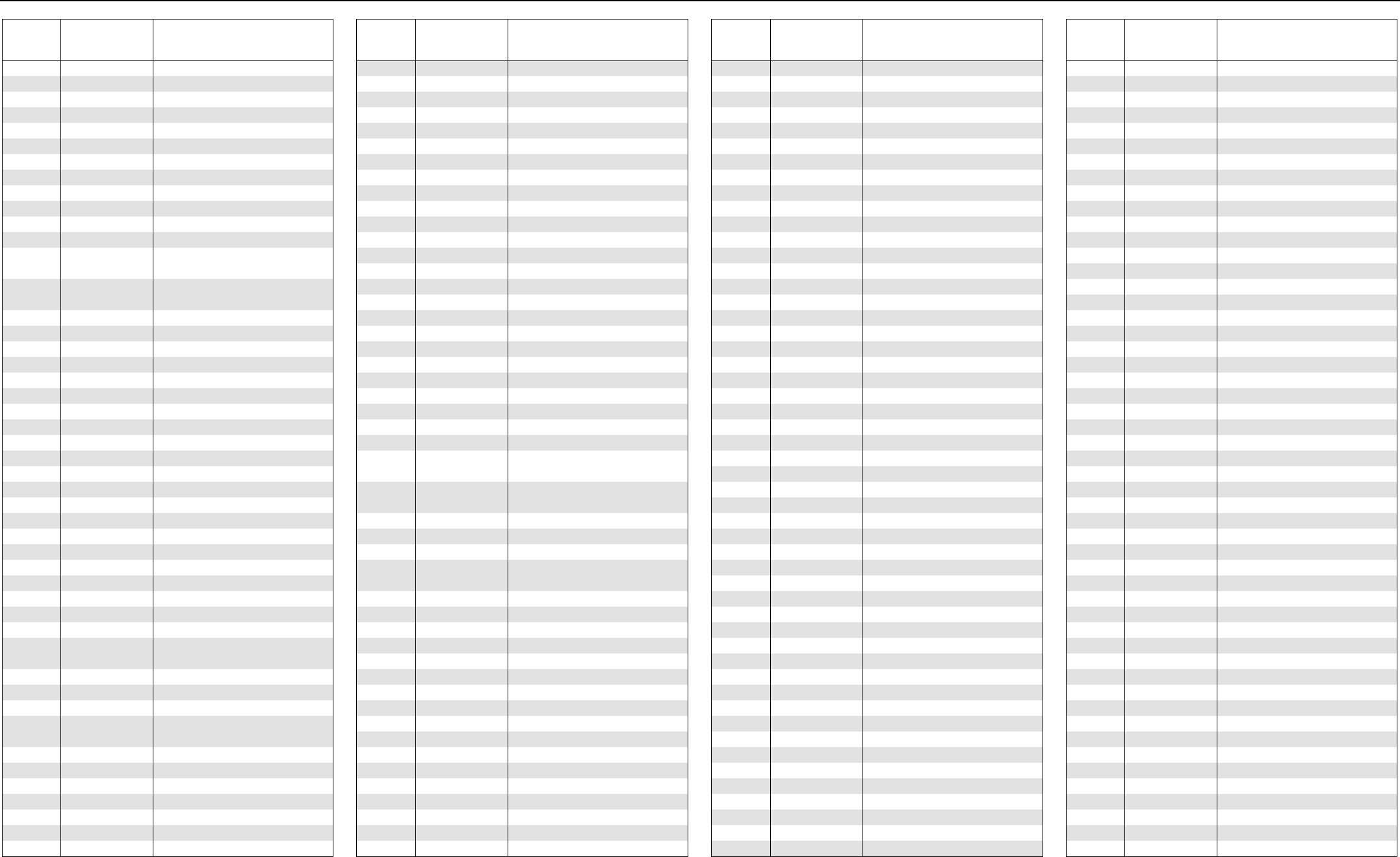

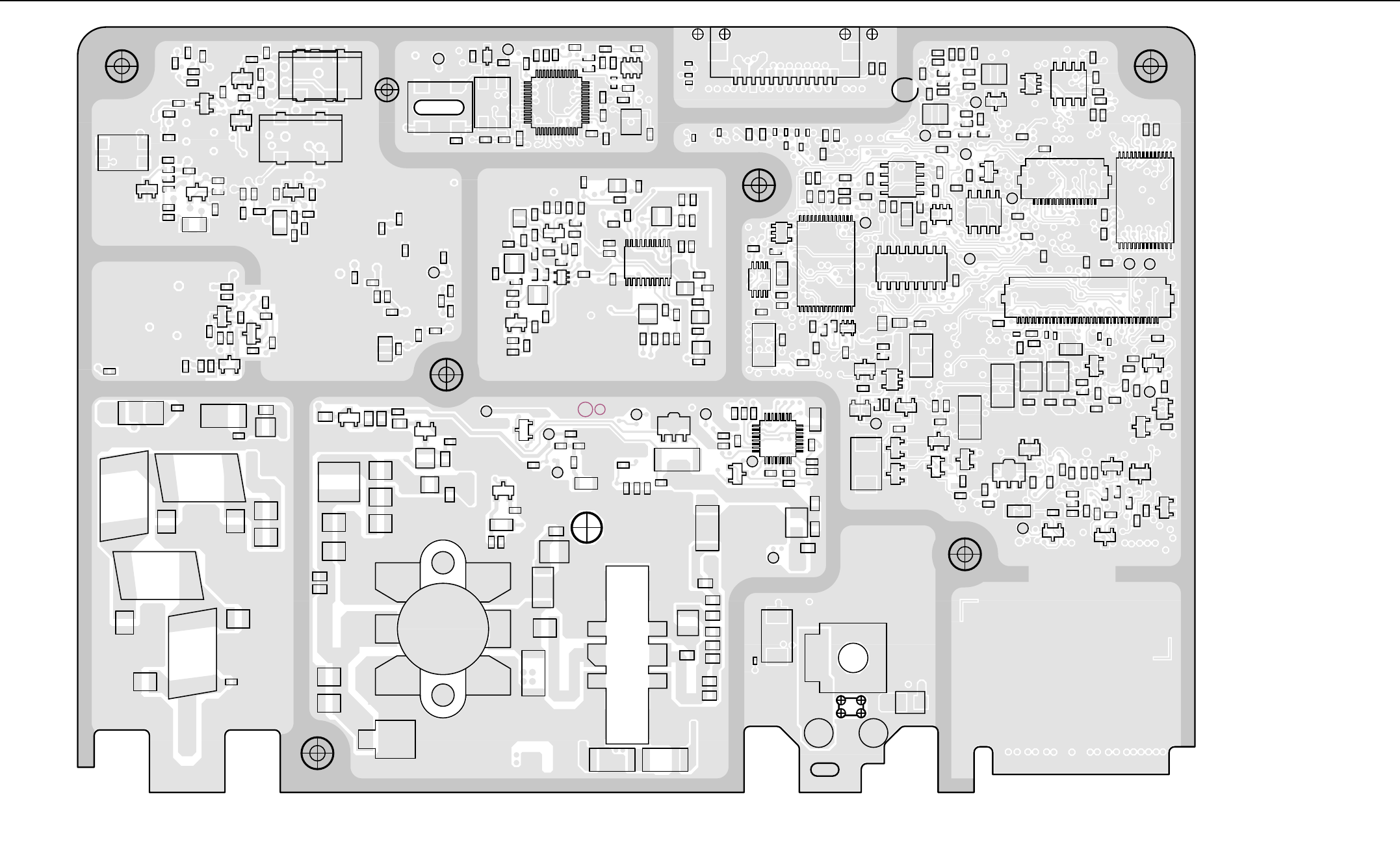

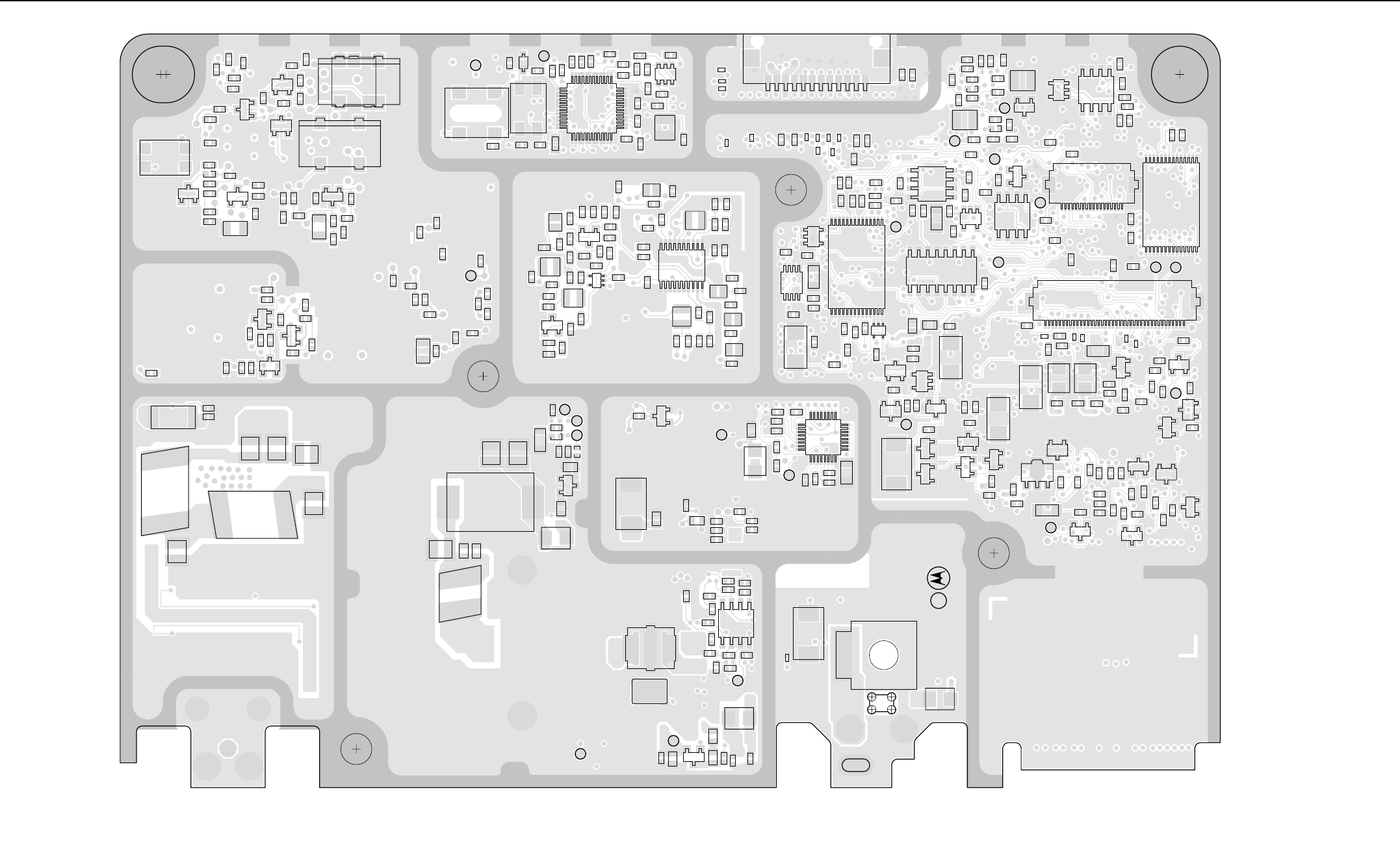

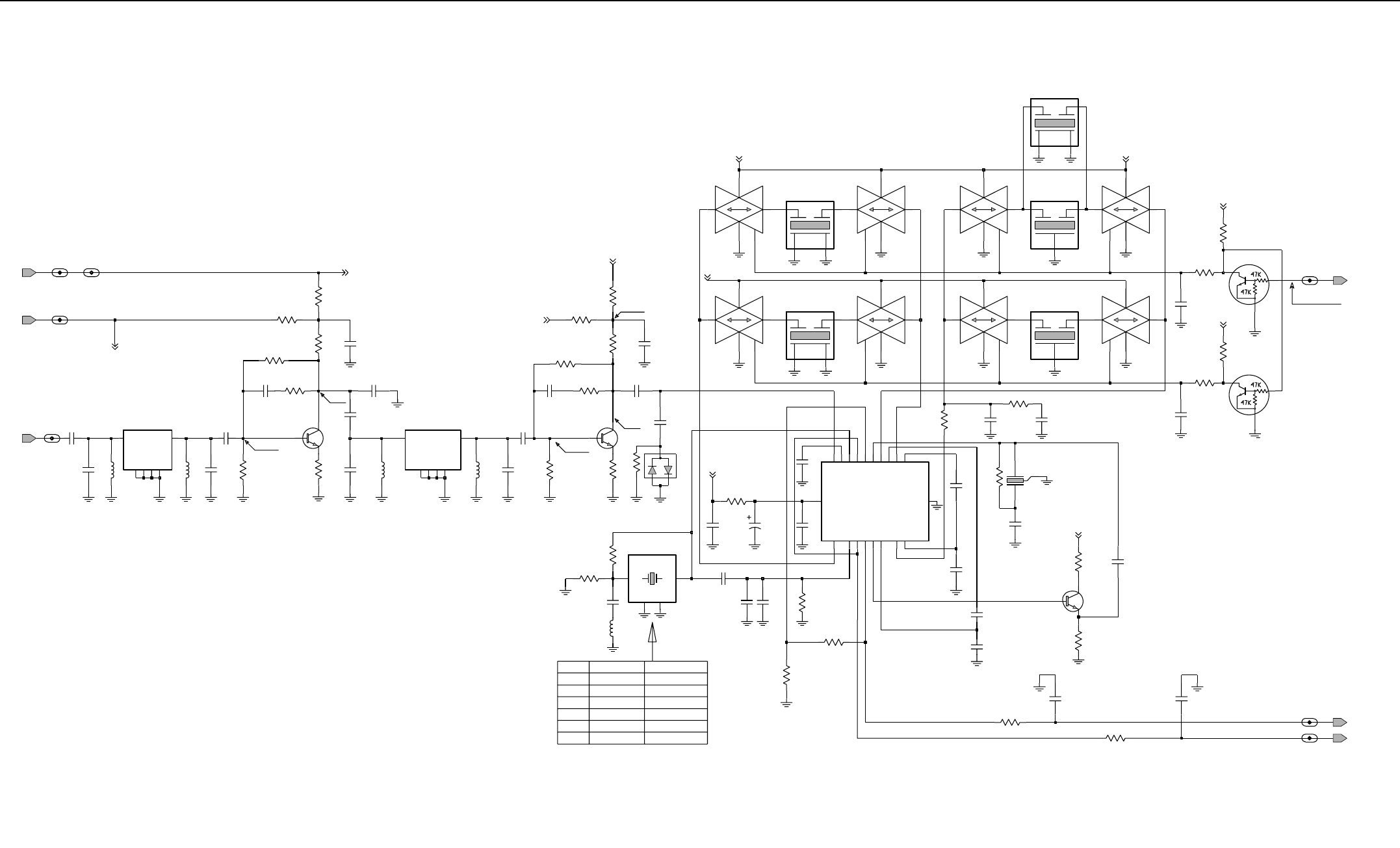

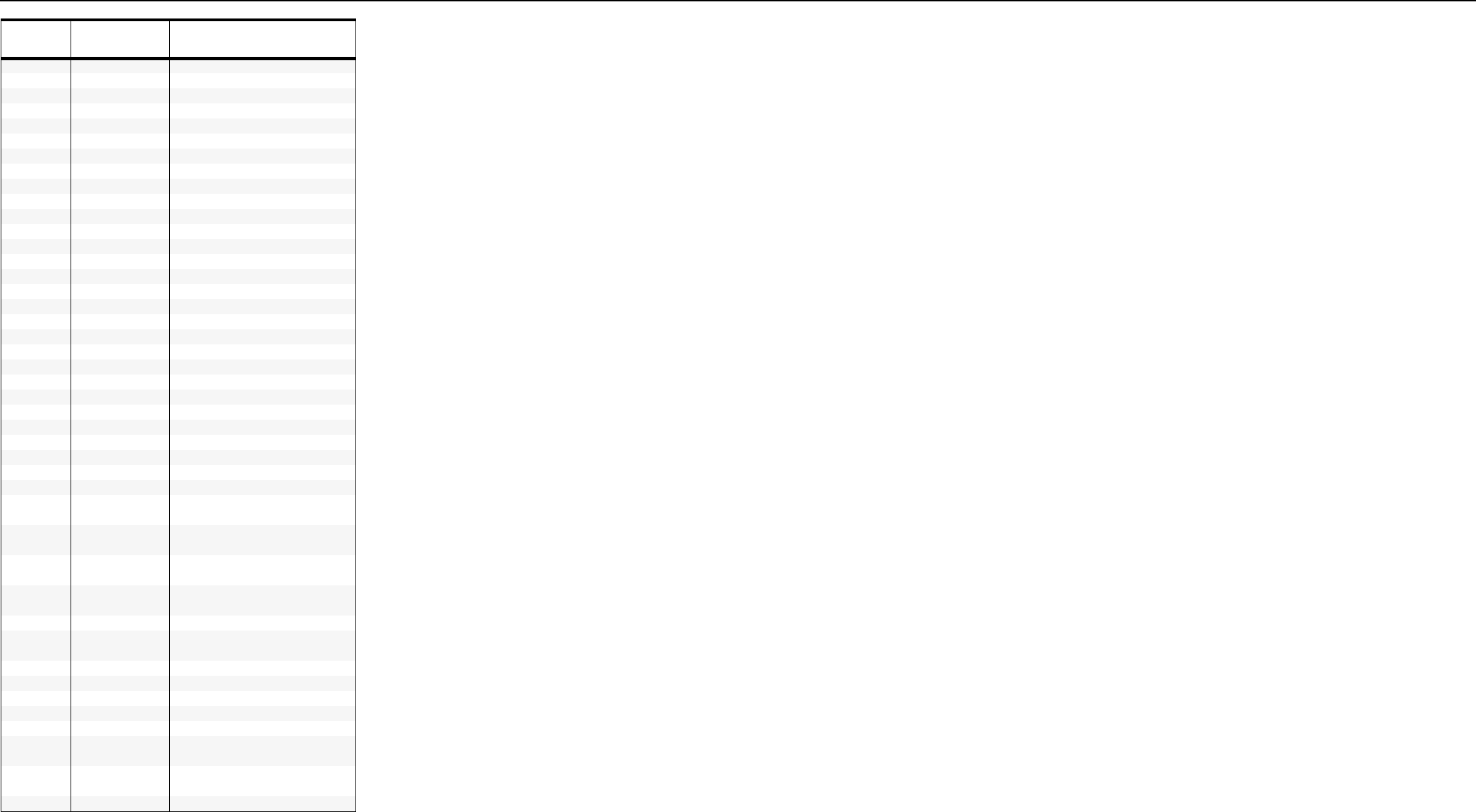

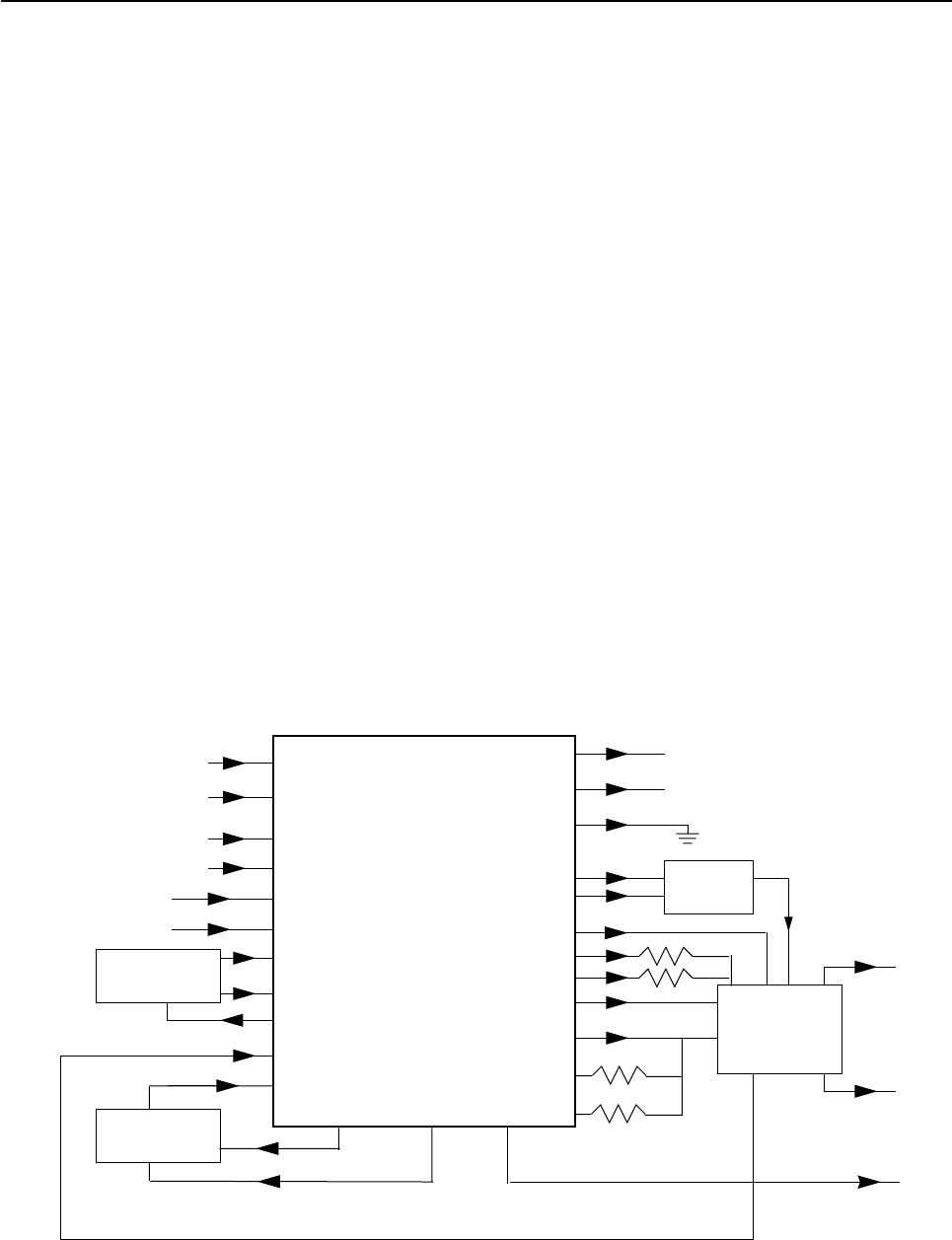

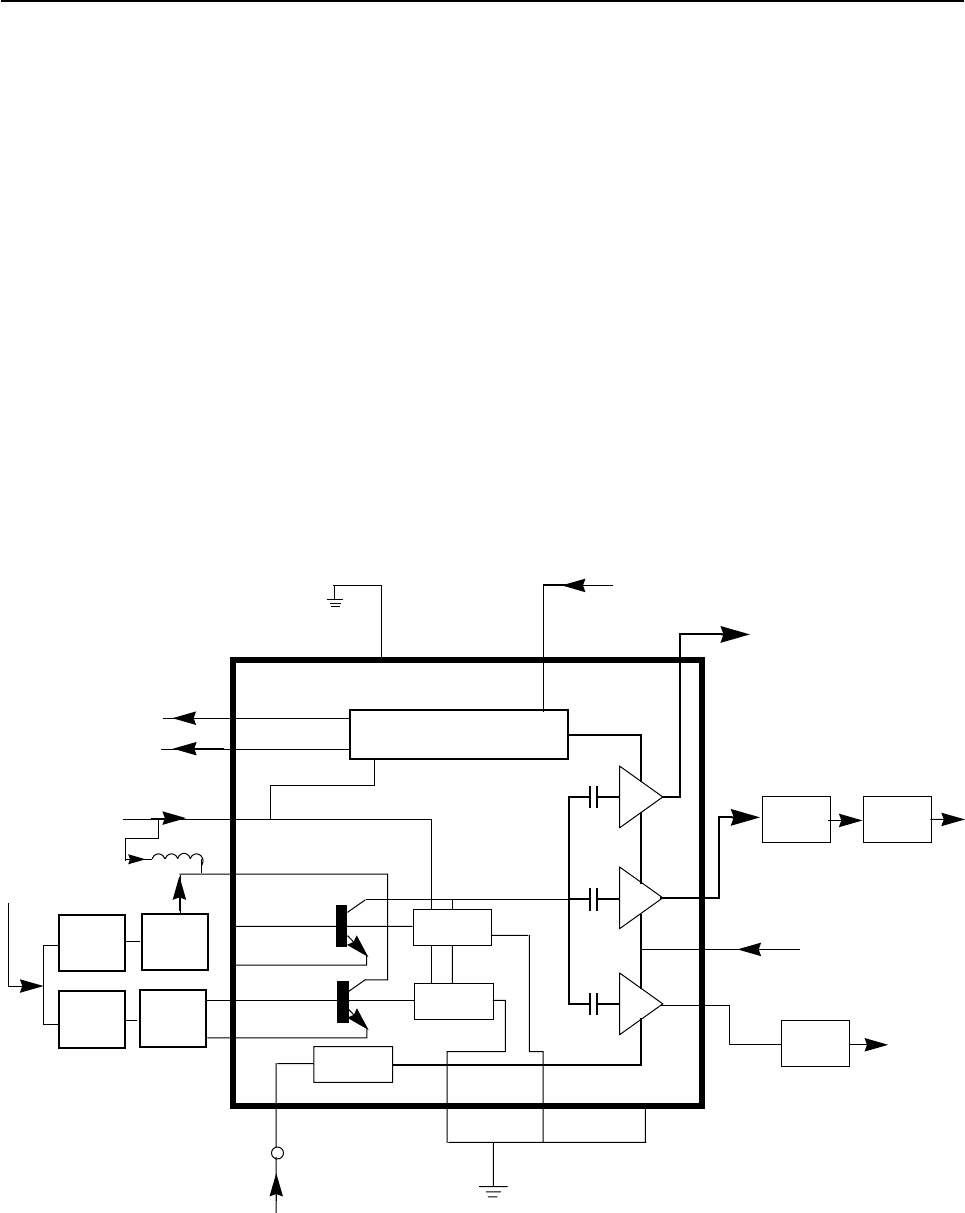

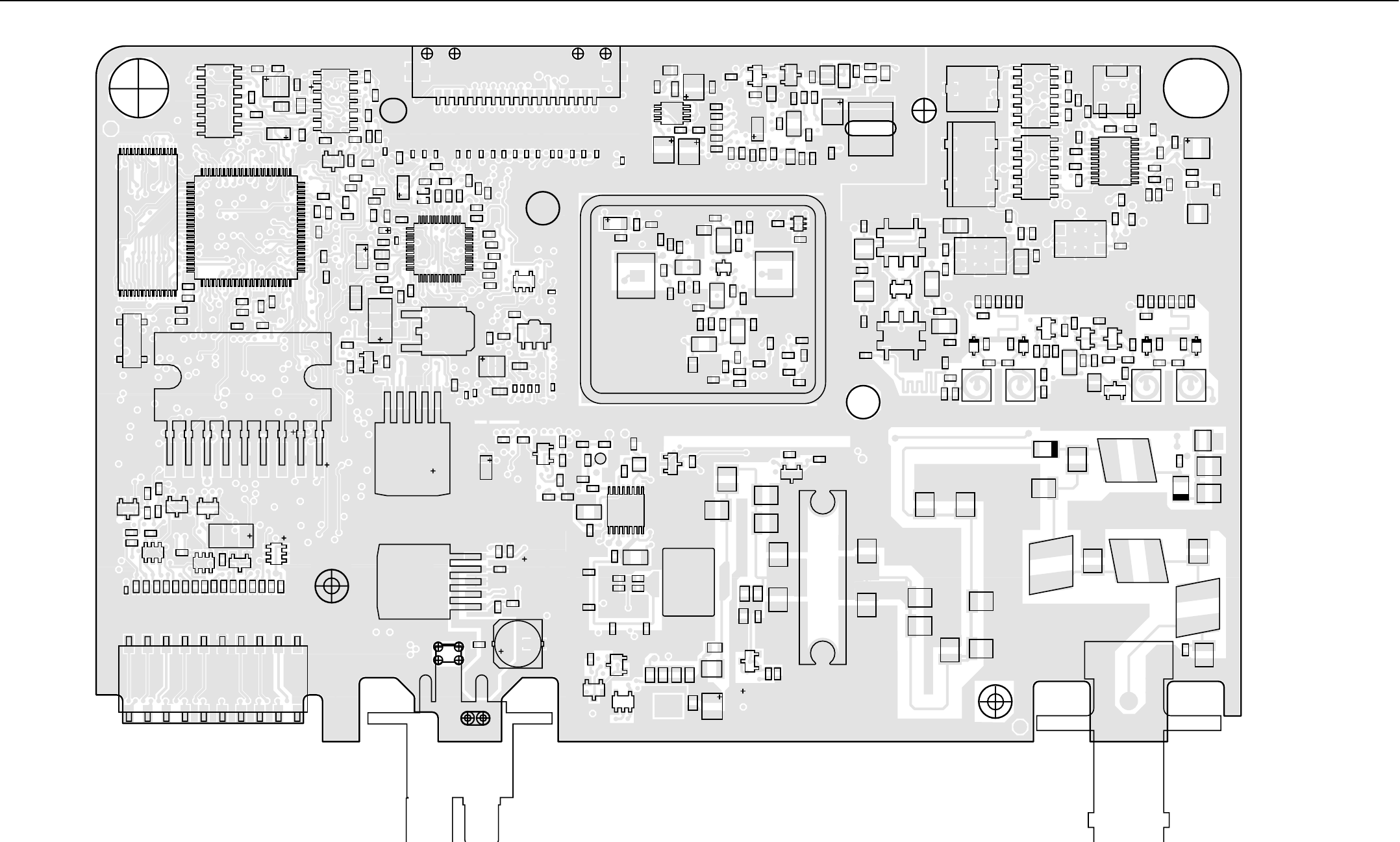

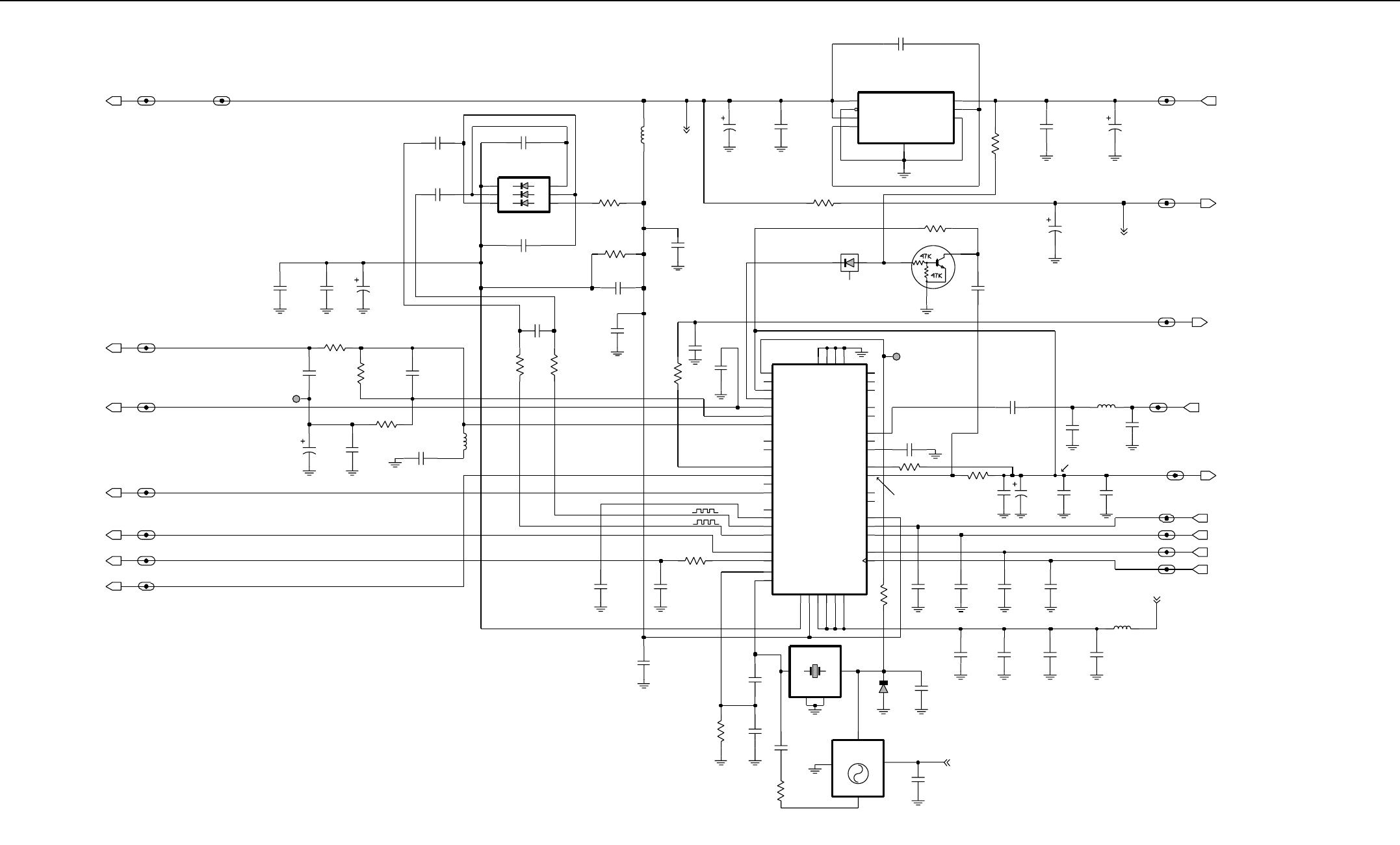

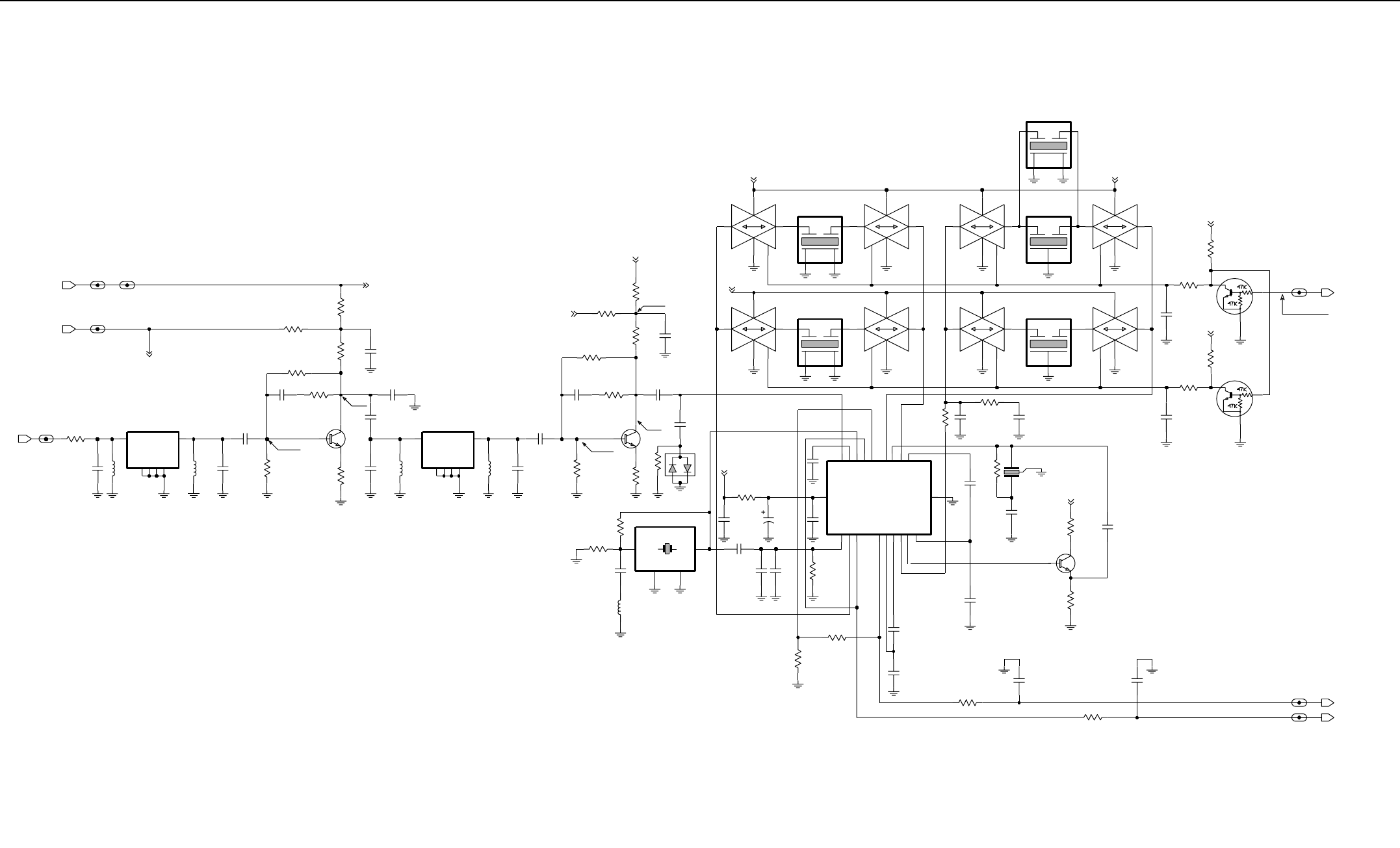

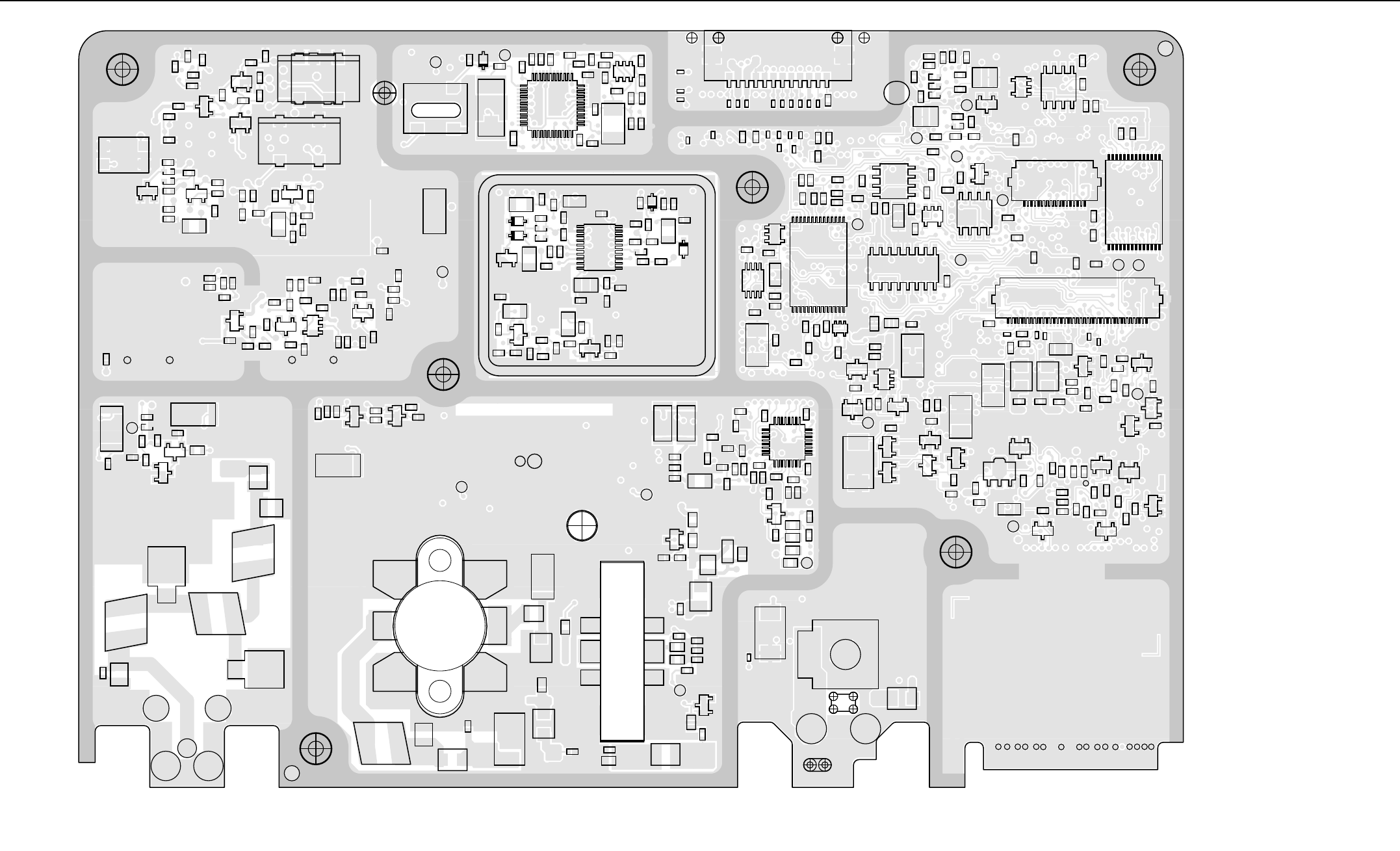

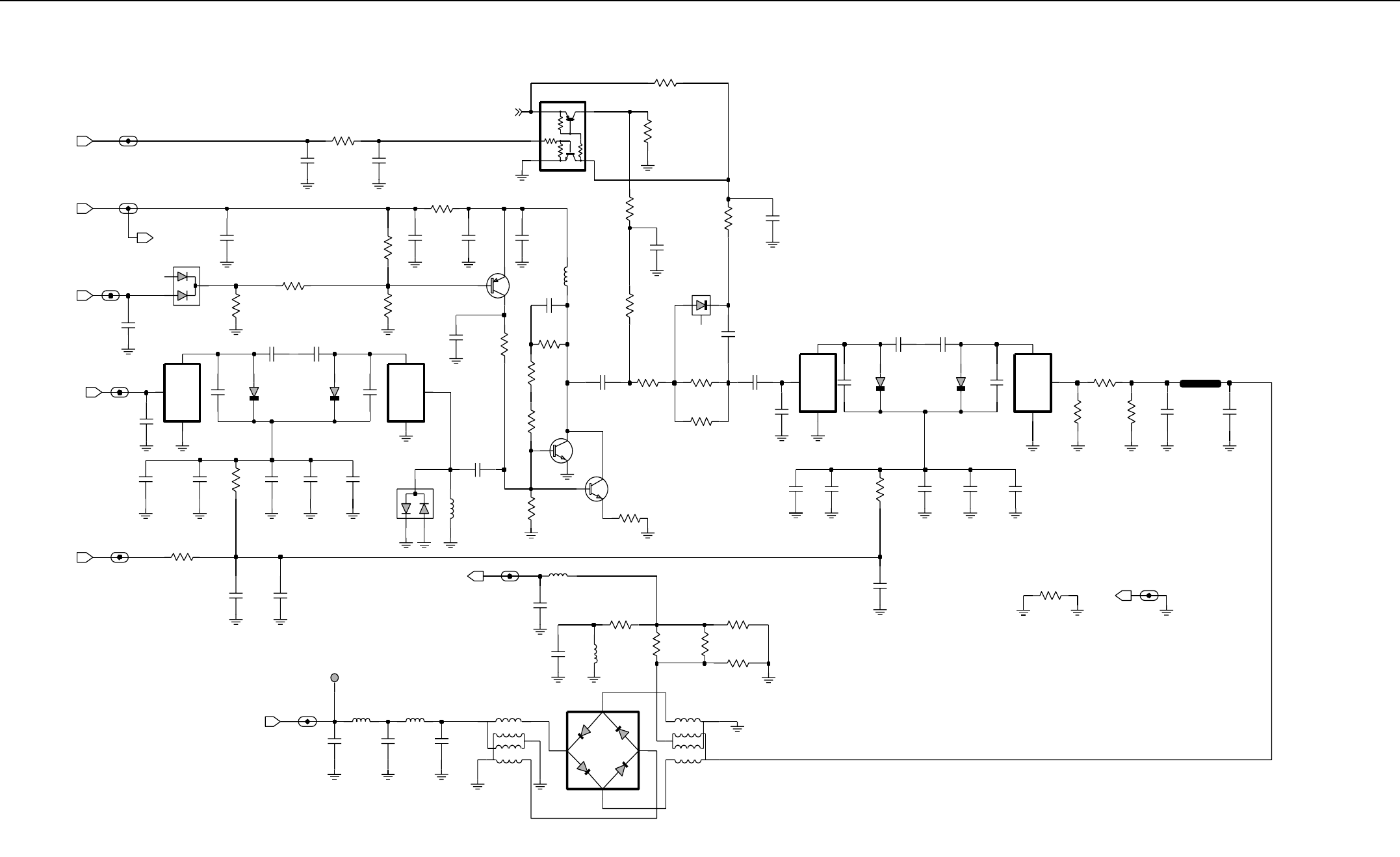

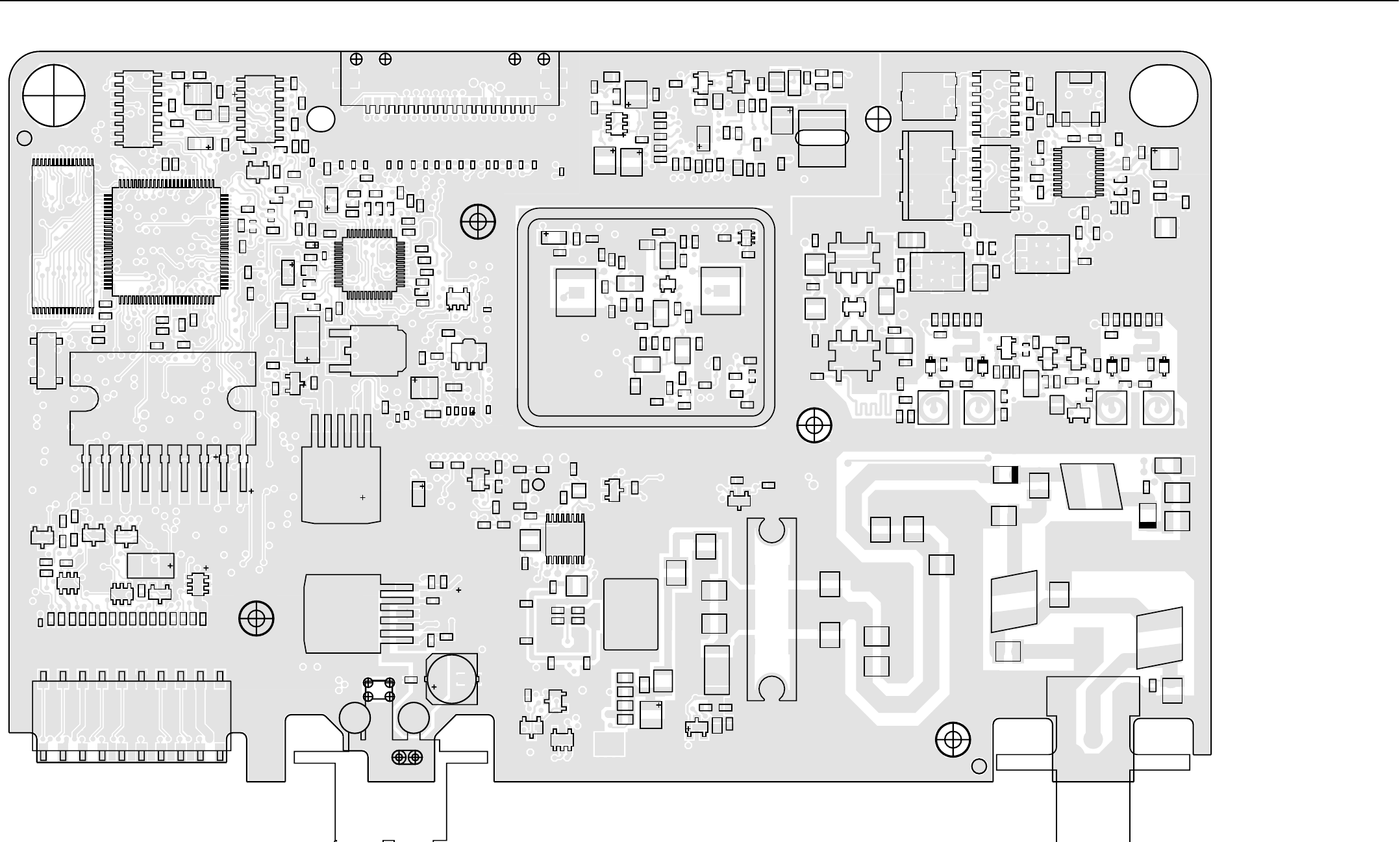

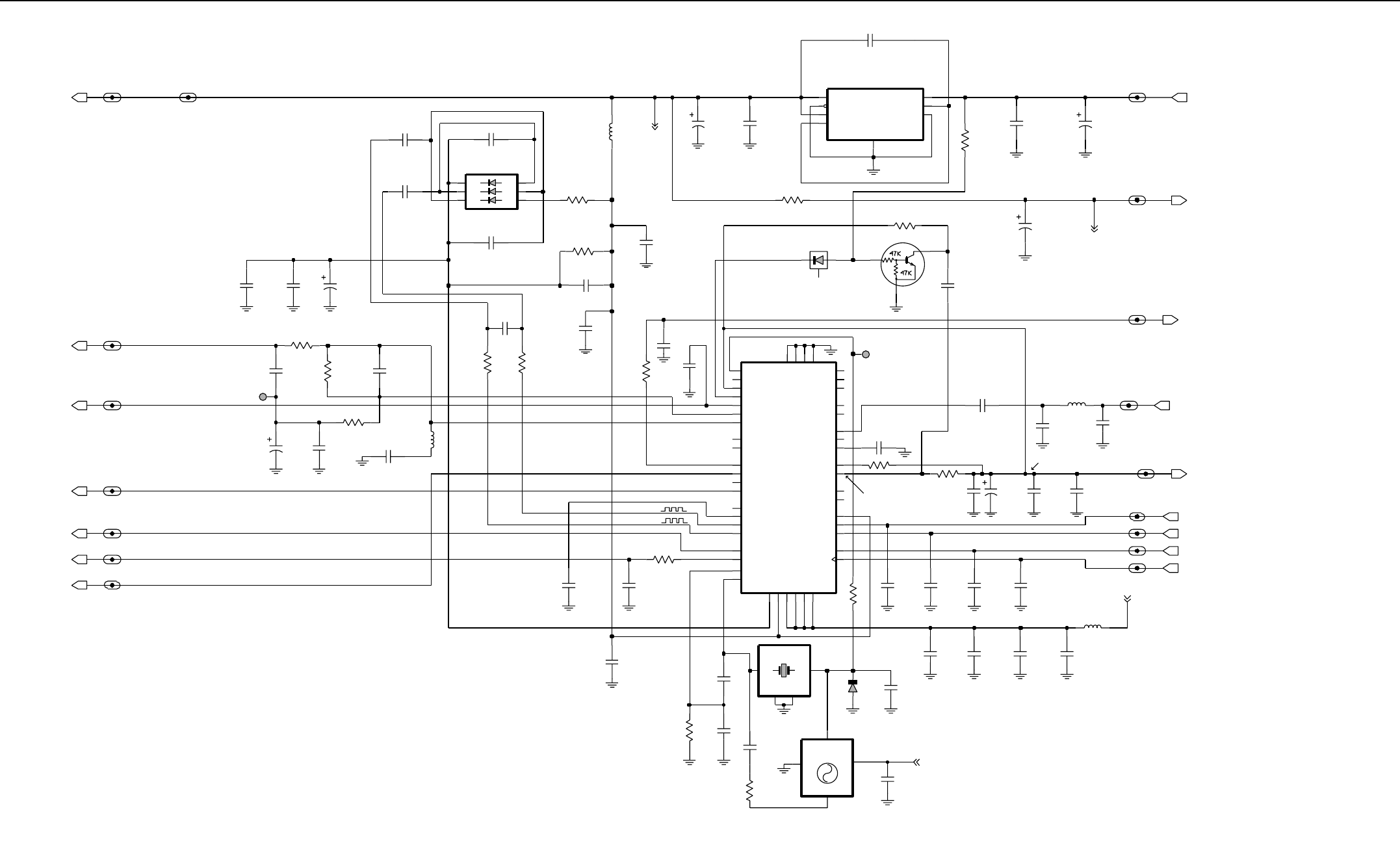

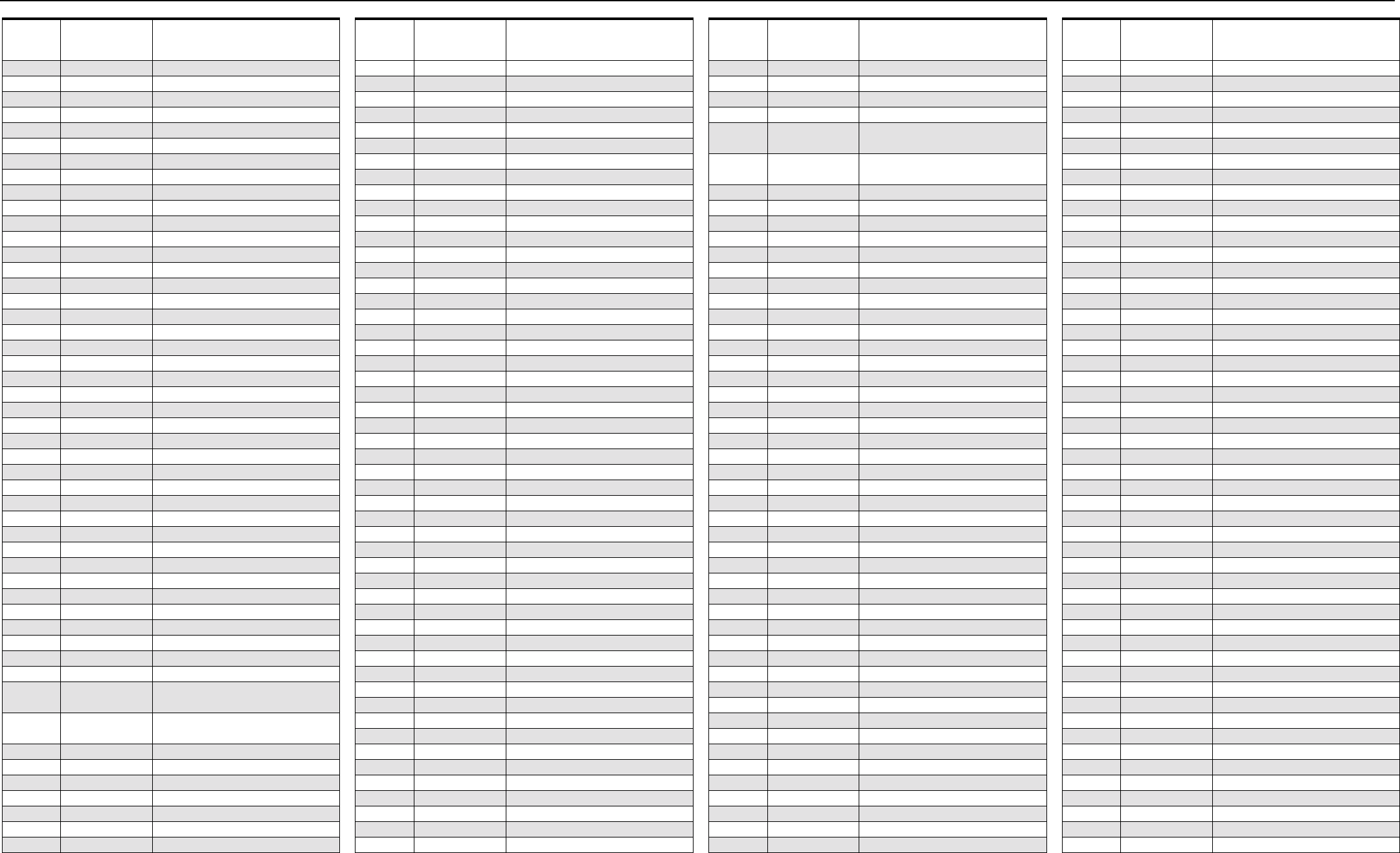

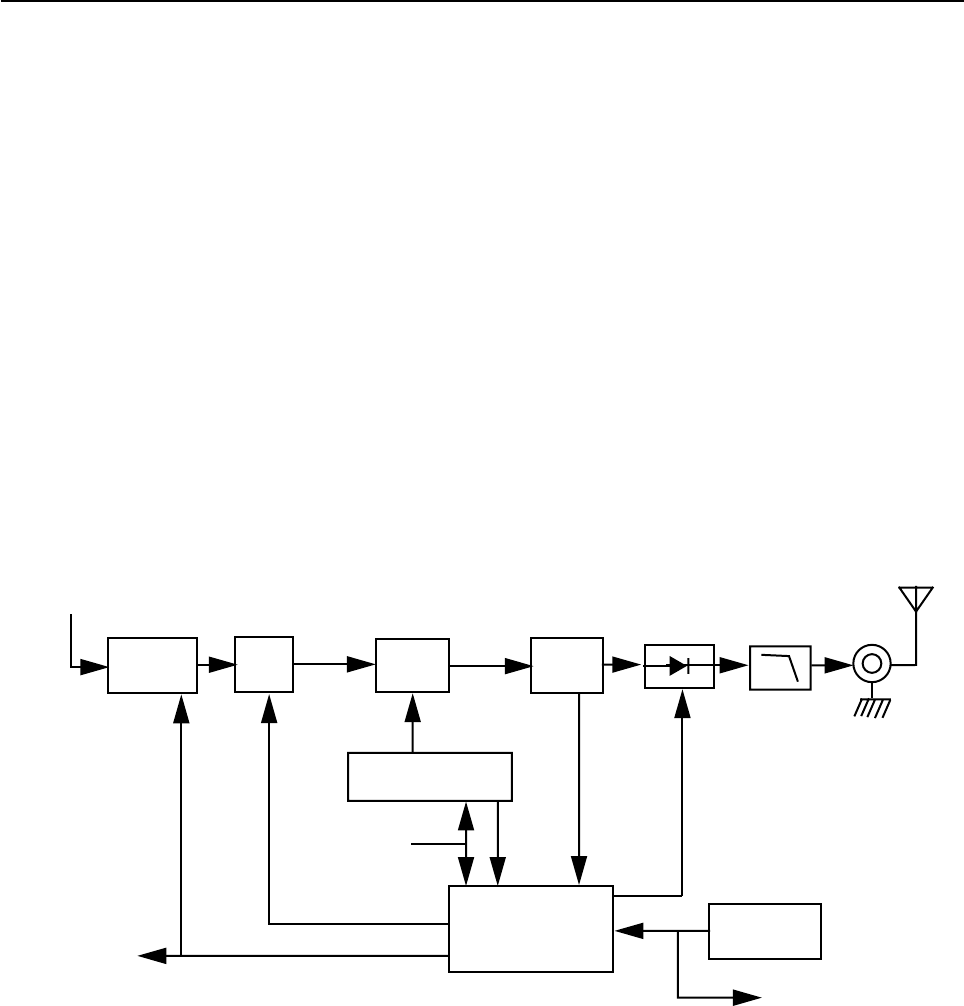

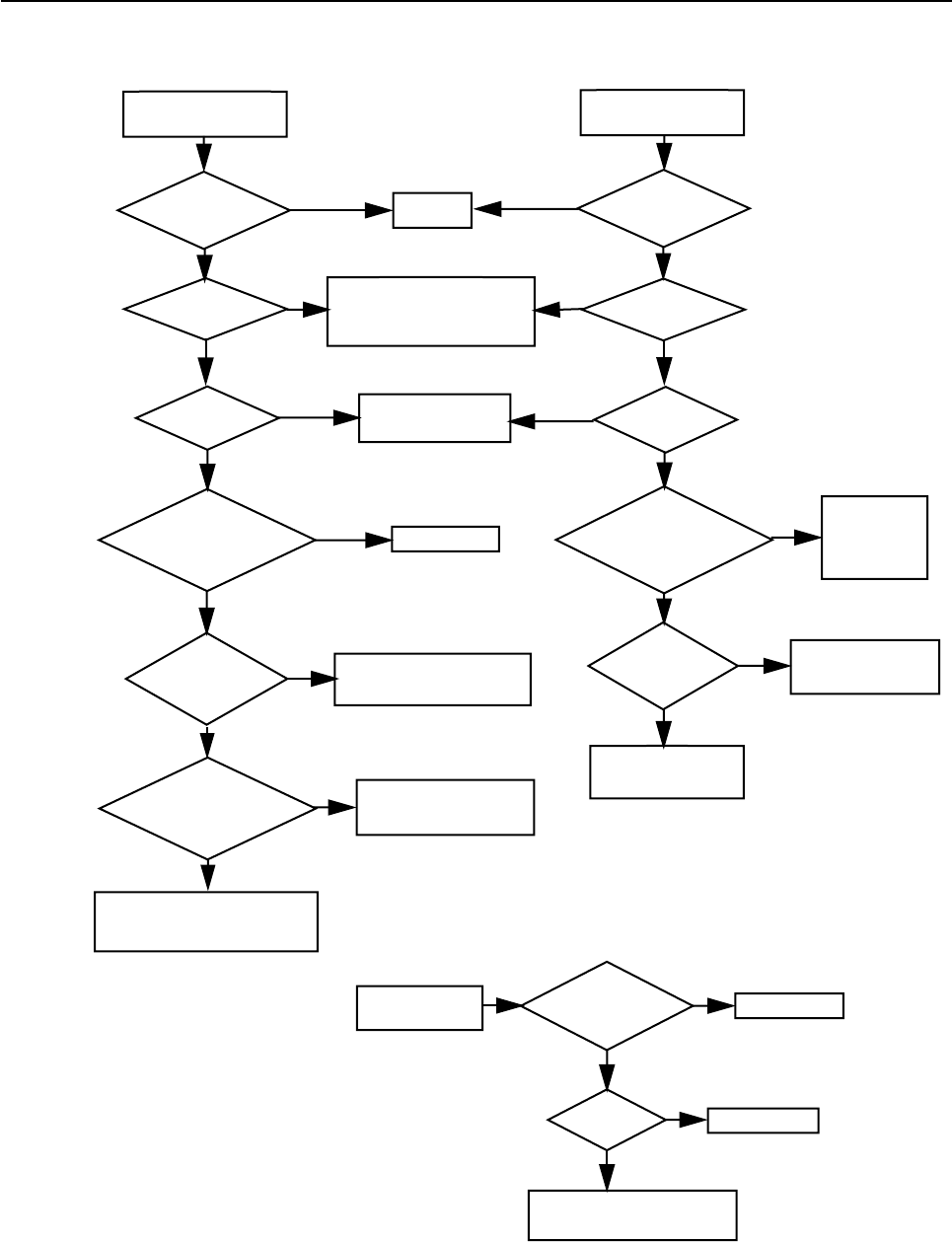

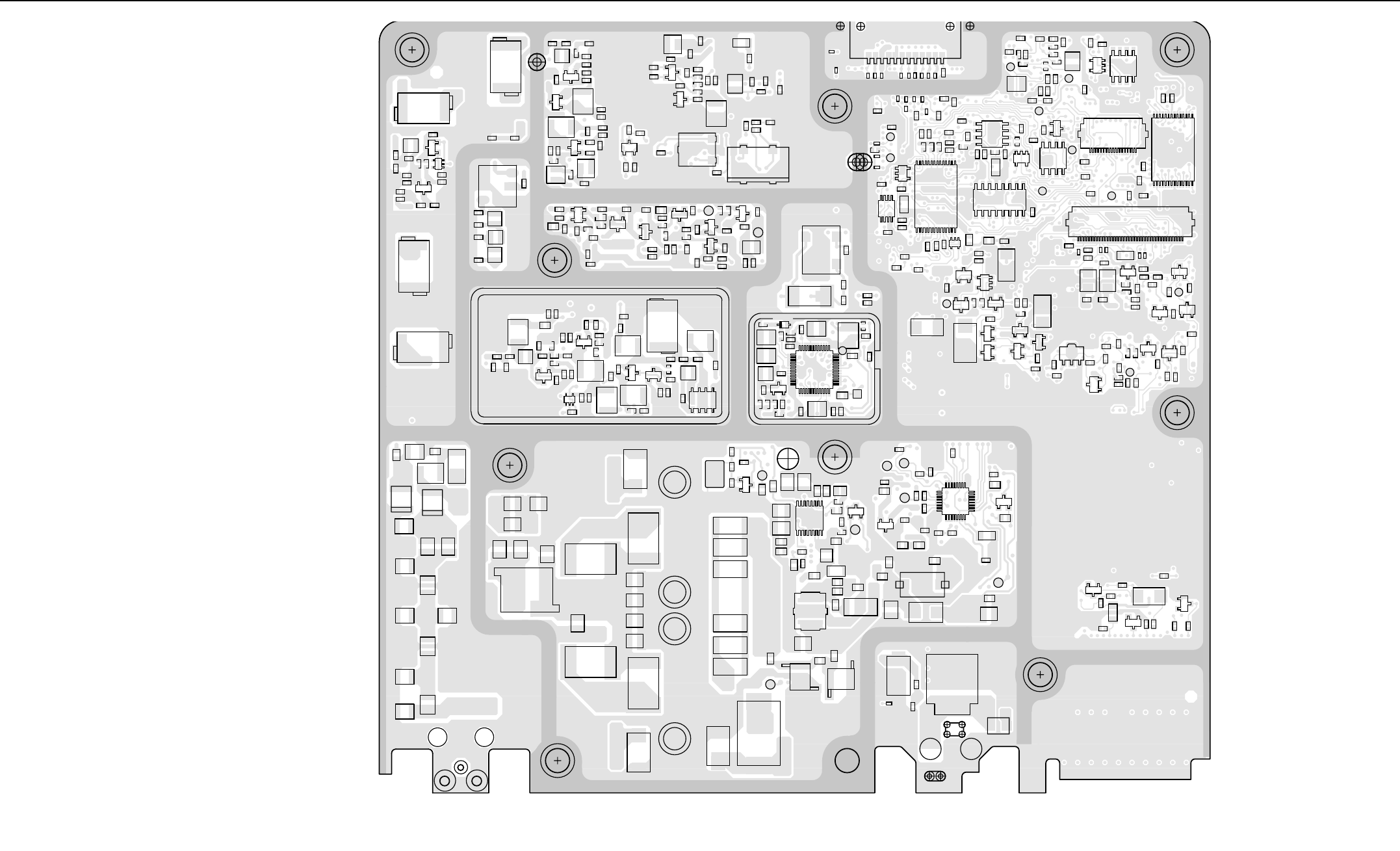

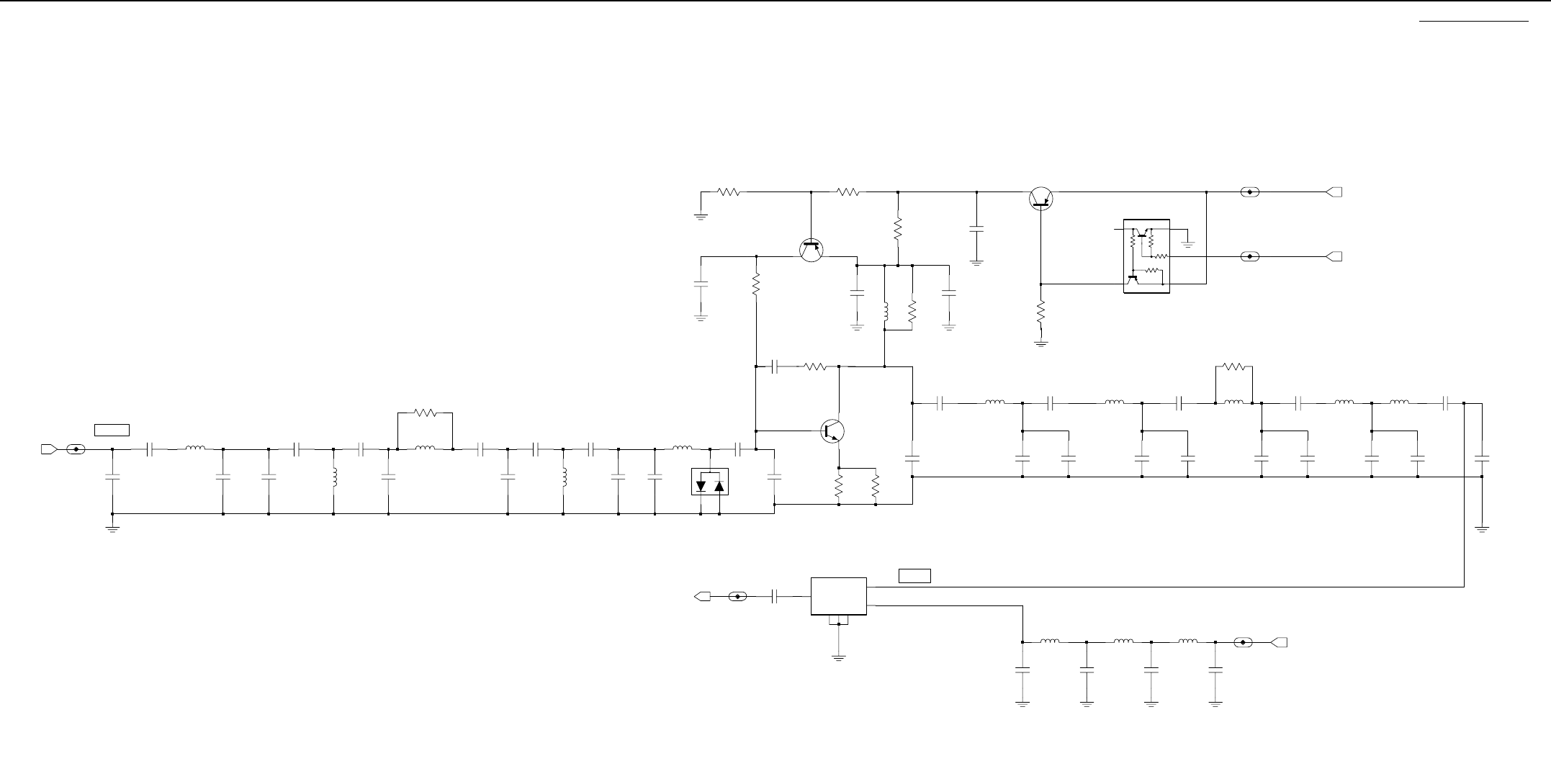

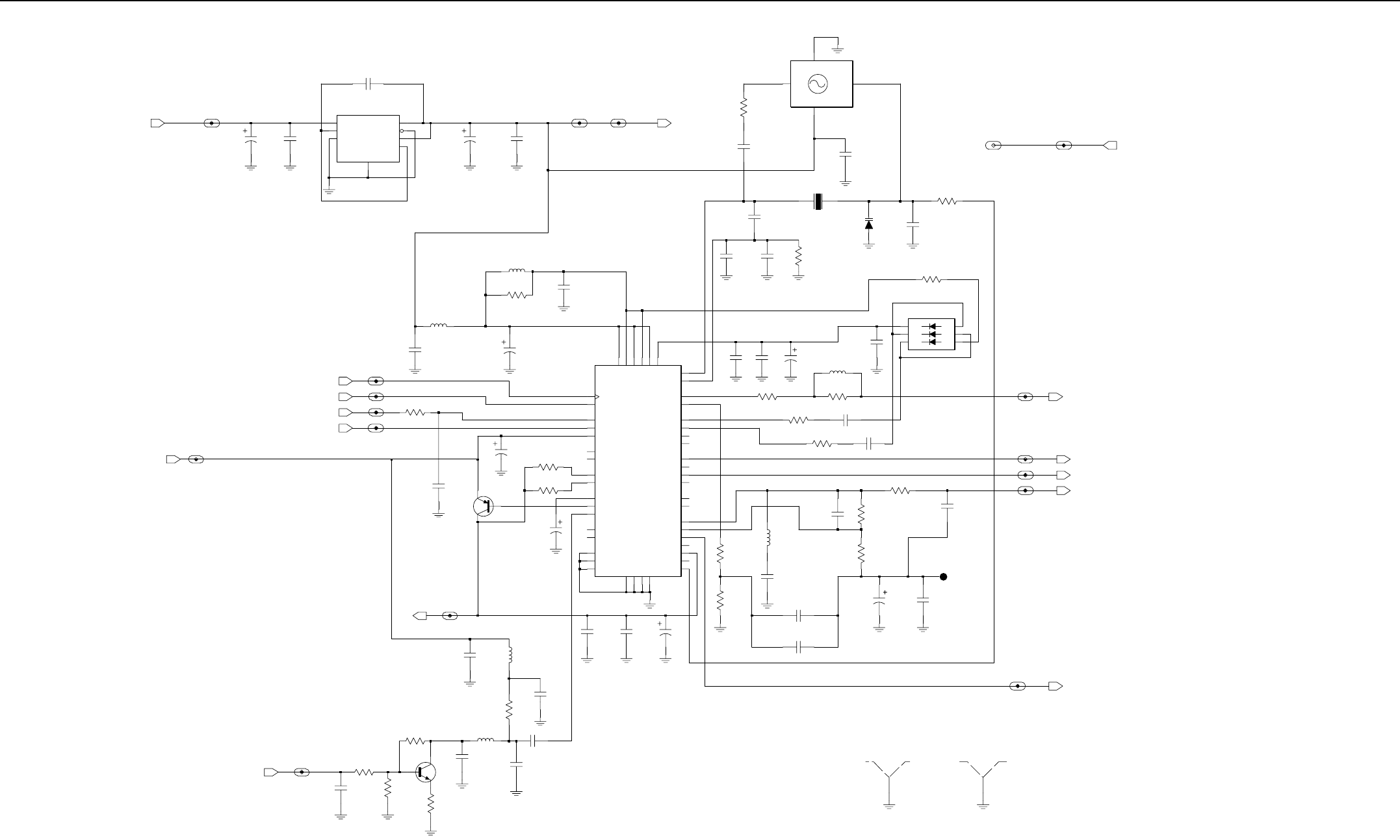

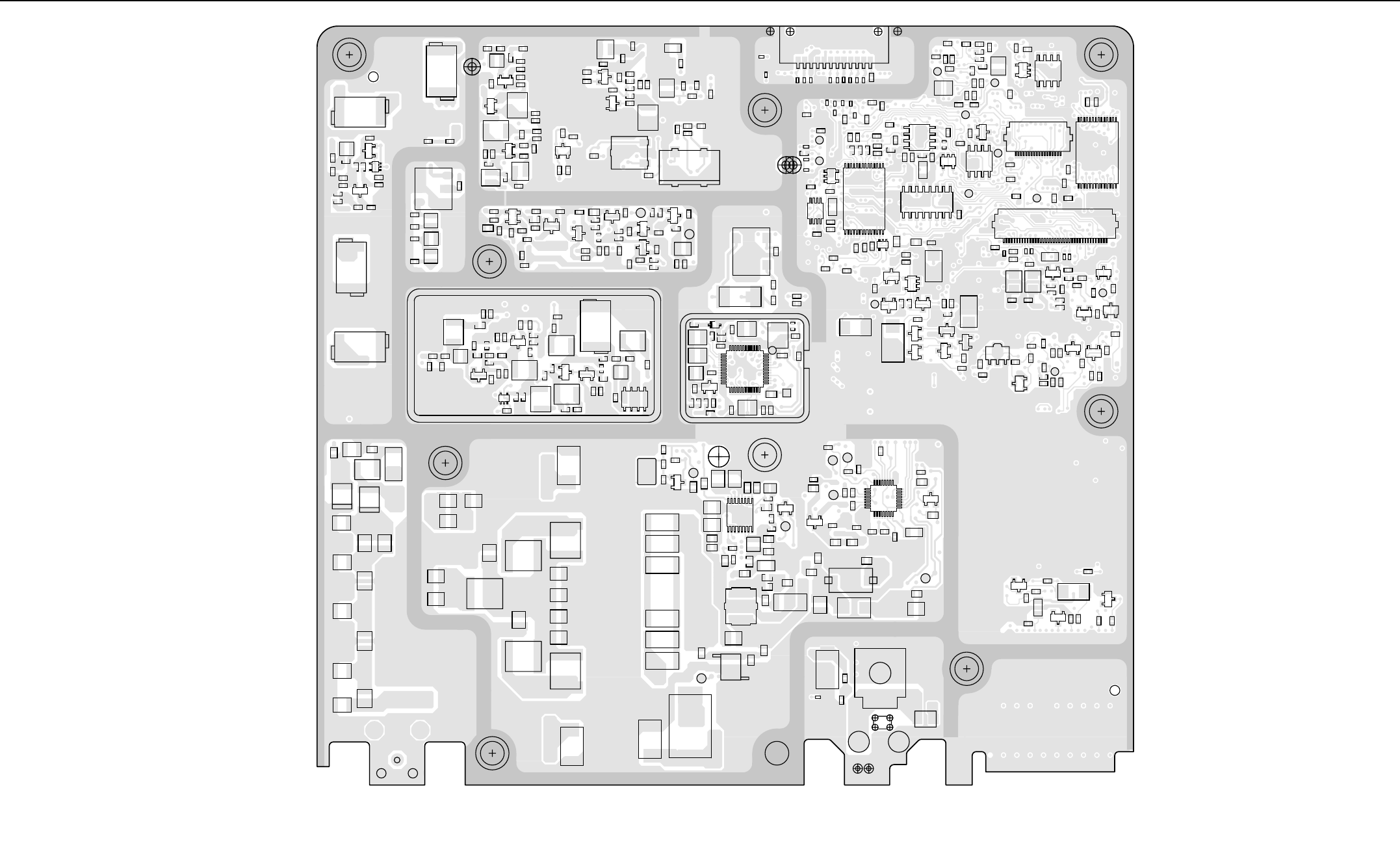

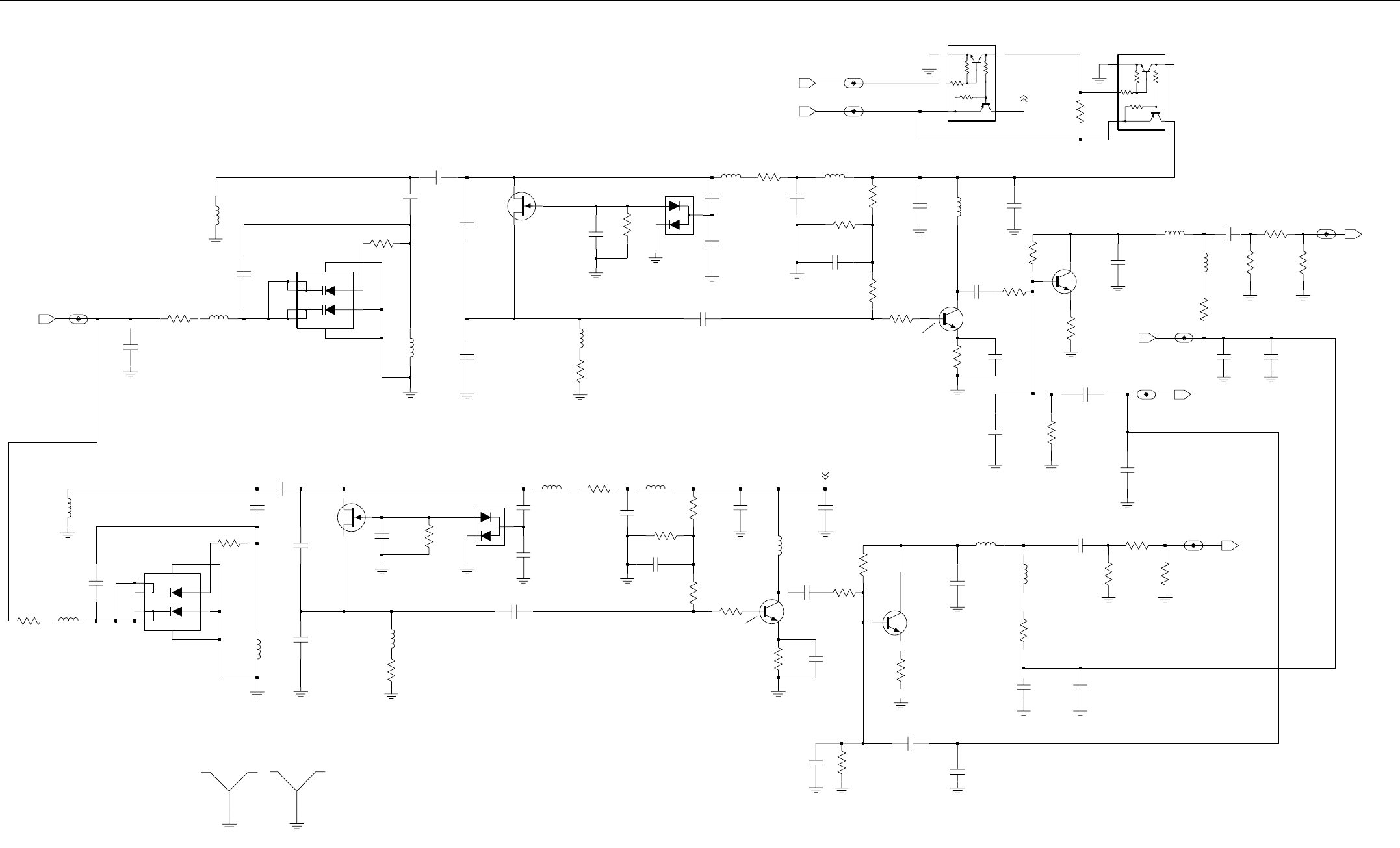

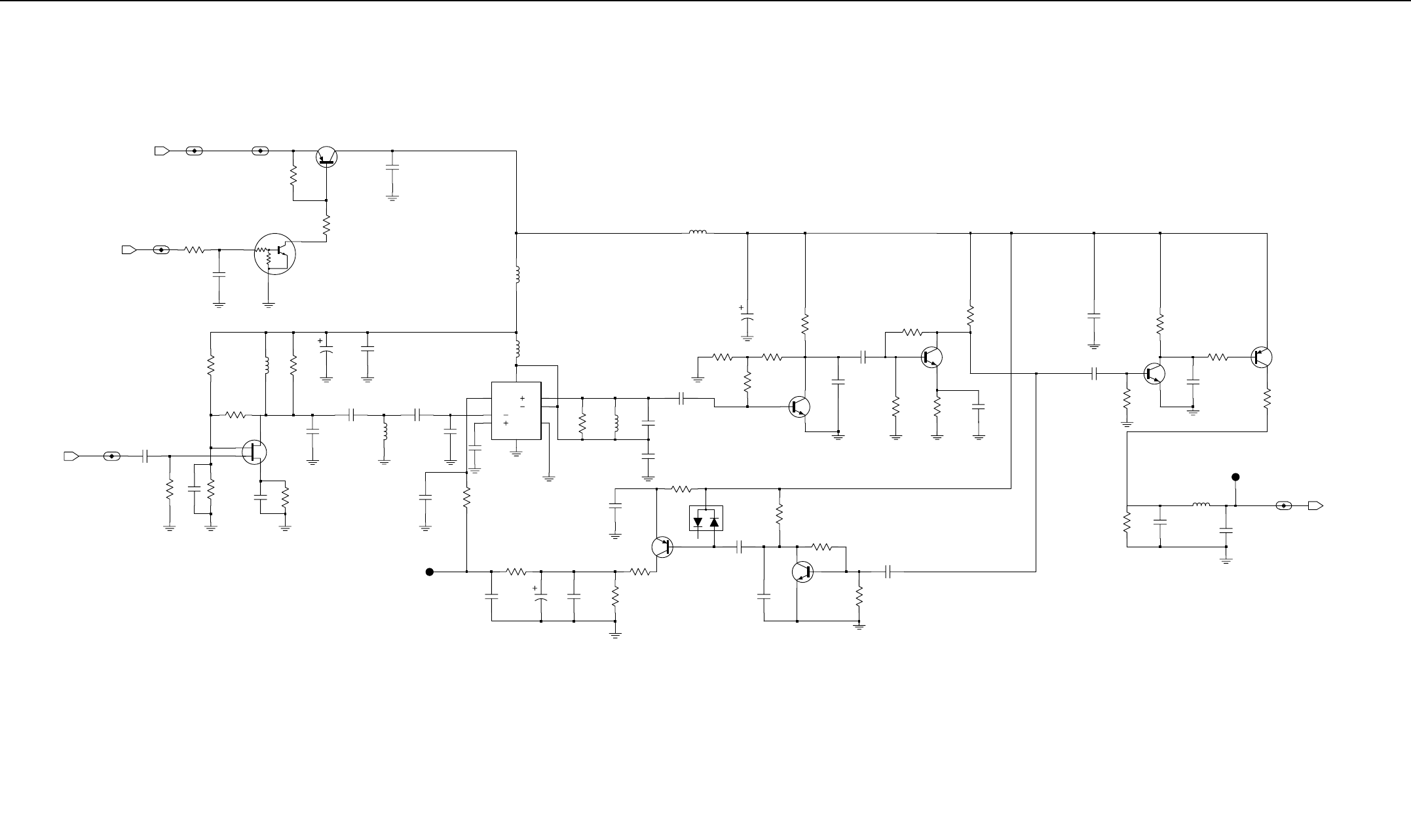

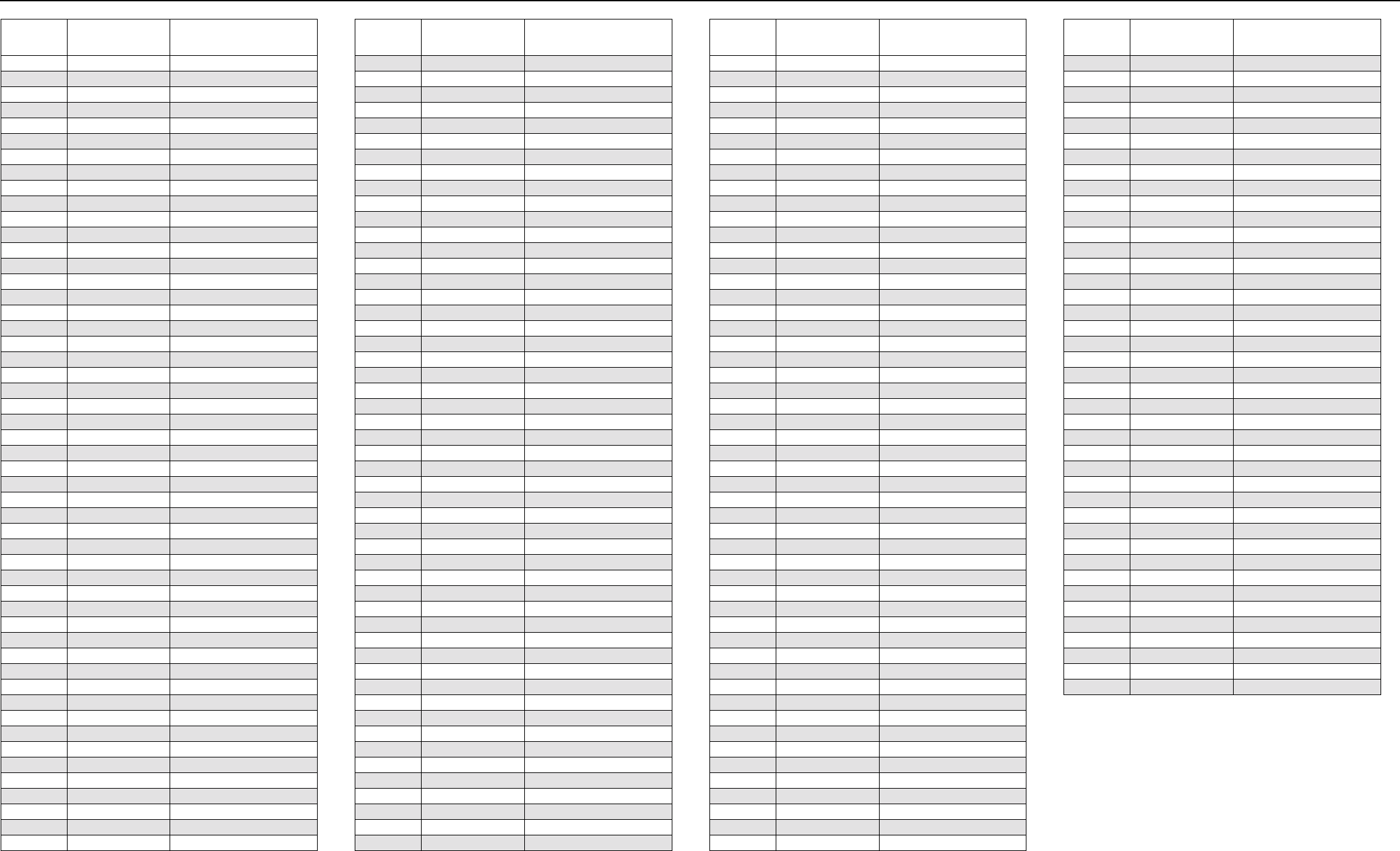

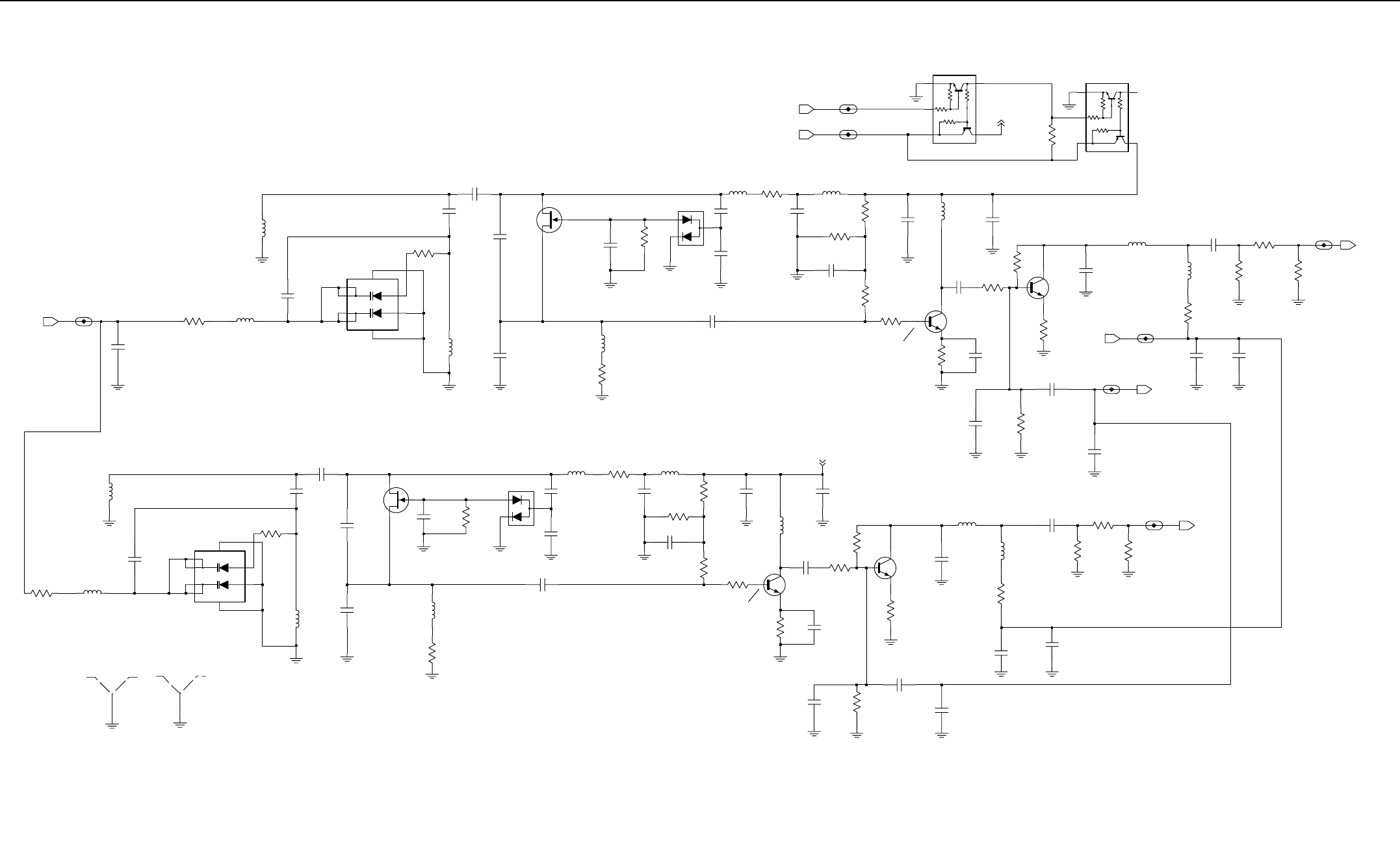

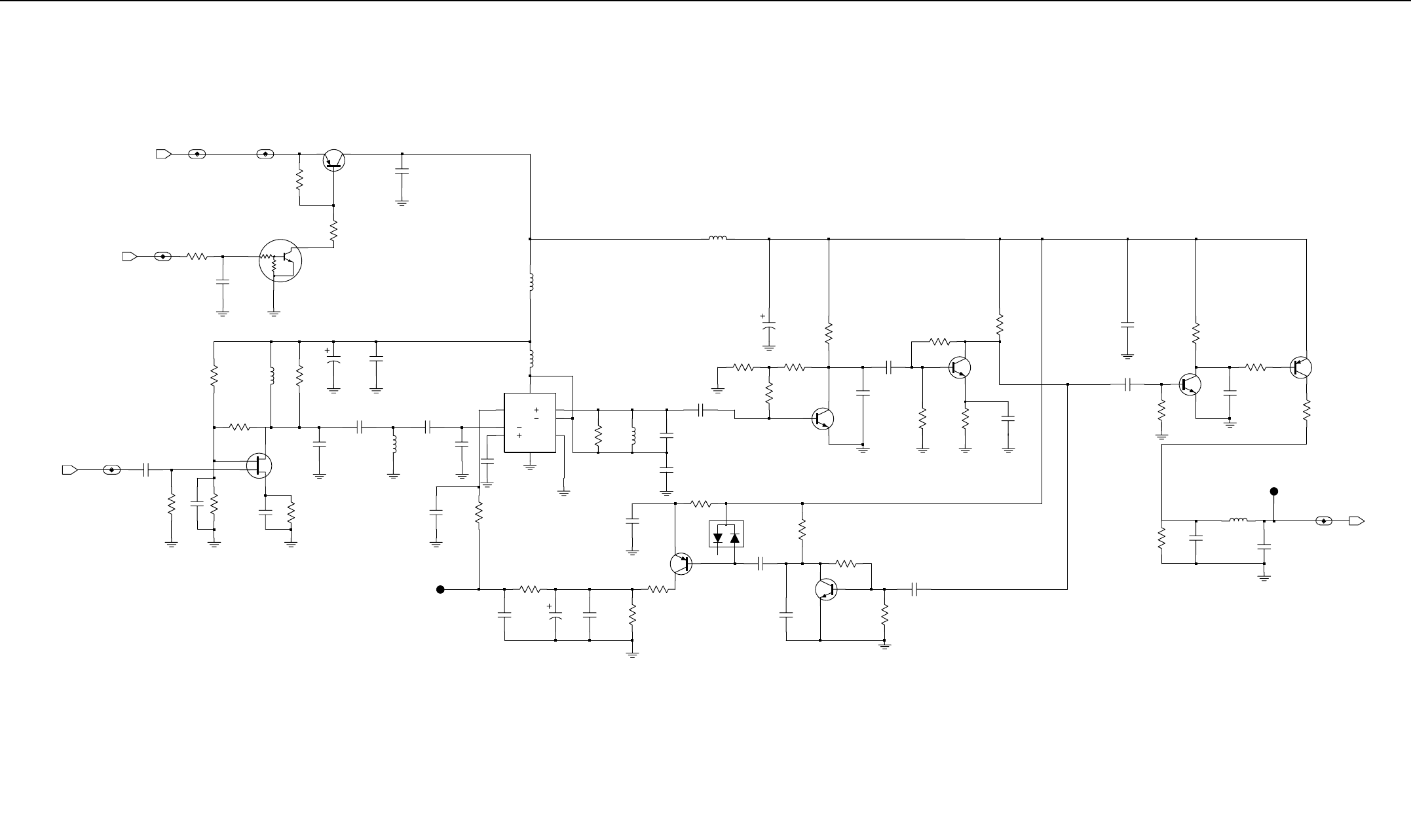

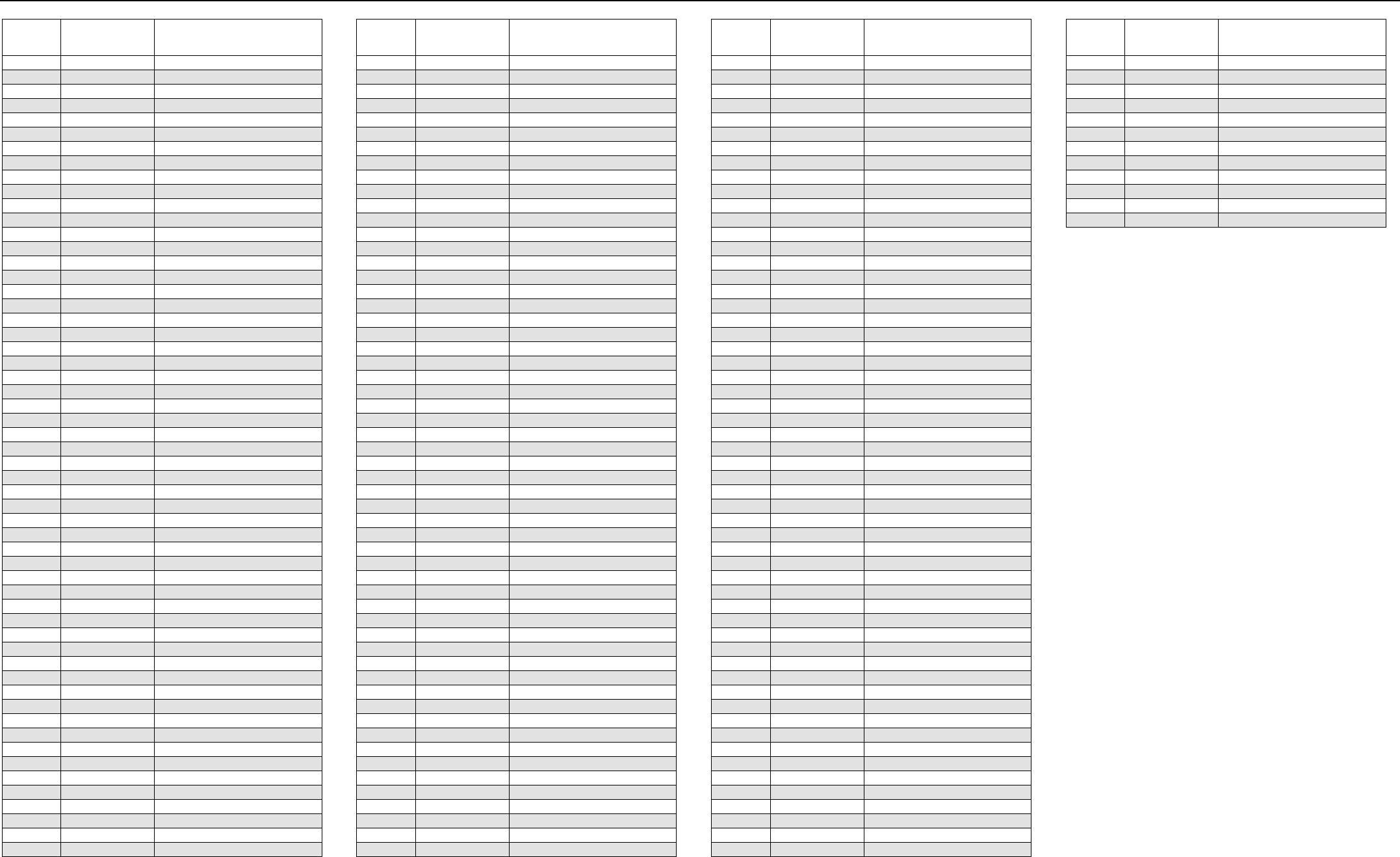

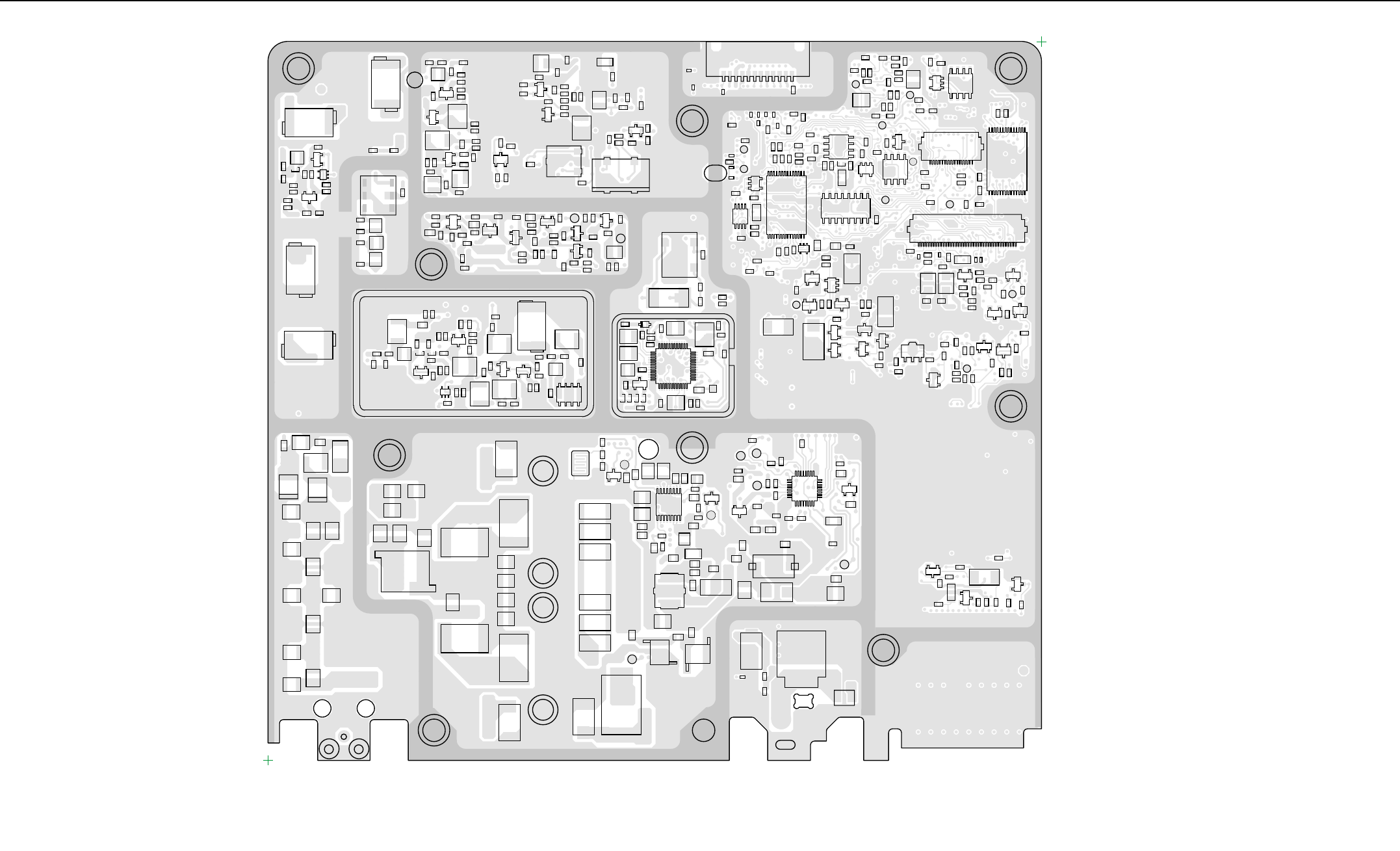

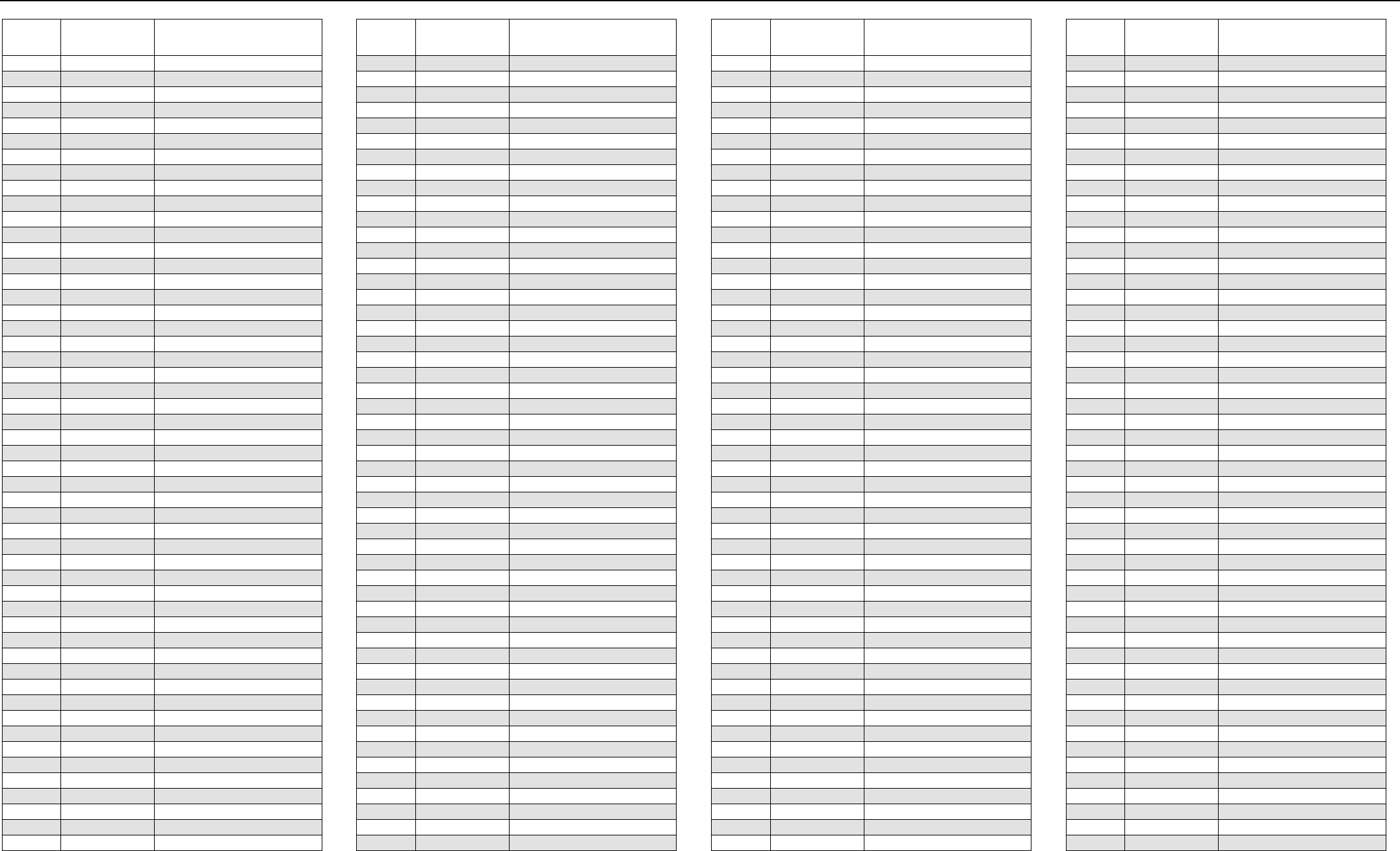

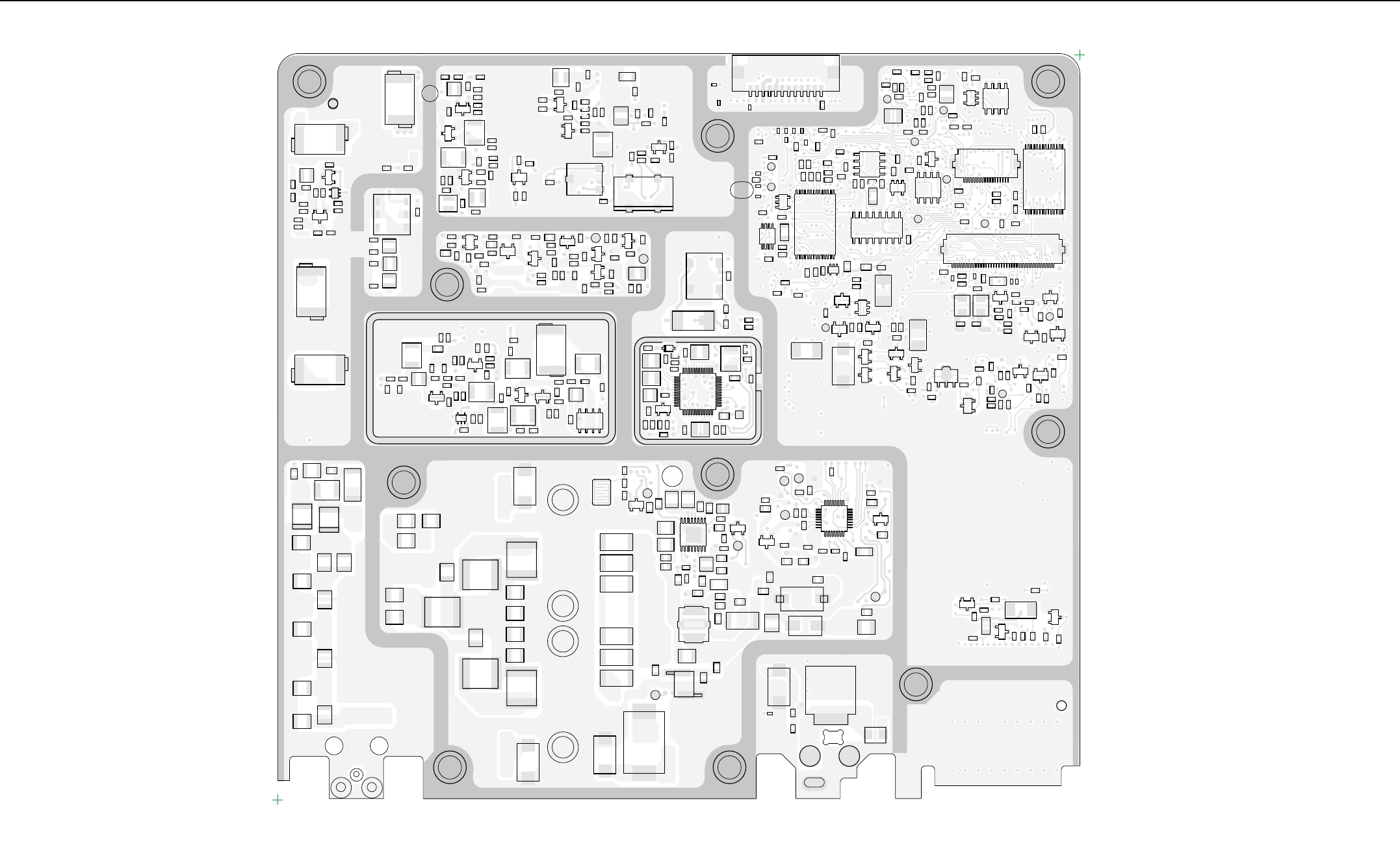

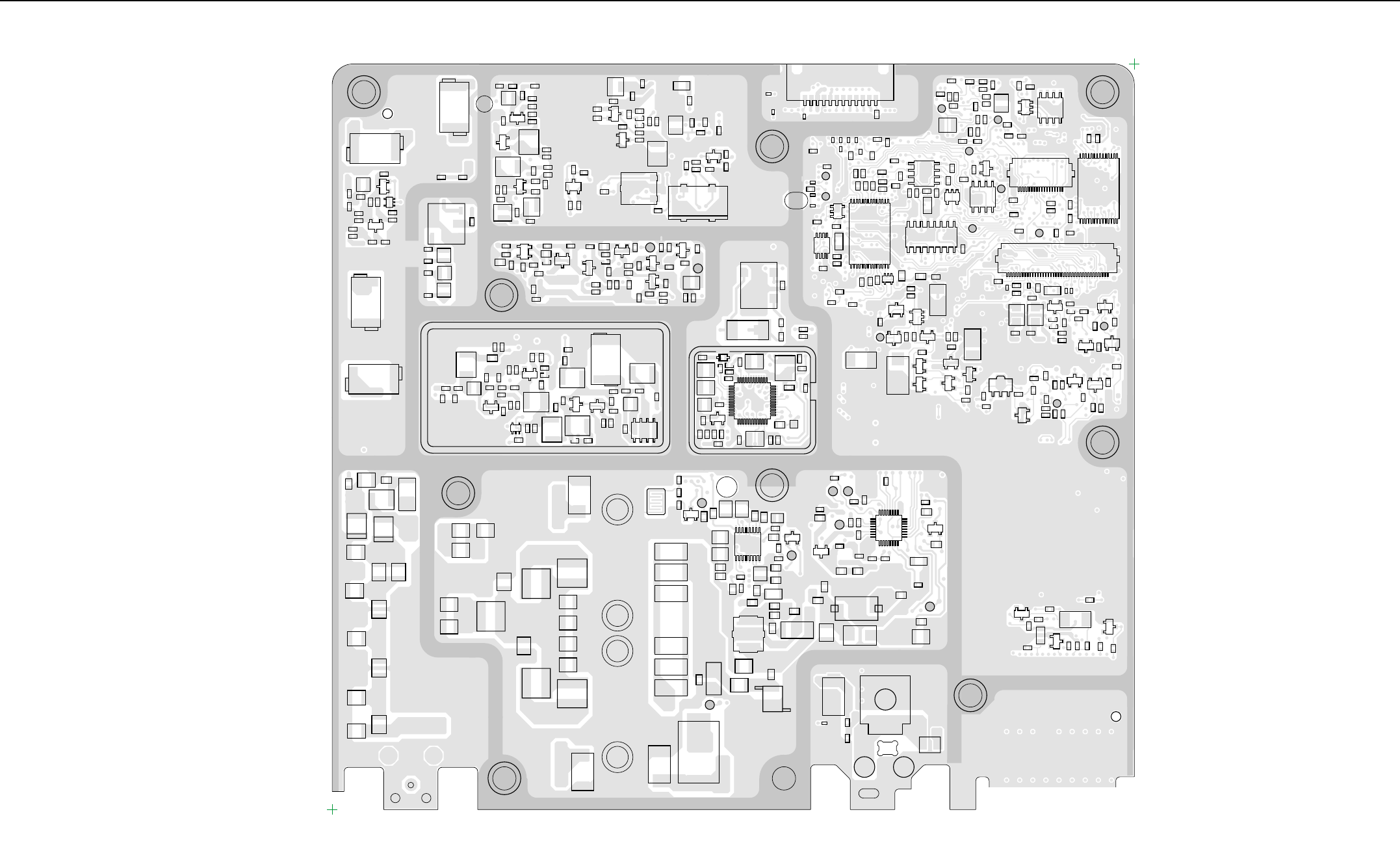

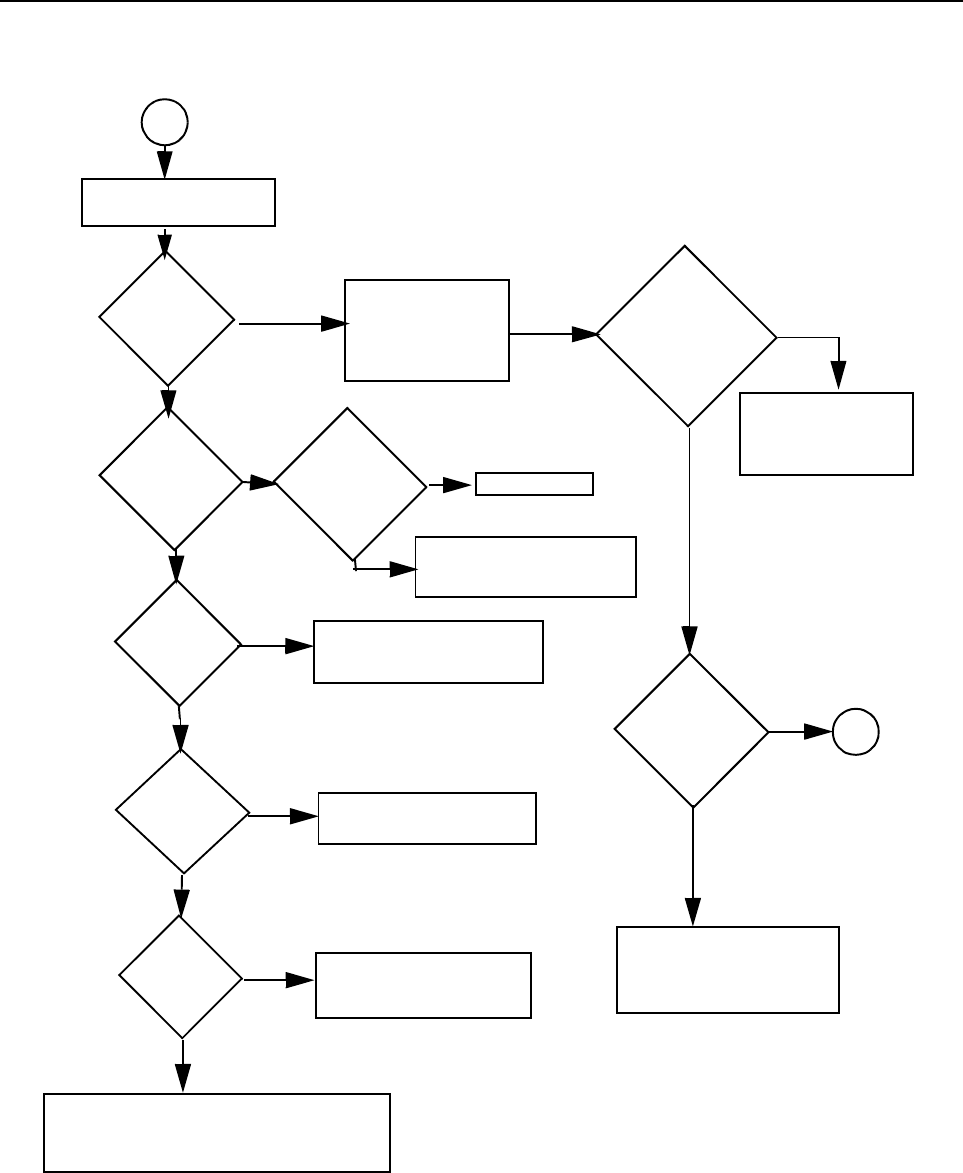

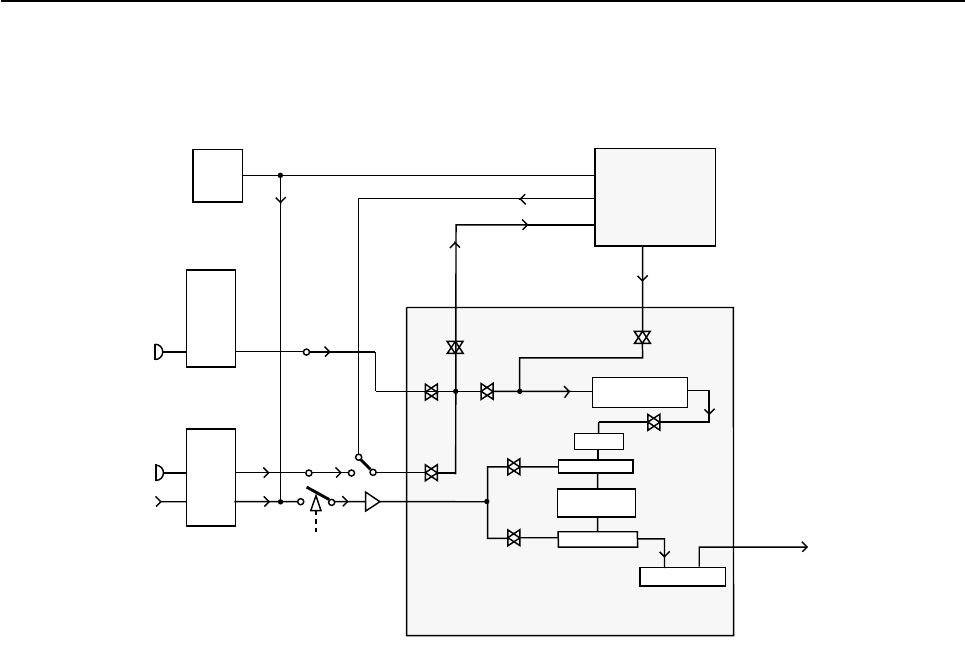

Controlhead GM160/360/660 - PCB 8486155B06 / Schematics 4-7

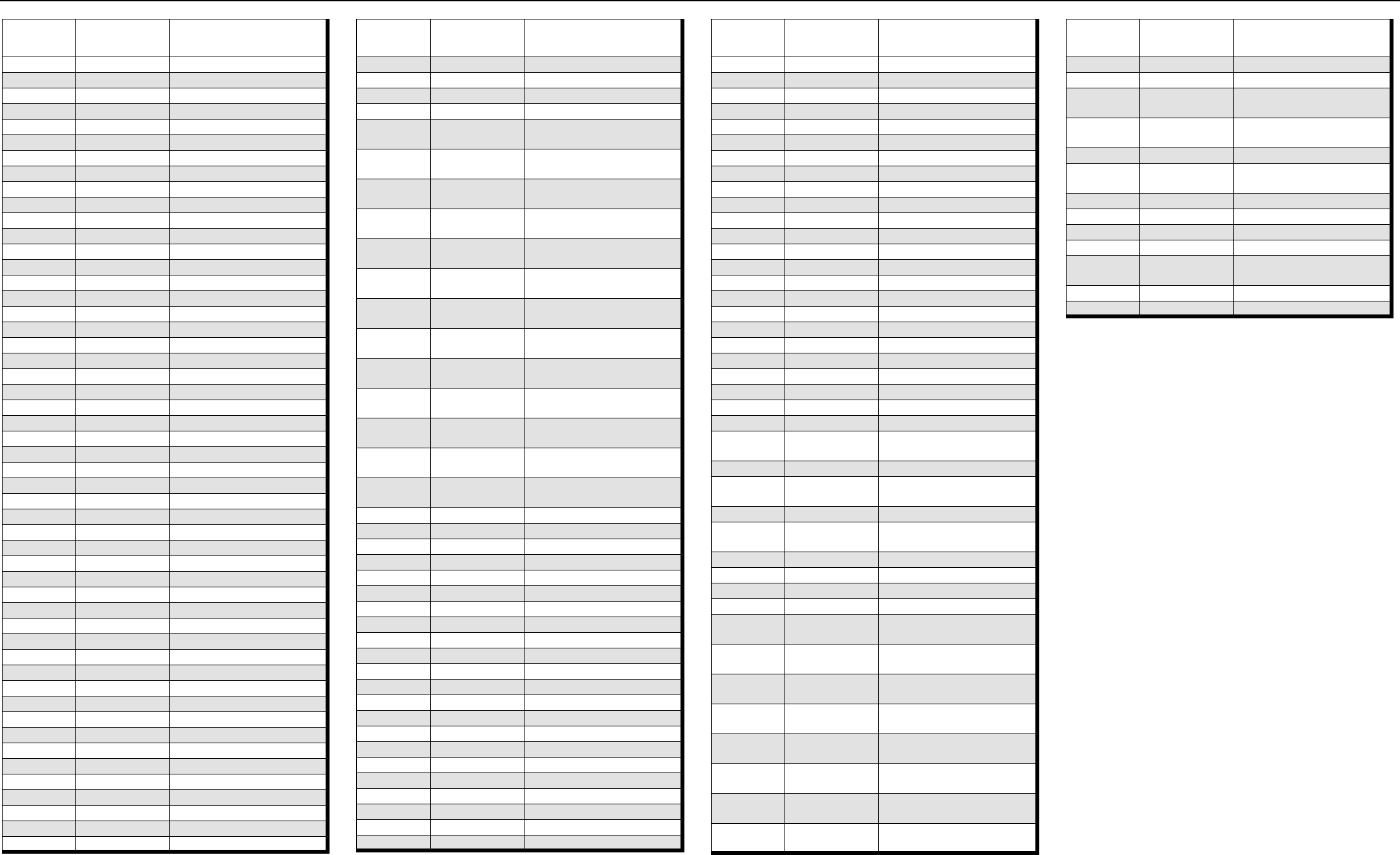

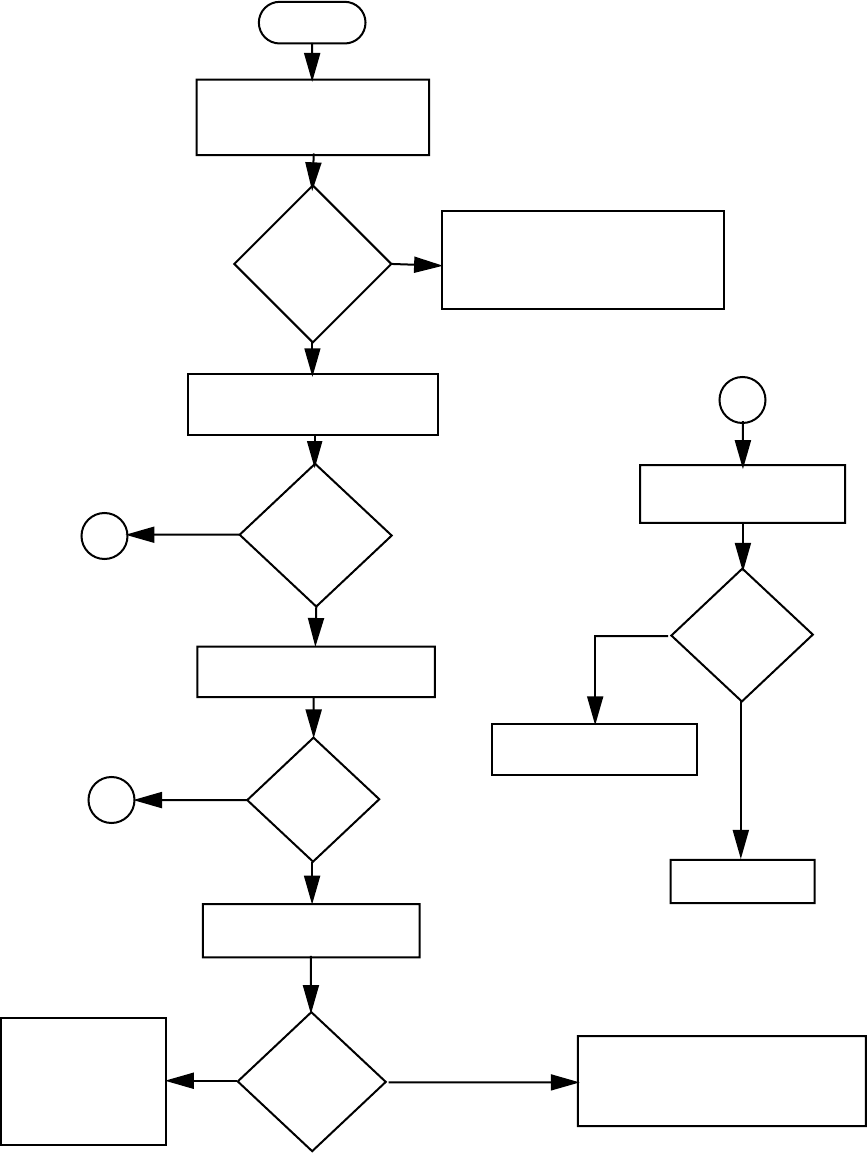

3.0 Controlhead GM160/360/660 - PCB 8486155B06 / Schematics

D0877 D0879

D0880

D0931

D0932

D0933

D0934

D0935

D0936 D0937

D0938

D0939

D0940

D0941

D0942

D0943

D0944 D0945

D0946

D0947

D0948

D0949

D0950 D0951

D0952 D0953

D0954

D0955

D0956

D0957

D0958

D0961

D0962

D0963

D0964

D0965

D0966 D0967

D0968

D0969

D0970

D0971

D0972

D0973

D0974 D0975

D0976

D0977

D0978

D0979

D0980 D0981

D0982 D0983

D0984

D0985

D0986

D0987

D0988

40

41 80

H0971

2

3579

864 10

J0811

4

1

23

5

R0823

S0852

S0853

S0854

S0901

S0902

S0903

S0904

S0905

S0906

S0907 S0908

S0909 S0910

U0834

110 30

20

60 70

50

1

ZWG0130136-A

C0802

C0803

C0804

C0805

C0806

C0807

C0808

C0810

C0811

C0812

C0813 C0815

C0816

C0817

C0818

C0819

C0821

C0822

C0823

C0831

C0832

C0833

C0842

C0843

C0931

C0932

C0933

C0971

C0972

C0973

C0974

C0975

C0976 C0977

C0978 C0979

C0980 C0981

C0982

C0983

C0984

C0985

D0821

D0822

D0831

12

J0801

1

2

P0801

Q0821

Q0822

Q0823

Q0841

Q0843

Q0877

Q0878

Q0879

1

2

3

4Q0931 Q0932

1

2

3

4Q0933

Q0934

R0810

R0811

R0812 R0813 R0814

R0815

R0816

R0817

R0821

R0822

R0824

R0825

R0831

R0832

R0833

R0834

R0835

R0836

R0837

R0838

R0841

R0842

R0843

R0844

R0845

R0847

R0848

R0849

R0850

R0851

R0852

R0853

R0854

R0855

R0856

R0857

R0858

R0859

R0860

R0861

R0862

R0863

R0864 R0865

R0877

R0878

R0879

R0901

R0902

R0903

R0904

R0905

R0906

R0907

R0908

R0909

R0910

R0931

R0932

R0933 R0934

R0935

R0936

R0937

R0938

R0941 R0942

R0943

R0944 R0945

R0946

R0947

R0948

R0972

R0973 R0974

R0975

R0976

R0977

R 0978

TP0831

TP0832

TP0833

TP0834

TP0835

TP0836

TP0837

TP0838

TP0971

TP0972

TP0973

TP0974 TP0975 1

49

17

33

U0831

1

4

58

U0832

3U0833

U0835

14

58

U0931

128

103

102

65

64 38

39

U0971

VR0811

VR0812

VR0816

VR0817

VR0821

VR0822

1

1

64

1

MOTOROLA

c8486155B06-0

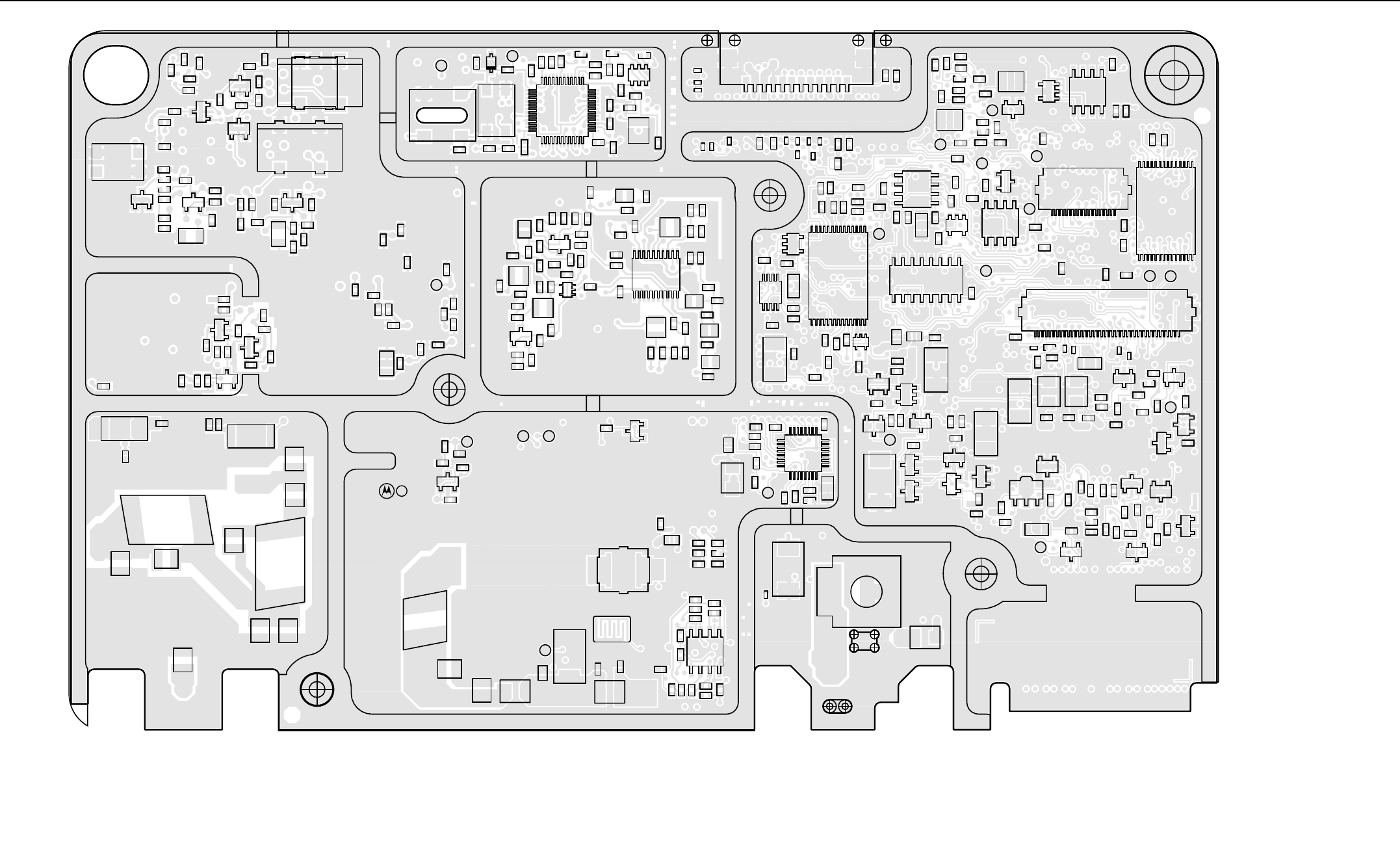

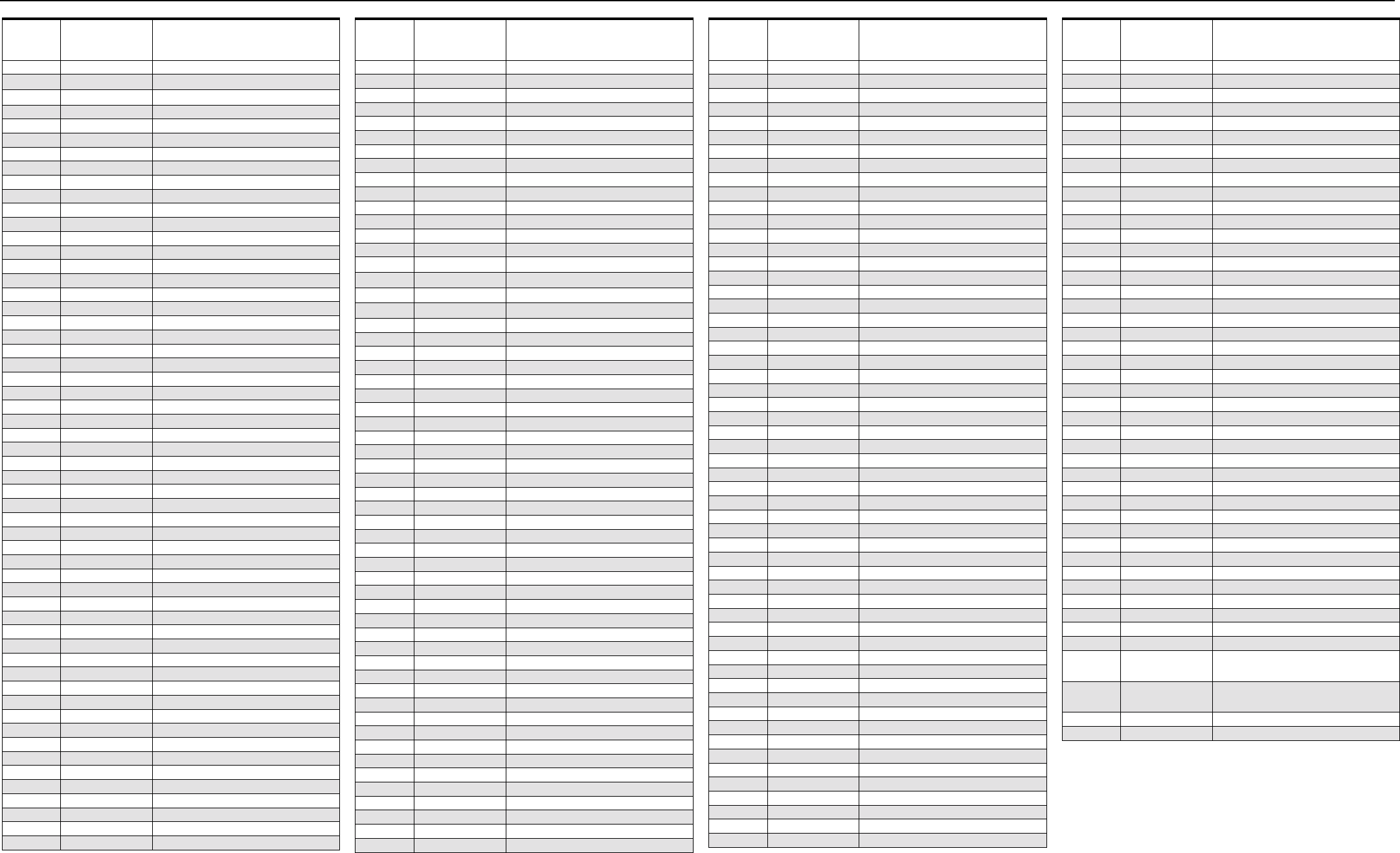

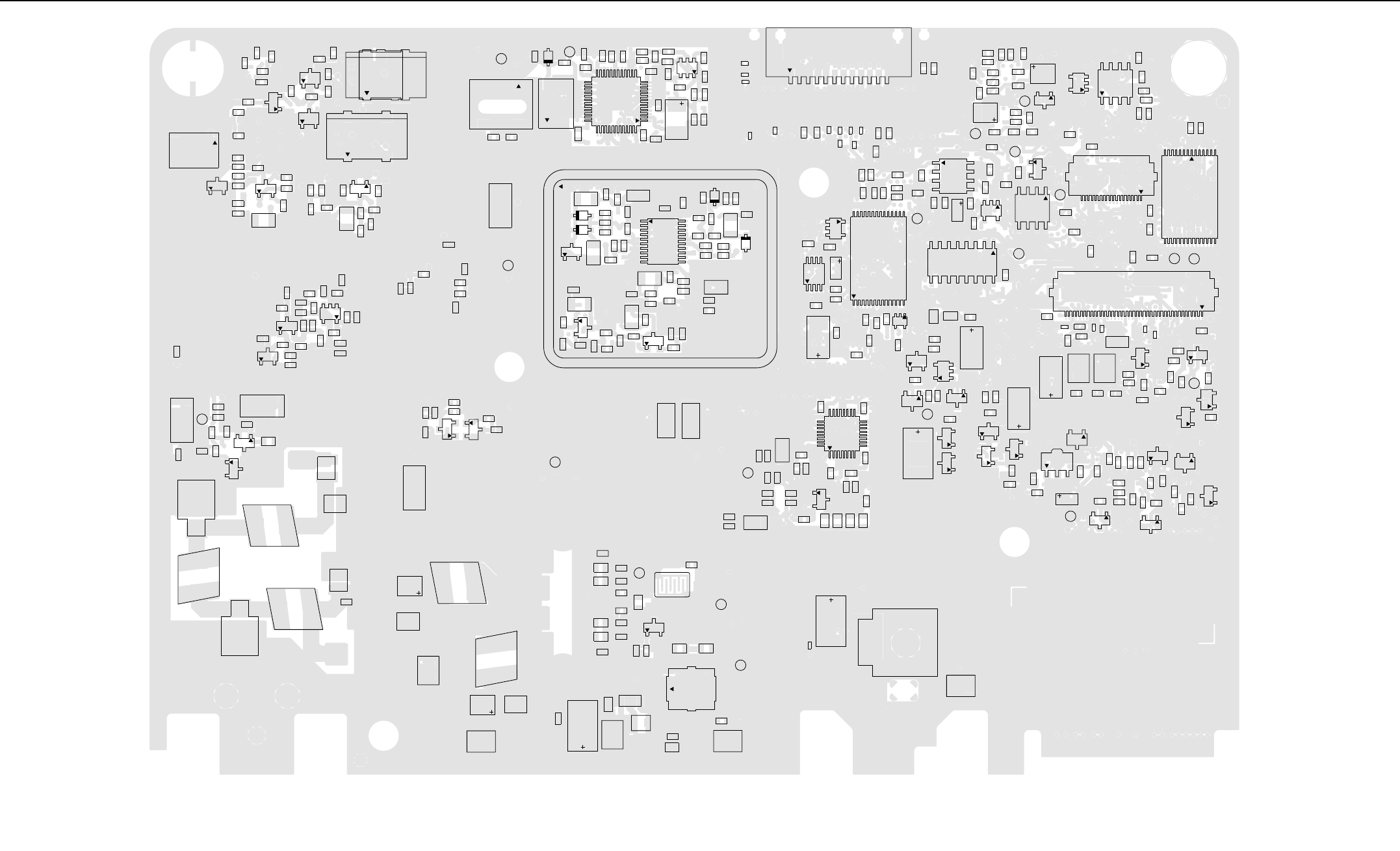

Controlhead GM160/360/660 - PCB8486155B06

ZWG0130136-A Top Side

ZWG0130137-B Bottom Side

4-8 Controlhead GM160/360/660 - PCB 8486155B06 / Schematics

MIC

PTT_IRDECODER

C

BUS+

KEYPAD ID

CONTROLLER

B

NOT PLACED

PLACED

VPP

HANDSET_AUDIO

ANALOG_INPUT_3

5V

BOOT_MODE

SCI_RX

SCI_TX

FLT_A+

RESET

TEMP_SENSE

CONTROL HEAD ID

5V

GND

HOOK

CONTROLHEAD

CONNECTOR

GROUND

ANALOG_INPUT_2

FLT_A+

J0801

J0801-8

4.7K

R0864

270

R0814

R0815

13K

R0810

13K

Q0841

J0801-5

6

0

R0833

47K

R0832

2.2K

R0837

33K

270

R0877

7

J0811-8

R0852

47K

GND

INPUT RESET_

NU

U0835

MC33464N-45ATR

S0854

SWITCH

SWITCH

S0853

J0801-3

S0852

SWITCH

J0801-10

J0801-13

J0811-9

J0801-14

J0811-10

10

6

7

R0813

J0801-7

5.6V

VR0822

D0831

Q0821 U0833

CSTCC8.00MG

C1 1

C2 3

GND

2

4

8

J0811-6

3

J0801-4

470pF

C0812

22

R0817

47K

7

NU

R0851

green

D0879

R0857

1

1

NU

47K

D0880

yellow

47K

NU

R0854

47K

R0859

10K

R0841

2.2K

R0843

51K

R0816

J0811-7

Q0823

R0831

TAB1

VAR

1MEG

R0823

50K

NEG

POS

TAB

J0801-12

J0801-9

R0848

68K

C0831

NU

NC4

NC5 8

1

RESET

3.3uF

MC33064

4

GND

2INPUT

3NC1

5NC2

6

NC3 7

U0832

R0812

22

5

0

R0879

270

R0878

270

D0822

J0811-5

R0844

10K

3

R0865

4.7K

100K

R0860

47K

NU

R0853

5

7

0

J0801-11

4

Q0822

4.7K

R0845

C0842

NU

2.2uF

Q0879Q0878

red

D0877

R0811

Q0877

51K

3

TP0833

1K

R0825

470pF

C0804

13K

TP0836

R0822

TP0834

470pF

C0821

4

NU

VR0812

5.6V

R0863

4.7K

NU

R0850

47K

4

R0856

47K

2

82pF

C0805

VDD 22

VRH 21

VRL

23 VSS1

24 VSS2

49 VSS3

45 XIRQ

33 XTAL

19

PE4_AN4

14

PE5_AN5

16

PE6_AN6

18

PE7_AN7

20

RESET

43

28

STRA_AS 30

STRB_RW*

55

50

PD2_MISO

51

PD3_MOSI

52

PD4_SCK

53

PD5_SS*

54

PE0_AN0

13

PE1_AN1

15

PE2_AN2

17

PE3_AN3

36

PC2_AD2 37

PC3_AD3 38

PC4_AD4 39

PC5_AD5 40

PC6_AD6 41

PC7_AD7 42

PD0_RXD

47

PD1_TXD 11

PB2_A10 10

PB3_A11 9

PB4_A12 8

PB5_A13 7

PB6_A14 6

PB7_A15 5

PC0_AD0 34

PC1_AD1

PA1_IC2 63

PA2_IC1 62

PA3_OC5_OC1 59

PA4_OC4_OC1 58

PA5_OC3_OC1 57

PA6_OC2_OC1 56

PA7_PA1_OC1

PB0_A8 12

PB1_A9

NC3

26 NC4

32 NC5

35

NC6 44

NC7 48

NC8 60

NC9

1

PA0_IC3 64

CLK_E

31 EXTAL

46 IRQ

27 MODA_LIR*

25 MODB_VSTBY

2NC1

61

NC10

3NC2

4

4

MC68HC711E9

U0831

29

J0811-4

J0811-3

J0811-2

1

C0822

2.2uF

R0838

10K

R0836

10K

VR0816

20V

VR0817

20V

2.2uF

C0843

0.1uF

2

C0832

C0833

0

0.1uF

47K

R0842

VR0821

5.6V

C0819

C0816

NU

470pF

470pF 82pF

C0817

TP0831

3

P0801-2

P0801-1

TP0835

C0806

470pF

47K

NU

R0849

47K

R0855

7

470pF

C0803

1

R084768K

470pF

C0813

C0815

470pF

47K

C0807

R0858

470pF

Q0843

VOUT

D0821

U0834

LM50

3

GND

1

POS

2

R0821

10K 6

6

3

5

J0801-1

270

R0834

1

0

5

3

2

2

J0801-6

R0824

4.7K

NU

470pF

C0802

470pF

C0810

VR0811

33V

NU

C0811 NU

470pF

470pF

C0818

2

NU

100K

R0862

TP0837

TP0832

TP0838

100

4

R0835

100K

R0861

56

J0801-2

J0811-1

82pF

C0808

NU

2

C0823

.01uF

BL_RED

BL_GREEN

5V

5V

5V

BUS+ 5V

RESET

5V

HOOK

MIC

5V

FLT_A+

5V

SCI_TX

5V

VOLTAGE_SENSE

HANDSET_AUDIO

PTT_IRDEC

BUS+

AN(0:4)

AN(0:4)

USW_5V

FLT_A+

5V

CH_REQUEST

ON_OFF_CONTROL

5V

5V

PTT_IRDEC

HOOK

5V

CH_REQUEST

ON_OFF_SENSE

5V

SCI_TX

5V

HANDSET_AUDIO

BUS+

MIC

FLT_A+

ON_OFF_CONTROL

5V

FLT_A+

LED_CNTRL(0:8)

LED_CNTRL(0:8)

ON_OFF_SENSE

PTT_IRDEC

FLT_A+

5V

AN(0:4)

USW_5V

FLT_A+

AN(0:4)

CH_KP_ID(0:7)

5V

CONTROLHEAD B NU NU NU USED USED USED USED NU

CONTROLHEAD C NU NU USED NU USED USED NU USED

R0850 R0851 R0852 R0853 R0855 R0856 R0857 R0858

10

GM300

789

MICROPHONE

CONNECTOR

J0811

WARIS

145623

Shown from Front Side

ZWG0130241-B

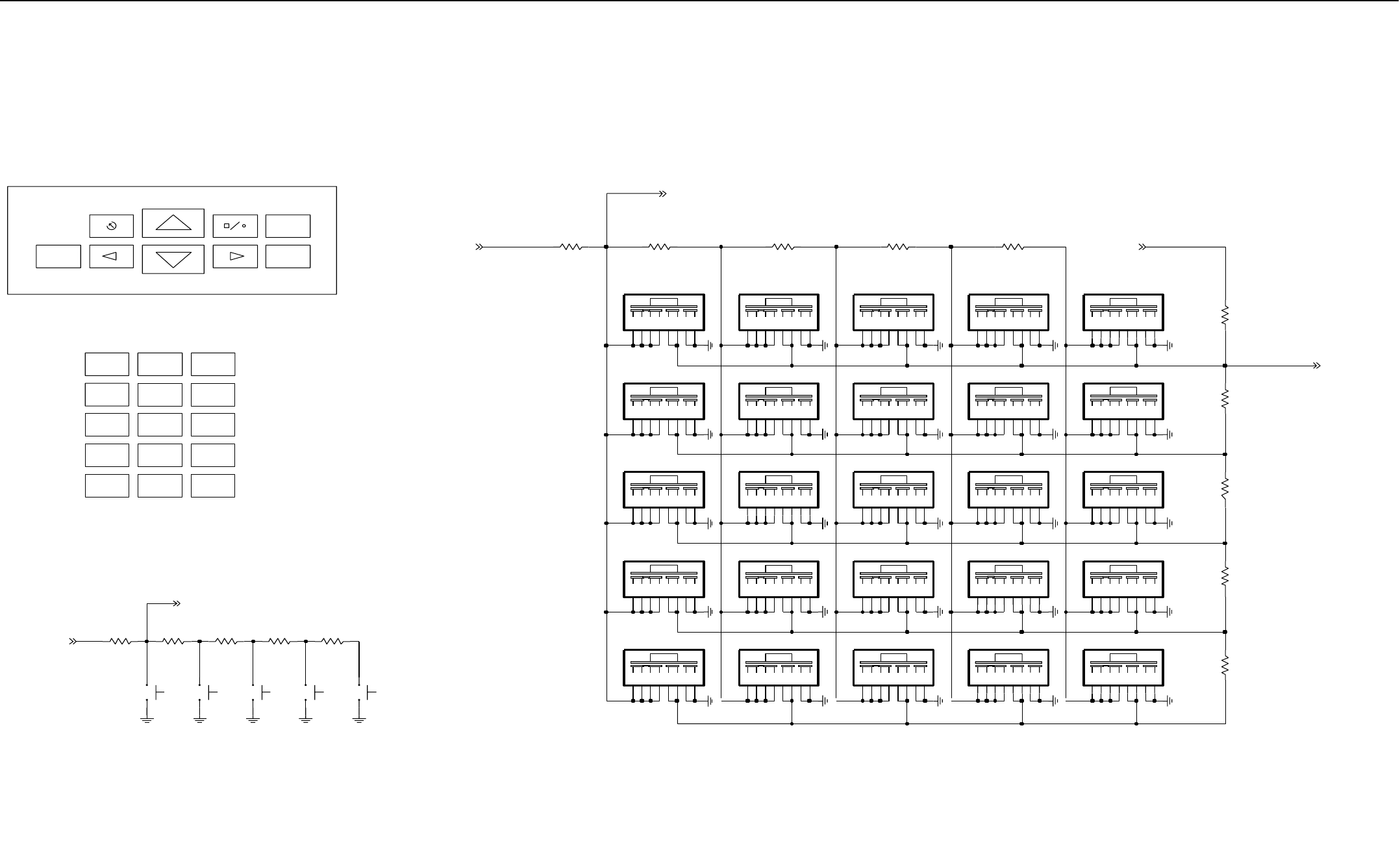

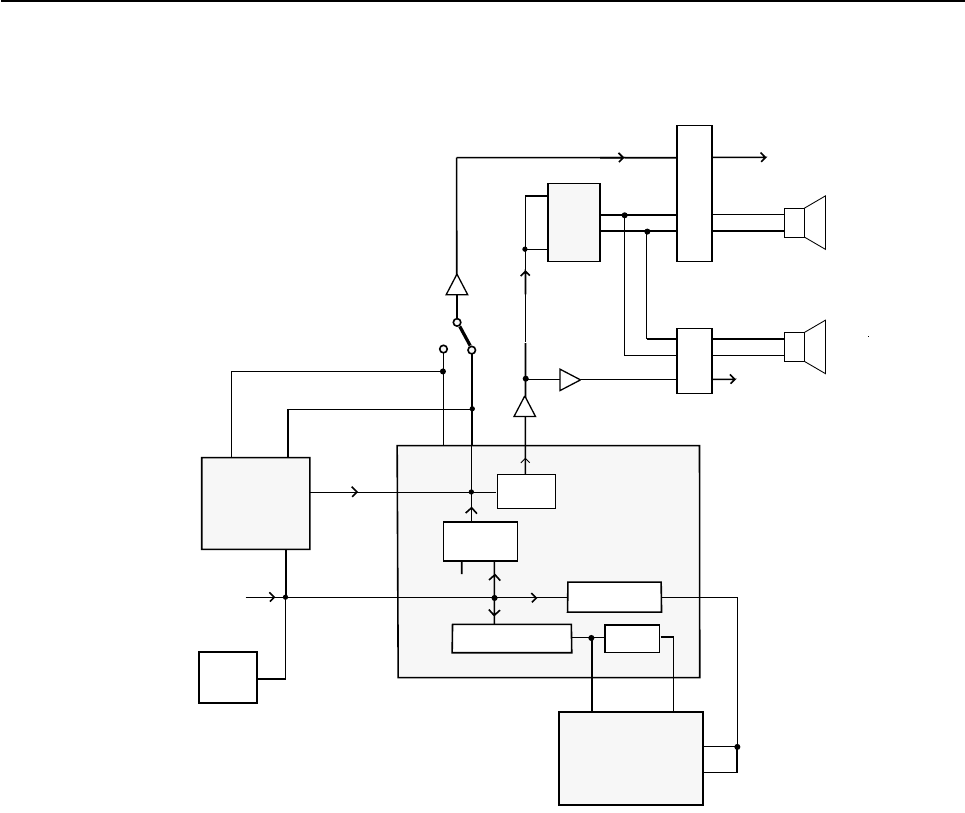

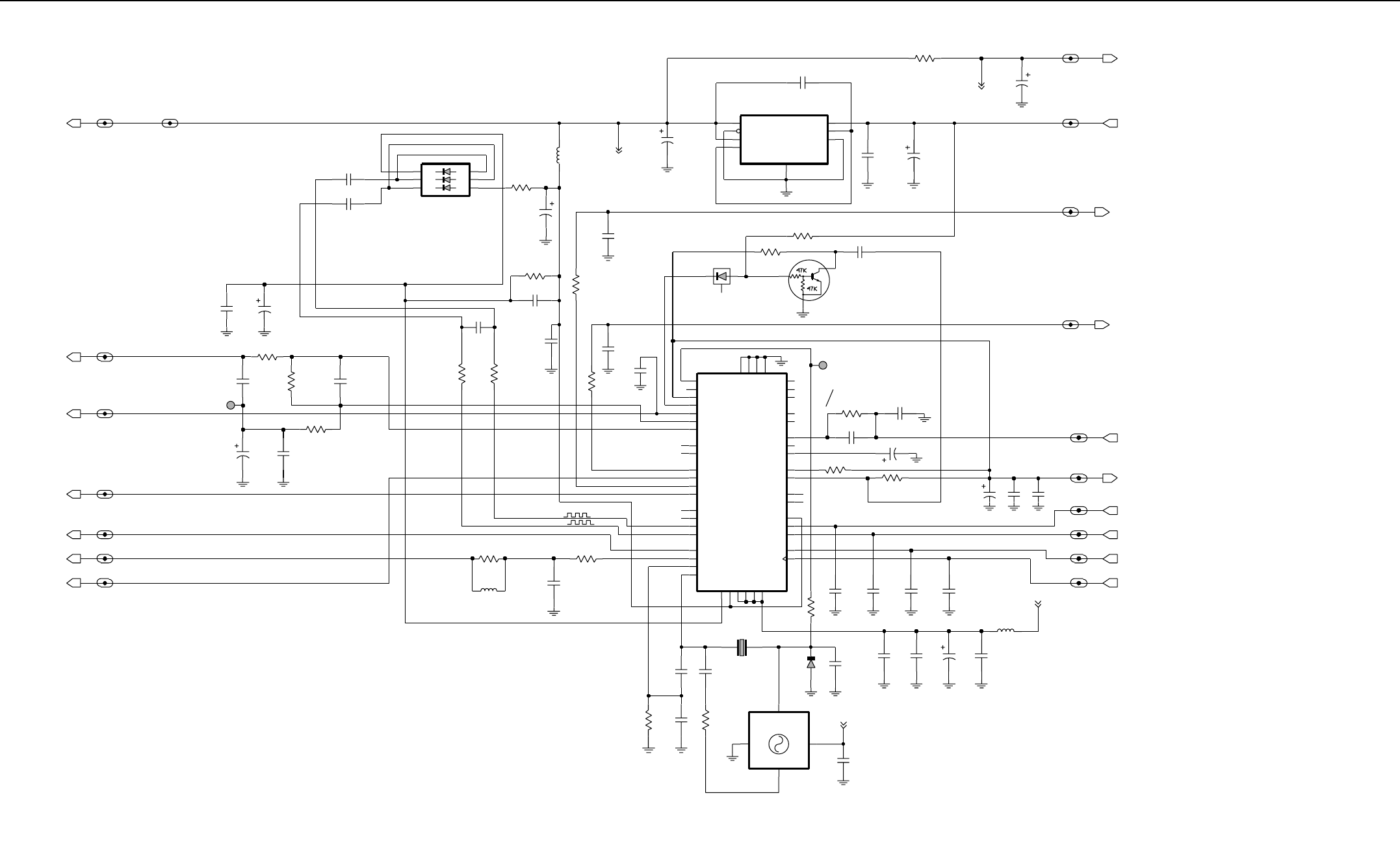

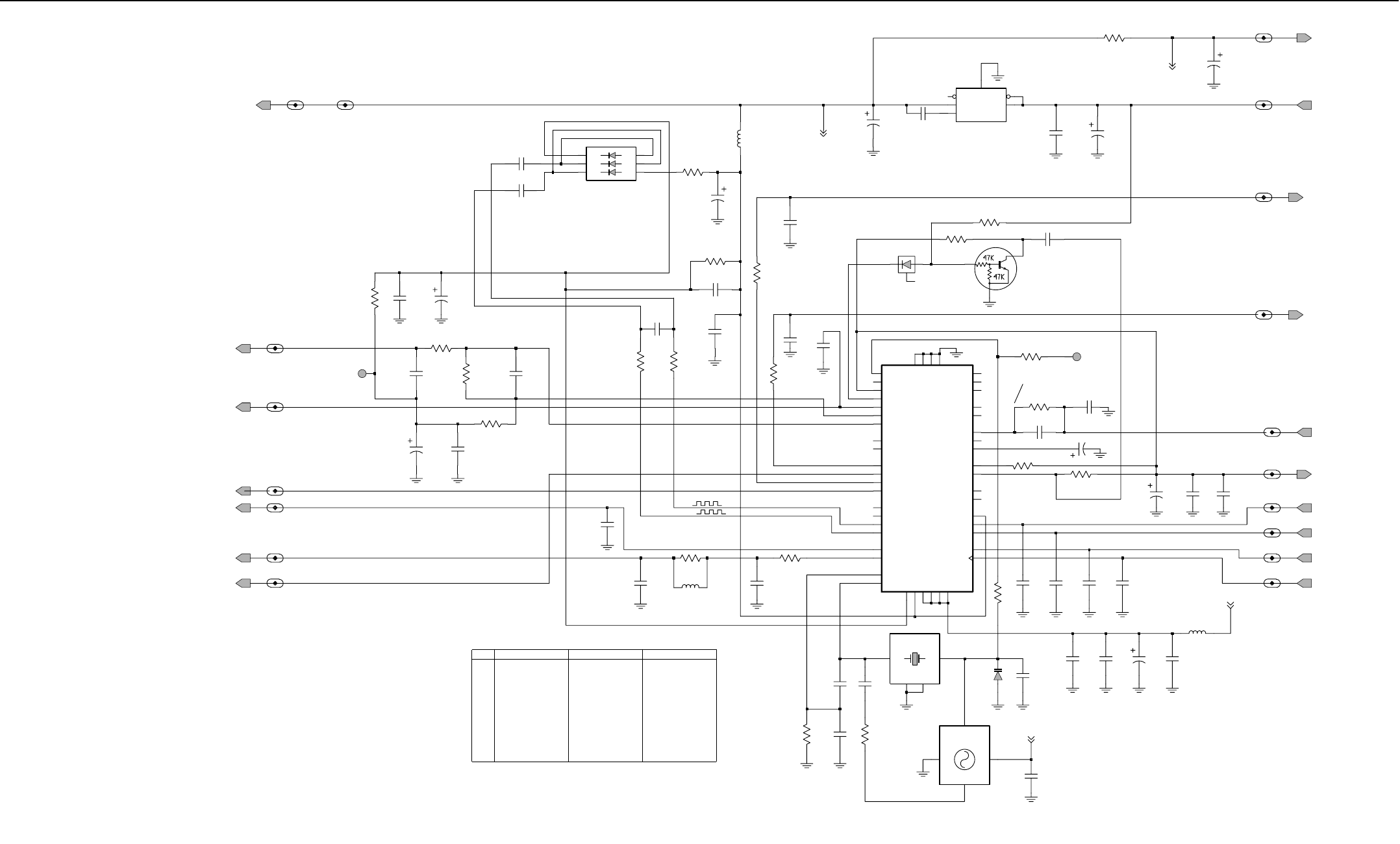

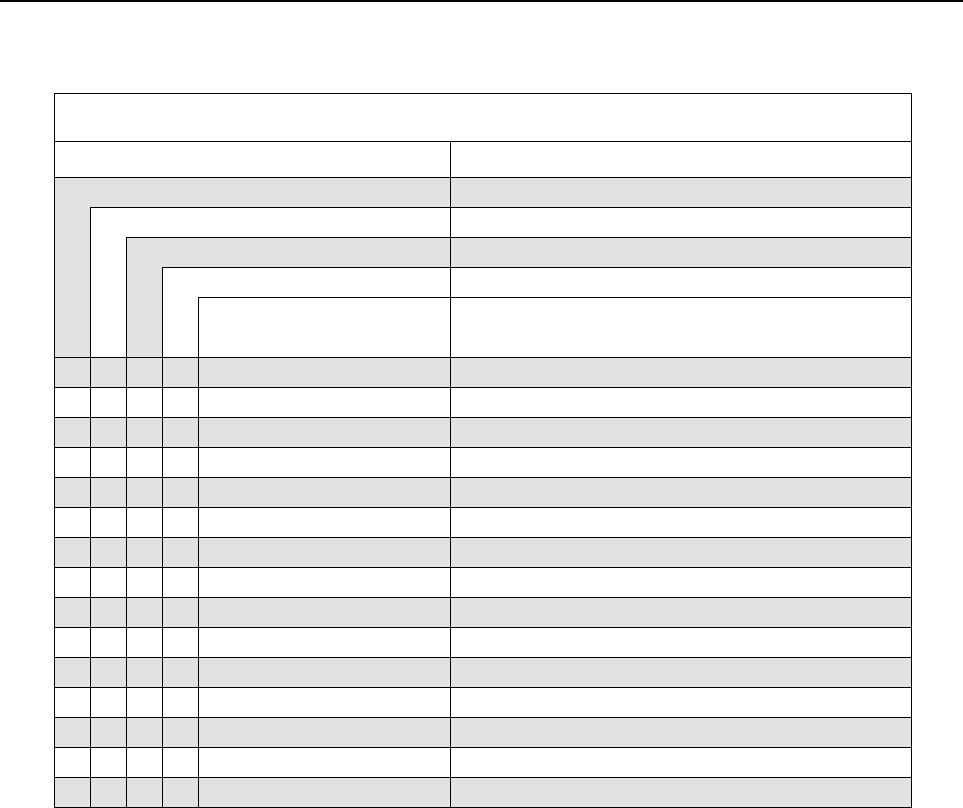

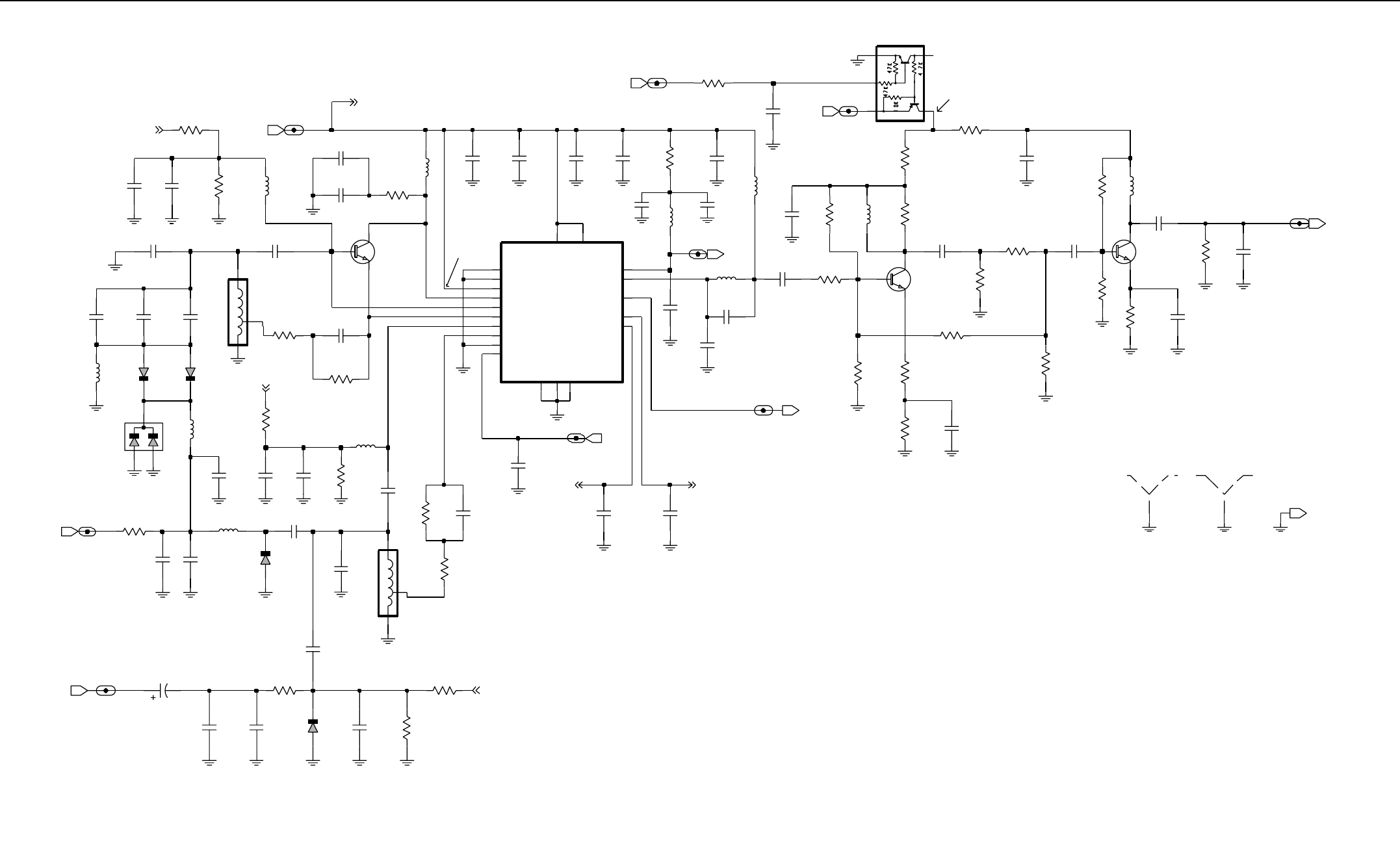

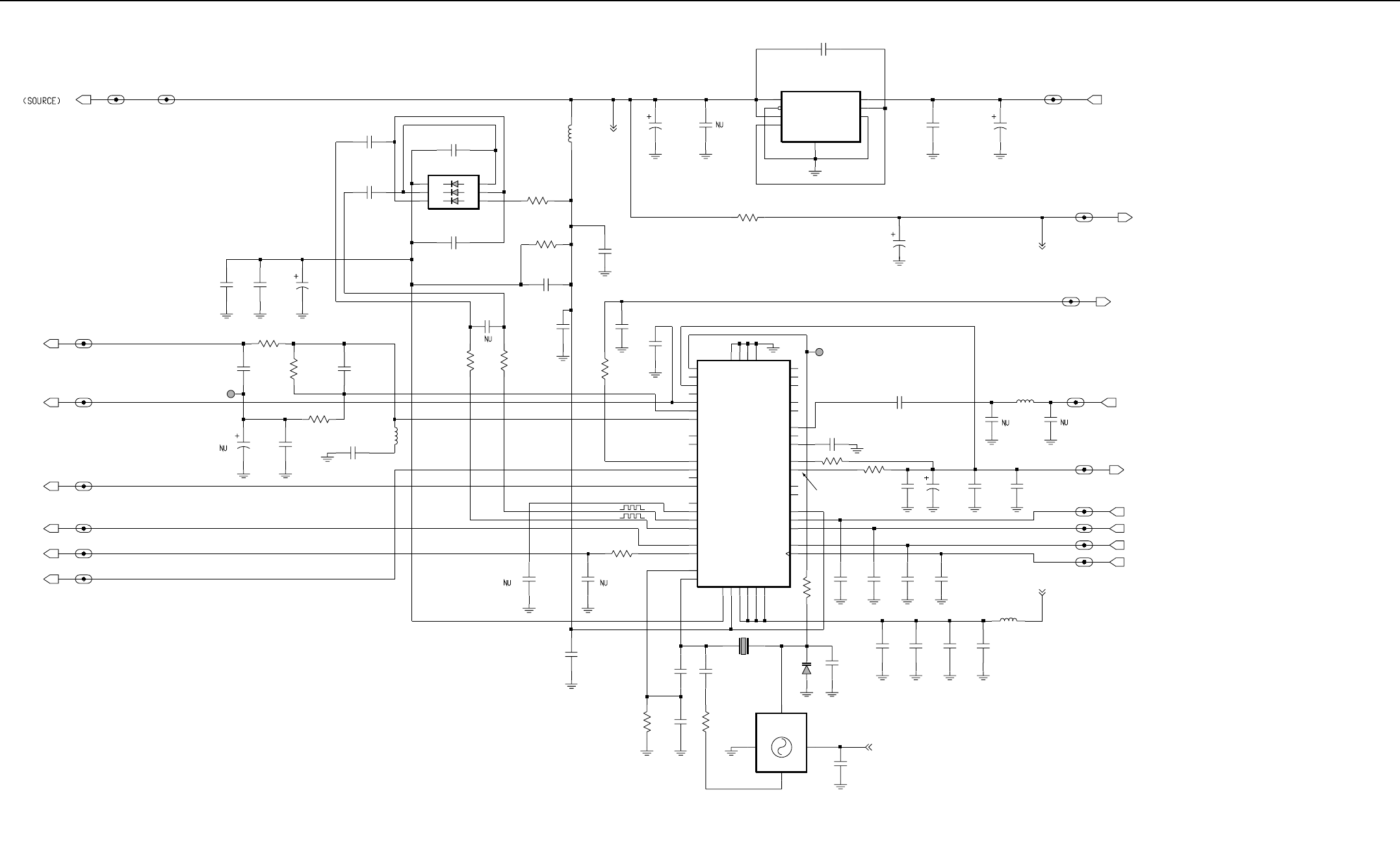

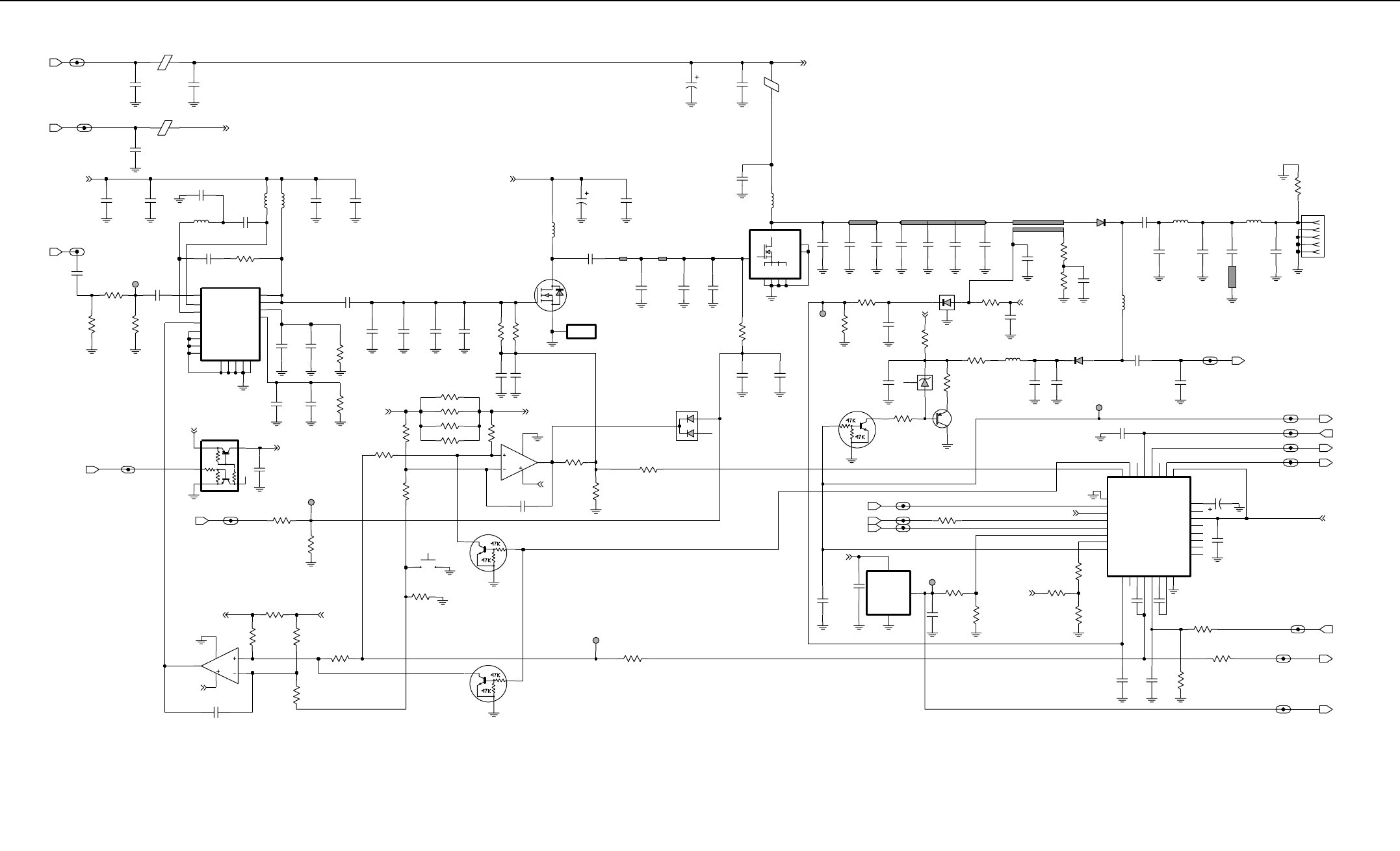

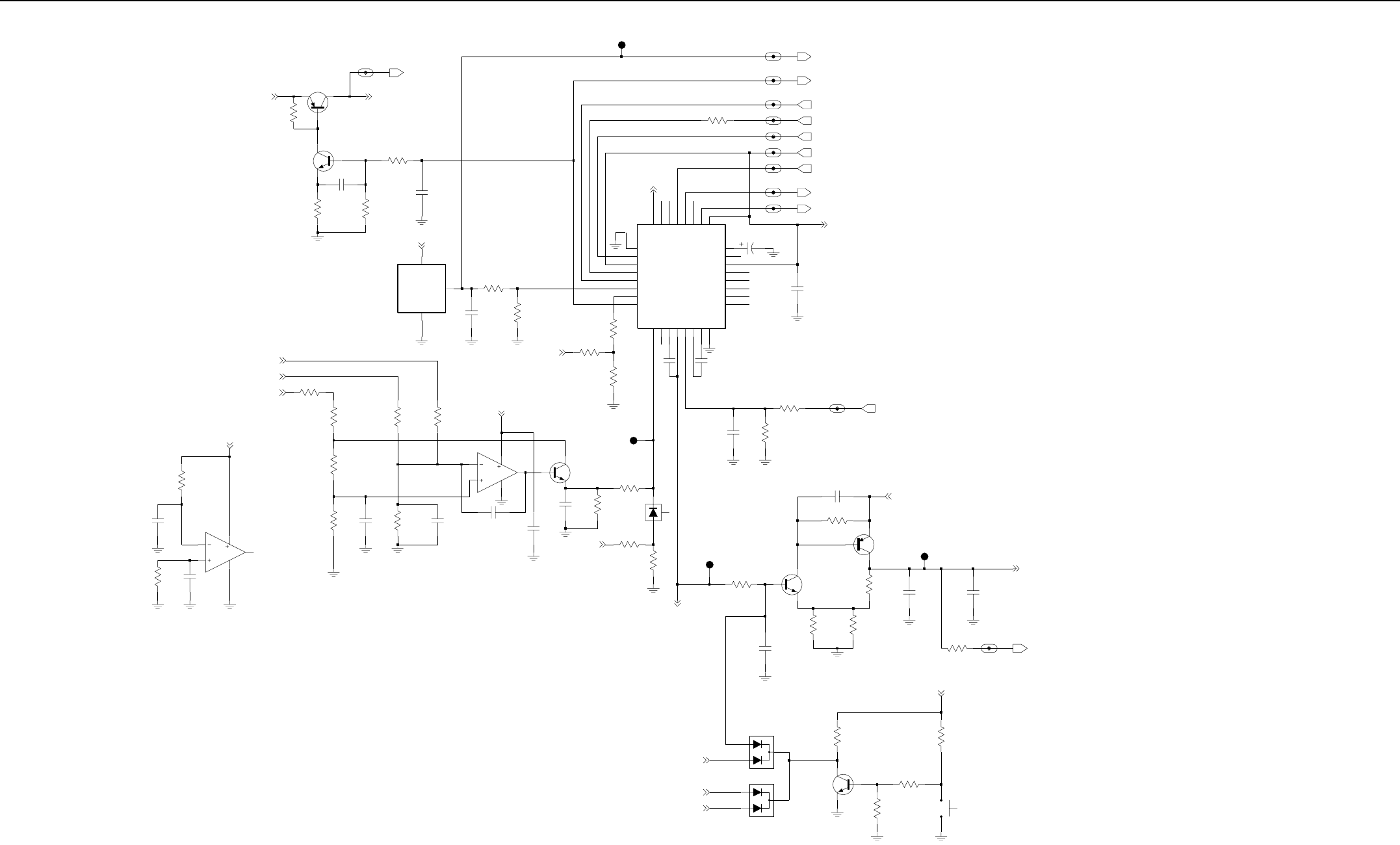

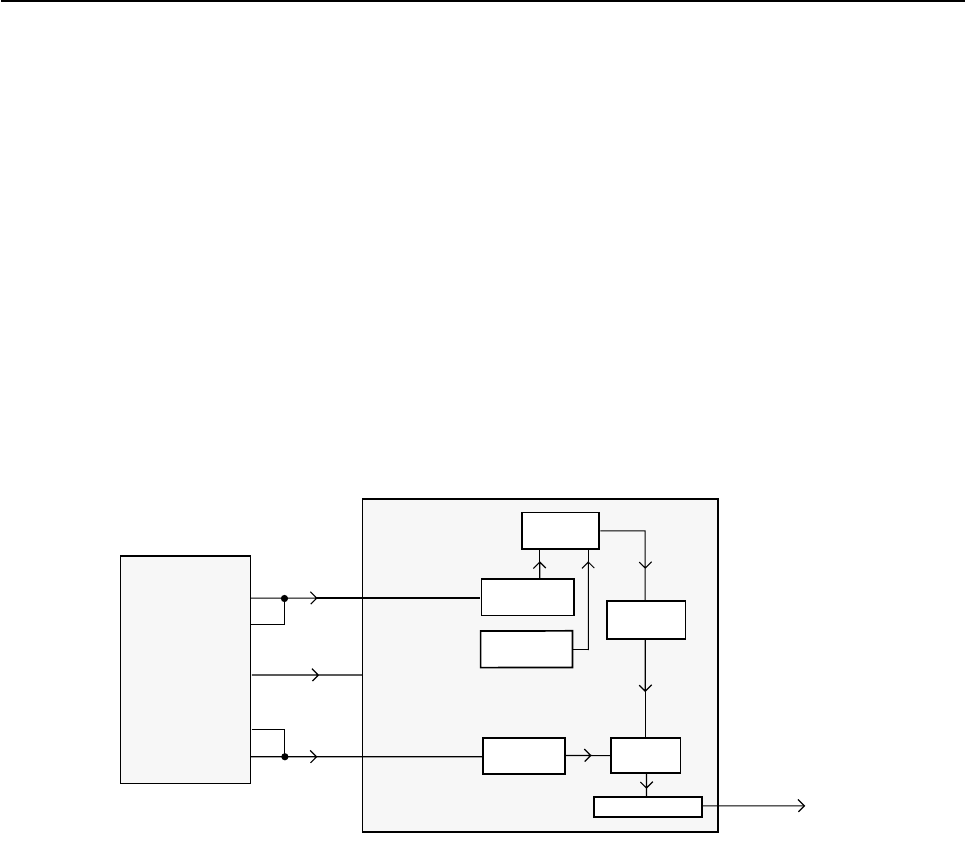

Controlhead GM160/360/660 - Schematic Sheet 1 of 4

ZWG0130241-B

Controlhead GM160/360/660 - PCB 8486155B06 / Schematics 4-9

P4

SW0906 SW0904

SW0903 SW0901

SW0909 SW0910

SW0908SW0907

SW0902

SW0905

KEYPAD C

SW0908

SW0905

SW0902

KEYPAD B

P3P1

P2 P4

P6

7P7

8P8

SW0906 SW0910

SW0903

P1

P2

P3

1P1

2P2

3P3

4P4

5P5

6

P5

6P6

7P7

8P8

SWITCH

S0901

1P1

2P2

3P3

4P4

5

4P4

5P5

6P6

7P7

8P8

SWITCH

S0905

1P1

2P2

3P3

3P3

4P4

5P5

6P6

7P7

8P8

SWITCH

S0902

SWITCH

S0910

1P1

2P2

2P2

3P3

4P4

5P5

6P6

7P7

8P8

P8

SWITCH

S0908

1P1

1P1

2P2

3P3

4P4

5P5

6P6

7P7

8

7P7

8P8

SWITCH

S0906

1P1

2P2

3P3

4P4

5P5

6P6

SWITCH

S0903

43K

0

1

R0909

43K

130K

R0904

130K

NU

R0910

NU

R0905

R0906

51K

R0901

51K

R0908

22K

R0903

22K

R0902

13K R0907

13K

P4

5P5

6P6

7P7

8P8

CH_C

sheet 2

CH_B

o

1P1

2P2

3P3

4

P3

4P4

5P5

6P6

7P7

8P8

SWITCH

S0909

1P1

2P2

3

P2

3P3

4P4

5P5

6P6

7P7

8P8

SWITCH

S0907

SWITCH

S0904

1P1

2

COL2

COL1

ROW2

ROW1

ROW3 COL3

5V

ROW5

ROW4

COL5

COL4

AN(0:4)

COL3 COL2

ROW1

ROW2

ROW3

ROW4

COL4

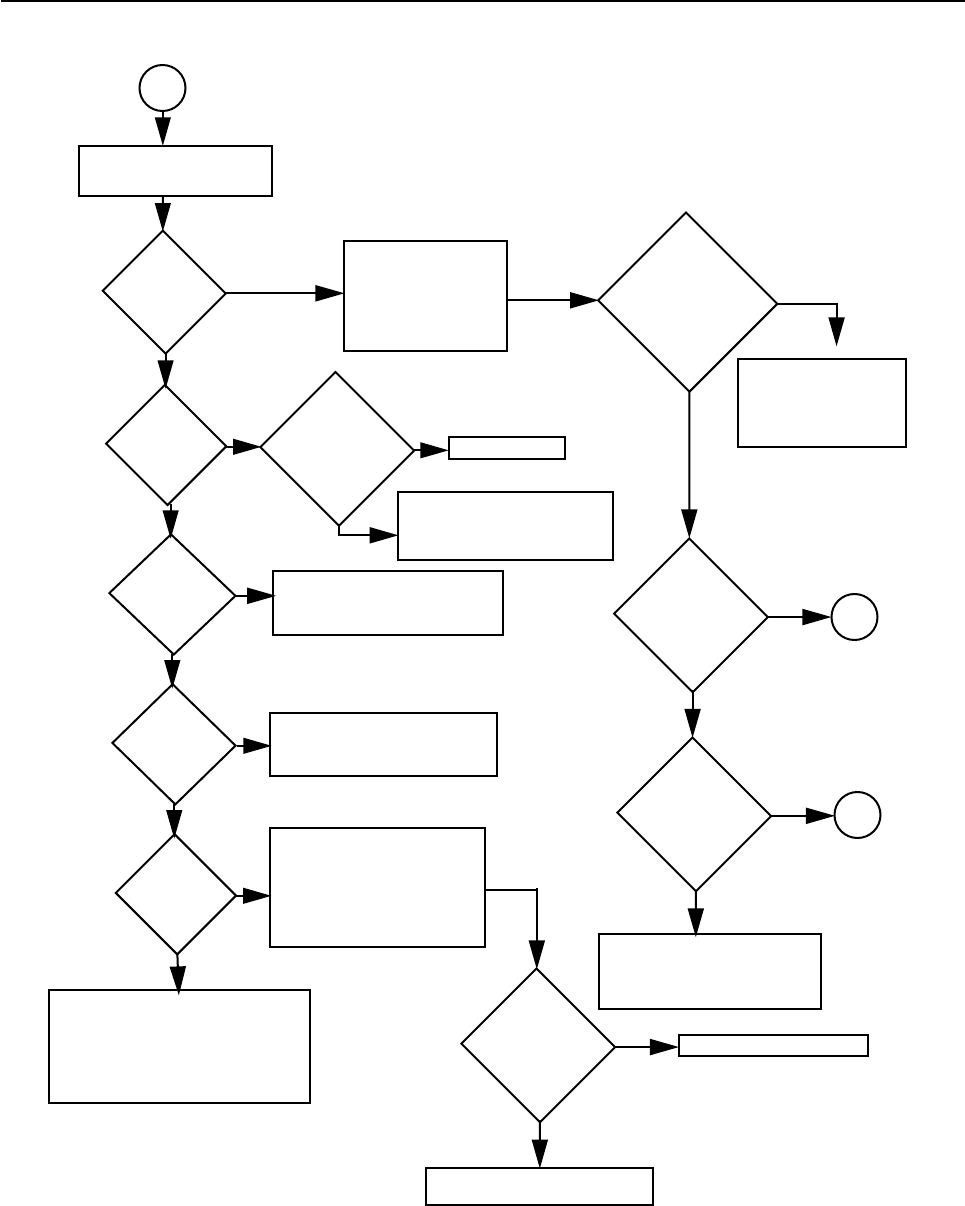

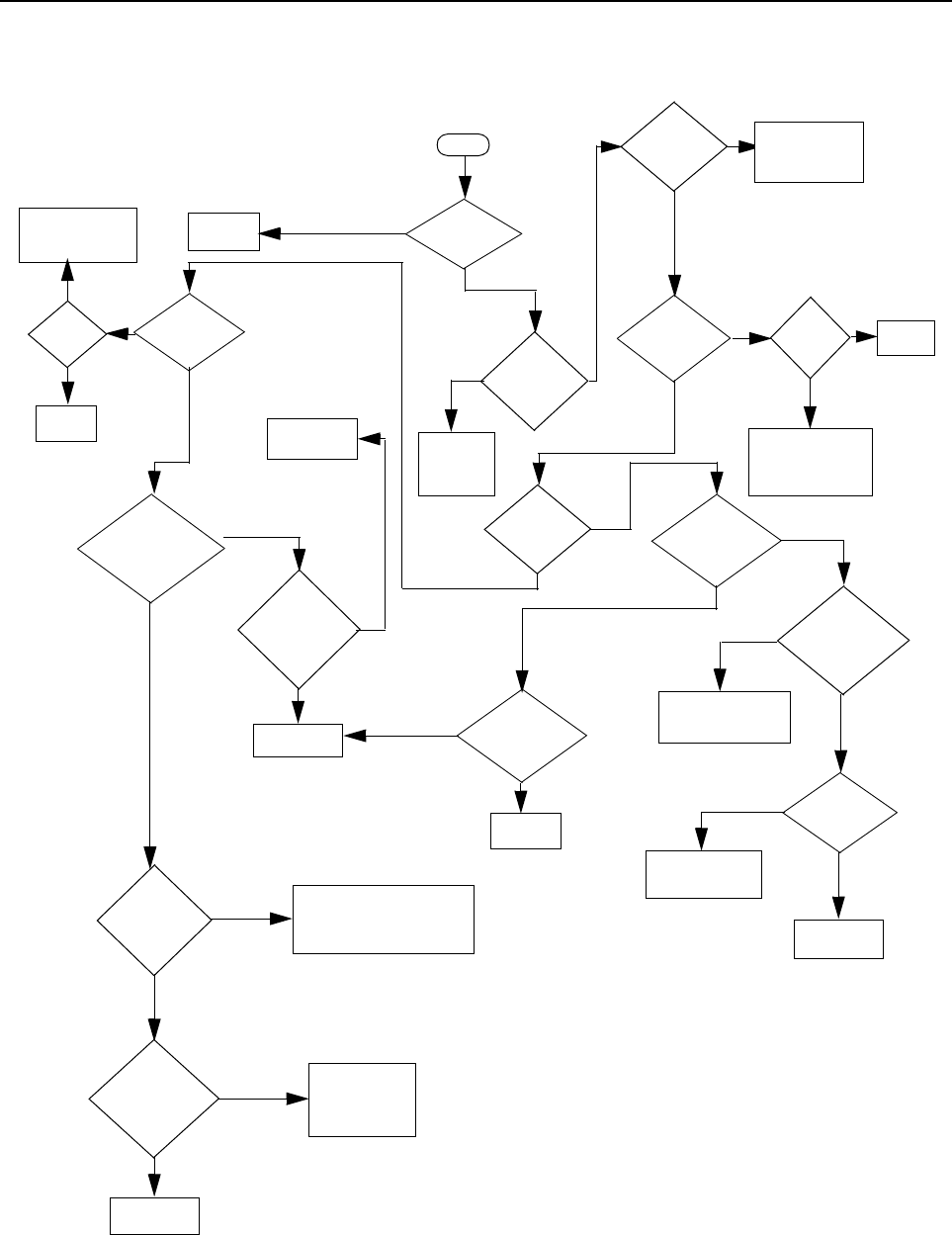

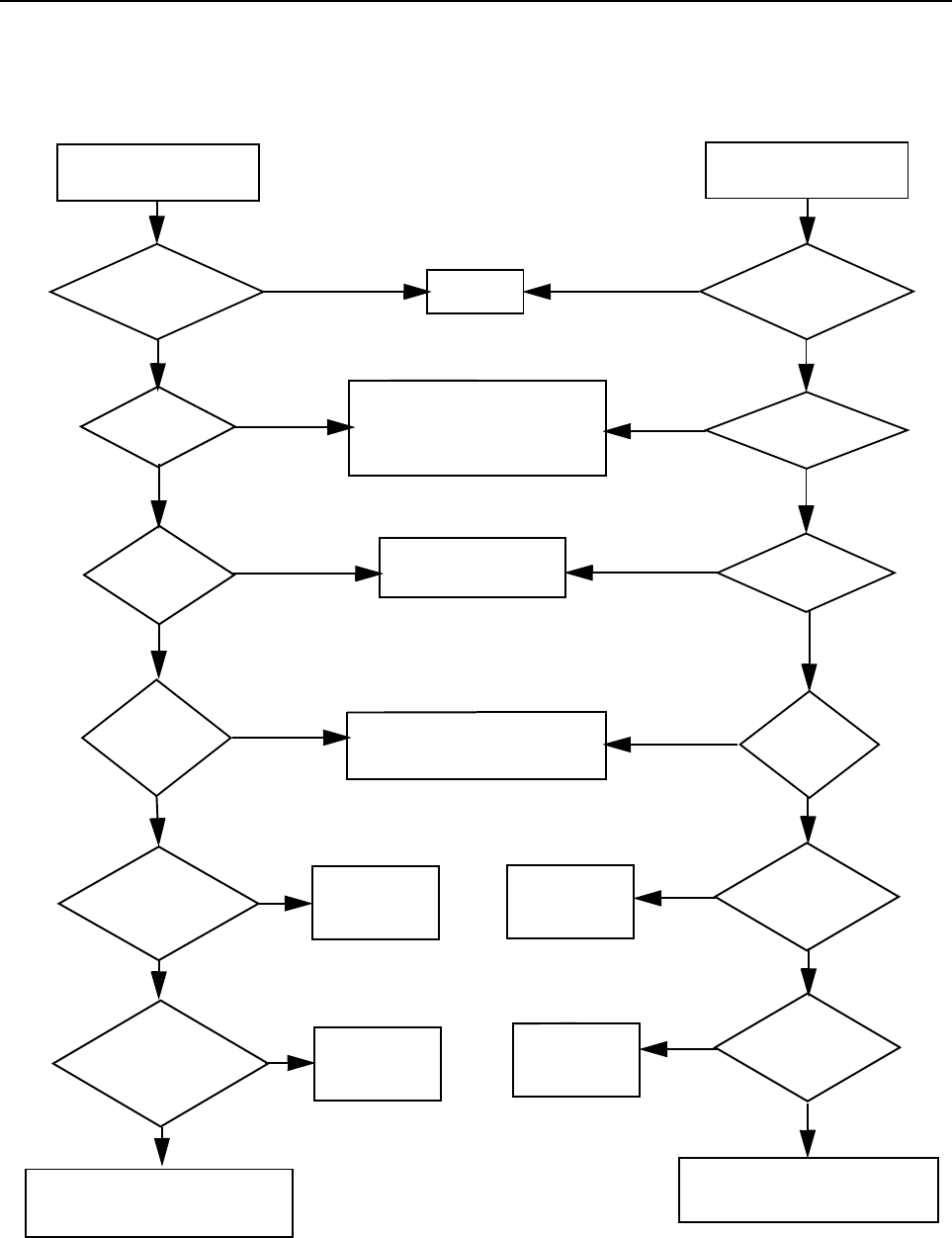

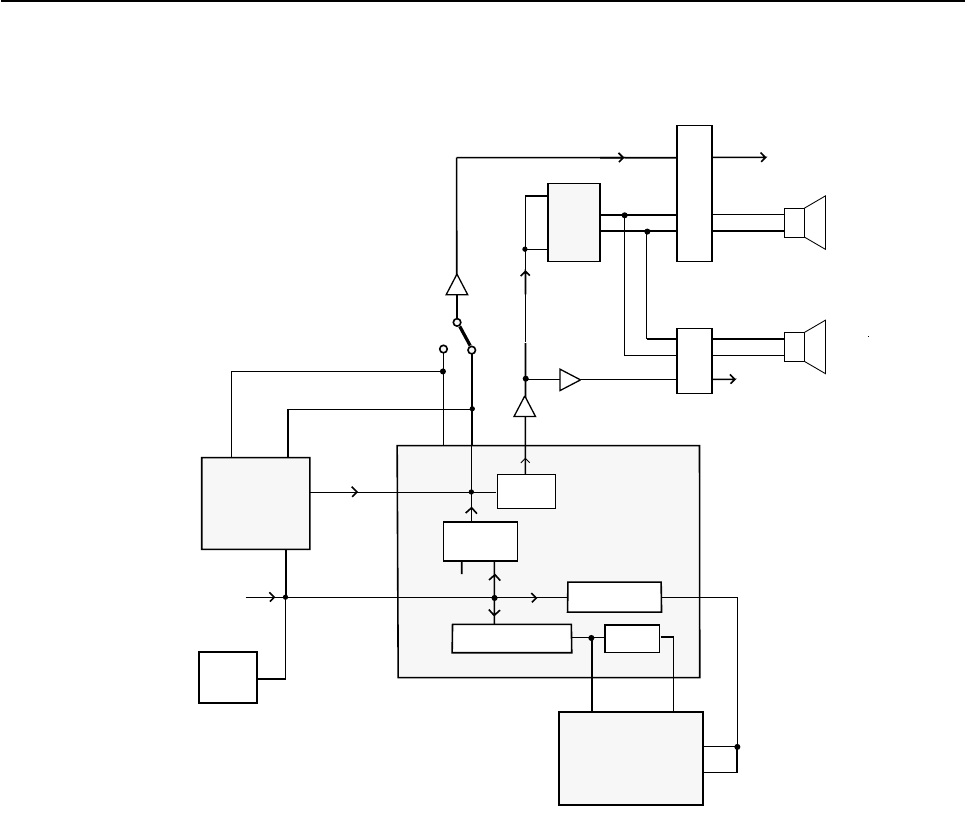

Controlhead GM160/360/660 - Schematic Sheet 2 of 4

ZWG0130242-A

4-10 Controlhead GM160/360/660 - PCB 8486155B06 / Schematics

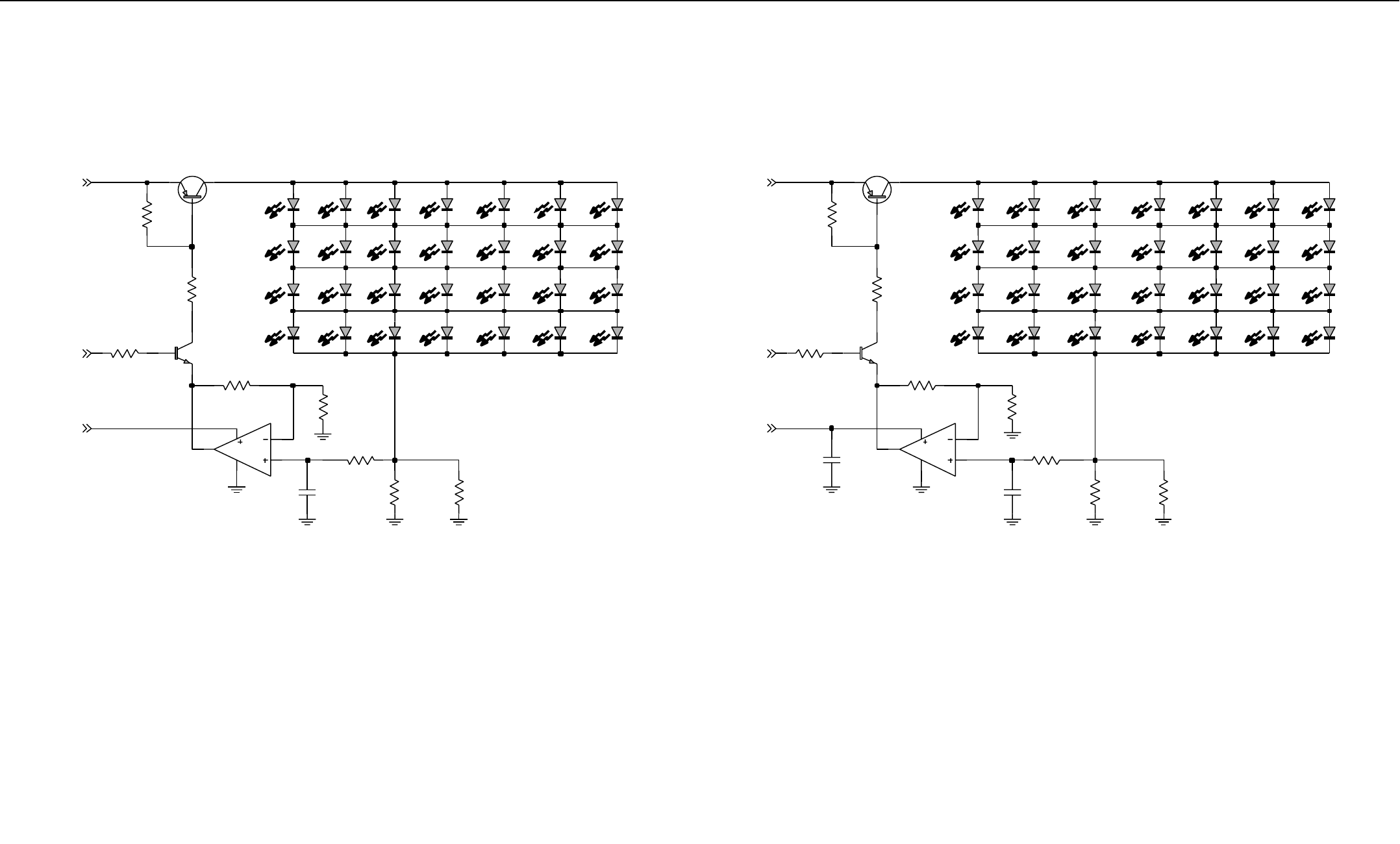

BACKLIGHT REDBACKLIGHT GREEN

NU

Q0931

D0980

D0979

D0978

R0946

D0977

R0945

10K

33K

10K

R0942

10K

R0941

D0972

R0944

10

100K

R0947 R0948

4

10

U0931-2

MC33072

6

5

78

100K

Q0933

D0987

NU

R0934

D0986

D0985

D0984

10K

R0935

D0969 NU

D0951

D0967

D0966

D0964

D0965

NU

NU

D0963

D0970

NU

D0962

D0971

NU

D0947

NU

D0943

Q0934

NU

D0932

4.7K

NU

D0931

R0943

C0931

0.1uF

10

R0938

R0937

10 NU

NU

C0932

0.1uF

R0936

10K

R0932 NU

D0949

NU

33K

NU

R0931

10K

Q0932

MC33072

U0931-1

2

3

18

4

NU

D0942

NU

NU

D0941

NU

D0940

NU

D0938

NU

D0937

NU

D0958

NU

D0957

NU

D0956

D0954

D0953

NU

D0952

NU

D0950

NU

NU

D0975

D0976

D0974

D0973 NU

D0939

NU

D0935

D0933

NU

D0934

NU

0.1uF

C0933

D0936

D0968

NU

D0988

4.7K

NU

R0933

NU

D0961

D0983

D0982

D0981 D0955

D0948

NU

D0946

NU

NU

D0944

NU

D0945

FLT_A+

FLT_A+

FLT_A+

BL_GREEN BL_RED

FLT_A+

NU

Controlhead GM160/360/660 - Schematic Sheet 3 of 4

ZWG0130243-A

Controlhead GM160/360/660 - PCB 8486155B06 / Schematics 4-11

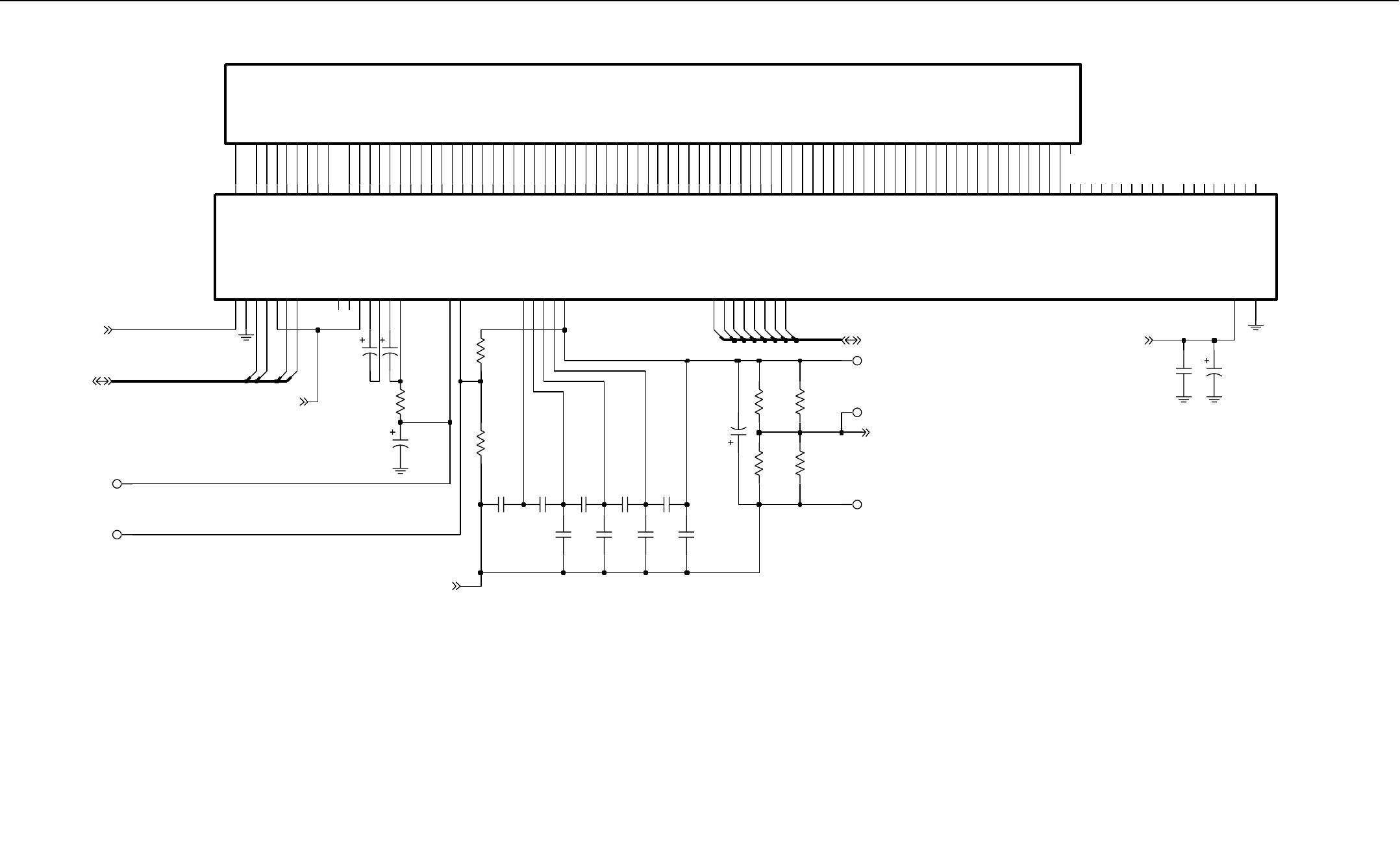

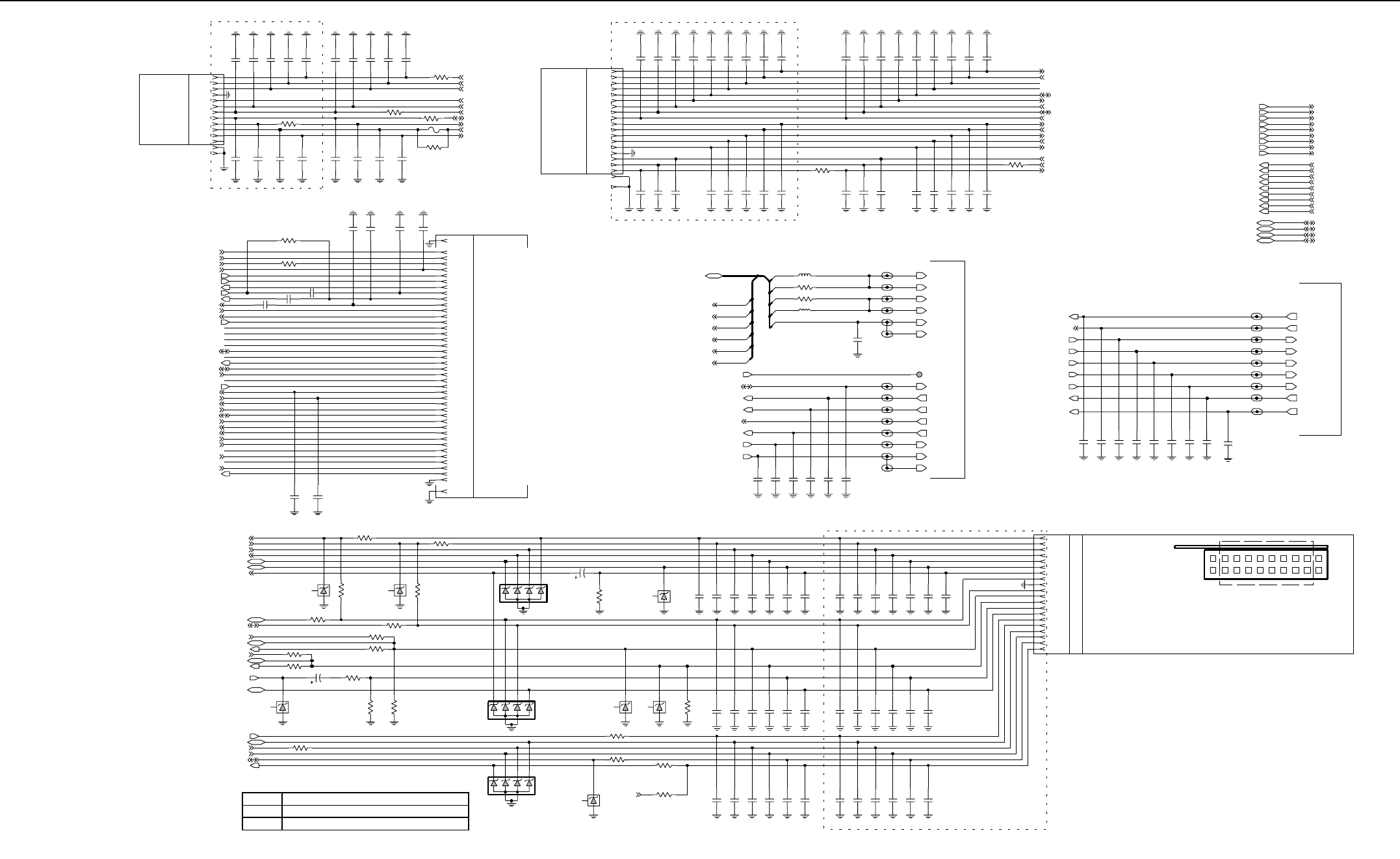

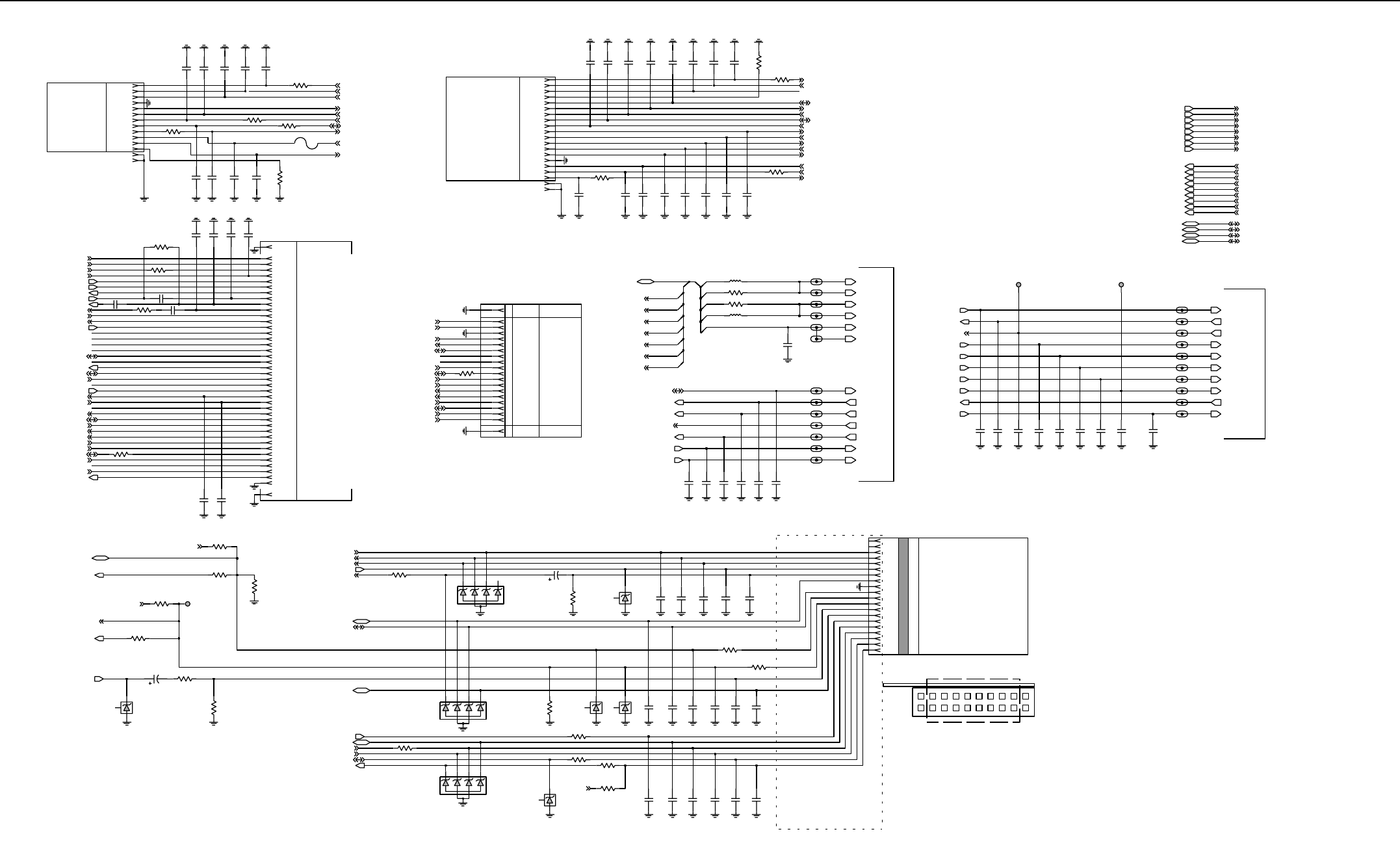

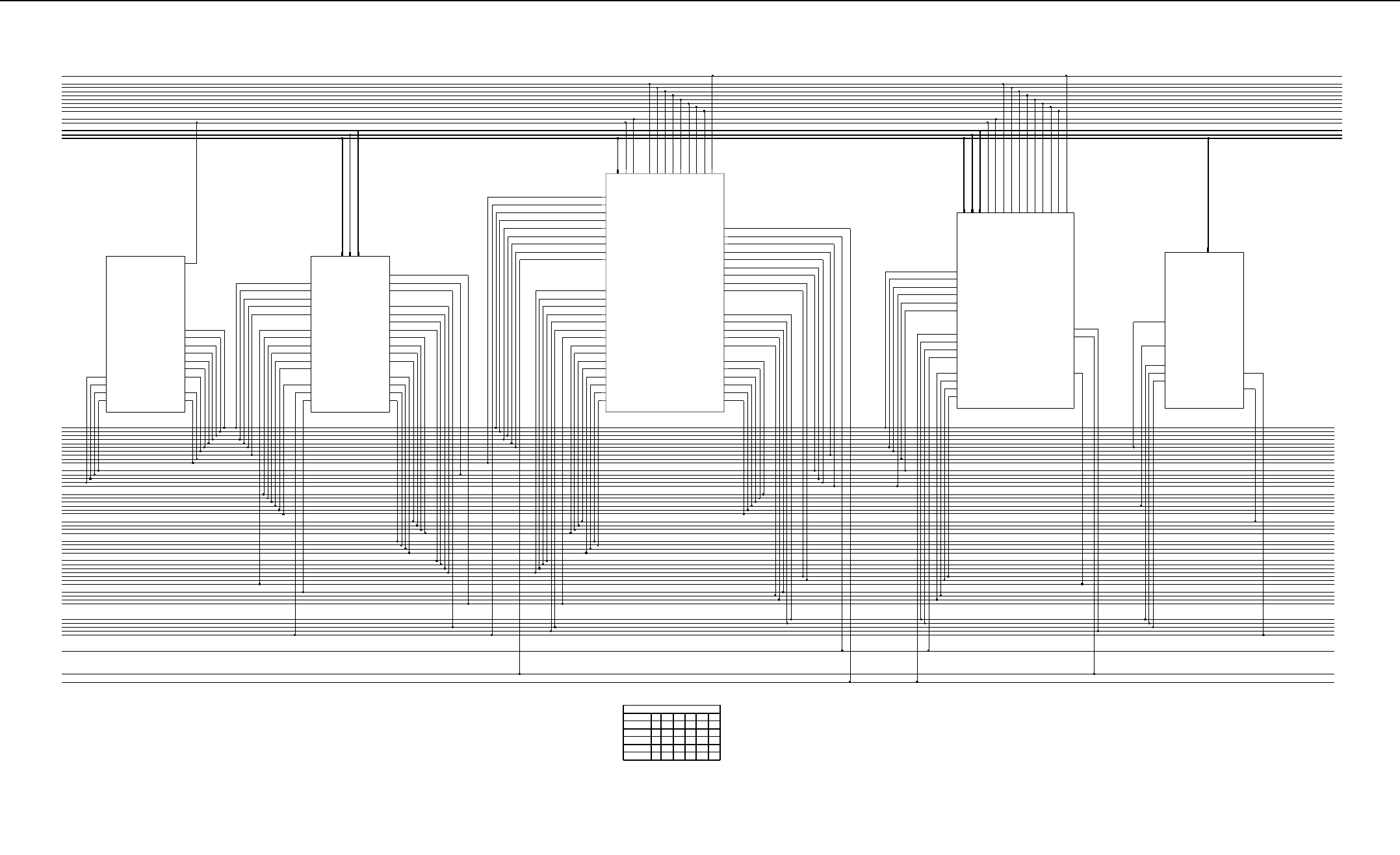

THE LCD IS PART OF HARDWAREKITS GLN7358A (EUR) AND GLN7359A (US)

R0974

1.8MEG

R0973

1.2MEG

R0972

C0972

0

NU

1uF

1uF

C0971

2.2uF

C0985

.01uF

1uF

C0984

C0973

0.1uF

C0980

0.1uF

C0976C0975

0.1uF

C0974

0.1uF

NU

C0982

0.1uF

0.1uF

C0981C0979

0.1uF NU

0.1uF

C0977

NU

1

2

NU

3

4

5

6

7

0

100K

R0978

200K

R0977

NU

NU

1

100K

R0976

SEG69_C70

SEG6_C7

SEG7_C8

SEG8_C9

SEG9_C10

0

SEG61_C62

SEG62_C63

SEG63_C64

SEG64_C65

SEG65_C66

SEG66_C67

SEG67_C68

SEG68_C69

SEG54_C55

SEG55_C56

SEG56_C57

SEG57_C58

SEG58_C59

SEG59_C60

SEG5_C6

SEG60_C61

SEG47_C48

SEG48_C49

SEG49_C50

SEG4_C5

SEG50_C51

SEG51_C52

SEG52_C53

SEG53_C54

SEG3_C4

SEG40_C41

SEG41_C42

SEG42_C43

SEG43_C44

SEG44_C45

SEG45_C46

SEG46_C47

SEG32_C33

SEG33_C34

SEG34_C35

SEG35_C36

SEG36_C37

SEG37_C38

SEG38_C39

SEG39_C40

SEG25_C26

SEG26_C27

SEG27_C28

SEG28_C29

SEG29_C30

SEG2_C3

SEG30_C31

SEG31_C32

SEG18_C19

SEG19_C20

SEG1_C2

SEG20_C21

SEG21_C22

SEG22_C23

SEG23_C24

SEG24_C25

SEG10_C11

SEG11_C12

SEG12_C13

SEG13_C14

SEG14_C15

SEG15_C16

SEG16_C17

SEG17_C18

COM3_R4

COM4_R5

COM5_R6

COM6_R7

COM7_NC

COMS

NC

SEG0_C1

04B01

H0971

COM0_R1

COM1_R2

COM2_R3

5V5

7VDD

8VOUT

6VR

13 VSS

17 WR

NU

57

SEG8 58

SEG9

16 SR1

15 SR2

1V1

2V2

3V3

4V4

121

SEG72 122

SEG73 123

SEG74 124

SEG75 125

SEG76 126

SEG77 127

SEG78 128

SEG79

114

SEG65 115

SEG66 116

SEG67 117

SEG68 118

SEG69

56

SEG7

119

SEG70 120

SEG71

107

SEG58 108

SEG59

55

SEG6

109

SEG60 110

SEG61 111

SEG62 112

SEG63 113

SEG64

99

SEG50 100

SEG51 101

SEG52 102

SEG53 103

SEG54 104

SEG55 105

SEG56 106

SEG57

92

SEG43 93

SEG44 94

SEG45 95

SEG46 96

SEG47 97

SEG48

SEG49 98

54

SEG5

85

SEG36 86

SEG37 87

SEG38 88

SEG39

53

SEG4

89

SEG40 90

SEG41 91

SEG42

78

SEG29

52

SEG3

79

SEG30 80

SEG31 81

SEG32 82

SEG33 83

SEG34 84

SEG35

70

SEG21 71

SEG22 72

SEG23 73

SEG24 74

SEG25 75

SEG26 76

SEG27 77

SEG28

63

SEG14 64

SEG15 65

SEG16 66

SEG17 67

SEG18 68

SEG19

51

SEG2

69

SEG20

14 M_S

18 RD

49

SEG0 50

SEG1

59

SEG10 60

SEG11 61

SEG12 62

SEG13

25 D1

26 D2

27 D3

28 D4

29 D5

30 D6

31 D7

22 FR

38

COM6 39

COM7

40

COM8 41

COM9

48

COMS

20 CS1

19 CS2

24 D0

44

COM12 45

COM13 46

COM14 47

COM15

34

COM2 35

COM3 36

COM4 37

COM5

12 CAP1_POS

9CAP2_NEG

10 CAP2_POS

23 CL

32

COM0 33

COM1

42

COM10 43

COM11

SED1526F0A

U0971

21 A0

11 CAP1_NEG

C0978

0.1uF

3

TP0974

TP0973

1

TP0975

1

TP0972

TP0971

2.2uF

C0983

200K

R0975

5V

RESET 5VCH_KP_ID(0:7)

LED_CNTRL(0:8)

5V

VOLTAGE_SENSE

2

Controlhead GM160/360/660 - Schematic Sheet 4 of 4

ZWG0130244-A

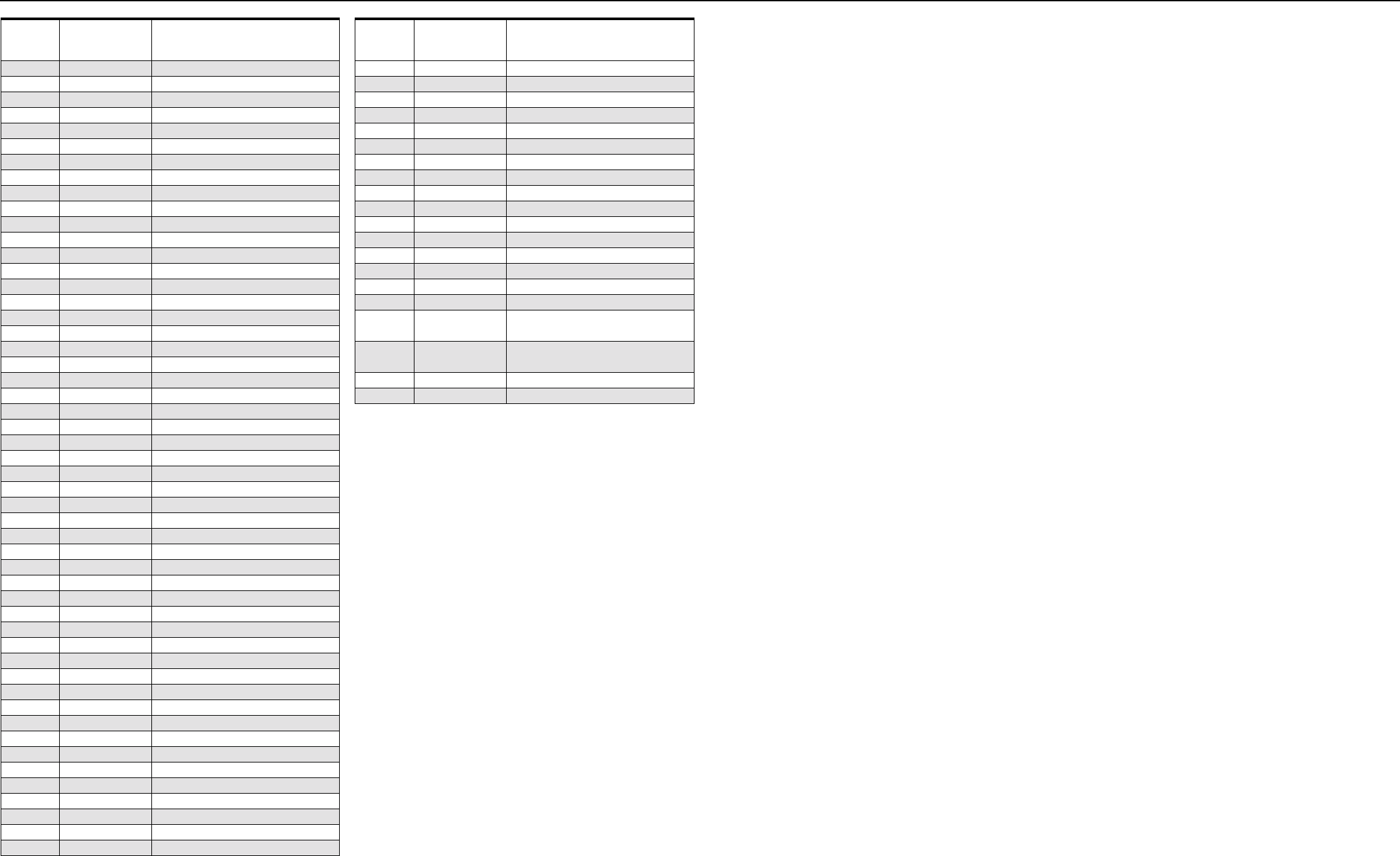

4-12 Controlhead GM160/360/660 - PCB 8486155B06 / Schematics

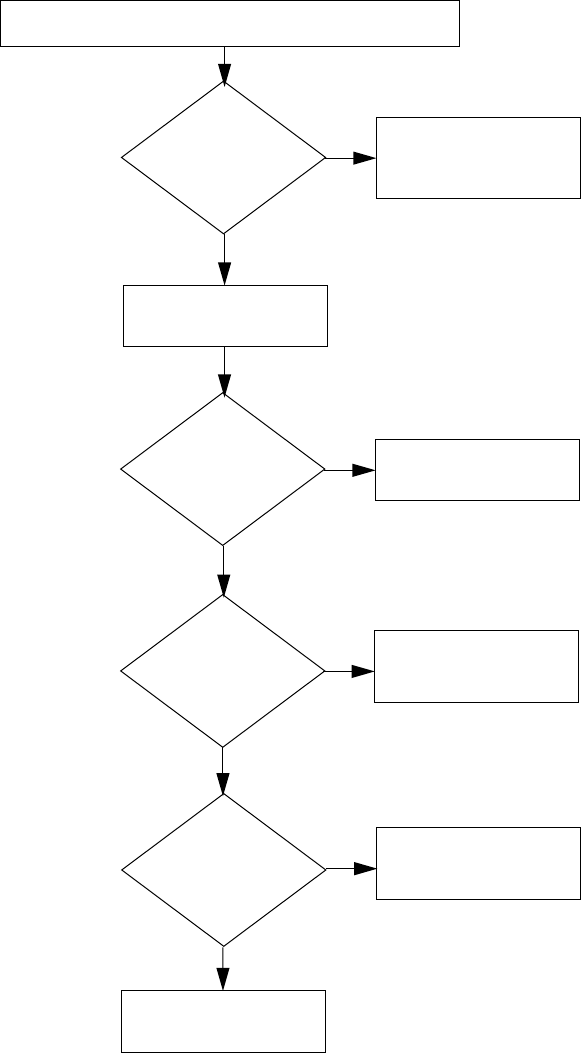

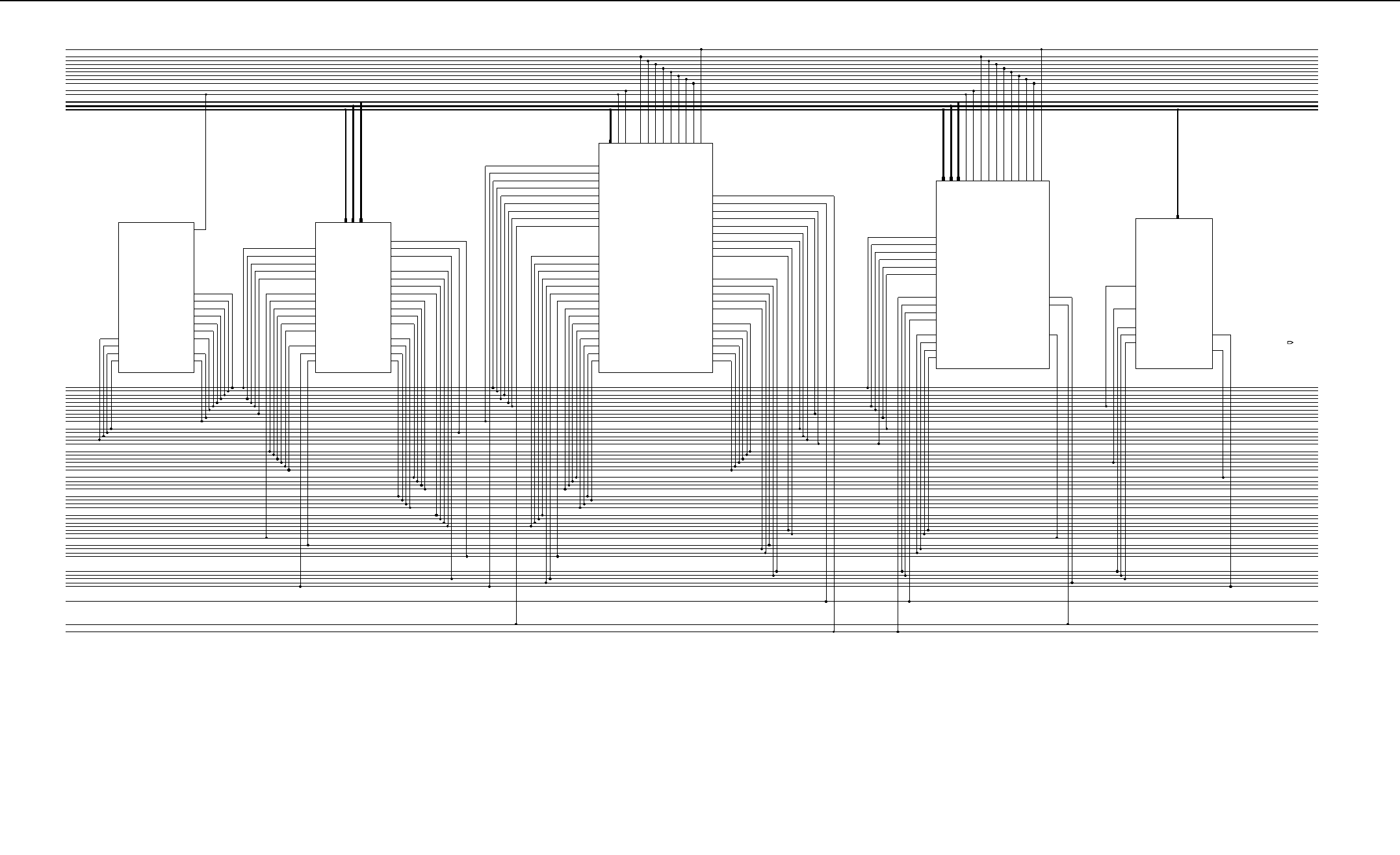

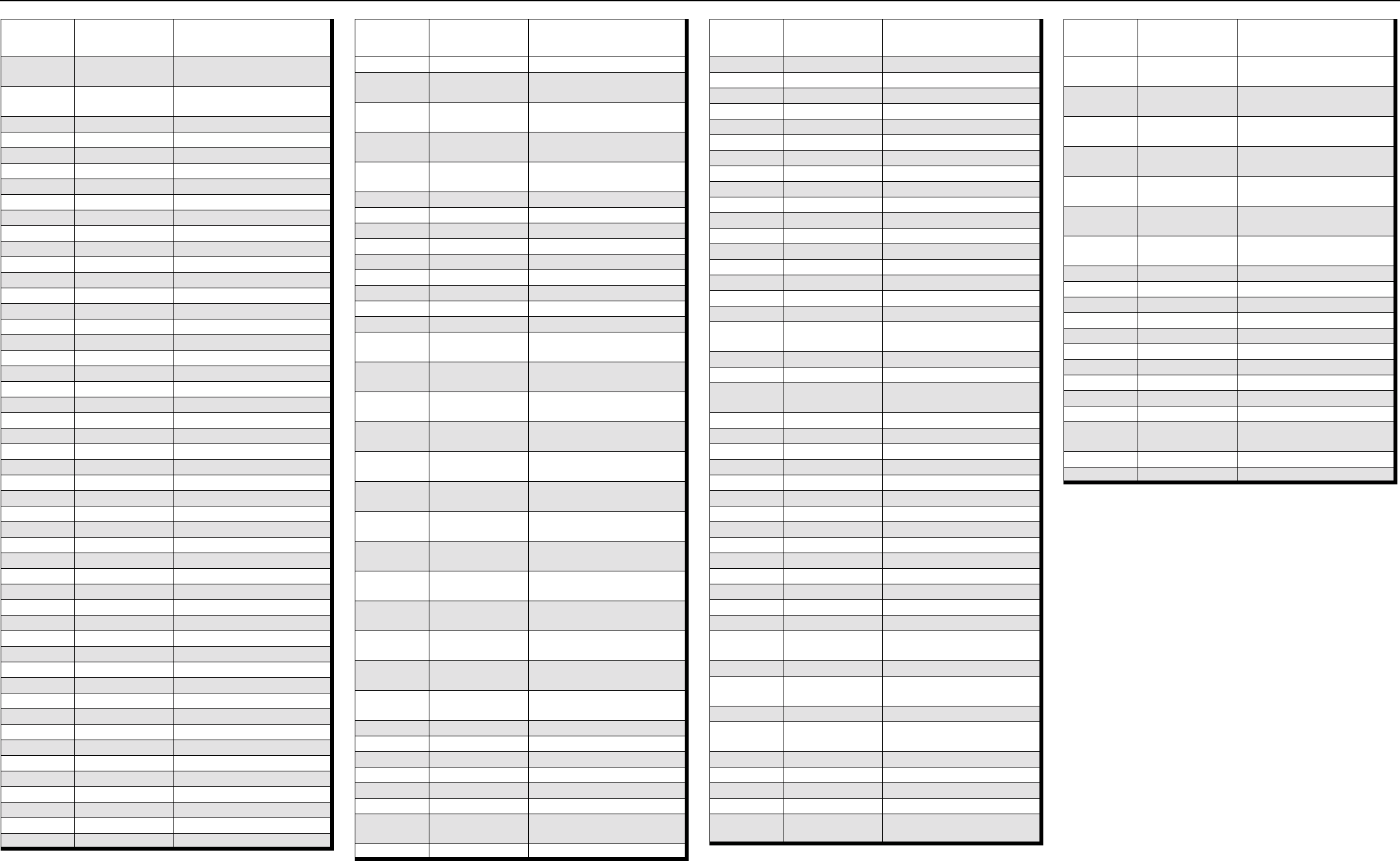

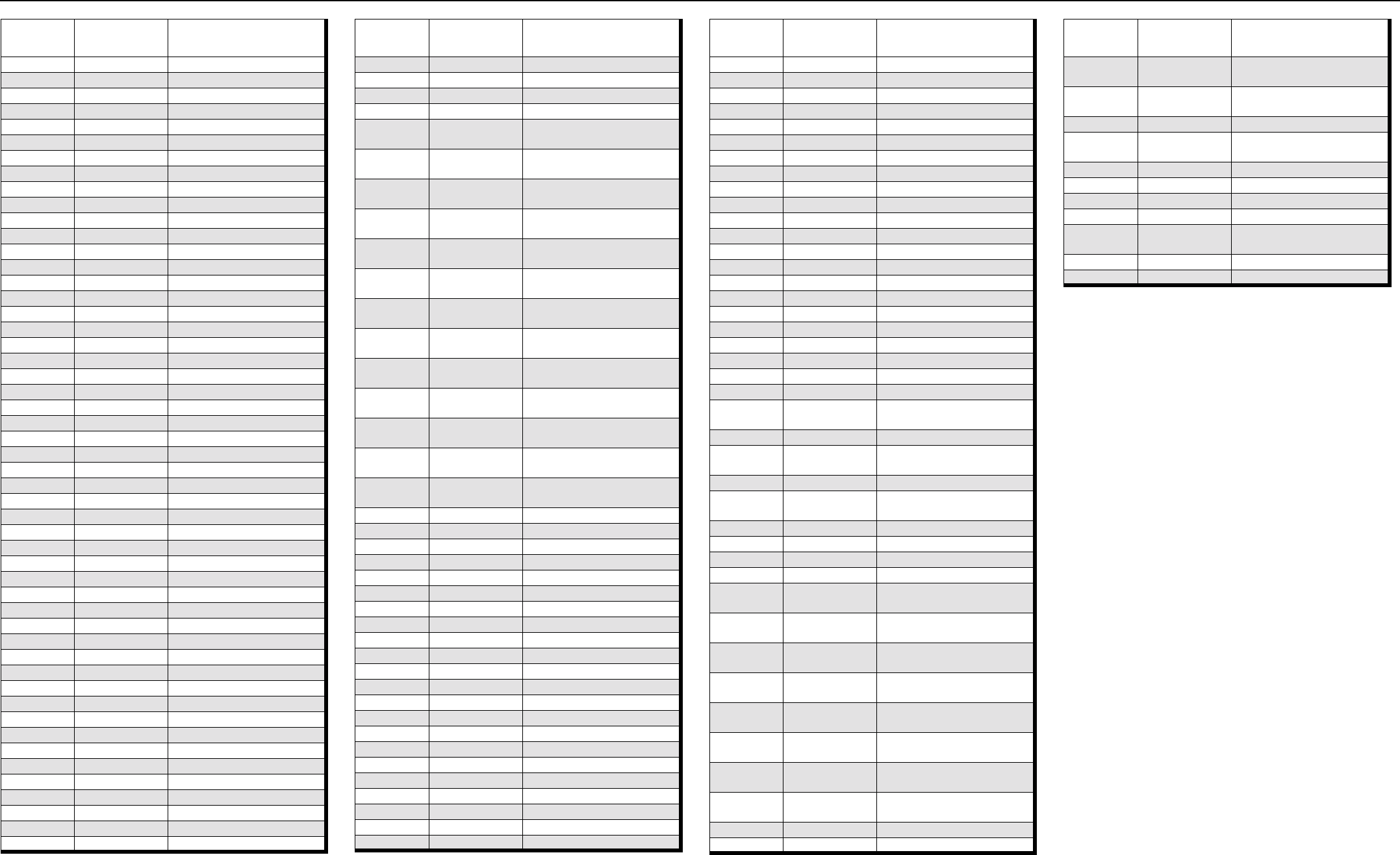

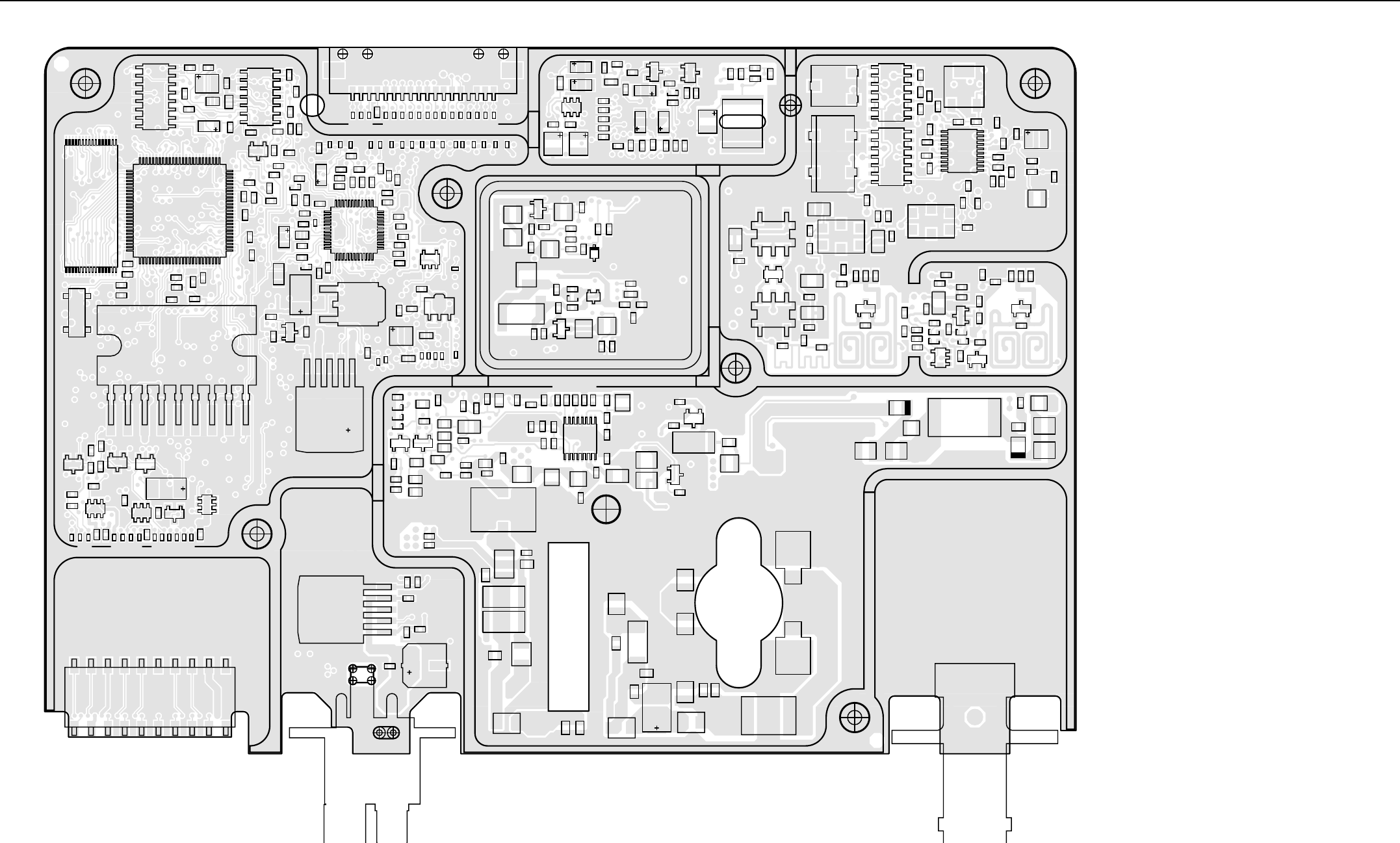

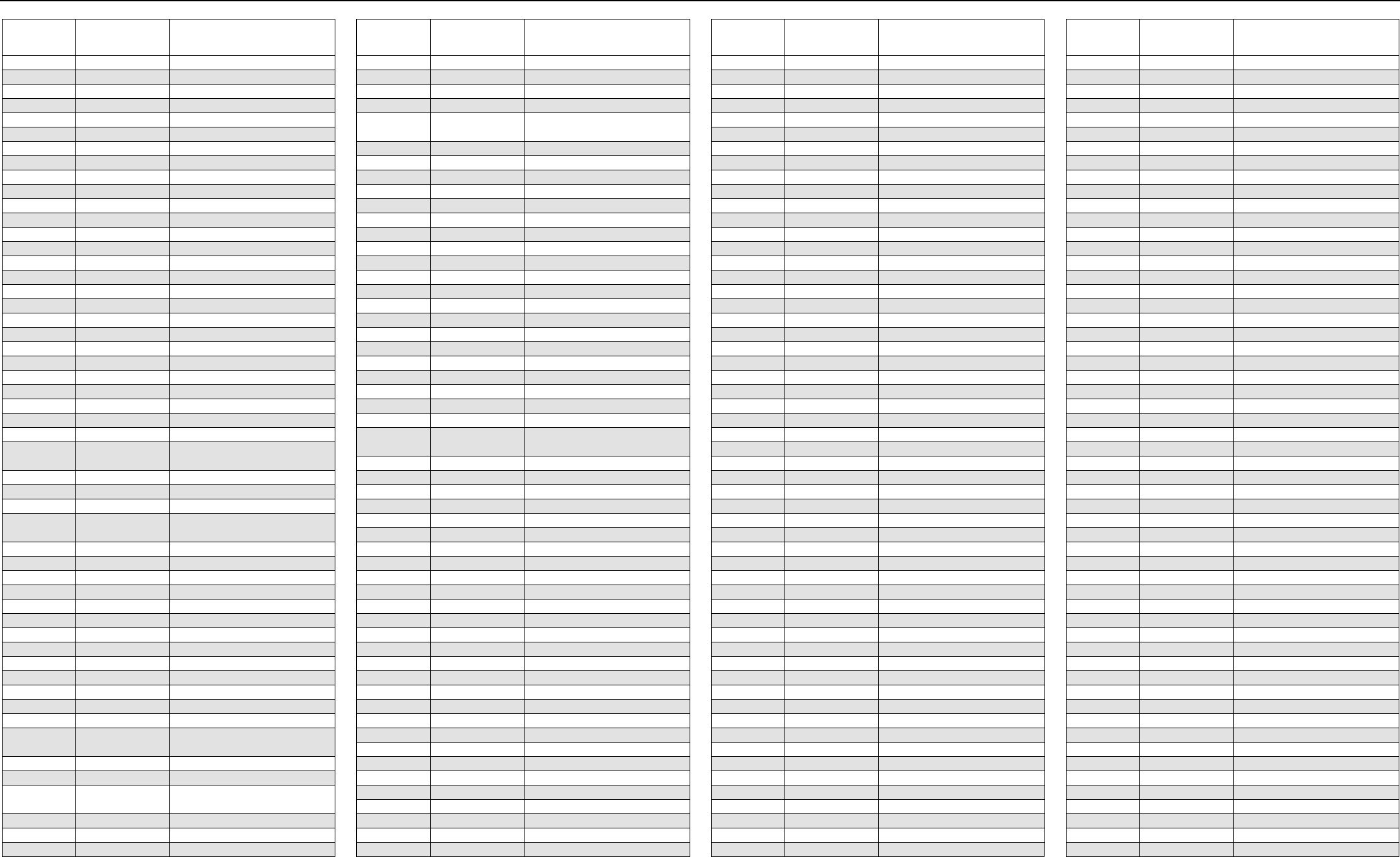

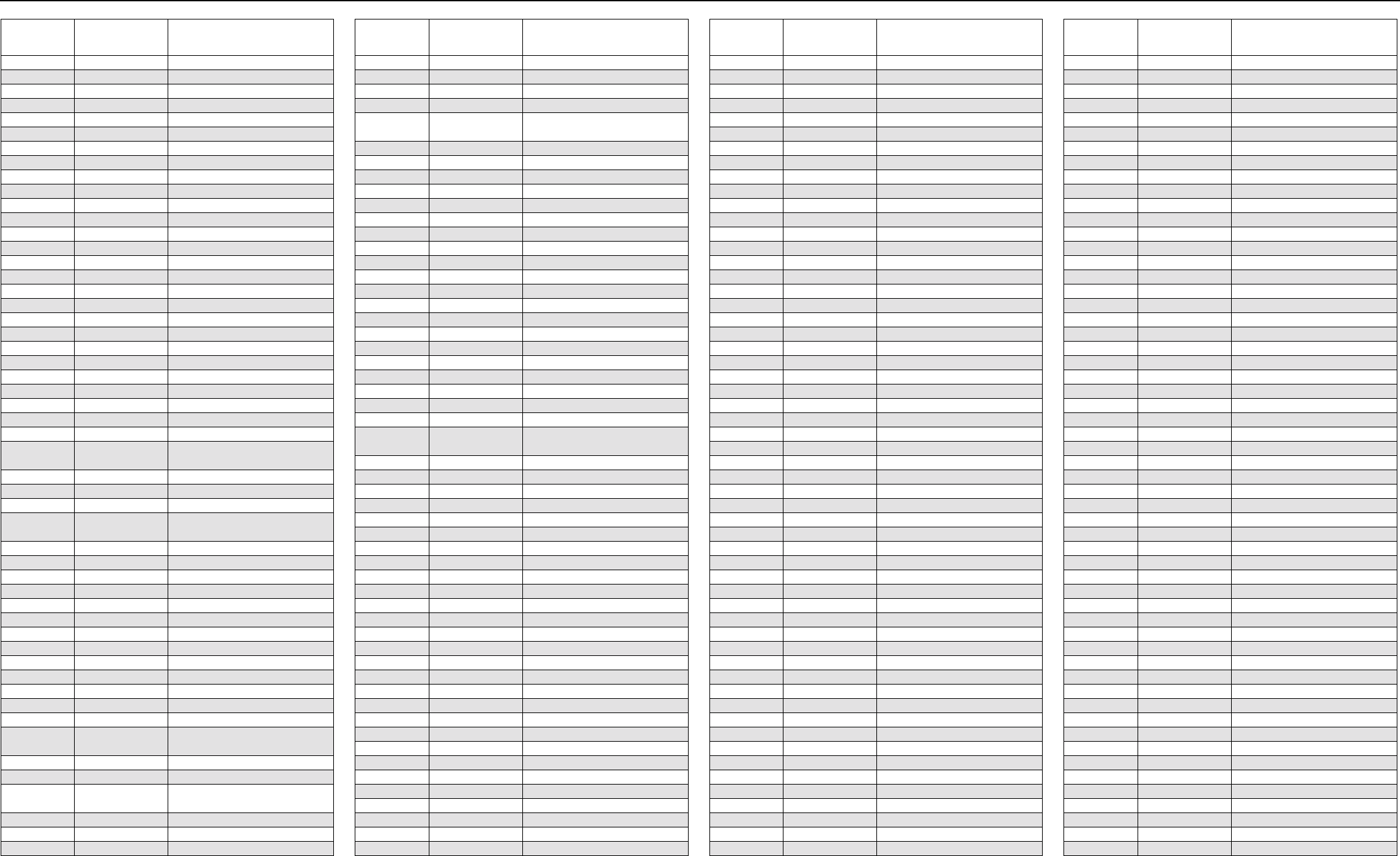

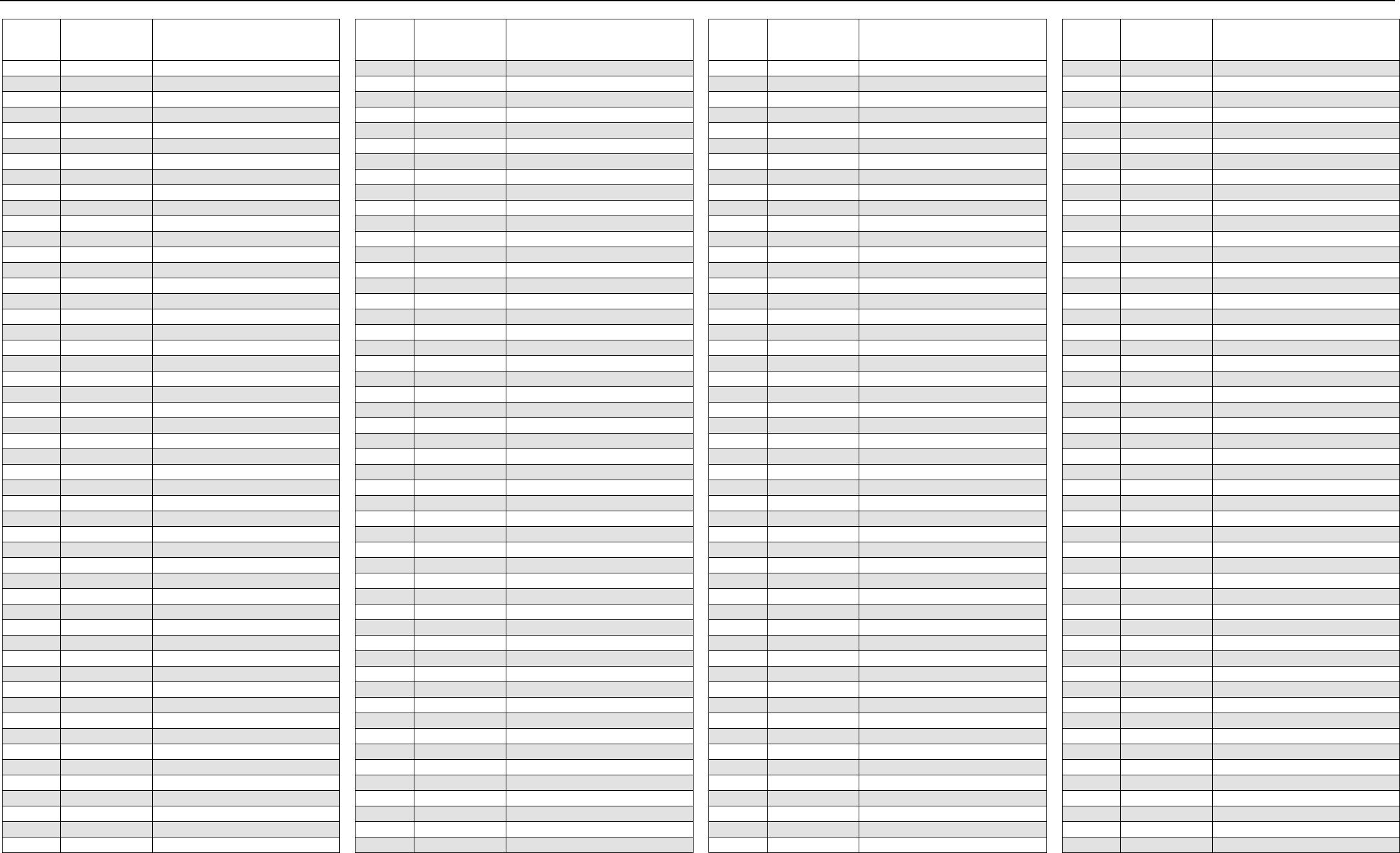

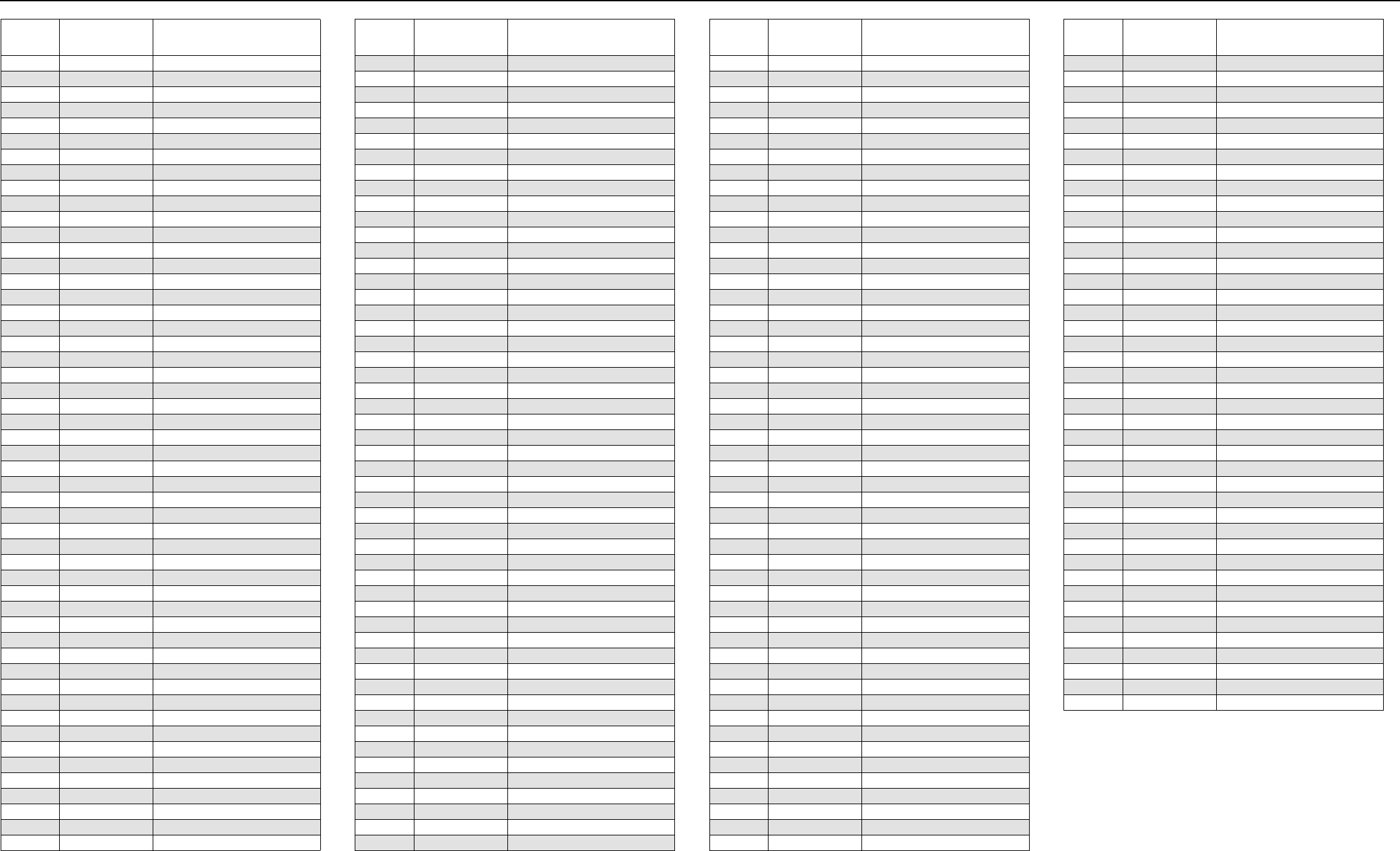

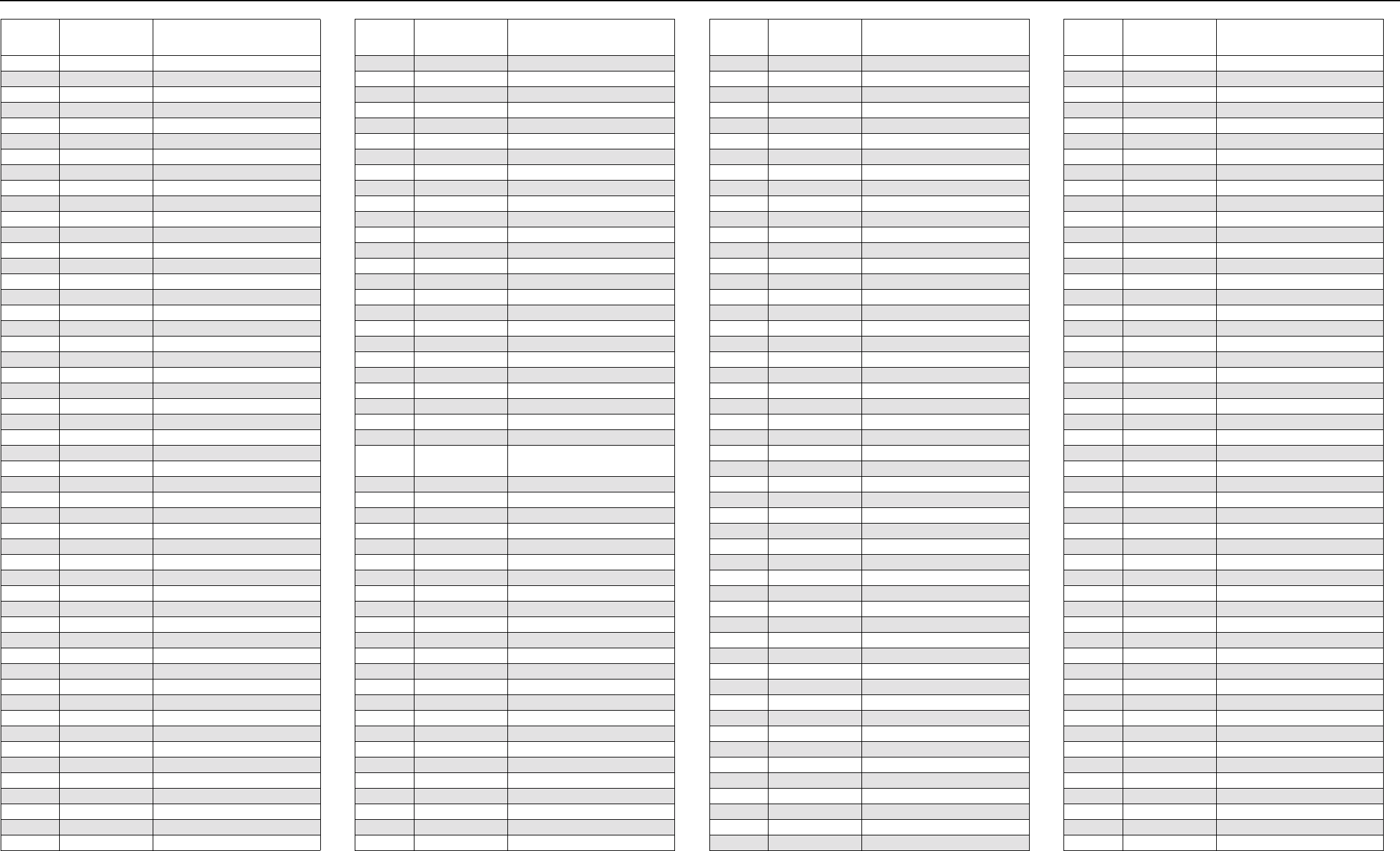

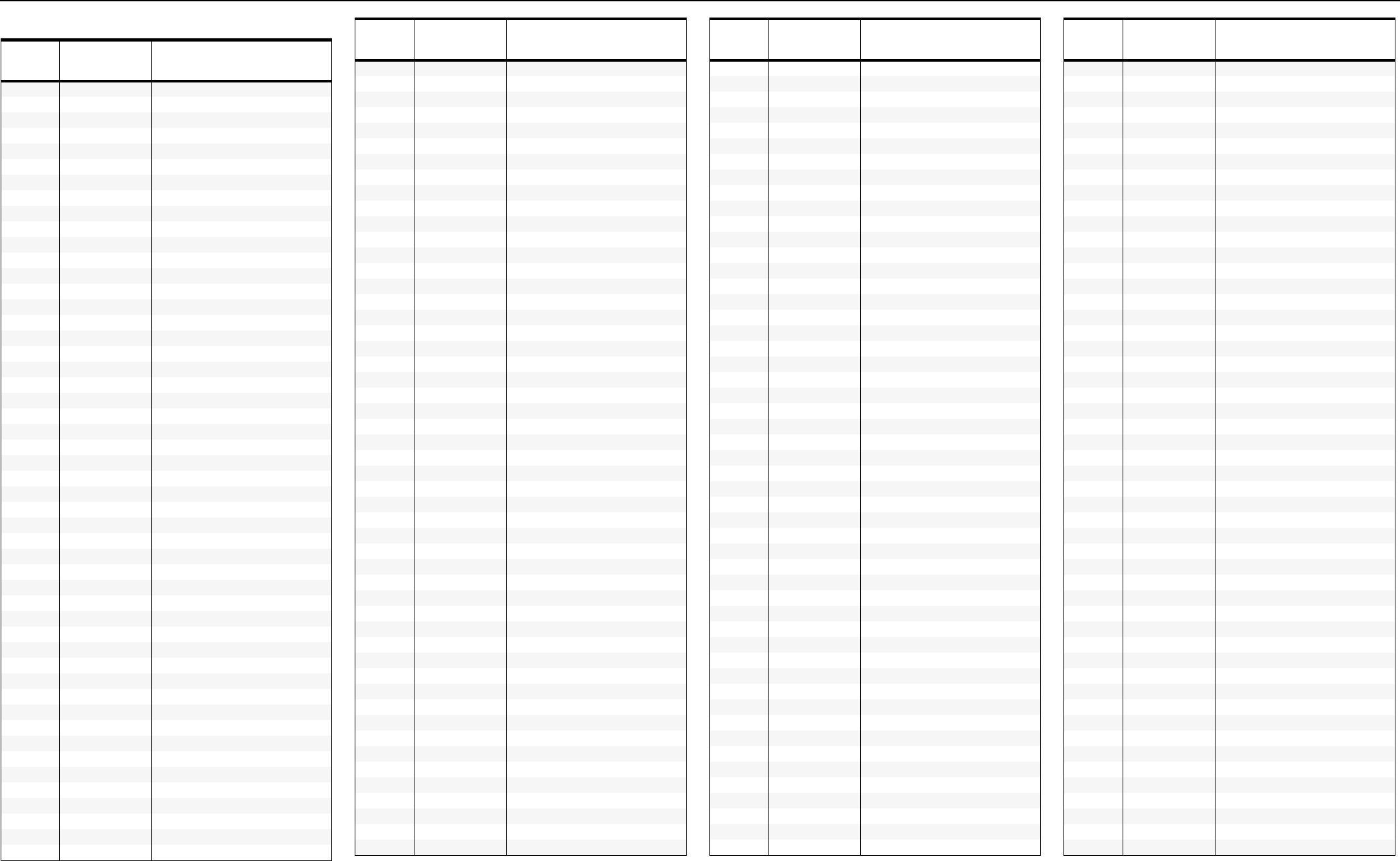

3.1 Controlhead PCB 8486155B06

Parts List

* Motorola Depot Servicing only

Reference designators with an asterisk indicate

components which are not fieldreplaceable

because they need to be calibrated with

specialized factory equipment after installation.

Radios in which these parts have been replaced in

the field will be off frequency at temperature

extremes.

Circuit

Ref Motorola

Part No Description

C0803 2113741F17 470pF 50V

C0804 2113741F17 470pF 50V

C0805 2113740F49 82pF 5% 50V NP0

C0807 2113741F17 470pF 50V

C0811 2113741F17 470pF 50V

C0812 2113741F17 470pF 50V

C0813 2113741F17 470pF 50V

C0815 2113741F17 470pF 50V

C0816 2113741F17 470pF 50V

C0817 2113740F49 82pF 5% 50V

C0822 2311049A40 TANT CP 2.2uF 10% 10V

C0823 2113741F49 10nF 50V

C0831 2311049A42 TANT CP 3.3uF 10% 6V

C0832 2113743E20 100nF 16V

C0833 2113743E20 100nF 16V

C0843 2311049A40 TANT CP 2.2uF 10% 10V

C0931 2113743E20 100nF 16V

C0933 2113743E20 100nF 16V

C0971 2311049A07 TANT CP 1uF 10% 16V

C0973 2311049A07 TANT CP 1uF 10% 16V

C0974 2113743E20 100nF 16V

C0975 2113743E20 100nF 16V

C0976 2113743E20 100nF 16V

C0978 2113743E20 100nF 16V

C0980 2113743E20 100nF 16V

C0983 2311049A09 TANT CP 2.2uF 10% 20V

C0984 2113741F49 10nF 50V

C0985 2311049A40 TANT CP 2.2uF 10% 10V

D0821 4813833C02 DIODE DUAL SOT

MMBD6100

D0822 4813833C02 DIODE DUAL SOT

MMBD6100

D0831 4880236E05 DIODE CHIP SCHOTTKY

D0877 4886171B01 LED RED

D0879 4886171B04 LED GREEN

D0880 4886171B03 LED YELLOW

D0965 4886171B04 LED GREEN

D0966 4886171B04 LED GREEN

D0967 4886171B04 LED GREEN