Joyce_History_of_the_AN_UYK 20_Sep76 Joyce History Of The AN UYK 20 Sep76

Joyce_History_of_the_AN_UYK-20_Sep76 Joyce_History_of_the_AN_UYK-20_Sep76

User Manual: Joyce_History_of_the_AN_UYK-20_Sep76

Open the PDF directly: View PDF ![]() .

.

Page Count: 123 [warning: Documents this large are best viewed by clicking the View PDF Link!]

- 000

- 001

- 002

- 003

- 004

- 005

- 006

- 007

- 008

- 009

- 010

- 011

- 012

- 013

- 014

- 015

- 016

- 017

- 018

- 019

- 020

- 021

- 022

- 023

- 024

- 025

- 026

- 027

- 028

- 029

- 030

- 031

- 032

- 033

- 034

- 035

- 036

- 037

- 038

- 039

- 040

- 041

- 042

- 043

- 044

- 045

- 046

- 047

- 048

- 049

- 050

- 051

- 052

- 053

- 054

- 055

- 056

- 057

- 058

- 059

- 060

- 061

- 062

- 063

- 064

- 065

- 066

- 067

- 068

- 069

- 070

- 071

- 072

- 073

- 074

- 075

- 076

- 077

- 078

- 079

- 080

- 081

- 082

- 083

- 084

- 085

- 086

- 087

- 088

- 089

- 090

- 091

- 092

- 093

- 094

- 095

- 096

- 097

- 098

- 099

- 100

- 101

- 102

- 103

- 104

- 105

- 106

- 107

- 108

- 109

- 110

- 111

- 112

- 113

- 114

- 115

- 116

- 117

- 118

- 119

- 120

- 121

- 122

HISTORY

OF

THE

AN/UYK-20(V)

DATA

PROCESSING

SYSTEM

ACQUISITION

AND

ITS

IMPACT

ON

TACTICAL

SYSTEMS

DEVELOPMENT

Robert

Richardson

Joyce

NPS-36Jo7609

1

NAVAL

POSTGRADUATE

SCHOOL

Monterey,

California

THESIS

HISTORY

OF

THE

~~/UYK-20(V)

DATA

PROCESSING

SYSTEM

ACQUISITION

Al'lD ITS

IMPACT

ON

TACTICAL

SYS~EMS

DEVELOPMENT

Robert

Richardson

Joyce

September

1976

Thesis

Advisors:

S.

Jauregui

&

E.

Zabrycki

Approved

for

public

release;

distribution

unli:nited

Prepared

for:

Naval

Electronic

Systems

Command

(E4E-107)

Washington,

D.C.

20360

T 1 7

hn

q 9

· UNCLASSIFIED

SECURITY

CL.ASSIFICATION

OF

THIS

~A.GE

(ft

..

Del.

Knl.,.d)

R!PORT

DOCUMENTATION

PAGE

READ

INSTRUCTIONS

BEFORE

COMPLETING

FORM

T.

~E~ORT

NUM.ER

2.

GOVT

ACCESSION

NO

1.

RECI~IENT'S

CAT

AL.OG

NUMSER

NPS-36Jo76091

••

TITL.E

(

..

d

Subtlt'.)

HISTORY

OF

THE

AN/UYK-20(V)

DATA

PROCESSING

SYST&~

ACQUISITION

AND

ITS

IMPACT

ON

TACTICAL

SYSTEMS

DEVELOPIIIlENT

7.

AUTHOR(.)

Robert

Richardson

Joyce

Naval

Postgraduate

School

Monterey,

California

93940

'I.

CONTROLL.ING

OFFICE

NAME

AND

ADDRESS

Naval

Electronic

Systems

Command(~4E-

Washington,

D.C.

20360 107)

Naval

Postgraduate

School

Monterey,

California

93940

16.

OISTRI.uTIOH

STATEMENT

(01

th,.

Report)

5.

TV~F'

Q.F-"'~PORT

•

~£RIOO

COVERED

Master's

Thesis;

(September

1976)-

••

~ERFORMING

ORG.

REPORT

NU.UER

'0.

~ROGRAM

ELEMENT,

PROJECT,

TASI(

AREA'

WORK

UNIT

NUM.ERS

12.

REPORT

OATE

September

1976

13.

NUM.ER

OF

~AGES

122

11.

IECURITY

CL.ASS.

(01

tlu.

~r1J

Unclassified

1S..

DECL.ASSIfI'ICATIONI

DOWNGIIUDING

SCHEDUL.E

Approved

for

public

release;

distribution

unlimited.

17.

OISTRI_UTIOH

STATEMENT

(01

tit.

".tree,

..

'end

'ft

.'00.30,

II

d,II.,

..

, IPo.I RefHWf)

18.

SUPPL.

EMENTARV

HOTES

't.

KEY

WORDS

(C«ttlnu.

on

,

...

.,

•••

'de

II

n.c

•••

~

end

ldentl",

bJ"

IJ'oclr

nu.tIJ.,)

Minicomputer

Standard

Data

Processing

System

Tactical

Digital

System

In

1972

the

Chief

of

Naval

~aterial

perceived

a

prolif-

eration

of

small

computer

types

in

the

Navy

inventory.

To

stem

that

prollferstlcn

:l

3t3.G.iar·d.~lniccffi;uter

W3.S

;:rocured,

to

be

used

in

all

current

and

future

tactical

systems

requir-

ing

a

small

digital

processor.

That

standard

was

designated

the

AN/UYK-20(V)

Data

Processing

System.

Lack

of

dedicated

DO

I

~~=~1

1A73

ED'TION

0"

I

NOV

81

IS

O.SOL.ETE

(Page

1)

SIN

0102-014-

6601

I

UNCLASSIFIED

SECURITY

CLASSIfI'ICATION

OF

TMIS

..

AGE

(""'"

D.,

••

I'I'erMJ

Unclas

s

ified

support

forced

the

Chief

of

Naval

Material

to

tax the

users

of

the

system

to

obtain

the

necessary

development

and

opera-

tional

support

funds.

Premature

delivery

of

the

system

to

meet

user

schedules

resulted

in

highly

unreliable

equipment

being

used

in

development

efforts.

A

significant

adverse

im-

pact

on

user

project

costs

and

schedules

resulted.

Examina-

tion

of

the

standard

minicomputer

acquisition

fosters

a num-

ber

of

recommendations

for

future

tactical

digital

processor

acquisitions.

DO

Form

1473

1

Jan

73

SIN

0102-014-6601

Unclassified

ABSTRACT

In

1972

the

Chief

of

Naval

Material

perceived

a

proliferation

of

small

computer

types

in

the

Navy

inventory.

To

stem

that

proliferation

a

standard

minicomputer

was

procured,

to

be

used

in

all

current

and

future

tactical

systems

requiring

a

small

digital

processor.

That

standard

was

designated

the

AN/UY

K-20

(V)

Da

ta

processing

System.

Lack

of

dedicated

appropriated

funds

for

procurement

and

support

forced

the

Chief

of

Naval

Material

to

tax

the

users

of

the

system

to

obtain

the

necessary

development

and

operational

support

funds.

Premature

delivery

of

the

system

to

meet

user

schedules

resulted

in

highly

unreliable

equipment

being

used

in

development

efforts.

A

significant

adverse

impact

on

user

project

costs

and

schedules

resulted.

Examination

of

the

standard

minicomputer

acquisition

fosters

a

number

of

recommendations

for

future

tactical

digital

processor

acquisitions.

4

TABLE

OF

CONTENTS

..

GLOSSARy..........

••••••••••

••••••••••

•..•

•••••••.

•.••••

8

ACKNOWLEDGEMENT

••••••••••••••••••••••••...•••••••.•••••.

11

I.

INTRODUCTION

••••••••••••••••••••••.•••••••.•.••••

12

A.

THESIS

OBJECTIVE.............................

12

B.

METHODOLOGy

••••••••••••••••••..•••••••.•.••••

13

II.

IDENTIFICATION

OF

THE

NEED

FOR

A

STANDARD

MINICOMPUTER

•••••••••••••••••••••••••••••••••••••.••••••

14

A.

DEFINITION

OF

A

MINICOMPUTER.................

16

B.

DEFINITION

AND

IMPLICATIONS

OF

A "STANDARDII..

17

C.

THE

RANGE

OF

CAPABILITIES

NEEDED

•••••••••••••

20

1.

Packaging

••

'.

• • •

•• •• ••

••

•

••

• • •

••

• •

••

•

.••

.•

21

2.

Reliability

and

Maintainability

••••••••••

22

3.

Architecture.............................

23

4.

Input/Output

••••••••••••••••••••••.••••.•

25

5 •

In

t

er

r up t

s.

. • • •

••

• • • • • • • • • • • • • . • • • • • . • • • • 27

6.

Control/Maintenance

Panel

••••••••••••••••

27

7.

Software.

• • • • • •

••

• • • •

••

•

.•

• • •

••

•• ••

•

••

•

.•

28

D.

CAPABILITIES

3F

EXISTING

NAVY

COMPUTERS

TO

MEET

THE

SPECIFICATIONS......................................

28

1.

CP-642B

.•••••••••••••••••••••••.•••••••••

30

2.

AN/UYK-15(V)

•••••••..•••••.•••.•..•••••••

30

3.

CP-890...................................

31

4.

AN/UYK-12(V)

••••••••••••••••••....•••••••

31

III.

DEVELOPMENT

AND PRODUCTION HISTORy

••.••.•••••••••

3~

IV.

EVALUATION

OF

THE

SySTEM.........................

54

A.

PRODUCT

B.

COMPARISON

OF

SPECIFICATION

AND

FINAL

• . . . • . . . . . . . . . . . • . • . . . . . . . . . . . . . . . . .

54

COMPARISON

OF

AN/UYK-20

DPS

WITH

THE

"OFF-THE-SHELF"

MINICOMPUrER

STATE-OF-THE-ART

••••••...•.

1972

57

57

1.

Architecture

•••••..•••..•••••••••••.••.•.

5

2.

Main

Memory

••••••••••••••••••••••••••••••

60

3.

Instruction

Set..........................

61

4 • I n p u

t/

0 u t

put.

• • • • • • • • • • • • • • • • • • • • • • • • • • • • 6 3

5.

Interrupt

Structure......................

64

6.

Construction..

• • • • •

••

• • • • • • • • • • • • • • • • • •

••

64

7.

Support

Software.........................

66

c. IMPACT OF

AN/UYK-20

DPS

ON

DEVELOPMENT OF USER

SySTEMS.............

•••••••••••••••••••••••••••.••••••••

67

1.

Establishment

of

AN/UYK-20

as

a

Standard.

68

2.

Hardware/Firmware

Capabilities

•••••••••••

70

3.

Availability

of

Support

Software

•••••••••

73

4.

Support

Software

capabilities

••••••••••••

76

5.

Availability

of

Peripherals

••••••••••••••

77

6.

Hardware

and

Software

Reliability

and

. "

b'l"

Ma~nta~na

~

~ty

••••••••••••••••••••••••••••••••

0

•••••••••

78

,7.

Lack

of

Dedicated

Appropriated

Funds

to

Su

pport

the

AN/UYK

-20

DPS...............................

80

V. SUMMARY, CONCLUSIONS

AND

RECOMMENDATIONS

•••••••••

82

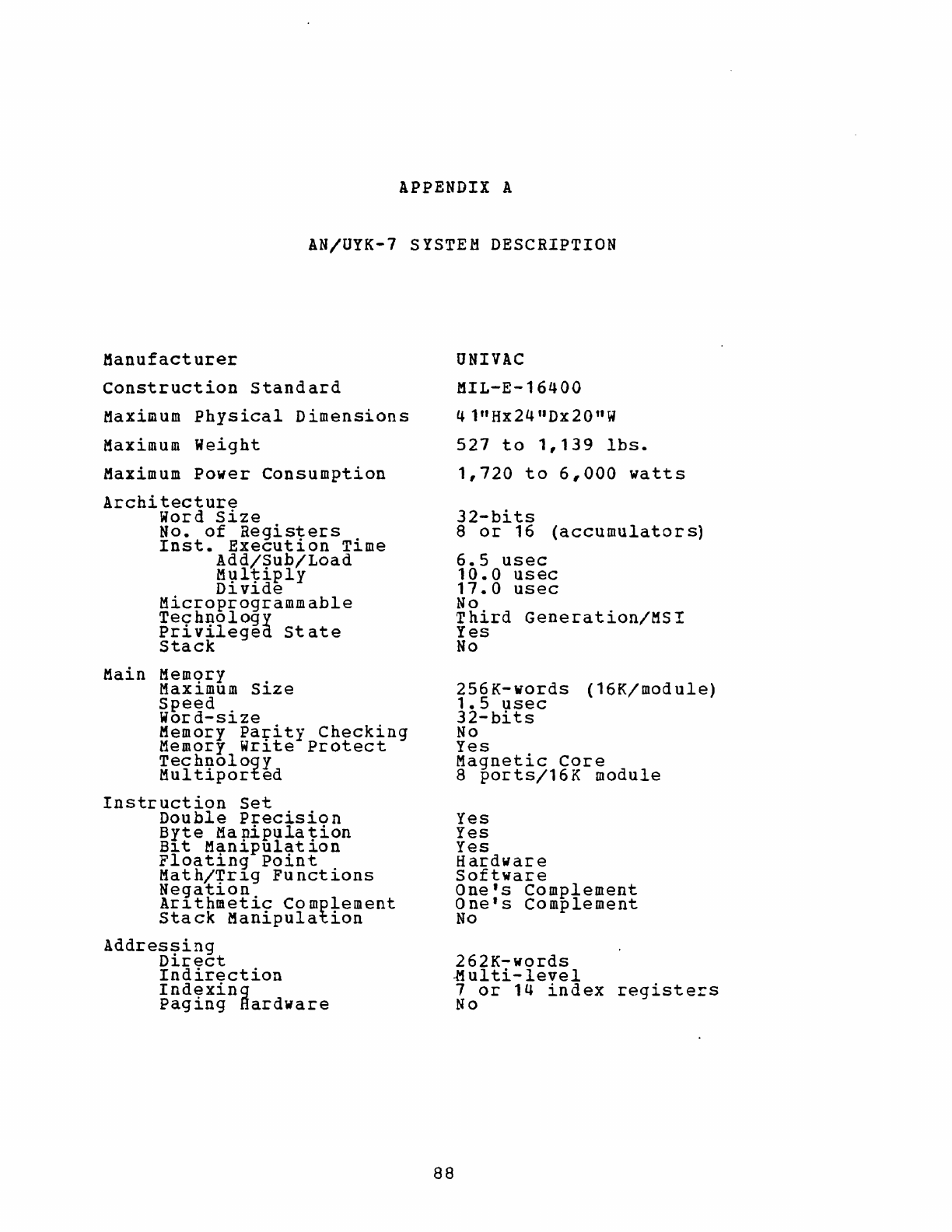

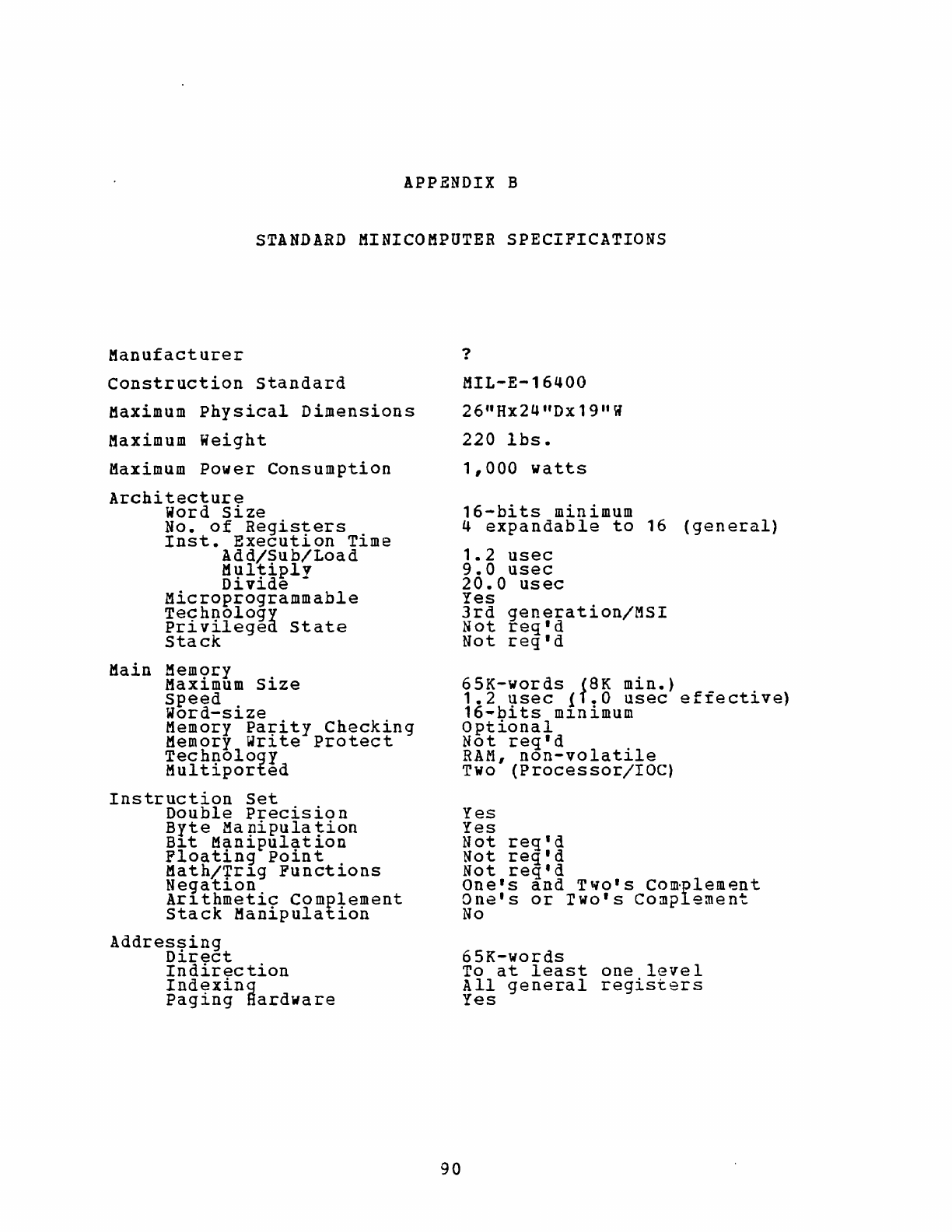

Appendix

A:

AN/OYK-7

SYSTEM

DESCRIPTION................

88

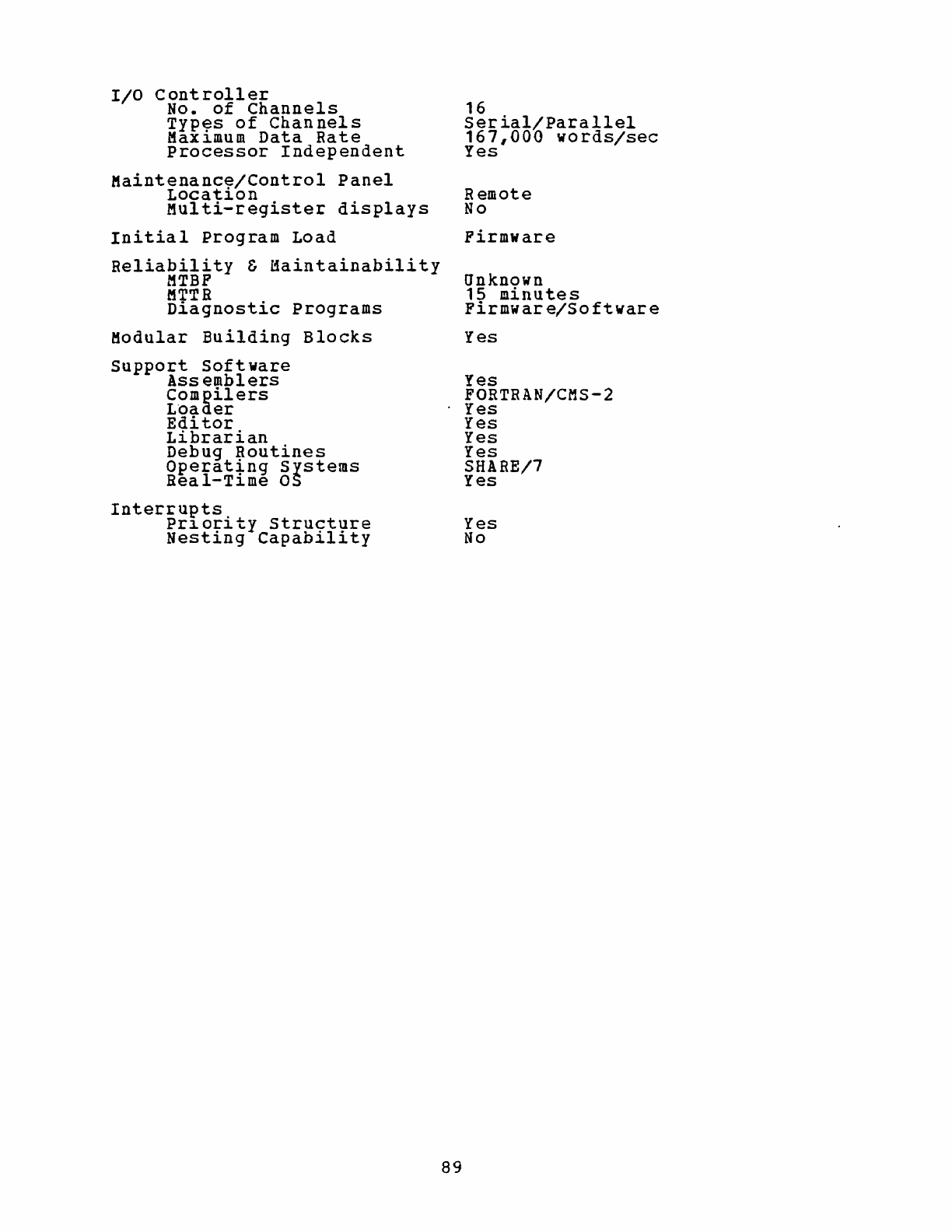

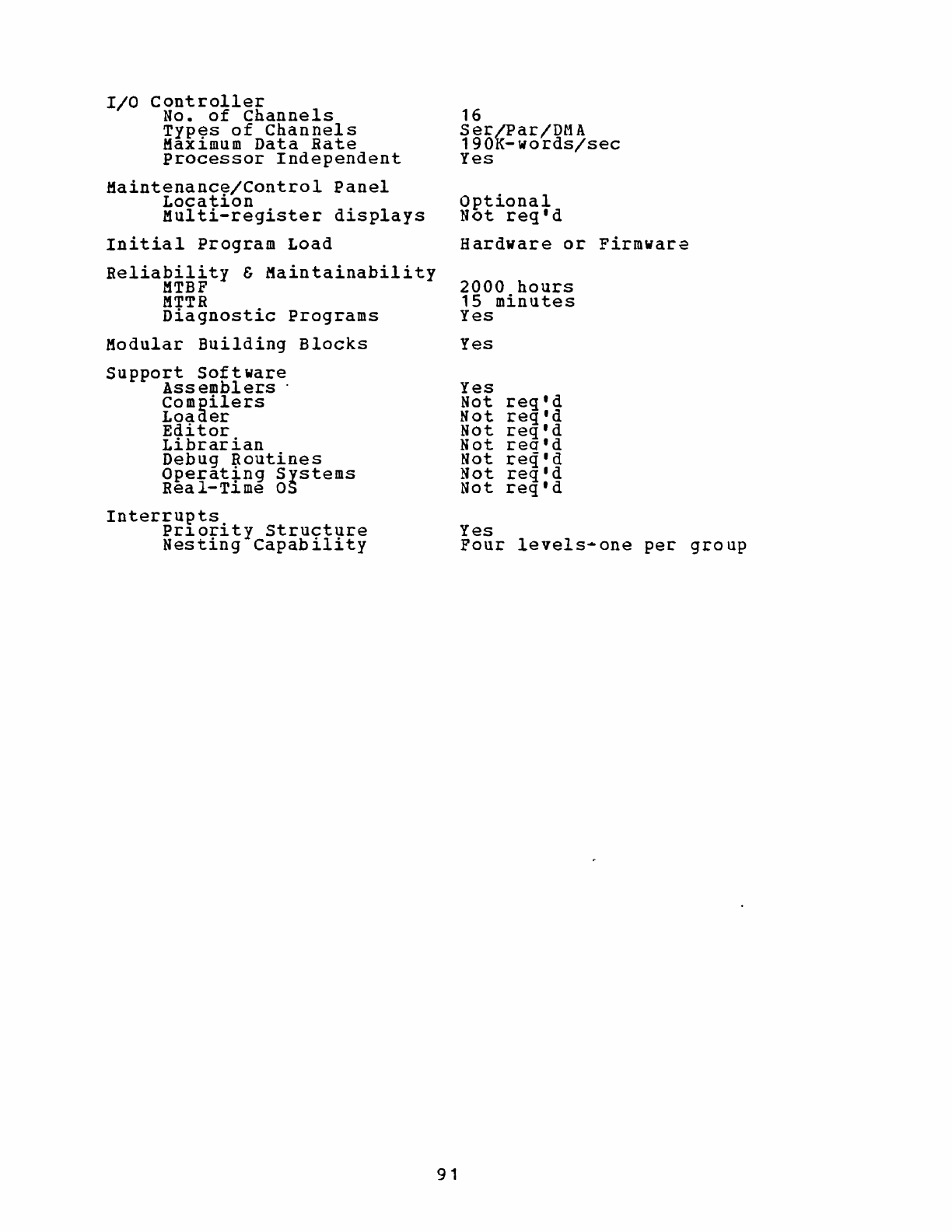

Appendix

B:

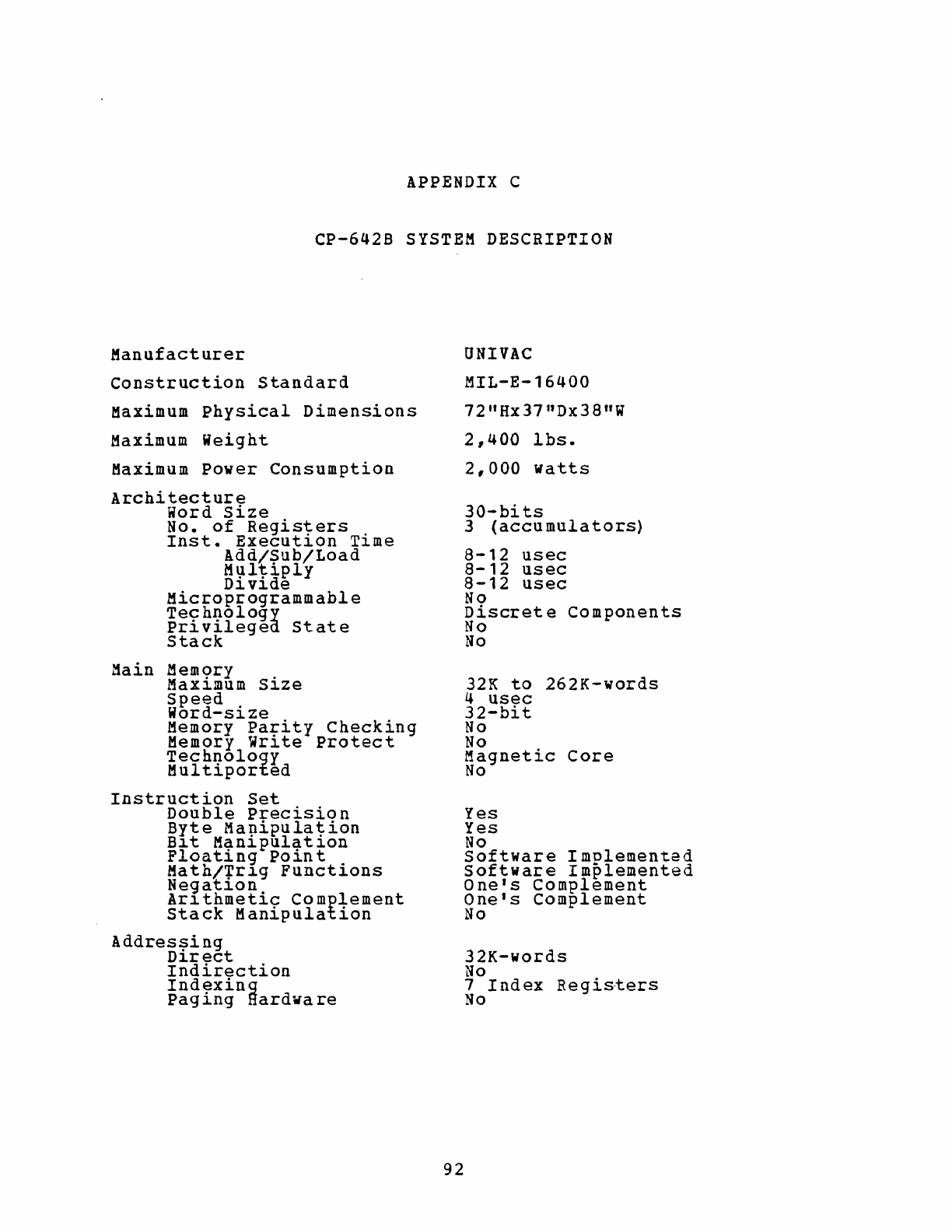

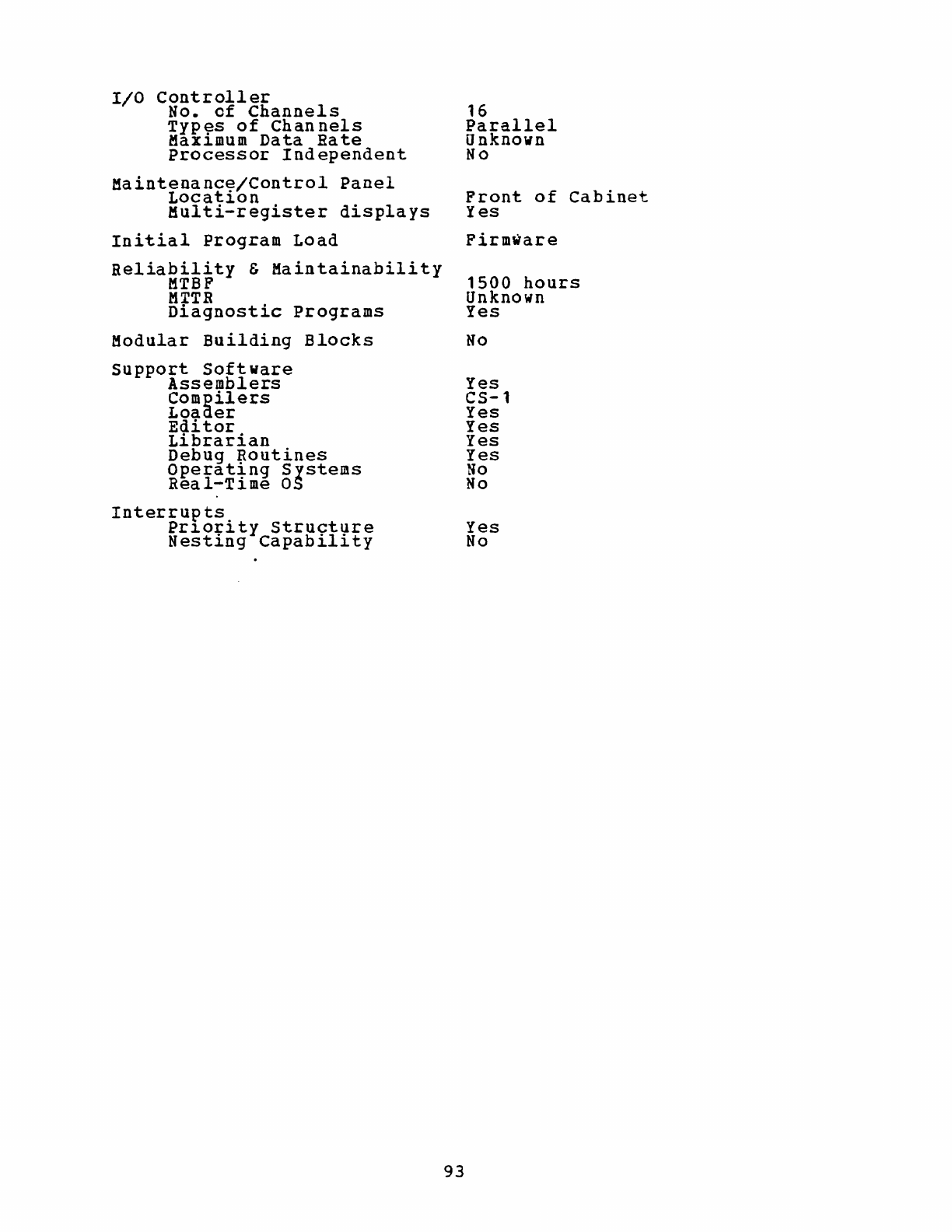

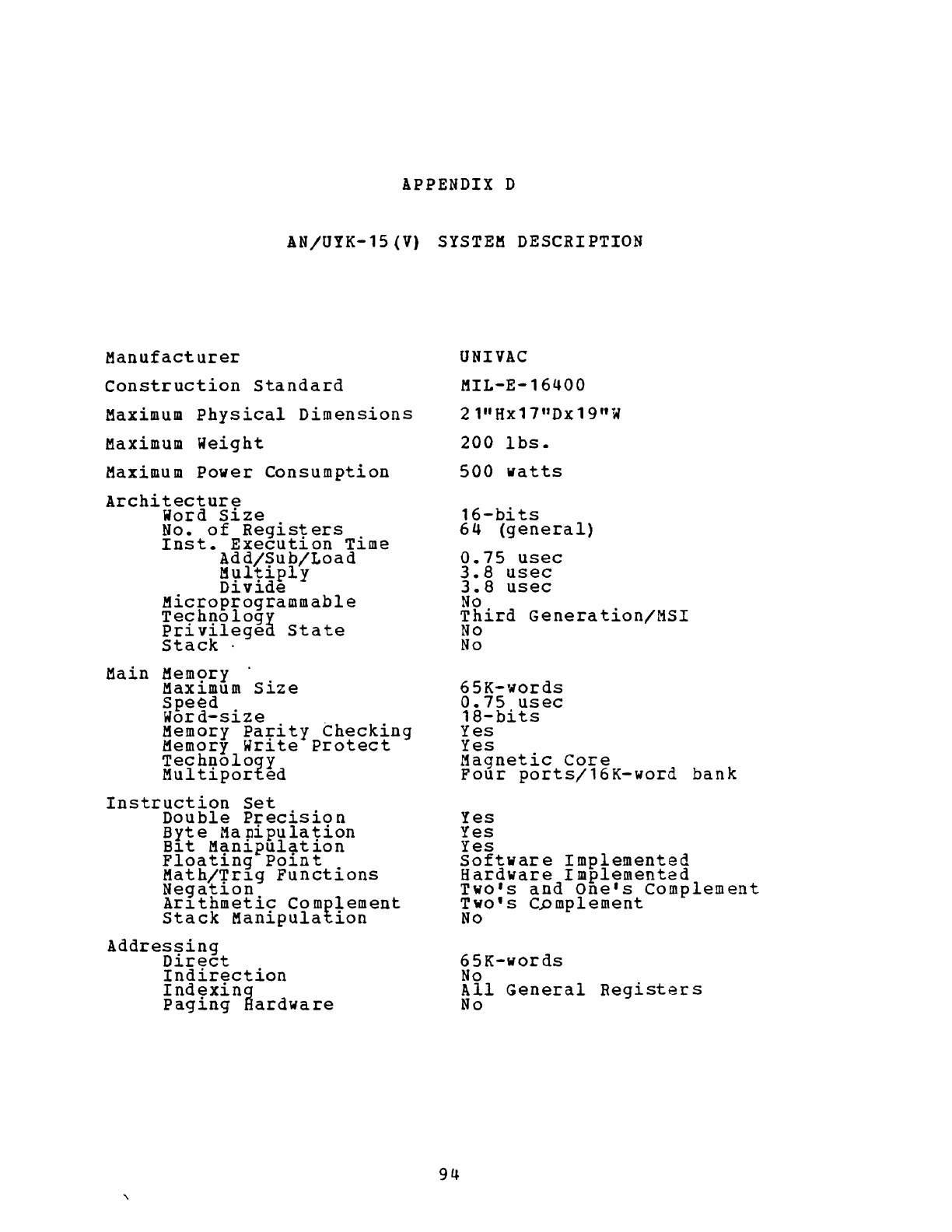

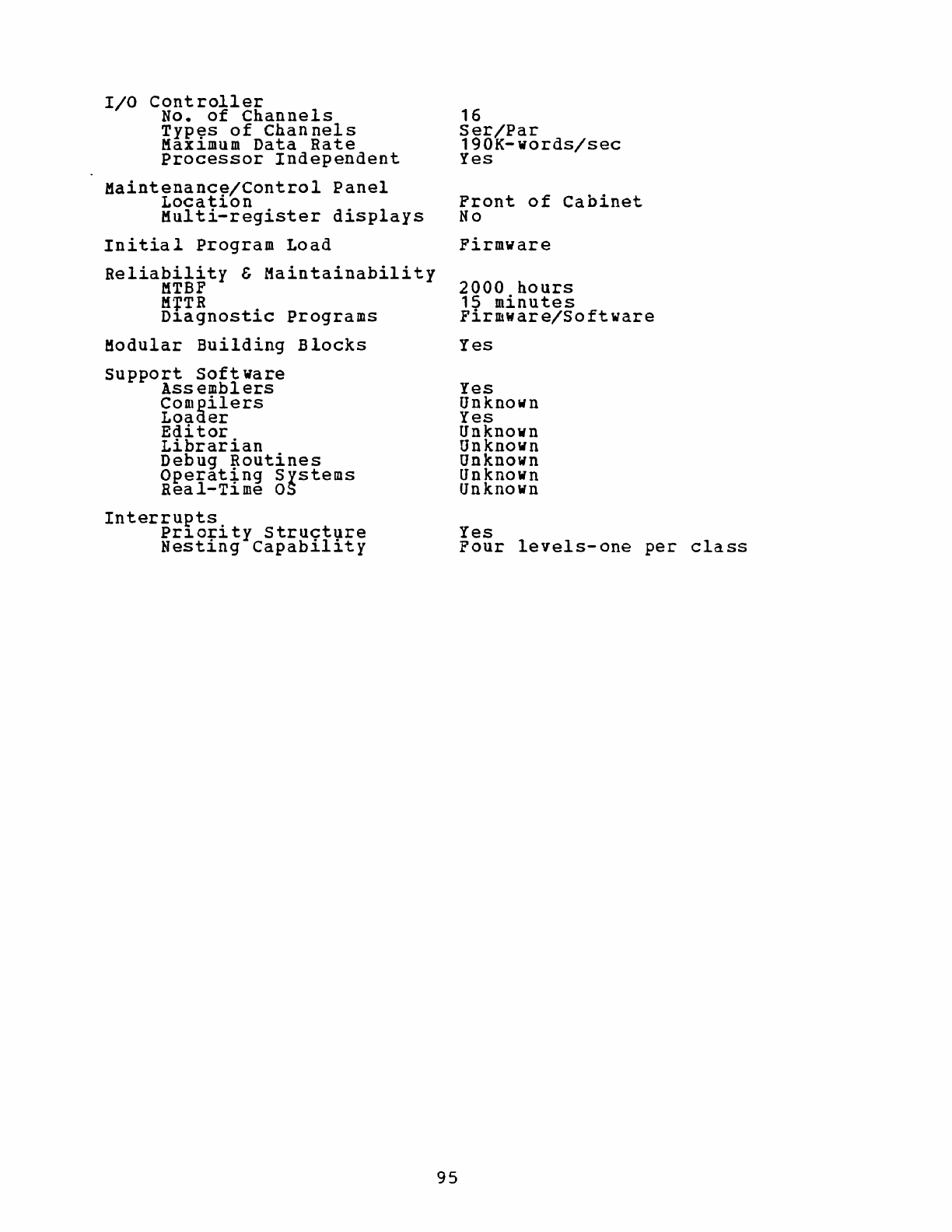

Appendix

C:

Appendix

D:

Appendix

E:

Appendix

F:

Appendix

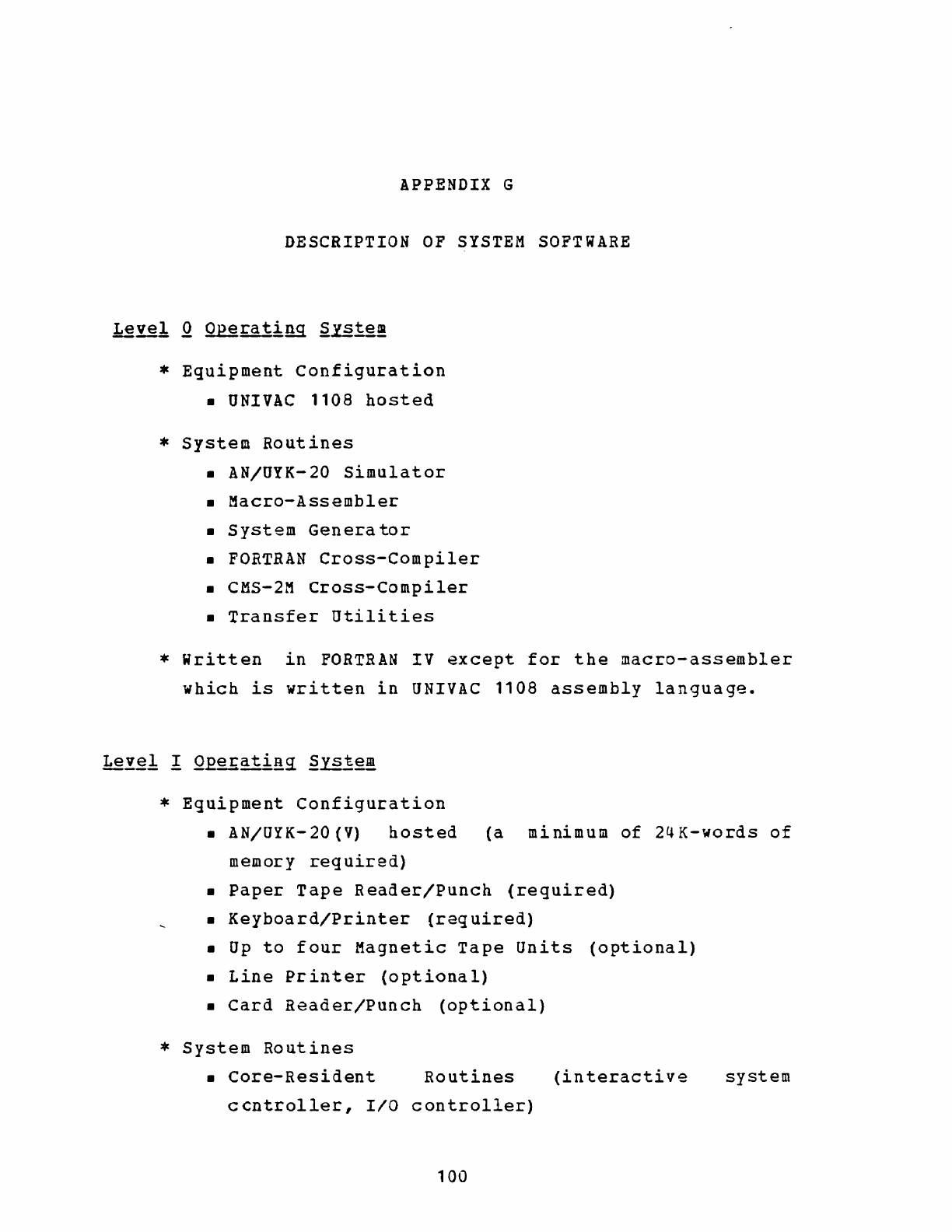

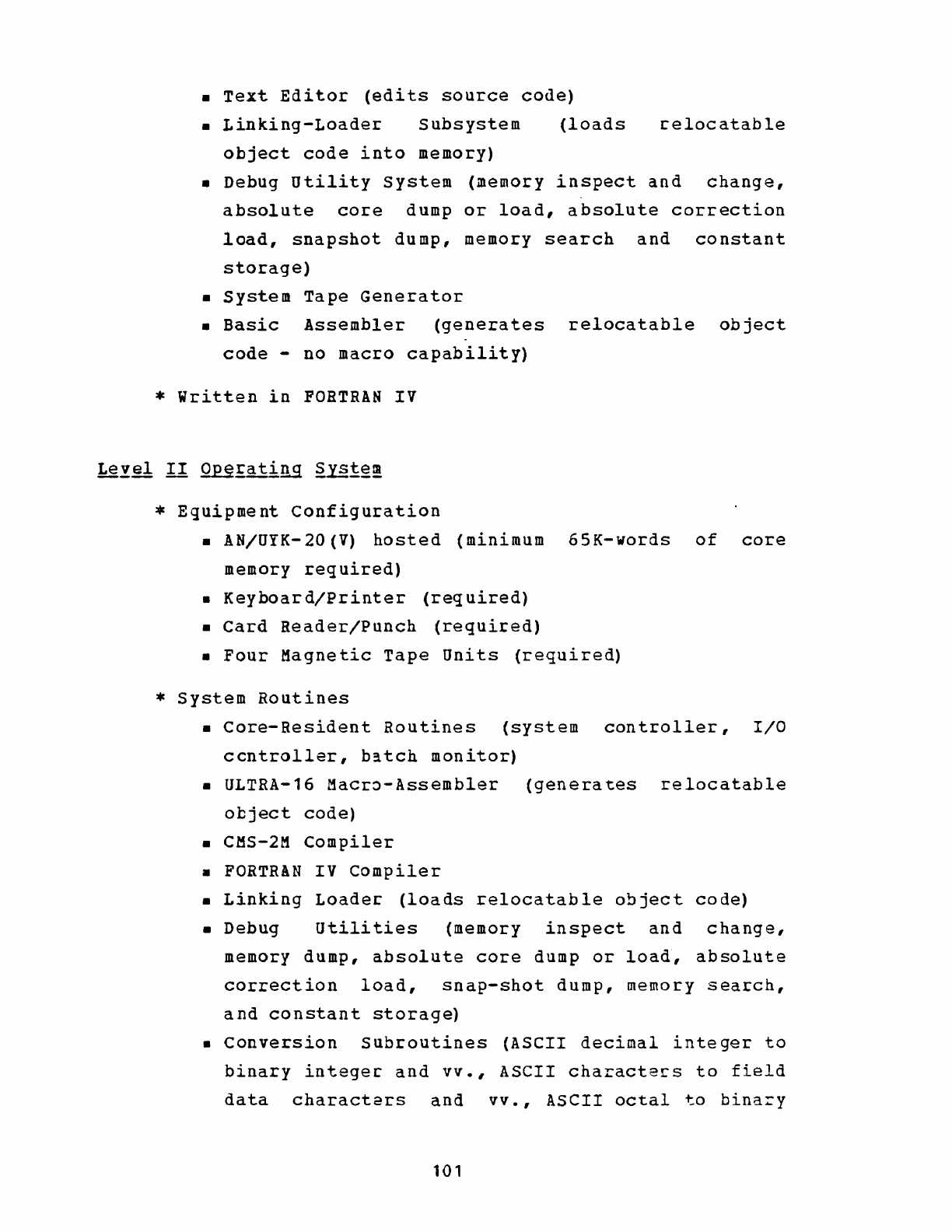

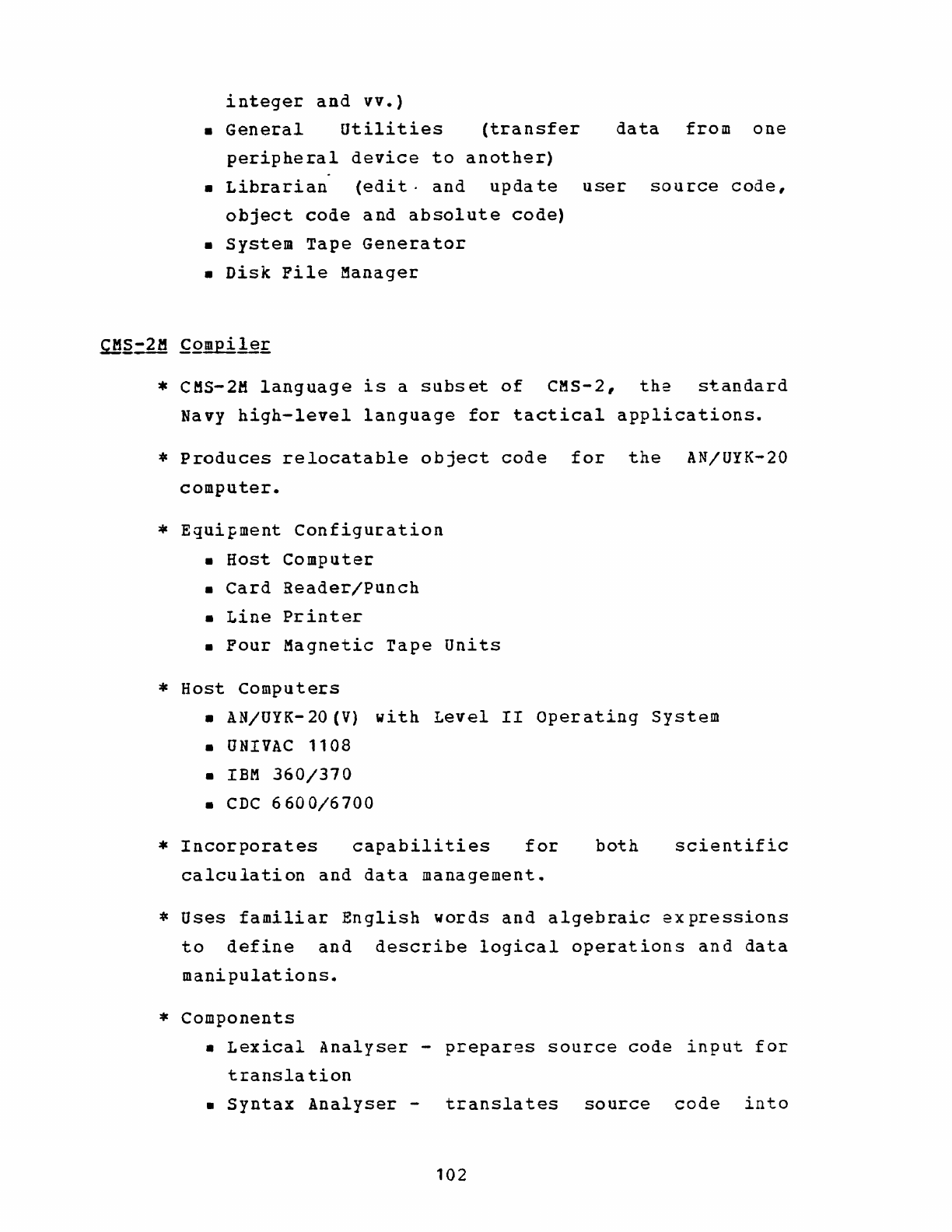

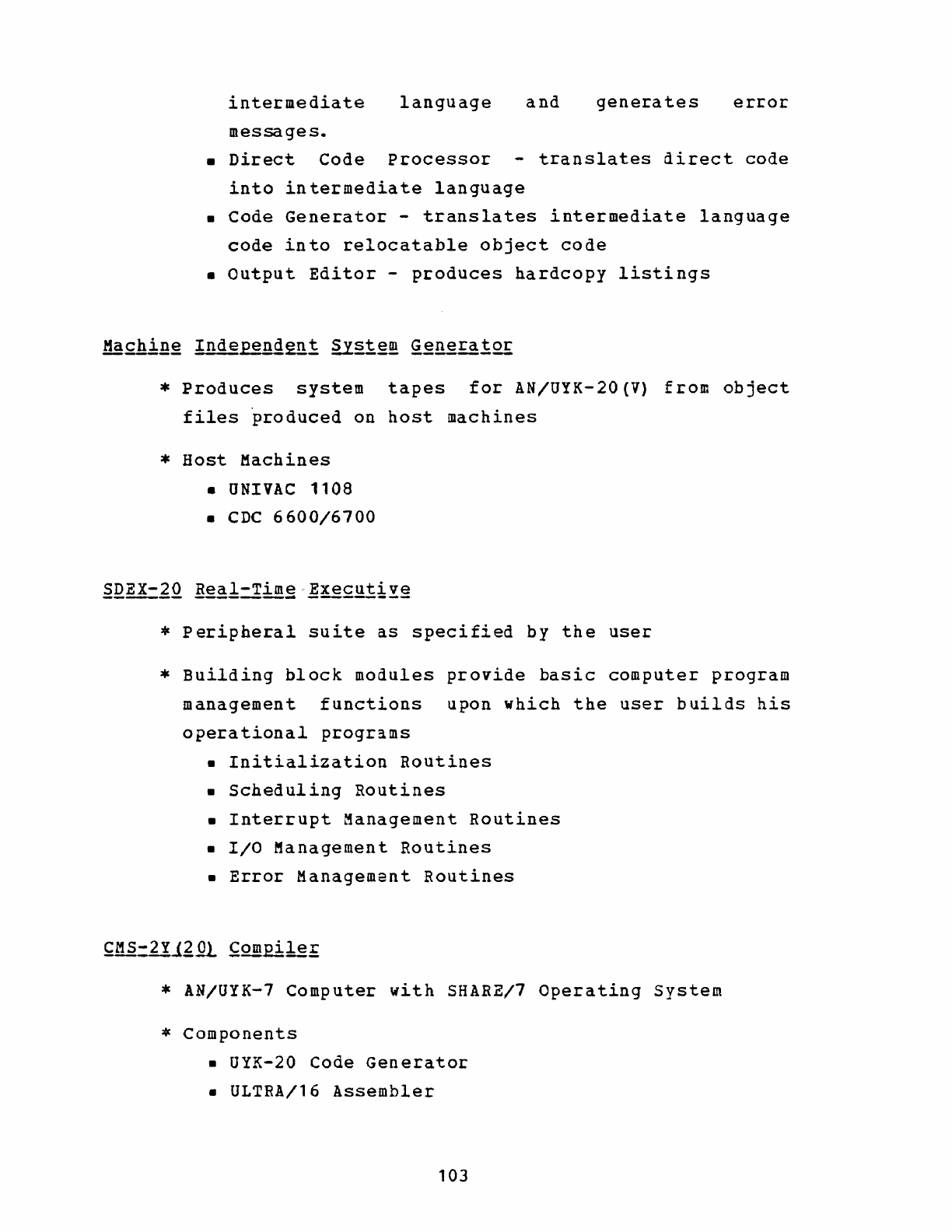

G:

Appendix

H:

Appendix

I:

STANDARD MINICOMPUTER

SPECIFICATIONS

•••••••

90

CP-642B

SYSTEM

DESCRIPTION.................

92

AN/OYK-15

(V) SYSTEM

DESCRIPTION............

94

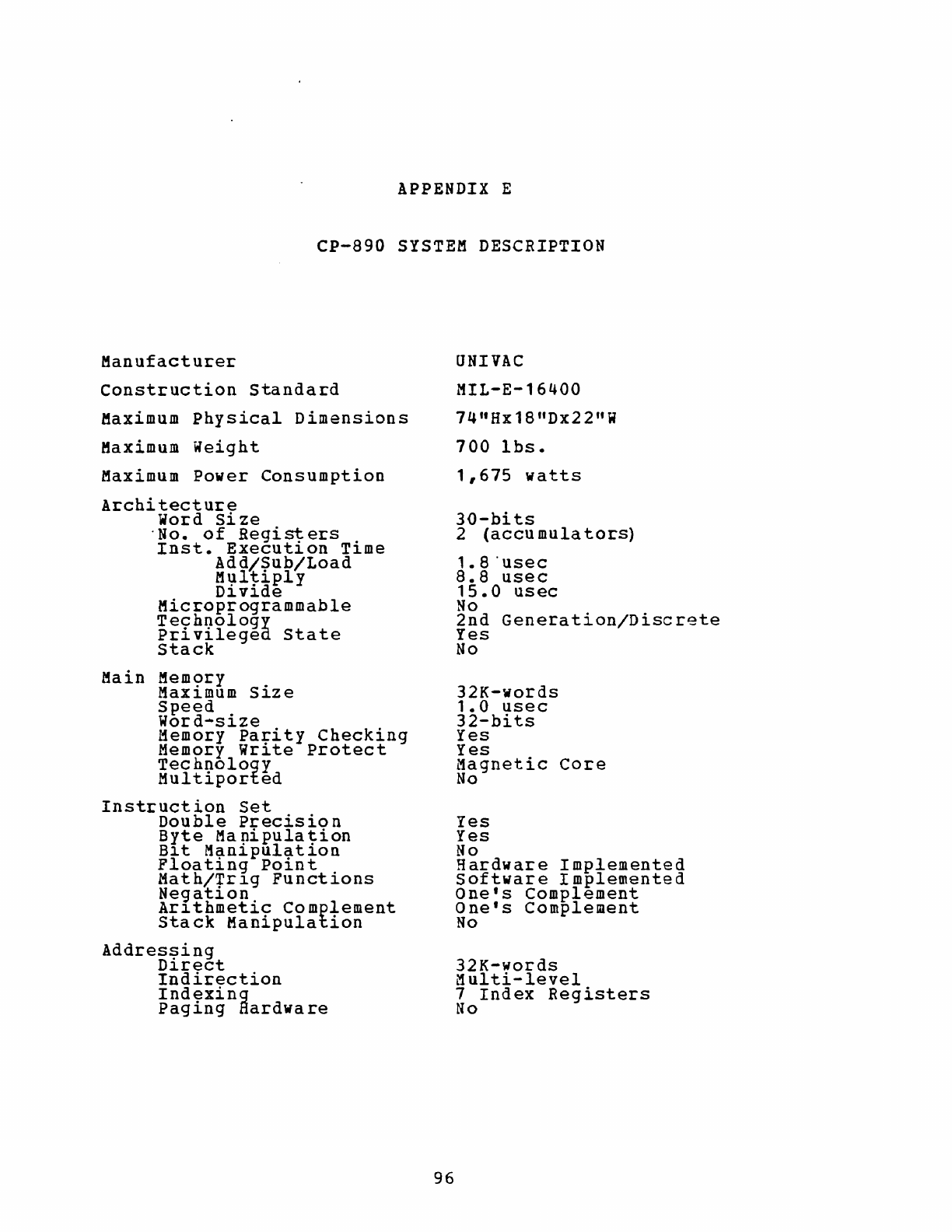

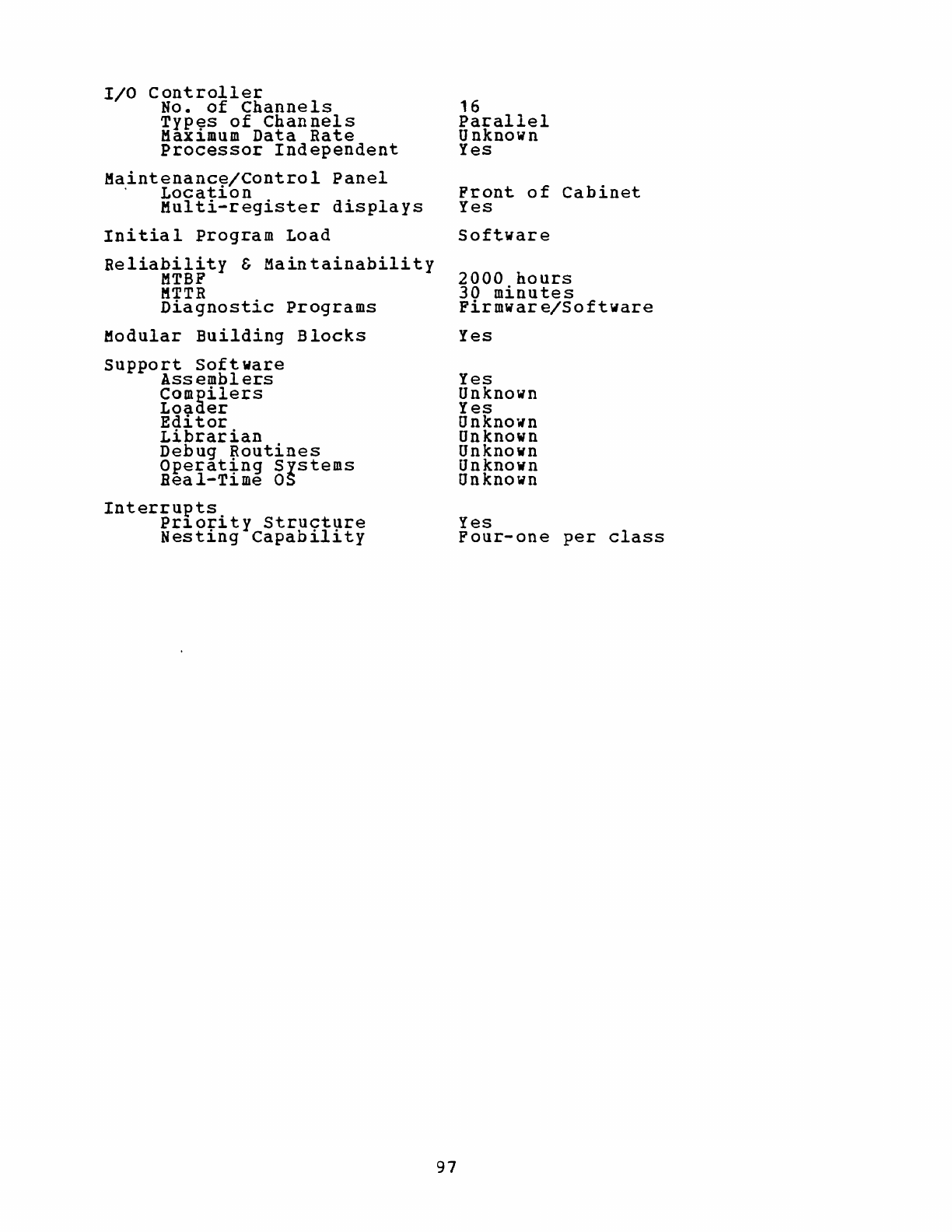

CP-890

SYSTEM

DESCRIPTION

••••••••••••••••••

96

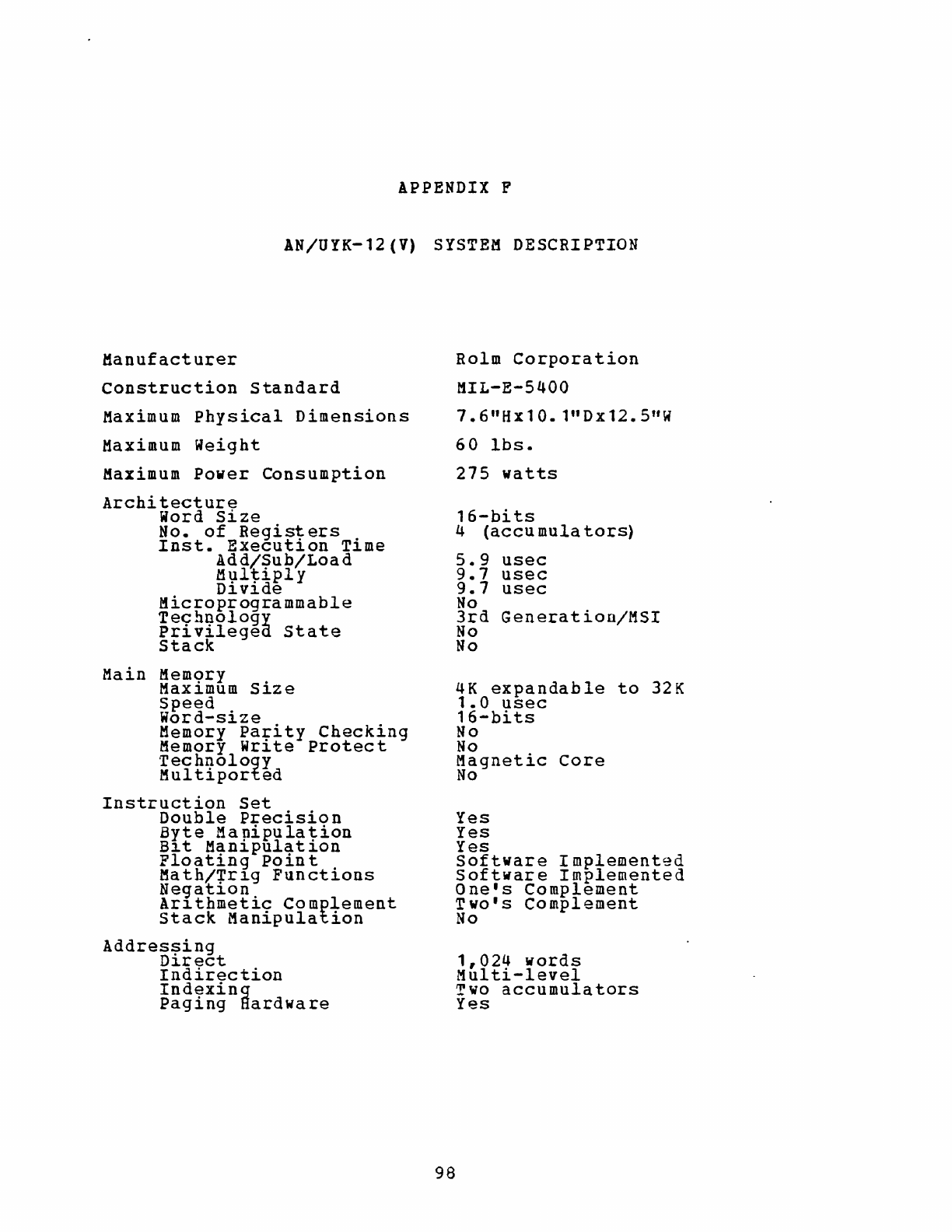

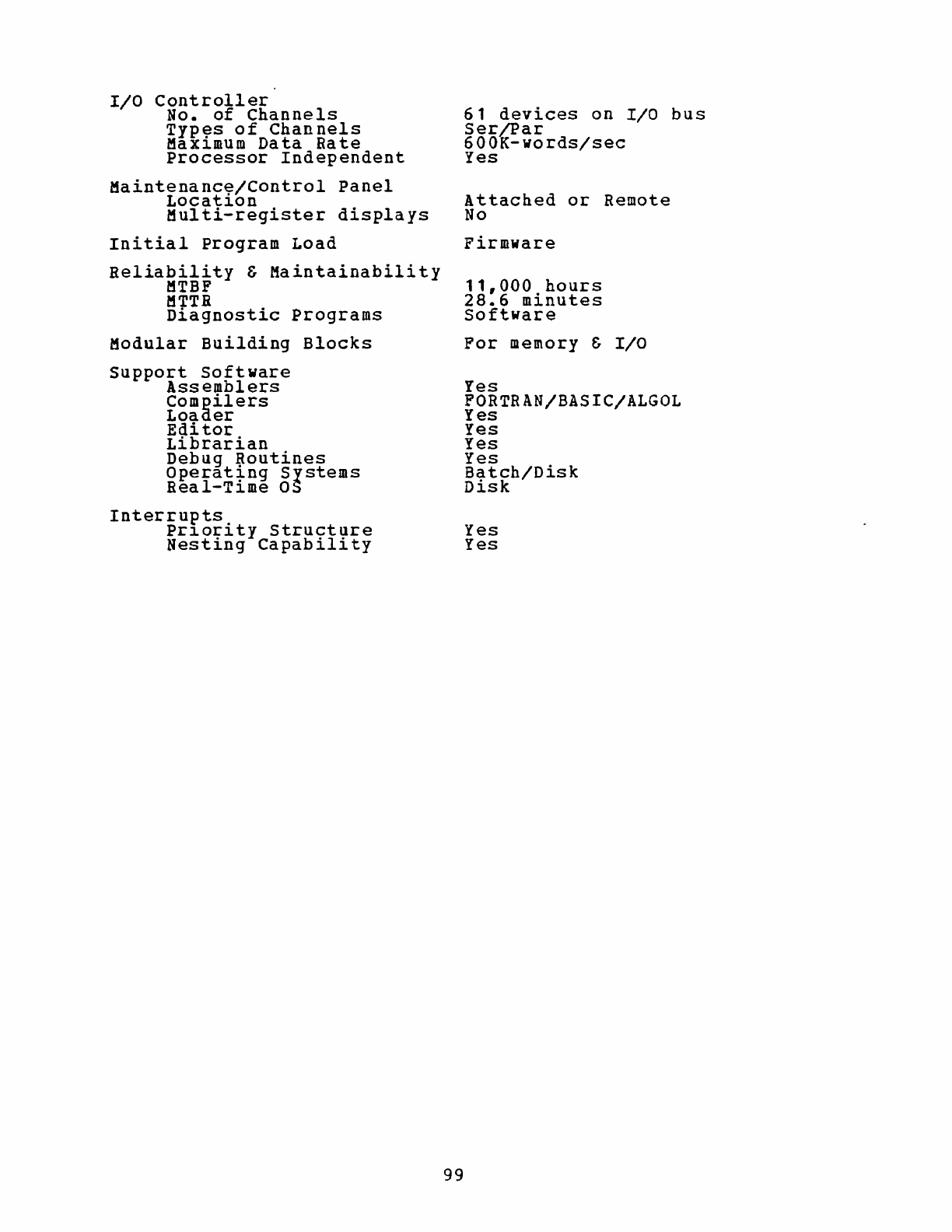

AN/UYK-12

(V)

SYSTEM

DESCRIPTION

••••••••••••

98

DESCRIPTION

OF

SYSTEM SOFTWARE

•••••••••••••

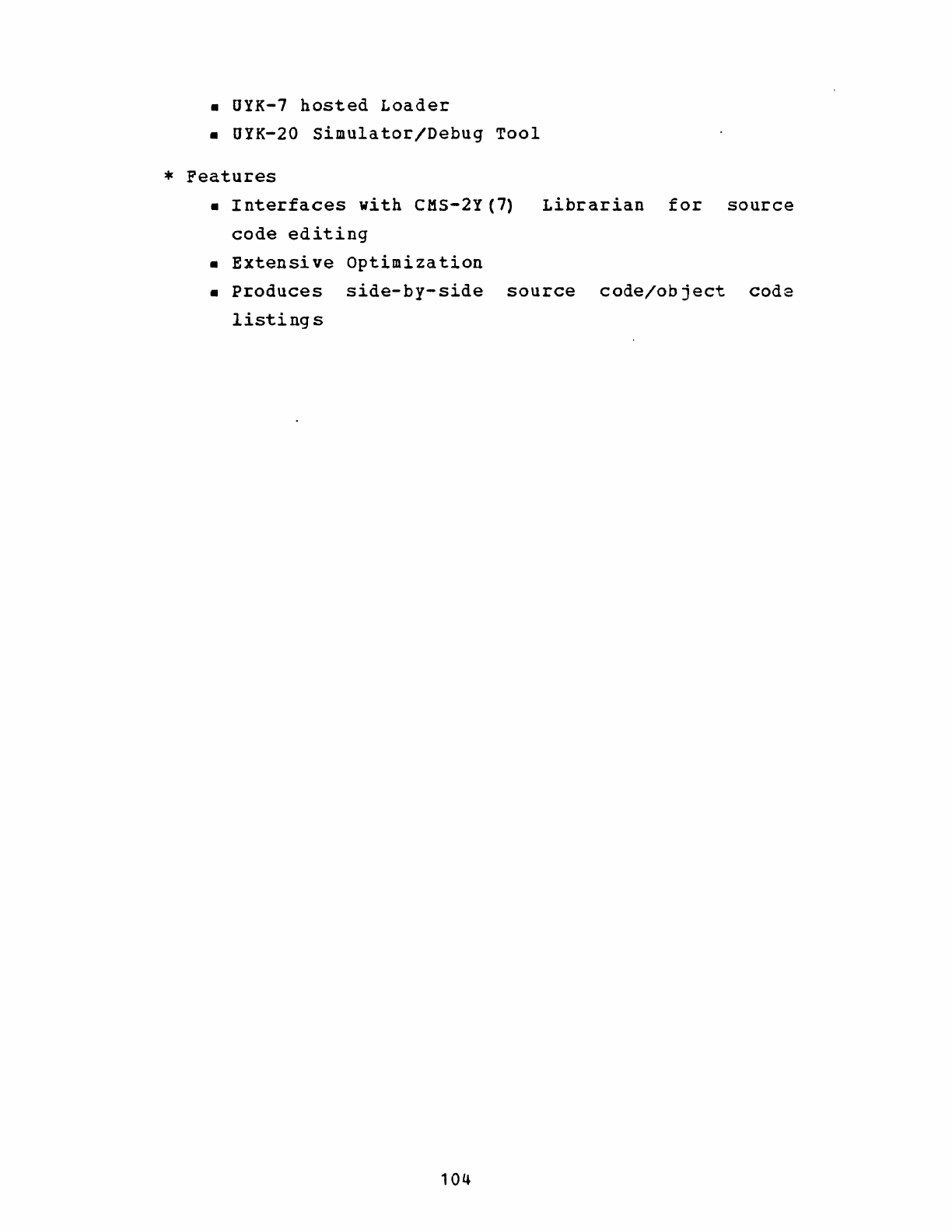

100

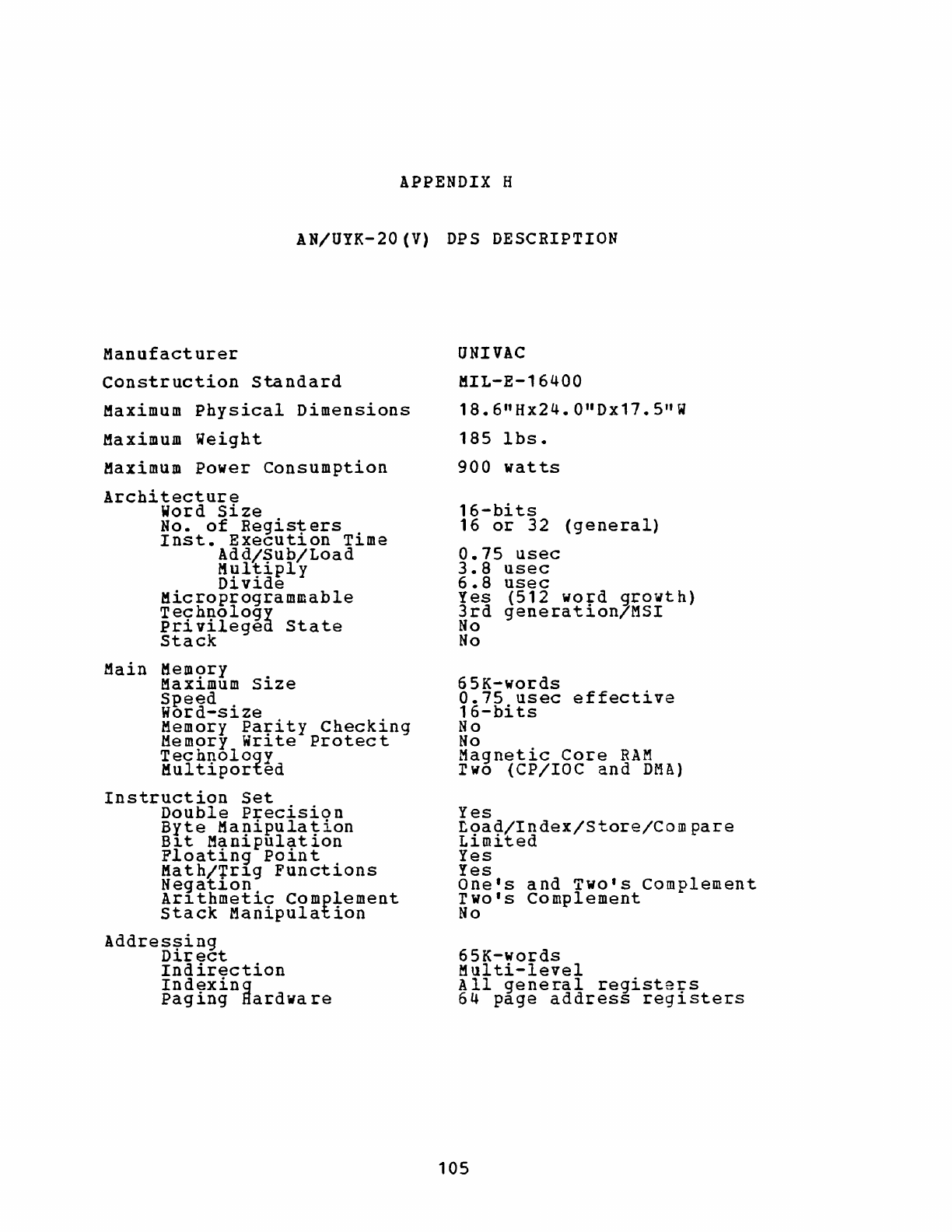

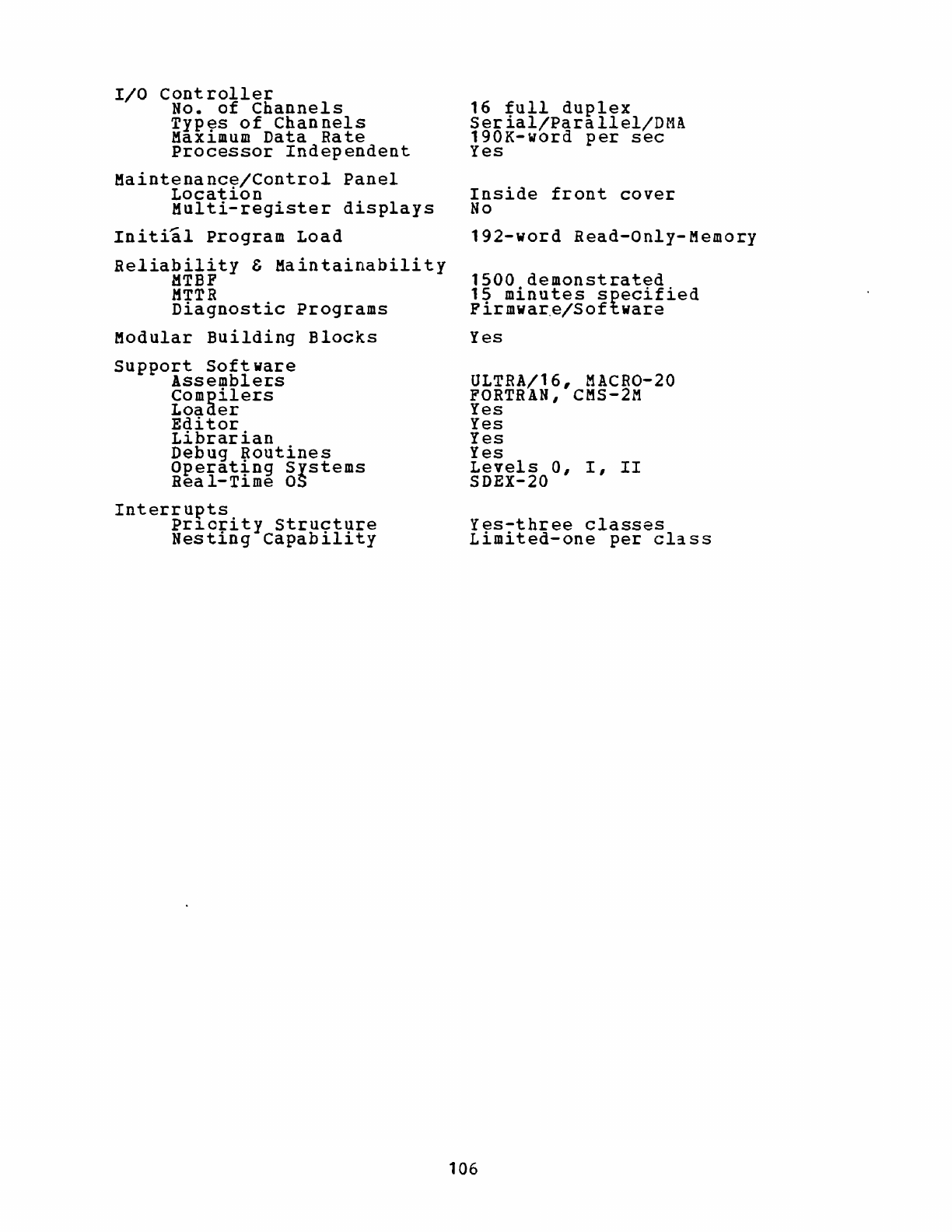

AN/OYK-20

(1)

DPS

DESCRIPTION

•••••••••••••••

105

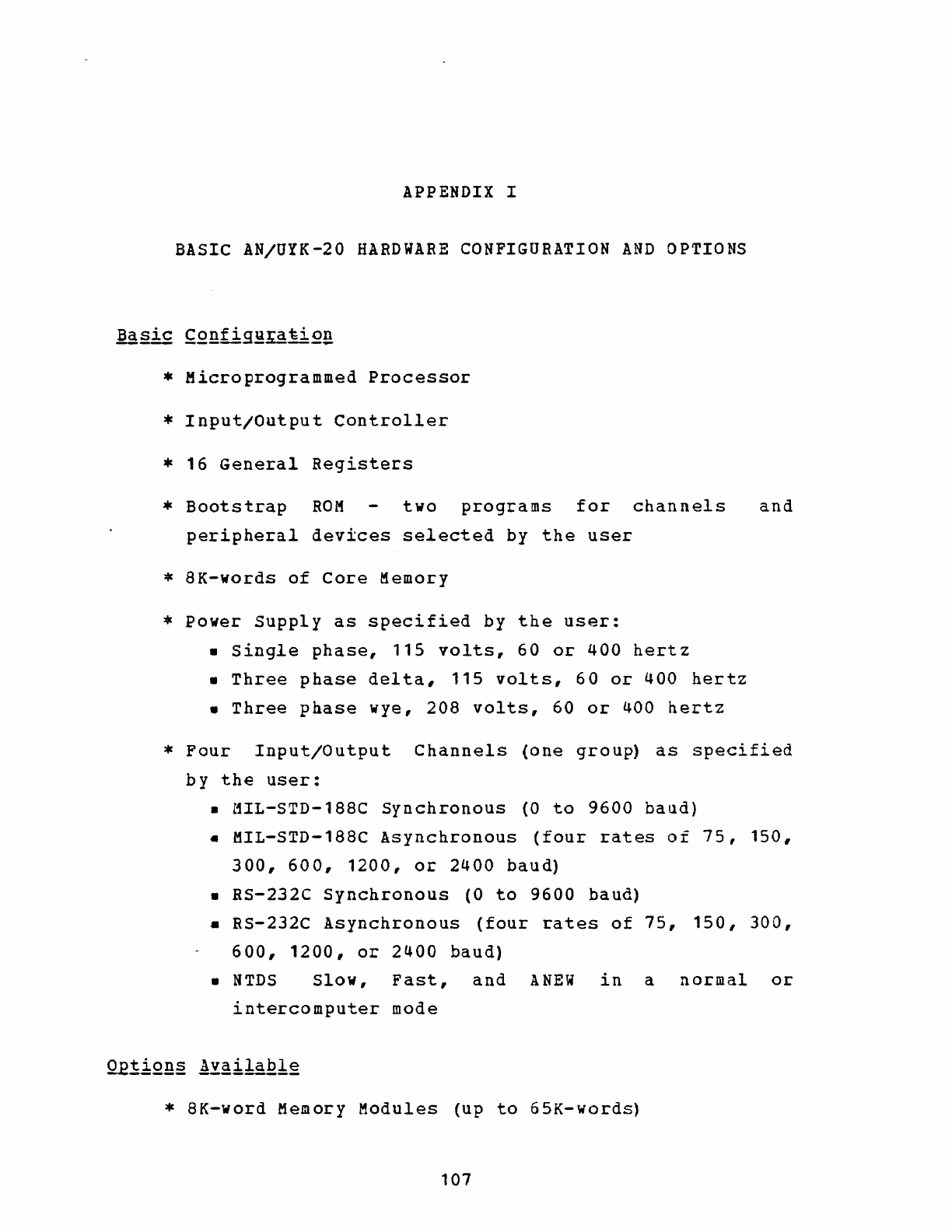

BASIC

AN/UYK-20

HARDWARE

CONFIGURATION AND

OPTIONS.

• • • •

••

• • • • • • • • • •

••

• • • • • • • • • • • • • • • • • • • • • • • • • • • •

••

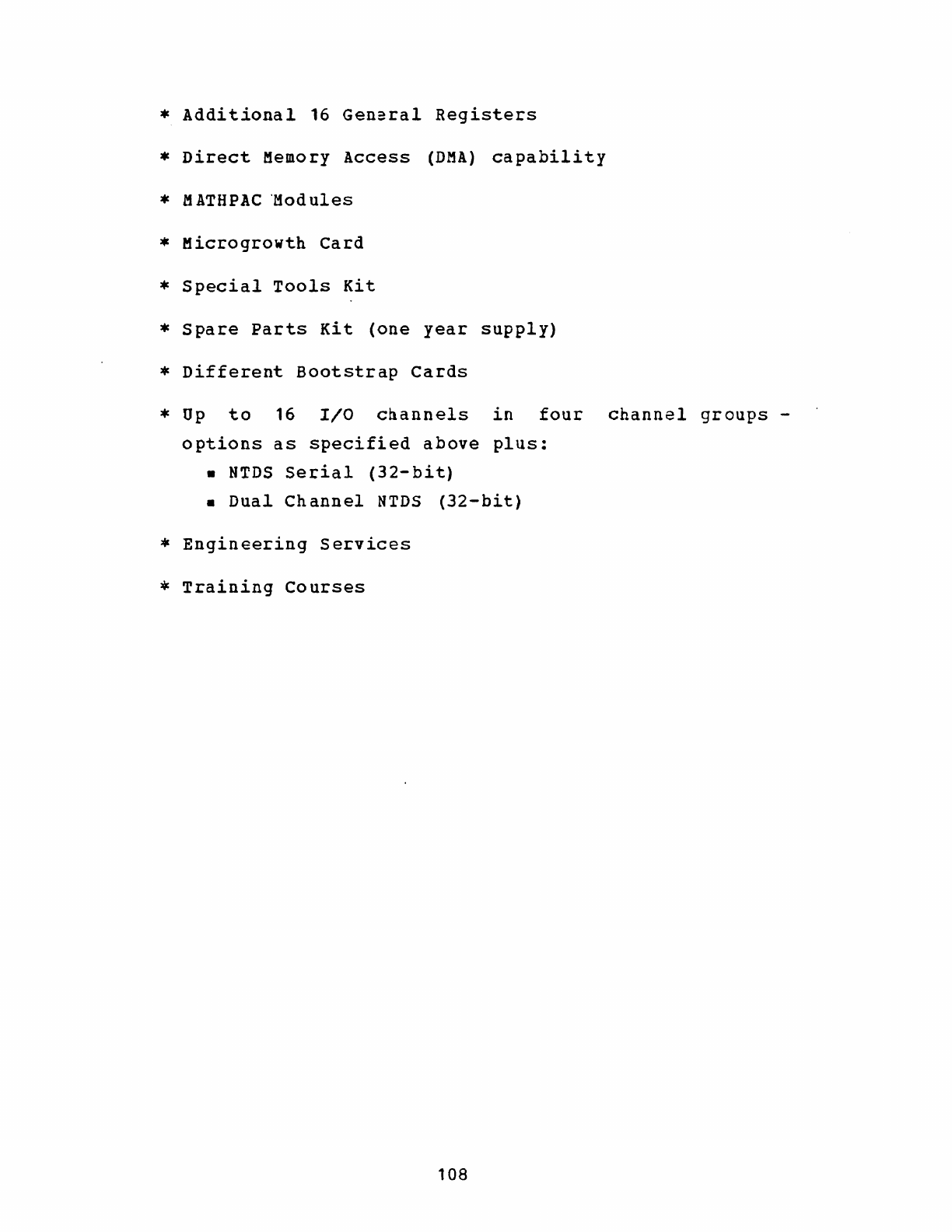

107

Appendix

J:

Appendix

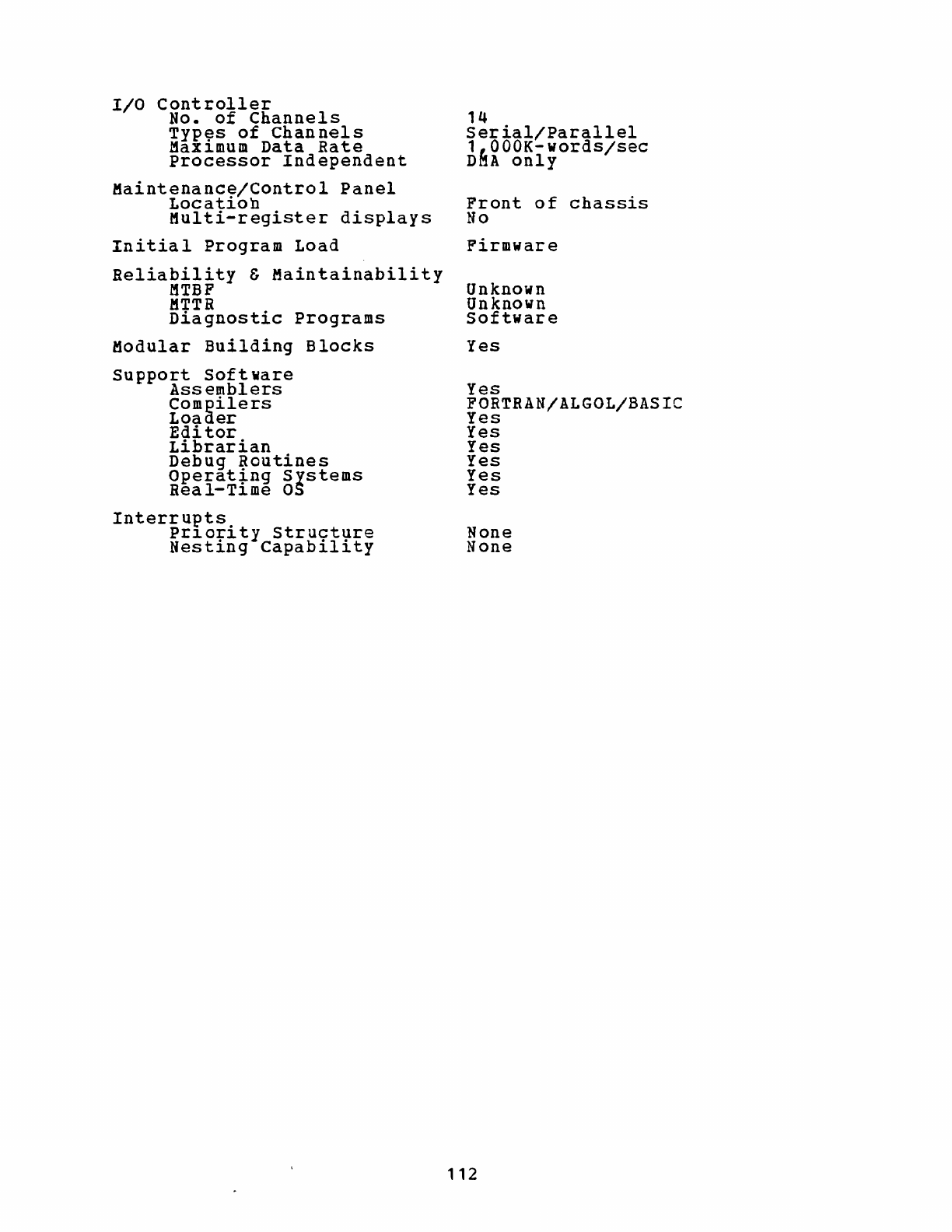

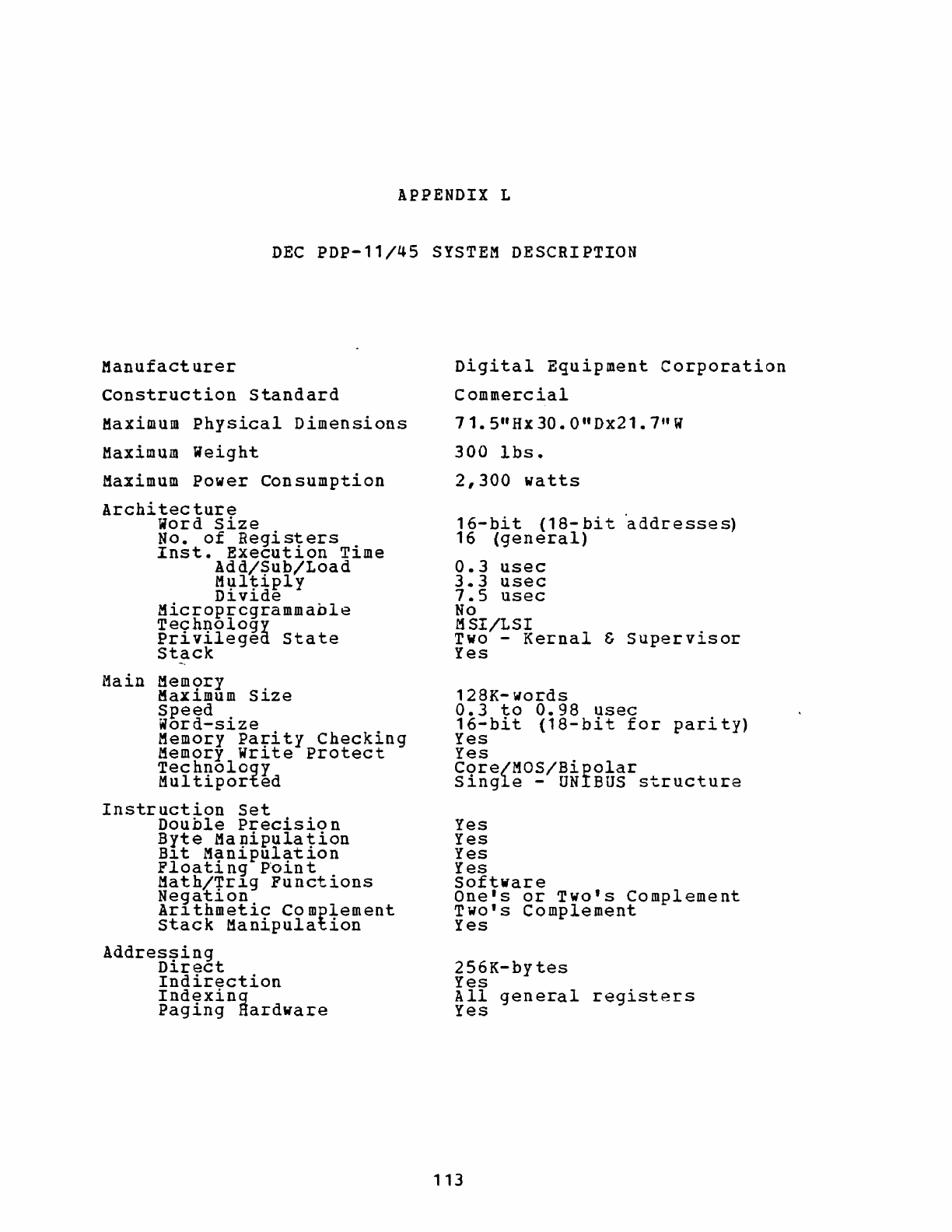

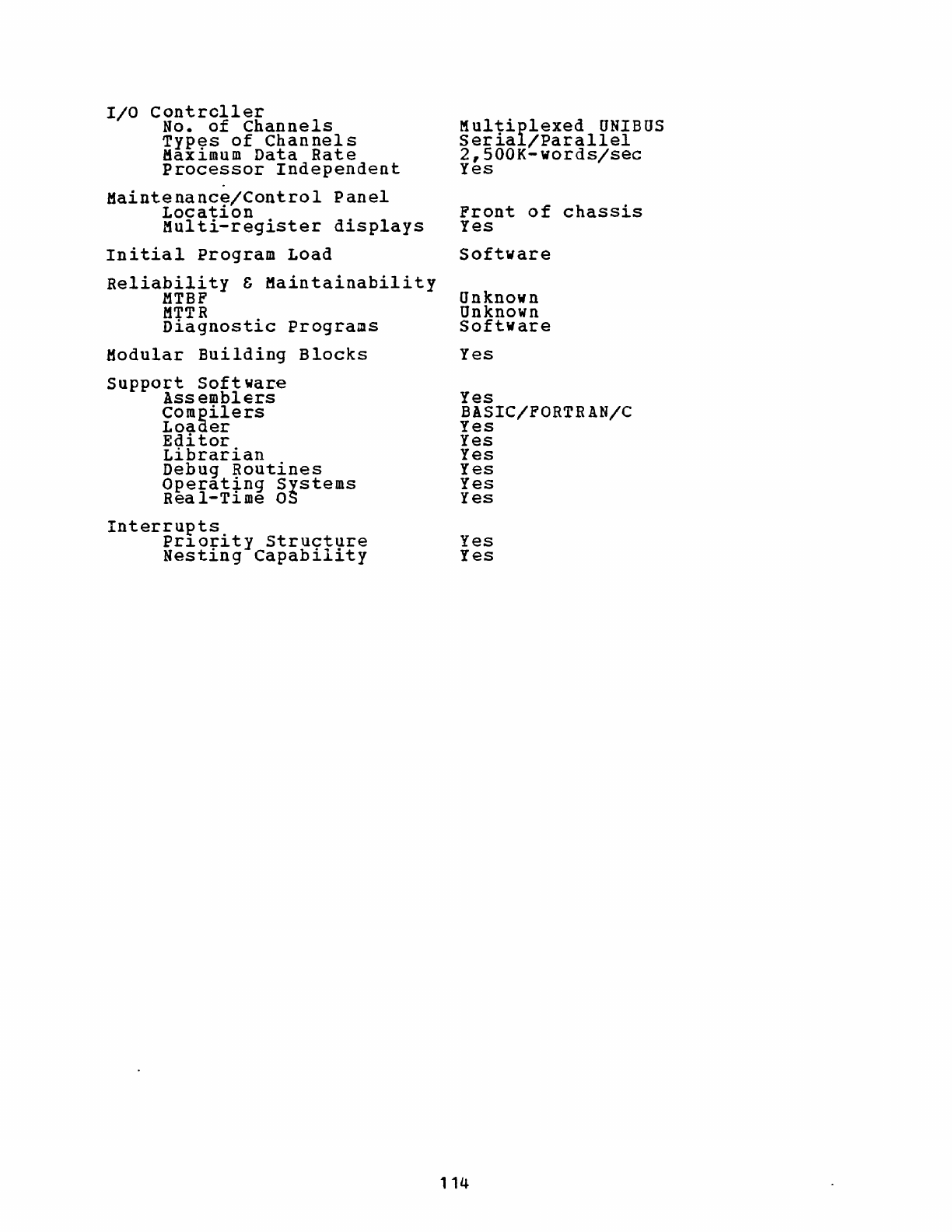

K:

Appendix

L:

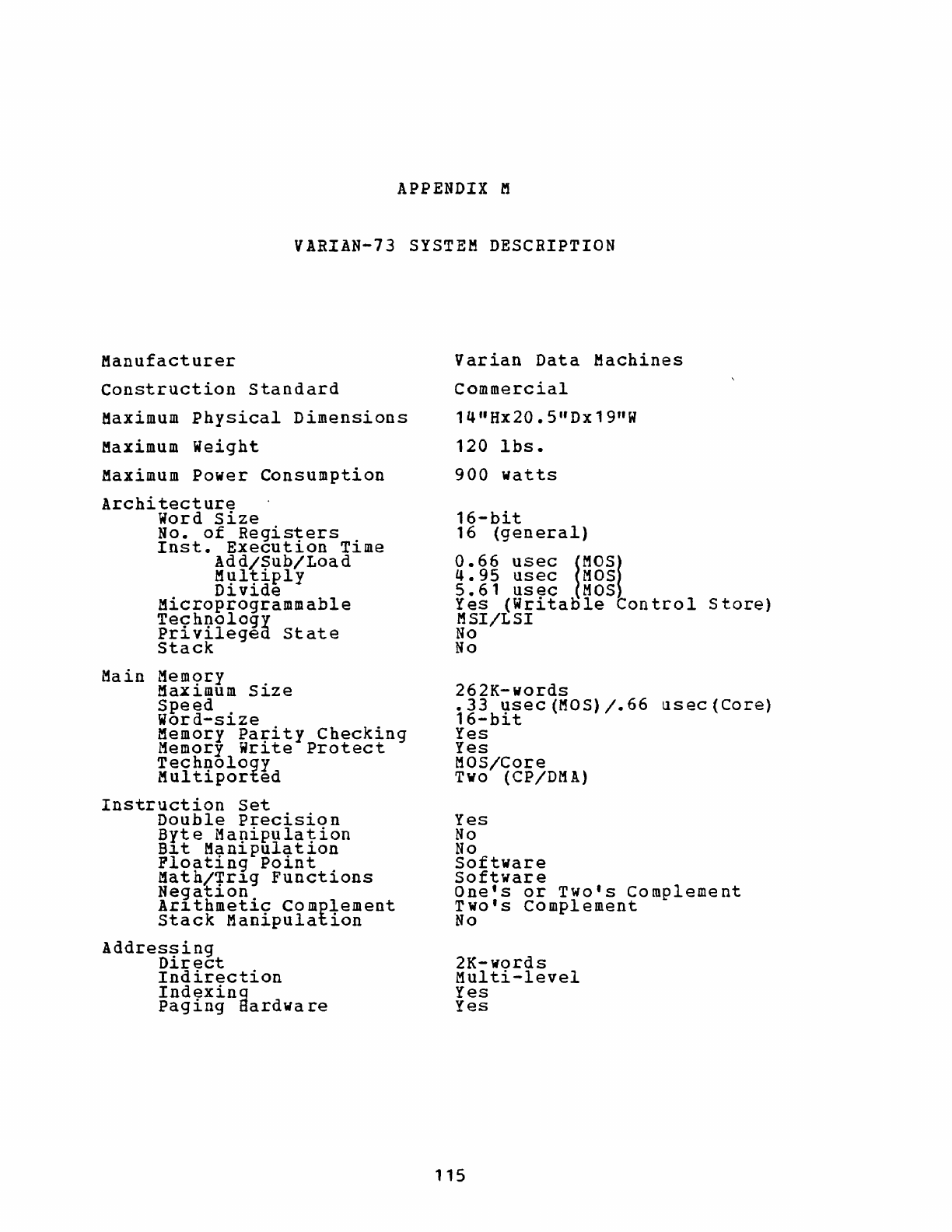

Appendix

M:

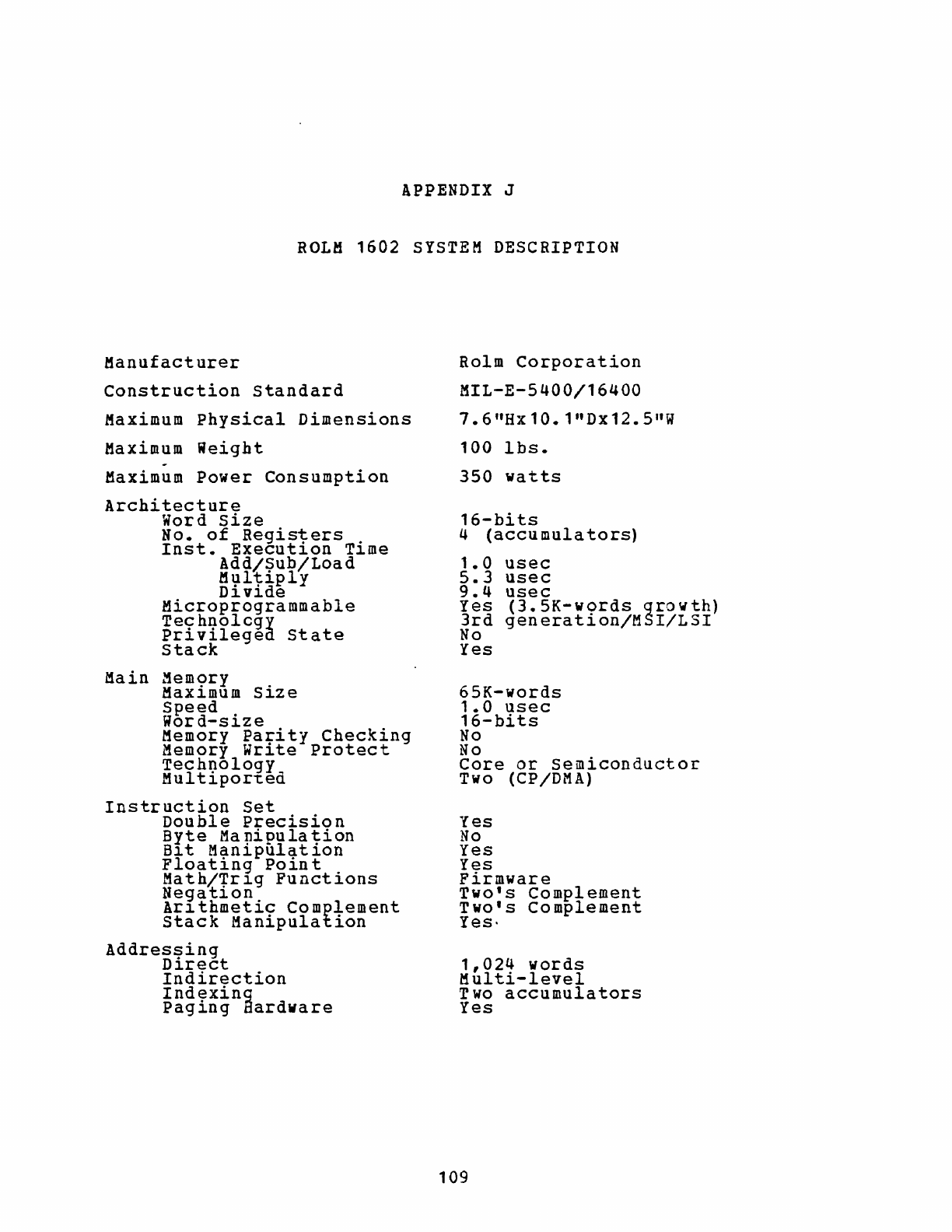

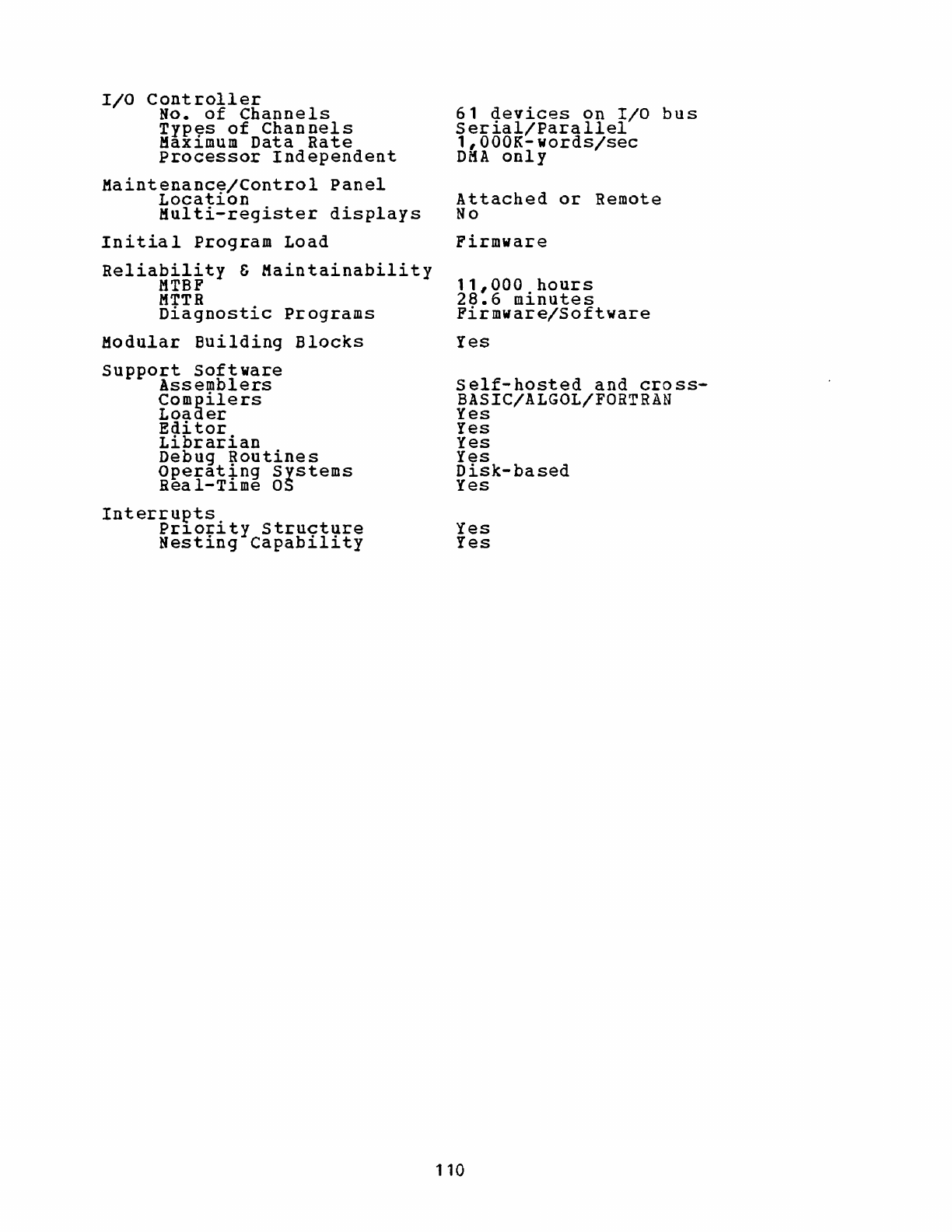

ROLM

1602

SYSTEK

DESCRIPTION...............

109

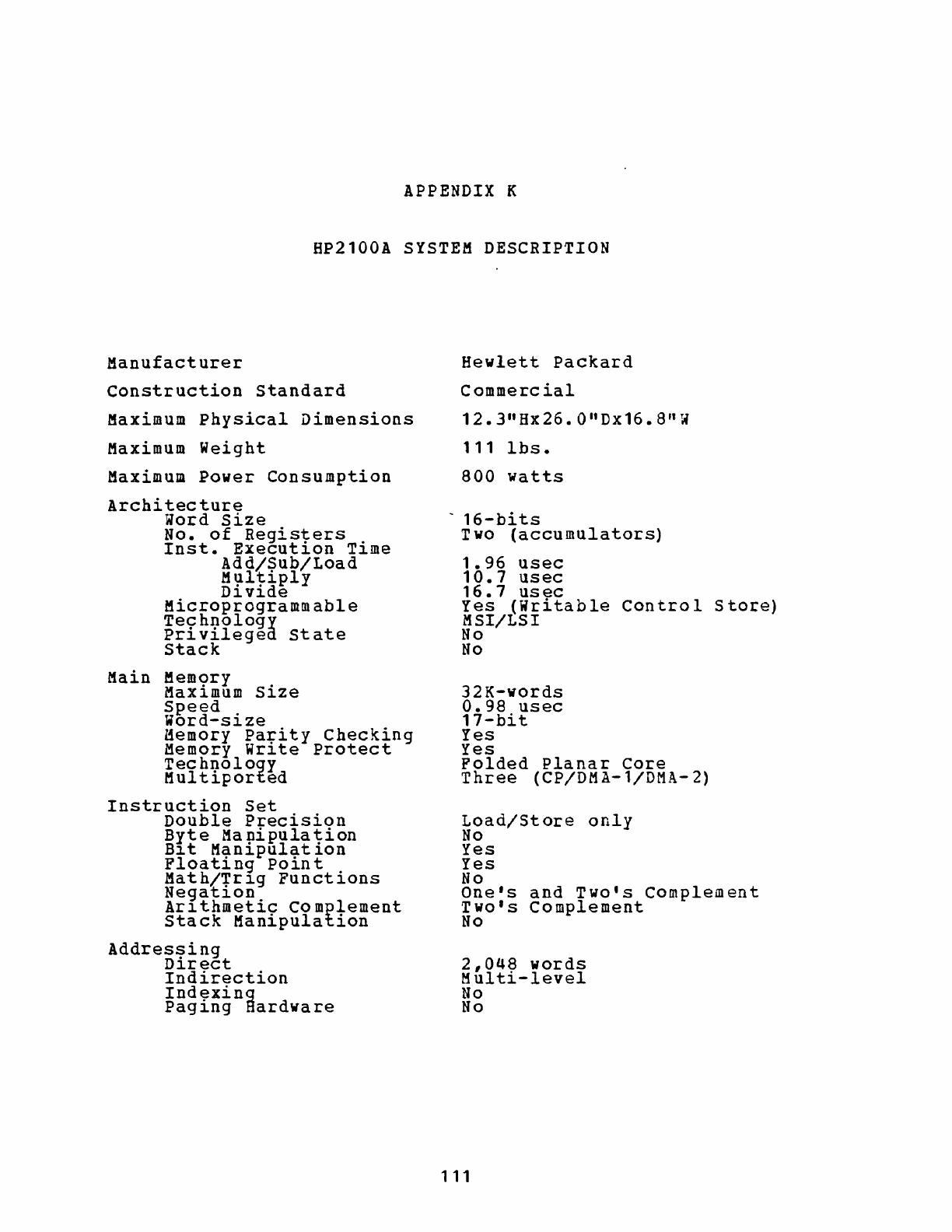

HP2100A

SYSTEM

DESCRIPTION

•••••••••••••••••

111

DEC

PDP-ll/45

SYSTEM

DESCRIPTION.........

••

113

VARIAN-73

SYSTEM

DESCRIPTION

•••••••••••••••

115

LIST

OF REFERENCES

••••••••••••••••••••••••••••••••••••••

117

INITIAL

DISTRIBUTION

LIST

................................

119

LIST

OF

FIGURES.........................................

7

6

LIST

OF

FIGURES

1.

Naval

Material

Command

Organization

•••••••••••••••••

33

2.

AN/UYK-20

(V)

System

Users

•••••••••••••••••••••••••••

34

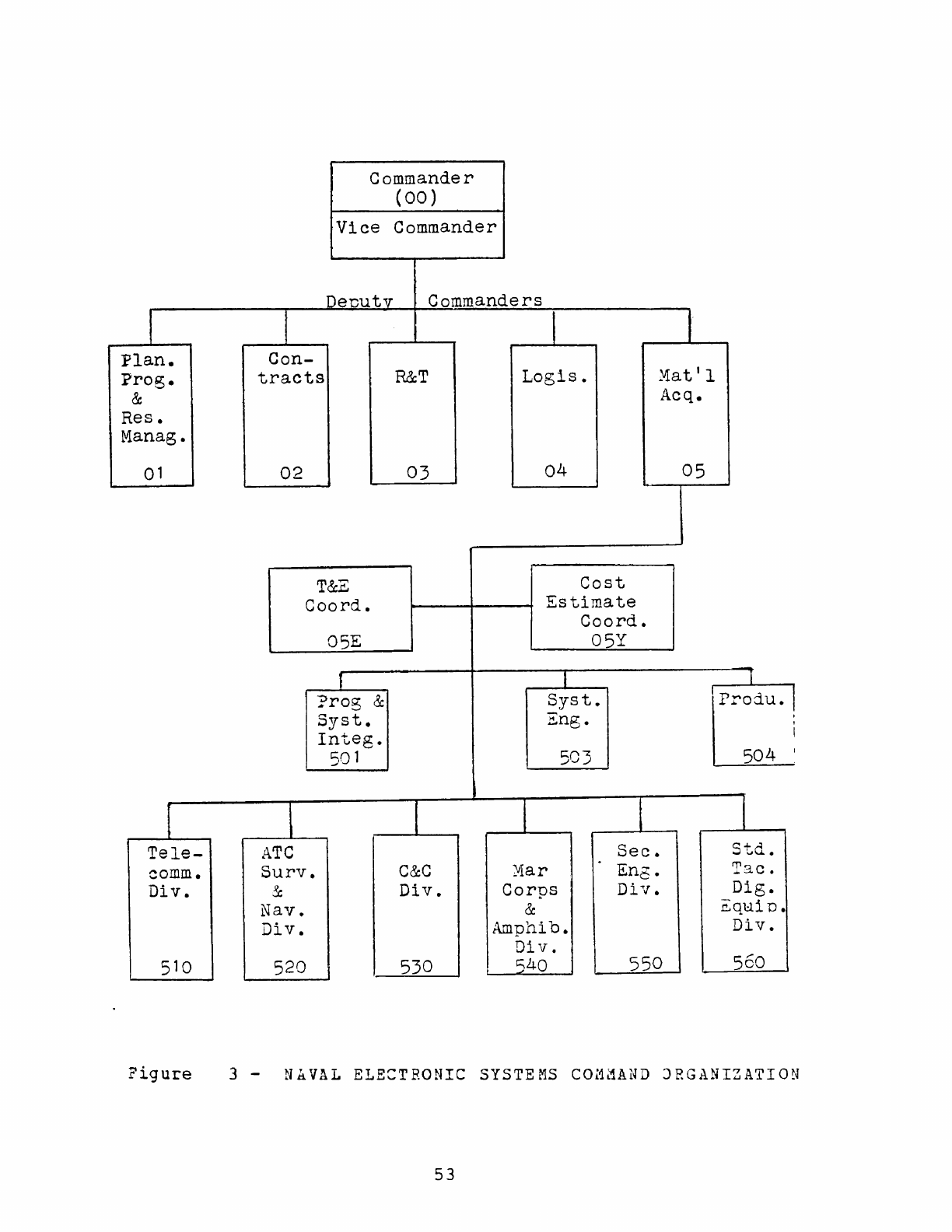

3.

Naval

Electronic

Systems

Command

Organization

•••••••

53

7

GLOSSARY

AADC

-

All

Applications

Digital

Computer

ADD

-

Alphanumeric

Display

Device

ADP

-

Automatic

Data

Processing

APE

-

Advanced

Production

Engineering

Model

- a

militarized

prototype

CDC

-

control

Data

corporation

CMTU

-

Cartridge

Magnetic

Tape

Unit

CNM

-

Chief

of

Naval

Material

CNO

-

Chief

of

Naval

Operations

COMNAVELEX

-

Commander,

Naval

Electronic

Systems

Command

CVTSC

-

Carrier

Tactical

Systems

Center

DCAS

-

Defense

Contract

Administration

Service

DEC

-

Digital

Equipment

:orporation

DMA

-

Direct

Memory

Access

DPS

-

Data

processing

System

DRG

-

Design

Review

Group

ESA

-

Externally

Specified

Addressing

FCDSSA -

Fleet

Combat

Direction

Systems

Software

Activity

FDM

-

Functional

Demonstration

Model

a

non-militariz~d

prototype

GFCS

-Gun

Fire

Control

System

GFE

-

Government

Furnished

Equipment

IBM

-'

International

Business

Machines

Corporation

ILS

-

Integrated

Logistics

Support

I/O

-

Input/Output

IOC -

Input/Output

Controller

ISADC -

Interim

Standard

Airborne

Digital

Computer

LSI

-

Large

Scale

Integration

MATHPAC

-

Plug-in

module

of

floating-point,

~rigonometric

and

hyperbolic

functions

implemented

in

microcode

8

MICROGROWTH

-

Plug-in

module

of

user

specified

microprograms

MOS

-

Metal

Oxide

Semiconductor

MSI

-Medium

Scale

Integration

MTBF

-Mean Time

Between

Failures

MTTR

-Mean Time To

Repair

NAFI

-

Naval

Avionics

Facility,

Indianapolis

NAVAIR

-

Naval

Air

Systems

Command

NAVELEX

-

Naval

Electronic

Systems

Command

HAVMACS

-

Naval

Message

Address

Communications

System

NAVHAT

-

Naval

Material

:ommand

HAVORD

-

Naval

Ordnance

Systems

Command

combined

with

NAVSHIPS

to

form

NAVSEA

NAVSEA

-

Naval

Sea

Systems

Command -

formed

by

combining

NAVORD

and

NAVSHIPS

NAVSEC

-

Naval

Systems

Engineering

Center

NAVSHIPS

-

Naval

Ships

Systems

Command

combined

with

HAVORD

to

form

NAVSEA

NELC

-

Naval

Electronics

Laboratory

Center

NESEC

-

Naval

Electronic

Systems

Engineering

Center

NTDS

-

Naval

Tactical

Data

System

OMB

-

Office

of

Management

and

Budget

O&MN

-

Operations

and

Maintenance

Navy

Appropriation

OPEVAL

-

Operational

Evaluation

OSD

-

Office

of

the

Secretary

of

Defense

QA

-

Quality

Assurance

RAM

-Random

Access

Memory

RDT&EN

-

Research,

Development,

Test

and

Evaluation

Navy

Appropriation

REiSON

-

Reconnaissance

Electronic

Warfare

Systems

Office

Navy

RFP

-

Request

for

Proposals

ROM

-

Read-Only-Memory

SECDEF

-

Secretary

of

Defense

SSA

-

Source

Selection

Authority

SSAC

-

Source

Selection

Advisory

Council

SSEB

-

Source

Selection

Evaluation

Board

9

TADSO

-

Tactical

Digital

systems

Office

of

the

Naval

Material

Command

TADSTAND

-

Tactical

Digital

Standard

TALOS

-

long-range,

surface-to-air

missile

TARTAR

-

short-range,

surface-to-air

missile

TECHEVAL

-

Technical

Evaluation

TERRIER -

intermediate-range,

surface-to-air

missile

TTL -

Transistor-Transistor

Logic

UNIVAC

-

UNIVAC

Defense

Systems

Division

of

Sperry-Rand

corporation

WCS

-

writable

Control

Store

10

ACKNOWLEDGEMENT

I

wish

to

thank

the

many

personnel

of

Navy

activities

and

private

contractor

firms

who

took

time

out

from

their

busy

schedules

to

answer

my

questions.

Thanks

also

to

my

two

thesis

advisors,

Professor

stephen

Jauregui

and

LCDR

Edward

Zabrycki,

who

waited

patiently

for

the

thesis

to

emerge

from

my

research.

Finally,

special

thanks

go

to

the

Commander,

Naval

Electronic

Systems

Command

(PME-107)

who

provided

funds

to

make

this

thesis

possible

and

to

my

wife,

Ann,

who

relieved

me

of

many

family

obligations

juring

the

final

crunch.

11

A.

THESIS

OBJECTIVE

In

1972

the

Navy

began

procurement

of

a

small

digital

computer

which

was

to

be

a

standard

minicomputer

for

tactical

system

applications.

That

standard

minicomputer

was

later

designated

the

AN/UYK-20(V)

Data

Processing

System.

The

acquisition

strategy

employed

and

the

resulting

events

of

the

first

three

years

of

production

caused

great

concern

among

project

m~nagers

who

were

required

to

use

the

standard

minicomputer.

At

least

one

user

project

manager

believed

that

~n

objective

look

at

the

standard

minicomputer

acquisition

was

necessary

to

prevent

recurrence

of

those

events

which

adversely

impacted

on

the

development

of

tactical

systems.

It

is

the

objective

of

this

thesis

to

examine

the

standard

minicomputer

acquisition

process,

to

ev~luate

the

system

in

light

of

user

needs

and

1972

state-of-the-art,

to

identify

those

events

which

contributed

to

the

adverse

impact

of

the

standard

minicomputer

on

development

efforts,

and

to

offer

some

recommendations

for

future

acquisitions

of

standard

tactical

digital

processors.

B.

METHODOLOGY

12

In

order

to

obtain

information

about

minicomputers

in

general

and

the

AN/UYK-20(V)

Data

Processing

System

in

particular,

a

literature

search

was

conducted.

references

are

listed

at

the

end

of

the

thesis.

Pertinent

To

obtain

a

complete

and

objective

picture

of

the

acquisition

process

it

was

then

necessary

to

contact

personnel

at

all

levels

in

user

pr~ject

organizations

and

also

personnel

in

the

standard

minicomputer

project

organization.

The

following

types

of

activities

were

contacted

to

obtain

information:

* Navy

field

activities

checkout,

delivery

responsible

for

assembly,

and

maintenance

of

tactical

systems

hardware

~nd

software.

* Navy

laboratories

-

responsible

for

certain

aspects

of

tactical

system

development

and

testing.

*

Private

contractors

responsible

for

hardware

and

software

development

of

tactical

systems

under

contract

to

Navy

project

offices.

* Navy

project

offices

-

responsible

for

management

of

the

acquisition

of

tactical

systems

utilizing

UYK-20

as

a

system

component.

Additional

information

was

obtained

by

attending

two

AN/UYK-20

User's

Group

meetings.

A

minimal

amount

of

laboratory

experience

was

gained

on

the

UYK-20

itself.

13

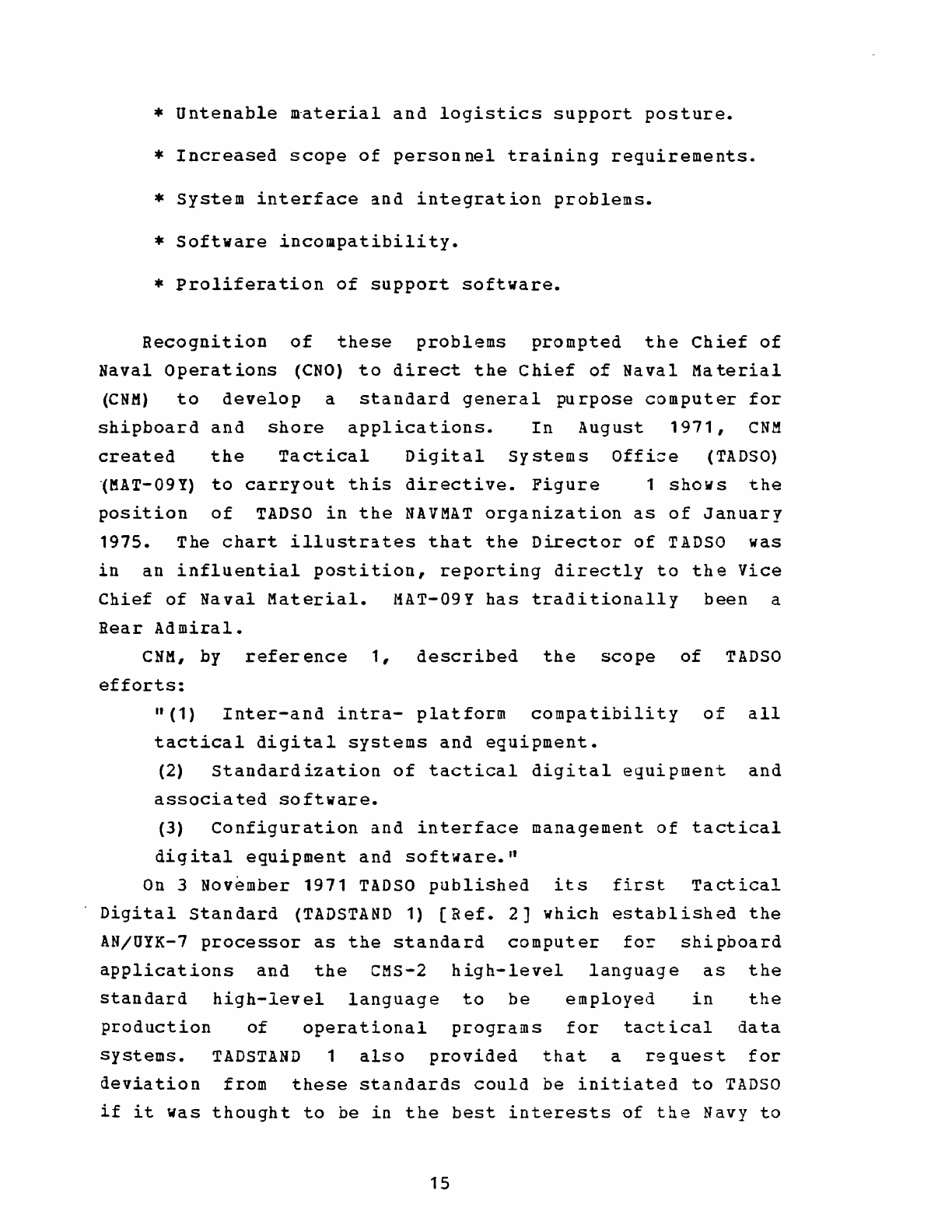

The

1960's

saw

the

first

successful

employment

of

a

general

purpose

digital

computer

in

a

shipboard

tactical

system.

This

event

precipitated

the

introduction

of

a

large

number

of

shipboard

computers

into

the

Navy

inventory

manufactured

by

several

different

companies

with

slightly

different

capabilities.

Some

of

these

computers

are

"listed

below.

Others

existed,

particularly

in

avionics

applications.

~Q!llput~£

MK

74

MK

76

MK

77

MK

86

AN/U5Q-17

AN/USQ-20

CP642

CP642A

CP642B

AN/OYK-7

AN/SYA-12

AN/UYK-15

(V)

CP890

AN/UYK-12

(V)

Cognizant

~§~2!!!

NAVORD

NAVORD

NAVORD

NAVORD

NAVSEC

NAVSEC

NAVSEC

NAVSEC

NAVSEC

NAVSEC

NAFI

NAVSEC

NAVSHIPS

NAVSBIPS

!E.21!cat

i211

TARTAR

Missile

System

TERRIER

Missile

System

TALOS

Missile

System

Gun

Fire

Control

System

NTDS

NTDS

NTDS

NTDS

NTDS

NTDS

Communications

General

Purpose

N~vigation

General

Purpose

This

proliferation

of

tactical

processors

created

the

following

tYFes

of

problems:

*

Small

and

uneconomical

procurement

programs.

14

*

Untenable

naterial

and

logistics

support

posture.

*

Increased

scope

of

personnel

training

requirements.

*

System

interface

and

integration

problems.

*

Software

incompatibility.

*

Proliferation

of

support

software.

Recognition

of

these

problems

prompted

the

Chief

of

Naval

Operations

(eNO)

to

direct

the

Chief

of

Naval

Material

(CNM)

to

develop

a

standard

general

purpose

computer

for

shipboard

and

shore

applications.

In

August

1971,

CNM

created

the

Tactical

Digital

Systems

Offi~e

(TADSO)

1MAT-09Y)

to

carryout

this

directive.

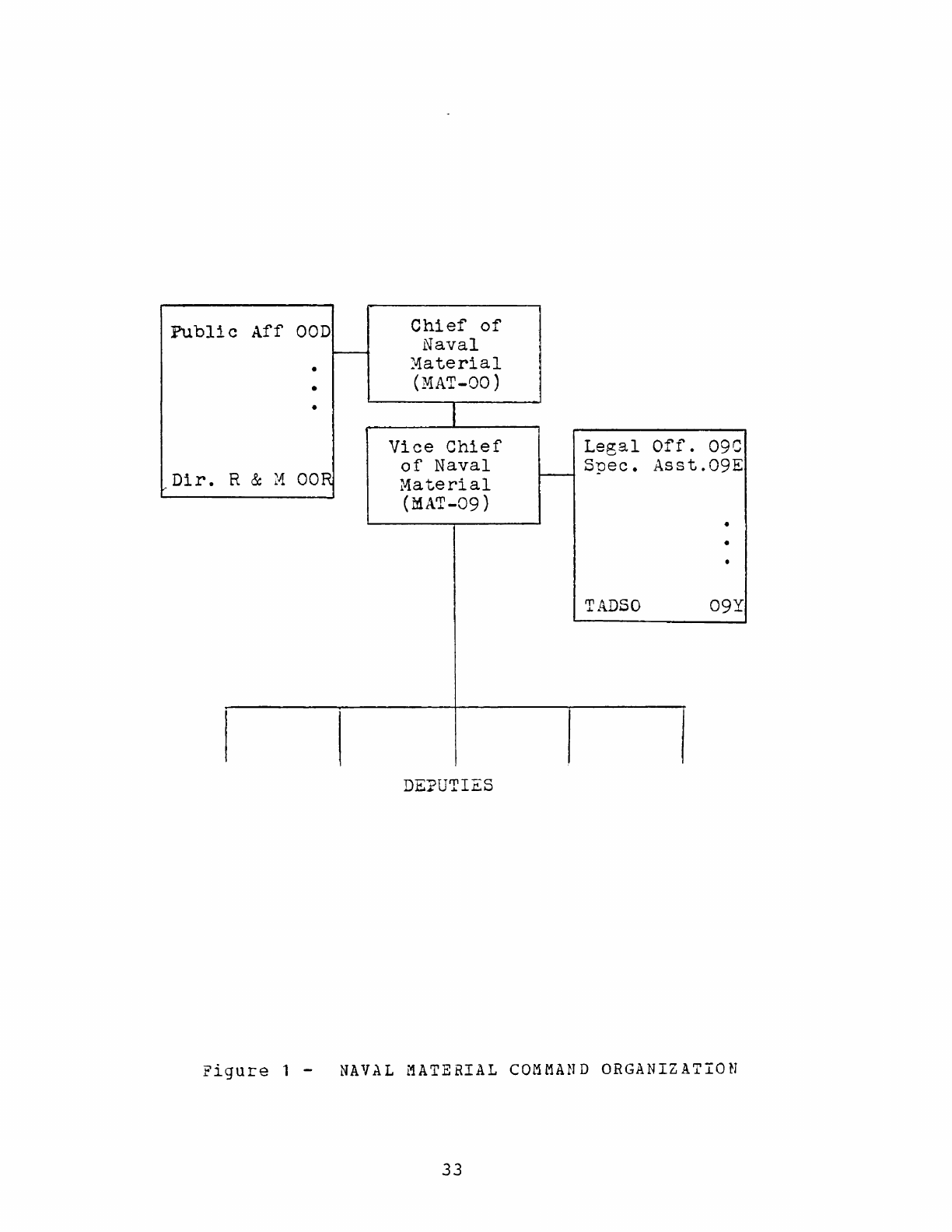

Figure

1

shows

the

position

of

TADSO

in

the

NAVMAT

organization

as

of

January

1975.

The

chart

illustrates

that

the

Director

of

TADSO

was

in

an

influential

postition,

reporting

directly

to

the

Vice

Chief

of

Naval

Material.

MAT-09Y

has

traditionally

been

a

Rear

Admiral.

CNM,

by

reference

1,

described

the

scope

of

TADSO

efforts:

11(1)

Inter-and

intra-

platform

compatibility

of

all

tactical

digital

systems

and

equipment.

(2)

Standardization

of

tactical

digital

eguipment

and

associated

software.

(3)

Configuration

and

interface

management

of

tactical

dig

ital

equipment

and

soft

ware.

"

On

3

November

1971

TADSO

published

its

first

Tactical

Digital

Standard

(TADSTAND

1)

[Ref.

2]

which

established

the

AN/UYK-7

processor

as

the

standard

computer

for

shipboard

applications

and

the

CMS-2

high-level

language

as

the

standard

high-level

language

to

be

employed

in

the

production

of

operational

programs

for

tactical

data

systems.

TADSTAND

1

also

provided

that

a

request

for

deviation

from

these

standards

could

be

initiated

to

TADSO

if

it

was

thought

to

be

in

the

best

interests

of

the

Navy

to

15

use

either

another

Navy

computer

or

a

computer

not

presently

in

the

Navy

inventory.

In

response

to

TADSfAND 1

some

requests

to

deviate

from

the

UYK-7

standard

were

received.

The

most

significant

justification

given

was

that

the

UYK-7

was

too

large

and

expensive

($720,000

average

cost)

for

the

intended

application.

(See

App.

A

for

a

description

of

the

UYK-7

computer.)

out

of

this

identified

need

for

a

smaller

computer

grew

the

AN/UYK-20(V)

Data

Processing

System

(DPS),

the

Navy

standard

m~nicomputer.

It

is

the

purpose

of

this

chapter

to

establish

the

meaning

and

implications

of

the

terms

"minicompu

terl1

and

"standard",

to

identify

the

capabilities

needed

within

the

Navy

in

a

standard

minicomputer

system,

and

to

establish

whether

or

not

these

capabilities

could

be

met

by

a

small

computer

existing

in

the

Navy

inventory

in

1972.

A.

DEFINITION

OF

A MINICOMPUTER

Commercially

available

computers

in

1972

formed

almost

a

continuous

spectrum

in

size,

power

and

capabilities.

Naturally,

it

is

is

difficult

to

separate

the

minicomputer

from

larger

or

smaller

types.

The

possibility

of

a

small

computer

with

useful

capabilities

and

memory

capacity

grew

with

tha

development

of

hybrid

and

integrated

circuits

in

the

mid-1960's.

In

1970

medium-

and

large-scale

integration

was

introduced,

allowing

even

more

capability

to

be

designed

into

a

small

package.

hardware

decade.

designed

At

the

same

time

these

advancements

were

reducing

costs

at

the

rate

of

an

order

of

magnitude

?er

The

advent

of

mini-peripherals

specifically

for

use

with

minicomputers

was

the

final

addition

to

complete,

low-cost

mini-systems.

At

that

time,

as

was

still

true

in

1976,

software

was

the

predomin~nt

cost

of

such

systems.

16

C.

weitzman

[Ref.

11]

defined

the

minicomputer

as

an

8-

to

18-

bit

word

size

machine

with

memory

size

from

1K

to

32K

words.

costs

range

from

$4,000

to

$100,000.

The

minicomputer

is

generally

catagorized

as

having

limited

accuracy,

low

speed

for

double-precision

arithmetic

operation.s

and

no

floating-point

hardware.

By

1972,

however,

many

minicomputers

had

multiple

Input/Ou

t

put'

(I/O)

access

features

and

microprogrammable

central

processors

allowing

extensive

instruction

repertoires

with

firmware

implementation

of

floating-point

and

special

mathmatical

functions.

A

more

detailed

discussion

of

the

minicomputer

technology

of

the

early

1970's

may

be

found

in

Chapter

IV,

section

B.

B. DEFINITION

AND

IMPLICATIONS

OF

A "STANDARD"

A

"standard"

could

be

defined

as

a

specific

entity

which

will

be

used

in

every

application

where

an

entity

of

that

general

description

is

required.

The

contents

of

the

several

TADSTANDS

published

by

TADSO

imply

the

following

Navy

policy

concerning

a

"standard":

The

entity

identified

as

a

"standard"

will

be

used

in

all

developing

and

future

tactical

digital

system

applications

except

where

deviation

is

specifically

provided

for,

requested

and

approved.

References

3

through

9

are

the

standards

promulgated

by

TADSO

as

of

May

1976.

Tne

impact

of

such

standards

in

user

system

design

will

be

discussed

in

Chapt.

IV.

The

implications

of

establishing

standards

are

summarized

in

the

following

paragraphs.

Standardization

allows

realization

of

the

economies

of

large

scale

production.

For

example,

as

of

~ay

1976,

824

AN/UYK-20

Data

Processing

Systems

had

been

ordered

and

637

17

units

delivered.

At

that

time

there

were

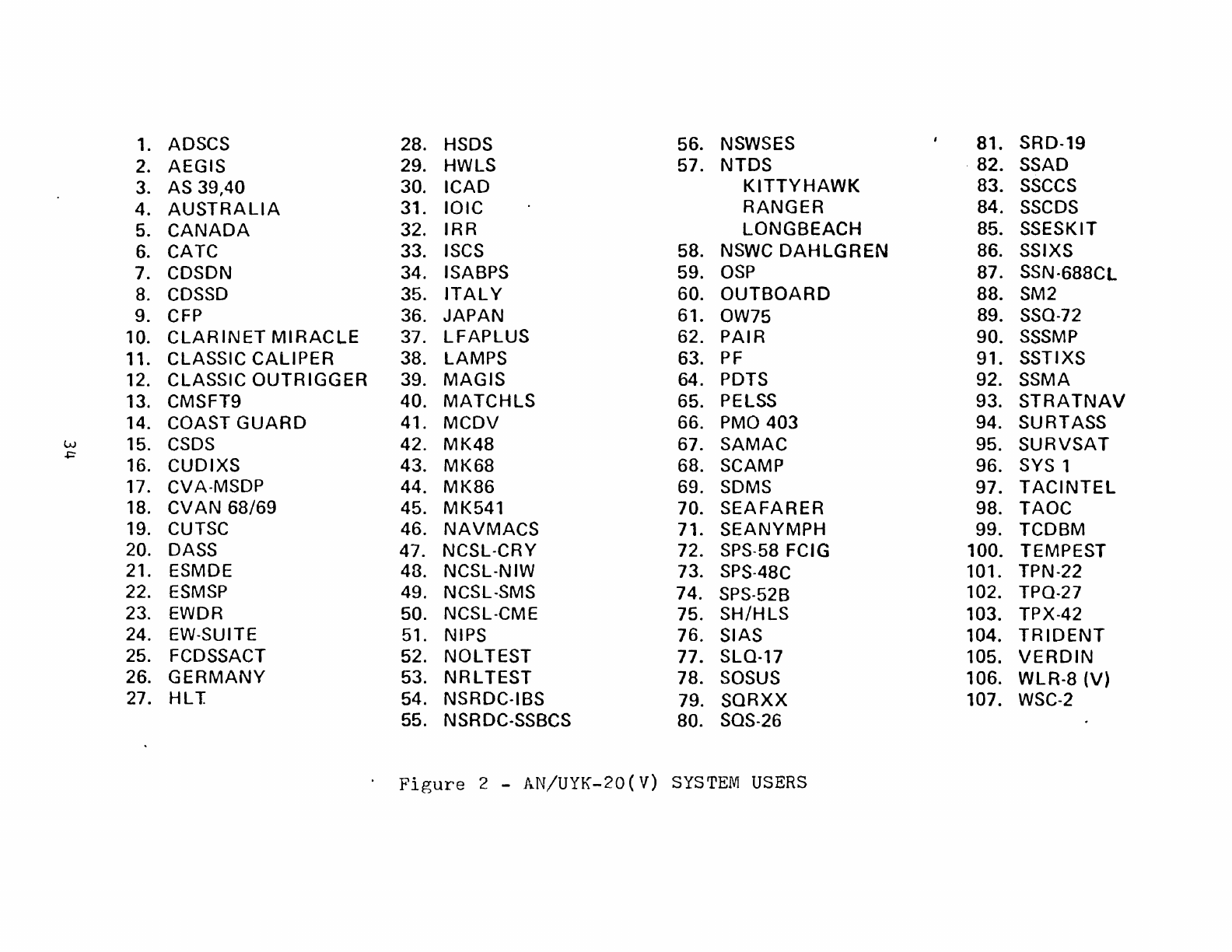

107

programs

using

the

system.[Fig.2]

At

the

outset

of

the

UYK-20

acquisition

the

estimated

production

run

was

in

excess

of

4500

units.

This

volume

is

over

an

oeder

of

magnitude

greater

than

any

one

program

would

require

in

an

independent

processor

acquisition.

Clearly,

the

economies

of

scale

would

be

realized

with

such

a

program.

Although

it

is

impossible

to

quantify

the

actual

savings

realized

by

using

UYK-20

in

any

particula.r

project,

the

economies

of

scale

are

demonstrated

in

the

volume

order

prices

for

an

AN/UYK-20(V)

DPS

basic

configuration

in

fiscal

year

1974:

Quantity

-

50

at

$25,966

each

Quantity

-

100

at

$24,735

each

Quantity

-

150

at

$24,324

each

It

is

also

interesting

tJ

note

that

the

Fiscal

Year

(FY)

1976

order

price

for

a

similar

$25,000

each,

approximately

the

same

despite

inflation.

configuration

as

the

FY

is

about

74

price

Standardization

realizes

cost

savings

in

material

support.

One

project

manager

estimated

that

the

cost

of

introducing

one

new

part

into

the

Navy

Supply

System

at

SPCC

is

about

$1500.

It

has

also

been

estimated

th~t

the

Navy

realizes

$20,000

to

$40,000

per

year

in

Integrated

Logistic

Support

(ILS)

cost

savings

through

a

standardized

system

like

UYK-20.

standardization

avoids

duplication

of

suppoct

software

costs.

A

project

manager

estimated

a

savings

of

$2,000,000

to

$4,000,000

per

year

in

software

maintainance

costs

for

a

project

using

a

standard

computer.

Standardization

reduces

the

scope

of

required

maintenance

training.

The

Chief

of

Naval

Technical

Training

emphasized

this

fact

in

a

letter

to

the

Director

of

TADSO,

pointing

out

that

it

was

becoming

increasingly

difficult

to

fill

technical

traininj

billets,

and

that

standardization

18

programs

like

AN/UYK-7

help

alleviate

this

problem.(Ref.10]

It

is

estimated

that

about

$409,000

per

year

savings

in

technical

training

costs

is

realized

through

the

existence

of

UYK-20.

standardization

can

required

for

operator

reduce

the

personnel.

amount

of

training

Lack

of

standardization

may

mean

that

as

an

operator

is

transferred

from

one

command

to

another

he

must

be

sent

back

to

school

to

learn

new

equipment.

such

an

occurrence

has

a

direct

impact

on

fleet

readiness

and

personnel

training

costs.

As

an

example,

the

REWSON

program

faces

this

problem

because

some

of

its

shore

installations

utilize

DEC

PDP-11

computers

while

the

associated

shipboard

installations

employ

AN/UYK-20

Data

Processing

Systems.

Standardization

saves

the

repetitive

acquisition

costs

of

procurements

of

unique

systems.

These

costs

include

the

recurring

costs

for

ILS,

software

maintenance,

etc.

and

also

the

one-time

development

costs.

As

an

example,

the

OYK-20

acquisition

required

$1.3

million

in

Research

&

Development

funding

for

militarization

of

commercial

hardware,

support

software,

documentation,

etc.

Despite

these

strong

arguments

in

favor

of

standardization,

there

is

much

resistance

to

any

standardization

program.

Mr.

Howard

Gantzler,

Deputy

Assistant

secretary

of

Defense

(Installations

&

Logistics),

recognized

that

attitude

when

he

stated

at

a

seminar

given

at

the

Naval

Postgraduate

School

in

January

1976,

"Everybody

is

in

favor

of

it

[standardization],

but

nobody

wants

to

adopt

someone

else'S

standards."

Rear

Admiral

E. B.

Fowler,

Vice

Commander

of

the

Naval

Electronics

systems

COmmand

identified

another

drawback

of

standardization

in

an

address

to

the

Naval

Postgraduate

School

chapter

of

the

IEEE

in

April

1976.

19

lIyou

have

to

standardize.

You

canlt

afford

not

to

do

so.

But

you

must

also

get

a

firm

grip

on

the

half-life

of

the

thing

you

are

standardizing...

AN/OYK-20

was

thought

at

first

to

be

a

five

year

investment.

We

are

currently

reprocurring,

and

it

looks

like

ten

to

fifteen

years.

The

CP-6~2Bls

[CP-642B

computer

(UNIVAC

1212).

See

Chapt.

II,

Sect.

D.]

have

been

~round

for

sixteen

to

seventeen

years,

and

we

put

them

on

the

Nimitz,

the

newest

capital

ship.

This

is

a

systems

engineering

problem."

In

that

statement

Admiral

Fowler

suggests

that

once

a

standard

is

established,

it

may

be

used

for

many

more

years

than

anticipated

unless

a

firm

policy

for

replacement

is

adopted

at

the

outset.

Understandably,

the

majo~ity

of

opposition

to

standardization

was

found

by

this

author

in

the

technical

community,

which

standardized

components

not

tasks

required.

must

desi9n

specifically

C.

THE

RANGE

OF

CAPABILITIES

NEEDED

systems

using

tailored

to

the

In

January

1972,

a

Design

Review

Group

(DRG)

was

convened

by

TADSO

to

translate

the

requirements

of

the

Navy

for

a

minicomputer

system

into

a

specification

which

could

be

used

as

the

basis

for

competitive

bidding.

It

is

significant

to

note

that

the

intent

was

not

to

fill

the

entire

range

of

size

and

power

below

the

UYK-7,

but

only

to

fill

the

identified

current

and

future

needs.

Thus,

from

the

outset

the

success

of

OYK-20

depended

on

accurate

prediction

of

those

needs

by

the

DRG.

The

composition

of

the

DRG

was

most

important,

and

it

is

interesting

to

note

the

commands

represented:

Naval

Ordnance

Systems

Command

(ORD-532),

Naval

Ships

systems

Command

(SHIPS-03524),

Naval

Air

Systems

Command

(AIR-5333F),

Naval

Ships

3ngineering

20

center

(SEC-6178D

and

SEC-6172),

H. Q.

Marine

Corps

(Code

AAM-4),

Fleet

Combat

Direction

System

Support

Activities

pacific

and

Atlantic,

and

Naval

Weapons

Laboratory

Dahlgren.

The

Naval

Ordnance

Systems

Command

and

the

Naval

Ships

systems

Command

have

since

been

combined

into

one

command

designated

the

Naval

Sea

Systems

Command (NAVSEA).

Thus

all

the

commands

responsible

for

systems

aevelopment

were

well

represented.

In

order

to

save

time

and

development

costs,

TADSO

had

conceived

an

"off-the-shelf"

procurement.

That

was

an

important

decision,

which

implied

that

the

intent

was

to

procure

a

market-tested

computer

system

which

would

only

need

to

be

militarized.

Since

the

computer

was

to

be

general

purpose

~nd

serve

a

wide

range

of

diverse

applications,

a

modular

building

block

approach

was

conceived.

A

basic

configuration

was

to

be

specified

and

plug-in

modules

provided

so

that

the

user

could

increase

the

size

and

power

of

the

processo~

up

to

his

individual

needs.

Add-on

modules

were

to

be

individually

priced

so

that

the

user

only

paid

for

the

capability

ne

needed.

The

following

p~ragraphs

summarize

the

range

of

capabilities

which

TADSO

and

the

DRG

foresaw

would

be

needed

to

meet

Navy

systems

requirements

of

1972

and

about

five

years

into

the

future~

The

computer

would

be

required

to

meet

military

specification

MIL-E-16400

for

shipboard,

groundbased,

and

submarine

electronic

systems.

This

decision

precluded

airborne

applications

of

the

computer,

which

would

have

required

the

more

stringent

and

expensive

MIL-E-5400

specification,

but

would

have

expanded

the

applications

and

thus

the

volume

of

production.

The

reason

behind

that

decision

was

the

intention

to

produce

an

interim

standard

shipboard

computer

to

be

eventually

replaced

by

the

All-Applications

Digital

Computer

(AADC)

which

was

then

21

"

under

development

by

the

Naval

Air

Systems

Command (NAVAIR).

The

AADC

never

materialized,

and

as

of

1975

the

AADC

project

had

been

redirected

to

produce

an

Interim

Standard

Airborne

Digital

Computer

(ISADC).

Out

of

the

ISADC

project

came

the

AN/AYK-14

computer

in

1976.

The

computer

was

to

be

packaged

in

one

enclosure

of

maximum

dimensions

26

inches

high,

24

inches

deep,

and

width

suitable

for

mounting

in

a

standard

19-inch

rack.

Maximum

power

consum~tion

was

to

be

one

kilowatt.

To

achieve

the

desired

building

block

capability,

the

following

units

were

to

be

strictly

plug-in

with

no

other

hardware

changes

necessary~to

install:

memory

modules

of

8K-words

per

module,

I/O

channels

in

groups

of

two

if

serial

and

in

groups

of

four

if

parallel,

real-time

clock,

general

registers,

and

microprogrammable

control

memory.

In

accordance

with

MIL-E-16400,

modular

construction

was

specified.

All

assemblies

with

a

cost

of

$200

or

less

would

be

throw-away

components.

only

those

assemblies

where

it

was.

determined

that

repair

would

be

more

cost-effective

than

throw-away/replacement

would

be

designated

as

repairable

modules.

It

was

further

specified

that

repairs

would

be

performed

by

the

contractor,

a

factor

which

had

a

later

impact

on

the

repairable

turn-around

time.

The

maximum

configuration

of

the

computer

was

to

have

a Mean

Time

Between

Failures

(MTBF)

of

2000

hours,

a

Mean

Time

to

Repair

(MTTR)

of

15

minutes

and

a Maximum

Time

to

Repair

of

12D

minutes.

The

MTBF

specified

was

a

figure

which

had

been

used

on

previous

military

computer

specifications.

As

far

as

the

author

of

this

thesis

could

determine,

the

basis

for

citing

the

2000

hour

figure

was

historical

rather

than

the

result

of

calculation.

The

computer

was

to

be

logically

and

electrically

designed

to

facilitate

the

isolation

of

malfunctioning

modules

through

diagnostic

programming.

The

diagnostic

22

program

was

to

isolate

93%

of

recurring

(non-intermittent)

active

logic

element

failures

to

not

more

than

three

printed

circuit

card

modules.

3.

Architectur~

The

computer

was

to

employ

third

generation

technology

with

the

use

of

medium-scale

integration.

Perhaps

the

most

significant

architectucal

requirement

was

th~t

the

processor

was

to

be

microprogram

mabIe.

The

rationale

for

requiring

this

capability

was

the

possibility

of

a

more

powerful

macro-instruction

set

and

the

flexibility

to

modify

or

add

to

the

macro-instruction

set

by

simply

modifying

the

contents

of

control

memory.

An

additional

requirement

was

therefore

for

at

least

500

words

(16-bit)

of

user

growth

capacity

in

the

control

memory.

Other

required

architecture

length

at

least

16-bits

including

sign

attributes

were:

word

but

not

including

parity,

random

access

non-volatile

memory

with

a

separate

high

speed

memory

desireaole

but

not

cequired,

main

memory

read-restore

cycle

time

less

than

1.2

microseconds,

asynchronous

timing

with

at

least

one

level

of

memory

fetch

instruction

overlap

to

cceate

an

effective

memory

cycle

time

of

less

than

one

microsec~nd,

minimum

storage

capacity

of

8K-words

expandable

to

at

least

65K-words

(directly

addressable)

in

8K-word

increments,

a minimum

of

four

general

registers

expandable

to

sixteen.

It

was

significant

that

no

requirement

was

made

for

a

capability

to.

expand

memory

capacity

beyond

65K-words.

Also

significant

was

the

absence

of

requirements

for

parity

checking,

memory

write

protection

or

executive

mode

with

privileged

instructions.

The

question

of

parity

checking

was

a much

discussed

attribute.

Those

in

favor

cited

the

need

to

identify

hardware

errors,

particularly

in

memory

accesses,

when

attempting

to

debug

software.

In

addition,

arguments

were

23

made

in

favor

of

identifying

errors

when

executing

operational

programs

to

prevent

miscalculations

of

target

information,

misrouting

of

data

(particularly

in

message

handling

systems),

mishandling

of

classified

information,

etc.

The

arguments

against

parity

pointed

to

the

significant

cost

in

real

estate

(extra

bits

and

about

10%

more

logic)

and

extra

memory

bits

per

word.

It

was

argued

that

parity

error

detection

had

little

value

in

modern

digital

equipment

since

this

attribute

was

designed

to

detect

single

bit

failures

rather

than

catastrophic

logic

failures

affect~ng

whole

blocks

of

addresses;

the

latter

type

of

failure

characterized

the

type

of

failure

most

often

encountered

in

modern

equipment.

Operationally

it

was

thought

undesireable

to

interrupt

processing

of

critical

targ'et-~data

to

process

pari

ty

errors

in

a comba t

si

tuation.

In

the

end

the

cost

considerations

prevailed.

Although

the

question

of

~emory

protection

was

not

discussed

to

the

same

extent

as

me~ory

parity

checking,

similar

cost

and

real

estate

savings

could

be

realized

by

not

including

a

hardware

memory

protection

feature

in

the

design.

The

macro-instruction

set

specified

pLovided

for

single

and

double

word

addition,

subtraction,

multiplication~

division,

logical

operations,

shifts,

jumps,

and

a

programmable

stop.

In

a

non-dual-state

machine

the

programmable

stop

would

be

non-privileged,

making

it

a

controversial

attribute.

Only

load,

add,

subtract

and

store

byte

operations

were

specified,

and

no

bit

manipulation

instructions

were

required.

It

is

significant

that

all

operations

specified

were

arithmetic

(recognizing

the

most

significant

bit

of

a

word

as

the

sign)

so

that

no

capability

for

full

16-bit

data

manipUlation

was

required.

Instruction

execution

times

were

specified

as

follows:

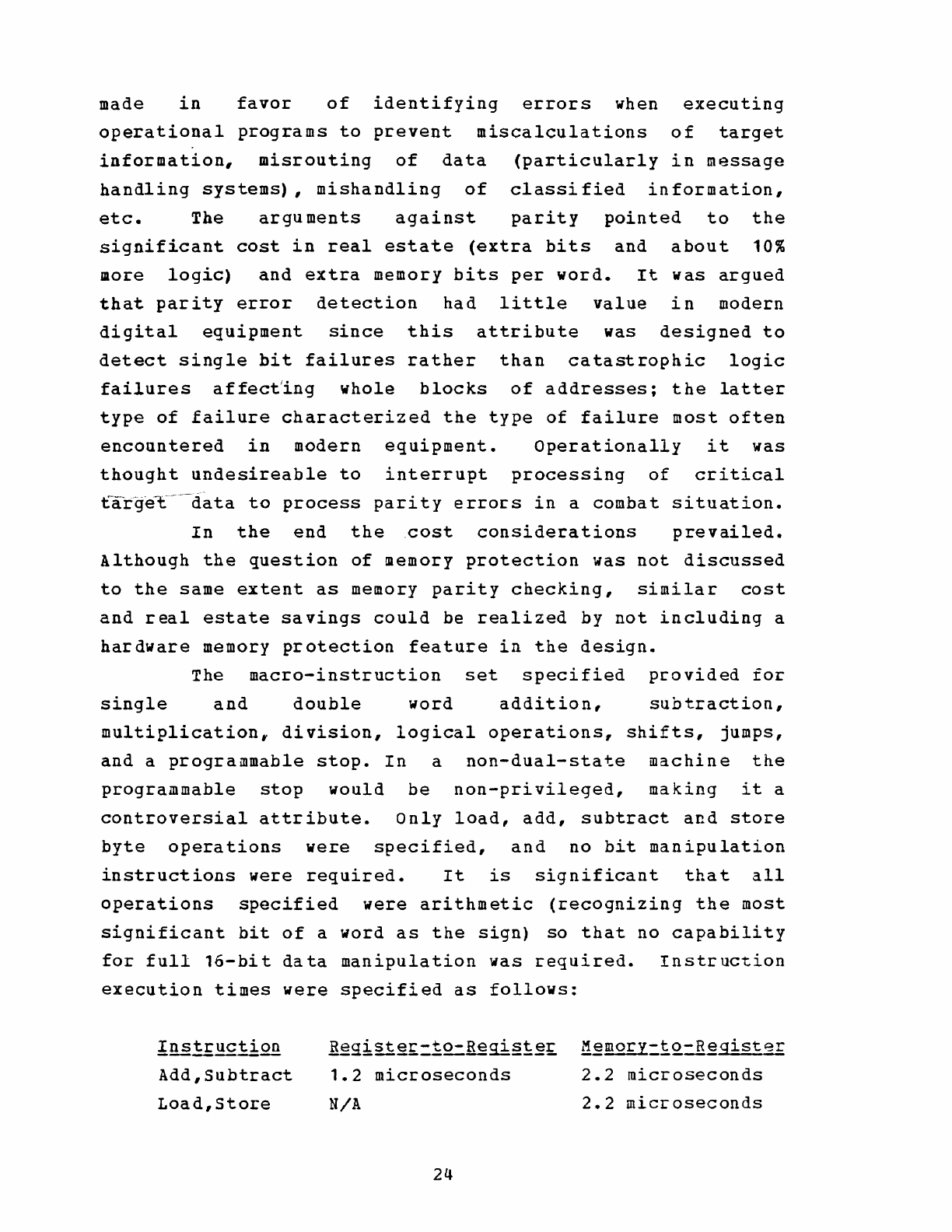

!~tr1!£ti.QQ

Add,Subtract

Load,Store

Regist~£=~2=Regi§i~£

~~mory-to-Register

1.2

microseconds

2.2

microseconds

N/A

2.2

microseconds

24

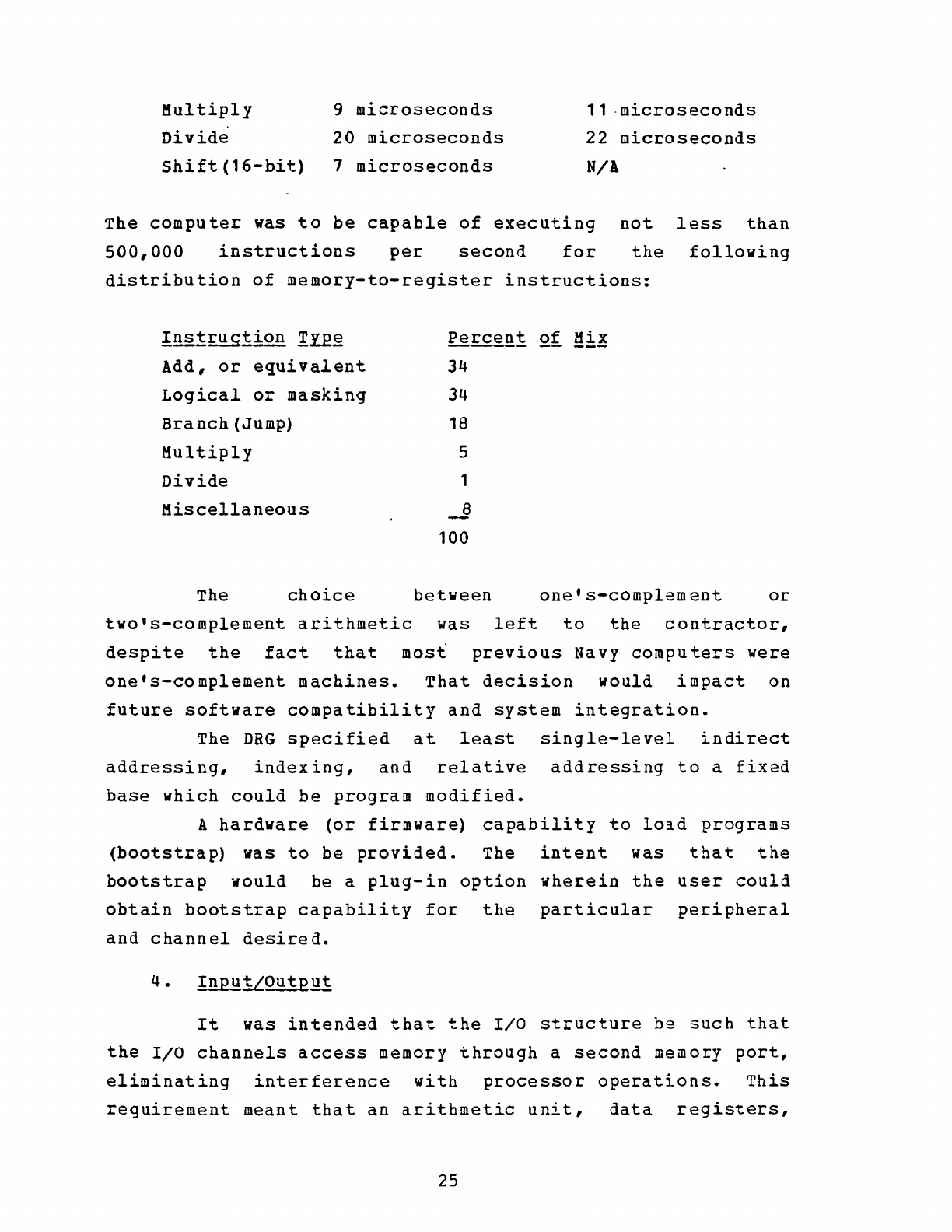

Multiply

9

microseconds

Divide

20

microseconds

11 .

microseconds

22

microseconds

Shift(16-bit)

1

microseconds

N/!

The

computer

was

to

be

capable

of

executing

500,000

instructions

per

second

for

not

less

than

the

following

distribution

of

memory-to-register

instructions:

!!l2~r.~~ion

!.ll~

Add,

or

equivalent

Logical

or

masking

Branch

(Jump)

Multiply

Divide

Miscellaneous

Pe~:!:

Qt

Hi!

34

34

18

5

1

~

100

The

choice

between

one's-complement

or

tvo's-complement

arithmetic

was

left

to

the

contractor,

despite

the

fact

that

most

previous

Navy

computers

were

one's-complement

machines.

That

decision

would

impact

on

future

software

compatibility

and

system

integration.

The

DRG

specified

at

least

single-level

indirect

addressing,

indexing,

and

relative

addressing

to

a

fixed

base

which

could

be

program

modified.

A

hardware

(or

firmware)

capability

to

lo~d

programs

(bootstrap)

was

to

be

provided.

The

intent

was

that

the

bootstrap

would

be

a

plug-in

option

wherein

the

user

could

obtain

bootstrap

capability

for

the

particular

peripheral

and

channel

desired.

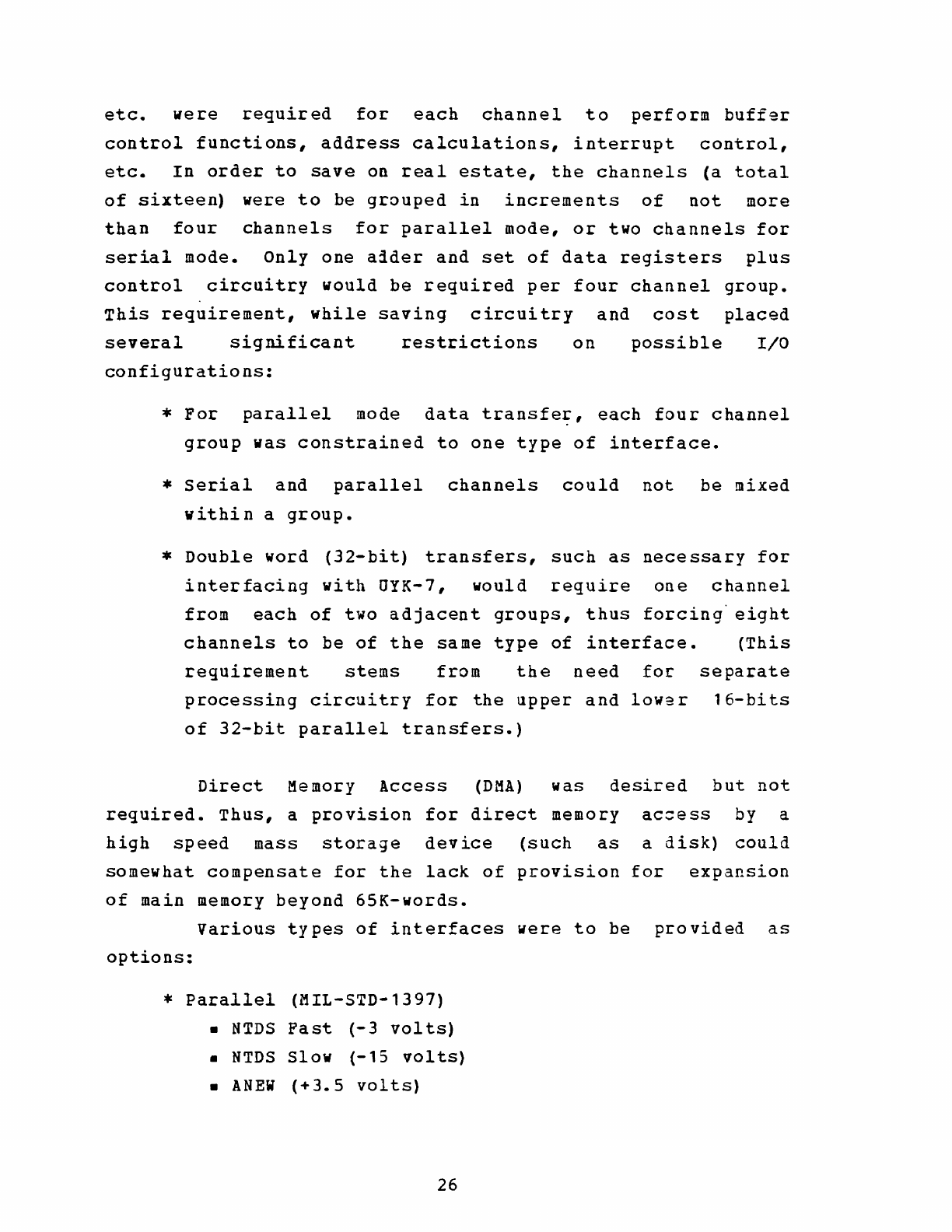

It

was

intended

that

the

110

structure

be

such

that

the

I/O

channels

access

memory

through

a

second

memory

port,

eliminating

interference

with

processor

operations.

This

requirement

meant

that

an

arithmetic

unit,

data

registers,

25

etc.

were

required

for

each

channel

to

perform

buffer

control

functions,

address

calculations,

interrupt

control,

etc.

In

order

to

save

on

real

estate,

the

channels

(a

total

of

sixteen)

were

to

be

grouped

in

increments

of

not

more

than

four

channels

for

parallel

mode,

or

two

channels

for

serial

mode.

Only

one

aider

and

set

of

data

registers

plus

control

circuitry

would

be

required

per

four

channel

group.

This

requirement,

while

saving

circuitry

and

cost

placed

several

significant

restrictions

on

possible

I/O

configurations:

*

For

parallel

mode

data

transfe~,

each

four

channel

group

was

constrained

to

one

type

of

interface.

*

Serial

and

parallel

channels

could

not

be

mixed

within

a

group.

*

Double

word

(32-bit)

transfers,

such

as

necessary

for

interfacing

with

UYK-7,

would

require

one

channel

from

each

of

two

adjacent

groups,

thus

forcing

eight

channels

to

be

of

the

same

type

of

interface.

(This

requirement

stems

from

the

need

for

separate

processing

circuitry

for

the

upper

and

lower

16-bits

of

32-hit

parallel

transfers.)

Direct

Memory

Access

(DMA)

was

desired

but

not

required.

Thus,

a

provision

for

direct

memory

ac~ess

by

a

high

speed

mass

storage

device

(such

as

a

disk)

could

somewhat

compensate

for

the

lack

of

provision

for

expansion

of

main

memory

beyond

65K-words.

Various

types

of

interfaces

were

to

be

provided

as

options:

*

Parallel

(MIL-STD-1397)

•

NTDS

Past

(-3

volts)

•

NTDS

Slow

(-15

volts)

•

ANEW

(+3.5

volts)

26

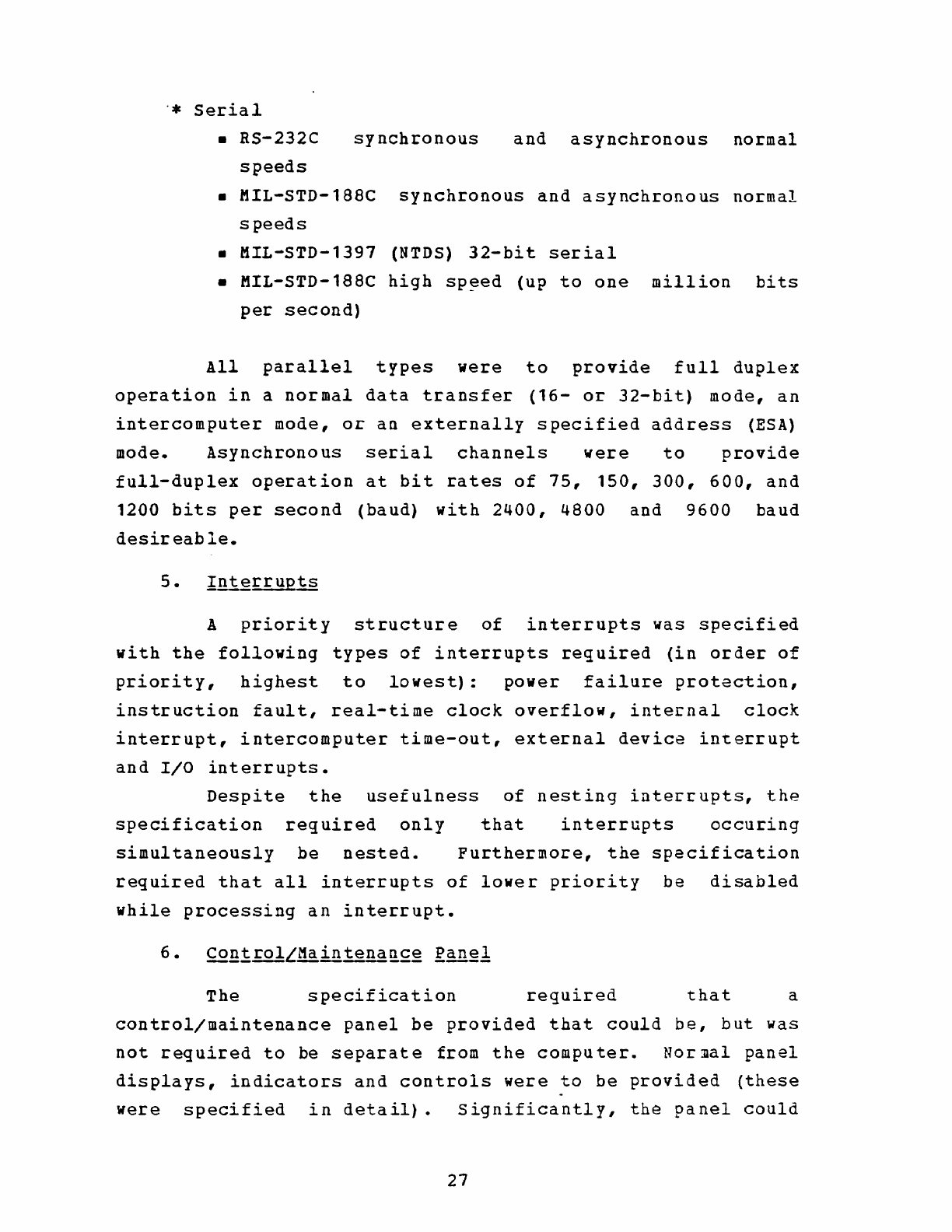

.•

Serial

•

RS-232C

synchronous

and

asynchronous

normal

speeds

•

MIL-STD-188C

synchronous

and

asynchronous

normal

speeds

•

MIL-STD-1397

(NTDS)

32-bit

serial

•

MIL-STD-188C

high

sp~ed

(up

to

one

million

bits

per

second)

All

parallel

types

were

to

provide

full

duplex

operation

in

a

normal

data

transfer

(16-

or

32-bit)

mode,

an

intercomputer

mode,

or

an

externally

specified

address

(ESA)

mode.

Asynchronous

serial

channels

were

to

provide

full-duplex

operation

at

bit

rates

of

75,

150,

300,

600,

and

1200

bits

per

second

(baud)

with

2400,

4800

and

9600

baud

desir

eab

Ie.

A

priority

structure

of

interrupts

was

specified

with

the

following

types

of

interrupts

required

(in

order

of

priority,

highest

to

lowest):

power

failure

protection,

instruction

fault,

real-time

clock

overflow,

inte~nal

clock

interrupt,

intercomputer

time-out,

external

device

interrupt

and

I/O

interrupts.

Despite

the

usefulness

of

nesting

interrupts,

the

specification

required

only

that

interrupts

occuring

simultaneously

be

nested.

Furthermore,

the

specification

required

that

all

interrupts

of

lower

priority

be

disabled

while

processing

an

interrupt.

The

specification

required

that

a

control/maintenance

panel

be

provided

that

could

be,

but

was

not

required

to

be

separate

from

the

computer.

Nor~al

panel

displays,

indicators

and

controls

were

to

be

provided

(these

were

specified

in

detail).

significantly,

the

panel

could

27

be

configured

to

display

only

one

register

at

a

time,

or

more,

as

the

manufacturer

wished.

It

is

significant

that

the

question

of

software

was

not

addressed

in

the

~pecification

generated

by

the

DRG.

In

the

Request-for-Proposals

(RFP)

only

an

assembler

was

required.

Ap~endix

B

summarizes

the

specifications

for

the

standard

minicomputer

system

as

determined

by

TADSO

and

the

DRG.

D.

CAPABILITIES

OF

EXISrING

NAVY

COMPUTERS

TO

MEET

THE

SPECI

FIC

ATIO

NS

It

is

valid

to

investigate

whether

the

perceived

present

and

future

needs

of

the

Navy

for

a

minicomputer,

as

defined

by

the

DRG,

could

be

met

by

an

existing

general

purpose

small

computer

in

the

Navy

inventory.

If

so,

this

computer

could

be

designated

a

standard

just

as

the

AN/OYK-7

had

been

a

year

before.

The

sections

below

discuss

the

pertinent

features

of

some

of

those

Navy

computers

which

woqld

have

been

most

likely

to

fill

the

need

for

a

standard

minicomputer.

Appendices

C

through

F

summarize

the

characteristics

of

those

computers.

Comparing

the

standard

minicomputer

specification

wi~h

the

existing

computers

reveals

that

none

met

the

specification

completely,

although

two

were

good

candidates

with

certain

exceptions.

The

AN/OYK-15

(V)

lacked

microprogramming

and

relative

addressing,

but

was

otherwise

acceptable.

It

had

additional

features

such

as

memory

parity

checking,

memory

write

protection

and

multi-ported

memory

banks

to

further

recommend

it.

The

AN/OYK-12(V)

also

lacked

microprogramming

and

did

not

meet

all

required

instruction

28

execution

speeds

or

memory

capacity,

but

had

an

extensive

support

software

package

to

recommend

it.

The

existence

of

UYK-12

and

UYK-15

brings

the

decision

to

specify

a

microprogrammed

processor

under

close

scrutiny.

As

discussed

in

the

previous

section,

the

advantages

of

microprogrammability

are

an

expanded

macro-instruction

set,

ability

to

implement

high

speed

floating-point,

mathematical

and

trigonometric

functions

as

needed,

and

flexibility

to

add

high-speed

user

macros

to

facilitate

real-time

processing.

The

disadvantages

were

best

summarized

in

enclosure

(1)

of

a

letter

to

TADSO

from

the

/Naval

Air

Systems

Command

(AIR-5333),

"The

latter

deficiency

(the

requirement

for

micro-programmability],

while

being

technically

feasible,

leads

to

unusual

hardware

and

software

configuration

management

problems.

NAVAIR

believes

that

a

requirement

for

micro-programmability

has

not

been

demonstrated

and

will

serve

only

to

eliminate

qualified

vendors.

lie

Ref.

13]

NAVAIR's

comments

about

configuration

management

refer

to

the

potential

user

capability

to

modify

the

macro-instruction

set.

It

must

be

pointed

out

that

configuration

control

can

be

maintained

by

requiring

that

all

modifications

to

the

macro-instruction

set

he

upward

compatible

with

the

basic

set.

The

foregoing

comments

not-withstanding,

microprogrammability

remained

a

requirement,

and

none

of

the

existing

Navy

computers

could

meet

the

specification.

It

is

also

interesting

to

note

that

a

majority

of

the

computers

in

the

Navy

inventory

were

manufactured

by

the

UNIVAC

Defense

Systems

Division

of

Sperry

Rand

Corporation

(UNIVAC).

Th9

Rolm

Corporation

manufactured

AN/UYK-12(V)

is

an

exception,

and

there

were

others.