1B数据手册 Loongson1B Processor User Manual V2.2

Loongson1B_processor_user_manual_V2.2

Loongson1B_processor_user_manual_V2.2

User Manual:

Open the PDF directly: View PDF ![]() .

.

Page Count: 204 [warning: Documents this large are best viewed by clicking the View PDF Link!]

- 1 概述

- 2 芯片引脚定义

- 3 地址空间分配

- 4 CPU

- 5 DDR2

- 6 LCD

- 7 GMAC0

- 8 GMAC1

- 9 USB HOST

- 10 SPI0

- 11 SPI1

- 12 Conf and Interrupt

- 13 DMA

- 14 UART

- 15 CAN

- 16 AC97

- 17 I2C

- 18 PWM

- 19 RTC

- 20 NAND

- 20.1 NAND控制器结构描述

- 20.2 NAND控制器寄存器配置描述

- 20.2.1 NAND_CMD(地址:BFE7_8000)

- 20.2.2 ADDR_L(地址:BFE7_8004)

- 20.2.3 ADDR_H(地址:BFE7_8008)

- 20.2.4 NAND_TIMING(地址:BFE7_800C)

- 20.2.5 ID_L(地址:BFE7_8010)

- 20.2.6 STATUS & ID_H(地址:BFE7_8014)

- 20.2.7 NAND_PARAMETER(地址:BFE7_8018)

- 20.2.8 NAND_OP_NUM(地址:BFE7_801C)

- 20.2.9 CS_RDY_MAP(地址:BFE7_8020)

- 20.2.10 DMA_ADDRESS(地址:BFE7_8040)

- 20.3 NAND ADDR说明

- 21 WATCHDOG

- 22 Clock Management

- 23 GPIO and MUX

- 24 AC/DC

龙芯 1B 处理器用户手册

2015

年

4

月

龙芯中科技术有限公司

龙芯 1B 处理器用户手册

版权声明

本文档版权归龙芯中科技术有限公司所有,并保留一切权利。未经书面许可,任何公司和

个人不得将此文档中的任何部分公开、转载或以其他方式散发给第三方。否则,必将追究

其法律责任。

免责声明

本文档仅提供阶段性信息,所含内容可根据产品的实际情况随时更新,恕不另行通知。如

因文档使用不当造成的直接或间接损失,本公司不承担任何责任。

龙芯中科技术有限公司

Loongson Technology Corporation Limited

地址:北京市海淀区中关村环保科技示范园龙芯产业园 2号楼

Building No.2, Loongson Industrial Park, Zhongguancun Environmental Protection Park,

电话(Tel):010-62546668

传真(Fax):010-62600826

I

龙芯 1B 处理器用户手册

阅读指南

《龙芯 1B 处理器用户手册》主要介绍龙芯 1B 架构与寄存器描述,包括用户手册和软件编程

指南两部分。软件编程指南介绍对 BIOS 和操作系统开发过程中的常见问题。

II

龙芯 1B 处理器用户手册

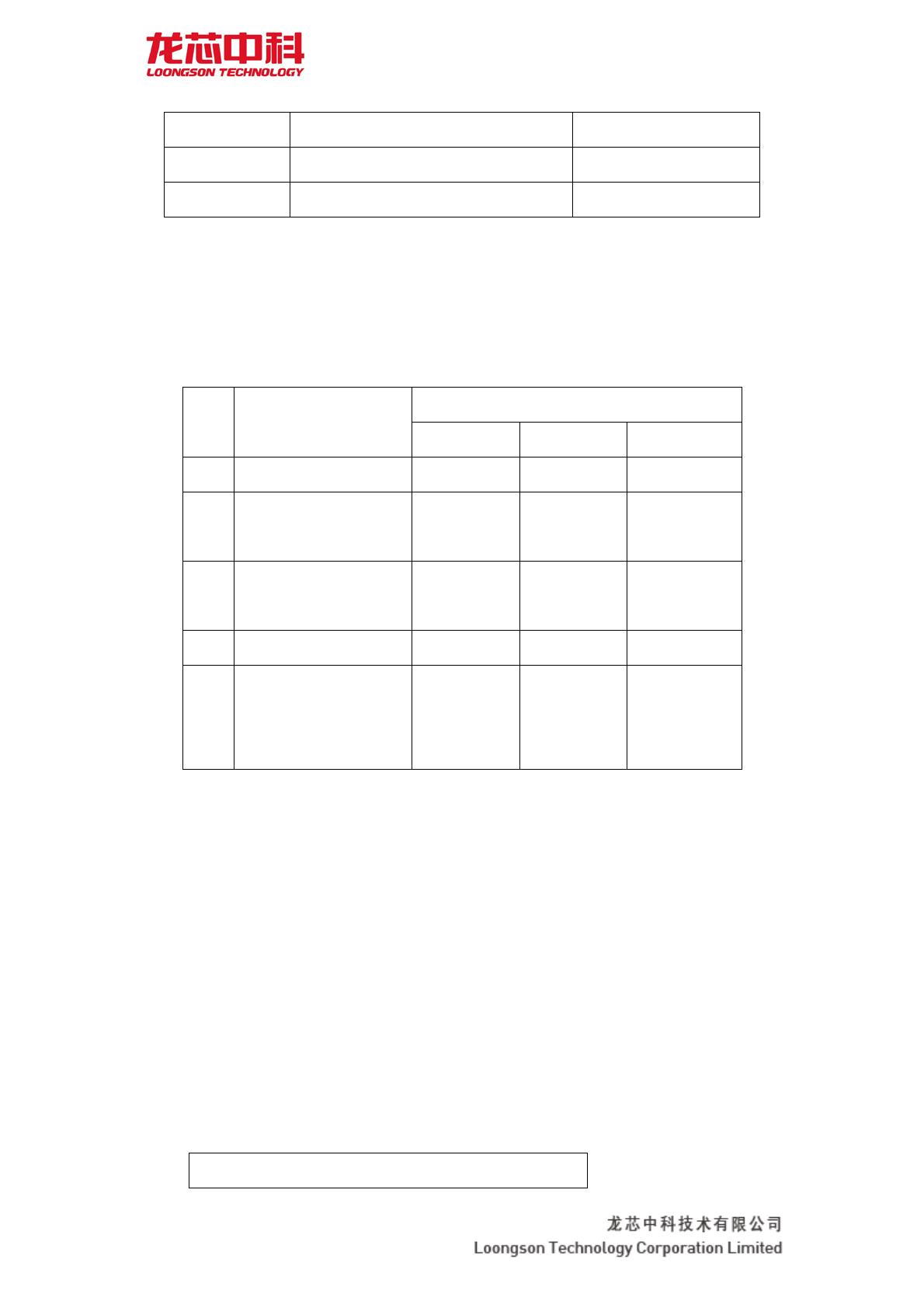

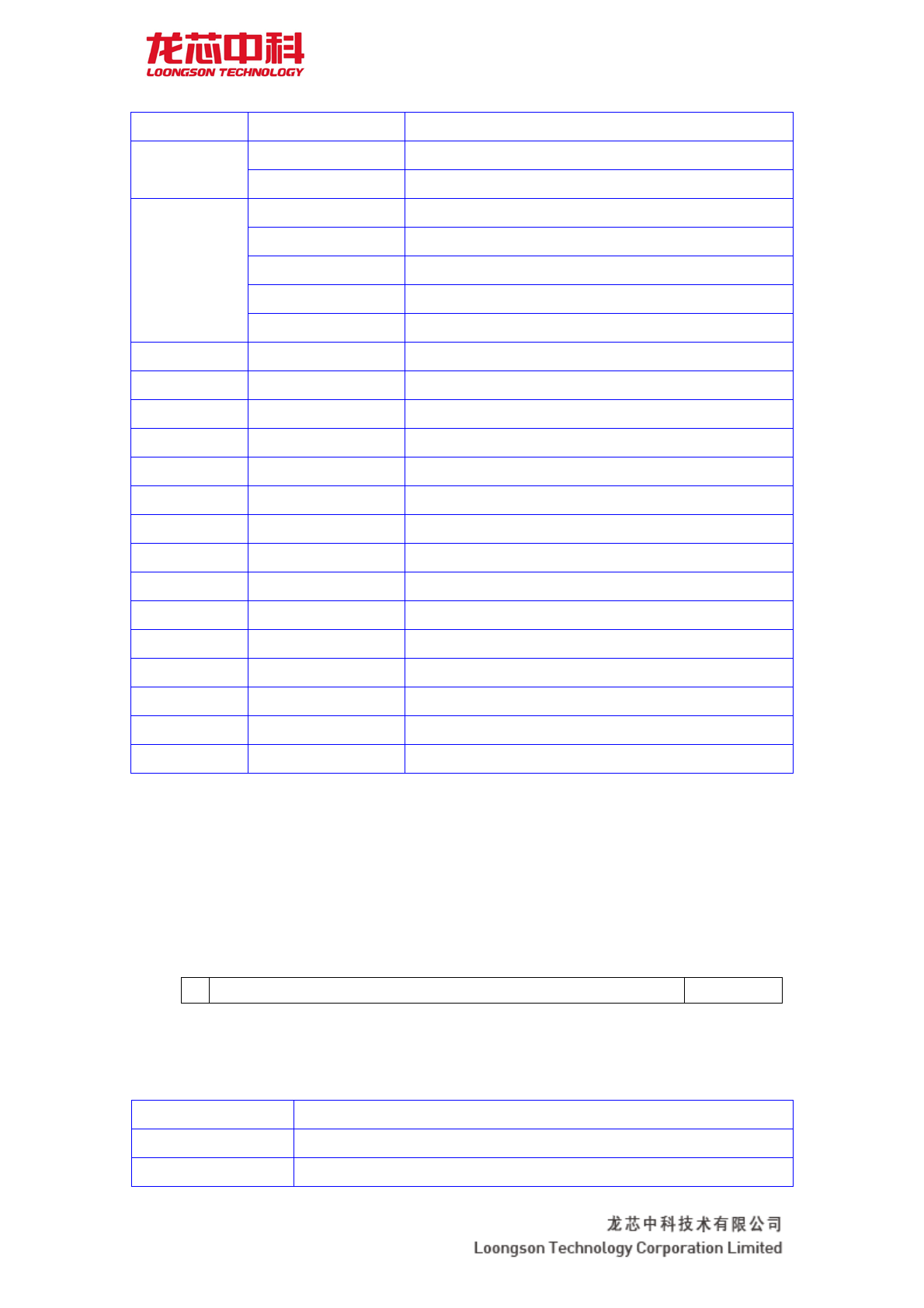

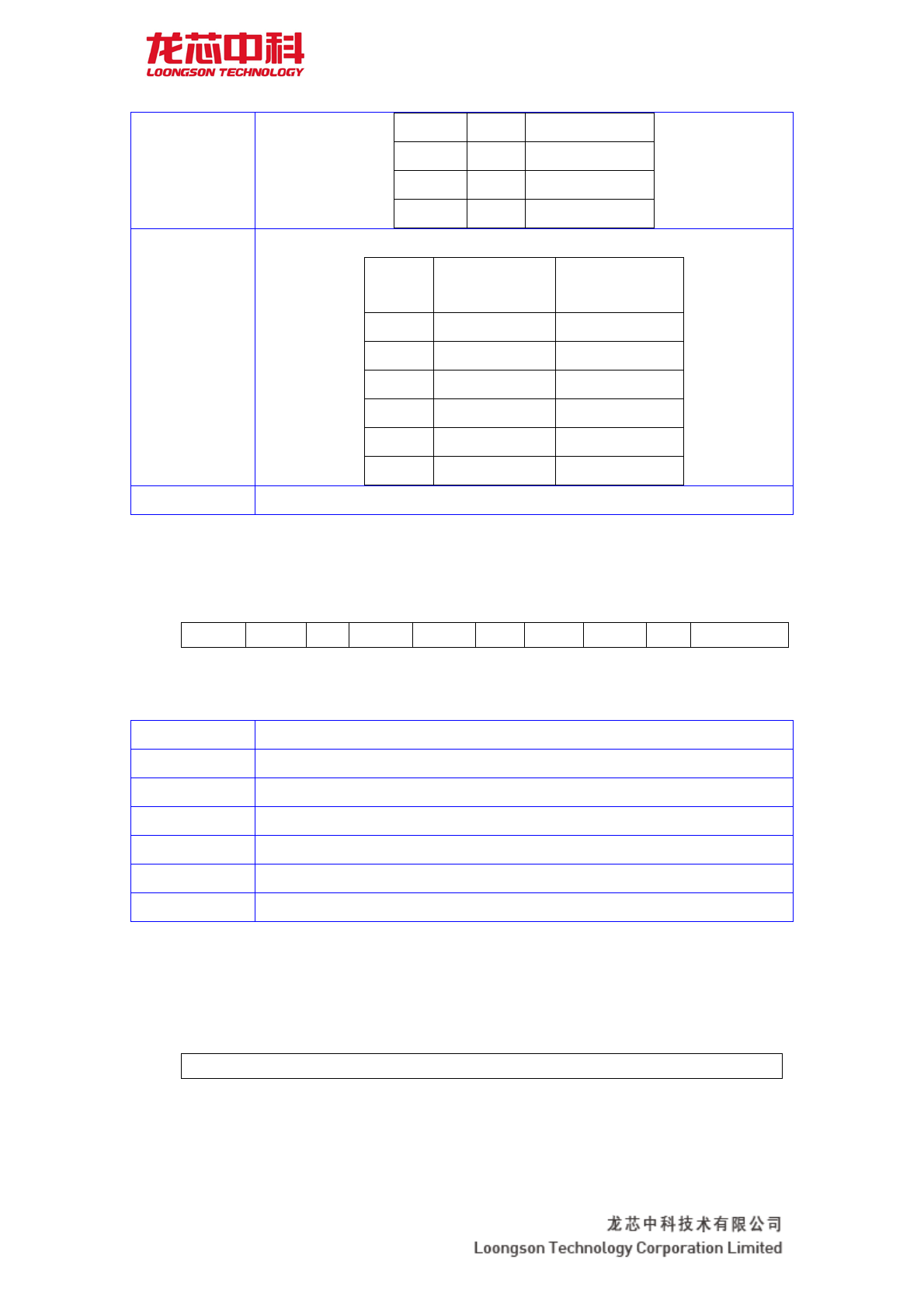

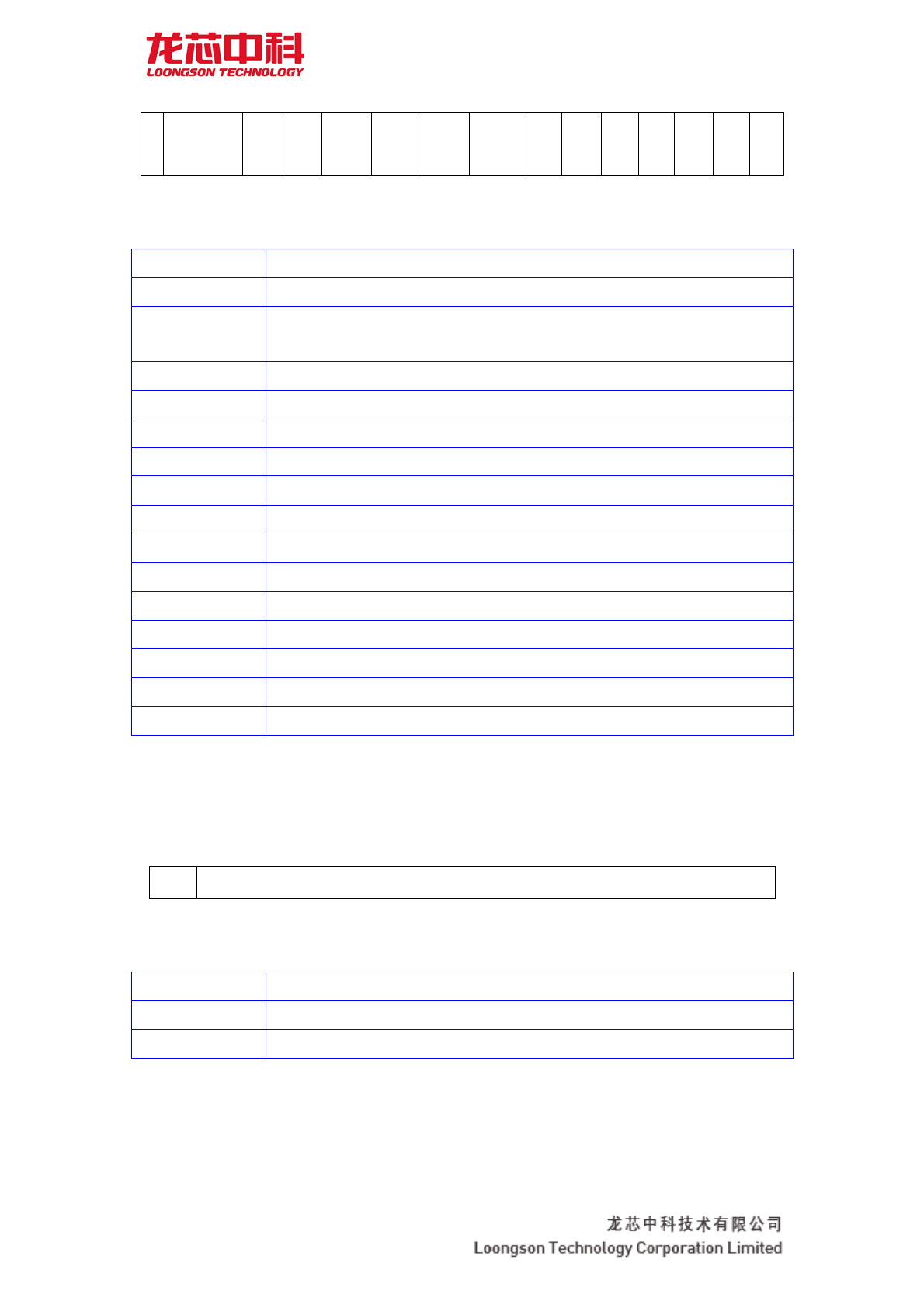

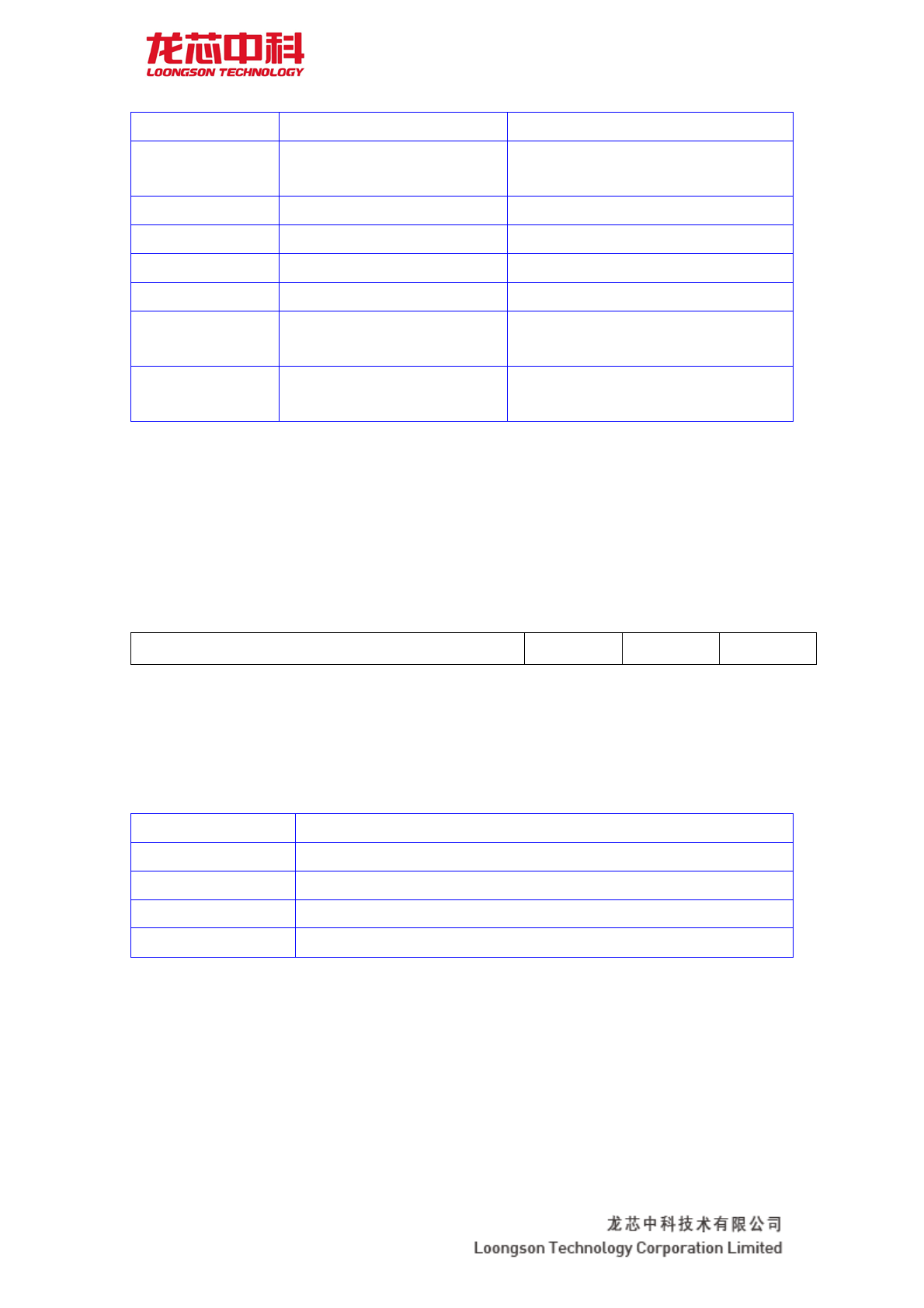

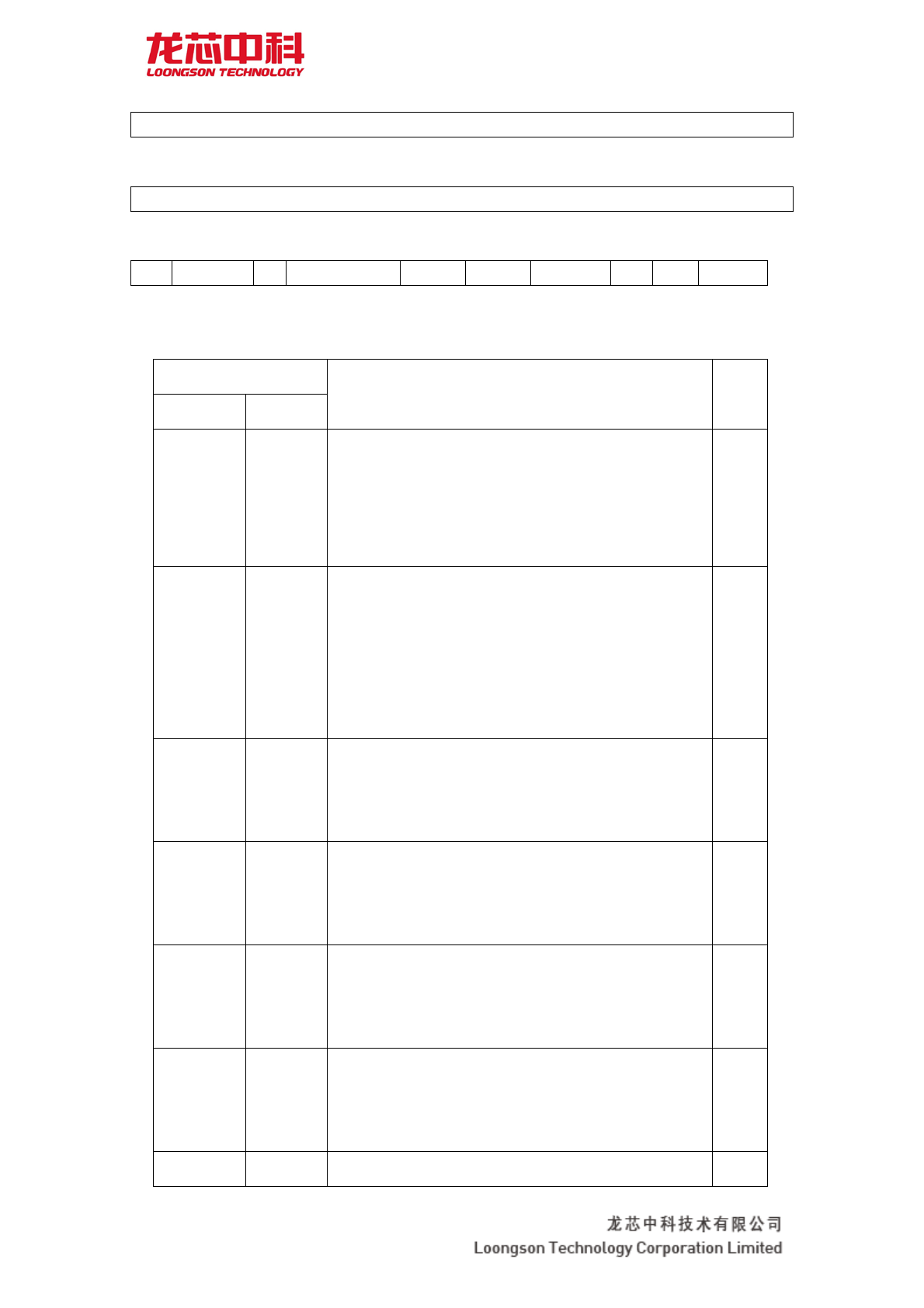

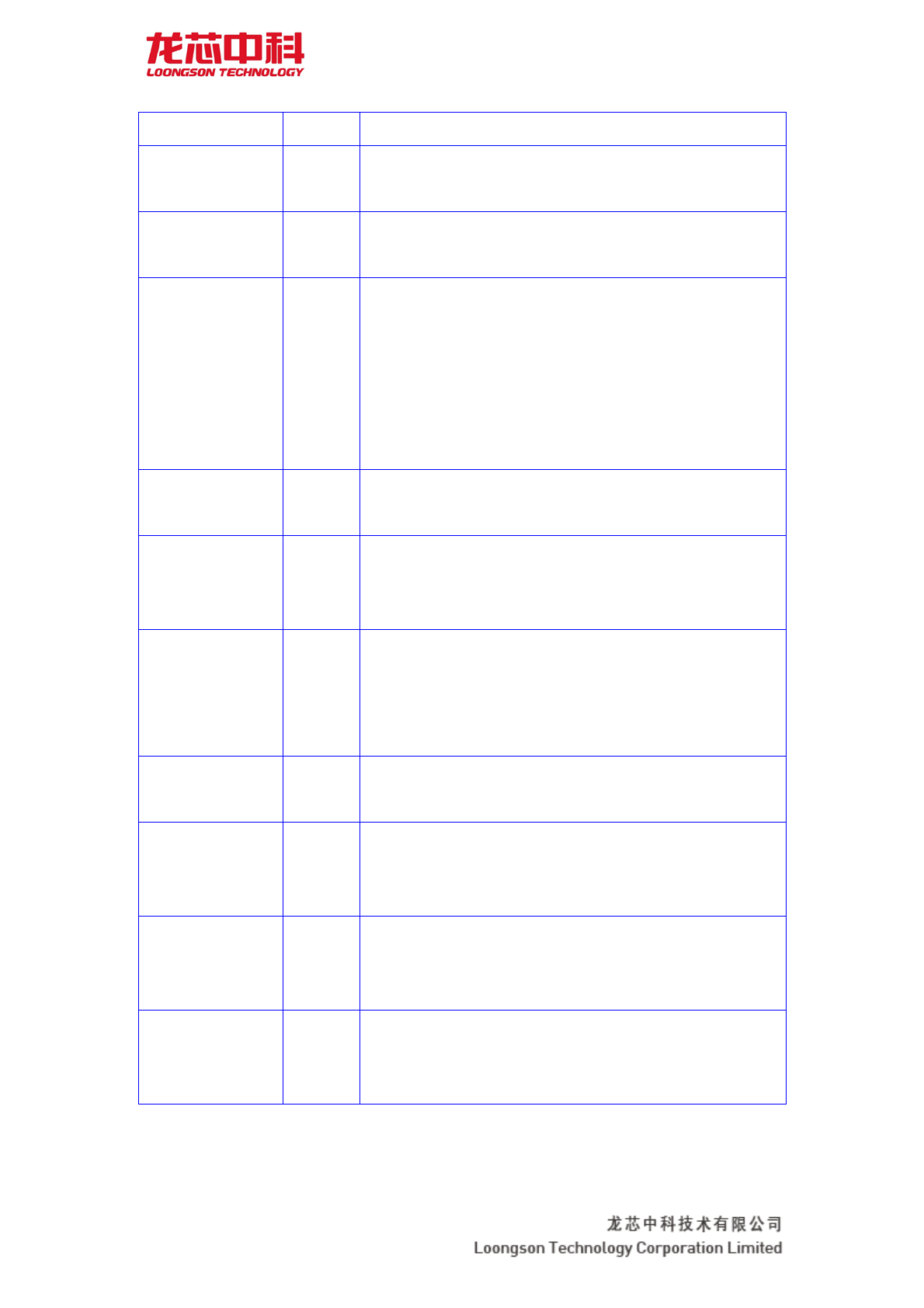

修订历史

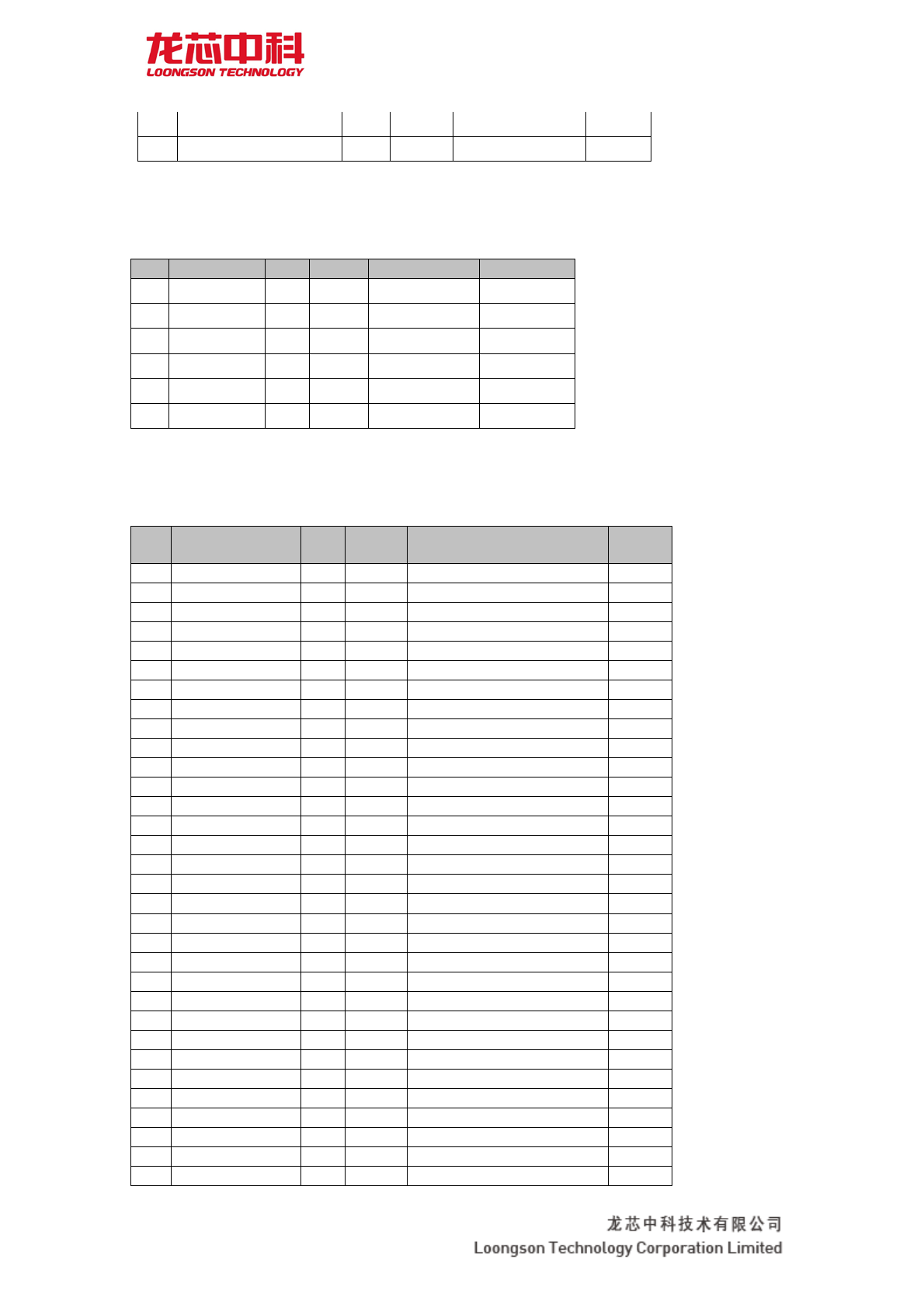

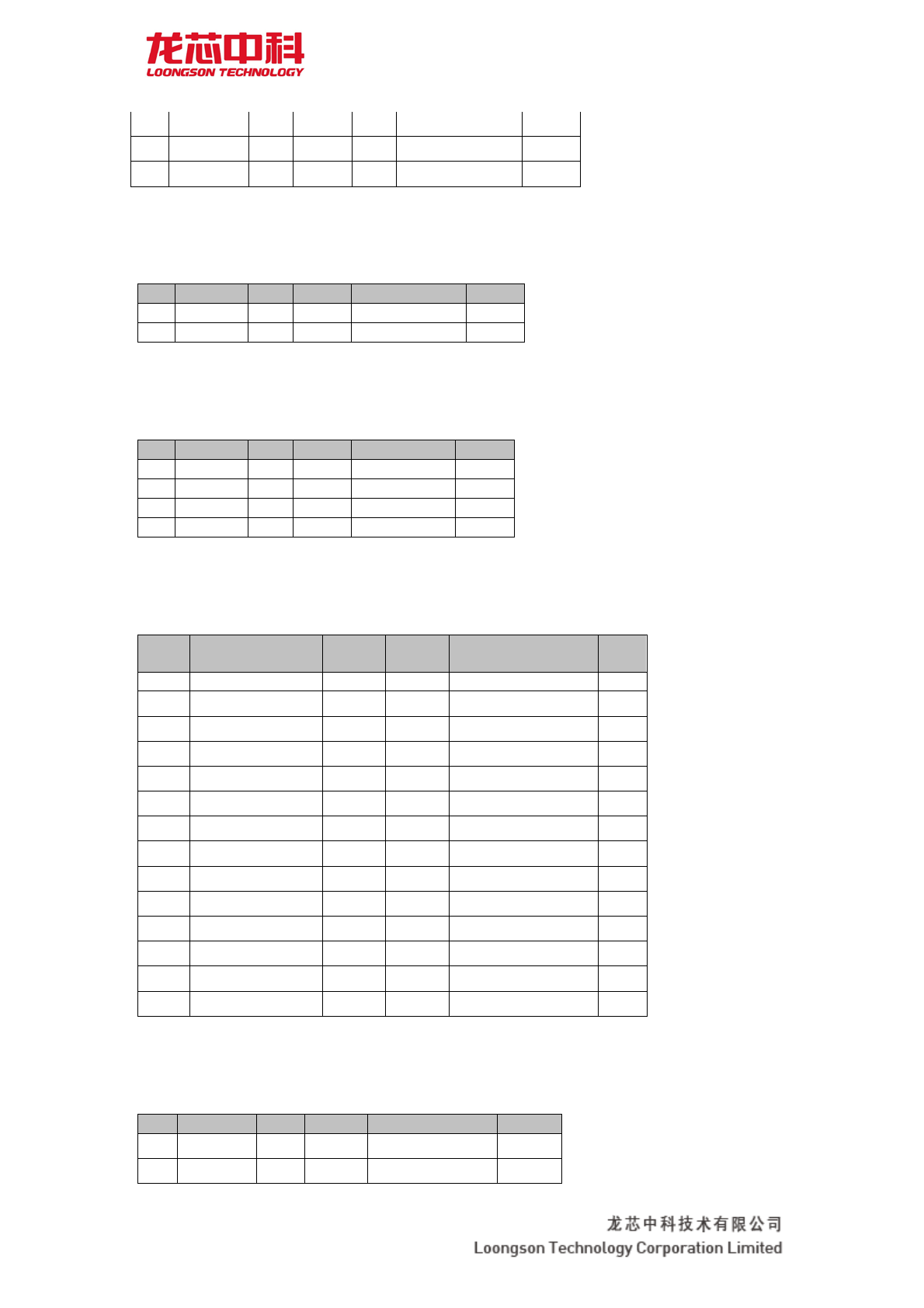

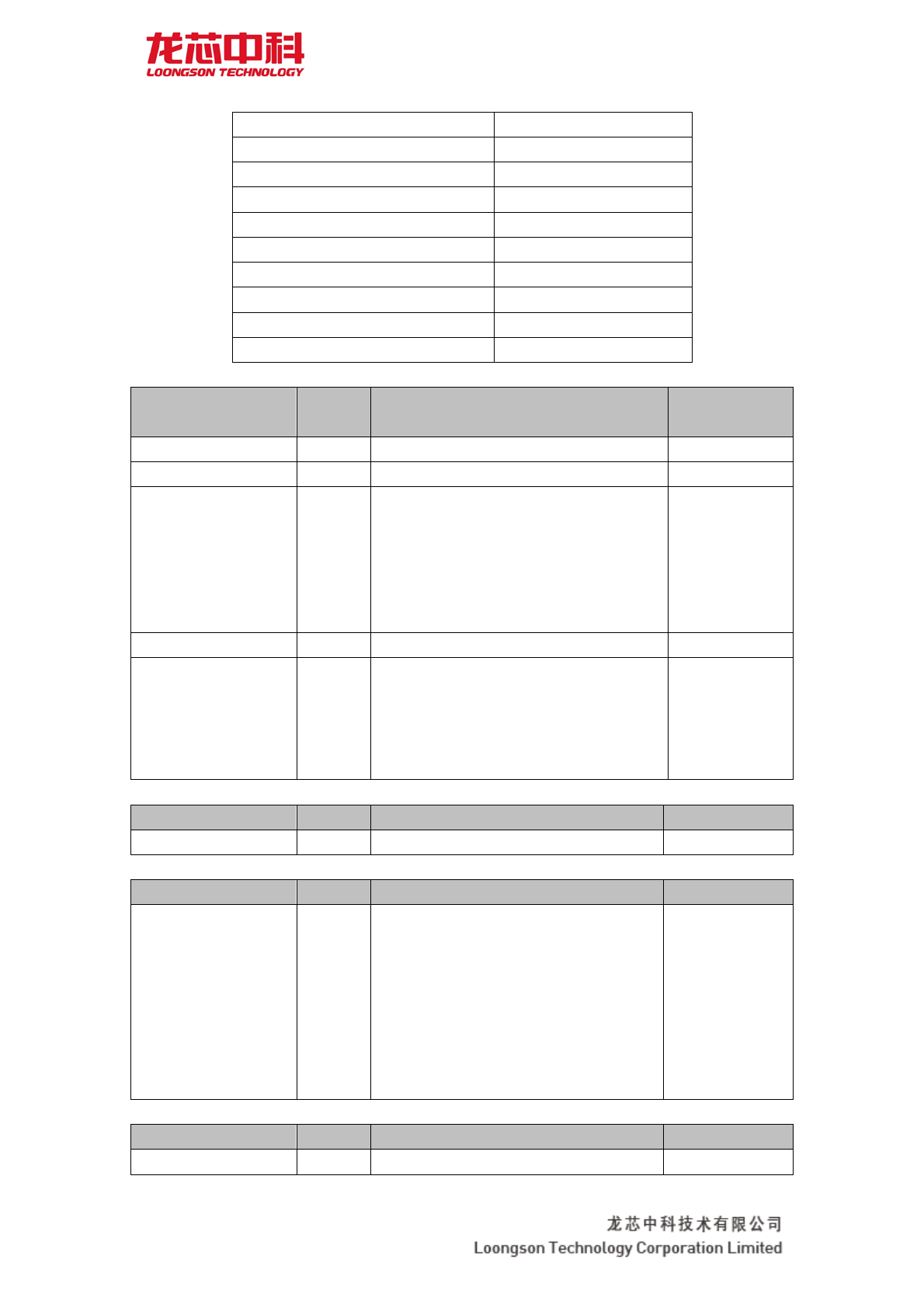

文档更新记录

文档编号:

文档名: 龙芯 1B 处理器用户手册

版本号 V2.2

创建人:

研发中心

创建日期 2015-4-1

更新历史

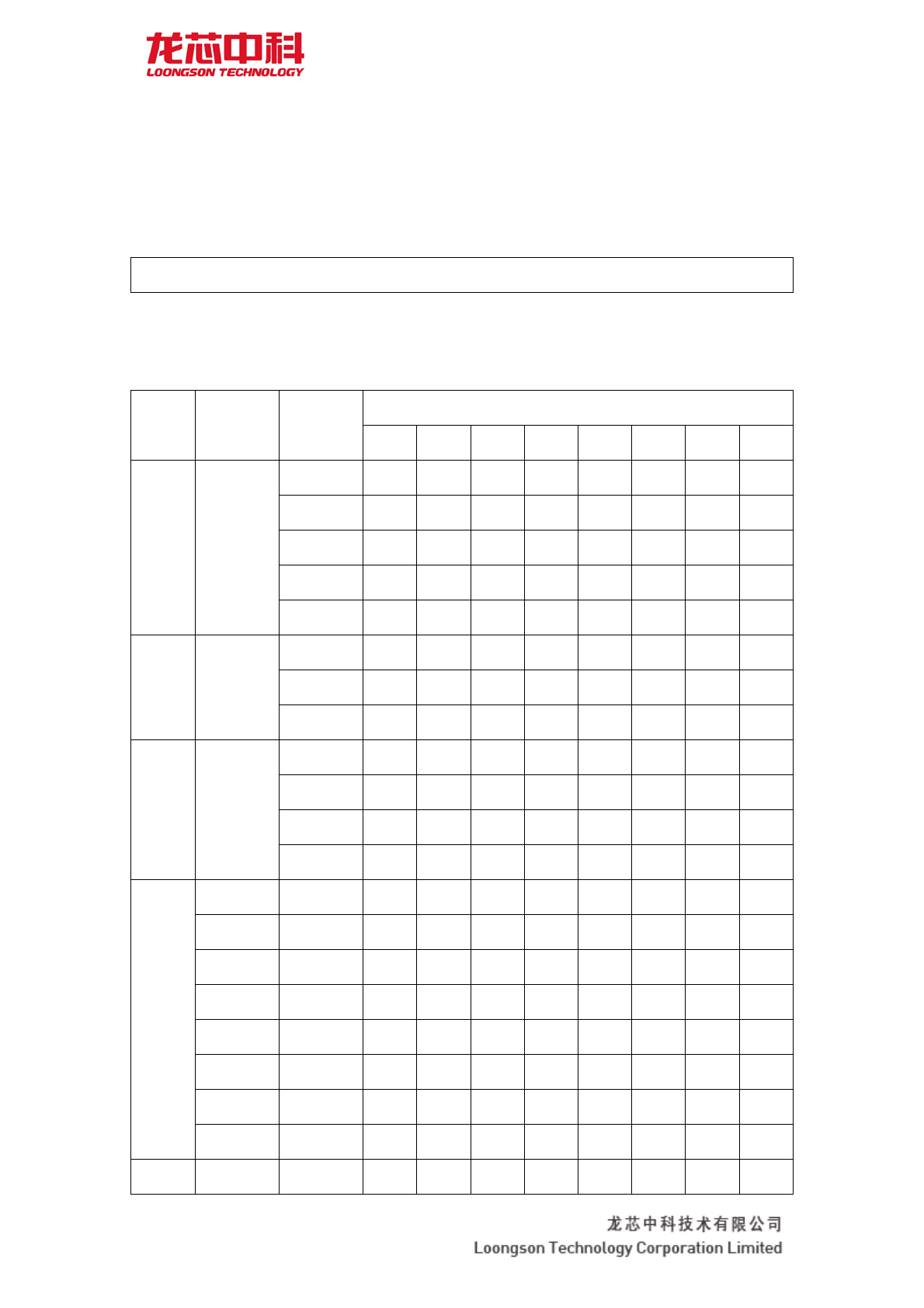

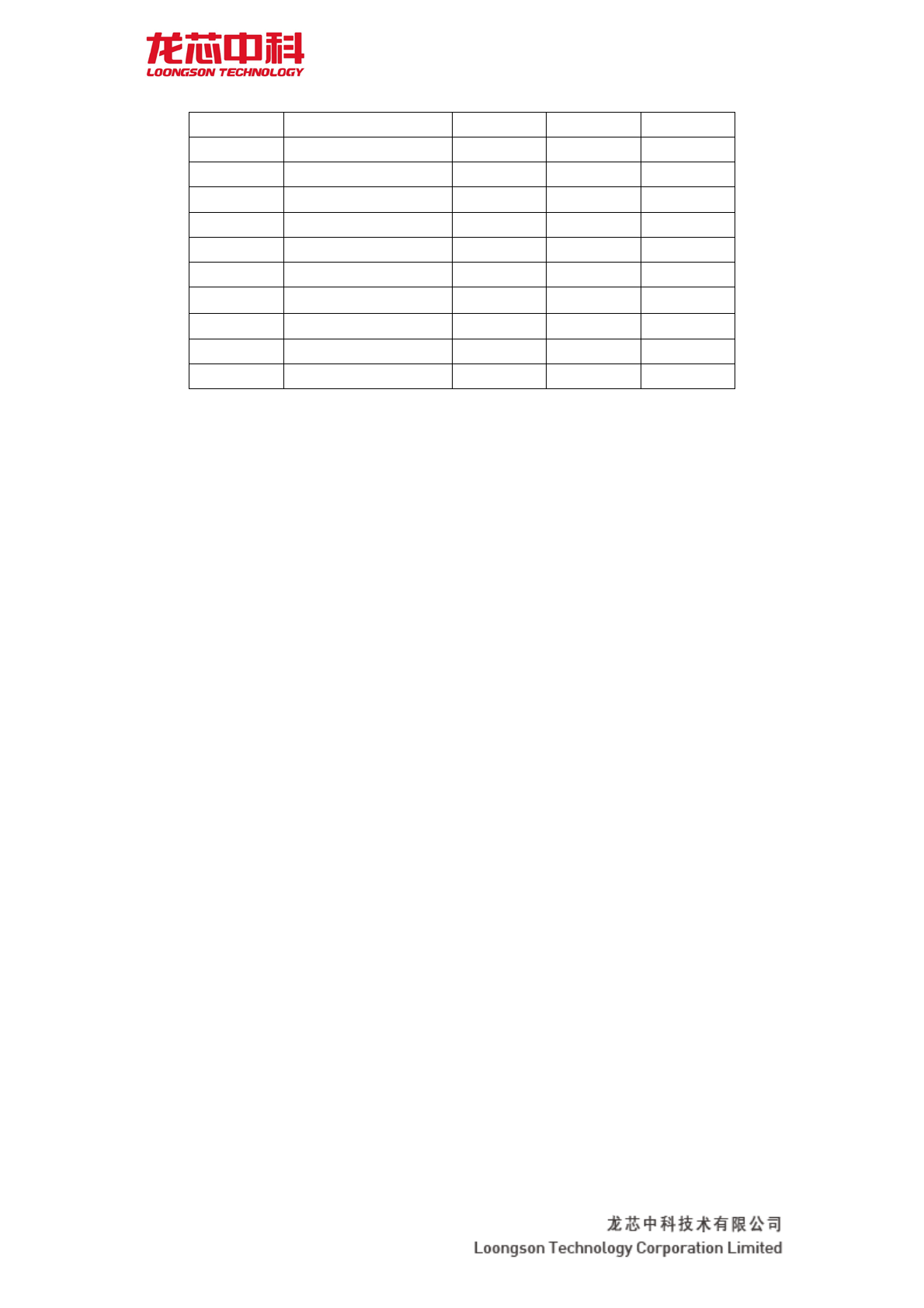

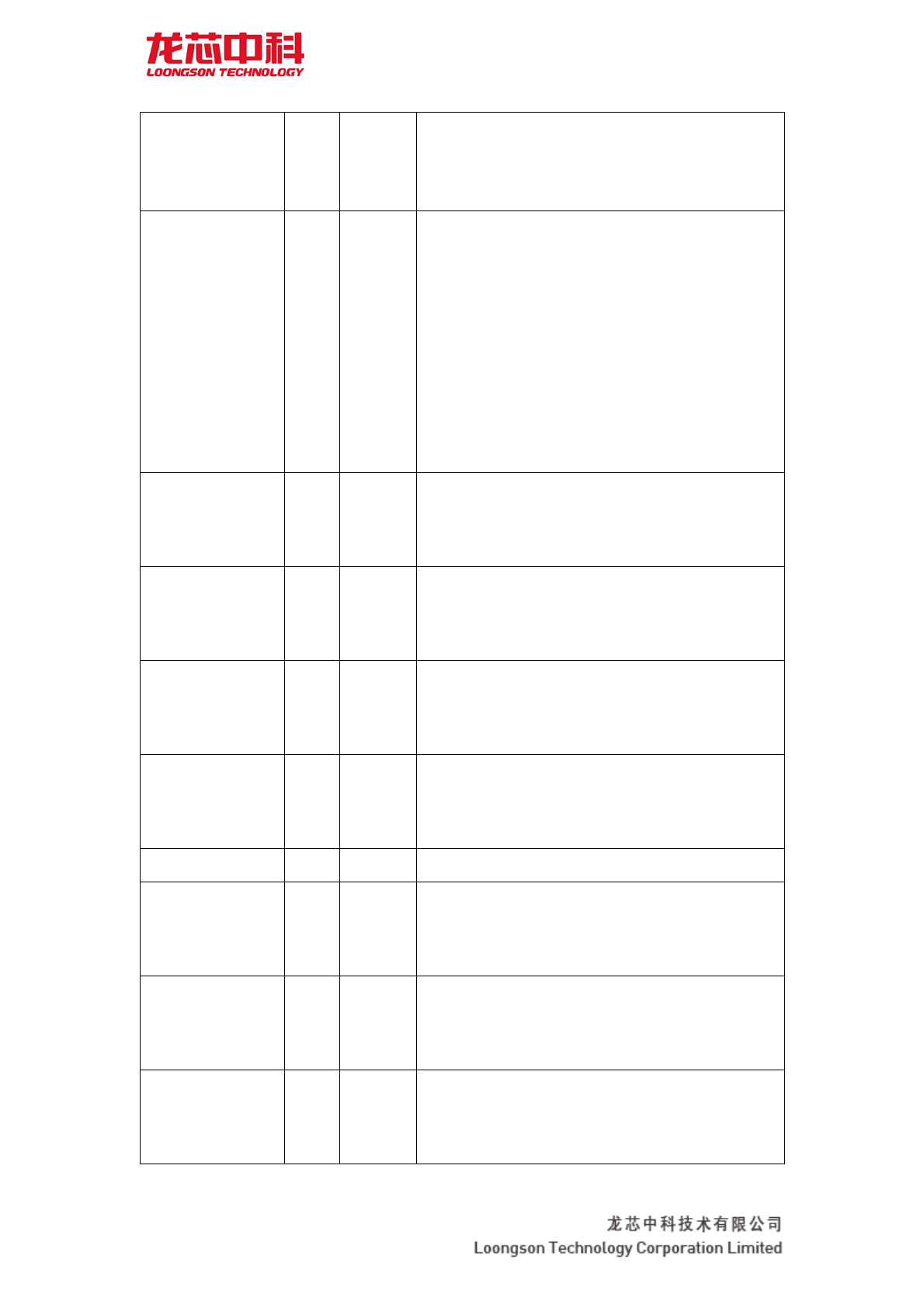

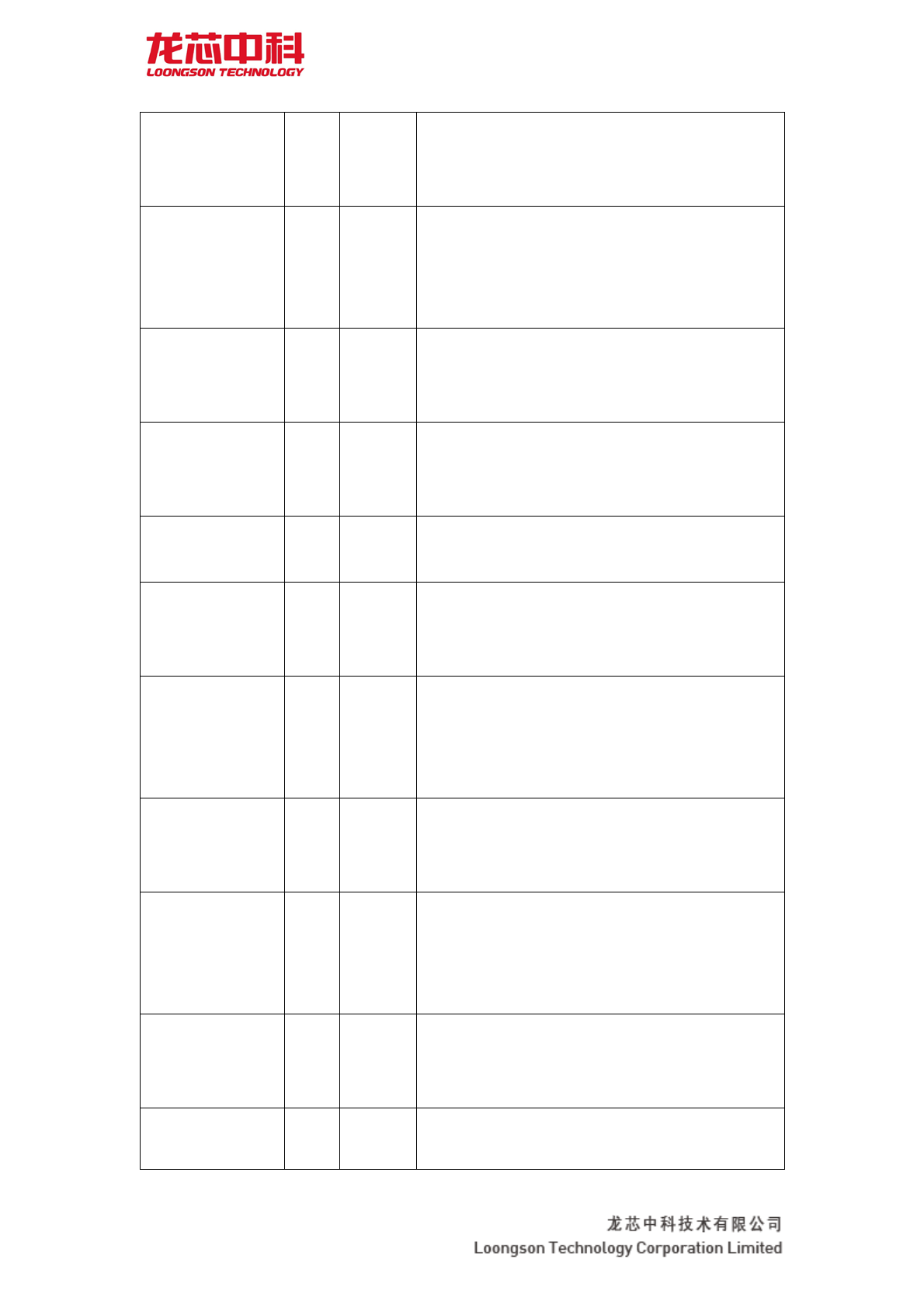

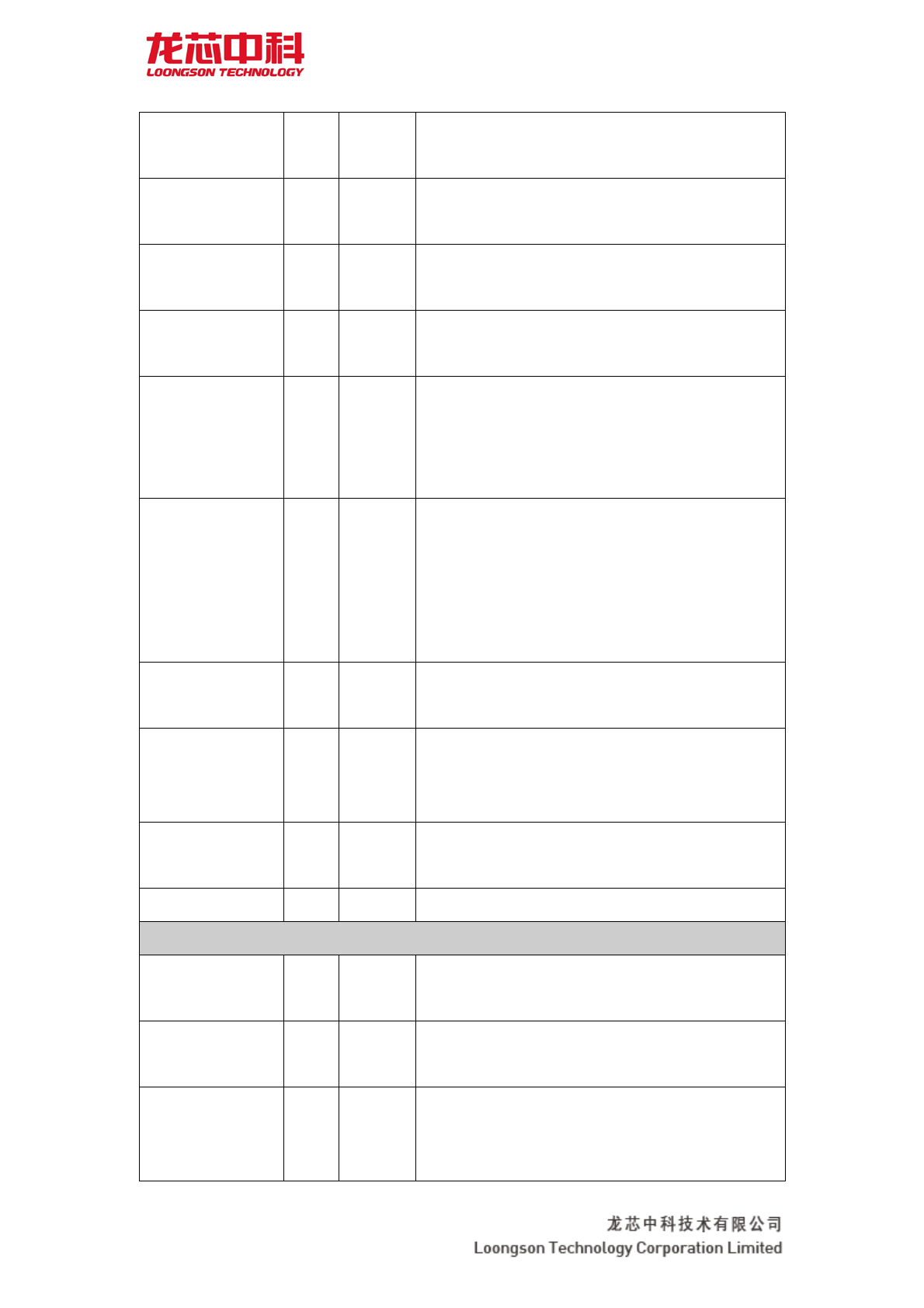

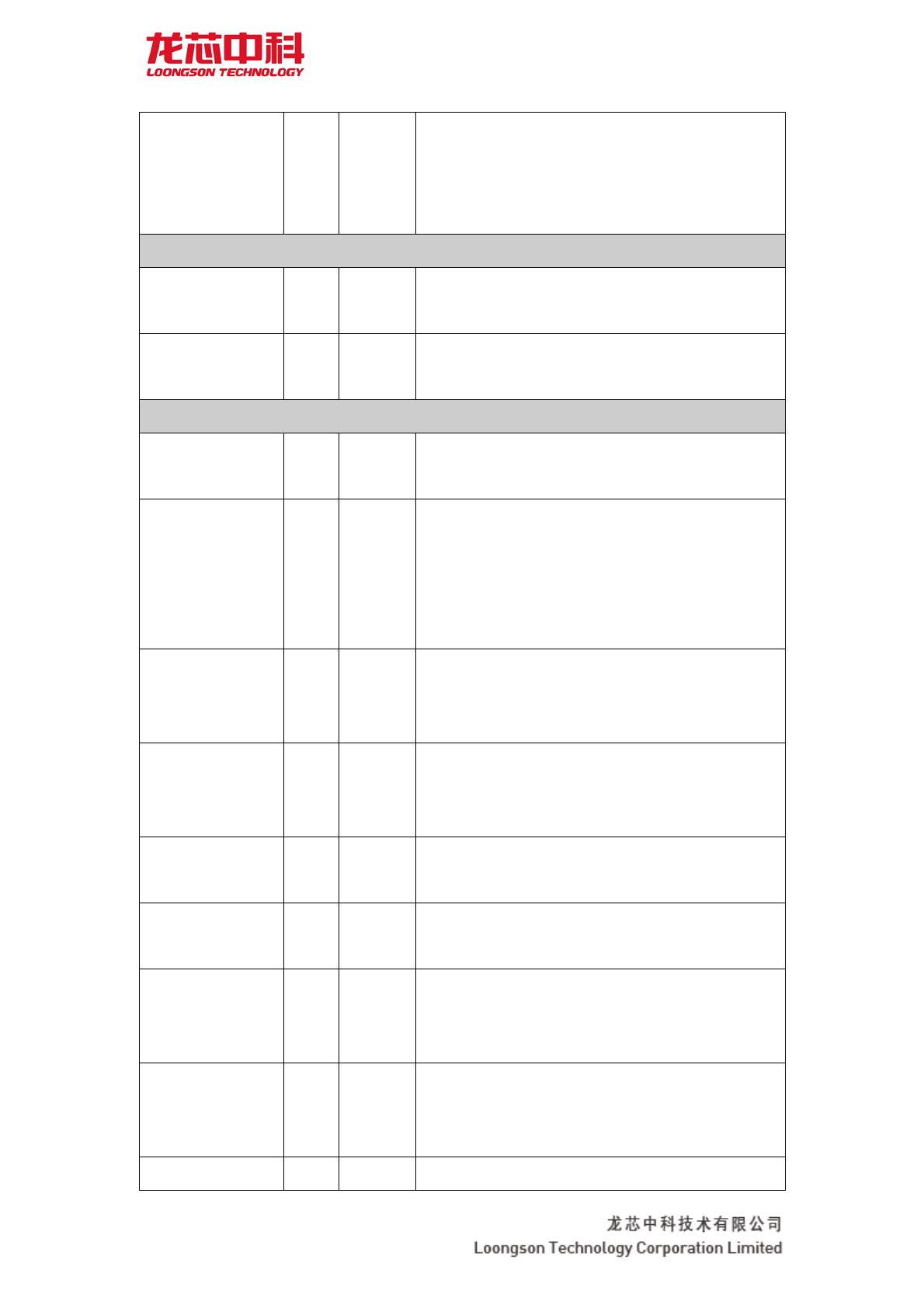

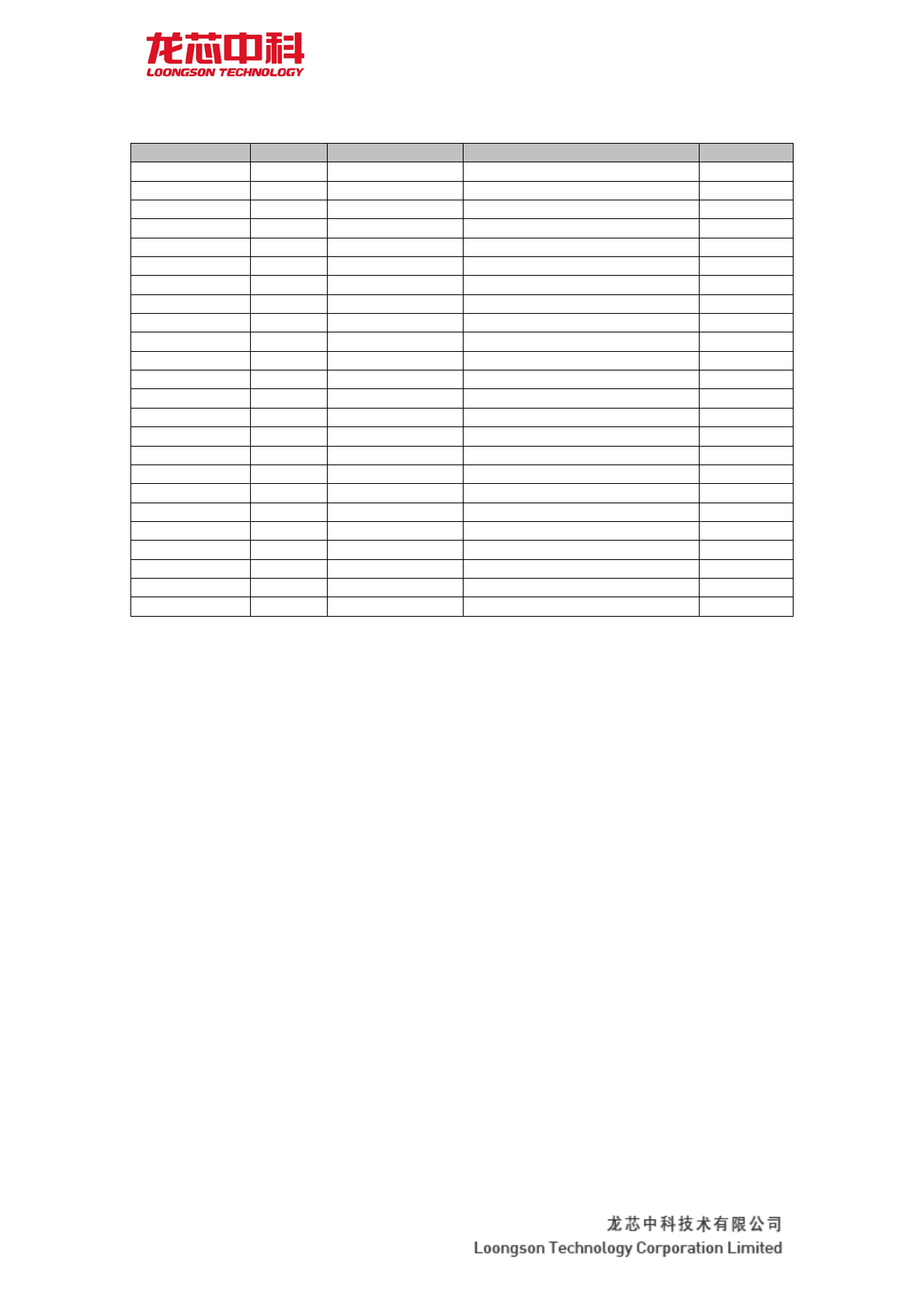

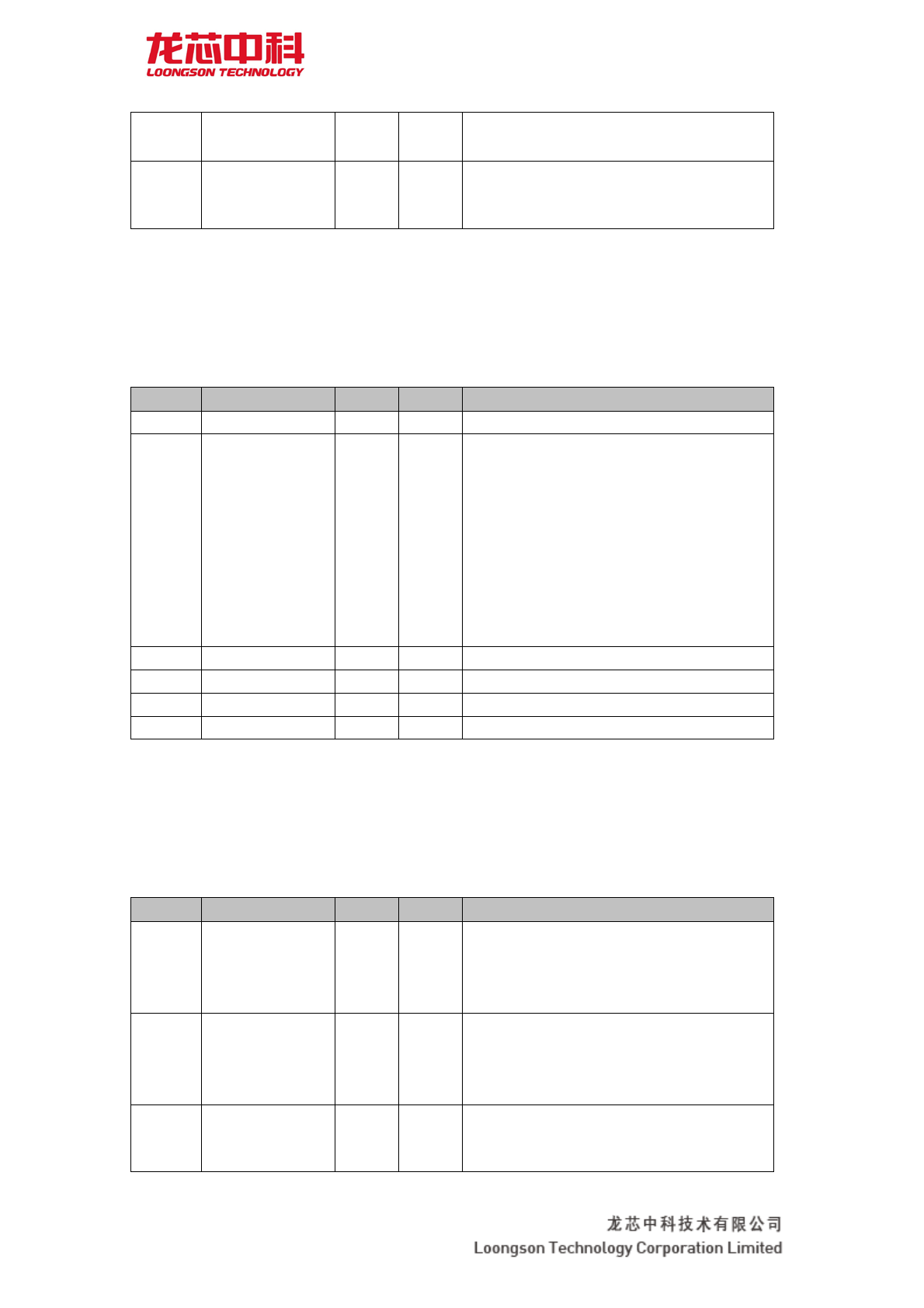

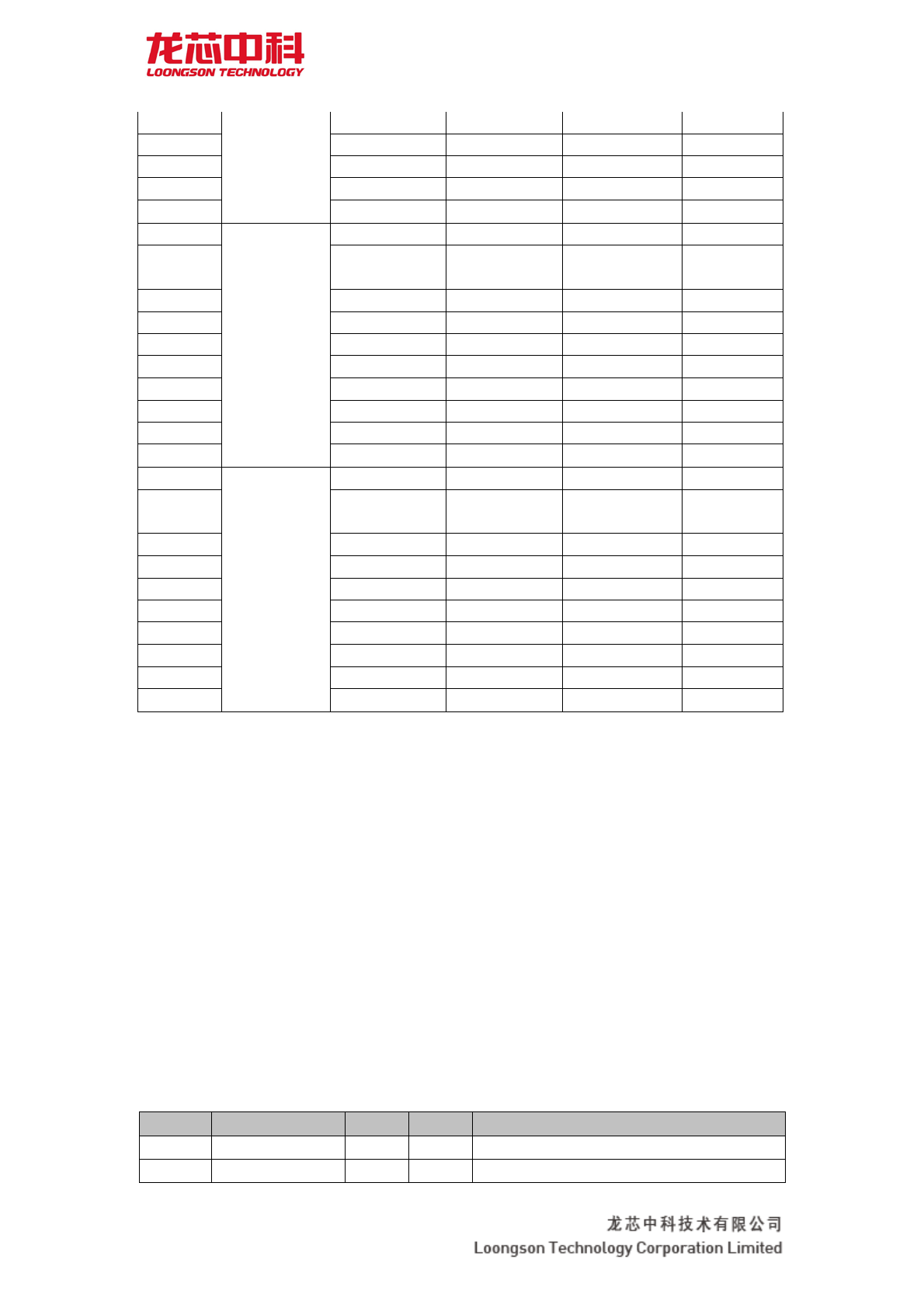

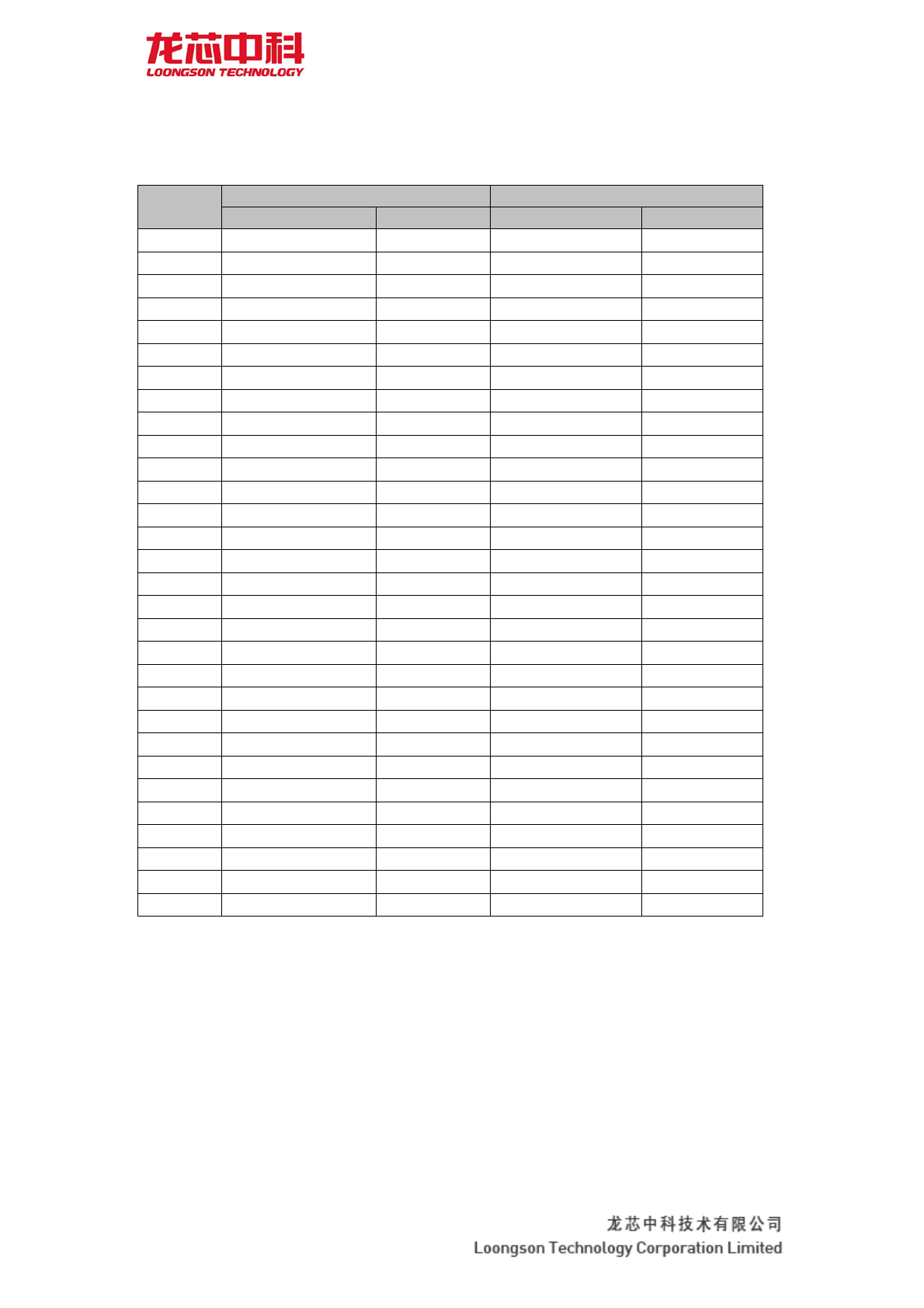

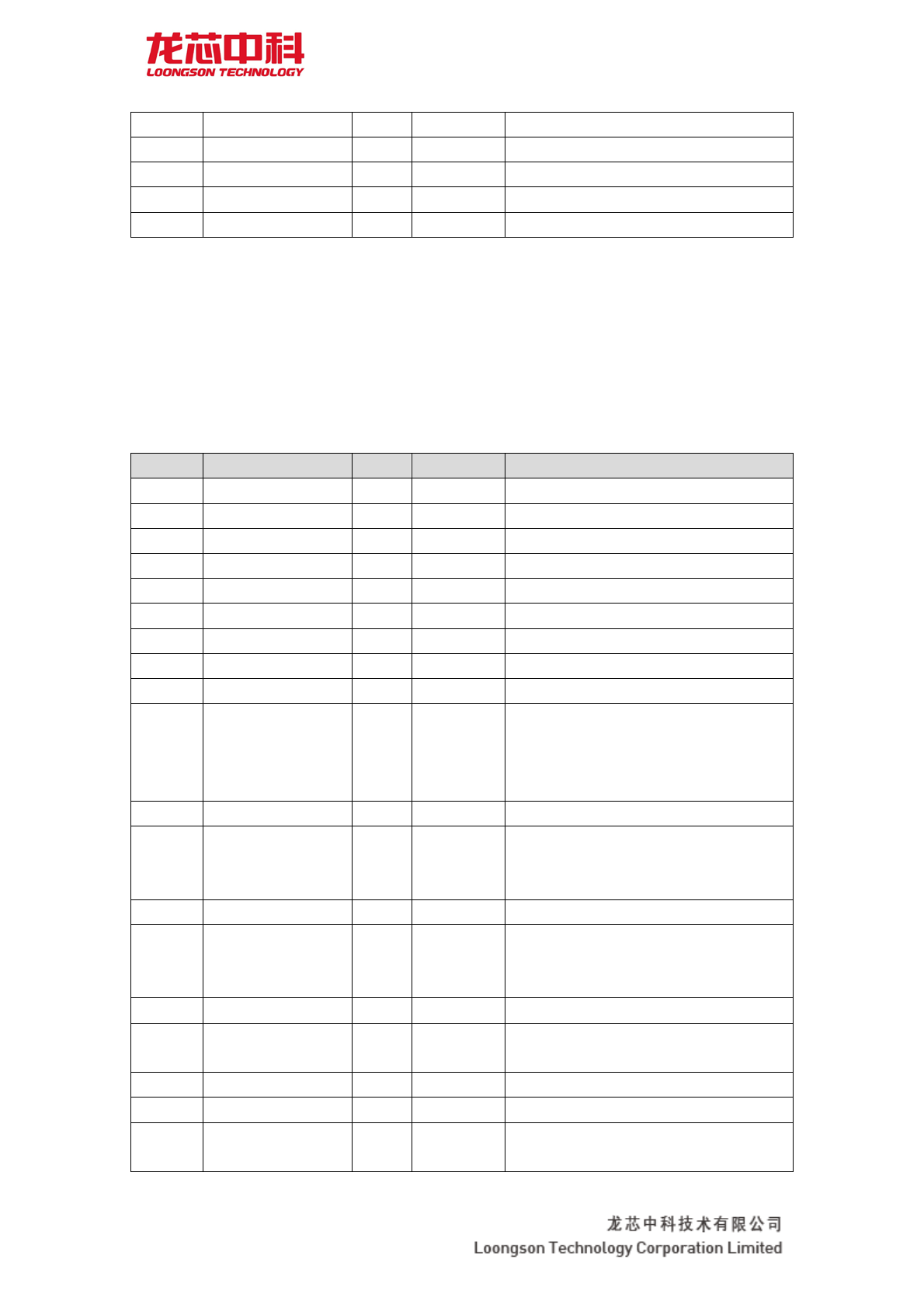

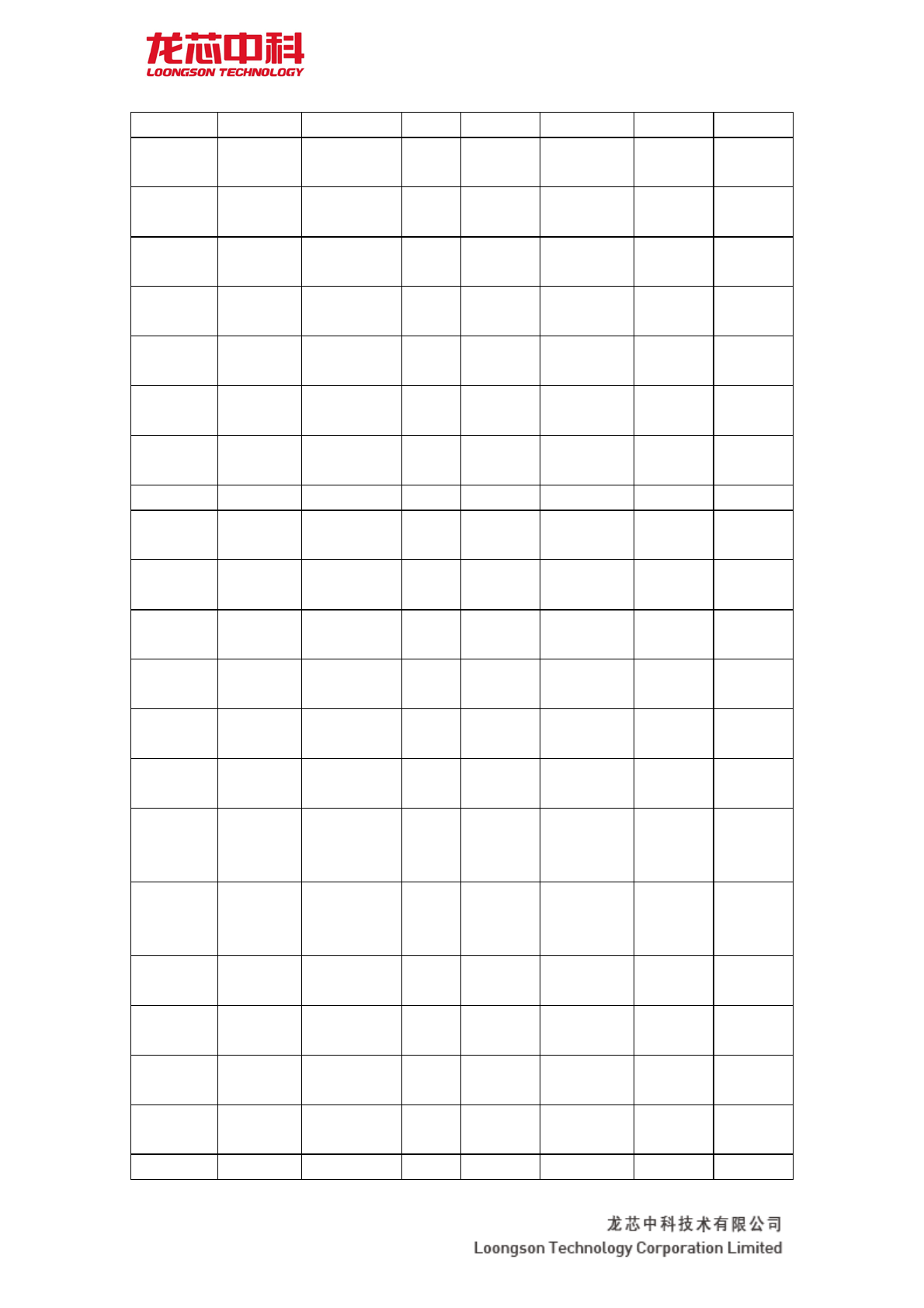

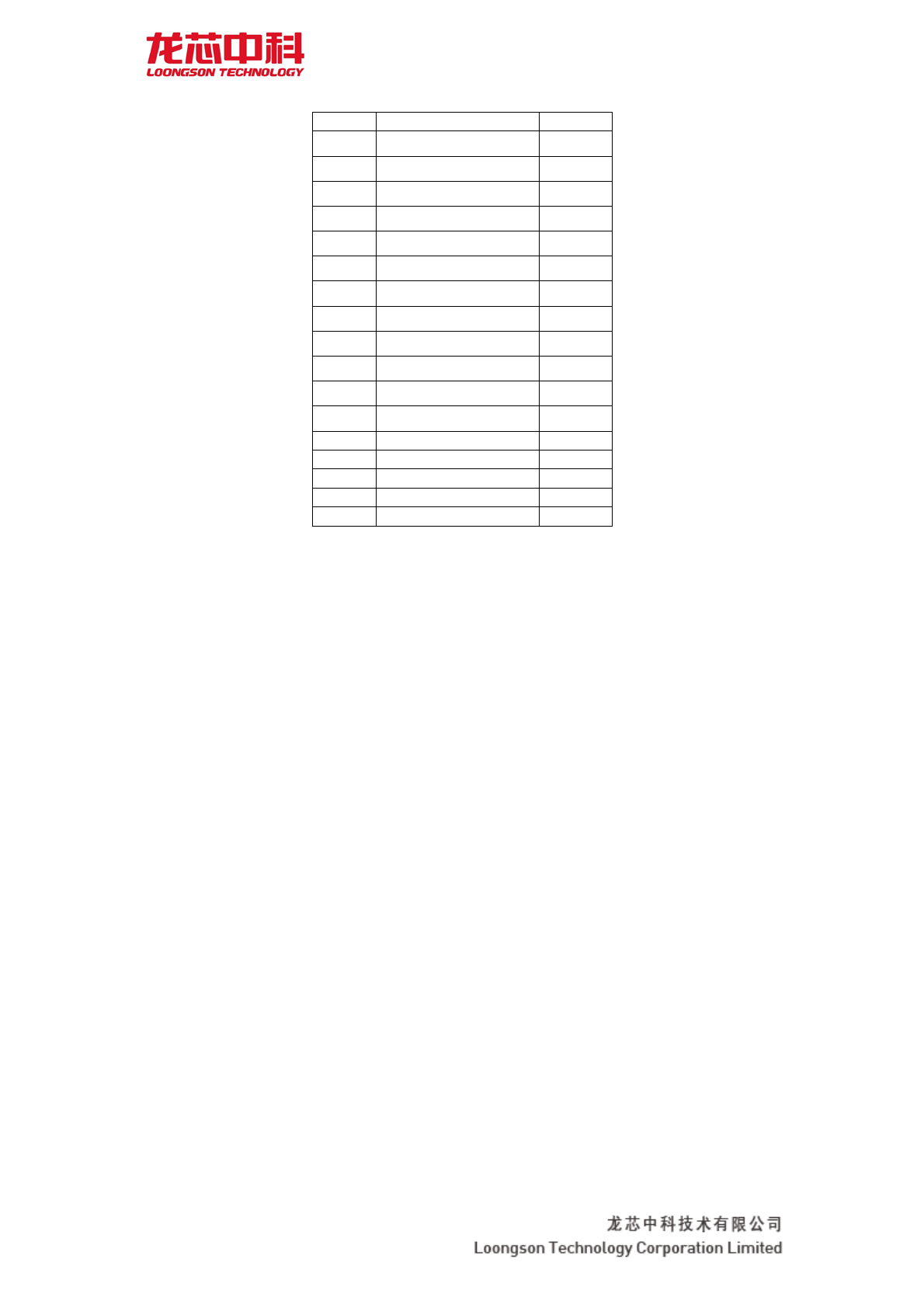

序号. 更新日期 更新人 版本号 更新内容

1

2010-6-7 研发中心 V1.0

1B 处理器初稿完成

2

2010-11-13 研发中心 V1.1

增加了芯片引脚排布,DDR 控制器信息等

3

2010-11-15 研发中心 V1.2

修改并进行标准排版

4

2010-11-15 研发中心 V1.3

修正了第五章 DDR 的部分错误

5

2011-05-08 研发中心 V1.4

修订了调试发现的错误

6

2011-05-17 研发中心 V1.5

修订了多个小问题

7

2011-11-15 研发中心 V1.6

GMAC0/1

的

RGMII

和

MII

模式需要配置才能使用

GPIO 配置和复用中修改 bug

SPI 部分,分频时钟明确是 DDR2_clk/2

DDR2 部分,配置 16/32 位可配置

时钟分频部分有改动

添加了 LCD PAD 在不同显示模式下的对应关系

GPIO

寄存器描述修改

8

2012-4-11 研发中心 V1.7

NAND

部分寄存器说明修改

XTALI/O 与外部有源晶振、无源晶体连接方法

9

2012-4-20 研发中心 V1.8

PAD

封装位置和封装延迟

GPIO 复位值和方向

GMAC0/1 在MII 模式下信号处理

Wdog 地址修改

USB

启动需要复位

10

2012-05-26

研发中心 V1.9 针对修改意见,做了

GPIO/ LCD/ DMA/ SPI/ UART

/I2C/ NAND /CLOCK 的修改

11

2014-07-30

研发中心 V2.0 增加质量等级和封装顶视图

12

2015-3-11

研发中心 V2.1 增加电特性,CAN 的速率计算

III

龙芯 1B 处理器用户手册

13

2015-4-1

研发中心 V2.1 补充质量等级描述

手册信息反馈: service@loongson.cn

IV

龙芯 1B 处理器用户手册目录

目

录

1 概述 ............................................................................................................................... 1

1.1 体系结构框图 ................................................................................................................... 1

1.2 芯片主要功能 ................................................................................................................... 2

1.2.1 GS232 CPU ................................................................................................ 2

1.2.2 DDR2 ......................................................................................................... 3

1.2.3 LCD Controller ...................................................................................... 3

1.2.4 USB2.0 ..................................................................................................... 3

1.2.5 AC97 ......................................................................................................... 3

1.2.6 GMAC ......................................................................................................... 4

1.2.7 SPI ........................................................................................................... 4

1.2.8 UART ......................................................................................................... 4

1.2.9 I2C ........................................................................................................... 4

1.2.10 PWM ........................................................................................................... 4

1.2.11 CAN ........................................................................................................... 5

1.2.12 RTC ........................................................................................................... 5

1.2.13 GPIO ......................................................................................................... 5

1.2.14 NAND ......................................................................................................... 5

1.2.15 INT controller ...................................................................................... 5

1.2.16 Watchdog ................................................................................................. 5

1.2.17 功耗 ......................................................................................................... 5

1.2.18 其它 ......................................................................................................... 7

1.3 质量等级 ........................................................................................................................... 7

2 芯片引脚定义 ................................................................................................................ 9

2.1 1B 引脚分布图 .................................................................................................................. 9

2.2 封装顶视图 ..................................................................................................................... 16

2.3 系统相关引脚定义(6) ............................................................................................... 17

2.4 LCD 引脚定义(20) ...................................................................................................... 17

2.5 PLL 引脚定义(4) ........................................................................................................ 17

2.6 VR 引脚定义(6) .......................................................................................................... 18

2.7 DDR2 引脚定义(71) .................................................................................................... 18

2.8 USB 引脚定义(10) .......................................................................................................... 19

2.9 EJTAG 引脚定义(6) ........................................................................................................ 20

2.10 GMAC0 引脚定义(15) ...................................................................................................... 20

2.11 GMAC1 引脚定义(4) ........................................................................................................ 20

2.12 AC97 引脚定义(5) .......................................................................................................... 21

2.13 SPI 引脚定义(7) ............................................................................................................ 21

2.14 UART 引脚定义(20) ........................................................................................................ 21

2.15 I2C 引脚定义(2) ............................................................................................................ 22

2.16 CAN 引脚定义(4) ............................................................................................................ 22

2.17 NAND 引脚定义(14) ........................................................................................................ 22

2.18 PWM 引脚定义(4) ............................................................................................................ 22

2.19 电源/地引脚(58) ................................................................................................... 23

I

龙芯 1B 处理器用户手册目录

3 地址空间分配 .............................................................................................................. 24

3.1 一级 AXI 交叉开关上模块的地址空间 ......................................................................... 24

3.2 AXI MUX 下各模块的地址空间 ...................................................................................... 24

3.3 APB 各模块的地址空间分配 .......................................................................................... 24

4 CPU ............................................................................................................................... 26

4.1 MIPS32 指令系统结构 .................................................................................................... 26

4.1.1 CPU 寄存器 ............................................................................................. 27

4.1.2 CPU 指令集 ............................................................................................. 27

4.1.3 CP0 指令集 ............................................................................................. 31

4.1.4 存储空间 ............................................................................................... 32

4.1.5 例外处理 ............................................................................................... 33

4.1.6 CP0 寄存器 ............................................................................................. 35

4.2 CP0 指令 .......................................................................................................................... 53

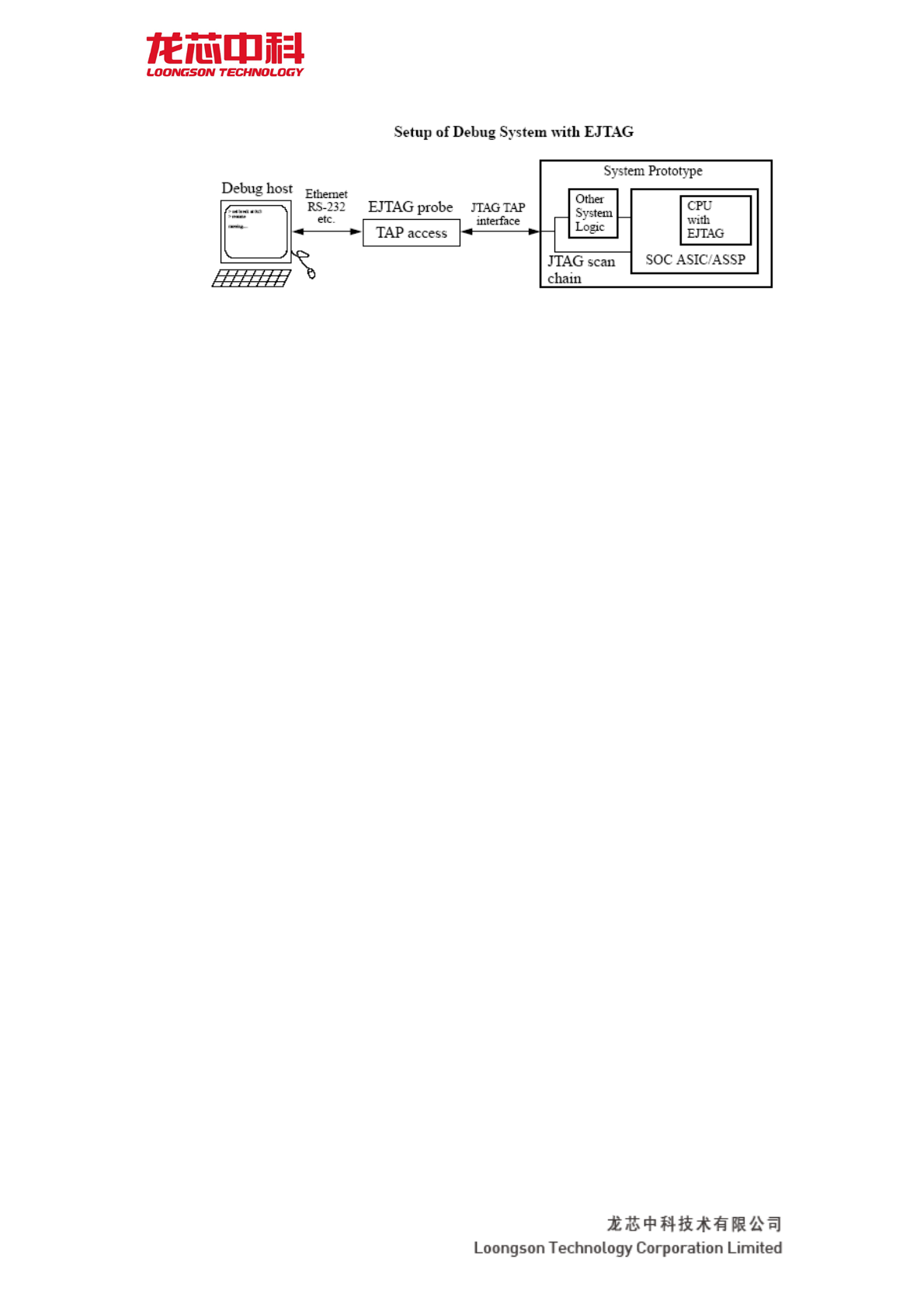

4.3 EJTAG 设计 ...................................................................................................................... 53

4.3.1 EJTAG 介绍 ............................................................................................. 53

4.3.2 调试控制寄存器(Debug Control Register) ..................................... 54

4.3.3 硬件断点 ............................................................................................... 56

4.3.4 EJTAG 相关的处理器核扩展 ................................................................... 61

4.3.5 TAP 接口 ................................................................................................ 64

5 DDR2 ............................................................................................................................. 72

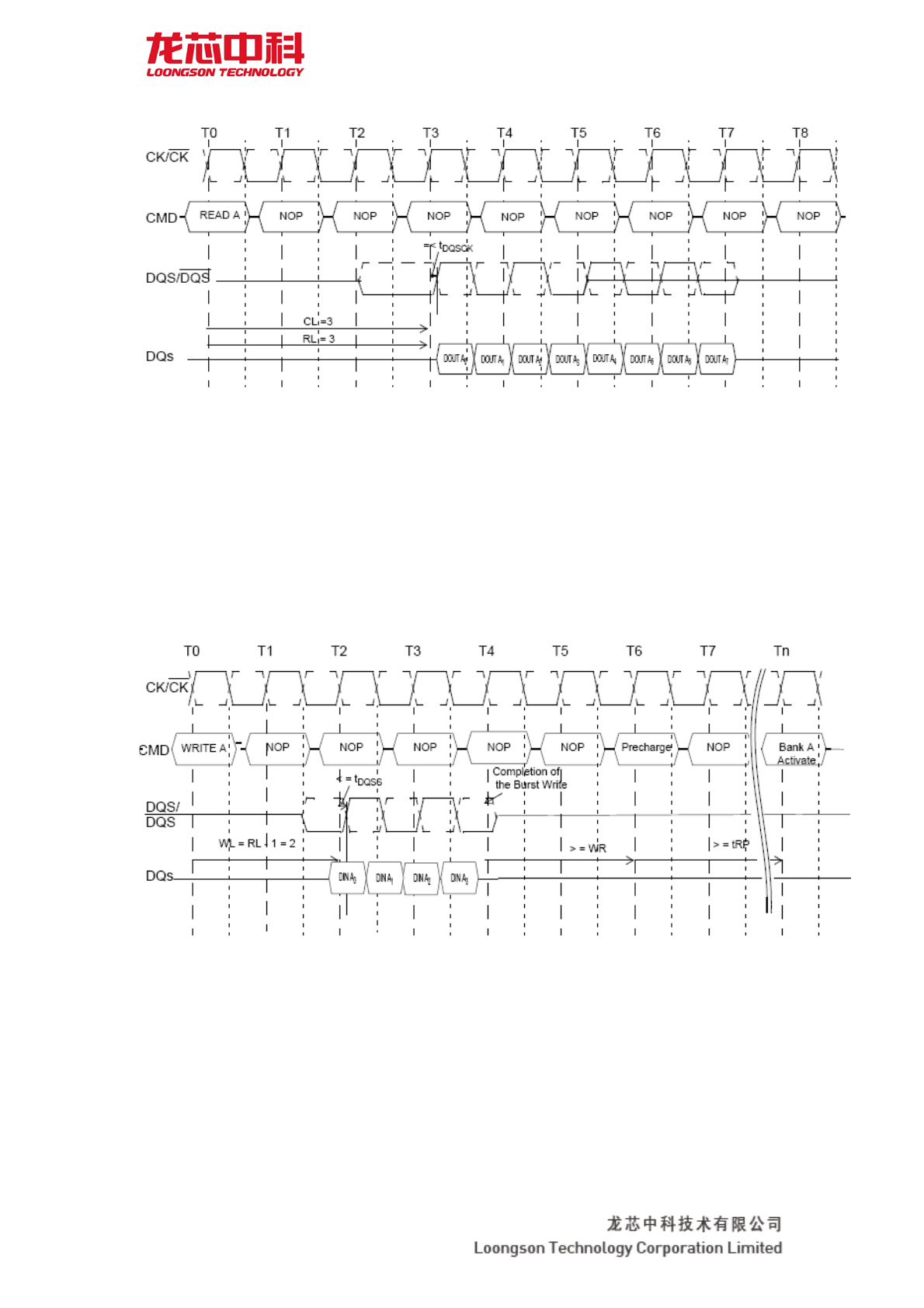

5.1 DDR2 SDRAM 控制器特性 ................................................................................................ 72

5.2 DDR2 SDRAM 读协议........................................................................................................ 72

5.3 DDR2 SDRAM 写协议 ........................................................................................................ 73

5.4 DDR2 SDRAM 参数设置顺序 ............................................................................................ 73

5.5 DDR2 SDRAM 采样模式配置 ............................................................................................ 74

5.6 DDR2 SDRAM PAD 驱动配置 ...................................................................................... 74

5.7 DDR2 16 位工作模式配置 ............................................................................................. 74

6 LCD ............................................................................................................................... 75

6.1 特性 ................................................................................................................................. 75

6.1.1 数据格式 ............................................................................................... 75

6.2 寄存器 ............................................................................................................................. 75

7 GMAC0 ........................................................................................................................... 81

7.1 配置成 MAC 的连接和复用方式 .................................................................................. 81

7.2 DMA 寄存器描述 .............................................................................................................. 81

7.3 GMAC 控制器寄存器描述 ................................................................................................ 90

7.4 DMA 描述符 .................................................................................................................... 101

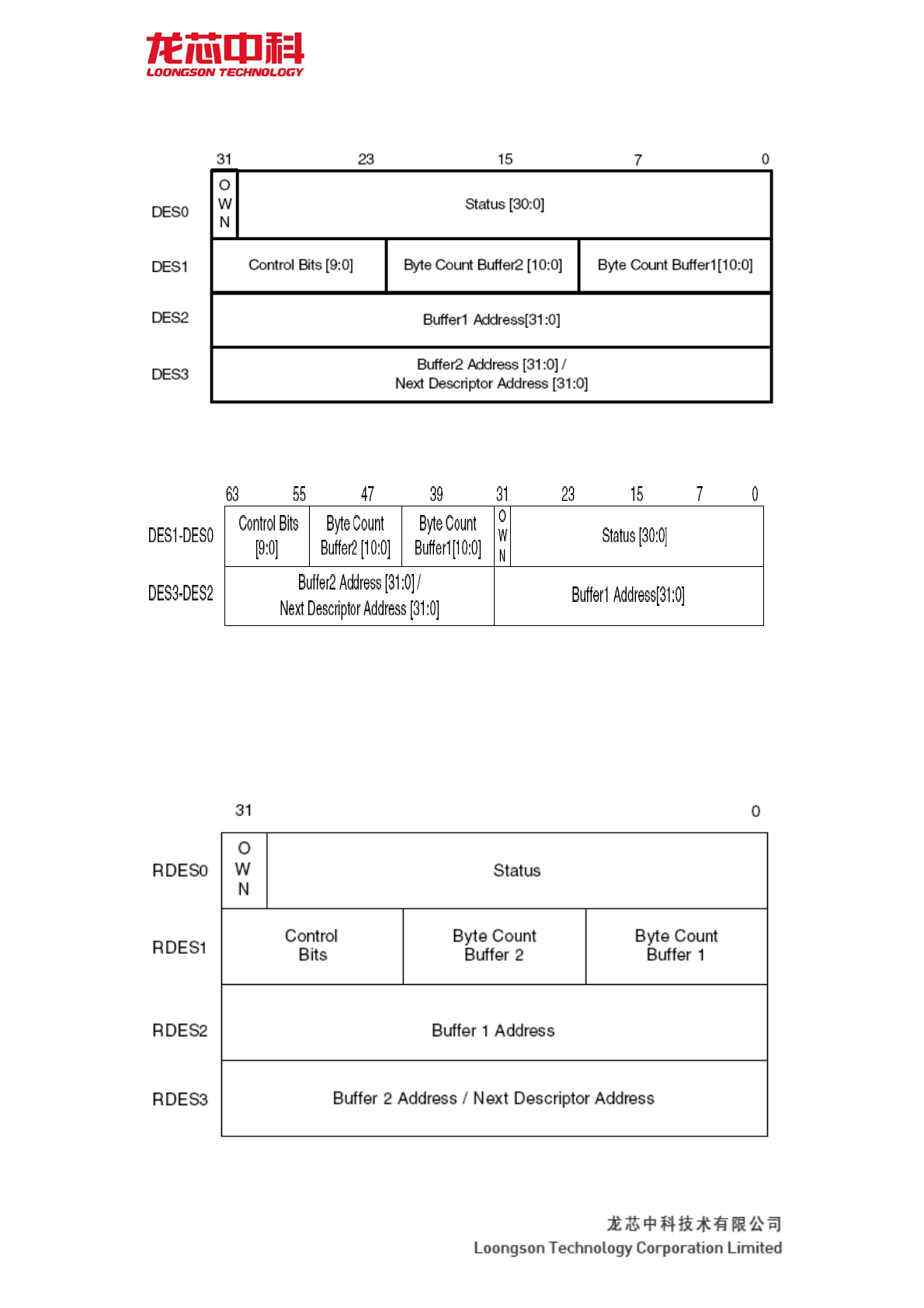

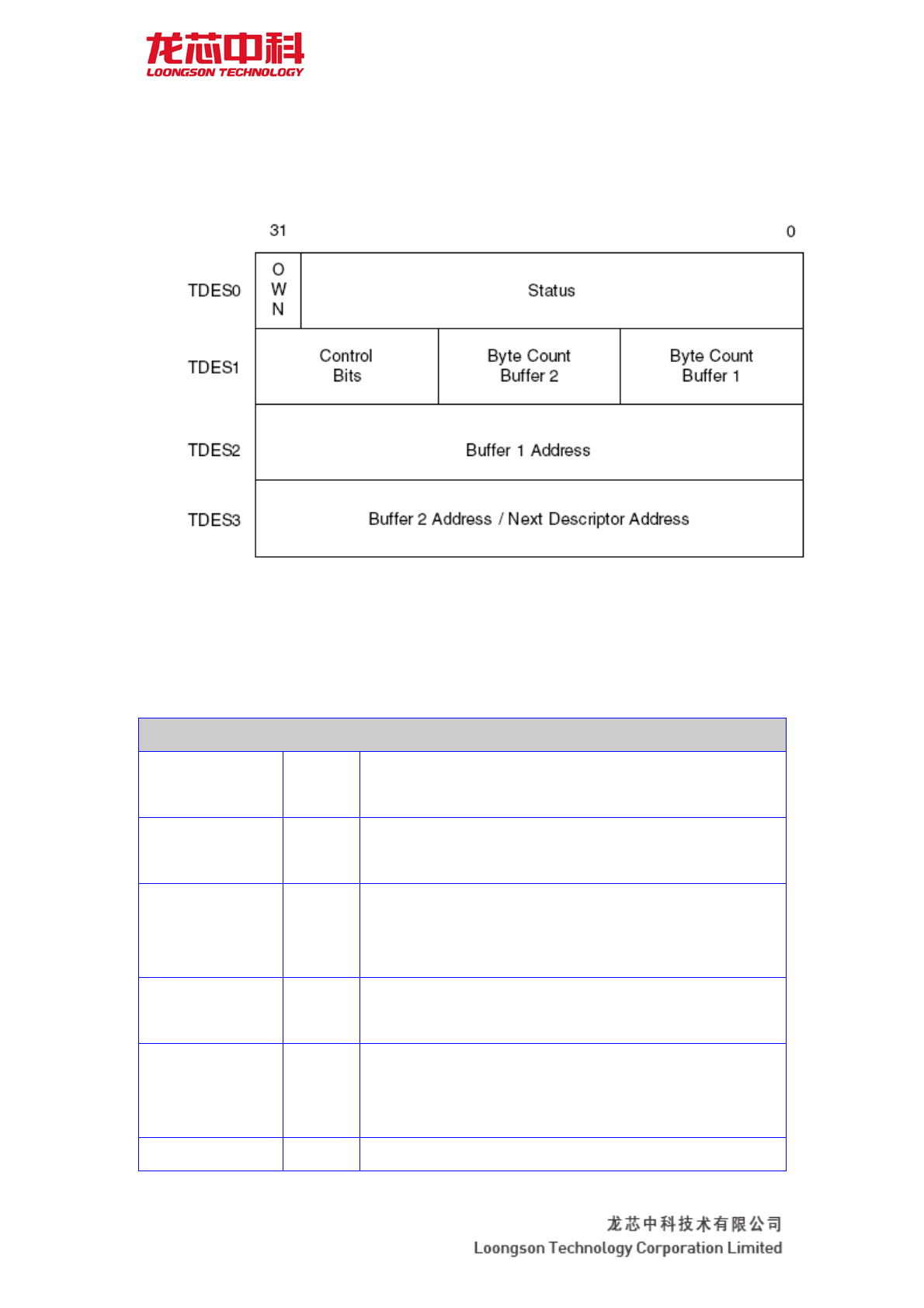

7.4.1 DMA 描述符的基本格式 ........................................................................ 101

7.4.2 DMA 接收描述符 ................................................................................... 102

7.4.3 RDES0 ................................................................................................... 103

7.4.4 RDES ..................................................................................................... 104

7.4.5 RDES2 ................................................................................................... 105

7.4.6 RDES3 ................................................................................................... 105

7.4.7 DMA 发送描述符 ................................................................................... 106

7.4.8 TDES0 ................................................................................................... 106

II

龙芯 1B 处理器用户手册目录

7.4.9 TDES1 ................................................................................................... 107

7.4.10 TDES2 ................................................................................................... 109

7.4.11 TDES3 ................................................................................................... 109

7.5 软件编程向导(SOFTWARE PROGRAMMING GUIDE):........................................................... 110

8 GMAC1 ......................................................................................................................... 112

8.1 配置成 MAC 的连接和复用方式 ................................................................................ 112

8.2 GMAC1 外部信号复用和配置 ........................................................................................ 112

8.3 寄存器描述 ................................................................................................................... 113

9 USB HOST .................................................................................................................... 114

9.1 总体概述 ....................................................................................................................... 114

9.2 USB 主机控制器寄存器 ................................................................................................ 115

9.2.1

EHCI 相关寄存器

.................................................................................. 115

9.2.2

Capability 寄存器

.............................................................................. 115

9.2.3

Operational 寄存器

............................................................................. 116

9.2.4 EHCI 实现相关寄存器 ......................................................................... 116

9.2.4.1 INSNREG00 寄存器(disable) ......................................................... 117

9.2.4.2 INSNREG01 寄存器 ............................................................................. 117

9.2.4.3 INSNREG02 寄存器............................................................................. 117

9.2.4.4 INSNREG03 寄存器............................................................................. 117

9.2.4.5 INSNRE04 寄存器(仅用于调试,软件不必更改此寄存器) ........ 117

9.2.4.6 INSNRE05 寄存器 ............................................................................... 118

9.2.4.7 INSNREG06 寄存器 ........................................................................ 118

9.2.4.8 INSNREG07 寄存器 ........................................................................ 118

9.2.4.9 INSNREG08 寄存器 ........................................................................ 118

9.3 OHCI 相关寄存器 .......................................................................................................... 119

9.3.1

Operational 寄存器

............................................................................. 119

9.3.2 OHCI 实现相关寄存器 ......................................................................... 119

9.3.2.1 INSNREG06 寄存器 ............................................................................. 120

9.3.2.2 INSNREG07 寄存器 ........................................................................ 120

9.4 USB 主机控制器时序 .................................................................................................... 120

9.4.1 数据接收时序 ...................................................................................... 120

9.4.2 数据传输时序 ...................................................................................... 121

10 SPI0 ................................................................................................................... 123

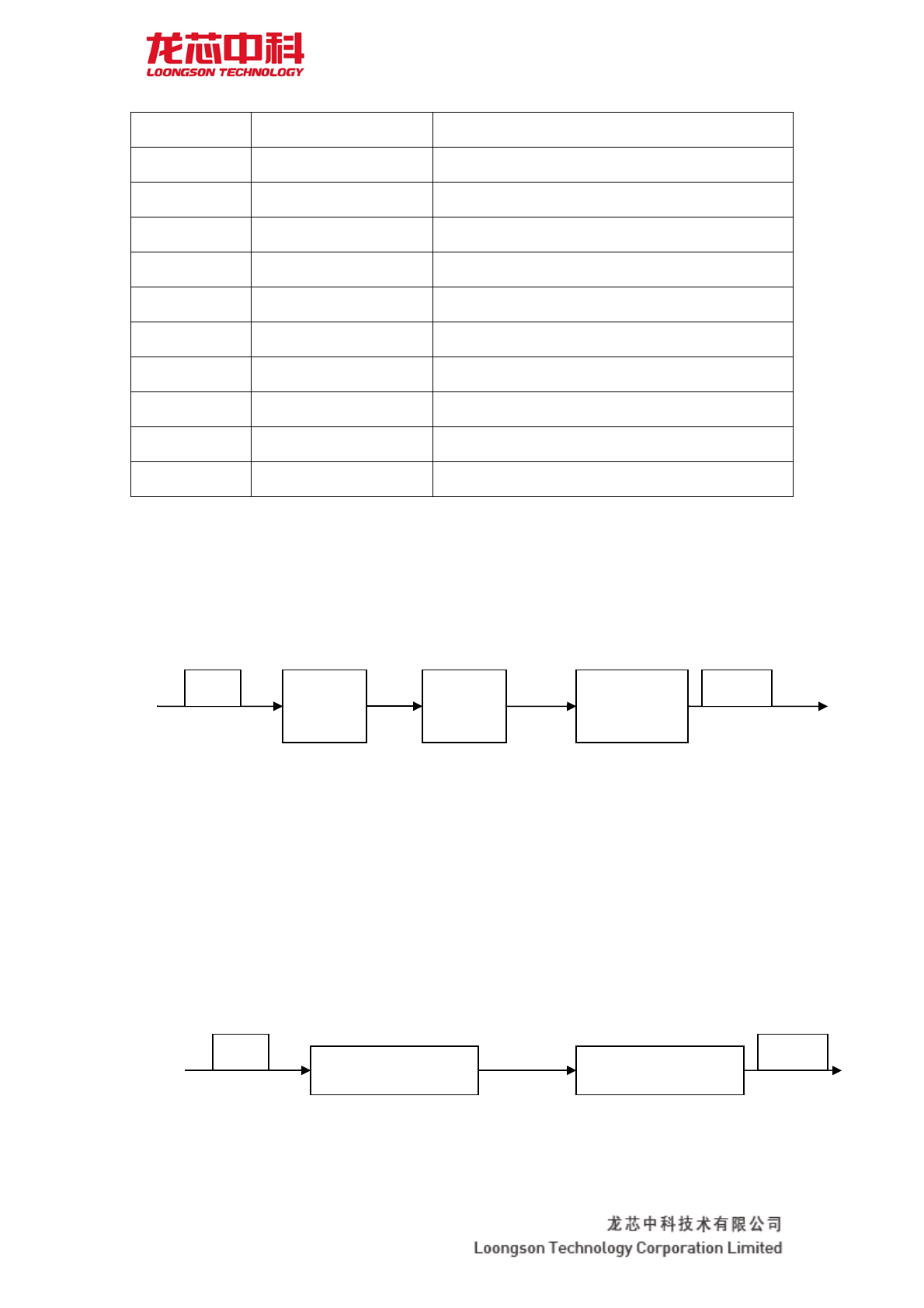

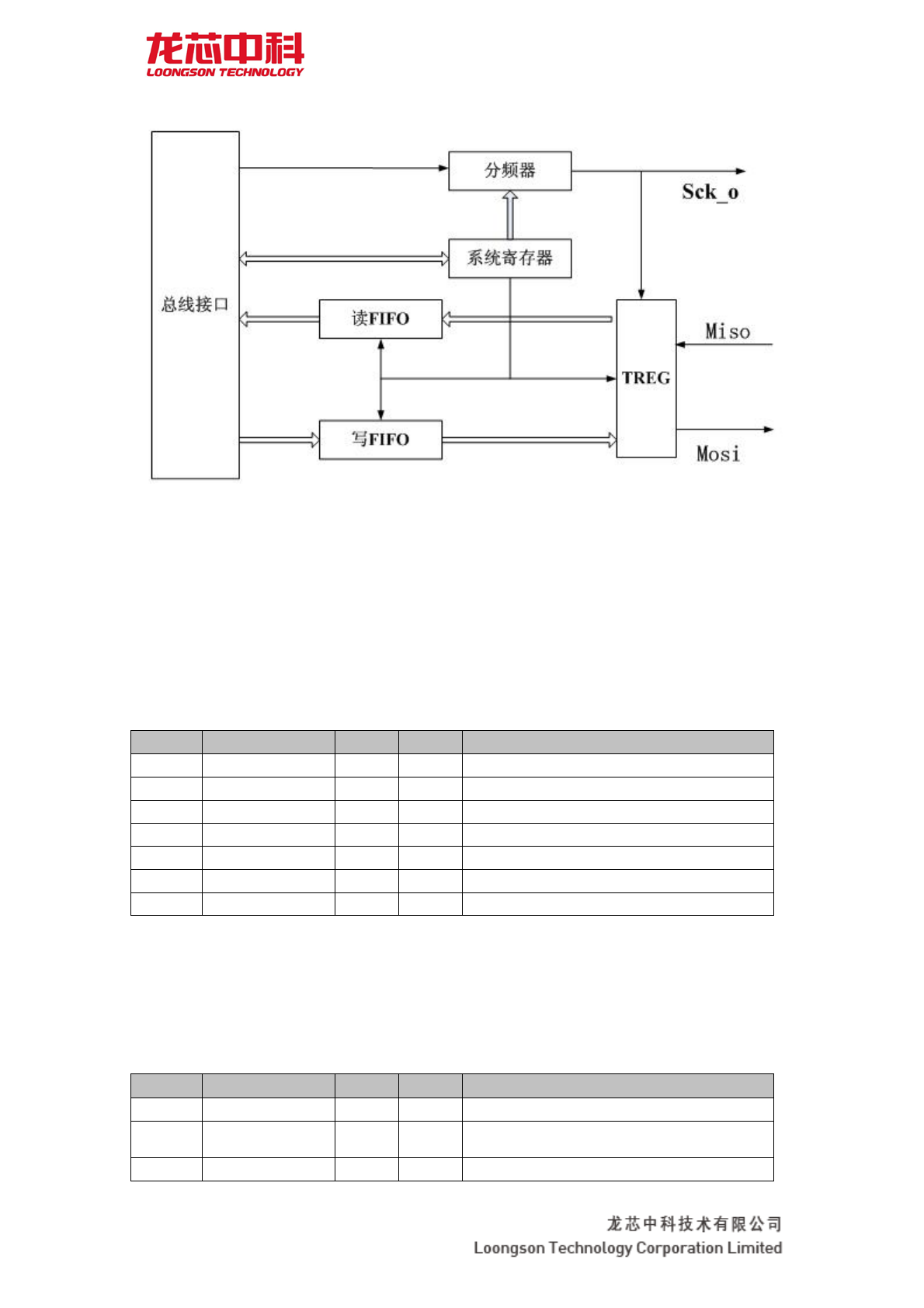

10.1 SPI 控制器结构 ............................................................................................................ 123

10.2 SPI 控制器寄存器 ........................................................................................................ 124

10.2.1 控制寄存器(SPCR) ........................................................................... 124

10.2.2 状态寄存器(SPSR) ........................................................................... 124

10.2.3 数据寄存器(TxFIFO/RxFIFO) ........................................................... 125

10.2.4 外部寄存器(SPER) ........................................................................... 125

10.2.5 参数控制寄存器(SFC_PARAM) ........................................................... 125

10.2.6 片选控制寄存器(SFC_SOFTCS) ......................................................... 126

10.2.7 时序控制寄存器(SFC_TIMING) ......................................................... 126

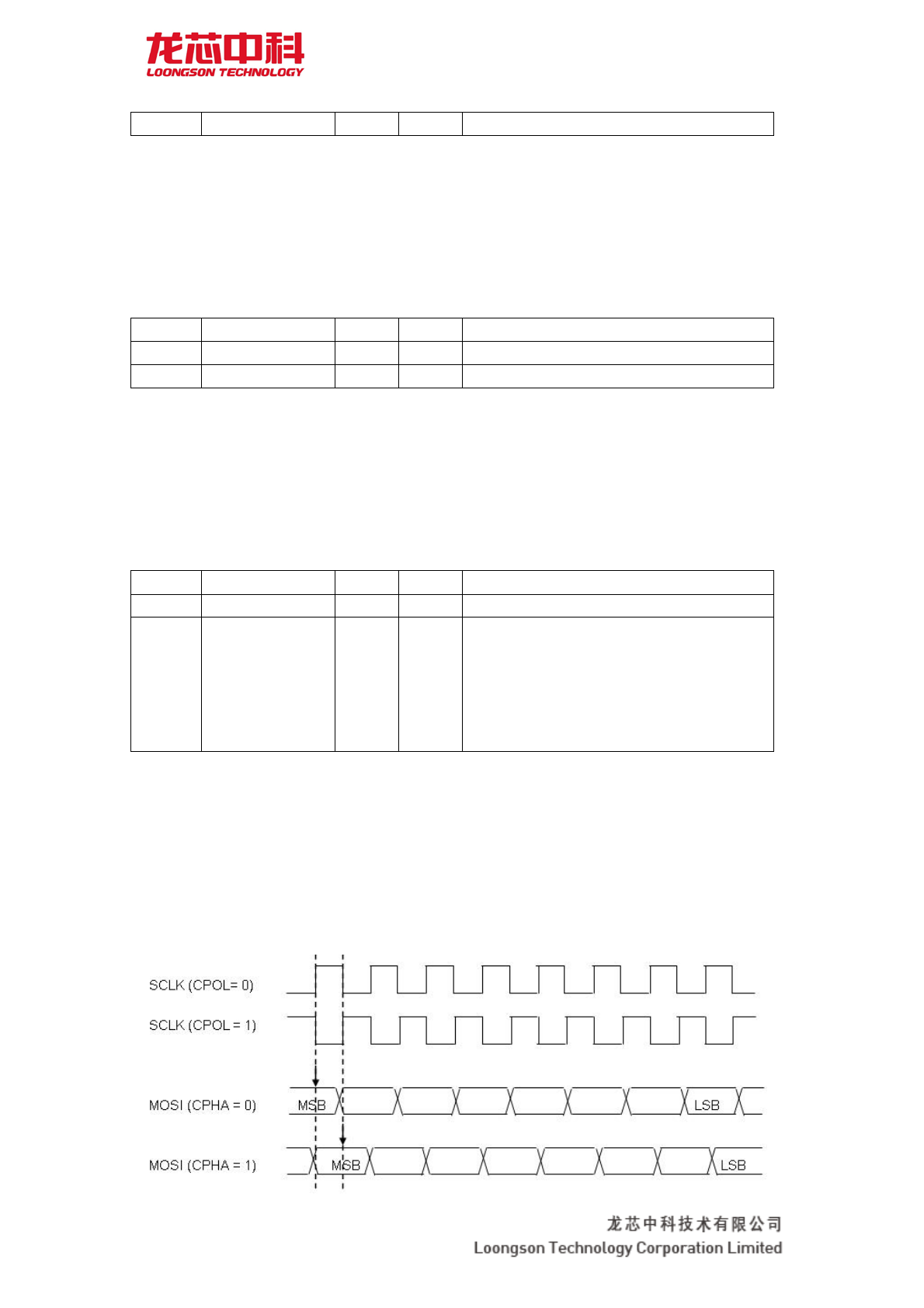

10.3 接口时序 ............................................................................................................... 126

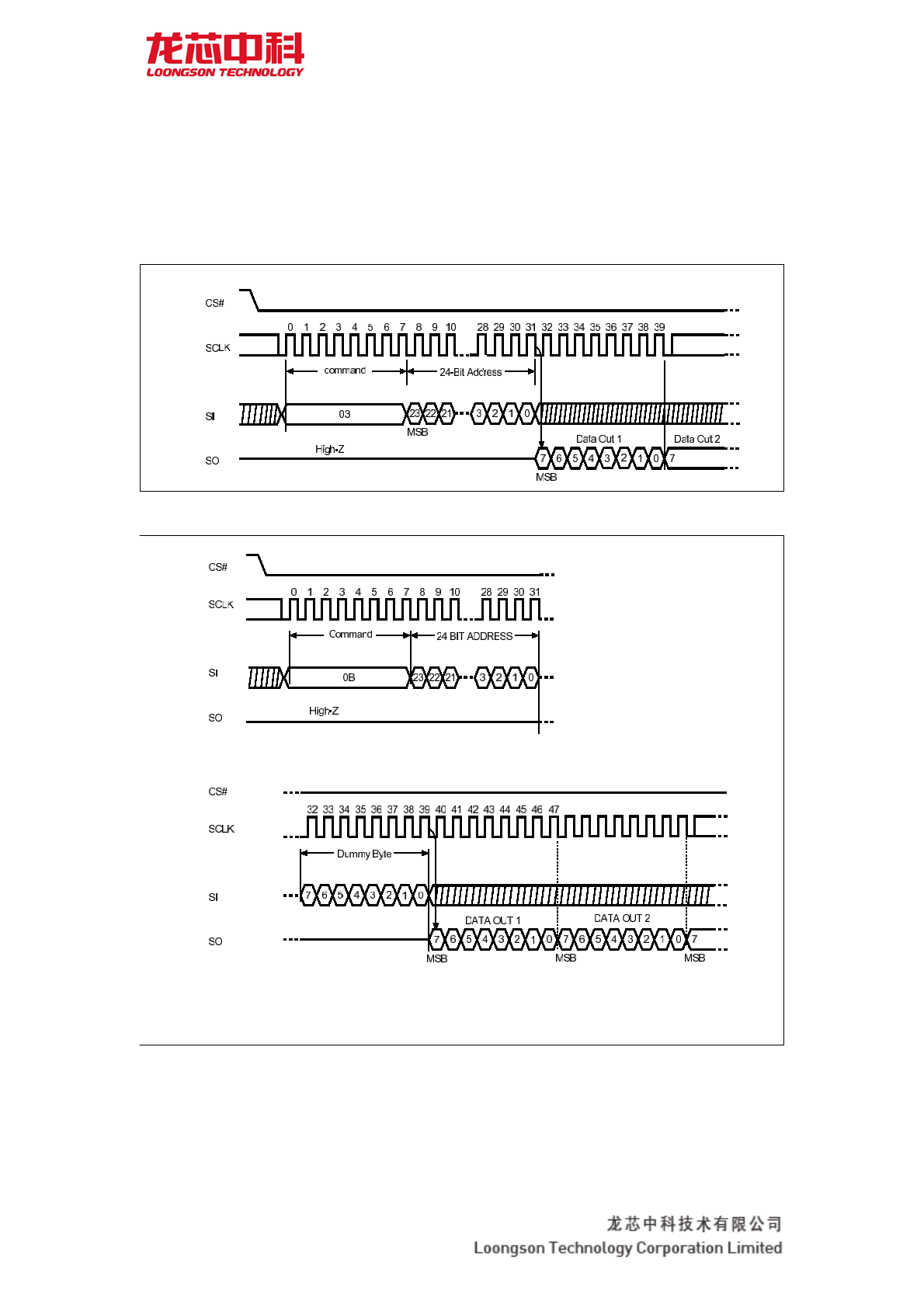

SPI 主控制器外部接口时序图 ............................................................................ 126

III

龙芯 1B 处理器用户手册目录

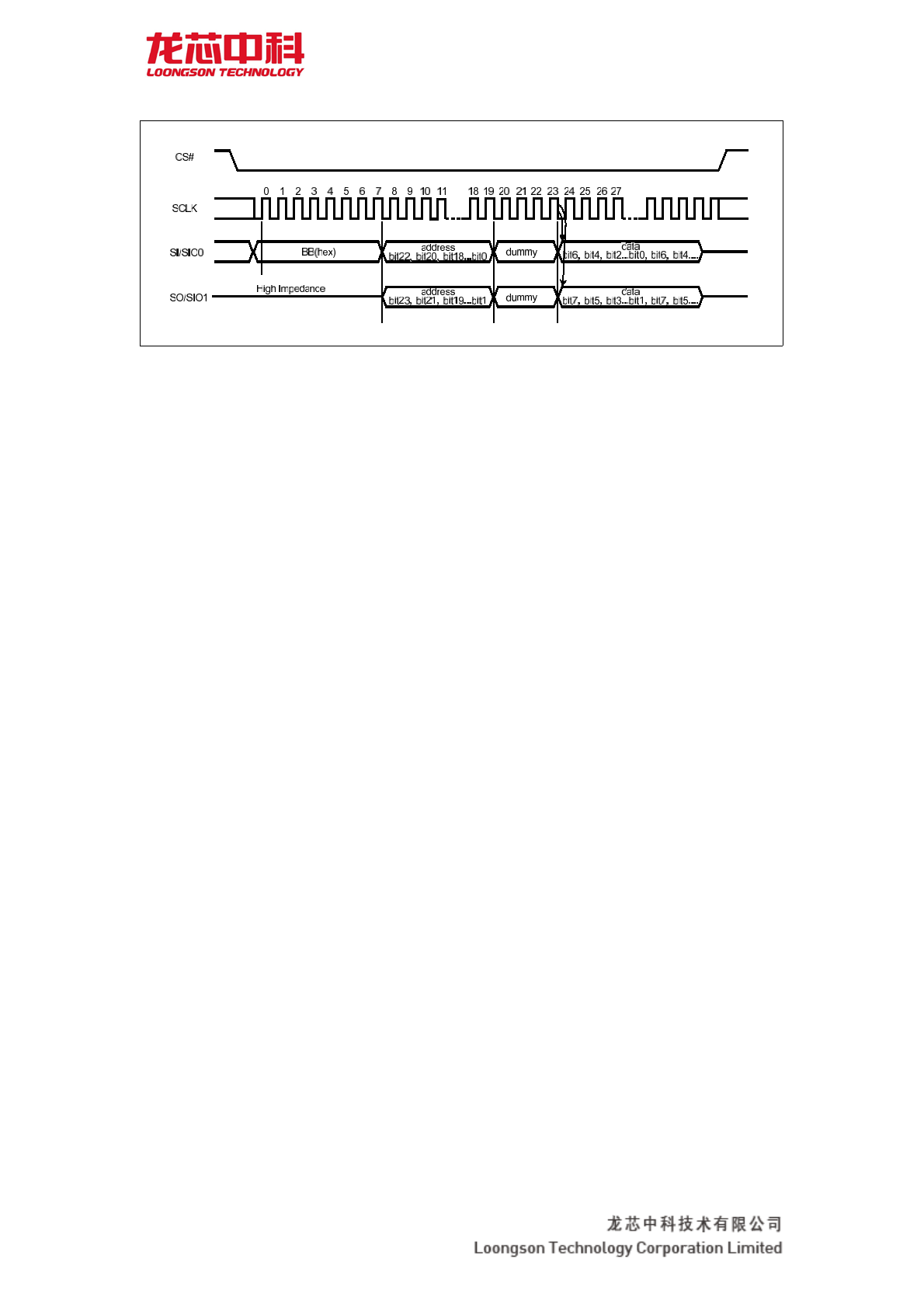

SPI Flash 访问时序图 ....................................................................................... 127

10.4 SPI FLASH 控制器使用指南 .......................................................................................... 128

SPI 主控制器的读写操作.................................................................................... 128

硬件 SPI Flash 读 .............................................................................................. 128

混合访问 SPI Flash 和SPI 主控制器 ................................................................ 129

11 SPI1 ................................................................................................................... 130

11.1 SPI 主控制器结构 ........................................................................................................ 130

12 Conf and Interrupt .......................................................................................... 131

12.1 配置和中断控制器总体描述 ............................................................................... 131

12.2 中断控制器寄存器描述 ....................................................................................... 132

13 DMA ..................................................................................................................... 134

13.1 DMA 控制器结构描述 .................................................................................................... 134

13.2 DMA 控制器与 APB 设备的交互 .................................................................................... 134

13.3 DMA 控制器 ................................................................................................................ 134

13.3.1 ORDER_ADDR_IN .................................................................................... 134

13.3.2 DMA_ORDER_ADDR .................................................................................. 135

13.3.3 DMA_SADDR ............................................................................................ 135

13.3.4 DMA_DADDR ............................................................................................ 136

13.3.5 DMA_LENGTH .......................................................................................... 136

13.3.6 DMA_STEP_LENGTH ................................................................................. 136

13.3.7 DMA_STEP_TIMES .................................................................................. 137

13.3.8 DMA_CMD ............................................................................................... 137

14 UART ................................................................................................................... 139

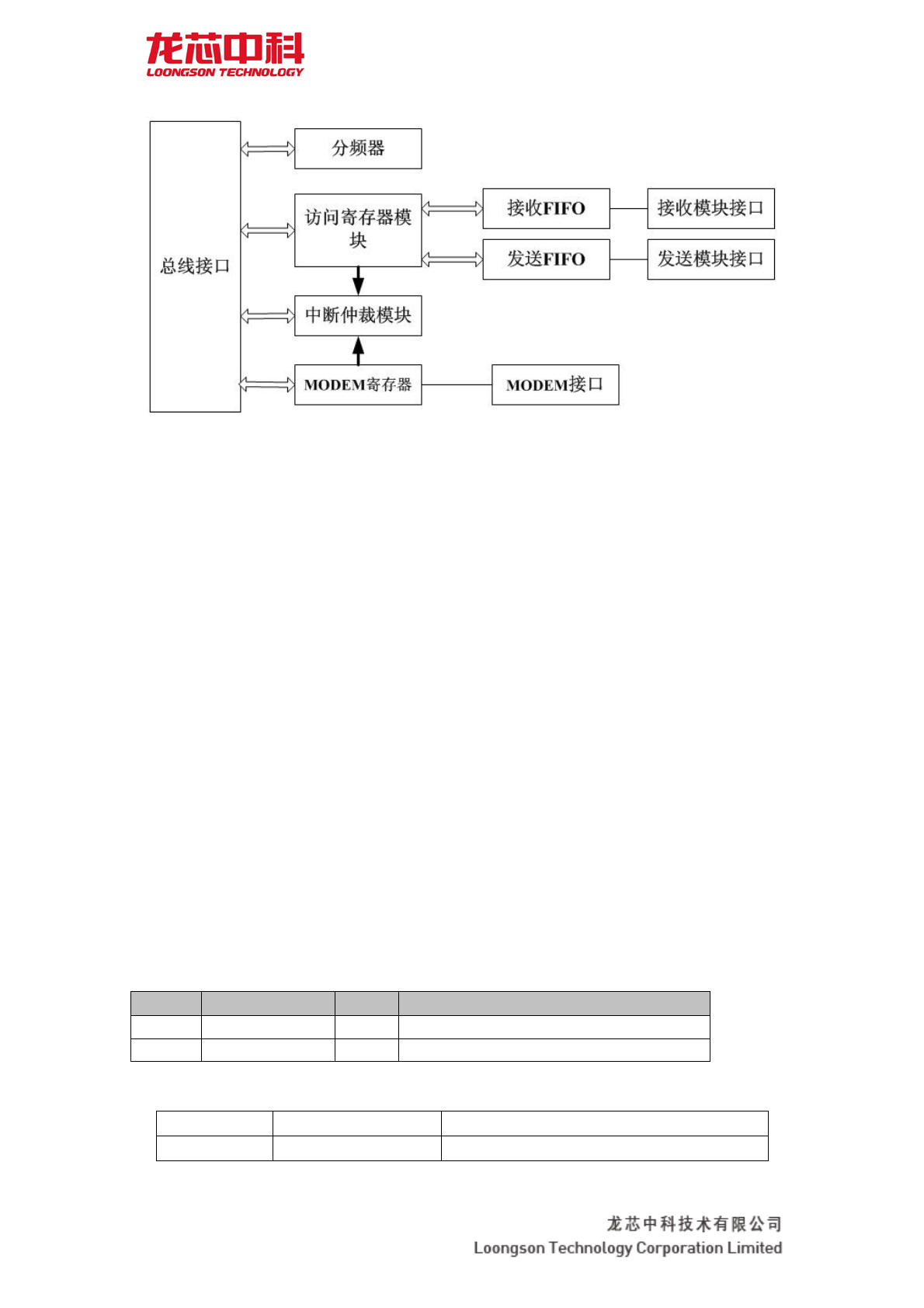

14.1 UART 控制器结构 .......................................................................................................... 139

14.2 UART 控制器寄存器 ...................................................................................................... 140

14.2.1 数据寄存器(DAT) ............................................................................. 141

14.2.2 中断使能寄存器(IER) ...................................................................... 141

14.2.3 中断标识寄存器(IIR) ...................................................................... 141

14.2.4 FIFO 控制寄存器(FCR) ..................................................................... 142

14.2.5 线路控制寄存器(LCR) ...................................................................... 142

14.2.6 MODEM 控制寄存器(MCR) ................................................................... 143

14.2.7 线路状态寄存器(LSR) ...................................................................... 143

14.2.8 MODEM 状态寄存器 (MSR) ................................................................. 144

14.2.9 分频锁存器 .......................................................................................... 144

15 CAN ..................................................................................................................... 146

15.1 概述 ....................................................................................................................... 146

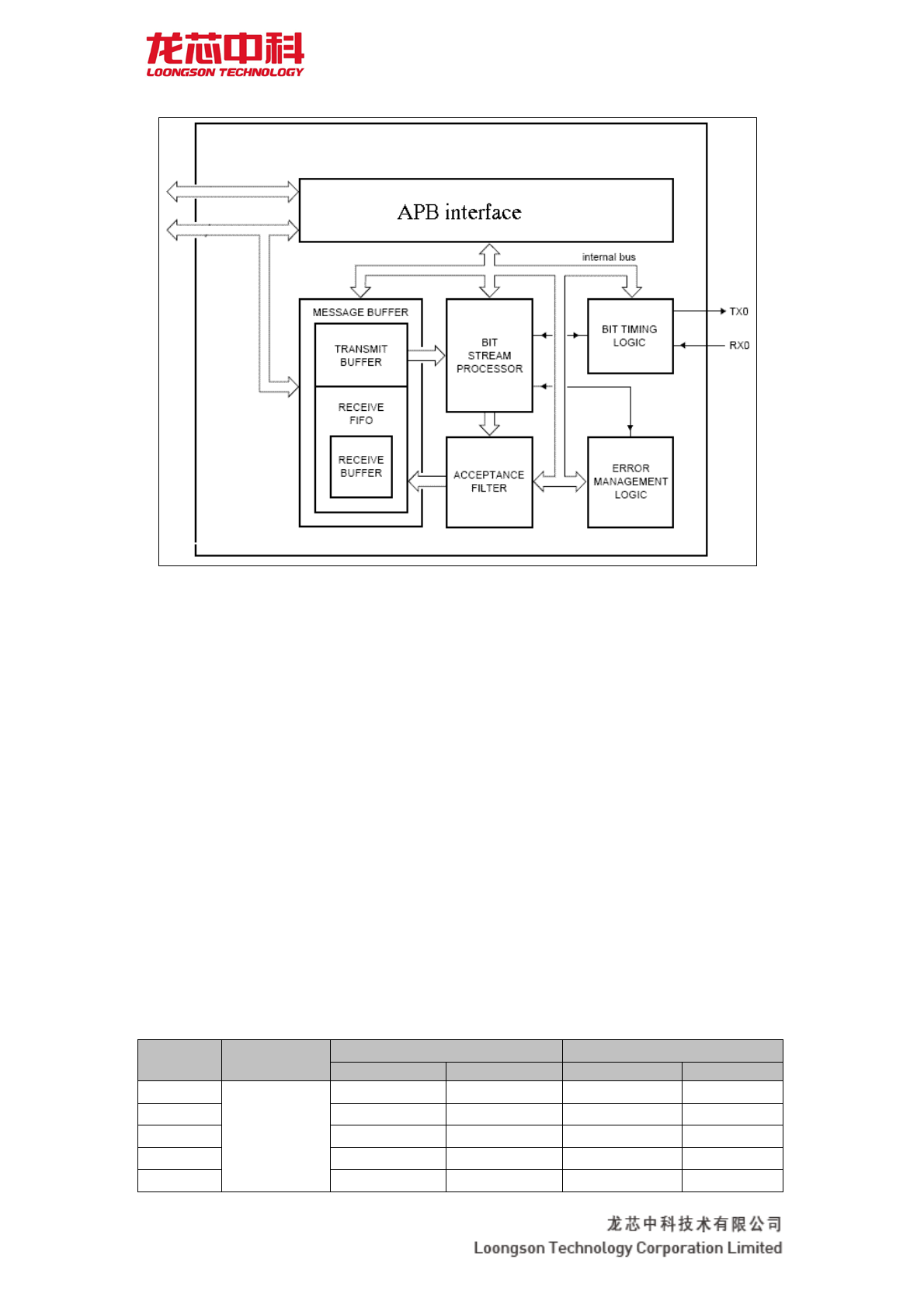

15.2 CAN 控制器结构 ............................................................................................................ 146

15.3 标准模式 ............................................................................................................... 147

15.3.1 标准模式地址表 .................................................................................. 147

15.3.2 控制寄存器(CR) ............................................................................... 148

15.3.3 命令寄存器(CMR) .......................................................................... 149

15.3.4 状态寄存器(SR) ............................................................................. 149

15.3.5 中断寄存器(IR) ............................................................................... 149

15.3.6 验收代码寄存器(ACR).................................................................... 150

IV

龙芯 1B 处理器用户手册目录

15.3.7 验收屏蔽寄存器(AMR) ................................................................... 150

15.3.8 发送缓冲区列表 .................................................................................. 150

15.3.9 接收缓冲区列表 .................................................................................. 150

15.4 扩展模式 ....................................................................................................................... 151

15.4.1 扩展模式地址表 .................................................................................. 151

15.4.2 模式寄存器(MOD) .......................................................................... 151

15.4.3 命令寄存器(CMR) .......................................................................... 152

15.4.4 状态寄存器(SR) ............................................................................. 152

15.4.5 中断寄存器(IR) ............................................................................... 152

15.4.6 中断使能寄存器(IER) ..................................................................... 153

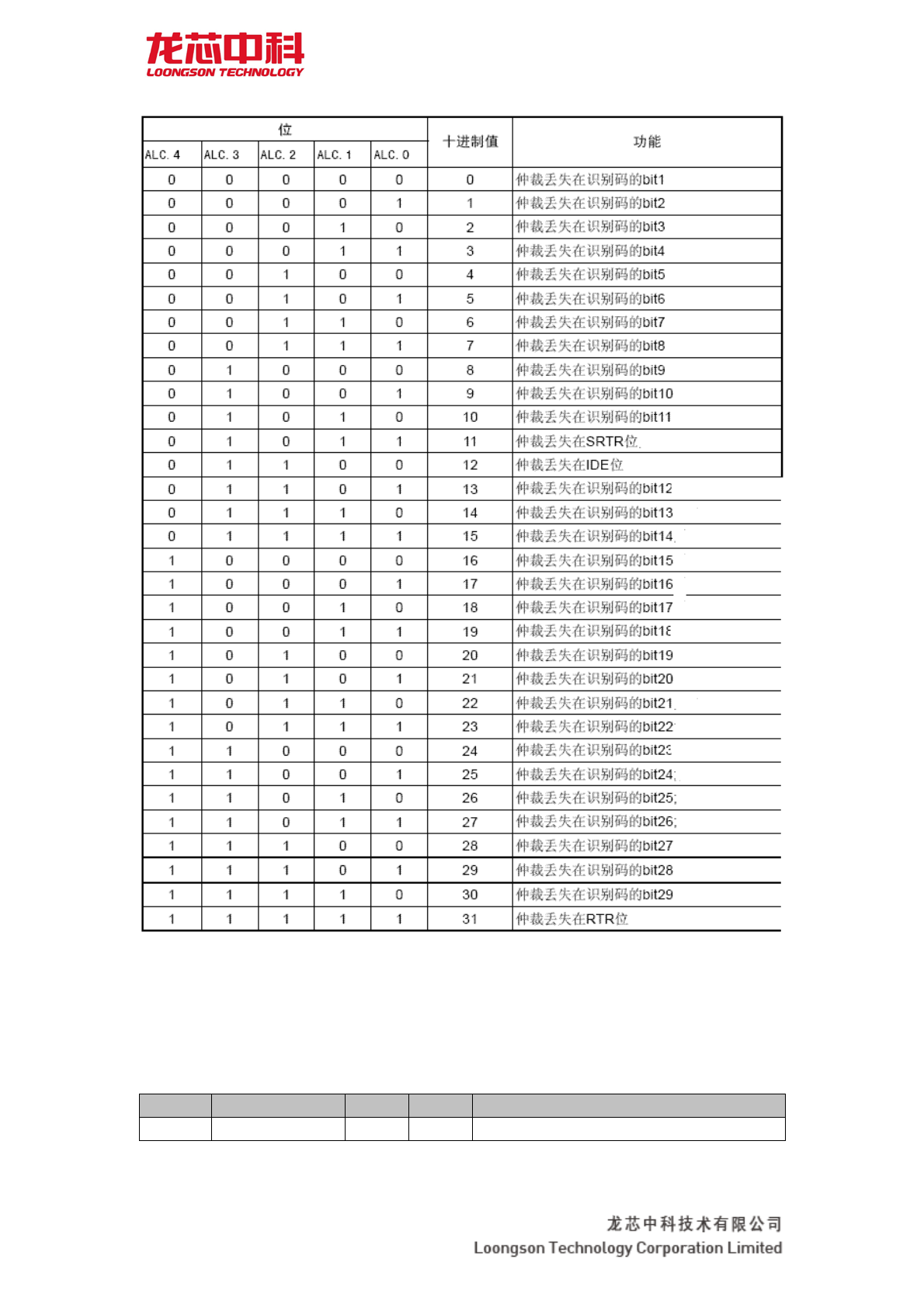

15.4.7 仲裁丢失捕捉寄存器(IER) .............................................................. 153

15.4.8 错误警报限制寄存器(EMLR) ............................................................. 154

15.4.9 RX 错误计数寄存器(RXERR) ........................................................ 155

15.4.10 TX 错误计数寄存器(TXERR) ......................................................... 155

15.4.11 验收滤波器 .......................................................................................... 155

15.4.12 RX 信息计数寄存器(RMCR) .......................................................... 155

15.5 公共寄存器 ................................................................................................................... 155

15.5.1 总线定时寄存器 0(BTR0) ............................................................... 155

15.5.2 总线定时寄存器 1(BTR1) ............................................................... 156

15.5.3 输出控制寄存器(OCR) ................................................................... 156

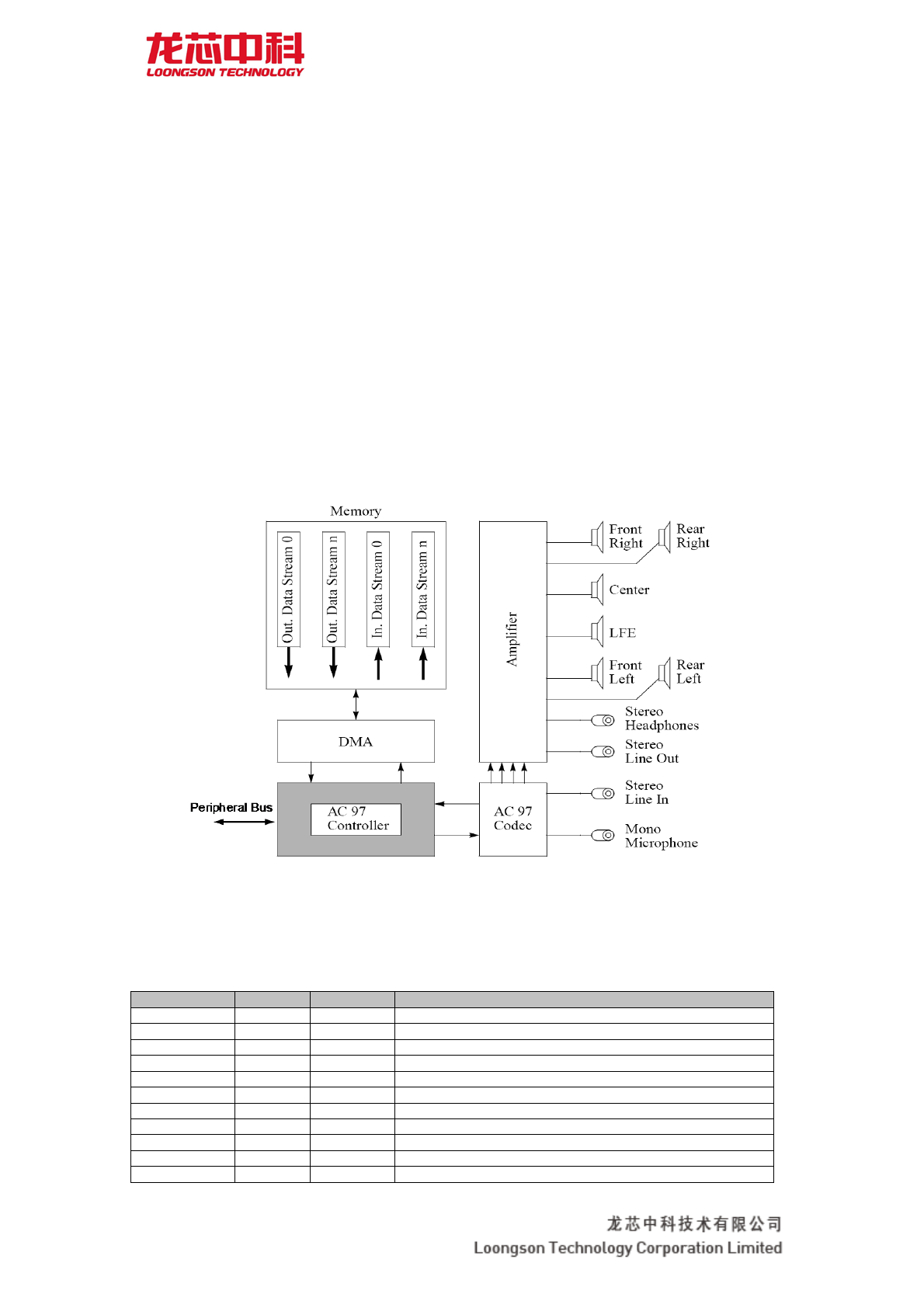

16 AC97 .................................................................................................................. 157

16.1 AC97 结构描述 ............................................................................................................ 157

16.2 AC97 控制器寄存器 .................................................................................................... 157

16.2.1 CSR 寄存器 ........................................................................................ 158

16.2.2 OCC 寄存器 ........................................................................................ 158

16.2.3 ICC 寄存器 .......................................................................................... 158

16.2.4 (输入输出)通道寄存器配置 ............................................................. 159

16.2.5 Codec 寄存器访问命令 ....................................................................... 159

16.2.6 中断状态寄存器/中断掩膜寄存器 ........................................................ 160

16.2.7 中断状态/清除寄存器 .......................................................................... 160

16.2.8 OC 中断清除寄存器 ............................................................................ 160

16.2.9 IC 中断清除寄存器 .............................................................................. 160

16.2.10 CODEC WRITE 中断清除寄存器 ....................................................... 161

16.2.11 CODEC READ 中断清除寄存器 ........................................................ 161

17 I2C ..................................................................................................................... 162

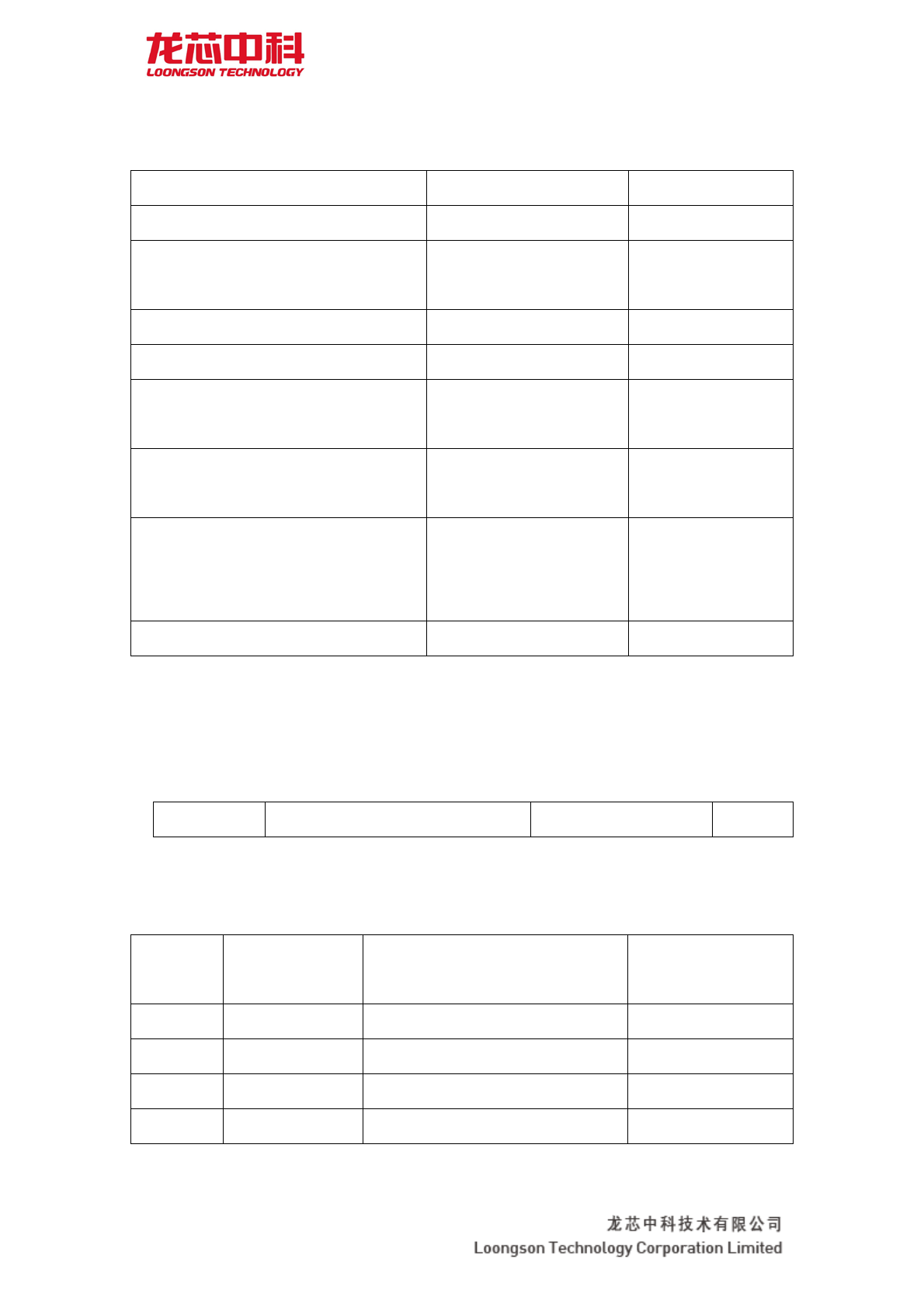

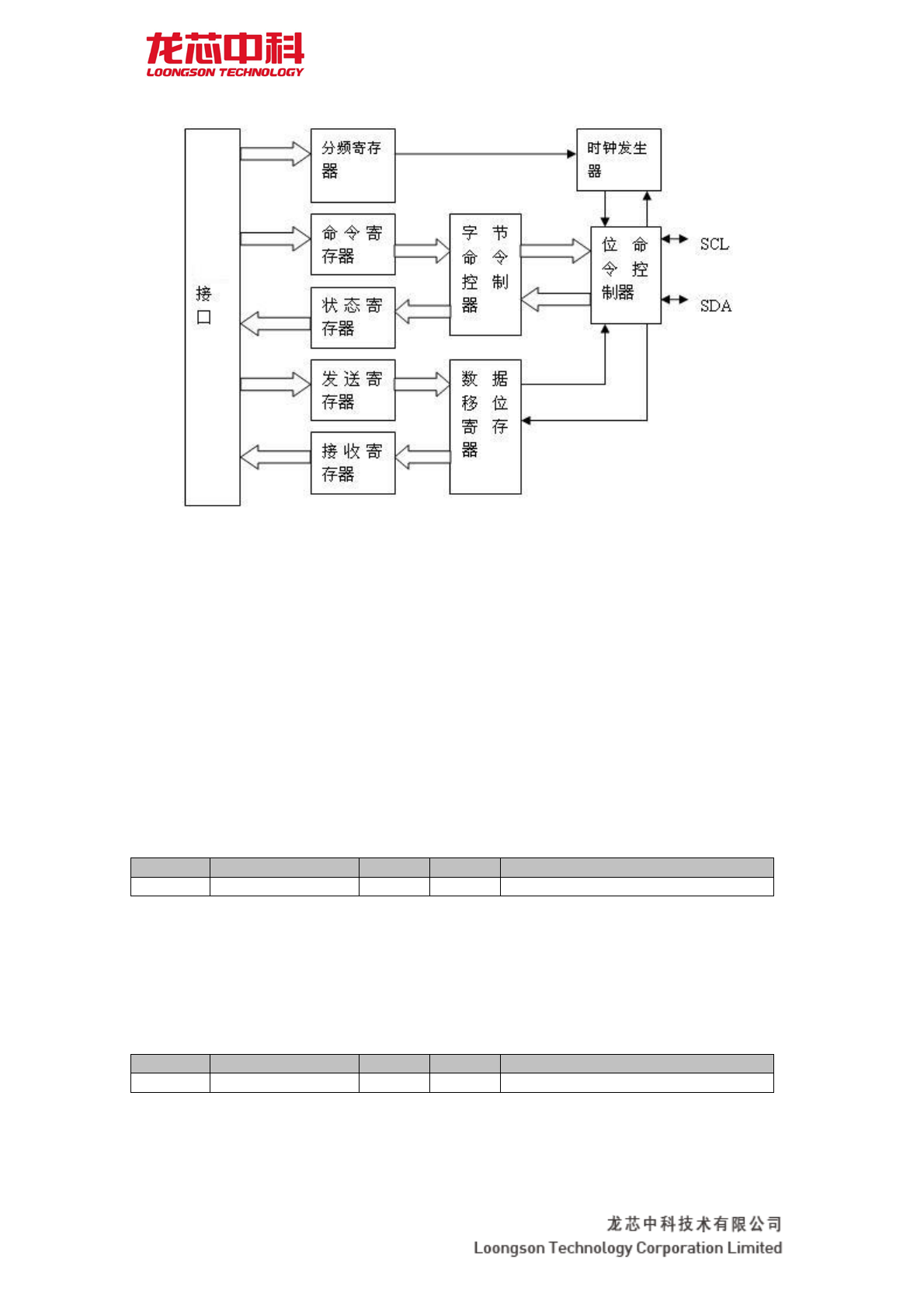

17.1 概述 ............................................................................................................................... 162

17.2 I2C 控制器结构 ............................................................................................................ 162

17.3 I2C控制器寄存器说明 ................................................................................................ 163

17.3.1 分频锁存器低字节寄存器(PRERlo) ................................................ 163

17.3.2 分频锁存器高字节寄存器(PRERhi) .................................................. 163

17.3.3 控制寄存器(CTR) ........................................................................... 164

17.3.4 发送数据寄存器(TXR) .................................................................... 164

17.3.5 接受数据寄存器(RXR).................................................................... 164

17.3.6 命令控制寄存器(CR) ...................................................................... 164

V

龙芯 1B 处理器用户手册目录

17.3.7 状态寄存器(SR) ............................................................................. 165

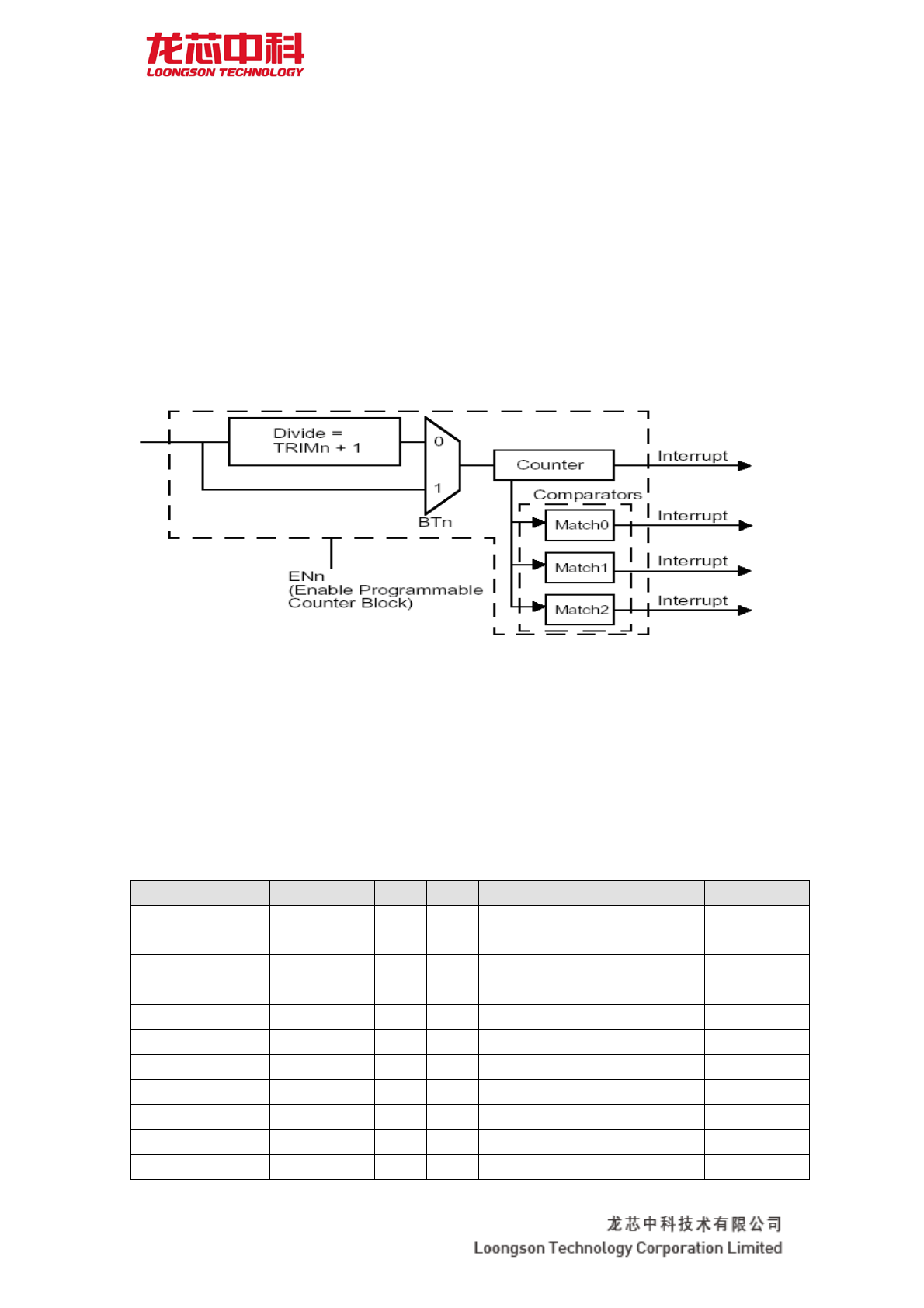

18 PWM .................................................................................................................. 166

18.1 概述 ............................................................................................................................... 166

18.2 PWM 寄存器说明 ............................................................................................................ 166

19 RTC ................................................................................................................... 168

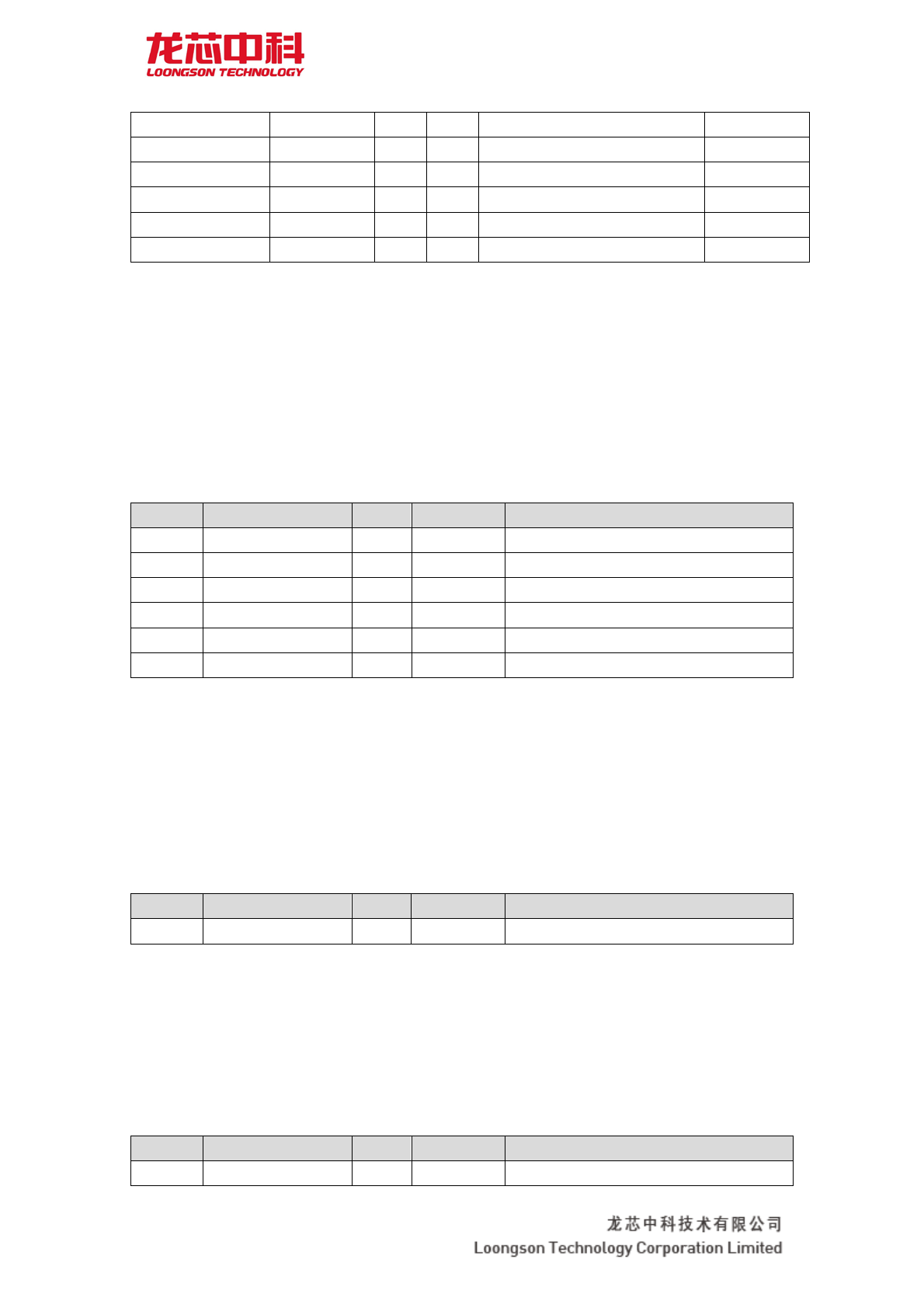

19.1 概述 ............................................................................................................................... 168

19.2 寄存器描述 ........................................................................................................... 168

19.2.1 寄存器地址列表 .................................................................................. 168

19.2.2 SYS_TOYWRITE0 ............................................................................. 169

19.2.3 SYS_TOYWRITE1 ............................................................................. 169

19.2.4 SYS_TOYMATCH0/1/2 ...................................................................... 169

19.2.5 SYS_RTCCTRL .................................................................................. 170

19.2.6 SYS_RTCMATCH0/1/2 ...................................................................... 171

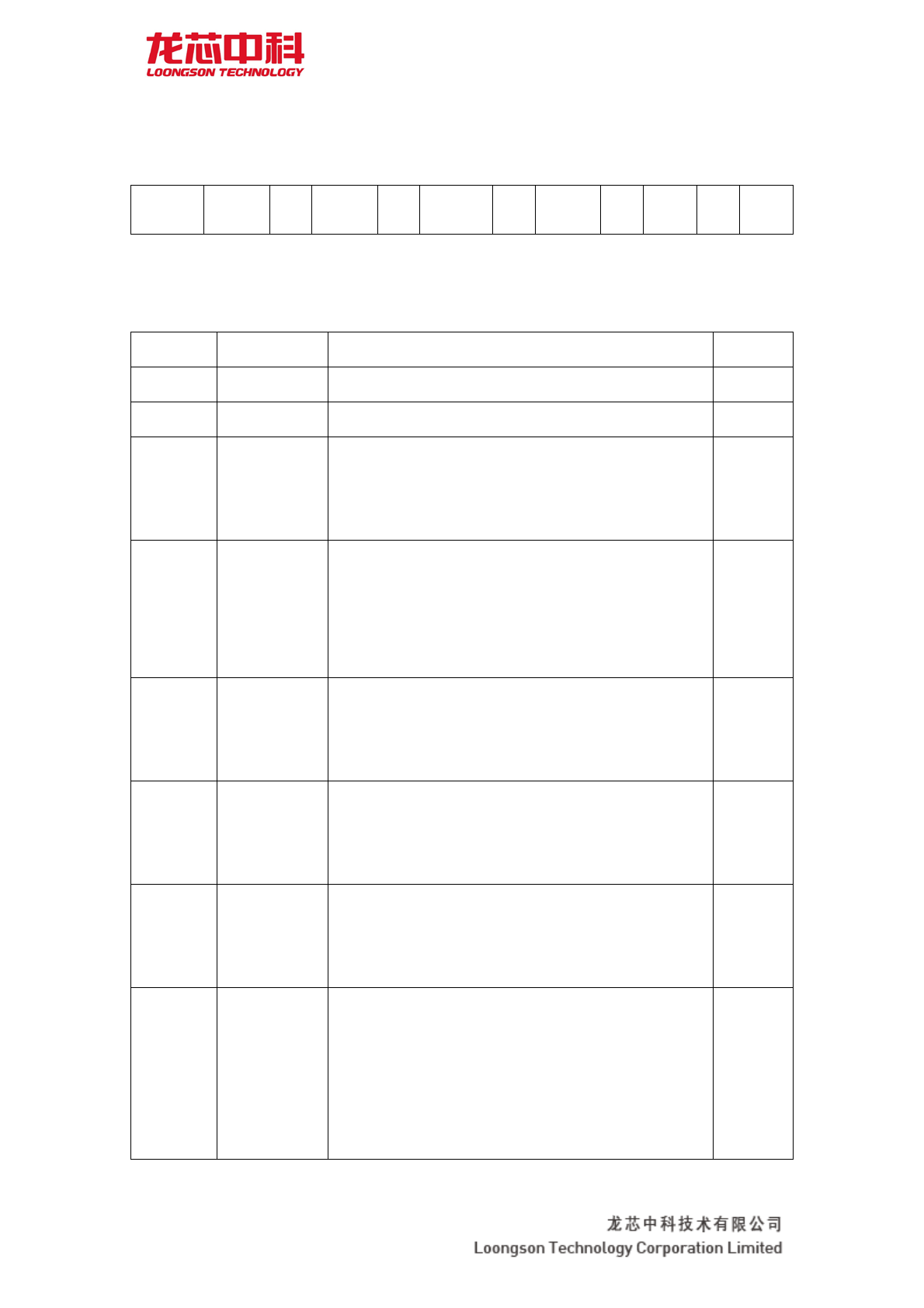

20 NAND ................................................................................................................ 172

20.1 NAND 控制器结构描述 .............................................................................................. 172

20.2 NAND 控制器寄存器配置描述 .................................................................................. 172

20.2.1 NAND_CMD(地址:BFE7_8000) .................................................. 172

20.2.2 ADDR_L(地址:BFE7_8004) ........................................................ 173

20.2.3 ADDR_H(地址:BFE7_8008) ........................................................ 173

20.2.4 NAND_TIMING(地址:BFE7_800C) ............................................. 173

20.2.5 ID_L(地址:BFE7_8010) ............................................................... 173

20.2.6 STATUS & ID_H(地址:BFE7_8014) ............................................ 173

20.2.7 NAND_PARAMETER(地址:BFE7_8018) .................................... 173

20.2.8 NAND_OP_NUM(地址:BFE7_801C) .......................................... 173

20.2.9 CS_RDY_MAP(地址:BFE7_8020) .............................................. 174

20.2.10 DMA_ADDRESS(地址:BFE7_8040) ........................................... 174

20.3 NAND ADDR 说明 ...................................................................................................... 174

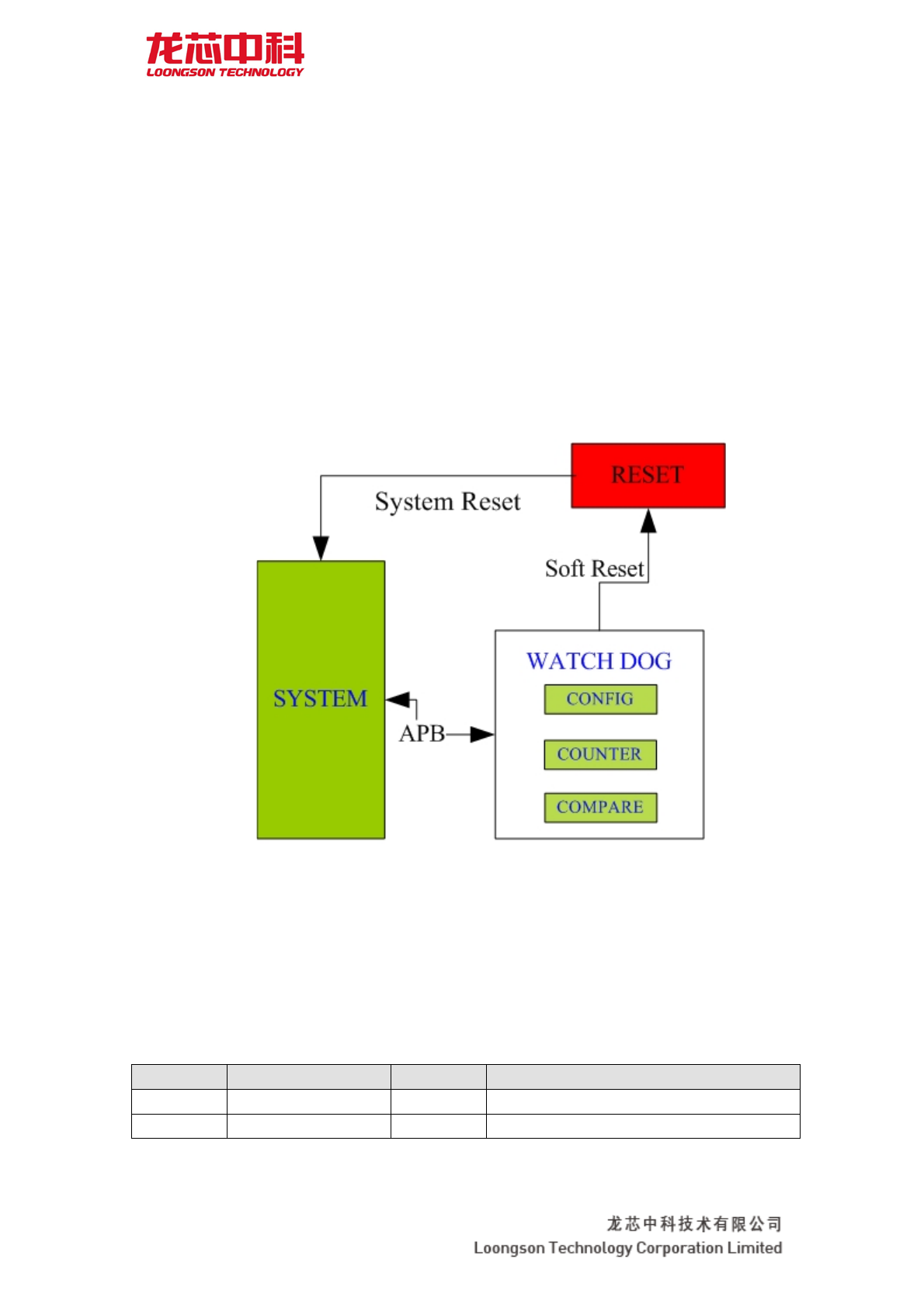

21 WATCHDOG ..................................................................................................... 177

21.1 概述 ............................................................................................................................... 177

21.2 WATCH DOG 寄存器描述 ........................................................................................... 177

21.2.1 WDT_EN 地址:(0XBFE5_C060) ................................................. 177

21.2.2 WDT_SET(地址:0XBFE5_C068) ................................................ 178

21.2.3 WDT_timer(地址:0XBFE5_C064) ............................................... 178

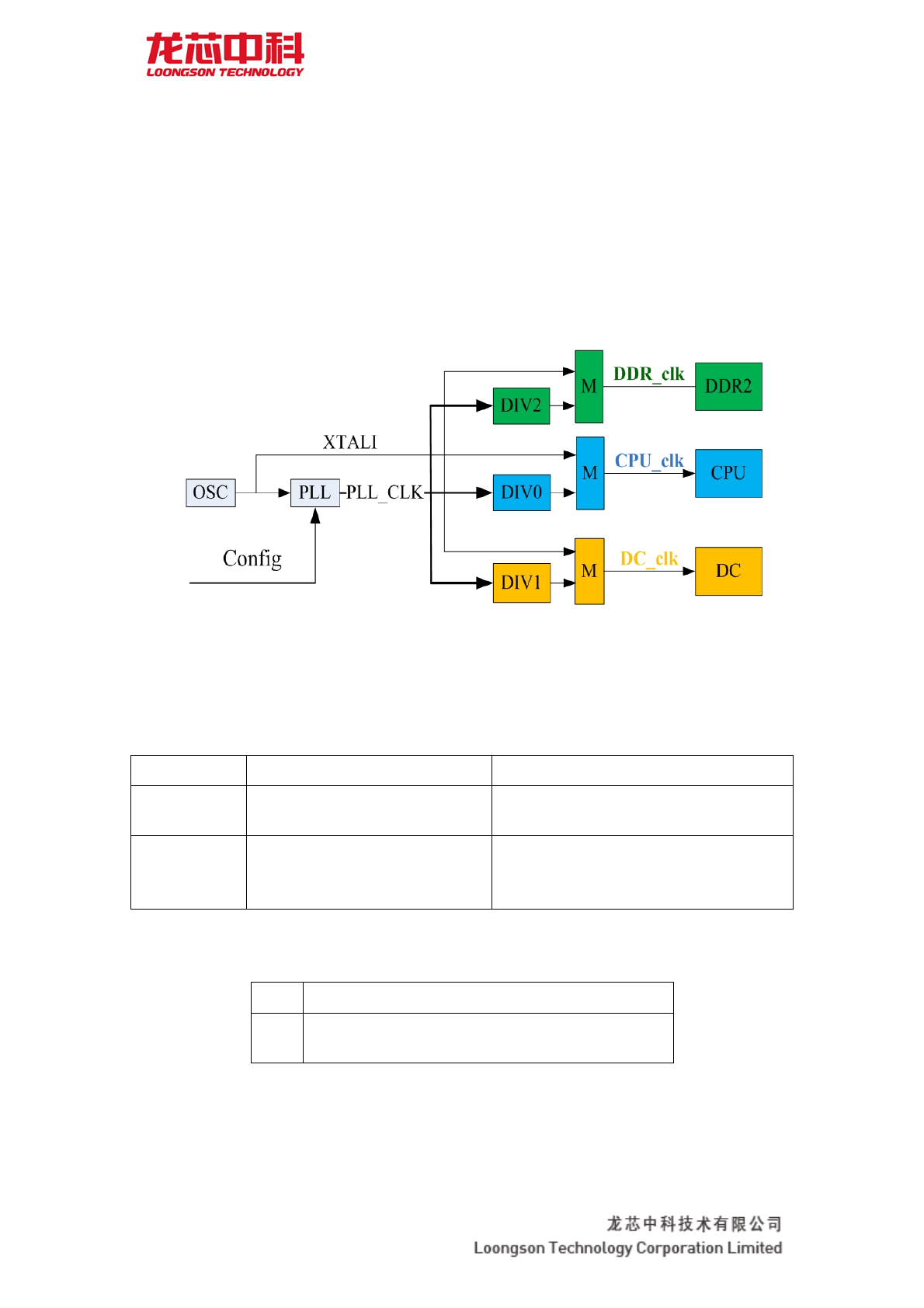

22 Clock Management ........................................................................................... 179

22.1 CLOCK 模块结构描述 .................................................................................................. 179

22.2 CLOCK 配置描述 .......................................................................................................... 179

22.3 系统其它 CLOCK 描述 ................................................................................................. 180

23 GPIO and MUX ................................................................................................. 181

23.1 GPIO 结构描述 ............................................................................................................ 181

23.2 GPIO 寄存器描述 ........................................................................................................ 184

23.3 MUX 寄存器描述 ........................................................................................................ 185

24 AC/DC ............................................................................................................... 187

24.1 时钟系统 ............................................................................................................... 187

24.2 系统复位 ....................................................................................................................... 187

VI

龙芯 1B 处理器用户手册 图目录

图

目

录

图 1-1 1B 芯片结构图 .................................................................................................. 2

图 4-1 TLB 表项内容 ................................................................................................. 33

图 4-2 Index 寄存器 ................................................................................................ 36

图 4-3 Random 寄存器 ............................................................................................... 37

图 4-4 EntryLo0 和EntryLo1 寄存器 ..................................................................... 37

图 4-5 Context 寄存器 ............................................................................................. 38

图 4-6 PageMask 寄存器 ........................................................................................... 38

图 4-7 Wired 寄存器界限 ......................................................................................... 39

图 4-8 Wired 寄存器 ................................................................................................. 40

图 4-9 HWREna 寄存器 ............................................................................................... 40

图 4-10 BadVAddr 寄存器 ......................................................................................... 40

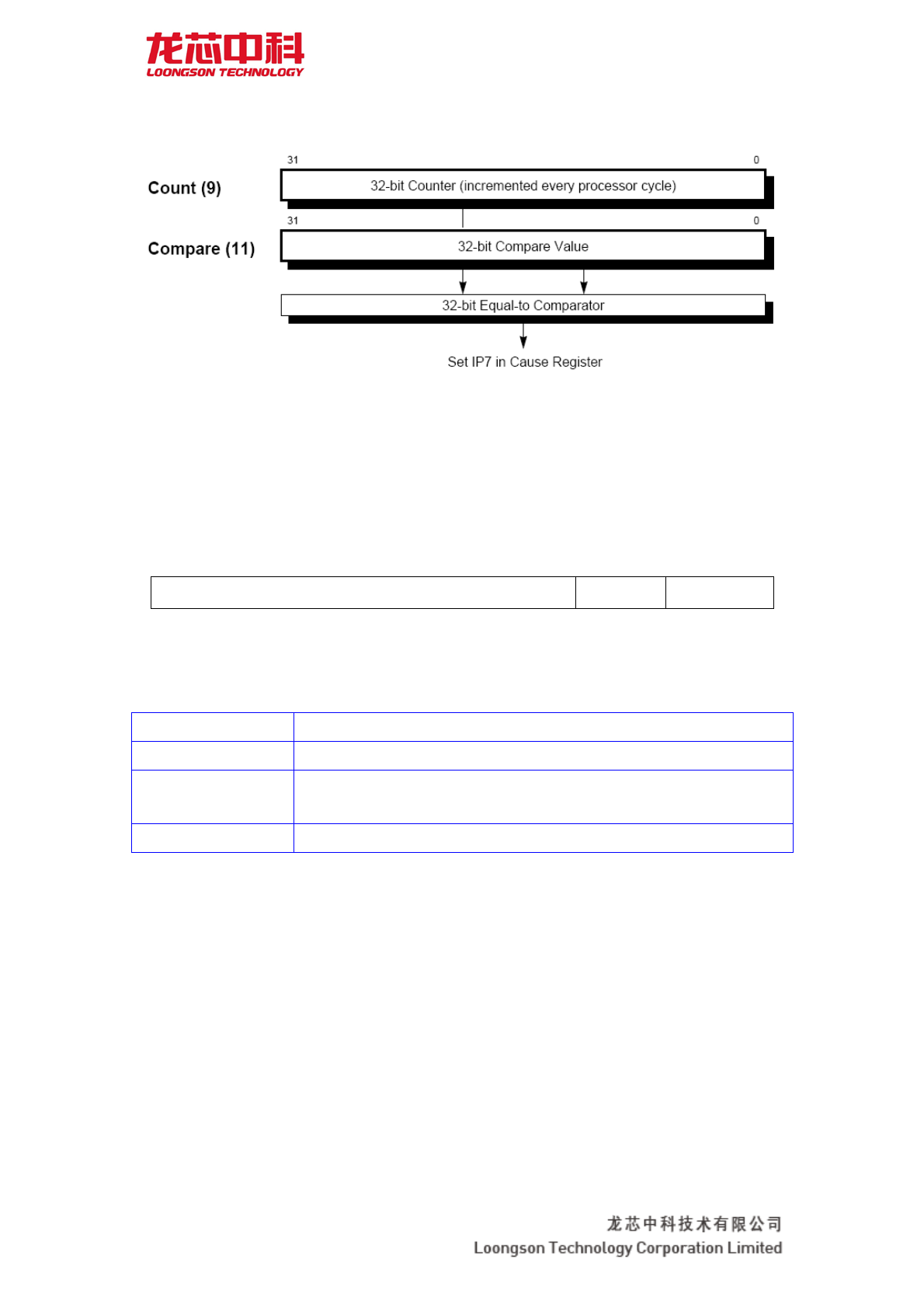

图 4-11 Count 寄存器和 Compare 寄存器 ............................................................... 41

图 4-12 EntryHi 寄存器 ........................................................................................... 41

图 4-13 Status 寄存器 ............................................................................................. 42

图 4-14 IntCtl 寄存器 ............................................................................................. 43

图 4-15SRSCtl 寄存器 ............................................................................................... 44

图 4-16 SRSMap 寄存器 ............................................................................................. 44

图 4-17 Cause 寄存器 ............................................................................................... 45

图 4-18 EPC 寄存器 ................................................................................................... 46

图 4-19 Processor Revision Identifier 寄存器 ........................................................... 46

图 4-20 Config 寄存器 ............................................................................................. 47

图 4-21 Config 寄存器 ............................................................................................. 48

图 4-22 Config 寄存器 ............................................................................................. 48

图 4-23 Config 寄存器 ............................................................................................. 49

图 4-24 Config 寄存器 ............................................................................................. 49

图 4-25 WatchLo 寄存器 ........................................................................................... 50

图 4-26 WatchHi 寄存器 ........................................................................................... 50

图 4-27 控制寄存器性能计数寄存器 ...................................................................... 51

图 4-28 性能计数器寄存器 ...................................................................................... 51

图 4-29 TagLo 寄存器(P-Cache) ............................................................................ 52

图 4-30 ErrorEPC 寄存器 ......................................................................................... 53

图 4-31 EJTAG 调试连接示意图 ............................................................................... 54

图 4-32 DCR 寄存器格式 ........................................................................................... 55

VIII

龙芯 1B 处理器用户手册 图目录

图 4-33 硬件指令、数据断点概况 .......................................................................... 56

图 4-34 IBS 寄存器格式 ........................................................................................... 57

图 4-35 IBAn 寄存器格式 ......................................................................................... 58

图 4-36 IBMn 寄存器格式 ......................................................................................... 58

图 4-37 IBCn 寄存器格式 ......................................................................................... 58

图 4-38 DBS 寄存器格式 ........................................................................................... 59

图 4-39 DBAn 寄存器格式 ......................................................................................... 60

图 4-40 DBMn 寄存器格式 ......................................................................................... 60

图 4-41 DBCn 寄存器格式 ......................................................................................... 60

图 4-42 TAP 主要部分 ............................................................................................... 64

图 4-43 ALL 指令示意图 .......................................................................................... 65

图 4-44 Fastdata 指令示意图 ................................................................................. 65

图 4-45 IDCODE 寄存器格式 ..................................................................................... 66

图 4-46 IMPCADE 寄存器示意图 ............................................................................... 67

图 4-47 数据寄存器格式 .......................................................................................... 68

图 4-48 地址寄存器格式 .......................................................................................... 69

图 4-49 ECR 格式 ....................................................................................................... 69

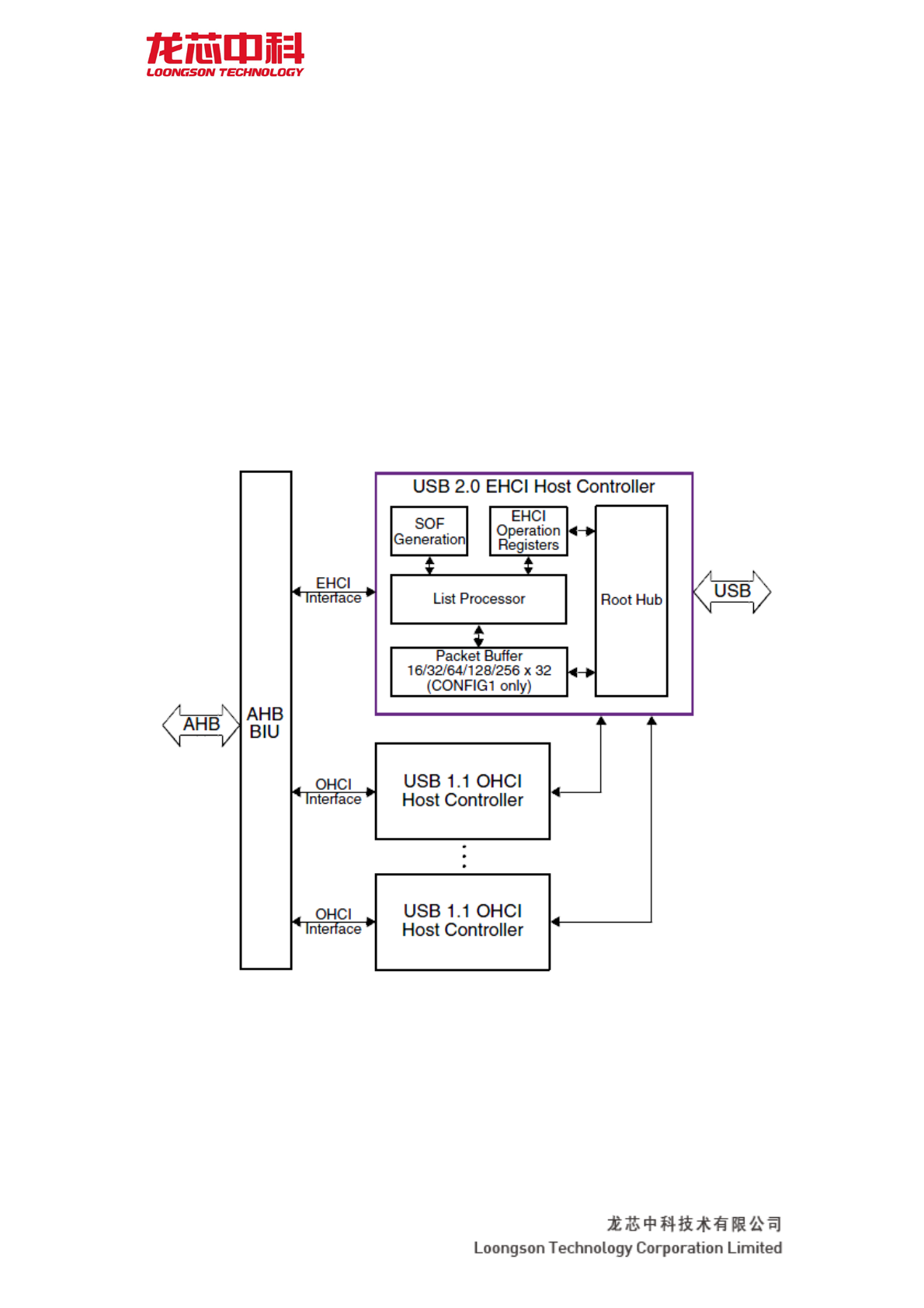

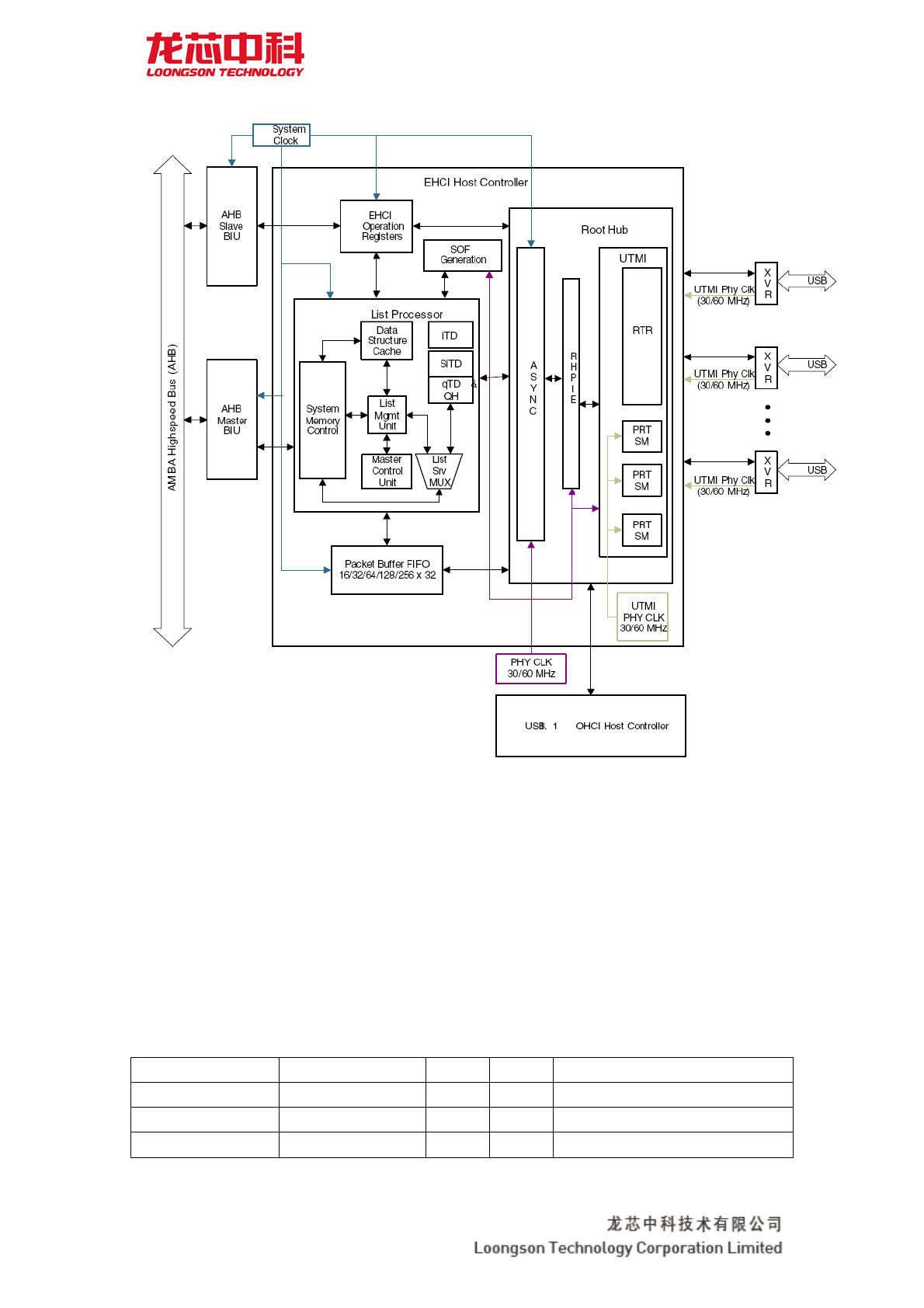

图 9-1 USB 主机控制器模块图 ......................................................................... 114

图 9-2 USB 主机控制器细节模块图(带 EHCI 控制器细节) ........................ 115

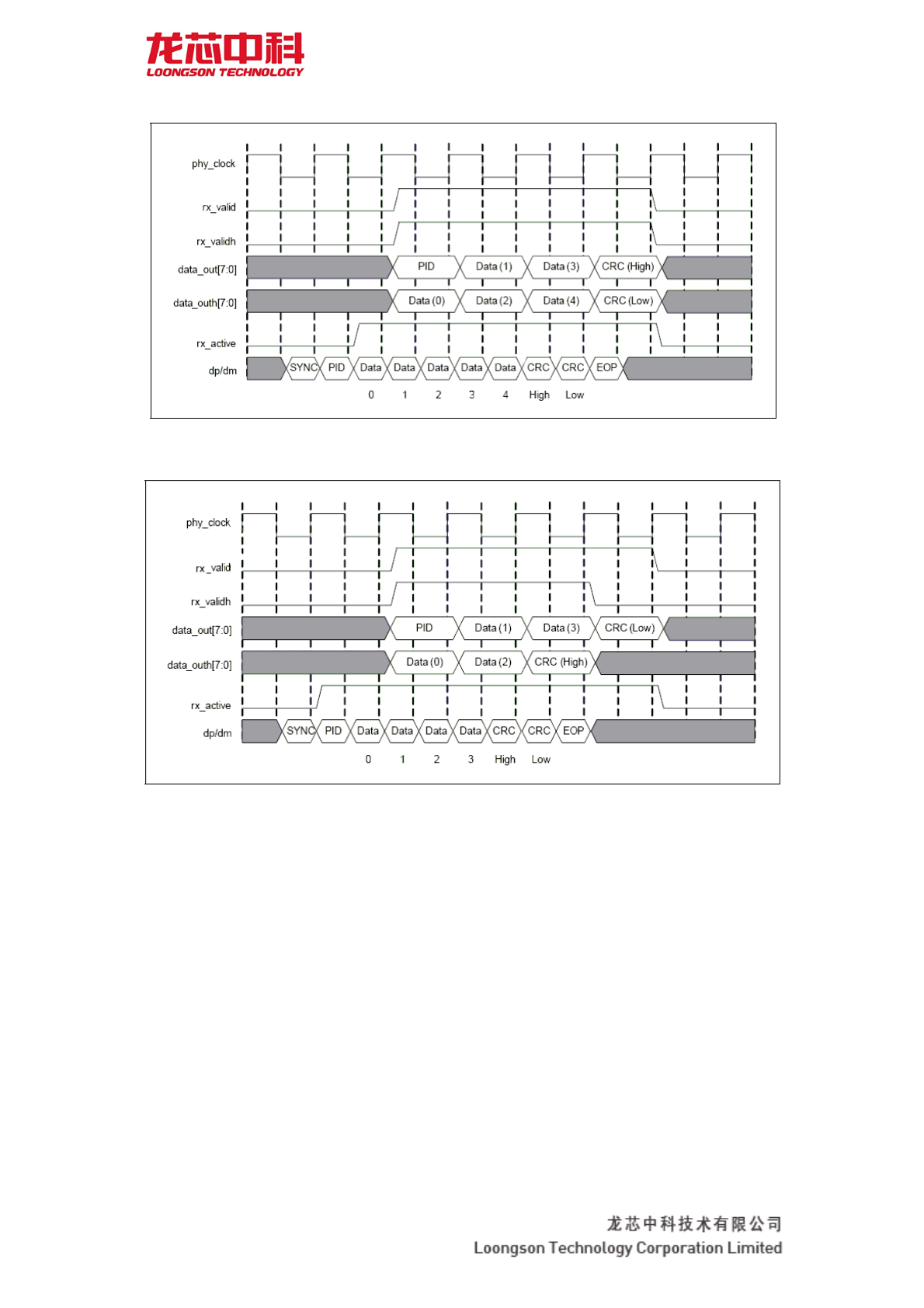

图 9-3 接收时序图(16 bit UTMI 接口,偶数个数据) ..................................... 121

图 9-4 接收时序图(16 bit UTMI 接口,奇数个数据) ................................... 121

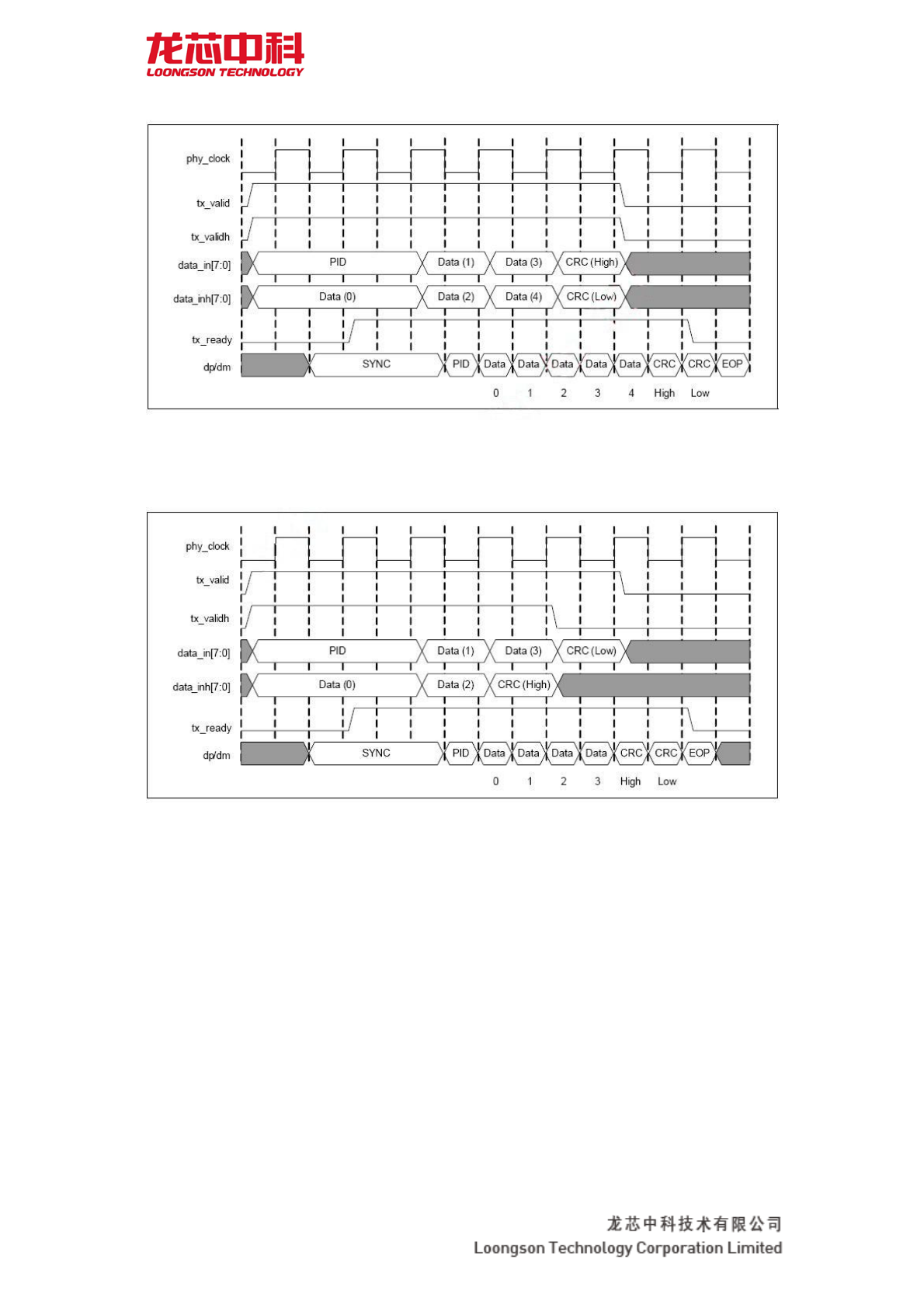

图 9-5 传输时序图(16 bit UTMI 接口,偶数个数据) ................................... 122

图 9-6 传输时序图(16bit UTMI 接口,奇数个数据) .................................... 122

图 10-1 SPI 主控制器结构 .................................................................................. 124

图 10-2 SPI 主控制器时序图 .................................................................................. 127

图 16-1 AC97 应用系统 ........................................................................................ 157

图 21-1 看门狗的结构图 ...................................................................................... 177

IX

龙芯 1B 处理器用户手册 表目录

表 目 录

表 4-1 CPU 指令集:访存指令 ................................................................................. 27

表 4-2 CPU 指令集:算术指令 (ALU 立即数) ...................................................... 28

表 4-3 CPU 指令集:算术指令 (2 操作数) ........................................................... 28

表 4-4 CPU 指令集:算术指令(3 操作数, R-型) .................................................. 28

表 4-5 CPU 指令集:乘法和除法指令 ..................................................................... 29

表 4-6 CPU 指令集:跳转和分支指令 ..................................................................... 29

表 4-7 CPU 指令集:移位指令 ................................................................................. 30

表 4-8 CPU 指令集:特殊指令 ................................................................................. 30

表 4-9 CPU 指令集:异常指令 ................................................................................. 30

表 4-10 CPU 指令集:CP0 指令 ................................................................................ 31

表 4-11 GS232 的CP0 指令 ....................................................................................... 31

表 4-12 GS232IP 地址空间的分配 ........................................................................... 32

表 4-13 例外编码及寄存器修改 .............................................................................. 33

表 4-14 例外入口地址 .............................................................................................. 34

表 4-15 GS232IP 实现的 CP0 寄存器 ...................................................................... 35

表 4-16 Index 寄存器各域描述 ............................................................................... 36

表 4-17 Random 寄存器各域 ..................................................................................... 37

表 4-18 EntryLo 寄存器域 ....................................................................................... 37

表 4-19 Context 寄存器域 ....................................................................................... 38

表 4-20 不同页大小的掩码(Mask)值 .................................................................. 39

表 4-21 Wired 寄存器域 ........................................................................................... 40

表 4-22 HWREna 寄存器域 ......................................................................................... 40

表 4-23 EntryHi 寄存器域 ....................................................................................... 41

表 4-24 Status 寄存器域 ........................................................................................ 42

表 4-25 IntCtl 寄存器域 ......................................................................................... 43

表 4-26 SRSCtl 寄存器域 ......................................................................................... 44

表 4-27Cause 寄存器域 ............................................................................................. 45

表 4-28 Cause 寄存器的 ExcCode 域 ....................................................................... 45

表 4-29 PRId 寄存器域 ............................................................................................ 46

表 4-30 Config 寄存器域 ........................................................................................ 47

表 4-31 Config 寄存器域 ........................................................................................ 48

表 4-32 Config 寄存器域 ........................................................................................ 48

表 4-33 Config 寄存器域 ........................................................................................ 49

X

龙芯 1B 处理器用户手册 表目录

表 4-34 Config 寄存器域 ........................................................................................ 49

表 4-35 WatchLo 寄存器域 ....................................................................................... 50

表 4-36 WatchHi 寄存器域 ....................................................................................... 50

表 4-37 控制域格式 ................................................................................................... 51

表 4-38 计数使能位定义 .......................................................................................... 51

表 4-39 计数器 0/1 事件 .......................................................................................... 51

表 4-40 Cache Tag 寄存器域 ................................................................................... 52

表 4-41 CP0 指令 ....................................................................................................... 53

表 4-42 DCR 寄存器域 ............................................................................................... 55

表 4-43 硬件断点寄存器 .......................................................................................... 56

表 4-44 IBS 域描述 ................................................................................................... 57

表 4-45 IBCn 域描述 ................................................................................................. 58

表 4-46 DBS 域描述 ................................................................................................... 59

表 4-47 DBCn 域描述 ................................................................................................. 60

表 4-48 调试例外优先级表 ...................................................................................... 61

表 4-49 例外屏蔽表 .................................................................................................. 62

表 4-50 Dseg 划分 ..................................................................................................... 63

表 4-51 Dmseg 的访问情况 ....................................................................................... 63

表 4-52 Drseg 的访问情况 ....................................................................................... 63

表 4-53 调试例外中断入口地址 .............................................................................. 64

表 4-54 EJTAG 指令 ................................................................................................... 64

表 4-55 TAP 数据寄存器 ........................................................................................... 66

表 4-56 IDCODE 寄存器说明 ..................................................................................... 66

表 4-57 IMPCODE 寄存器说明 ................................................................................... 67

表 4-58 Psz 位的含义 ............................................................................................... 68

表 4-59 ECR 域描述 ................................................................................................... 69

表 4-60 Sample 寄存器说明 ..................................................................................... 70

表 18-18-1 四路控制器描述 ................................................................................... 166

表18-18-2 控制寄存器描述 .................................................................................. 166

表 18-18-3 主计数器设置 ..................................................................................... 166

表 18-18-4 高脉冲计数器设置 ............................................................................. 166

表 18-18-5 低脉冲计数器设置 ............................................................................... 167

表 18-18-6 控制寄存器设置 ................................................................................. 167

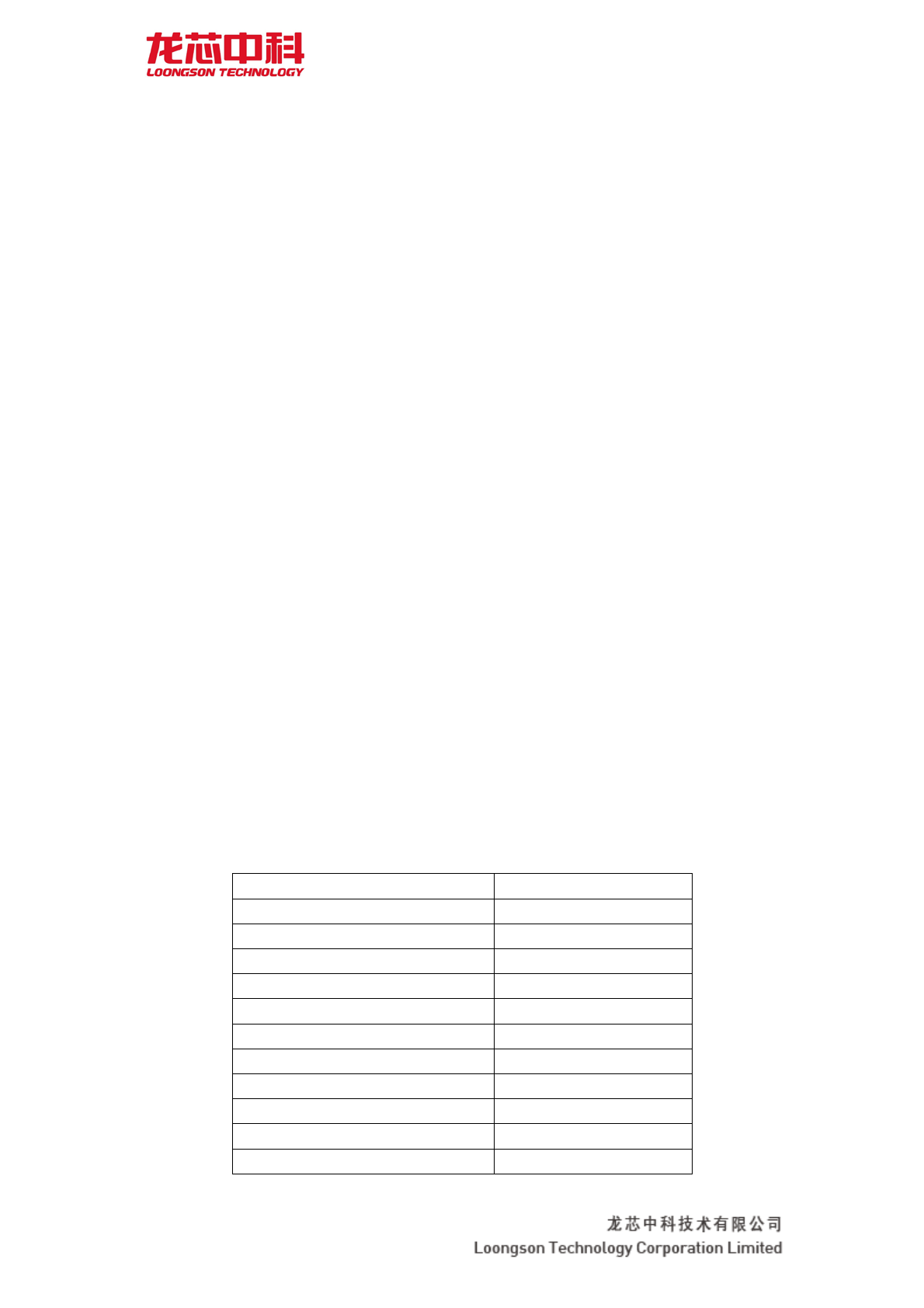

表 24-1 1B 电源域 .................................................................................................... 187

XI

龙芯 1B 处理器用户手册 表目录

表 24-2 1B 上电配置引脚汇总 ................................................................................ 187

表 24-3 推荐的工作条件 ......................................................................................... 187

表 24-4 绝对最大额定值 ......................................................................................... 188

XII

龙芯 1B 处理器用户手册

1 概述

龙芯 1B 芯片是基于 GS232 处理器核的片上系统,具有高性价比,可广泛应用于工业控

制、家庭网关、信息家电、医疗器械和安全应用等领域。1B 采用 SMIC0.13 微米工艺实现,

采用 Wire Bond BGA256 封装。

1B 芯片具有以下关键特性:

• 集成一个 GS232 双发射龙芯处理器核,指令和数据 L1 Cache 各8KB

• 集成一路 LCD 控制器,最大分辨率可支持到 1920*1080@60Hz/16bit

• 集成 2个10M/100M/1000M 自适应 GMAC

• 集成 1个16/32 位133MHz DDR2 控制器

• 集成 1个USB 2.0 接口,兼容 EHCI 和OHCI

• 集成 1个8位NAND FLASH 控制器,最大支持 32GB

• 集成中断控制器,支持灵活的中断设置

• 集成 2个SPI 控制器,支持系统启动

• 集成 AC97 控制器

• 集成 1个全功能串口、1个四线串口和 10 个两线串口

• 集成 3路I2C 控制器,兼容 SMBUS

• 集成 2个CAN 总线控制器

• 集成 61 个GPIO 端口

• 集成 1个RTC 接口

• 集成 4个PWM 控制器

• 集成看门狗电路

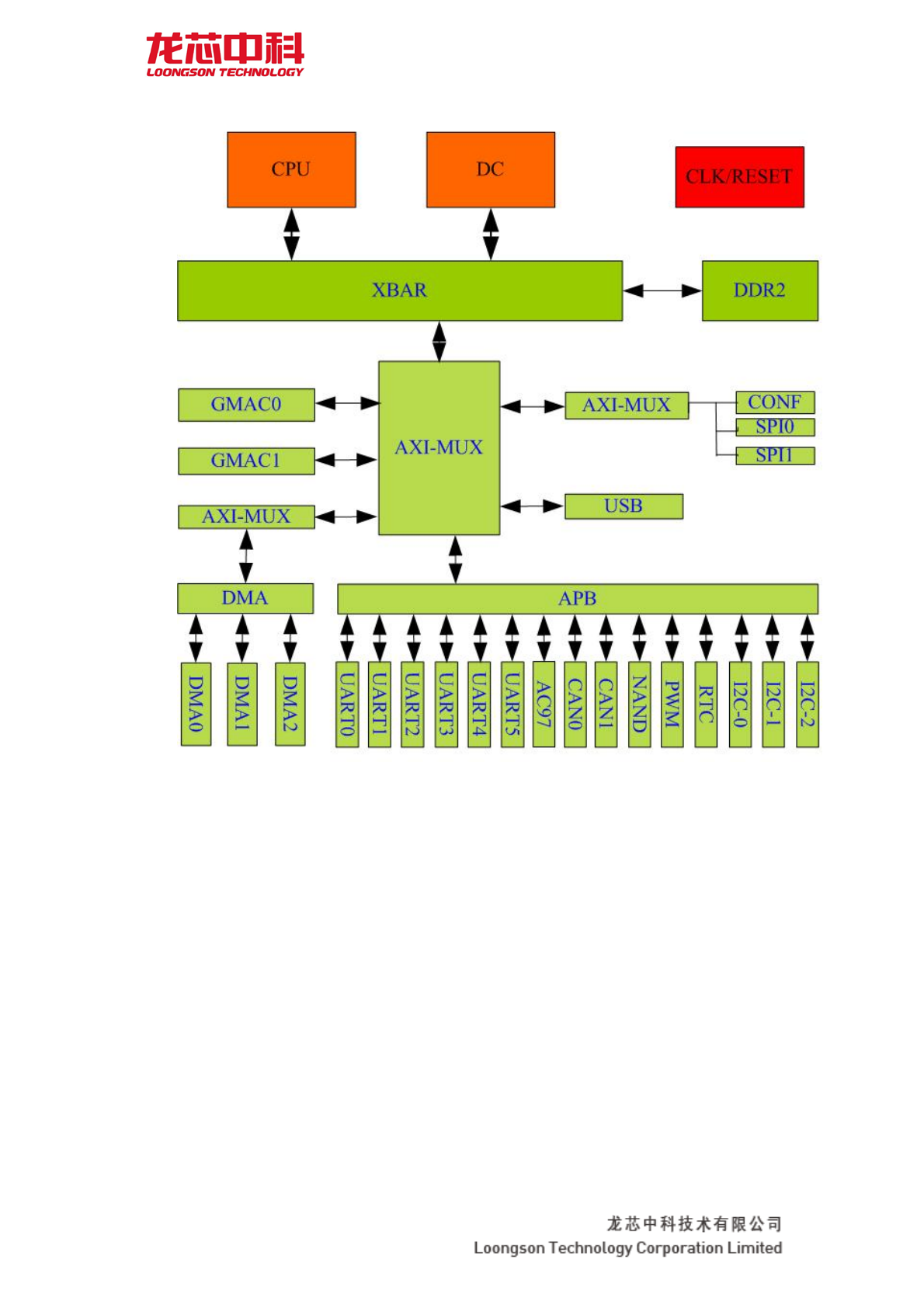

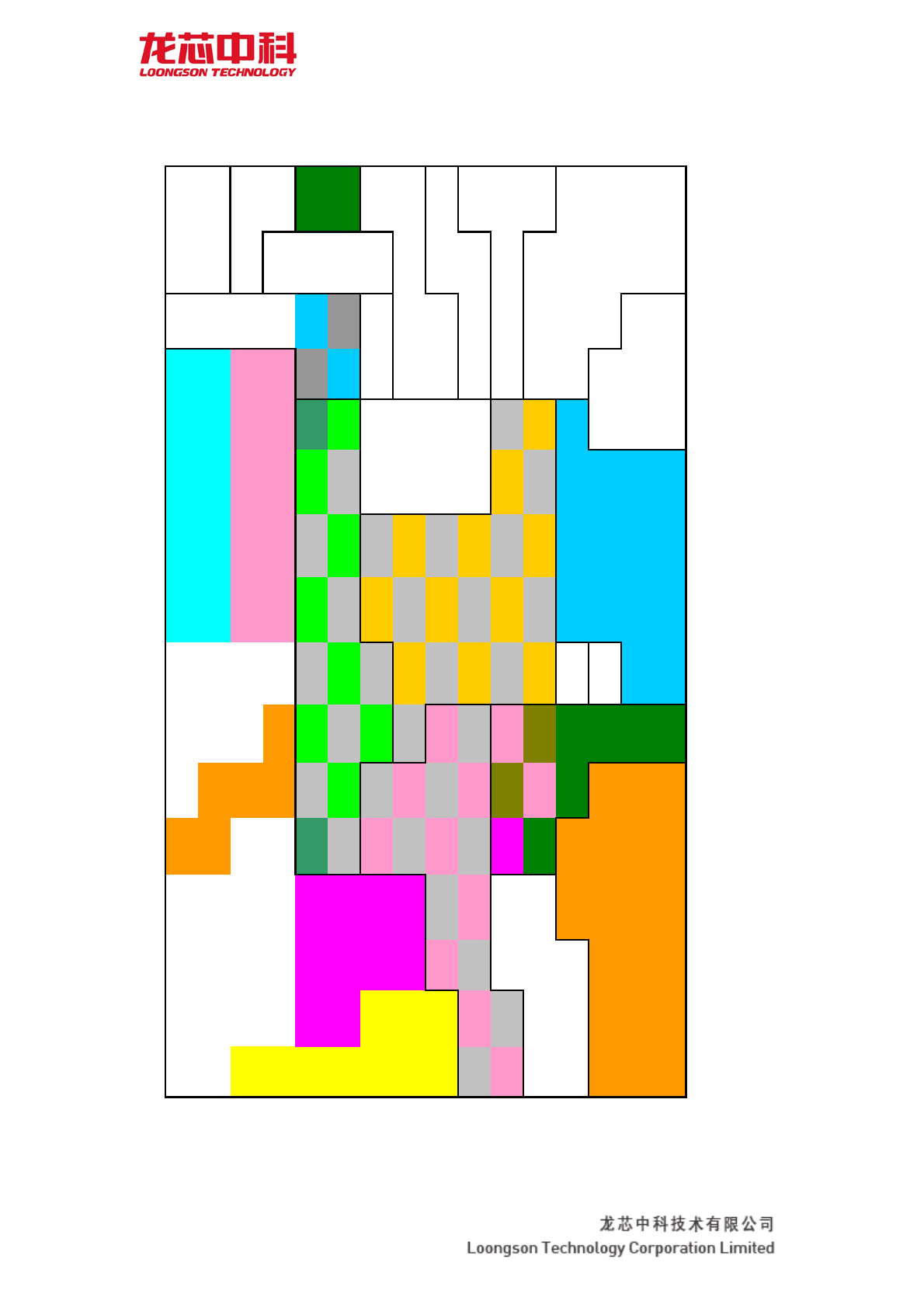

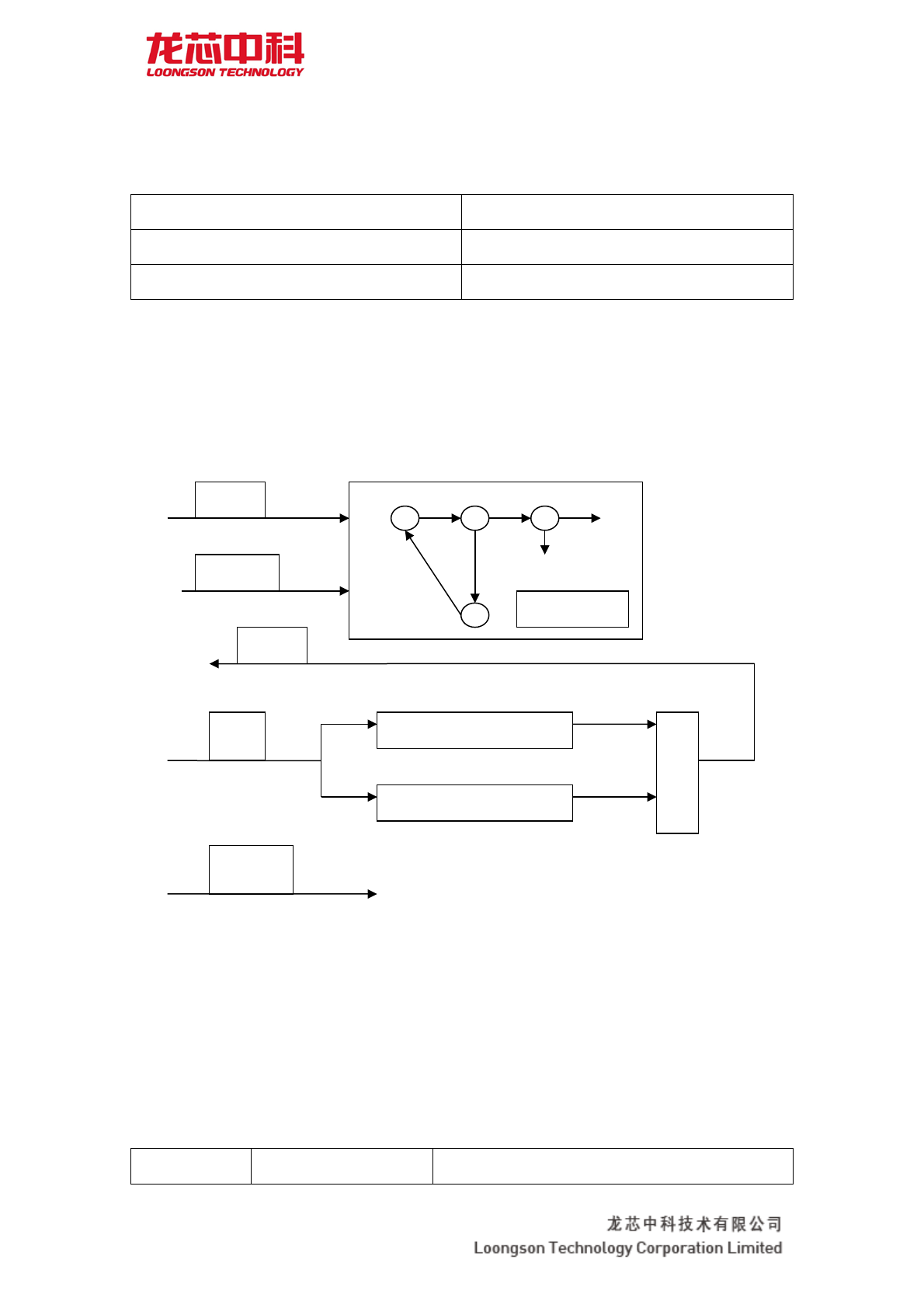

1.1 体系结构框图

1B 芯片内部顶层结构由 AXI XBAR 交叉开关互连,其中 GS232、DC、AXI_MUX 作为主设

备通过 3X3 交叉开关连接到系统; DC、AXI_MUX 和DDR2 作为从设备通过 3X3 交叉开关连接

到系统。在 AXI_MUX 内部实现了多个 AHB 和APB 模块到顶层 AXI 交叉开关的连接,其中

DMA_MUX、GMAC0、GMAC1、USB 被AXI_MUX 选择作为主设备访问交叉开关;AXI_MUX(包括

confreg、SPI0、SPI1)、 AXI2APB、GMAC0、GMAC1、USB 等作为从设备被来自 AXI_MUX 的

主设备访问。在 AXI2APB 内部实现了系统对内部 APB 接口设备的访问,这些设备包括 Watch

Dog、RTC、PWM、I2C、CAN、NAND、UART 等。

1

龙芯 1B 处理器用户手册

图 1-1 1B 芯片结构图

1.2 芯片主要功能

1B 芯片支持以下功能:

1.2.1 GS232 CPU

龙芯 232 核是一款实现 MIPS32 兼容且支持 EJTAG 调试的双发射处理器,通过采用转移

预测、寄存器重命名、乱序发射、路预测的指令 CACHE、非阻塞的数据 CACHE、写合并收集

等技术来提高流水线的效率。

• 双发射五级流水、乱序发射、乱序执行

• 8KB 指令 Cache+8KB 数据 Cache,4路组相连,指令 CACHE 支持路预测

• 6项BRQ、16 项的 QUEUE

• 动态转移预测、地址返回栈

• 32 项JTLB,4项ITLB 、8项DTLB

• 两个定点 ALU 部件。

• 支持非阻塞的 Cache 访问技术,4项load 队列、2项store 队列、3项miss 队列,最

2

龙芯 1B 处理器用户手册

多容忍 5条store 指令 Cache 不命中和 4条load 指令 Cache 不命中。

• 支持 cached store 指令的写合并和 uncache 写加速技术

• 支持 cache lock 技术和预取指令

• 支持流水线暂停模式

• 支持向量中断,可配置支持快速中断响应,最多 8个时钟周期进入中断处理程序

• 支持 EJTAG 调试

1.2.2 DDR2

• 32 位 DDR2 控制器

• 遵守 DDR2 DDR 的行业标准(JESD79-2B)

• 一共含有 18 位的地址总线(即:15 位的行列地址总线和 3位的逻辑 Bank 总线)。

• 接口上命令、读写数据全流水操作

• 内存命令合并、排序提高整体带宽

• 配置寄存器读写端口,可以修改内存设备的基本参数

• 内建动态延迟补偿电路(DCC),用于数据的可靠发送和接收

• 支持 33-133MHZ 工作频率

1.2.3 LCD Controller

• 屏幕大小可达 1920*1080

• 硬件光标

• 伽玛校正

• 最高像素时钟 172MHz

• 支持线性显示缓冲

• 上电序列控制

• 支持 16 位/24 位LCD

1.2.4 USB2.0

• 1个独立的 USB2.0 的HOST ports 及PHY

• 兼容 USB1.1 和 USB2.0

• 内部 EHCI 控制和实现高速传输可达 480Mbps

• 内部 OHCI 控制和实现全速和低速传输 12Mbps 和1.5Mbps

1.2.5 AC97

• 支持 16,18 和20 位采样精度,支持可变速率

• 最高达 48KHz

• 2频道立体声输出

• 支持麦克风输入

3

龙芯 1B 处理器用户手册

1.2.6 GMAC

• 两路 10/100/1000Mbps 自适应以太网控制器

• 双网卡均兼容 IEEE 802.3

• 对外部 PHY 实现 RGMII 和MII 接口

• 半双工/全双工自适应

• 半双工时,支持碰撞检测与重发(CSMA/CD)协议

• 支持 CRC 校验码的自动生成与校验

1.2.7 SPI

• 支持 2路SPI 接口

• 支持系统启动

• 极性和相位可编程的串行时钟

• 可在等待模式下对 SPI 进行控制

1.2.8 UART

• 集成 1个全功能串口、1个四线串口和 10 个两线串口

• 在寄存器与功能上兼容 NS16550A

• 全双工异步数据接收/发送

• 可编程的数据格式

• 16 位可编程时钟计数器

• 支持接收超时检测

• 带仲裁的多中断系统

1.2.9 I2C

• 兼容 SMBUS(100Kbps)

• 与PHILIPS I2C 标准相兼容

• 履行双向同步串行协议

• 只实现主设备操作

• 能够支持多主设备的总线

• 总线的时钟频率可编程

• 可以产生开始/停止/应答等操作

• 能够对总线的状态进行探测

• 支持低速和快速模式

• 支持 7位寻址和 10 位寻址

• 支持时钟延伸和等待状态

1.2.10 PWM

• 提供 4路可配置 PWM 输出,

• 数据宽度 32 位

4

龙芯 1B 处理器用户手册

• 定时器功能

• 计数器功能

1.2.11 CAN

• 支持 2个独立 CAN 总线接口

• 每路 CAN 接口均支持 CAN2.0A/B 协议

• 支持 CAN 协议扩展

1.2.12 RTC

• 计时精确到 0.1 秒

• 可产生 3个计时中断

• 支持定时开关机功能

1.2.13 GPIO

• 61 位GPIO

• 支持位操作

1.2.14 NAND

- 支持最大单颗 NAND FLASH 为32GB

- 共4个片选 CS

- 数据宽度 8bit

- 支持 SLC

- 支持页大小 2048Byte

1.2.15 INT controller

• 支持软件设置中断

• 支持电平与边沿触发

• 支持中断屏蔽与使能

• 支持固定中断优先级

1.2.16 Watchdog

• 16 比特计数器及初始化寄存器

• 低功耗模式暂停功能

1.2.17 功耗

• 典型工作状态 0.3-0.5W

5

龙芯 1B 处理器用户手册

1.2.18 其它

• 测试访问口控制器 JTAG

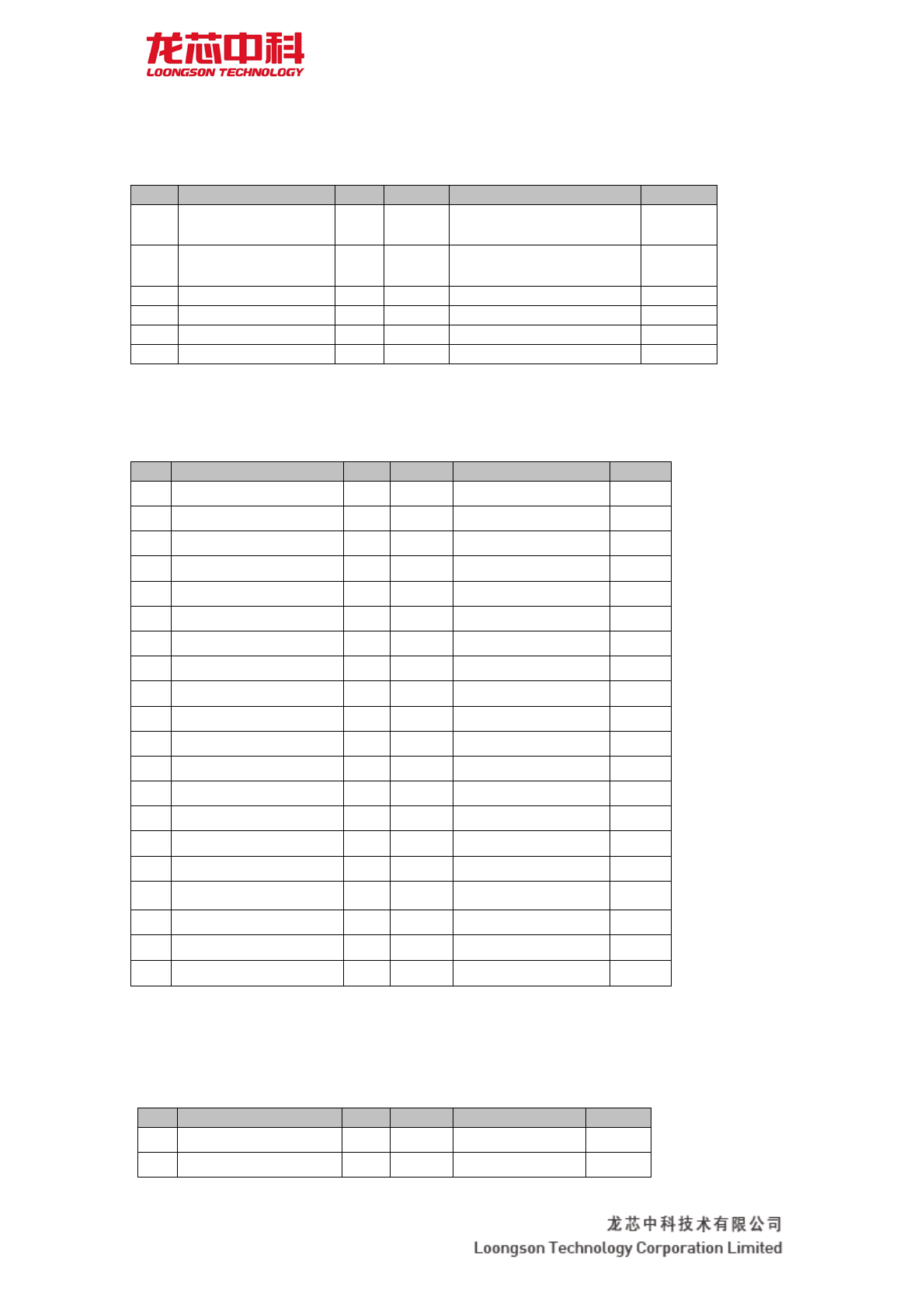

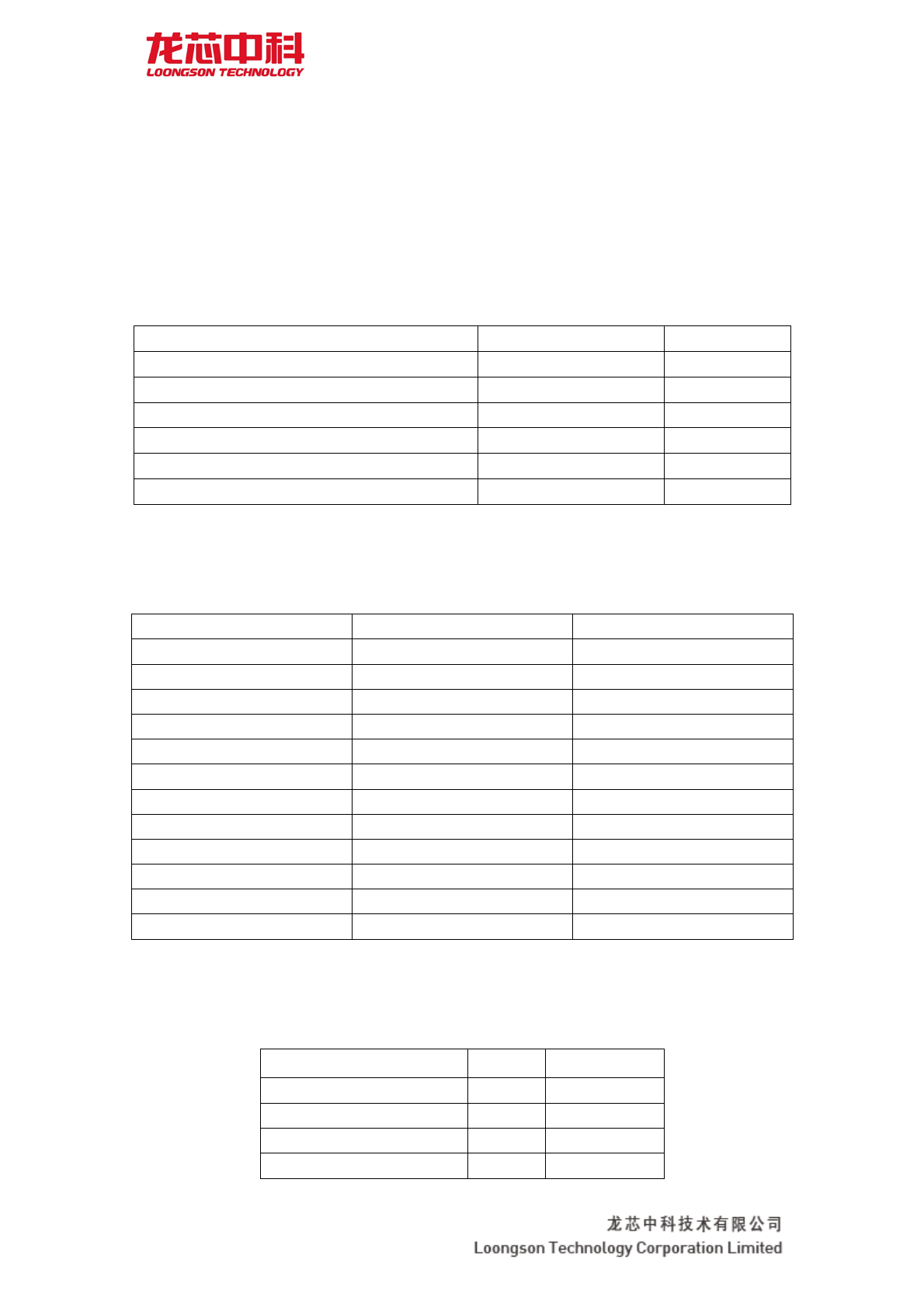

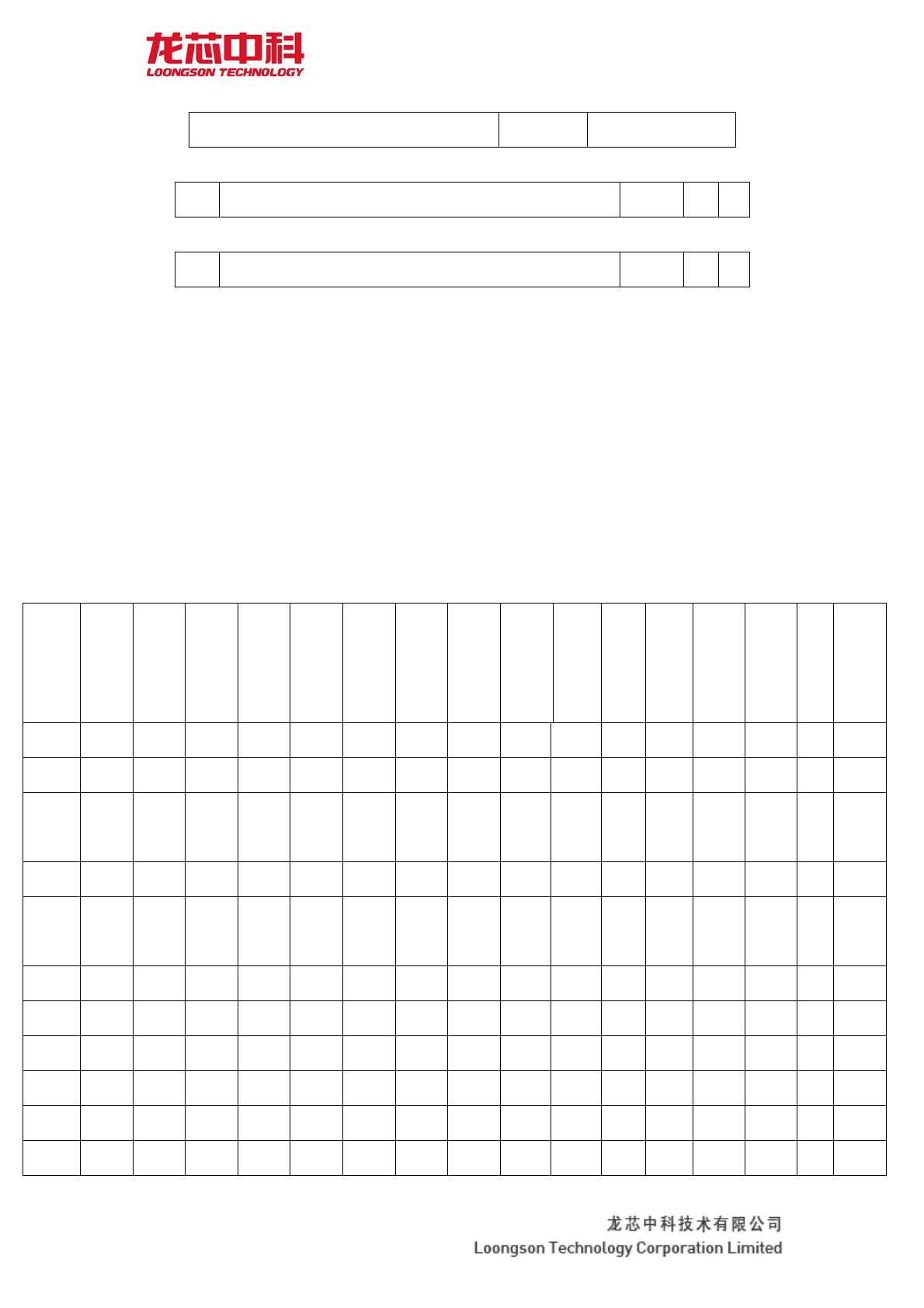

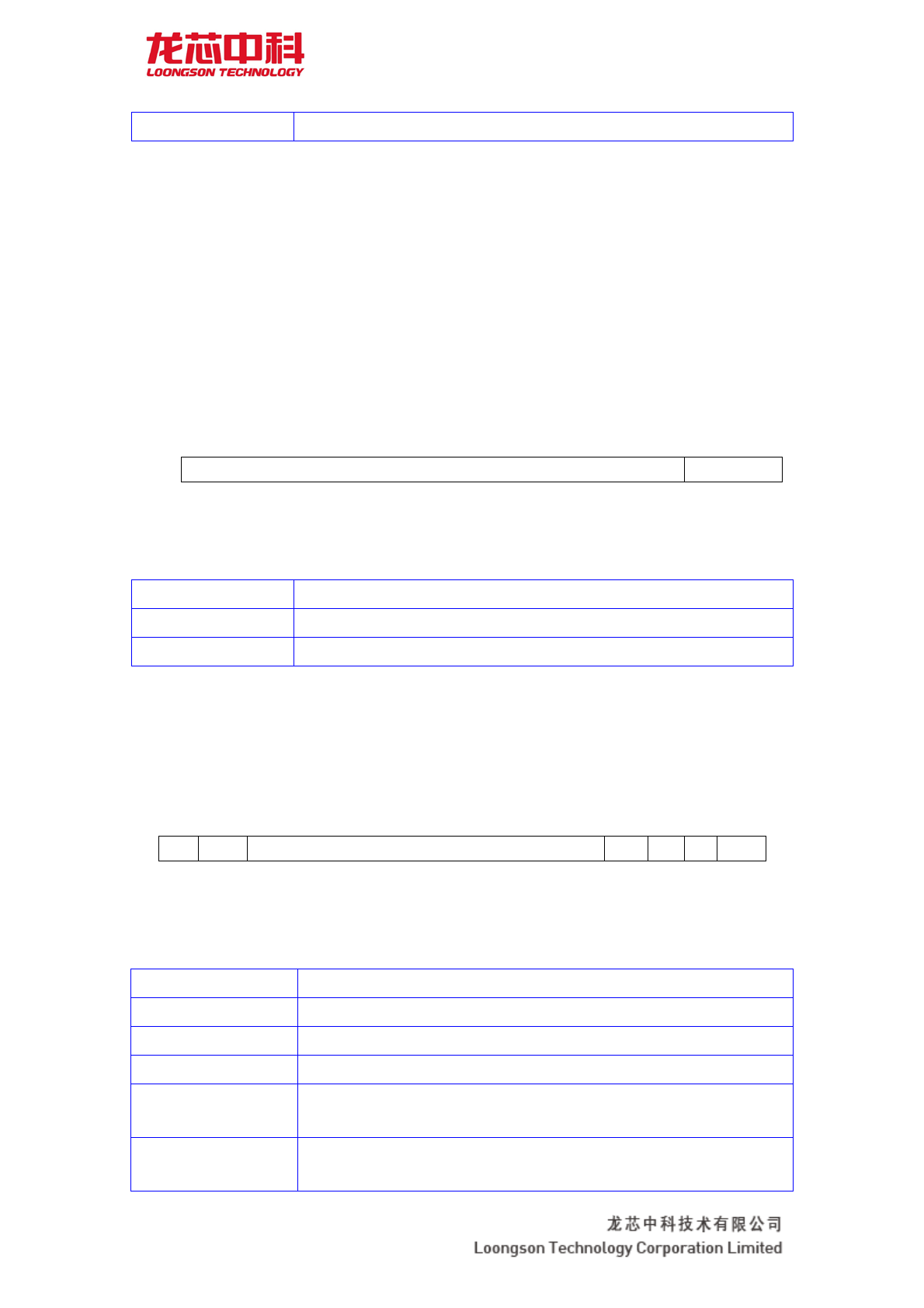

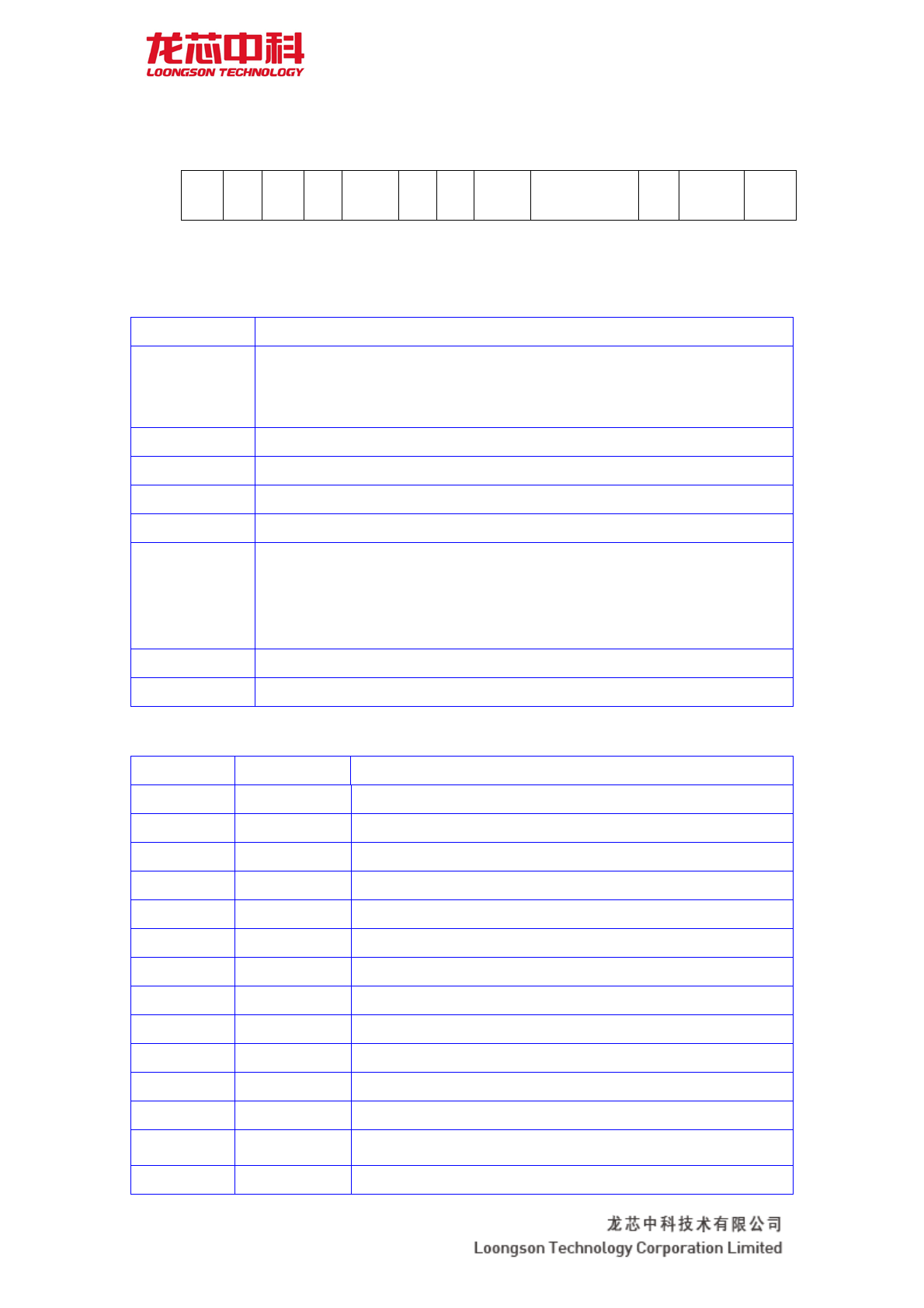

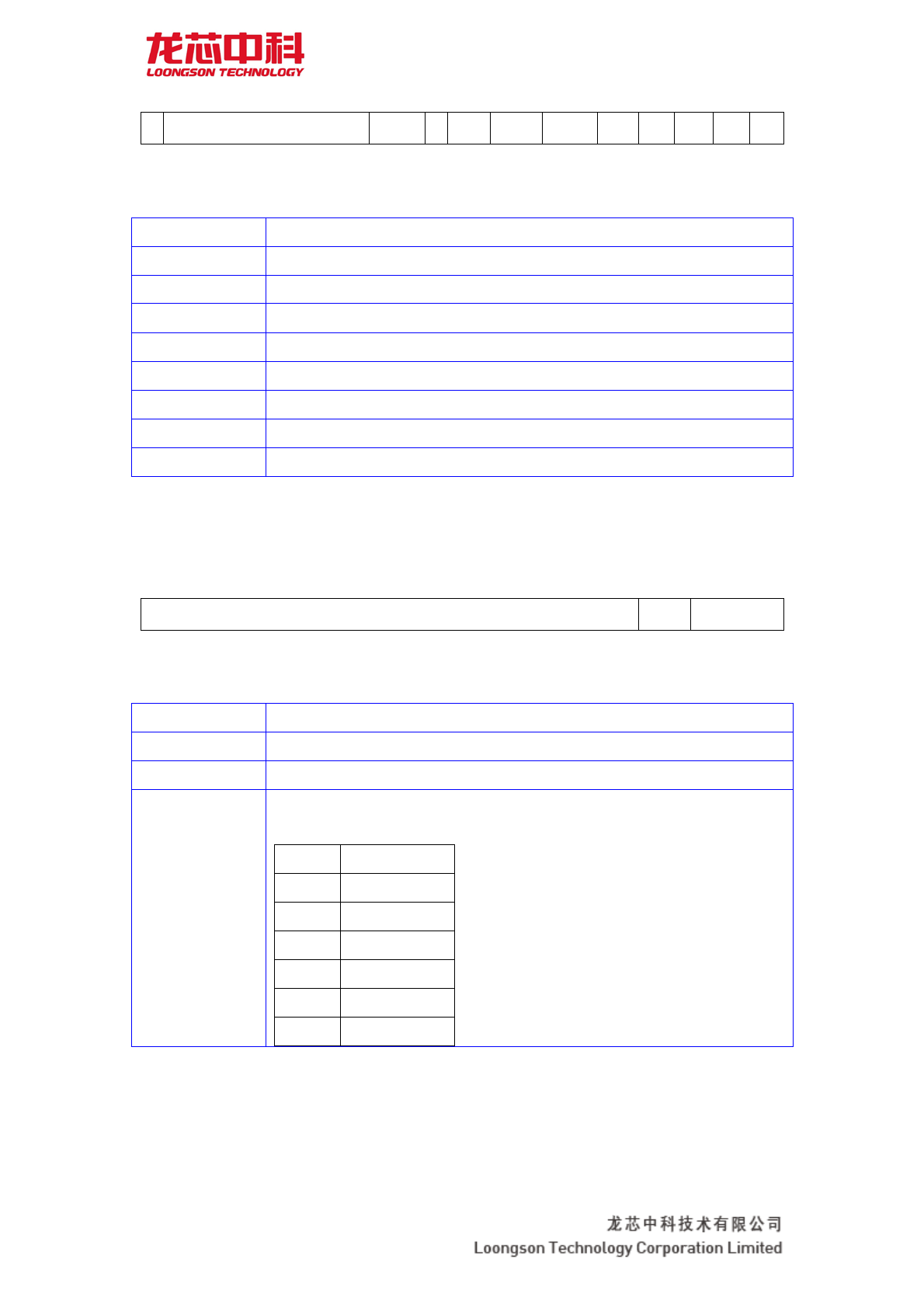

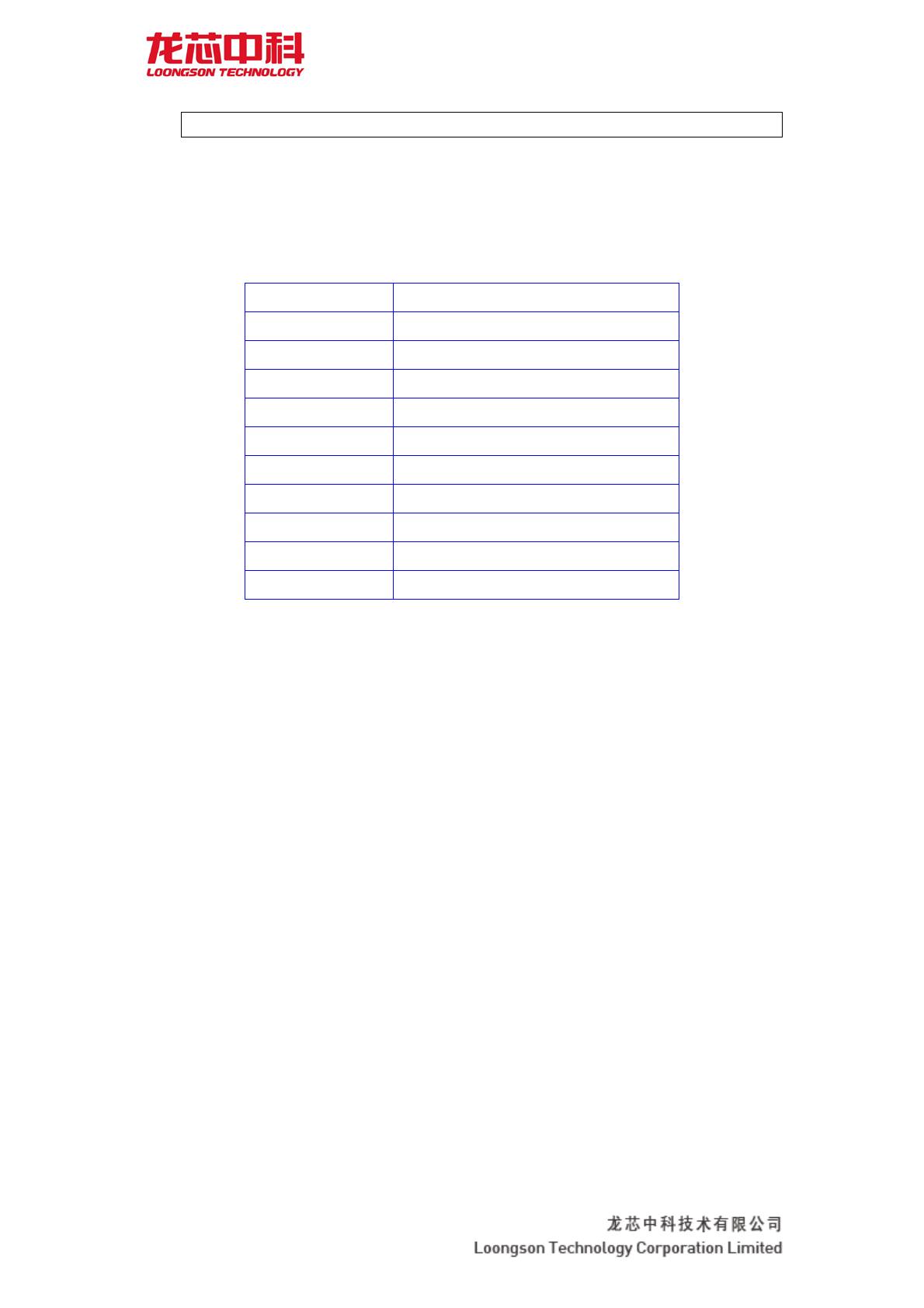

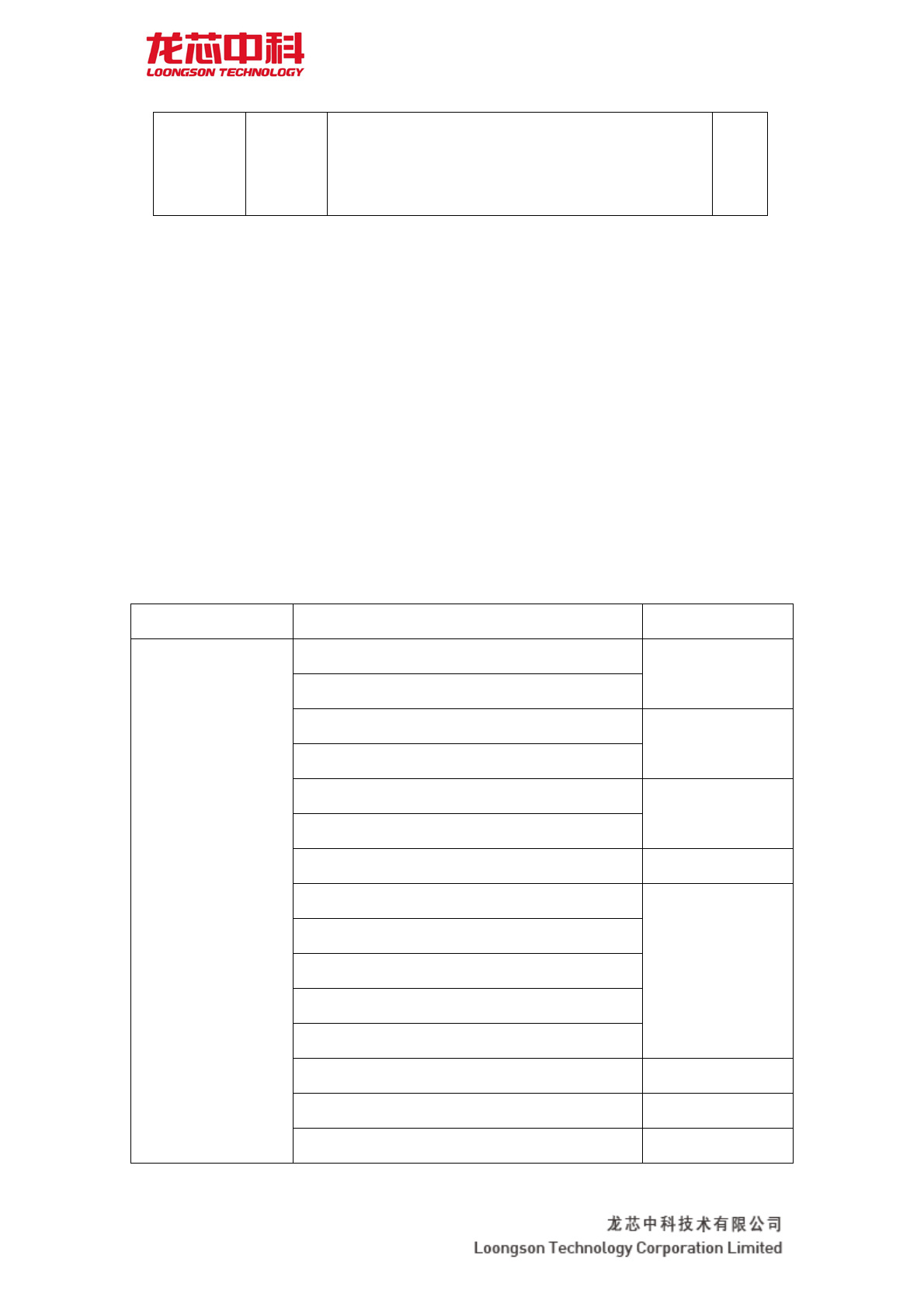

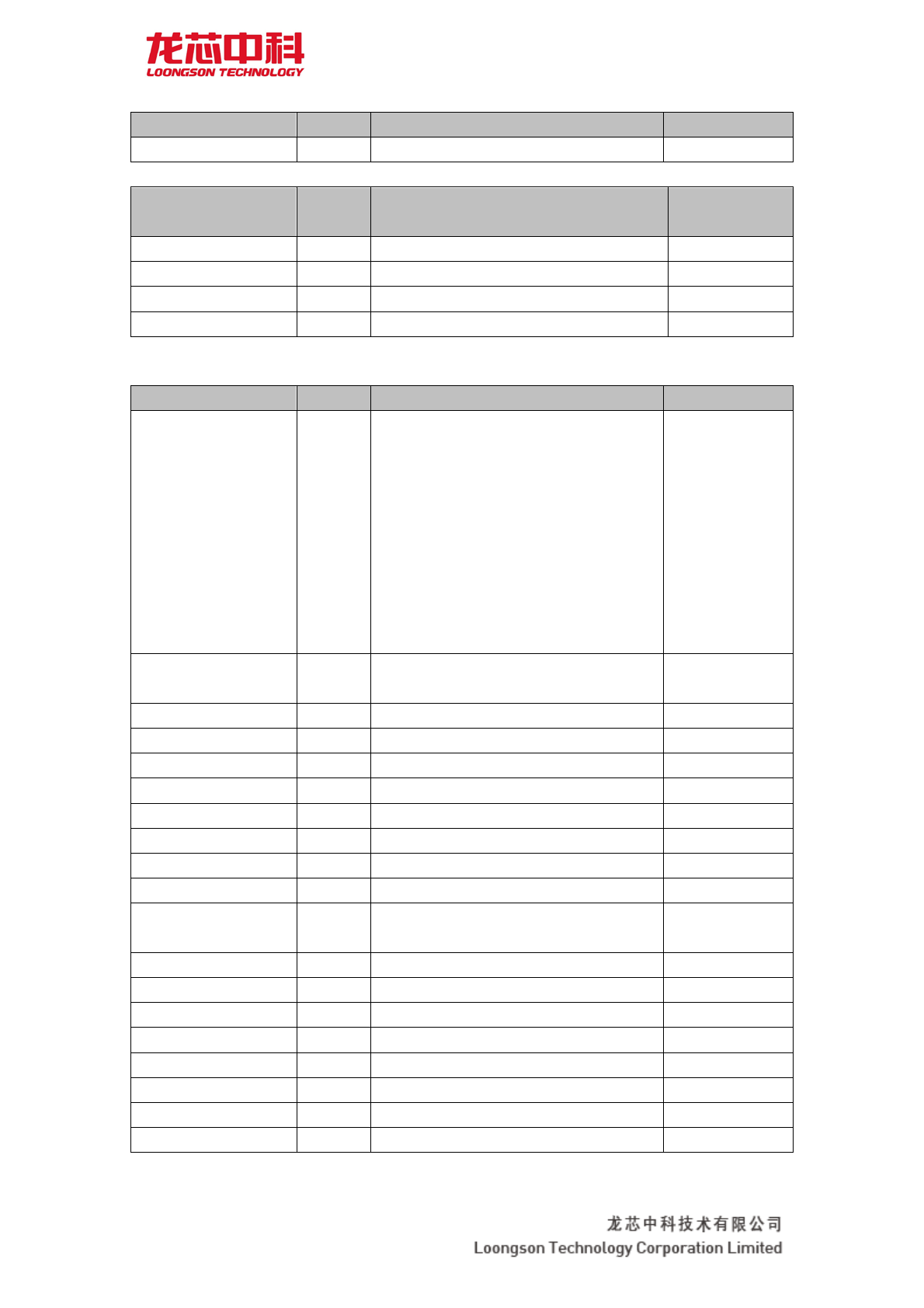

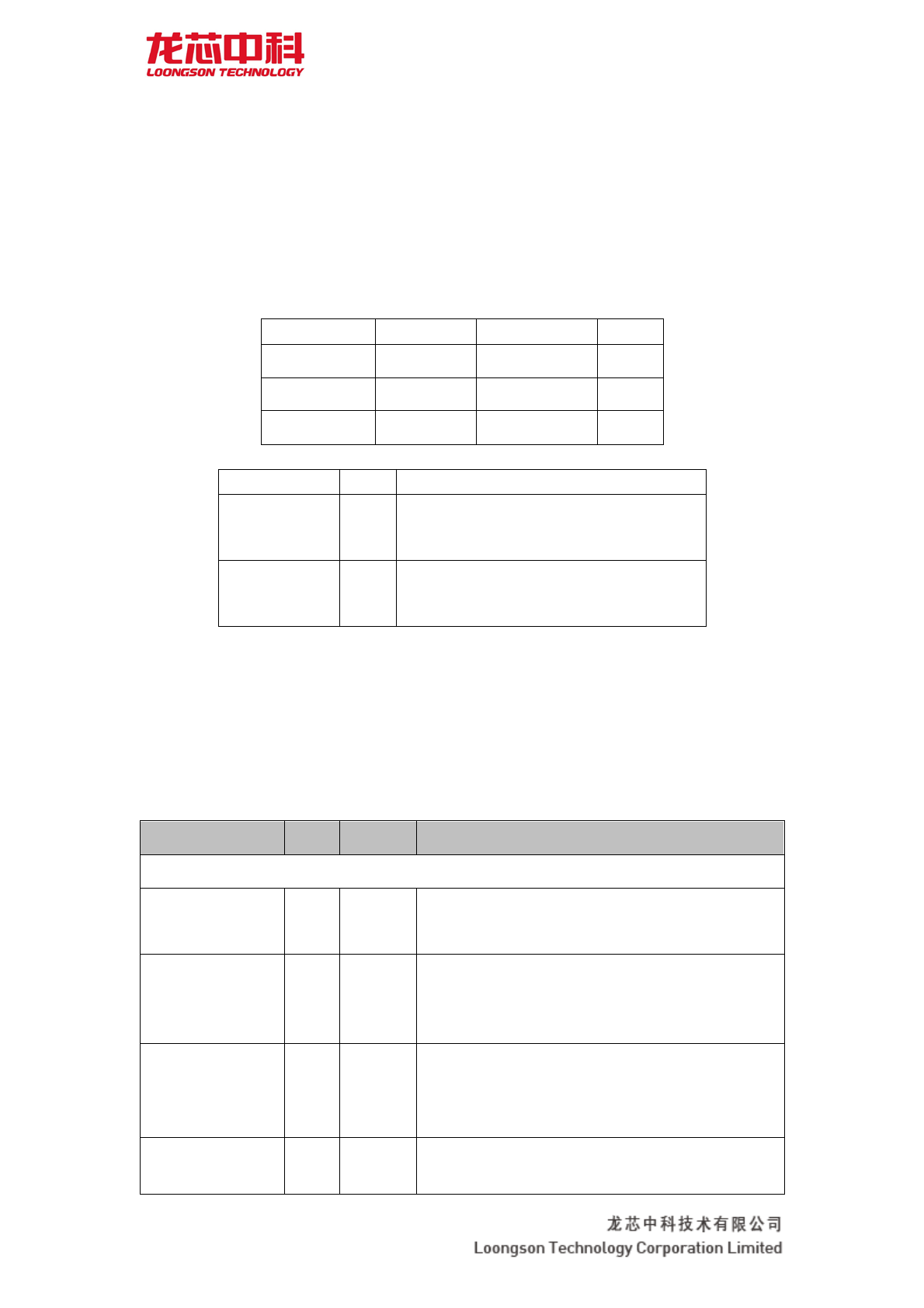

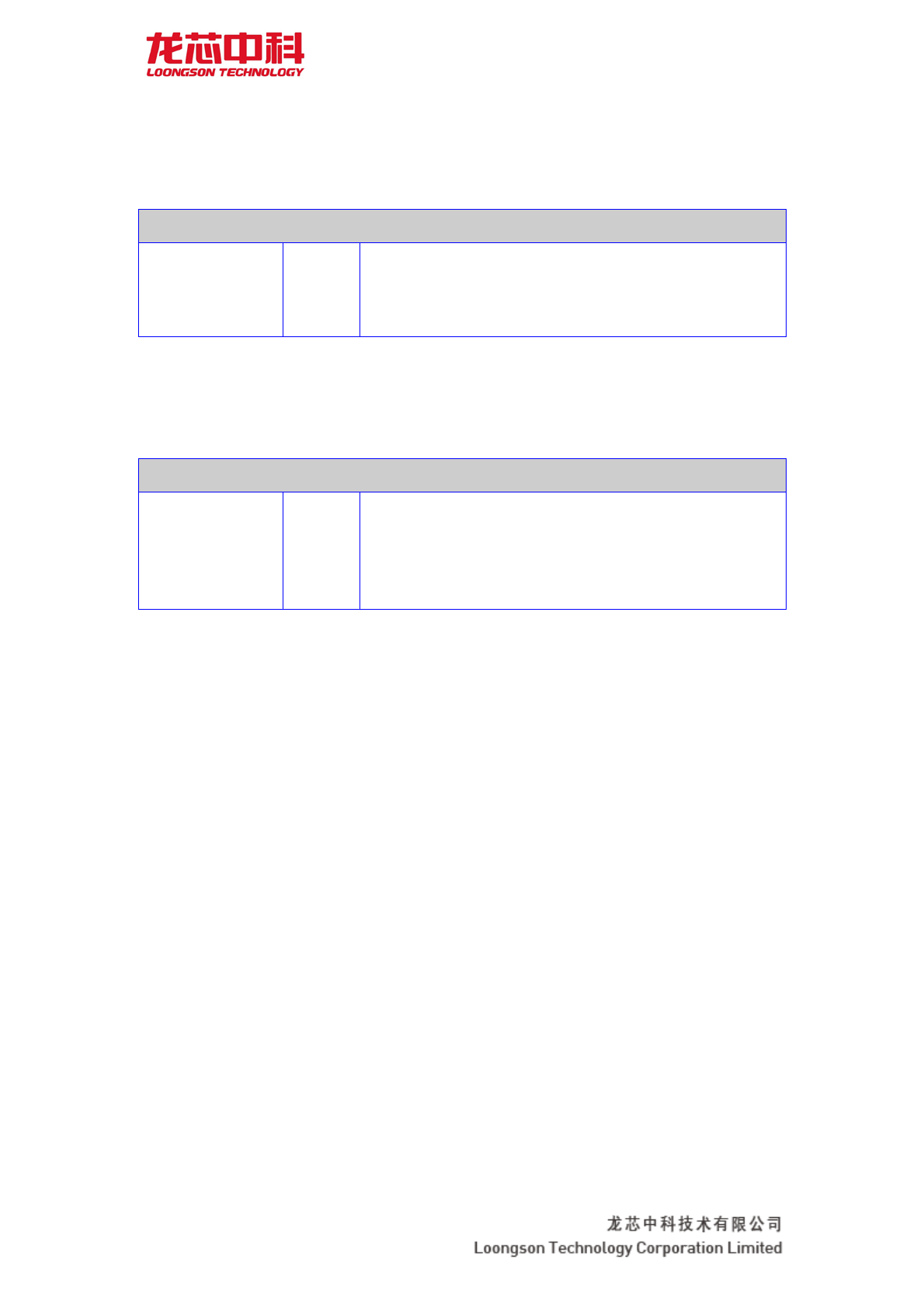

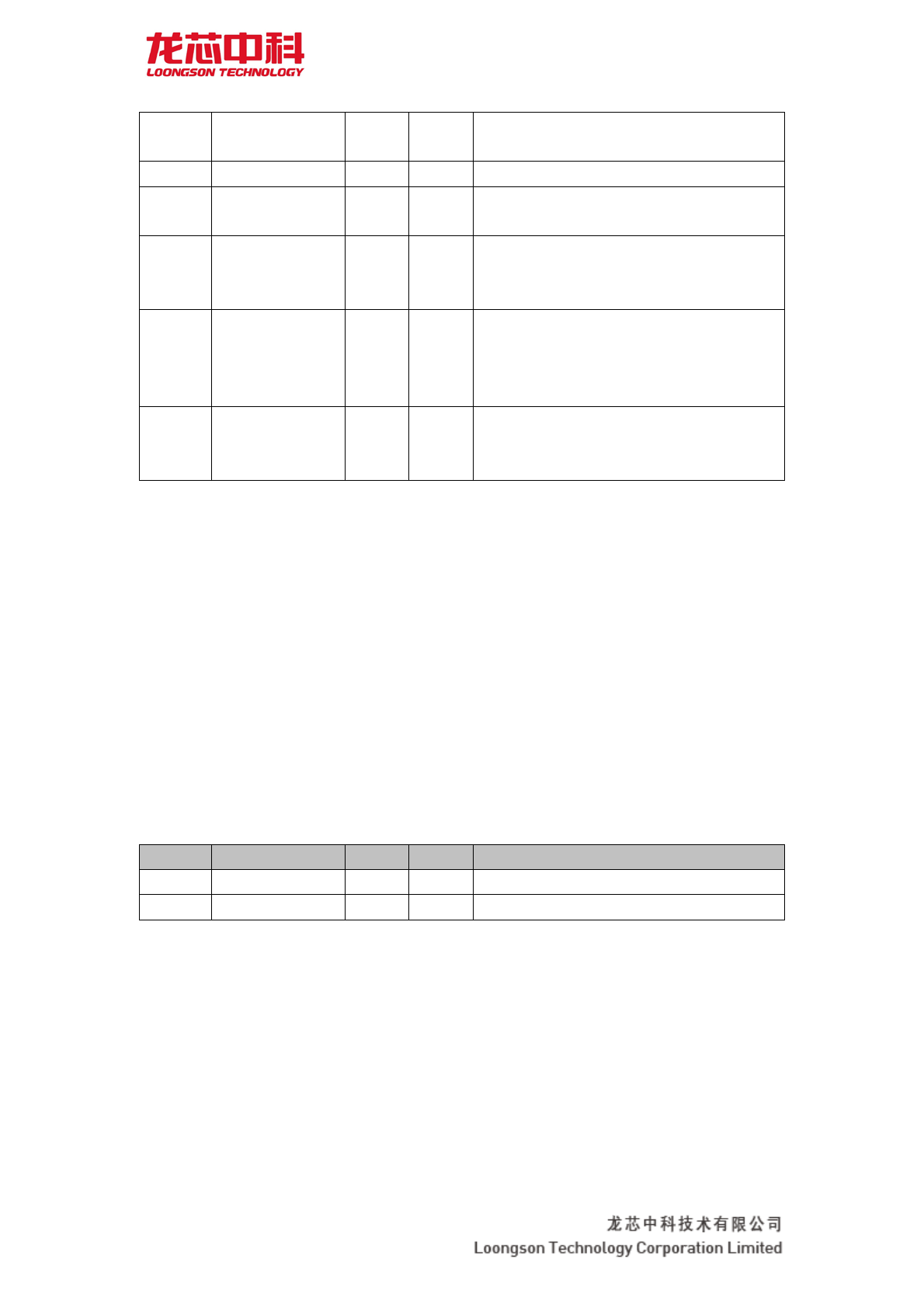

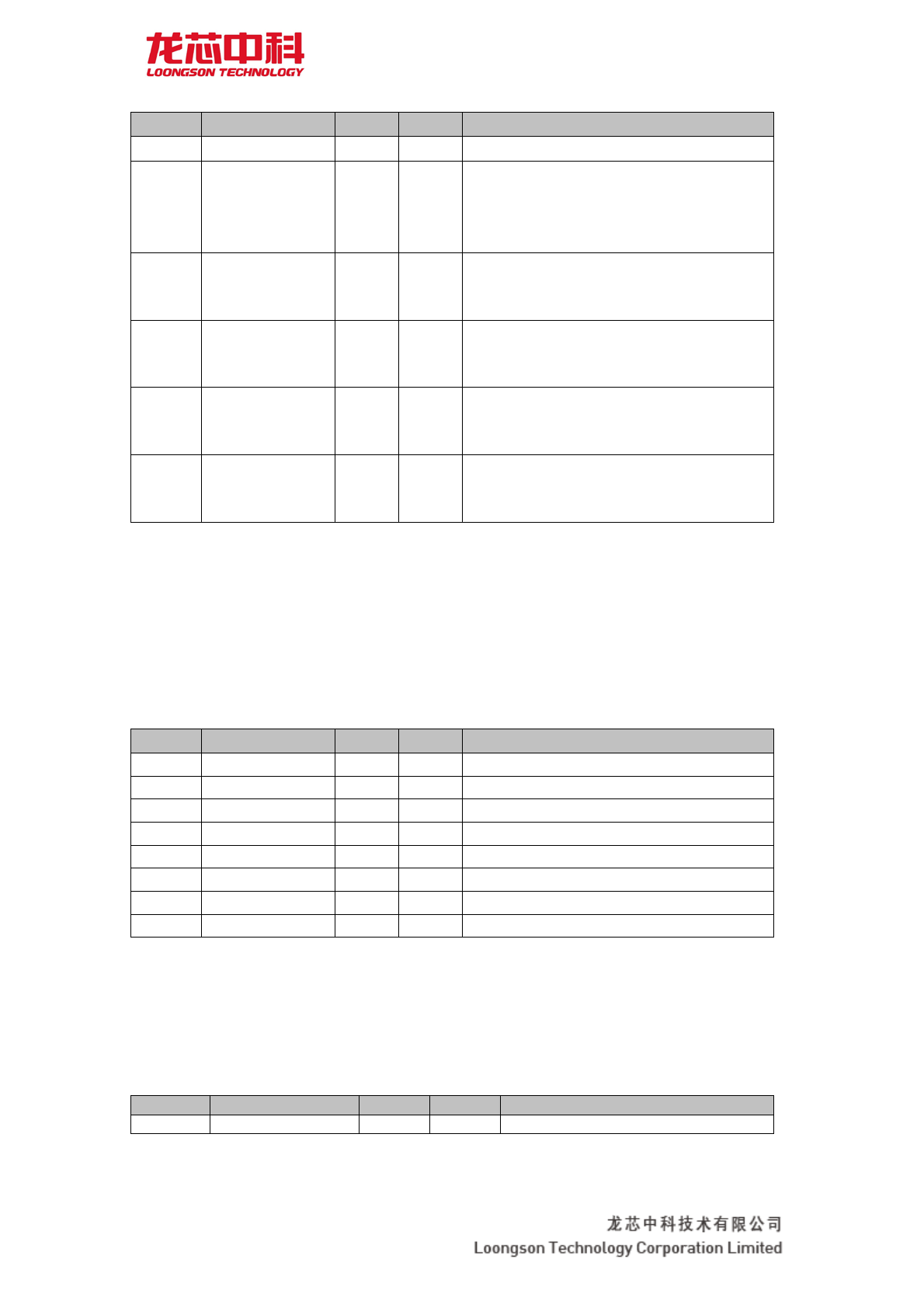

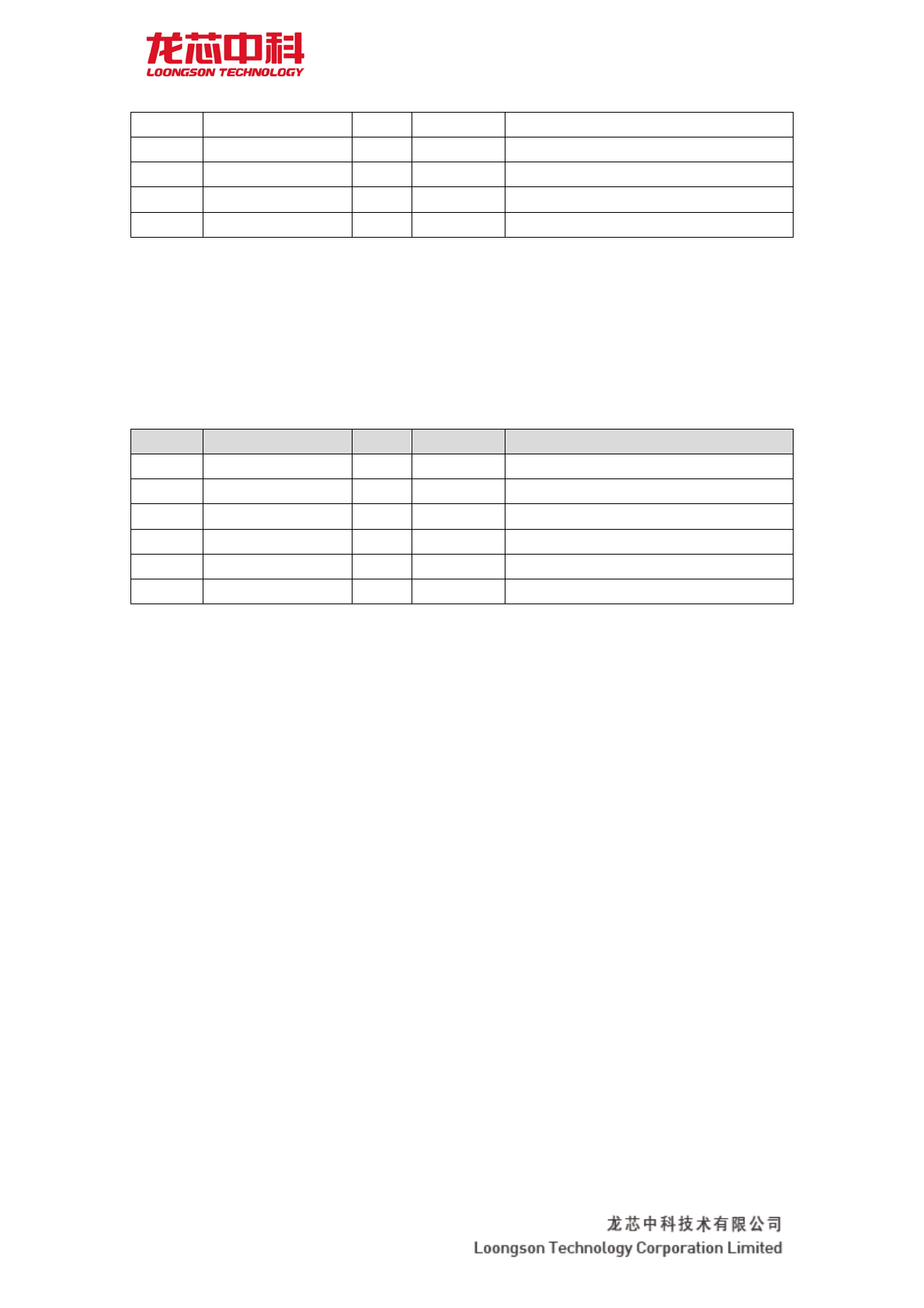

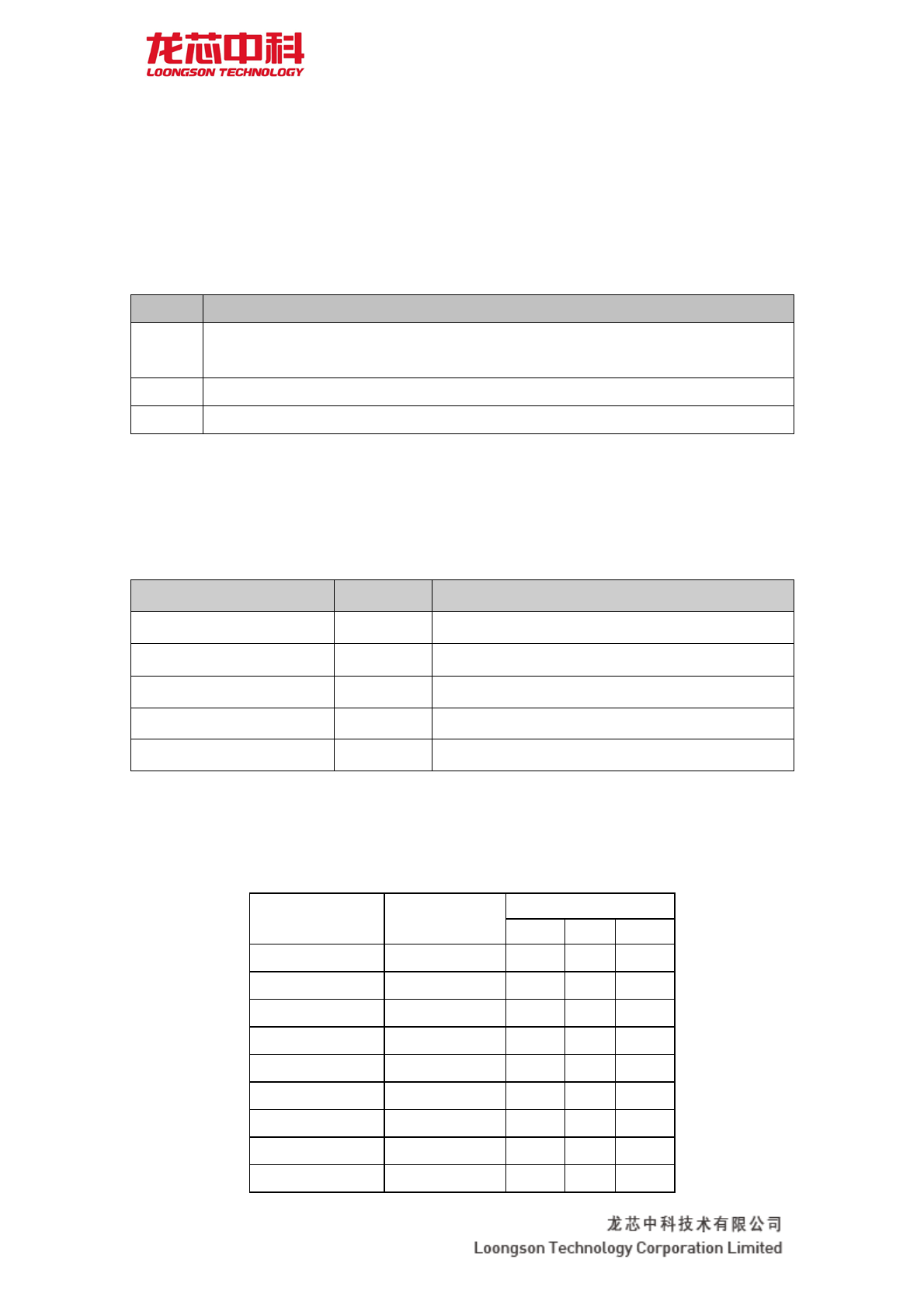

1.3 质量等级

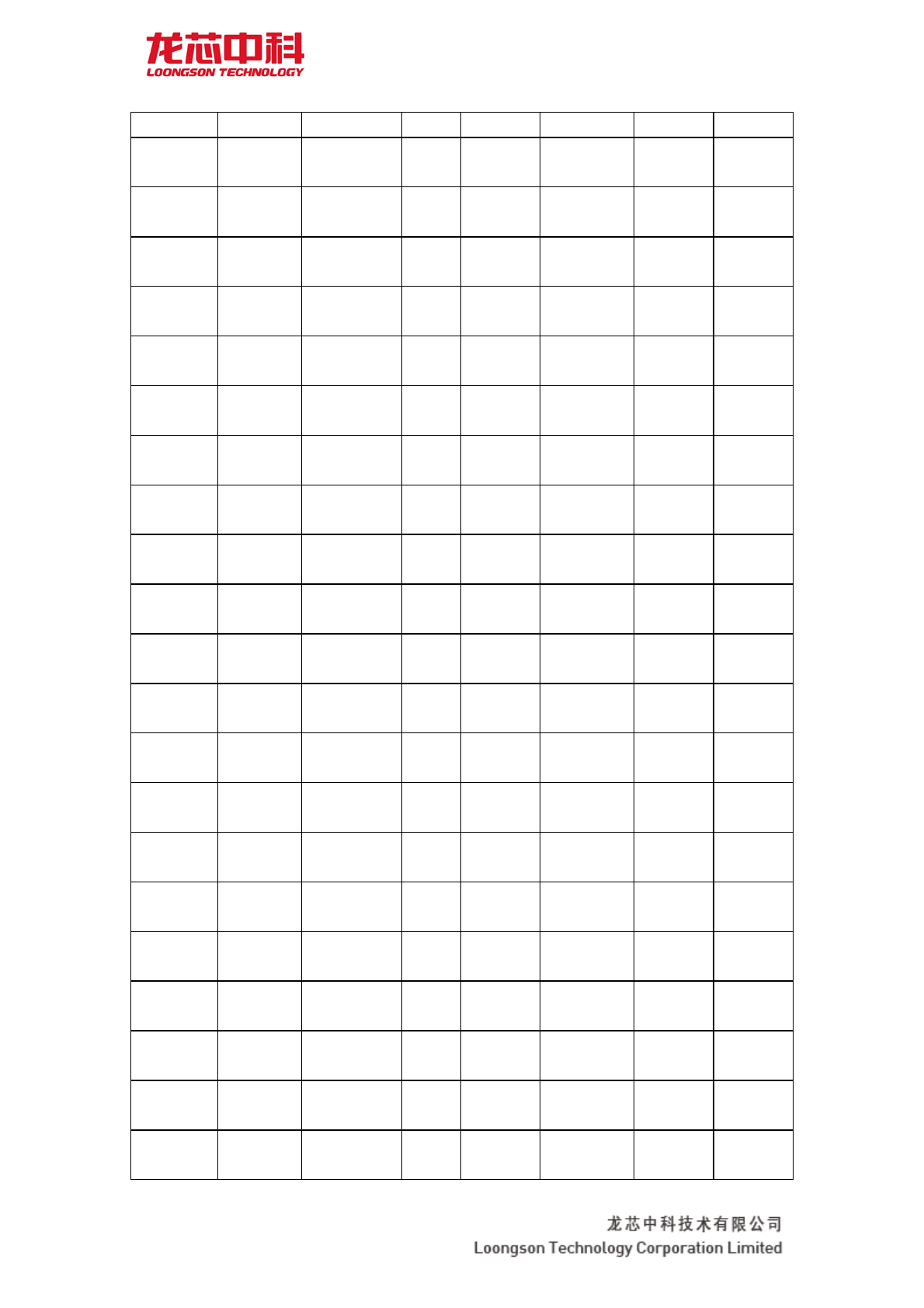

龙芯 1B 芯片有工业级和商业级两种,其主要特征如下:

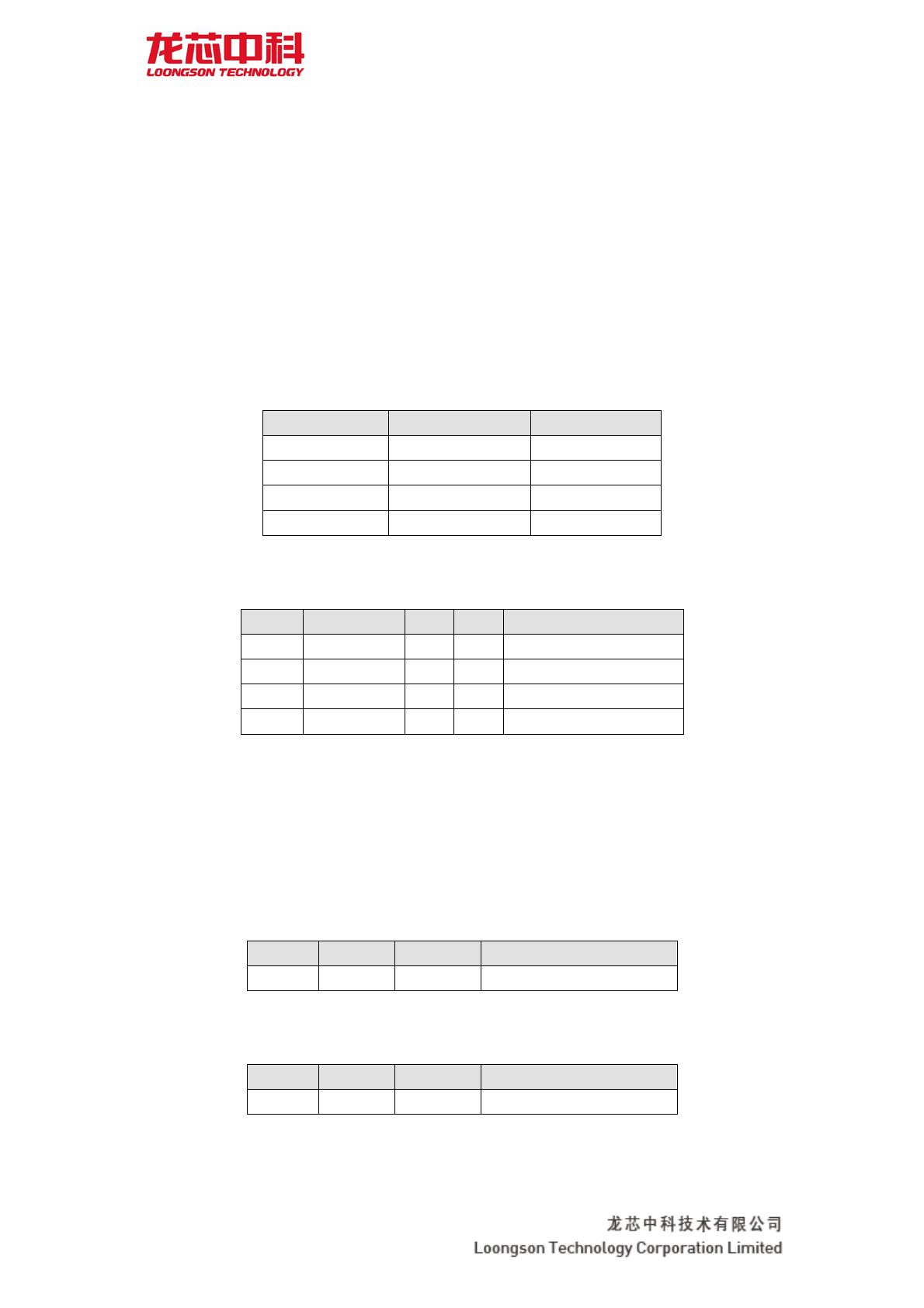

配置 商业级 工业级

工作温度 0℃~70℃ -40℃~85℃

是否筛选 — √

是否质量一致性试验 — √

质量一致性试验标准 — GB 12750-2006

GB 4937-1995

GJB 548B-2005

龙芯 1B 芯片为验证是否符合国标以及其他标准的相关质量要求,依据国家标准,制定

了器件专用的详细规范,并依据详细规范,进行了鉴定检验试验。鉴定检验试验中包含器件

详细规范中规定的各种高温、高湿、老化寿命以及 ESD 等一系列可靠性试验。关键试验项

目见下表,其余所有试验项目详见器件的详细规范。

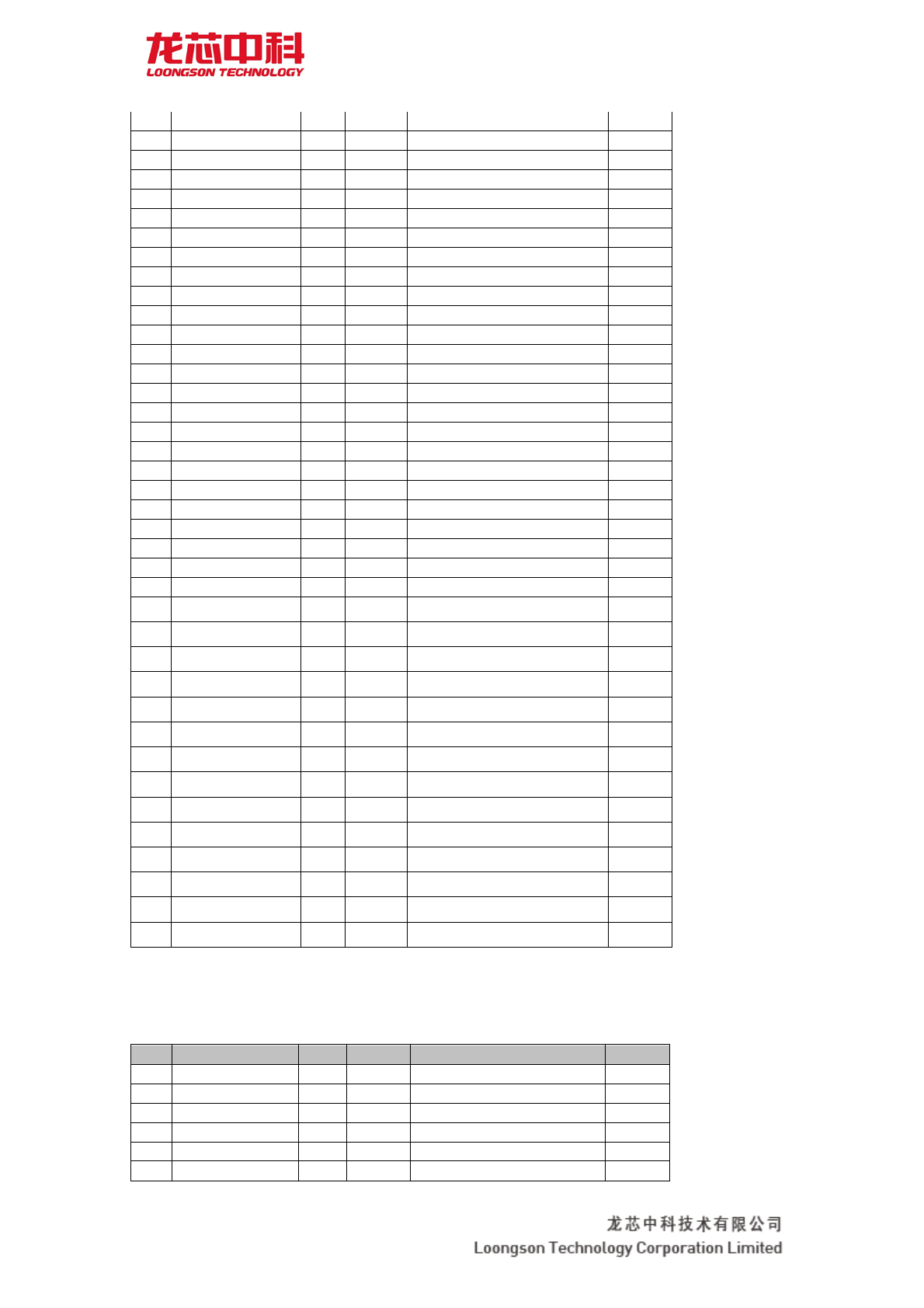

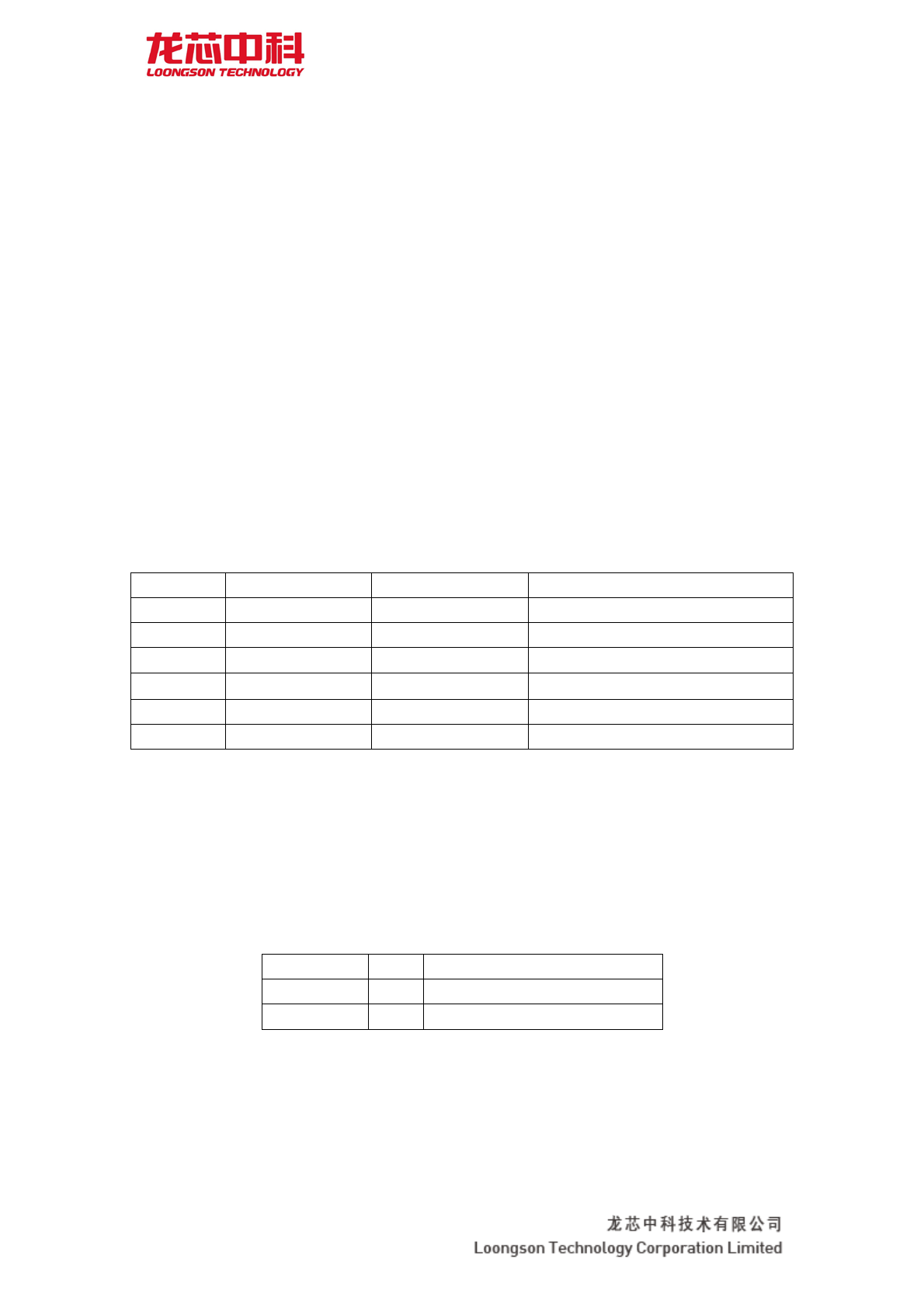

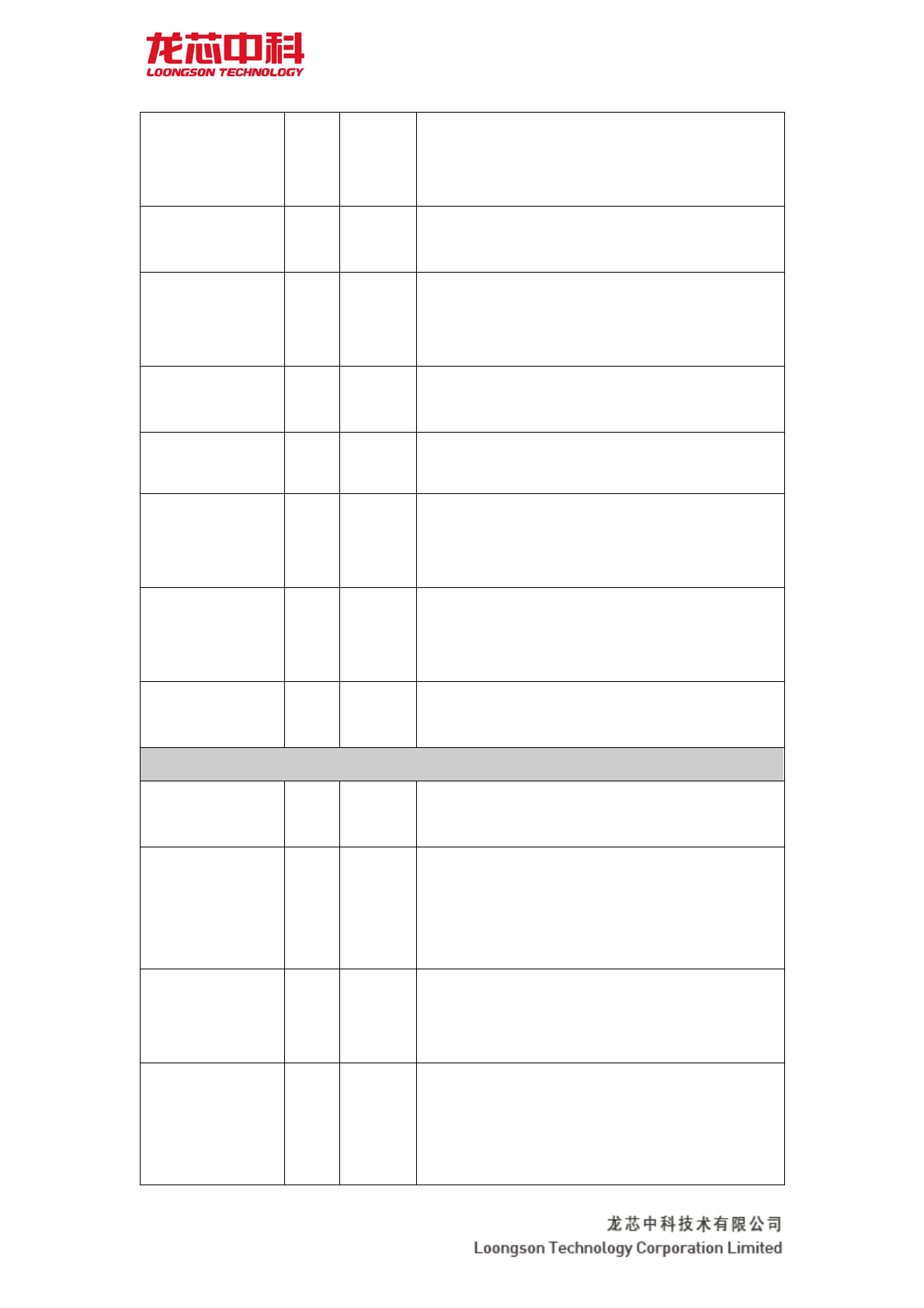

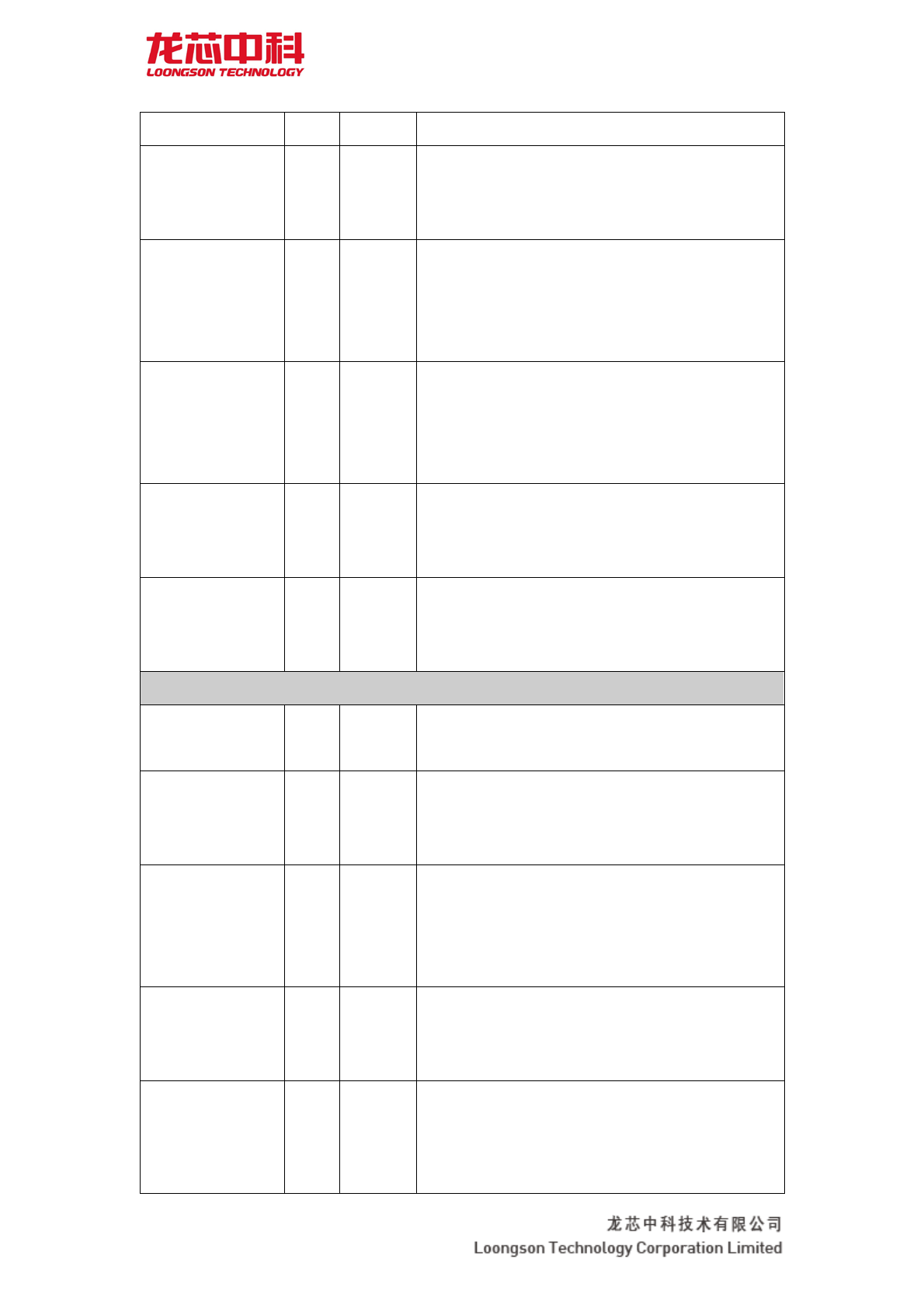

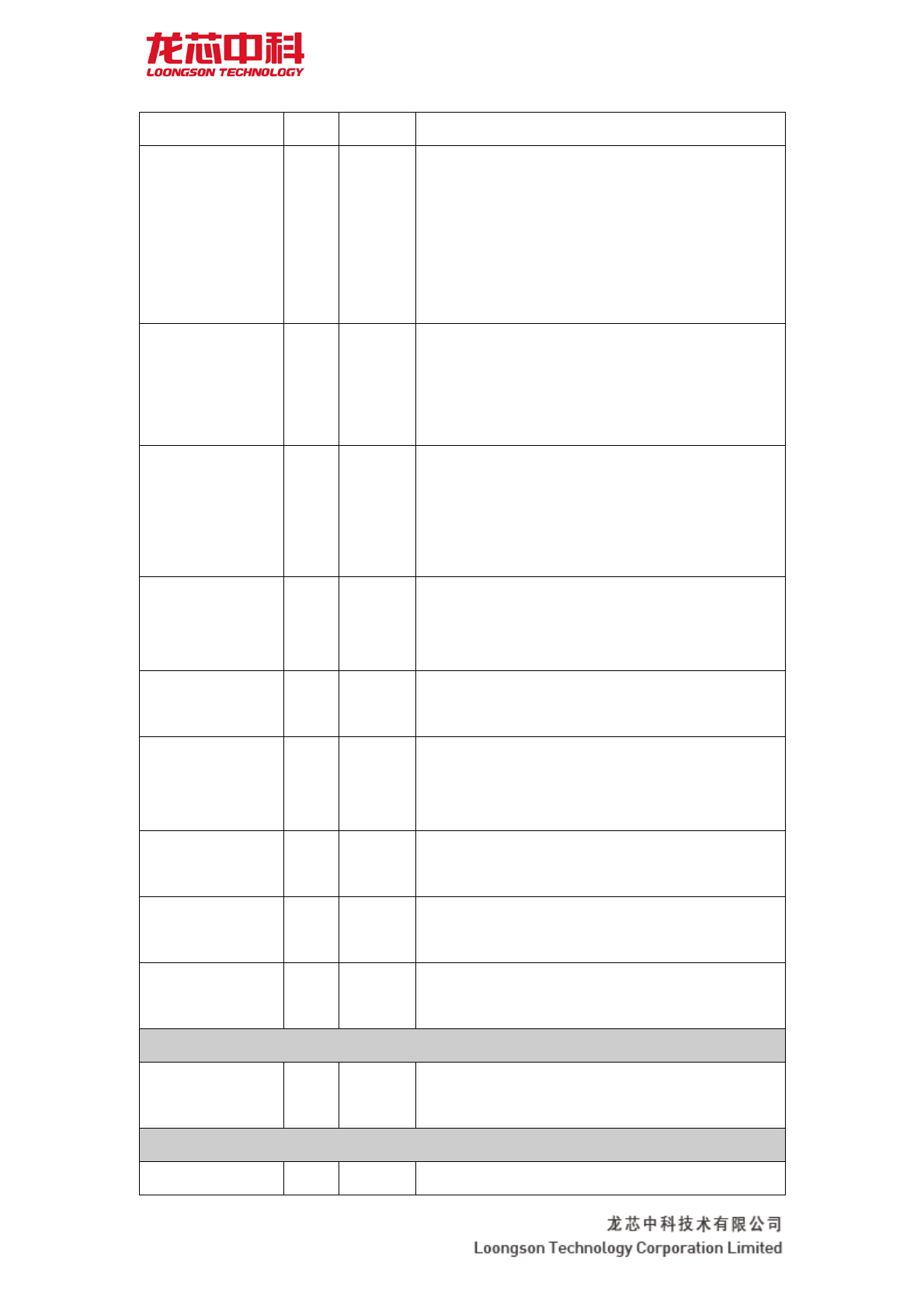

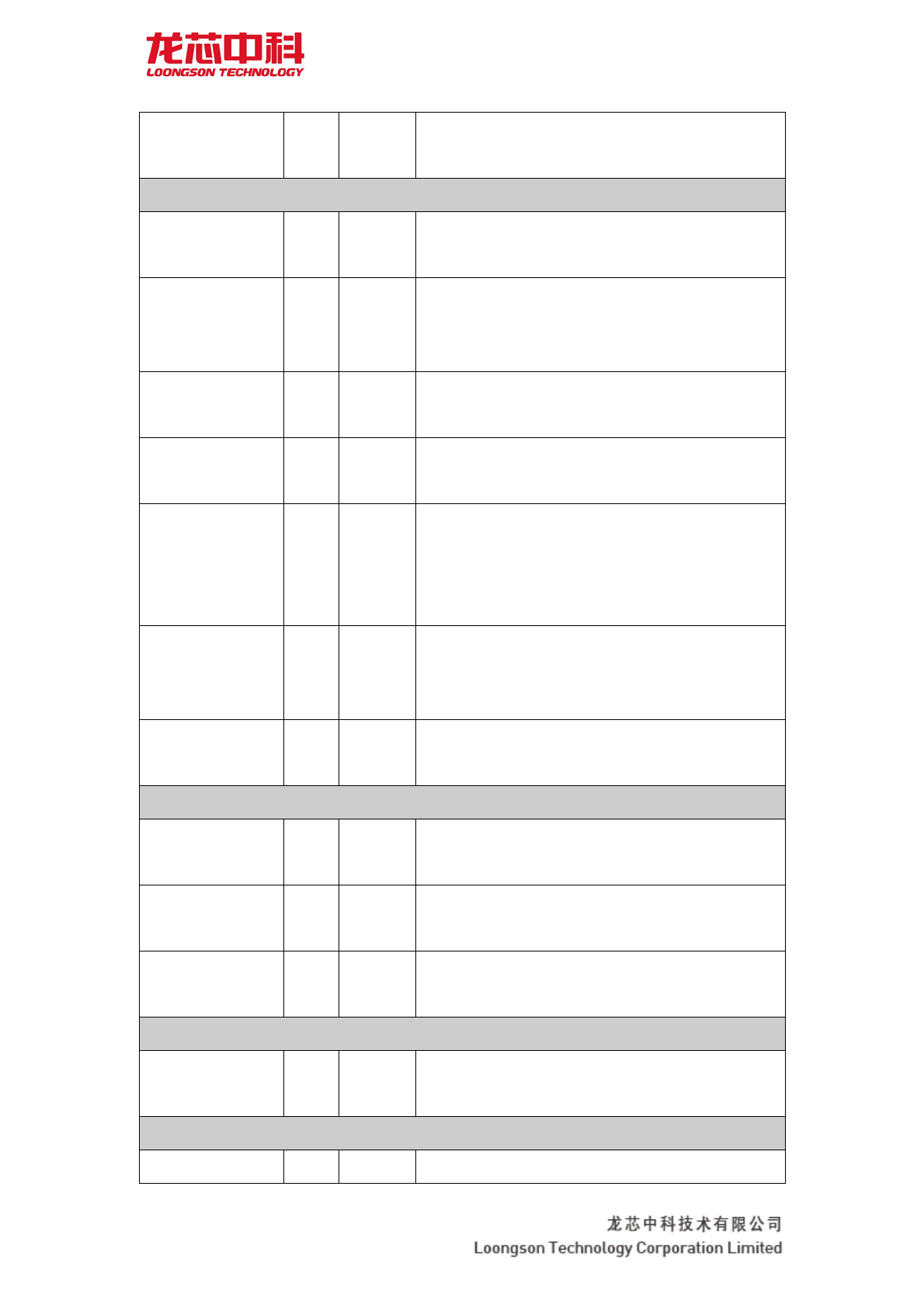

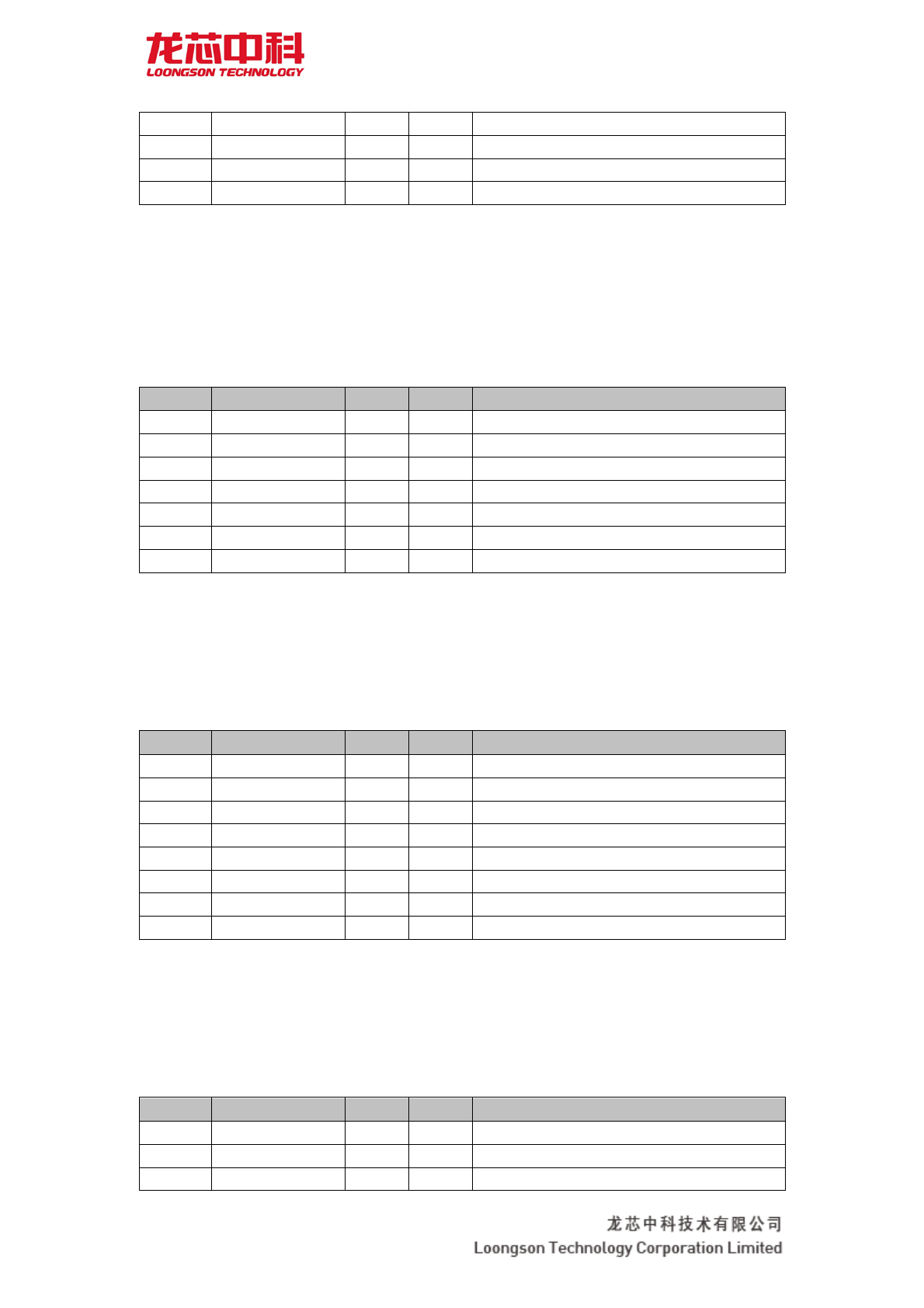

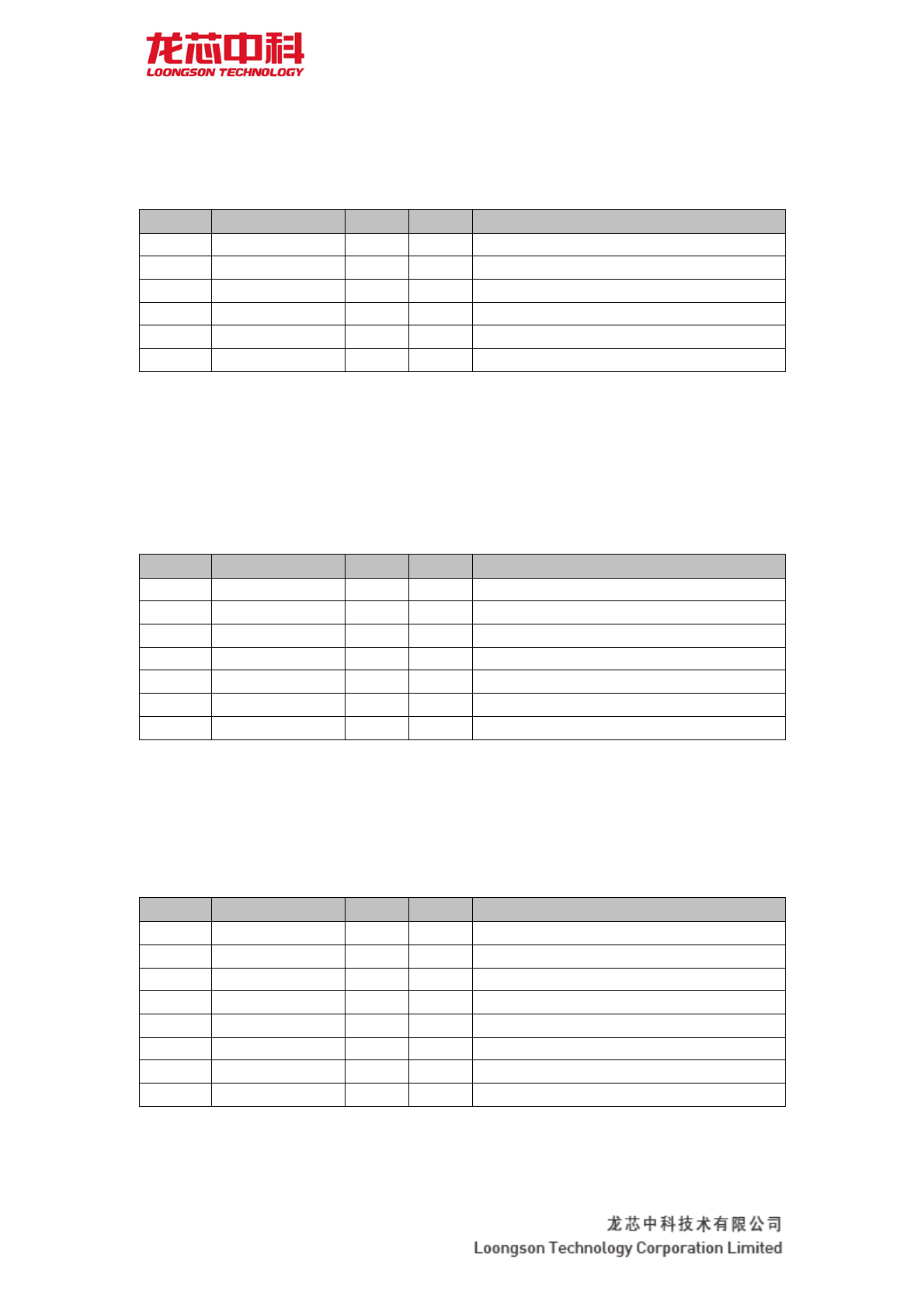

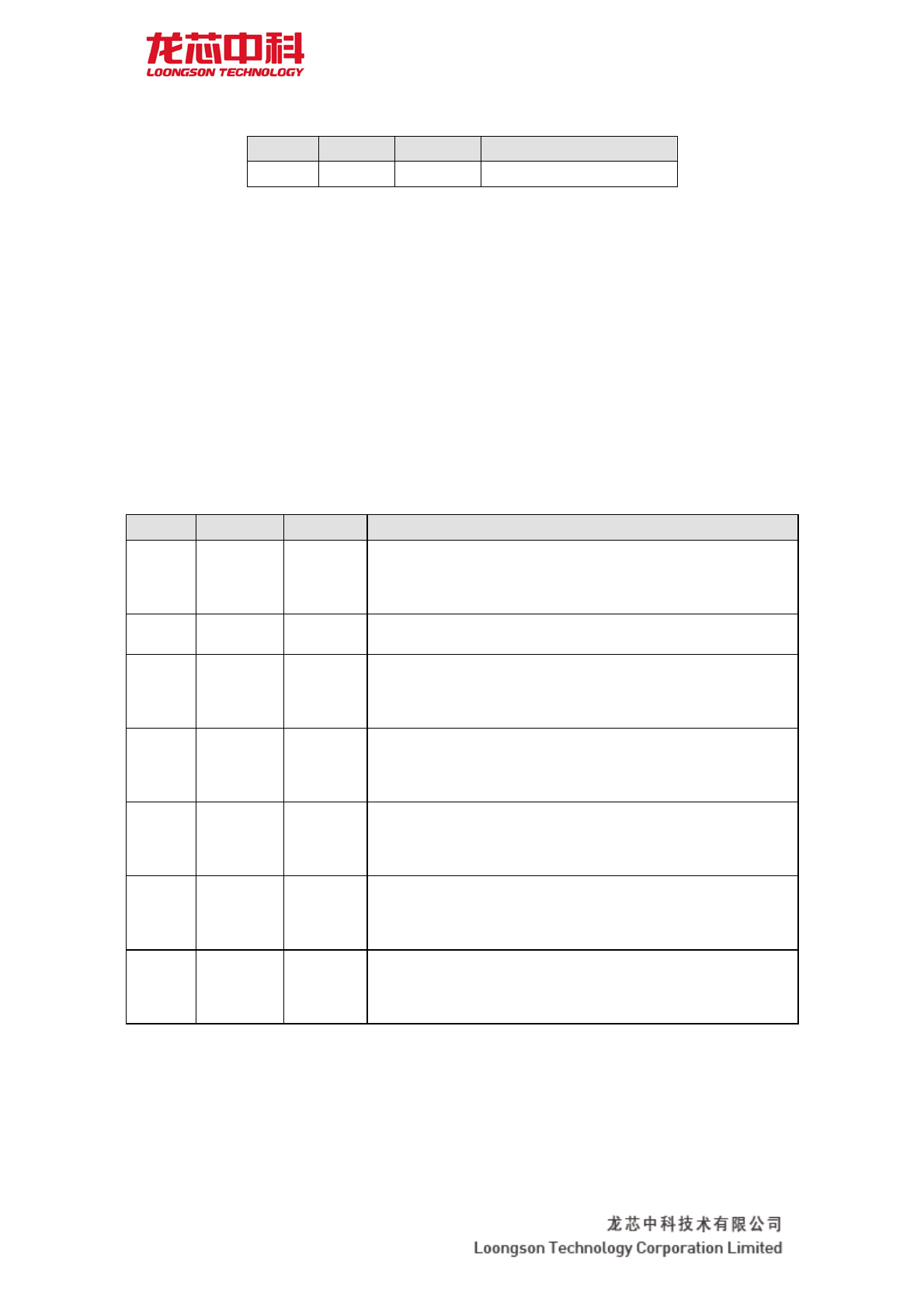

分组 试验项目 方法 条件 LTPD(c=0)或样品

数(允许失效数)

B5 a) 温度快速变化

b) 外部目检

c) 强加速稳态湿热 a

d) 电测试

GB/T 4937 第III 篇1.1

GB/T 4589.1 4.3.1.1

GB/T 4937 第III 篇5C

10 次循环

130℃/85%RH, 24h

或85℃/85%RH, 24h

A2、A3 分组

10

C2 静电放电敏感度(ESD) ESDA/JEDEC JS-001-2012 2000V 18(0)

C5 a

a)温度快速变化

b)外部目检

c)强加速稳态湿热 a

GB/T 4937 第III 篇1.1

GB/T 4589.1 4.3.1.1

GB/T 4937 第III 篇

5C(或 5B)

500 次循环

130℃/85%RH,24h

或85℃/85%RH, 24h

10

C6 盐雾 GB/T 4937 第III 篇8 24h 50

C7 a)加速稳态湿热

b)电测试

GB/T 4937 第III 篇5B 85℃/85%RH,500h

A2、A3 分组 15

C8 电耐久性(寿命) 附录 A Ta=85℃,1000h 5

a

工业级按照 130℃标准试验,商业级按照 85℃标准试验。

龙芯 1B 芯片和多数半导体器件一样,其失效率符合浴盆曲线模型。龙芯 1B 工业级芯

片为了保证能够更长期、稳定、可靠地工作,并且能够适应更苛刻的环境温度要求,对芯

片进行了可靠性筛选,以剔除早期失效的芯片。这种可靠性筛选是 100%的试验,通过筛

选的为符合工业级要求的芯片。

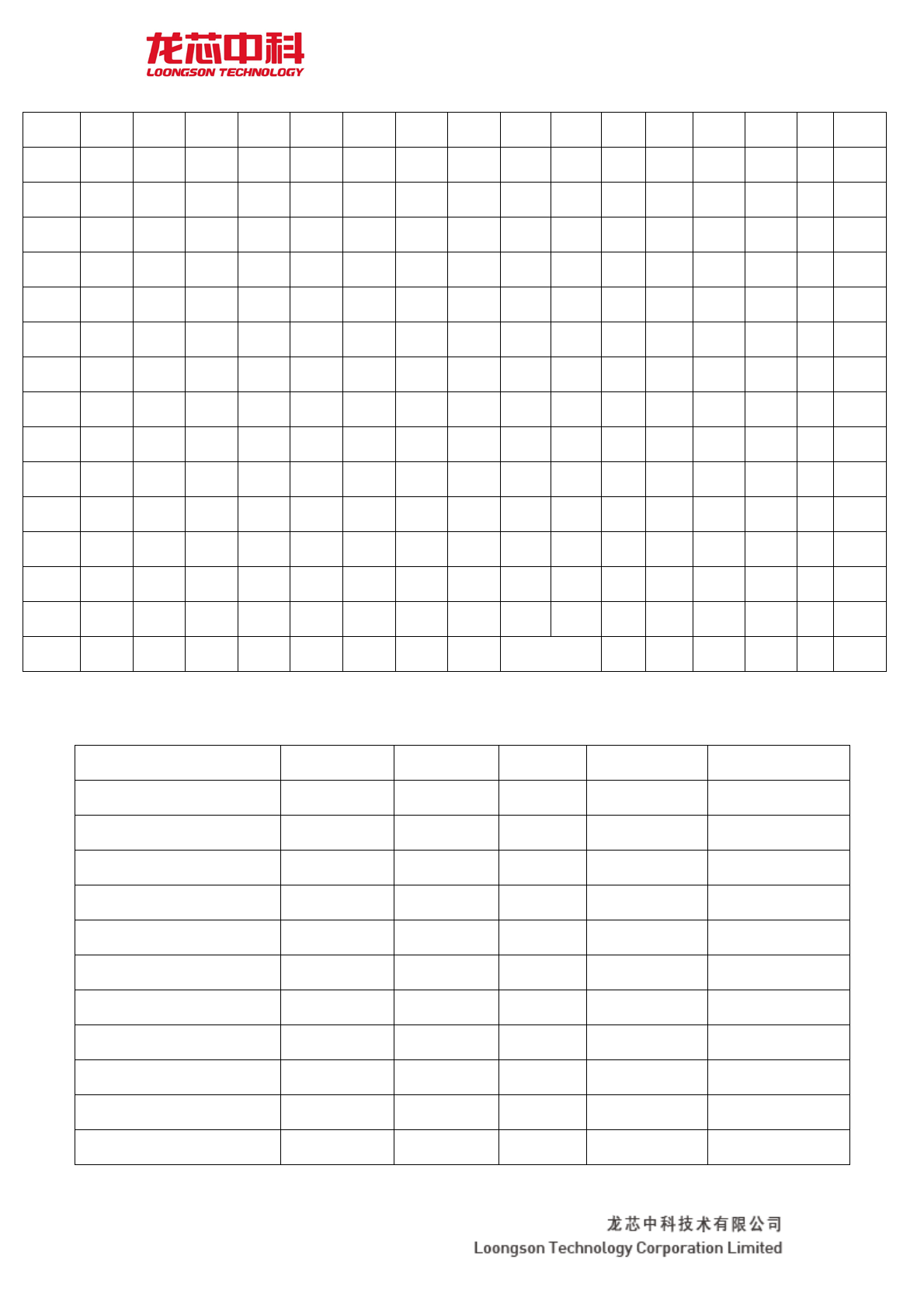

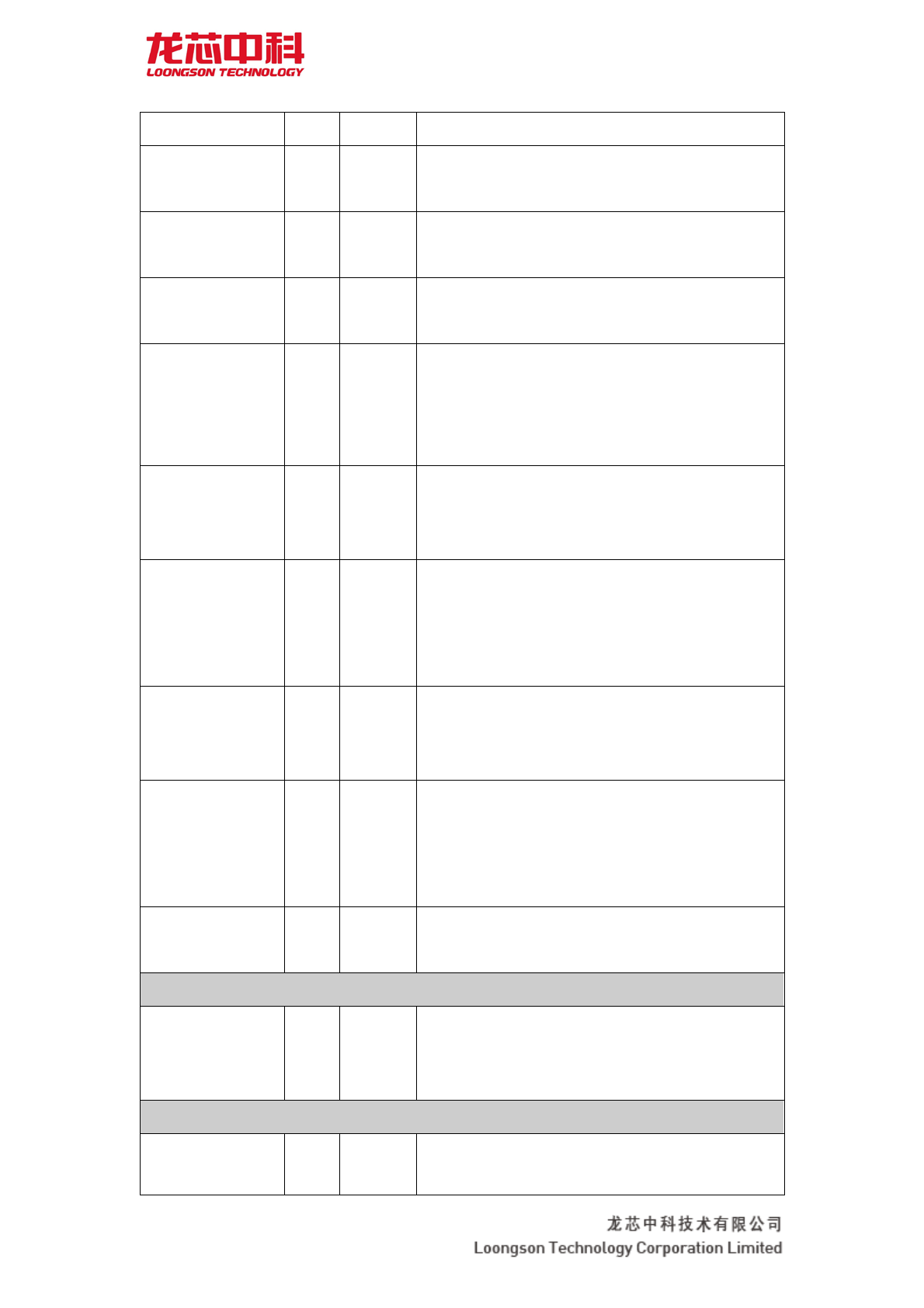

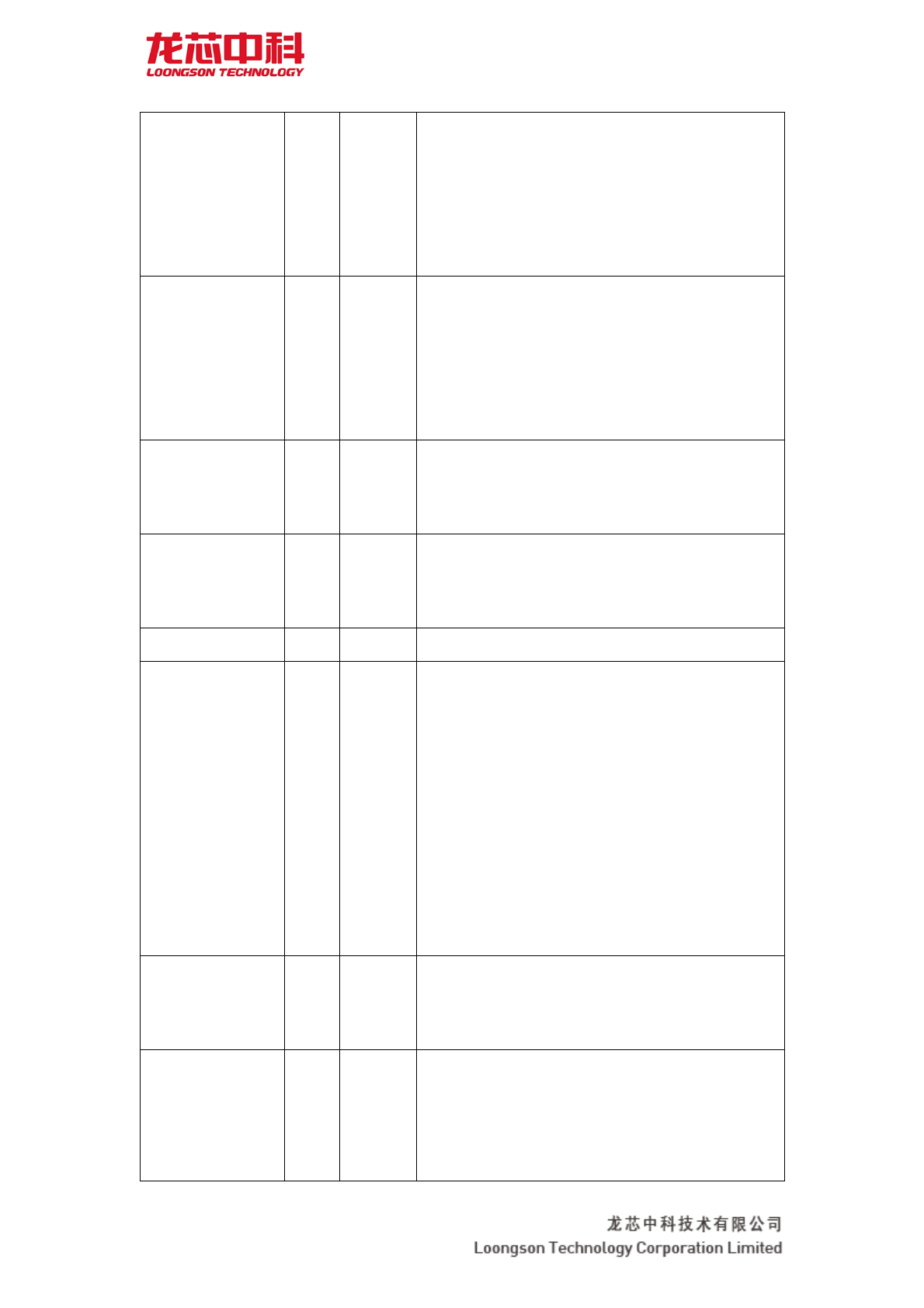

龙芯 1B 筛选试验主要内容如下:

7

龙芯 1B 处理器用户手册

筛选项目 方法和条件(概要) 要求

1、目检 标识清晰,无沾污,焊球无氧化,芯片完好 100%

2、稳定性烘培 125℃,24h 100%

3、温度快速变化

最高和最低储存温度下,10次循环 100%

4、编序列号 100%

5、终点电测试 三温,记录所有测试数据 100%

6、外部目检 标识清晰,无沾污,焊球无氧化,芯片完好 100%

8

龙芯 1B 处理器用户手册

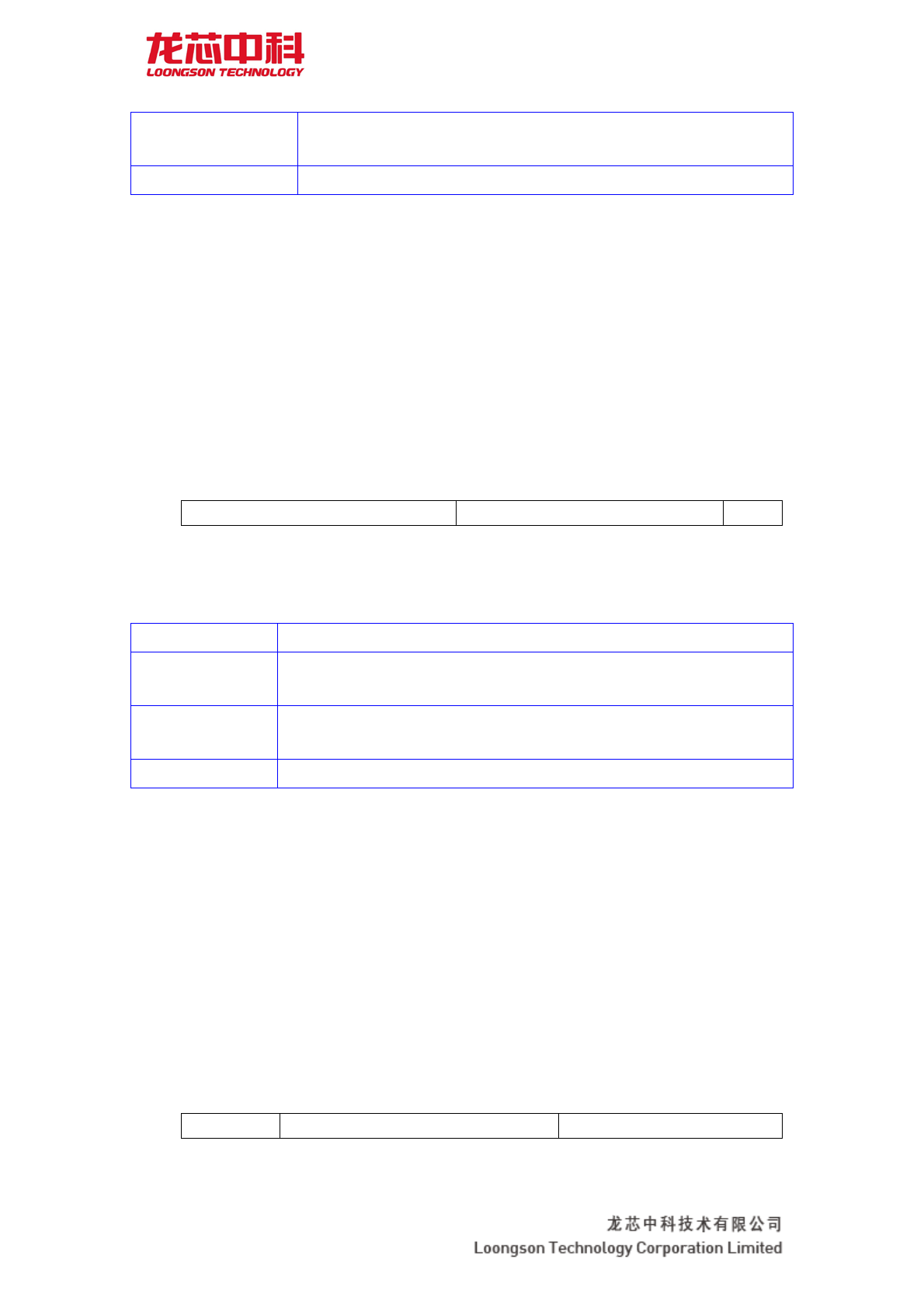

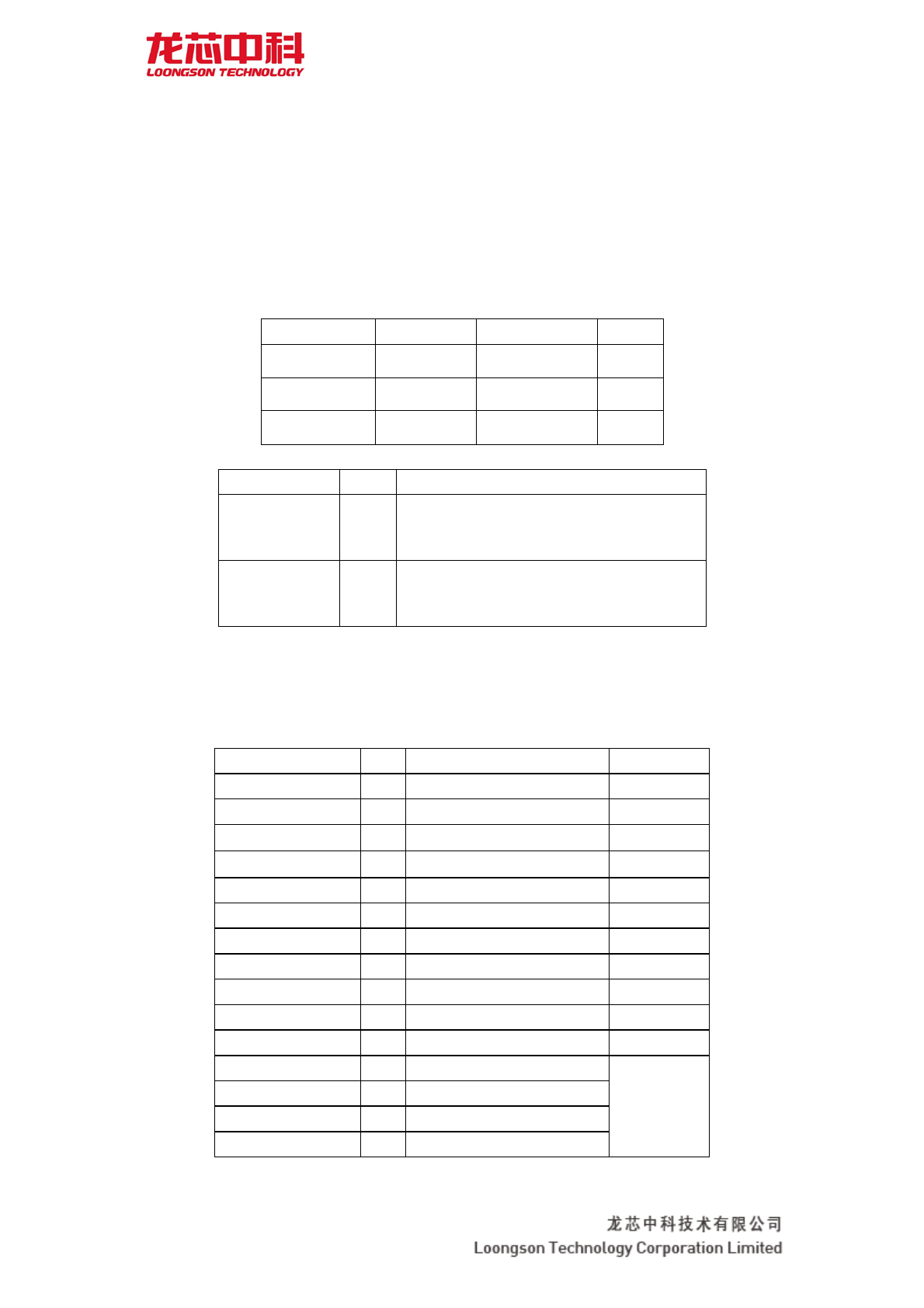

2 芯片引脚定义

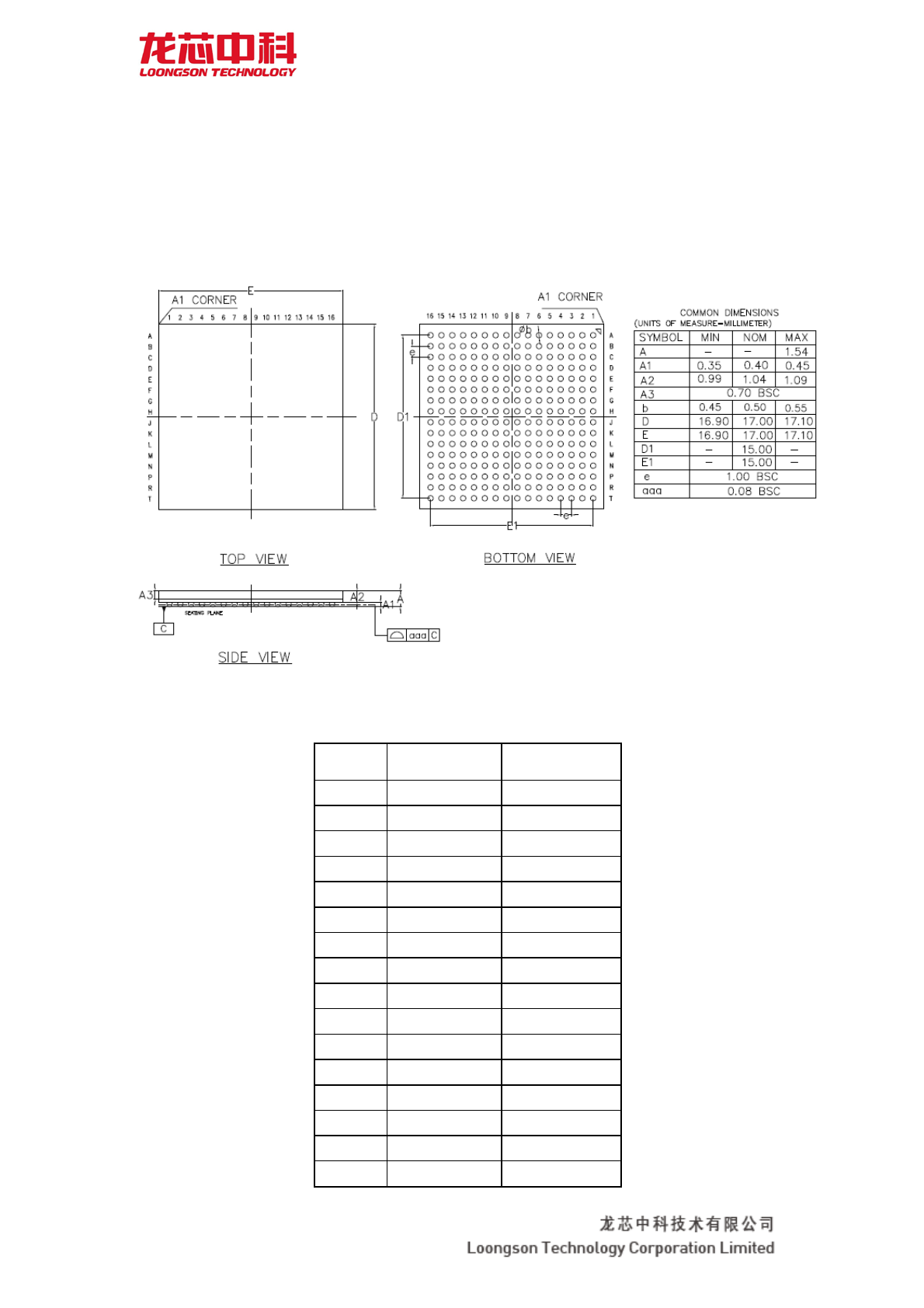

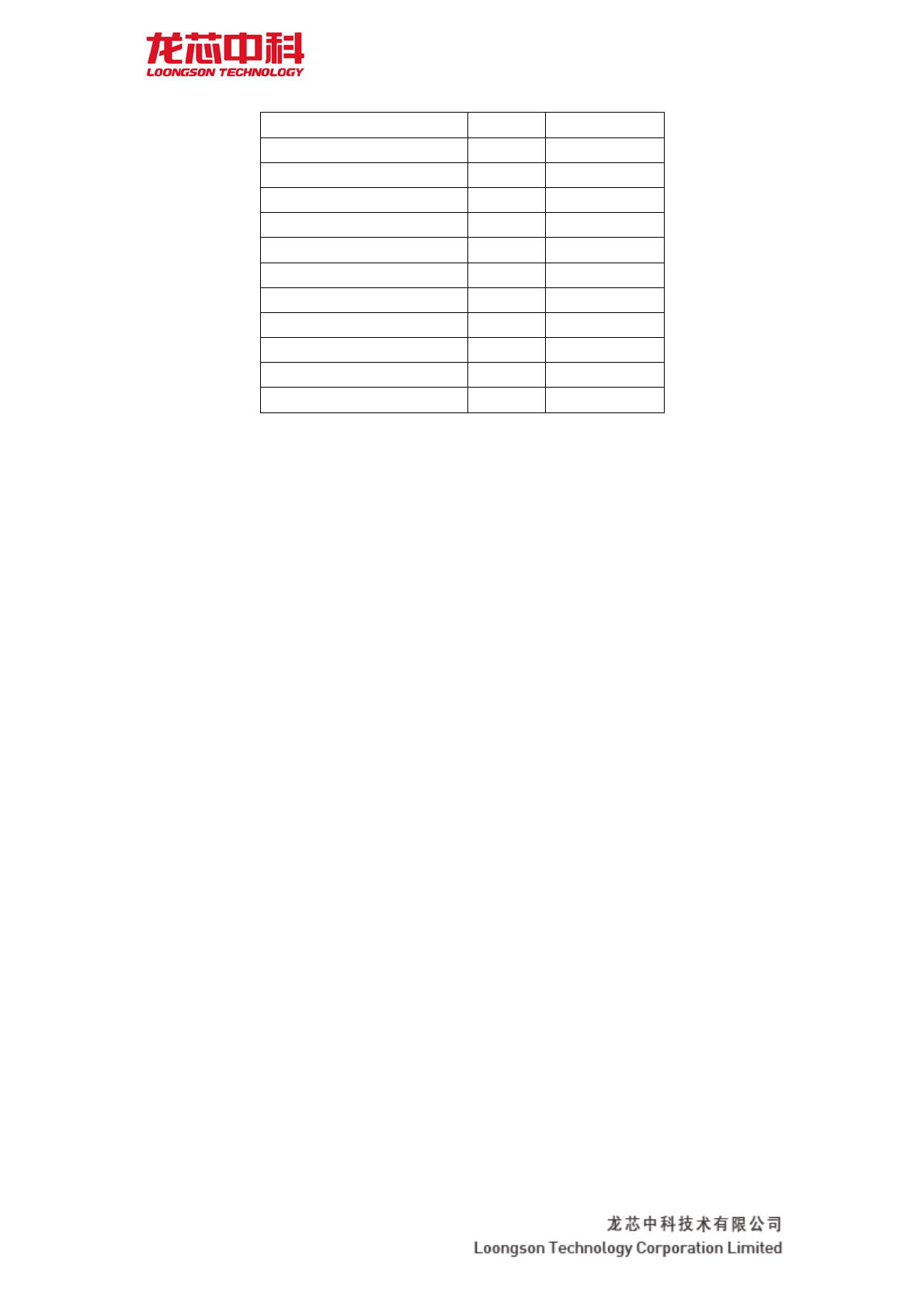

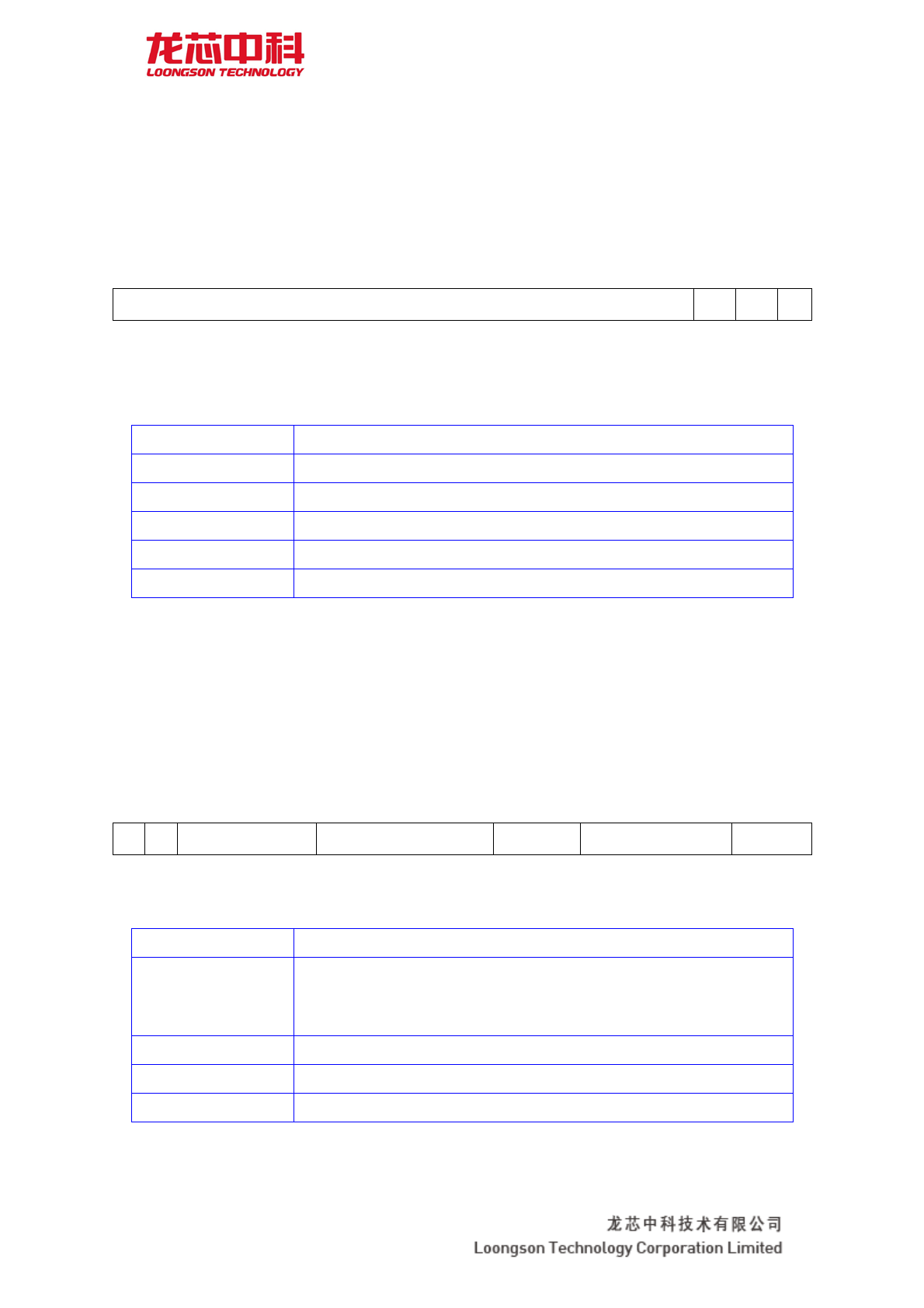

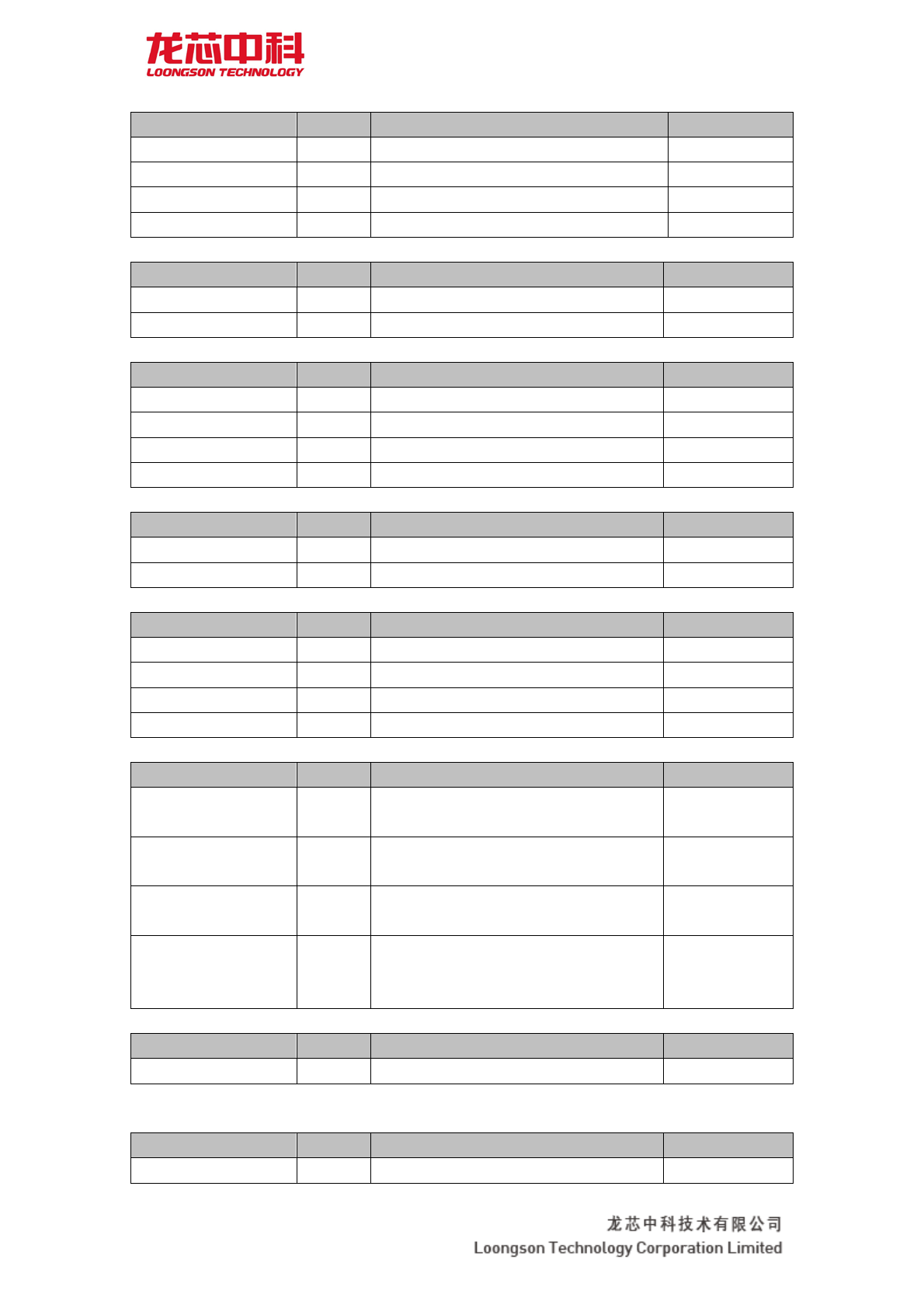

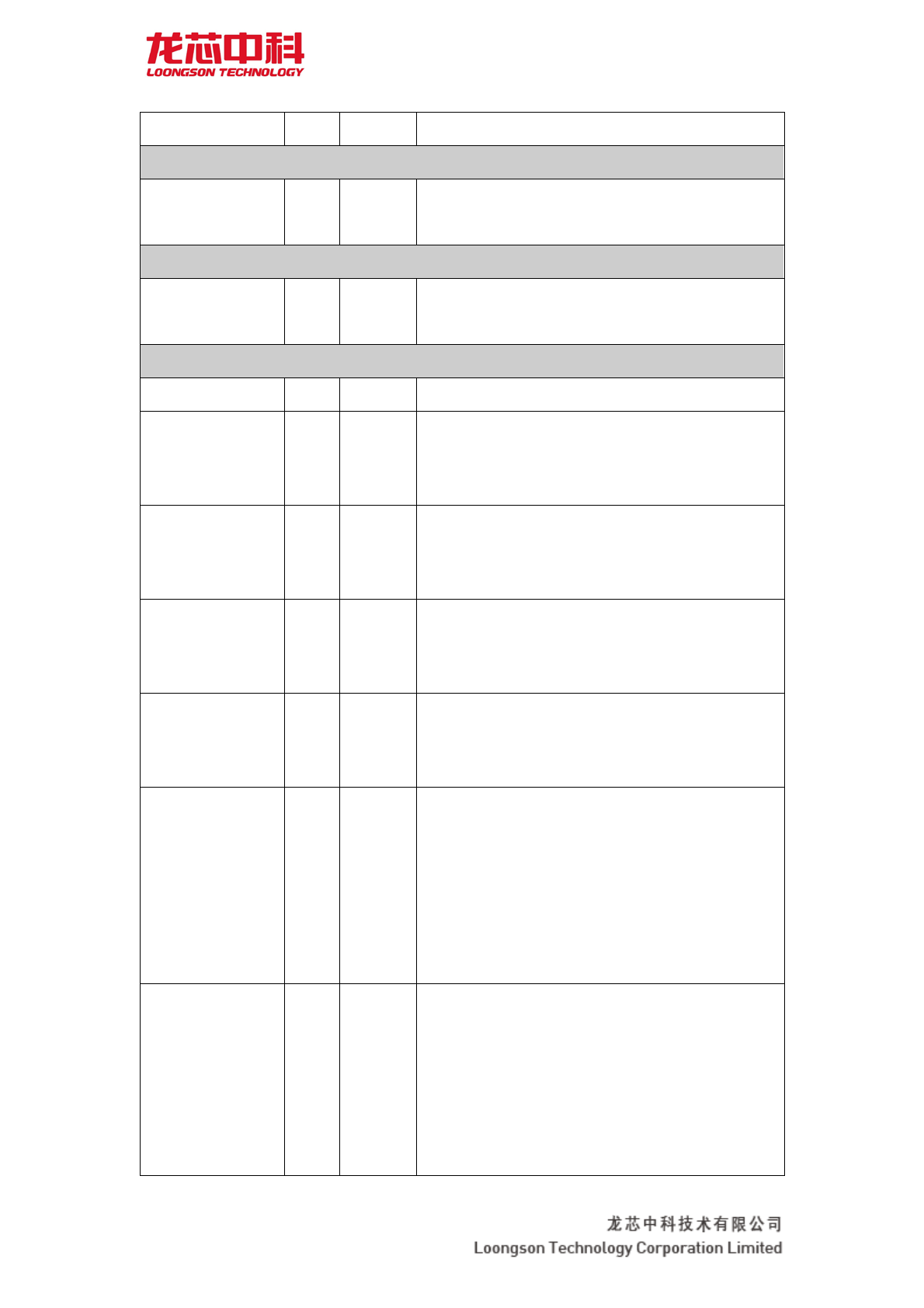

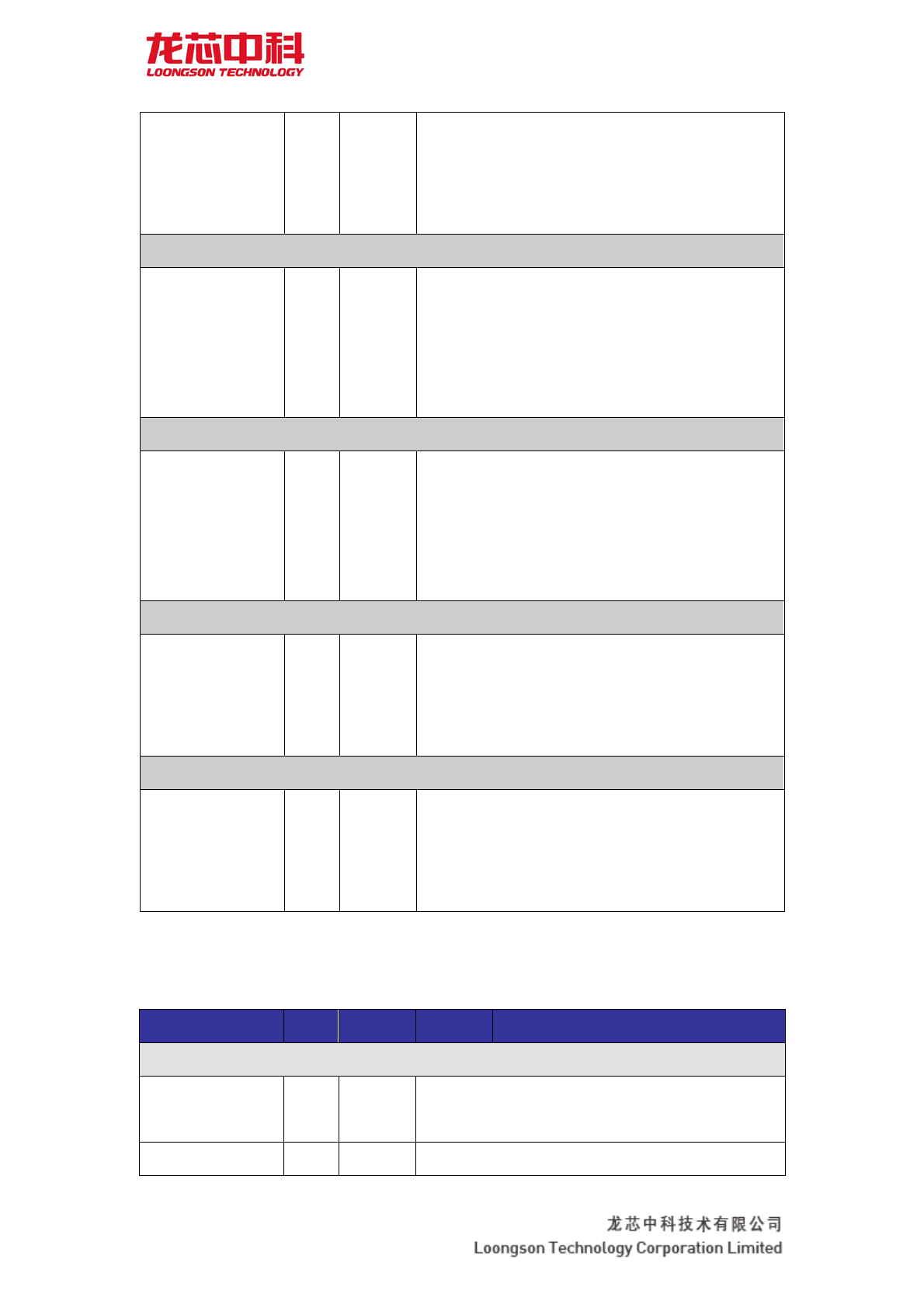

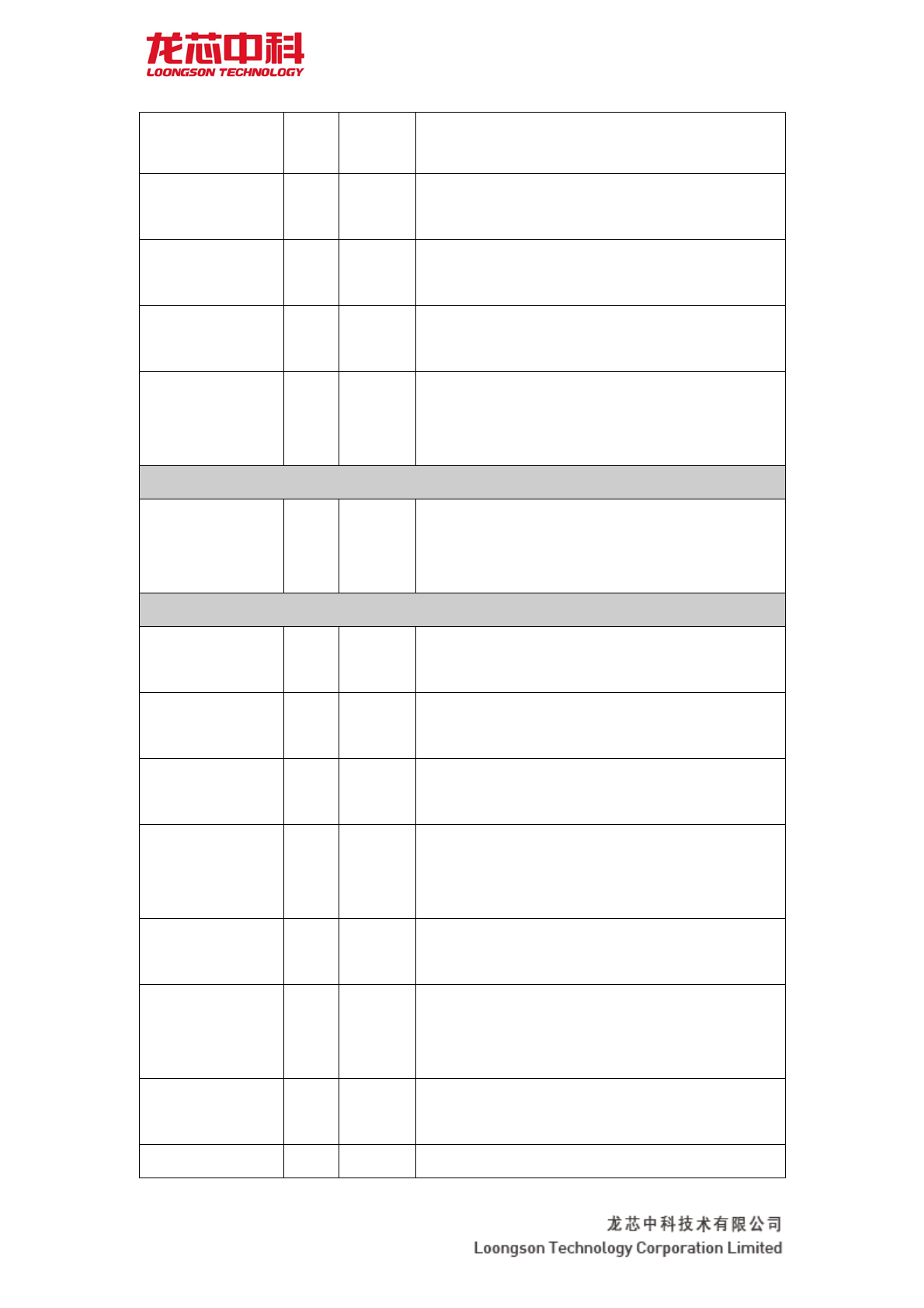

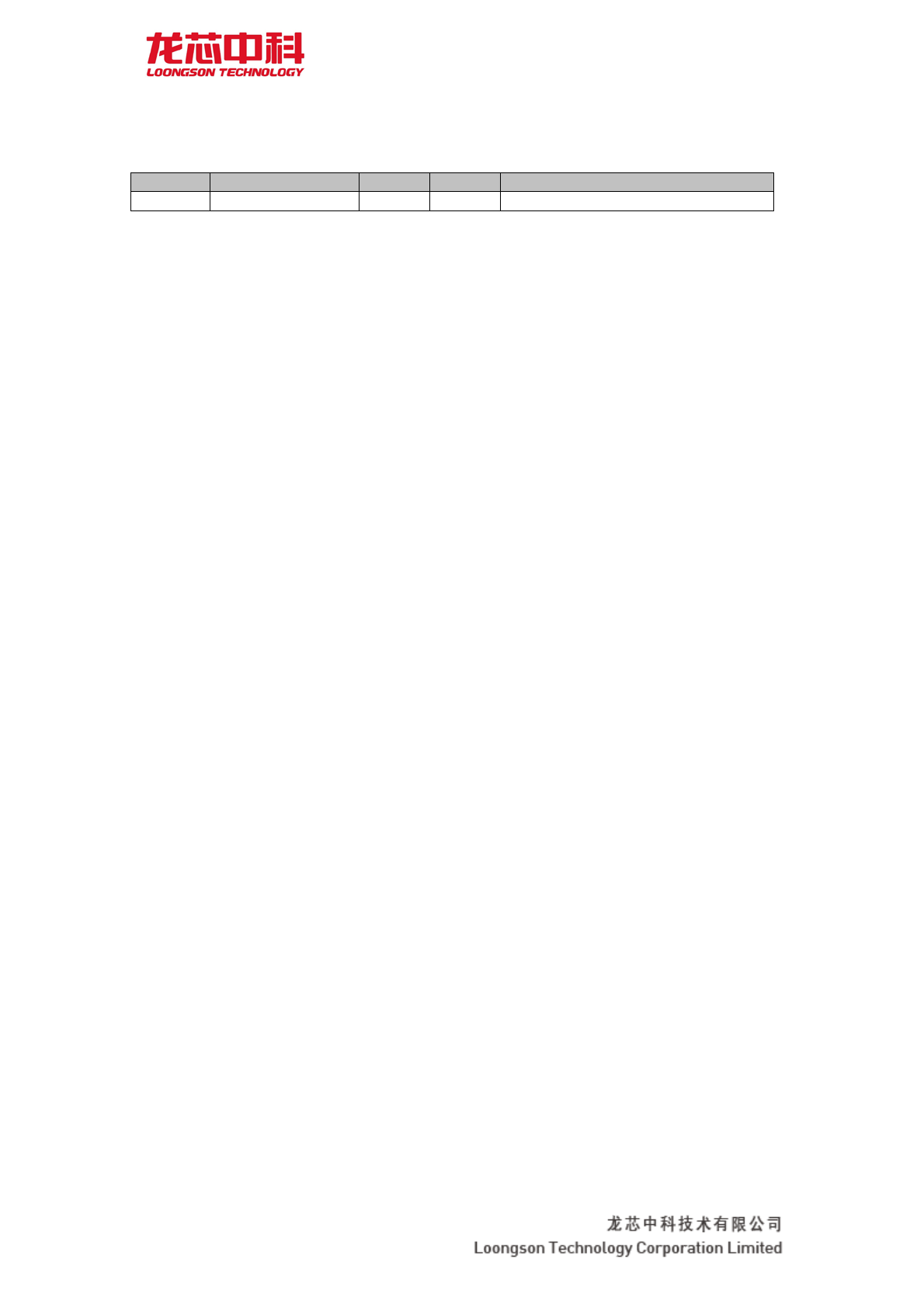

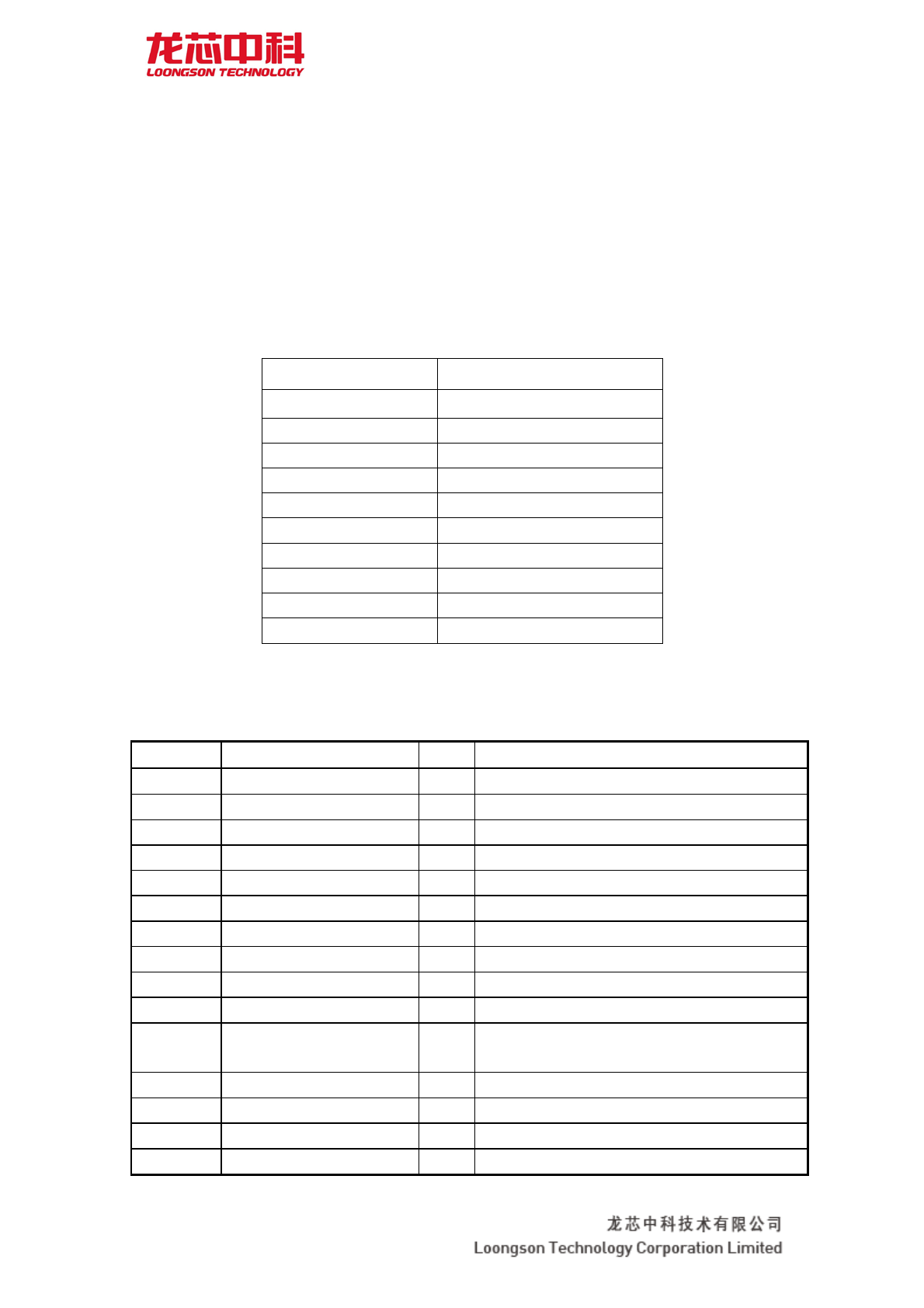

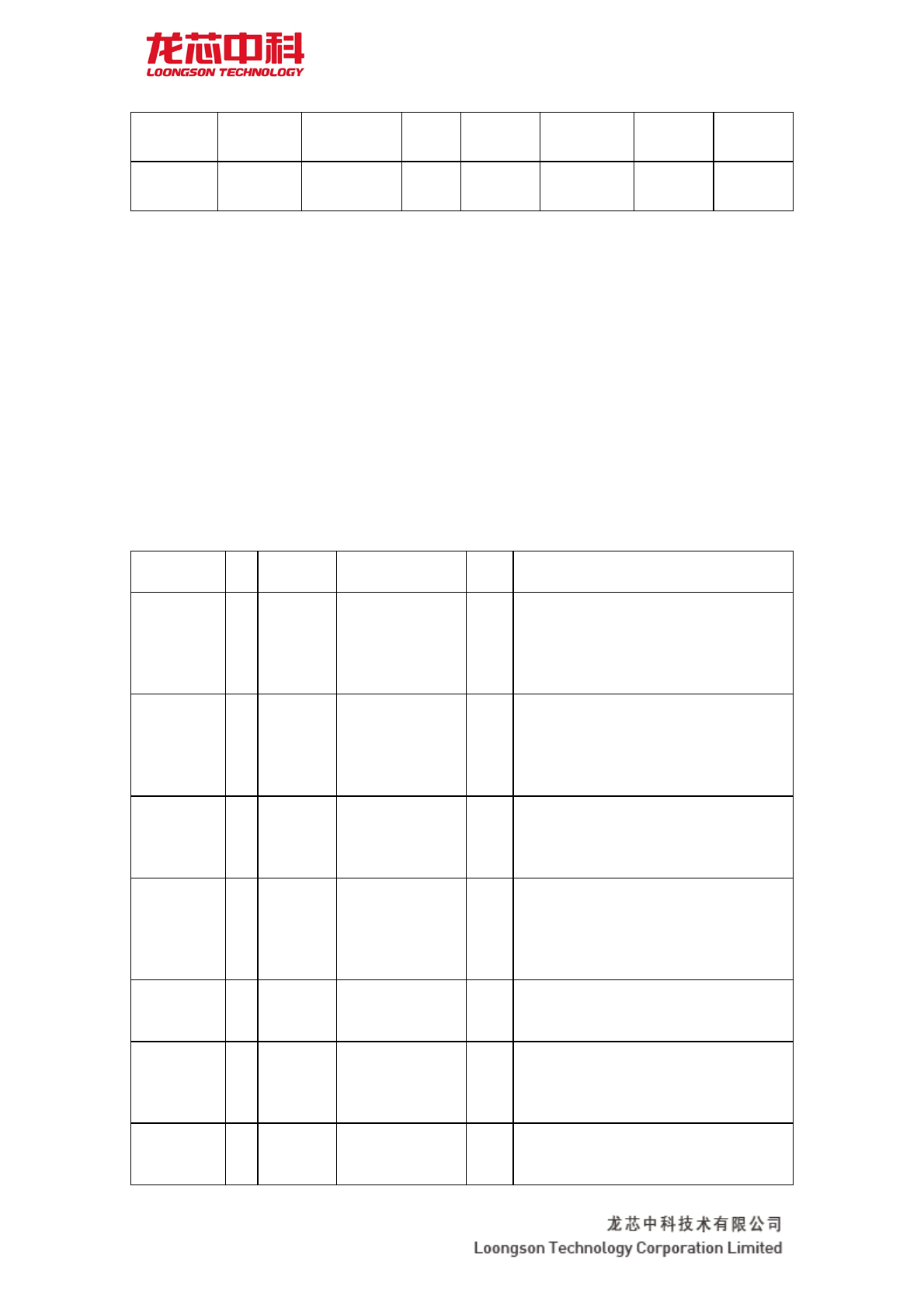

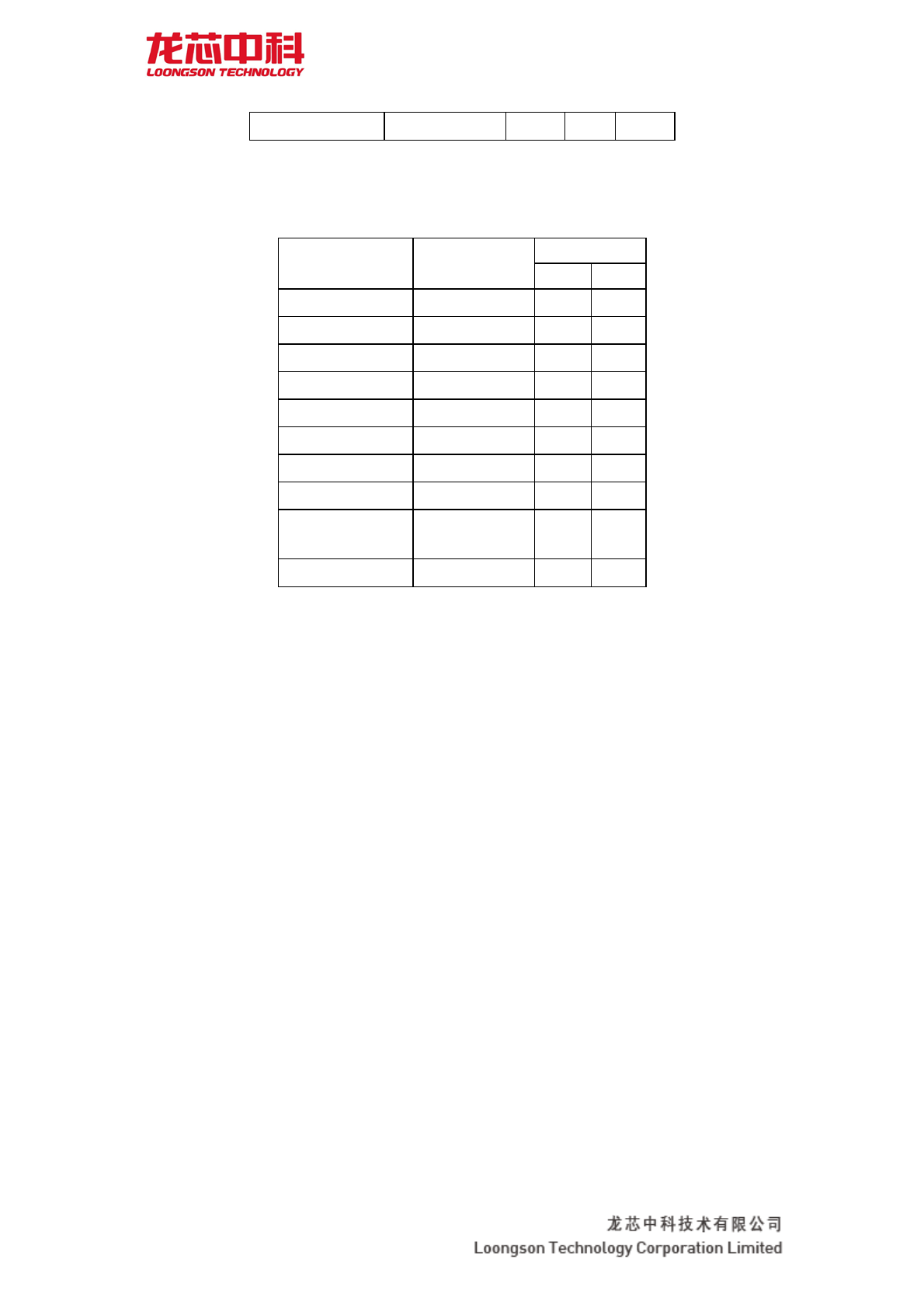

2.1 1B 引脚分布图

1B 采用 BGA256 封装形式,封装尺寸入下图所示:

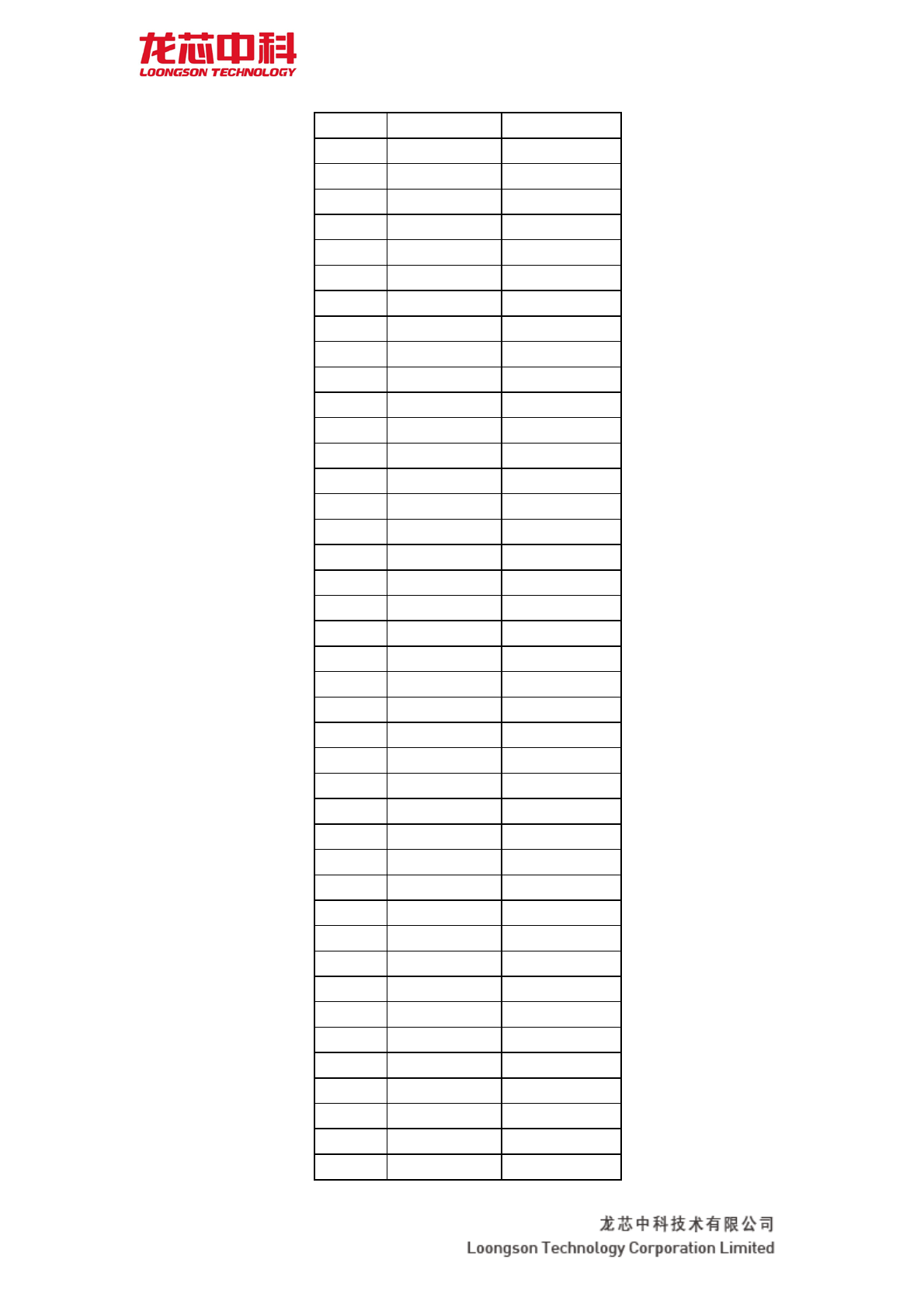

芯片的引脚 PAD 的排布列常用信号延迟如下表所示:

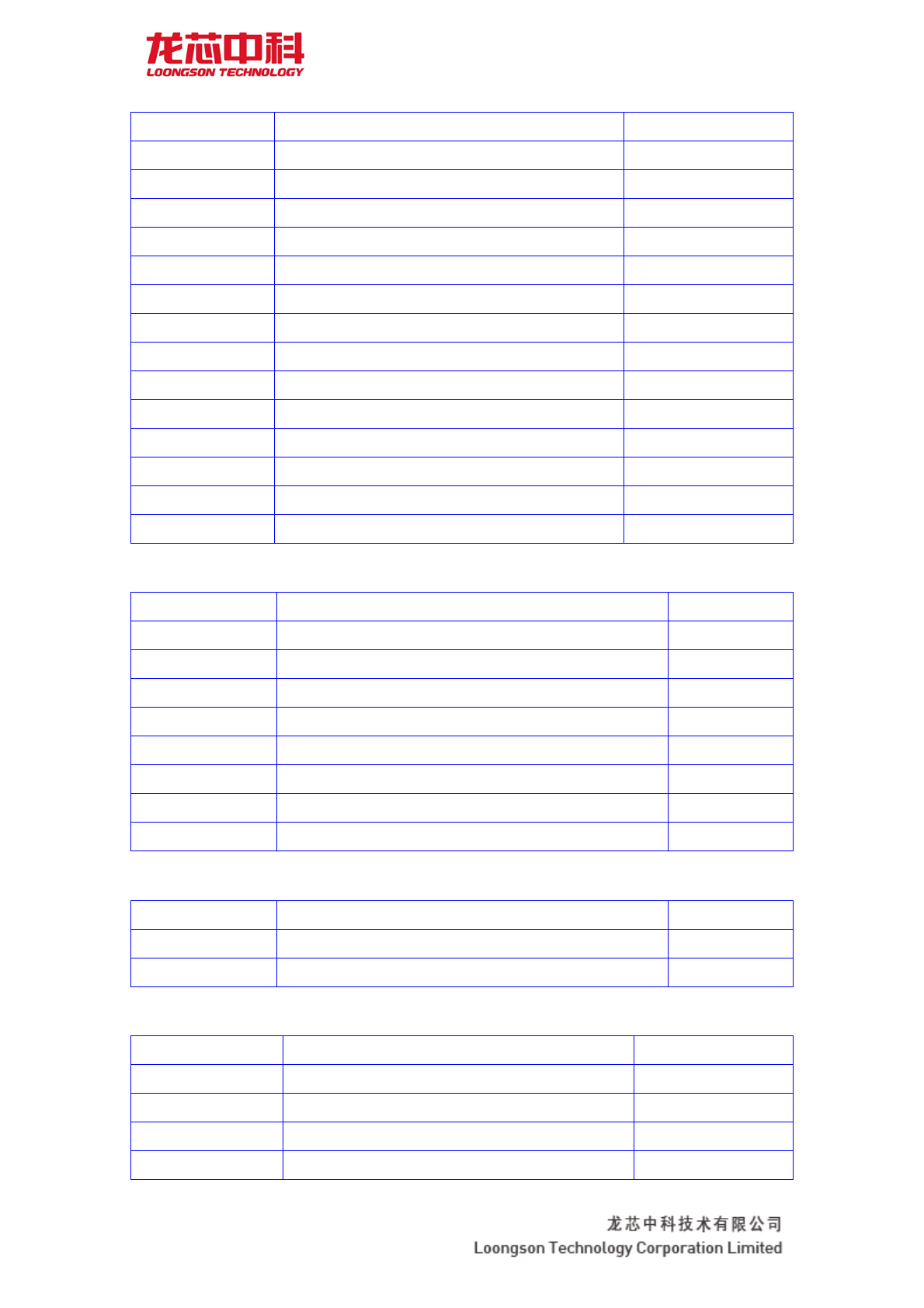

表2- 1 芯片引脚 PAD 的排布列表

Location

Name Delay(um)

K15 AC97_BIT_CLK 7630

J16 AC97_DATA_I 8471

J15 AC97_DATA_O 8426

K14 AC97_RESET 7351

K13 AC97_SYNC 6592

T12 CAN0_RX 9501

R12 CAN0_TX 8338

P12 CAN1_RX 7521

P13 CAN1_TX 8717

B01 DDR2_A00 12623

A01 DDR2_A01 13928

D02 DDR2_A02 9792

C02 DDR2_A03 11318

B02 DDR2_A04 11496

A02 DDR2_A05 12195

D03 DDR2_A06 9037

9

龙芯 1B 处理器用户手册

C03 DDR2_A07 9723

B03 DDR2_A08 10375

A03 DDR2_A09 11434

D04 DDR2_A10 8109

C04 DDR2_A11 8373

B04 DDR2_A12 9582

A04 DDR2_A13 9438

D05 DDR2_A14 6126

C07 DDR2_BA0 6741

B07 DDR2_BA1 7790

A07 DDR2_BA2 8917

C08 DDR2_CASN 6745

C05 DDR2_CKE0 8537

A05 DDR2_CKN0 9282

B05 DDR2_CKP0 9209

H01 DDR2_DQ00 10204

E01 DDR2_DQ01 12521

J02 DDR2_DQ02 8263

G02 DDR2_DQ03 9832

F01 DDR2_DQ04 11482

J01 DDR2_DQ05 9568

C01 DDR2_DQ06 13879

H02 DDR2_DQ07 10212

G03 DDR2_DQ08 8558

E02 DDR2_DQ09 10758

H04 DDR2_DQ10 6724

E03 DDR2_DQ11 10387

E04 DDR2_DQ12 10798

H03 DDR2_DQ13 6836

F04 DDR2_DQ14 6311

G04 DDR2_DQ15 3884

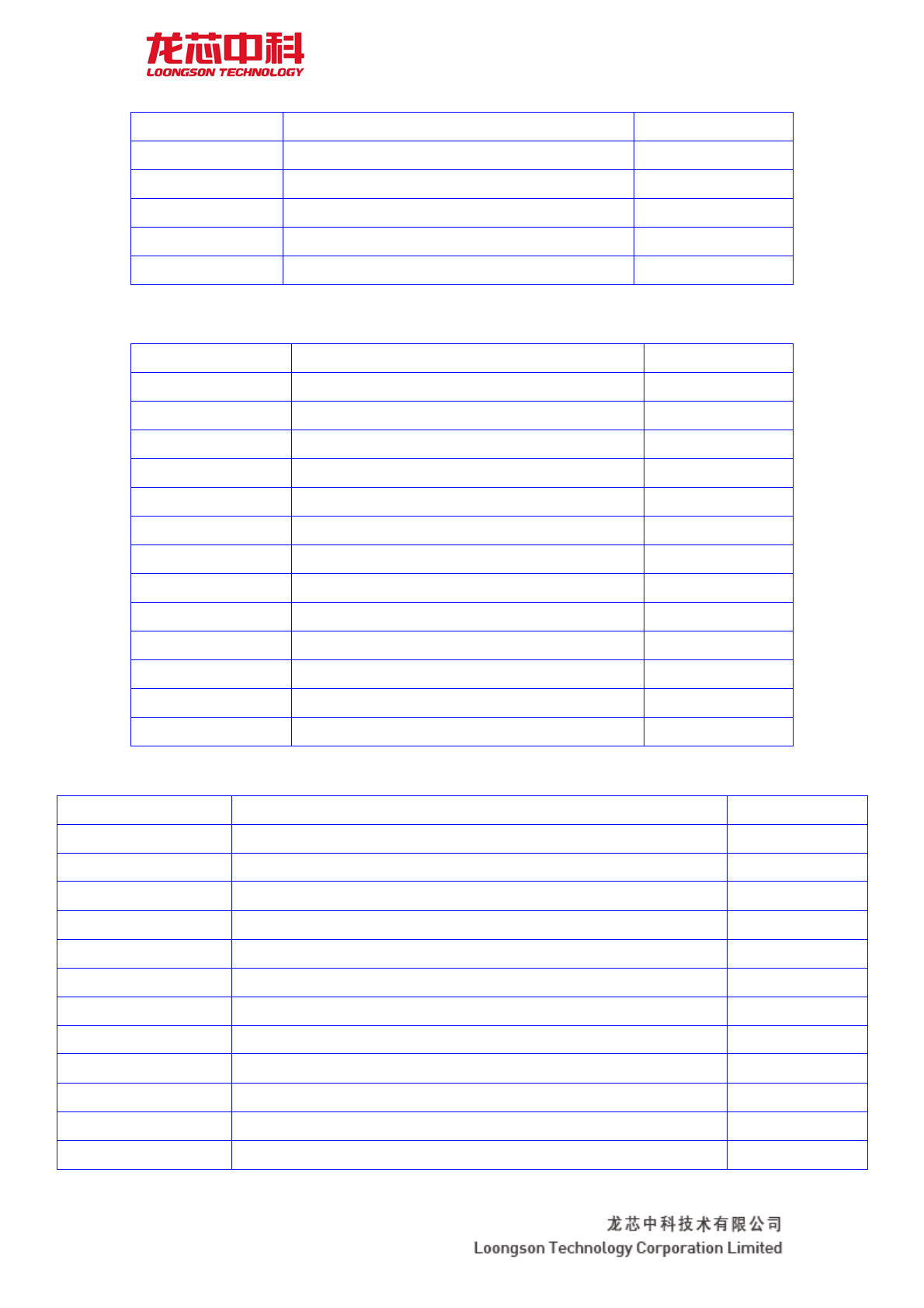

B10 DDR2_DQ16 8866

A12 DDR2_DQ17 12093

A09 DDR2_DQ18 9068

B11 DDR2_DQ19 10432

B12 DDR2_DQ20 10116

B09 DDR2_DQ21 7961

B13 DDR2_DQ22 10991

A10 DDR2_DQ23 9302

D10 DDR2_DQ24 6637

C12 DDR2_DQ25 9230

C09 DDR2_DQ26 6748

10

龙芯 1B 处理器用户手册

D13 DDR2_DQ27 9679

C13 DDR2_DQ28 9341

D09 DDR2_DQ29 7575

D12 DDR2_DQ30 7419

C10 DDR2_DQ31 6687

D01 DDR2_DQM0 12838

F03 DDR2_DQM1 8257

A13 DDR2_DQM2 11310

C11 DDR2_DQM3 6869

G01 DDR2_DQS0 10939

F02 DDR2_DQS1 8533

A11 DDR2_DQS2 10187

D11 DDR2_DQS3 7020

D06 DDR2_GATEI0 6628

D07 DDR2_GATEI1 3705

C06 DDR2_GATEO0 6888

B06 DDR2_GATEO1 8649

A06 DDR2_ODT0 8994

D08 DDR2_RASN 5651

A08 DDR2_SCSN0 8745

B08 DDR2_WEN 7745

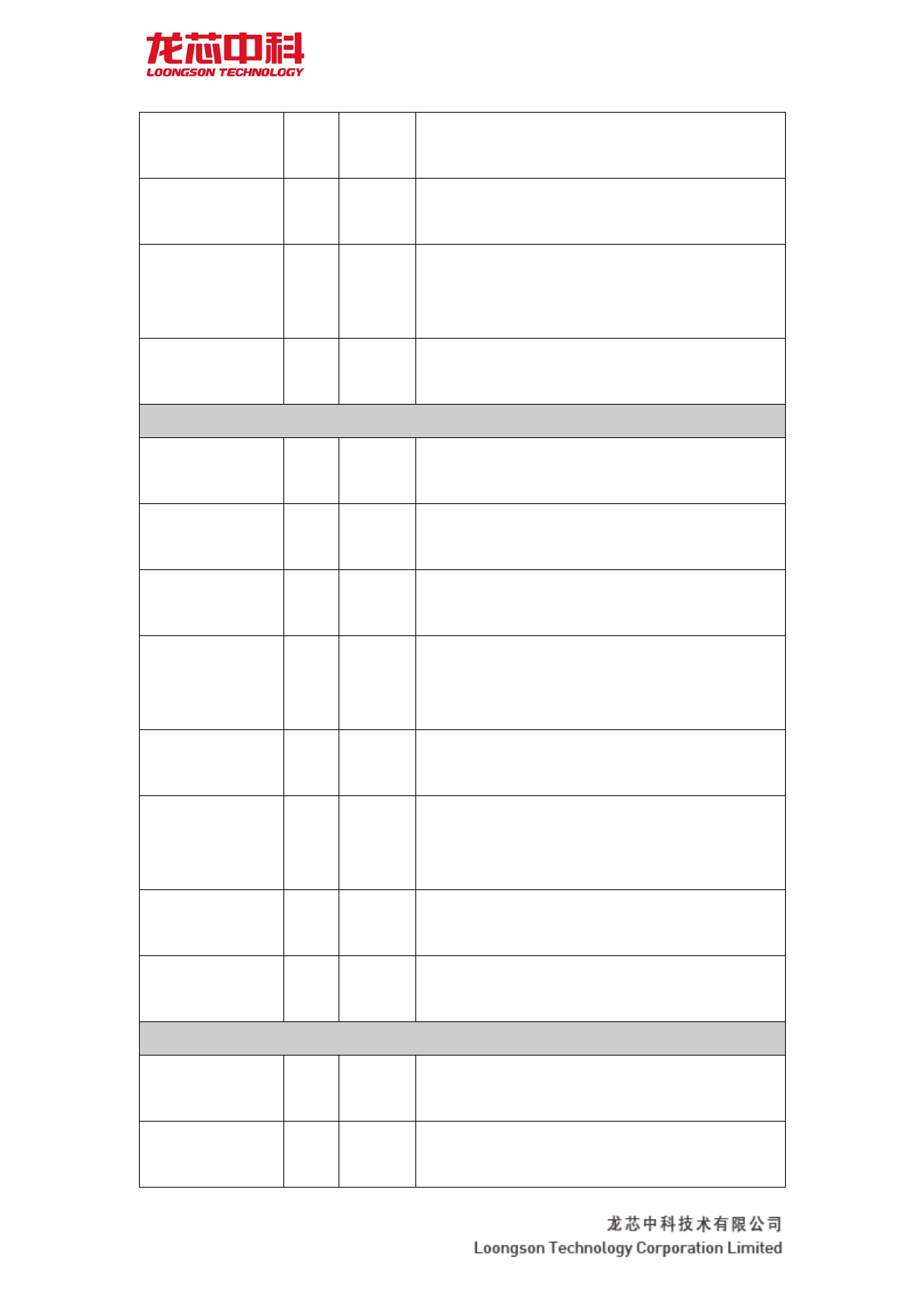

L16 EJTAG_TCK 8933

L15 EJTAG_TDI 7868

K16 EJTAG_TDO 8685

L14 EJTAG_TMS 7823

L13 EJTAG_TRST 7524

N11 GMAC0_MDCK 6878

N12 GMAC0_MDIO 8206

R08 GMAC0_RX_CLK_I

6849

N09 GMAC0_RX_CTL_I

7076

P09 GMAC0_RX0 6973

N10 GMAC0_RX1 7360

P10 GMAC0_RX2 9231

P11 GMAC0_RX3 6844

T08 GMAC0_TX_CLK_I

8736

R11 GMAC0_TX_CLK_O

9410

T11 GMAC0_TX_CTL_O

7991

R10 GMAC0_TX0 8973

T10 GMAC0_TX1 9242

R09 GMAC0_TX2 9905

T09 GMAC0_TX3 10857

M04 GMAC1_RX_CLK_I

7499

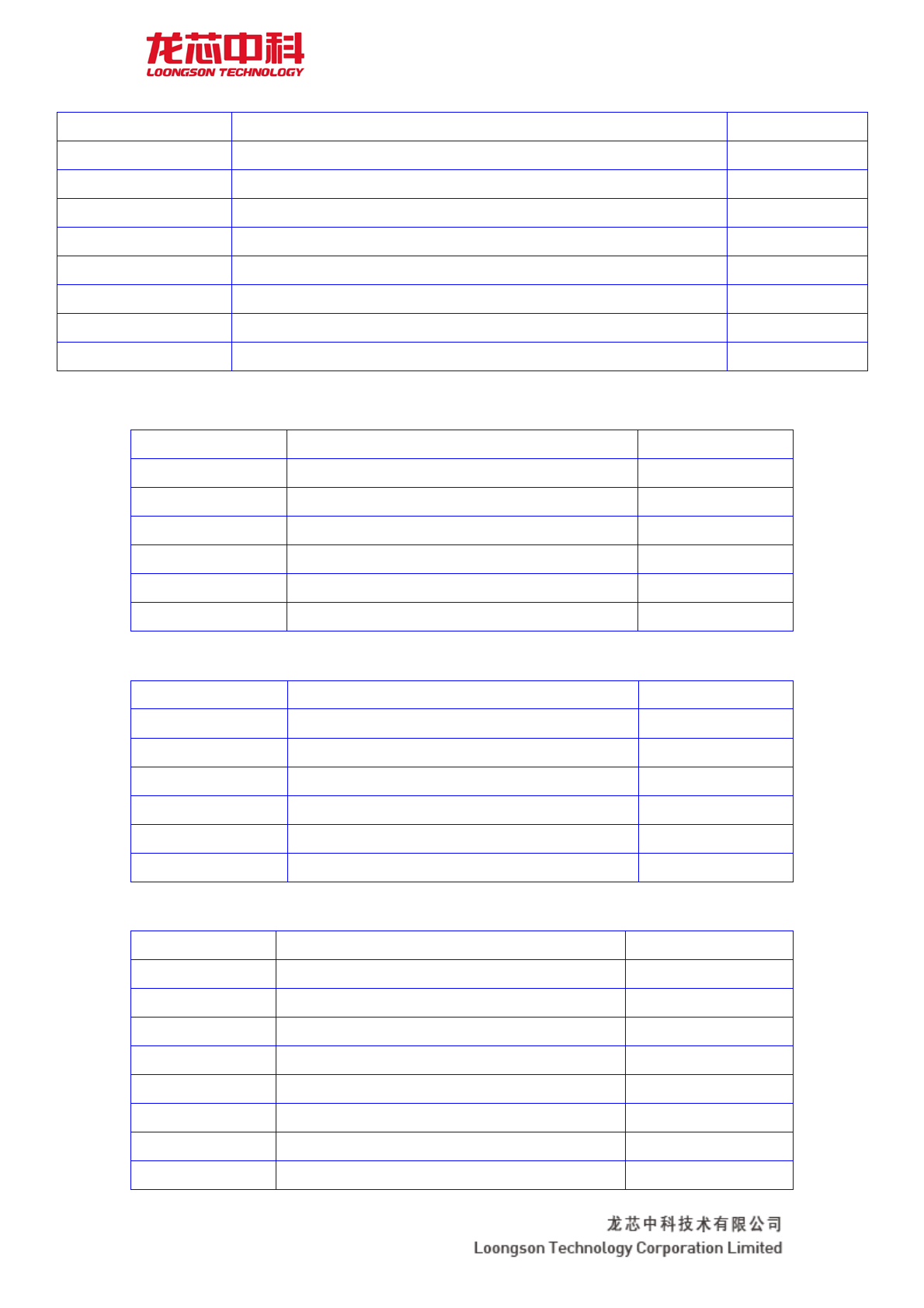

11

龙芯 1B 处理器用户手册

D16 GMAC1_TX_CLK_I

10743

C16 GMAC1_TX_CLK_O

11938

C15 GMAC1_TX_CTL_O

10929

G13 I2C_SCL 9062

G14 I2C_SDA 7886

T06 LCD_CLK 9050

N05 LCD_DAT_B0 7837

N04 LCD_DAT_B1 9278

P03 LCD_DAT_B2 9723

P04 LCD_DAT_B3 9653

P05 LCD_DAT_B4 7609

P01 LCD_DAT_G0 11258

P02 LCD_DAT_G1 10460

R01 LCD_DAT_G2 13011

T01 LCD_DAT_G3 12938

R02 LCD_DAT_G4 11774

T02 LCD_DAT_G5 11960

R03 LCD_DAT_R0 10699

T03 LCD_DAT_R1 13006

R04 LCD_DAT_R2 9332

T04 LCD_DAT_R3 9489

R05 LCD_DAT_R4 8482

P06 LCD_EN 7889

T05 LCD_HSYNC 9617

R06 LCD_VSYNC 8085

N13 NAND_ALE 9117

M15 NAND_CE 9198

N14 NAND_CLE 8809

T16 NAND_D0 11717

R16 NAND_D1 11235

R15 NAND_D2 10371

P14 NAND_D3 9032

P15 NAND_D4 9769

P16 NAND_D5 10210

N16 NAND_D6 9839

N15 NAND_D7 8909

M13 NAND_RD 7573

T15 NAND_RDY 10896

M14 NAND_WR 7961

B16 PLL_CPU_AVDD33

17840

B15 PLL_CPU_AVSS33

18831

A16 PLL_CPU_DVDD12

12759

12

龙芯 1B 处理器用户手册

A15 PLL_CPU_DVSS12

12807

R13 PWM0 9034

T13 PWM1 9503

T14 PWM2 10205

R14 PWM3 9905

A14 RTC_CLK_I 11584

B14 RTC_CLK_O 10493

E14 RTC_VDD33 33449

F13 RTC_VDD33

C14 RTC_VR_CEXT 12177

D14 RTC_VR_VOUT 11997

E13 RTC_VSS33 23636

F14 RTC_VSS33

H16 SPI0_CLK 9620

H14 SPI0_CS0 7708

J14 SPI0_CS1 6530

J13 SPI0_CS2 6324

H13 SPI0_CS3 7239

G16 SPI0_MISO 9904

H15 SPI0_MOSI 8645

P08 SYS_RSTN

N08 TEST_CFG_MODEN

M16 TEST_JTAG_SEL

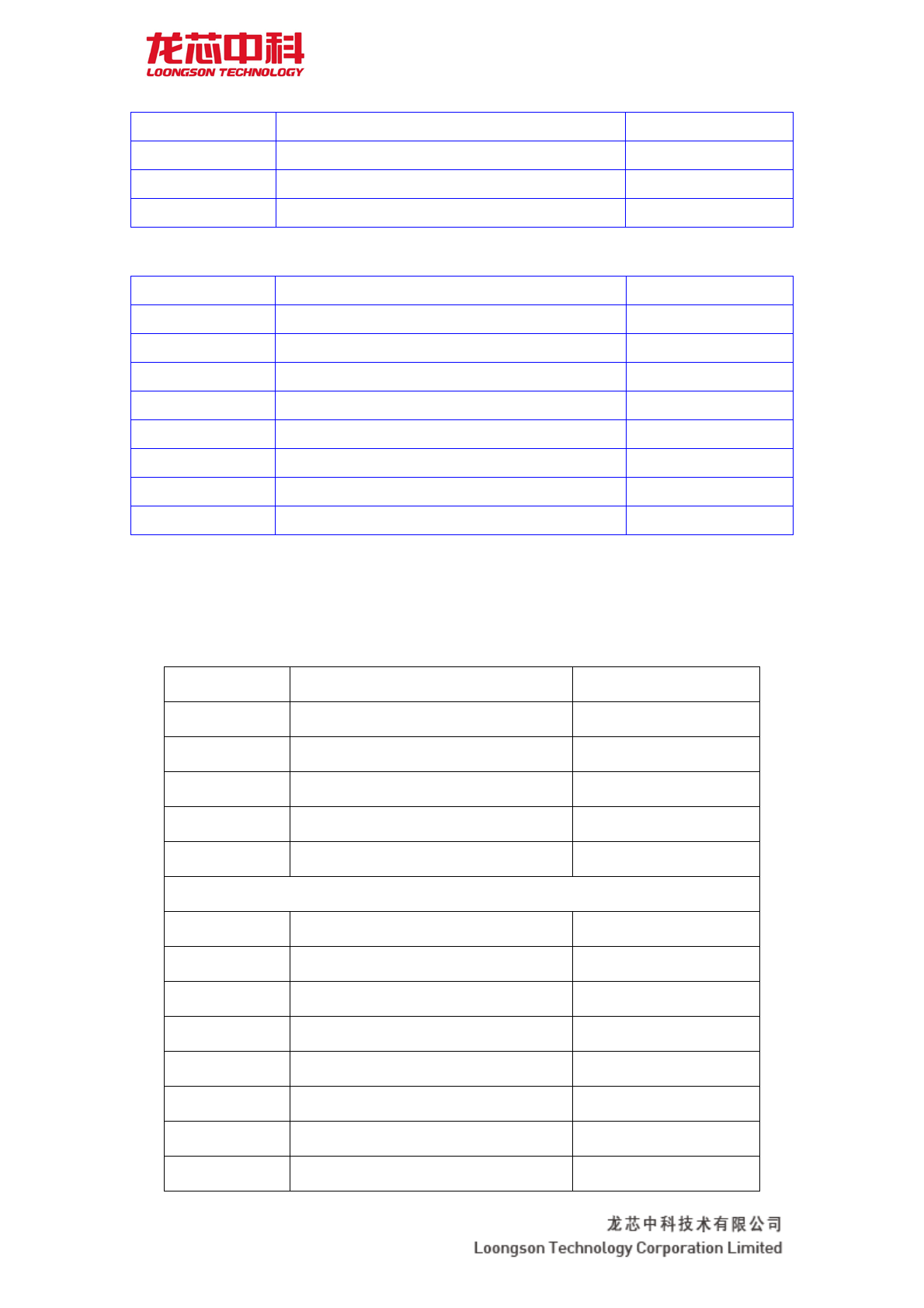

N01 UART0_CTS 9660

L03 UART0_DCD 6806

N03 UART0_DSR 8056

M01 UART0_DTR 9219

L04 UART0_RI 6301

N02 UART0_RTS 8689

M03 UART0_RX 7353

M02 UART0_TX 8201

D15 UART1_CTS 10124

E15 UART1_RTS 9692

G15 UART1_RX 7806

F15 UART1_TX 8614

K12 UART2_RX 10114

K11 UART2_TX 7963

J11 UART3_RX 8783

J12 UART3_TX 7119

H12 UART4_RX 7246

H11 UART4_TX 6701

G11 UART5_RX 9284

13

龙芯 1B 处理器用户手册

G12 UART5_TX 6569

L07 USB_AVDD33

M06 USB_AVDD33

L06 USB_AVSS33

M07 USB_AVSS33

L05 USB_VDD1V2

M05 USB_VSS

N06 USB0_DM

N07 USB0_DP

P07 USB0_REXT

R07 USB0_XI

T07 USB0_XO

G05 VDD1V2

H06 VDD1V2

J03 VDD1V2

J05 VDD1V2

J07 VDD1V2

K02 VDD1V2

K04 VDD1V2

K06 VDD1V2

L01 VDD1V2

E07 VDD1V8

E09 VDD1V8

E11 VDD1V8

F06 VDD1V8

F08 VDD1V8

F10 VDD1V8

F12 VDD1V8

G07 VDD1V8

G09 VDD3V3

H08 VDD3V3

H10 VDD3V3

J09 VDD3V3

K08 VDD3V3

K10 VDD3V3

L09 VDD3V3

L11 VDD3V3

M08 VDD3V3

M10 VDD3V3

M12 VDD3V3

E05 VREF_0V9

E12 VREF_0V9

14

龙芯 1B 处理器用户手册

E06 VSS

E08 VSS

E10 VSS

F05 VSS

F07 VSS

F09 VSS

F11 VSS

G06 VSS

G08 VSS

G10 VSS

H05 VSS

H07 VSS

H09 VSS

J04 VSS

J06 VSS

J08 VSS

J10 VSS

K01 VSS

K03 VSS

K05 VSS

K07 VSS

K09 VSS

L02 VSS

L08 VSS

L10 VSS

L12 VSS

M09 VSS

M11 VSS

E16 XTALI 10899

F16 XTALO 10414

15

龙芯 1B 处理器用户手册

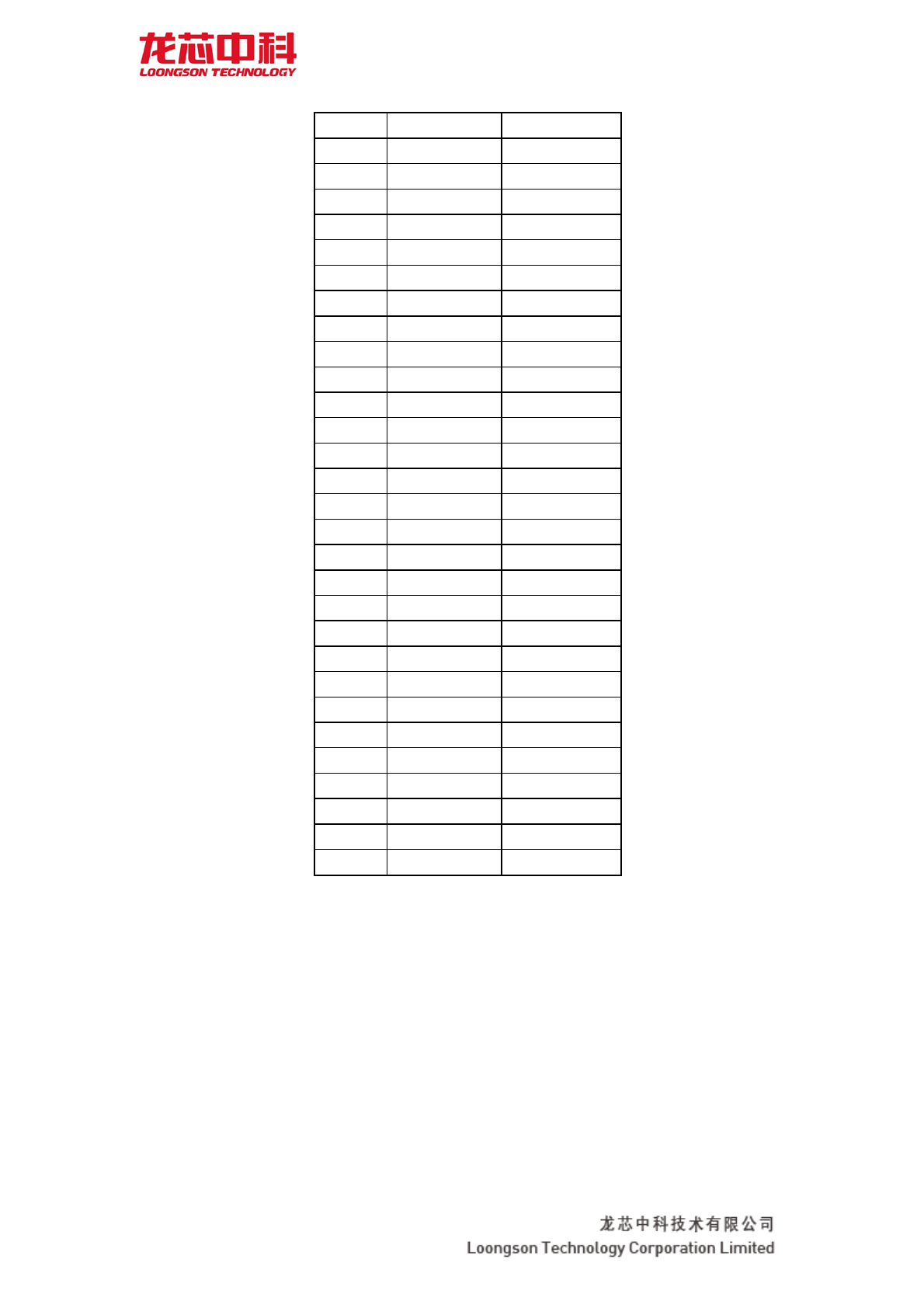

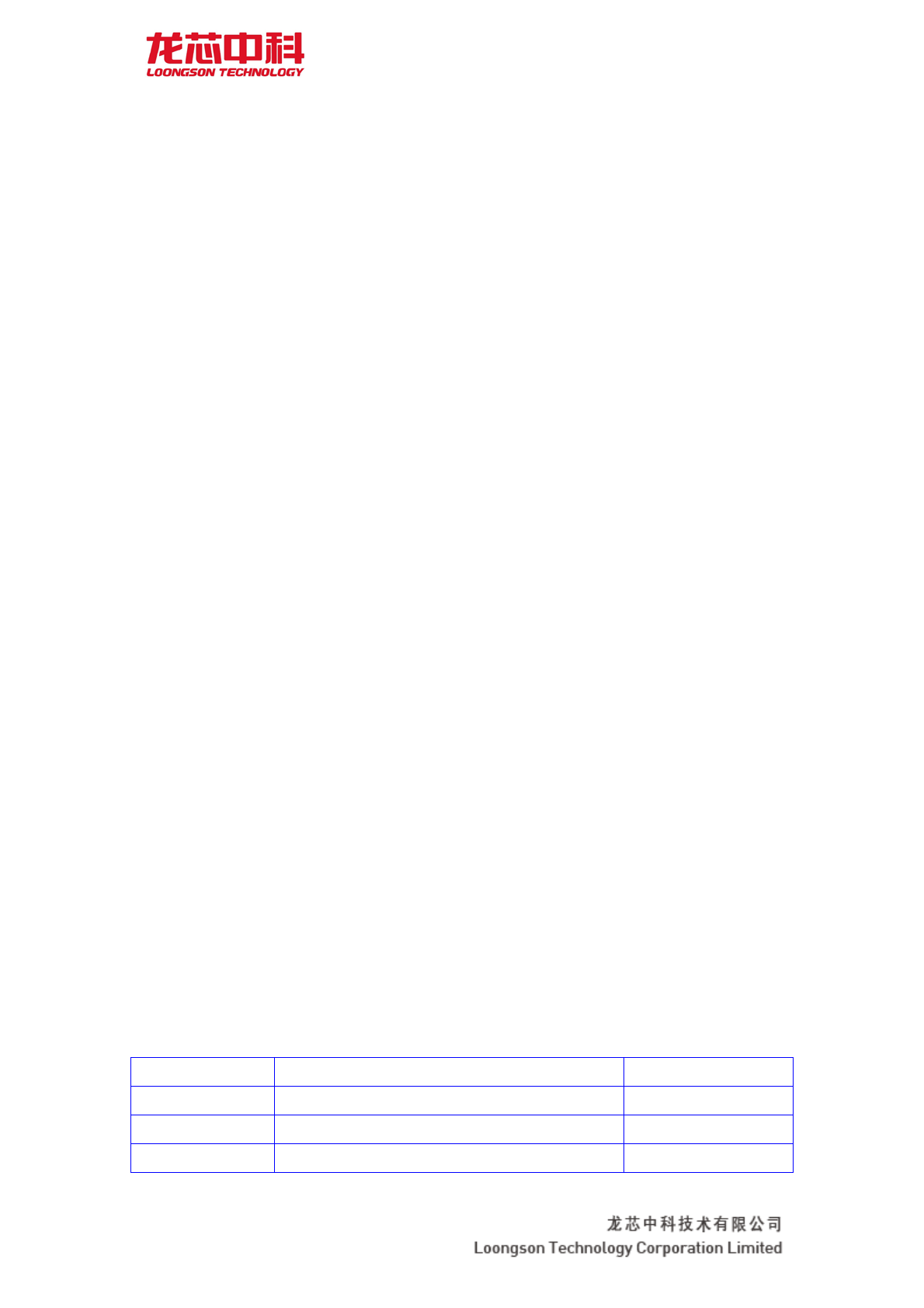

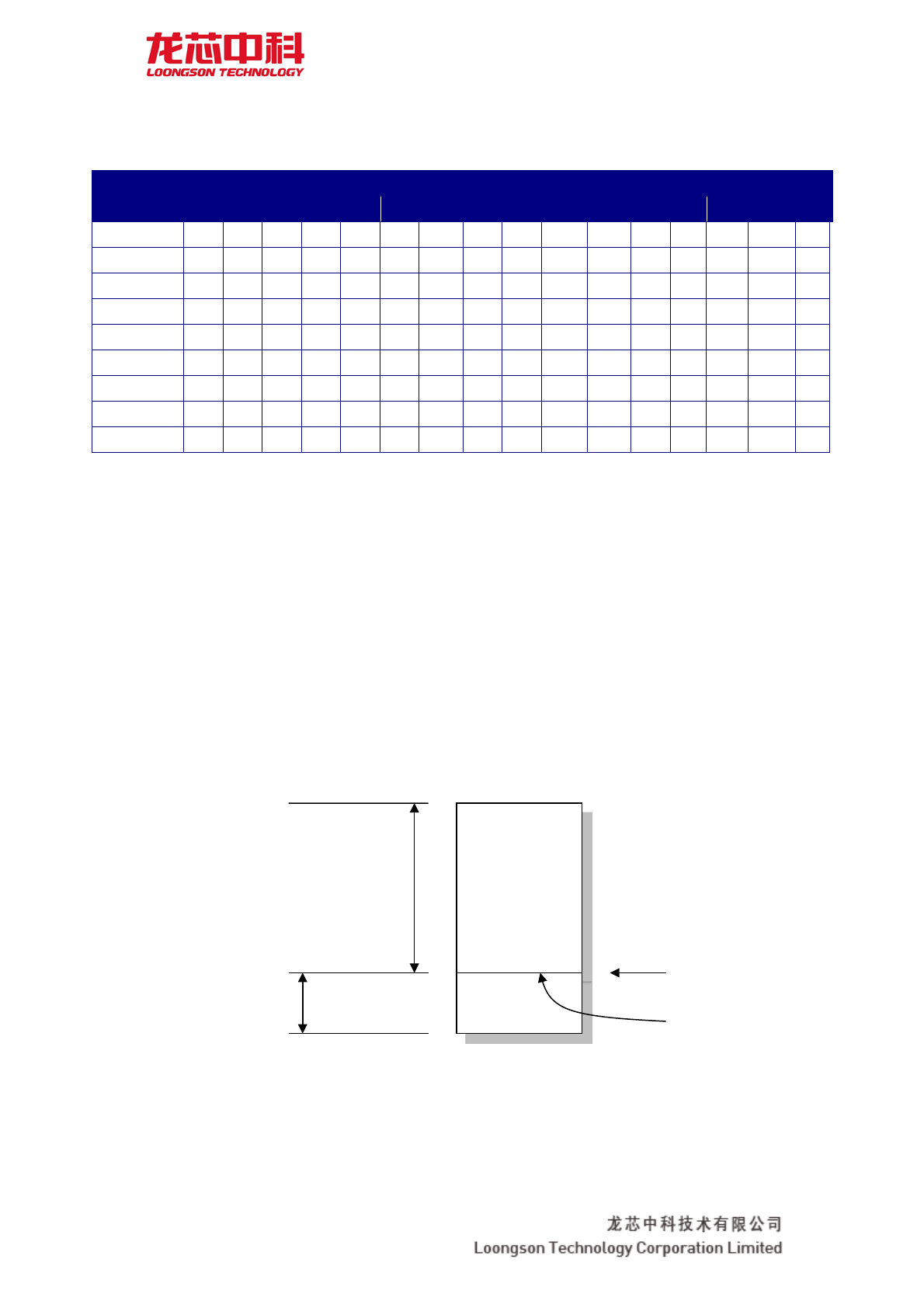

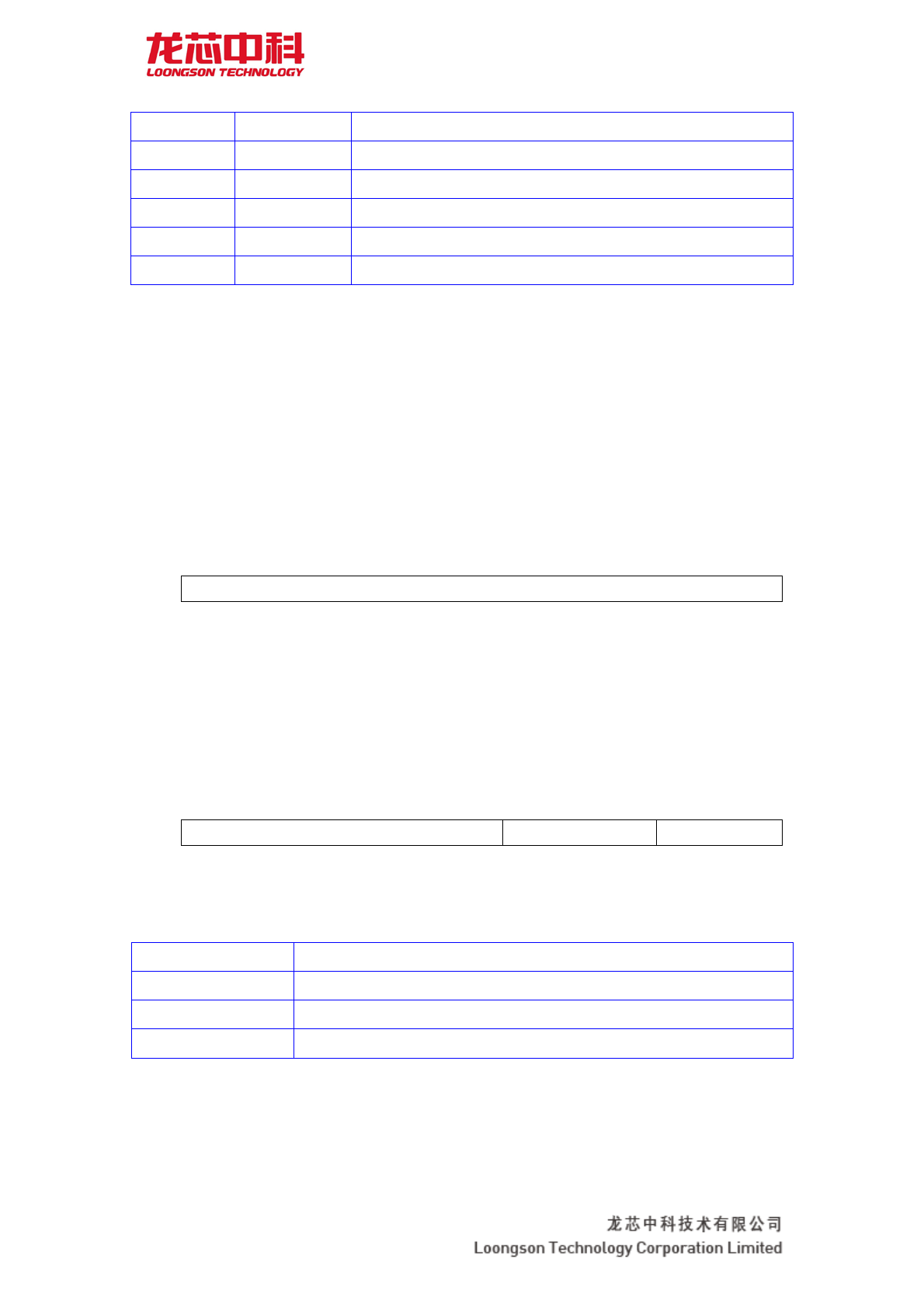

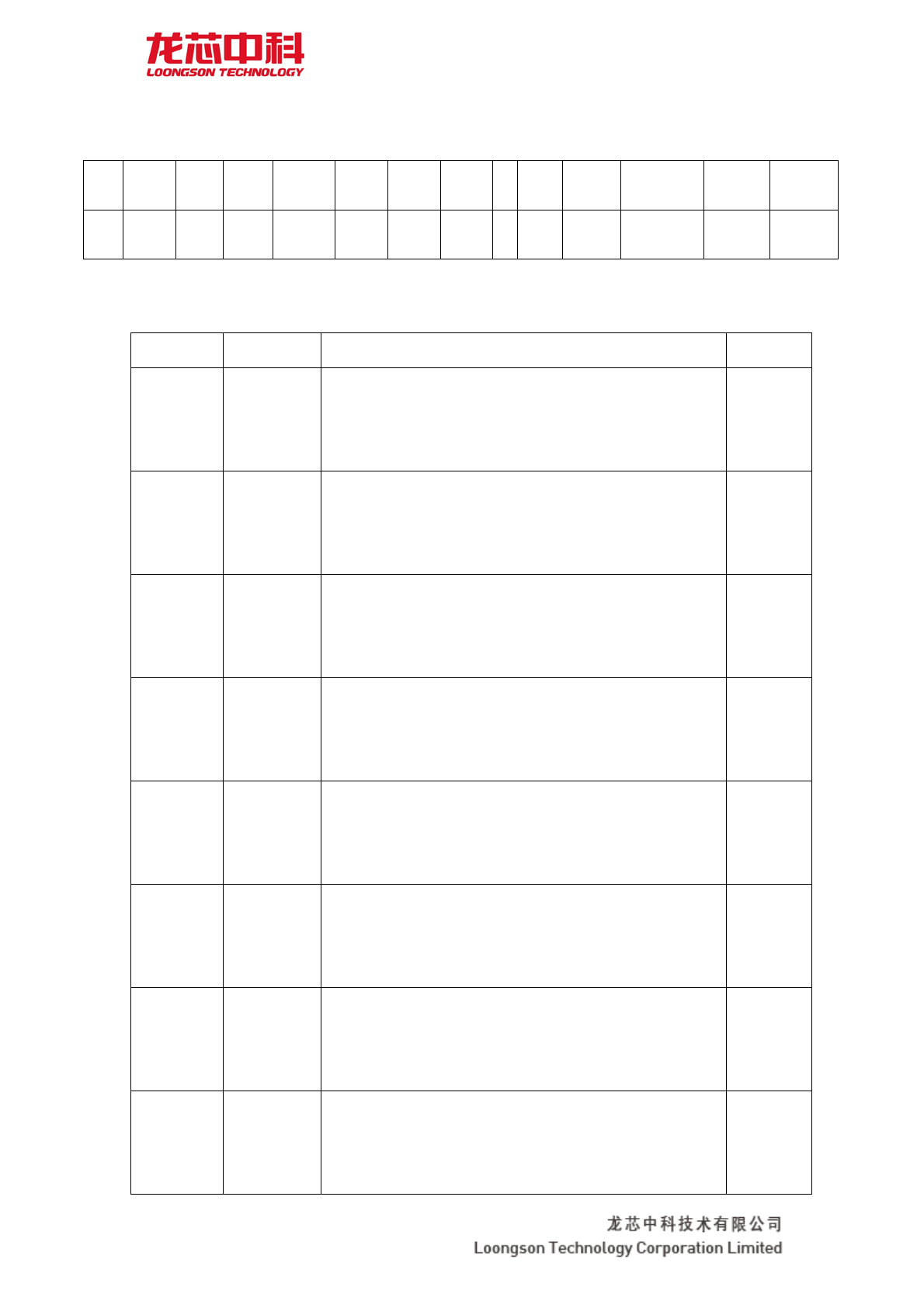

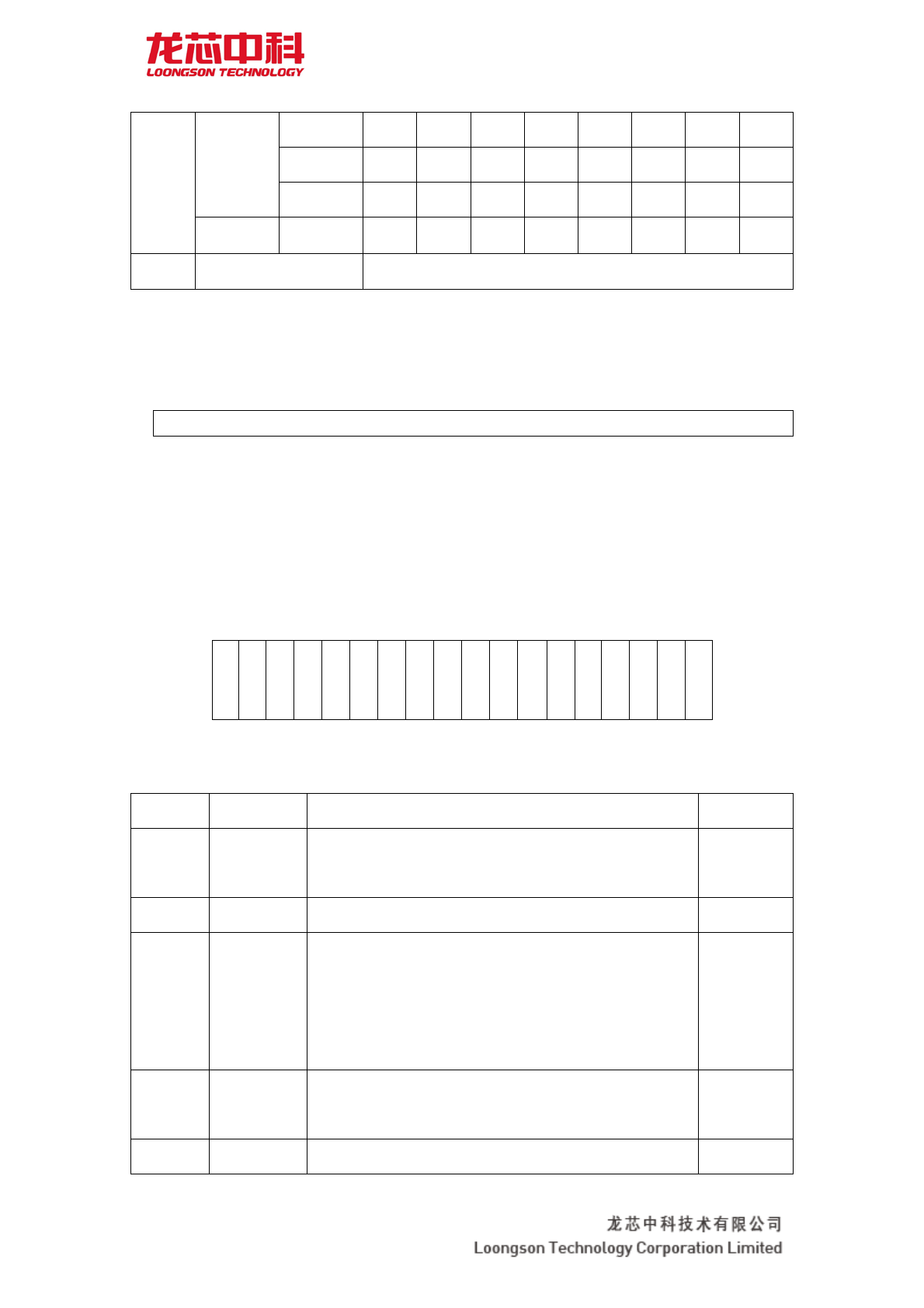

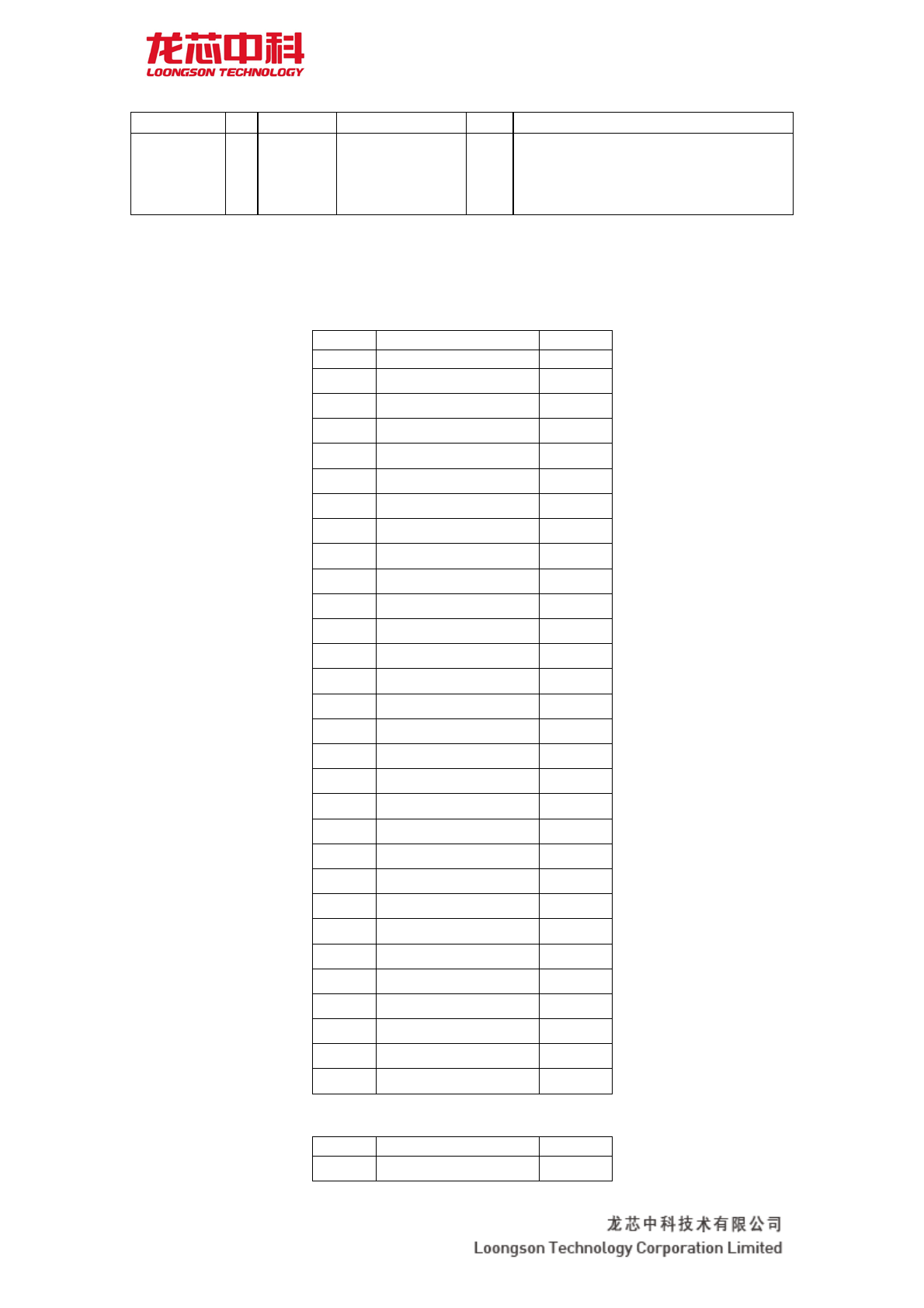

2.2 封装顶视图

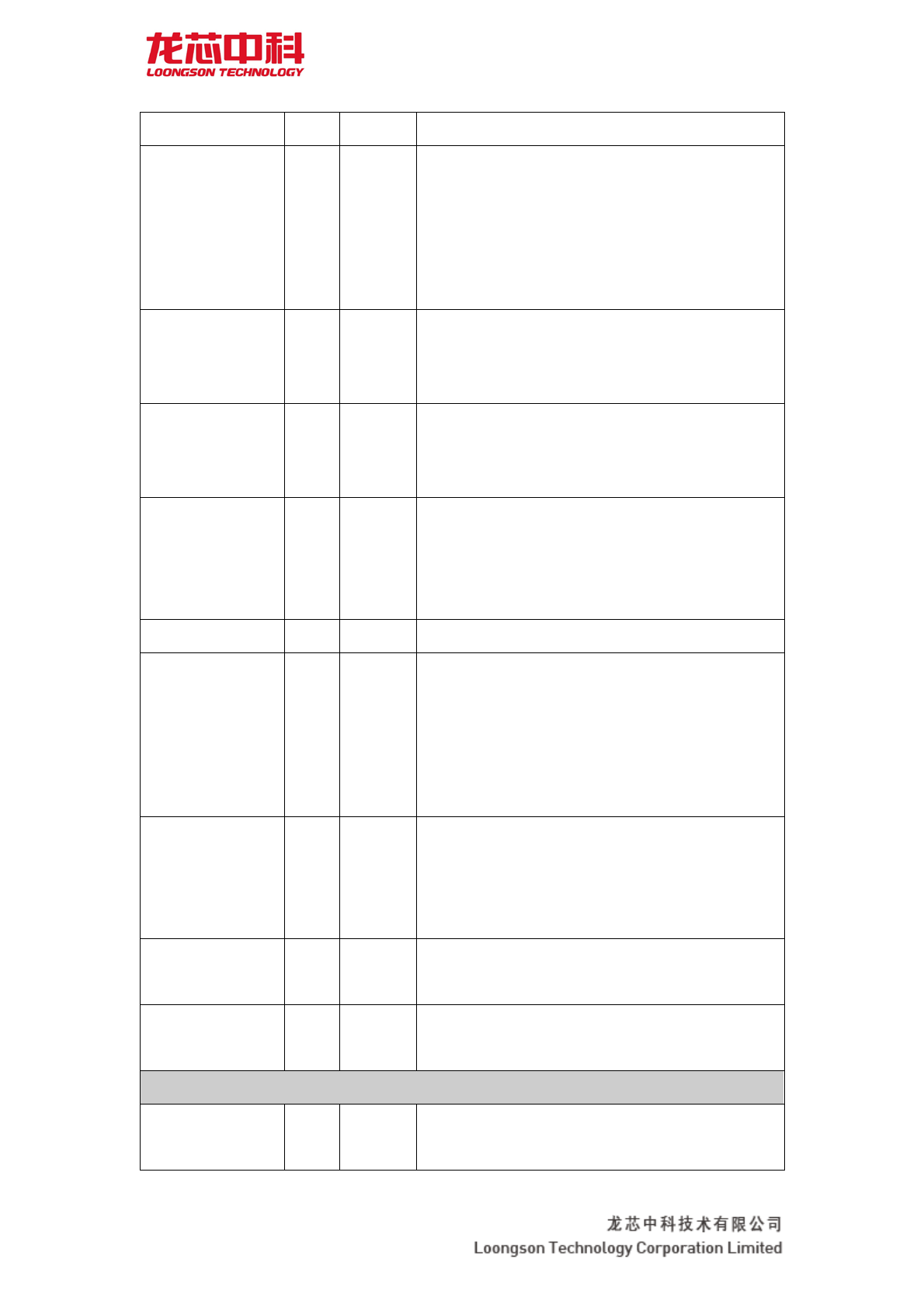

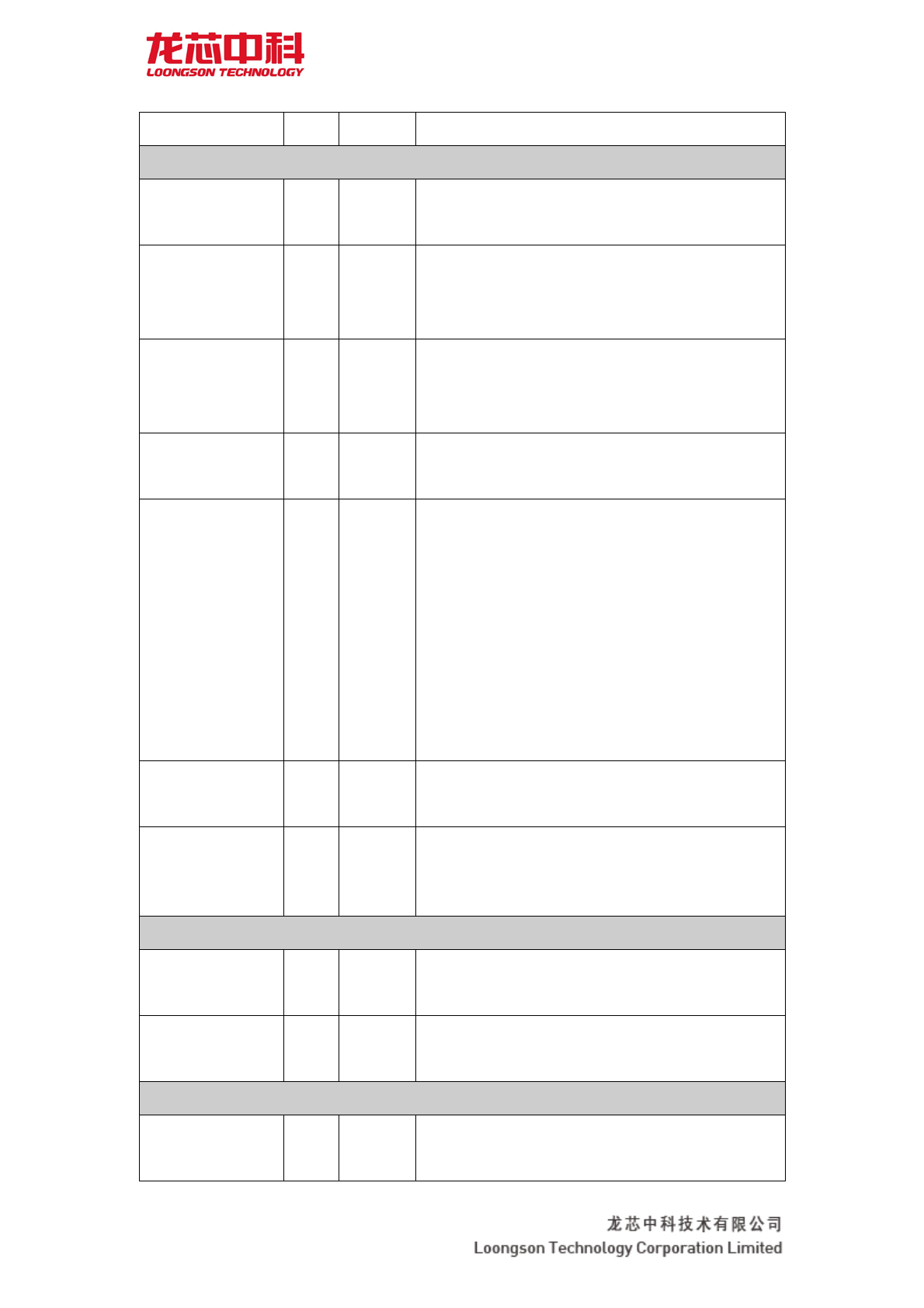

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

ADDR2_A01 DDR2_A05 DDR2_A09 DDR2_A13 DDR2_CKN0 DDR2_ODT0 DDR2_BA2 DDR2_SCSN0 DDR2_DQ18 DDR2_DQ23 DDR2_DQS2 DDR2_DQ17 DDR2_DQM2 RTC_CLK_I PLL_CPU_DVSS12 PLL_CPU_DVDD12

BDDR2_A00 DDR2_A04 DDR2_A08 DDR2_A12 DDR2_CKP0 DDR2_GATEO1 DDR2_BA1 DDR2_WEN DDR2_DQ21 DDR2_DQ16 DDR2_DQ19 DDR2_DQ20 DDR2_DQ22 RTC_CLK_O PLL_CPU_AVSS33 PLL_CPU_AVDD33

CDDR2_DQ06 DDR2_A03 DDR2_A07 DDR2_A11 DDR2_CKE0 DDR2_GATEO0 DDR2_BA0 DDR2_CASN DDR2_DQ26 DDR2_DQ31 DDR2_DQM3 DDR2_DQ25 DDR2_DQ28 RTC_VR_CEXT GMAC1_TX_CTL_O GMAC1_TX_CLK_O

DDDR2_DQM0 DDR2_A02 DDR2_A06 DDR2_A10 DDR2_A14 DDR2_GATEI0 DDR2_GATEI1 DDR2_RASN DDR2_DQ29 DDR2_DQ24 DDR2_DQS3 DDR2_DQ30 DDR2_DQ27 RTC_VR_VOUT UART1_CTS GMAC1_TX_CLK_I

EDDR2_DQ01 DDR2_DQ09 DDR2_DQ11 DDR2_DQ12 VREF_0V9 VSS VDD1V8 VSS VDD1V8 VSS VDD1V8 VREF_0V9 RTC_VSS33 RTC_VDD33 UART1_RTS XTALI

FDDR2_DQ04 DDR2_DQS1 DDR2_DQM1 DDR2_DQ14 VSS VDD1V8 VSS VDD1V8 VSS VDD1V8 VSS VDD1V8 RTC_VDD33 RTC_VSS33 UART1_TX XTALO

GDDR2_DQS0 DDR2_DQ03 DDR2_DQ08 DDR2_DQ15 VDD1V2 VSS VDD1V8 VSS VDD3V3 VSS UART5_RX UART5_TX I2C_SCL I2C_SDA UART1_RX SPI0_MISO

HDDR2_DQ00 DDR2_DQ07 DDR2_DQ13 DDR2_DQ10 VSS VDD1V2 VSS VDD3V3 VSS VDD3V3 UART4_TX UART4_RX SPI0_CS3 SPI0_CS0 SPI0_MOSI SPI0_CLK

JDDR2_DQ05 DDR2_DQ02 VDD1V2 VSS VDD1V2 VSS VDD1V2 VSS VDD3V3 VSS UART3_RX UART3_TX SPI0_CS2 SPI0_CS1 AC97_DATA_O AC97_DATA_I

KVSS VDD1V2 VSS VDD1V2 VSS VDD1V2 VSS VDD3V3 VSS VDD3V3 UART2_TX UART2_RX AC97_SYNC AC97_RESET AC97_BIT_CLK EJTAG_TDO

LVDD1V2 VSS UART0_DCD UART0_RI USB_VDD1V2 USB_AVSS33 USB_AVDD33 VSS VDD3V3 VSS VDD3V3 VSS EJTAG_TRST EJTAG_TMS EJTAG_TDI EJTAG_TCK

MUART0_DTR UART0_TX UART0_RX GMAC1_RX_CLK_I USB_VSS USB_AVDD33 USB_AVSS33 VDD3V3 VSS VDD3V3 VSS VDD3V3 NAND_RD NAND_WR NAND_CE TEST_JTAG_SEL

NUART0_CTS UART0_RTS UART0_DSR LCD_DAT_B1 LCD_DAT_B0 USB0_DM USB0_DP TEST_CFG_MODEN GMAC0_RX_CTL_I GMAC0_RX1 GMAC0_MDCK GMAC0_MDIO NAND_ALE NAND_CLE NAND_D7 NAND_D6

PLCD_DAT_G0 LCD_DAT_G1 LCD_DAT_B2 LCD_DAT_B3 LCD_DAT_B4 LCD_EN USB0_REXT SYS_RSTN GMAC0_RX0 GMAC0_RX2 GMAC0_RX3 CAN1_RX CAN1_TX NAND_D3 NAND_D4 NAND_D5

RLCD_DAT_G2 LCD_DAT_G4 LCD_DAT_R0 LCD_DAT_R2 LCD_DAT_R4 LCD_VSYNC USB0_XI GMAC0_RX_CLK_I GMAC0_TX2 GMAC0_TX0 GMAC0_TX_CLK_O CAN0_TX PWM0 PWM3 NAND_D2 NAND_D1

TLCD_DAT_G3 LCD_DAT_G5 LCD_DAT_R1 LCD_DAT_R3 LCD_HSYNC LCD_CLK USB0_XO GMAC0_TX_CLK_I GMAC0_TX3 GMAC0_TX1 GMAC0_TX_CTL_O CAN0_RX PWM1 PWM2 NAND_RDY NAND_D0

123 4 5 6 7 8 9 10 11 12 13 14 15 16

16

龙芯 1B 处理器用户手册

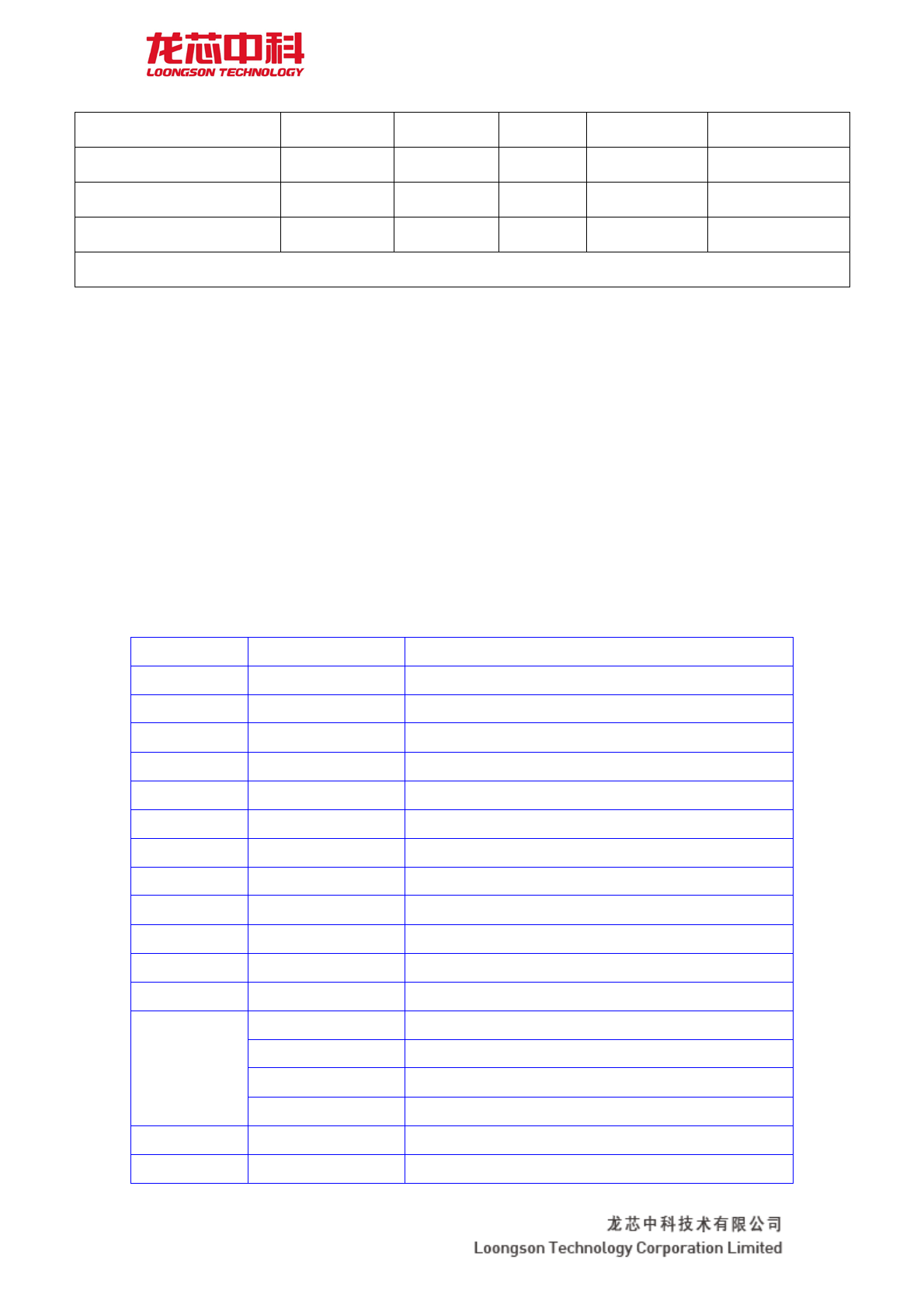

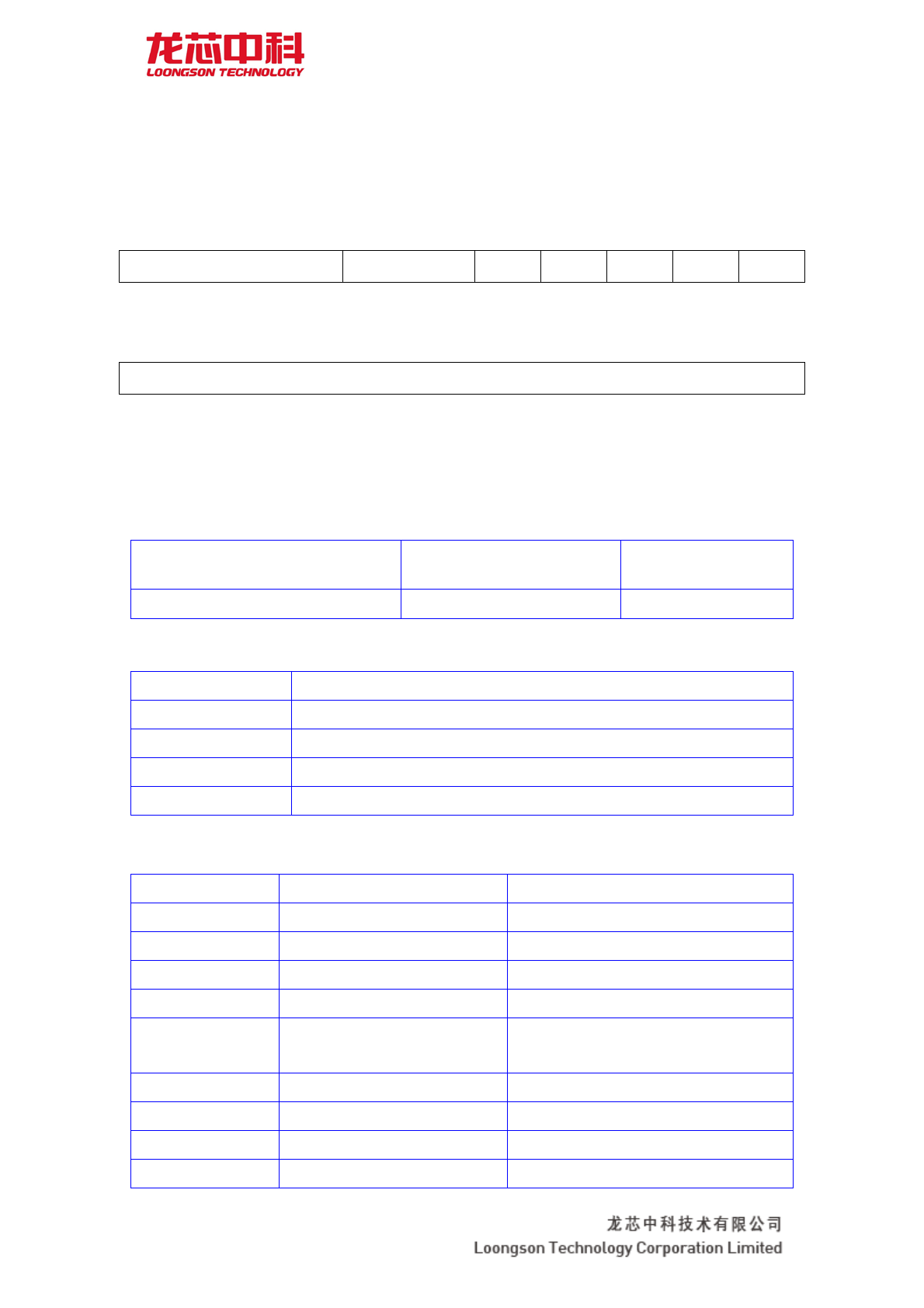

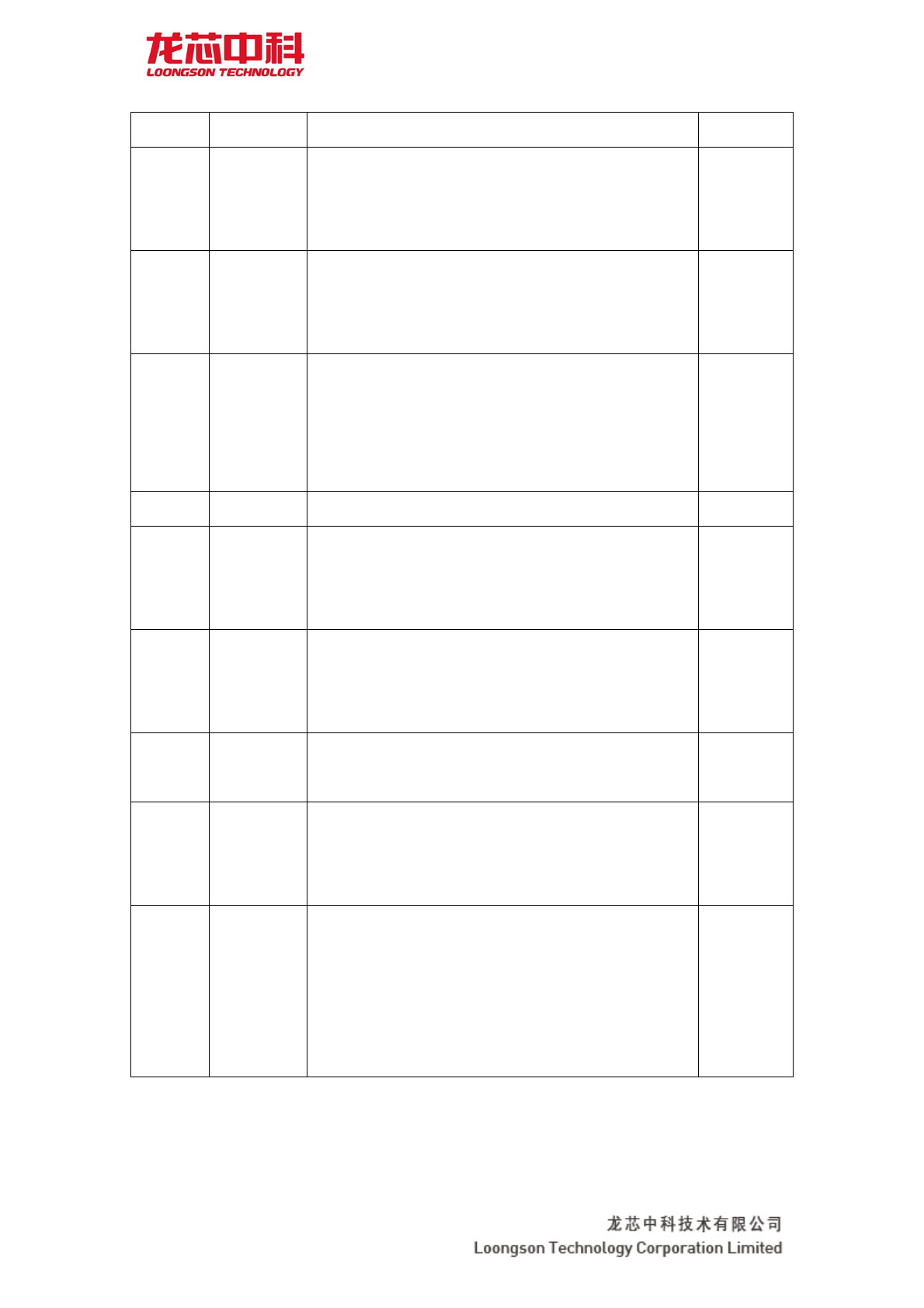

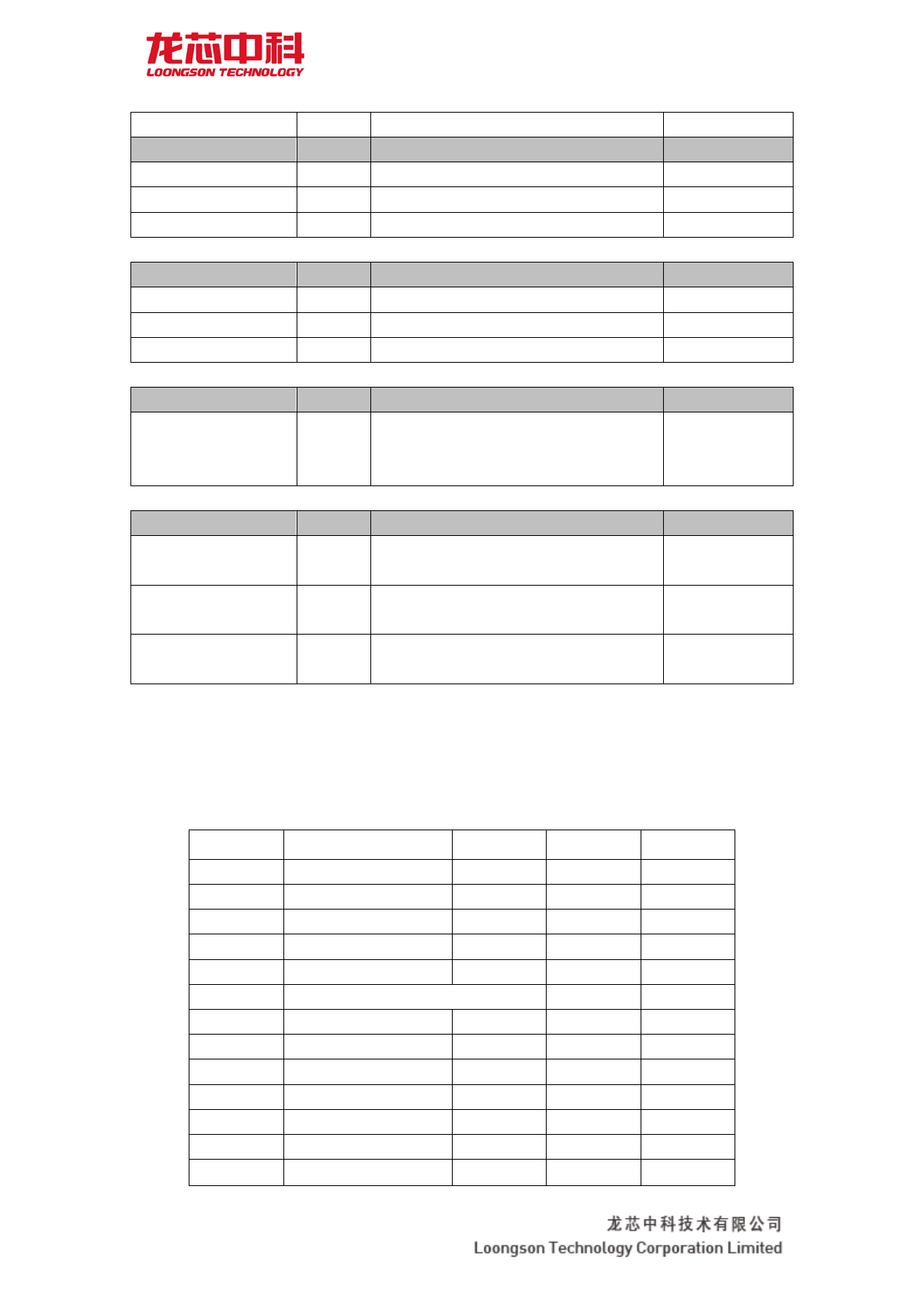

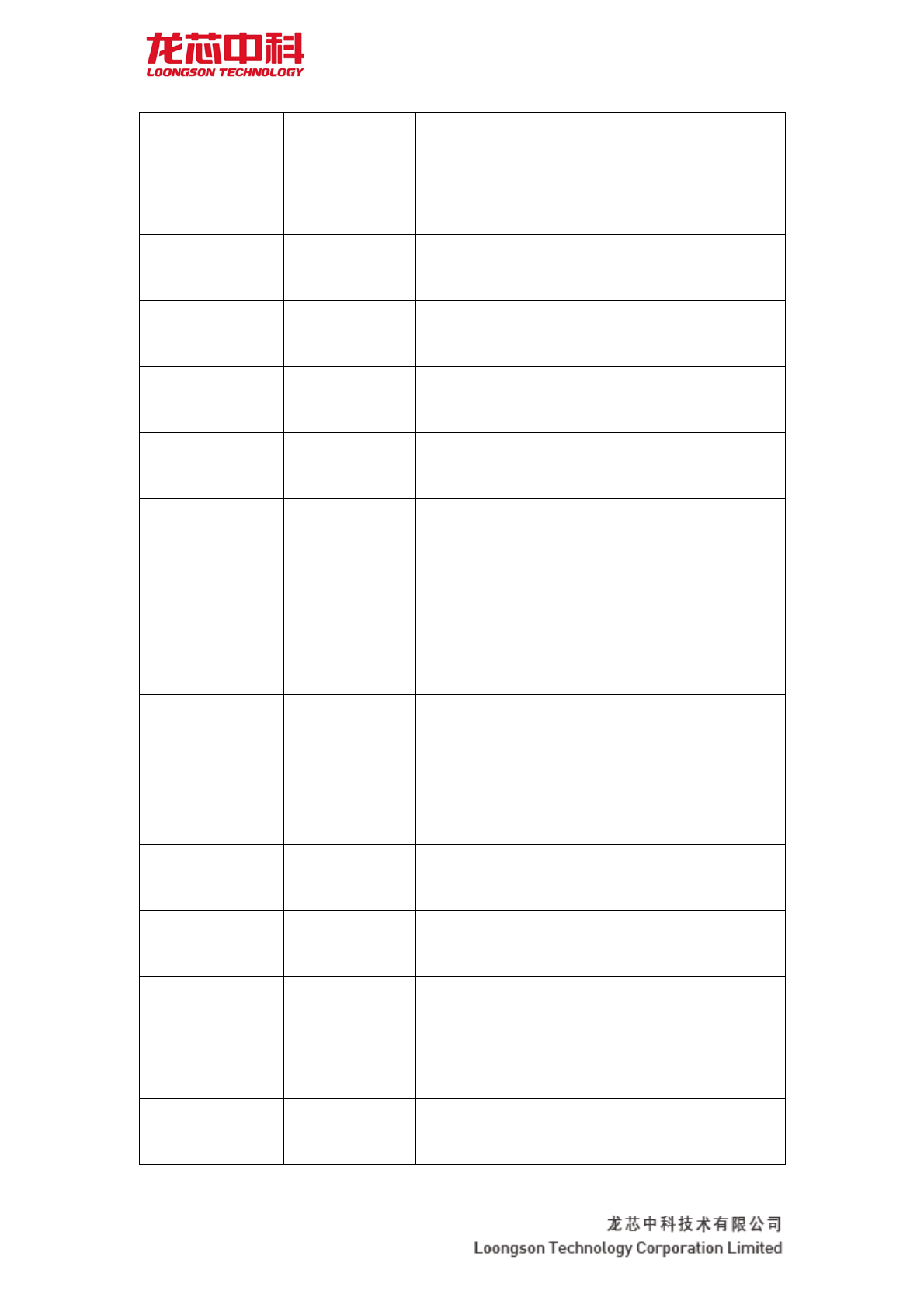

2.3 系统相关引脚定义(6)

表 2-1 系统时钟引脚定义

No. 信号名称 方向 上下拉 描述 电压域

1

XTALI

I

外部无源晶体时钟输入;

外部有源晶振悬空连接

core

2

XTALO

O

外部无源晶体时钟回送;

外部有源晶振输入

core

3

RTC_CKI

I

RTC

时钟晶体输入

RTC

4

RTC_CKO

O

RTC

时钟晶体回送

RTC

5

TEST_CFG_MODEN

I

测试模块

core

6

SYS_RSTN

I

系统复位

core

2.4 LCD 引脚定义(20)

表 2-2 LCD 引脚定义

No. 信号名称 方向 上下拉 描述 电压域

1 LCD_CLK O LCD 时钟 core

2 LCD_VSYNC O LCD 列同步 core

3 LCD_HSYNC O LCD 行同步 core

4 LCD_EN O LCD 可视使能信号 core

5 LCD_DAT_B0 O LCD 蓝色数据信号 0 core

6 LCD_DAT_B1 O LCD 蓝色数据信号 1 core

7 LCD_DAT_B2 O LCD 蓝色数据信号 2 core

8 LCD_DAT_B3 O LCD 蓝色数据信号 3 core

9 LCD_DAT_B4 O LCD 蓝色数据信号 4 core

10 LCD_DAT_G0 O LCD 绿色数据信号 0 core

11 LCD_DAT_G1 O LCD 绿色数据信号 1 core

12 LCD_DAT_G2 O LCD 绿色数据信号 2 core

13 LCD_DAT_G3 O LCD 绿色数据信号 3 core

14 LCD_DAT_G4 O LCD 绿色数据信号 4 core

15 LCD_DAT_G5 O LCD 绿色数据信号 5 core

16 LCD_DAT_R0 O LCD 红色数据信号 0 core

17 LCD_DAT_R1 O LCD 红色数据信号 1 core

18 LCD_DAT_R2 O LCD 红色数据信号 2 core

19 LCD_DAT_R3 O LCD红色数据信号 3 core

20 LCD_DAT_R4 O LCD 红色数据信号 4 core

2.5 PLL 引脚定义(4)

表 2-3 PLL 引脚定义

No. 信号名称 方向 上下拉 描述 电压域

1 PLL_DVDD12 I

1.2

伏数字电源

2 PLL_DVSS12 I

1.2

伏数字地

17

龙芯 1B 处理器用户手册

3 PLL_AVDD33 I

3.3

伏模拟电源

4 PLL_AVSS33 I

3.3

伏模拟地

2.6 VR 引脚定义(6)

表 2-4 VR 引脚定义

No. 信号名称 方向 上下拉 描述 电压域

1 VR_VDDD-0 I 电源 VR_VDDD-0

2 VR_VDDA-0 I 电源 VR_VDDA-0

3 VR_VDDA-1 I 电源 VR_VDDA-1

4 VR_VDDD-1 I 电源 VR_VDDD-1

5 VR_VOUT O 外接 10nf 电容

6 VR_TOCAP O 外接 4.7uf 电容

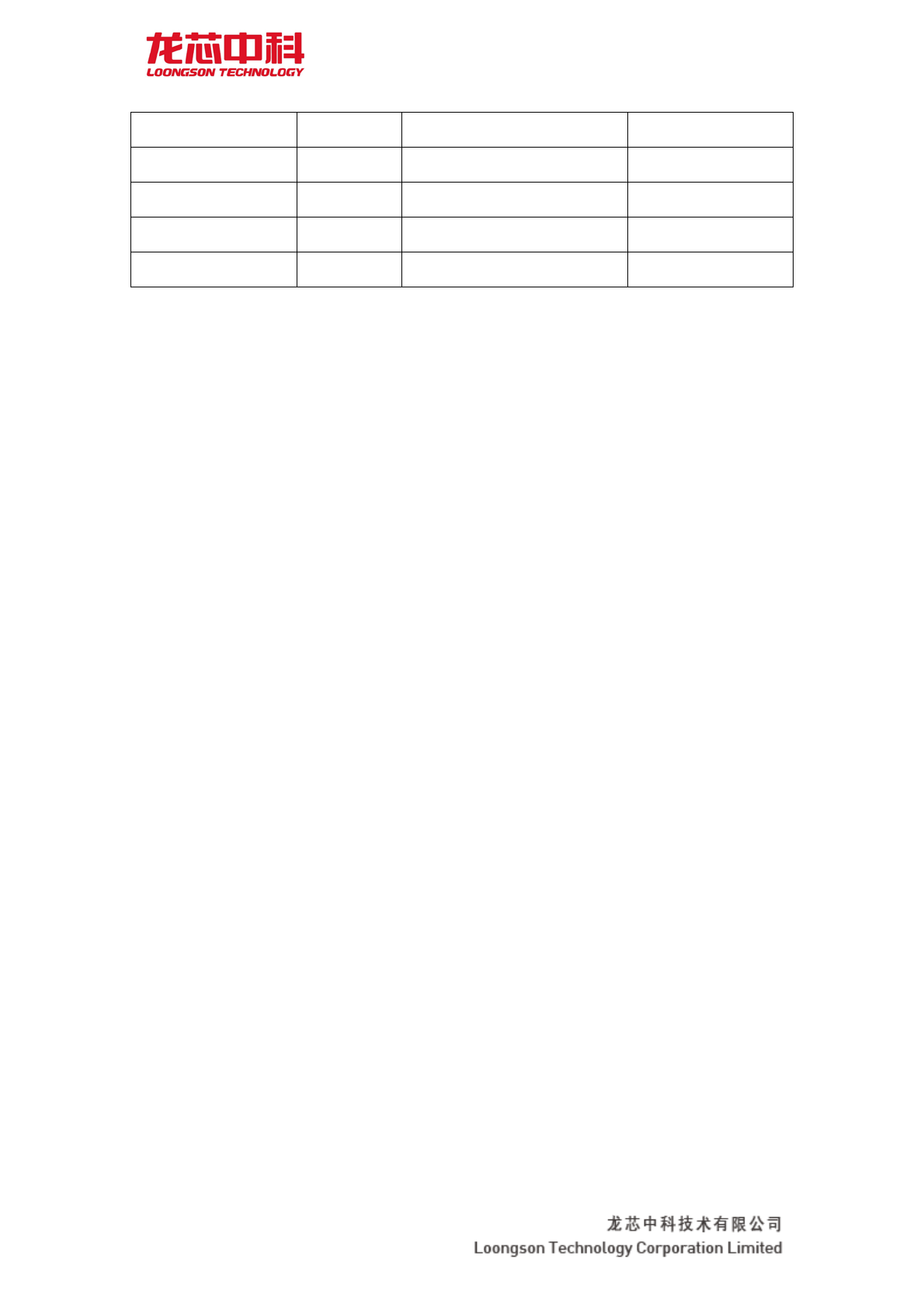

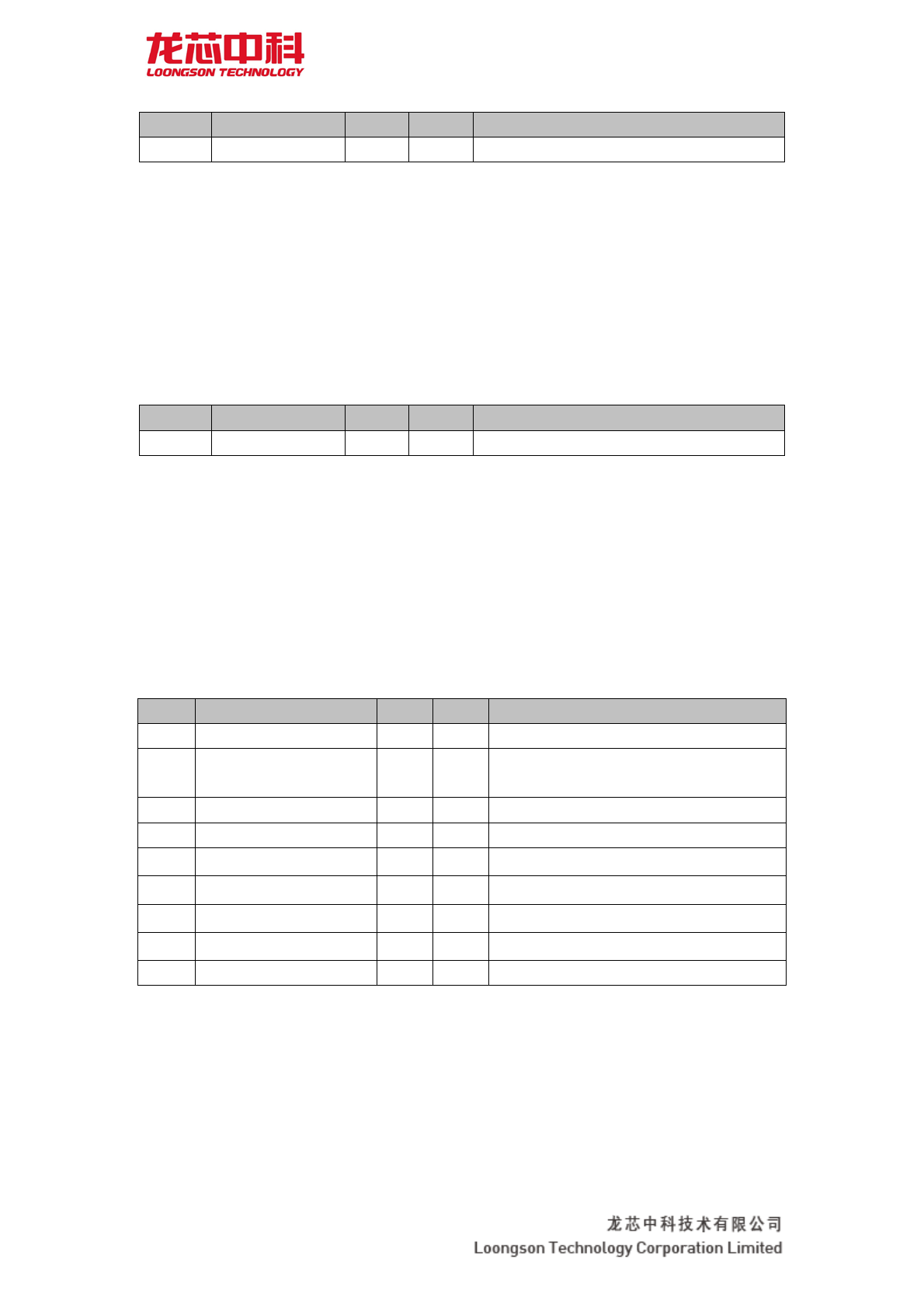

2.7 DDR2引脚定义(71)

表 2-5 DDR 引脚定义

No. 信号名称 方

向

上下拉 描述 电压域

1 DDR2_DQ00 B 外部存储数据总线第 0位

2 DDR2_DQ01 B 外部存储数据总线第 1位

3 DDR2_DQ02 B 外部存储数据总线第 2位

4 DDR2_DQ03 B 外部存储数据总线第 3位

5 DDR2_DQ04 B 外部存储数据总线第 4位

6 DDR2_DQ05 B 外部存储数据总线第 5位

7 DDR2_DQ06 B 外部存储数据总线第 6位

8 DDR2_DQ07 B 外部存储数据总线第 7位

9 DDR2_DQ08 B 外部存储数据总线第 8位

10 DDR2_DQ09 B 外部存储数据总线第 9位

11 DDR2_DQ10 B 外部存储数据总线第 10 位

12 DDR2_DQ11 B 外部存储数据总线第 11 位

13 DDR2_DQ12 B 外部存储数据总线第 12 位

14 DDR2_DQ13 B 外部存储数据总线第 13 位

15 DDR2_DQ14 B 外部存储数据总线第 14 位

16 DDR2_DQ15 B 外部存储数据总线第 15 位

17 DDR2_DQ16 B 外部存储数据总线第 16 位

18 DDR2_DQ17 B 外部存储数据总线第 17 位

19 DDR2_DQ18 B 外部存储数据总线第 18 位

20 DDR2_DQ19 B 外部存储数据总线第 19 位

21 DDR2_DQ20 B 外部存储数据总线第 20 位

22 DDR2_DQ21 B 外部存储数据总线第 21 位

23 DDR2_DQ22 B 外部存储数据总线第 22 位

24 DDR2_DQ23 B 外部存储数据总线第 23 位

25 DDR2_DQ24 B 外部存储数据总线第 24 位

26 DDR2_DQ25 B 外部存储数据总线第 25 位

27 DDR2_DQ26 B 外部存储数据总线第 26 位

28 DDR2_DQ27 B 外部存储数据总线第 27 位

29 DDR2_DQ28 B 外部存储数据总线第 28 位

30 DDR2_DQ29 B 外部存储数据总线第 29 位

31 DDR2_DQ30 B 外部存储数据总线第 30 位

32 DDR2_DQ31 B 外部存储数据总线第 31 位

18

龙芯 1B 处理器用户手册

33 DDR2_A00 O 外部存储地址总线第 0位

34 DDR2_A01 O 外部存储地址总线第 1位

35 DDR2_A02 O 外部存储地址总线第 2位

36 DDR2_A03 O 外部存储地址总线第 3位

37 DDR2_A04 O 外部存储地址总线第 4位

38 DDR2_A05 O 外部存储地址总线第 5位

39 DDR2_A06 O 外部存储地址总线第 6位

40 DDR2_A07 O 外部存储地址总线第 7位

41 DDR2_A08 O 外部存储地址总线第 8位

42 DDR2_A09 O 外部存储地址总线第 9位

43 DDR2_A10 O 外部存储地址总线第 10 位

44 DDR2_A11 O 外部存储地址总线第 11 位

45 DDR2_A12 O 外部存储地址总线第 12 位

46 DDR2_A13 O 外部存储地址总线第 13 位

47 DDR2_A14 O 外部存储地址总线第 14 位

48 DDR2_DQS0 B 输入输出数据 strobe 信号

49 DDR2_DQS1 B 输入输出数据 strobe 信号

50 DDR2_DQS2 B 输入输出数据 strobe 信号

51 DDR2_DQS3 B 输入输出数据 strobe 信号

52 DDR2_DQM0 O 写数据屏蔽信号

53 DDR2_DQM1 O 写数据屏蔽信号

54 DDR2_DQM2 O 写数据屏蔽信号

55 DDR2_DQM3 O 写数据屏蔽信号

56 DDR2_CKp0 O 时钟信号

57 DDR2_CKn0 O 时钟信号

58 DDR2_CKE0 O 时钟有限信号

59 DDR2_ODT0 O ODT 信号

60 DDR2_SCSn0 O 片选信号

61 DDR2_BA0 O bank 选择信号

62 DDR2_BA1 O bank 选择信号

63 DDR2_BA2 O bank 选择信号

64 DDR2_RASn O 行选择

65 DDR2_CASn O 列选择

66 DDR2_WEn O 写信号

67 DDR2_GATEI0 I GATE 信号

68 DDR2_GATEI1 I GATE 信号

69 DDR2_GATEO0 O GATE 信号

70 DDR2_GATEO1 O GATE 信号

71 VREF_0V9 I 0.9V 参考电压

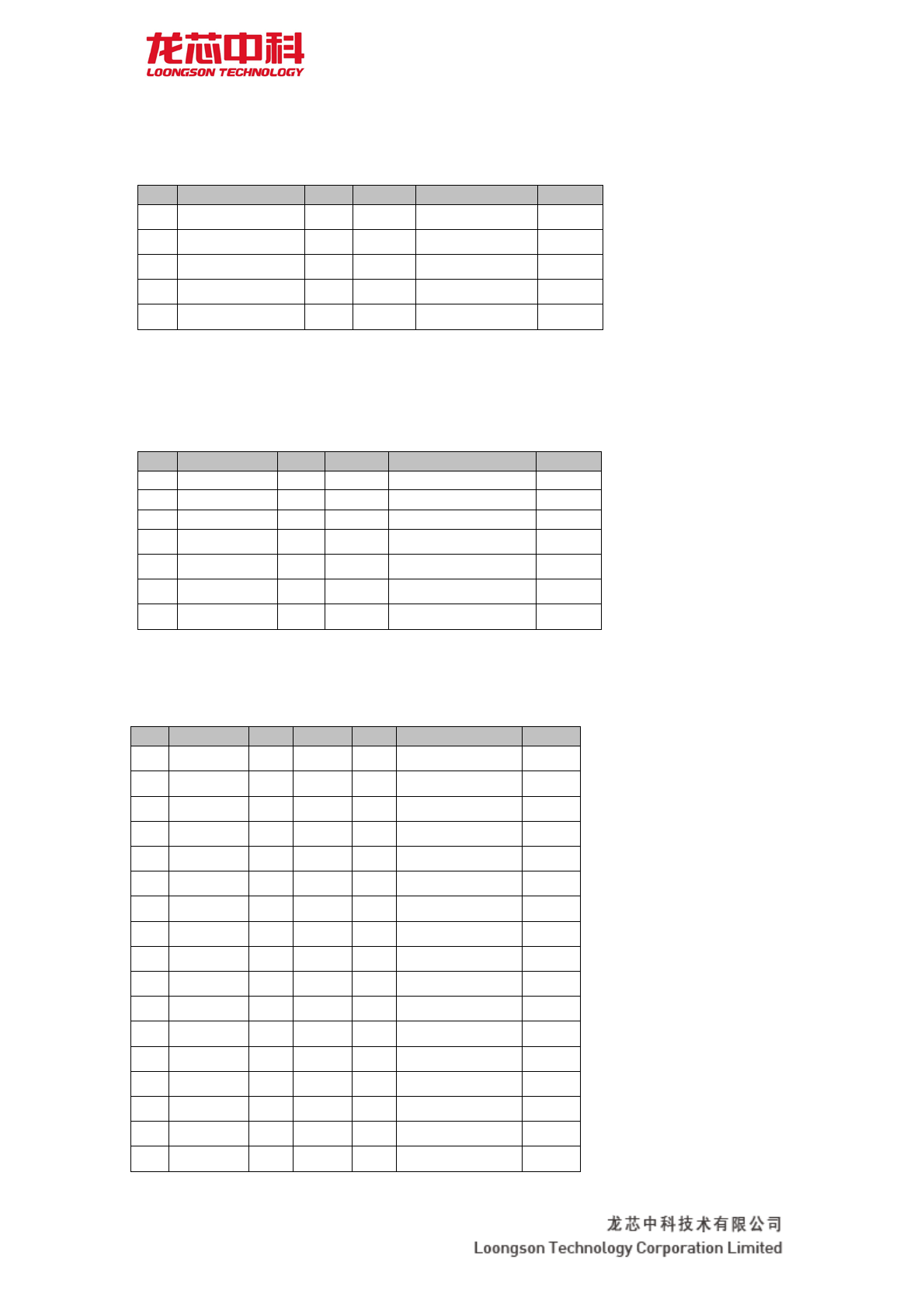

2.8 USB 引脚定义(10)

表 2-6 USB 引脚定义

No. 信号名称 方向 上下拉 描述 电压域

1 USB_AVDD33 I 3.3 伏模拟电源

2 USB_AVSS33 I 模拟地

3 USB0_REXT I 外部参考电阻 44.2ohm 对地

4 USB_VSS33 I 模拟地

5 USB_VDD33 I 3.3 伏模拟电源

6 USB_DVDD I 1.2 伏数字电源

19

龙芯 1B 处理器用户手册

7 USB_DVSS I 数字地

8 USB0_XI I 接地(或者接 12M 晶体)

9 USB0_XO I 外部 12Mhz 参考时钟输入

(或者接 12M 晶体)

10 USB0_DP B USB 差分数据

11 USB0_DM B USB 差分数据

2.9 EJTAG 引脚定义(6)

表 2-7 JTAG 引脚定义

No. 信号名称 方向 上下拉 描述 电压域

1 EJTAG_TCK I PU TAP 时钟(内置上拉) core

2 EJTAG_TRST I PU TAP 复位(内置上拉) core

3 EJTAG_TDI I PU TAP 数据输入(内置上拉) core

4 EJTAG_TDO O TAP 数据输出 core

5 EJTAG_TMS I PU TAP 工作模式(内置上拉) core

6 TEST_JTAG_SEL I JTAG/EJTAG 选择 core

2.10 GMAC0引脚定义(15)

表 2-8 GMAC 引脚定义

No. 信号名称 方

向

上下拉 描述 电压

域

1 GMAC0_TCKI I GMAC 传输时钟输入 core

2 GMAC0_TCKO O GMAC 传输时钟输出 core

3 GMAC0_TX0 O GMAC 传输数据输出 0 core

4 GMAC0_TX1 O GMAC 传输数据输出 1 core

5 GMAC0_TX2 O GMAC 传输数据输出 2 core

6 GMAC0_TX3 O GMAC 传输数据输出 3 core

7 GMAC0_TCTL O GMAC 传输控制 core

8 GMAC0_RCKI I GMAC 接收时钟输入 core

9 GMAC0_RX0 I GMAC 接收数据输入 0 core

10 GMAC0_RX1 I GMAC 接收数据输入 1 core

11 GMAC0_RX2 I GMAC 接收数据输入 2 core

12 GMAC0_RX3 I GMAC 接收数据输入 3 core

13 GMAC0_RCTL I GMAC 接受控制 core

14 GMAC0_MDC O 读写 PHY 的时钟信号 core

15 GMAC0_MDIO B 读写 PHY 的数据信号 core

注:GMAC 引脚电压为 3.3V

2.11 GMAC1引脚定义(4)

表 2-9 GMAC 引脚定义

No. 信号名称 方

向

上下拉 描述 电压

域

1 GMAC1_TX_CLK_I I GMAC1 传输时钟输入 core

2 GMAC1_TX_CLK_O O GMAC1 传输时钟输出 core

3 GMAC1_RX_CLK_I I GMAC1 接收时钟输入 core

4 GMAC1_TX_CTL_O O GMAC1 传输控制 core

20

龙芯 1B 处理器用户手册

2.12 AC97 引脚定义(5)

表 2-10 AC97 引脚定义

No. 信号名称 方向 上下拉 描述 电压域

1 AC97_BIT_CLK I AC97 时钟输入 core

2 AC97_DATA_I I AC97 数据输入 core

3 AC97_DATA_O O AC97 数据输出 core

4 AC97_SYNC O AC97 同步信号 core

5 AC97_RESET O AC97 复位信号 core

2.13 SPI 引脚定义(7)

表 2-11 SPI 引脚定义

No. 信号名称 方向 上下拉 描述 电压域

1 SPI0_CLK O SPI0 时钟 core

2 SPI0_MISO I SPI0 主入从出数据 core

3 SPI0_MOSI O SPI0 主出从入数据 core

4 SPI0_CS0 O SPI0 选通信号 0 core

5 SPI0_CS1 O SPI0 选通信号 1 core

6 SPI0_CS2 O SPI0 选通信号 2 core

7 SPI0_CS3 O SPI0 选通信号 3 core

2.14 UART 引脚定义(20)

表 2-12 UART 引脚定义

No. 信号名称 方向 上下拉 频率 描述 电压域

1 UART0_RX I 1MHz UART0 发送数据 core

2 UART0_TX O 1MHz UART0 接收数据 core

3 UART0_RTS O 1MHz UART0 请求发送 core

4 UART0_CTS I 1MHz UART0 允许发送 core

5 UART0_DSR I 1MHz UART0 设备准备好

core

6 UART0_DTR O 1MHz UART0 终端准备好

core

7 UART0_DCD I 1MHz UART0 载波检测 core

8 UART0_RI I 1MHz UART0 振铃提示 core

9 UART1_TX O 1MHz UART1 发送数据 core

10 UART1_RX I 1MHz UART1 接收数据 core

11 UART1_RTS O 1MHz UART1 请求发送 core

12 UART1_CTS I 1MHz UART1 允许发送 core

13 UART2_TX O 1MHz UART2 发送数据 core

14 UART2_RX I 1MHz UART2 接收数据 core

15 UART3_TX O 1MHz UART3 发送数据 core

16 UART3_RX I 1MHz UART3 接收数据 core

17 UART4_TX O 1MHz UART4发送数据 core

21

龙芯 1B 处理器用户手册

18 UART4_RX I 1MHz UART4接收数据 core

19 UART5_TX O 1MHz UART5发送数据 core

20 UART5_RX I 1MHz UART5接收数据 core

2.15 I2C 引脚定义(2)

表 2-13 I2C 引脚定义

No.

信号名称 方向 上下拉 描述 电压域

1

I2C_SCL O 第一路 I2C 时钟 core

2

I2C_SDA B 第一路 I2C 数据 core

2.16 CAN 引脚定义(4)

表 2-14 CAN 引脚定义

No.

信号名称 方向 上下拉 描述 电压域

1

CAN0_RX I CAN0 数据输入 core

2

CAN0_TX O CAN0 数据输出 core

3

CAN1_RX I CAN1 数据输入 core

4

CAN1_TX O CAN1数据输出 core

2.17 NAND 引脚定义(14)

表 2-15 NAND 引脚定义

No. 信号名称 方向 上下拉 描述 电压

域

1 NAND_CLE O NAND 读信号 core

2 NAND_ALE O NAND 写信号 core

3 NAND_RD O NAND 命令锁存 core

4 NAND_WR O NAND 地址锁存 core

5 NAND_CE O NAND 片选信号 core

6 NAND_RDY I NAND 忙信号 core

7 NAND_D0 O NAND 数据信号 0 core

8 NAND_D1 O NAND 数据信号 1 core

9 NAND_D2 O NAND 数据信号 2 core

10 NAND_D3 O NAND 数据信号 3 core

11 NAND_D4 O NAND 数据信号 4 core

12 NAND_D5 O NAND 数据信号 5 core

13 NAND_D6 O NAND 数据信号 6 core

14 NAND_D7 O NAND 数据信号 7 core

2.18 PWM 引脚定义(4)

表 2-18 PWM 引脚定义

No. 信号名称 方向 上下拉 描述 电压域

1 PWM0 O PWM0 波形输出 core

2 PWM1 O PWM1 波形输出 core

22

龙芯 1B 处理器用户手册

3 PWM2 O PWM2 波形输出 core

4 PWM3 O PWM3 波形输出 core

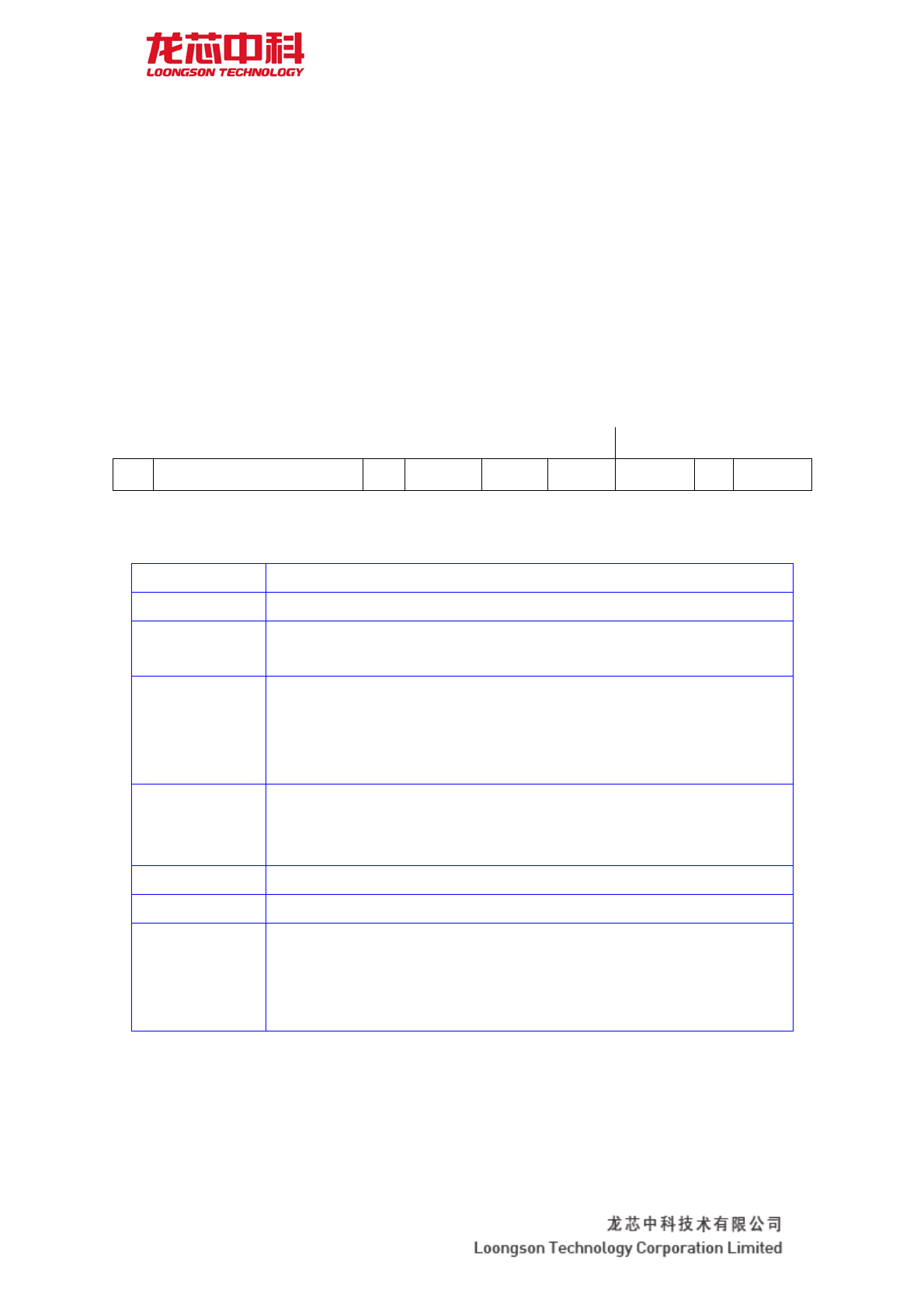

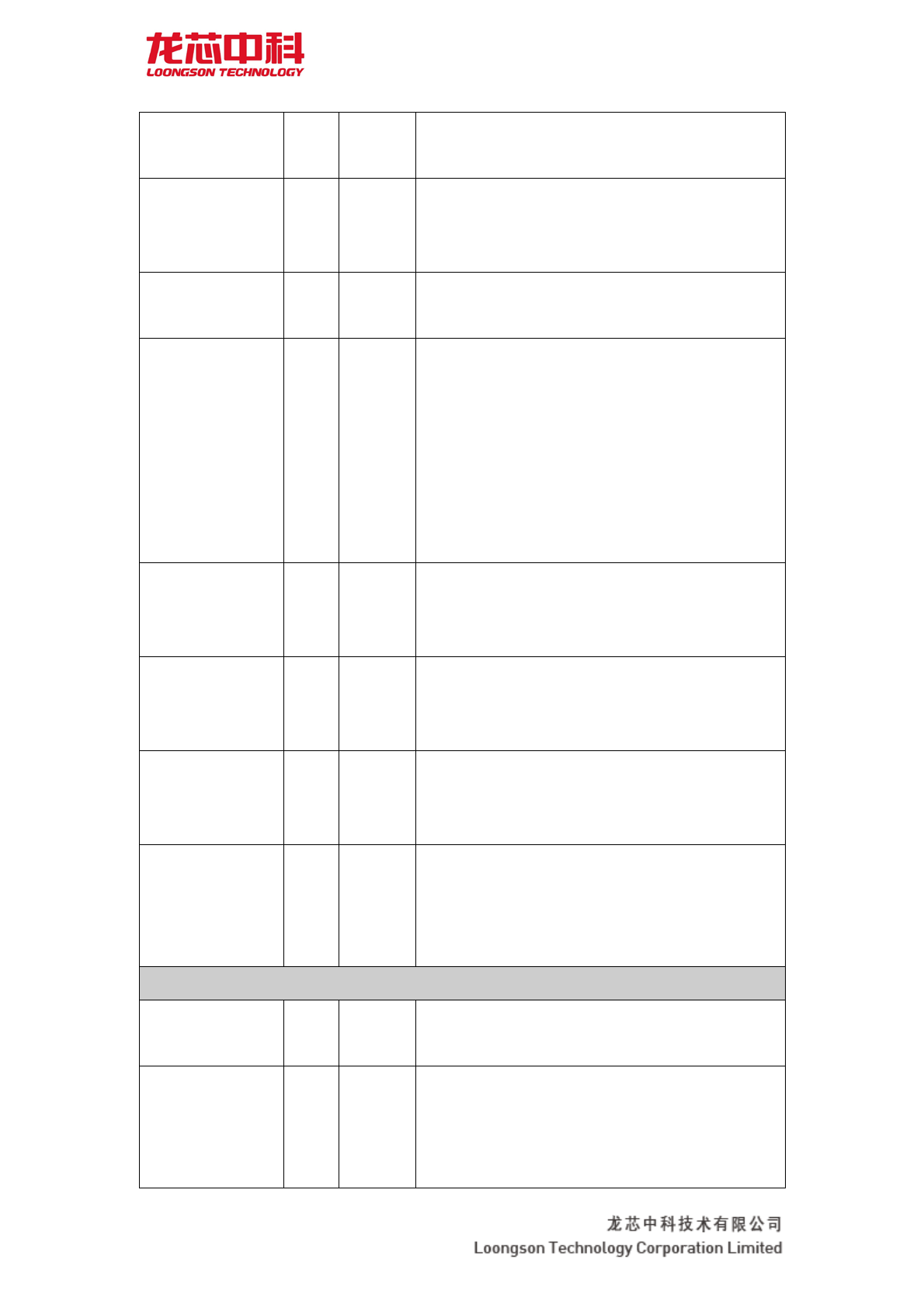

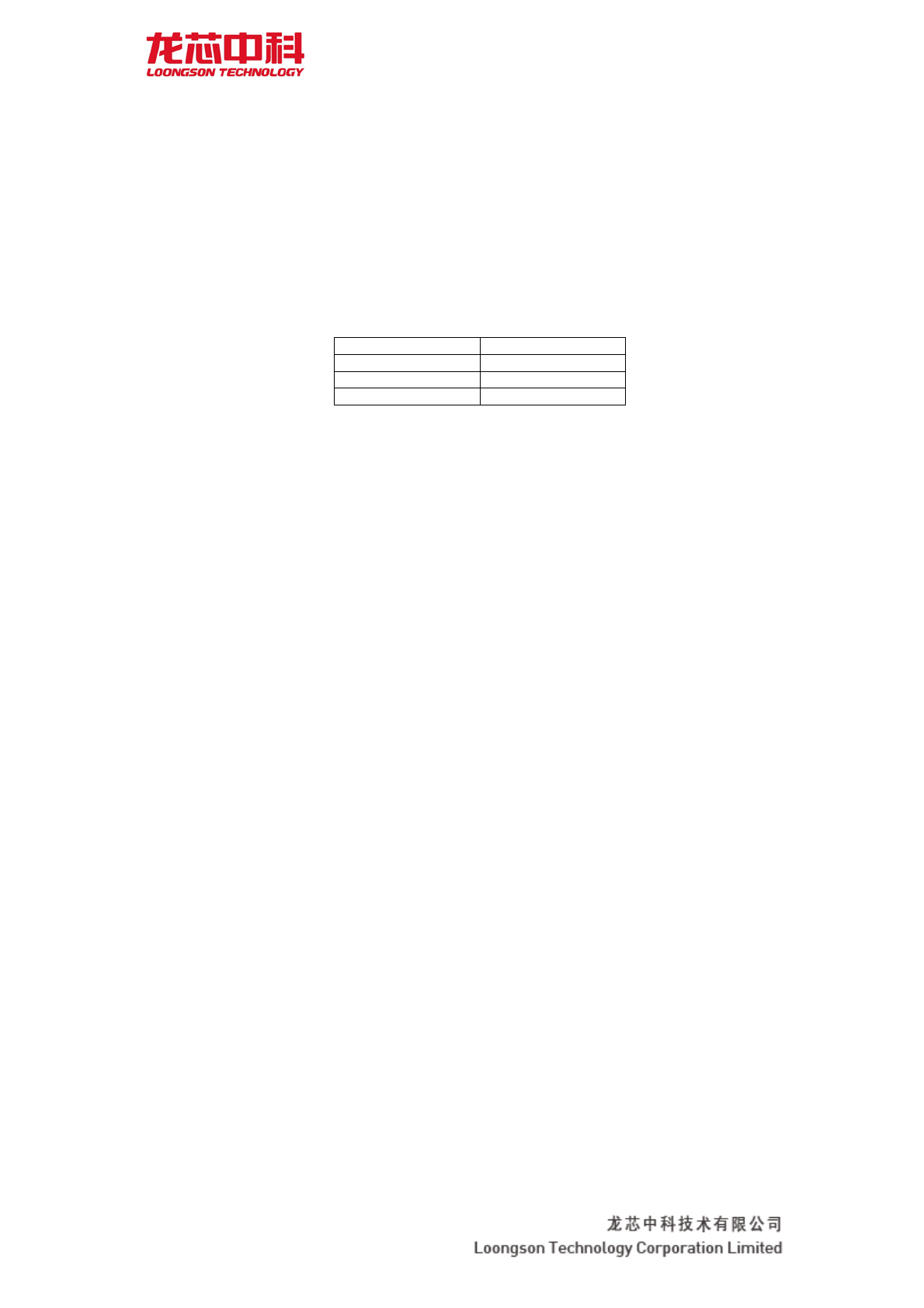

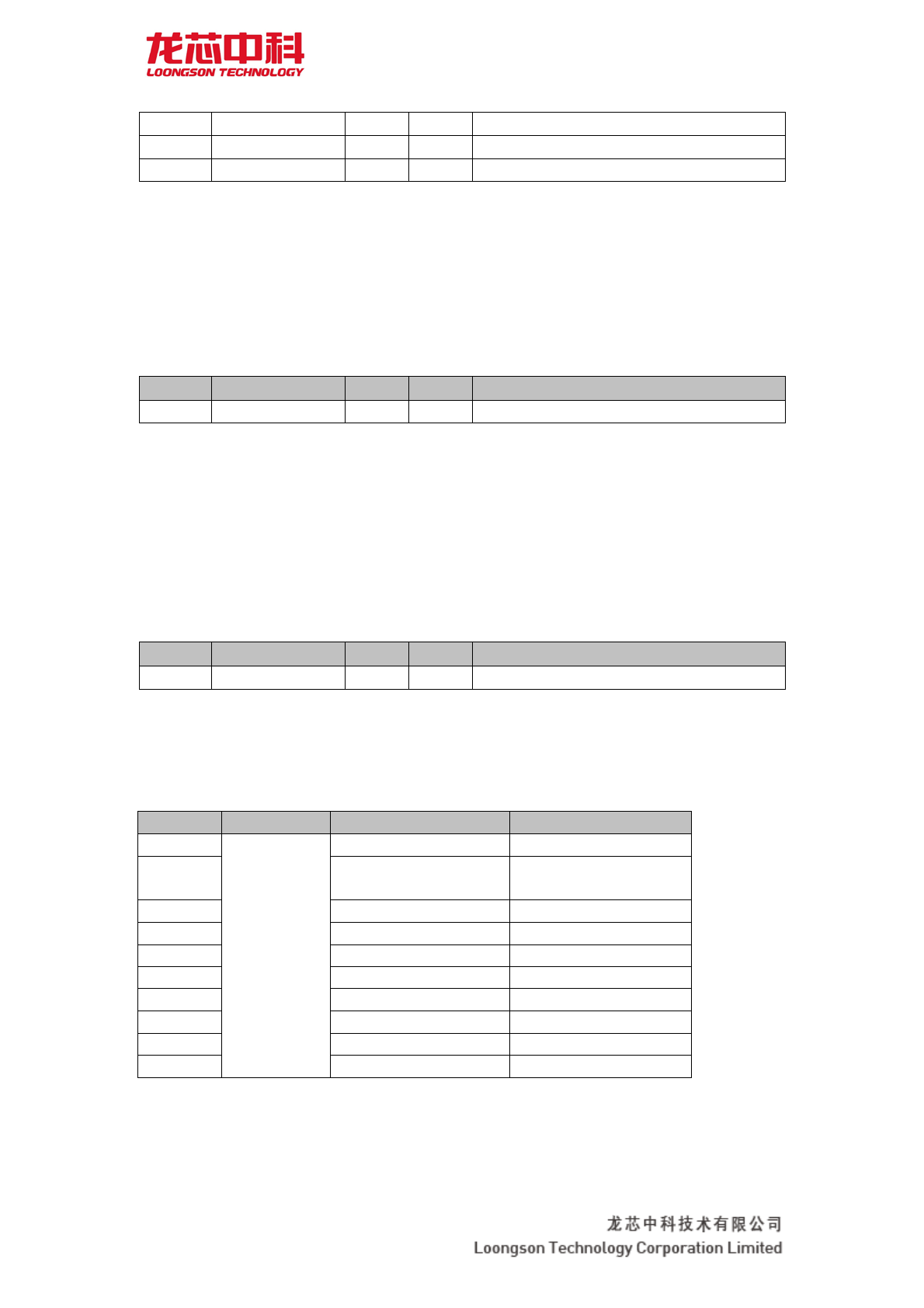

2.19 电源/地引脚(58)

表 2-19 电源地引脚

No. 信号名称 方向 描述 电压值 电压域 数目

1 VDD1V2 CORE 域 1.2v CORE 10

2 VDD1V8 DDR2 电压域 1.8v DDR2 8

3 VDD3V3 PAD 电压域 3.3v PAD 11

4 RTC_VDD33 RTC 电源 3.3v RTC 2

5 VSS 接地 0v 接地 27

6 RTC_VSS33 RTC 地 0v RTC 2

23

龙芯 1B 处理器用户手册

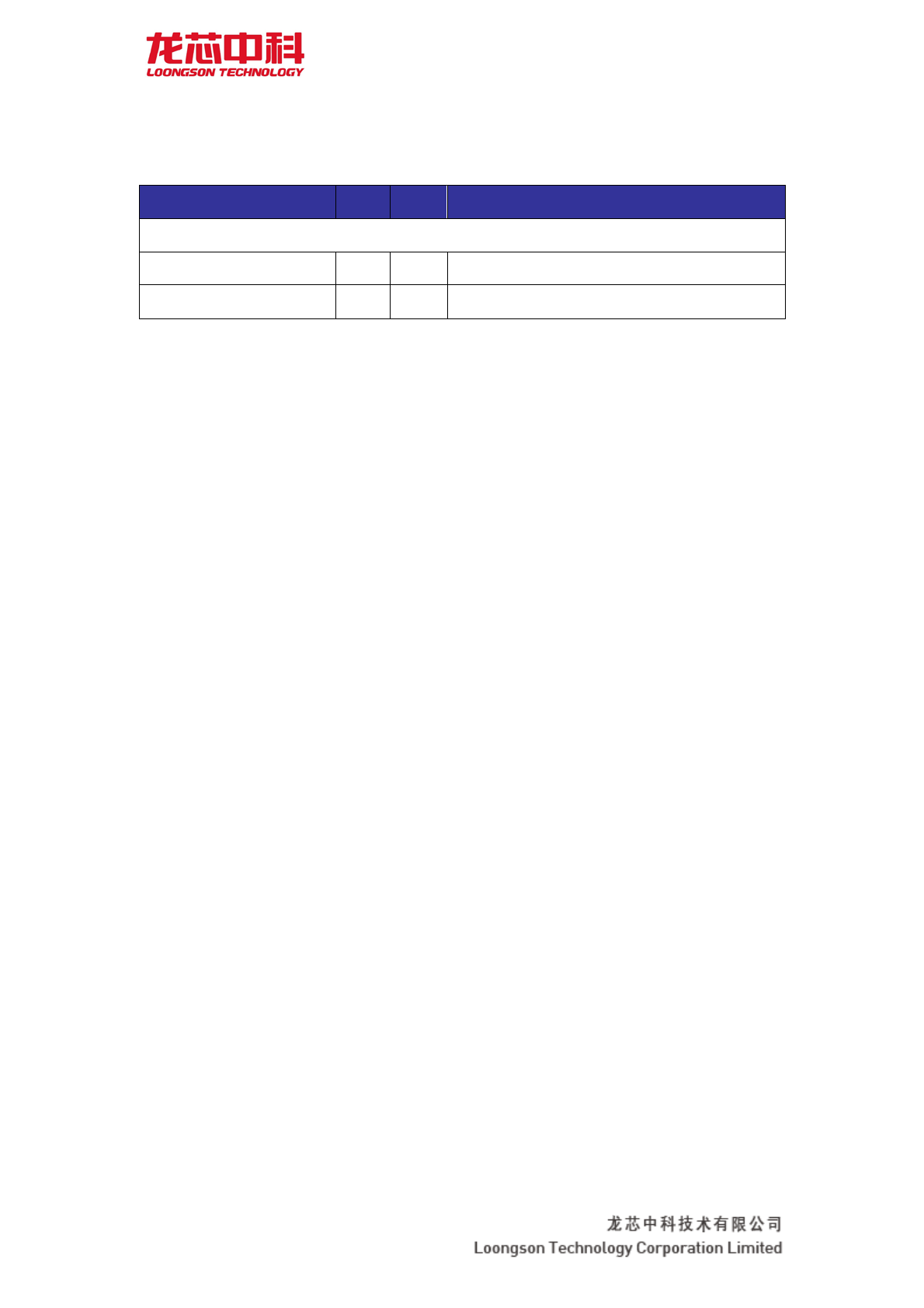

3 地址空间分配

本章给出 1B 芯片各模块的地址空间分配。

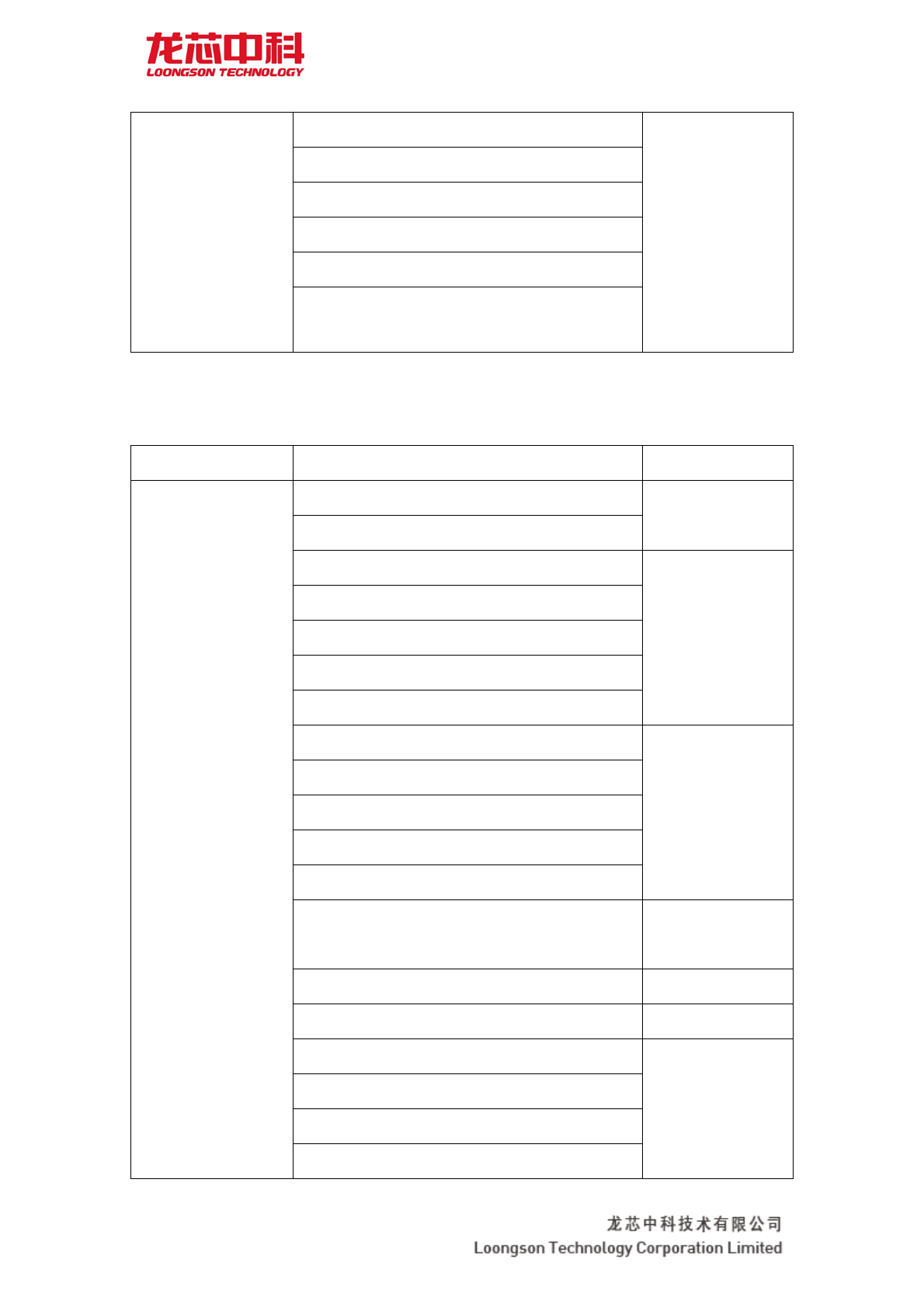

3.1 一级 AXI 交叉开关上模块的地址空间

表3- 1 AXI 各模块地址分配

地址空间 模块 说明

0x0000,0000 – 0x0fff,ffff DDR 256MB

0x1000,0000 – 0x1c19,ffff

RESERVED

0x1c20,0000 – 0x1c2f,ffff DC Slave 1MB

0x1c30,0000 – 0x1eff,ffff RESERVED

0x1f00,0000 – 0x1fff,ffff AXI MUX Slave 16MB

0x2000,0000 – 0x7fff,ffff RESERVED

3.2 AXI MUX 下各模块的地址空间

表 3-2 AXI MUX 各模块地址分配

地址空间 模块 说明

0xbf00,0000 – 0xbf7f,ffff SPI0-memory 8MB

0xbf80,0000 – 0xbfbf,ffff SPI1-memory 4MB

0xbfc0,0000 – 0xbfcf,ffff SPI0 1MB

0xbfd0,0000 – 0xbfdf,ffff CONFREG 1MB

0xbfe0,0000 – 0xbfe0,ffff USB 64KB

0xbfe1,0000 – 0xbfe1,ffff GMAC0 64KB

0xbfe2,0000 – 0xbfe2,ffff GMAC1 64KB

0xbfe3,0000 – 0xbfe3,ffff

RESERVED

0xbfe4,0000 – 0xbfe7,ffff APB-devices 256KB

0xbfe8,0000 – 0xbfeb,ffff SPI0-IO 256KB

0xbfec,0000 – 0xbfef,ffff SPI1-IO 256KB

0xbff0,0000 – 0xbfff,ffff

RESERVED

3.3 APB 各模块的地址空间分配

表 3-3 APB 各模块地址分配

地址空间 模块 说明

0xbfe40000-0xbfe43fff UART0 16KB

0xbfe44000-0xbfe47fff UART1 16KB

0xbfe48000-0xbfe4bfff UART2 16KB

0xbfe4c000-0xbfe4ffff UART3 16KB

24

龙芯 1B 处理器用户手册

0xbfe50000-0xbfe53fff CAN0 16KB

0xbfe54000-0xbfe57fff CAN1 16KB

0xbfe58000-0xbfe5bfff I2C-0 16KB

0xbfe5c000-0xbfe5ffff PWM 16KB

0xbfe60000-0xbfe63fff

RESERVED

0xbfe64000-0xbfe67fff RTC 16KB

0xbfe68000-0xbfe6bfff I2C-1 16KB

0xbfe6c000-0xbfe6ffff UART4 16KB

0xbfe70000-0xbfe73fff I2C-2 16KB

0xbfe74000-0xbfe77fff AC97 16KB

0xbfe78000-0xbfe7bfff NAND 16KB

0xbfe7c000-0xbfe7ffff UART5 16KB

25

龙芯 1B 处理器用户手册

4 CPU

本章给出 1B 芯片内 CPU 的详细说明。GS232 核是一款实现 MIPS32 兼容且支持 DSP 扩

展和 EJTAG 调试的双发射处理器,通过采用转移预测、寄存器重命名、乱序发射、路预测

的指令 CACHE、非阻塞的数据 CACHE、写合并收集等技术来提高流水线的效率,形成了一款

具有突出的性能价格比及性能功耗比的 32 位嵌入式处理器 IP。

GS232 处理器 IP 具有如下主要特点:

MIPS32 兼容的 32 位处理器,包含可配置的 DSP 部件和 64 位浮点部件(FPU)。

高效的双发射+五级流水结构(取指、译码、发射、执行并写回、提交)

支持寄存器重命名、动态调度、转移预测等乱序发射、乱序执行技术。其中包含 6

项的转移队列、16 项重命名队列,采用 Gshare 转移猜测,BHT 为256 项。

包含两个定点、一个浮点、一个访存四个功能部件。

定点部件支持 DSP 扩展指令的运算。

浮点部件支持全流水的 64 位浮点加法和浮点乘法运算,硬件实现浮点除法运算。

专门的 SIMD 型多媒体加速指令。

32 项全相联 JTLB,每项映射两页,页大小可变,并具有可执行位设置以防止缓冲

区溢出攻击。

4项的指令 TLB 和8项的数据 TLB,每项映射一页,页大小可变。

分离的一级指令 Cache 和数据 Cache,可配置为 1路/2 路/4 路组相联,每路大小各

为4KB。

支持非阻塞的 Cache 访问技术,4项load 队列、2项store 队列、3项miss 队列,

最多容忍 5条store 指令 Cache 不命中和 4条load 指令 Cache 不命中。

支持 cached store 指令的写合并和 uncache 写加速技术

支持 cache lock 技术和预取指令

软IP 级可配置:是否包含 DSP 指令支持、浮点部件、指令和数据 Cache 的大小

(4KB/8KB/16KB)、定点乘法规模(半规模/全规模/串行)等可配置以满足不同应用的

要求。

标准的 EJTAG 调试标准,方便软硬件调试。

标准的 32 位AMBA AHB 接口。

上述特点使得 GS232 处理器 IP 具有执行效率高,功耗和成本低的优势,可在面向

嵌入式的应用领域中得到广泛采用。

4.1 MIPS32 指令系统结构

MIPS 公司开发的 MIPS 体系结构(ISA)已经发展了 6个版本,依次分别为 MIPS I,MIPS

II,MIPS III,MIPS IV,MIPS V 和MIPS 32/64,版本之间向前兼容。目前最新的是 MIPS

32/64 体系结构的 Release2 版本,其中,MIPS32 体系结构基于 MIPSII 体系结构的指令集,

并补充了 MIPS III,IV 和V中的部分指令增强其生成代码和移动数据的效率;MIPS64 体

系结构基于 MIPS V 体系结构的指令集,兼容 MIPS 32 体系结构。

MIPS32 是MIPS 公司为了统一 MIPS 指令系统的不同版本,在 MIPS II 的基础上进行扩

充,并对系统态的指令进行规范而定义的。MIPS32 指令系统的用户态指令融合了不同指令

系统的优点,系统态指令也更加规范。

26

龙芯 1B 处理器用户手册

GS232 处理器兼容 MIPS32 的Release2 体系结构。MIPS32 主要包括 ISA(Instruction

Set Architecture)、 PRA(Privileged Resource Architecture)、 ASEs(Application

Specific Extensions)和 UDI(User Defined Instructions)四个部分,GS232 处理器实

现了 ISA、PRA,以及 DSP ASE。

本章从 CPU,DSP,FPU,PRA 四个方面描述 GS232 指令结构系统,并分别给出指令列表,

以及 GS232 实现的 CP0 寄存器的定义。GS232 与MIPS32 Release1 兼容,具体的指令说明

以及寄存器描述可以参见 MIPS32 用户手册。

4.1.1 CPU 寄存器

MIPS32 体系结构定义了如下 CPU 寄存器:

(1)32 个32 位的通用寄存器。GPRs(general purpose registers)。其中有两个被

赋予了特殊含义:R0,0号通用寄存器,值永远为 0;R31,31 号通用寄存器,被 JAL,BLTZAL,

BLTZALL,BGEZAL,和 BGEZALL 指令隐式的用作目标寄存器,存放返回地址。

(2)一对用于保存乘法、除法和乘加操作的结果的特殊寄存器。HI 和LO。HI 寄存器

用于存放乘或者除运算结果的高位;LO 寄存器用于存放乘或者除运算结果的低位。

(3)一个特殊的程序计数器(PC)。这个寄存器程序不可直接访问。

4.1.2 CPU 指令集

MIPS32 体系结构的定义把 CPU 指令集按照功能划分为以下几组:存取、计算、跳转分

支、协处理器和杂项指令。①Load 和Store 访存指令在主存和通用寄存器之间移动数据。

访存指令都是立即数指令(I型),因为该指令模式所支持的唯一访存模式就是基址寄存器

加上 16 位的对齐的偏移量。②Computational 计算型指令完成寄存器值的算术、逻辑、移

位、乘法和除法操作。计算型指令包含了寄存器指令格式(R型,操作数和运算结果均保

存在寄存器中)和立即数指令格式(I型,其中一个操作数为一个 16 位的立即数)。③Jump

and Branch 跳转和分支指令改变程序的控制流。绝对地址跳转被称为“Jump( 跳 转 )”( J

型或者 R型 ), PC(指令计数器)相关的跳转指令被称为“Branch(分支)”(I型 )。 ④

Coprocessor 协处理器指令完成协处理器内部的操作。协处理器的访存操作是 I型指令。

在MIPS32 定义了 0号协处理器(系统处理器)和 1号协处理器(浮点协处理器),用户可

以自定义 2号协处理器的功能。⑤Special 特殊指令完成系统调用和断点操作。这些指令

通常是 R型的。⑥Exception 异常指令引起跳转,根据异常号比较结果跳转到通用异常处

理向量。这些指令包括 R型和 I型指令格式。

GS232 IP 虽然与 MIPS32 Release2 版本兼容,从功能上实现了 MIPS32 体系结构规定

的所有 CPU 指令,但是有些指令在实现了有细微的并不影响兼容性的差别,以下值得编程

人员注意。

pref、prefx 指令。

表 4-1 到表 4-10 列出了 GS232IP 实现的 MIPS32 指令中的 CPU 指令。MIPS32 的浮点

和CP0 协处理器指令在后面章节介绍。

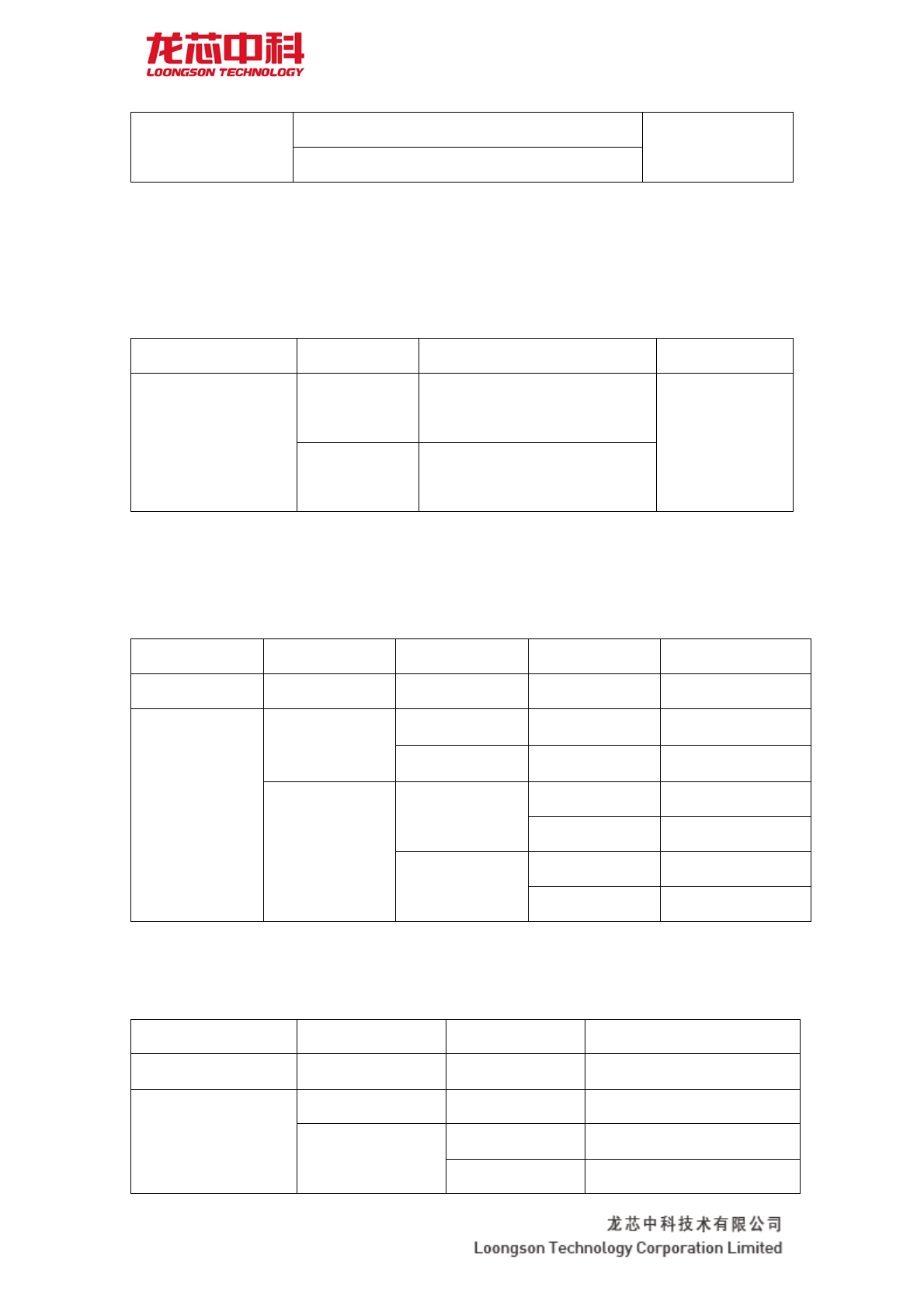

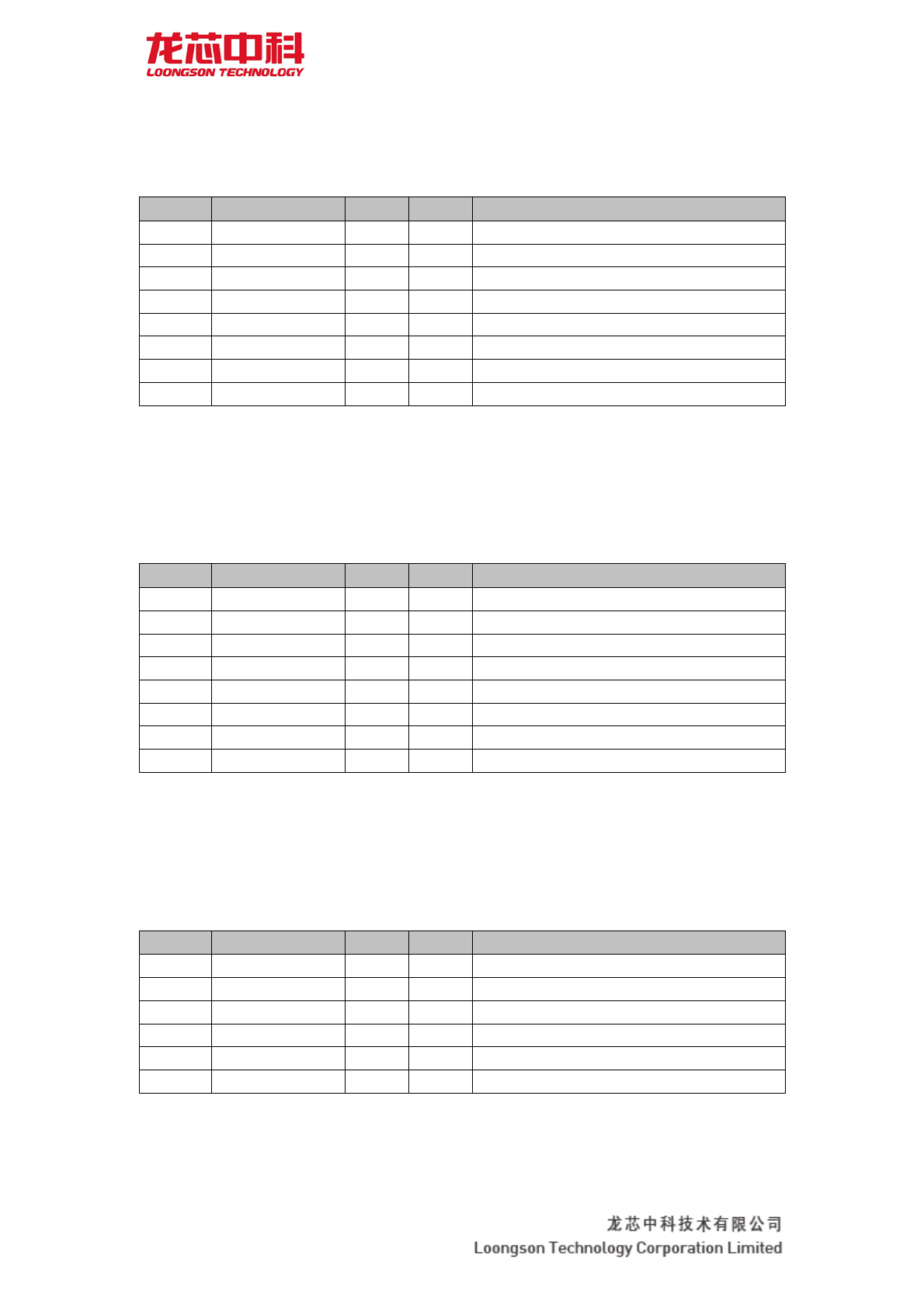

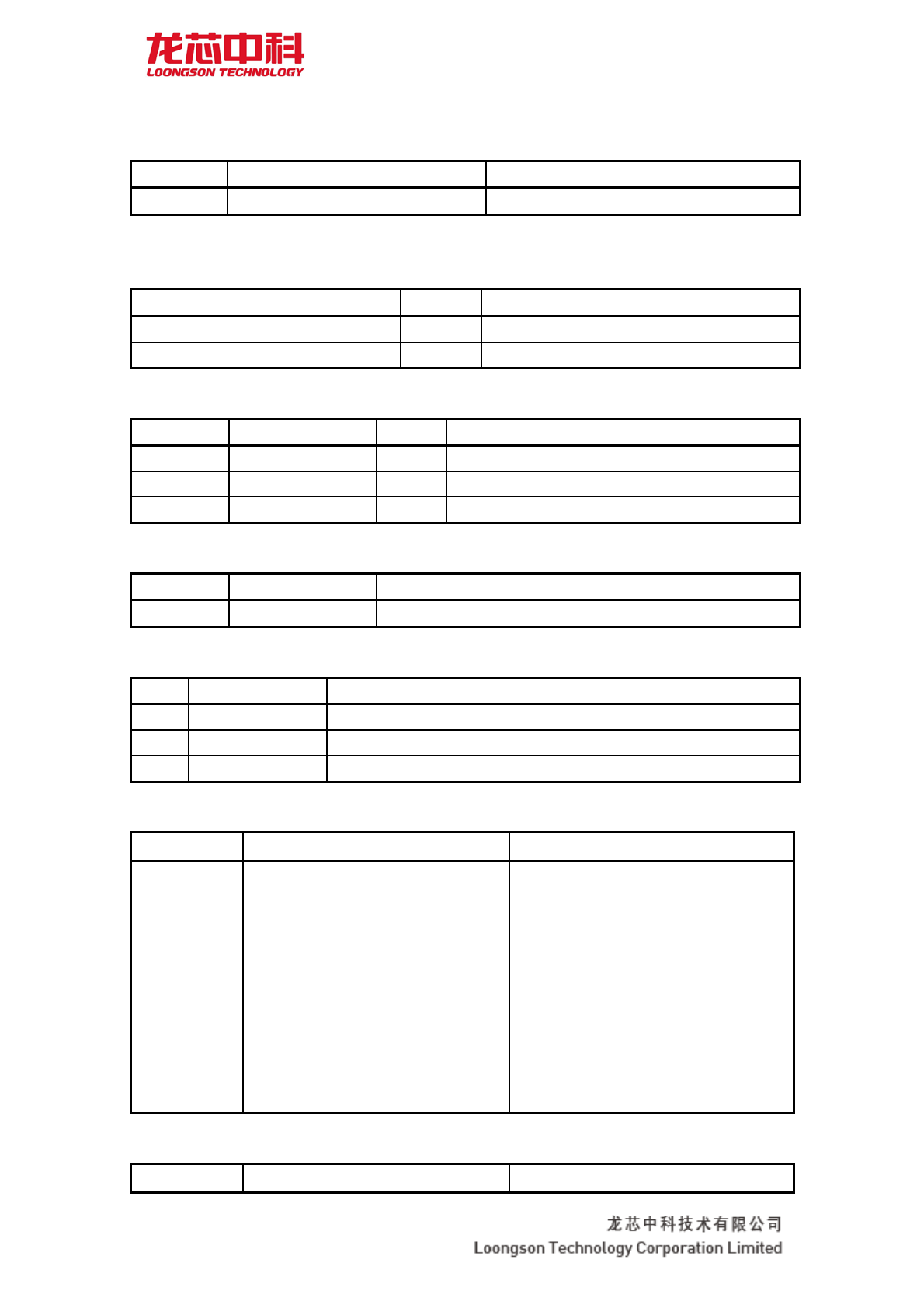

表 4-1 CPU 指令集:访存指令

OpCode

Description

MIPS ISA

LB 取字节 I

LBU 取无符号字节 I

LH 取半字 I

27

龙芯 1B 处理器用户手册

OpCode

Description

MIPS ISA

LHU 取无符号半字 I

LW 取字 I

LWU 取无符号字 I

LWL 取字左部 I

LWR 取字右部 I

LL 取标志处地址 I

SB 存字节 I

SH 存半字 I

SW 存字 I

SWL 存字左部 I

SWR 存字右部 I

SC 满足条件下存 I

SYNC 同步 I

PREF 预取 MIPS32

表 4-2 CPU 指令集:算术指令 (ALU 立即数)

OpCode

Description

MIPS ISA

ADDI 加立即数 I

ADDIU 加无符号立即数 I

SLTI 小于立即数设置 I

SLTIU 无符号小于立即数设置 I

ANDI 与立即数 I

ORI 或立即数 I

XORI 异或立即数 I

LUI 取立即数到高位 I

表 4-3 CPU 指令集:算术指令 (2 操作数)

OpCode

Description

MIPS ISA

CLO 计算前导 0的个数 MIPS32

CLZ 计算前导 1的个数 MIPS32

表 4-4 CPU 指令集:算术指令(3 操作数, R-型)

OpCode

Description

MIPS ISA

ADD 加 I

ADDU 无符号加 I

SUB 减 I

SUBU 无符号减 I

28

龙芯 1B 处理器用户手册

SLT 小于设置 I

SLTU 无符号小于设置 I

AND 与 I

OR 或 I

XOR 异或 I

NOR 或非 I

表 4-5 CPU指令集:乘法和除法指令

OpCode

Description

MIPS ISA

MADD 乘加 MIPS32

MADDU 无符号乘加 MIPS32

MSUB 乘减 MIPS32

MSUBU 无符号乘减 MIPS32

MUL 乘(结果放到 GPR) MIPS32

MULT 乘(结果放到 HI,LO) I

MULTU 无符号乘 I

DIV 除 I

DIVU 无符号除 I

MFHI 从hi 寄存器取数到通用寄存器 I

MTHI 从通用寄存器存数到 hi 寄存器 I

MFLO 从lo 寄存器取数到通用寄存器 I

MTLO 从通用寄存器存数到 lo 寄存器 I

表 4-6 CPU 指令集:跳转和分支指令

Opcode

Description

MIPS ISA

J 跳转 I

JAL 立即数调用子程序 I

JR 跳转到寄存器指向的指令 I

JALR 寄存器调用子程序 I

BEQ 相等则跳转 I

BNE 不等则跳转 I

BLEZ 小于等于 0跳转 I

BGTZ 大于 0跳转 I