( MPRH01TSU 02_603_604_Reference_Design_2.1_Aug95 02 603 604 Reference Design 2.1 Aug95

MPRH01TSU-02_603_604_Reference_Design_2.1_Aug95 MPRH01TSU-02_603_604_Reference_Design_2.1_Aug95

User Manual: MPRH01TSU-02_603_604_Reference_Design_2.1_Aug95

Open the PDF directly: View PDF ![]() .

.

Page Count: 200 [warning: Documents this large are best viewed by clicking the View PDF Link!]

R

PowerPC 603/604 Reference

Design Technical Specification

This document provides a detailed

technical description of the PowerPC

603/604 Reference Design. It is in-

tended as a first source of information

for both hardware and software de-

signers. Where appropriate, other

documents are referenced.

Document Number:

MPRH01TSU-02

August, 9 1995

Release 2.1

2MPRH08TSU-02

International Business Machines Corporation, 1995. Printed in the United States of America 8/95. All Rights

reserved.

IBM Microelectronics, PowerPC, PowerPC 601, PowerPC 603, PowerPC 603e, PowerPC 604, RISCWatch,

and AIX are trademarks of the IBM corporation. IBM and the IBM logo are registered trademarks of the IBM

corporation. Other company names and product identifiers are trademarks of the respective companies.

This document contains information which is subject to change by IBM without notice. IBM assumes no re-

sponsibility or liability for any use of the information contained herein. Nothing in this document shall operate

as an express or implied license or indemnity under the intellectual property rights of IBM or third parties. The

products described in this document are not intended for use in implantation or other direct life-support ap-

plications where malfunction may result in physical harm or injury to persons. NO WARRANTIES OF ANY

KIND, INCLUDING BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY OR

FITNESS FOR A PARTICULAR PURPOSE, ARE OFFERED IN THIS DOCUMENT.

Contacts

USA and Canada:

IBM Microelectronics Division

1580 Route 52, Bldg. 504

Hopewell Junction, NY 12533-6531

Tel: (800) PowerPC

Fax: (800) PowerFax

Japan:

IBM

800, Ichimiyake

Yasu–cho, Yasu–gun

Shiga–ken, Japan 520–23

Tel: (81) 775–87–4745

Fax: (81) 775–87–4735

Europe:

IBM

La Pompignane BP 1021

34006 Montpellier, France

Tel: (33) 6713–5757 (Français)

(33) 6713–5756 (Italiano)

Fax: (33) 6713–5750

( from Paris add 16)

Europe:

IBM

Informations Systeme GmbH

Laatzener Str. 1

30539 Hannover, Germany

Tel: (49) 511–516–3444 (English)

(49) 511–516–3555 (Deutsche)

Fax: (49) 511–516–3888

ESD Warning

The motherboard and memory cards contain CMOS devices which are very susceptible

to ElectroStatic Discharge (ESD). DO NOT remove them from the antistatic bags until you

have connected yourself to an acceptable ESD grounding strap. Work in a static free envi-

ronment and be sure any person or equipment coming into contact with the cards do not

have a static charge. The cards are particularly susceptible until they are placed in a prop-

erly designed enclosure. Bench work should be done by persons connected to ESD

grounding straps.

3

MPRH08TSU-02

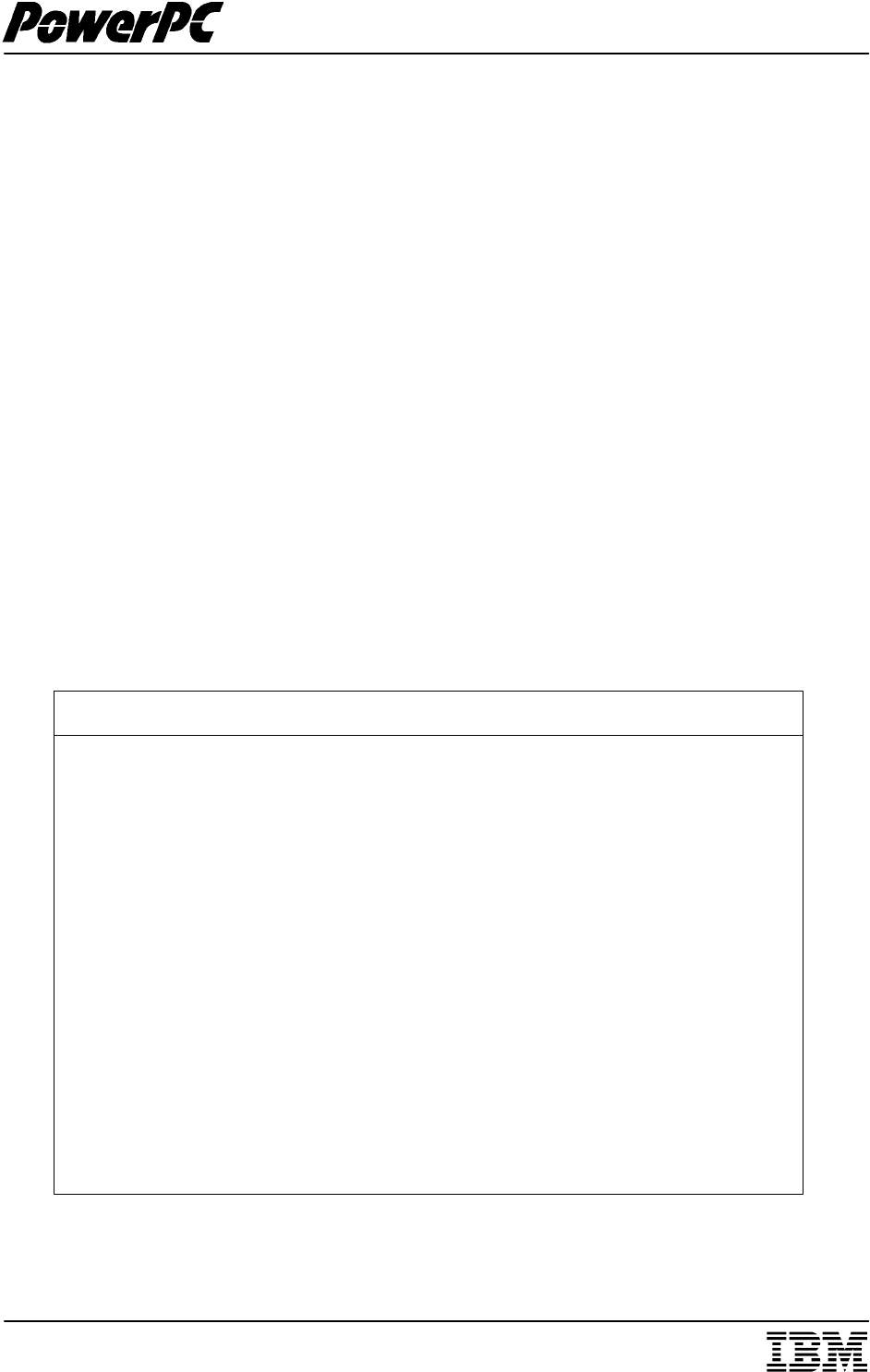

IBM POWERPCTM 603/604 REFERENCE DESIGN AGREEMENT

BEFORE READING THE REST OF THE DOCUMENT, YOU SHOULD CAREFULLY READ THE FOLLOWING TERMS

AND CONDITIONS. OPENING THE PACKAGE INDICATES YOUR ACCEPTANCE OF THESE TERMS AND CONDI-

TIONS. IF YOU DO NOT AGREE WITH THEM, YOU SHOULD PROMPTLY RETURN THE PACKAGE UNOPENED TO

YOUR IBM SALES OFFICE.

International Business Machines Corporation (”IBM”) agrees to provide you a PowerPC 603/604 Reference Design (Reference Design)

in return for your promise to use reasonable efforts to develop a system based on the technology in the Reference Design. The Reference

Design contains documentation and software listed below:

Documentation

PowerPC 603e RISC Microprocessor Hardware Specification

PowerPC 603e RISC Microprocessor Technical Summary

PowerPC 603/604 RISC Microprocessor Hardware Specification

PowerPC 603/604 Reference Design Technical Specification

IBM PowerPC 603/604 Reference Board Design Files (on 8mm tape)

IBM PowerPC 604 Reference Board Mfg. Data Files (in Gerber format)

IBM14N1372 Data Sheet

IBM11D4360B Data Sheet

Motorola MPC970 Data Sheet

Altera 5130 Data Sheet

Integrated Device Technology IDT71216 Data Sheet

LICENSE TO SOFTWARE

The software is licensed not sold. IBM, or the applicable IBM country organization, grants you a license for the software only in the country

where you received the software. Title to the physical software and documentation (not the information contained in such documentation)

transfers to you upon your acceptance of these terms and conditions. The term ”software” means the original and all whole or partial copies

of it, including modified copies or portions merged into other programs. IBM retains title to the software. IBM owns, or has licensed from

the owner, copyrights to the software provided under this agreement. The terms of this Agreement apply to all of the hardware, software

and documentation provided to you as part of the Reference Design.

With regard to the software provided hereunder, it is understood and agreed that you intend to use the software solely for the purpose of

designing PowerPC compatible products, testing your designs, and making your own independent determination of whether you wish to

eventually manufacture PowerPC compatible products commercially. In accordance with this understanding, IBM hereby grants you the

rights to: a) use, run, and copy the software, but only make such number of copies and run on such number of machines as are reasonably

necessary for the purpose of designing PowerPC compatible products and testing such designs; and b) copy the software for the purpose

of making one archival or backup copy.

With regard to any copy made in accordance with the foregoing license, you must reproduce any copyright notice appearing thereon. With

regard to the software provided hereunder, you may not: a) use, copy, modify or merge the software, except as provided in this license;

b) reverse assemble or reverse compile it; or c) sell, sublicense, rent. lease, assign or otherwise transfer it. In the event that you no longer

wish to use the software, you will return it to IBM.

LICENSE TO DESIGN DOCUMENTATION

With regard to the design documentation provided hereunder, it is understood that you intend to use such documentation solely for the pur-

pose of designing your own PowerPC compatible products, testing your designs, and making your own independent determination of wheth-

er you wish to eventually manufacture PowerPC compatible products commercially. In accordance with this understanding, IBM hereby

grants you the right to: a) use the design documentation for the purpose of designing PowerPC compatible products and testing such de-

signs; b) make derivative works of the design documentation for the purpose of designing PowerPC compatible products, and testing such

designs; and c) make copies of the design documentation and any such derivative works, but only such numbers as are reasonably neces-

sary for designing PowerPC compatible products and testing such designs.

With regard to any copy made in accordance with the forgoing license, you must reproduce any copyright notice appearing thereon. With

regard to the design documentation provided hereunder, you may not: a) use, copy, modify, or merge the design documentation as provided

in this license; or b) sell, sublicense, rent, lease, assign, or otherwise transfer it.

In the event you no longer wish to use the design documentation or any derivative versions thereof, you must return them to IBM.

DISCLAIMER OF WARRANTY

IBM does not represent or warrant that the Reference Design (which may contain prototype items): a) meets any particular requirements;

b) operates uninterrupted; c) is error free; or d) is non–infringing of any patent, copyright, or other intellectual property right of any third party.

IBM makes no representation or warranty regarding the performance or compatibility that may be obtained from the use of the Reference

Design or that the Reference Design is adequate for any use. The Reference Design may contain errors and may not provide the level

of completeness, functionality, support, performance, reliability, or ease of use available with other products, whether or not similar to the

Reference Design. IBM does not represent or warrant that errors or other defects will be identified or corrected.

THE REFERENCE DESIGN IS PROVIDED ”AS IS” WITH ALL FAULTS, WITHOUT WARRANTY OF ANY KIND, EX-

PRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND

FITNESS FOR A PARTICULAR PURPOSE. THE ENTIRE RISK AS TO THE QUALITY AND PERFORMANCE OF THE

REFERENCE DESIGN IS WITH YOU.

Some jurisdictions do not allow exclusion of implied warranties, so the above exclusions may not apply to you.

4MPRH08TSU-02

LIMITATION OF REMEDIES

IBM’s entire cumulative liability and your exclusive remedy for damages for all causes, claims or actions wherever and whenever asserted

relating in any way to the subject matter of this agreement including the contents of the Reference Design and any components thereof,

is limited to twenty five thousand dollars ($25,000.00) or its equivalent in your local currency and is without regard to the number of items

in the Reference Design that caused the damage. This limitation will apply, except as otherwise stated in this Section, regardless of the

form of the action, including negligence. This limitation will not apply to claims by you for bodily injury or damages to real property or tangible

personal property. In no event will IBM be liable for any lost profits, lost savings, or any incidental damages or economic consequential dam-

ages, even if IBM has been advised of the possibility of such damages, or for any damages caused by your failure to perform your responsibi-

lities. In addition, IBM will not be liable for any damages claimed by you based on any third party claim. Some jurisdictions do not allow these

limitations or exclusions, so they may not apply to you.

RISK OF LOSS

You are responsible for all risk of loss or damage to the Reference Design upon its delivery to you.

IBM TRADEMARKS AND TRADE NAMES

This Agreement does not give you any rights to use any of IBM’s trade names or trademarks. You agree that should IBM determine that

any of your advertising, promotional, or other materials are inaccurate or misleading with respect to IBM trademarks or trade names, that

you will, upon written notice from IBM, change or correct such materials at your expense.

NO IMPLIED LICENSE TO IBM INTELLECTUAL PROPERTY

Notwithstanding the fact that IBM is hereby providing design information for your convenience, you expressly understand and agree that,

except for the rights granted under sections 1 and 2 above, no right or license of any type is granted, expressly or impliedly, under any pat-

ents, copyrights, trade secrets, trademarks, or other intellectual property rights of IBM. Moreover, you understand and agree that in the

event you wish to be granted any license beyond the scope of the expressly stated herein, you will contact IBM’s Intellectual Property Licens-

ing and Services Office (currently located at 500 Columbus Avenue, Thornwood, N.Y.), or such other IBM offices responsible for the licens-

ing of IBM intellectual property, when you seek the license.

YOUR ASSUMPTION OF RISK

You shall be solely responsible for your success in designing, developing, manufacturing, distributing, and marketing any product(s), or

portion(s), where use of all or any part of the Reference Design is involved. You are solely responsible for any claims, warranties, represen-

tations, indemnities and liabilities you undertake with your customers, distributors, resellers or others, concerning any product(s) or por-

tion(s) of product(s) where use of all or any part of the Reference Design is involved. You assume the risk that IBM may introduce other

Reference Design that are somehow better than the Reference Design which is the subject of this Agreement. Furthermore, you accept

sole responsibility for your decision to select and use the Reference Design; for attainment or non-attainment of any schedule, performance,

cost, reliability, maintainability, quality, manufacturability or the like, requirements, or goals, self–imposed by you or accepted by you from

others, concerning any product(s) or portion(s) of product(s), or for any delays, costs, penalties, charges, damages, expenses, claims or

the like, resulting from such non-attainment, where use of all or any part of the Reference Design is involved.

GENERAL

In the event there is a conflict between the terms of this Agreement and the terms printed or stamped on any item or any ambiguities with

respect thereto, including documentation, contained in the Reference Design, the terms of this Agreement control to the extent IBM is af-

forded greater protection thereby. IBM may terminate this Agreement if you fail to comply with the terms and conditions of this Agreement.

Upon termination of this Agreement, you must destroy all copies of the software and documentation. You are responsible for payment of

any taxes, including personal property taxes, resulting from this Agreement. Neither party may bring an action hereunder, regardless of form,

more than one (1) year after the cause of the action arose. If you acquired the Reference Design in the United States, this Agreement is

governed by the laws of the State of New York. In the event of litigations, trial shall be in New York without a jury. If you acquired the Refer-

ence Design in Canada, this Agreement is governed by the laws of the Province of Ontario; otherwise, this Agreement is governed by the

laws of the country in which you acquired the Reference Design. All obligations and duties which, by their nature, survive termination or

expiration of this Agreement, shall remain in effect beyond termination or expiration of this Agreement, and shall bind IBM, you and your

successors and assigns. If any section or paragraph of this Agreement is found by competent authority to be invalid, illegal or unenforceable

in any respect for any reason, the validity, legality, and enforceability of any such section or paragraph in every other respect, and the remain-

der of this Agreement, shall continue in effect so long as it still expresses the intent of the parties. If the intent of the parties cannot be pre-

served, the parties will attempt to renegotiate this Agreement and failing renegotiation, this Agreement will then be terminated. The headings

in this Agreement shall not affect the meaning or interpretation of this Agreement in any way. No failure by IBM in exercising any right, power

or remedy under this Agreement shall serve as a waiver of any such right, power or remedy. Neither this Agreement nor any activities here-

under will impair any right of IBM to develop, manufacture, use or market, directly or indirectly, alone or with others, any products or services

competitive with those offered or to be offered by you; nor will this Agreement or any activities hereunder require IBM to disclose any busi-

ness planning information to you. You agree to comply with all applicable government laws and regulations. Any changes to this Agreement

must be in writing and signed by the parties.

5

MPRH08TSU-02

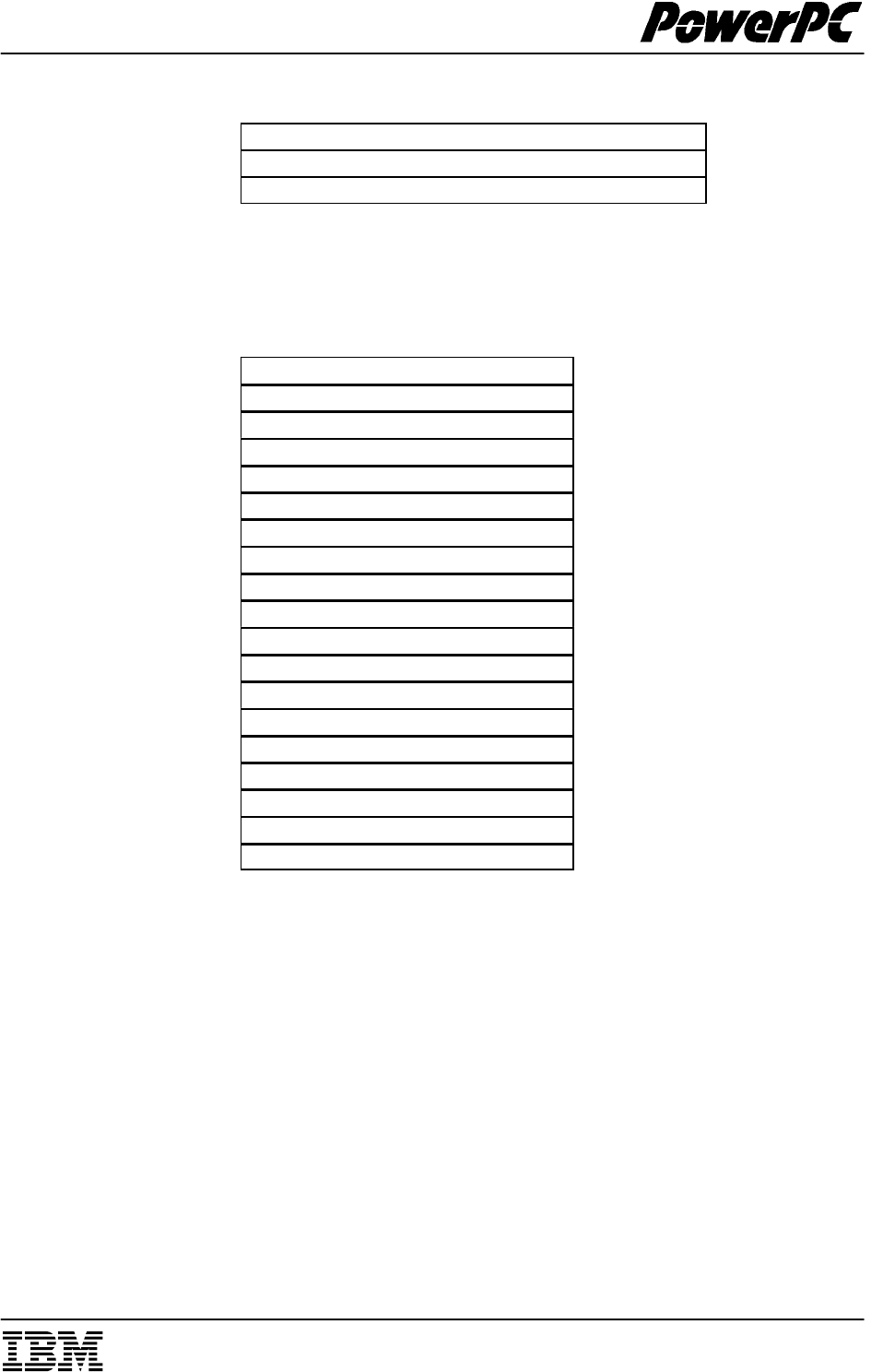

Table of Contents

Section 1 Introduction 17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.1 IBM Reference Products 17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.1.1 Reference Design 17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.1.2 Reference Board 17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.1.3 Reference Firmware 17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.1.4 Reference System 18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2 Purpose 18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3 Reference Design Overview 19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3.1 The CPU 19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3.2 IBM27-82660 Bridge 19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3.3 L2 Cache 19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3.4 System Memory 20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3.5 PCI Bus 21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3.6 Flash ROM 21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3.7 ISA Bus 21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3.8 Time of Day Clock 21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3.9 PS/2t Compatible Keyboard/Mouse Controller 21. . . . . . . . . . . . . . . . .

1.3.10 System Clocks 21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3.11 System I/O EPLD 21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.4 Quickstart Peripheral List 22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.5 Reference Design Level 22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Section 2 CPU and CPU Bus 25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1 CPU Bus Masters 25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.1 603e CPU 25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.2 604 CPU 26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2 System Response by CPU Bus Transfer Type 26. . . . . . . . . . . . . . . . . . . . .

2.3 System Response by CPU Bus Address Range 28. . . . . . . . . . . . . . . . . . . .

2.3.1 Address Mapping for Non-Contiguous I/O 28. . . . . . . . . . . . . . . . . . . . . .

2.3.2 Address Mapping for Contiguous I/O 30. . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3.3 PCI Final Address Formation 30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.4 CPU to Memory Transfers 30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.4.1 LE Mode 31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.5 CPU to PCI Transactions 31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.5.1 CPU to PCI Read 31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.5.2 CPU to PCI Write 31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.5.2.1 Eight-Byte Writes to the PCI (Memory and I/O) 31. . . . . . . . . . . . . . . . .

2.5.3 CPU to PCI Memory Transactions 32. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.5.4 CPU to PCI I/O Transactions 32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.5.5 CPU to PCI Configuration Transactions 32. . . . . . . . . . . . . . . . . . . . . . . .

2.5.5.1 Preferred Method of Generating PCI Configuration Transactions 32.

6MPRH08TSU-02

2.5.5.2 650 Bridge compatible method 32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.5.6 CPU to PCI Interrupt Acknowledge Transaction 33. . . . . . . . . . . . . . . . .

2.5.7 PCI Lock 33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6 CPU to ROM Transfers 33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6.1 CPU to ROM Read 34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6.2 CPU to ROM Write 34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6.2.1 ROM Write Protection 34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6.3 CPU to BCR Transfers 34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Section 3 PCI Bus 35. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1 PCI Transaction Decoding 35. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1.1 PCI Transaction Decoding By Bus Command 36. . . . . . . . . . . . . . . . . . .

3.1.2 PCI Memory Transaction Decoding By Address Range 36. . . . . . . . . . .

3.1.3 PCI I/O Transaction Decoding 38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1.4 ISA Master Considerations 38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2 PCI Transaction Details 38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.1 Bus Snooping on PCI to Memory Cycles 39. . . . . . . . . . . . . . . . . . . . . . .

3.2.2 PCI to PCI Peer Transactions 39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.3 PCI to System Memory Transactions 39. . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3 Bus Arbitration Logic 41. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4 Other PCI Considerations 41. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Section 4 ISA Bus 43. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.1 The ISA Bridge 43. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2 Address Ranges 44. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3 ISA Bus Concurrency 44. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4 ISA Bus Masters and IGN_PCI_AD31 44. . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.5 DMA 46. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.5.1 Supported DMA Paths 46. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.5.2 DMA Timing 46. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.5.3 Scatter-Gather 46. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.6 X-Bus 47. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.6.1 Control Signal Decodes 47. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.6.2 Keyboard/Mouse Controller 47. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.6.3 Real Time Clock (RTC) 47. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.6.4 PCI Adapter Card Presence Detect Register 47. . . . . . . . . . . . . . . . . . . .

4.6.5 L2 SRAM Identification Register 46. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.6.6 Planar ID Detection Register 48. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.6.7 DRAM Presence Detection 49. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.6.7.1 DRAM SIMM 1-2 Memory ID Register 49. . . . . . . . . . . . . . . . . . . . . . . . .

4.6.7.2 DRAM SIMM 3-4 Memory ID Register 49. . . . . . . . . . . . . . . . . . . . . . . . .

4.7 Miscellaneous 50. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.7.1 Speaker Support 60. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Section 5 System I/O EPLD 51. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1 System Register Support 51. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7

MPRH08TSU-02

5.1.1 External Register Support 51. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1.2 Internal Registers 52. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1.2.1 Storage Light Register 52. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1.2.2 Power Management Control Register 1 52. . . . . . . . . . . . . . . . . . . . . . .

5.1.2.3 Power Management Control Register 2 53. . . . . . . . . . . . . . . . . . . . . . .

5.1.2.4 Freeze Clock Register (FCR) Low 53. . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1.2.5 Freeze Clock Register (FCR) High 53. . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2 Signal Descriptions 54. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3 EPLD Design Equations 57. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3.1 Fit File 57. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3.2 TDF File 59. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Section 6 Memory Systems 67. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

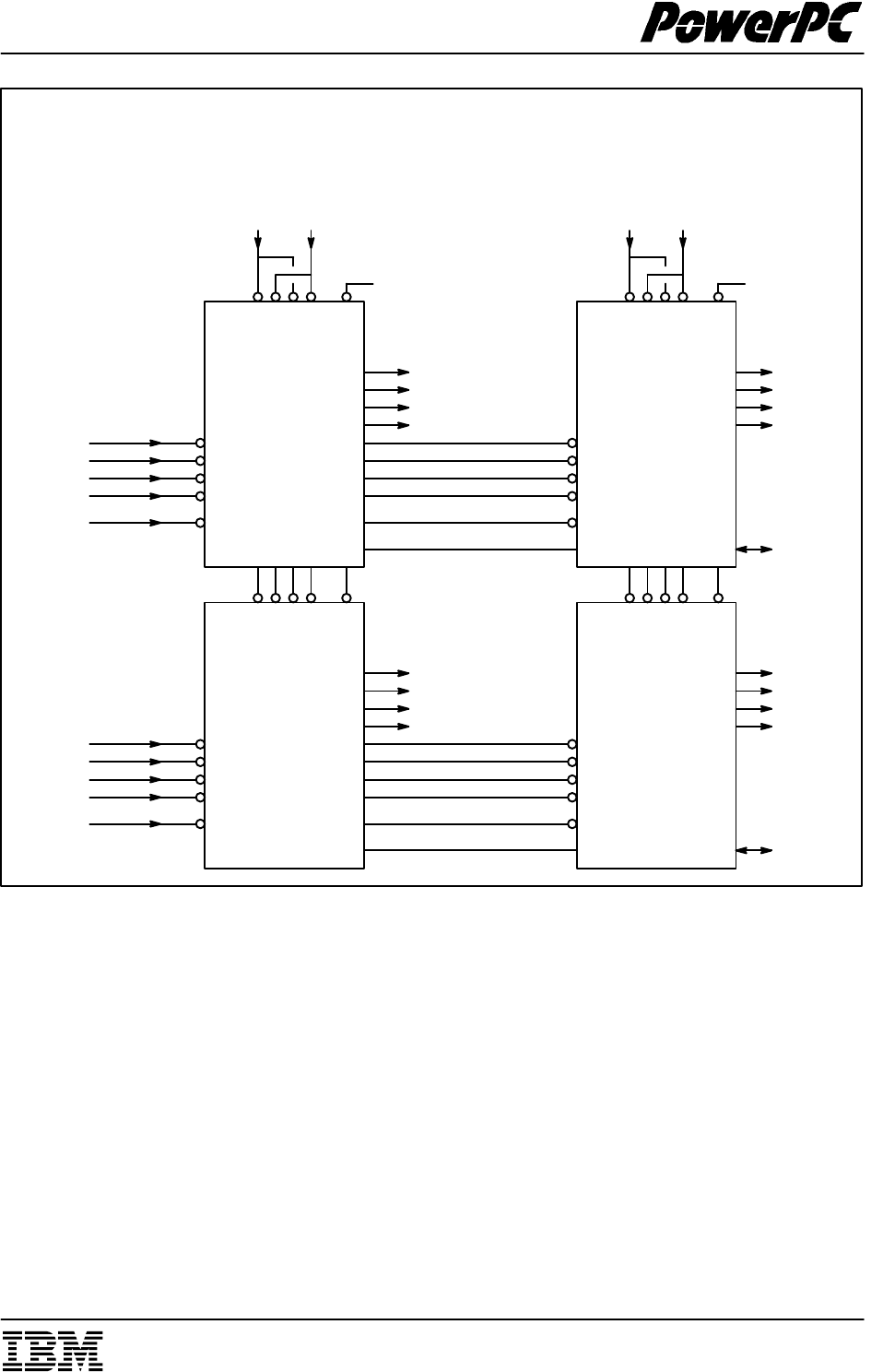

6.1 DRAM 67. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.1.1 Refresh 67. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.1.2 DRAM Presence Detection 67. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.1.3 Organization 68. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

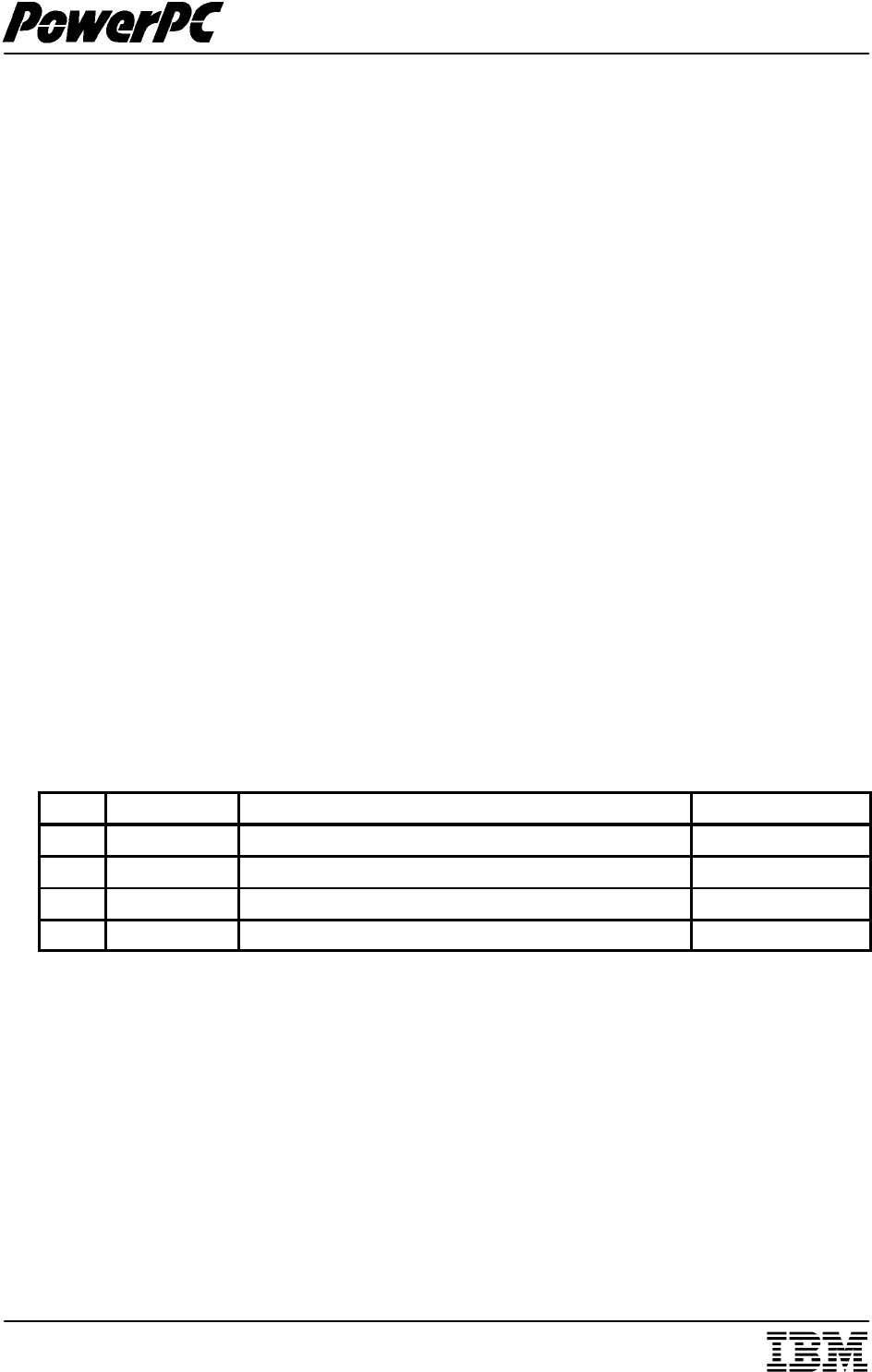

6.2 L2 Cache 69. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

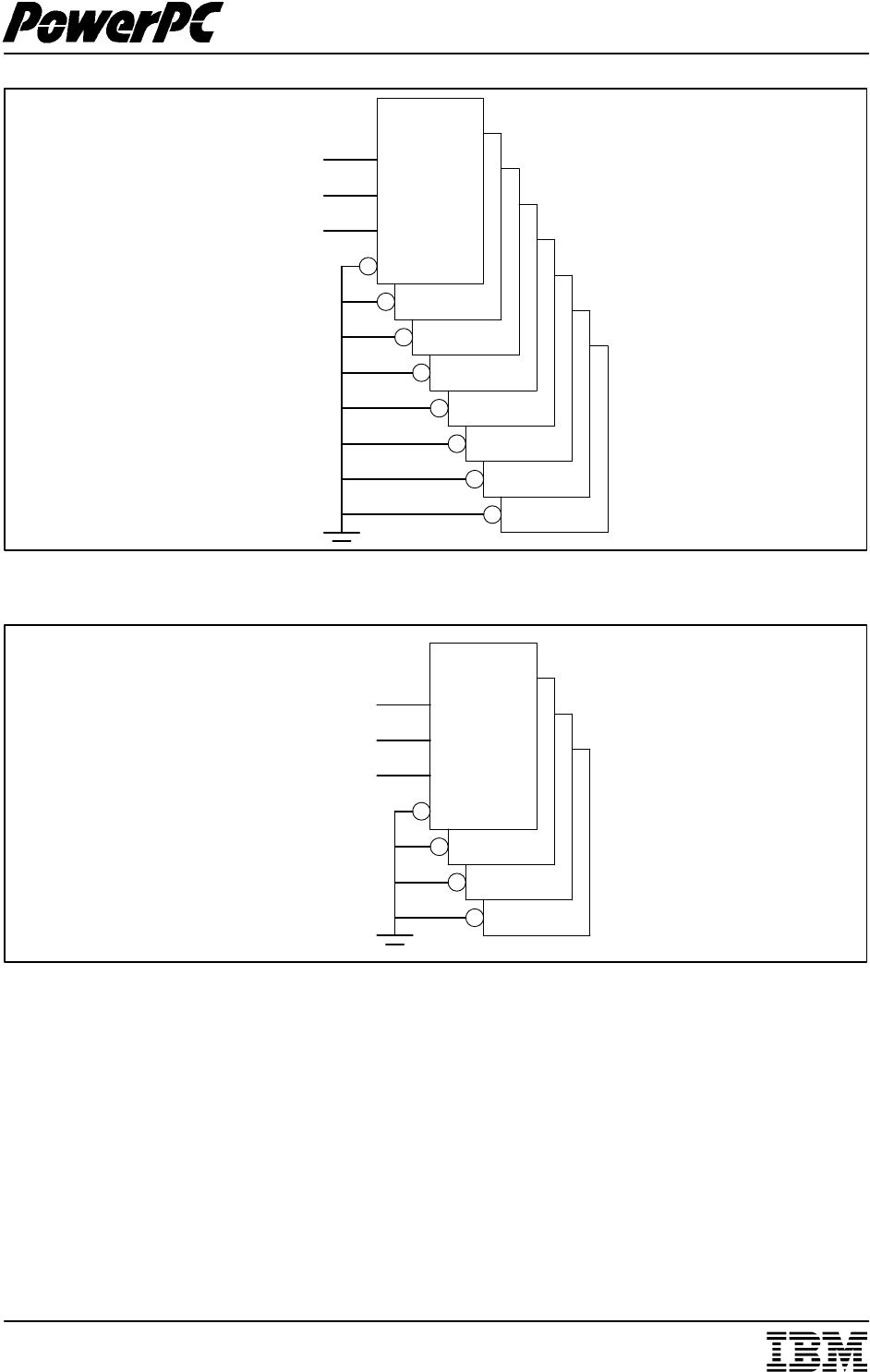

6.2.1 SRAM 69. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.2.2 TagRAM 72. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.2.3 L2 Cache Configuration 73. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3 ROM 74. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.4 CPU to ROM Transfers 74. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.4.1 CPU to ROM Read 74. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.4.2 CPU to ROM Write 74. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.4.2.1 ROM Write Protection 75. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Section 7 Endian Mode Considerations 77. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

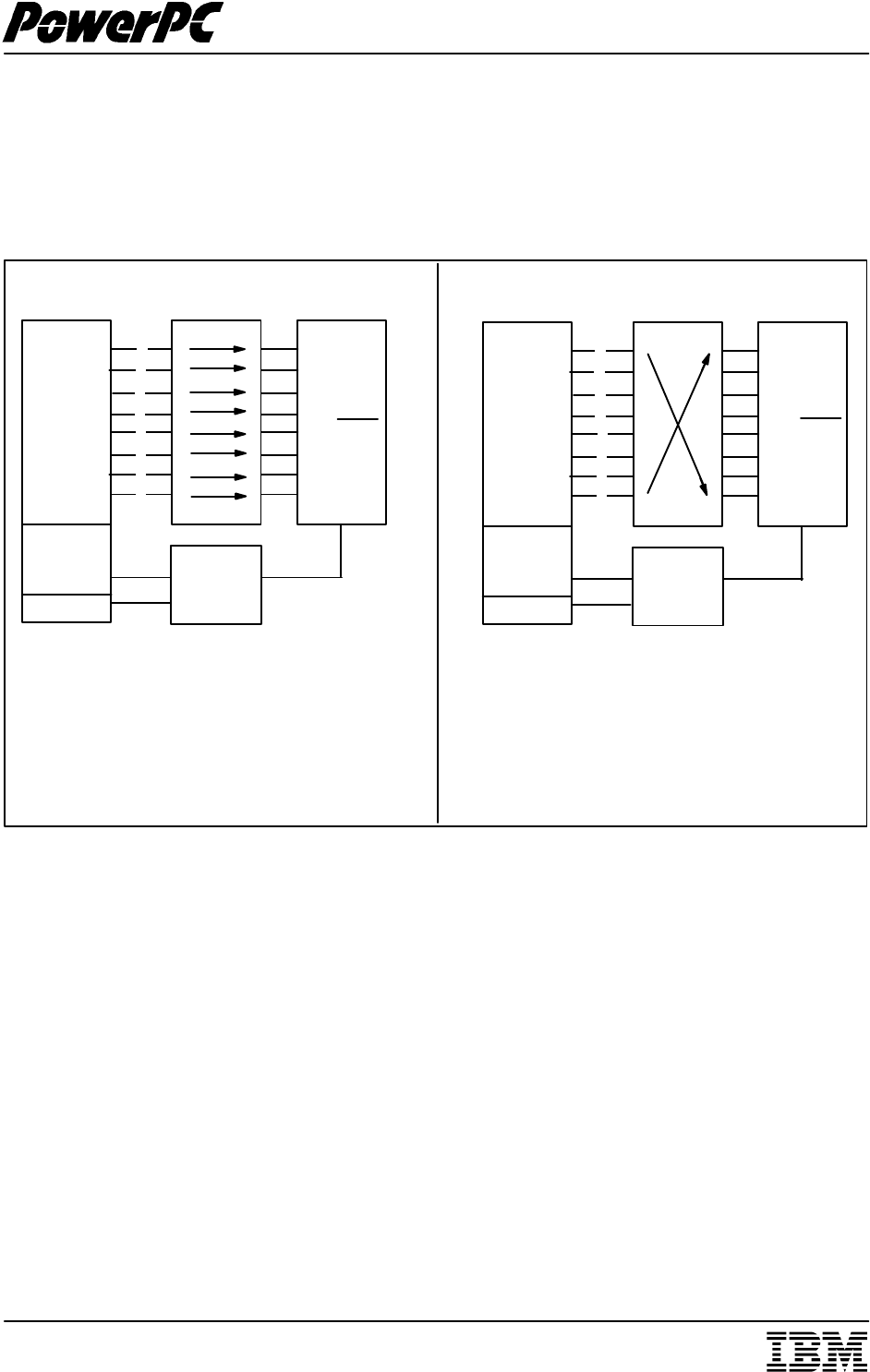

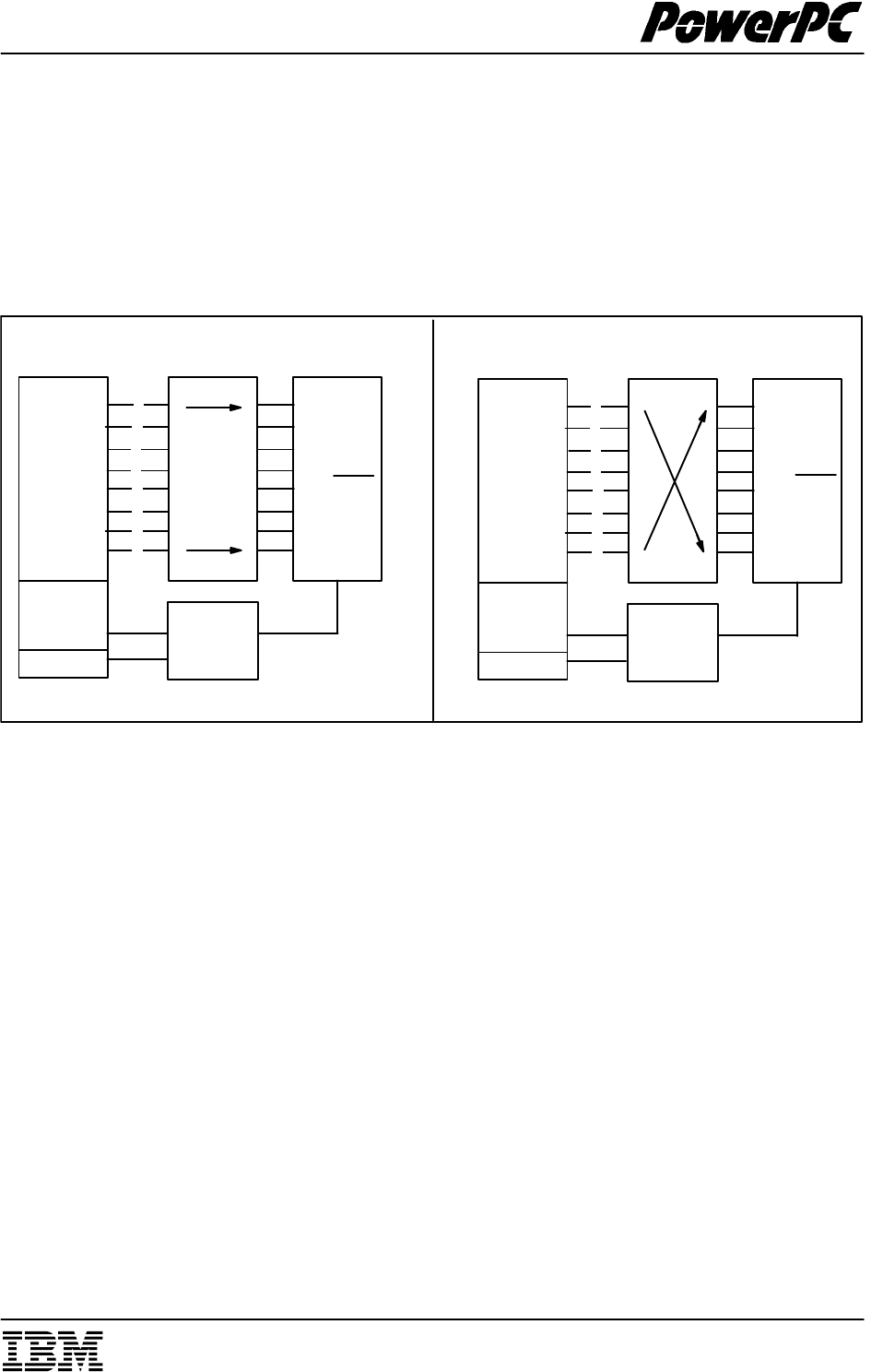

7.1 What the 603/604 CPU Does 77. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.2 What the 660 Bridge Does 78. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.3 Bit Ordering Within Bytes 79. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.4 Byte Swap Instructions 79. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.5 603/604 CPU Alignment Exceptions In LE Mode 80. . . . . . . . . . . . . . . . . . .

7.6 Single–Byte Transfers 80. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.7 Two–Byte Transfers 84. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.8 Four–Byte Transfers 86. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.9 Three byte Transfers 88. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.10 Instruction Fetches and Endian Modes 89. . . . . . . . . . . . . . . . . . . . . . . . . . .

7.11 Changing BE/LE Mode 90. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.12 Summary of Bi–Endian Operation and Notes 92. . . . . . . . . . . . . . . . . . . . . .

Section 8 Exceptions 93. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

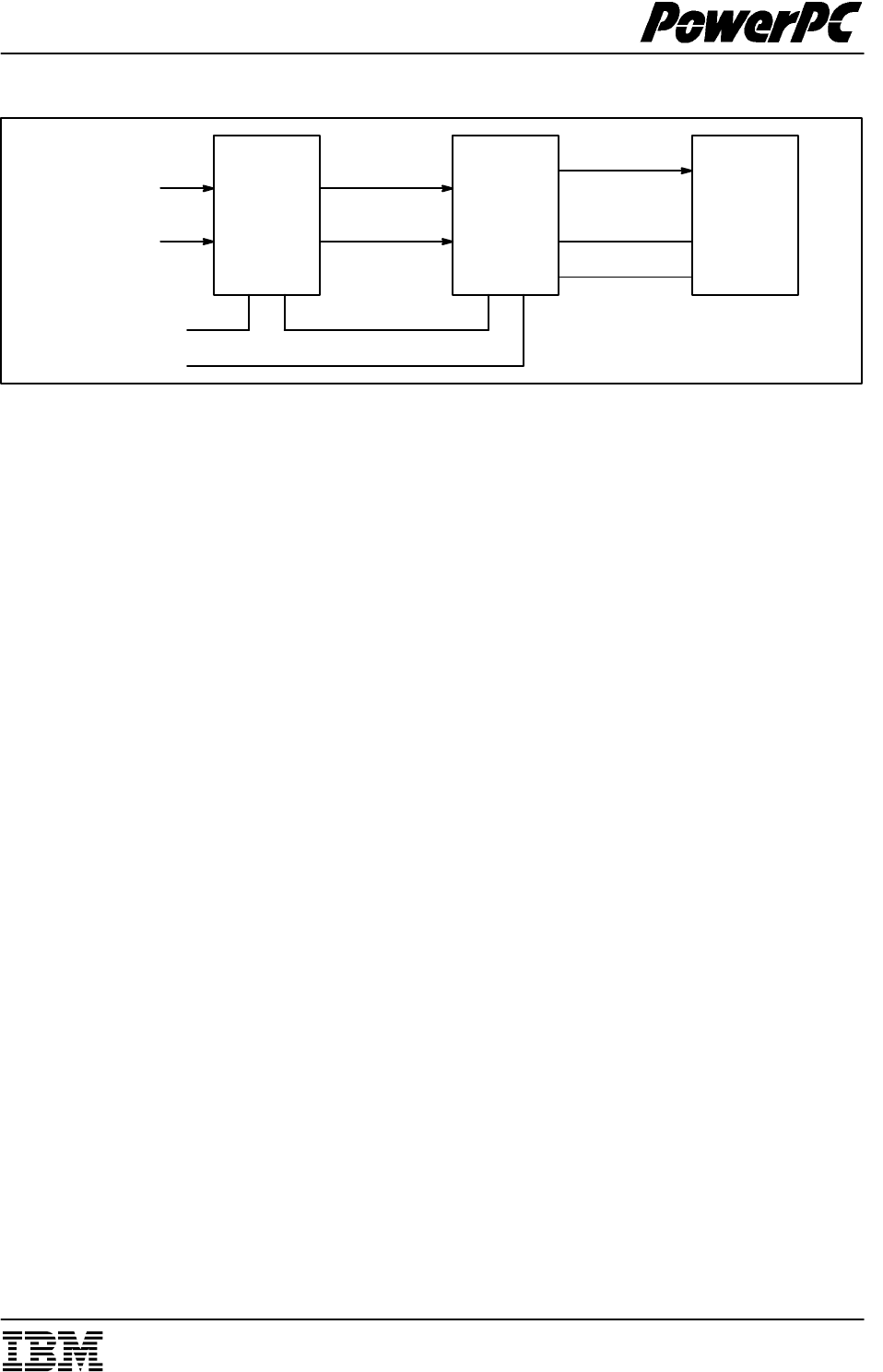

8.1 Interrupts 93. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.1.1 System Interrupt Handler 93. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.1.2 Interrupt Handling 94. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8MPRH08TSU-02

8.1.3 Interrupt Assignments 95. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.1.4 Scatter-Gather Interrupts 95. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.2 Error Handling 96. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.2.1 Data Error Checking 96. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.2.1.1 CPU to Memory Writes 96. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.2.1.2 CPU to Memory Reads 96. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.2.1.3 PCI to Memory Parity Errors 97. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.2.1.4 CPU to PCI Transaction Data Parity Errors 97. . . . . . . . . . . . . . . . . . . .

8.2.2 Illegal CPU cycles 97. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.2.3 SERR, I/O Channel Check, and NMI Logic 97. . . . . . . . . . . . . . . . . . . . . .

8.2.4 Out of Bounds PCI Memory Accesses 97. . . . . . . . . . . . . . . . . . . . . . . . . .

8.2.5 No Response on CPU to PCI Cycles – Master Abort 98. . . . . . . . . . . . .

8.2.6 CPU to PCI Cycles That Are Target Aborted 98. . . . . . . . . . . . . . . . . . . .

8.2.7 Error Status Registers 98. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.2.8 Reporting Error Addresses 98. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.2.9 Errant Masters 98. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.2.10 Special Events Not Reported as Errors 99. . . . . . . . . . . . . . . . . . . . . . . . .

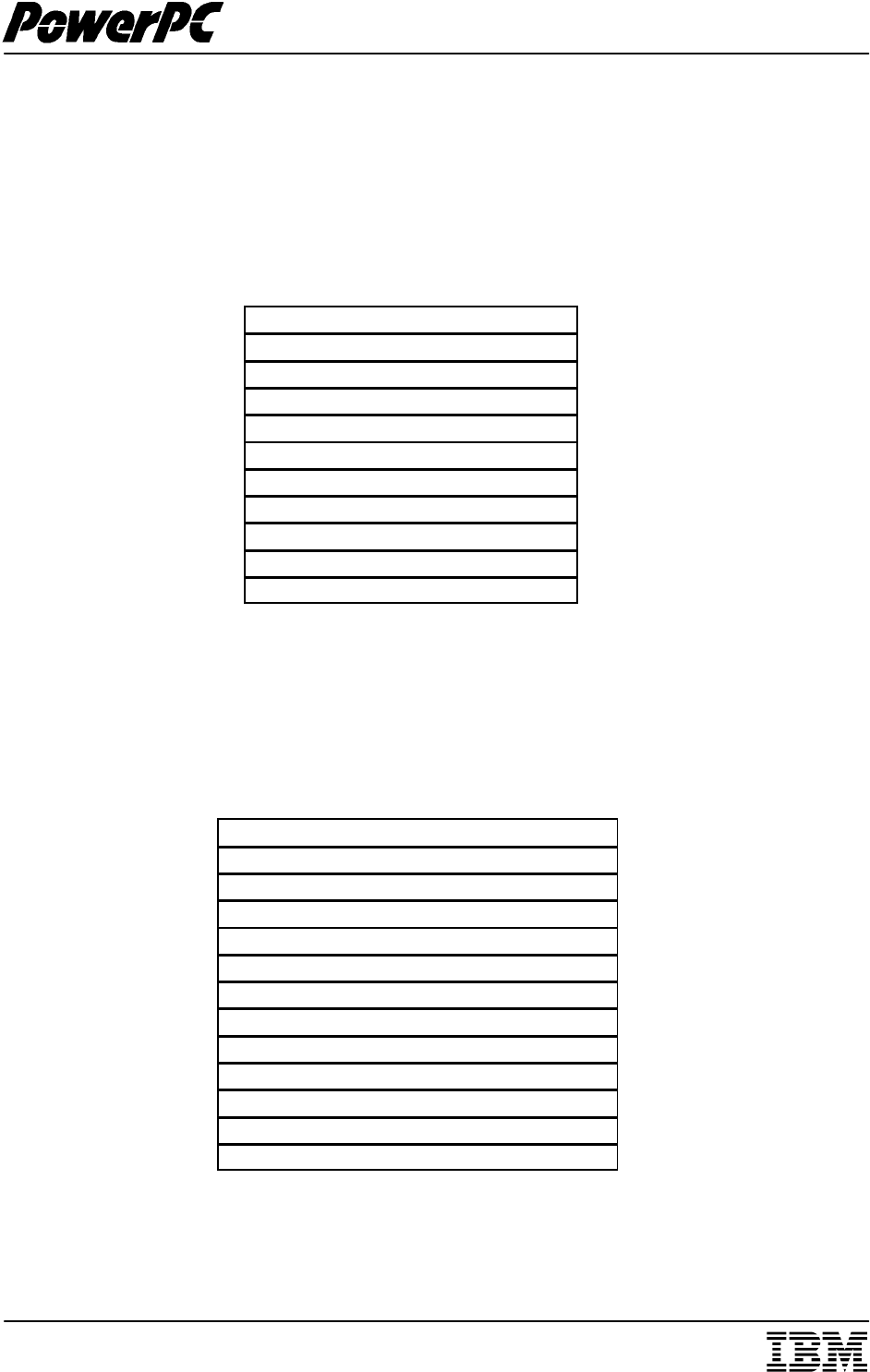

Section 9 System Setup and Initialization 101. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.1 CPU Initialization 101. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.2 660 Bridge Initialization 102. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.3 ISA Bridge (SIO) Initialization 103. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.3.1 Summary of SIO Configuration Registers 106. . . . . . . . . . . . . . . . . . . . . . .

9.4 PCI Configuration Scan 107. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.4.1 Multi-function Adaptors 107. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.4.2 PCI to PCI Bridges 107. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

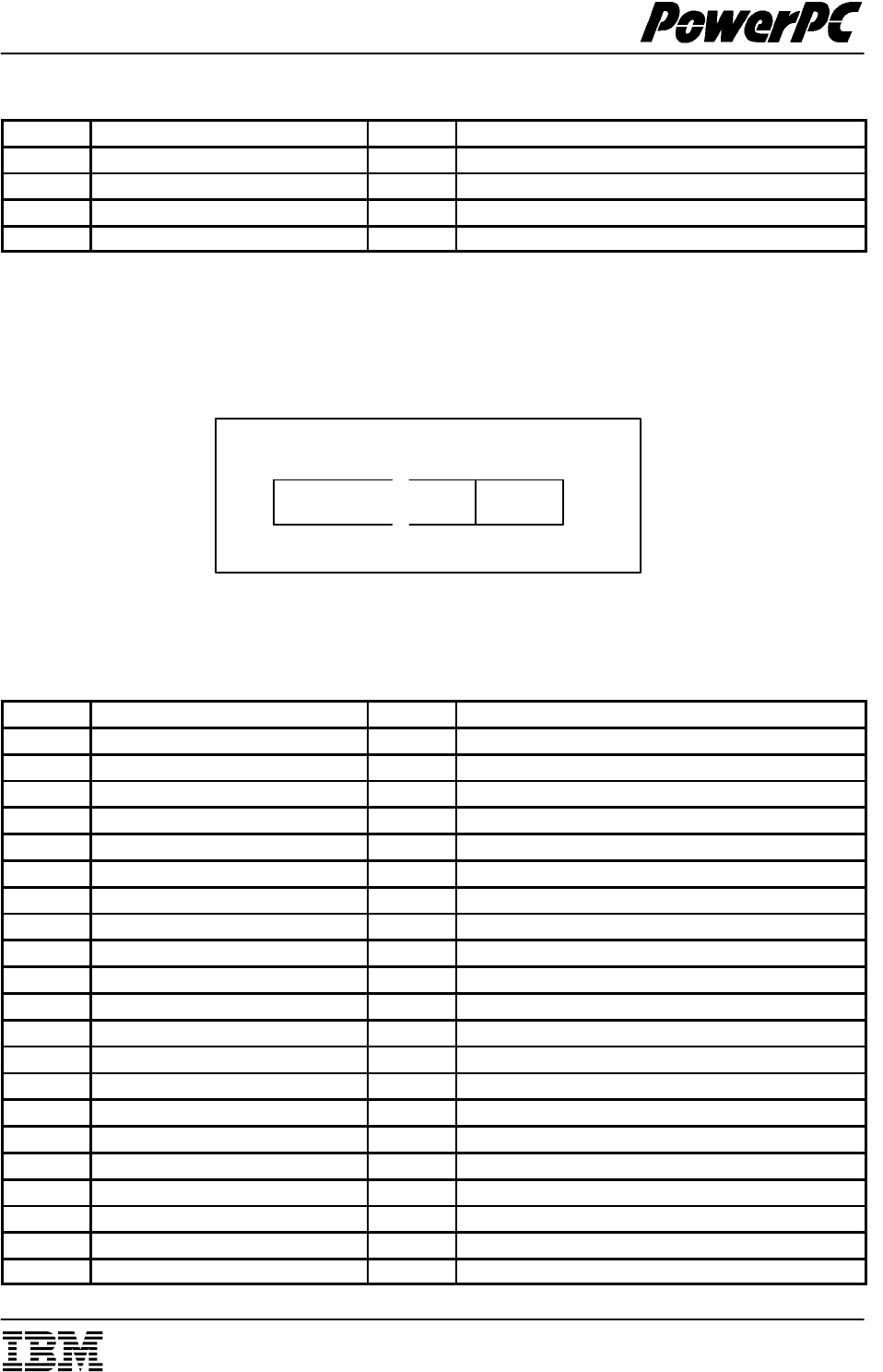

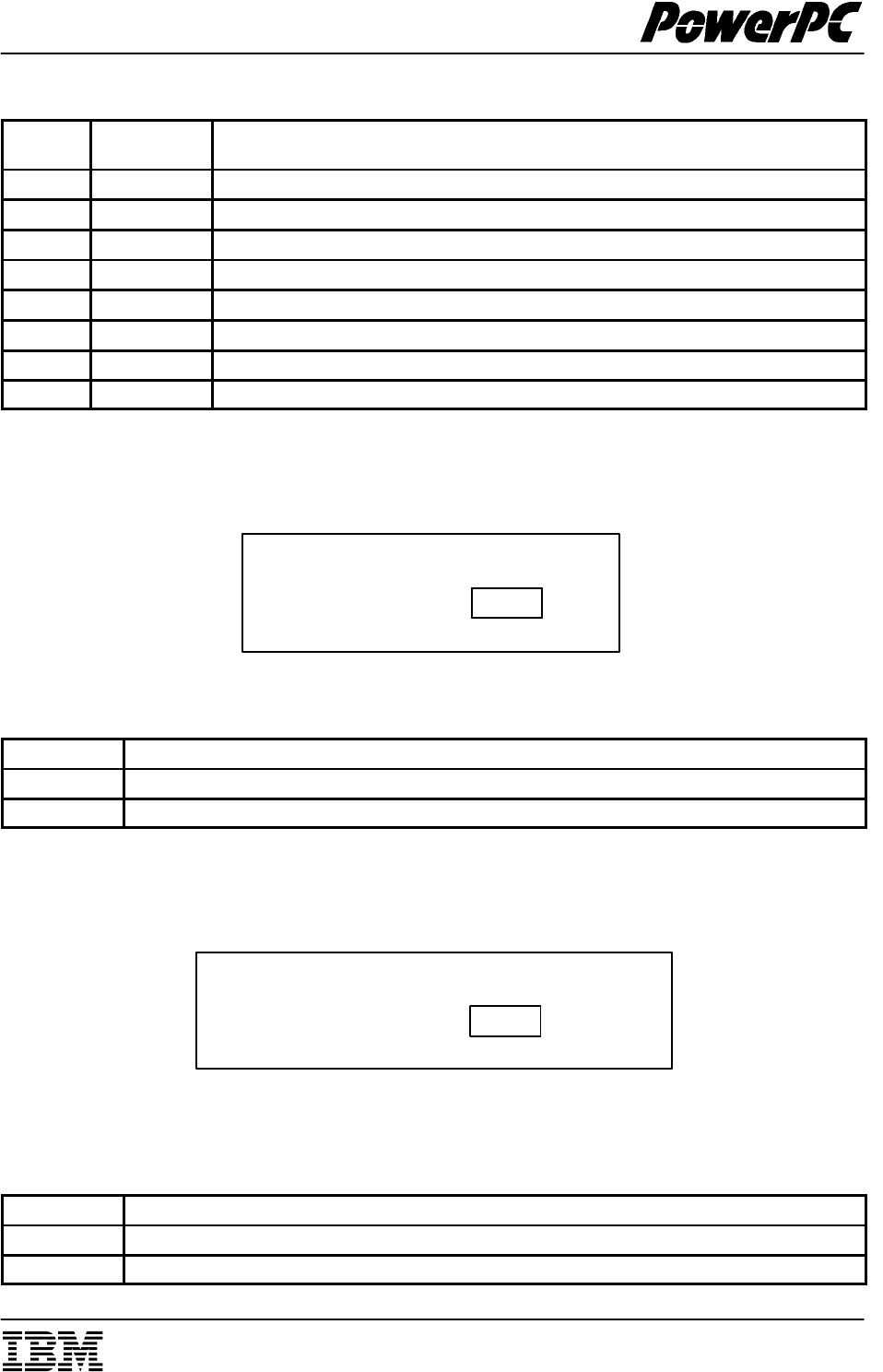

9.5 Reference Design Combined Register Listing 108. . . . . . . . . . . . . . . . . . . . . .

9.5.1 Direct Access Registers 108. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.5.2 Indexed BCR Summary 114. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.6 ISA Bus Register Suggestions 116. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Section 10 System Firmware 119. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.1 Introduction 119. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.2 Power On System Test 119. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.2.1 Hardware Requirements 119. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.3 Boot Record Format 119. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.3.1 Boot Record 120. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.3.1.1 PC Partition Table Entry 120. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.3.1.2 Extended DOS Partition 121. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.3.1.3 PowerPC Reference Platform Partition Table Entry 122. . . . . . . . . . . . .

10.3.2 Loading the Load Image 123. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.4 System Configuration 125. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.4.1 System Console 125. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.4.2 System Initialization 125. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.4.3 Main Menu 126. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9

MPRH08TSU-02

10.4.3.1 System Configuration Menu 127. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.4.3.2 Run a Program 133. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.4.3.3 Reprogram Flash Memory 134. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.4.3.4 Exit Options 135. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.4.4 Default Configuration Values 135. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Section 11 Electromechanical 137. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.1 Electrical 137. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.1.1 Power Requirements 137. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

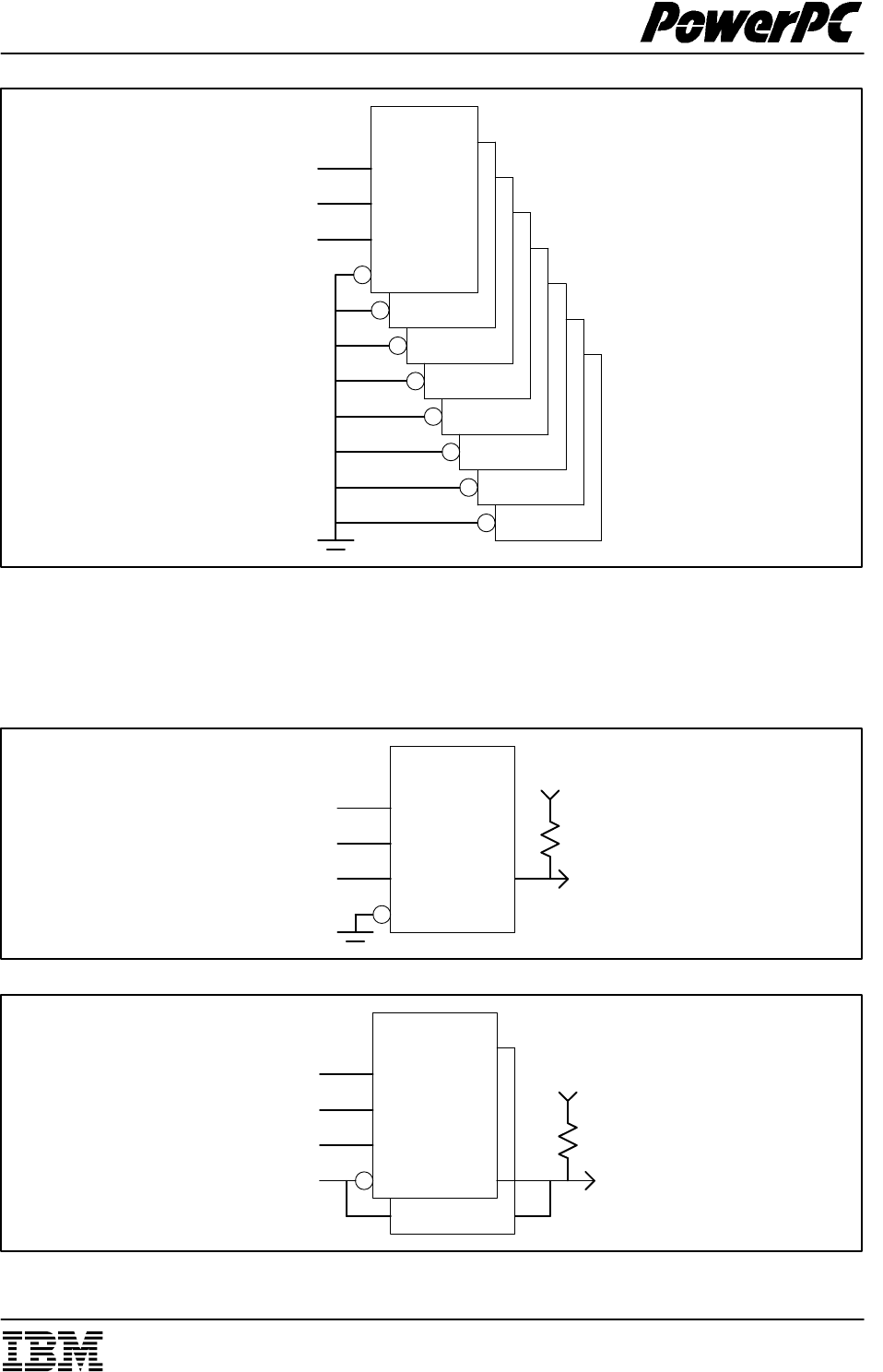

11.1.2 Onboard 3.3V Regulator 138. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.1.3 Onboard 2.5V Regulator 138. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.2 Thermal 139. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.2.1 Thermal Requirements for the 603/604 Processor 139. . . . . . . . . . . . . . .

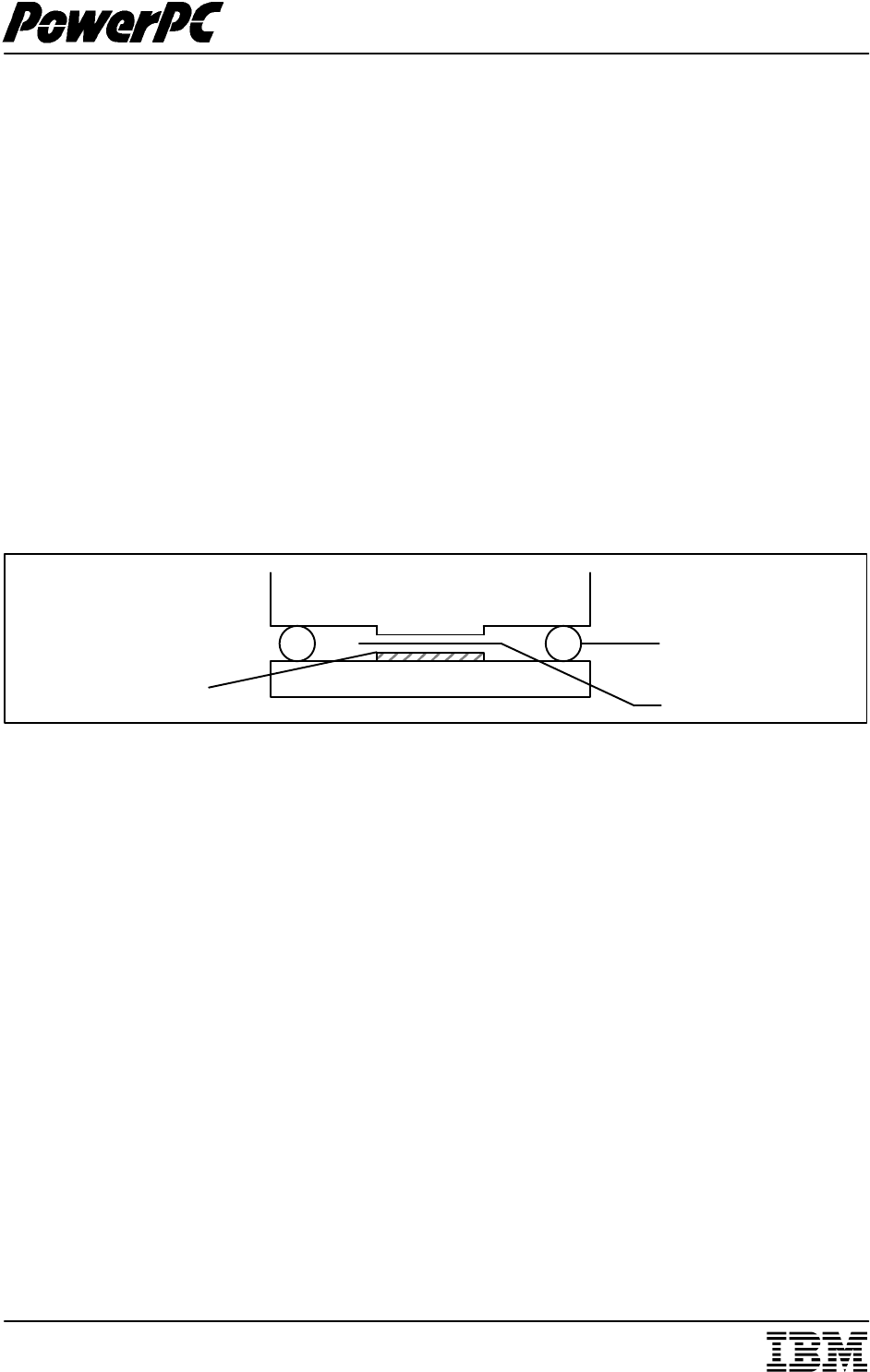

11.2.1.1 604 Fan-Sink Installation 139. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.2.1.2 604 Fan-Sink Experimentation 140. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.2.1.3 Thermal Requirements for the 3.3V Regulator 140. . . . . . . . . . . . . . . . .

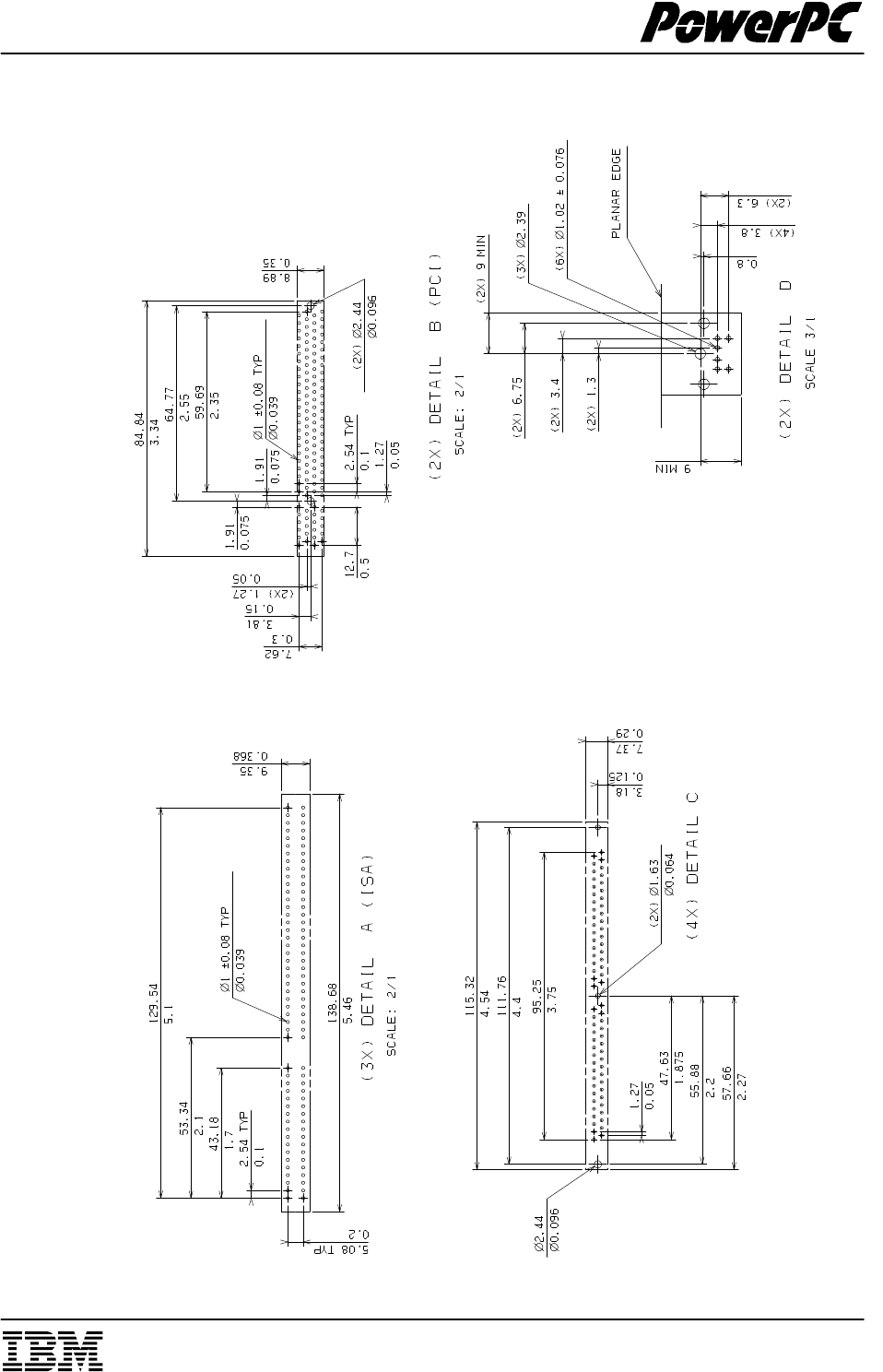

11.3 Mechanical 141. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

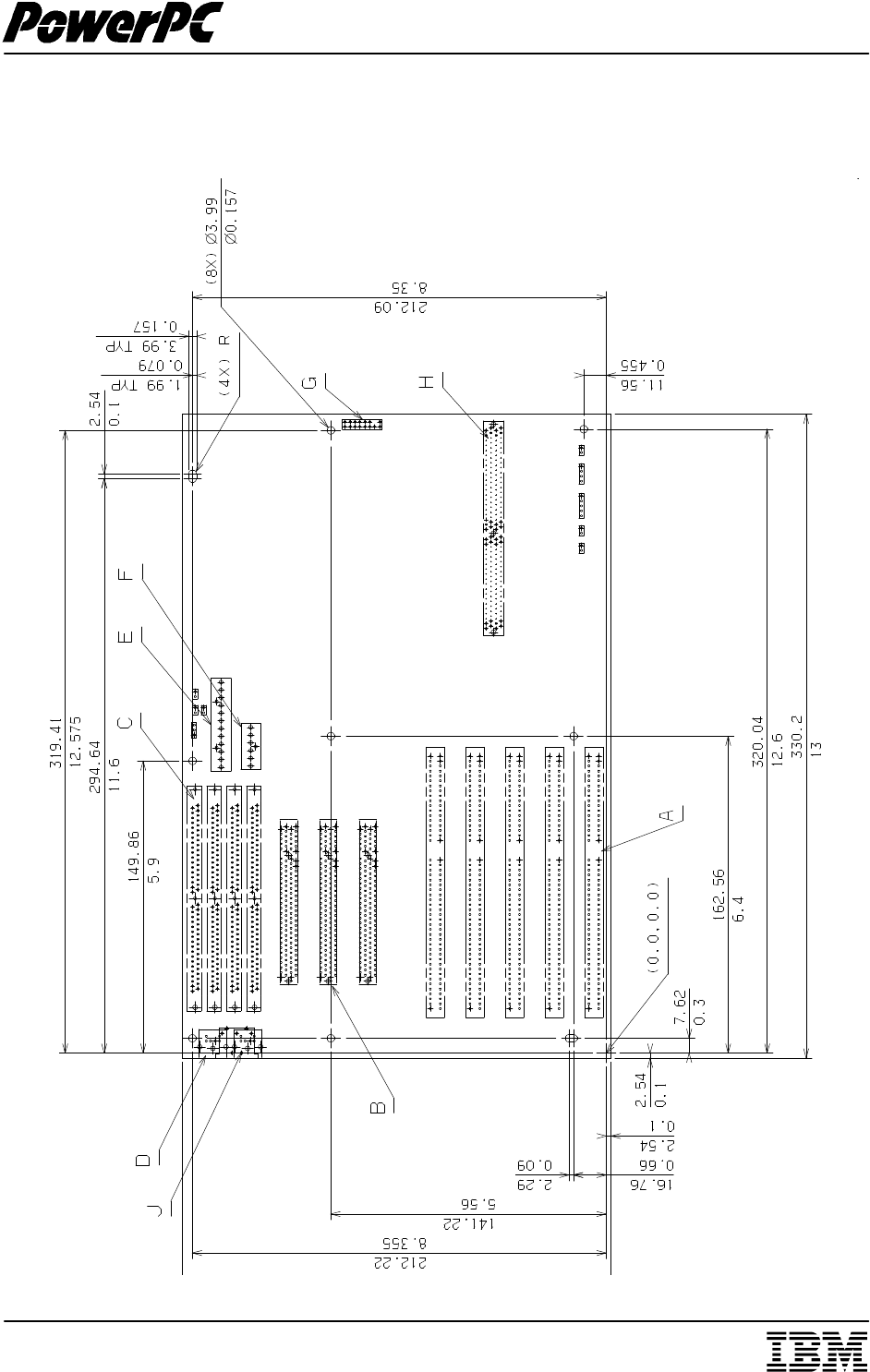

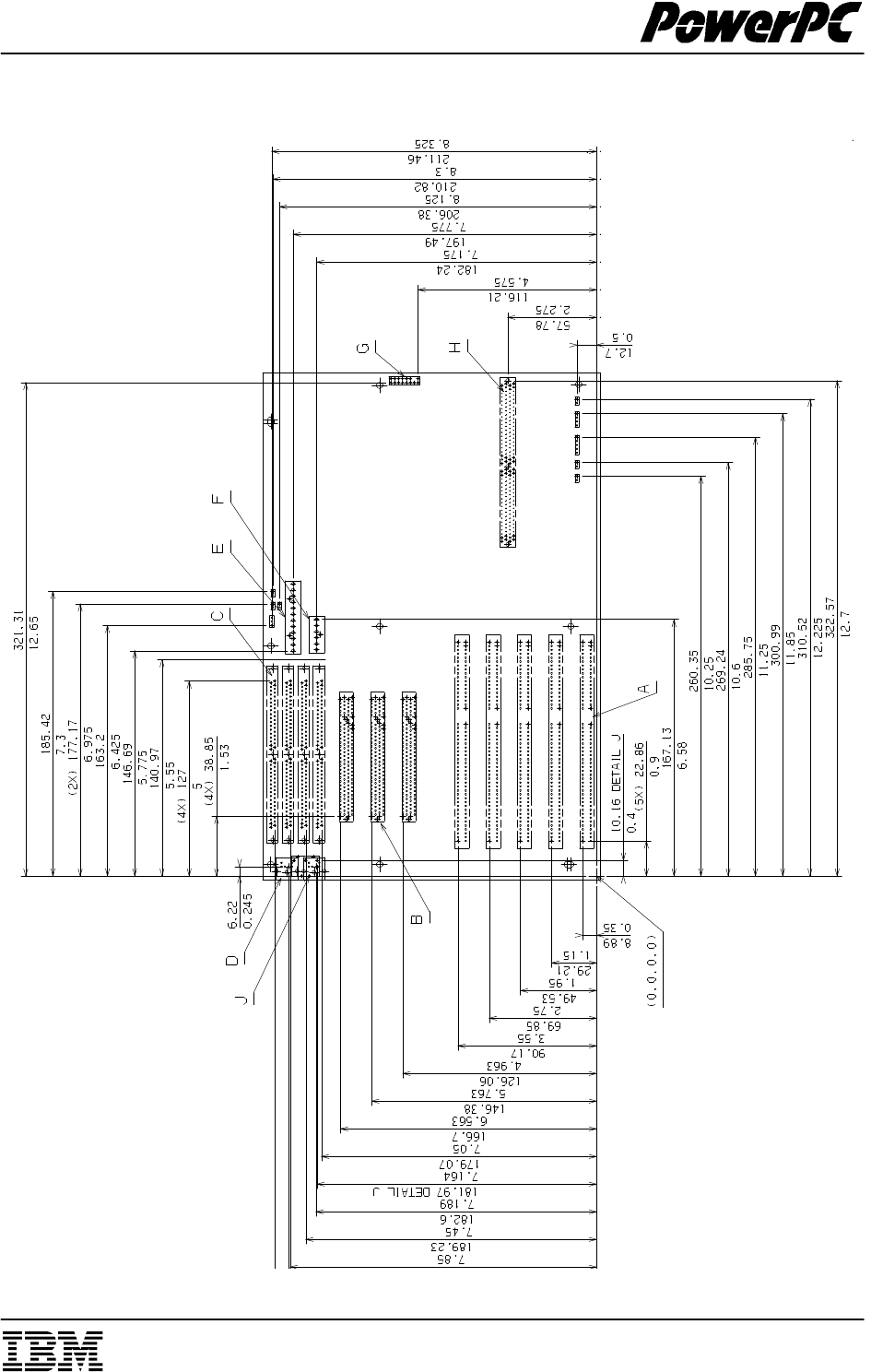

11.3.1 Reference Design Board Mechanical 141. . . . . . . . . . . . . . . . . . . . . . . . . . .

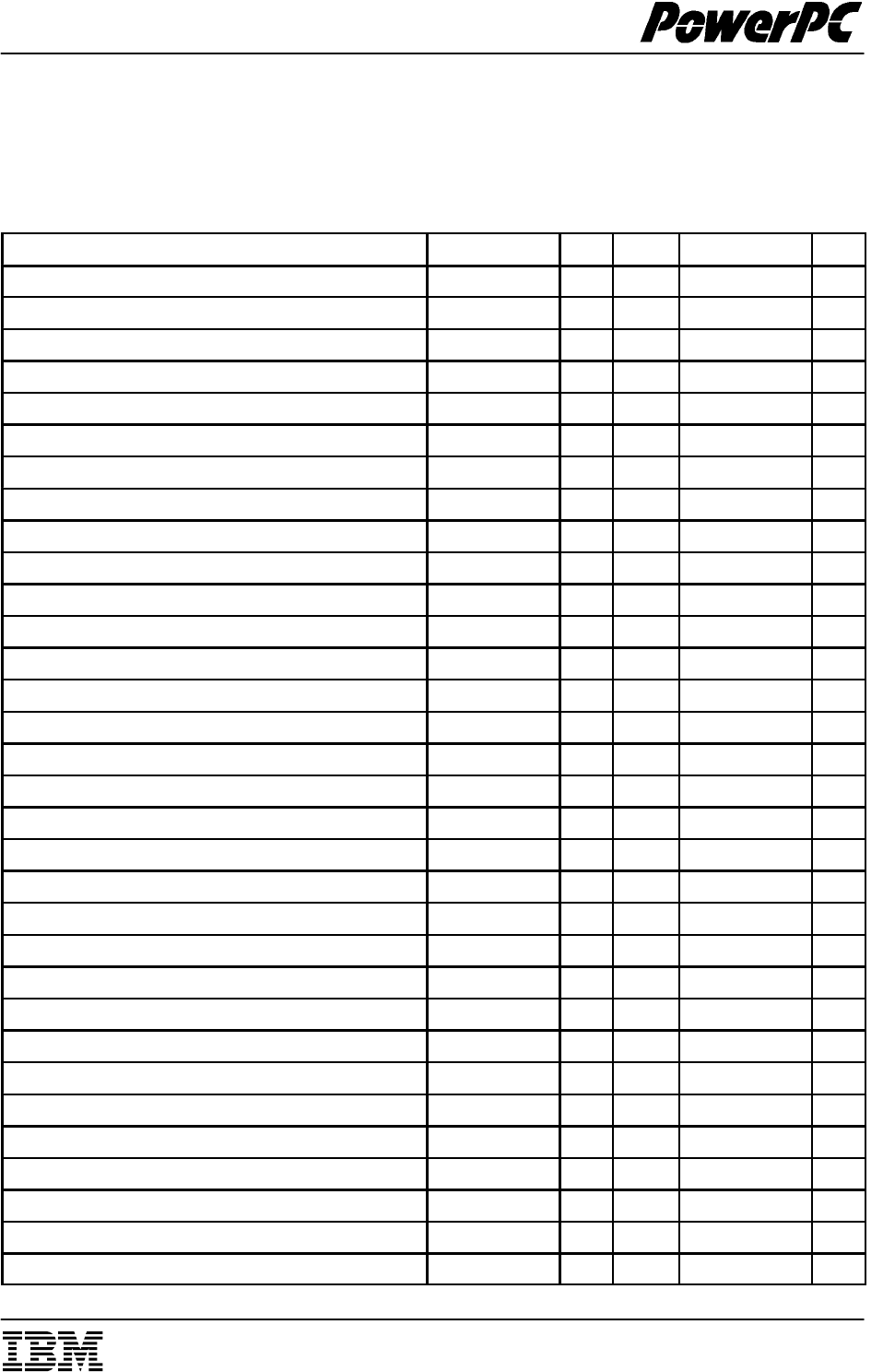

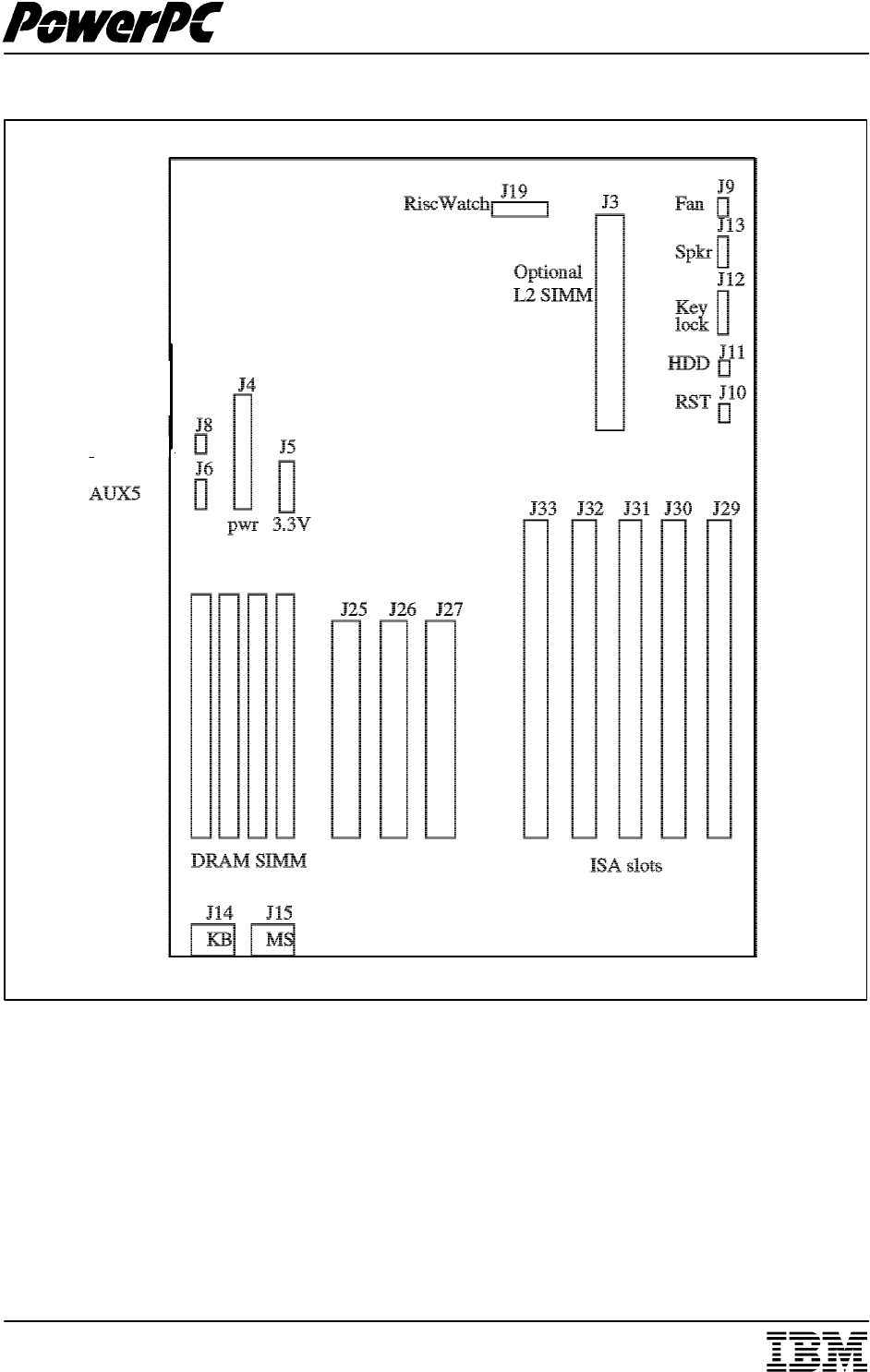

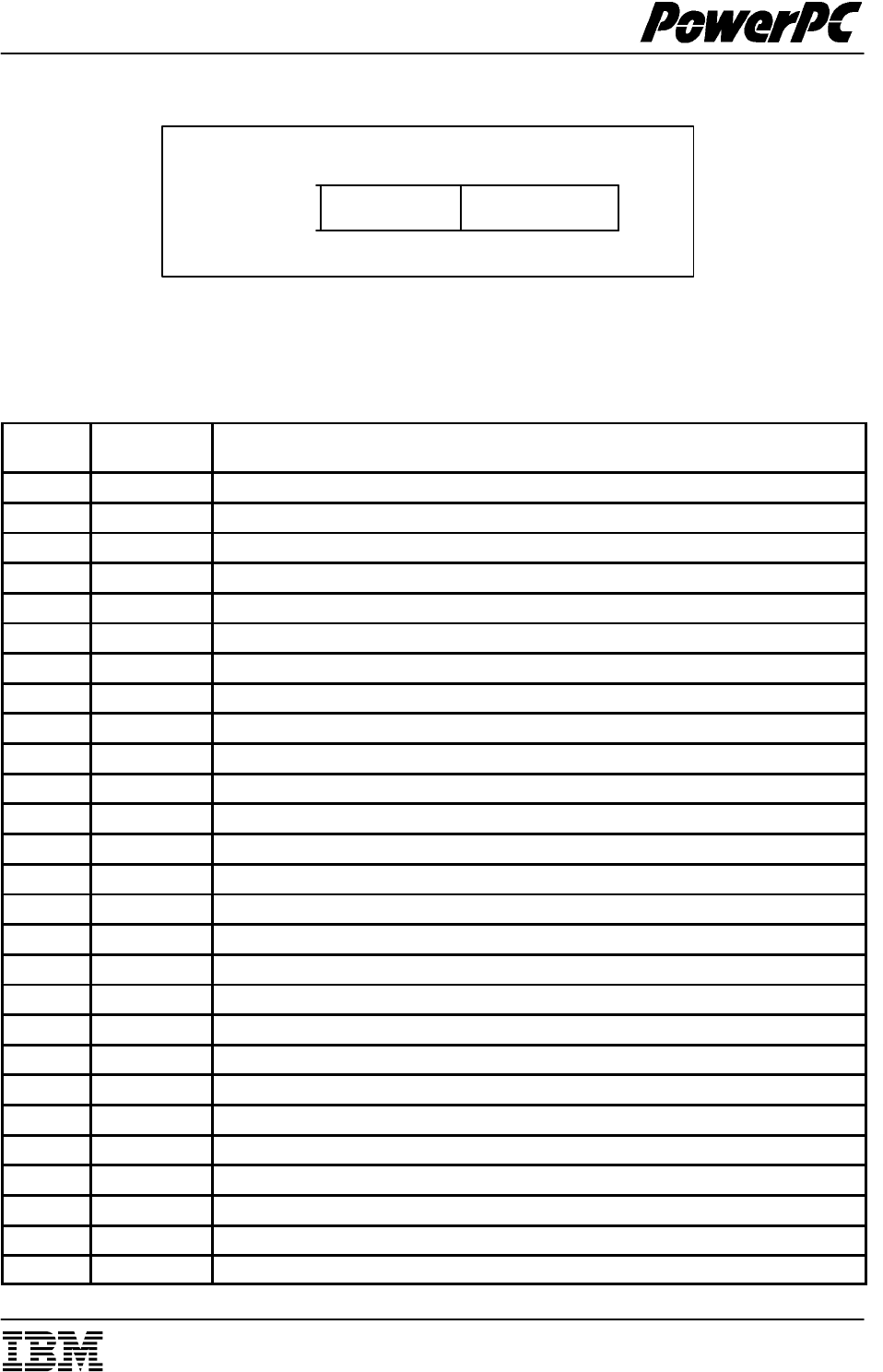

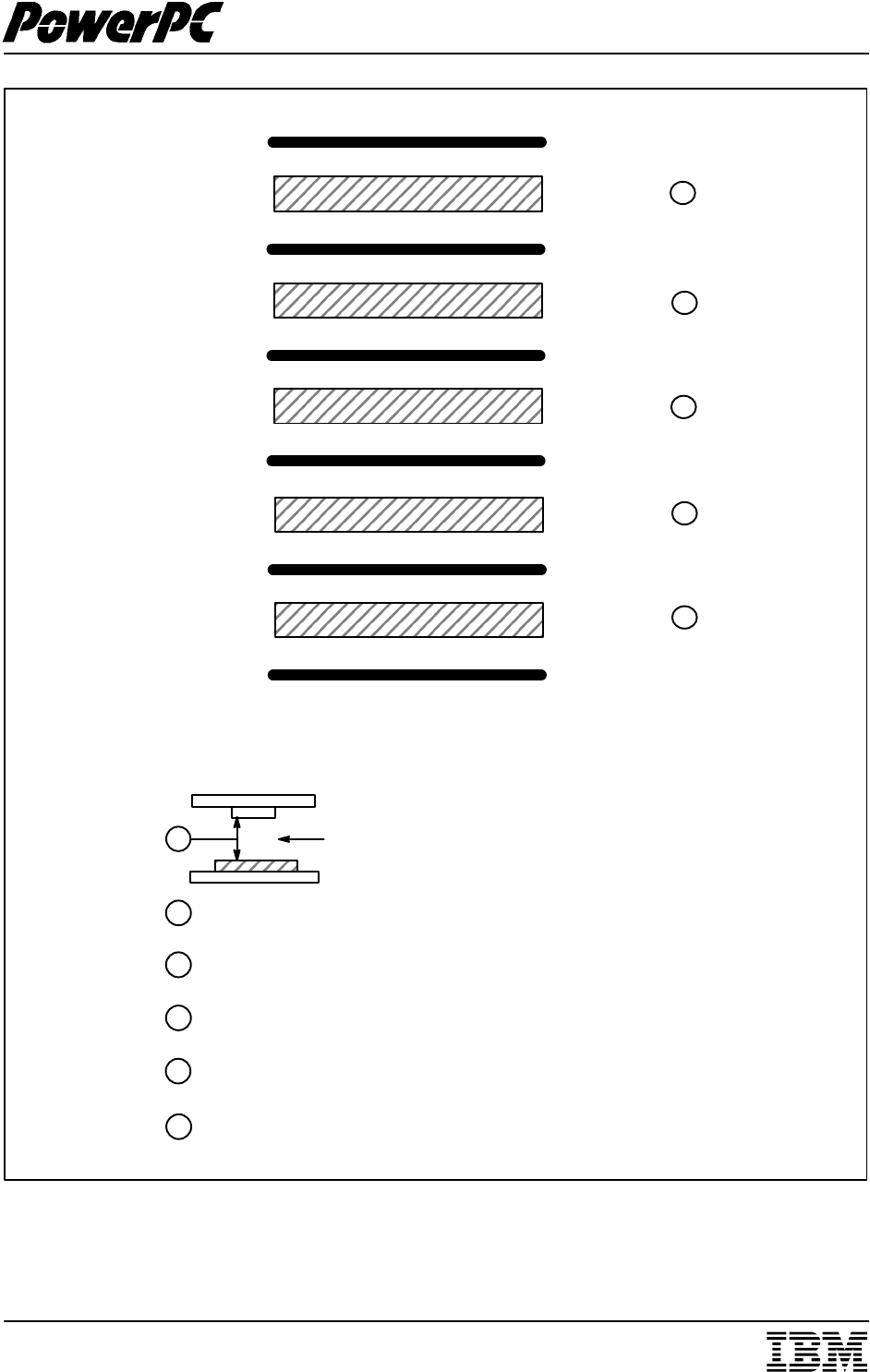

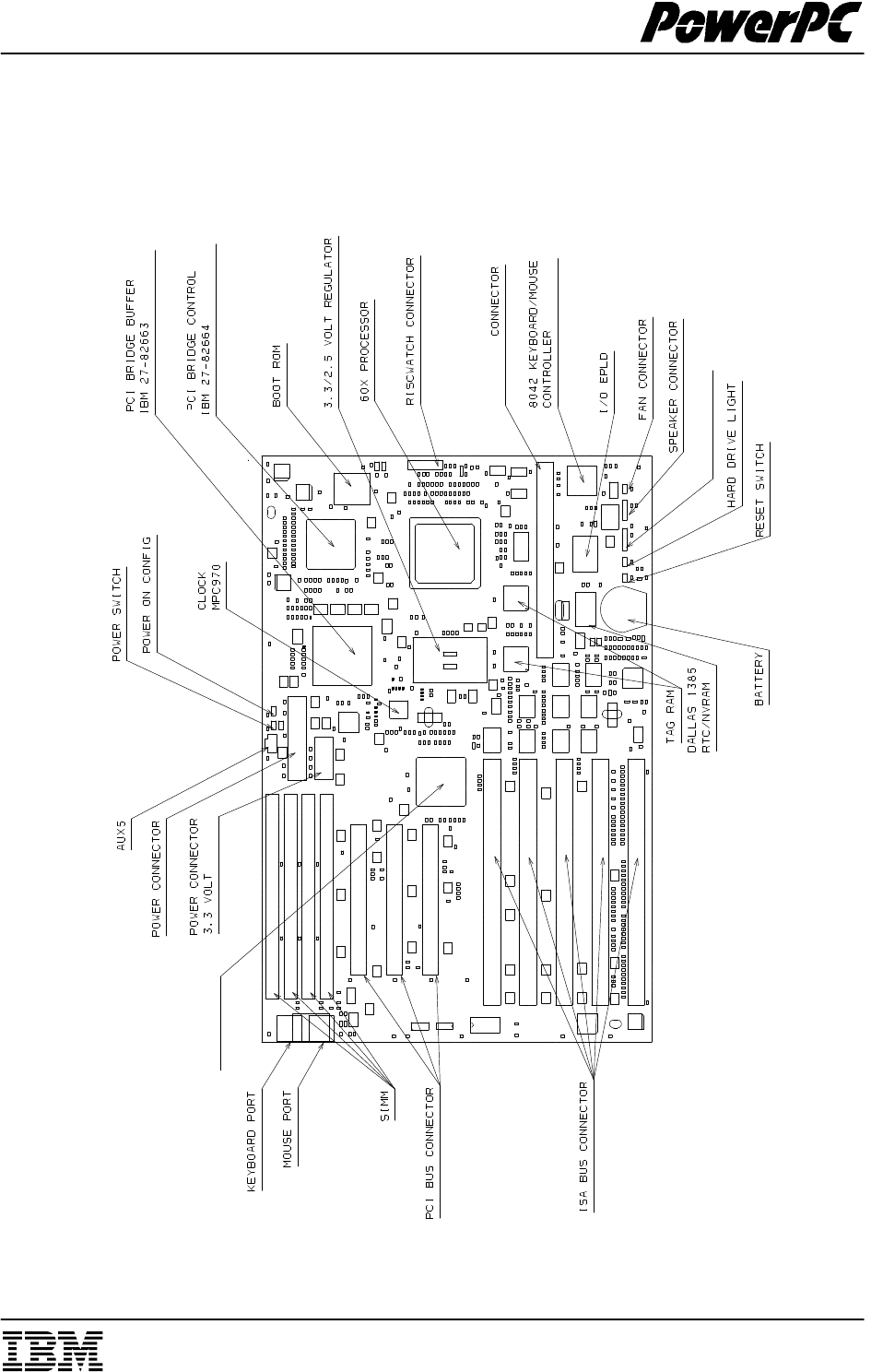

11.3.2 Connector Locations 142. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.3.3 Connector Locator Diagram 143. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

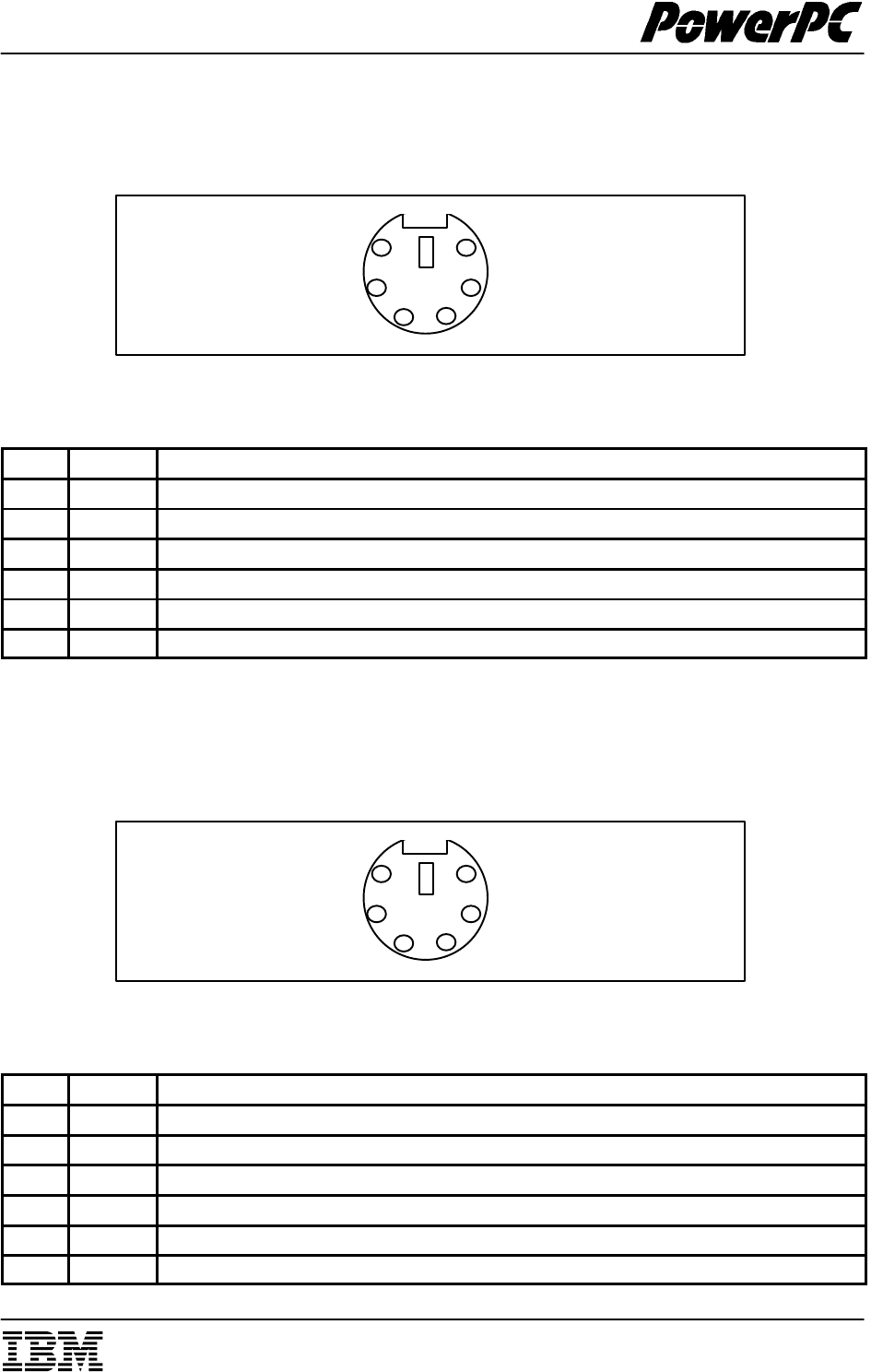

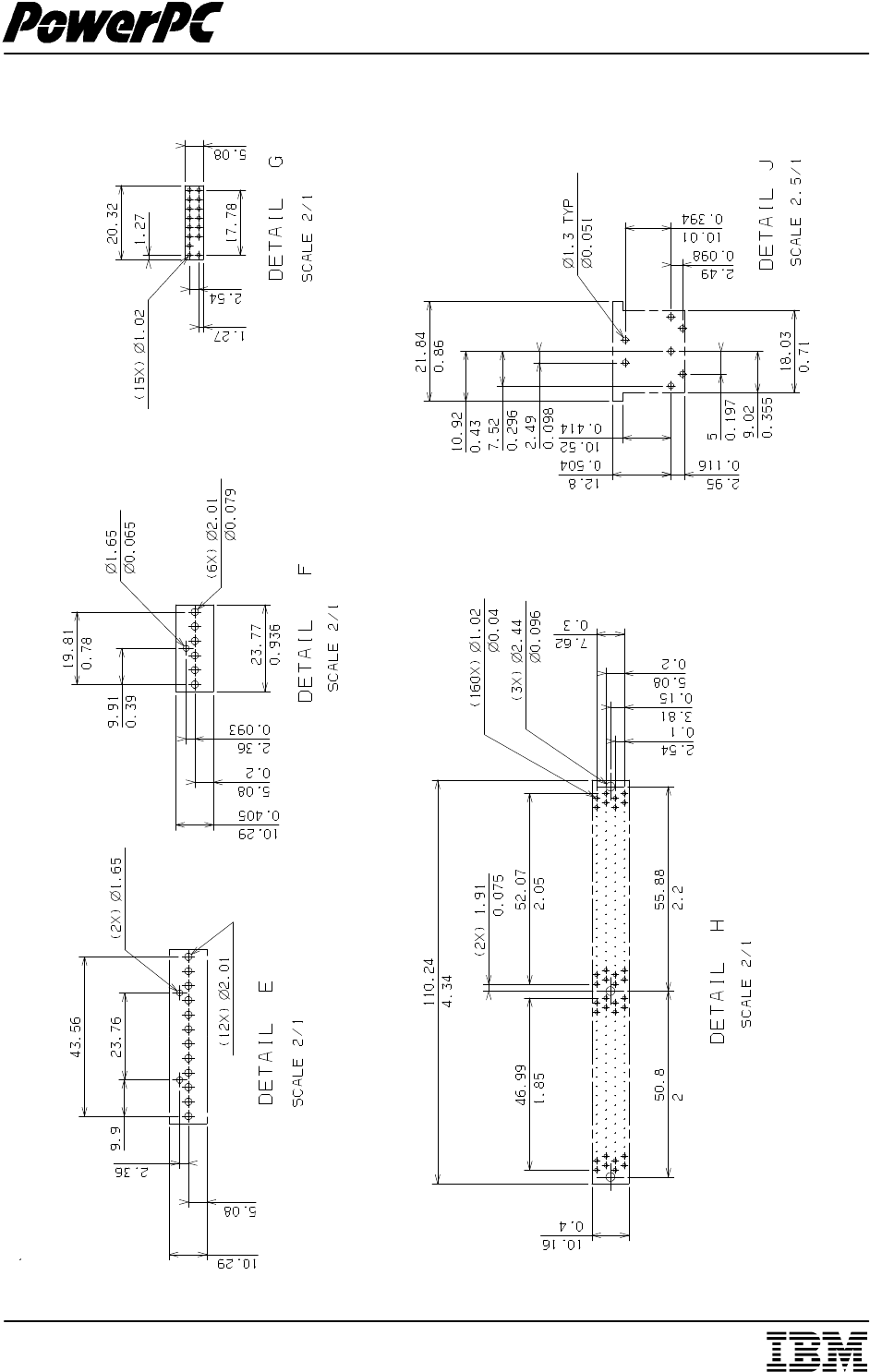

11.3.4 Keyboard Connector J14 144. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.3.5 Mouse Connector J15 144. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.3.6 Speaker Connector J13 145. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.3.7 Power Good LED/KEYLOCK# Connector J12 145. . . . . . . . . . . . . . . . . . .

11.3.8 HDD LED Connector J11 (1 x 2 Berg) 145. . . . . . . . . . . . . . . . . . . . . . . . . .

11.3.9 Reset Switch Connector J10 (1 x 2 Berg) 146. . . . . . . . . . . . . . . . . . . . . . .

11.3.10 Fan Connector J9 146. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.3.11 3.3V Power Connector J5 147. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.3.12 Power Connector J4 147. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.3.13 AUX5/ON-OFF Connector J6 148. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

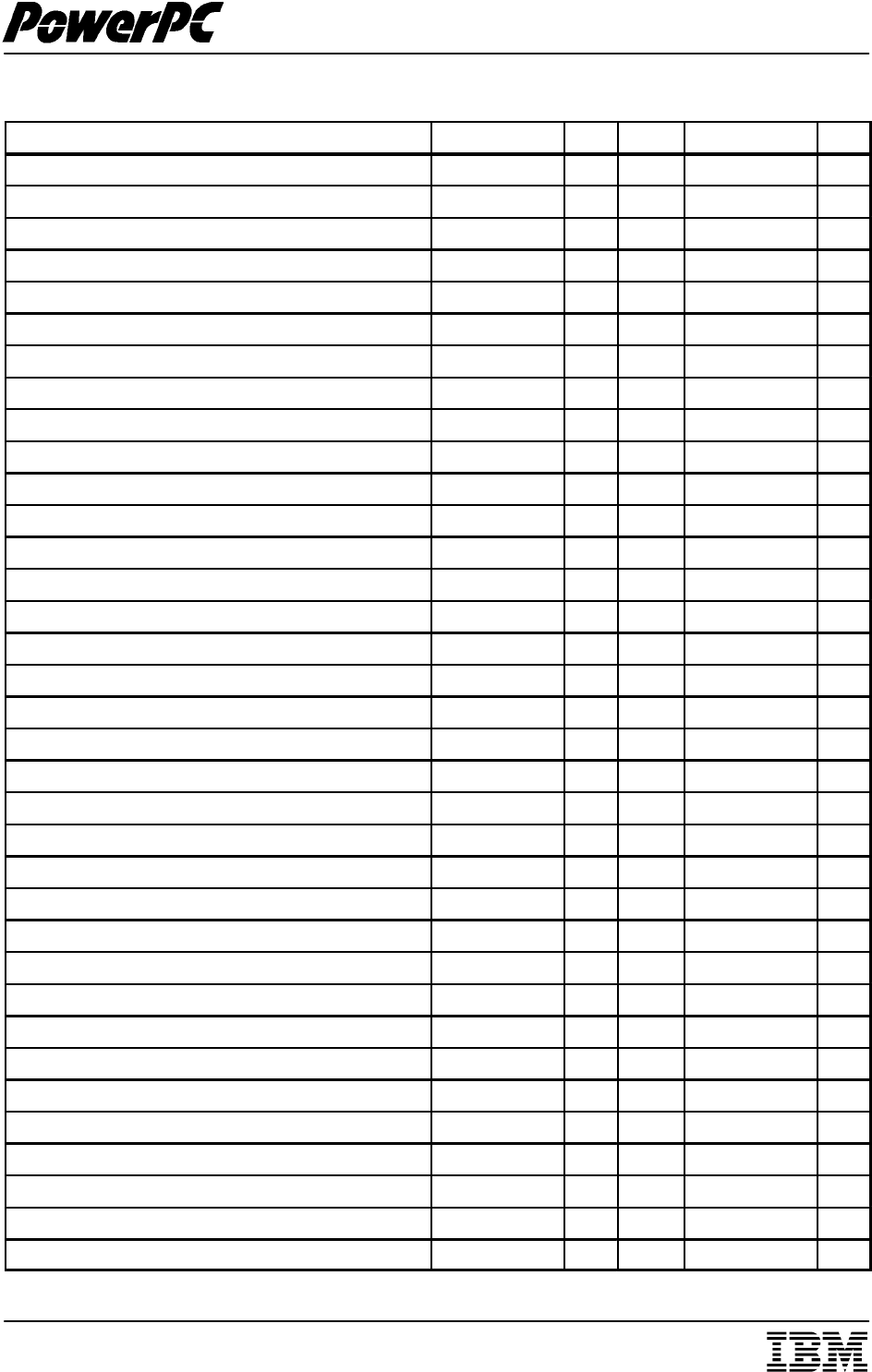

11.3.14 PCI Connectors J25, J26, and J27 148. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.3.15 ISA Connectors J29, J30, J31, J32, and J33 150. . . . . . . . . . . . . . . . . . . .

11.3.16 SIMM Connectors J21, J22, J23, and J24 152. . . . . . . . . . . . . . . . . . . . . .

11.3.17 Power Switch Connector J8 154. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.3.18 Power Up Configuration Connector J7 154. . . . . . . . . . . . . . . . . . . . . . . . .

11.3.19 L2 Cache Data SIMM Connector J3 155. . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.3.20 RISCWatch Connector J19 157. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.3.21 Battery Connector BT2 157. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.3.22 Reference Design Board Connector Footprint #1 158. . . . . . . . . . . . . . . .

11.3.23 Reference Design Board Connector Footprint #2 159. . . . . . . . . . . . . . . .

11.4 Enclosure 160. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Section 12 Physical Design Guidelines 161. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.1 General Considerations 161. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.1.1 Construction 161. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10 MPRH08TSU-02

12.1.2 General Wiring Guidelines 164. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.2 Clock Nets 164. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.3 CPU Bus Nets 165. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.4 Timing Critical Nets 166. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.5 PCI Bus Nets 167. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.6 Group 2A: Noise Sensitive Wires 167. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.7 8mm Tape Contents and Extract Instructions 168. . . . . . . . . . . . . . . . . . . . . .

12.7.1 Download Instructions 168. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.7.2 Cadence Version 168. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.7.3 Tape Contents 168. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Section 13 Errata for Reference Design Release 2.1 169. . . . . . . . . . . . . . . . . . . . .

13.1 PowerPC 603/604 Reference Design Roadmap 169. . . . . . . . . . . . . . . . . . . .

13.2 Release 2.1 Board Level Errata 171. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.2.1 Driving 32MB 72-pin DRAM SIMMs 171. . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.2.2 CPU Data Bus 33 Ohm Series Resistors 171. . . . . . . . . . . . . . . . . . . . . . .

13.3 Reference Design Errata for Revision 1.1 of the 660 Bridge 172. . . . . . . . .

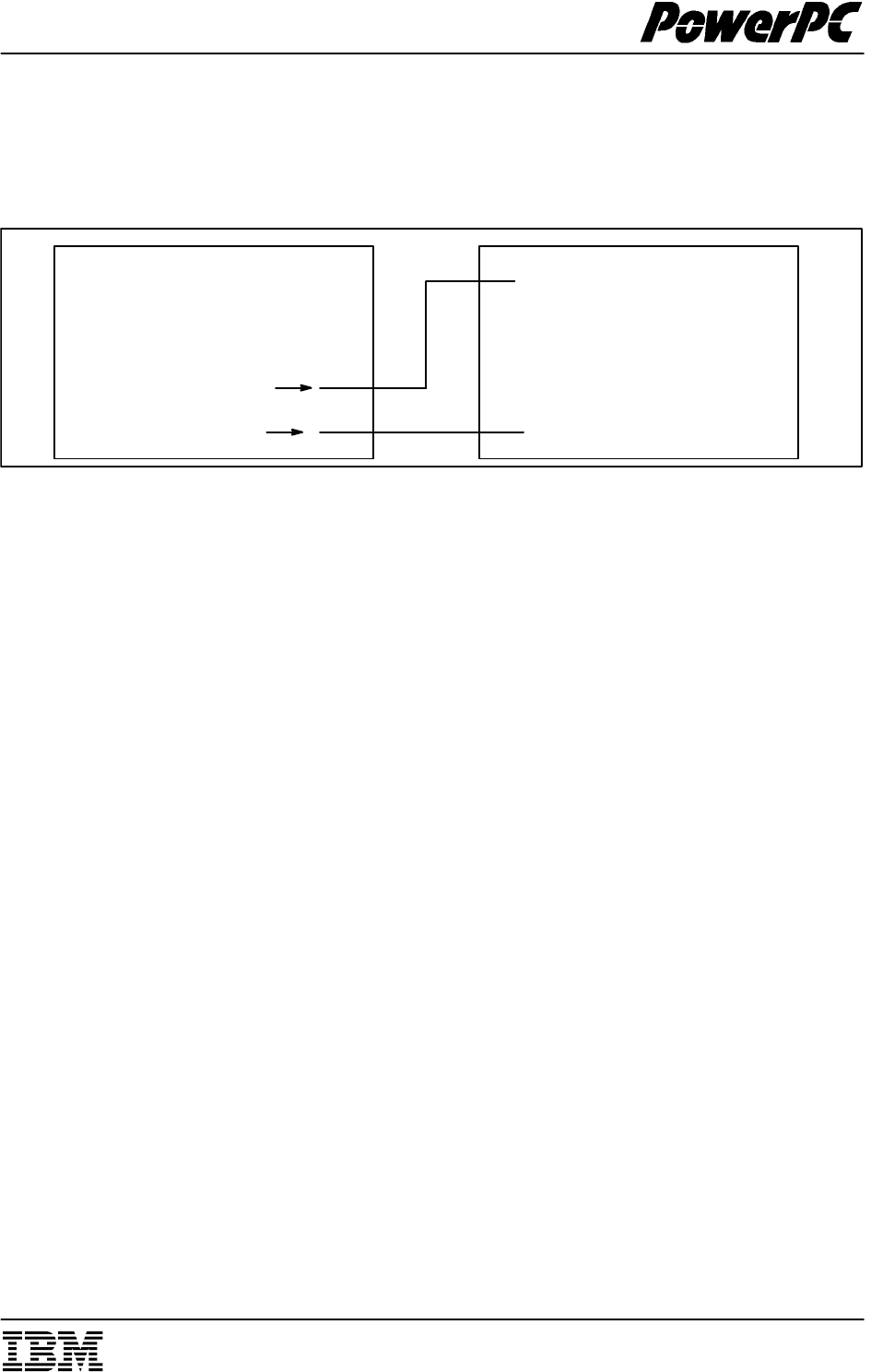

13.3.1 Workaround Implementation 172. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.3.2 HPP1 Reference Design Workaround PAL 172. . . . . . . . . . . . . . . . . . . . . .

13.3.3 HCn Reference Design Workaround PAL 173. . . . . . . . . . . . . . . . . . . . . . .

13.3.4 HBROOM Reference Design Workaround PAL 175. . . . . . . . . . . . . . . . . .

13.4 660 Bridge Revision 1.1 Errata, 8/9/95 Release 177. . . . . . . . . . . . . . . . . . . .

13.4.1 Individual 66 Bridge Errata 177. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.4.2 IPAL Design Files 182. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.4.2.1 HPP1 Design File 182. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.4.2.2 C3 PAL Design File 184. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.4.2.3 Broom PAL Design File 186. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

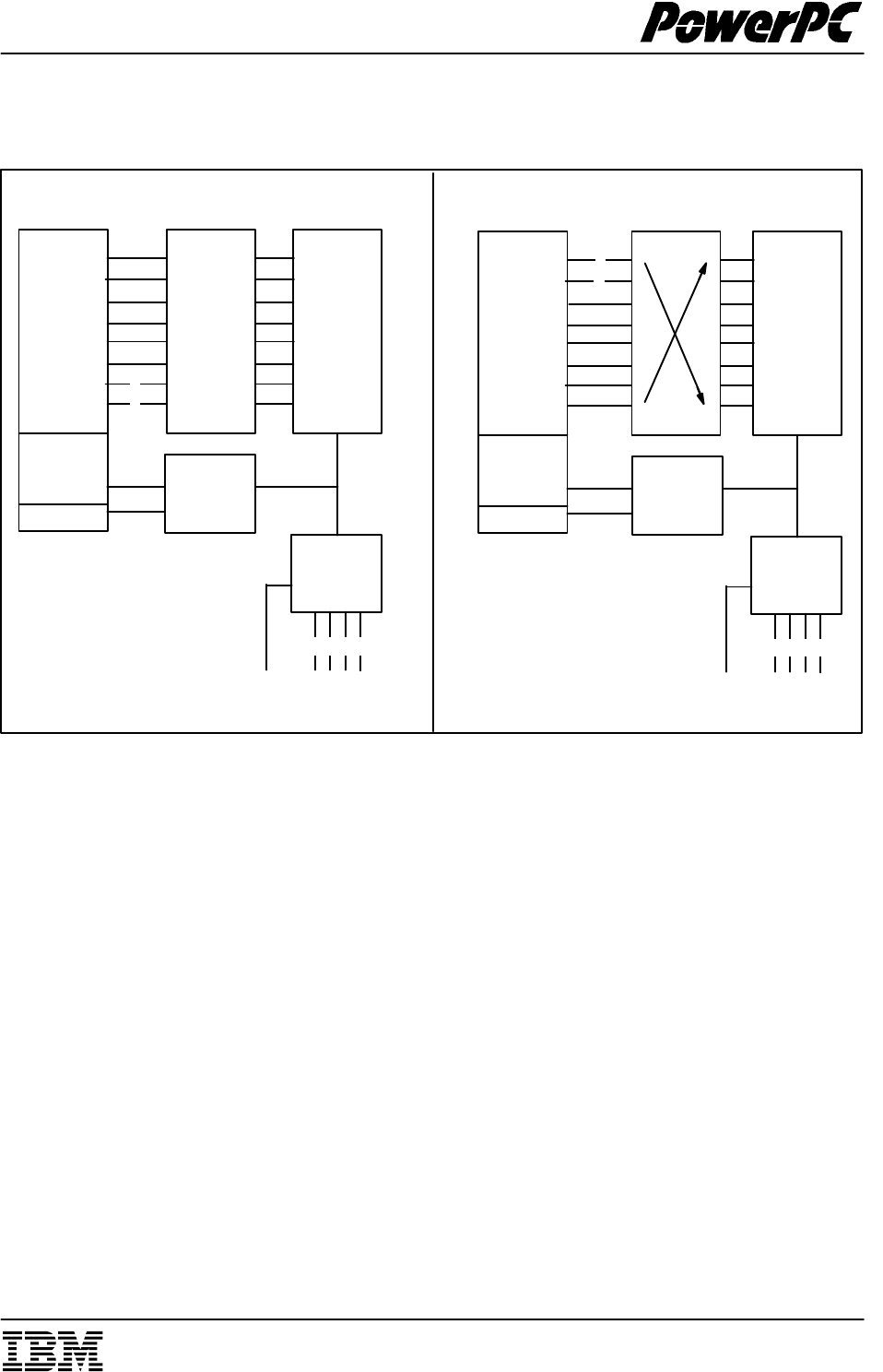

13.4.3 Workaround PAL Installation 188. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

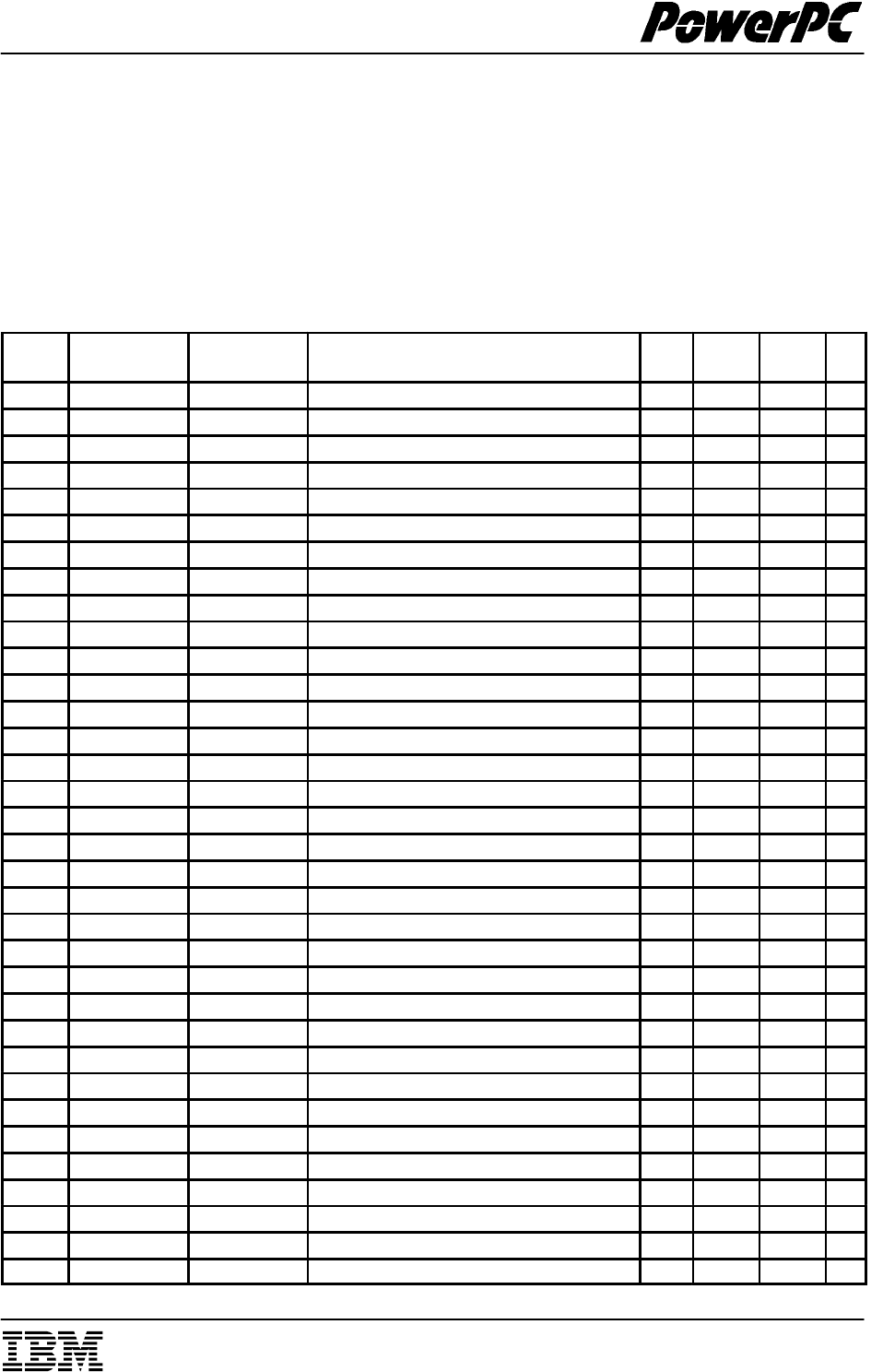

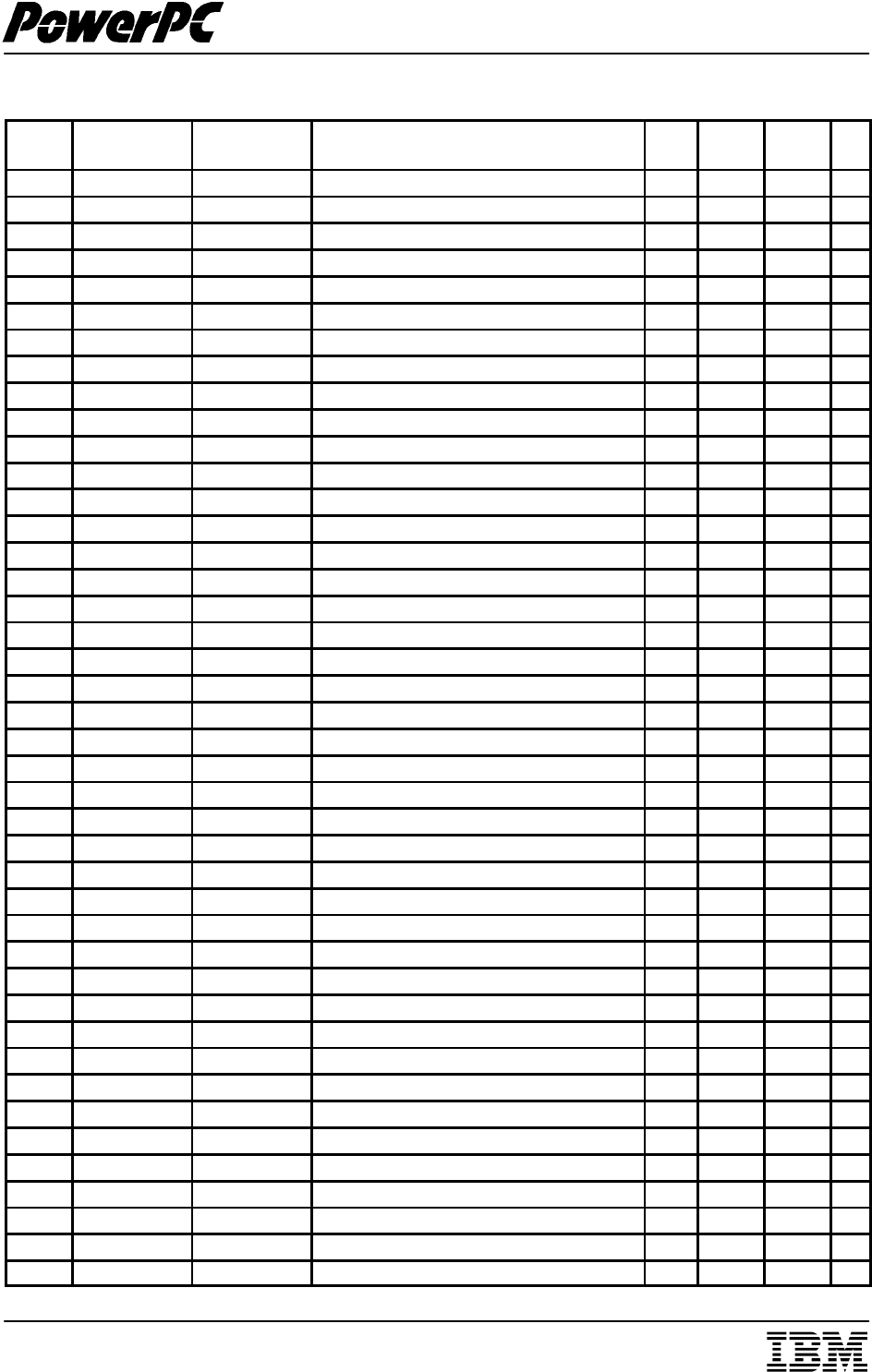

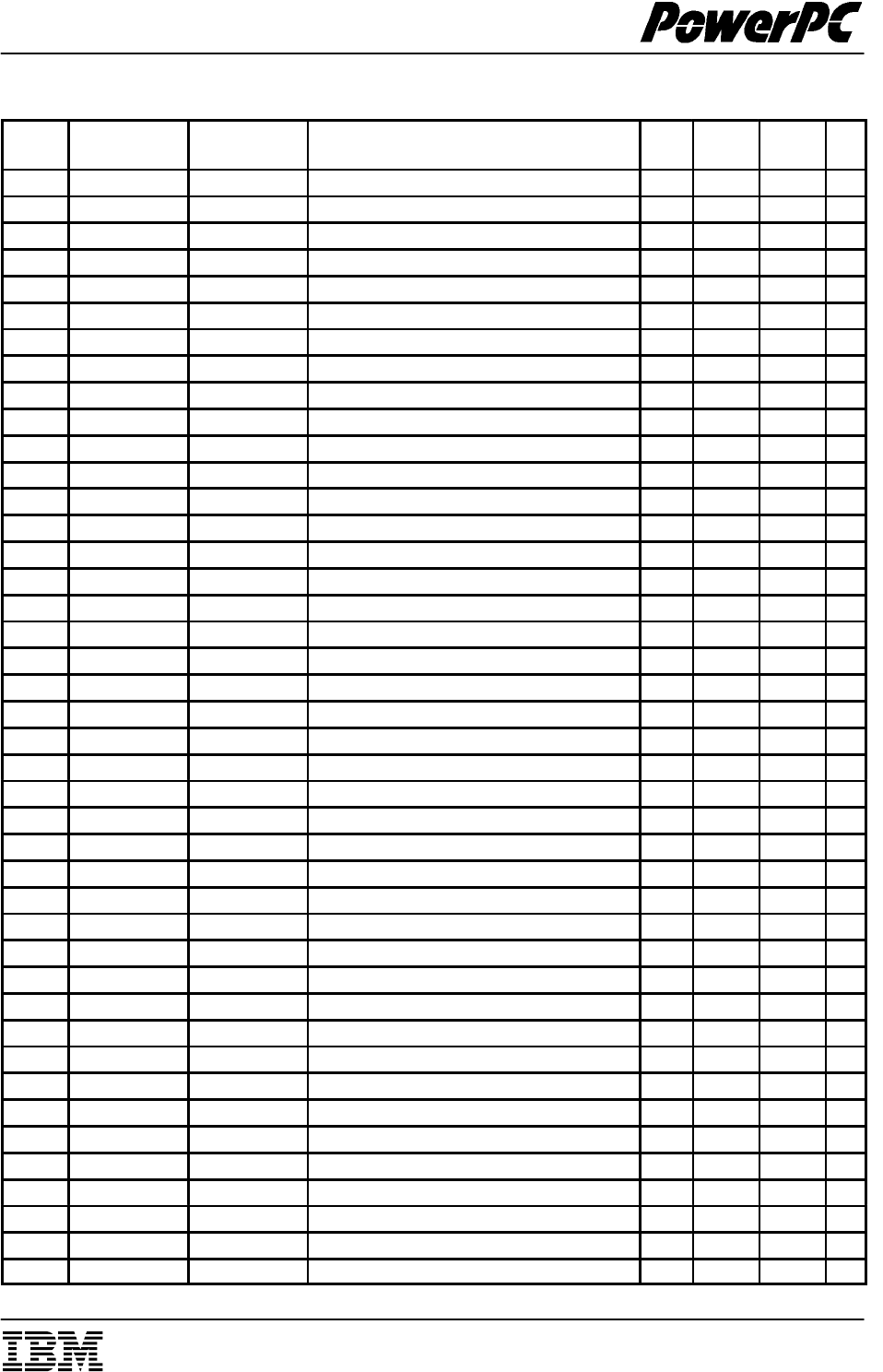

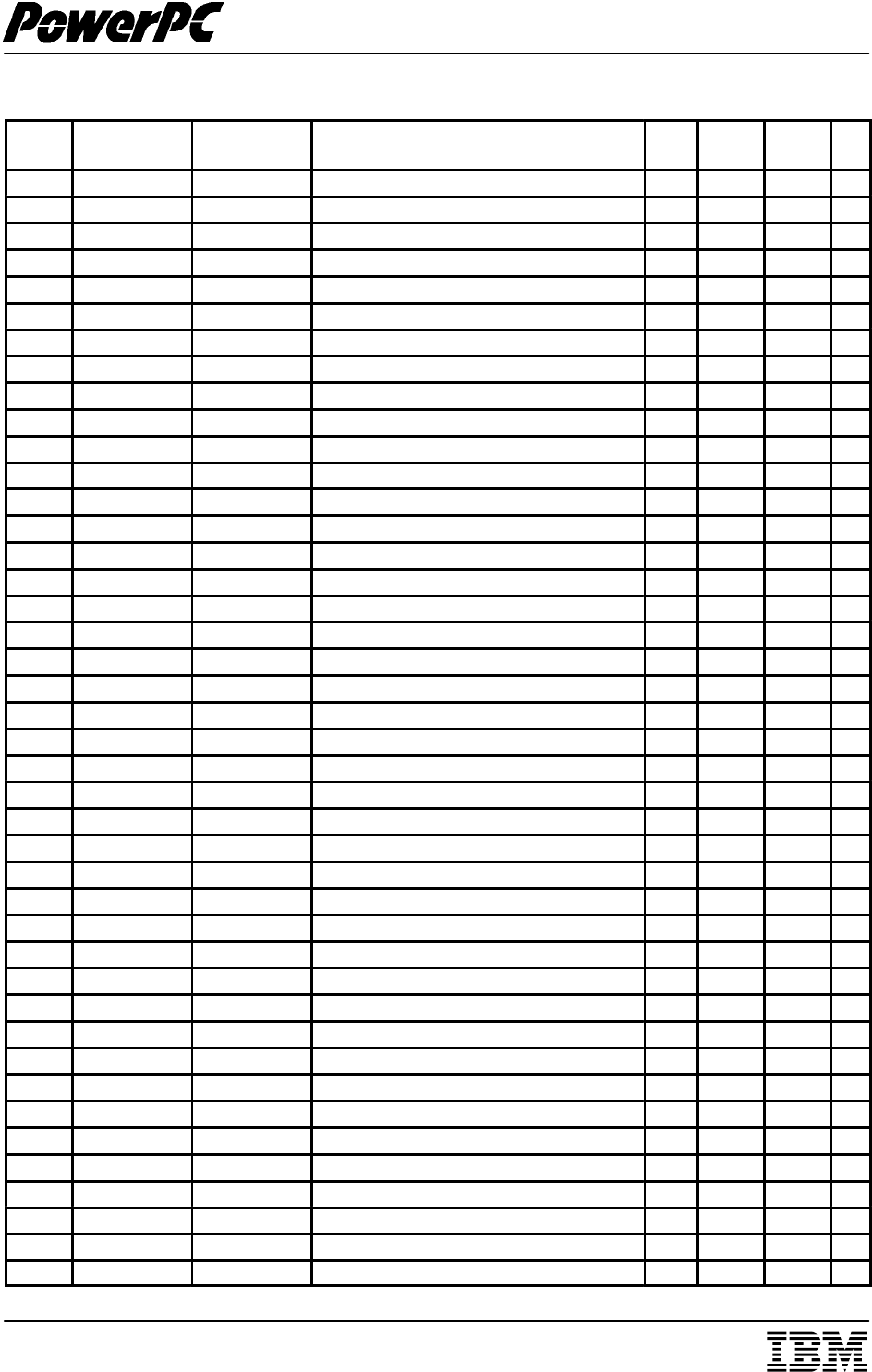

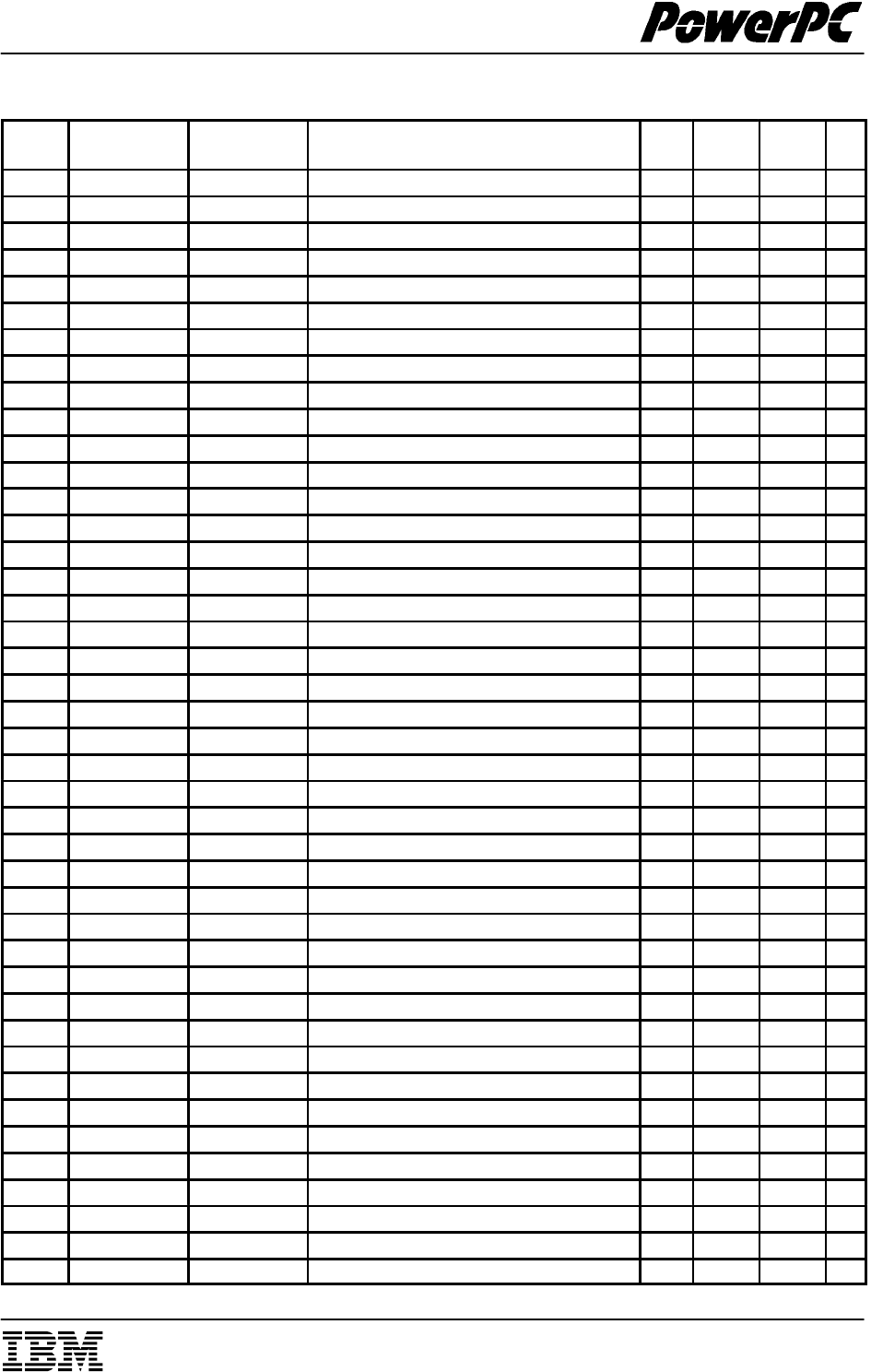

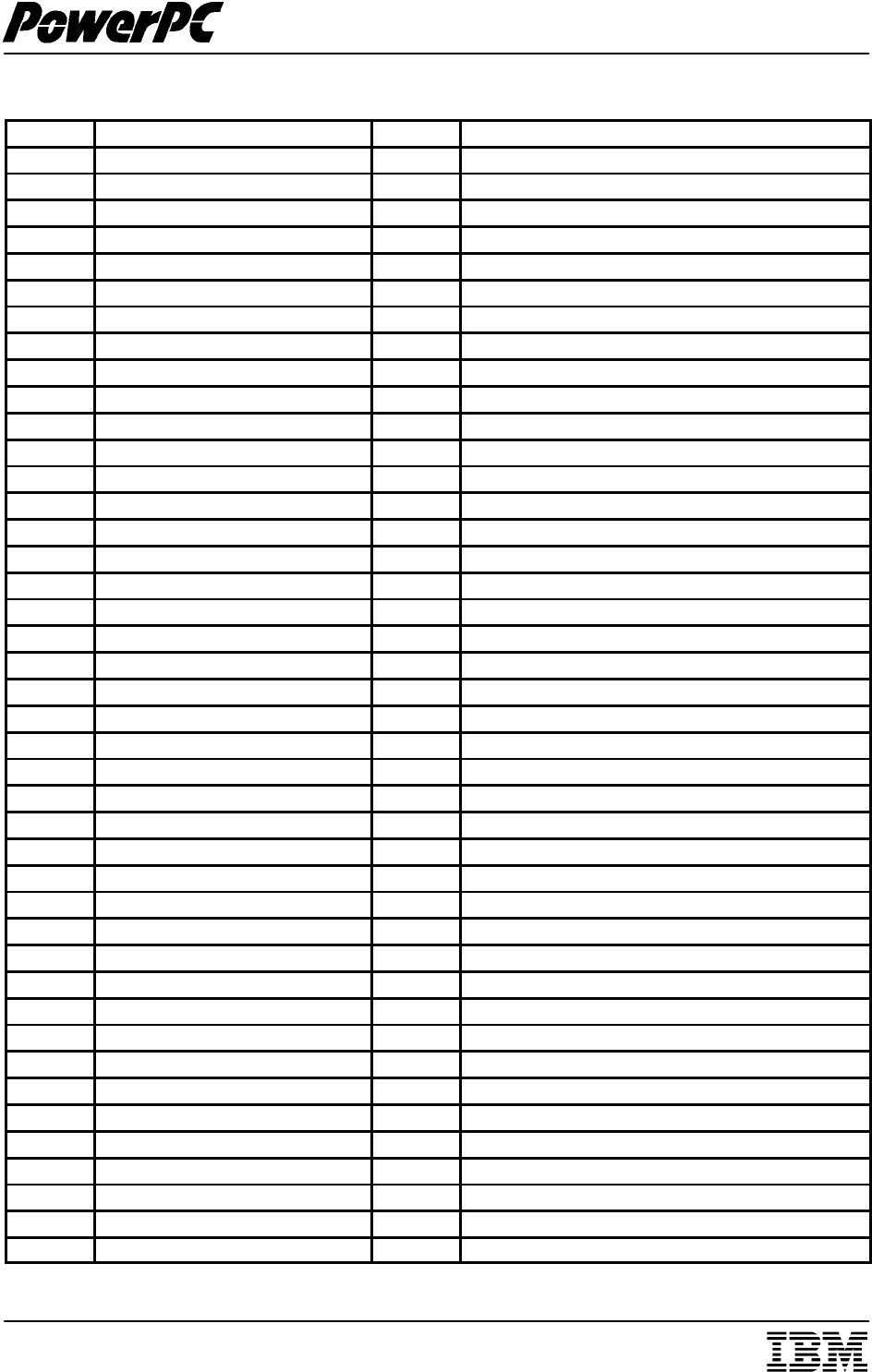

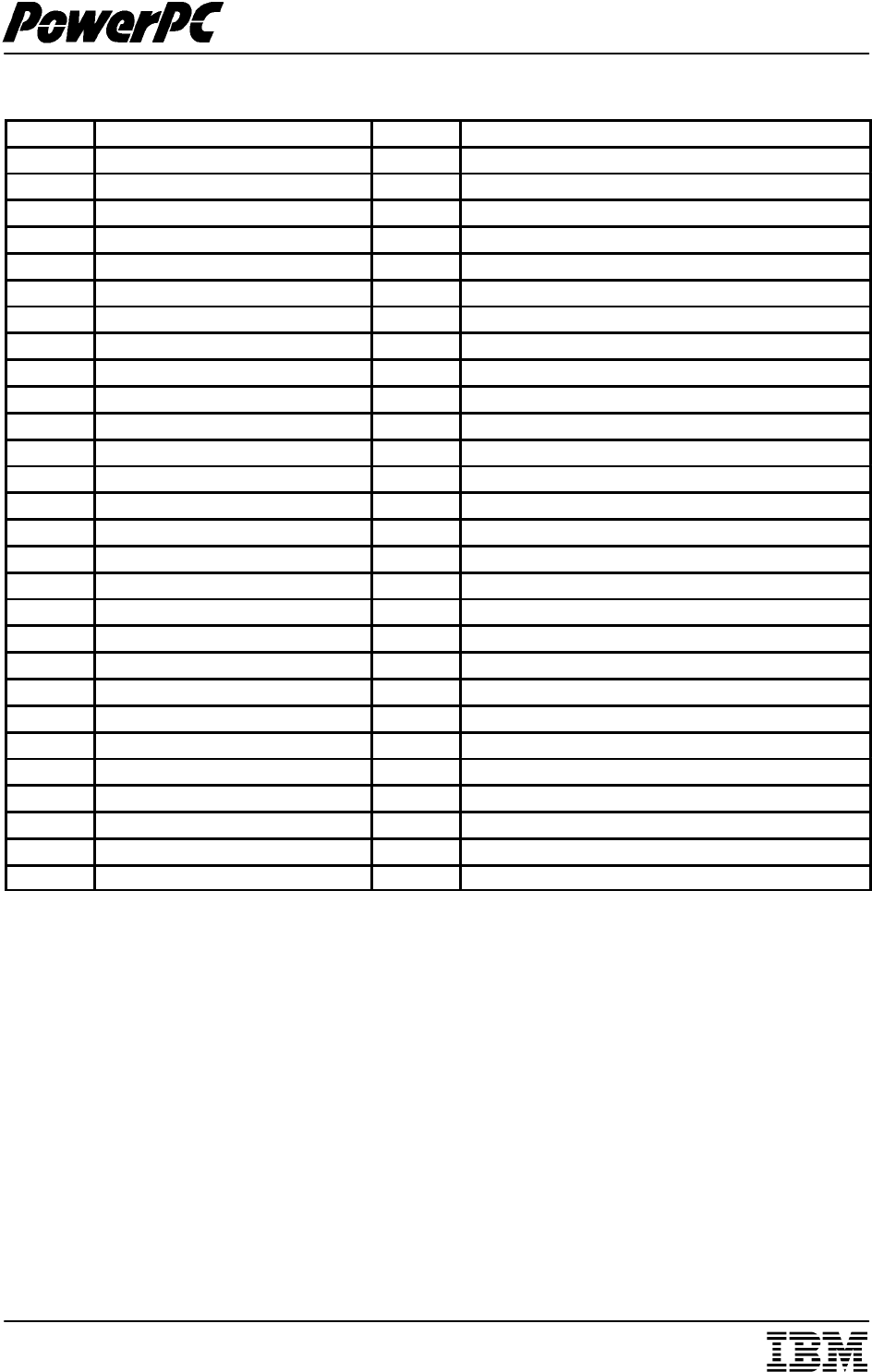

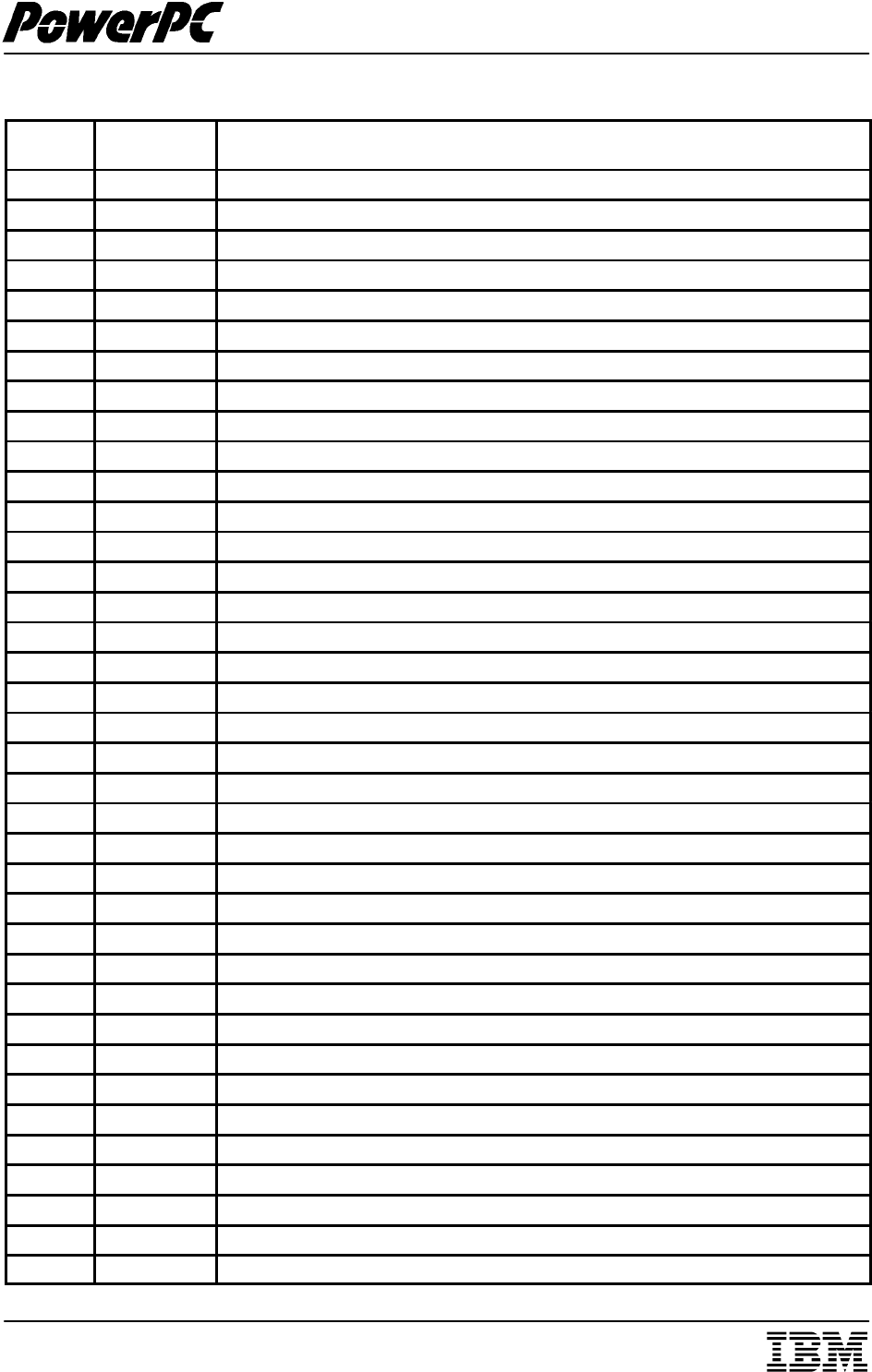

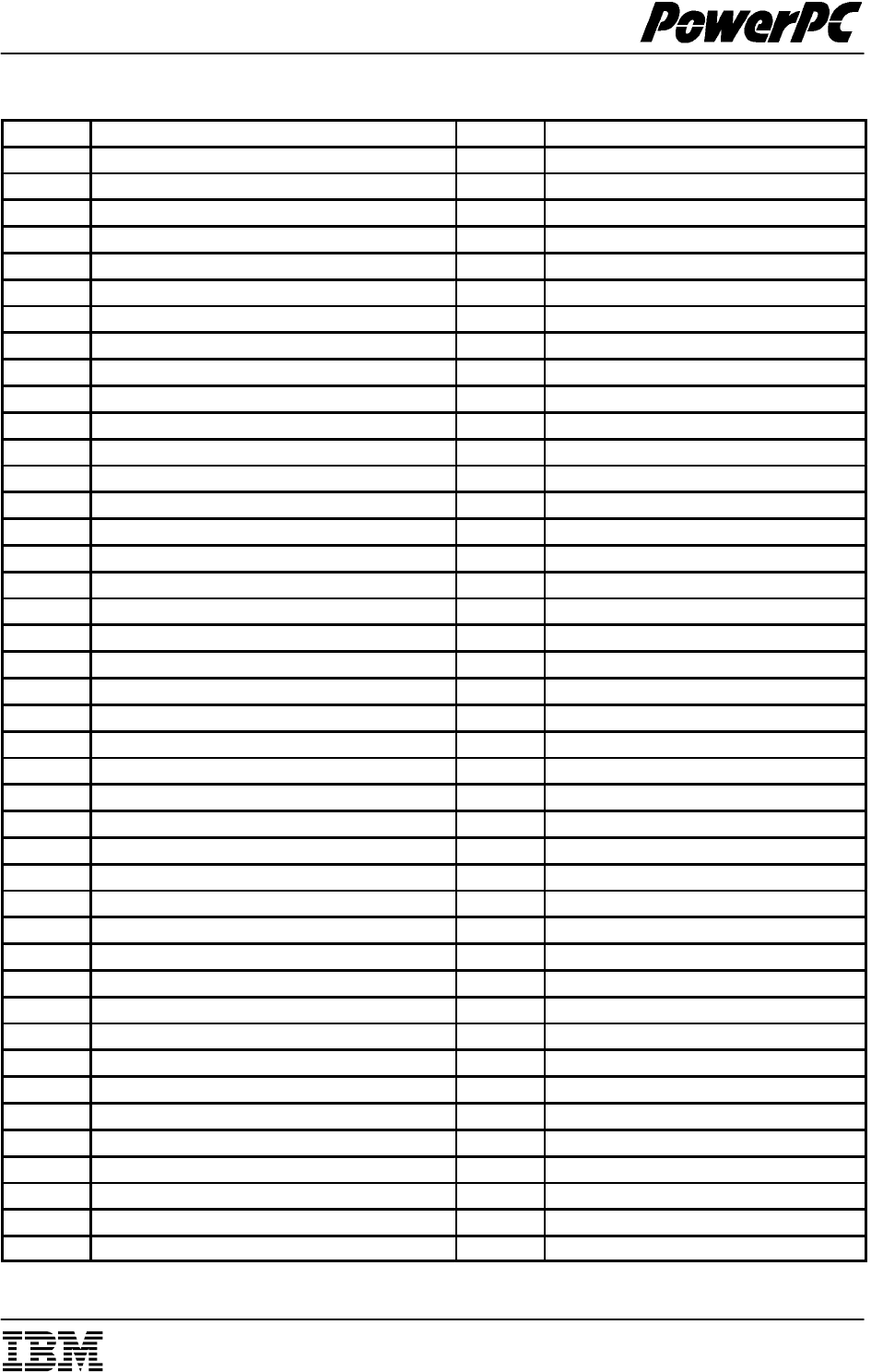

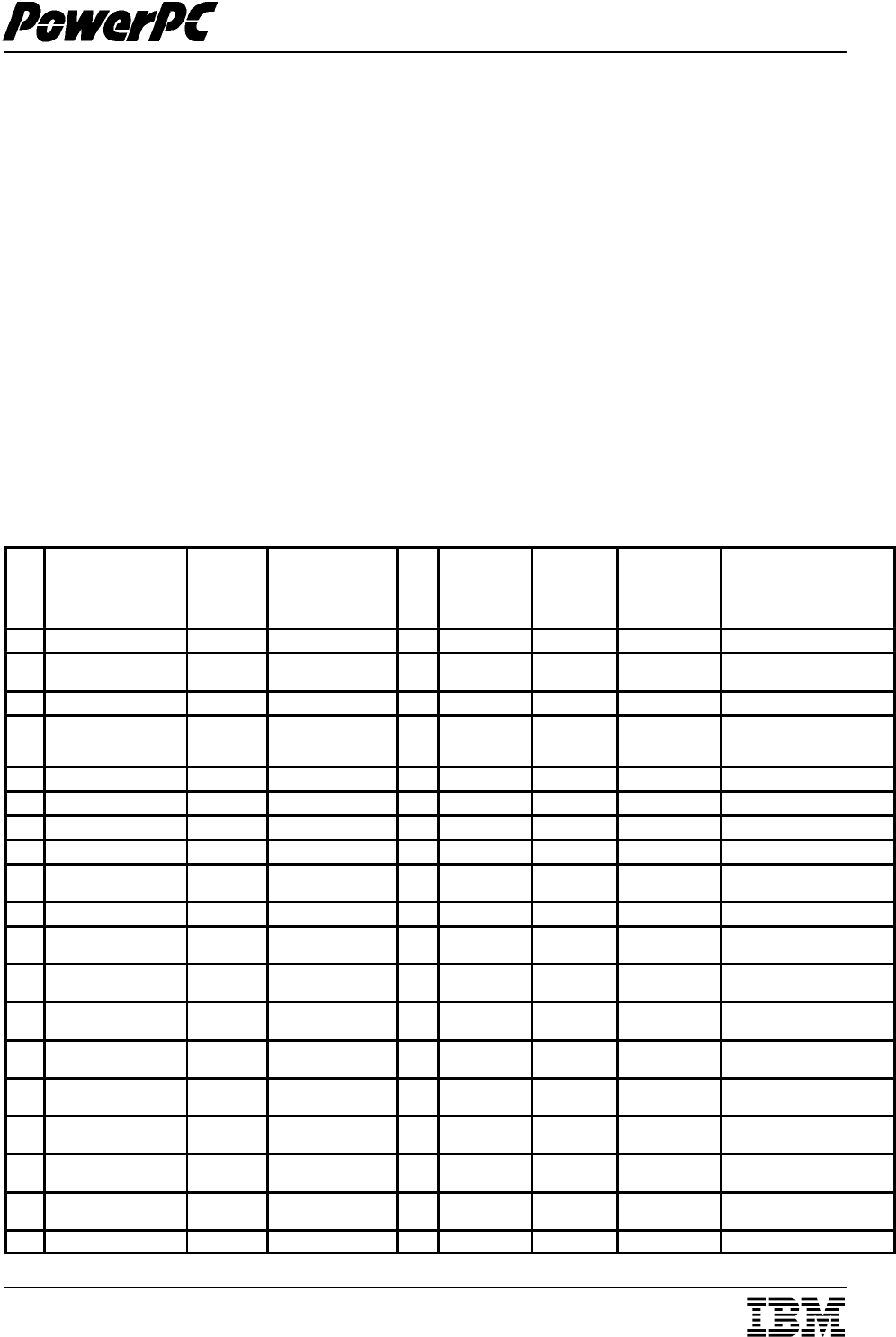

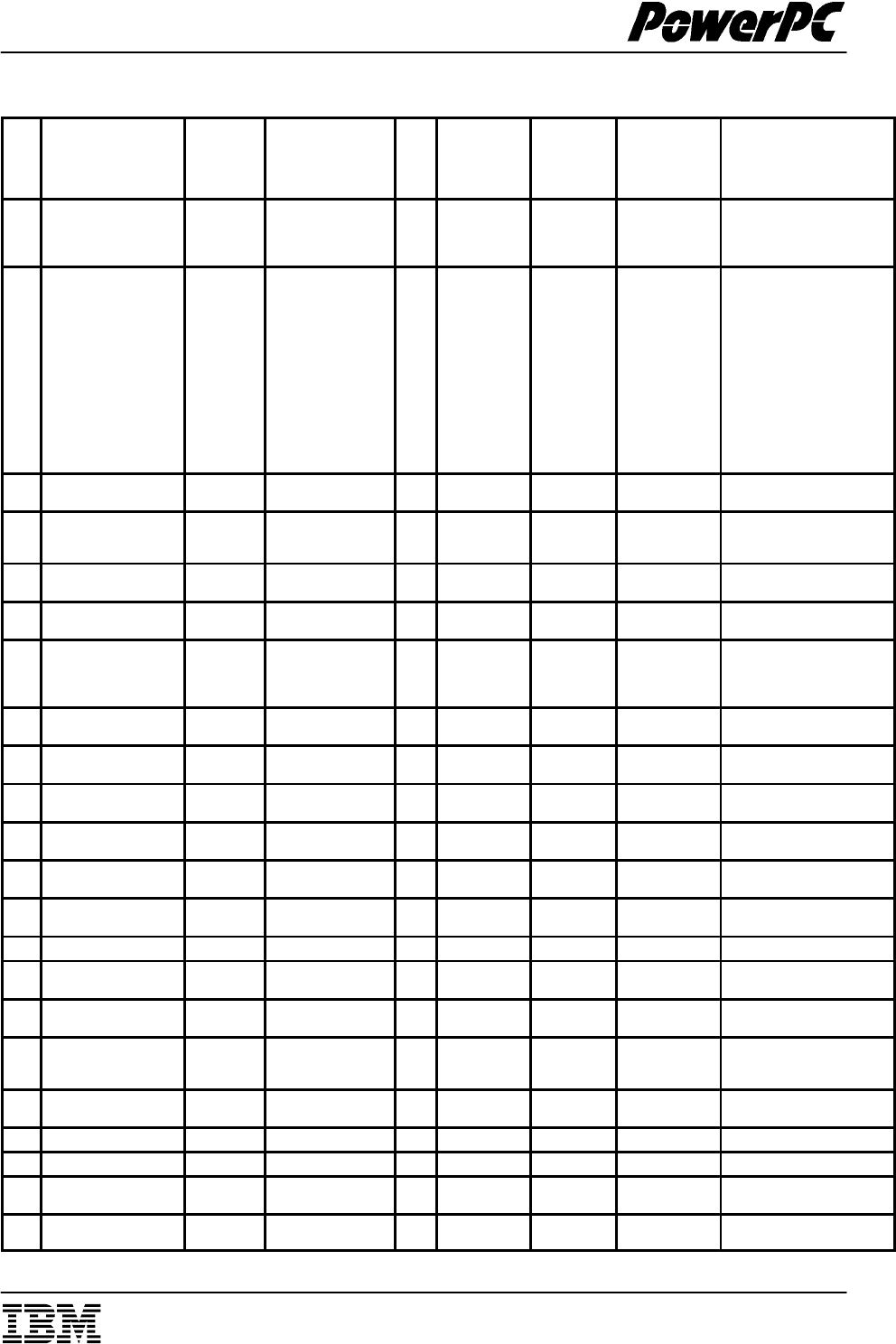

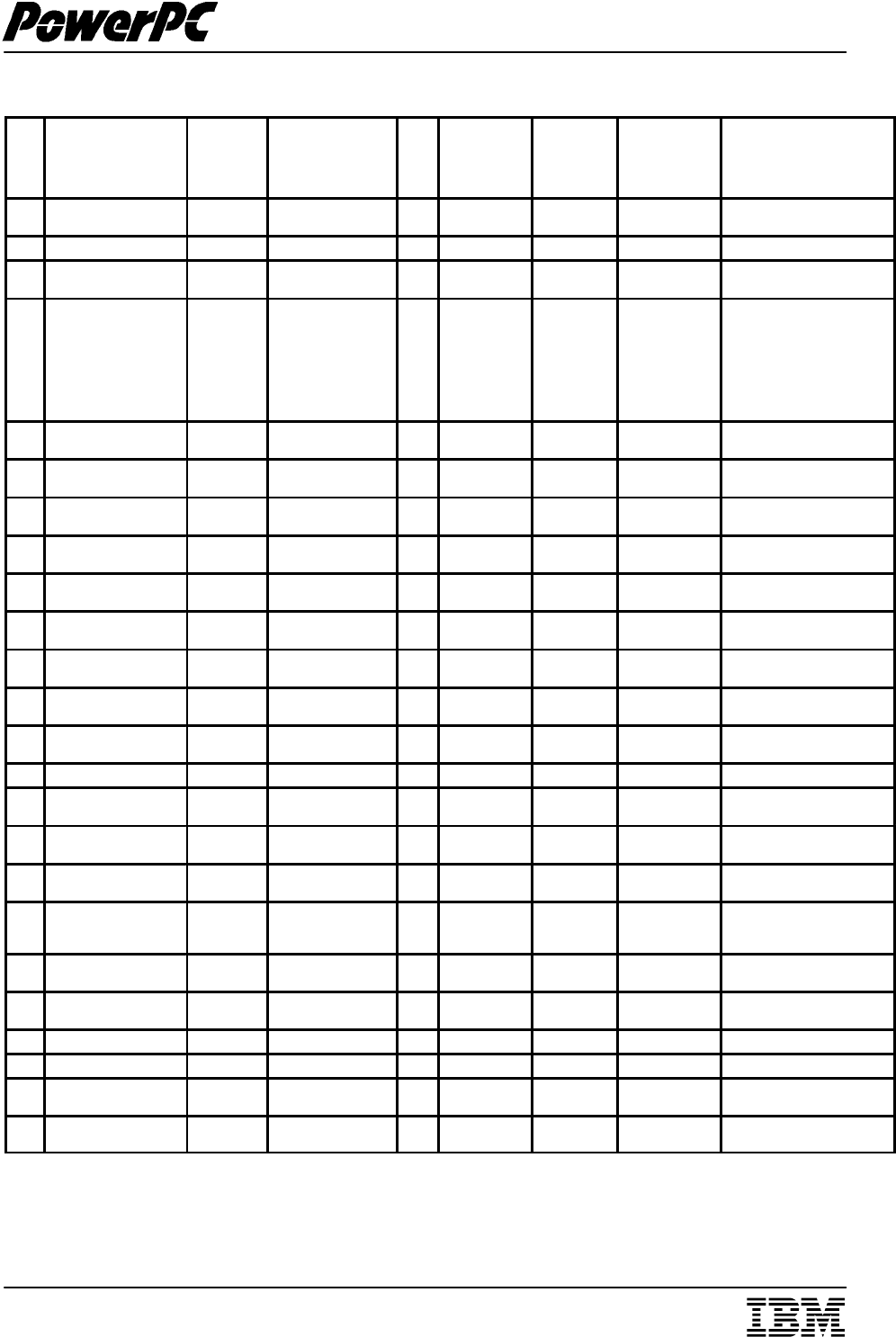

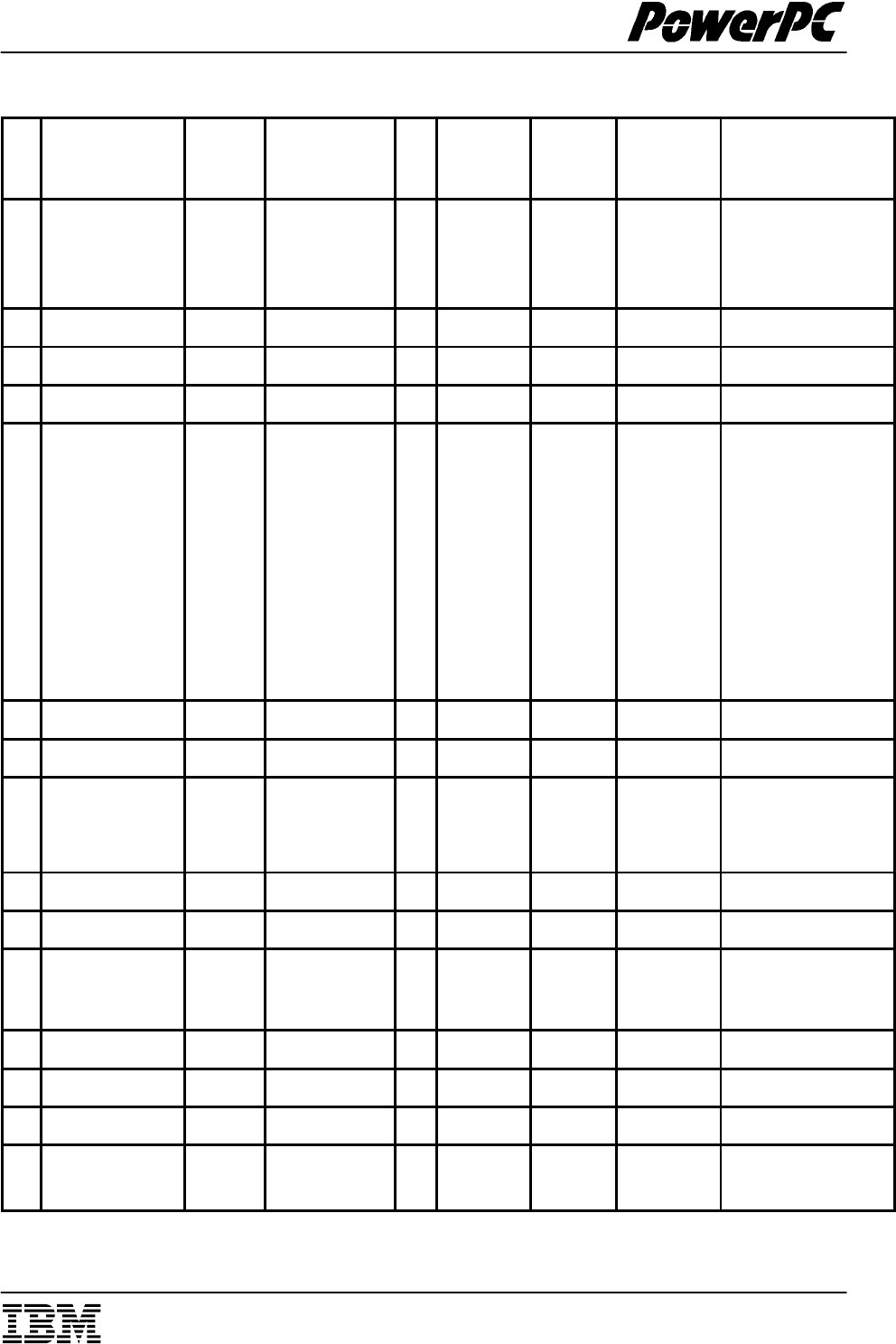

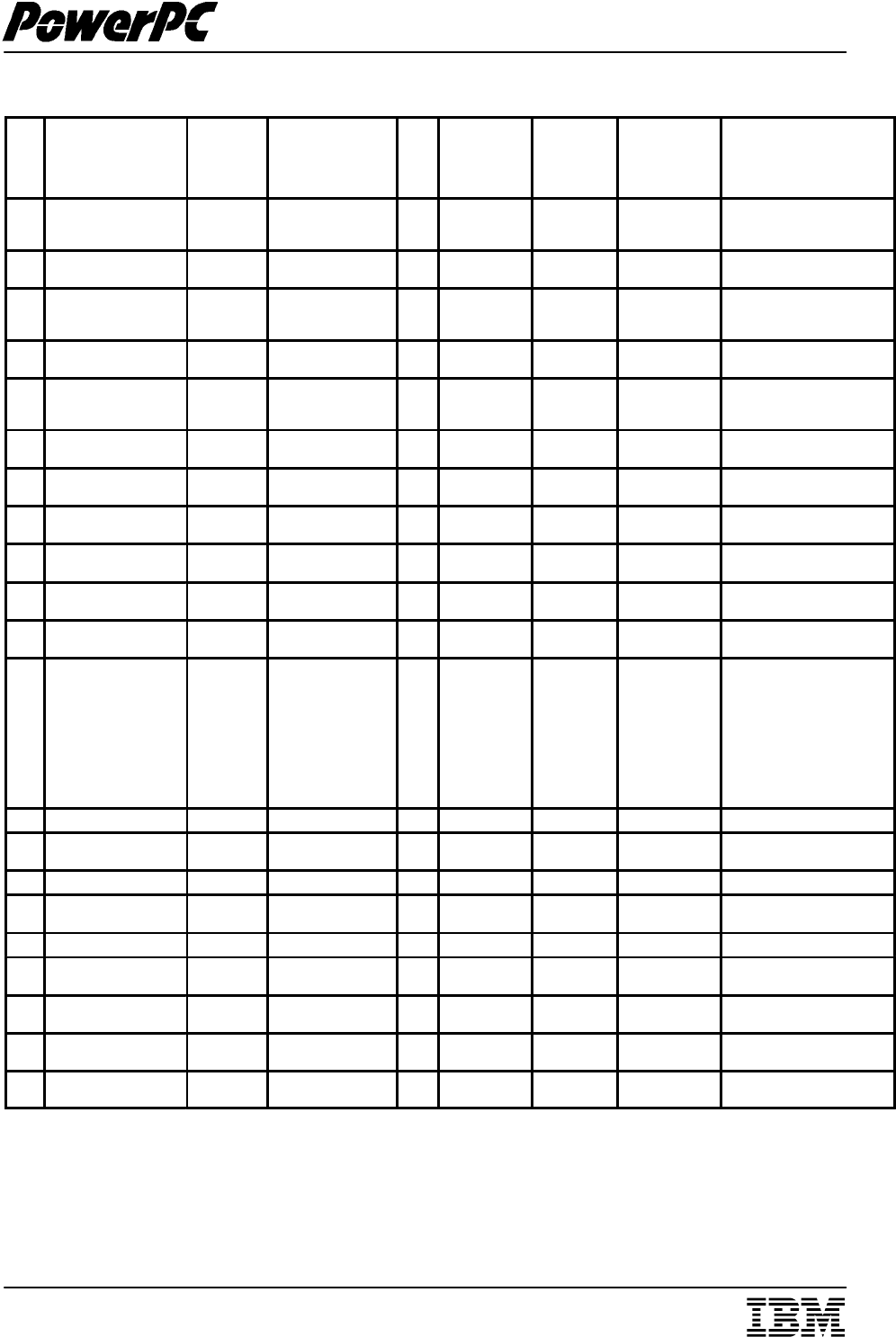

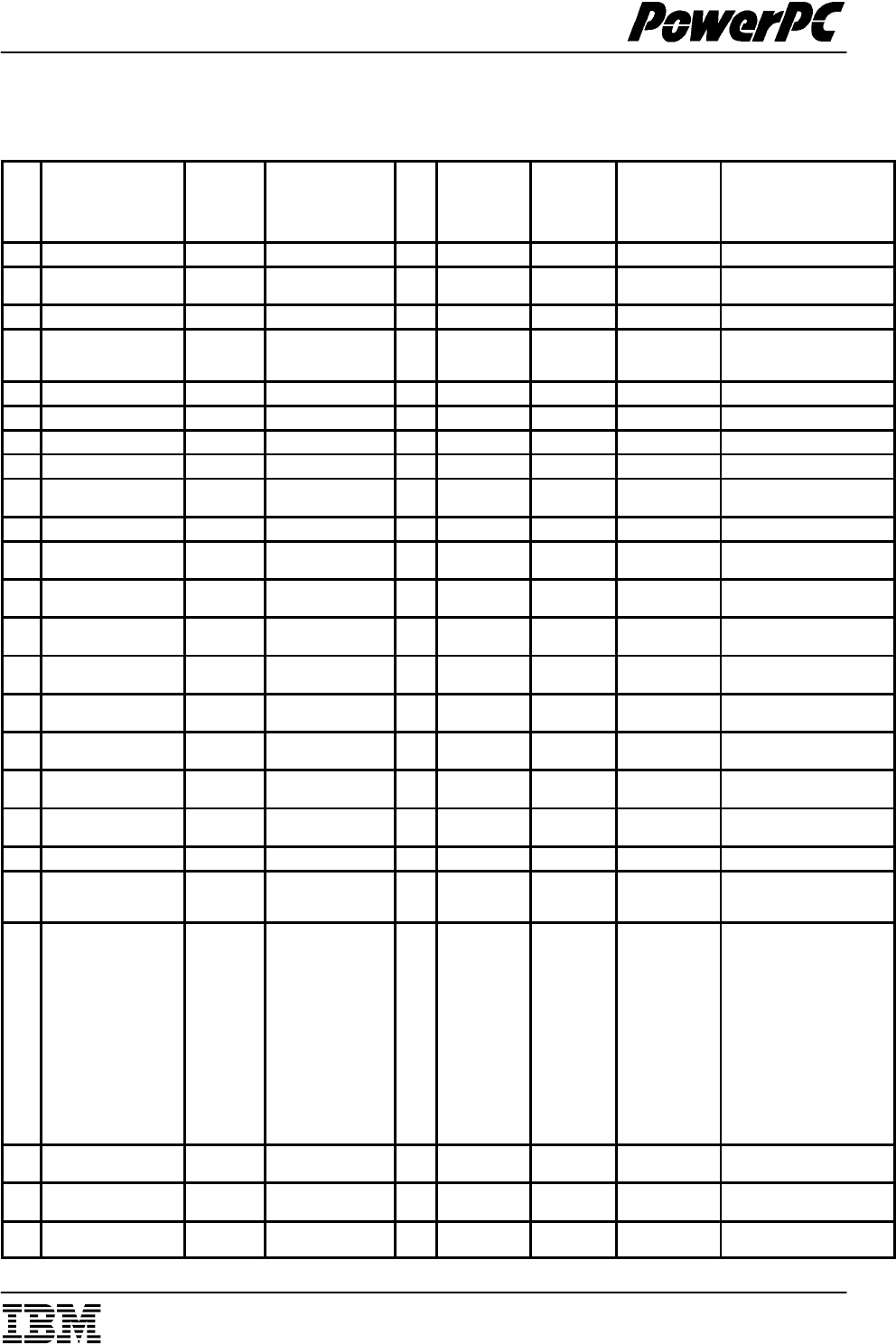

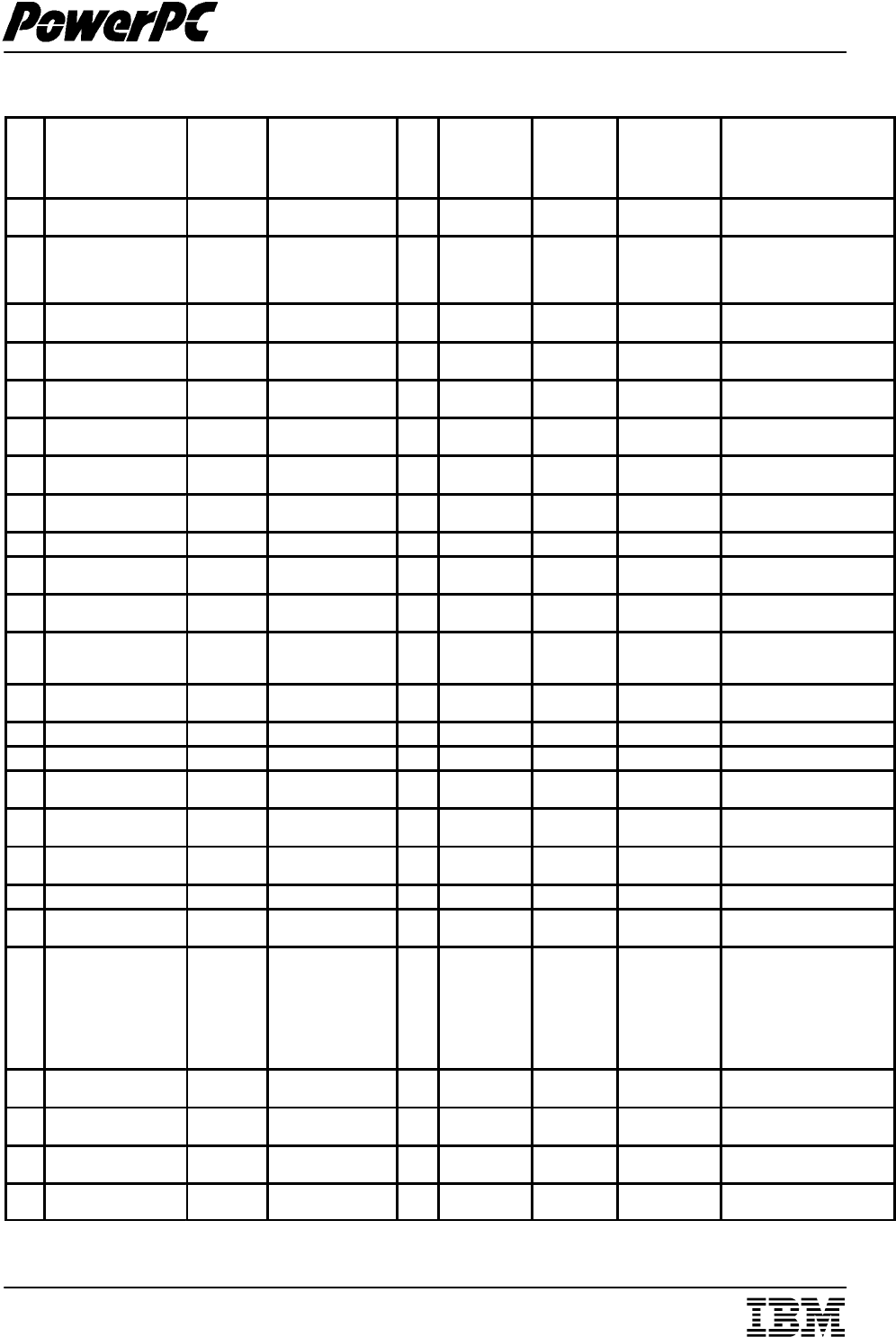

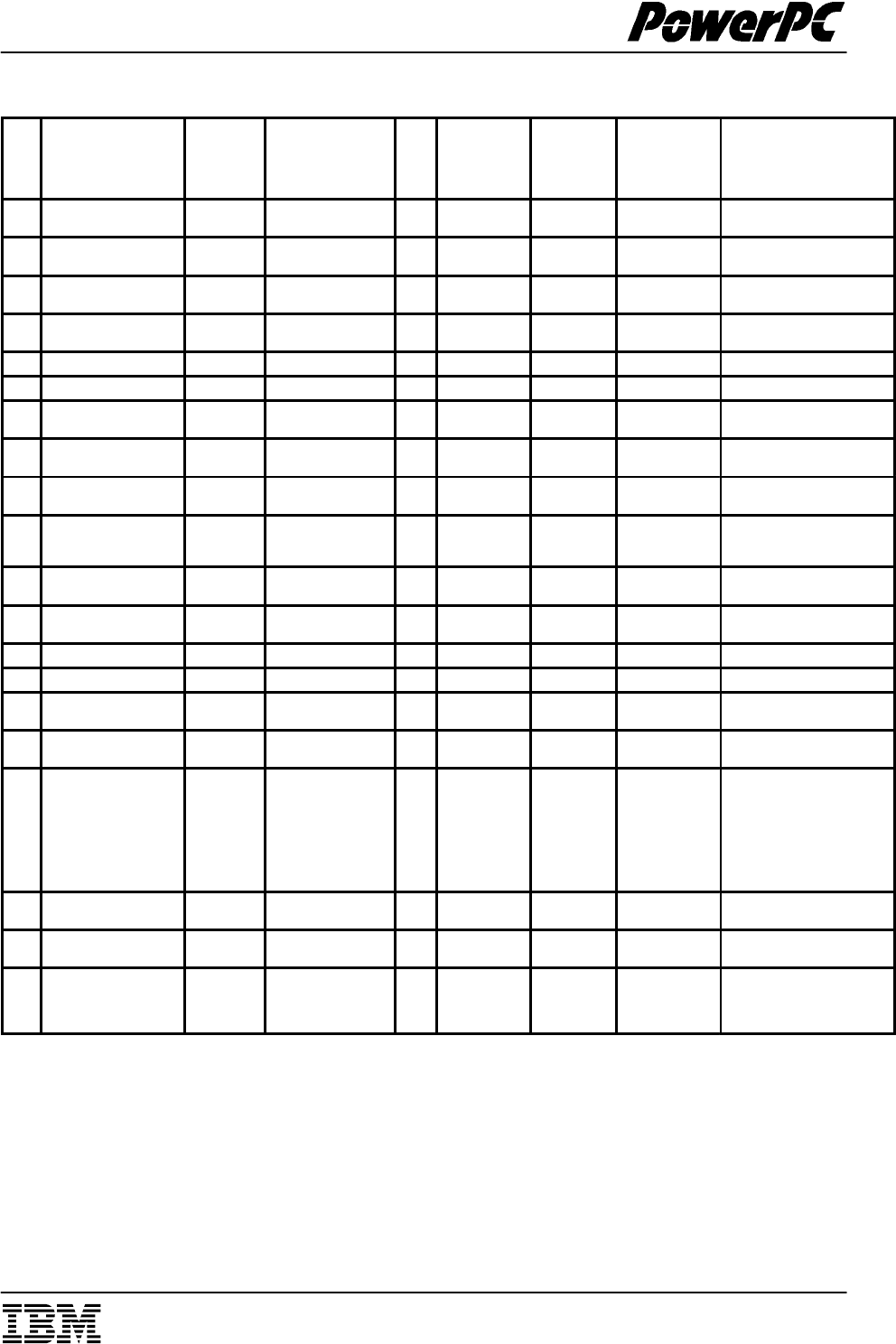

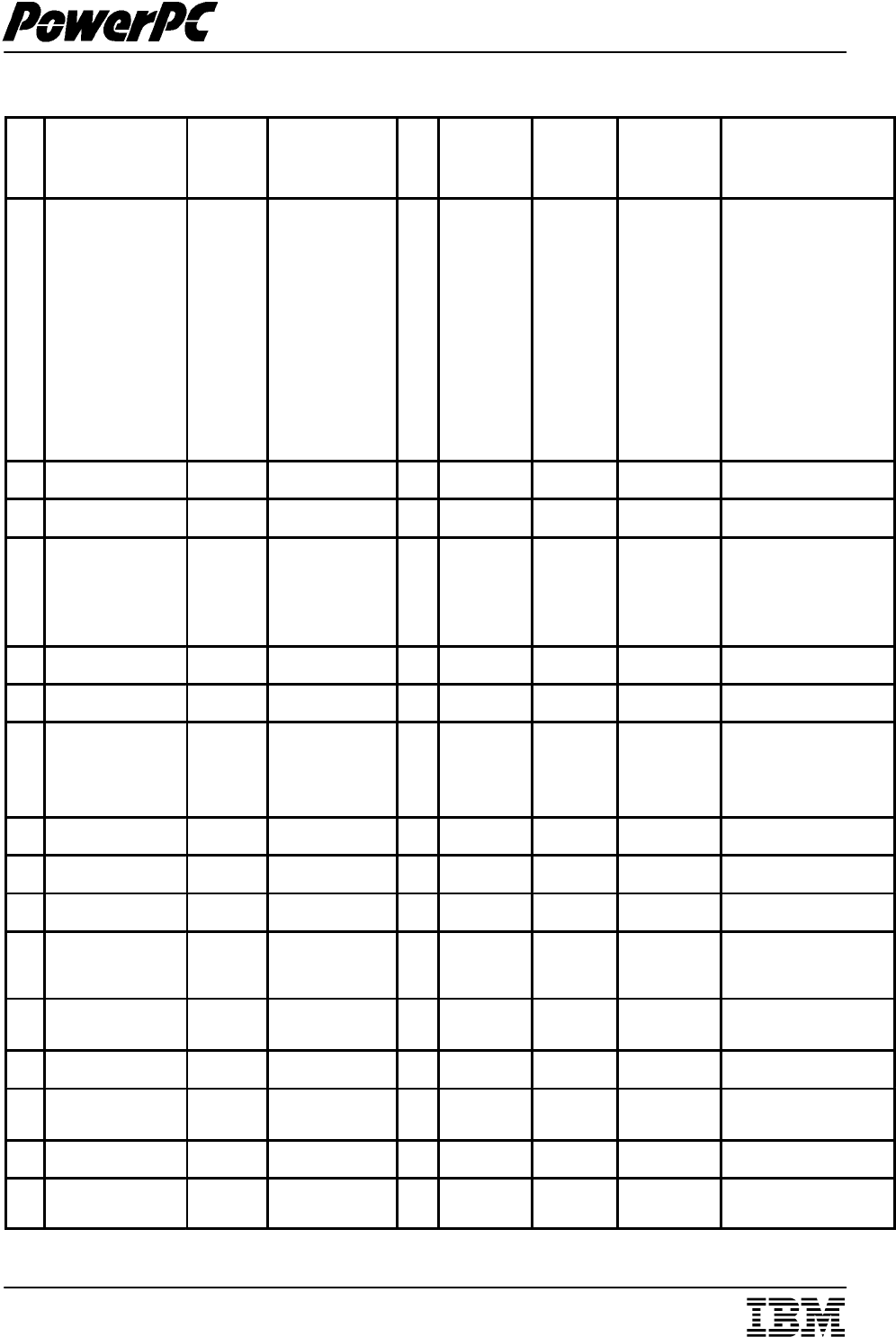

Section 14 Bill of Materials 189. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14.1 603e/604 Reference Design Bill of Materials 189. . . . . . . . . . . . . . . . . . . . . . .

14.1.1 603e Bill of Materials 189. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14.1.2 604 Bill of Materials 194. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Section 15 Schematics 199. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15.1 Reference Board Component Placement 200. . . . . . . . . . . . . . . . . . . . . . . . . .

Section 16 Selected Component Data Sheets . . . . . . . . . . . . . . . . . . . . . . . . . . .

11

MPRH08TSU-02

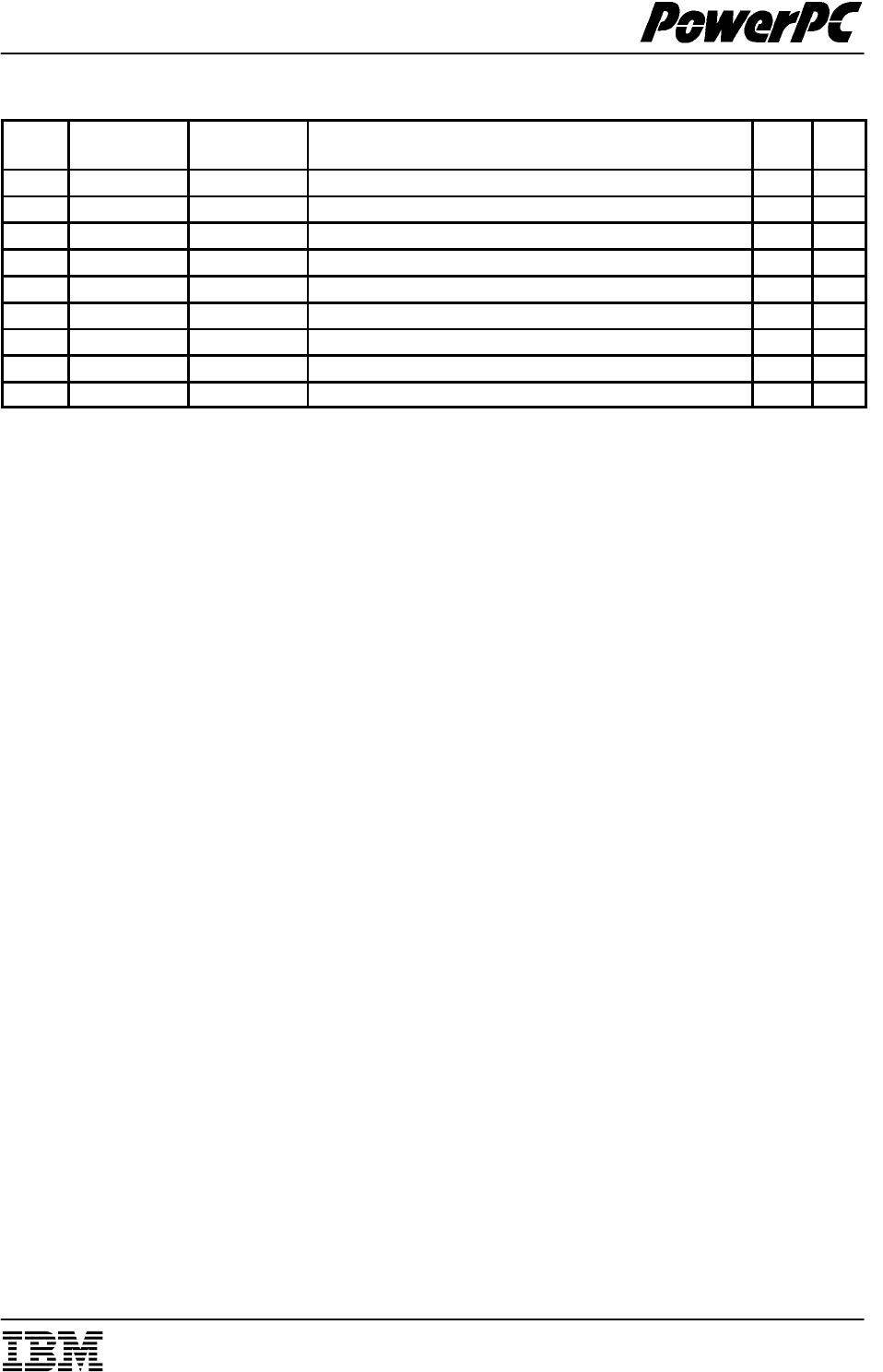

Figures

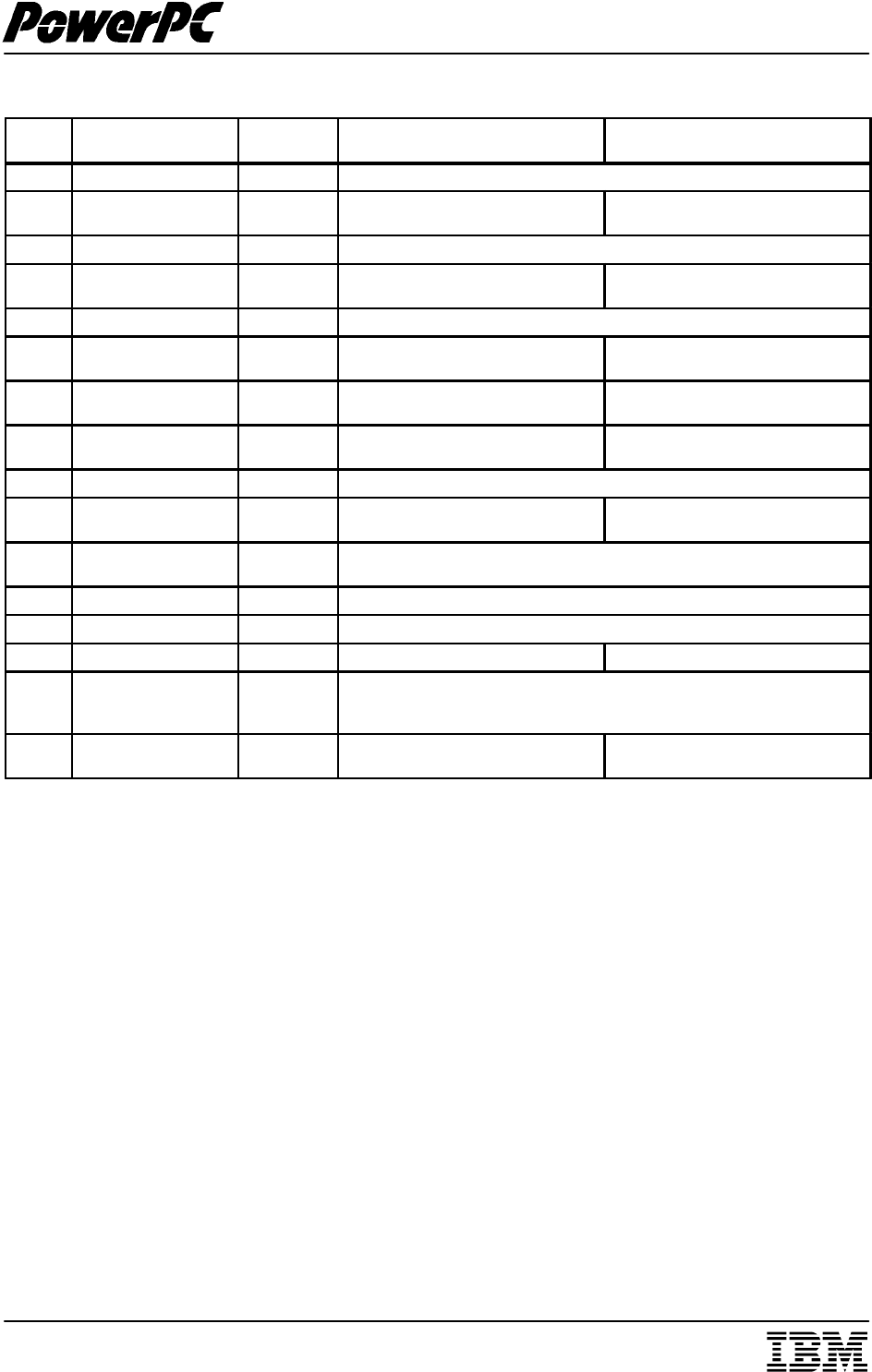

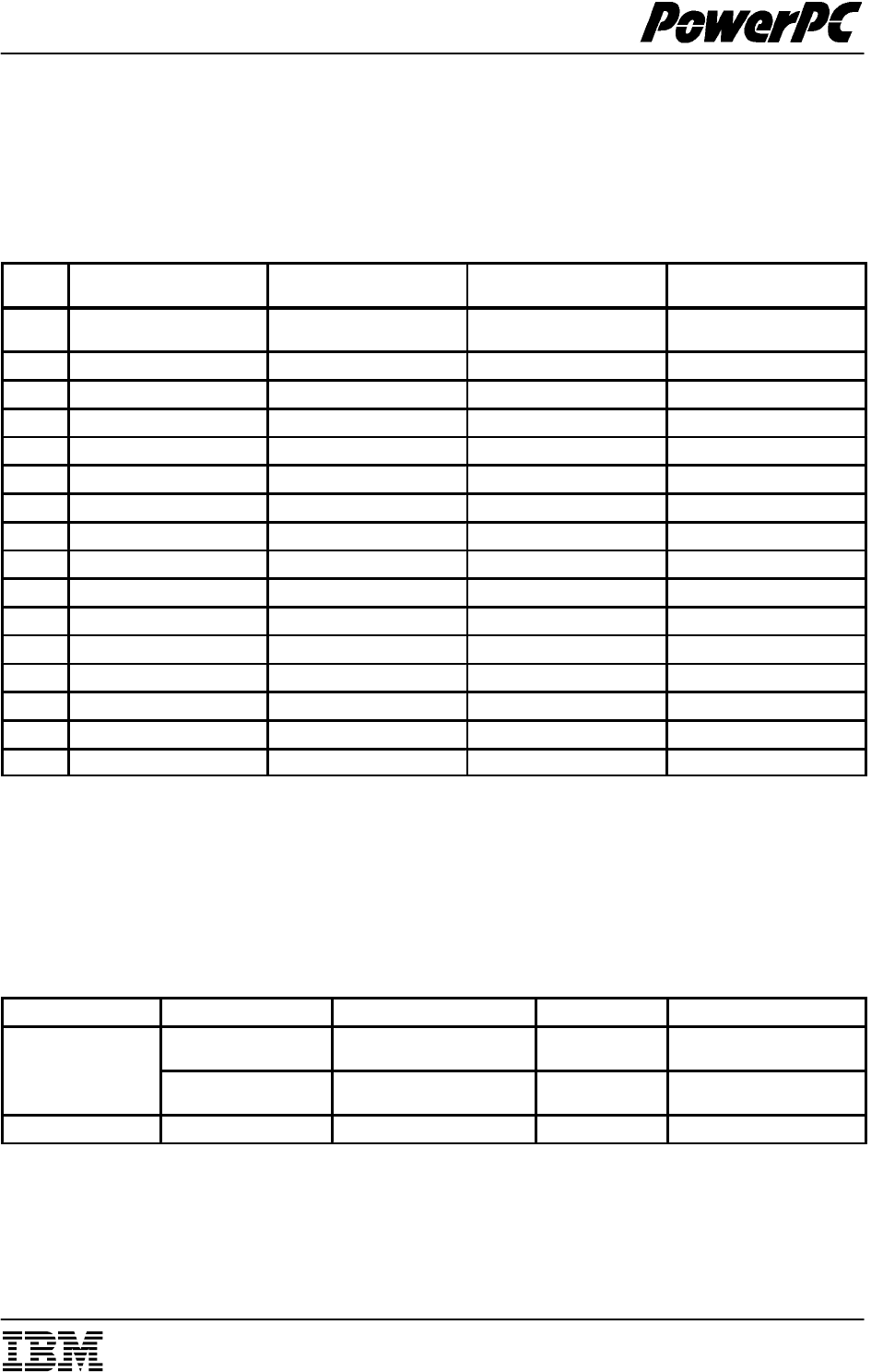

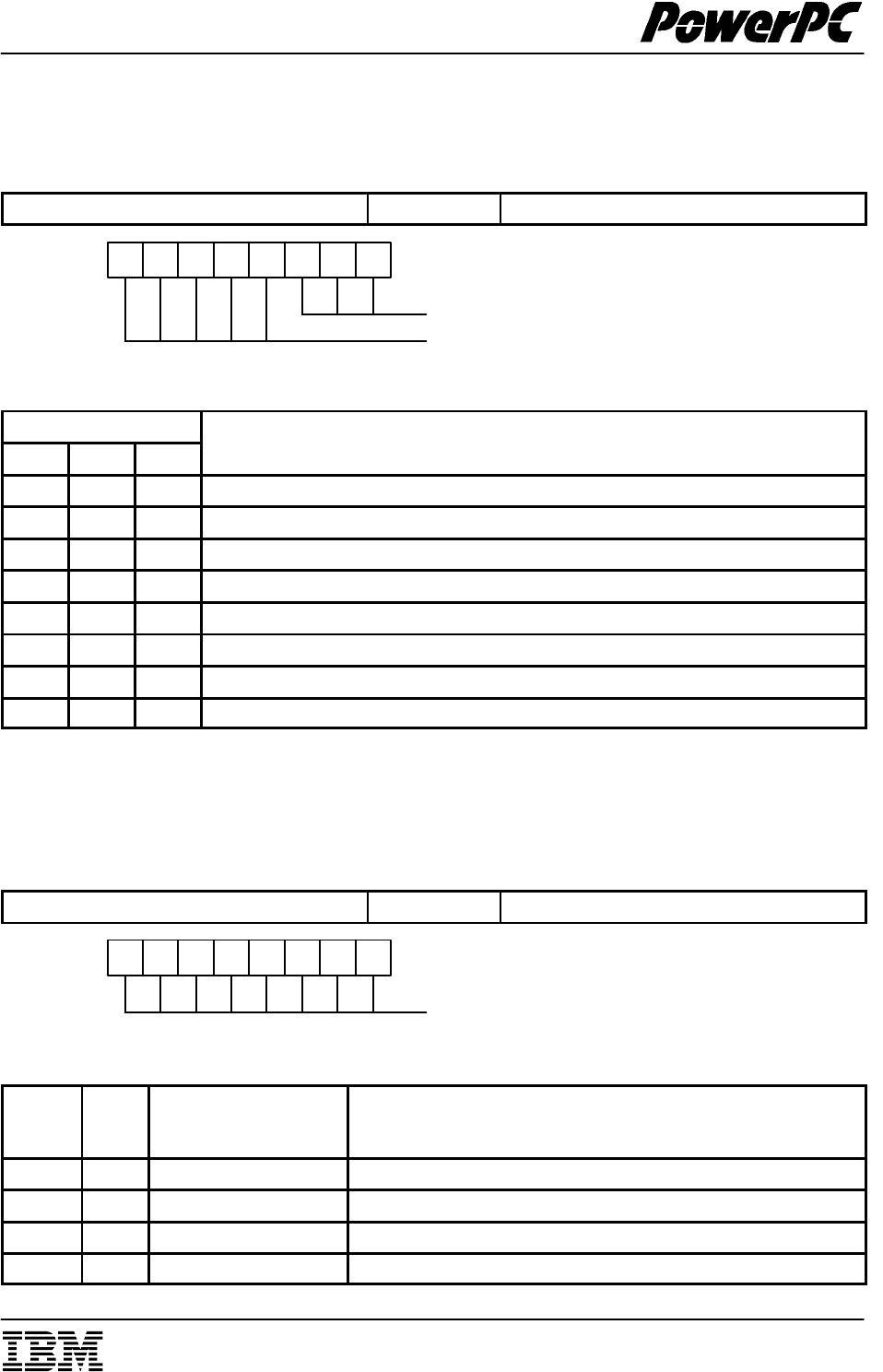

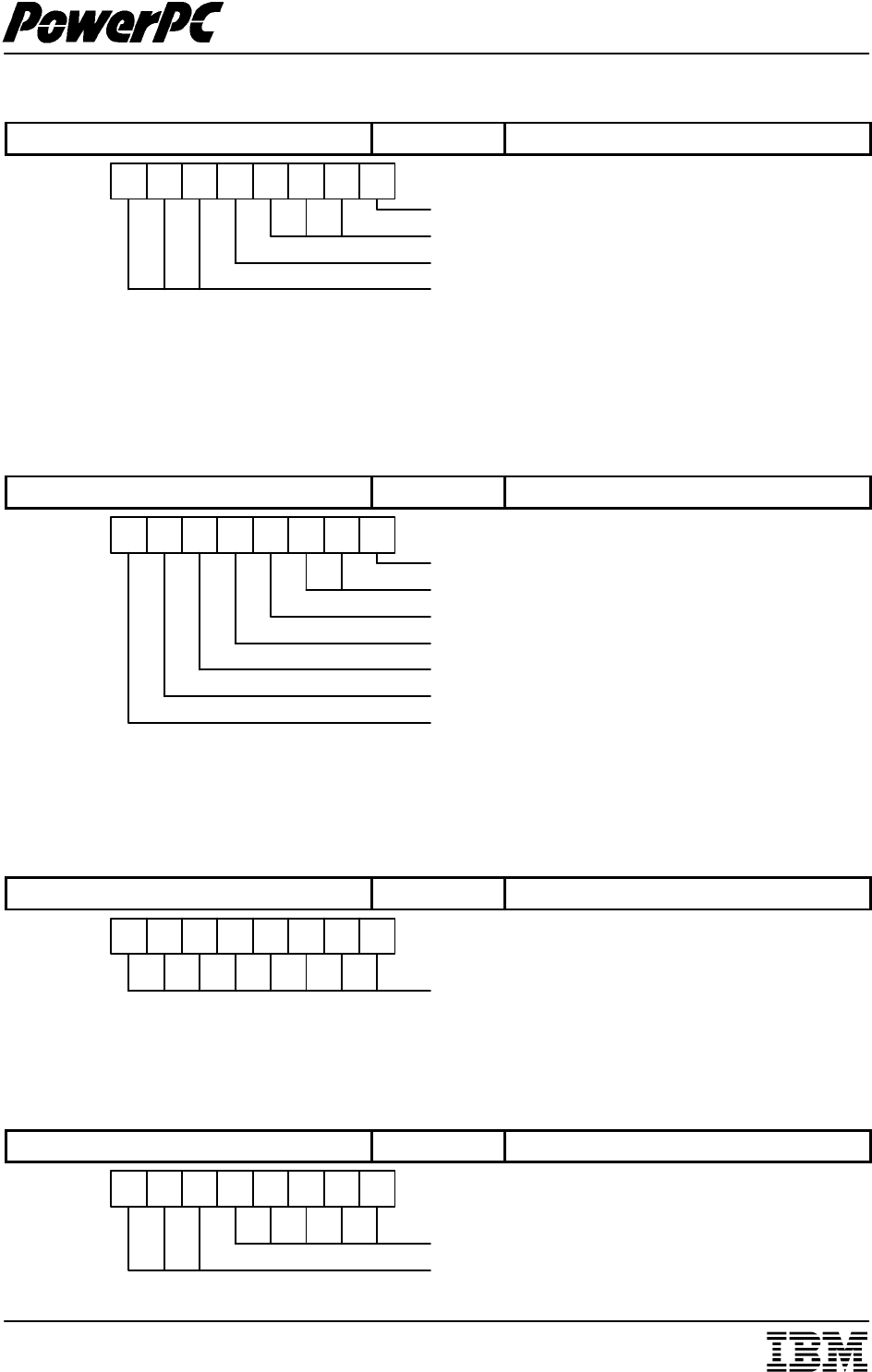

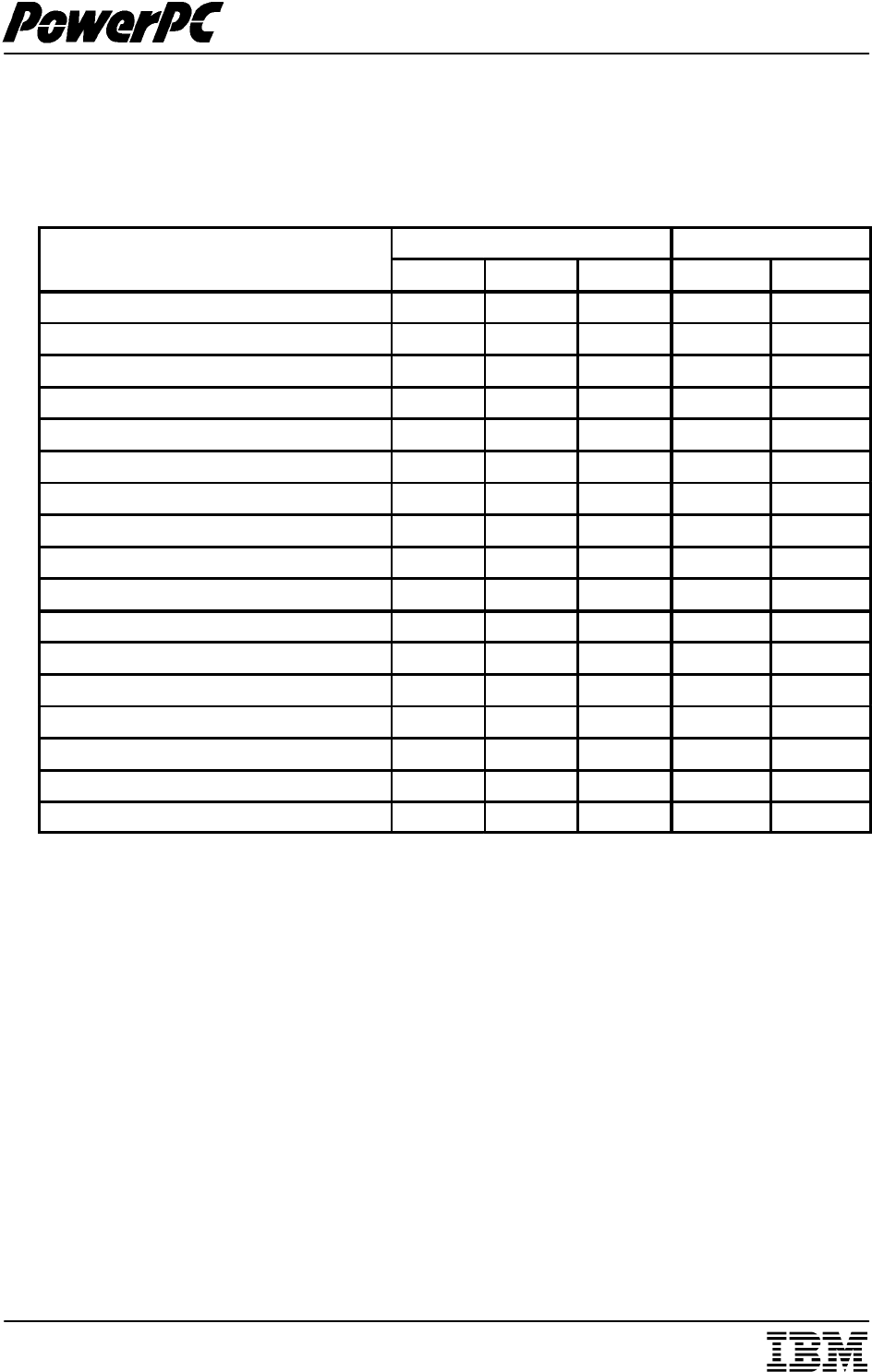

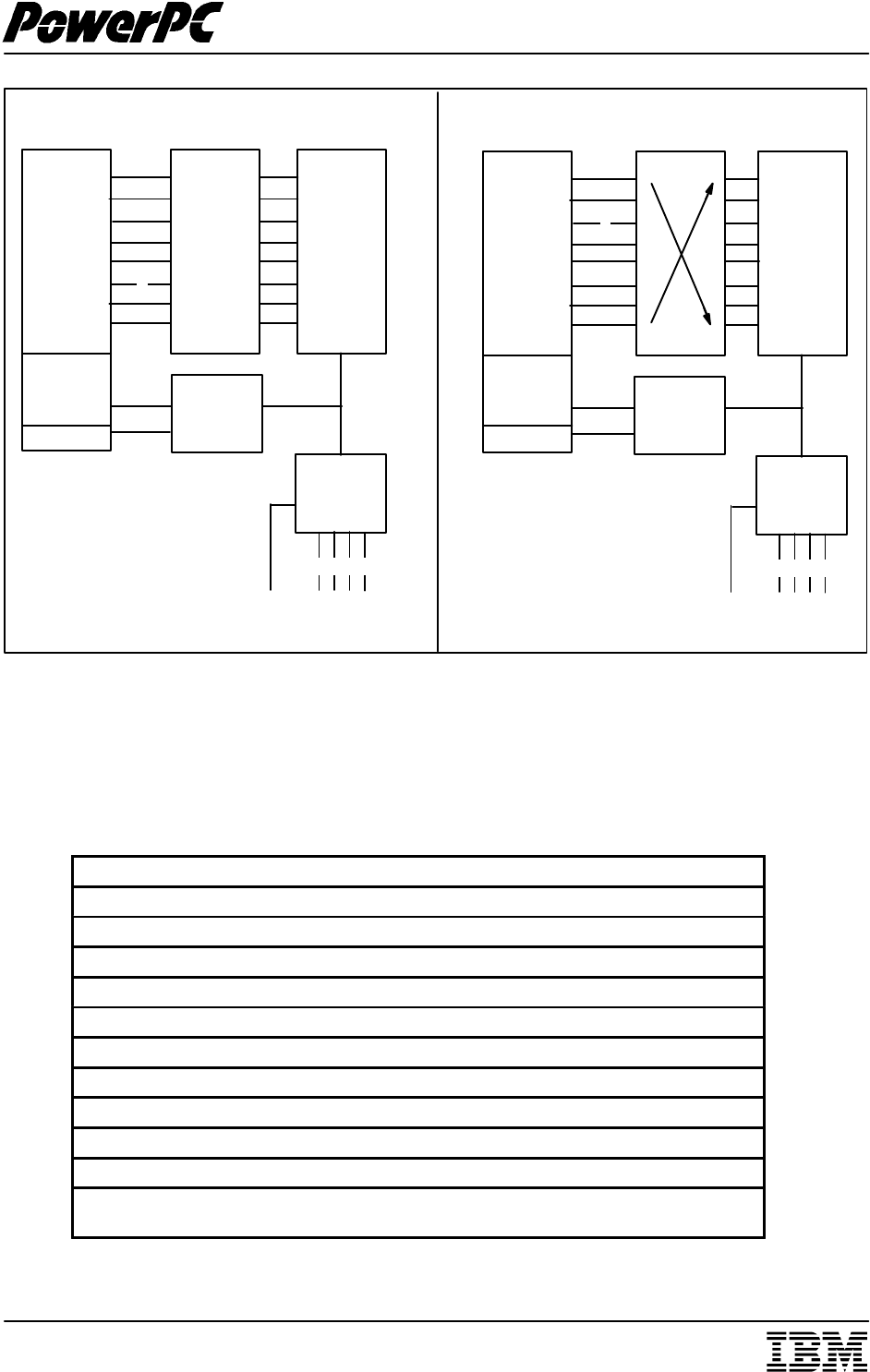

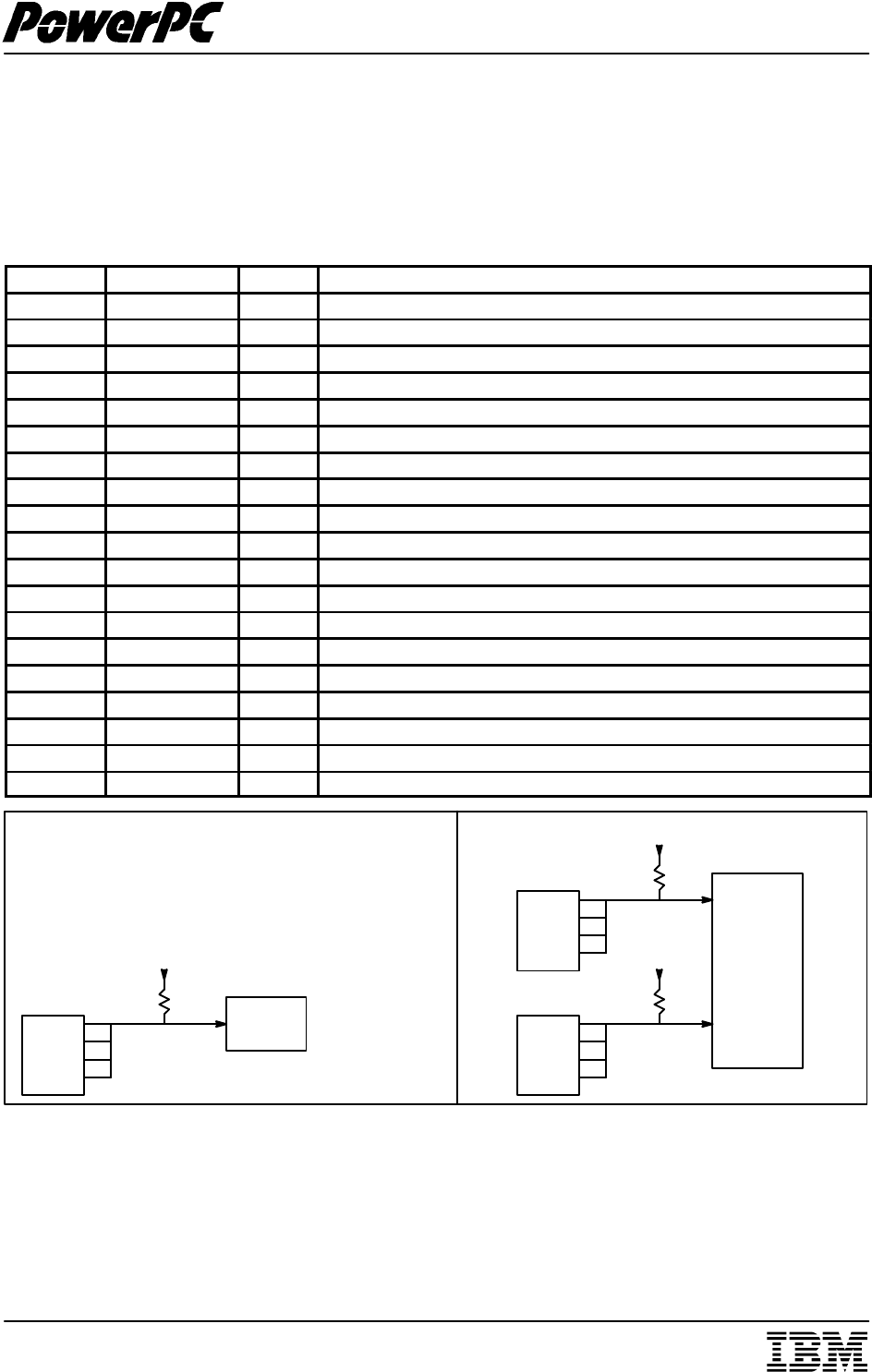

Figure 1. 603/604 Reference Design Block Diagram 20. . . . . . . . . . . . . . . . . . .

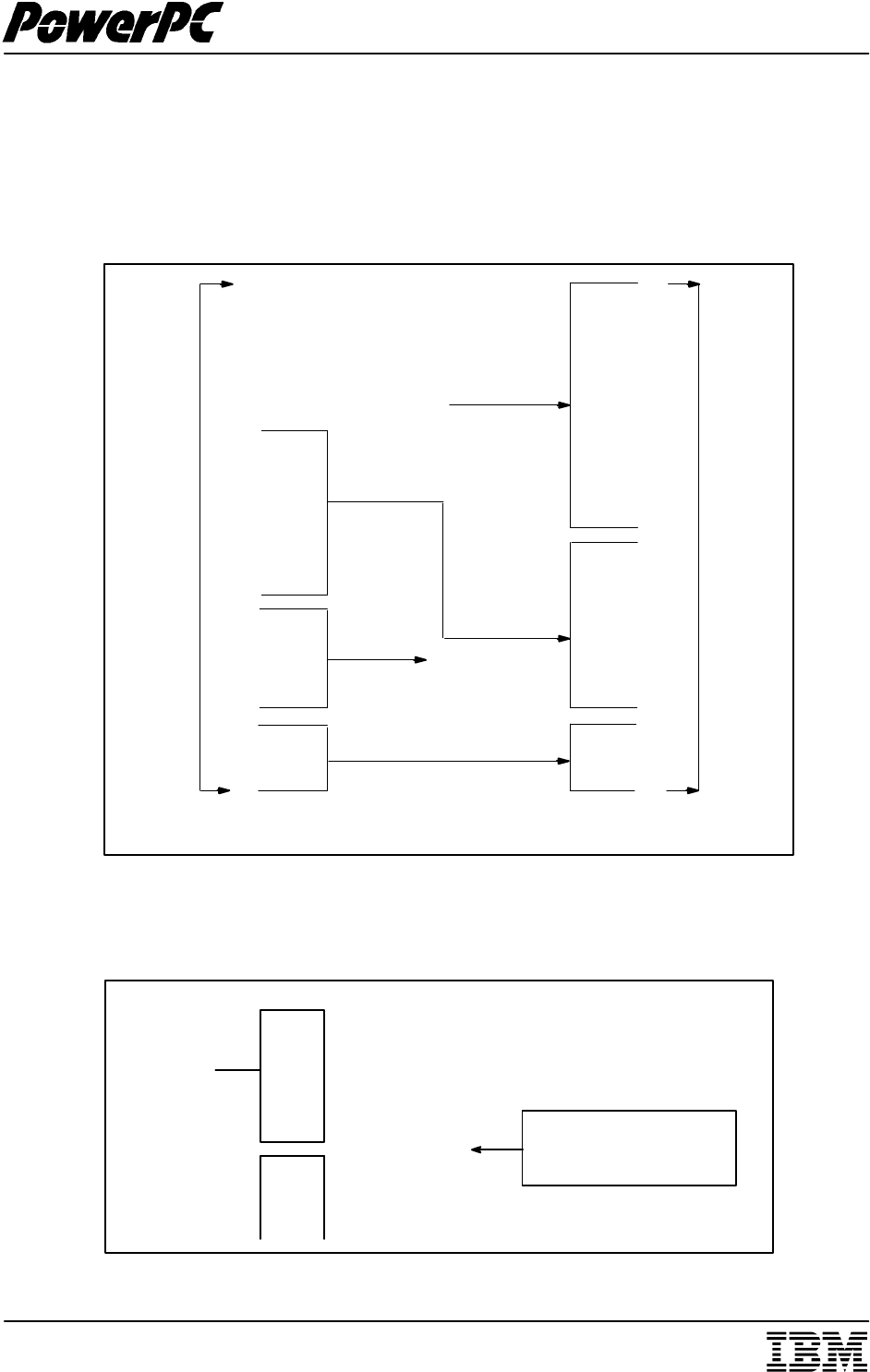

Figure 2. Non-Contiguous PCI I/O Address Transformation 29. . . . . . . . . . . . .

Figure 3. Non-Contiguous PCI I/O Address Translation 29. . . . . . . . . . . . . . . . .

Figure 4. Contiguous PCI I/O Address Translation 30. . . . . . . . . . . . . . . . . . . . .

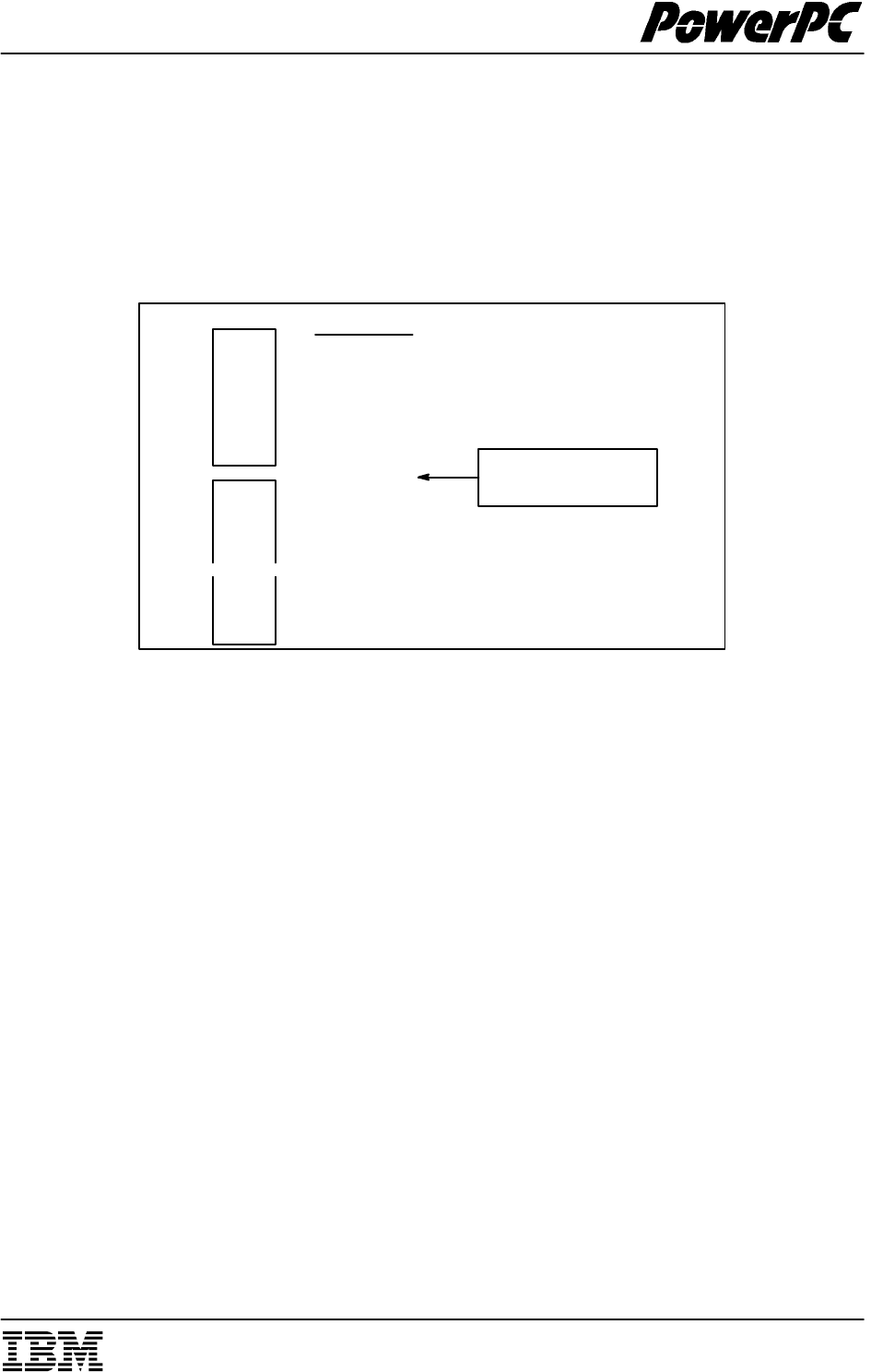

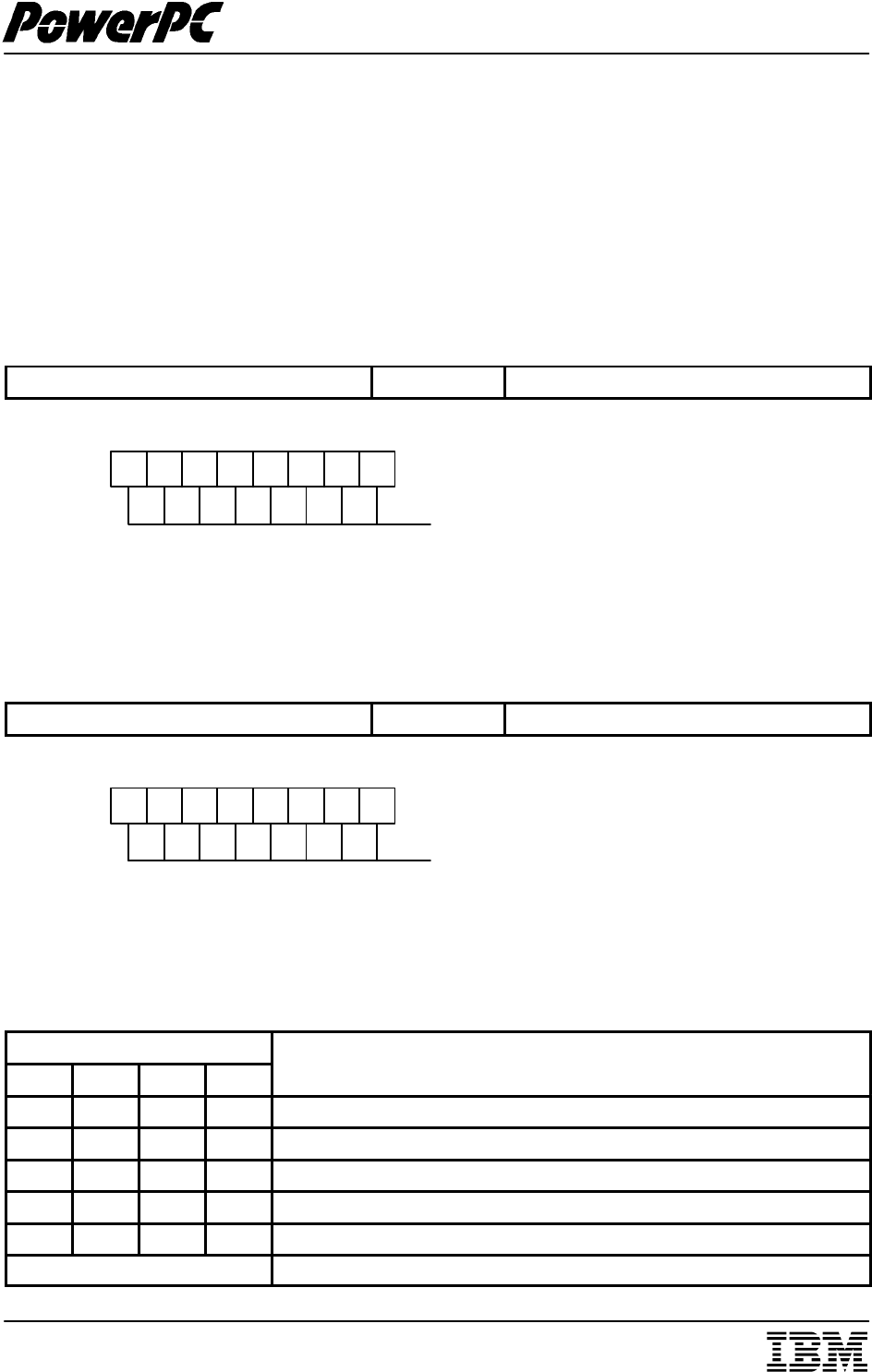

Figure 5. Typical External Register 51. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 6. DRAM Bank Organization 68. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

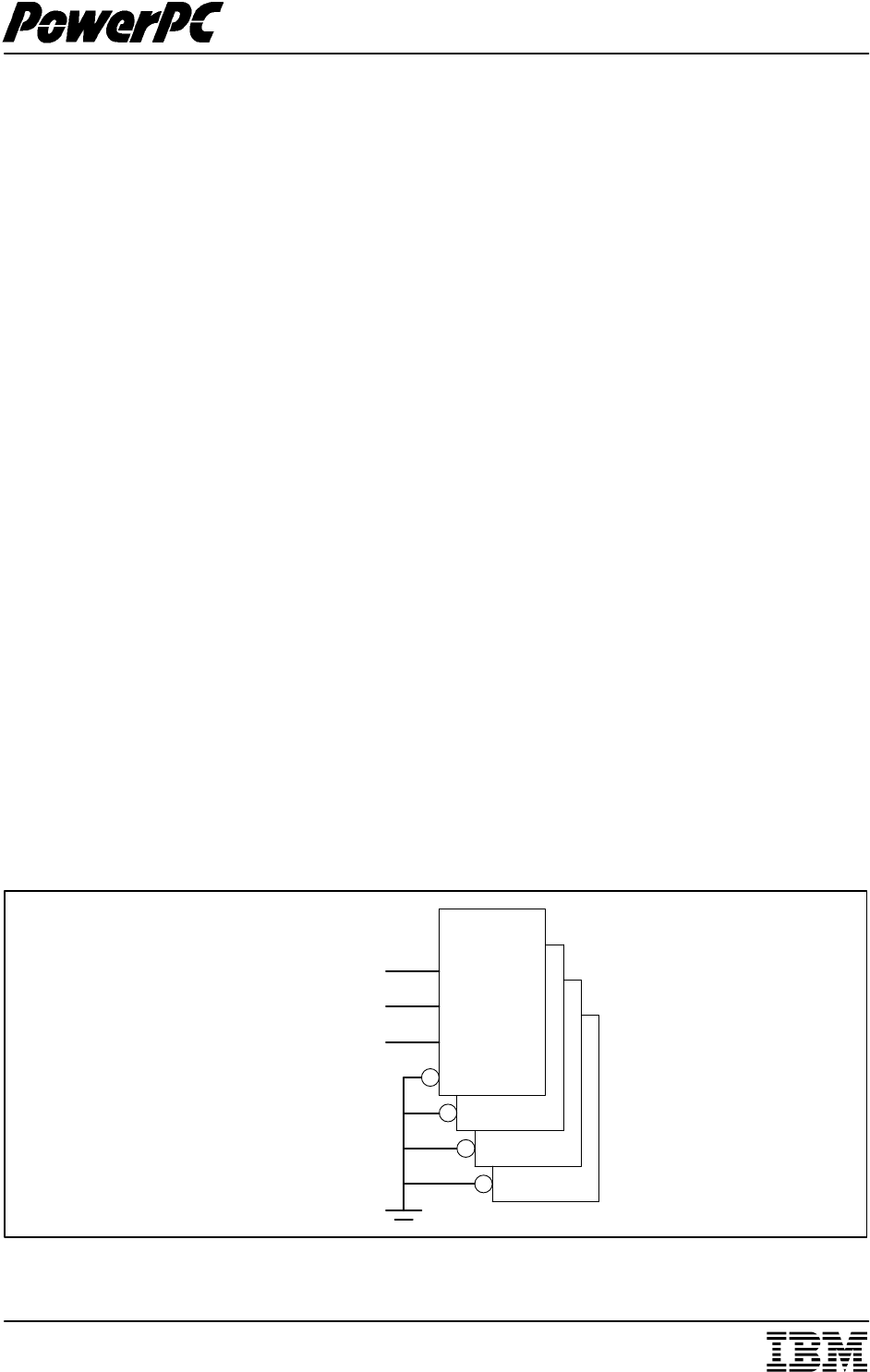

Figure 7. Synchronous SRAM, 256K L2 69. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 8. Synchronous SRAM, 512K L2 70. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 9. Synchronous SRAM, 1M L2 70. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

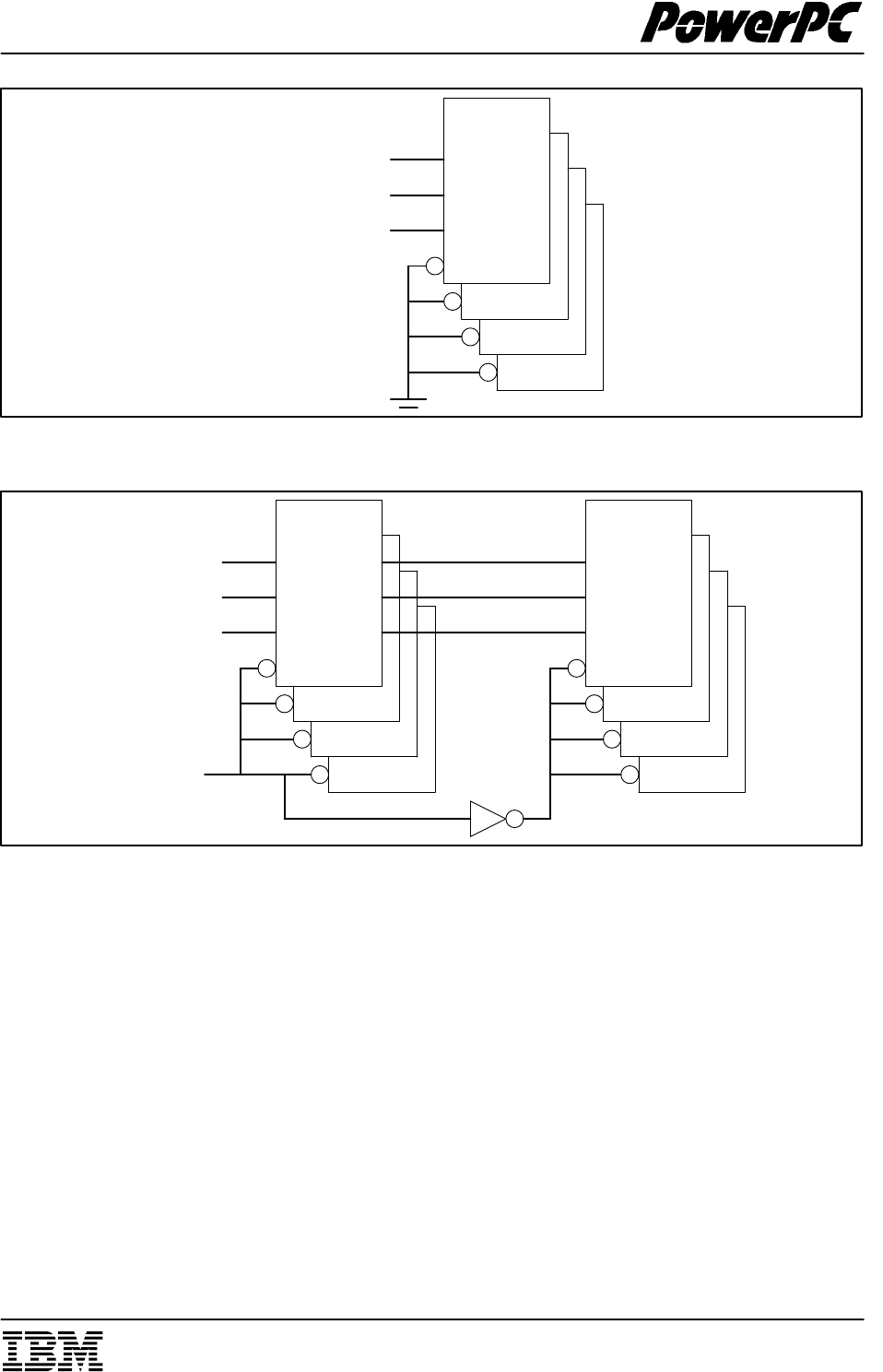

Figure 10. Asynchronous SRAM, 256K L2 71. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 11. Asynchronous SRAM, 512K L2 71. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 12. Asynchronous SRAM, 1M L2 72. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 13. Synchronous TagRAM, 512K L2 72. . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 14. Synchronous TagRAM, 1M L2 72. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

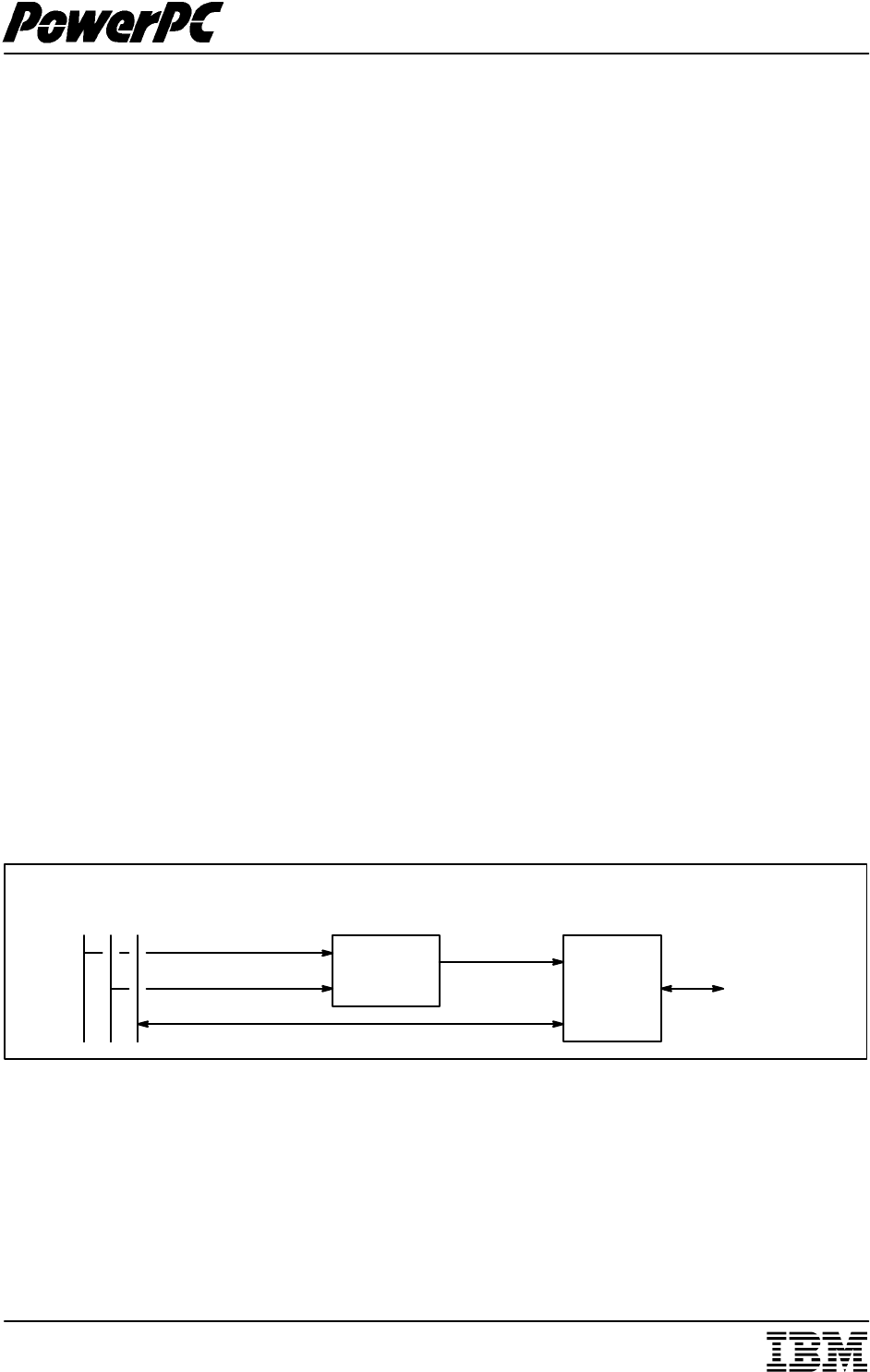

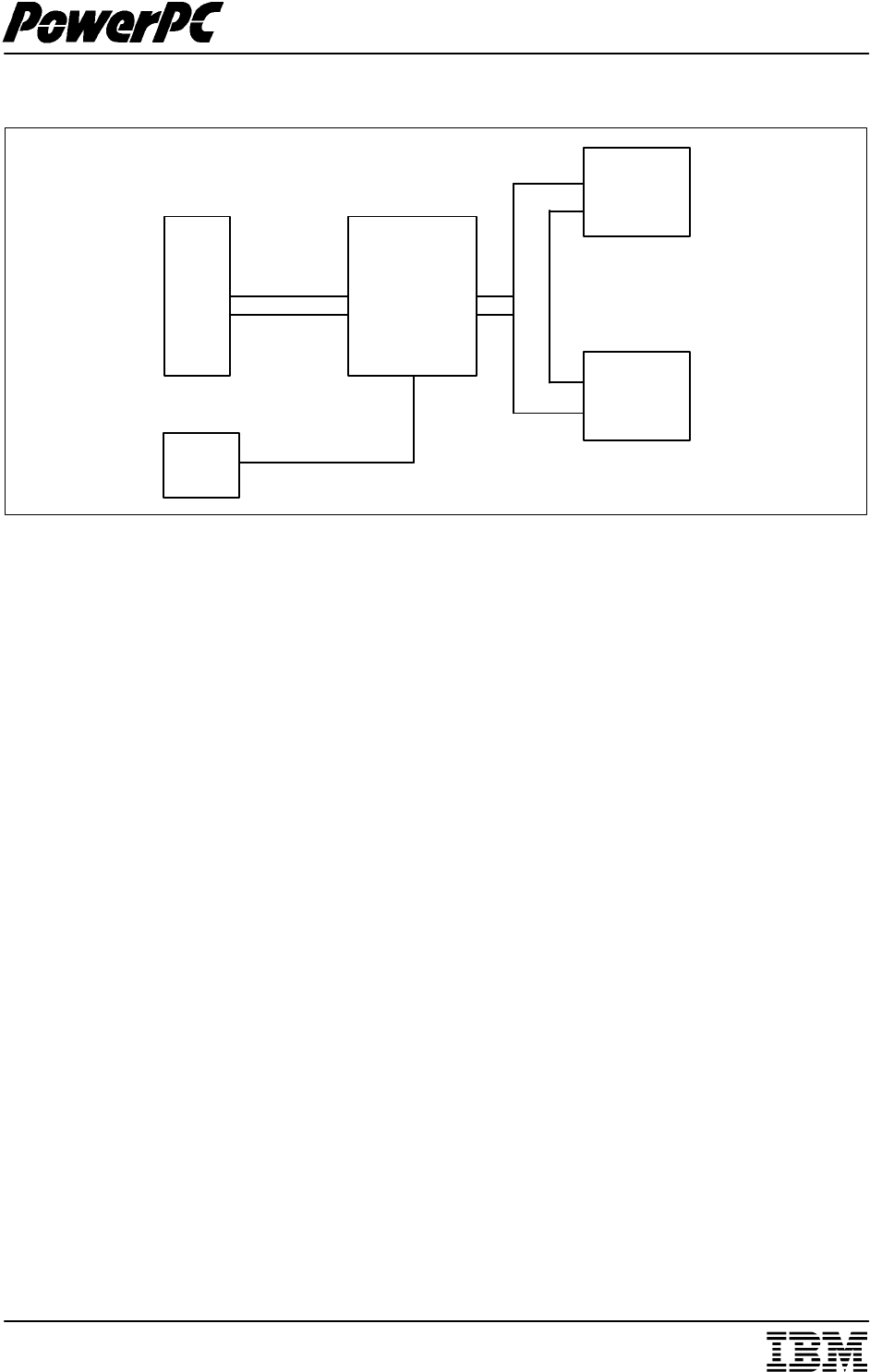

Figure 15. Endian Mode Block Diagram 79. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

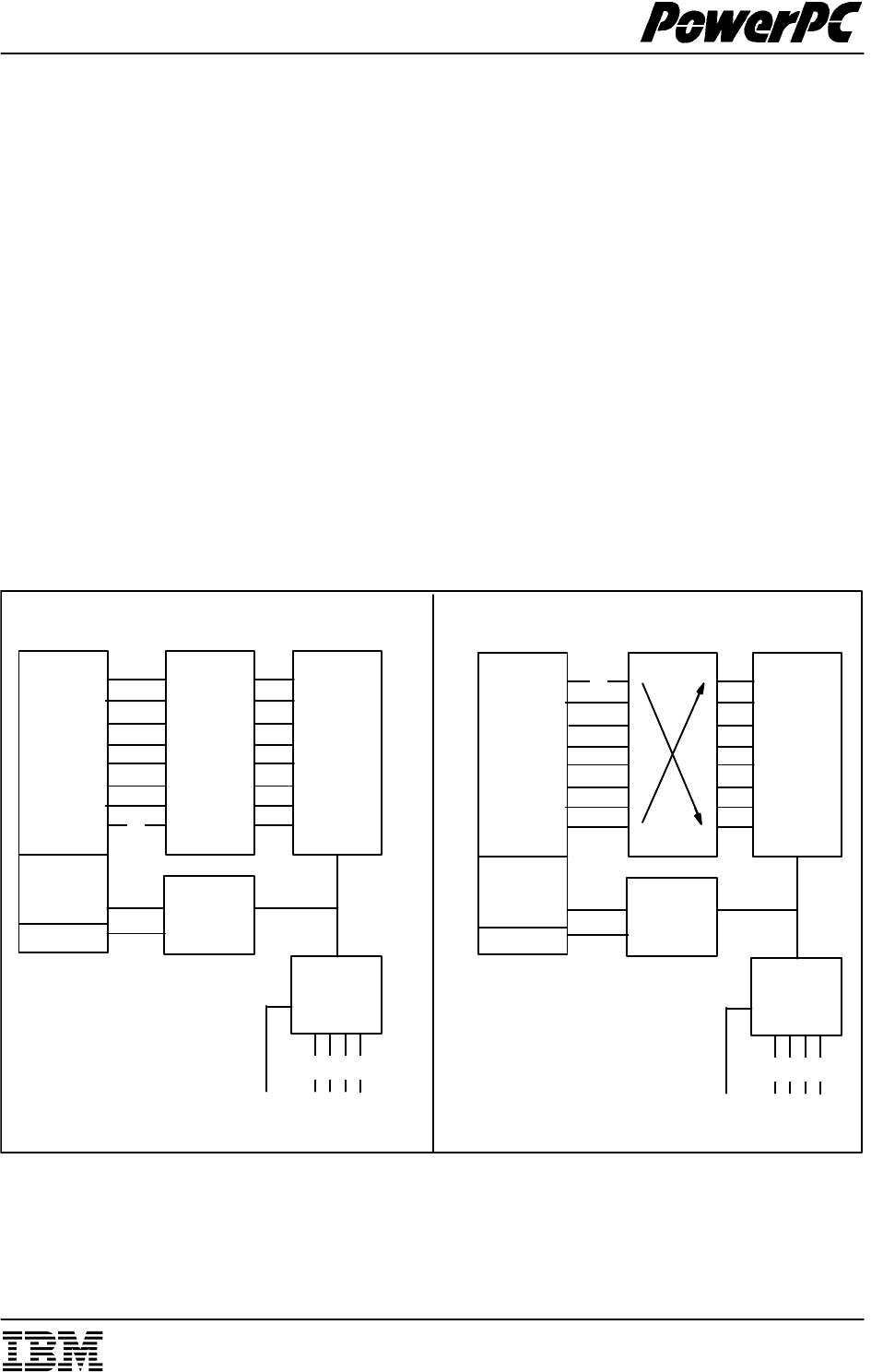

Figure 16. Example at Address XXXX XXX0 80. . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 17. Example at Address XXXX XXX2 81. . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 18. Double Byte Write Data ab at Address XXXX XXX0 84. . . . . . . . . . .

Figure 19. Word (4-Byte) Write of 0a0b0c0dh at Address XXXX XXX4 84. . . . .

Figure 20. Instruction Alignment Example 89. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 21. Wrong Instruction Read When Unmunger is used 90. . . . . . . . . . . . .

Figure 22. Instruction Stream to Switch Endian Modes 91. . . . . . . . . . . . . . . . . . .

Figure 23. Interrupt Handling 94. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 24. PCI Interrupt Connections 95. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 25. Boot Record 120. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 26. Partition Table Entry 120. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 27. Partition Table Entry Format for an Extended Partition 122. . . . . . . . .

Figure 28. Partition Table Entry for PowerPC Reference Platform 122. . . . . . . . .

Figure 29. PowerPC Reference Platform Partition 123. . . . . . . . . . . . . . . . . . . . . . .

Figure 30. System Initialization Screen 125. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 31.Configuration Utility Main Menu 126. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 32. System Configuration Menu 127. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 33. System Information Screen 128. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 34. Device Configuration Screen 129. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 35. SCSI Devices Screen 130. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 36. Boot Devices Screen 131. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 37. Set Date and Time Screen 132. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 38. Run a Program Screen 133. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 39. Reprogram the Flash Memory Screen 134. . . . . . . . . . . . . . . . . . . . . . .

Figure 40. 604 Heat Sink Assembly 139. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 41. Connector Location Diagram 143. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12 MPRH08TSU-02

Figure 42. The Keyboard Connector 144. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 43. The Mouse Connector 144. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 44. 1x4 Speaker Connector 145. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 45. 1x5 Power Good LED Connector 145. . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 46. 1x2 HDD LED Connector 145. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 47. 1x2 Reset Switch Connector 146. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 48. 1x2 Fan Connector 146. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 49. 1x6 3.3V Power Connector J5 147. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 50. 1x12 Power Connector 147. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 51. AUX5/ON-OFF Connector 148. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 52. PCI Connector 148. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 53. ISA Connector 150. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 54. SIMM Connector 152. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 55. 1x2 Power Switch Connector 154. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 56. 1x2 Power Up Configuration Connector 154. . . . . . . . . . . . . . . . . . . . . .

Figure 57. L2 SRAM Module Connector 155. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 58. 2x8 RISCWatch Connector 157. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 59. Signal and Power Layers 161. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 60. Typical Wiring Channel Top View 162. . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 61. PowerPC 603/604 Board Fabrication 163. . . . . . . . . . . . . . . . . . . . . . . .

Figure 62. Power Plane Split 164. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 63. PCI Interrupt Slot 0 Connections 171. . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 64. Generic Implementation PAL Installation 188. . . . . . . . . . . . . . . . . . . . .

13

MPRH08TSU-02

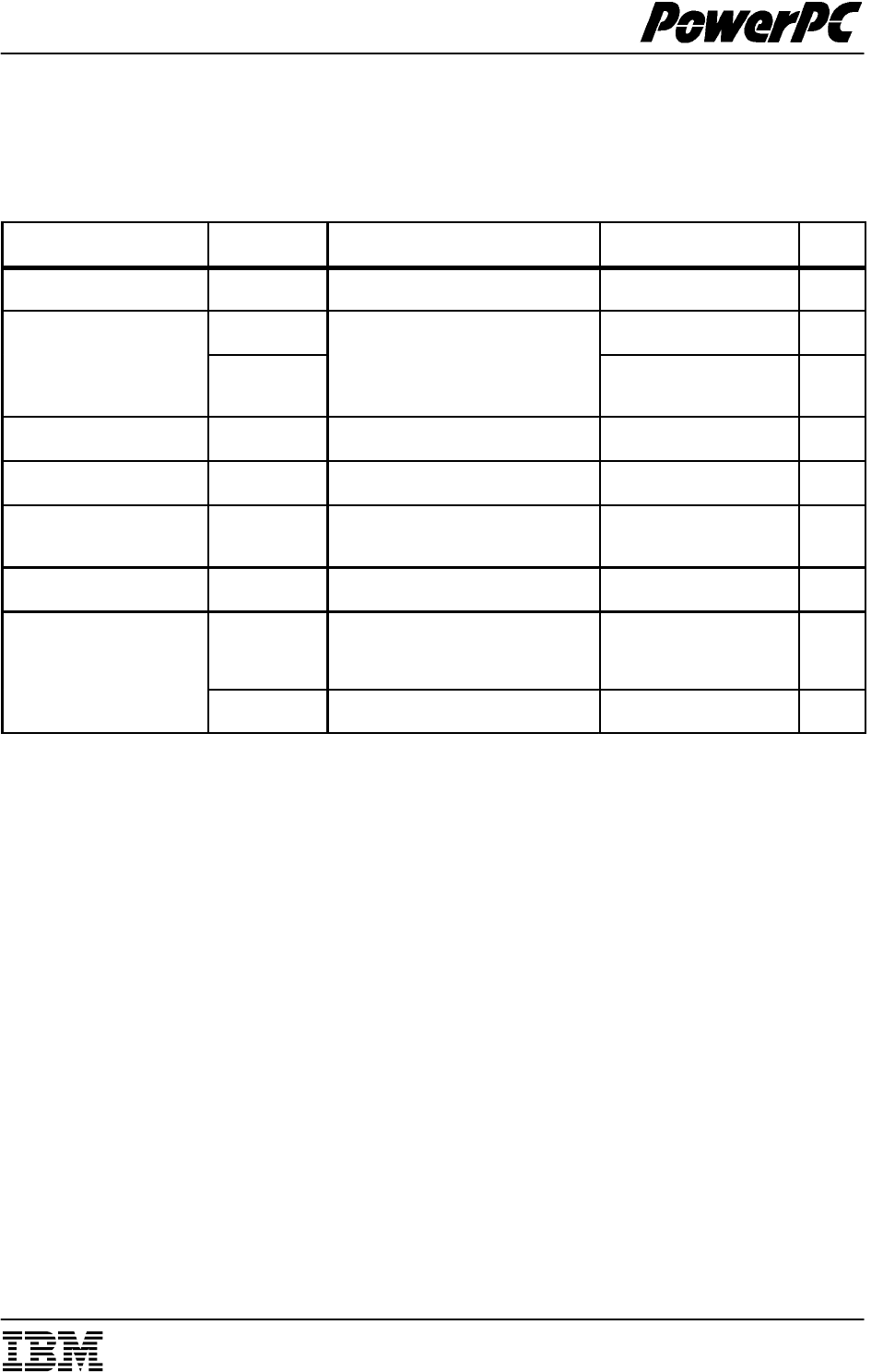

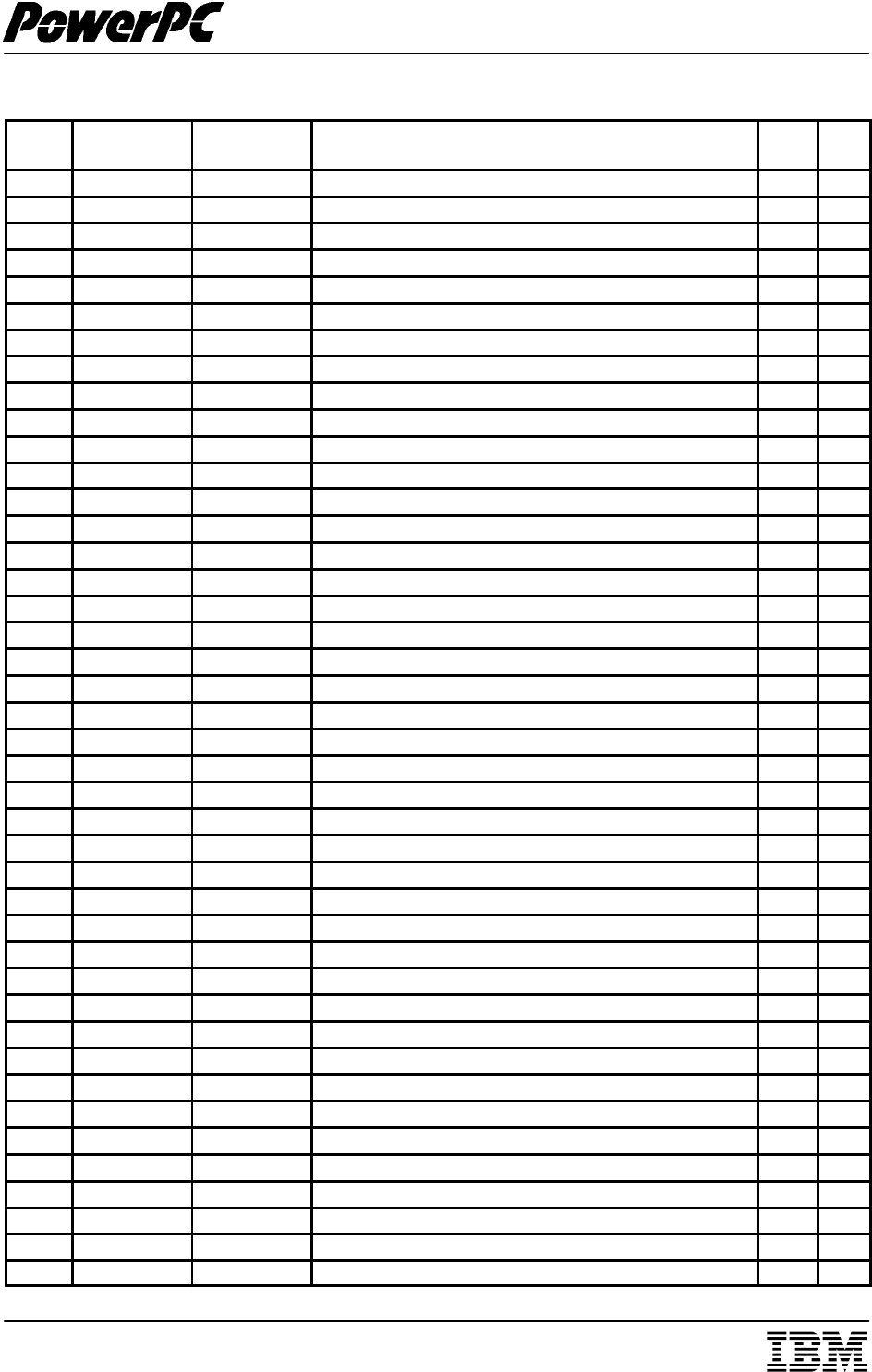

Tables

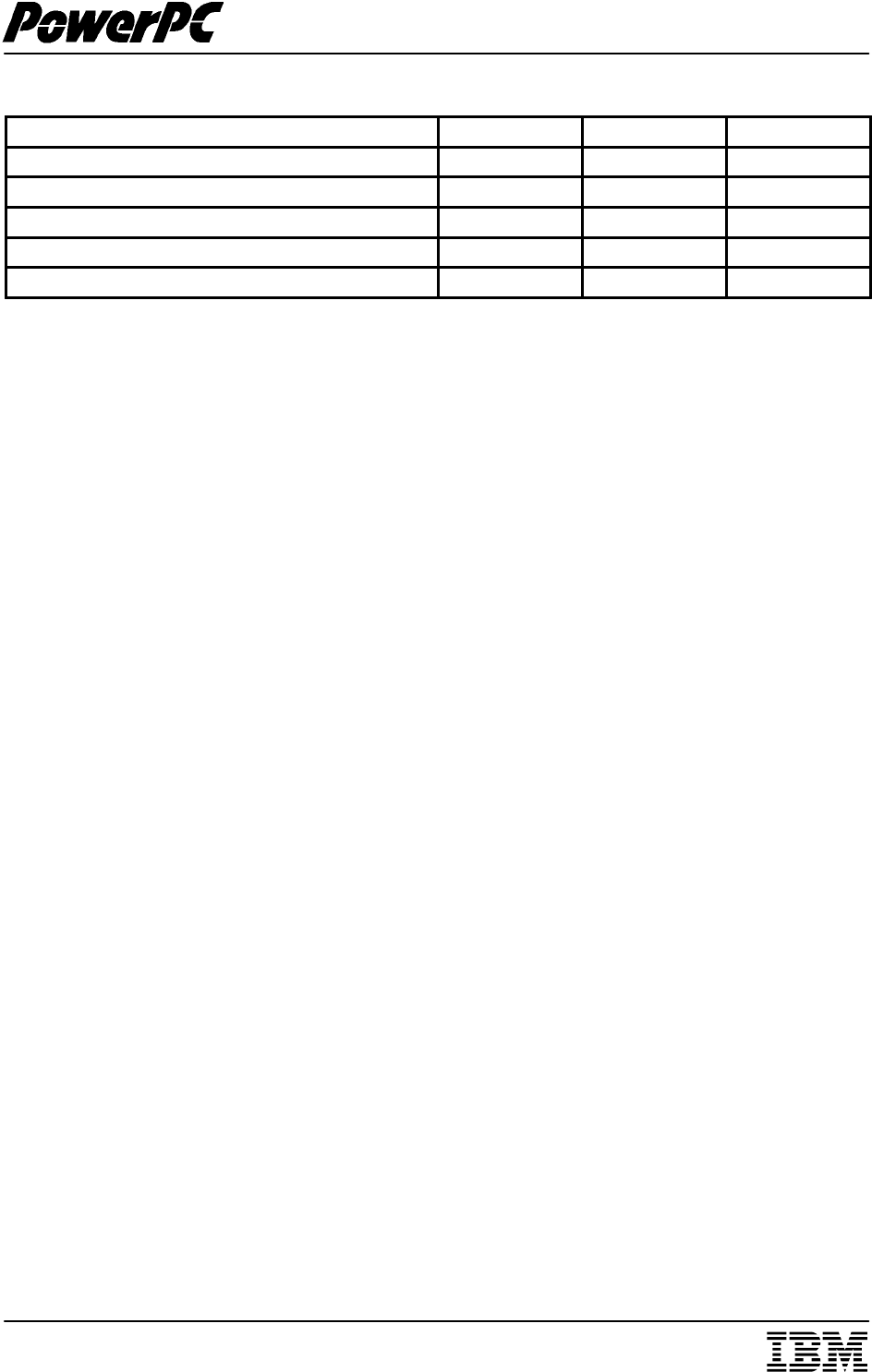

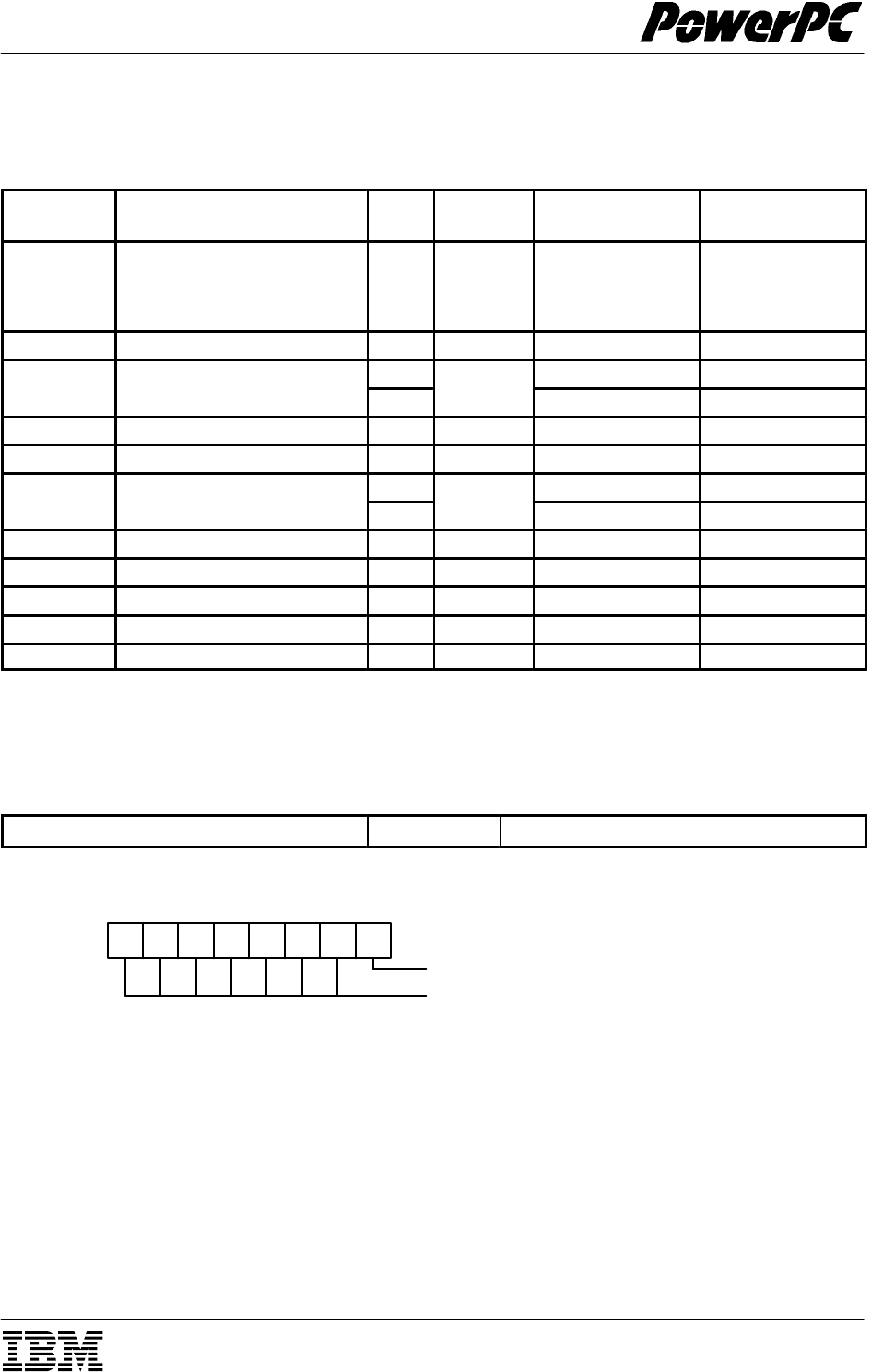

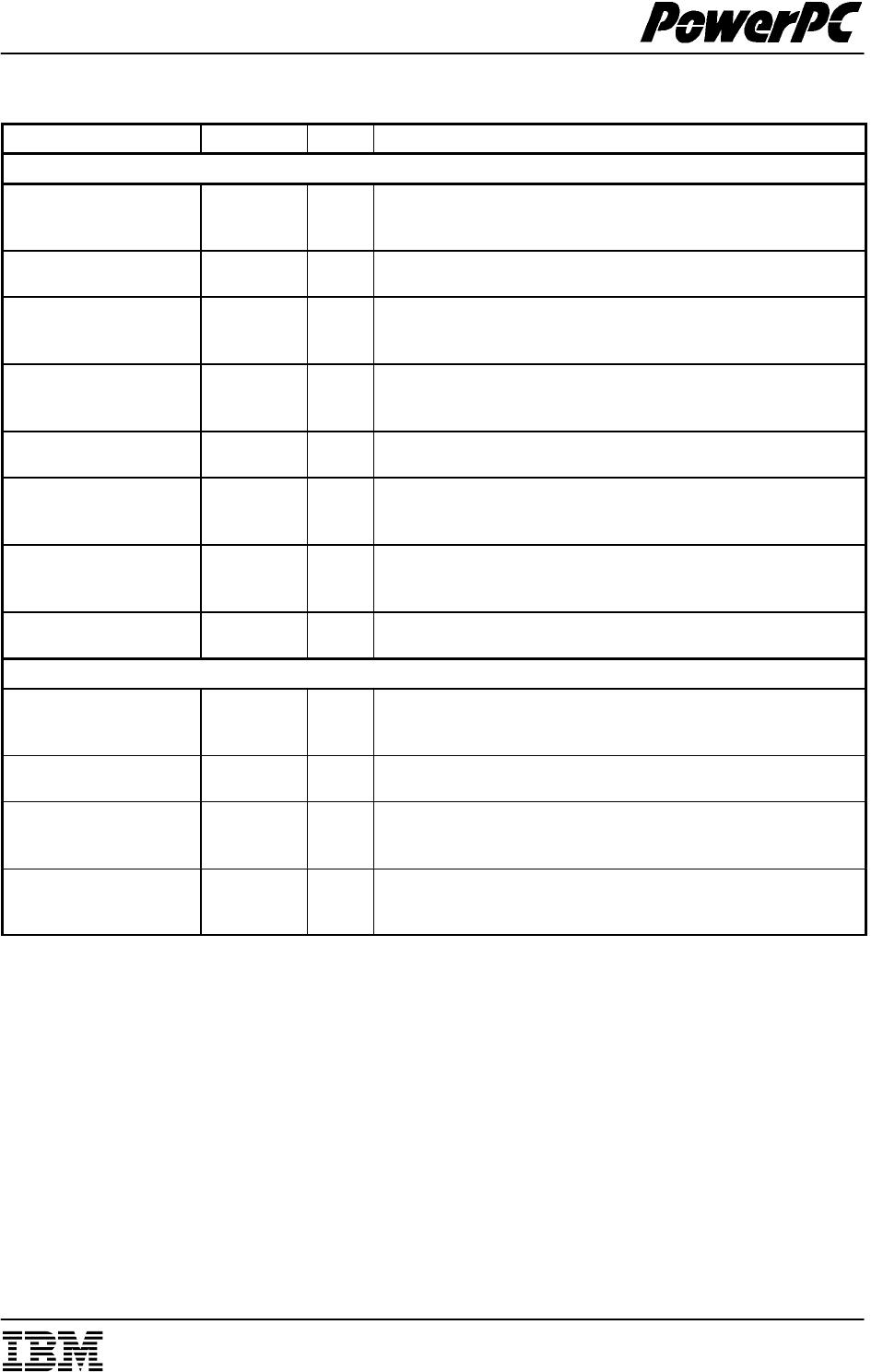

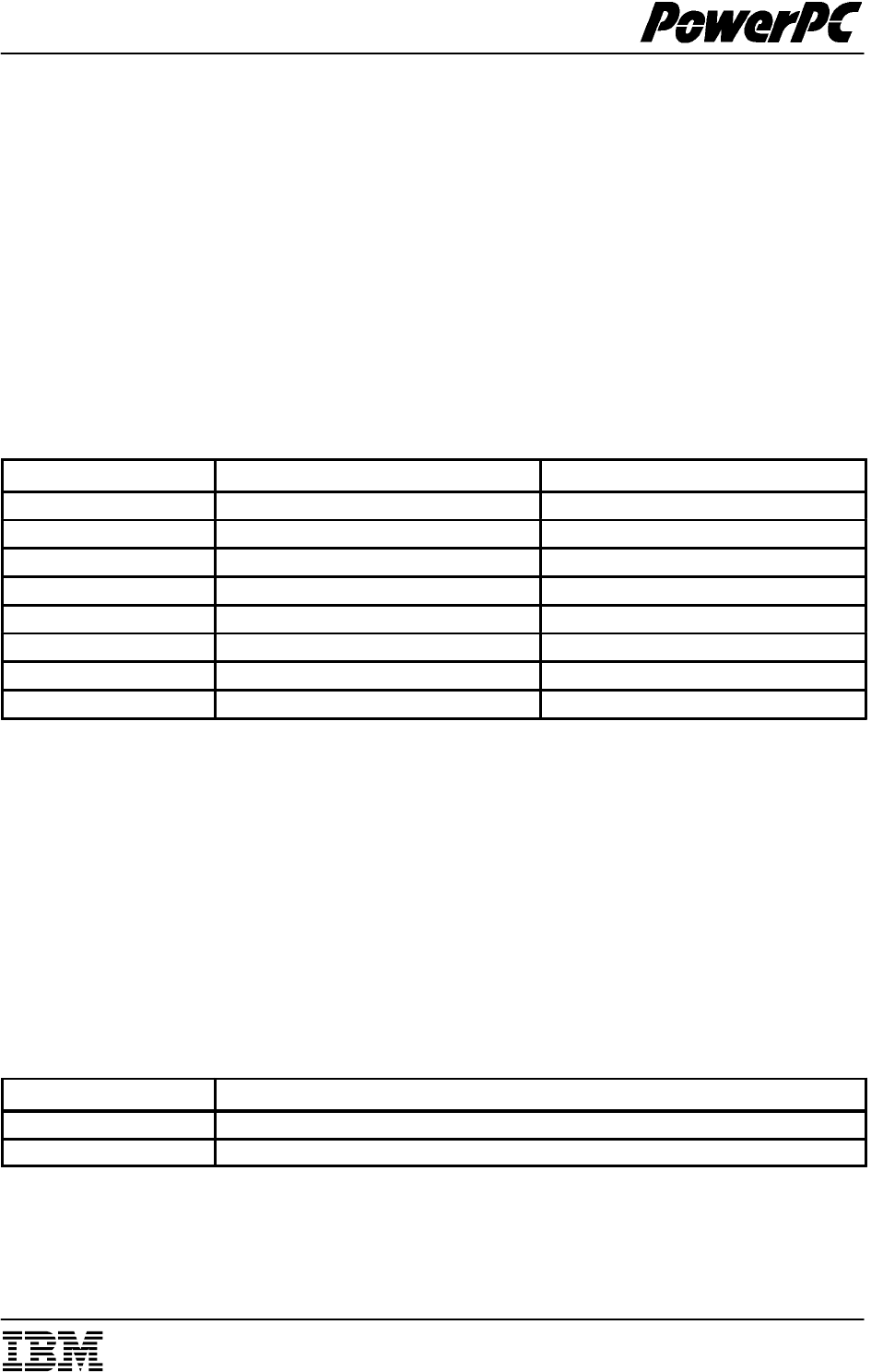

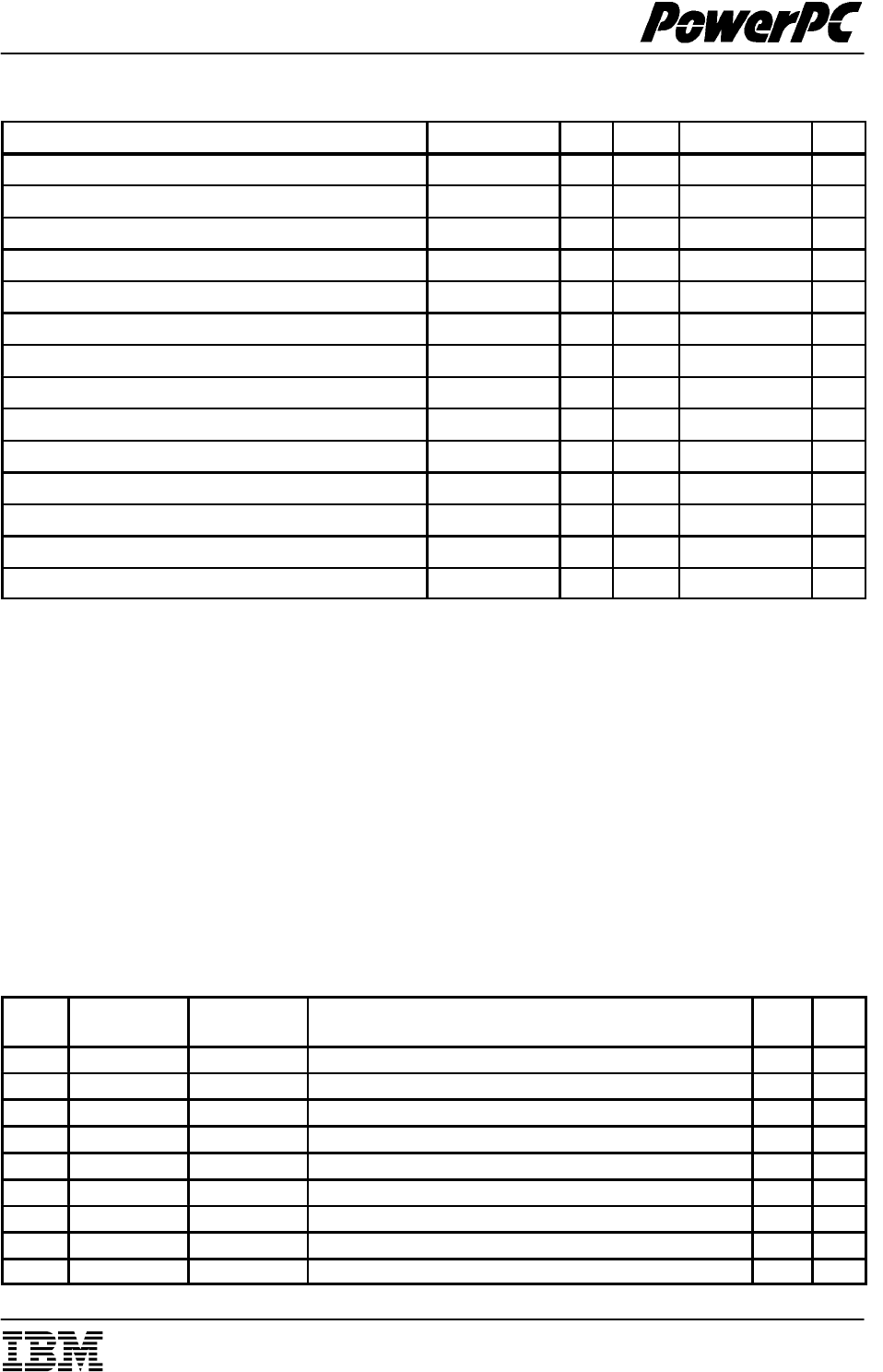

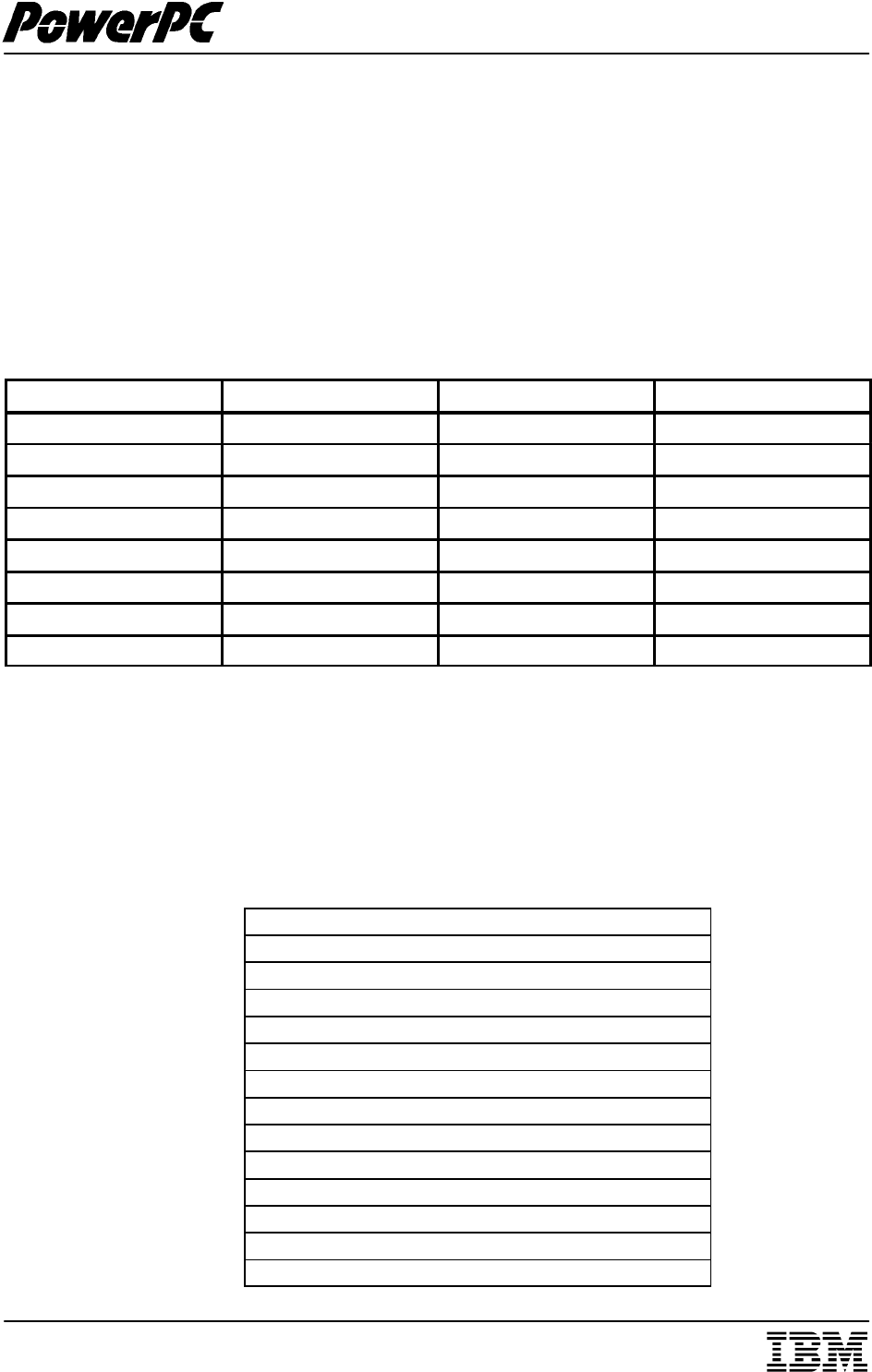

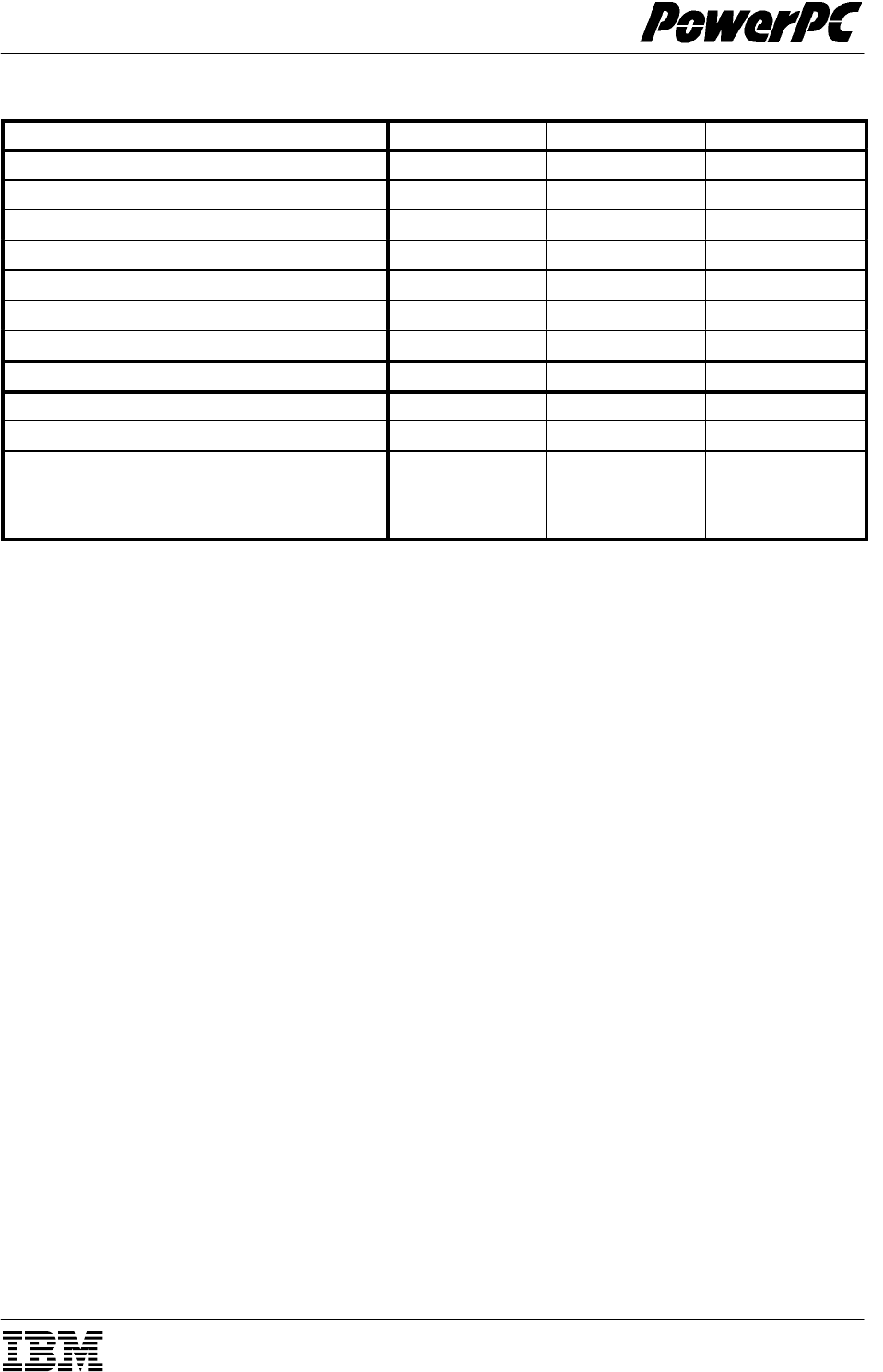

Table 1. Quickstart Peripheral List 23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

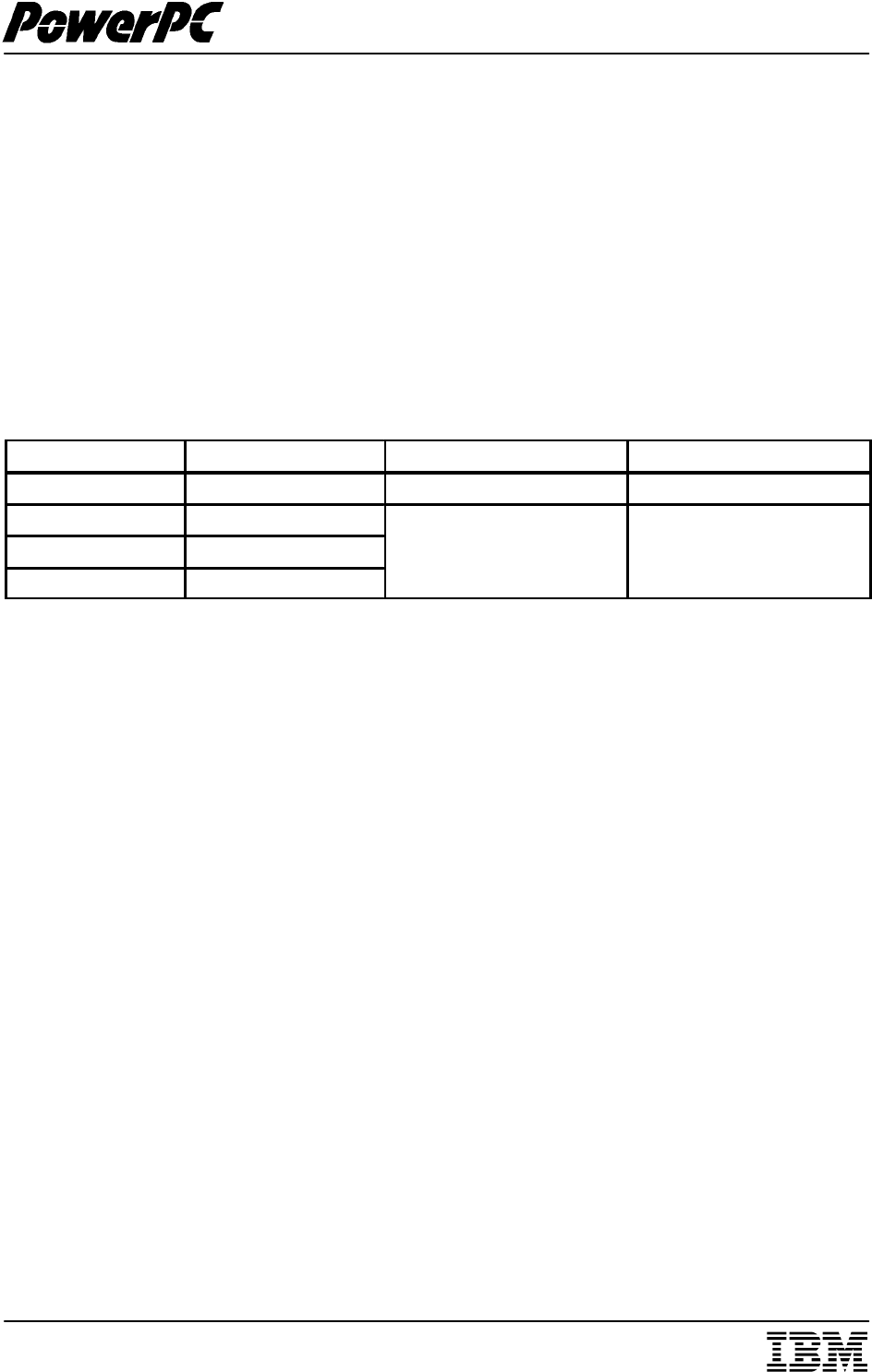

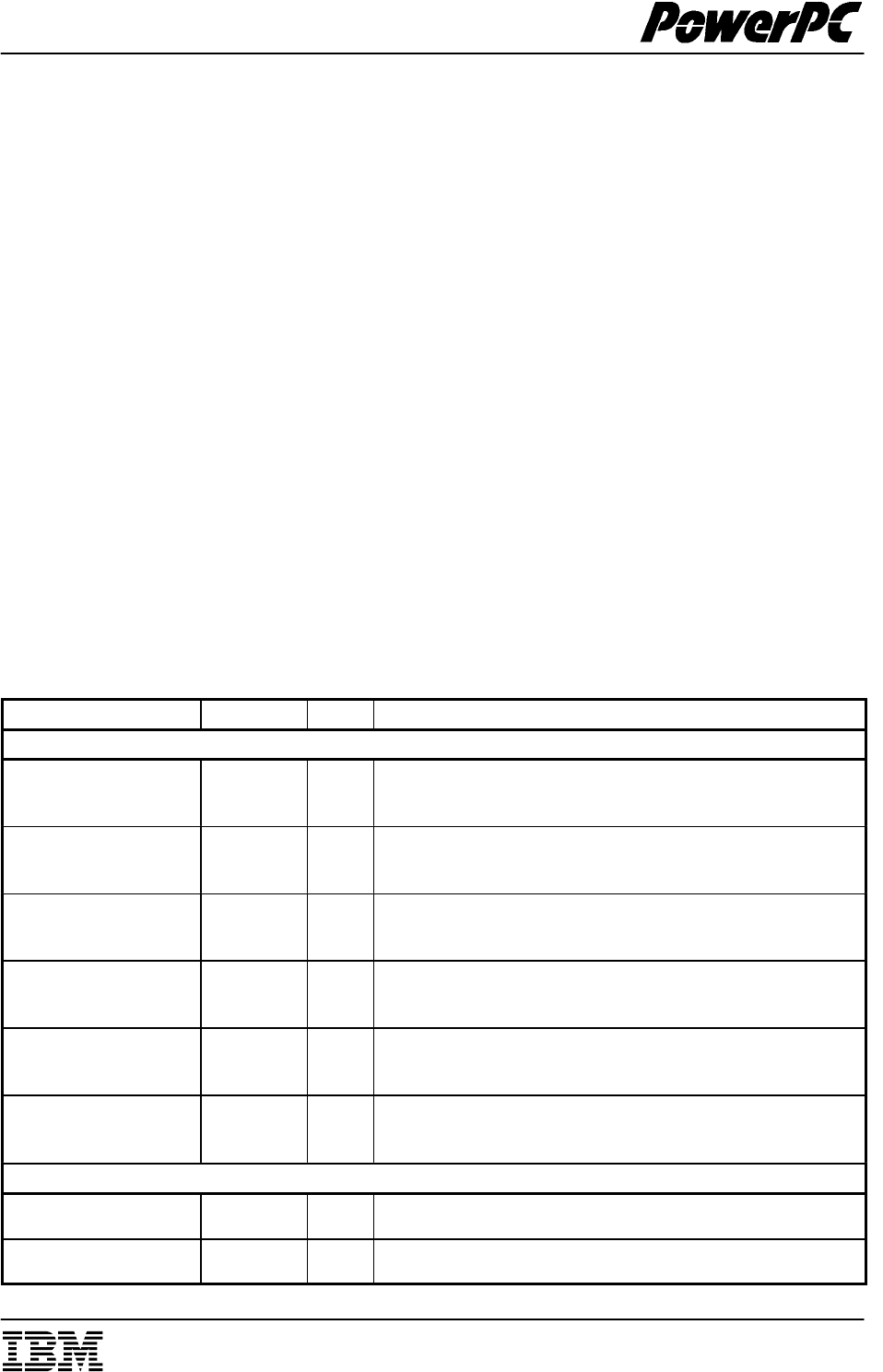

Table 2. Example Clock Generator Frequencies 26. . . . . . . . . . . . . . . . . . . . . . . .

Table 3. TT[0:3] (Transfer Type) Decoding by 660 Bridge 27. . . . . . . . . . . . . . . .

Table 4. 660 Bridge Address Mapping of CPU Bus Transactions 28. . . . . . . . . .

Table 5. 660 Bridge Address Mapping of CPU Bus Transactions 33. . . . . . . . . .

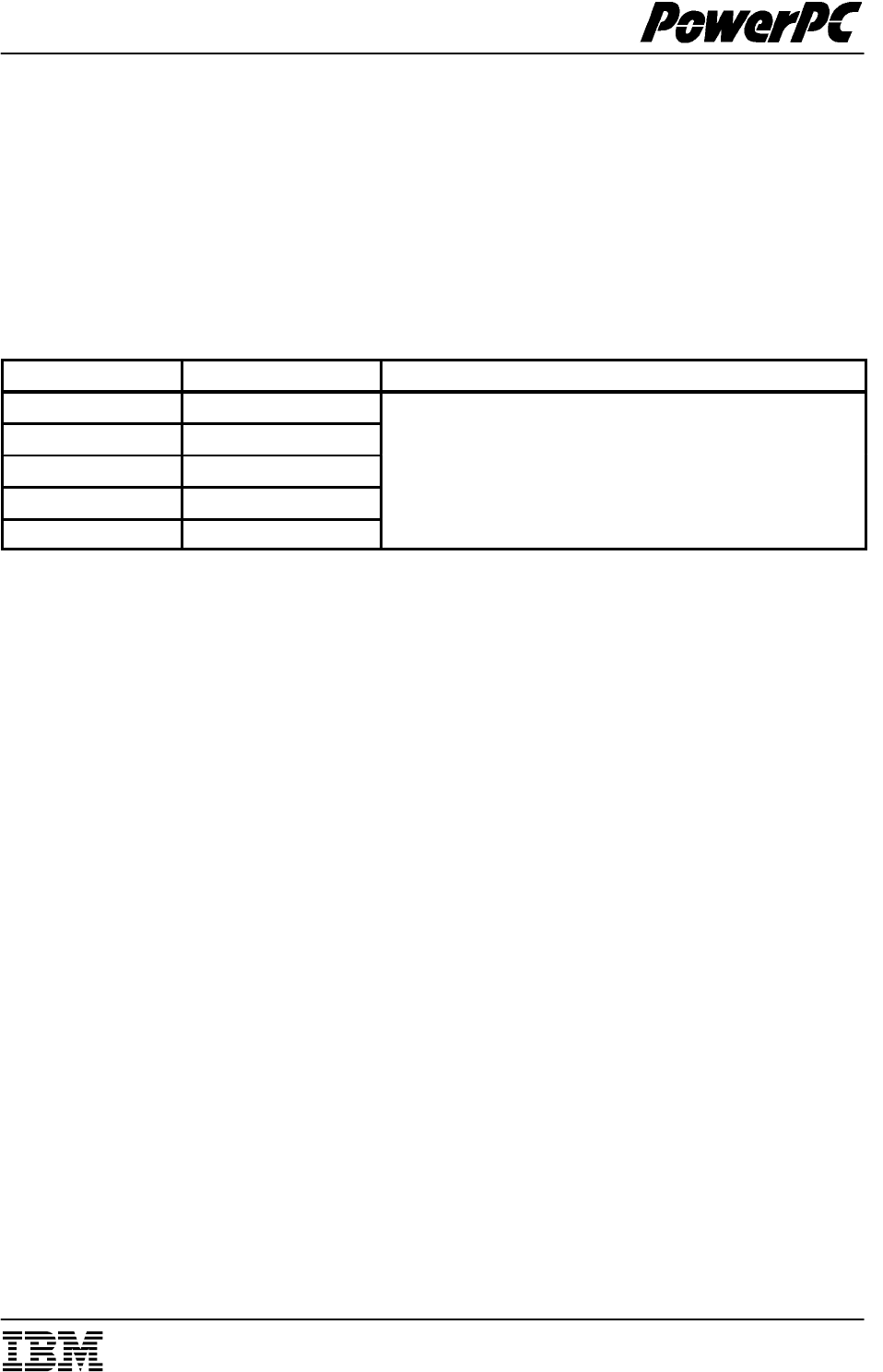

Table 6. Reference Design Responses to PCI_C[3:0] Bus Commands 36. . . . .

Table 7. Mapping of PCI Memory Space, Part 1 36. . . . . . . . . . . . . . . . . . . . . . . . .

Table 8. Mapping of PCI Memory Space, Part 2 37. . . . . . . . . . . . . . . . . . . . . . . . .

Table 9. Mapping of PCI Master I/O Transactions 38. . . . . . . . . . . . . . . . . . . . . . .

Table 10. Active CAS# Lines – PCI to Memory Writes, BE or LE Mode 40. . . . .

Table 11. DMA Assignments 46. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 12. DRAM Module Presence Detect Bit Encoding 48. . . . . . . . . . . . . . . . . .

Table 13. Planar ID Encoding 48. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 14. DRAM Module Presence Detect Bit Encoding 49. . . . . . . . . . . . . . . . . .

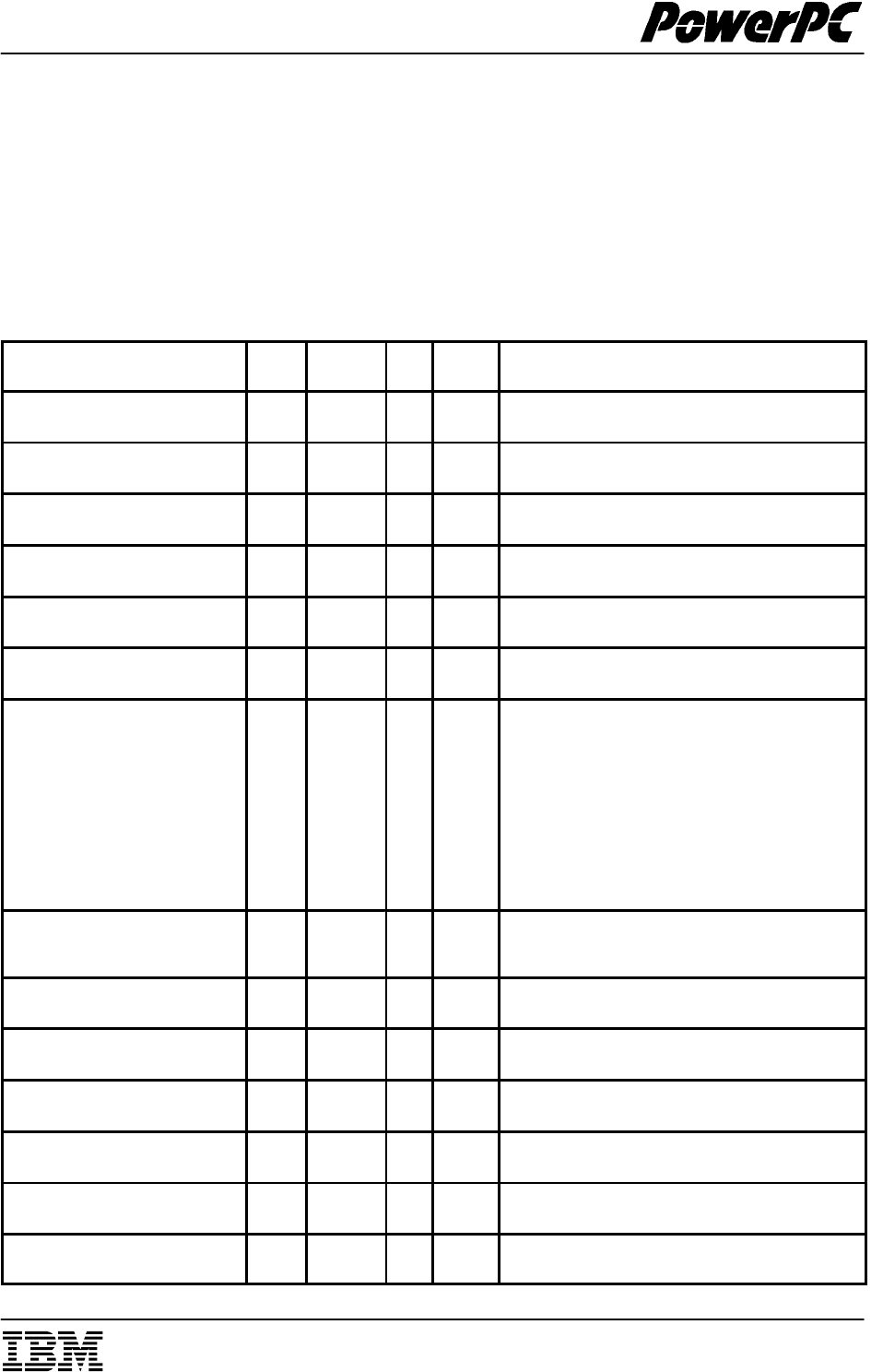

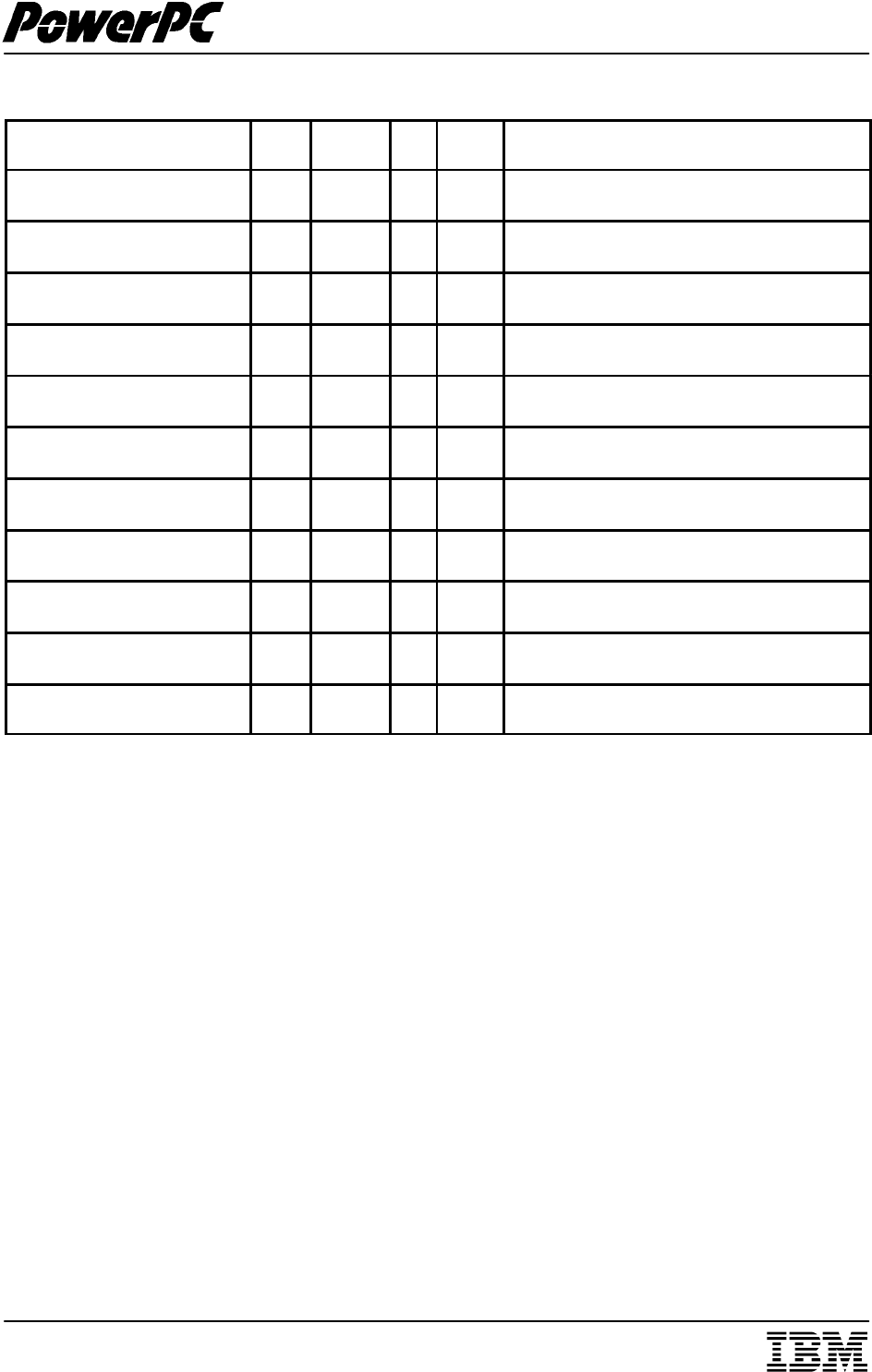

Table 15. External Register Support 51. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 16. Signal Descriptions 54. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 17. Supported DRAM Modules 67. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 18. L2 Configuration Implementation 73. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 19. Endian Mode Byte Lane Steering 78. . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 20. Endian Mode 6–3/604 Address Translation 78. . . . . . . . . . . . . . . . . . . .

Table 21. Memory in BE Mode 81. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 22. Memory in LE Mode 82. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 23. PCI in BE Mode 82. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 24. PCI in LE Mode 83. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 25. Two Byte Transfer Information 85. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 26. Rearranged 2-Byte Transfer Information 85. . . . . . . . . . . . . . . . . . . . . .

Table 27. 4-Byte Transfer Information 87. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 28. Rearranged 4–Byte Transfer Information 88. . . . . . . . . . . . . . . . . . . . . .

Table 29. Mapping of PCI Memory Space, Part 1 95. . . . . . . . . . . . . . . . . . . . . . .

Table 30. Summary of SIO Register Setup

(Configuration Address = 8080 08xx) 104. . . . . . . . . . . . . . . . . . . . . . . .

Table 31. Summary of SIO Configuration Registers 106. . . . . . . . . . . . . . . . . . . . .

Table 32. Configuration Address Assignments 107. . . . . . . . . . . . . . . . . . . . . . . . . .

Table 33. Combined Register Listing 108. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 34. 660 Bridge Indexed BCR Listing 114. . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 35. Compatible ISA Ports (Not on Reference Board) 116. . . . . . . . . . . . . .

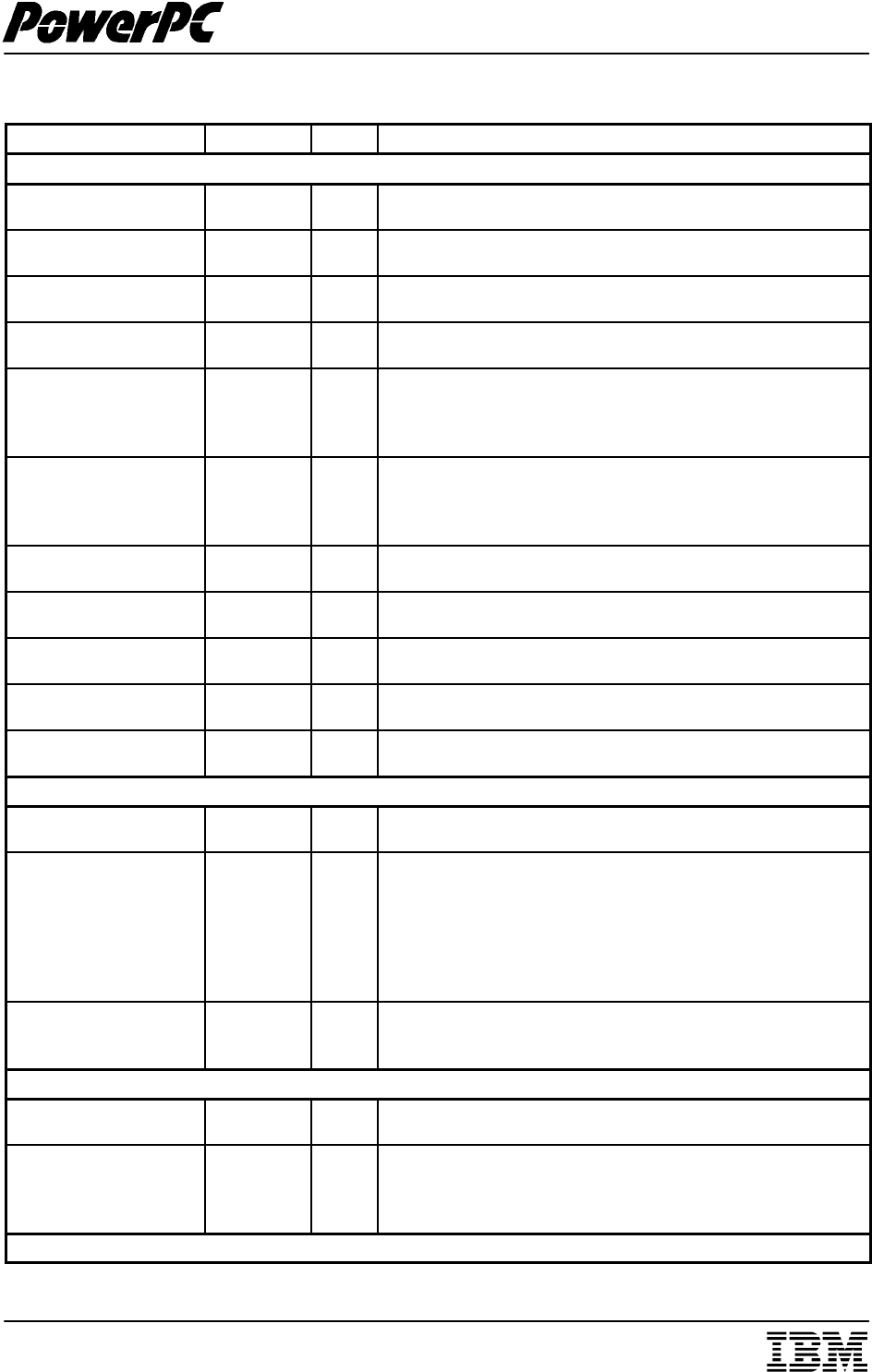

Table 36. Power Supply Specification 137. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 37. Approximate Power Consumption 137. . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 38. Specifications for 3.3V Regulator on the Motherboard 138. . . . . . . . . . .

Table 39. Specifications for 2.5V Regulator on the Motherboard 138. . . . . . . . . . .

Table 40. Keyboard Connector Pin Assignments 144. . . . . . . . . . . . . . . . . . . . . . . .

Table 41. Mouse Connector Pin Assignments 144. . . . . . . . . . . . . . . . . . . . . . . . . .

14 MPRH08TSU-02

Table 42. Speaker Connector Pin Assignments 145. . . . . . . . . . . . . . . . . . . . . . . . .

Table 43. Power Good LED Connector 145. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 44. HDD LED Connector 145. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 45. Reset Switch Connector 146. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 46. Fan Connector Pin Assignments 146. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 47. 3.3V Power Connector J5 Pin Assignments 147. . . . . . . . . . . . . . . . . . .

Table 48. Power Connector J4 Pin Assignments 147. . . . . . . . . . . . . . . . . . . . . . . .

Table 49. AUX5/ON-OFF Connector Pin Assignments 148. . . . . . . . . . . . . . . . . . .

Table 50. PCI Connector Pin Assignments 148. . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 51. ISA Connector Pin Assignments 150. . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 52. SIMM Connector Pin Assignments 152. . . . . . . . . . . . . . . . . . . . . . . . . .

Table 53. Power Switch Connector Pin Assignments 154. . . . . . . . . . . . . . . . . . . .

Table 54. Power Up Configuration Connector Pin Assignments 154. . . . . . . . . . .

Table 55. L2 SRAM Module Connector Pin Assignments 155. . . . . . . . . . . . . . . .

Table 56. RISCWatch Connector Pin Assignments 157. . . . . . . . . . . . . . . . . . . . . .

Table 57. Height Considerations 160. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 58. Clock Net Lengths ( 7 a 10 ) 165. . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 59. CPU Bus Nets 165. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 60. Timing Critical Nets 166. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 61. PCI Bus Nets 167. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 62. Noise Sensitive Nets 167. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

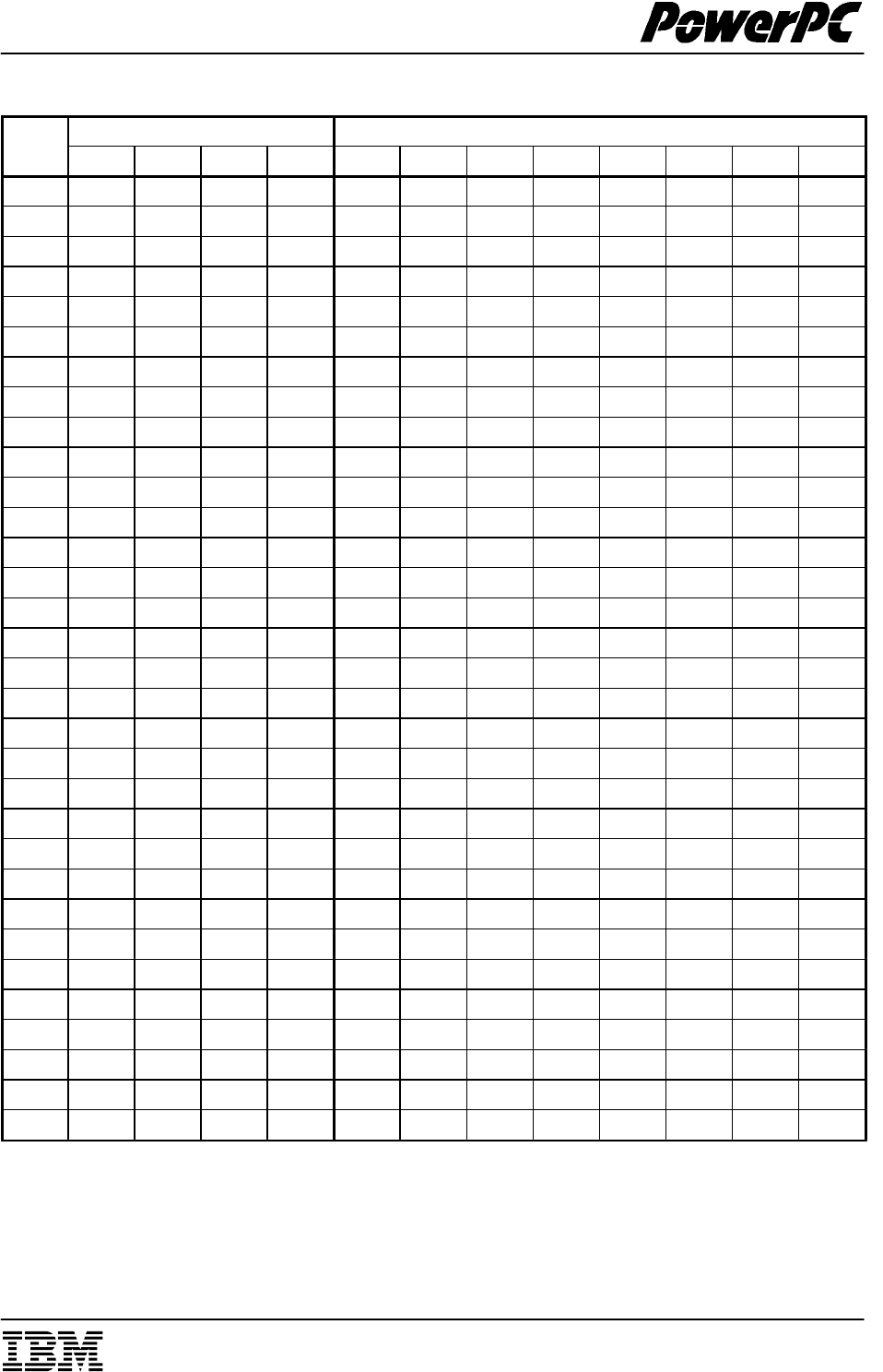

Table 63. PowerPC 603/604 Reference Design Roadmap 170. . . . . . . . . . . . . . . .

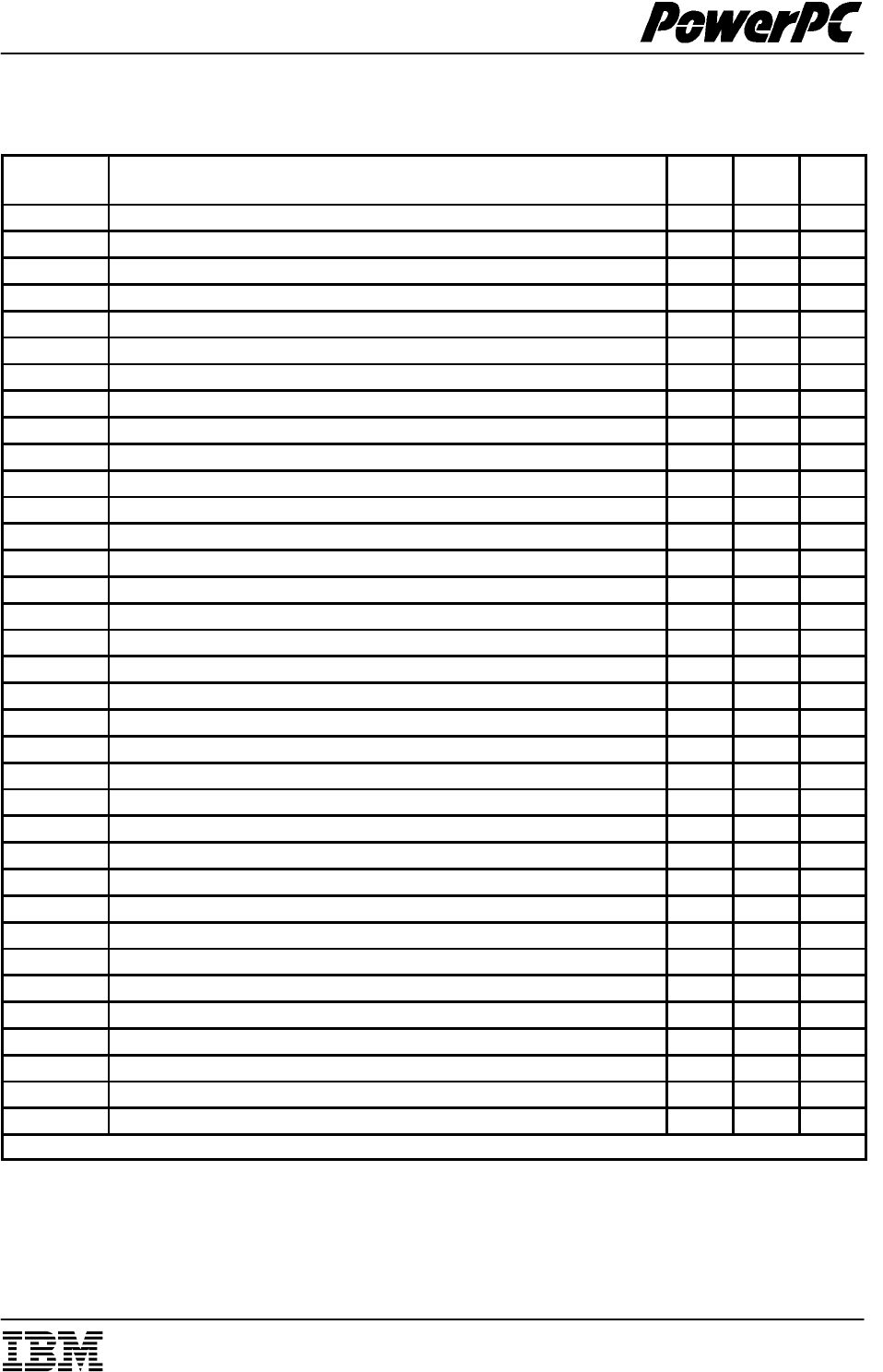

Table 64. 603e Bill of Materials 189. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 65. 604 Bill of Materials 194. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15

MPRH08TSU-02

About This Book

Notice:

The 603 version of the PowerPC 603/604 Reference Design is no longer supported. It is replaced by the 603e

version of the 603/604 PowerPC Reference Design. In this document, the term 603 also refers to the Pow-

erPC 603e RISC microprocessor unless otherwise specified.

Power management is beyond the scope of this document.

Audience:

This reference design is designed for engineers and system designers who are interested in implementing

PowerPC systems that are compliant with the PowerPC Reference Platform Specification. The material re-

quires a detailed understanding of computer systems at the hardware and software level.

Reference Material:

Understanding of the relevant areas of the following documents is required for a good understanding of the

reference design:

SPowerPC 604 User’s Manual, IBM document MPR604UMU-01

SPowerPC 604 Hardware Specification, IBM document MPR604HSU-01

SPowerPC 603 User’s Manual, IBM document MPR603UMU-01

SPowerPC 603e Hardware Specification, IBM document MPR603EHS-01

SPowerPC 603e Technical Summary, IBM document MPR603TSU-04

SIBM27-82660 PowerPC to PCI Bridge User’s Manual, IBM document number MPR660UMU–01

SPCI Local Bus Specification, Revision 2.1, available from the PCI SIG

SPowerPC Reference Platform Specification, Version 1.1, IBM document MPRPRPPKG

SThe Power PC Architecture, second edition, Morgan Kaufmann Publishers

(800) 745–7323, IBM document MPRPPCARC–02

SIntel 82378ZB System I/O (SIO) Data Book, Intel order number 290473-004.

The following documents are useful as sources of tutorial and supplementary information about the reference

design.

SPowerPC System Architecture, Tom Shanley, Mindshare Press (800) 420-2677.

SIBM27-82650 PowerPC to PCI Bridge User’s Manual, IBM document number MPR650UMU–01

Document Conventions:

Kilobytes, megabytes, and gigabytes are indicated by a single capital letter after the numeric value. For exam-

ple, 4K means 4 kilobytes, 8M means 8 megabytes, and 4G means 4 gigabytes.

The terms DIMM and SIMM are often used to mean DRAM module.

Hexadecimal values are identified (where not clear from context) with a lower-case letter h at the end of the

value. Binary values are identified (where not clear from context) with a lower-case letter b at the end of the

value.

In identifying ranges of values from and to are used whenever possible. The range statement from 0 to 2M

means from and including zero up to (but not including) two megabytes. The hexadecimal value for the range

from 0 to 64K is: 0000h to FFFFh.

The terms asserted and negated are used extensively. The term asserted indicates that a signal is active

(logically true), regardless of whether that level is represented by a high or low voltage. The term negated

means that a signal is not asserted. The # symbol at the end of a signal name indicates that the active state

of the signal occurs with a low voltage level.

16 MPRH08TSU-02

Introduction

17

MPRH01TSU-02

Section 1

Introduction

This document provides a detailed technical description of the PowerPCt 603/604 Refer-

ence Design, and is intended to be used by hardware, software, test, simulation, and other

engineers as a first source of information. Software developers should read through the

entire document because pertinent facts may be located in hardware sections.

The focus of this document is mainly the motherboard electronics and firmware. Where ap-

propriate this document references detailed information in other documents. Consult other

documents for information on specific I/O devices such as hard drives, CD–ROMs, L2

cache cards, video cards, etc. that comprise a total system.

Recommendations for memory mappings, software implementations, and the like are only

recommendations and may or may not represent the algorithms implemented in boot code

or operating systems.

Note: This document contains several references to the 603/604 Reference Design Power

Management Specification; however, the specification was not yet available at the date of

printing.

1.1 IBM Reference Products

IBM offers several different PowerPC reference products for a given PowerPC system.

1.1.1 Reference Design

The PowerPC 603/604 Reference Design (reference design) is composed of both the in-

tangible design and the documentation describing that design. The reference design docu-

mentation addresses the motherboard electronics, firmware, and various system related

issues. The reference design contains this reference design Technical Specification, Gerb-

er format physical design files on an 8mm tape, electrical device model files in Cadencet

format, system firmware guidelines, schematics, contact information for commented boot

ROM source code, and such other device and system information as is deemed helpful.

1.1.2 Reference Board

The PowerPC 603/604 Reference Board (reference board) is the physical implementation

of the motherboard part of the reference design. It includes the reference design, the popu-

lated motherboard, the boot ROM, and other components as appropriate.

1.1.3 Reference Firmware

The PowerPC 603/604 Reference Firmware (reference firmware) is described in the refer-

ence design, and consists of the commented source code of the software contained in the

boot ROM. This is available from IBM as discussed in section 10.1.

Introduction

18 MPRH01TSU-02

1.1.4 Reference System

The PowerPC 603/604 Reference System (reference system) consists of a complete

603/604 PowerPC computer system, including the motherboard, enclosure, power supply,

cooling devices, and such other adaptors and peripherals as are described in the detailed

product offering.

1.2 Purpose

The reference design is aimed at the market for low cost desk top PowerPC personal com-

puters. The motherboard is sized to fit within a BabyAT form factor enclosure, although the

enclosure may need to be modified to provide additional cooling and/or additional space

for I/O cards.

The reference design is intended to help companies develop their own products using the

PowerPC architecture. The reference design may be used:

SAs a baseline system in order to gauge the effects of changes on the design

STo test new boot code

STo test operating systems and/or applications

SFor performance measuring.

The reference design is:

SA compliant implementation of the PowerPC Hardware Reference Platform Specifi-

cation, version 1.1

STested for functionality to the level of software available at the time of shipping

SA prototype of a system under development which may have prototype ASICs, erra-

ta, and/or wiring changes.

The reference design is not:

SA complete market ready design

STested for compliance to FCC and other regulatory requirements.

Introduction

19

MPRH01TSU-02

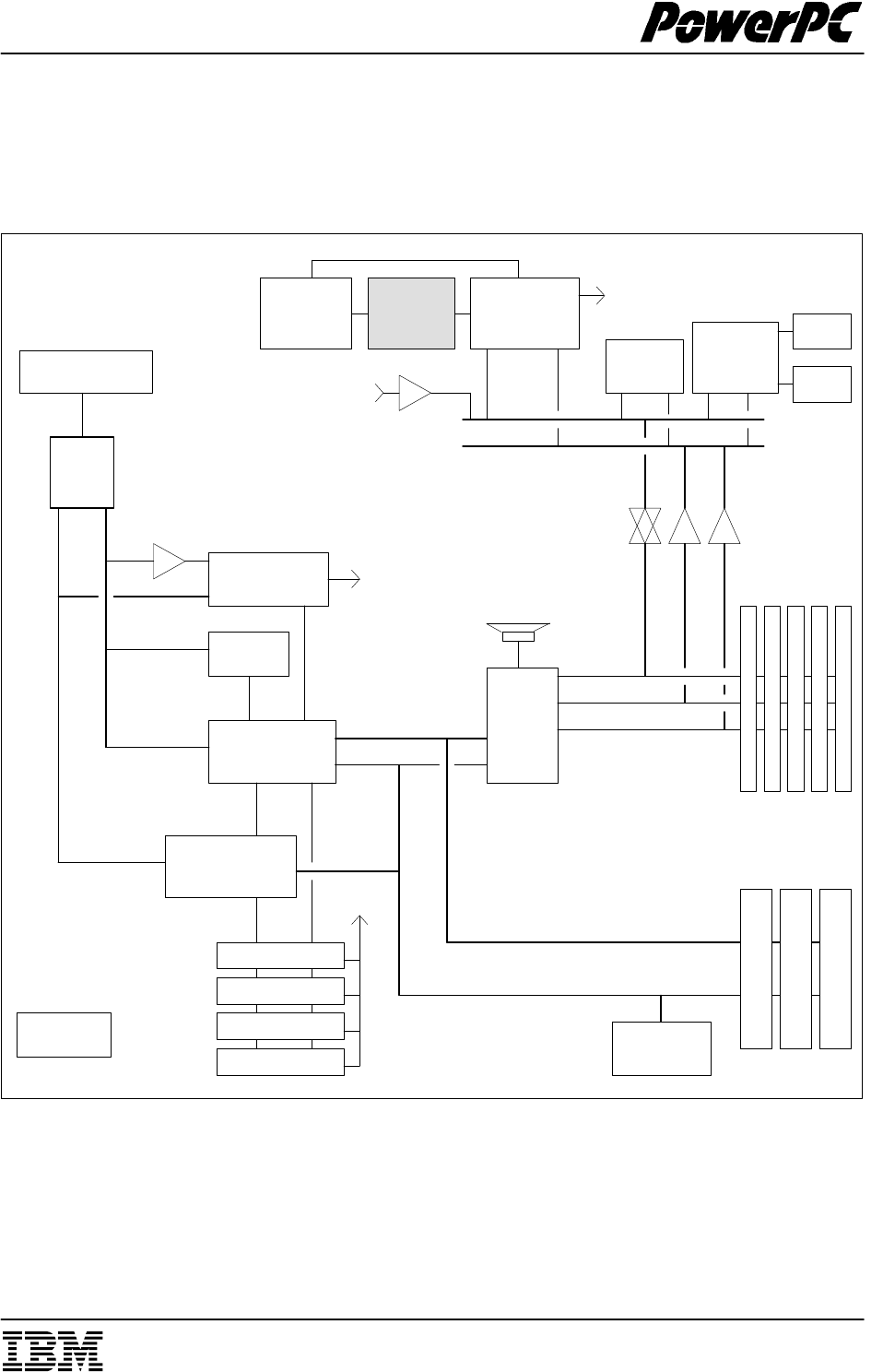

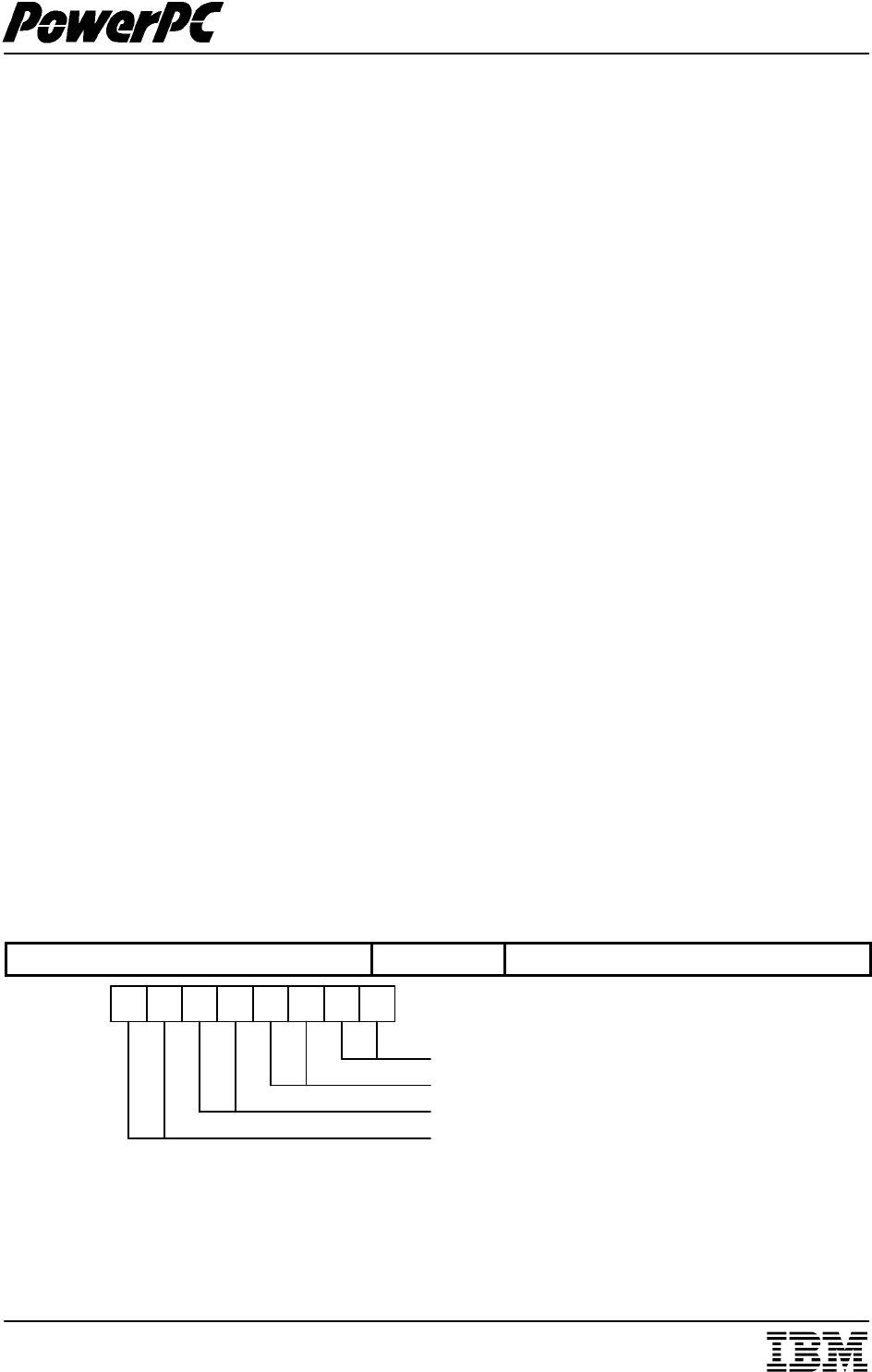

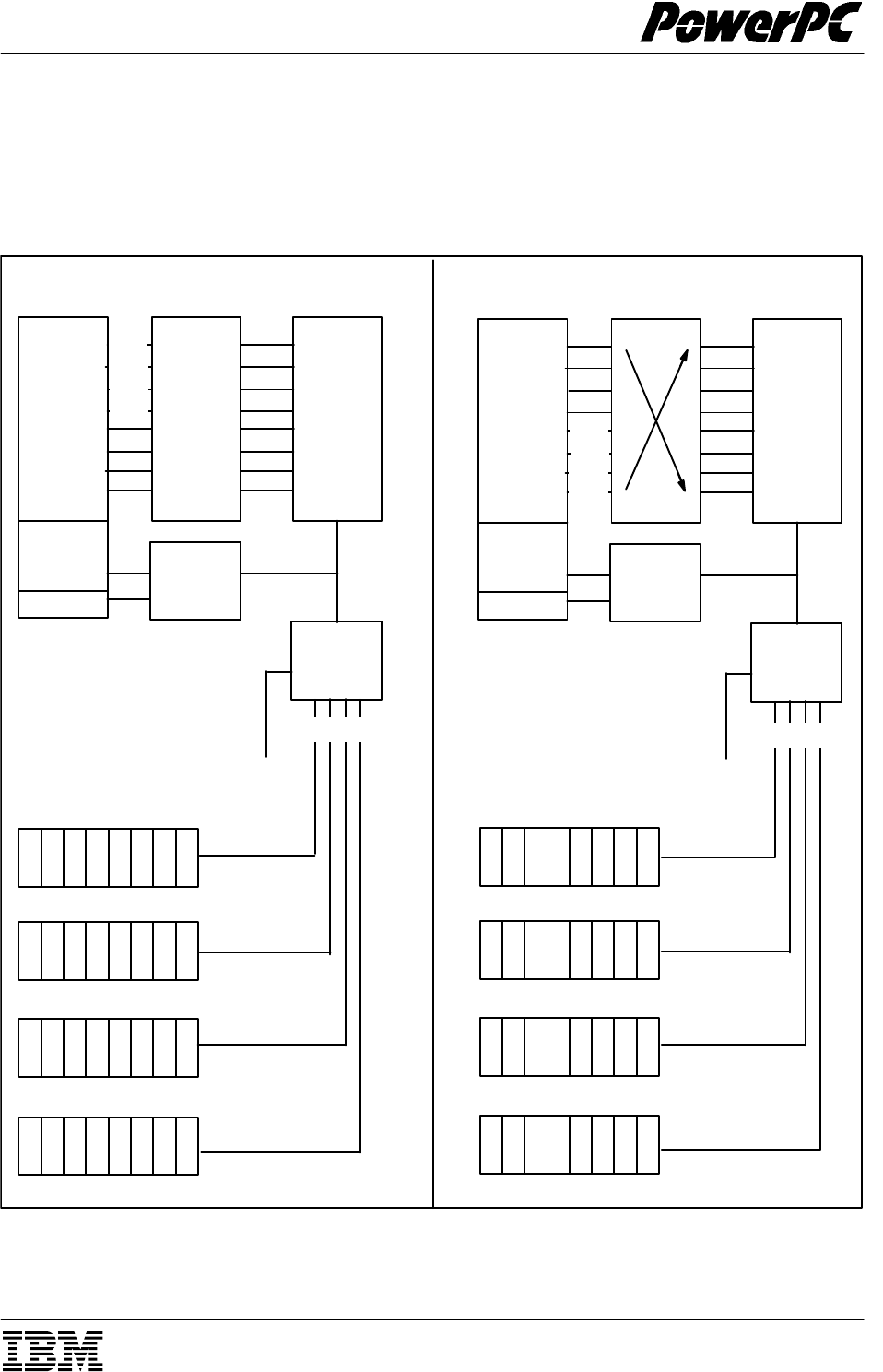

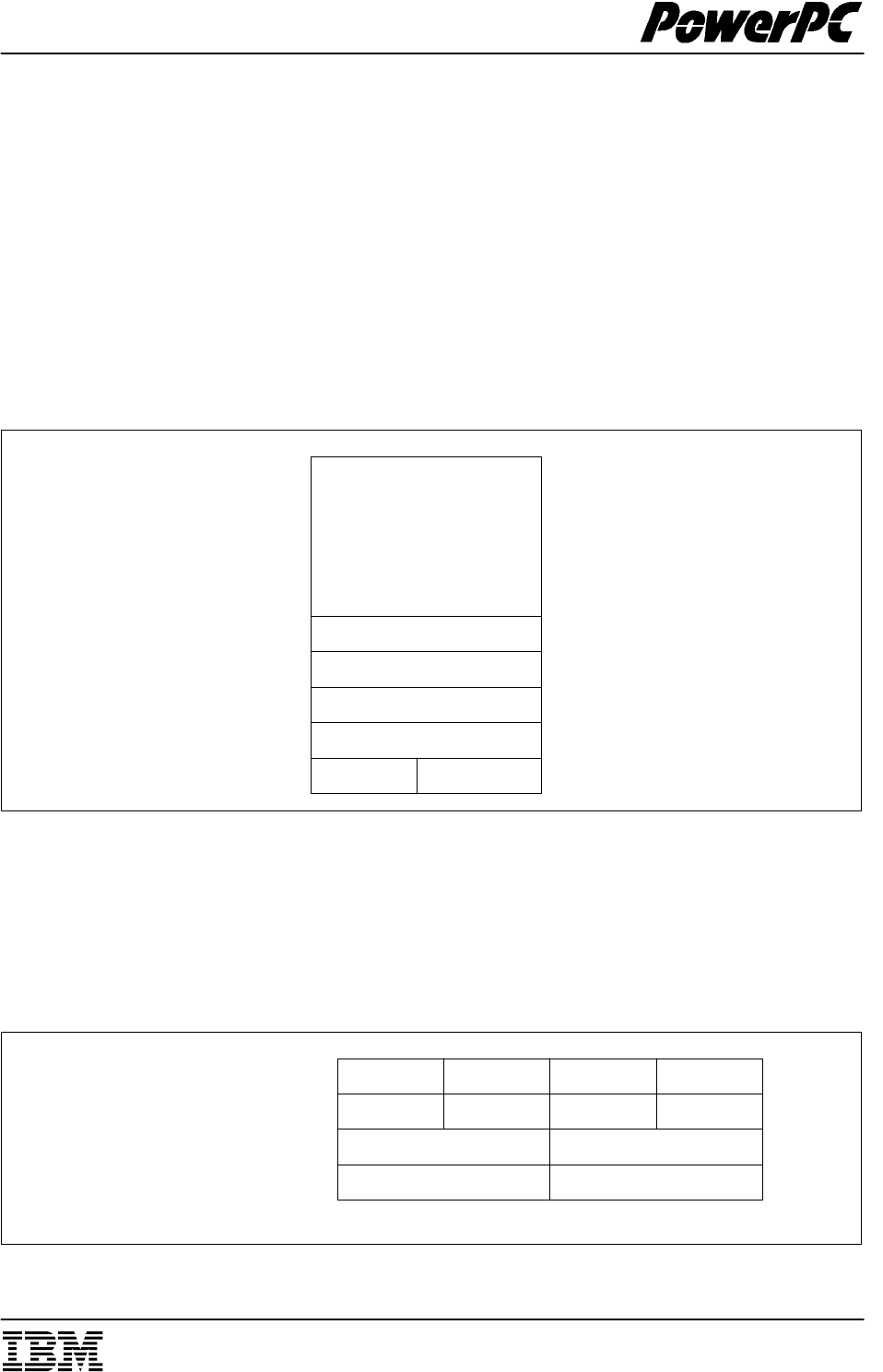

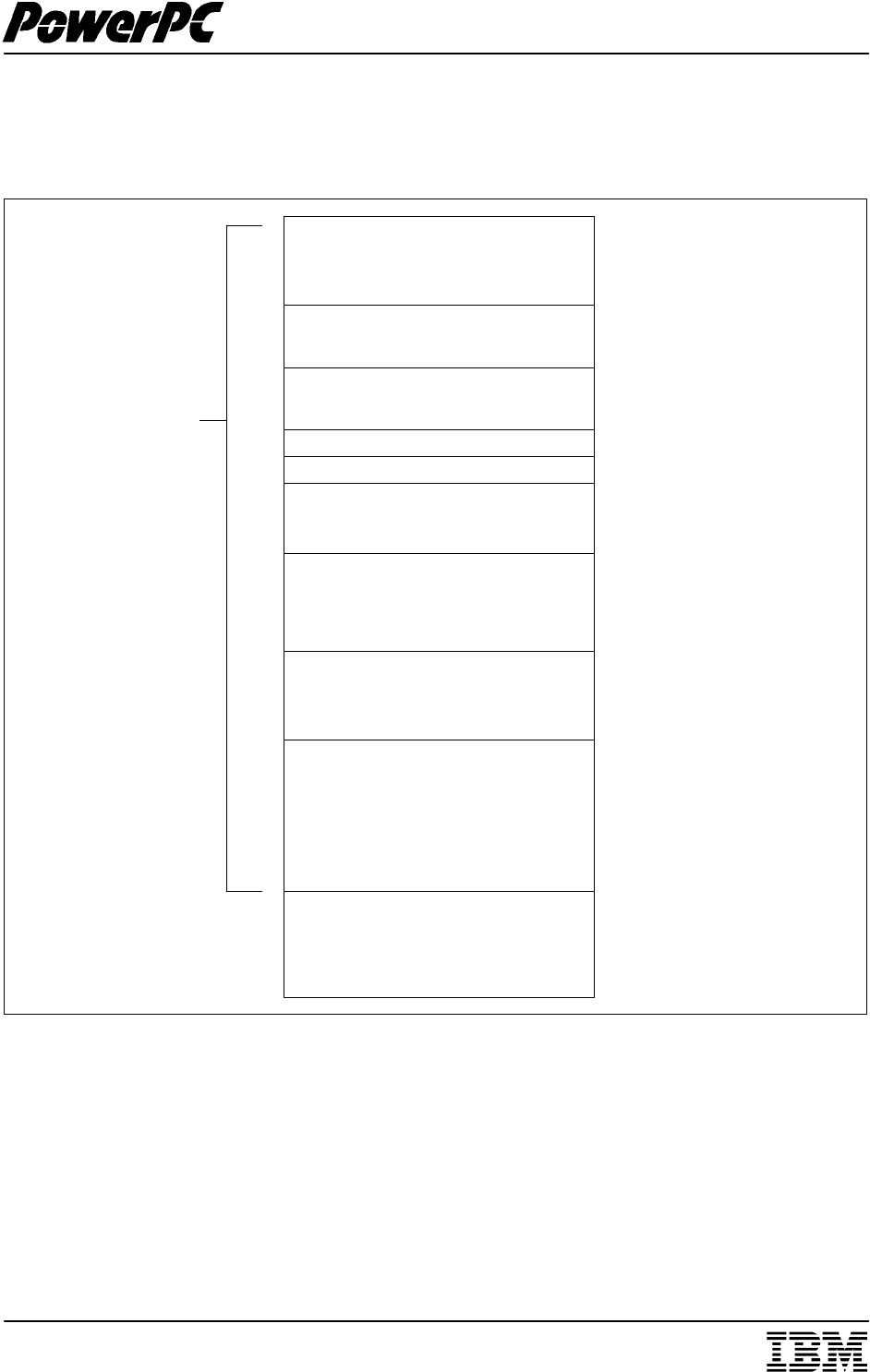

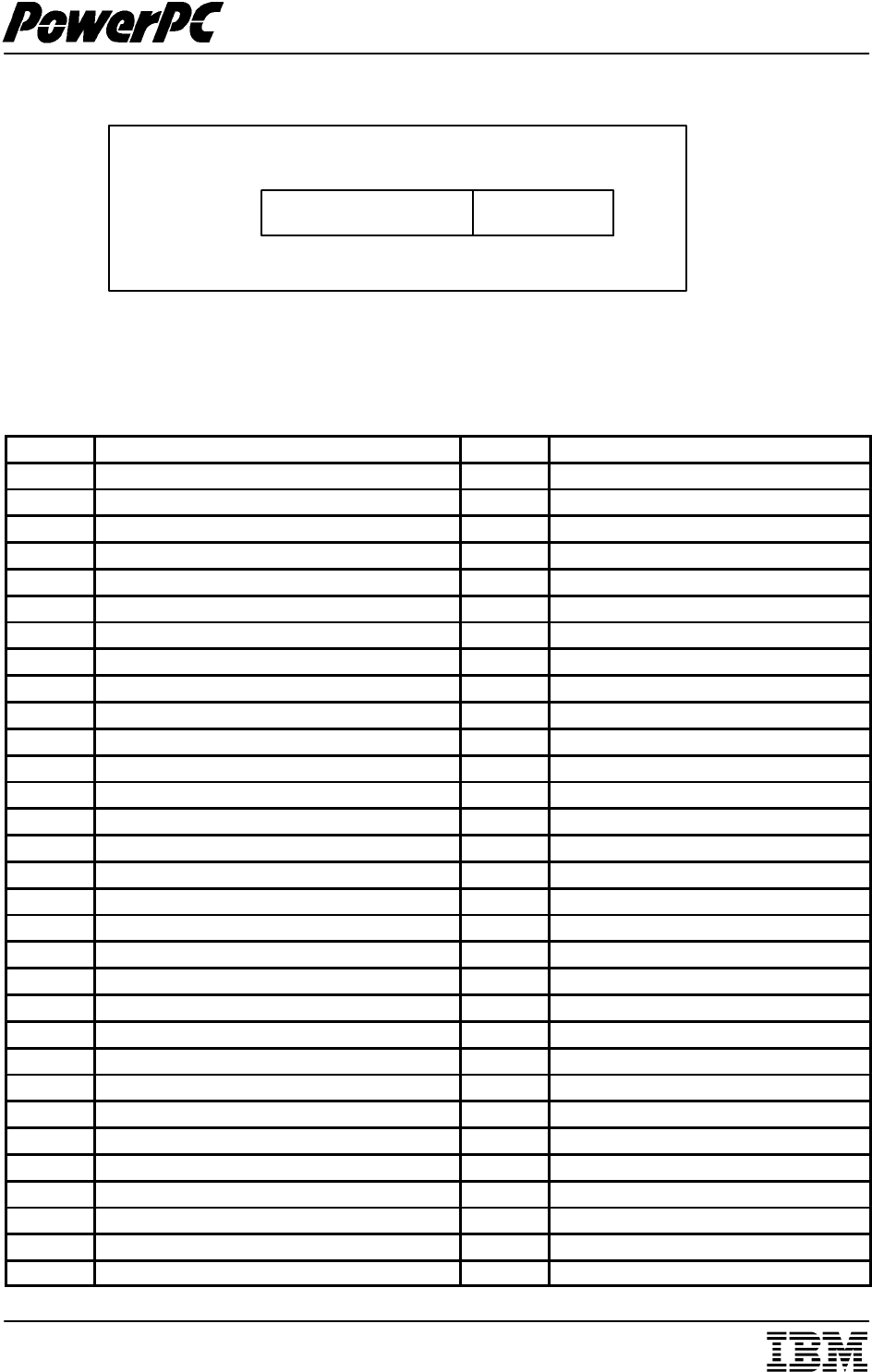

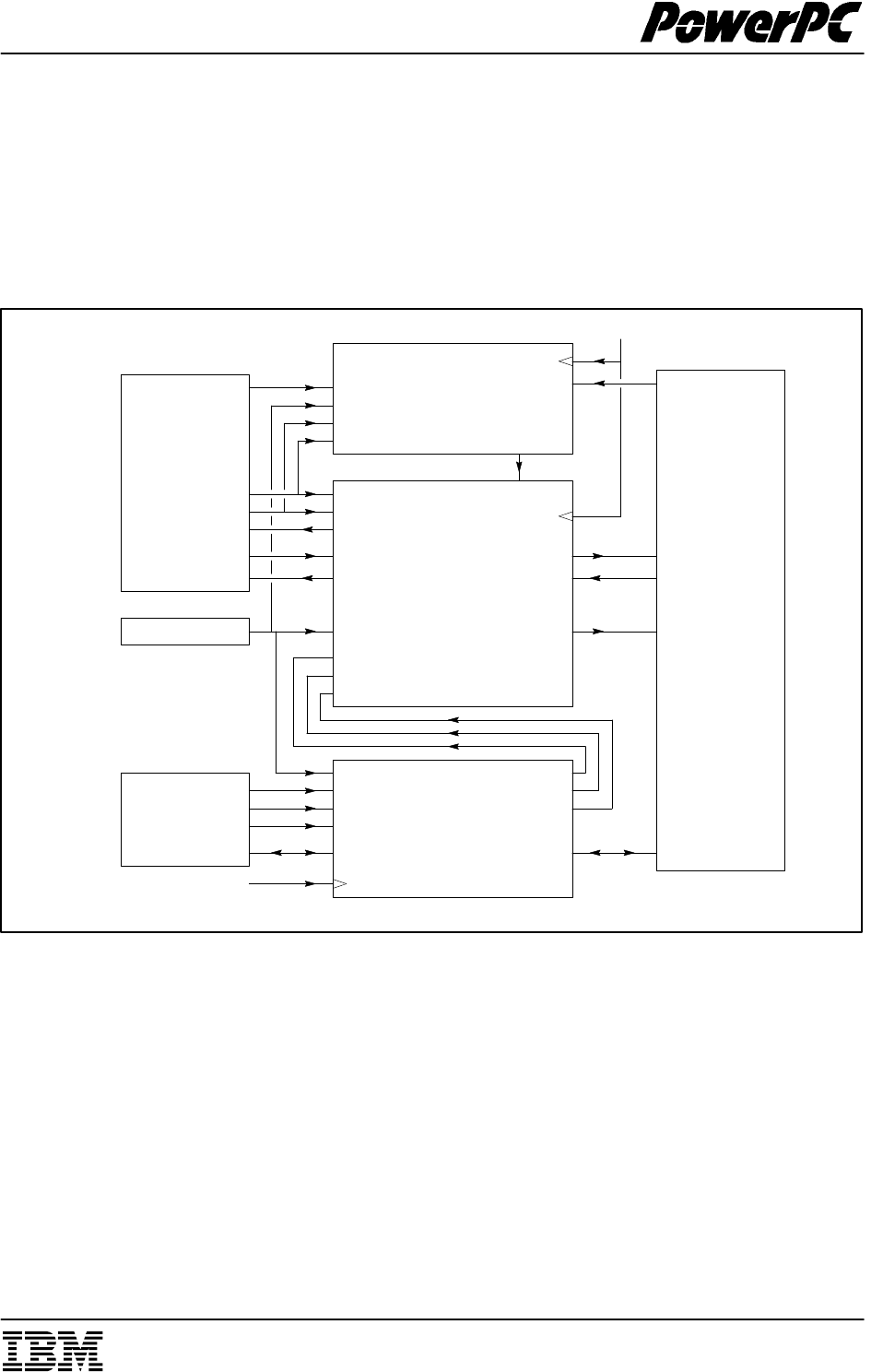

1.3 Reference Design Overview

This section contains an overview of the reference design. The block diagram of the refer-

ence design is shown in Figure 1.

The reference design is compliant with the PowerPC Reference Platform Specification Ver-

sion 1.1.

The core of the system is the PowerPC 603et or PowerPC 604t RISC microprocessor.

The IBM27-82660 Bridge chipset (660 Bridge) interfaces the CPU to the DRAM memory,

and provides L2 cache control for the tagRAM and SRAM components that are located on

the CPU bus.

The 660 Bridge also interfaces the CPU to the PCI bus. On the motherboard, the ISA bus

bridge is located on the PCI bus. The boot ROM is also physically located on the PCI bus,

but is accessed using a special protocol. PCI devices are unable to activate the ROM, and

ROM operations do not interfere with the PCI bus protocol.

The reference design also provides three PCI slots, by which major I/O subsystems, such

as SCSI and video adaptors, can be connected to the system. The reference design also

provides five ISA slots.

The motherboard is designed to an industry standard BabyAT (8.6 in. by 13 in.) form factor.

It requires +5V to power most of the components. The motherboard also requires 12 V

to support some of the peripheral features. Components that require +3.3V (such as the

PCI bus agents) are supported using a regulator mounted on the motherboard to convert

+5V to +3.3V.

1.3.1 The CPU

The reference board can be configured with either the 603e, or the 604 implementation of

the PowerPC architecture. Only one CPU may be installed at a time.

These CPUs use a CPU bus clock, and are in general capable of running their internal clock

at several different multiples of the bus clock frequency. The reference design runs the PCI

bus clock at a fixed frequency multiple of one half of the CPU bus clock frequency. The CPU

bus clock frequency is adjustable, and is nominally 66MHz.

The reference design supports bi-endian operation, and is equipped with an ESP connec-

tor to support RISCWatch debugging and monitor systems.

Consult your IBM representative for currently available choices of CPU type and operating

frequency.

1.3.2 IBM27-82660 Bridge

The IBM27-82660 Bridge (660 Bridge) chipset supplies many of the functions of the refer-

ence design. The 660 Bridge interfaces the CPU to the L2, system memory, the PCI bus,

the ROM, and other reference design components.

1.3.3 L2 Cache

The reference design supplies an L2 cache controller, located inside the 660 Bridge chip-

set. The motherboard provides a socket for an SRAM module, and the L2 tag RAM (16K

x 15, synchronous) is supplied installed on the board. The L2 is a unified, write-thru, direct-

Introduction

20 MPRH01TSU-02

mapped, look-aside cache that supports 1M of SRAM to cache the low 1G of CPU memory

space. The L2 supplies data to the CPU bus on write hits and snarfs the data (updates the

SRAM data while the memory controller is accessing DRAM memory) on read/write mis-

ses. It snoops PCI to memory transactions. Typical read performance with 9ms SRAM is

3-1-1-1, followed by -2-1-1-1 on pipelined reads for sync.

Regulator 29F040

KYBD

Mouse

8042

Mouse

DC1385

RTC

IBM27-82663

Buffer

ESP Connector

X-Bus

ISA Bus

Data

Address

Control

ISA Expansion

Slots (5)

System I/O

EPLD

X-Buffers

Data

Addr/Cntrl

MPC970

Clock Gen X-Bus

Strobes

ISA Bus

Bridge

SIO

Keyboard

Speaker

Control

PCI_AD

Address/Data

PCI Expansion

Slots (3)

Flash ROM

IBM27-82664

Controller

DRAM Module

DRAM Module

DRAM Module

DRAM Module

604

603

TagRAM

L2 SRAM

Module

Address

Data

CC

PD

PD

PD

5v to 3.3v

PCI Bus

60X Bus

Power

Mgt Cntrlr

87C750

Figure 1. 603/604 Reference Design Block Diagram

EPM5130C

1.3.4 System Memory

The reference design memory subsystem can support up to 128M of 70ns DRAM memory

on four 72 pin modules via sockets. Each SIMM socket can support an 8M or 32M 72 pin

SIMM. The DRAM subsystem is 72 bits wide: 64 data bits and eight parity bits. One parity

bit is generated for each byte of data written. The 660 Bridge can also be configured to per-

Introduction

21

MPRH01TSU-02

form ECC memory data checking and correction using standard parity DRAM modules. Or

it can be configured to disable DRAM parity checking for systems using non-parity DRAM.

The 660 Bridge also provides DRAM refresh and supports EDO hyper-page mode DRAM.

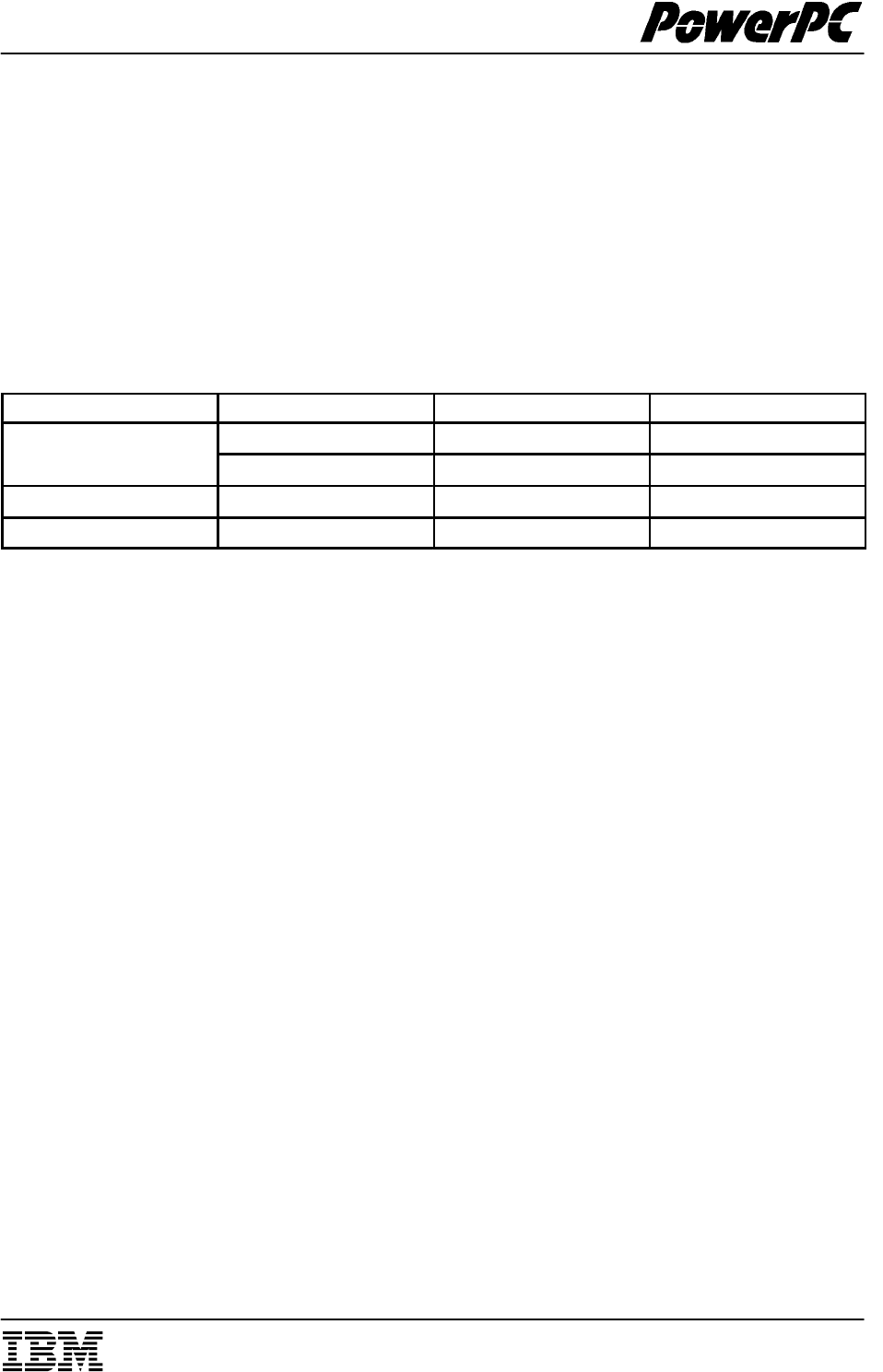

Memory access performance from the CPU bus at 66MHz with 70ns DRAM is typically:

SPipelined burst read: 4-4-4-4 CPU bus clocks—16 CPU clocks for 32 bytes of data

SPipelined burst write: 5-4-4-4 CPU bus clocks—17 CPU clocks for 32 bytes of data

Memory access performance from the PCI bus at 33MHz with 70ns DRAM is typically:

SRead bursts 5-1-1-1 -1-1-1-1 6-1-1-1 -1-1-1-1 6-1-1-1 -1-1-1-1 ... 6-1-1-1 -1-1-1-1,

SWrite bursts 5-1-1-1 -1-1-1-1 3-1-1-1 -1-1-1-1 3-1-1-1 -1-1-1-1 ... 3-1-1-1 -1-1-1-1.

1.3.5 PCI Bus

The 660 Bridge includes the interface between the PCI bus and the rest of the system. The

reference design allows CPU to PCI access and PCI bus master to memory access (with

snooping), and handles all PCI related system memory cache coherency issues. Three PCI

expansion slots are provided.

The reference design also supports memory block locking, types 0 and 1 configuration

cycles, and ISA master access to system memory thru the ISA bridge.

1.3.6 Flash ROM

The reference design uses an AMD AM29F040-120 Flasht ROM to contain the POST and

boot code. It is recommended that Vital Product Data (VPD) such as the motherboard

speed and native I/O complement be programmed into in this device. It is possible to pro-

gram the Flash before or during the manufacturing process.

After power on, the initial code fetched is supplied from this device. The 660 Bridge man-

ages ROM access and control. The reference design supports a 512K Flash.

1.3.7 ISA Bus

The ISA bridge function is provided by an Intel 82378ZB chip (SIO). It provides a PCI to

ISA bus bridge where the native I/O and the ISA slots reside, and it provides system ser-

vices such as ISA bus DMA, PCI bus arbitration, and interrupt control.

1.3.8 Time of Day Clock

The reference design uses a Dallas Semiconductort DS1385S to provide the real time

clock (TOD or RTC) function. This device is PC compatible and resides on the X-bus. It fea-

tures an additional 4K of NVRAM and a replaceable battery.

1.3.9 PS/2t Compatible Keyboard/Mouse Controller

The reference design uses an Intel 8042AH as a keyboard and mouse controller.

The code used is the same version as used in IBM Personal System/2 machines. This mi-

crocode may differ from other 8042 type keyboard controllers.

1.3.10 System Clocks

The primary clock generation is accomplished with a Motorolat MPC970 PLL clock gener-

ator, which uses a seed oscillator to generate the CPU and PCI clocks needed by the sys-

tem.

Introduction

22 MPRH01TSU-02

1.3.11 System I/O EPLD

The system I/O EPLD is a programmable logic device that uses the X-bus signals and the

partial decode signals from the SIO to decode chip selects for various components.

1.3.12 Power Management

Power management hardware is included on the board; however, power managenent ca-

pability will be implemented at a later date and will be described in a separate document.

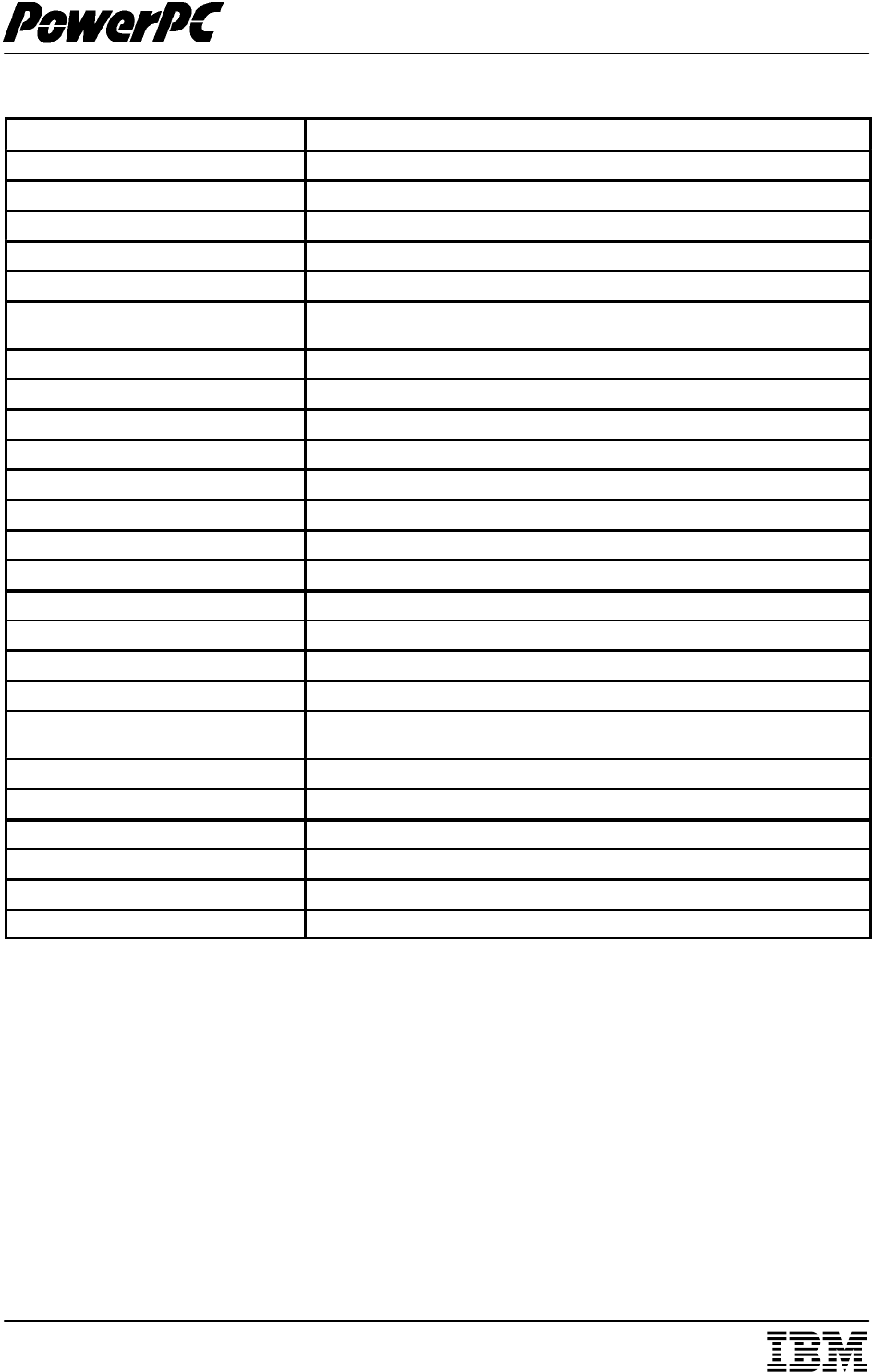

1.4 Quickstart Peripheral List

The reference design is intended for typical PC peripherals. Products from a large number

of manufacturers should work satisfactorily (see Table 1 for a list of peripherals and materi-

als). Reference boards do not come with the all of the required peripherals, cables, speak-

er, indicator LEDs, switches, and such that are needed to configure a properly working sys-

tem.

Table 1 outlines the generic requirements for peripherals and gives examples of some de-

vices that have been used for testing. It is not a recommendation of any particular vendor.

The purpose of this table is to outline at least one set of peripherals that may be used to

begin testing.

Table 1 does not include cables for a parallel port, indicators, a switch, or a speaker.

An IBM 3101 asynchronous terminal or equivalent is required for testing with the bring up

driver (BUD) code. Settings are 8-bit, no parity, one stop bit, and 9600 baud. VT100 or VT52

emulator terminals may be acceptable. It is desirable to also have a video monitor for BUD

tests. The boot code will boot with either an async console, a video on motherboard, or

both.

1.5 Reference Design Level

This documentation supports the release 2.1 version of the 603/604 reference design and

reference board. Except as noted, the information herein is believed to be correct for the

release 3.0 version of the reference design, once all of the errata are cured (see section

13, Errata for the reference design roadmap).

The reference board schematics are of the release 2.0 reference board, and correctly show

the workarounds that are installed on that board in order to work around certain errata.

Introduction

23

MPRH01TSU-02

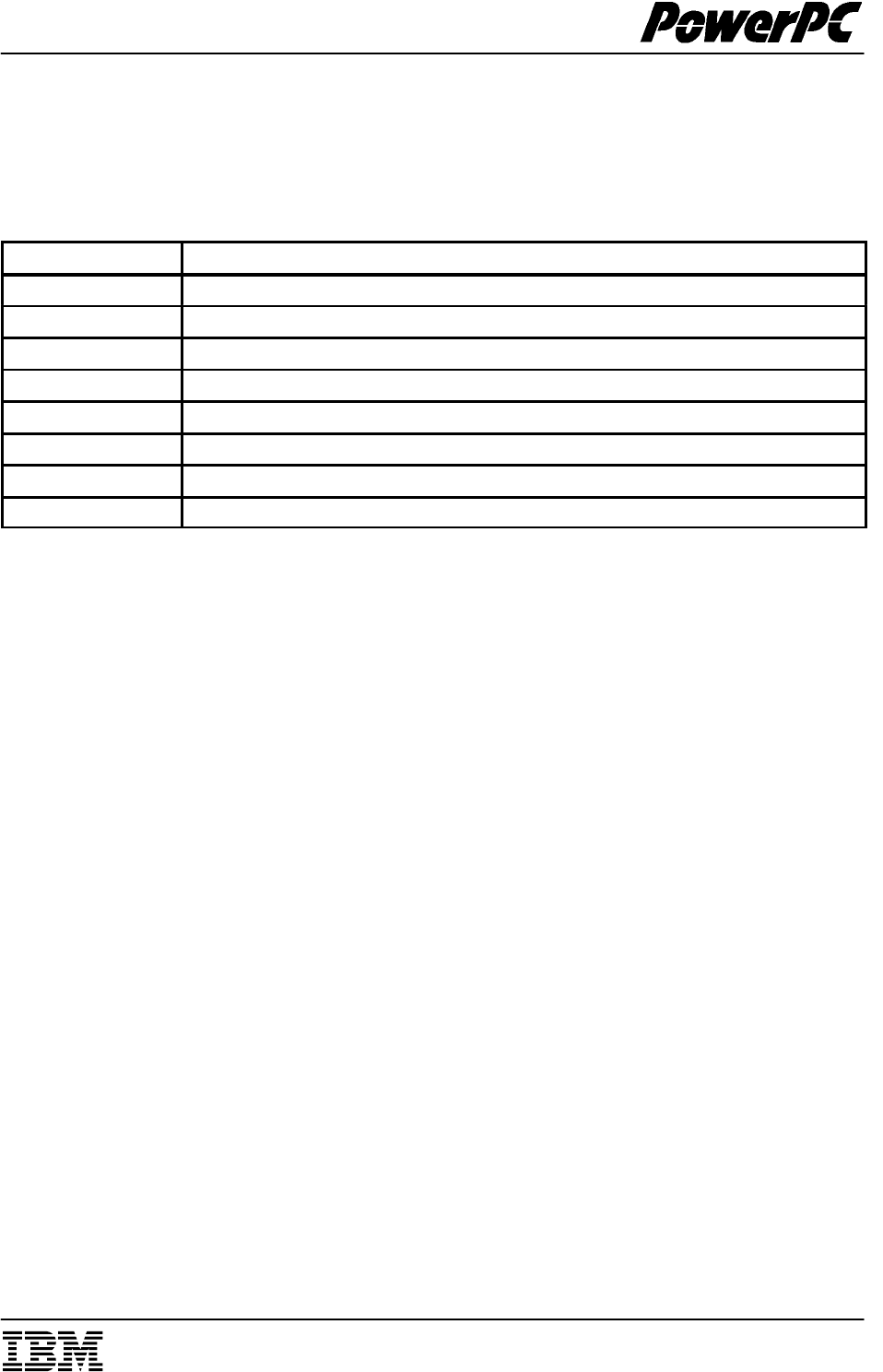

Table 1. Quickstart Peripheral List

Generic Description Example Device

L2 SRAM card, 256KB Alliance Semiconductor AS7M64P3256–15C

Loctite 384 adhesive, 300ml cartridge Loctite Corp. 17041

Loctite 384 activator, 10 liter can Loctite Corp. 17101

Video adapter card, PCI S3 Diamond Stealth (S3) 864

SCSI adaptor card, PCI NCR 8100S with 609–039–1635 controller

Super I/O adaptor ( IDE, floppy, serial

ports, parallel ports, etc.) Acculogic sIDE–4/HP (110–00139–00E00)

Audio adaptor card Creative Labs Soundblaster 16

Floppy disk drive, 3.5”x1.44MB Alps DFR723F, IBM 73G4514, Mitsubishi MF355F–258UG

Hard disk drive, SCSI–2, 8 bit Quantum LPS270/5405, Maxtor MXT–540SL, IBM WDS–3200 (79F4042)

Hard disk drive, SCSI 1GB IBM 94G3187

Hard disk drive, IDE 1GB Maxtor HDMC71260AC

CD_ROM drive, internal SCSI Toshiba XM–4101BMY

CD_ROM drive, internal SCSI, 4x Toshiba 5301–4x

CD_ROM drive, internal IDE, 4x Chinnon CDS5451

Chassis, Baby AT Olsen Metal Products CC300249–17

Power supply, 200W Energy Star API-3186S, IBM 06H2968

Box fan Panaflow FBA08T12M

Box fan shock mounts IBM 81F7977

Internal cables, floppy, SCSI, and CD–

ROM Standard cables

Speaker, internal 8W .5W 2pin

LED, 2.5 ma drive

Asynchronous terminal IBM 3101

Super VGA monitor IBM 6324, 6325, 6327, 9524, 9525, 9527, 9521

Keyboard, PS/2 compatible

Mouse, PS/2 compatible

Introduction

24 MPRH01TSU-02

CPU

25

MPRH01TSU-02

Section 2

CPU and CPU Bus

This section discusses topics that are directly related to the CPU, including how the 660

bridge decodes CPU initiated transfers as a function of the transfer type and address range.

For more information, refer to the 660 Bridge User’s Manual.

The reference design supports CPU bus speeds up to 66MHz, and PCI bus speeds up to

33MHz. The reference design is initially configured with a CPU:PCI bus speed ratio of 2:1.

The CPU:PCI clock ratio can be changed to 1:1 or 3:1 by reconfiguring the clock generator

and the 660 bridge, as long as other system considerations are handled correctly.

2.1 CPU Bus Masters

The reference design uses a single CPU, of either the PowerPC 603e or PowerPC 604 fam-

ily, and an external L2 cache is not allowed. Thus there are only two bus masters on the

CPU bus, the CPU and the 660 bridge. CPU bus arbitration is greatly simplified, and the

multi-processor capabilities of the 660 bridge are not used. The remaining arbitration on

the CPU bus is between the CPU and the snoop broadcasting logic in the 660 bridge. Since

the 660 bridge parks the CPU bus on CPU1 whenever the bus is idle, CPU latency is mini-

mized.

One level of address bus pipelining is supported, and most data writes are posted. Precise

exceptions are reported via TEA#, and imprecise exceptions are reported via MCP#. PIO,

or programmed I/O transactions (XATS# type) are not supported.

2.1.1 603e CPU

The 603e version of the reference design operates the 603e in 64 bit data bus mode.

The reference design is initially configured for DRTRY# mode, and can be reconfigured to

no-DRTRY# mode by populating R440 = 0 ohm. In DRTRY# mode, data is assumed to

have been speculatively presented to the CPU, and so is held for one clock in an internal

CPU latch before being presented to the CPU data consumers. In no-DRTRY# mode, the

data is assumed to be good when TA# is sampled active, so it is immediately forwarded

without the delay cycle. Use of this mode mainly speeds up reads from the L2.

The 603e version of the reference design runs at 3:2 603e internal clock to bus clock ratio

at 99MHz:66MHz. CPU PLL_CFG[0:3] is set to 1100.

On the 603e version of the reference board, the following are populated: R425 and R426

with 1k ohm resistors, and R423 and R424 with with 10k ohm resistors. The following are

not populated: R421, R422, R427, and R428, R377.

CPU

26 MPRH01TSU-02

2.1.2 604 CPU

The reference design is initially configured for DRTRY# mode, and can be reconfigured to

no-DRTRY# mode by populating R440 = 0 ohm.

The 604 version of the reference design is initially configured to run at 2:1 604 internal clock