Rockchip Developer Guide Linux4.4 Devfreq

Rockchip-Developer-Guide-Linux4.4-Devfreq

User Manual:

Open the PDF directly: View PDF ![]() .

.

Page Count: 25

4.1.5 PVTM OPP Table

4.1.5.1 PVTM

4.1.6 IR-Drop OPP Table

4.1.7

4.1.8

4.2 DMC DVFS

4.2.1 Clock

4.2.2 Regulator

4.2.3 OPP Table

4.2.3.1 OPP Table

4.2.3.2 OPP

4.2.4 leakage OPP Table

4.2.4.1 leakage

4.2.5 PVTM OPP Table

4.2.5.1 PVTM

4.2.6 IR-Drop OPP Table

4.2.7

4.2.8

4.2.9 VOP

4.3 BUS DVFS

4.3.1 PLL DVFS

5

6

6.1

6.2

6.3

6.4

6.5

6.6

6.7 leakage

6.8

1

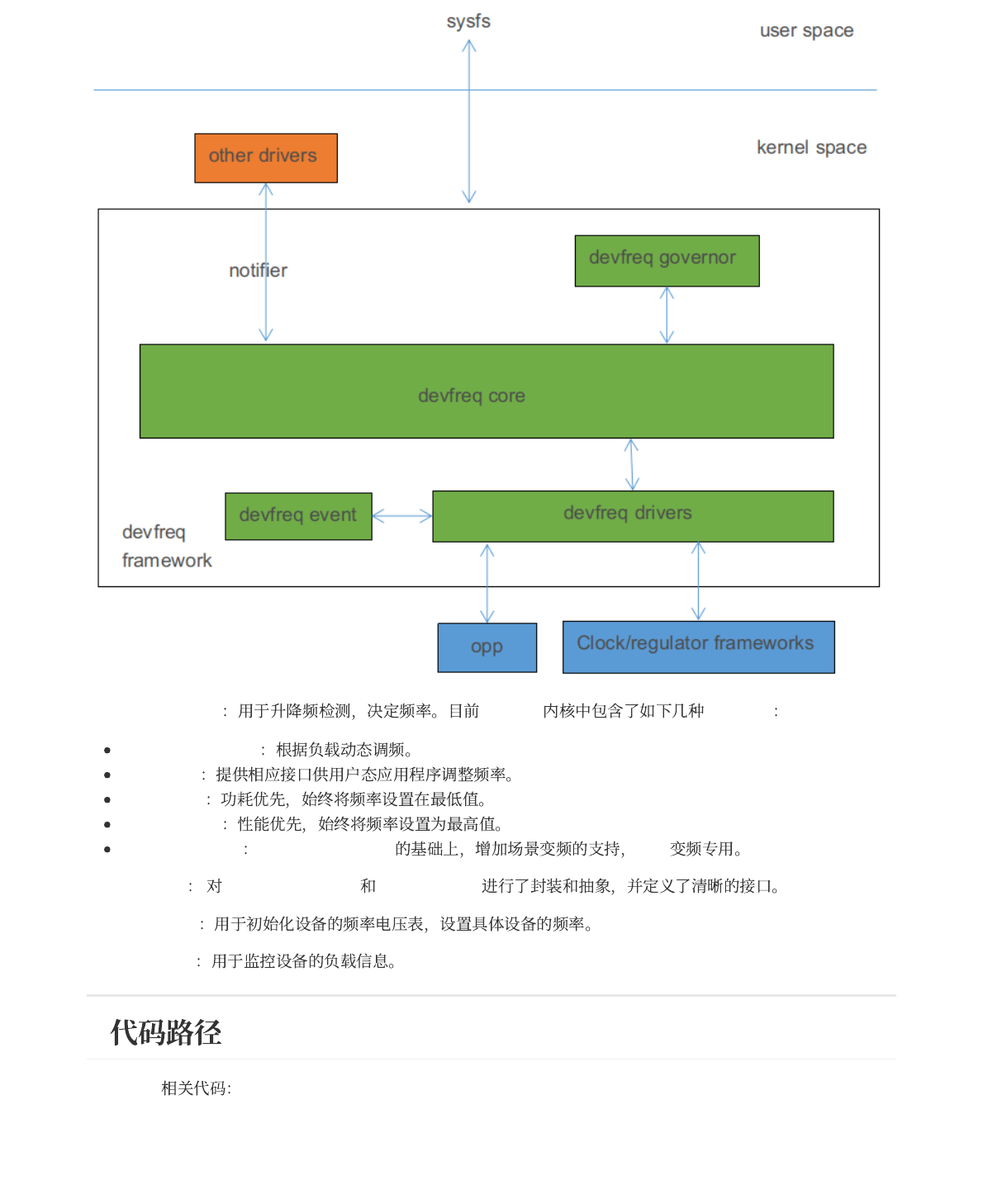

Devfreq governor

Devfreq CPUFreq CPUFreq CPU devfreq CPU

Devfreq framework governor core driver event

Event

Core

Driver

3 Menuconfig

drivers/devfreq/governor_simpleondemand.c /* simple ondemand */

drivers/devfreq/governor_performance.c /* performance */

drivers/devfreq/governor_powersave.c /* powersave */

drivers/devfreq/governor_userspace.c /* userspace */

drivers/devfreq/devfreq-event.c

drivers/devfreq/event/rockchip-dfi.c /* DDR cycle */

drivers/devfreq/event/rockchip-nocp.c /* DDR */

drivers/devfreq/devfreq.c

drivers/devfreq/rockchip_dmc.c /* dmc ondemand DMC driver */

drivers/gpu/arm/midgard/backend/gpu/mali_kbase_devfreq.c /* GPU driver */

drivers/gpu/arm/bifrost_for_linux/backend/gpu/mali_kbase_devfreq.c /* GPU driver */

drivers/gpu/arm/bifrost/backend/gpu/mali_kbase_devfreq.c /* GPU driver */

drivers/gpu/arm/mali400/mali/linux/mali_devfreq.c /* GPU driver */

drivers/devfreq/rockchip_bus.c /* bus driver */

drivers/soc/rockchip/rockchip_opp_select.c /* */

Device Drivers --->

[*] Generic Dynamic Voltage and Frequency Scaling (DVFS) support --->

--- Generic Dynamic Voltage and Frequency Scaling (DVFS) support

*** DEVFREQ Governors *** /* devfreq governor */

-*- Simple Ondemand

<*> Performance

<*> Powersave

*** DEVFREQ Drivers ***

<*> ARM ROCKCHIP BUS DEVFREQ Driver /* bus devfreq driver */

<*> ARM ROCKCHIP DMC DEVFREQ Driver /* dmc devfreq driver */

[*] DEVFREQ-Event device Support --->

--- DEVFREQ-Event device Support

-*- ROCKCHIP DFI DEVFREQ event Driver /* dfi event driver */

/* nocp event driver */

<*> ROCKCHIP NoC (Network On Chip) Probe DEVFREQ event Driver

4 Device Tree

4.1 GPU DVFS

4.1.1 Clock

GPU “clock” “clock-names” DTSI Clock

clock RK3399

4.1.2 Regulator

GPU “mali-supply” DTS

Regulator regulator PMIC RK3399

gpu: gpu@ff9a0000 {

compatible = "arm,malit860",

"arm,malit86x",

"arm,malit8xx",

"arm,mali-midgard";

...

clocks = <&cru ACLK_GPU>;

clock-names = "clk_mali";

...

};

&i2c0 {

...

vdd_gpu: syr828@41 {

compatible = "silergy,syr828";

reg = <0x41>;

vin-supply = <&vcc5v0_sys>;

regulator-compatible = "fan53555-reg";

pinctrl-0 = <&vsel2_gpio>;

vsel-gpios = <&gpio1 14 GPIO_ACTIVE_HIGH>;

regulator-name = "vdd_gpu";

regulator-min-microvolt = <712500>;

regulator-max-microvolt = <1500000>;

regulator-ramp-delay = <1000>;

fcs,suspend-voltage-selector = <1>;

regulator-always-on;

regulator-boot-on;

regulator-initial-state = <3>;

regulator-state-mem {

regulator-off-in-suspend;

};

};

};

&gpu {

status = "okay";

4.1.3 OPP Table

Linux4.4 devicetree

OPP Table OPP Table OPP leaakge PVTM

OPP

4.1.3.1 OPP Table

OPP Table GPU “operating-points-v2”

DTSI RK3399

4.1.3.2 OPP

OPP “status = "disabeld";”

mali-supply = <&vdd_gpu>;

};

Documentation/devicetree/bindings/opp/opp.txt

Documentation/power/opp.txt

&gpu {

operating-points-v2 = <&gpu_opp_table>;

};

gpu_opp_table: opp-table2 {

compatible = "operating-points-v2";

opp-200000000 {

opp-hz = /bits/ 64 <200000000>; /* Hz */

opp-microvolt = <800000>; /* uV */

};

...

opp-800000000 {

opp-hz = /bits/ 64 <800000000>;

opp-microvolt = <1100000>;

};

}

gpu_opp_table: opp-table2 {

compatible = "operating-points-v2";

opp-200000000 {

opp-hz = /bits/ 64 <200000000>; /* Hz */

opp-microvolt = <800000>; /* uV */

};

...

DTSI OPP Table OPP “status = "disabeld";”

4.1.4 leakage OPP Table

IDDQ(Integrated Circuit Quiescent Current) CMOS

leakage GPU leakage GPU GPU VD logic

GPU leakage logic leakage logic

leakage eFuse OTP

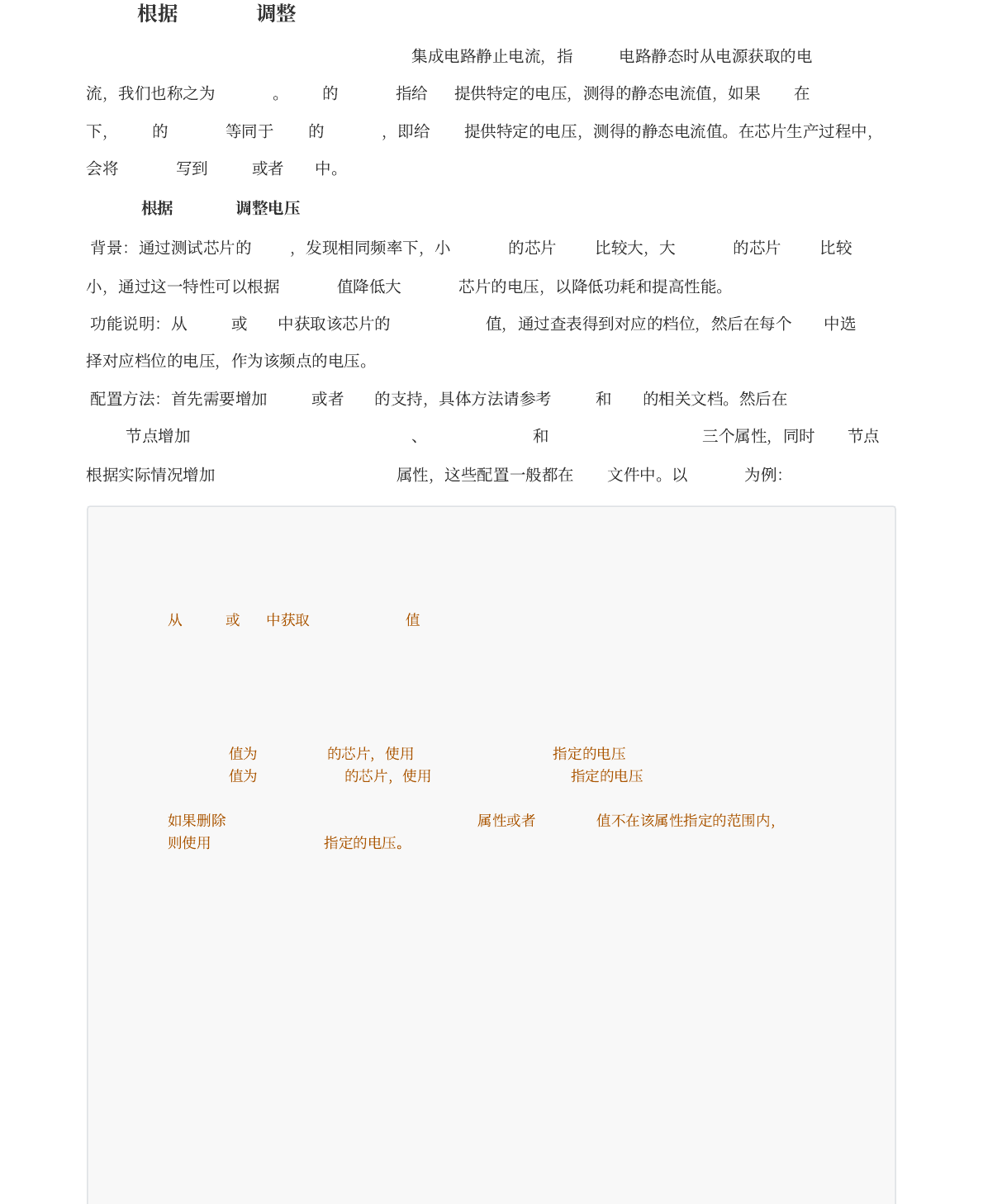

4.1.4.1 leakage

Vmin leakage Vmin leakage Vmin

leakage leakage

eFuse OTP GPU leakage OPP

eFuse OTP eFuse OTP OPP

Table “rockchip,leakage-voltage-sel” “nvmem-cells” “nvmem-cell-names” OPP

“opp-microvolt-<name>” DTSI RK3328

opp-800000000 {

opp-hz = /bits/ 64 <800000000>;

opp-microvolt = <1100000>;

status = "disabled";

};

}

&gpu_opp_table {

opp-800000000 {

status = "disabled";

}

};

gpu_opp_table: gpu-opp-table {

compatible = "operating-points-v2";

/*

* eFuse OTP GPU leakage

*/

nvmem-cells = <&gpu_leakage>;

nvmem-cell-names = "gpu_leakage";

/*

* leakage 1mA-10mA opp-microvolt-L0

* leakage 11mA-254mA opp-microvolt-L1

*

* rockchip,leakage-voltage-sell leakage

“rockchip,leakage-voltage-sel” opp-microvolt

4.1.5 PVTM OPP Table

GPU PVTM(Process-Voltage-Temperature Monitor) GPU

4.1.5.1 PVTM

Vmin PVTM Vmin PVTM

Vmin PVTM PVTM

PVTM PVTM

OPP

PVTM PVTM OPP Table

“rockchip,pvtm-voltage-sel” “rockchip,thermal-zone” “rockchip,pvtm-<name>”

“nvmem-cells” “nvmem-cell-names” OPP “opp-microvolt-<name>”

DTSI RK3399

* opp-microvolt

*/

rockchip,leakage-voltage-sel = <

1 10 0

11 254 1

>;

opp-200000000 {

opp-hz = /bits/ 64 <200000000>;

opp-microvolt = <950000>;

opp-microvolt-L0 = <950000>;

opp-microvolt-L1 = <950000>;

};

...

opp-500000000 {

opp-hz = /bits/ 64 <500000000>;

opp-microvolt = <1150000>;

opp-microvolt-L0 = <1150000>;

opp-microvolt-L1 = <1100000>;

};

};

gpu_opp_table: opp-table2 {

compatible = "operating-points-v2";

/*

* PVTM 0-121000 opp-microvolt-L0

* PVTM 121001-125500 opp-microvolt-L1

* PVTM 125501-128500 opp-microvolt-L2

“rockchip,pvtm-voltage-sel” opp-microvolt

4.1.6 IR-Drop OPP Table

IR-Drop

EVB

IR-Drop OPP Ttable

EVB

* PVTM 128501-999999 opp-microvolt-L3

*

* rockchip,pvtm-voltage-sel PVTM

* opp-microvolt

*/

rockchip,pvtm-voltage-sel = <

0 121000 0

121001 125500 1

125501 128500 2

128501 999999 3

>;

rockchip,pvtm-freq = <200000>; /* PVTM GPU Khz */

rockchip,pvtm-volt = <900000>; /* PVTM GPU uV */

rockchip,pvtm-ch = <3 0>; /* PVTM < sel > */

rockchip,pvtm-sample-time = <1000>; /* PVTM us */

rockchip,pvtm-number = <10>; /* PVTM */

rockchip,pvtm-error = <1000>; /* */

rockchip,pvtm-ref-temp = <41>; /* */

/* PVTM < > */

rockchip,pvtm-temp-prop = <46 12>;

rockchip,thermal-zone = "gpu-thermal"; /* thermal-zone */

opp-200000000 {

opp-hz = /bits/ 64 <200000000>;

opp-microvolt = <800000>;

opp-microvolt-L0 = <800000>;

opp-microvolt-L1 = <800000>;

opp-microvolt-L2 = <800000>;

opp-microvolt-L3 = <800000>;

};

...

opp-800000000 {

opp-hz = /bits/ 64 <800000000>;

opp-microvolt = <1100000>;

opp-microvolt-L0 = <1100000>;

opp-microvolt-L1 = <1075000>;

opp-microvolt-L2 = <1050000>;

opp-microvolt-L3 = <1025000>;

};

};

OPP Table “rockchip,max-volt ” “rockchip,evb-irdrop”

“rockchip,board-irdrop” “rockchip,board-irdrop” DTS DTSI

RK3326 DTSI

DTS

“rockchip,board-irdrop”

4.1.7

-40~85

OPP Table “rockchip,temp-hysteresis” “rockchip,low-temp“

”rockchip,low-temp-min-volt“ “rockchip,low-temp-adjust-volt” “rockchip,max-volt”

DTSI RK3399

gpu_opp_table: gpu-opp-table {

compatible = "operating-points-v2";

/* uV */

rockchip,max-volt = <1175000>;

rockchip,evb-irdrop = <25000>;/* EVB SDK */

...

}

&gpu_opp_table {

/*

* max IR-drop values on different freq condition for this board!

*/

/*

* :

* 200Mhz-520MHz 50000uV 25000uV 50000-25000 EVB

*/

rockchip,board-irdrop = <

/* MHz MHz uV */

200 520 50000

>;

};

gpu_opp_table: opp-table2 {

compatible = "operating-points-v2";

4.1.8

Simple ondemand upthreshold downdifferential 90

5 90% 90% 90%-5% 90%-5%

90%-5%/2 GPU

GPU “upthreshold” downdifferential“ DTSI

RK3288

4.2 DMC DVFS

DMC Dynamic Memory Controller DVFS DDR

4.2.1 Clock

DMC “clock” DTSI Clock

clock RK3399

/*

* millicelsius

* 0 0+5 85 85-5

*/

rockchip,temp-hysteresis = <5000>;

rockchip,low-temp = <0>; /* millicelsius*/

rockchip,low-temp-min-volt = <900000>; /* uV */

rockchip,low-temp-adjust-volt = <

/* MHz MHz uV */

0 800 25000 /* 0-800MHz 25mV */

>;

rockchip,max-volt = <1150000>; /* */

...

}

gpu: gpu@ffa30000 {

compatible = "arm,malit764",

"arm,malit76x",

"arm,malit7xx",

"arm,mali-midgard";

reg = <0x0 0xffa30000 0x0 0x10000>;

upthreshold = <75>;

downdifferential = <10>;

...

}

4.2.2 Regulator

DMC “center-supply” DTS

Regulator regulator PMIC RK3399

4.2.3 OPP Table

Linux4.4 devicetree

OPP Table OPP Table OPP leaakge PVTM

OPP

4.2.3.1 OPP Table

dmc: dmc {

compatible = "rockchip,rk3399-dmc";

...

clocks = <&cru SCLK_DDRCLK>;

clock-names = "dmc_clk";

...

};

&i2c0 {

...

rk808: pmic@1b {

...

regulators {

vdd_center: DCDC_REG1 {

regulator-always-on;

regulator-boot-on;

regulator-min-microvolt = <750000>;

regulator-max-microvolt = <1350000>;

regulator-ramp-delay = <6001>;

regulator-name = "vdd_center";

regulator-state-mem {

regulator-off-in-suspend;

};

};

};

};

};

&dmc {

status = "okay";

center-supply = <&vdd_center>;

};

Documentation/devicetree/bindings/opp/opp.txt

Documentation/power/opp.txt

OPP Table DMC “operating-points-v2”

DTSI RK3399

4.2.3.2 OPP

OPP “status = "disabeld";”

DTS OPP Table OPP “status = "disabeld";”

&dmc {

operating-points-v2 = <&dmc_opp_table>;

};

dmc_opp_table: opp-table3 {

compatible = "operating-points-v2";

opp-200000000 {

opp-hz = /bits/ 64 <200000000>; /* Hz */

opp-microvolt = <900000>; /* uV */

};

...

opp-800000000 {

opp-hz = /bits/ 64 <800000000>;

opp-microvolt = <900000>;

};

};

dmc_opp_table: opp-table3 {

compatible = "operating-points-v2";

opp-200000000 {

opp-hz = /bits/ 64 <200000000>; /* Hz */

opp-microvolt = <800000>; /* uV */

};

...

opp-800000000 {

opp-hz = /bits/ 64 <800000000>;

opp-microvolt = <900000>;

status = "disabled";

};

}

&dmc_opp_table {

opp-800000000 {

status = "disabled";

}

};

4.2.4 leakage OPP Table

IDDQ(Integrated Circuit Quiescent Current) CMOS

leakage DDR leakage ddr DDR VD logic

DDR leakage logic leakage logic

leakage eFuse OTP

4.2.4.1 leakage

Vmin leakage Vmin leakage Vmin

leakage leakage

eFuse OTP DDR leakage OPP

eFuse OTP eFuse OTP OPP

Table “rockchip,leakage-voltage-sel” “nvmem-cells” “nvmem-cell-names” OPP

“opp-microvolt-<name>” DTSI RK3328

dmc_opp_table: dmc-opp-table {

compatible = "operating-points-v2";

/*

* eFuse OTP DDR leakage

*/

nvmem-cells = <&logic_leakage>;

nvmem-cell-names = "ddr_leakage";

/*

* leakage 1mA-10mA opp-microvolt-L0

* leakage 11mA-254mA opp-microvolt-L1

*

* rockchip,leakage-voltage-sell leakage

* opp-microvolt

*/

rockchip,leakage-voltage-sel = <

1 10 0

11 254 1

>;

opp-400000000 {

opp-hz = /bits/ 64 <400000000>;

opp-microvolt = <950000>;

opp-microvolt-L0 = <950000>;

opp-microvolt-L1 = <950000>;

};

...

opp-1066000000 {

opp-hz = /bits/ 64 <1066000000>;

“rockchip,leakage-voltage-sel” opp-microvolt

4.2.5 PVTM OPP Table

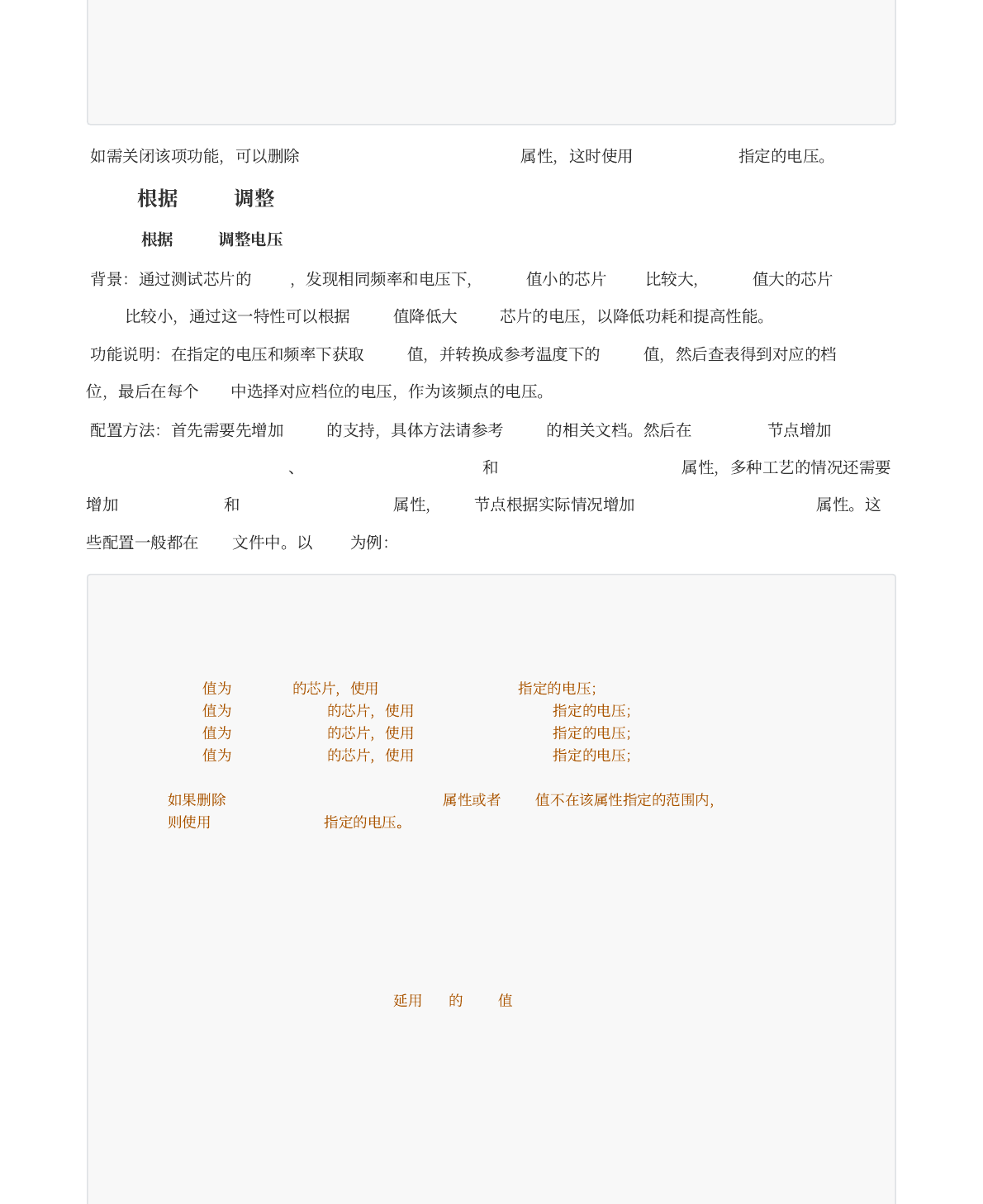

4.2.5.1 PVTM

Vmin PVTM Vmin PVTM

Vmin PVTM PVTM

PVTM PVTM

OPP

PVTM PVTM OPP Table

“rockchip,pvtm-voltage-sel” “rockchip,thermal-zone” “rockchip,pvtm-<name>”

“nvmem-cells” “nvmem-cell-names” OPP “opp-microvolt-<name>”

DTSI PX30

opp-microvolt = <1175000>;

opp-microvolt-L0 = <1175000>;

opp-microvolt-L1 = <1150000>;

};

};

dmc_opp_table: dmc-opp-table {

compatible = "operating-points-v2";

/*

* PVTM 0-50000 opp-microvolt-L0

* PVTM 50001-54000 opp-microvolt-L1

* PVTM 54001-60000 opp-microvolt-L2

* PVTM 60001-99999 opp-microvolt-L3

*

* rockchip,pvtm-voltage-sel PVTM

* opp-microvolt

*/

rockchip,pvtm-voltage-sel = <

0 50000 0

50001 54000 1

54001 60000 2

60001 99999 3

>;

rockchip,pvtm-ch = <0 0>; /* CPU PVTM */

opp-194000000 {

opp-hz = /bits/ 64 <194000000>;

opp-microvolt = <950000>;

opp-microvolt-L0 = <950000>;

opp-microvolt-L1 = <950000>;

opp-microvolt-L2 = <950000>;

opp-microvolt-L3 = <950000>;

“rockchip,pvtm-voltage-sel” opp-microvolt

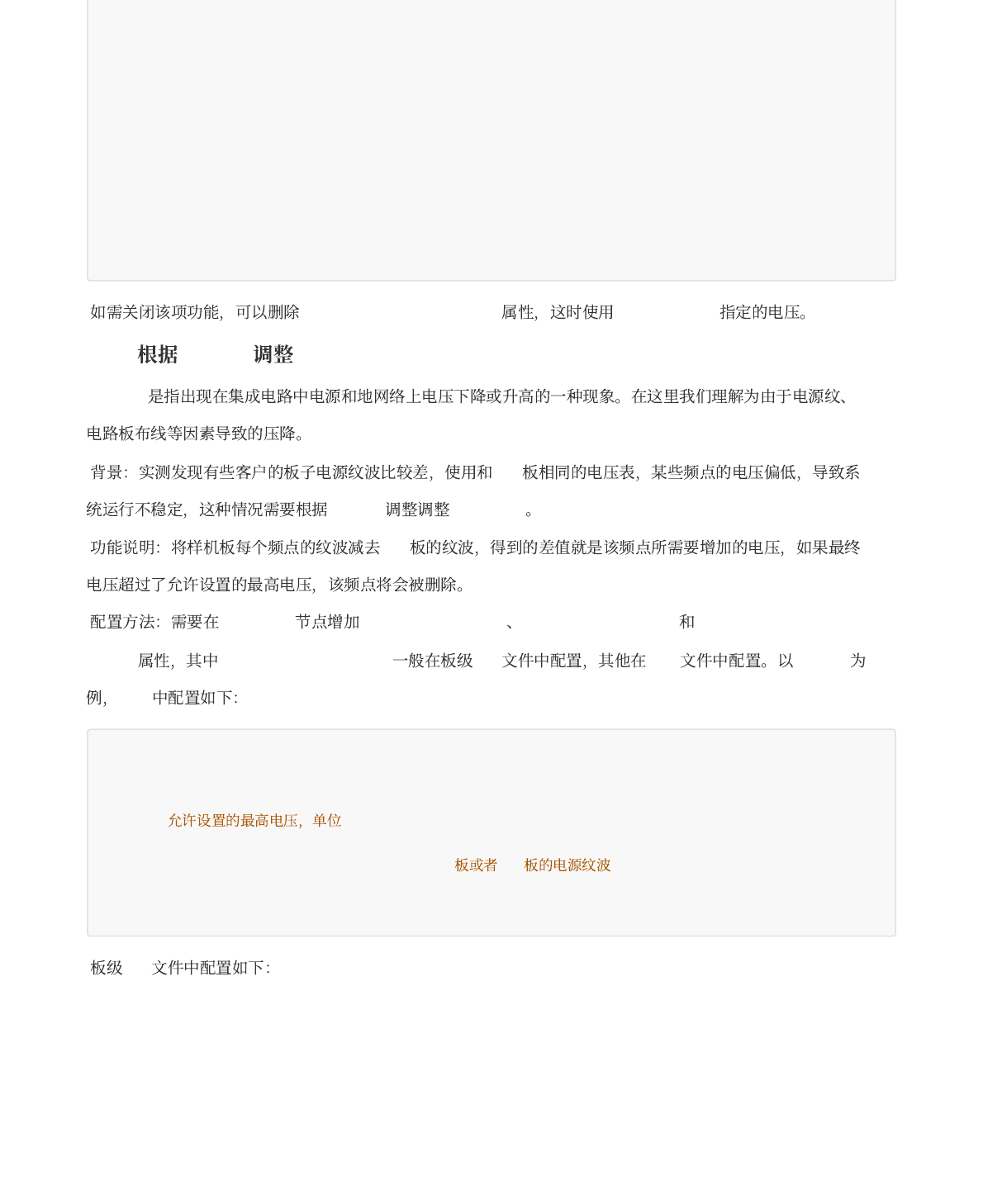

4.2.6 IR-Drop OPP Table

IR-Drop

EVB

IR-Drop OPP Table

EVB

OPP Table “rockchip,max-volt ” “rockchip,evb-irdrop” “rockchip,board-

irdrop” “rockchip,board-irdrop” DTS DTSI RK3326

DTSI

DTS

};

...

opp-786000000 {

opp-hz = /bits/ 64 <786000000>;

opp-microvolt = <1100000>;

opp-microvolt-L0 = <1100000>;

opp-microvolt-L1 = <1050000>;

opp-microvolt-L2 = <1025000>;

opp-microvolt-L3 = <1000000>;

status = "disabled";

};

};

dmc_opp_table: dmc-opp-table {

compatible = "operating-points-v2";

/* uV */

rockchip,max-volt = <1150000>;

rockchip,evb-irdrop = <25000>;/* EVB SDK */

...

}

“rockchip,board-irdrop”

4.2.7

DDR DDR

DDR

DDR

SYS_STATUS_DUALVIEW SYS_STATUS_DUALVIEW DDR

DDR DDR

DMC “system-status-freq ” RK3399

4.2.8

DDR DDR

&dmc_opp_table {

/*

* max IR-drop values on different freq condition for this board!

*/

/*

* :

* 451Mhz-800MHz 75000uV 50000uV 75000-25000 EVB

*/

rockchip,board-irdrop = <

/* MHz MHz uV */

451 800 75000

>;

};

&dmc {

status = "okay";

...

system-status-freq = <

/* system status freq(KHz) */

SYS_STATUS_NORMAL 800000 /* */

SYS_STATUS_REBOOT 528000 /* reboot reboot DDR */

SYS_STATUS_SUSPEND 200000 /* DDR */

SYS_STATUS_VIDEO_1080P 200000 /* 1080 DDR */

SYS_STATUS_VIDEO_4K 600000 /* 4k DDR */

SYS_STATUS_VIDEO_4K_10B 800000 /* 4k 10bit DDR */

SYS_STATUS_PERFORMANCE 800000 /* DDR */

SYS_STATUS_BOOST 400000 /* DDR */

SYS_STATUS_DUALVIEW 600000 /* DDR */

SYS_STATUS_ISP 600000 /* ISP DDR */

>;

}

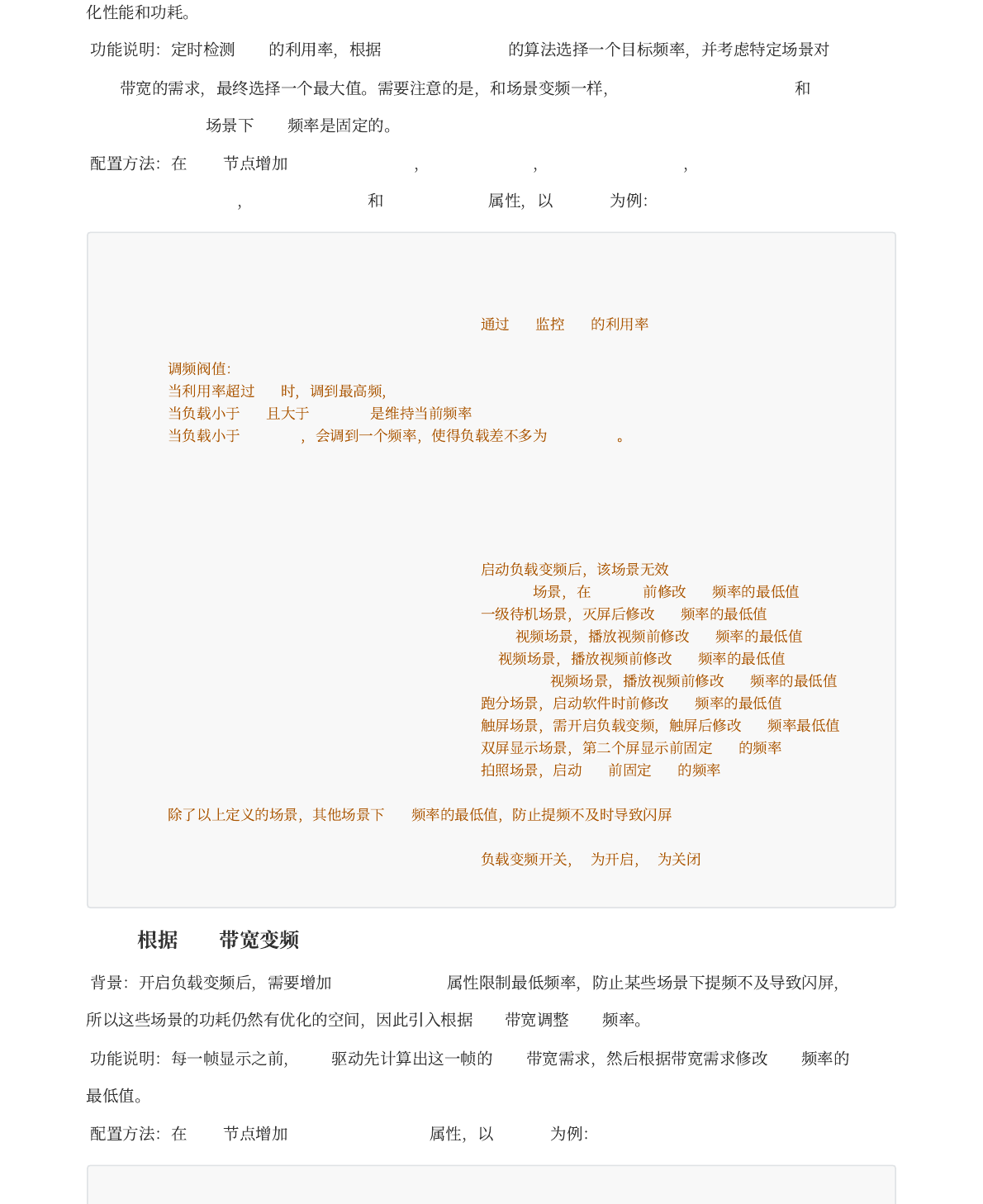

DDR simple ondeman

DDR SYS_STATUS_DUALVIEW

SYS_STATUS_ISP DDR

DMC “devfreq-events ” “upthreshold” “downdifferential”

“system-status-freq” “auto-min-freq” “auto-freq-en” RK3399

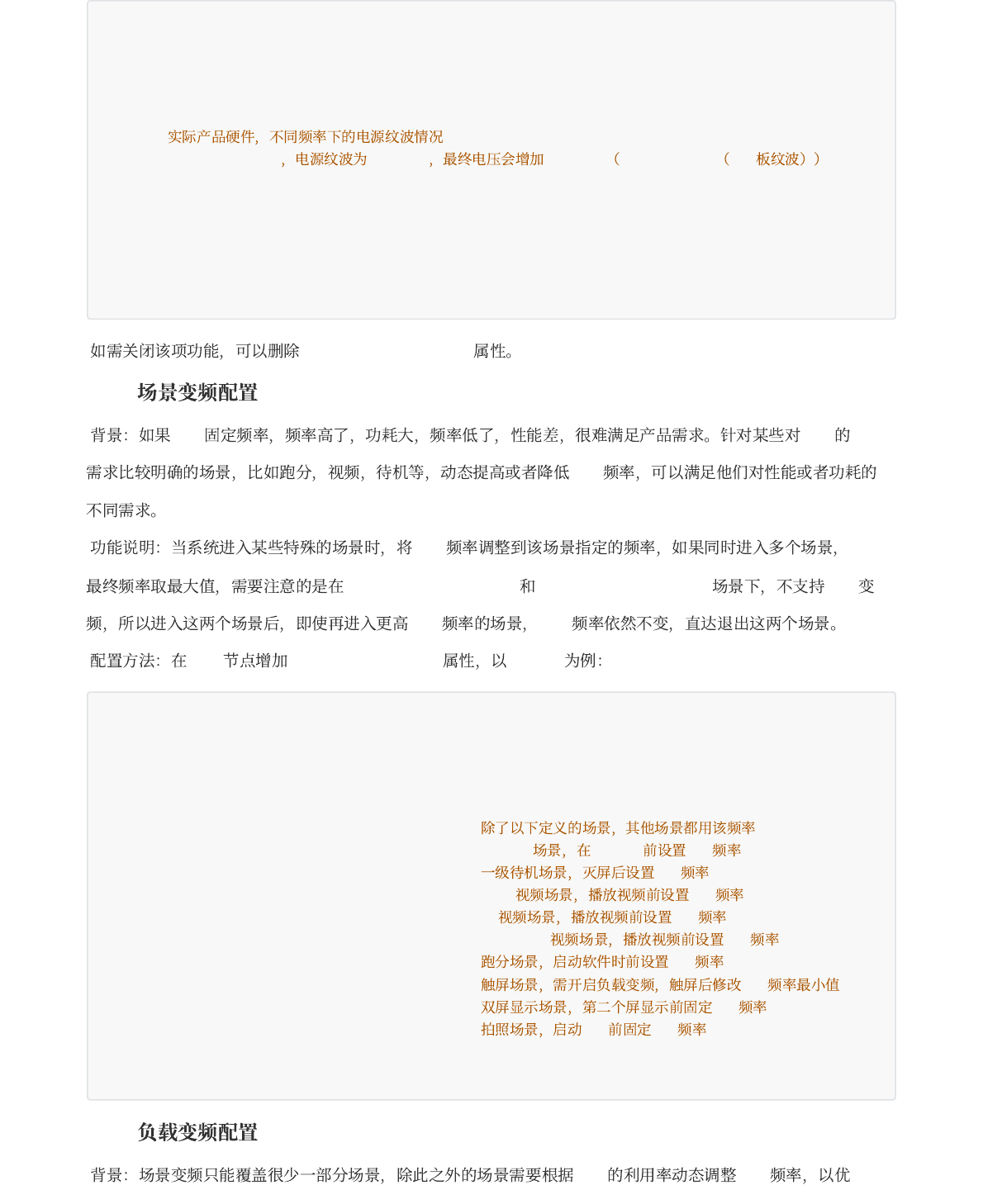

4.2.9 VOP

“auto-min-freq”

VOP DDR

VOP DDR DDR

DMC "vop-bw-dmc-freq" RK3399

&dmc {

status = "okay";

...

devfreq-events = <&dfi>; /* dfi DDR */

/*

*

* 40%

* 40% 40%-20%

* 40%-20% 40%-2%/2

*/

upthreshold = <40>;

downdifferential = <20>;

system-status-freq = <

/* system status freq(KHz) */

SYS_STATUS_NORMAL 800000 /* */

SYS_STATUS_REBOOT 528000 /* reboot reboot DDR */

SYS_STATUS_SUSPEND 200000 /* DDR */

SYS_STATUS_VIDEO_1080P 200000 /* 1080 DDR */

SYS_STATUS_VIDEO_4K 600000 /* 4k DDR */

SYS_STATUS_VIDEO_4K_10B 800000 /* 4k 10bit DDR */

SYS_STATUS_PERFORMANCE 800000 /* DDR */

SYS_STATUS_BOOST 400000 /* DDR */

SYS_STATUS_DUALVIEW 600000 /* DDR */

SYS_STATUS_ISP 600000 /* ISP DDR */

>;

/* DDR */

auto-min-freq = <400000>;

auto-freq-en = <1>; /* 1 0 */

};

&dmc {

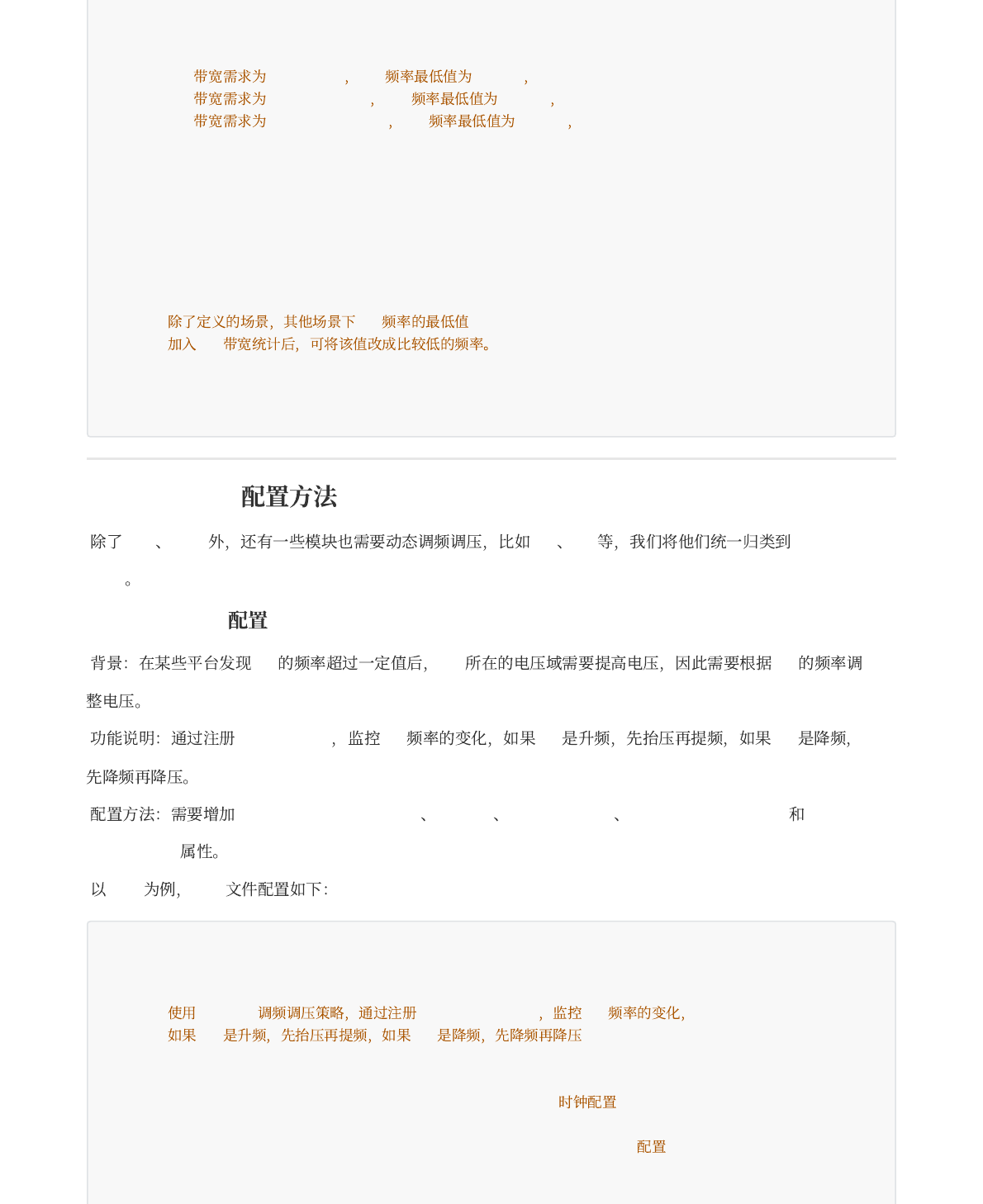

4.3 BUS DVFS

GPU DMC PLL CCI BUS

DVFS

4.3.1 PLL DVFS

PLL PLL PLL

clock notifier PLL PLL PLL

”rockchip,busfreq-policy“ ”clocks“ ”clock-names“ ”operating-points-v2“

“bus-supply”

PX30 DTSI

status = "okay";

...

/*

* VOP 0-577MB/s DDR 200MHz

* VOP 578-1701MB/s DDR 300MHz

* VOP 1702-99999MB/s DDR 400MHz

*/

vop-bw-dmc-freq = <

/* min_bw(MB/s) max_bw(MB/s) freq(KHz) */

0 577 200000

578 1701 300000

1702 99999 400000

>;

/*

* DDR

* VOP

*/

auto-min-freq = <200000>;

};

bus_apll: bus-apll {

compatible = "rockchip,px30-bus";

/*

* clkfreq clock notifier PLL

* PLL PLL .

*/

rockchip,busfreq-policy = "clkfreq";

clocks = <&cru PLL_APLL>; /* */

clock-names = "bus";

operating-points-v2 = <&bus_apll_opp_table>; /* OPP Table */

status = "disabled";

5

devfreq /sys/class/devfreq/

};

bus_apll_opp_table: bus-apll-opp-table {

compatible = "operating-points-v2";

opp-shared;

/* PLL 1008MHz 950mV 1008MHz 1000mV */

opp-1512000000 {

opp-hz = /bits/ 64 <1512000000>;

opp-microvolt = <1000000>;

opp-1008000000 {

opp-hz = /bits/ 64 <1008000000>;

opp-microvolt = <950000>;

};

};

&i2c0 {

status = "okay";

rk809: pmic@20 {

compatible = "rockchip,rk809";

reg = <0x20>;

...

regulators {

vdd_logic: DCDC_REG1 {

regulator-always-on;

regulator-boot-on;

regulator-min-microvolt = <950000>;

regulator-max-microvolt = <1350000>;

regulator-ramp-delay = <6001>;

regulator-initial-mode = <0x2>;

regulator-name = "vdd_logic";

regulator-state-mem {

regulator-on-in-suspend;

regulator-suspend-microvolt = <950000>;

};

};

}

}

}

&bus_apll {

bus-supply = <&vdd_logic>; /* regulator */

status = "okay";

};

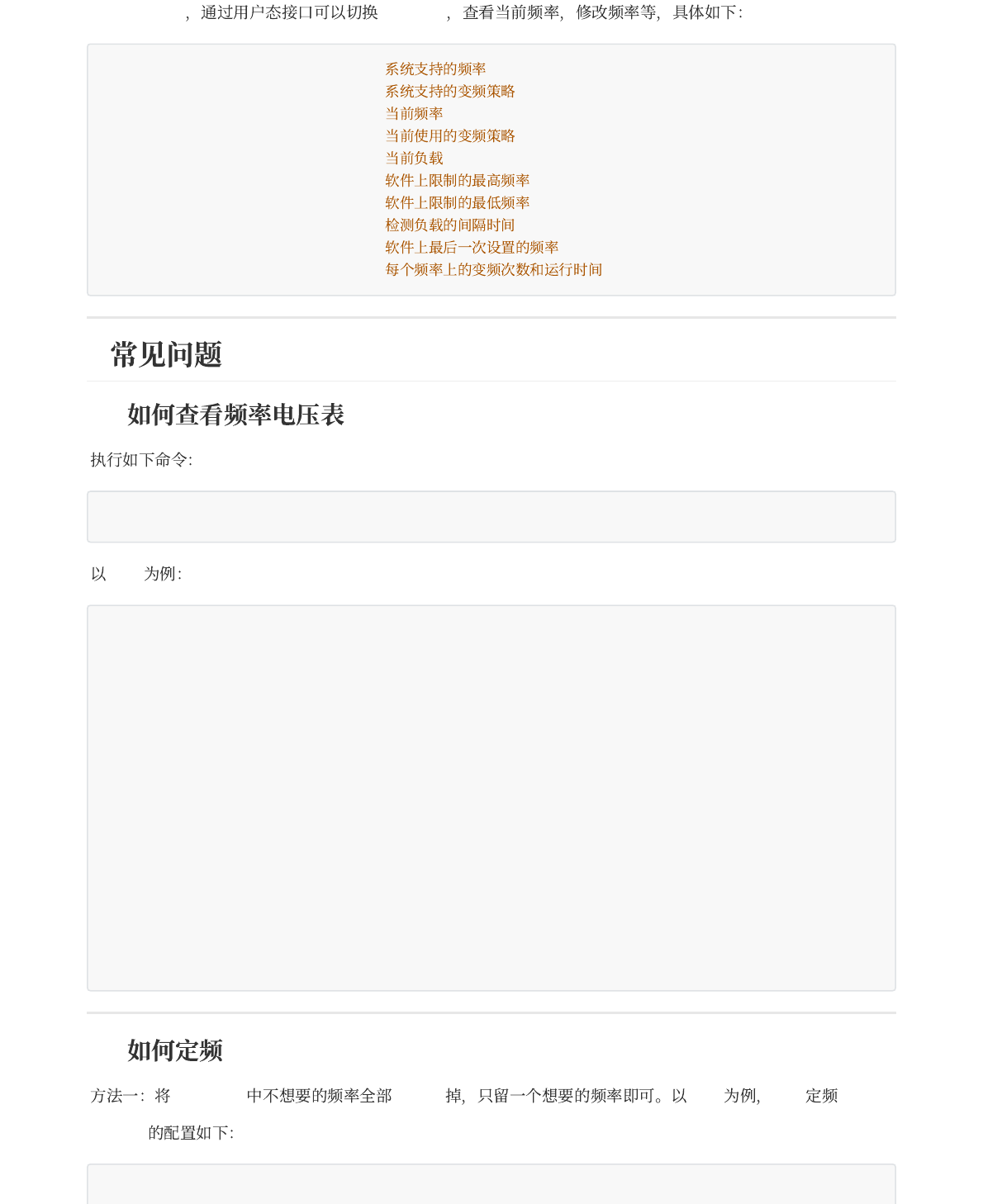

ff9a0000.gpu governor

6

6.1

PX30

6.2

OPP Table disable PX30 GPU

400MHz

available_frequencies /* */

available_governors /* */

cur_freq /* */

governor /* */

load /* */

max_freq /* */

min_freq /* */

polling_interval /* */

target_freq /* */

trans_stat /* */

cat /sys/kernel/debug/opp/opp_summary

device rate(Hz) target(uV) min(uV) max(uV)

-------------------------------------------------------------------

platform-dmc

194000000 950000 950000 950000

328000000 950000 950000 950000

450000000 950000 950000 950000

528000000 975000 975000 975000

666000000 1000000 1000000 1000000

platform-ff400000.gpu

200000000 950000 950000 950000

300000000 950000 950000 950000

400000000 1025000 1025000 1025000

480000000 1100000 1100000 1100000

platform-bus-apll

1008000000 950000 950000 950000

1512000000 1000000 1000000 1000000

gpu_opp_table: gpu-opp-table {

PX30 GPU 400MHz

6.3

devfreq clock debug PX30 GPU

compatible = "operating-points-v2";

...

opp-200000000 {

opp-hz = /bits/ 64 <200000000>;

opp-microvolt = <950000>;

opp-microvolt-L0 = <950000>;

opp-microvolt-L1 = <950000>;

opp-microvolt-L2 = <950000>;

opp-microvolt-L3 = <950000>;

status = "disabled";

};

opp-300000000 {

opp-hz = /bits/ 64 <300000000>;

opp-microvolt = <975000>;

opp-microvolt-L0 = <975000>;

opp-microvolt-L1 = <950000>;

opp-microvolt-L2 = <950000>;

opp-microvolt-L3 = <950000>;

status = "disabled";

};

opp-400000000 {

opp-hz = /bits/ 64 <400000000>;

opp-microvolt = <1050000>;

opp-microvolt-L0 = <1050000>;

opp-microvolt-L1 = <1025000>;

opp-microvolt-L2 = <975000>;

opp-microvolt-L3 = <950000>;

};

opp-480000000 {

opp-hz = /bits/ 64 <480000000>;

opp-microvolt = <1125000>;

opp-microvolt-L0 = <1125000>;

opp-microvolt-L1 = <1100000>;

opp-microvolt-L2 = <1050000>;

opp-microvolt-L3 = <1000000>;

status = "disabled";

};

};

/* userspace ff400000.gpu */

echo userspace > /sys/class/devfreq/ff400000.gpu/governor

/* 400MHz */

echo 400000000 > /sys/class/devfreq/ff400000.gpu/userspace/set_freq

/* */

cat /sys/class/devfreq/ff400000.gpu/cur_freq

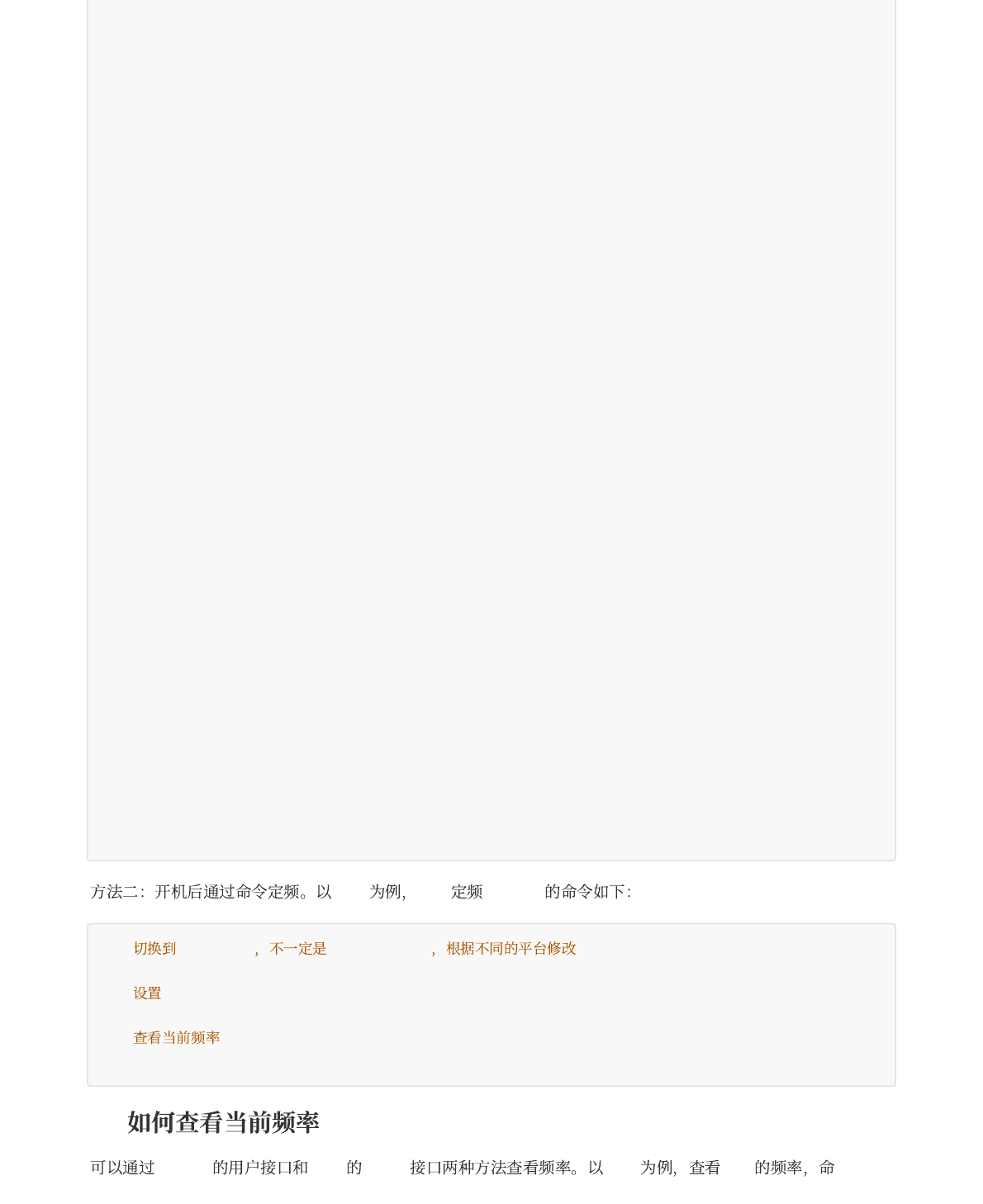

6.4

regulator debug PX30 GPU

6.5

PX30 GPU 400MHz 1000mV

6.6

PVTM

RK3399 GPU

/* devfreq ff400000.gpu */

cat /sys/class/devfreq/ff400000.gpu/cur_freq

/* clock debug aclk_gpu clock */

cat /sys/kernel/debug/clk/aclk_gpu/clk_rate

/* vdd_logic regulator */

cat /sys/kernel/debug/regulator/vdd_logic/voltage

/* ff400000.gpu */

echo userspace > /sys/class/devfreq/ff400000.gpu/governor

/* aclk_gpu clock */

echo 400000000 > /sys/kernel/debug/clk/aclk_gpu/clk_rate

cat /sys/kernel/debug/clk/aclk_gpu/clk_rate

/* vdd_logic regulator */

echo 1000000 > /sys/kernel/debug/regulator/vdd_logic/voltage

cat /sys/kernel/debug/regulator/vdd_logic/voltage

dmesg | grep pvtm

leakage

6.7 leakage

RK3399 GPU

6.8

GPU 200MHz 25000uV

200MHz OPP

[ 0.669456] cpu cpu0: temp=22222, pvtm=138792 (140977 + -2185)

[ 0.670601] cpu cpu0: pvtm-volt-sel=0

[ 0.683008] cpu cpu4: temp=22222, pvtm=148761 (150110 + -1349)

[ 0.683109] cpu cpu4: pvtm-volt-sel=0

[ 1.495247] rockchip-dmc dmc: Failed to get pvtm

[ 3.366028] mali ff9a0000.gpu: temp=22777, pvtm=120824 (121698 + -874)

/* pvtm-volt-sel=0 GPU opp-microvolt-L0 */

[ 3.366915] mali ff9a0000.gpu: pvtm-volt-sel=0

dmesg | grep leakage

dmesg | grep leakage

[ 0.656175] cpu cpu0: leakage=10

[ 0.671092] cpu cpu4: leakage=20

[ 1.492769] rockchip-dmc dmc: Failed to get leakage

/* leakage=15 GPU leakage 15mA */

[ 3.341084] mali ff9a0000.gpu: leakage=15

opp-200000000 {

opp-hz = /bits/ 64 <200000000>;

opp-microvolt = <800000>;

opp-microvolt-L0 = <800000>;

opp-microvolt-L1 = <800000>;

opp-microvolt-L2 = <800000>;

opp-microvolt-L3 = <800000>;

};

IR-Drop GPU 200MHz 25000uV

IR-Drop

opp-200000000 {

opp-hz = /bits/ 64 <200000000>;

/* 25000uV */

opp-microvolt = <825000>;

opp-microvolt-L0 = <825000>;

opp-microvolt-L1 = <825000>;

opp-microvolt-L2 = <825000>;

opp-microvolt-L3 = <825000>;

};

&gpu_opp_table {

/*

* max IR-drop values on different freq condition for this board!

*/

/*

* :

* 200Mhz-520MHz 50000uV 25000uV 50000-25000 EVB

*/

rockchip,board-irdrop = <

/* MHz MHz uV */

200 520 50000

>;

};

&gpu_opp_table {

/*

* max IR-drop values on different freq condition for this board!

*/

/*

* :

* 200Mhz-299MHz 75000uV 50000uV 75000-25000 EVB

* 300Mhz-520MHz 50000uV 25000uV 50000-25000 EVB

*/

rockchip,board-irdrop = <

/* MHz MHz uV */

200 299 75000 /* 200MHz-299MHz 50000 75000 */

300 520 50000

>;

};