STM32 Technical Reference Manual (Chinese)

User Manual:

Open the PDF directly: View PDF ![]() .

.

Page Count: 754 [warning: Documents this large are best viewed by clicking the View PDF Link!]

- 导言

- 相关文档

- 1 文中的缩写

- 2 存储器和总线构架

- 3 CRC计算单元(CRC)

- 4 电源控制(PWR)

- 5 备份寄存器(BKP)

- 6 小容量、中容量和大容量产品的复位和时钟控制(RCC)

- 7 互联型产品的复位和时钟控制(RCC)

- 7.1 复位

- 7.2 时钟

- 7.3 RCC寄存器

- 7.3.1 时钟控制寄存器(RCC_CR)

- 7.3.2 时钟配置寄存器(RCC_CFGR)

- 7.3.3 时钟中断寄存器(RCC_CIR)

- 7.3.4 APB2外设复位寄存器(RCC_APB2RSTR)

- 7.3.5 APB1外设复位寄存器(RCC_APB1RSTR)

- 7.3.6 AHB外设时钟使能寄存器(RCC_AHBENR)

- 7.3.7 APB2外设时钟使能寄存器(RCC_APB2ENR)

- 7.3.8 APB1外设时钟使能寄存器(RCC_APB1ENR)

- 7.3.9 备份域控制寄存器(RCC_BDCR)

- 7.3.10 控制/状态寄存器(RCC_CSR)

- 7.3.11 AHB外设时钟复位寄存器(RCC_AHBRSTR)

- 7.3.12 时钟配置寄存器2(RCC_CFGR2)

- 7.3.13 RCC寄存器地址映像

- 8 通用和复用功能I/O(GPIO和AFIO)

- 9 中断和事件

- 10 DMA控制器(DMA)

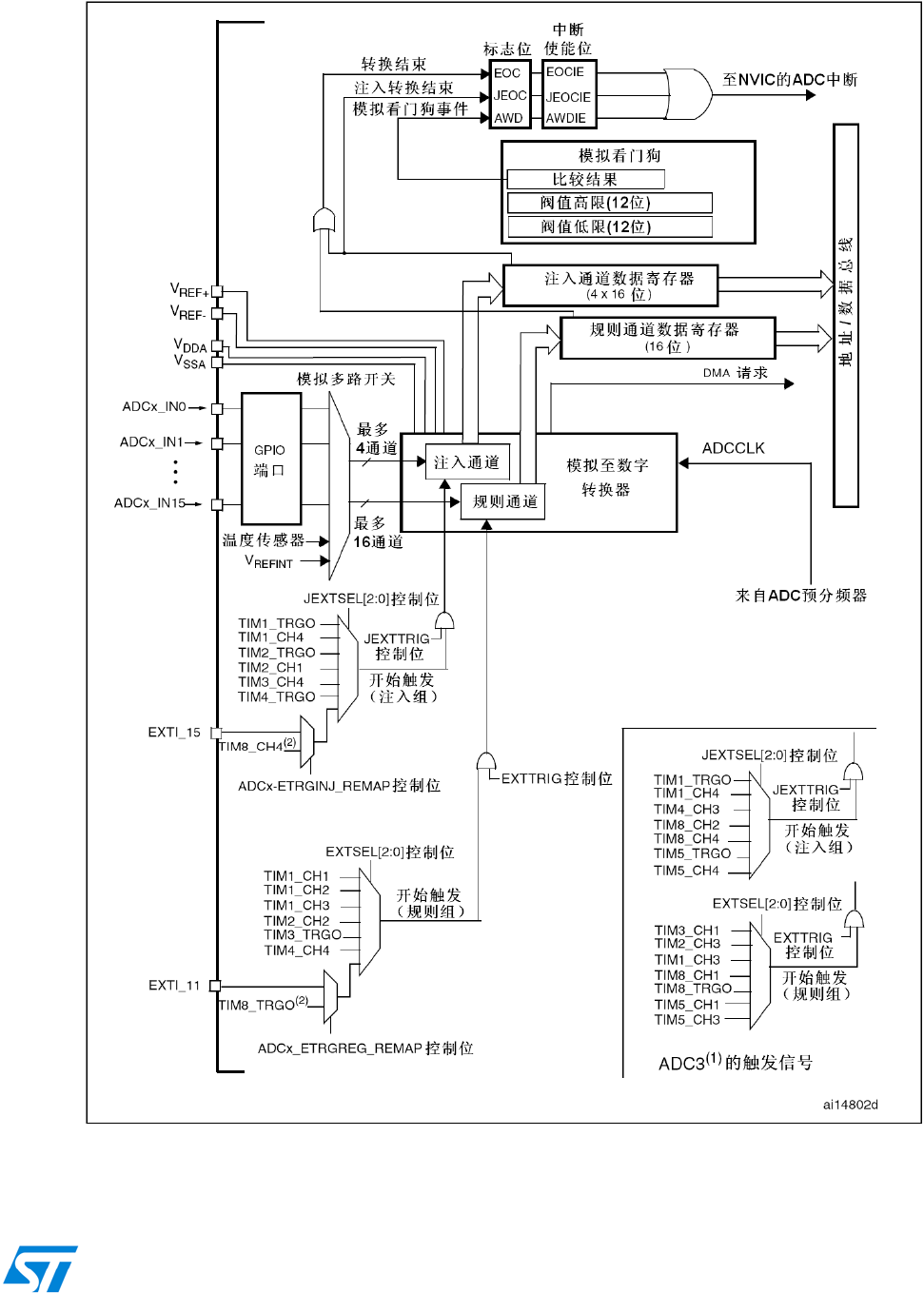

- 11 模拟/数字转换(ADC)

- 11.1 ADC介绍

- 11.2 ADC主要特征

- 11.3 ADC功能描述

- 11.4 校准

- 11.5 数据对齐

- 11.6 可编程的通道采样时间

- 11.7 外部触发转换

- 11.8 DMA请求

- 11.9 双ADC模式

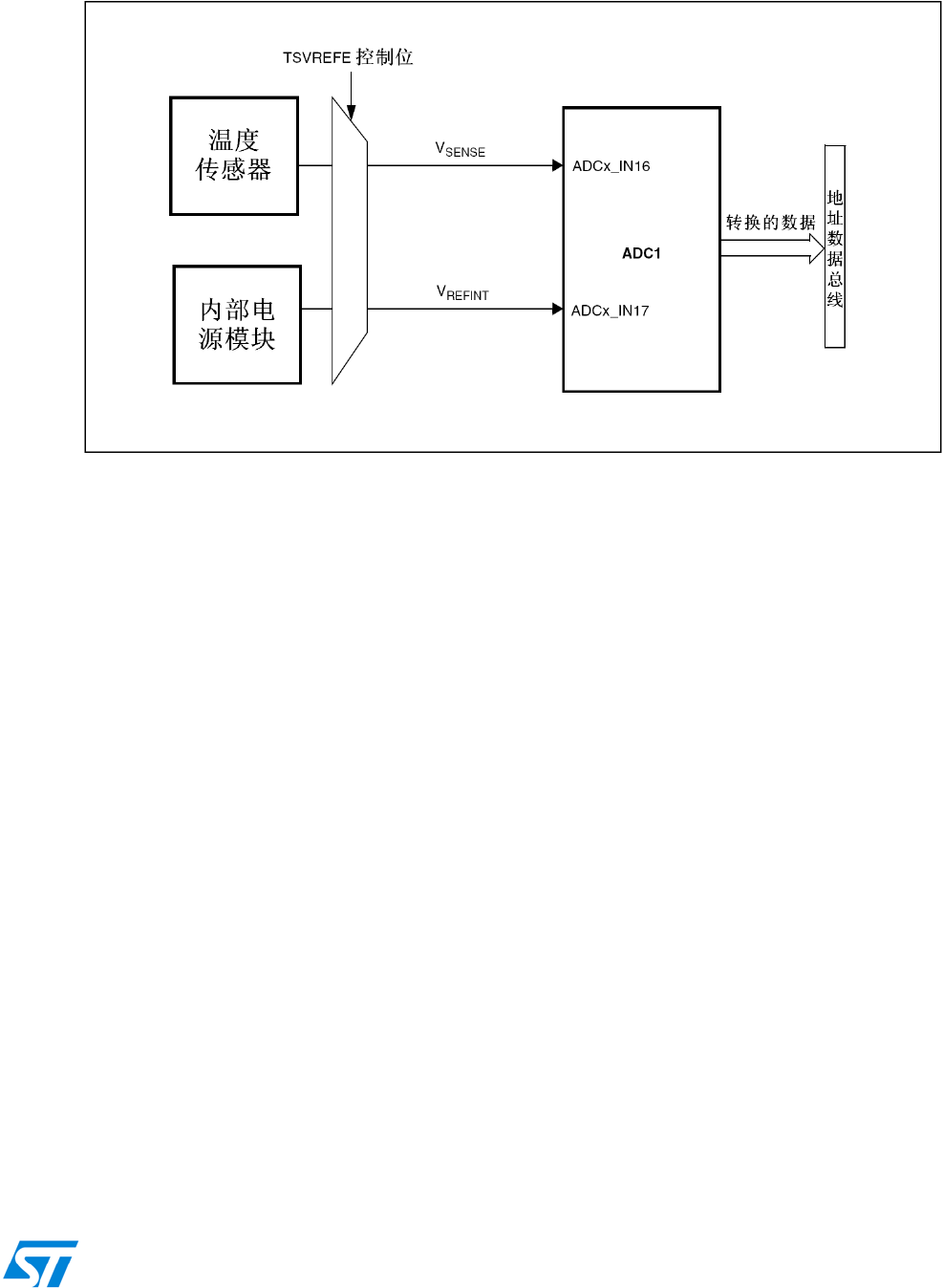

- 11.10 温度传感器

- 11.11 ADC中断

- 11.12 ADC寄存器

- 11.12.1 ADC状态寄存器(ADC_SR)

- 11.12.2 ADC控制寄存器1(ADC_CR1)

- 11.12.3 ADC控制寄存器2(ADC_CR2)

- 11.12.4 ADC采样时间寄存器1(ADC_SMPR1)

- 11.12.5 ADC采样时间寄存器2(ADC_SMPR2)

- 11.12.6 ADC注入通道数据偏移寄存器x (ADC_JOFRx)(x=1..4)

- 11.12.7 ADC看门狗高阀值寄存器(ADC_HTR)

- 11.12.8 ADC看门狗低阀值寄存器(ADC_LRT)

- 11.12.9 ADC规则序列寄存器1(ADC_SQR1)

- 11.12.10 ADC规则序列寄存器2(ADC_SQR2)

- 11.12.11 ADC规则序列寄存器3(ADC_SQR3)

- 11.12.12 ADC注入序列寄存器(ADC_JSQR)

- 11.12.13 ADC 注入数据寄存器x (ADC_JDRx) (x= 1..4)

- 11.12.14 ADC规则数据寄存器(ADC_DR)

- 11.12.15 ADC寄存器地址映像

- 12 数字/模拟转换(DAC)

- 12.1 DAC简介

- 12.2 DAC主要特征

- 12.3 DAC功能描述

- 12.4 双DAC通道转换

- 12.5 DAC寄存器

- 12.5.1 DAC控制寄存器(DAC_CR)

- 12.5.2 DAC软件触发寄存器(DAC_SWTRIGR)

- 12.5.3 DAC通道1的12位右对齐数据保持寄存器(DAC_DHR12R1)

- 12.5.4 DAC通道1的12位左对齐数据保持寄存器(DAC_DHR12L1)

- 12.5.5 DAC通道1的8位右对齐数据保持寄存器(DAC_DHR8R1)

- 12.5.6 DAC通道2的12位右对齐数据保持寄存器(DAC_DHR12R2)

- 12.5.7 DAC通道2的12位左对齐数据保持寄存器(DAC_DHR12L2)

- 12.5.8 DAC通道2的8位右对齐数据保持寄存器(DAC_DHR8R2)

- 12.5.9 双DAC的12位右对齐数据保持寄存器(DAC_DHR12RD)

- 12.5.10 双DAC的12位左对齐数据保持寄存器(DAC_DHR12LD)

- 12.5.11 双DAC的8位右对齐数据保持寄存器(DAC_DHR8RD)

- 12.5.12 DAC通道1数据输出寄存器(DAC_DOR1)

- 12.5.13 DAC通道2数据输出寄存器(DAC_DOR2)

- 12.5.14 DAC寄存器映像

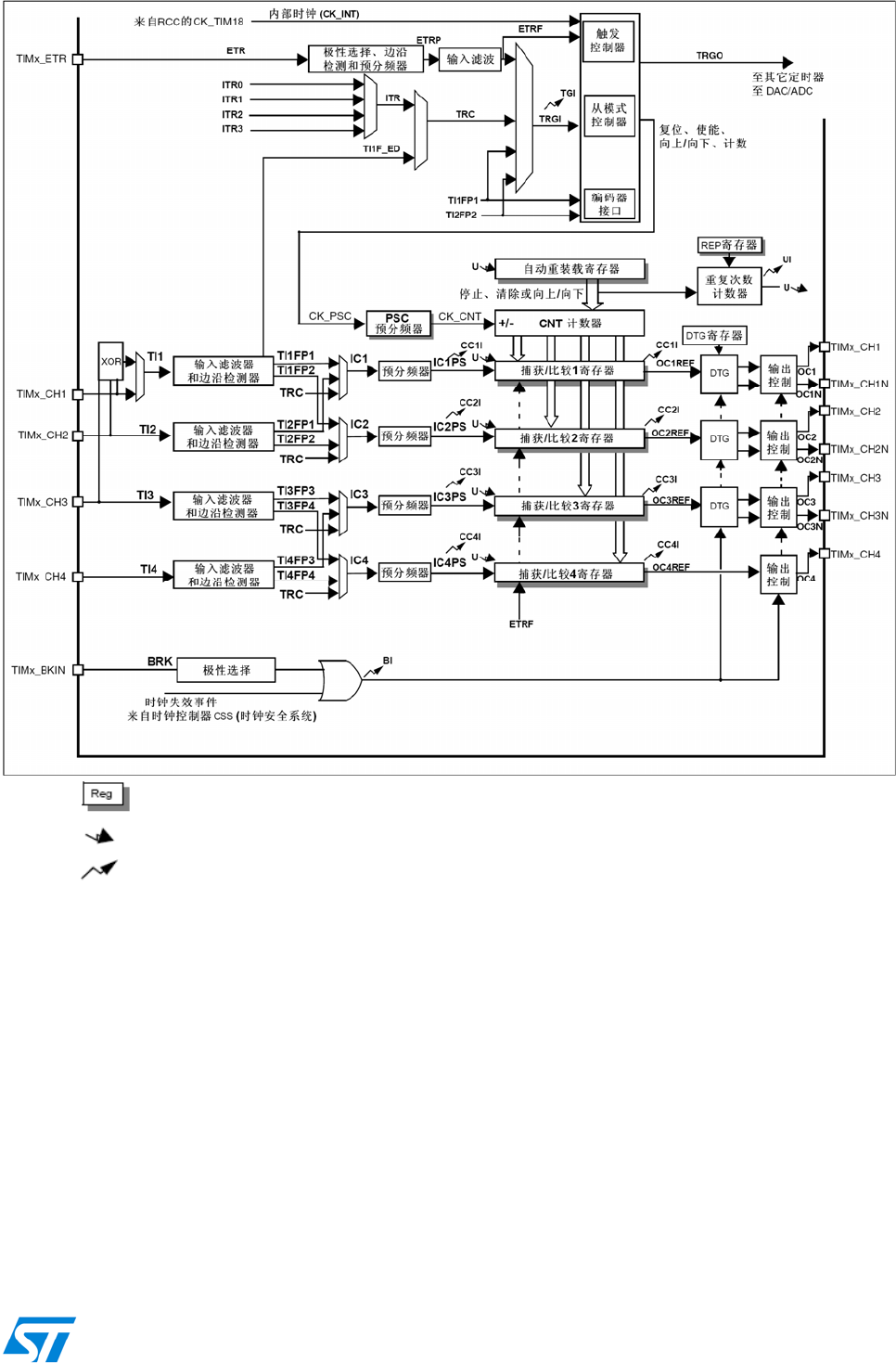

- 13 高级控制定时器(TIM1和TIM8)

- 13.1 TIM1和TIM8简介

- 13.2 TIM1和TIM8主要特性

- 13.3 TIM1和TIM8功能描述

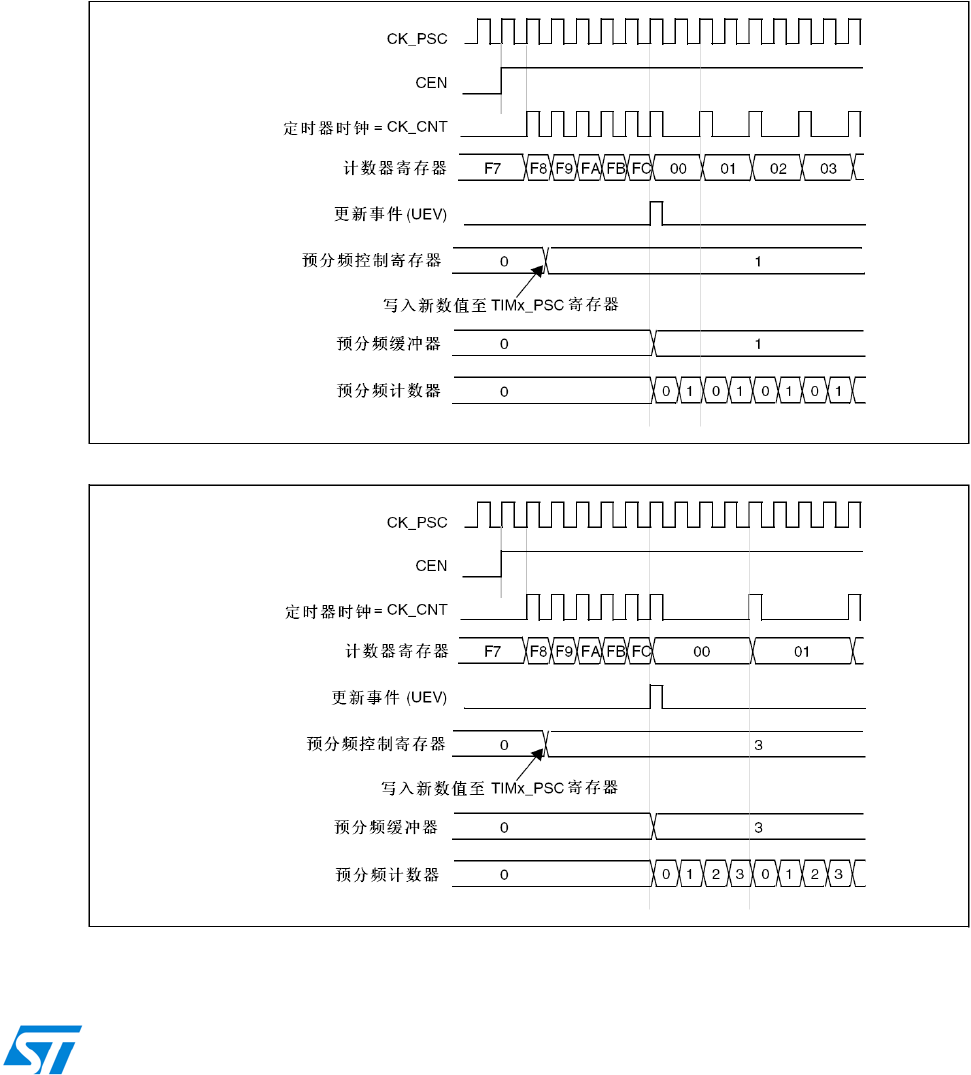

- 13.3.1 时基单元

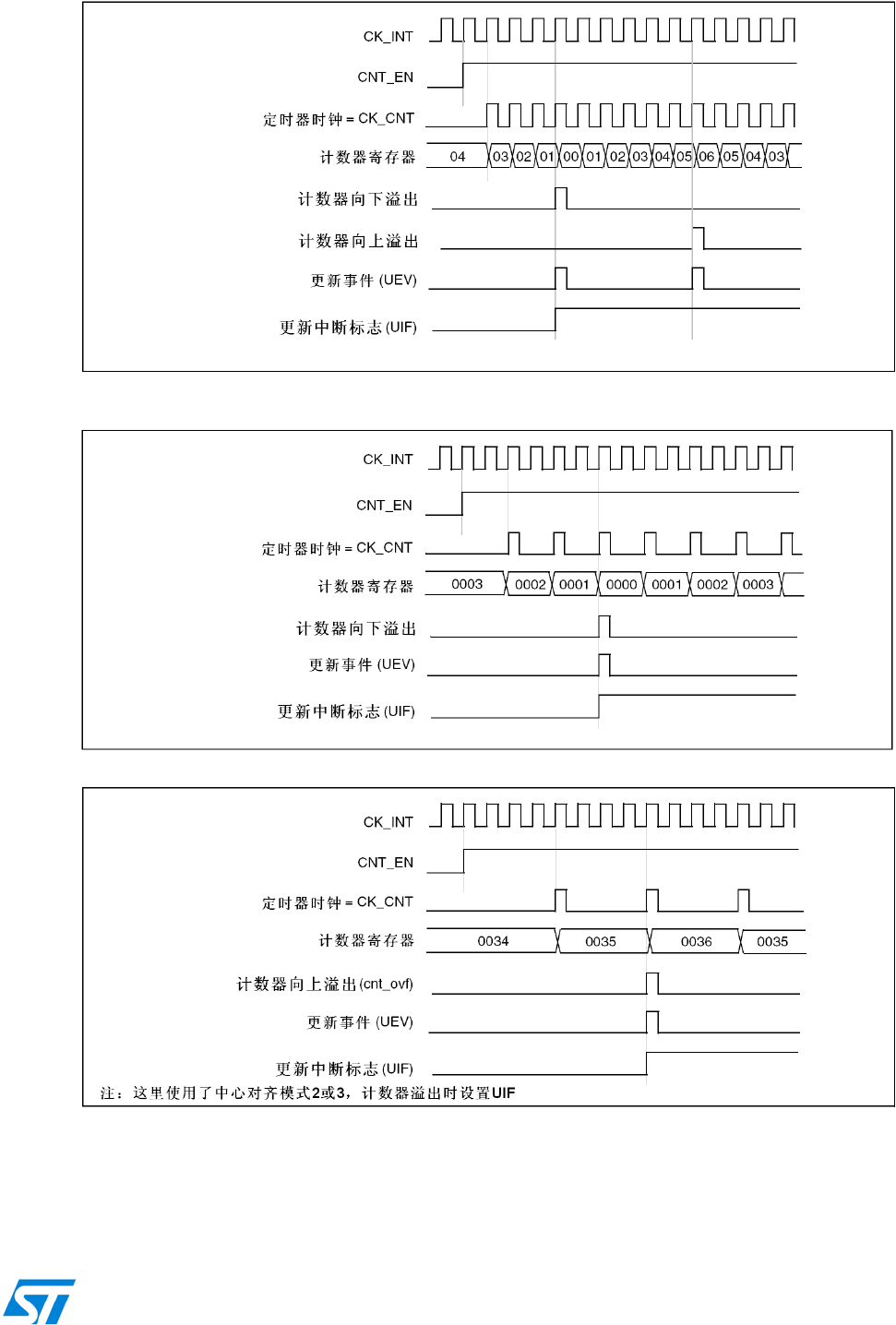

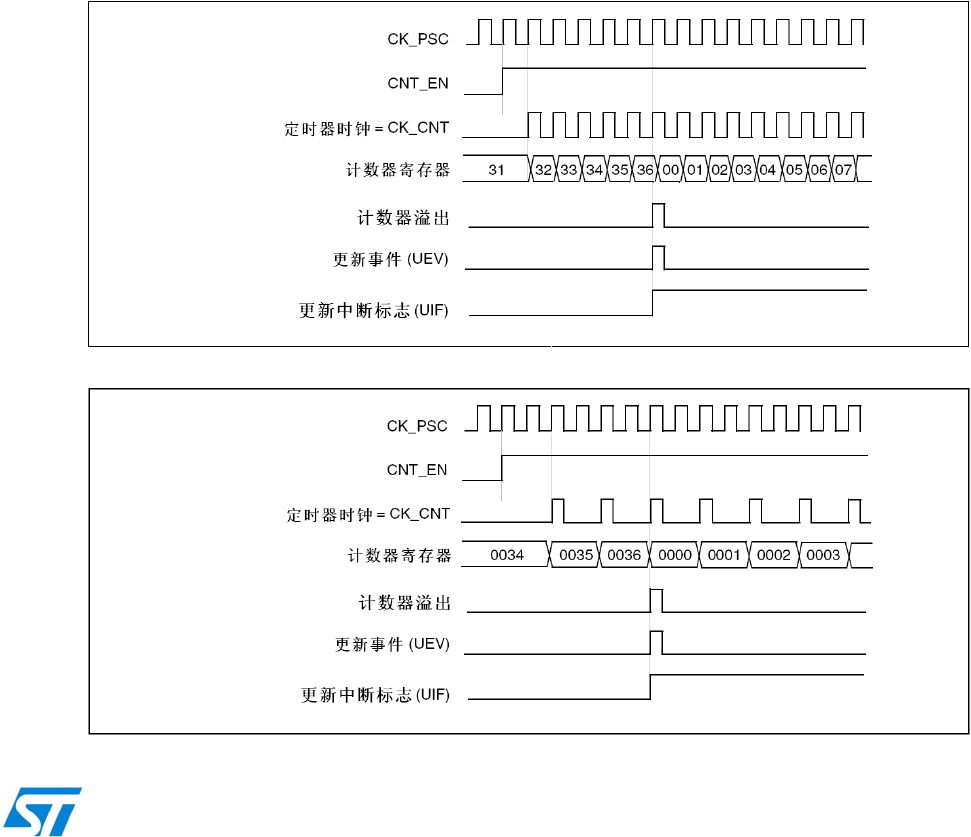

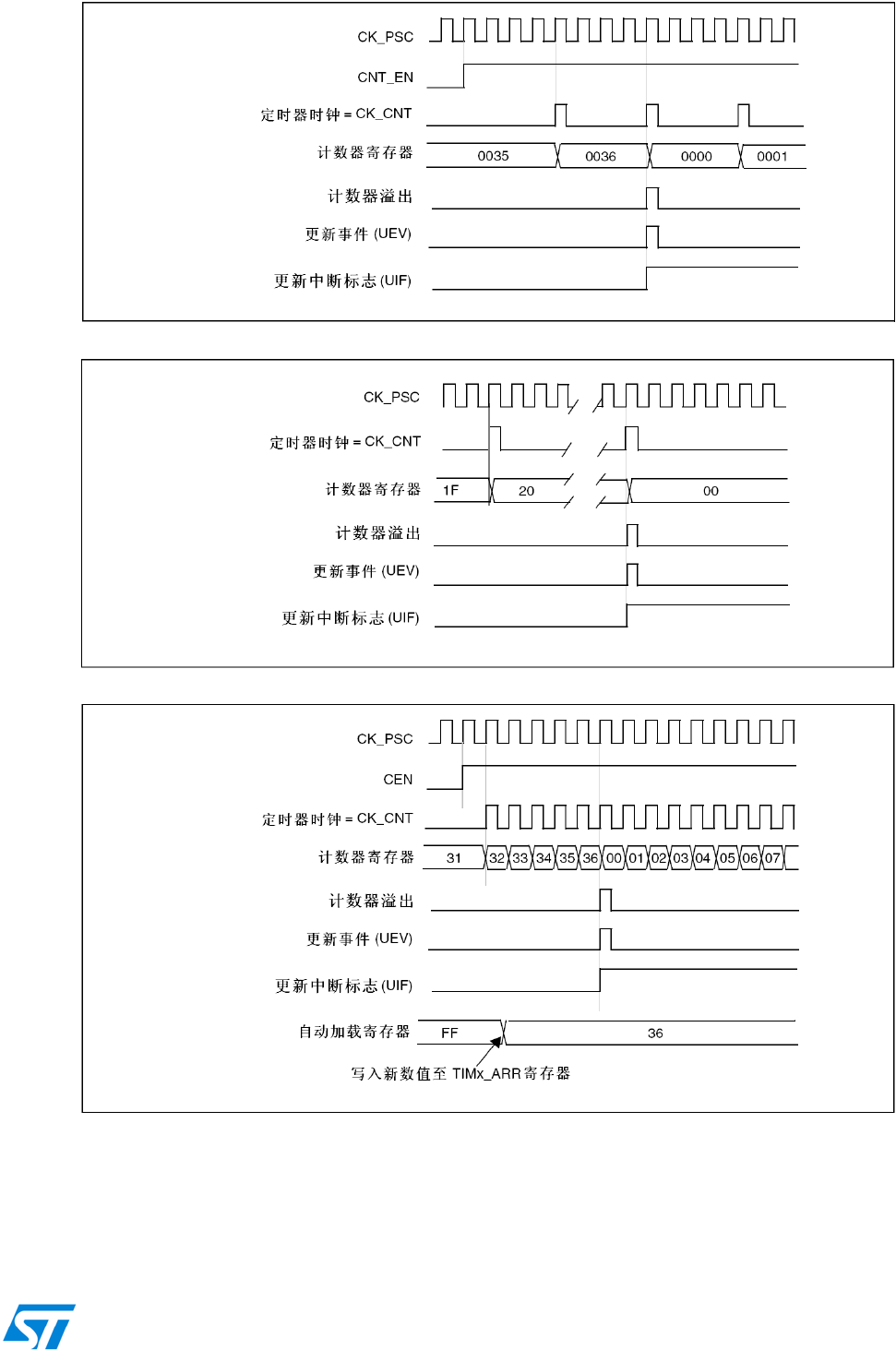

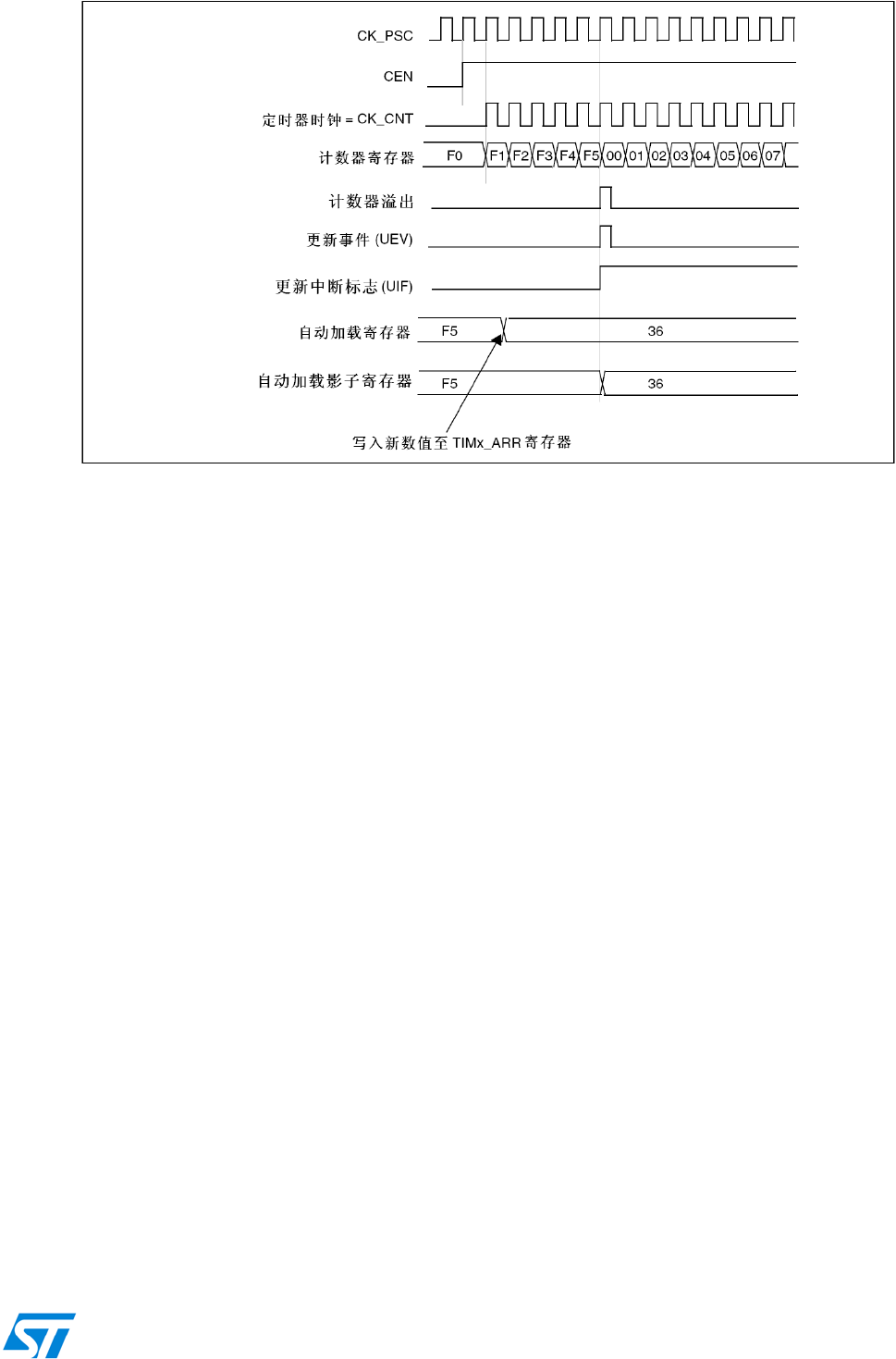

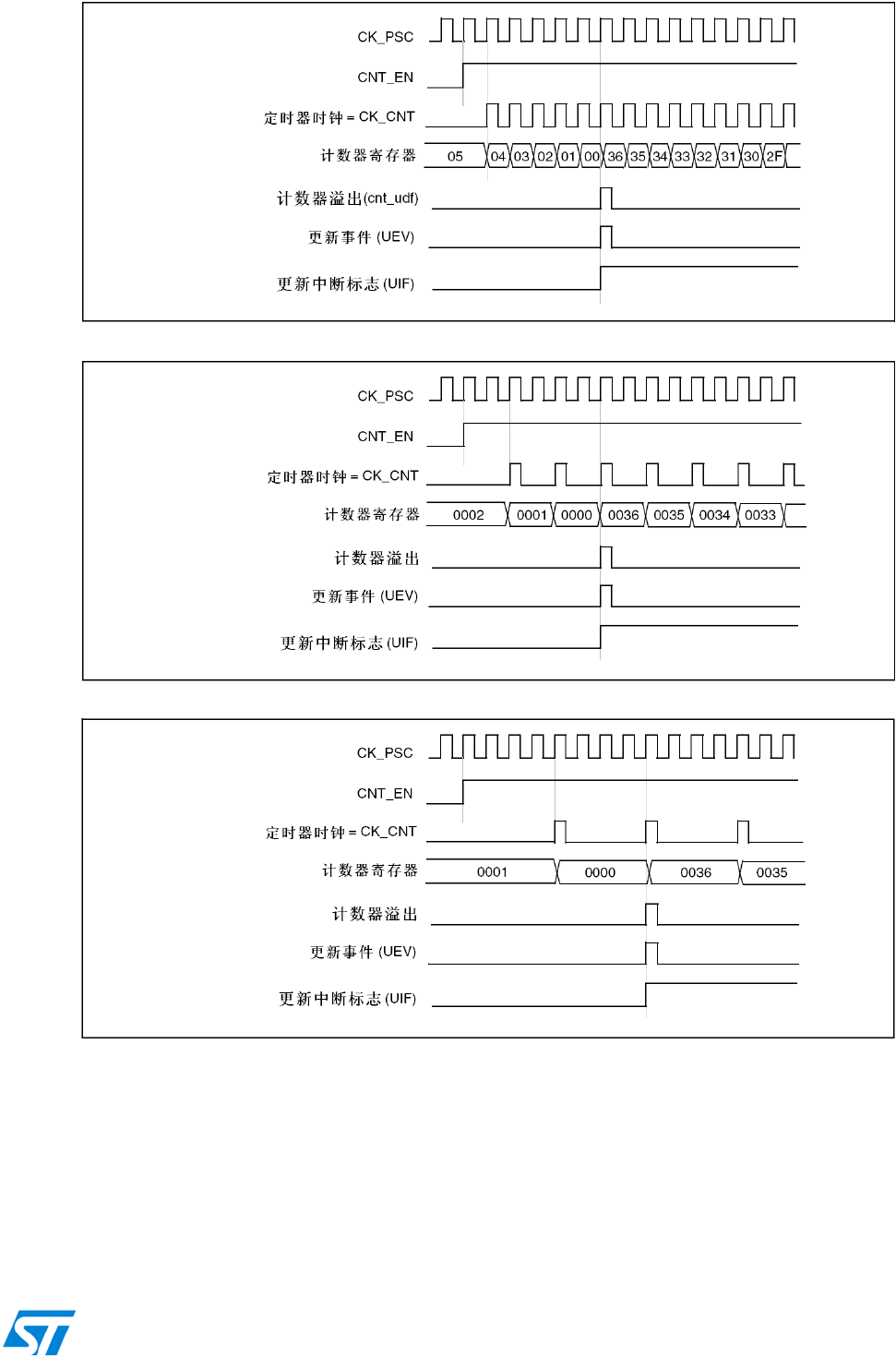

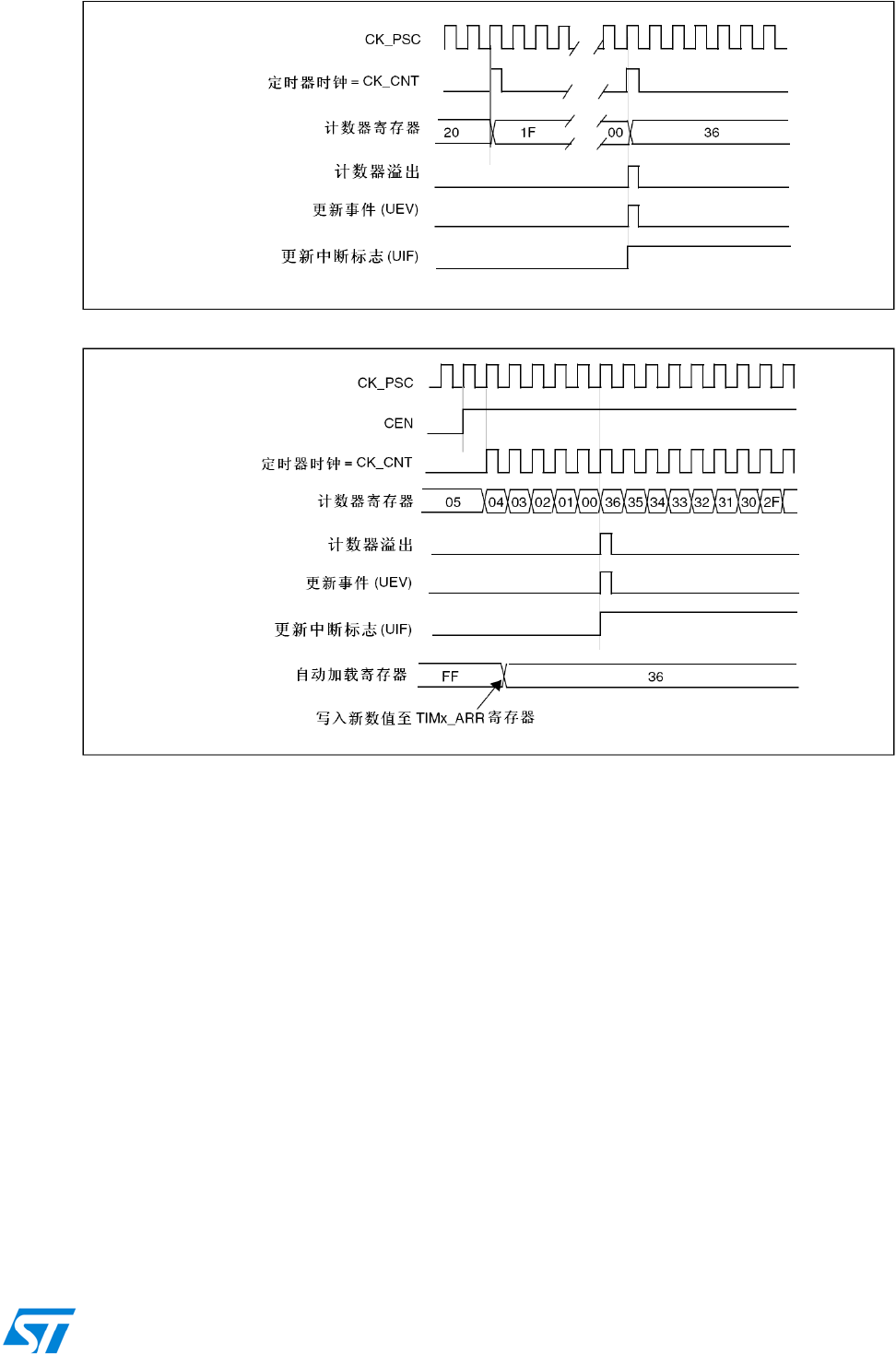

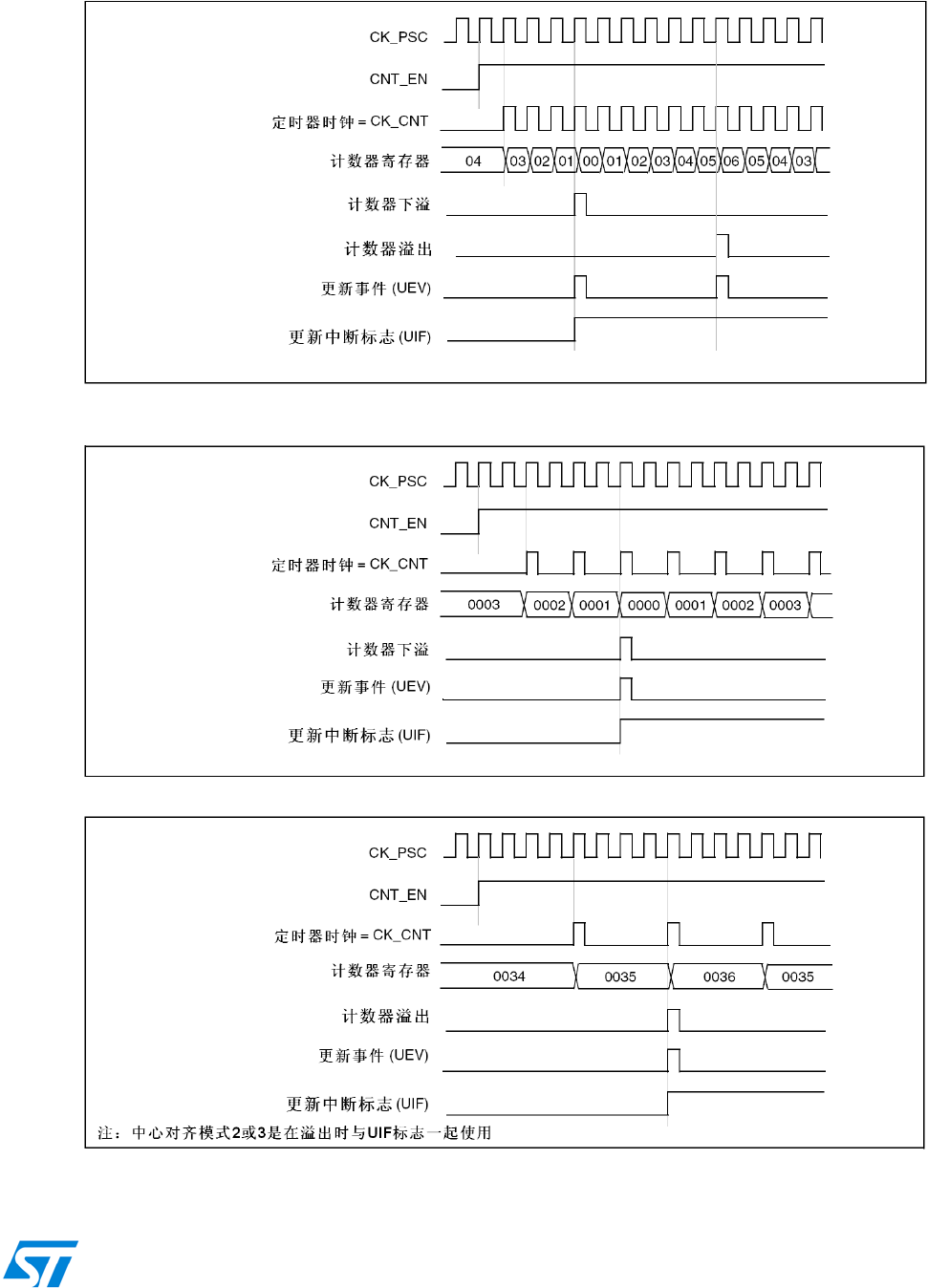

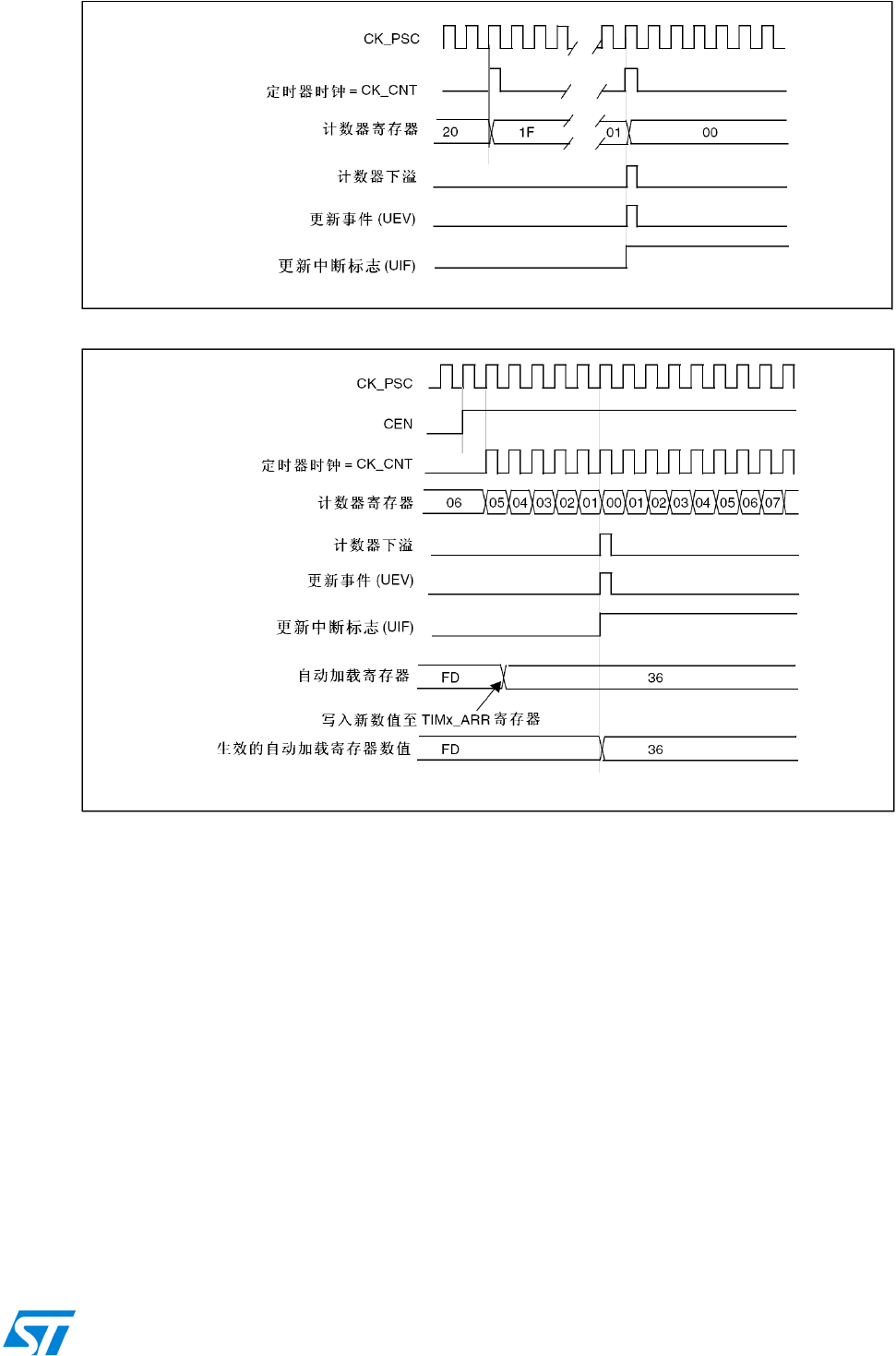

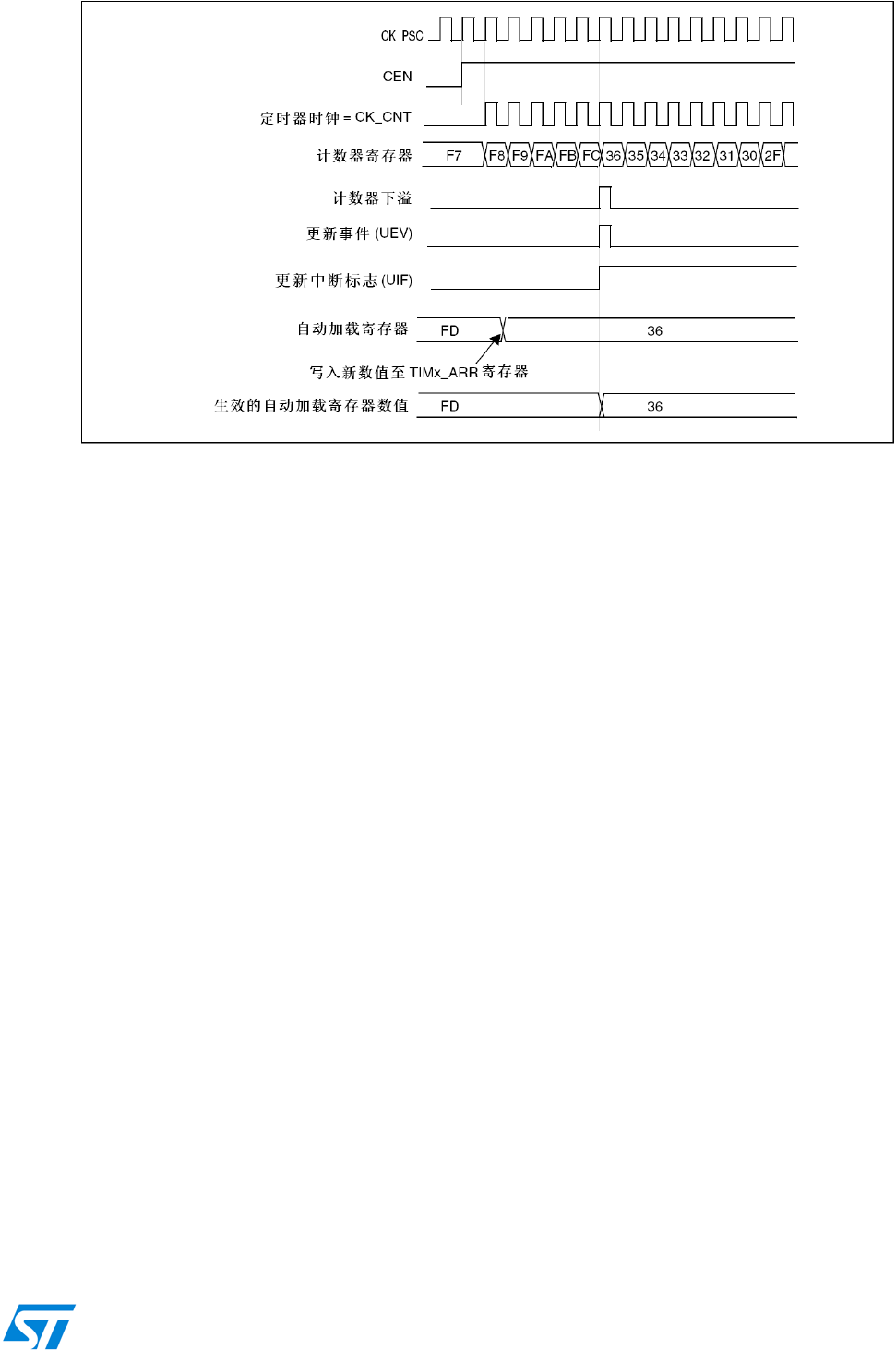

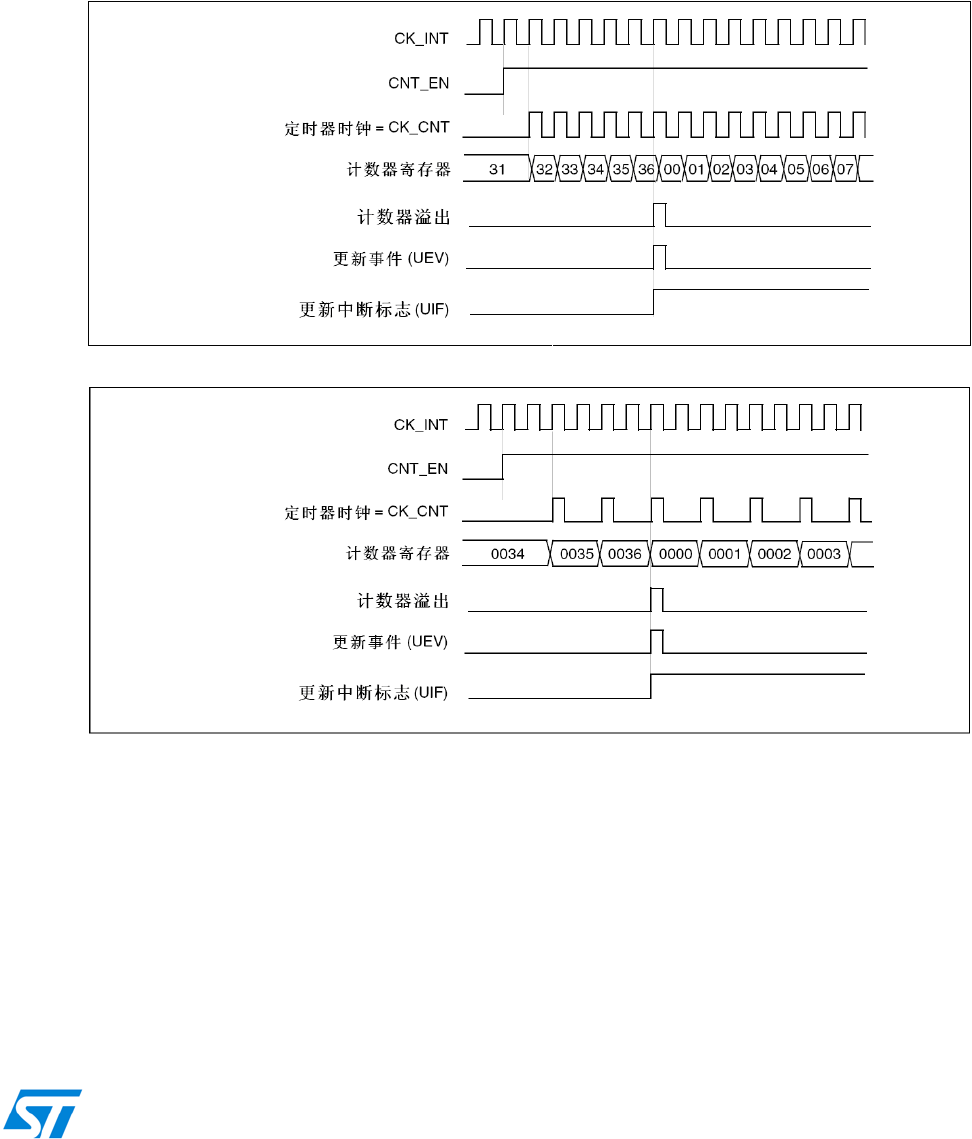

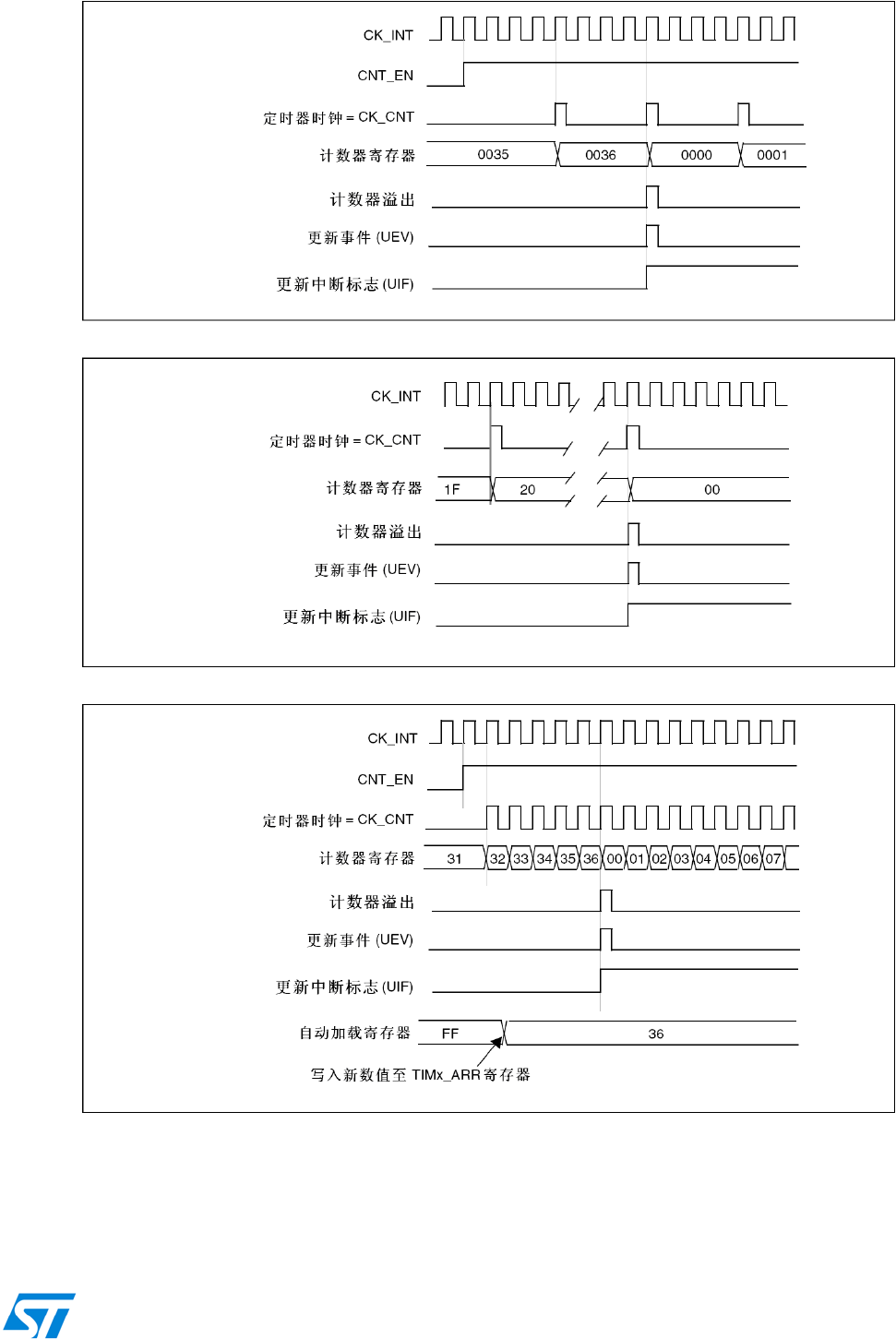

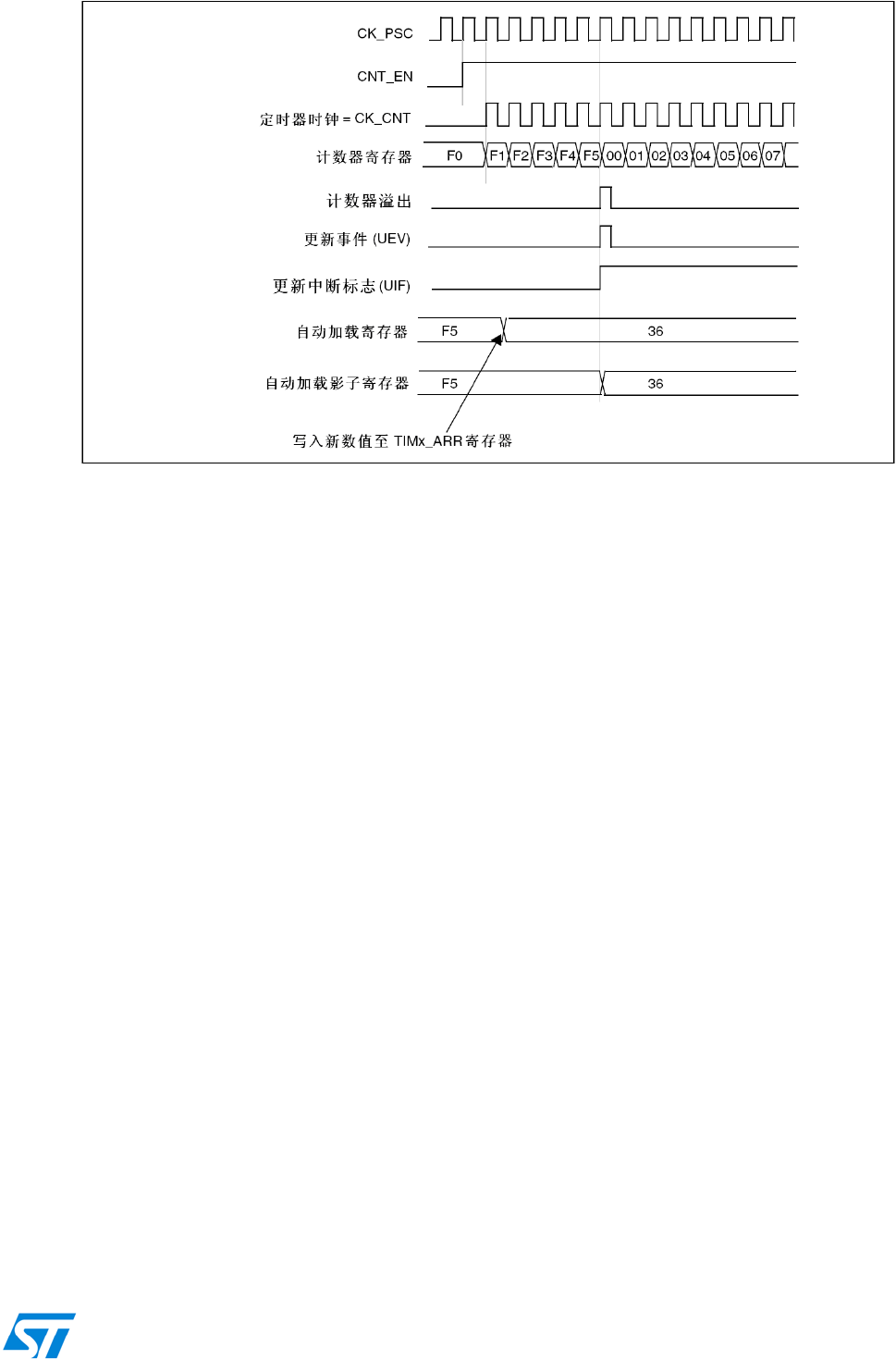

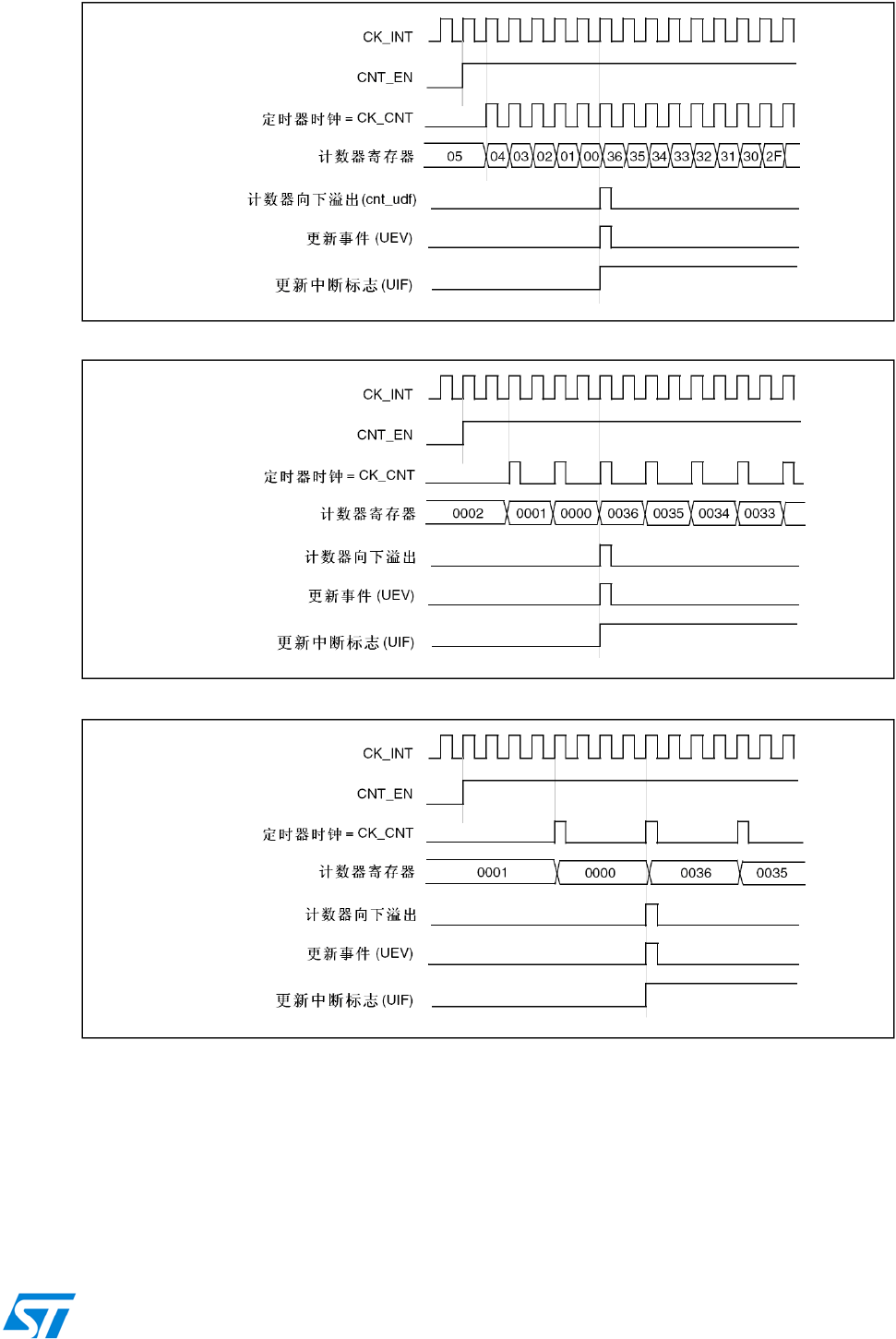

- 13.3.2 计数器模式

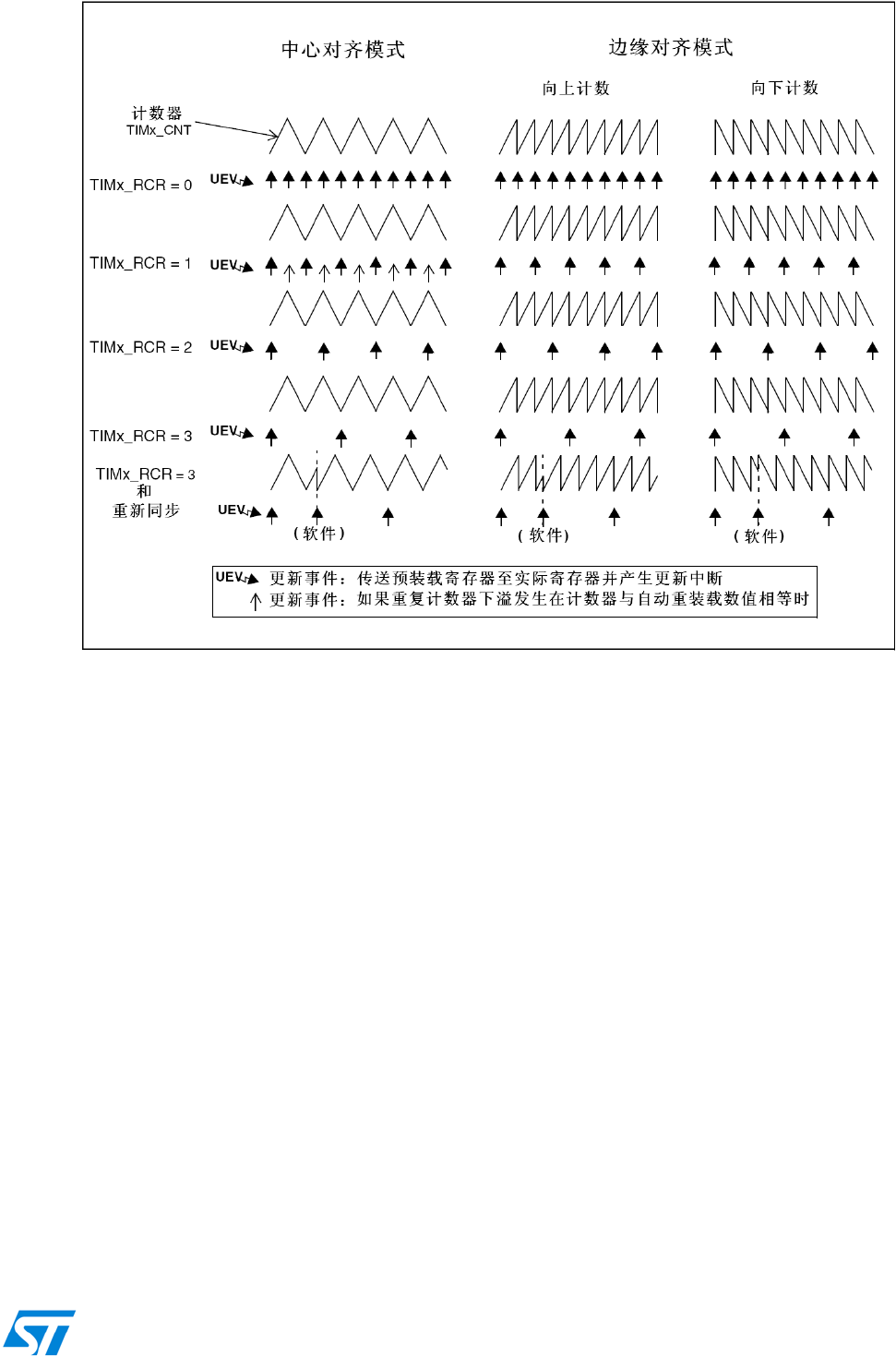

- 13.3.3 重复计数器

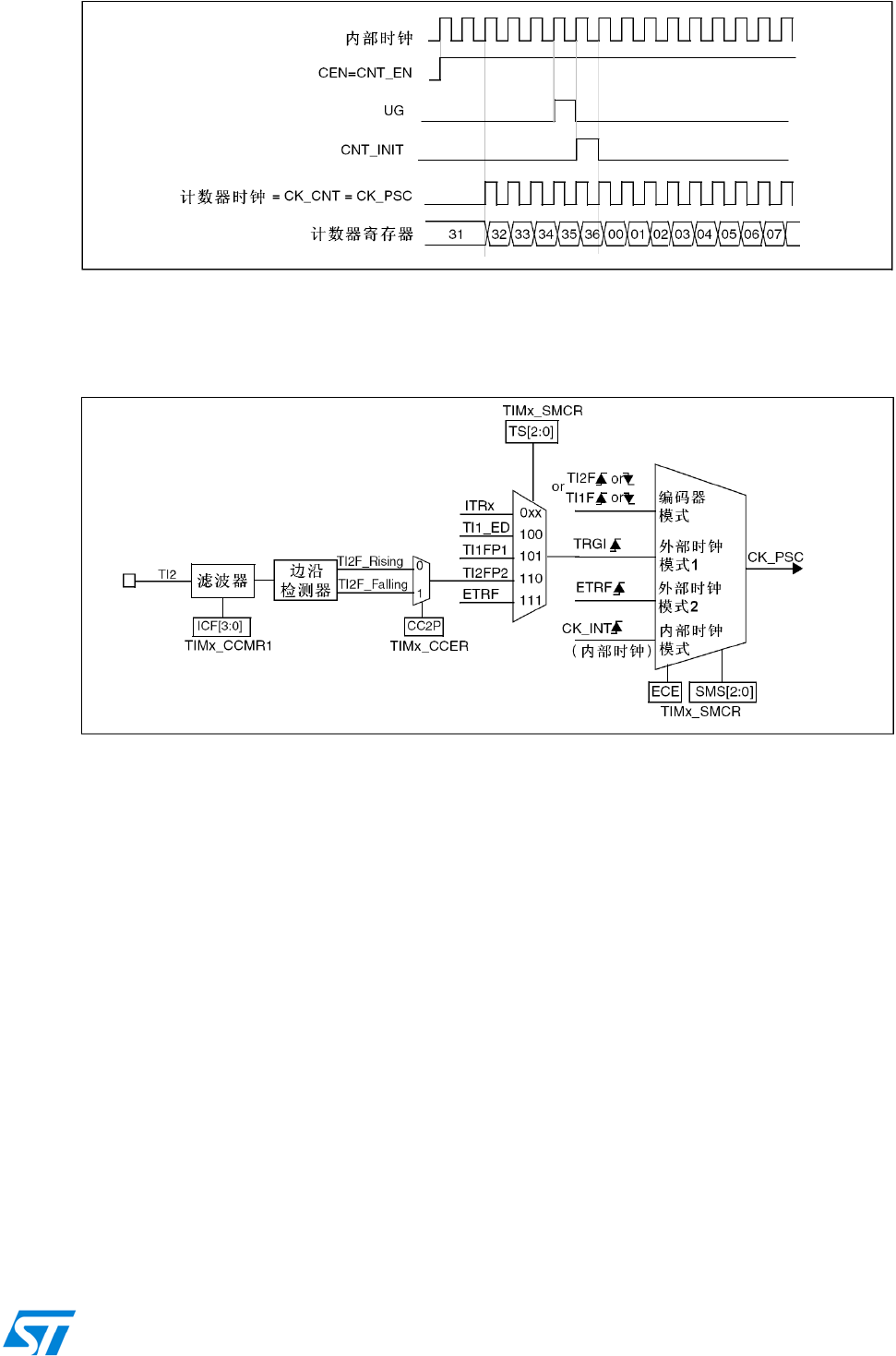

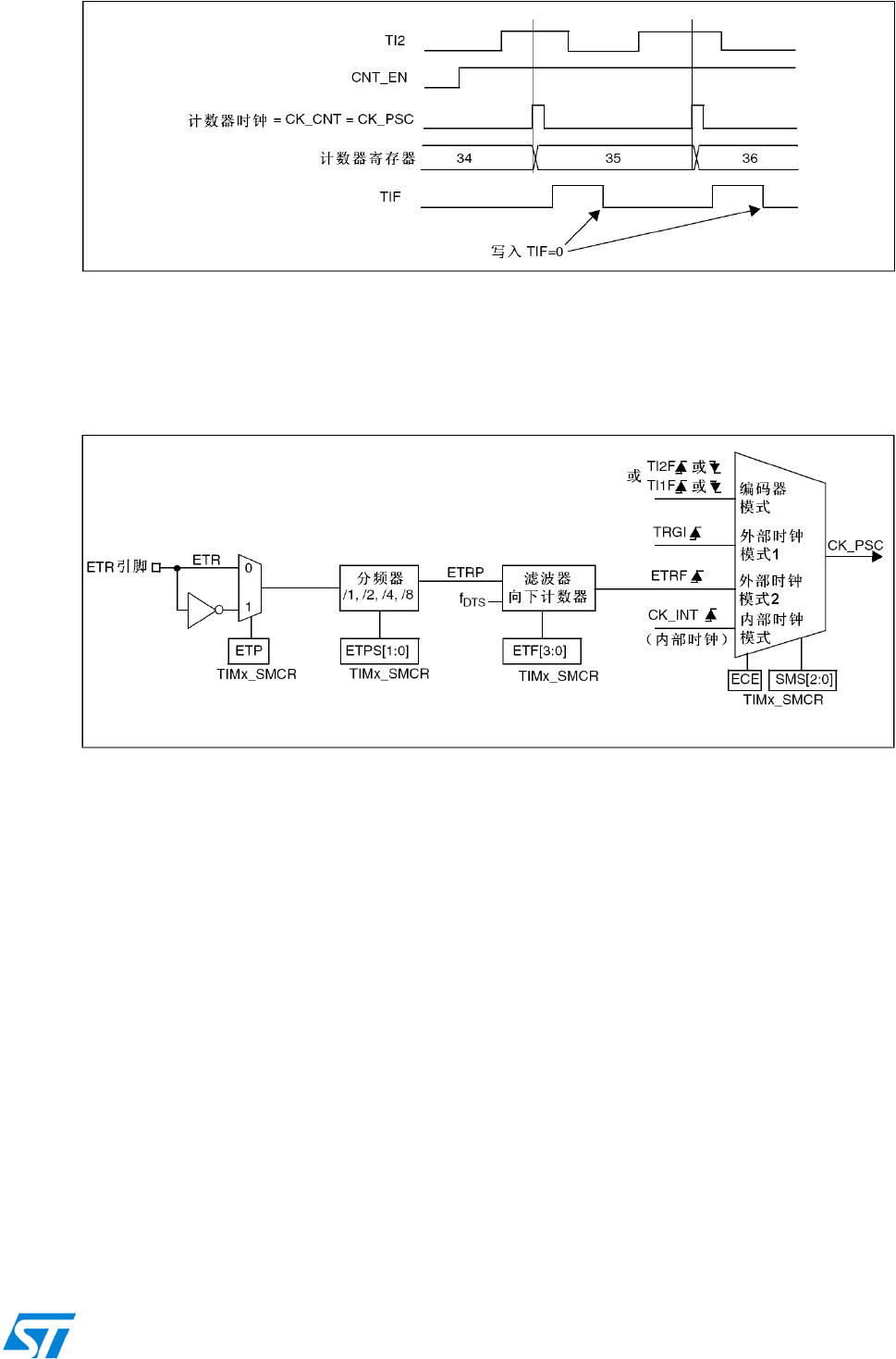

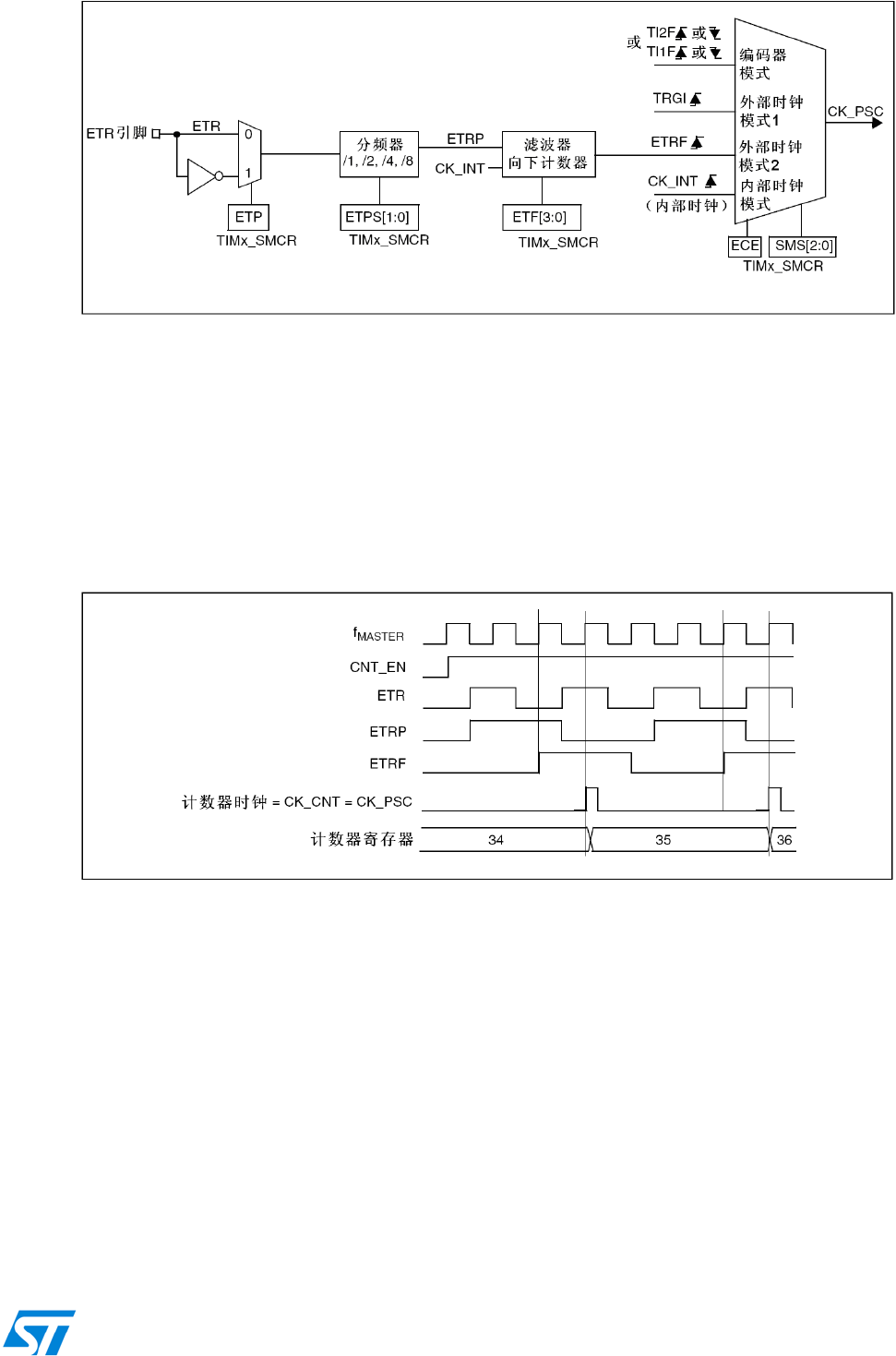

- 13.3.4 时钟选择

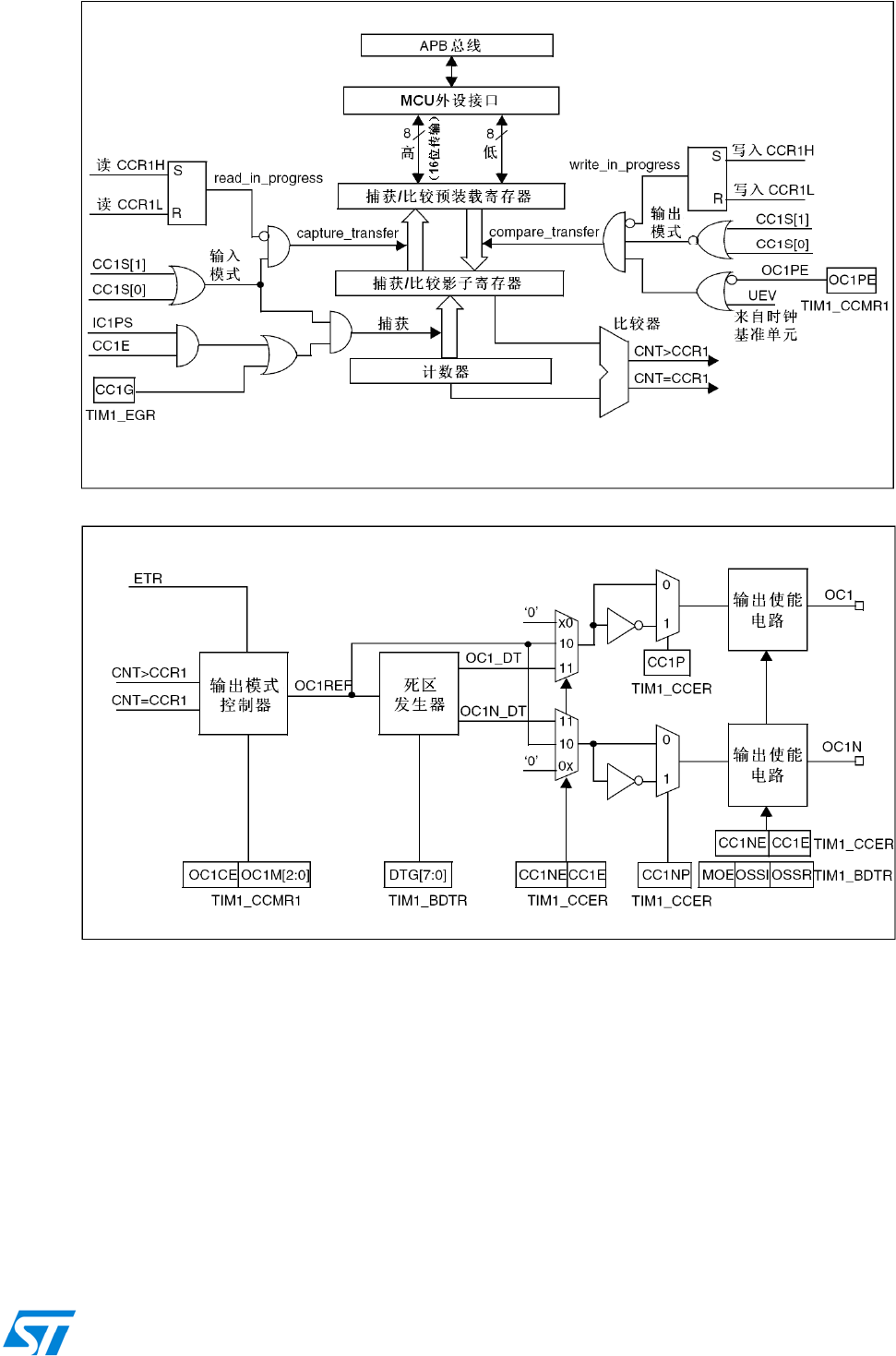

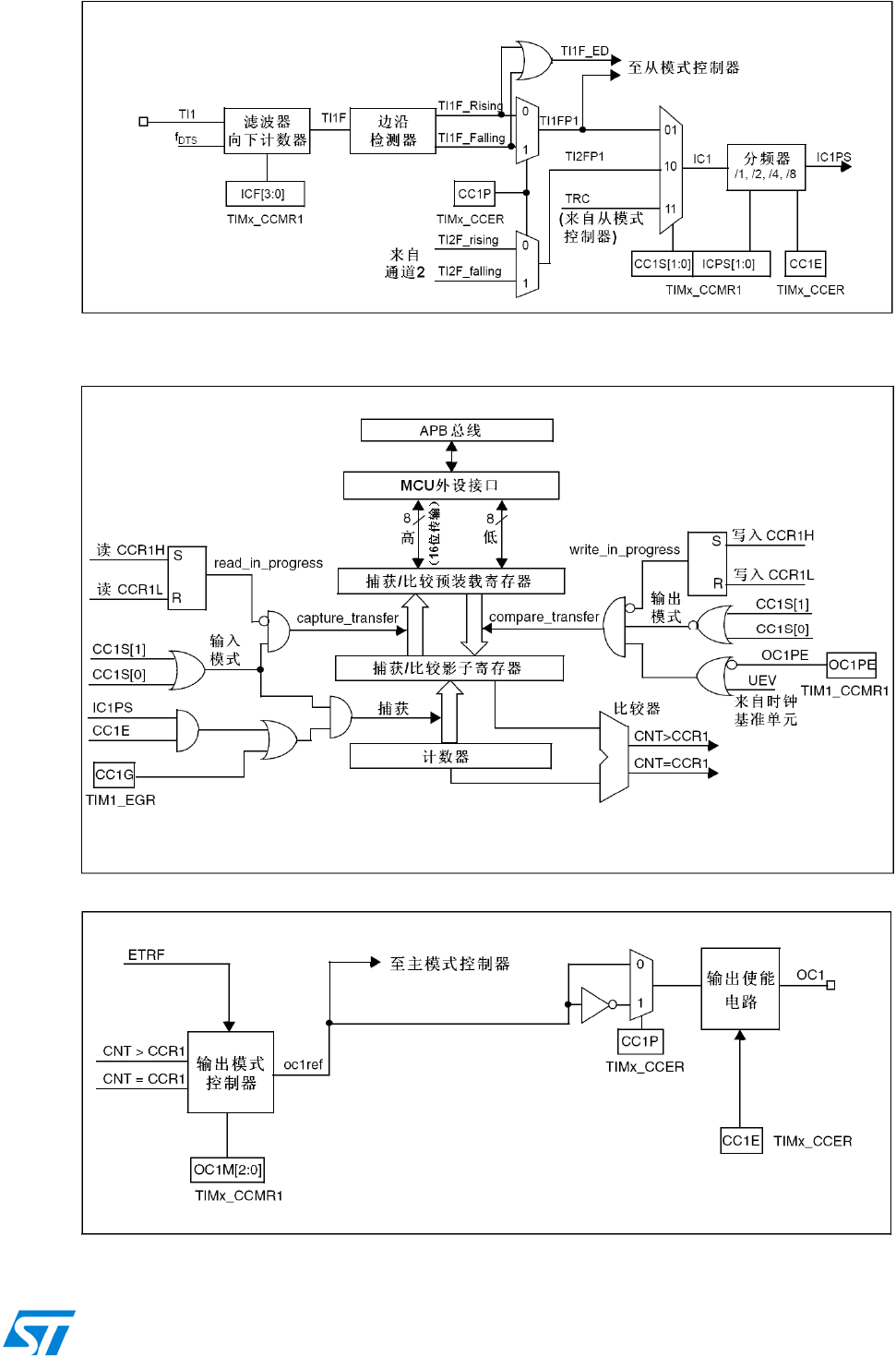

- 13.3.5 捕获/比较通道

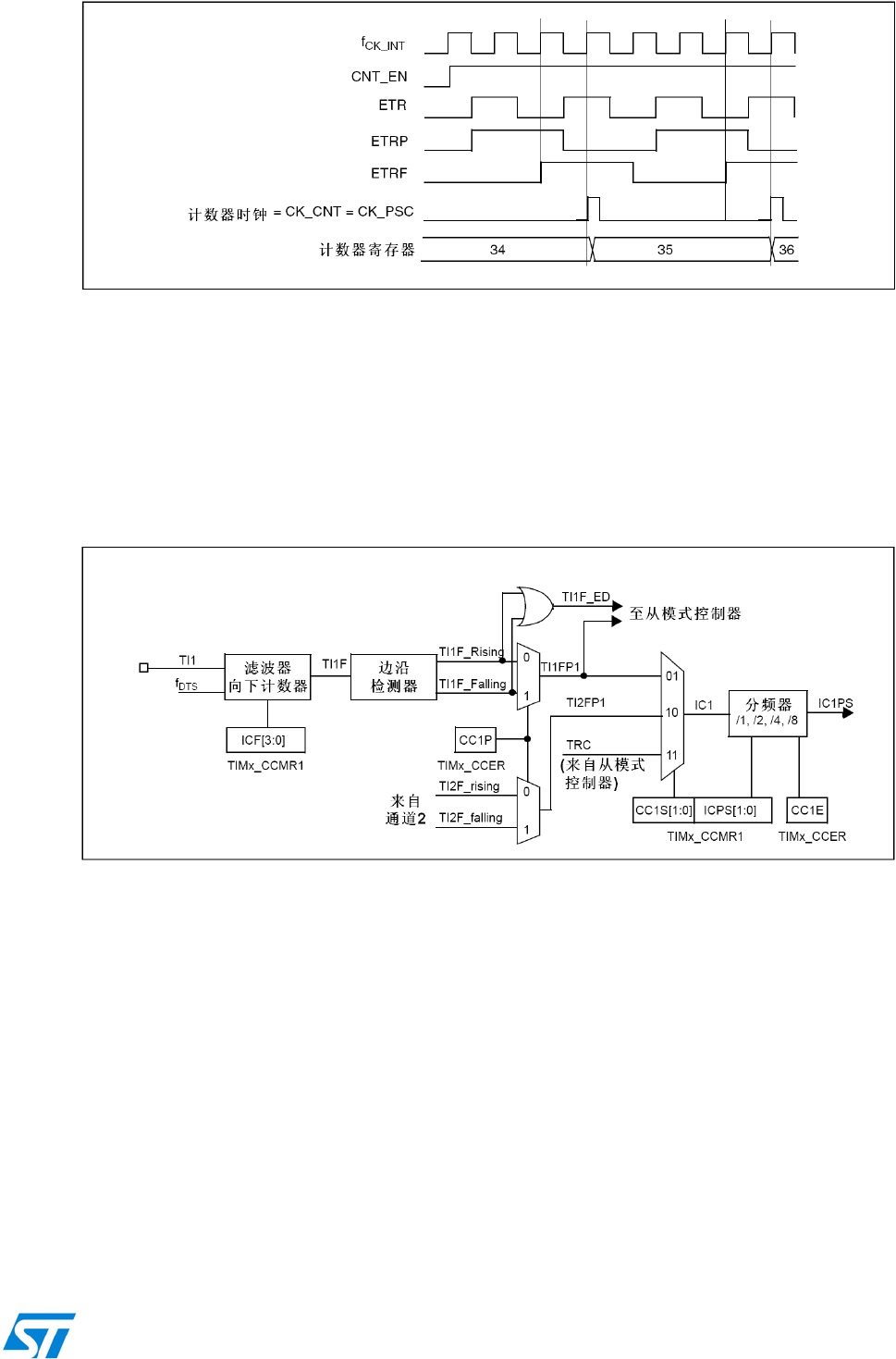

- 13.3.6 输入捕获模式

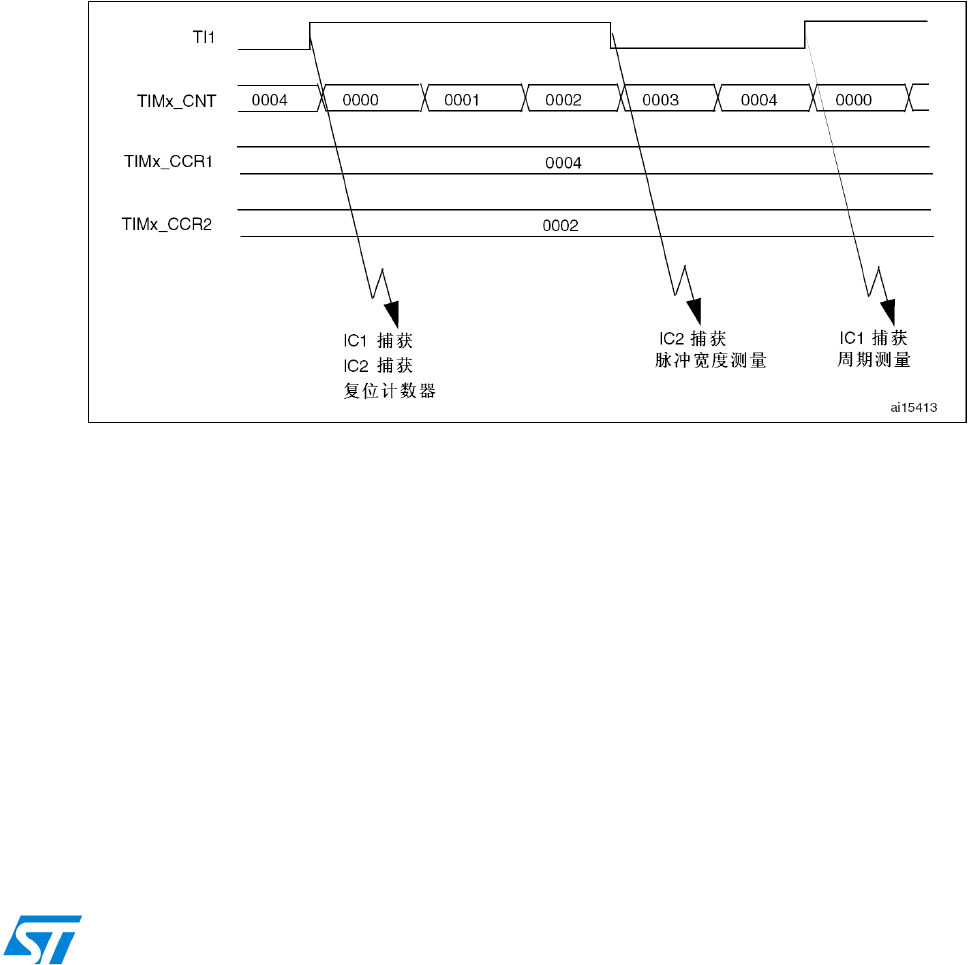

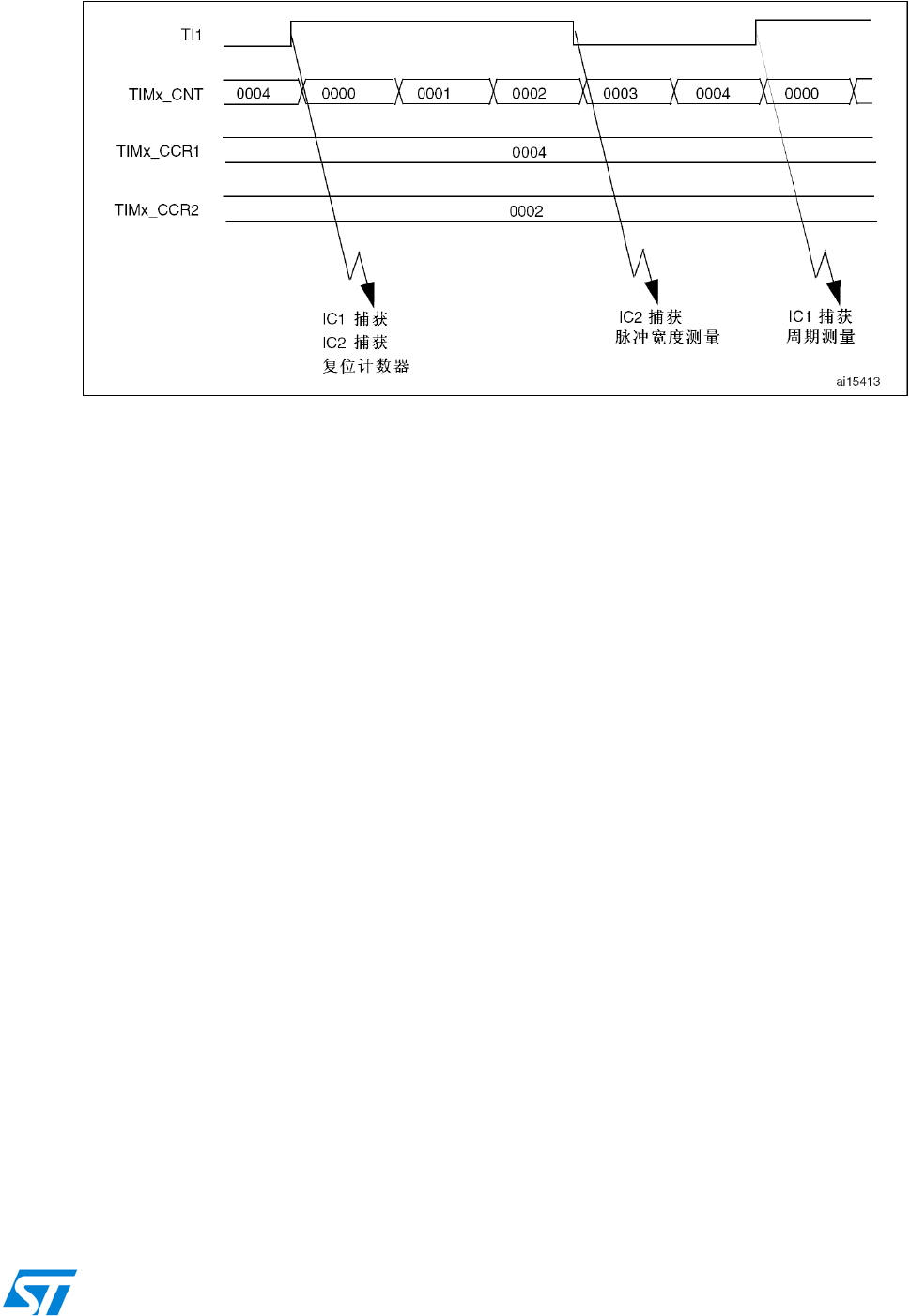

- 13.3.7 PWM输入模式

- 13.3.8 强置输出模式

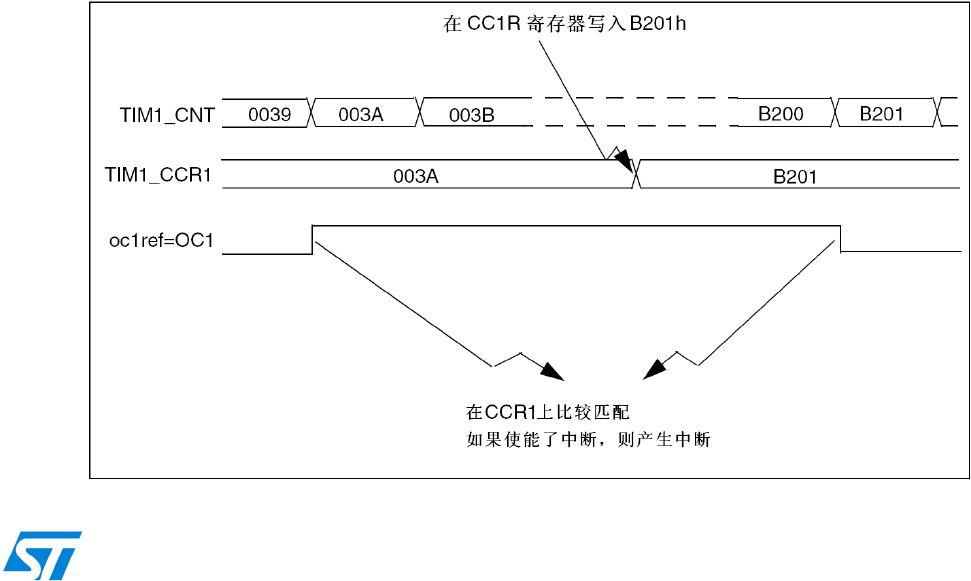

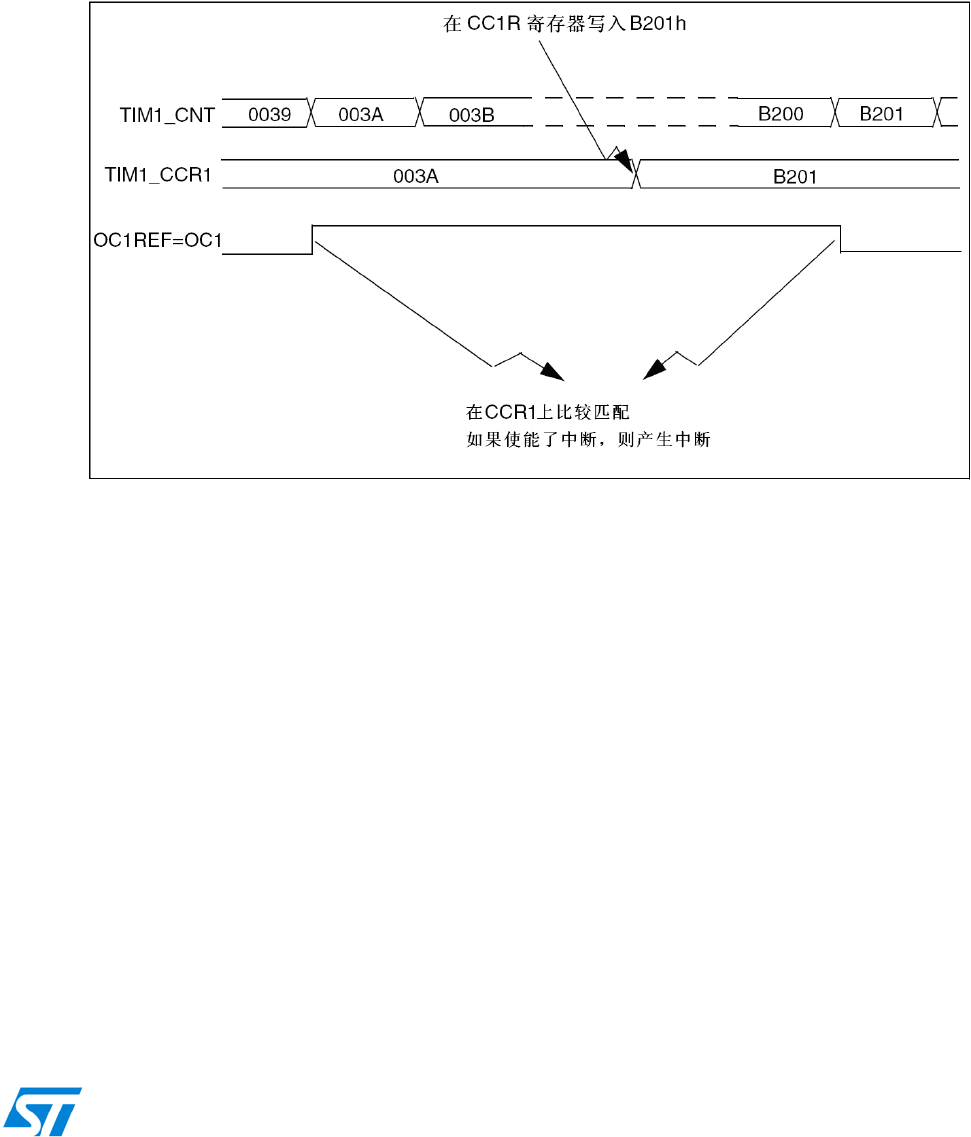

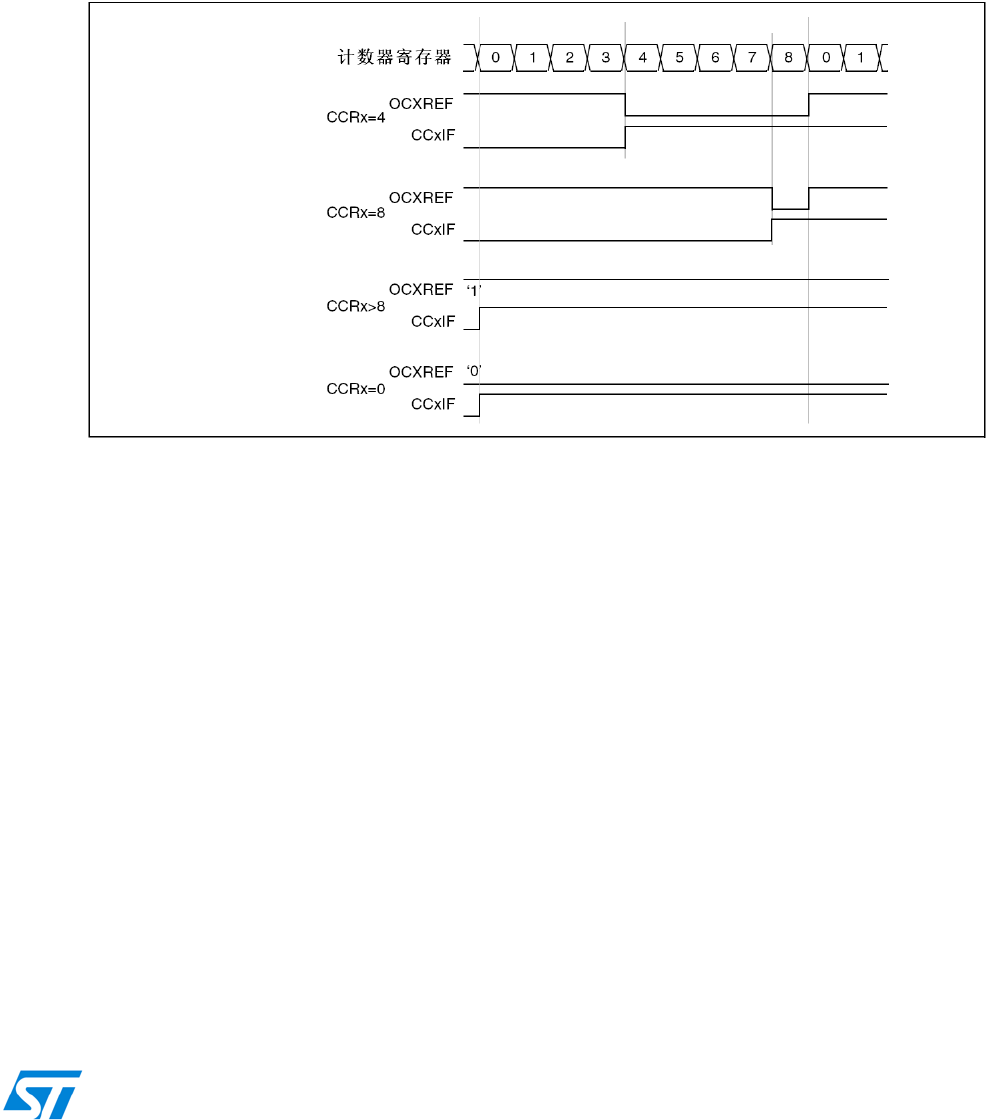

- 13.3.9 输出比较模式

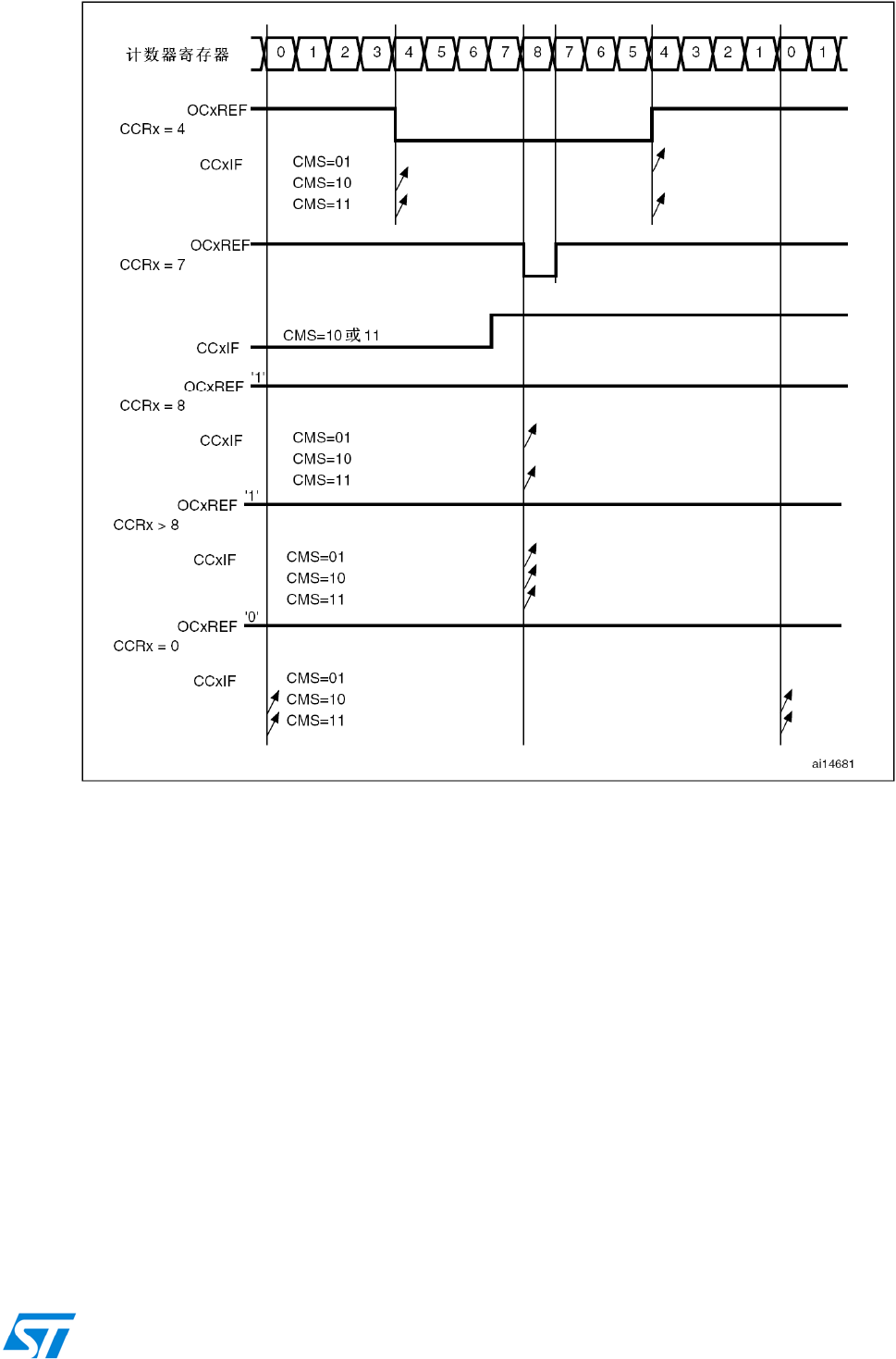

- 13.3.10 PWM模式

- 13.3.11 互补输出和死区插入

- 13.3.12 使用刹车功能

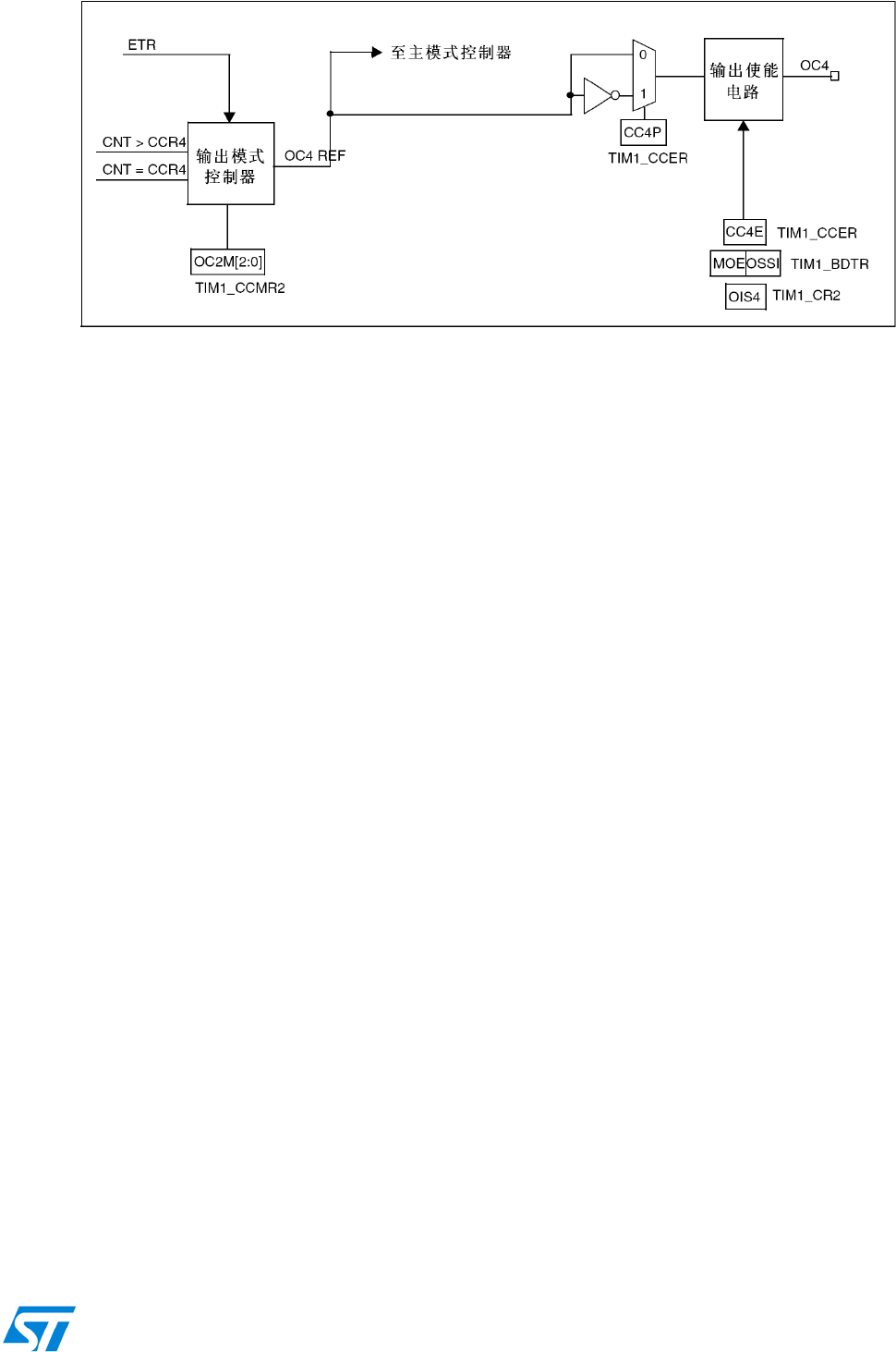

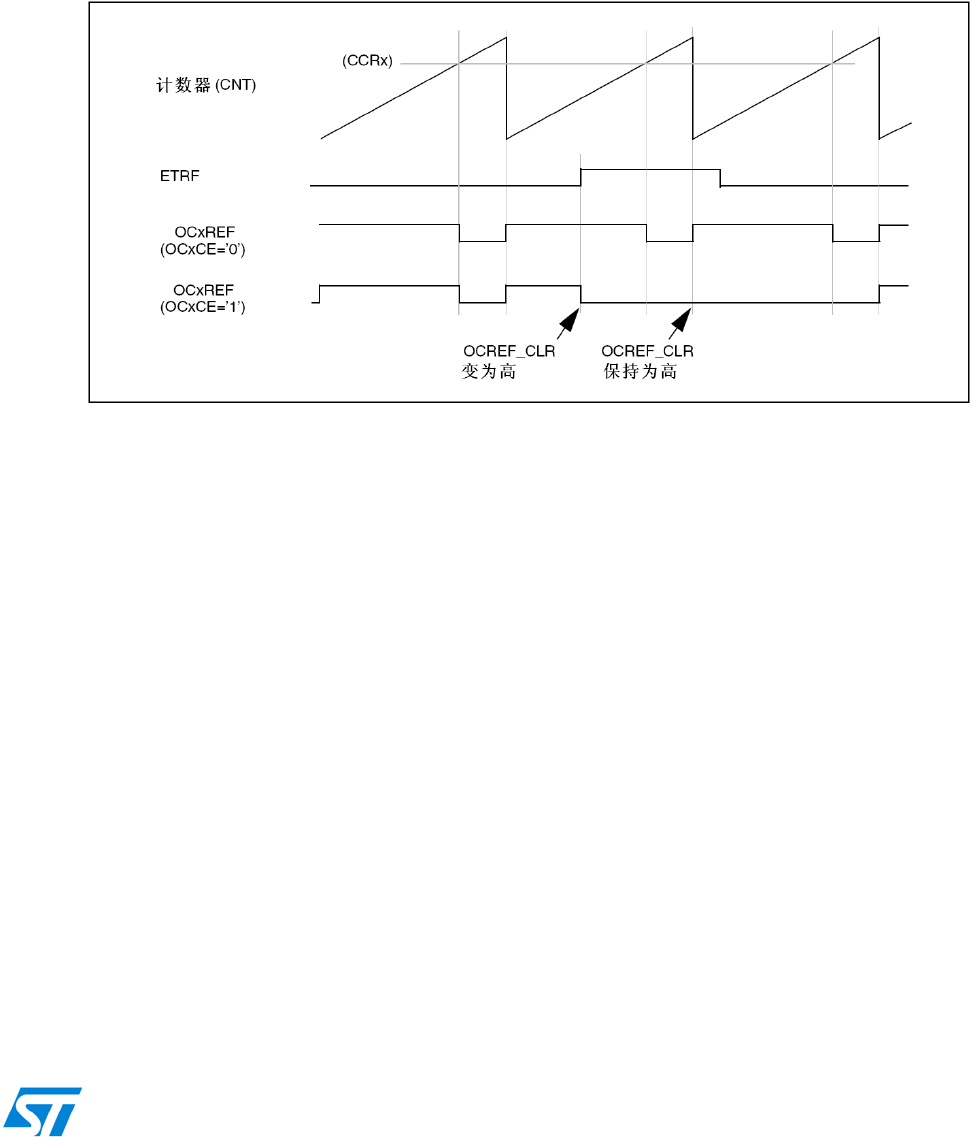

- 13.3.13 在外部事件时清除OCxREF信号

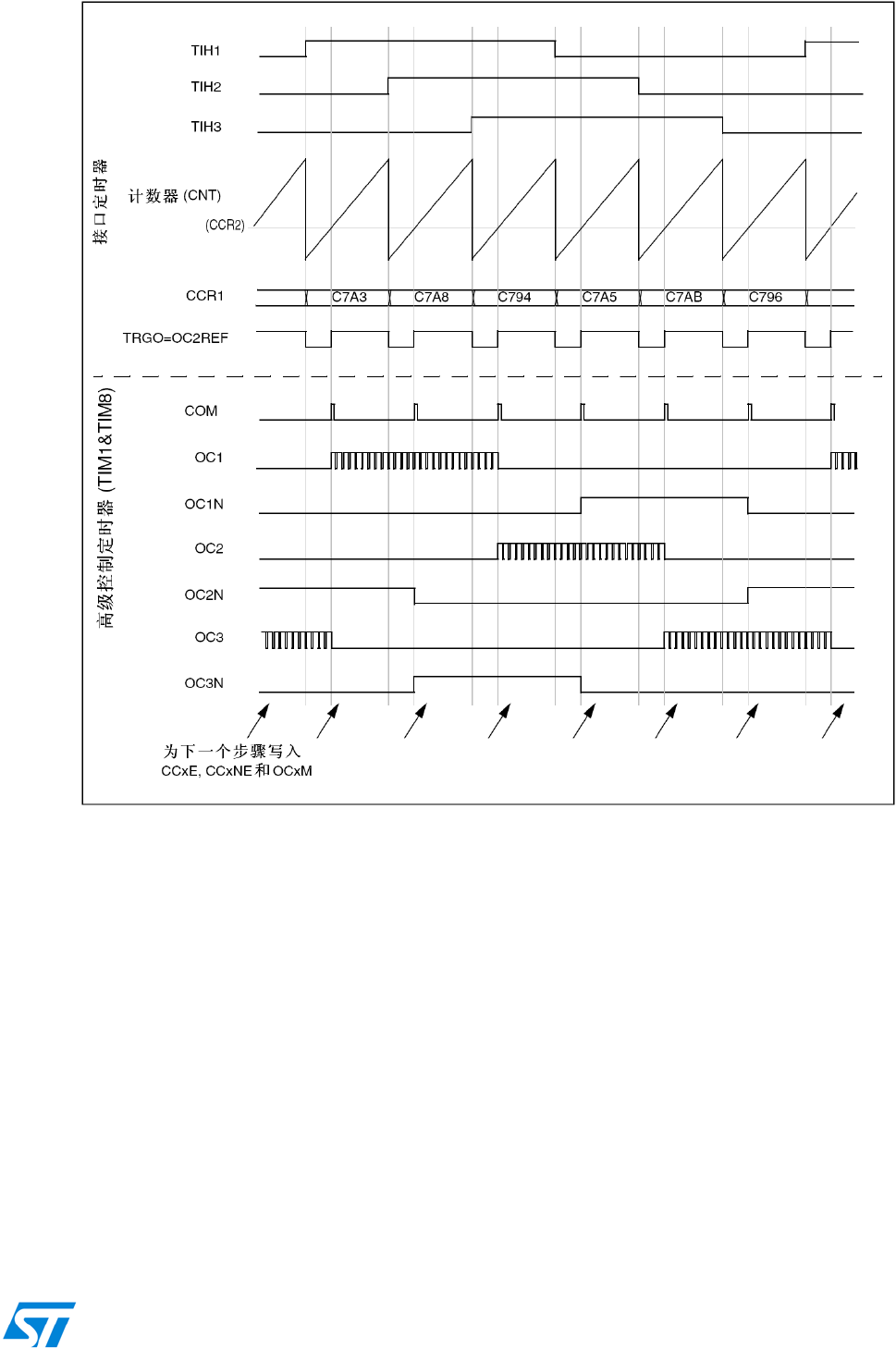

- 13.3.14 产生六步PWM输出

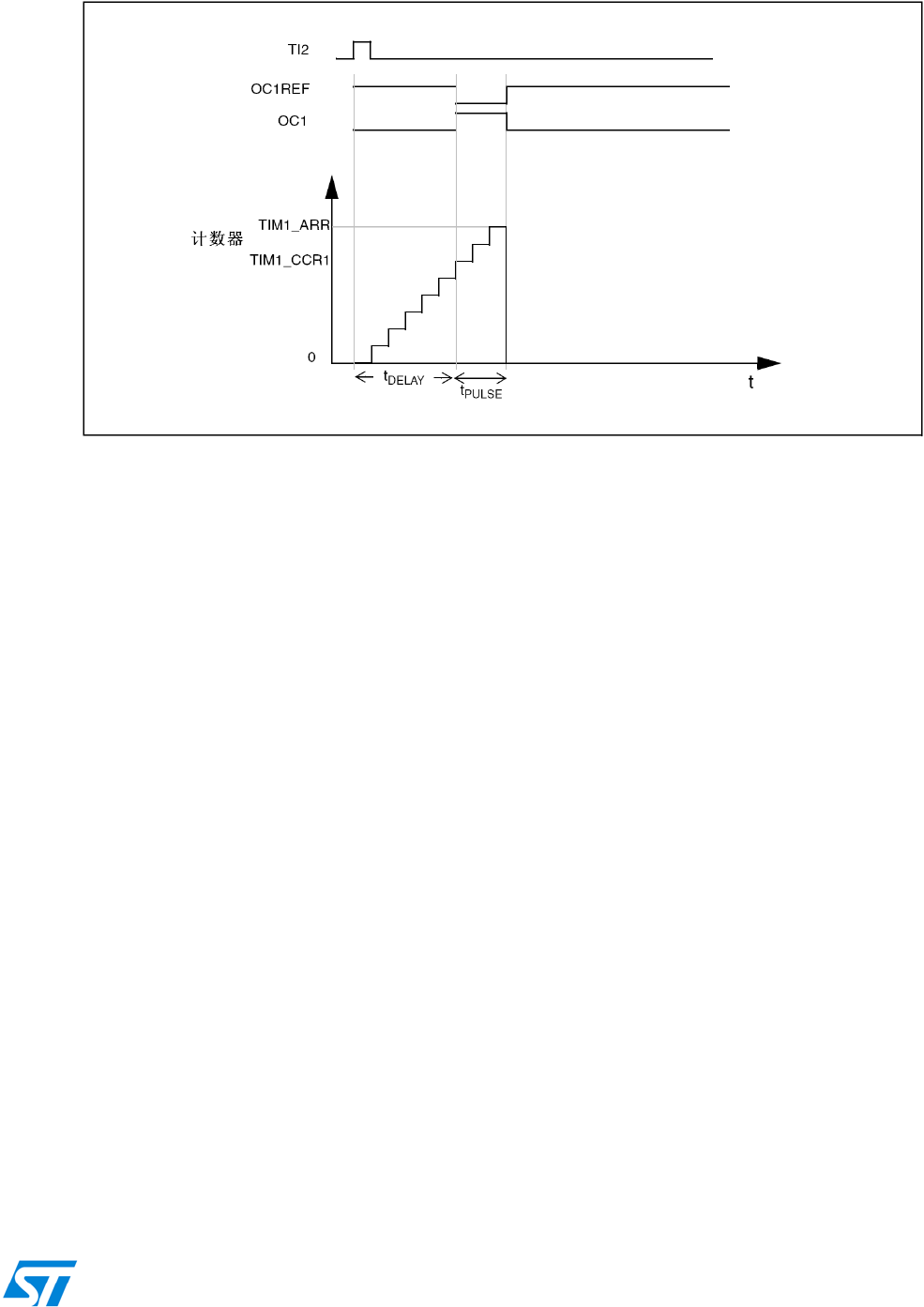

- 13.3.15 单脉冲模式

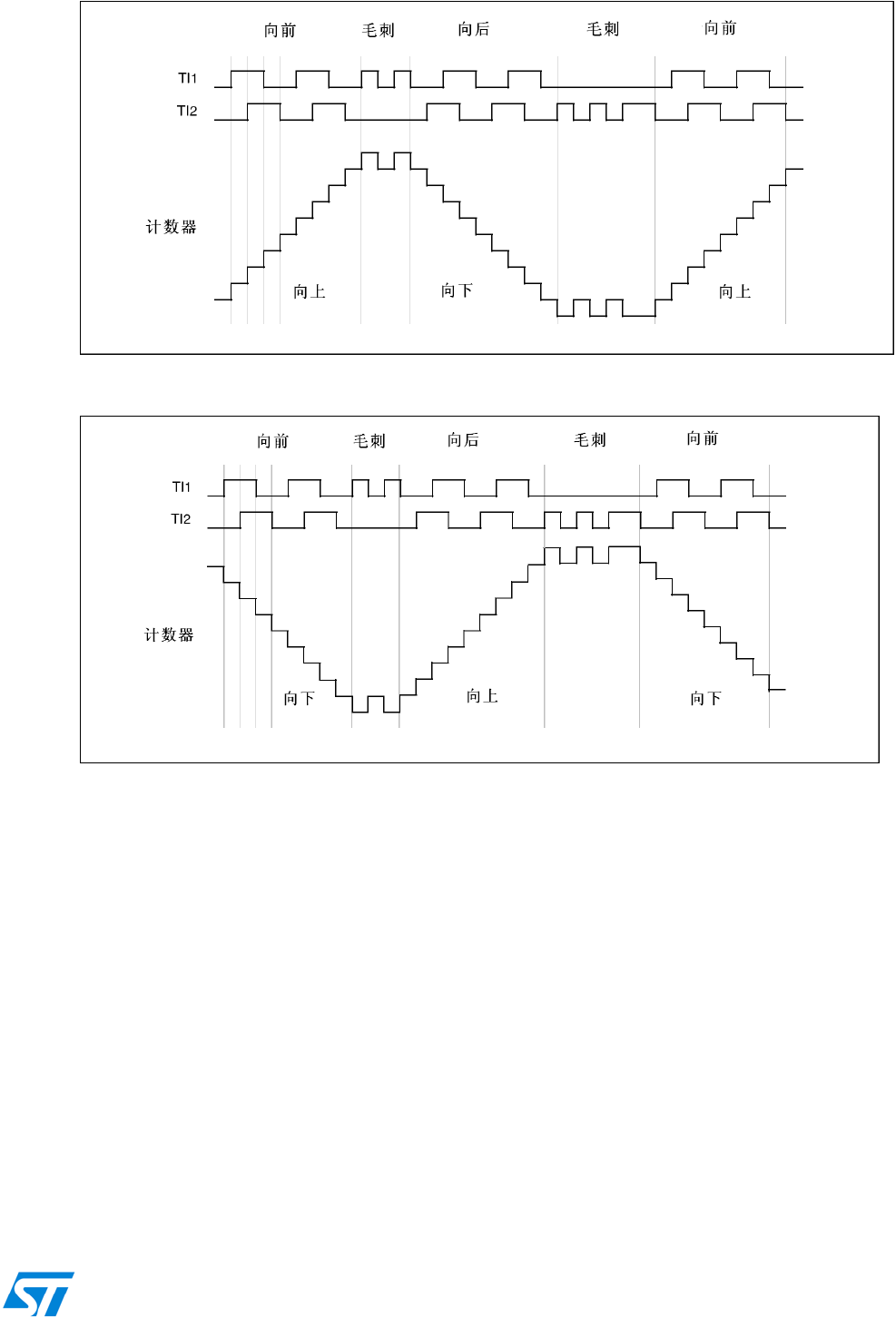

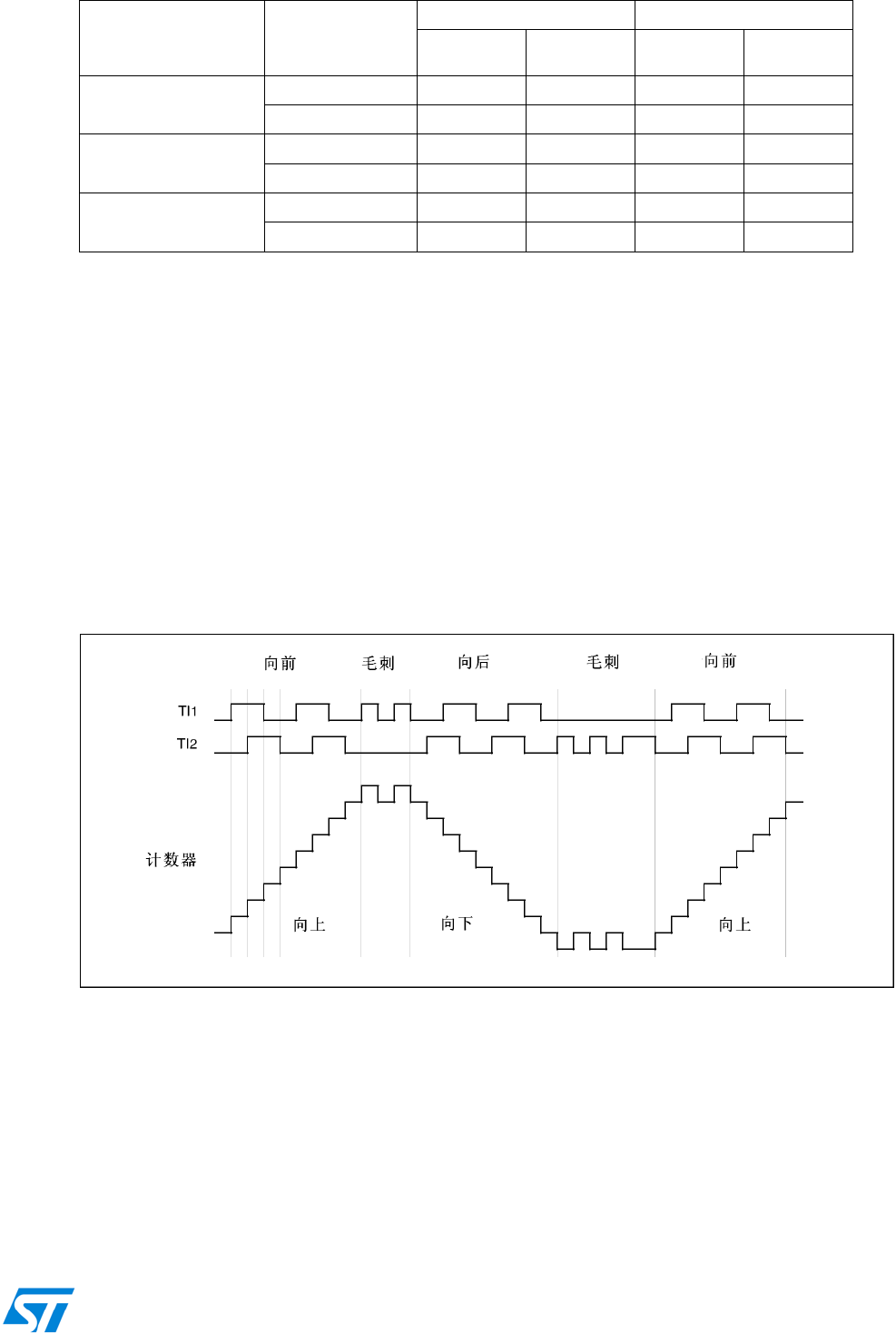

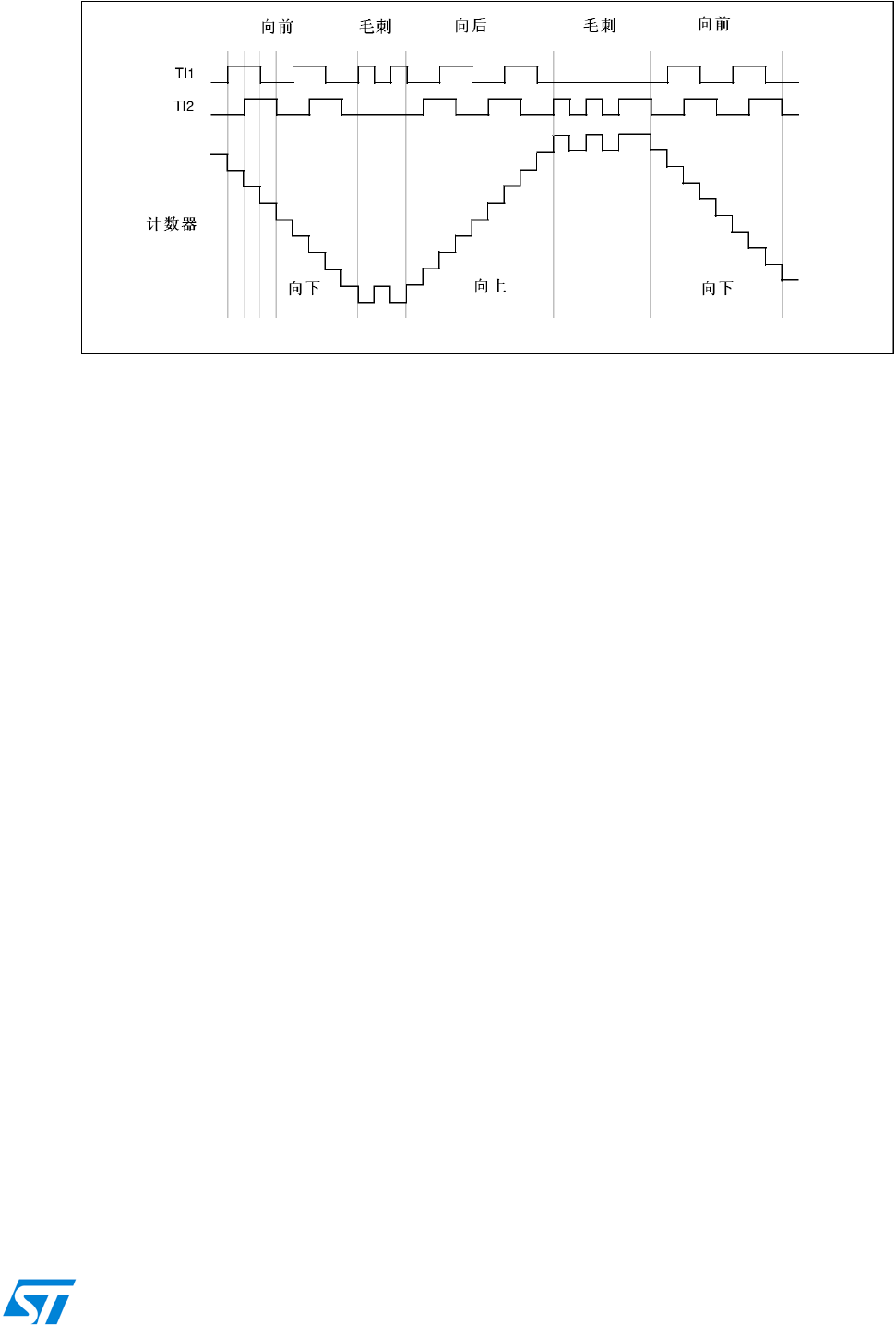

- 13.3.16 编码器接口模式

- 13.3.17 定时器输入异或功能

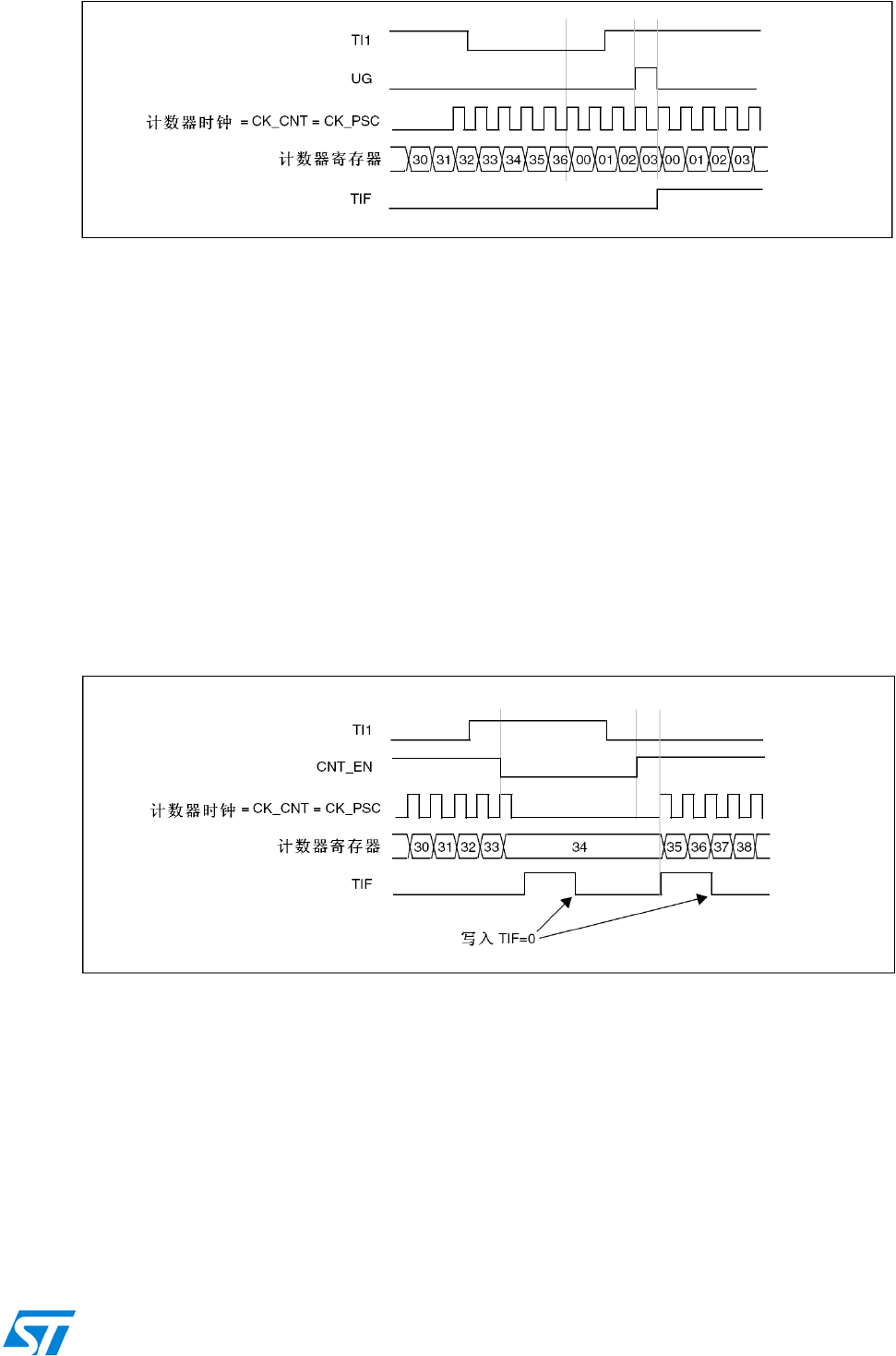

- 13.3.18 与霍尔传感器的接口

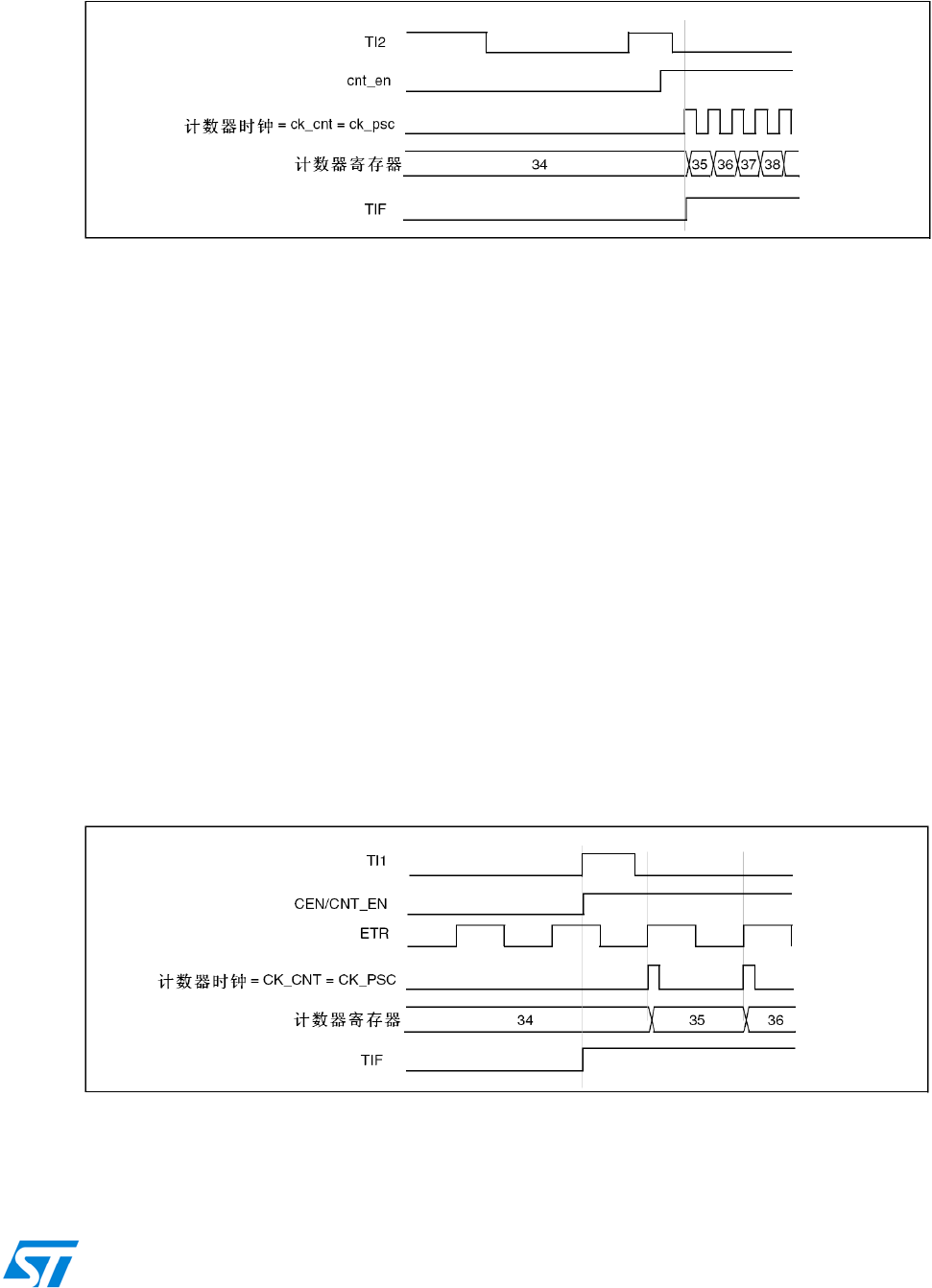

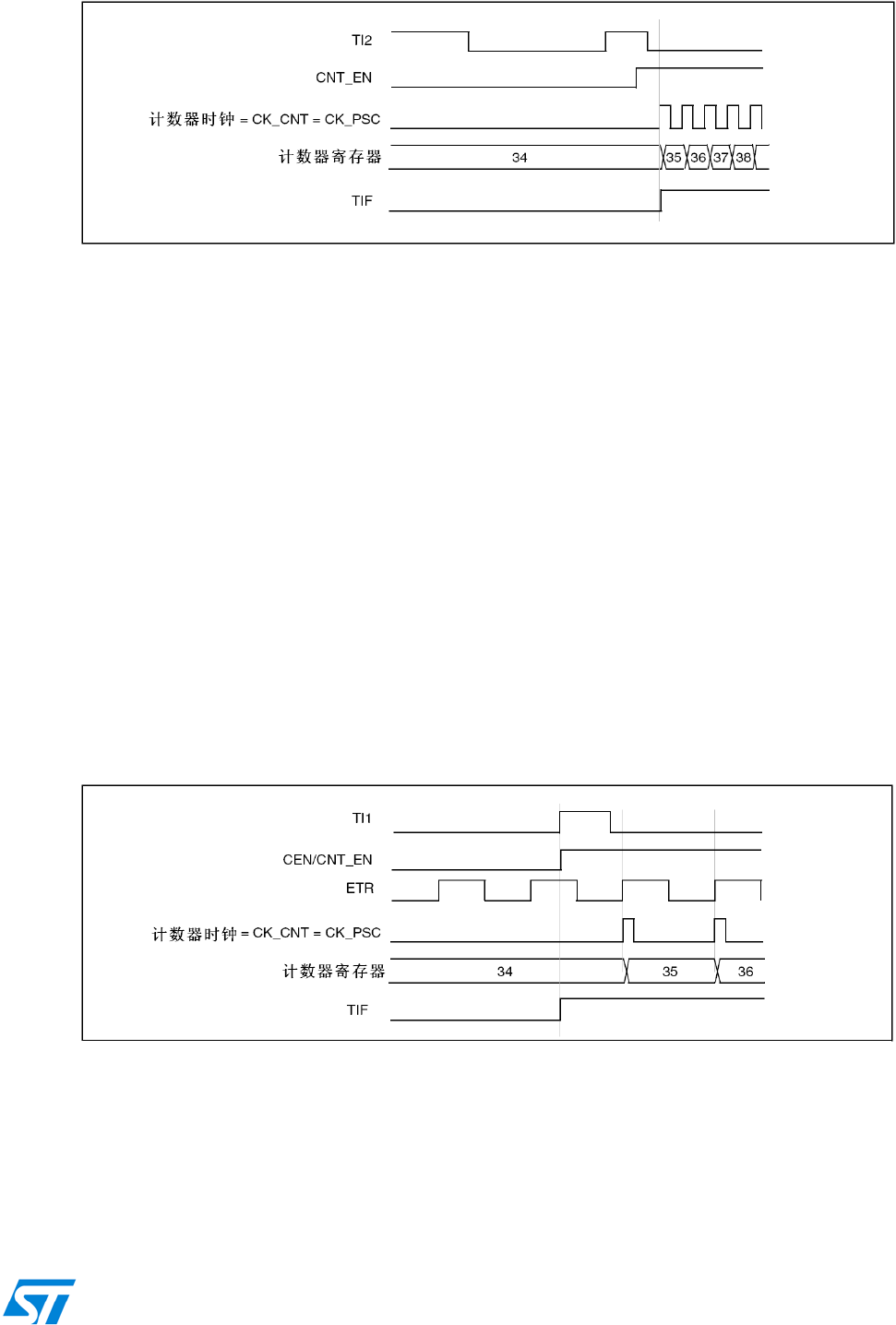

- 13.3.19 TIMx定时器和外部触发的同步

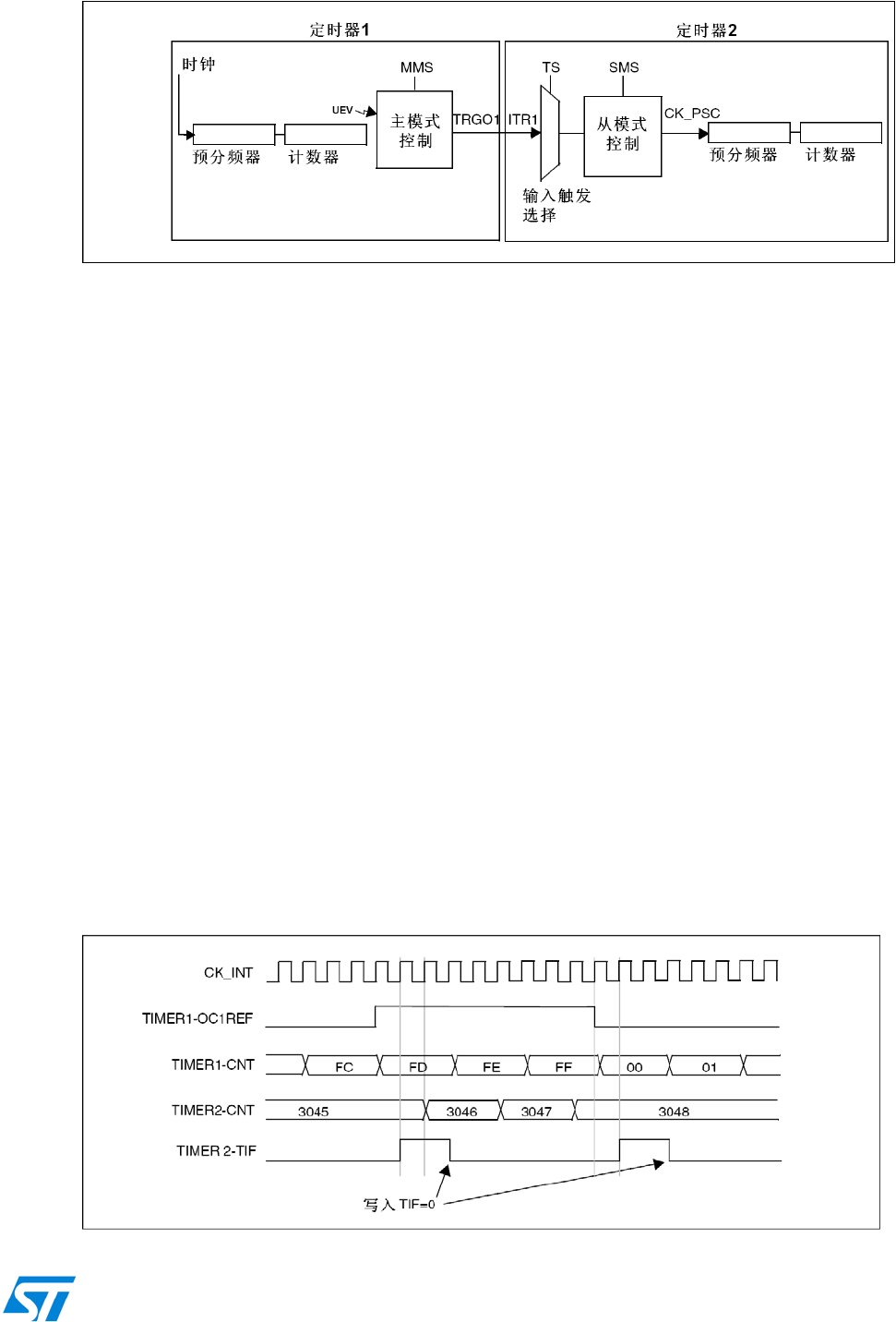

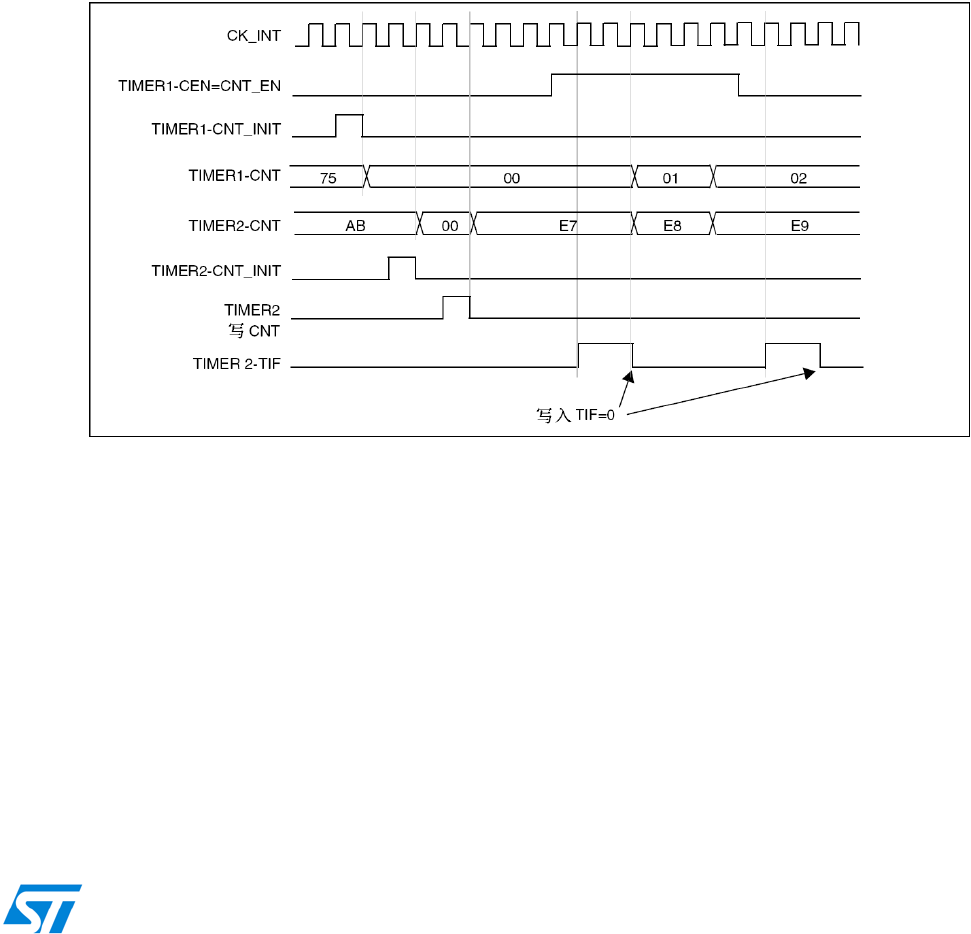

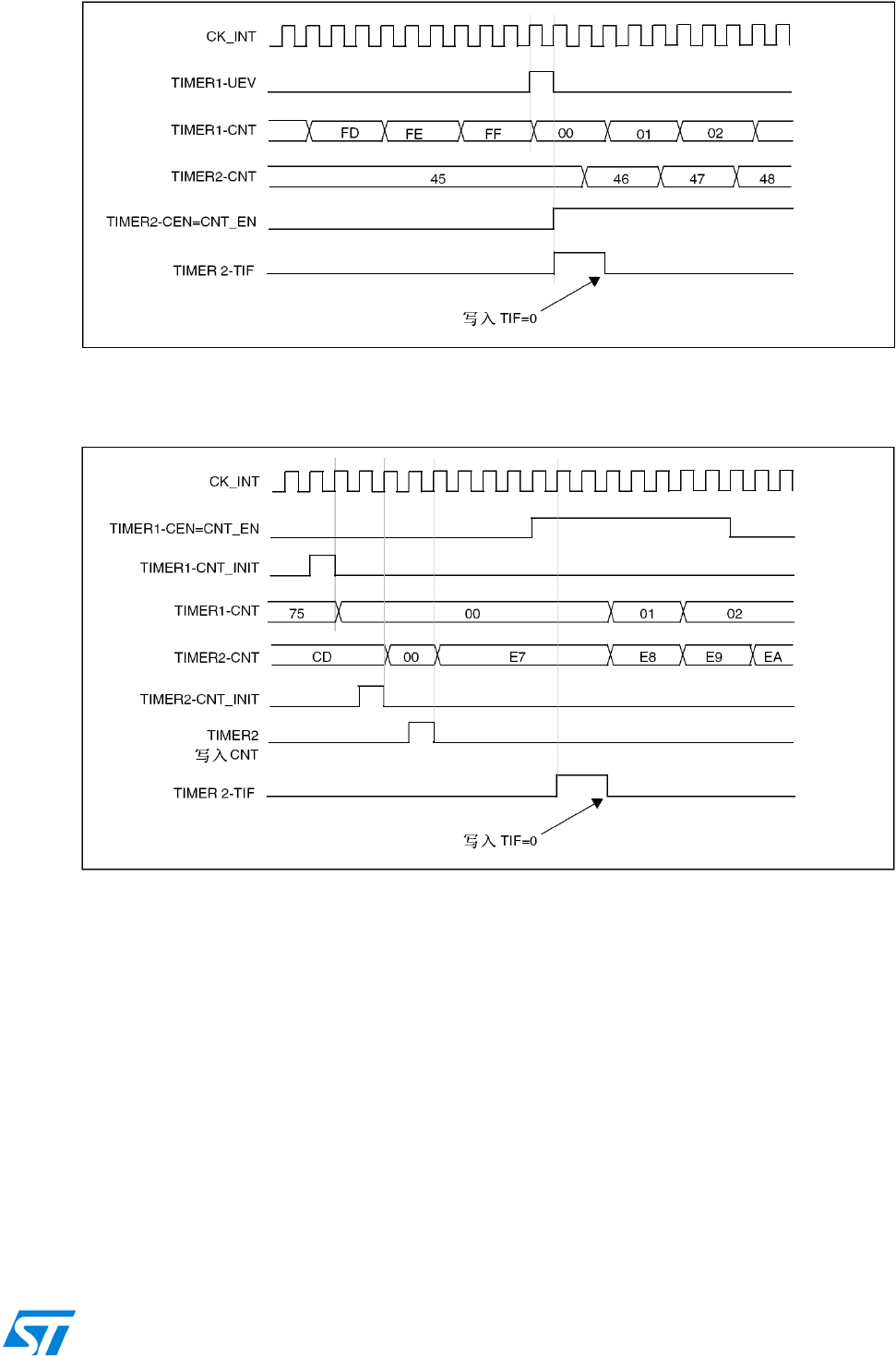

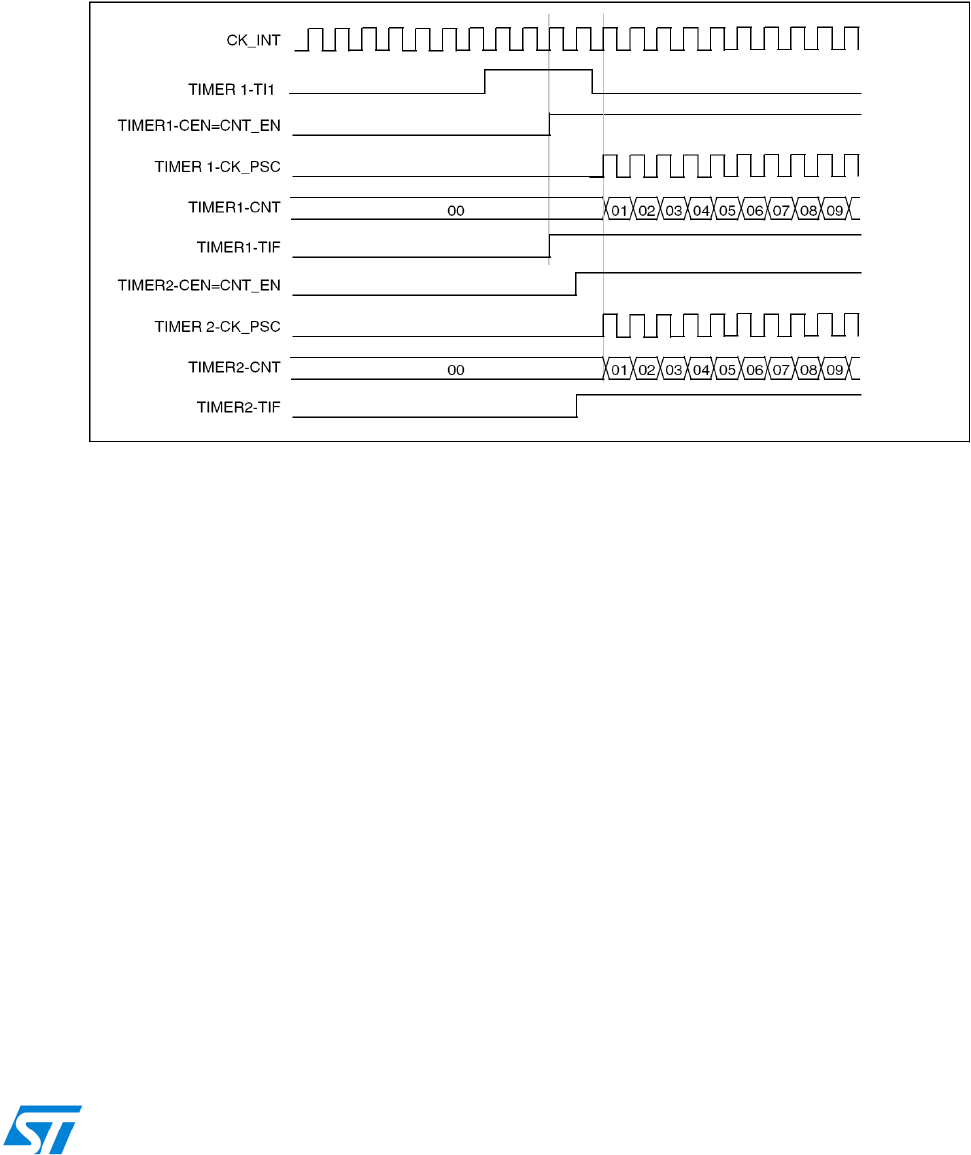

- 13.3.20 定时器同步

- 13.3.21 调试模式

- 13.4 TIM1和TIM8寄存器描述

- 13.4.1 TIM1和TIM8控制寄存器1(TIMx_CR1)

- 13.4.2 TIM1和TIM8控制寄存器2(TIMx_CR2)

- 13.4.3 TIM1和TIM8从模式控制寄存器(TIMx_SMCR)

- 13.4.4 TIM1和TIM8 DMA/中断使能寄存器(TIMx_DIER)

- 13.4.5 TIM1和TIM8状态寄存器(TIMx_SR)

- 13.4.6 TIM1和TIM8事件产生寄存器(TIMx_EGR)

- 13.4.7 TIM1和TIM8捕获/比较模式寄存器1(TIMx_CCMR1)

- 13.4.8 TIM1和TIM8捕获/比较模式寄存器2(TIMx_CCMR2)

- 13.4.9 TIM1和TIM8捕获/比较使能寄存器(TIMx_CCER)

- 13.4.10 TIM1和TIM8计数器(TIMx_CNT)

- 13.4.11 TIM1和TIM8预分频器(TIMx_PSC)

- 13.4.12 TIM1和TIM8自动重装载寄存器(TIMx_ARR)

- 13.4.13 TIM1和TIM8重复计数寄存器(TIMx_RCR)

- 13.4.14 TIM1和TIM8捕获/比较寄存器1(TIMx_CCR1)

- 13.4.15 TIM1和TIM8捕获/比较寄存器2(TIMx_CCR2)

- 13.4.16 TIM1和TIM8捕获/比较寄存器3(TIMx_CCR3)

- 13.4.17 TIM1和TIM8捕获/比较寄存器(TIMx_CCR4)

- 13.4.18 TIM1和TIM8刹车和死区寄存器(TIMx_BDTR)

- 13.4.19 TIM1和TIM8 DMA控制寄存器(TIMx_DCR)

- 13.4.20 TIM1和TIM8连续模式的DMA地址(TIMx_DMAR)

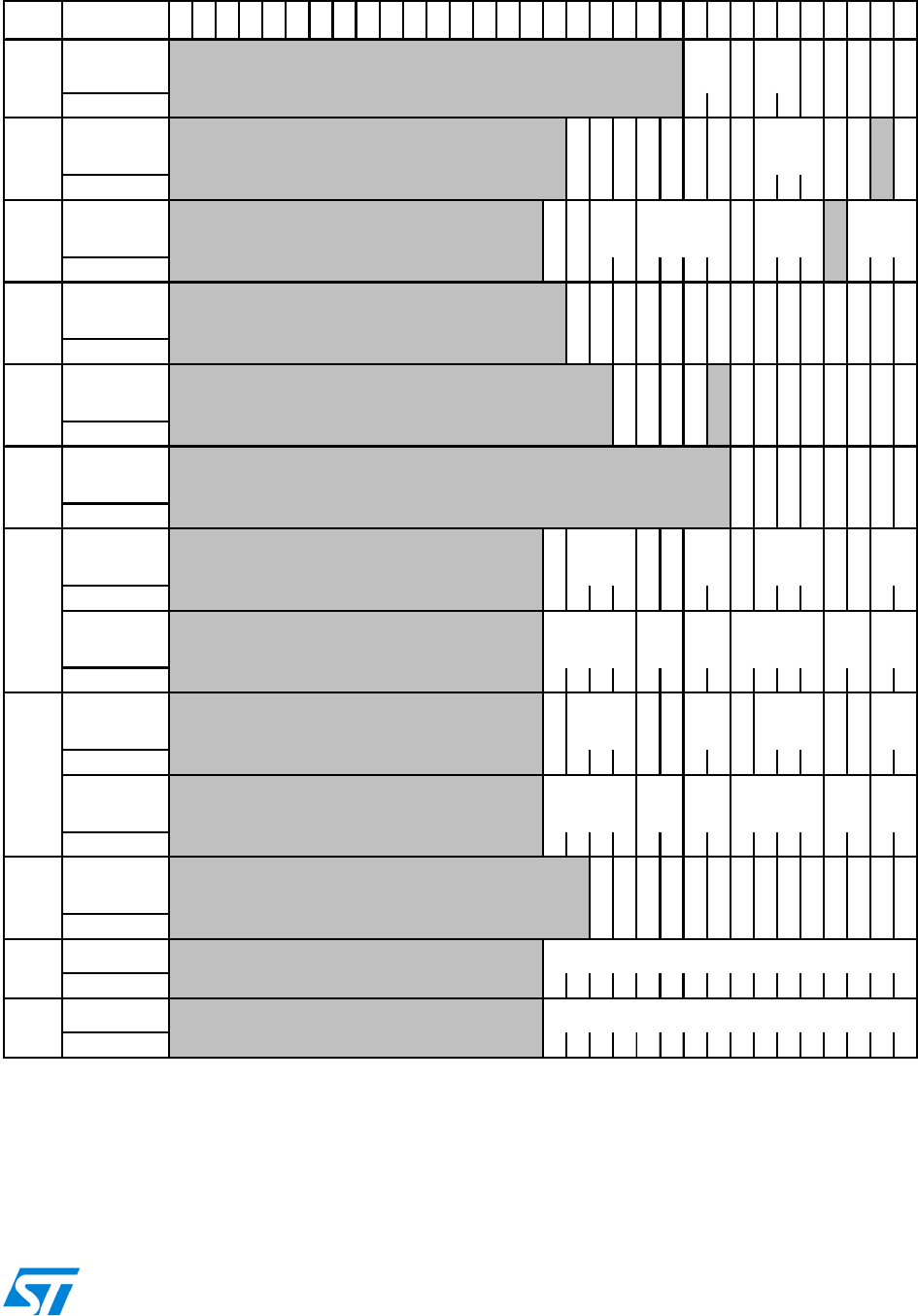

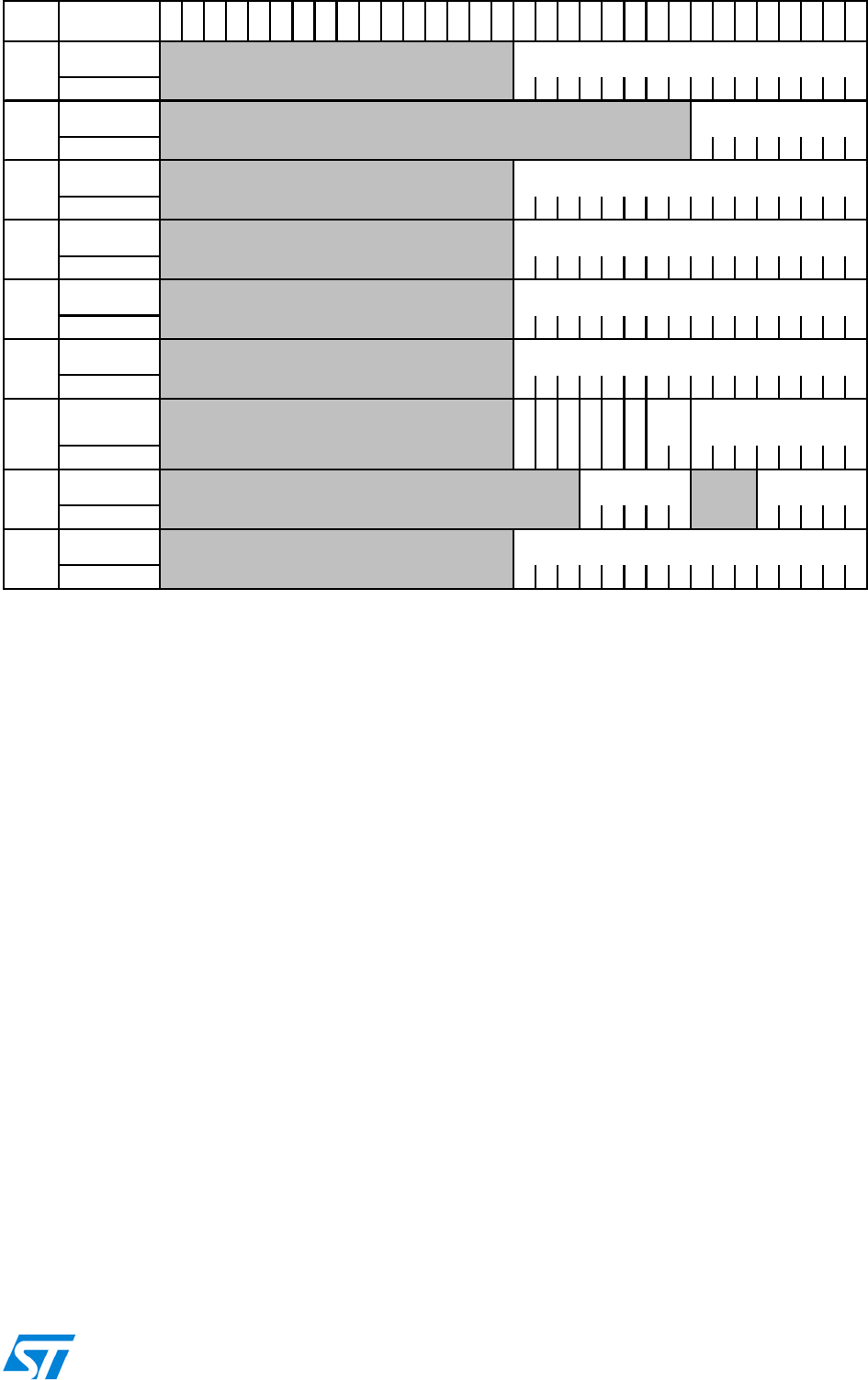

- 13.4.21 TIM1和TIM8寄存器图

- 14 通用定时器(TIMx)

- 14.1 TIMx简介

- 14.2 TIMx主要功能

- 14.3 TIMx功能描述

- 14.4 TIMx寄存器描述

- 14.4.1 控制寄存器1(TIMx_CR1)

- 14.4.2 控制寄存器2(TIMx_CR2)

- 14.4.3 从模式控制寄存器(TIMx_SMCR)

- 14.4.4 DMA/中断使能寄存器(TIMx_DIER)

- 14.4.5 状态寄存器(TIMx_SR)

- 14.4.6 事件产生寄存器(TIMx_EGR)

- 14.4.7 捕获/比较模式寄存器1(TIMx_CCMR1)

- 14.4.8 捕获/比较模式寄存器2(TIMx_CCMR2)

- 14.4.9 捕获/比较使能寄存器(TIMx_CCER)

- 14.4.10 计数器(TIMx_CNT)

- 14.4.11 预分频器(TIMx_PSC)

- 14.4.12 自动重装载寄存器(TIMx_ARR)

- 14.4.13 捕获/比较寄存器1(TIMx_CCR1)

- 14.4.14 捕获/比较寄存器2(TIMx_CCR2)

- 14.4.15 捕获/比较寄存器3(TIMx_CCR3)

- 14.4.16 捕获/比较寄存器4(TIMx_CCR4)

- 14.4.17 DMA控制寄存器(TIMx_DCR)

- 14.4.18 连续模式的DMA地址(TIMx_DMAR)

- 14.4.19 TIMx寄存器图

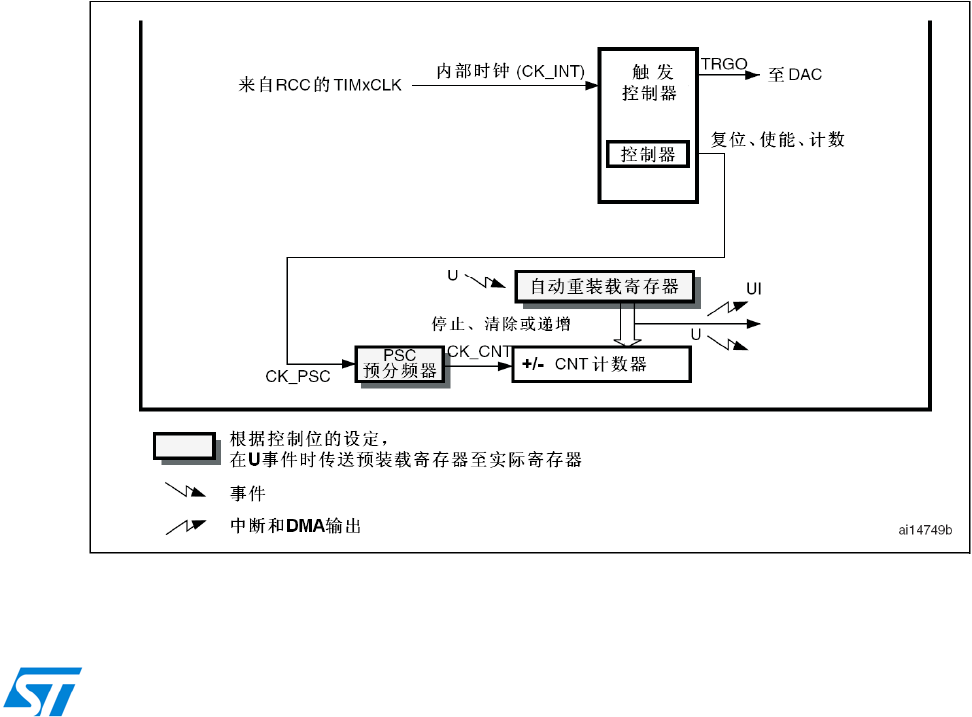

- 15 基本定时器(TIM6和TIM7)

- 16 实时时钟(RTC)

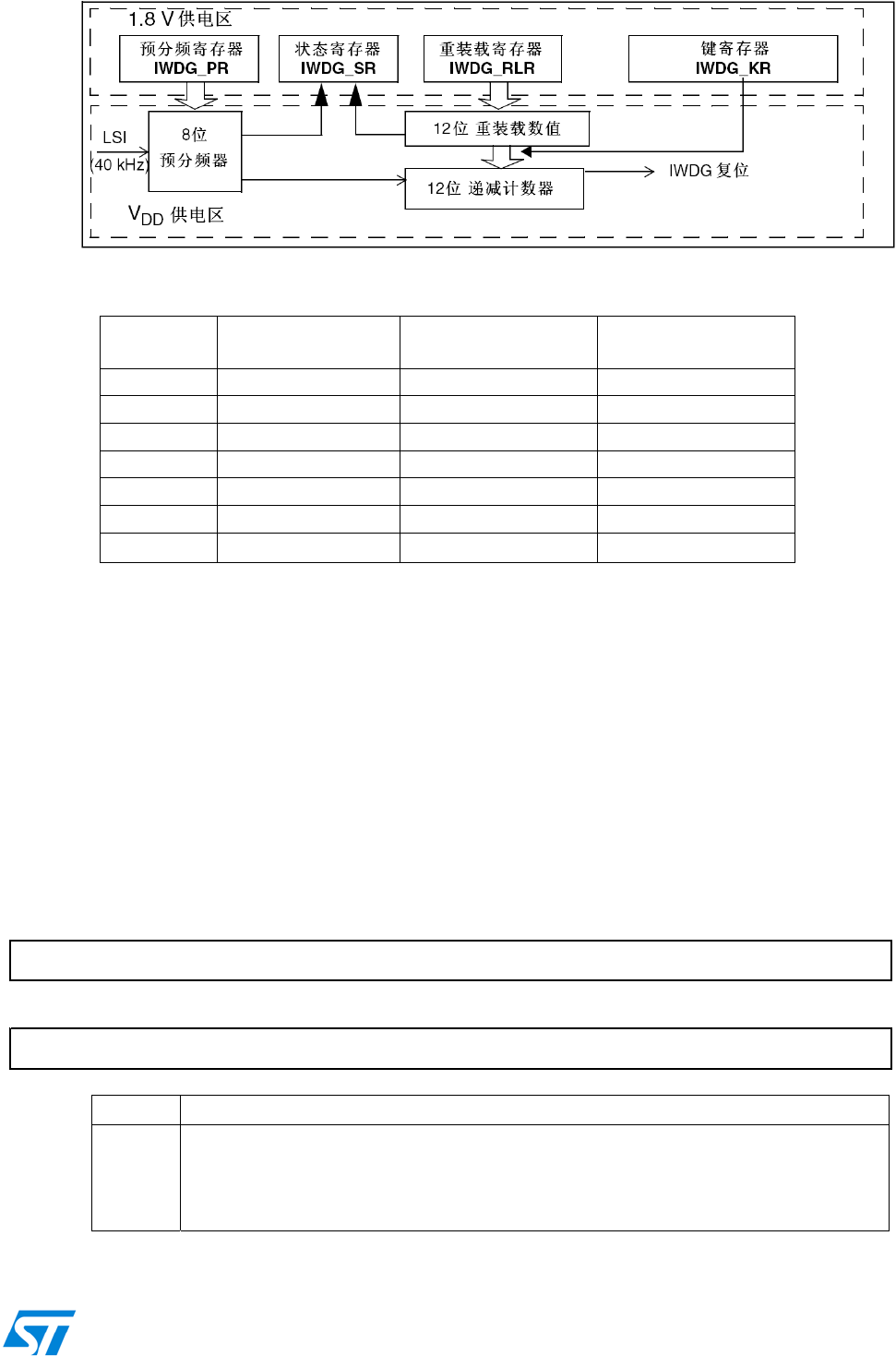

- 17 独立看门狗(IWDG)

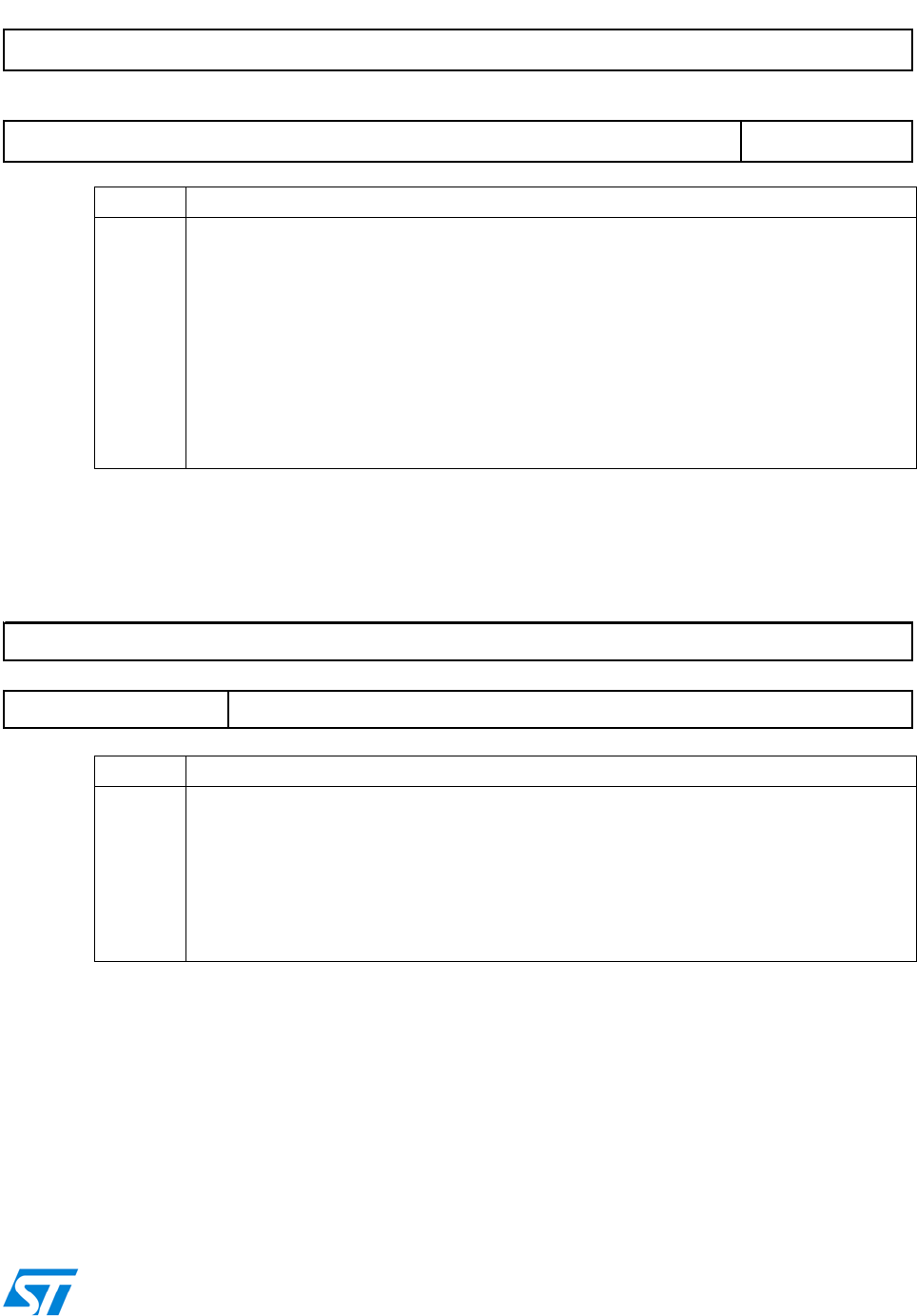

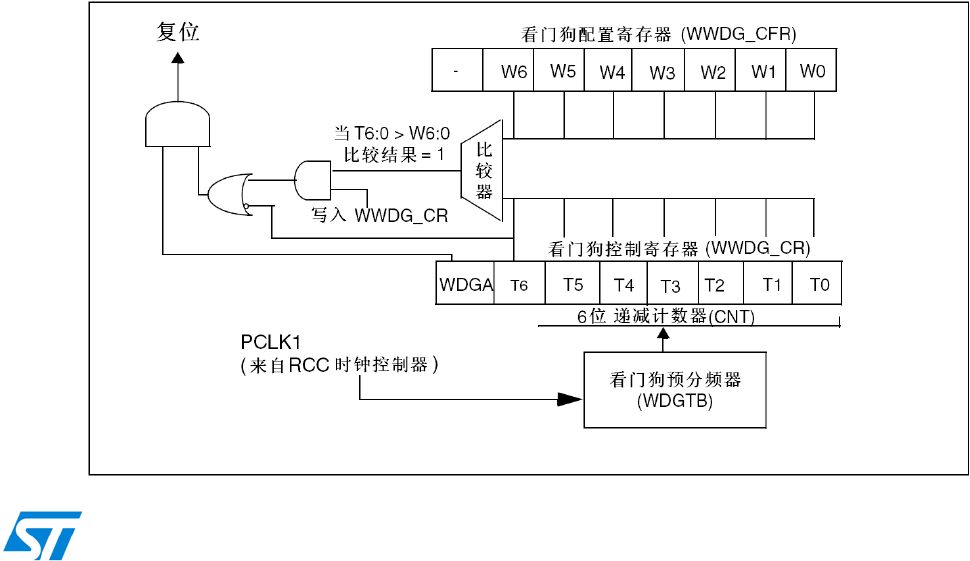

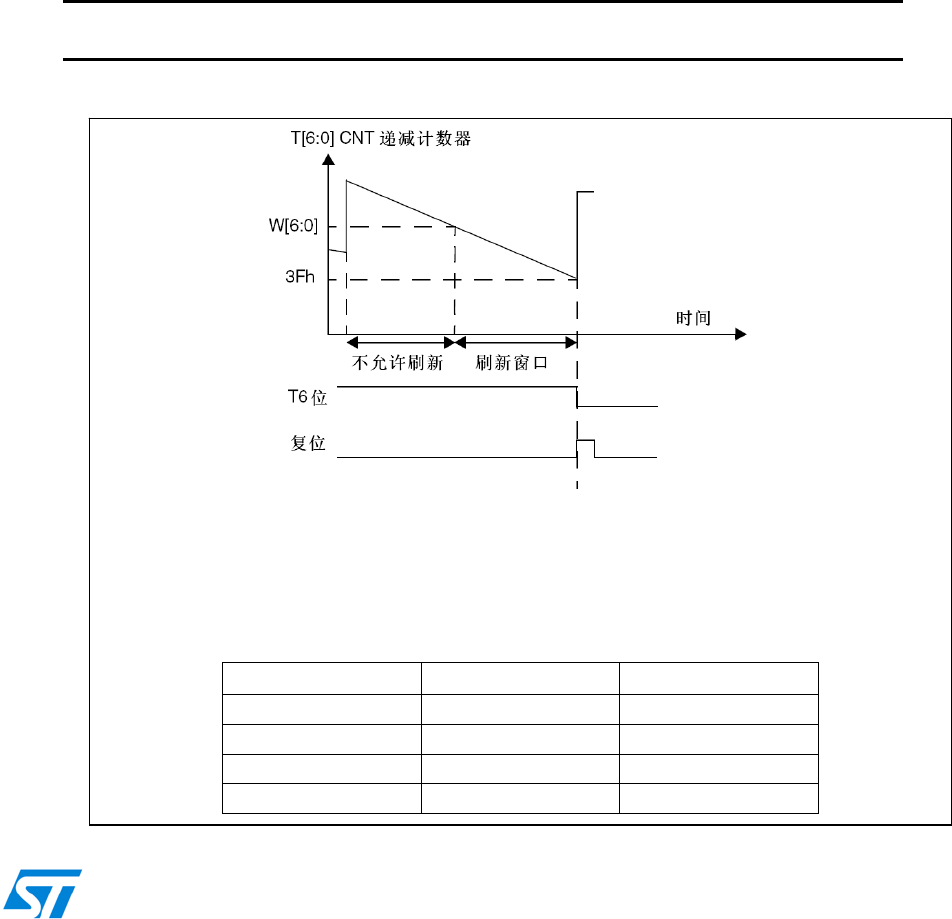

- 18 窗口看门狗(WWDG)

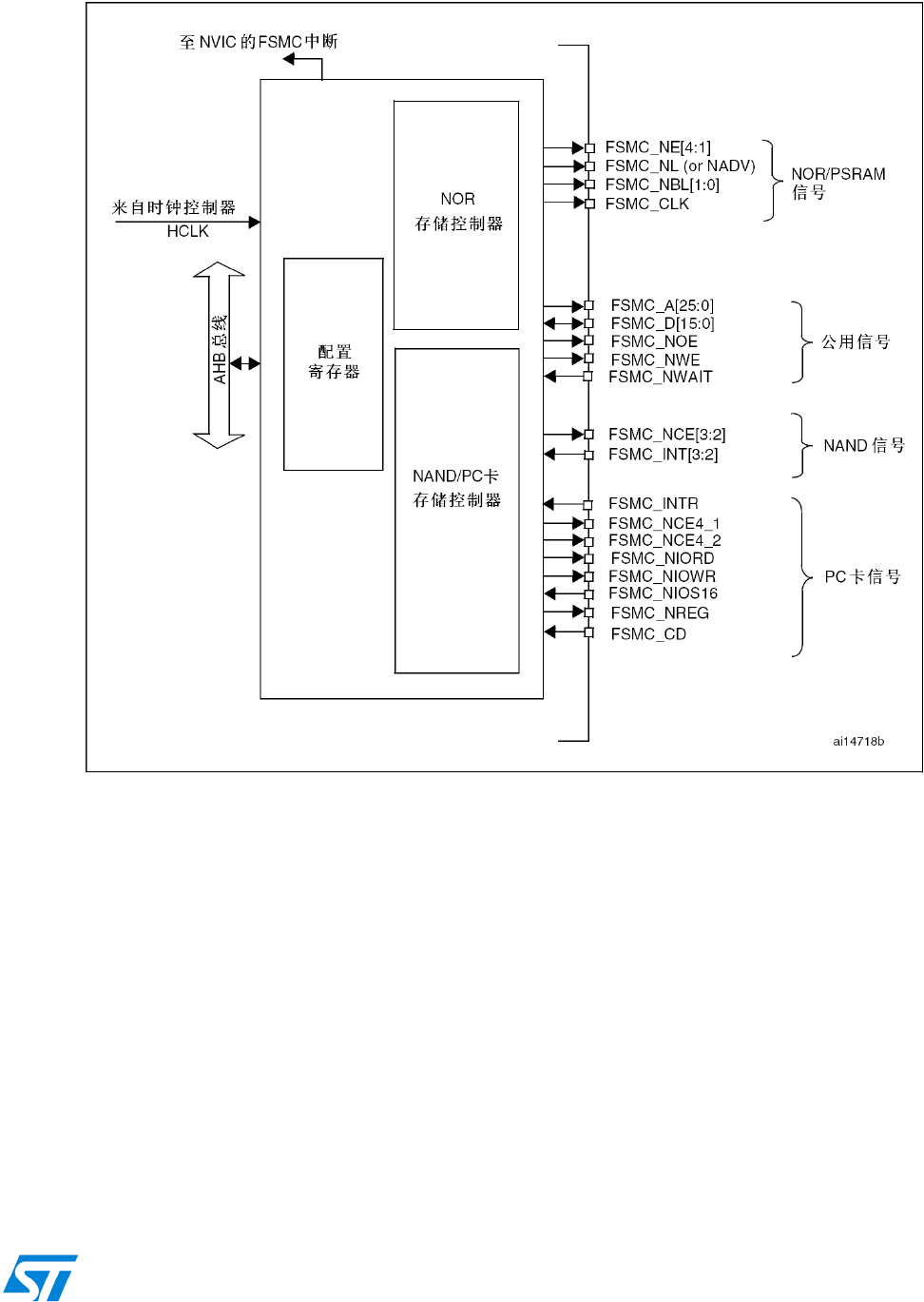

- 19 灵活的静态存储器控制器(FSMC)

- 19.1 FSMC功能描述

- 19.2 框图

- 19.3 AHB接口

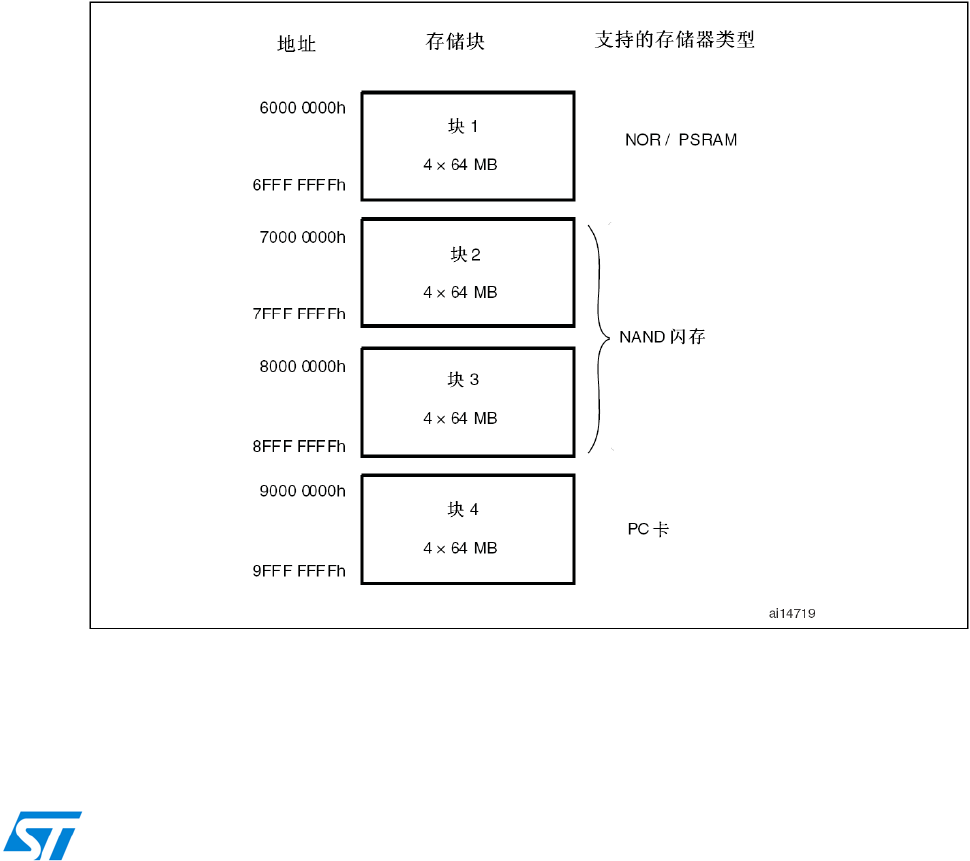

- 19.4 外部设备地址映像

- 19.5 NOR闪存和PSRAM控制器

- 19.6 NAND闪存和PC卡控制器

- 19.7 FSMC寄存器地址映象

- 20 SDIO接口(SDIO)

- 20.1 SDIO主要功能

- 20.2 SDIO总线拓扑

- 20.3 SDIO功能描述

- 20.4 卡功能描述

- 20.5 响应格式

- 20.6 SDIO I/O卡特定的操作

- 20.7 CE-ATA特定操作

- 20.8 硬件流控制

- 20.9 SDIO寄存器

- 20.9.1 SDIO电源控制寄存器(SDIO_POWER)

- 20.9.2 SDIO时钟控制寄存器(SDIO_CLKCR)

- 20.9.3 SDIO参数寄存器(SDIO_ARG)

- 20.9.4 SDIO命令寄存器(SDIO_CMD)

- 20.9.5 SDIO命令响应寄存器(SDIO_RESPCMD)

- 20.9.6 SDIO响应1..4寄存器(SDIO_RESPx)

- 20.9.7 SDIO数据定时器寄存器(SDIO_DTIMER)

- 20.9.8 SDIO数据长度寄存器(SDIO_DLEN)

- 20.9.9 SDIO数据控制寄存器(SDIO_DCTRL)

- 20.9.10 SDIO数据计数器寄存器(SDIO_DCOUNT)

- 20.9.11 SDIO状态寄存器(SDIO_STA)

- 20.9.12 SDIO清除中断寄存器(SDIO_ICR)

- 20.9.13 SDIO中断屏蔽寄存器(SDIO_MASK)

- 20.9.14 SDIO FIFO计数器寄存器(SDIO_FIFOCNT)

- 20.9.15 SDIO数据FIFO寄存器(SDIO_FIFO)

- 20.9.16 SDIO寄存器映像

- 21 USB全速设备接口(USB)

- 22 控制器局域网(bxCAN)

- 23 串行外设接口(SPI)

- 23.1 SPI简介

- 23.2 SPI和I2S主要特征

- 23.3 SPI功能描述

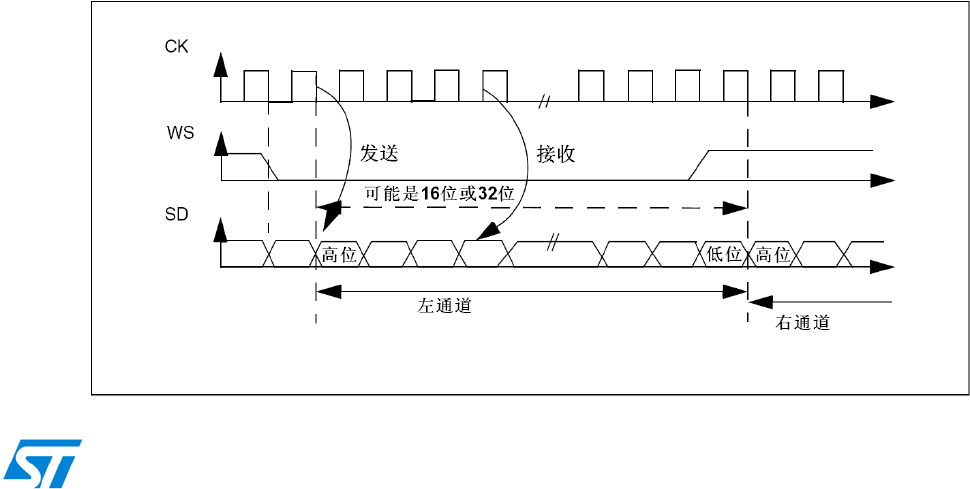

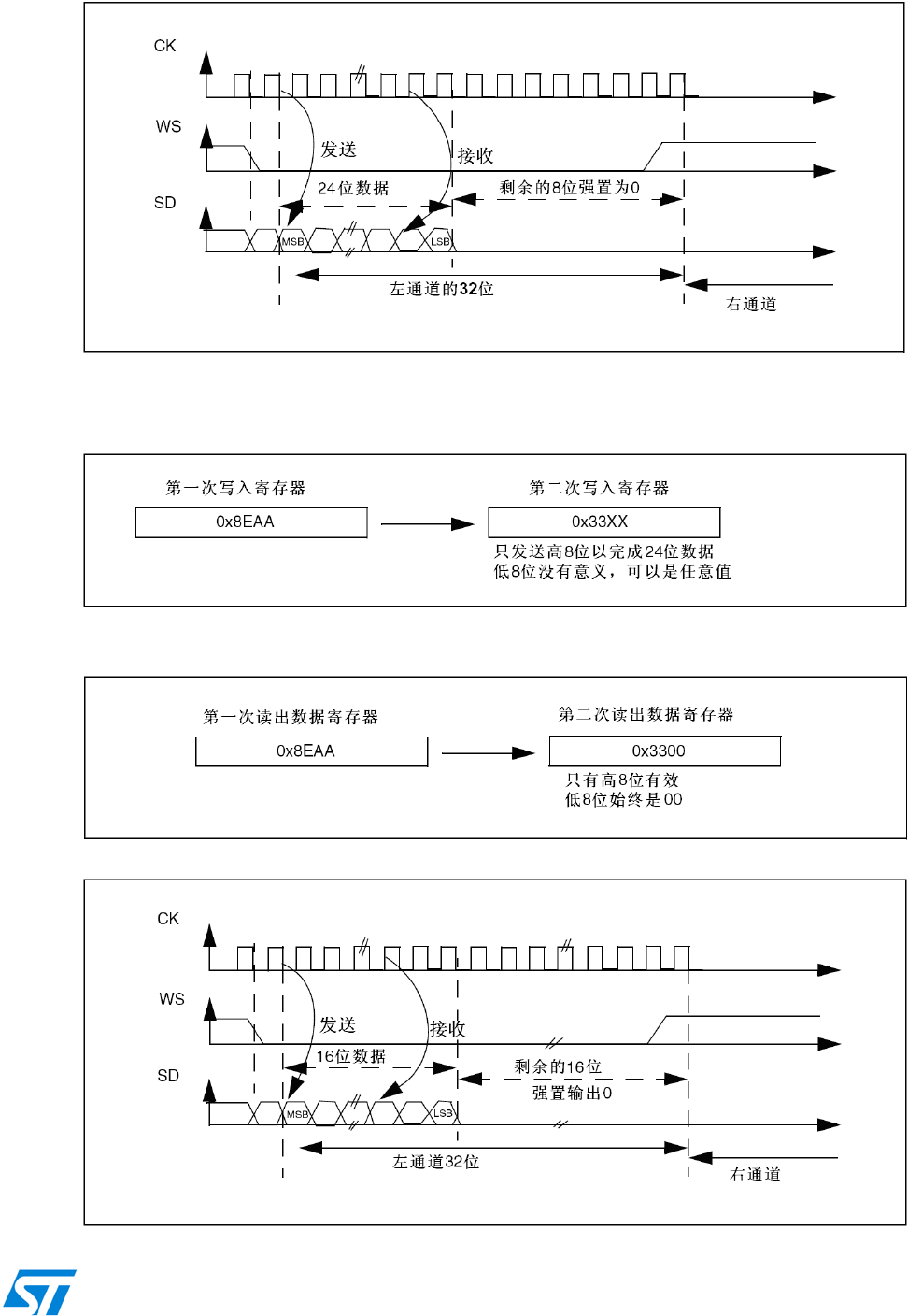

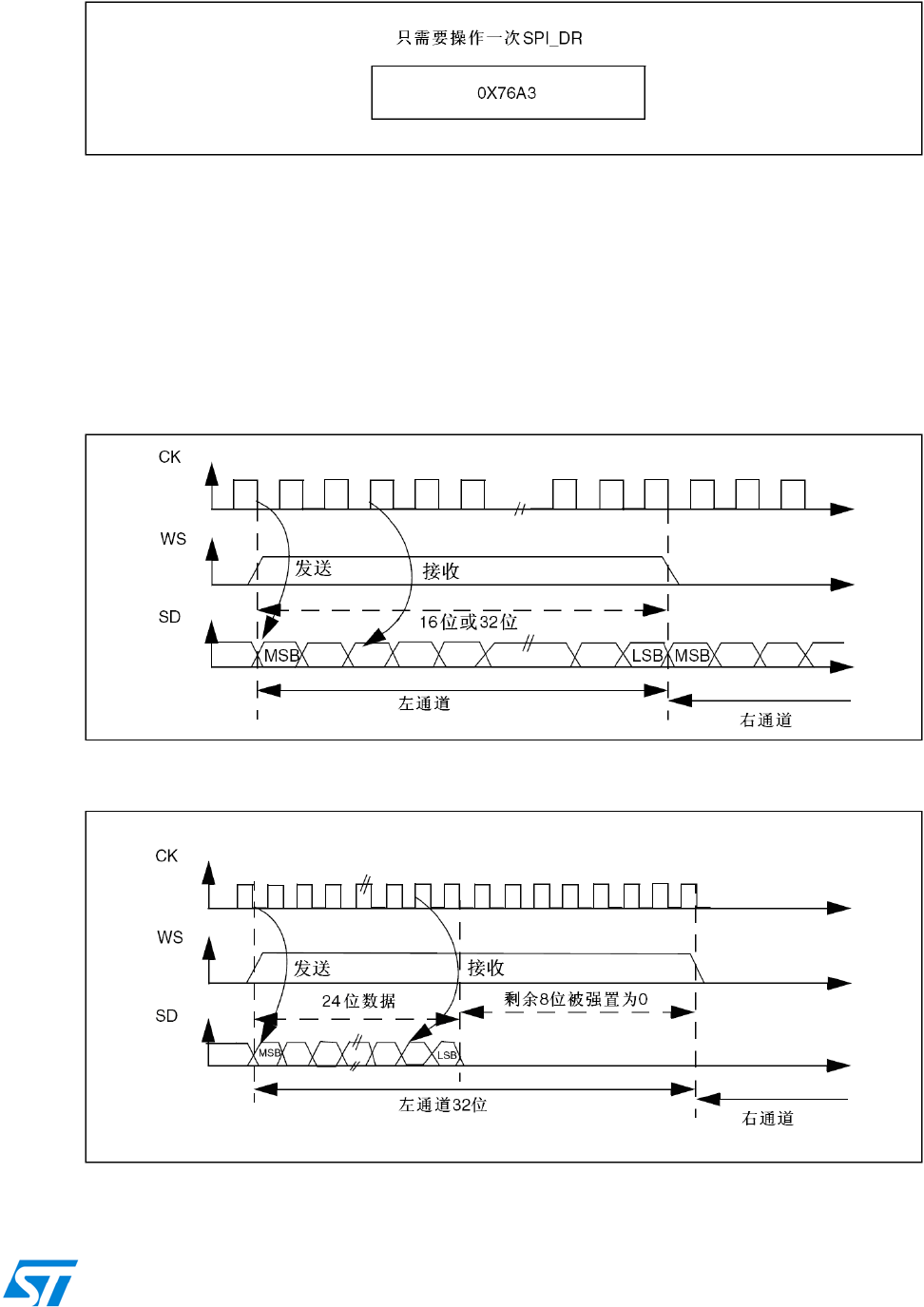

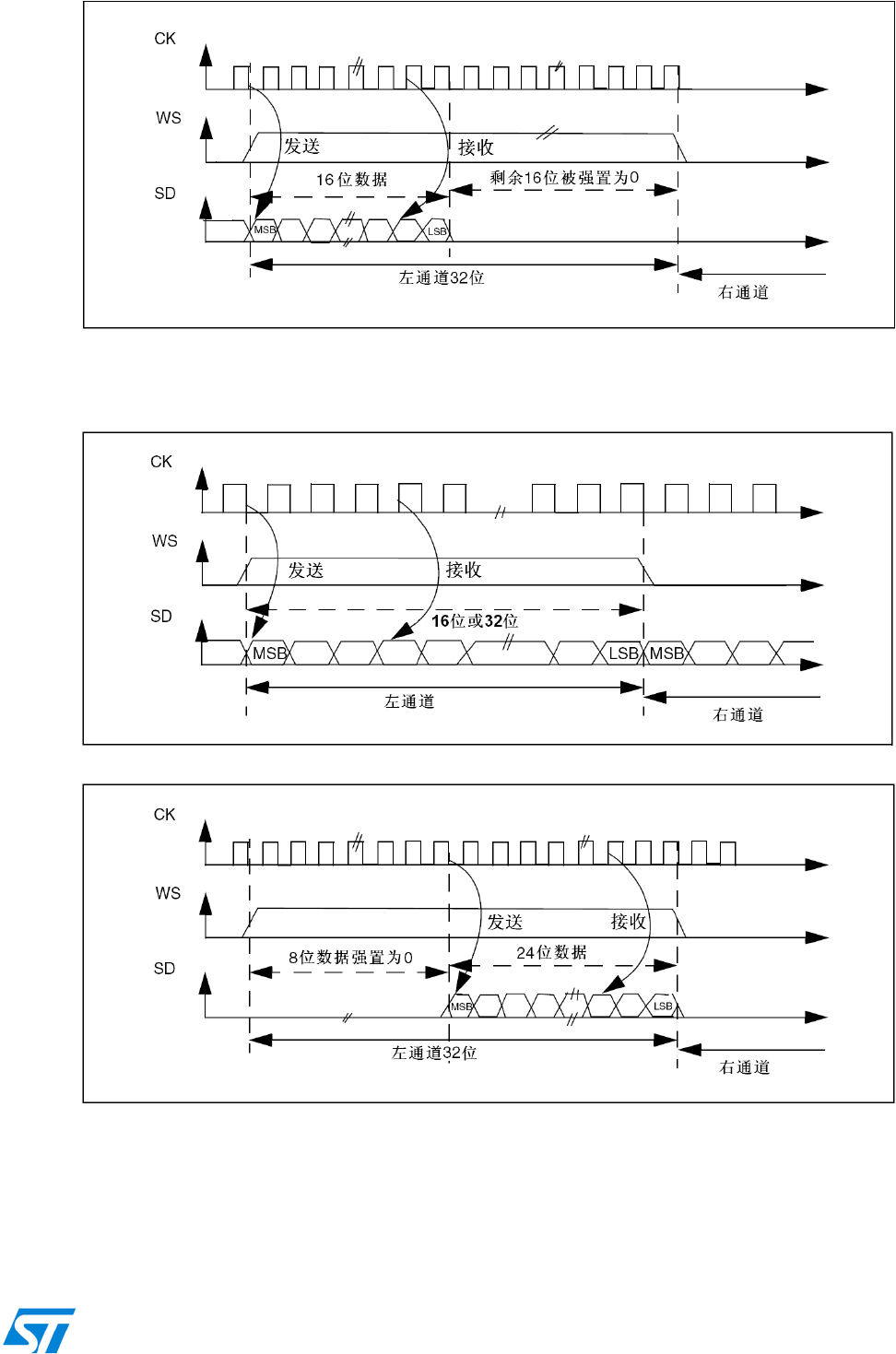

- 23.4 I2S功能描述

- 23.5 SPI和I2S寄存器描述

- 23.5.1 SPI控制寄存器1(SPI_CR1)(I2S模式下不使用)

- 23.5.2 SPI控制寄存器2(SPI_CR2)

- 23.5.3 SPI 状态寄存器(SPI_SR)

- 23.5.4 SPI 数据寄存器(SPI_DR)

- 23.5.5 SPI CRC多项式寄存器(SPI_CRCPR)(I2S模式下不使用)

- 23.5.6 SPI Rx CRC寄存器(SPI_RXCRCR)(I2S模式下不使用)

- 23.5.7 SPI Tx CRC寄存器(SPI_TXCRCR)

- 23.5.8 SPI_I2S配置寄存器(SPI_I2S_CFGR)

- 23.5.9 SPI_I2S预分频寄存器(SPI_I2SPR)

- 23.5.10 SPI 寄存器地址映象

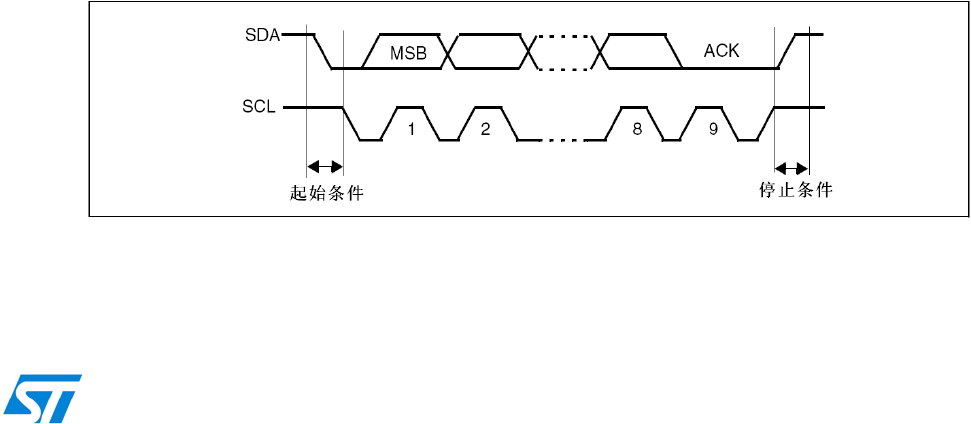

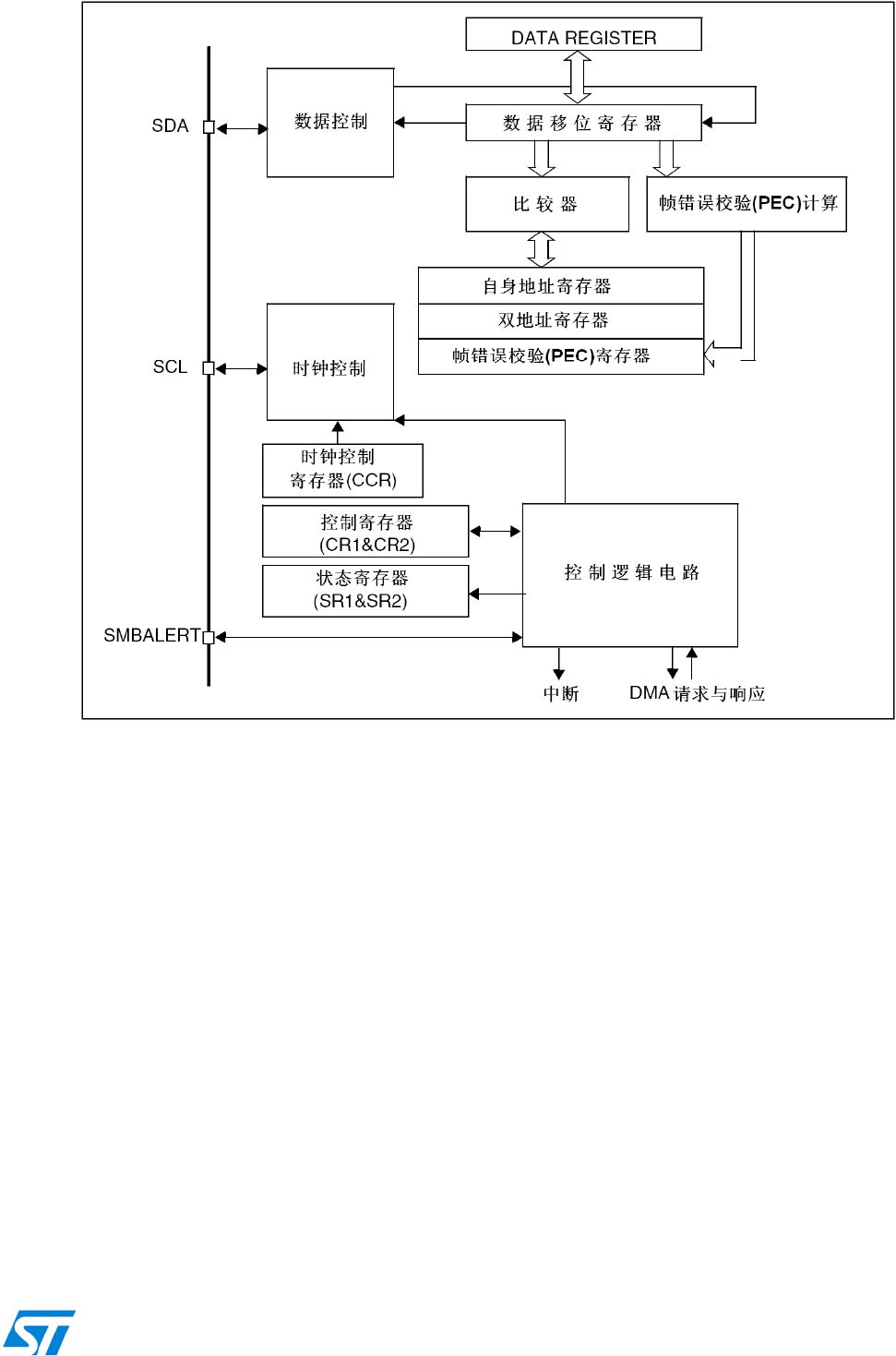

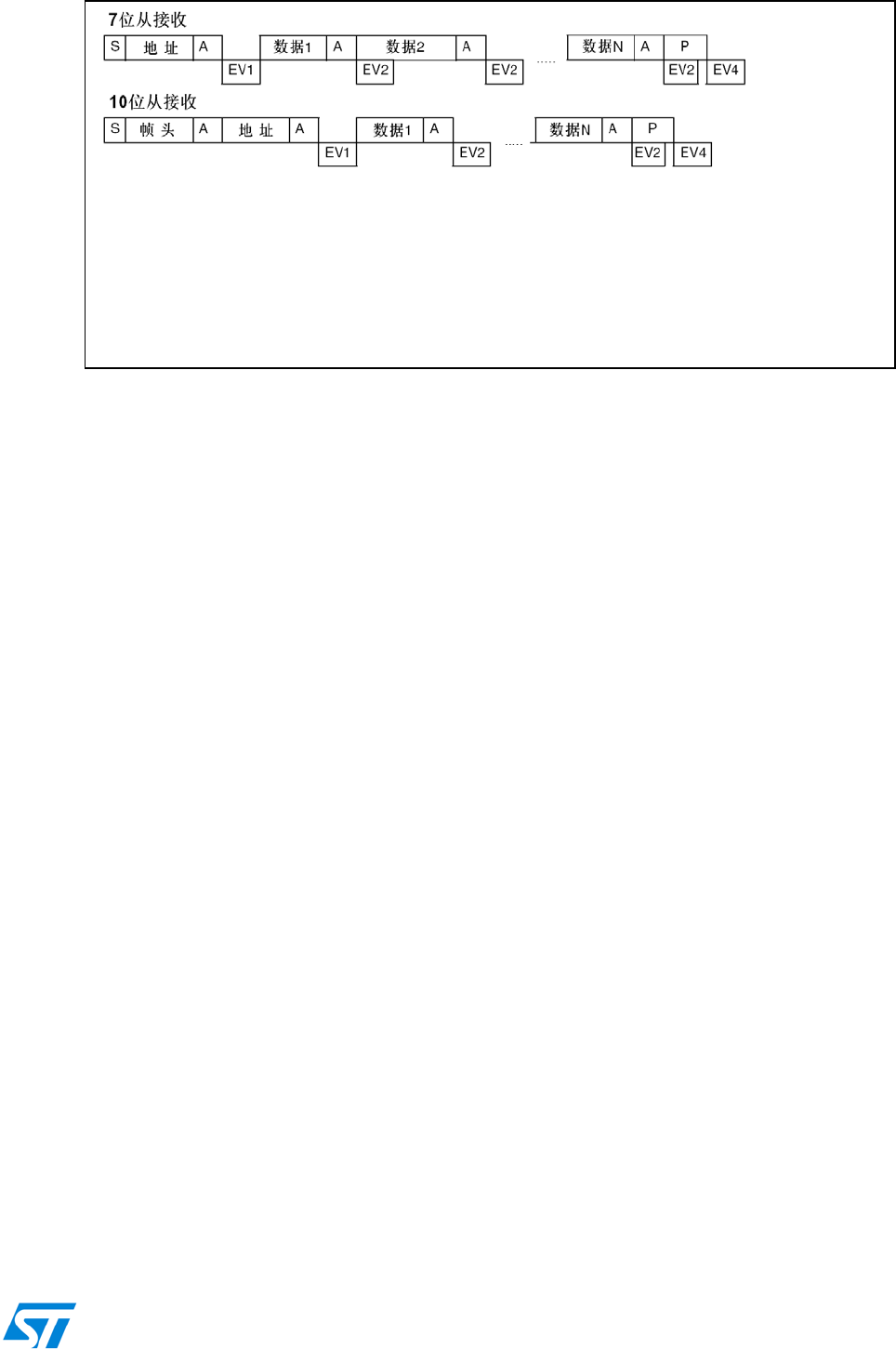

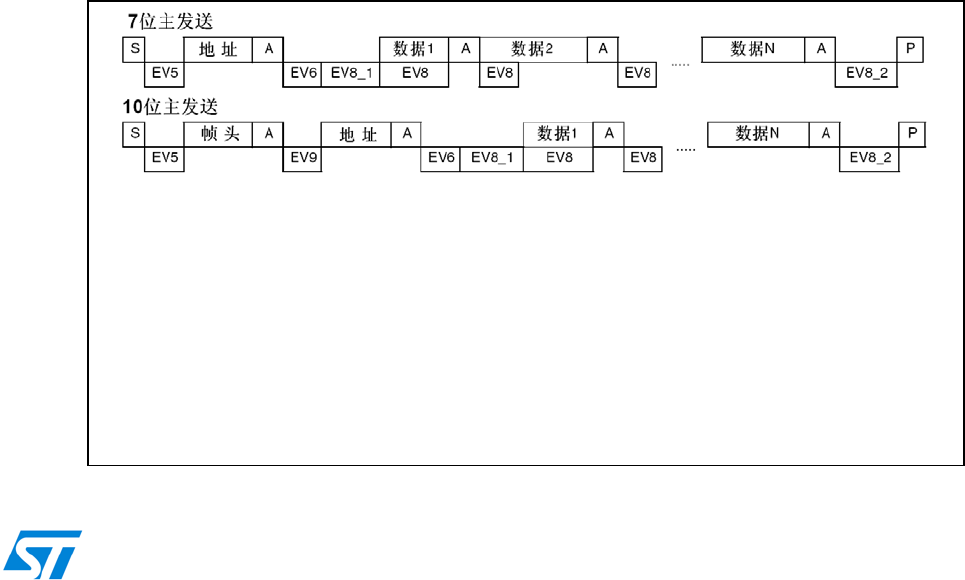

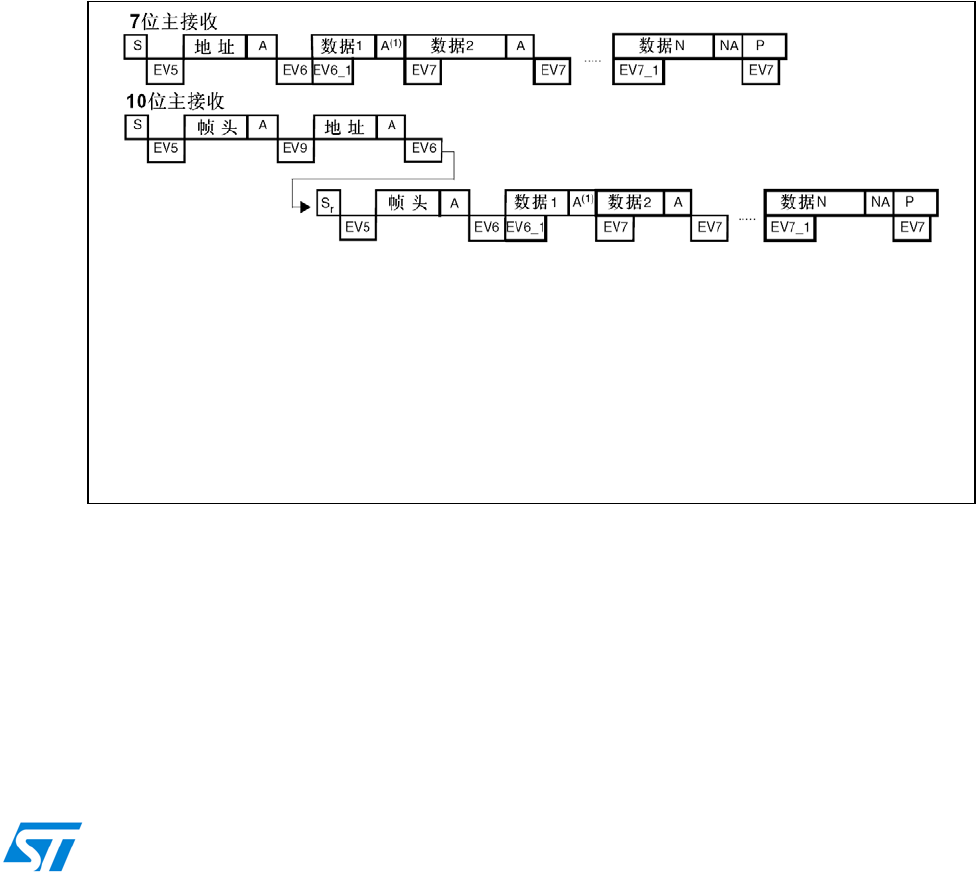

- 24 I2C接口

- 25 通用同步异步收发器(USART)

- 25.1 USART介绍

- 25.2 USART主要特性

- 25.3 USART功能概述

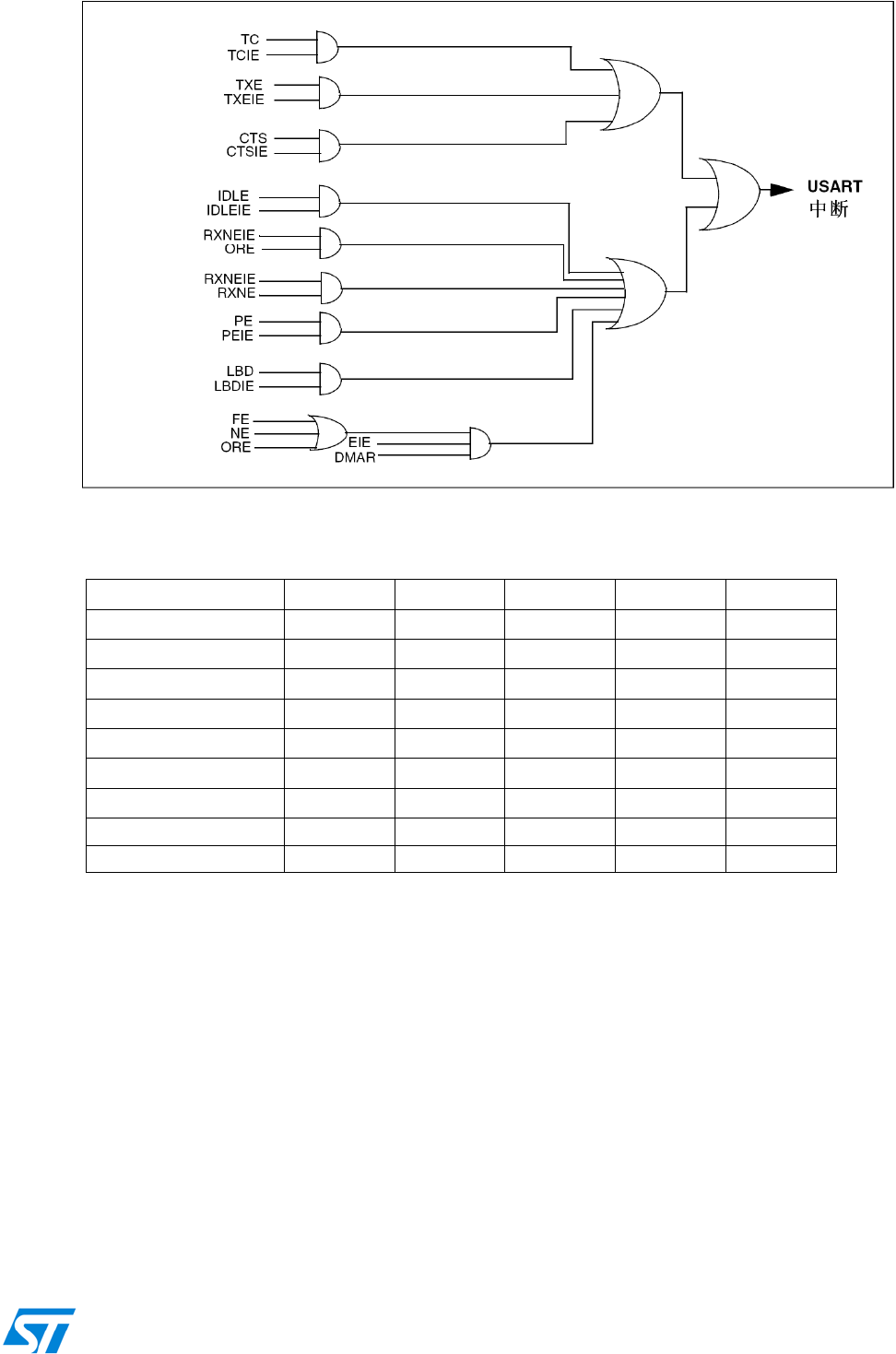

- 25.4 USART中断请求

- 25.5 USART模式配置

- 25.6 USART寄存器描述

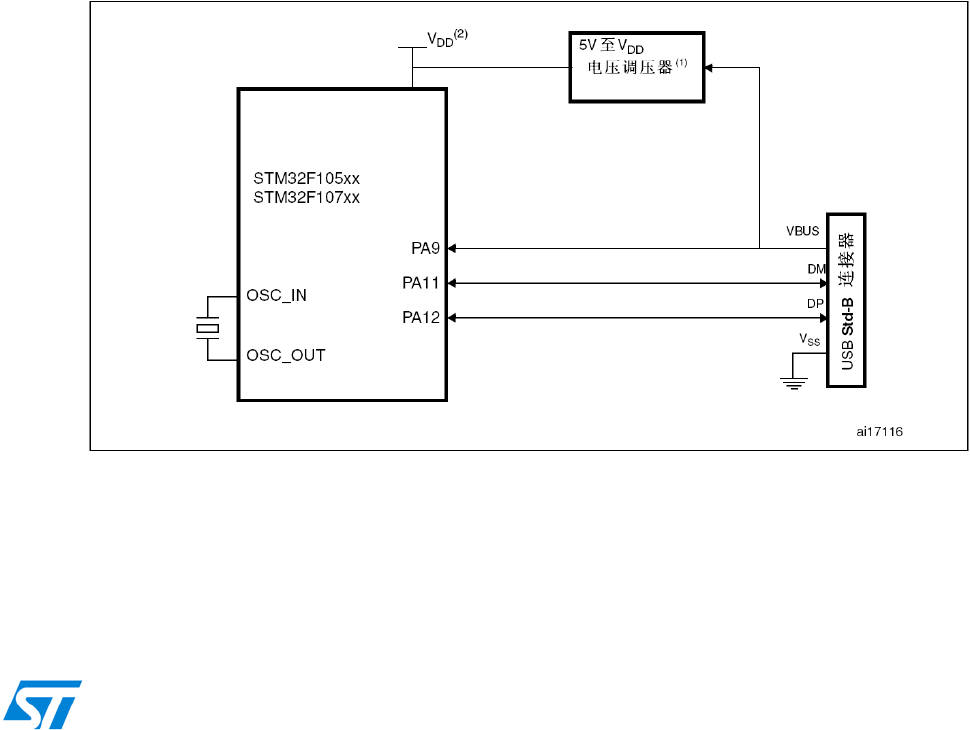

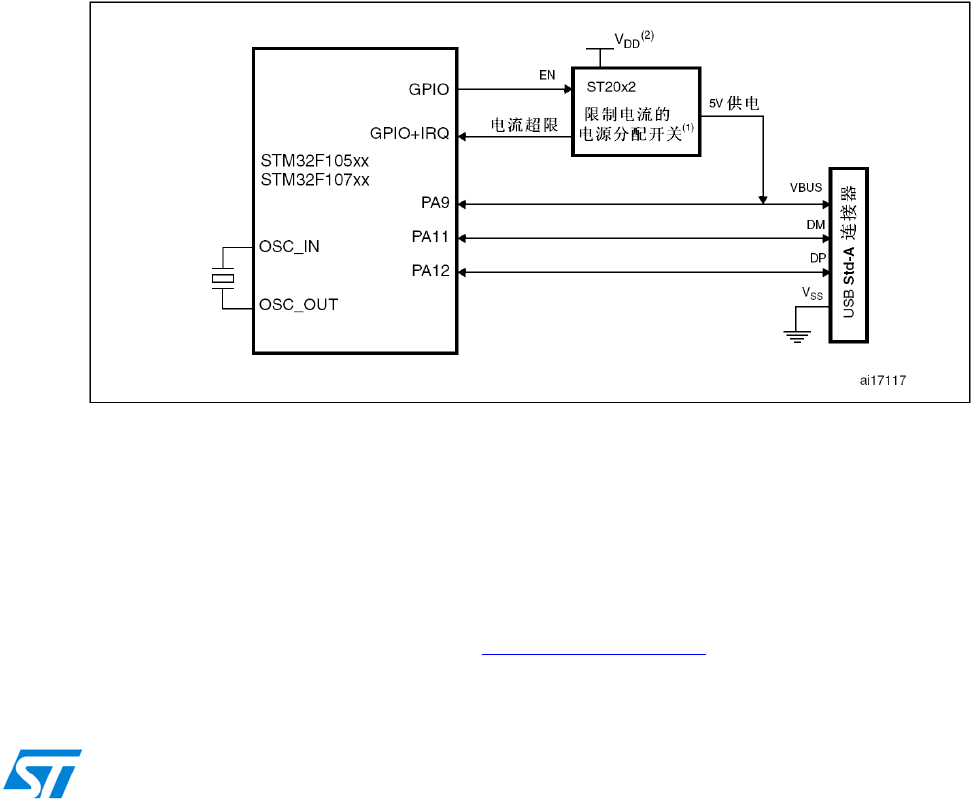

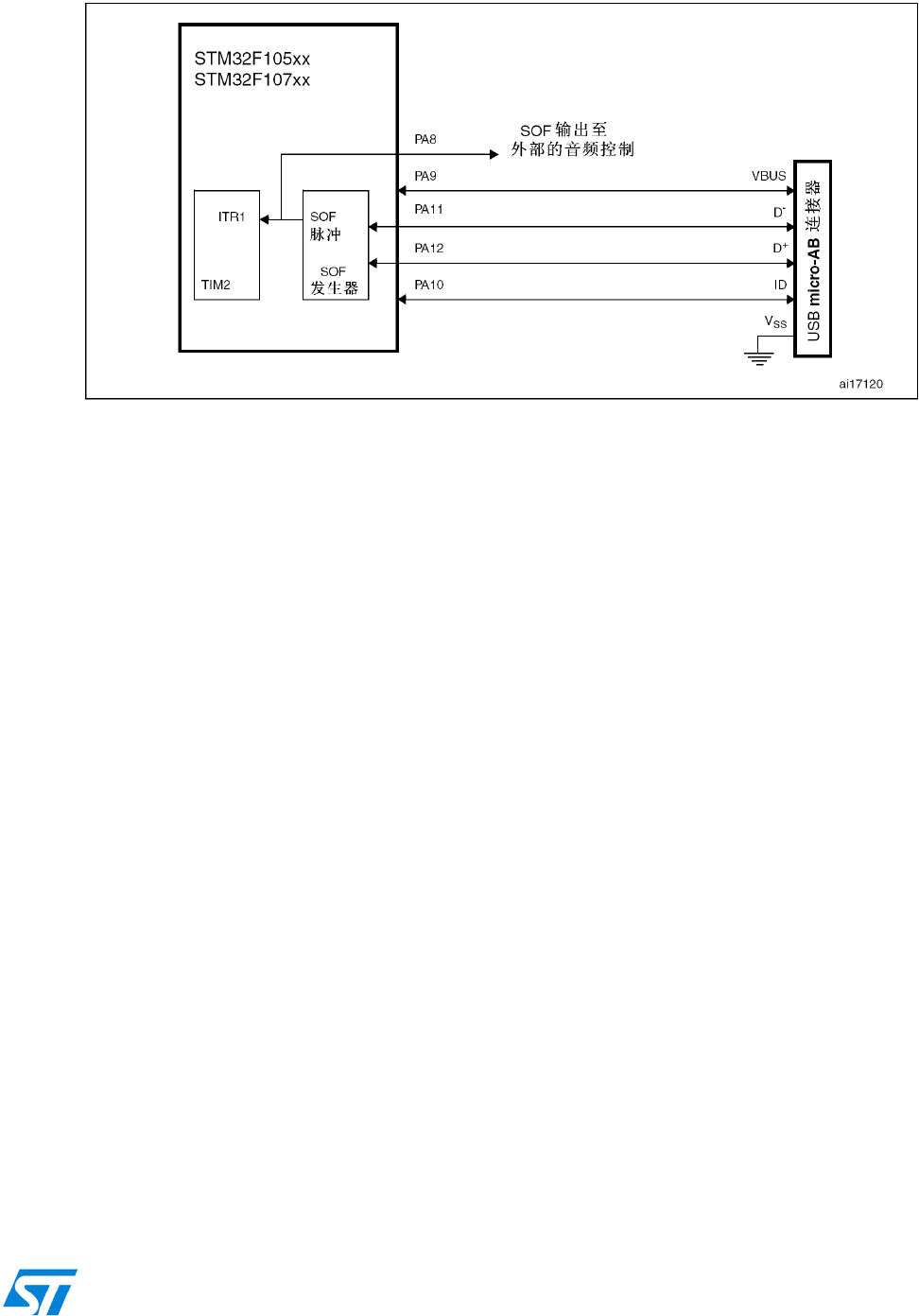

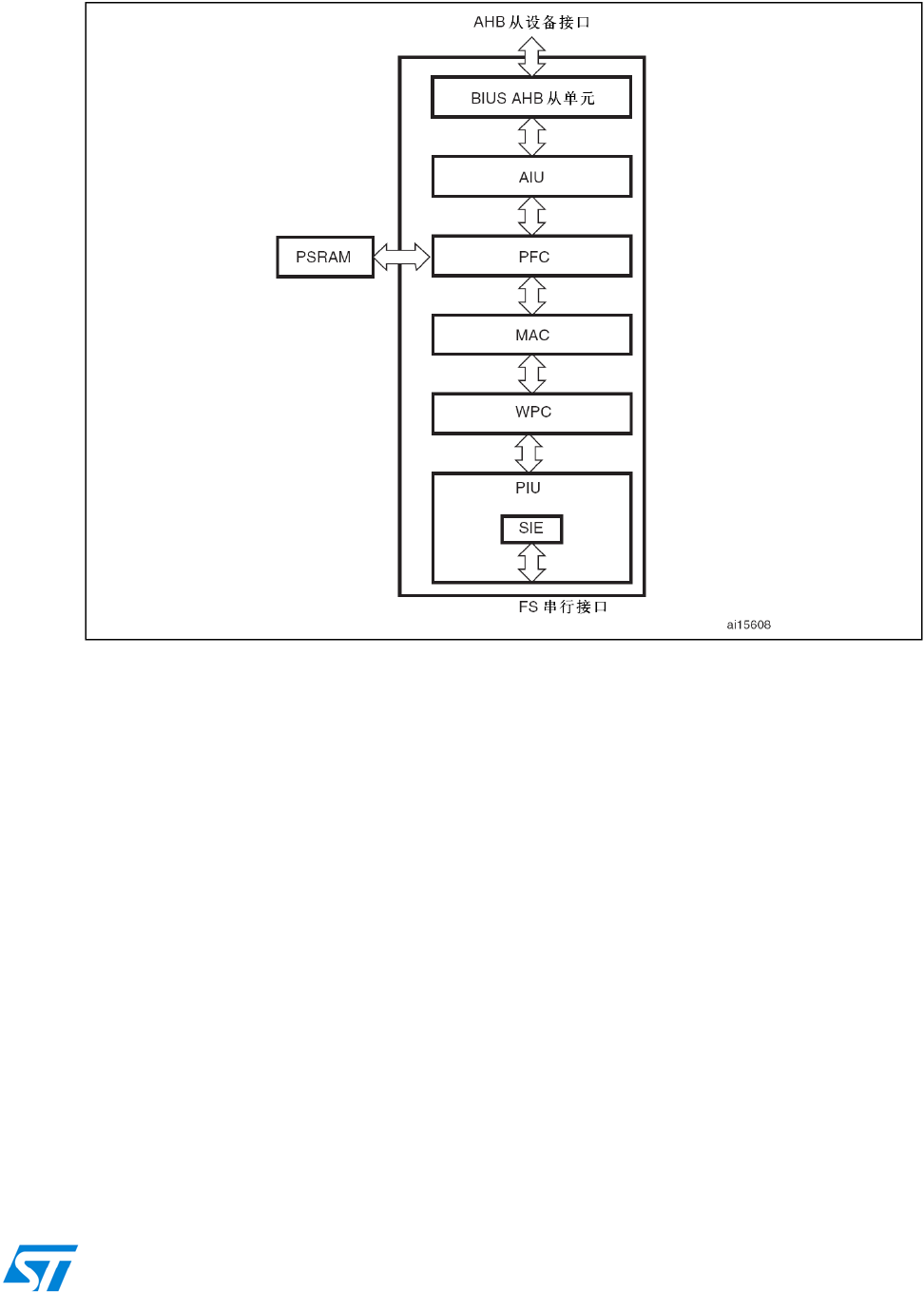

- 26 USB OTG全速(OTG_FS)

- 26.1 OTG模块介绍

- 26.2 OTG_FS主要功能

- 26.3 OTG_FS功能描述

- 26.4 OTG双角色设备(DRD)

- 26.5 USB设备模式

- 26.6 USB主机

- 26.7 SOF触发

- 26.8 供电选项

- 26.9 USB数据FIFO

- 26.10 设备模式下的FIFO结构

- 26.11 主机模式下的FIFO结构

- 26.12 USB系统性能

- 26.13 OTG_FS中断

- 26.14 OTG_FS控制和状态寄存器

- 26.14.1 CSR存储器映像

- 26.14.2 OTG_FS全局寄存器

- OTG_FS控制和状态寄存器(OTG_FS_GOTGCTL)

- OTG_FS中断寄存器(OTG_FS_GOTGINT)

- OTG_FS AHB配置寄存器(OTG_FS_GAHBCFG)

- OTG_FS_USB配置寄存器(OTG_FS_GUSBCFG)

- OTG_FS复位寄存器(OTG_FS_GRSTCTL)

- OTG_FS控制器中断寄存器(OTG_FS_GINTSTS)

- OTG_FS中断屏蔽寄存器(OTG_FS_GINTMSK)

- OTG_FS接收状态调试读/OTG状态读和POP寄存器(OTG_FS_GRXSTSR / OTG_FS_GRXSTSP)

- OTG_FS接收FIFO长度寄存器(OTG_FS_GRXFSIZ)

- OTG_FS非周期性TX FIFO长度寄存器(OTG_FS_GNPTXFSIZ)

- OTG_FS非周期性TX FIFO/请求队列状态寄存器(OTG_FS_GNPTXSTS)

- OTG_FS通用控制器配置寄存器(OTG_FS_GCCFG)

- OTG_FS控制器ID寄存器(OTG_FS_CID)

- OTG_FS主机周期性发送FIFO长度寄存器(OTG_FS_HPTXFSIZ)

- OTG_FS设备IN端点发送FIFO长度寄存器(OTG_FS_DIEPTXFx)(其中x是FIFO的编号,x=1…4)

- 26.14.3 主机模式下的寄存器

- OTG_FS主机模式配置寄存器(OTG_FS_HCFG)

- OTG_FS主机帧间隔寄存器(OTG_FS_HFIR)

- OTG_FS主机帧号/帧时间剩余寄存器(OTG_FS_HFNUM)

- OTG_FS主机周期性发送FIFO/请求队列寄存器(OTG_FS_HPTXSTS)

- OTG_FS主机所有通道中断寄存器(OTG_FS_HAINT)

- OTG_FS主机所有通道中断屏蔽寄存器(OTG_FS_HAINTMSK)

- OTG_FS主机端口控制和状态寄存器(OTG_FS_HPRT)

- OTG_FS主机通道x特性寄存器(OTG_FS_HCCHARx)(此处x代码通道号,x = 0...7)

- OTG_FS主机通道x中断寄存器(OTG_FS_HCINTx)(其中x代表通道号,x=0...7,)

- OTG_FS主机通道x中断屏蔽寄存器(OTG_FS_HCINTMSKx)(其中x为通道号,x=0...7)

- OTG_FS主机通道x传输长度寄存器(OTG_FS_HCTSIZx)(其中x为通道号,x=0...7)

- 26.14.4 设备模式下的寄存器

- OTG_FS设备配置寄存器(OTG_FS_DCFG)

- OTG_FS设备控制寄存器(OTG_FS_DCTL)

- OTG_FS设备状态寄存器(OTG_FS_DSTS)

- OTG_FS设备IN端点通用中断屏蔽寄存器(OTG_FS_DIEPMSK)

- OTG_FS设备OUT端点通用中断屏蔽寄存器(OTG_FS_DOEPMSK)

- OTG_FS设备所有端点中断寄存器(OTG_FS_DAINT)

- OTG_FS所有端点中断屏蔽寄存器(OTG_FS_DAINTMSK)

- OTG_FS设备VBUS放电时间寄存器(OTG_FS_DVBUSDIS)

- OTG_FS设备VBUS脉冲时间寄存器(OTG_FS_DVBUSPULSE)

- OTG_FS设备IN端点FIFO空中断屏蔽寄存器(OTG_FS_DIEPEMPMSK)

- OTG_FS设备控制IN端点0控制寄存器(OTG_FS_DIEPCTL0)

- OTG设备端点x控制寄存器(OTG_FS_DIEPCTLx)(其中x为端点号,x=1…3)

- OTG_FS设备控制OUT端点0控制寄存器(OTG_FS_DOEPCTL0)

- OTG_FS设备OUT端点x控制寄存器(OTG_FS_DOEPCTLx)(其中x为端点号,x=1…3)

- OTG_FS设备端点x中断寄存器(OTG_FS_DIEPINTx)(其中x为端点号,x=0…3)

- OTG_FS设备端点x中断寄存器(OTG_FS_DOEPINTx)(其中x为端点号,x=0…3)

- OTG_FS设备IN端点0传输长度寄存器(OTG_FS_DIEPTSIZ0)

- OTG_FS设备OUT端点0传输长度寄存器(OTG_FS_DOEPTSIZ0)

- OTG_FS设备端点x传输长度寄存器(OTG_FS_DIEPTSIZx)(其中x为端点号,x=1…3)

- OTG_FS设备IN端点传输FIFO状态寄存器(OTG-FS_DTXFSTSx)(其中x为端点号,x=0…3)

- OTG_FS设备端点x传输长度寄存器(OTG_FS_DOEPTSIZx)(其中x为端点号,x=1…3)

- 26.14.5 OTG_FS电源和时钟门控寄存器(OTG_FS_PCGCCTL)

- 26.14.6 OTG_FS寄存器映像

- 26.15 OTG_FS编程规则

- 27 以太网(ETH):具有DMA控制器的介质访问控制(MAC)

- 27.1 以太网模块介绍

- 27.2 以太网模块主要功能

- 27.3 以太网模块引脚和内部信号

- 27.4 以太网模块功能描述:SMI、MII和RMII

- 27.5 以太网模块功能描述:MAC 802.3

- 27.6 以太网功能描述:DMA控制器操作

- 27.7 以太网中断

- 27.8 以太网寄存器描述

- 27.8.1 MAC寄存器描述

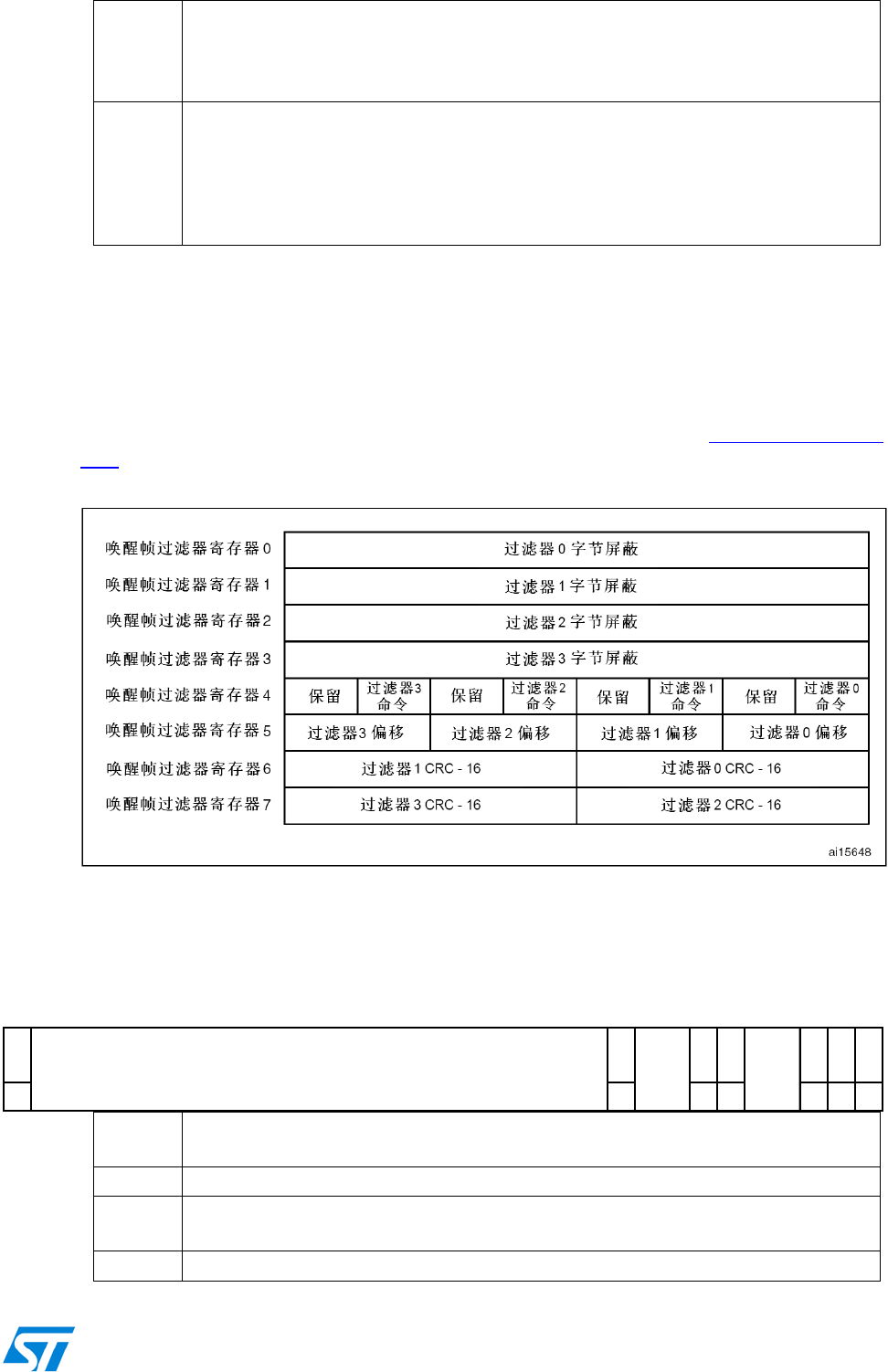

- 以太网MAC设置寄存器(ETH_MACCR)

- 以太网MAC帧过滤器寄存器(ETH_MACFFR)

- 以太网MAC Hash列表高寄存器(ETH_MACHTHR)

- 以太网MAC Hash列表低寄存器(ETH_MACHTLR)

- 以太网MAC MII地址寄存器(ETH_MACMIIAR)

- 以太网MAC MII数据寄存器(ETH_MACMIIDR)

- 以太网MAC流控寄存器(ETH_MACFCR)

- 以太网MAC VLAN标签寄存器(ETH_MACVLANTR)

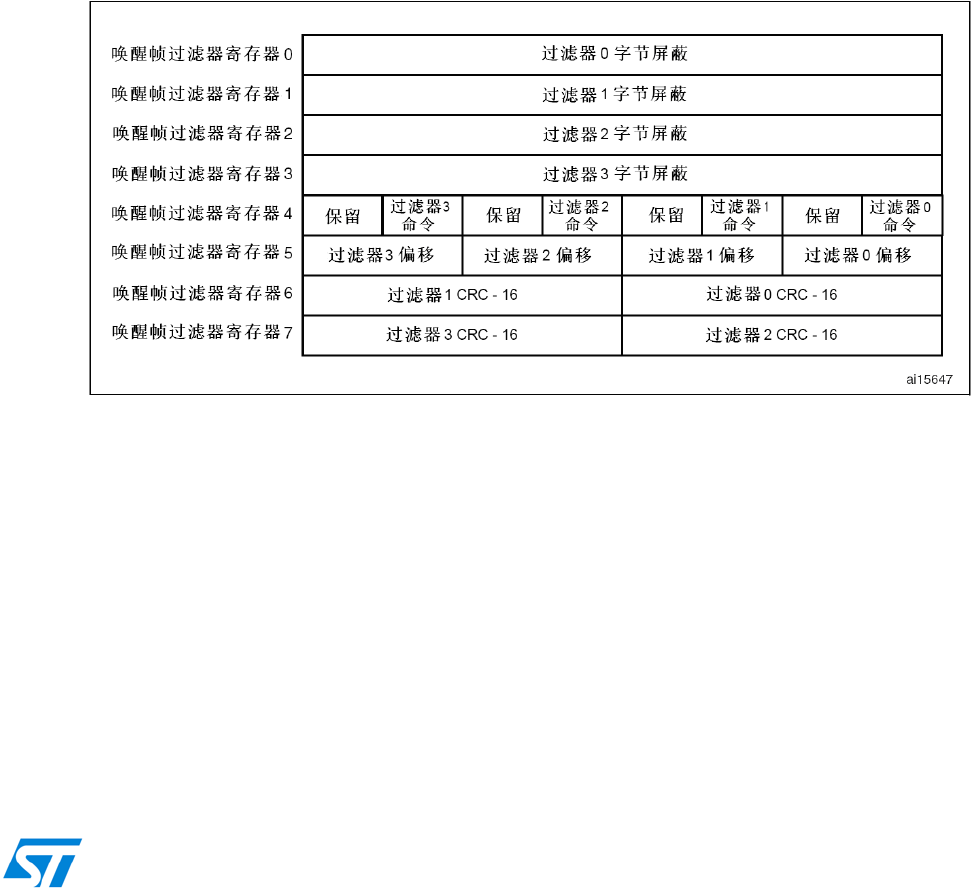

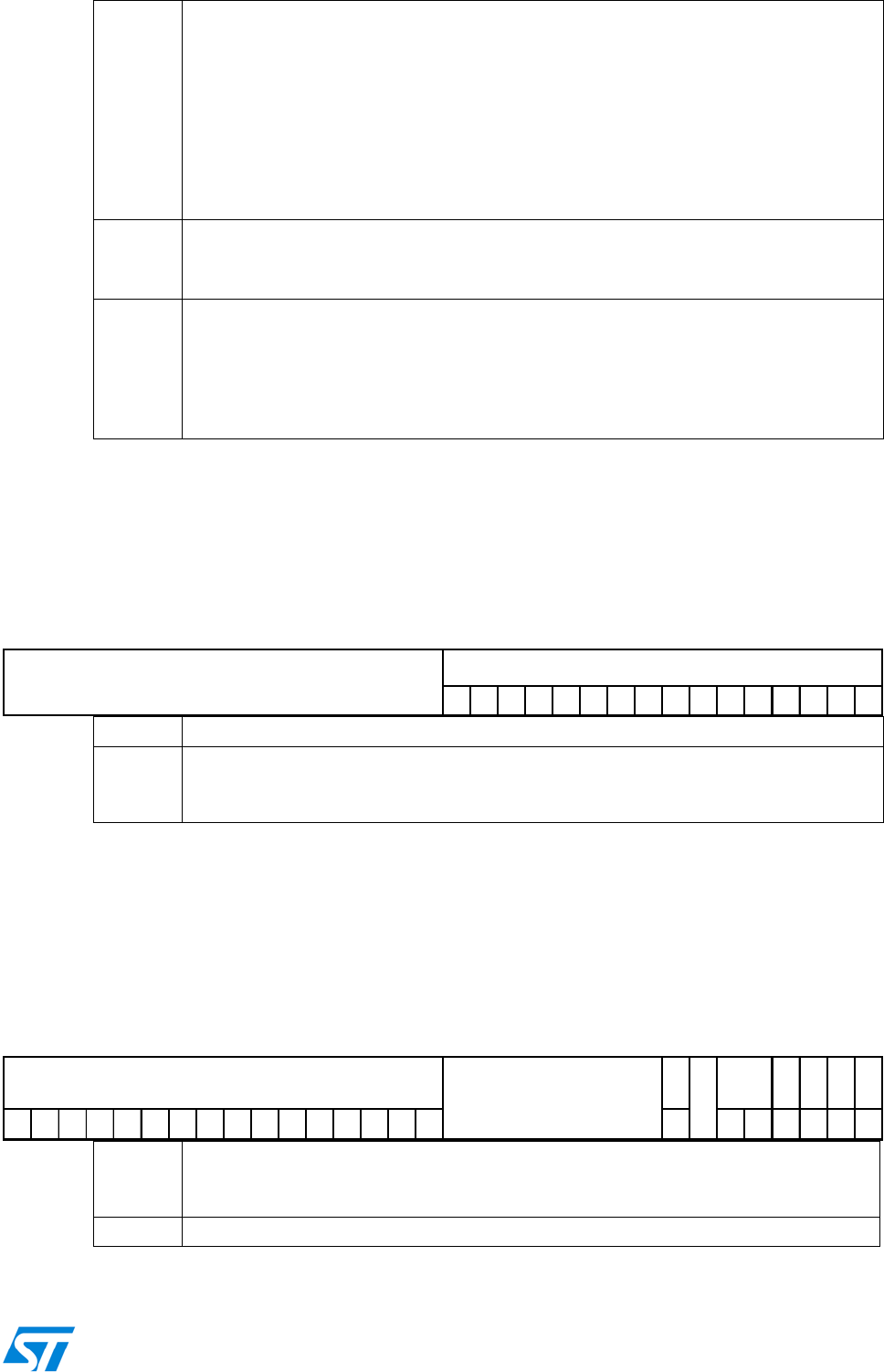

- 以太网MAC远程唤醒帧过滤器寄存器(ETH_MACRWUFFR)

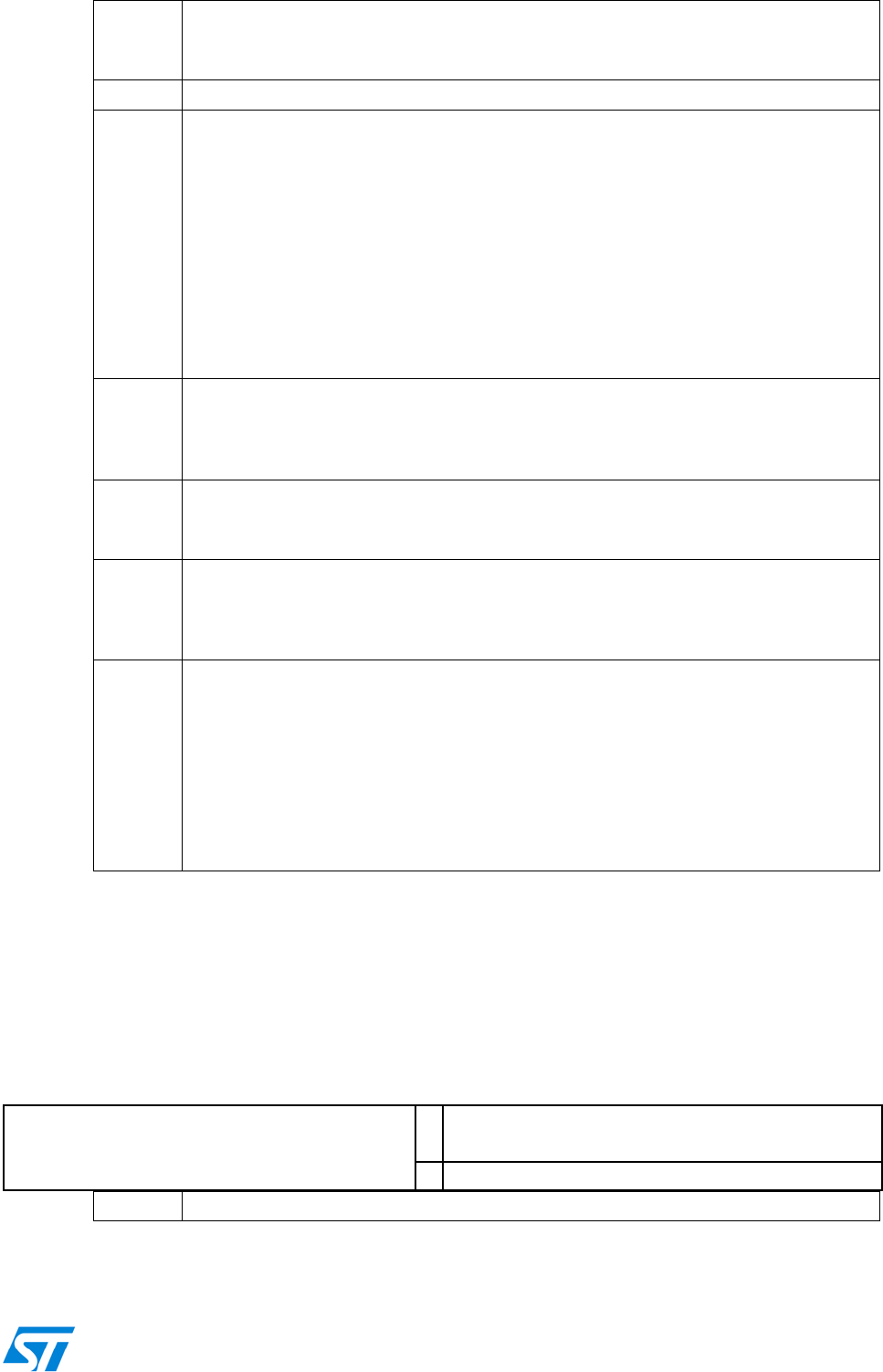

- 以太网MAC PMT控制和状态寄存器(ETH_MACPMTCSR)

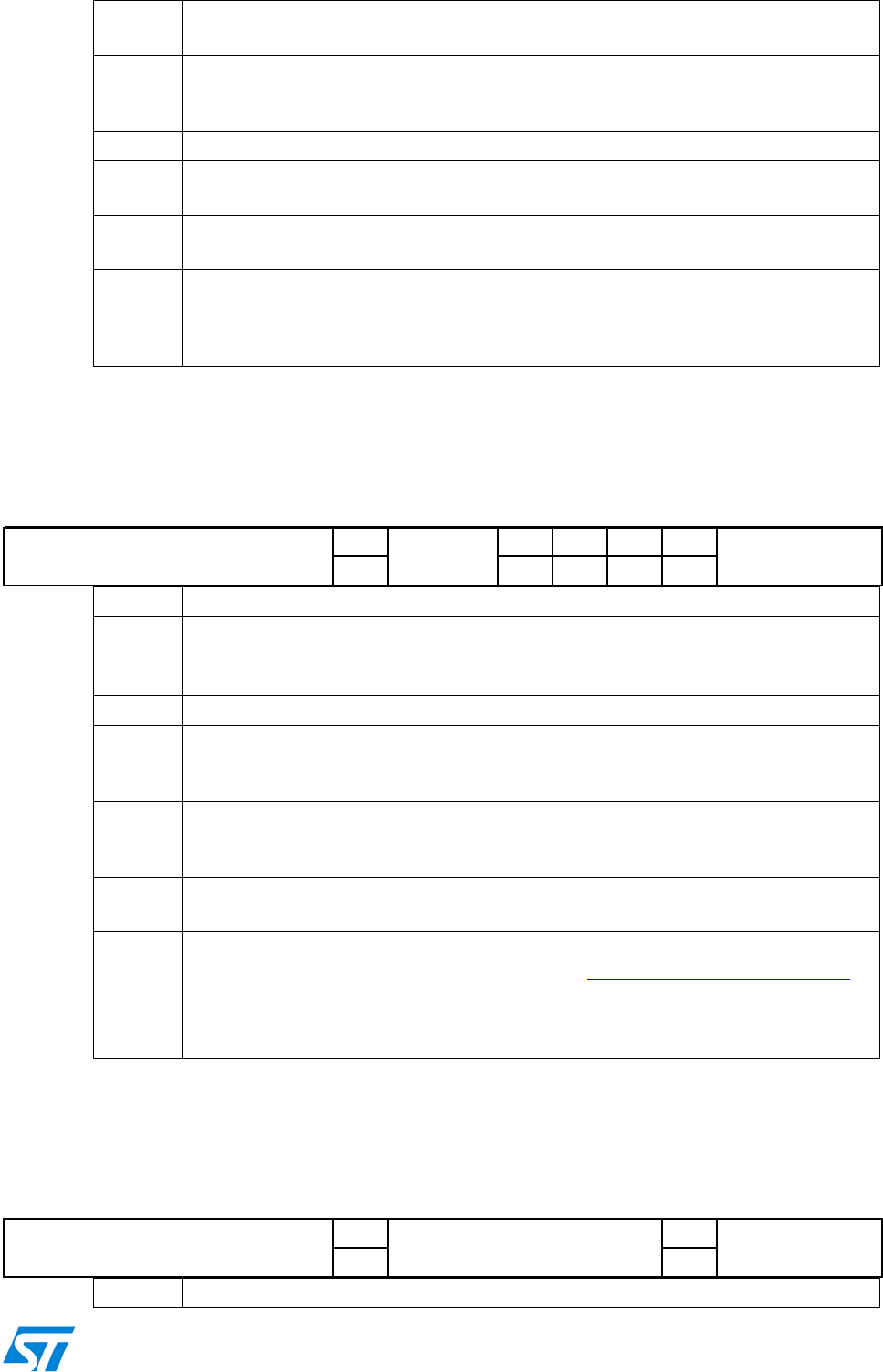

- 以太网MAC中断状态寄存器(ETH_MACSR)

- 以太网MAC中断屏蔽寄存器(ETH_MAIMR)

- 以太网MAC地址0高寄存器(ETH_MACA0HR)

- 以太网MAC地址0低寄存器(ETH_MACA0LR)

- 以太网MAC地址1高寄存器(ETH_MACA1HR)

- 以太网MAC地址1低寄存器(ETH_MACA1LR)

- 以太网MAC地址2高寄存器(ETH_MACA2HR)

- 以太网MAC地址2低寄存器(ETH_MACA2LR)

- 以太网MAC地址3高寄存器(ETH_MACA3HR)

- 以太网MAC地址3低寄存器(ETH_MACA1LR)

- 27.8.2 MMC寄存器描述

- 以太网MMC控制寄存器(ETH_MMCCR)

- 以太网MMC接收中断寄存器(ETH_MMCRIR)

- 以太网MMC发送中断寄存器(ETH_MMCTIR)

- 以太网MMC接收中断屏蔽寄存器(ETH_MMCRIMR)

- 以太网MMC发送中断屏蔽寄存器(ETH_MMCTIMR)

- 以太网MMC 1次冲突后发送”好”帧的计数器寄存器(ETH_MMCTGFSCCR)

- 以太网MMC 1次以上冲突后发送”好”帧的计数器寄存器(ETH_ MMCTGFMSCCR)

- 以太网MMC发送”好”帧计数器寄存器(ETH_ MMCTGFCR)

- 以太网MMC CRC错误接收帧计数器寄存器(ETH_ MMCRFCECR)

- 以太网MMC对齐错误接收帧计数器寄存器(ETH_ MMCRFAECR)

- 以太网MMC 接收帧”好”单播帧计数器寄存器(ETH_ MMCRGUFCR)

- 27.8.3 IEEE 1588时间戳寄存器

- 27.8.4 DMA寄存器描述

- 以太网DMA总线模式寄存器(ETH_DMABMR)

- 以太网DMA发送查询请求寄存器(ETH_DMATPDR)

- 以太网DMA接收查询请求寄存器(ETH_DMARPDR)

- 以太网DMA接收描述符列表地址寄存器(ETH_DMARDLAR)

- 以太网DMA发送描述符列表地址寄存器(ETH_DMATDLAR)

- 以太网DMA状态寄存器(ETH_DMASR)

- 以太网DMA工作模式寄存器(ETH_DMAOMR)

- 以太网DMA中断使能寄存器(ETH_DMAIER)

- 以太网DMA丢失帧和缓存溢出计数器寄存器(ETH_DMAMFBOCR)

- 以太网DMA当前发送描述符寄存器(ETH_DMACHTDR)

- 以太网DMA当前接收描述符寄存器(ETH_DMACHRDR)

- 以太网DMA当前发送缓存地址寄存器(ETH_DMACHTBDR)

- 以太网DMA当前接收缓存地址寄存器(ETH_ DMACHRBDR)

- 27.8.5 以太网寄存器映像

- 27.8.1 MAC寄存器描述

- 28 器件电子签名

- 29 调试支持(DBG)

- 29.1 概况

- 29.2 ARM参考文献

- 29.3 SWJ调试端口(serial wire and JTAG)

- 29.4 引脚分布和调试端口脚

- 29.5 STM32F10xxx JTAG TAP 连接

- 29.6 ID 代码和锁定机制

- 29.7 JTAG调试端口

- 29.8 SW调试端口

- 29.9 对于JTAG-DP或SWDP都有效的AHB-AP (AHB 访问端口)

- 29.10 内核调试

- 29.11 调试器主机在系统复位下的连接能力

- 29.12 FPB (Flash patch breakpoint)

- 29.13 DWT(数据观察点触发data watchpoint trigger)

- 29.14 ITM (指令跟踪微单元 instrumentation trace macrocell)

- 29.15 ETM模块(嵌入式跟踪微单元Embedded Trace Macrocell)

- 29.16 MCU调试模块(MCUDBG)

- 29.17 TPIU (跟踪端口接口单元 Trace Port Interface Unit)

- 29.18 DBG寄存器地址映象

STM32F10xxx参考手册

翻译说明

本文档是依据STM32 Reference Manual (RM0008)翻译的,已经与2009年6月的英文第9版(Doc ID

13902 Rev 9)进行了全面校对,更正了不少以前版本的错误。

在校对即将结束时,ST于2009年12月中旬又发布了英文第10版(Doc ID 13902 Rev 10),为了与最新的

英文版同步,我们按照英文第10版结尾的”文档版本历史”中的指示,在翻译的文档中快速地校对更正了对

应的部分。由于时间的关系,没有逐字逐句地按照英文第10版进行通篇校对,鉴于芯片本身没有改变,

我们相信除了”文档版本历史”中指出的差别外,英文第10版与英文第9版不会再有更多的变化,遂定稿现

在这个翻译版本为对应的中文第10版文档。

由于我们的水平有限以及文档篇幅的庞大,翻译的过程中难免会有错误和遗漏的地方,希望广大读者们

能够及时向我们反馈您在阅读期间所发现的错误和问题,我们会尽快在下一个版本中更正。您可以发邮

件到mcu.china@st.com向我们提出您的意见和建议,谢谢。

意法半导体(中国)投资有限公司

MCU技术支持

2010年1月10日

参照2009年12月 RM0008 Reference Manual 英文第10版

本译文仅供参考,如有翻译错误,请以英文原稿为准。请读者随时注意在ST网站下载更新版本

STM32F10xxx参考手册

文档使用说明

本手册是STM32微控制器产品的技术参考手册

参照2009年12月 RM0008 Reference Manual 英文第10版

,技术参考手册是有关如何使用该产品的具体信息,包含

各个功能模块的内部结构、所有可能的功能描述、各种工作模式的使用和寄存器配置等详细信息。

技术参考手册不包含有关产品技术特征的说明,这些内容在数据手册中。数据手册中的内容包括:产品

的基本配置(如内置Flash和RAM的容量、外设模块的种类和数量等),管脚的数量和分配,电气特性,封

装信息,和定购代码等。

STM32是一个微控制器产品系列的总称,目前这个系列中已经包含了多个子系列,分别是:STM32小容

量产品、STM32中容量产品、STM32大容量产品和STM32互联型产品;按照功能上的划分,又可分为

STM32F101xx、STM32F102xx和STM32F103xx系列;因此STM32产品系列有以下这些数据手册:

小容量STM32F101xx:http://www.st.com/stonline/products/literature/ds/15058.pdf

中容量STM32F101xx:http://www.st.com/stonline/products/literature/ds/13586.pdf

大容量STM32F101xx:http://www.st.com/stonline/products/literature/ds/14610.pdf

小容量STM32F102xx:http://www.st.com/stonline/products/literature/ds/15057.pdf

中容量STM32F102xx:http://www.st.com/stonline/products/literature/ds/15056.pdf

小容量STM32F103xx:http://www.st.com/stonline/products/literature/ds/15060.pdf

中容量STM32F103xx:http://www.st.com/stonline/products/literature/ds/13587.pdf

大容量STM32F103xx:http://www.st.com/stonline/products/literature/ds/14611.pdf

互联型STM32F105xx/STM32F107xx:http://www.st.com/stonline/products/literature/ds/15274.pdf

STM32微控制器产品中大多数功能模块都是在多个产品(或所有产品)中共有的并且是相同的,因此只有一

份STM32微控制器产品的技术参考手册对应所有这些产品。技术参考手册对每种功能模块都有专门的一

个章节对应,每章的开始申明了这个功能模块的适用范围;例如第5章”备份寄存器”适用于整个STM32微

控制器系列,第27章”以太网”只适用于STM32F107xx互联型产品。

为了方便阅读,下一页的表格列出了每个产品子系列所对应功能模块在技术参考手册中的章节一览。

数据手册通常在芯片选型的初期,首先要看 以评估该产品是否能够满足设计上的功能需求;在基本选定

所需产品后,需要察看技术参考手册以确定各功能模块的工作模式是否符合要求;在确定选型进入编程

设计阶段时,需要详细阅读技术参考手册获知各项功能的具体实现方式和寄存器的配置使用。 在设计硬

件时还需参考数据手册以获得电压、电流、管脚分配、驱动能力等信息。

关于Cortex-M3核心、SysTick定时器和NVIC的详细说明,请参考另一篇ST的文档和一篇ARM的文档:

《STM32F10xxx Cortex-M3编程手册》和《Cortex™-M3技术参考手册》。

本译文仅供参考,如有翻译错误,请以英文原稿为准。请读者随时注意在ST网站下载更新版本

STM32F10xxx参考手册

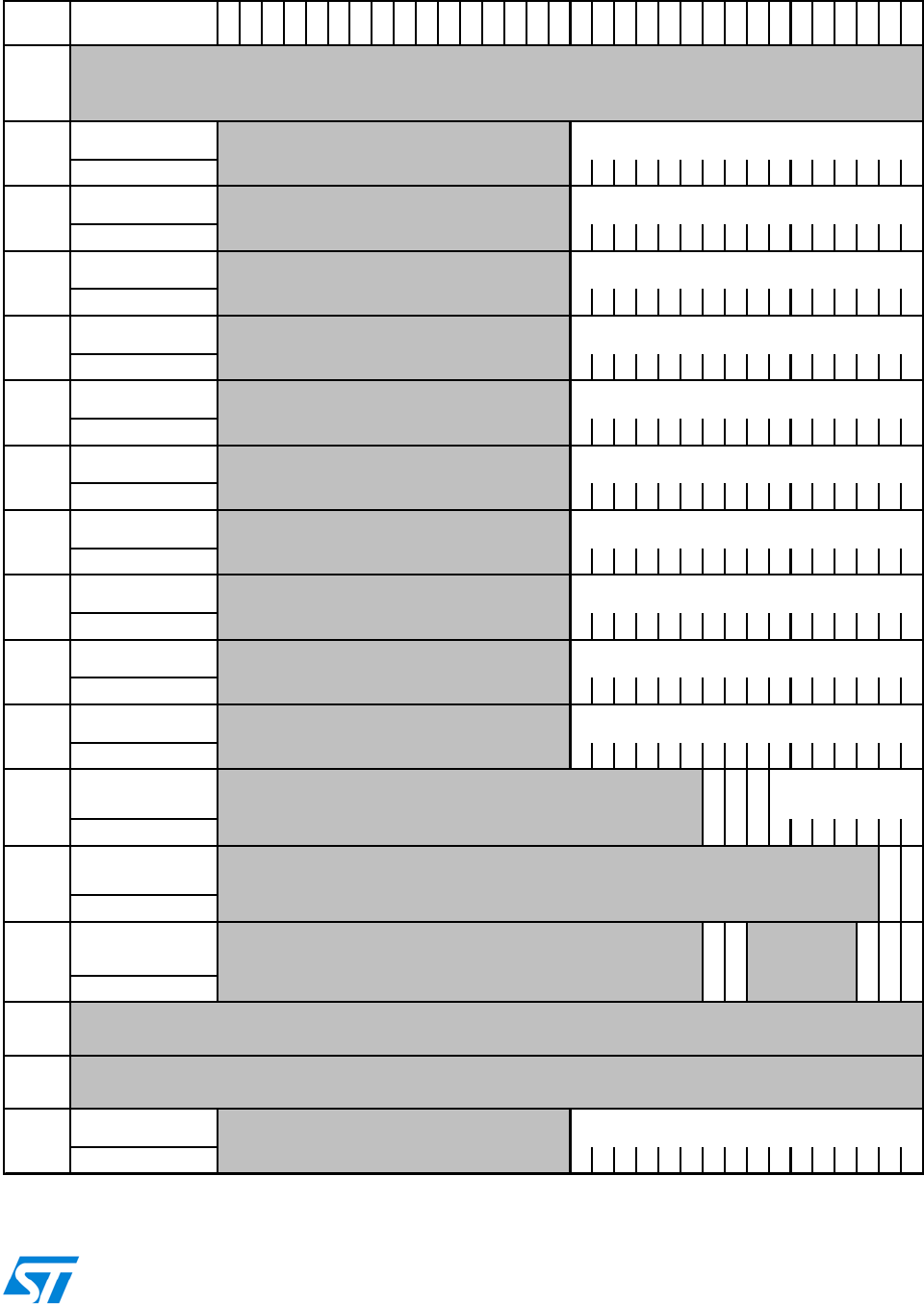

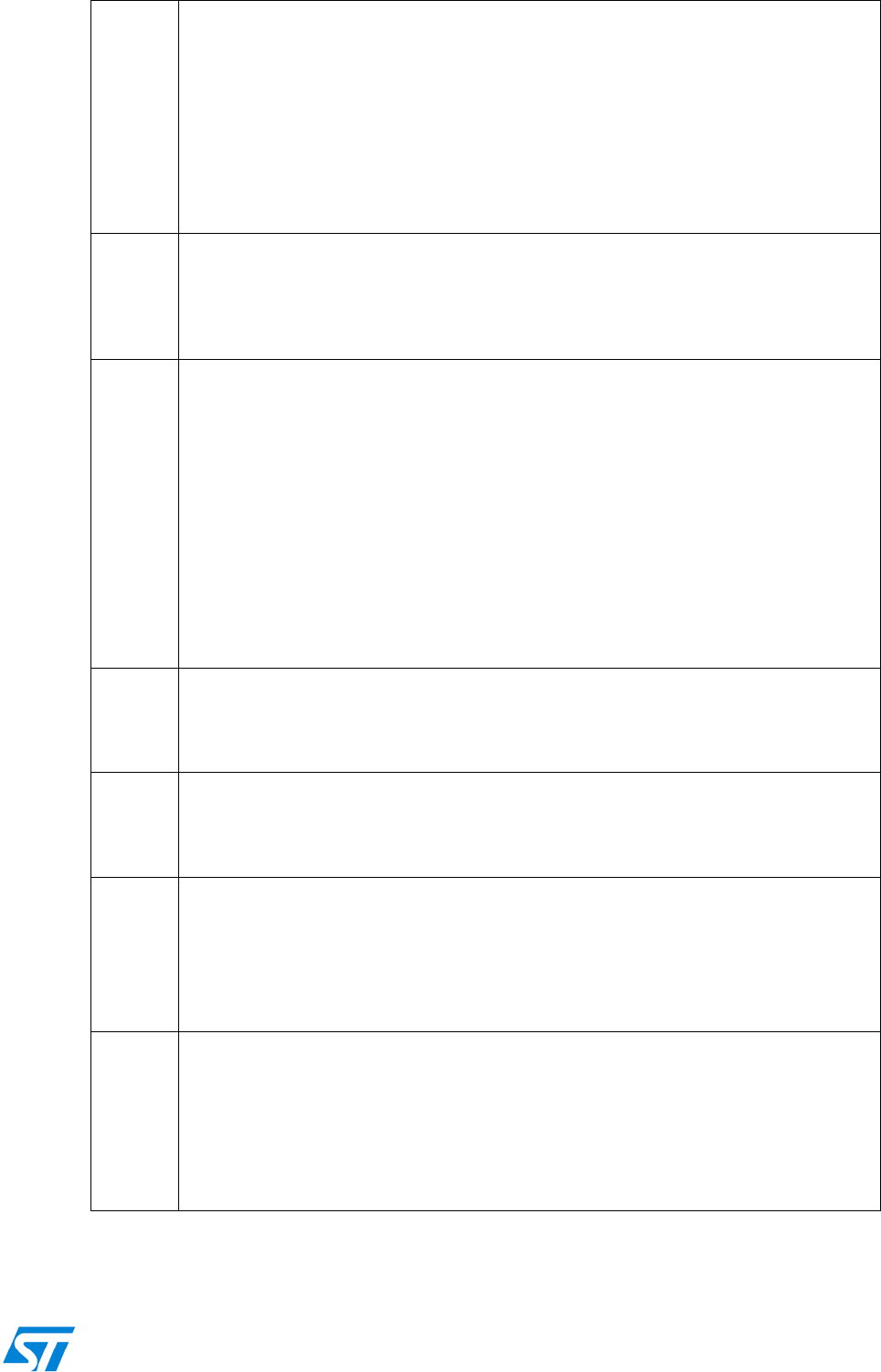

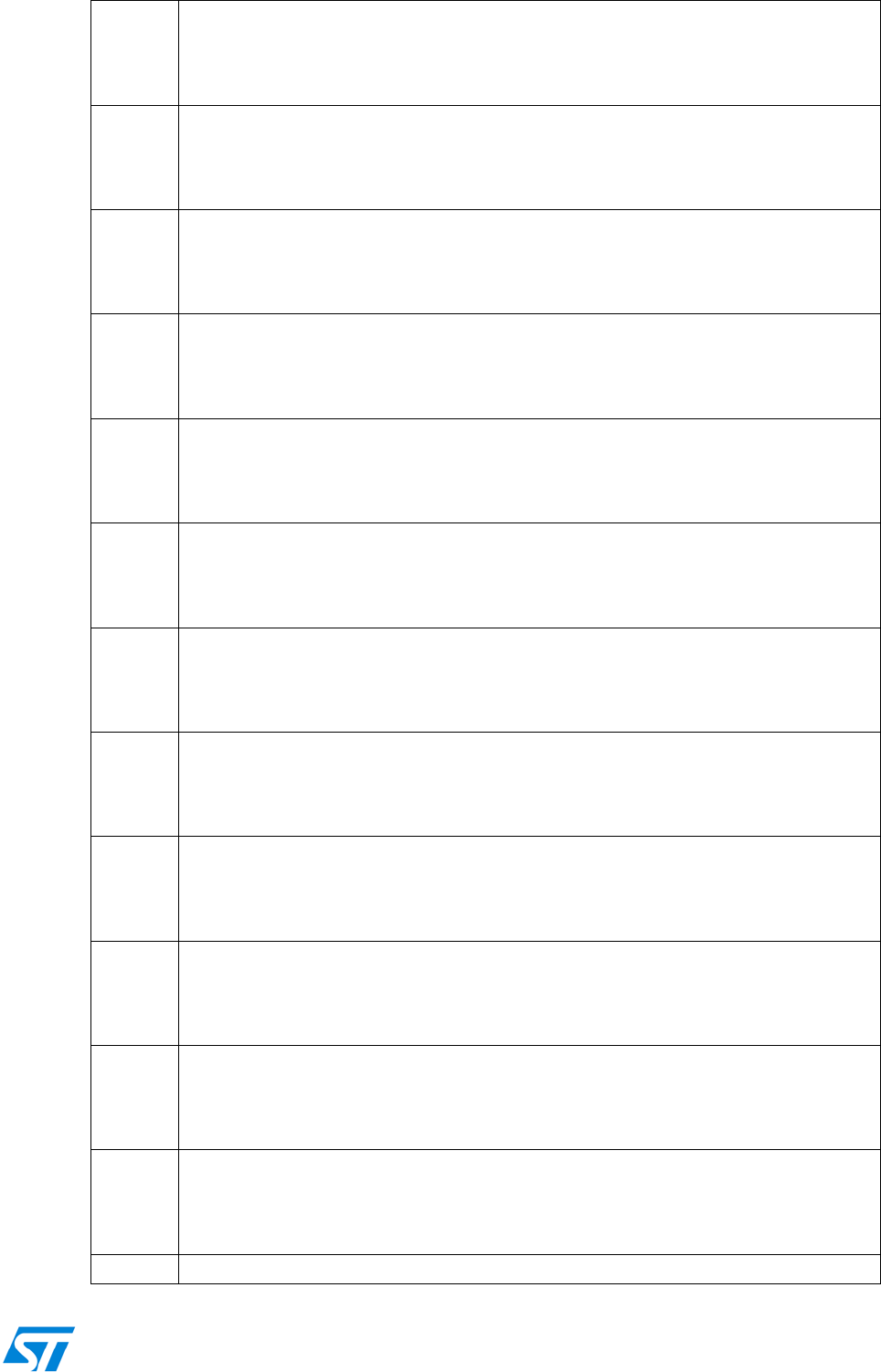

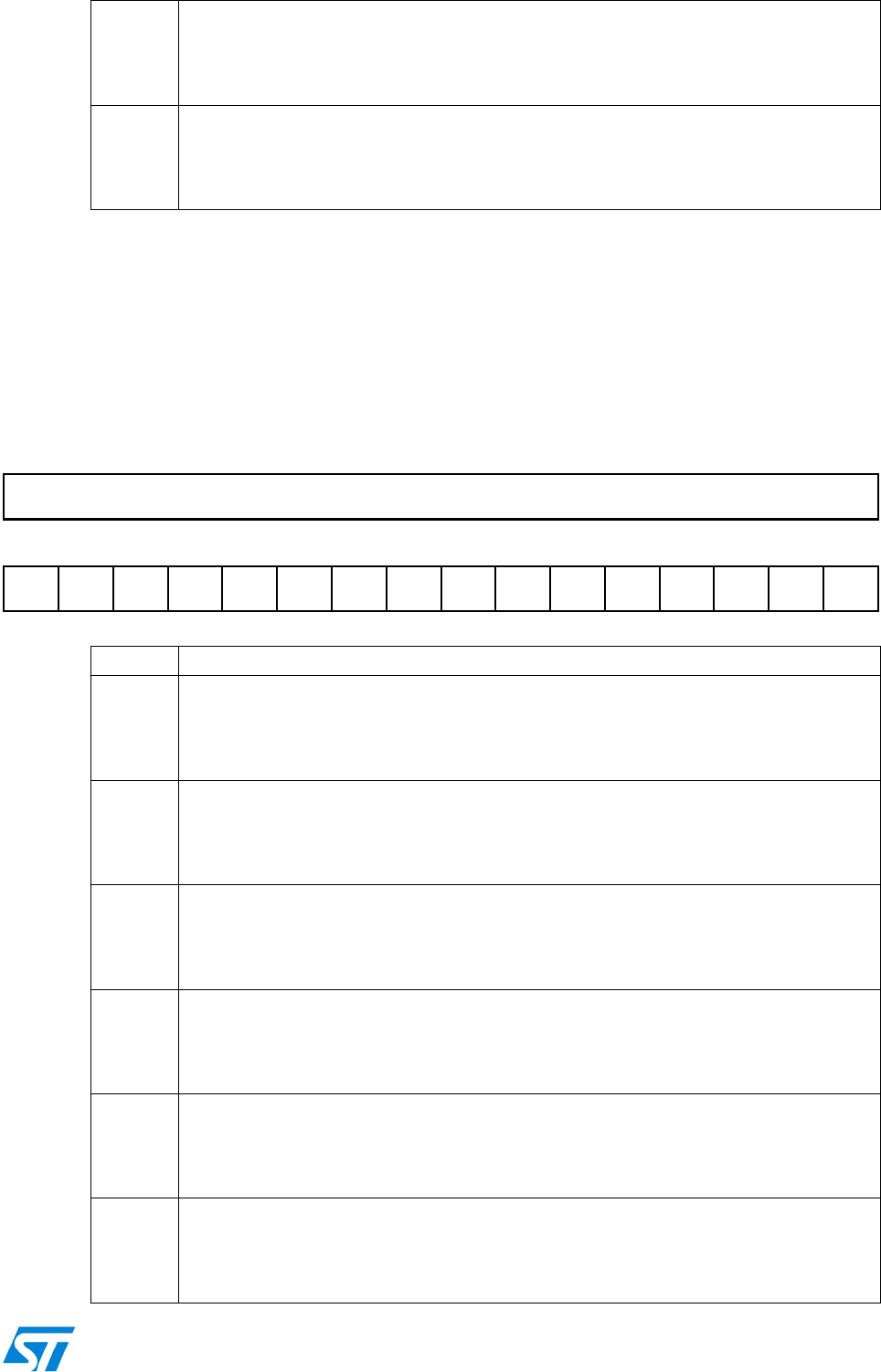

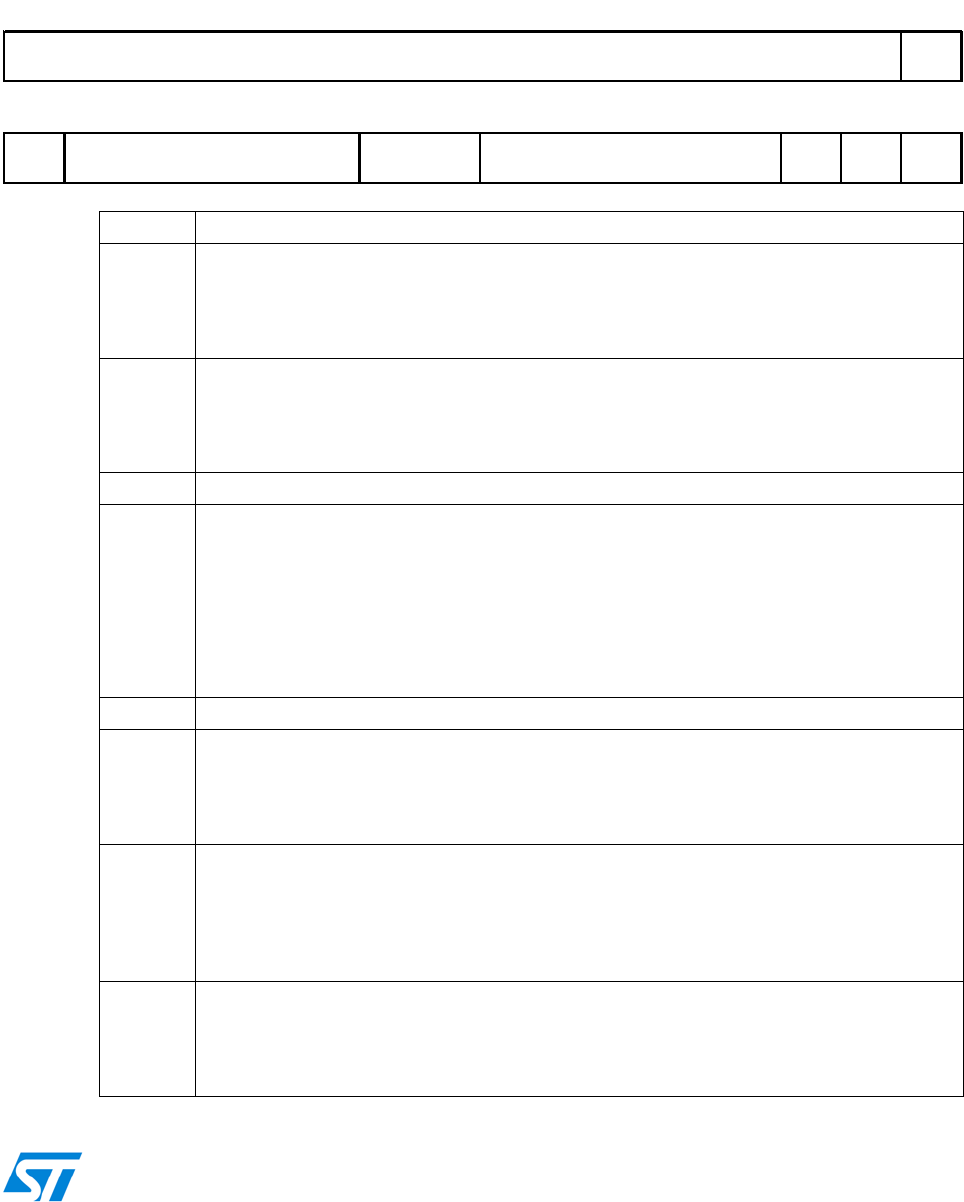

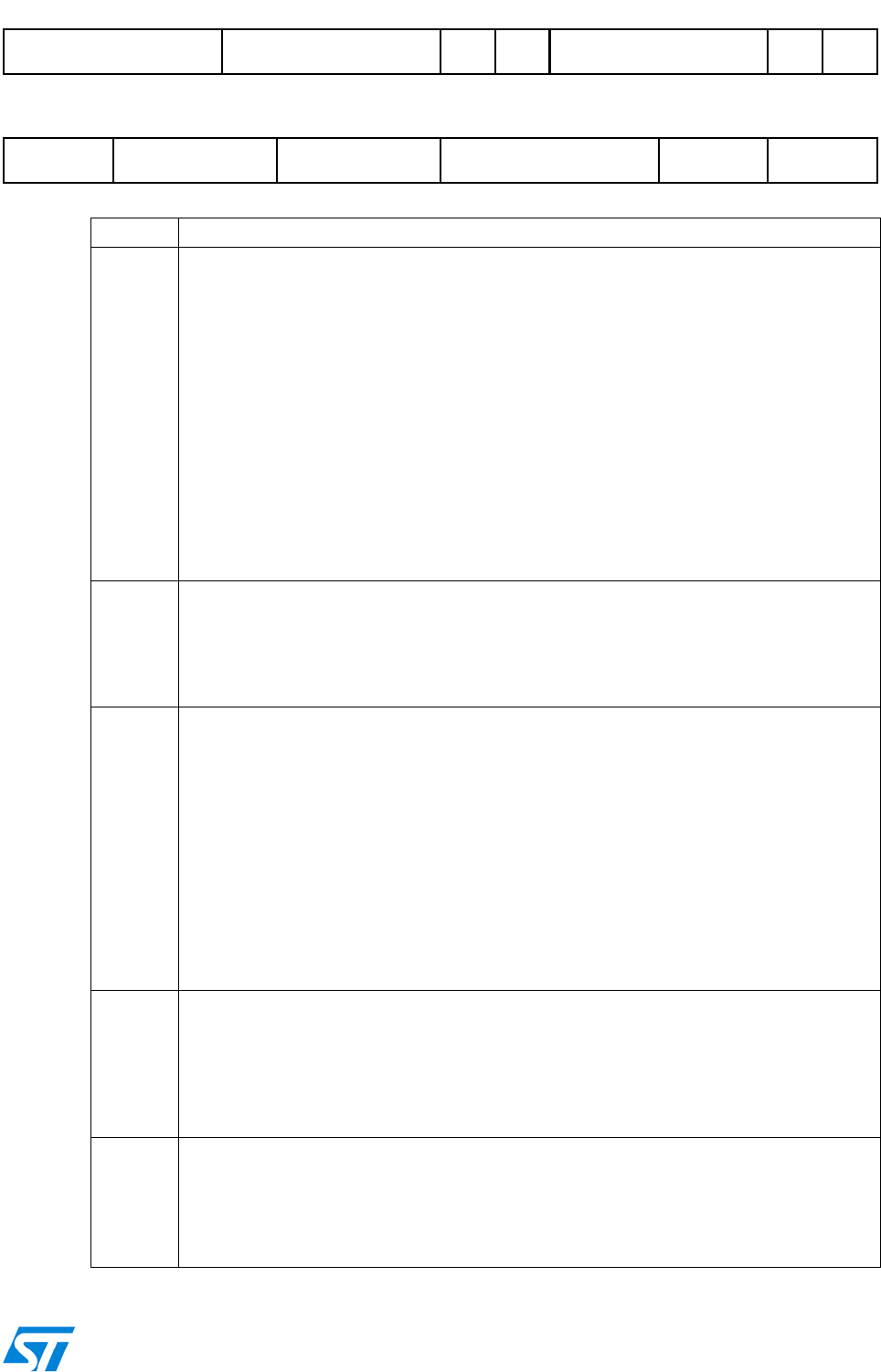

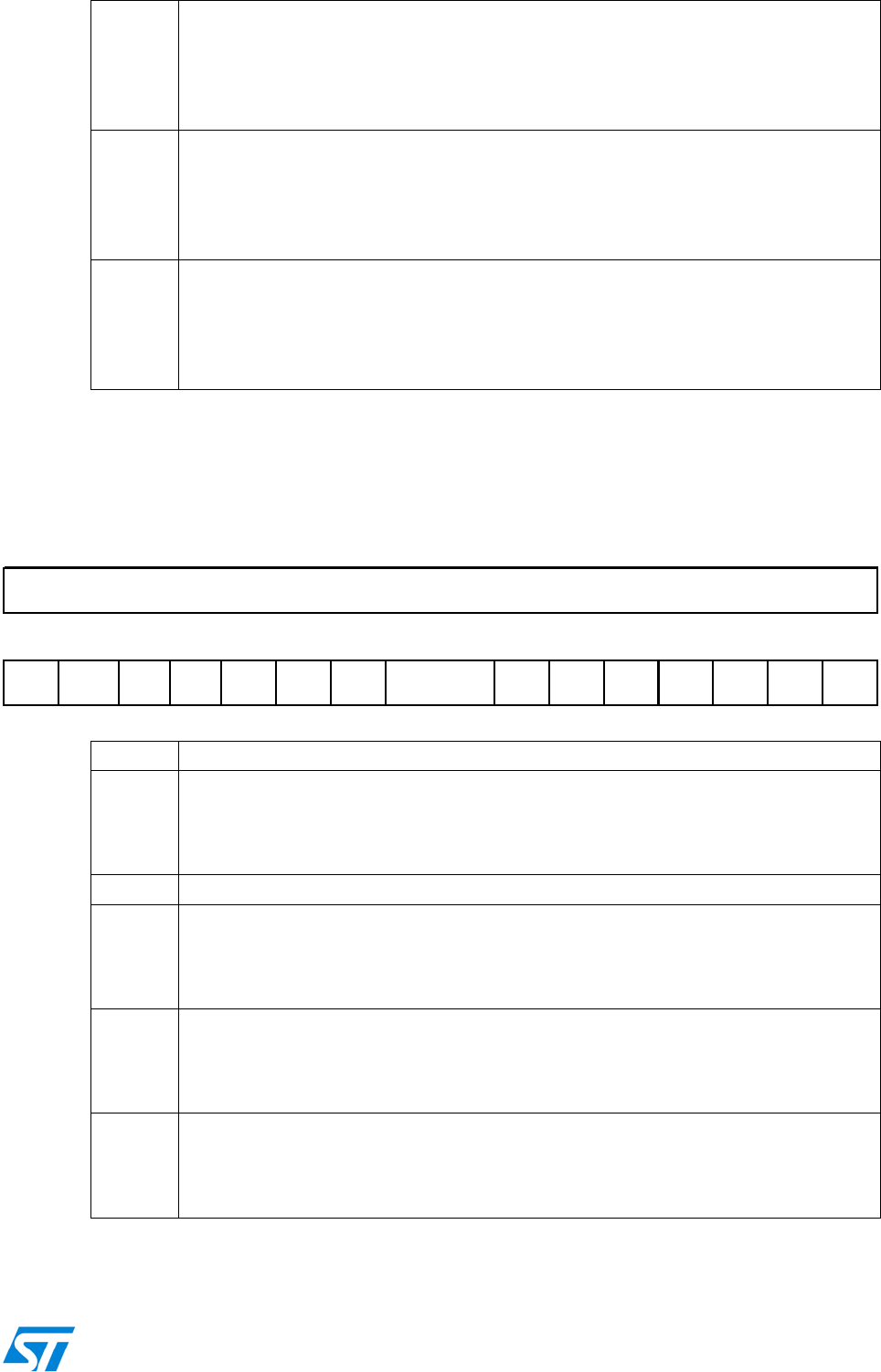

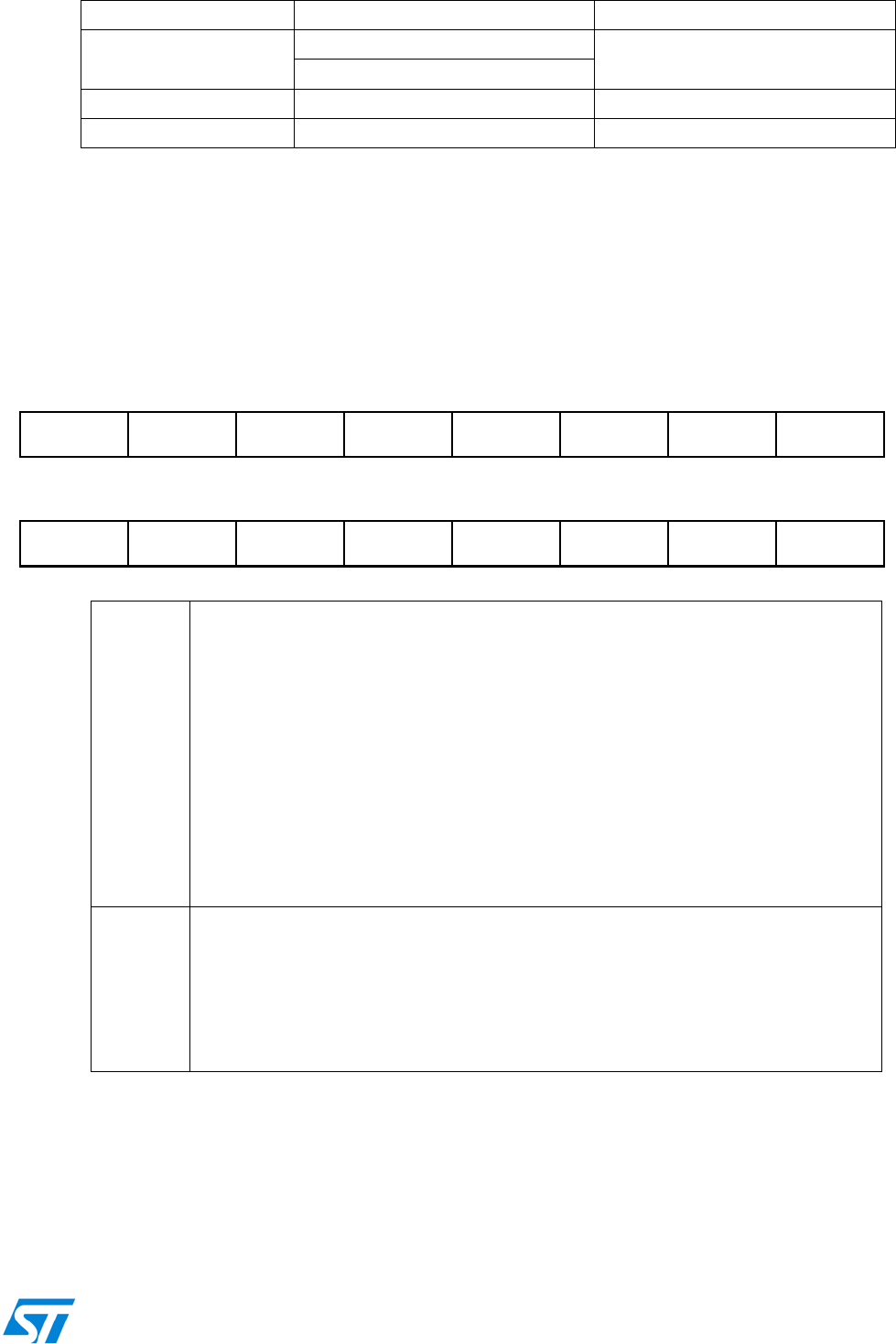

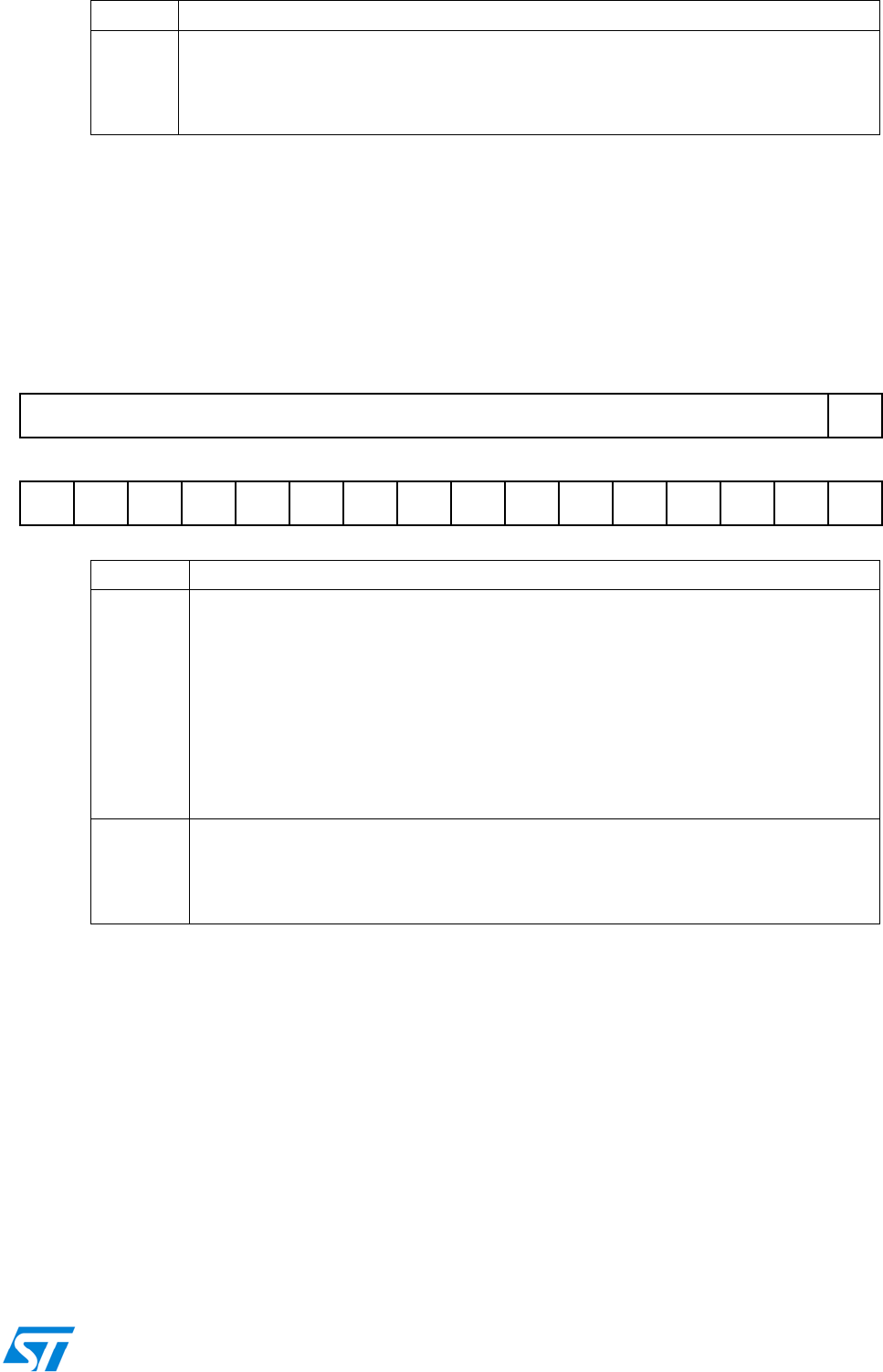

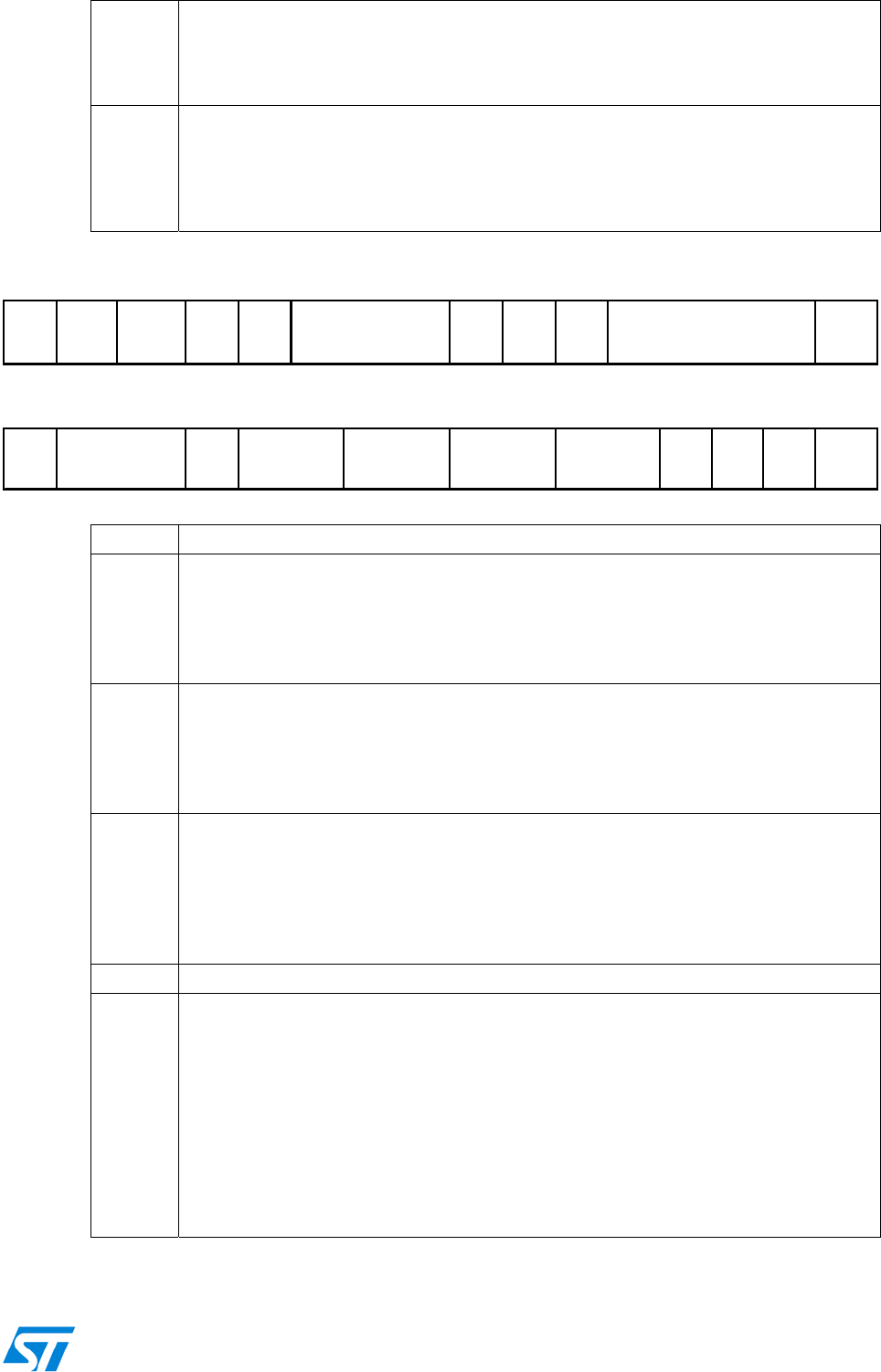

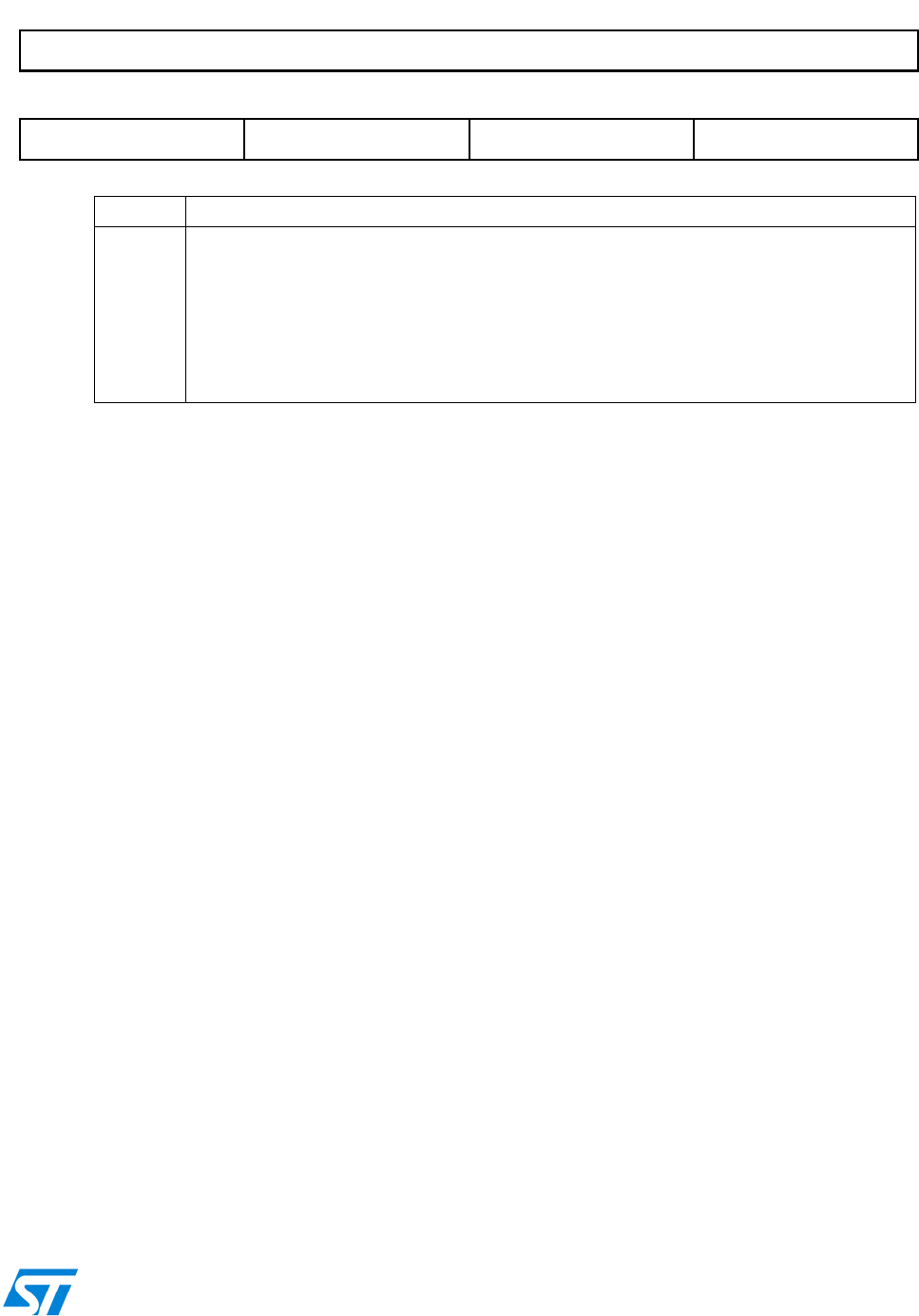

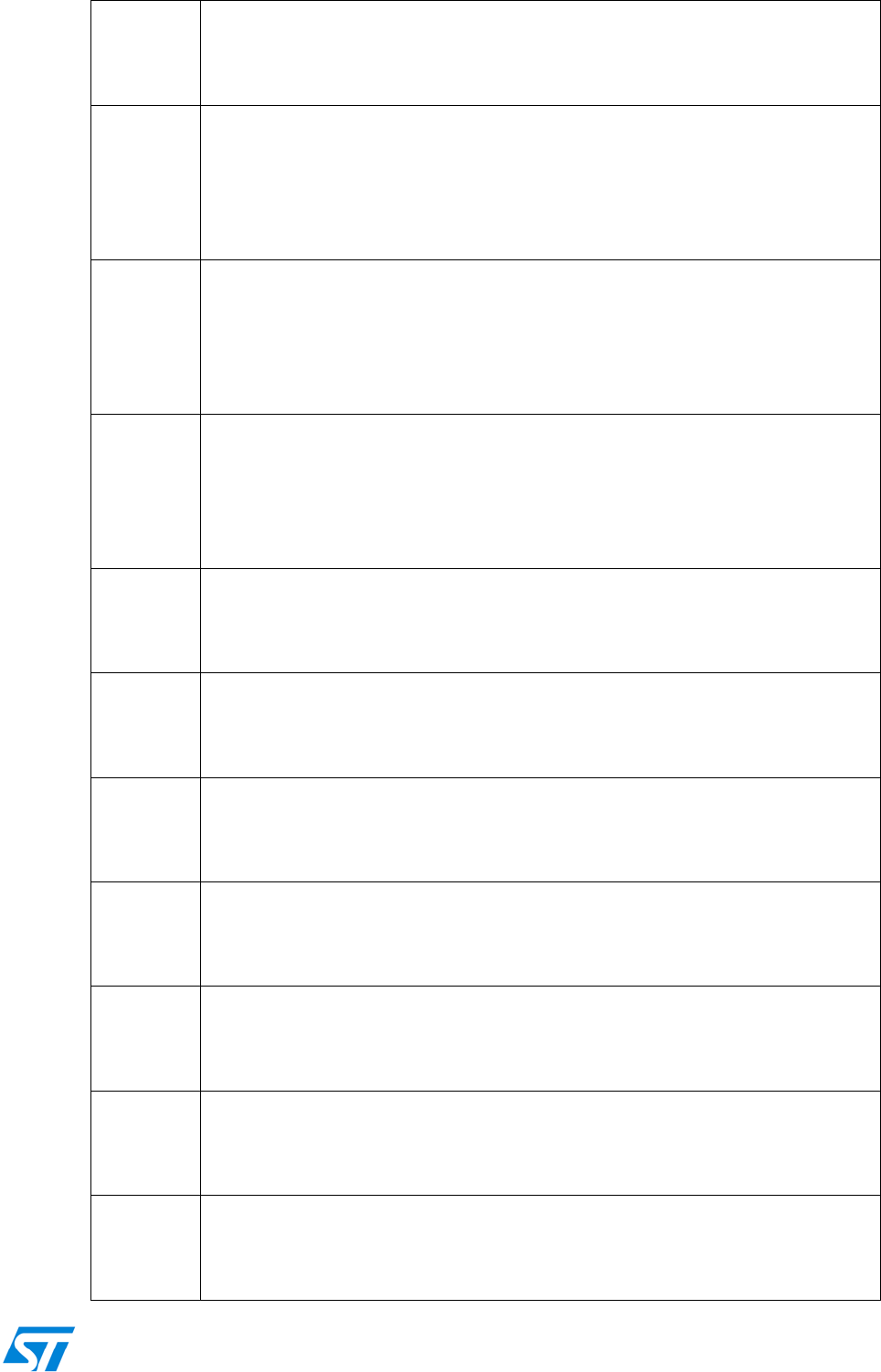

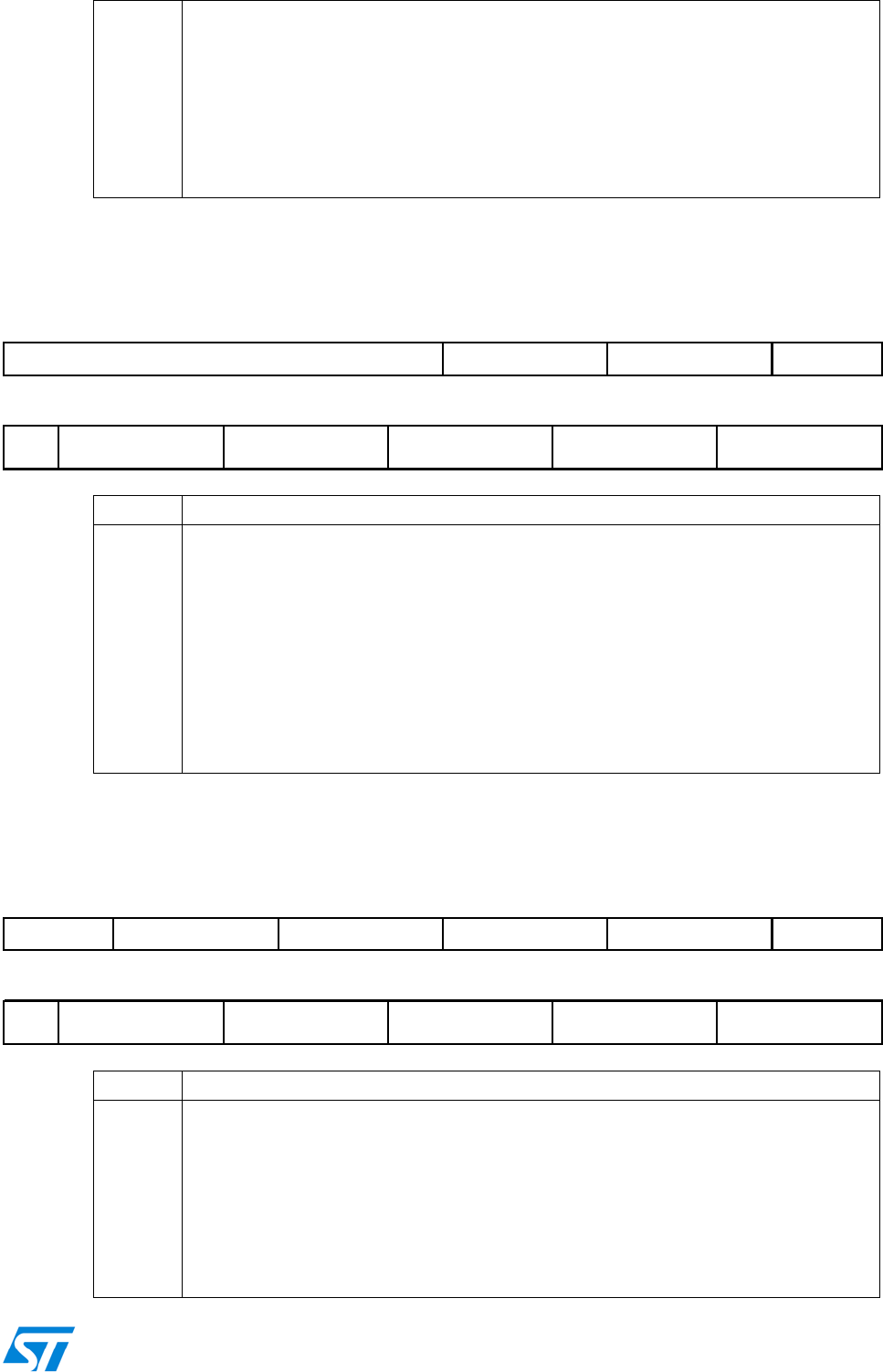

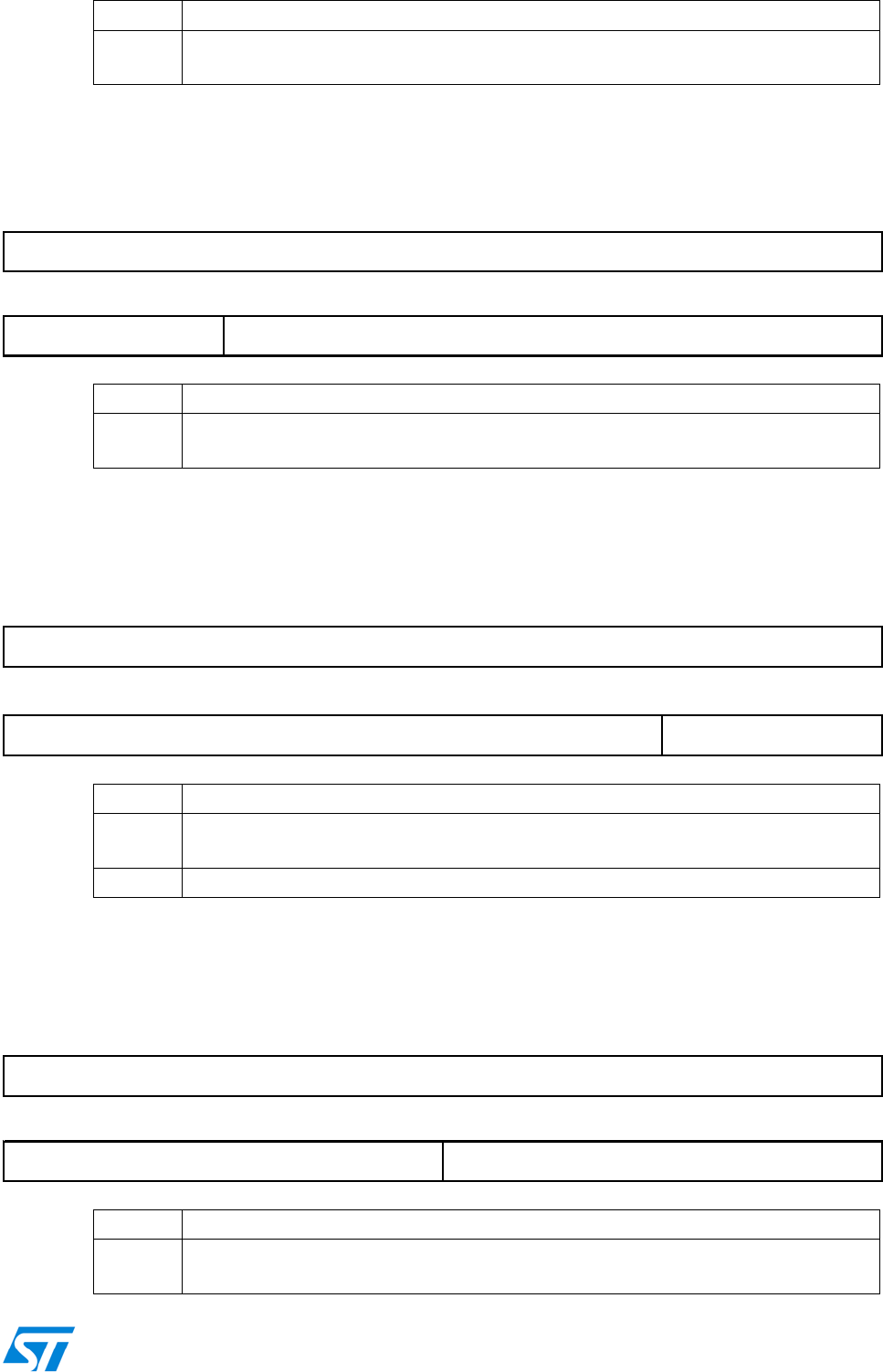

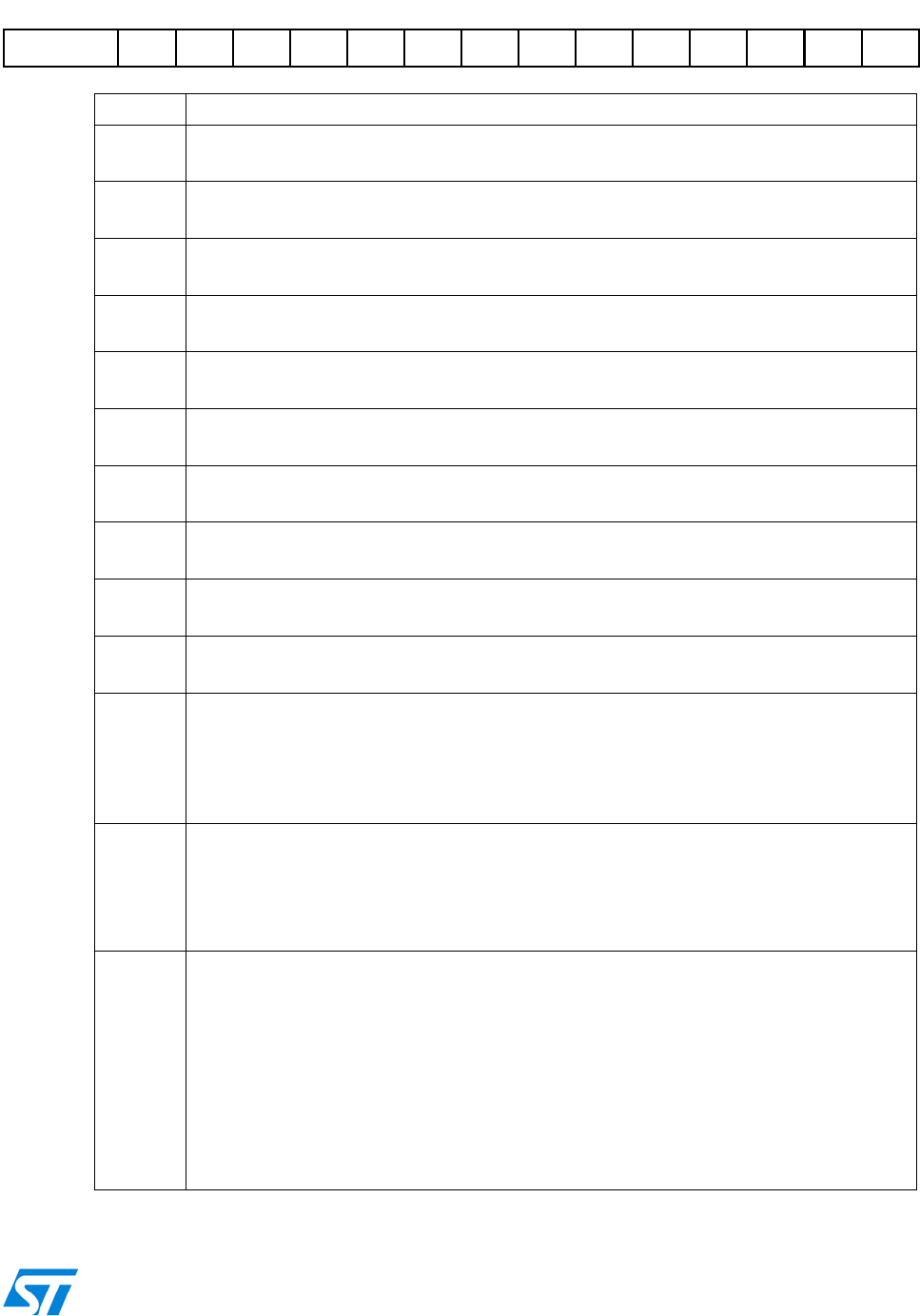

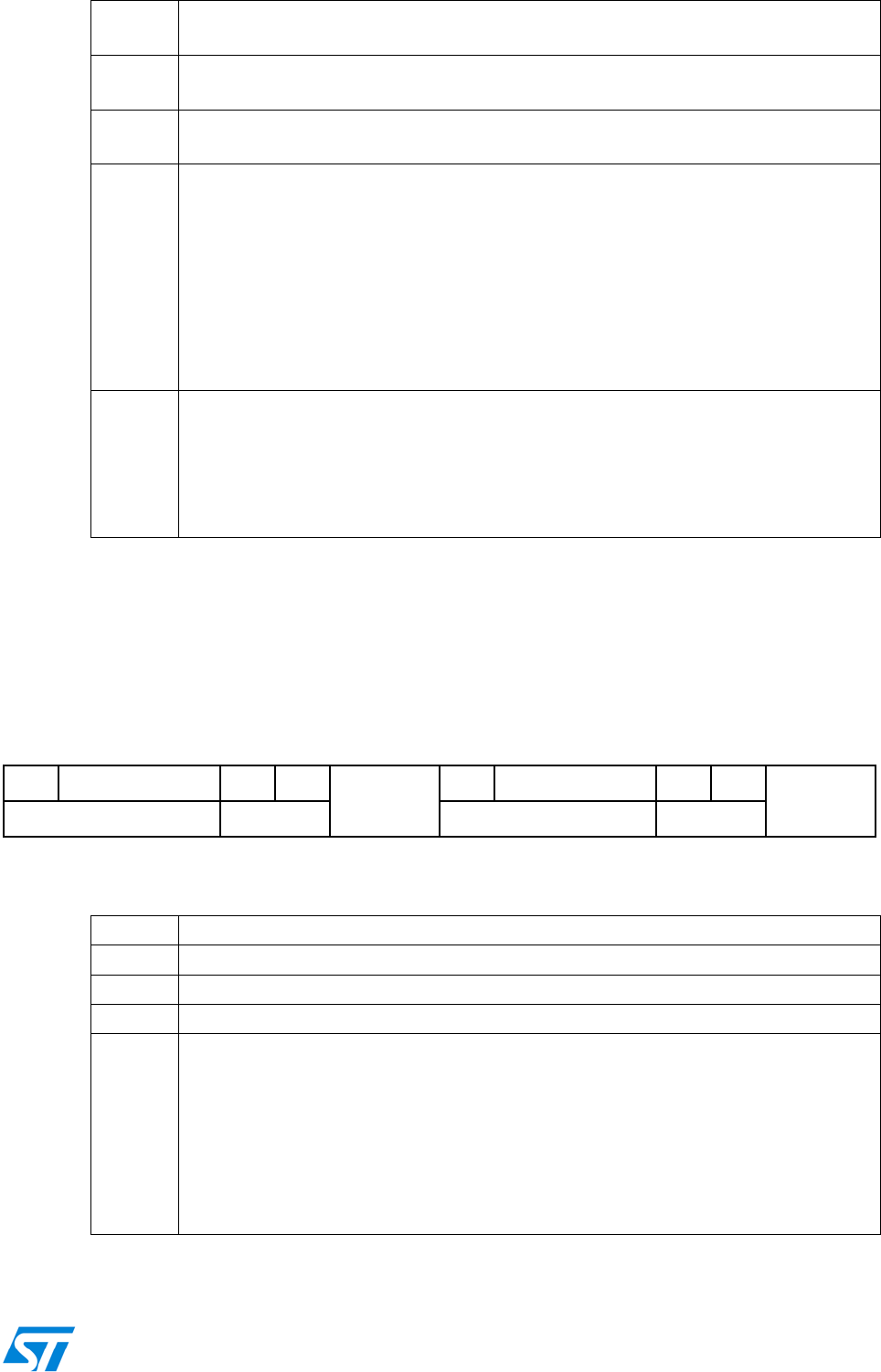

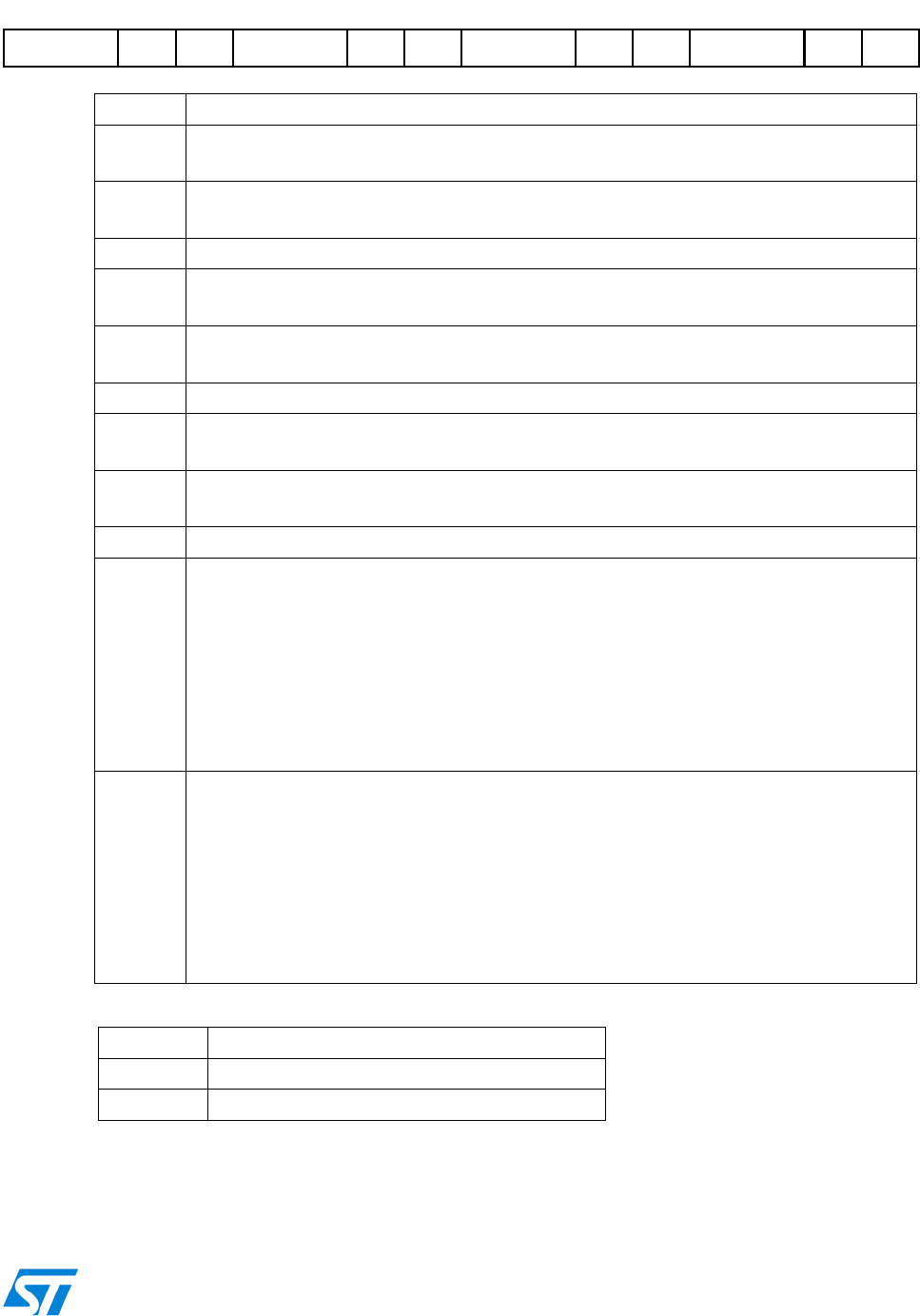

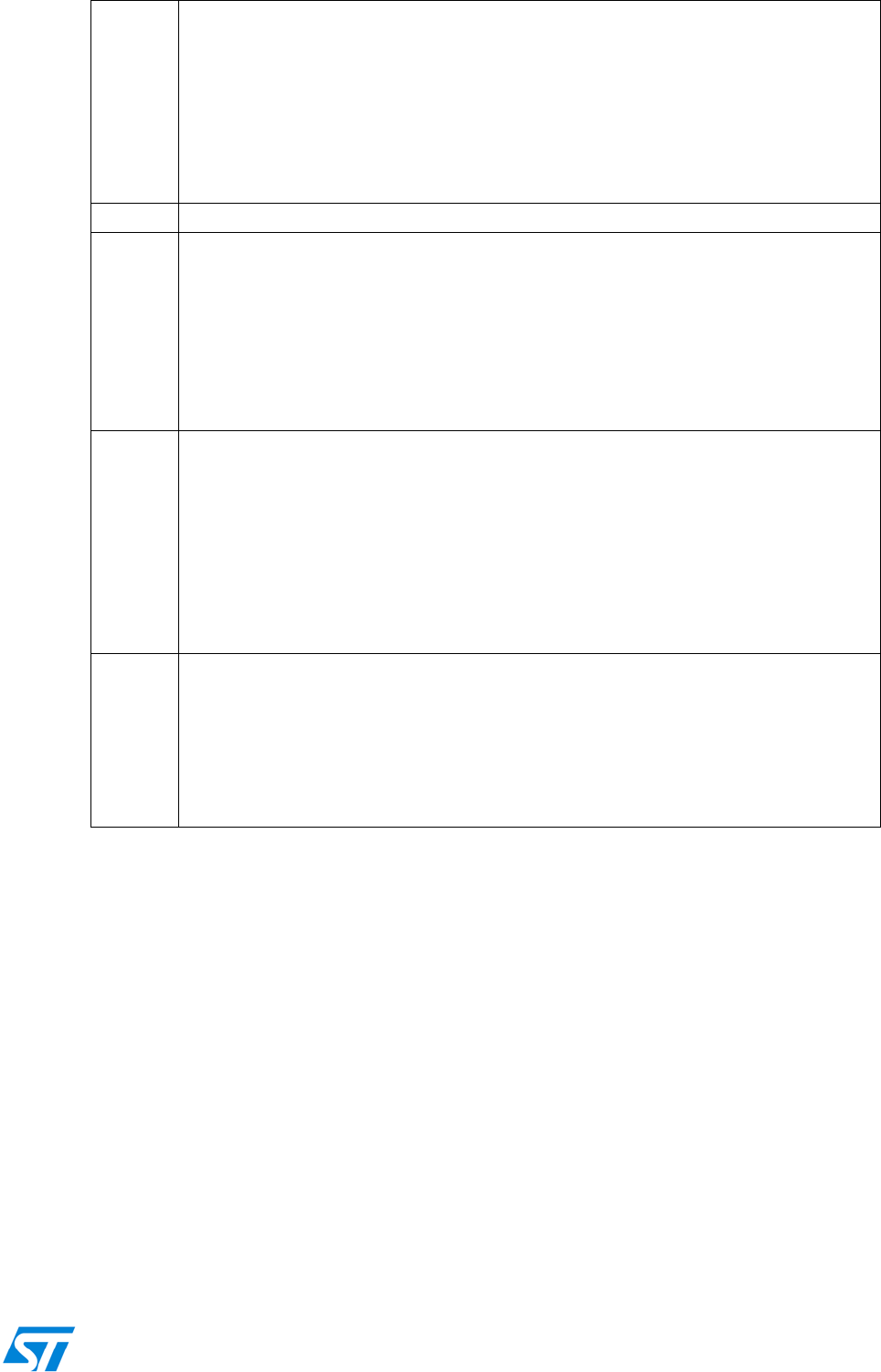

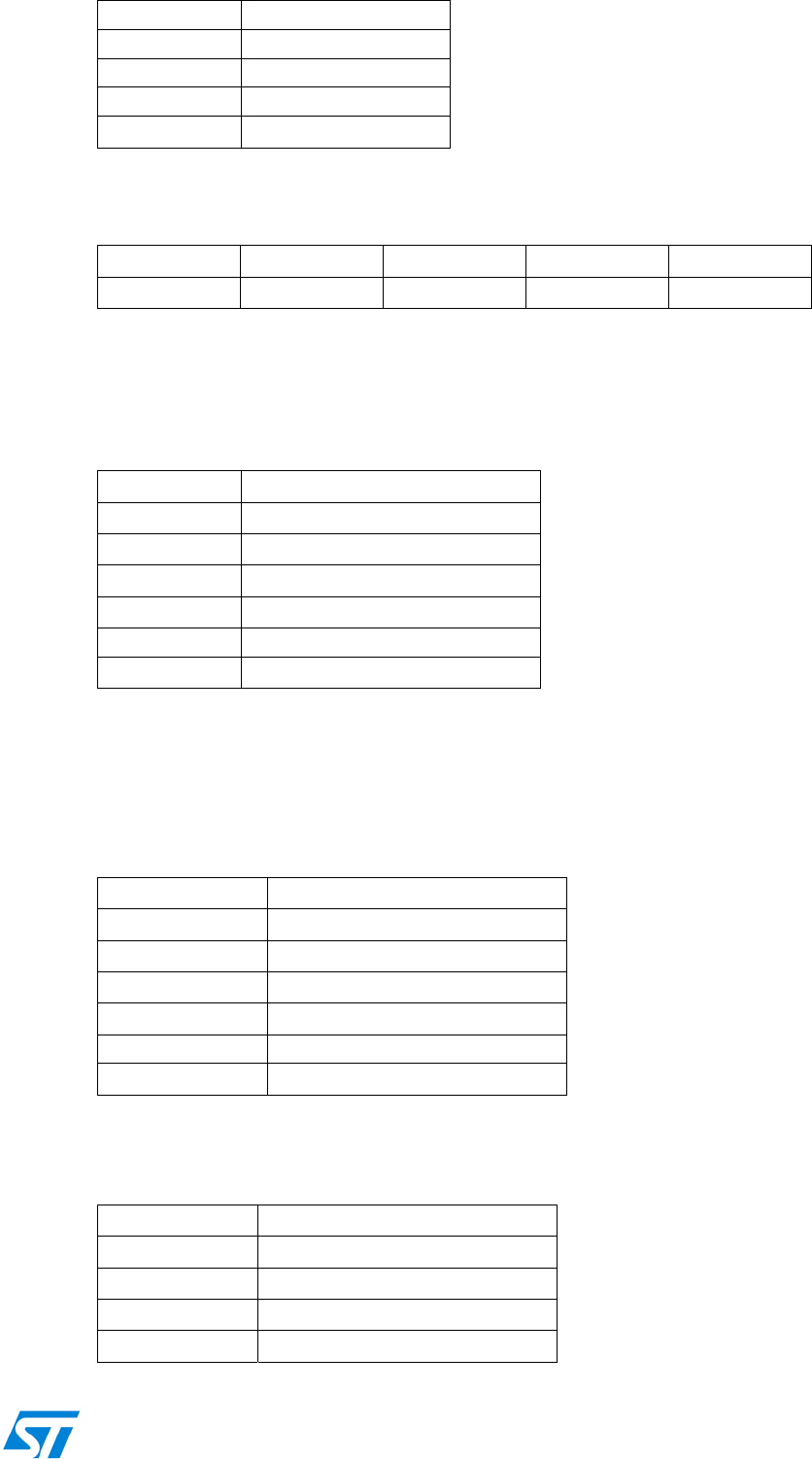

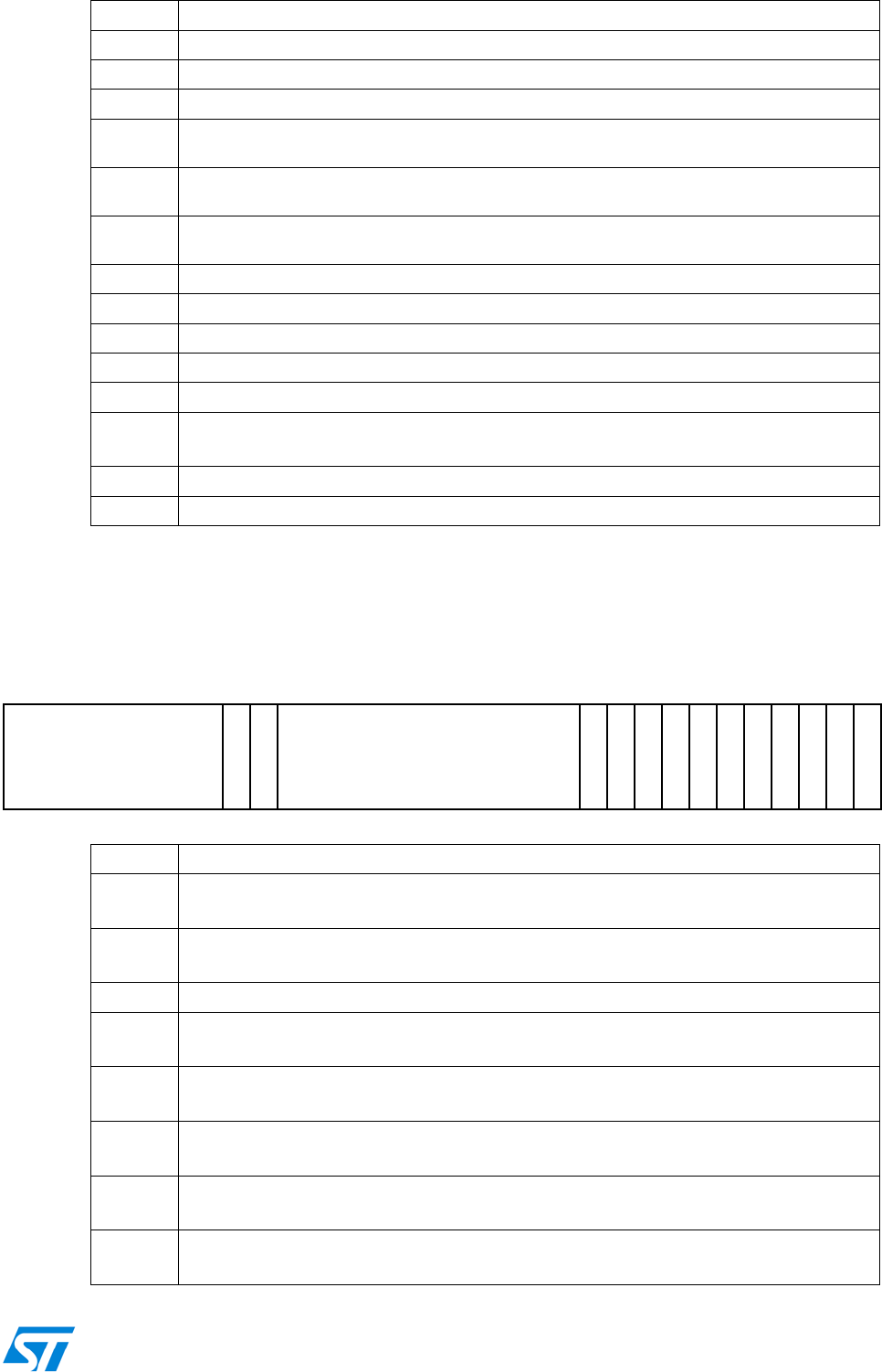

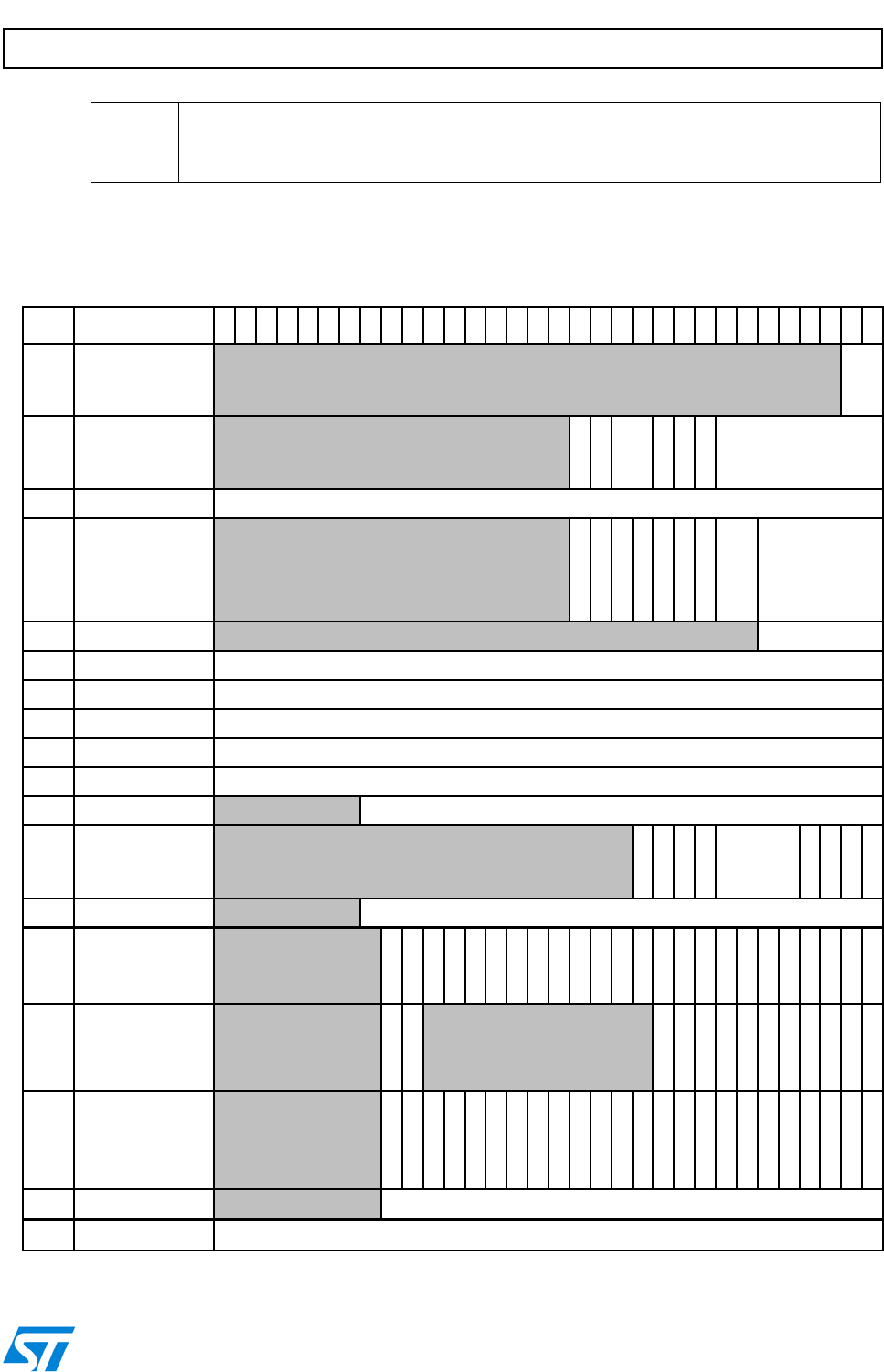

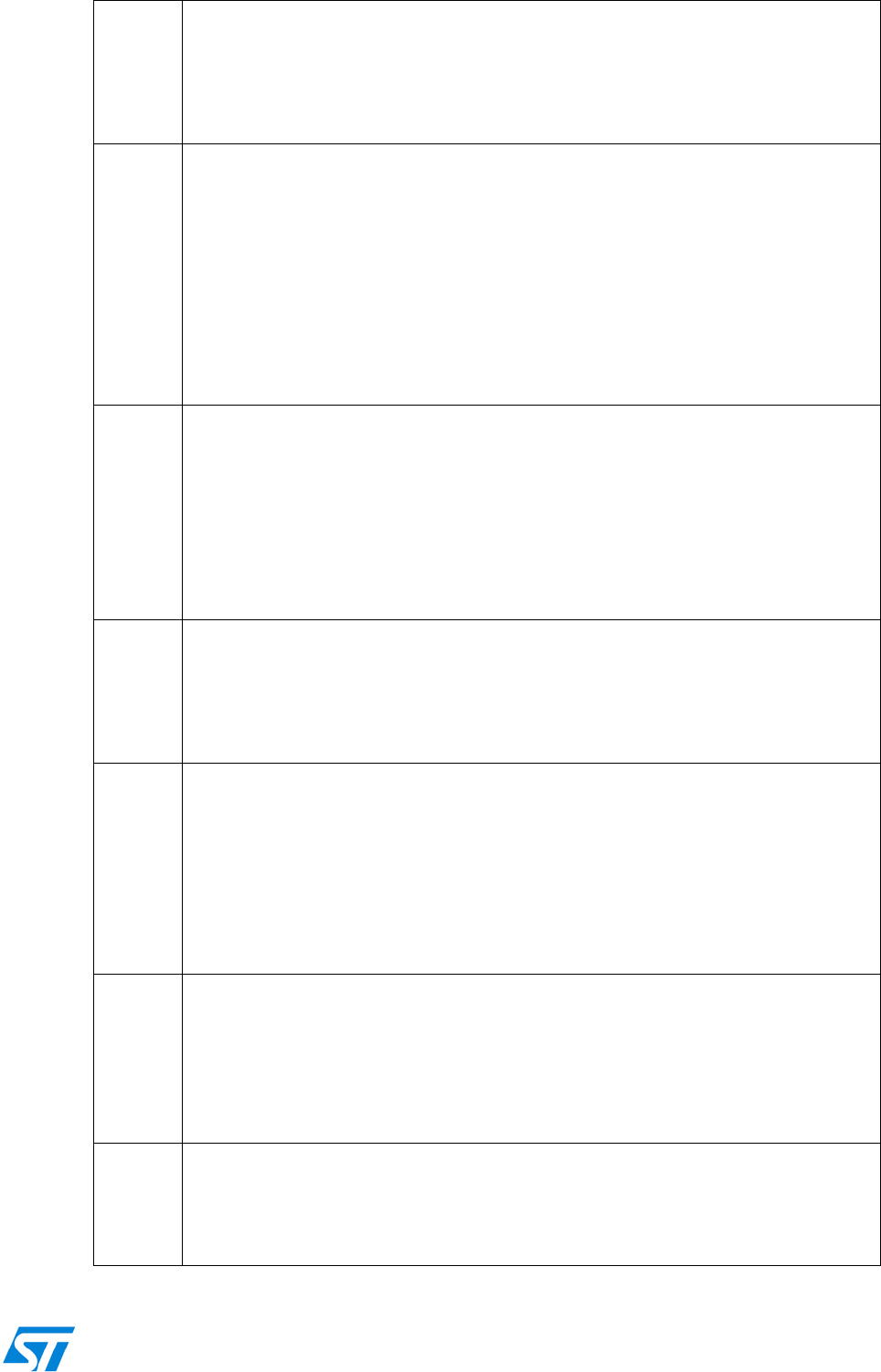

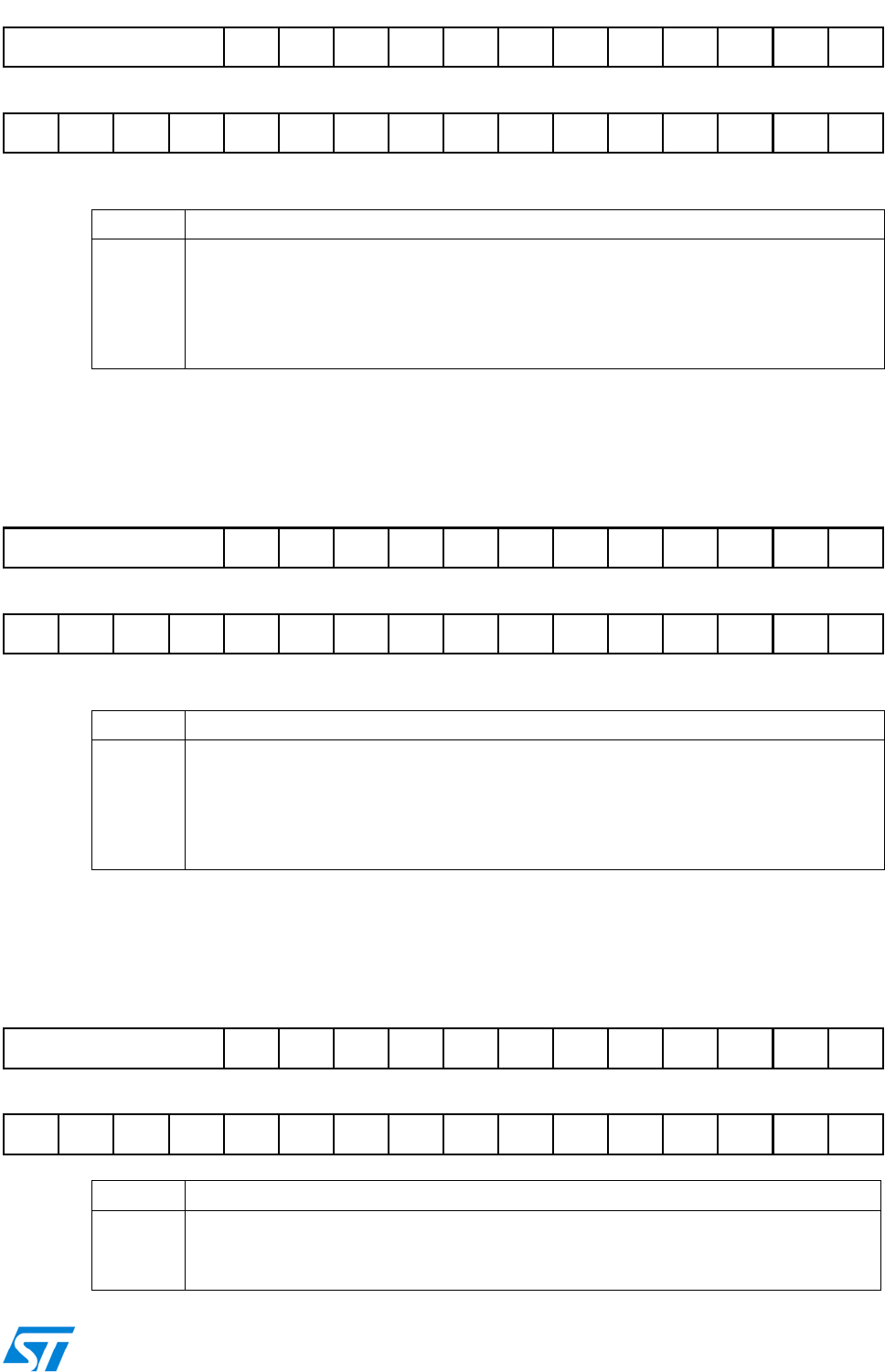

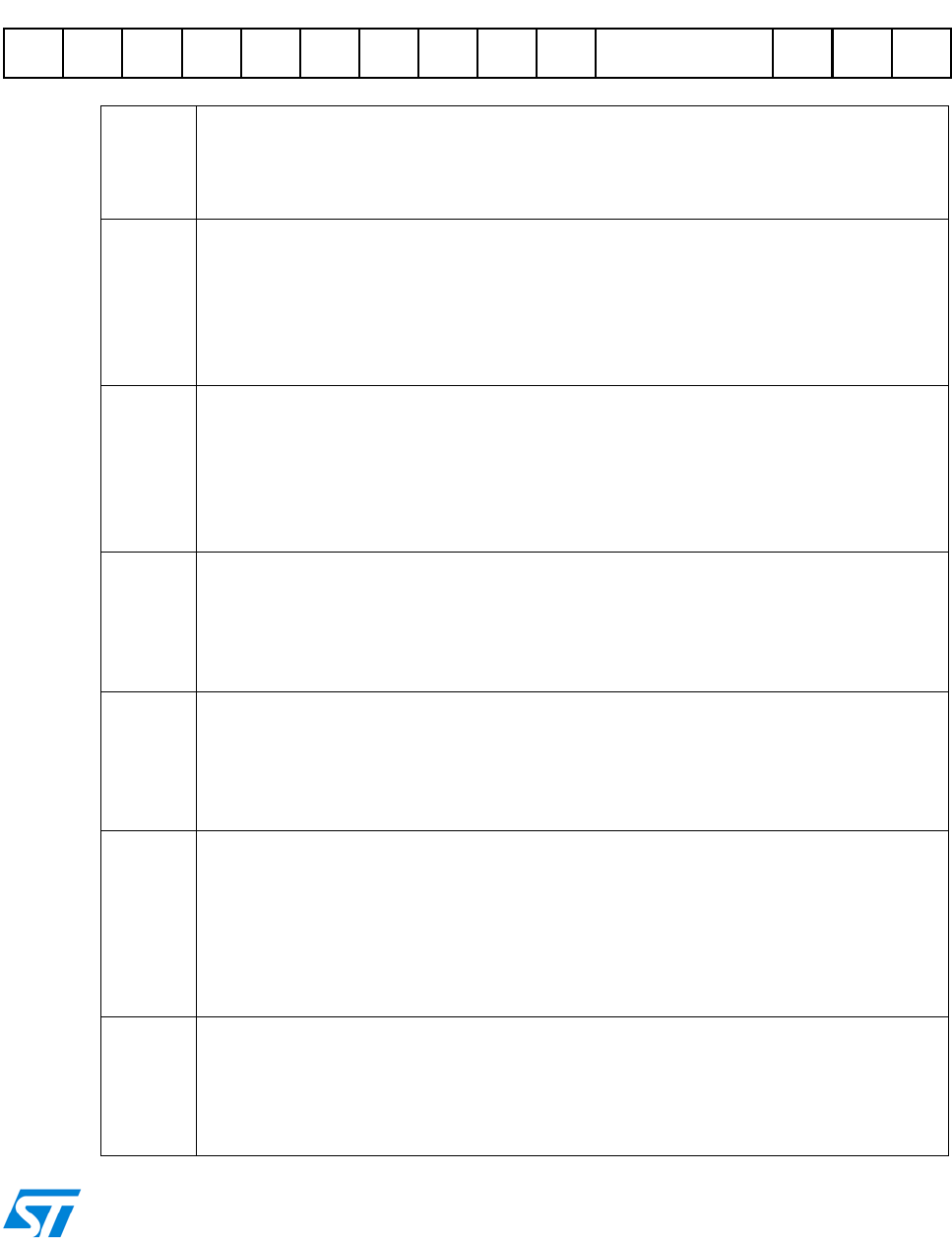

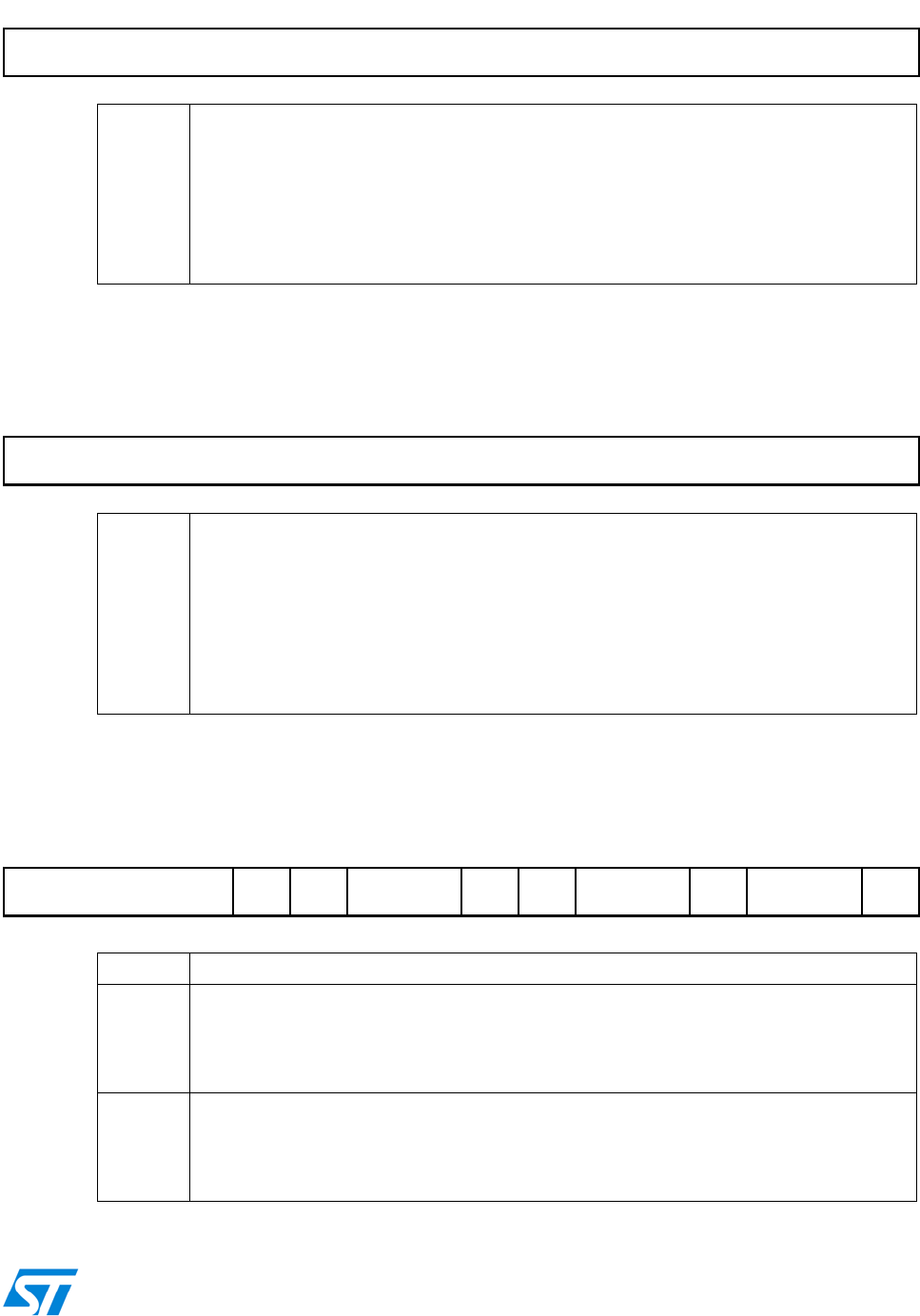

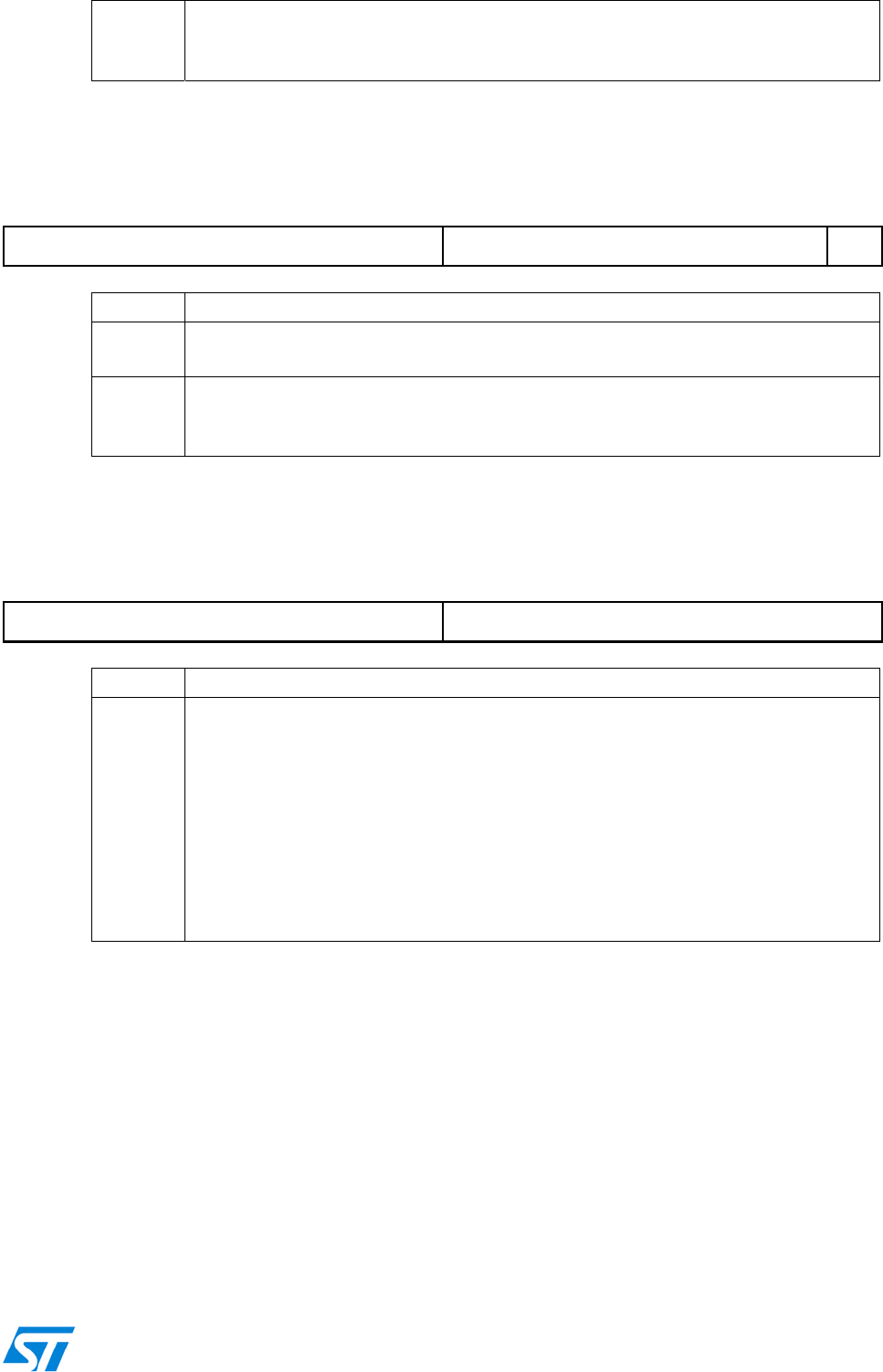

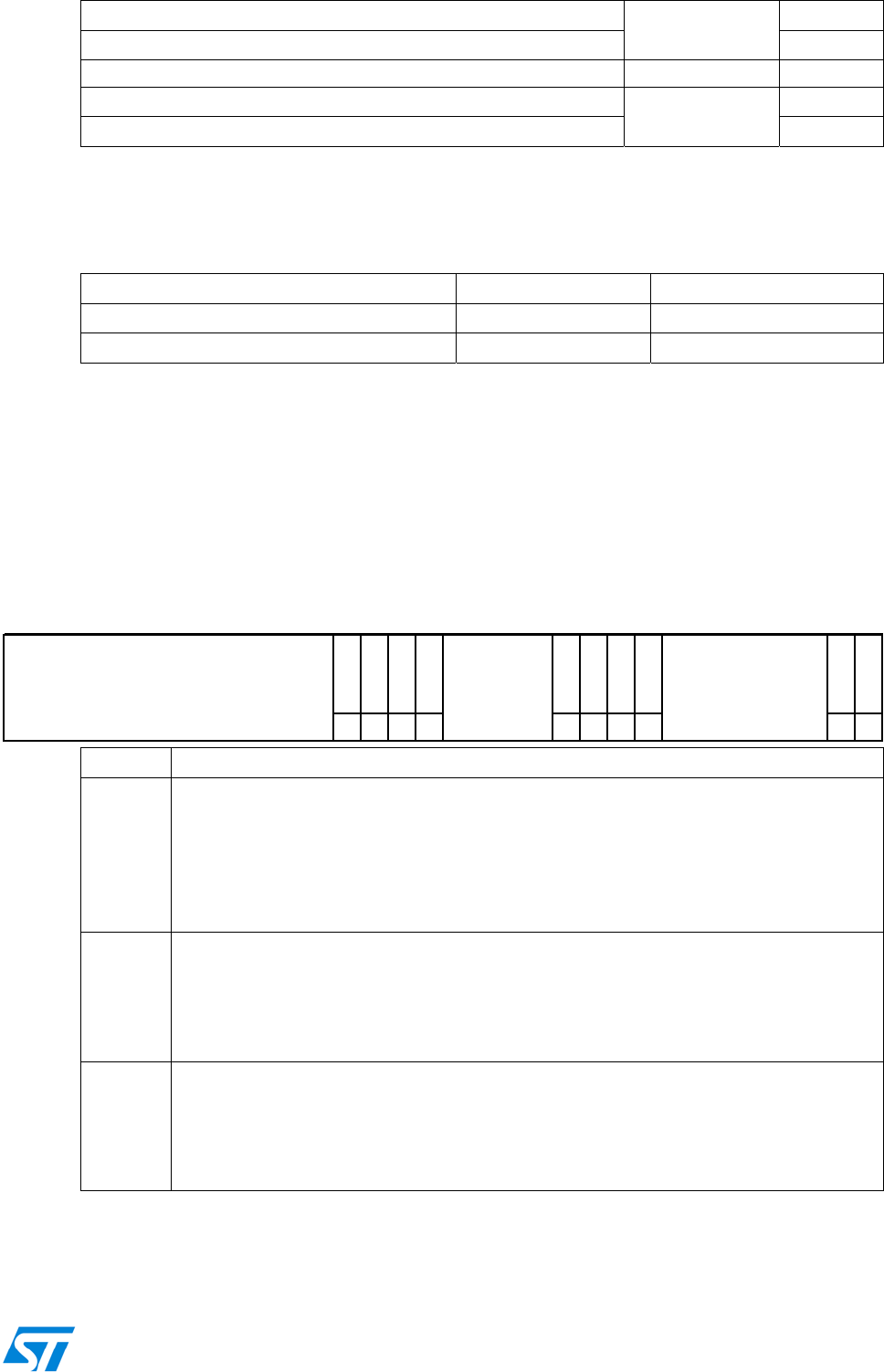

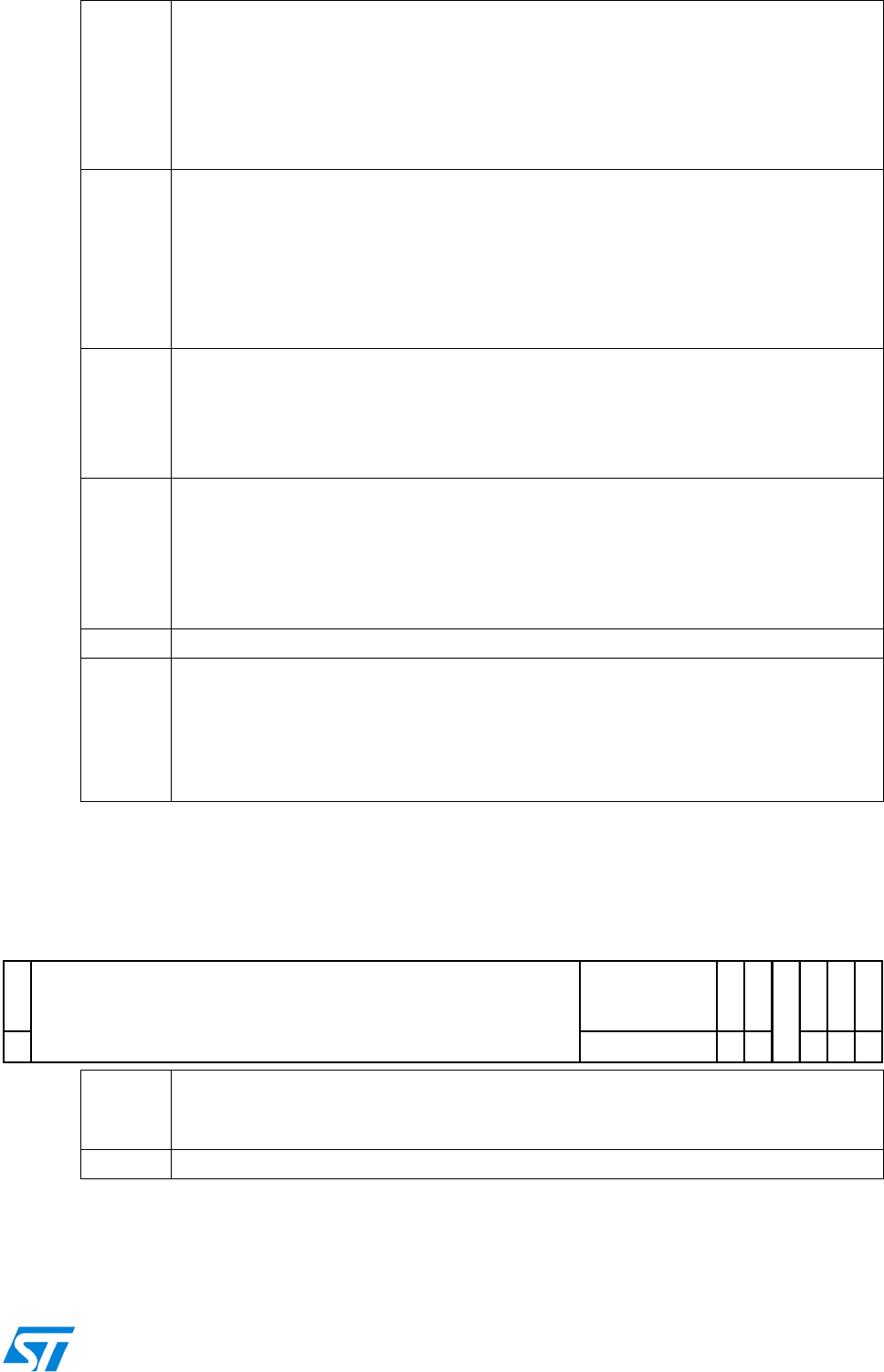

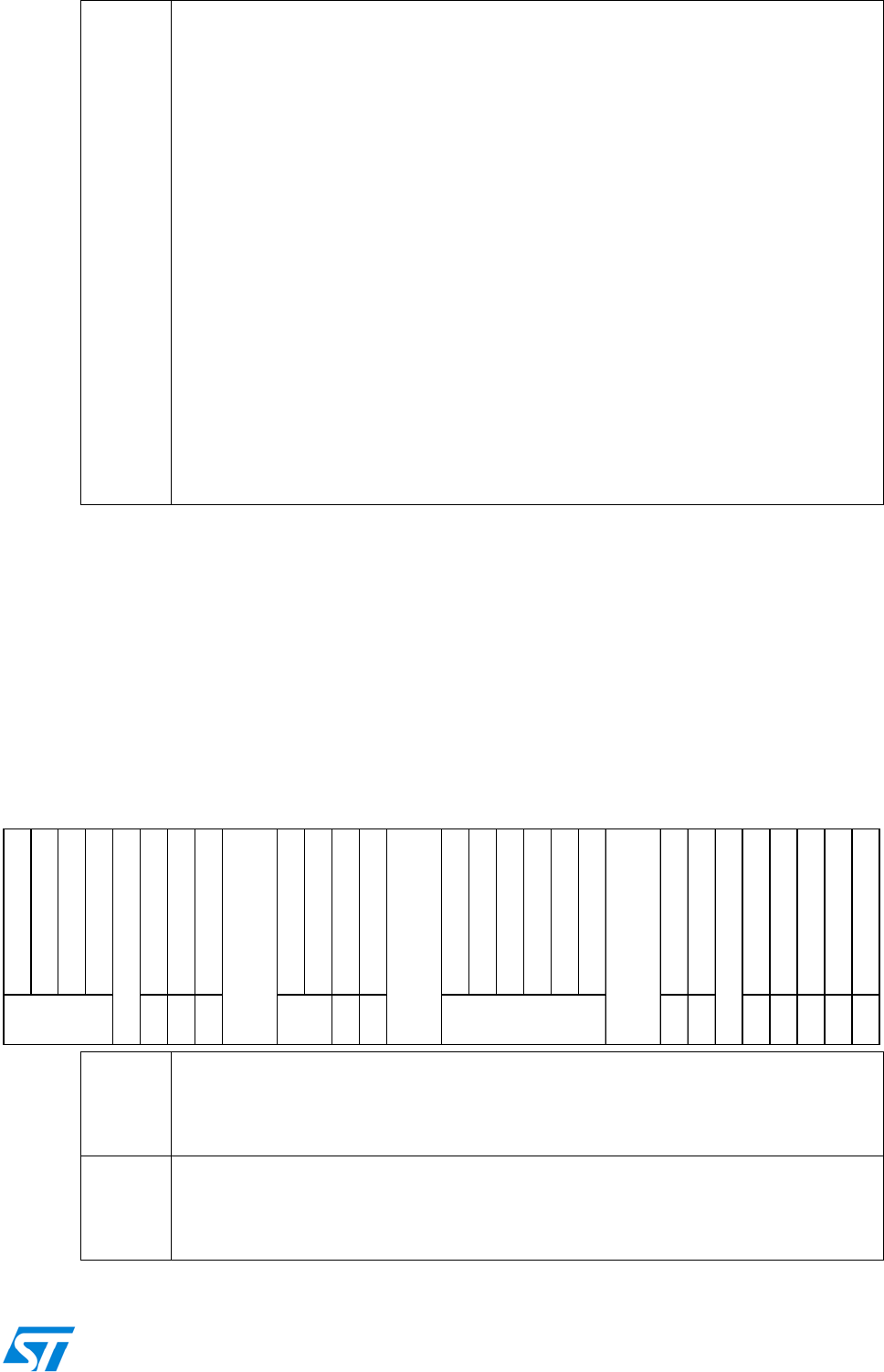

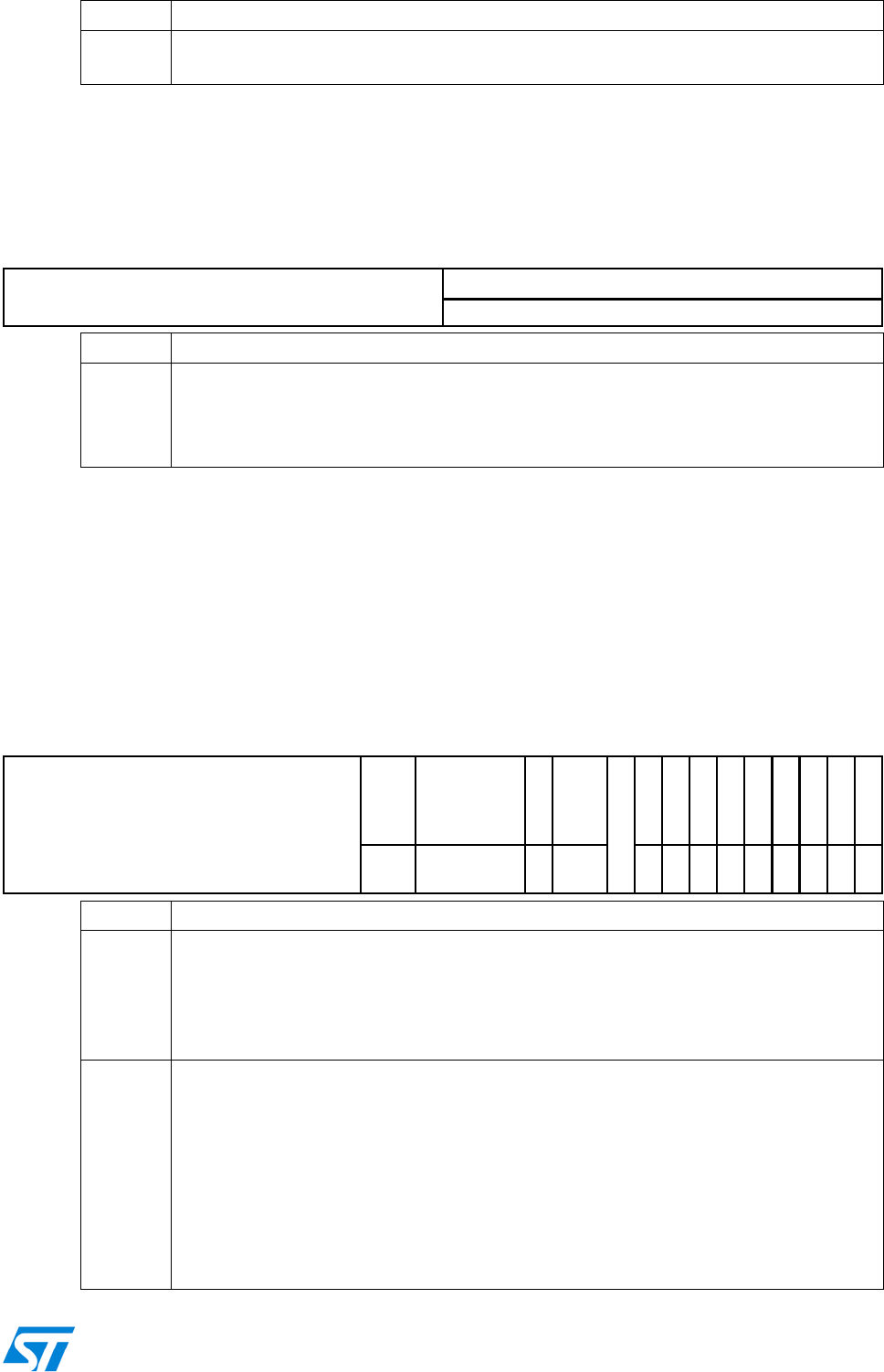

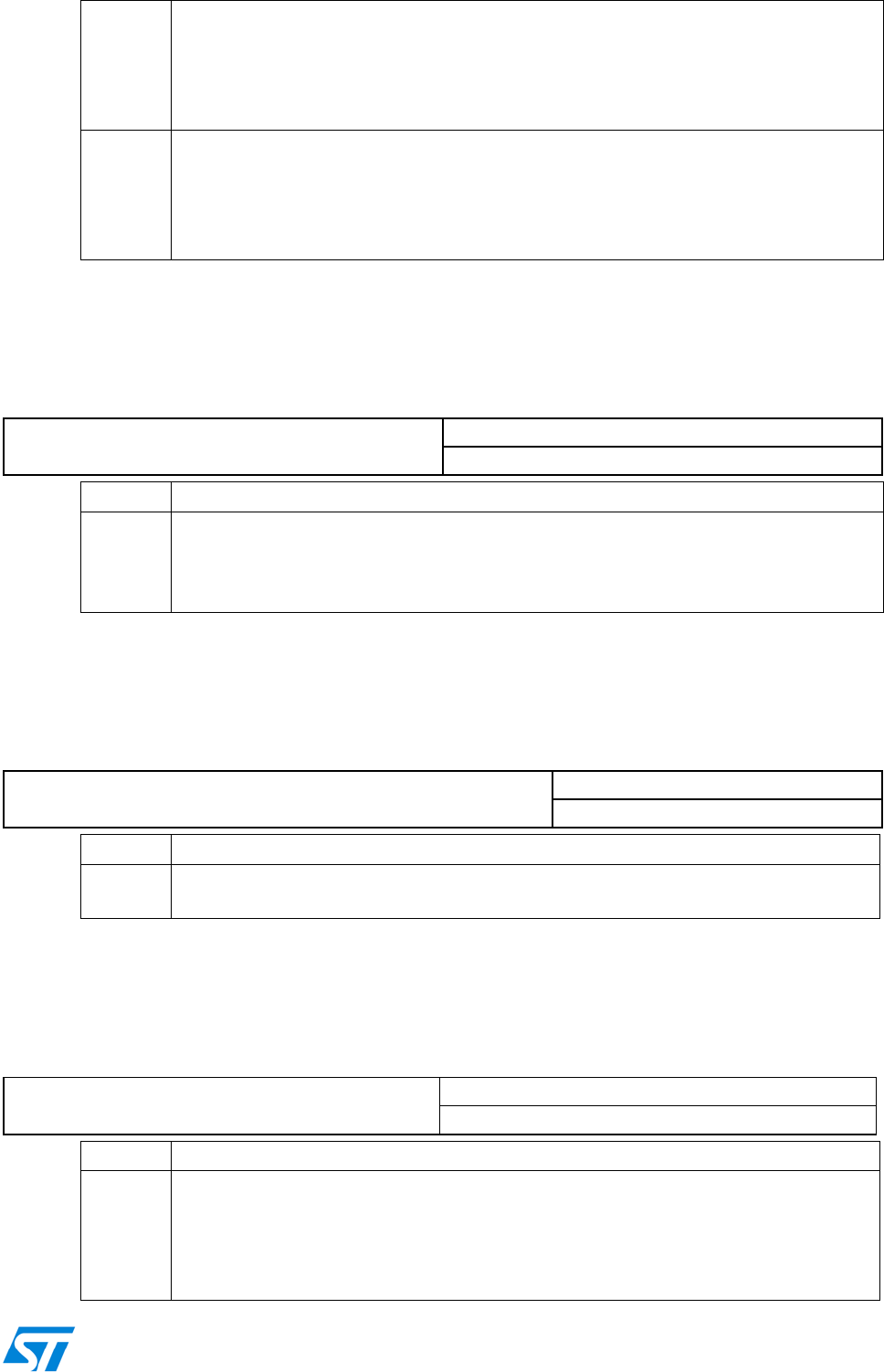

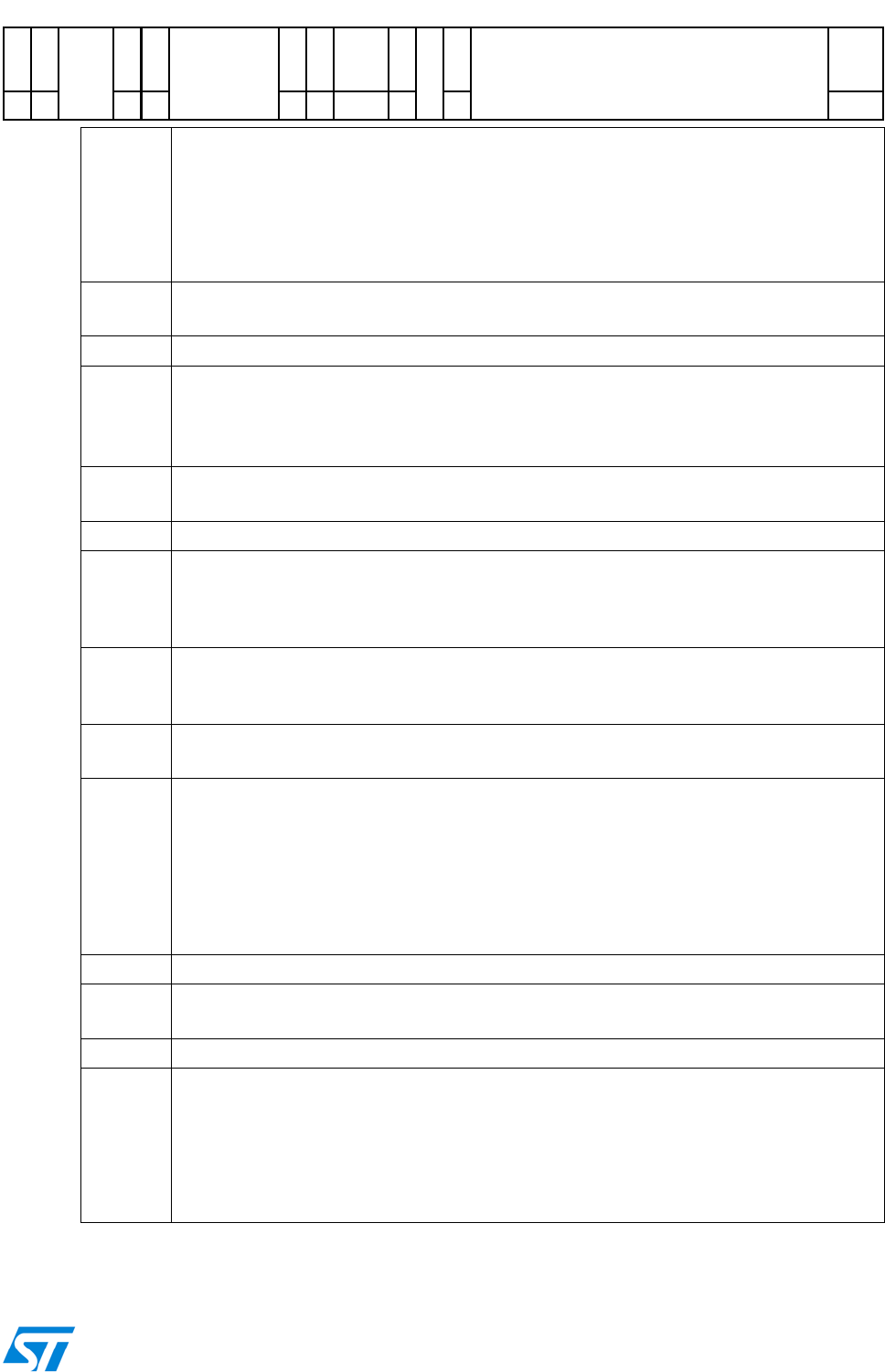

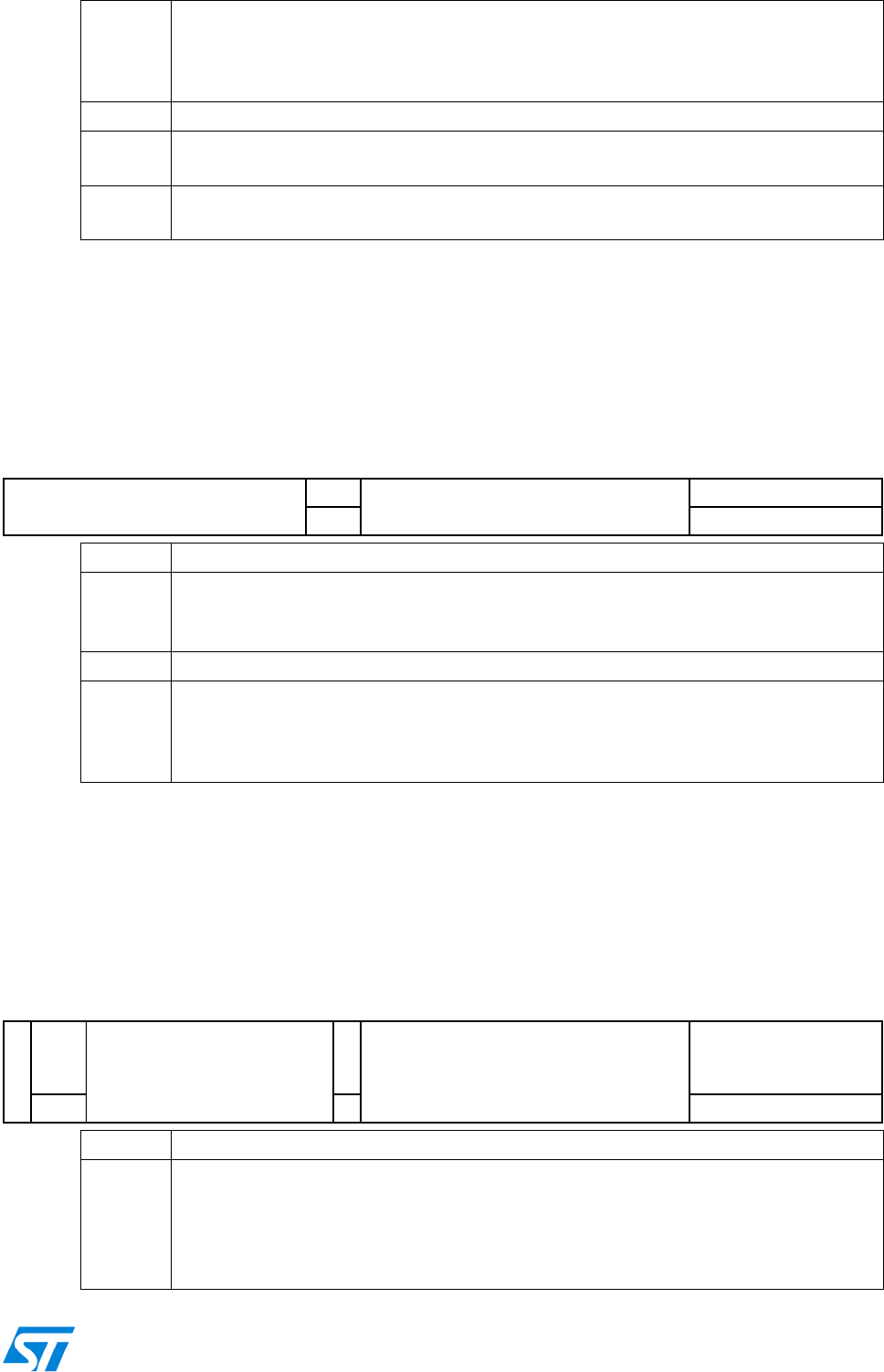

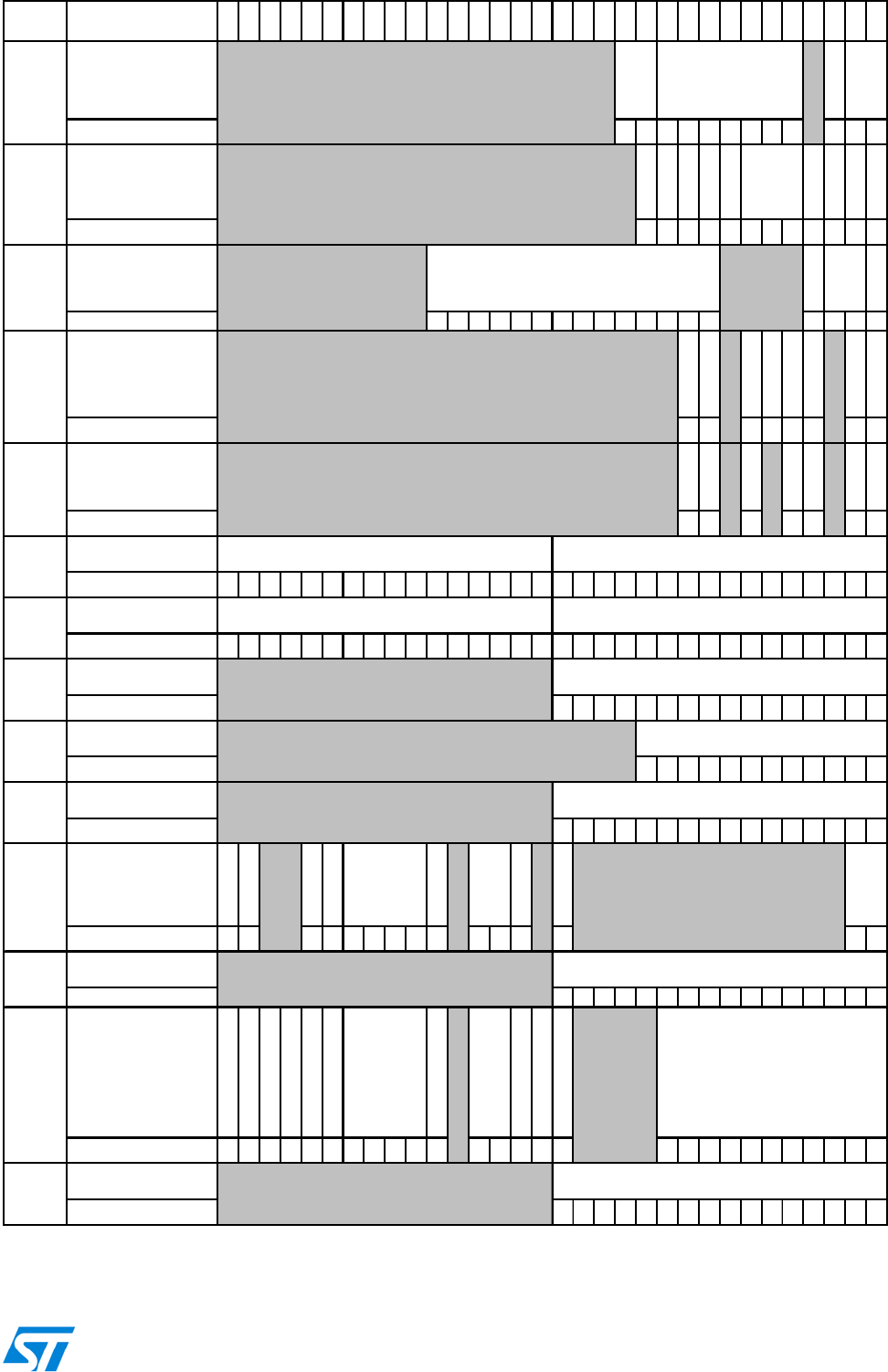

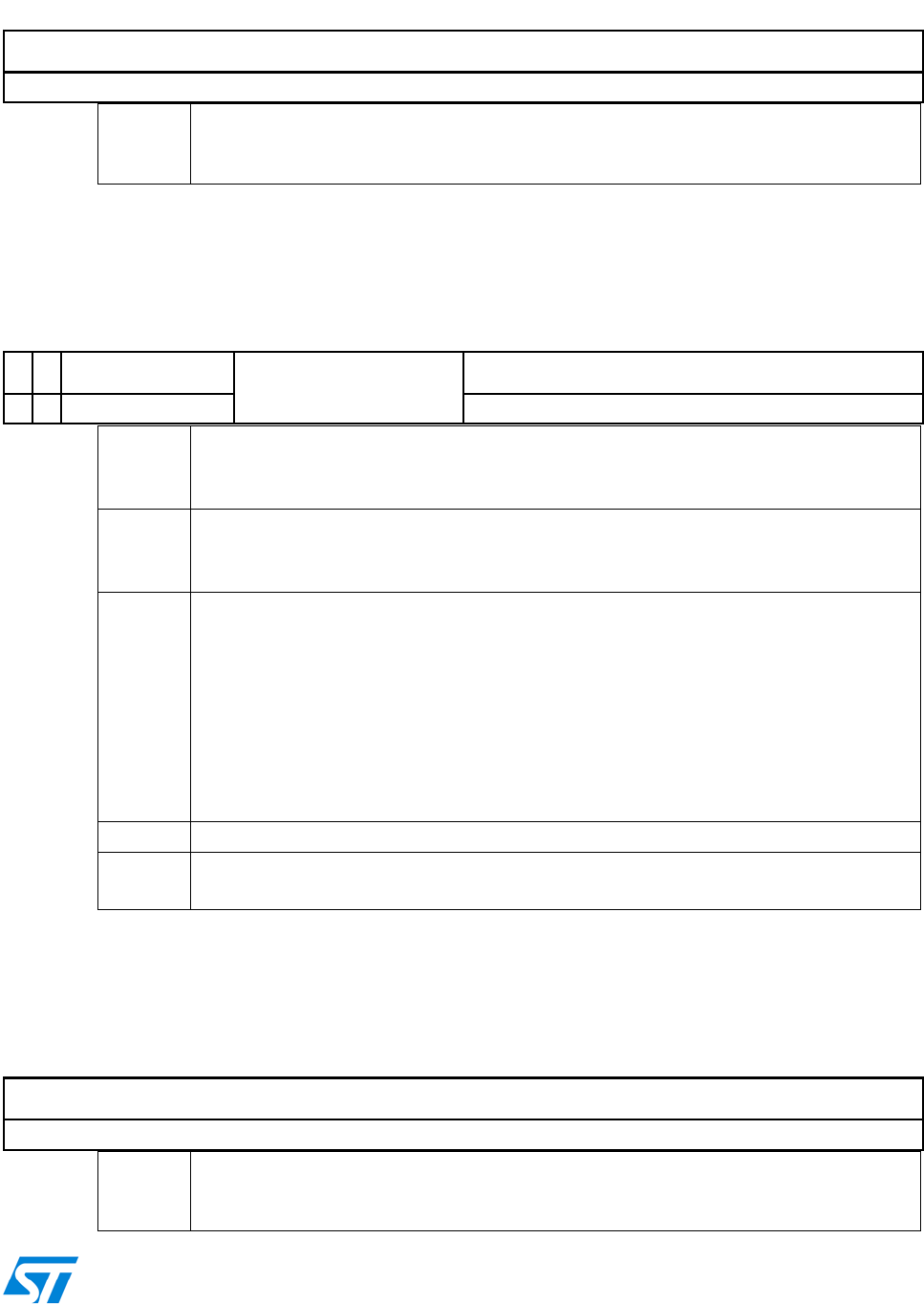

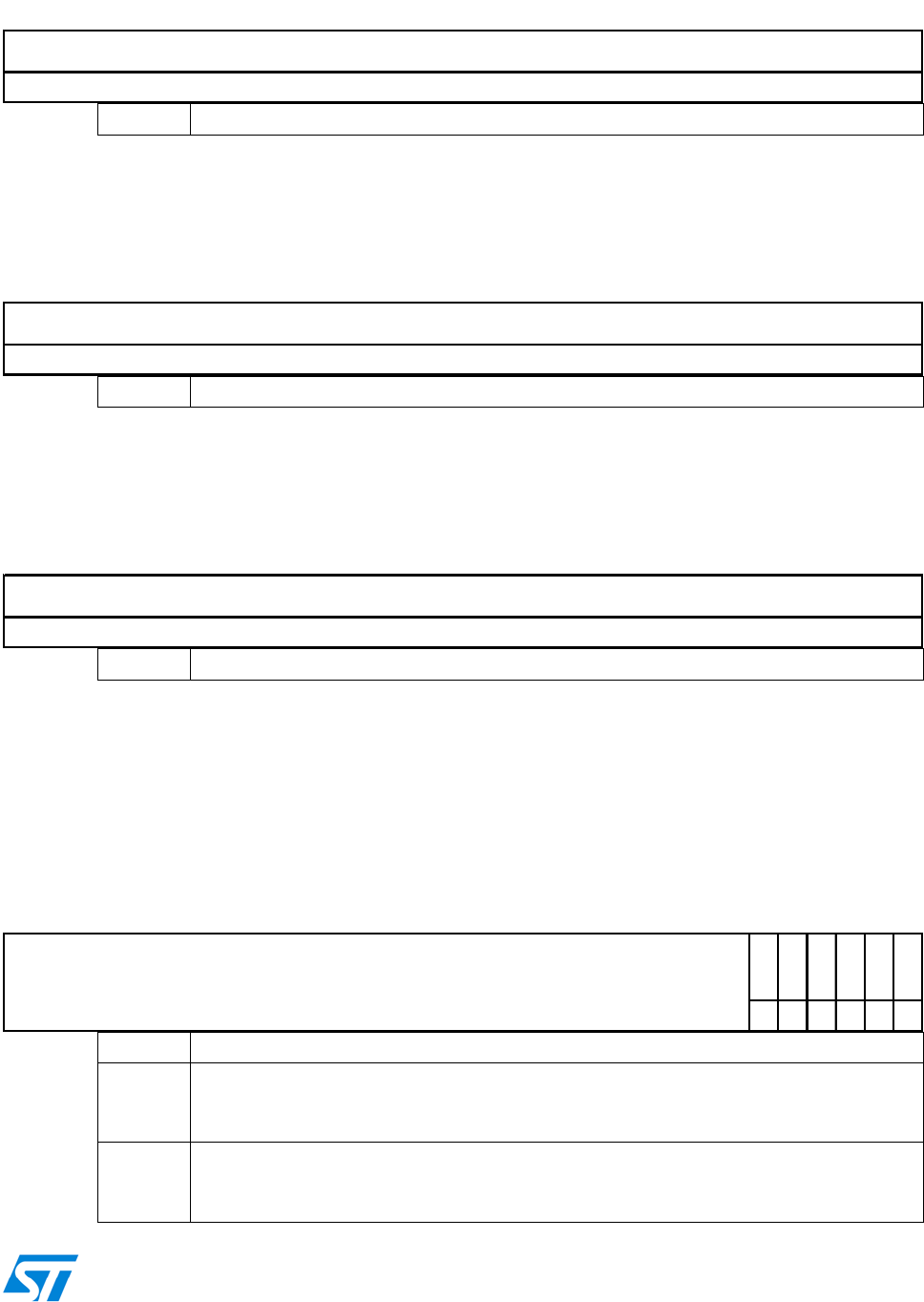

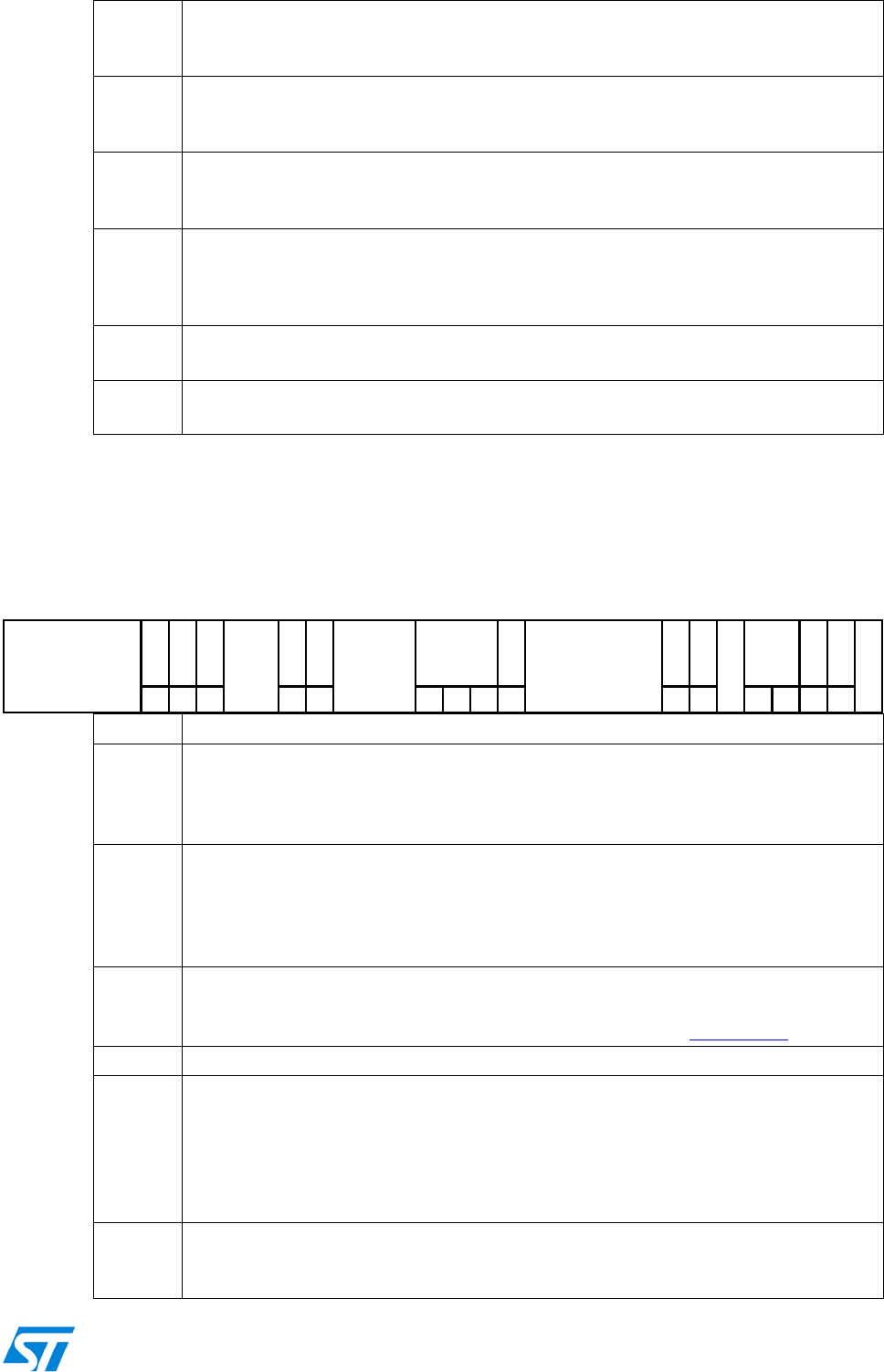

STM32系列产品命名规则

示例:

产品系列

STM32 = 基于ARM®的32位微控制器

产品类型

F = 通用类型

产品子系列

101 = 基本型

102 = USB基本型,USB 2.0全速设备

103 = 增强型

105或107 = 互联型

引脚数目

T = 36脚

C = 48脚

R = 64脚

V = 100脚

Z = 144脚

闪存存储器容量

4 = 16K字节的闪存存储器

6 = 32K字节的闪存存储器

8 = 64K字节的闪存存储器

B = 128K字节的闪存存储器

C = 256K字节的闪存存储器

D = 384K字节的闪存存储器

E = 512

K

字节的闪存存储器

封装

H = BGA

T = LQFP

U = VFQFPN

Y = WLCSP64

温度范围

6 = 工业级温度范围,-40°C~85°C

7 = 工业级温度范围,-40°C~105°C

内部代码

A 或者空 (详见产品数据手册)

选项

xxx = 已编程的器件代号(3个数字)

TR = 卷带式包装

STM32 F 103 C xxx8T6A

参照2009年12月 RM0008 Reference Manual 英文第10版

本译文仅供参考,如有翻译错误,请以英文原稿为准。请读者随时注意在ST网站下载更新版本

STM32F10xxx参考手册

参照2009年12月 RM0008 Reference Manual 英文第10版

本译文仅供参考,如有翻译错误,请以英文原稿为准。请读者随时注意在ST网站下载更新版本

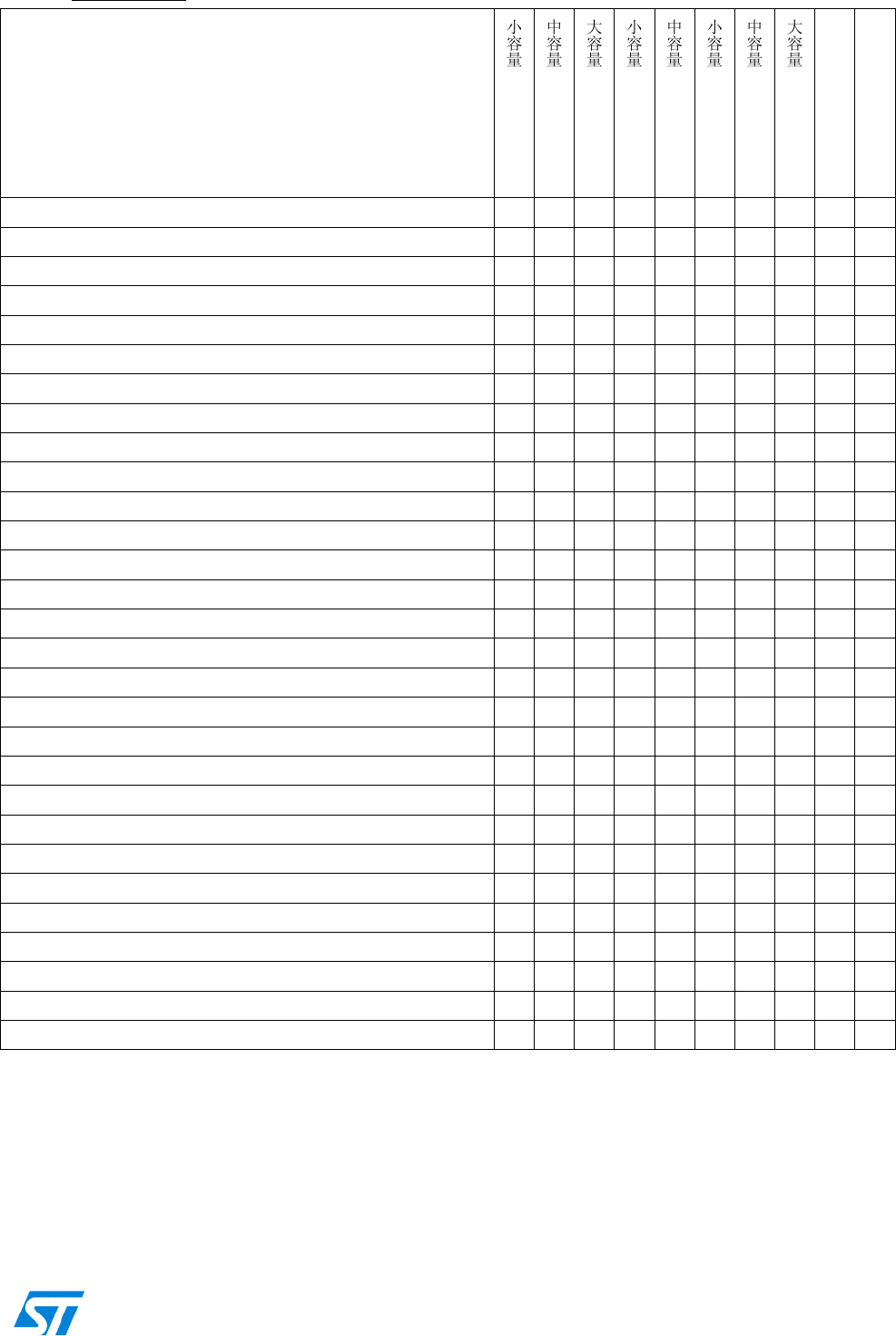

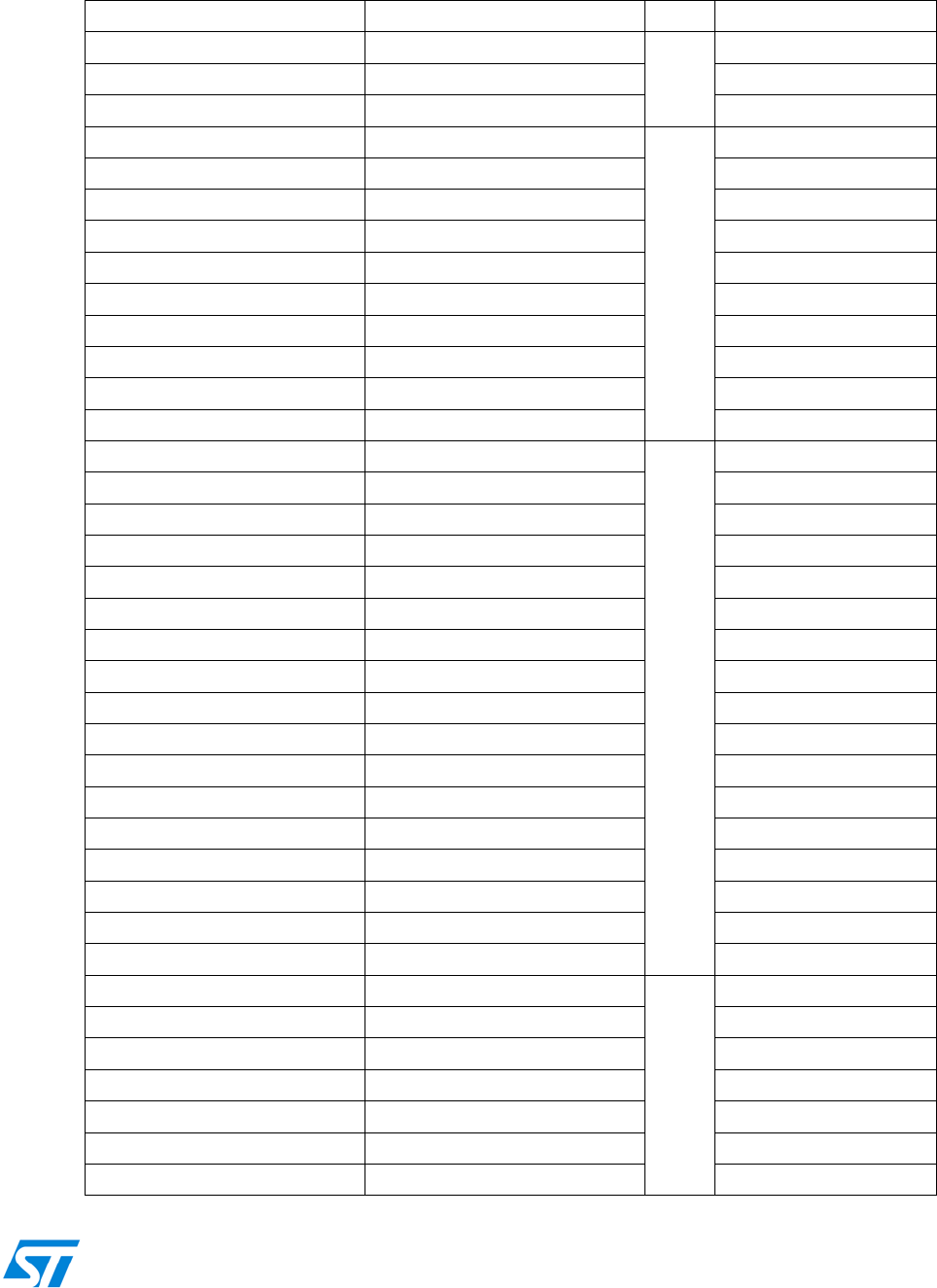

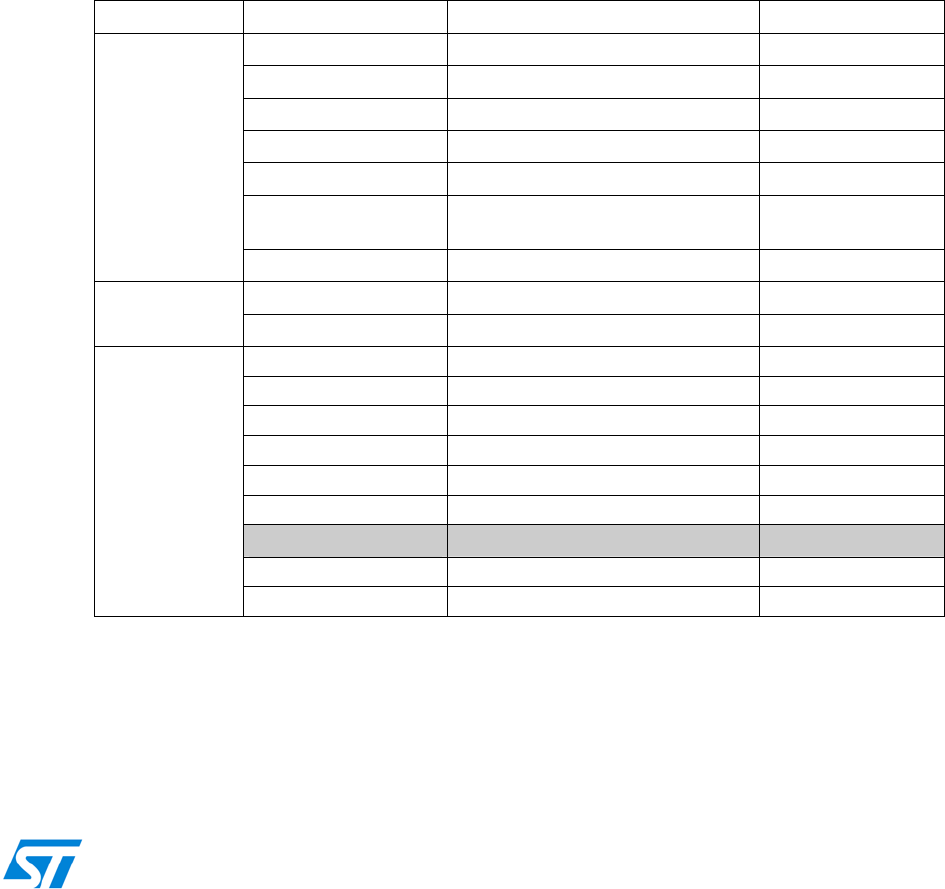

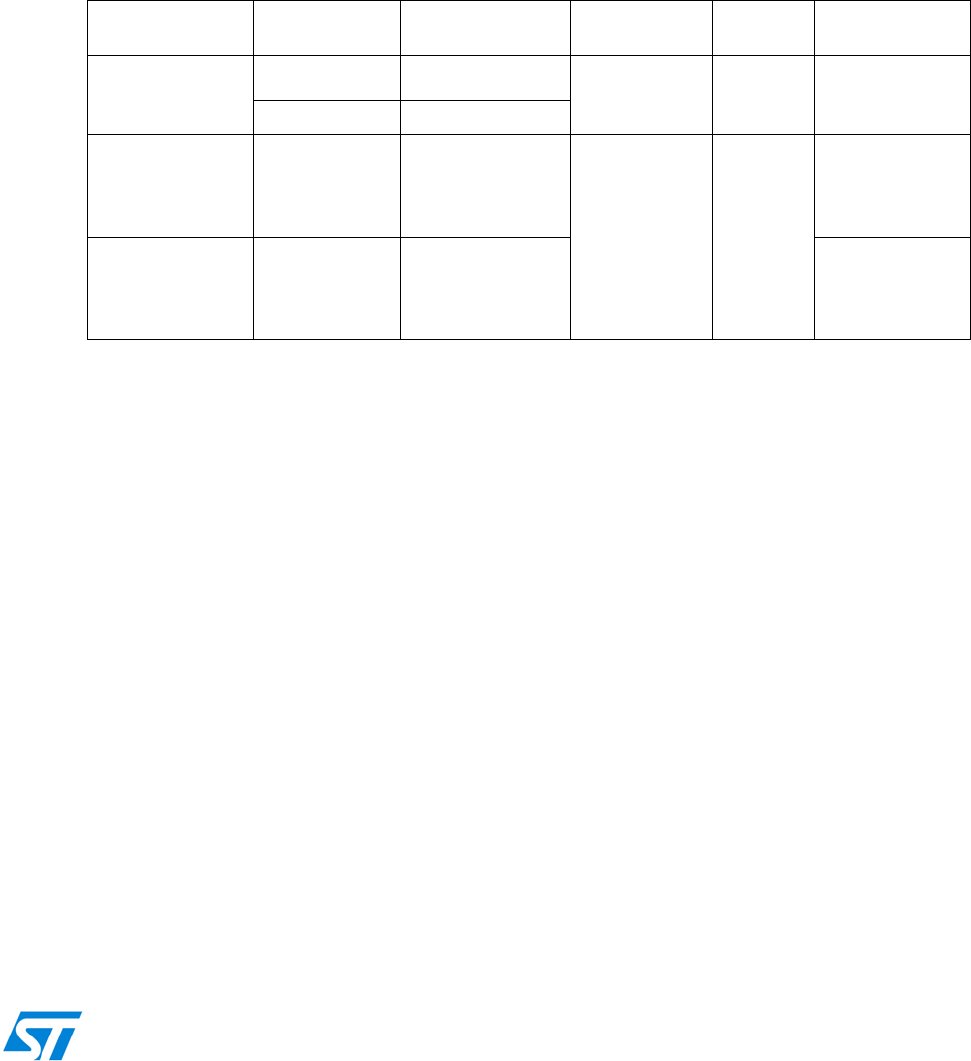

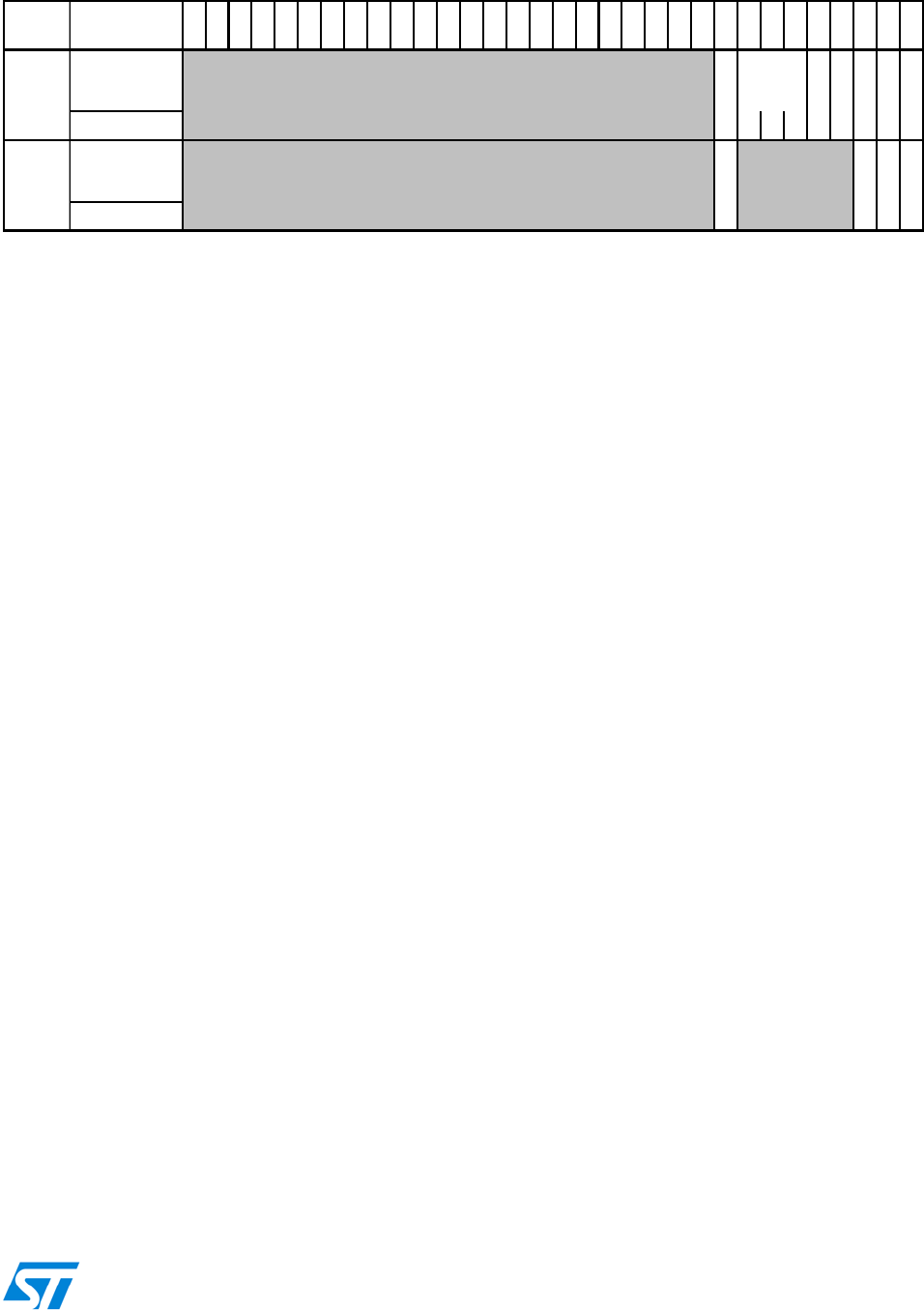

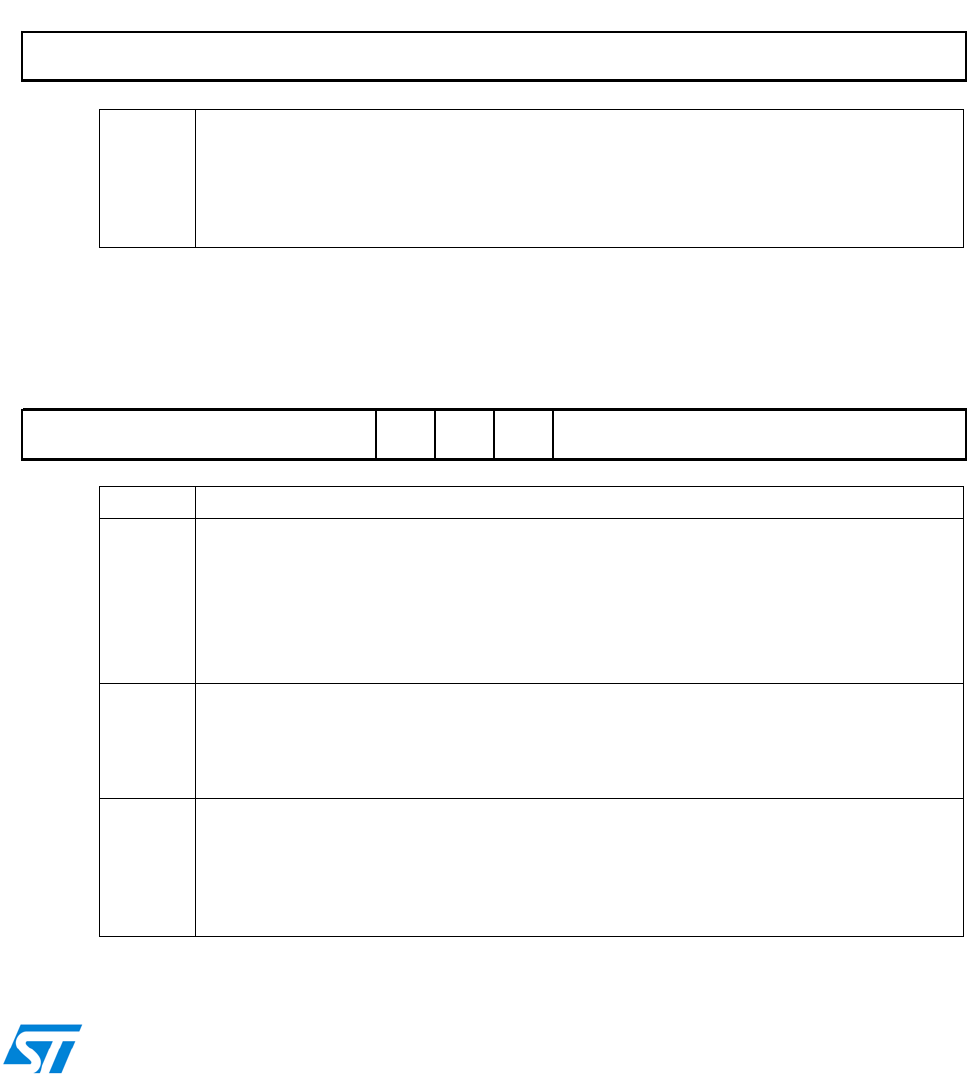

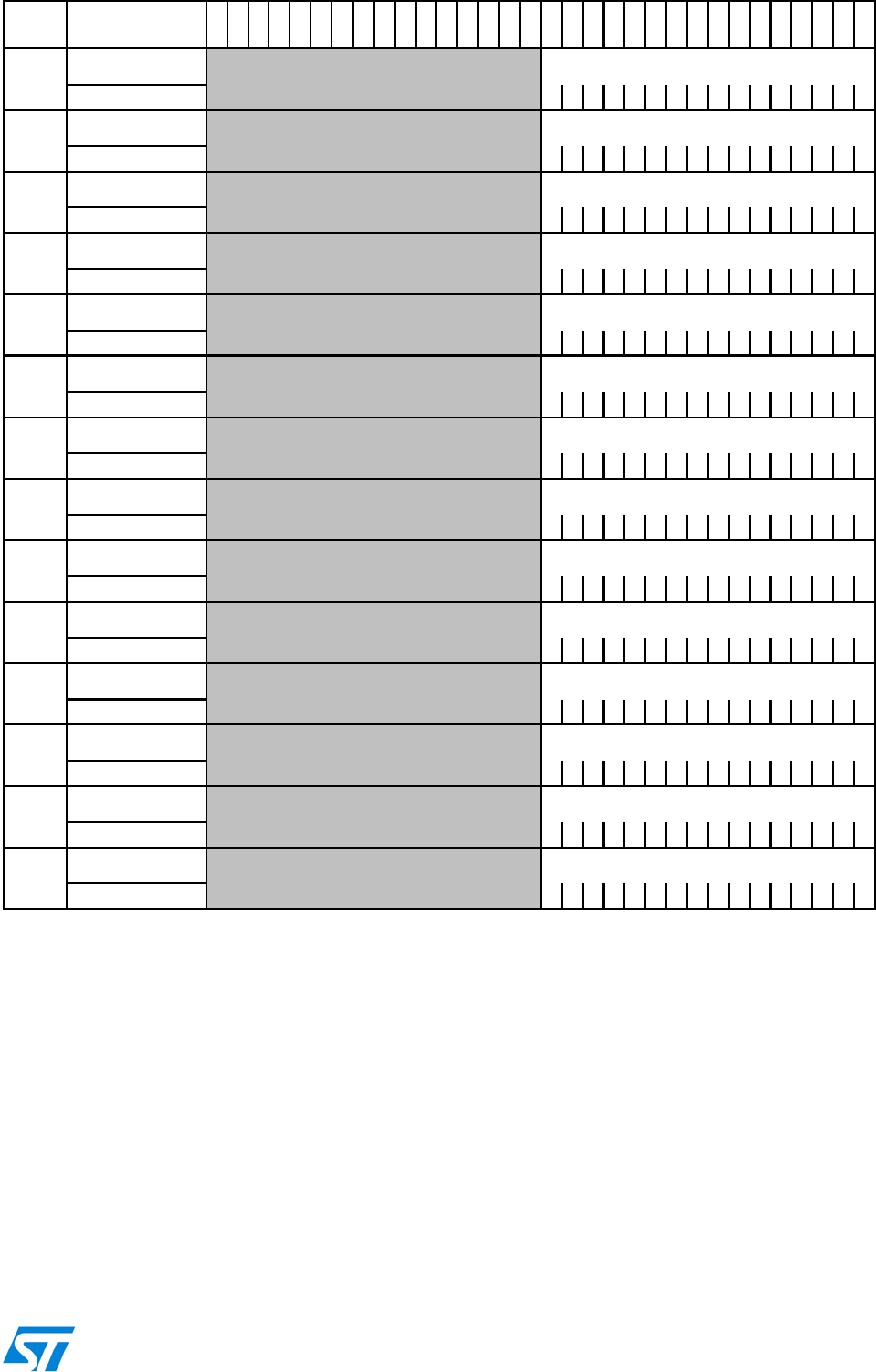

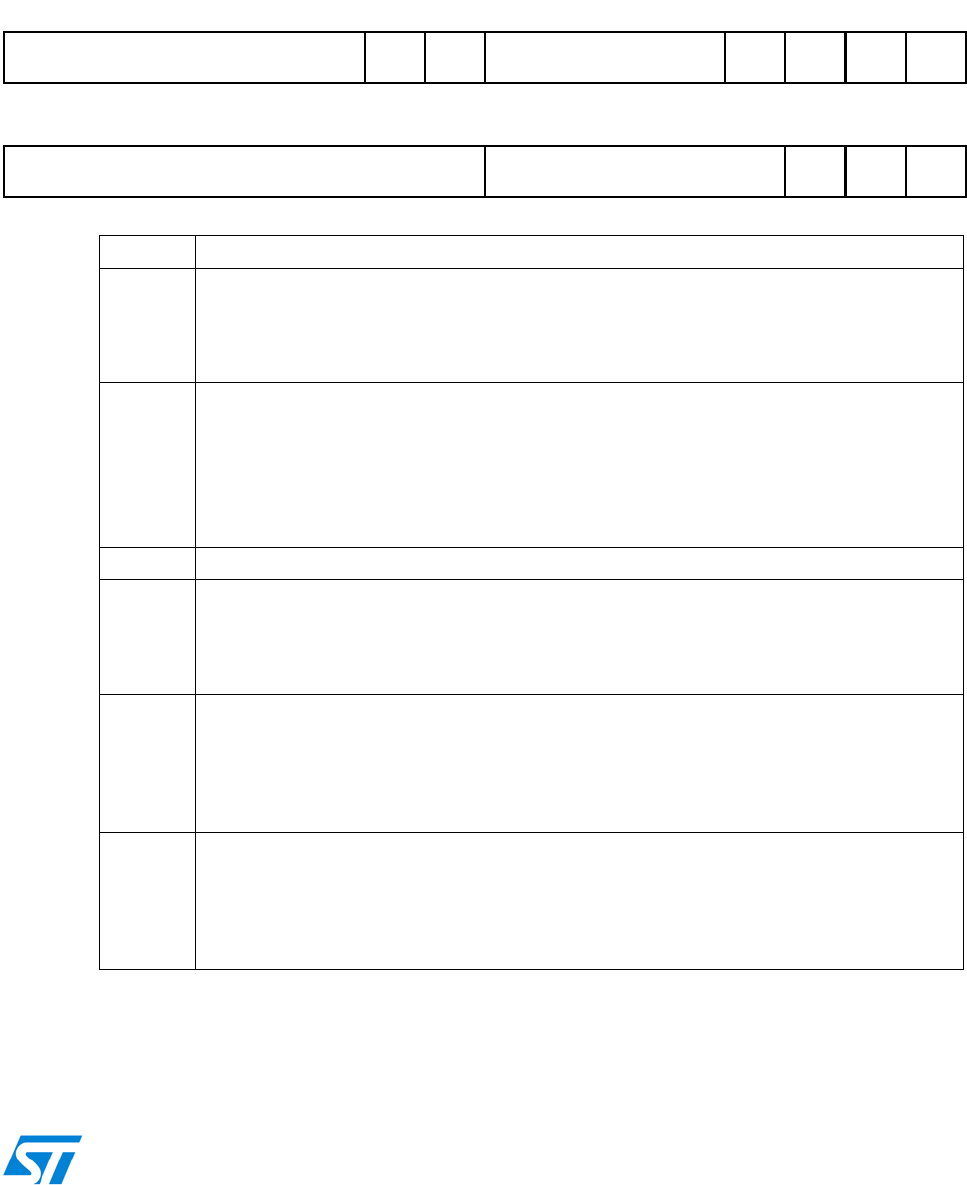

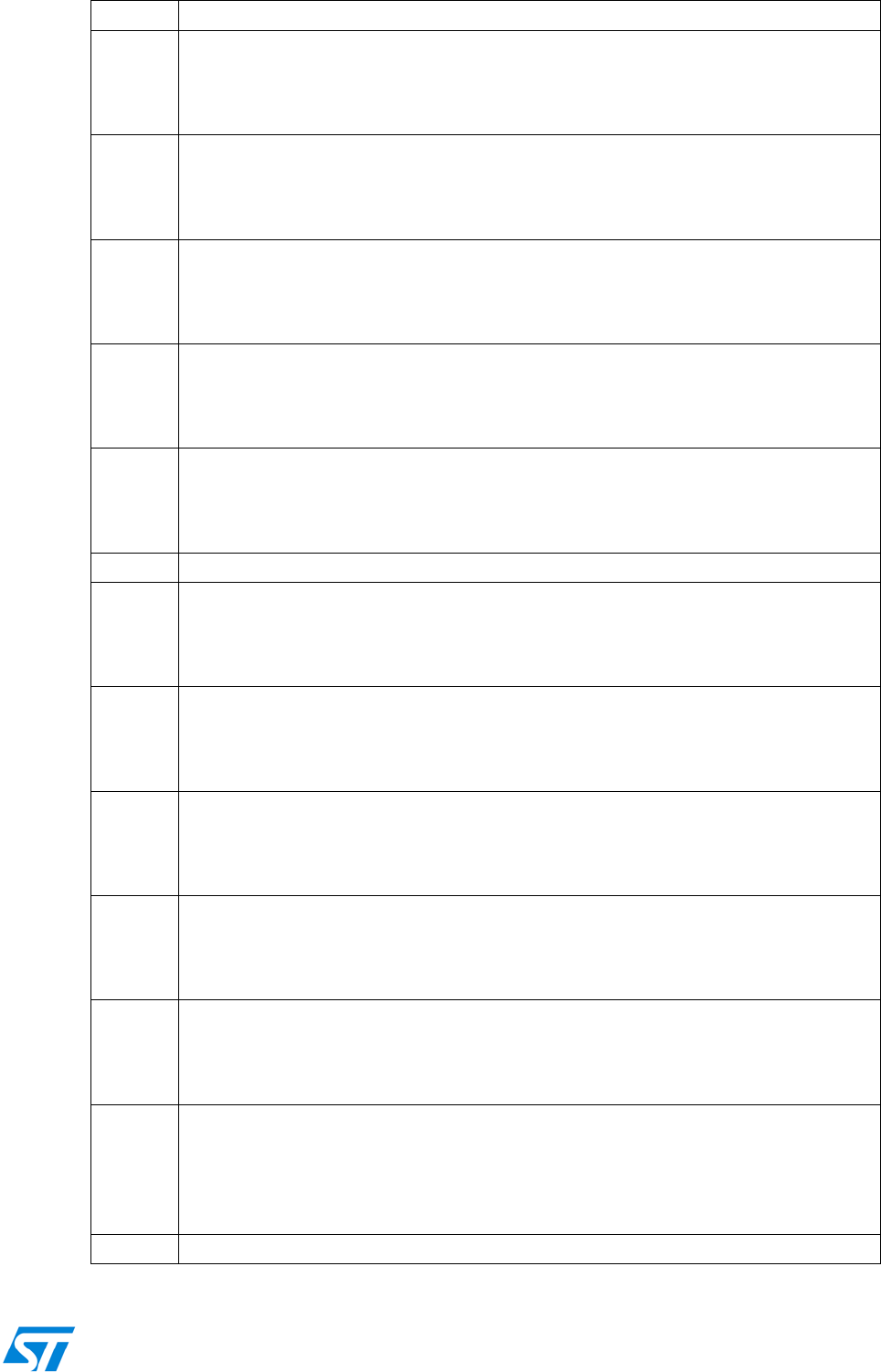

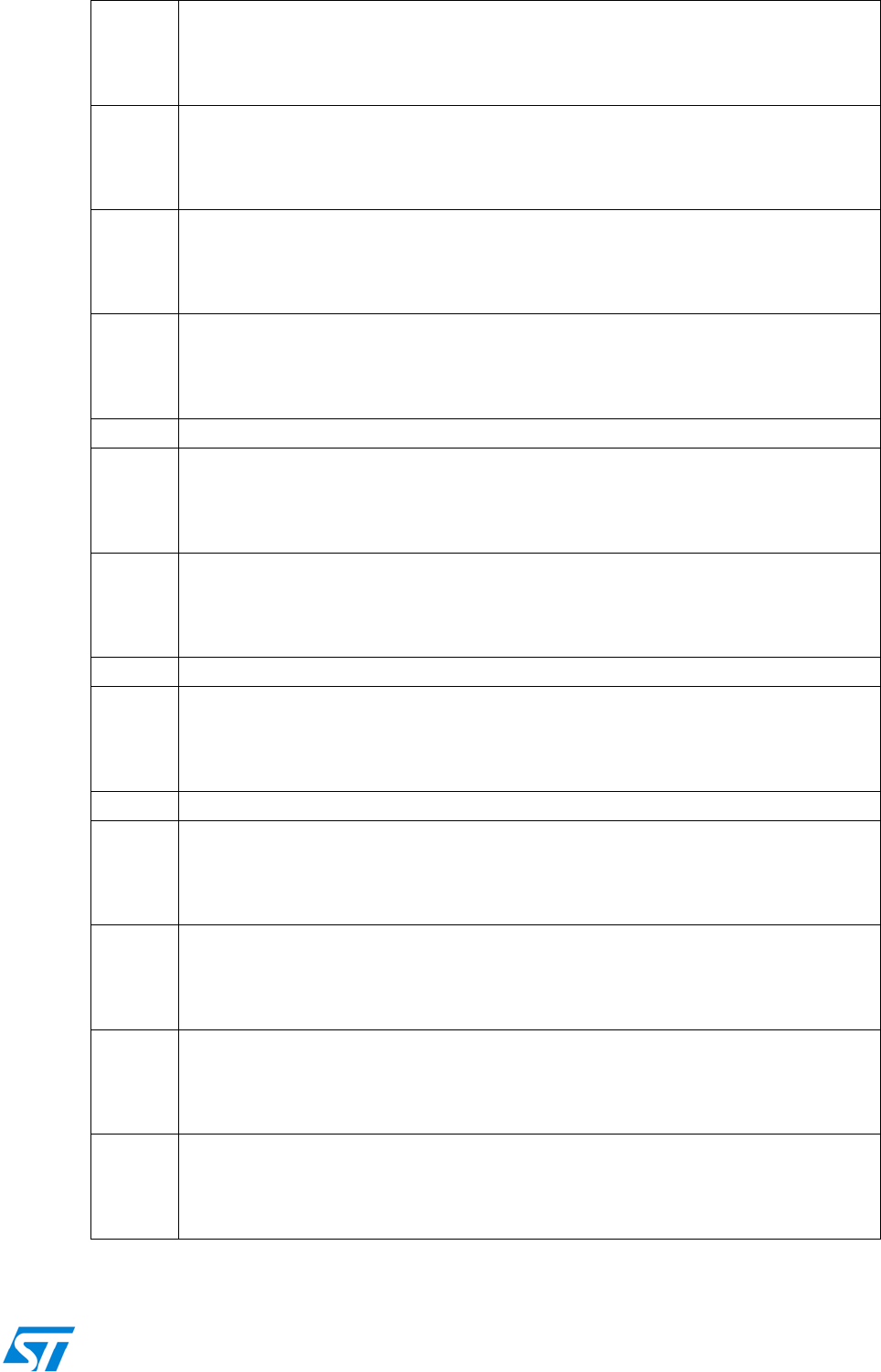

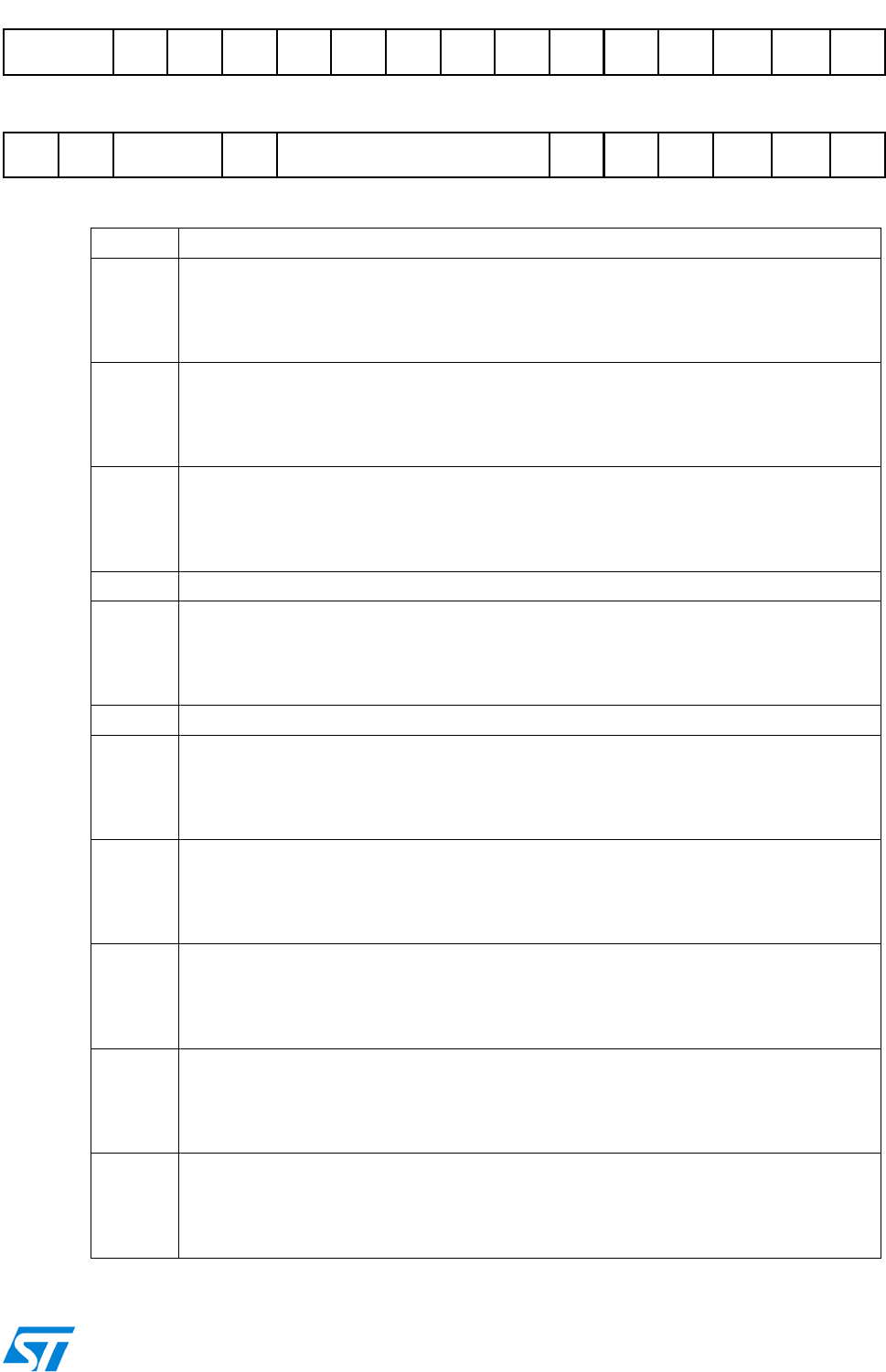

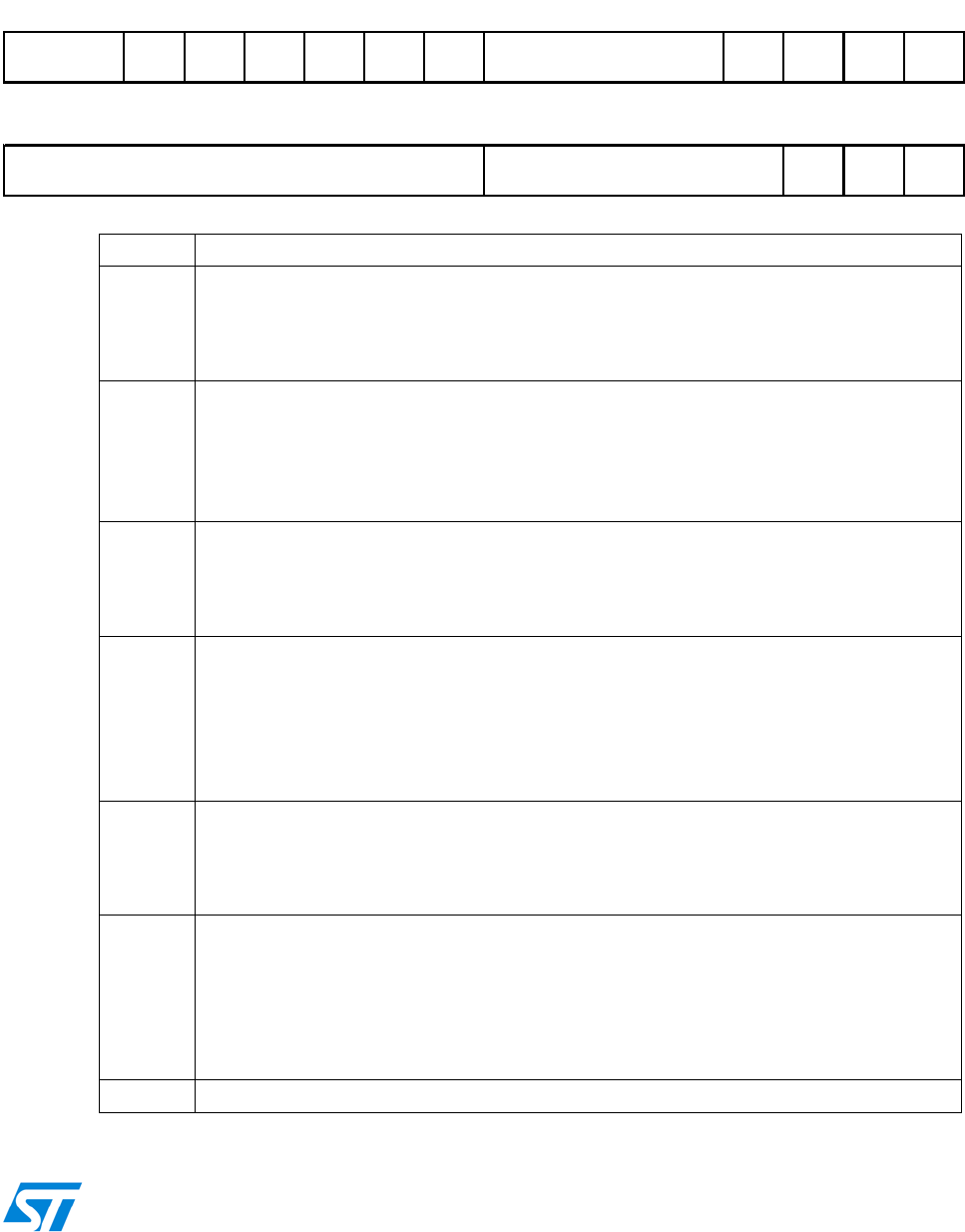

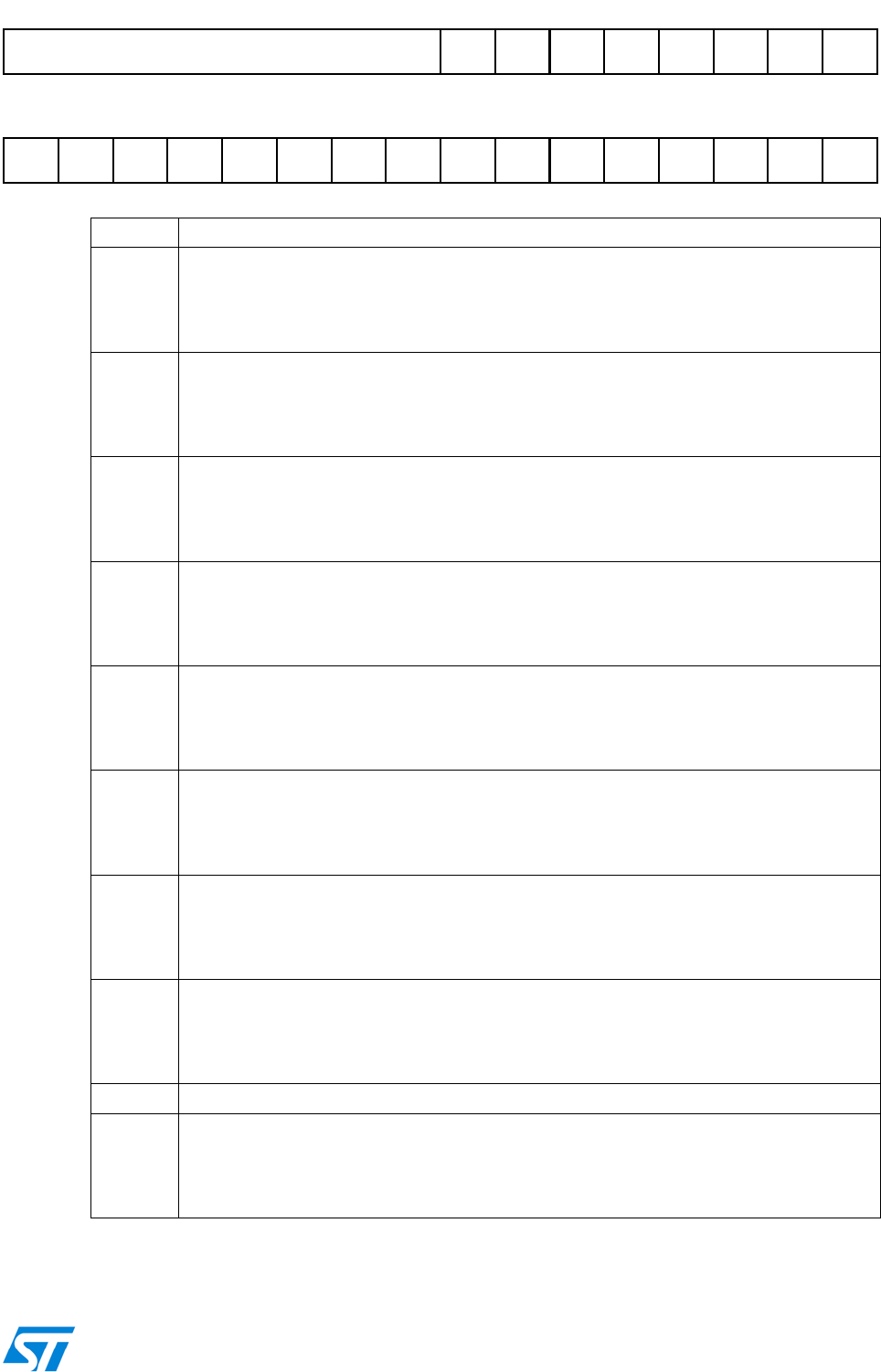

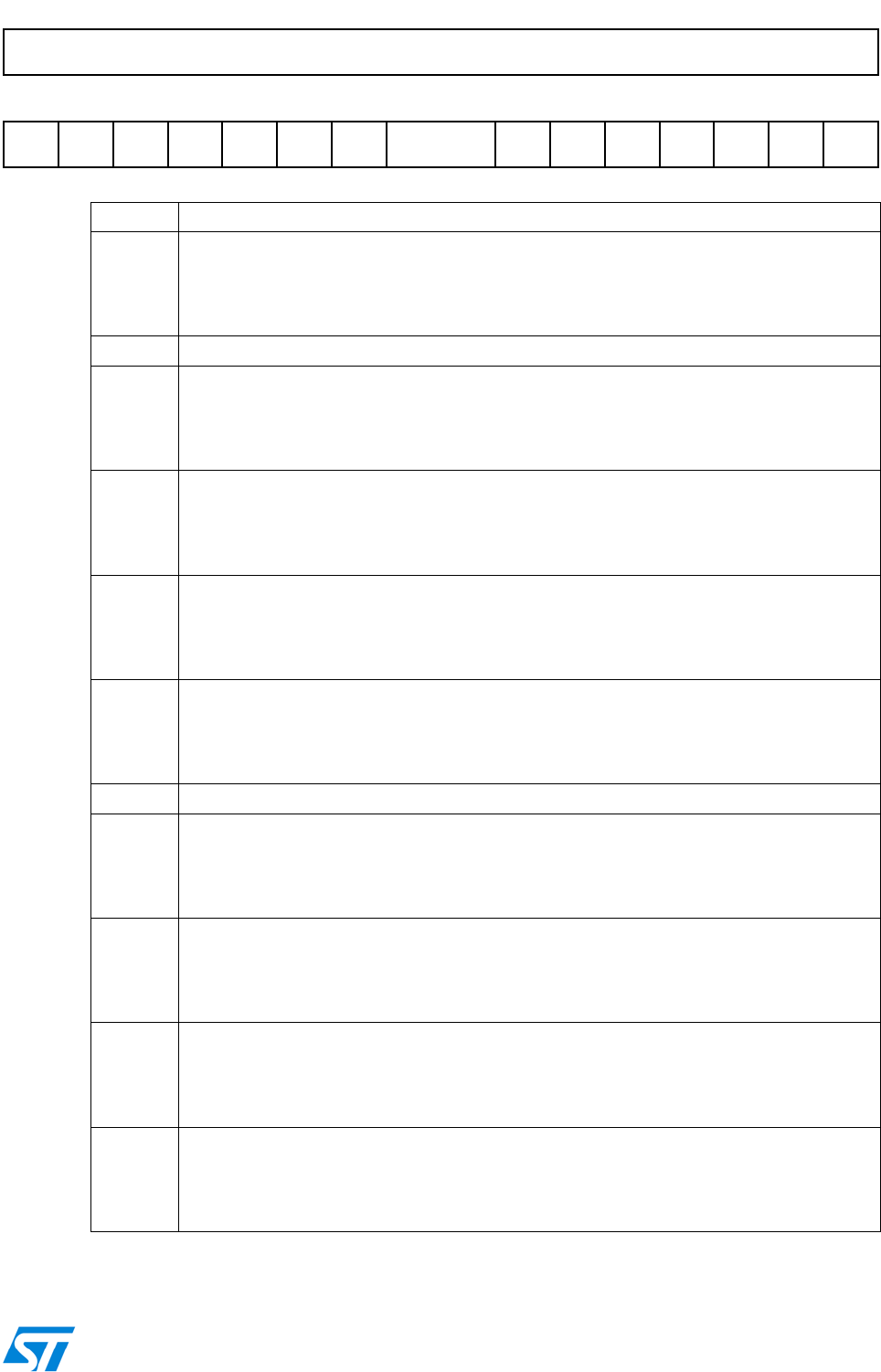

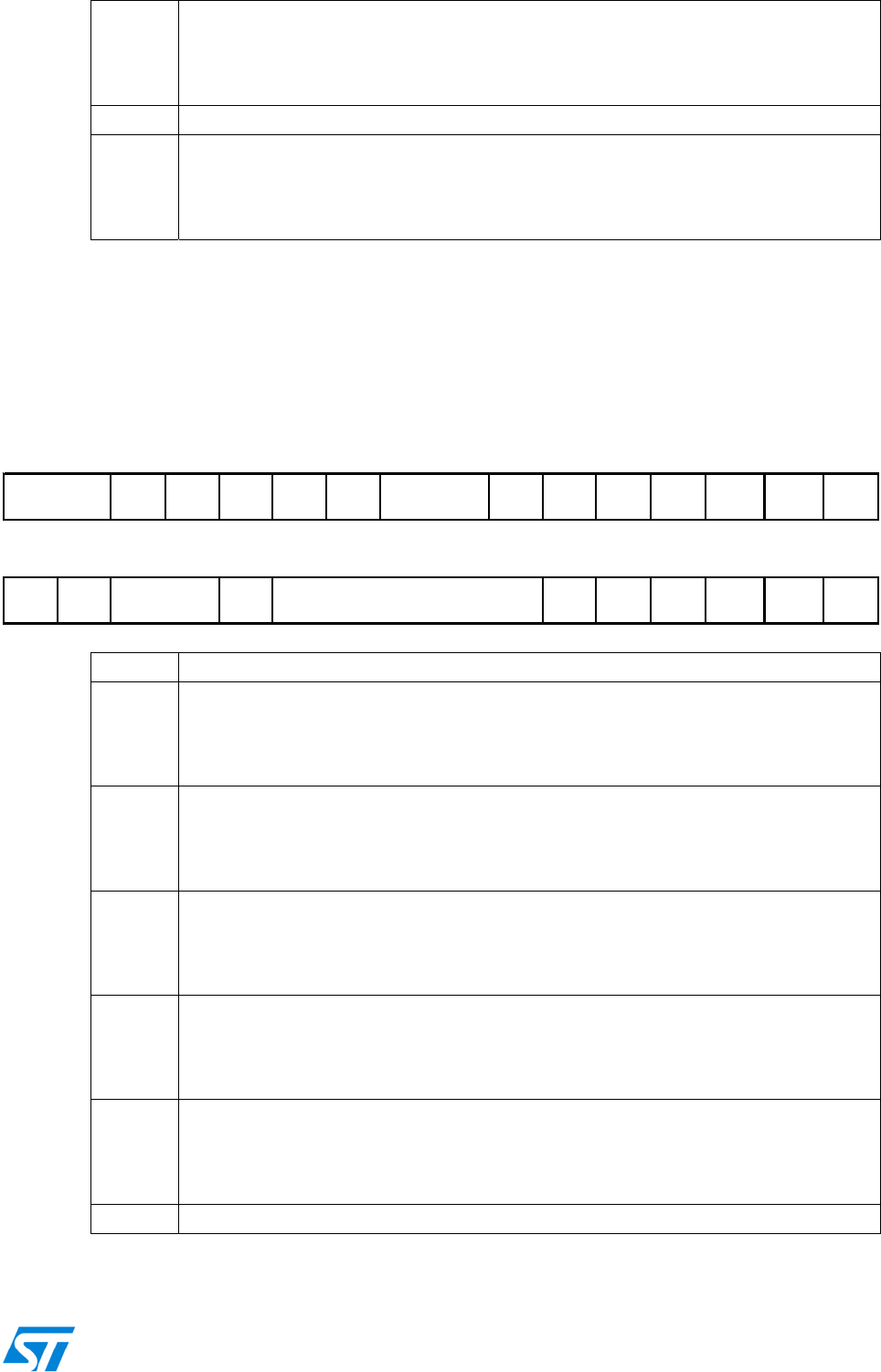

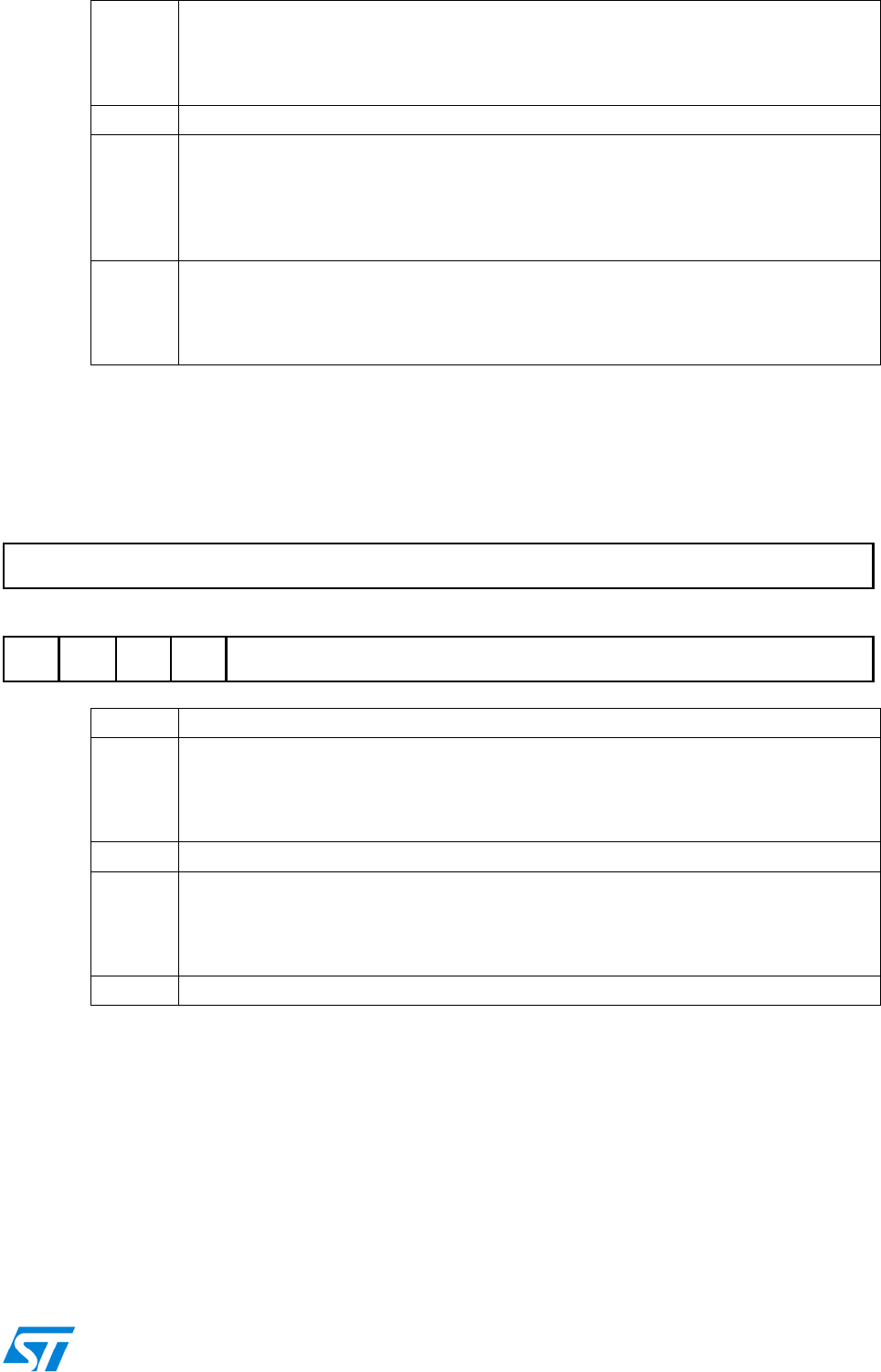

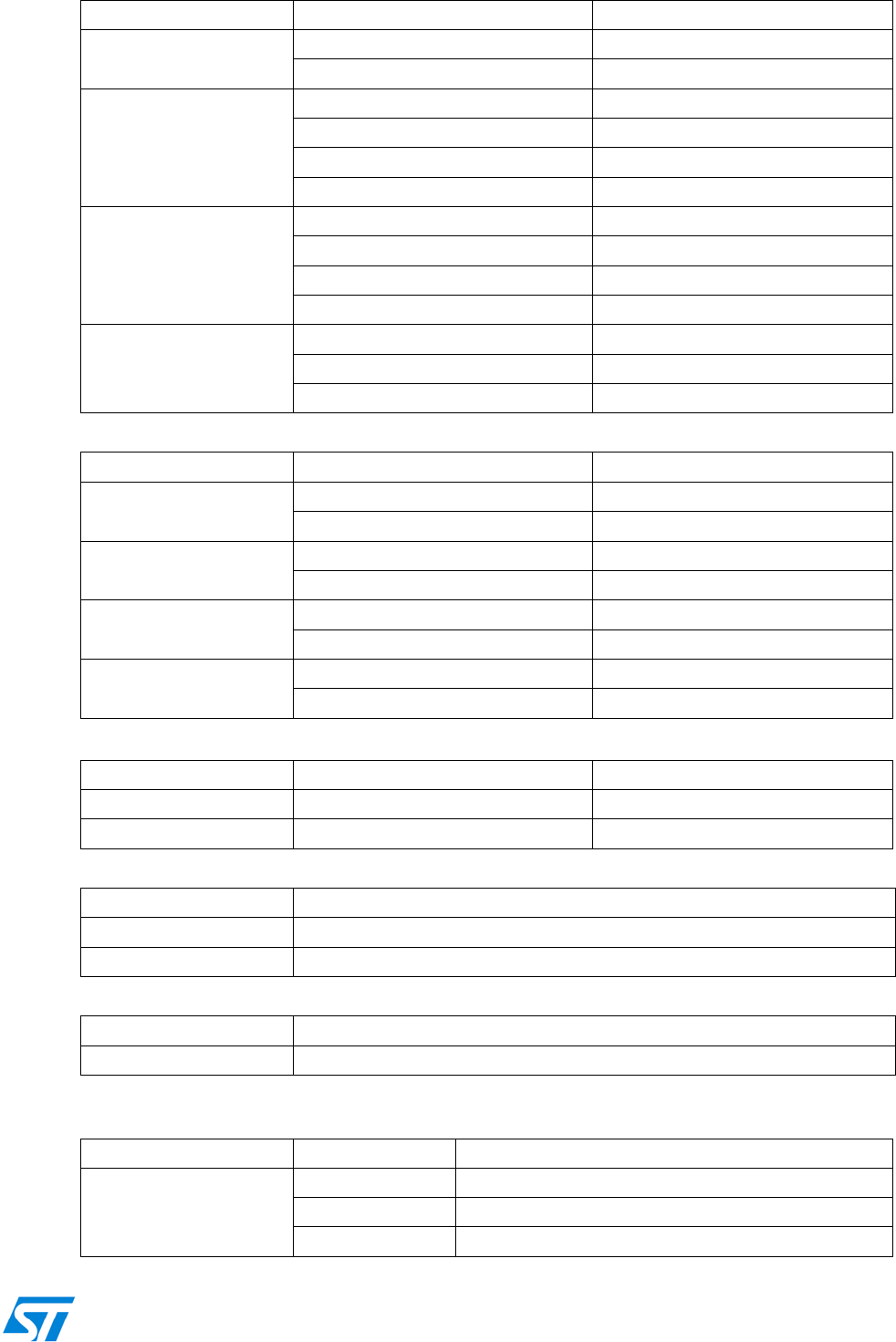

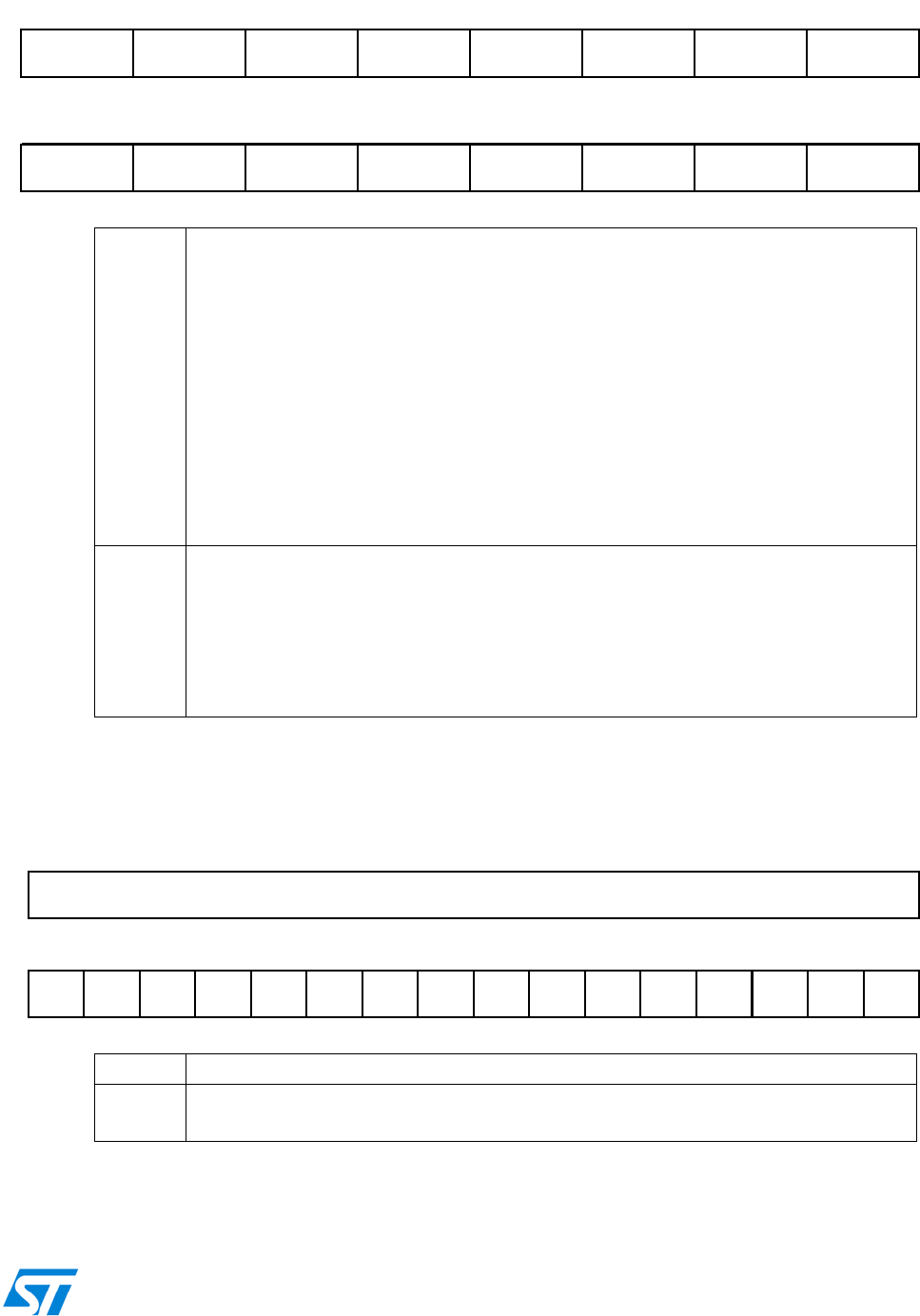

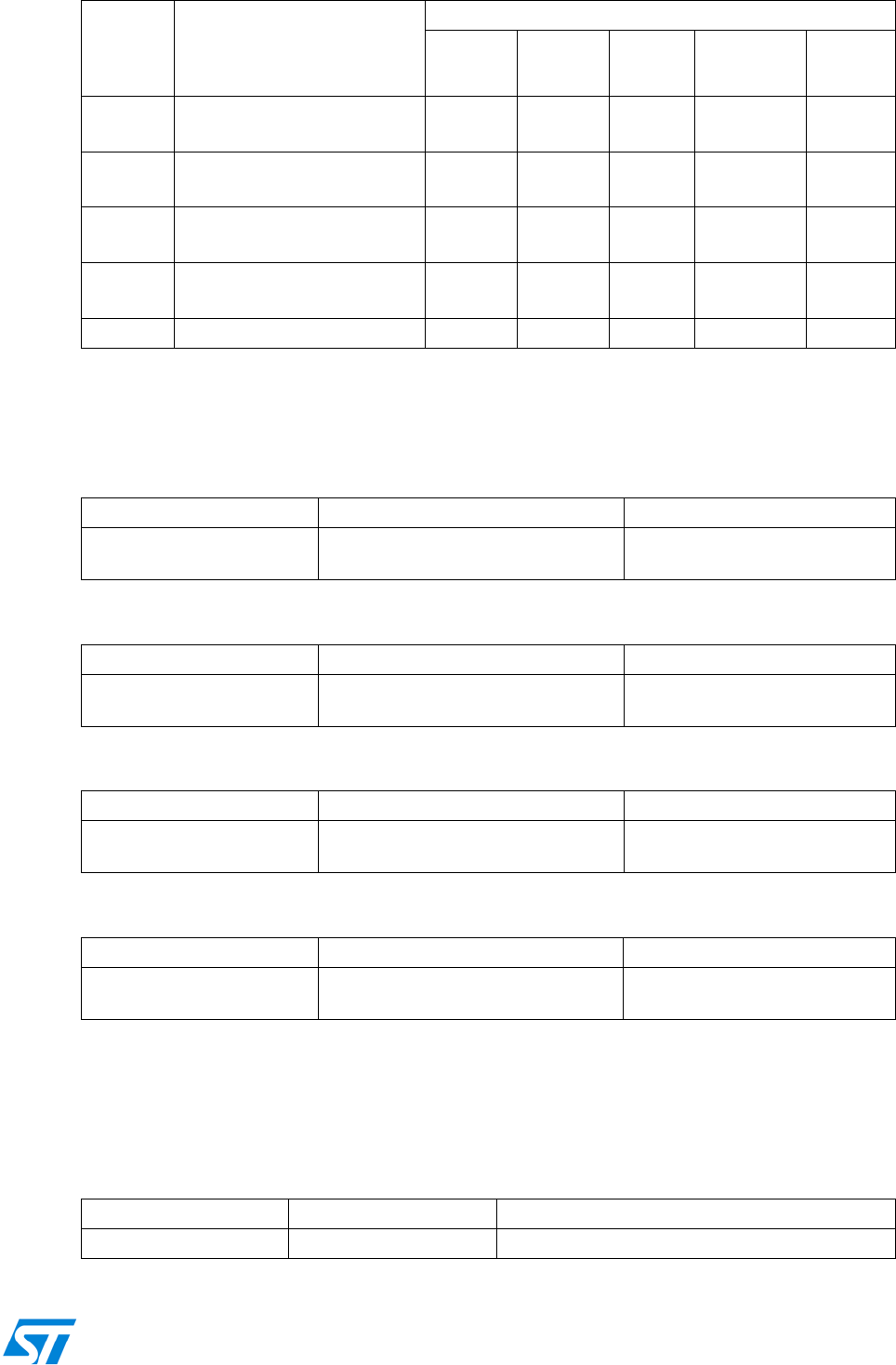

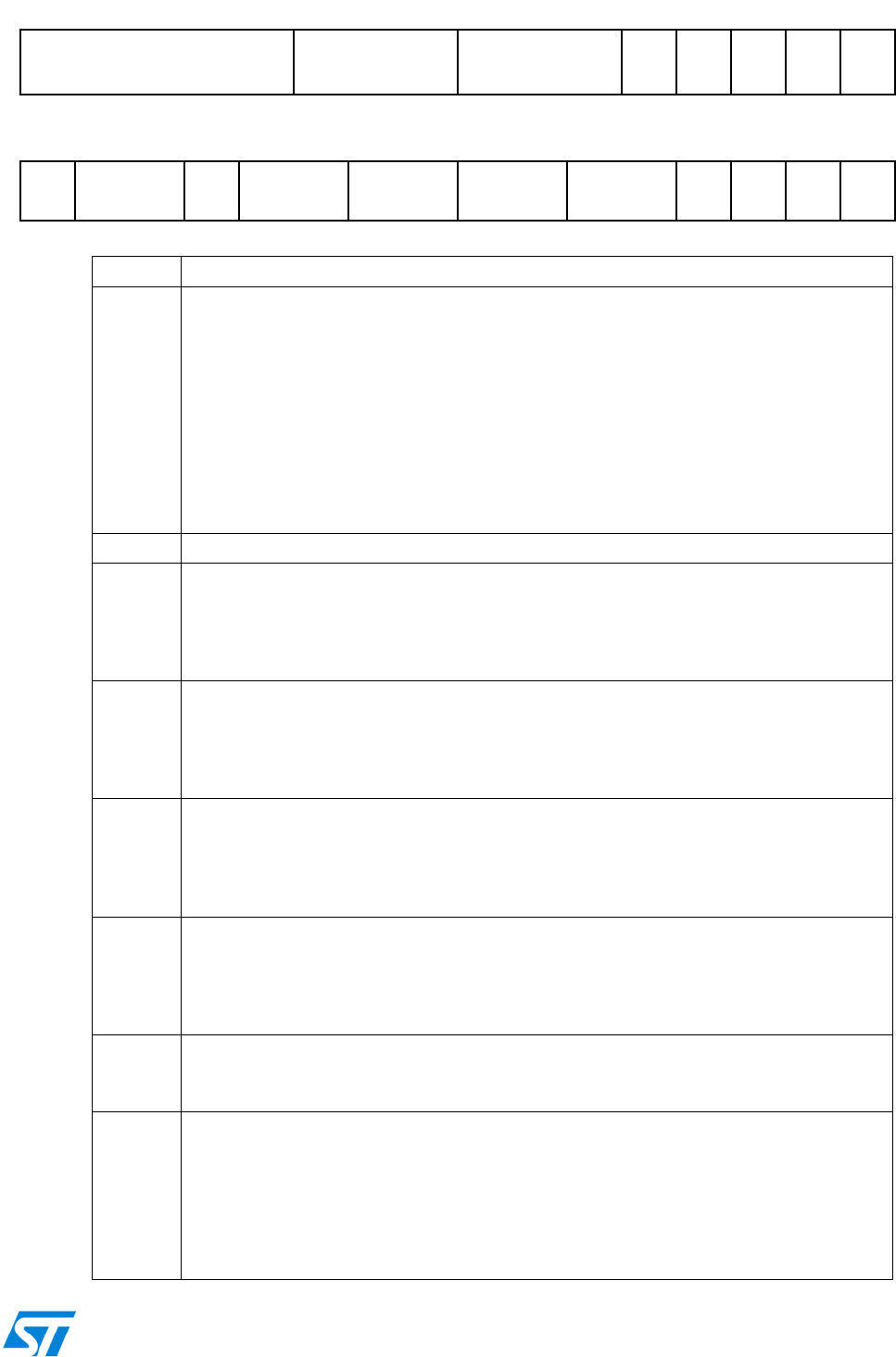

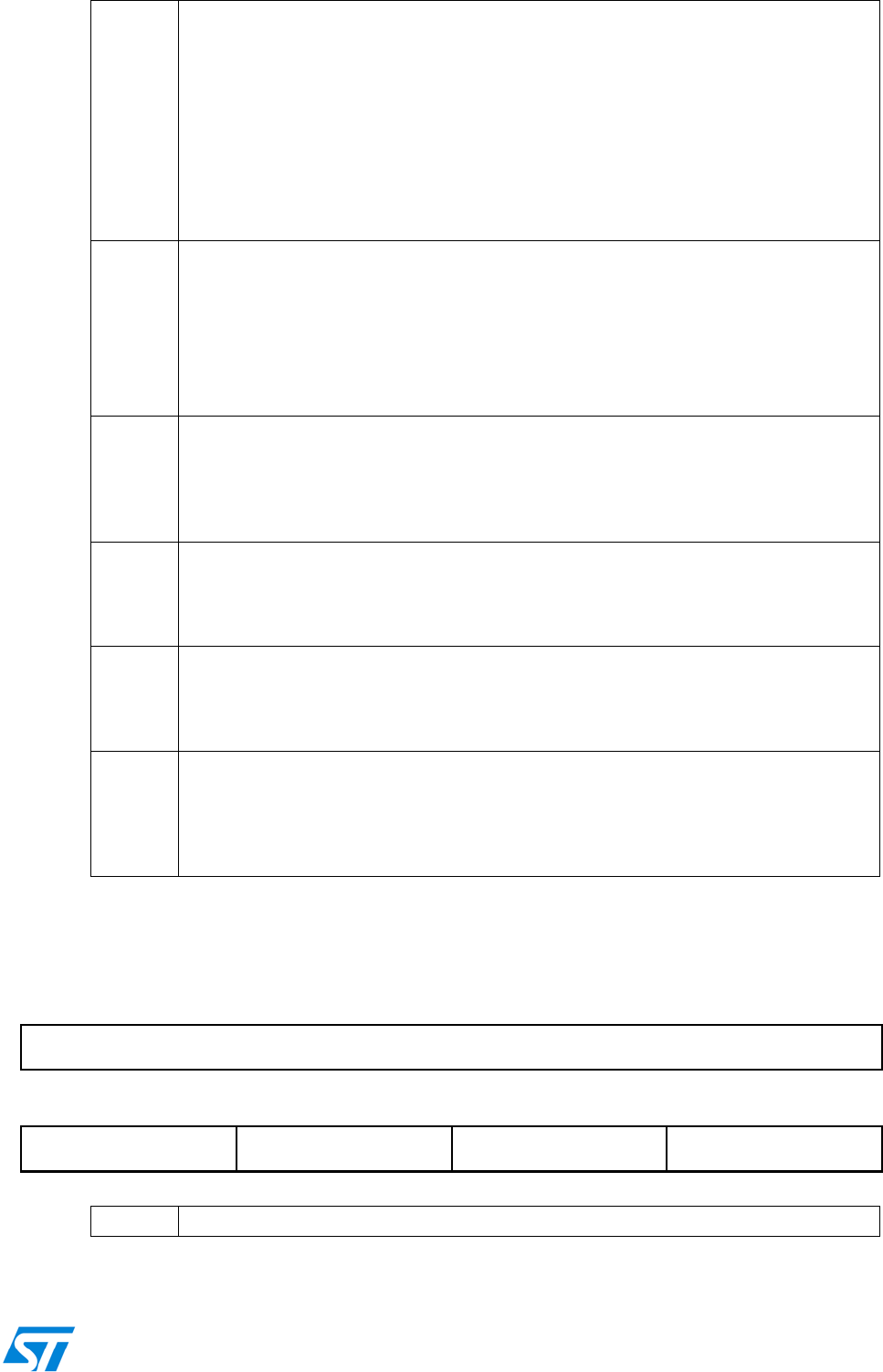

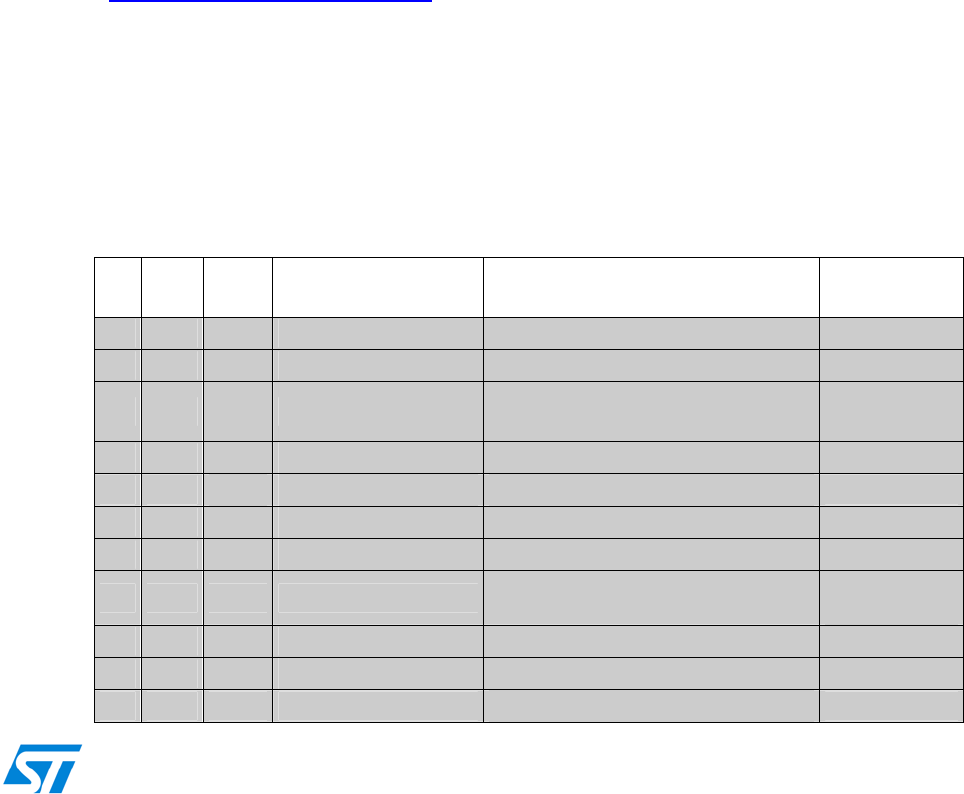

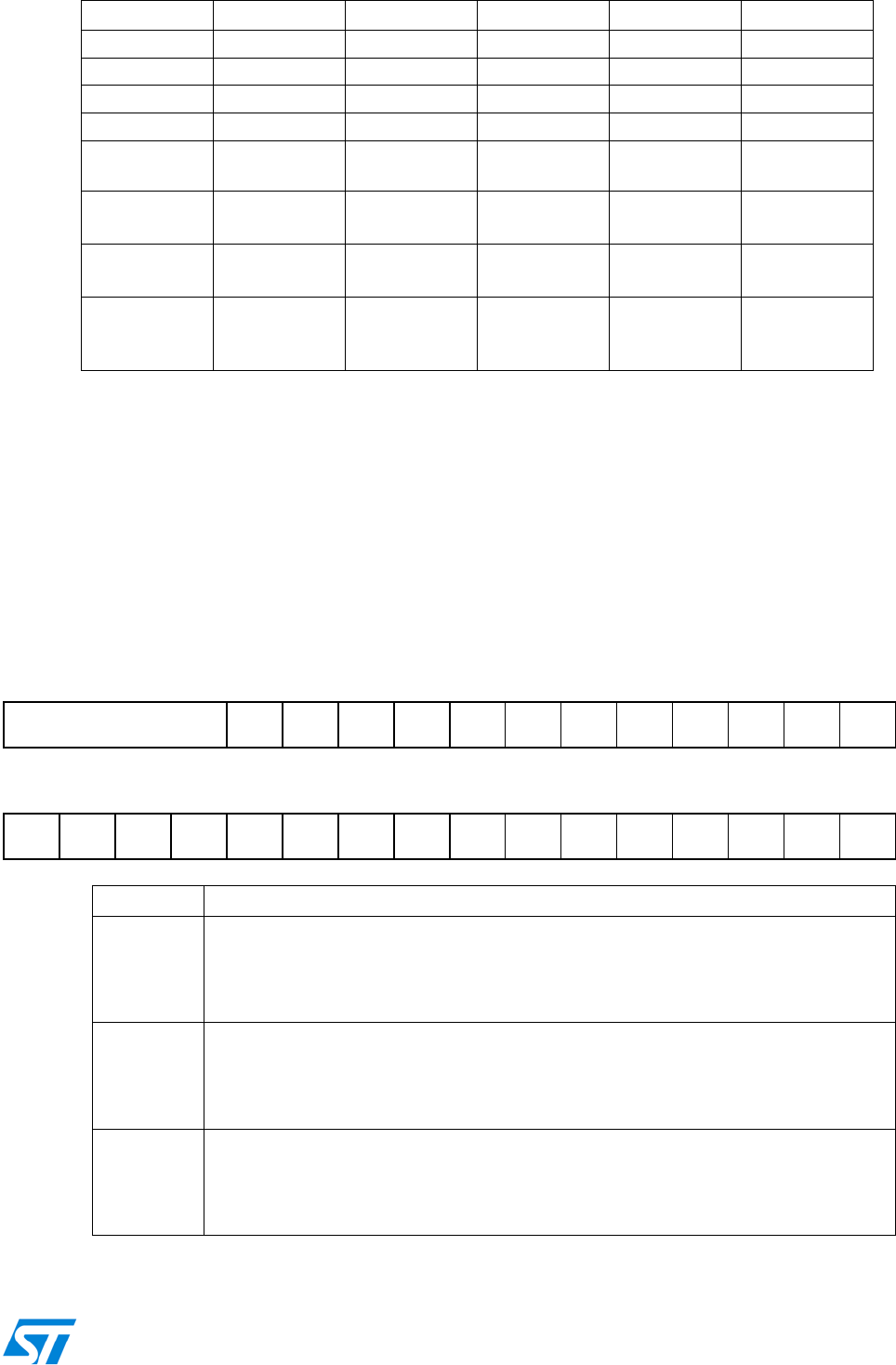

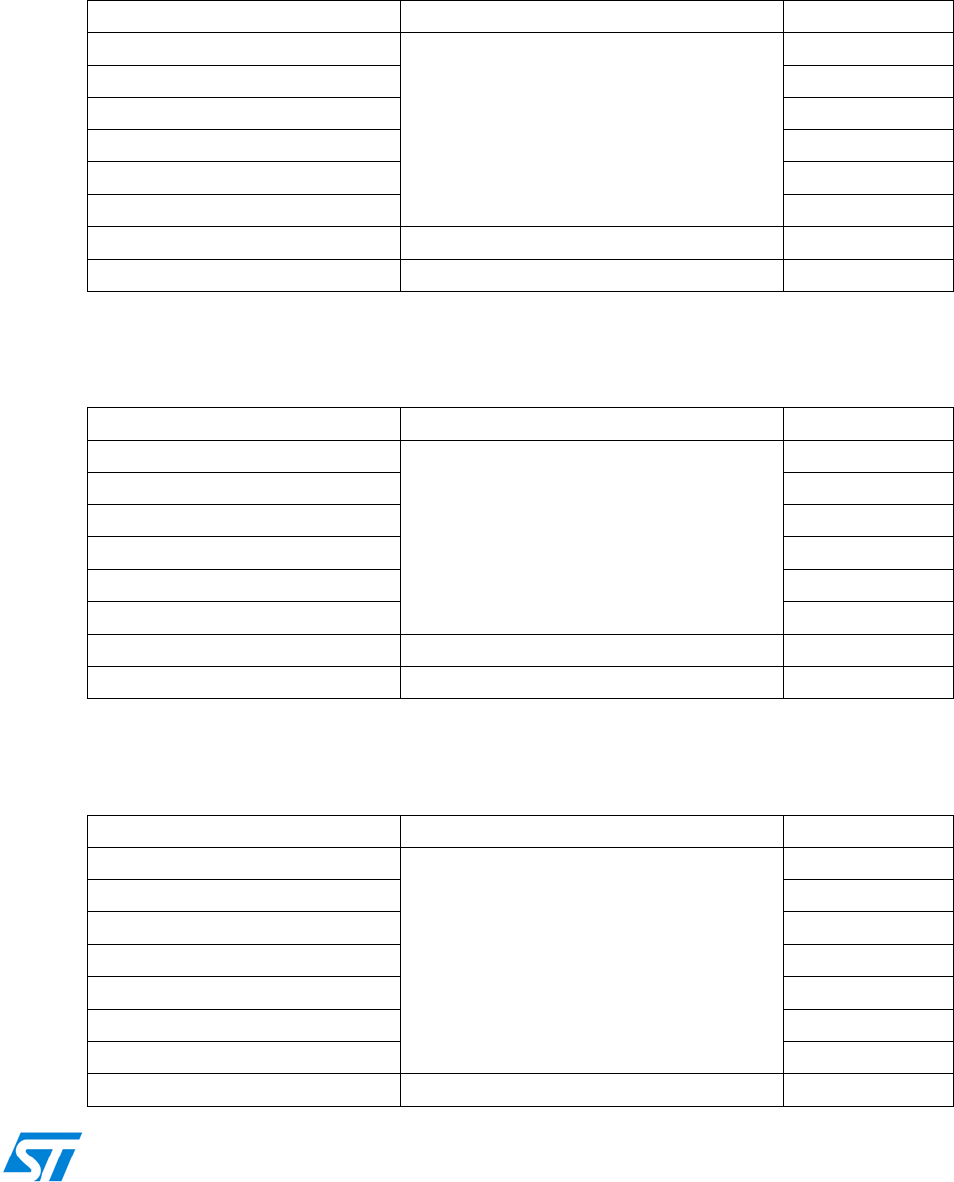

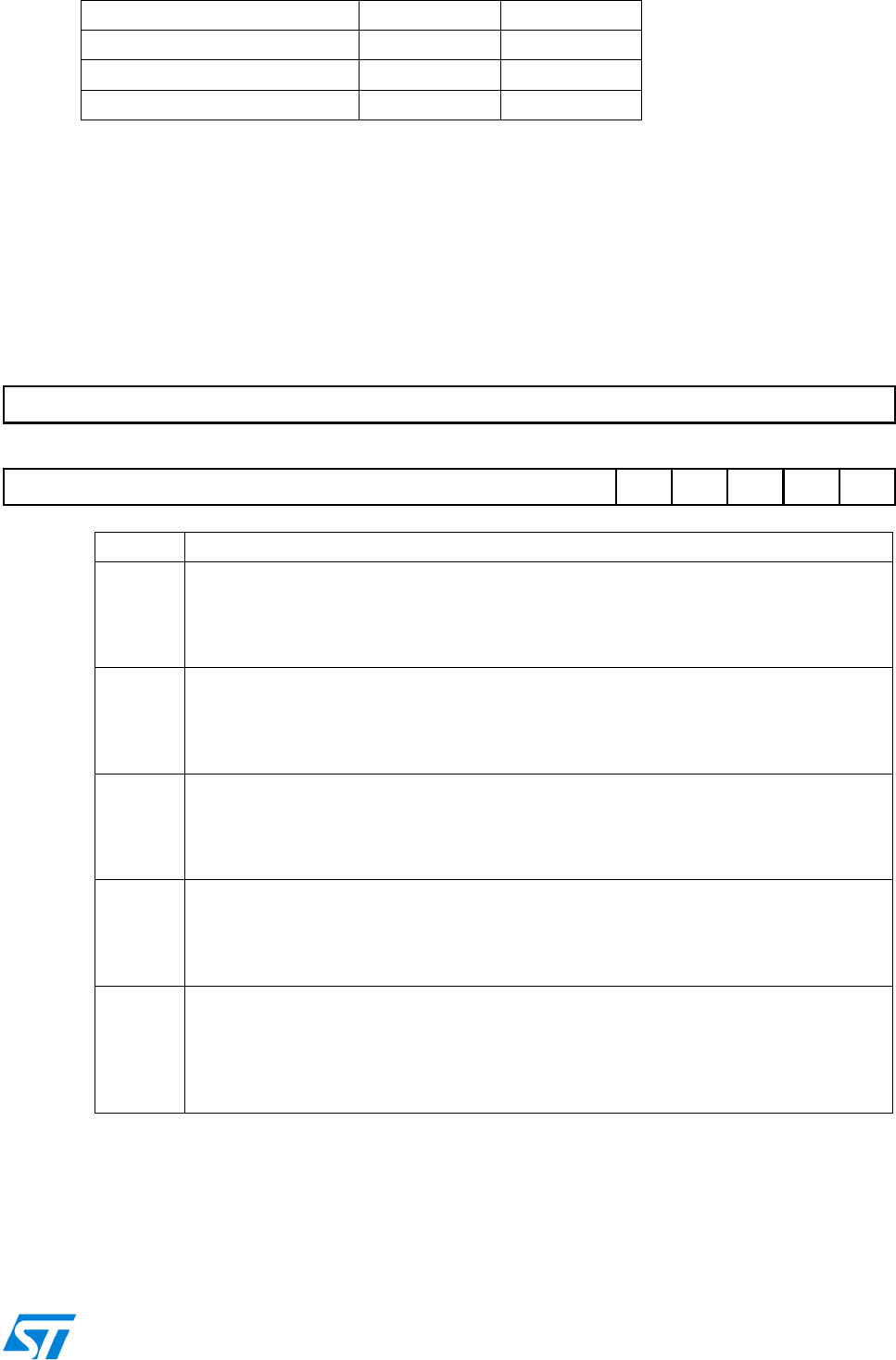

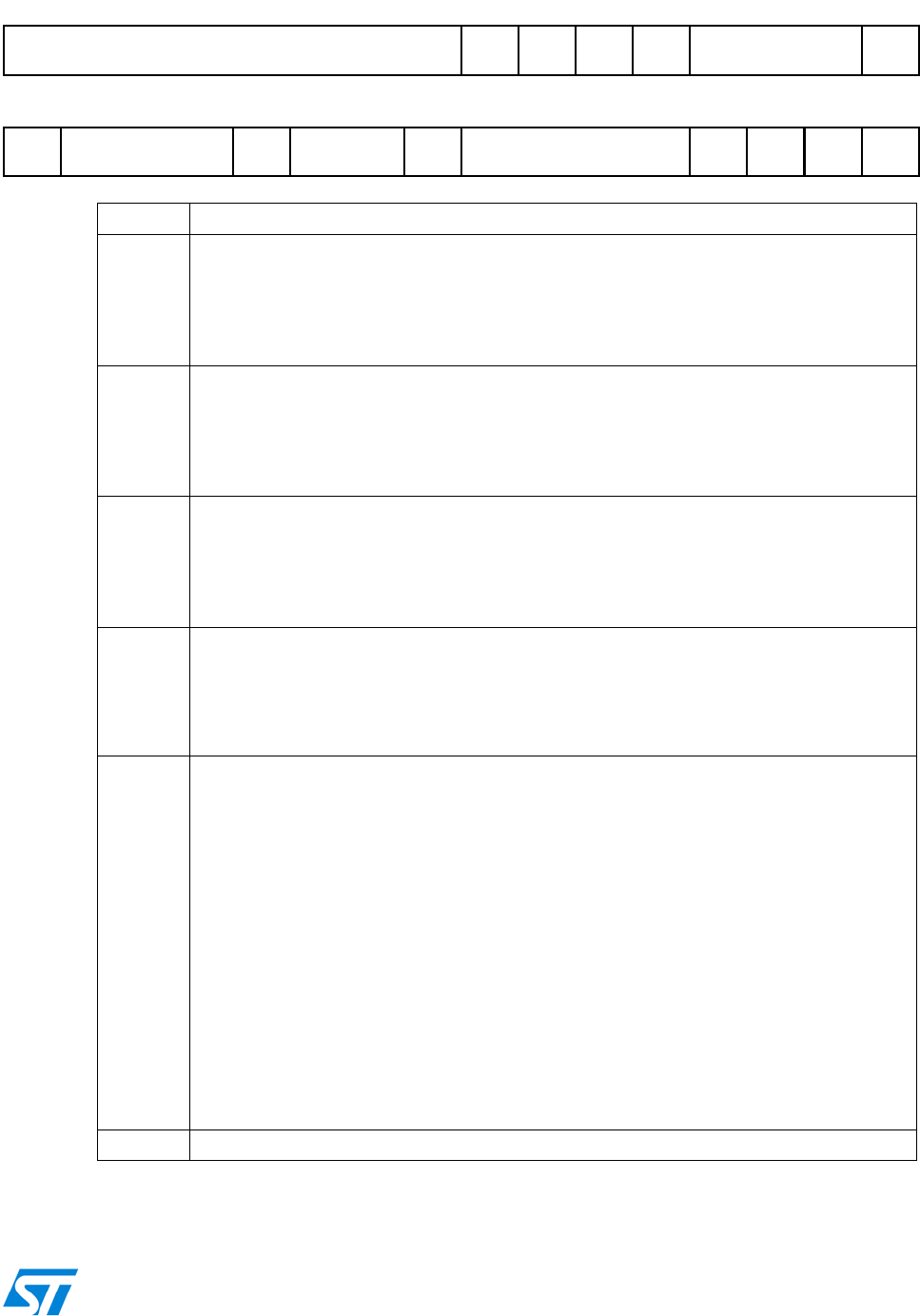

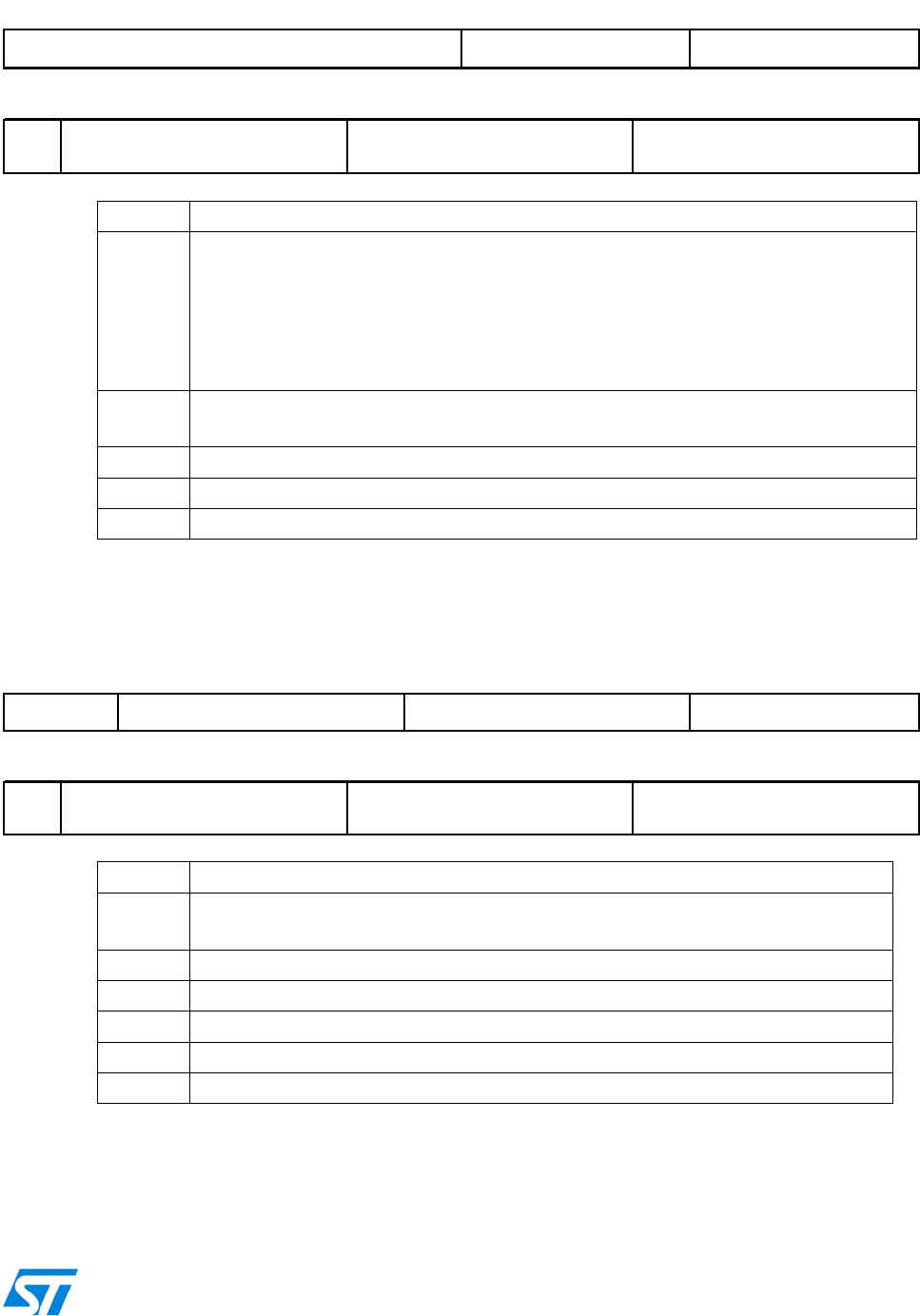

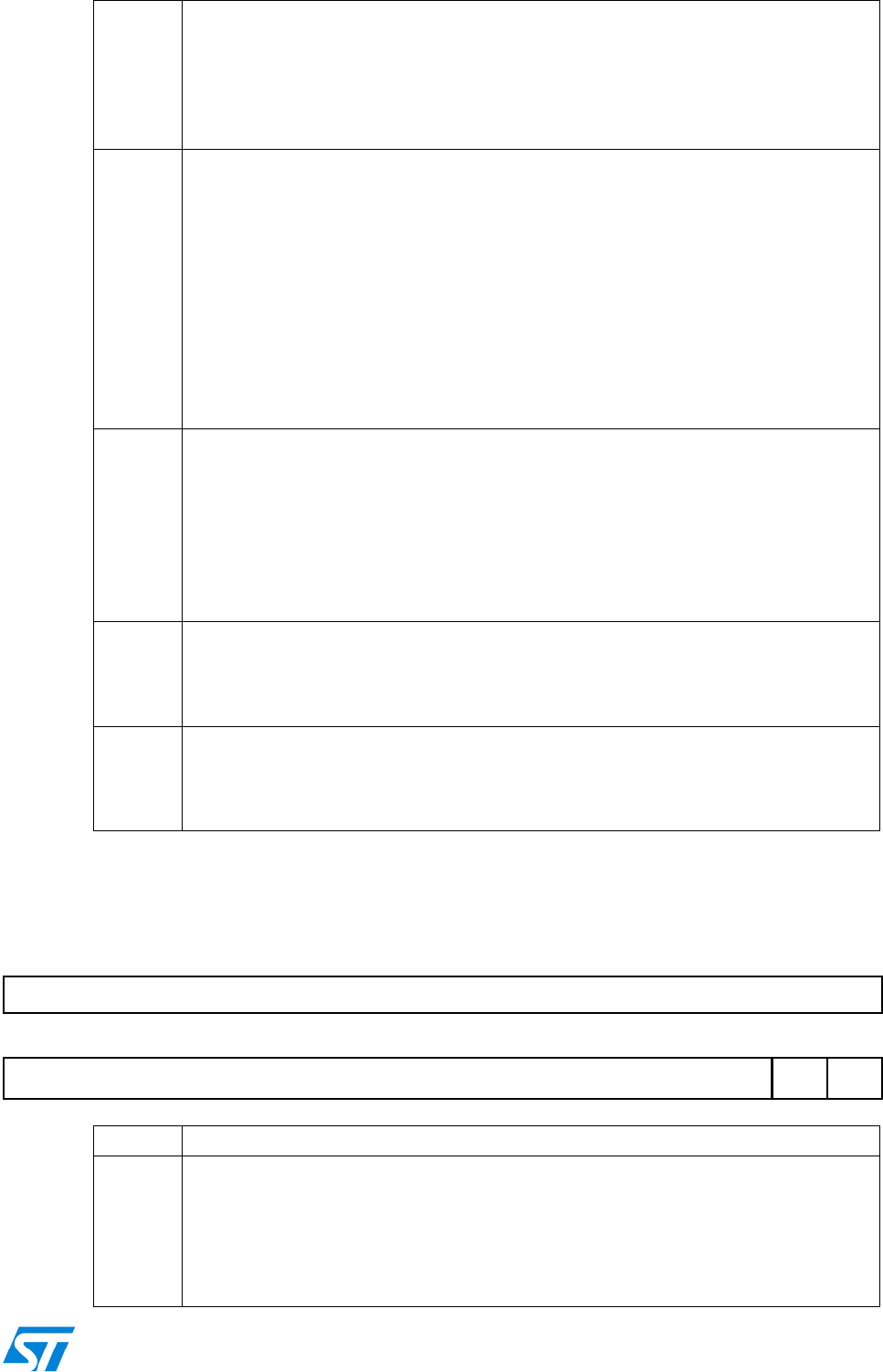

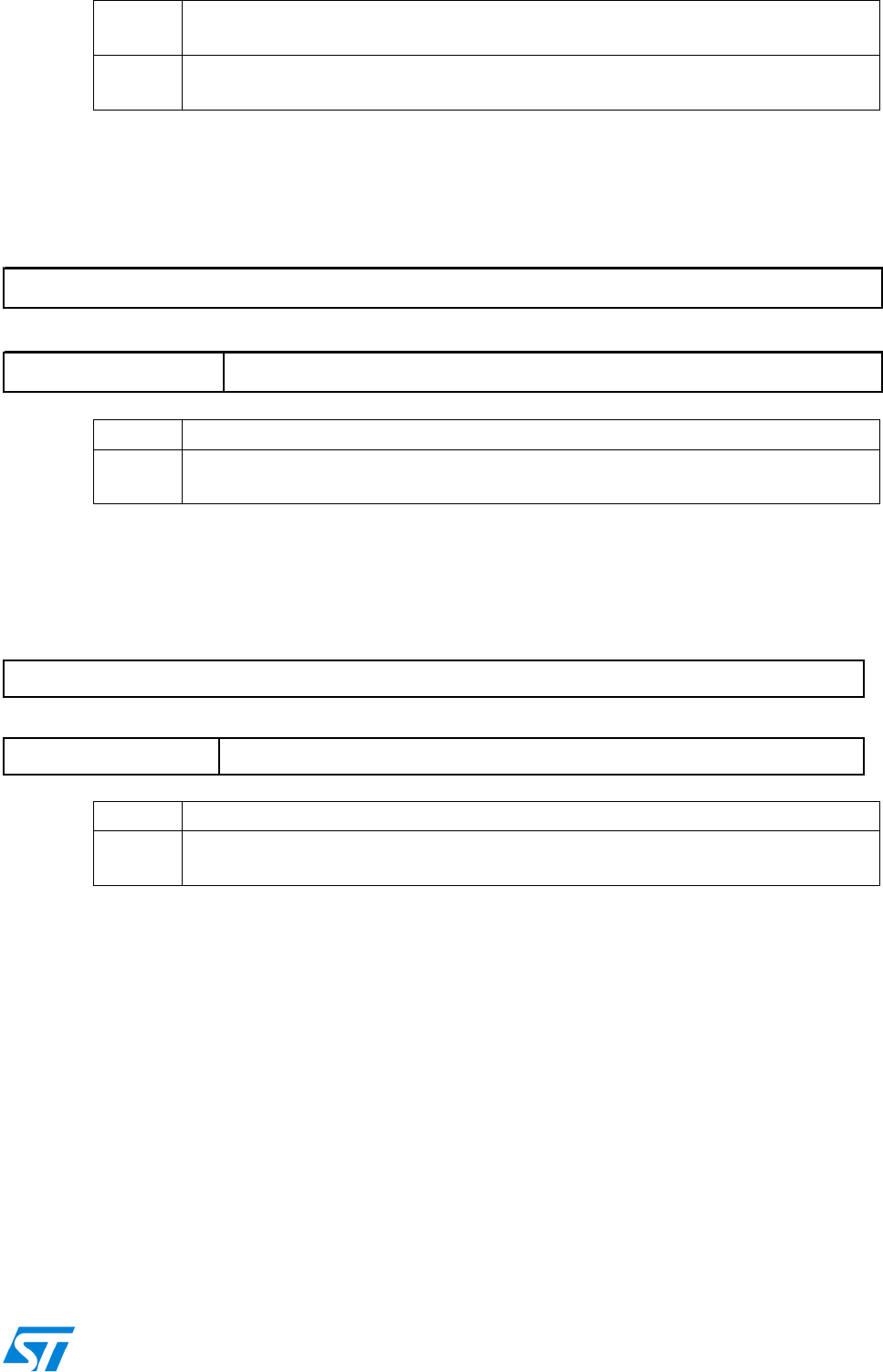

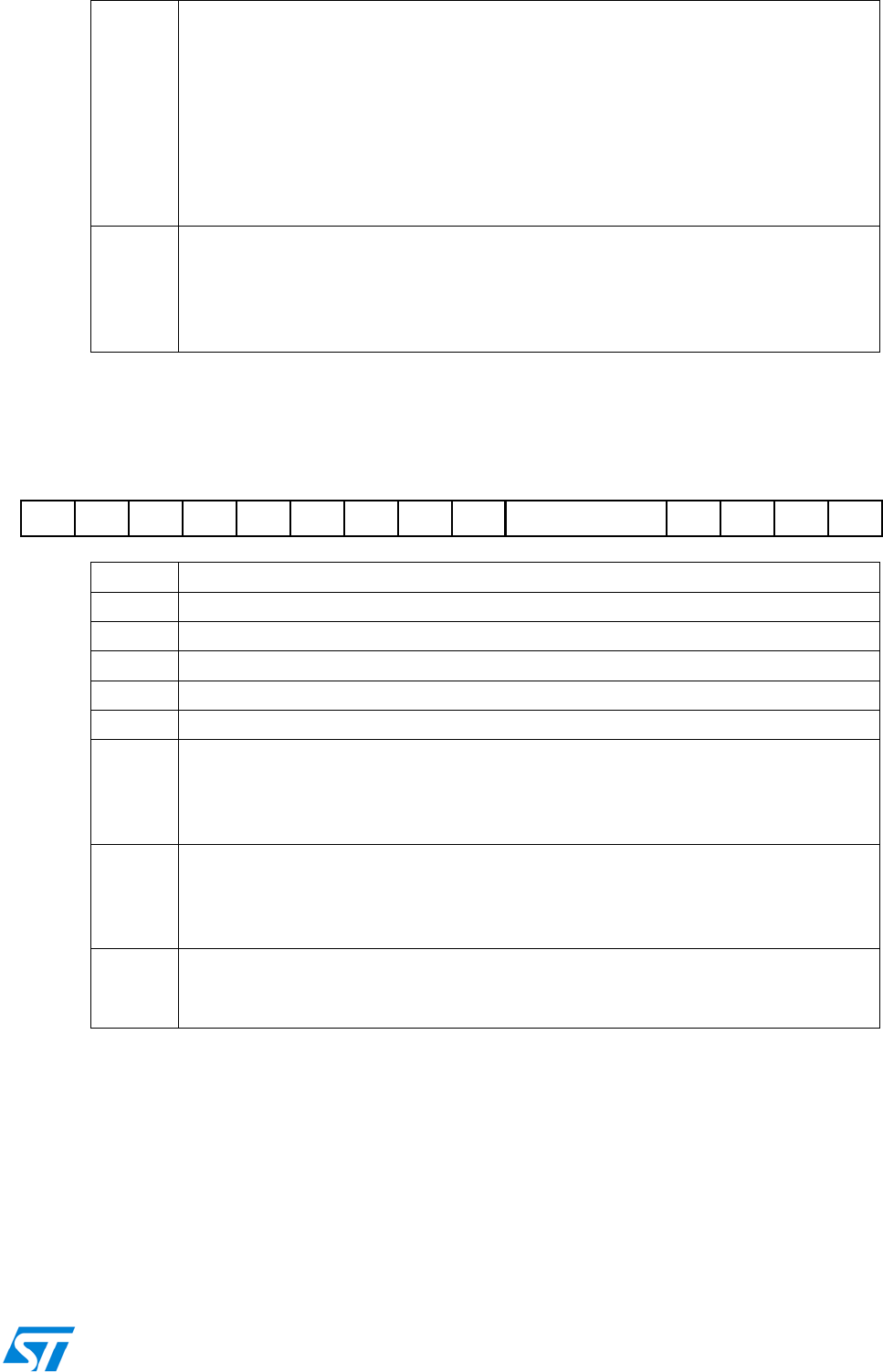

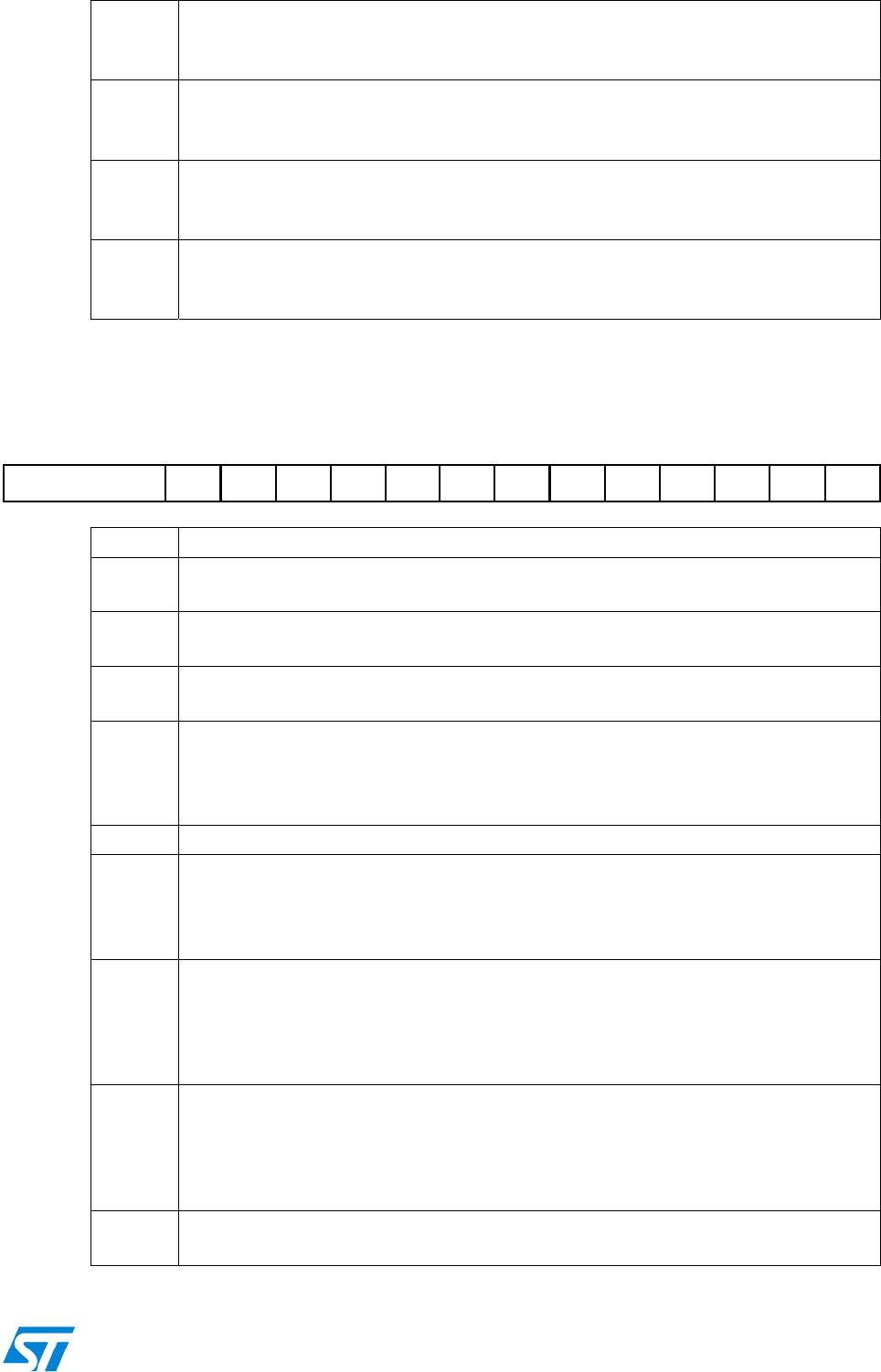

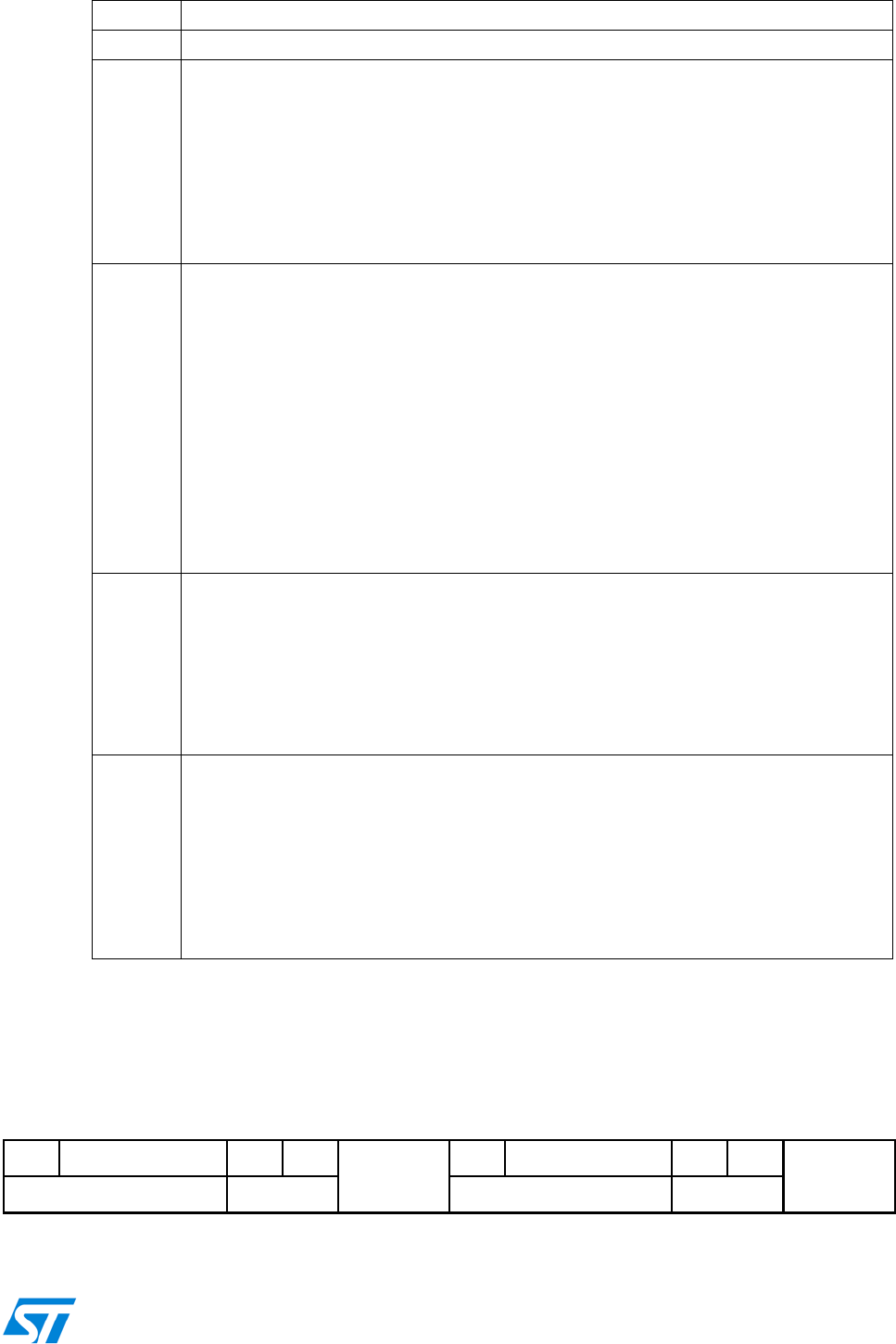

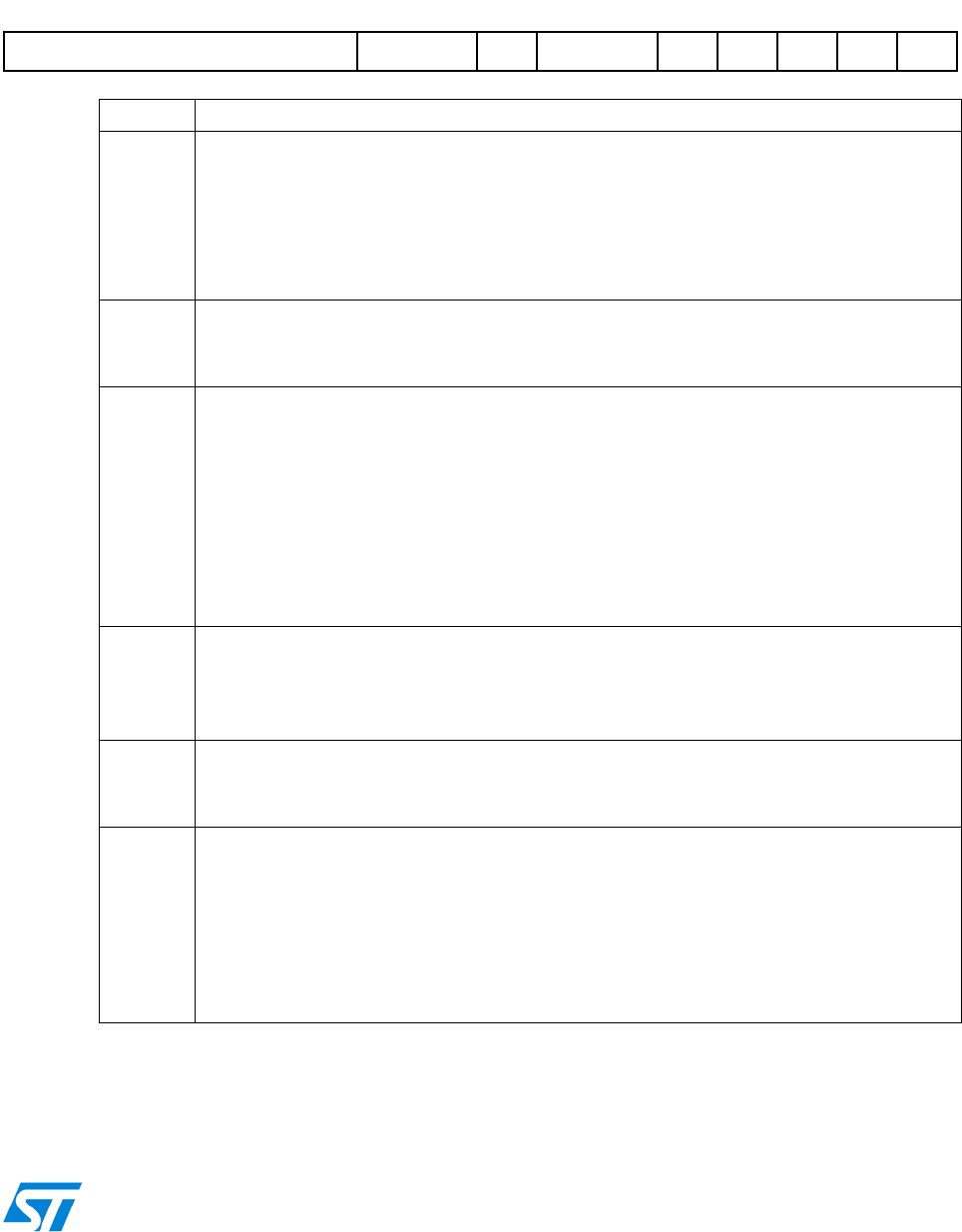

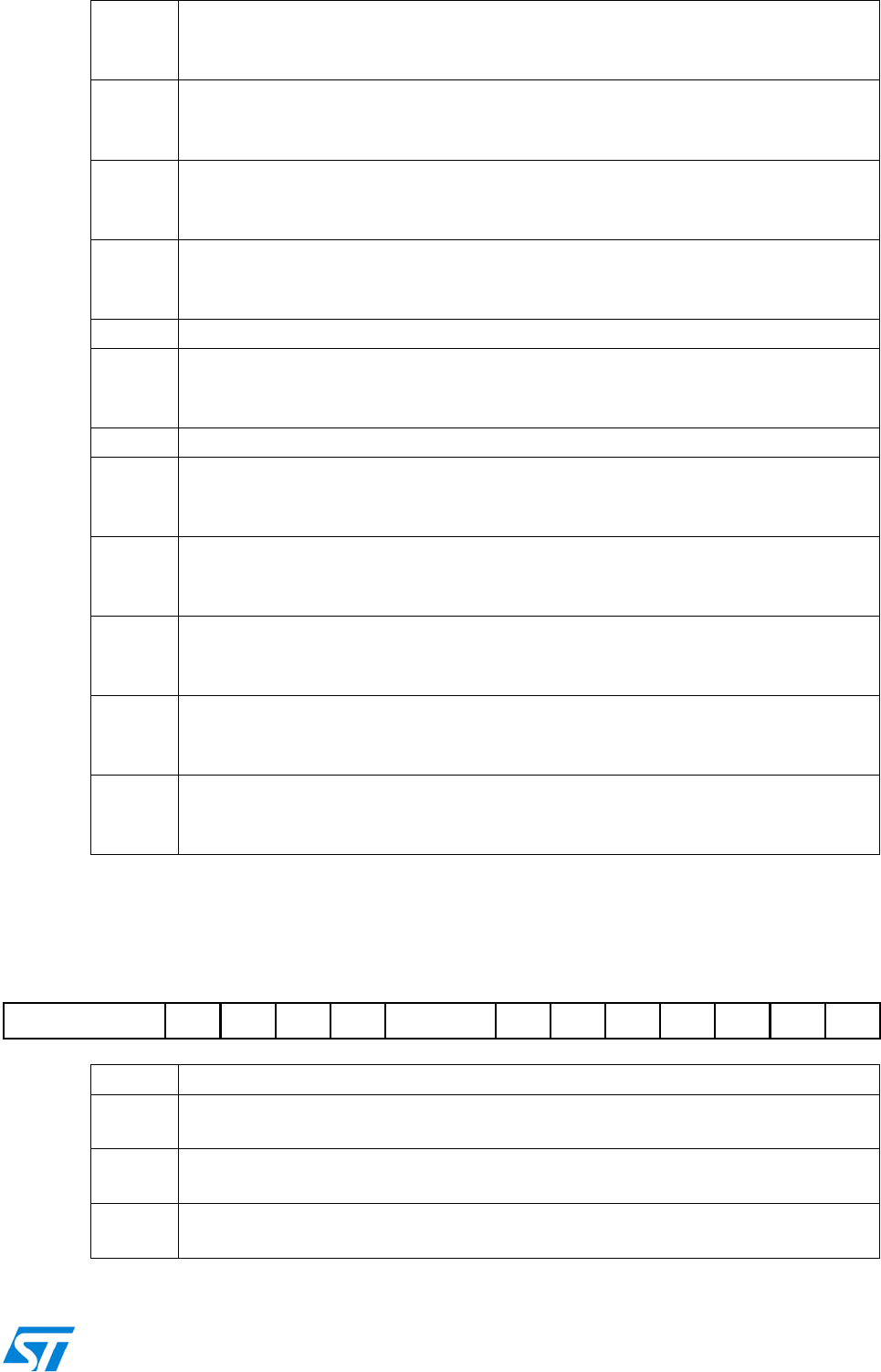

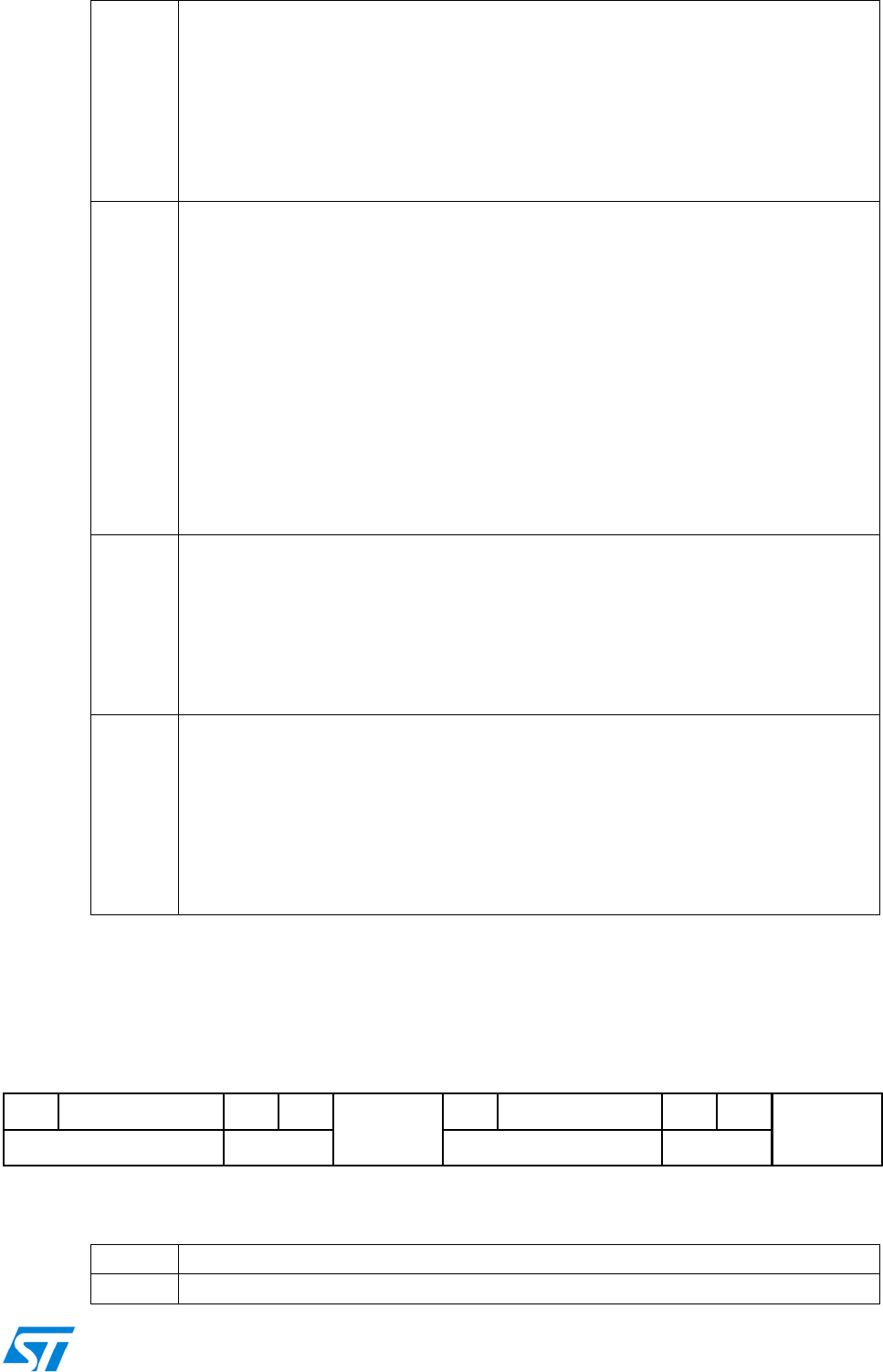

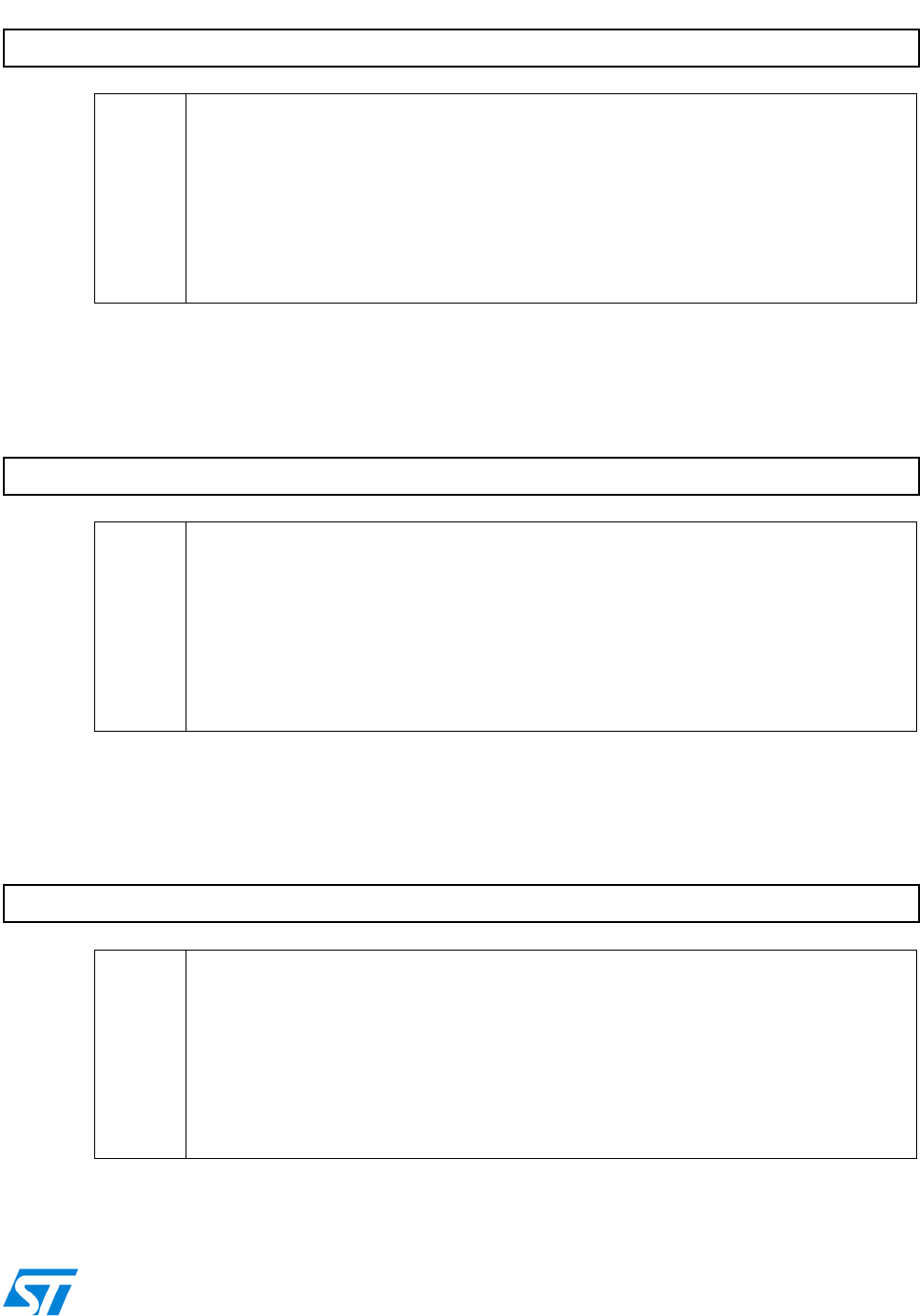

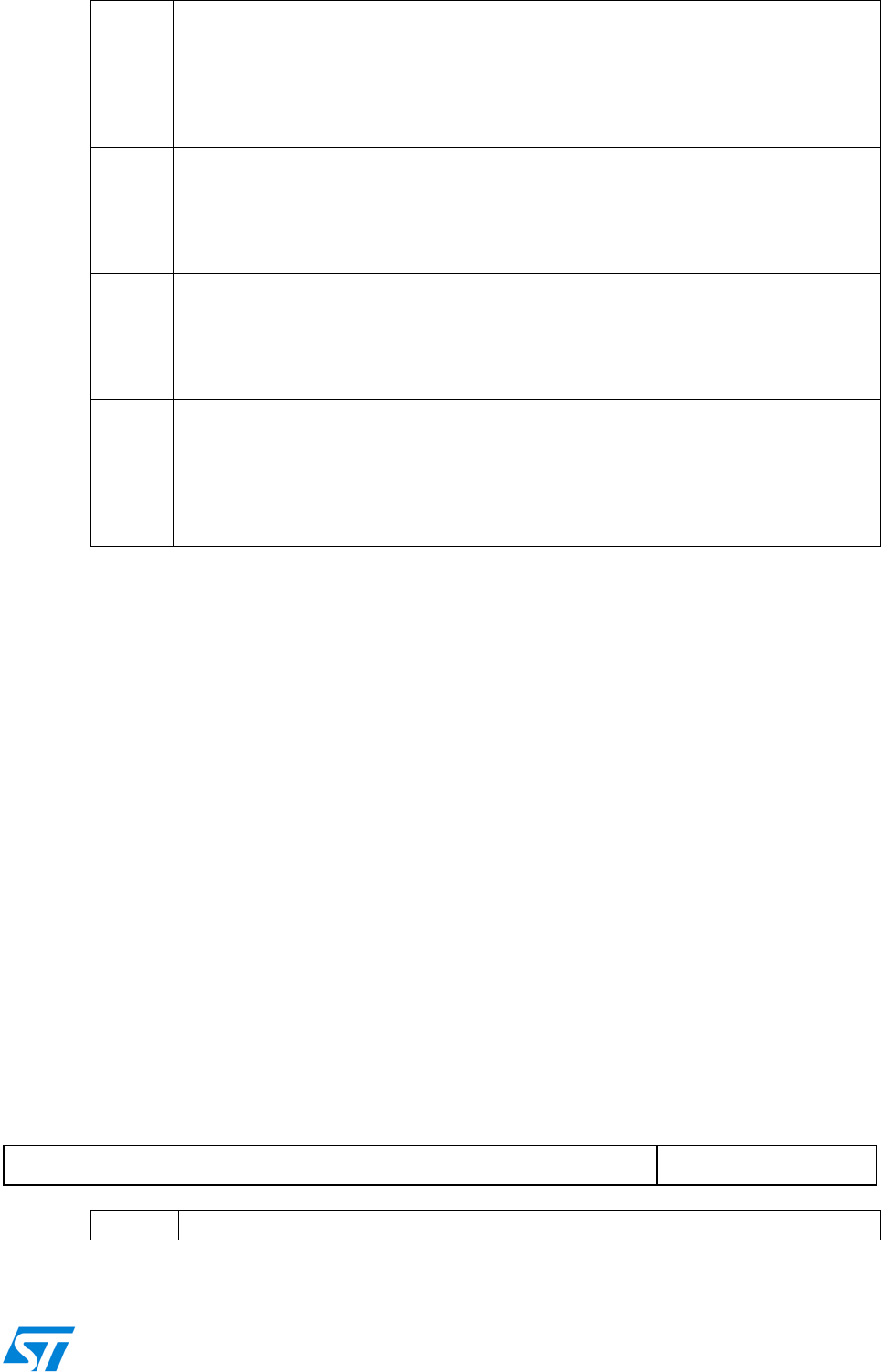

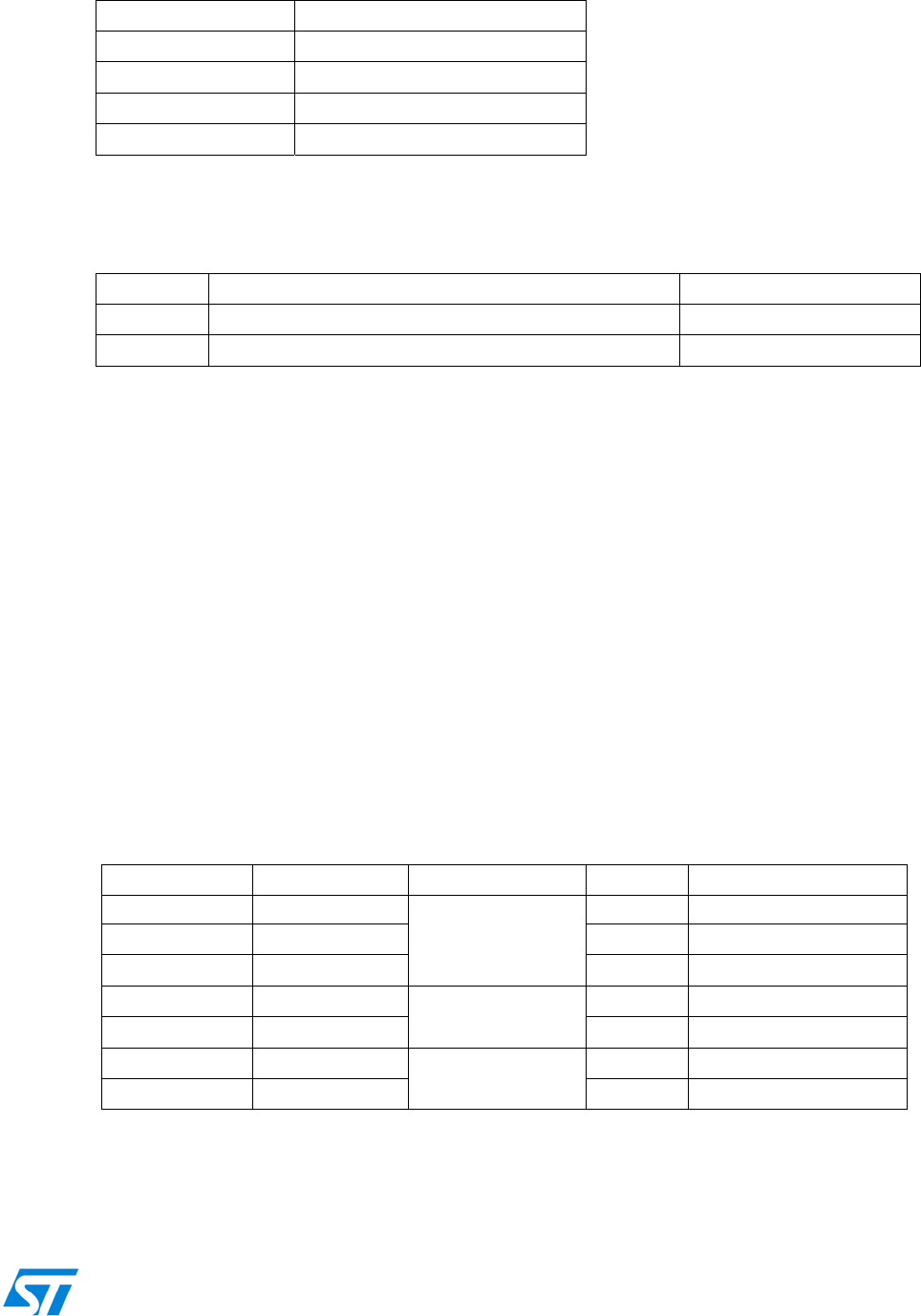

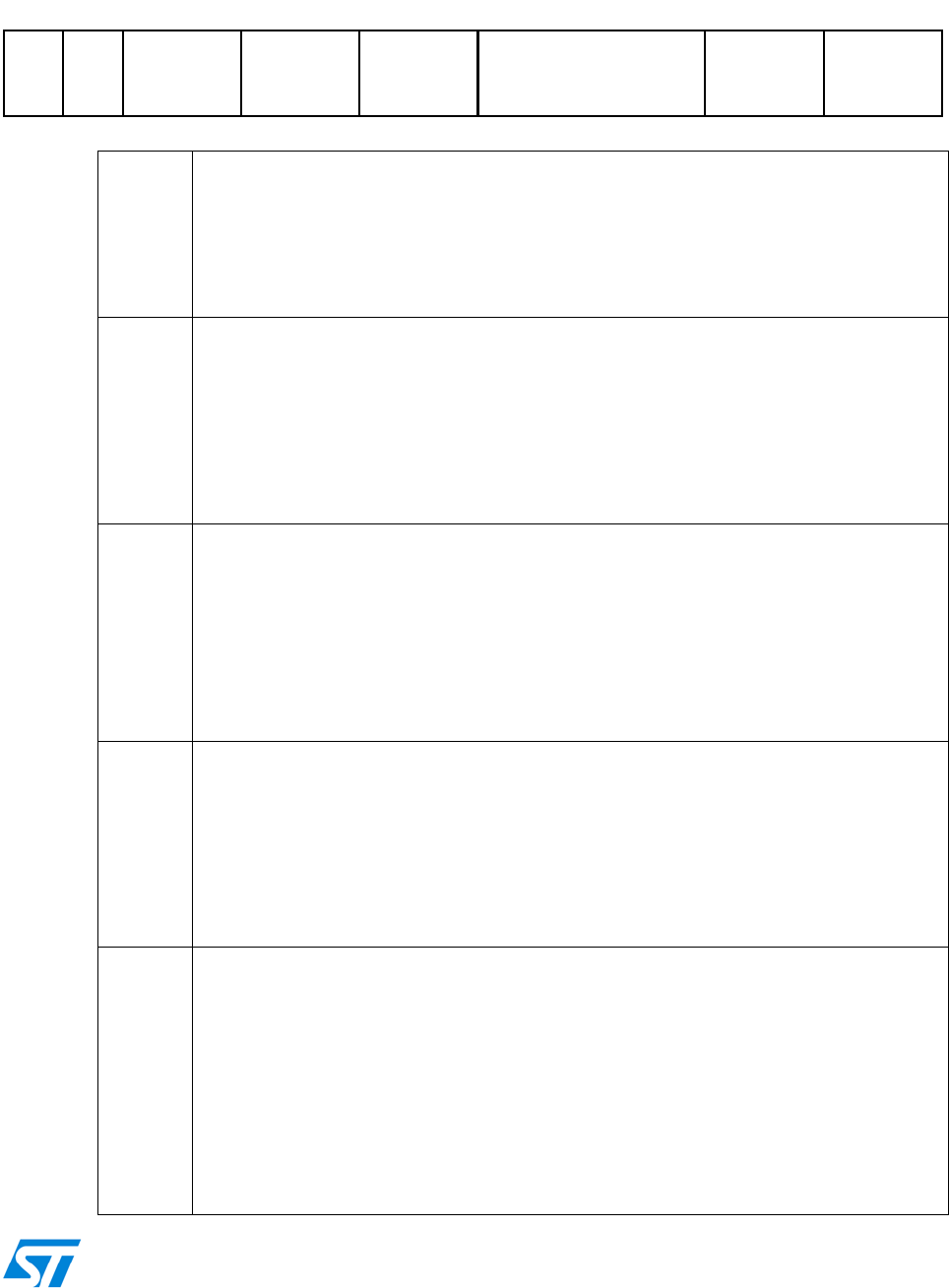

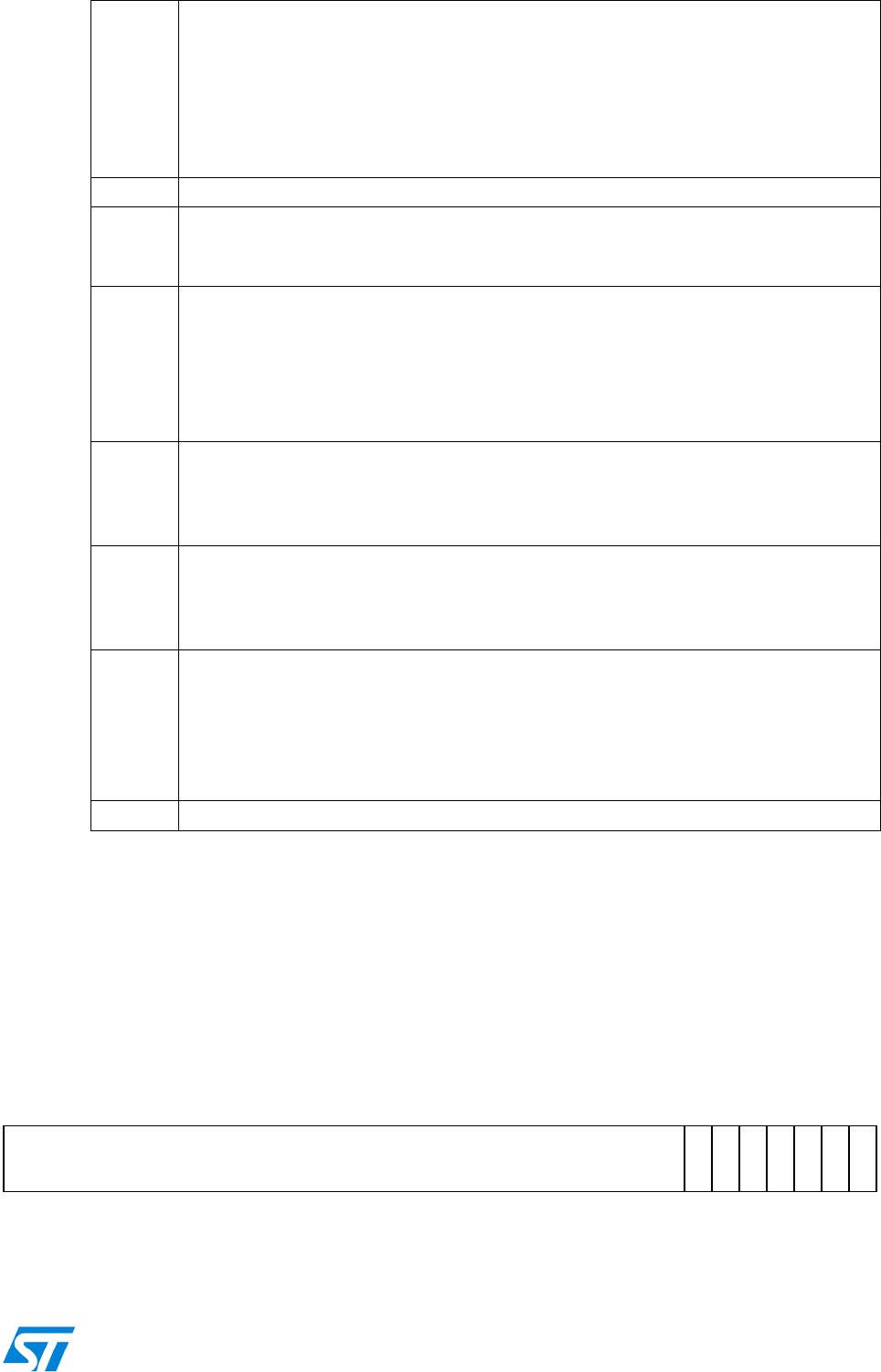

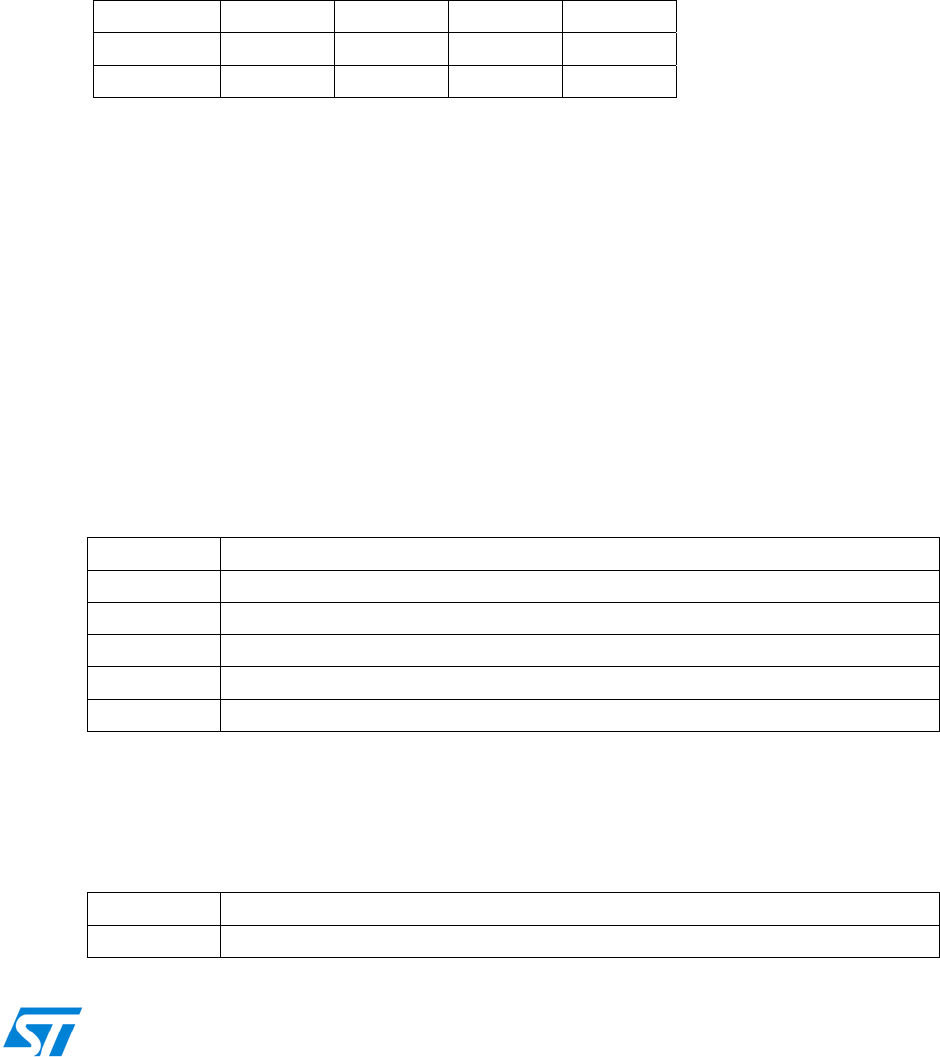

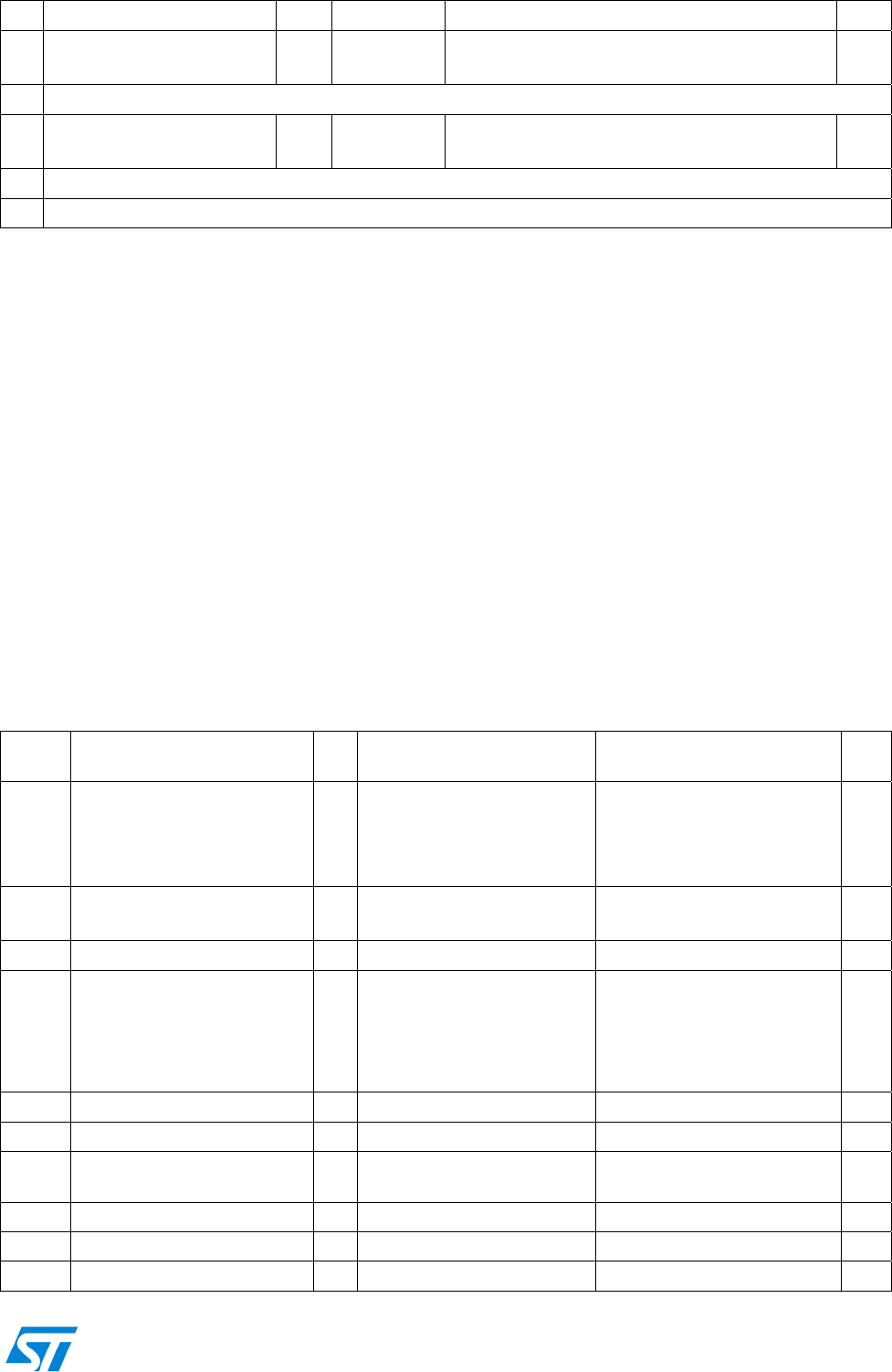

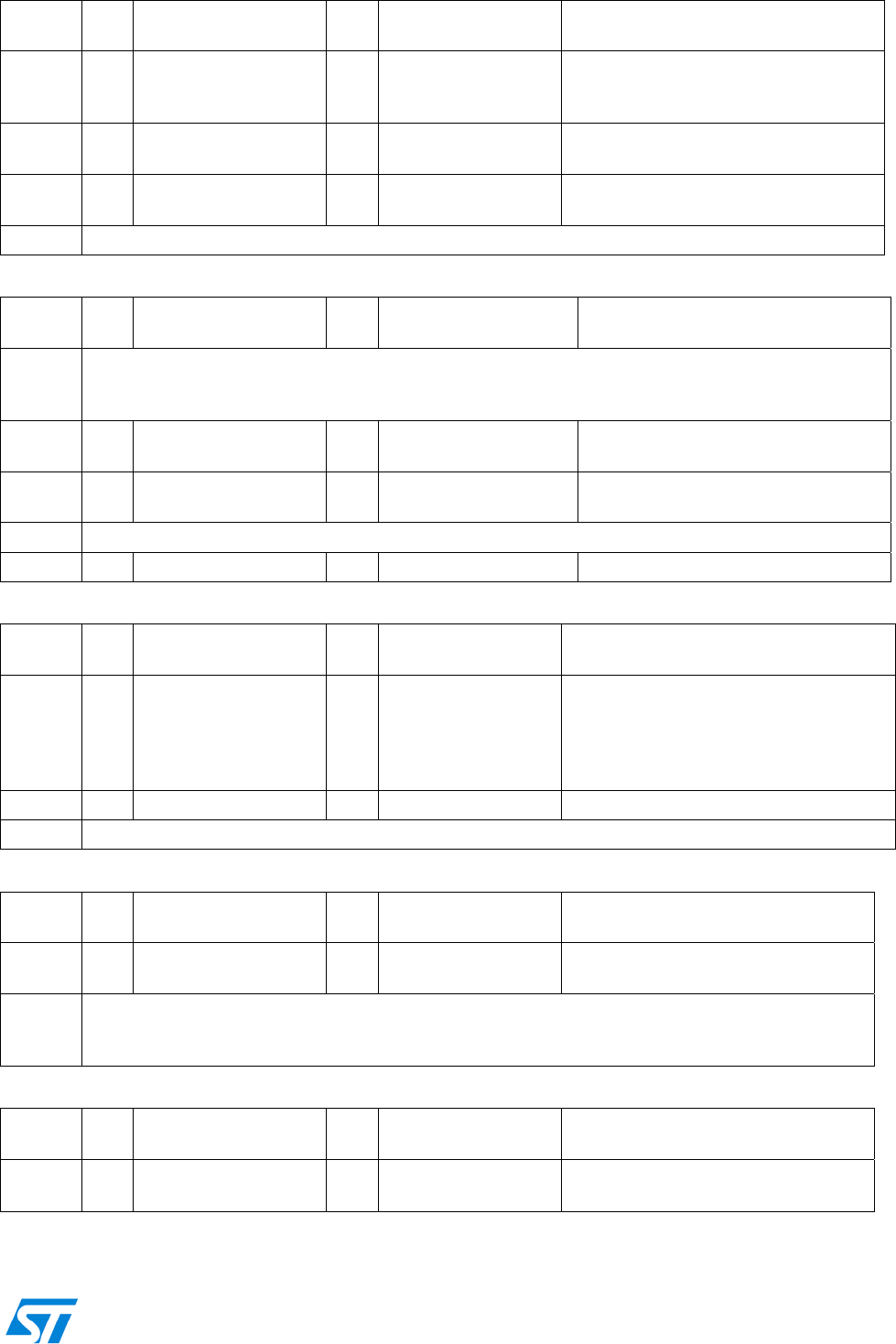

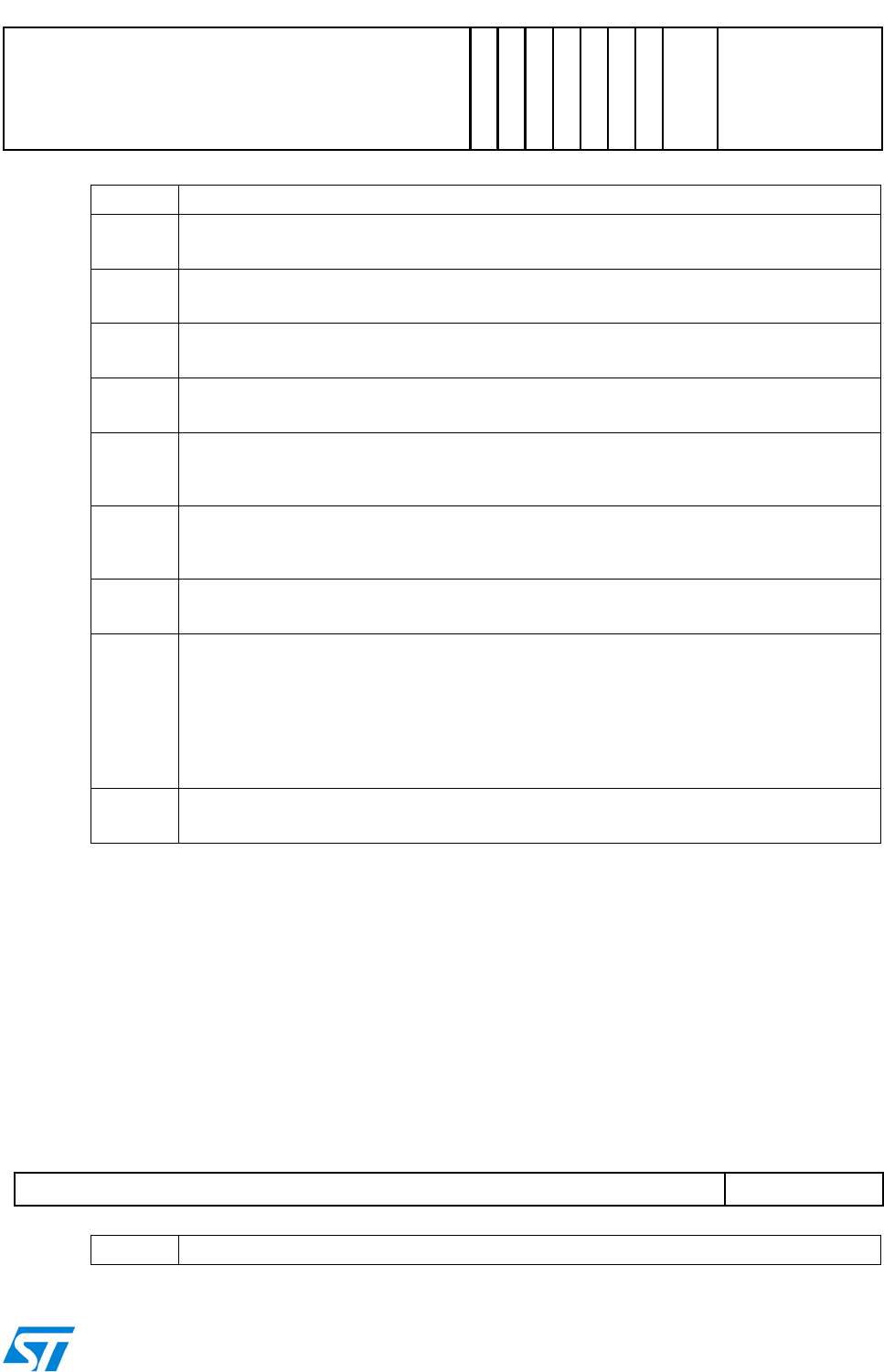

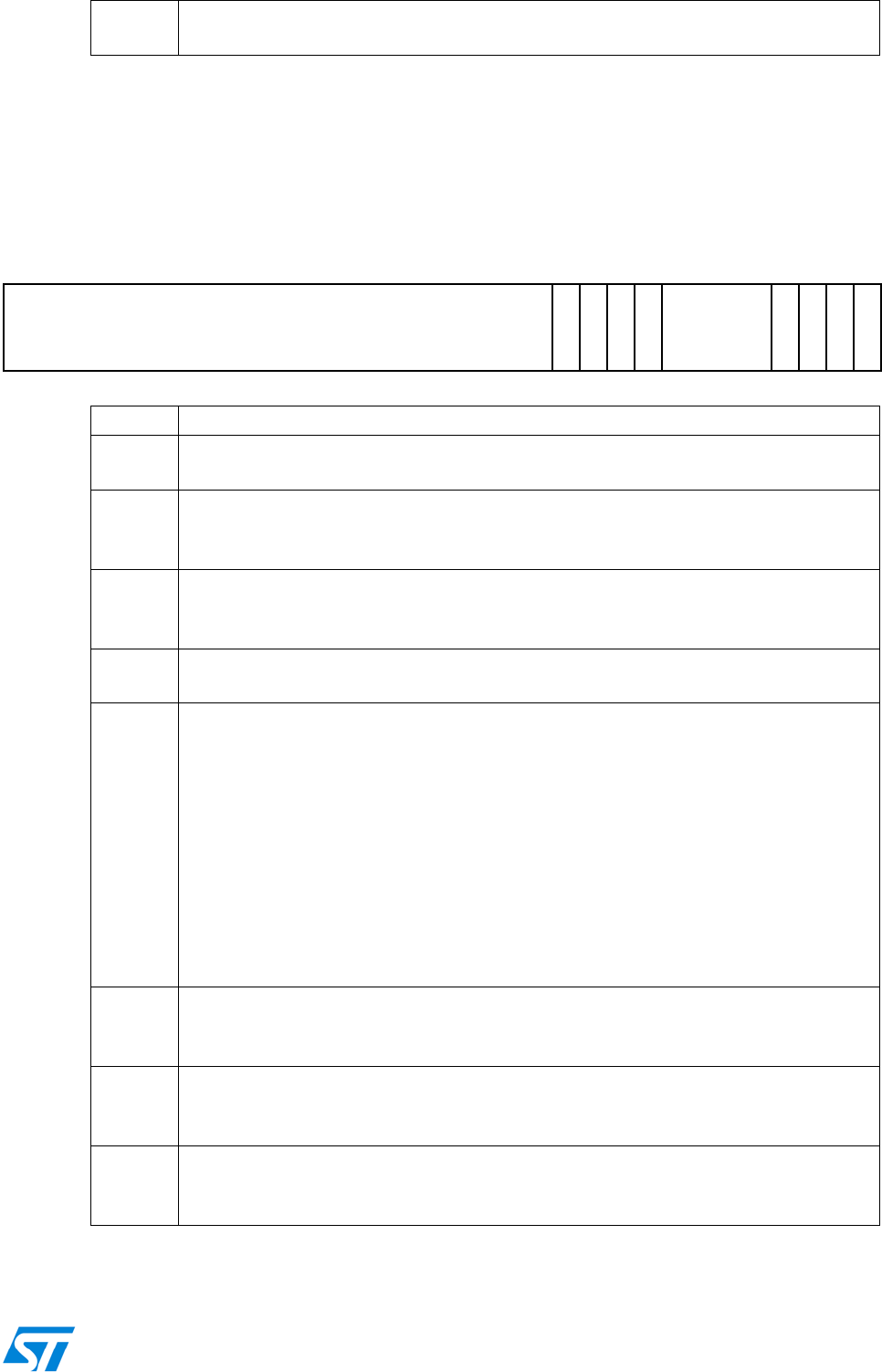

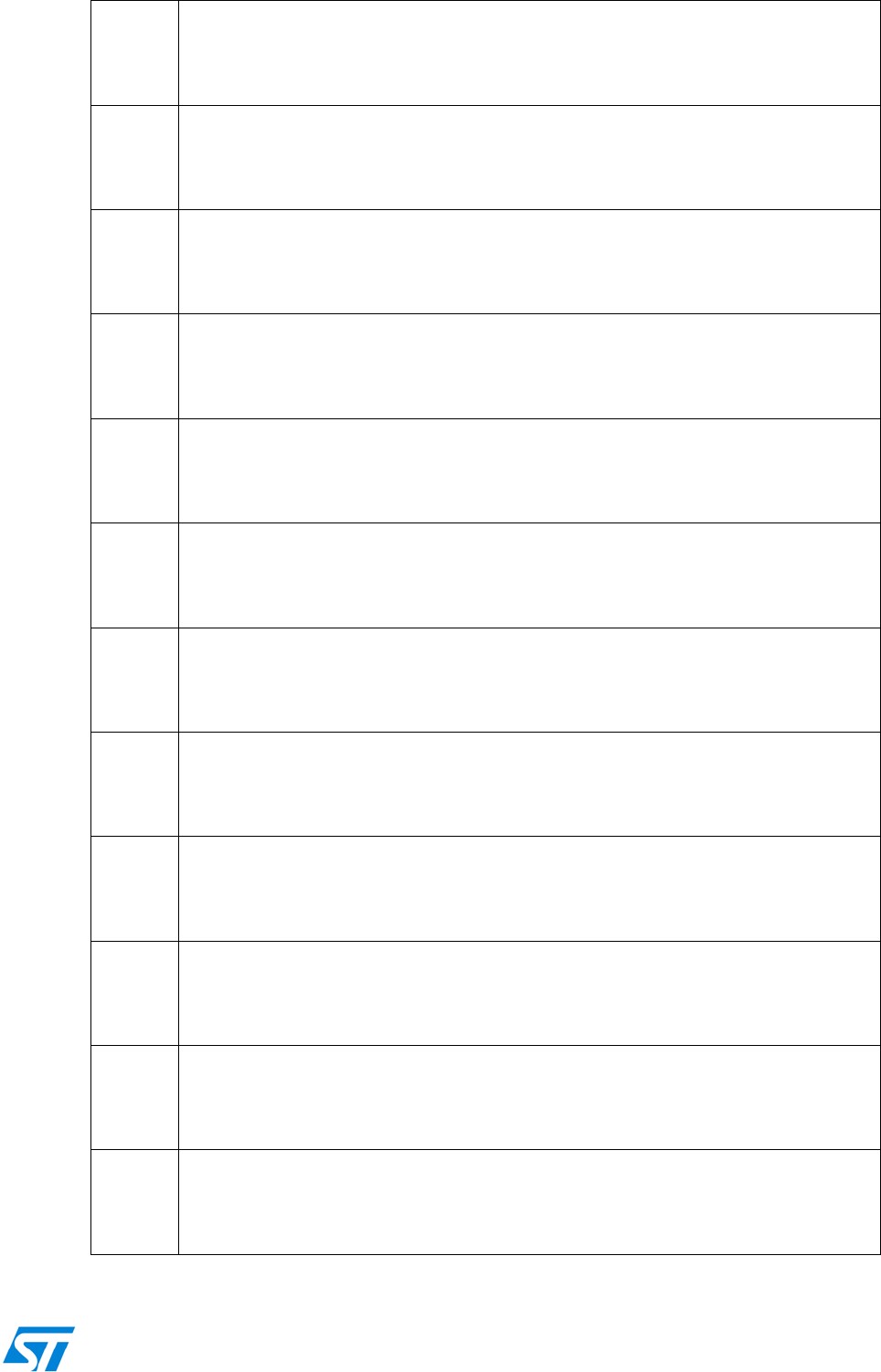

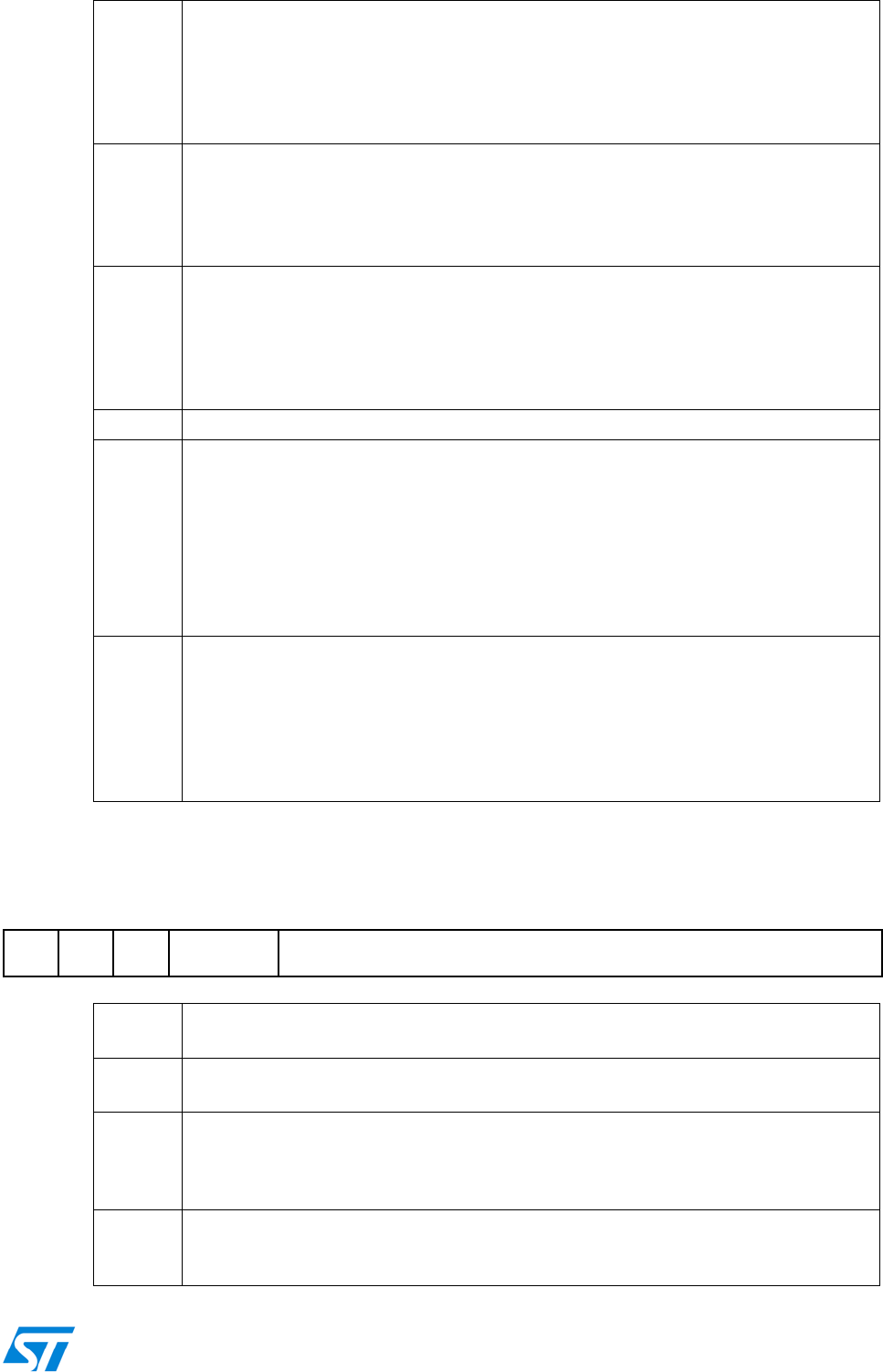

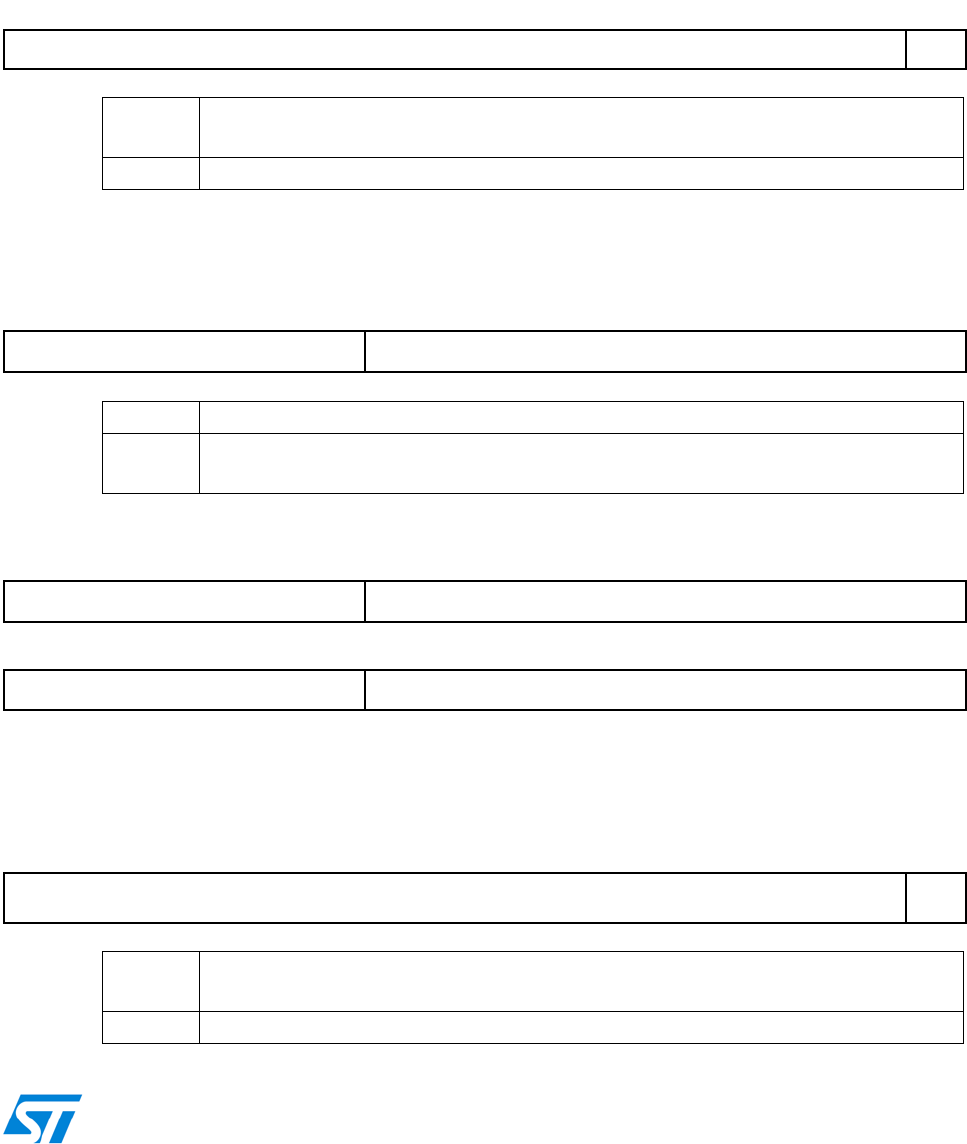

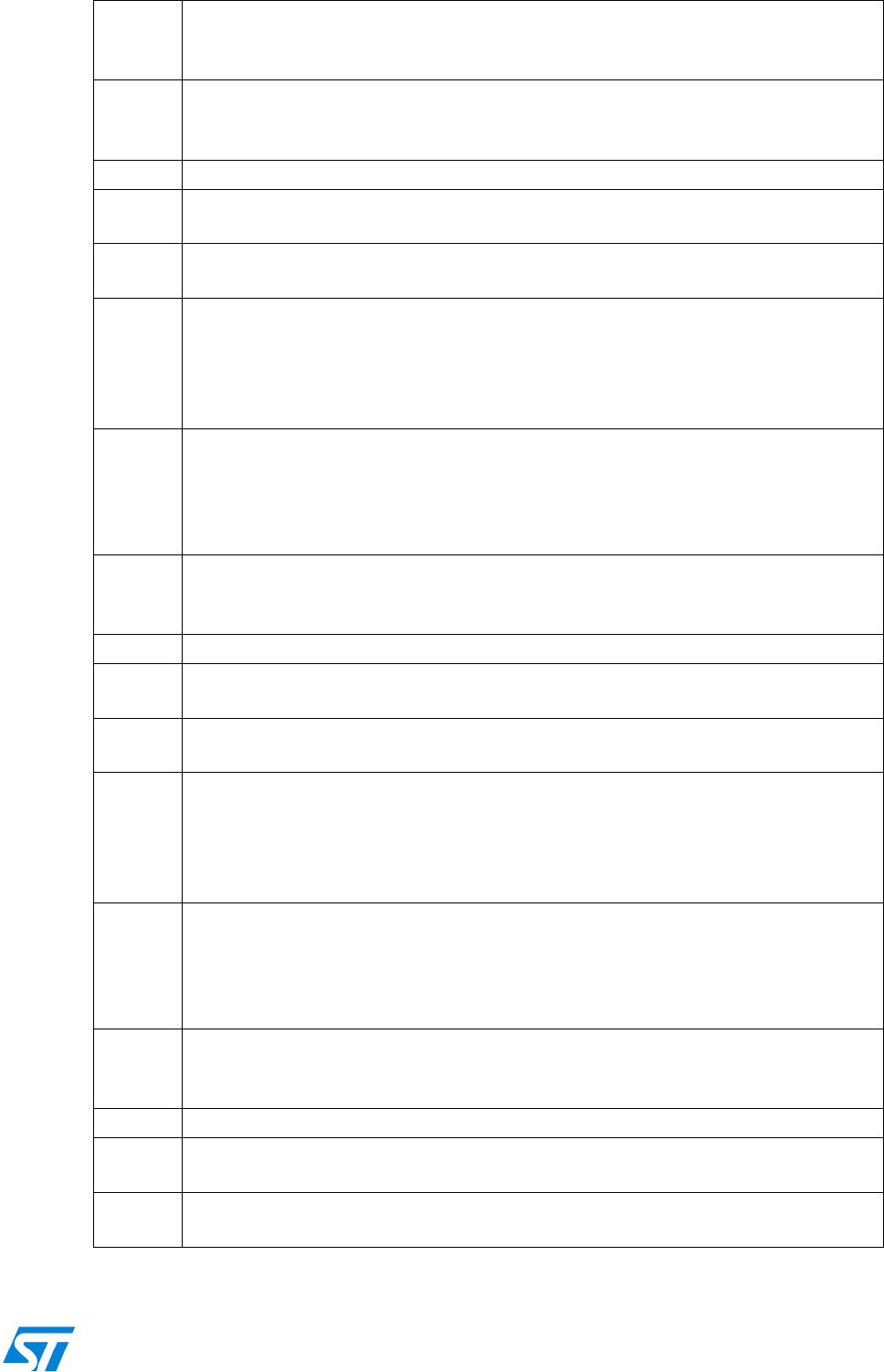

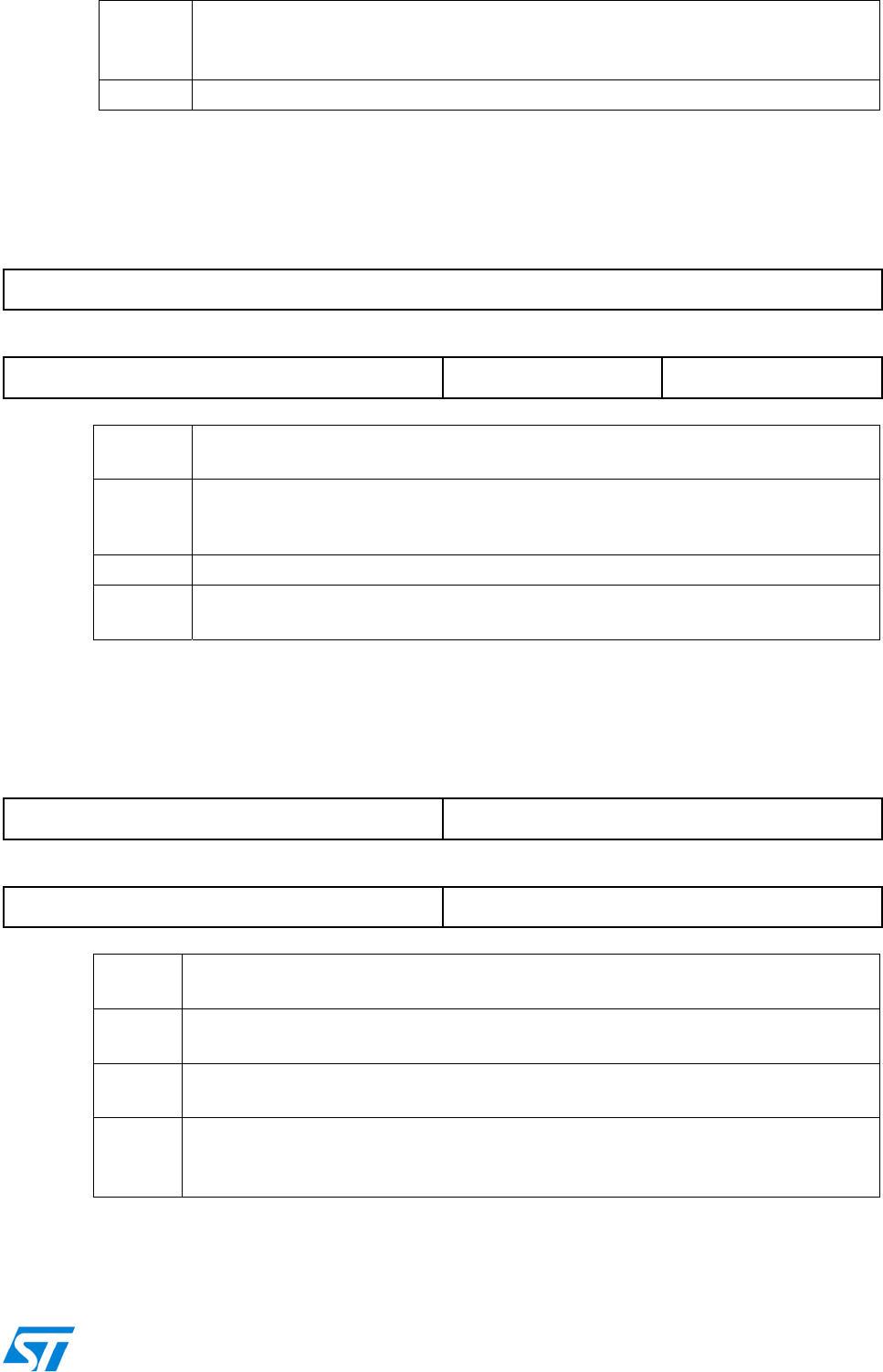

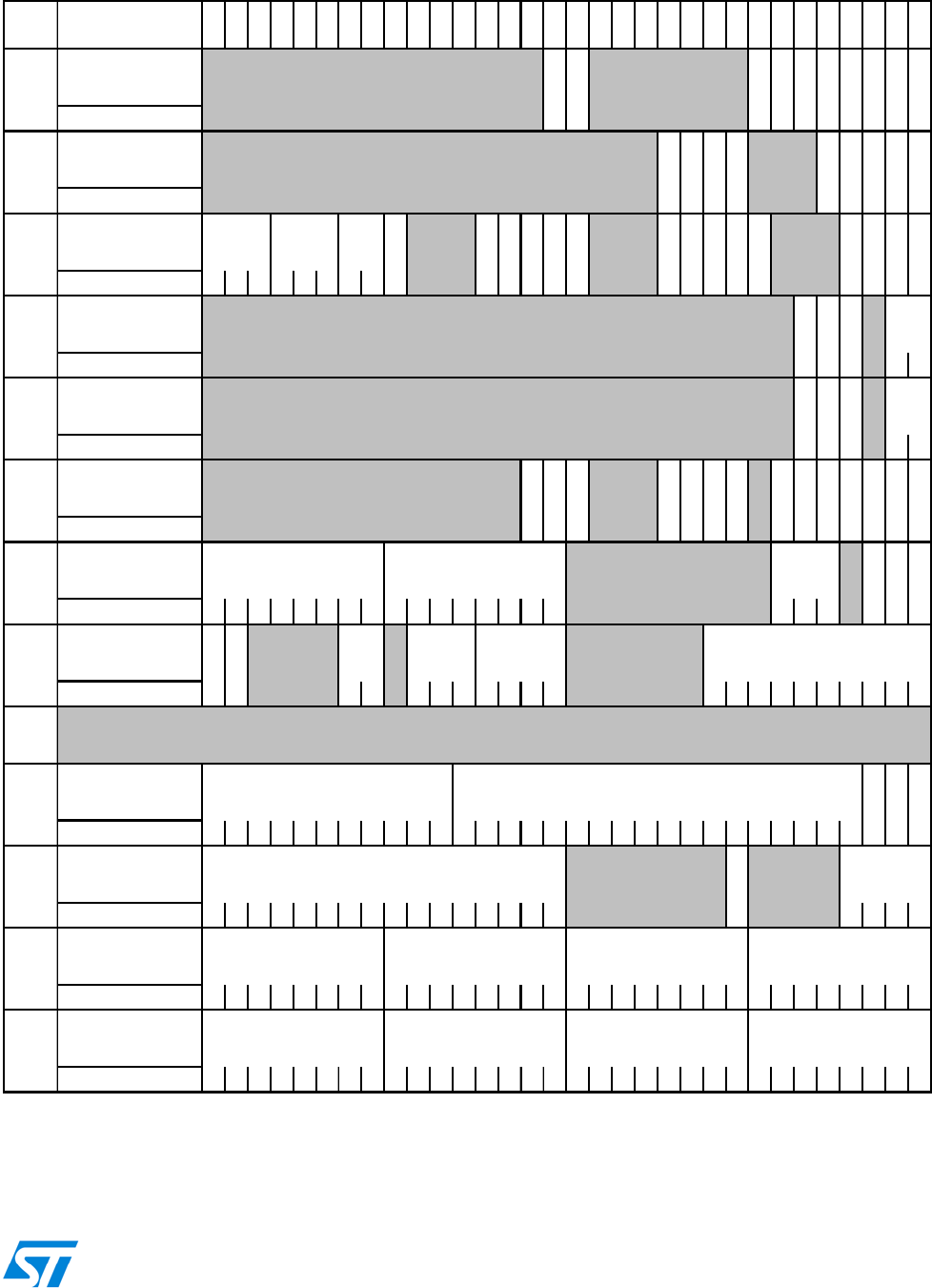

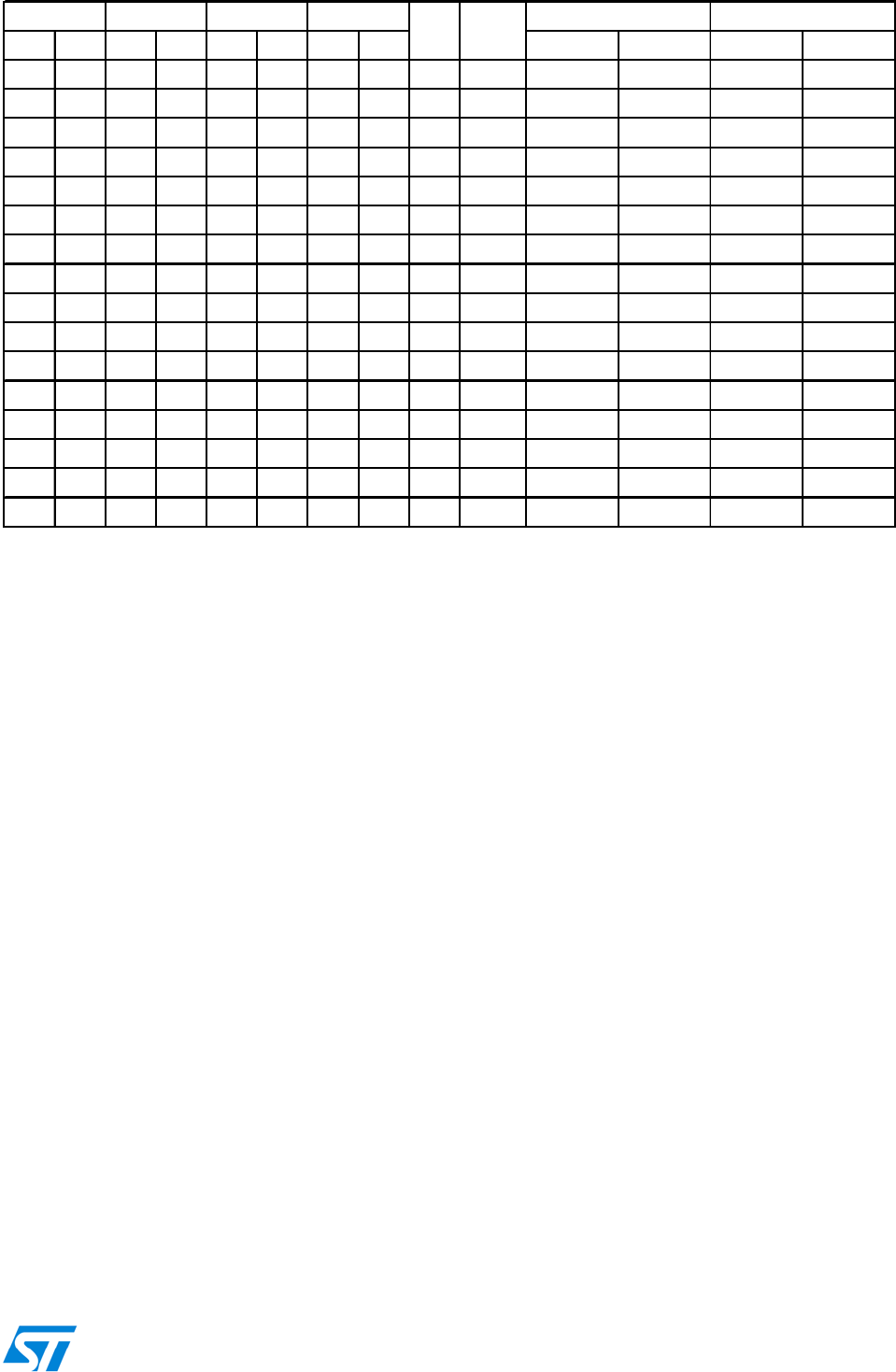

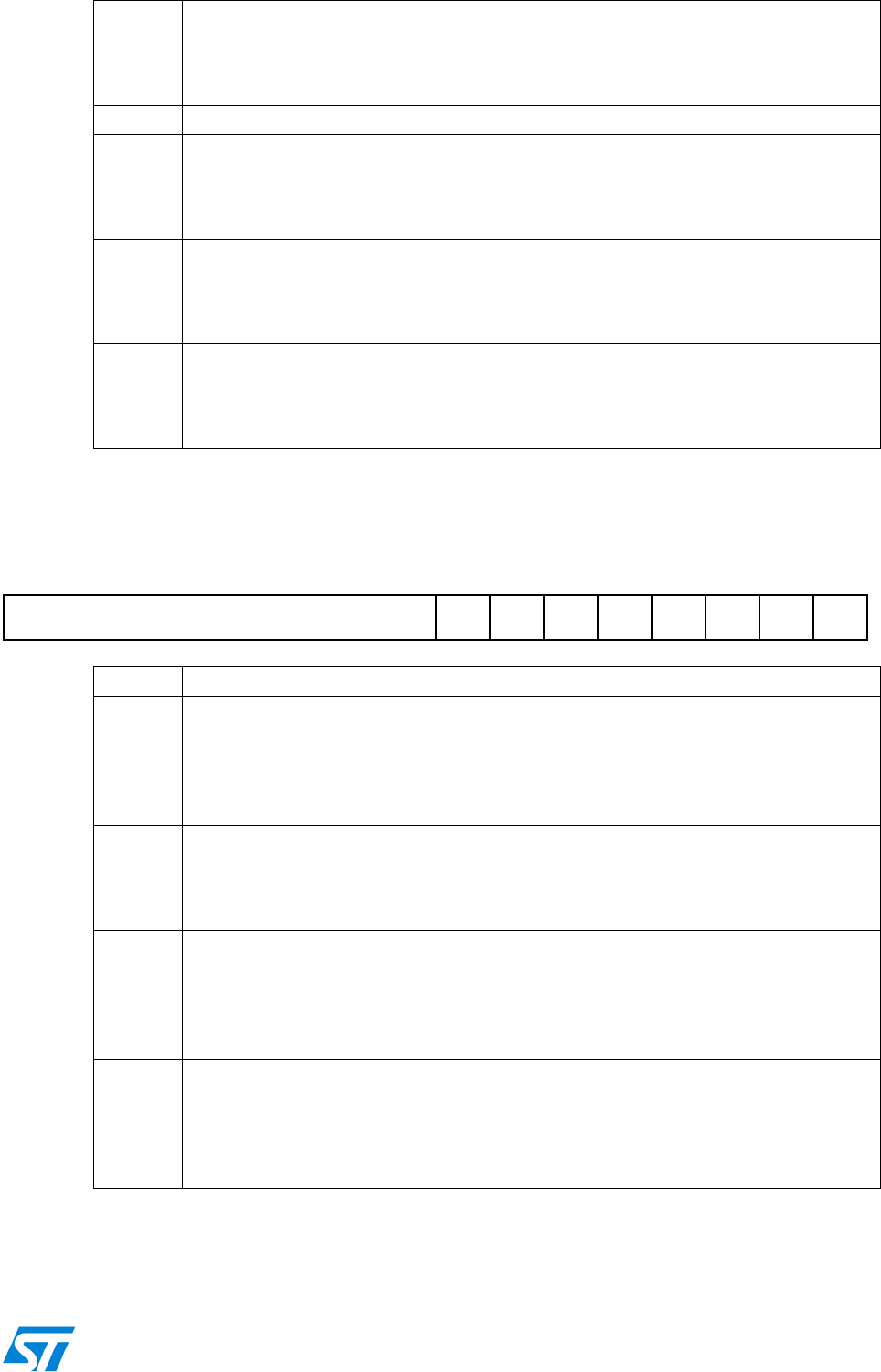

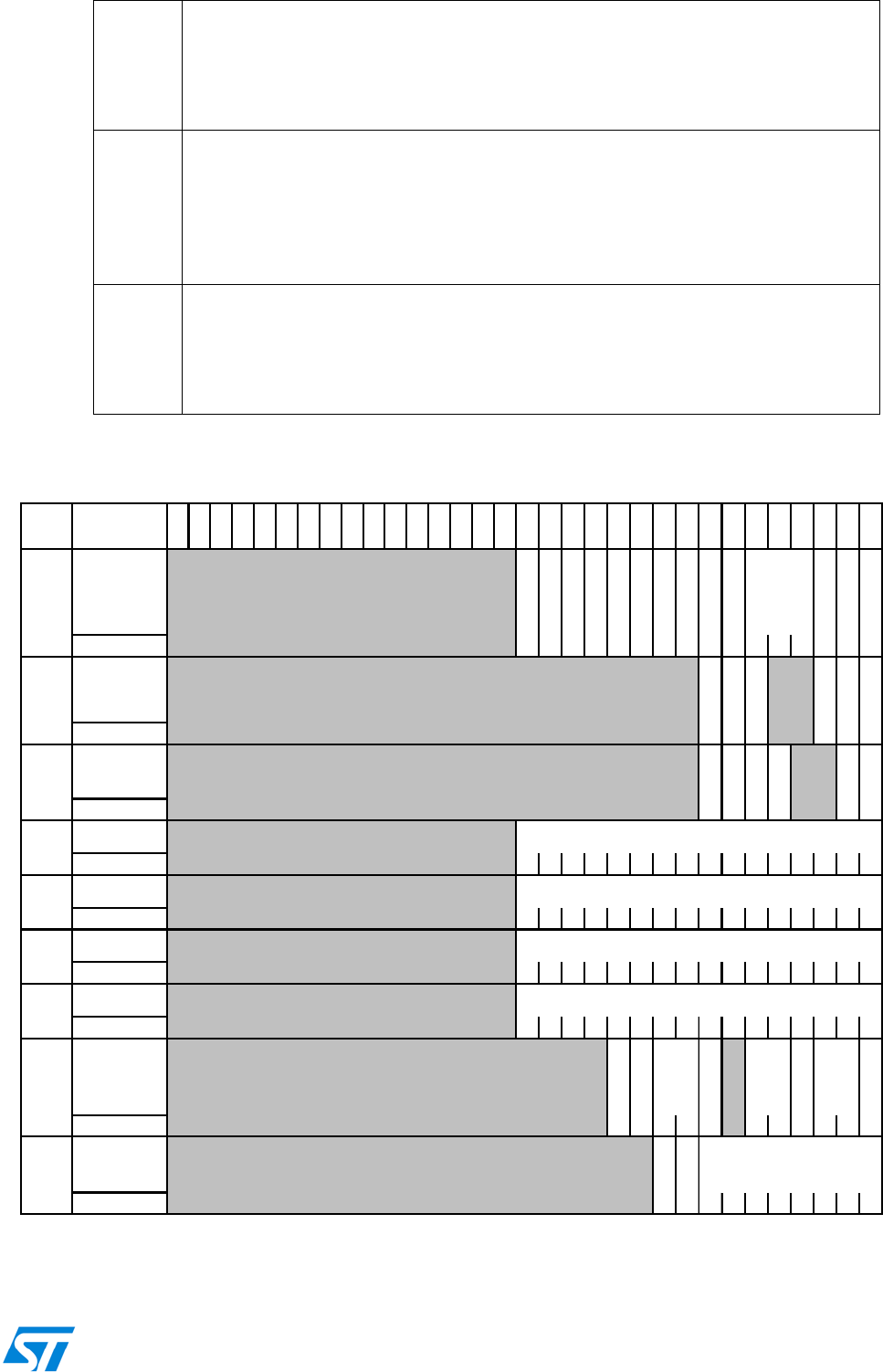

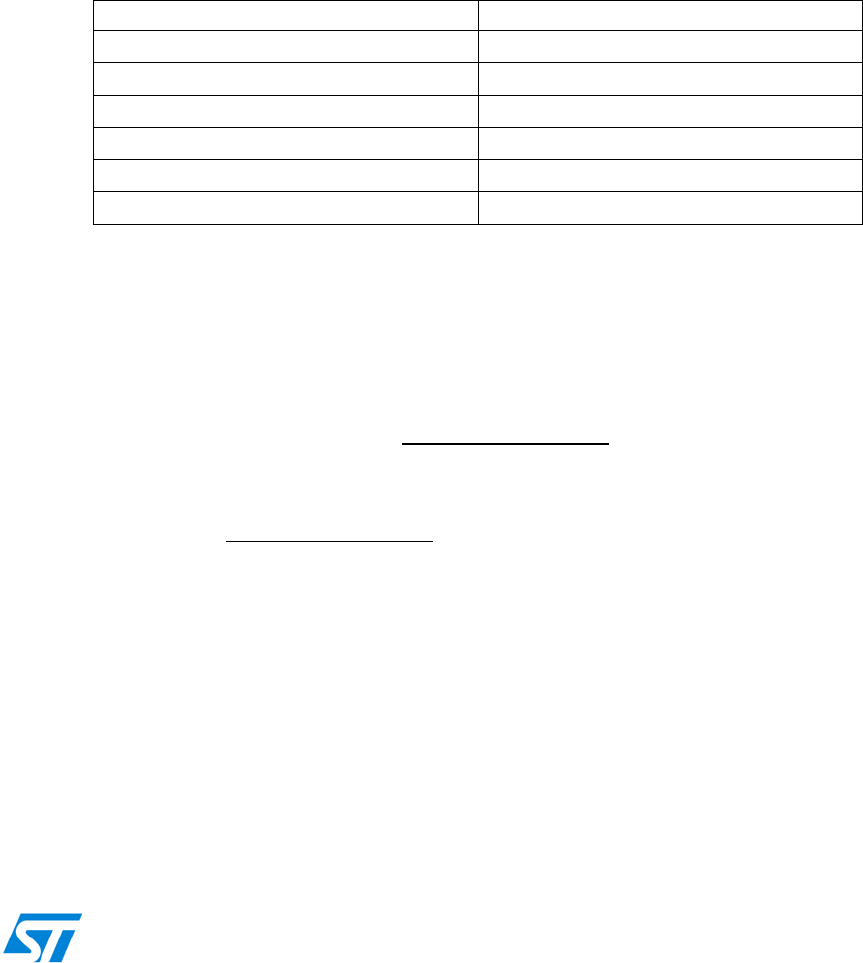

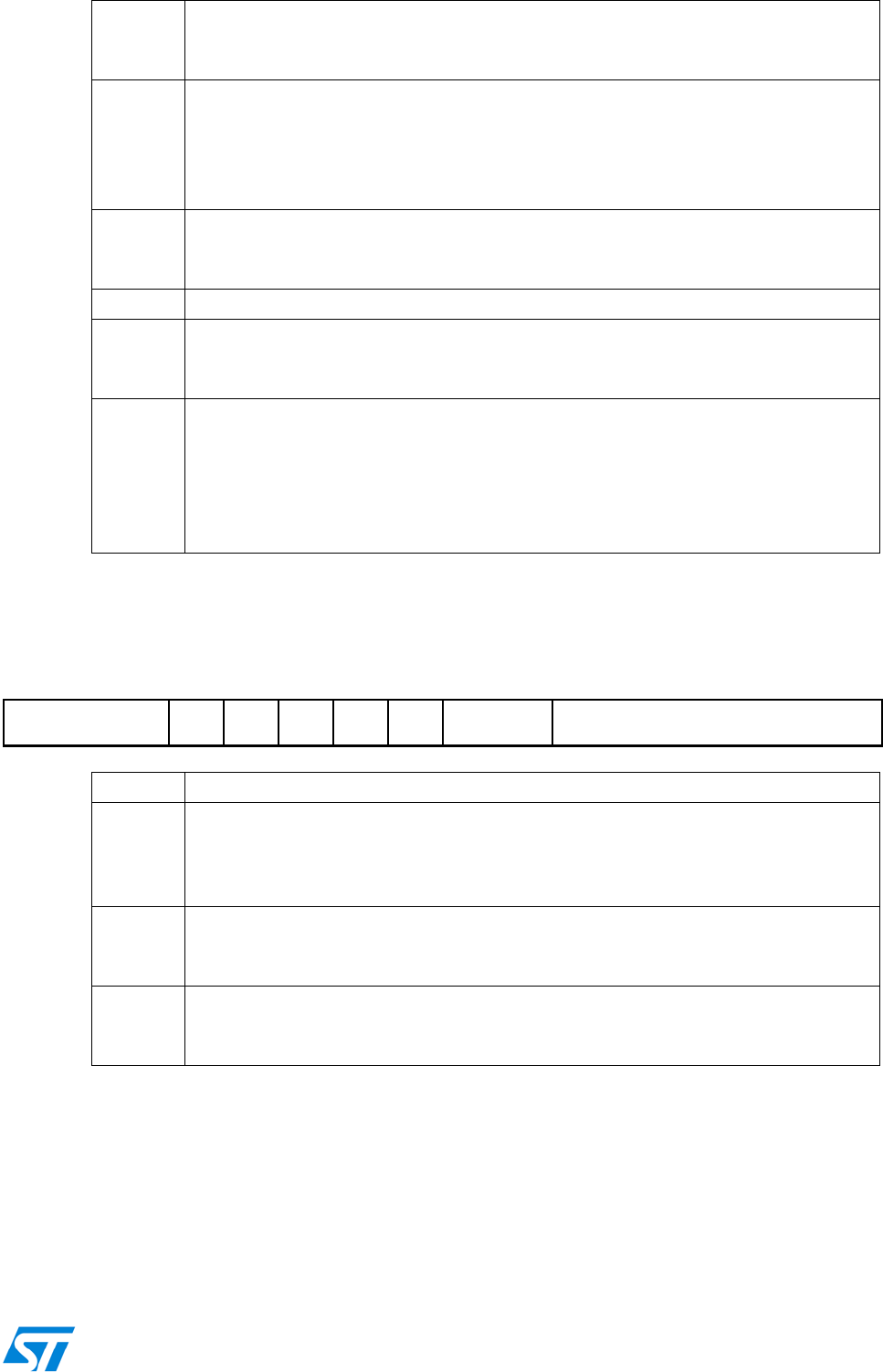

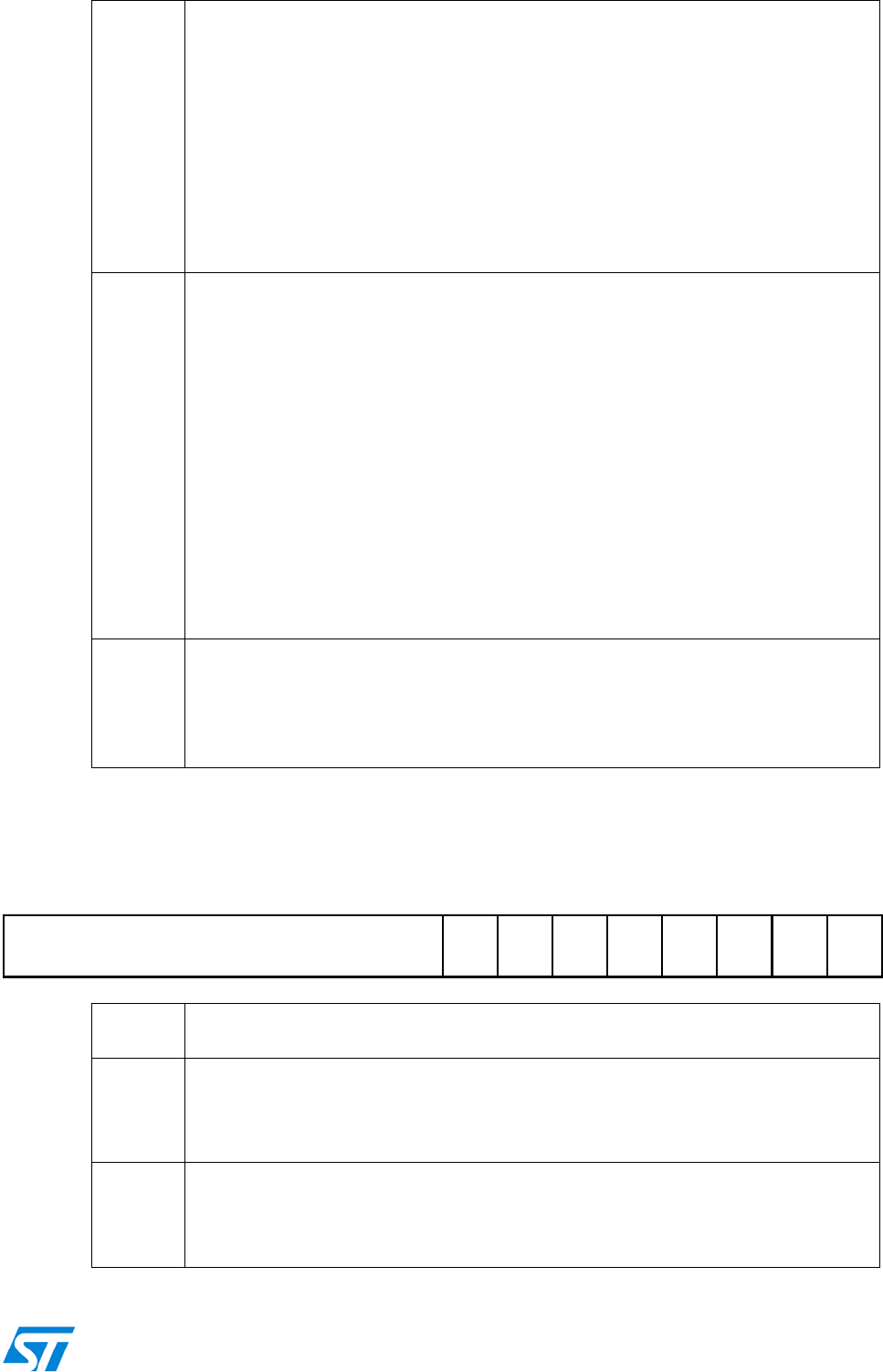

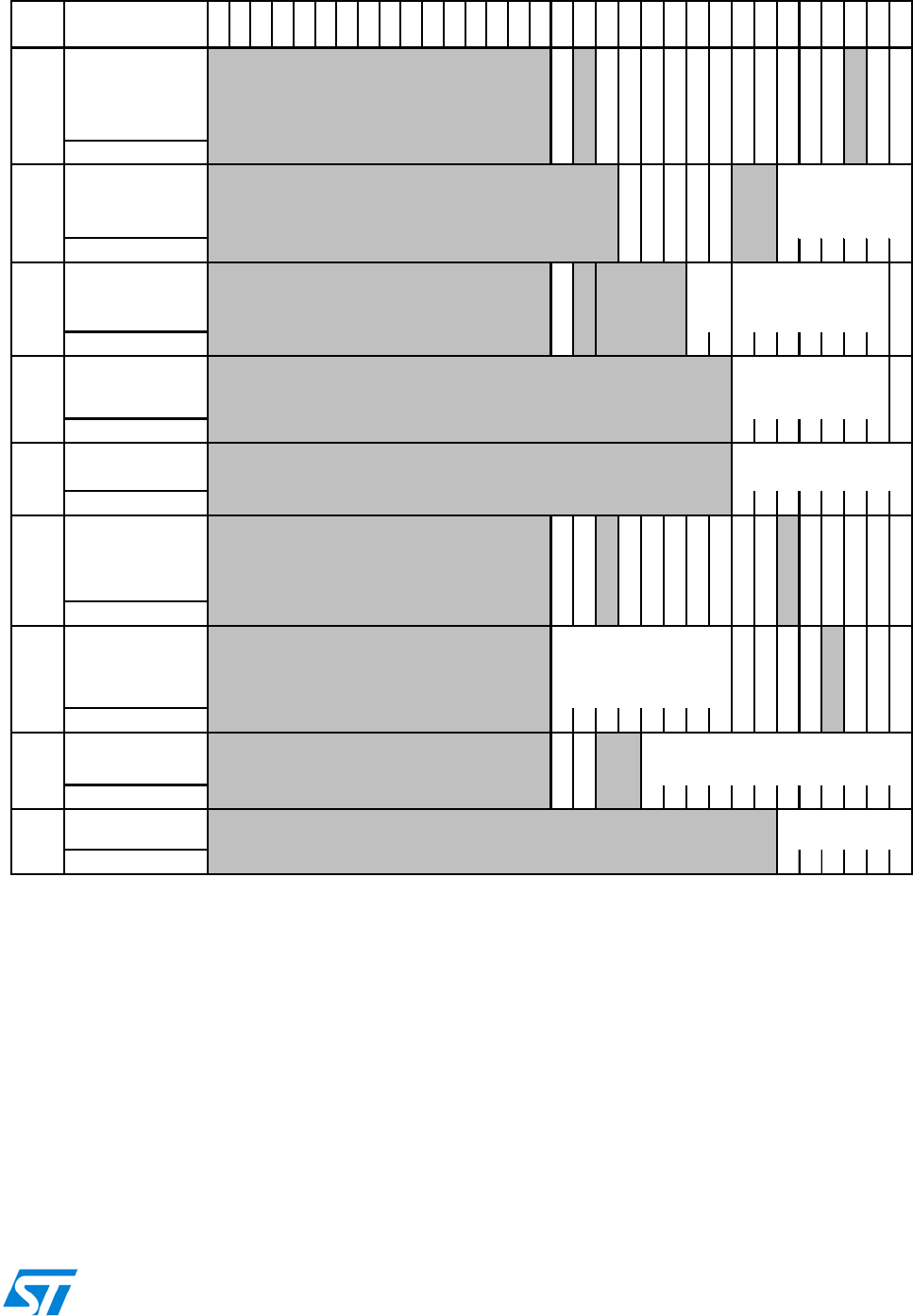

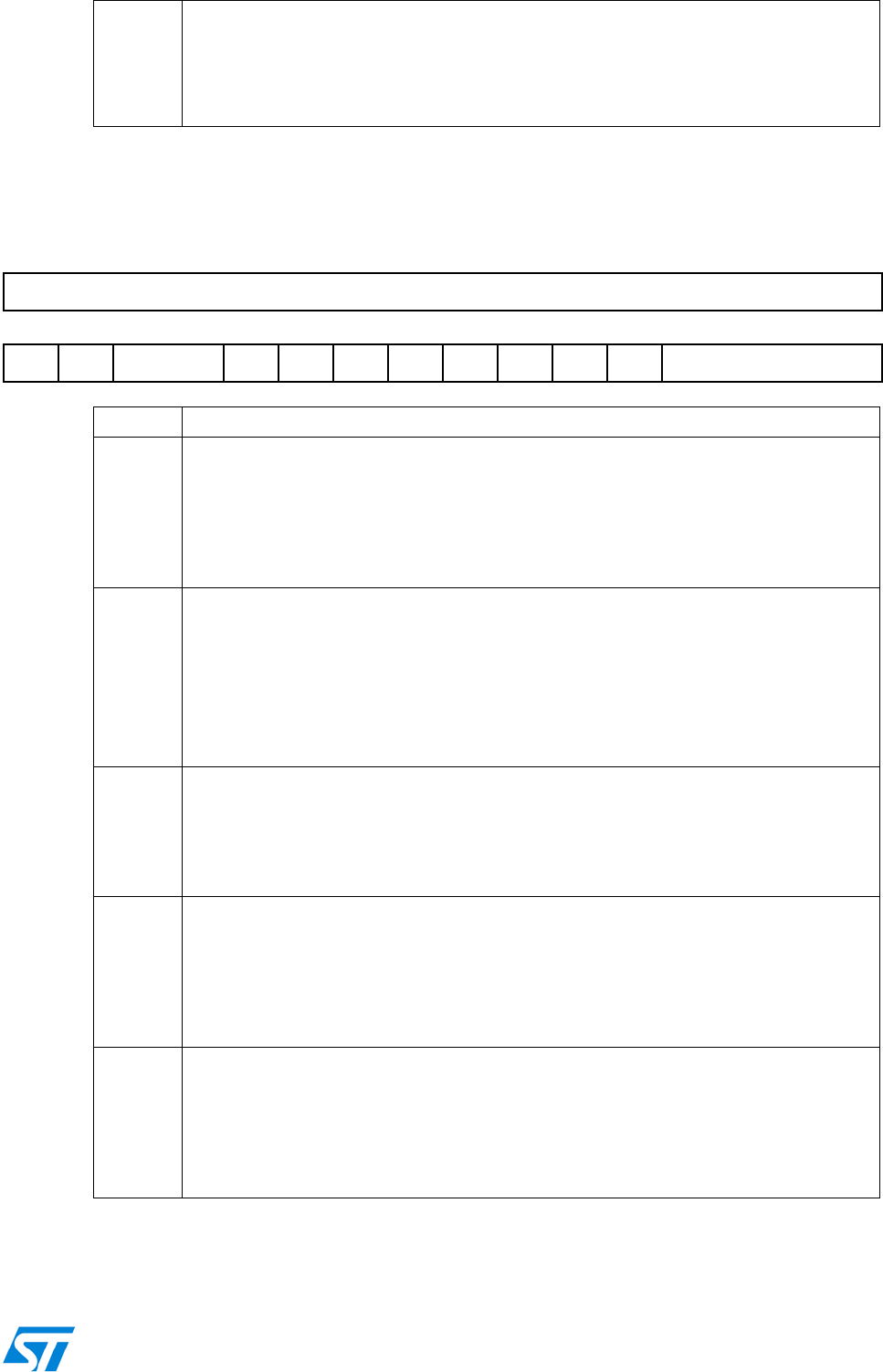

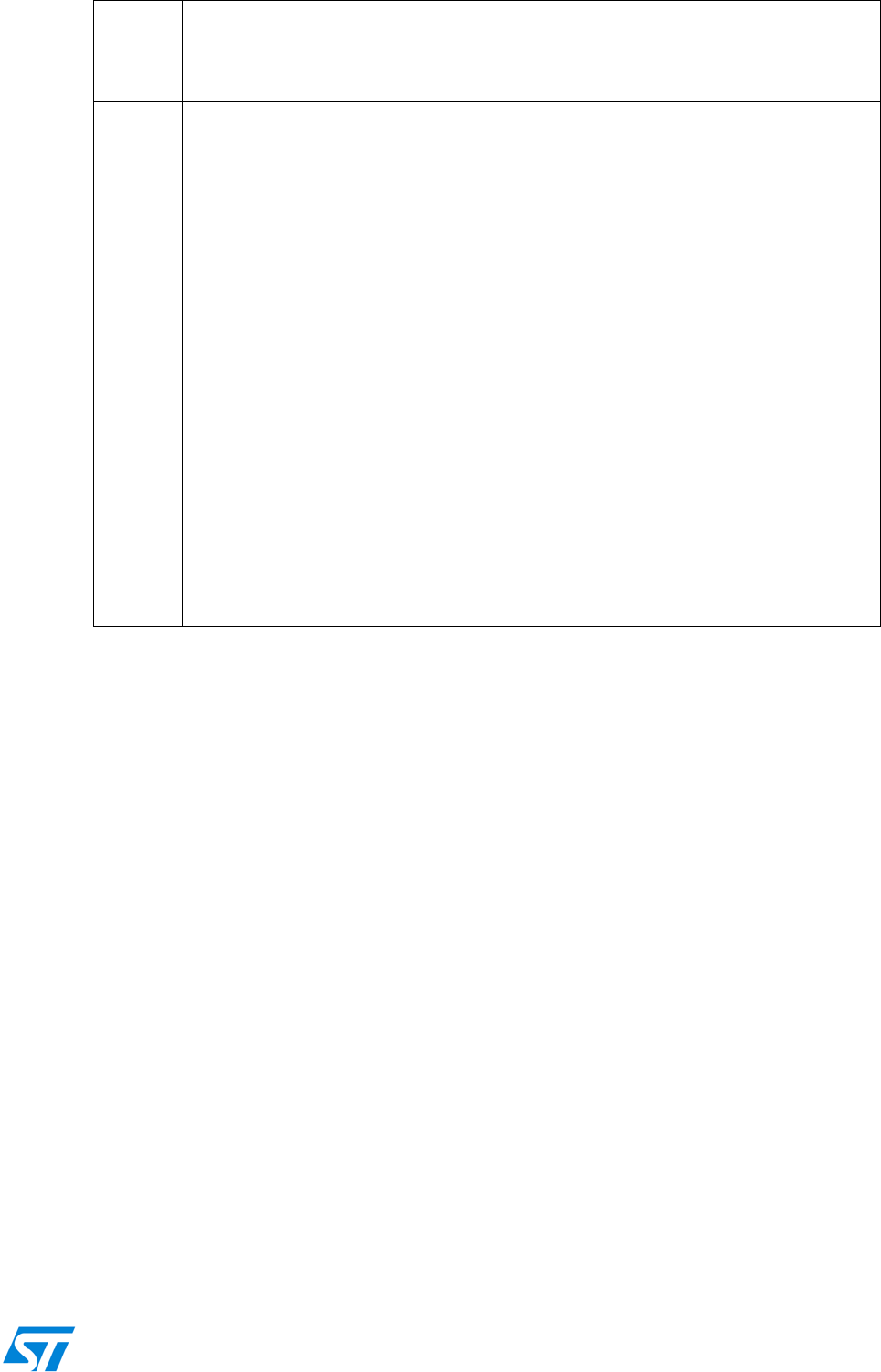

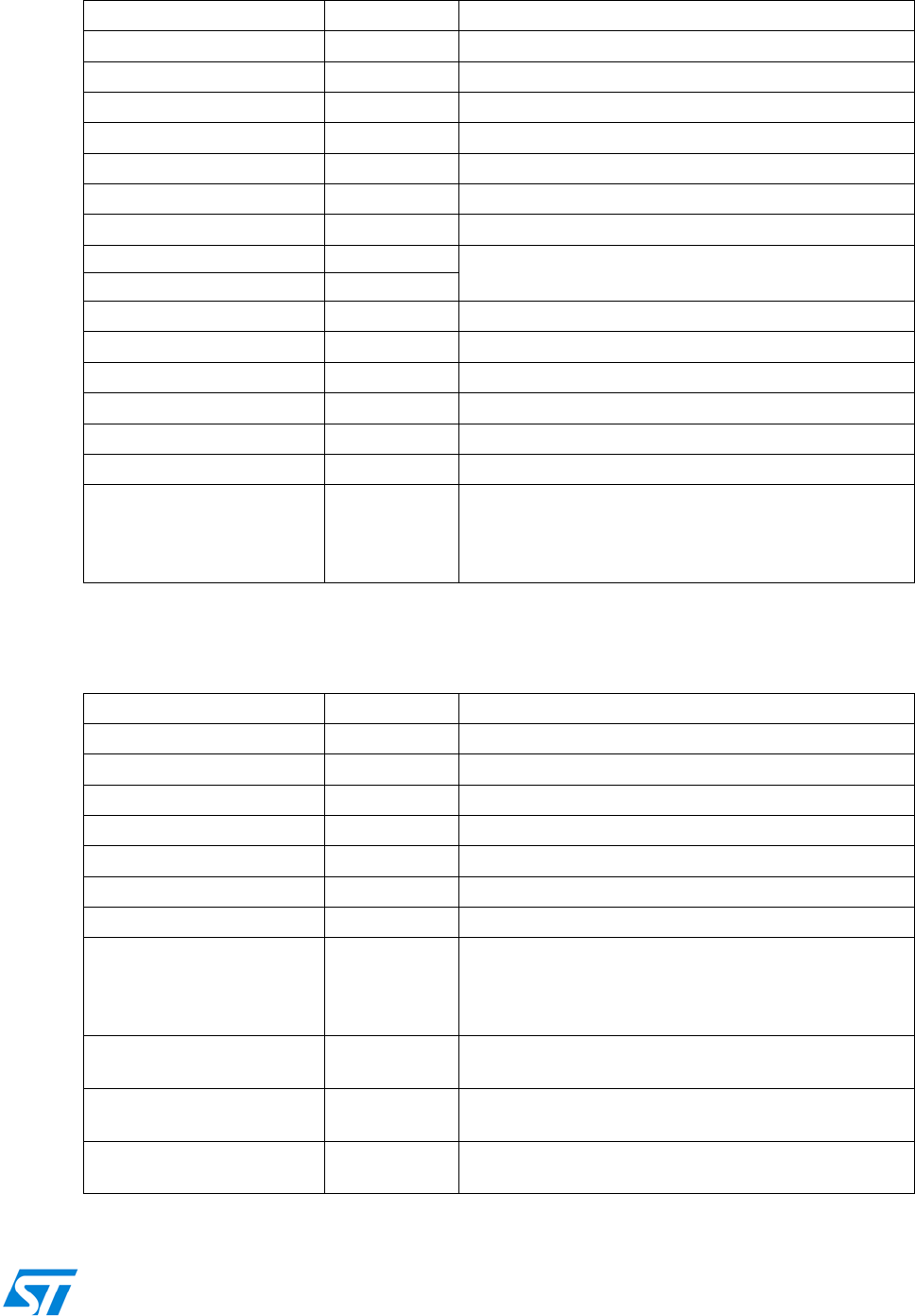

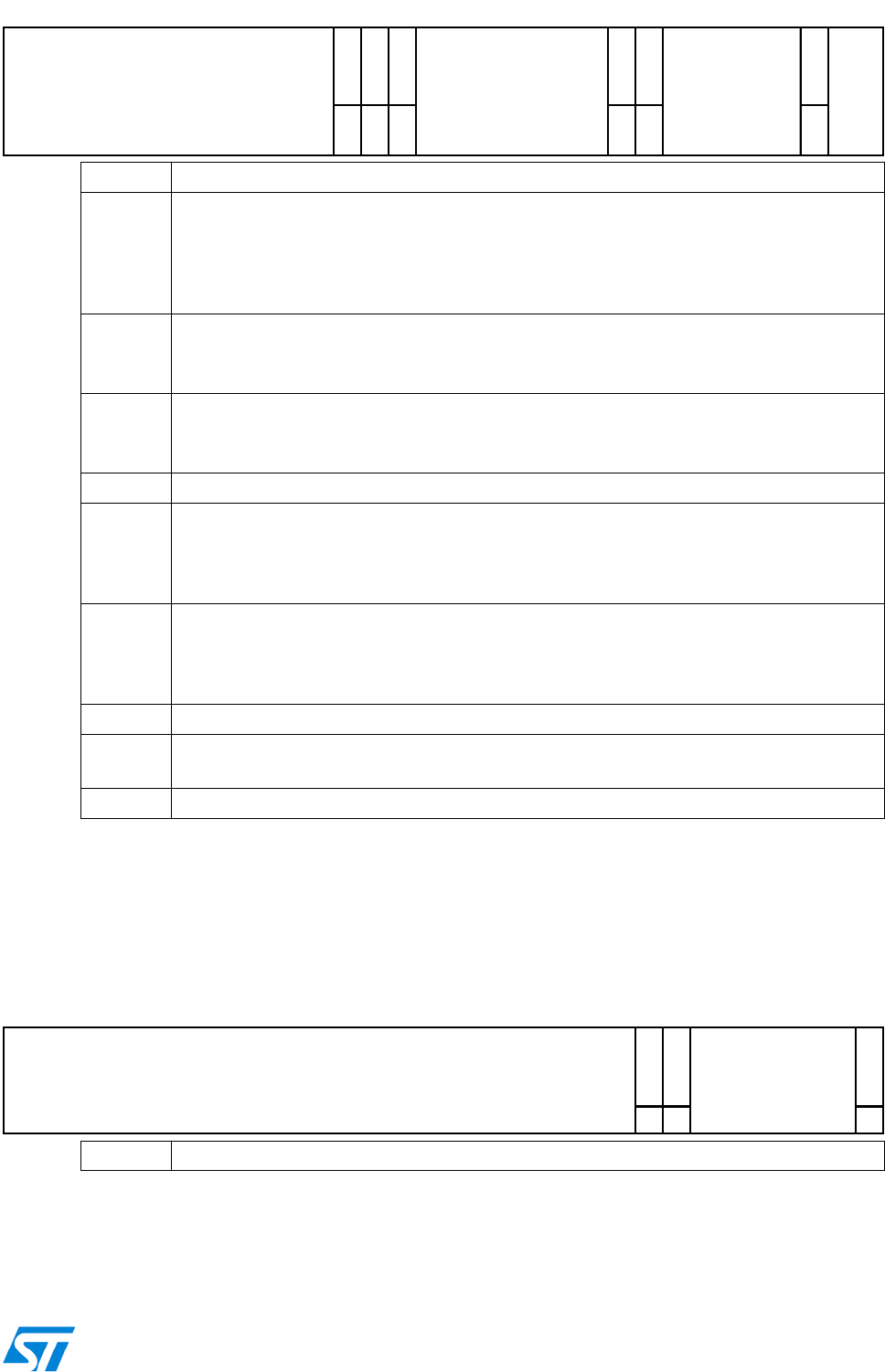

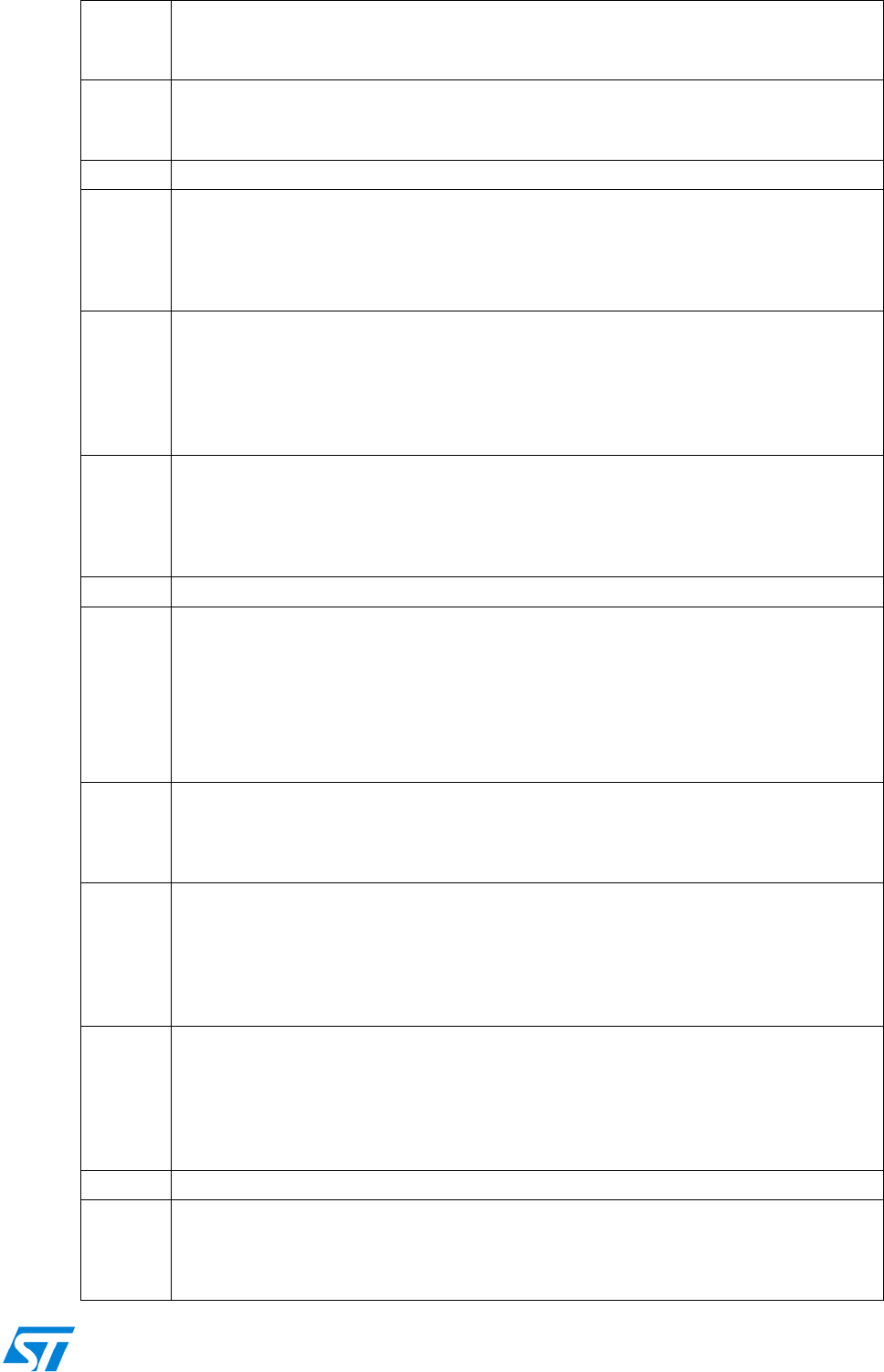

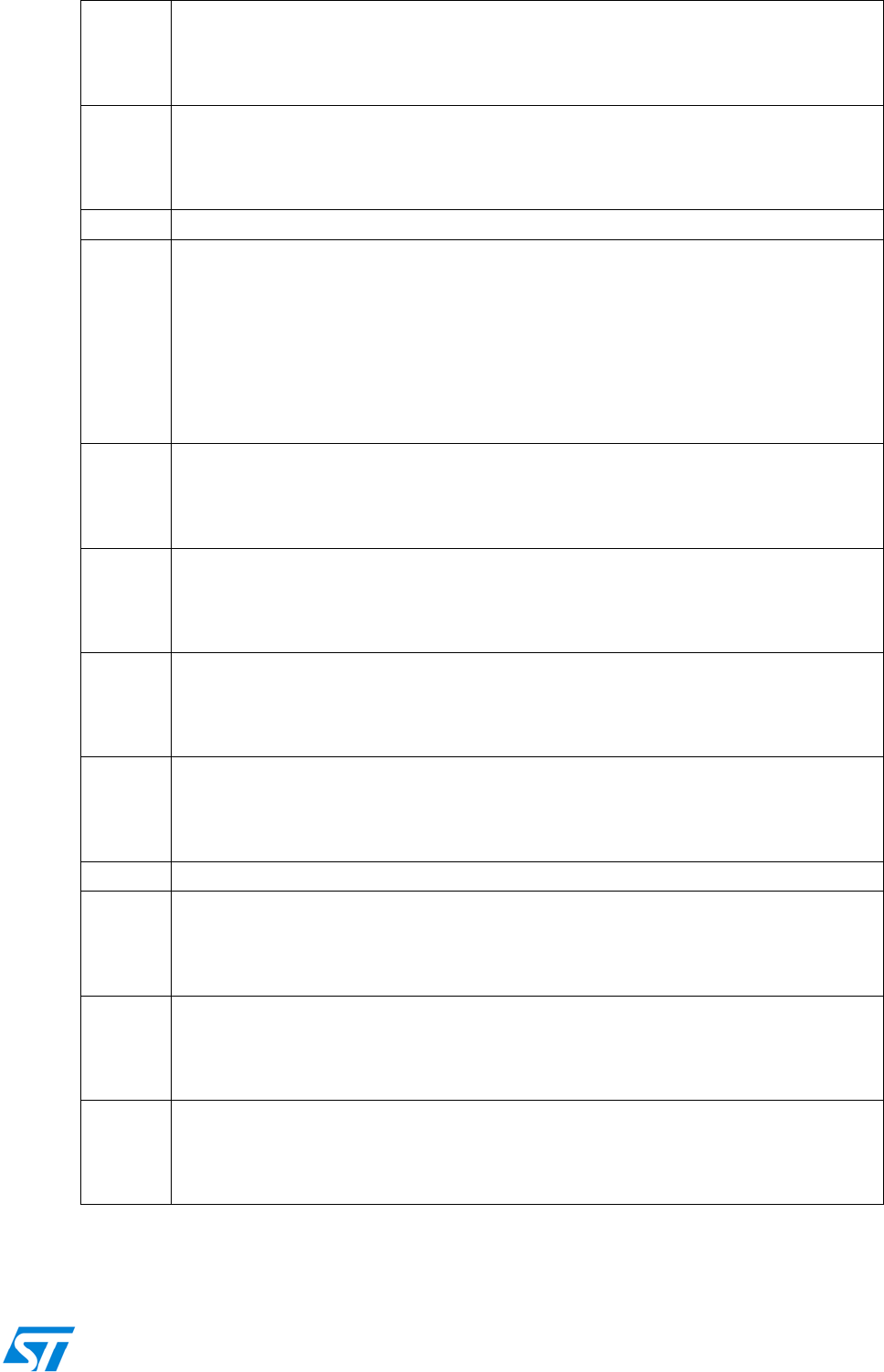

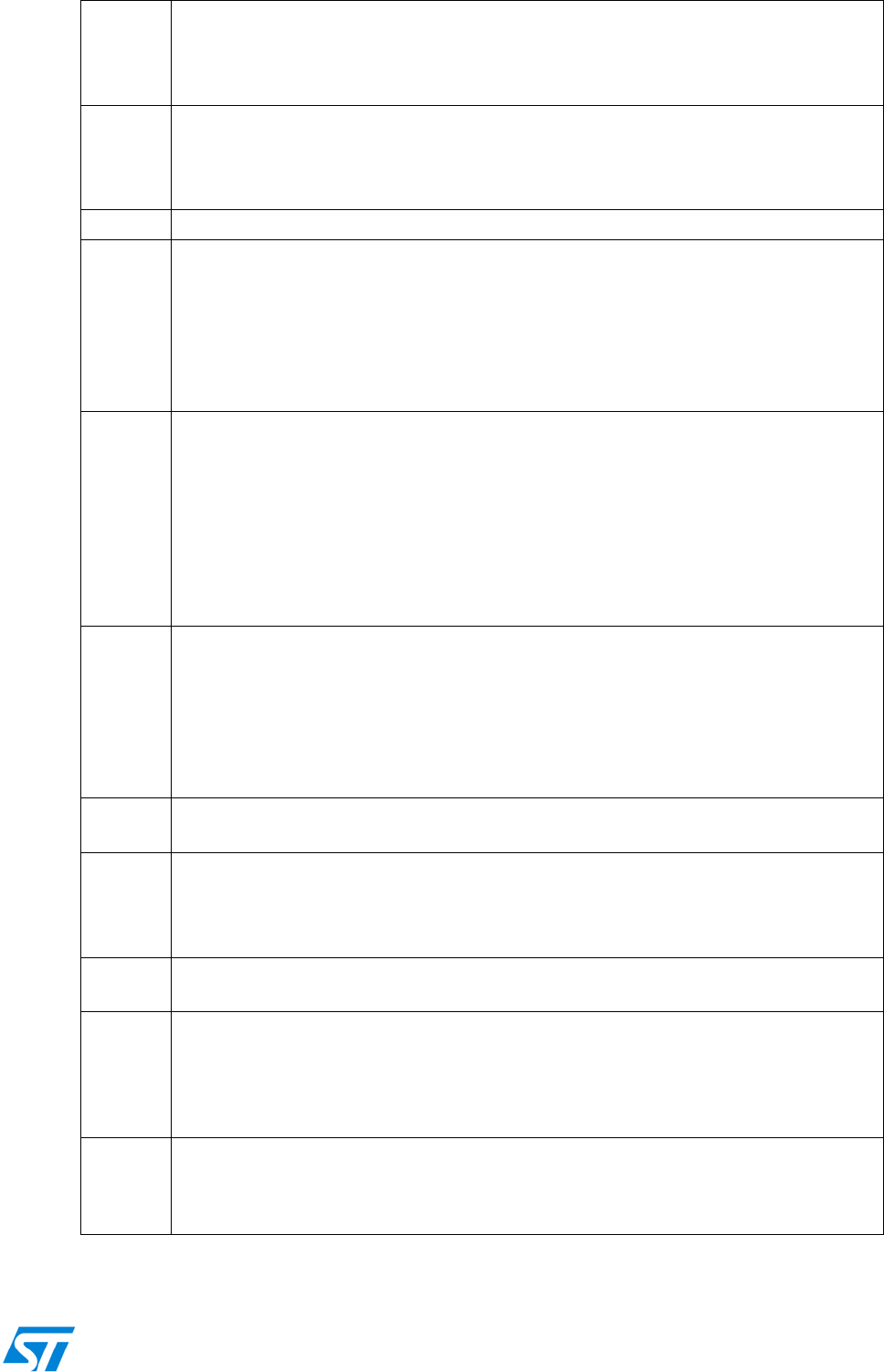

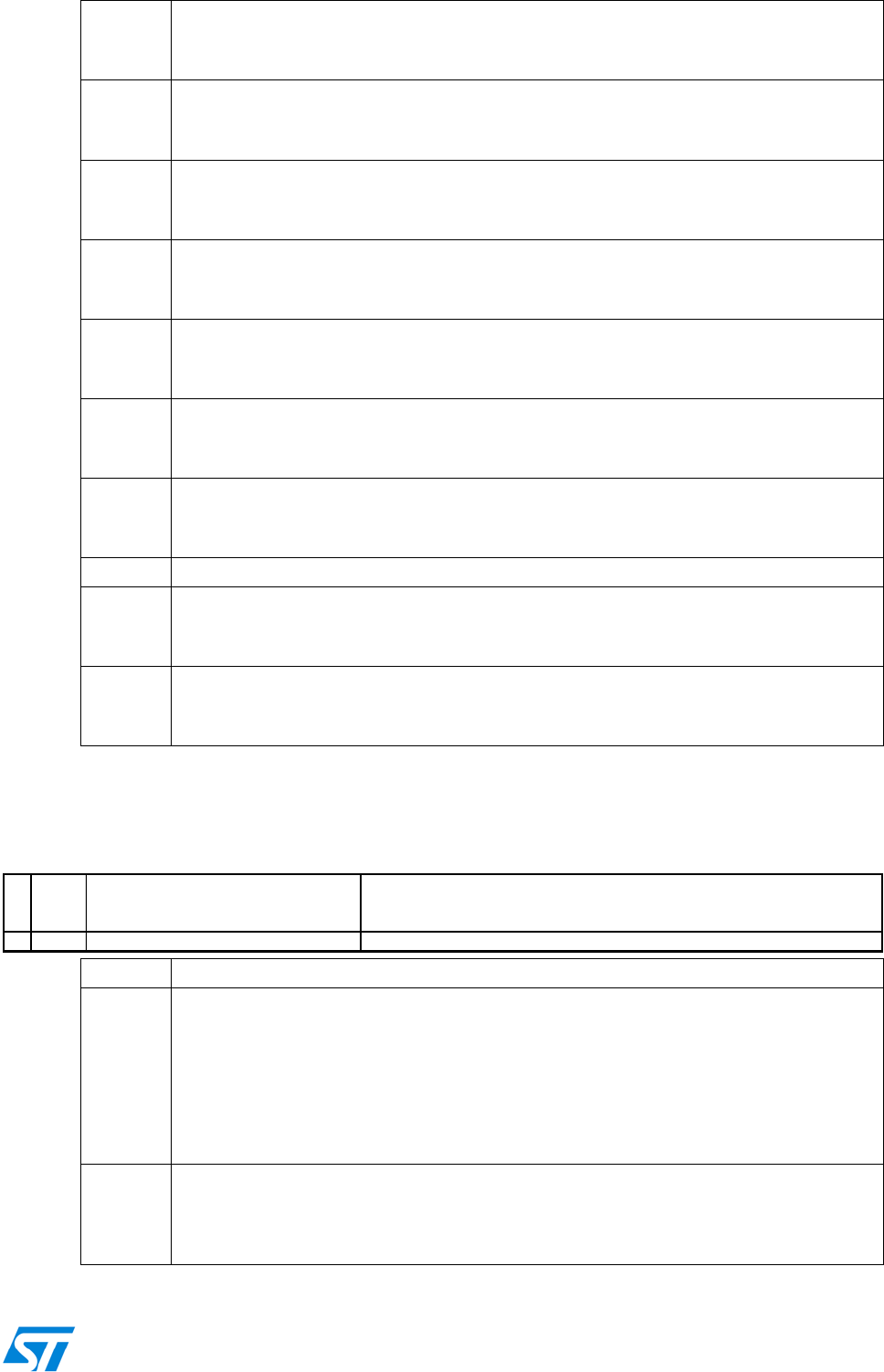

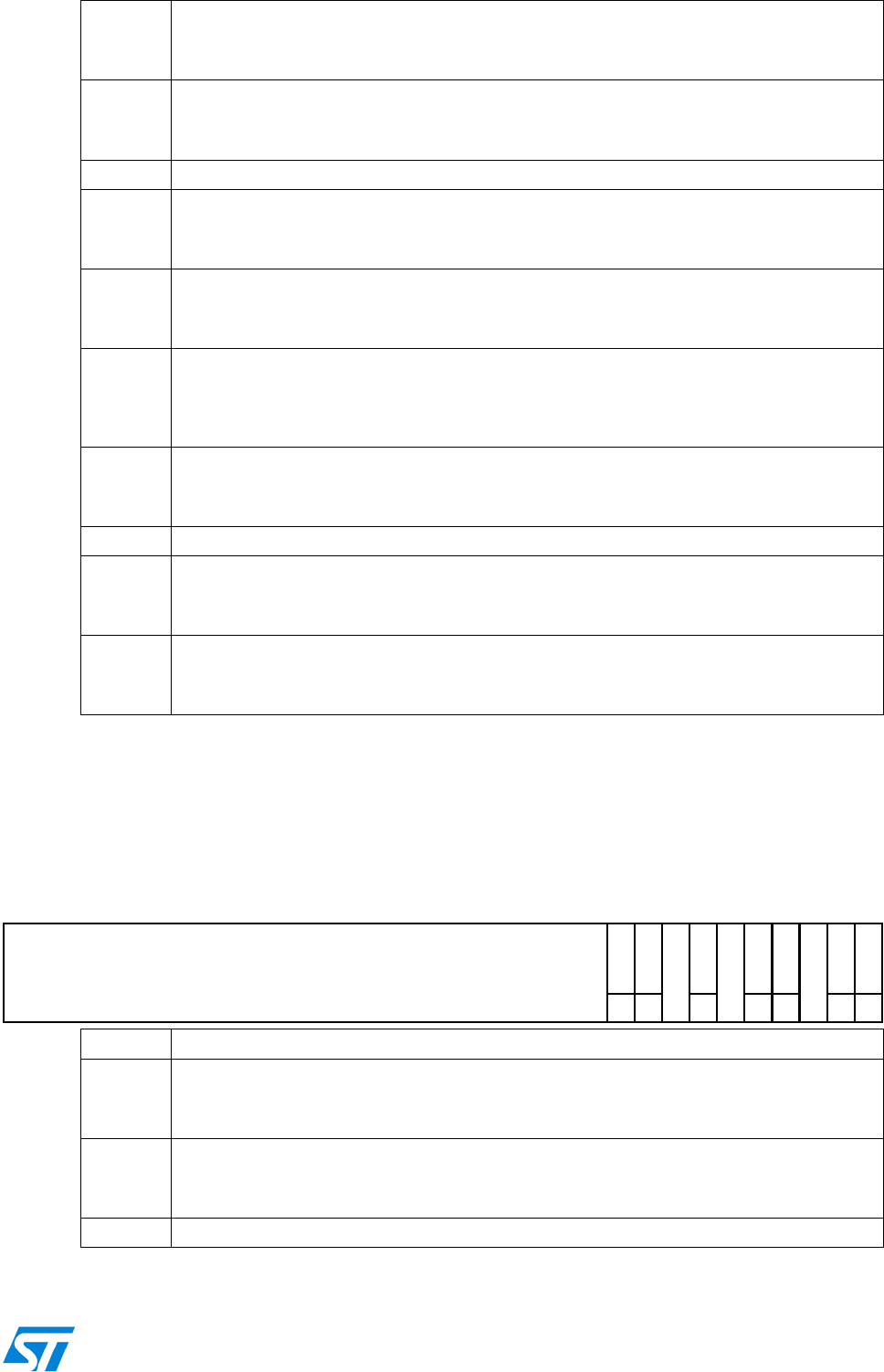

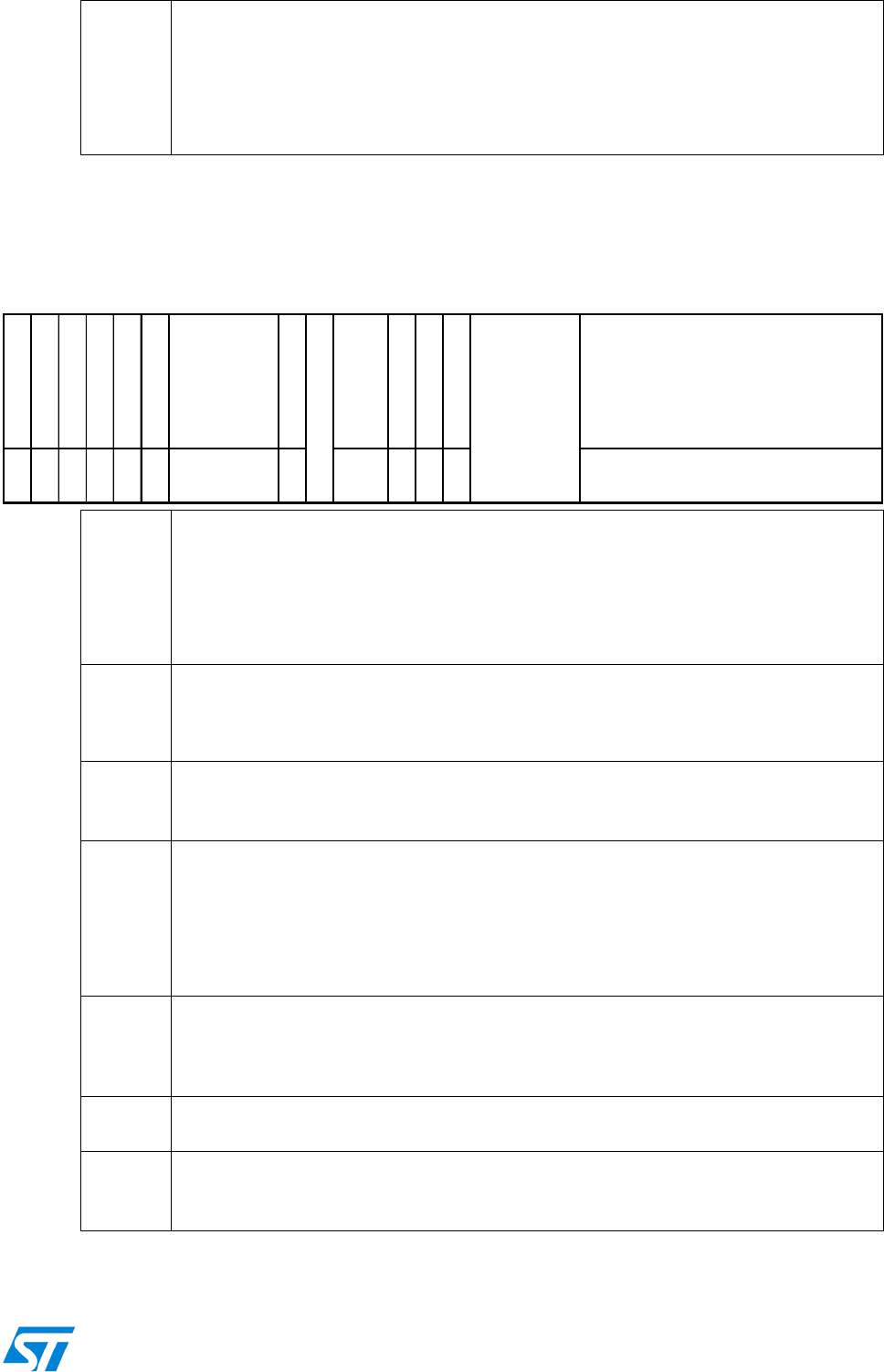

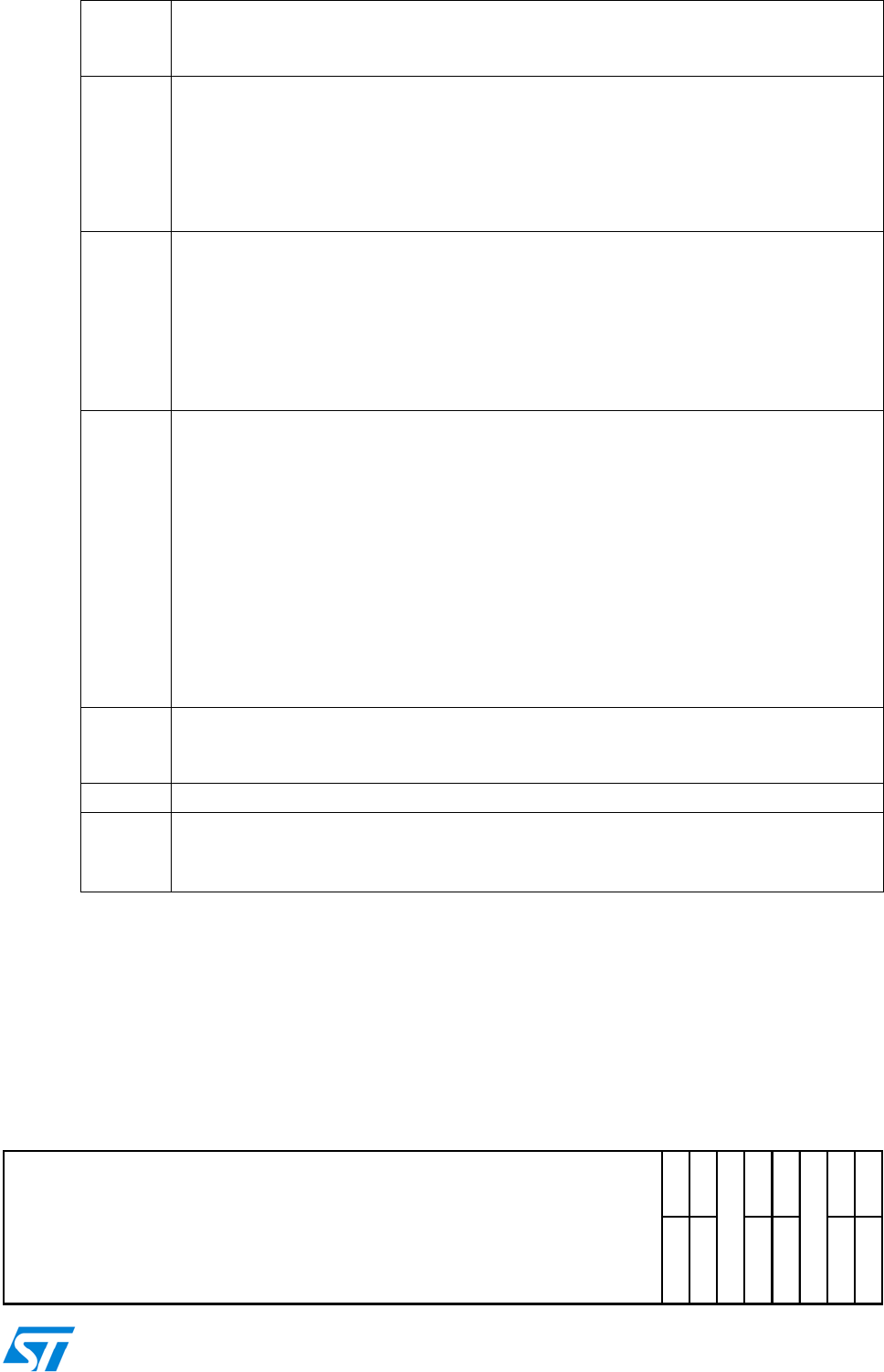

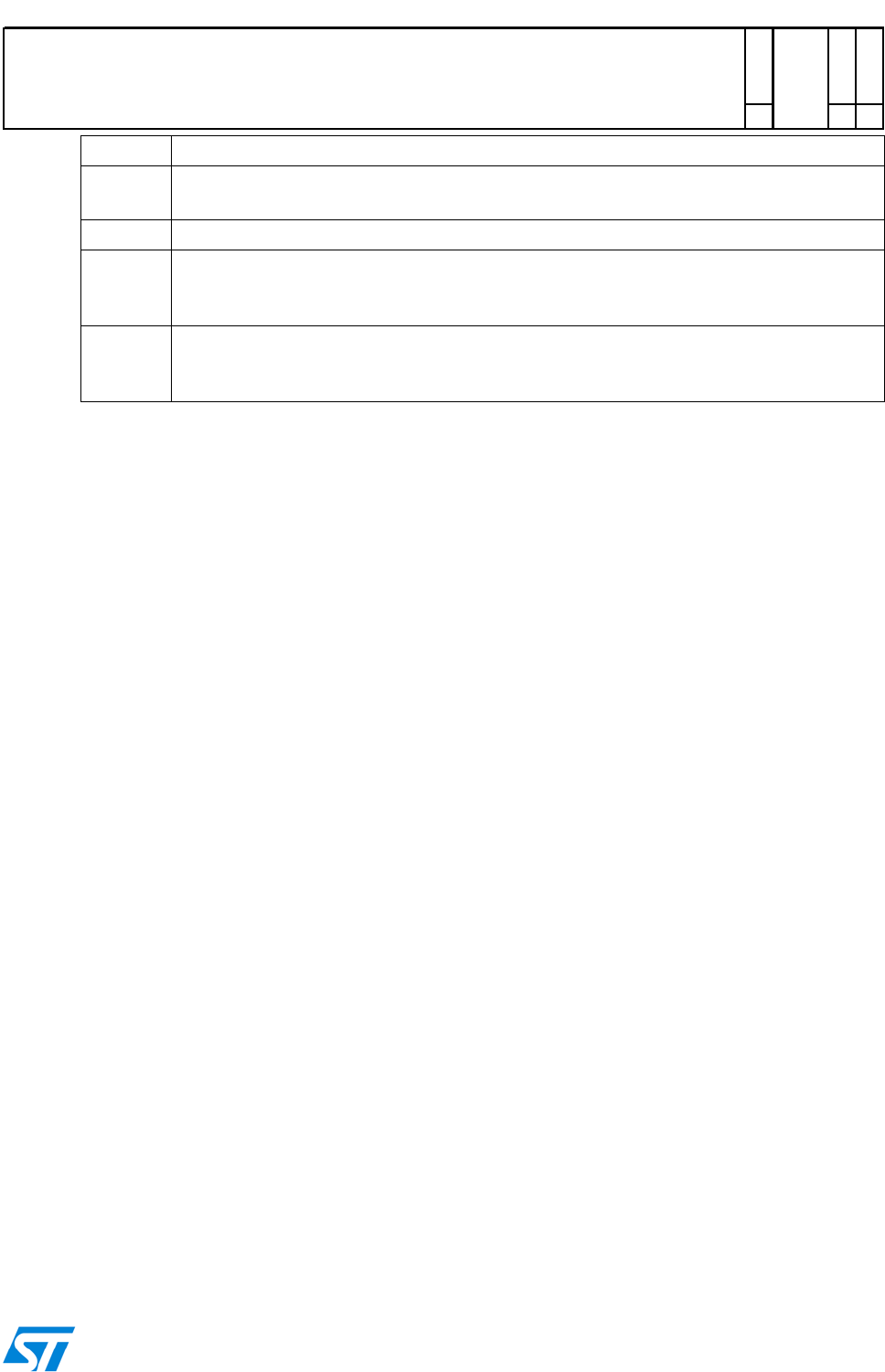

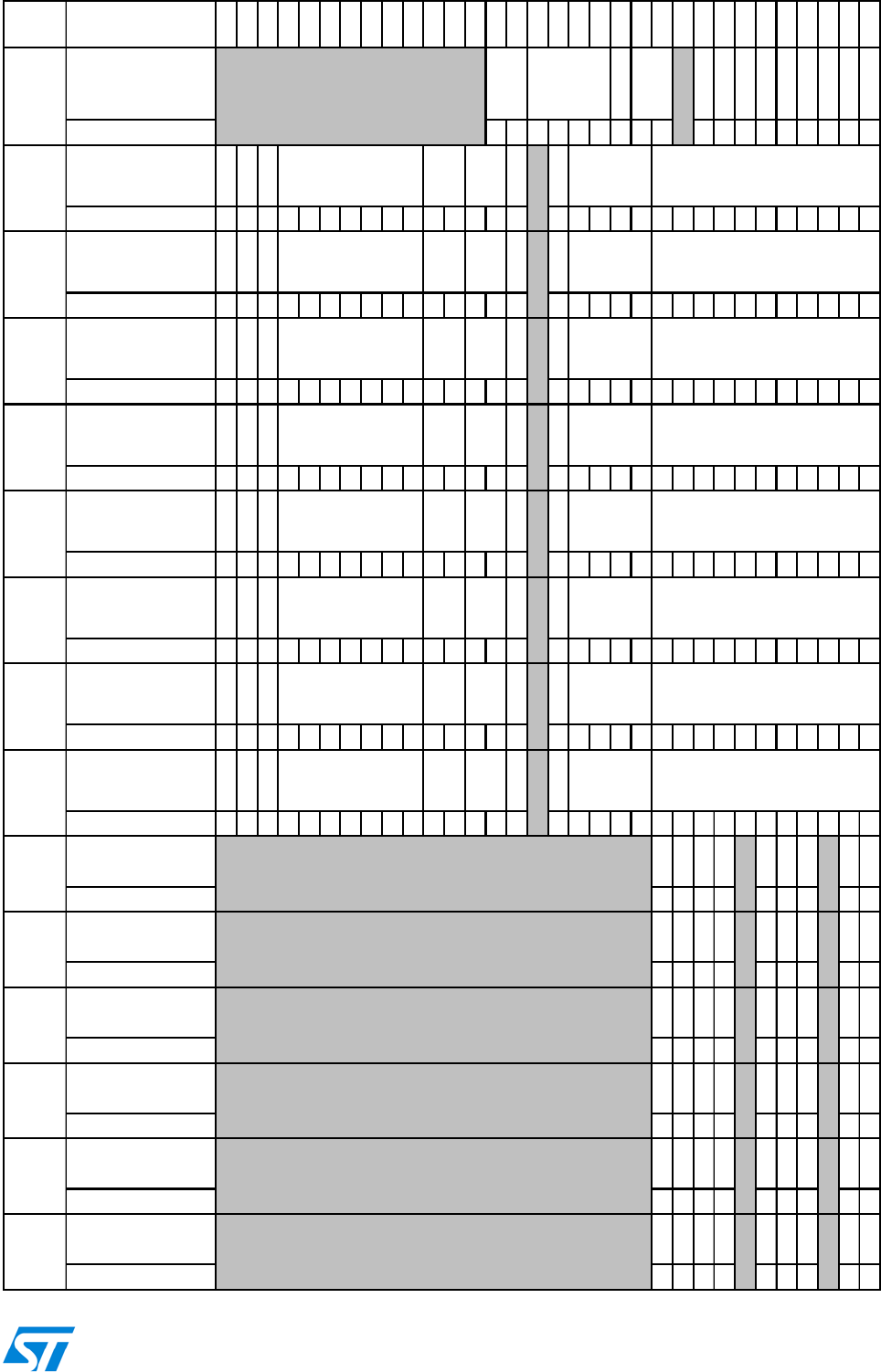

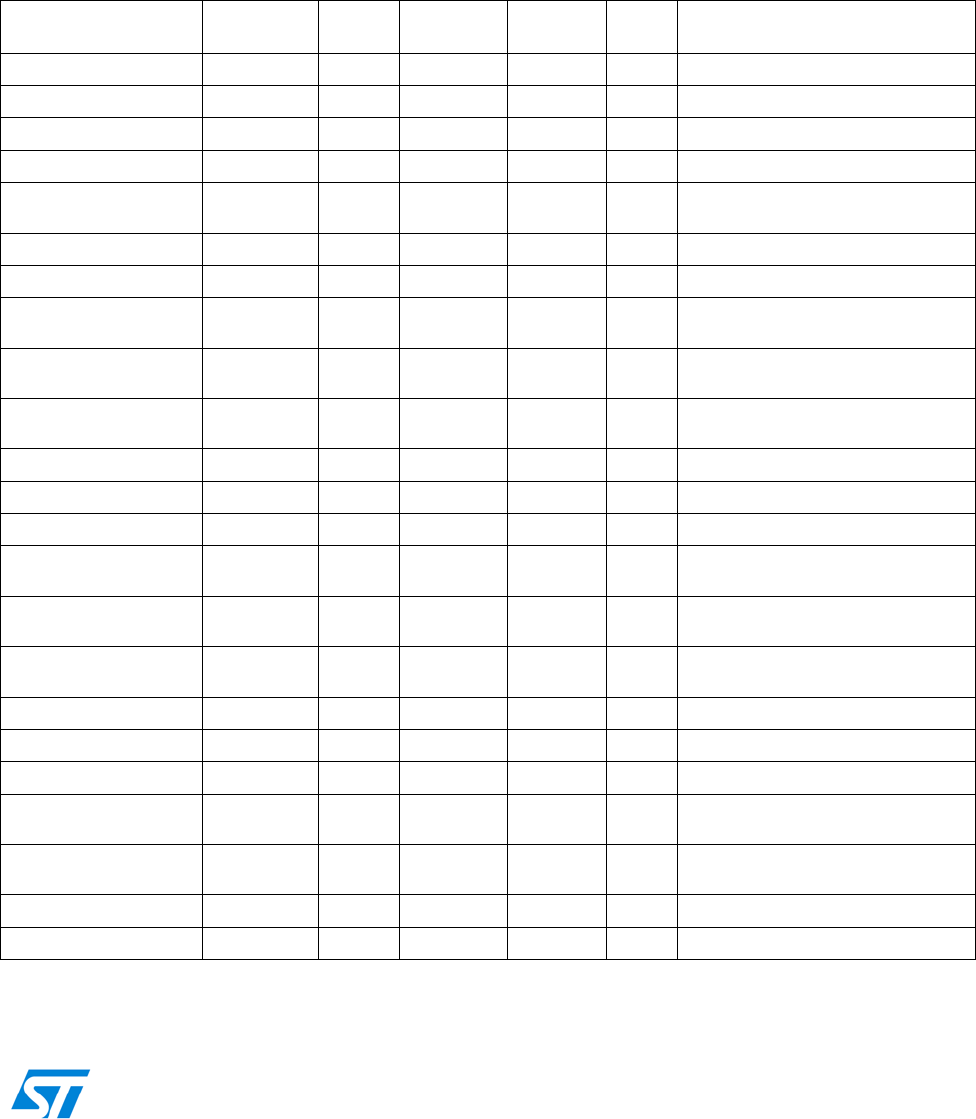

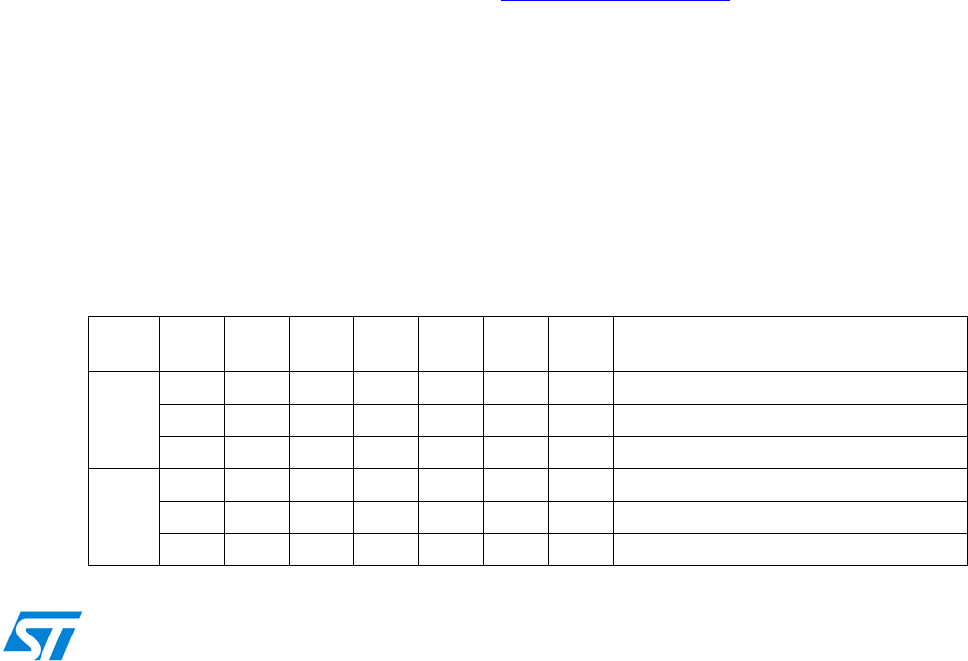

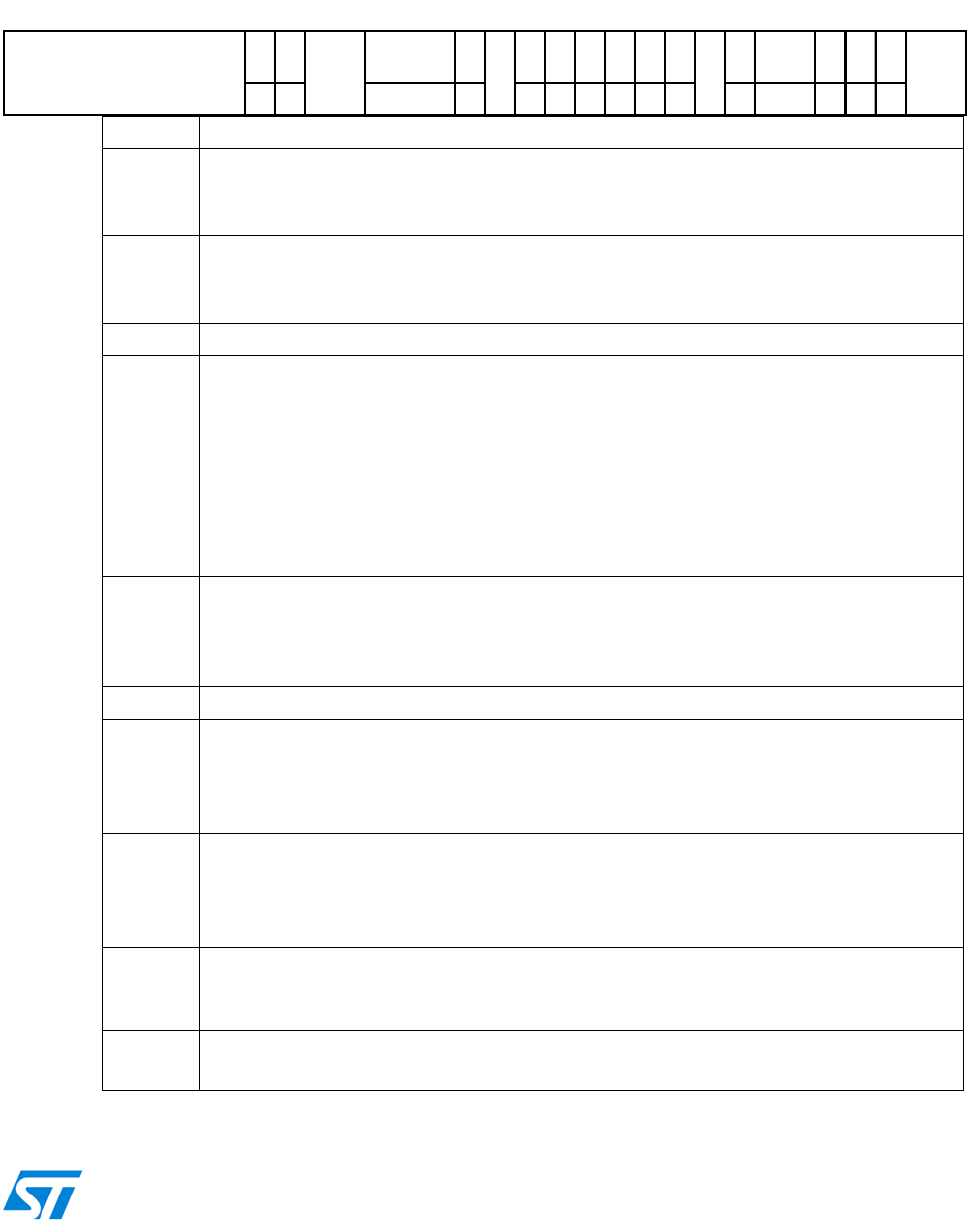

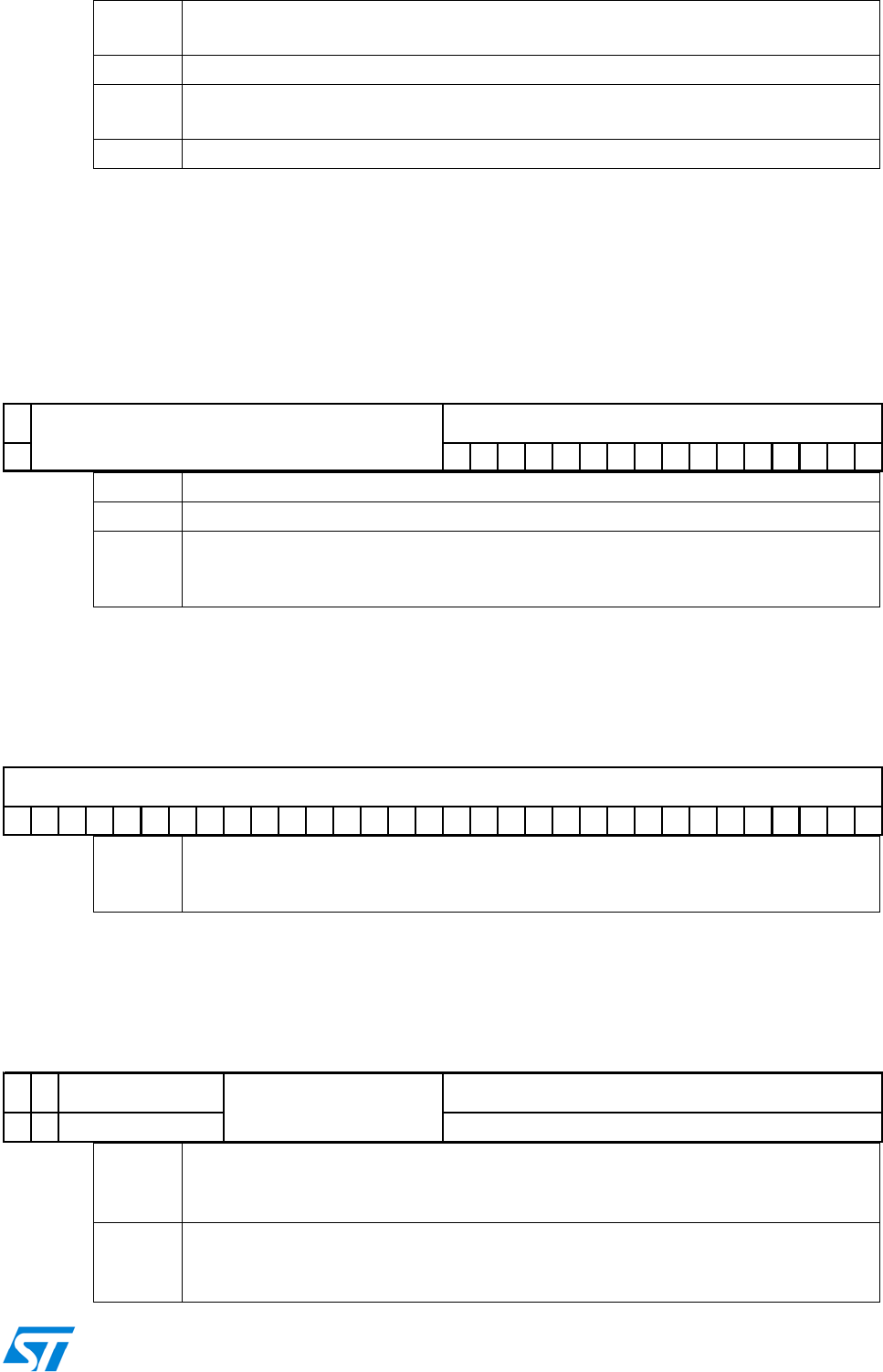

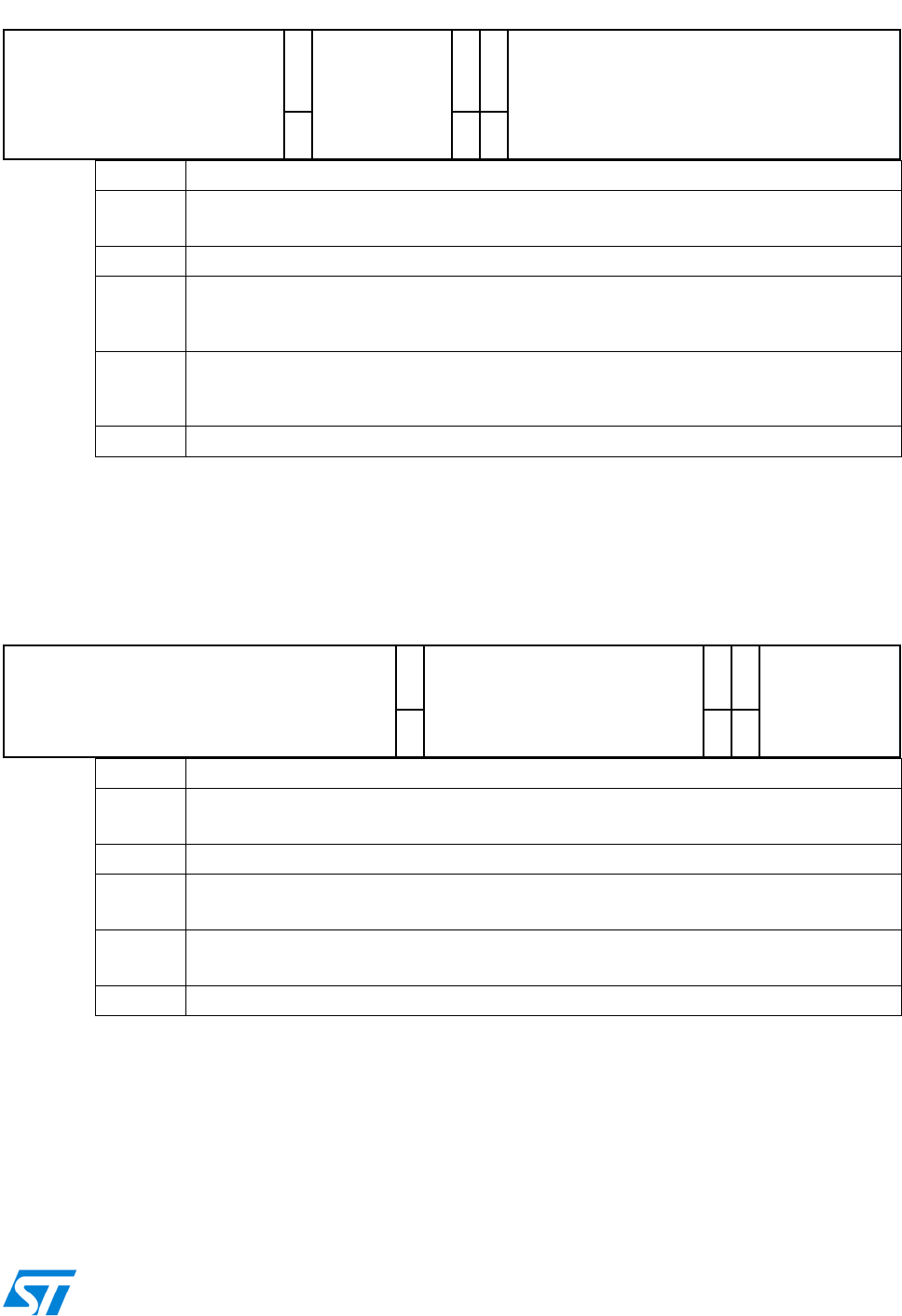

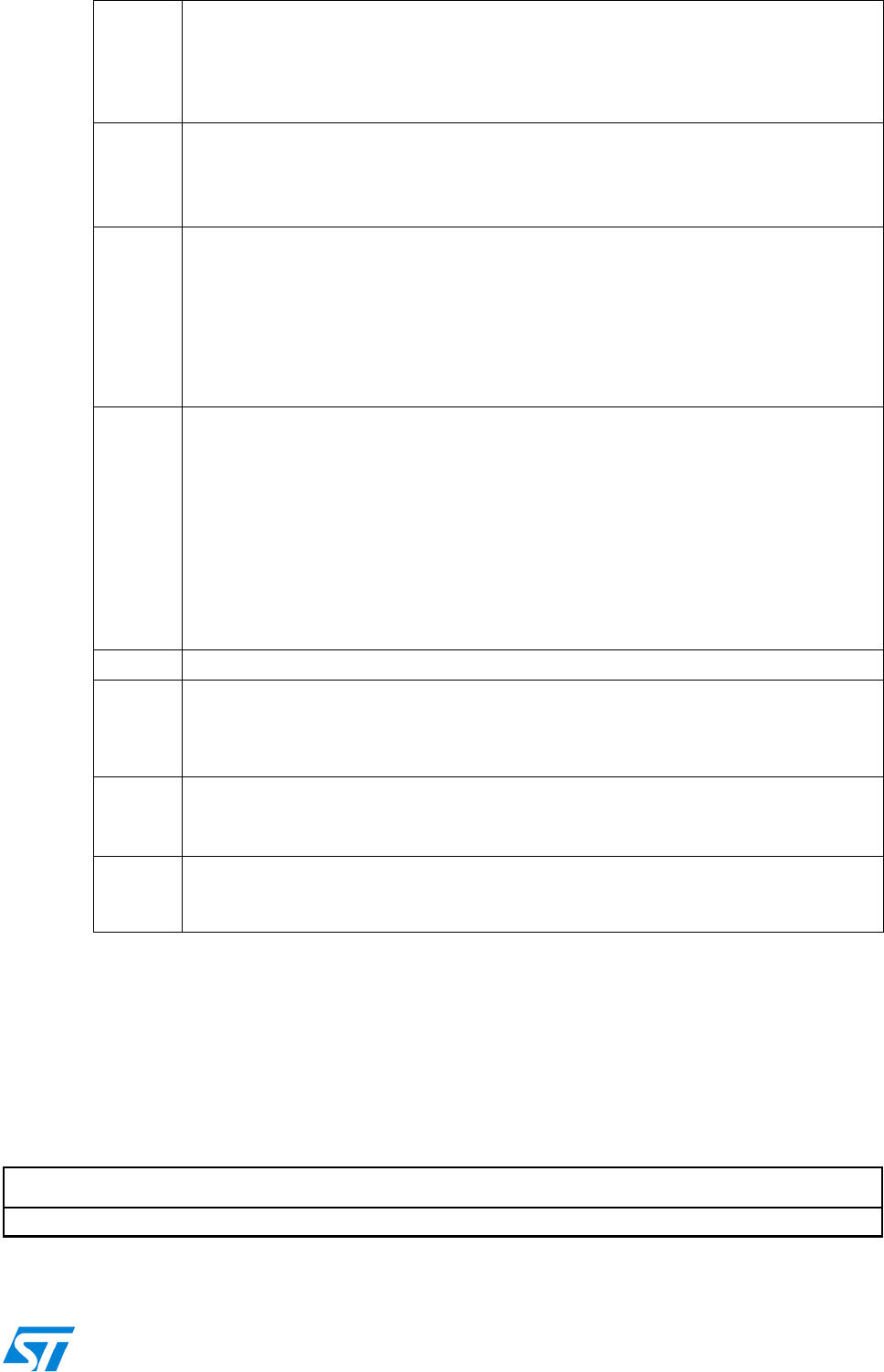

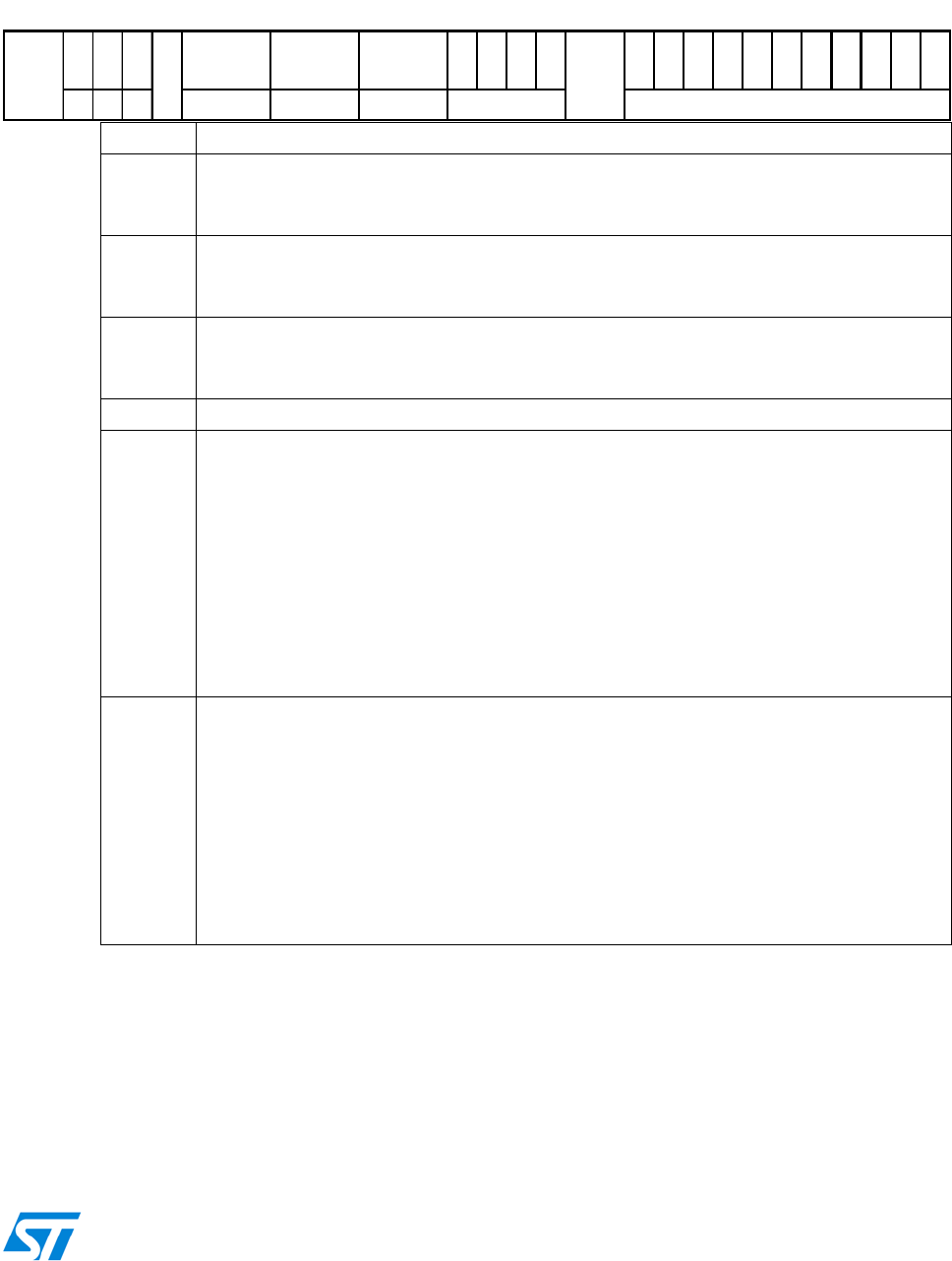

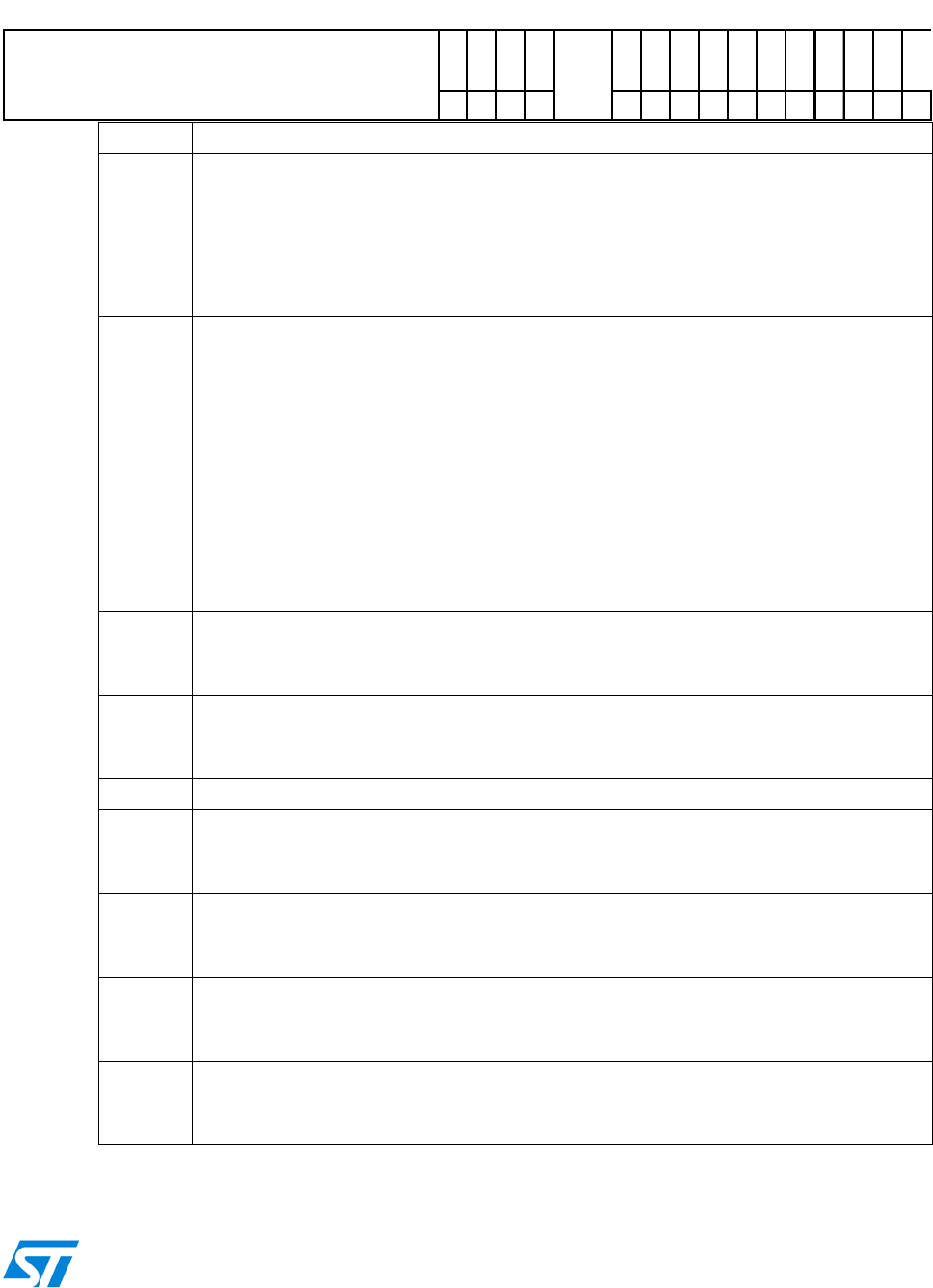

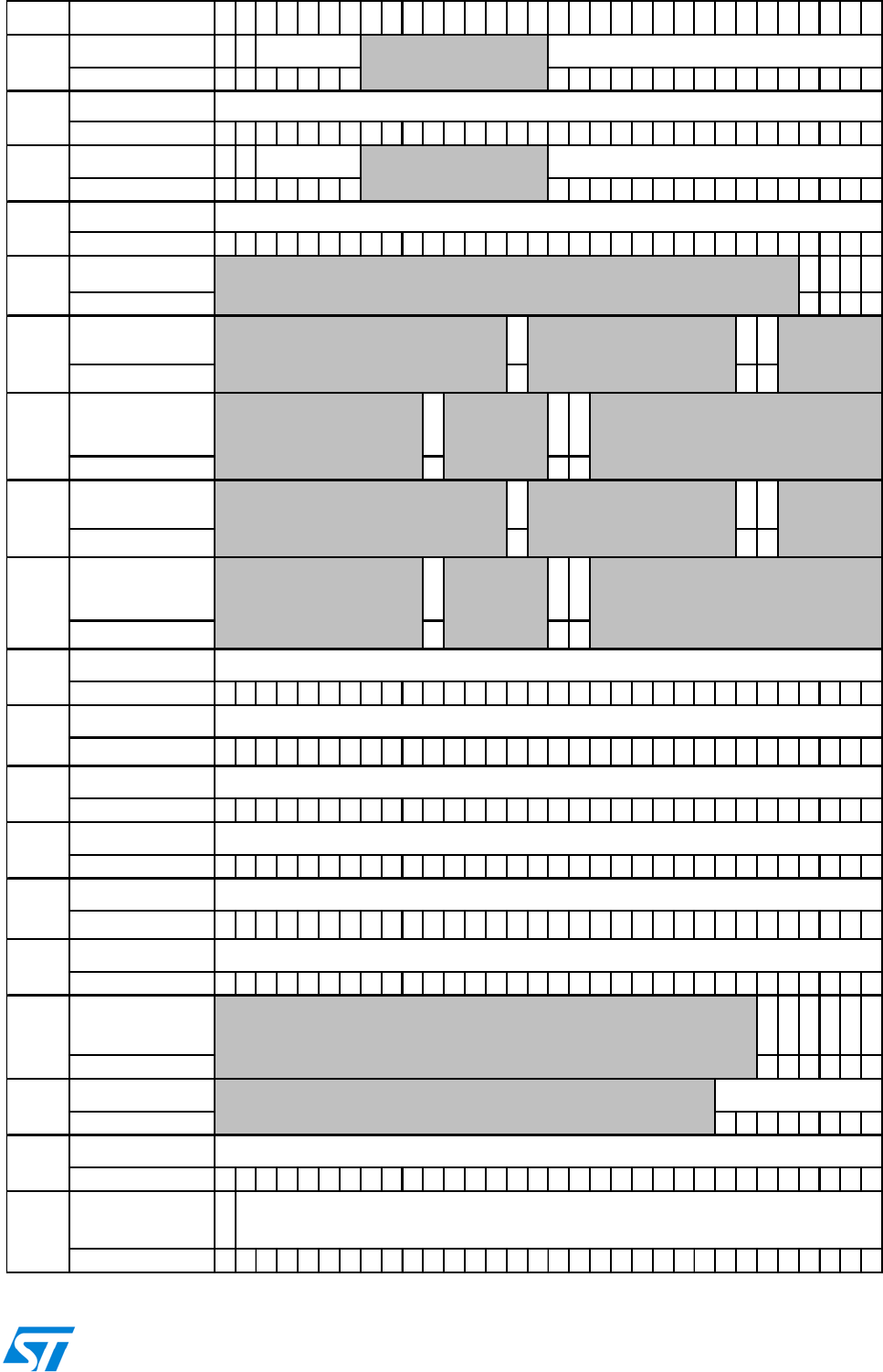

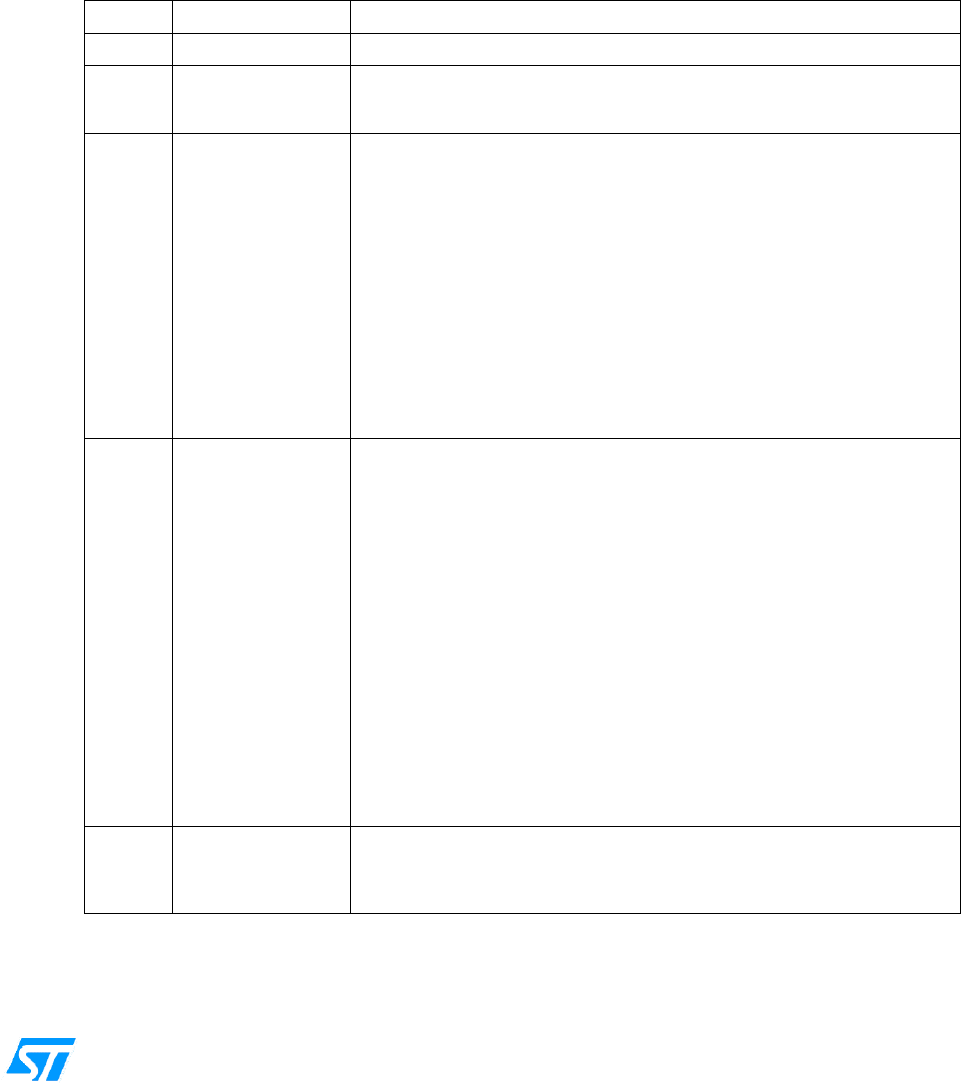

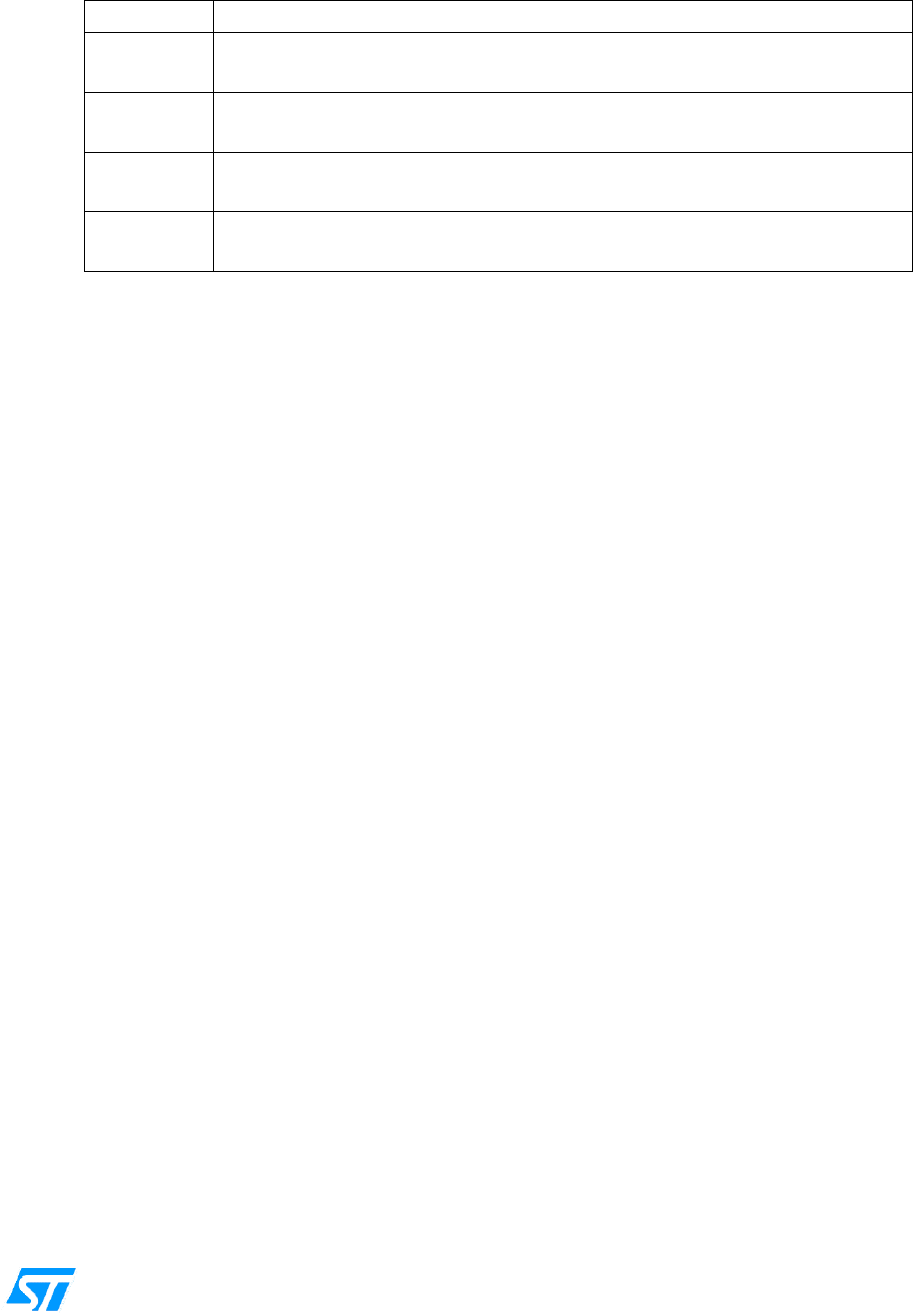

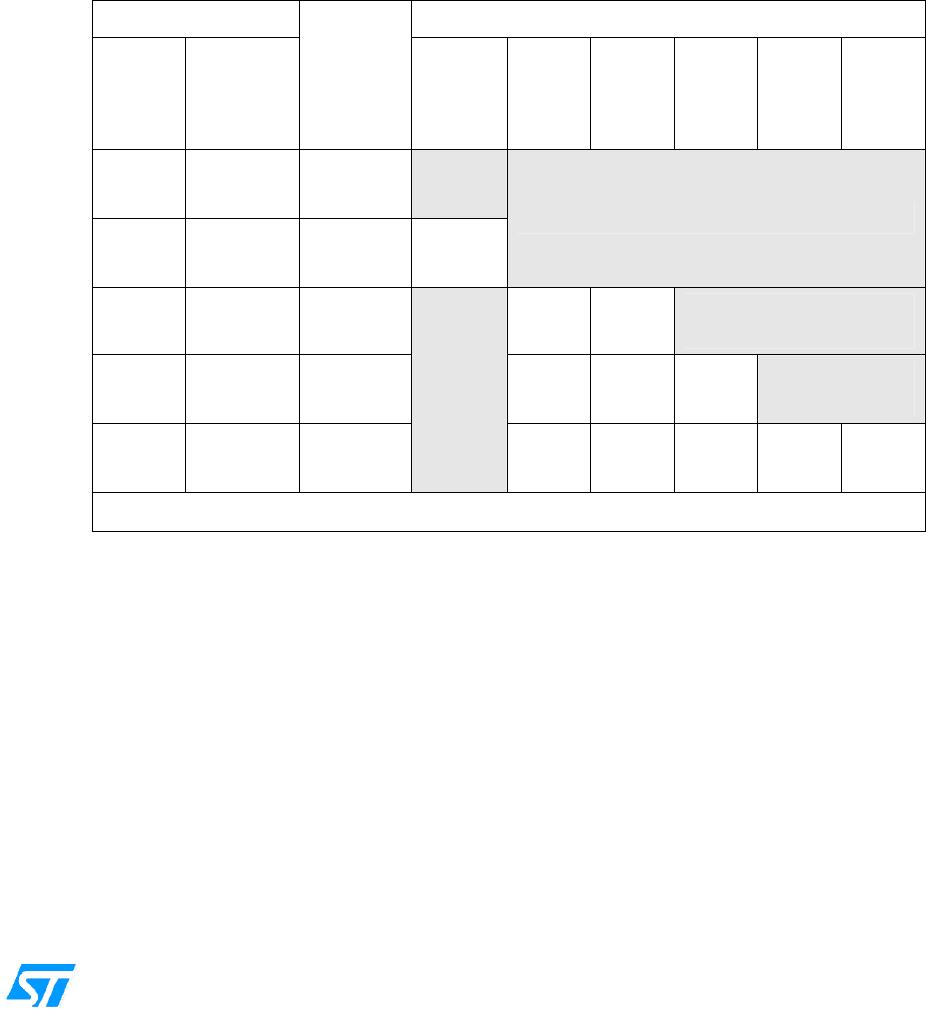

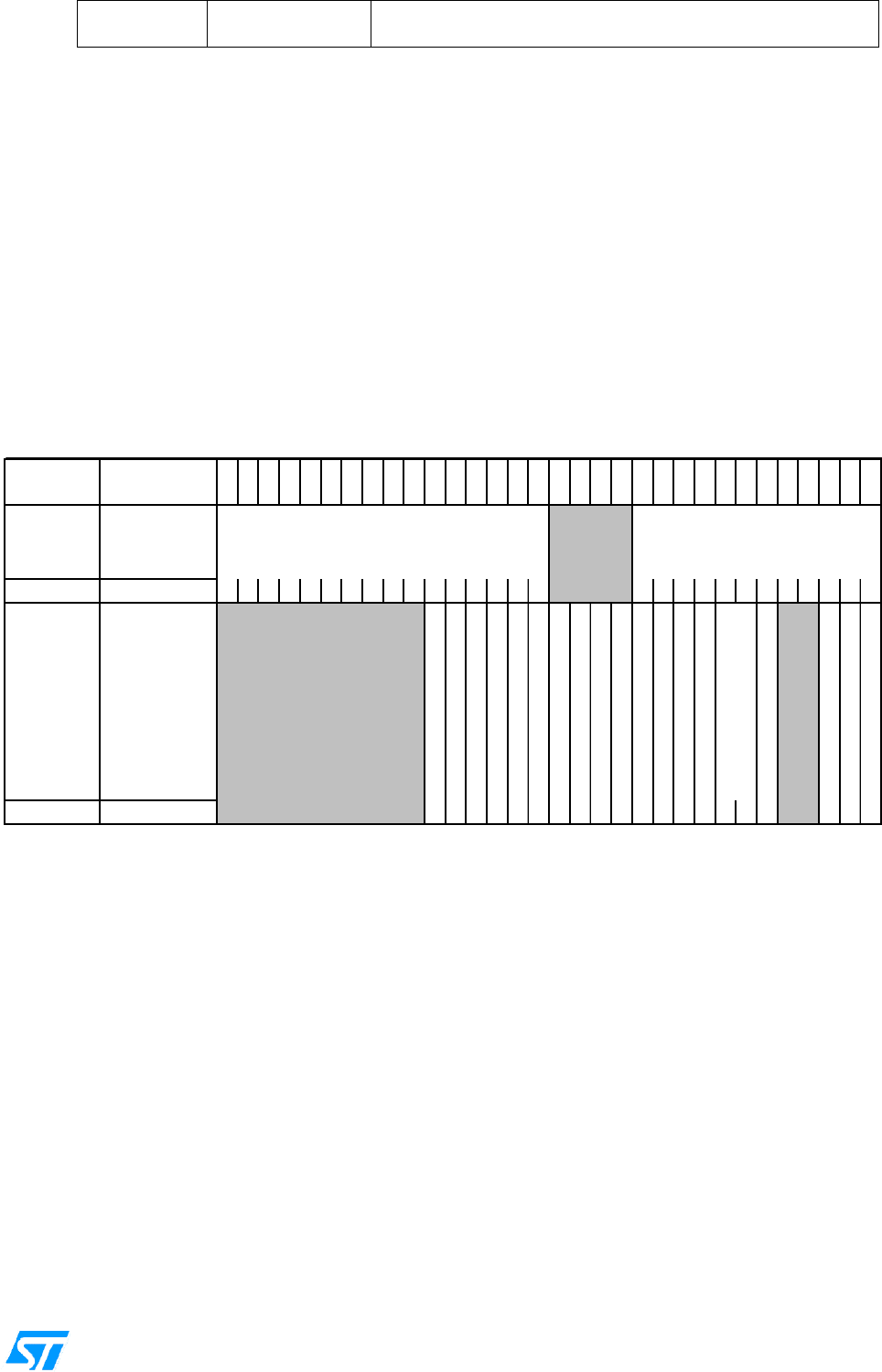

STM32技术参考手册各章节与各产品系列交叉对照表

STM32F101xx

STM32F101xx

STM32F101xx

STM32F102xx

STM32F102xx

STM32F103xx

STM32F103xx

STM32F103xx

STM32F105xx

STM32F107xx

第1章:文中的缩写 ●●●●● ● ● ●●●

第2章:存储器和总线构架 ●●●●● ● ● ●●●

第3章:CRC计算单元(CRC) ●●●●● ● ● ●●●

第4章:电源控制(PWR) ●●●●● ● ● ●●●

第5章:备份寄存器(BKP) ●●●●● ● ● ●●●

第6章:小容量、中容量和大容量产品的复位和时钟控制(RCC) ●●●●● ● ● ●

第7章:互联型产品的复位和时钟控制(RCC) ● ●

第8章:通用和复用功能I/O(GPIO和AFIO) ●●●●● ● ● ●●●

第9章:中断和事件 ●●●●● ● ● ●●●

第10章:DMA控制器(DMA) ●●●●● ● ● ●●●

第11章:模拟/数字转换(ADC) ●●●●● ● ● ●●●

第12章:数字/模拟转换(DAC) ● ●●●

第13章:高级控制定时器(TIM1和TIM8) ● ● ●●●

第14章:通用定时器(TIMx) ●●●●● ● ● ●●●

第15章:基本定时器(TIM6和TIM7) ● ●●●

第16章:实时时钟(RTC) ●●●●● ● ● ●●●

第17章:独立看门狗(IWDG) ●●●●● ● ● ●●●

第18章:窗口看门狗(WWDG) ●●●●● ● ● ●●●

第19章:灵活的静态存储器控制器(FSMC) ● ●

第20章:SDIO接口(SDIO) ●

第21章:USB全速设备接口(USB) ● ● ● ● ●

第22章:控制器局域网(bxCAN) ● ● ●●●

第23章:串行外设接口(SPI) ●●●●● ● ● ●●●

第24章:I2C接口 ●●●●● ● ● ●●●

第25章:通用同步异步收发器(USART) ●●●●● ● ● ●●●

第26章:USB OTG全速(OTG_FS) ● ●

第27章:以太网(ETH):具有DMA控制器的介质访问控制(MAC) ●

第28章:器件电子签名 ●●●●● ● ● ●●●

第29章:调试支持(DBG) ●●●●● ● ● ●●●

● 表示所在行对应的章节适用于该列标示的产品系列

提示:点击上表中的章节名字可以直接跳转到对应的章节。

STM32F10xxx参考手册

参照2009年12月 RM0008 Reference Manual 英文第10版

本译文仅供参考,如有翻译错误,请以英文原稿为准。请读者随时注意在ST网站下载更新版本

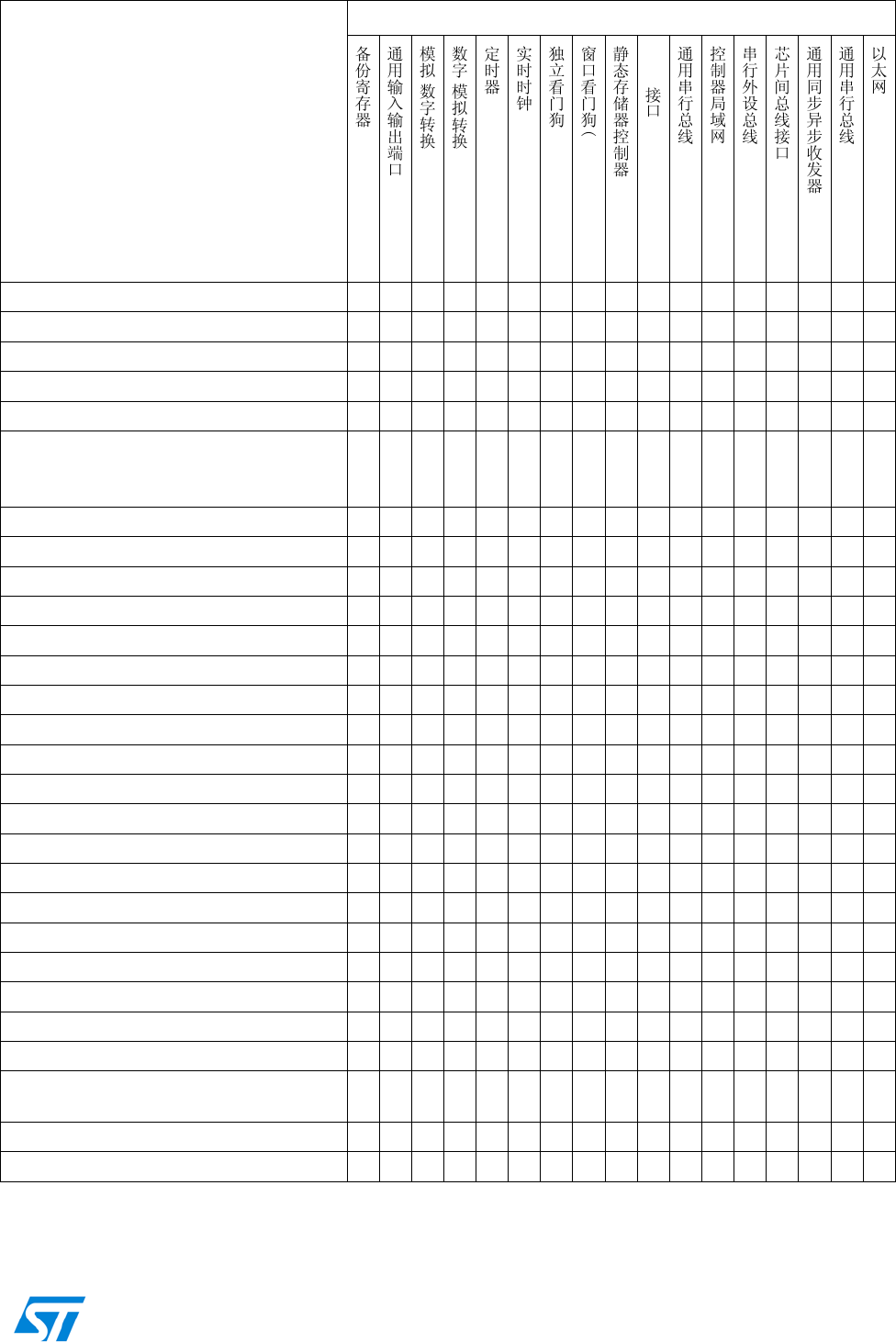

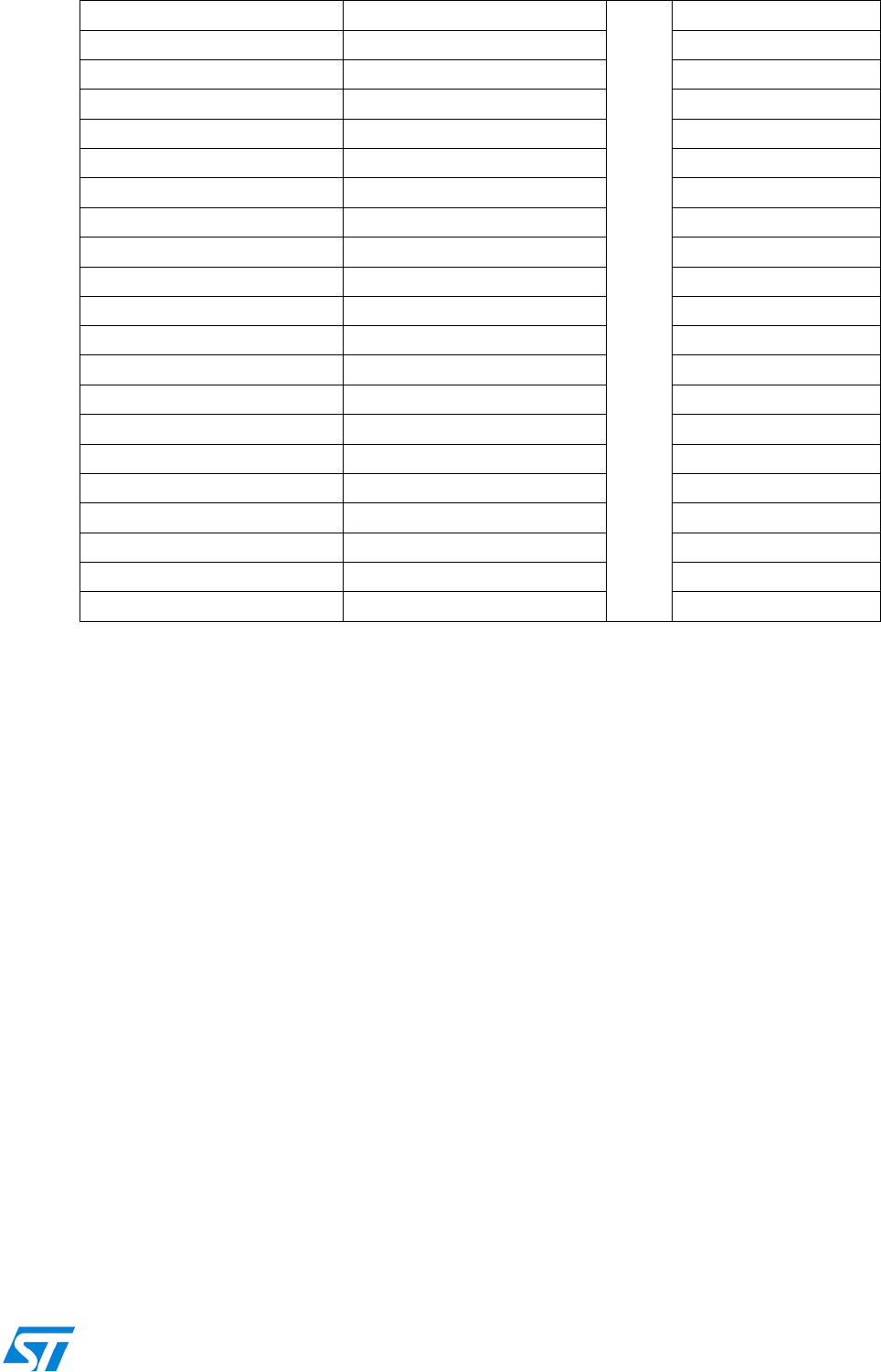

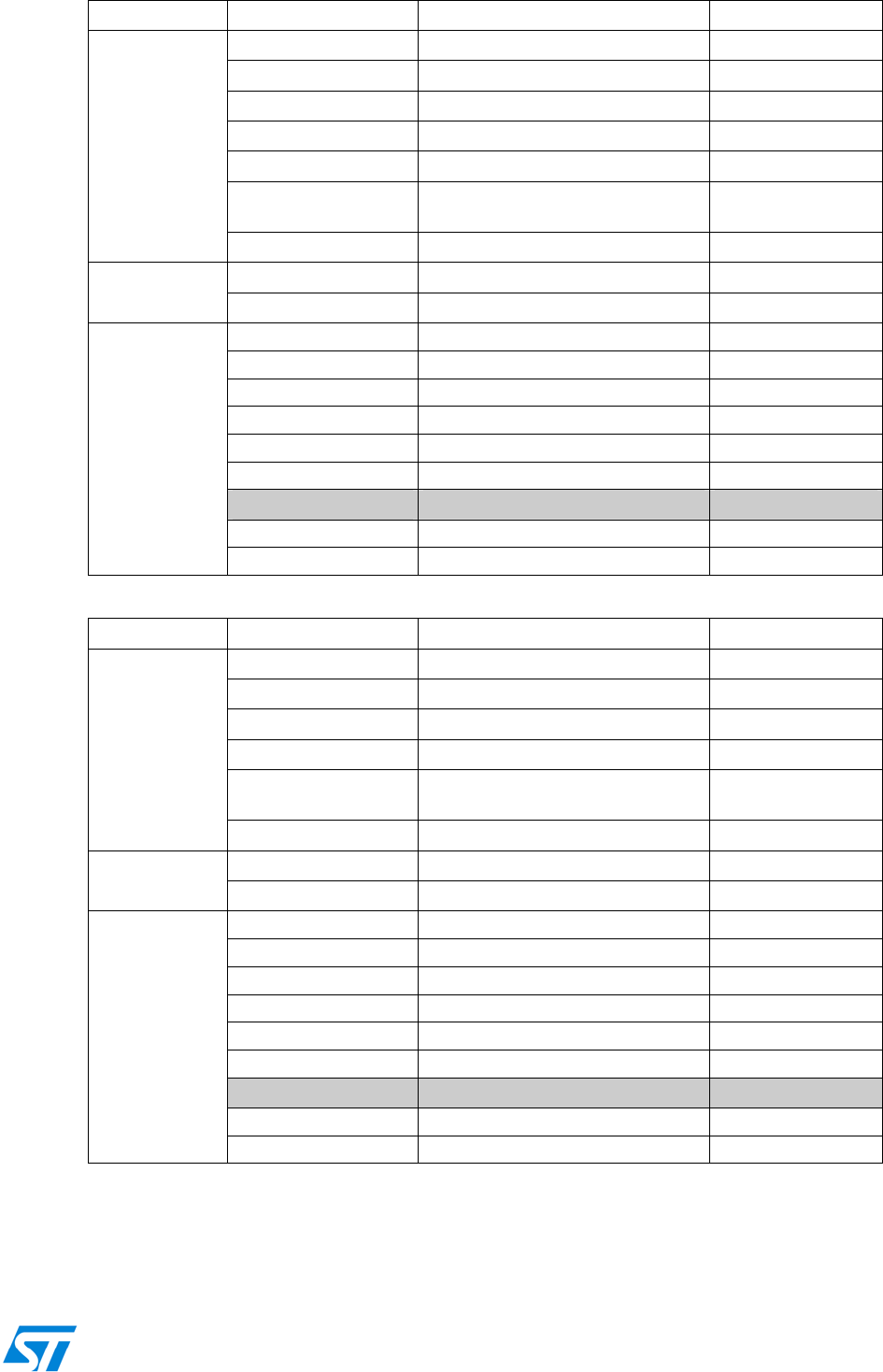

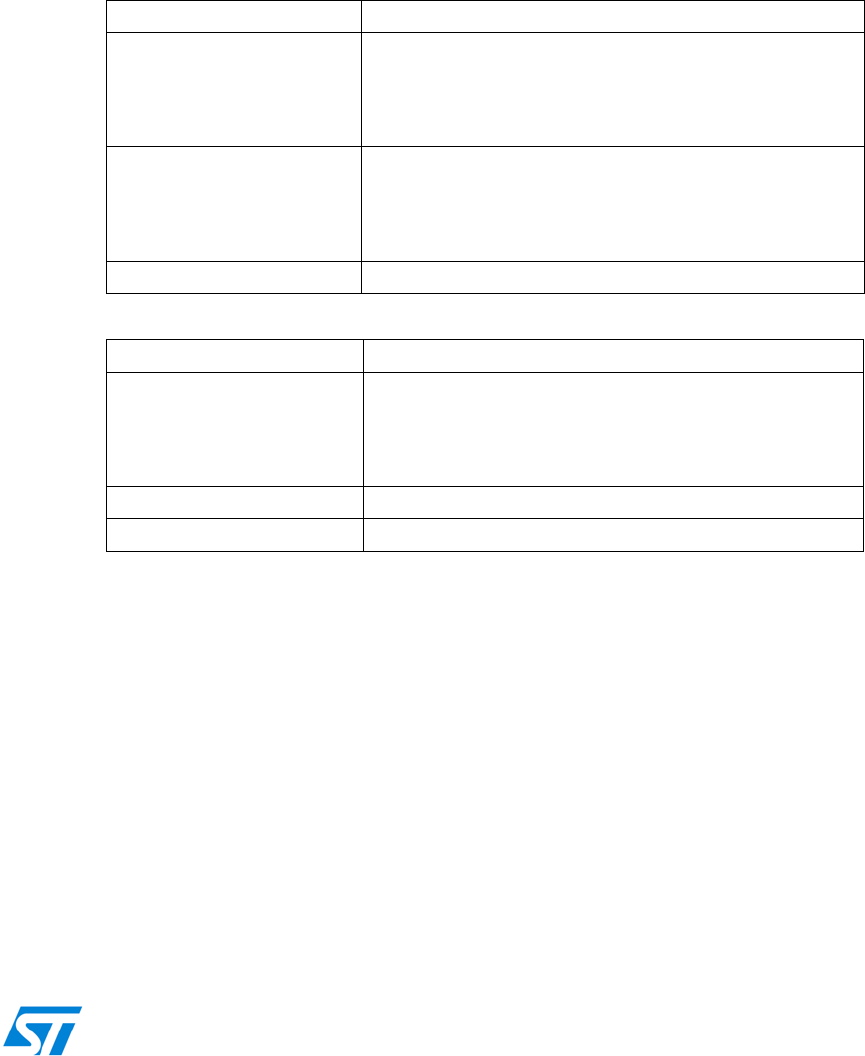

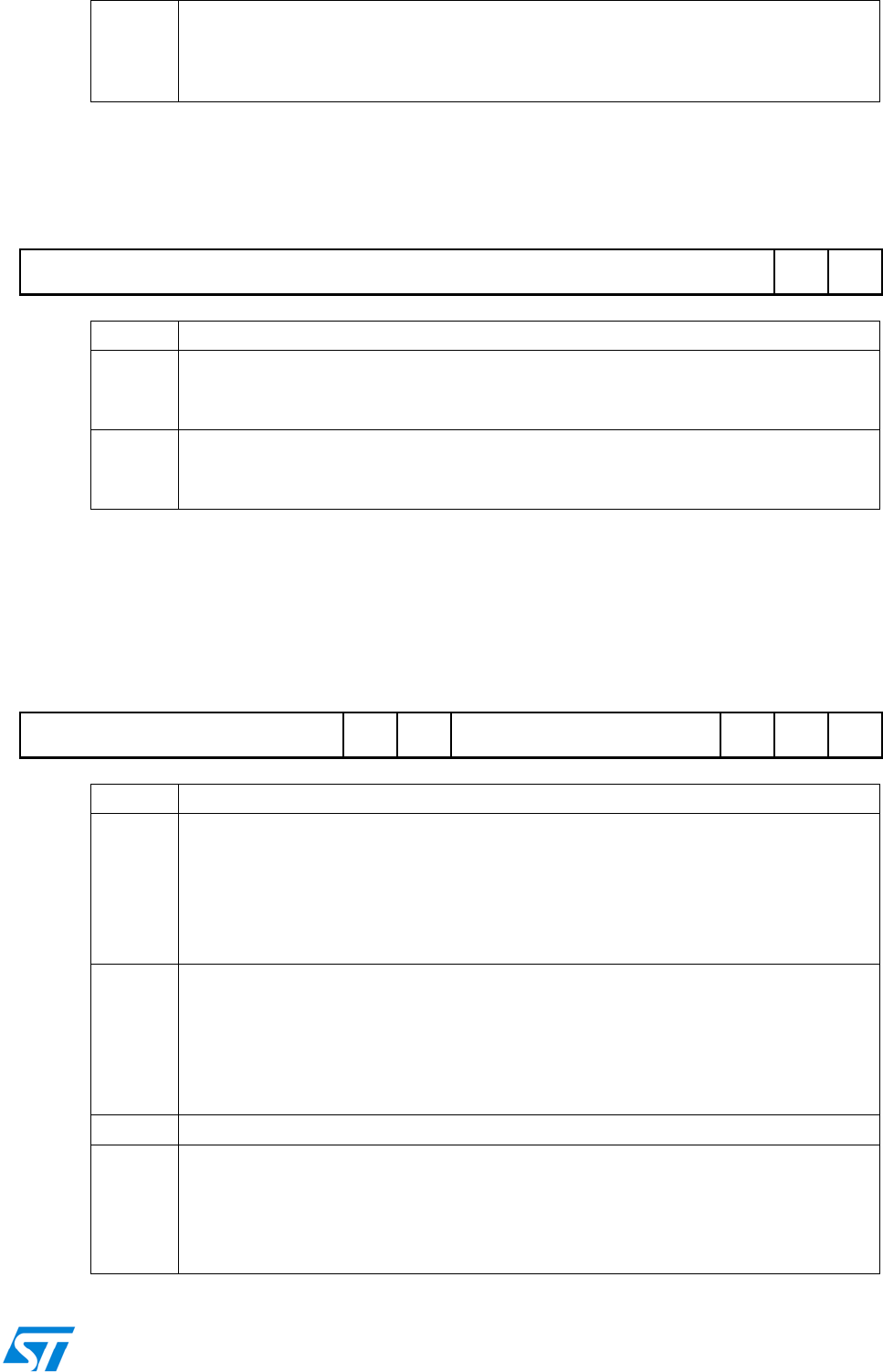

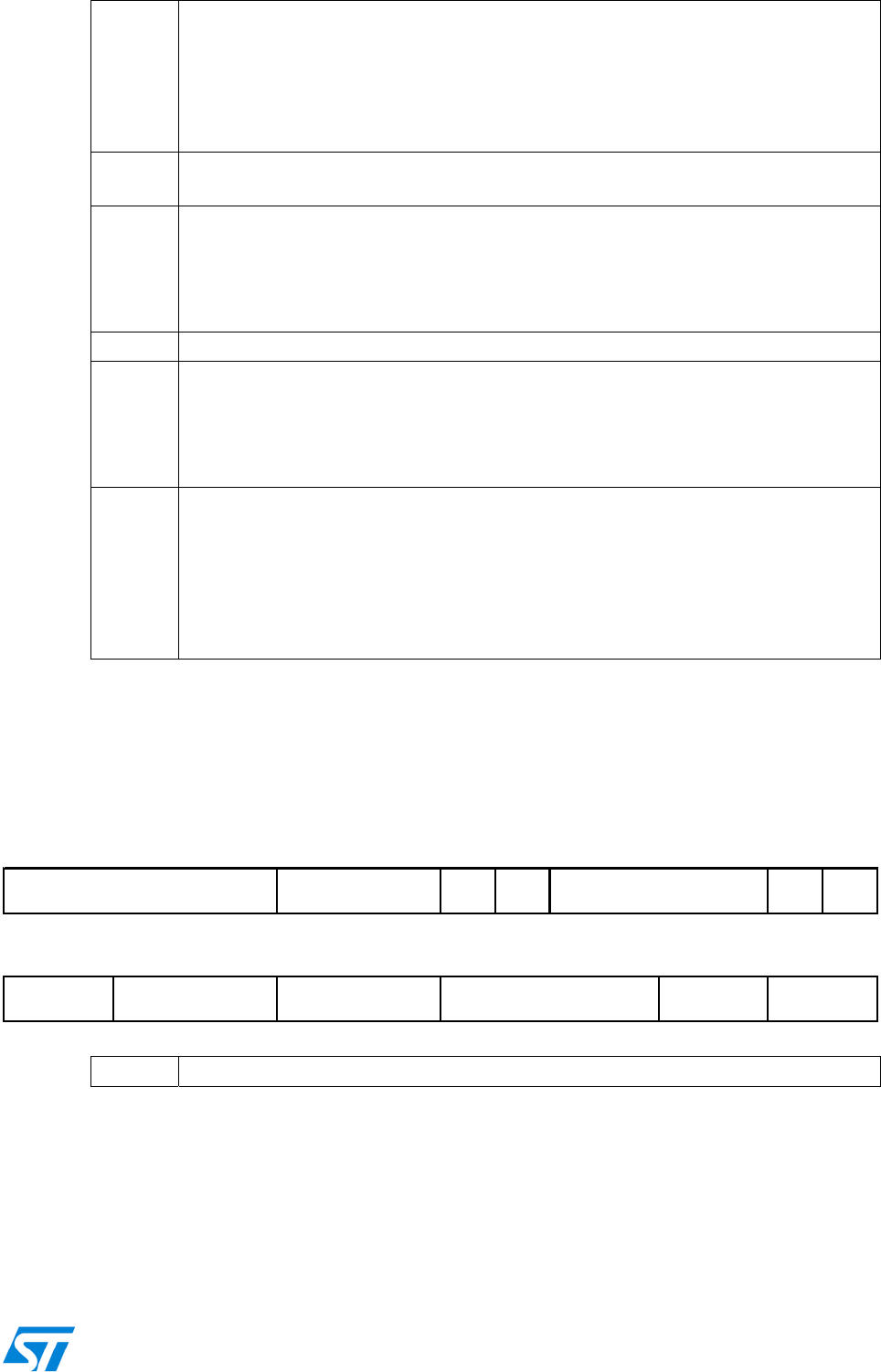

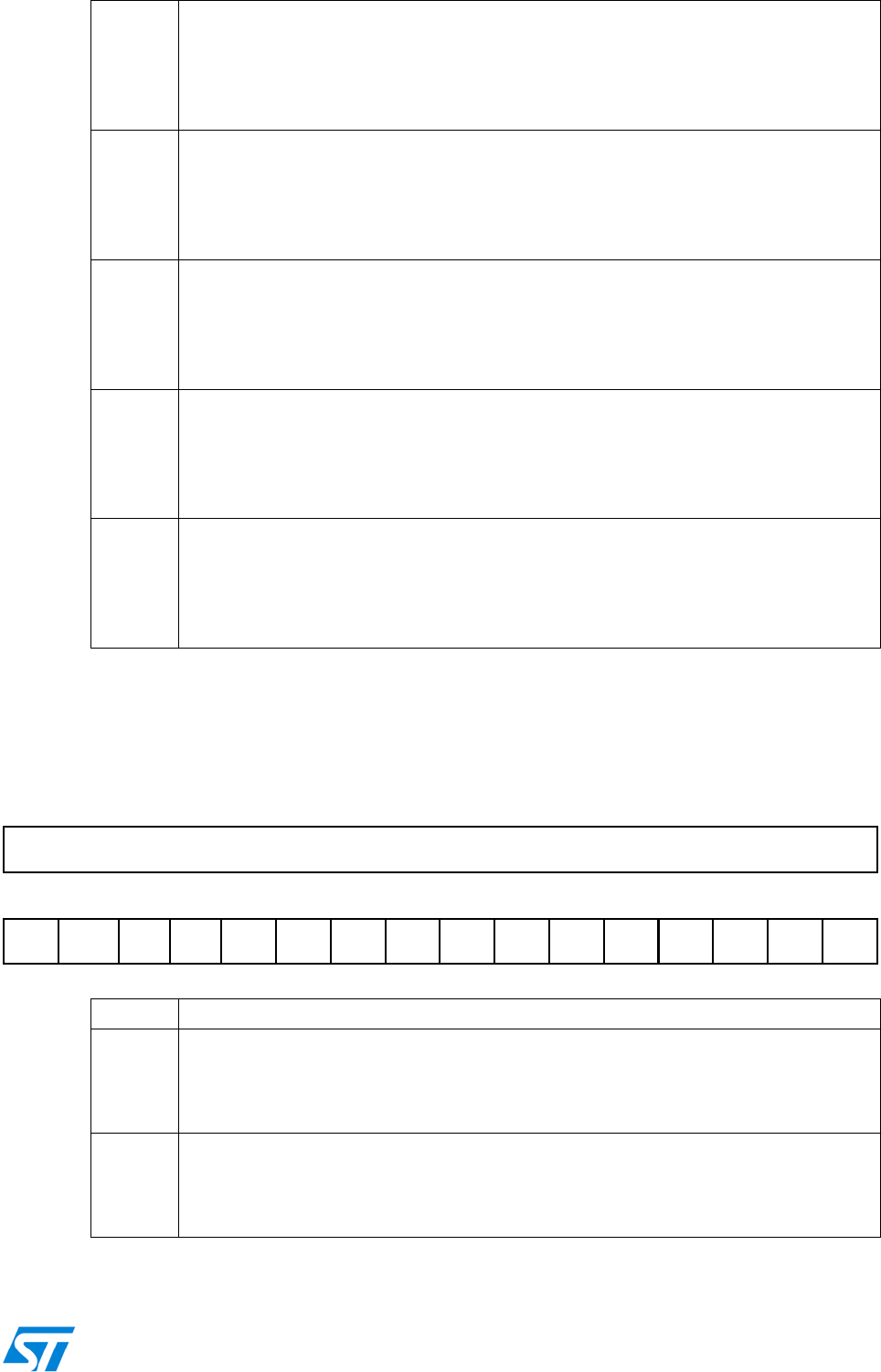

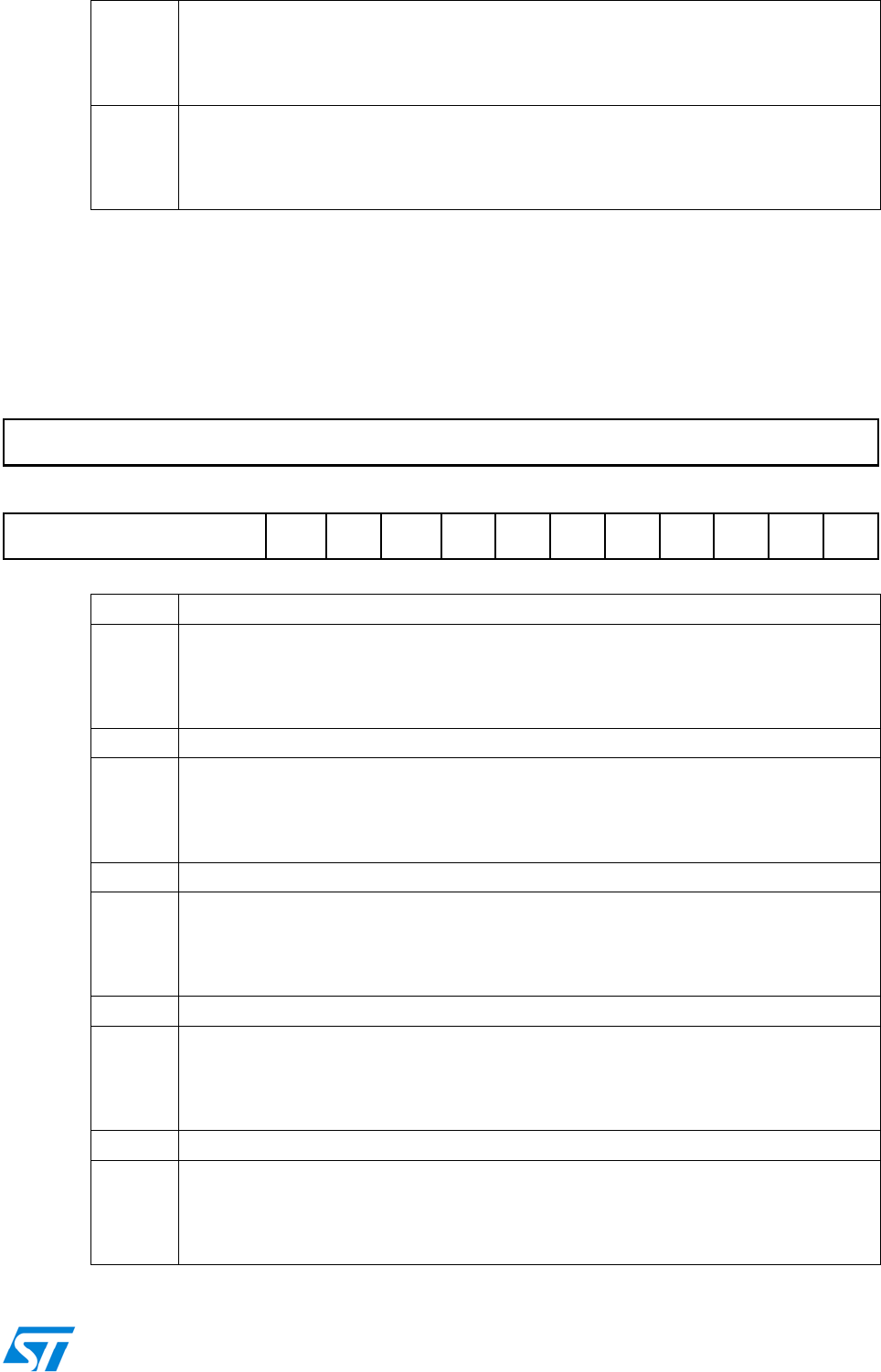

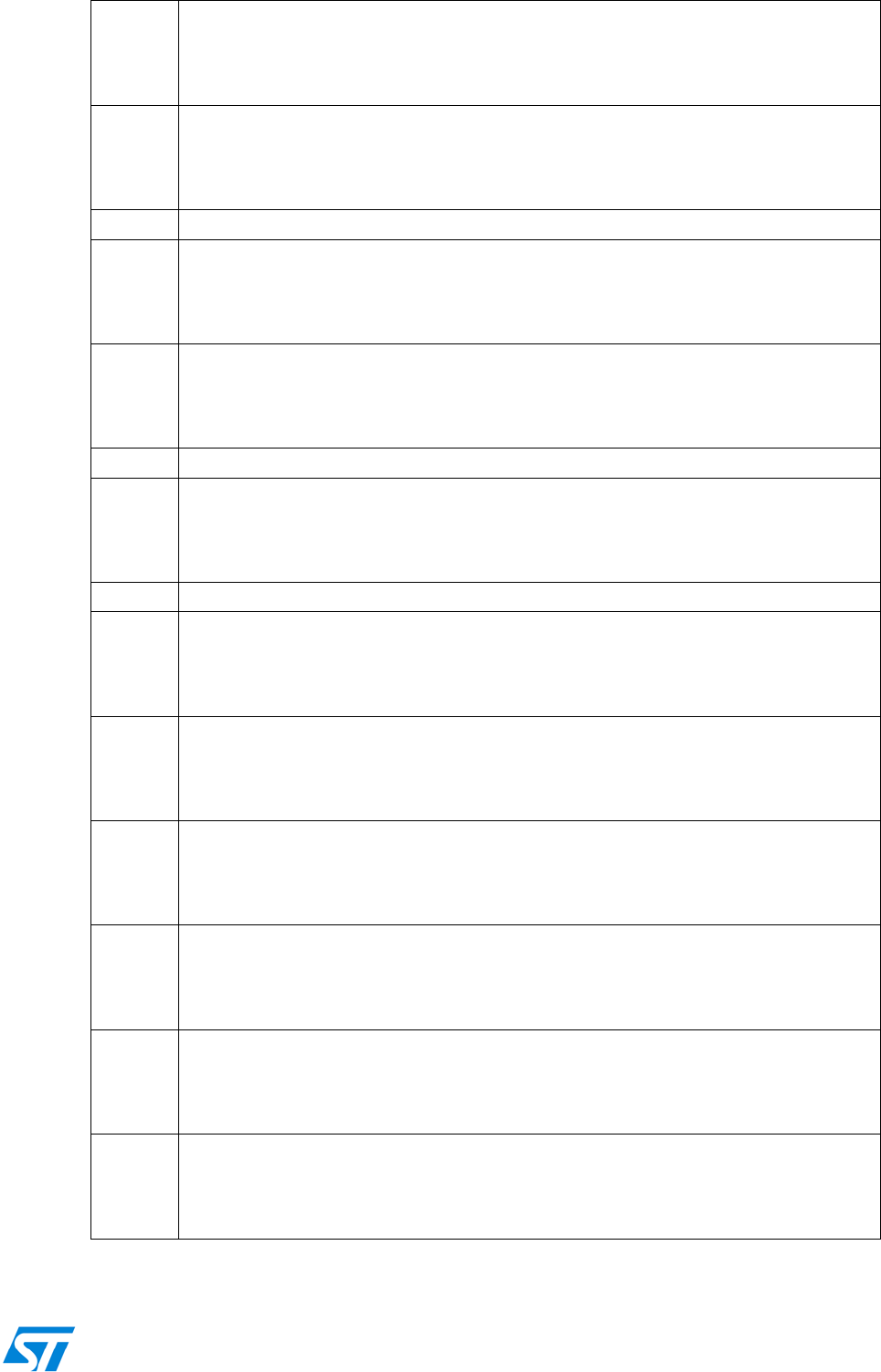

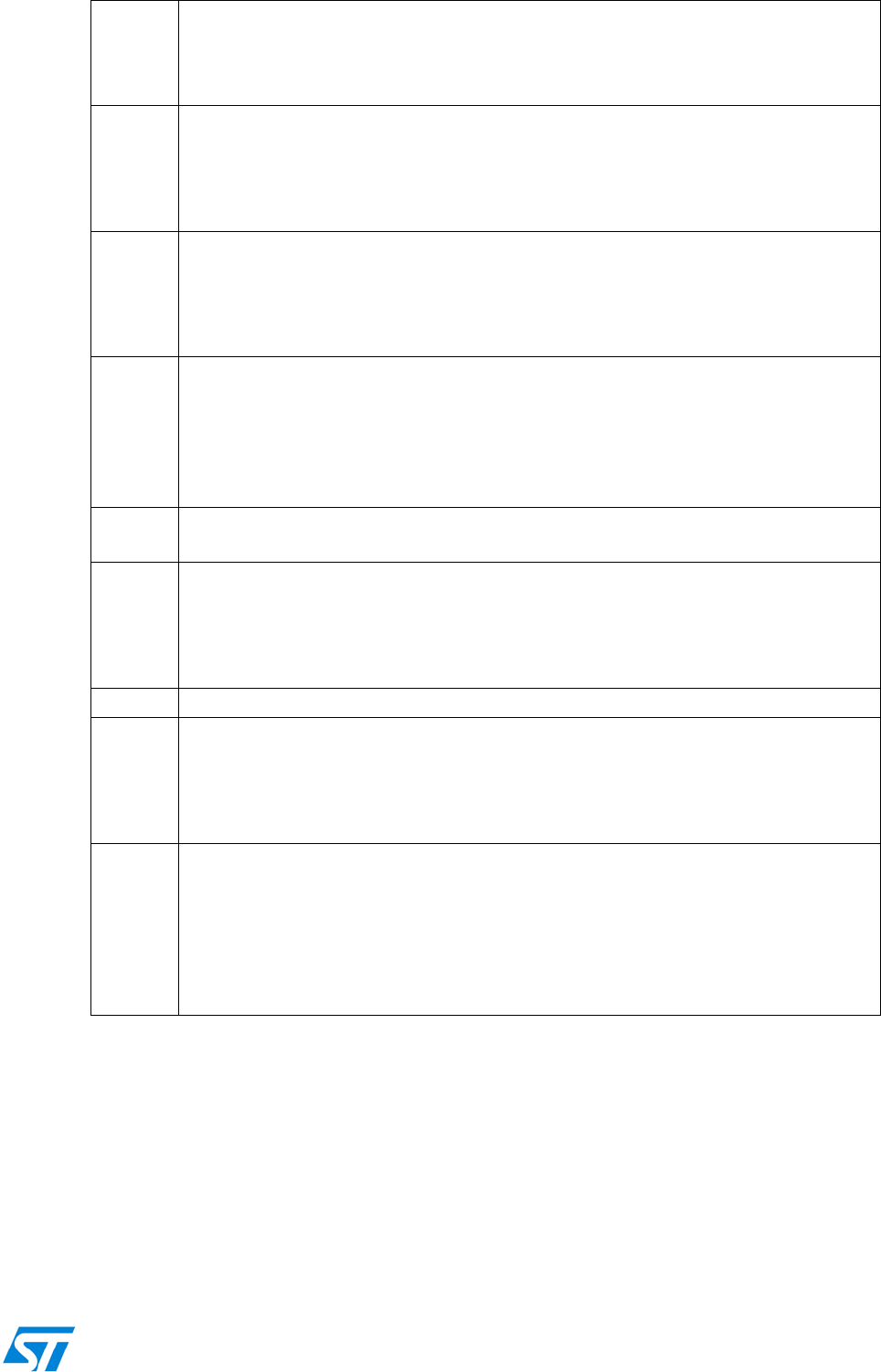

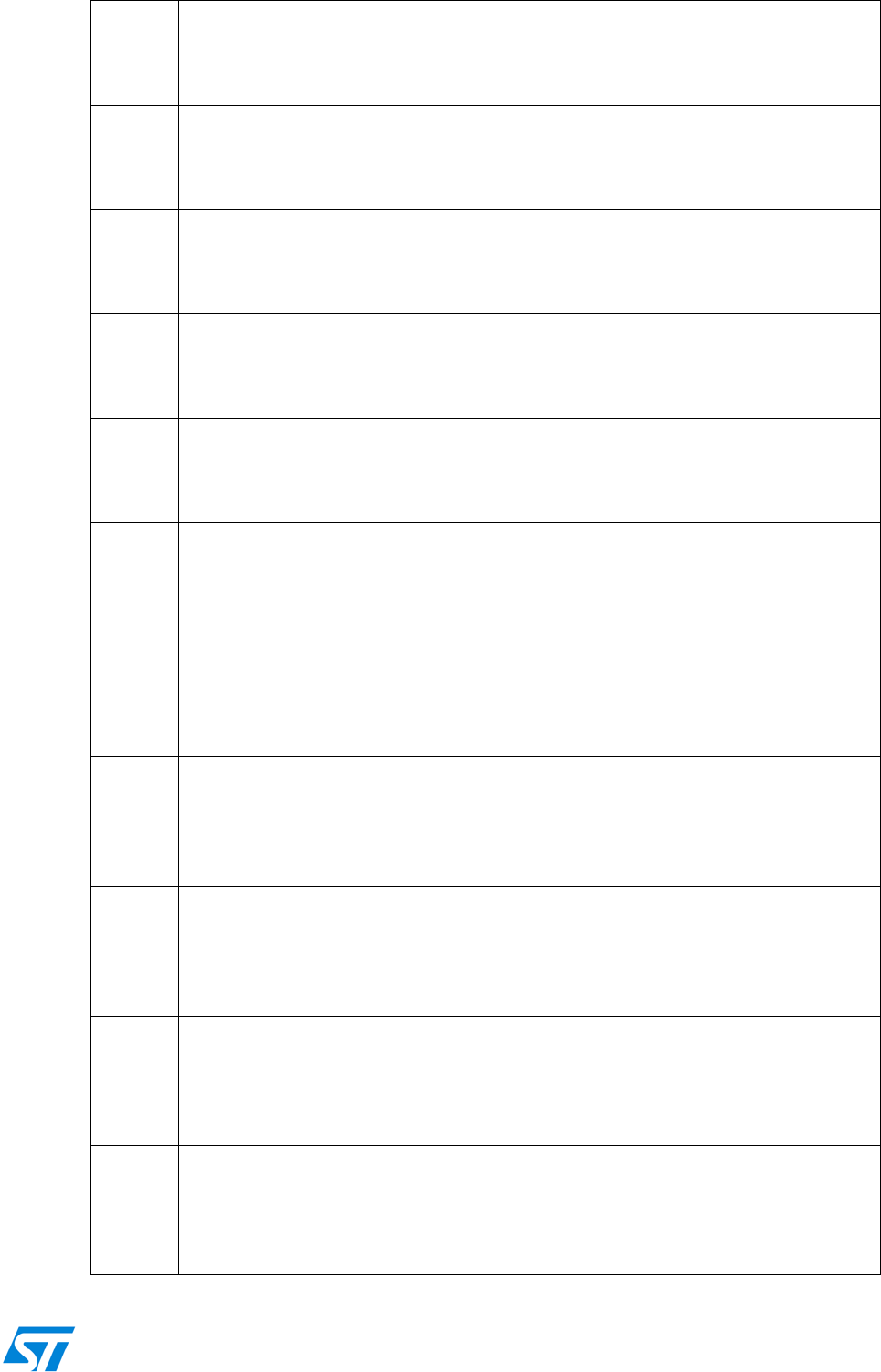

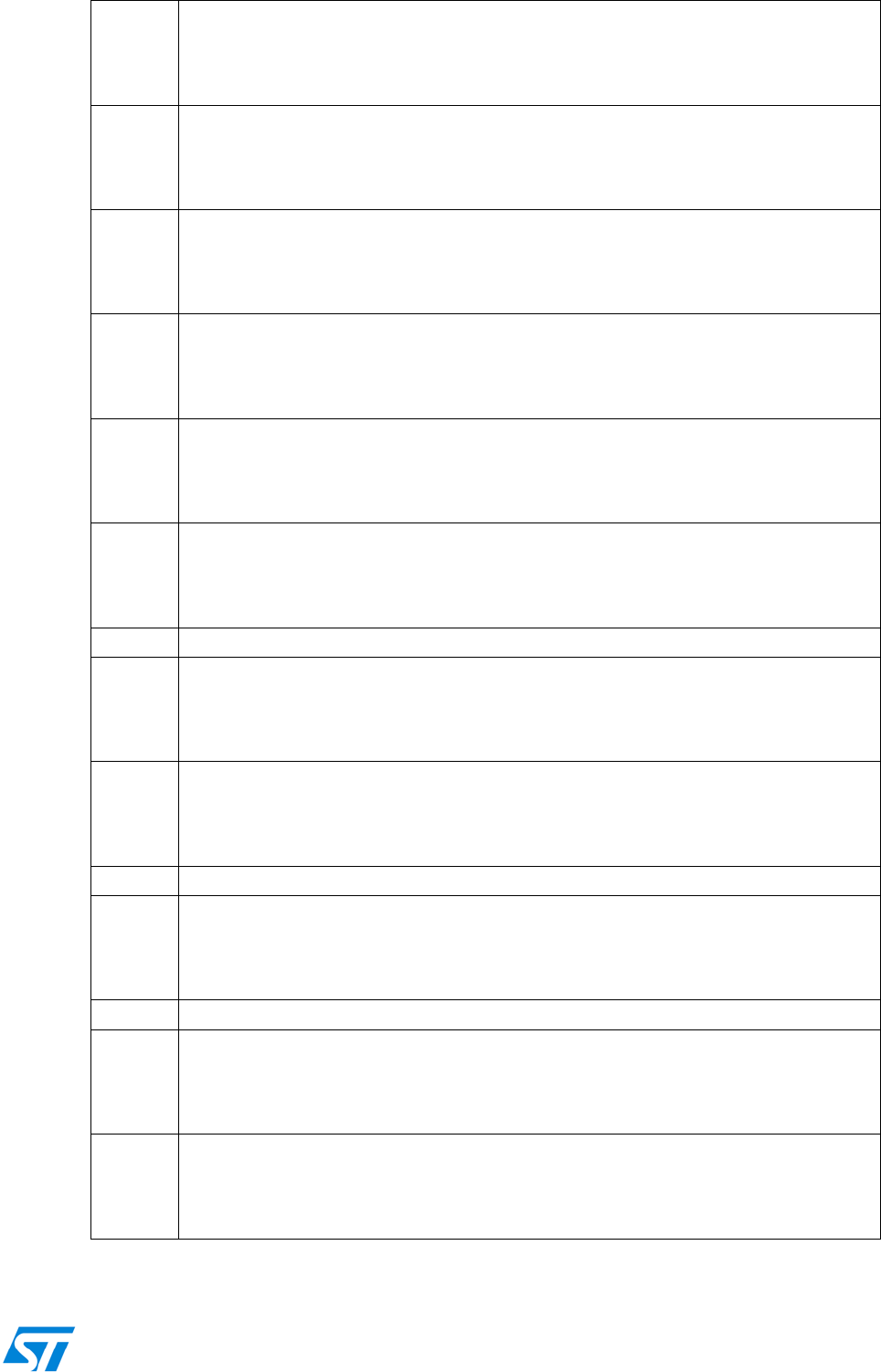

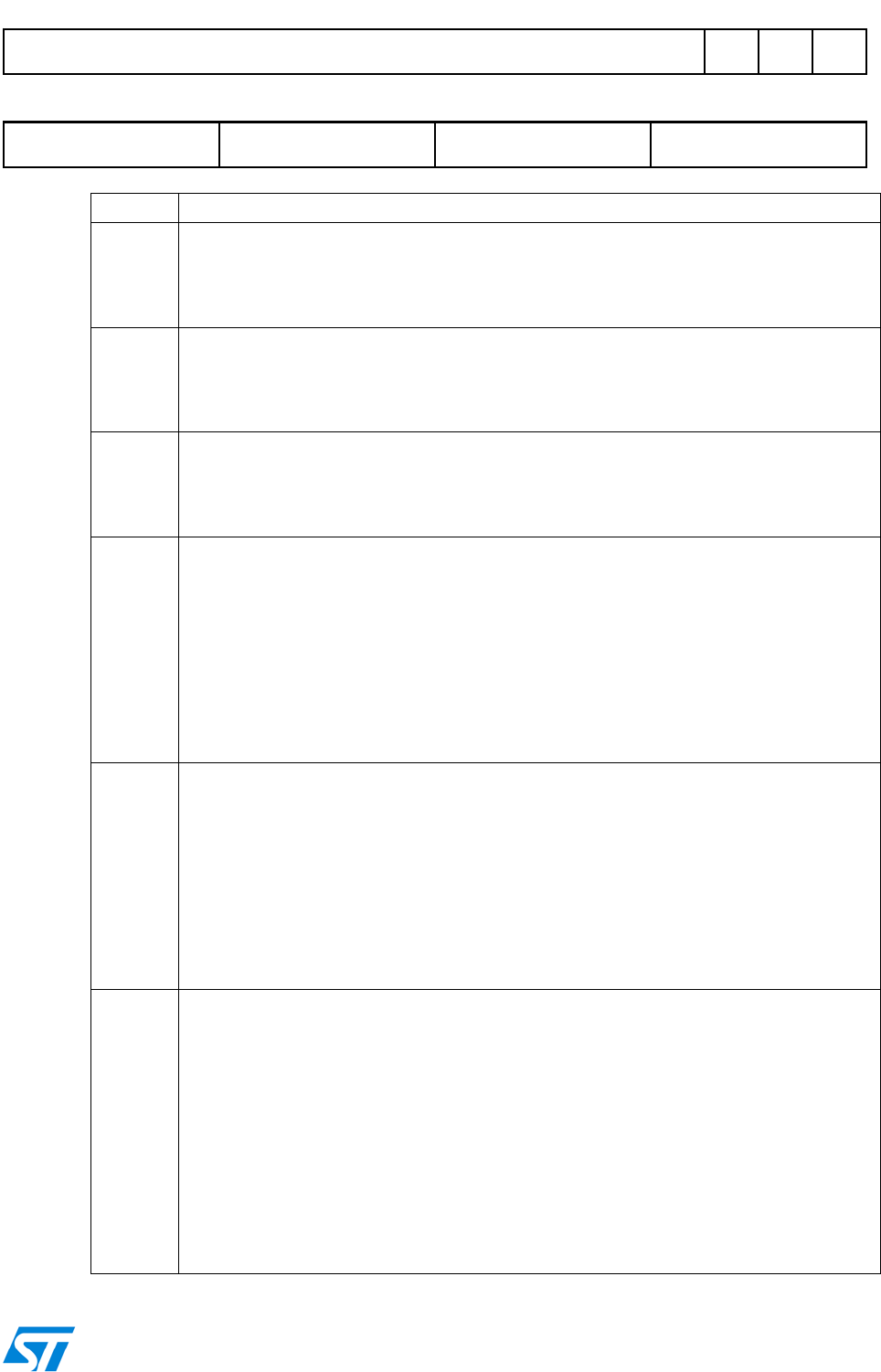

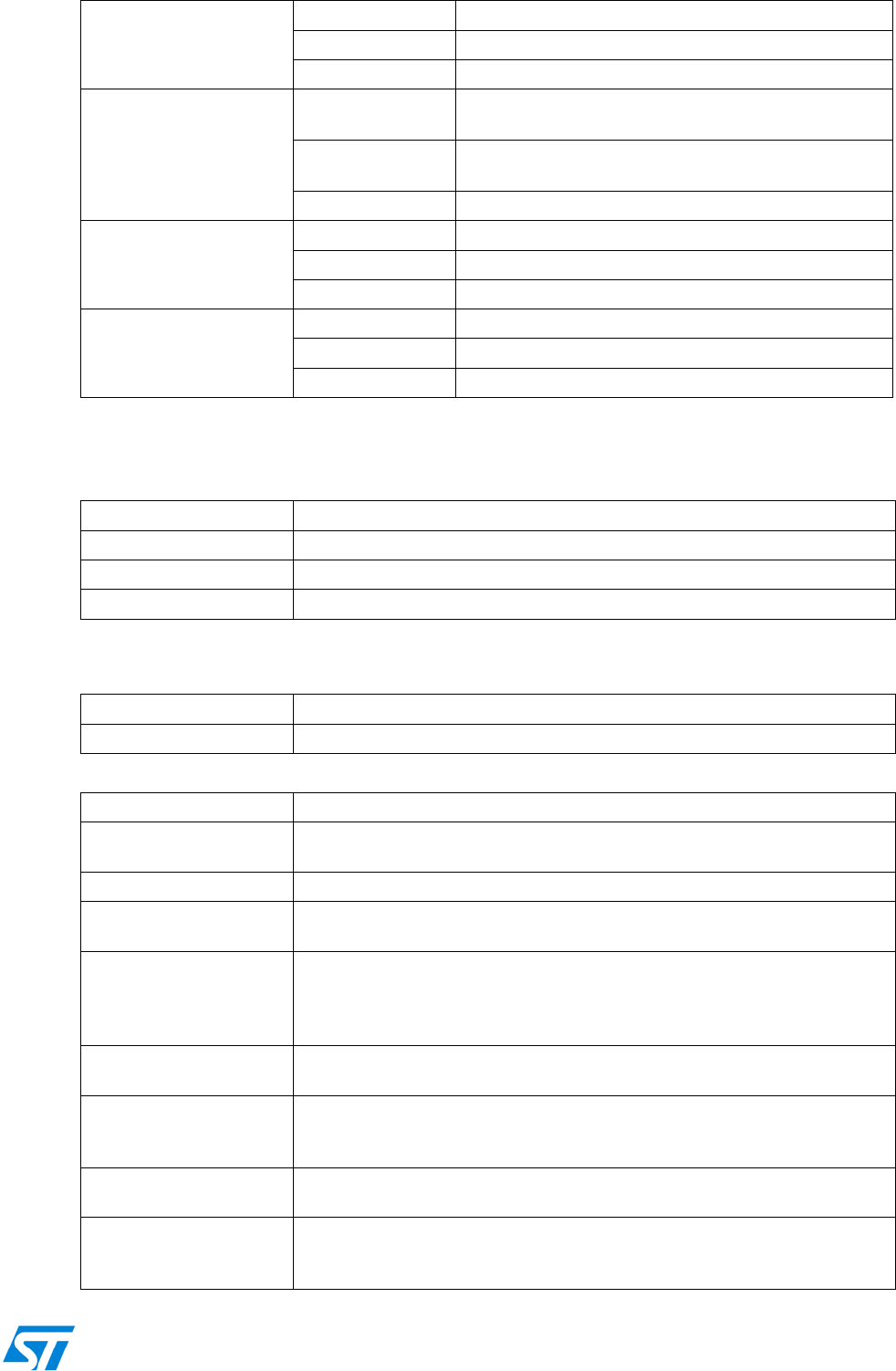

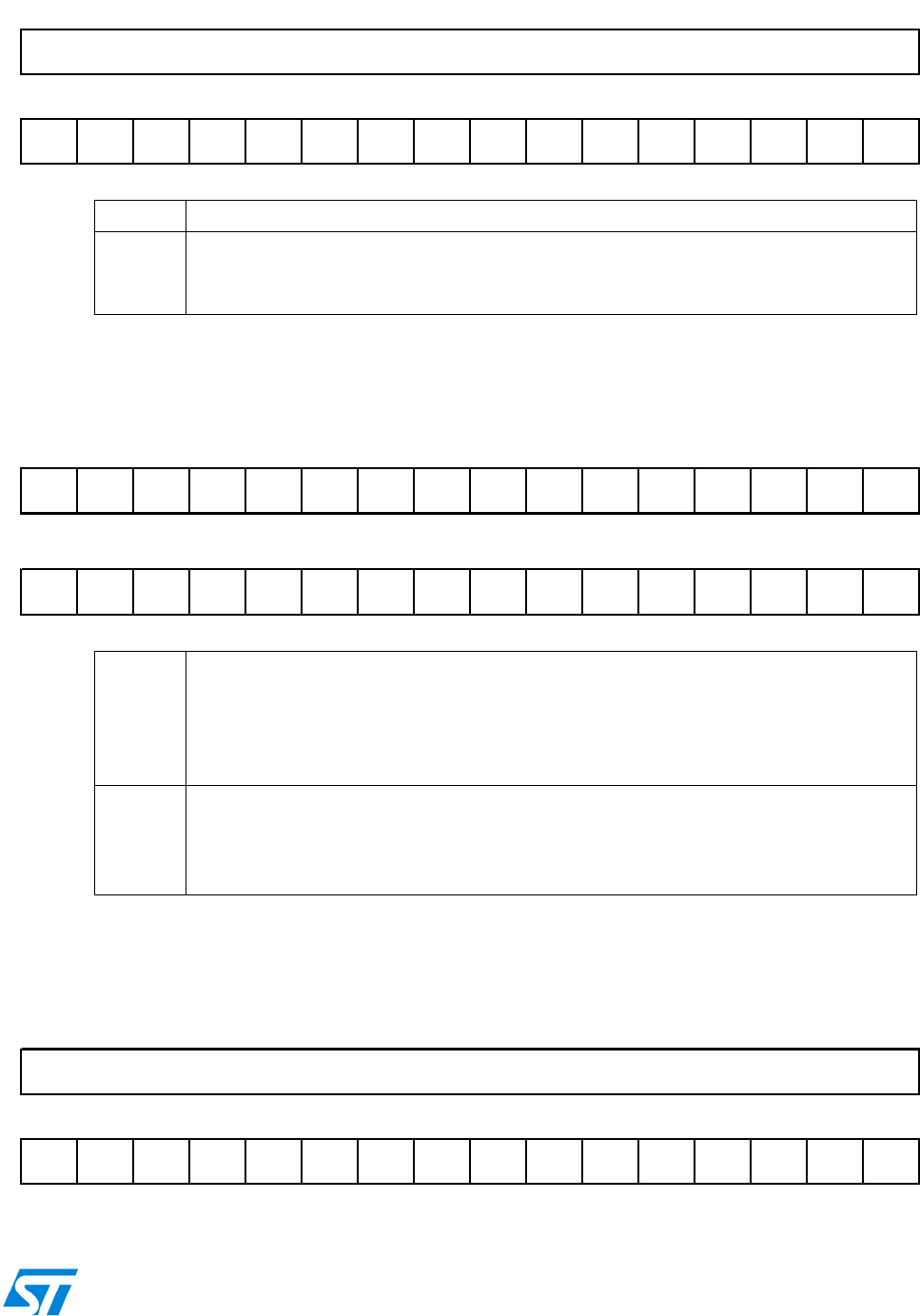

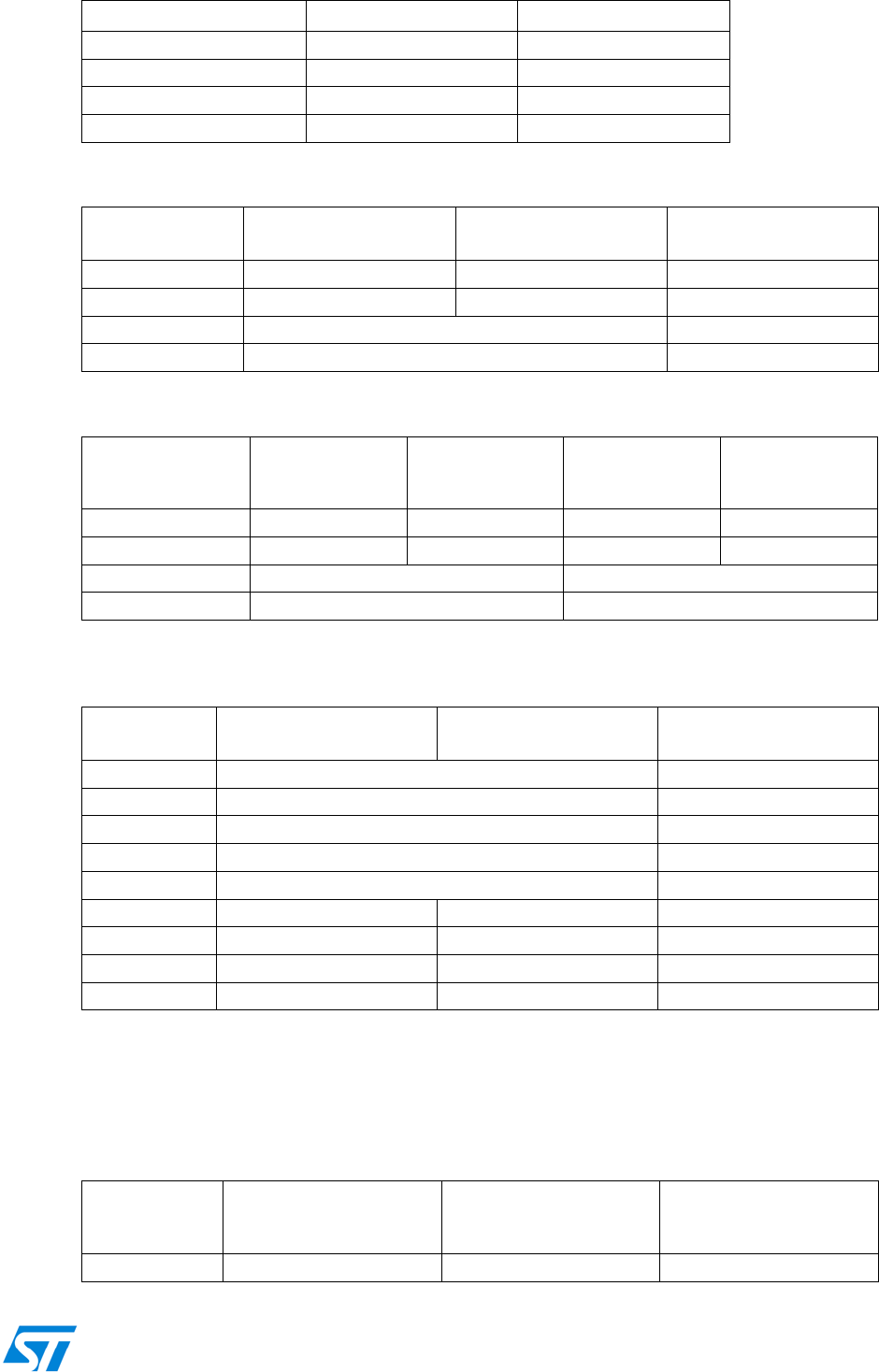

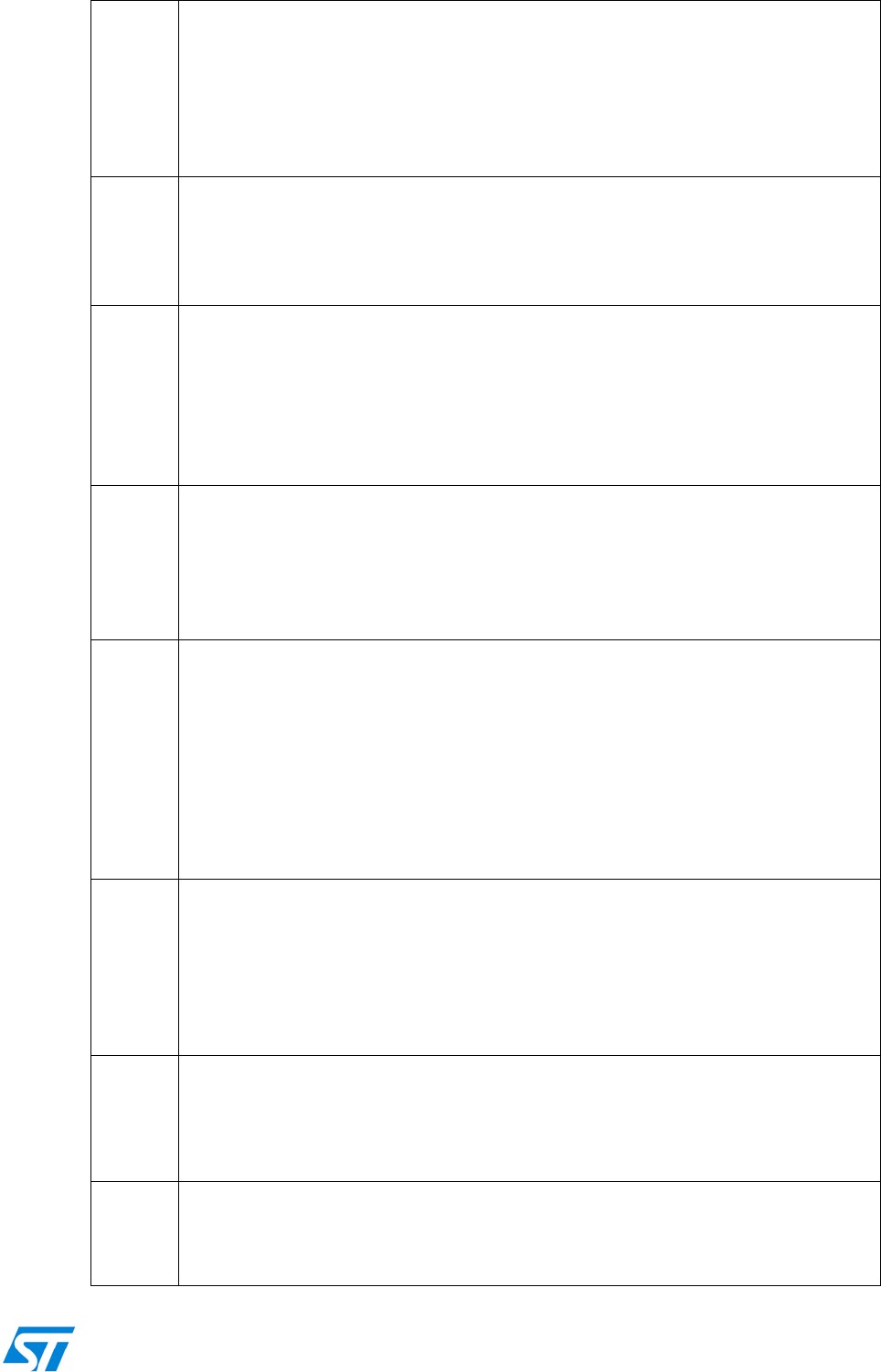

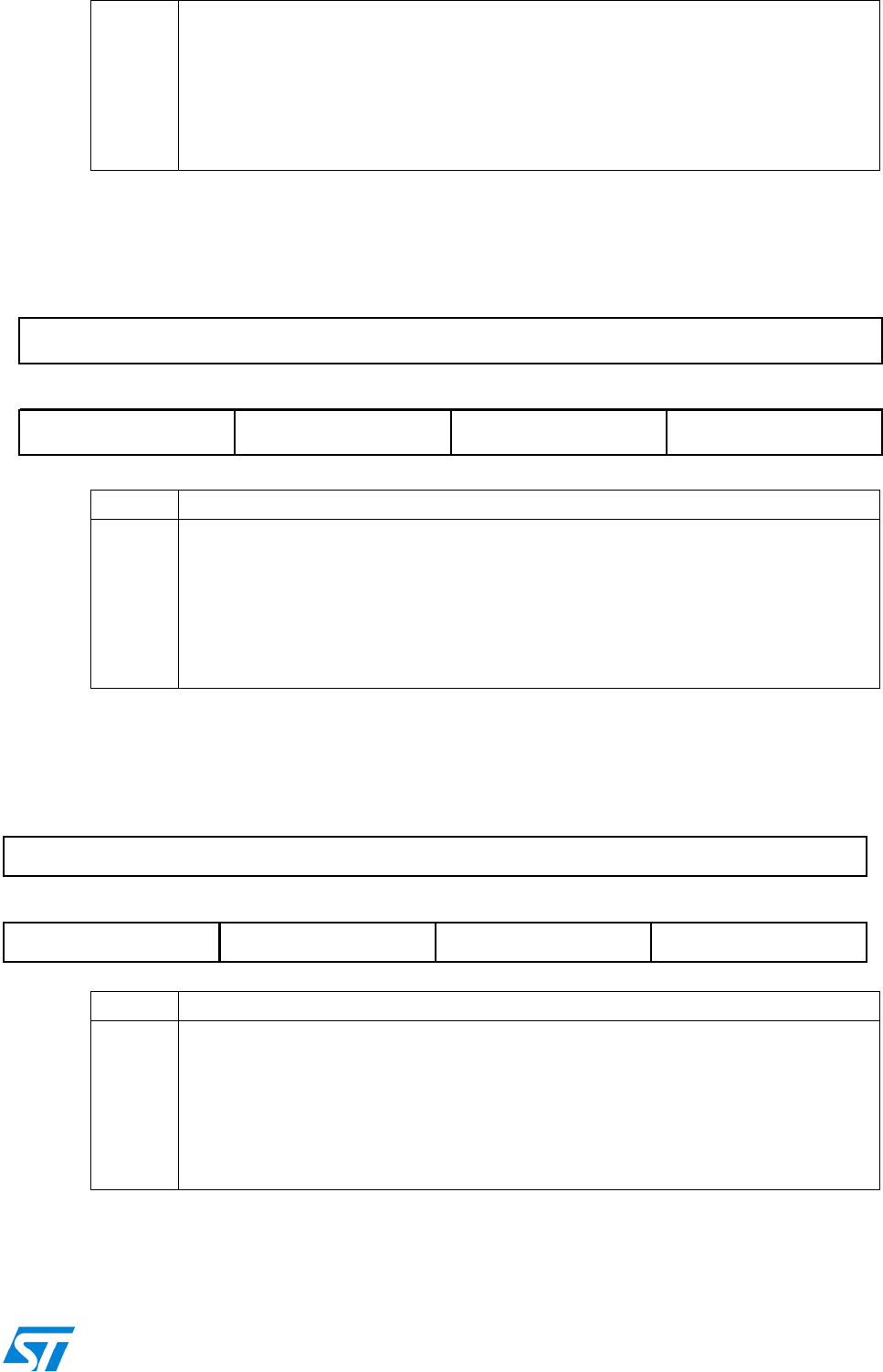

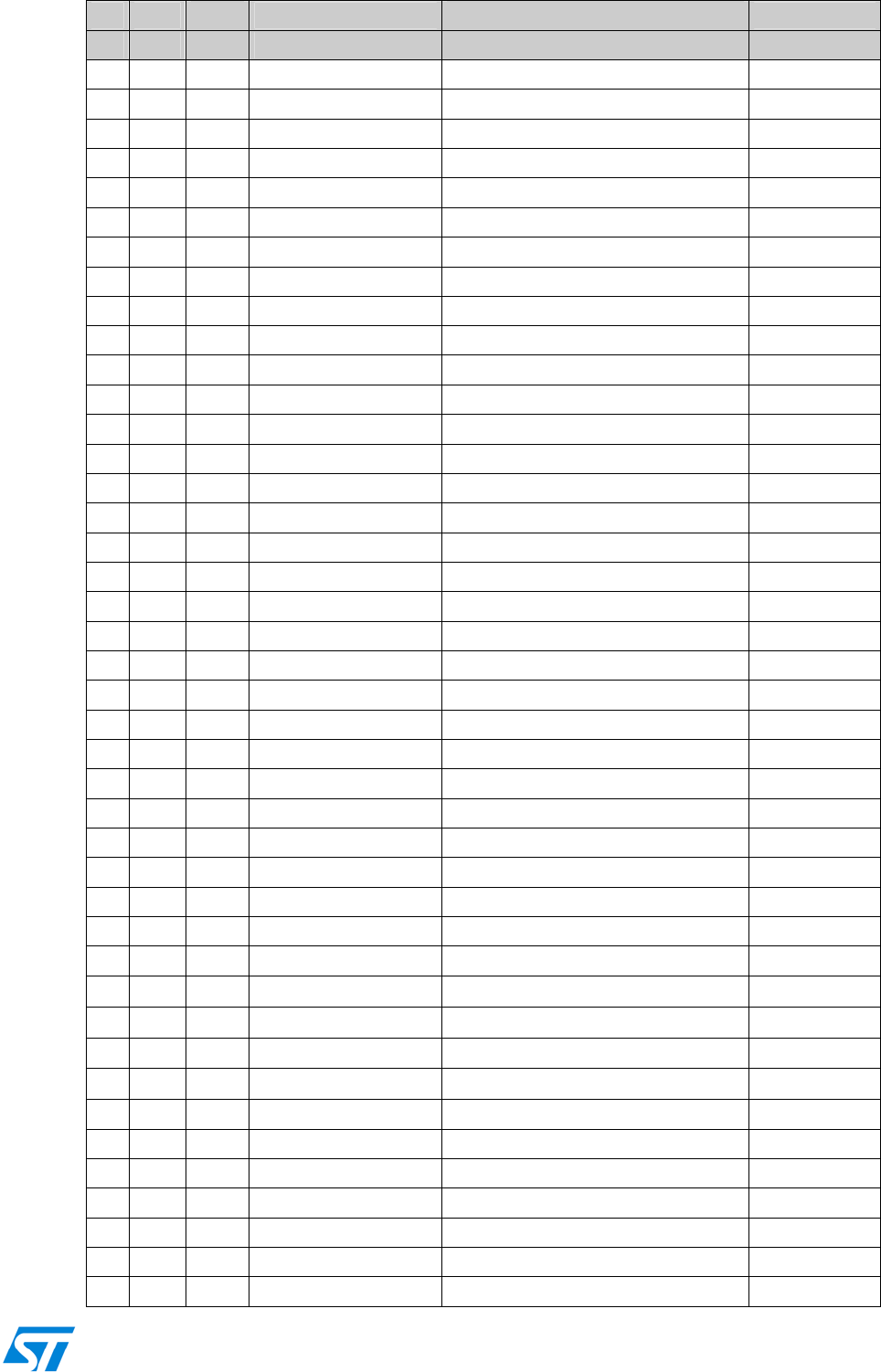

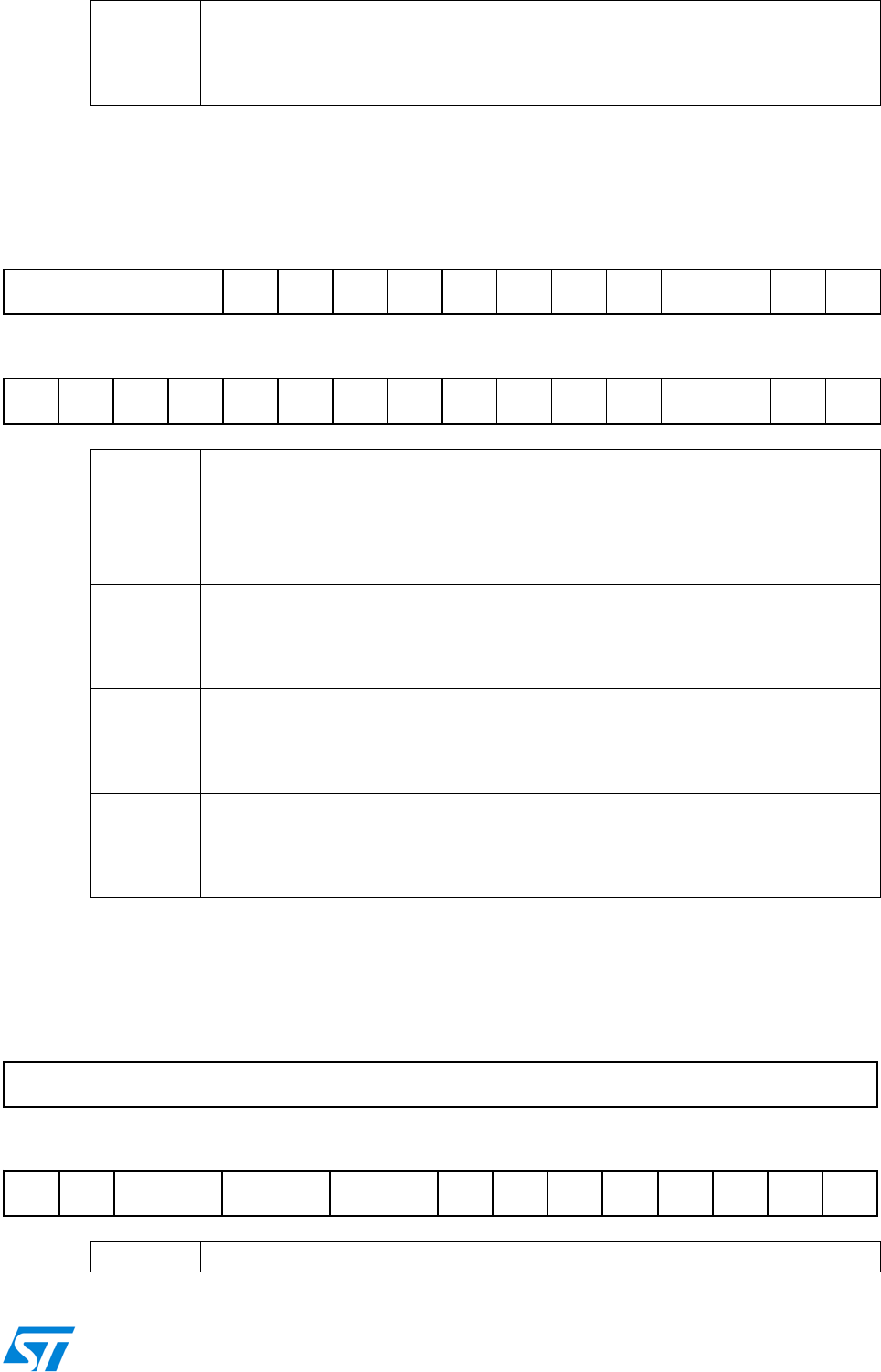

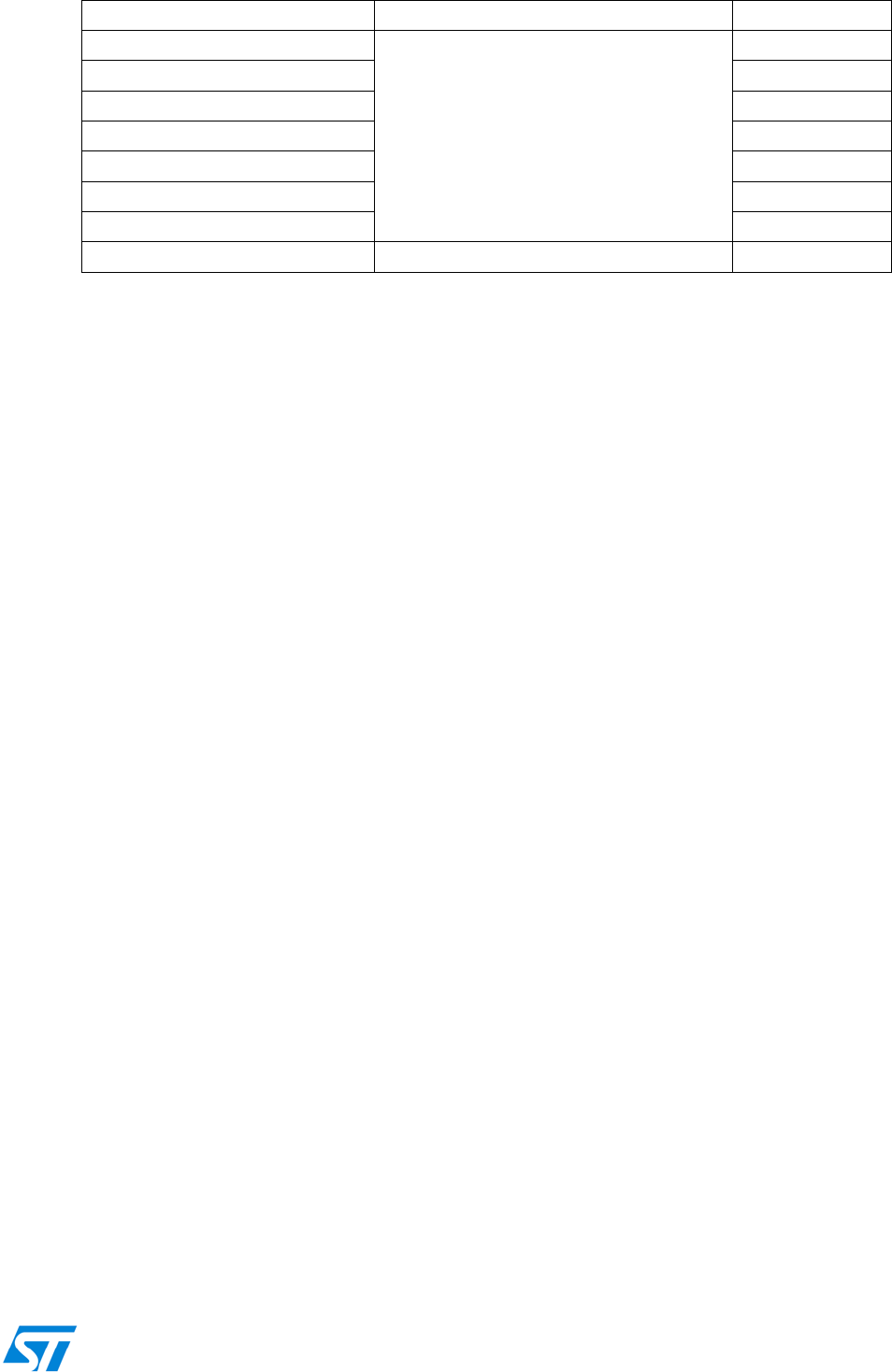

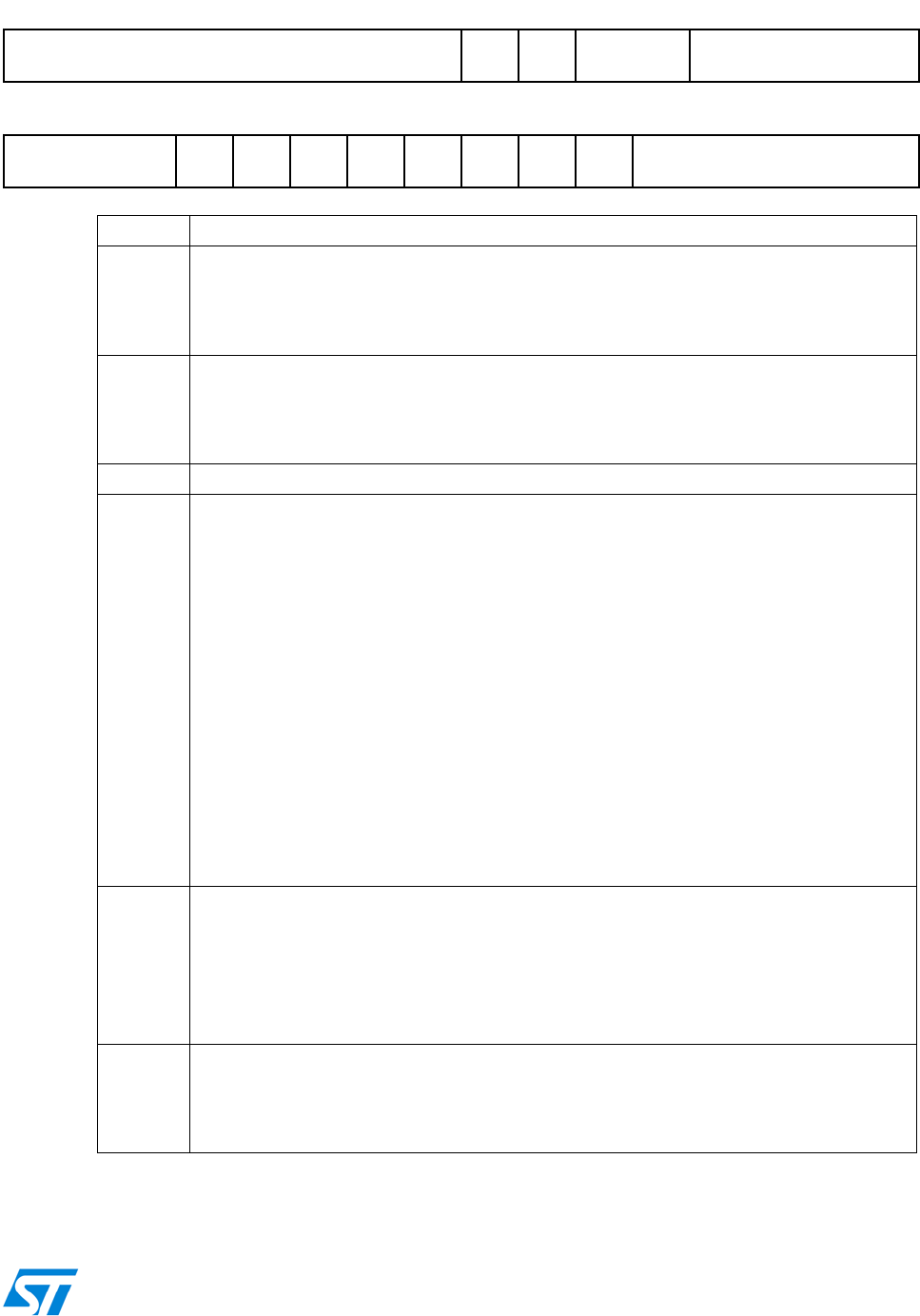

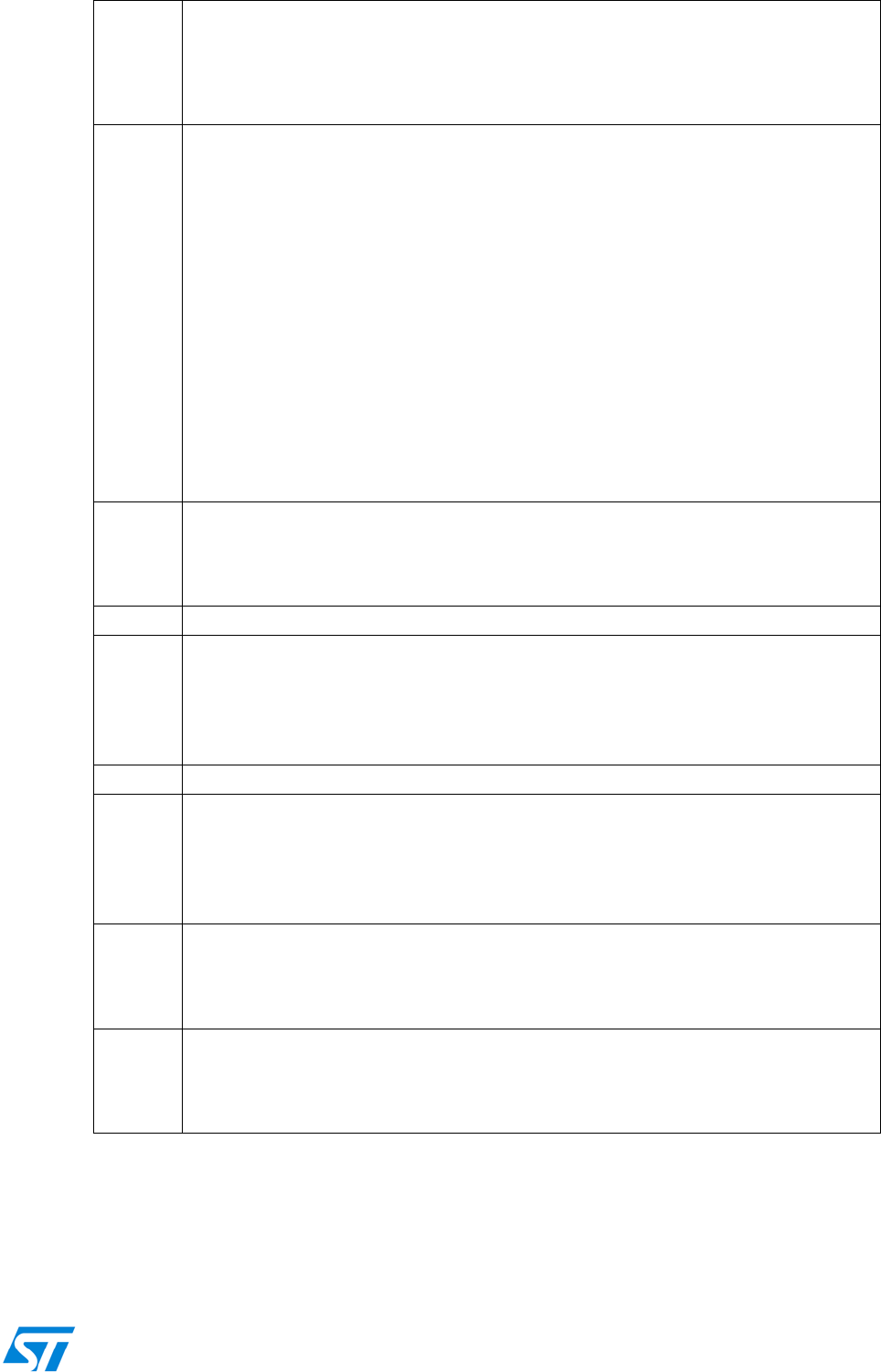

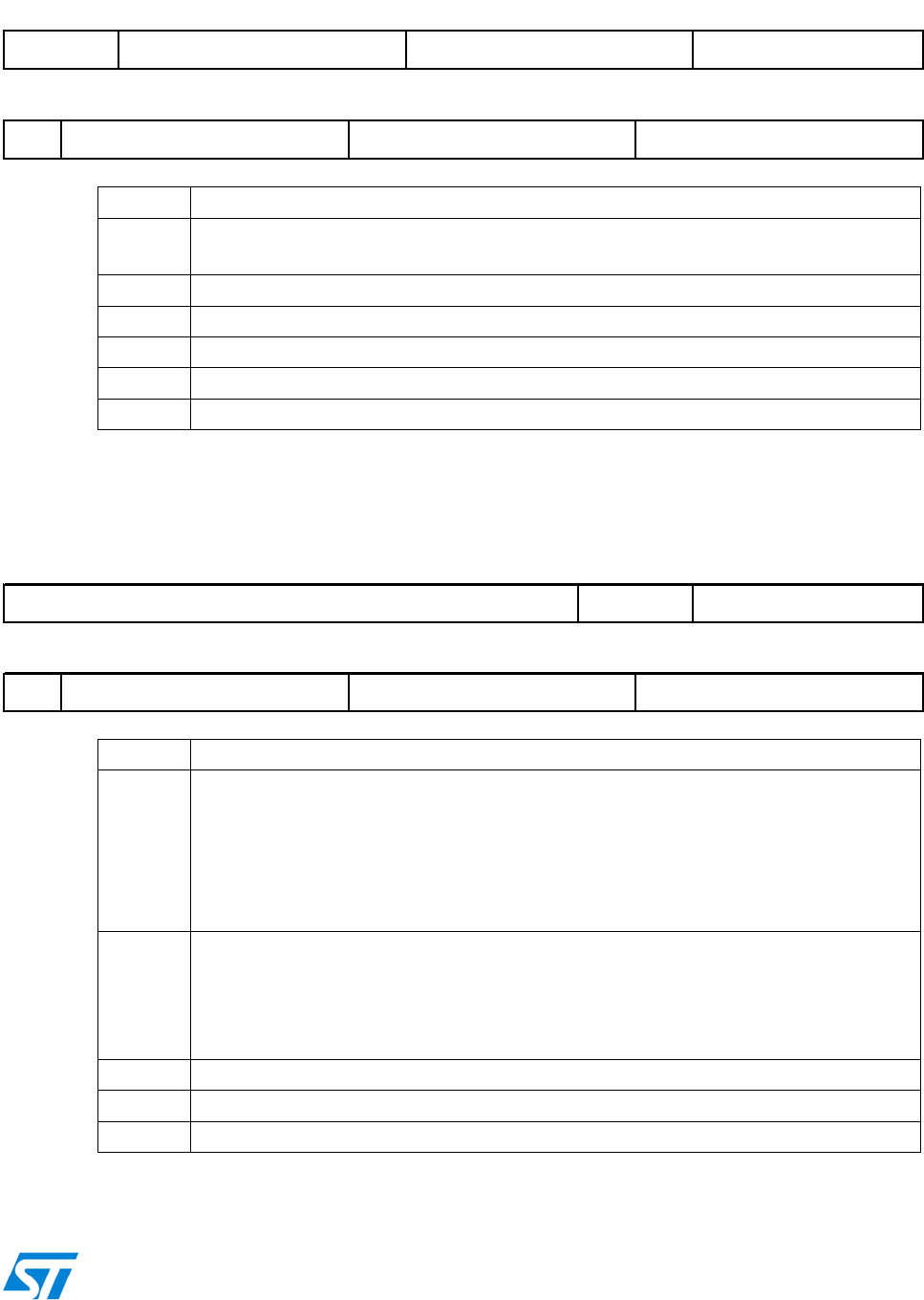

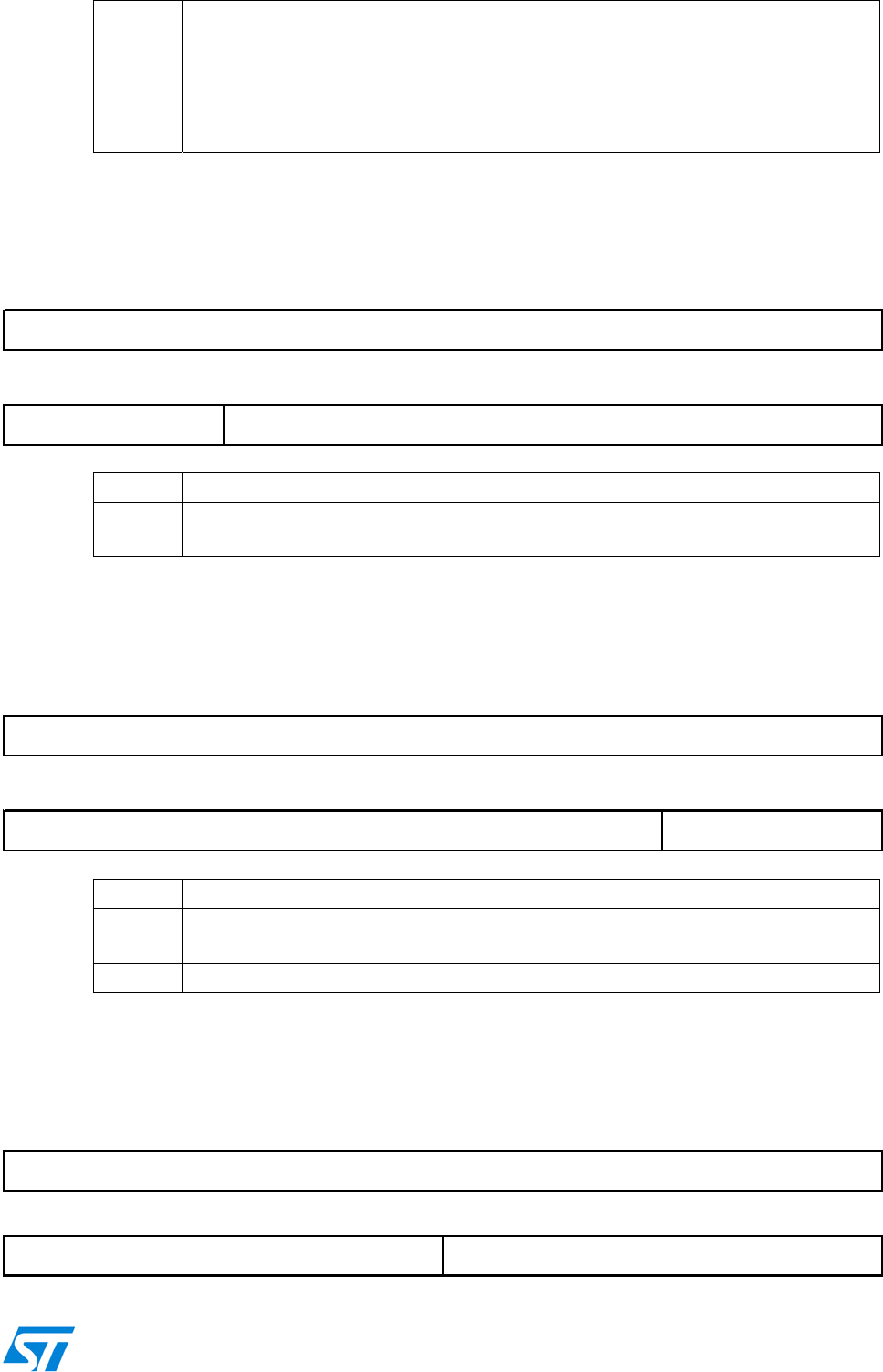

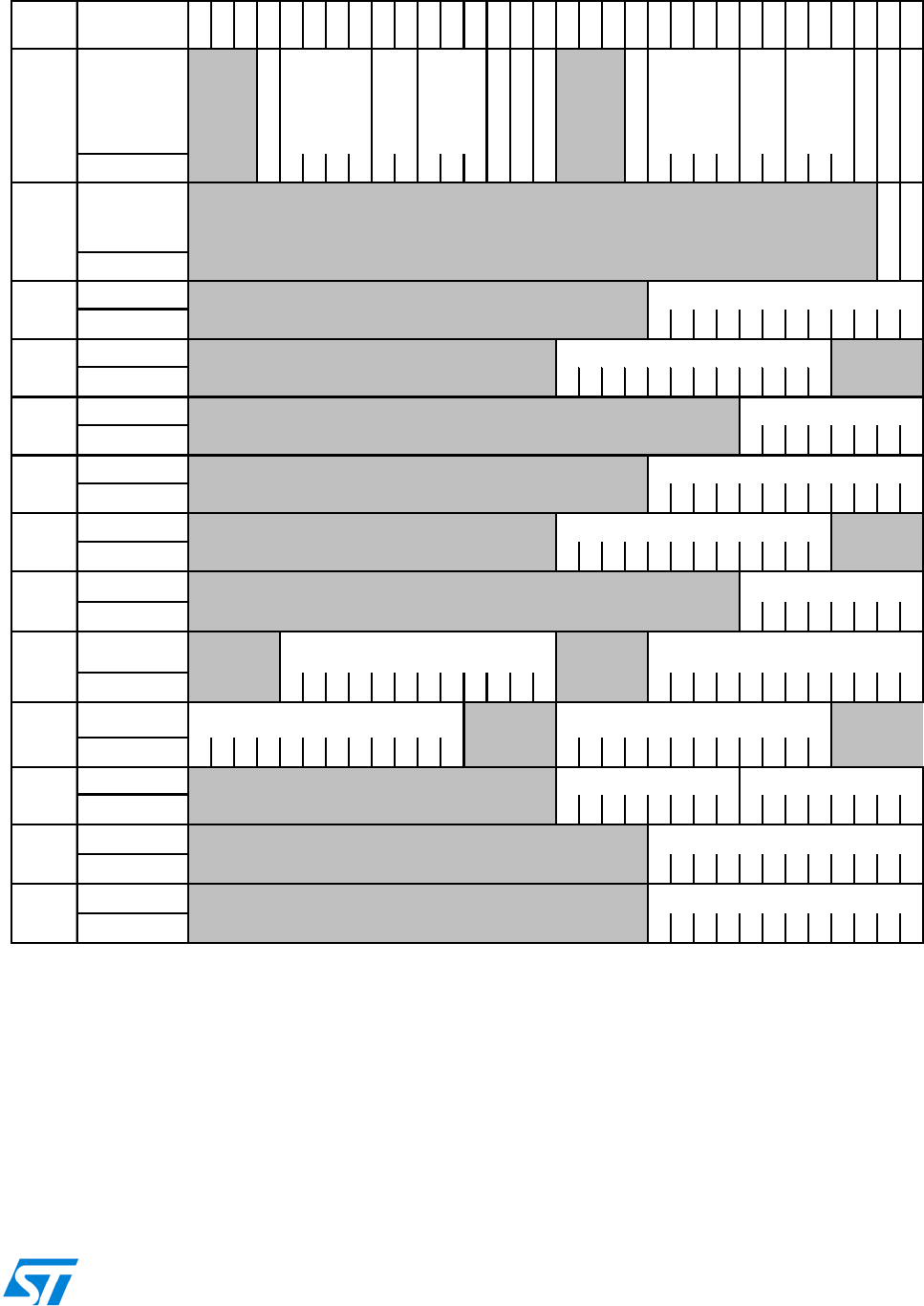

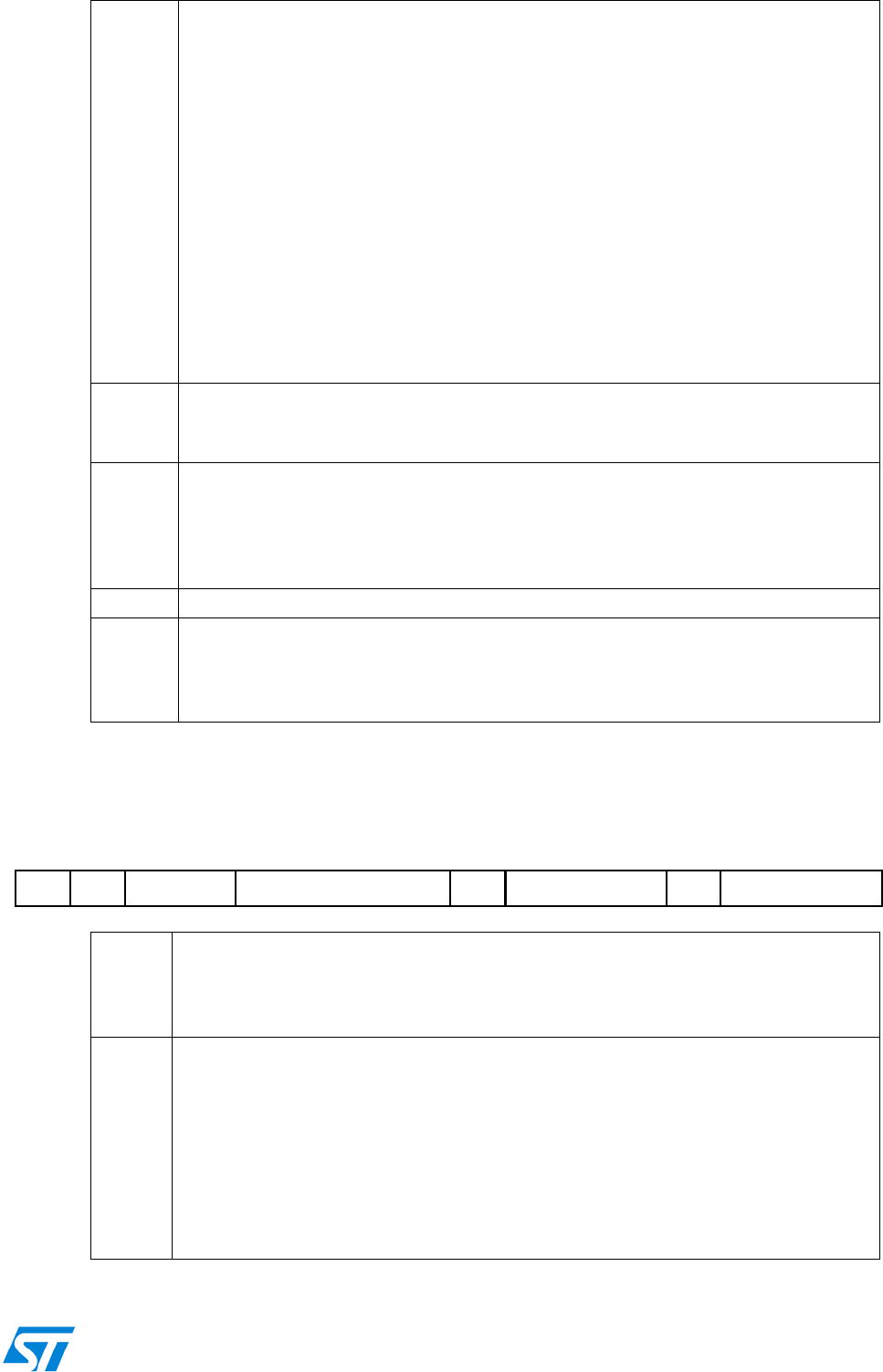

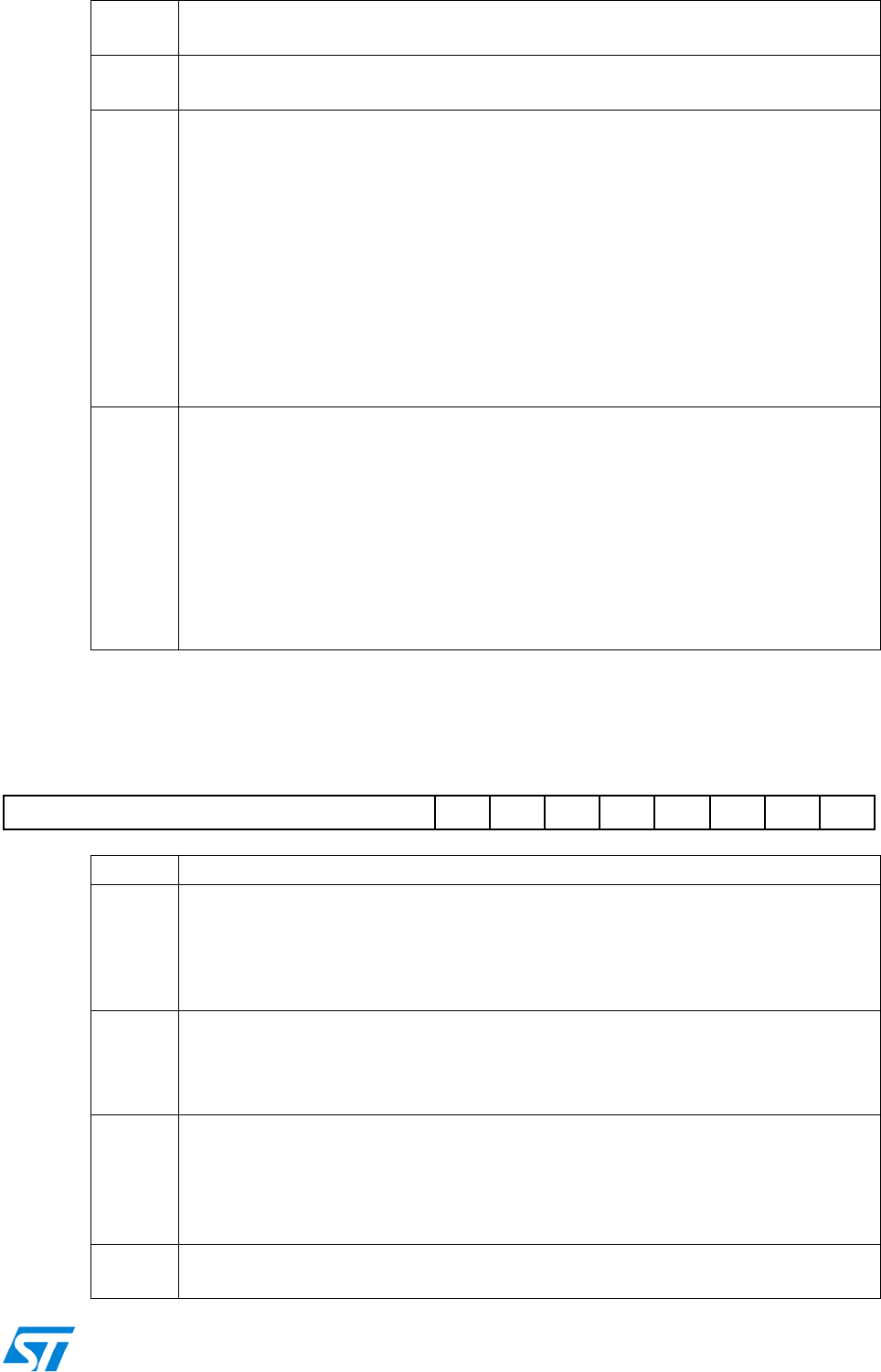

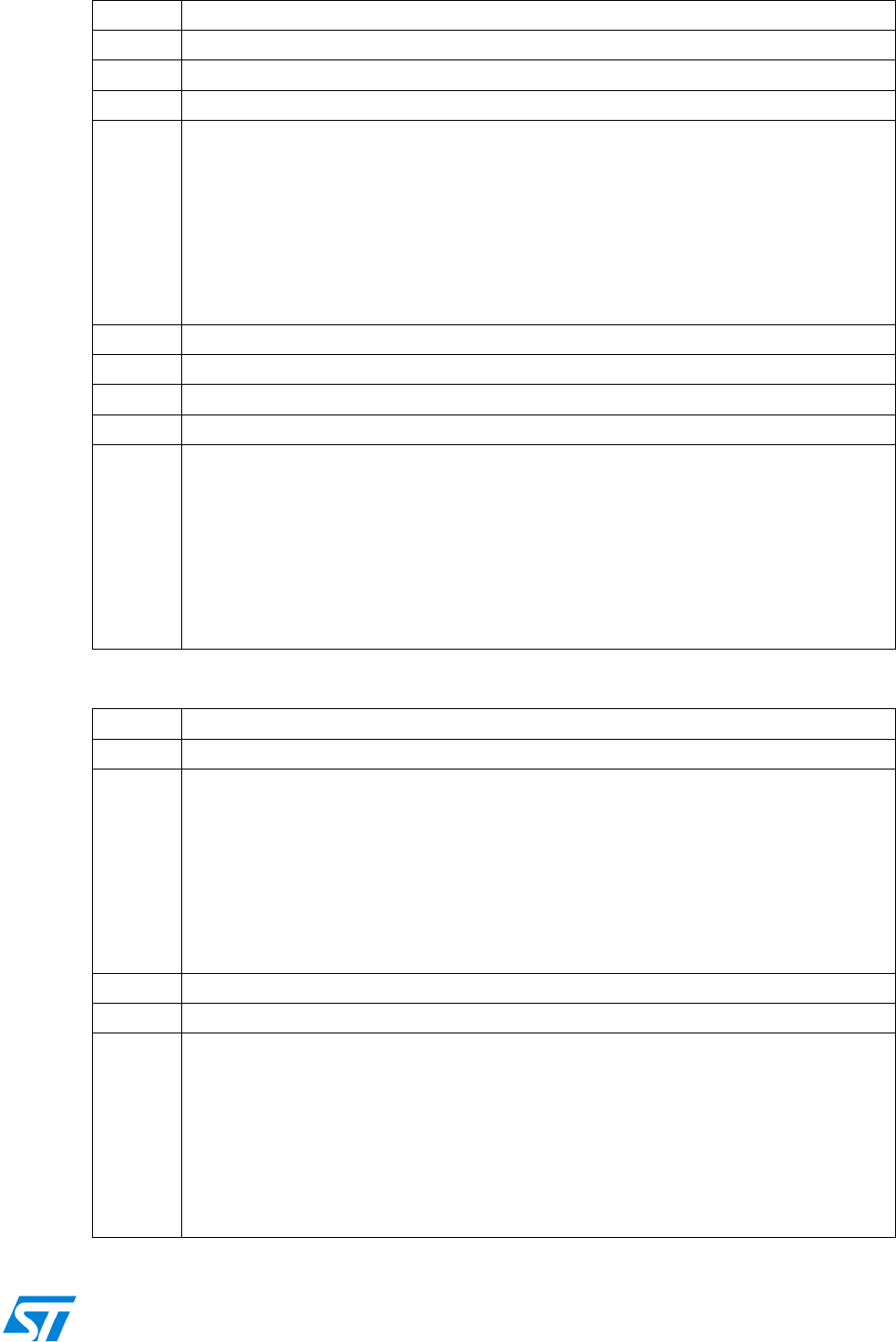

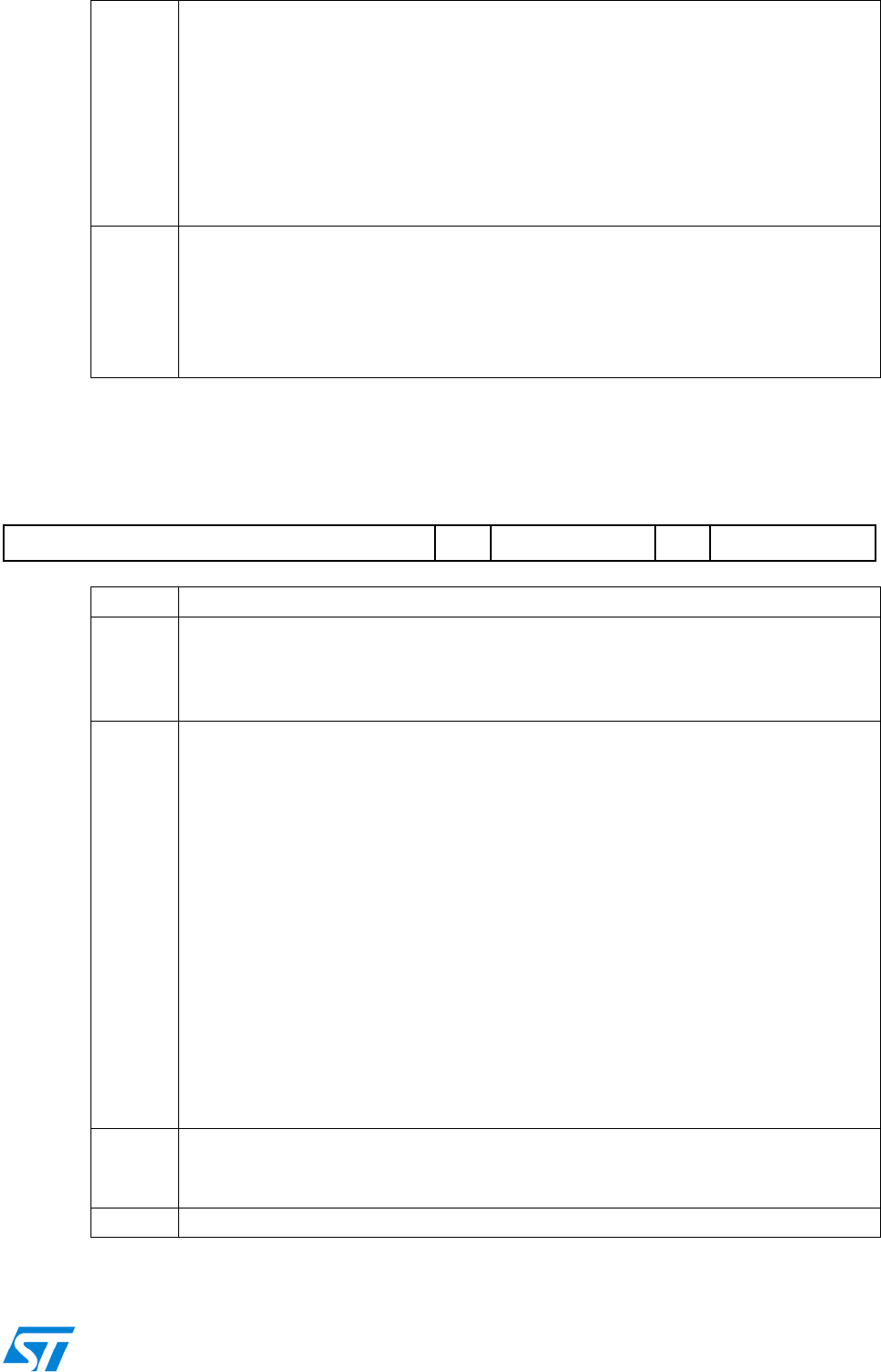

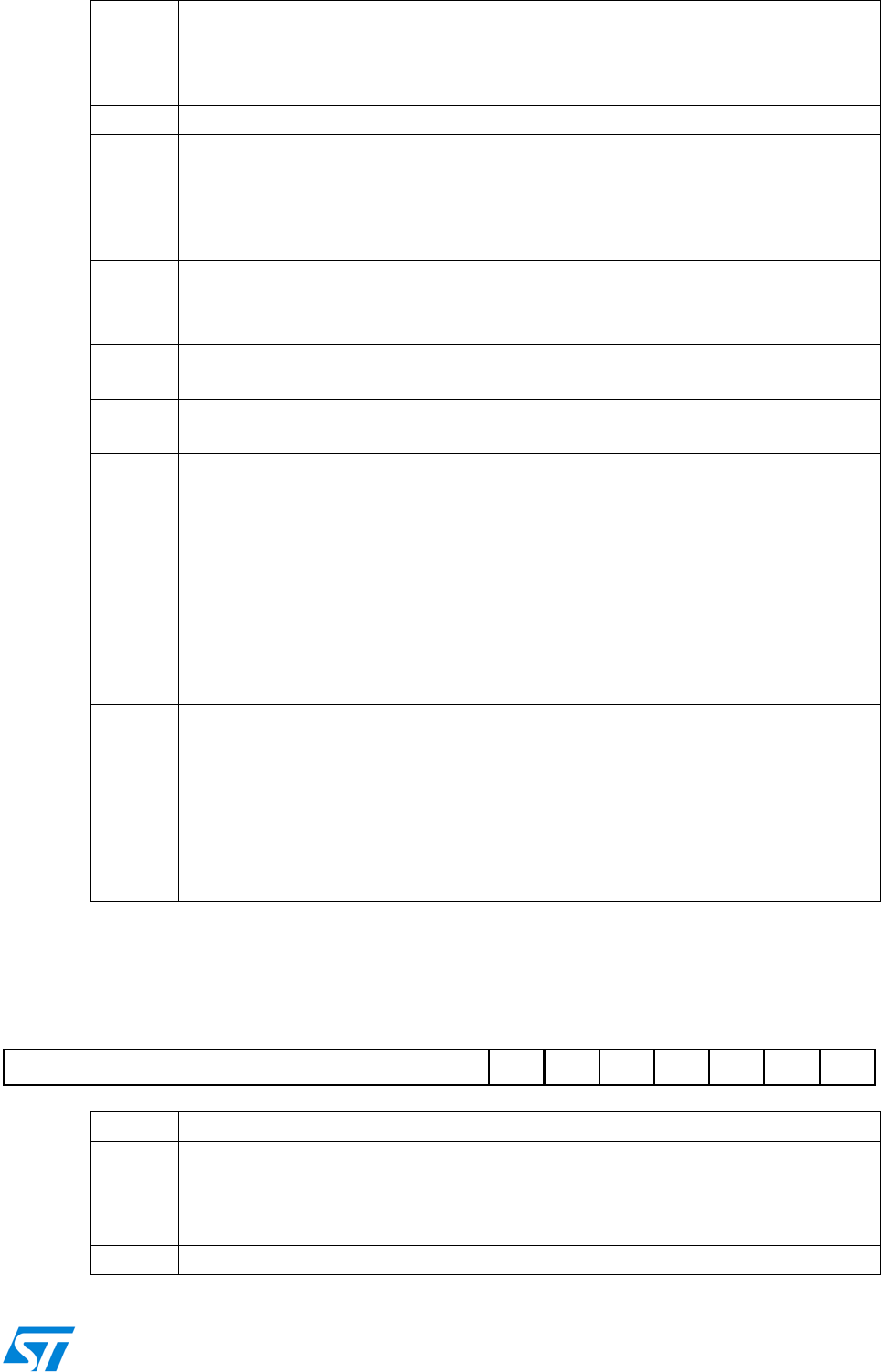

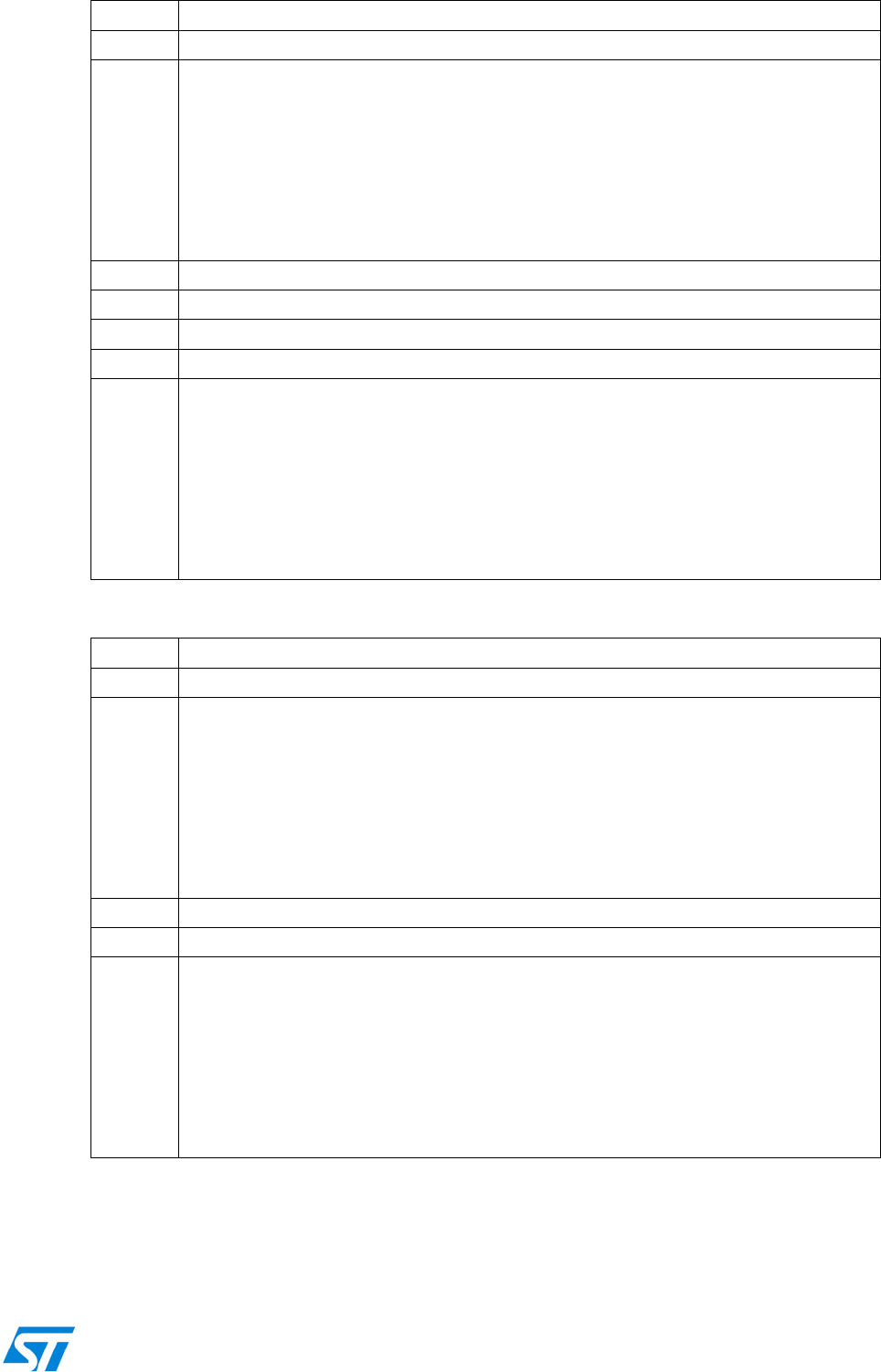

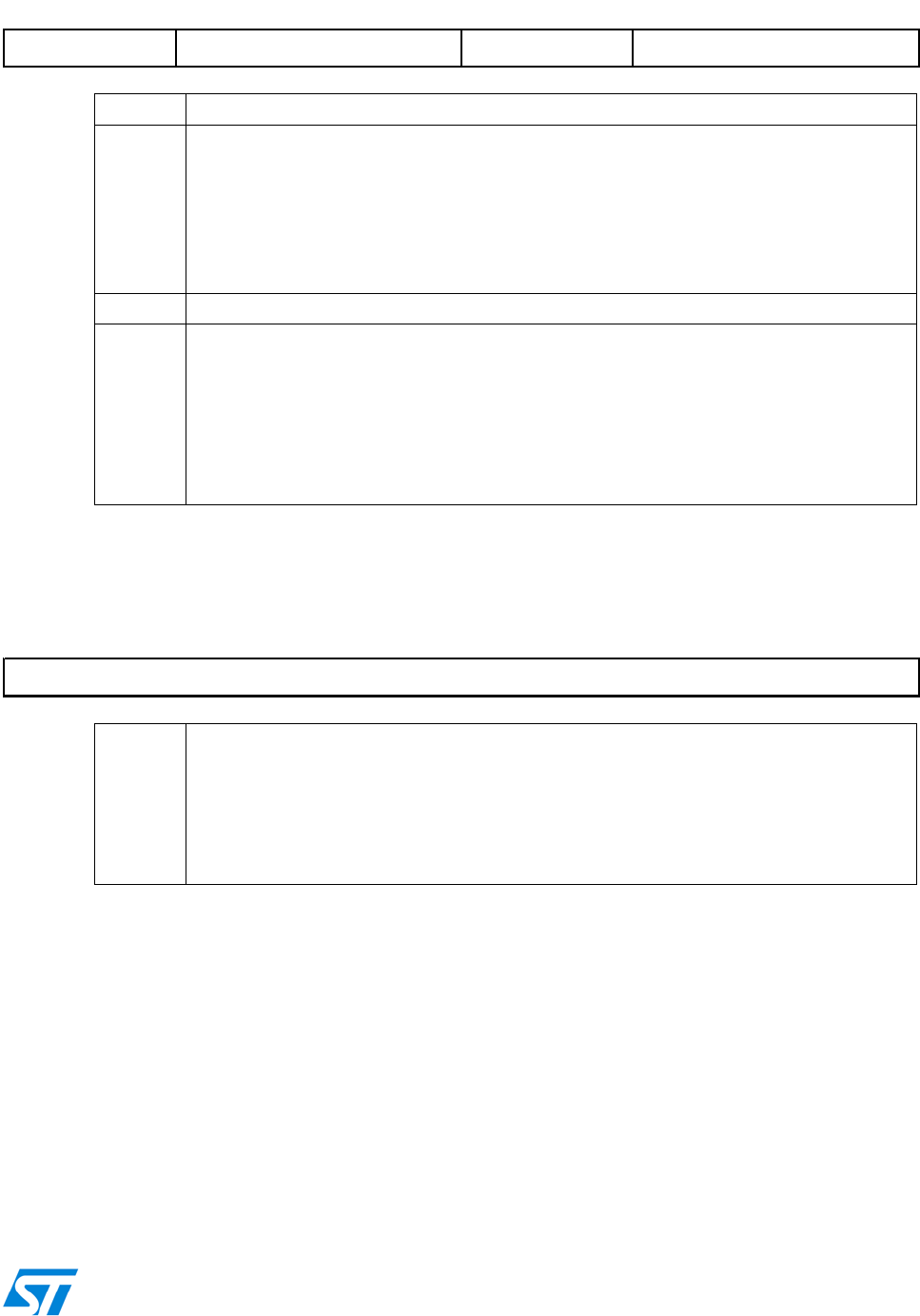

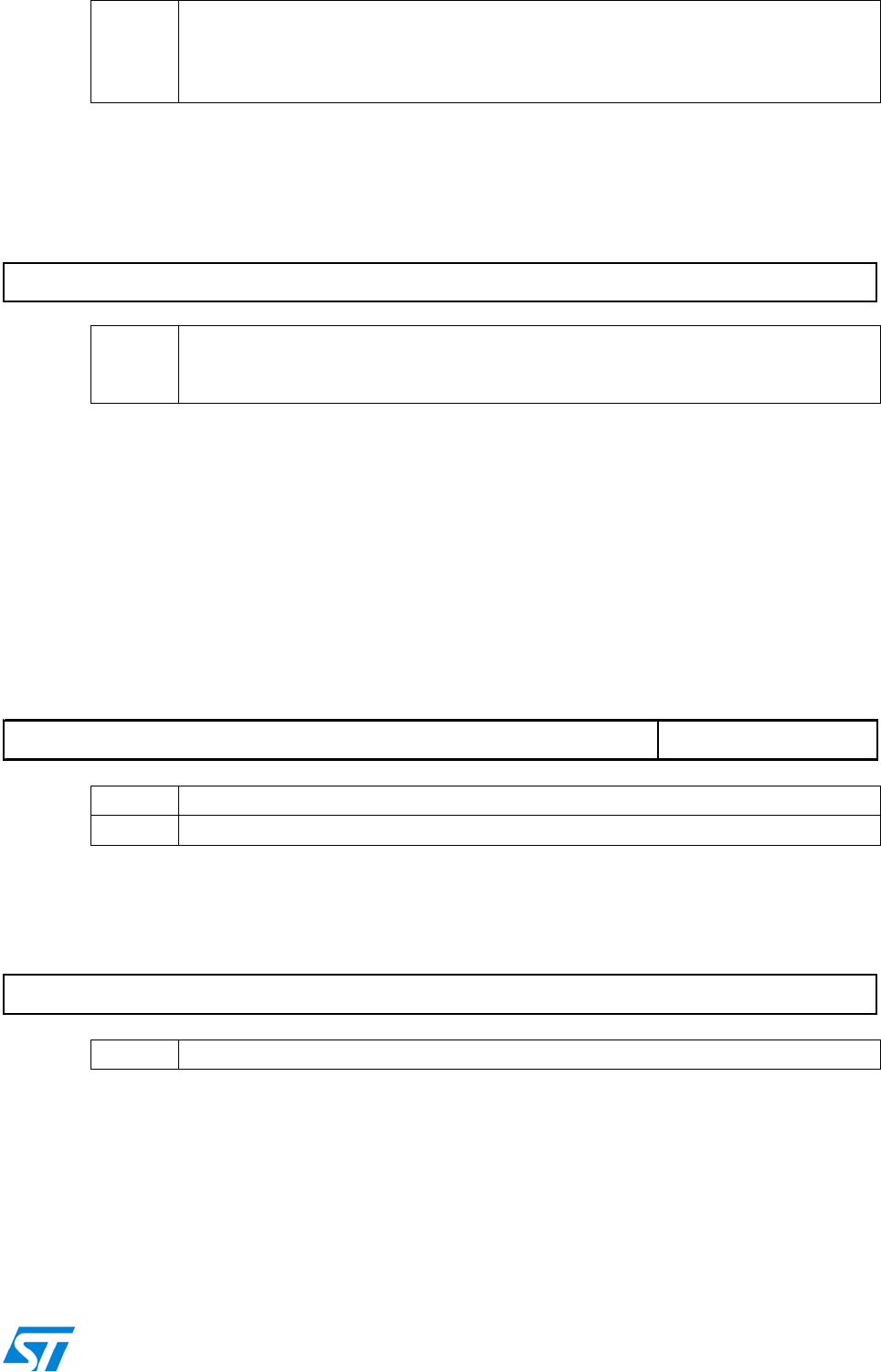

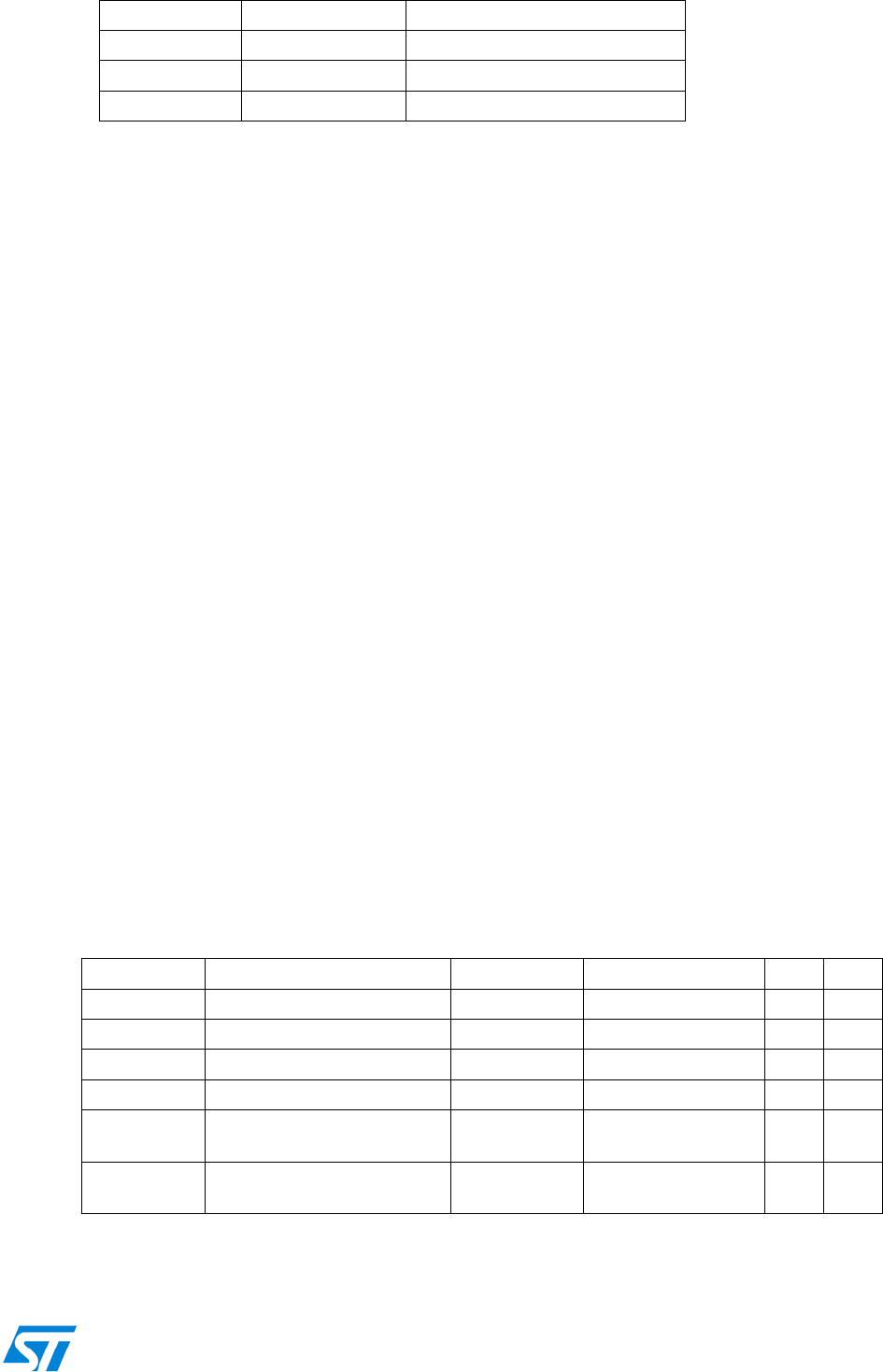

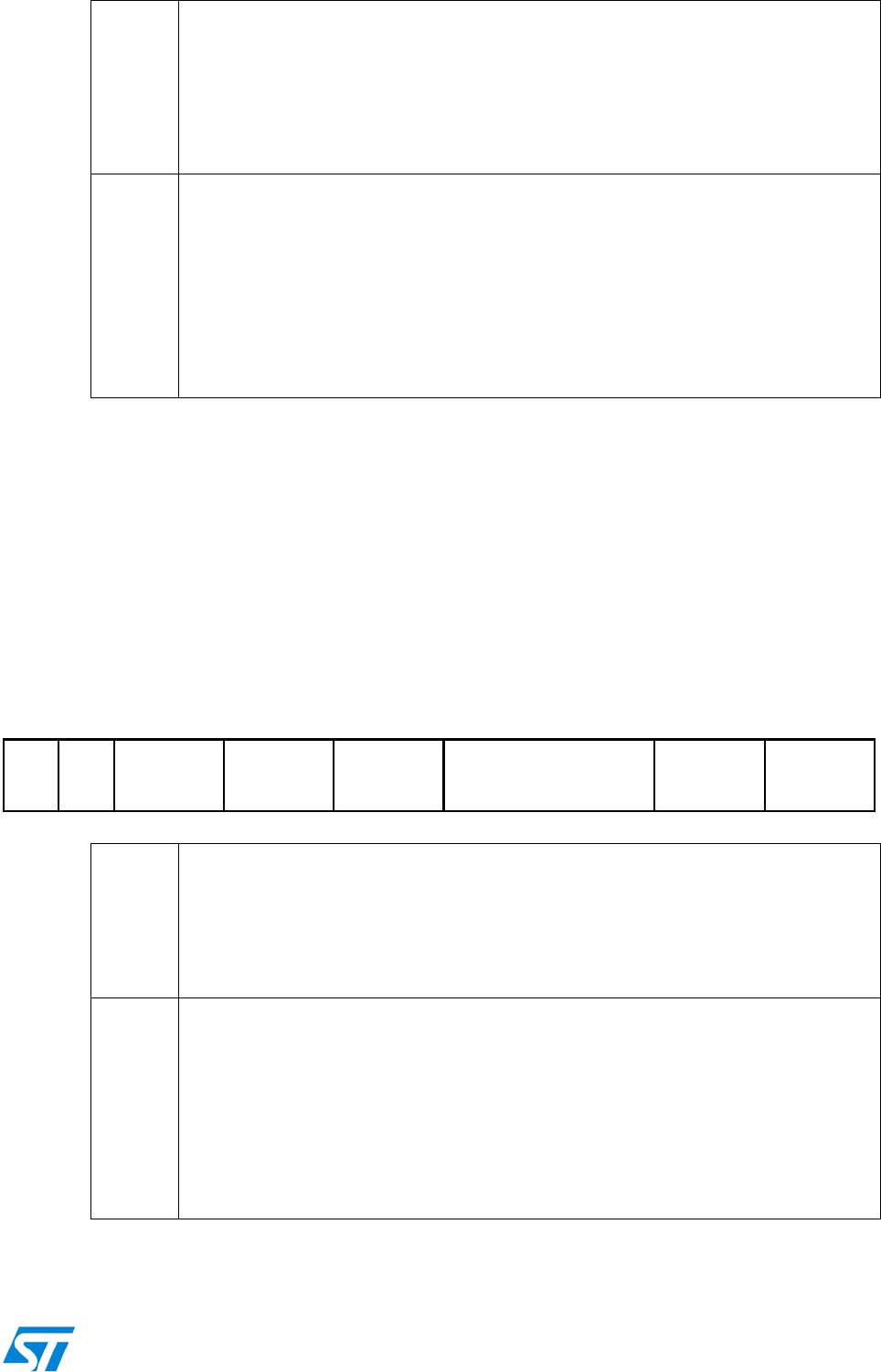

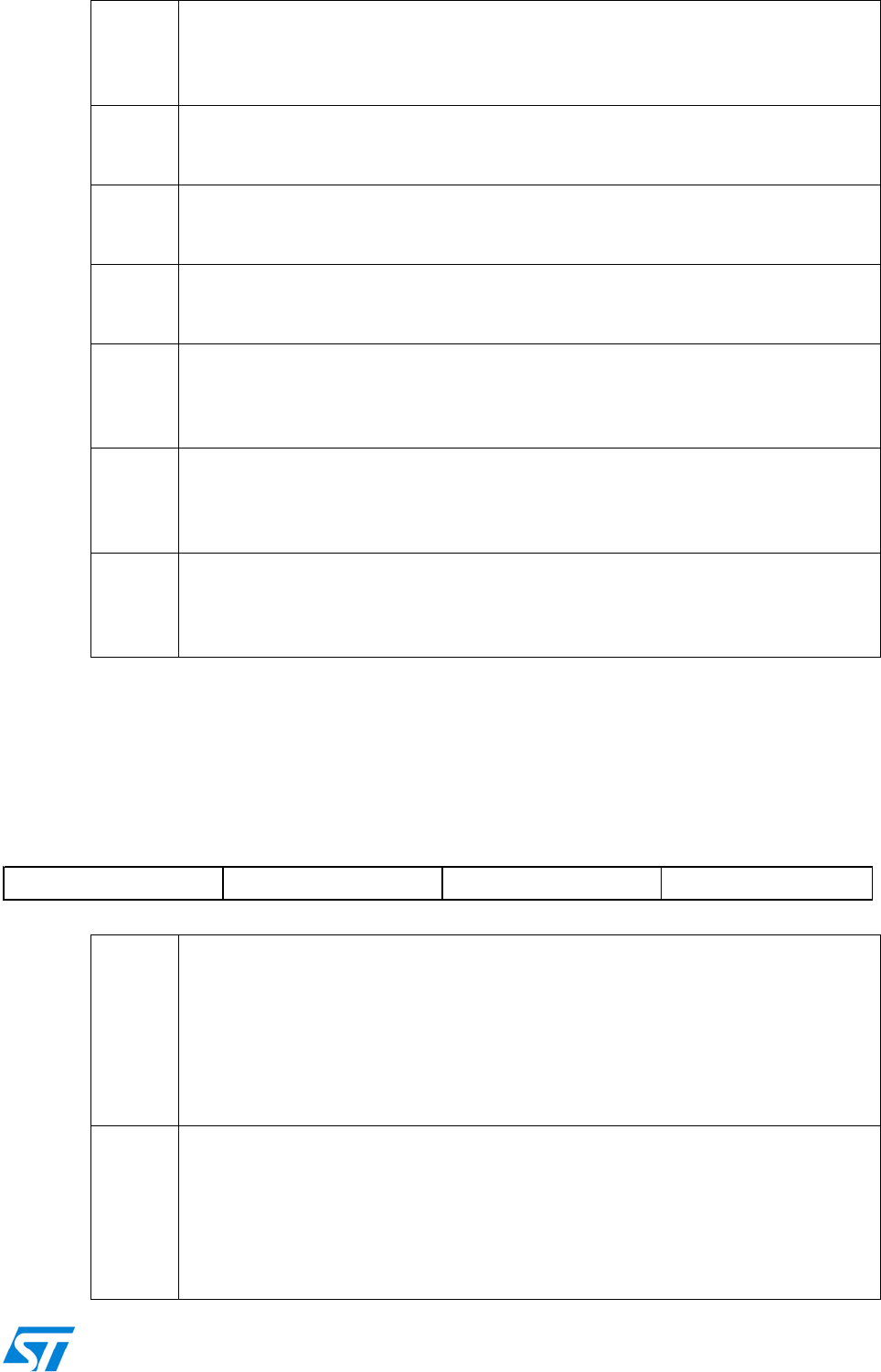

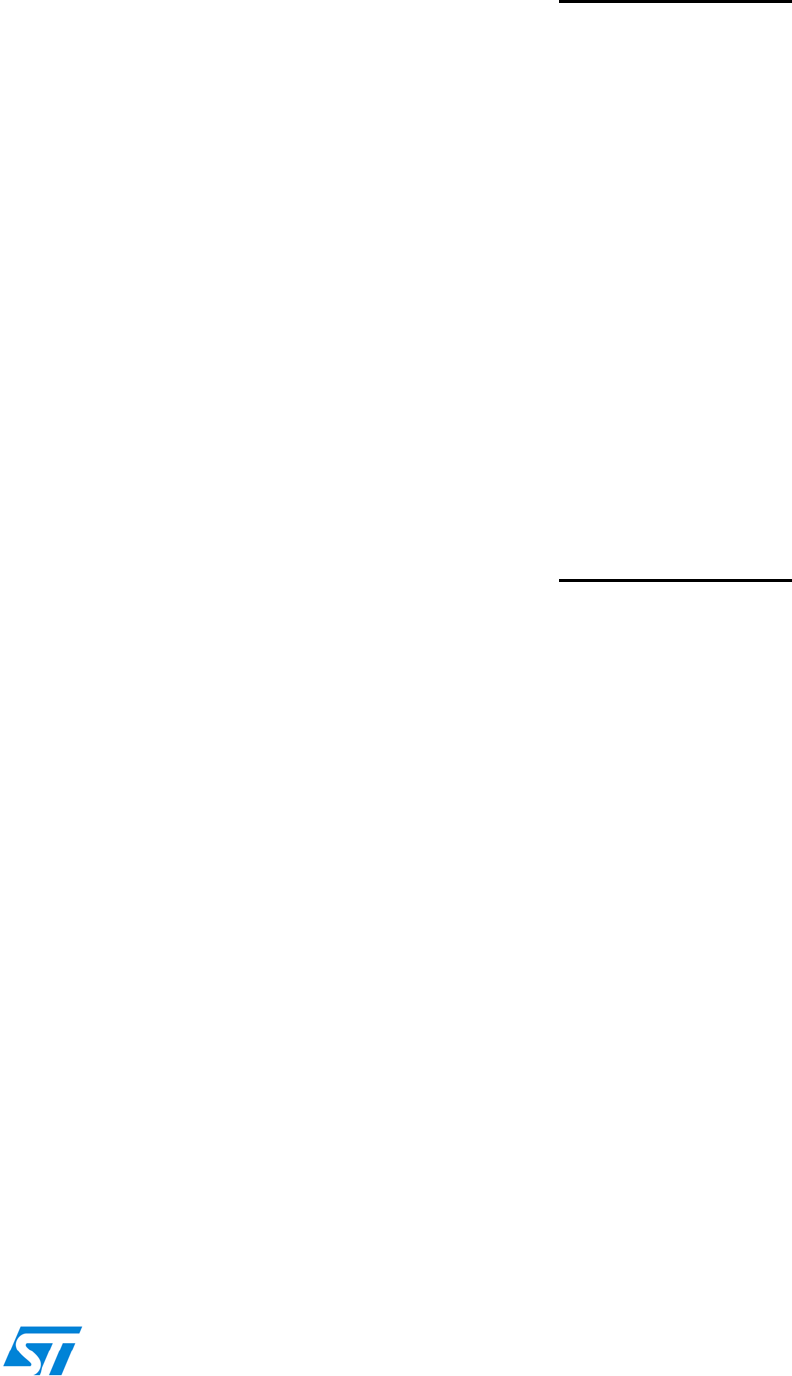

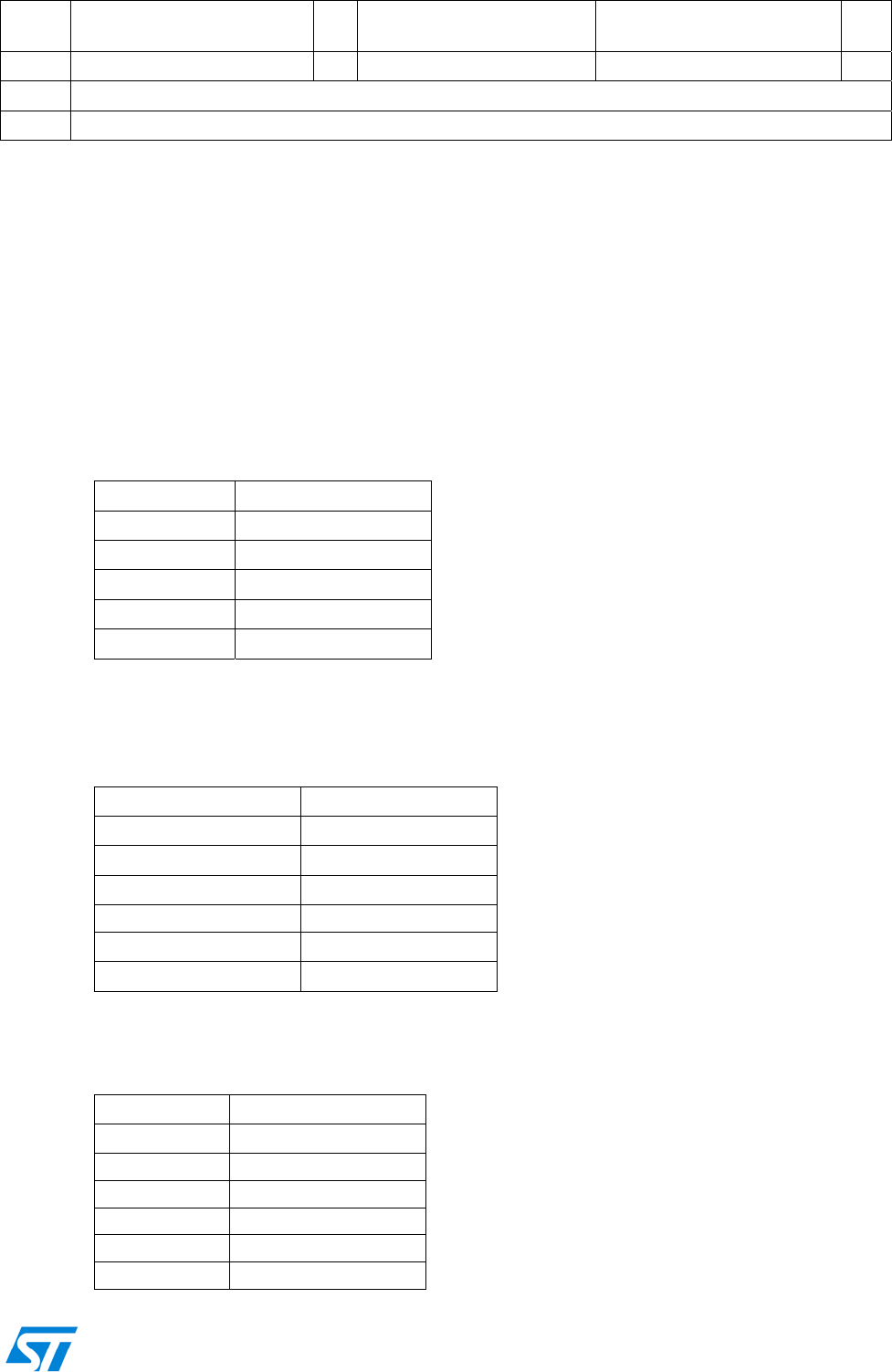

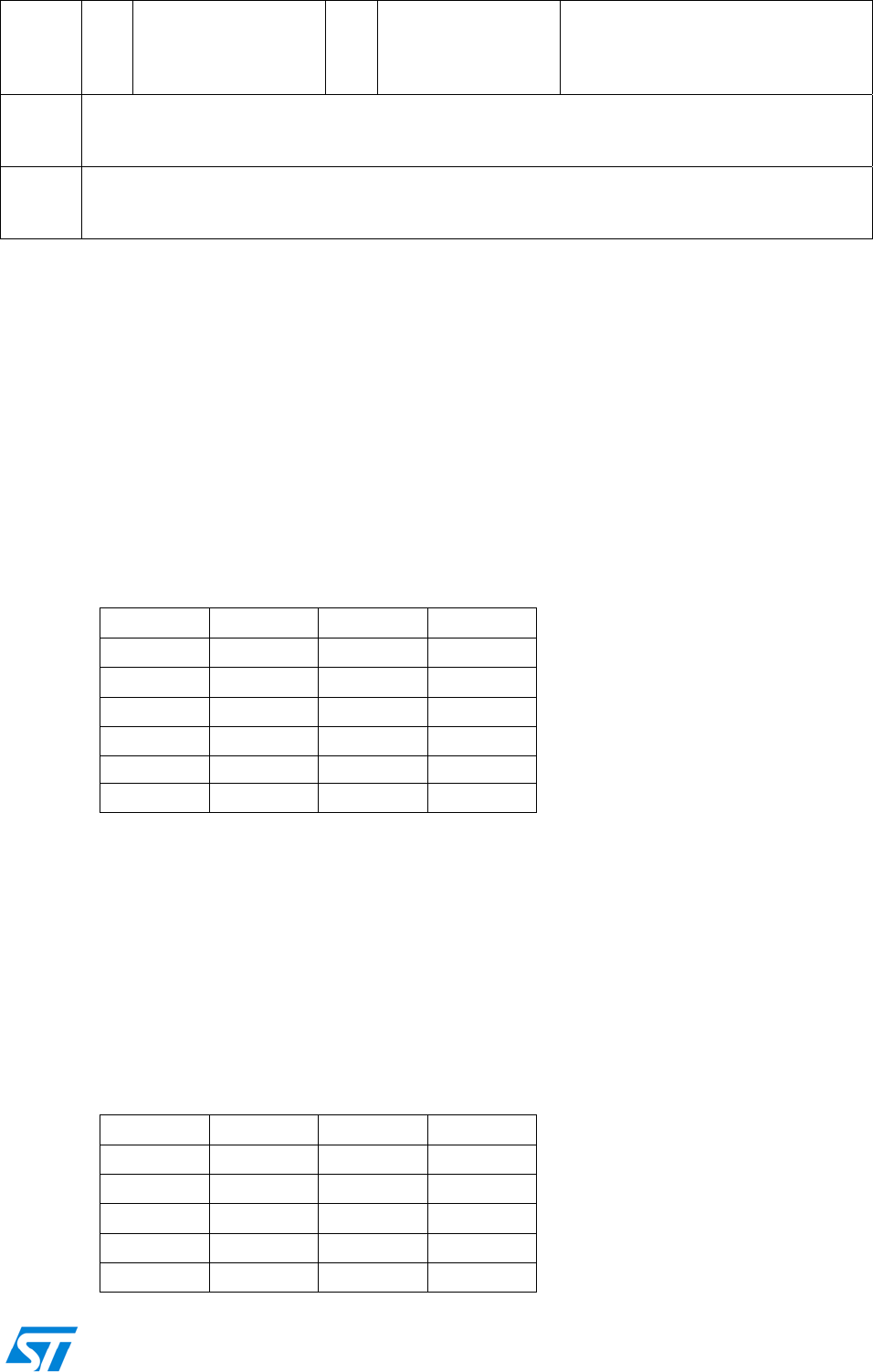

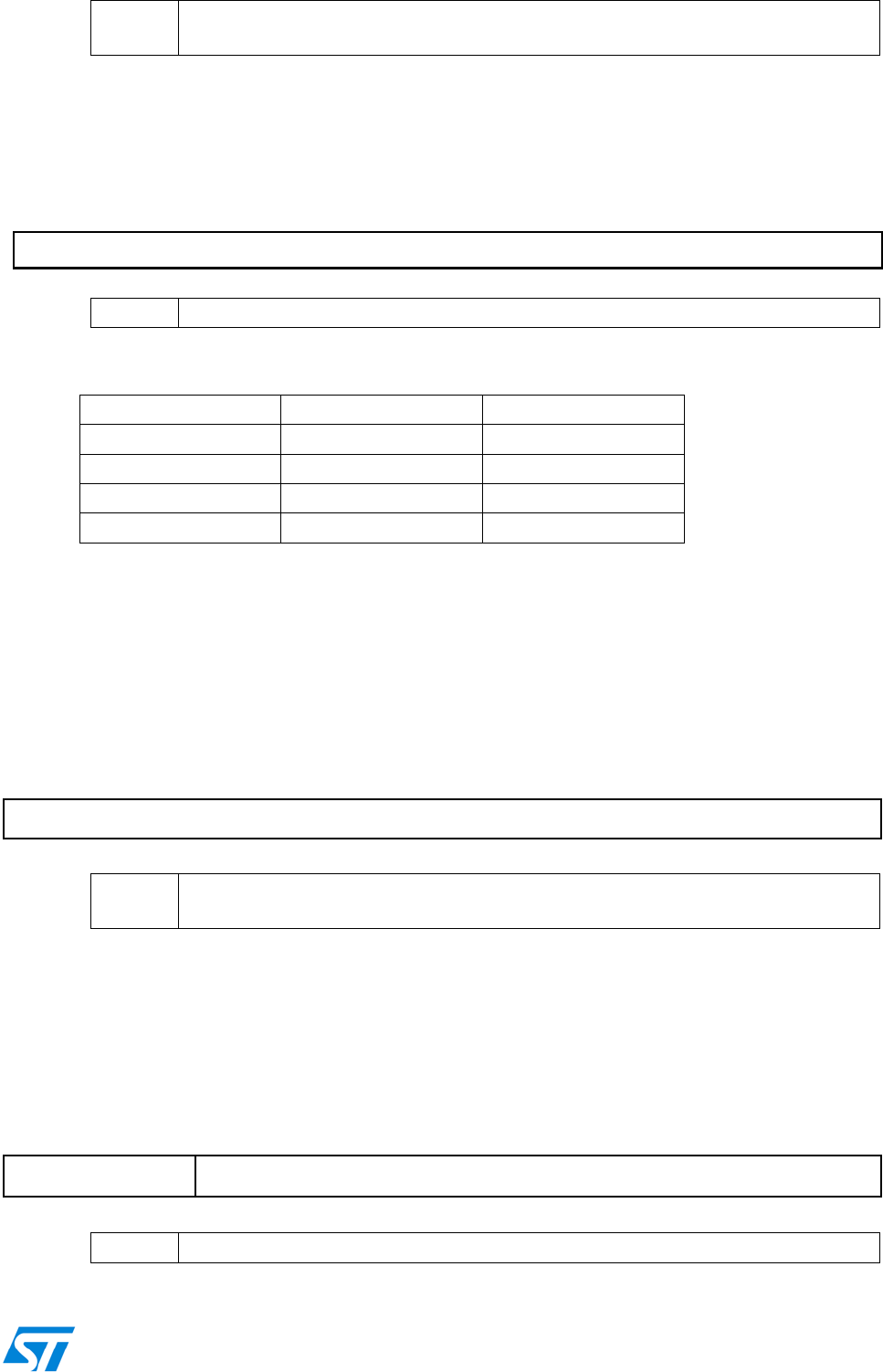

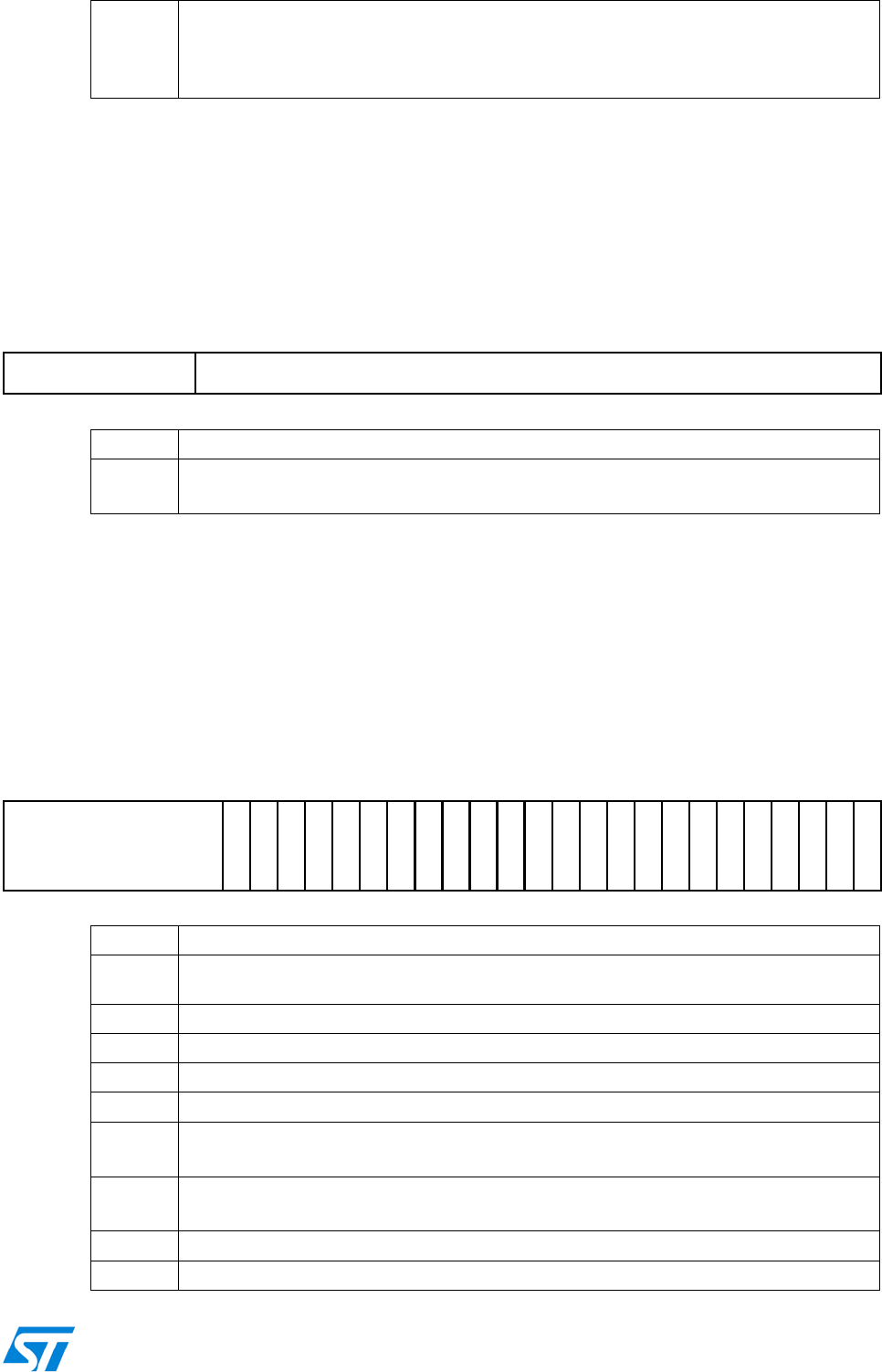

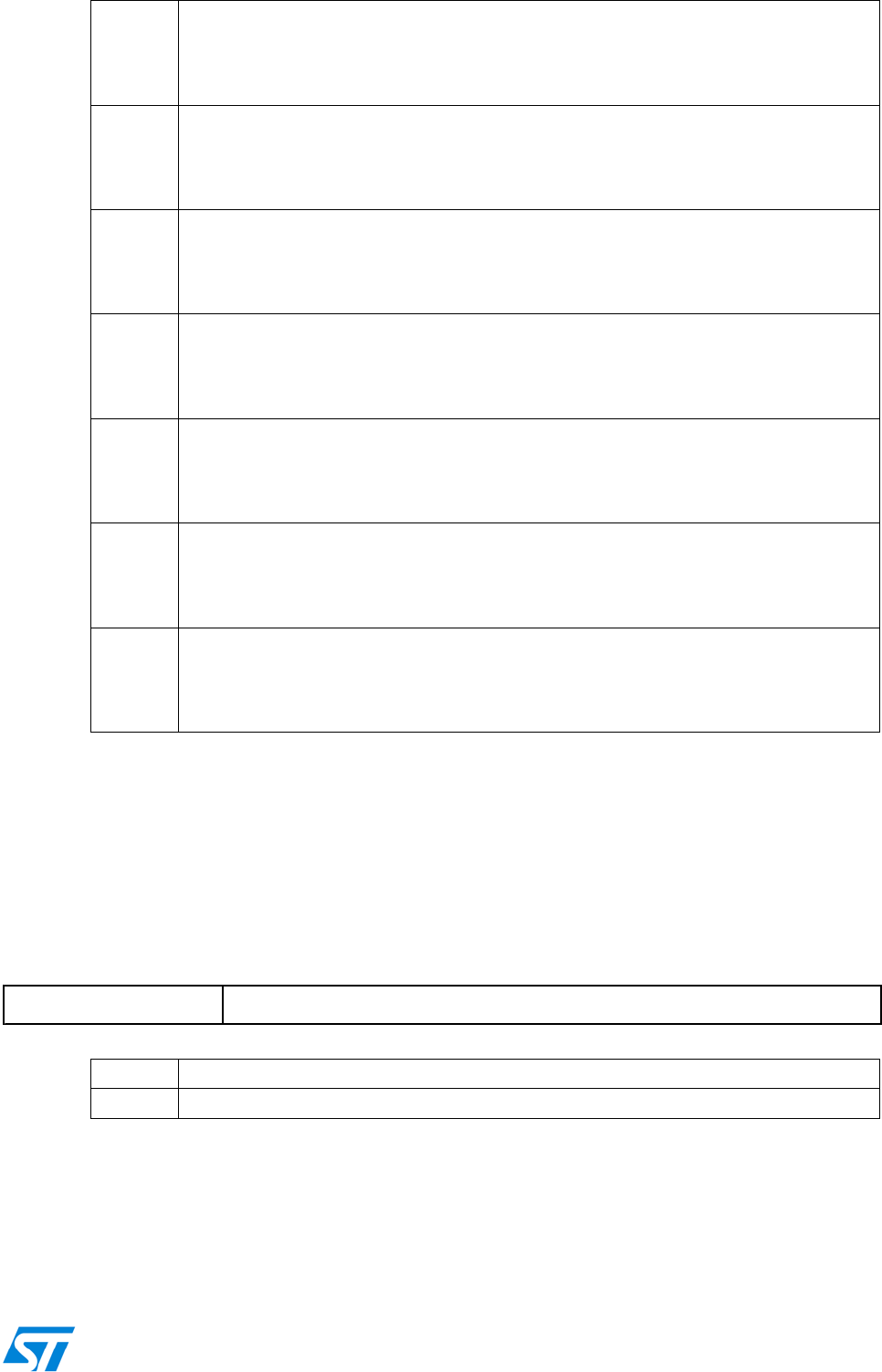

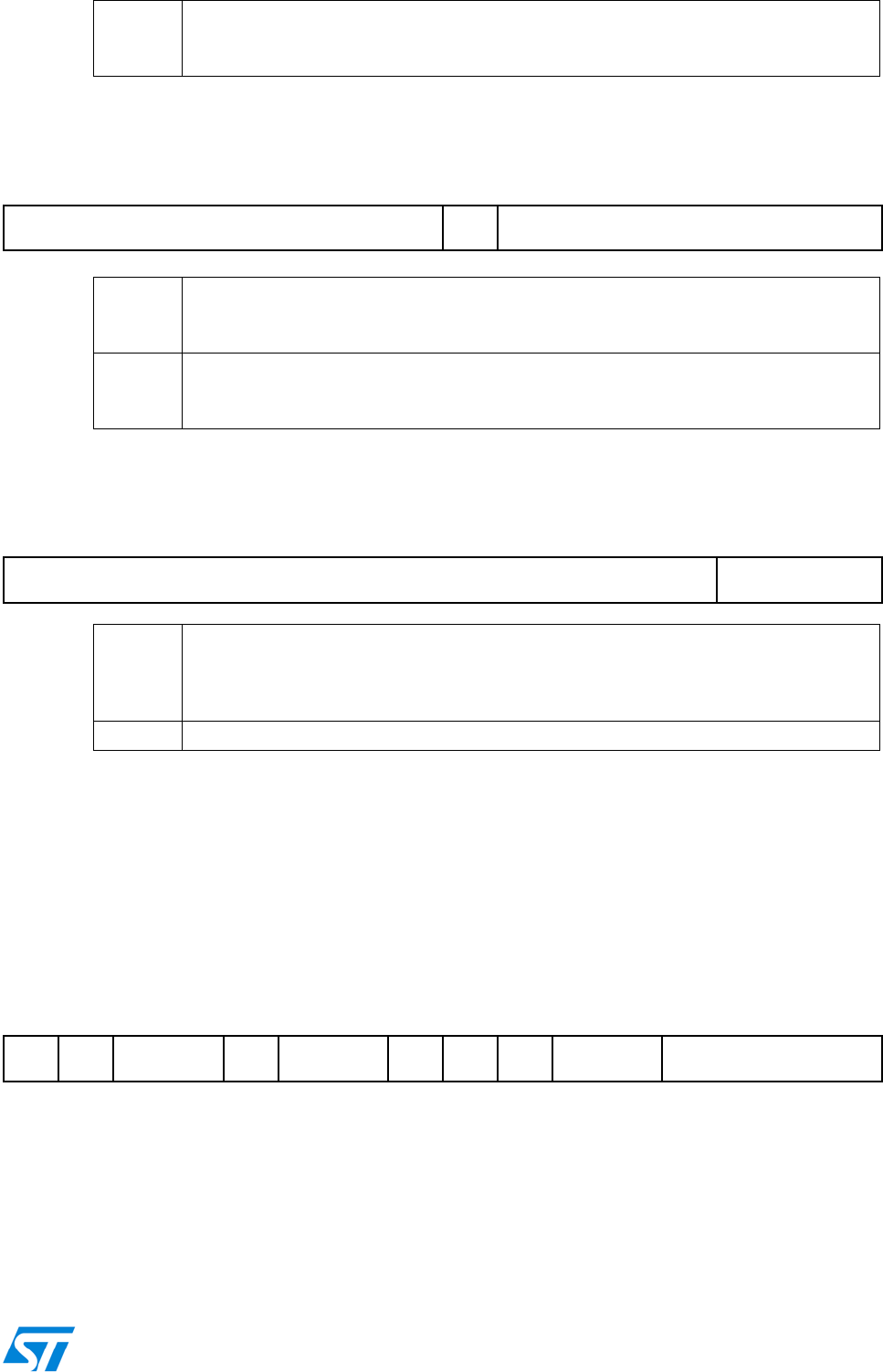

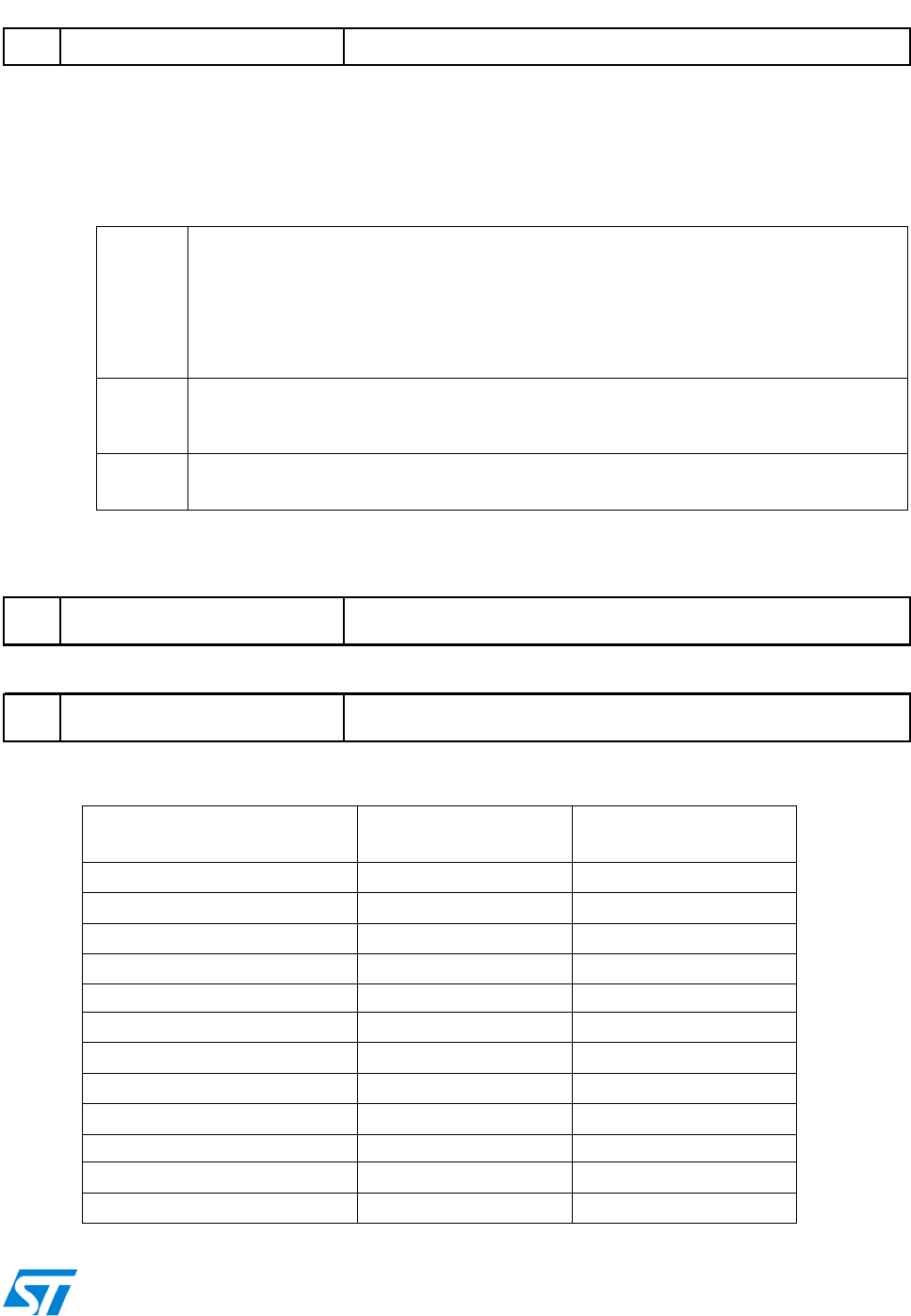

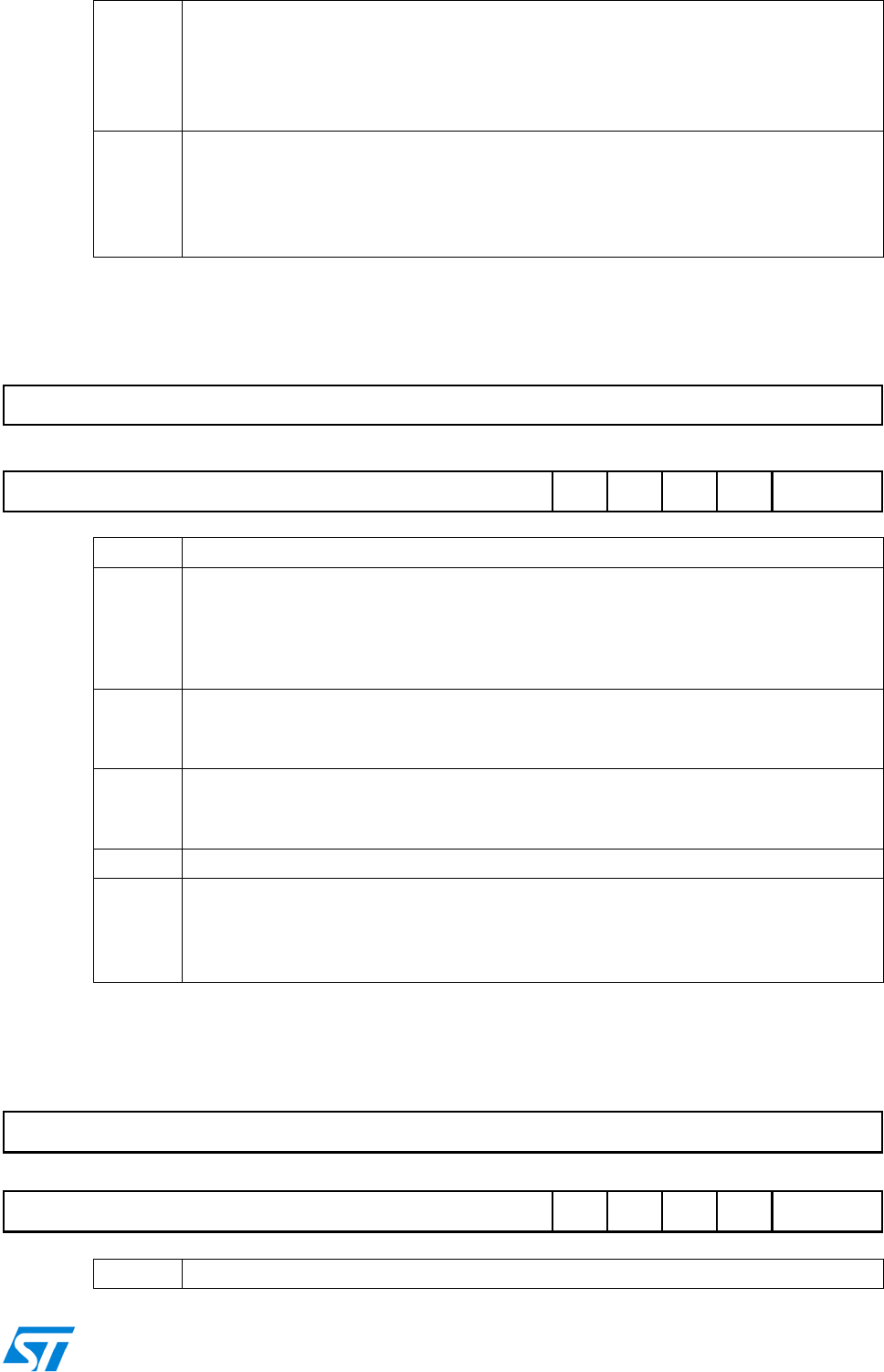

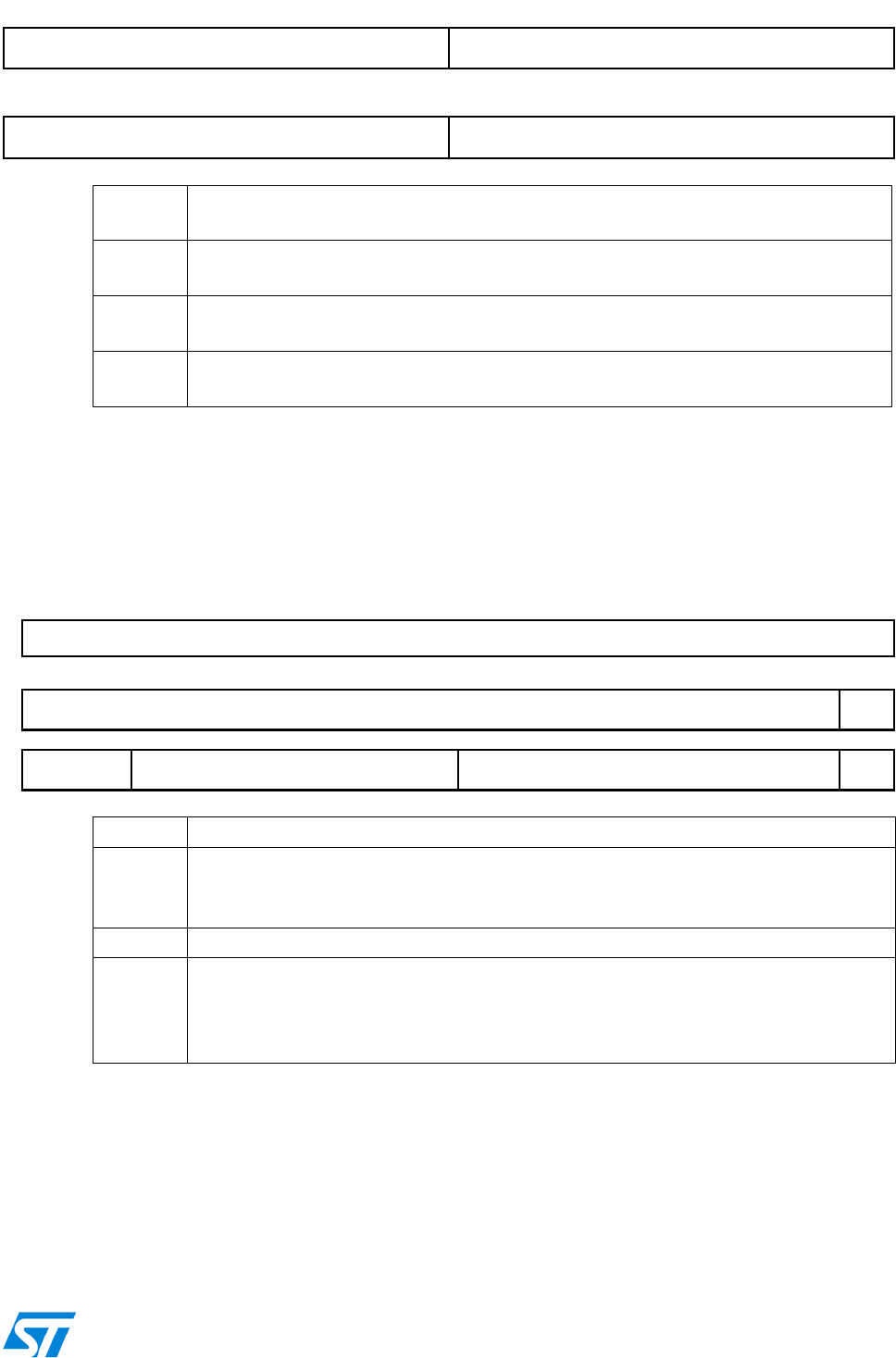

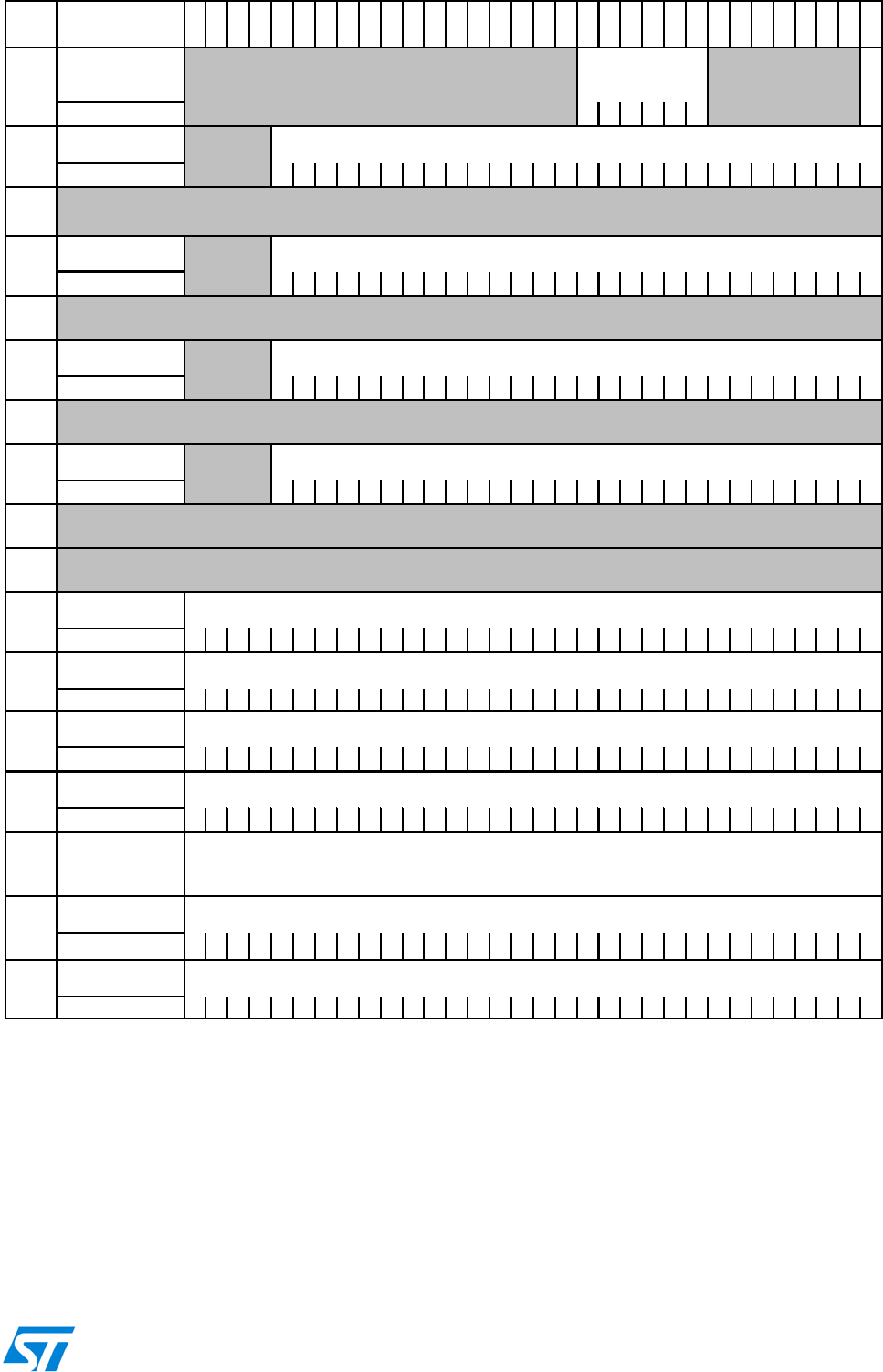

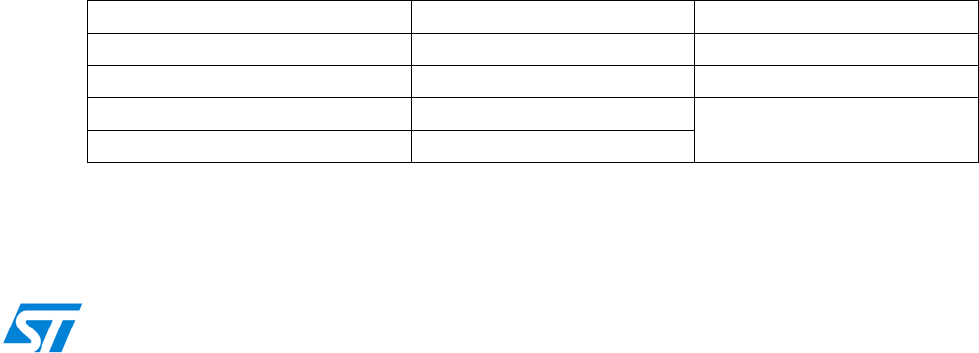

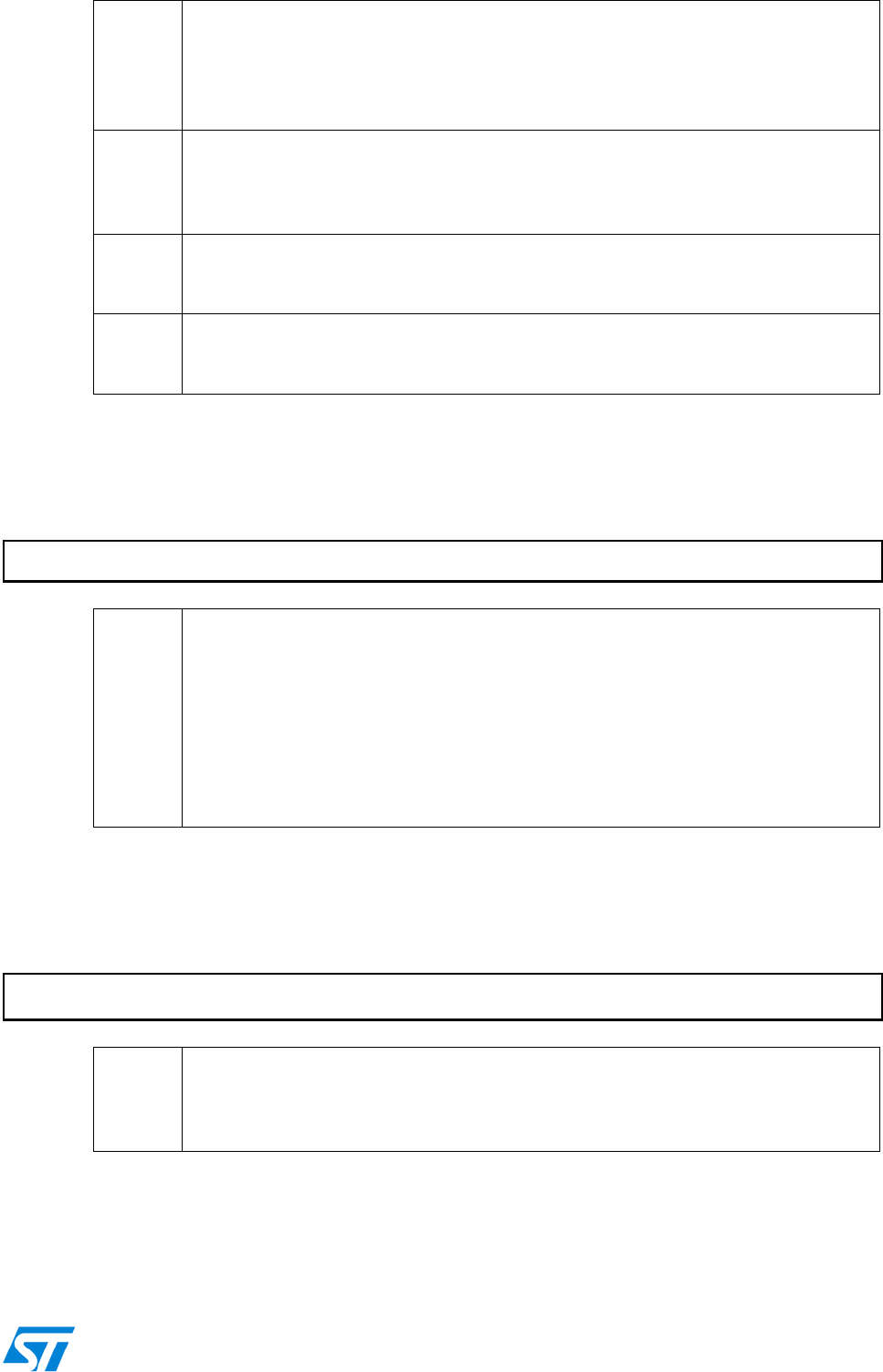

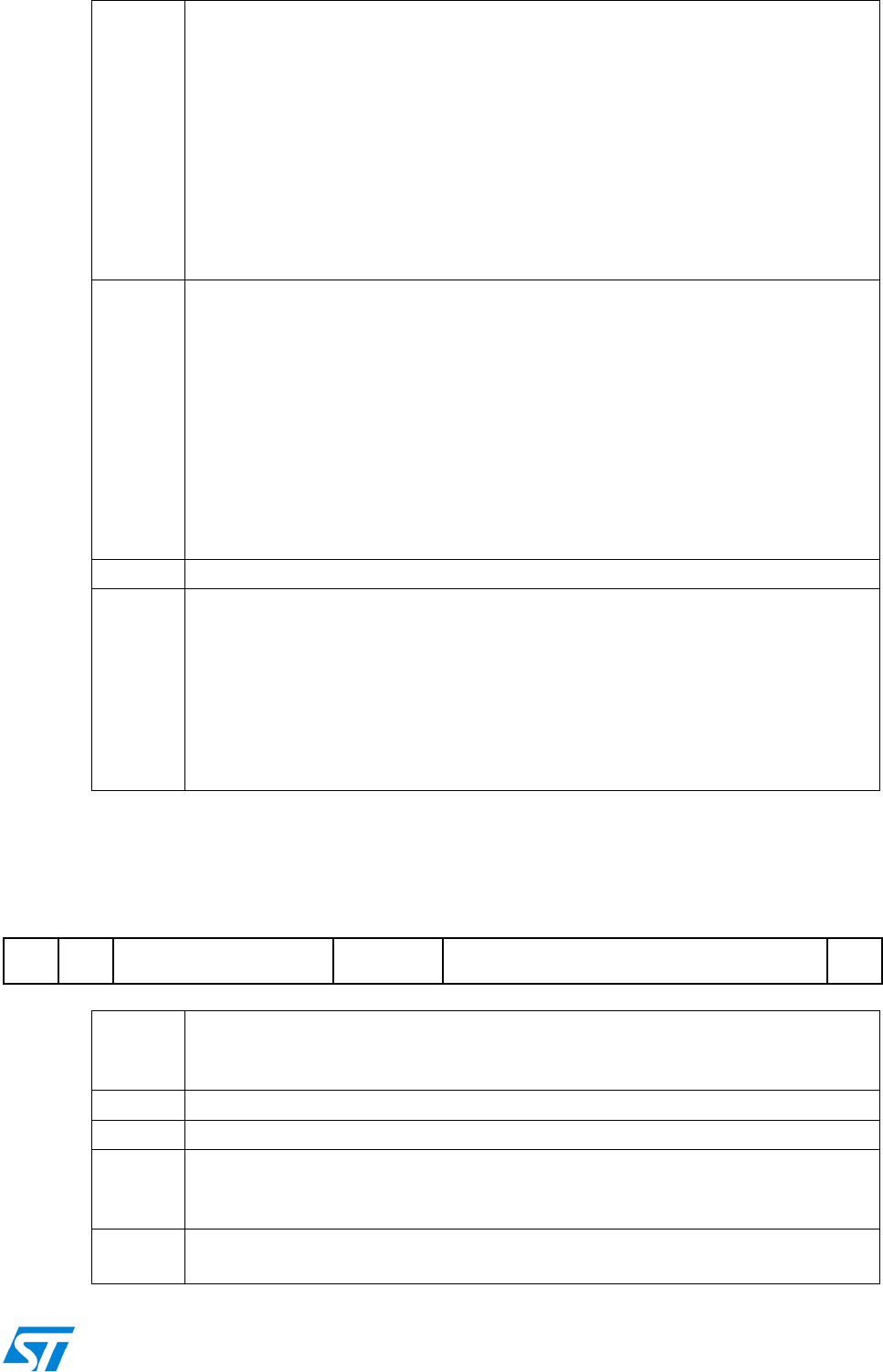

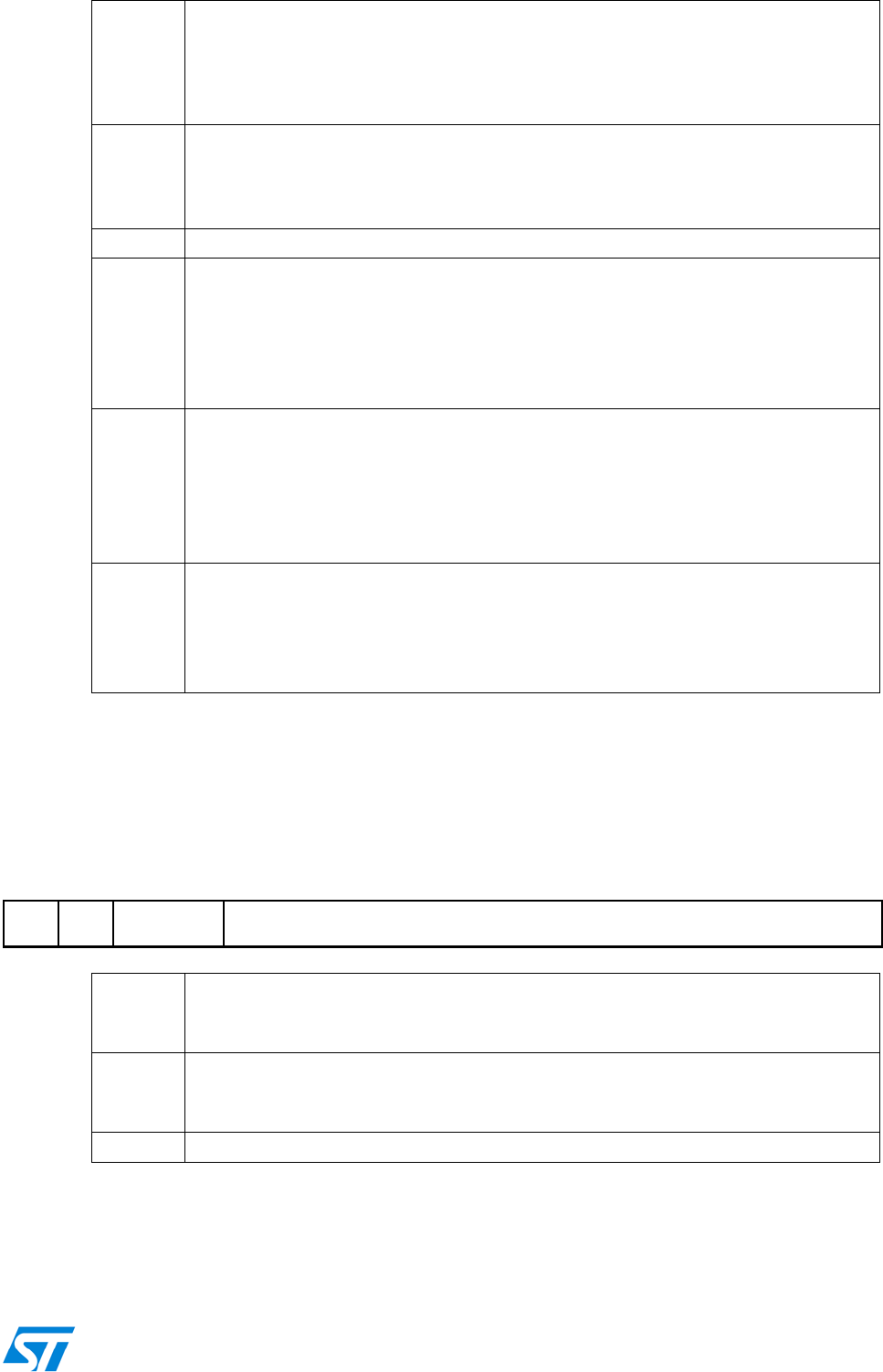

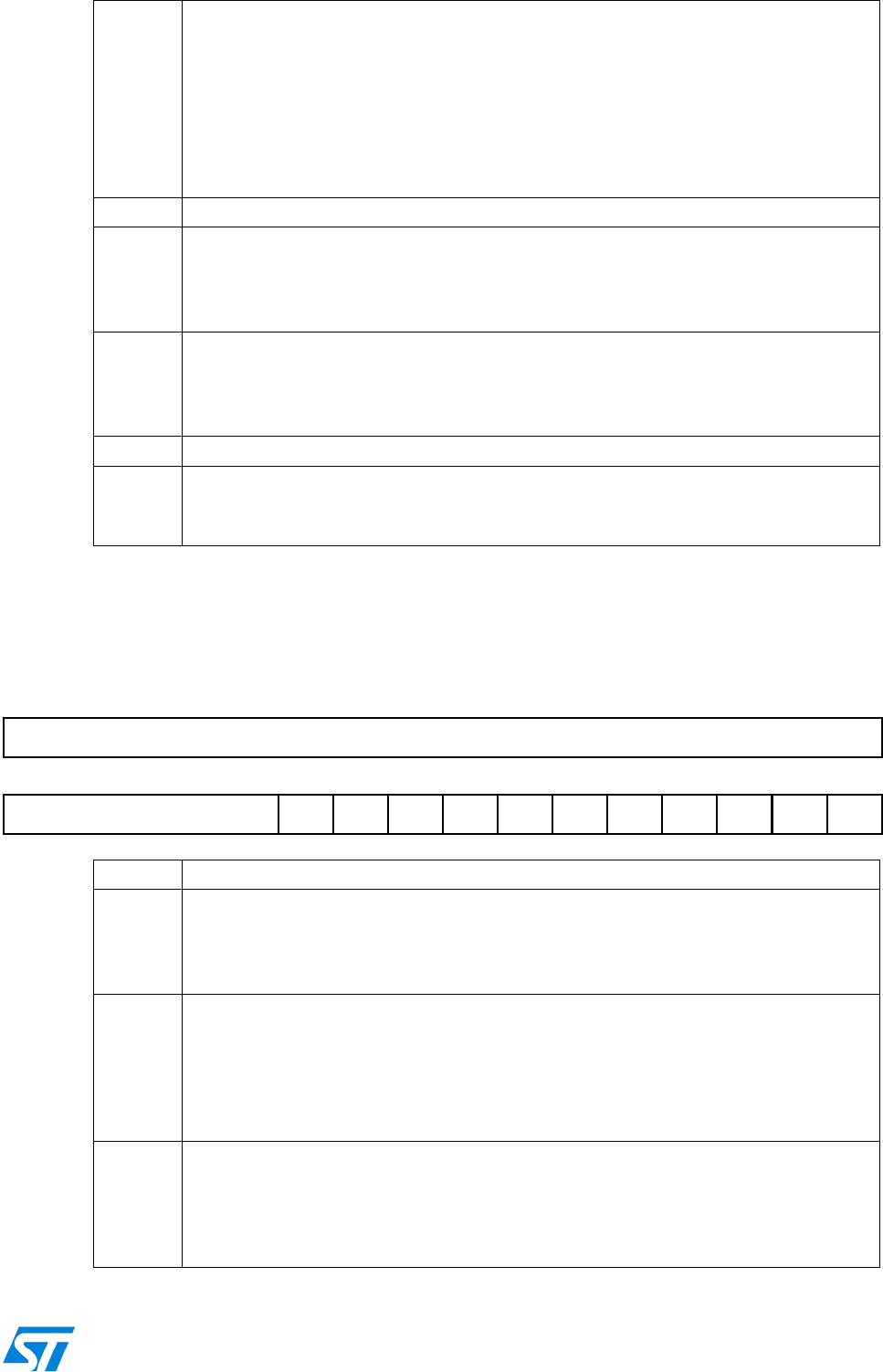

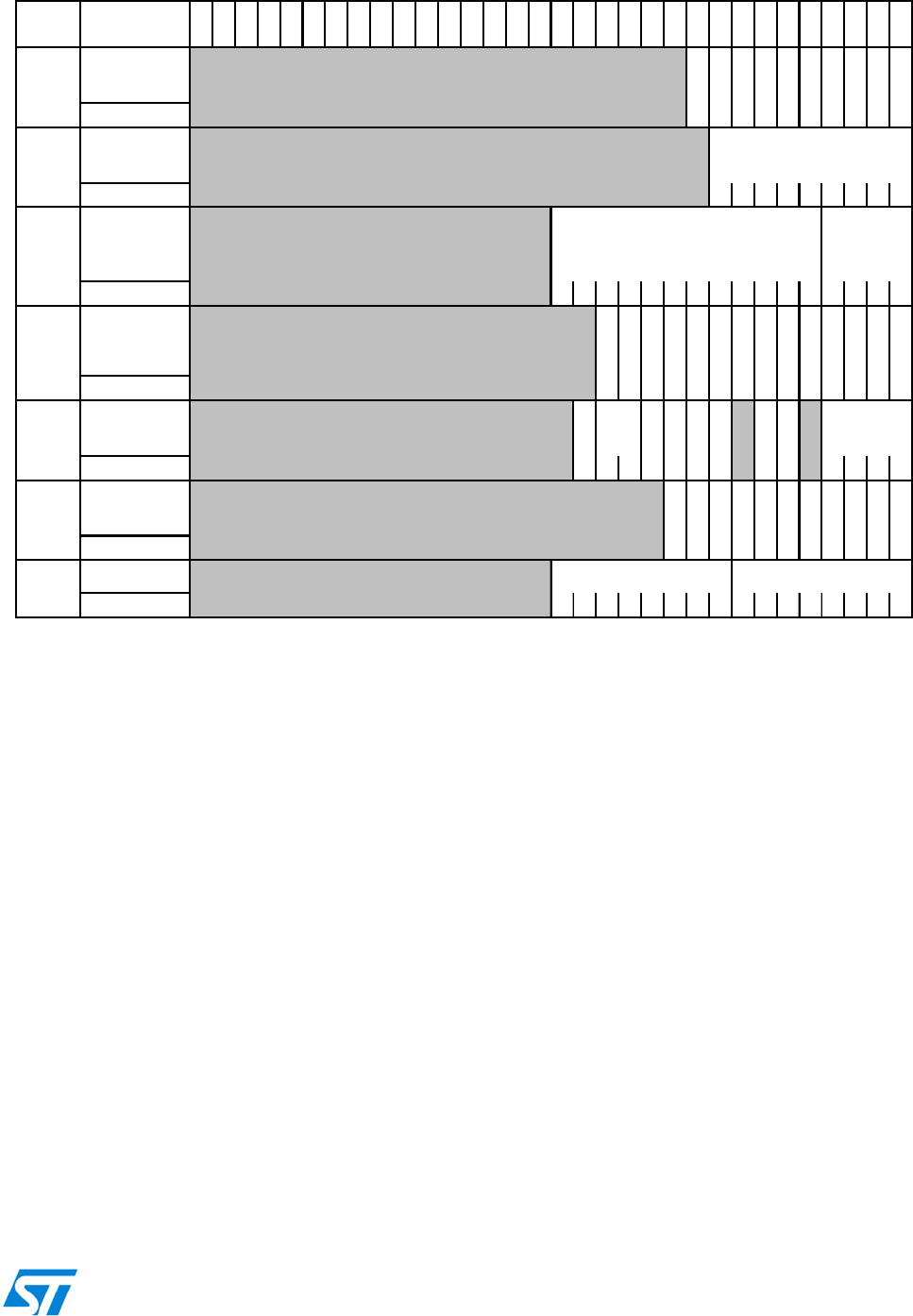

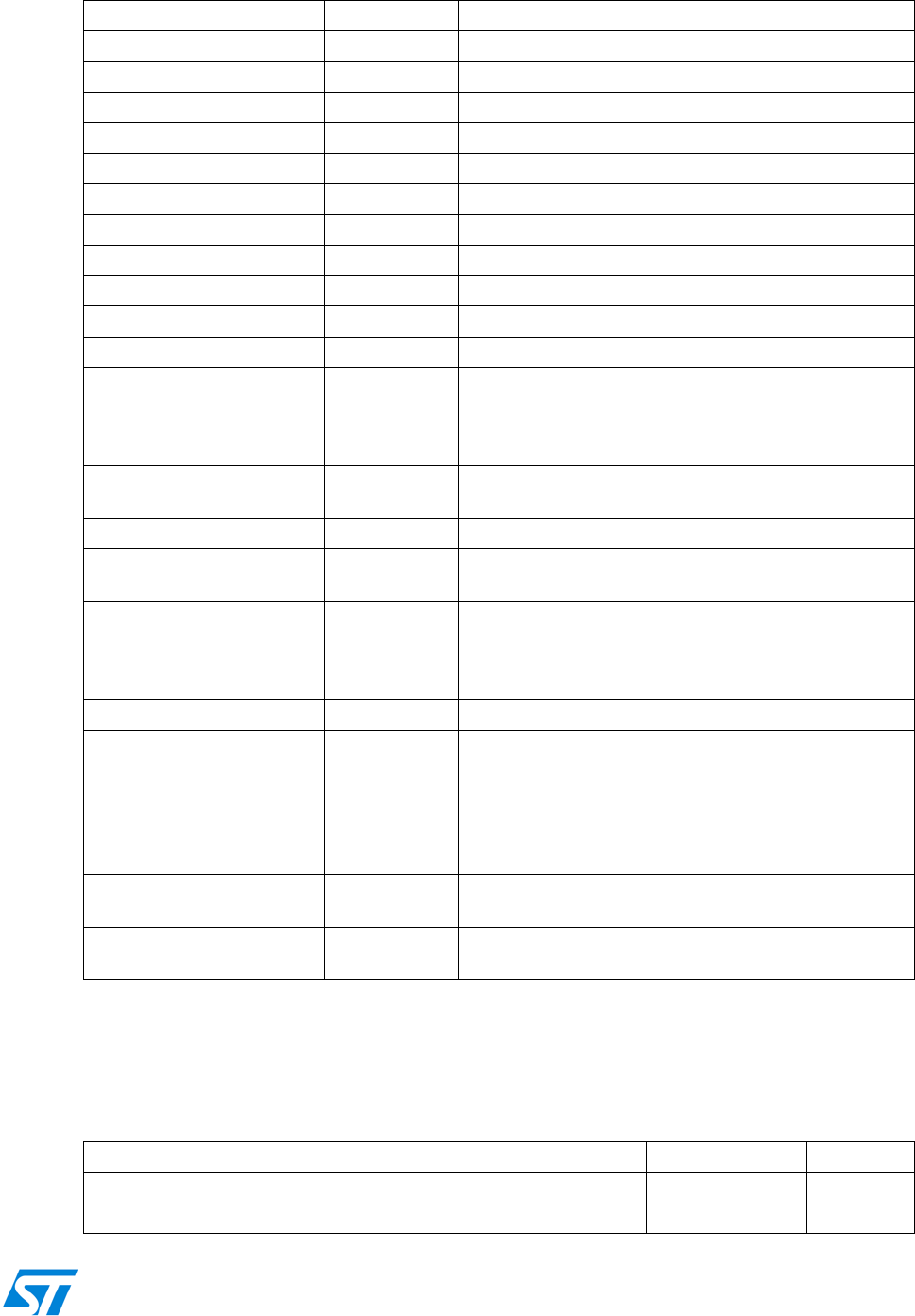

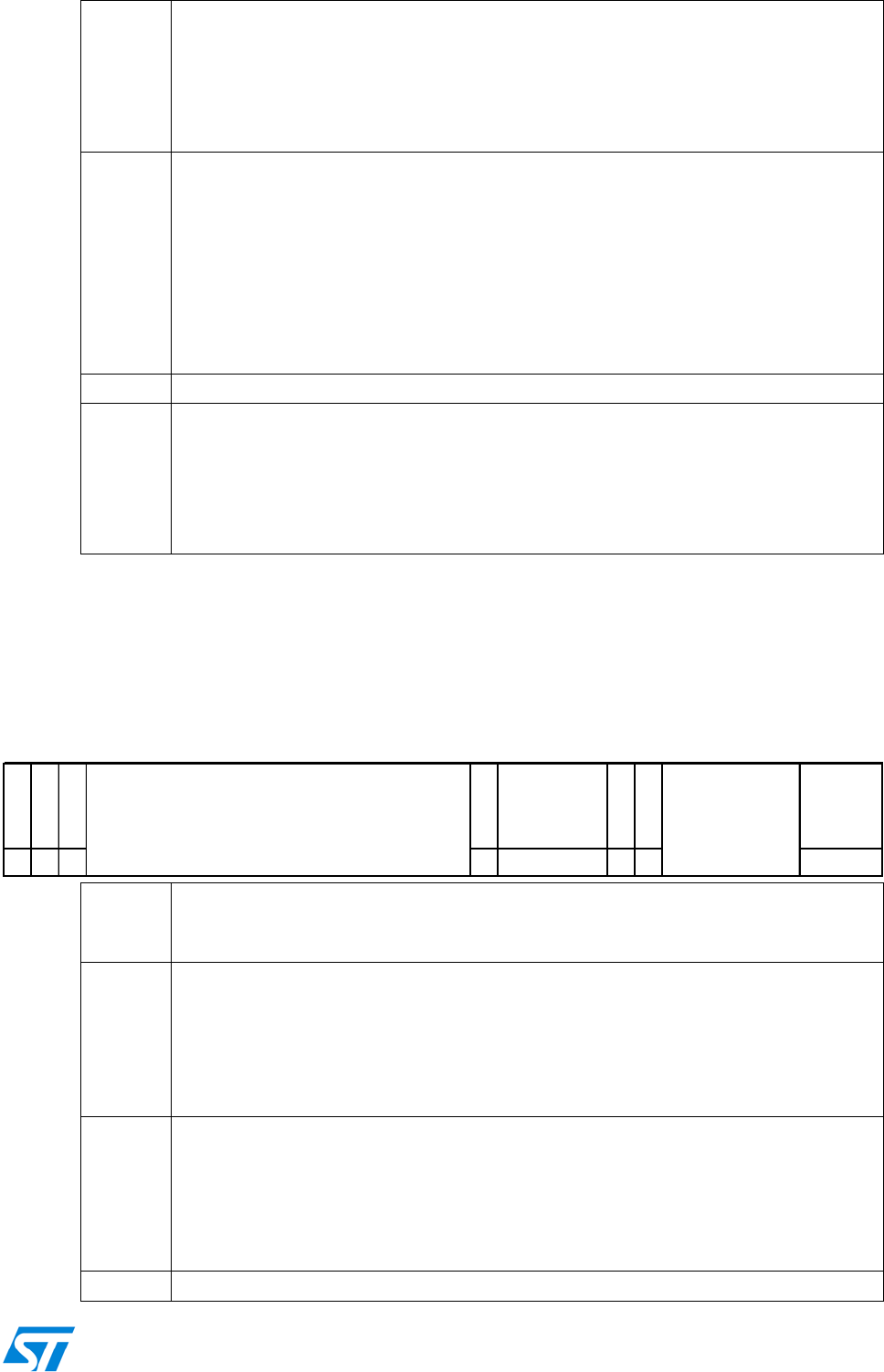

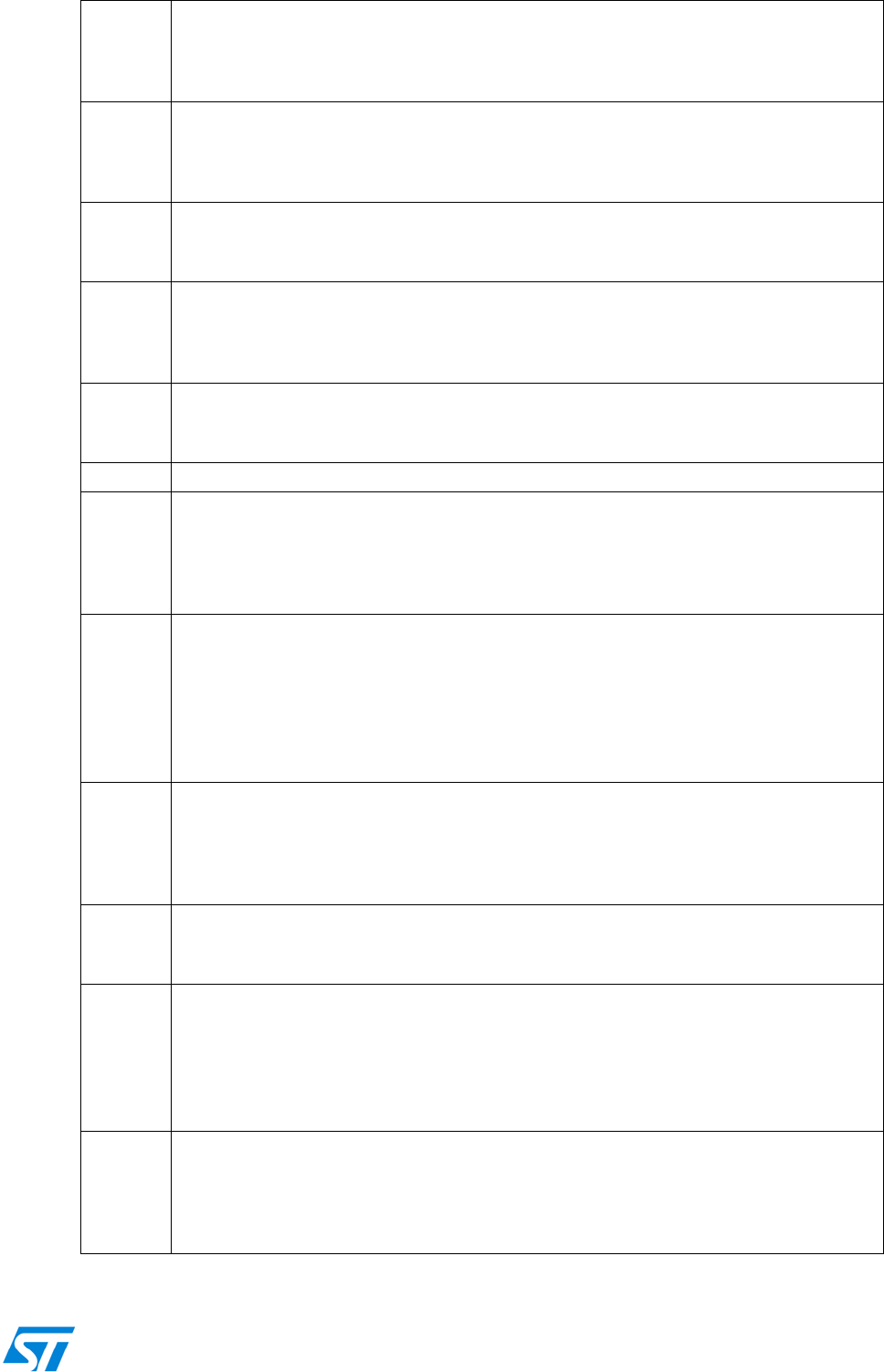

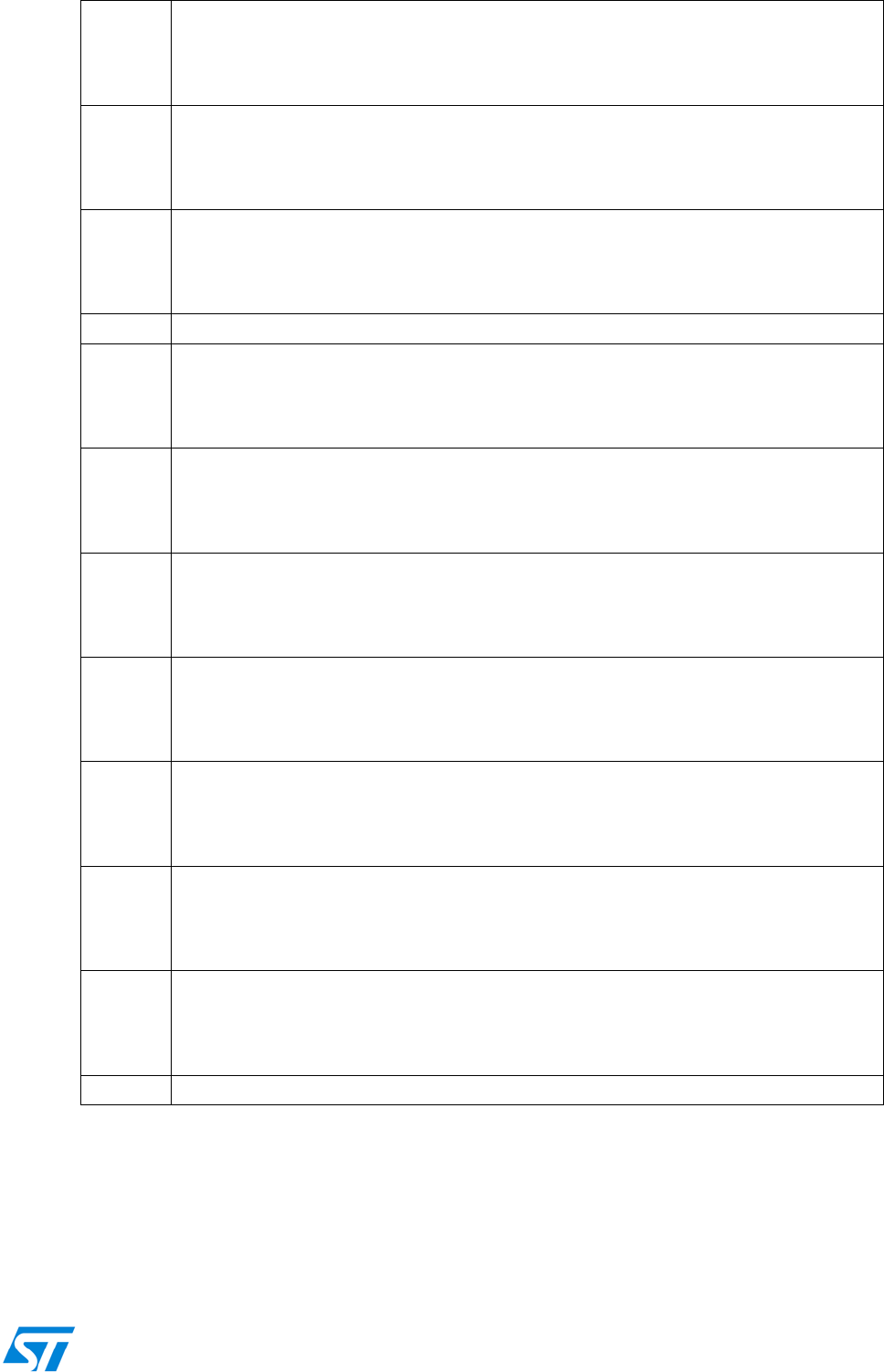

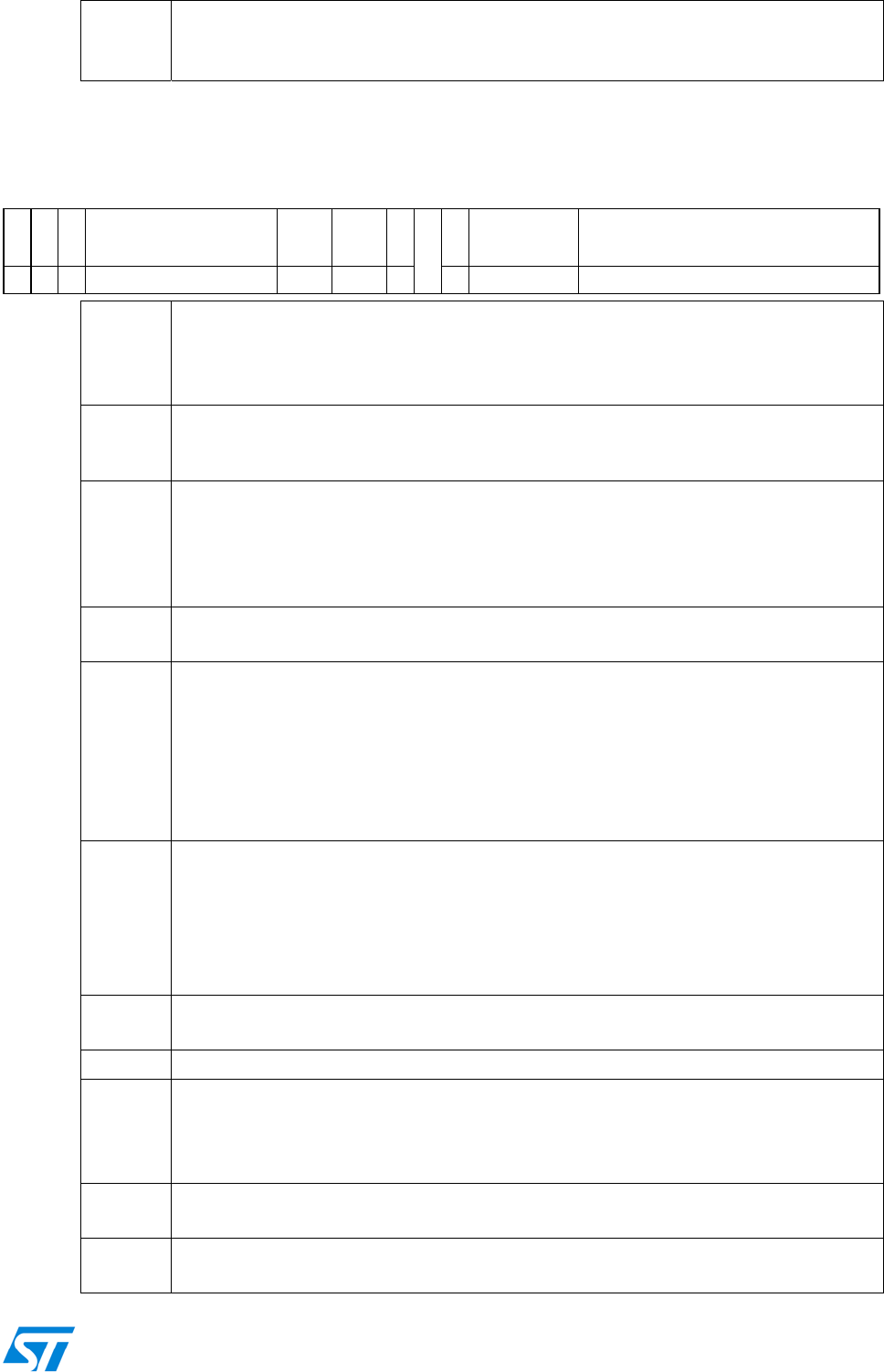

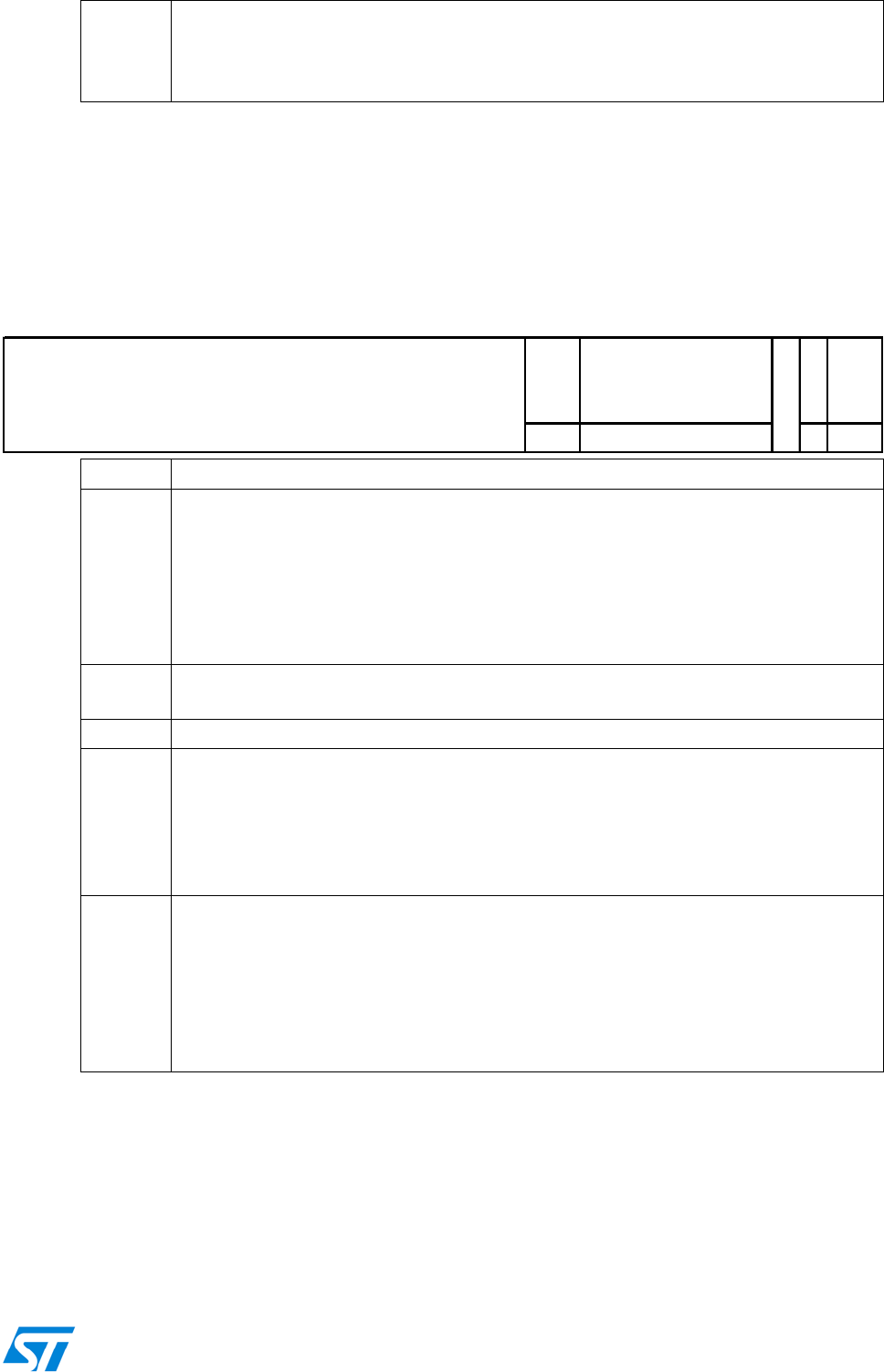

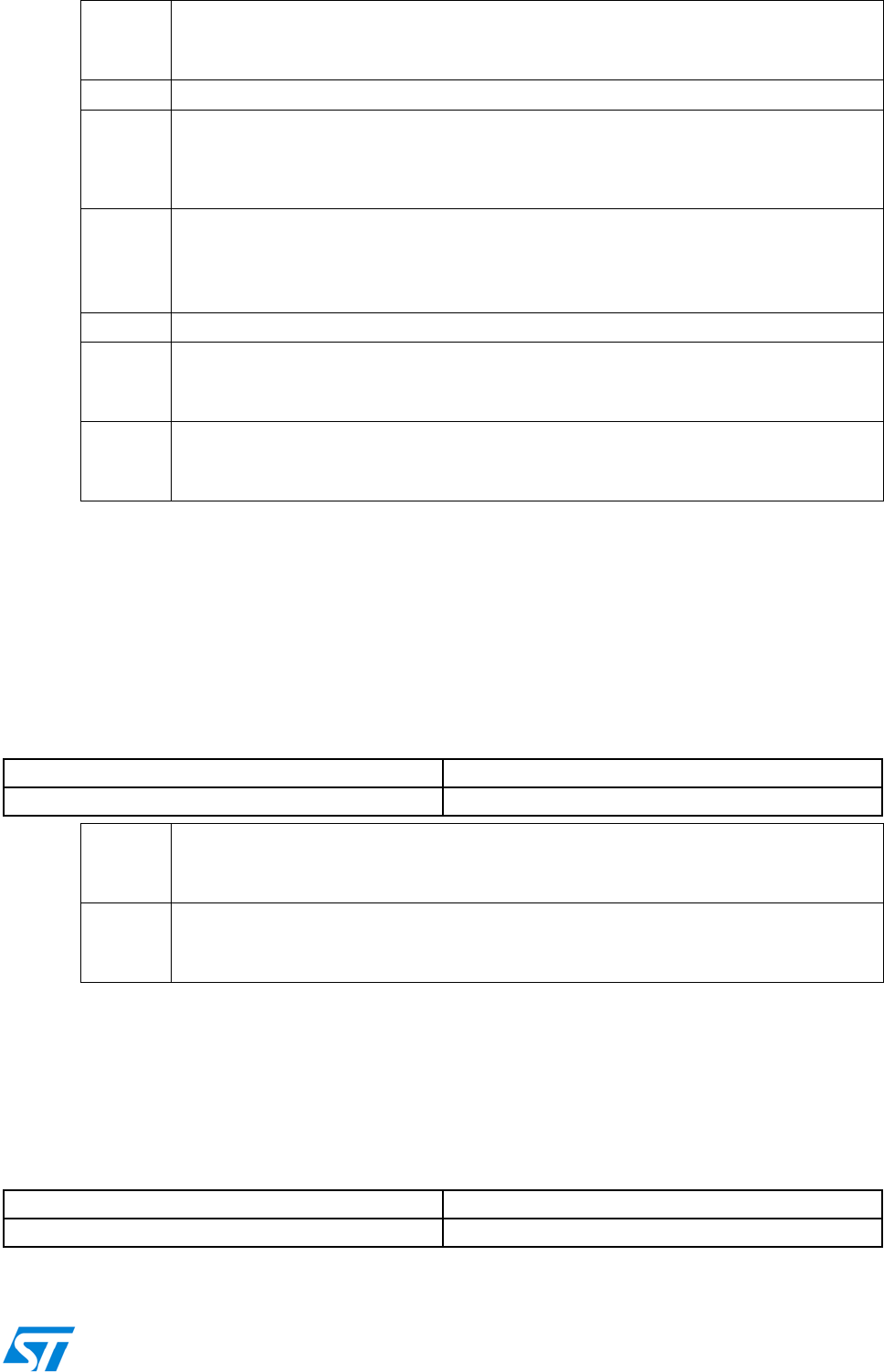

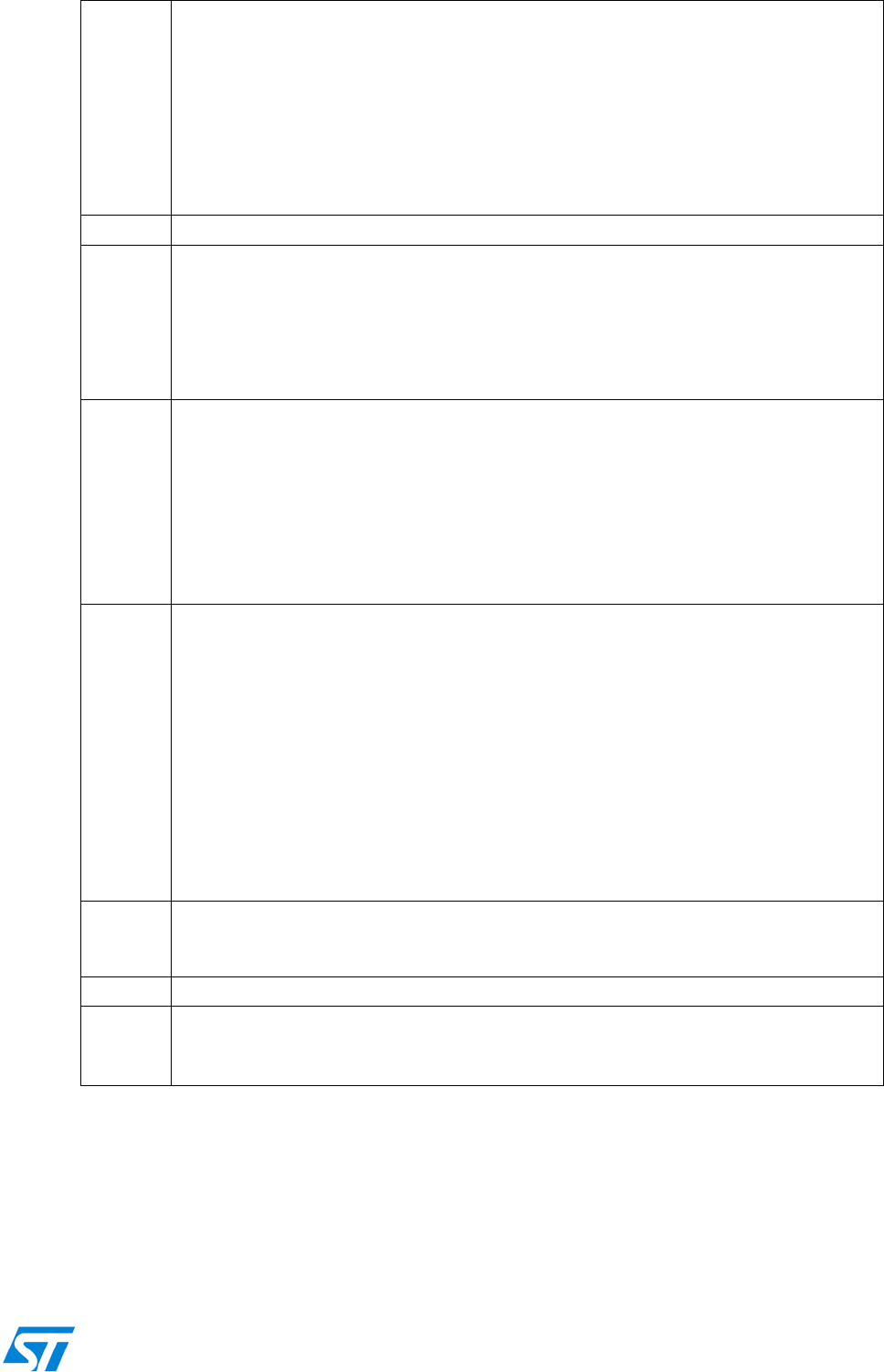

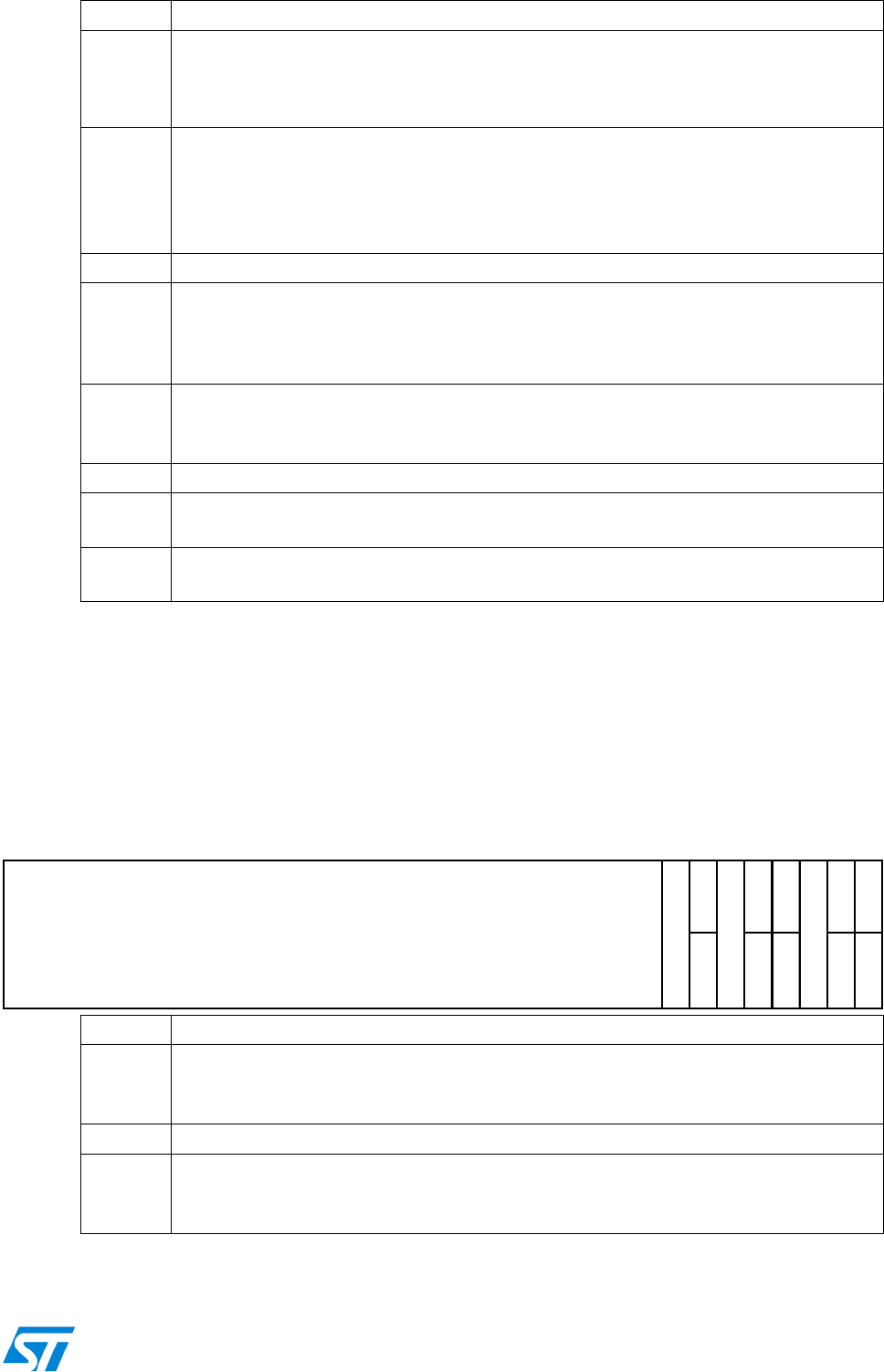

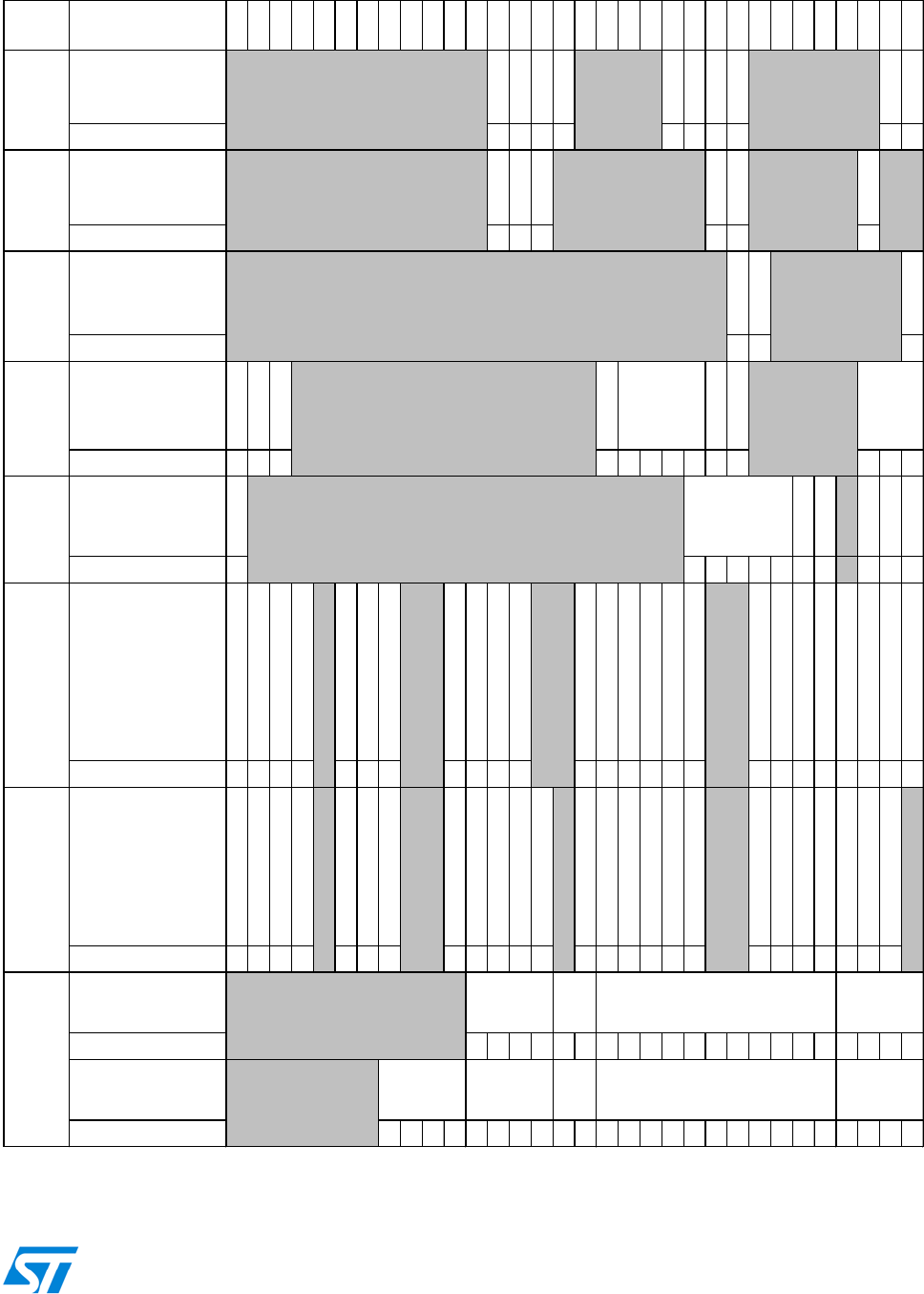

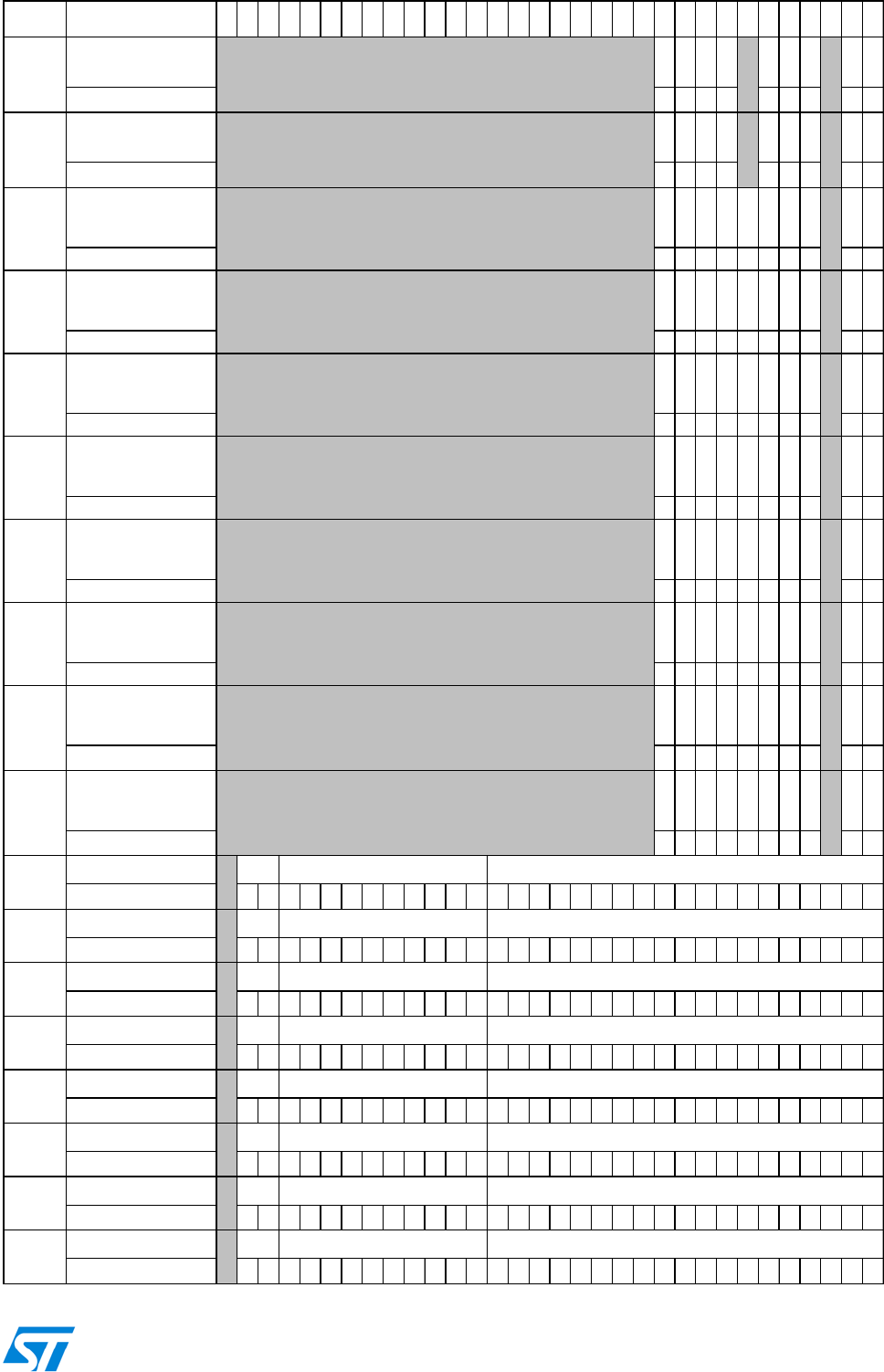

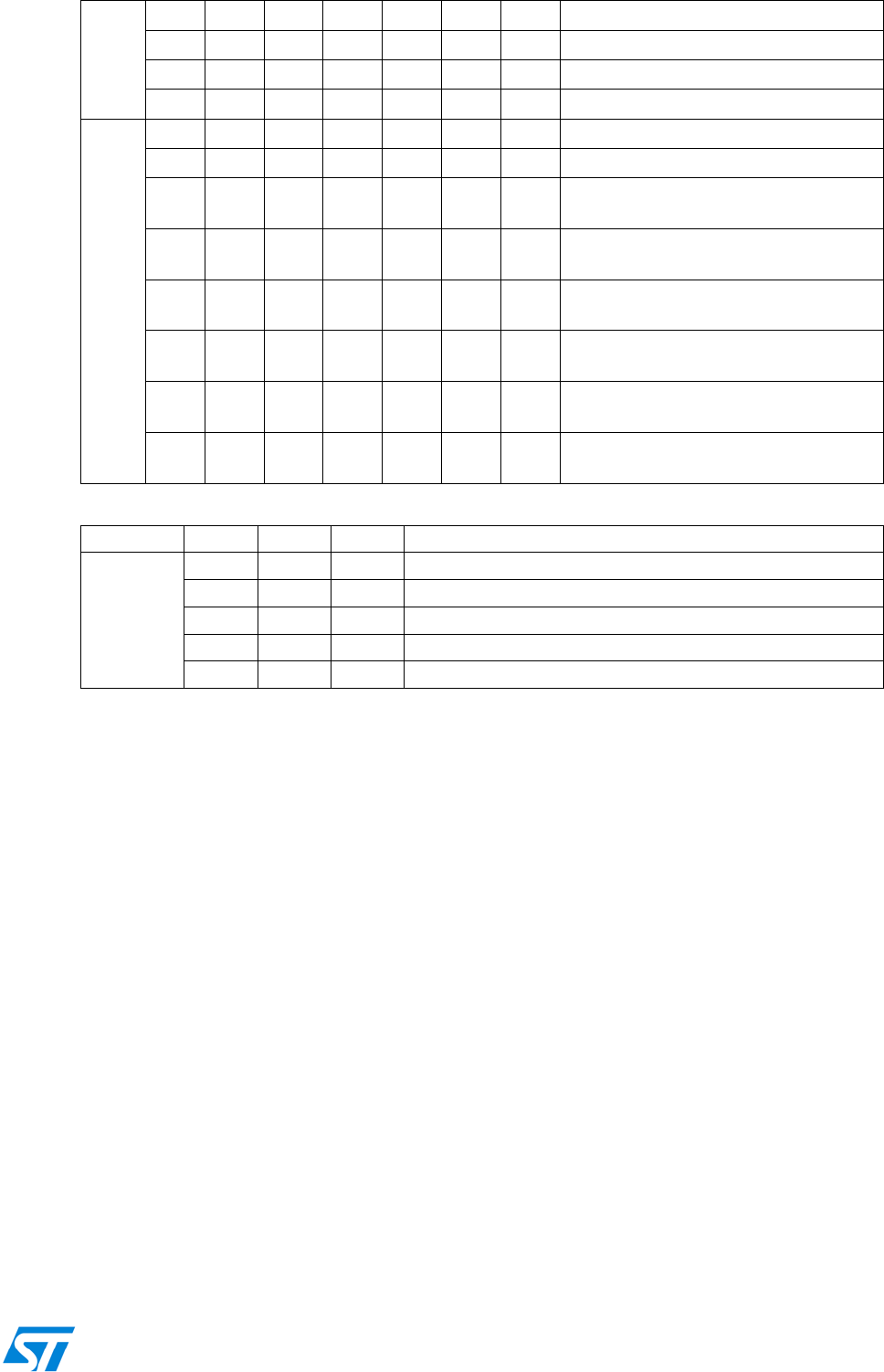

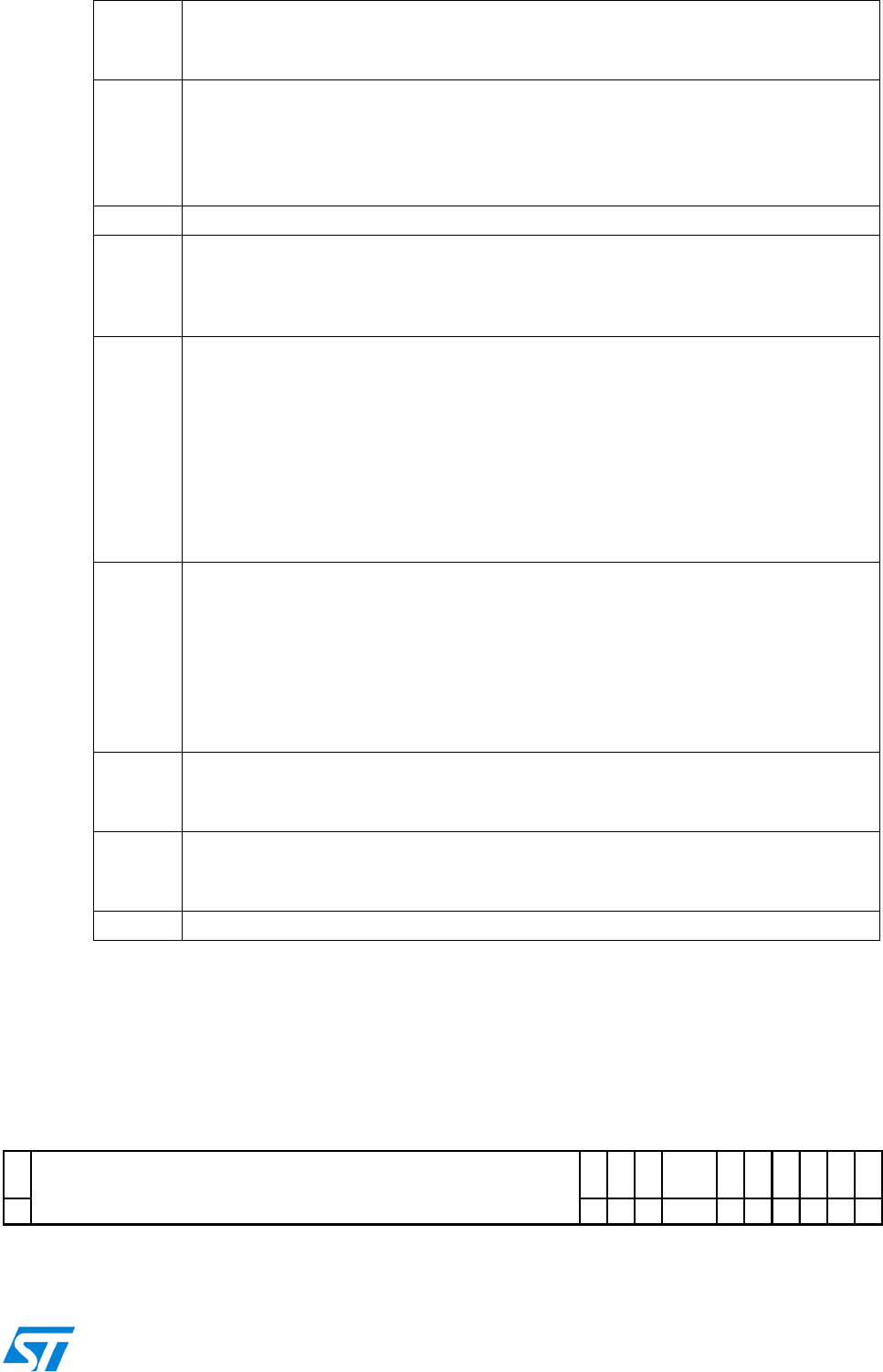

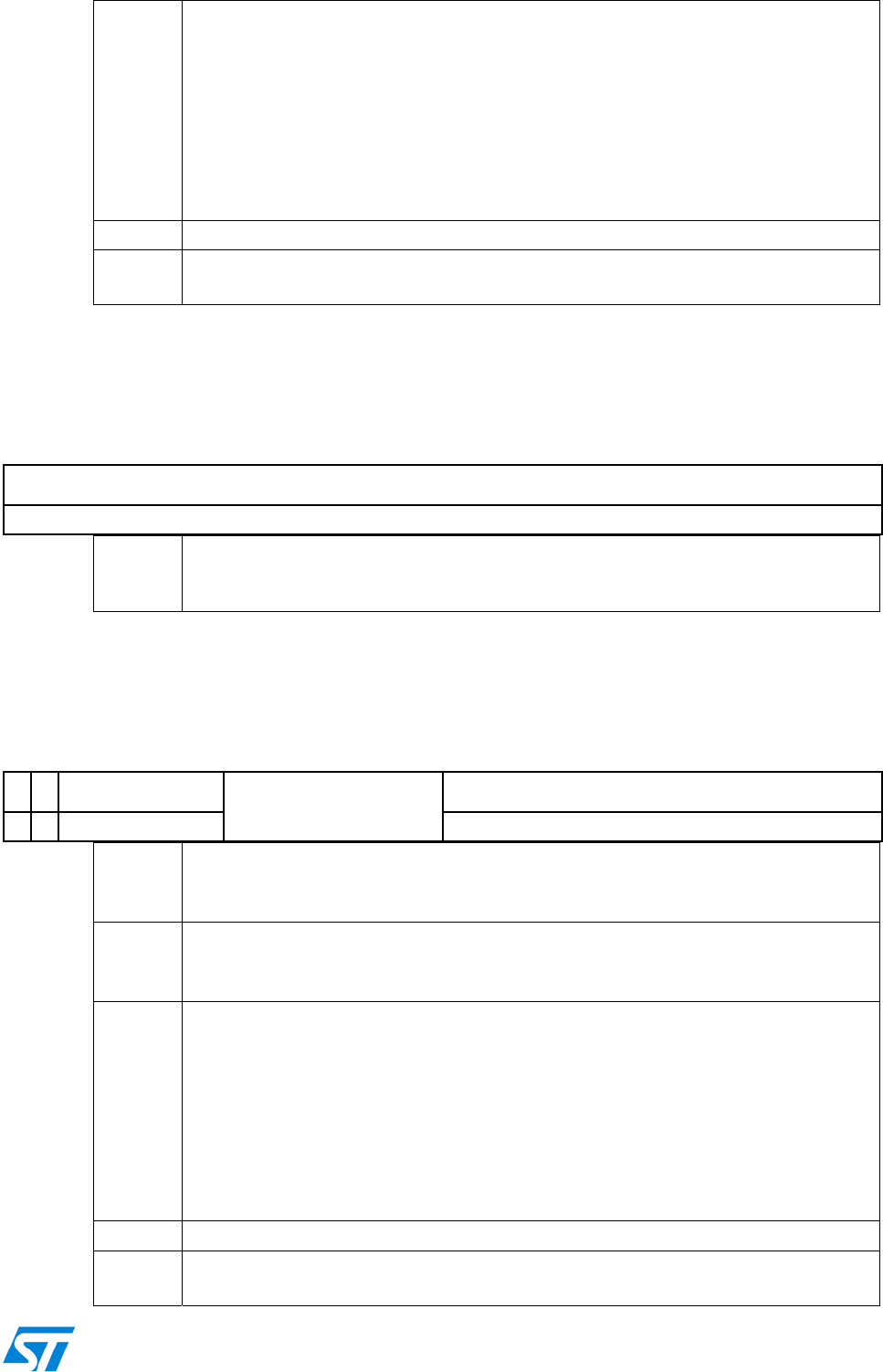

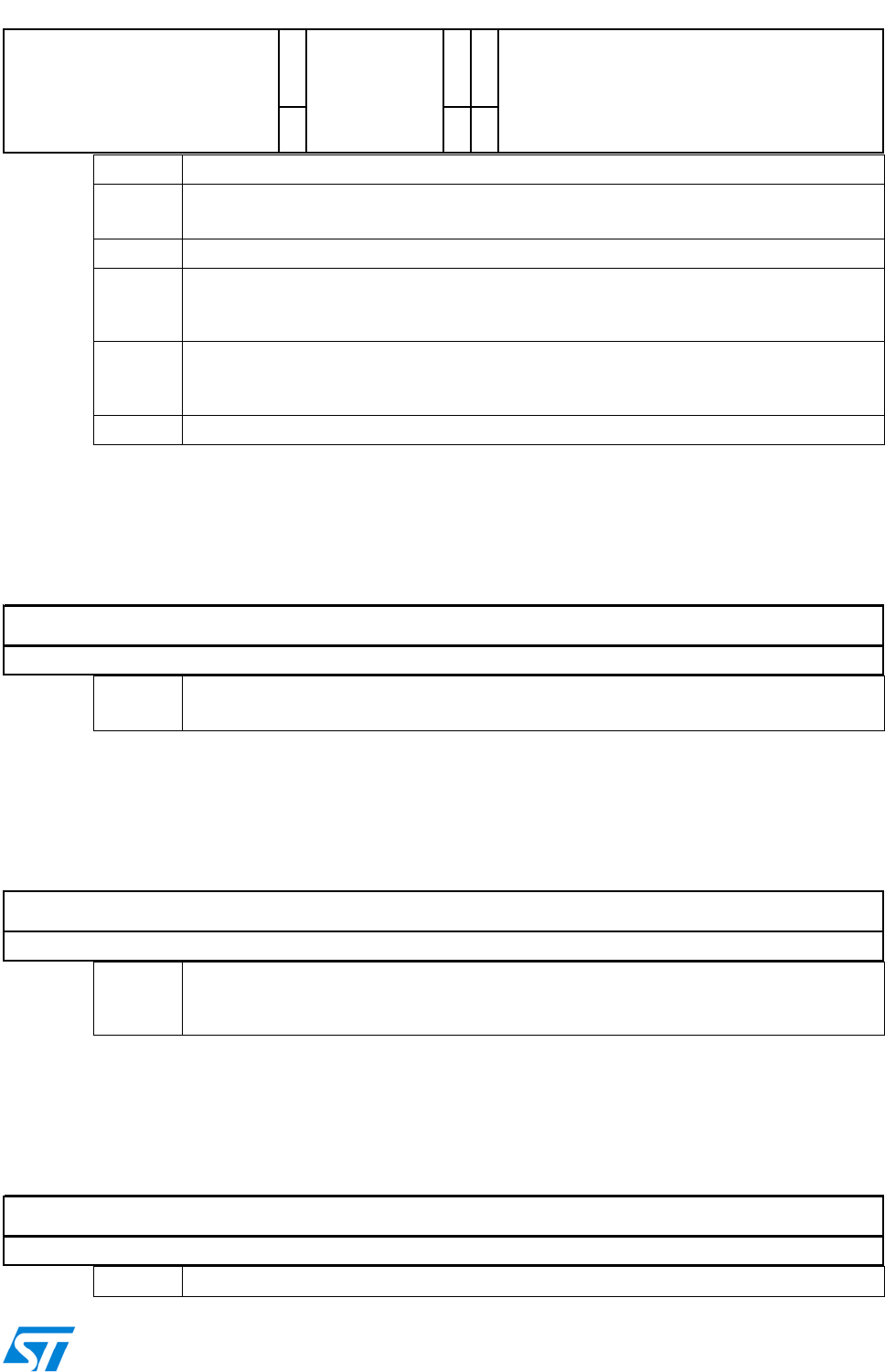

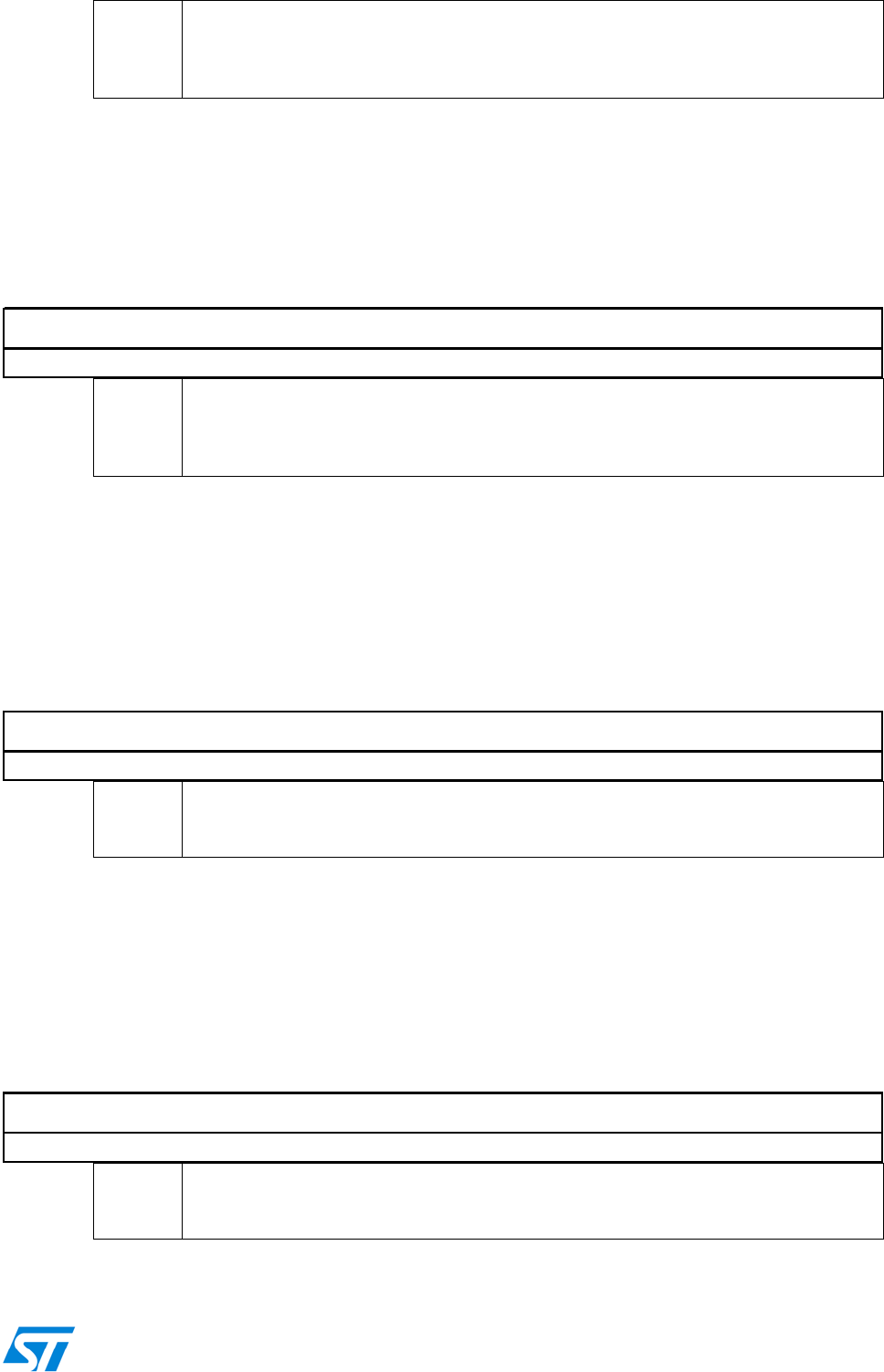

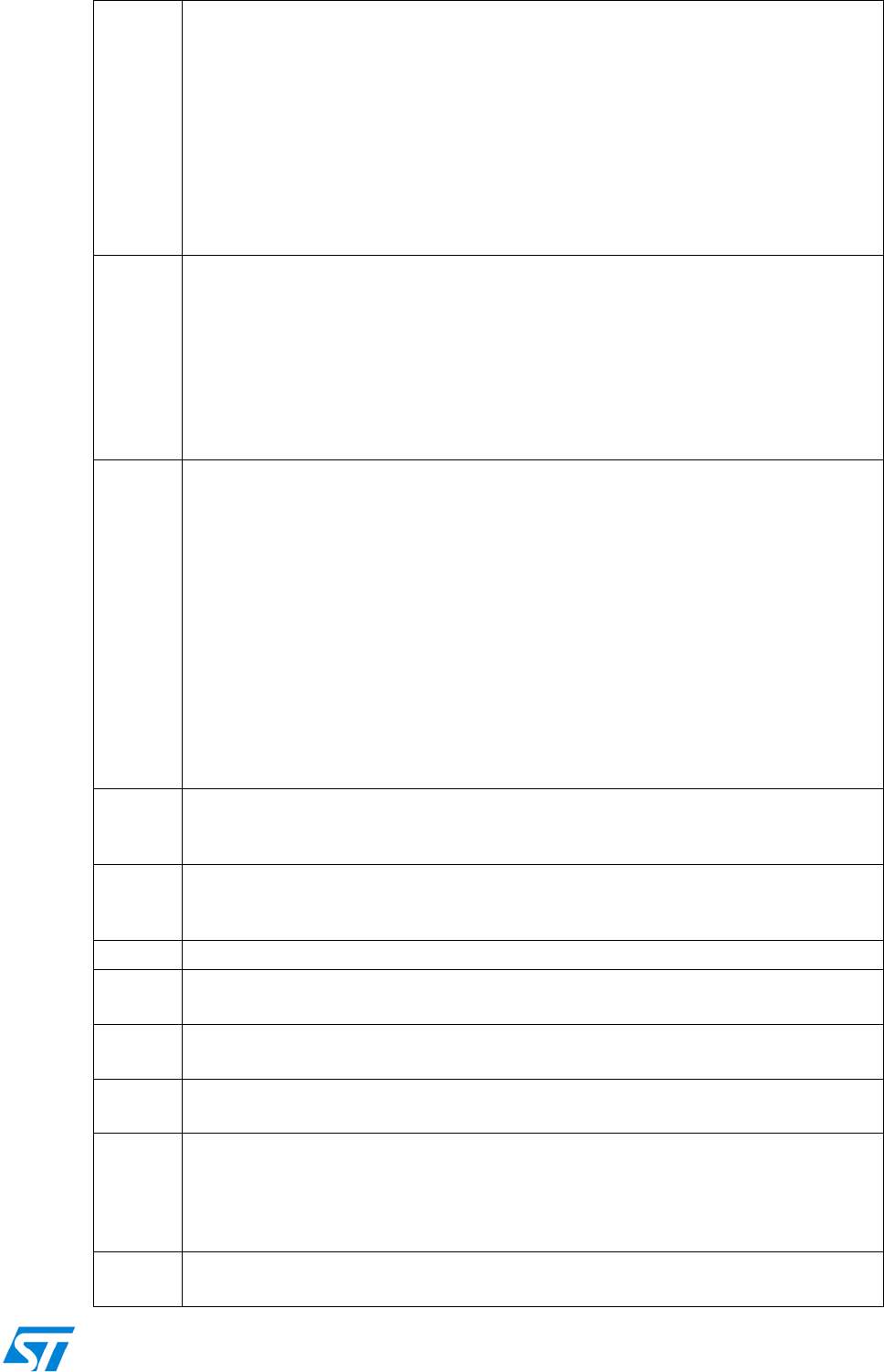

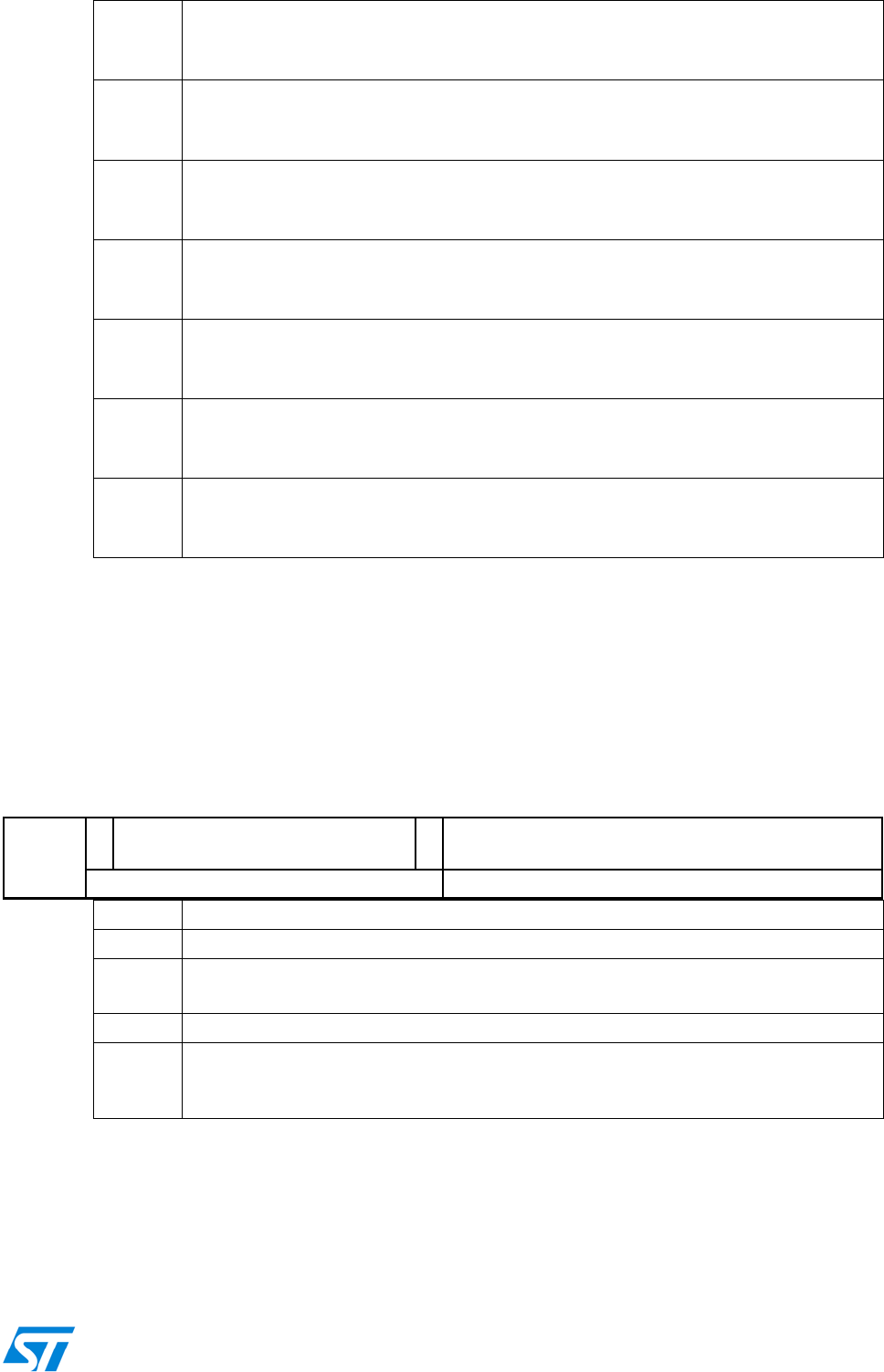

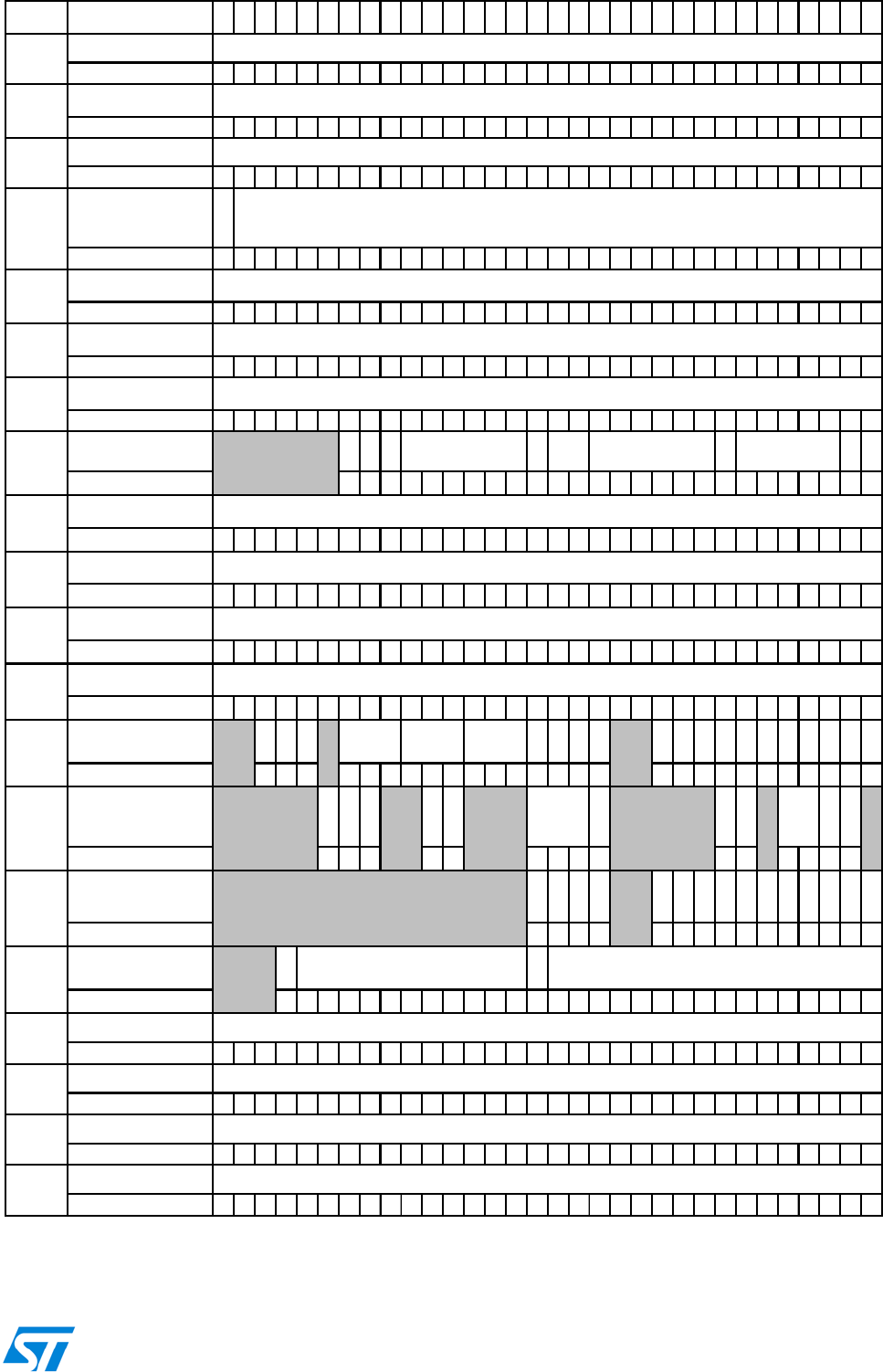

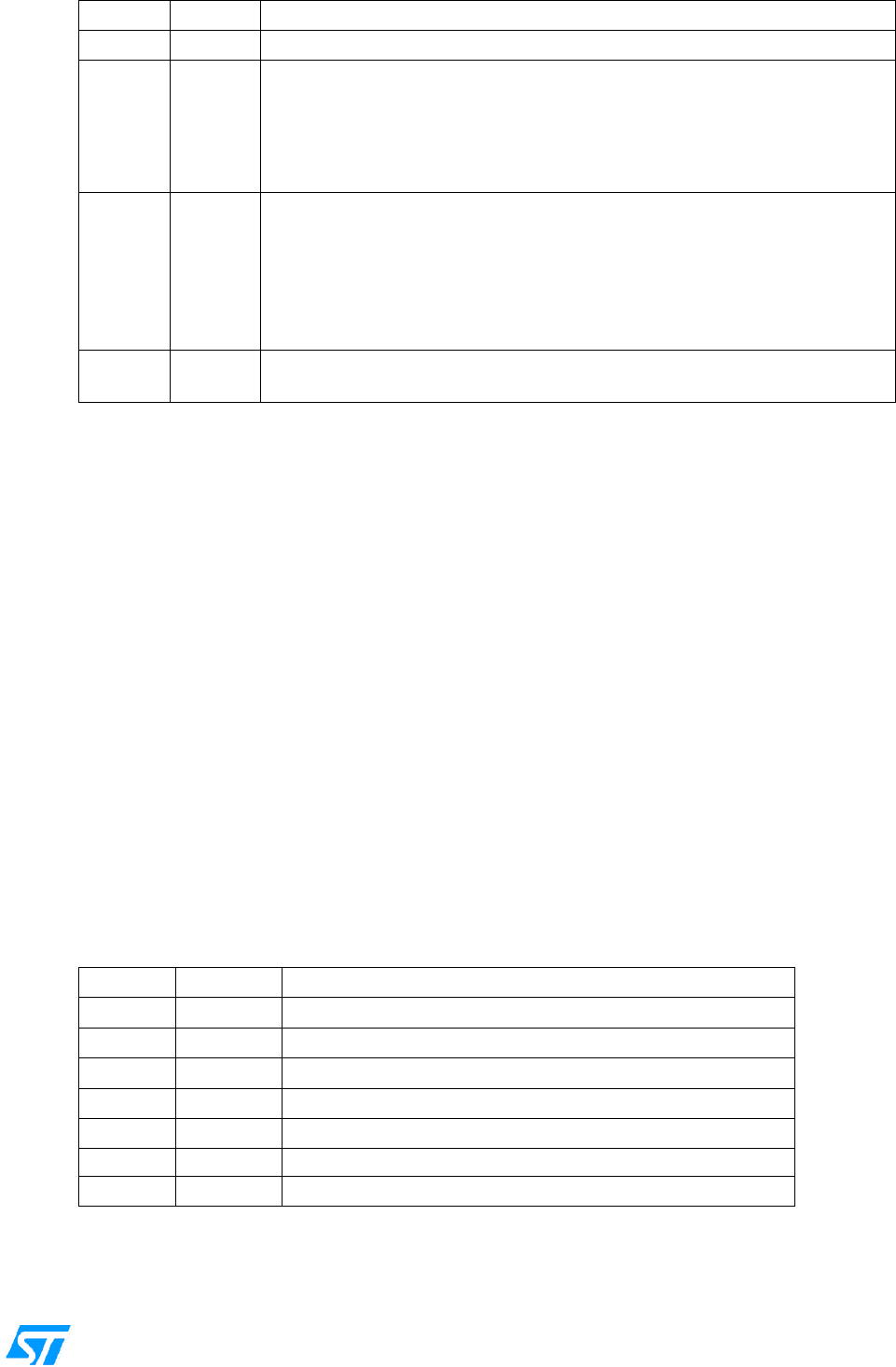

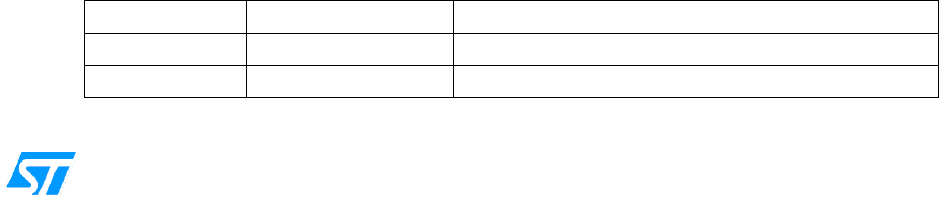

下表给出了一个交叉参考,在使用各功能模块时应重点阅读哪些章节:

功能模块

(BKP)

(GPIO)

/(ADC)

/(DAC)

(TIMx(x=1…8))

(RTC)

(IWDG)

WWDG)

(FSMC)

SDIO (SDIO)

(USB)

(bxCAN)

(SPI)

(I2C)

(USART)

OTG(OTG_FS)

(ETH)

第1章:文中的缩写 ●●●●●●●●●●● ● ● ● ● ● ●

第2章:存储器和总线构架 ●●●●●●●●●●● ● ● ● ● ● ●

第3章:CRC计算单元(CRC)

第4章:电源控制(PWR) ●●●●●●●●●●● ● ● ● ● ● ●

第5章:备份寄存器(BKP) ● ◎

第6章:小容量、中容量和大容量产品的复位

和时钟控制(RCC) 或

第7章:互联型产品的复位和时钟控制(RCC)

●●●●●●●●●●● ● ● ● ● ● ●

第8章:通用和复用功能I/O(GPIO和AFIO) ◎●●●●◎●●●●● ● ● ● ● ● ●

第9章:中断和事件 ◎◎◎◎◎ ◎◎◎◎ ◎ ◎ ◎ ◎ ◎ ◎

第10章:DMA控制器(DMA) ◎◎◎ ◎◎ ◎ ◎ ◎

第11章:模拟/数字转换(ADC) ●

第12章:数字/模拟转换(DAC) ●

第13章:高级控制定时器(TIM1和TIM8) ◎ ●

第14章:通用定时器(TIMx) ◎ ●

第15章:基本定时器(TIM6和TIM7) ◎◎●

第16章:实时时钟(RTC) ● ●

第17章:独立看门狗(IWDG) ●

第18章:窗口看门狗(WWDG) ●

第19章:灵活的静态存储器控制器(FSMC) ●

第20章:SDIO接口(SDIO) ●

第21章:USB全速设备接口(USB) ●

第22章:控制器局域网(bxCAN) ●

第23章:串行外设接口(SPI) ●

第24章:I2C接口 ●

第25章:通用同步异步收发器(USART) ●

第26章:USB OTG全速(OTG_FS) ●

第27章:以太网(ETH):具有DMA控制器的

介质访问控制(MAC)

●

第28章:器件电子签名

第29章:调试支持(DBG) ◎◎◎◎◎◎◎◎◎◎◎ ◎ ◎ ◎ ◎ ◎ ◎

● 表示对应的章节是必读的

◎ 表示对应的章节是选读的

注:请区分第

7

章的内容只适合于互联型产品,第

6

章的内容适合于除互联型产品以外的产品。

STM32F10xxx参考手册

参考手册

STM32F101xx, STM32F102xx、STM32F103xx、STM32F105xx

和STM32F107xx,ARM 内核 32 位高性能微控制器

导言

本参考手册针对应用开发,提供关于如何使用STM32F101xx、STM32F102xx、STM32F103和

STM32F105xx/STM32F107xx 微控制器的存储器和外设的详细信息。在本参考手册中

STM32F101xx 、STM32F102xx 、STM32F103 和STM32F105xx/STM32F107xx 被统称为

STM32F10xxx。

STM32F10xxx系列拥有不同的存储器容量、封装和外设配置。

关于订货编号、电气和物理性能参数,请参考小容量、中容量和大容量的STM32F101xx和

STM32F103xx 的数据手册,小容量和中容量的STM32F102xx 数据手册和STM32F105xx/

STM32F107xx互联型产品的数据手册。

STM32F10xxx闪存编程手册

参照2009年12月 RM0008 Reference Manual 英文第10版

关于芯片内部闪存的编程,擦除和保护操作,请参考 。

关于ARM Cortex™-M3内核的具体信息,请参考Cortex™-M3技术参考手册。

相关文档

● Cortex™-M3技术参考手册,可按下述链接下载:

http://infocenter.arm.com/help/topic/com.arm.doc.ddi0337e/DDI0337E_cortex_m3_r1p1_trm.pdf

下述文档可在ST网站下载(http://www.st.com/mcu/):

● STM32F101xx、STM32F102xx和STM32F103xx的数据手册。

● STM32F10xxx闪存编程手册。

相关数据手册下载地址:

小容量STM32F101xx:http://www.st.com/stonline/products/literature/ds/15058.pdf

中容量STM32F101xx:http://www.st.com/stonline/products/literature/ds/13586.pdf

大容量STM32F101xx:http://www.st.com/stonline/products/literature/ds/14610.pdf

小容量STM32F102xx:http://www.st.com/stonline/products/literature/ds/15057.pdf

中容量STM32F102xx:http://www.st.com/stonline/products/literature/ds/15056.pdf

小容量STM32F103xx:http://www.st.com/stonline/products/literature/ds/15060.pdf

中容量STM32F103xx:http://www.st.com/stonline/products/literature/ds/13587.pdf

大容量STM32F103xx:http://www.st.com/stonline/products/literature/ds/14611.pdf

互联型STM32F105xx/STM32F107xx:http://www.st.com/stonline/products/literature/ds/15274.pdf

STM32F10xxx Cortex-M3编程手册:http://www.st.com/stonline/products/literature/pm/15491.pdf

本译文仅供参考,如有翻译错误,请以英文原稿为准。请读者随时注意在ST网站下载更新版本

目录 STM32F10xxx参考手册

目录

1 文中的缩写 24

1.1 寄存器描述表中使用的缩写列表 24

1.2 术语表 24

1.3 可用的外设 24

2 存储器和总线构架 25

2.1 系统构架 25

2.2 存储器组织 27

2.3 存储器映像 28

2.3.1 嵌入式SRAM 29

2.3.2 位段 29

2.3.3 嵌入式闪存 30

2.4 启动配置 33

3 CRC计算单元(CRC) 34

3.1 CRC简介 34

3.2 CRC主要特性 34

3.3 CRC功能描述 34

3.4 CRC寄存器 35

3.4.1 数据寄存器(CRC_DR) 35

3.4.2 独立数据寄存器(CRC_IDR) 35

3.4.3 控制寄存器(CRC_CR) 36

3.4.4 CRC寄存器映像 36

4 电源控制(PWR) 37

4.1 电源 37

4.1.1 独立的A/D转换器供电和参考电压 37

4.1.2 电池备份区域 38

4.1.3 电压调节器 38

4.2 电源管理器 38

4.2.1 上电复位(POR)和掉电复位(PDR) 38

4.2.2 可编程电压监测器(PVD) 39

4.3 低功耗模式 40

4.3.1 降低系统时钟 40

4.3.2 外部时钟的控制 40

4.3.3 睡眠模式 40

4.3.4 停止模式 41

4.3.5 待机模式 42

4.3.6 低功耗模式下的自动唤醒(AWU) 43

4.4 电源控制寄存器 44

4.4.1 电源控制寄存器(PWR_CR) 44

4.4.2 电源控制/状态寄存器(PWR_CSR) 45

4.4.3 PWR寄存器地址映像 46

5 备份寄存器(BKP) 47

5.1 BKP简介 47

5.2 BKP特性 47

7/754

参照2009年12月 RM0008 Reference Manual 英文第10版

本译文仅供参考,如有翻译错误,请以英文原稿为准。请读者随时注意在ST网站下载更新版本

目录 STM32F10xxx参考手册

5.3 BKP功能描述 47

5.3.1 侵入检测 47

5.3.2 RTC校准 48

5.4 BKP寄存器描述 48

5.4.1 备份数据寄存器x(BKP_DRx) (x = 1 … 10) 48

5.4.2 RTC时钟校准寄存器(BKP_RTCCR) 48

5.4.3 备份控制寄存器(BKP_CR) 49

5.4.4 备份控制/状态寄存器(BKP_CSR) 49

5.4.5 BKP寄存器映像 51

6 小容量、中容量和大容量产品的复位和时钟控制(RCC) 54

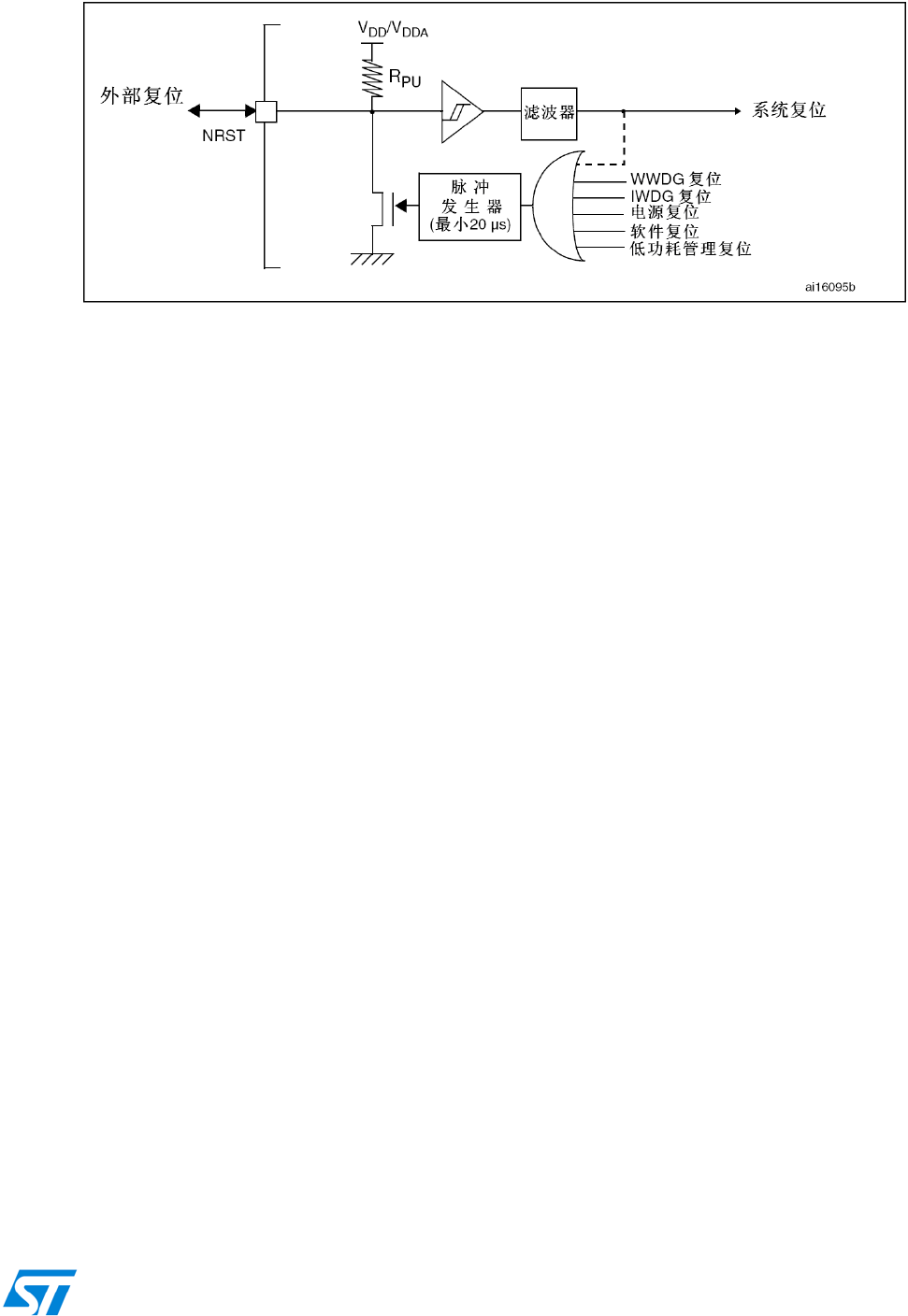

6.1 复位 54

6.1.1 系统复位 54

6.1.2 电源复位 54

6.1.3 备份域复位 55

6.2 时钟 55

6.2.1 HSE时钟 57

6.2.2 HSI时钟 57

6.2.3 PLL 58

6.2.4 LSE时钟 58

6.2.5 LSI时钟 58

6.2.6 系统时钟(SYSCLK)选择 59

6.2.7 时钟安全系统(CSS) 59

6.2.8 RTC时钟 59

6.2.9 看门狗时钟 59

6.2.10 时钟输出 59

6.3 RCC寄存器描述 60

6.3.1 时钟控制寄存器(RCC_CR) 60

6.3.2 时钟配置寄存器(RCC_CFGR) 61

6.3.3 时钟中断寄存器 (RCC_CIR) 63

6.3.4 APB2外设复位寄存器 (RCC_APB2RSTR) 65

6.3.5 APB1外设复位寄存器 (RCC_APB1RSTR) 67

6.3.6 AHB外设时钟使能寄存器 (RCC_AHBENR) 69

6.3.7 APB2外设时钟使能寄存器(RCC_APB2ENR) 70

6.3.8 APB1外设时钟使能寄存器(RCC_APB1ENR) 71

6.3.9 备份域控制寄存器 (RCC_BDCR) 74

6.3.10 控制/状态寄存器 (RCC_CSR) 75

6.3.11 RCC寄存器地址映像 77

7 互联型产品的复位和时钟控制(RCC) 78

7.1 复位 78

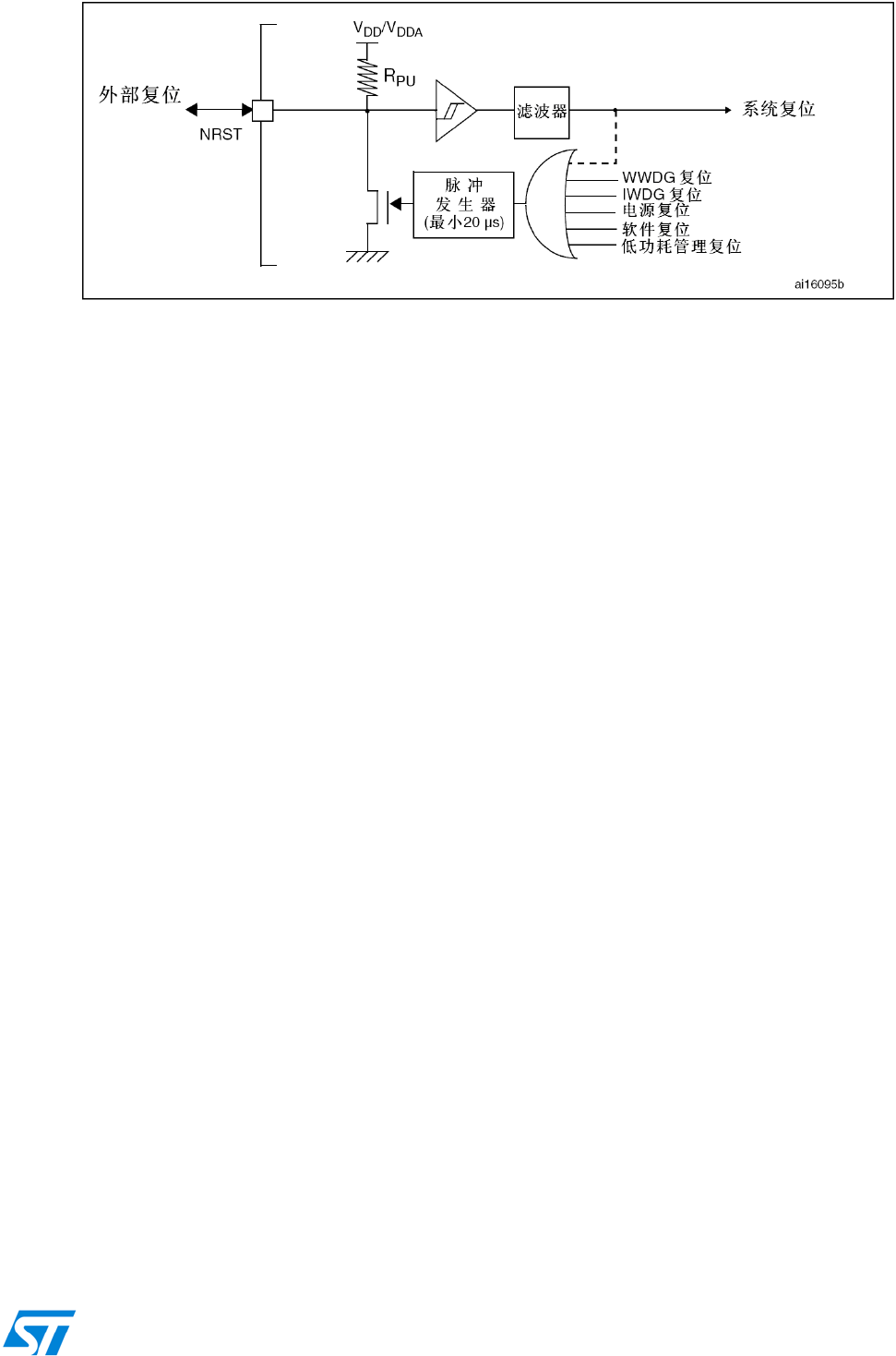

7.1.1 系统复位 78

7.1.2 电源复位 78

7.1.3 备份域复位 79

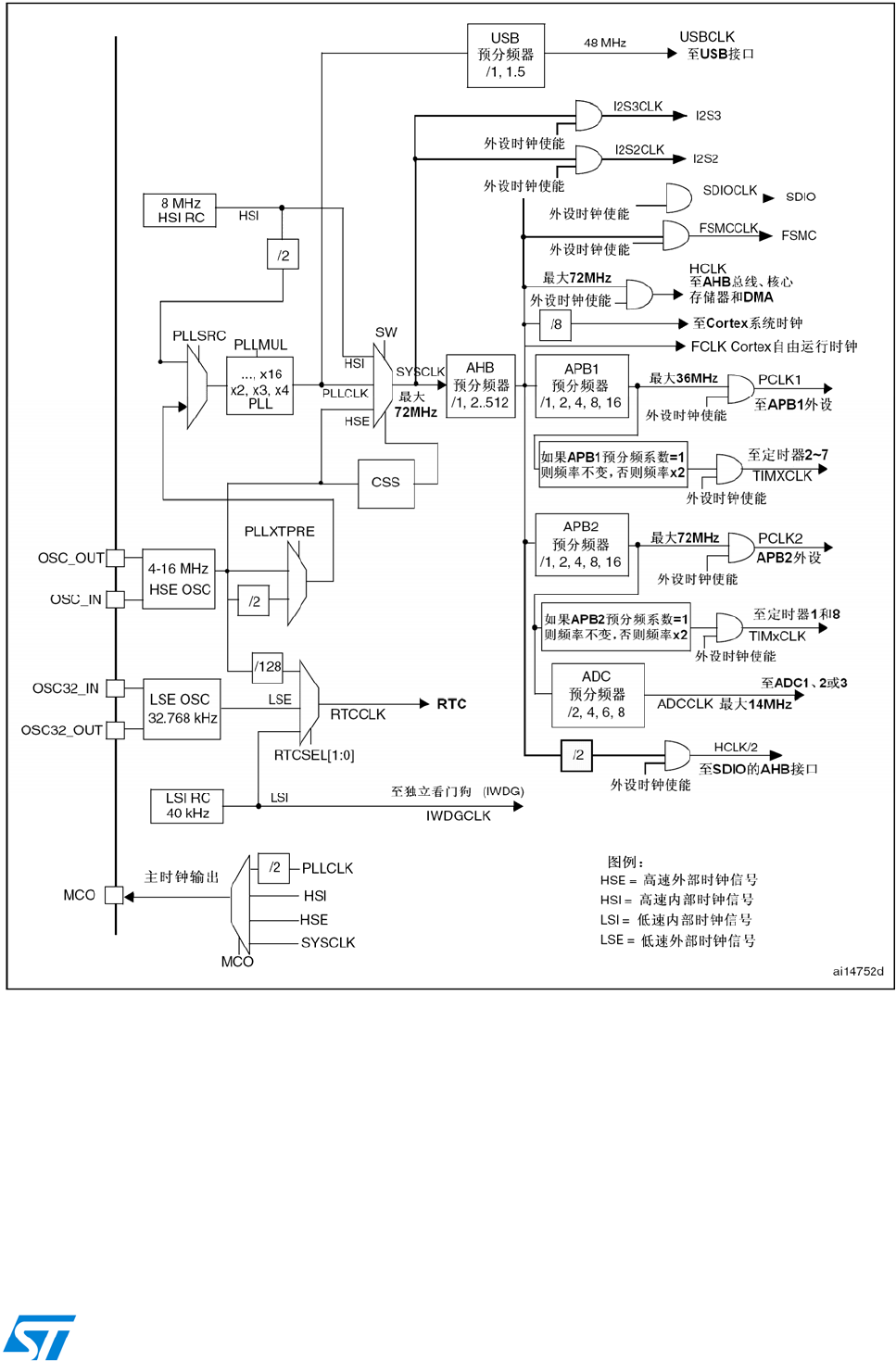

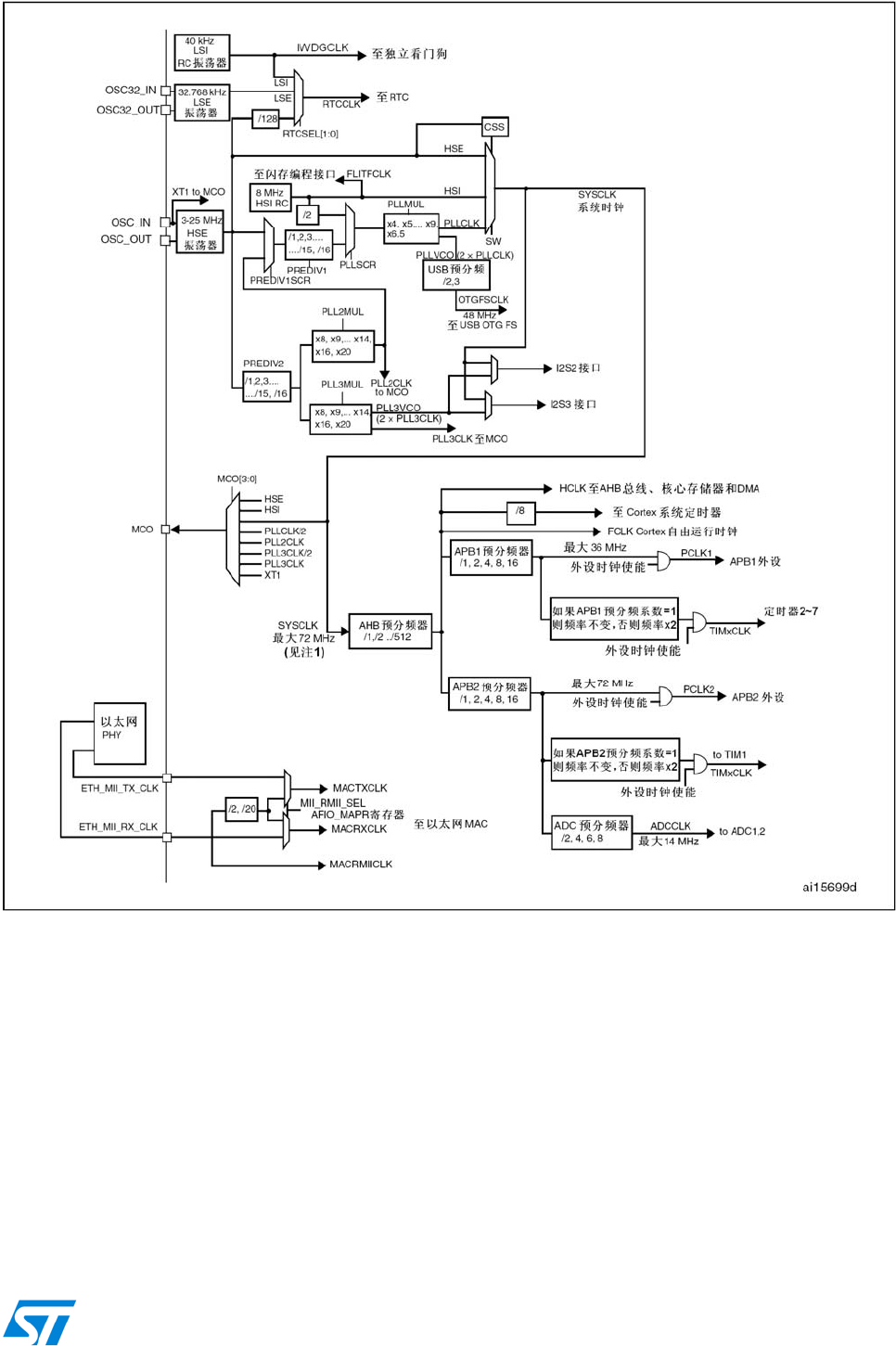

7.2 时钟 79

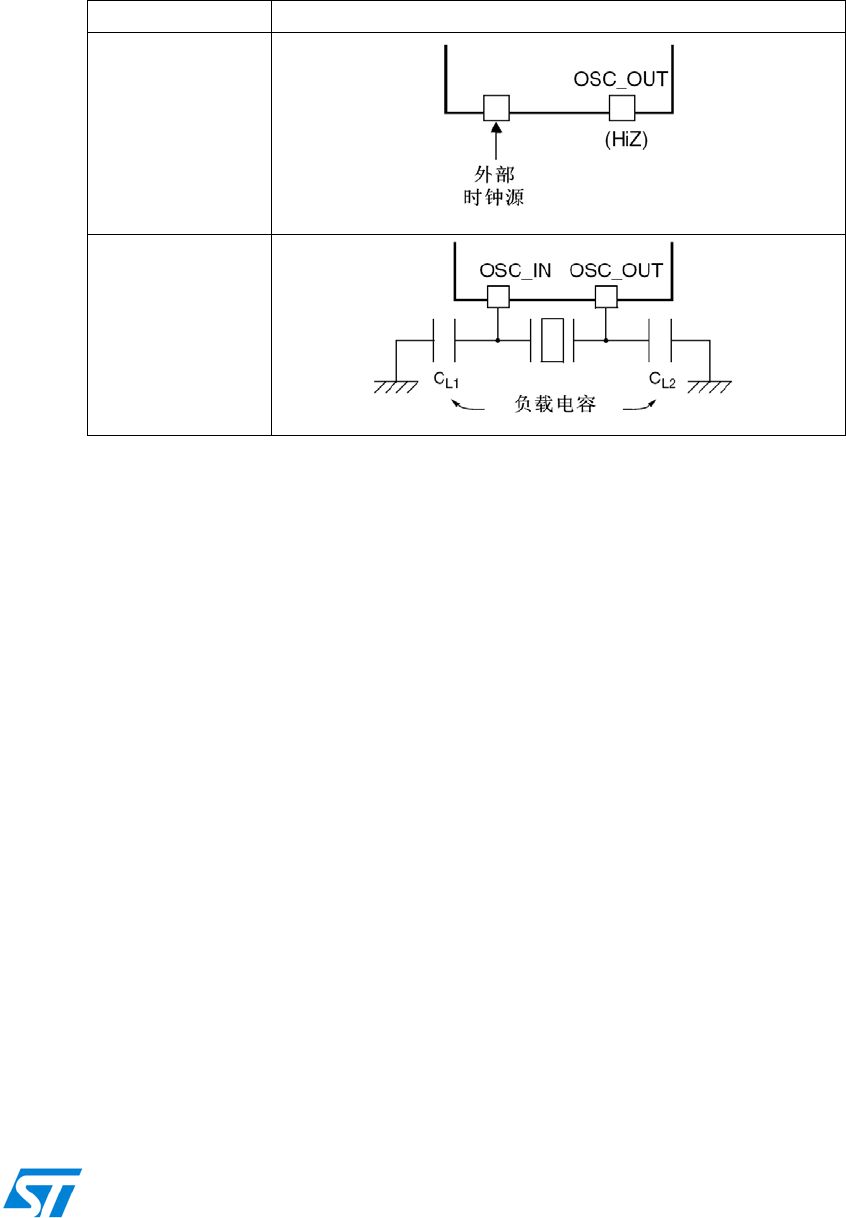

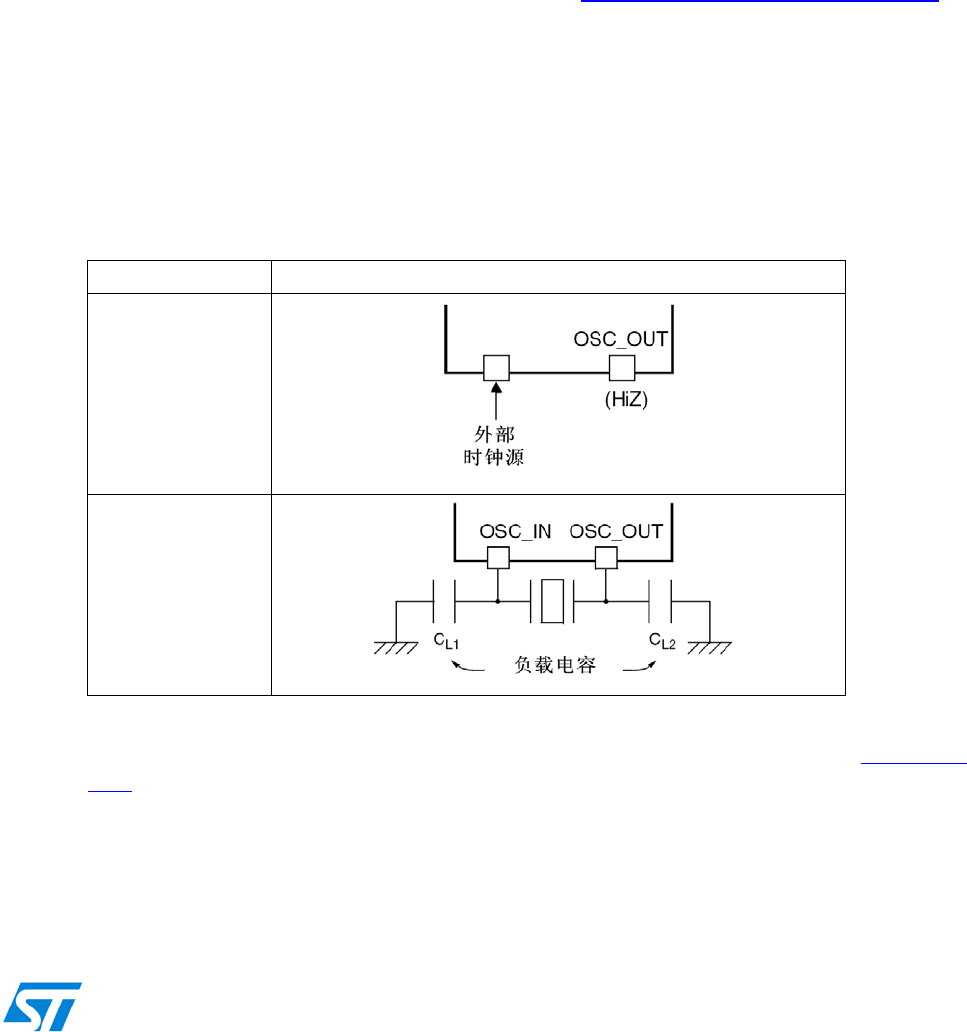

7.2.1 HSE时钟 81

7.2.2 HSI时钟 82

7.2.3 PLL 82

7.2.4 LSE时钟 82

7.2.5 LSI时钟 83

7.2.6 系统时钟(SYSCLK)选择 83

8/754

参照2009年12月 RM0008 Reference Manual 英文第10版

本译文仅供参考,如有翻译错误,请以英文原稿为准。请读者随时注意在ST网站下载更新版本

目录 STM32F10xxx参考手册

7.2.7 时钟安全系统(CSS) 83

7.2.8 RTC时钟 83

7.2.9 看门狗时钟 84

7.2.10 时钟输出 84

7.3 RCC寄存器 85

7.3.1 时钟控制寄存器(RCC_CR) 85

7.3.2 时钟配置寄存器(RCC_CFGR) 86

7.3.3 时钟中断寄存器(RCC_CIR) 88

7.3.4 APB2外设复位寄存器(RCC_APB2RSTR) 91

7.3.5 APB1外设复位寄存器(RCC_APB1RSTR) 92

7.3.6 AHB外设时钟使能寄存器(RCC_AHBENR) 94

7.3.7 APB2外设时钟使能寄存器(RCC_APB2ENR) 95

7.3.8 APB1外设时钟使能寄存器(RCC_APB1ENR) 97

7.3.9 备份域控制寄存器(RCC_BDCR) 99

7.3.10 控制/状态寄存器(RCC_CSR) 100

7.3.11 AHB外设时钟复位寄存器(RCC_AHBRSTR) 101

7.3.12 时钟配置寄存器2(RCC_CFGR2) 101

7.3.13 RCC寄存器地址映像 103

8 通用和复用功能I/O(GPIO和AFIO) 105

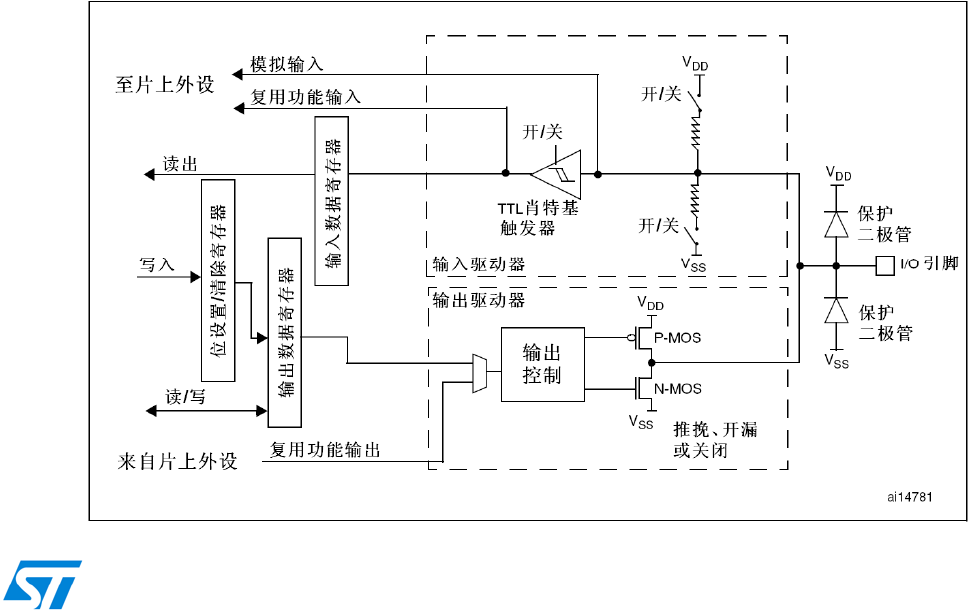

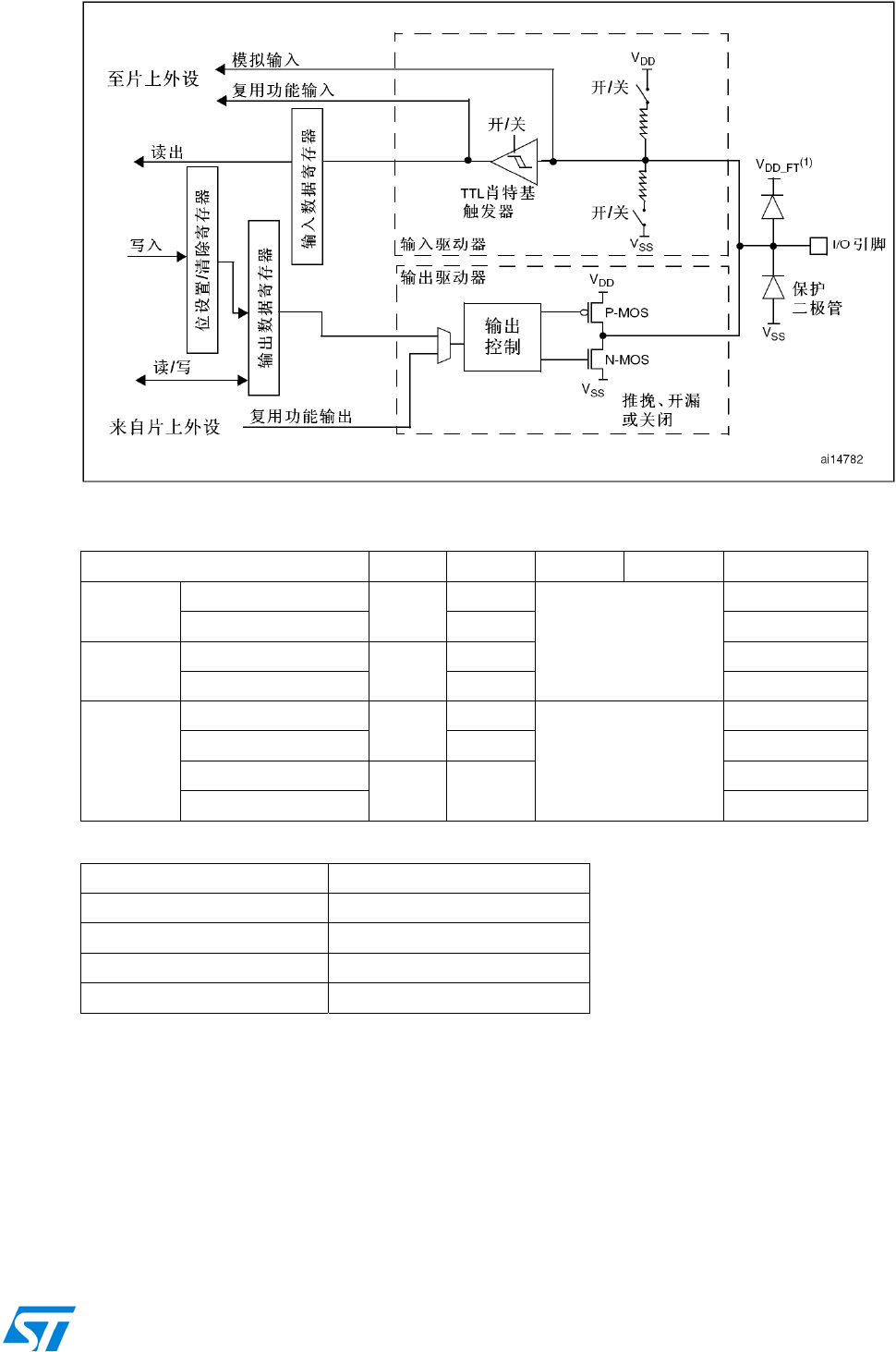

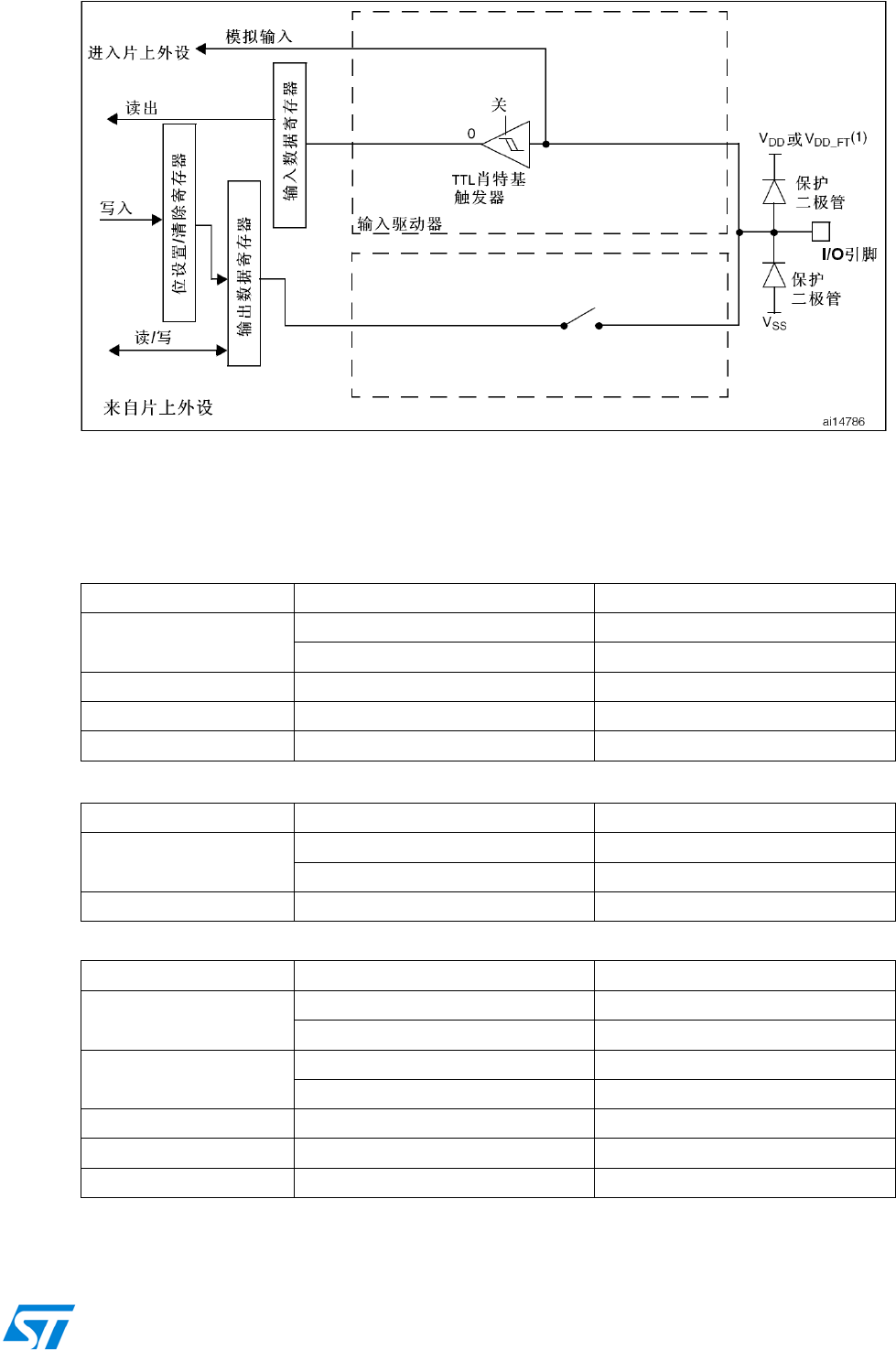

8.1 GPIO功能描述 105

8.1.1 通用I/O(GPIO) 106

8.1.2 单独的位设置或位清除 107

8.1.3 外部中断/唤醒线 107

8.1.4 复用功能(AF) 107

8.1.5 软件重新映射I/O复用功能 107

8.1.6 GPIO锁定机制 107

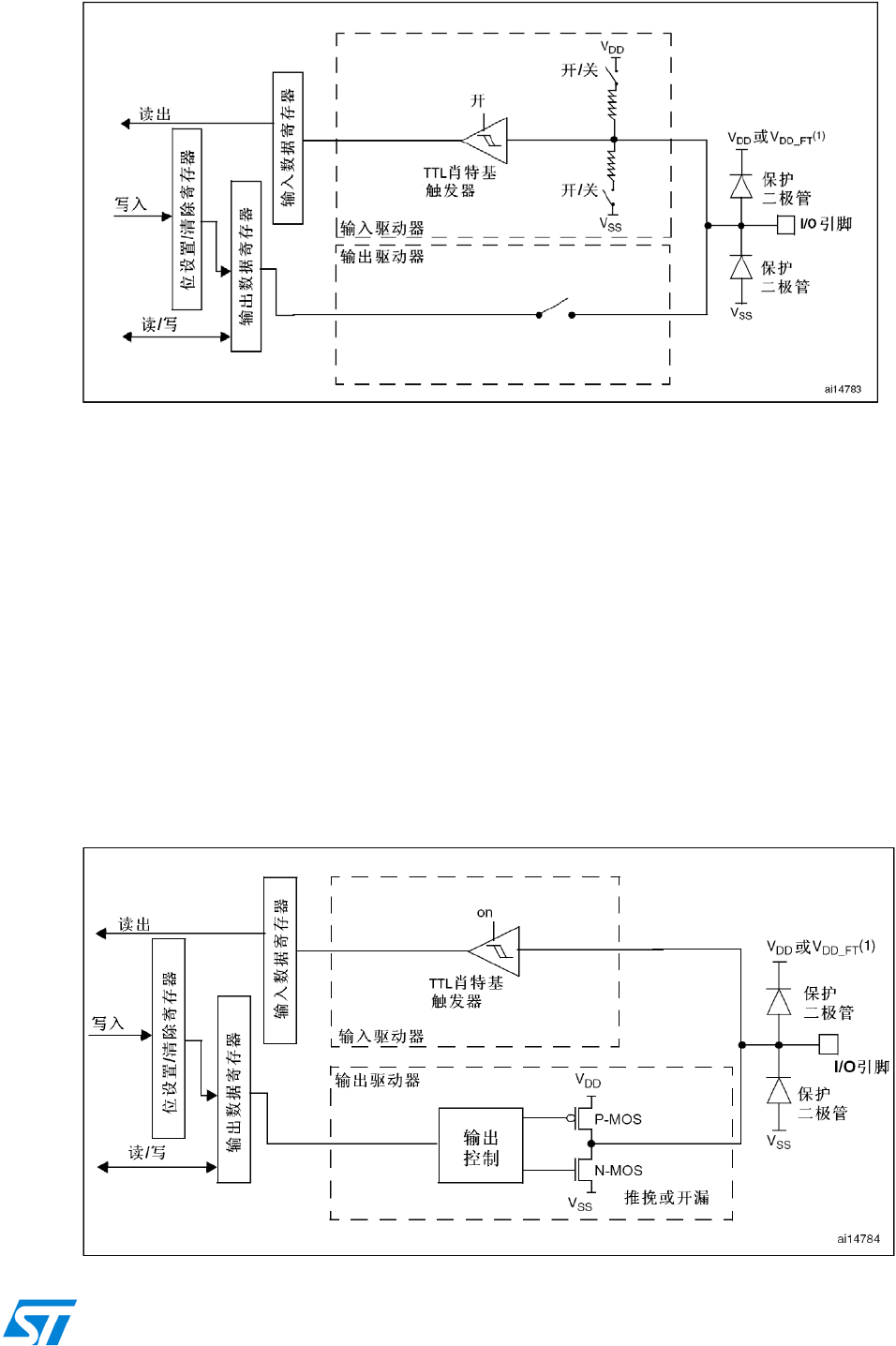

8.1.7 输入配置 107

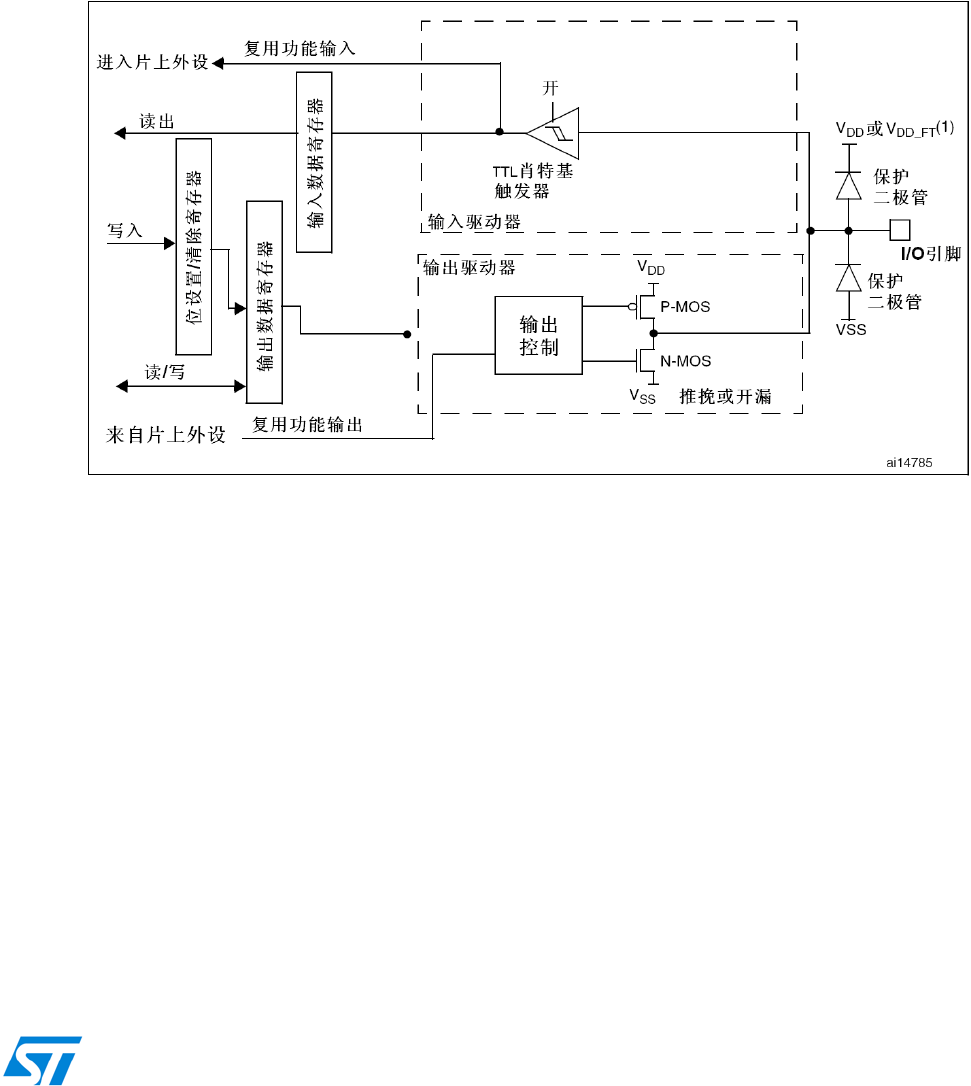

8.1.8 输出配置 108

8.1.9 复用功能配置 109

8.1.10 模拟输入配置 109

8.1.11 外设的GPIO配置 110

8.2 GPIO寄存器描述 113

8.2.1 端口配置低寄存器(GPIOx_CRL) (x=A..E) 113

8.2.2 端口配置高寄存器(GPIOx_CRH) (x=A..E) 114

8.2.3 端口输入数据寄存器(GPIOx_IDR) (x=A..E) 114

8.2.4 端口输出数据寄存器(GPIOx_ODR) (x=A..E) 115

8.2.5 端口位设置/清除寄存器(GPIOx_BSRR) (x=A..E) 115

8.2.6 端口位清除寄存器(GPIOx_BRR) (x=A..E) 115

8.2.7 端口配置锁定寄存器(GPIOx_LCKR) (x=A..E) 116

8.3 复用功能I/O和调试配置(AFIO) 116

8.3.1 把OSC32_IN/OSC32_OUT作为GPIO 端口PC14/PC15 116

8.3.2 把OSC_IN/OSC_OUT引脚作为GPIO端口PD0/PD1 117

8.3.3 CAN1复用功能重映射 117

8.3.4 CAN2复用功能重映射 117

8.3.5 JTAG/SWD复用功能重映射 117

8.3.6 ADC复用功能重映射 118

8.3.7 定时器复用功能重映射 118

8.3.8 USART复用功能重映射 119

8.3.9 I2C1复用功能重映射 120

8.3.10 SPI 1复用功能重映射 120

9/754

参照2009年12月 RM0008 Reference Manual 英文第10版

本译文仅供参考,如有翻译错误,请以英文原稿为准。请读者随时注意在ST网站下载更新版本

目录 STM32F10xxx参考手册

8.3.11 SPI3复用功能重映射 120

8.3.12 以太网复用功能重映射 121

8.4 AFIO寄存器描述 121

8.4.1 事件控制寄存器(AFIO_EVCR) 121

8.4.2 复用重映射和调试I/O配置寄存器(AFIO_MAPR) 121

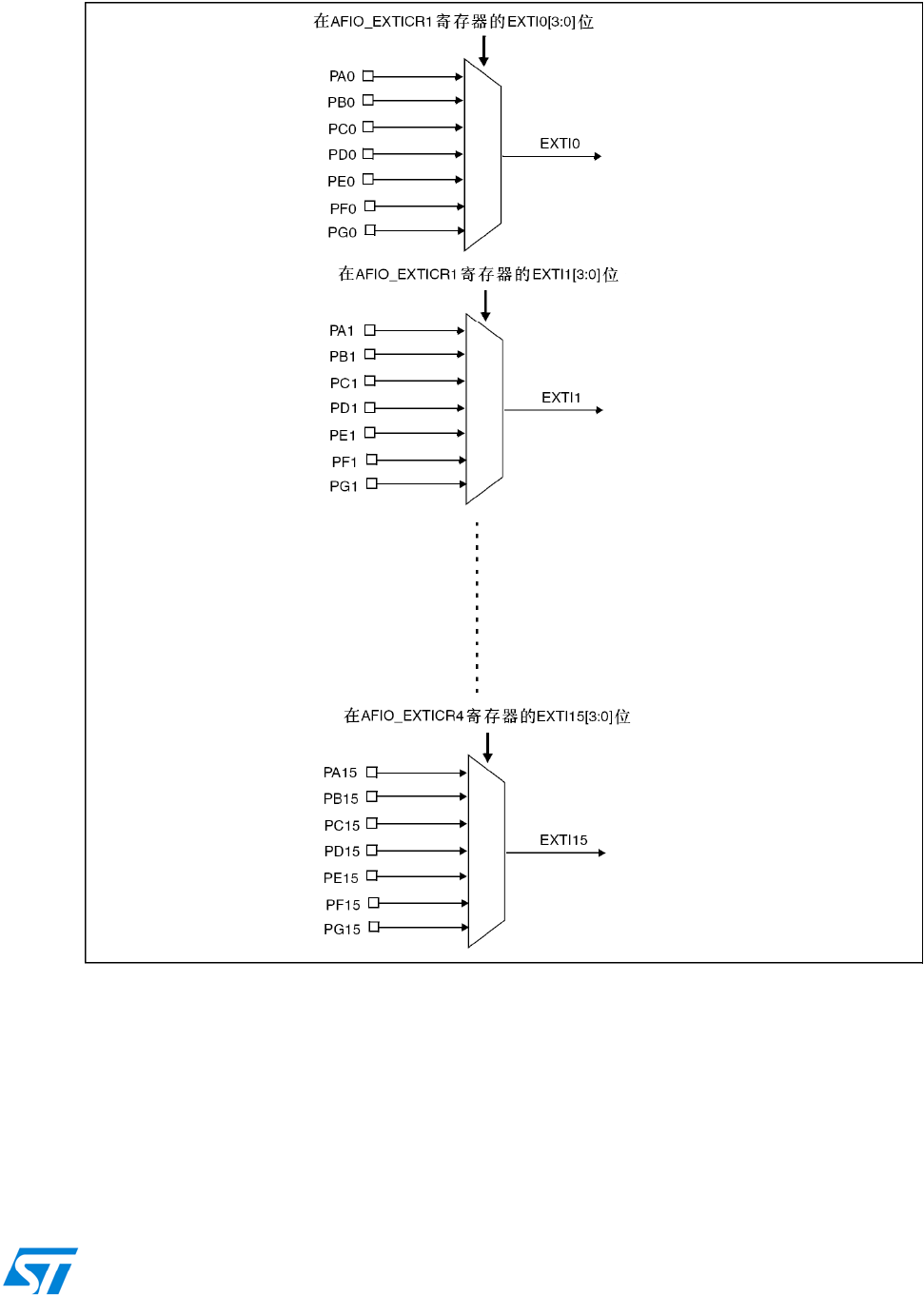

8.4.3 外部中断配置寄存器1(AFIO_EXTICR1) 126

8.4.4 外部中断配置寄存器2(AFIO_EXTICR2) 127

8.4.5 外部中断配置寄存器3(AFIO_EXTICR3) 127

8.4.6 外部中断配置寄存器4(AFIO_EXTICR4) 128

8.5 GPIO 和AFIO寄存器地址映象 129

9 中断和事件 130

9.1 嵌套向量中断控制器 130

9.1.1 系统嘀嗒(SysTick)校准值寄存器 130

9.1.2 中断和异常向量 130

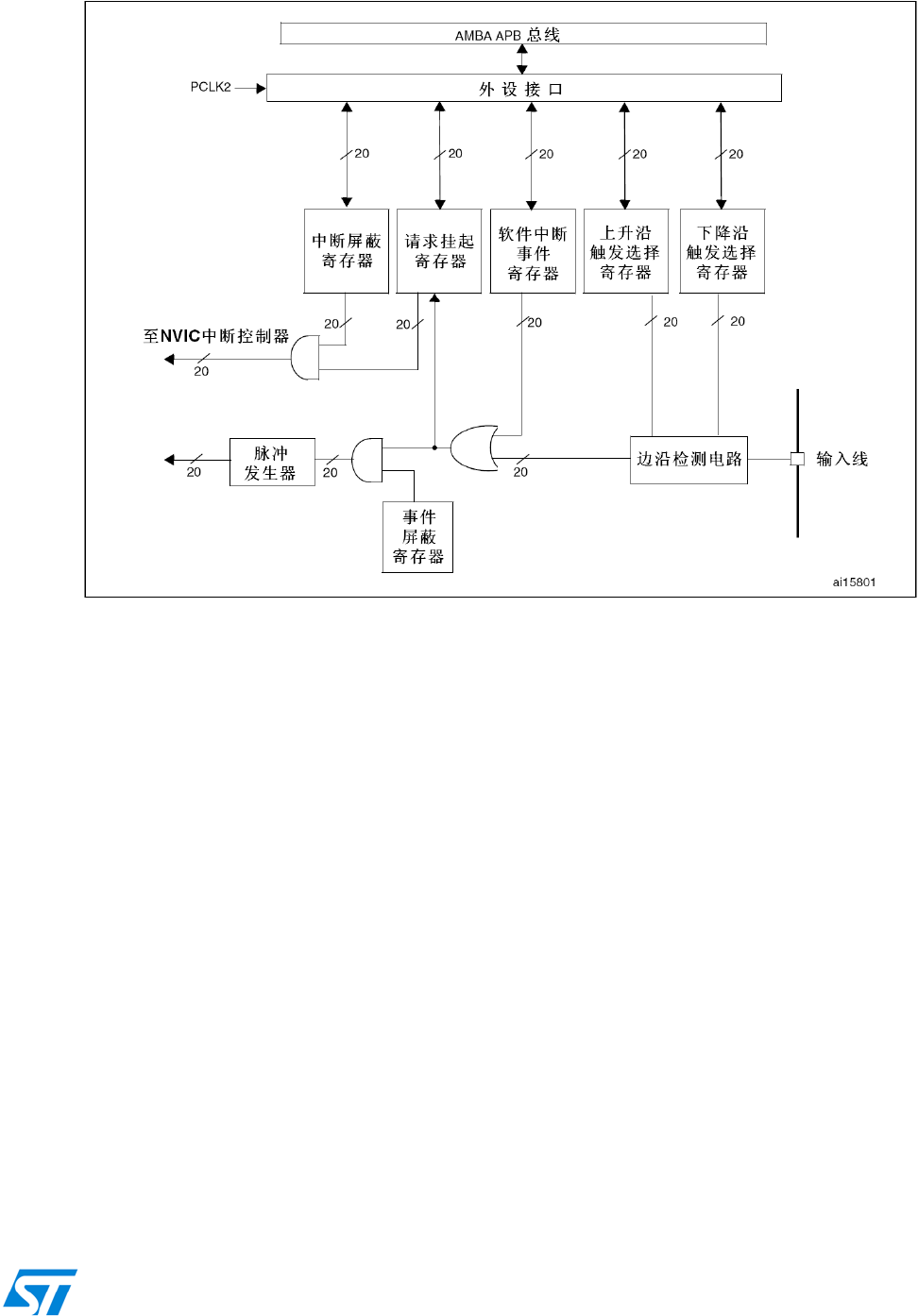

9.2 外部中断/事件控制器(EXTI) 134

9.2.1 主要特性 134

9.2.2 框图 135

9.2.3 唤醒事件管理 135

9.2.4 功能说明 135

9.2.5 外部中断/事件线路映像 137

9.3 EXTI 寄存器描述 138

9.3.1 中断屏蔽寄存器(EXTI_IMR) 138

9.3.2 事件屏蔽寄存器(EXTI_EMR) 138

9.3.3 上升沿触发选择寄存器(EXTI_RTSR) 139

9.3.4 下降沿触发选择寄存器(EXTI_FTSR) 139

9.3.5 软件中断事件寄存器(EXTI_SWIER) 140

9.3.6 挂起寄存器(EXTI_PR) 140

9.3.7 外部中断/事件寄存器映像 141

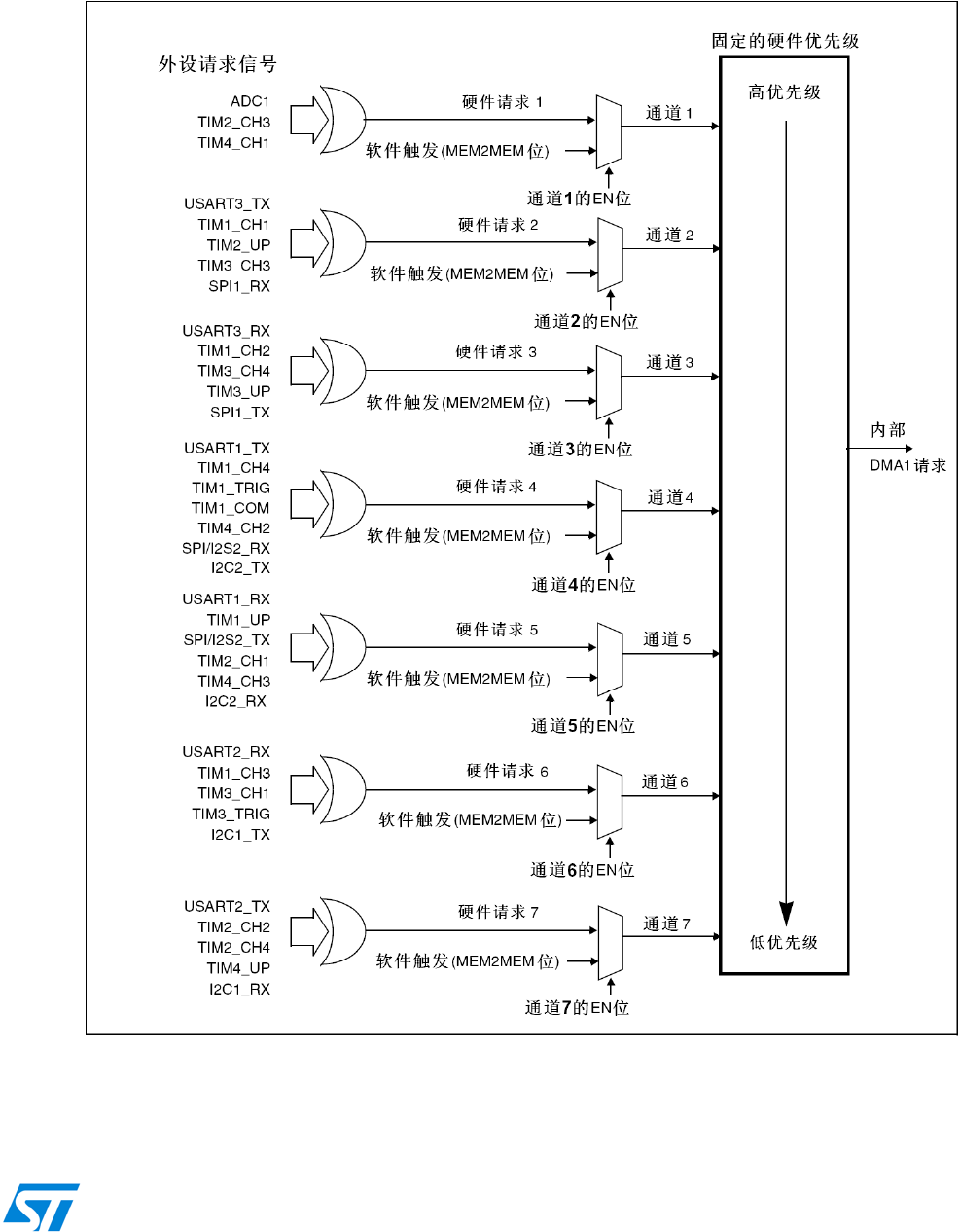

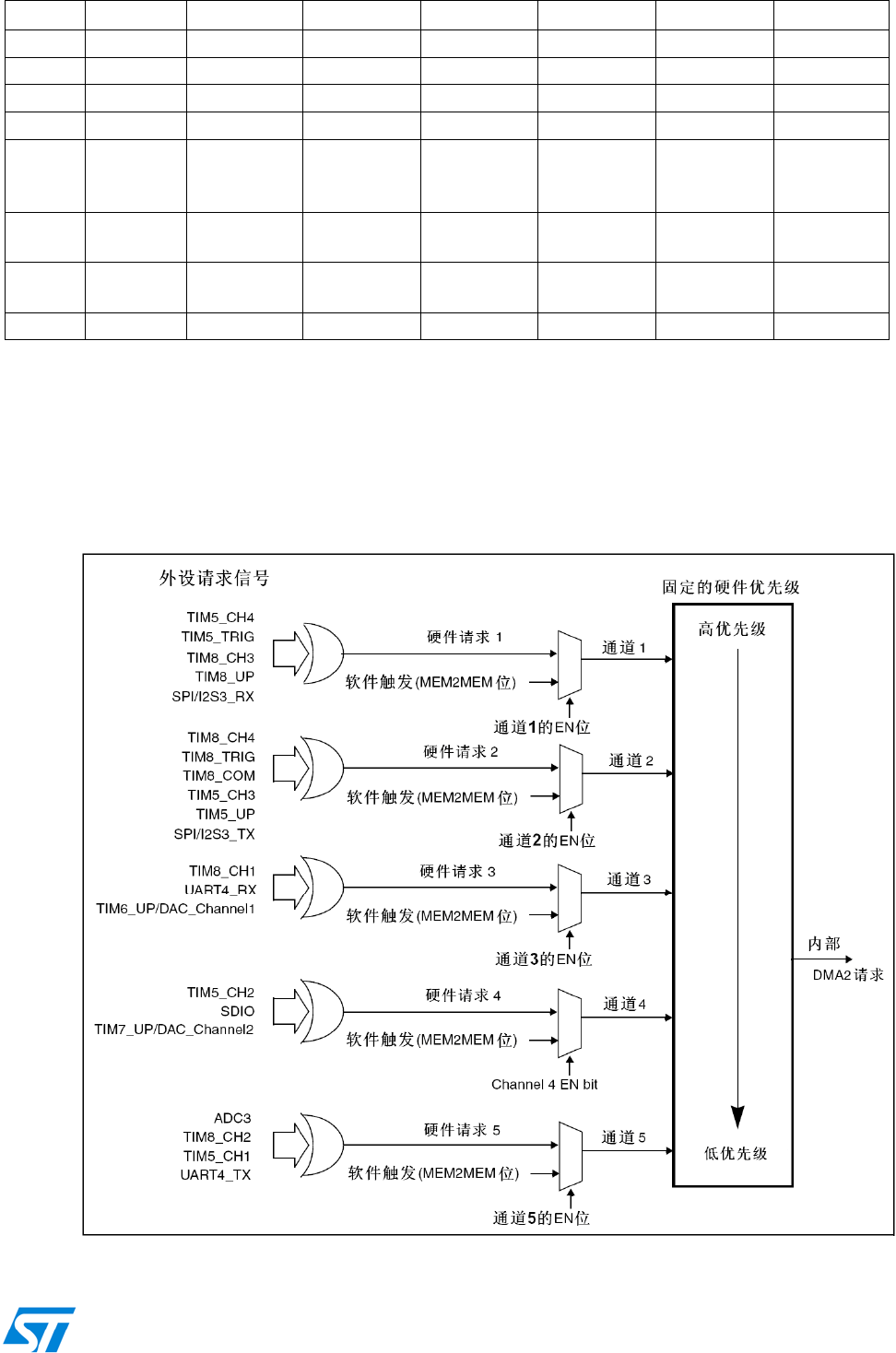

10 DMA控制器(DMA) 142

10.1 DMA简介 142

10.2 DMA主要特性 142

10.3 功能描述 143

10.3.1 DMA处理 143

10.3.2 仲裁器 144

10.3.3 DMA 通道 144

10.3.4 可编程的数据传输宽度、对齐方式和数据大小端 145

10.3.5 错误管理 146

10.3.6 中断 146

10.3.7 DMA请求映像 147

10.4 DMA寄存器 149

10.4.1 DMA中断状态寄存器(DMA_ISR) 149

10.4.2 DMA中断标志清除寄存器(DMA_IFCR) 150

10.4.3 DMA通道x配置寄存器(DMA_CCRx)(x = 1…7) 150

10.4.4 DMA通道x传输数量寄存器(DMA_CNDTRx)(x = 1…7) 152

10.4.5 DMA通道x外设地址寄存器(DMA_CPARx)(x = 1…7) 152

10.4.6 DMA通道x存储器地址寄存器(DMA_CMARx)(x = 1…7) 152

10.4.7 DMA寄存器映像 153

11 模拟/数字转换(ADC) 155

10/754

参照2009年12月 RM0008 Reference Manual 英文第10版

本译文仅供参考,如有翻译错误,请以英文原稿为准。请读者随时注意在ST网站下载更新版本

目录 STM32F10xxx参考手册

11.1 ADC介绍 155

11.2 ADC主要特征 155

11.3 ADC功能描述 156

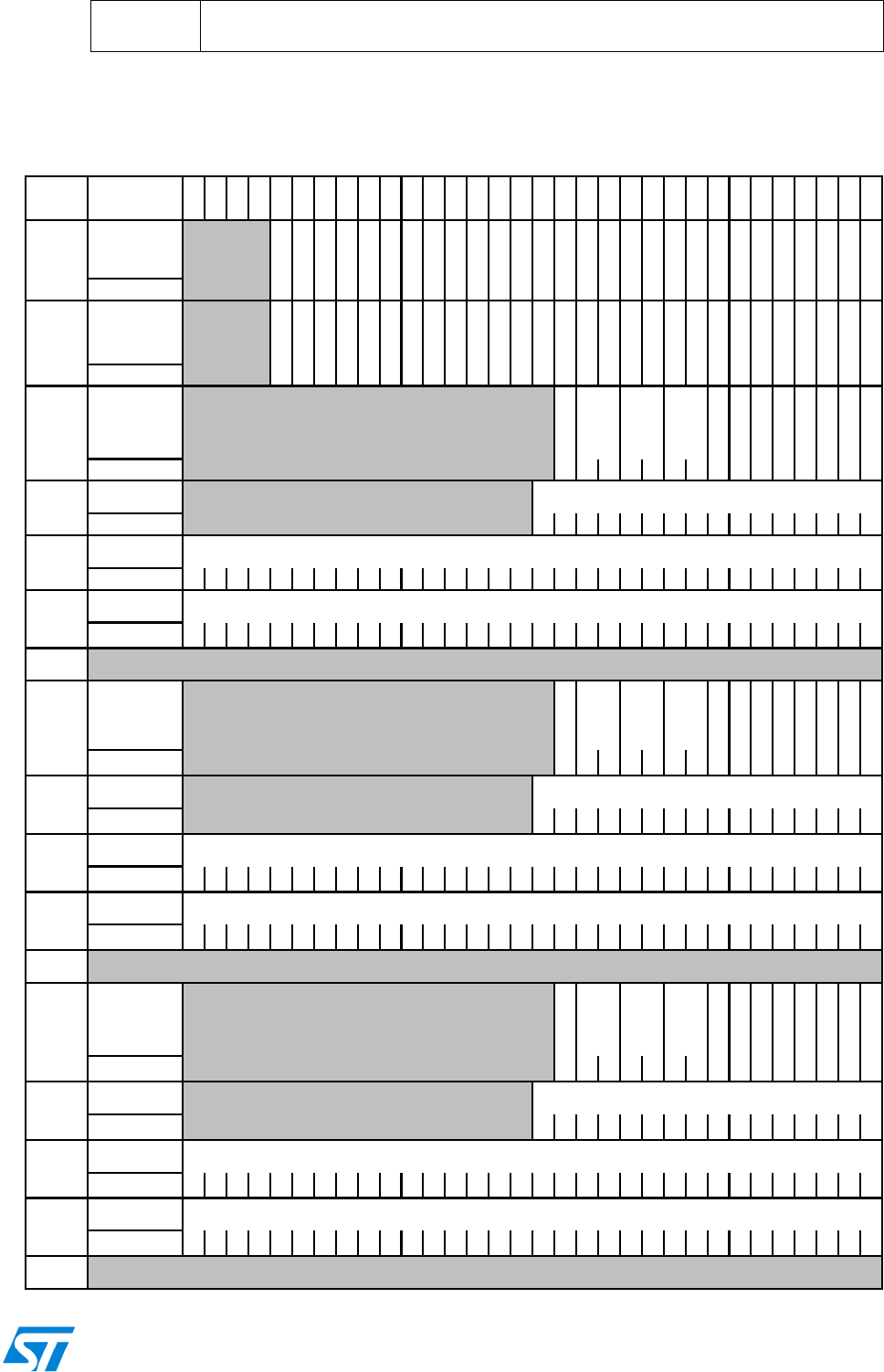

11.3.1 ADC开关控制 157

11.3.2 ADC时钟 157

11.3.3 通道选择 157

11.3.4 单次转换模式 157

11.3.5 连续转换模式 158

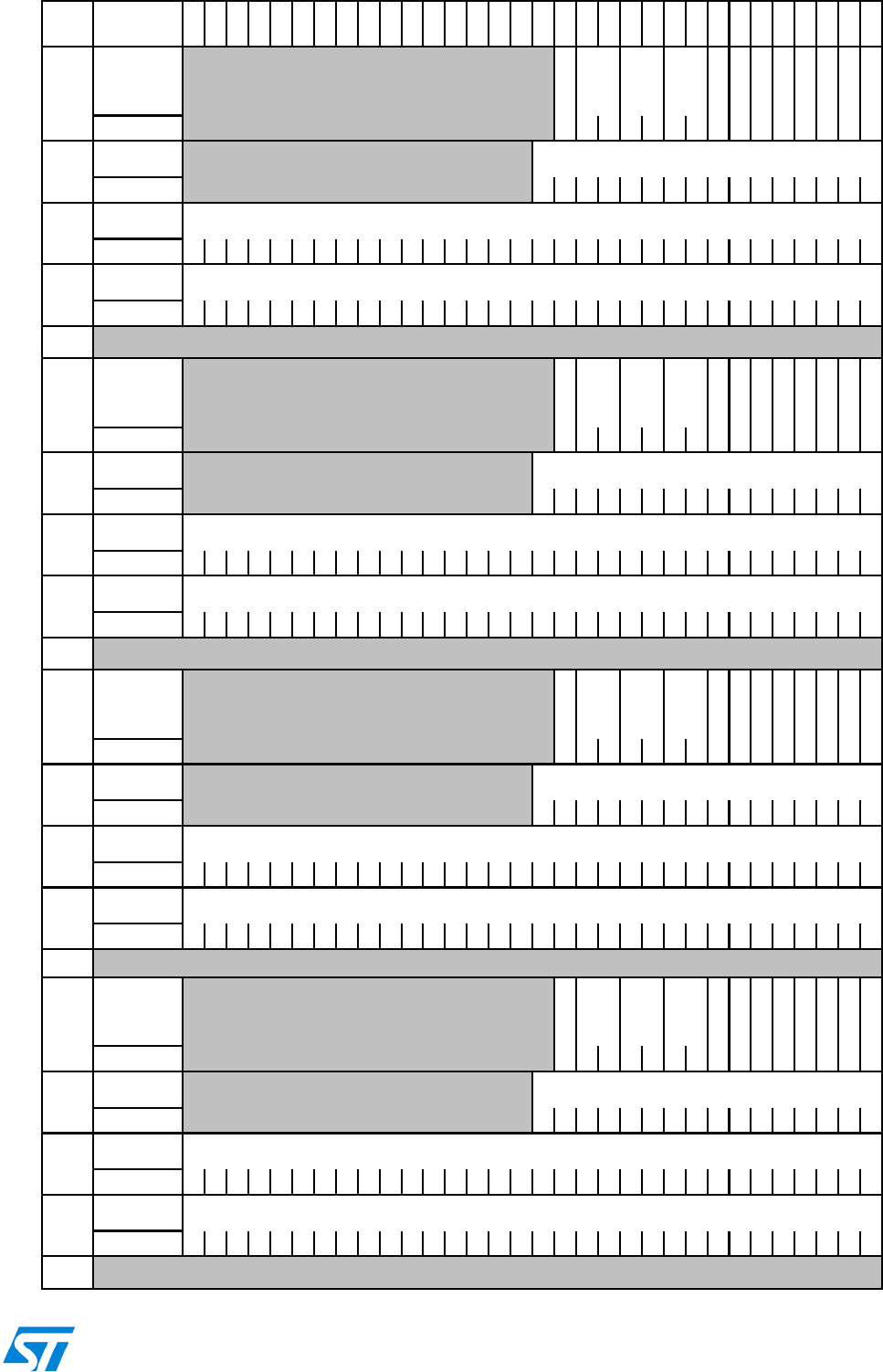

11.3.6 时序图 158

11.3.7 模拟看门狗 158

11.3.8 扫描模式 159

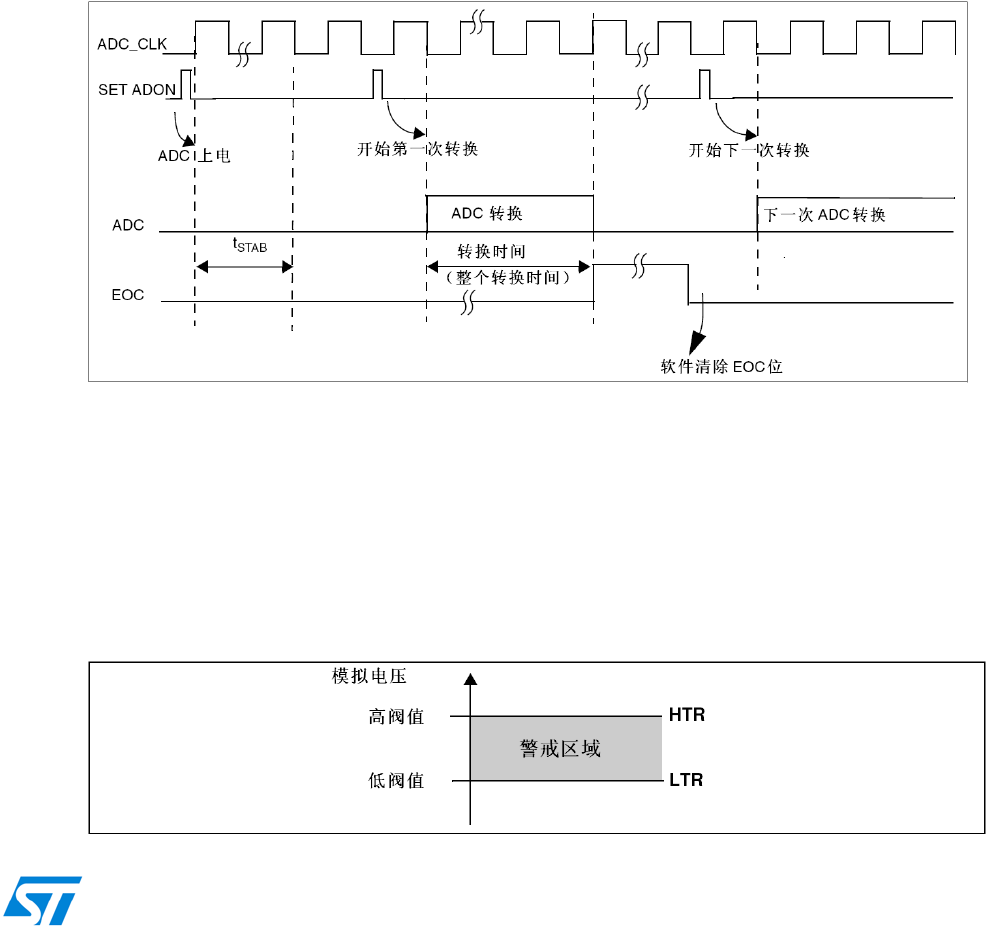

11.3.9 注入通道管理 159

11.3.10 间断模式 160

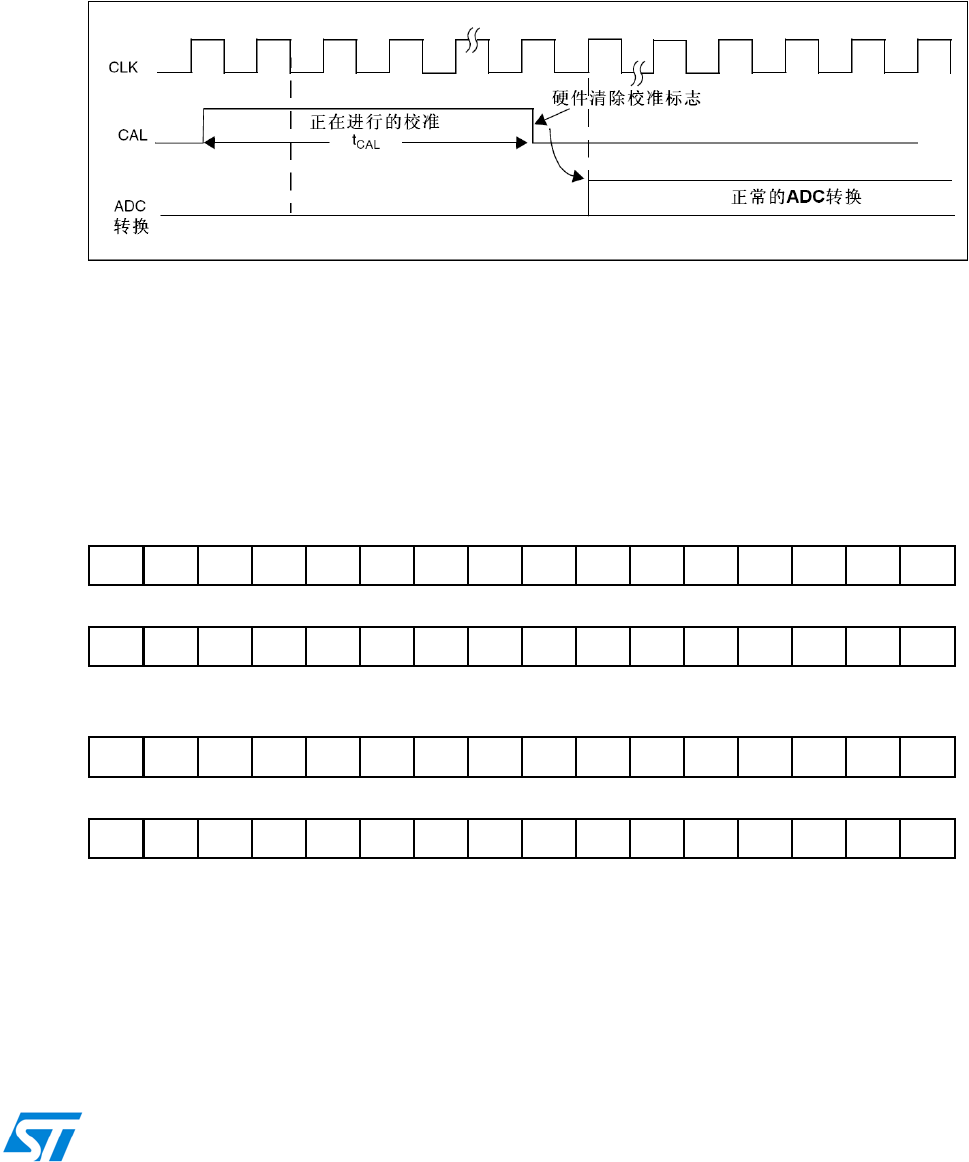

11.4 校准 161

11.5 数据对齐 161

11.6 可编程的通道采样时间 161

11.7 外部触发转换 162

11.8 DMA请求 163

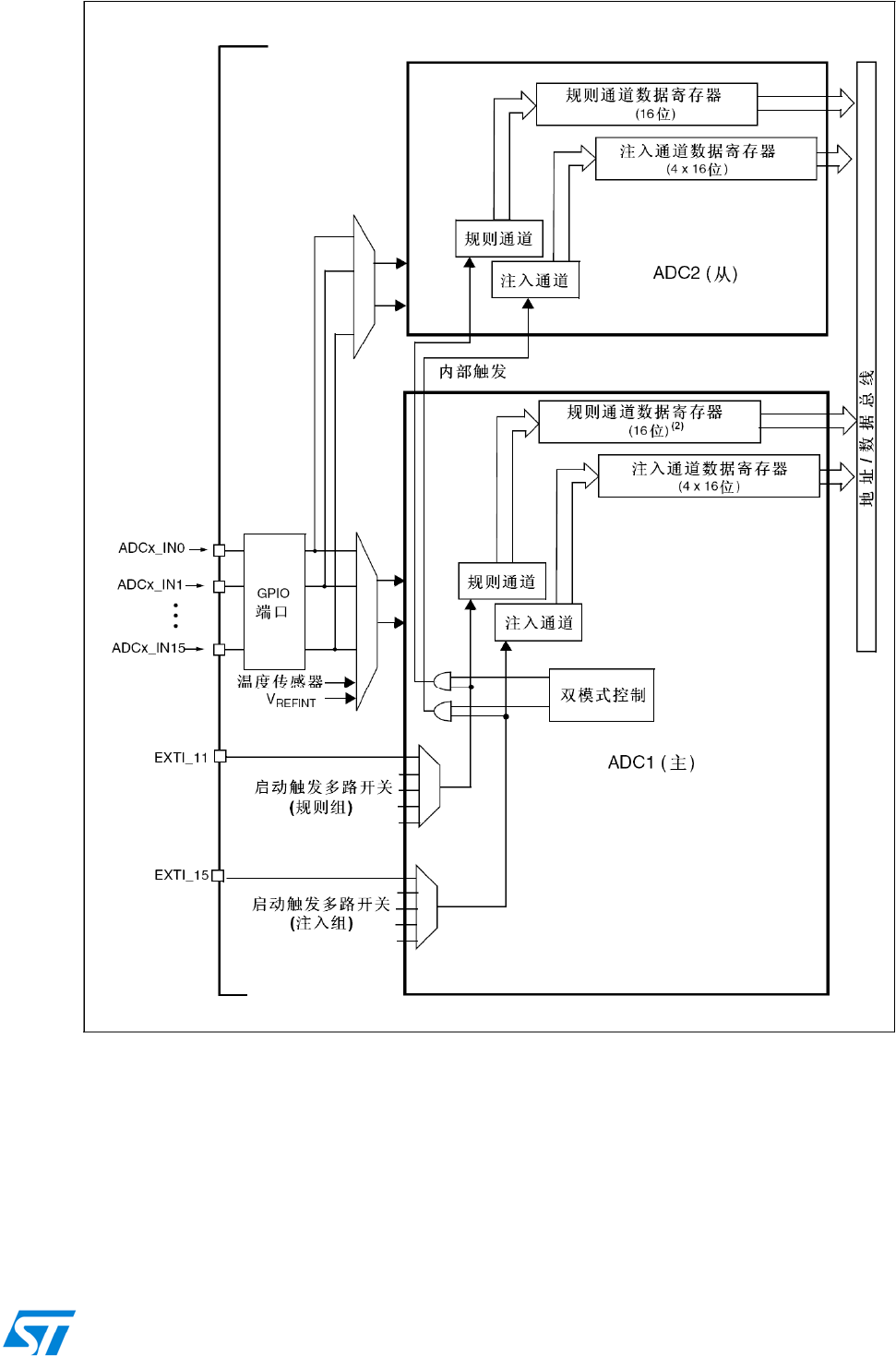

11.9 双ADC模式 163

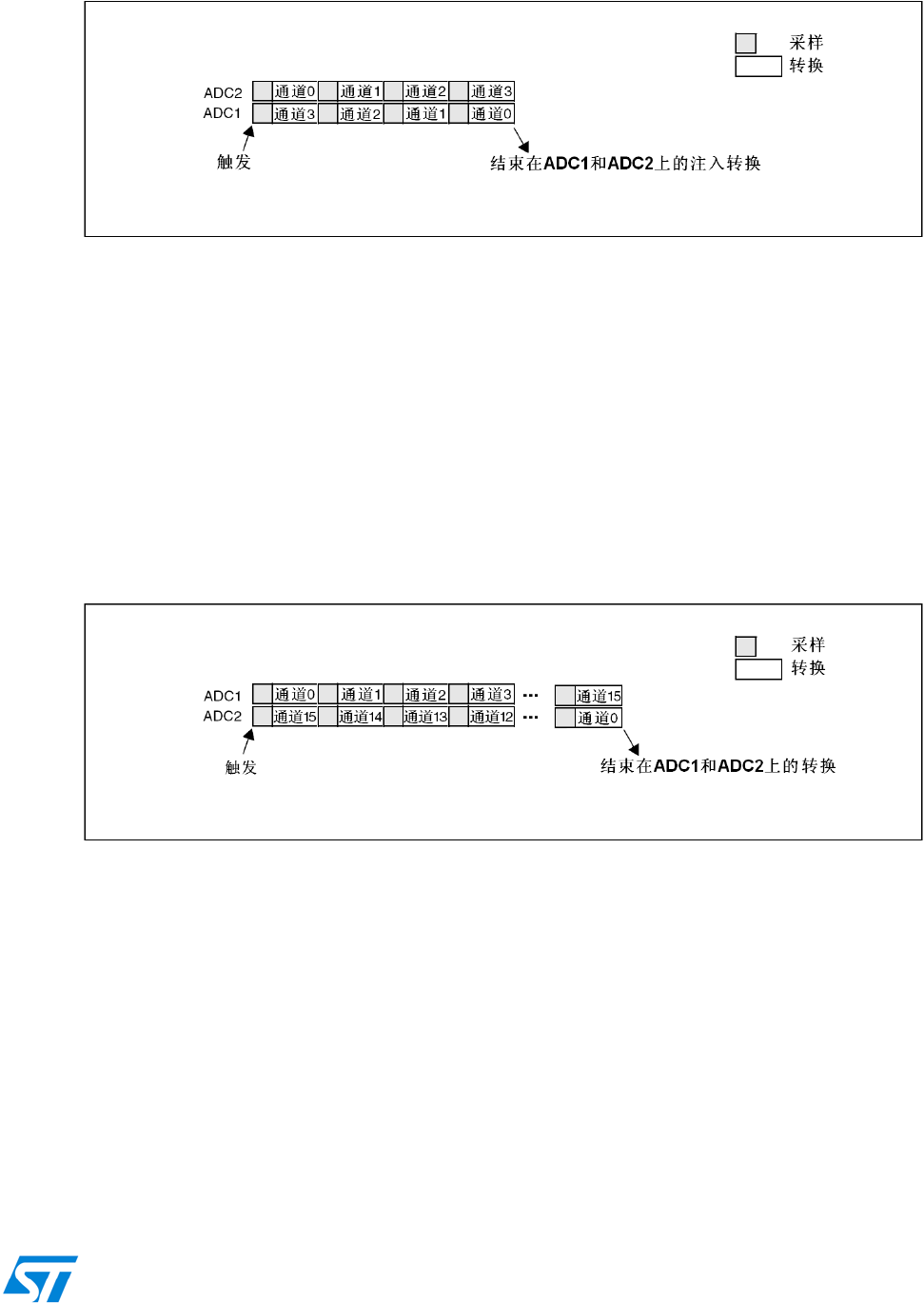

11.9.1 同步注入模式 164

11.9.2 同步规则模式 165

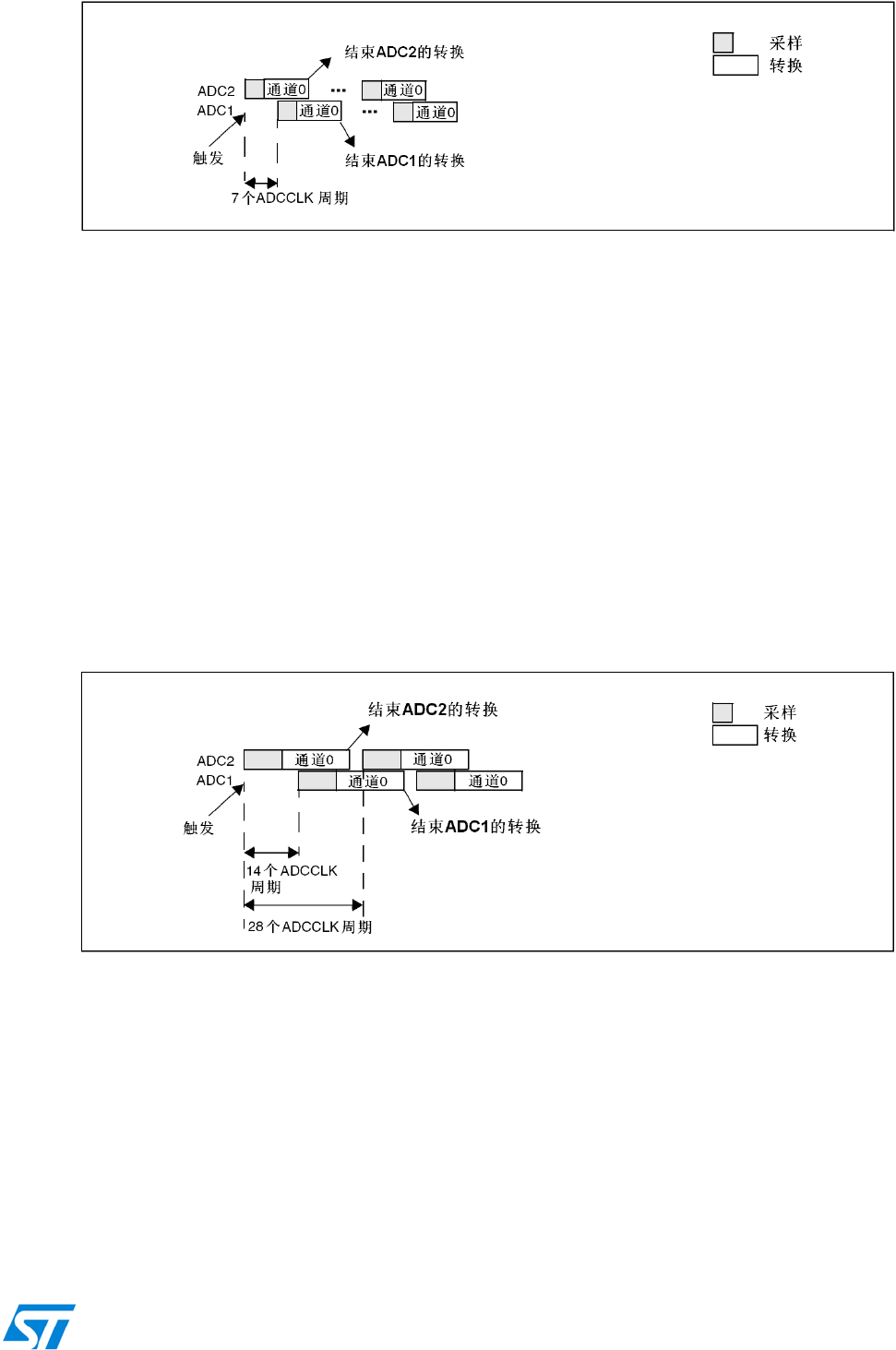

11.9.3 快速交叉模式 165

11.9.4 慢速交叉模式 166

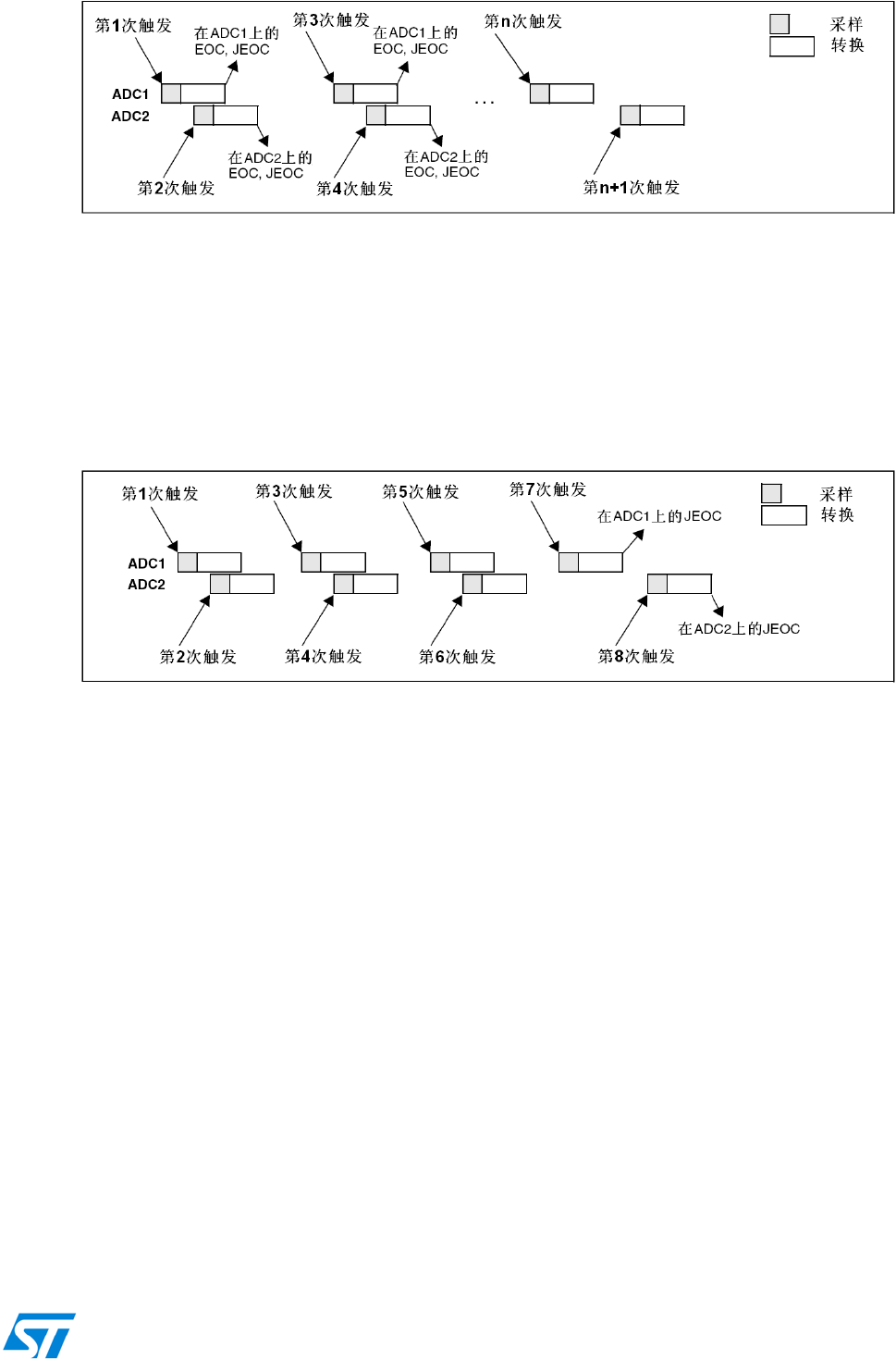

11.9.5 交替触发模式 166

11.9.6 独立模式 167

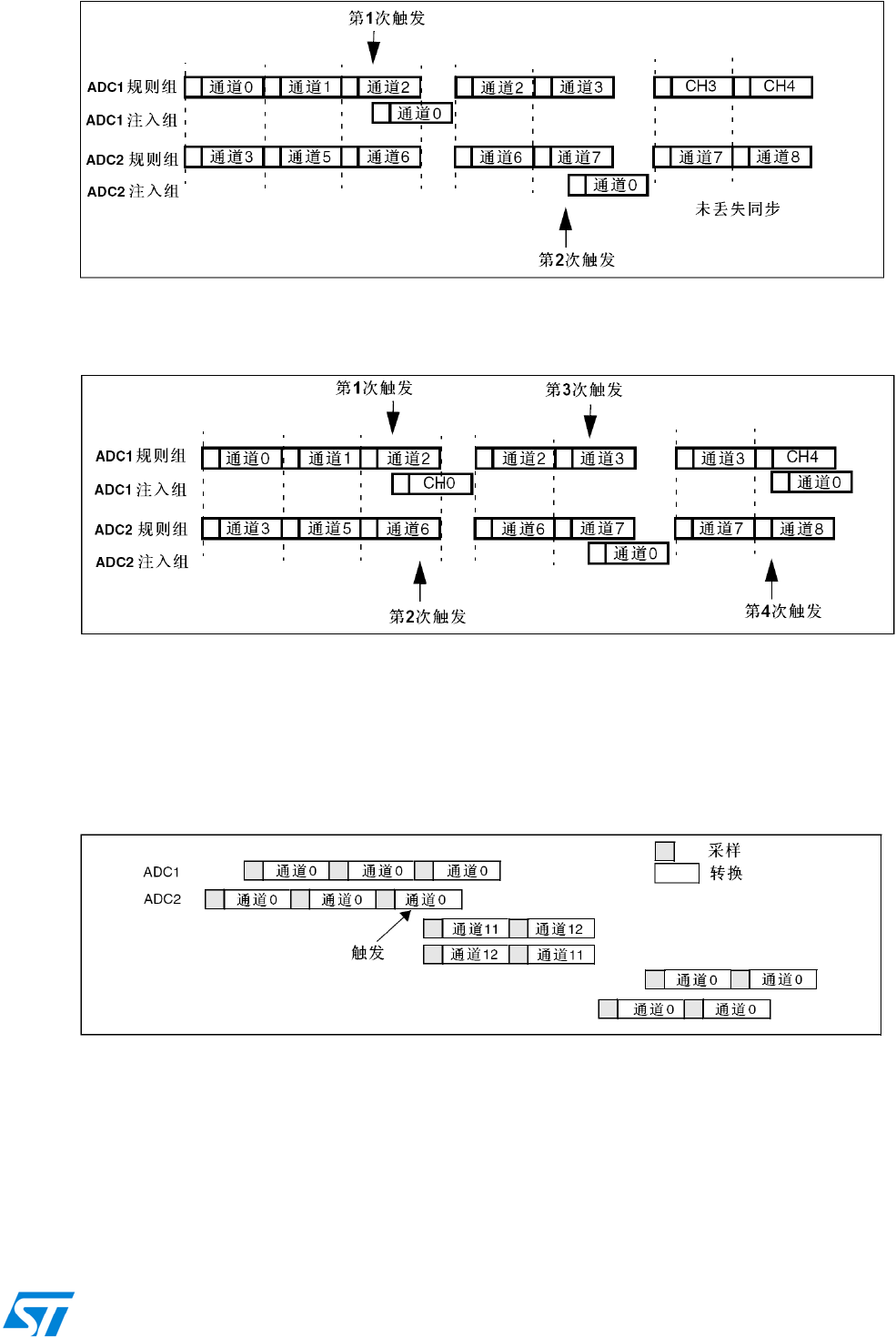

11.9.7 混合的规则/注入同步模式 167

11.9.8 混合的同步规则+交替触发模式 167

11.9.9 混合同步注入 + 交叉模式 168

11.10 温度传感器 168

11.11 ADC中断 169

11.12 ADC寄存器 170

11.12.1 ADC状态寄存器(ADC_SR) 170

11.12.2 ADC控制寄存器1(ADC_CR1) 171

11.12.3 ADC控制寄存器2(ADC_CR2) 173

11.12.4 ADC采样时间寄存器1(ADC_SMPR1) 175

11.12.5 ADC采样时间寄存器2(ADC_SMPR2) 175

11.12.6 ADC注入通道数据偏移寄存器x (ADC_JOFRx)(x=1..4) 176

11.12.7 ADC看门狗高阀值寄存器(ADC_HTR) 176

11.12.8 ADC看门狗低阀值寄存器(ADC_LRT) 176

11.12.9 ADC规则序列寄存器1(ADC_SQR1) 177

11.12.10 ADC规则序列寄存器2(ADC_SQR2) 177

11.12.11 ADC规则序列寄存器3(ADC_SQR3) 178

11.12.12 ADC注入序列寄存器(ADC_JSQR) 178

11.12.13 ADC 注入数据寄存器x (ADC_JDRx) (x= 1..4) 179

11.12.14 ADC规则数据寄存器(ADC_DR) 179

11.12.15 ADC寄存器地址映像 180

12 数字/模拟转换(DAC) 182

12.1 DAC简介 182

11/754

参照2009年12月 RM0008 Reference Manual 英文第10版

本译文仅供参考,如有翻译错误,请以英文原稿为准。请读者随时注意在ST网站下载更新版本

目录 STM32F10xxx参考手册

12.2 DAC主要特征 182

12.3 DAC功能描述 183

12.3.1 使能DAC通道 183

12.3.2 使能DAC输出缓存 184

12.3.3 DAC数据格式 184

12.3.4 DAC转换 185

12.3.5 DAC输出电压 185

12.3.6 选择DAC触发 185

12.3.7 DMA请求 186

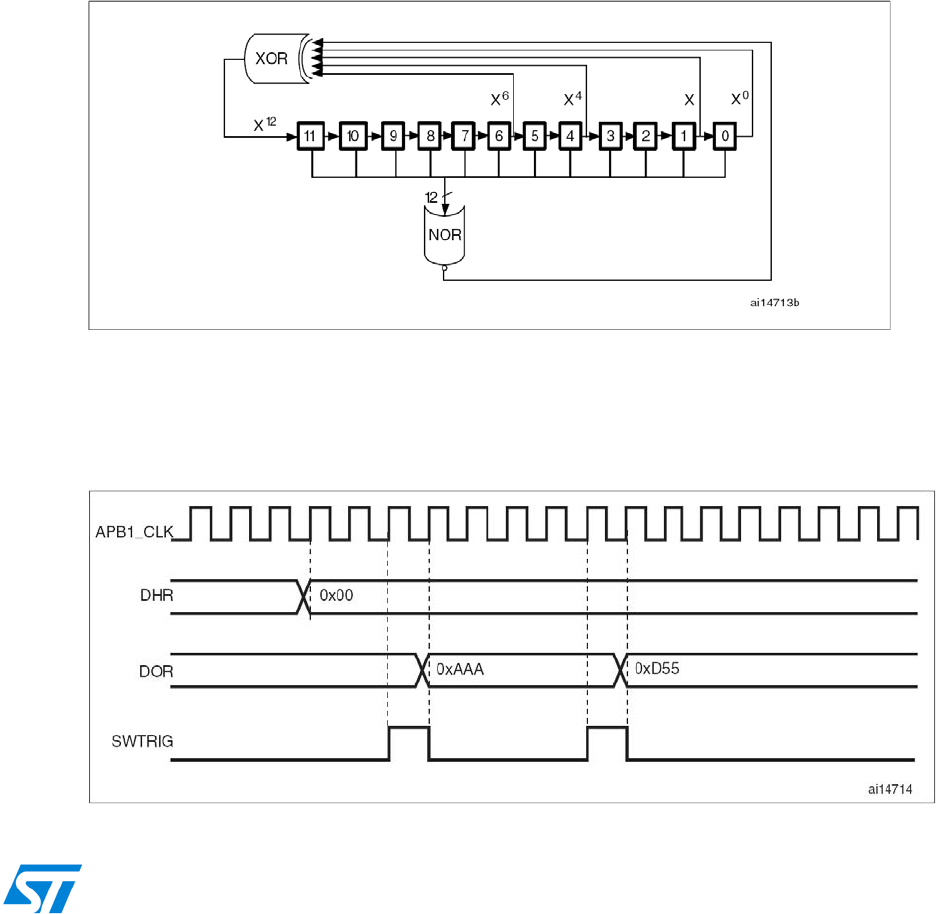

12.3.8 噪声生成 186

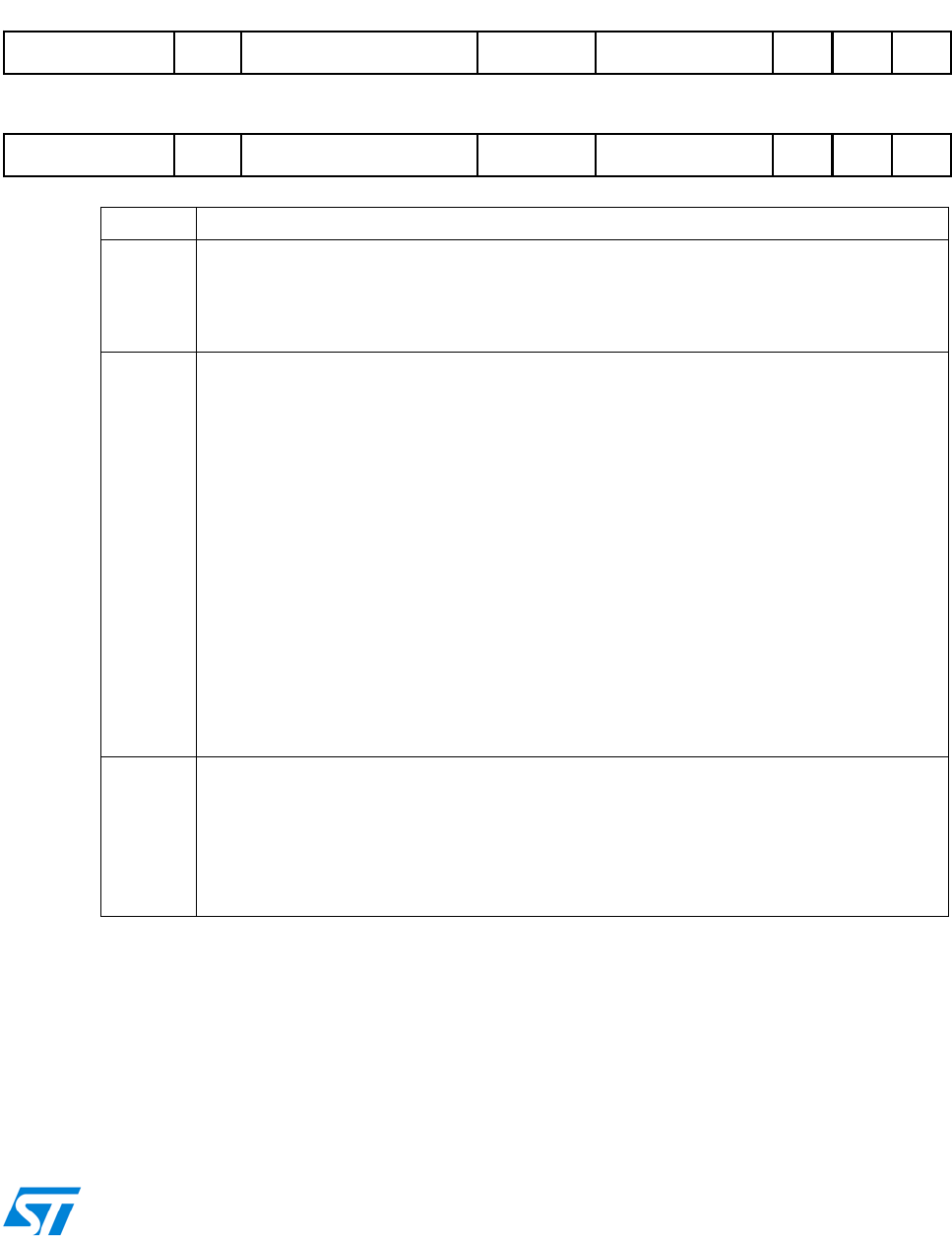

12.3.9 三角波生成 187

12.4 双DAC通道转换 187

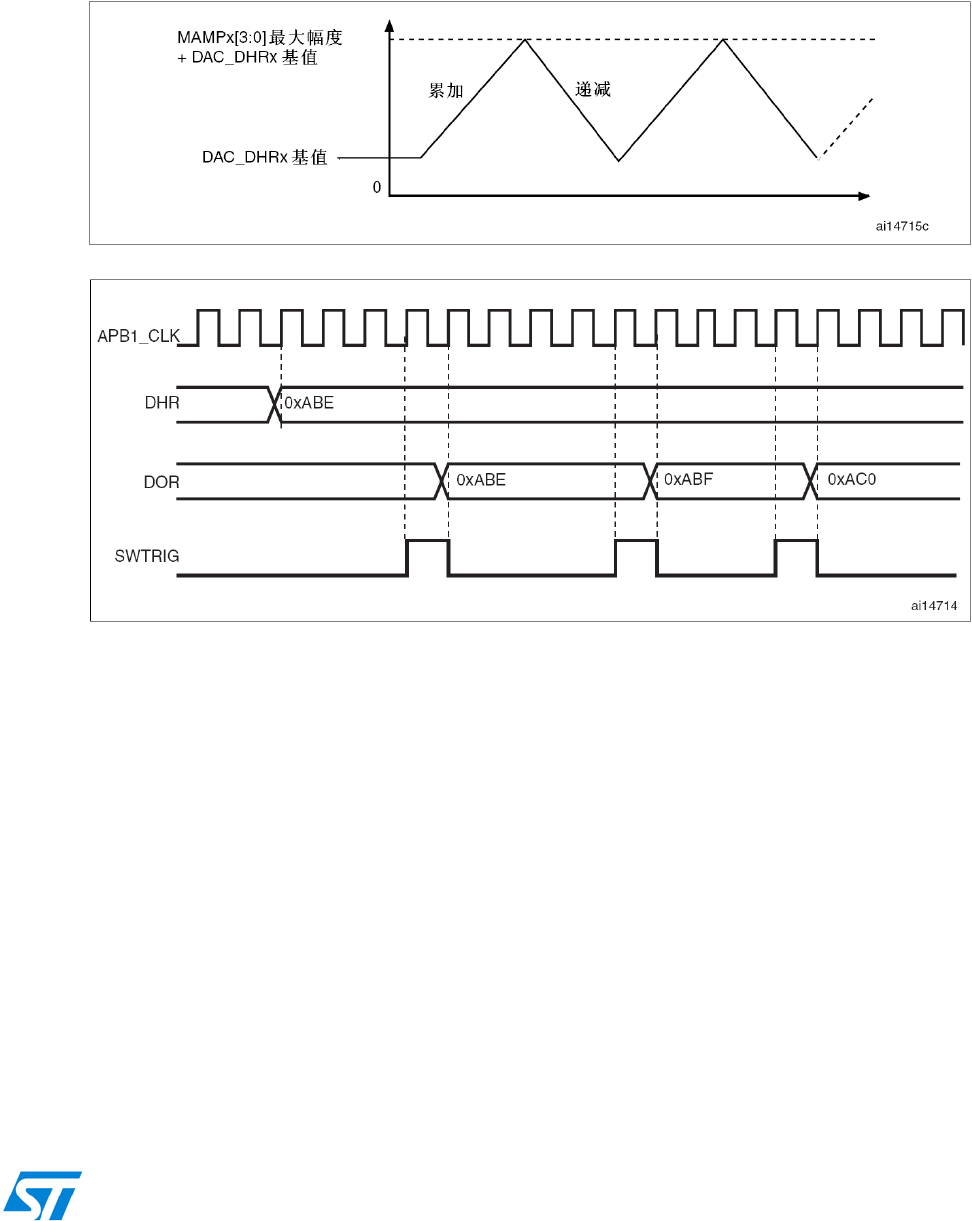

12.4.1 不使用波形发生器的独立触发 187

12.4.2 使用相同LFSR的独立触发 188

12.4.3 使用不同LFSR的独立触发 188

12.4.4 产生相同三角波的独立触发 188

12.4.5 产生不同三角波的独立触发 188

12.4.6 同时软件启动 189

12.4.7 不使用波形发生器的同时触发 189

12.4.8 使用相同LFSR的同时触发 189

12.4.9 使用不同LFSR的同时触发 189

12.4.10 使用相同三角波发生器的同时触发 189

12.4.11 使用不同三角波发生器的同时触发 190

12.5 DAC寄存器 191

12.5.1 DAC控制寄存器(DAC_CR) 191

12.5.2 DAC软件触发寄存器(DAC_SWTRIGR) 193

12.5.3 DAC通道1的12位右对齐数据保持寄存器(DAC_DHR12R1) 194

12.5.4 DAC通道1的12位左对齐数据保持寄存器(DAC_DHR12L1) 194

12.5.5 DAC通道1的8位右对齐数据保持寄存器(DAC_DHR8R1) 194

12.5.6 DAC通道2的12位右对齐数据保持寄存器(DAC_DHR12R2) 195

12.5.7 DAC通道2的12位左对齐数据保持寄存器(DAC_DHR12L2) 195

12.5.8 DAC通道2的8位右对齐数据保持寄存器(DAC_DHR8R2) 195

12.5.9 双DAC的12位右对齐数据保持寄存器(DAC_DHR12RD) 196

12.5.10 双DAC的12位左对齐数据保持寄存器(DAC_DHR12LD) 196

12.5.11 双DAC的8位右对齐数据保持寄存器(DAC_DHR8RD) 196

12.5.12 DAC通道1数据输出寄存器(DAC_DOR1) 197

12.5.13 DAC通道2数据输出寄存器(DAC_DOR2) 197

12.5.14 DAC寄存器映像 198

13 高级控制定时器(TIM1 和TIM8) 199

13.1 TIM1和TIM8简介 199

13.2 TIM1和TIM8主要特性 199

13.3 TIM1和TIM8功能描述 200

13.3.1 时基单元 200

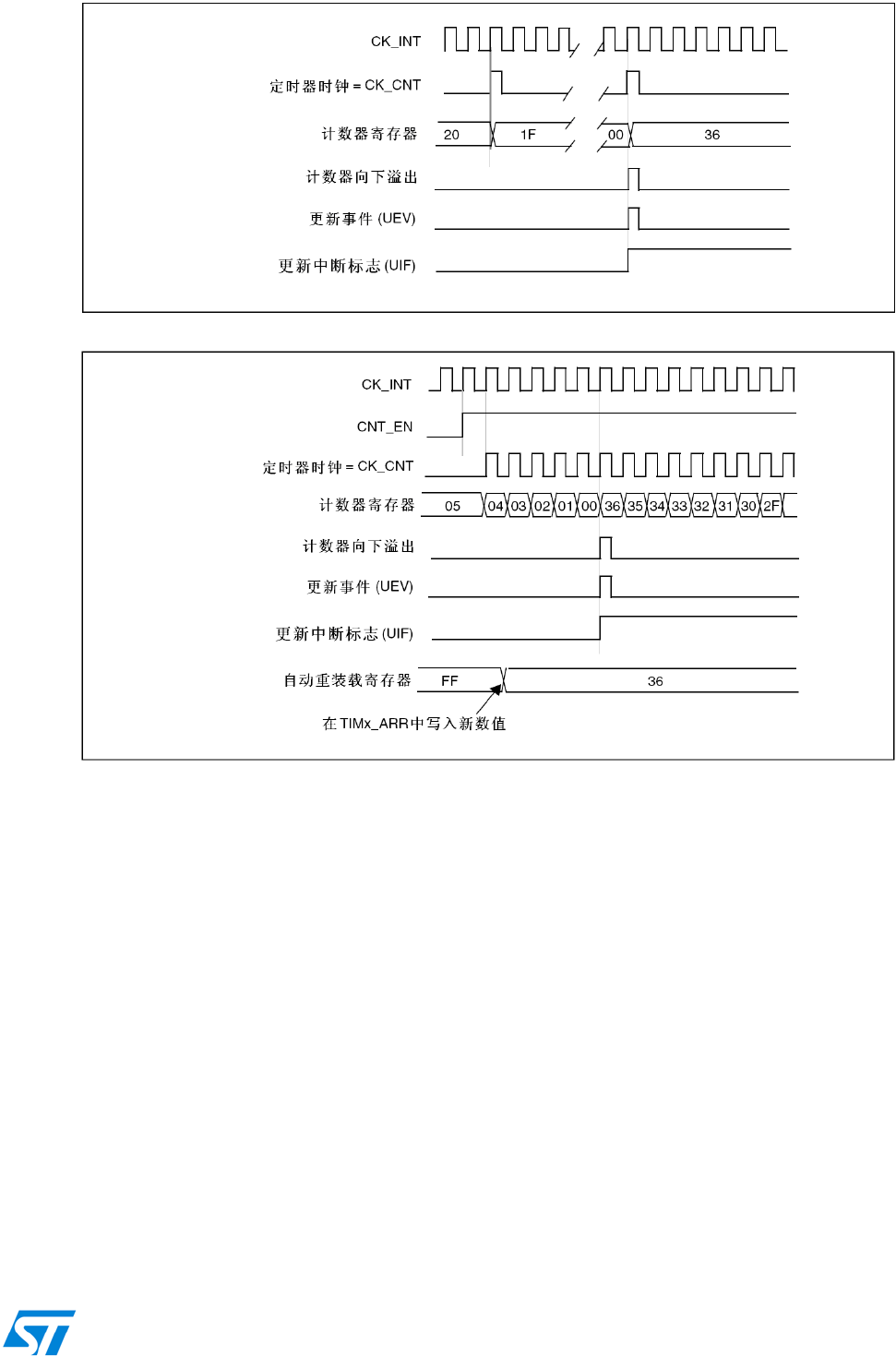

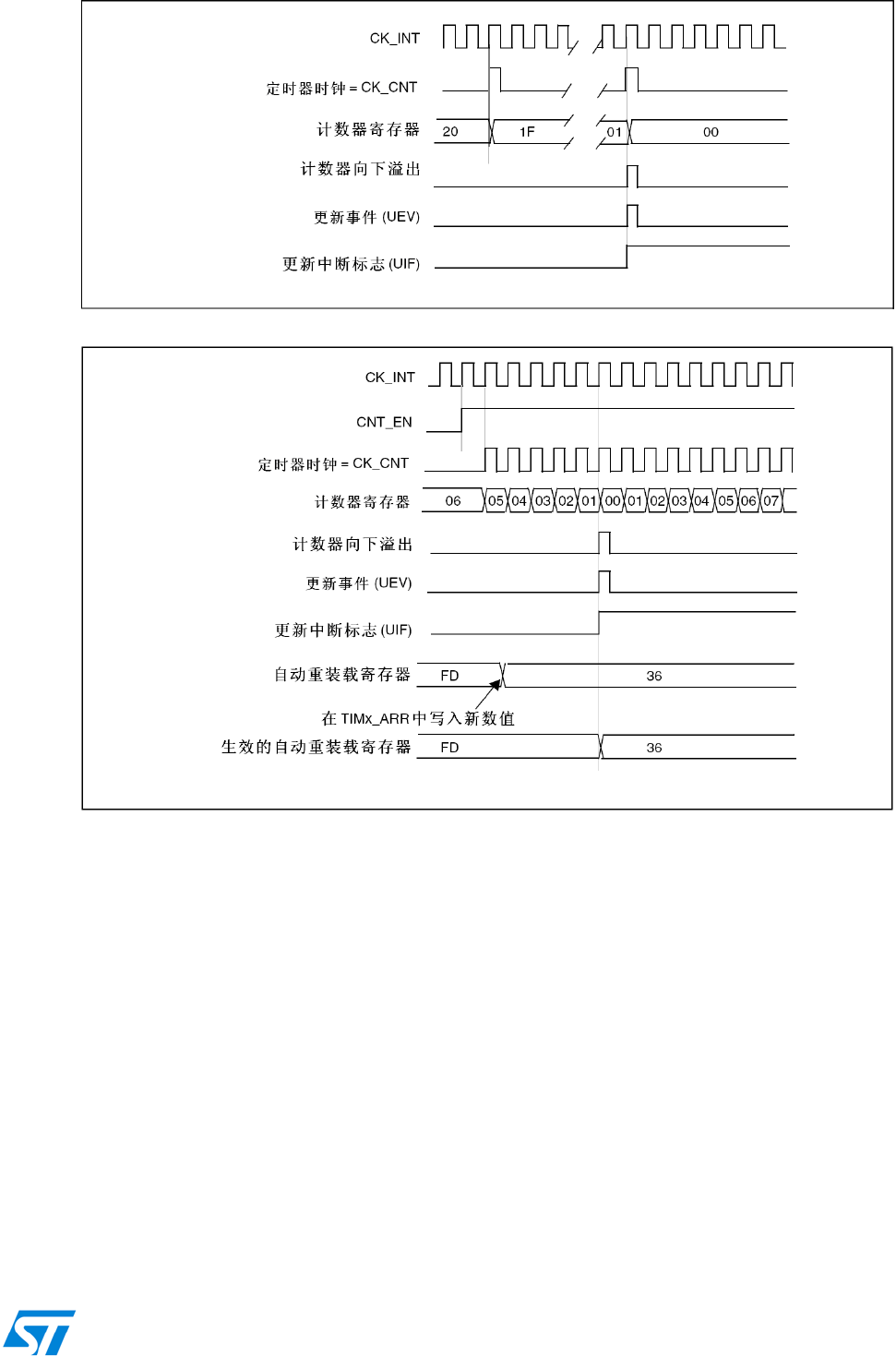

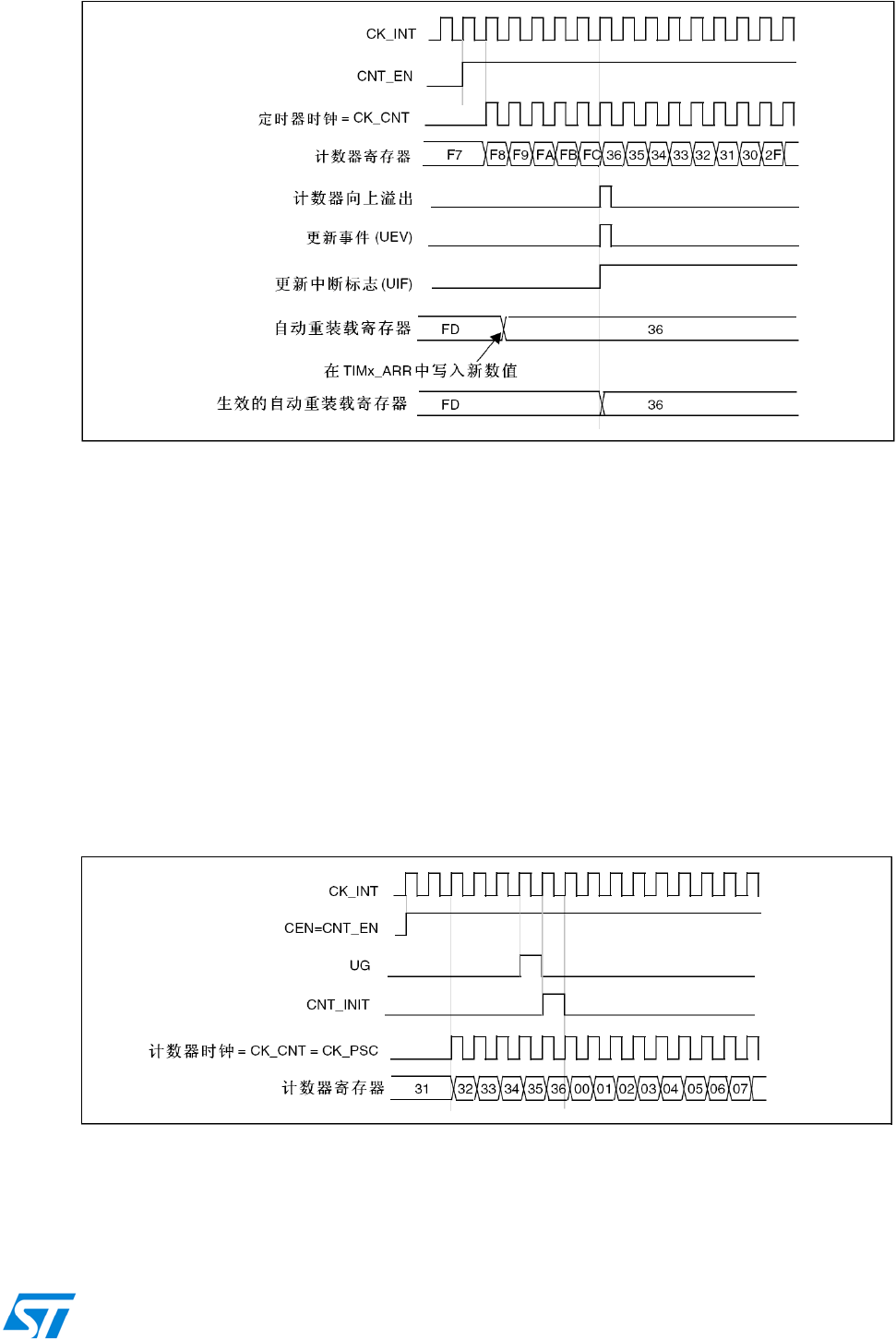

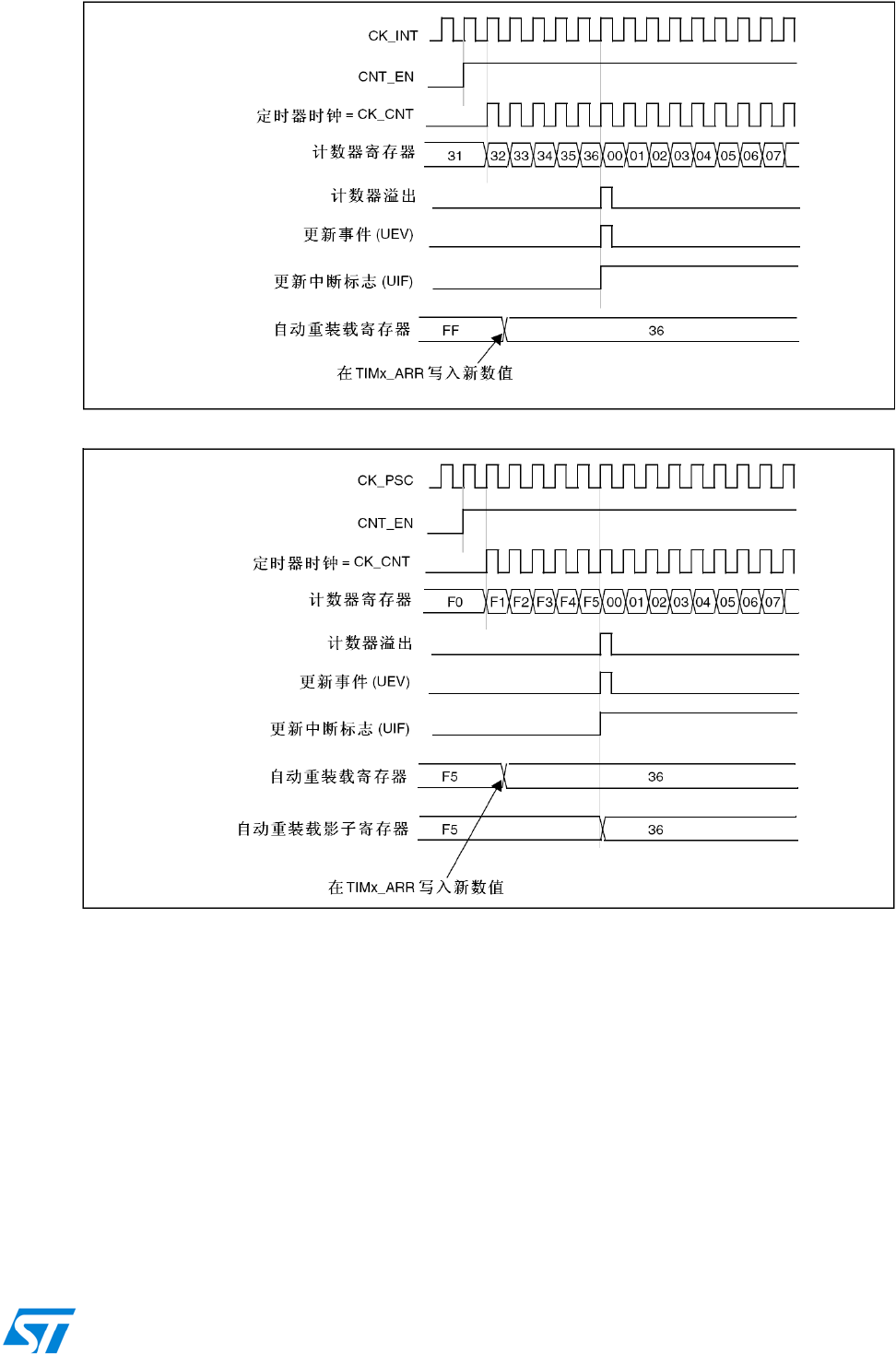

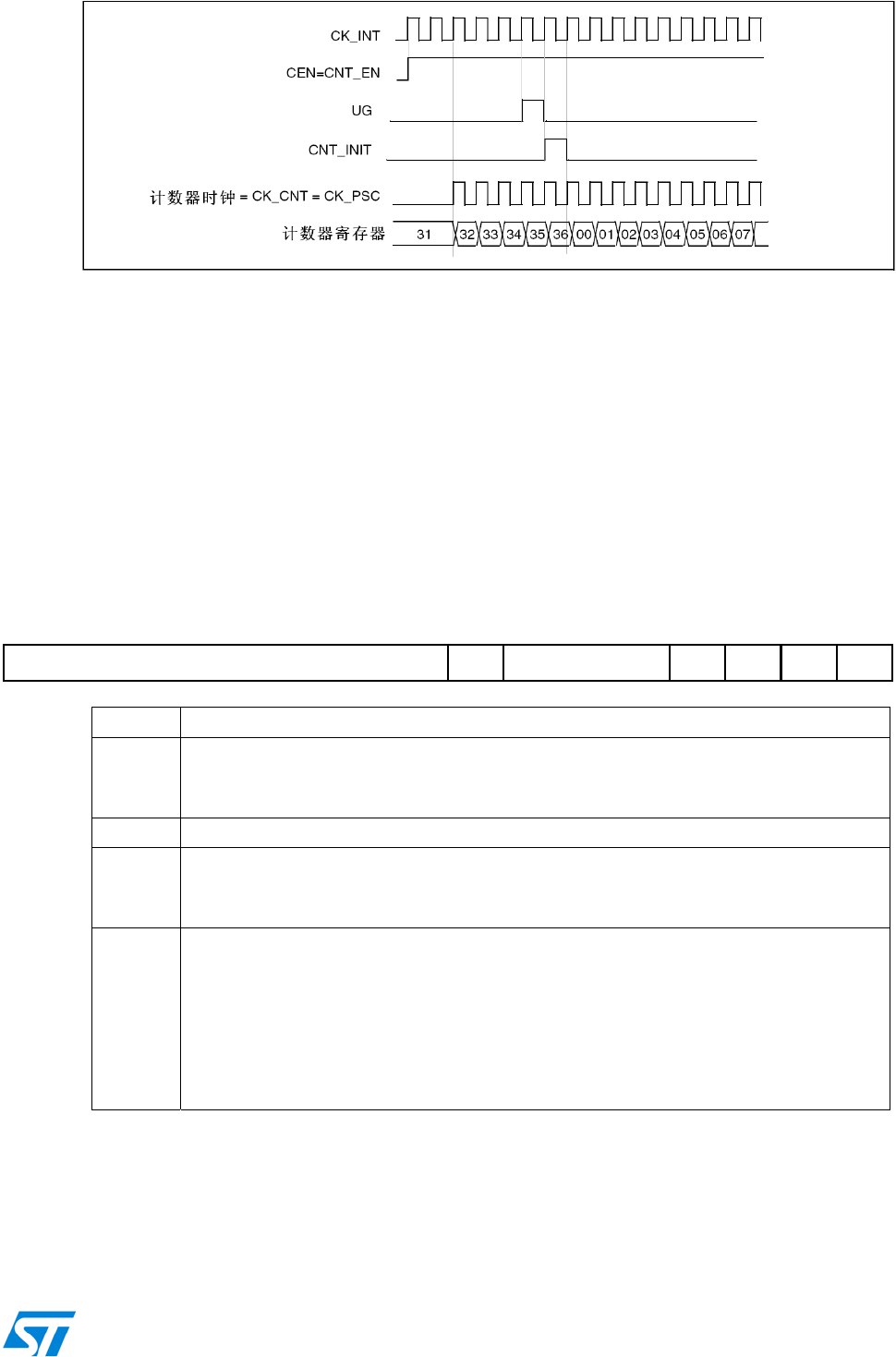

13.3.2 计数器模式 202

13.3.3 重复计数器 209

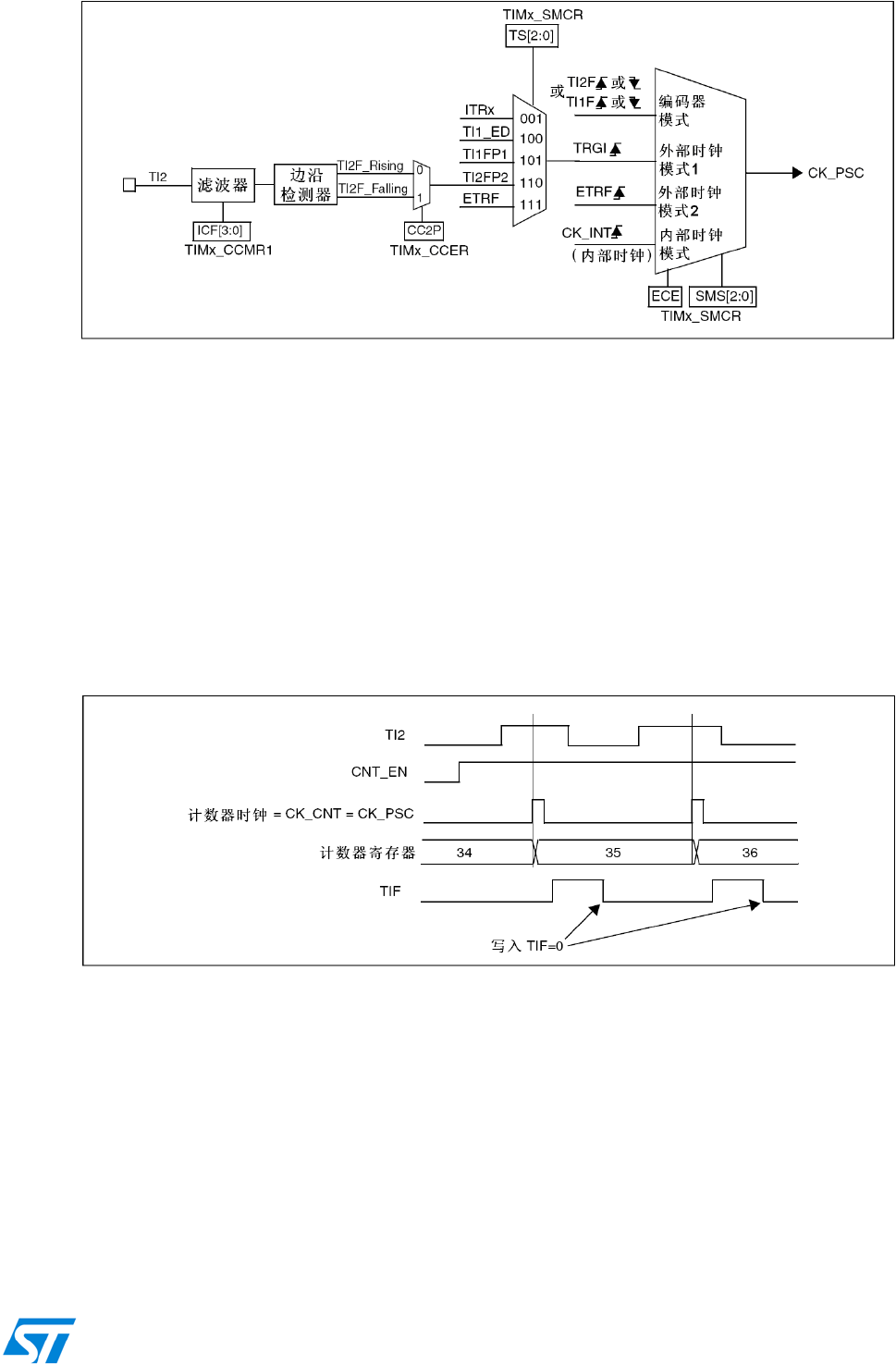

13.3.4 时钟选择 210

13.3.5 捕获/比较通道 213

13.3.6 输入捕获模式 215

13.3.7 PWM输入模式 216

13.3.8 强置输出模式 216

12/754

参照2009年12月 RM0008 Reference Manual 英文第10版

本译文仅供参考,如有翻译错误,请以英文原稿为准。请读者随时注意在ST网站下载更新版本

目录 STM32F10xxx参考手册

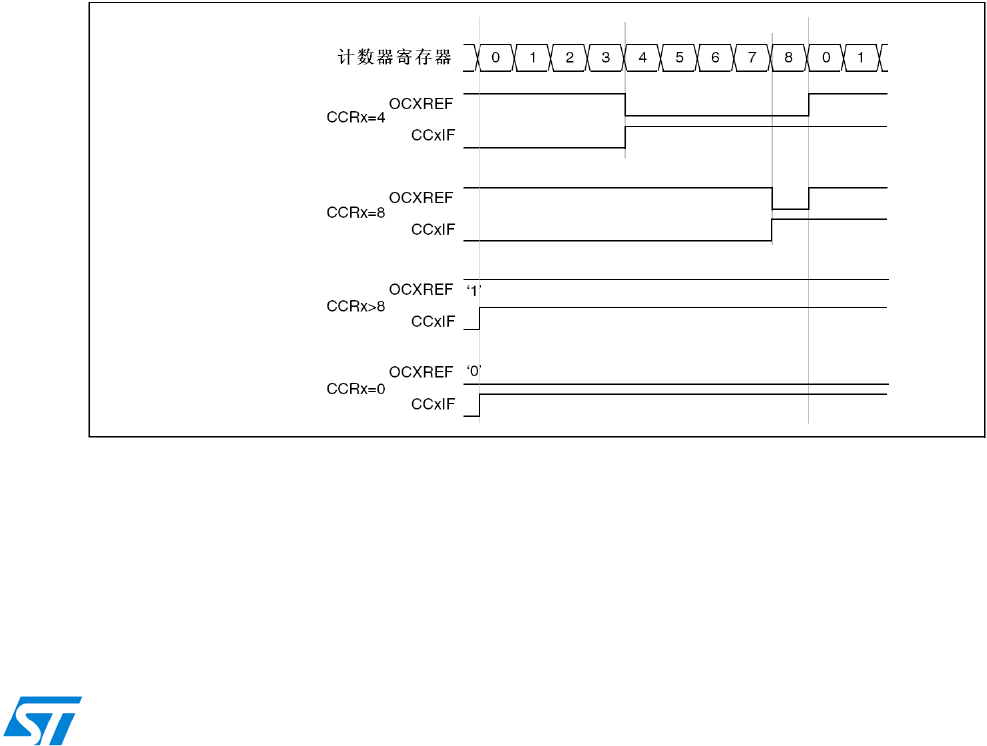

13.3.9 输出比较模式 217

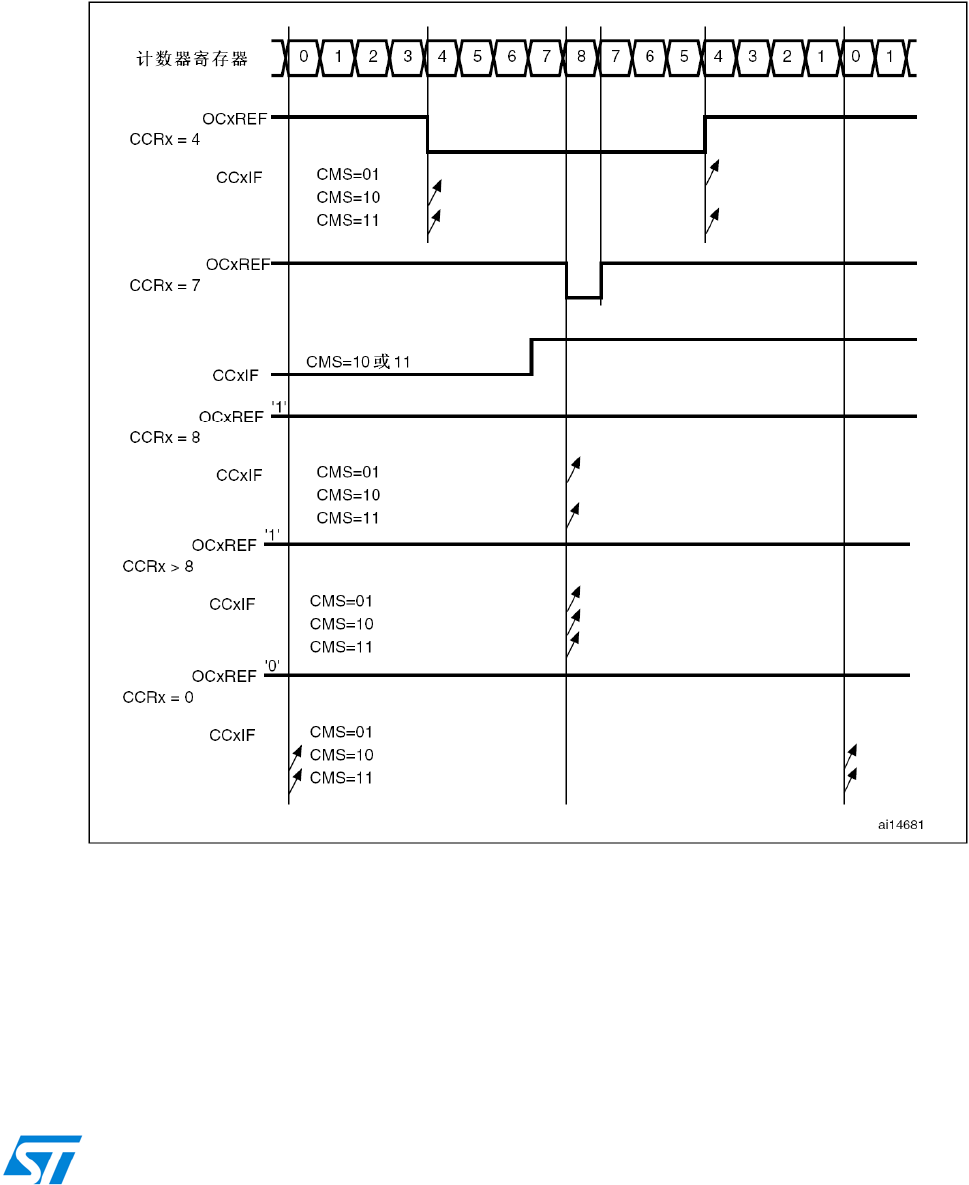

13.3.10 PWM模式 218

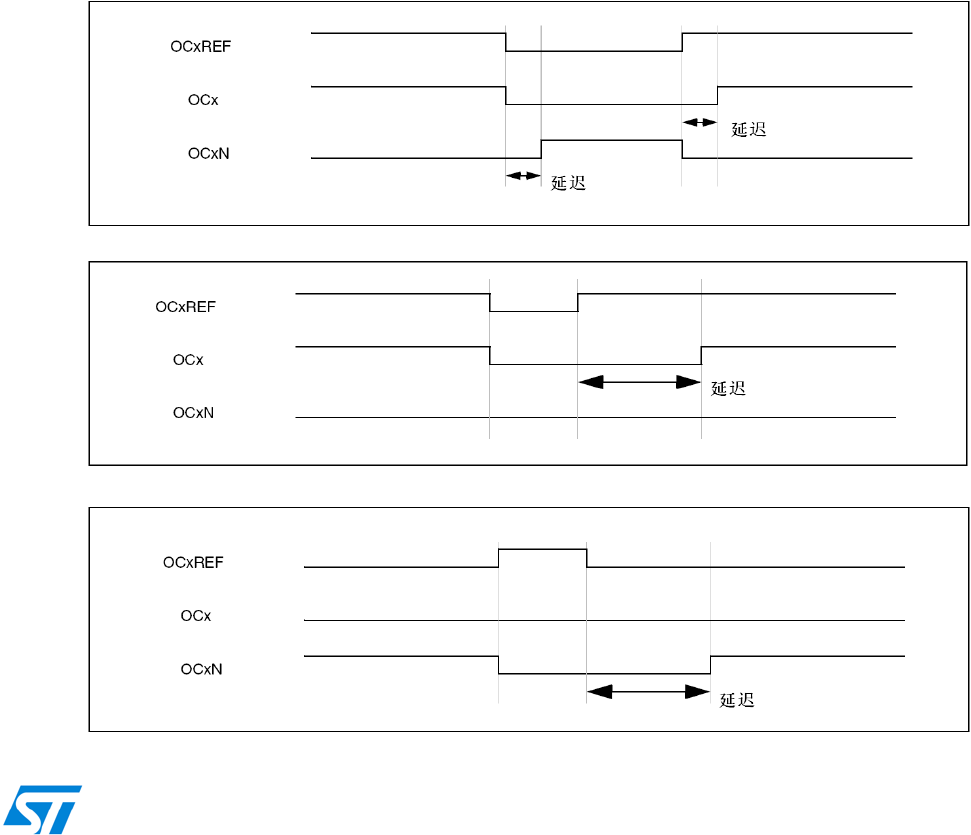

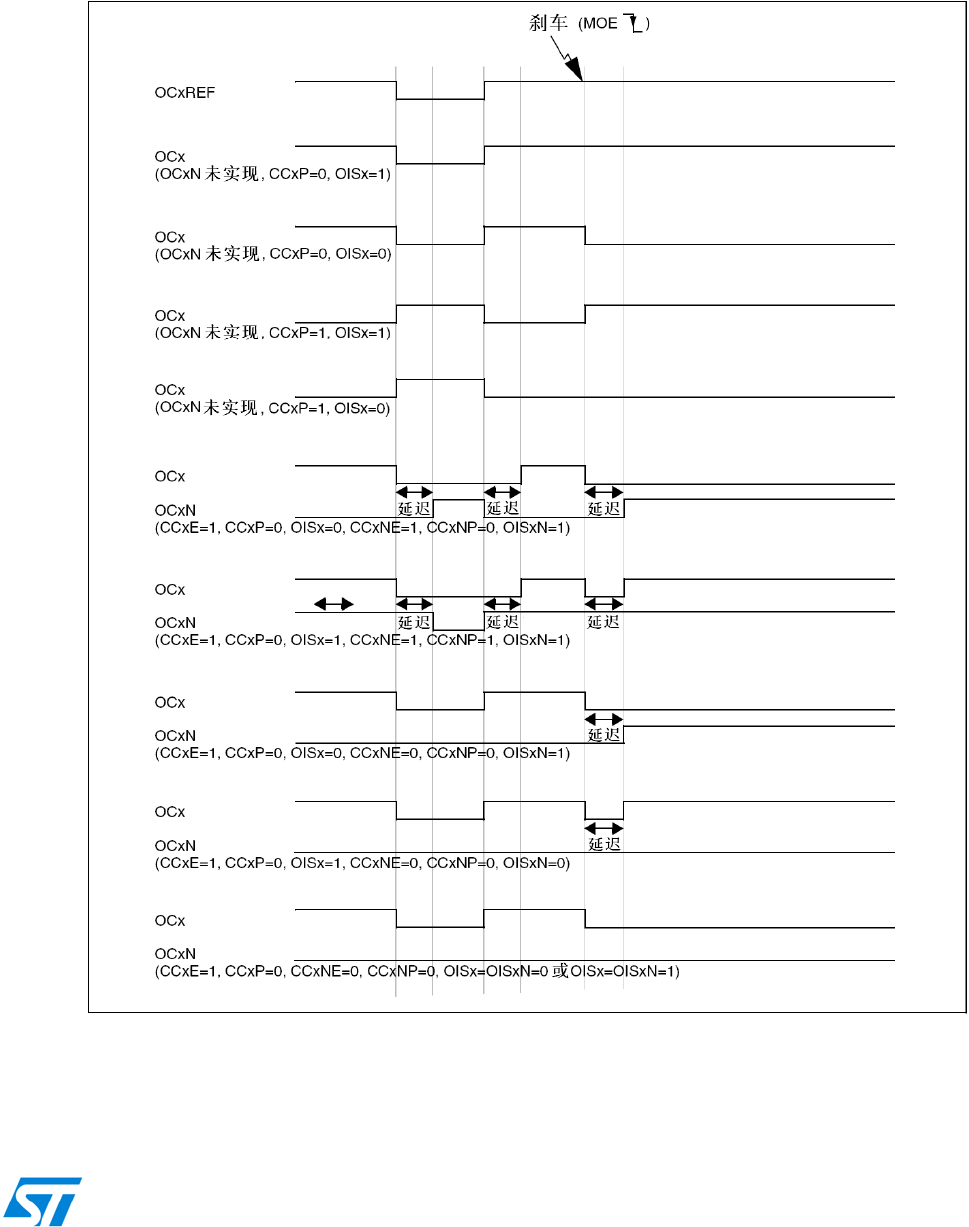

13.3.11 互补输出和死区插入 220

13.3.12 使用刹车功能 221

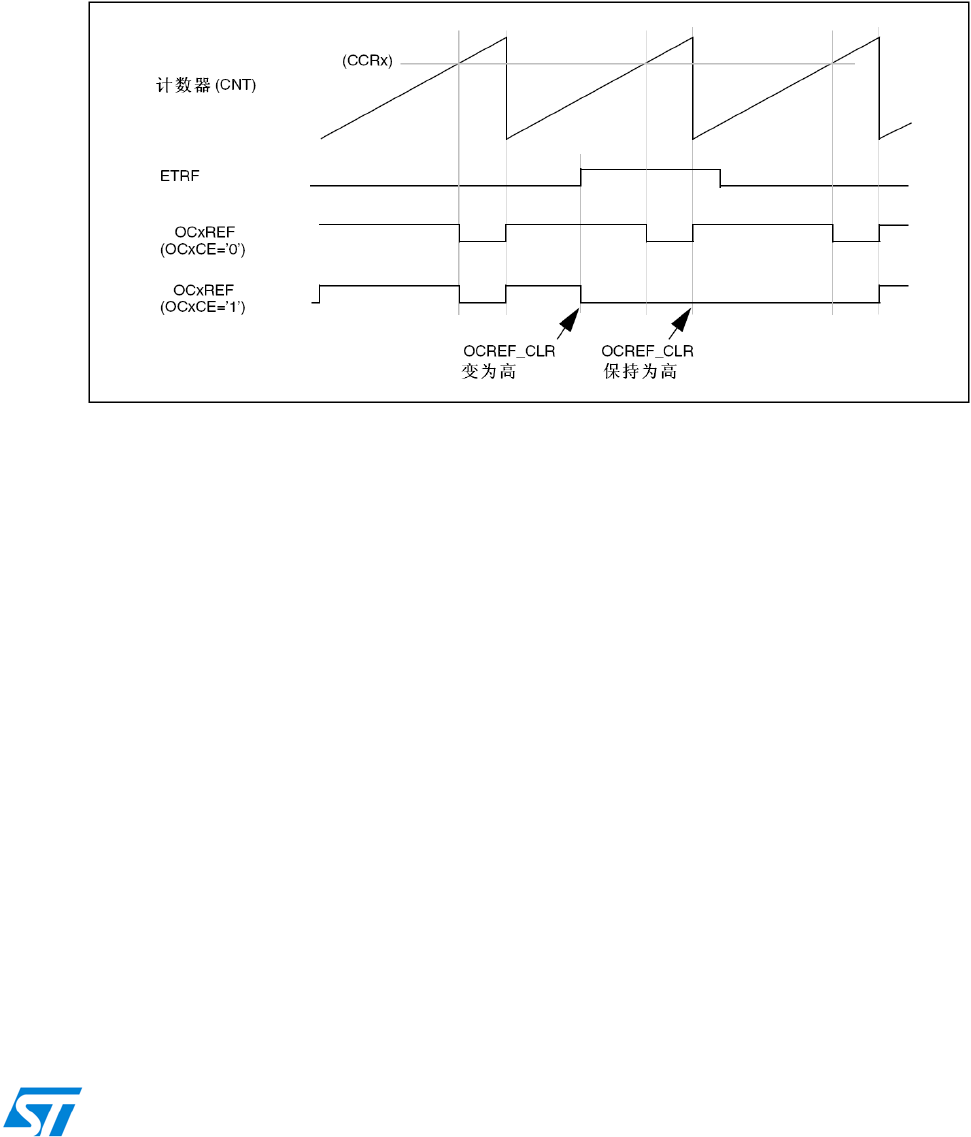

13.3.13 在外部事件时清除OCxREF信号 223

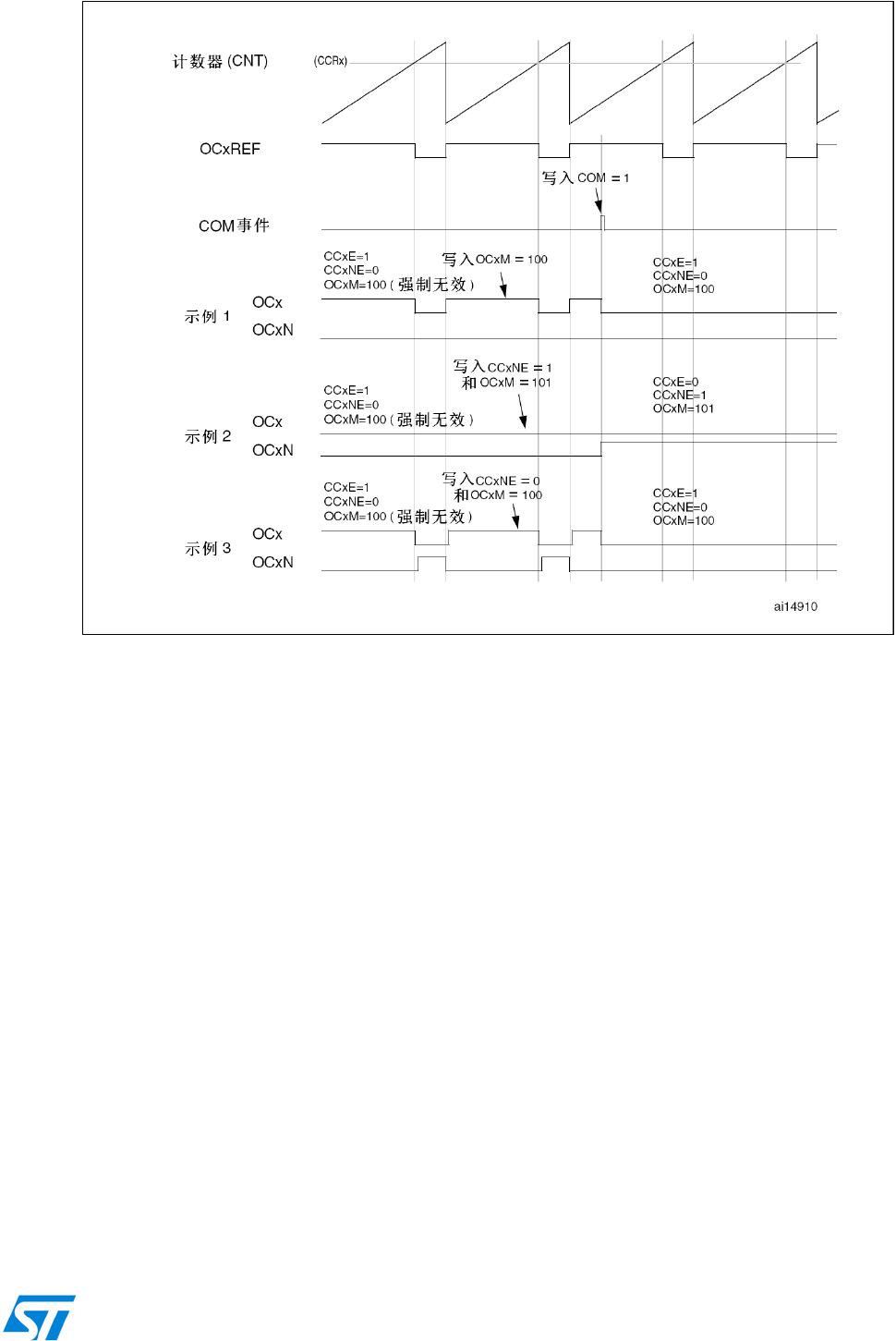

13.3.14 产生六步PWM输出 223

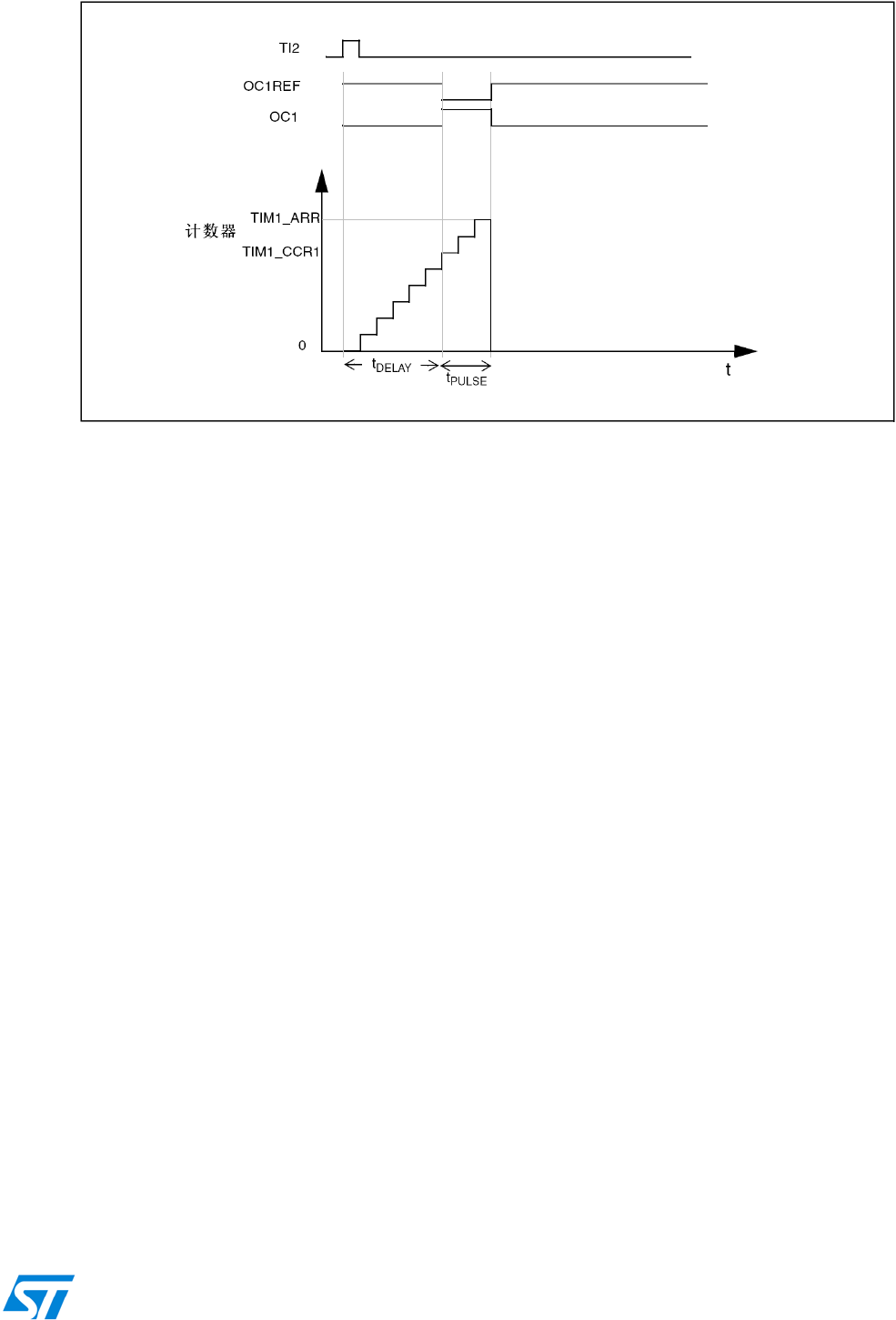

13.3.15 单脉冲模式 224

13.3.16 编码器接口模式 225

13.3.17 定时器输入异或功能 227

13.3.18 与霍尔传感器的接口 227

13.3.19 TIMx定时器和外部触发的同步 229

13.3.20 定时器同步 232

13.3.21 调试模式 232

13.4 TIM1和TIM8寄存器描述 233

13.4.1 TIM1和TIM8控制寄存器1(TIMx_CR1) 233

13.4.2 TIM1和TIM8控制寄存器2(TIMx_CR2) 234

13.4.3 TIM1和TIM8从模式控制寄存器(TIMx_SMCR) 235

13.4.4 TIM1和TIM8 DMA/中断使能寄存器(TIMx_DIER) 237

13.4.5 TIM1和TIM8状态寄存器(TIMx_SR) 238

13.4.6 TIM1和TIM8事件产生寄存器(TIMx_EGR) 239

13.4.7 TIM1和TIM8捕获/比较模式寄存器1(TIMx_CCMR1) 240

13.4.8 TIM1和TIM8捕获/比较模式寄存器2(TIMx_CCMR2) 242

13.4.9 TIM1和TIM8捕获/比较使能寄存器(TIMx_CCER) 244

13.4.10 TIM1和TIM8计数器(TIMx_CNT) 246

13.4.11 TIM1和TIM8预分频器(TIMx_PSC) 246

13.4.12 TIM1和TIM8自动重装载寄存器(TIMx_ARR) 246

13.4.13 TIM1和TIM8重复计数寄存器(TIMx_RCR) 246

13.4.14 TIM1和TIM8捕获/比较寄存器1(TIMx_CCR1) 247

13.4.15 TIM1和TIM8捕获/比较寄存器2(TIMx_CCR2) 247

13.4.16 TIM1和TIM8捕获/比较寄存器3(TIMx_CCR3) 247

13.4.17 TIM1和TIM8捕获/比较寄存器(TIMx_CCR4) 248

13.4.18 TIM1和TIM8刹车和死区寄存器(TIMx_BDTR) 248

13.4.19 TIM1和TIM8 DMA控制寄存器(TIMx_DCR) 249

13.4.20 TIM1和TIM8连续模式的DMA地址(TIMx_DMAR) 250

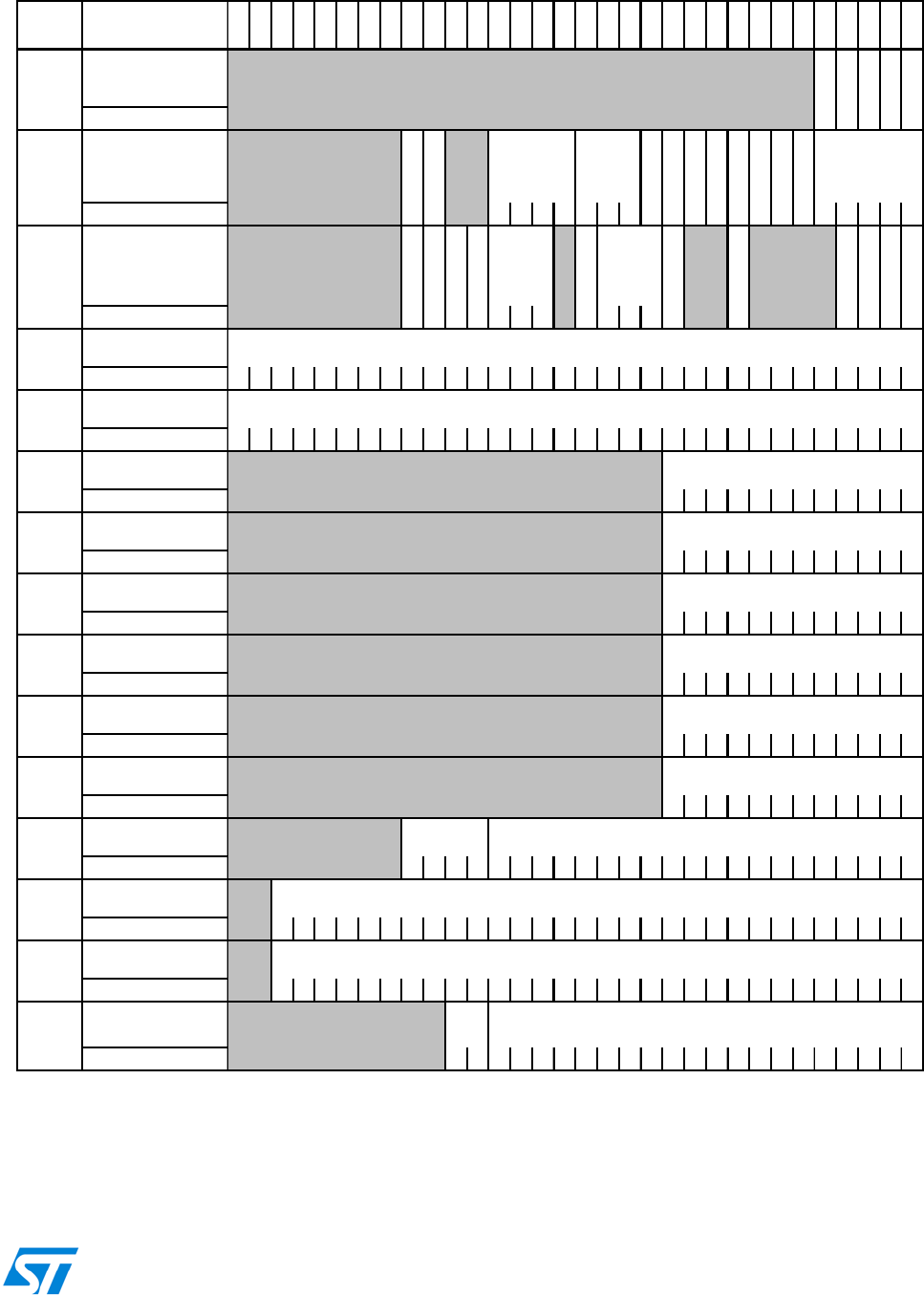

13.4.21 TIM1和TIM8寄存器图 251

14 通用定时器(TIMx) 253

14.1 TIMx简介 253

14.2 TIMx主要功能 253

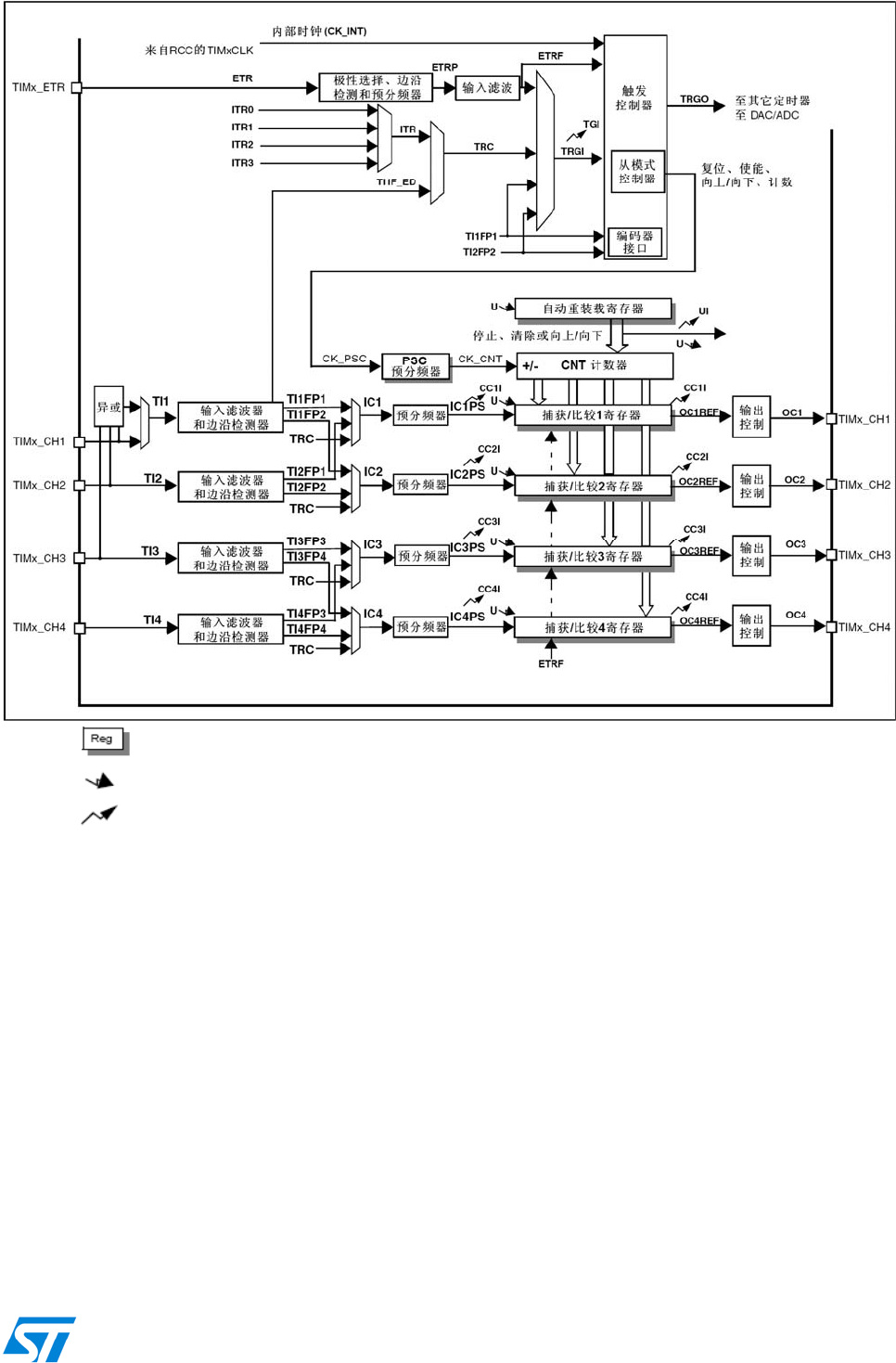

14.3 TIMx功能描述 254

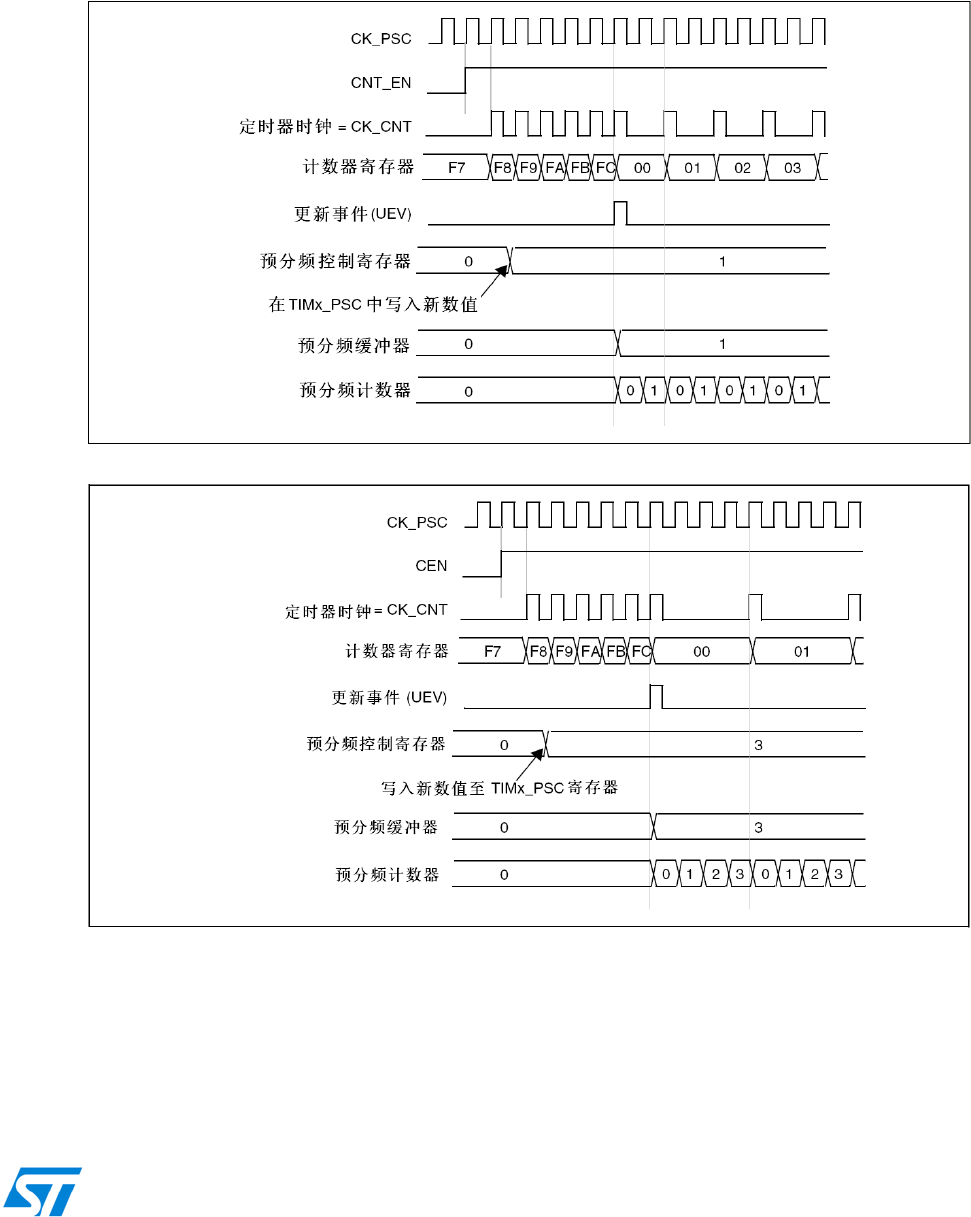

14.3.1 时基单元 254

14.3.2 计数器模式 255

14.3.3 时钟选择 263

14.3.4 捕获/比较通道 265

14.3.5 输入捕获模式 267

14.3.6 PWM输入模式 267

14.3.7 强置输出模式 268

14.3.8 输出比较模式 268

14.3.9 PWM 模式 269

14.3.10 单脉冲模式 271

14.3.11 在外部事件时清除OCxREF信号 273

14.3.12 编码器接口模式 273

13/754

参照2009年12月 RM0008 Reference Manual 英文第10版

本译文仅供参考,如有翻译错误,请以英文原稿为准。请读者随时注意在ST网站下载更新版本

目录 STM32F10xxx参考手册

14.3.13 定时器输入异或功能 275

14.3.14 定时器和外部触发的同步 275

14.3.15 定时器同步 277

14.3.16 调试模式 281

14.4 TIMx寄存器描述 282

14.4.1 控制寄存器1(TIMx_CR1) 282

14.4.2 控制寄存器2(TIMx_CR2) 283

14.4.3 从模式控制寄存器(TIMx_SMCR) 284

14.4.4 DMA/中断使能寄存器(TIMx_DIER) 285

14.4.5 状态寄存器(TIMx_SR) 286

14.4.6 事件产生寄存器(TIMx_EGR) 287

14.4.7 捕获/比较模式寄存器1(TIMx_CCMR1) 288

14.4.8 捕获/比较模式寄存器2(TIMx_CCMR2) 290

14.4.9 捕获/比较使能寄存器(TIMx_CCER) 292

14.4.10 计数器(TIMx_CNT) 293

14.4.11 预分频器(TIMx_PSC) 293

14.4.12 自动重装载寄存器(TIMx_ARR) 293

14.4.13 捕获/比较寄存器1(TIMx_CCR1) 293

14.4.14 捕获/比较寄存器2(TIMx_CCR2) 294

14.4.15 捕获/比较寄存器3(TIMx_CCR3) 294

14.4.16 捕获/比较寄存器4(TIMx_CCR4) 294

14.4.17 DMA控制寄存器(TIMx_DCR) 295

14.4.18 连续模式的DMA地址(TIMx_DMAR) 295

14.4.19 TIMx寄存器图 296

15 基本定时器(TIM6 和TIM7) 298

15.1 TIM6和TIM7简介 298

15.2 TIM6和TIM7的主要特性 298

15.3 TIM6和TIM7的功能 299

15.3.1 时基单元 299

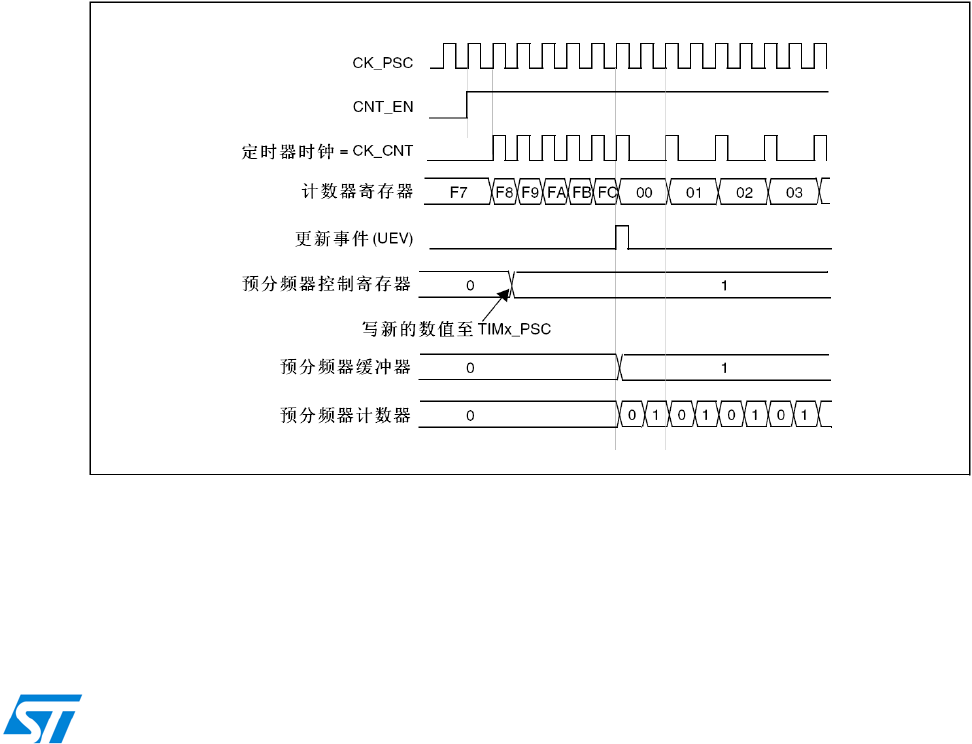

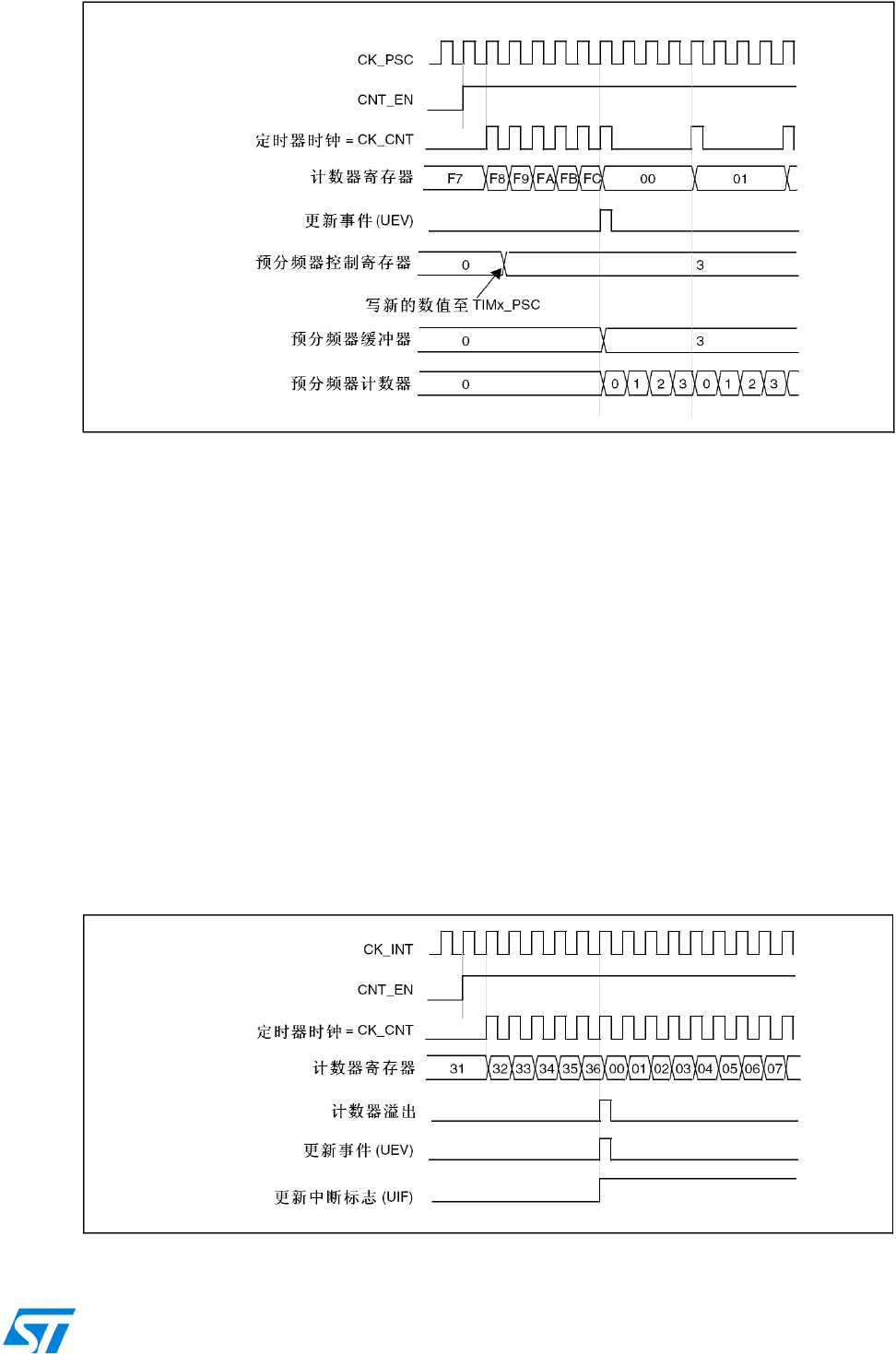

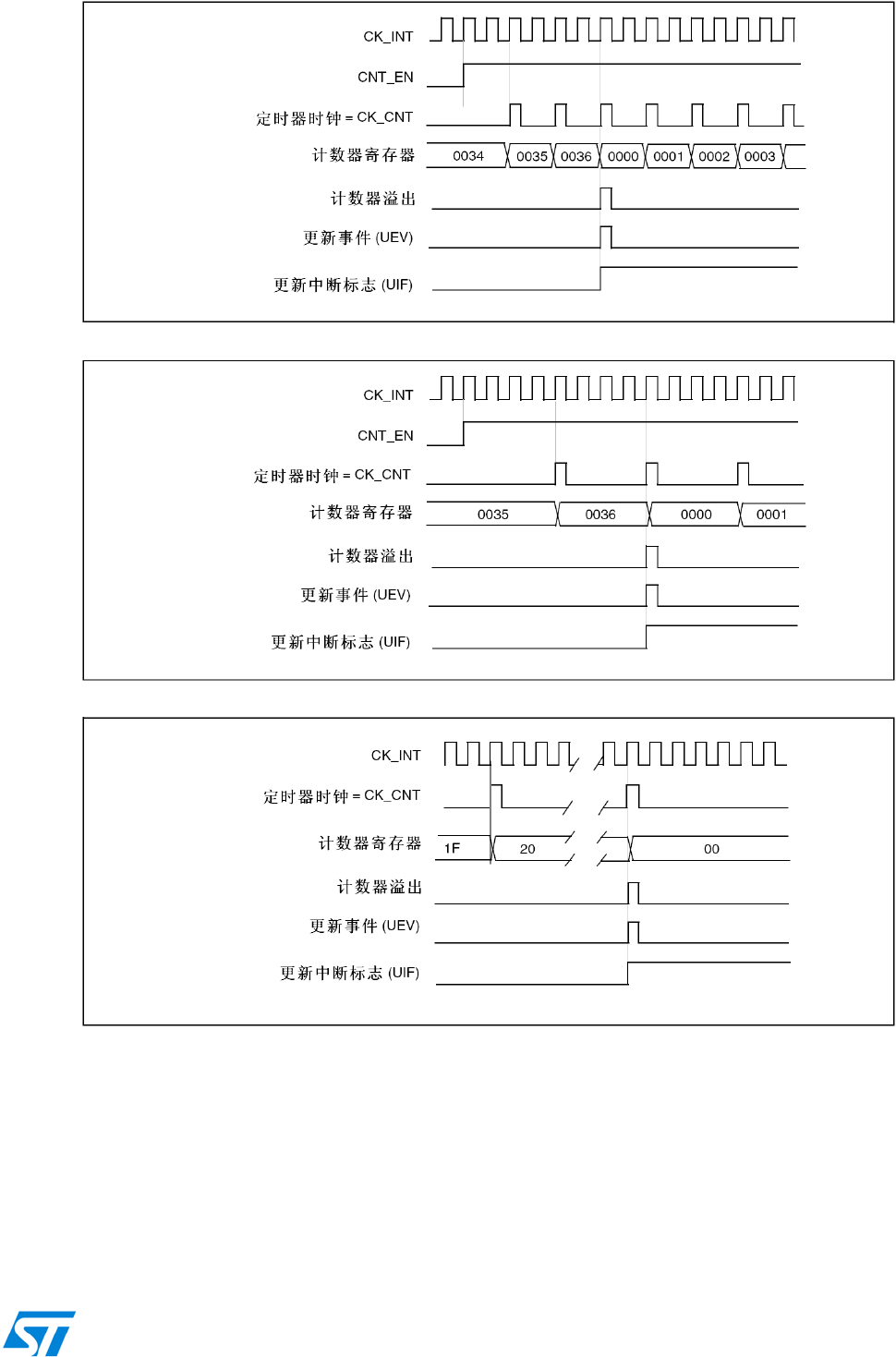

15.3.2 计数模式 300

15.3.3 时钟源 302

15.3.4 调试模式 303

15.4 TIM6和TIM7寄存器 303

15.4.1 TIM6和TIM7控制寄存器1(TIMx_CR1) 303

15.4.2 TIM6和TIM7控制寄存器2(TIMx_CR2) 304

15.4.3 TIM6和TIM7 DMA/中断使能寄存器(TIMx_DIER) 304

15.4.4 TIM6和TIM7状态寄存器(TIMx_SR) 305

15.4.5 TIM6和TIM7事件产生寄存器(TIMx_EGR) 305

15.4.6 TIM6和TIM7计数器(TIMx_CNT) 305

15.4.7 TIM6和TIM7预分频器(TIMx_PSC) 306

15.4.8 TIM6和TIM7自动重装载寄存器(TIMx_ARR) 306

15.4.9 TIM6和TIM7寄存器图 307

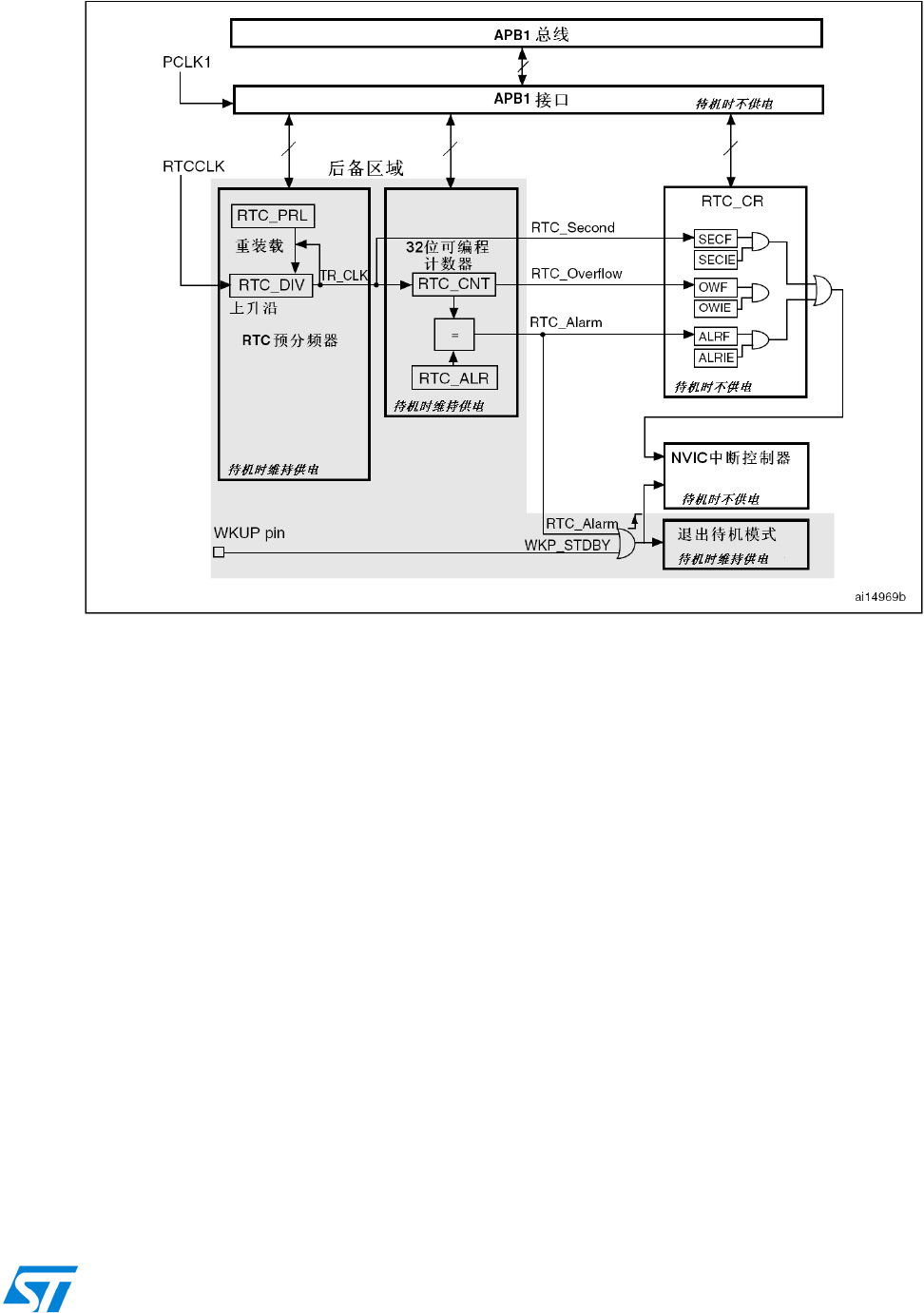

16 实时时钟(RTC) 308

16.1 RTC简介 308

16.2 主要特性 308

16.3 功能描述 308

16.3.1 概述 308

16.3.2 复位过程 309

16.3.3 读RTC寄存器 309

14/754

参照2009年12月 RM0008 Reference Manual 英文第10版

本译文仅供参考,如有翻译错误,请以英文原稿为准。请读者随时注意在ST网站下载更新版本

目录 STM32F10xxx参考手册

16.3.4 配置RTC寄存器 310

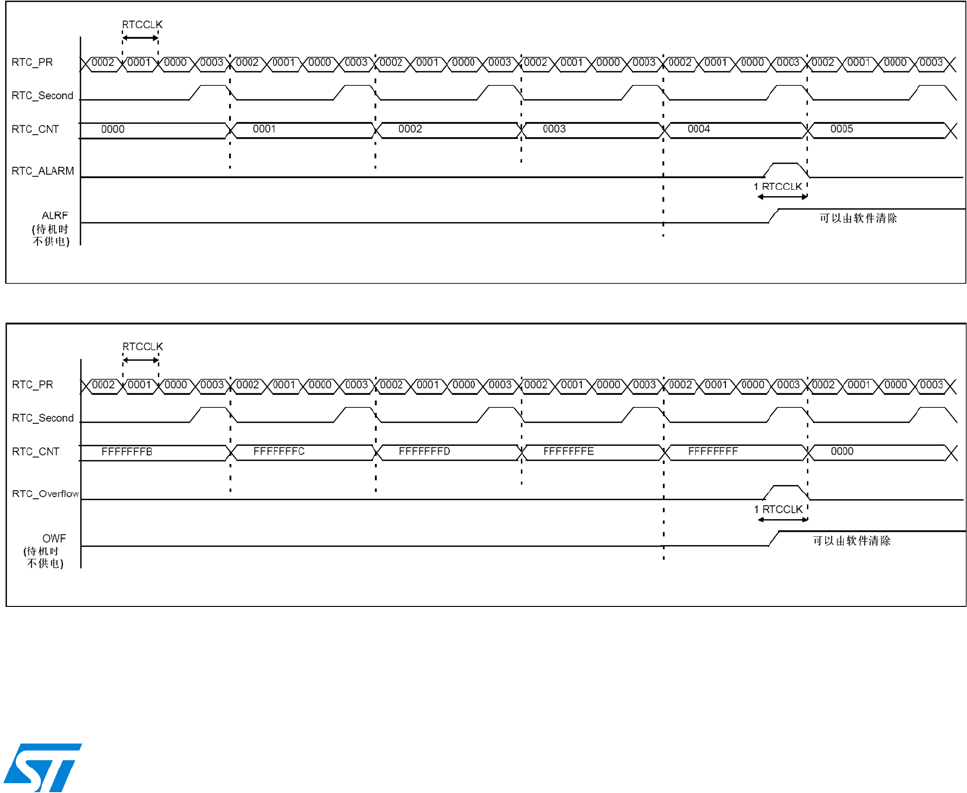

16.3.5 RTC标志的设置 310

16.4 RTC寄存器描述 311

16.4.1 RTC控制寄存器高位(RTC_CRH) 311

16.4.2 RTC控制寄存器低位(RTC_CRL) 311

16.4.3 RTC预分频装载寄存器(RTC_PRLH/RTC_PRLL) 312

16.4.4 RTC预分频器余数寄存器(RTC_DIVH / RTC_DIVL) 313

16.4.5 RTC计数器寄存器 (RTC_CNTH / RTC_CNTL) 313

16.4.6 RTC闹钟寄存器(RTC_ALRH/RTC_ALRL) 314

16.4.7 RTC寄存器映像 315

17 独立看门狗(IWDG) 316

17.1 简介 316

17.2 IWDG主要性能 316

17.3 IWDG功能描述 316

17.3.1 硬件看门狗 316

17.3.2 寄存器访问保护 316

17.3.3 调试模式 316

17.4 IWDG寄存器描述 317

17.4.1 键寄存器(IWDG_KR) 317

17.4.2 预分频寄存器(IWDG_PR) 318

17.4.3 重装载寄存器(IWDG_RLR) 318

17.4.4 状态寄存器(IWDG_SR) 319

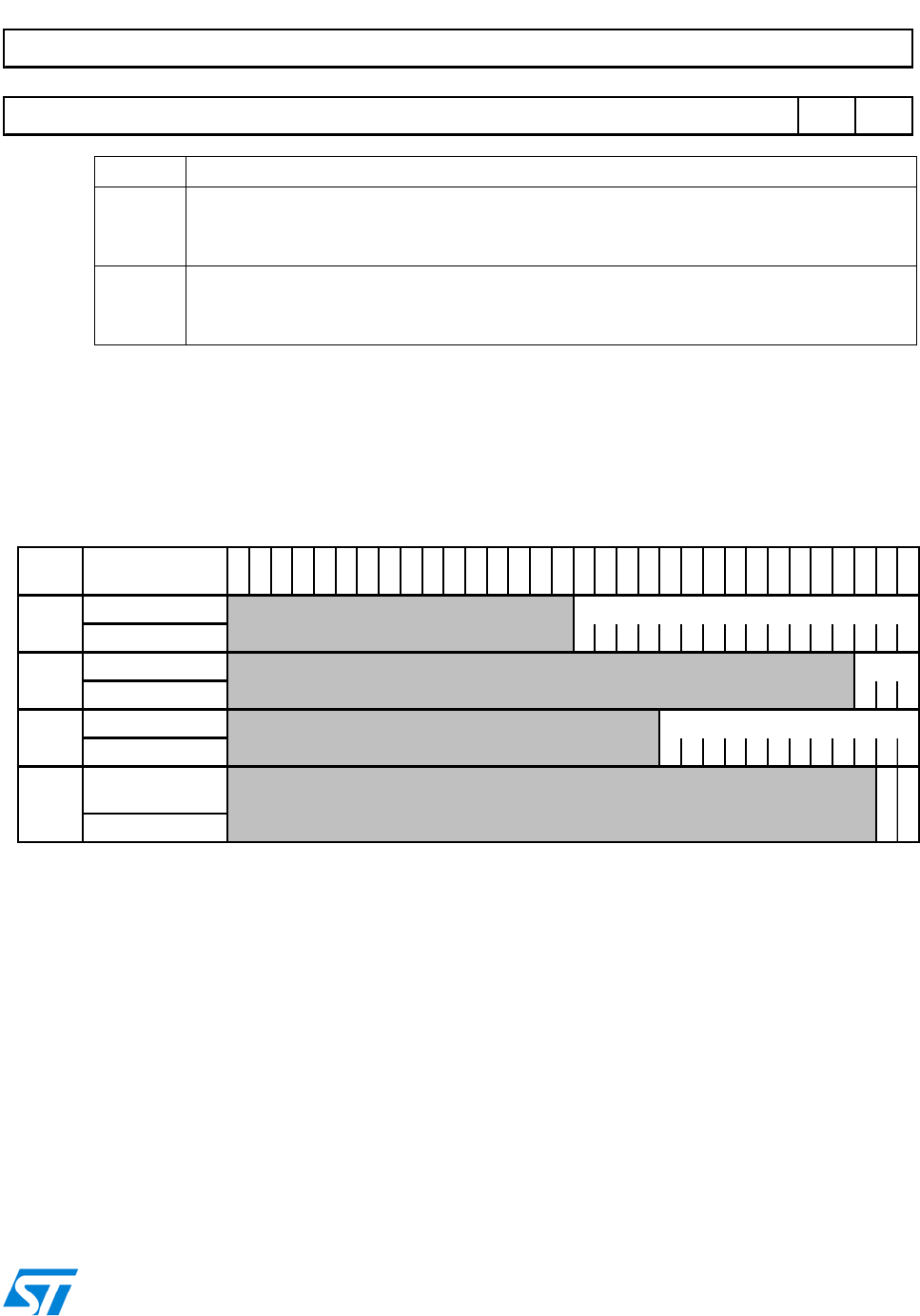

17.4.5 IWDG寄存器映像 319

18 窗口看门狗(WWDG) 320

18.1 WWDG简介 320

18.2 WWDG主要特性 320

18.3 WWDG功能描述 320

18.4 如何编写看门狗超时程序 321

18.5 调试模式 322

18.6 寄存器描述 322

18.6.1 控制寄存器(WWDG_CR) 322

18.6.2 配置寄存器(WWDG_CFR) 322

18.6.3 状态寄存器(WWDG_SR) 323

18.6.4 WWDG寄存器映像 323

19 灵活的静态存储器控制器(FSMC) 324

19.1 FSMC功能描述 324

19.2 框图 324

19.3 AHB接口 325

19.3.1 支持的存储器和操作 325

19.4 外部设备地址映像 326

19.4.1 NOR和PSRAM地址映像 327

19.4.2 NAND和PC卡地址映像 327

19.5 NOR闪存和PSRAM控制器 328

19.5.1 外部存储器接口信号 329

19.5.2 支持的存储器及其操作 330

19.5.3 时序规则 330

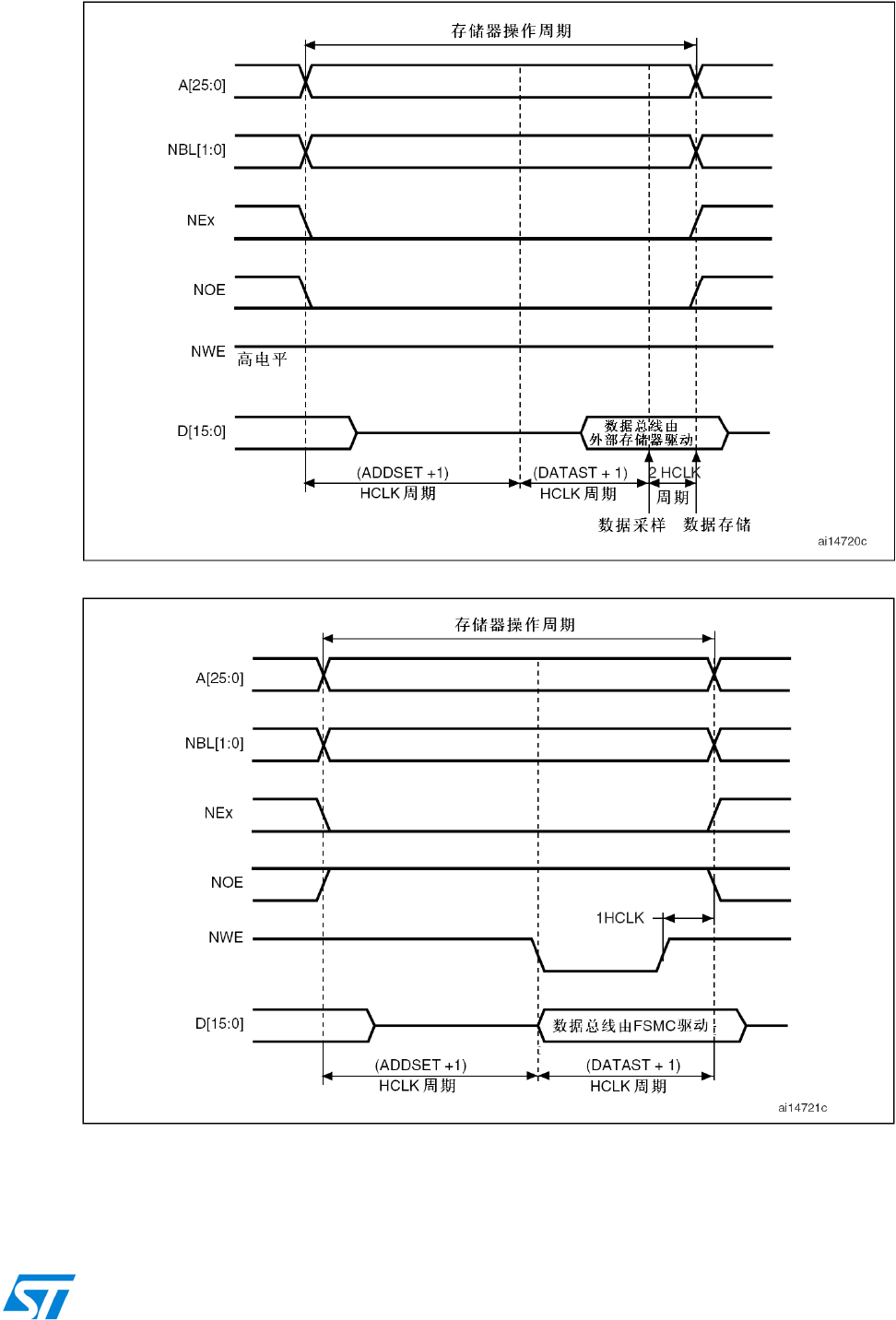

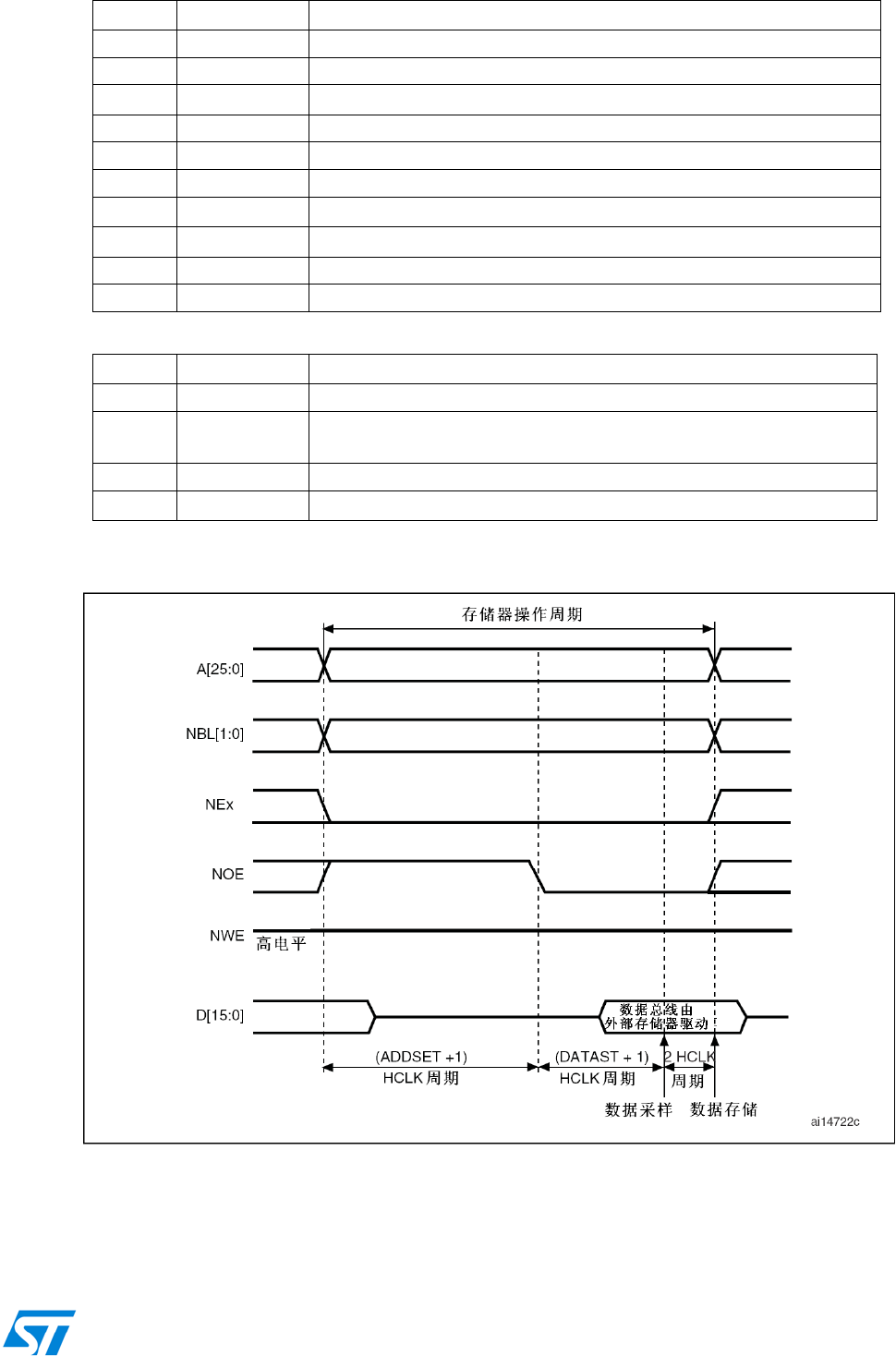

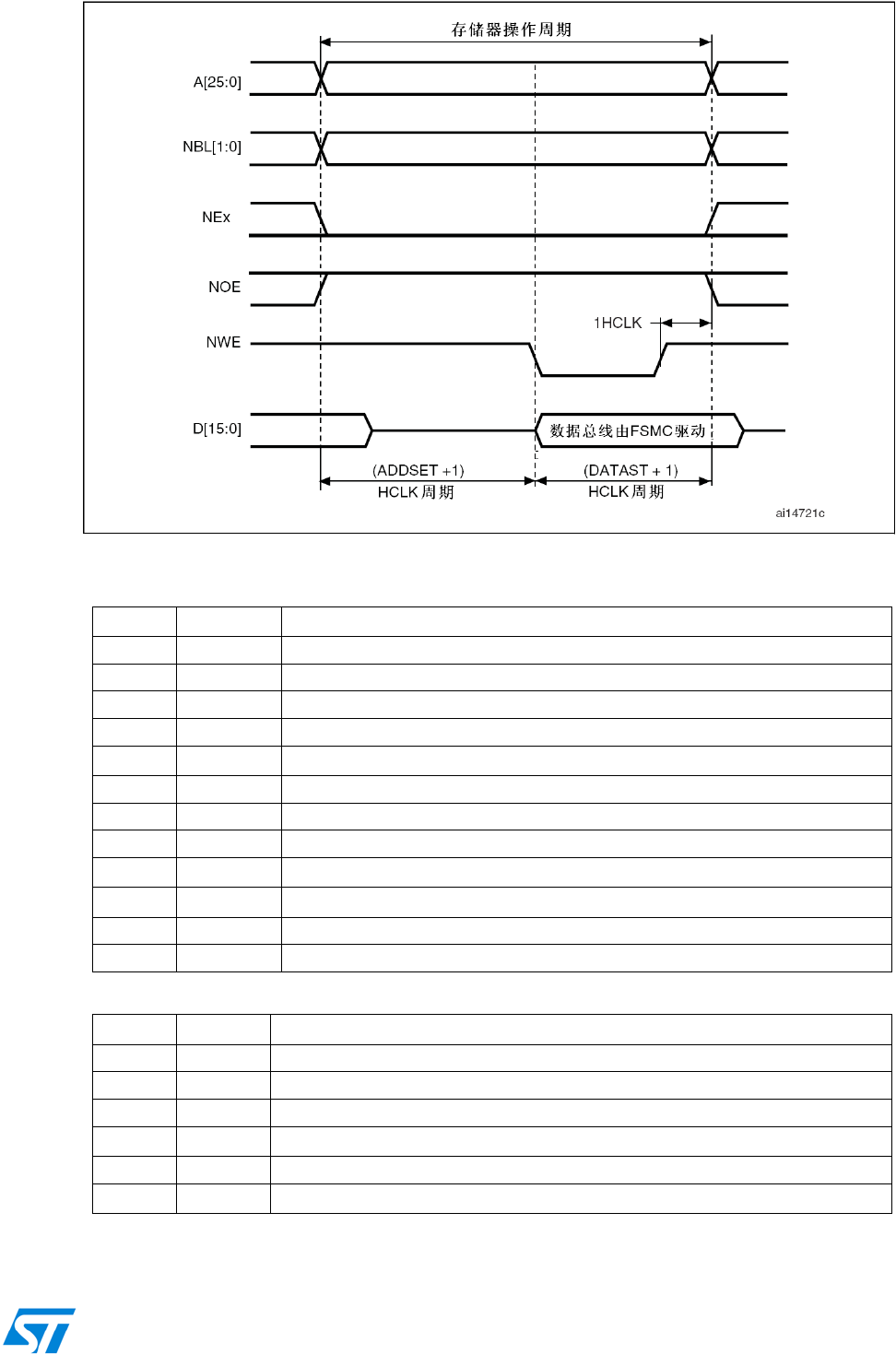

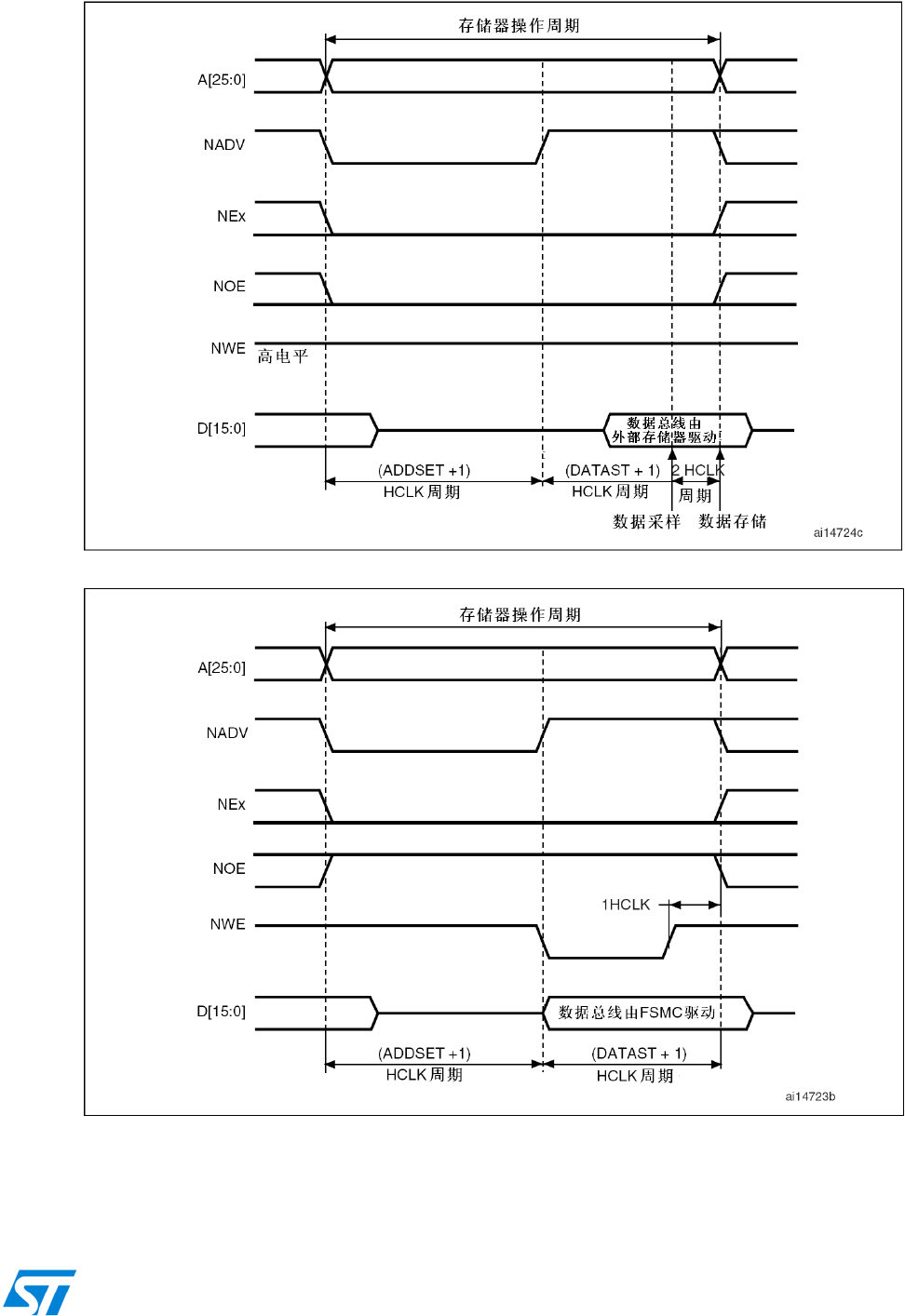

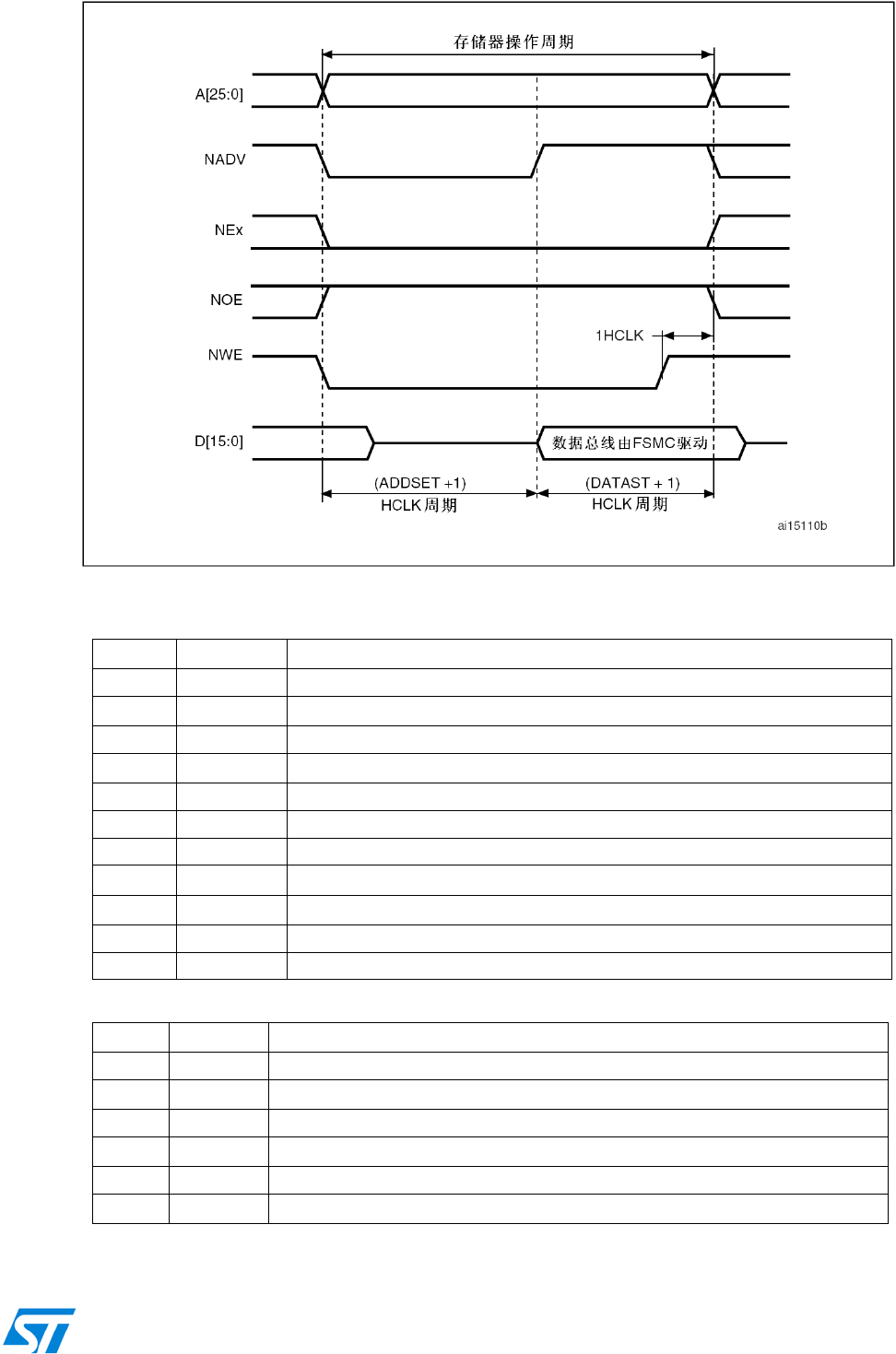

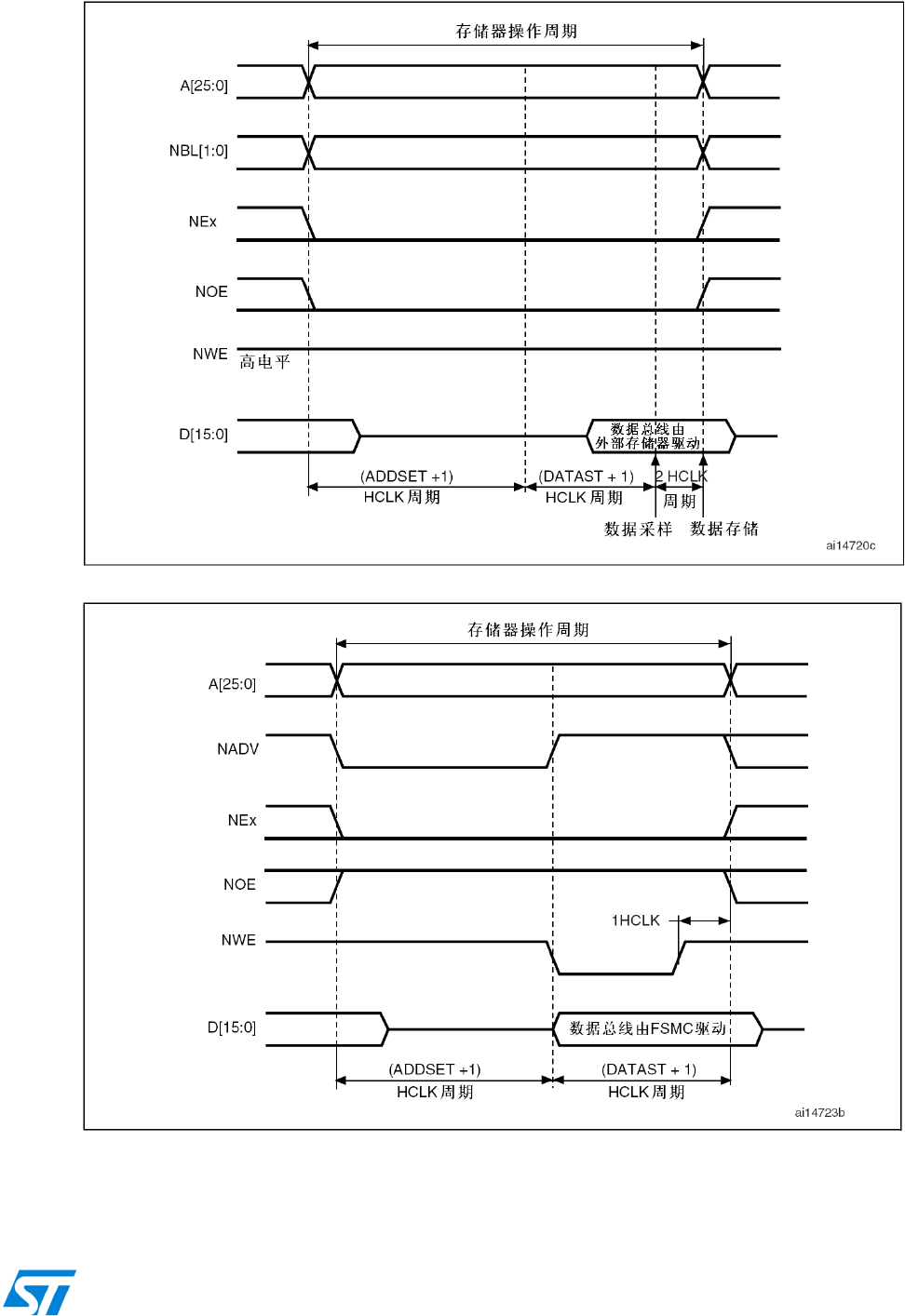

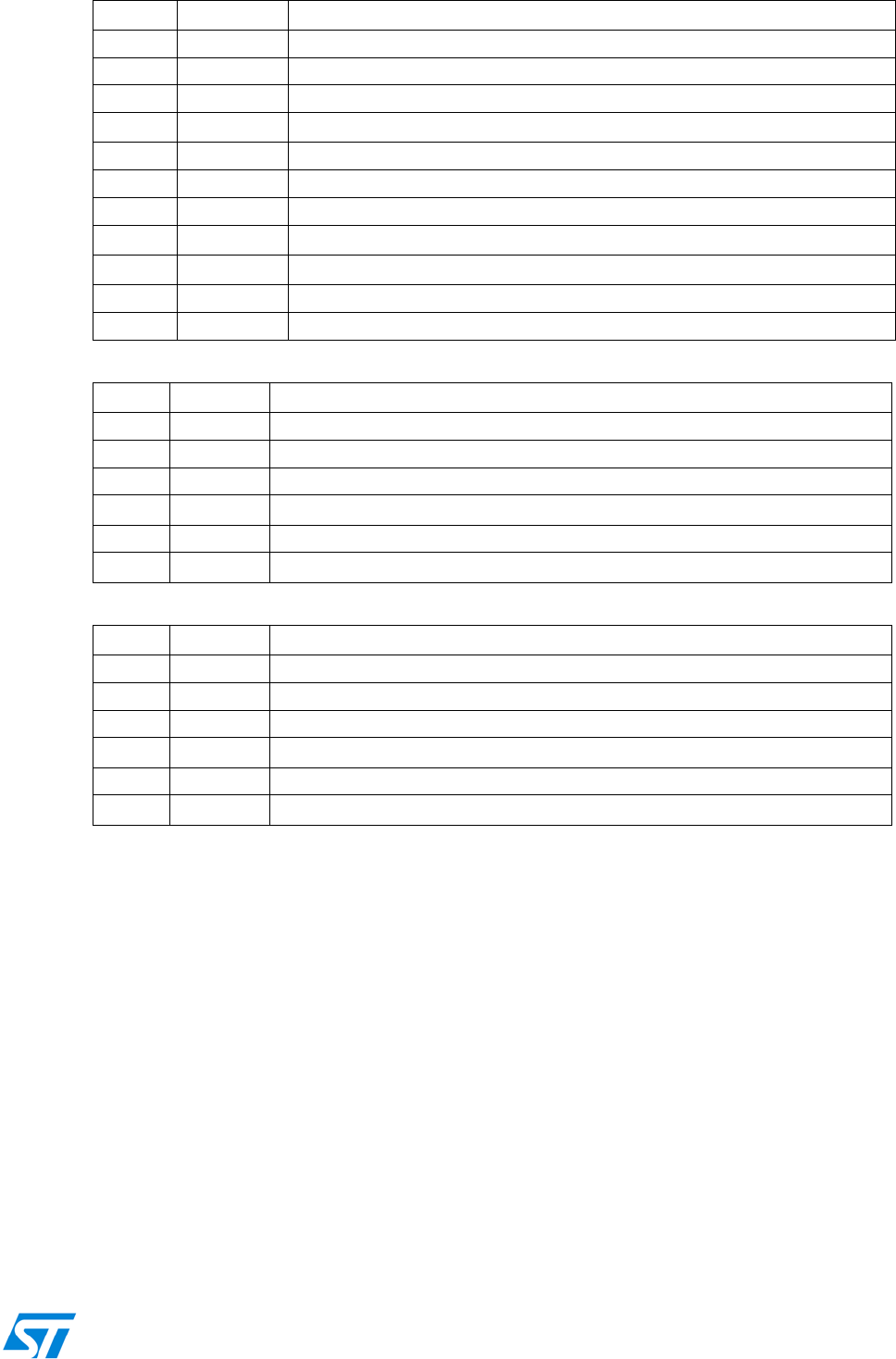

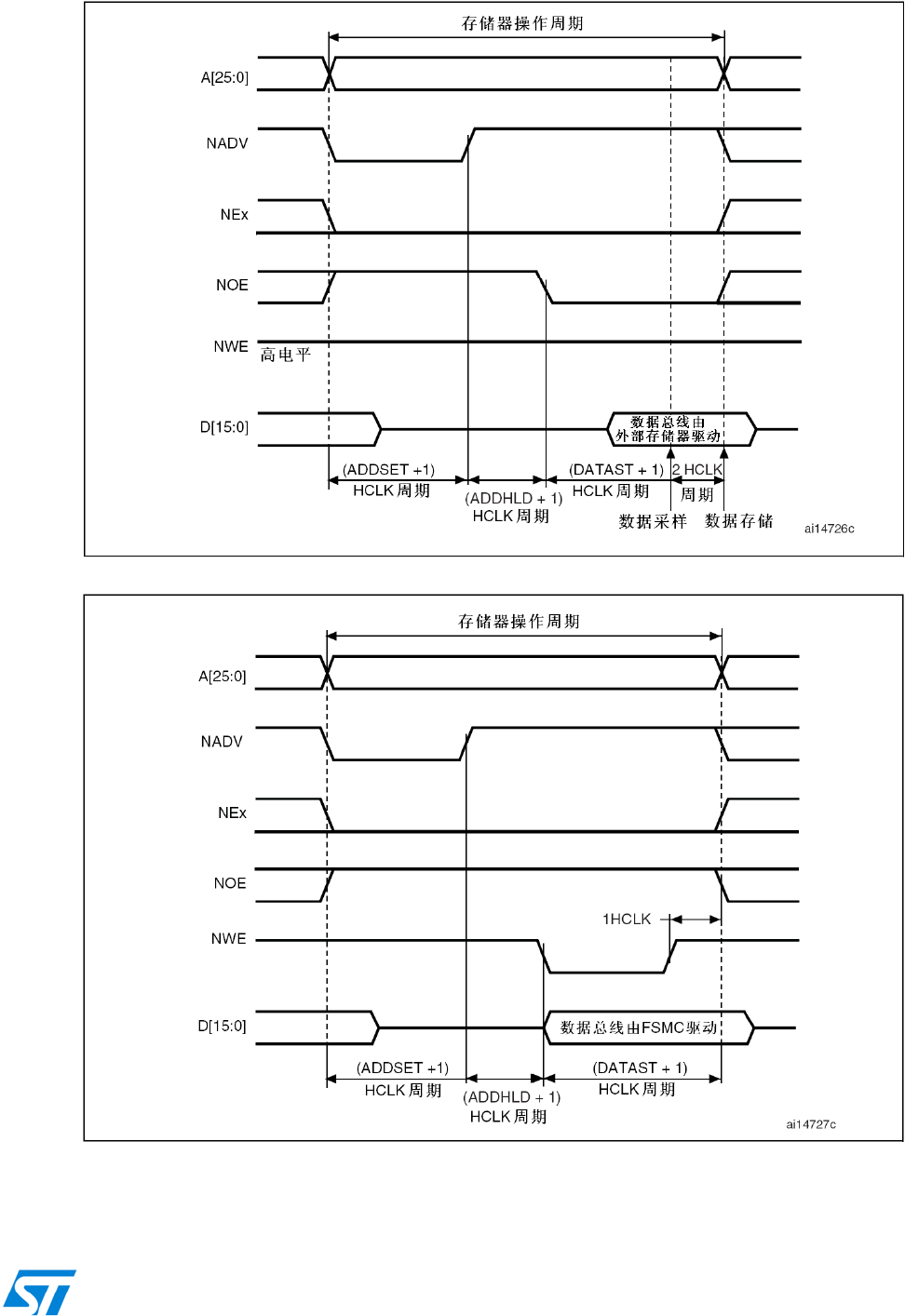

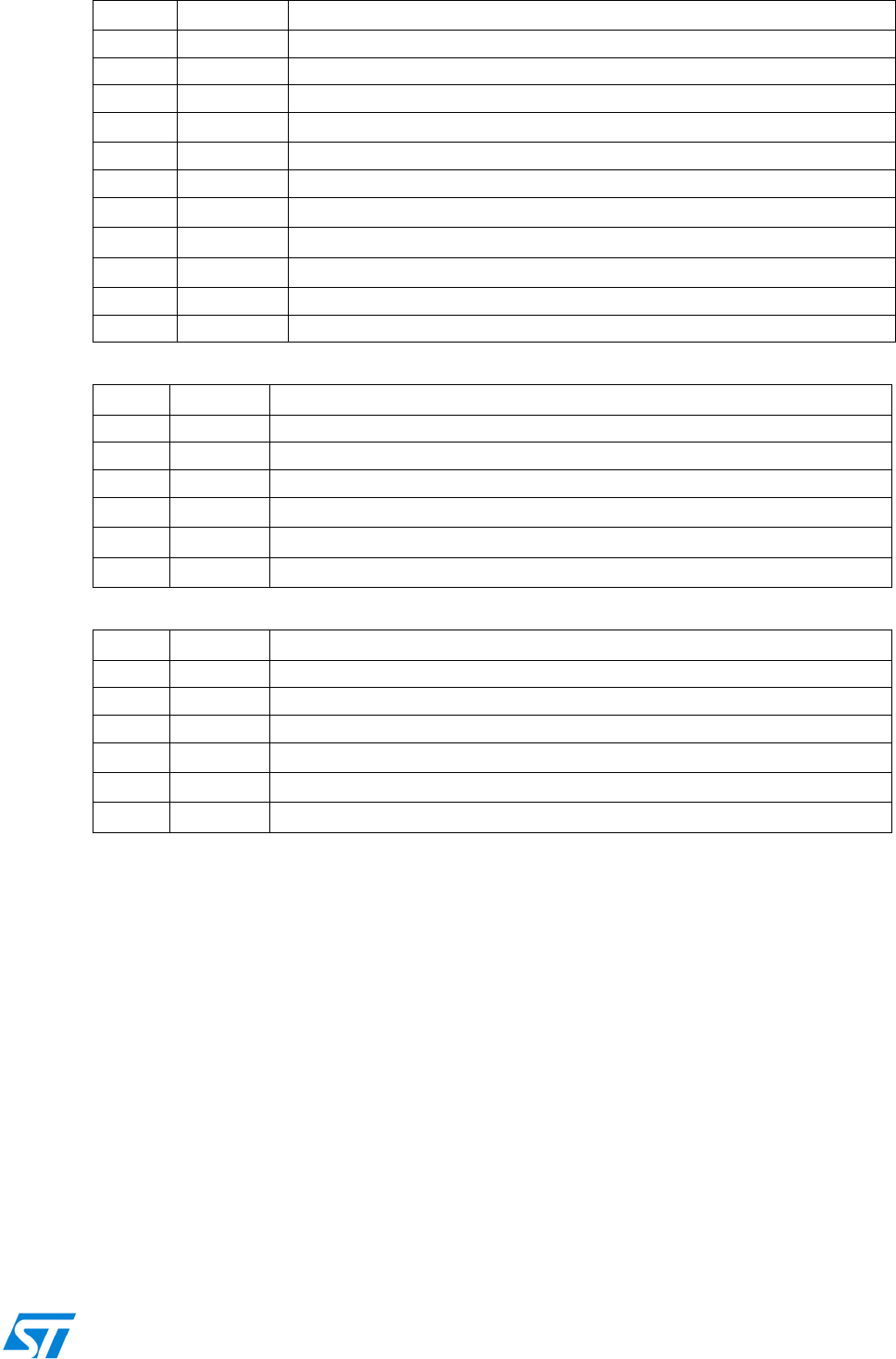

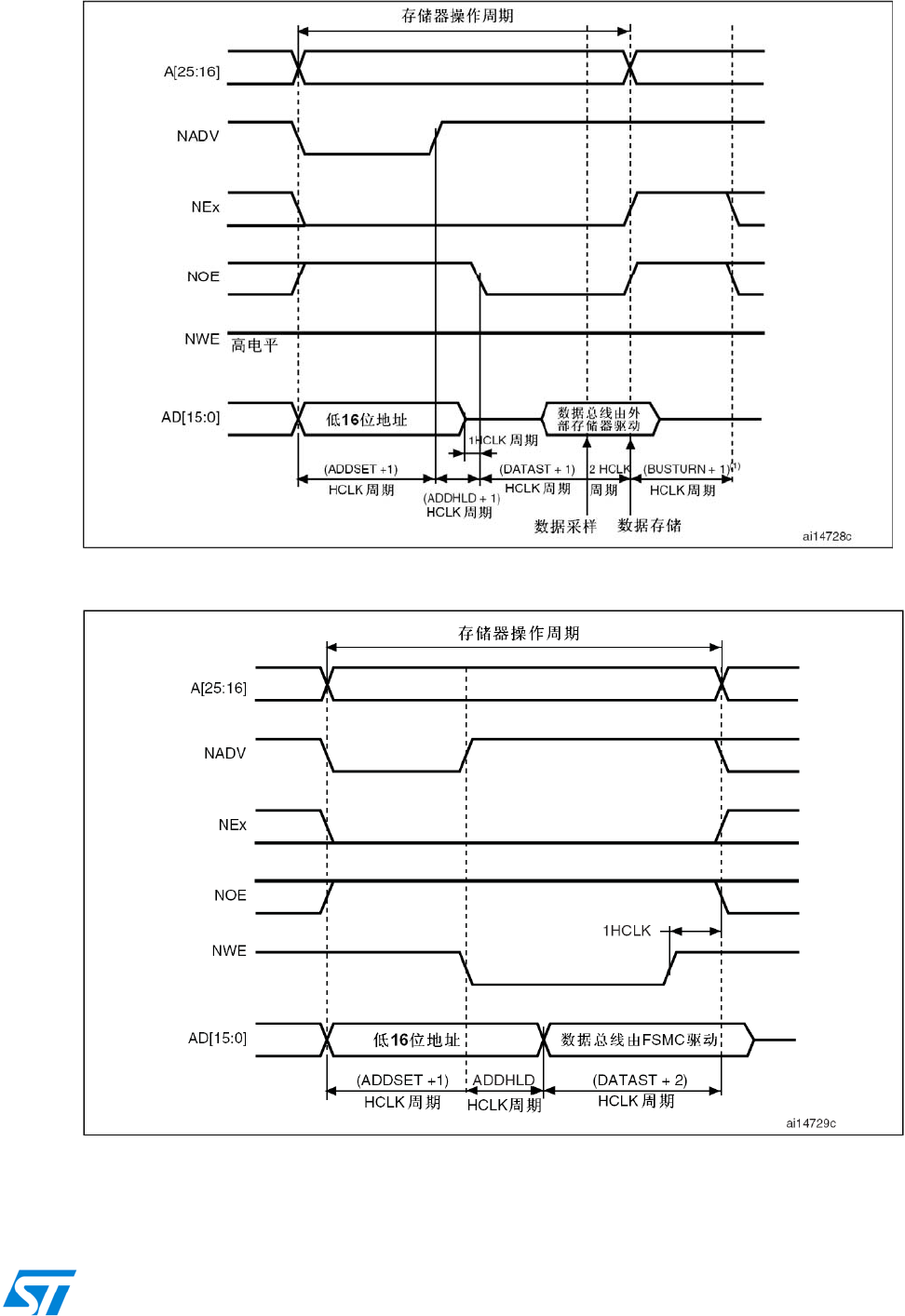

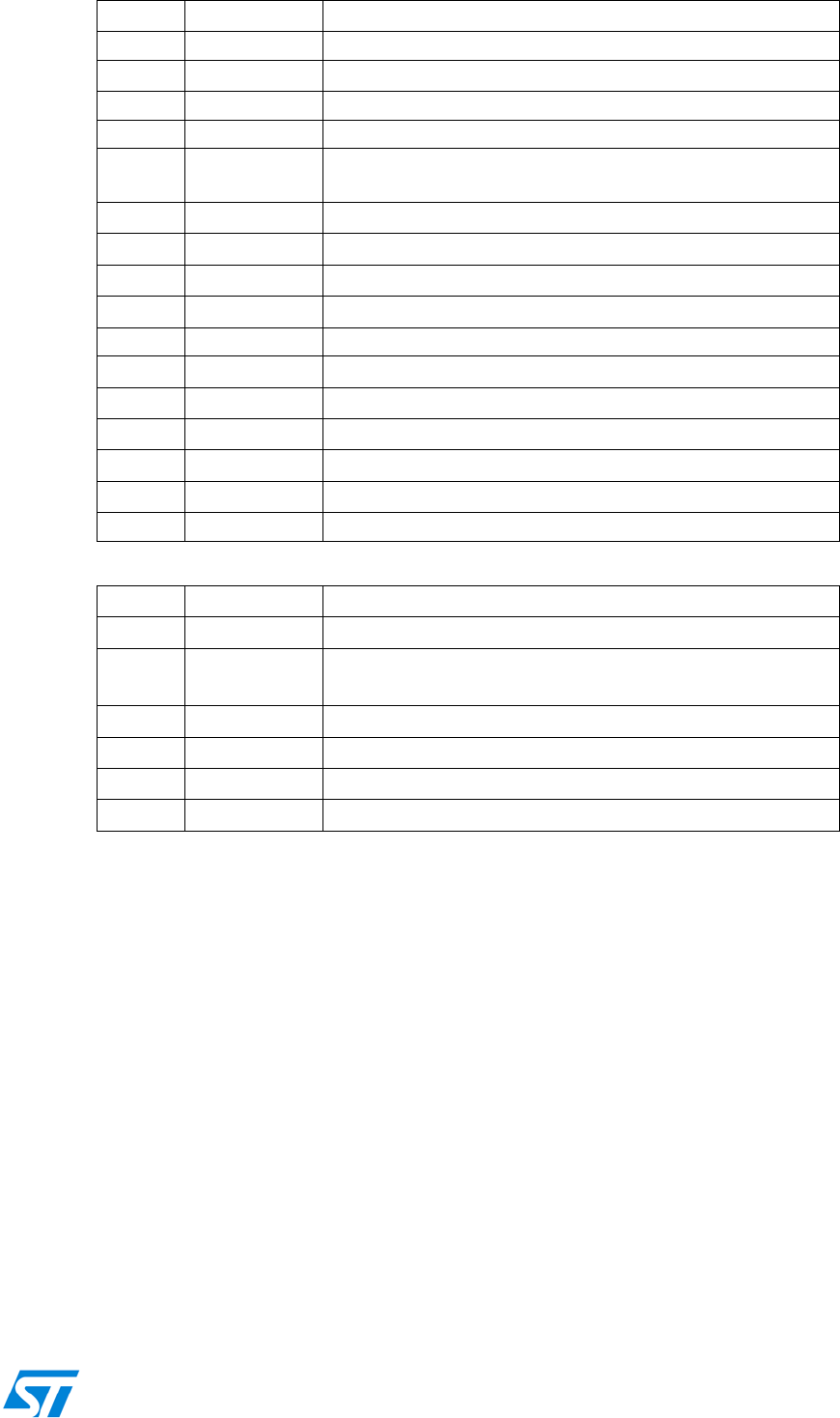

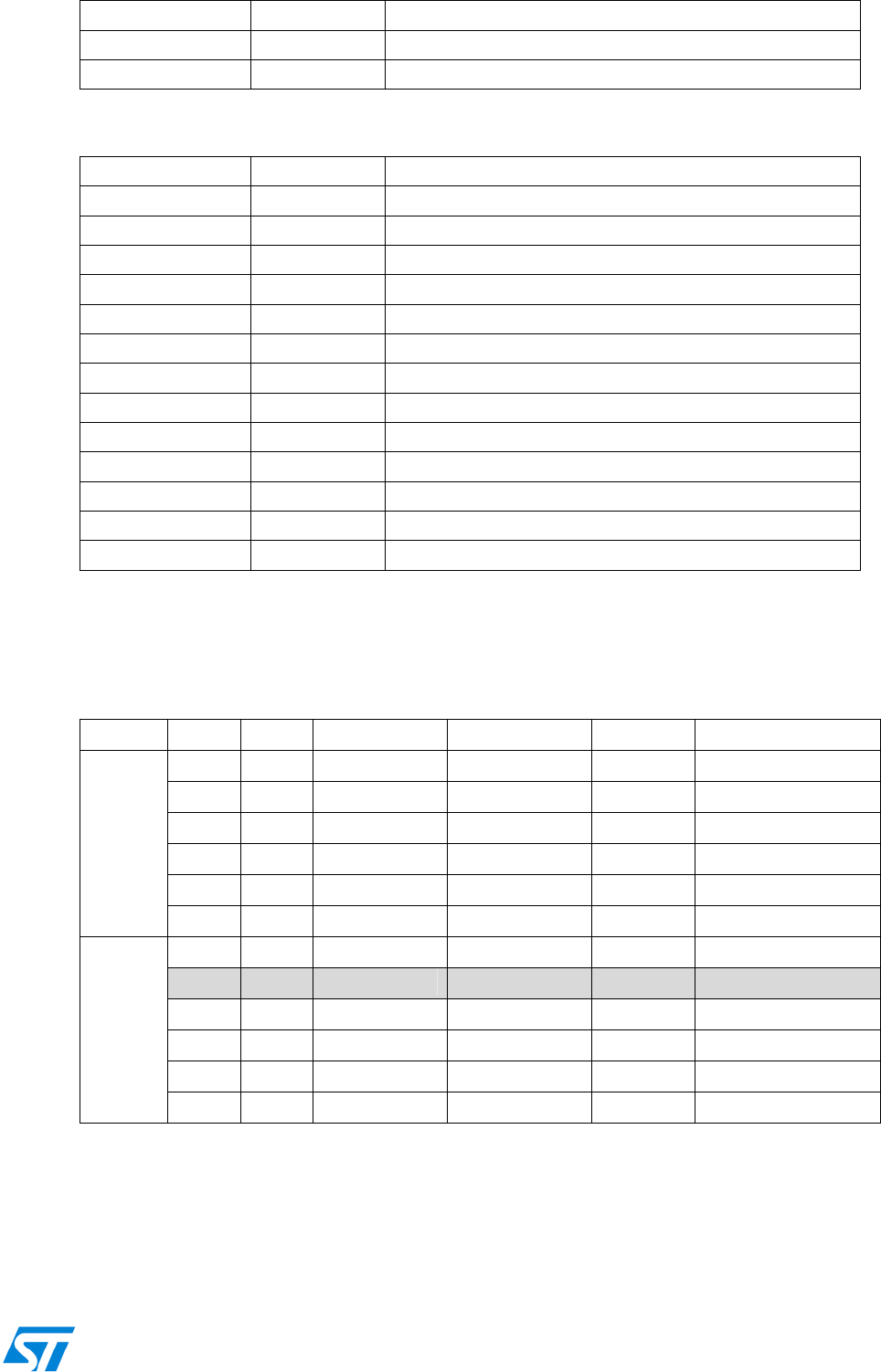

19.5.4 NOR闪存和PSRAM控制器时序图 330

15/754

参照2009年12月 RM0008 Reference Manual 英文第10版

本译文仅供参考,如有翻译错误,请以英文原稿为准。请读者随时注意在ST网站下载更新版本

目录 STM32F10xxx参考手册

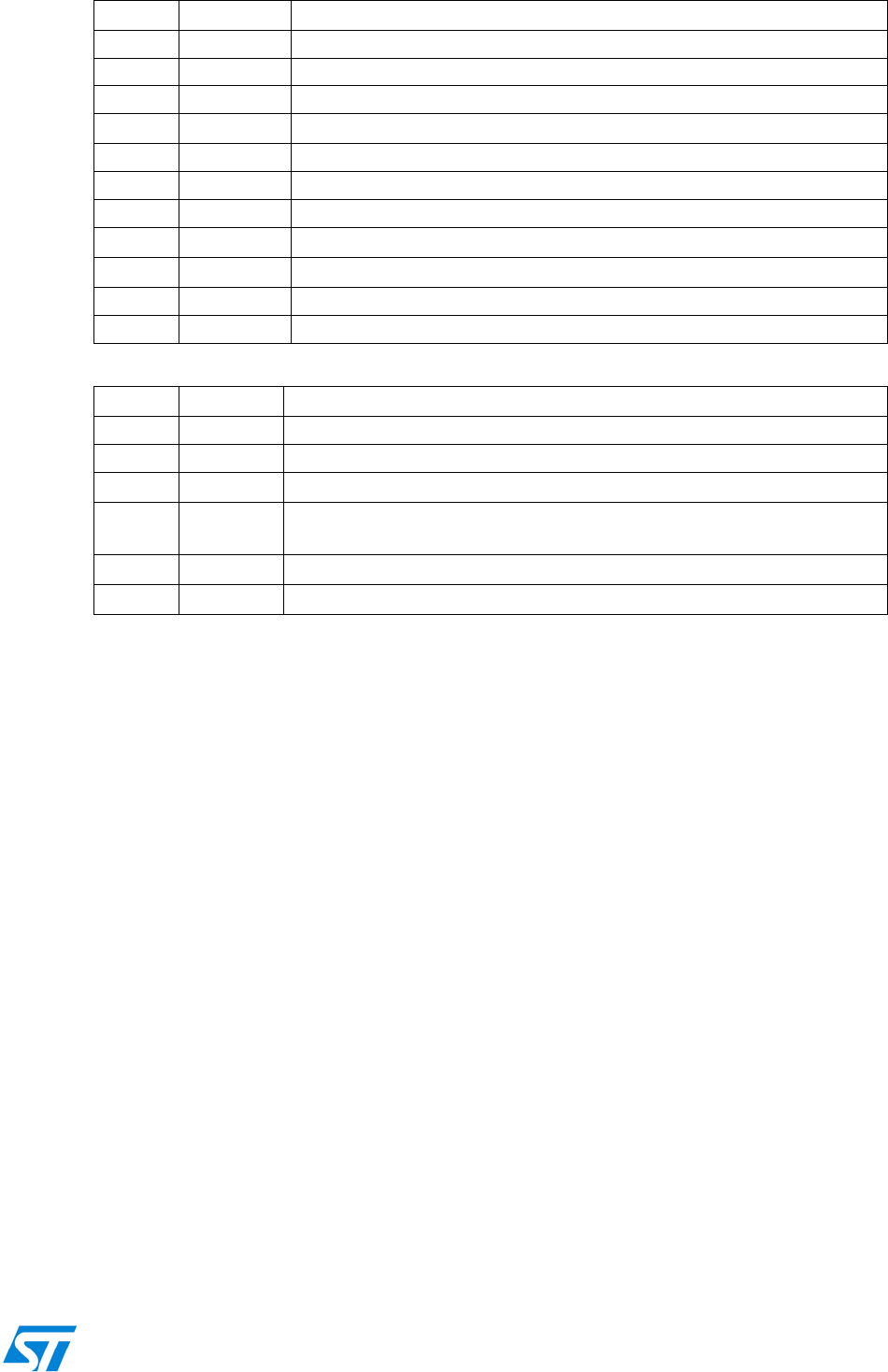

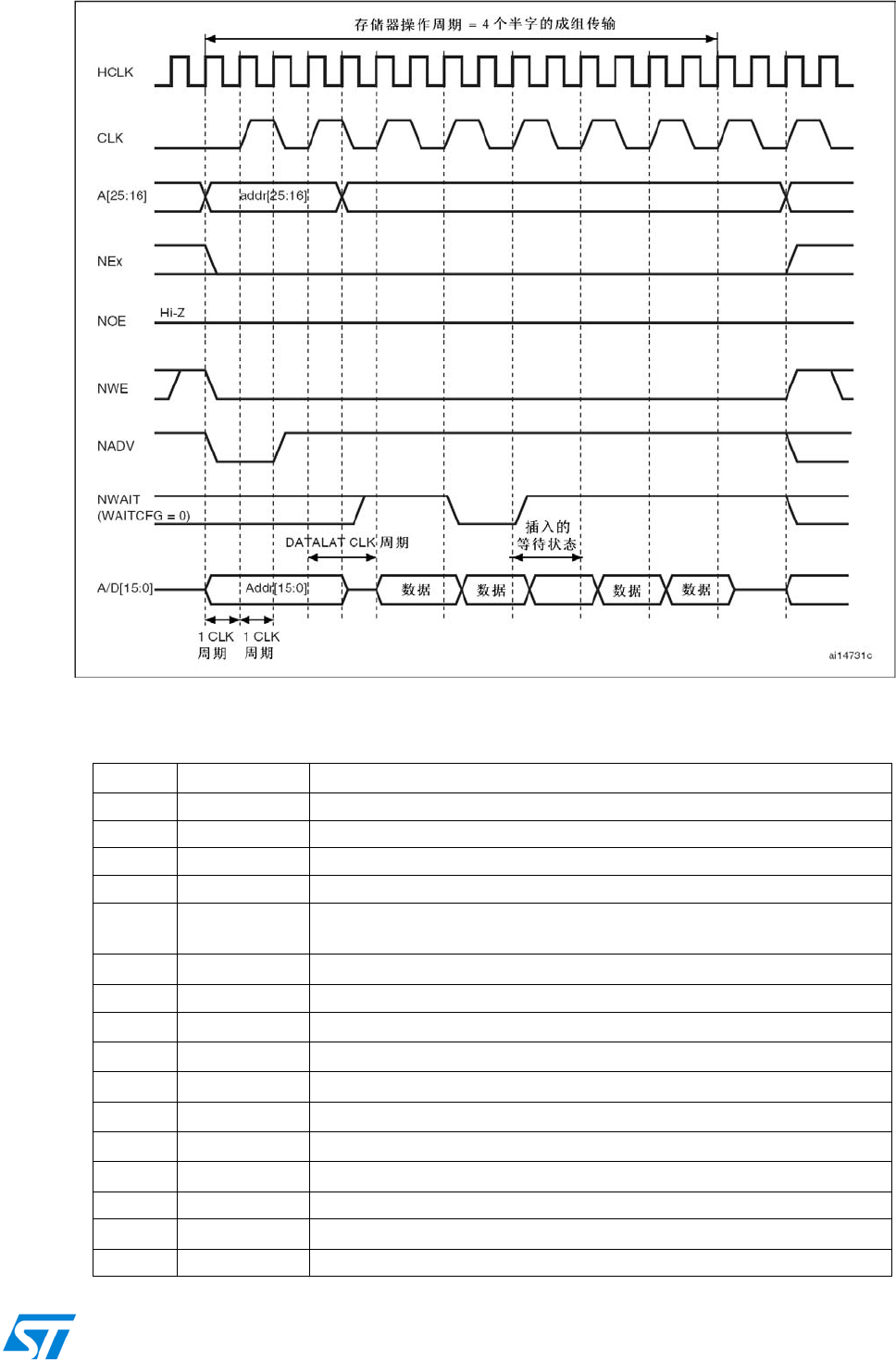

19.5.5 同步的成组读 343

19.5.6 NOR闪存和PSRAM控制器寄存器 347

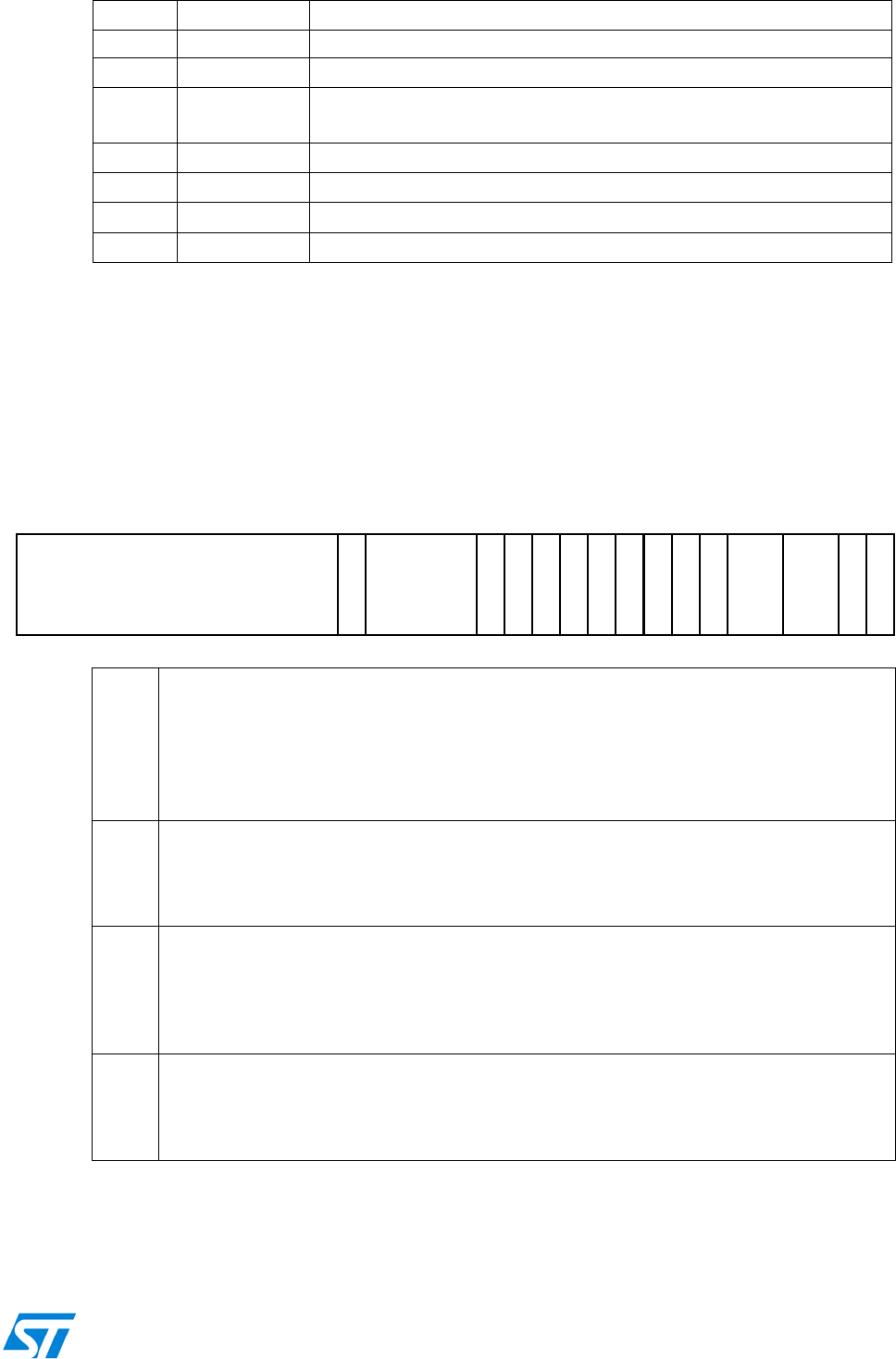

19.6 NAND闪存和PC卡控制器 352

19.6.1 外部存储器接口信号 352

19.6.2 NAND闪存/PC卡支持的存储器及其操作 353

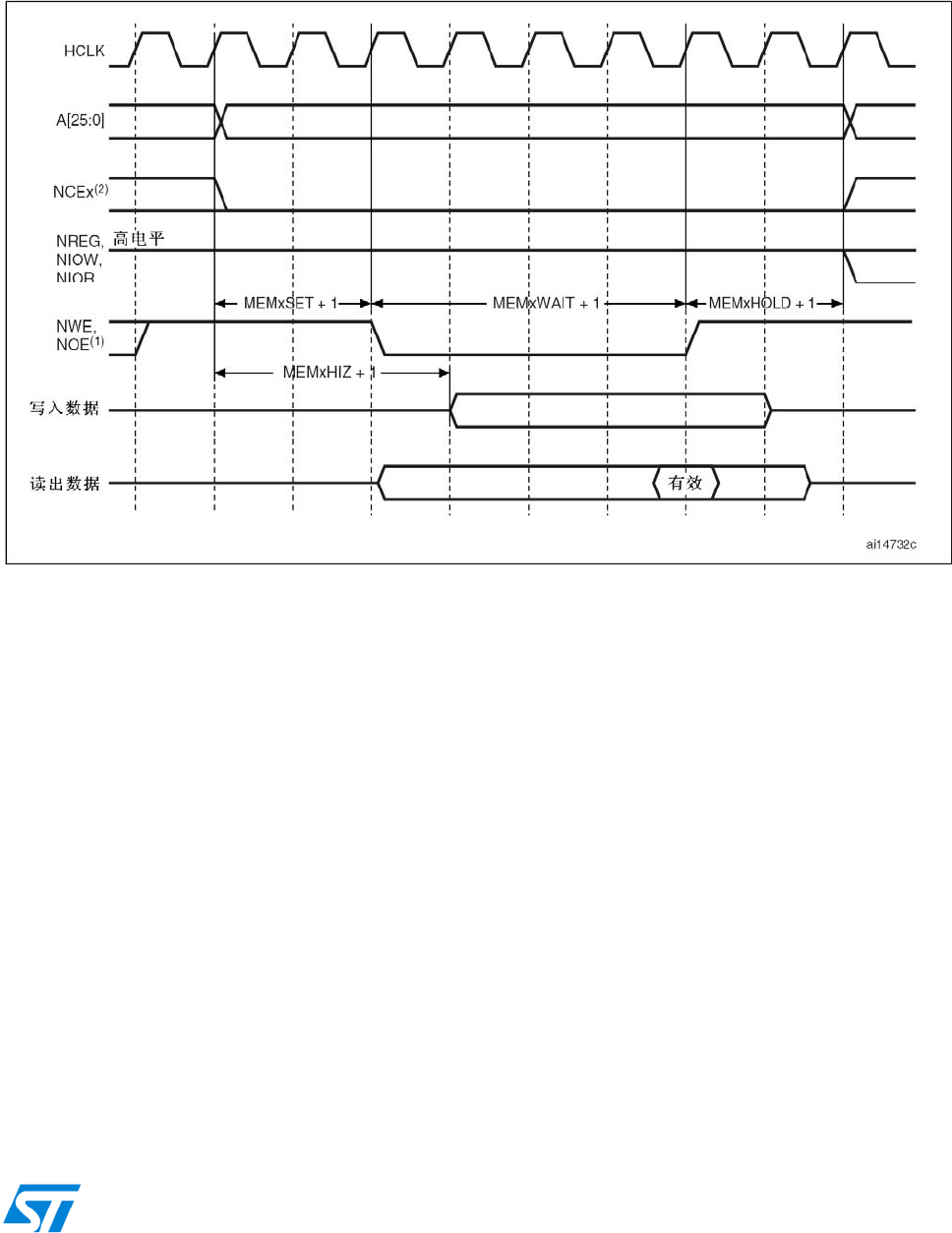

19.6.3 NAND闪存、ATA和PC卡时序图 353

19.6.4 NAND闪存操作 354

19.6.5 NAND闪存预等待功能 355

19.6.6 NAND闪存的纠错码ECC计算(NAND闪存) 356

19.6.7 NAND闪存和PC卡控制器寄存器 356

19.7 FSMC寄存器地址映象 362

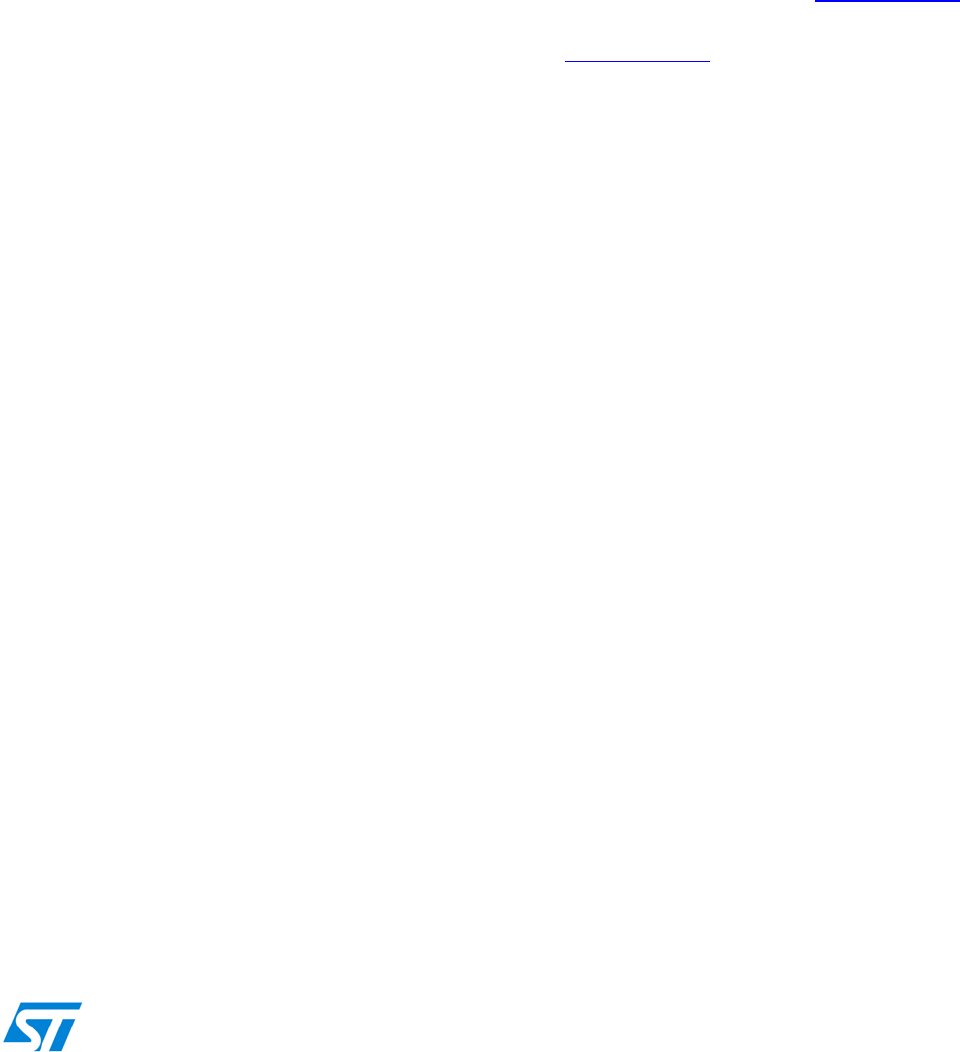

20 SDIO接口(SDIO) 363

20.1 SDIO主要功能 363

20.2 SDIO总线拓扑 363

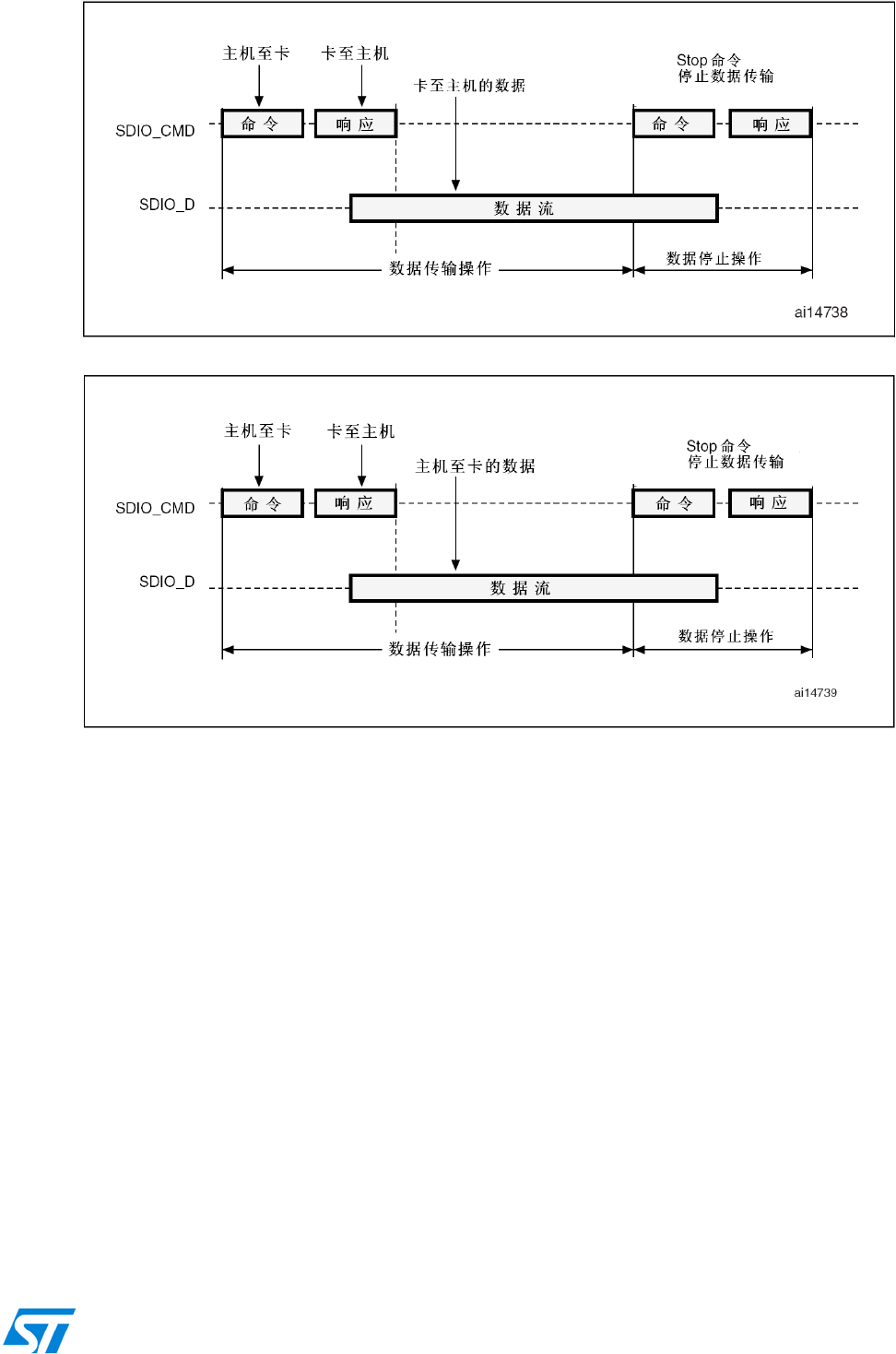

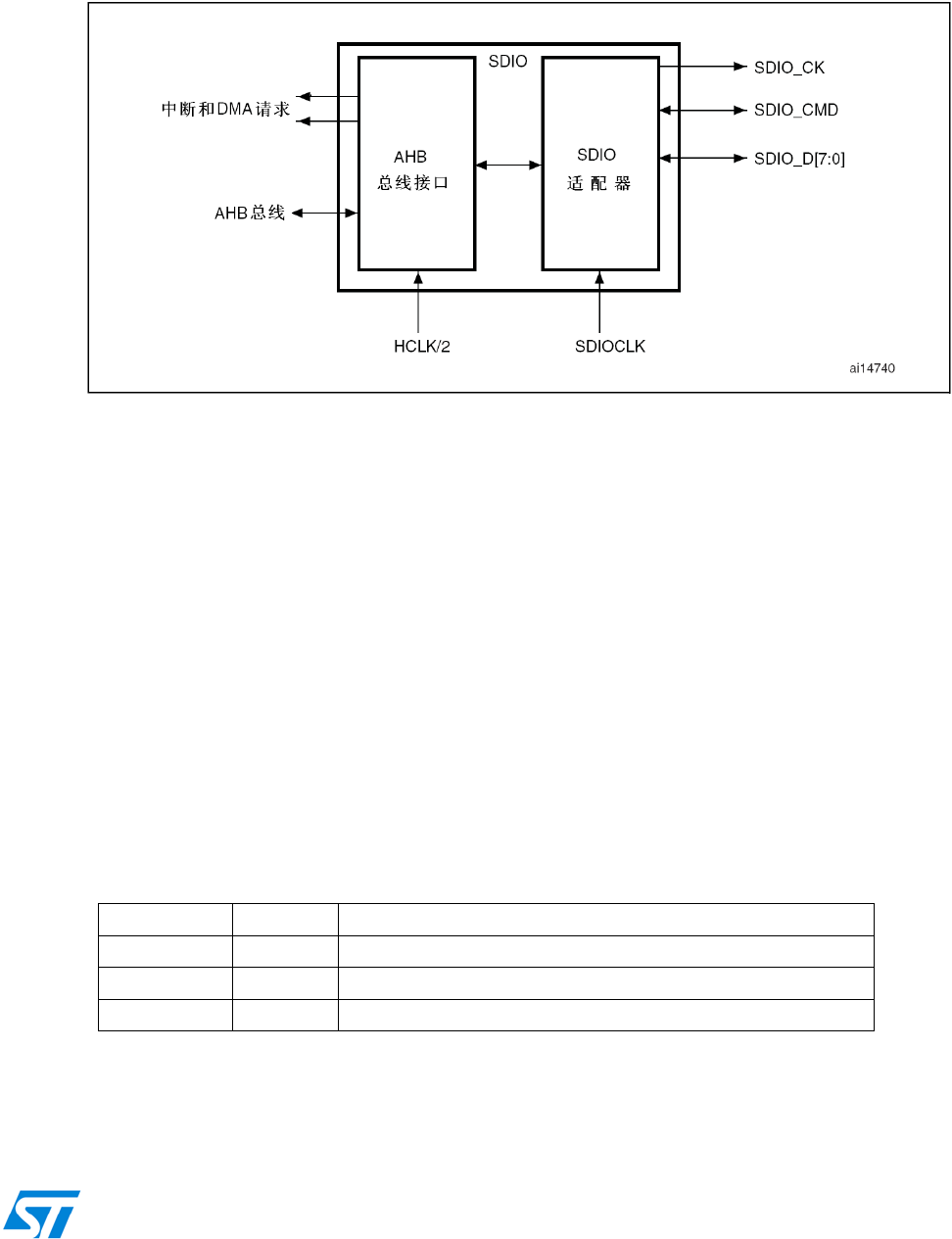

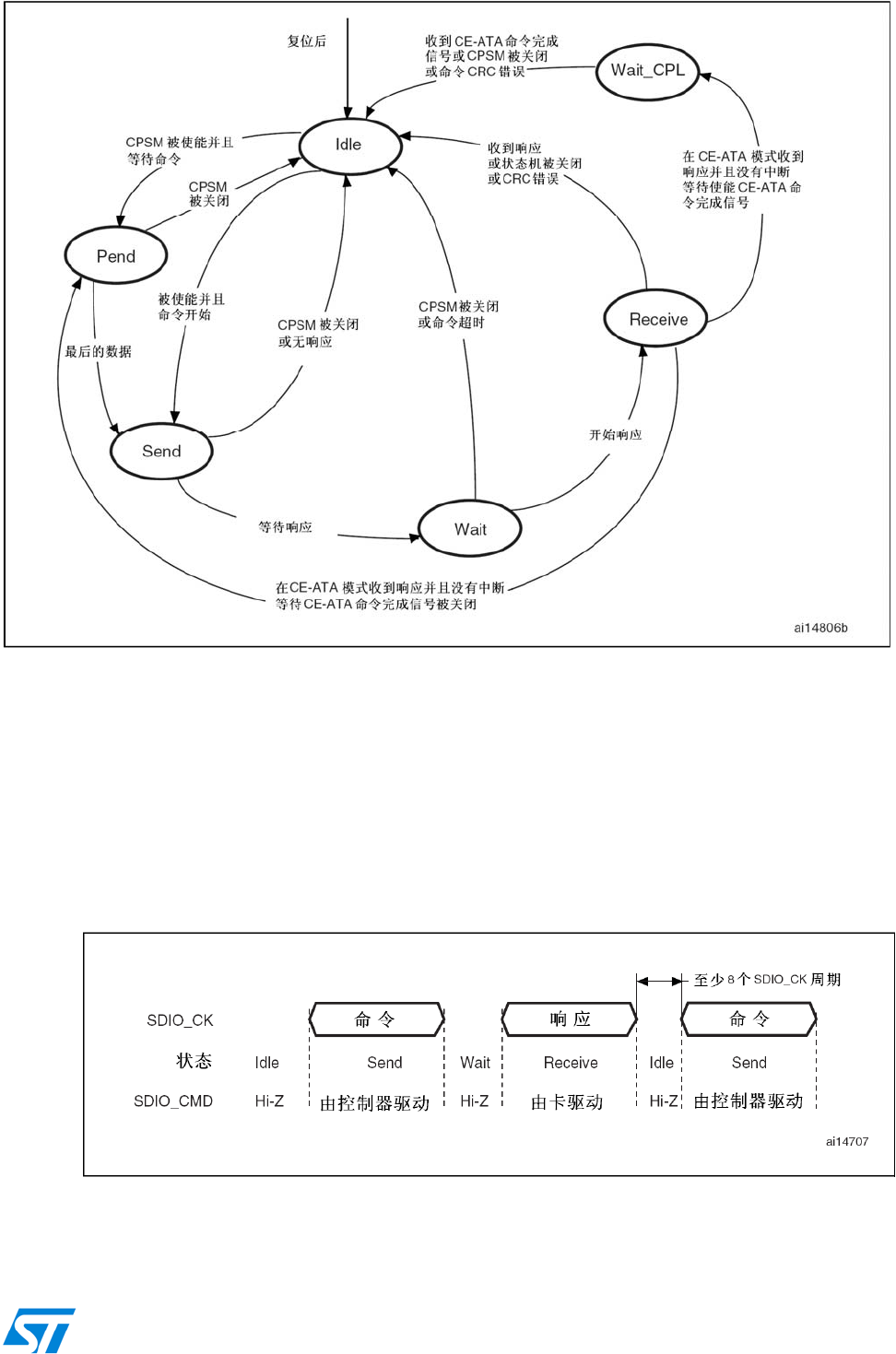

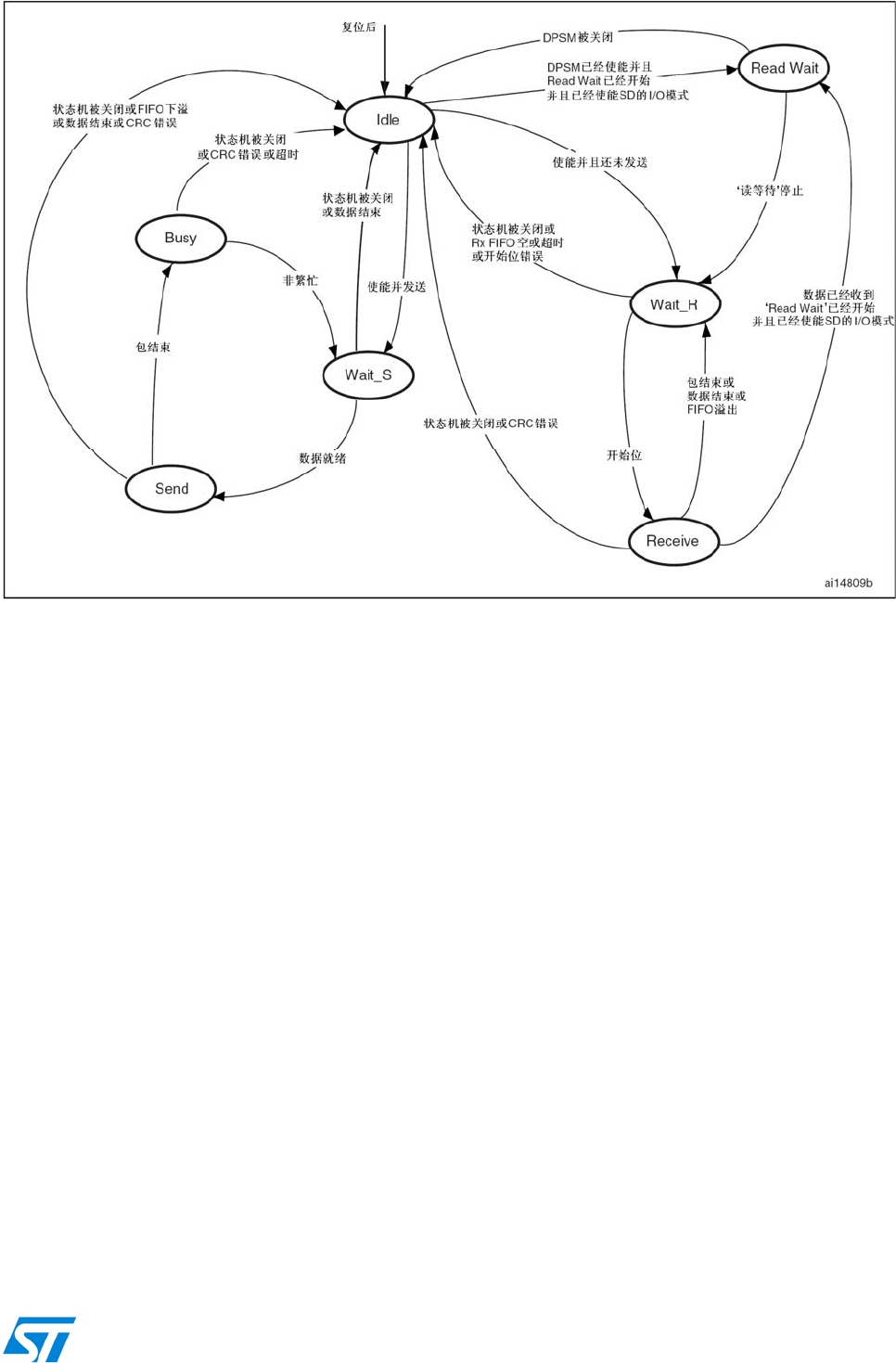

20.3 SDIO功能描述 366

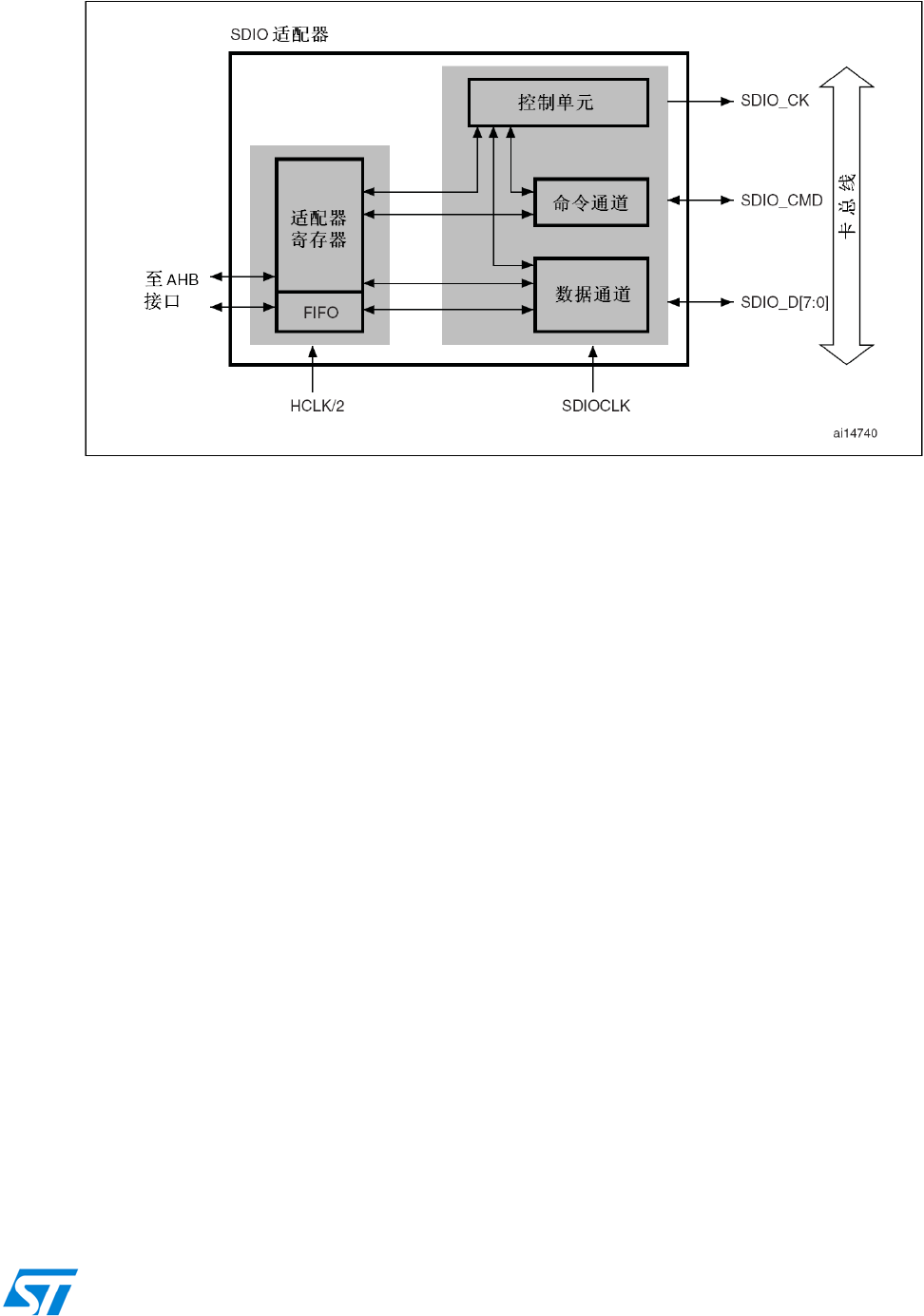

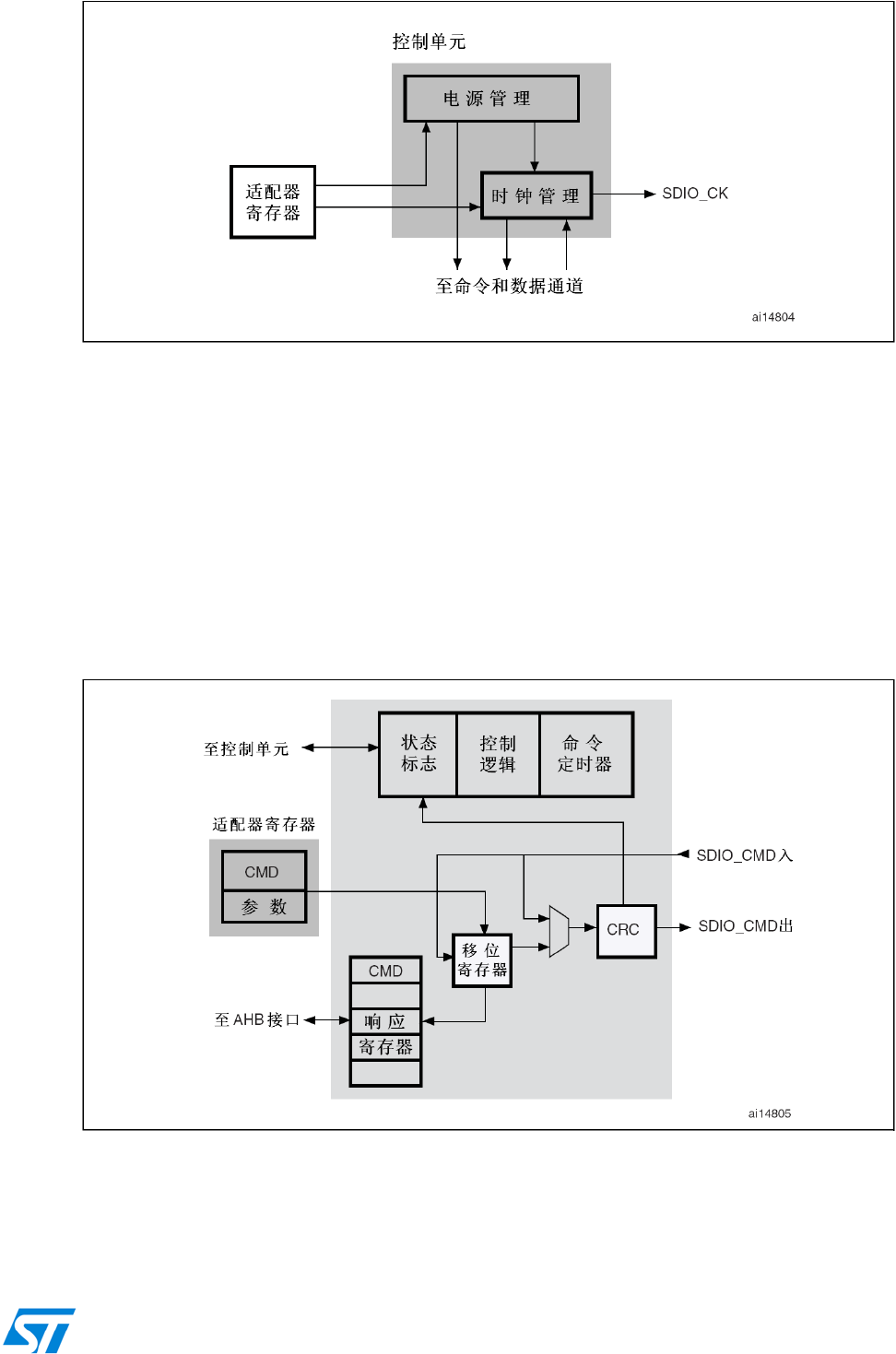

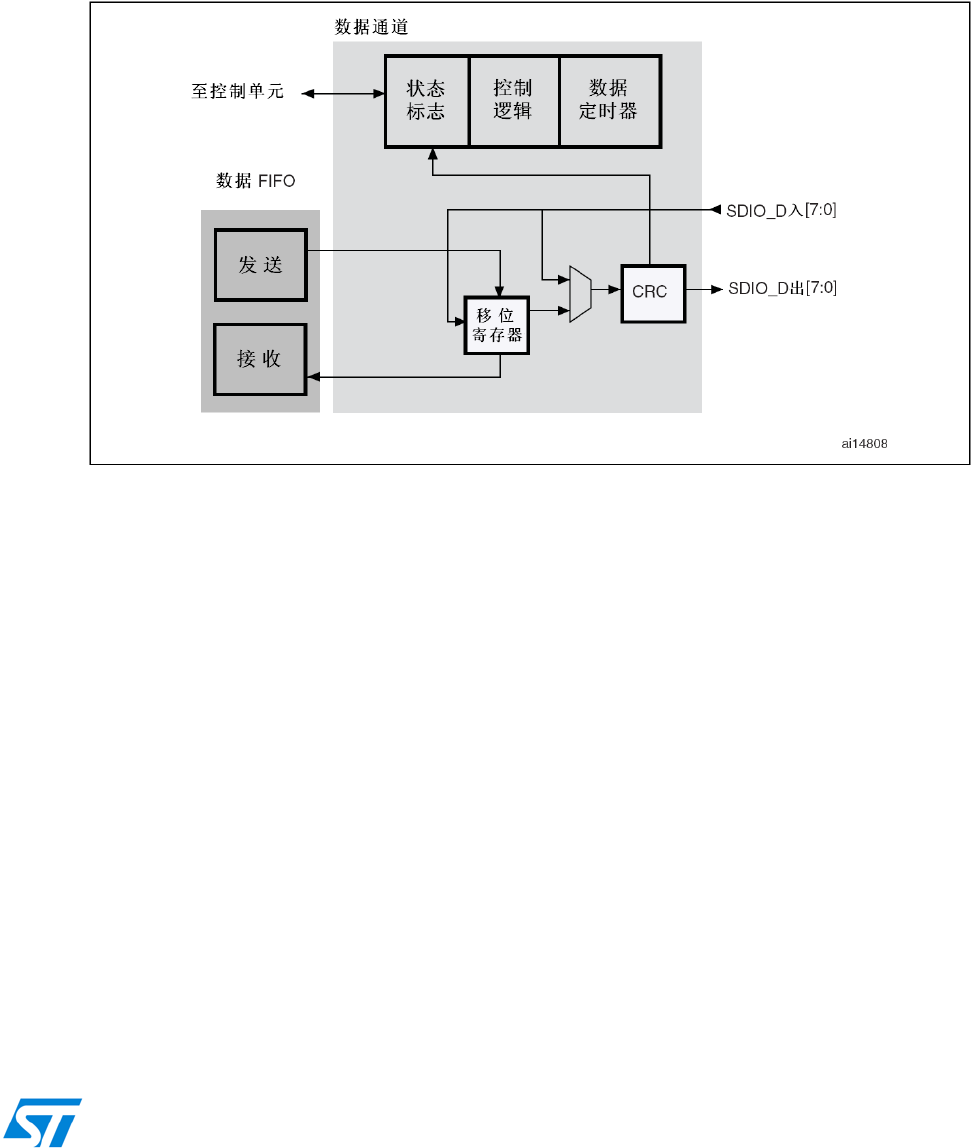

20.3.1 SDIO适配器 367

20.3.2 SDIO AHB接口 374

20.4 卡功能描述 374

20.4.1 卡识别模式 374

20.4.2 卡复位 374

20.4.3 操作电压范围确认 375

20.4.4 卡识别过程 375

20.4.5 写数据块 376

20.4.6 读数据块 376

20.4.7 数据流操作,数据流写入和数据流读出(只适用于多媒体卡) 376

20.4.8 擦除:成组擦除和扇区擦除 377

20.4.9 宽总线选择和解除选择 378

20.4.10 保护管理 378

20.4.11 卡状态寄存器 380

20.4.12 SD状态寄存器 382

20.4.13 SD的I/O模式 385

20.4.14 命令与响应 385

20.5 响应格式 388

20.5.1 R1(普通响应命令) 388

20.5.2 R1b 388

20.5.3 R2(CID、CSD寄存器) 388

20.5.4 R3(OCR寄存器) 389

20.5.5 R4(快速I/O) 389

20.5.6 R4b 389

20.5.7 R5(中断请求) 390

20.5.8 R6(中断请求) 390

20.6 SDIO I/O卡特定的操作 390

20.6.1 使用SDIO_D2信号线的SDIO I/O读等待操作 390

20.6.2 使用停止SDIO_CK的SDIO读等待操作 391

20.6.3 SDIO暂停/恢复操作 391

20.6.4 SDIO中断 391

20.7 CE-ATA特定操作 391

20.7.1 命令完成指示关闭 391

20.7.2 命令完成指示使能 391

16/754

参照2009年12月 RM0008 Reference Manual 英文第10版

本译文仅供参考,如有翻译错误,请以英文原稿为准。请读者随时注意在ST网站下载更新版本

目录 STM32F10xxx参考手册

20.7.3 CE-ATA中断 392

20.7.4 中止CMD61 392

20.8 硬件流控制 392

20.9 SDIO寄存器 392

20.9.1 SDIO电源控制寄存器(SDIO_POWER) 392

20.9.2 SDIO时钟控制寄存器(SDIO_CLKCR) 392

20.9.3 SDIO参数寄存器(SDIO_ARG) 393

20.9.4 SDIO命令寄存器(SDIO_CMD) 393

20.9.5 SDIO命令响应寄存器(SDIO_RESPCMD) 394

20.9.6 SDIO响应1..4寄存器(SDIO_RESPx) 395

20.9.7 SDIO数据定时器寄存器(SDIO_DTIMER) 395

20.9.8 SDIO数据长度寄存器(SDIO_DLEN) 395

20.9.9 SDIO数据控制寄存器(SDIO_DCTRL) 396

20.9.10 SDIO数据计数器寄存器(SDIO_DCOUNT) 397

20.9.11 SDIO状态寄存器(SDIO_STA) 397

20.9.12 SDIO清除中断寄存器(SDIO_ICR) 398

20.9.13 SDIO中断屏蔽寄存器(SDIO_MASK) 399

20.9.14 SDIO FIFO计数器寄存器(SDIO_FIFOCNT) 401

20.9.15 SDIO数据FIFO寄存器(SDIO_FIFO) 401

20.9.16 SDIO寄存器映像 402

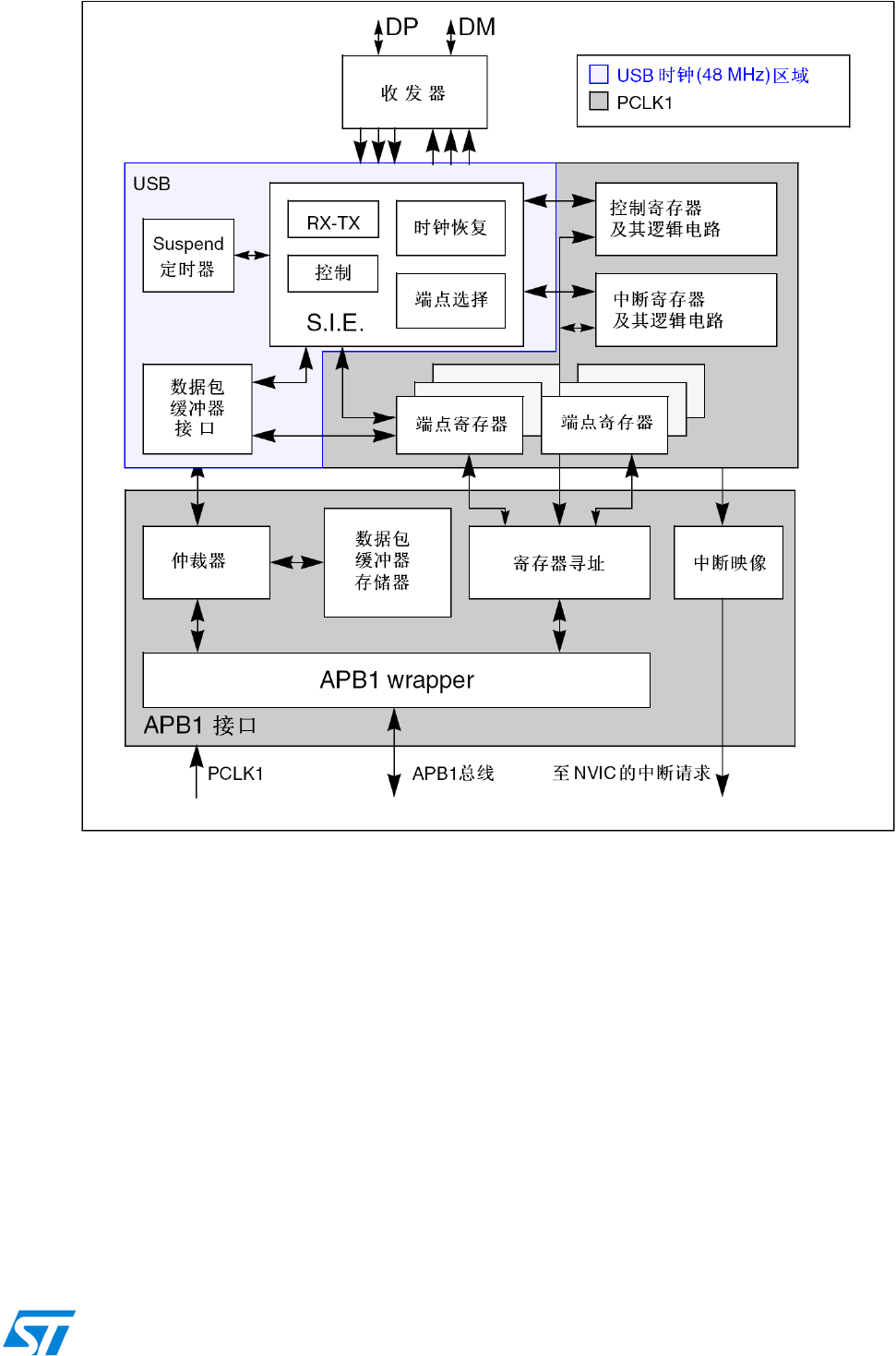

21 USB全速设备接口(USB) 403

21.1 USB简介 403

21.2 USB主要特征 403

21.3 USB功能描述 404

21.3.1 USB功能模块描述 405

21.4 编程中需要考虑的问题 406

21.4.1 通用USB设备编程 406

21.4.2 系统复位和上电复位 406

21.4.3 双缓冲端点 409

21.4.4 同步传输 410

21.4.5 挂起/恢复事件 411

21.5 USB寄存器描述 412

21.5.1 通用寄存器 412

21.5.2 端点寄存器 416

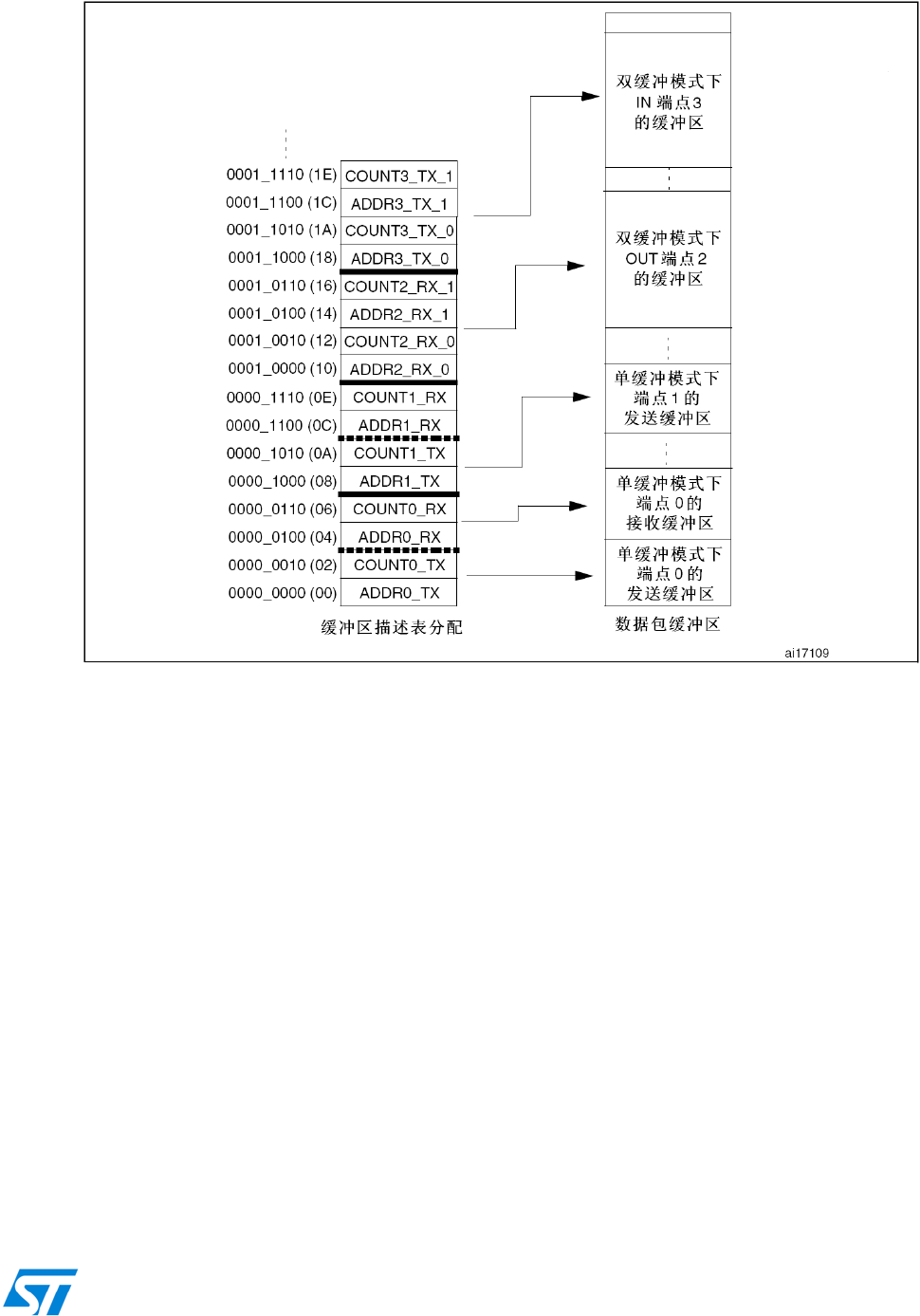

21.5.3 缓冲区描述表 419

21.5.4 USB寄存器映像 421

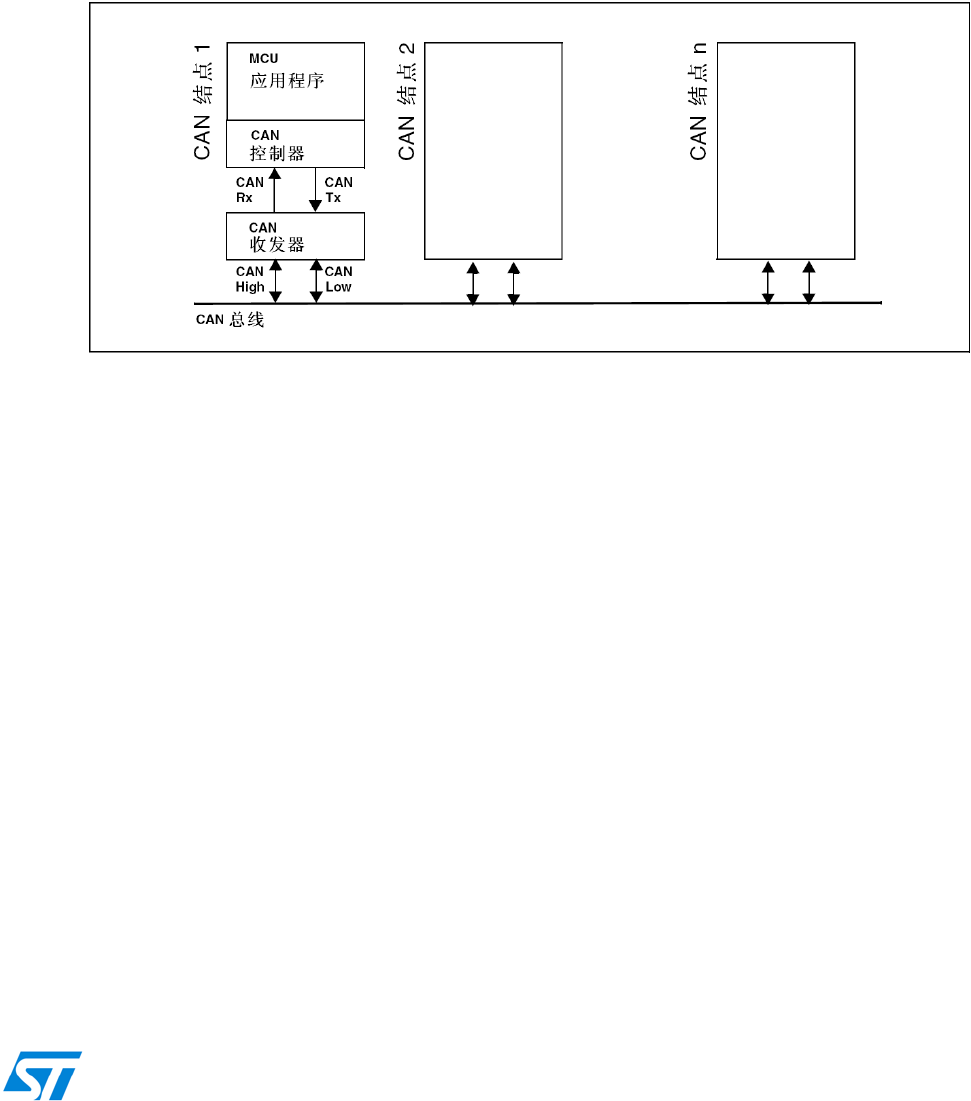

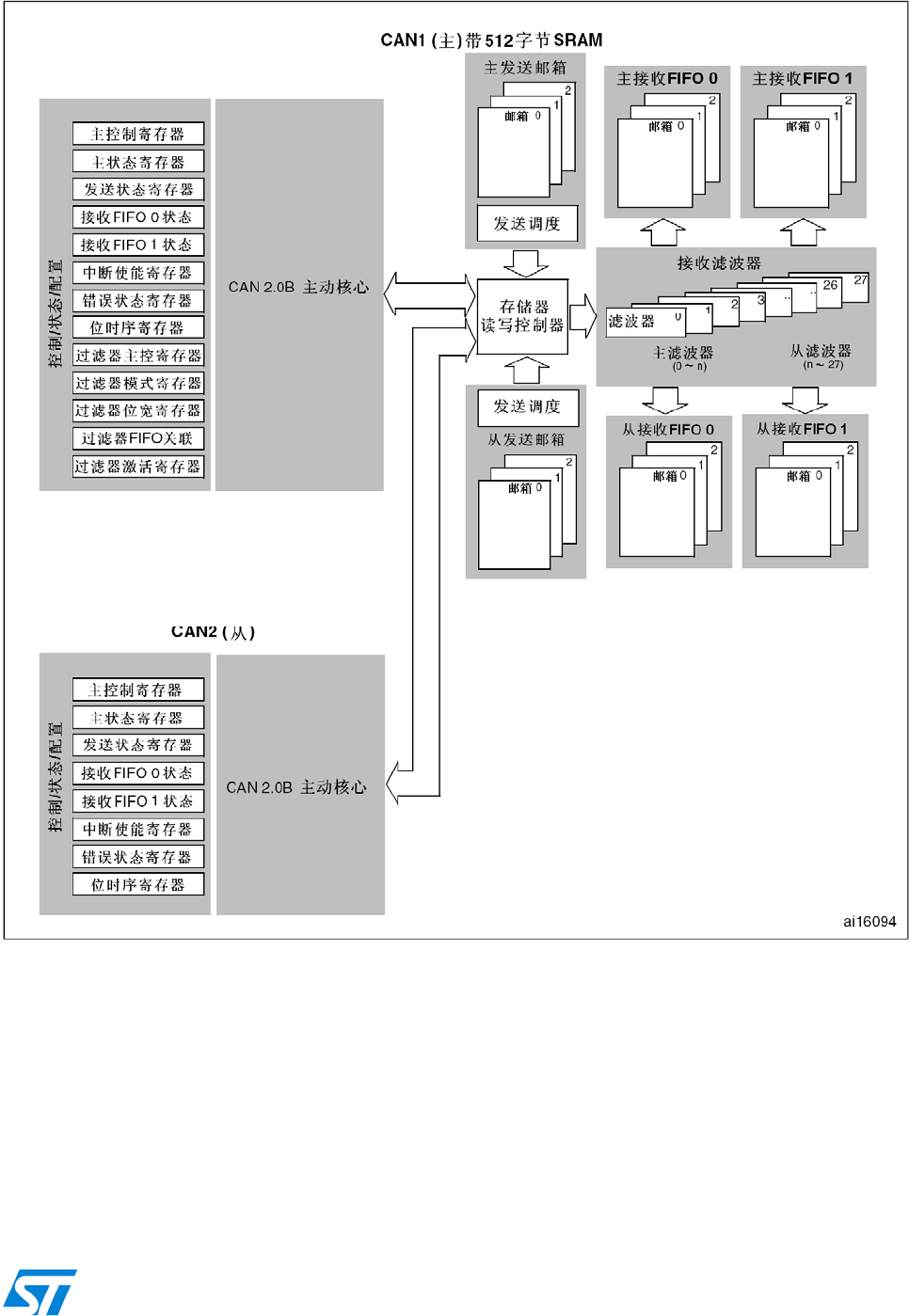

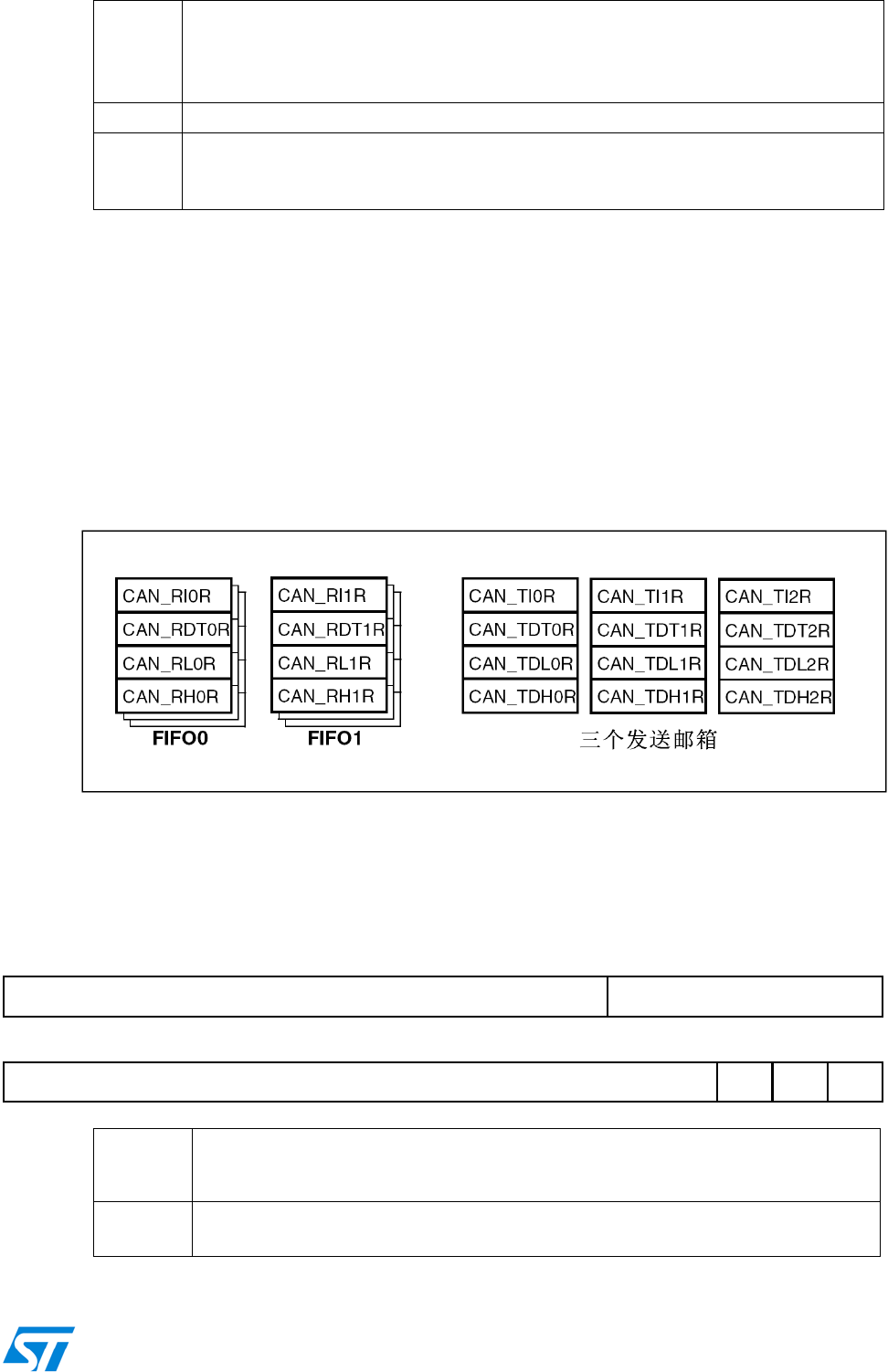

22 控制器局域网(bxCAN) 423

22.1 bxCAN简介 423

22.2 bxCAN主要特点 423

22.3 bxCAN总体描述 424

22.3.1 CAN 2.0B主动内核 424

22.3.2 控制、状态和配置寄存器 424

22.3.3 发送邮箱 424

22.3.4 接收过滤器 424

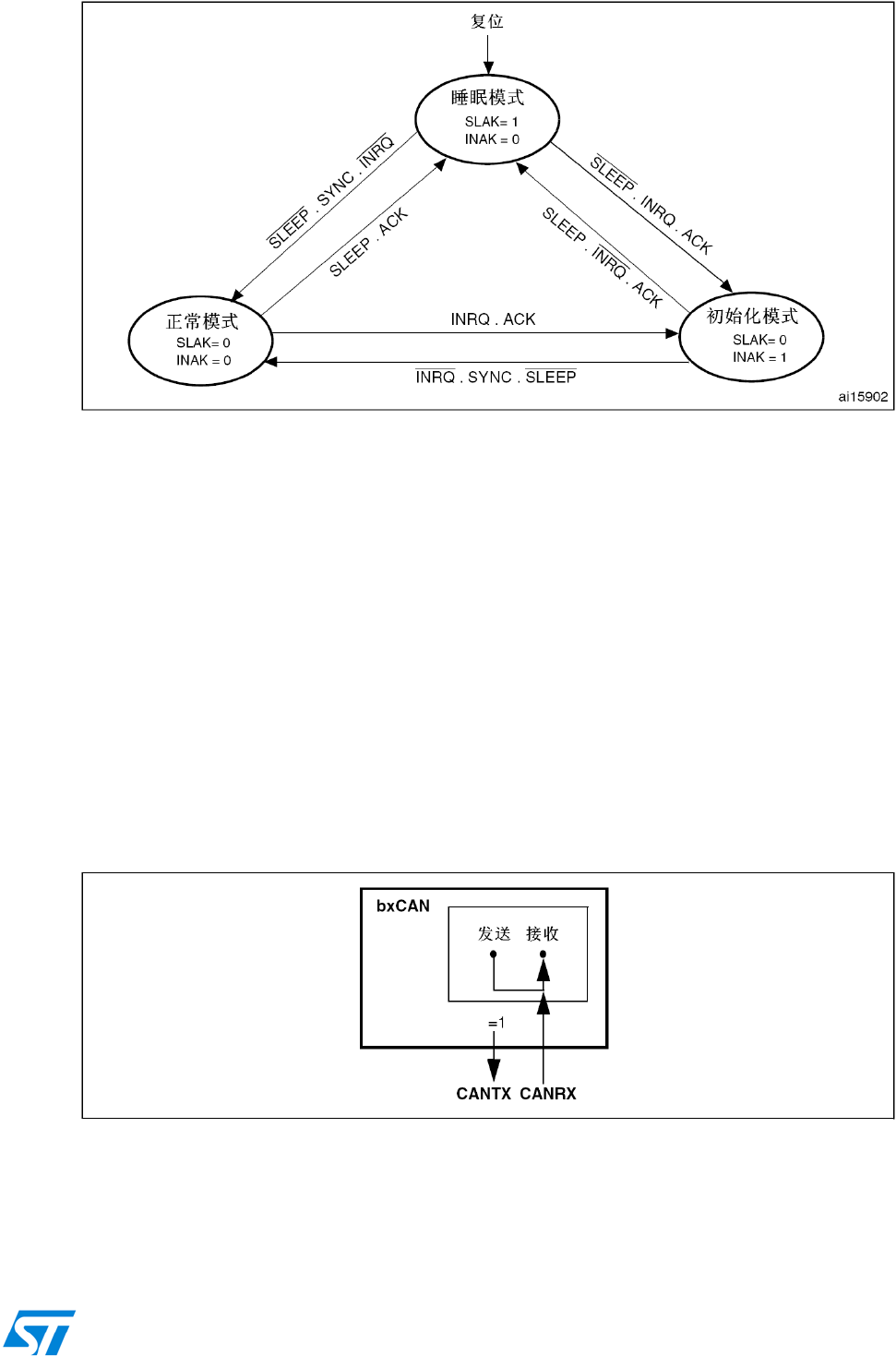

22.4 bxCAN工作模式 426

22.4.1 初始化模式 426

22.4.2 正常模式 426

22.4.3 睡眠模式(低功耗) 426

17/754

参照2009年12月 RM0008 Reference Manual 英文第10版

本译文仅供参考,如有翻译错误,请以英文原稿为准。请读者随时注意在ST网站下载更新版本

目录 STM32F10xxx参考手册

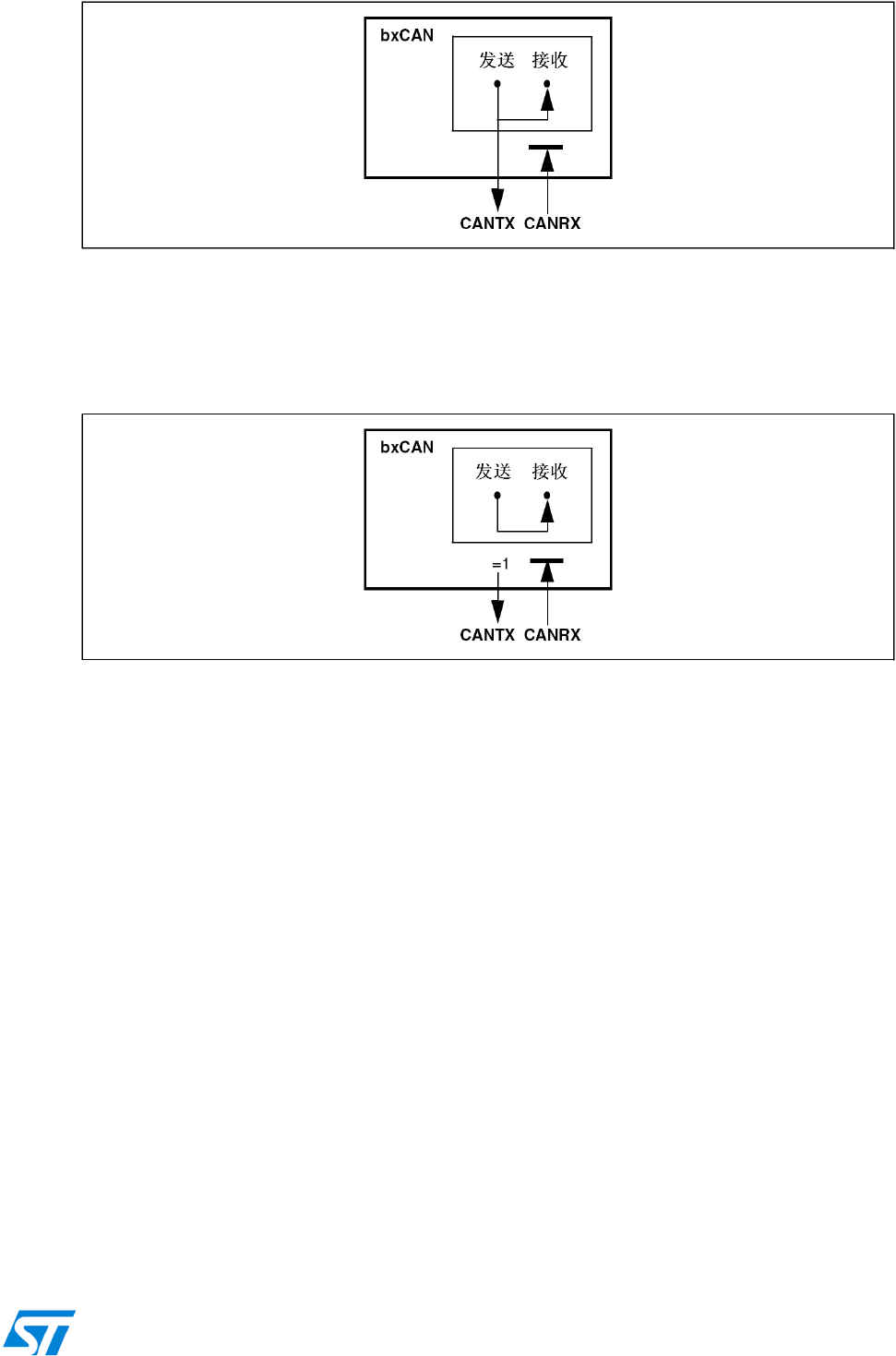

22.5 测试模式 427

22.5.1 静默模式 427

22.5.2 环回模式 427

22.5.3 环回静默模式 428

22.6 STM32F10xxx处于调试模式时 428

22.7 bxCAN功能描述 428

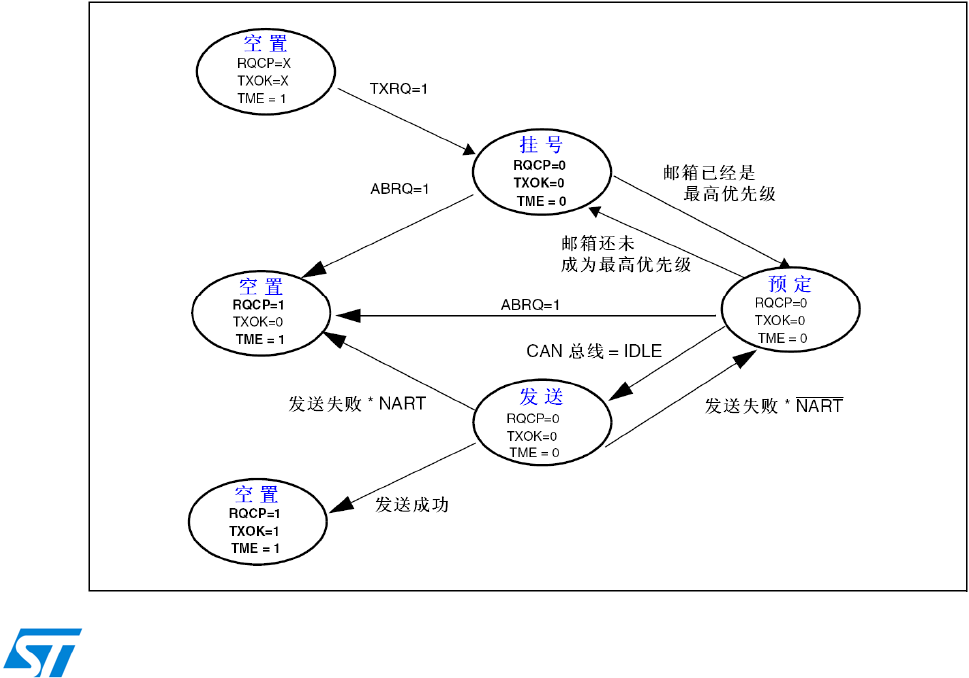

22.7.1 发送处理 428

22.7.2 时间触发通信模式 430

22.7.3 接收管理 430

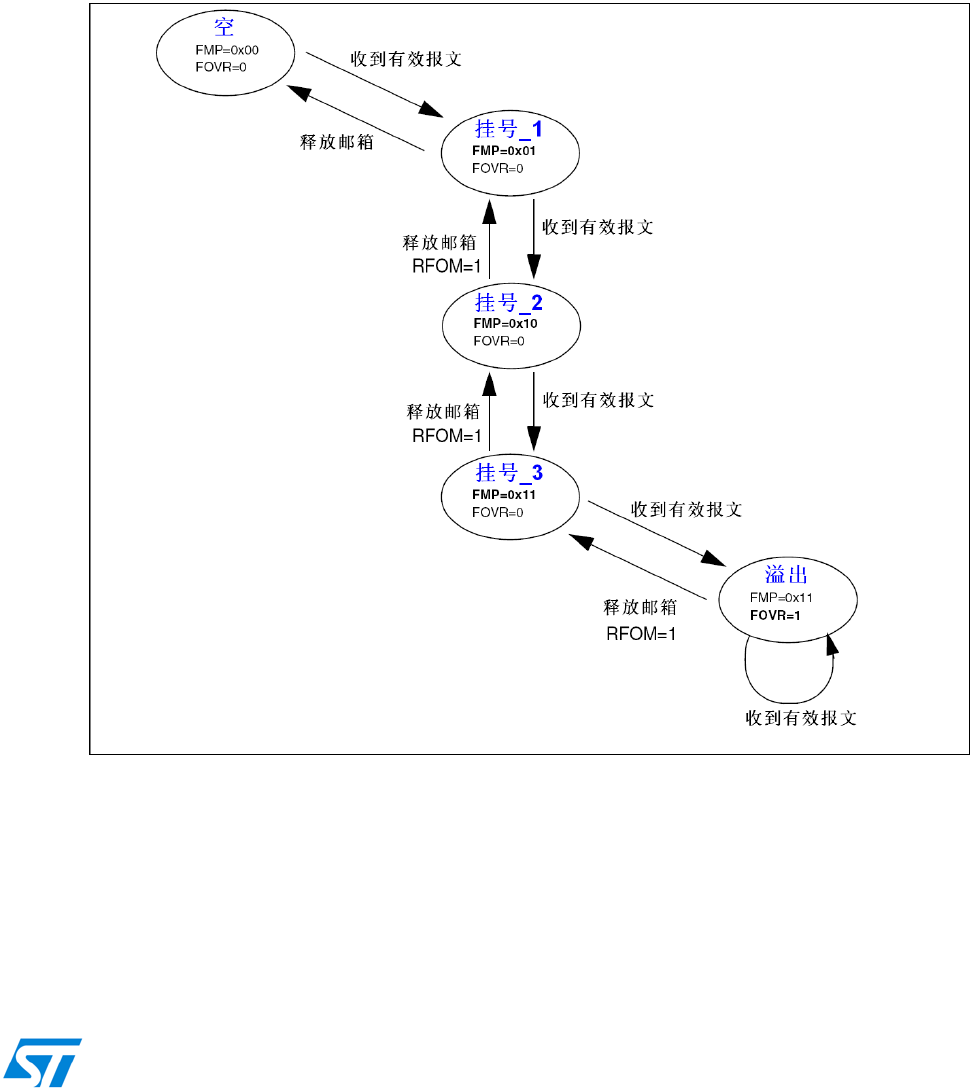

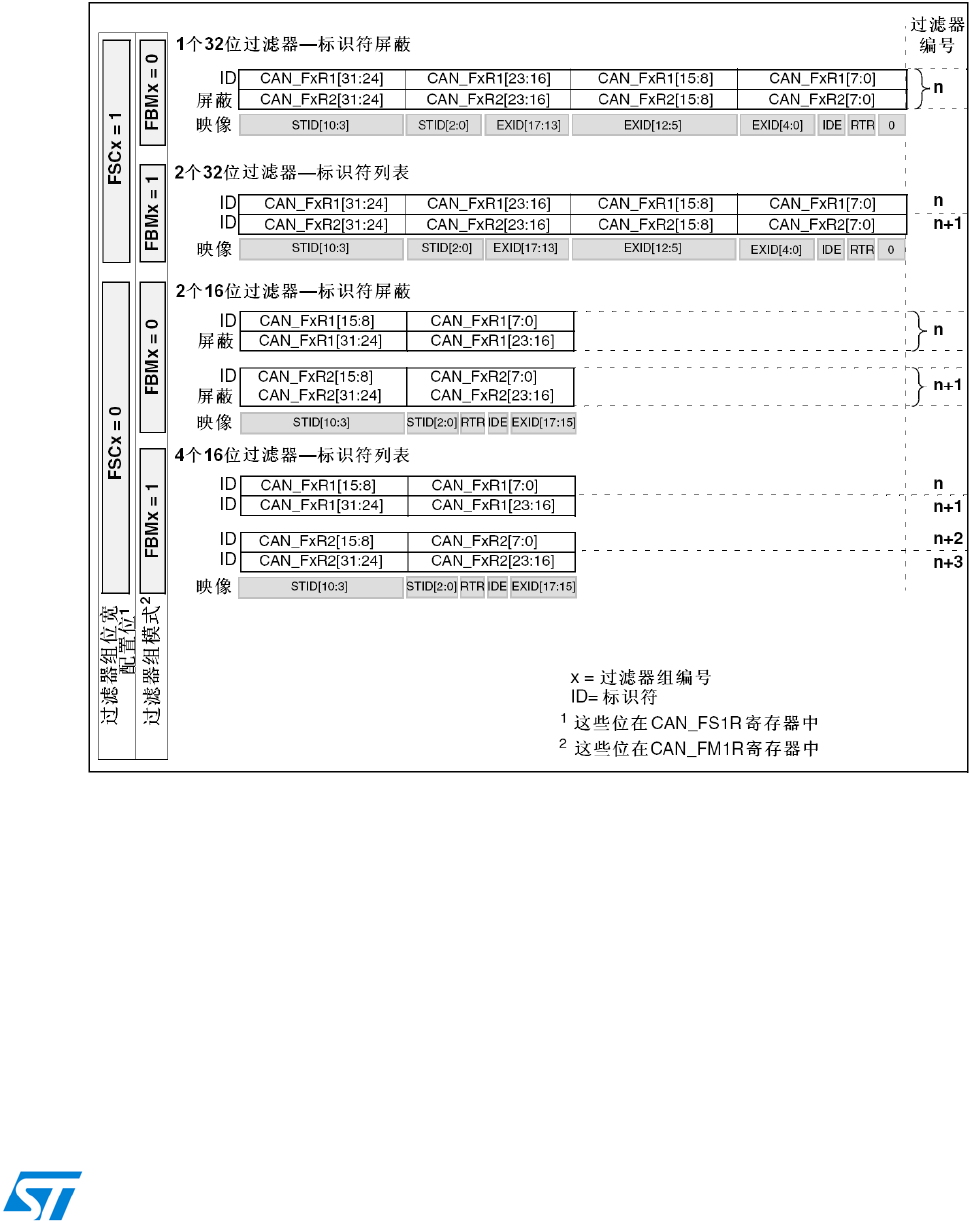

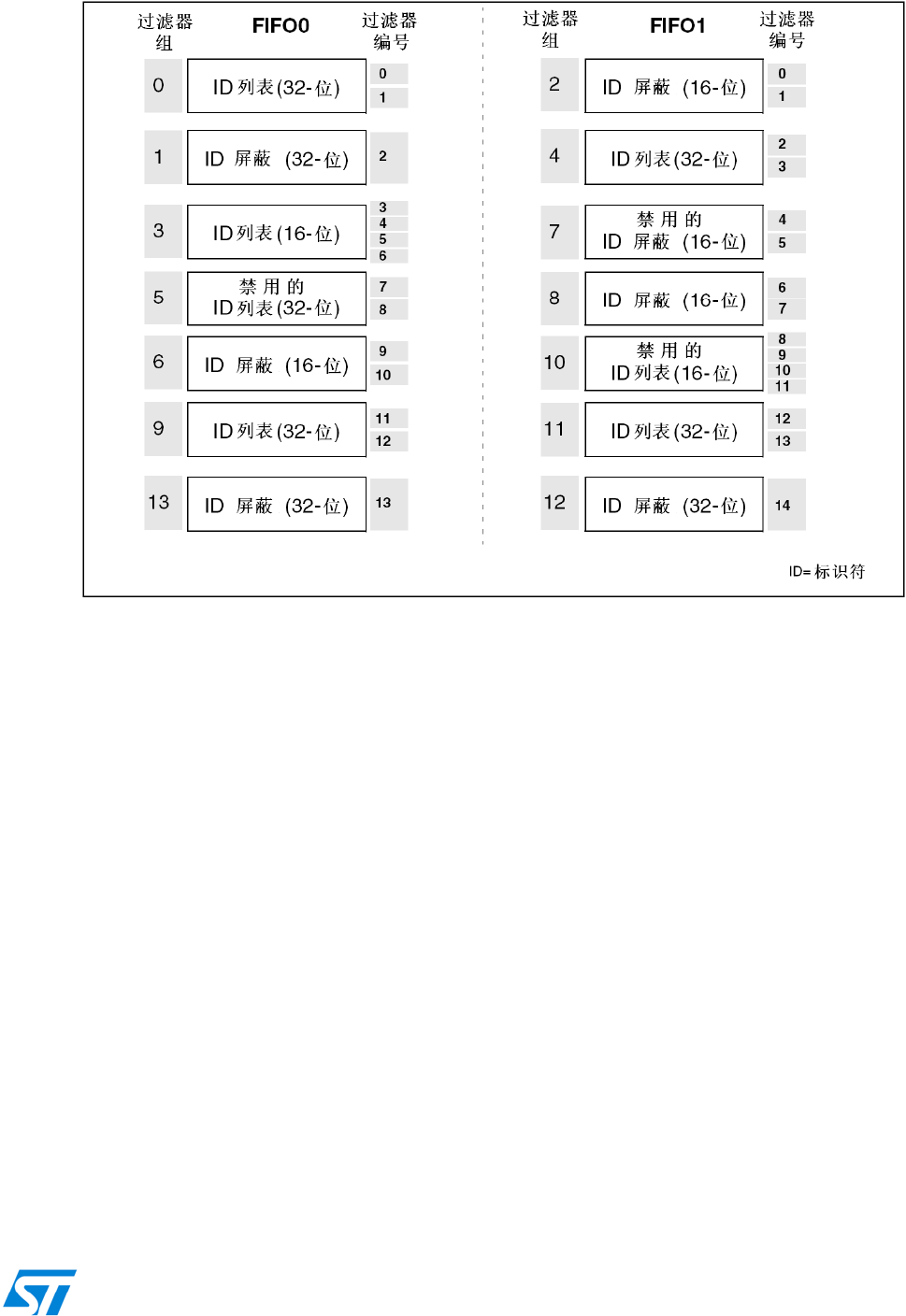

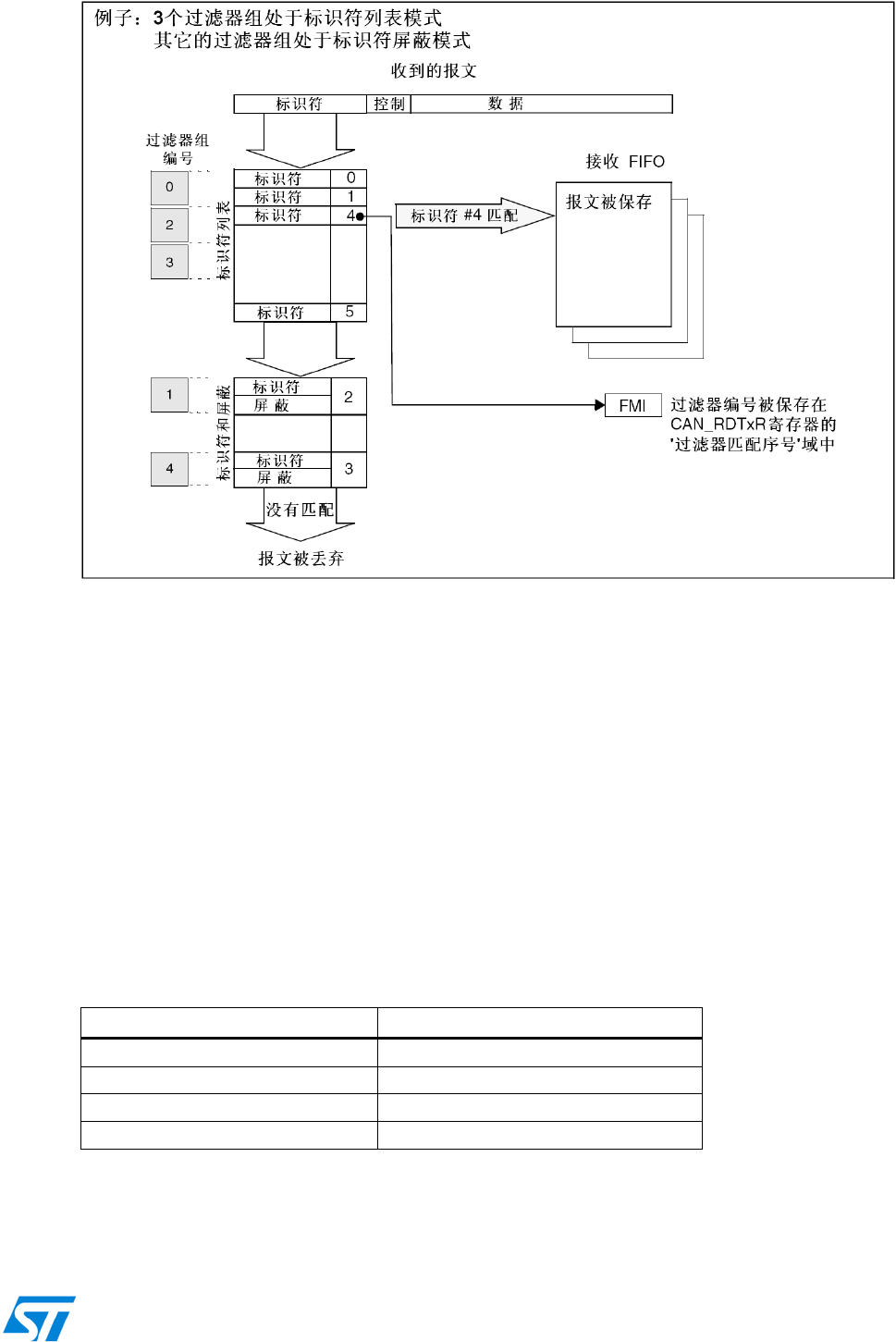

22.7.4 标识符过滤 431

22.7.5 报文存储 434

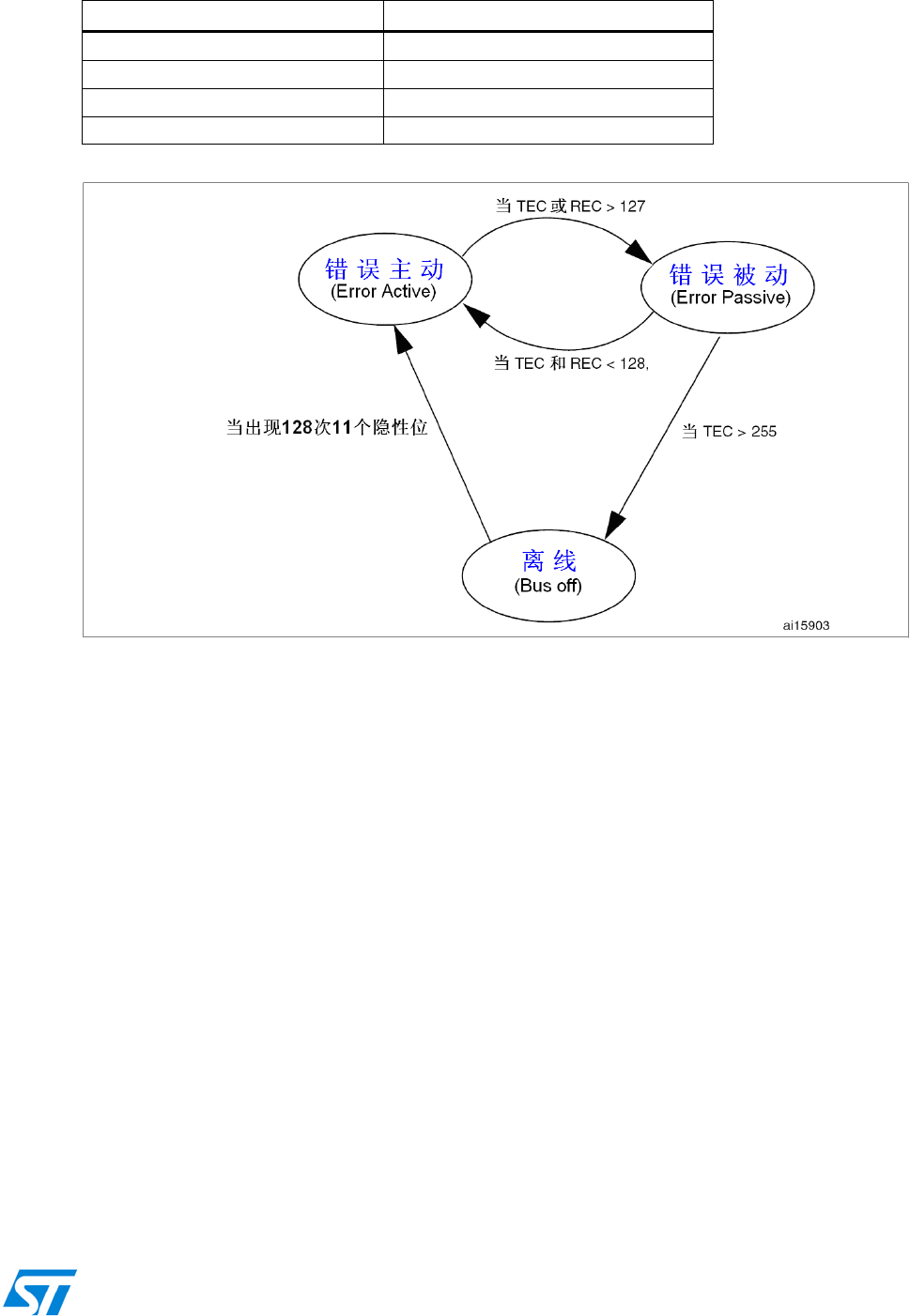

22.7.6 出错管理 435

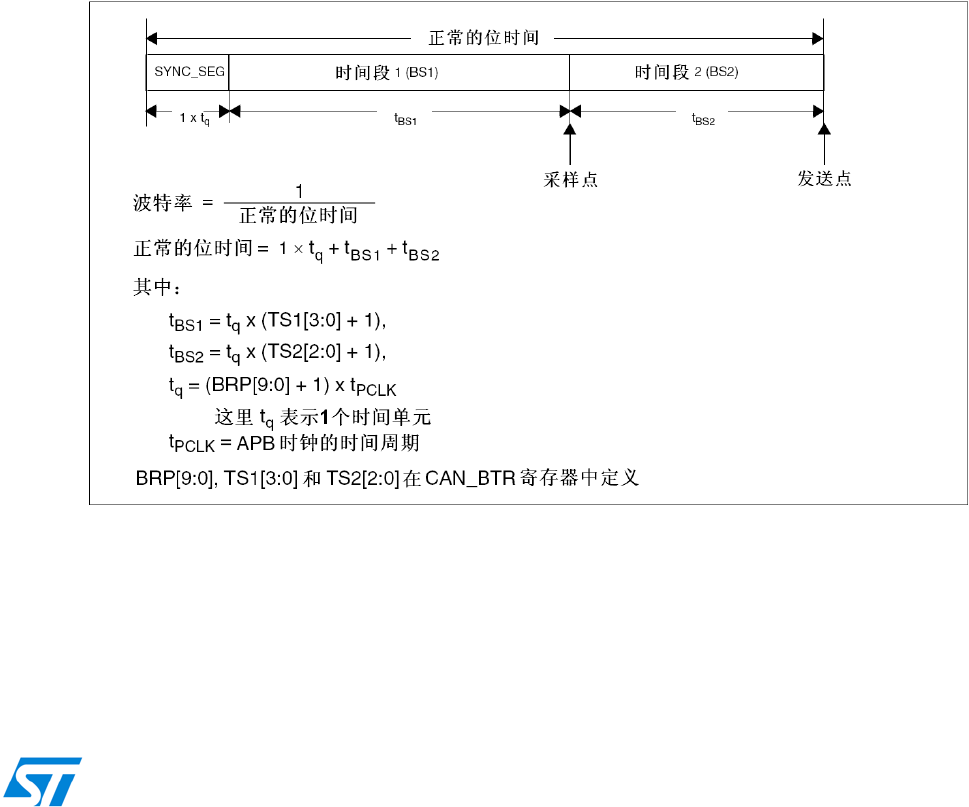

22.7.7 位时间特性 436

22.8 bxCAN中断 438

22.9 CAN 寄存器描述 439

22.9.1 寄存器访问保护 439

22.9.2 CAN控制和状态寄存器 439

22.9.3 CAN邮箱寄存器 447

22.9.4 CAN过滤器寄存器 451

22.9.5 bxCAN寄存器列表 454

23 串行外设接口(SPI) 457

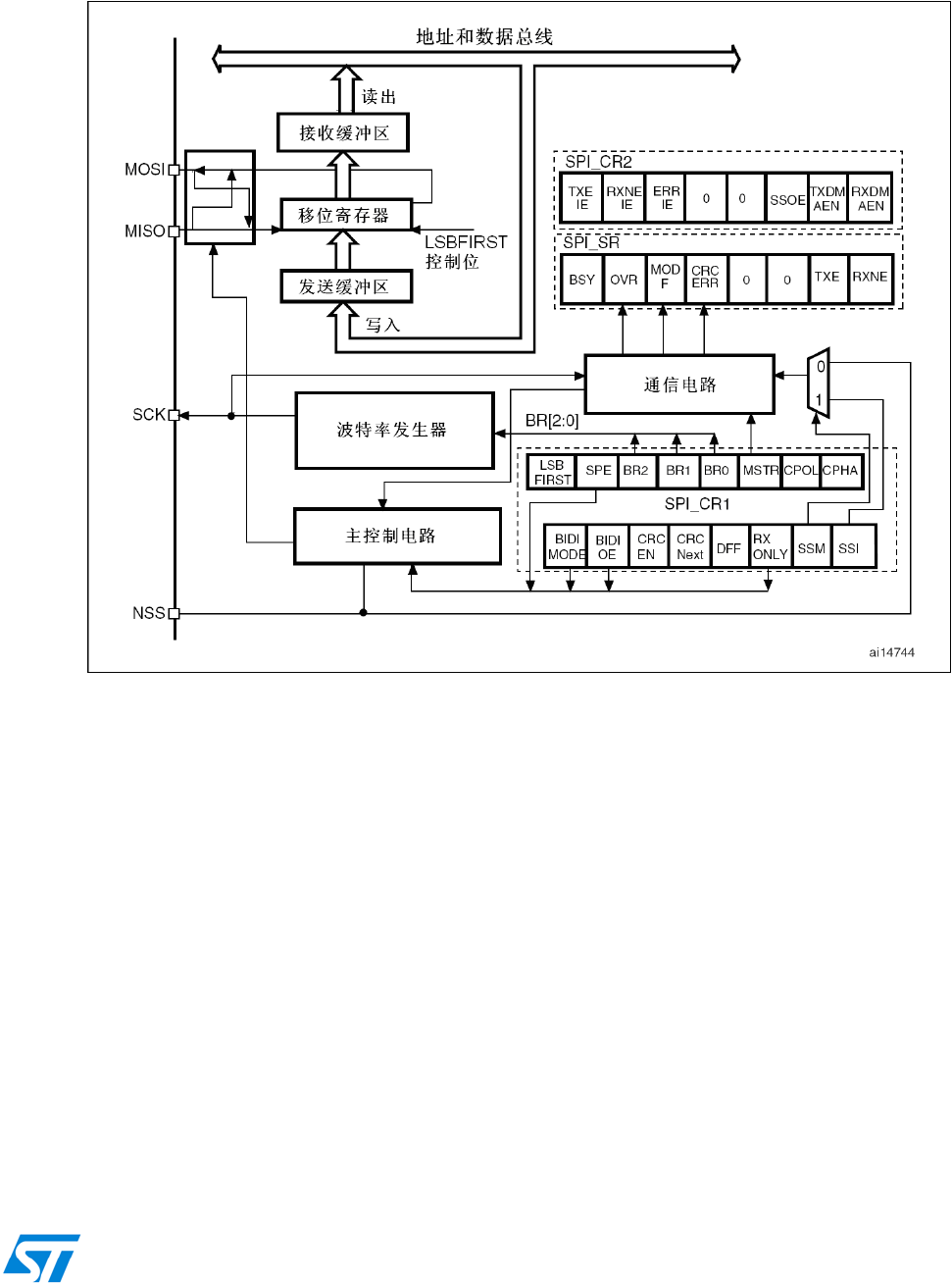

23.1 SPI简介 457

23.2 SPI和I2S主要特征 457

23.2.1 SPI特征 457

23.2.2 I2S功能 458

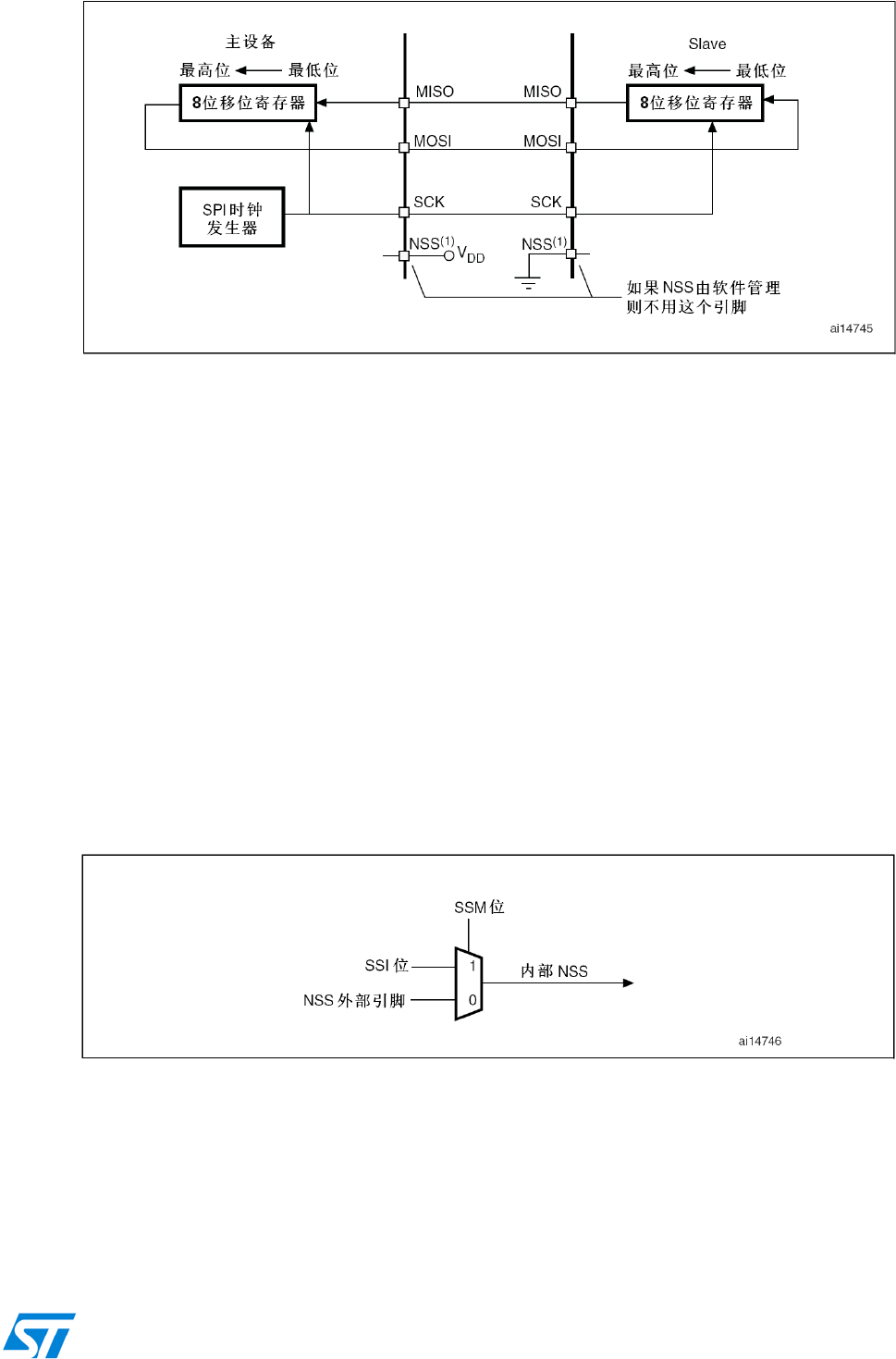

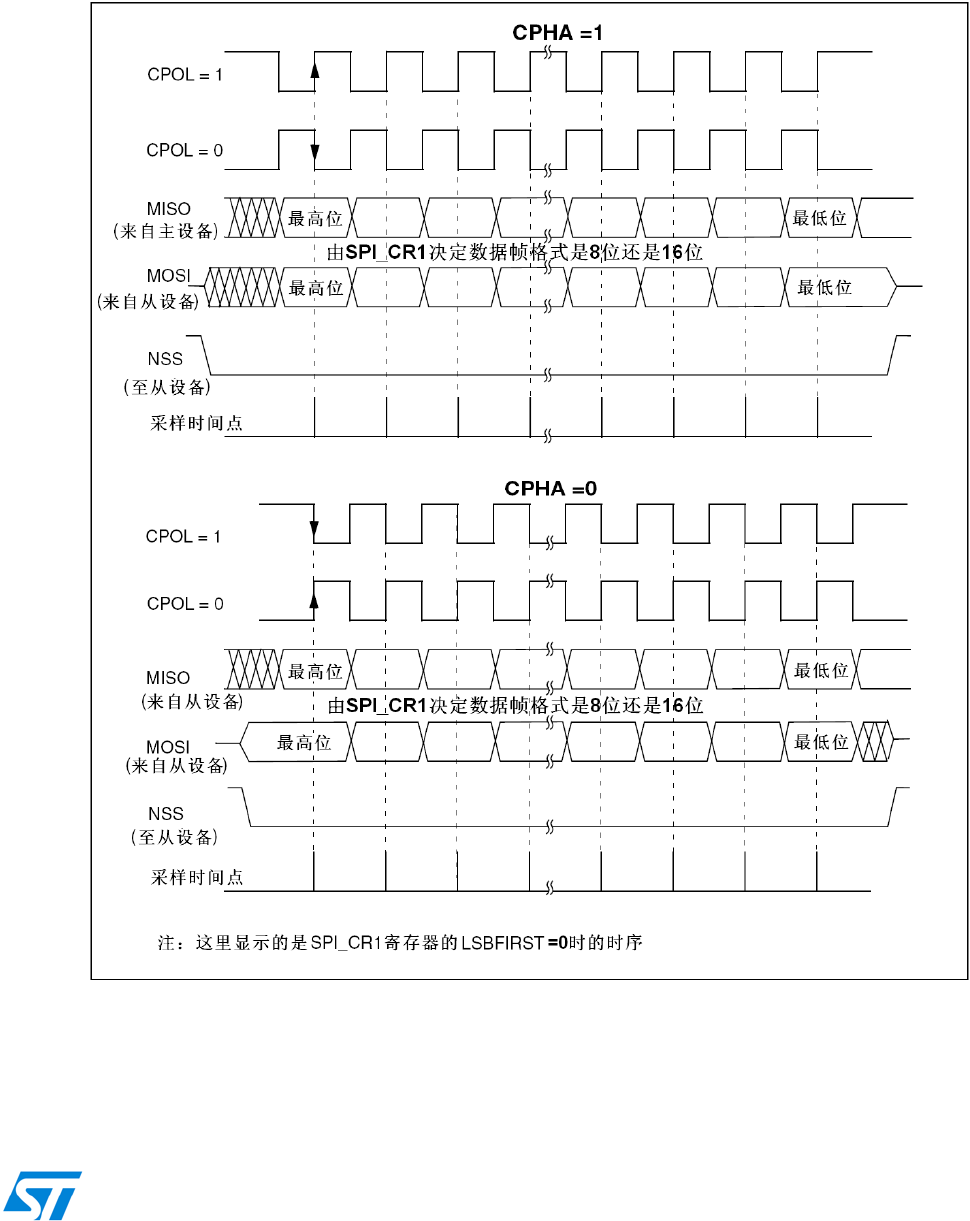

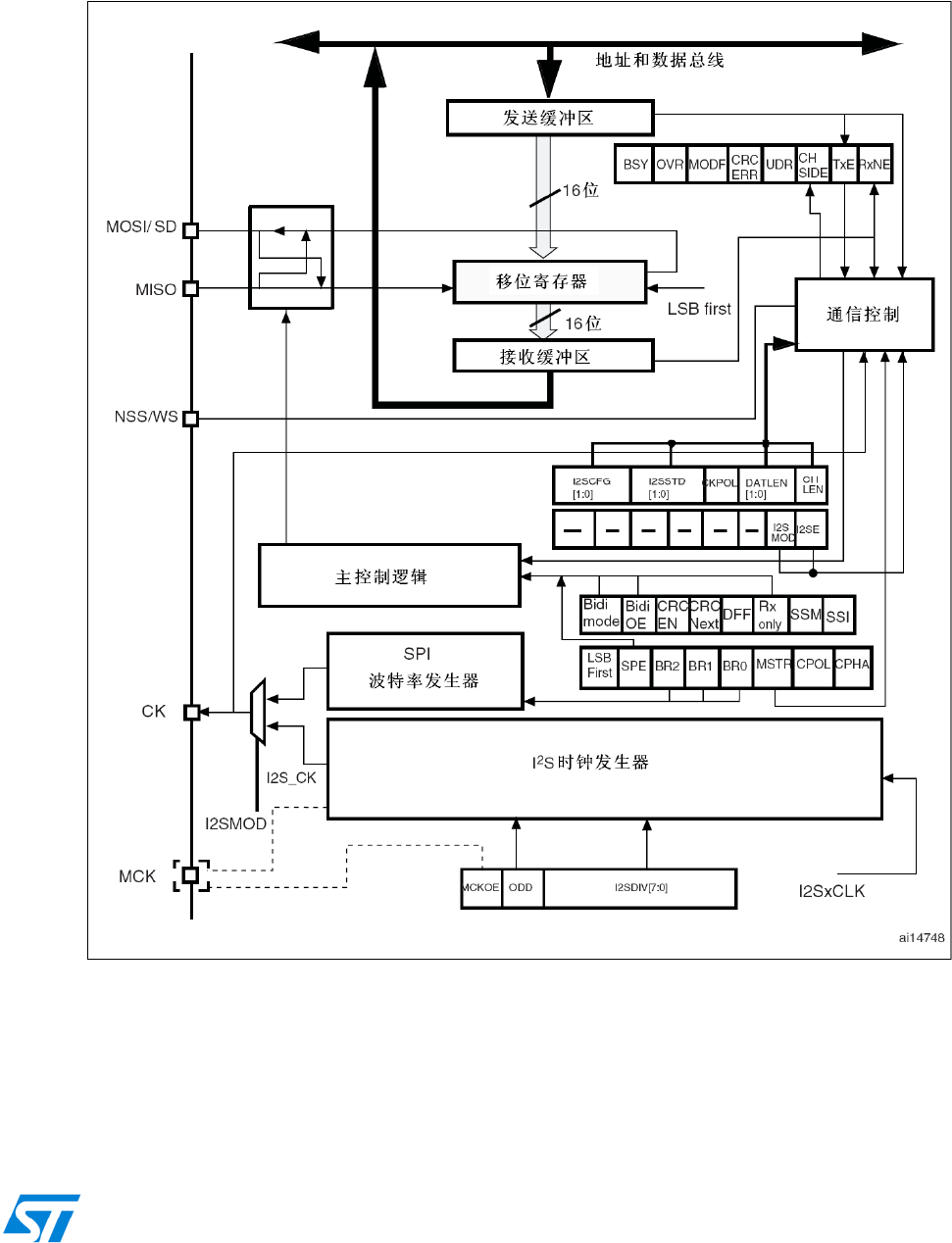

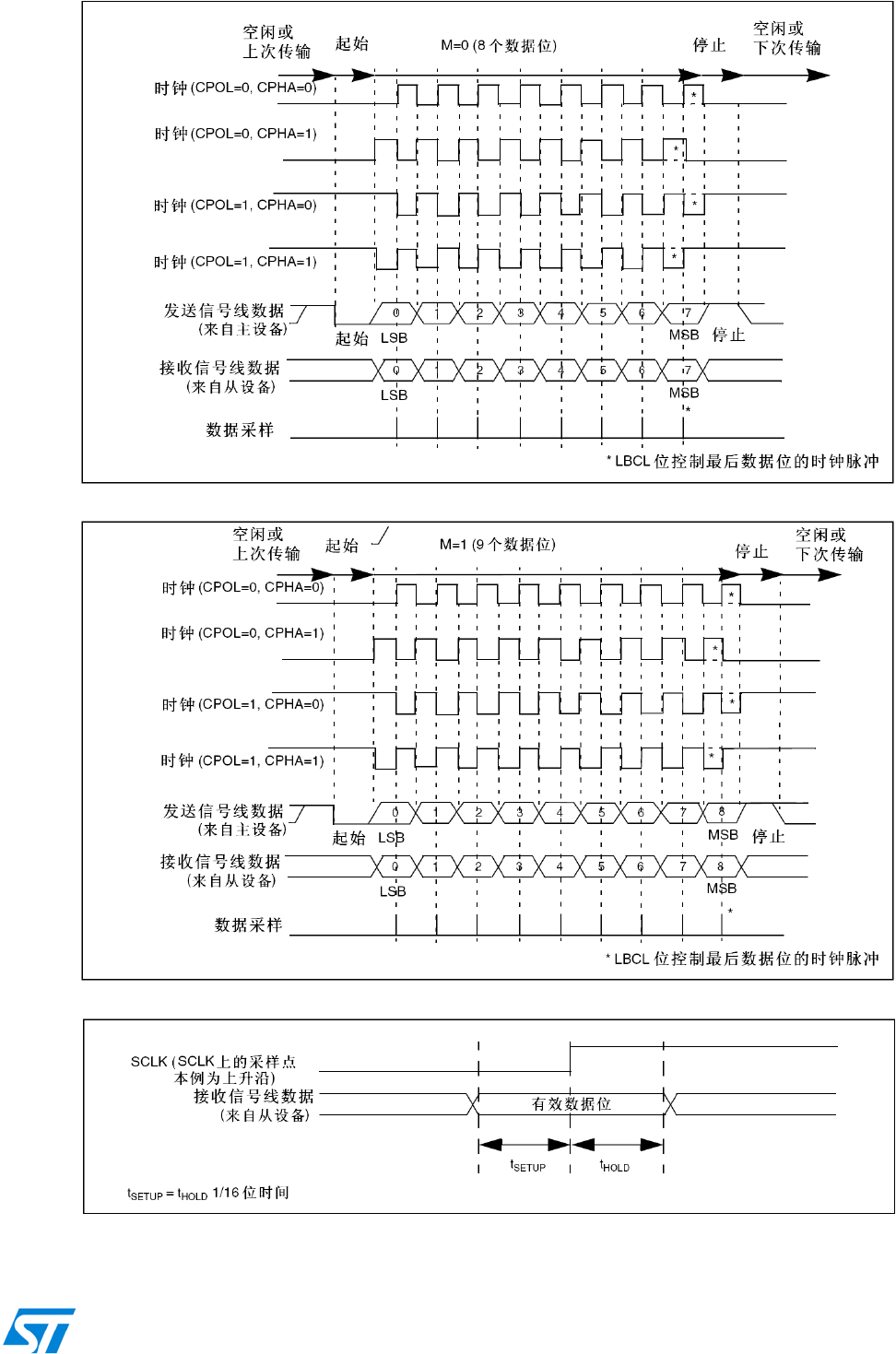

23.3 SPI功能描述 459

23.3.1 概述 459

23.3.2 配置SPI为从模式 462

23.3.3 配置SPI为主模式 462

23.3.4 配置SPI为单工通信 463

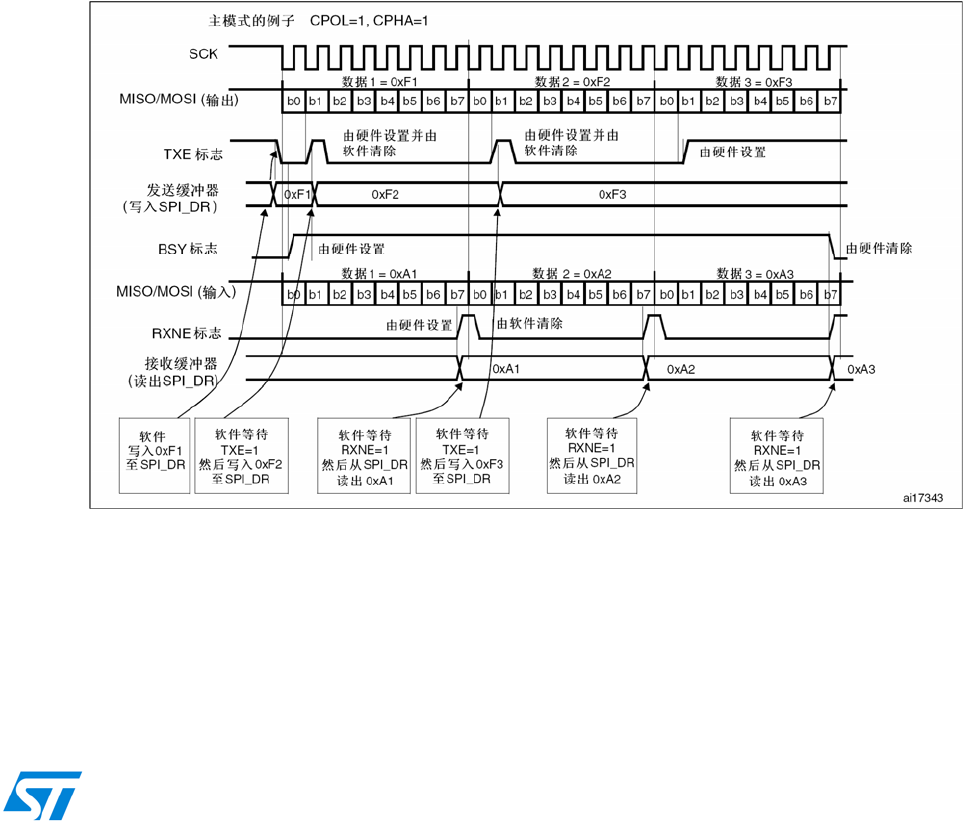

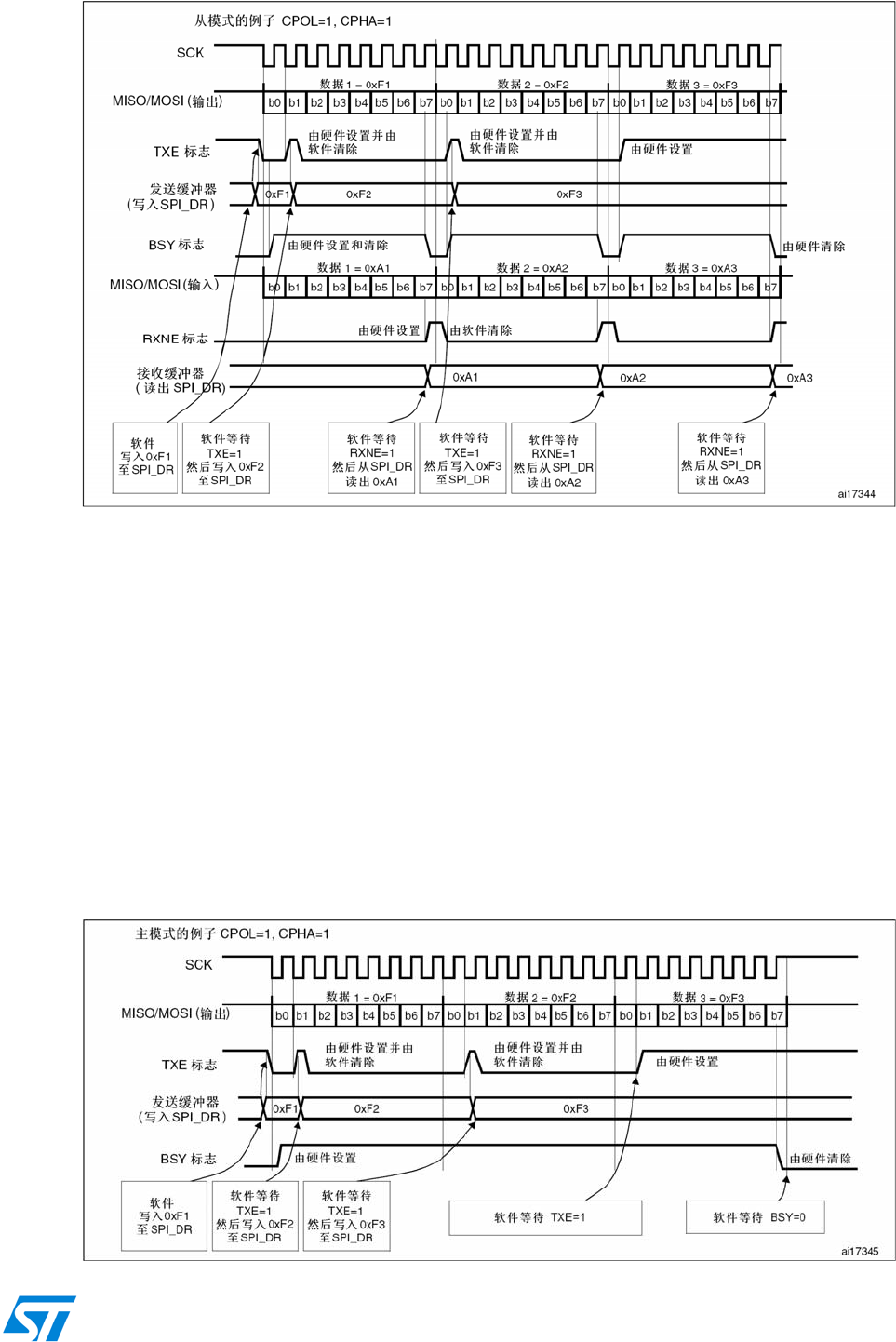

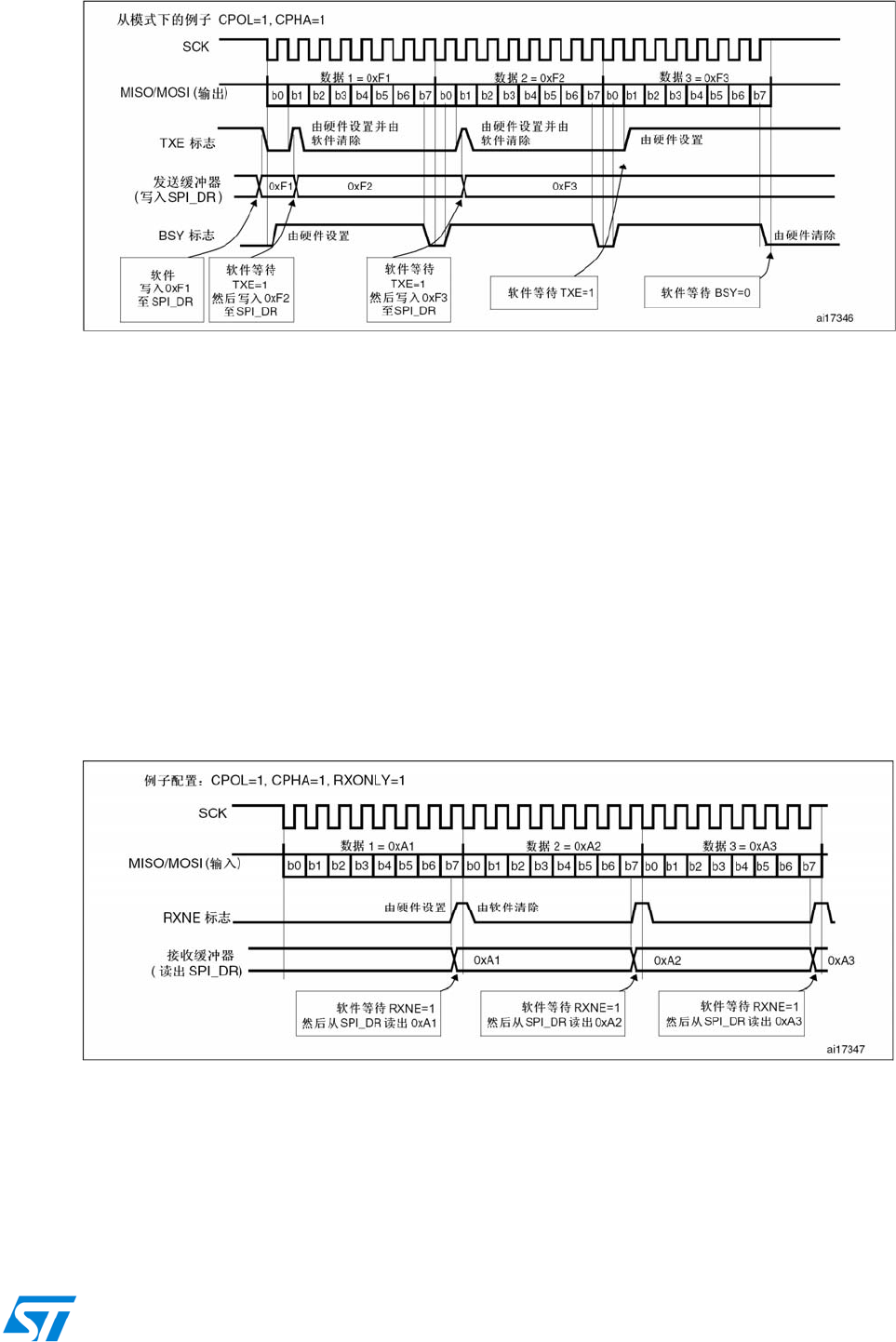

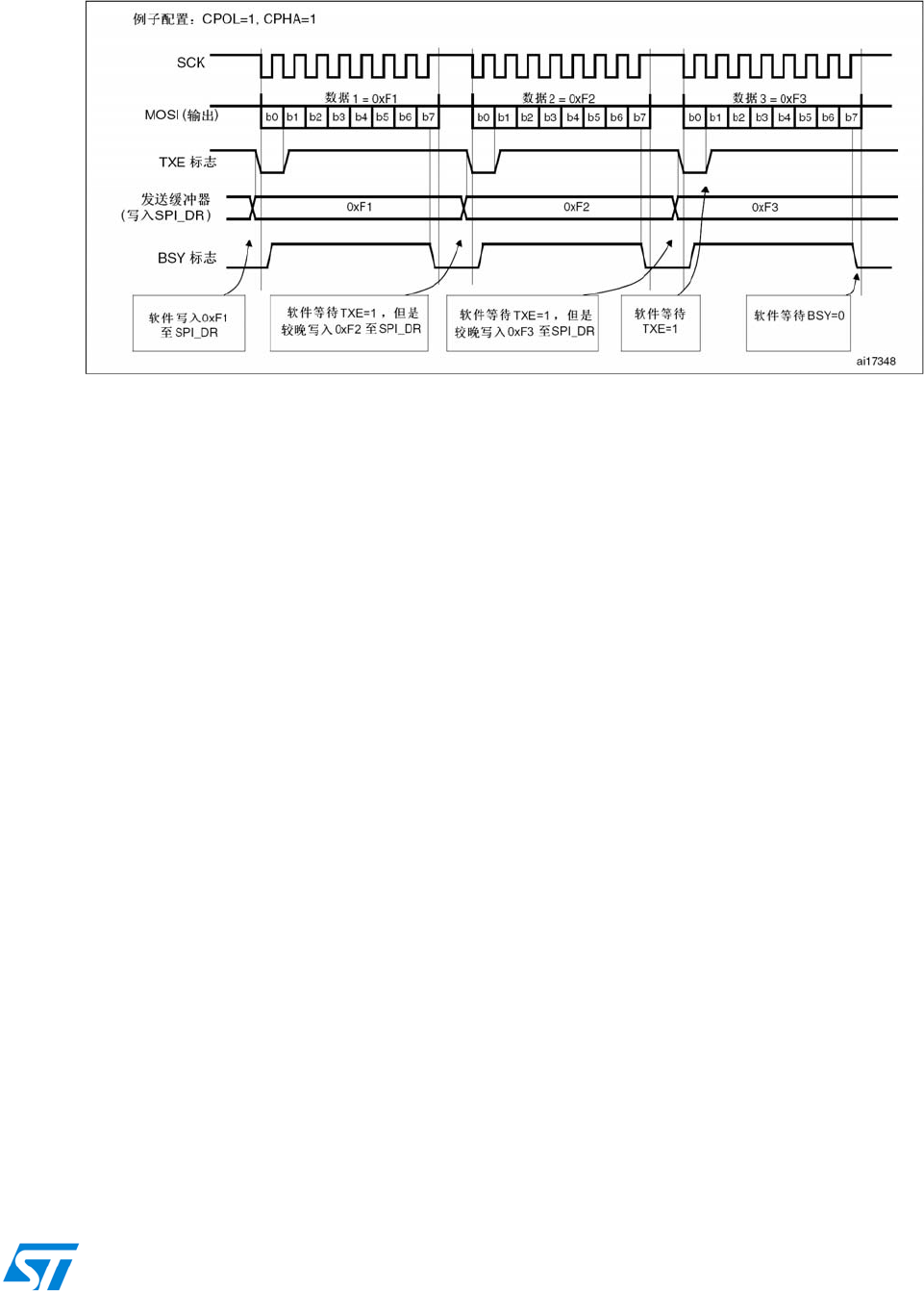

23.3.5 数据发送与接收过程 463

23.3.6 CRC计算 468

23.3.7 状态标志 469

23.3.8 关闭SPI 470

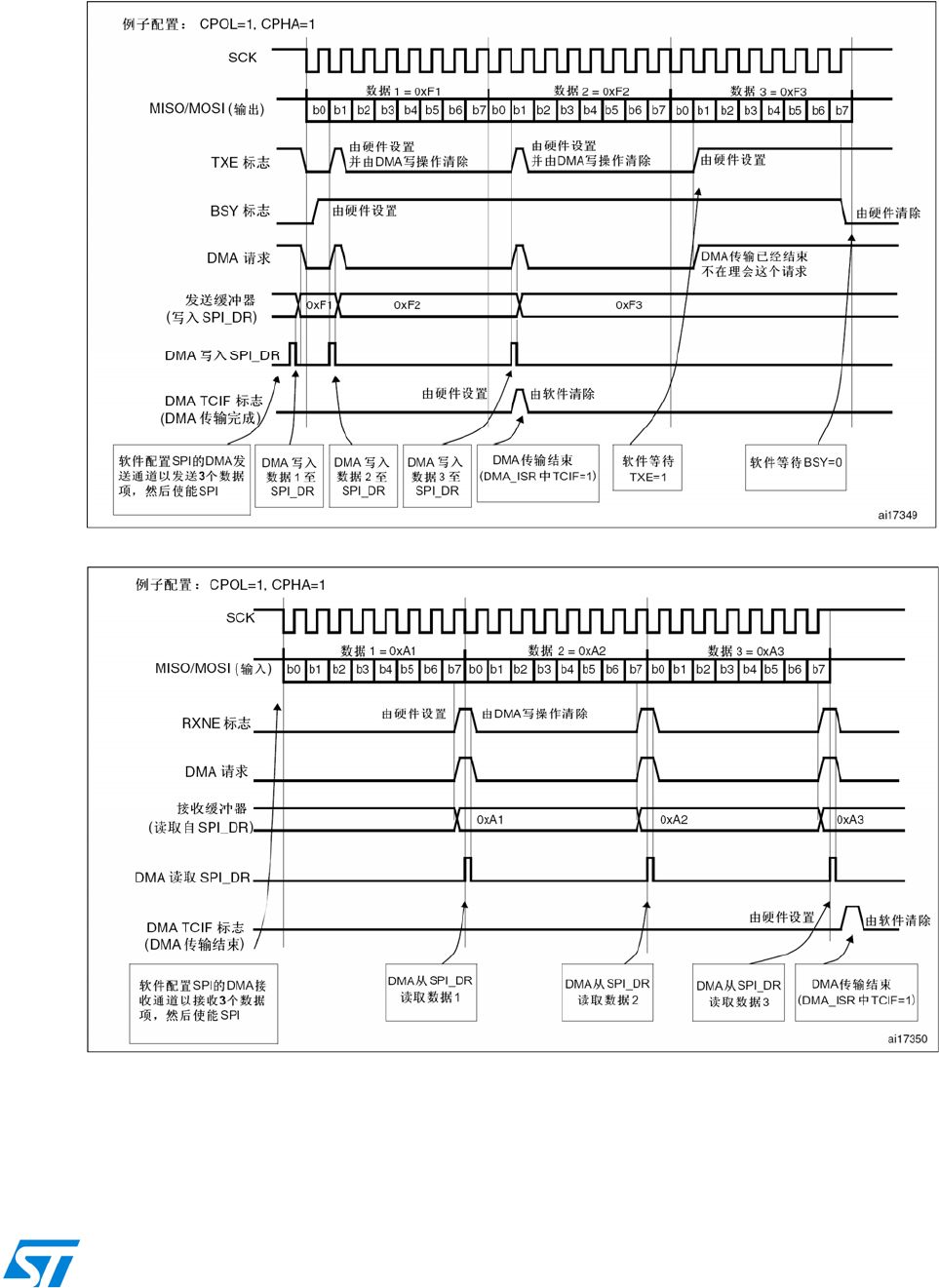

23.3.9 利用DMA的SPI通信 470

23.3.10 错误标志 472

23.3.11 SPI中断 472

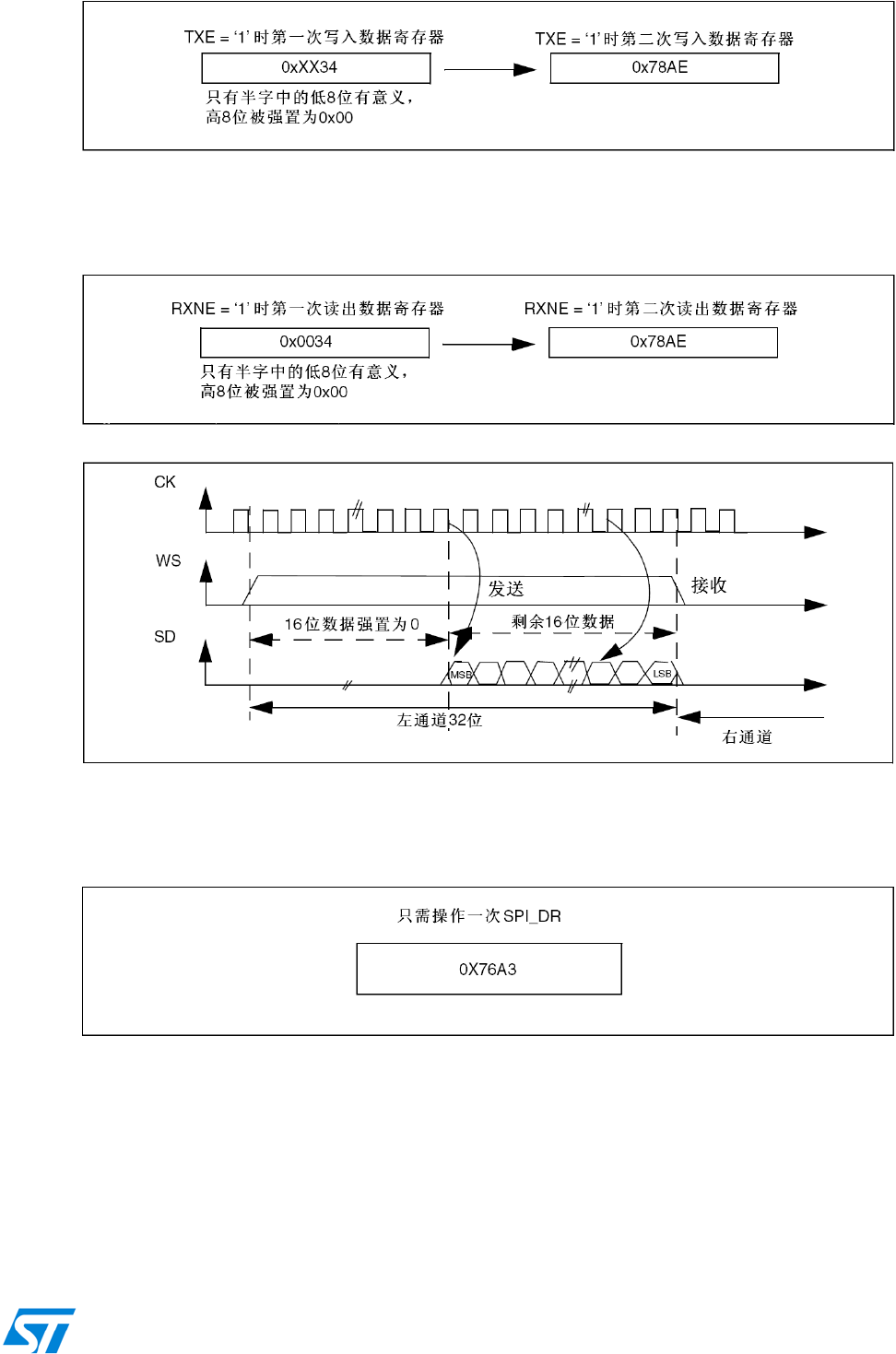

23.4 I2S功能描述 473

23.4.1 I2S功能描述 473

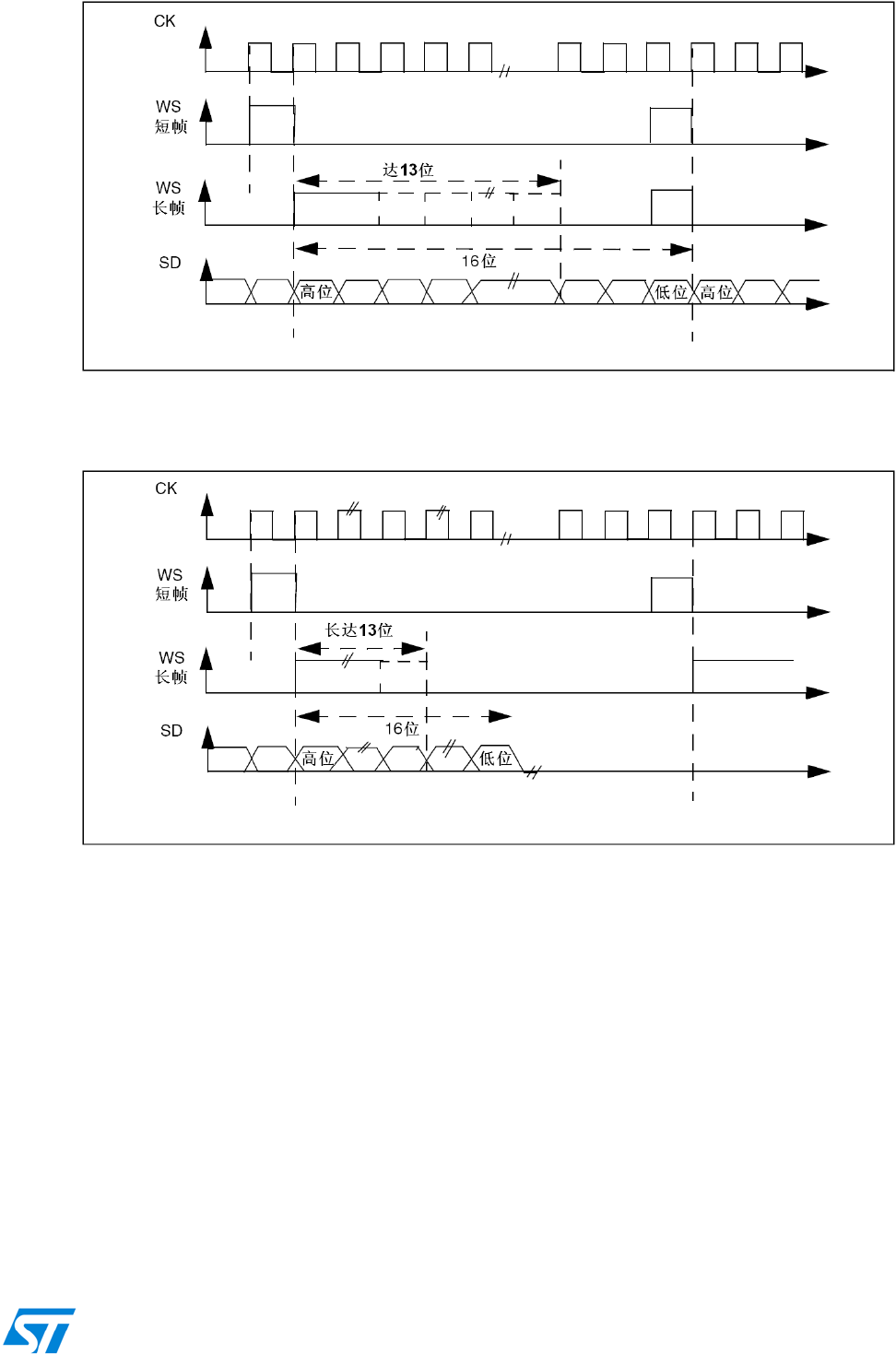

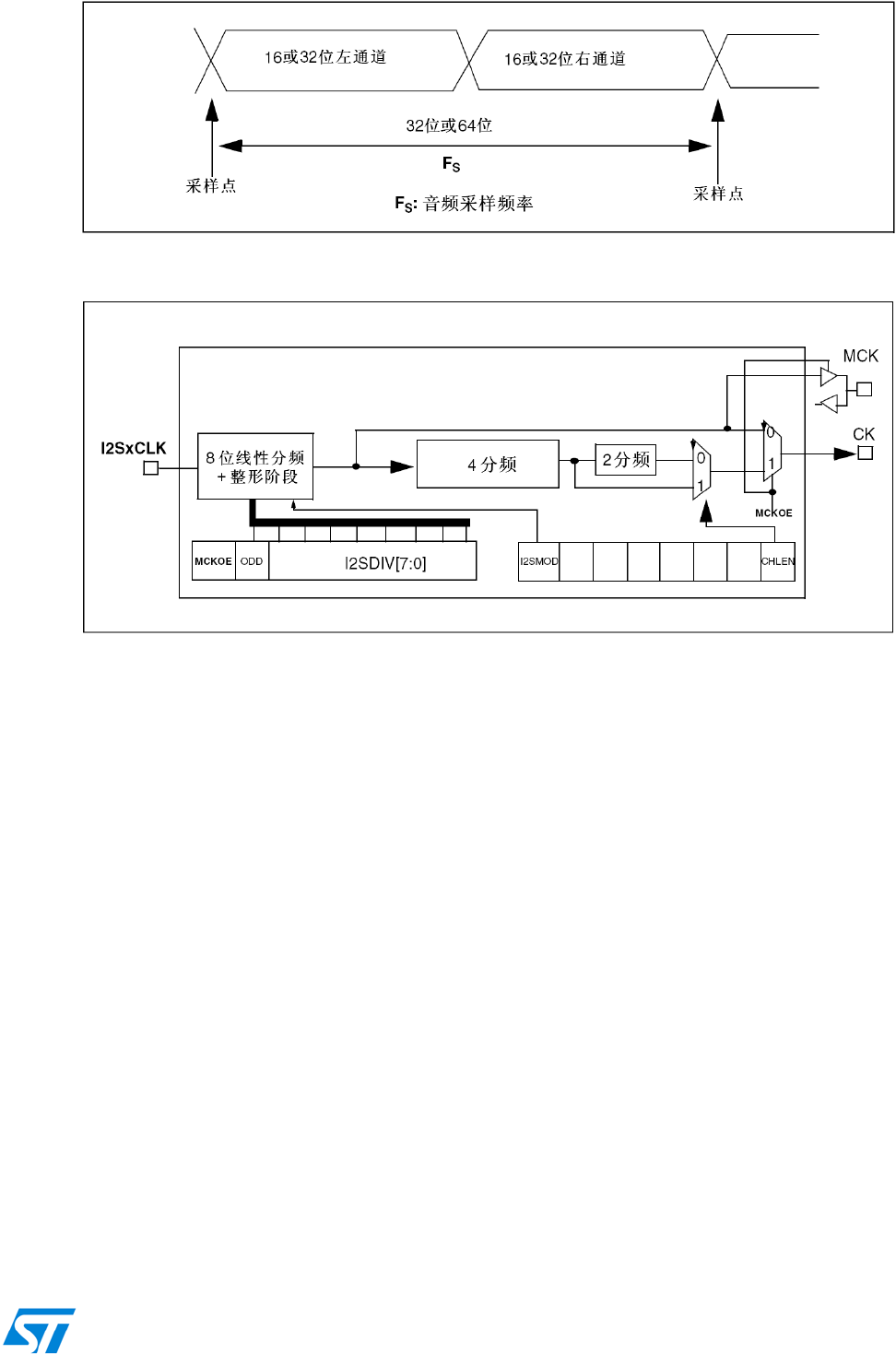

23.4.2 支持的音频协议 474

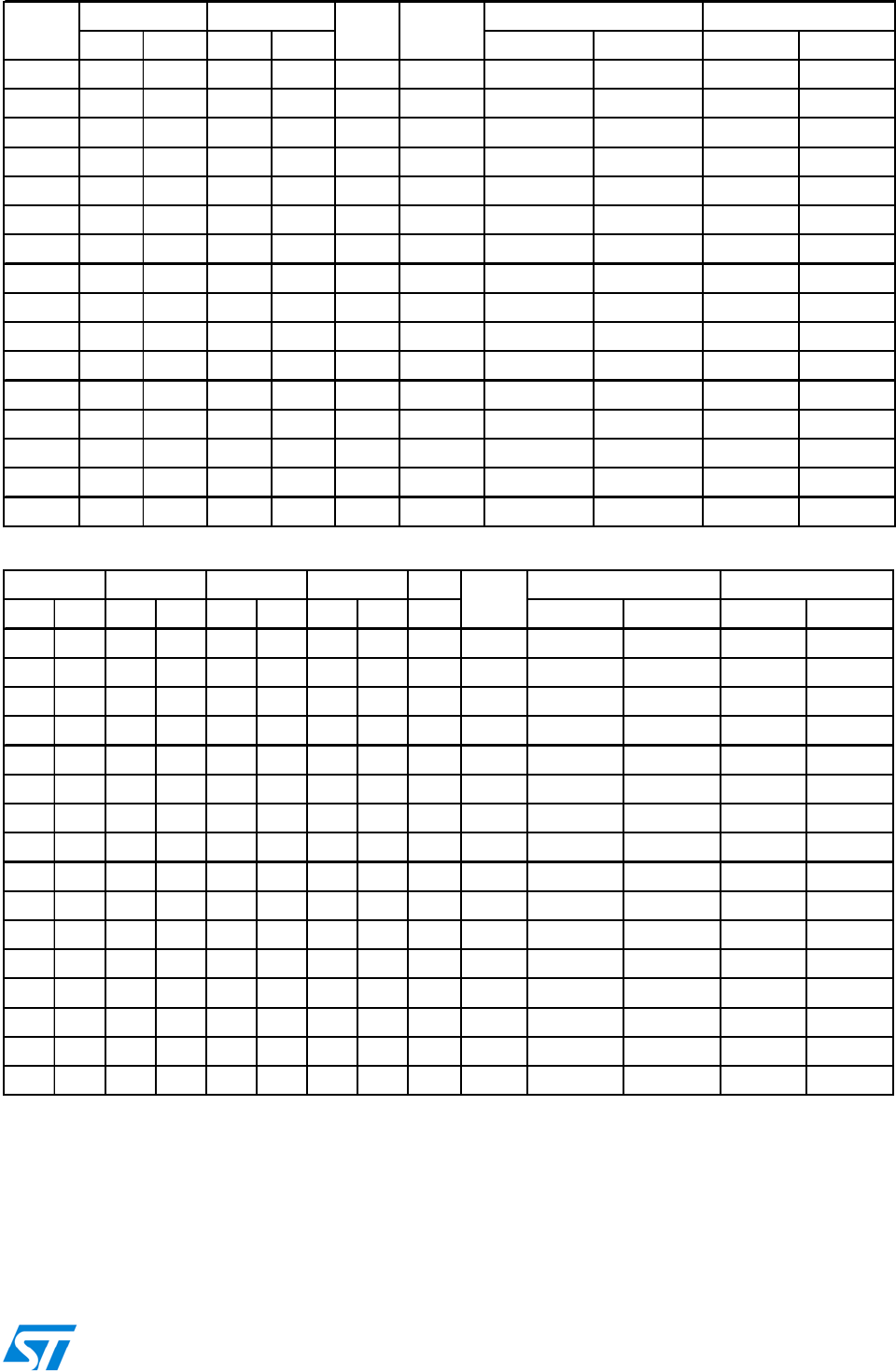

23.4.3 时钟发生器 479

23.4.4 I2S主模式 482

23.4.5 I2S从模式 483

23.4.6 状态标志位 484

23.4.7 错误标志位 485

23.4.8 I2S中断 485

23.4.9 DMA功能 485

23.5 SPI和I2S寄存器描述 486

18/754

参照2009年12月 RM0008 Reference Manual 英文第10版

本译文仅供参考,如有翻译错误,请以英文原稿为准。请读者随时注意在ST网站下载更新版本

目录 STM32F10xxx参考手册

23.5.1 SPI控制寄存器1(SPI_CR1)(I2S模式下不使用) 486

23.5.2 SPI控制寄存器2(SPI_CR2) 487

23.5.3 SPI 状态寄存器(SPI_SR) 488

23.5.4 SPI 数据寄存器(SPI_DR) 489

23.5.5 SPI CRC多项式寄存器(SPI_CRCPR)(I2S模式下不使用) 489

23.5.6 SPI Rx CRC寄存器(SPI_RXCRCR)(I2S模式下不使用) 490

23.5.7 SPI Tx CRC寄存器(SPI_TXCRCR) 490

23.5.8 SPI_I2S配置寄存器(SPI_I2S_CFGR) 490

23.5.9 SPI_I2S预分频寄存器(SPI_I2SPR) 491

23.5.10 SPI 寄存器地址映象 492

24 I2C接口 493

24.1 I2C简介 493

24.2 I2C主要特点 493

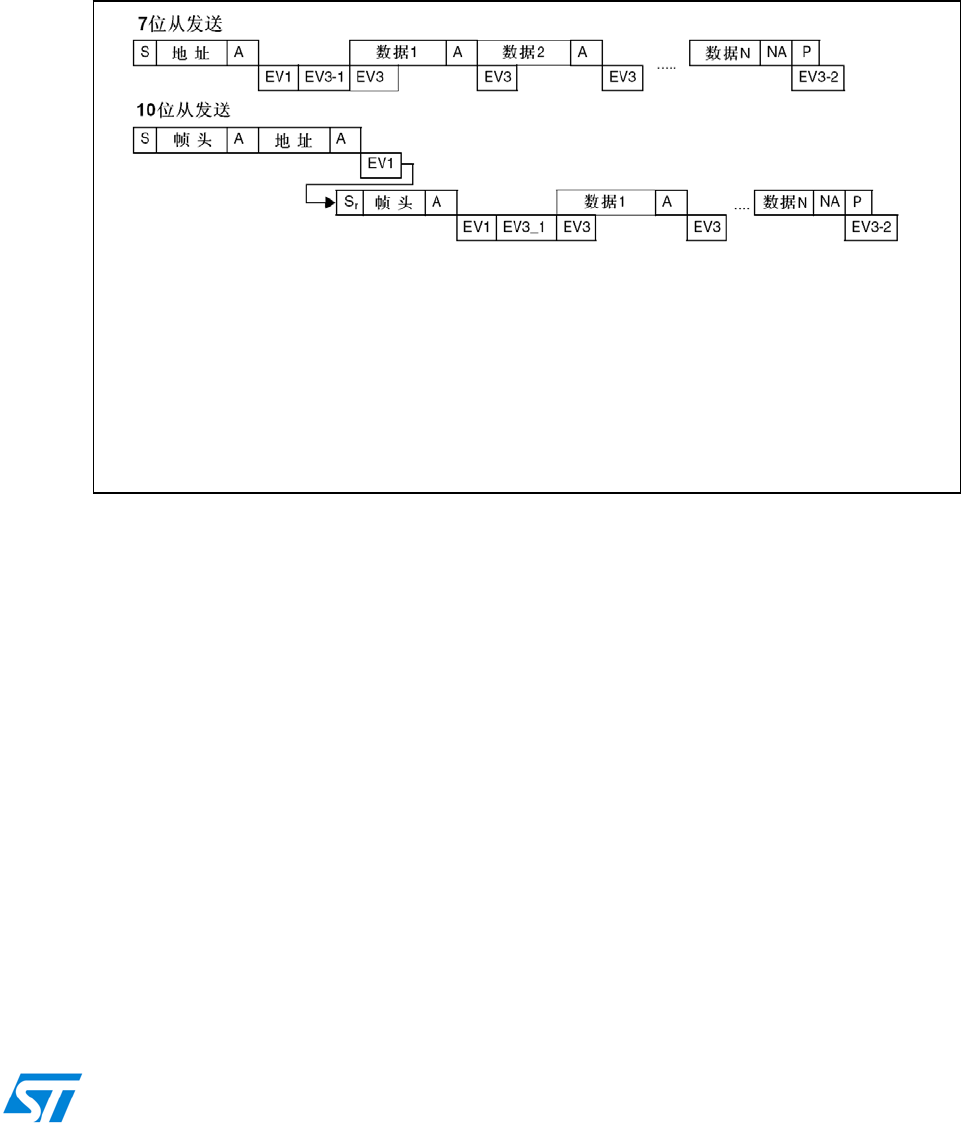

24.3 I2C功能描述 494

24.3.1 模式选择 494

24.3.2 I2C从模式 495

24.3.3 I2C主模式 497

24.3.4 错误条件 499

24.3.5 SDA/SCL线控制 500

24.3.6 SMBus 501

24.3.7 DMA请求 502

24.3.8 包错误校验(PEC) 503

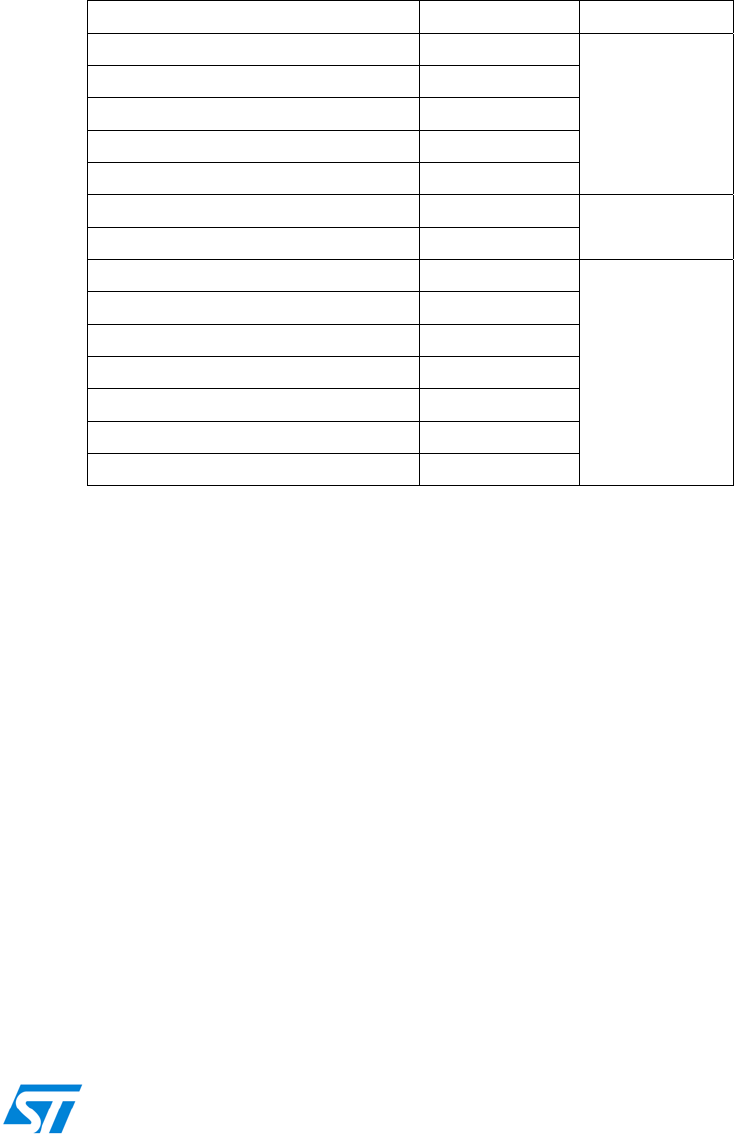

24.4 I2C中断请求 504

24.5 I2C调试模式 505

24.6 I2C寄存器描述 505

24.6.1 控制寄存器1(I2C_CR1) 505

24.6.2 控制寄存器2(I2C_CR2) 507

24.6.3 自身地址寄存器1(I2C_OAR1) 508

24.6.4 自身地址寄存器2(I2C_OAR2) 509

24.6.5 数据寄存器(I2C_DR) 509

24.6.6 状态寄存器1(I2C_SR1) 510

24.6.7 状态寄存器2 (I2C_SR2) 512

24.6.8 时钟控制寄存器(I2C_CCR) 513

24.6.9 TRISE寄存器(I2C_TRISE) 514

24.6.10 I2C寄存器地址映象 515

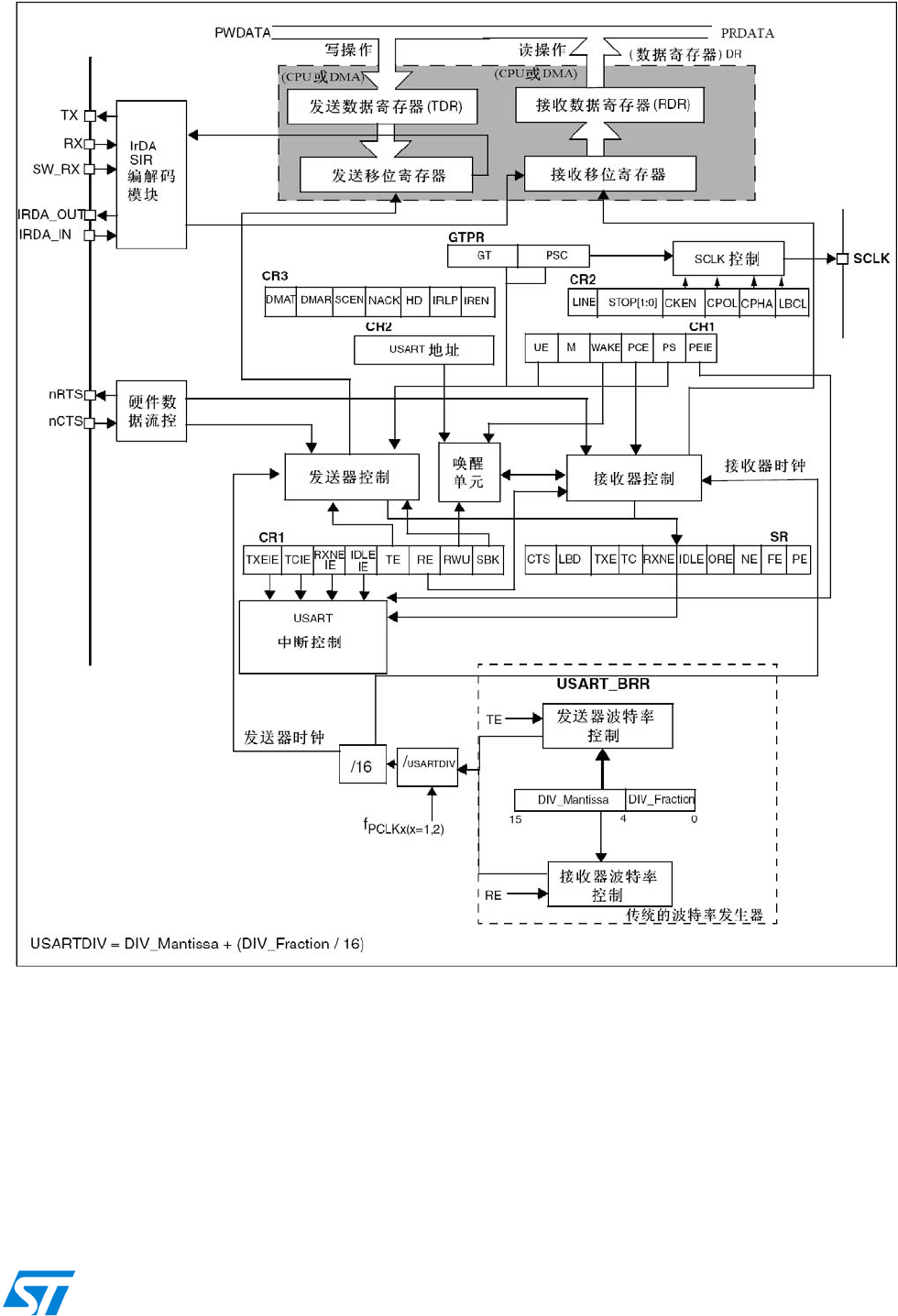

25 通用同步异步收发器(USART) 516

25.1 USART介绍 516

25.2 USART主要特性 516

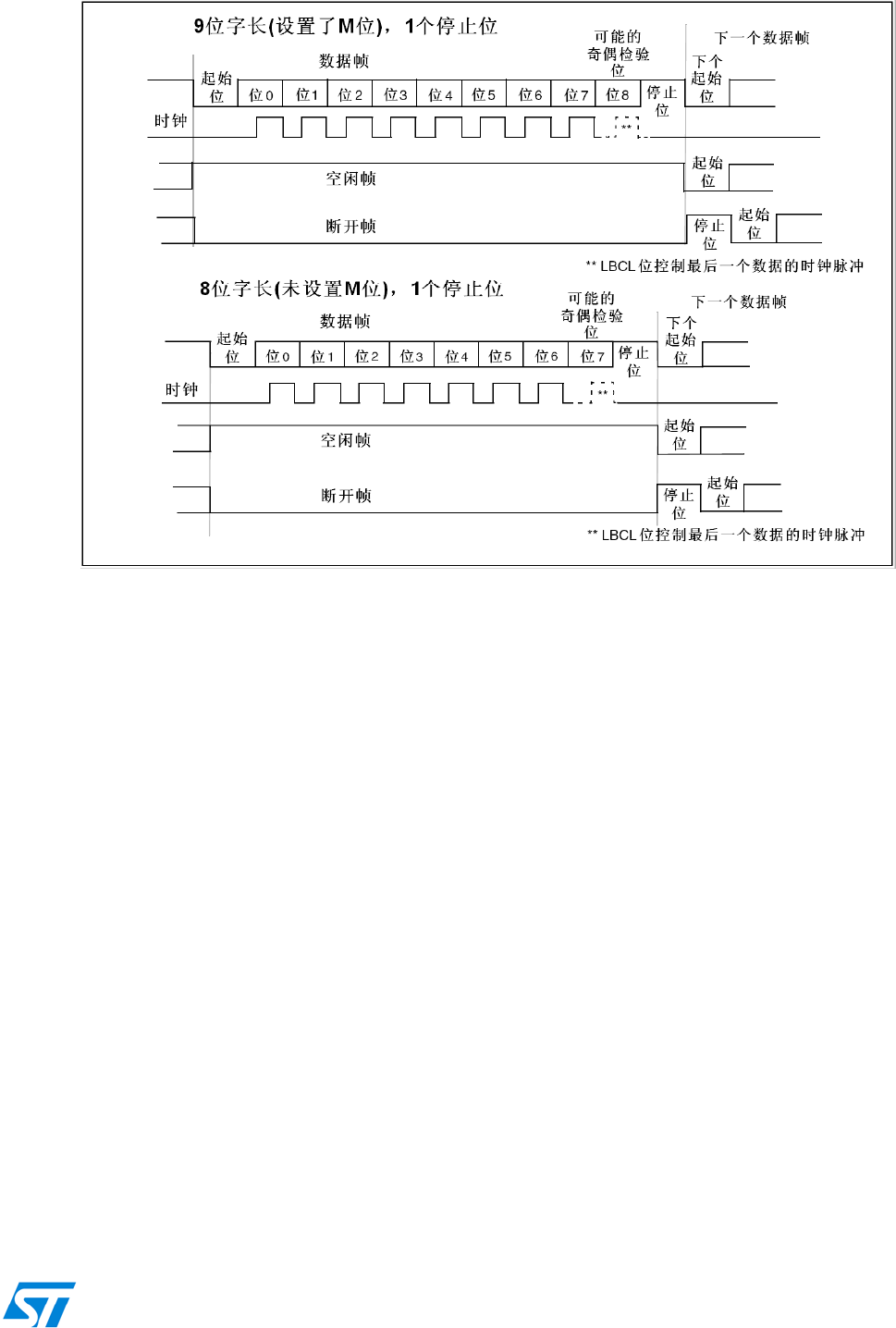

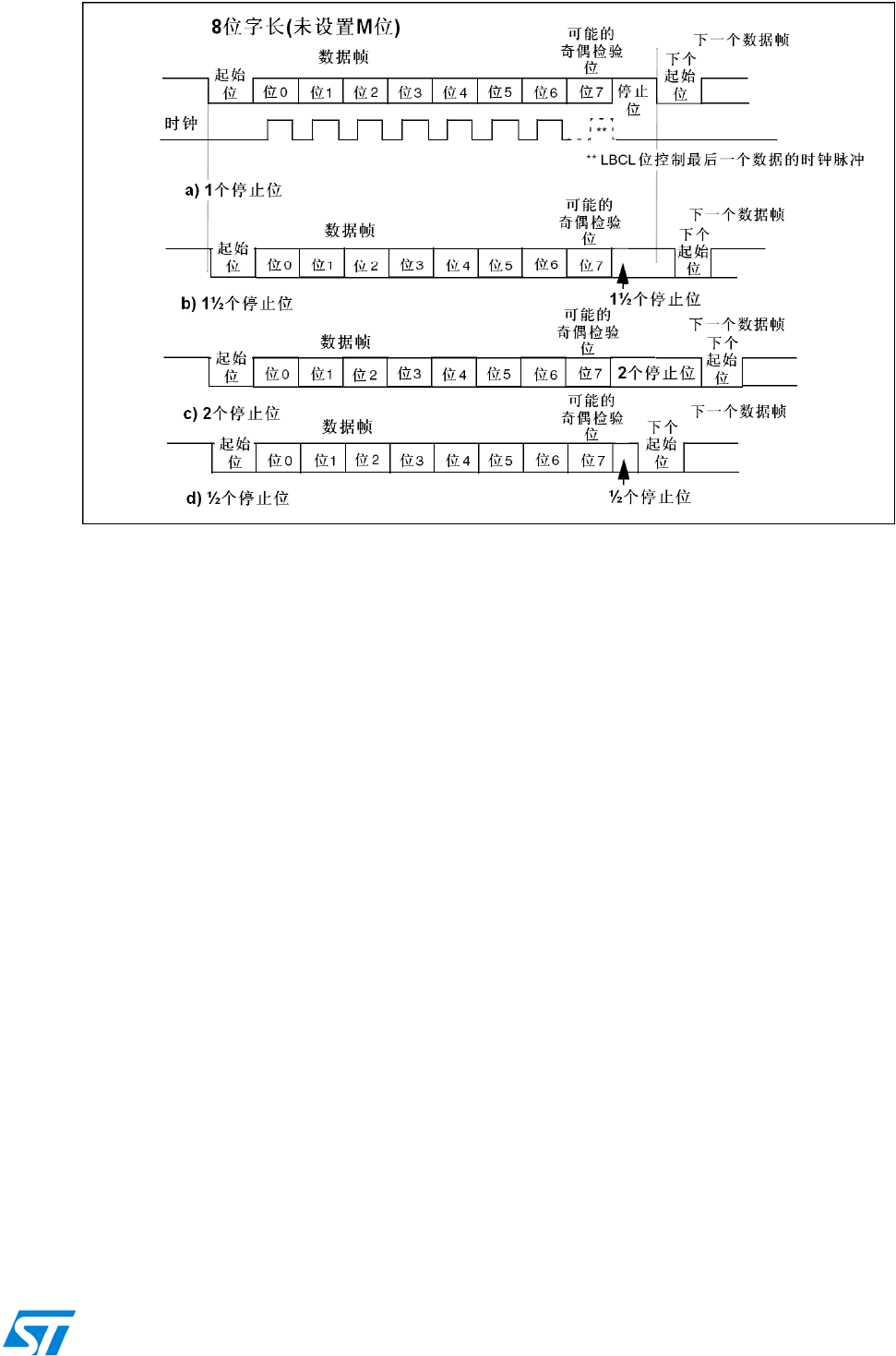

25.3 USART功能概述 517

25.3.1 USART 特性描述 518

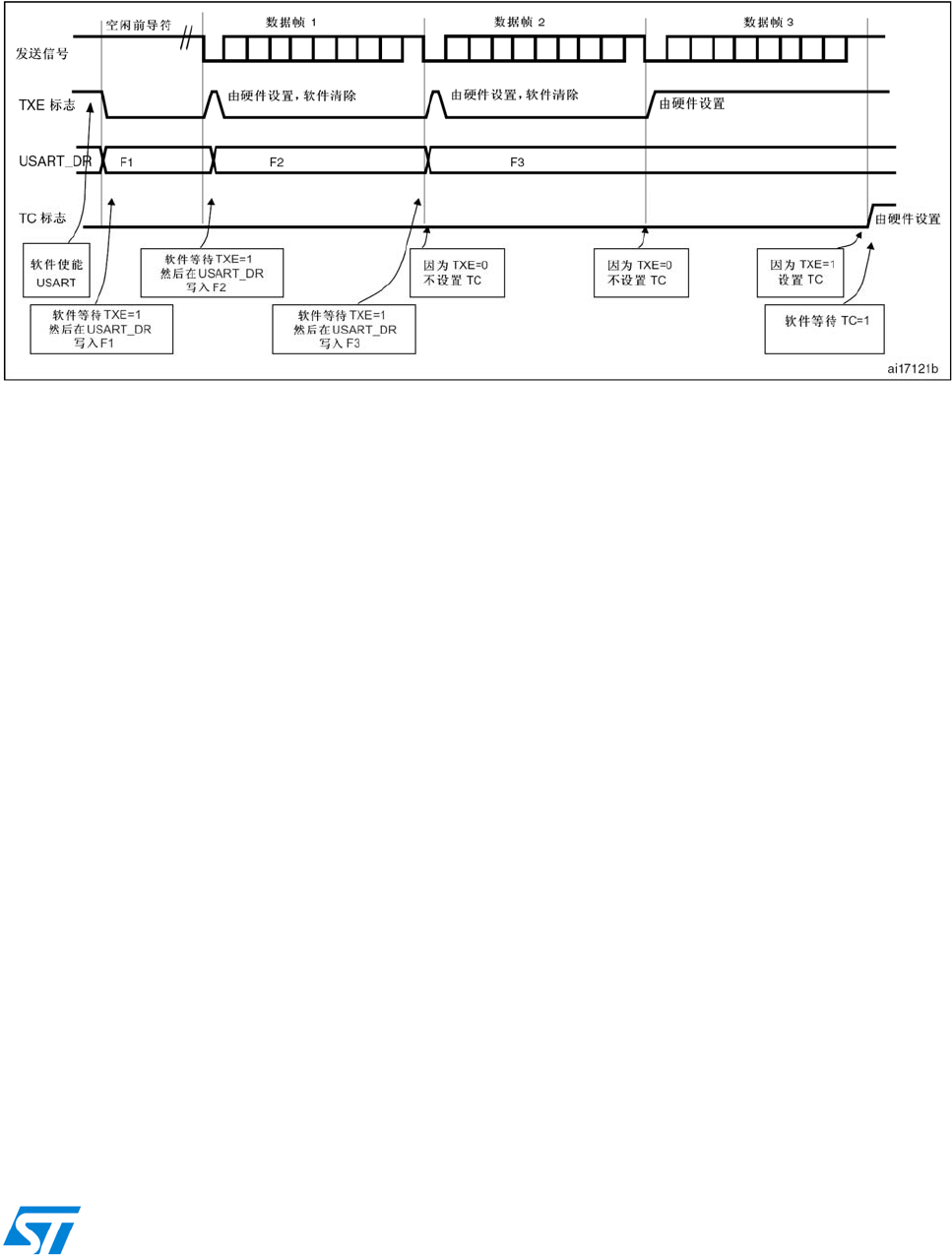

25.3.2 发送器 519

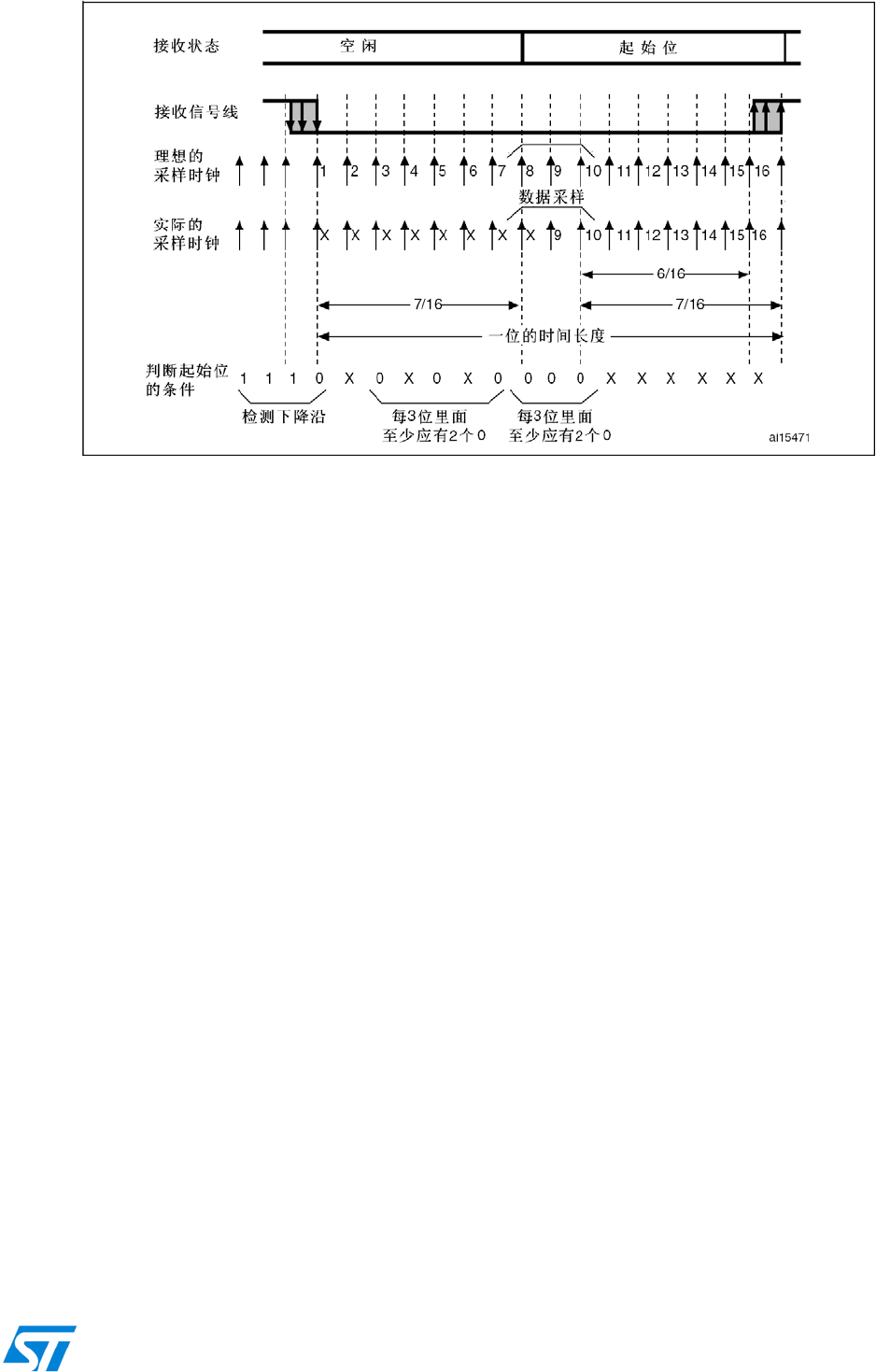

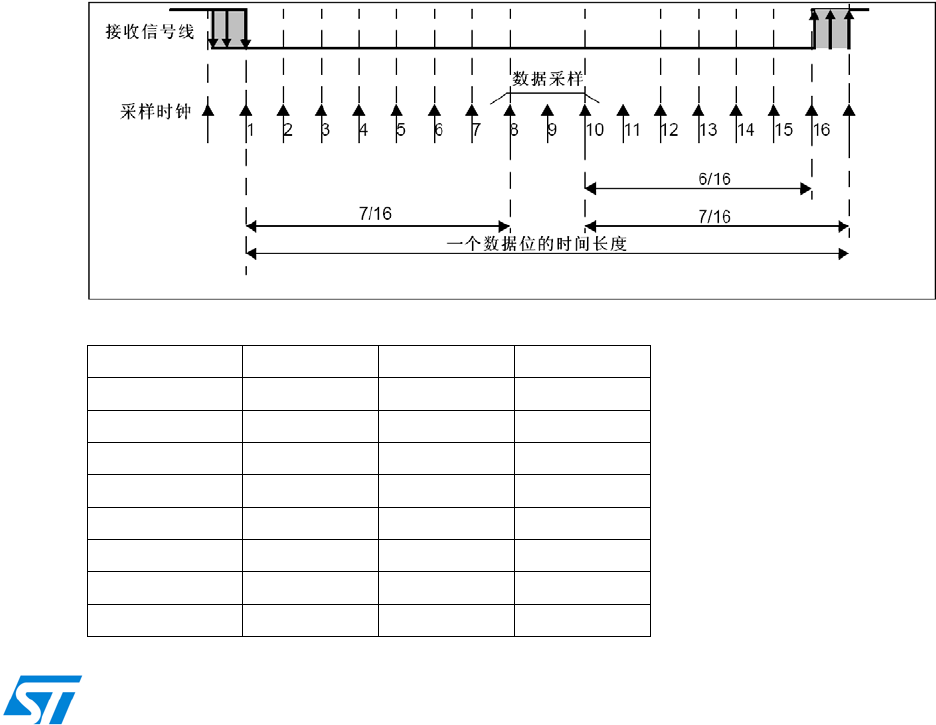

25.3.3 接收器 521

25.3.4 分数波特率的产生 524

25.3.5 USART接收器容忍时钟的变化 525

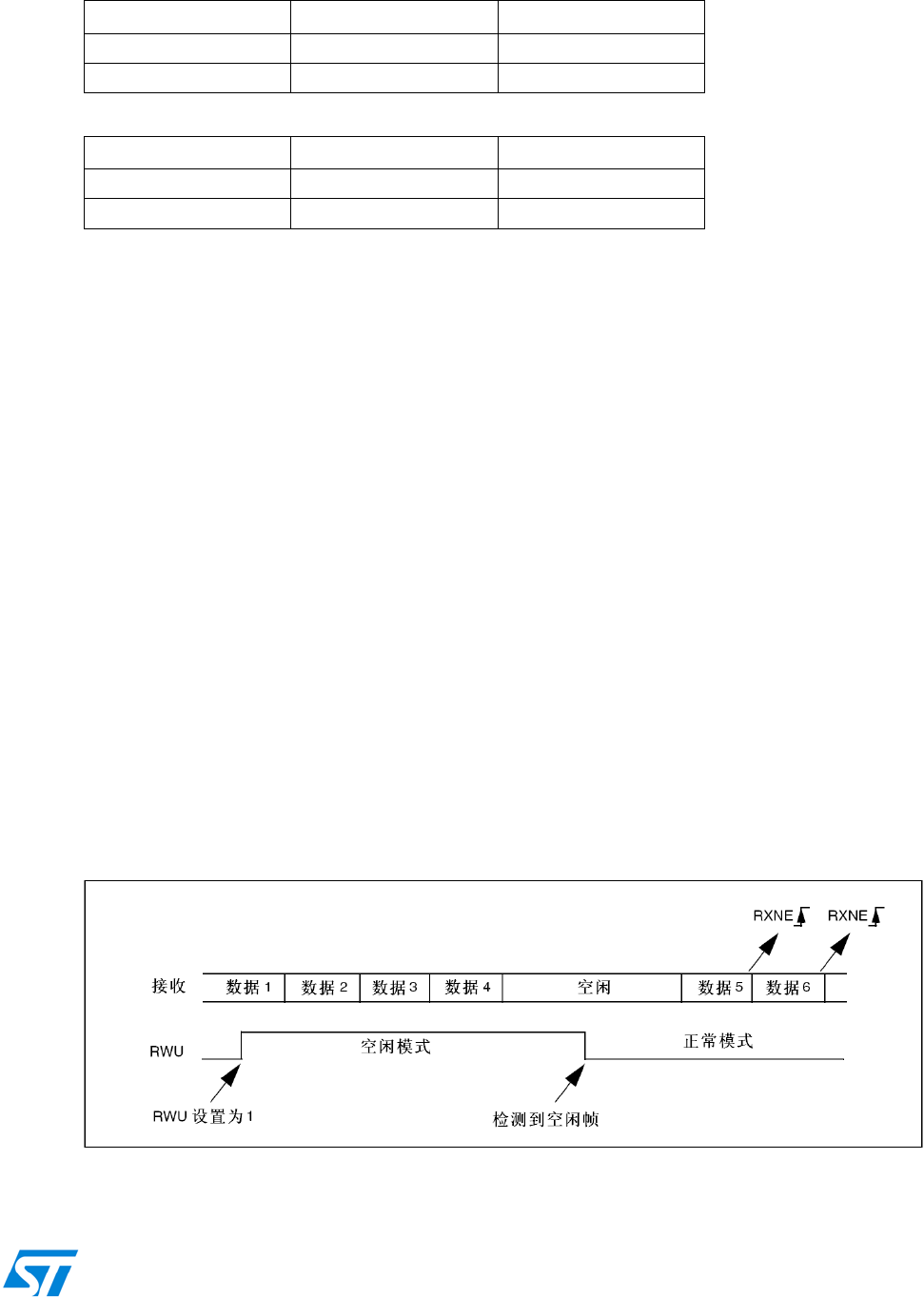

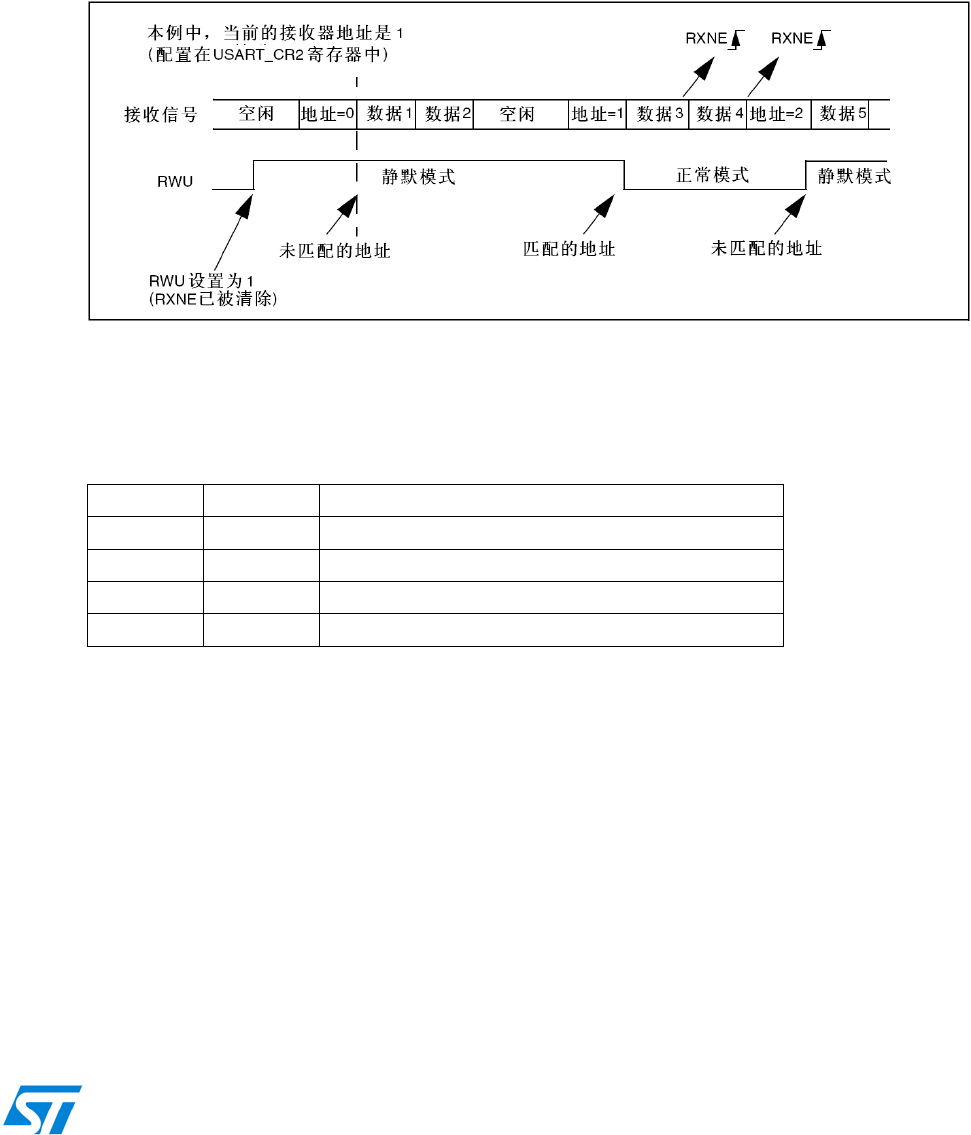

25.3.6 多处理器通信 526

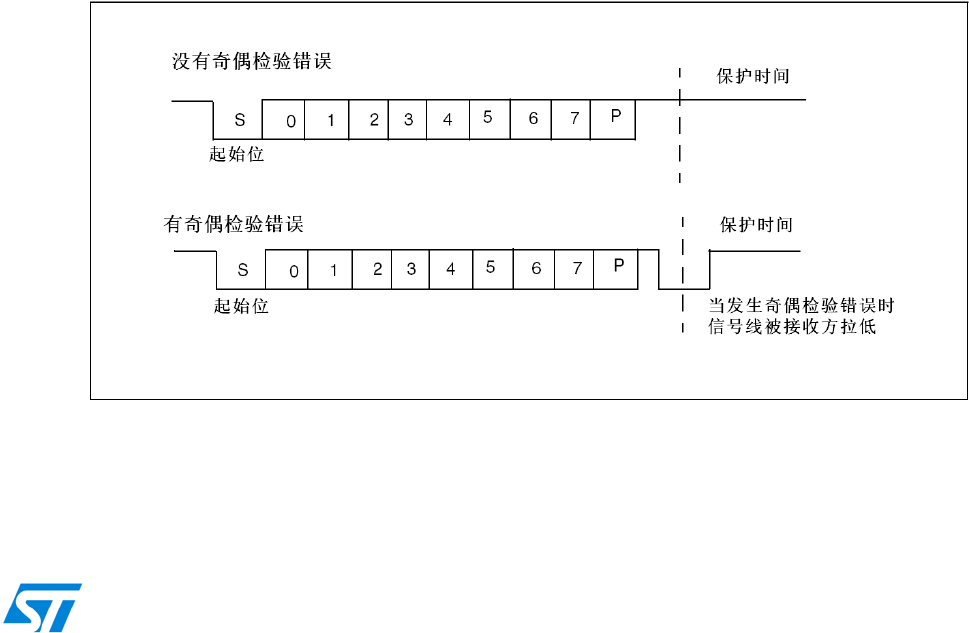

25.3.7 校验控制 527

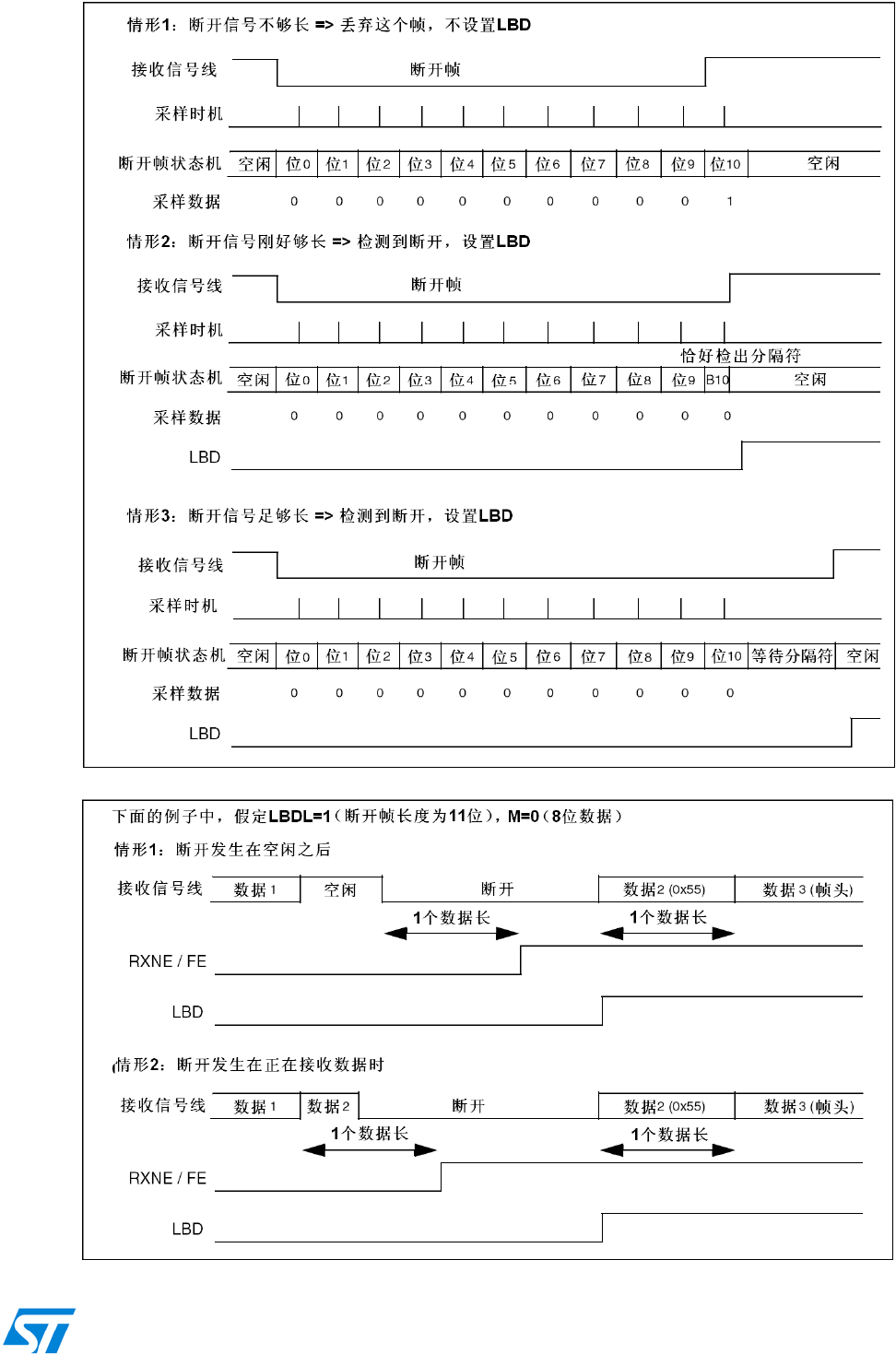

25.3.8 LIN(局域互联网)模式 528

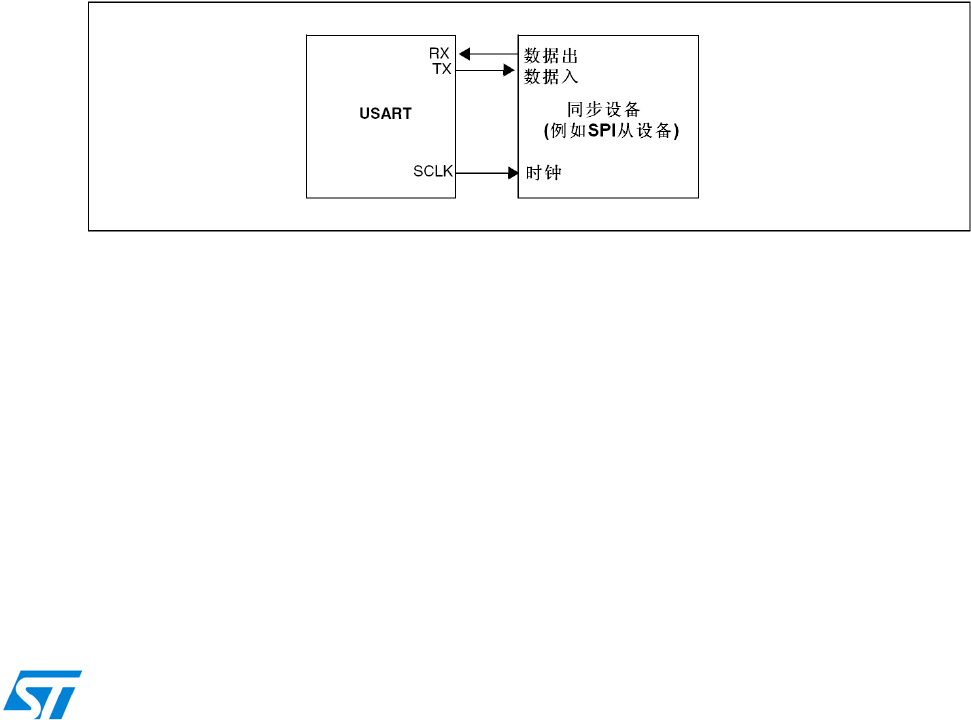

25.3.9 USART 同步模式 530

25.3.10 单线半双工通信 532

19/754

参照2009年12月 RM0008 Reference Manual 英文第10版

本译文仅供参考,如有翻译错误,请以英文原稿为准。请读者随时注意在ST网站下载更新版本

目录 STM32F10xxx参考手册

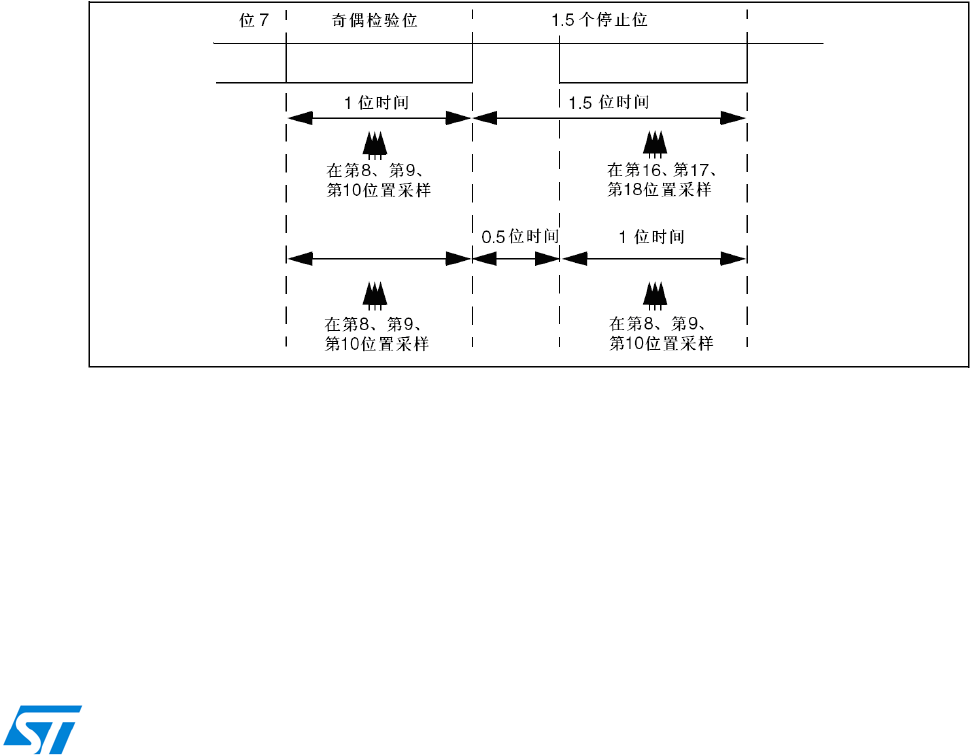

25.3.11 智能卡 532

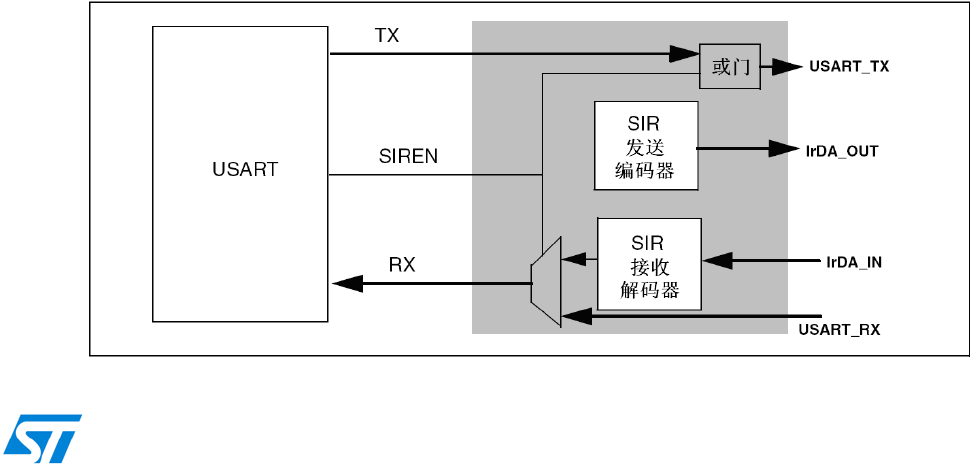

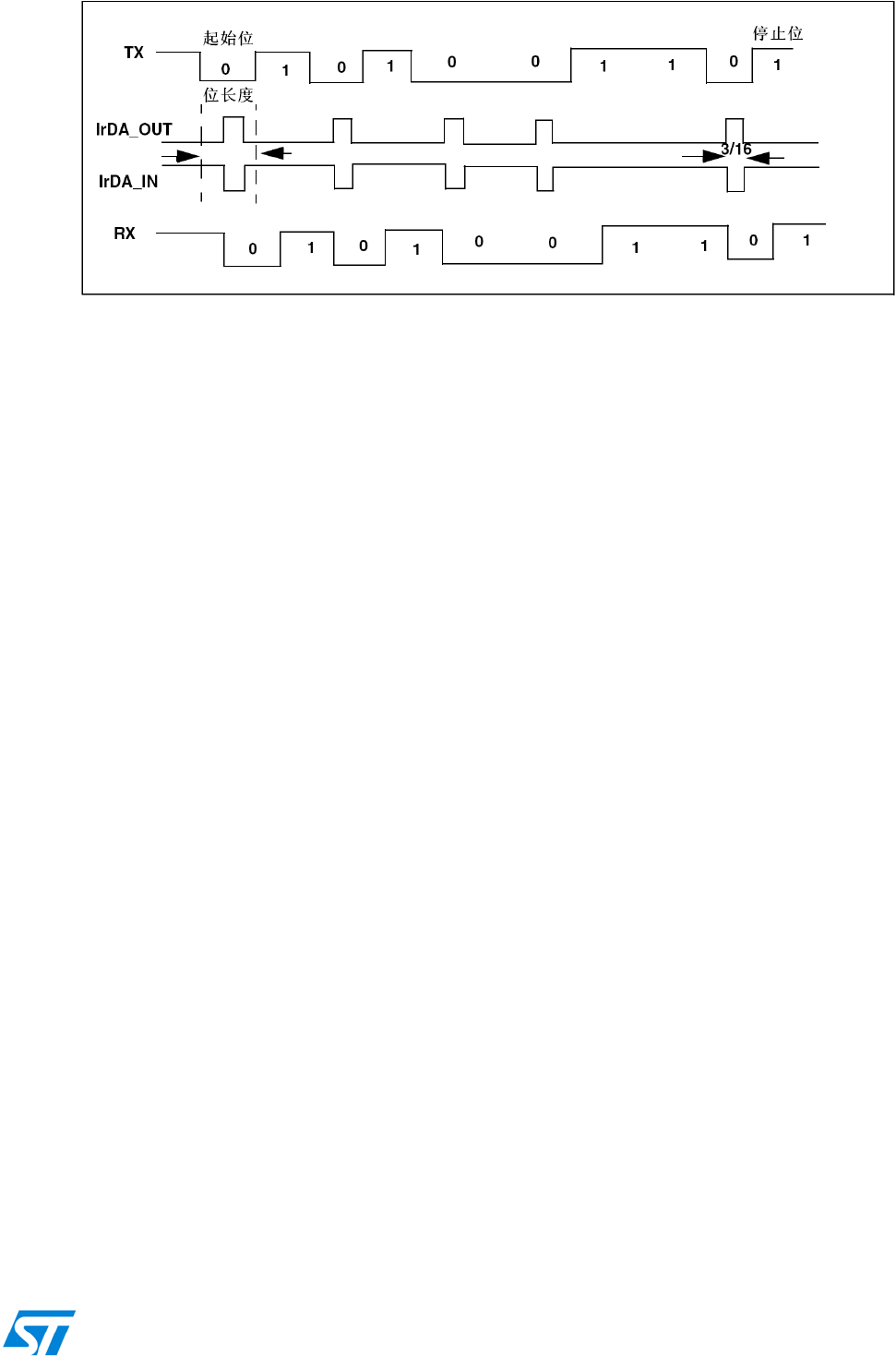

25.3.12 IrDA SIR ENDEC 功能模块 533

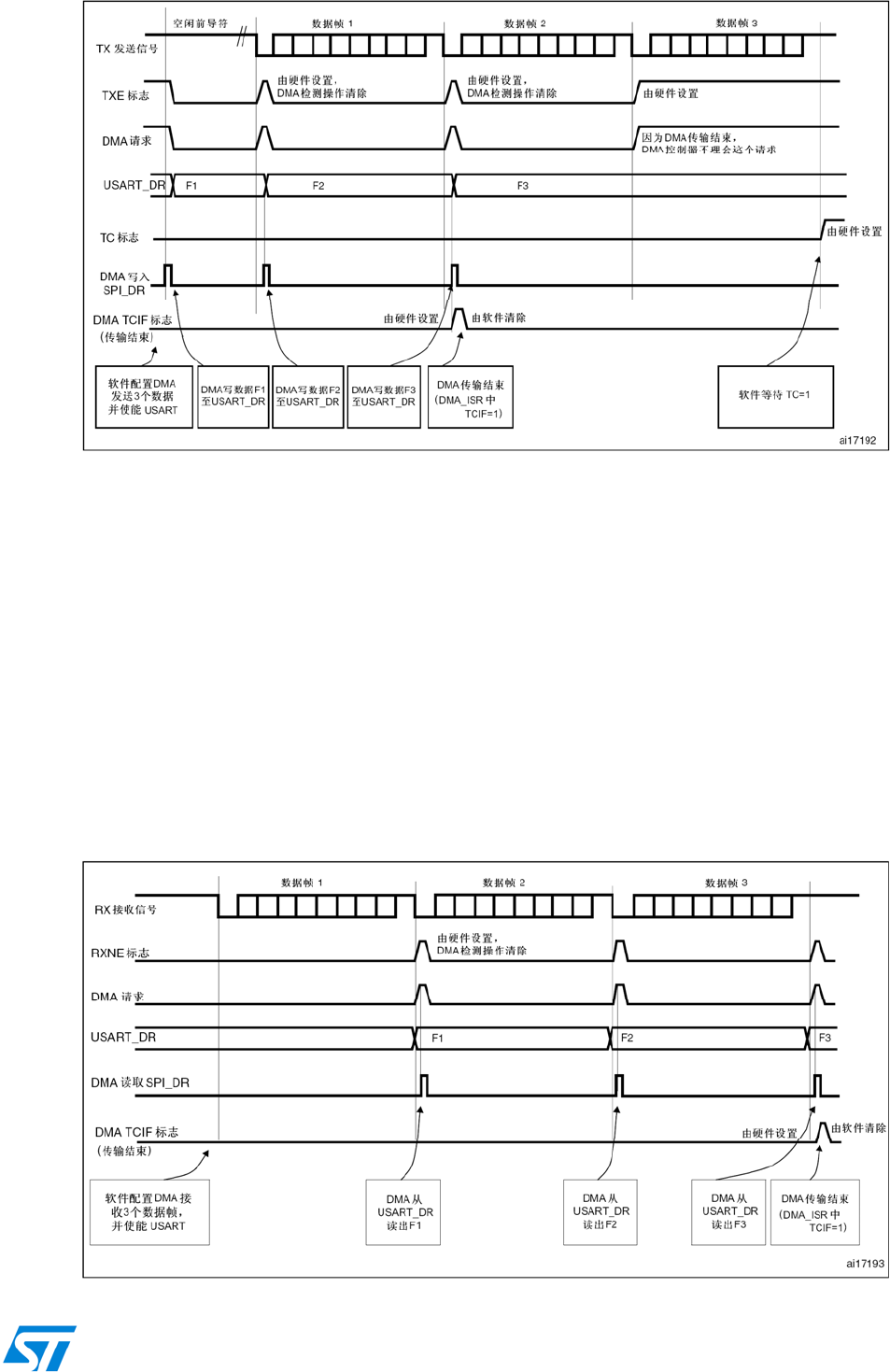

25.3.13 利用DMA连续通信 535

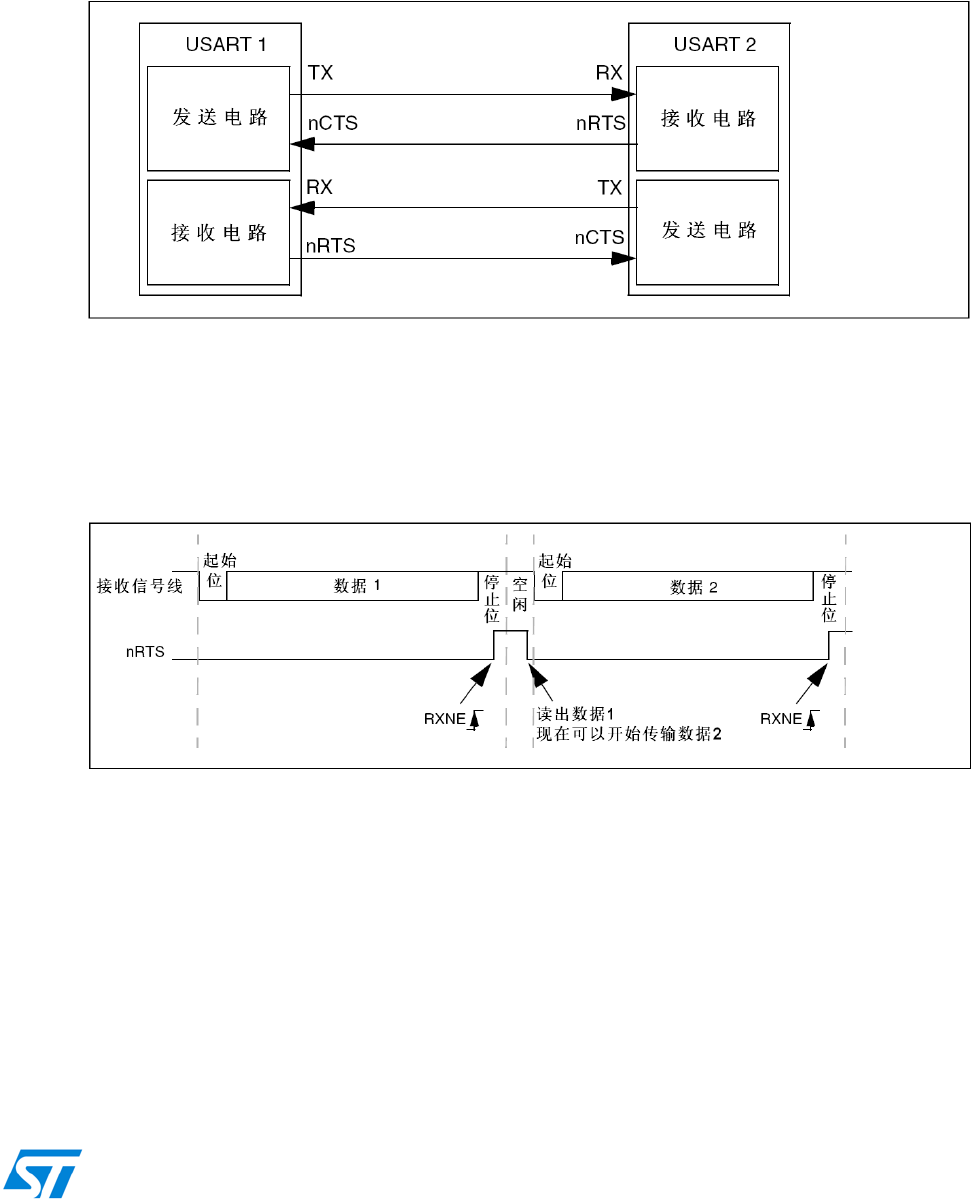

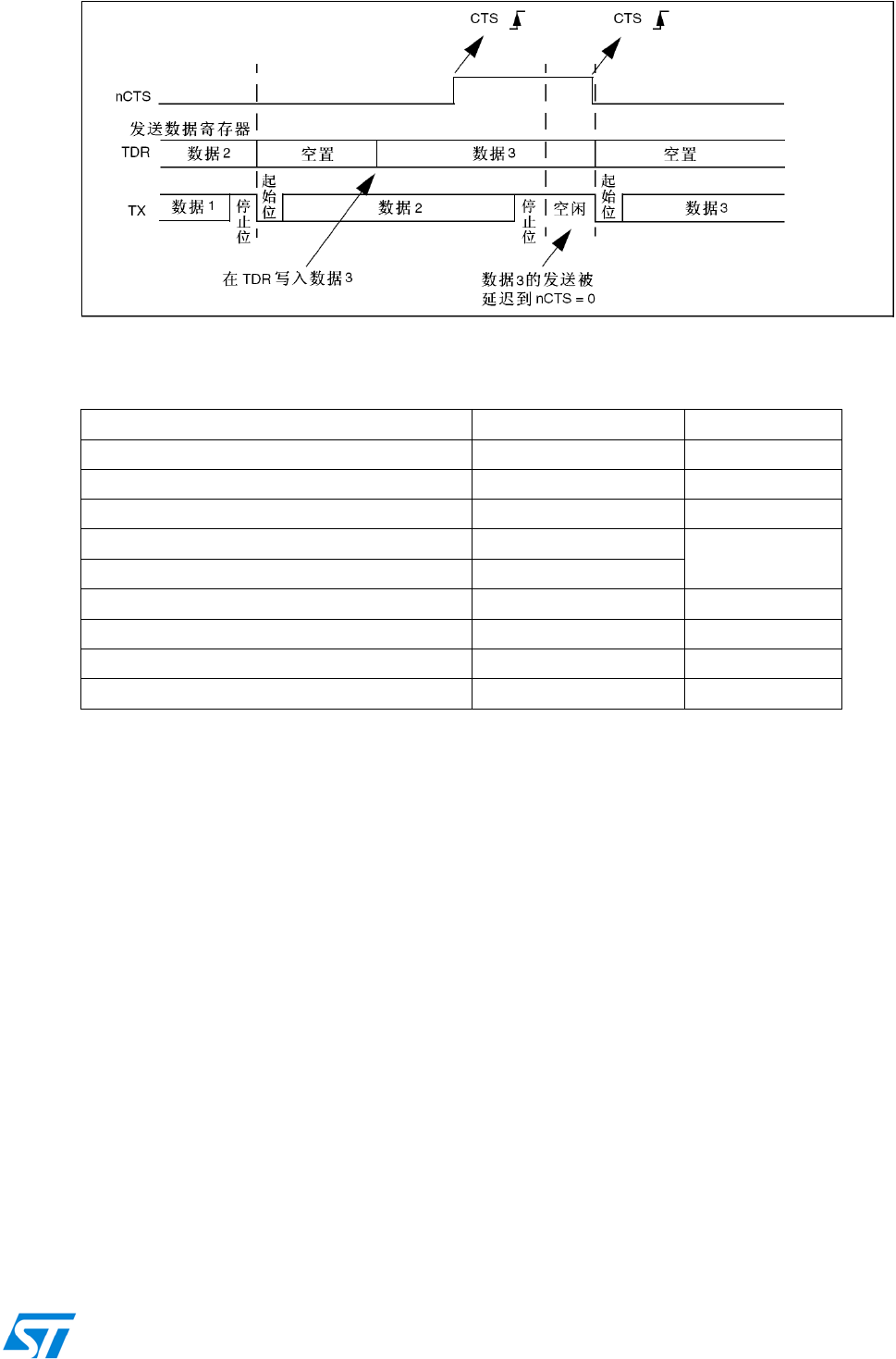

25.3.14 硬件流控制 537

25.4 USART中断请求 538

25.5 USART模式配置 539

25.6 USART寄存器描述 540

25.6.1 状态寄存器(USART_SR) 540

25.6.2 数据寄存器(USART_DR) 541

25.6.3 波特比率寄存器(USART_BRR) 542

25.6.4 控制寄存器1(USART_CR1) 542

25.6.5 控制寄存器2(USART_CR2) 544

25.6.6 控制寄存器3(USART_CR3) 545

25.6.7 保护时间和预分频寄存器(USART_GTPR) 546

25.6.8 USART寄存器地址映象 548

26 USB OTG全速(OTG_FS) 549

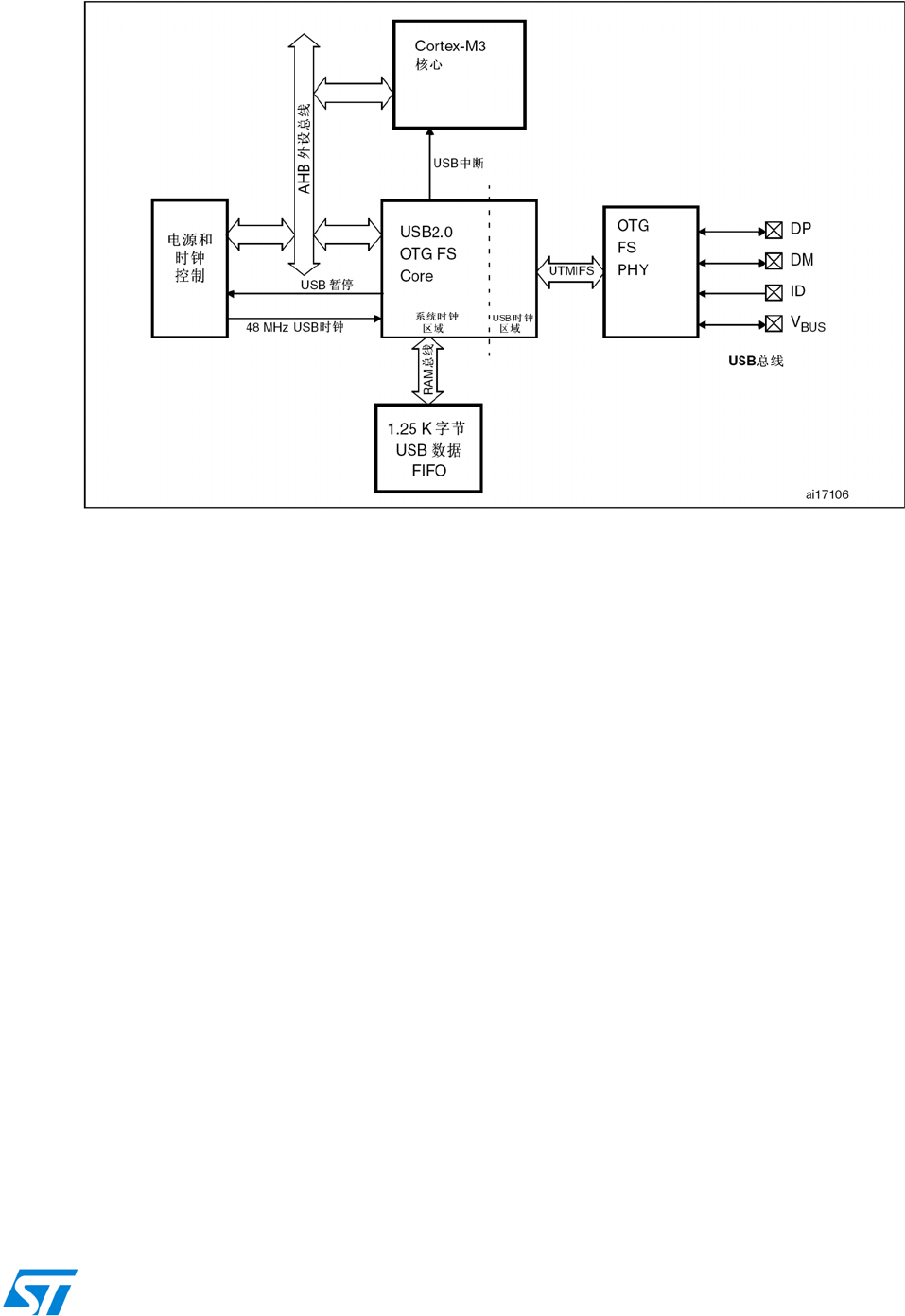

26.1 OTG模块介绍 549

26.2 OTG_FS主要功能 549

26.2.1 通用功能 549

26.2.2 主机模式功能 550

26.2.3 设备模式功能 550

26.3 OTG_FS功能描述 551

26.3.1 OTG全速控制器 551

26.3.2 全速OTG PHY(物理接口) 551

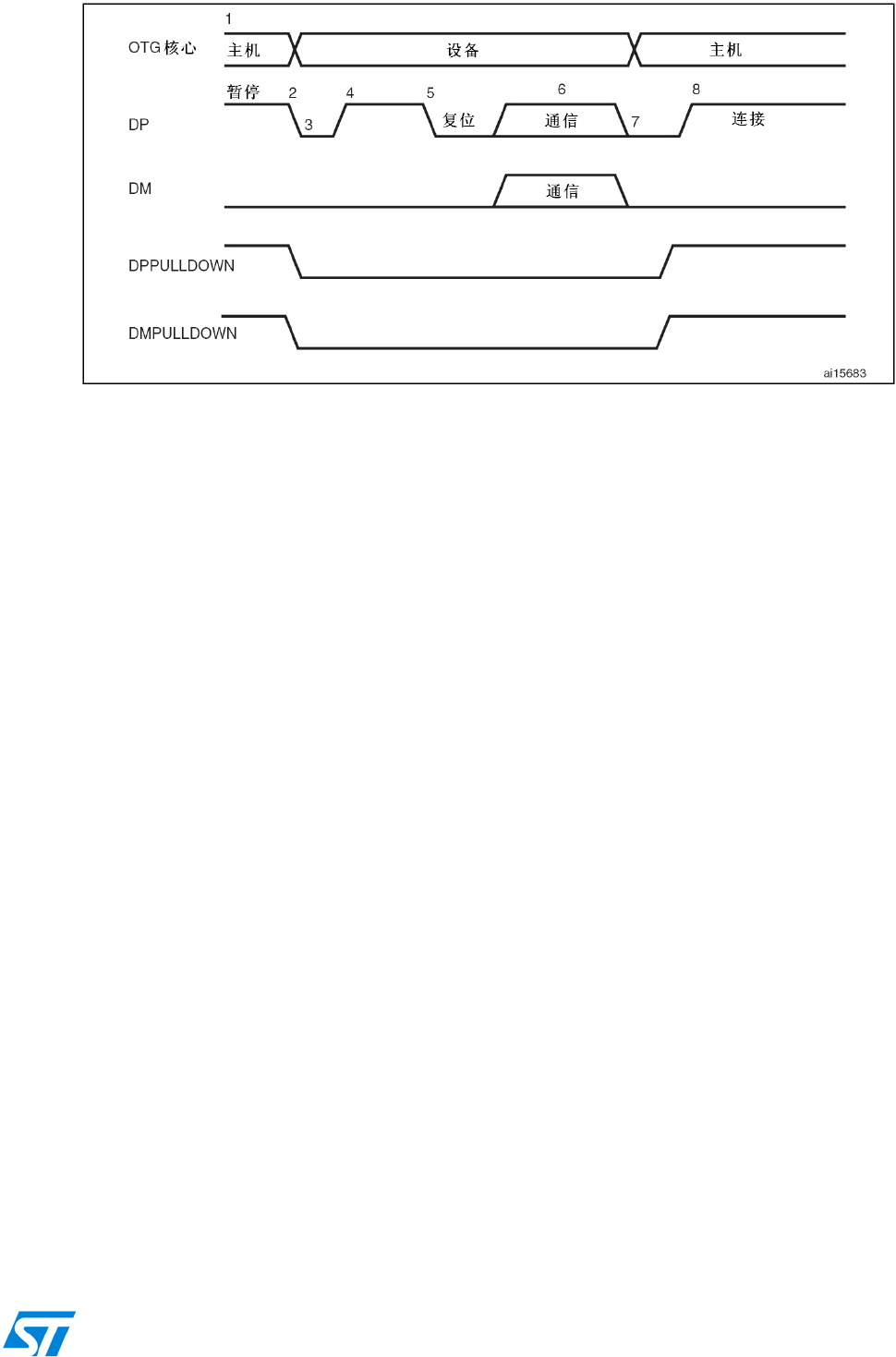

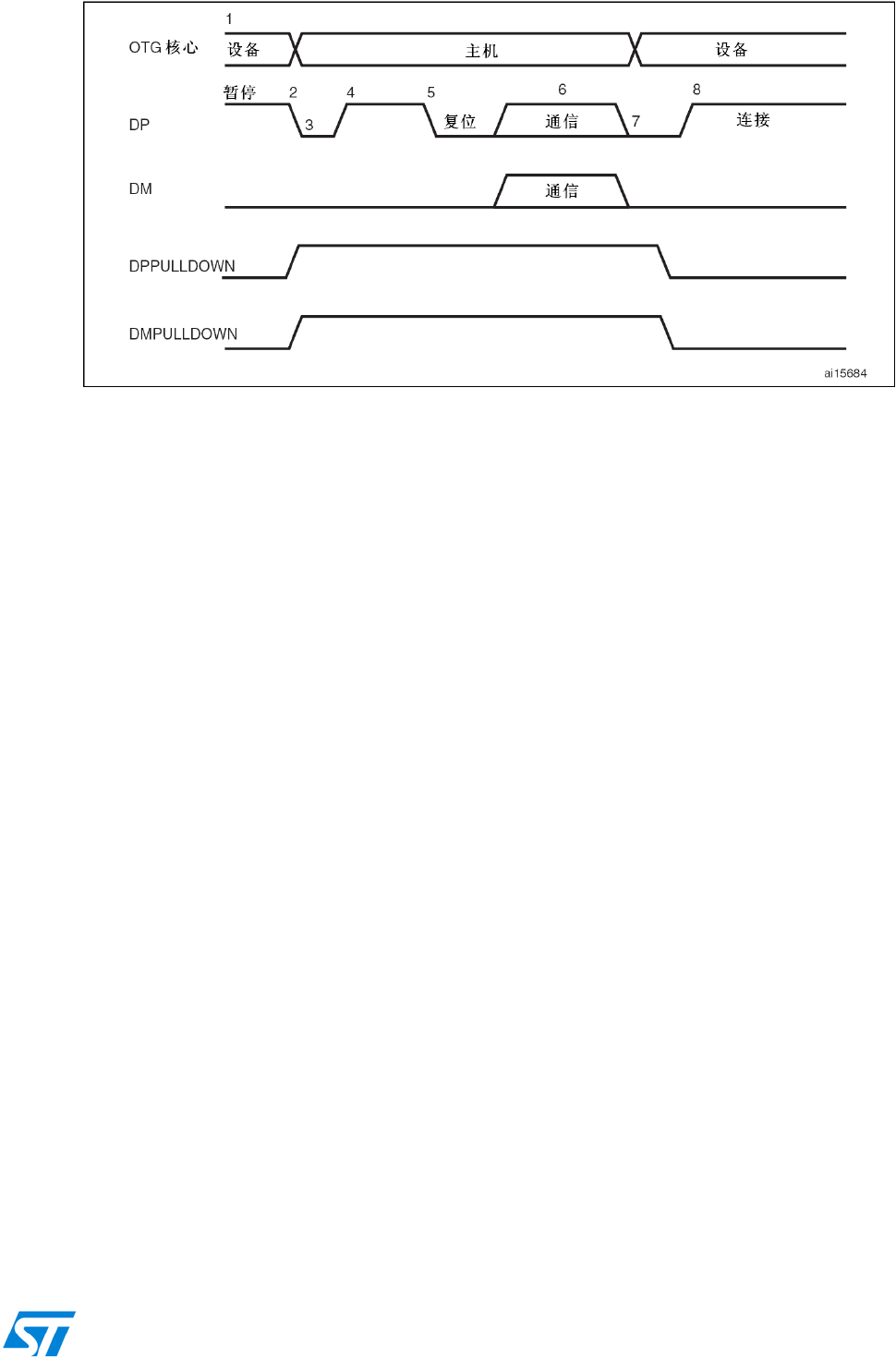

26.4 OTG双角色设备(DRD) 552

26.4.1 ID信号检测 552

26.4.2 HNP双角色设备 552

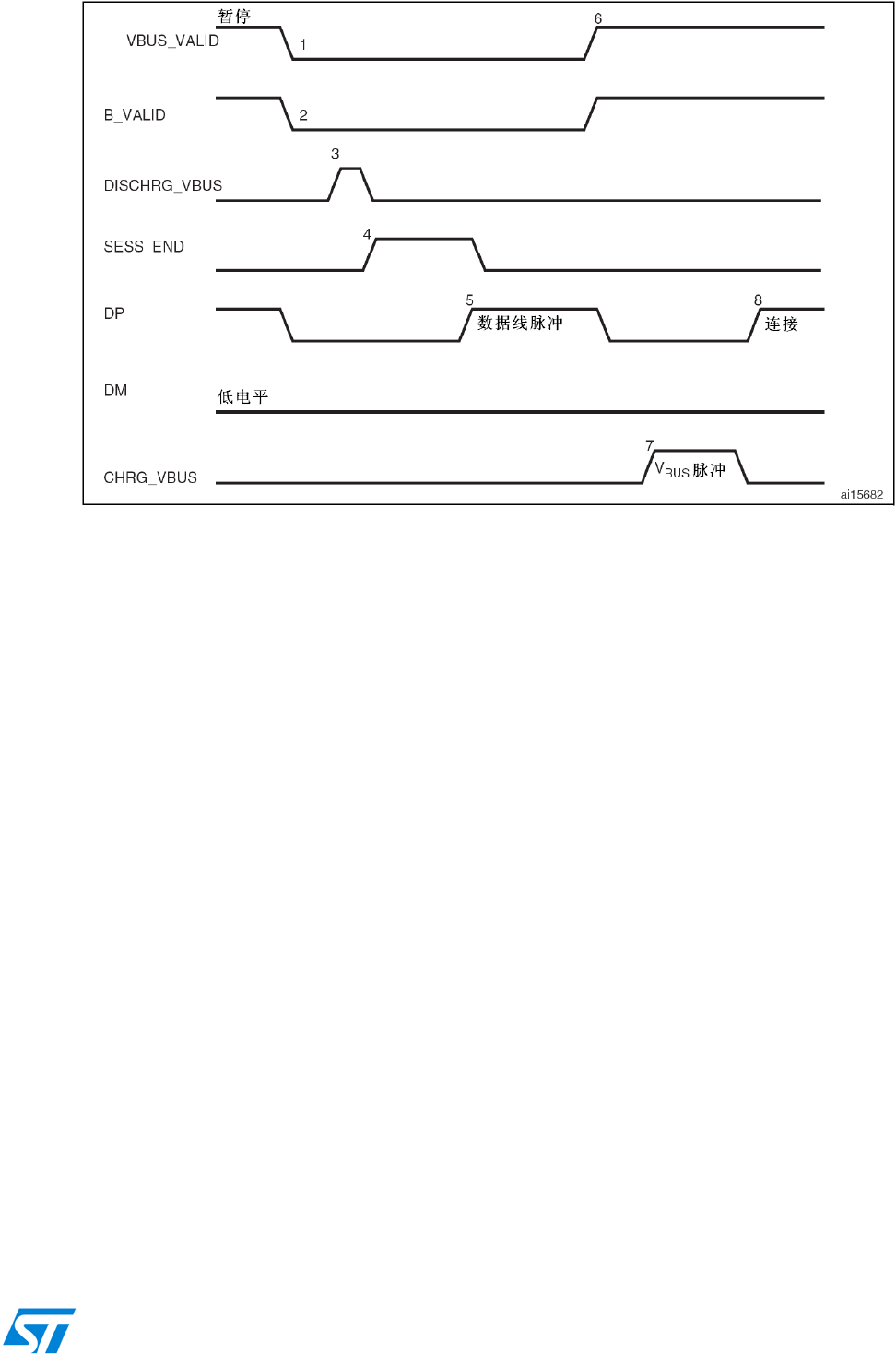

26.4.3 SRP双角色设备 553

26.5 USB设备模式 553

26.5.1 具备SRP功能的设备 553

26.5.2 设备状态 554

26.5.3 设备端点 554

26.6 USB主机 556

26.6.1 具备SRP功能的主机 556

26.6.2 USB主机状态 557

26.6.3 主机通道 558

26.6.4 主机调度器 558

26.7 SOF触发 560

26.7.1 主机SOF 560

26.7.2 设备SOF 560

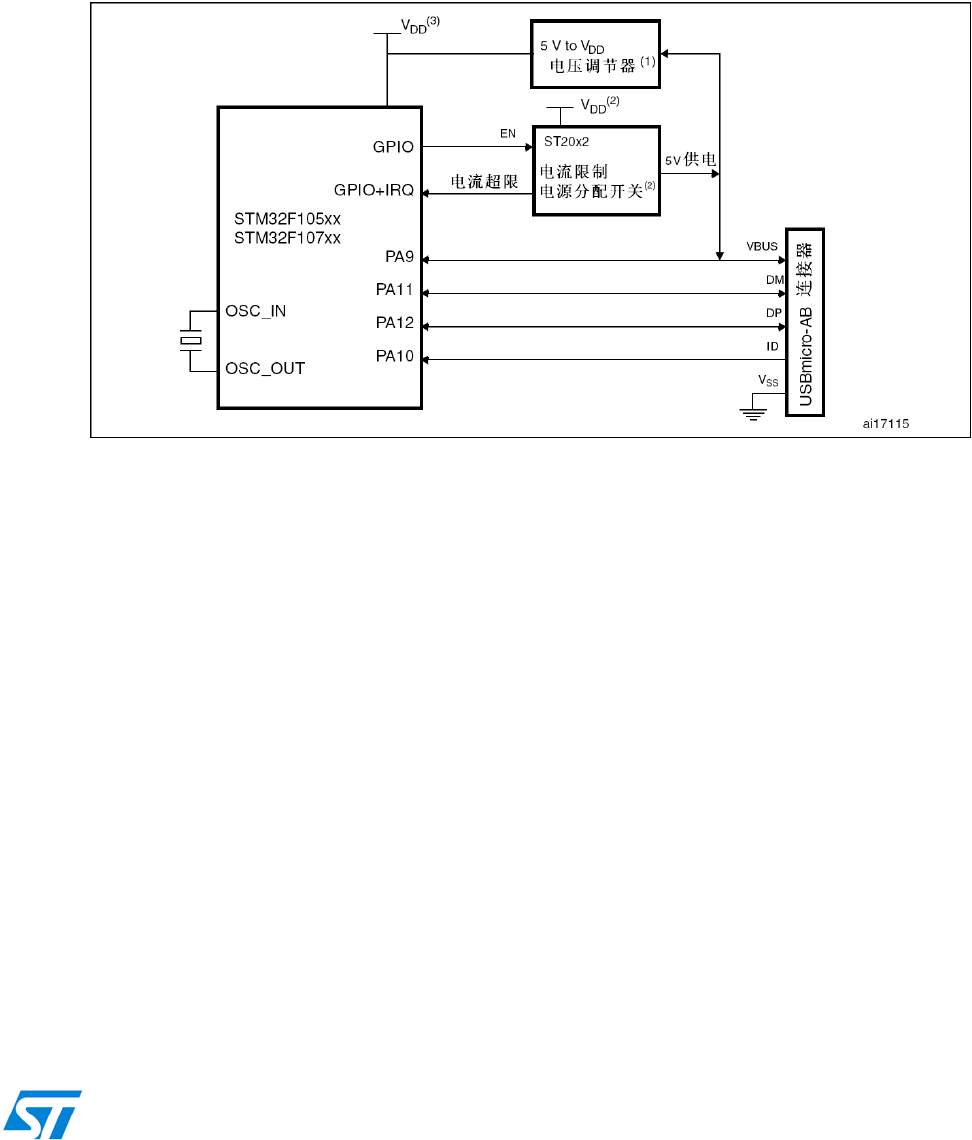

26.8 供电选项 560

26.9 USB数据FIFO 562

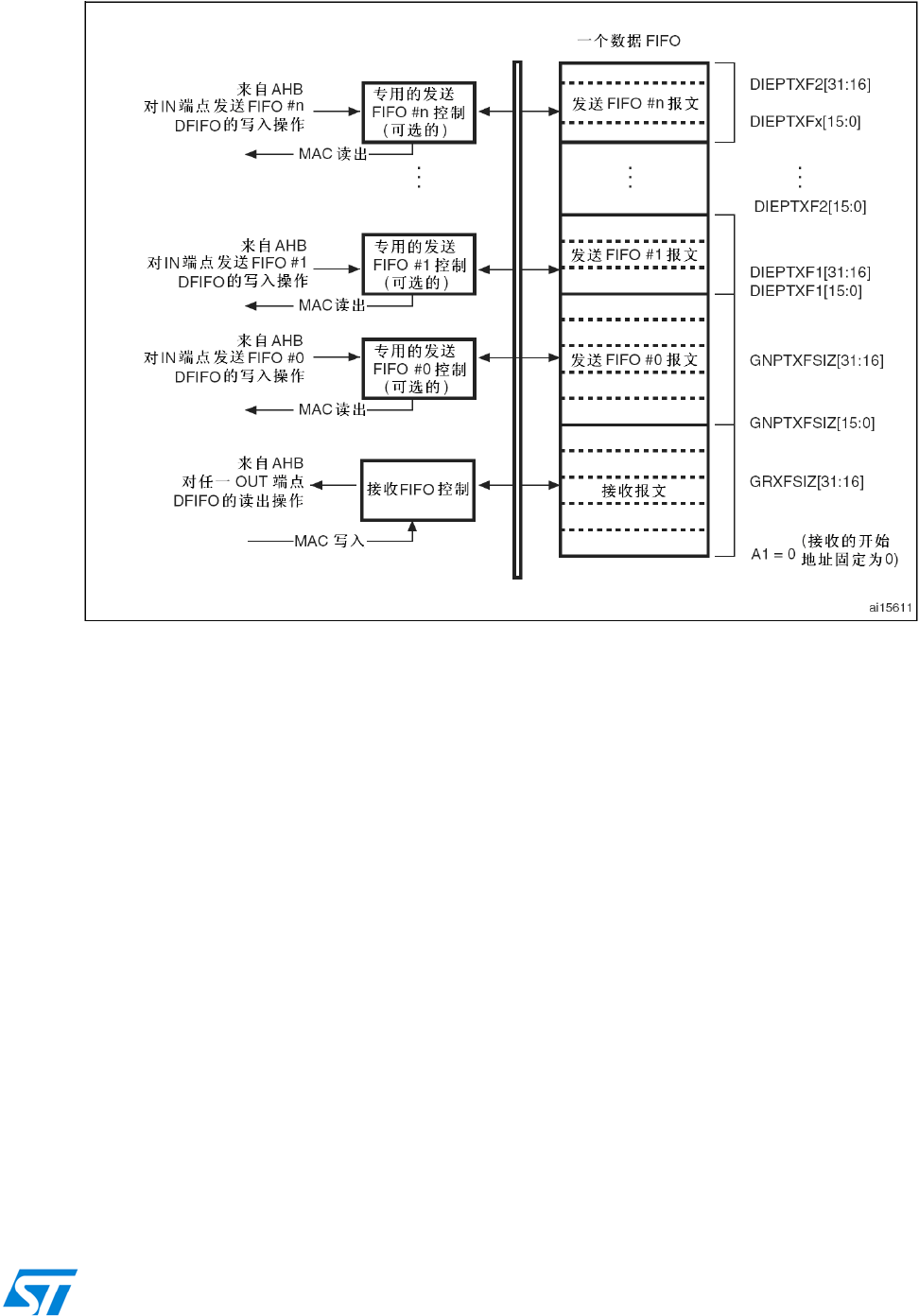

26.10 设备模式下的FIFO结构 563

26.10.1 设备模式下的接收FIFO 563

26.10.2 设备模式下的发送FIFO 563

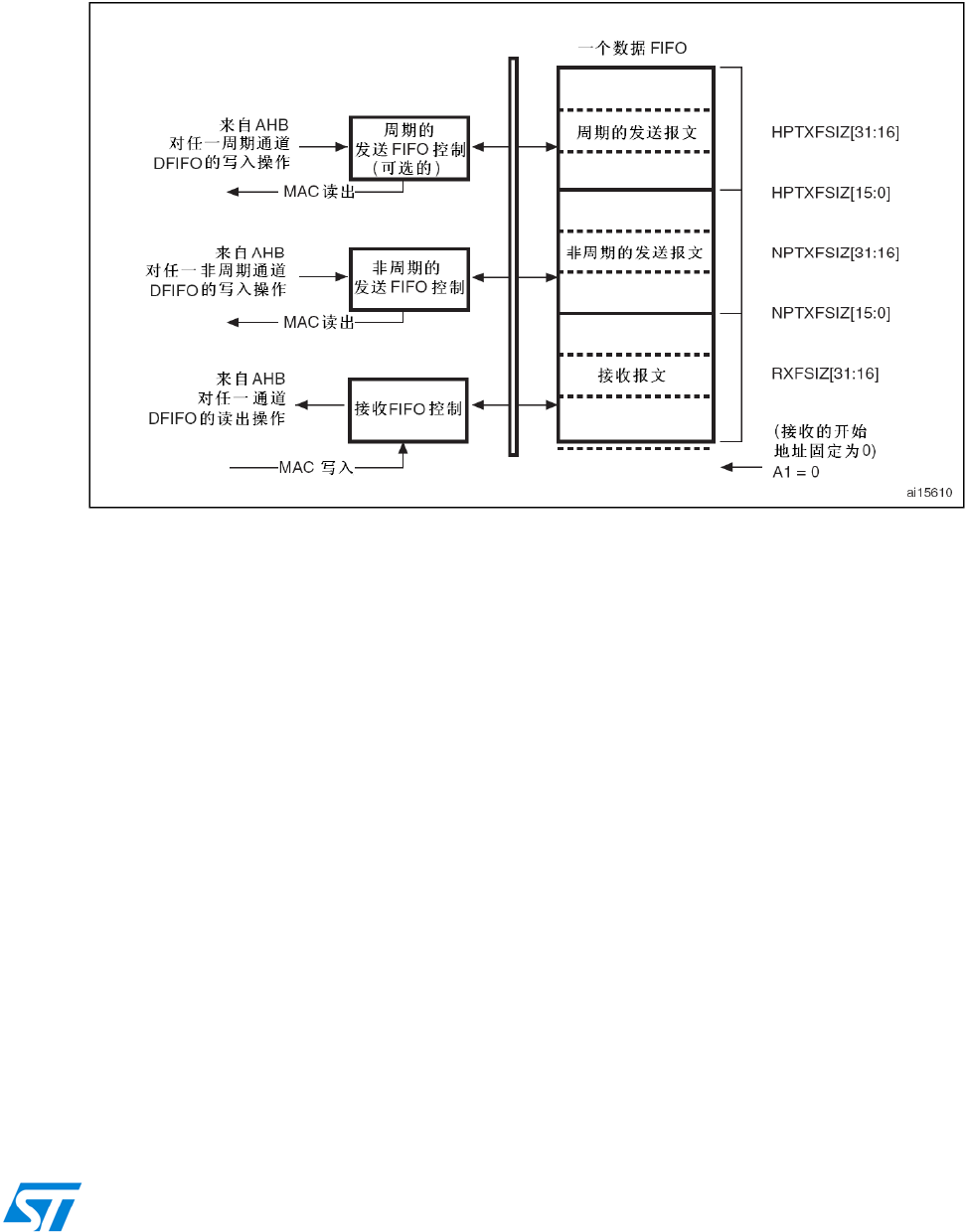

26.11 主机模式下的FIFO结构 564

26.11.1 主机模式下的接收FIFO 564

20/754

参照2009年12月 RM0008 Reference Manual 英文第10版

本译文仅供参考,如有翻译错误,请以英文原稿为准。请读者随时注意在ST网站下载更新版本

目录 STM32F10xxx参考手册

26.11.2 主机模式下的发送FIFO 564

26.12 USB系统性能 565

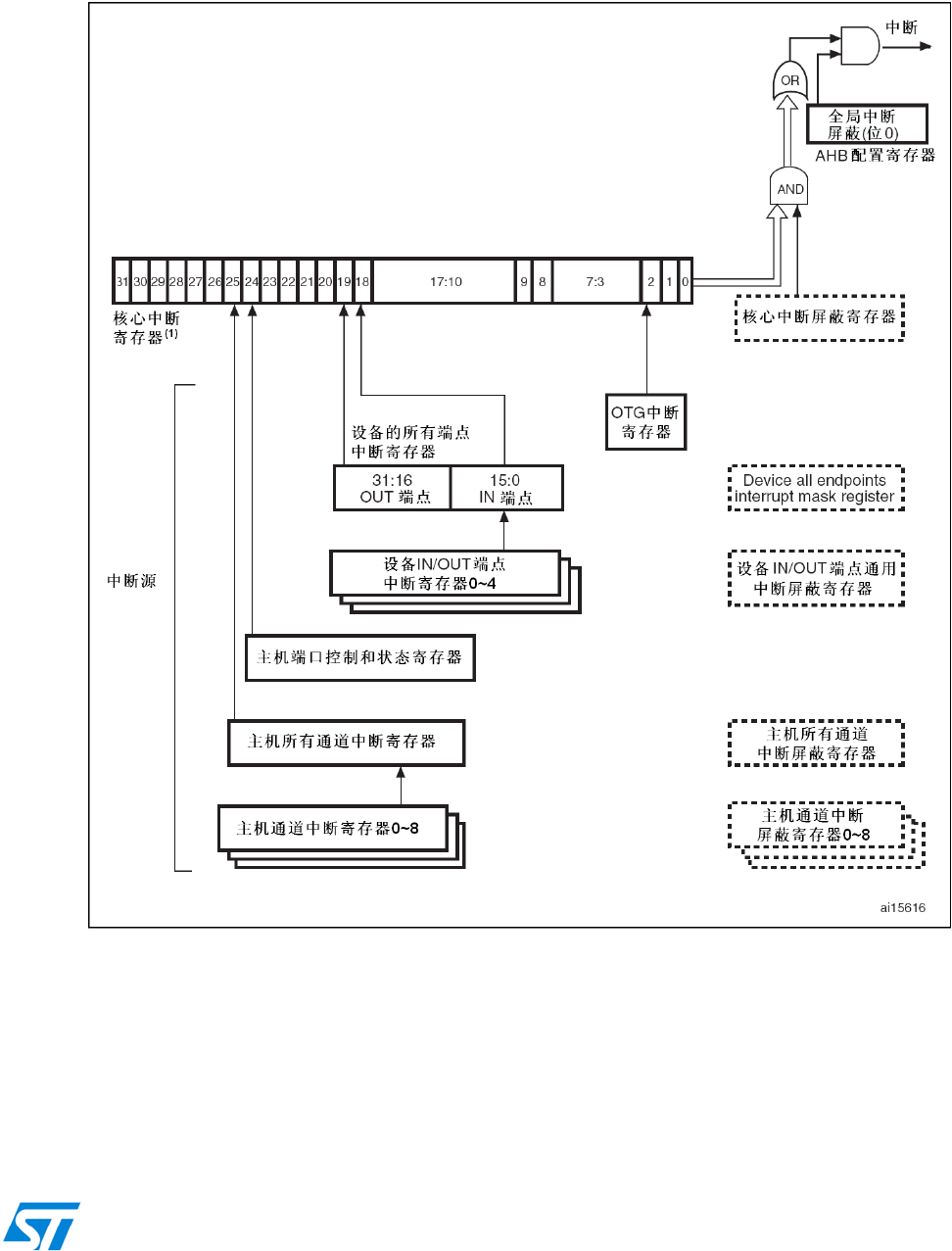

26.13 OTG_FS中断 566

26.14 OTG_FS控制和状态寄存器 566

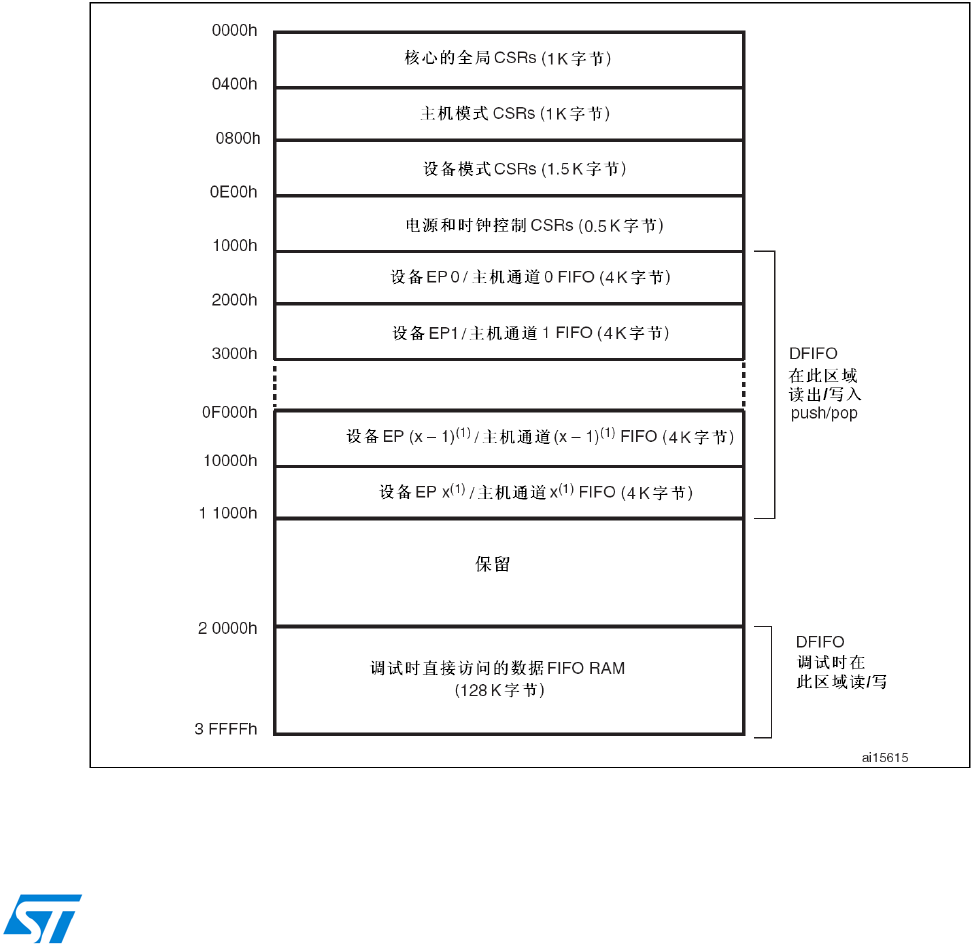

26.14.1 CSR存储器映像 567

26.14.2 OTG_FS全局寄存器 570

26.14.3 主机模式下的寄存器 585

26.14.4 设备模式下的寄存器 593

26.14.5 OTG_FS电源和时钟门控寄存器(OTG_FS_PCGCCTL) 608

26.14.6 OTG_FS寄存器映像 610

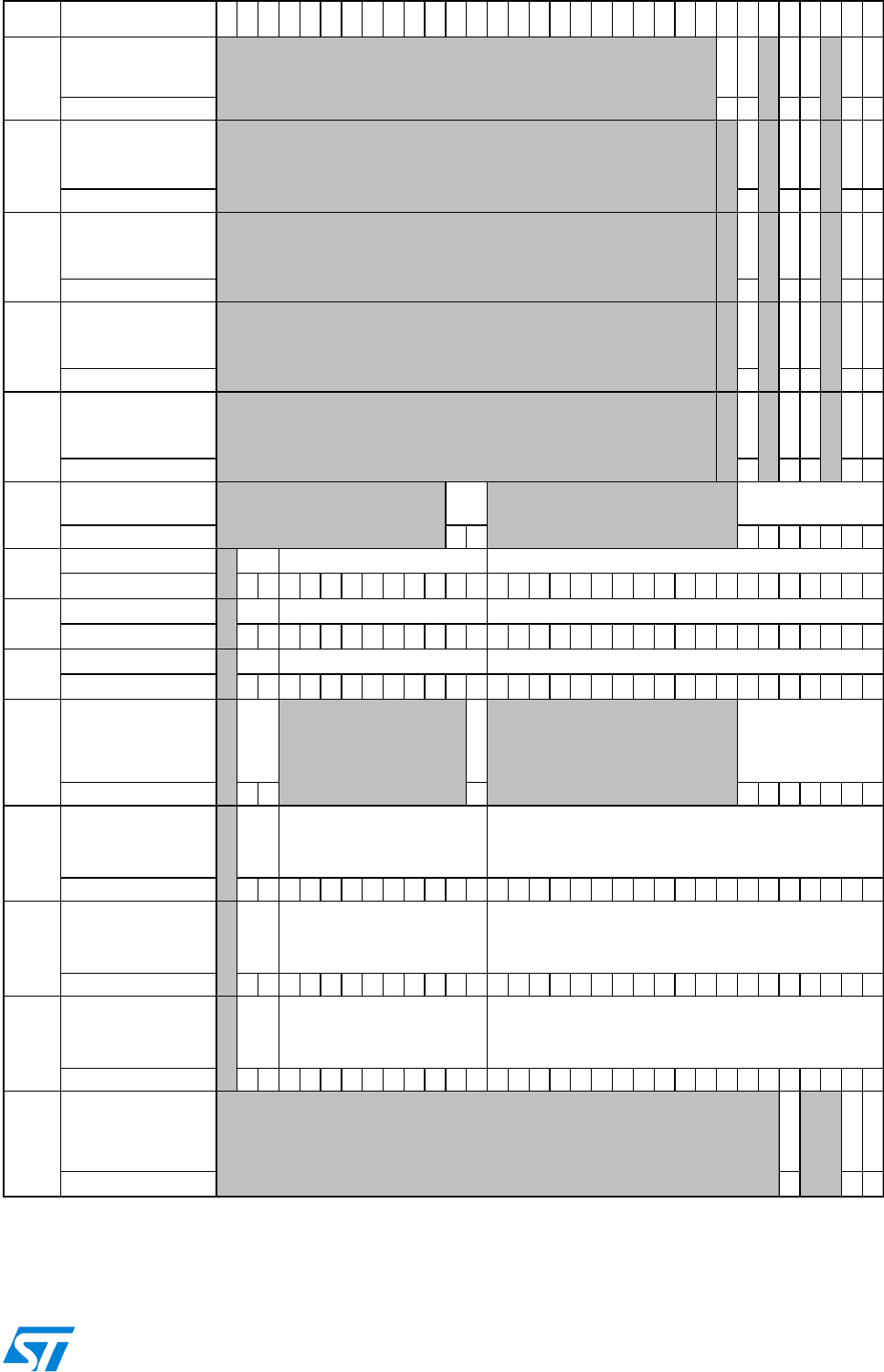

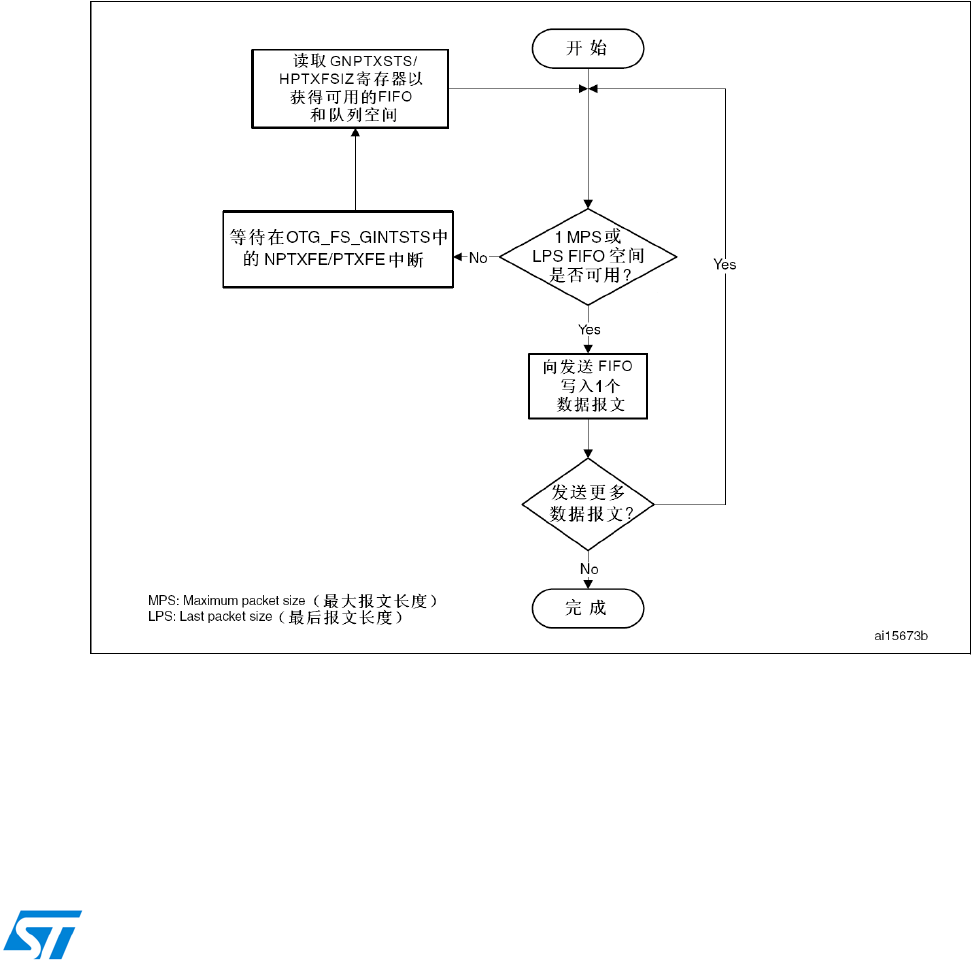

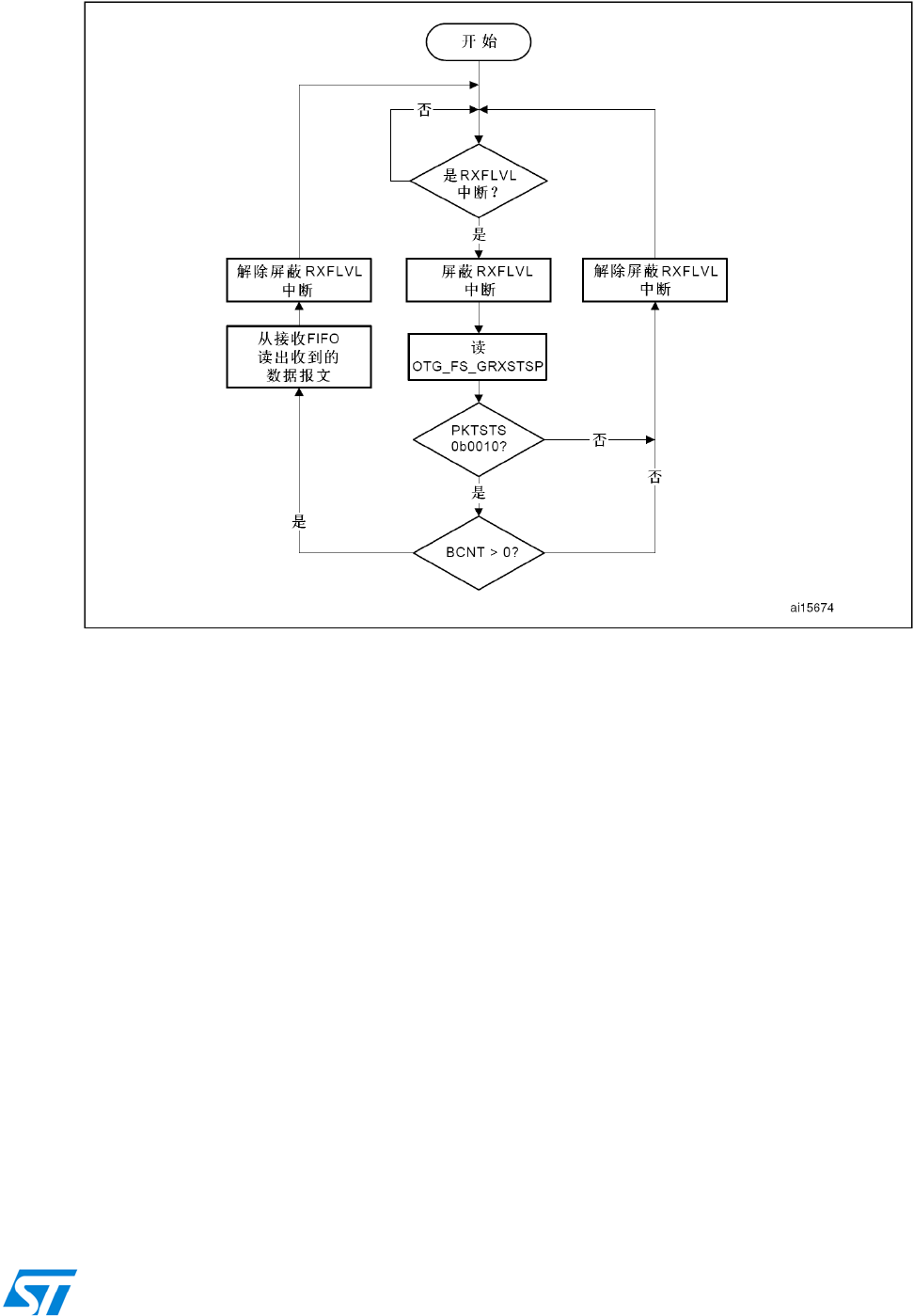

26.15 OTG_FS编程规则 617

26.15.1 控制器初始化 617

26.15.2 主机模式下的初始化 617

26.15.3 设备模式下的初始化 617

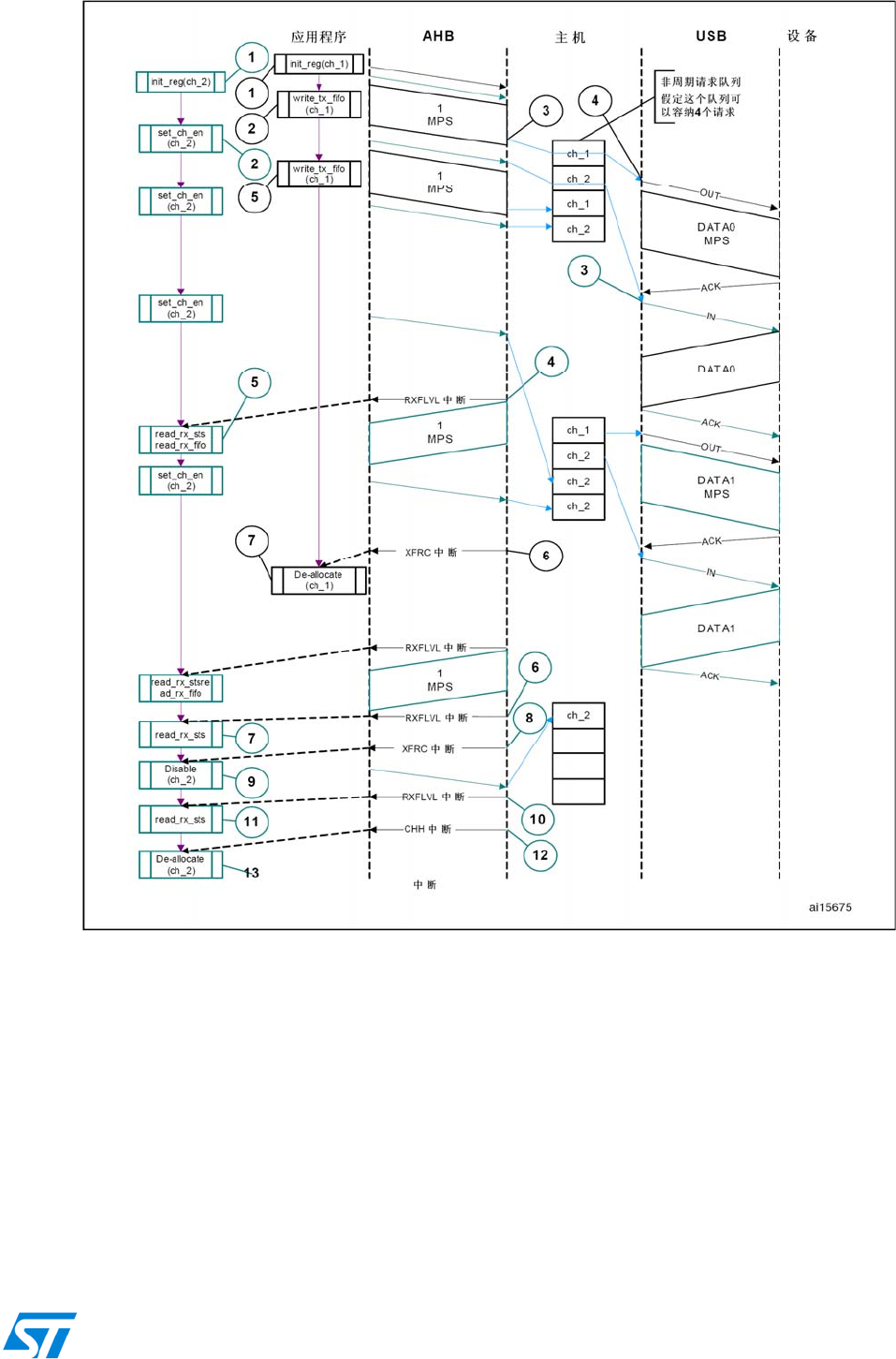

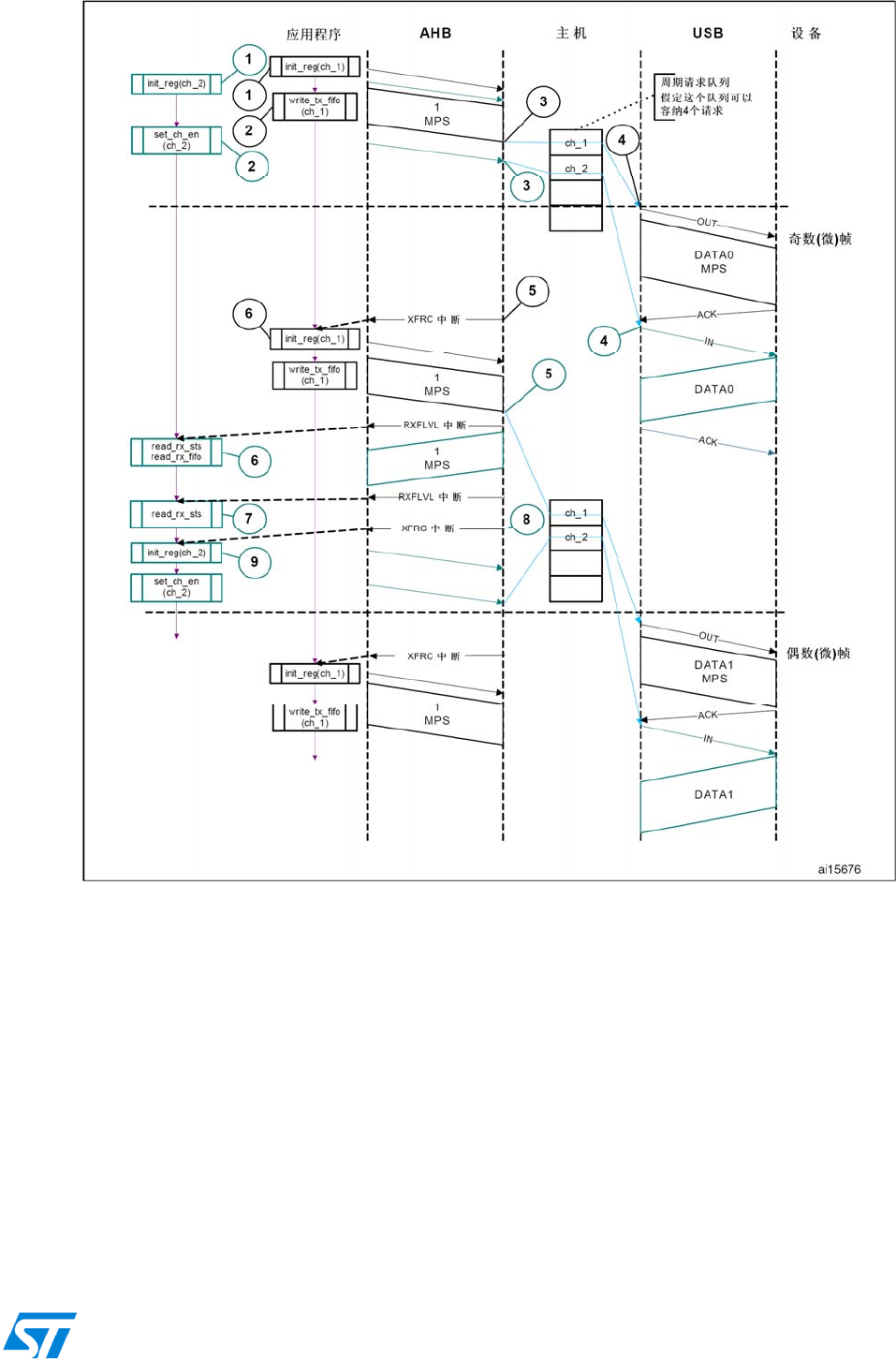

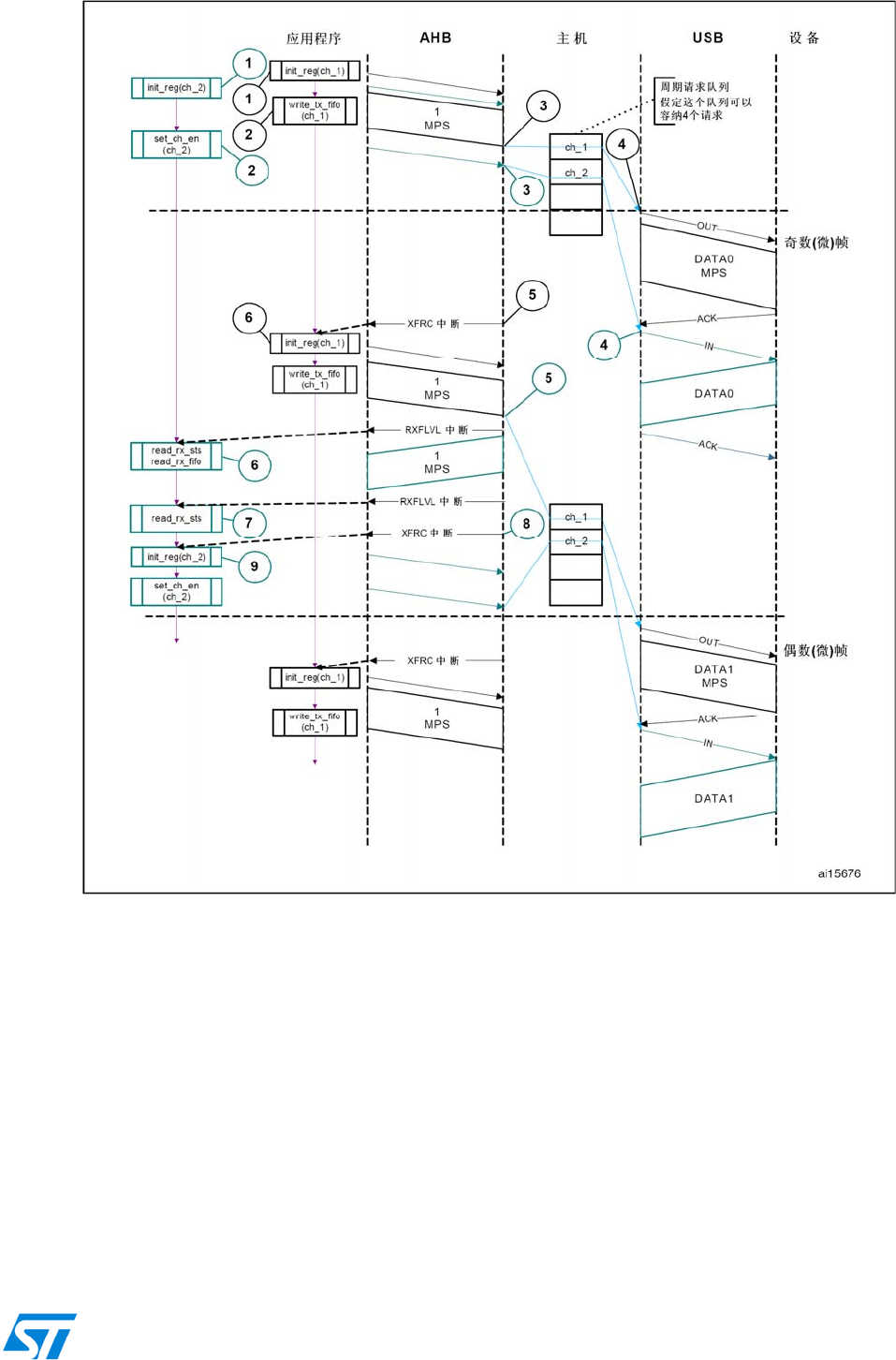

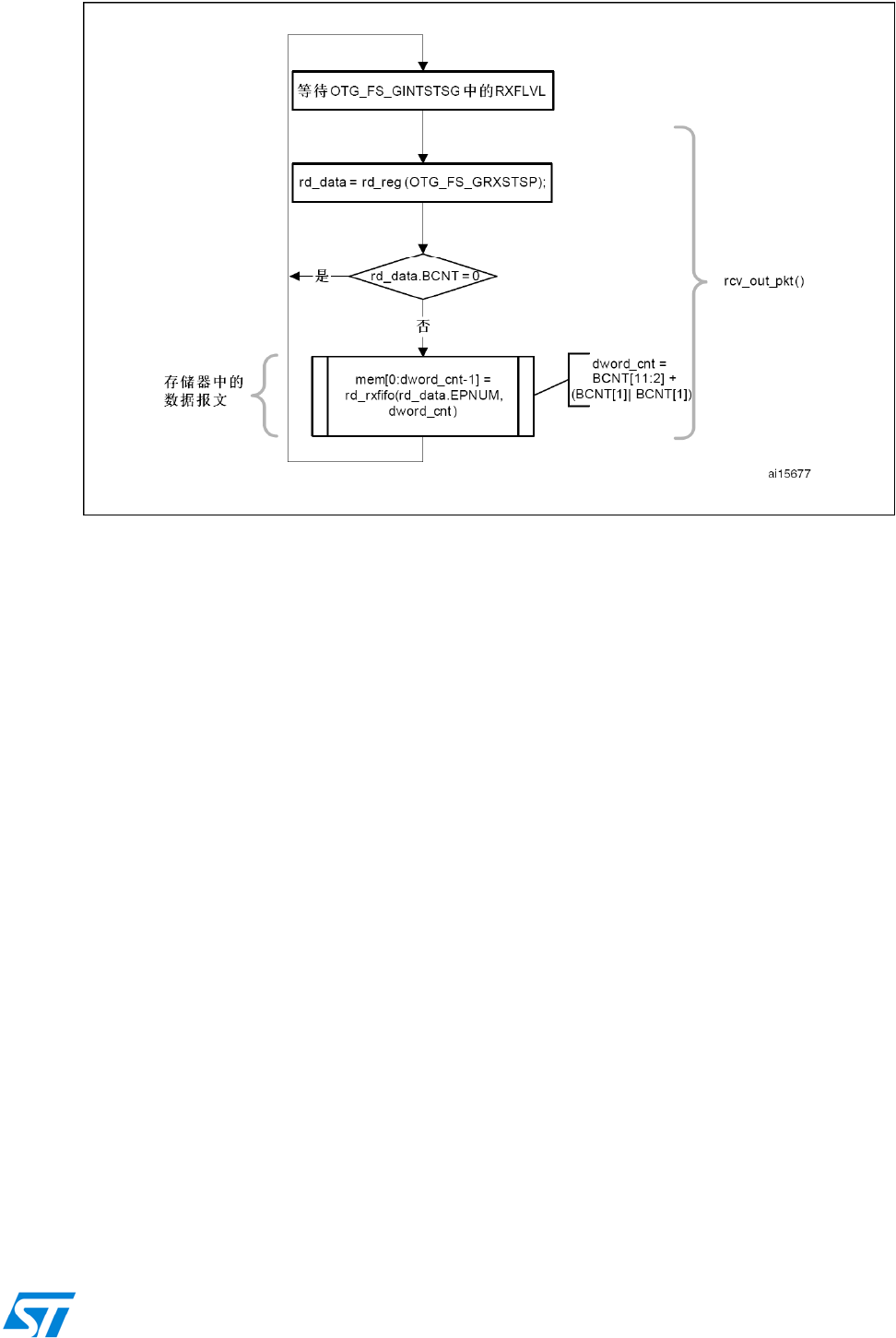

26.15.4 主机模式下的编程规则 618

26.15.5 设备模式下的编程规则 632

26.15.6 操作流程 633

26.15.7 最差情况下的响应时间 646

26.15.8 OTG编程规则 648

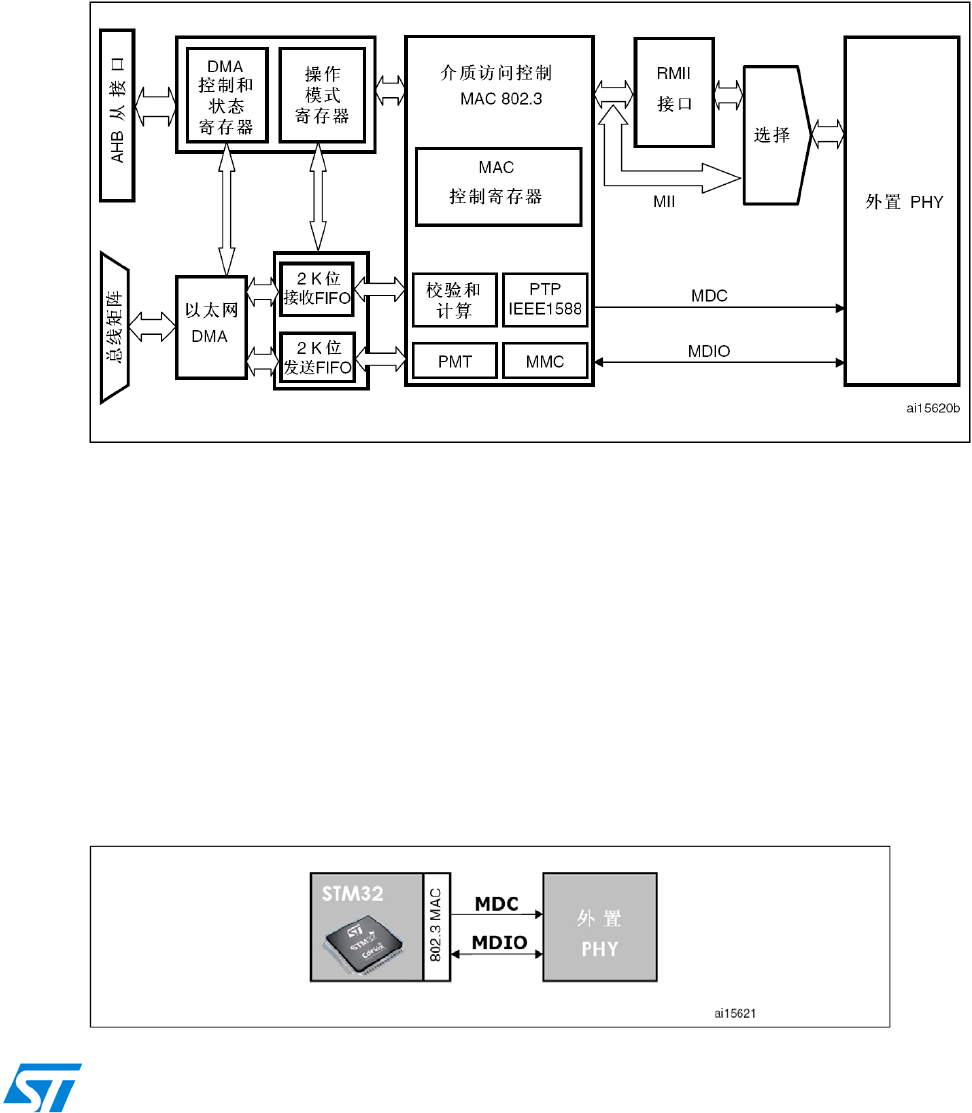

27 以太网(ETH):具有DMA控制器的介质访问控制(MAC) 652

27.1 以太网模块介绍 652

27.2 以太网模块主要功能 652

27.2.1 MAC控制器功能 652

27.2.2 DMA功能 653

27.2.3 PTP功能 654

27.3 以太网模块引脚和内部信号 654

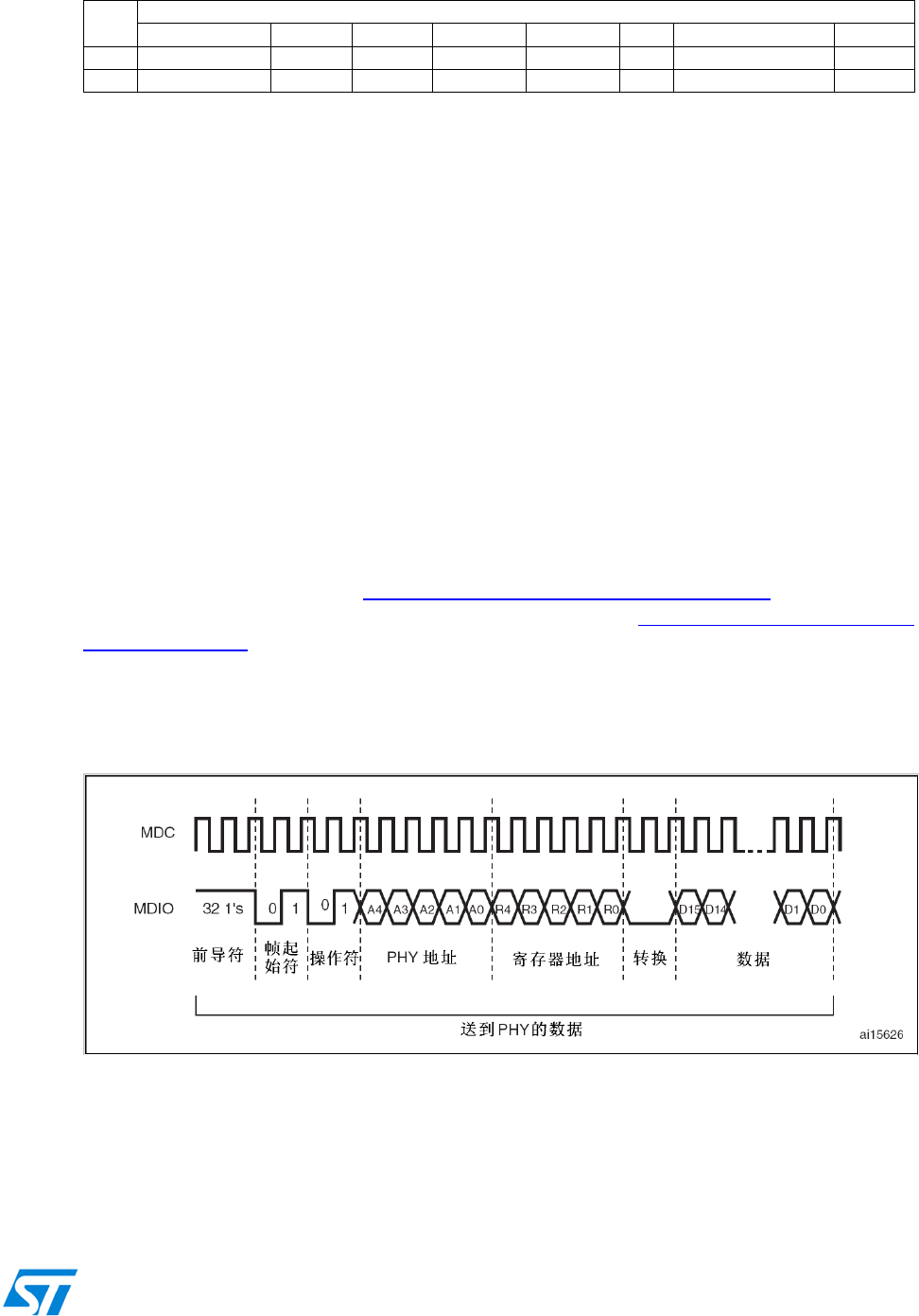

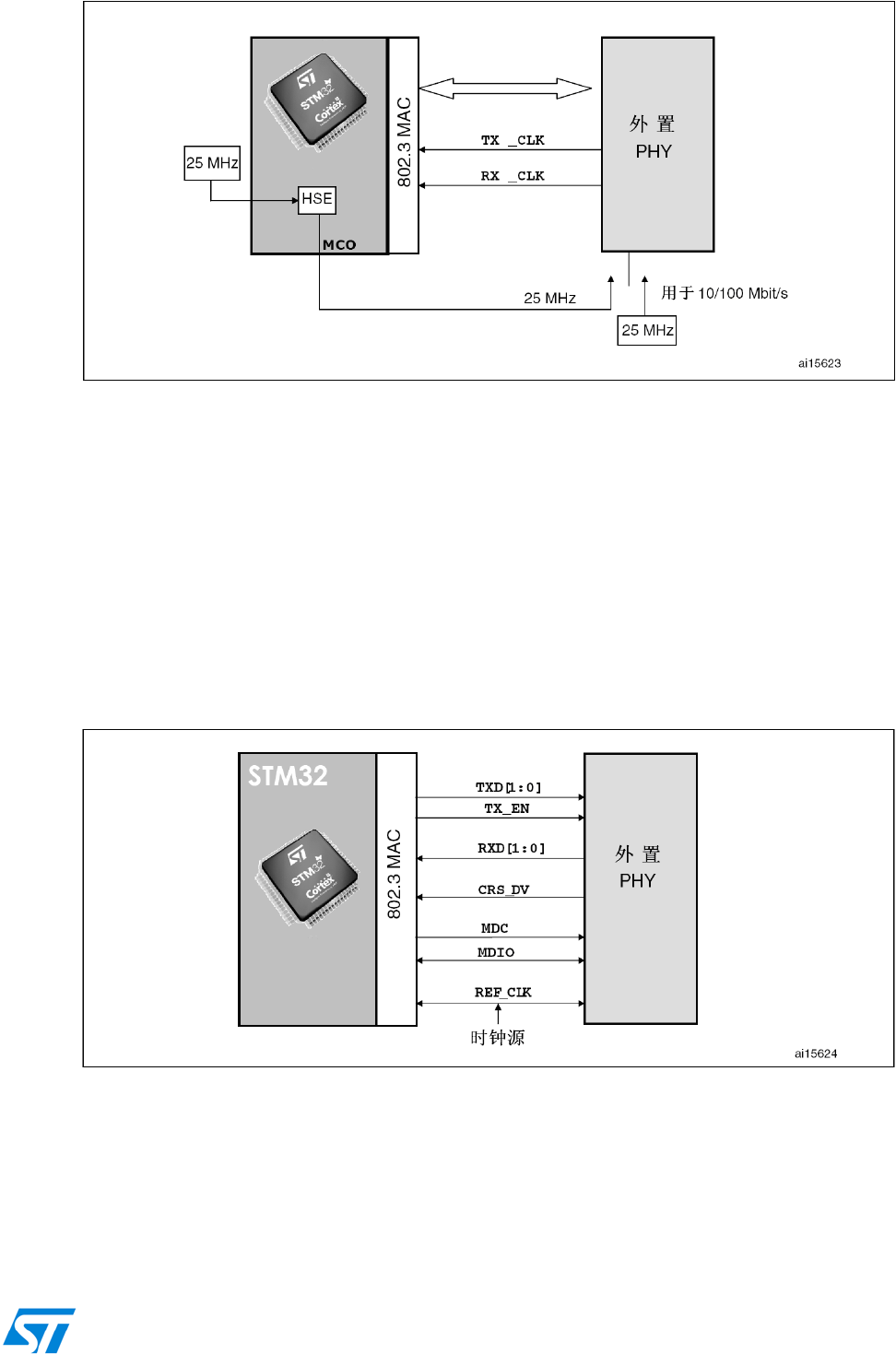

27.4 以太网模块功能描述:SMI、MII和RMII 655

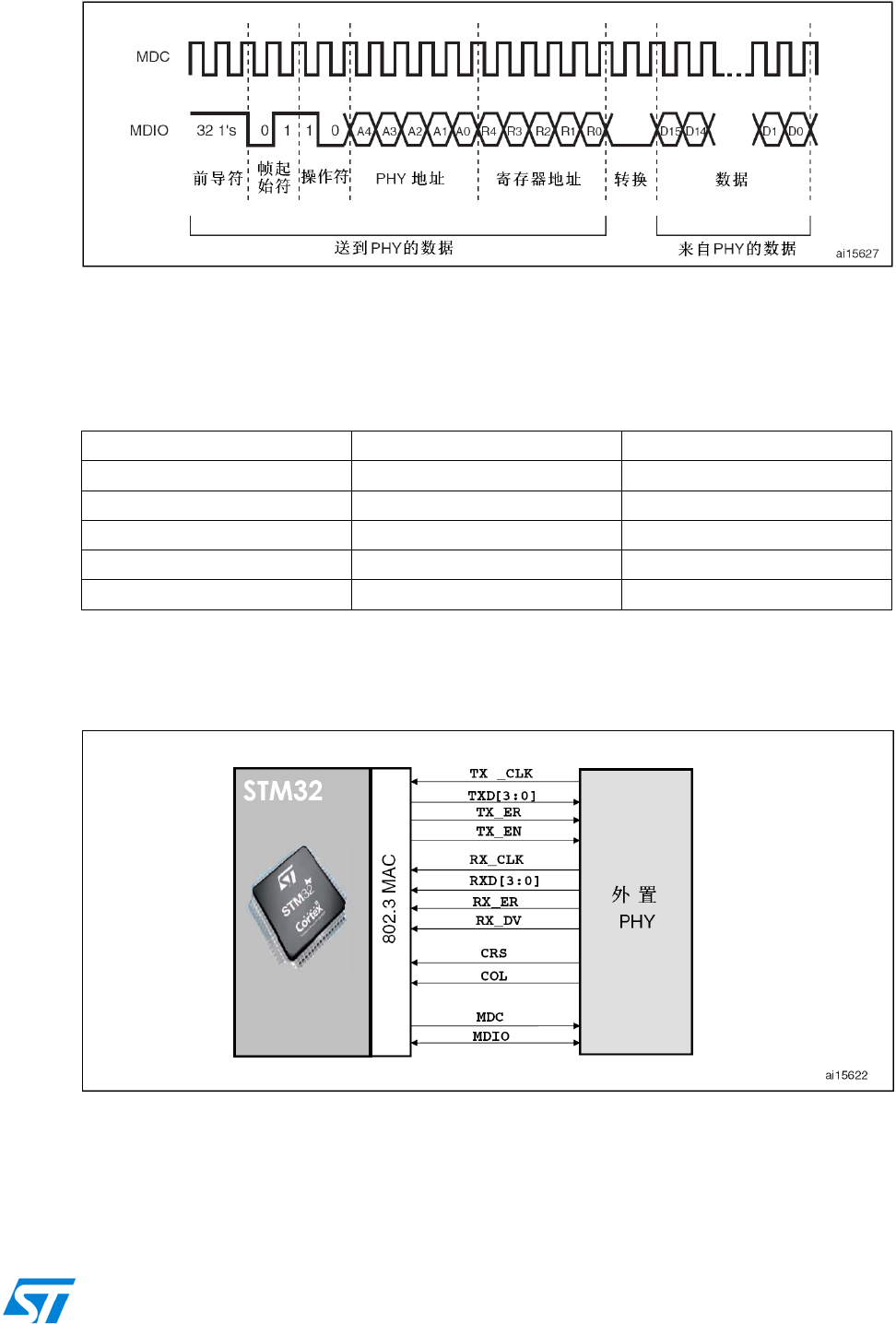

27.4.1 站点管理接口(SMI) 655

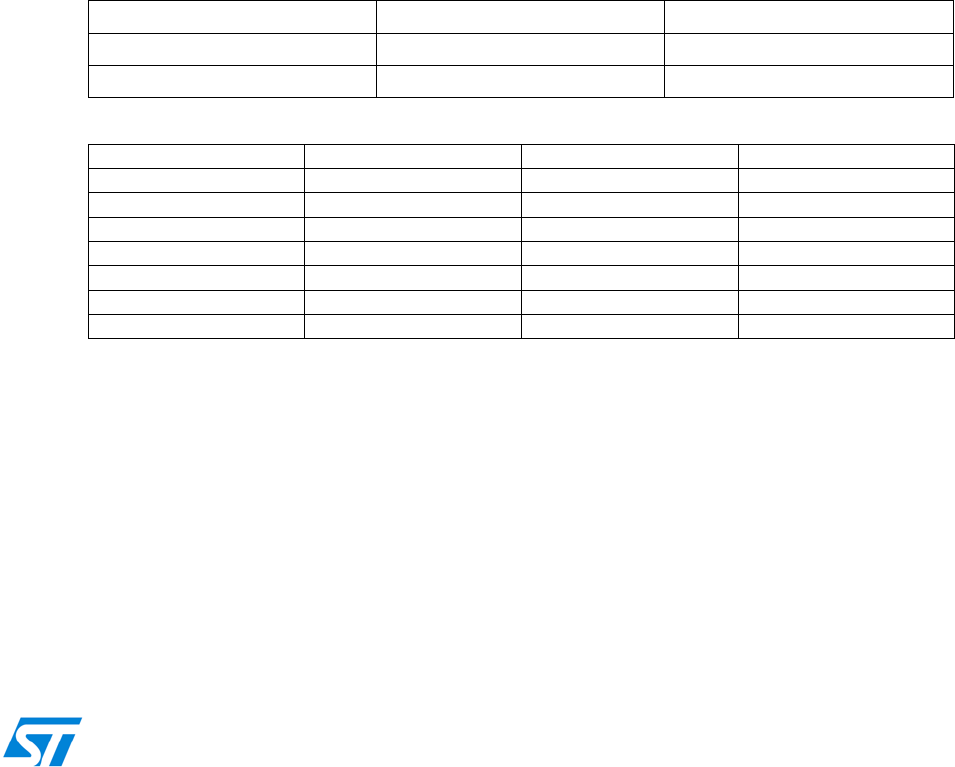

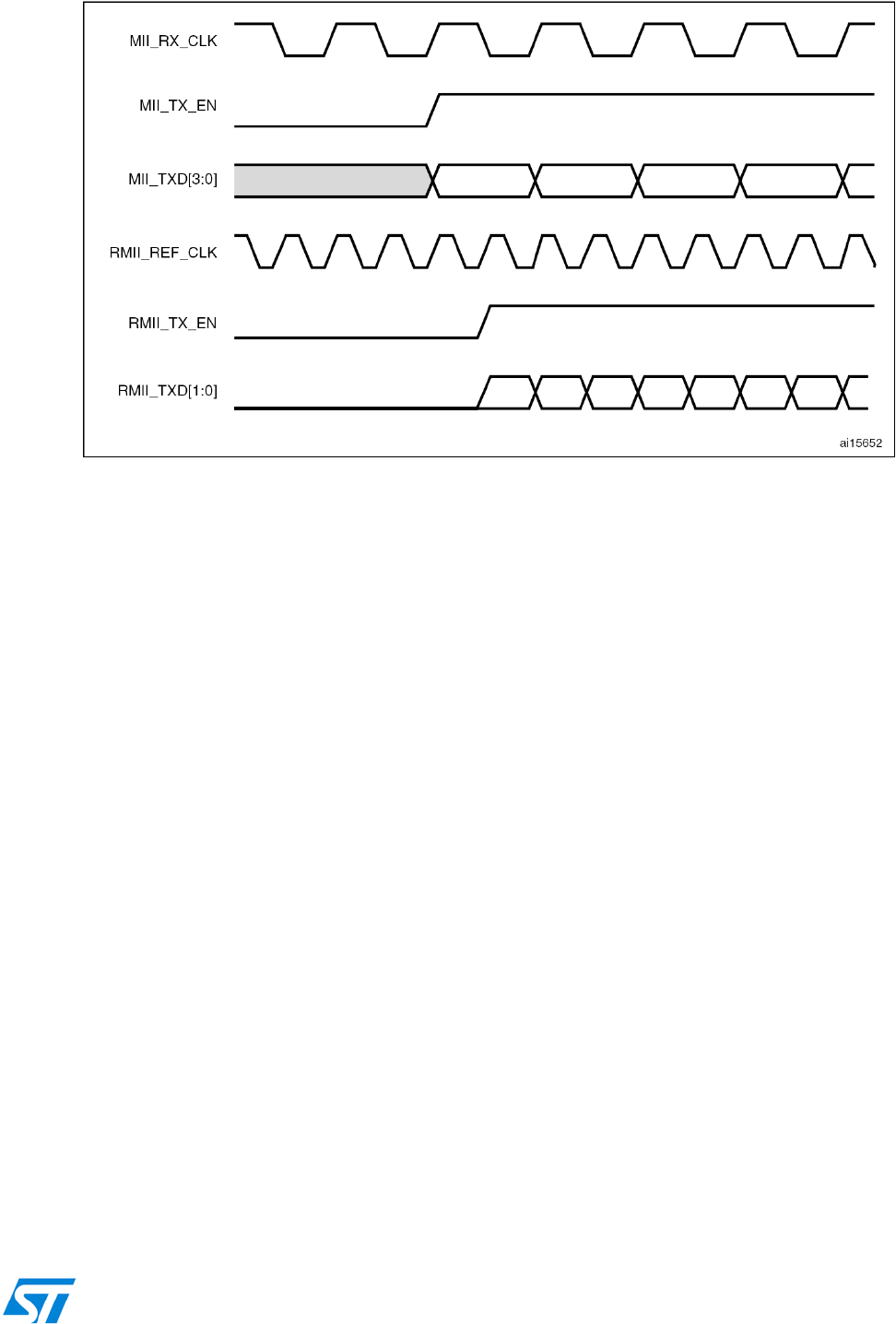

27.4.2 独立于介质的接口:MII 657

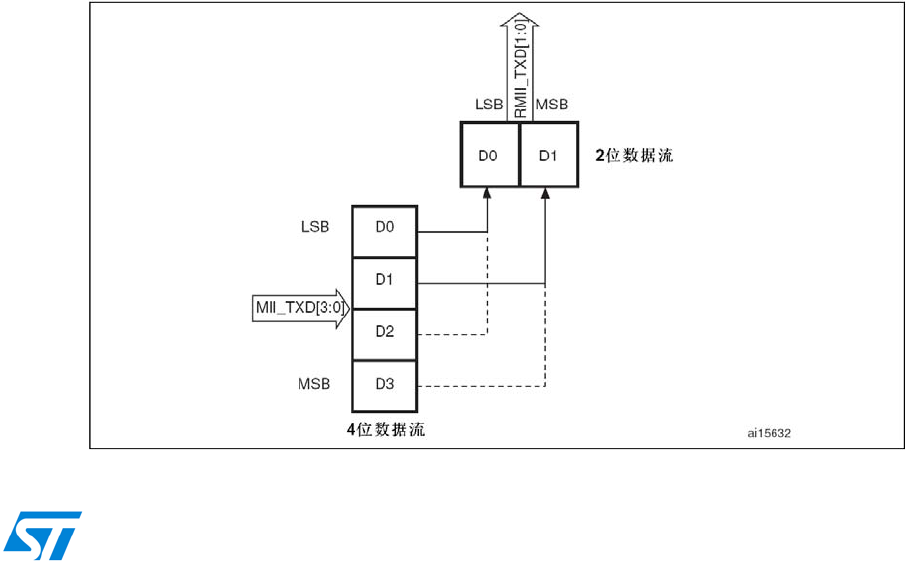

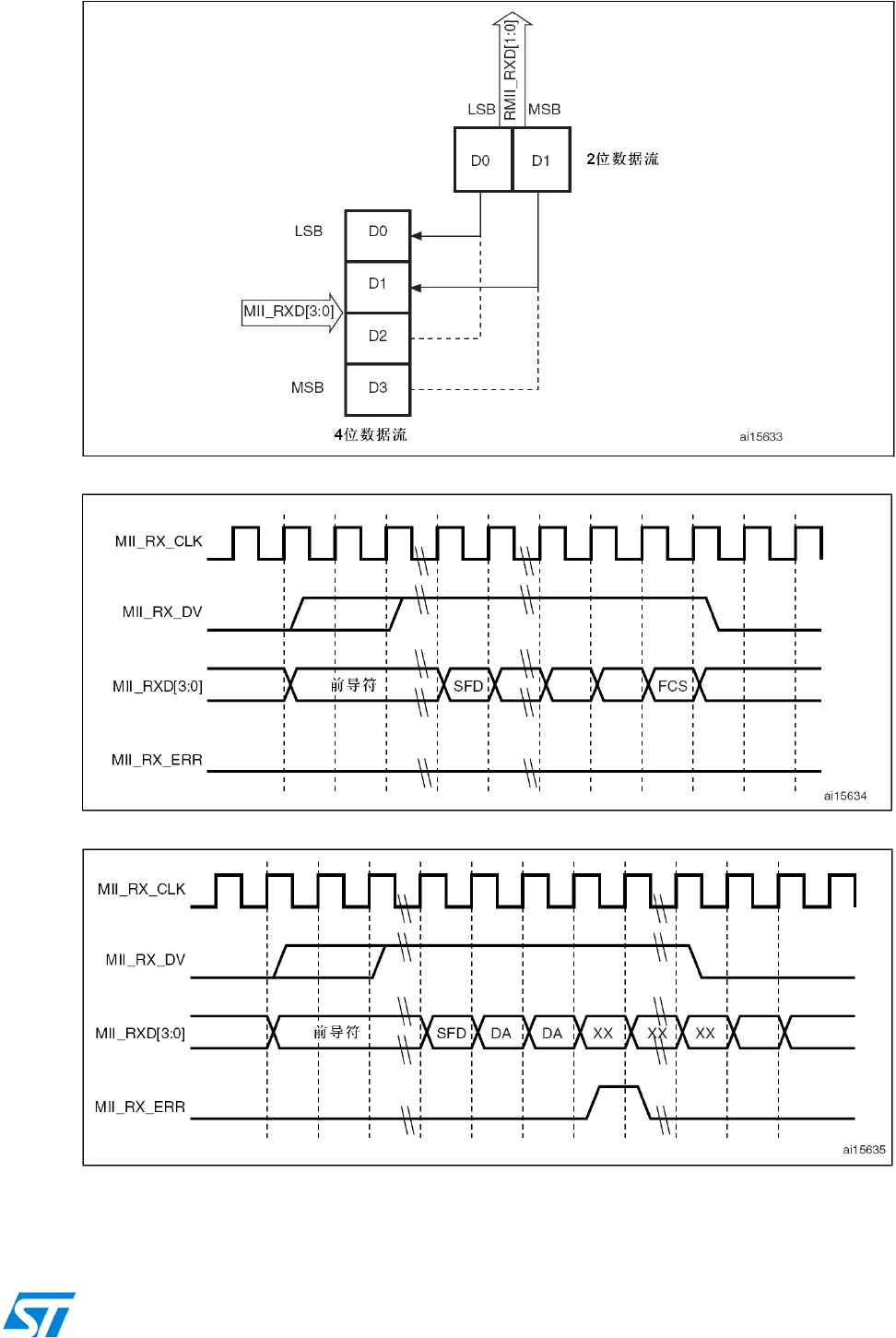

27.4.3 精简的独立于介质的接口:RMII 659

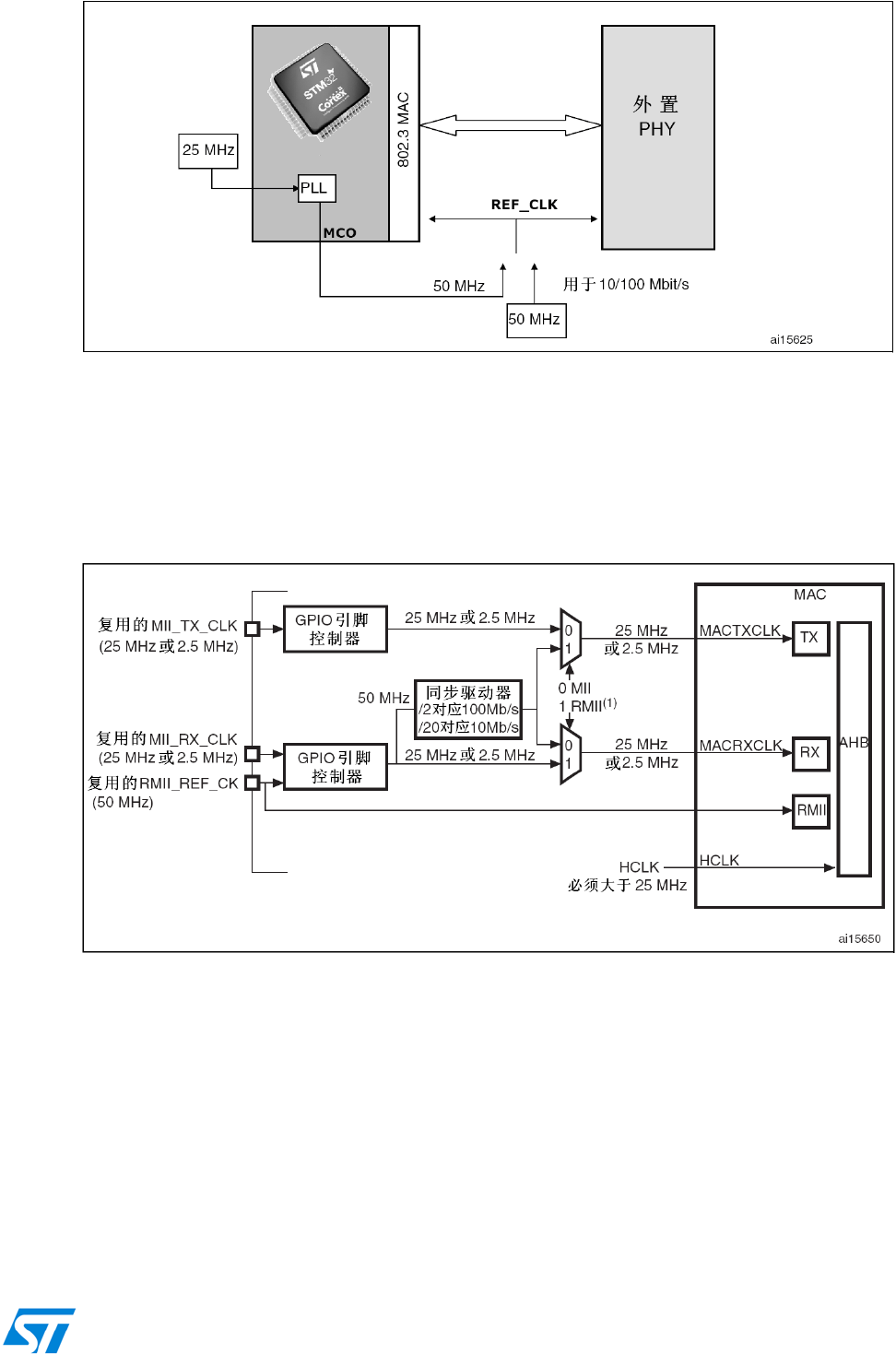

27.4.4 MII/RMII的选择 660

27.5 以太网模块功能描述:MAC 802.3 660

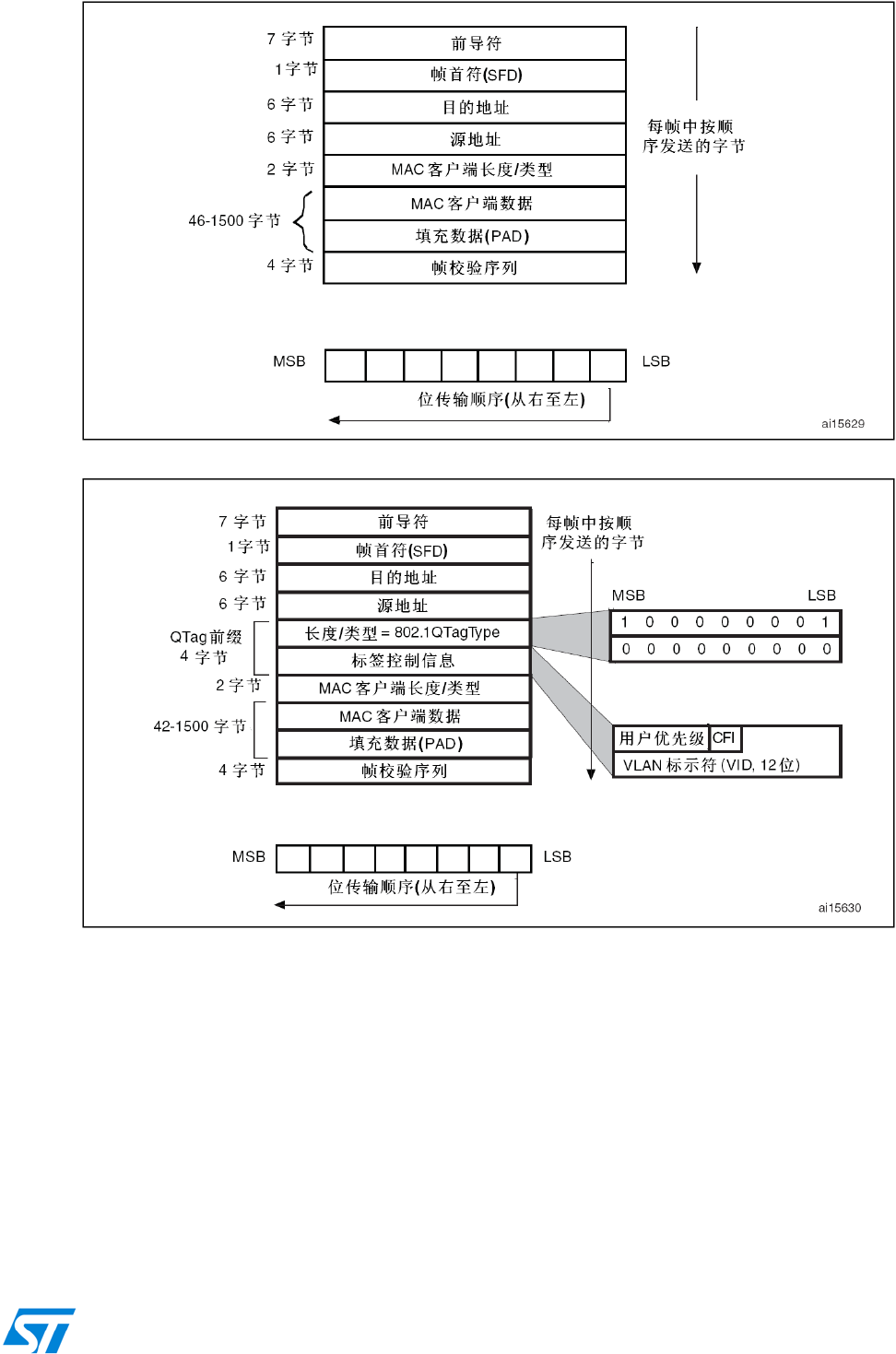

27.5.1 MAC 802.3帧格式 661

27.5.2 MAC帧的传输 663

27.5.3 MAC帧的接收 669

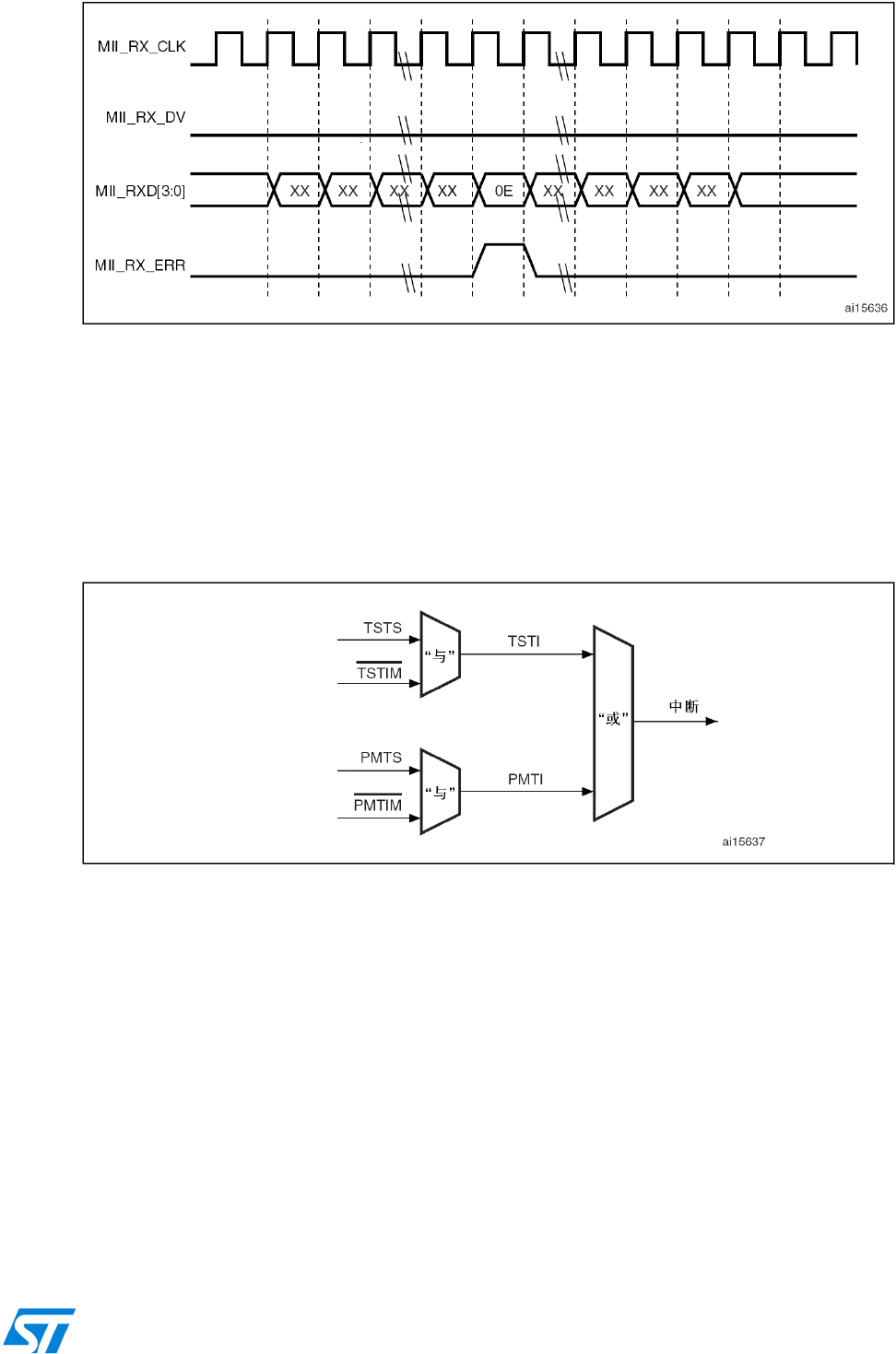

27.5.4 MAC中断 673

27.5.5 MAC过滤 673

27.5.6 MAC自循环模式 675

27.5.7 MAC管理计数器:MMC 675

27.5.8 电源管理:PMT 676

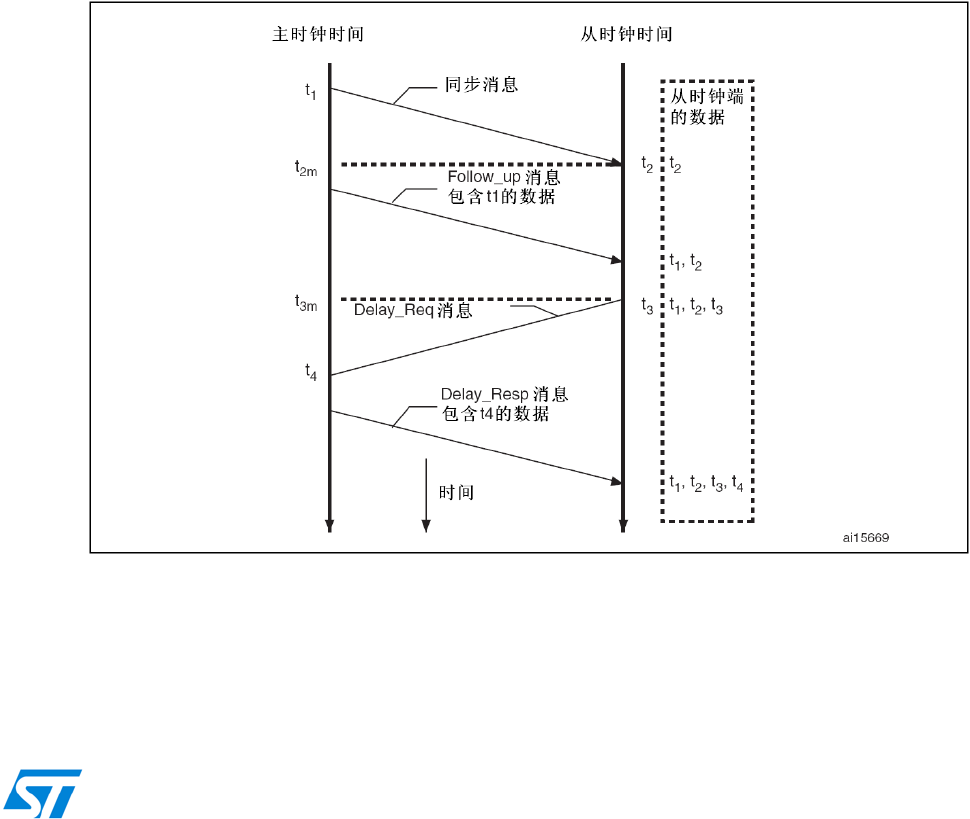

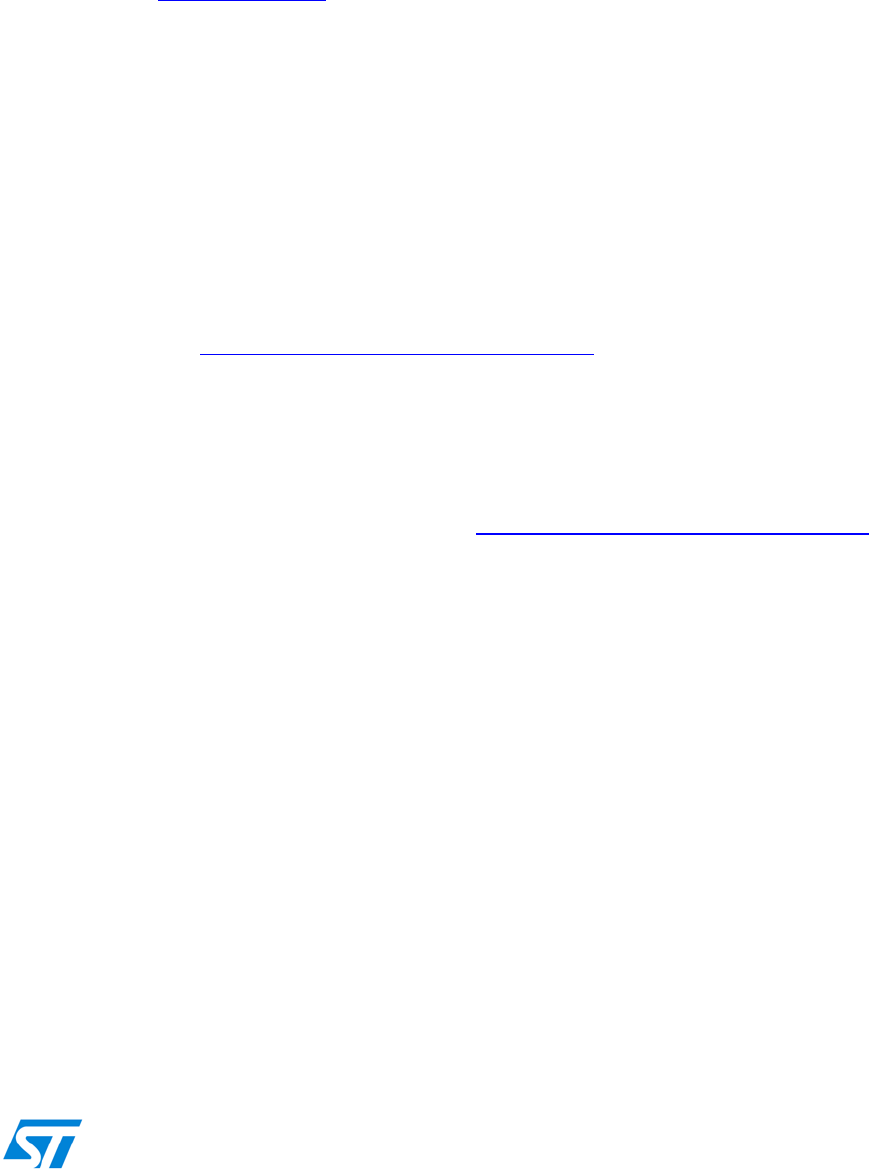

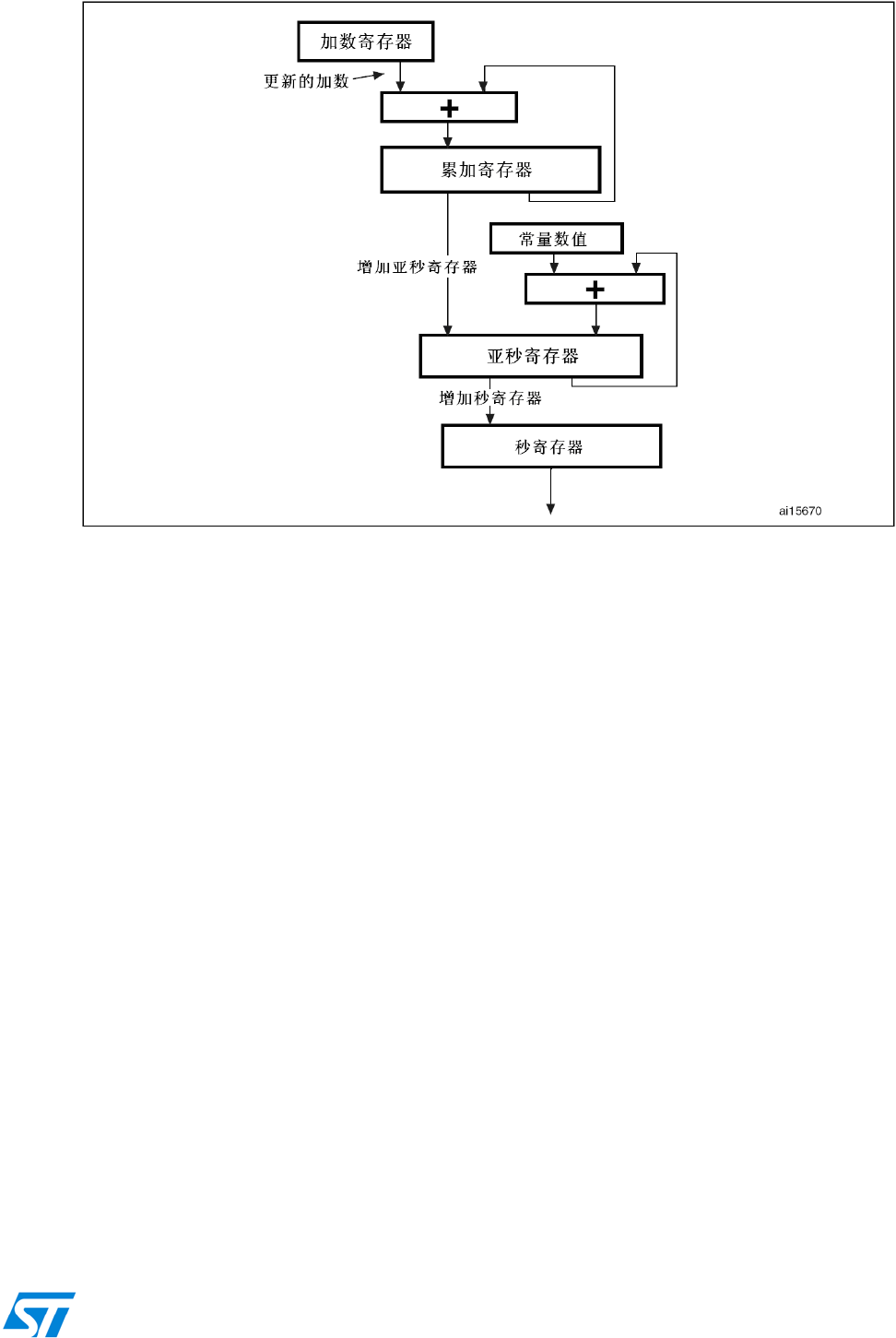

27.5.9 精确时间协议(IEEE1588 PTP) 678

27.6 以太网功能描述:DMA控制器操作 682

27.6.1 使用DMA发送的初始化步骤 683

27.6.2 主机总线突发访问 683

27.6.3 主机数据缓存对齐 684

27.6.4 缓冲区大小计算 684

27.6.5 DMA仲裁器 684

27.6.6 DMA错误响应 684

21/754

参照2009年12月 RM0008 Reference Manual 英文第10版

本译文仅供参考,如有翻译错误,请以英文原稿为准。请读者随时注意在ST网站下载更新版本

目录 STM32F10xxx参考手册

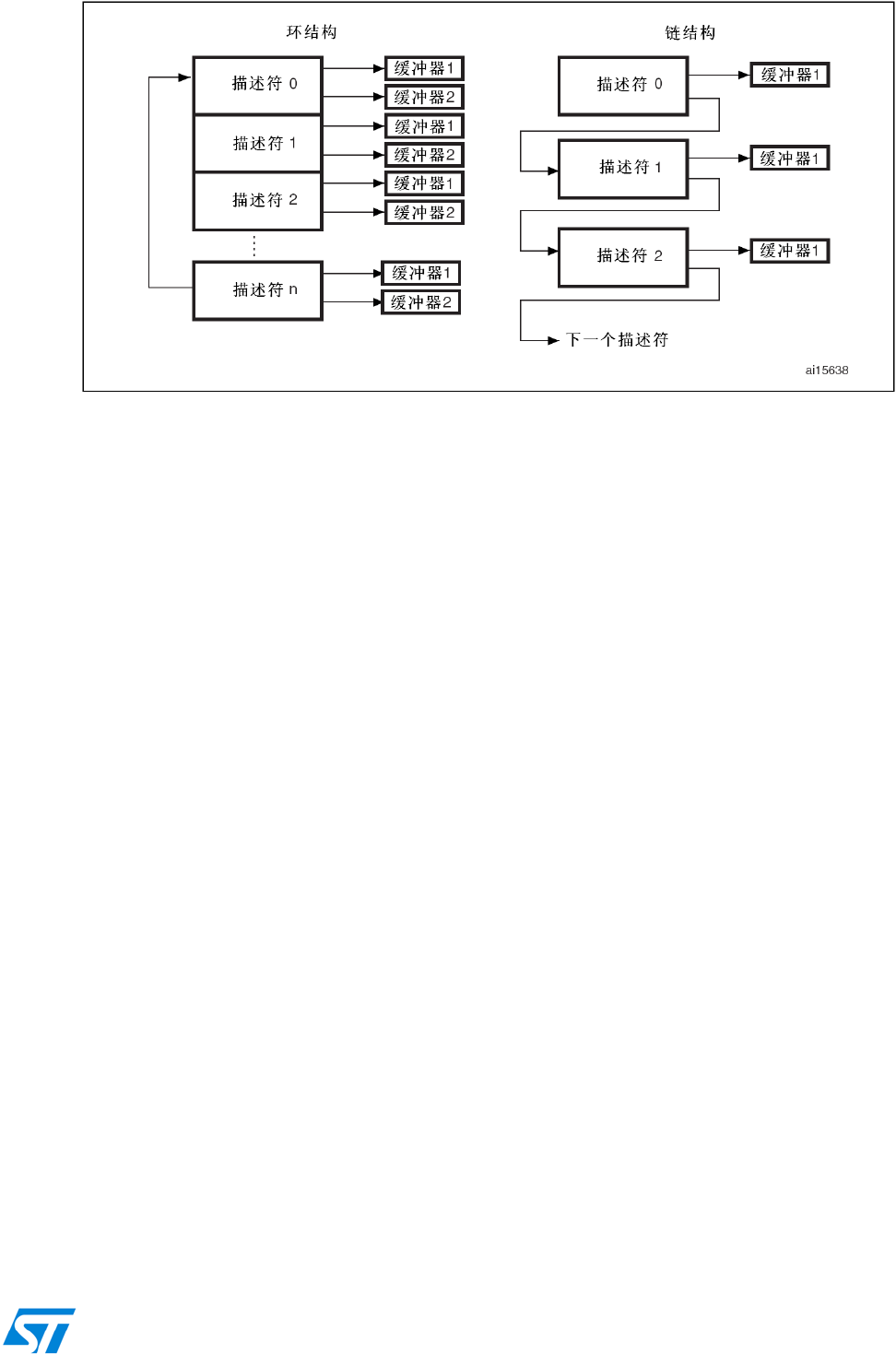

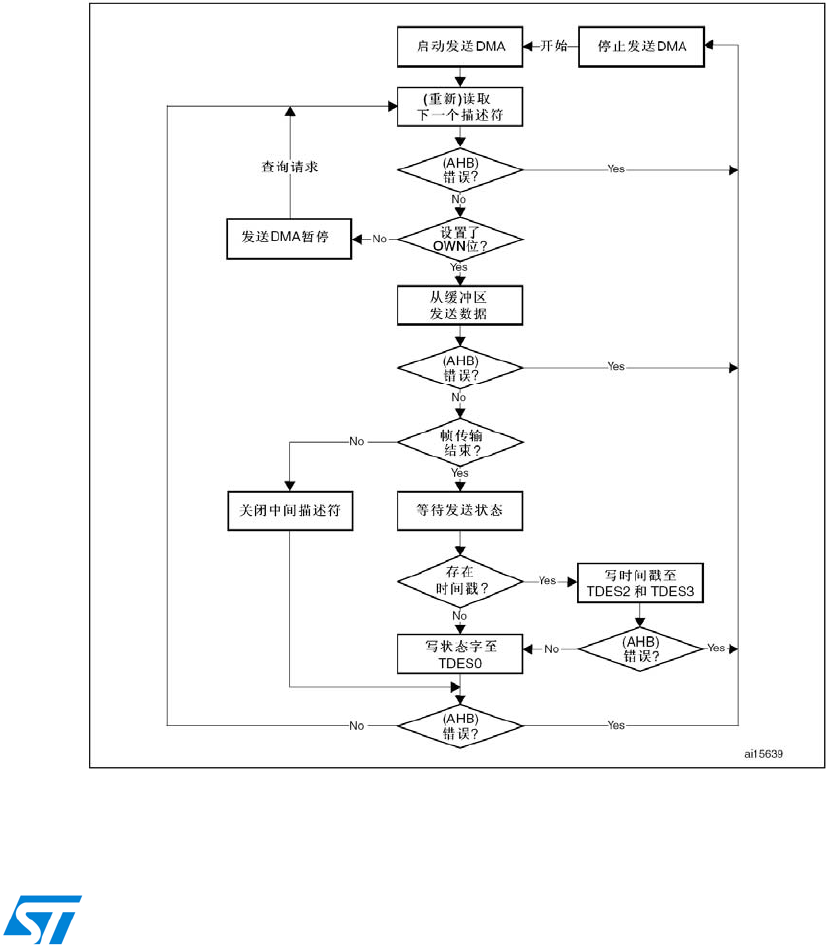

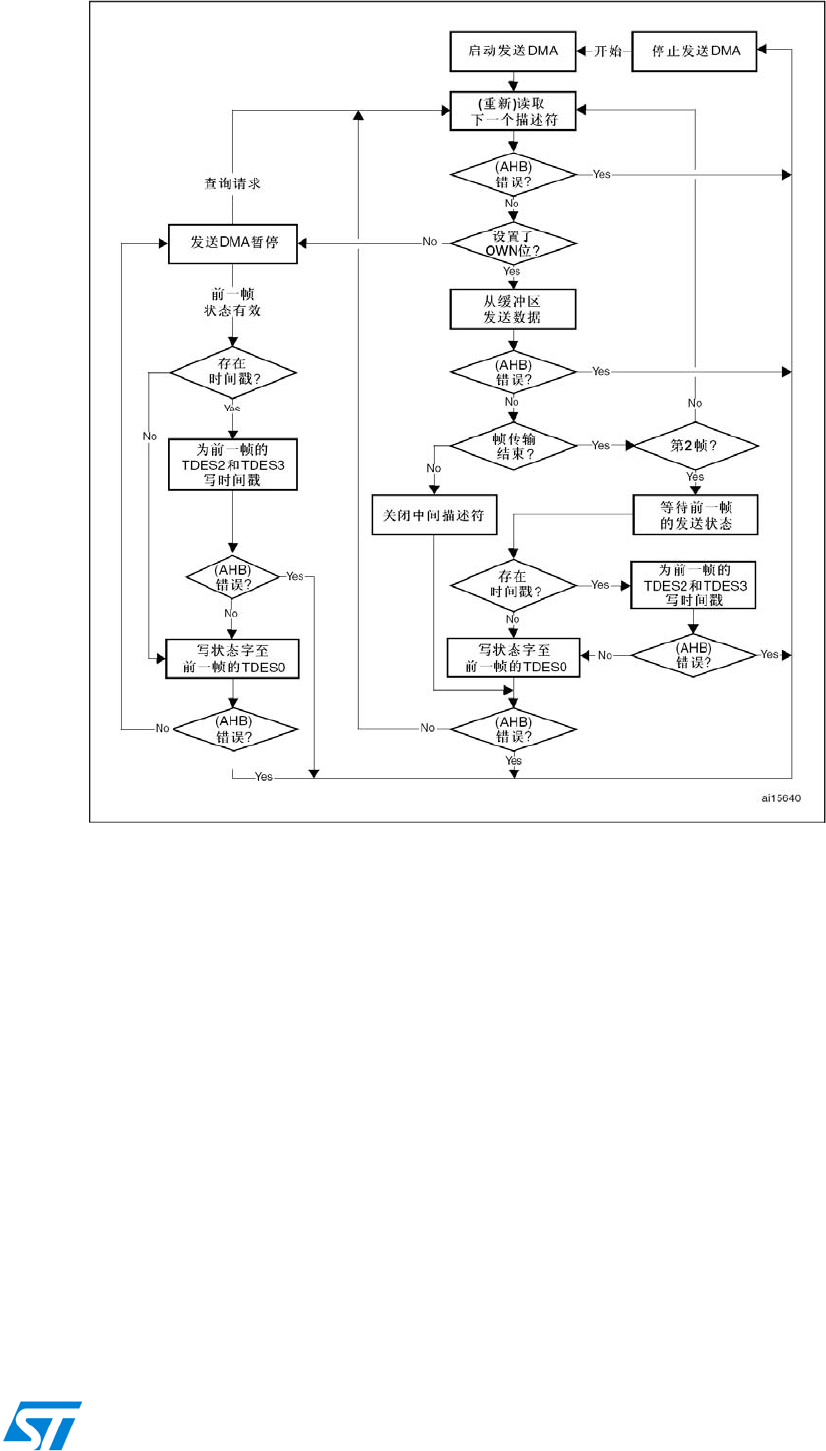

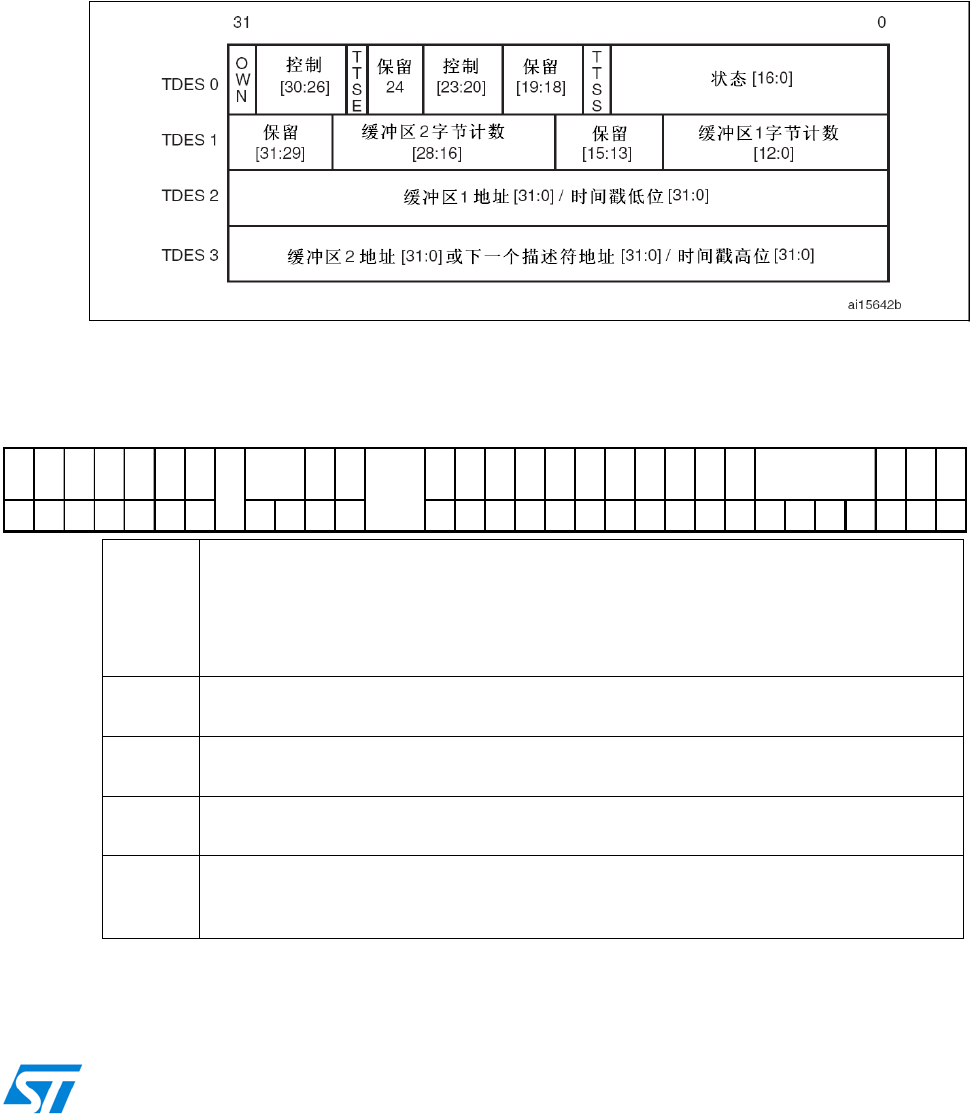

27.6.7 发送DMA设置 684

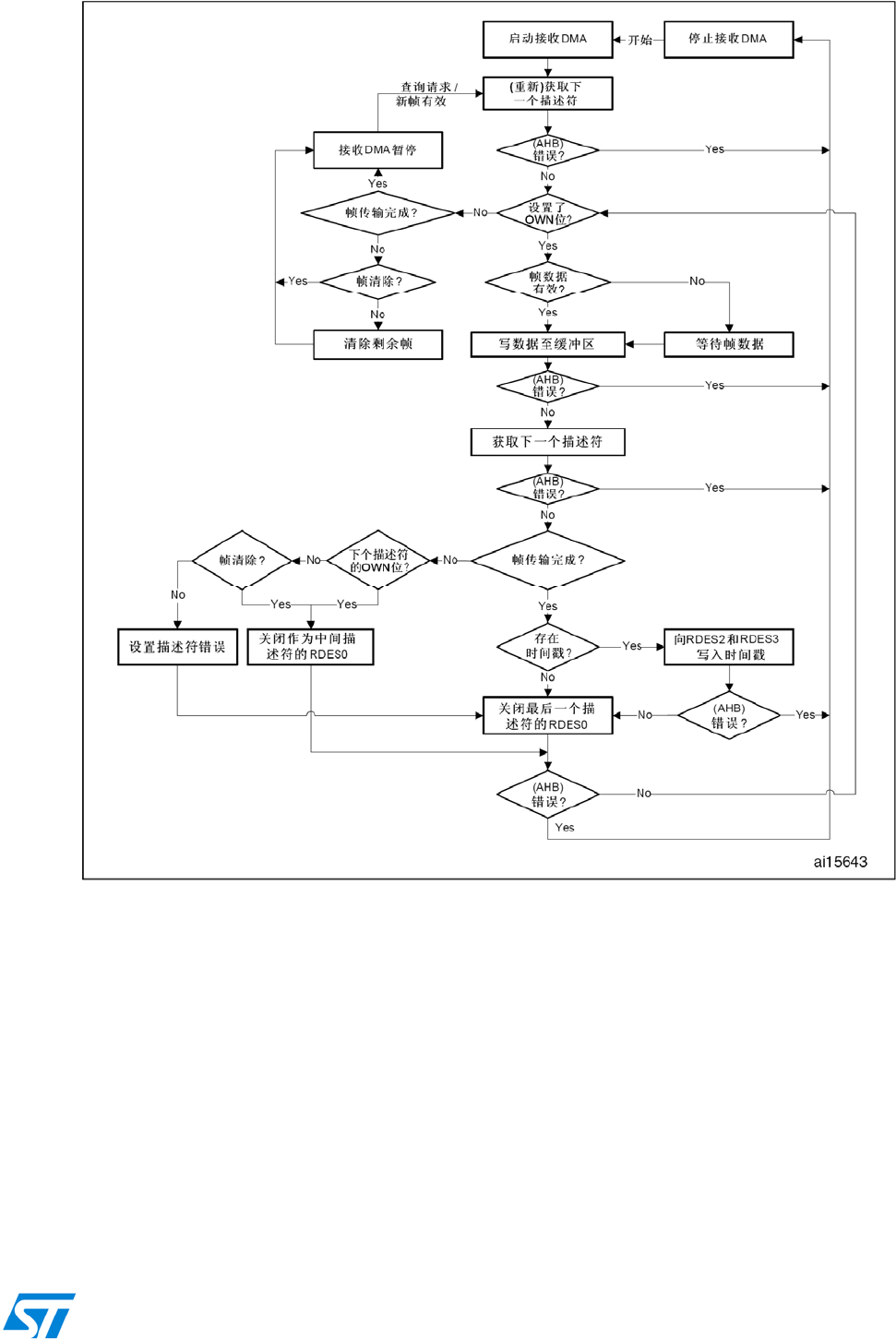

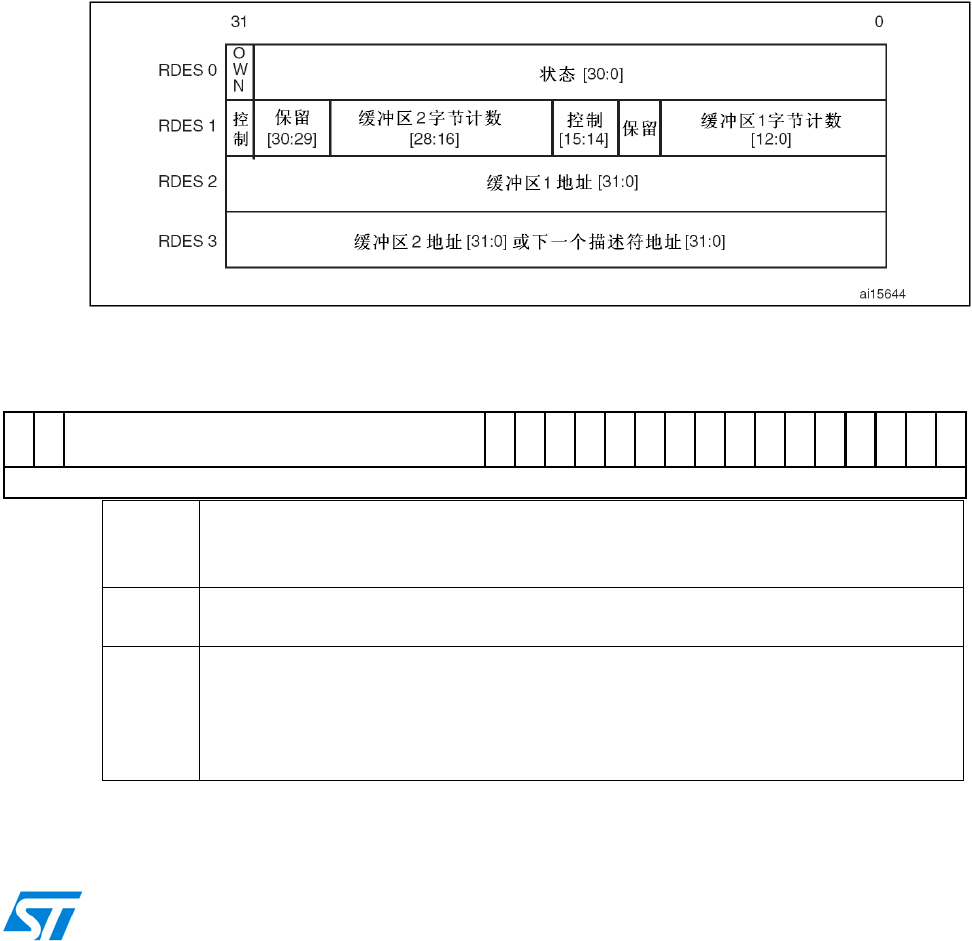

27.6.8 接收DMA设置 694

27.6.9 DMA中断 700

27.7 以太网中断 701

27.8 以太网寄存器描述 702

27.8.1 MAC寄存器描述 702

27.8.2 MMC寄存器描述 713

27.8.3 IEEE 1588时间戳寄存器 716

27.8.4 DMA寄存器描述 719

27.8.5 以太网寄存器映像 729

28 器件电子签名 732

28.1 存储器容量寄存器 732

28.1.1 闪存容量寄存器 732

28.2 产品唯一身份标识寄存器(96位) 732

29 调试支持(DBG) 734

29.1 概况 734

29.2 ARM参考文献 735

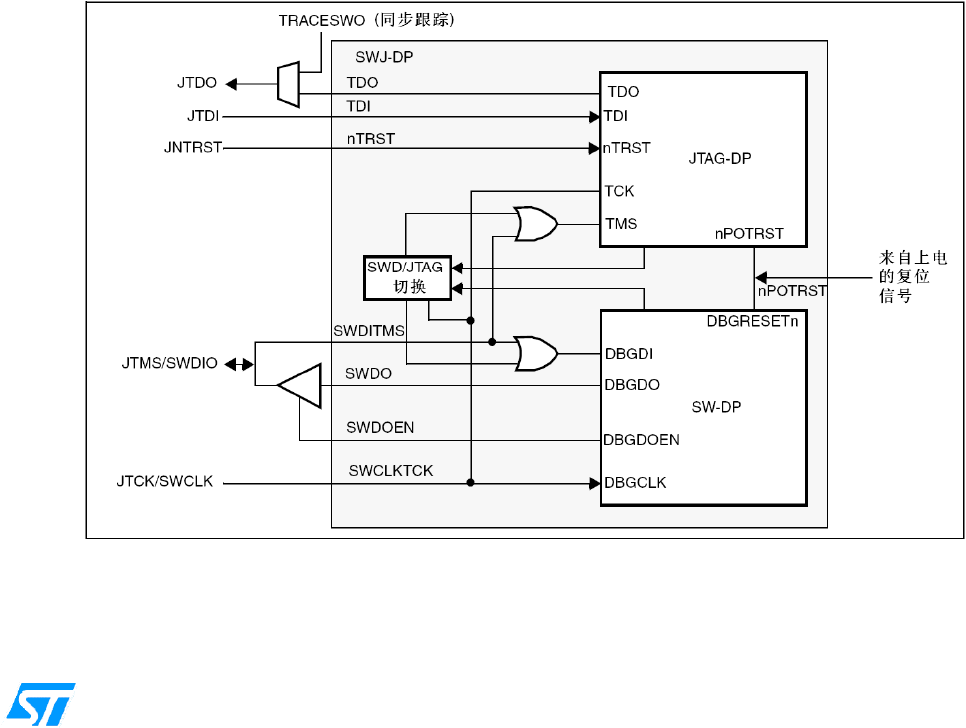

29.3 SWJ调试端口(serial wire and JTAG) 735

29.3.1 JTAG-DP和SW-DP切换的机制 736

29.4 引脚分布和调试端口脚 736

29.4.1 SWJ调试端口脚 736

29.4.2 灵活的SWJ-DP脚分配 736

29.4.3 JTAG脚上的内部上拉和下拉 737

29.4.4 利用串行接口并释放不用的调试脚作为普通I/O口 737

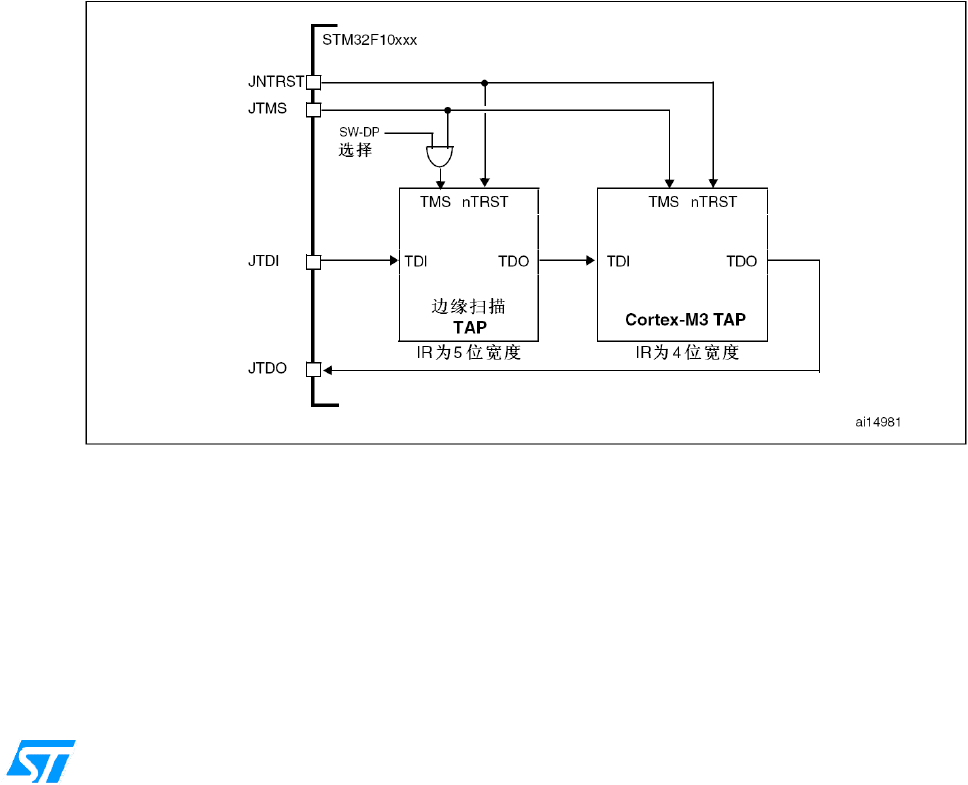

29.5 STM32F10xxx JTAG TAP 连接 738

29.6 ID 代码和锁定机制 738

29.6.1 微控制器设备ID编码 738

29.6.2 边界扫描TAP 739

29.6.3 Cortex-M3 TAP 740

29.6.4 Cortex-M3 JEDEC-106 ID代码 740

29.7 JTAG调试端口 740

29.8 SW调试端口 741

29.8.1 SW协议介绍 741

29.8.2 SW协议序列 741

29.8.3 SW-DP状态机(Reset, idle states, ID code) 742

29.8.4 DP和AP读/写访问 742

29.8.5 SW-DP寄存器 742

29.8.6 SW-AP寄存器 743

29.9 对于JTAG-DP或SWDP都有效的AHB-AP (AHB 访问端口) 743

29.10 内核调试 744

29.11 调试器主机在系统复位下的连接能力 744

29.12 FPB (Flash patch breakpoint) 744

29.13 DWT(数据观察点触发data watchpoint trigger) 745

29.14 ITM (指令跟踪微单元 instrumentation trace macrocell) 745

29.14.1 概述 745

29.14.2 时间戳包,同步和溢出包 745

22/754

参照2009年12月 RM0008 Reference Manual 英文第10版

本译文仅供参考,如有翻译错误,请以英文原稿为准。请读者随时注意在ST网站下载更新版本

目录 STM32F10xxx参考手册

23/754

参照2009年12月 RM0008 Reference Manual 英文第10版

本译文仅供参考,如有翻译错误,请以英文原稿为准。请读者随时注意在ST网站下载更新版本

29.15 ETM模块(嵌入式跟踪微单元Embedded Trace Macrocell) 746

29.15.1 概述 746

29.15.2 信号协议和包类型 746

29.15.3 主要的ETM寄存器 747

29.15.4 配置实例 747

29.16 MCU调试模块(MCUDBG) 747

29.16.1 低功耗模式的调试支持 747

29.16.2 支持定时器、看门狗、bxCAN和I2C的调试 747

29.16.3 调试MCU配置寄存器 748

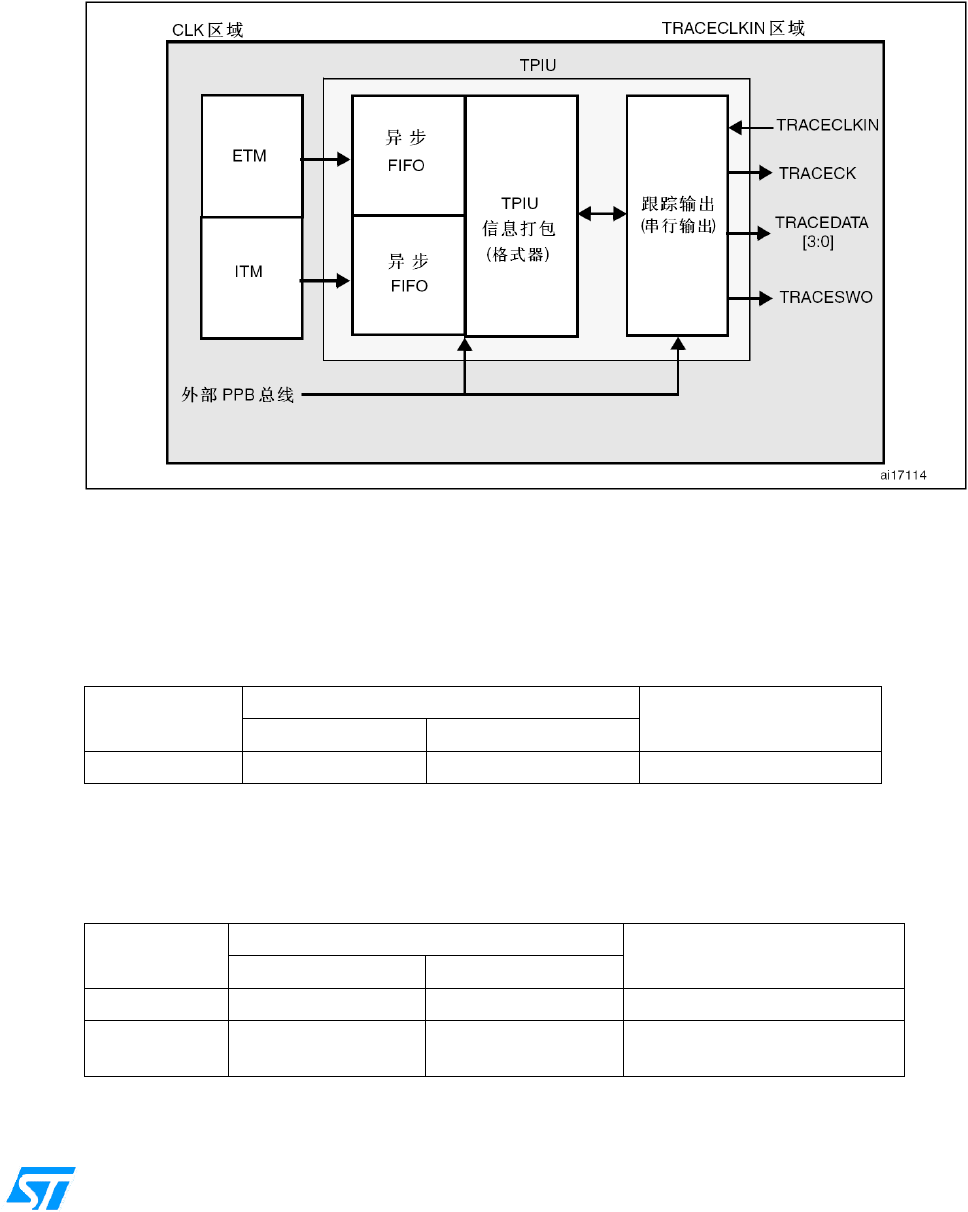

29.17 TPIU (跟踪端口接口单元 Trace Port Interface Unit) 750

29.17.1 导言 750

29.17.2 跟踪引脚分配 750

29.17.3 TPUI格式器 752

29.17.4 TPUI帧异步包 752

29.17.5 同步帧包的发送 752

29.17.6 同步模式 752

29.17.7 异步模式 753

29.17.8 TRACECLKIN在STM32F10xxx内部的连接 753

29.17.9 TPIU寄存器 753

29.17.10 配置的例子 754

29.18 DBG寄存器地址映象 754

存储器和总线架构 STM32F10xxx参考手册

1 文中的缩写

1.1 寄存器描述表中使用的缩写列表

在对寄存器的描述中使用了下列缩写:

read / write (rw) 软件能读写此位。

read-only (r) 软件只能读此位。

write-only (w) 软件只能写此位,读此位将返回复位值。

read/clear (rc_w1) 软件可以读此位,也可以通过写’1’清除此位,写’0’对此位无影响。

read / clear (rc_w0) 软件可以读此位,也可以通过写’0’清除此位,写’1’对此位无影响。

read / clear by read (rc_r) 软件可以读此位;读此位将自动地清除它为’0’,写’0’对此位无影响。

read / set (rs) 软件可以读也可以设置此位,写’0’对此位无影响。

read-only write trigger (rt_w) 软件可以读此位;写’0’或’1’触发一个事件但对此位数值没有影响。

toggle (t) 软件只能通过写’1’来翻转此位,写’0’对此位无影响。

Reserved(Res.) 保留位,必须保持默认值不变

1.2 术语表

● 小容量产品是指闪存存储器容量在16K至32K字节之间的STM32F101xx、STM32F102xx和

STM32F103xx微控制器。

● 中容量产品是指闪存存储器容量在64K至128K字节之间的STM32F101xx、STM32F102xx

和STM32F103xx微控制器。

● 大容量产品是指闪存存储器容量在256K至512K字节之间的STM32F101xx和STM32F103xx

微控制器。

● 互联型产品是STM32F105xx和STM32F107xx微控制器。

1.3 可用的外设

有关STM32微控制器系列全部型号中,某外设存在与否及其数目,请查阅相应的小容量、中容

量或者大容量STM32F101xx和STM32F103xx以及小容量和中容量STM32F102xx的数据手册,

以及STM32F105xx/STM32F107xx数据手册。

24/754

参照2009年12月 RM0008 Reference Manual 英文第10版

本译文仅供参考,如有翻译错误,请以英文原稿为准。请读者随时注意在ST网站下载更新版本

存储器和总线架构 STM32F10xxx参考手册

2 存储器和总线构架

2.1 系统构架

在小容量、中容量和 大容量产品中,主系统由以下部分构成:

● 四个驱动单元:

─ Cortex™-M3内核DCode总线(D-bus),和系统总线(S-bus)

─ 通用DMA1和通用DMA2

● 四个被动单元

─ 内部SRAM

─ 内部闪存存储器

─ FSMC

─ AHB到APB的桥(AHB2APBx),它连接所有的APB设备

25/754

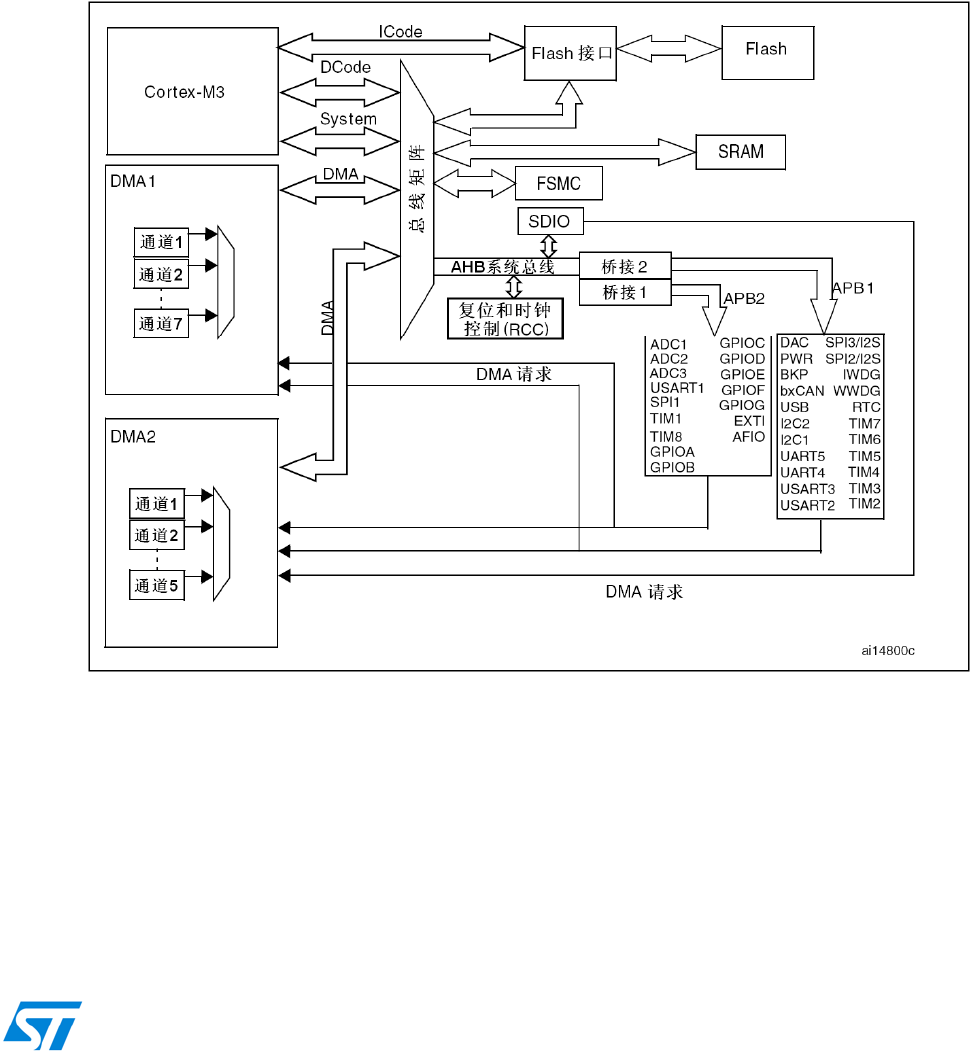

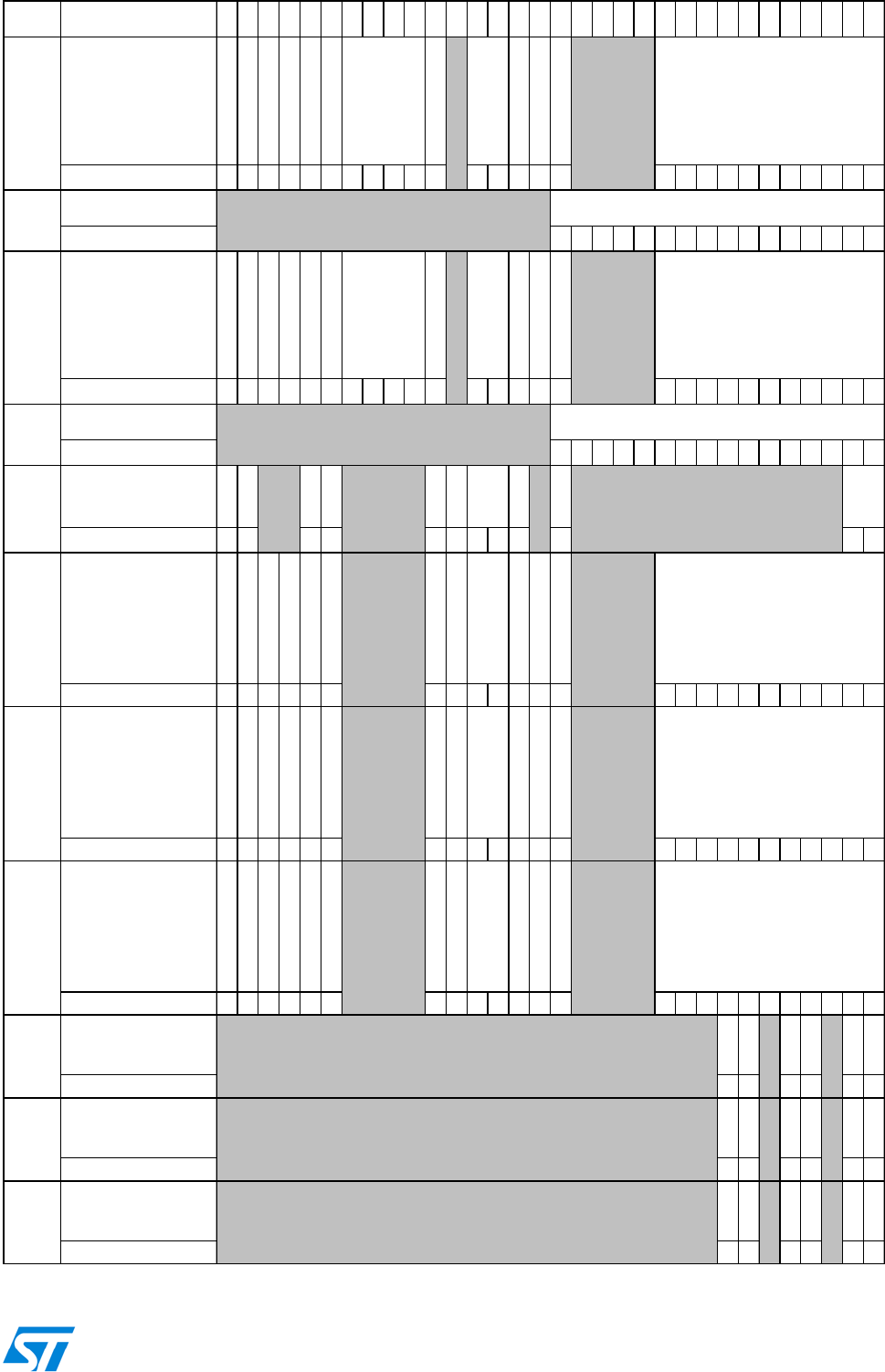

这些都是通过一个多级的AHB总线构架相互连接的,如下图图1所示:

图1 系统结构

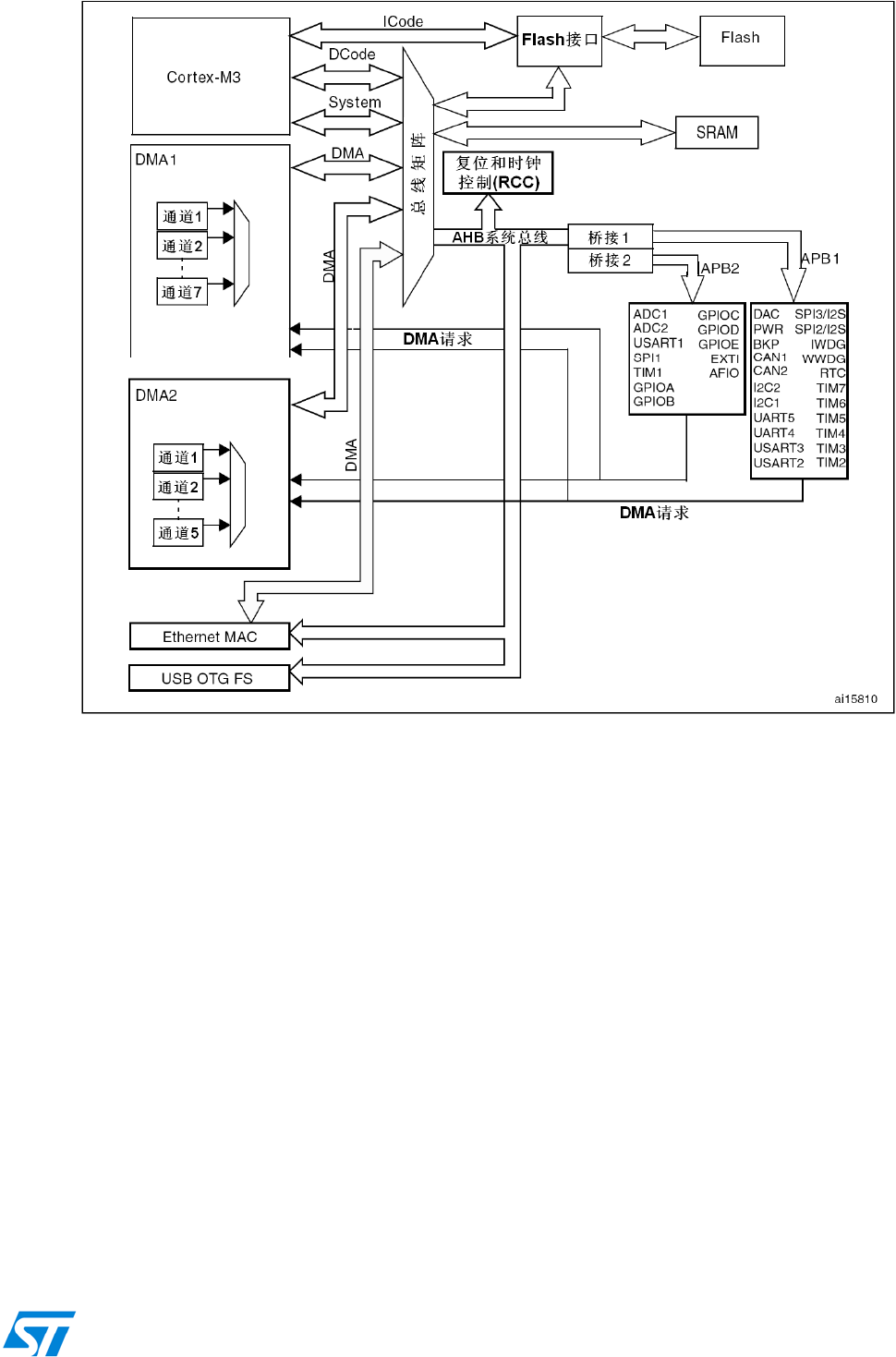

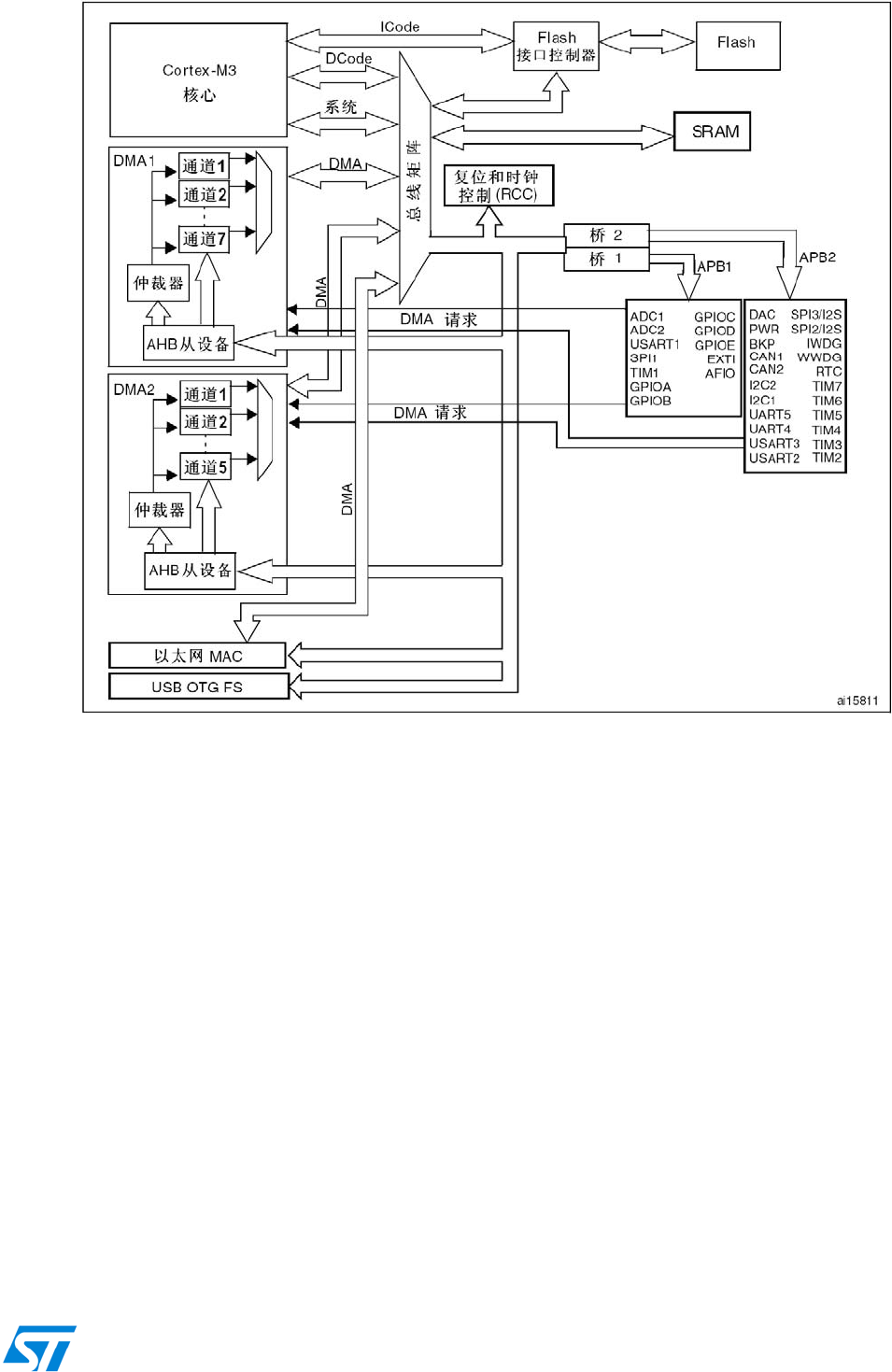

在互联型产品中,主系统由以下部分构成:

● 五个驱动单元:

─ Cortex™-M3内核DCode总线(D-bus),和系统总线(S-bus)

─ 通用DMA1和通用DMA2

─ 以太网DMA

● 三个被动单元

─ 内部SRAM

─ 内部闪存存储器

─ AHB到APB的桥(AHB2APBx),它连接所有的APB设备

这些都是通过一个多级的AHB总线构架相互连接的,如图2所示:

参照2009年12月 RM0008 Reference Manual 英文第10版

本译文仅供参考,如有翻译错误,请以英文原稿为准。请读者随时注意在ST网站下载更新版本

存储器和总线架构 STM32F10xxx参考手册

图2 互联型产品的系统结构

ICode总线

该总线将Cortex™-M3内核的指令总线与闪存指令接口相连接。指令预取在此总线上完成。

DCode总线

该总线将Cortex™-M3内核的DCode总线与闪存存储器的数据接口相连接(常量加载和调试访

问)。

系统总线

此总线连接Cortex™-M3内核的系统总线(外设总线)到总线矩阵,总线矩阵协调着内核和DMA间

的访问。

DMA总线

此总线将DMA的AHB主控接口与总线矩阵相联,总线矩阵协调着CPU的DCode和DMA 到

SRAM、闪存和外设的访问。

总线矩阵

总线矩阵协调内核系统总线和DMA主控总线之间的访问仲裁,仲裁利用轮换算法。在互联型产

品中,总线矩阵包含5个驱动部件(CPU的DCode、系统总线、以太网DMA、DMA1总线和

DMA2总线)和3个从部件(闪存存储器接口(FLITF)、SRAM和AHB2APB桥)。在其它产品中总线

矩阵包含4个驱动部件(CPU的DCode、系统总线、DMA1总线和DMA2总线)和4个被动部件(闪存

存储器接口(FLITF)、SRAM、FSMC和AHB2APB桥)。

AHB外设通过总线矩阵与系统总线相连,允许DMA访问。

26/754

参照2009年12月 RM0008 Reference Manual 英文第10版

本译文仅供参考,如有翻译错误,请以英文原稿为准。请读者随时注意在ST网站下载更新版本

存储器和总线架构 STM32F10xxx参考手册

AHB/APB桥(APB)

两个AHB/APB桥在AHB和2个APB总线间提供同步连接。APB1操作速度限于36MHz,APB2操

作于全速(最高72MHz)。

表1有关连接到每个桥的不同外设的地址映射请参考 。在每一次复位以后,所有除SRAM和

FLITF以外的外设都被关闭,在使用一个外设之前,必须设置寄存器RCC_AHBENR来打开该外

设的时钟。

注意:

当对

APB

寄存器进行

8

位或者

16

位访问时,该访问会被自动转换成

32

位的访问:桥会自动将

8

位

或者

32

位的数据扩展以配合

32

位的向量。

2.2 存储器组织

程序存储器、数据存储器、寄存器和输入输出端口被组织在同一个4GB的线性地址空间内。

数据字节以小端格式存放在存储器中。一个字里的最低地址字节被认为是该字的最低有效字

节,而最高地址字节是最高有效字节。

外设寄存器的映像请参考相关章节。

可访问的存储器空间被分成8个主要块,每个块为512MB。

其他所有没有分配给片上存储器和外设的存储器空间都是保留的地址空间,请参考相应器件的

数据手册中的存储器映像图。

27/754

参照2009年12月 RM0008 Reference Manual 英文第10版

本译文仅供参考,如有翻译错误,请以英文原稿为准。请读者随时注意在ST网站下载更新版本

存储器和总线架构 STM32F10xxx参考手册

2.3 存储器映像

表1请参考相应器件的数据手册中的存储器映像图。 列出了所用STM32F10xxx中内置外设的起

始地址。

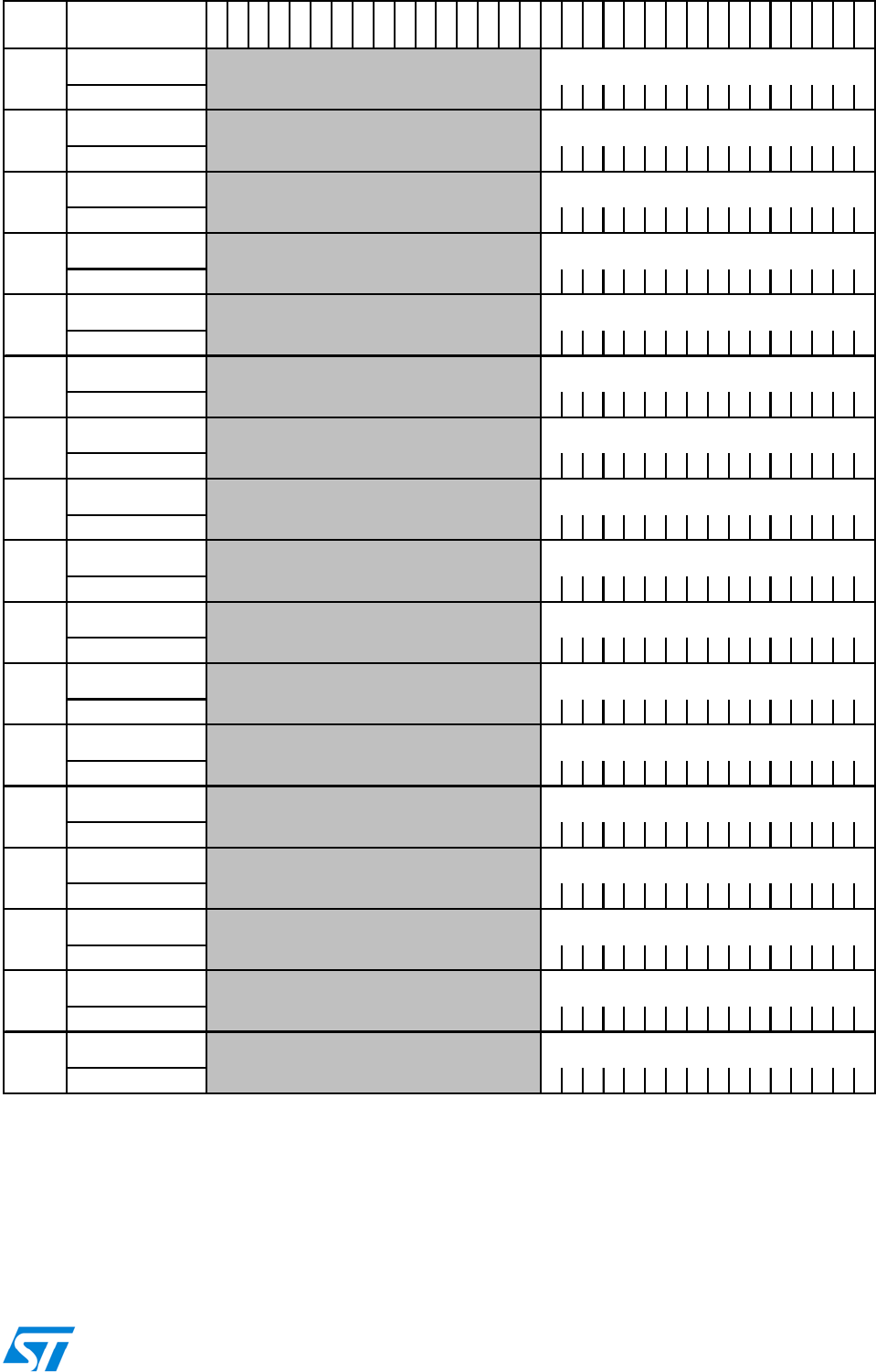

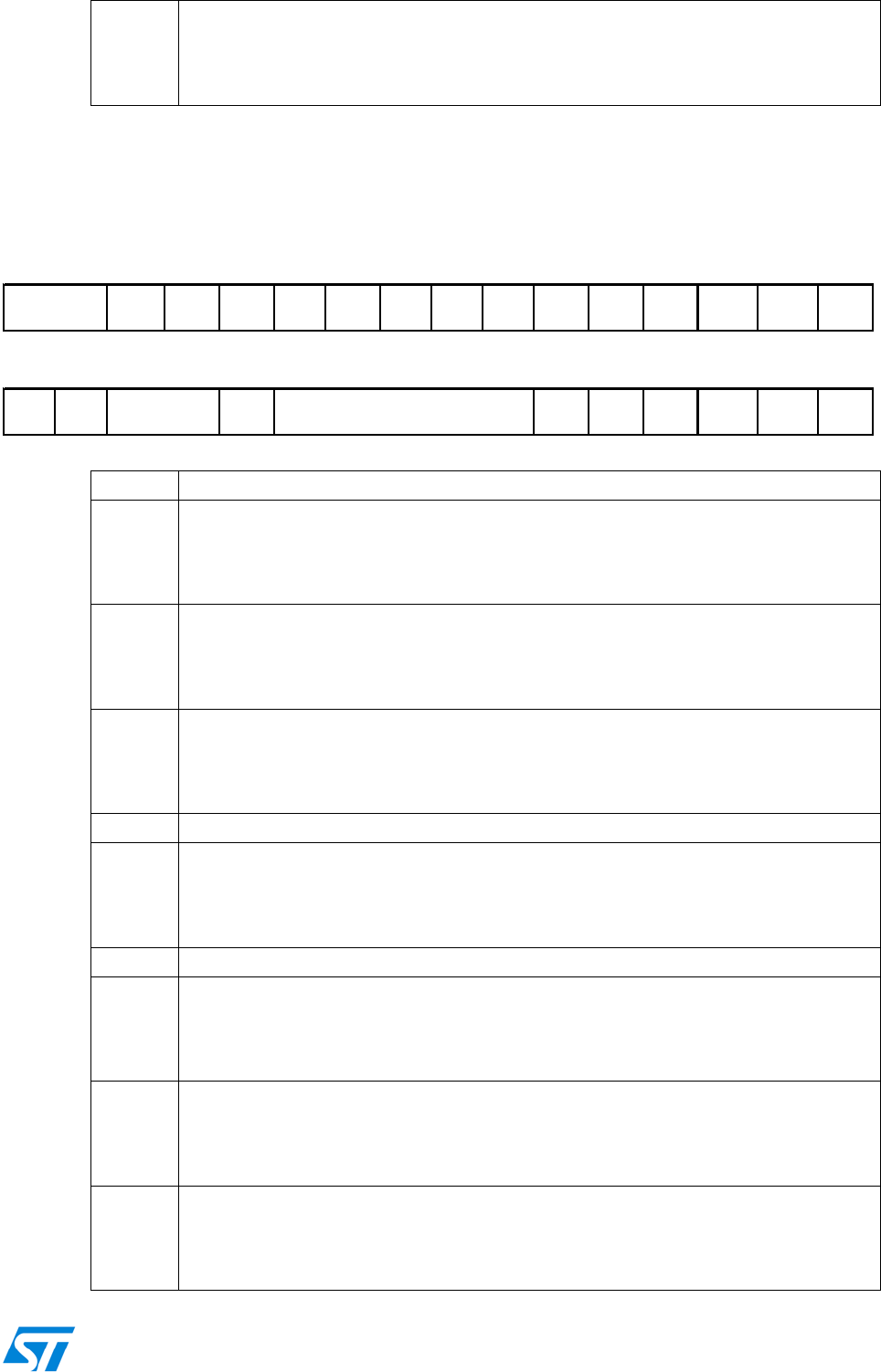

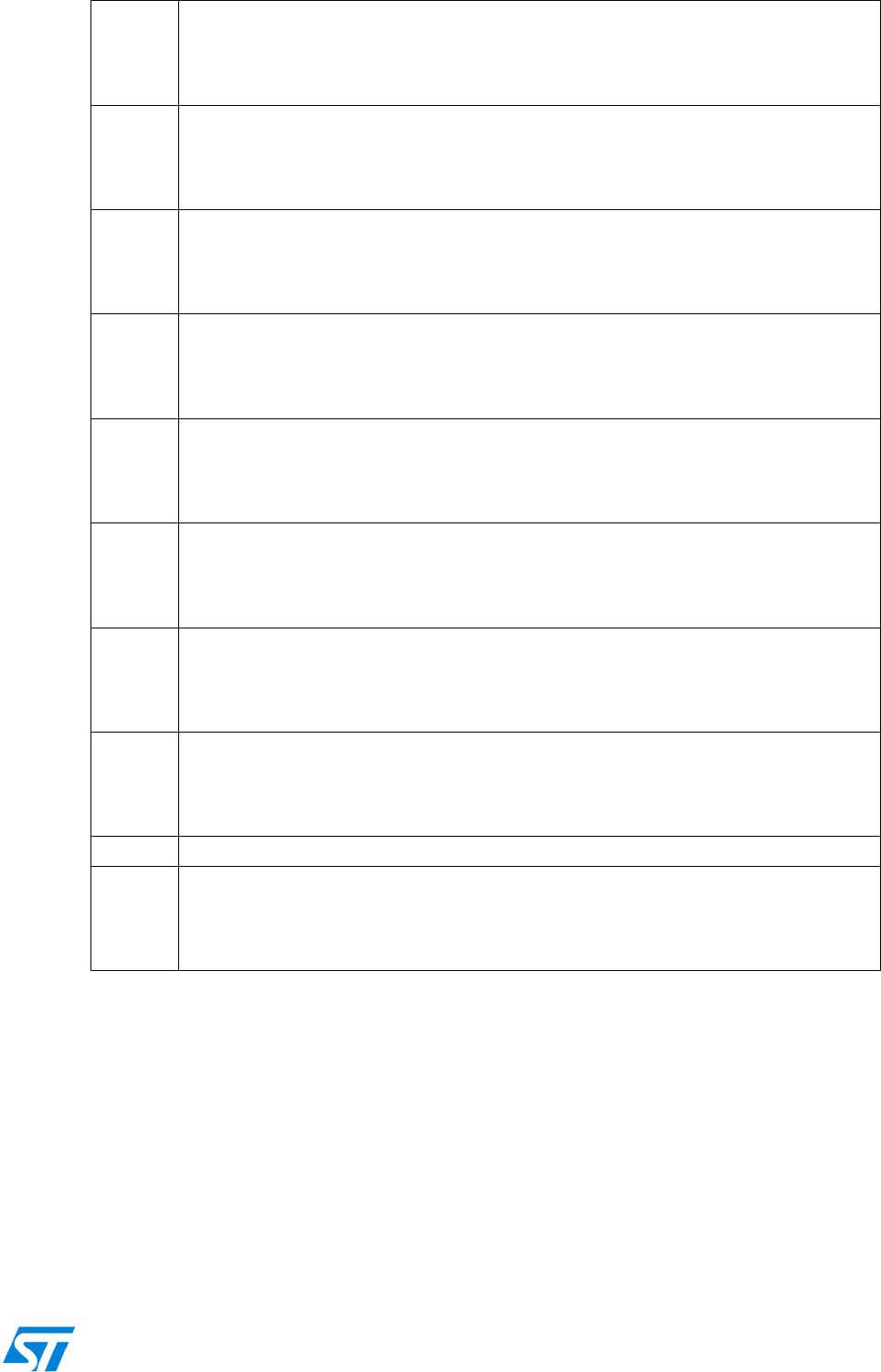

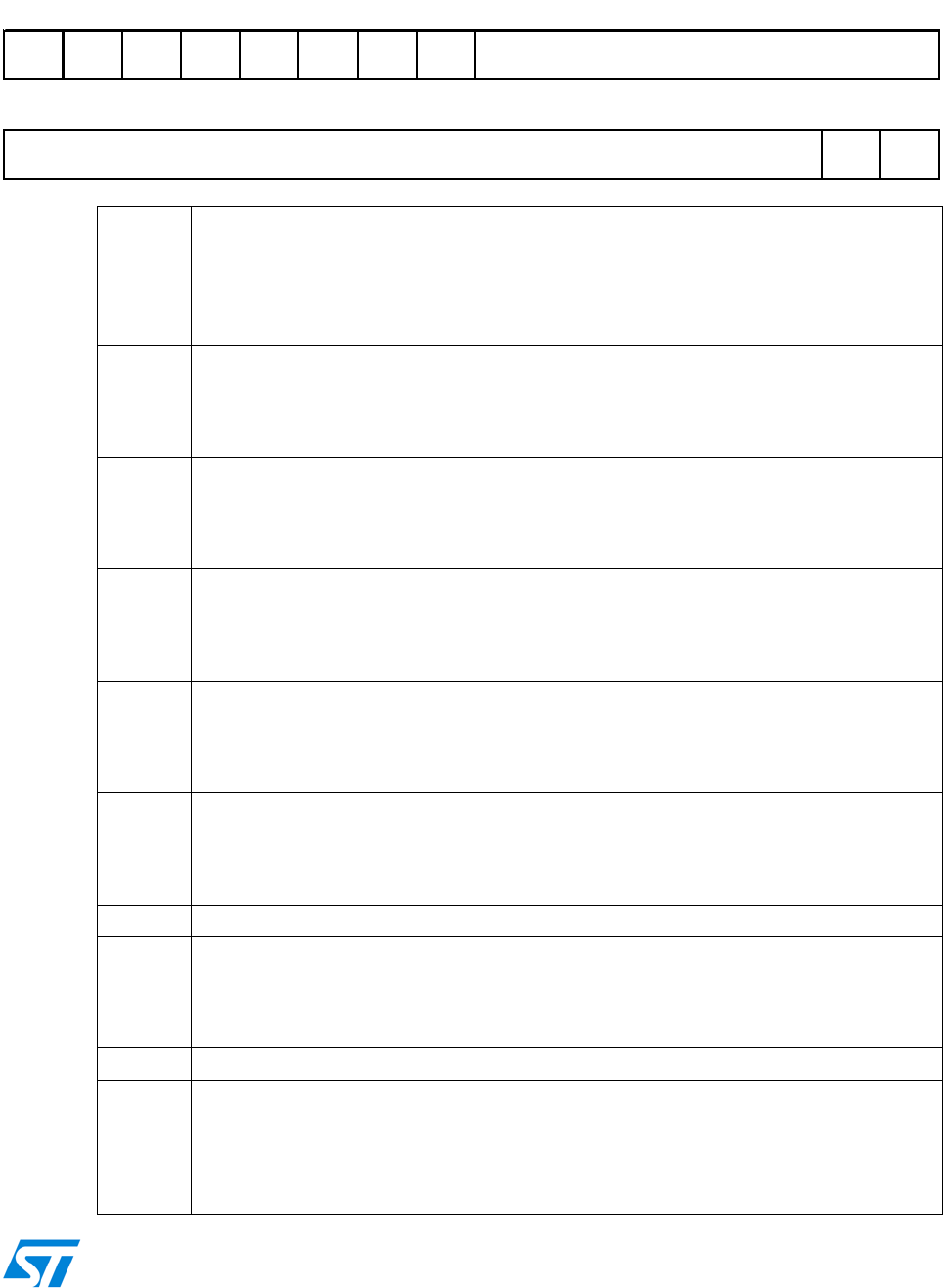

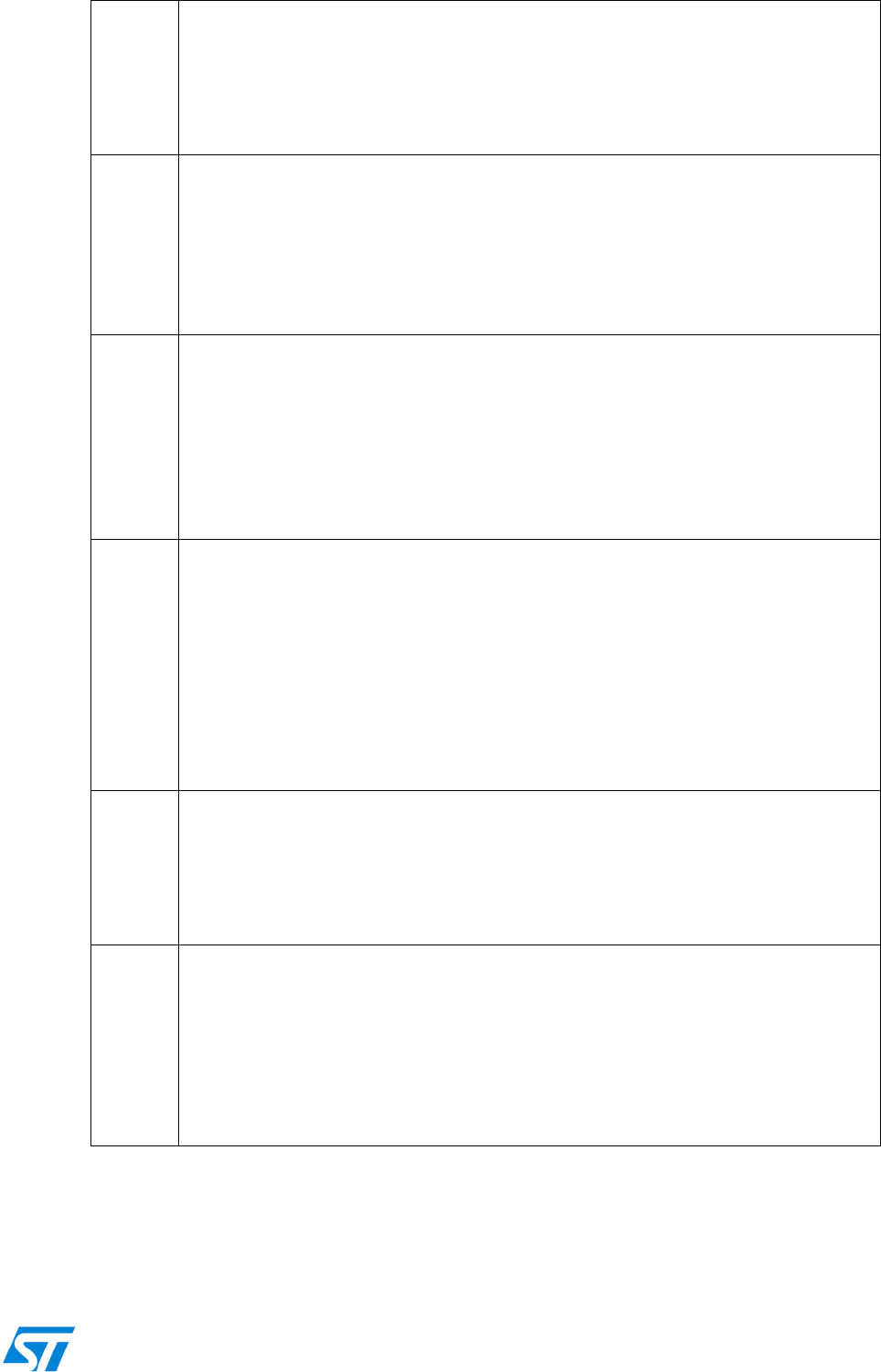

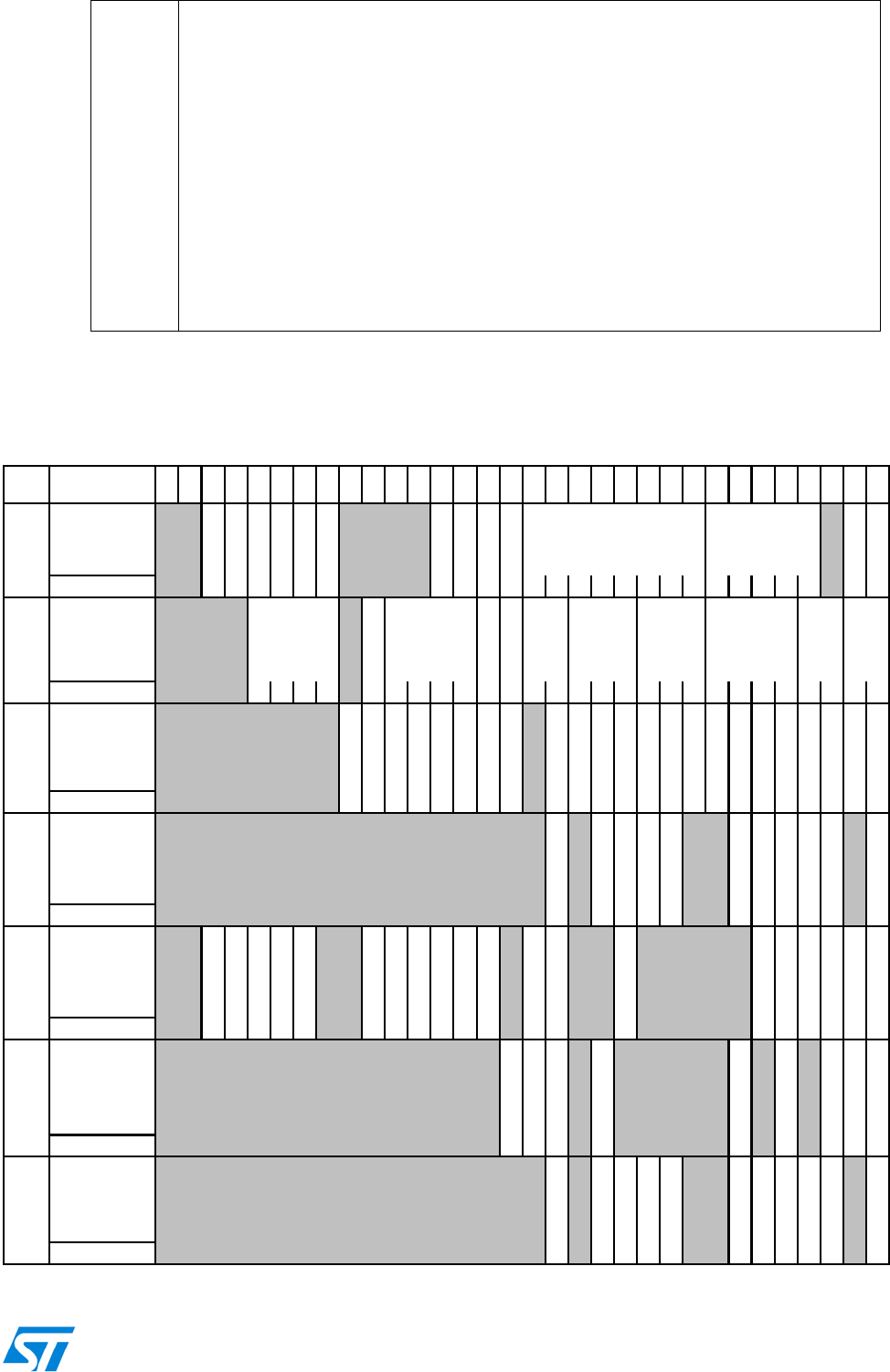

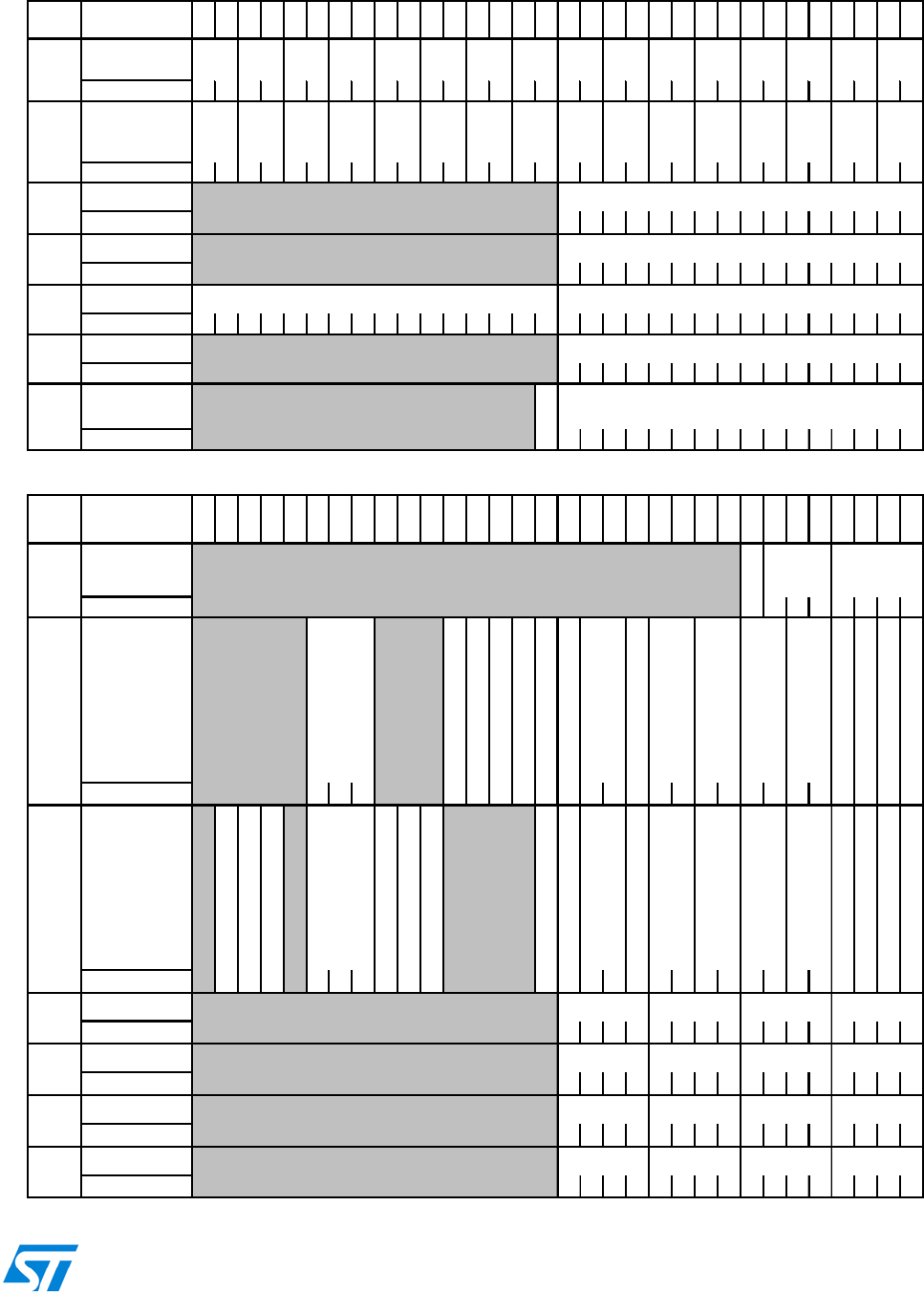

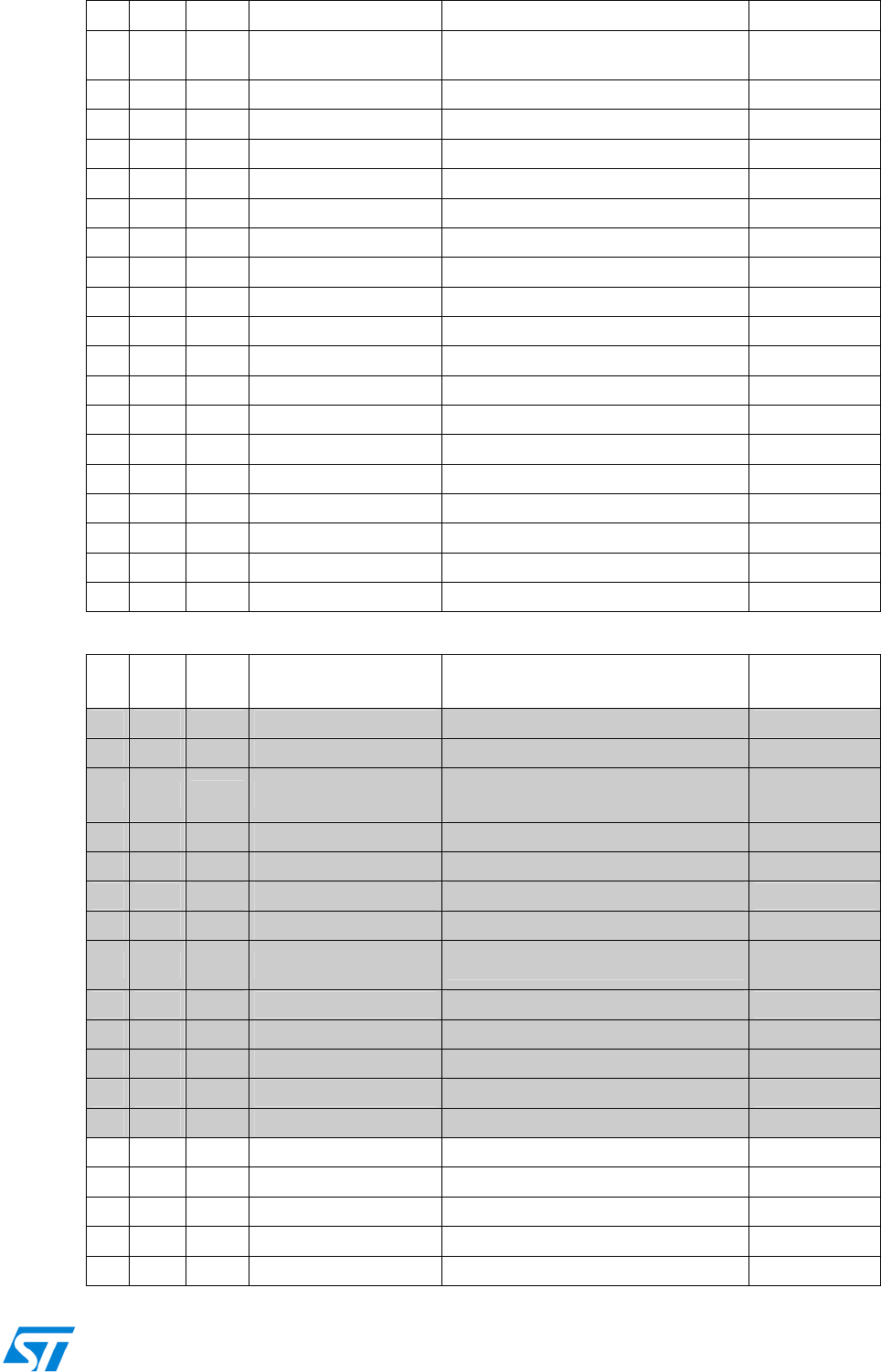

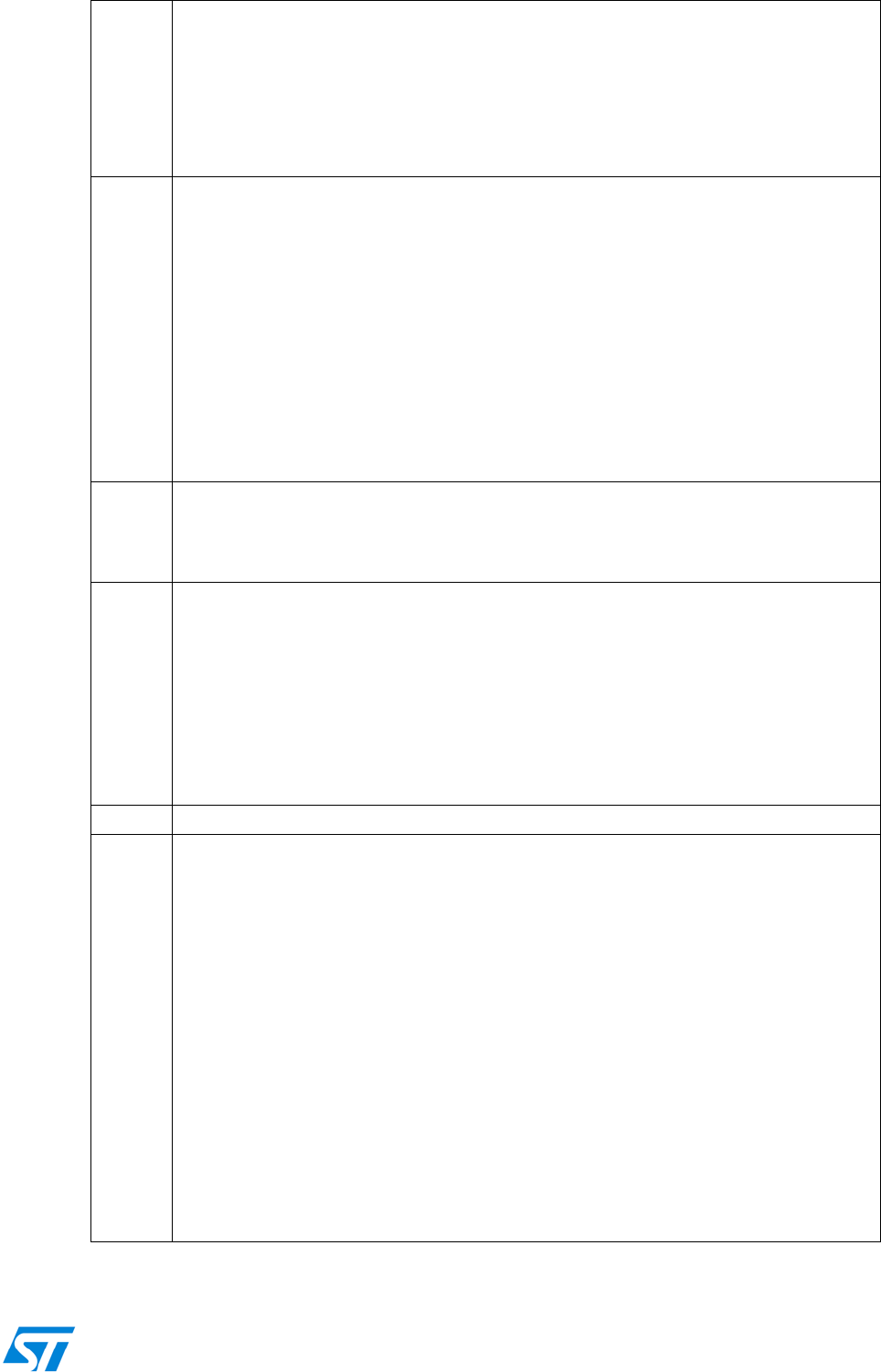

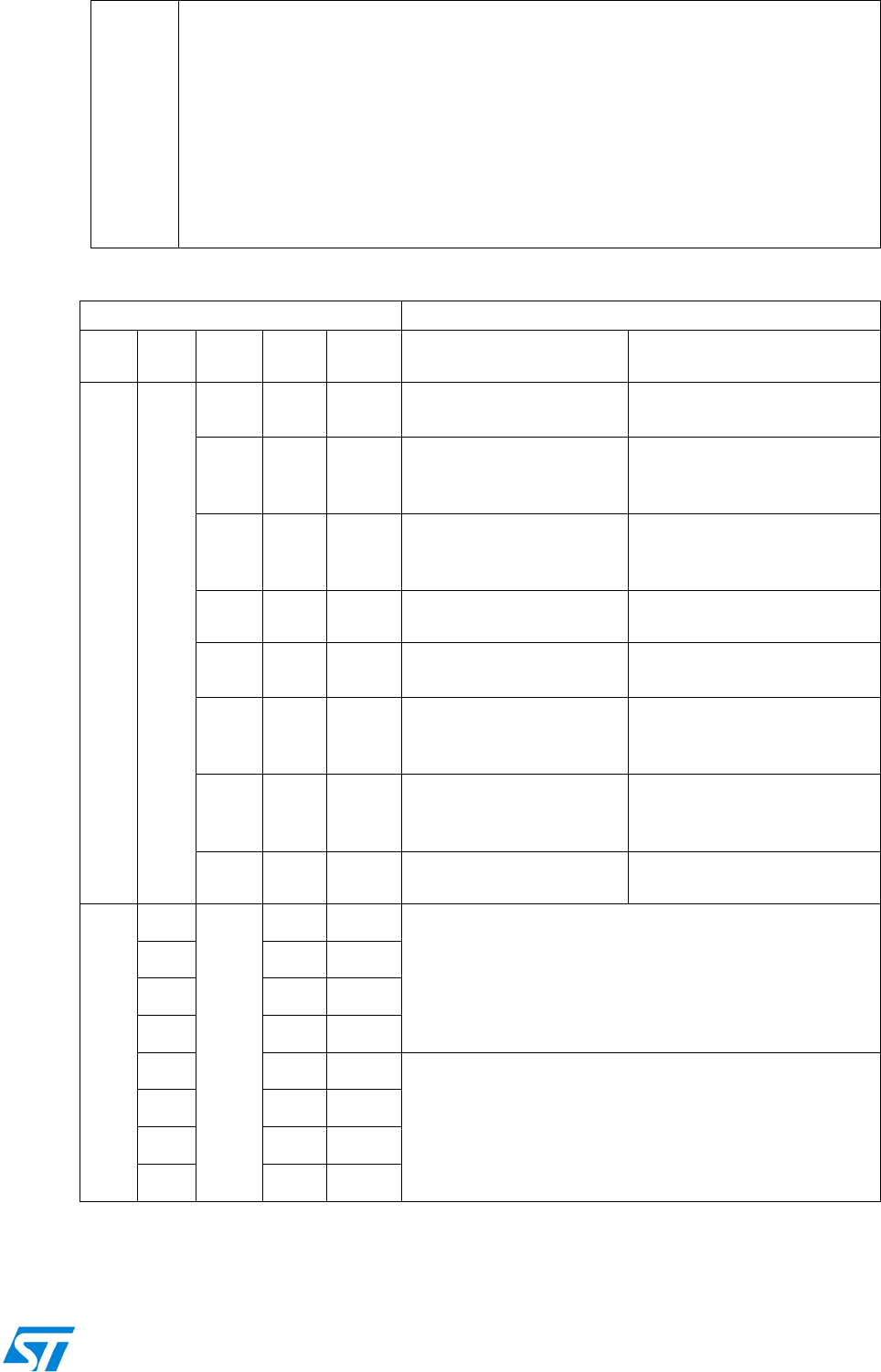

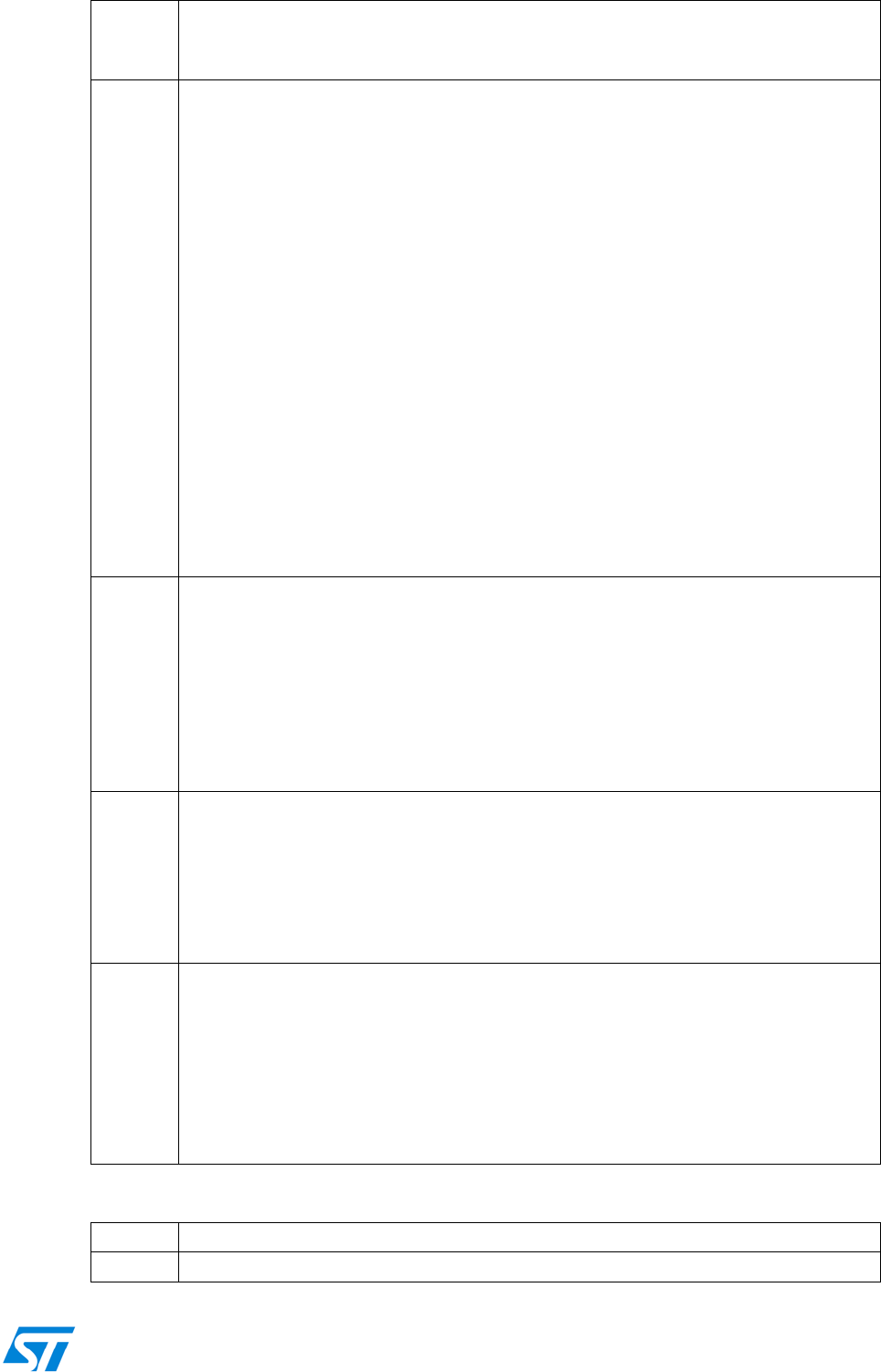

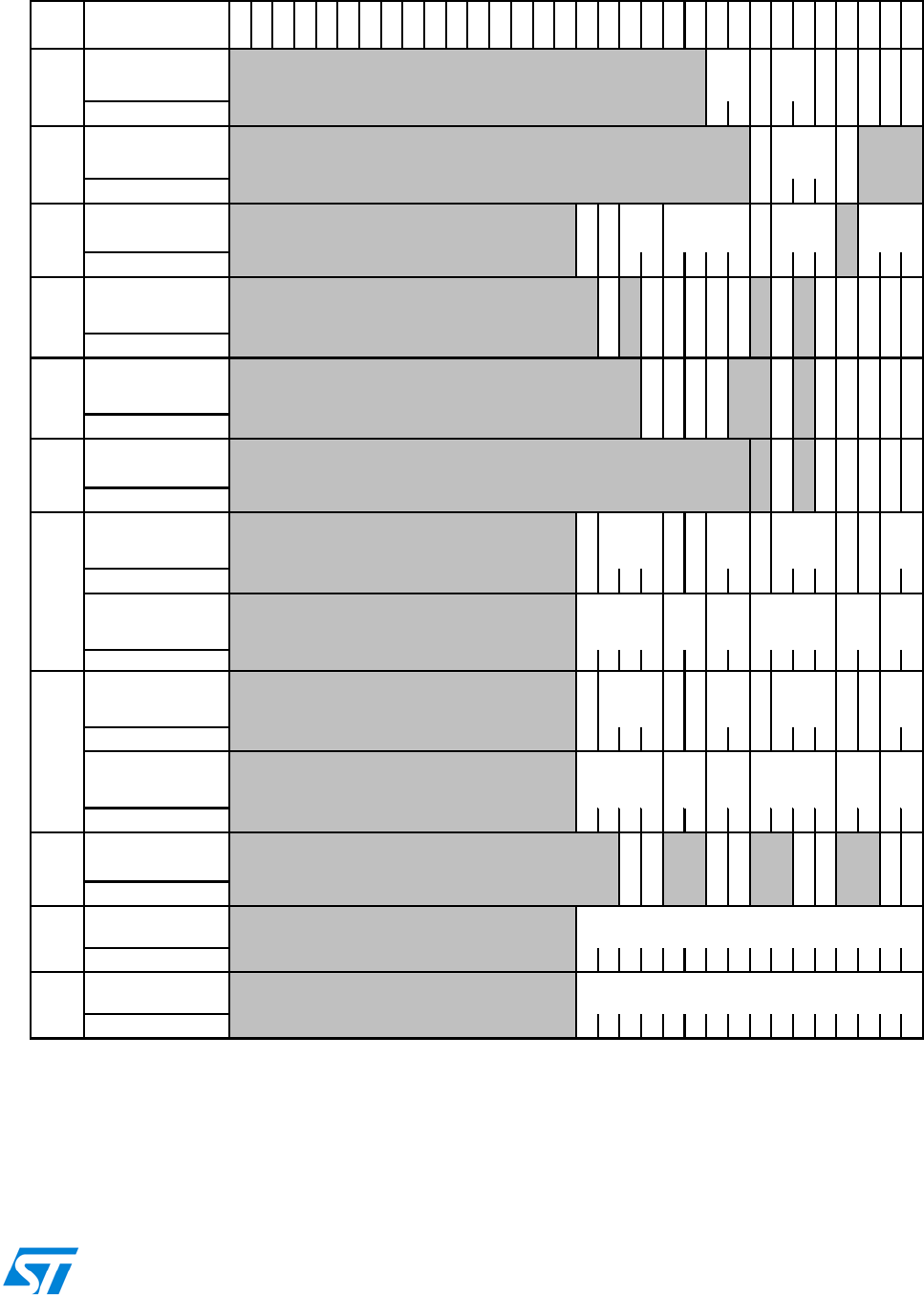

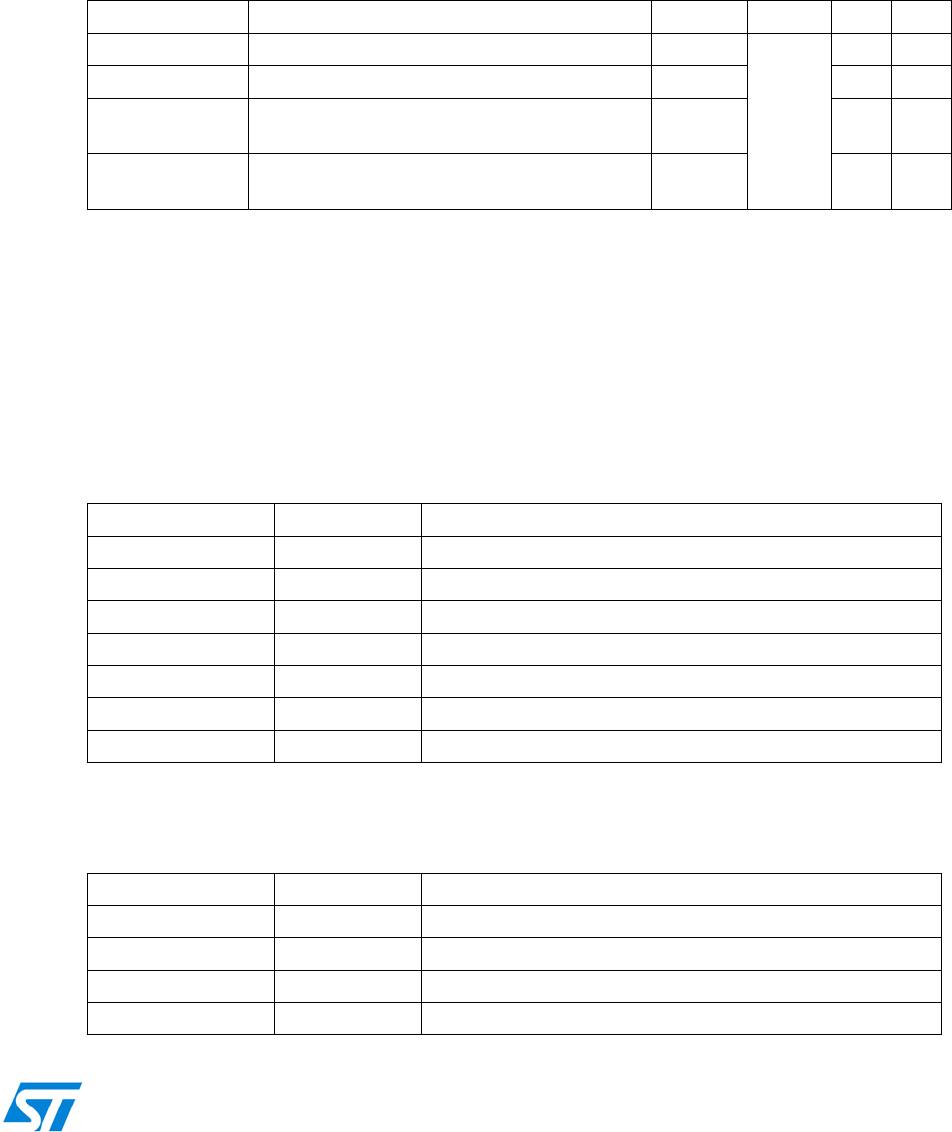

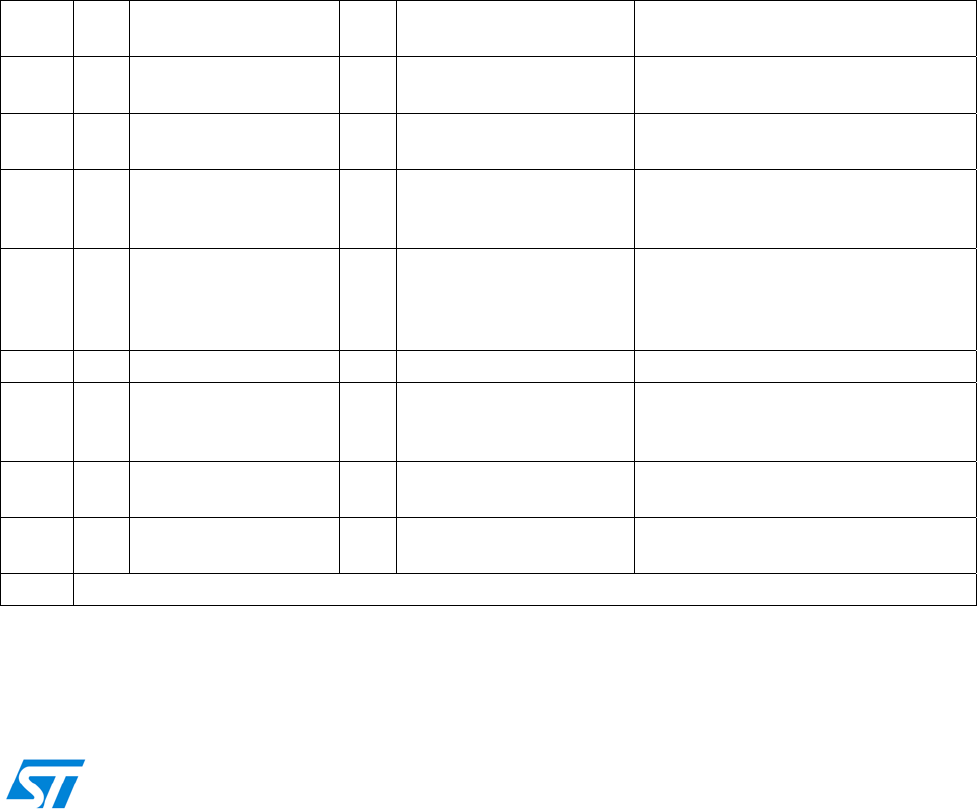

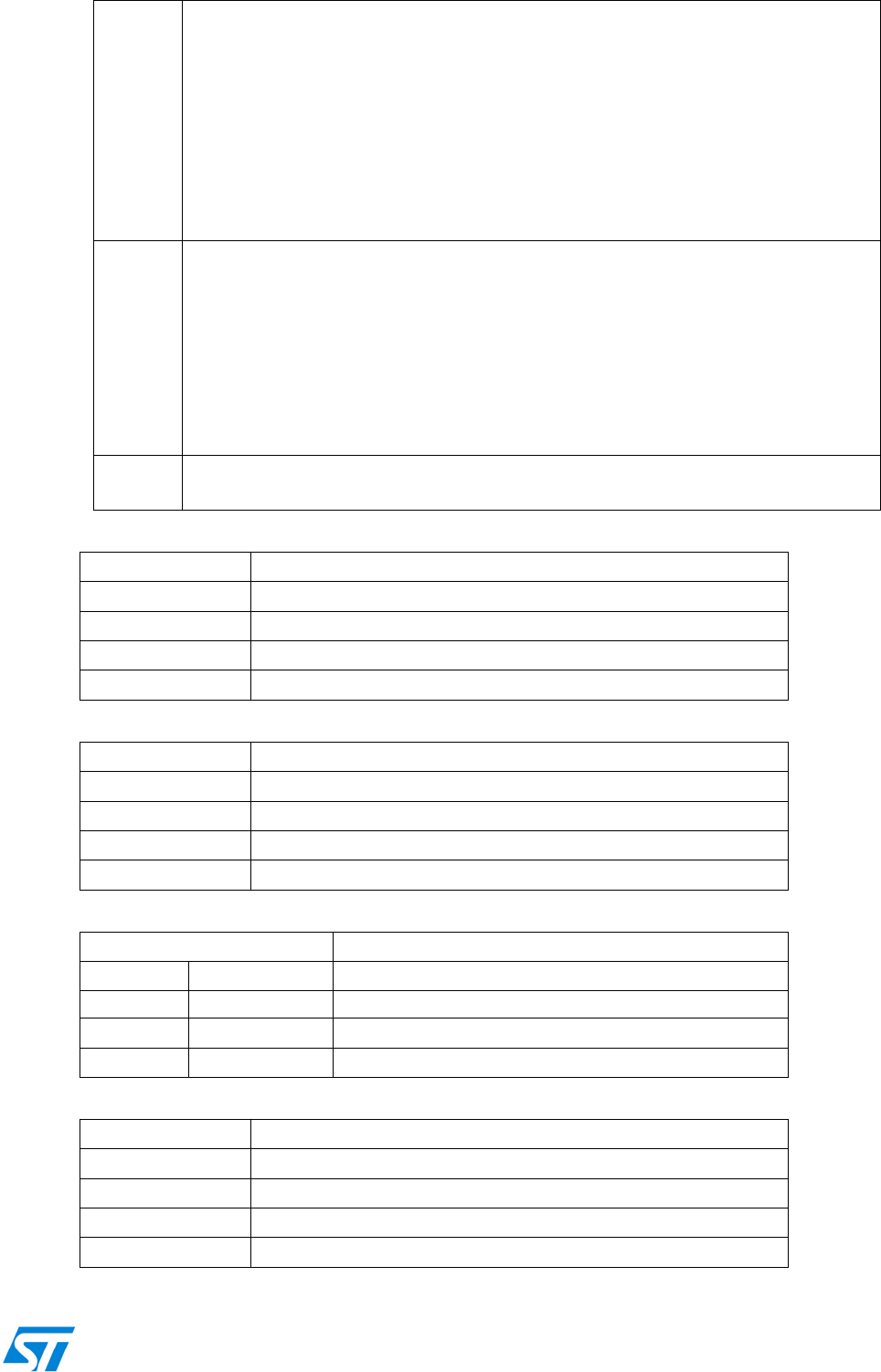

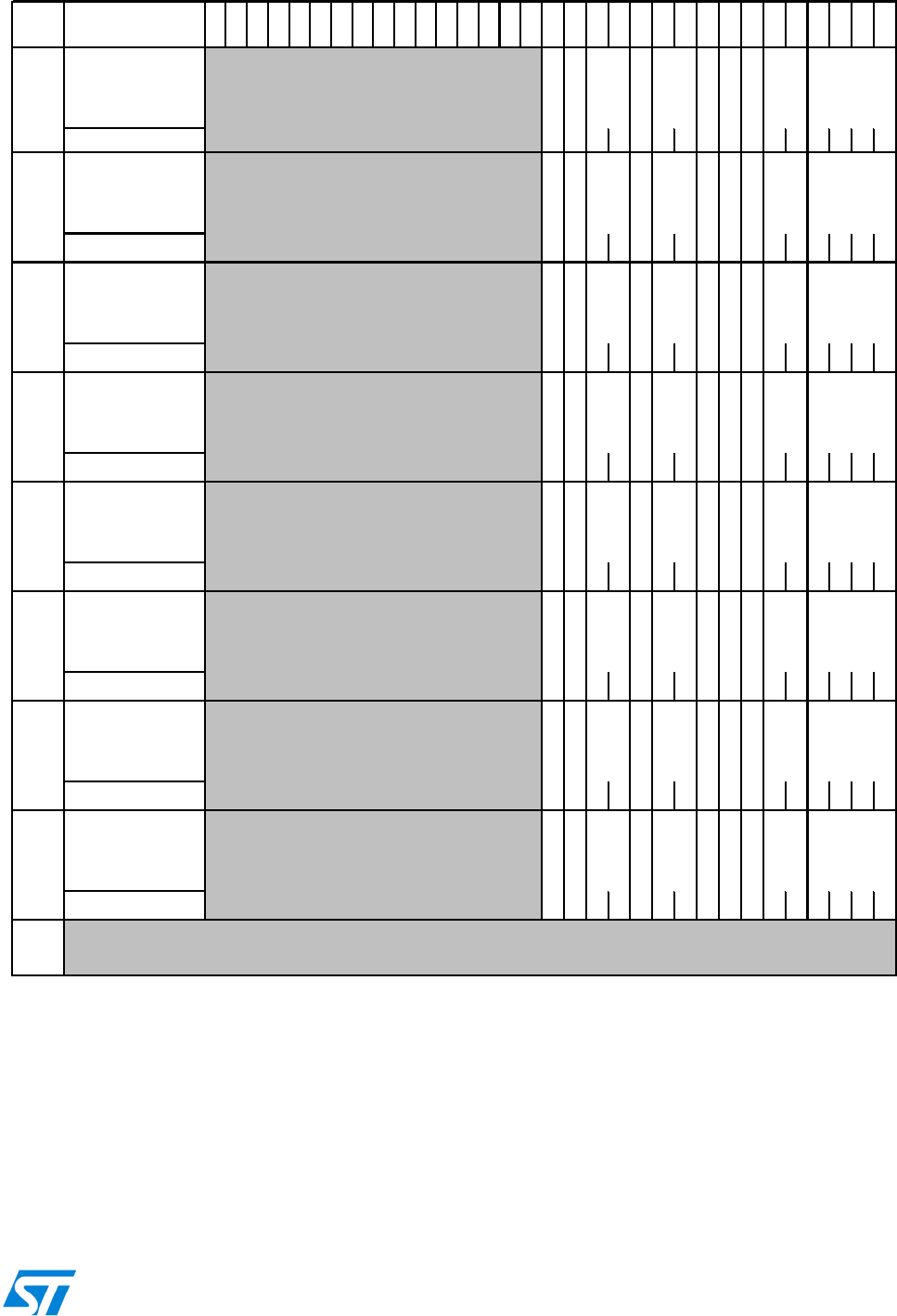

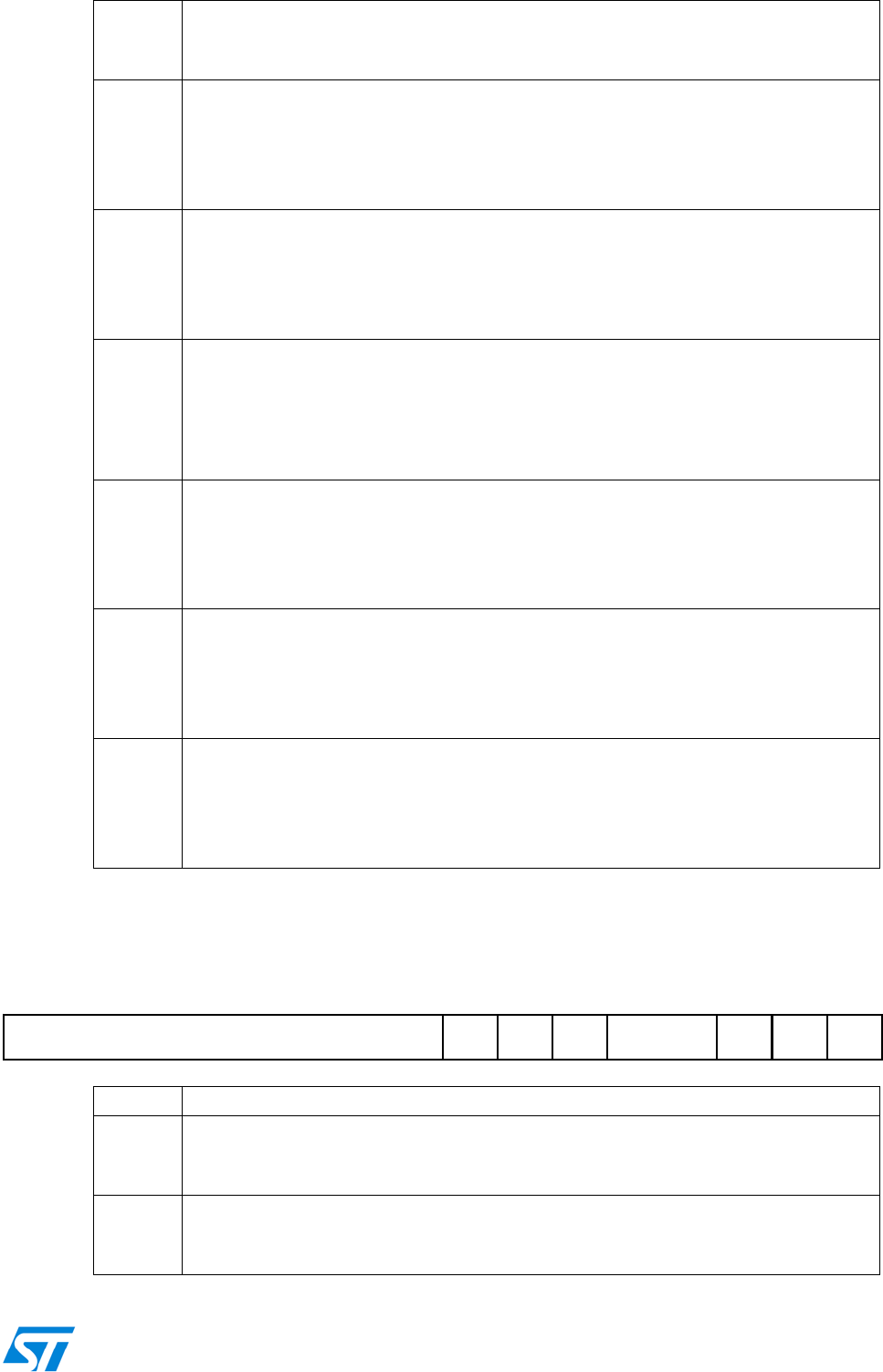

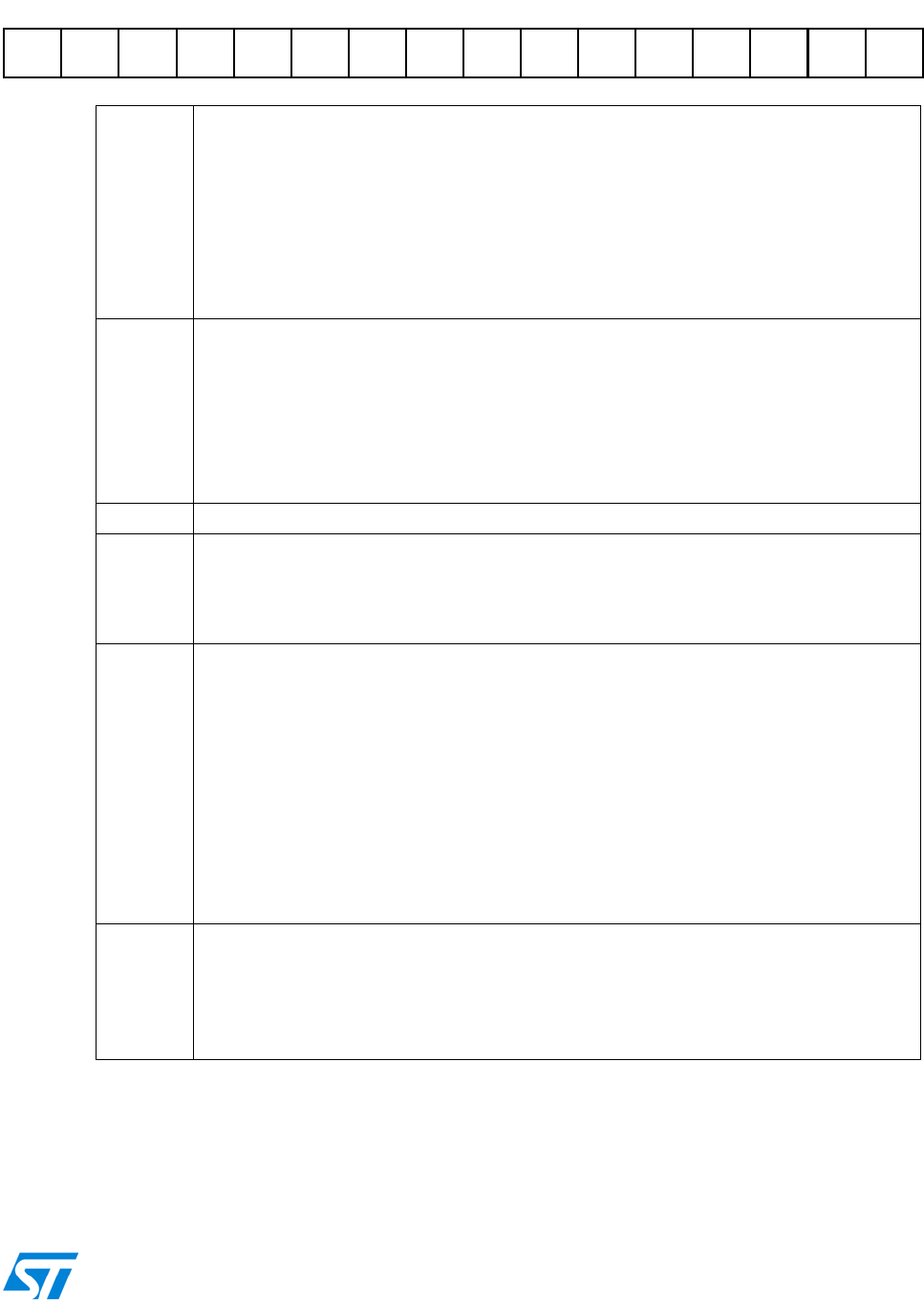

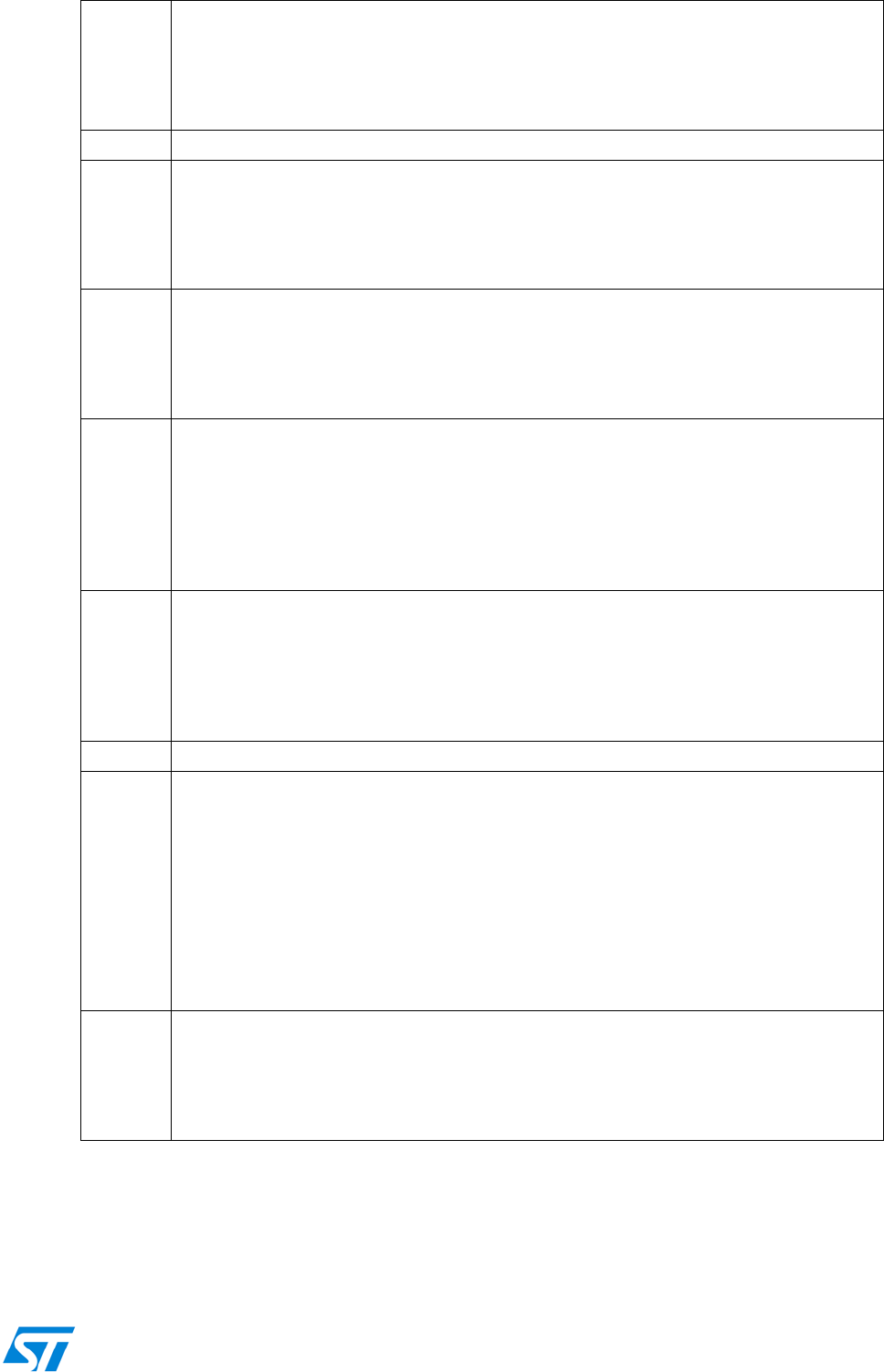

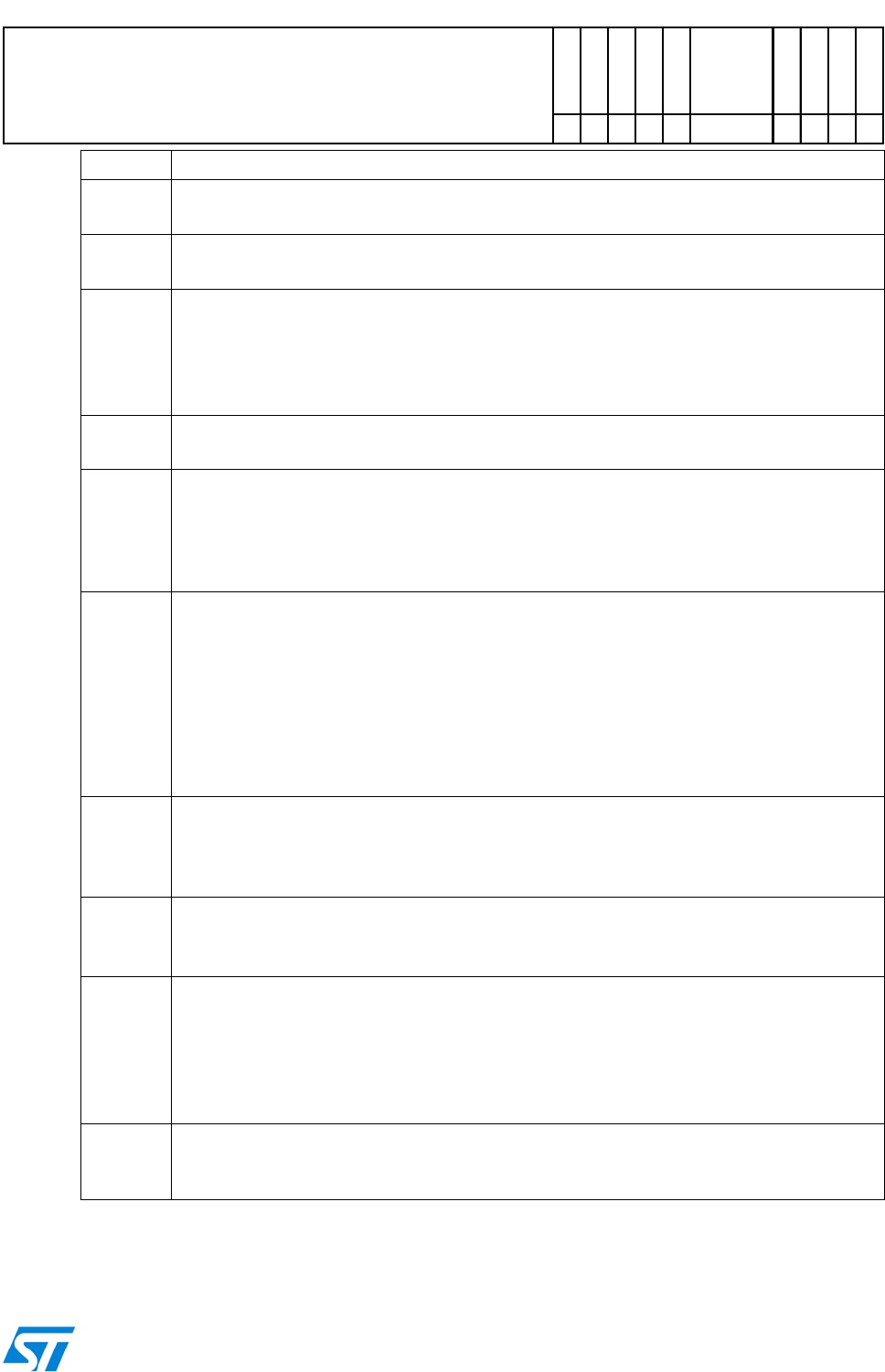

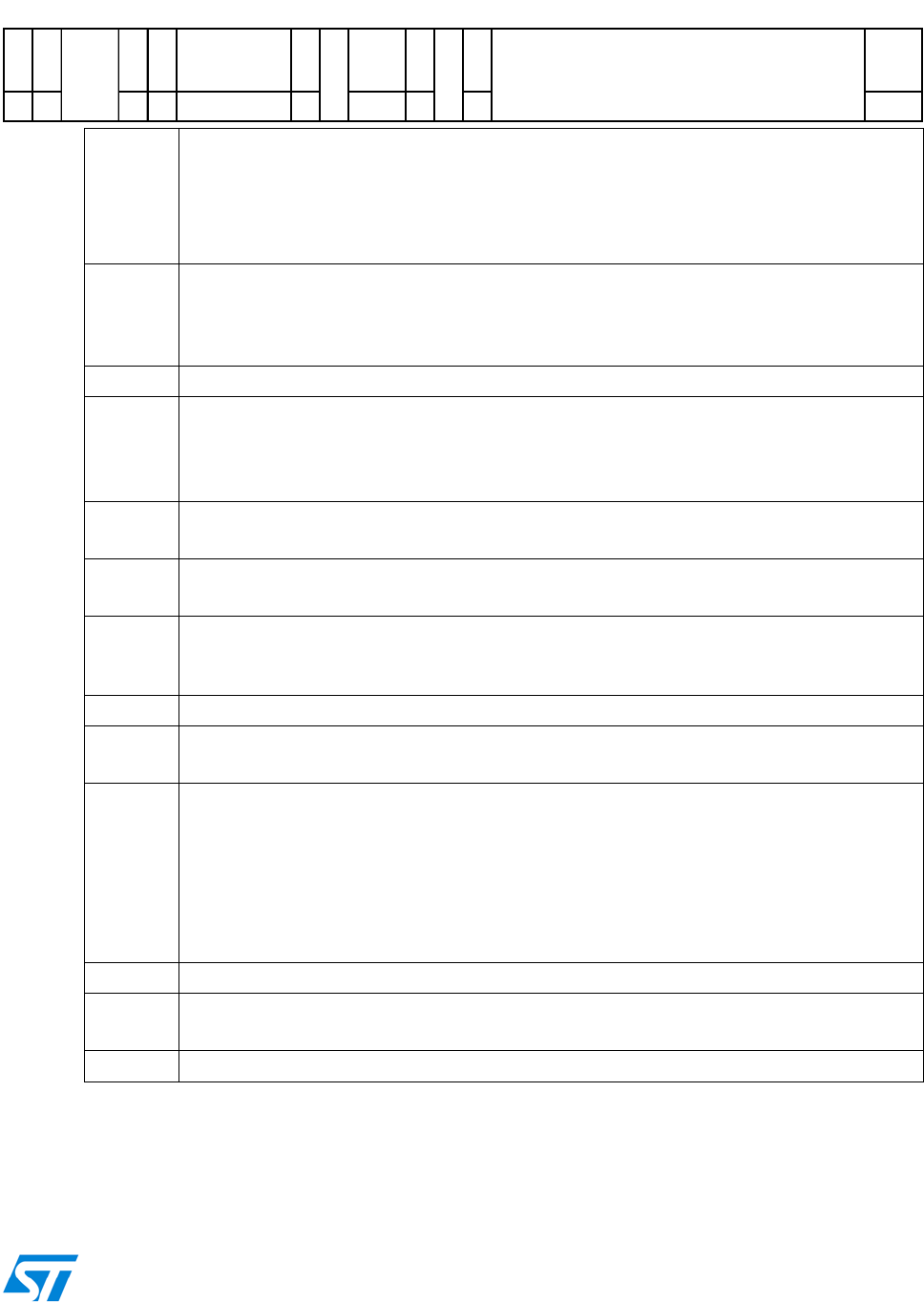

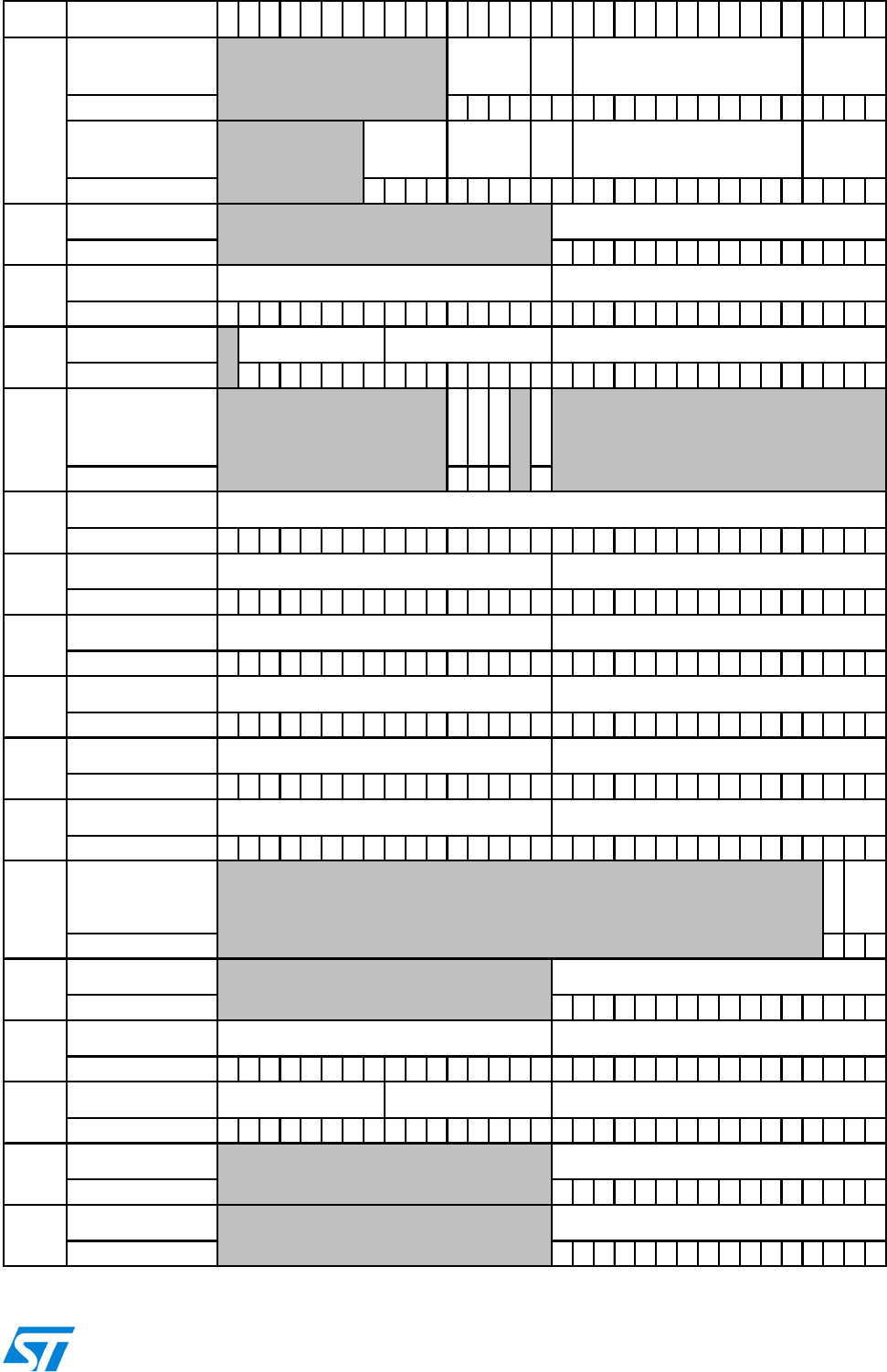

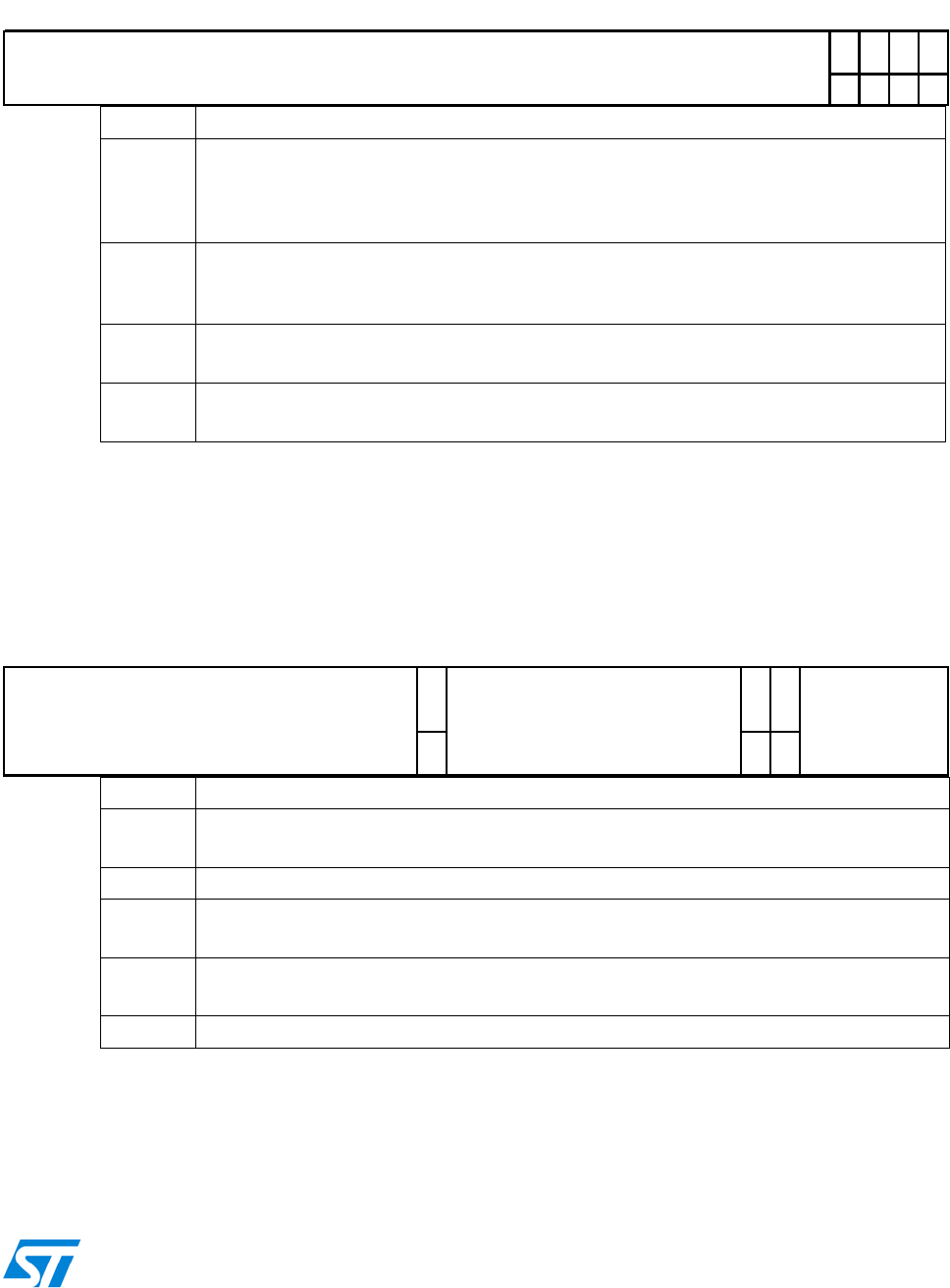

表1 寄存器组起始地址

起始地址 外设 总线 寄存器映像

0x5000 0000 – 0x5003 FFFF USB OTG 全速

28/754

参见26.14.6节

0x4003 0000 – 0x4FFF FFFF

保留 AHB

0x4002 8000 – 0x4002 9FFF 以太网 参见27.8.5节

0x4002 3400 - 0x4002 3FFF

保留

0x4002 3000 - 0x4002 33FF CRC 参见3.4.4节

0x4002 2000 - 0x4002 23FF

闪存存储器接口

0x4002 1400 - 0x4002 1FFF

保留

0x4002 1000 - 0x4002 13FF 复位和时钟控制(RCC) 参见6.3.11节

0x4002 0800 - 0x4002 0FFF 保留

AHB

0x4002 0400 - 0x4002 07FF DMA2 参见10.4.7节

0x4002 0000 - 0x4002 03FF DMA1 参见10.4.7节

0x4001 8400 - 0x4001 7FFF

保留

0x4001 8000 - 0x4001 83FF SDIO 参见20.9.16节

0x4001 4000 - 0x4001 7FFF

保留

0x4001 3C00 - 0x4001 3FFF ADC3 参见11.12.15节

0x4001 3800 - 0x4001 3BFF USART1 参见25.6.8节

0x4001 3400 - 0x4001 37FF TIM8定时器 参见13.4.21节

0x4001 3000 - 0x4001 33FF SPI1 参见23.5节

0x4001 2C00 - 0x4001 2FFF TIM1定时器 参见13.4.21节

0x4001 2800 - 0x4001 2BFF ADC2 参见11.12.15节

0x4001 2400 - 0x4001 27FF ADC1 参见11.12.15节

0x4001 2000 - 0x4001 23FF GPIO端口G 参见8.5节

APB2

0x4001 2000 - 0x4001 23FF GPIO端口F 参见8.5节

0x4001 1800 - 0x4001 1BFF GPIO端口E 参见8.5节

0x4001 1400 - 0x4001 17FF GPIO端口D 参见8.5节

0x4001 1000 - 0x4001 13FF GPIO端口C 参见8.5节

0X4001 0C00 - 0x4001 0FFF GPIO端口B 参见8.5节

0x4001 0800 - 0x4001 0BFF GPIO端口A 参见8.5节

0x4001 0400 - 0x4001 07FF EXTI 参见9.3.7节

0x4001 0000 - 0x4001 03FF AFIO 参见8.5节

0x4000 7800 - 0x4000FFFF

保留 APB1

0x4000 7400 - 0x4000 77FF DAC 参见12.5.14节

0x4000 7000 - 0x4000 73FF 电源控制(PWR) 参见4.4.3节

0x4000 6C00 - 0x4000 6FFF 后备寄存器(BKP) 参见5.4.5节

0x4000 6800 - 0x4000 6BFF bxCAN2 参见22.9.5节

0x4000 6400 - 0x4000 67FF bxCAN1 参见22.9.5节

0x4000 6000(1) - 0x4000 63FF

USB/CAN共享的512字节SRAM

参照2009年12月 RM0008 Reference Manual 英文第10版

本译文仅供参考,如有翻译错误,请以英文原稿为准。请读者随时注意在ST网站下载更新版本

存储器和总线架构 STM32F10xxx参考手册

0x4000 5C00 - 0x4000 5FFF USB全速设备寄存器

29/754

参见21.5.4节

0x4000 5800 - 0x4000 5BFF I2C2 参见24.6.10节

0x4000 5400 - 0x4000 57FF I2C1 参见24.6.10节

0x4000 5000 - 0x4000 53FF UART5 参见25.6.8节

0x4000 4C00 - 0x4000 4FFF UART4 参见25.6.8节

0x4000 4800 - 0x4000 4BFF USART3 参见25.6.8节

0x4000 4400 - 0x4000 47FF USART2 参见25.6.8节

0x4000 4000 - 0x4000 3FFF

保留

0x4000 3C00 - 0x4000 3FFF SPI3/I2S3 参见23.5节

0x4000 3800 - 0x4000 3BFF SPI2/I2S3 参见23.5节

0x4000 3400 - 0x4000 37FF

保留

0x4000 3000 - 0x4000 33FF 独立看门狗(IWDG) 参见17.4.5节

0x4000 2C00 - 0x4000 2FFF 窗口看门狗(WWDG) 参见18.6.4节

0x4000 2800 - 0x4000 2BFF RTC 参见16.4.7节

0x4000 1800 - 0x4000 27FF

保留

0x4000 1400 - 0x4000 17FF TIM7定时器 参见15.4.9节

0x4000 1000 - 0x4000 13FF TIM6定时器 参见15.4.9节

0x4000 0C00 - 0x4000 0FFF TIM5定时器 参见14.4.19节

0x4000 0800 - 0x4000 0BFF TIM4定时器 参见14.4.19节

0x4000 0400 - 0x4000 07FF TIM3定时器 参见14.4.19节

0x4000 0000 - 0x4000 03FF TIM2定时器 参见14.4.19节

1.只在小容量、中容量和大容量的产品中才有这个共享的SRAM区域,互联型产品中没有这个区域。

2.3.1 嵌入式SRAM

STM32F10xxx内置64K字节的静态SRAM。它可以以字节、半字(16位)或全字(32位)访问。

SRAM的起始地址是0x2000 0000。

2.3.2 位段

Cortex™-M3存储器映像包括两个位段(bit-band)区。这两个位段区将别名存储器区中的每个字

映射到位段存储器区的一个位,在别名存储区写入一个字具有对位段区的目标位执行读-改-写操

作的相同效果。

在STM32F10xxx里,外设寄存器和SRAM都被映射到一个位段区里,这允许执行单一的位段的

写和读操作。

下面的映射公式给出了别名区中的每个字是如何对应位带区的相应位的:

bit_word_addr = bit_band_base + (byte_offset×32) + (bit_number×4)

其中:

bit_word_addr是别名存储器区中字的地址,它映射到某个目标位。

bit_band_base是别名区的起始地址。

byte_offset是包含目标位的字节在位段里的序号

bit_number是目标位所在位置(0-31)

例子:

下面的例子说明如何映射别名区中SRAM地址为0x20000300的字节中的位2:

0x22006008 = 0x22000000 + (0x300×32) + (2×4).

对0x22006008地址的写操作与对SRAM中地址0x20000300字节的位2执行读-改-写操作有着相

同的效果。

参照2009年12月 RM0008 Reference Manual 英文第10版

本译文仅供参考,如有翻译错误,请以英文原稿为准。请读者随时注意在ST网站下载更新版本

存储器和总线架构 STM32F10xxx参考手册

读0x22006008地址返回SRAM中地址0x20000300字节的位2的值(0x01 或 0x00)。

请参考《Cortex™-M3技术参考手册》以了解更多有关位段的信息。

2.3.3 嵌入式闪存

高性能的闪存模块有以下的主要特性:

● 高达512K字节闪存存储器结构:闪存存储器有主存储块和信息块组成:

─ 主存储块容量:

小容量产品主存储块最大为4K×64位,每个存储块划分为32个1K字节的页(见表2)。

中容量产品主存储块最大为16K×64位,每个存储块划分为128个1K字节的页(见表3)。

大容量产品主存储块最大为64K×64位,每个存储块划分为256个2K字节的页(见表4)。

互联型产品主存储块最大为32K×64位,每个存储块划分为128个2K字节的页(见表5)。

─ 信息块容量:

互联型产品有2360×64位(见表5)。

其它产品有258×64位(见表2

30/754

、表3表4)。 、

闪存存储器接口的特性为:

● 带预取缓冲器的读接口(每字为2×64位)

● 选择字节加载器

● 闪存编程/擦除操作

● 访问/写保护

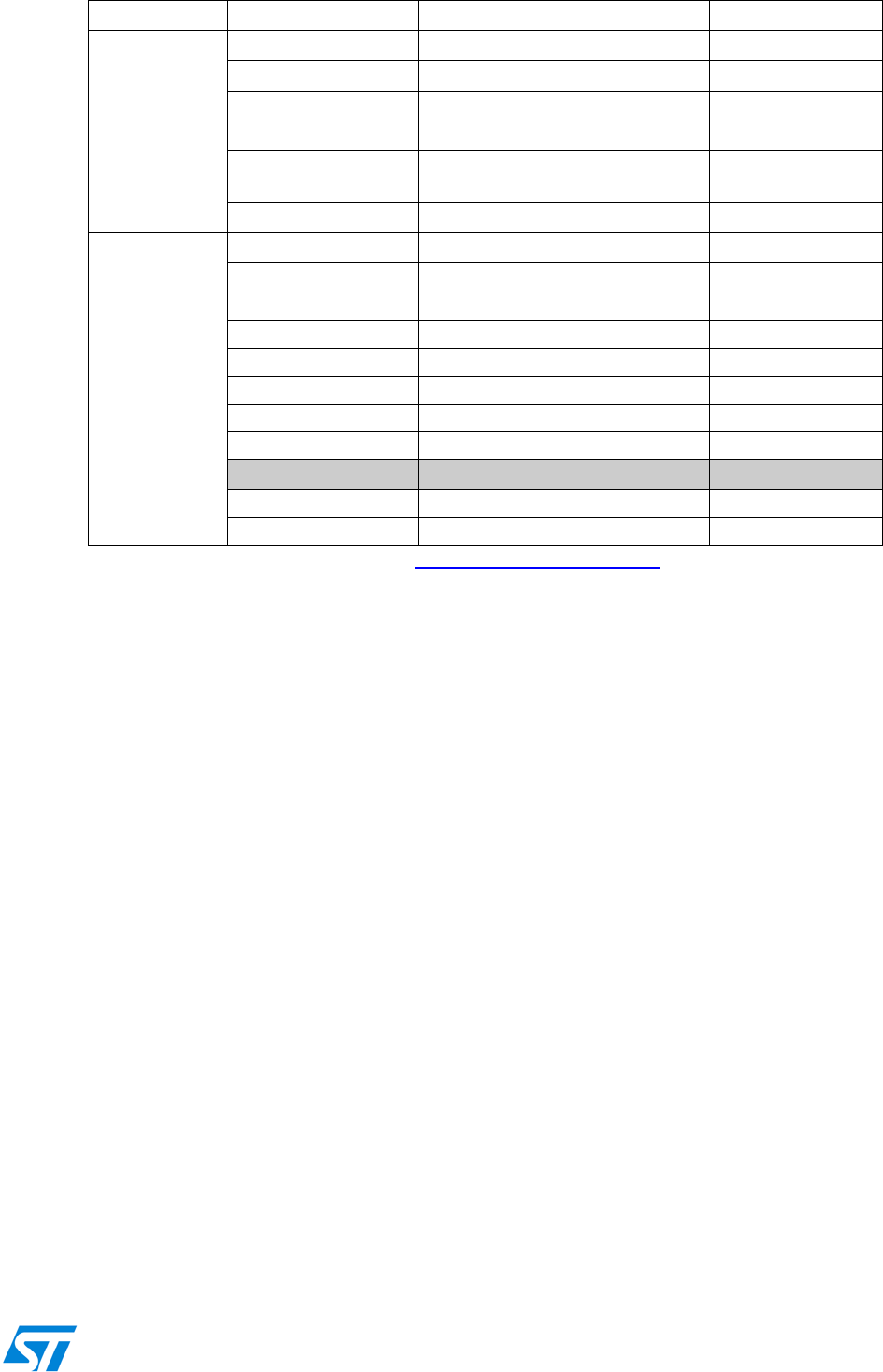

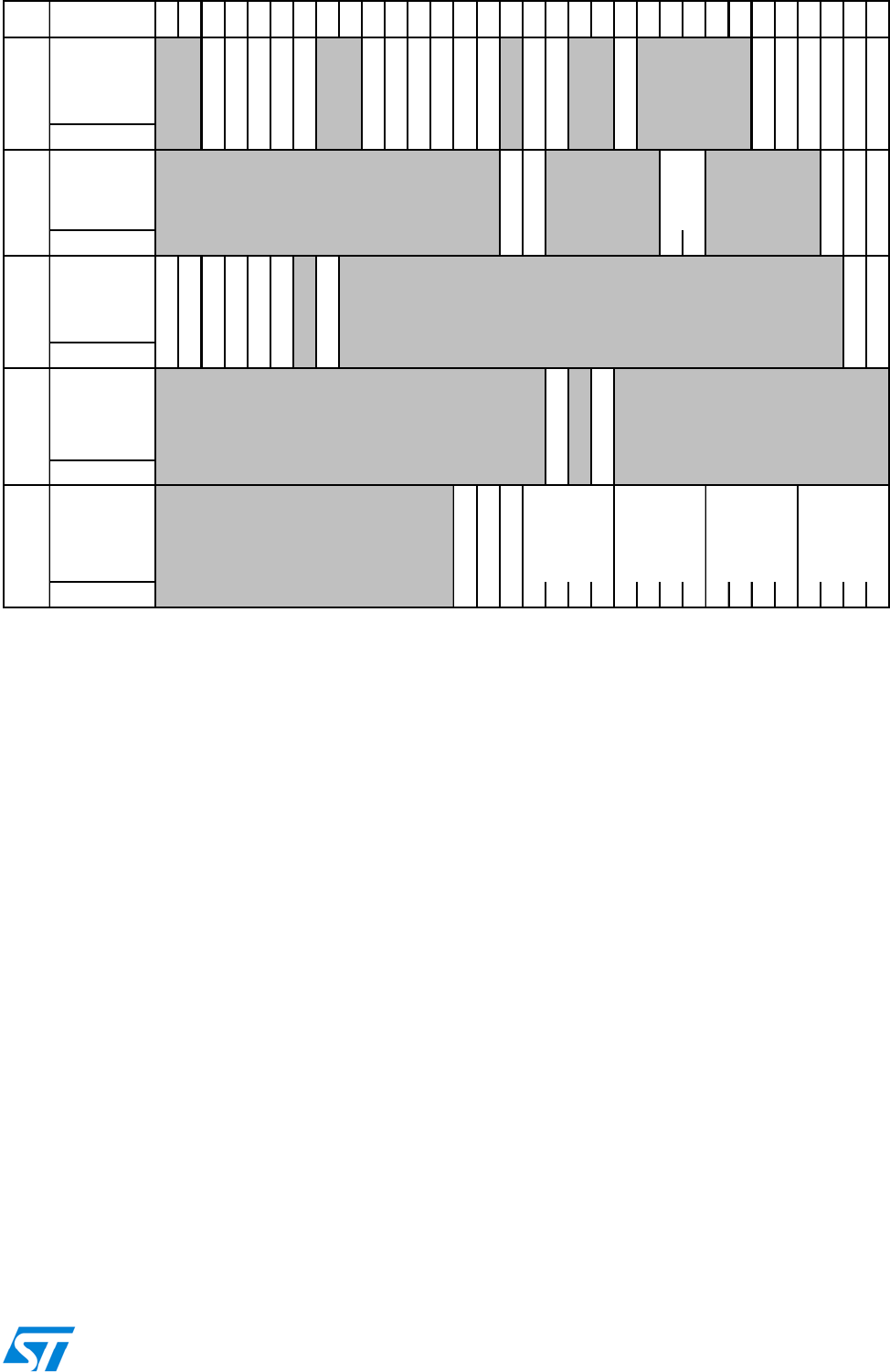

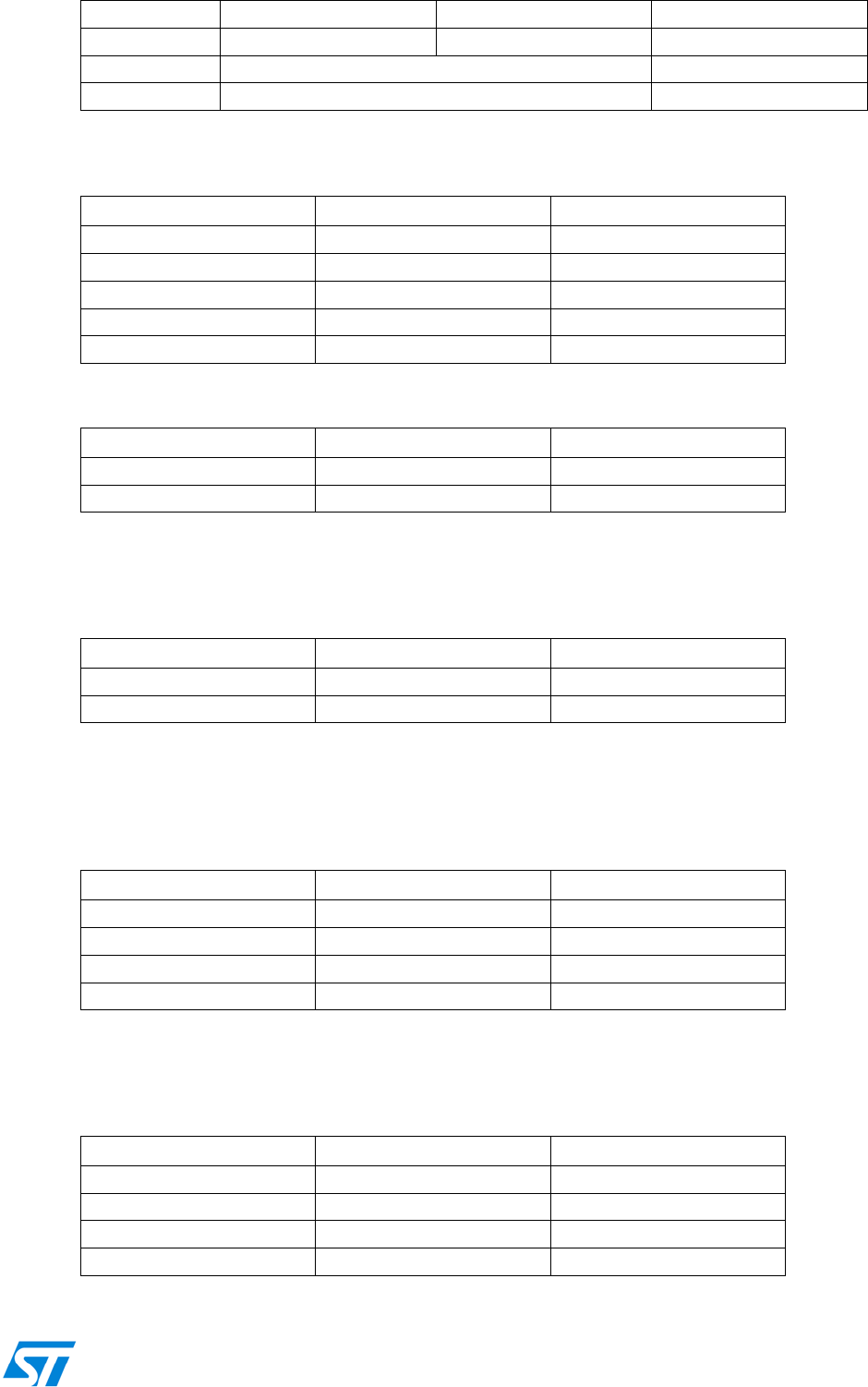

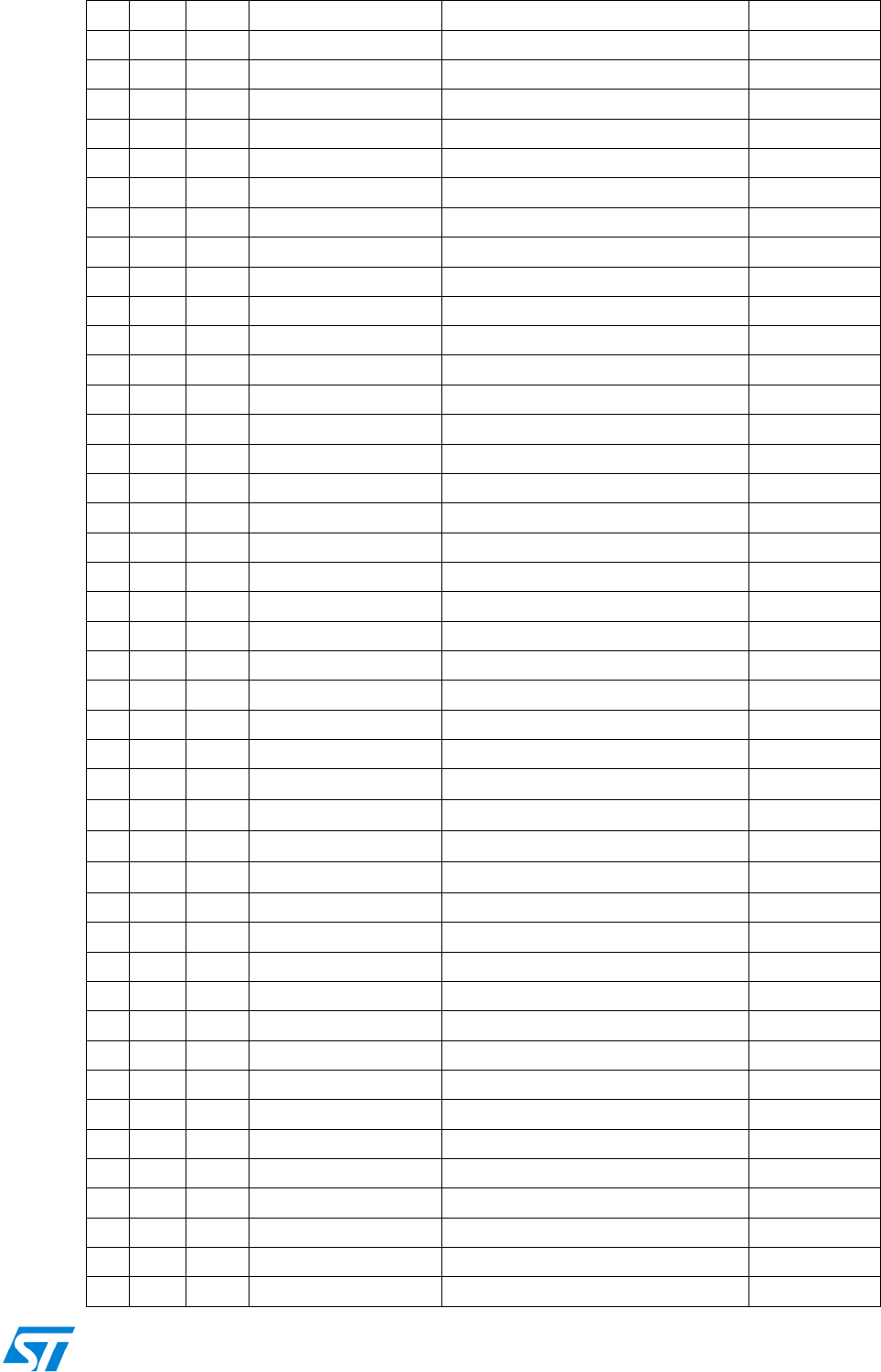

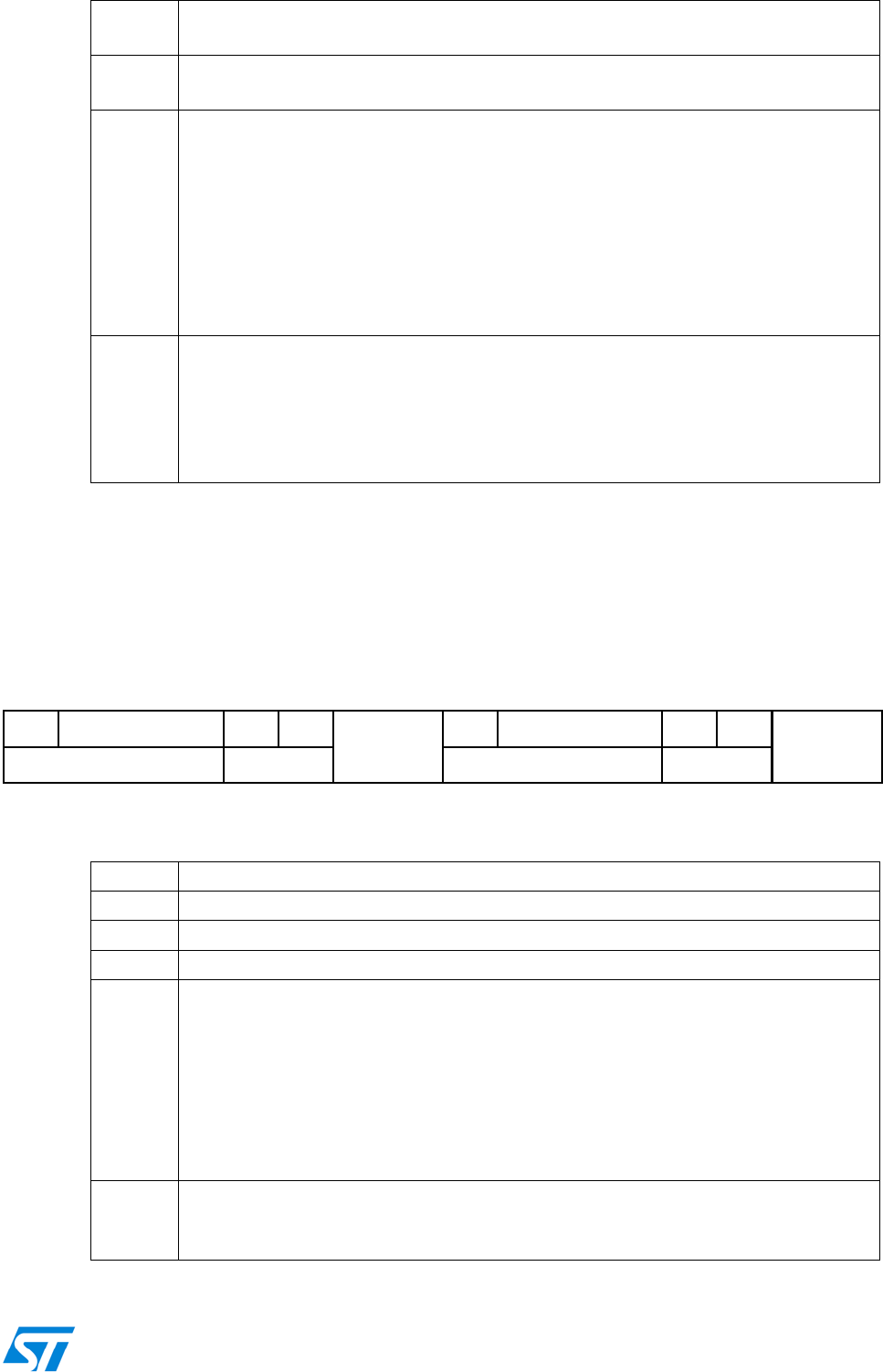

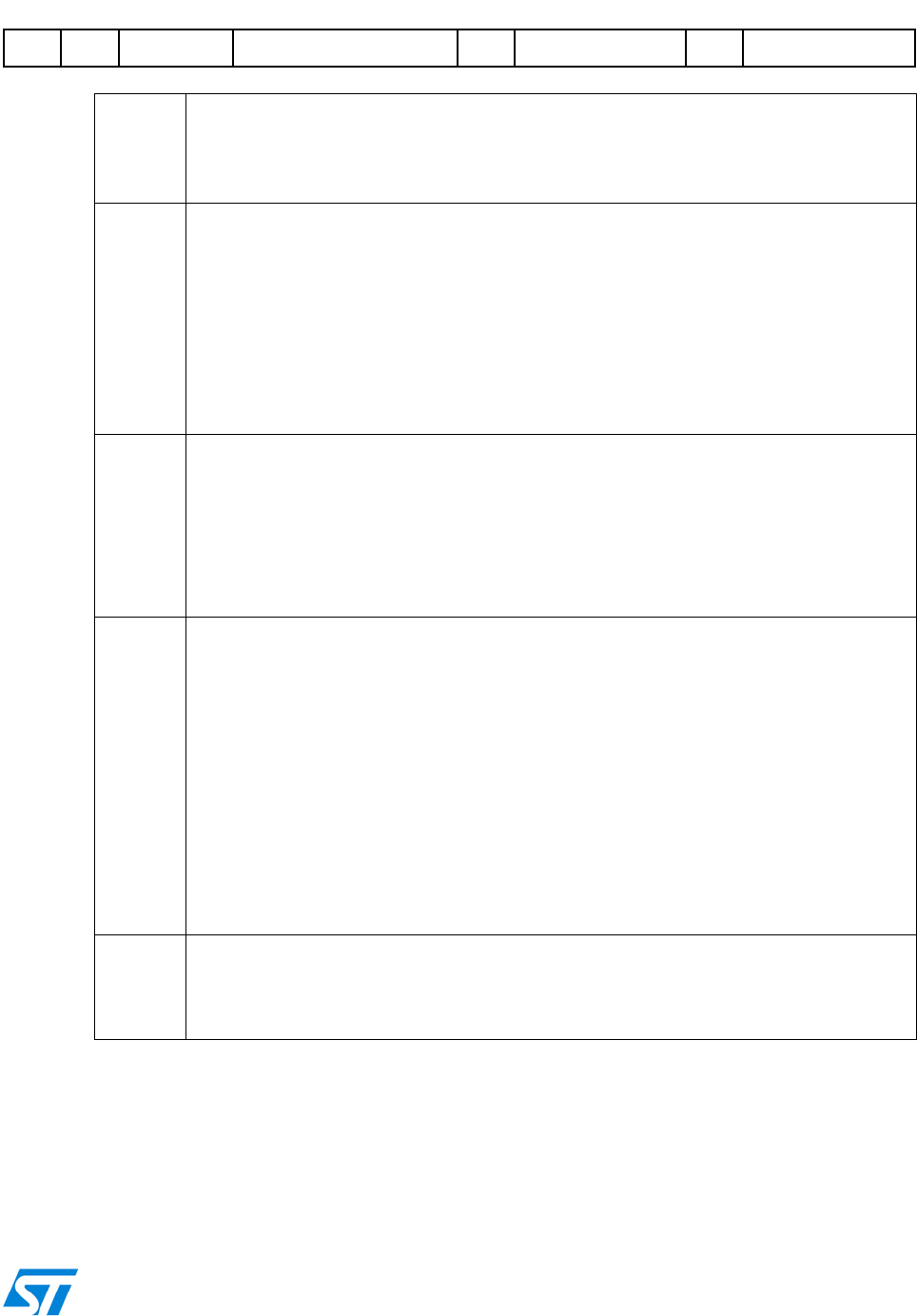

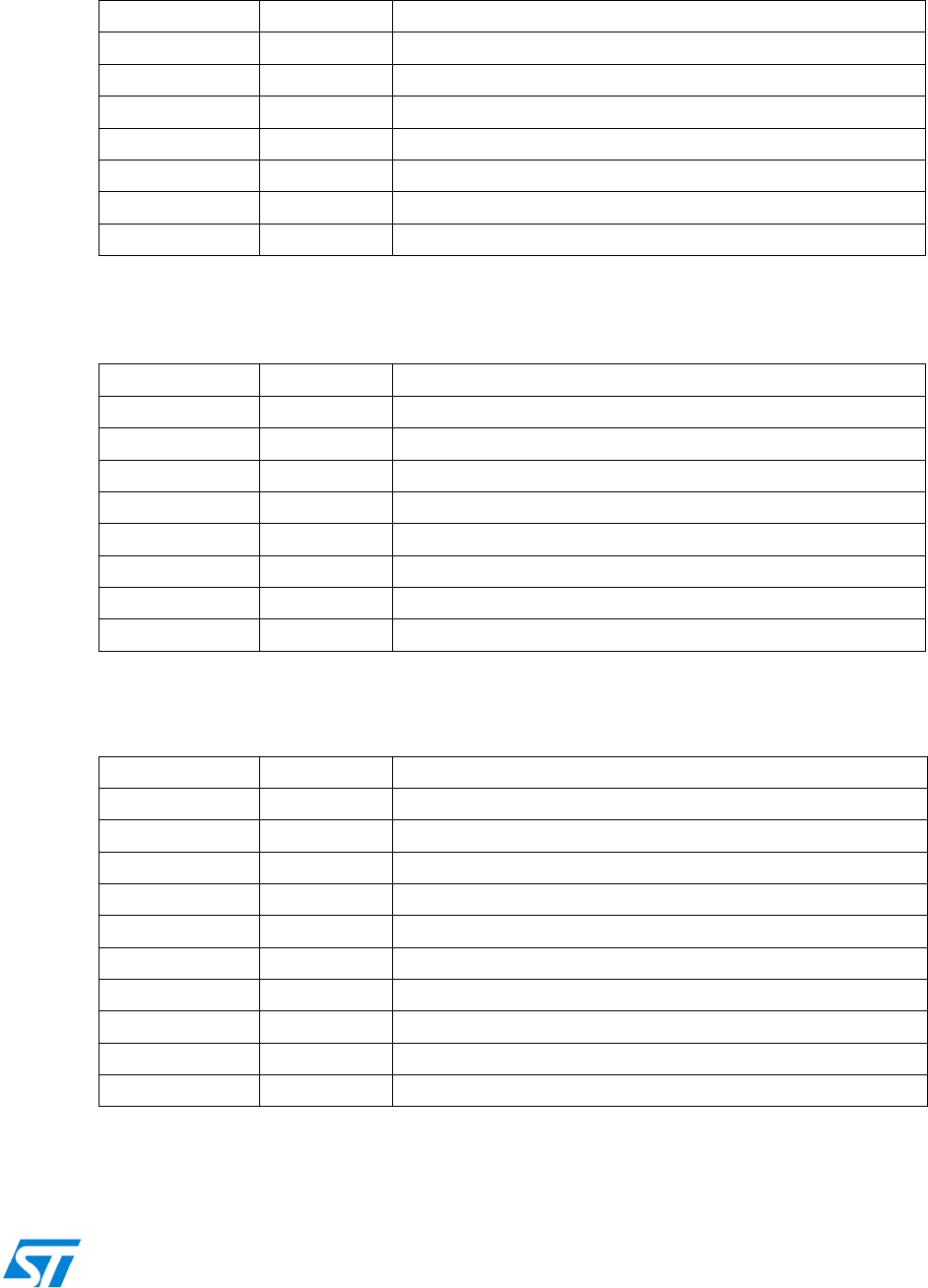

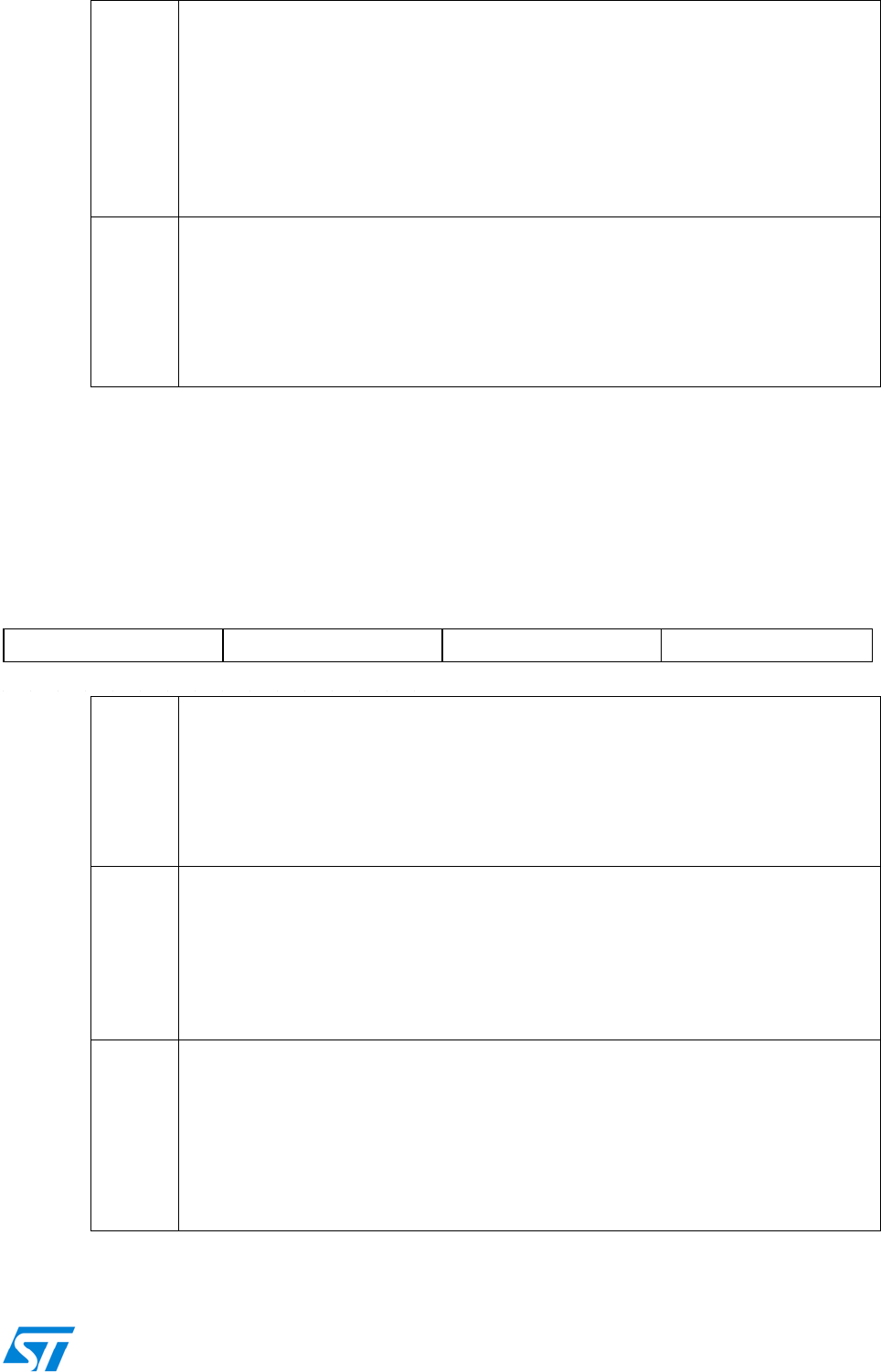

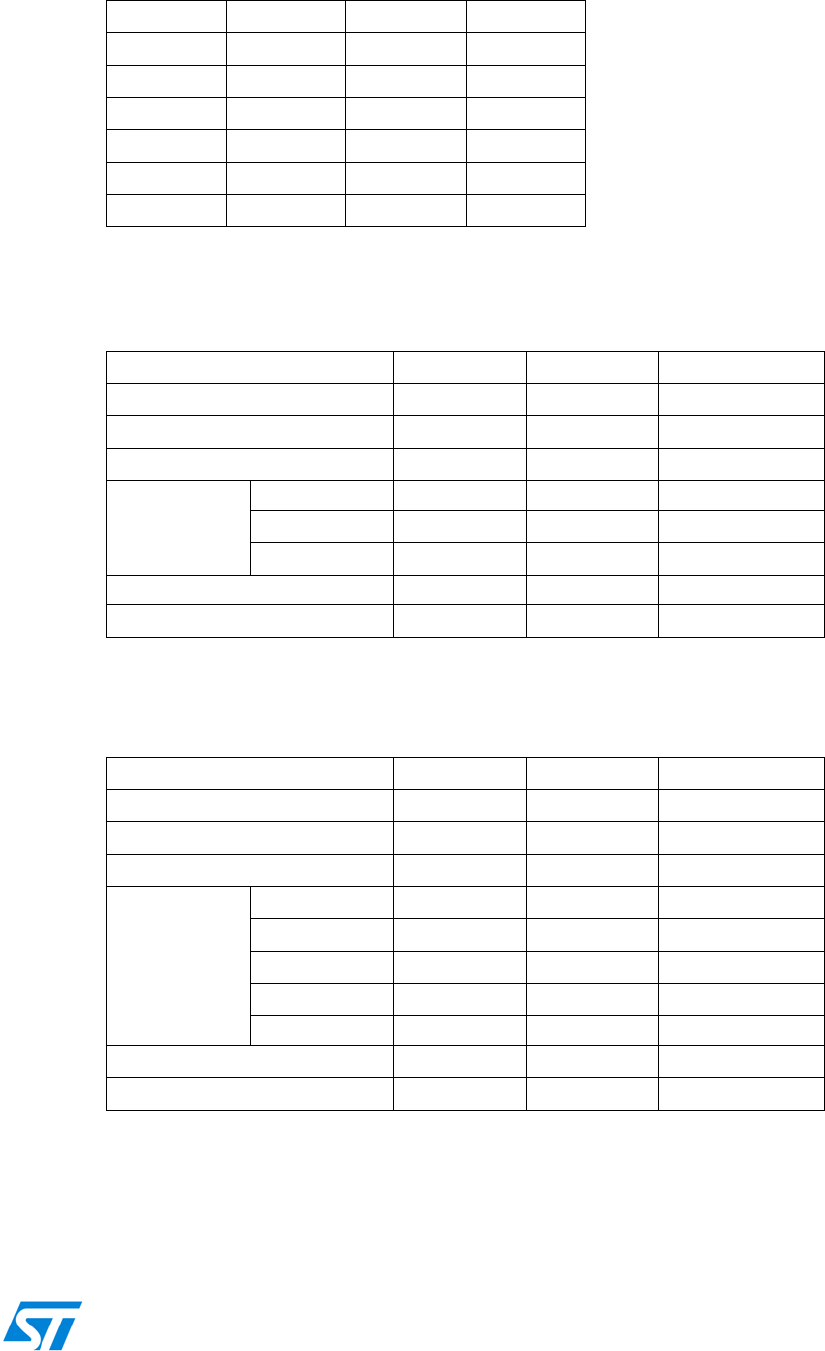

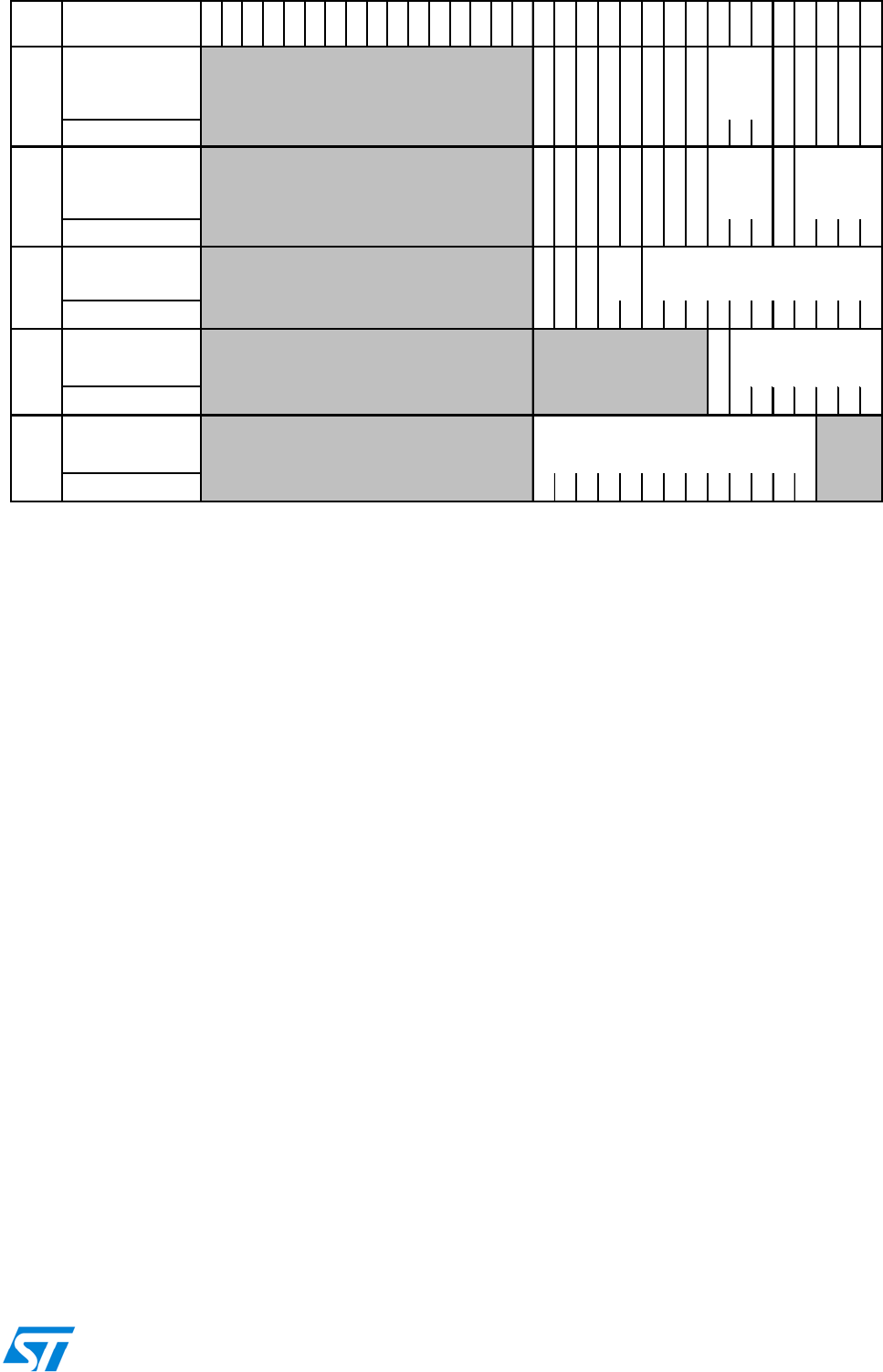

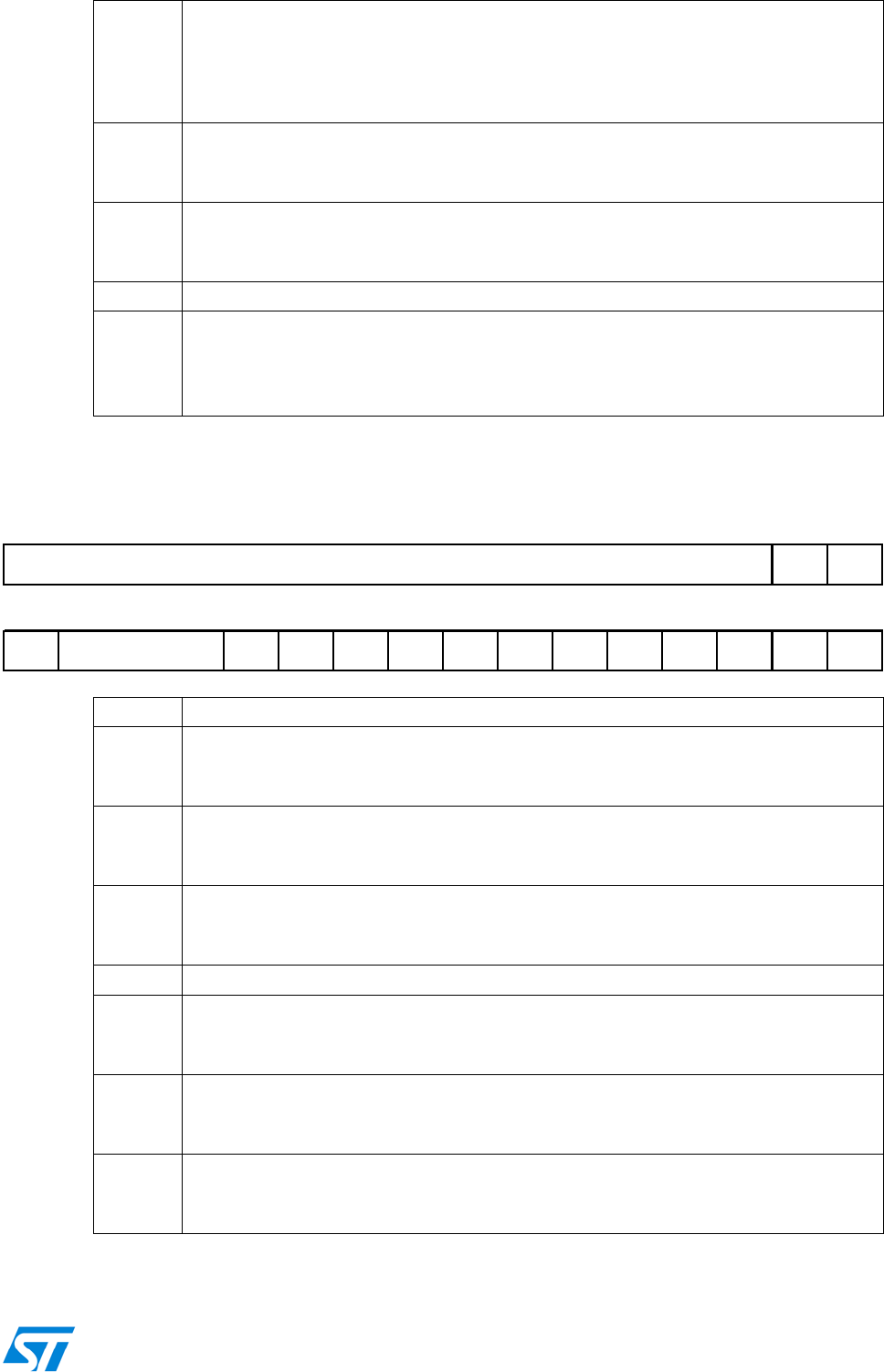

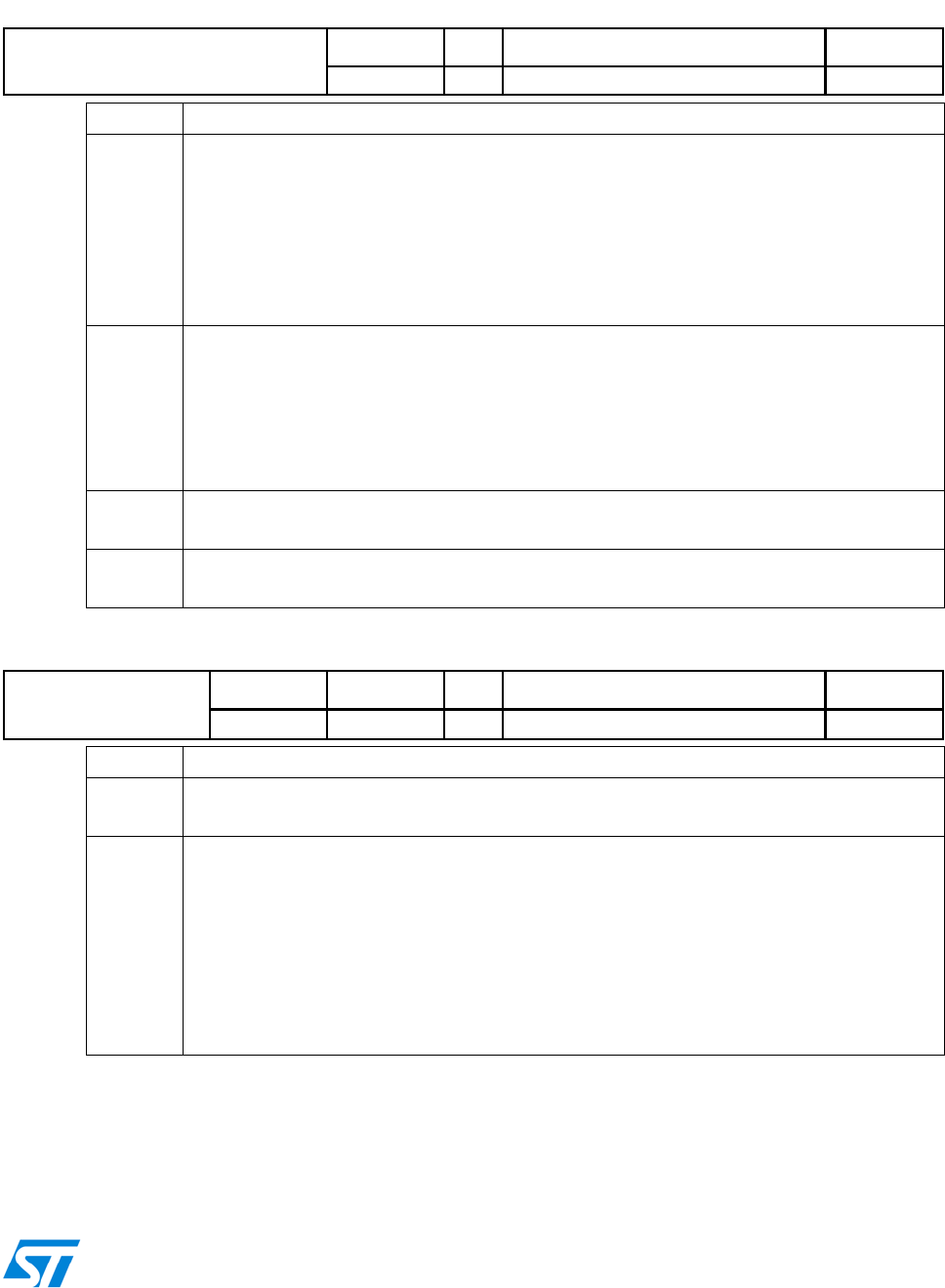

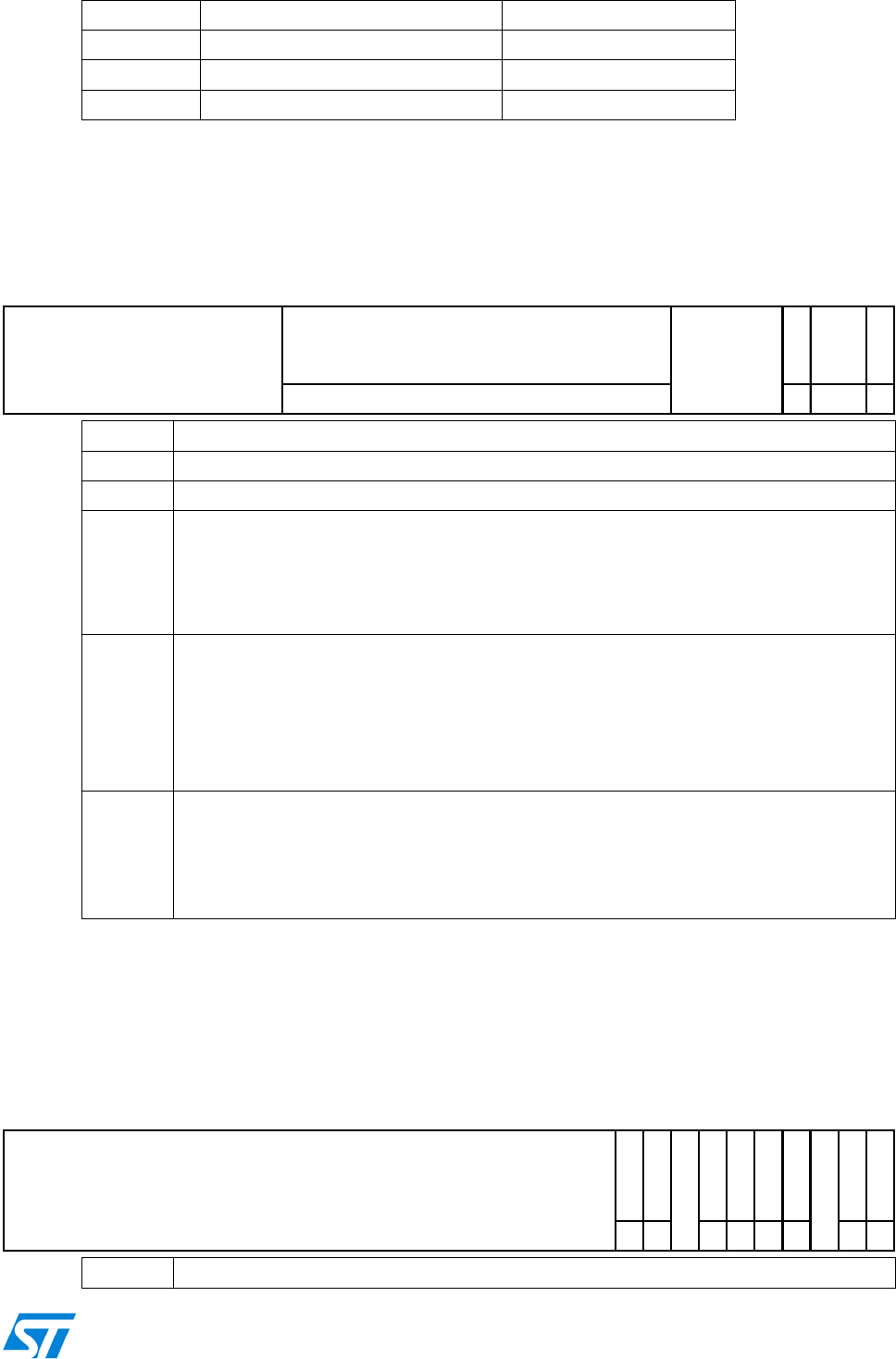

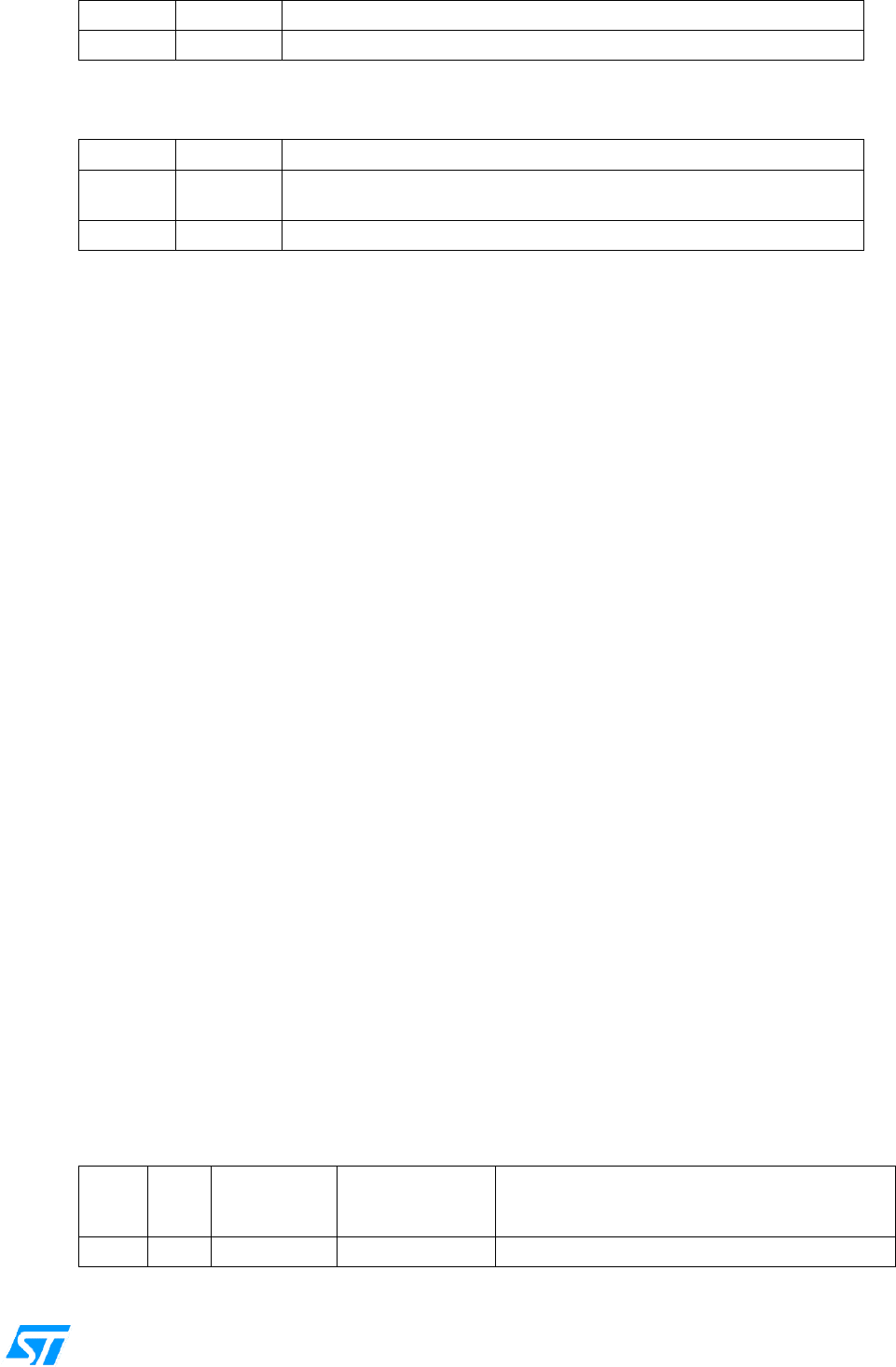

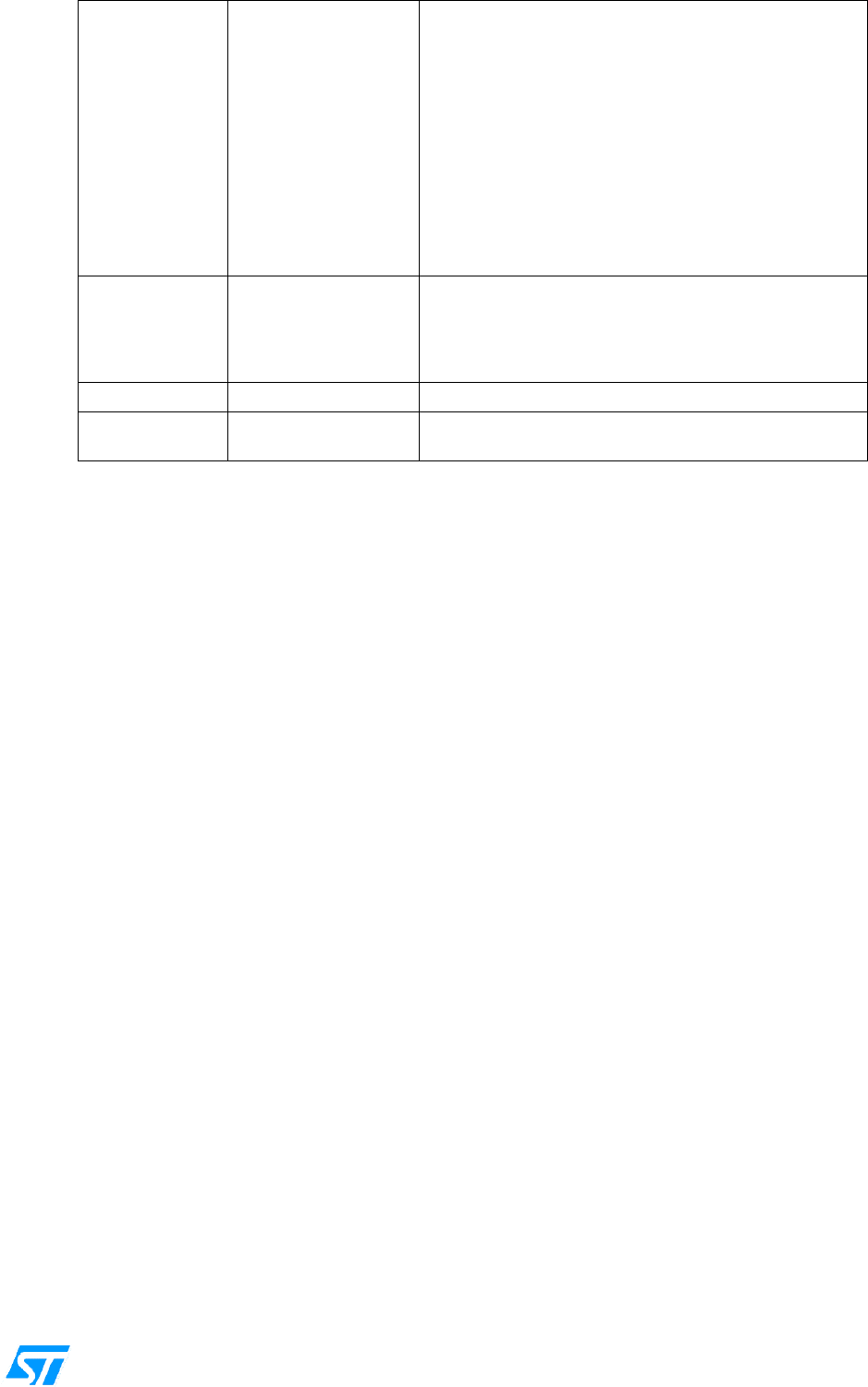

表2 闪存模块的组织(小容量产品)

模块 名称 地址 大小(字节)

0x0800 0000 - 0x0800 03FF 页0 1K

0x0800 0400 - 0x0800 07FF 页1 1K

0x0800 0800 - 0x0800 0BFF 页2 1K

0x0800 0C00 - 0x0800 0FFF 页3 1K

页4 0x0800 1000 - 0x0800 13FF 1K

主存储块

… … …

… … …

0x0800 7C00 - 0x0800 7FFF

页31 1K

0x1FFF F000 - 0x1FFF F7FF 系统存储器 2K

信息块 0x1FFF F800 - 0x1FFF F80F 16 选择字节

0x4002 2000 - 0x4002 2003 FLASH_ACR 4

0x4002 2004 - 0x4002 2007 FALSH_KEYR 4

0x4002 2008 - 0x4002 200B FLASH_OPTKEYR 4

0x4002 200C - 0x4002 200F FLASH_SR 4

FLASH_CR 0x4002 2010 - 0x4002 2013 4

闪存存储器

FLASH_AR 0x4002 2014 - 0x4002 2017 4

接口寄存器

0x4002 2018 - 0x4002 201B 4

保留

0x4002 201C - 0x4002 201F FLASH_OBR 4

0x4002 2020 - 0x4002 2023 FLASH_WRPR 4

参照2009年12月 RM0008 Reference Manual 英文第10版

本译文仅供参考,如有翻译错误,请以英文原稿为准。请读者随时注意在ST网站下载更新版本

存储器和总线架构 STM32F10xxx参考手册

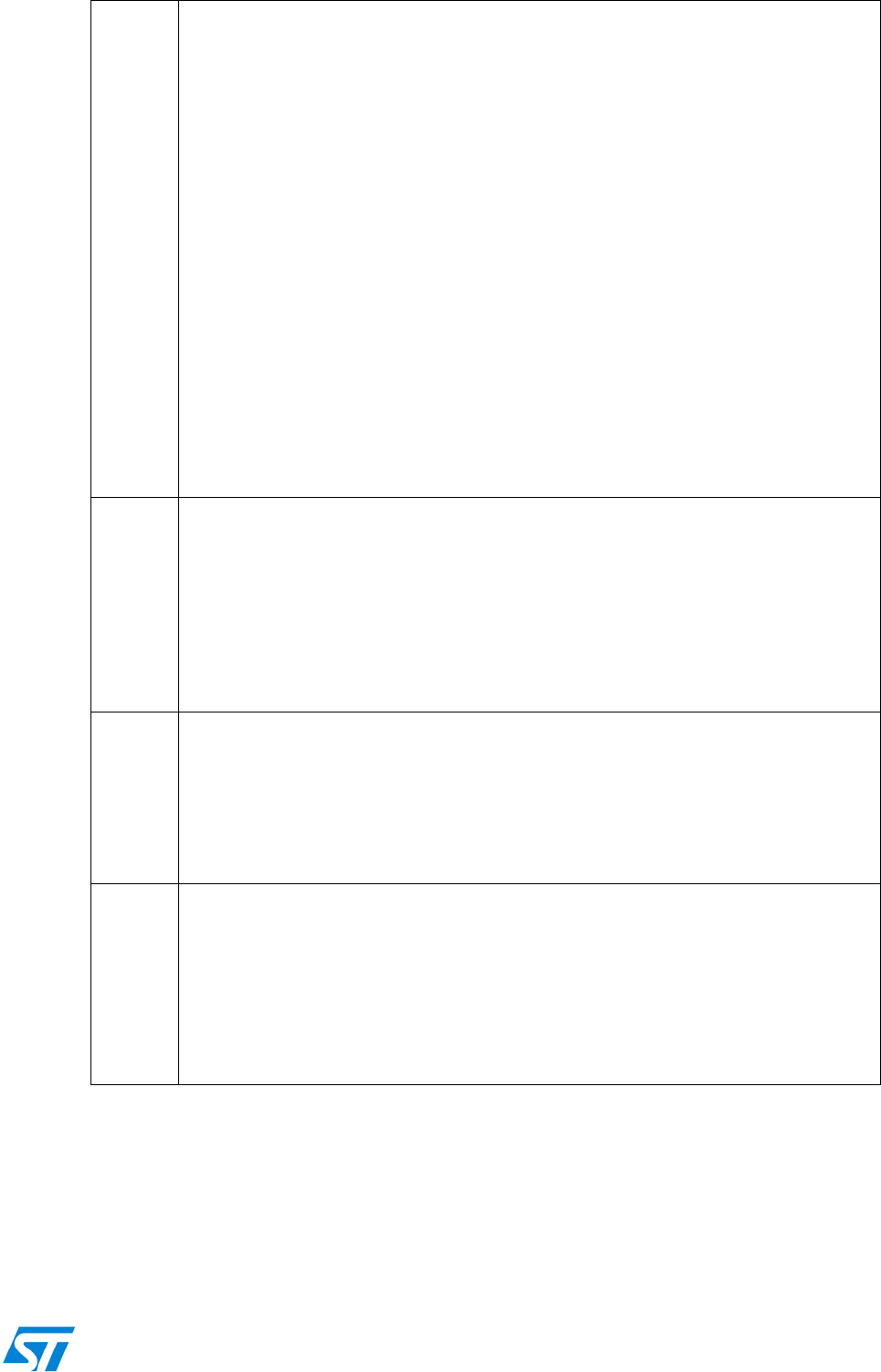

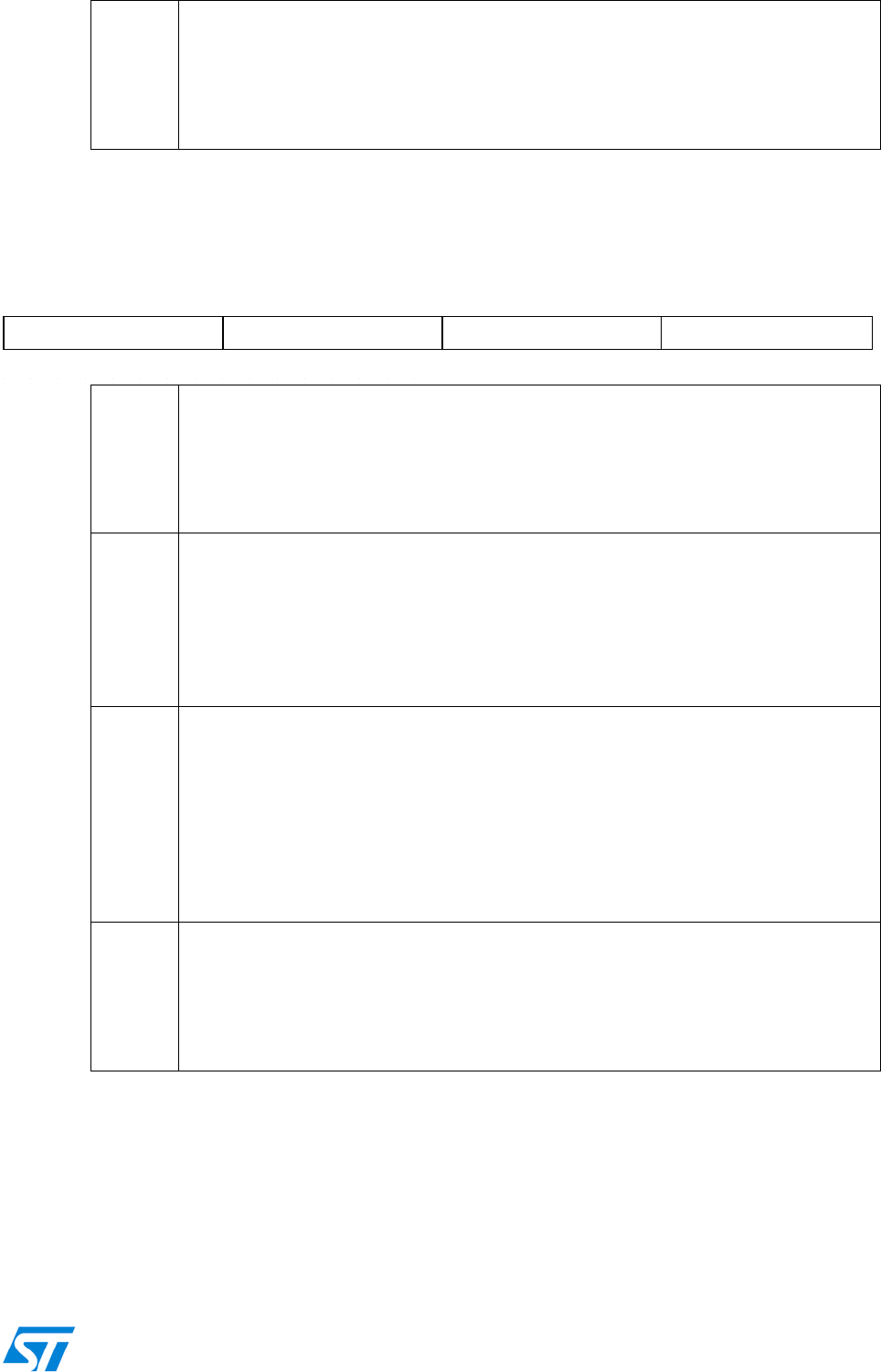

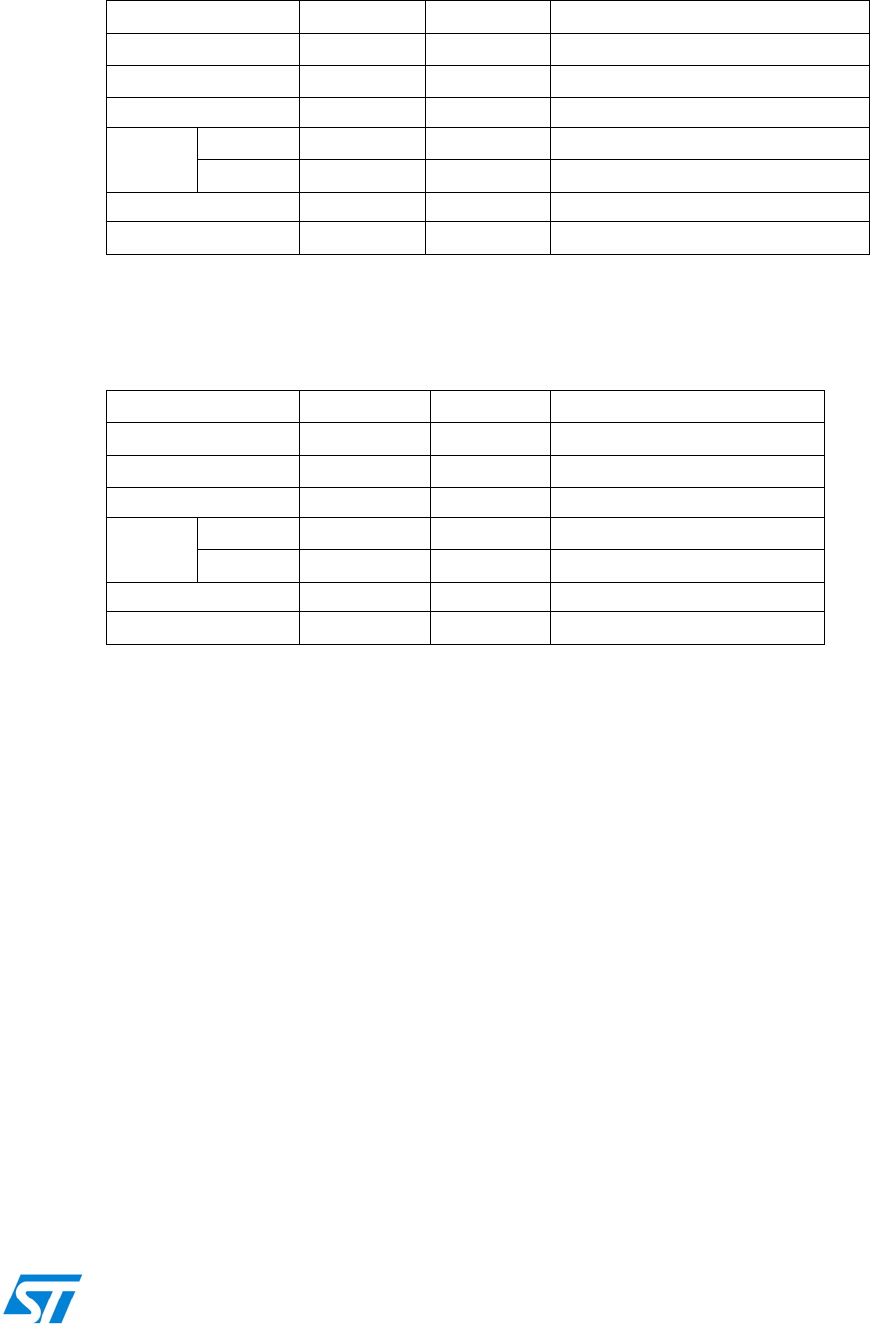

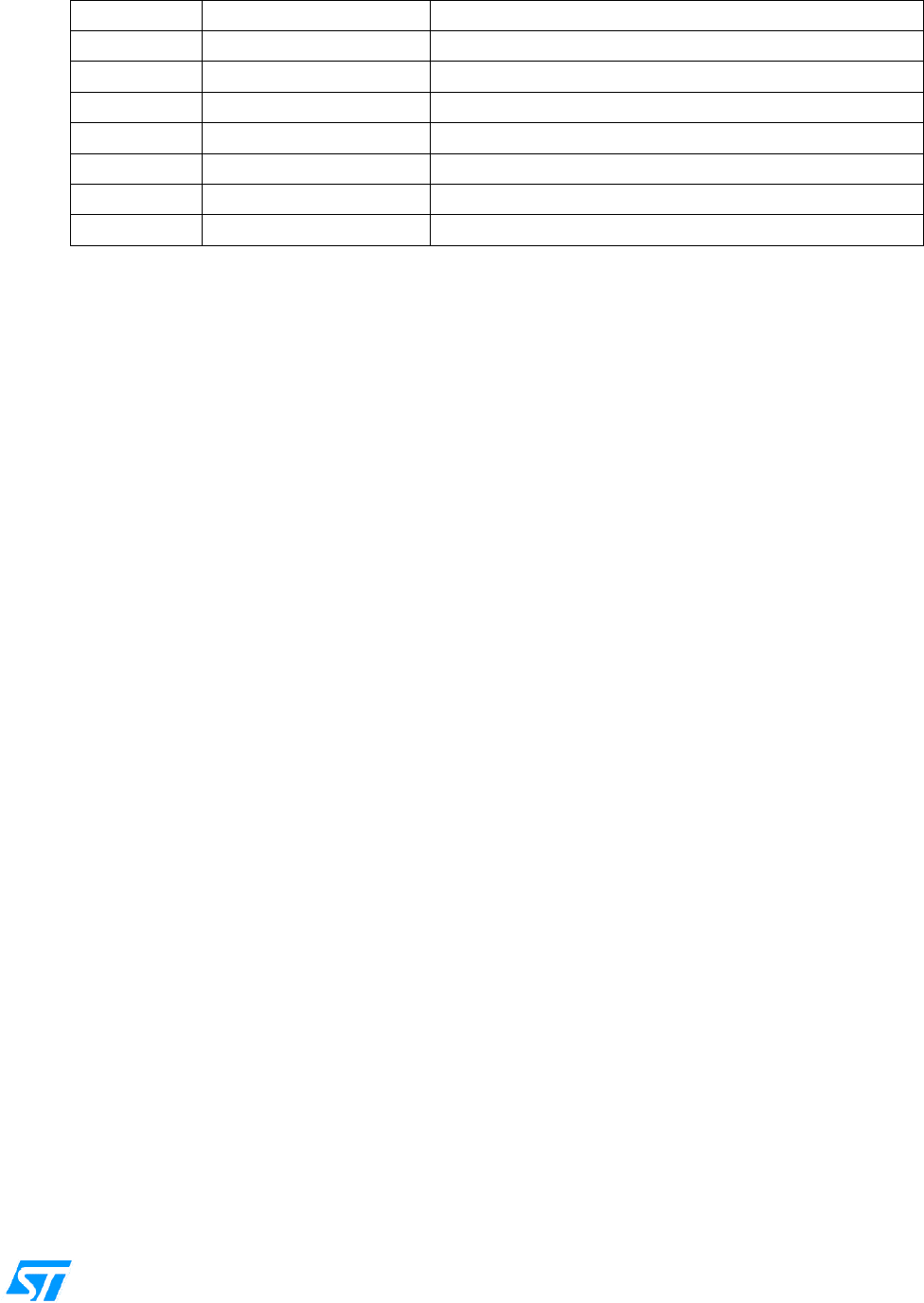

表3 闪存模块的组织(中容量产品)

模块 名称 地址 大小(字节)

0x0800 0000 - 0x0800 03FF 页0 1K

0x0800 0400 - 0x0800 07FF 页1 1K

0x0800 0800 - 0x0800 0BFF 页2 1K

0x0800 0C00 - 0x0800 0FFF 页3 1K

31/754

页4 0x0800 1000 - 0x0800 13FF 1K

主存储块

… … …

… … …

0x0801 FC00 - 0x0801 FFFF

页127 1K

0x1FFF F000 - 0x1FFF F7FF 系统存储器 2K

信息块 0x1FFF F800 - 0x1FFF F80F 16 选择字节

0x4002 2000 - 0x4002 2003 FLASH_ACR 4

0x4002 2004 - 0x4002 2007 FALSH_KEYR 4

0x4002 2008 - 0x4002 200B FLASH_OPTKEYR 4

0x4002 200C - 0x4002 200F FLASH_SR 4

FLASH_CR 0x4002 2010 - 0x4002 2013 4

闪存存储器

FLASH_AR 0x4002 2014 - 0x4002 2017 4

接口寄存器

0x4002 2018 - 0x4002 201B 4

保留

0x4002 201C - 0x4002 201F FLASH_OBR 4

0x4002 2020 - 0x4002 2023 FLASH_WRPR 4

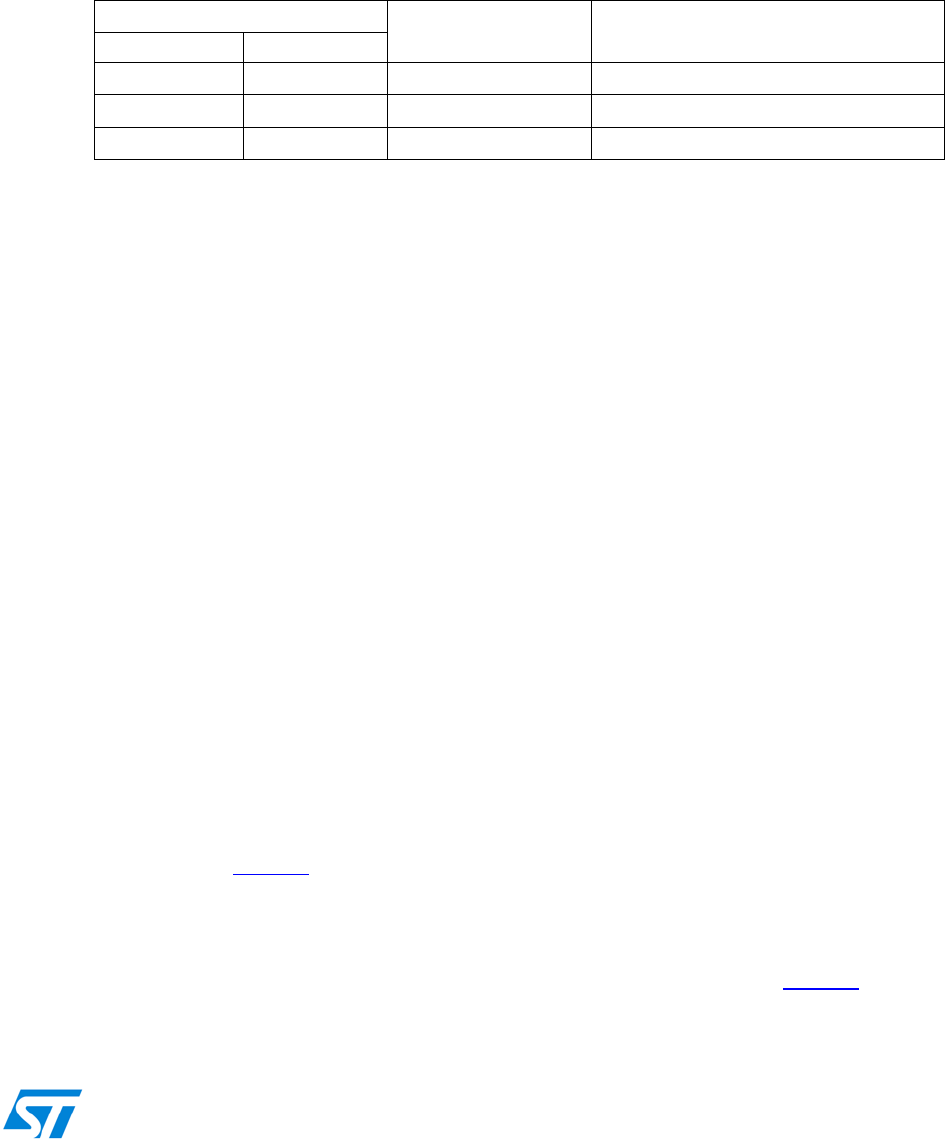

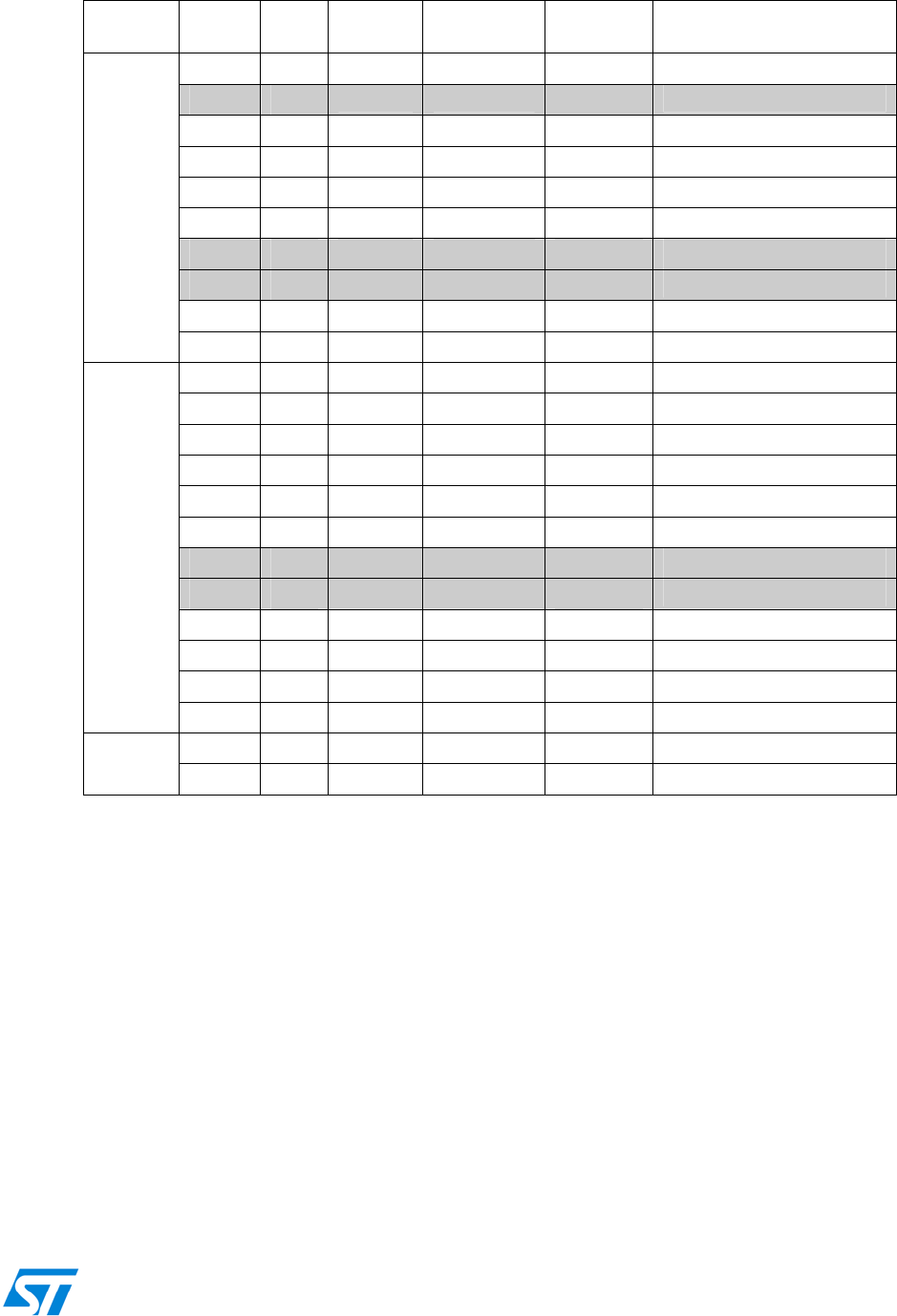

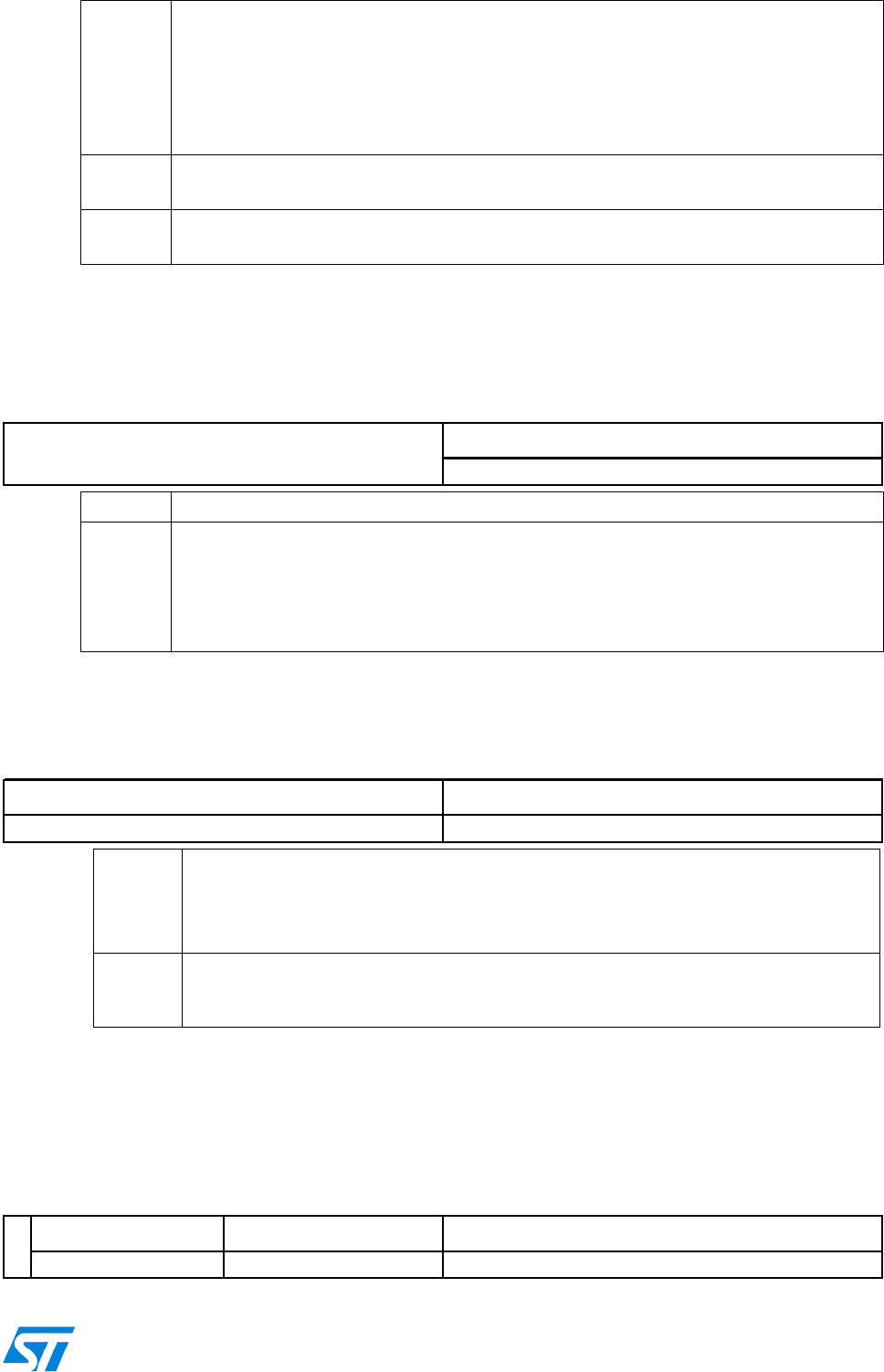

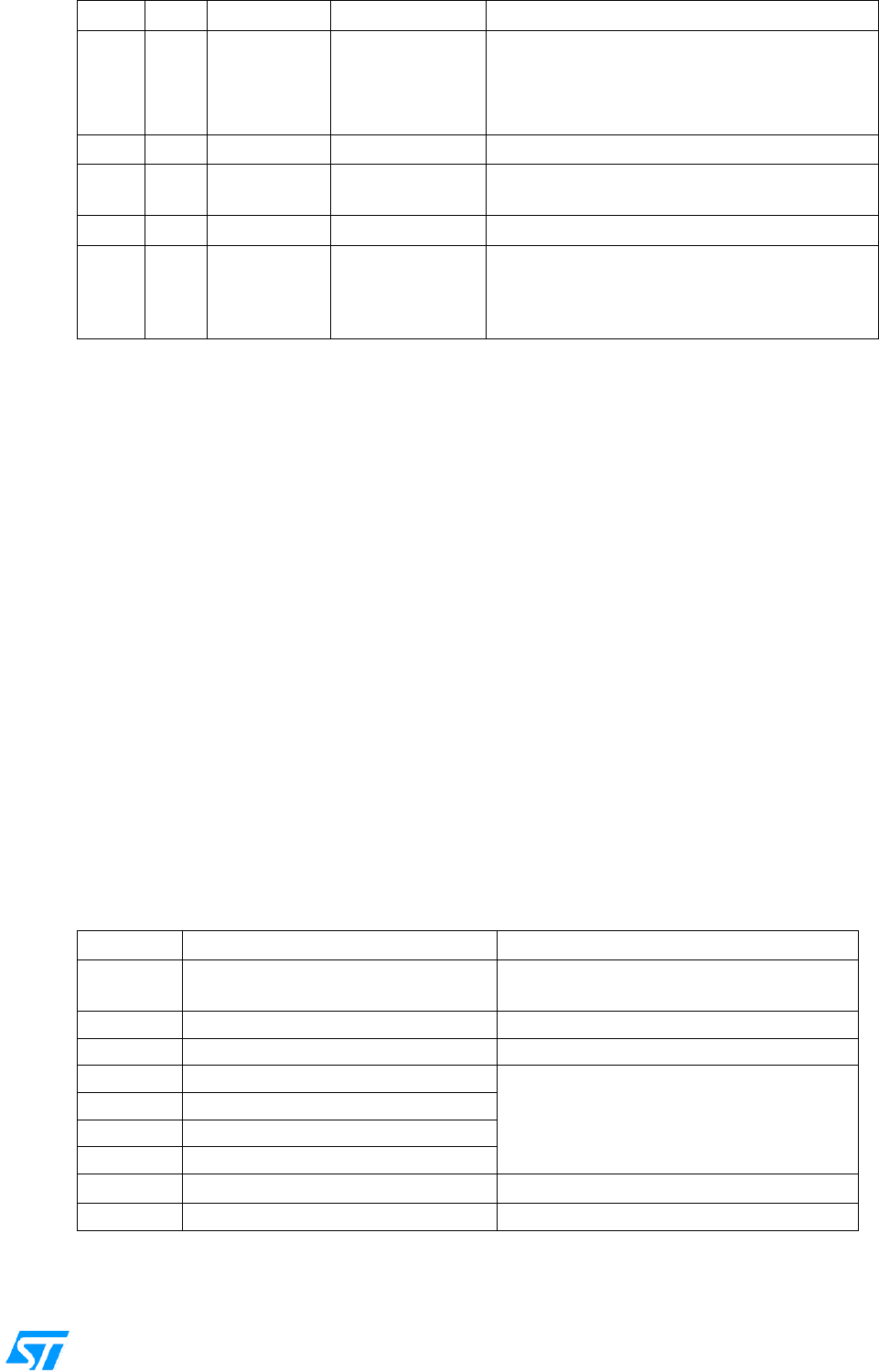

表4 闪存模块的组织(大容量产品)

模块 名称 地址 大小(字节)

0x0800 0000 - 0x0800 07FF 页0 2K

0x0800 0800 - 0x0800 0FFF 页1 2K

0x0800 1000 - 0x0800 17FF 页2 2K

页3 0x0800 1800 - 0x0800 1FFF 2K

主存储块

… … …

… … …

0x0807 F800 - 0x0807 FFFF

页255 2K

0x1FFF F000 - 0x1FFF F7FF 系统存储器 2K

信息块 0x1FFF F800 - 0x1FFF F80F 16 选择字节

0x4002 2000 - 0x4002 2003 FLASH_ACR 4

0x4002 2004 - 0x4002 2007 FALSH_KEYR 4

0x4002 2008 - 0x4002 200B FLASH_OPTKEYR 4

0x4002 200C - 0x4002 200F FLASH_SR 4

FLASH_CR 0x4002 2010 - 0x4002 2013 4

闪存存储器

FLASH_AR 0x4002 2014 - 0x4002 2017 4

接口寄存器

0x4002 2018 - 0x4002 201B 4

保留

0x4002 201C - 0x4002 201F FLASH_OBR 4

0x4002 2020 - 0x4002 2023 FLASH_WRPR 4

参照2009年12月 RM0008 Reference Manual 英文第10版

本译文仅供参考,如有翻译错误,请以英文原稿为准。请读者随时注意在ST网站下载更新版本

存储器和总线架构 STM32F10xxx参考手册

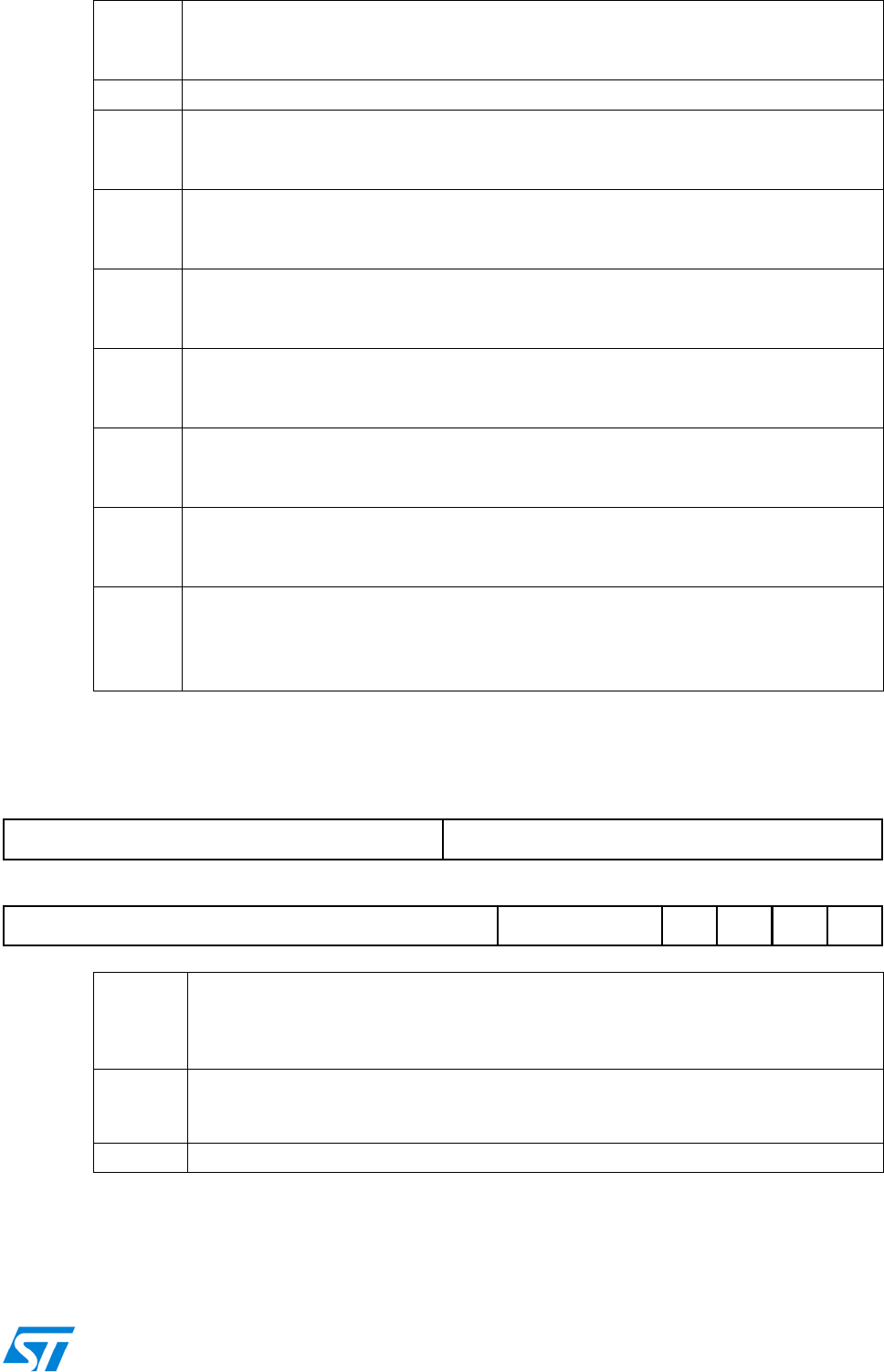

表5 闪存模块的组织(互联型产品)

模块 名称 地址 大小(字节)

0x0800 0000 - 0x0800 07FF 页0 2K

0x0800 0800 - 0x0800 0FFF 页1 2K

0x0800 1000 - 0x0800 17FF 页2 2K

32/754

页3 0x0800 1800 - 0x0800 1FFF 2K

主存储块

… … …

… … …

0x0803 F800 - 0x0803 FFFF

页127 2K

0x1FFF B000 - 0x1FFF F7FF 系统存储器 18K

信息块 0x1FFF F800 - 0x1FFF F80F 16 选择字节

0x4002 2000 - 0x4002 2003 FLASH_ACR 4

0x4002 2004 - 0x4002 2007 FALSH_KEYR 4

0x4002 2008 - 0x4002 200B FLASH_OPTKEYR 4

0x4002 200C - 0x4002 200F FLASH_SR 4

FLASH_CR 0x4002 2010 - 0x4002 2013 4

闪存存储器

FLASH_AR 0x4002 2014 - 0x4002 2017 4

接口寄存器

0x4002 2018 - 0x4002 201B 4

保留

0x4002 201C - 0x4002 201F FLASH_OBR 4

0x4002 2020 - 0x4002 2023

FLASH_WRPR 4

注:

有关闪存寄存器的详细信息,请参考《

STM32F10xxx

闪存编程手册》

闪存读取

闪存的指令和数据访问是通过AHB总线完成的。预取模块是用于通过ICode总线读取指令的。仲

裁是作用在闪存接口,并且DCode总线上的数据访问优先。

读访问可以有以下配置选项:

● 等待时间:可以随时更改的用于读取操作的等待状态的数量。

● 预取缓冲区(2个64位):在每一次复位以后被自动打开,由于每个缓冲区的大小(64位)与闪

存的带宽相同,因此只通过需一次读闪存的操作即可更新整个缓冲区的内容。由于预取缓

冲区的存在,CPU可以工作在更高的主频。CPU每次取指最多为32位的字,取一条指令

时,下一条指令已经在缓冲区中等待。

● 半周期:用于功耗优化。

注:

1.

这些选项应与闪存存储器的访问时间一起使用。等待周期体现了系统时钟

(SYSCLK)

频率与闪

存访问时间的关系:

0

等待周期,当

0 < SYSCLK < 24MHz

1

等待周期,当

24MHz < SYSCLK

≤

48MHz

2

等待周期,当

48MHz < SYSCLK

≤

72MHz

2 .

半周期配置不能与使用了预分频器的

AHB

一起使用,时钟系统应该等于

HCLK

时钟。该特性

只能用在时钟频率为

8MHz

或低于

8MHz

时,可以直接使用的内部

RC

振荡器

(HSI)

,或者是主振

荡器

(HSE)

,但不能用

PLL

。

3.

当

AHB

预分频系数不为

1

时,必须置预取缓冲区处于开启状态。

4.

只有在系统时钟

(SYSCLK)

小于

24MHz

并且没有打开

AHB

的预分频器

(

即

HCLK

必须等于

SYSHCLK)

时,才能执行预取缓冲器的打开和关闭操作。一般而言,在初始化过程中执行预取

缓冲器的打开和关闭操作,这时微控制器的时钟由

8MHz

的内部

RC

振荡器

(HSI)

提供。

5.

使用

DMA

:

DMA

在

DCode

总线上访问闪存存储器,它的优先级比

ICode

上的取指高。

DMA

在

每次传送完成后具有一个空余的周期。有些指令可以和

DMA

传输一起执行。

参照2009年12月 RM0008 Reference Manual 英文第10版

本译文仅供参考,如有翻译错误,请以英文原稿为准。请读者随时注意在ST网站下载更新版本

存储器和总线架构 STM32F10xxx参考手册

33/754

参照2009年12月 RM0008 Reference Manual 英文第10版

本译文仅供参考,如有翻译错误,请以英文原稿为准。请读者随时注意在ST网站下载更新版本

编程和擦除闪存

闪存编程一次可以写入16位(半字)。

闪存擦除操作可以按页面擦除或完全擦除(全擦除)。全擦除不影响信息块。

为了确保不发生过度编程, 闪存编程和擦除控制器块是由一个固定的时钟控制的。

写操作(编程或擦除)结束时可以触发中断。仅当闪存控制器接口时钟开启时,此中断可以用来从

WFI模式退出。

注:

有关闪存存储器的操作和寄存器配置,请参考

STM32F10xxx

闪存编程手册。

2.4 启动配置

在STM32F10xxx里,可以通过BOOT[1:0]引脚选择三种不同启动模式。

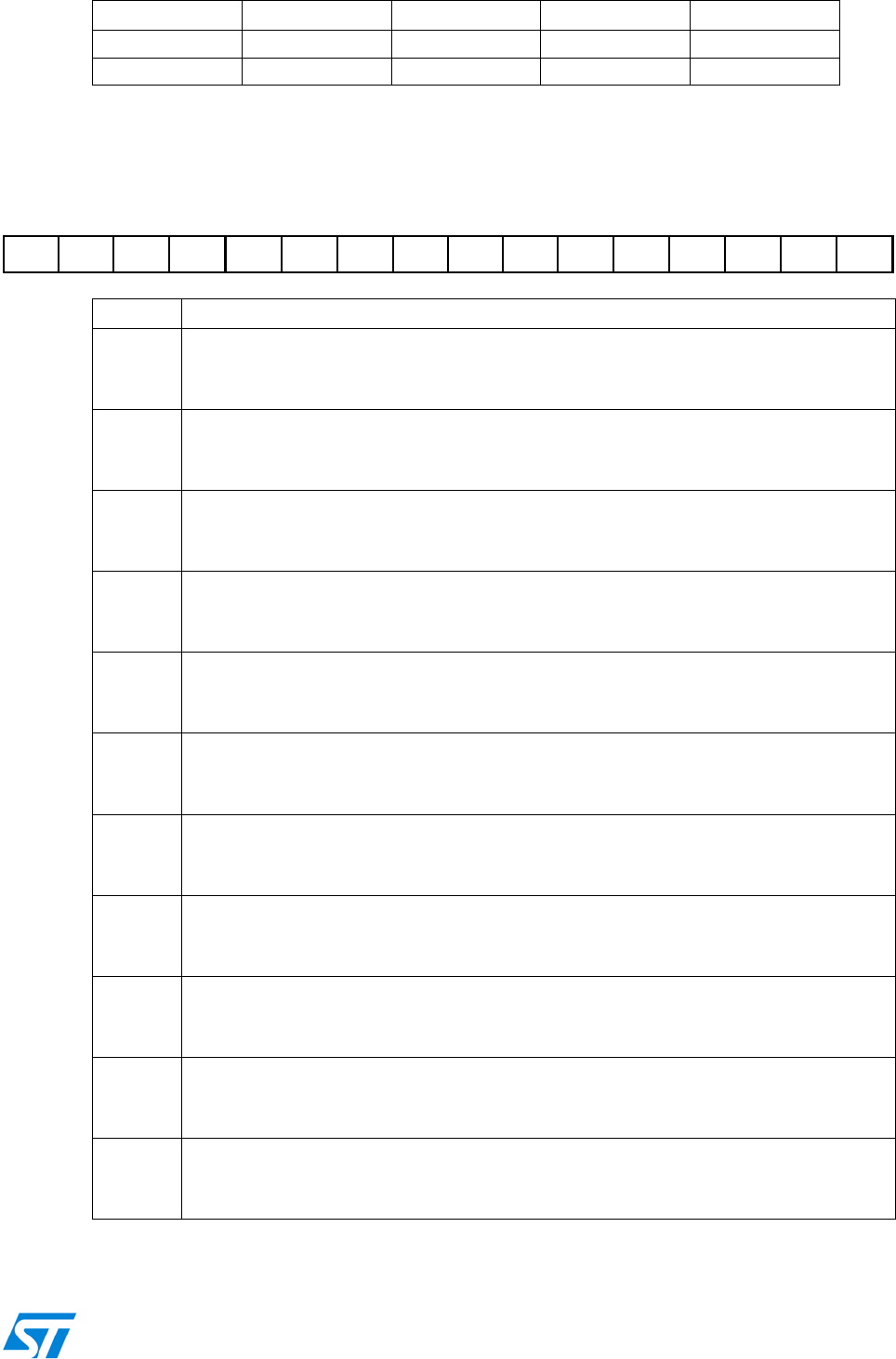

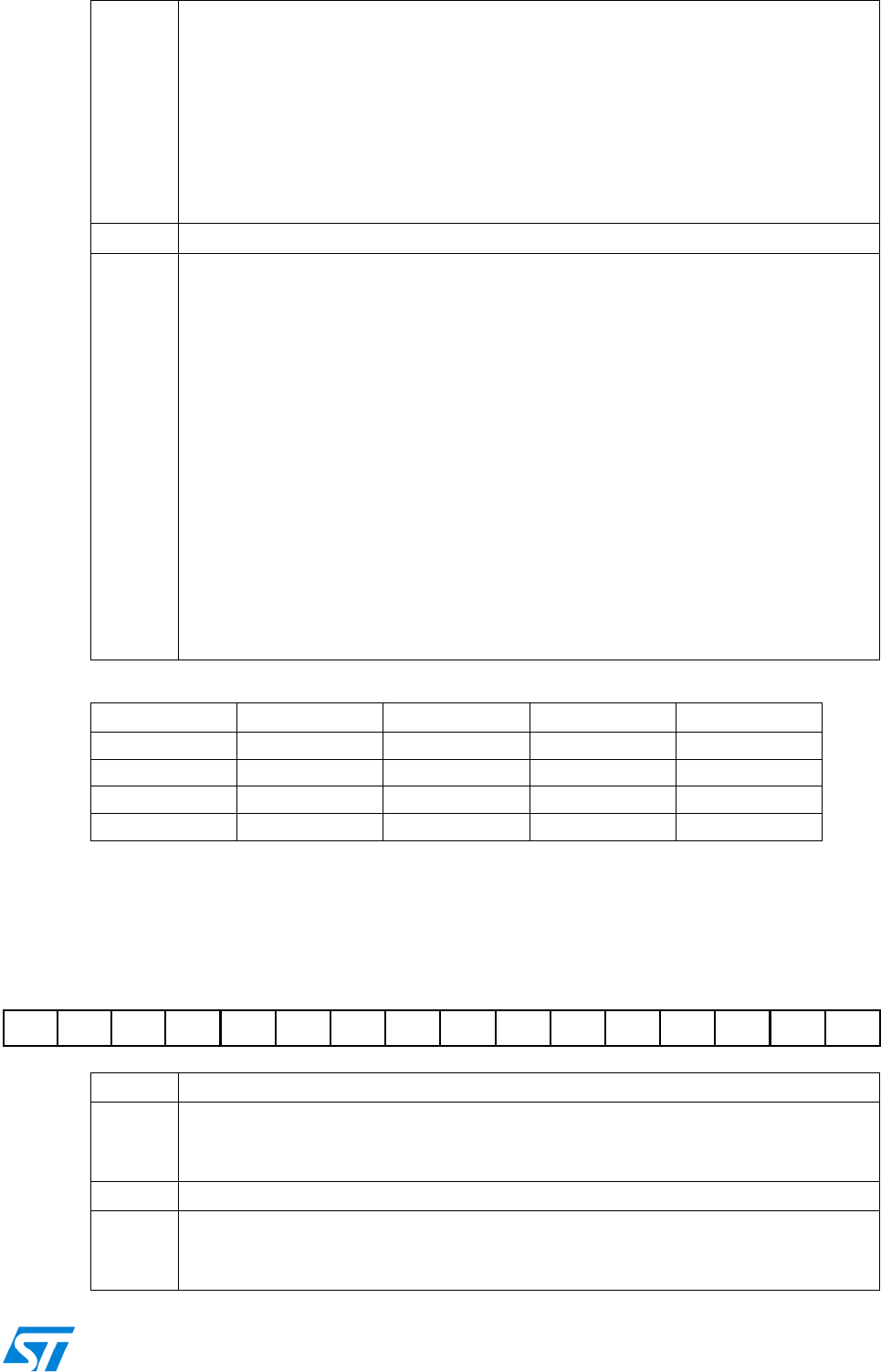

表6 启动模式

启动模式选择引脚

BOOT1 BOOT0 启动模式 说明

X 0 主闪存存储器 主闪存存储器被选为启动区域

0 1 系统存储器 系统存储器被选为启动区域

1 1 内置SRAM 内置SRAM被选为启动区域

在系统复位后,SYSCLK的第4个上升沿,BOOT引脚的值将被锁存。用户可以通过设置BOOT1

和BOOT0引脚的状态,来选择在复位后的启动模式。

在从待机模式退出时,BOOT引脚的值将被被重新锁存;因此,在待机模式下BOOT引脚应保持

为需要的启动配置。在启动延迟之后,CPU从地址0x0000 0000获取堆栈顶的地址,并从启动

存储器的0x0000 0004指示的地址开始执行代码。

因为固定的存储器映像,代码区始终从地址0x0000 0000开始(通过ICode和DCode总线访问),

而数据区(SRAM)始终从地址0x2000 0000开始(通过系统总线访问)。Cortex-M3的CPU始终从

ICode总线获取复位向量,即启动仅适合于从代码区开始(典型地从Flash启动)。STM32F10xxx

微控制器实现了一个特殊的机制,系统可以不仅仅从Flash存储器或系统存储器启动,还可以从

内置SRAM启动。

根据选定的启动模式,主闪存存储器、系统存储器或SRAM可以按照以下方式访问:

● 从主闪存存储器启动:主闪存存储器被映射到启动空间(0x0000 0000),但仍然能够在它原

有的地址(0x0800 0000)访问它,即闪存存储器的内容可以在两个地址区域访问,0x0000

0000或0x0800 0000。

● 从系统存储器启动:系统存储器被映射到启动空间(0x0000 0000),但仍然能够在它原有的

地址(互联型产品原有地址为0x1FFF B000,其它产品原有地址为0x1FFF F000)访问它。

● 从内置SRAM启动:只能在0x2000 0000开始的地址区访问SRAM。

注意: 当从内置

SRAM

启动,在应用程序的初始化代码中,必须使用

NVIC

的异常表和偏移寄存器,从

新映射向量表之

SRAM

中。

内嵌的自举程序

内嵌的自举程序存放在系统存储区,由ST在生产线上写入,用于通过可用的串行接口对闪存存

储器进行重新编程:

● 对于小容量、中容量和大容量的产品而言,可以通过USART1接口启用自举程序。进一步的

细节请查询AN2606。

● 对于互联型产品而言,可以通过以下某个接口启用自举程序:USART1、USART2(重映像

的)、CAN2(重映像的)或USB OTG全速接口的设备模式(通过设备固件更新DFU协议)。

USART接口依靠内部8MHz振荡器(HSI)运行。CAN和USB OTG接口只能当外部有一个

8MHz、14.7456MHz或25MHz时钟(HSE)时运行。进一步的细节请查询AN2606。

CRC计算单元(CRC) STM32F10xxx参考手册

3 CRC计算单元(CRC)

小容量产品是指闪存存储器容量在16K至32K字节之间的STM32F101xx、STM32F102xx和

STM32F103xx微控制器。

中容量产品是指闪存存储器容量在64K至128K字节之间的STM32F101xx、STM32F102xx和

STM32F103xx微控制器。

大容量产品是指闪存存储器容量在256K至512K字节之间的STM32F101xx和STM32F103xx微控

制器。

互联型产品是指STM32F105xx和STM32F107xx微控制器。

除非特别说明,本章描述的模块适用于整个STM32F10xxx微控制器系列。

3.1 CRC简介

循环冗余校验(CRC)计算单元是根据固定的生成多项式得到任一32位全字的CRC计算结果。

在其他的应用中, CRC技术主要应用于核实数据传输或者数据存储的正确性和完整性。标准

EN/IEC 60335-1即提供了一种核实闪存存储器完整性的方法。CRC计算单元可以在程序运行时

计算出软件的标识,之后与在连接时生成的参考标识比较,然后存放在指定的存储器空间。

3.2 CRC主要特性

● 使用CRC-32(以太网)多项式:0x4C11DB7

─ X

32 + X26 + X23 + X22 + X16 + X12 + X11 + X10 + X8 + X7 + X4 + X2 + X +1

● 一个32位数据寄存器用于输入 / 输出

● CRC计算时间:4个AHB时钟周期(HCLK)

● 通用8位寄存器(可用于存放临时数据)

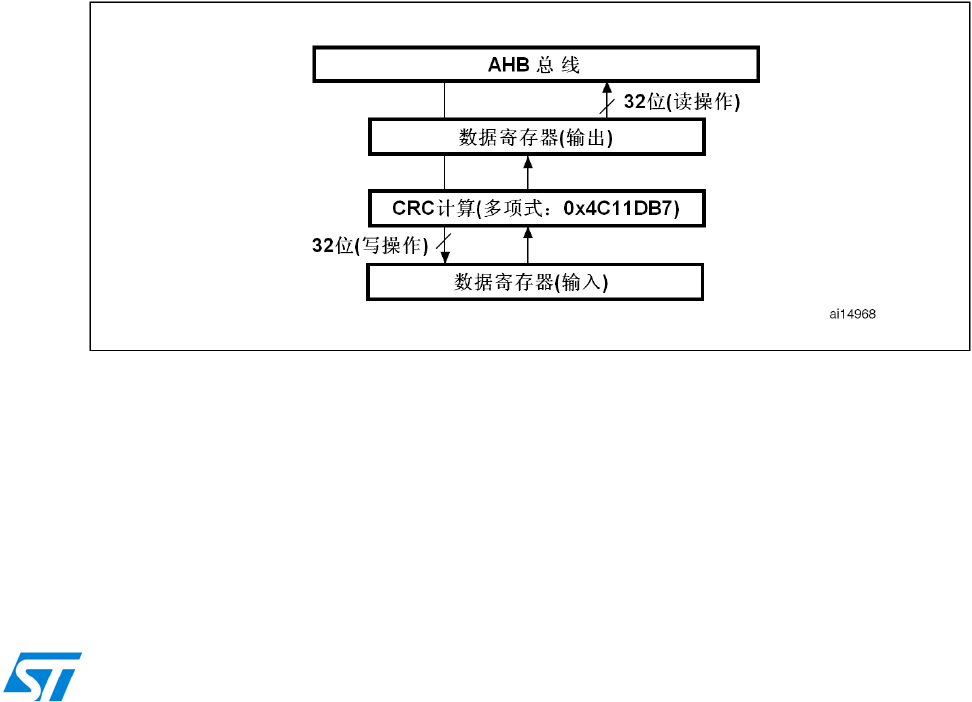

下图为CRC计算单元框图

图3 CRC 计算单元框图

3.3 CRC功能描述

CRC计算单元含有1个32位数据寄存器:

● 对该寄存器进行写操作时,作为输入寄存器,可以输入要进行CRC计算的新数据。

● 对该寄存器进行读操作时,返回上一次CRC计算的结果。

每一次写入数据寄存器,其计算结果是前一次CRC计算结果和新计算结果的组合(对整个32位字

进行CRC计算,而不是逐字节地计算)。

34/754

参照2009年12月 RM0008 Reference Manual 英文第10版

本译文仅供参考,如有翻译错误,请以英文原稿为准。请读者随时注意在ST网站下载更新版本

CRC计算单元(CRC) STM32F10xxx参考手册

在CRC计算期间会暂停CPU的写操作,因此可以对寄存器CRC_DR进行背靠背写入或者连续地

写-读操作。

可以通过设置寄存器CRC_CR的RESET位来重置寄存器CRC_DR为0xFFFF FFFF。该操作不

影响寄存器CRC_IDR内的数据。

3.4 CRC寄存器

CRC计算单元包括2个数据寄存器和1个控制寄存器

3.4.1 数据寄存器(CRC_DR)

地址偏移:0x00

复位值:0xFFFF FFFF

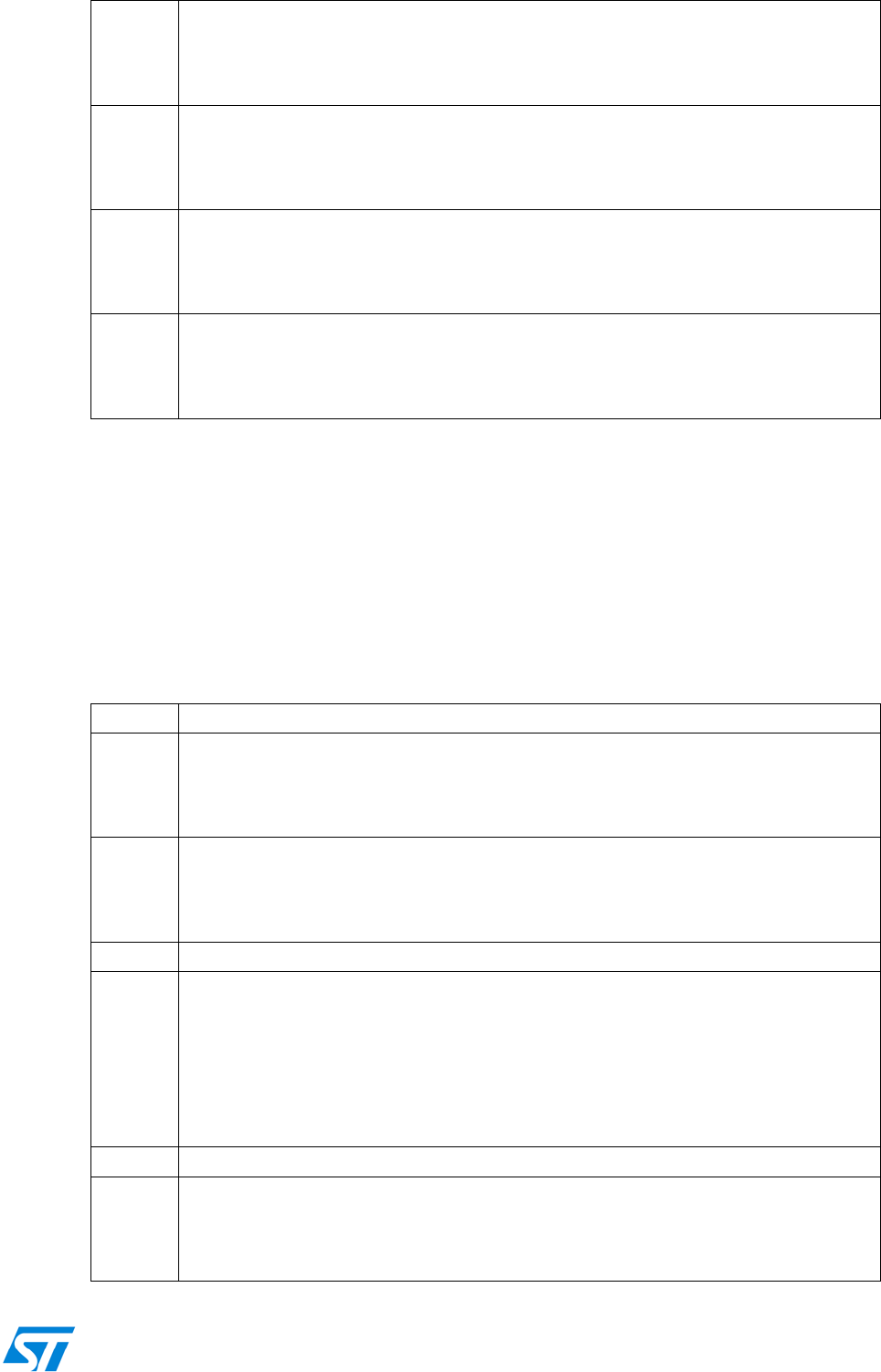

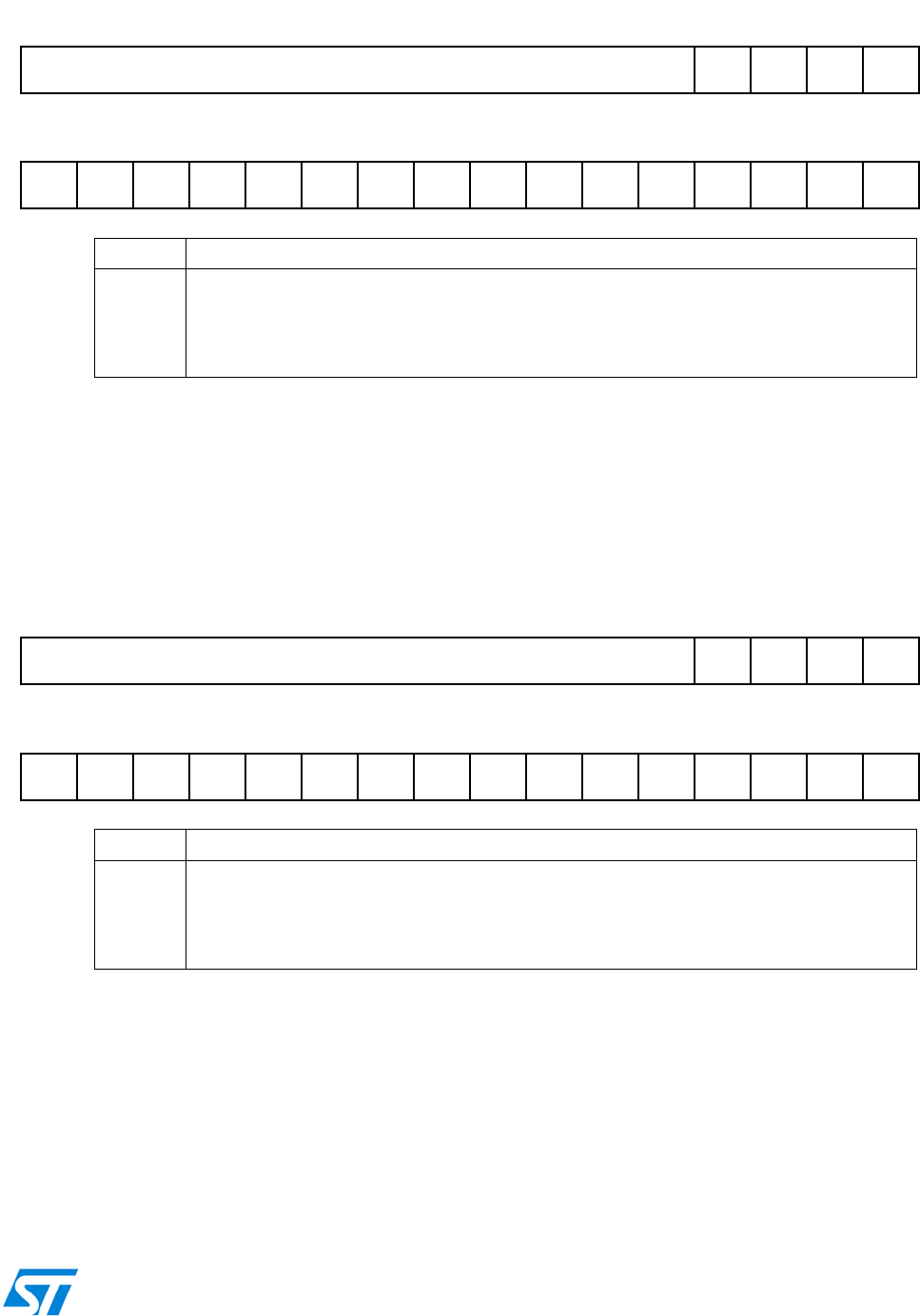

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

1514131211109876543210

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

DR[31:16]

DR[15:0]

位31: 0 数据寄存器位

写入CRC计算器的新数据时,作为输入寄存器

读取时返回CRC计算的结果

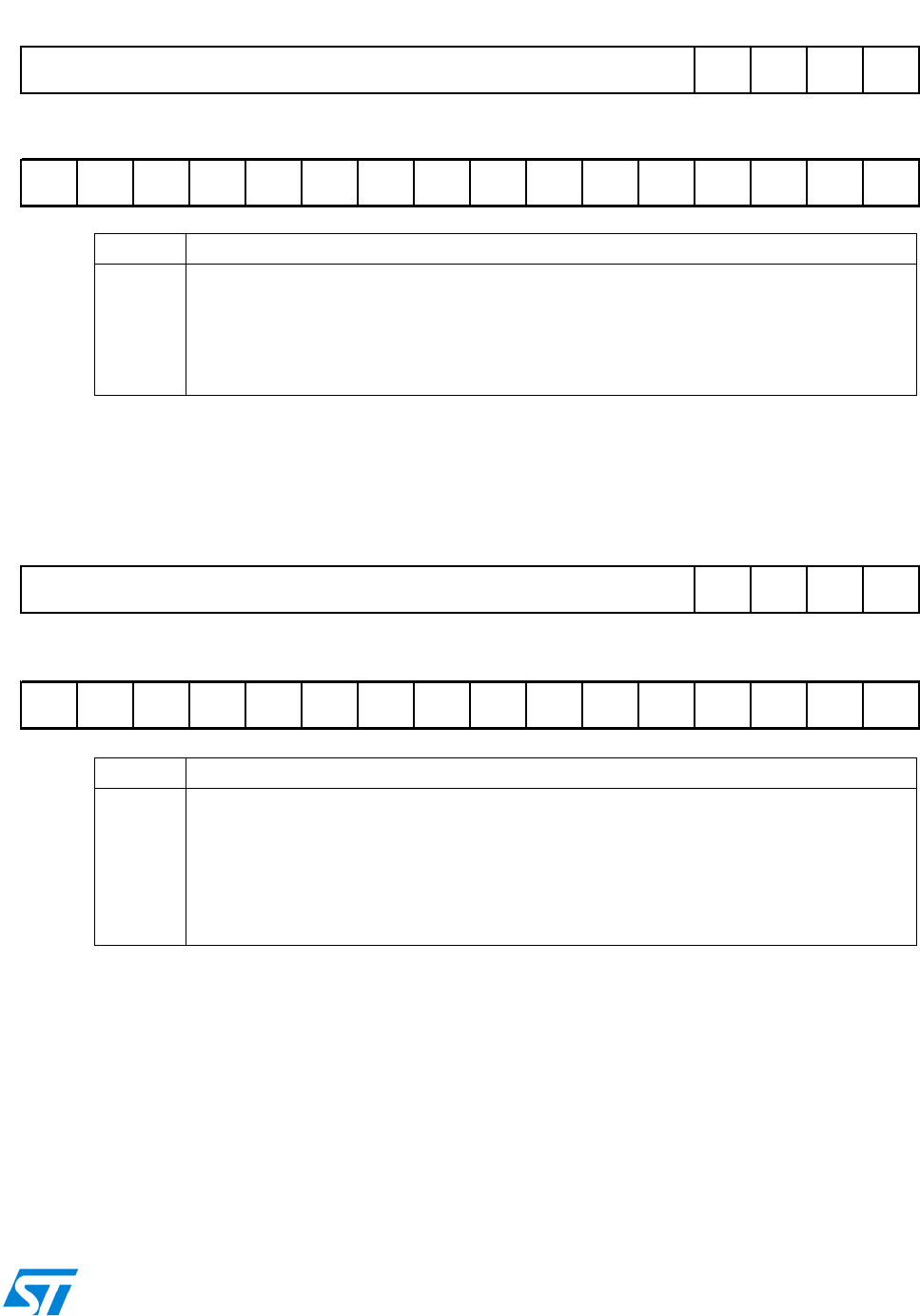

3.4.2 独立数据寄存器(CRC_IDR)

地址偏移:0x04

复位值:0x0000 0000

1514131211109876543210

rw rw rw rw rw rw rw rw

保留 IDR[7:0]

位31:8 保留。

位7:0 通用8位数据寄存器位

可用于临时存放1字节的数据。

寄存器CRC_CR的RESET位产生的CRC复位对本寄存器没有影响

译注:此寄存器不参与CRC计算,可以存放任何数据。

35/754

参照2009年12月 RM0008 Reference Manual 英文第10版

本译文仅供参考,如有翻译错误,请以英文原稿为准。请读者随时注意在ST网站下载更新版本

CRC计算单元(CRC) STM32F10xxx参考手册

36/754

参照2009年12月 RM0008 Reference Manual 英文第10版

3.4.3 控制寄存器(CRC_CR)

地址偏移:0x08

复位值:0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

1514131211109876543210

RESET

保留

保留

w

位31:1 保留。

位0 RESET位

复位CRC计算单元,设置数据寄存器为0xFFFF FFFF。

只能对该位写’1’,它由硬件自动清’0’。

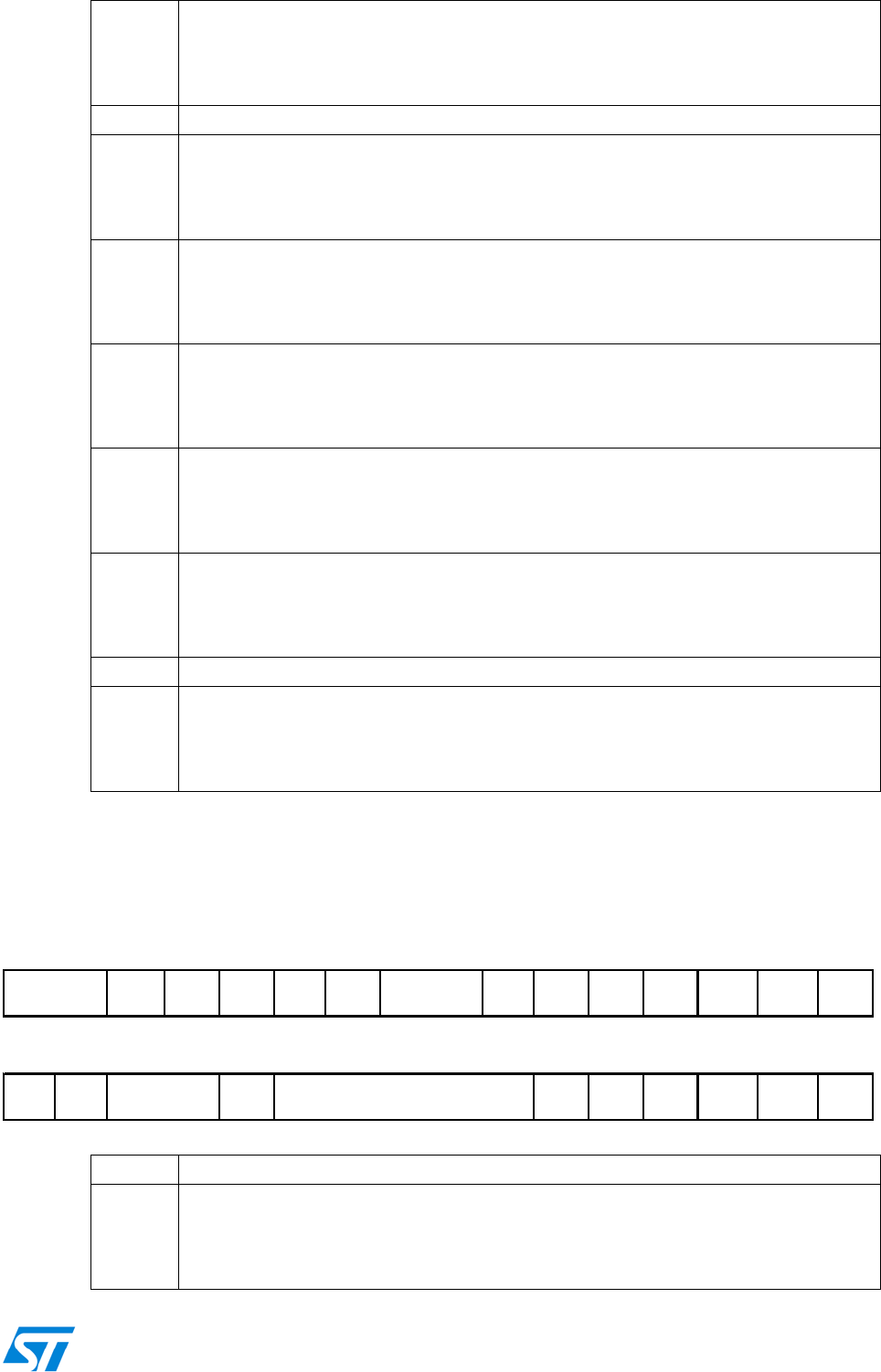

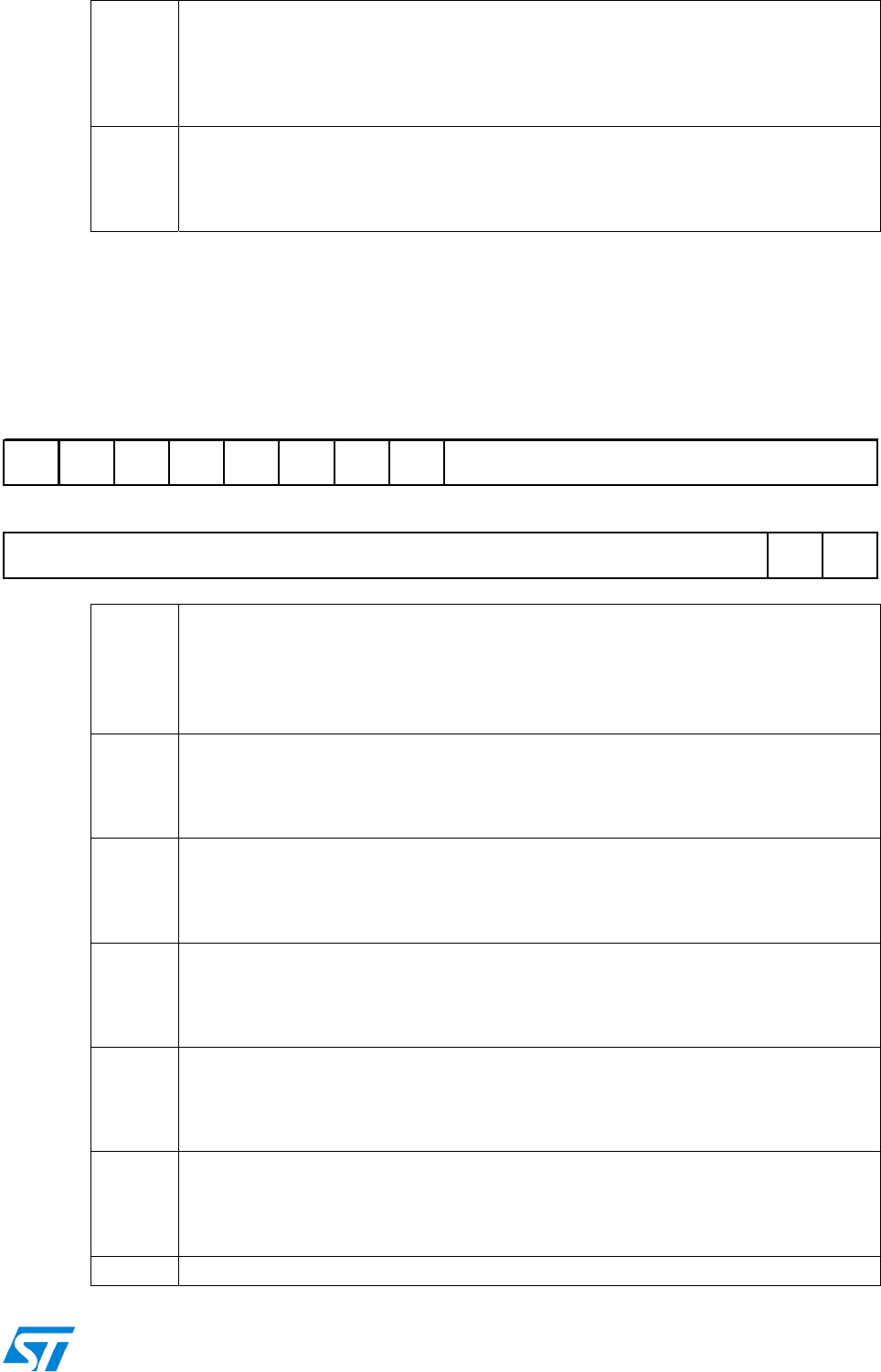

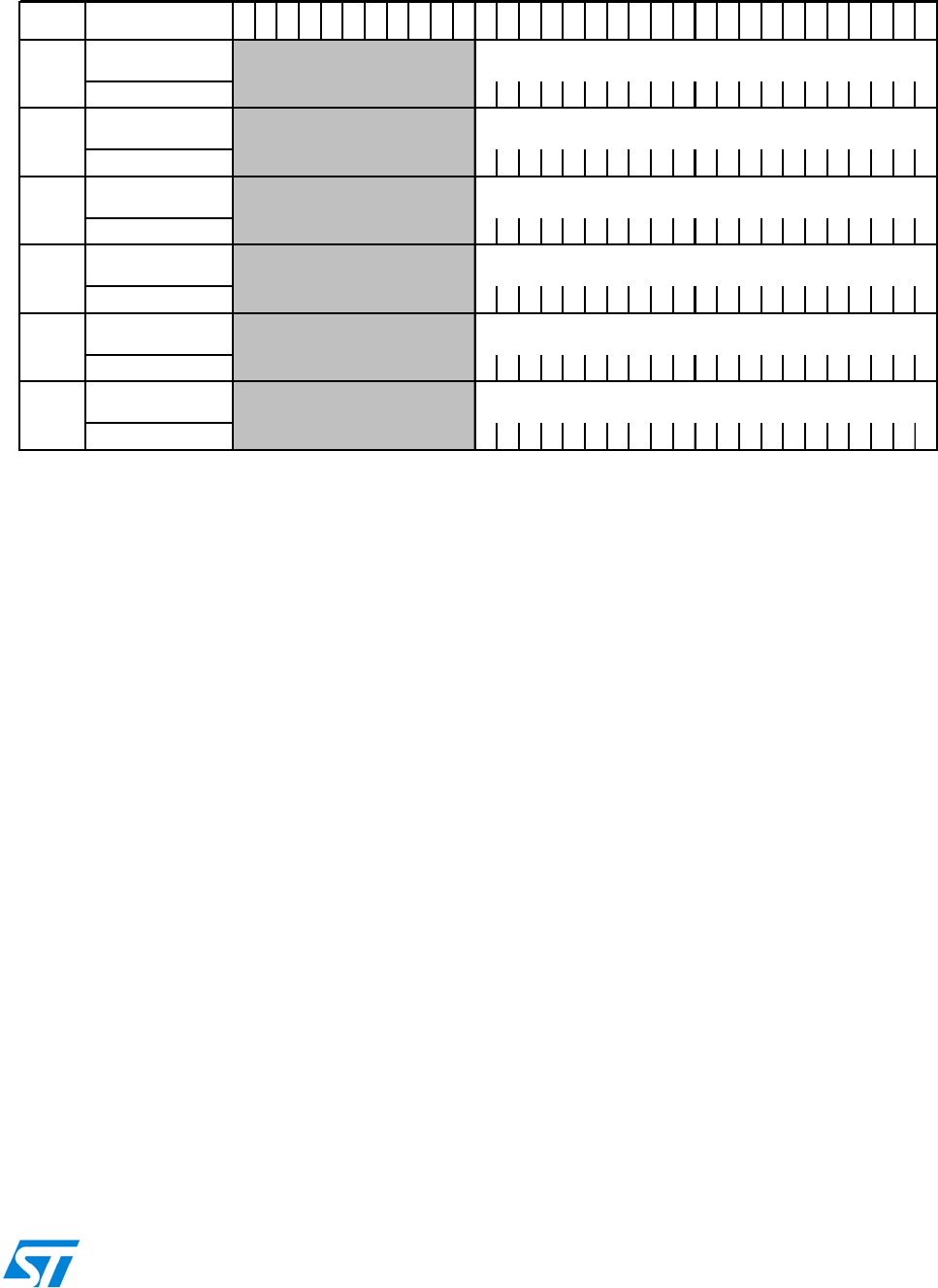

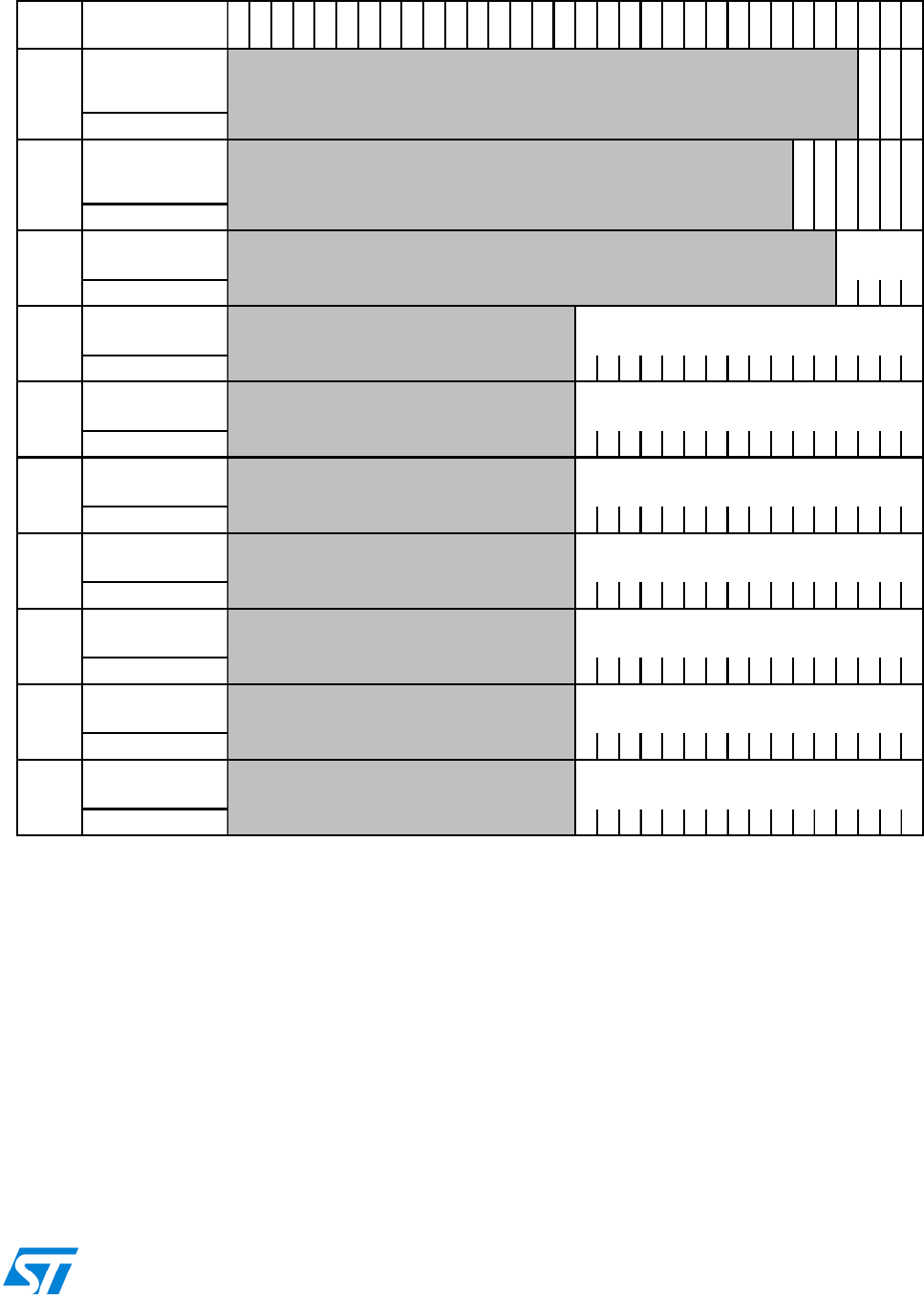

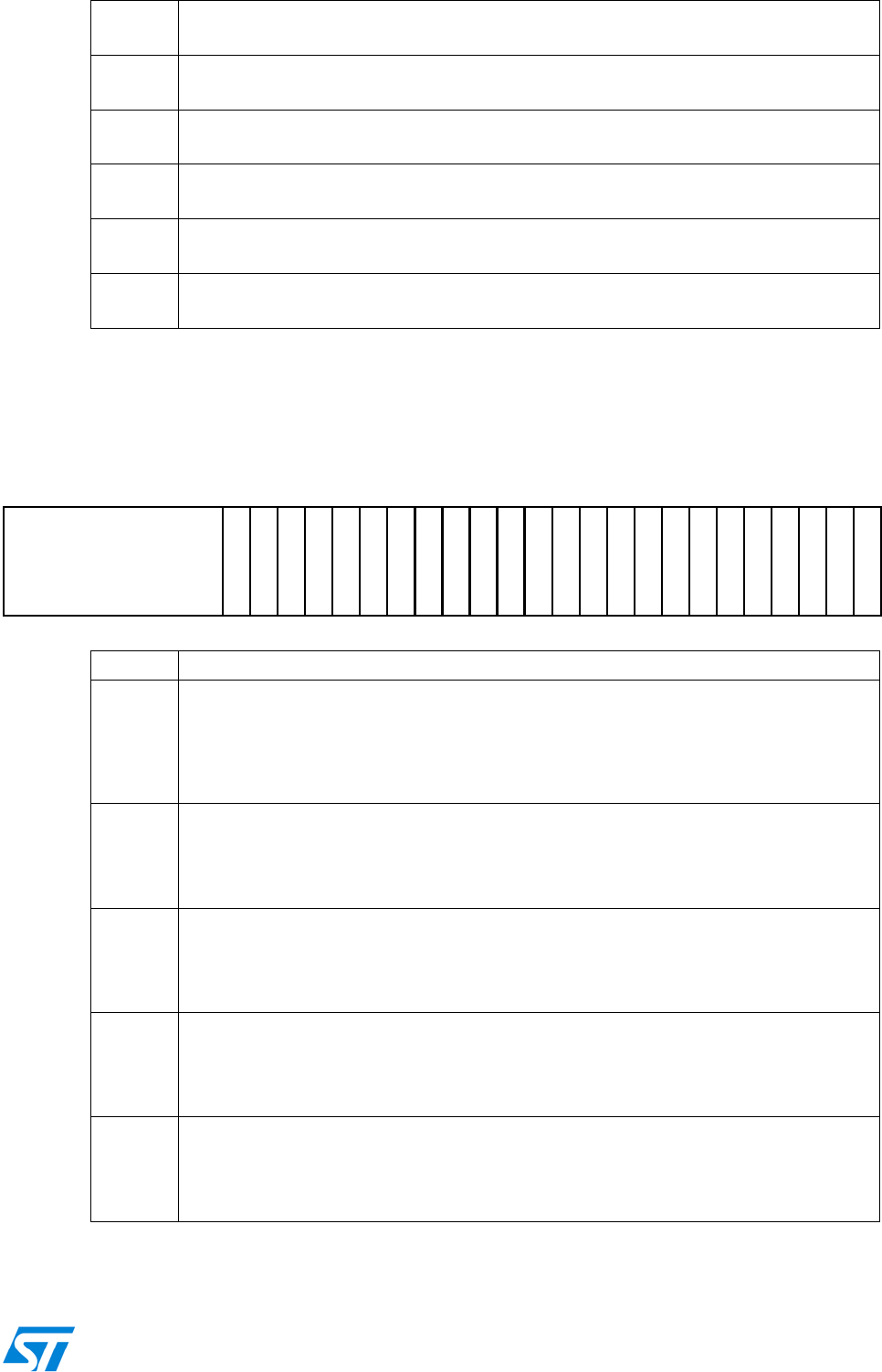

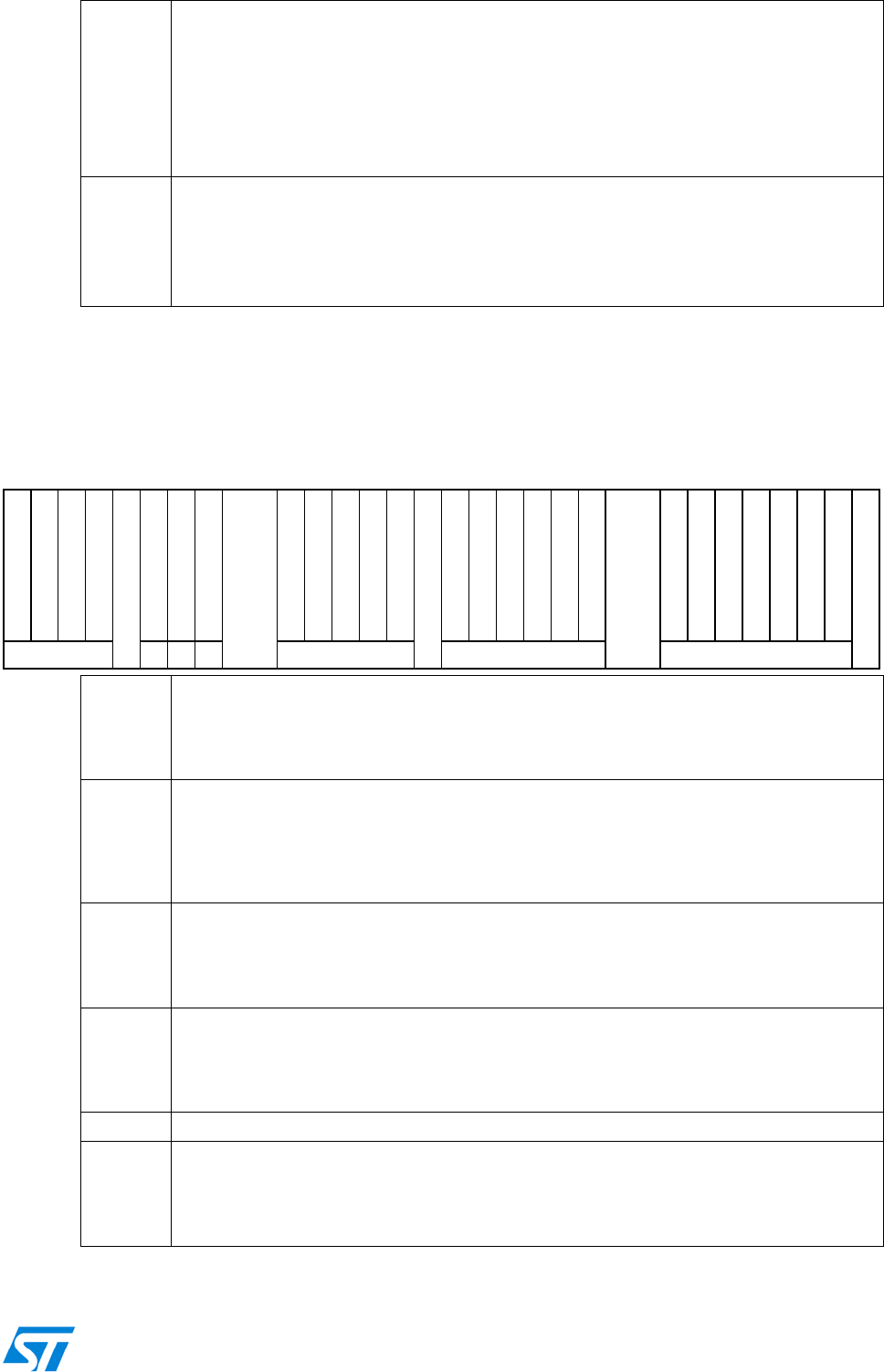

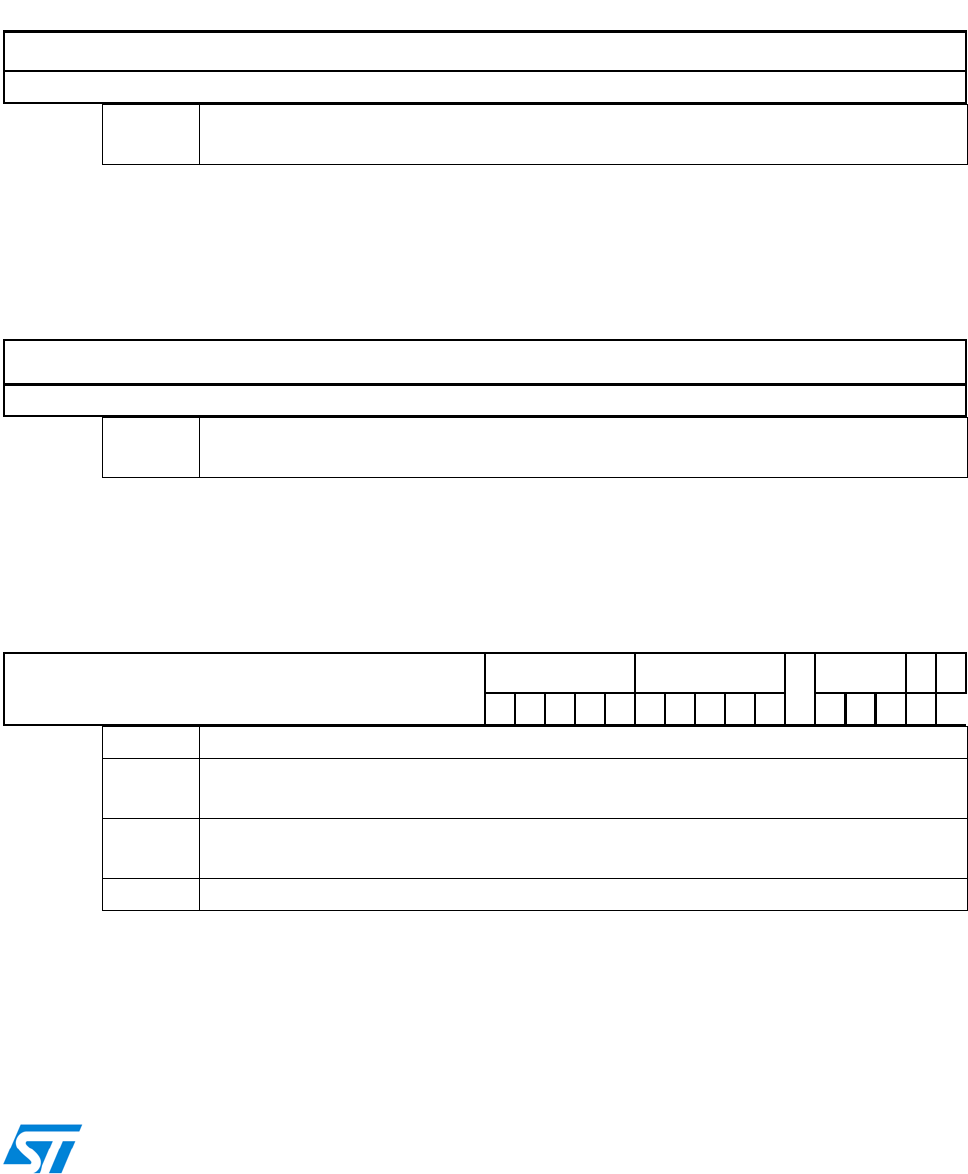

3.4.4 CRC寄存器映像

下表列出了CRC的寄存器映像和复位值

表7 CRC 计算单元寄存器映像和复位值

偏移 寄存器 31~24 23~16 15~8 76543210

CRC_DR

复位值

CRC_IDR

复位值

CRC_CR RESET

复位值 0

保留

0

0x00

0x08

0x04

数据寄存器

保留 独立的数据寄存器

0xFFFF FFFF

0x00

保留

本译文仅供参考,如有翻译错误,请以英文原稿为准。请读者随时注意在ST网站下载更新版本

电源控制(PWR) STM32F10xxx参考手册

4 电源控制(PWR)

小容量产品是指闪存存储器容量在16K至32K字节之间的STM32F101xx、STM32F102xx和

STM32F103xx微控制器。

中容量产品是指闪存存储器容量在64K至128K字节之间的STM32F101xx、STM32F102xx和

STM32F103xx微控制器。

大容量产品是指闪存存储器容量在256K至512K字节之间的STM32F101xx和STM32F103xx微控

制器。

互联型产品是指STM32F105xx和STM32F107xx微控制器。

除非特别说明,本章描述的模块适用于整个STM32F10xxx微控制器系列。

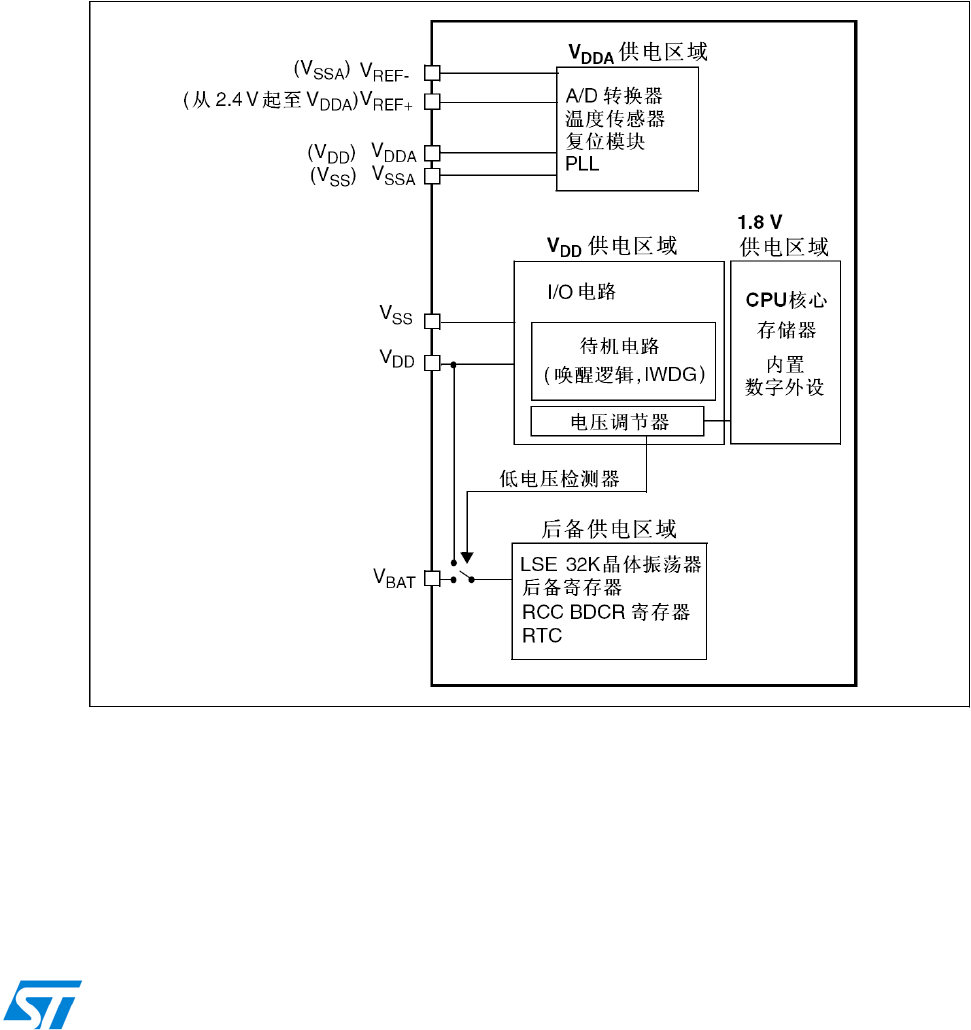

4.1 电源

STM32的工作电压(VDD)为2.0~3.6V。通过内置的电压调节器提供所需的1.8V电源。

当主电源VDD掉电后,通过VBAT脚为实时时钟(RTC)和备份寄存器提供电源。

图4 电源框图

注:

V

DDA

和

VSSA

必须分别联到

VDD

和

VSS

。

4.1.1 独立的A/D转换器供电和参考电压

为了提高转换的精确度,ADC使用一个独立的电源供电,过滤和屏蔽来自印刷电路板上的毛刺

干扰。

● ADC的电源引脚为VDDA

● 独立的电源地VSSA

如果有VREF-引脚(根据封装而定),它必须连接到VSSA。

37/754

参照2009年12月 RM0008 Reference Manual 英文第10版

本译文仅供参考,如有翻译错误,请以英文原稿为准。请读者随时注意在ST网站下载更新版本

电源控制(PWR) STM32F10xxx参考手册

100脚和144脚封装:

为了确保输入为低压时获得更好精度,用户可以连接一个独立的外部参考电压ADC到VREF+和

VREF-脚上。在VREF+的电压范围为2.4V~VDDA。

64脚或更少封装:

没有VREF+和VREF-引脚,他们在芯片内部与ADC的电源(VDDA)和地(VSSA)相联。

4.1.2 电池备份区域

使用电池或其他电源连接到VBAT脚上,当VDD断电时,可以保存备份寄存器的内容和维持RTC的

功能。

VBAT脚也为RTC、LSE振荡器和PC13至PC15供电,这保证当主要电源被切断时RTC能继续工

作。切换到VBAT供电由复位模块中的掉电复位功能控制。

如果应用中没有使用外部电池,VBAT必须连接到VDD引脚上。

注意:

在VDD上升阶段(tRSTTEMPO)或者探测到PVD之后,VBAT和VDD之间的电源开关仍会保持连接在

VBAT。在VDD上升阶段,如果VDD在小于tRSTTEMPO的时间内达到稳定状态(关于tRSTTEMPO可参考数

据手册中的相关部分),且VDD > VBAT + 0.6V时,电流可能通过VDD和VBAT之间的内部二极管注

入到VBAT。

如果与VBAT连接的电源或者电池不能承受这样的注入电流,强烈建议在外部VBAT和电源之间连

接一个低压降二极管。

如果在应用中没有外部电池,建议VBAT在外部通过一个100nF的陶瓷电容与VDD相连,更多细节

参阅AN2586。

当备份区域由VDD(内部模拟开关连到VDD)供电时,下述功能可用:

● PC14和PC15可以用于GPIO或LSE引脚

5● PC13可以作为通用I/O口、TAMPER引脚、RTC校准时钟、RTC闹钟或秒输出(参见第

38/754

章:备份寄存器(BKP))

注:

因为模拟开关只能通过少量的电流

(3mA)

,在输出模式下使用

PC13

至

PC15

的

I/O

口功能是有限

制的:速度必须限制在

2MHz

以下,最大负载为

30pF

,而且这些

I/O

口绝对不能当作电流源

(

如驱

动

LED)

。

当后备区域由VBAT供电时(VDD消失后模拟开关连到VBAT),可以使用下述功能:

● PC14和PC15只能用于LSE引脚

5.4.2● PC13可以作为TAMPER引脚、RTC闹钟或秒输出(参见第 节:RTC时钟校准寄存器

(BKP_RTCCR))

4.1.3 电压调节器

复位后调节器总是使能的。根据应用方式它以3种不同的模式工作。

● 运转模式:调节器以正常功耗模式提供1.8V电源(内核,内存和外设)。

● 停止模式:调节器以低功耗模式提供1.8V电源,以保存寄存器和SRAM的内容。

● 待机模式:调节器停止供电。除了备用电路和备份域外,寄存器和SRAM的内容全部丢失。

4.2 电源管理器

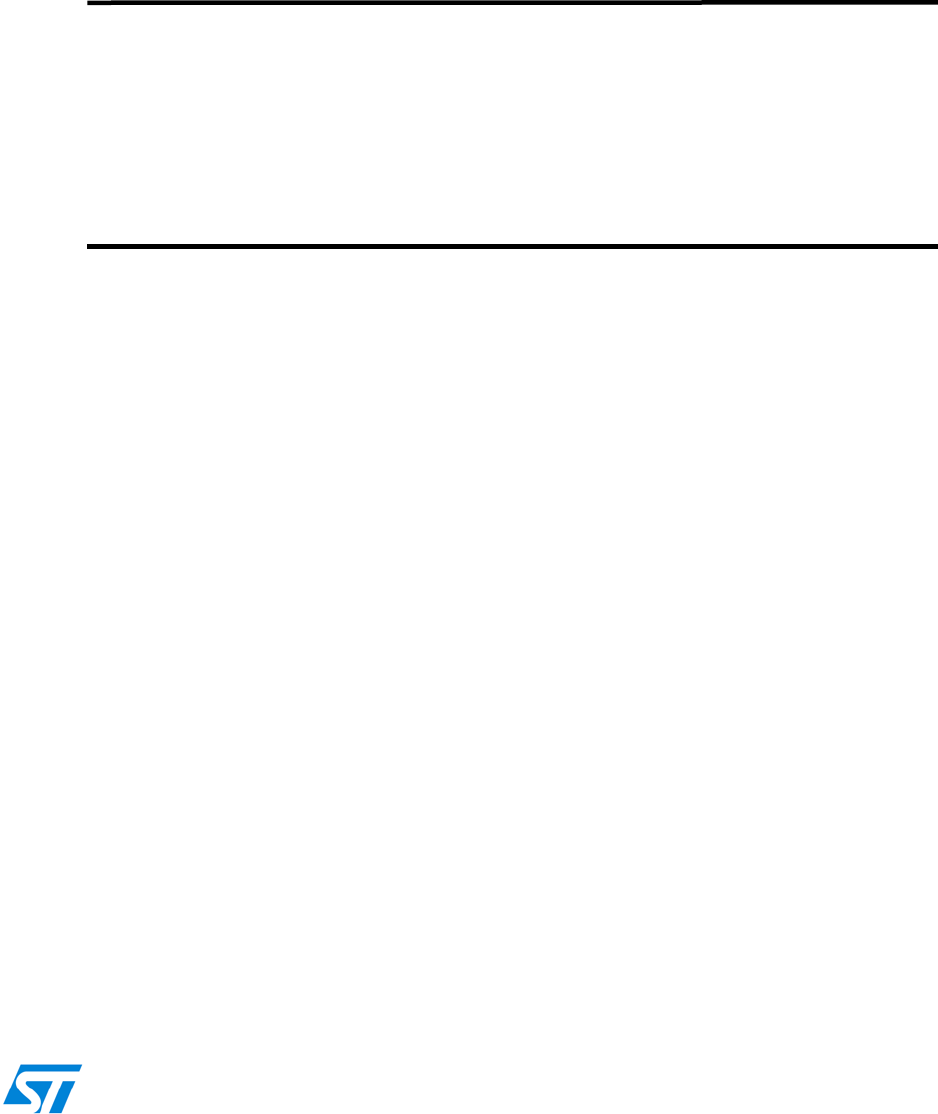

4.2.1 上电复位(POR)和掉电复位(PDR)

STM32内部有一个完整的上电复位(POR)和掉电复位(PDR)电路,当供电电压达到2V时系统既

能正常工作。

参照2009年12月 RM0008 Reference Manual 英文第10版

本译文仅供参考,如有翻译错误,请以英文原稿为准。请读者随时注意在ST网站下载更新版本

电源控制(PWR) STM32F10xxx参考手册

当VDD/VDDA低于指定的限位电压VPOR/VPDR时,系统保持为复位状态,而无需外部复位电路。关

于上电复位和掉电复位的细节请参考数据手册的电气特性部分。

图5 上电复位和掉电复位的波形图

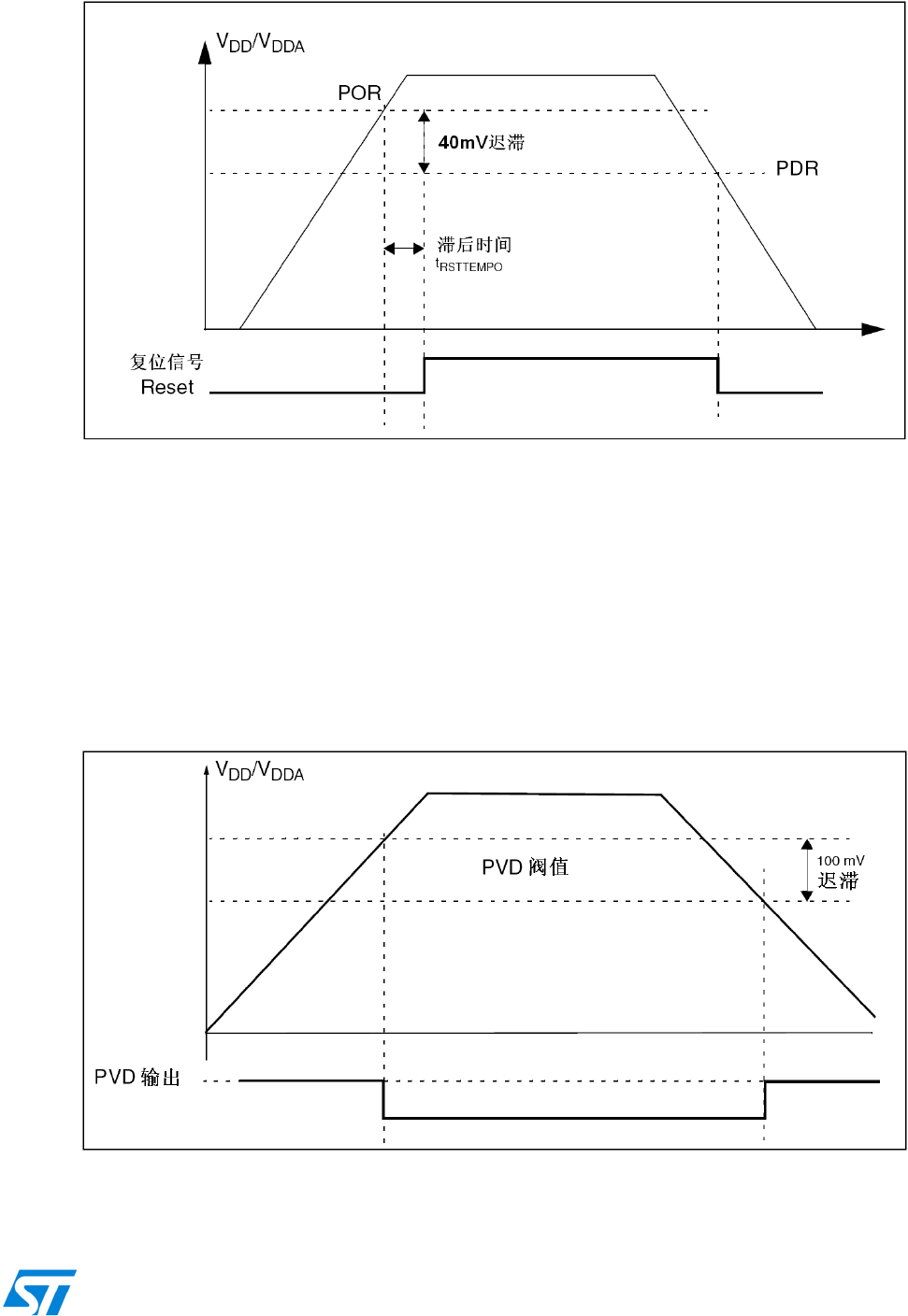

4.2.2 可编程电压监测器(PVD)

用户可以利用PVD对VDD电压与电源控制寄存器(PWR_CR)中的PLS[2:0]位进行比较来监控电

源,这几位选择监控电压的阀值。

通过设置PVDE位来使能PVD。

电源控制/状态寄存器(PWR_CSR)中的PVDO标志用来表明VDD是高于还是低于PVD的电压阀

值。该事件在内部连接到外部中断的第16线,如果该中断在外部中断寄存器中是使能的,该事

件就会产生中断。当VDD下降到PVD阀值以下和(或)当VDD上升到PVD阀值之上时,根据外部中

断第16线的上升/下降边沿触发设置,就会产生PVD中断。例如,这一特性可用于用于执行紧急

关闭任务。

图6 PVD的门限

39/754

参照2009年12月 RM0008 Reference Manual 英文第10版

本译文仅供参考,如有翻译错误,请以英文原稿为准。请读者随时注意在ST网站下载更新版本

电源控制(PWR) STM32F10xxx参考手册

4.3 低功耗模式

在系统或电源复位以后,微控制器处于运行状态。当CPU不需继续运行时,可以利用多种低功

耗模式来节省功耗,例如等待某个外部事件时。用户需要根据最低电源消耗、最快速启动时间

和可用的唤醒源等条件,选定一个最佳的低功耗模式。

STM32F10xxx有三种低功耗模式:

● 睡眠模式(Cortex™-M3内核停止,所有外设包括Cortex-M3核心的外设,如NVIC、系统时

钟(SysTick)等仍在运行)

● 停止模式(所有的时钟都已停止)

● 待机模式(1.8V电源关闭)

此外,在运行模式下,可以通过以下方式中的一种降低功耗:

● 降低系统时钟

● 关闭APB和AHB总线上未被使用的外设时钟。

表8 低功耗模式一览

对VDD区域

时钟的影响

对1.8V区域

时钟的影响 电压调节器 模式 进入 唤醒

40/754

WFI 任一中断 CPU时钟关,对

其他时钟和ADC

时钟无影响

睡眠

(SLEEP-NOW或

SLEEP-ON-EXIT)

无 开

WFE 唤醒事件

开启或处于低功耗

模式(依据电源控制

寄存器(PWR_CR)

的设定)

PDDS和LPDS位

+SLEEPDEEP位

+WFI或WFE

任一外部中断(在外

部中断寄存器中设

置)

停机

HSI 和HSE

的振荡器关

闭

关闭所有1.8V区

域的时钟

WKUP引脚的上升

沿、RTC闹钟事件、

NRST引脚上的外部

复位、IWDG复位

PDDS位

+SLEEPDEEP位

+WFI或WFE

待机 关

4.3.1 降低系统时钟

在运行模式下,通过对预分频寄存器进行编程,可以降低任意一个系统时钟(SYSCLK 、

HCLK、PCLK1、PCLK2)的速度。进入睡眠模式前,也可以利用预分频器来降低外设的时钟。

详见第6.3.2节:时钟配置寄存器(RCC_CFGR)。

4.3.2 外部时钟的控制

在运行模式下,任何时候都可以通过停止为外设和内存提供时钟(HCLK和PCLKx)来减少功耗。

为了在睡眠模式下更多地减少功耗,可在执行WFI或WFE指令前关闭所有外设的时钟。

通过设置AHB 外设时钟使能寄存器 (RCC_AHBENR) 、APB2 外设时钟使能寄存器

(RCC_APB2ENR)和APB1外设时钟使能寄存器(RCC_APB1ENR)来开关各个外设模块的时钟。

4.3.3 睡眠模式

进入睡眠模式

通过执行WFI或WFE指令进入睡眠状态。根据Cortex™-M3系统控制寄存器中的SLEEPONEXIT

位的值,有两种选项可用于选择睡眠模式进入机制:

● SLEEP-NOW:如果SLEEPONEXIT位被清除,当WRI或WFE被执行时,微控制器立即进

入睡眠模式。

● SLEEP-ON-EXIT:如果SLEEPONEXIT位被置位,系统从最低优先级的中断处理程序中退

出时,微控制器就立即进入睡眠模式。

在睡眠模式下,所有的I/O引脚都保持它们在运行模式时的状态。

参照2009年12月 RM0008 Reference Manual 英文第10版

本译文仅供参考,如有翻译错误,请以英文原稿为准。请读者随时注意在ST网站下载更新版本

电源控制(PWR) STM32F10xxx参考手册

41/754

关于如何进入睡眠模式,更多的细节参考表9和表10。

退出睡眠模式

如果执行WFI指令进入睡眠模式,任意一个被嵌套向量中断控制器响应的外设中断都能将系统从

睡眠模式唤醒。

如果执行WFE指令进入睡眠模式,则一旦发生唤醒事件时,微处理器都将从睡眠模式退出。唤

醒事件可以通过下述方式产生:

● 在外设控制寄存器中使能一个中断,而不是在NVIC(嵌套向量中断控制器)中使能,并且在

Cortex-M3系统控制寄存器中使能SEVONPEND位。当MCU从WFE中唤醒后,外设的中断

挂起位和外设的NVIC中断通道挂起位(在NVIC中断清除挂起寄存器中)必须被清除。

● 配置一个外部或内部的EXIT线为事件模式。当MCU从WFE中唤醒后,因为与事件线对应的

挂起位未被设置,不必清除外设的中断挂起位或外设的NVIC中断通道挂起位。

该模式唤醒所需的时间最短,因为没有时间损失在中断的进入或退出上。

关于如何退出睡眠模式,更多的细节参考表9和表10。

表9 SLEEP-NOW模式

SLEEP-NOW模式 说明

在以下条件下执行WFI(等待中断)或WFE(等待事件)指令:

– SLEEPDEEP = 0 和

进入 – SLEEPONEXIT = 0

参考Cortex-M3系统控制寄存器。

如果执行WFI进入睡眠模式:

中断:参考中断向量表(表54)

退出 如果执行WFE进入睡眠模式:

唤醒事件:参考唤醒事件管理(第9.2.3节)

唤醒延时 无

表10 SLEEP-ON-EXIT模式

SLEEP-ON_EXIT模式 说明

在以下条件下执行WFI指令:

– SLEEPDEEP = 0和

进入 – SLEEPONEXIT = 1

参考Cortex™-M3系统控制寄存器

退出 中断:参考中断向量表(表54)

唤醒延时 无

4.3.4 停止模式

停止模式是在Cortex™-M3的深睡眠模式基础上结合了外设的时钟控制机制,在停止模式下电压

调节器可运行在正常或低功耗模式。此时在1.8V供电区域的的所有时钟都被停止,PLL、HSI和

HSE RC振荡器的功能被禁止,SRAM和寄存器内容被保留下来。

在停止模式下,所有的I/O引脚都保持它们在运行模式时的状态。

进入停止模式

关于如何进入停止模式,详见表11。

电源控制寄存器(PWR_CR)在停止模式下,通过设置 的LPDS位使内部调节器进入低功耗模式,

能够降低更多的功耗。

如果正在进行闪存编程,直到对内存访问完成,系统才进入停止模式。

如果正在进行对APB的访问,直到对APB访问完成,系统才进入停止模式。

可以通过对独立的控制位进行编程,可选择以下功能:

参照2009年12月 RM0008 Reference Manual 英文第10版

本译文仅供参考,如有翻译错误,请以英文原稿为准。请读者随时注意在ST网站下载更新版本

电源控制(PWR) STM32F10xxx参考手册

● 独立看门狗(IWDG):可通过写入看门狗的键寄存器或硬件选择来启动IWDG。一旦启动了

独立看门狗,除了系统复位,它不能再被停止。详见17.3节。

● 实时时钟(RTC):通过备份域控制寄存器 (RCC_BDCR)的RTCEN位来设置。

● 内部RC振荡器(LSI RC):通过控制/状态寄存器 (RCC_CSR)的LSION位来设置。

42/754

● 外部32.768kHz振荡器(LSE):通过备份域控制寄存器 (RCC_BDCR)的LSEON位设置。

在停止模式下,如果在进入该模式前ADC和DAC没有被关闭,那么这些外设仍然消耗电流。通

过设置寄存器ADC_CR2的ADON位和寄存器DAC_CR的ENx位为0可关闭这2个外设。

退出停止模式

关于如何退出停止模式,详见下表。

当一个中断或唤醒事件导致退出停止模式时,HSI RC振荡器被选为系统时钟。

当电压调节器处于低功耗模式下,当系统从停止模式退出时,将会有一段额外的启动延时。如

果在停止模式期间保持内部调节器开启,则退出启动时间会缩短,但相应的功耗会增加。

表11 停止模式

停止模式 说明

在以下条件下执行WFI(等待中断)或WFE(等待事件)指令:

– 设置Cortex-M3系统控制寄存器中的SLEEPDEEP位

– 清除电源控制寄存器(PWR_CR)中的PDDS位

进入 – 通过设置PWR_CR中LPDS位选择电压调节器的模式

注:为了进入停止模式,所有的外部中断的请求位(挂起寄存器(EXTI_PR))和RTC的闹钟标志

都必须被清除,否则停止模式的进入流程将会被跳过,程序继续运行。

如果执行WFI进入停止模式:

设置任一外部中断线为中断模式(在NVIC中必须使能相应的外部中断向量)。参见中断向量

表(表54)。

退出

如果执行WFE进入停止模式:

设置任一外部中断线为事件模式。参见唤醒事件管理(第9.2.3节)。

唤醒延时 HSI RC唤醒时间 + 电压调节器从低功耗唤醒的时间。

4.3.5 待机模式

待机模式可实现系统的最低功耗。该模式是在Cortex-M3深睡眠模式时关闭电压调节器。整个

1.8V供电区域被断电。PLL、HSI和HSE振荡器也被断电。SRAM和寄存器内容丢失。只有备份

的寄存器和待机电路维持供电(见图4)。

进入待机模式

关于如何进入待机模式,详见表12。

可以通过设置独立的控制位,选择以下待机模式的功能:

● 独立看门狗(IWDG):可通过写入看门狗的键寄存器或硬件选择来启动IWDG。一旦启动了

独立看门狗,除了系统复位,它不能再被停止。详见17.3节。

● 实时时钟(RTC):通过备用区域控制寄存器(RCC_BDCR)的RTCEN位来设置。

● 内部RC振荡器(LSI RC):通过控制/状态寄存器(RCC_CSR)的LSION位来设置。

● 外部32.768kHz振荡器(LSE):通过备用区域控制寄存器(RCC_BDCR)的LSEON位设置。

退出待机模式

当一个外部复位(NRST引脚)、IWDG复位、WKUP引脚上的上升沿或RTC闹钟事件的上升沿发

生时(见图154 简化的RTC框图),微控制器从待机模式退出。从待机唤醒后,除了:电源控制/状

态寄存器(PWR_CSR)(见第4.4.2节),所有寄存器被复位。

从待机模式唤醒后的代码执行等同于复位后的执行(采样启动模式引脚、读取复位向量等)。电源

控制/状态寄存器(PWR_CSR)(见第4.4.2节)将会指示内核由待机状态退出。

关于如何退出待机模式,详见下表。

参照2009年12月 RM0008 Reference Manual 英文第10版

本译文仅供参考,如有翻译错误,请以英文原稿为准。请读者随时注意在ST网站下载更新版本

电源控制(PWR) STM32F10xxx参考手册

表12 待机模式

待机模式 说明

在以下条件下执行WFI(等待中断)或WFE(等待事件)指令:

– 设置Cortex™-M3系统控制寄存器中的SLEEPDEEP位

进入 – 设置电源控制寄存器(PWR_CR)中的PDDS位

– 清除电源控制/状态寄存器(PWR_CSR)中的WUF位

退出 WKUP引脚的上升沿、RTC闹钟事件的上升沿、NRST引脚上外部复位、IWDG复位。

唤醒延时 复位阶段时电压调节器的启动。

待机模式下的输入/输出端口状态

在待机模式下,所有的I/O引脚处于高阻态,除了以下的引脚:

● 复位引脚(始终有效)

● 当被设置为防侵入或校准输出时的TAMPER引脚

● 被使能的唤醒引脚

调试模式

默认情况下,如果在进行调试微处理器时,使微处理器进入停止或待机模式,将失去调试连

接。这是因为Cortex™-M3的内核失去了时钟。

然而,通过设置DBGMCU_CR寄存器中的某些配置位,可以在使用低功耗模式下调试软件。更

多的细节请参考第29.16.1

43/754

节:低功耗模式的调试支持。

4.3.6 低功耗模式下的自动唤醒(AWU)

RTC可以在不需要依赖外部中断的情况下唤醒低功耗模式下的微控制器(自动唤醒模式)。RTC提

供一个可编程的时间基数,用于周期性从停止或待机模式下唤醒。通过对备份区域控制寄存器

(RCC_BDCR)的RTCSEL[1:0]位的编程,三个RTC时钟源中的二个时钟源可以选作实现此功

能。

● 低功耗32.768kHz外部晶振(LSE)

该时钟源提供了一个低功耗且精确的时间基准。(在典型情形下消耗小于1µA)

● 低功耗内部RC振荡器(LSI RC)

使用该时钟源,节省了一个32.768kHz晶振的成本。但是RC振荡器将少许增加电源消耗。

为了用RTC闹钟事件将系统从停止模式下唤醒,必须进行如下操作:

● 配置外部中断线17为上升沿触发。

● 配置RTC使其可产生RTC闹钟事件。

如果要从待机模式中唤醒,不必配置外部中断线17。

参照2009年12月 RM0008 Reference Manual 英文第10版

本译文仅供参考,如有翻译错误,请以英文原稿为准。请读者随时注意在ST网站下载更新版本

电源控制(PWR) STM32F10xxx参考手册

4.4 电源控制寄存器

可以用半字(16位)或字(32位)的方式操作这些外设寄存器。

4.4.1 电源控制寄存器(PWR_CR)

地址偏移:0x00

复位值:0x0000 0000 (从待机模式唤醒时清除)

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

1514131211109876543210

DBP PVDE CSBF CWUF PDDS LPDS

rw rw rw rw rw rc_w1 rc_w1 rw rw

保留

保留

PLS[2:0]

位 31:9 保留。始终读为0。

DBP:取消后备区域的写保护 位 8

在复位后,RTC和后备寄存器处于被保护状态以防意外写入。设置这位允许写入这些寄存器。

0:禁止写入RTC和后备寄存器

1:允许写入RTC和后备寄存器

注:如果RTC的时钟是HSE/128,该位必须保持为’1’。

PLS[2:0]:PVD电平选择 位 7:5

这些位用于选择电源电压监测器的电压阀值

000:2.2V 100:2.6V

001:2.3V 101:2.7V

010:2.4V 110:2.8V

011:2.5V 111:2.9V

注:详细说明参见数据手册中的电气特性部分。

PVDE:电源电压监测器(PVD)使能 位 4

0:禁止PVD

1:开启PVD

CSBF:清除待机位 位 3

始终读出为0

0:无功效

1:清除SBF待机位(写)

CWUF:清除唤醒位 位 2

始终读出为0

0:无功效

1:2个系统时钟周期后清除WUF唤醒位(写)

PDDS:掉电深睡眠 位 1

与LPDS位协同操作

0:当CPU进入深睡眠时进入停机模式,调压器的状态由LPDS位控制。

1:CPU进入深睡眠时进入待机模式。

LPDS:深睡眠下的低功耗 位 0

PDDS=0时,与PDDS位协同操作

0:在停机模式下电压调压器开启

1:在停机模式下电压调压器处于低功耗模式

44/754

参照2009年12月 RM0008 Reference Manual 英文第10版

本译文仅供参考,如有翻译错误,请以英文原稿为准。请读者随时注意在ST网站下载更新版本

电源控制(PWR) STM32F10xxx参考手册

4.4.2 电源控制/状态寄存器(PWR_CSR)

地址偏移:0x04

复位值:0x0000 0000 (从待机模式唤醒时不被清除)

与标准的APB读相比,读此寄存器需要额外的APB周期

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

1514131211109876543210

EWUP PVDO SBF WUF

rw rrr

保留

保留 保留

位31:9 保留。始终读为0。

EWUP:使能WKUP引脚 位 8

0:WKUP引脚为通用I/O。WKUP引脚上的事件不能将CPU从待机模式唤醒

1:WKUP引脚用于将CPU从待机模式唤醒,WKUP引脚被强置为输入下拉的配置(WKUP引脚

上的上升沿将系统从待机模式唤醒)

注:在系统复位时清除这一位。

位 7:3 保留。始终读为0。

PVDO:PVD输出 位 2

当PVD被PVDE位使能后该位才有效

0:VDD/VDDA高于由PLS[2:0]选定的PVD阀值

1:VDD/VDDA低于由PLS[2:0]选定的PVD阀值

注:在待机模式下PVD被停止。因此,待机模式后或复位后,直到设置PVDE位之前,该位为

0。

SBF:待机标志 位 1

该位由硬件设置,并只能由POR/PDR(上电/掉电复位)或设置电源控制寄存器(PWR_CR)的

CSBF位清除。

0:系统不在待机模式

1:系统进入待机模式

WUF:唤醒标志 位 0

该位由硬件设置,并只能由POR/PDR(上电/掉电复位)或设置电源控制寄存器(PWR_CR)的

CWUF位清除。

0:没有发生唤醒事件

1:在WKUP引脚上发生唤醒事件或出现RTC闹钟事件。

注:当WKUP引脚已经是高电平时,在(通过设置EWUP位)使能WKUP引脚时,会检测到一个额外的

事件。

45/754

参照2009年12月 RM0008 Reference Manual 英文第10版

本译文仅供参考,如有翻译错误,请以英文原稿为准。请读者随时注意在ST网站下载更新版本

电源控制(PWR) STM32F10xxx参考手册

46/754

参照2009年12月 RM0008 Reference Manual 英文第10版

4.4.3 PWR寄存器地址映像

以下表格列出所有PWR寄存器。

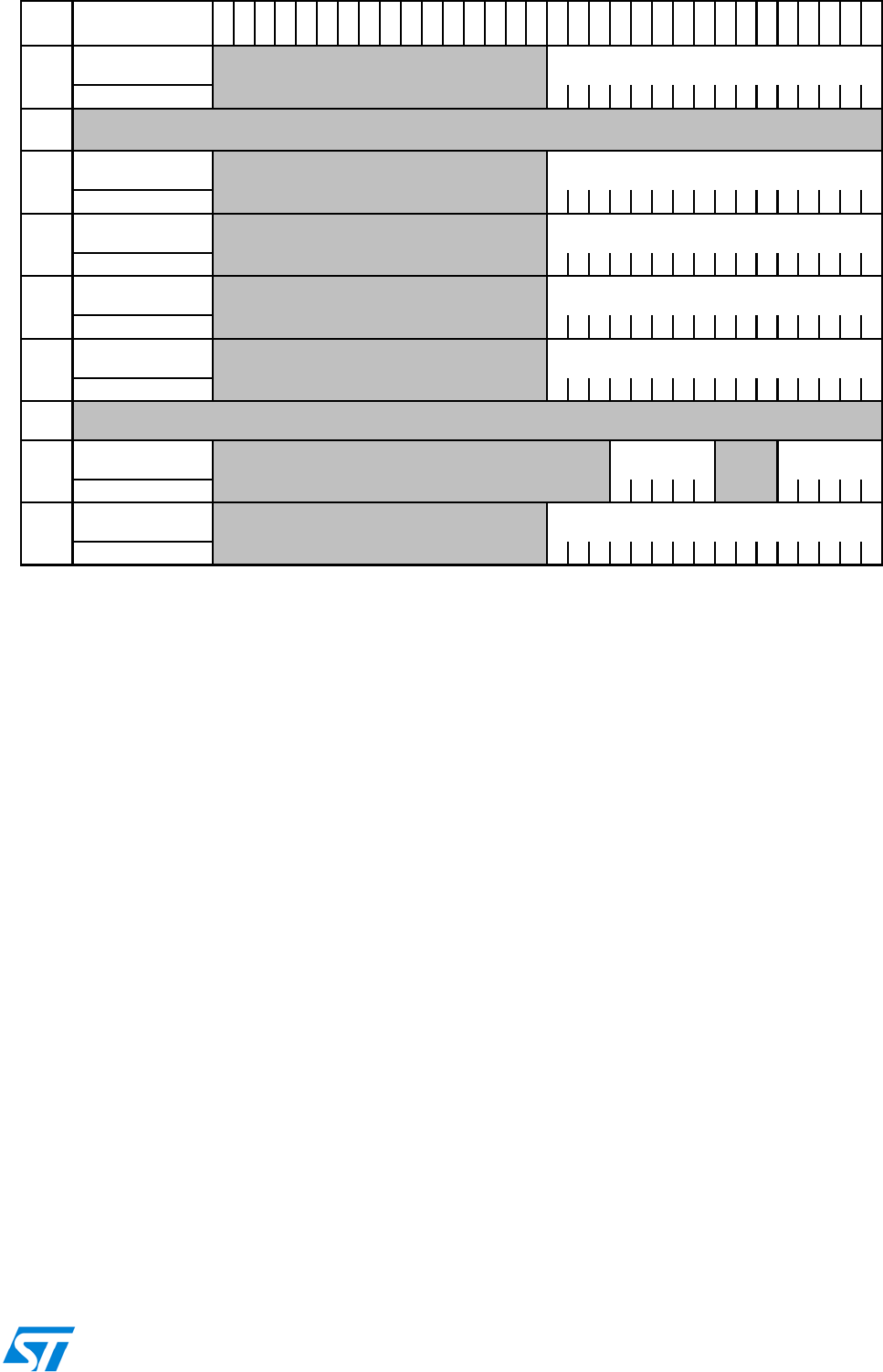

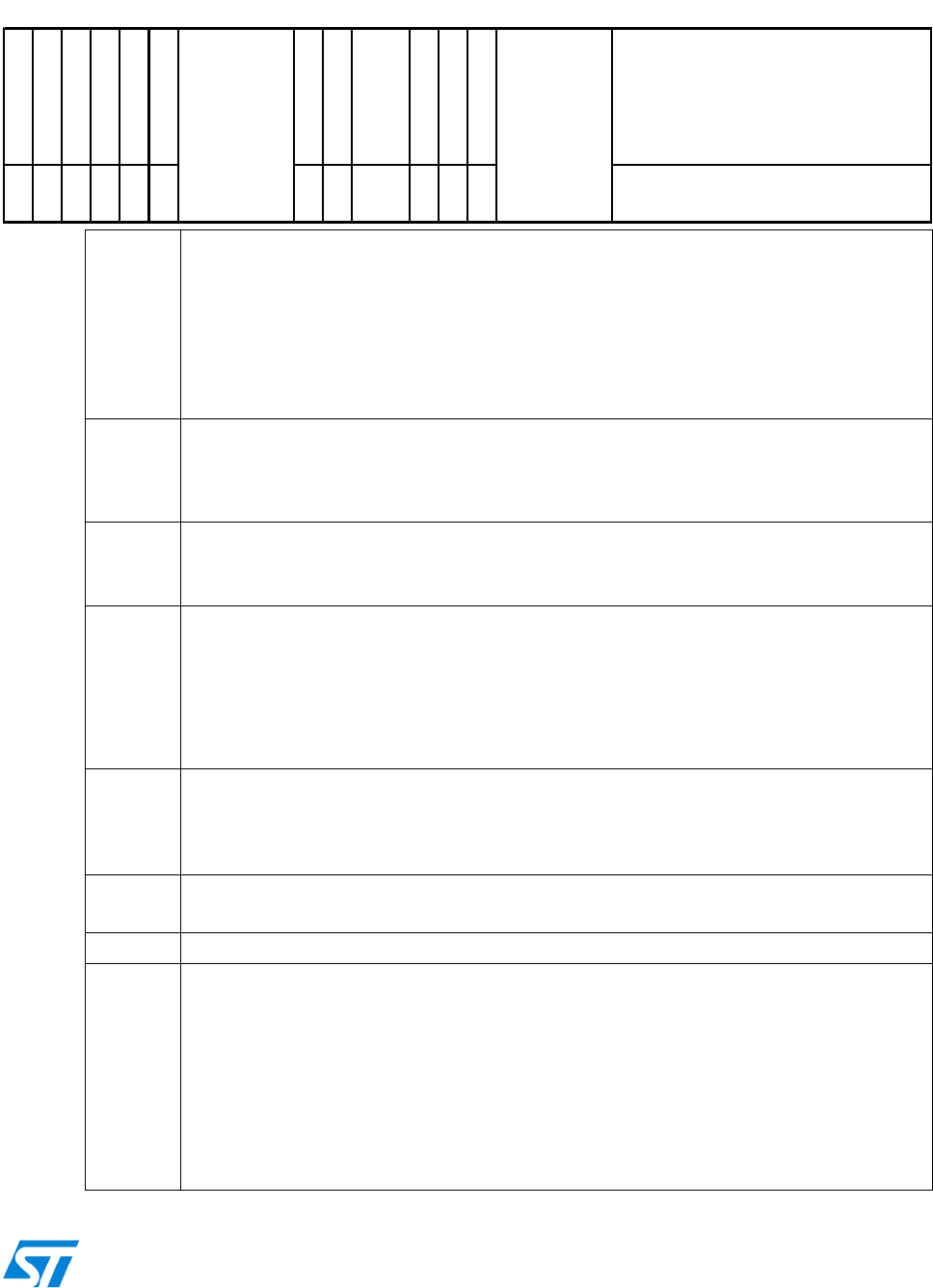

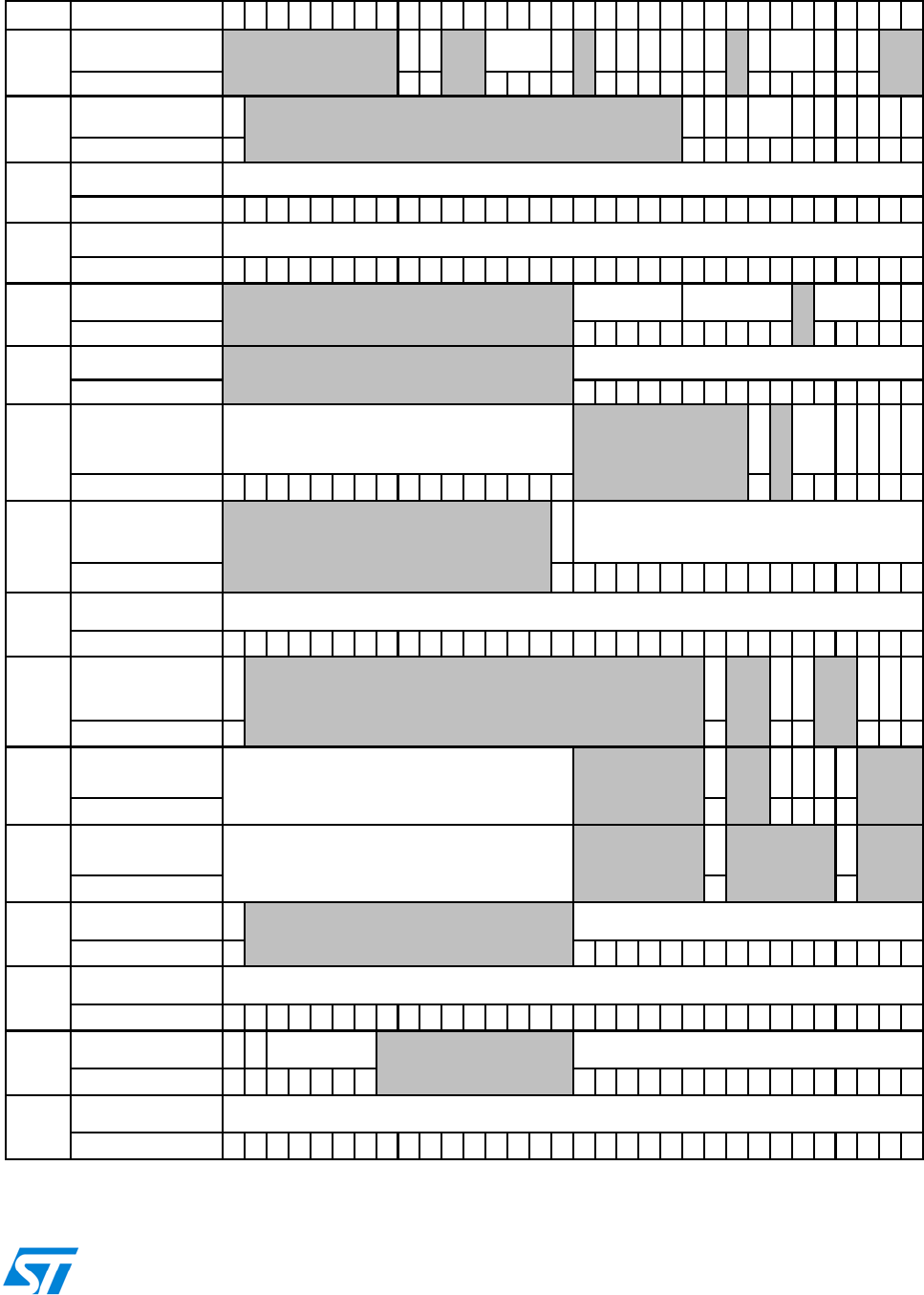

表13 PWR寄存器地址映像和复位值

偏移 寄存器

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

PWR_CR

DBP

PVDE

CSBF

CWUF

PDDS

LPDS

PLS

[2:0]

000h 保留

复位值 000000000

PWR_CSR

EWUP

PVDO

SBF

WUF

复位值 0 0 0 0

004h 保留 保留

本译文仅供参考,如有翻译错误,请以英文原稿为准。请读者随时注意在ST网站下载更新版本

关于寄存器的起始地址,参见表1。

备份寄存器(BKP) STM32F10xxx参考手册

5 备份寄存器(BKP)

小容量产品是指闪存存储器容量在16K至32K字节之间的STM32F101xx、STM32F102xx和

STM32F103xx微控制器。

中容量产品是指闪存存储器容量在64K至128K字节之间的STM32F101xx、STM32F102xx和

STM32F103xx微控制器。

大容量产品是指闪存存储器容量在256K至512K字节之间的STM32F101xx和STM32F103xx微控

制器。

互联型产品是指STM32F105xx和STM32F107xx微控制器。

除非特别说明,本章描述的模块适用于整个STM32F10xxx微控制器系列。

5.1 BKP简介

备份寄存器是42个16位的寄存器,可用来存储84个字节的用户应用程序数据。他们处在备份域

里,当VDD电源被切断,他们仍然由VBAT维持供电。当系统在待机模式下被唤醒,或系统复位或

电源复位时,他们也不会被复位。

此外,BKP控制寄存器用来管理侵入检测和RTC校准功能。

复位后,对备份寄存器和RTC的访问被禁止,并且备份域被保护以防止可能存在的意外的写操

作。执行以下操作可以使能对备份寄存器和RTC的访问。

● 通过设置寄存器RCC_APB1ENR的PWREN和BKPEN位来打开电源和后备接口的时钟

● 电源控制寄存器(PWR_CR)的DBP位来使能对后备寄存器和RTC的访问。

5.2 BKP特性

● 20字节数据后备寄存器(中容量和小容量产品),或84字节数据后备寄存器(大容量和互联型

产品)

● 用来管理防侵入检测并具有中断功能的状态/控制寄存器

● 用来存储RTC校验值的校验寄存器。

● 在PC13引脚(当该引脚不用于侵入检测时)上输出RTC校准时钟,RTC闹钟脉冲或者秒脉冲

5.3 BKP功能描述

5.3.1 侵入检测

当TAMPER引脚上的信号从0变成1或者从1变成0(取决于备份控制寄存器BKP_CR的TPAL位),

会产生一个侵入检测事件。侵入检测事件将所有数据备份寄存器内容清除。

然而为了避免丢失侵入事件,侵入检测信号是边沿检测的信号与侵入检测允许位的逻辑与,从

而在侵入检测引脚被允许前发生的侵入事件也可以被检测到。

● 当TPAL=0时:如果在启动侵入检测TAMPER引脚前(通过设置TPE位)该引脚已经为高电

平,一旦启动侵入检测功能,则会产生一个额外的侵入事件(尽管在TPE位置’1’后并没有出

现上升沿)。

● 当TPAL=1时:如果在启动侵入检测引脚TAMPER前(通过设置TPE位)该引脚已经为低电

平,一旦启动侵入检测功能,则会产生一个额外的侵入事件(尽管在TPE位置’1’后并没有出

现下降沿)。

设置BKP_CSR寄存器的TPIE位为’1’,当检测到侵入事件时就会产生一个中断。

在一个侵入事件被检测到并被清除后,侵入检测引脚TAMPER应该被禁止。然后,在再次写入

备份数据寄存器前重新用TPE位启动侵入检测功能。这样,可以阻止软件在侵入检测引脚上仍

然有侵入事件时对备份数据寄存器进行写操作。这相当于对侵入引脚TAMPER进行电平检测。

注:

当

VDD

电源断开时,侵入检测功能仍然有效。为了避免不必要的复位数据备份寄存器,

TAMPER

引脚应该在片外连接到正确的电平。

47/754

参照2009年12月 RM0008 Reference Manual 英文第10版

本译文仅供参考,如有翻译错误,请以英文原稿为准。请读者随时注意在ST网站下载更新版本

备份寄存器(BKP) STM32F10xxx参考手册

5.3.2 RTC校准

为方便测量,RTC时钟可以经64分频输出到侵入检测引脚TAMPER上。通过设置RTC校验寄存

器(BKP_RTCCR)的CCO位来开启这一功能。

通过配置CAL[6:0]位,此时钟可以最多减慢121ppm。

关于RTC校准和如何提高精度,请看AN2604“STM32F101xx和STM32F103xx的RTC校准”

5.4 BKP寄存器描述

48/754