ARM Assembly Language Tools V5.0 User's Guide (Rev. K) TI Assembler Manual

User Manual:

Open the PDF directly: View PDF ![]() .

.

Page Count: 326 [warning: Documents this large are best viewed by clicking the View PDF Link!]

- Table of Contents

- Preface

- 1 Introduction to the Software Development Tools

- 2 Introduction to Object Modules

- 3 Assembler Description

- 3.1 Assembler Overview

- 3.2 The Assembler's Role in the Software Development Flow

- 3.3 Invoking the Assembler

- 3.4 Naming Alternate Directories for Assembler Input

- 3.5 Source Statement Format

- 3.6 Constants

- 3.7 Character Strings

- 3.8 Symbols

- 3.9 Expressions

- 3.10 Built-in Functions

- 3.11 Unified Assembly Language Syntax Support

- 3.12 Source Listings

- 3.13 Debugging Assembly Source

- 3.14 Cross-Reference Listings

- 4 Assembler Directives

- 4.1 Directives Summary

- 4.2 Directives That Define Sections

- 4.3 Directives That Change the Instruction Type

- 4.4 Directives That Initialize Constants

- 4.5 Directives That Perform Alignment and Reserve Space

- 4.6 Directives That Format the Output Listings

- 4.7 Directives That Reference Other Files

- 4.8 Directives That Enable Conditional Assembly

- 4.9 Directives That Define Union or Structure Types

- 4.10 Directives That Define Enumerated Types

- 4.11 Directives That Define Symbols at Assembly Time

- 4.12 Miscellaneous Directives

- 4.13 Directives Reference

- 5 Macro Description

- 5.1 Using Macros

- 5.2 Defining Macros

- 5.3 Macro Parameters/Substitution Symbols

- 5.4 Macro Libraries

- 5.5 Using Conditional Assembly in Macros

- 5.6 Using Labels in Macros

- 5.7 Producing Messages in Macros

- 5.8 Using Directives to Format the Output Listing

- 5.9 Using Recursive and Nested Macros

- 5.10 Macro Directives Summary

- 6 Archiver Description

- 7 Linker Description

- 7.1 Linker Overview

- 7.2 The Linker's Role in the Software Development Flow

- 7.3 Invoking the Linker

- 7.4 Linker Options

- 7.4.1 Wild Cards in File, Section, and Symbol Patterns

- 7.4.2 Relocation Capabilities (--absolute_exe and --relocatable Options)

- 7.4.3 Allocate Memory for Use by the Loader to Pass Arguments (--arg_size Option)

- 7.4.4 Changing Encoding of Big-Endian Instructions

- 7.4.5 Compression (--cinit_compression and --copy_compression Option)

- 7.4.6 Compress DWARF Information (--compress_dwarf Option)

- 7.4.7 Control Linker Diagnostics

- 7.4.8 Disable Automatic Library Selection (--disable_auto_rts Option)

- 7.4.9 Controlling Unreferenced and Unused Sections

- 7.4.10 Link Command File Preprocessing (--disable_pp, --define and --undefine Options)

- 7.4.11 Define an Entry Point (--entry_point Option)

- 7.4.12 Set Default Fill Value (--fill_value Option)

- 7.4.13 Generate List of Dead Functions (--generate_dead_funcs_list Option)

- 7.4.14 Define Heap Size (--heap_size Option)

- 7.4.15 Hiding Symbols

- 7.4.16 Alter the Library Search Algorithm (--library Option, --search_path Option, and TI_ARM_C_DIR Environment Variable)

- 7.4.17 Change Symbol Localization

- 7.4.18 Create a Map File (--map_file Option)

- 7.4.19 Managing Map File Contents (--mapfile_contents Option)

- 7.4.20 Disable Name Demangling (--no_demangle)

- 7.4.21 Disable Merge of Symbolic Debugging Information (--no_sym_merge Option)

- 7.4.22 Strip Symbolic Information (--no_symtable Option)

- 7.4.23 Name an Output Module (--output_file Option)

- 7.4.24 Prioritizing Function Placement (--preferred_order Option)

- 7.4.25 C Language Options (--ram_model and --rom_model Options)

- 7.4.26 Retain Discarded Sections (--retain Option)

- 7.4.27 Create an Absolute Listing File (--run_abs Option)

- 7.4.28 Scan All Libraries for Duplicate Symbol Definitions (--scan_libraries)

- 7.4.29 Define Stack Size (--stack_size Option)

- 7.4.30 Enforce Strict Compatibility (--strict_compatibility Option)

- 7.4.31 Mapping of Symbols (--symbol_map Option)

- 7.4.32 Generate Far Call Trampolines (--trampolines Option)

- 7.4.33 Introduce an Unresolved Symbol (--undef_sym Option)

- 7.4.34 Display a Message When an Undefined Output Section Is Created (--warn_sections Option)

- 7.4.35 Generate XML Link Information File (--xml_link_info Option)

- 7.4.36 Zero Initialization (--zero_init Option)

- 7.5 Linker Command Files

- 7.5.1 Reserved Names in Linker Command Files

- 7.5.2 Constants in Linker Command Files

- 7.5.3 The MEMORY Directive

- 7.5.4 The SECTIONS Directive

- 7.5.4.1 SECTIONS Directive Syntax

- 7.5.4.2 Allocation

- 7.5.4.3 Specifying Input Sections

- 7.5.4.4 Using Multi-Level Subsections

- 7.5.4.5 Specifying Library or Archive Members as Input to Output Sections

- 7.5.4.6 Allocation Using Multiple Memory Ranges

- 7.5.4.7 Automatic Splitting of Output Sections Among Non-Contiguous Memory Ranges

- 7.5.5 Specifying a Section's Run-Time Address

- 7.5.6 Using UNION and GROUP Statements

- 7.5.7 Special Section Types (DSECT, COPY, NOLOAD, and NOINIT)

- 7.5.8 Assigning Symbols at Link Time

- 7.5.8.1 Syntax of Assignment Statements

- 7.5.8.2 Assigning the SPC to a Symbol

- 7.5.8.3 Assignment Expressions

- 7.5.8.4 Symbols Defined by the Linker

- 7.5.8.5 Assigning Exact Start, End, and Size Values of a Section to a Symbol

- 7.5.8.6 Why the Dot Operator Does Not Always Work

- 7.5.8.7 Address and Dimension Operators

- 7.5.9 Creating and Filling Holes

- 7.6 Object Libraries

- 7.7 Default Allocation Algorithm

- 7.8 Linker-Generated Copy Tables

- 7.8.1 A Current Boot-Loaded Application Development Process

- 7.8.2 An Alternative Approach

- 7.8.3 Overlay Management Example

- 7.8.4 Generating Copy Tables Automatically With the Linker

- 7.8.5 The table() Operator

- 7.8.6 Boot-Time Copy Tables

- 7.8.7 Using the table() Operator to Manage Object Components

- 7.8.8 Compression Support

- 7.8.9 Copy Table Contents

- 7.8.10 General Purpose Copy Routine

- 7.8.11 Linker-Generated Copy Table Sections and Symbols

- 7.8.12 Splitting Object Components and Overlay Management

- 7.9 Linker-Generated CRC Tables

- 7.10 Partial (Incremental) Linking

- 7.11 Linking C/C++ Code

- 7.12 Linker Example

- 8 Absolute Lister Description

- 9 Cross-Reference Lister Description

- 10 Object File Utilities

- 11 Hex Conversion Utility Description

- 11.1 The Hex Conversion Utility's Role in the Software Development Flow

- 11.2 Invoking the Hex Conversion Utility

- 11.3 Understanding Memory Widths

- 11.4 The ROMS Directive

- 11.5 The SECTIONS Directive

- 11.6 The Load Image Format (--load_image Option)

- 11.7 Excluding a Specified Section

- 11.8 Assigning Output Filenames

- 11.9 Image Mode and the --fill Option

- 11.10 Building a Table for an On-Chip Boot Loader

- 11.11 Controlling the ROM Device Address

- 11.12 Control Hex Conversion Utility Diagnostics

- 11.13 Description of the Object Formats

- 11.13.1 ASCII-Hex Object Format (--ascii Option)

- 11.13.2 Intel MCS-86 Object Format (--intel Option)

- 11.13.3 Motorola Exorciser Object Format (--motorola Option)

- 11.13.4 Extended Tektronix Object Format (--tektronix Option)

- 11.13.5 Texas Instruments SDSMAC (TI-Tagged) Object Format (--ti_tagged Option)

- 11.13.6 TI-TXT Hex Format (--ti_txt Option)

- 12 Sharing C/C++ Header Files With Assembly Source

- 12.1 Overview of the .cdecls Directive

- 12.2 Notes on C/C++ Conversions

- 12.2.1 Comments

- 12.2.2 Conditional Compilation (#if/#else/#ifdef/etc.)

- 12.2.3 Pragmas

- 12.2.4 The #error and #warning Directives

- 12.2.5 Predefined symbol _ _ASM_HEADER_ _

- 12.2.6 Usage Within C/C++ asm( ) Statements

- 12.2.7 The #include Directive

- 12.2.8 Conversion of #define Macros

- 12.2.9 The #undef Directive

- 12.2.10 Enumerations

- 12.2.11 C Strings

- 12.2.12 C/C++ Built-In Functions

- 12.2.13 Structures and Unions

- 12.2.14 Function/Variable Prototypes

- 12.2.15 C Constant Suffixes

- 12.2.16 Basic C/C++ Types

- 12.3 Notes on C++ Specific Conversions

- 12.4 Special Assembler Support

- A Symbolic Debugging Directives

- B XML Link Information File Description

- C Hex Conversion Utility Examples

- D Glossary

ARM Assembly Language Tools

v5.0

User's Guide

Literature Number: SPNU118K

August 2012

Contents

Preface ...................................................................................................................................... 10

1 Introduction to the Software Development Tools ................................................................... 13

1.1 Software Development Tools Overview ................................................................................ 14

1.2 Tools Descriptions ......................................................................................................... 15

2 Introduction to Object Modules ........................................................................................... 16

2.1 Sections ..................................................................................................................... 17

2.2 How the Assembler Handles Sections .................................................................................. 18

2.2.1 Uninitialized Sections ............................................................................................ 18

2.2.2 Initialized Sections ................................................................................................ 19

2.2.3 Named Sections .................................................................................................. 20

2.2.4 Subsections ....................................................................................................... 20

2.2.5 Section Program Counters ...................................................................................... 21

2.2.6 Using Sections Directives ....................................................................................... 21

2.3 How the Linker Handles Sections ....................................................................................... 23

2.3.1 Default Memory Allocation ...................................................................................... 24

2.3.2 Placing Sections in the Memory Map .......................................................................... 24

2.4 Relocation .................................................................................................................. 25

2.5 Run-Time Relocation ...................................................................................................... 26

2.6 Loading a Program ........................................................................................................ 26

2.7 Symbols in an Object File ................................................................................................ 27

2.7.1 External Symbols ................................................................................................. 27

2.8 Object File Format Specifications ....................................................................................... 27

3 Assembler Description ....................................................................................................... 28

3.1 Assembler Overview ...................................................................................................... 29

3.2 The Assembler's Role in the Software Development Flow .......................................................... 30

3.3 Invoking the Assembler ................................................................................................... 31

3.4 Naming Alternate Directories for Assembler Input .................................................................... 32

3.4.1 Using the --include_path Assembler Option .................................................................. 33

3.4.2 Using the TI_ARM_C_DIR Environment Variable ............................................................ 33

3.5 Source Statement Format ................................................................................................ 35

3.5.1 Label Field ......................................................................................................... 35

3.5.2 Mnemonic Field ................................................................................................... 36

3.5.3 Operand Field ..................................................................................................... 36

3.5.4 Comment Field .................................................................................................... 38

3.6 Constants ................................................................................................................... 38

3.6.1 Binary Integers .................................................................................................... 38

3.6.2 Octal Integers ..................................................................................................... 38

3.6.3 Decimal Integers .................................................................................................. 38

3.6.4 Hexadecimal Integers ............................................................................................ 39

3.6.5 Character Constants ............................................................................................. 39

3.6.6 Assembly-Time Constants ...................................................................................... 39

3.7 Character Strings .......................................................................................................... 40

3.8 Symbols ..................................................................................................................... 40

3.8.1 Labels .............................................................................................................. 40

3.8.2 Local Labels ....................................................................................................... 40

2Contents SPNU118K–August 2012

Submit Documentation Feedback

Copyright © 2012, Texas Instruments Incorporated

www.ti.com

3.8.3 Symbolic Constants .............................................................................................. 42

3.8.4 Defining Symbolic Constants (--asm_define Option) ........................................................ 42

3.8.5 Predefined Symbolic Constants ................................................................................ 43

3.8.6 Substitution Symbols ............................................................................................. 45

3.9 Expressions ................................................................................................................ 46

3.9.1 Operators .......................................................................................................... 46

3.9.2 Expression Overflow and Underflow ........................................................................... 46

3.9.3 Well-Defined Expressions ....................................................................................... 47

3.9.4 Conditional Expressions ......................................................................................... 47

3.9.5 Relocatable Symbols and Legal Expressions ................................................................ 47

3.9.6 Expression Examples ............................................................................................ 48

3.10 Built-in Functions .......................................................................................................... 49

3.11 Unified Assembly Language Syntax Support .......................................................................... 50

3.12 Source Listings ............................................................................................................ 51

3.13 Debugging Assembly Source ............................................................................................ 54

3.14 Cross-Reference Listings ................................................................................................. 55

4 Assembler Directives ......................................................................................................... 56

4.1 Directives Summary ....................................................................................................... 57

4.2 Directives That Define Sections ......................................................................................... 61

4.3 Directives That Change the Instruction Type .......................................................................... 63

4.4 Directives That Initialize Constants ..................................................................................... 63

4.5 Directives That Perform Alignment and Reserve Space ............................................................. 65

4.6 Directives That Format the Output Listings ............................................................................ 67

4.7 Directives That Reference Other Files .................................................................................. 68

4.8 Directives That Enable Conditional Assembly ......................................................................... 69

4.9 Directives That Define Union or Structure Types ..................................................................... 69

4.10 Directives That Define Enumerated Types ............................................................................. 70

4.11 Directives That Define Symbols at Assembly Time ................................................................... 70

4.12 Miscellaneous Directives ................................................................................................. 71

4.13 Directives Reference ...................................................................................................... 72

5 Macro Description ............................................................................................................ 132

5.1 Using Macros ............................................................................................................. 133

5.2 Defining Macros .......................................................................................................... 133

5.3 Macro Parameters/Substitution Symbols ............................................................................. 135

5.3.1 Directives That Define Substitution Symbols ................................................................ 136

5.3.2 Built-In Substitution Symbol Functions ....................................................................... 137

5.3.3 Recursive Substitution Symbols .............................................................................. 138

5.3.4 Forced Substitution ............................................................................................. 138

5.3.5 Accessing Individual Characters of Subscripted Substitution Symbols .................................. 139

5.3.6 Substitution Symbols as Local Variables in Macros ........................................................ 140

5.4 Macro Libraries ........................................................................................................... 141

5.5 Using Conditional Assembly in Macros ............................................................................... 142

5.6 Using Labels in Macros ................................................................................................. 144

5.7 Producing Messages in Macros ........................................................................................ 145

5.8 Using Directives to Format the Output Listing ....................................................................... 146

5.9 Using Recursive and Nested Macros ................................................................................. 147

5.10 Macro Directives Summary ............................................................................................. 148

6 Archiver Description ........................................................................................................ 149

6.1 Archiver Overview ........................................................................................................ 150

6.2 The Archiver's Role in the Software Development Flow ............................................................ 151

6.3 Invoking the Archiver .................................................................................................... 152

6.4 Archiver Examples ....................................................................................................... 153

3

SPNU118K–August 2012 Contents

Submit Documentation Feedback Copyright © 2012, Texas Instruments Incorporated

www.ti.com

6.5 Library Information Archiver Description .............................................................................. 154

6.5.1 Invoking the Library Information Archiver .................................................................... 154

6.5.2 Library Information Archiver Example ........................................................................ 155

6.5.3 Listing the Contents of an Index Library ..................................................................... 155

6.5.4 Requirements .................................................................................................... 156

7 Linker Description ........................................................................................................... 157

7.1 Linker Overview .......................................................................................................... 158

7.2 The Linker's Role in the Software Development Flow .............................................................. 159

7.3 Invoking the Linker ....................................................................................................... 160

7.4 Linker Options ............................................................................................................ 161

7.4.1 Wild Cards in File, Section, and Symbol Patterns .......................................................... 163

7.4.2 Relocation Capabilities (--absolute_exe and --relocatable Options) ..................................... 163

7.4.3 Allocate Memory for Use by the Loader to Pass Arguments (--arg_size Option) ...................... 164

7.4.4 Changing Encoding of Big-Endian Instructions ............................................................. 165

7.4.5 Compression (--cinit_compression and --copy_compression Option) ................................... 165

7.4.6 Compress DWARF Information (--compress_dwarf Option) .............................................. 165

7.4.7 Control Linker Diagnostics ..................................................................................... 165

7.4.8 Disable Automatic Library Selection (--disable_auto_rts Option) ......................................... 166

7.4.9 Controlling Unreferenced and Unused Sections ............................................................ 166

7.4.10 Link Command File Preprocessing (--disable_pp, --define and --undefine Options) ................. 167

7.4.11 Define an Entry Point (--entry_point Option) ............................................................... 168

7.4.12 Set Default Fill Value (--fill_value Option) .................................................................. 168

7.4.13 Generate List of Dead Functions (--generate_dead_funcs_list Option) ................................ 168

7.4.14 Define Heap Size (--heap_size Option) ..................................................................... 168

7.4.15 Hiding Symbols ................................................................................................. 169

7.4.16 Alter the Library Search Algorithm (--library Option, --search_path Option, and TI_ARM_C_DIR

Environment Variable) .......................................................................................... 169

7.4.17 Change Symbol Localization ................................................................................. 172

7.4.18 Create a Map File (--map_file Option) ...................................................................... 173

7.4.19 Managing Map File Contents (--mapfile_contents Option) ............................................... 174

7.4.20 Disable Name Demangling (--no_demangle) .............................................................. 175

7.4.21 Disable Merge of Symbolic Debugging Information (--no_sym_merge Option) ....................... 175

7.4.22 Strip Symbolic Information (--no_symtable Option) ....................................................... 175

7.4.23 Name an Output Module (--output_file Option) ............................................................ 176

7.4.24 Prioritizing Function Placement (--preferred_order Option) .............................................. 176

7.4.25 C Language Options (--ram_model and --rom_model Options) ......................................... 176

7.4.26 Retain Discarded Sections (--retain Option) ................................................................ 176

7.4.27 Create an Absolute Listing File (--run_abs Option) ........................................................ 177

7.4.28 Scan All Libraries for Duplicate Symbol Definitions (--scan_libraries) .................................. 177

7.4.29 Define Stack Size (--stack_size Option) .................................................................... 177

7.4.30 Enforce Strict Compatibility (--strict_compatibility Option) ................................................ 177

7.4.31 Mapping of Symbols (--symbol_map Option) .............................................................. 177

7.4.32 Generate Far Call Trampolines (--trampolines Option) ................................................... 177

7.4.33 Introduce an Unresolved Symbol (--undef_sym Option) .................................................. 180

7.4.34 Display a Message When an Undefined Output Section Is Created (--warn_sections Option) ..... 180

7.4.35 Generate XML Link Information File (--xml_link_info Option) ............................................ 180

7.4.36 Zero Initialization (--zero_init Option) ........................................................................ 180

7.5 Linker Command Files .................................................................................................. 181

7.5.1 Reserved Names in Linker Command Files ................................................................. 182

7.5.2 Constants in Linker Command Files ......................................................................... 182

7.5.3 The MEMORY Directive ........................................................................................ 183

7.5.4 The SECTIONS Directive ...................................................................................... 185

7.5.5 Specifying a Section's Run-Time Address ................................................................... 197

4Contents SPNU118K–August 2012

Submit Documentation Feedback

Copyright © 2012, Texas Instruments Incorporated

www.ti.com

7.5.6 Using UNION and GROUP Statements ...................................................................... 199

7.5.7 Special Section Types (DSECT, COPY, NOLOAD, and NOINIT) ........................................ 203

7.5.8 Assigning Symbols at Link Time .............................................................................. 204

7.5.9 Creating and Filling Holes ..................................................................................... 209

7.6 Object Libraries ........................................................................................................... 212

7.7 Default Allocation Algorithm ............................................................................................ 213

7.7.1 How the Allocation Algorithm Creates Output Sections ................................................... 213

7.7.2 Reducing Memory Fragmentation ............................................................................ 214

7.8 Linker-Generated Copy Tables ........................................................................................ 214

7.8.1 A Current Boot-Loaded Application Development Process ............................................... 214

7.8.2 An Alternative Approach ....................................................................................... 215

7.8.3 Overlay Management Example ............................................................................... 216

7.8.4 Generating Copy Tables Automatically With the Linker ................................................... 216

7.8.5 The table() Operator ............................................................................................ 217

7.8.6 Boot-Time Copy Tables ........................................................................................ 218

7.8.7 Using the table() Operator to Manage Object Components ............................................... 218

7.8.8 Compression Support .......................................................................................... 219

7.8.9 Copy Table Contents ........................................................................................... 222

7.8.10 General Purpose Copy Routine .............................................................................. 223

7.8.11 Linker-Generated Copy Table Sections and Symbols .................................................... 224

7.8.12 Splitting Object Components and Overlay Management ................................................. 225

7.9 Linker-Generated CRC Tables ......................................................................................... 227

7.9.1 The crc_table() Operator ....................................................................................... 227

7.9.2 Restrictions ...................................................................................................... 227

7.9.3 Examples ......................................................................................................... 228

7.9.4 Interface .......................................................................................................... 229

7.9.5 A Note on the TMS570_CRC64_ISO Algorithm ............................................................ 232

7.10 Partial (Incremental) Linking ............................................................................................ 233

7.11 Linking C/C++ Code ..................................................................................................... 234

7.11.1 Run-Time Initialization ......................................................................................... 234

7.11.2 Object Libraries and Run-Time Support .................................................................... 234

7.11.3 Setting the Size of the Stack and Heap Sections ......................................................... 234

7.11.4 Autoinitialization of Variables at Run Time ................................................................. 235

7.11.5 Initialization of Variables at Load Time ...................................................................... 235

7.11.6 The --rom_model and --ram_model Linker Options ....................................................... 236

7.12 Linker Example ........................................................................................................... 237

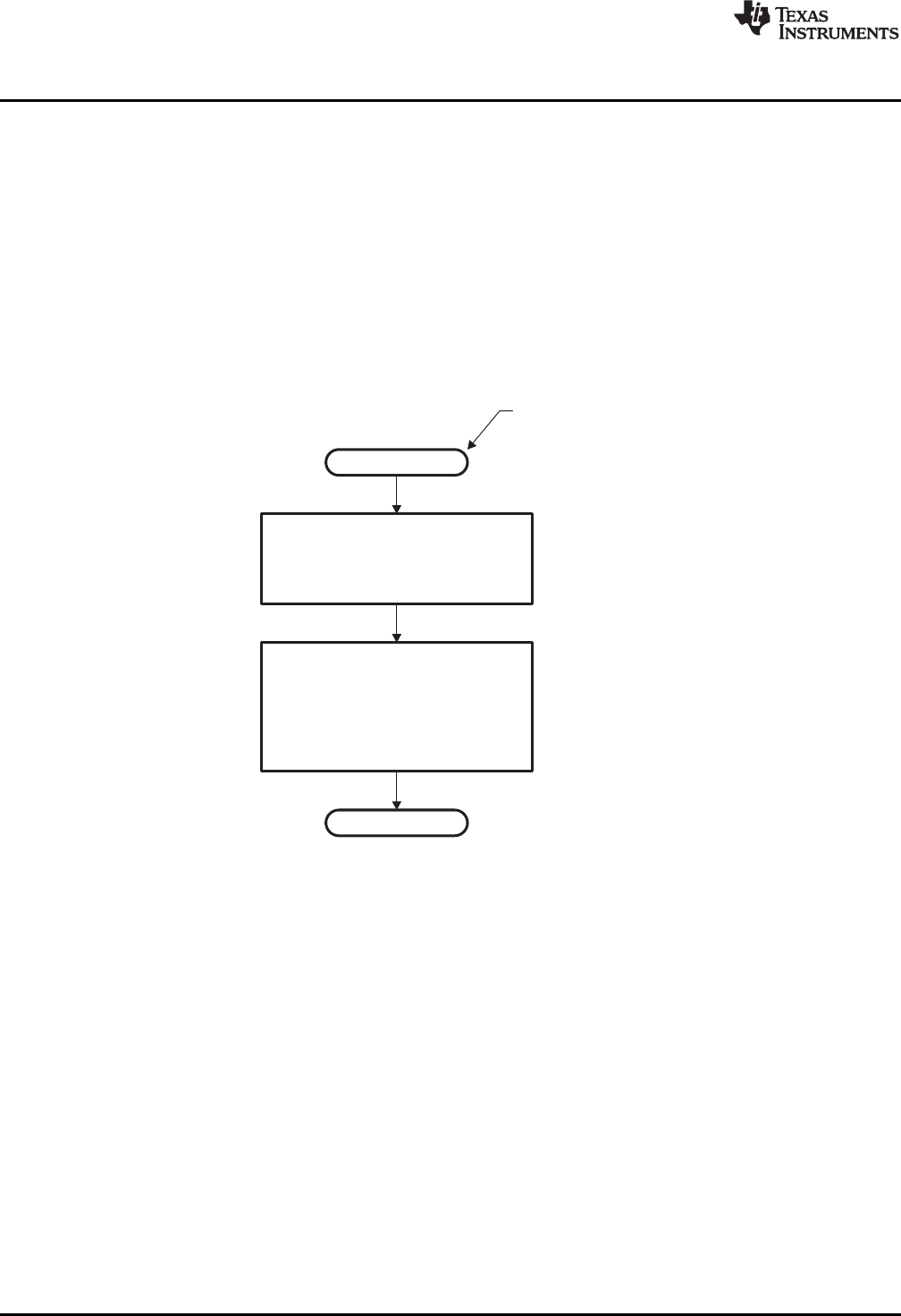

8 Absolute Lister Description ............................................................................................... 240

8.1 Producing an Absolute Listing .......................................................................................... 241

8.2 Invoking the Absolute Lister ............................................................................................ 242

8.3 Absolute Lister Example ................................................................................................ 243

9 Cross-Reference Lister Description ................................................................................... 246

9.1 Producing a Cross-Reference Listing ................................................................................. 247

9.2 Invoking the Cross-Reference Lister .................................................................................. 248

9.3 Cross-Reference Listing Example ..................................................................................... 249

10 Object File Utilities ........................................................................................................... 251

10.1 Invoking the Object File Display Utility ................................................................................ 252

10.2 Invoking the Disassembler .............................................................................................. 253

10.3 Invoking the Name Utility ............................................................................................... 255

10.4 Invoking the Strip Utility ................................................................................................. 256

11 Hex Conversion Utility Description .................................................................................... 257

11.1 The Hex Conversion Utility's Role in the Software Development Flow ........................................... 258

11.2 Invoking the Hex Conversion Utility ................................................................................... 259

5

SPNU118K–August 2012 Contents

Submit Documentation Feedback Copyright © 2012, Texas Instruments Incorporated

www.ti.com

11.2.1 Invoking the Hex Conversion Utility From the Command Line .......................................... 259

11.2.2 Invoking the Hex Conversion Utility With a Command File .............................................. 261

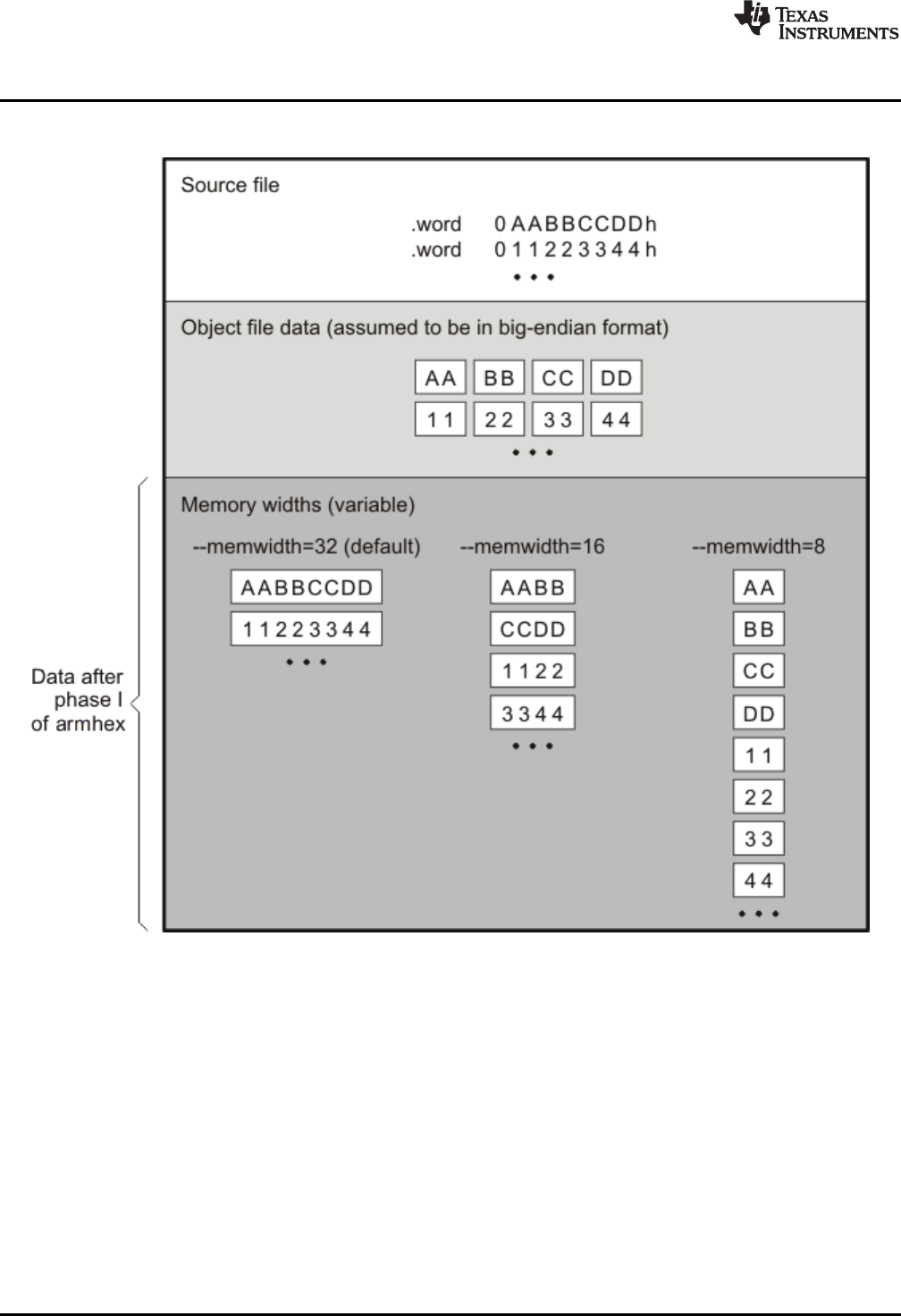

11.3 Understanding Memory Widths ........................................................................................ 262

11.3.1 Target Width .................................................................................................... 262

11.3.2 Specifying the Memory Width ................................................................................ 263

11.3.3 Partitioning Data Into Output Files ........................................................................... 264

11.4 The ROMS Directive ..................................................................................................... 267

11.4.1 When to Use the ROMS Directive ........................................................................... 268

11.4.2 An Example of the ROMS Directive ......................................................................... 268

11.5 The SECTIONS Directive ............................................................................................... 270

11.6 The Load Image Format (--load_image Option) ..................................................................... 271

11.6.1 Load Image Section Formation .............................................................................. 271

11.6.2 Load Image Characteristics .................................................................................. 271

11.7 Excluding a Specified Section .......................................................................................... 272

11.8 Assigning Output Filenames ............................................................................................ 272

11.9 Image Mode and the --fill Option ....................................................................................... 273

11.9.1 Generating a Memory Image ................................................................................. 273

11.9.2 Specifying a Fill Value ......................................................................................... 274

11.9.3 Steps to Follow in Using Image Mode ...................................................................... 274

11.10 Building a Table for an On-Chip Boot Loader ....................................................................... 275

11.10.1 Description of the Boot Table ............................................................................... 275

11.10.2 The Boot Table Format ...................................................................................... 275

11.10.3 How to Build the Boot Table ................................................................................ 275

11.10.4 Booting From a Device Peripheral ......................................................................... 276

11.10.5 Setting the Entry Point for the Boot Table ................................................................ 276

11.10.6 Using the ARM Boot Loader ................................................................................ 277

11.11 Controlling the ROM Device Address ................................................................................. 281

11.12 Control Hex Conversion Utility Diagnostics .......................................................................... 282

11.13 Description of the Object Formats ..................................................................................... 283

11.13.1 ASCII-Hex Object Format (--ascii Option) ................................................................. 283

11.13.2 Intel MCS-86 Object Format (--intel Option) .............................................................. 284

11.13.3 Motorola Exorciser Object Format (--motorola Option) .................................................. 285

11.13.4 Extended Tektronix Object Format (--tektronix Option) ................................................. 286

11.13.5 Texas Instruments SDSMAC (TI-Tagged) Object Format (--ti_tagged Option) ...................... 287

11.13.6 TI-TXT Hex Format (--ti_txt Option) ........................................................................ 288

12 Sharing C/C++ Header Files With Assembly Source ............................................................. 289

12.1 Overview of the .cdecls Directive ...................................................................................... 290

12.2 Notes on C/C++ Conversions .......................................................................................... 290

12.2.1 Comments ...................................................................................................... 290

12.2.2 Conditional Compilation (#if/#else/#ifdef/etc.) .............................................................. 291

12.2.3 Pragmas ......................................................................................................... 291

12.2.4 The #error and #warning Directives ......................................................................... 291

12.2.5 Predefined symbol _ _ASM_HEADER_ _ .................................................................. 291

12.2.6 Usage Within C/C++ asm( ) Statements .................................................................... 291

12.2.7 The #include Directive ......................................................................................... 291

12.2.8 Conversion of #define Macros ............................................................................... 291

12.2.9 The #undef Directive .......................................................................................... 292

12.2.10 Enumerations ................................................................................................. 292

12.2.11 C Strings ....................................................................................................... 292

12.2.12 C/C++ Built-In Functions .................................................................................... 293

12.2.13 Structures and Unions ....................................................................................... 293

12.2.14 Function/Variable Prototypes ............................................................................... 293

12.2.15 C Constant Suffixes .......................................................................................... 294

6Contents SPNU118K–August 2012

Submit Documentation Feedback

Copyright © 2012, Texas Instruments Incorporated

www.ti.com

12.2.16 Basic C/C++ Types ........................................................................................... 294

12.3 Notes on C++ Specific Conversions ................................................................................... 294

12.3.1 Name Mangling ................................................................................................ 294

12.3.2 Derived Classes ................................................................................................ 294

12.3.3 Templates ....................................................................................................... 295

12.3.4 Virtual Functions ............................................................................................... 295

12.4 Special Assembler Support ............................................................................................. 295

12.4.1 Enumerations (.enum/.emember/.endenum) ............................................................... 295

12.4.2 The .define Directive ........................................................................................... 295

12.4.3 The .undefine/.unasg Directives ............................................................................. 295

12.4.4 The $defined( ) Built-In Function ............................................................................. 296

12.4.5 The $sizeof Built-In Function ................................................................................. 296

12.4.6 Structure/Union Alignment and $alignof( ) .................................................................. 296

12.4.7 The .cstring Directive .......................................................................................... 296

A Symbolic Debugging Directives ......................................................................................... 297

A.1 DWARF Debugging Format ............................................................................................ 298

A.2 COFF Debugging Format ............................................................................................... 298

A.3 Debug Directive Syntax ................................................................................................. 299

B XML Link Information File Description ................................................................................ 300

B.1 XML Information File Element Types .................................................................................. 301

B.2 Document Elements ..................................................................................................... 301

B.2.1 Header Elements ................................................................................................ 301

B.2.2 Input File List .................................................................................................... 302

B.2.3 Object Component List ......................................................................................... 303

B.2.4 Logical Group List ............................................................................................... 304

B.2.5 Placement Map .................................................................................................. 306

B.2.6 Far Call Trampoline List ........................................................................................ 307

B.2.7 Symbol Table .................................................................................................... 308

C Hex Conversion Utility Examples ....................................................................................... 309

C.1 Scenario 1: Building a Hex Conversion Command File for a Single 8-Bit EPROM ............................. 310

C.2 Scenario 2: Building a Hex Conversion Command File for 16-BIS Code ........................................ 314

C.3 Scenario 3: Building a Hex Conversion Command File for Two 8-Bit EPROMs ................................ 317

D Glossary ......................................................................................................................... 321

7

SPNU118K–August 2012 Contents

Submit Documentation Feedback Copyright © 2012, Texas Instruments Incorporated

www.ti.com

List of Figures

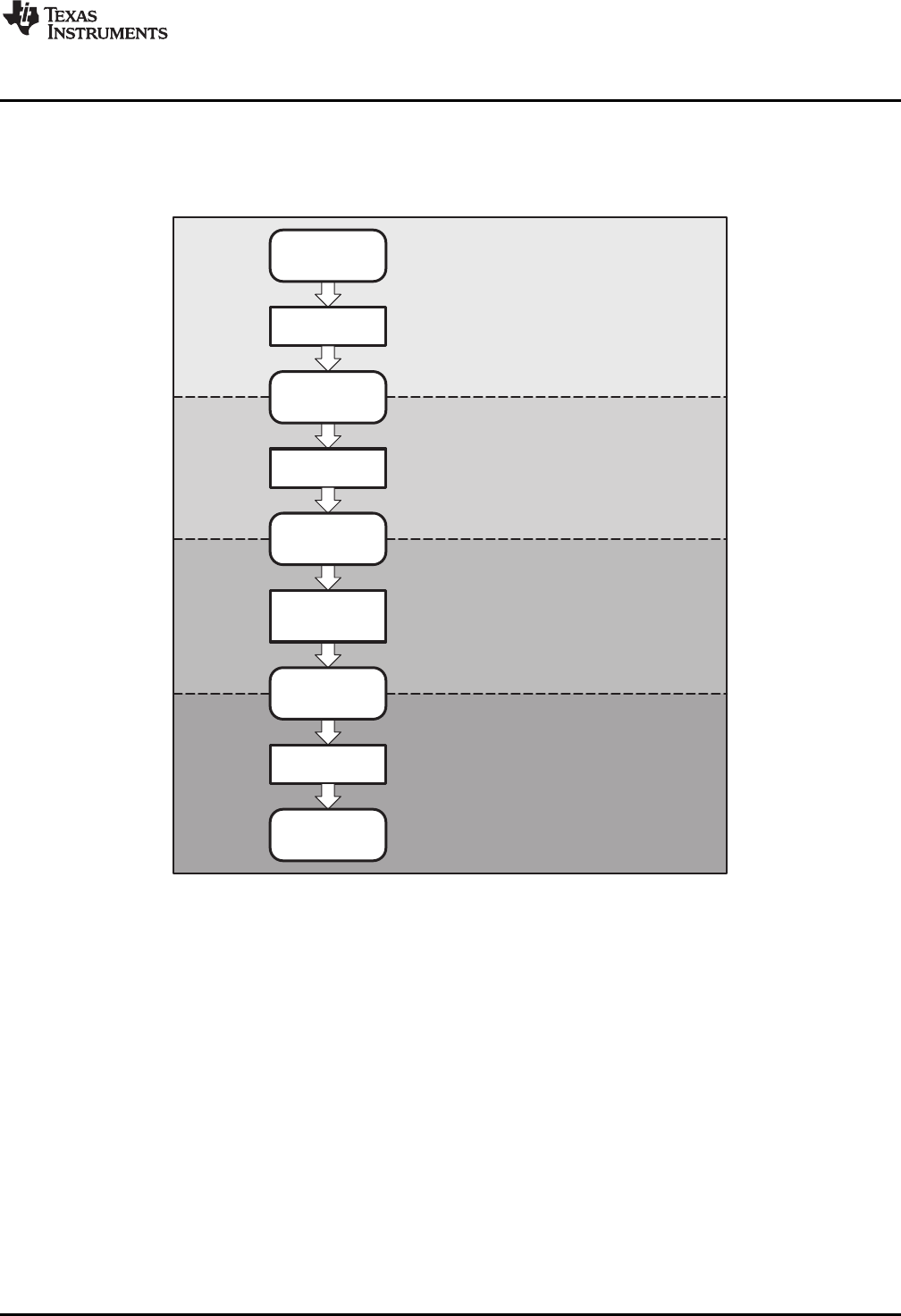

1-1. ARM Device Software Development Flow ............................................................................ 14

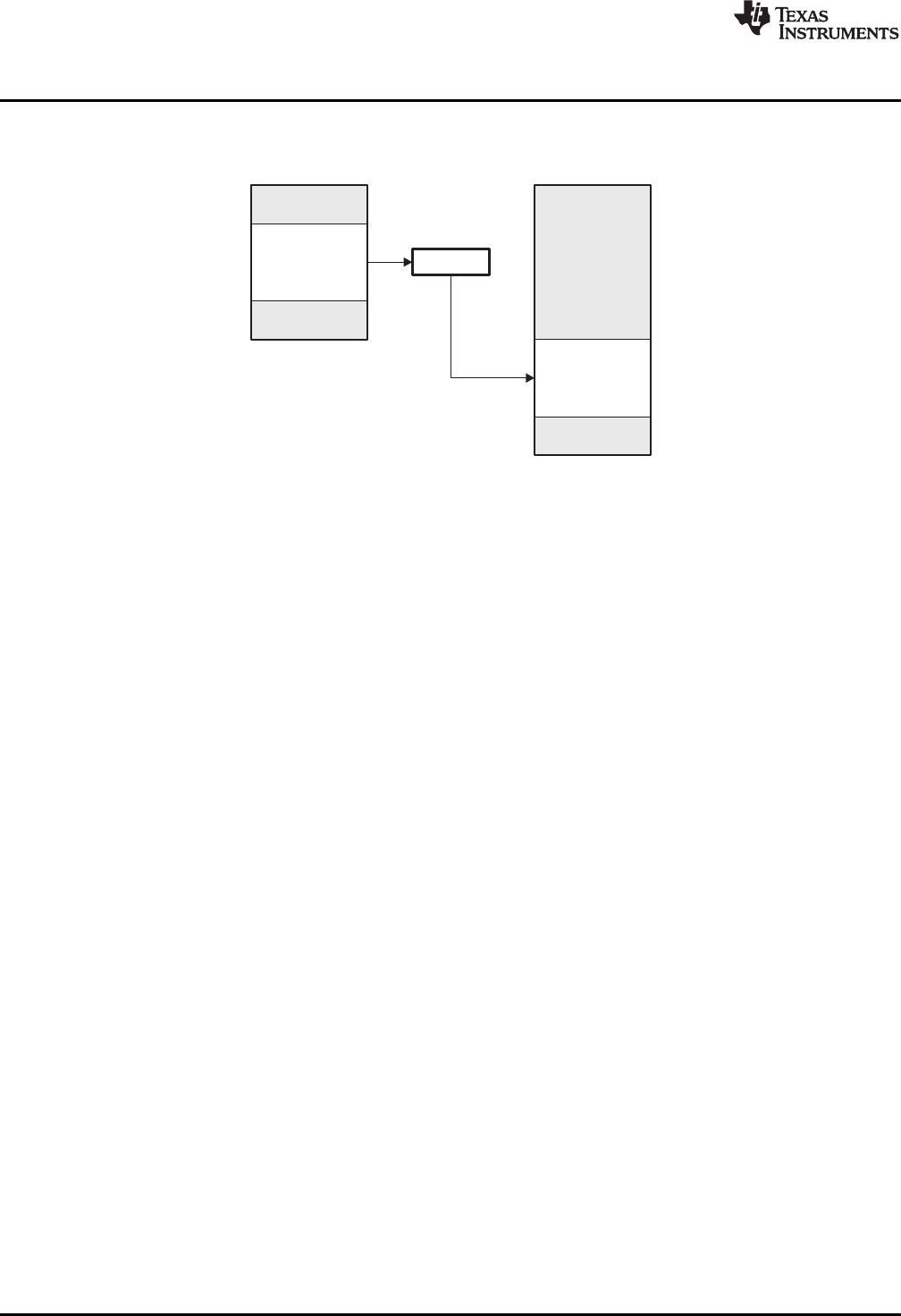

2-1. Partitioning Memory Into Logical Blocks ............................................................................... 17

2-2. Using Sections Directives Example ..................................................................................... 22

2-3. Object Code Generated by the File in ................................................................................. 23

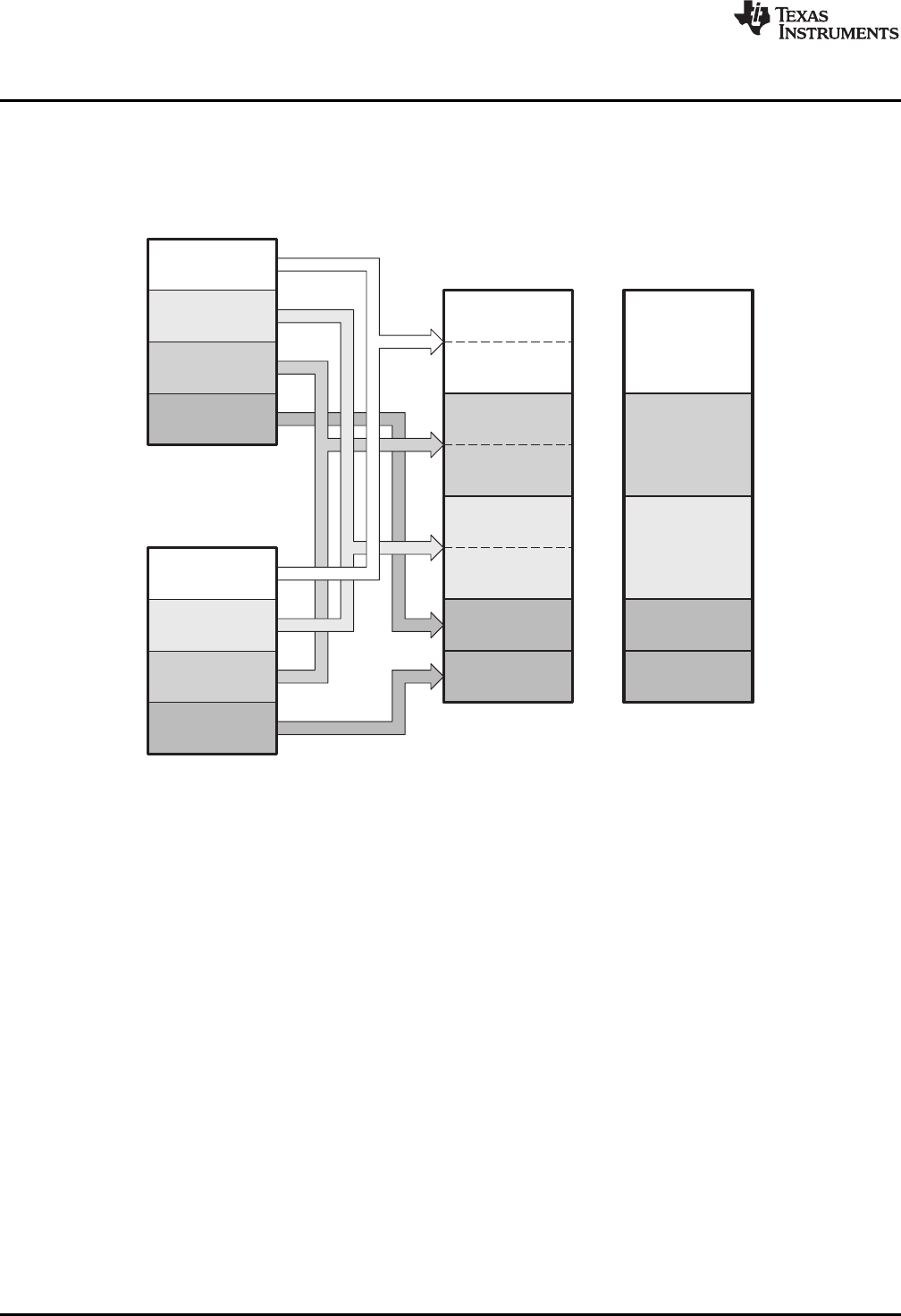

2-4. Combining Input Sections to Form an Executable Object Module.................................................. 24

3-1. The Assembler in the ARM Software Development Flow............................................................ 30

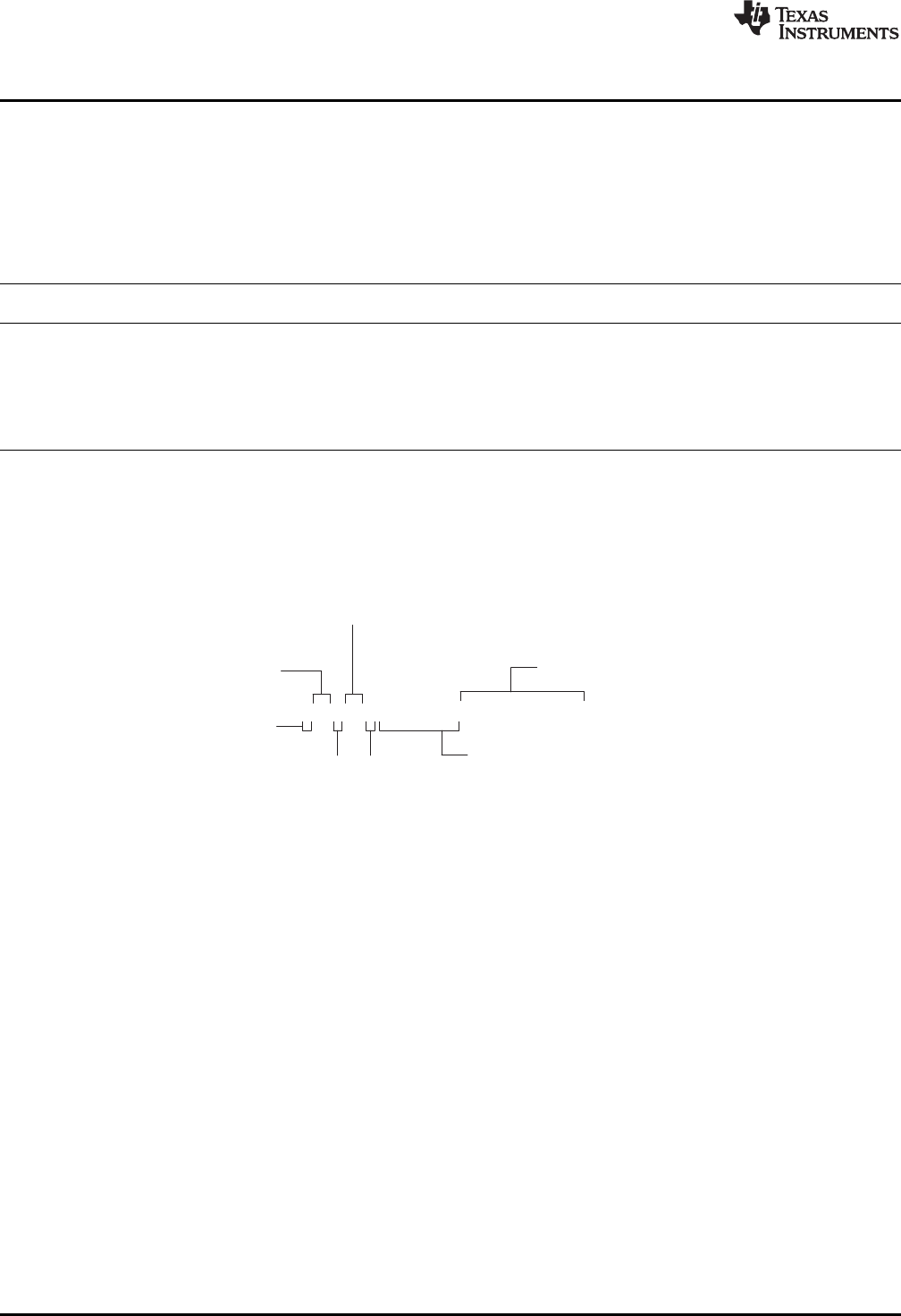

3-2. Example Assembler Listing .............................................................................................. 52

4-1. The .field Directive ........................................................................................................ 64

4-2. Initialization Directives .................................................................................................... 65

4-3. The .align Directive........................................................................................................ 66

4-4. The .space and .bes Directives.......................................................................................... 67

4-5. Double-Precision Floating-Point Format................................................................................ 88

4-6. The .field Directive ........................................................................................................ 95

4-7. Single-Precision Floating-Point Format................................................................................. 96

4-8. The .usect Directive ..................................................................................................... 130

6-1. The Archiver in the ARM Software Development Flow ............................................................. 151

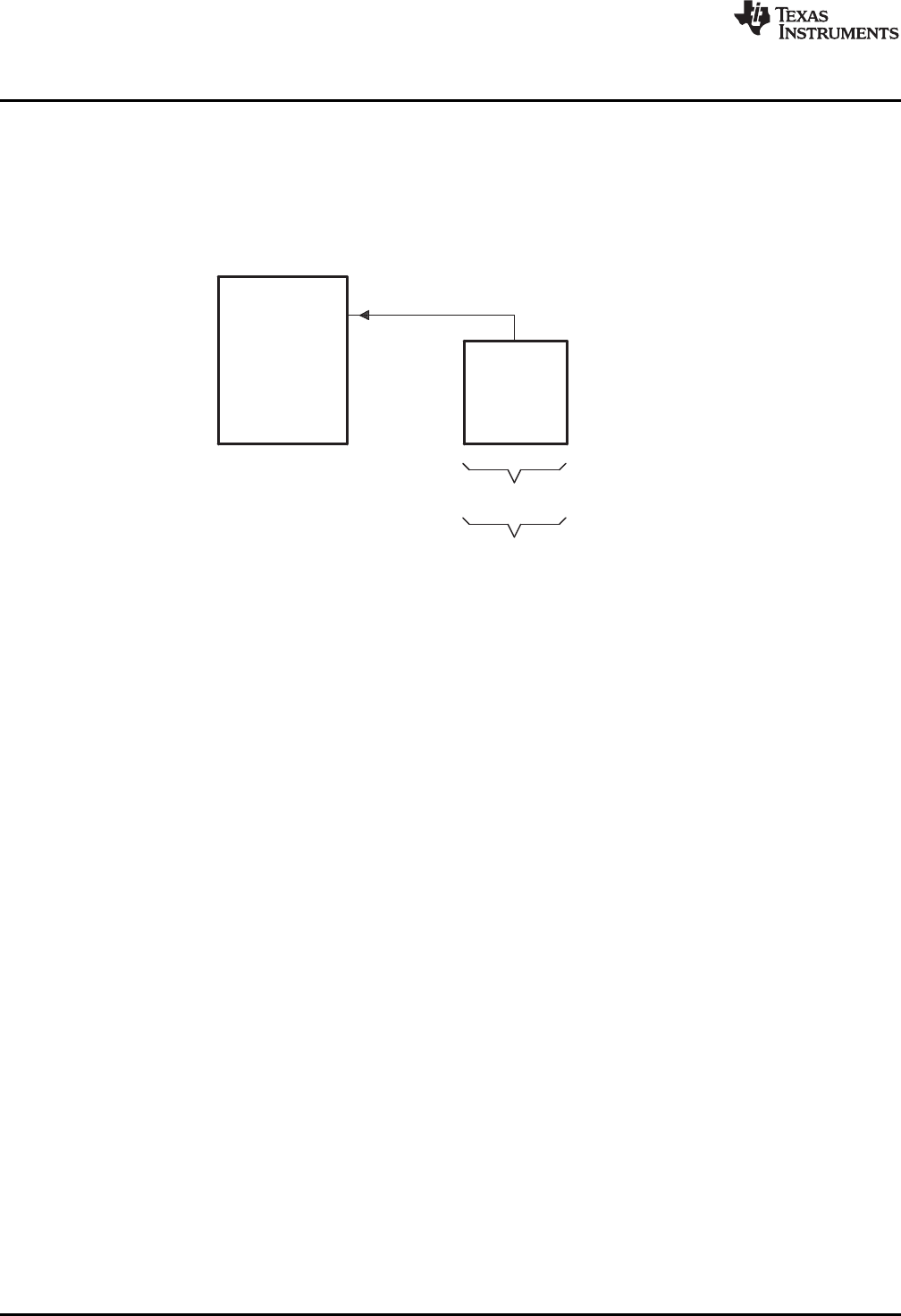

7-1. The Linker in the ARM Software Development Flow................................................................ 159

7-2. Section Allocation Defined by ......................................................................................... 187

7-3. Run-Time Execution of ................................................................................................. 199

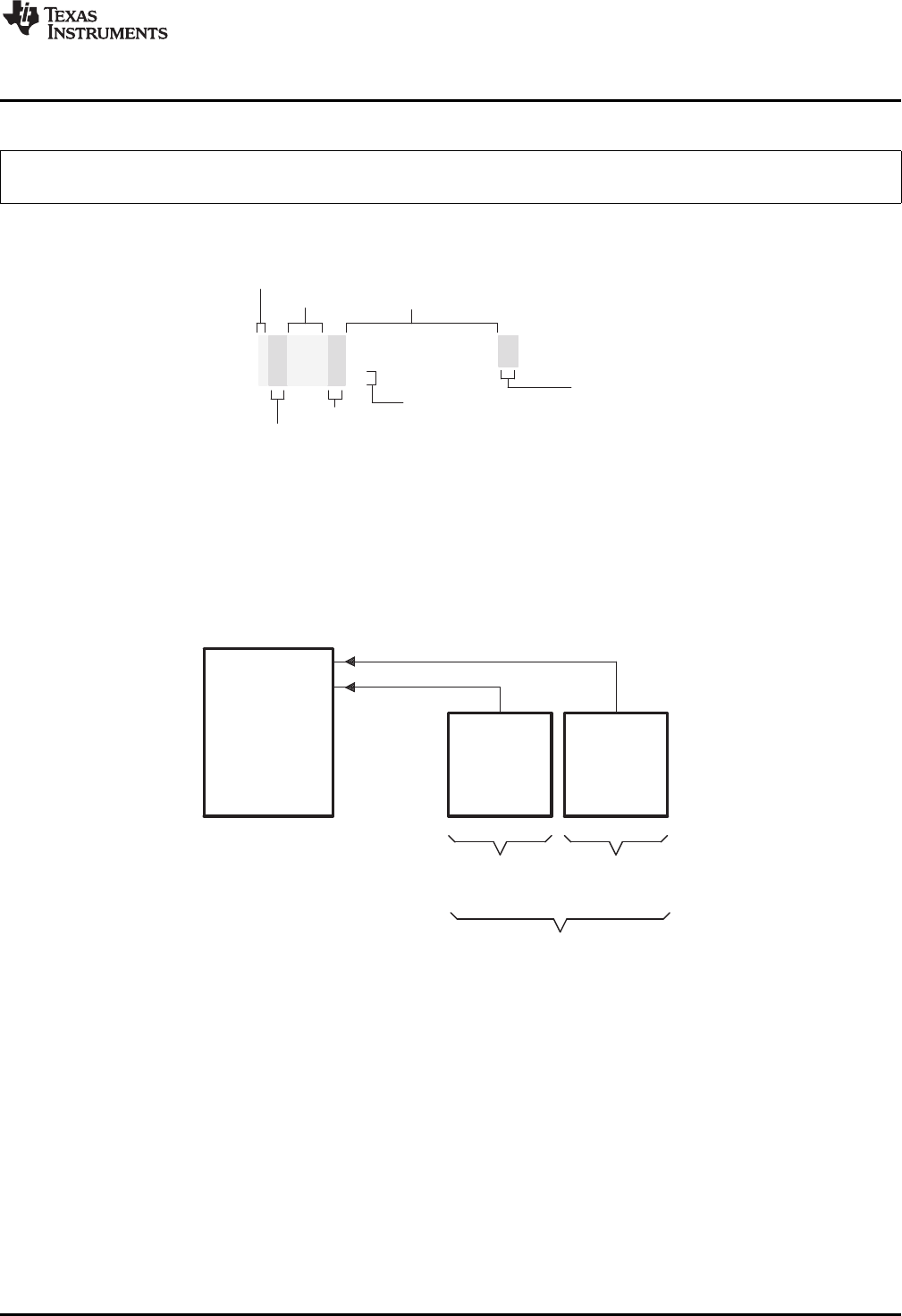

7-4. Memory Allocation Shown in and ..................................................................................... 200

7-5. Compressed Copy Table................................................................................................ 219

7-6. Handler Table ............................................................................................................ 220

7-7. CRC_TABLE Conceptual Model ....................................................................................... 230

7-8. Autoinitialization at Run Time .......................................................................................... 235

7-9. Initialization at Load Time............................................................................................... 236

8-1. Absolute Lister Development Flow .................................................................................... 241

9-1. The Cross-Reference Lister Development Flow ..................................................................... 247

11-1. The Hex Conversion Utility in the ARM Software Development Flow ............................................ 258

11-2. Hex Conversion Utility Process Flow.................................................................................. 262

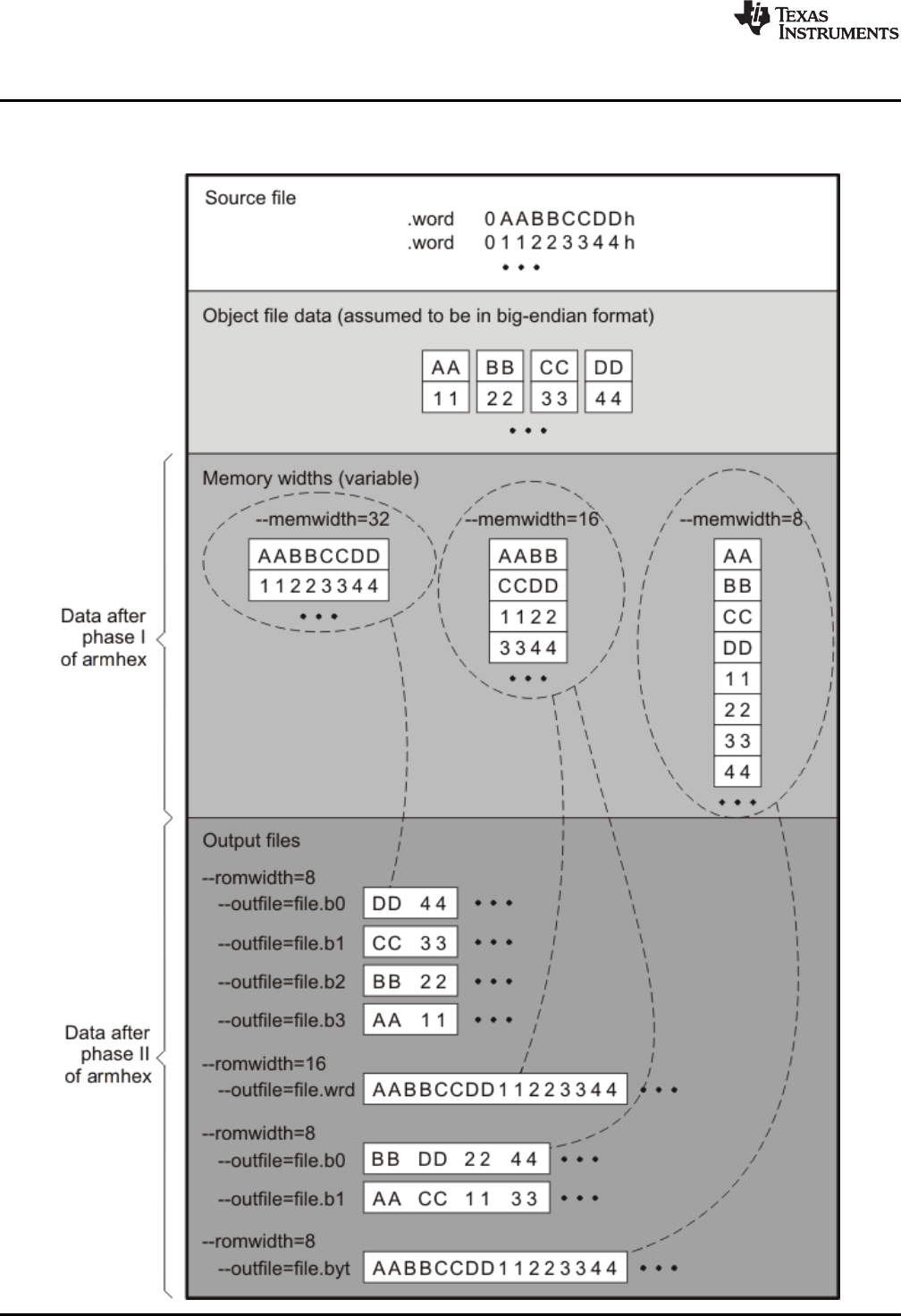

11-3. Object File Data and Memory Widths ................................................................................. 264

11-4. Data, Memory, and ROM Widths ...................................................................................... 266

11-5. The infile.out File Partitioned Into Four Output Files ................................................................ 269

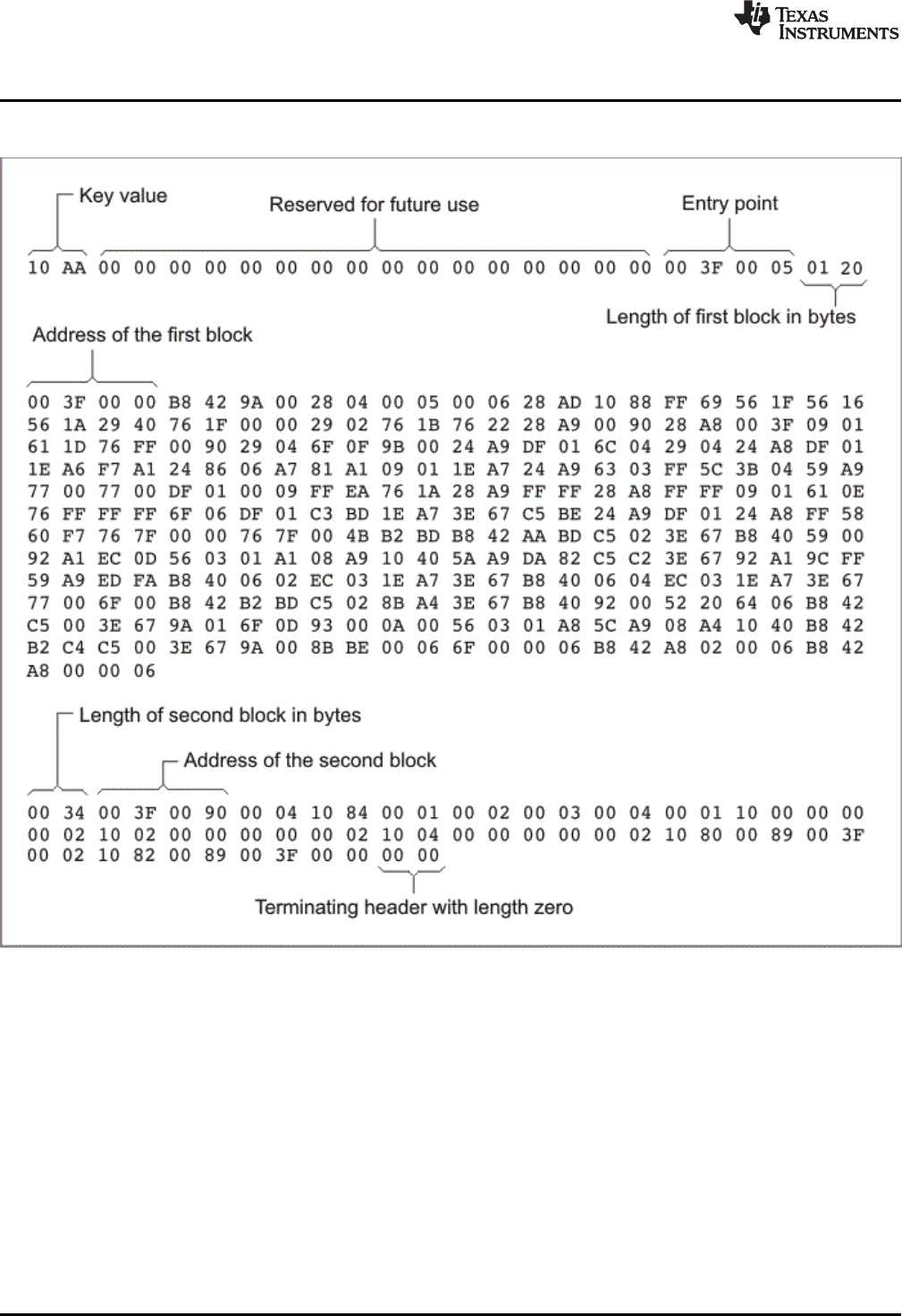

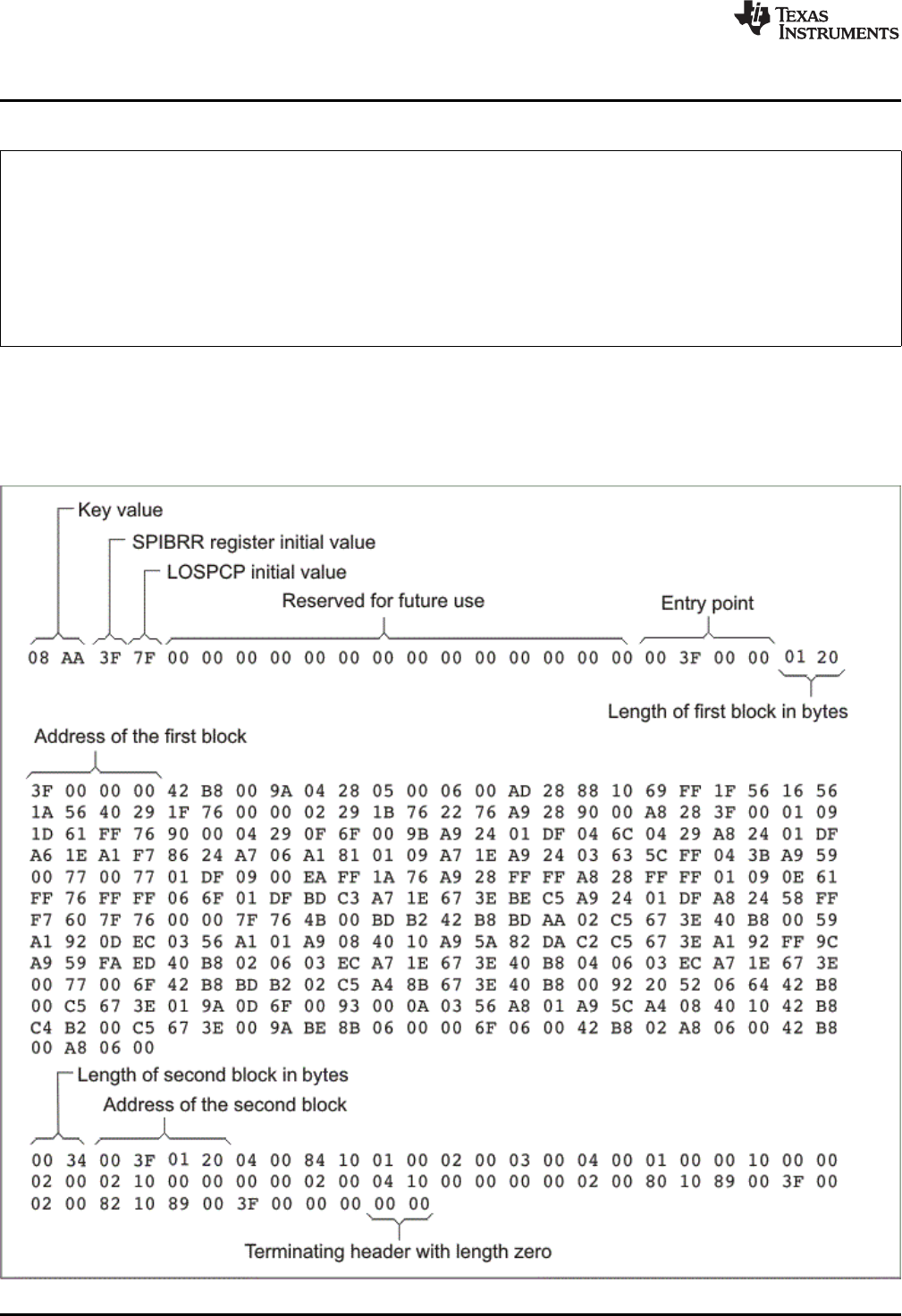

11-6. Sample Hex Converter Out File for Booting From 8-Bit SPI Boot................................................. 278

11-7. Sample Hex Converter Out File for ARM 16-Bit Parallel Boot GP I/O............................................ 280

11-8. ASCII-Hex Object Format............................................................................................... 283

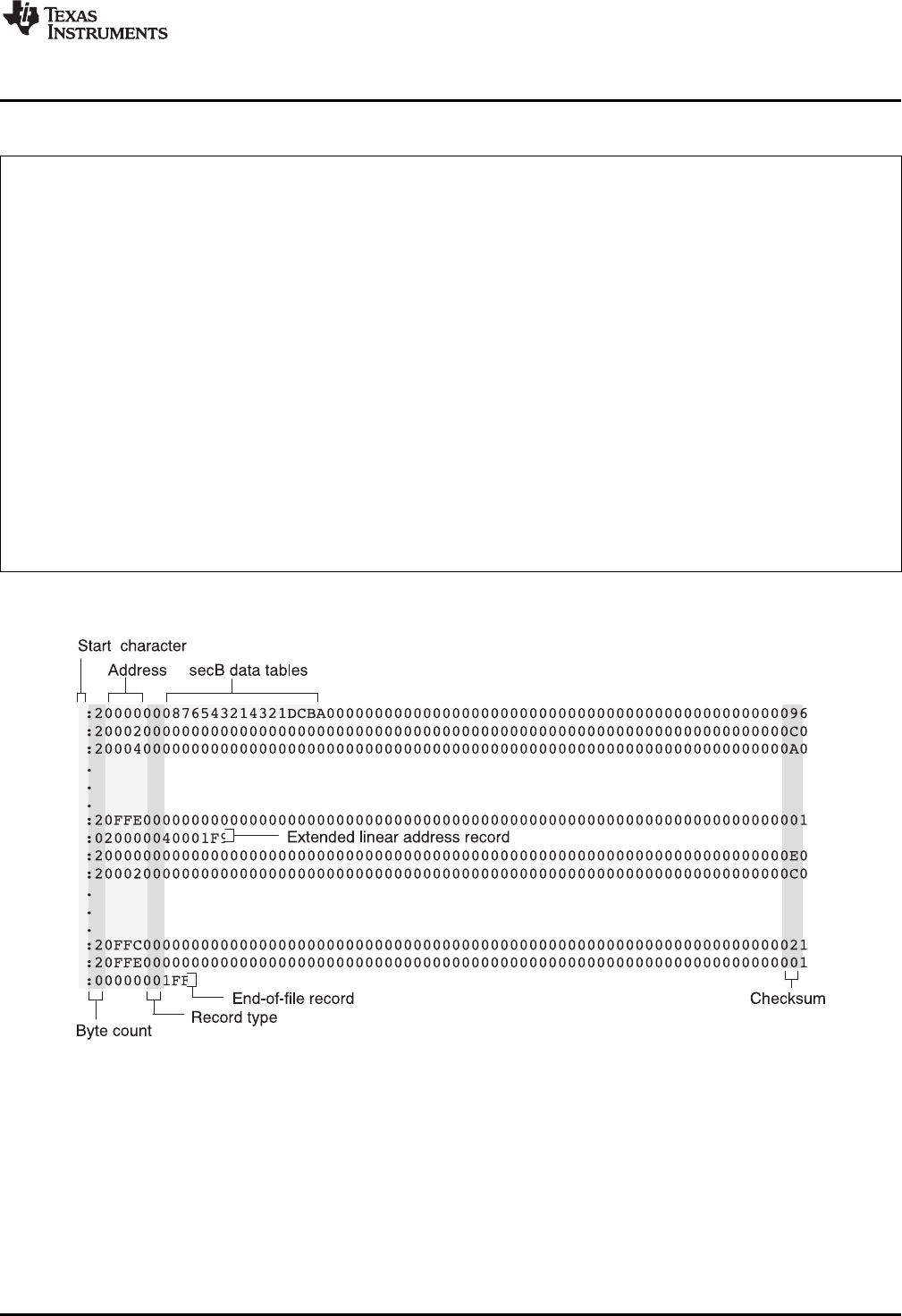

11-9. Intel Hexadecimal Object Format ...................................................................................... 284

11-10. Motorola-S Format....................................................................................................... 285

11-11. Extended Tektronix Object Format .................................................................................... 286

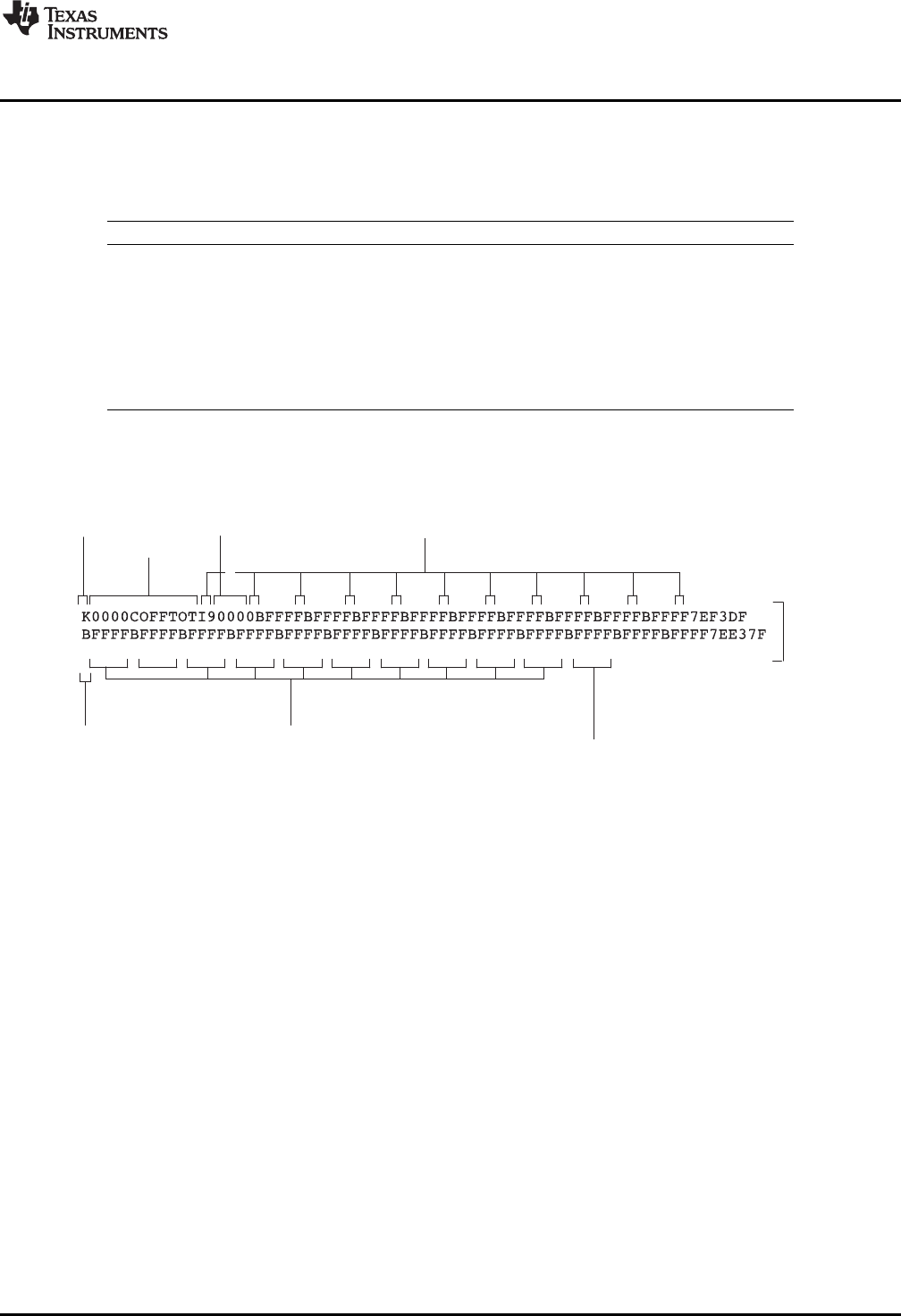

11-12. TI-Tagged Object Format ............................................................................................... 287

11-13. TI-TXT Object Format ................................................................................................... 288

C-1. EPROM Memory System for Scenario 1 ............................................................................. 310

C-2. Contents of Hex Output File example1.hex .......................................................................... 313

C-3. EPROM Memory System for Scenario 2 ............................................................................. 314

C-4. Contents of Hex Output File example2.hex .......................................................................... 317

C-5. EPROM Memory System for Scenario 3 ............................................................................. 317

C-6. Contents of Hex Output File lower16.bit .............................................................................. 320

C-7. Contents of Hex Output File upper16.bit.............................................................................. 320

8List of Figures SPNU118K–August 2012

Submit Documentation Feedback

Copyright © 2012, Texas Instruments Incorporated

www.ti.com

List of Tables

3-1. ARM Assembler Options ................................................................................................. 31

3-2. Operators Used in Expressions (Precedence) ........................................................................ 46

3-3. Expressions With Absolute and Relocatable Symbols ............................................................... 47

3-4. Built-In Mathematical Functions ......................................................................................... 49

3-5. Symbol Attributes.......................................................................................................... 55

4-1. Directives That Define Sections ......................................................................................... 57

4-2. Directives That Initialize Values (Data and Memory) ................................................................. 57

4-3. Directives That Perform Alignment and Reserve Space ............................................................. 58

4-4. Directives That Change the Instruction Type .......................................................................... 58

4-5. Directives That Format the Output Listing ............................................................................. 58

4-6. Directives That Reference Other Files.................................................................................. 58

4-7. Directives That Effect Symbol Linkage and Visibility ................................................................. 59

4-8. Directives That Enable Conditional Assembly......................................................................... 59

4-9. Directives That Define Union or Structure Types ..................................................................... 59

4-10. Directives That Define Symbols ......................................................................................... 59

4-11. Directives That Define Common Data Sections....................................................................... 60

4-12. Directives That Create or Effect Macros ............................................................................... 60

4-13. Directives That Control Diagnostics..................................................................................... 60

4-14. Directives That Perform Assembly Source Debug.................................................................... 60

4-15. Directives That Are Used by the Absolute Lister...................................................................... 60

4-16. Directives That Perform Miscellaneous Functions .................................................................... 61

5-1. Substitution Symbol Functions and Return Values.................................................................. 137

5-2. Creating Macros.......................................................................................................... 148

5-3. Manipulating Substitution Symbols .................................................................................... 148

5-4. Conditional Assembly ................................................................................................... 148

5-5. Producing Assembly-Time Messages................................................................................. 148

5-6. Formatting the Listing ................................................................................................... 148

7-1. Basic Options Summary ................................................................................................ 161

7-2. File Search Path Options Summary ................................................................................... 161

7-3. Command File Preprocessing Options Summary ................................................................... 161

7-4. Diagnostic Options Summary .......................................................................................... 161

7-5. Linker Output Options Summary....................................................................................... 162

7-6. Symbol Management Options Summary ............................................................................. 162

7-7. Run-Time Environment Options Summary ........................................................................... 162

7-8. Link-Time Optimization Options Summary ........................................................................... 162

7-9. Miscellaneous Options Summary...................................................................................... 163

7-10. Groups of Operators Used in Expressions (Precedence) .......................................................... 205

9-1. Symbol Attributes in Cross-Reference Listing........................................................................ 250

11-1. Basic Hex Conversion Utility Options ................................................................................. 259

11-2. Boot-Loader Options..................................................................................................... 275

11-3. Boot Table Source Formats ............................................................................................ 277

11-4. Boot Table Format ....................................................................................................... 277

11-5. Options for Specifying Hex Conversion Formats .................................................................... 283

A-1. Symbolic Debugging Directives ........................................................................................ 299

9

SPNU118K–August 2012 List of Tables

Submit Documentation Feedback Copyright © 2012, Texas Instruments Incorporated

Preface

SPNU118K–August 2012

Read This First

About This Manual

The ARM Assembly Language Tools User's Guide explains how to use these assembly language tools:

• Assembler

• Archiver

• Linker

• Library information archiver

• Absolute lister

• Cross-reference lister

• Disassembler

• Object file display utility

• Name utility

• Strip utility

• Hex conversion utility

How to Use This Manual

This book helps you learn how to use the Texas Instruments assembly language tools designed

specifically for the ARM®32-bit devices. This book consists of four parts:

•Introductory information, consisting of Chapter 1 and Chapter 2, gives you an overview of the

assembly language development tools. It also discusses object modules, which helps you to use the

ARM tools more effectively. Read Chapter 2 before using the assembler and linker.

•Assembler description, consisting of Chapter 3 through Chapter 5, contains detailed information

about using the assembler. This portion explains how to invoke the assembler and discusses source

statement format, valid constants and expressions, assembler output, and assembler directives. It also

describes the macro language.

•Additional assembly language tools description, consisting of Chapter 6 through Chapter 11,

describes in detail each of the tools provided with the assembler to help you create executable object

files. For example, Chapter 7 explains how to invoke the linker, how the linker operates, and how to

use linker directives; Chapter 11 explains how to use the hex conversion utility.

•Reference material, consisting of Appendix A through Appendix D, provides supplementary

information including symbolic debugging directives that the ARM C/C++ compiler uses. It also

provides hex utility examples, a description of the XML link information file and a glossary.

10 Read This First SPNU118K–August 2012

Submit Documentation Feedback

Copyright © 2012, Texas Instruments Incorporated

www.ti.com

Notational Conventions

Notational Conventions

This document uses the following conventions:

• Program listings, program examples, and interactive displays are shown in a special typeface.

Interactive displays use a bold version of the special typeface to distinguish commands that you enter

from items that the system displays (such as prompts, command output, error messages, etc.).

Here is a sample of C code:

#include <stdio.h>

main()

{ printf("hello, cruel world\n");

}

• In syntax descriptions, the instruction, command, or directive is in a bold typeface and parameters are

in an italic typeface. Portions of a syntax that are in bold should be entered as shown; portions of a

syntax that are in italics describe the type of information that should be entered.

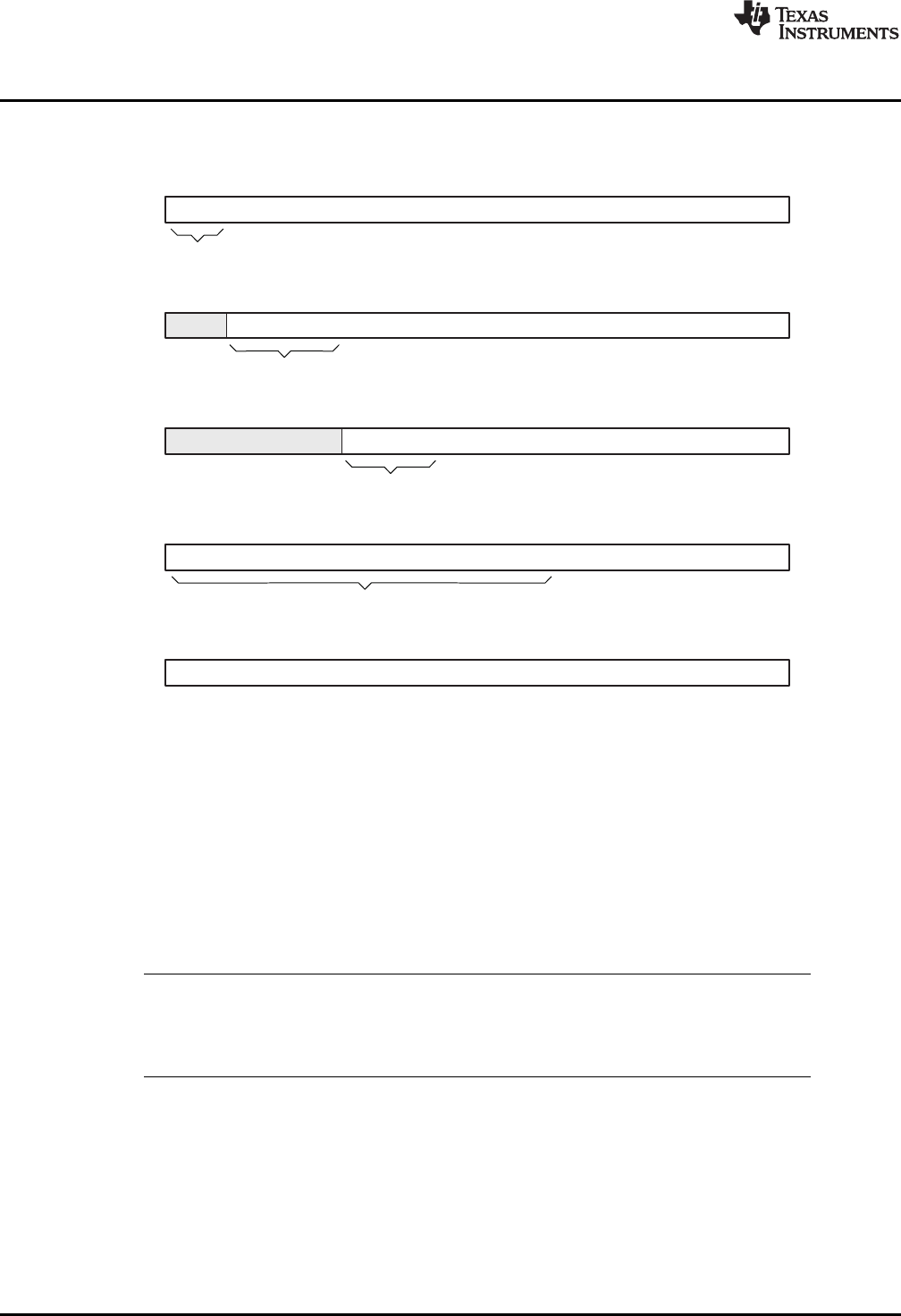

• Square brackets ( [ and ] ) identify an optional parameter. If you use an optional parameter, you specify

the information within the brackets. Unless the square brackets are in the bold typeface, do not enter

the brackets themselves. The following is an example of a command that has an optional parameter:

armcl [options] [filenames] [--run_linker [link_options] [object files]]

• Braces ( { and } ) indicate that you must choose one of the parameters within the braces; you do not

enter the braces themselves. This is an example of a command with braces that are not included in the

actual syntax but indicate that you must specify either the --rom_model or --ram_model option:

armcl --run_linker {--rom_model | --ram_model}filenames [--output_file= name.out]

--library= libraryname

• In assembler syntax statements, column 1 is reserved for the first character of a label or symbol. If the

label or symbol is optional, it is usually not shown. If it is a required parameter, it is shown starting

against the left margin of the box, as in the example below. No instruction, command, directive, or

parameter, other than a symbol or label, can begin in column 1.

symbol .usect "section name", size in bytes[, alignment]

• Some directives can have a varying number of parameters. For example, the .byte directive can have

multiple parameters. This syntax is shown as [, ..., parameter].

• The TMS470 and TMS570 devices are collectively referred to as ARM.

• The ARM 16-bit instruction set is referred to as 16-BIS.

• The ARM 32-bit instruction set is referred to as 32-BIS.

• Following are other symbols and abbreviations used throughout this document:

Symbol Definition

B,b Suffix — binary integer

H, h Suffix — hexadecimal integer

LSB Least significant bit

MSB Most significant bit

0x Prefix — hexadecimal integer

Q, q Suffix — octal integer

11

SPNU118K–August 2012 Read This First

Submit Documentation Feedback Copyright © 2012, Texas Instruments Incorporated

Related Documentation From Texas Instruments

www.ti.com

Related Documentation From Texas Instruments

You can use the following books to supplement this user's guide:

SPRAAO8 — Common Object File Format Application Report. Provides supplementary information on

the internal format of COFF object files. Much of this information pertains to the symbolic

debugging information that is produced by the C compiler.

SPNU134 —TMS470R1x User's Guide. Describes the TMS470R1x RISC microcontroller, its architecture

(including registers), ICEBreaker module, interfaces (memory, coprocessor, and debugger), 16-bit

and 32-bit instruction sets, and electrical specifications.

SPNU151 —ARM Optimizing C/C++ Compiler v4.6 User's Guide. Describes the ARM C/C++ compiler.

This C/C++ compiler accepts ANSI standard C/C++ source code and produces assembly language

source code for the ARM platform of devices.

ARM is a registered trademark of ARM Limited.

All other trademarks are the property of their respective owners.

12 Read This First SPNU118K–August 2012

Submit Documentation Feedback

Copyright © 2012, Texas Instruments Incorporated

Chapter 1

SPNU118K–August 2012

Introduction to the Software Development Tools

The ARM®is supported by a set of software development tools, which includes an optimizing C/C++

compiler, an assembler, a linker, and assorted utilities. This chapter provides an overview of these tools.

The ARM device is supported by the following assembly language development tools:

• Assembler

• Archiver

• Linker

• Library information archiver

• Absolute lister

• Cross-reference lister

• Object file display utility

• Disassembler

• Name utility

• Strip utility

• Hex conversion utility

This chapter shows how these tools fit into the general software tools development flow and gives a brief

description of each tool. For convenience, it also summarizes the C/C++ compiler and debugging tools.

For detailed information on the compiler and debugger, and for complete descriptions of the ARM device,

refer to the books listed in Related Documentation From Texas Instruments.

Topic ........................................................................................................................... Page

1.1 Software Development Tools Overview ................................................................ 14

1.2 Tools Descriptions ............................................................................................ 15

13

SPNU118K–August 2012 Introduction to the Software Development Tools

Submit Documentation Feedback Copyright © 2012, Texas Instruments Incorporated

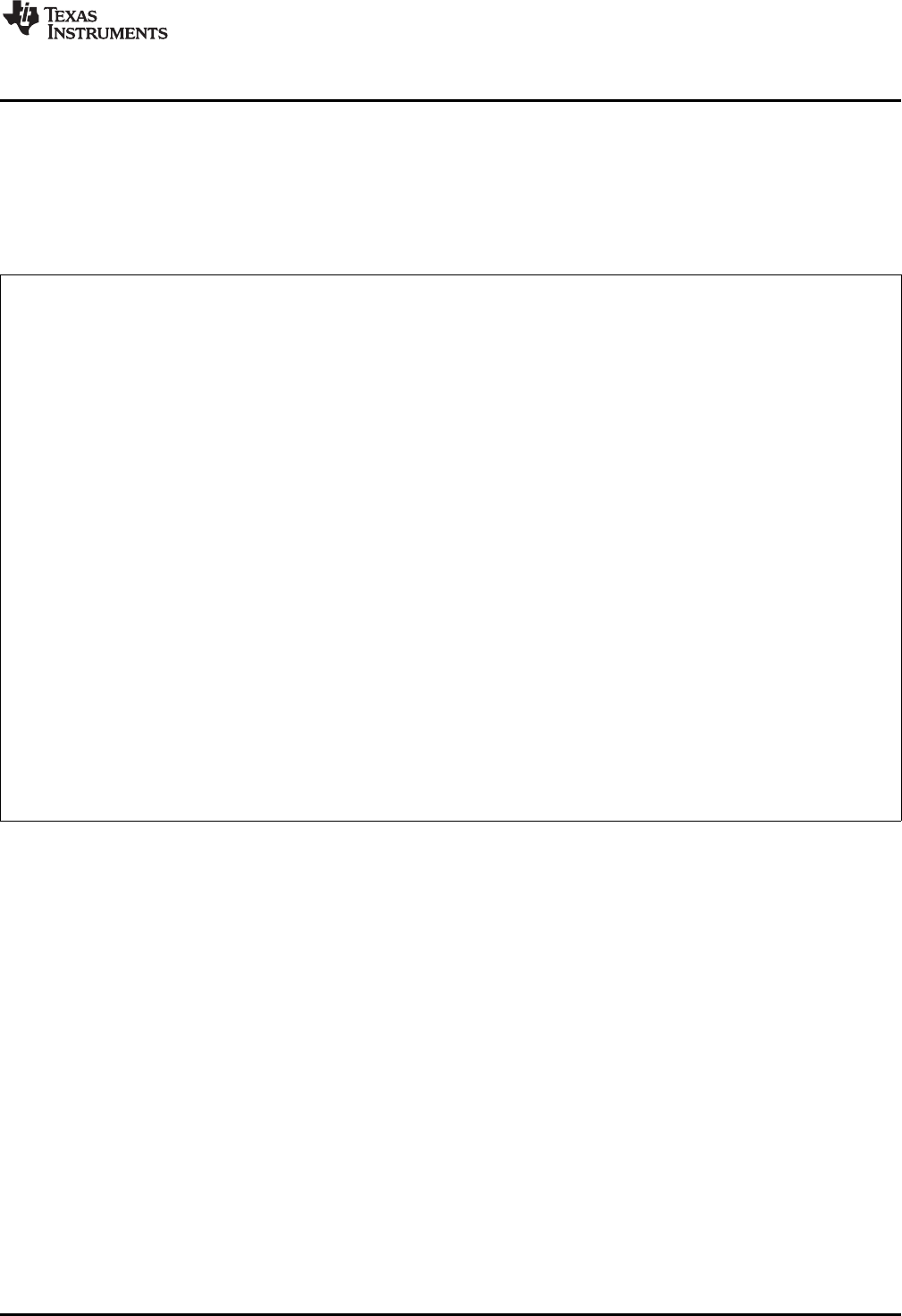

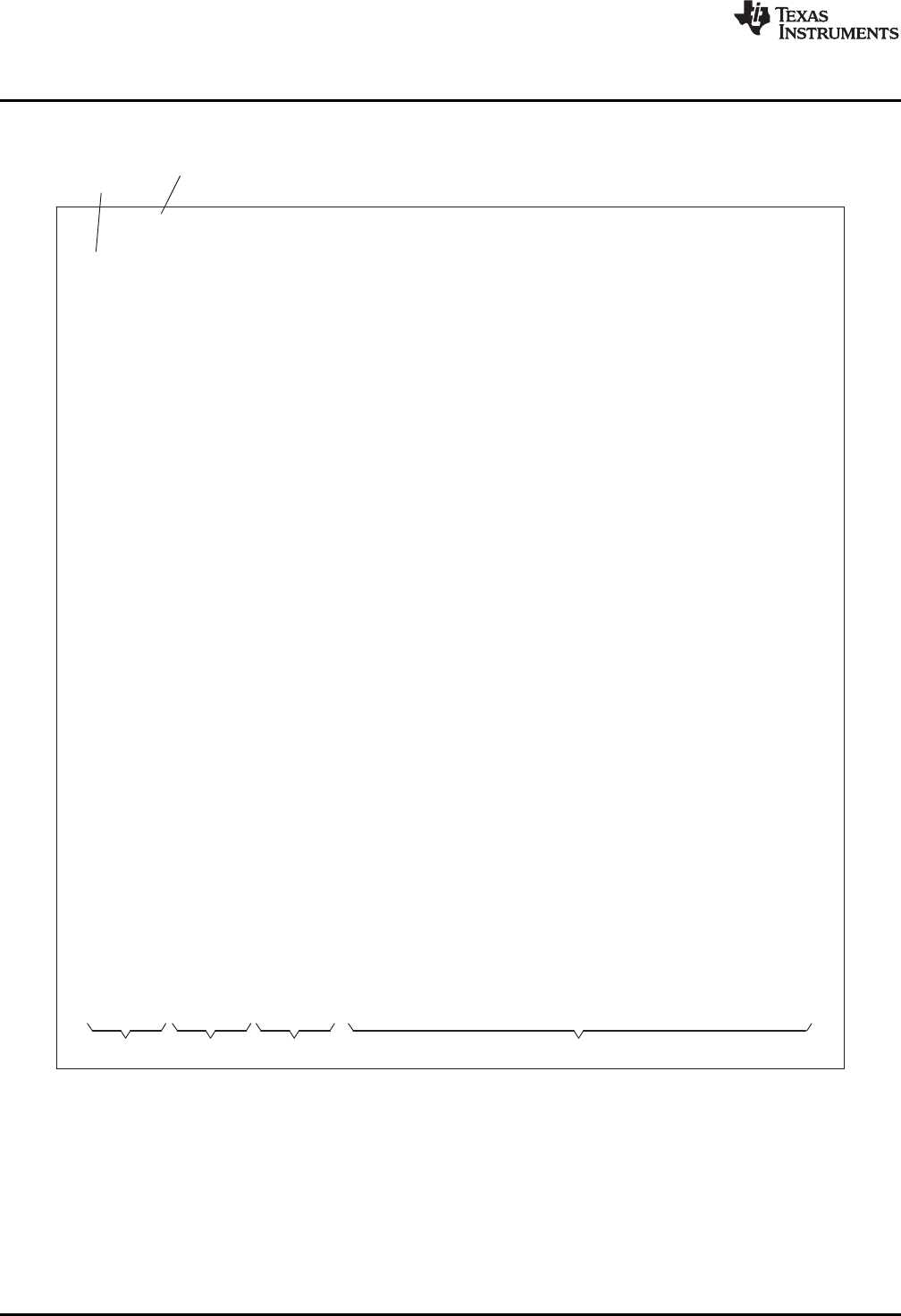

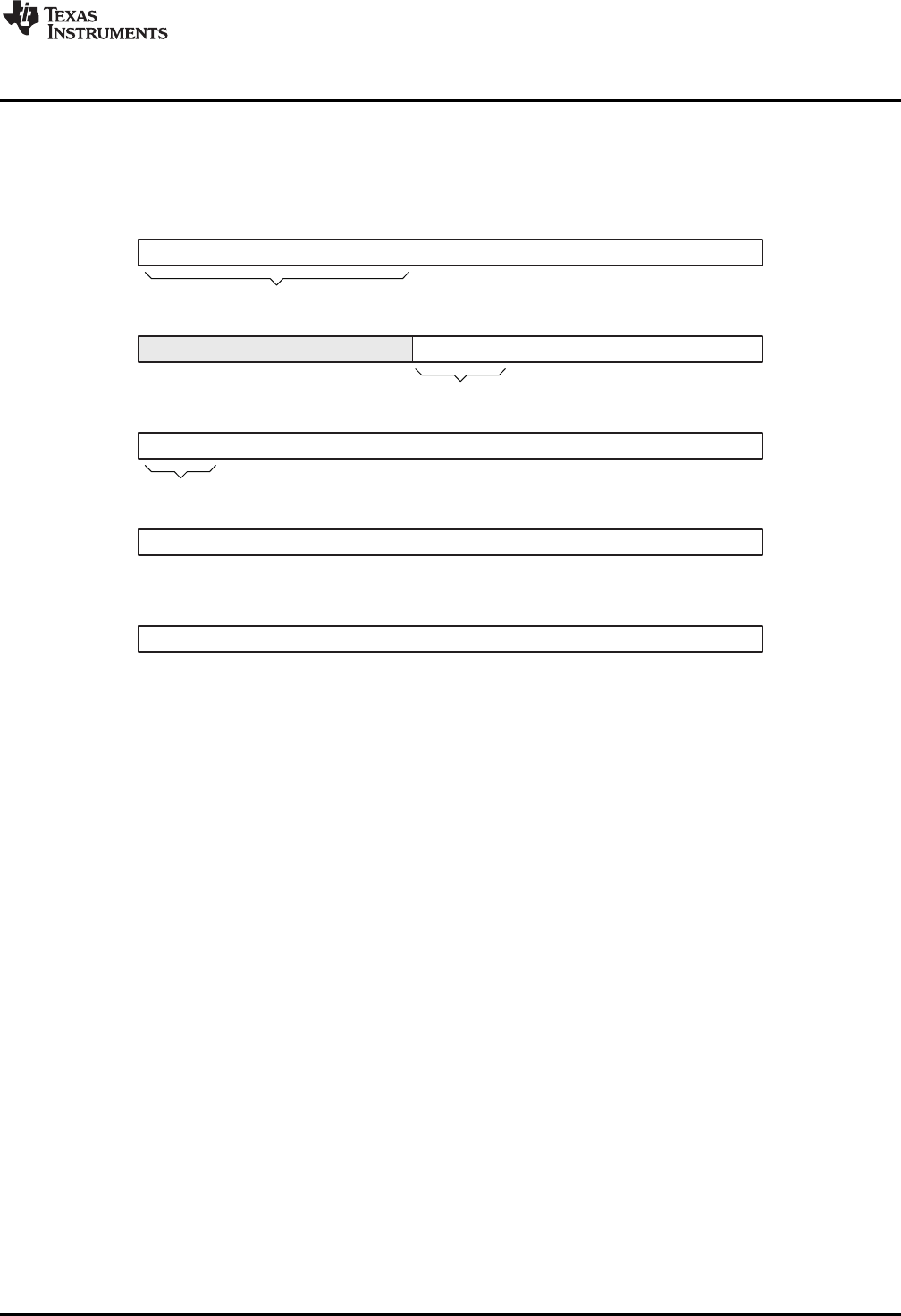

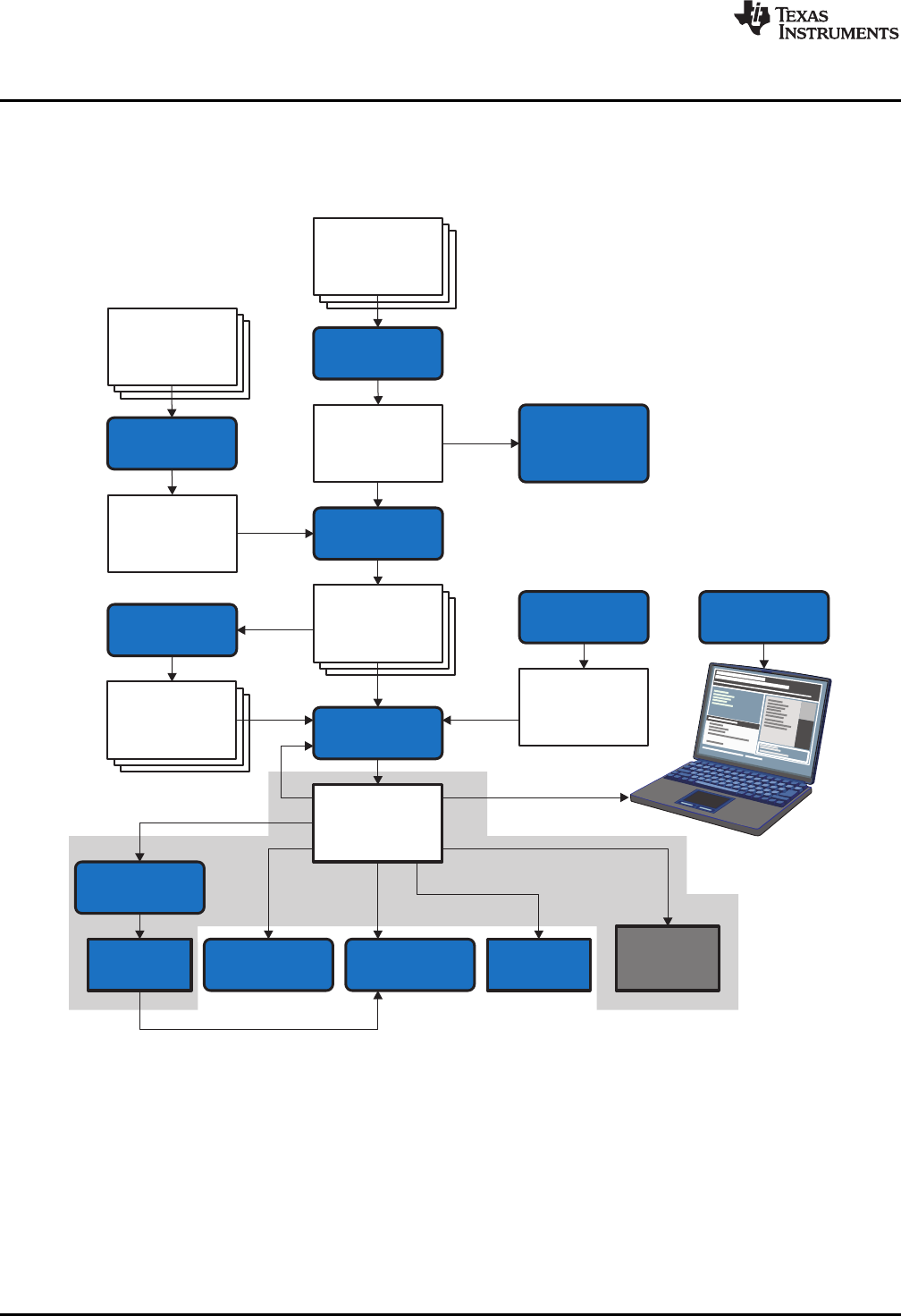

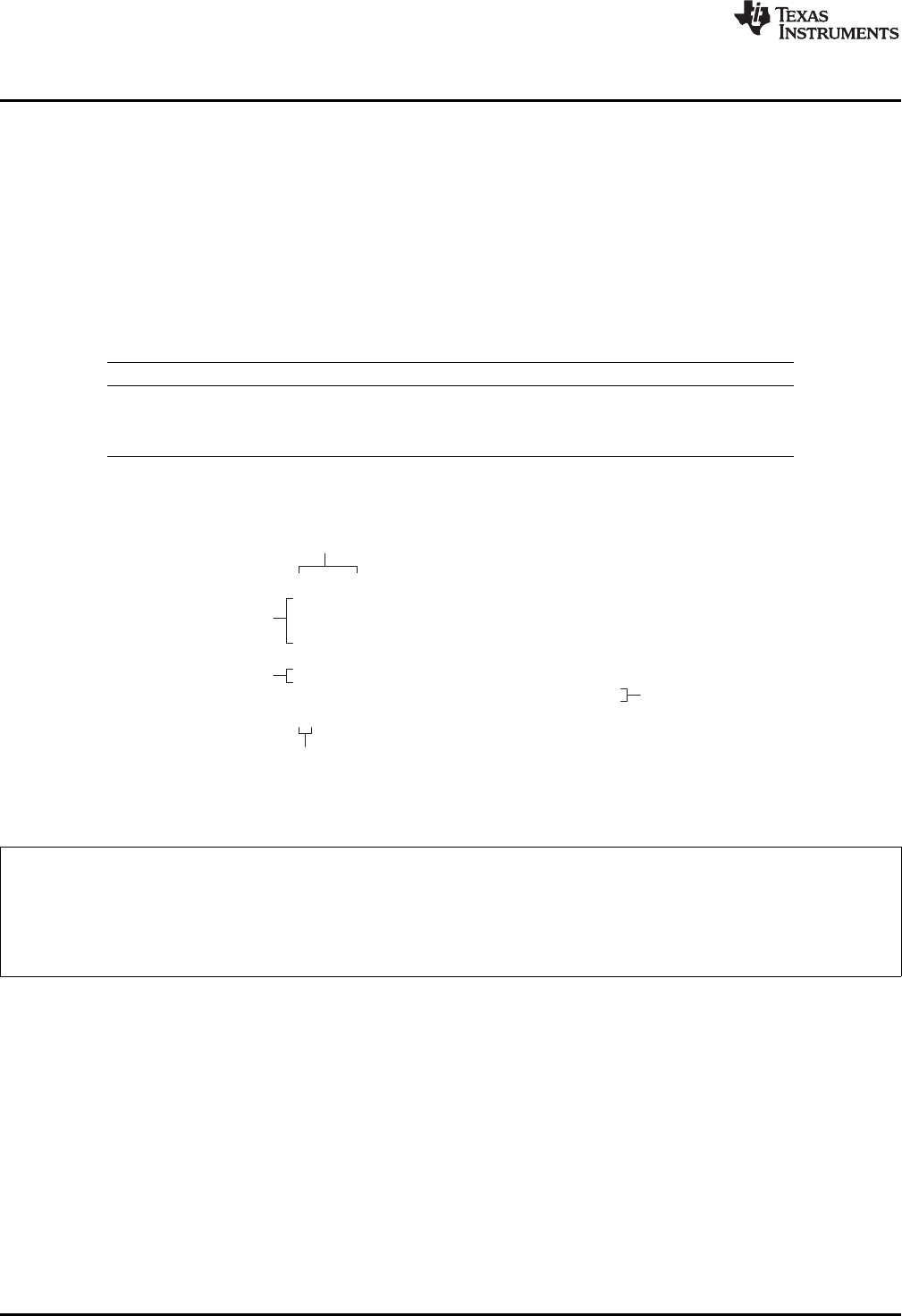

C/C++

source

files

C/C++

compiler

Assembler

source

Assembler

Executable

object file

Debugging

tools

Library-build

utility

Run-time-

support

library

Archiver

Archiver

Macro

library

Absolute lister

Hex-conversion

utility

Cross-reference

lister

Object file

utilities

ARM

Linker

Macro

source

files

Object

files

EPROM

programmer

Library of

object

files

C/C++ name

demangling

utility

Software Development Tools Overview

www.ti.com

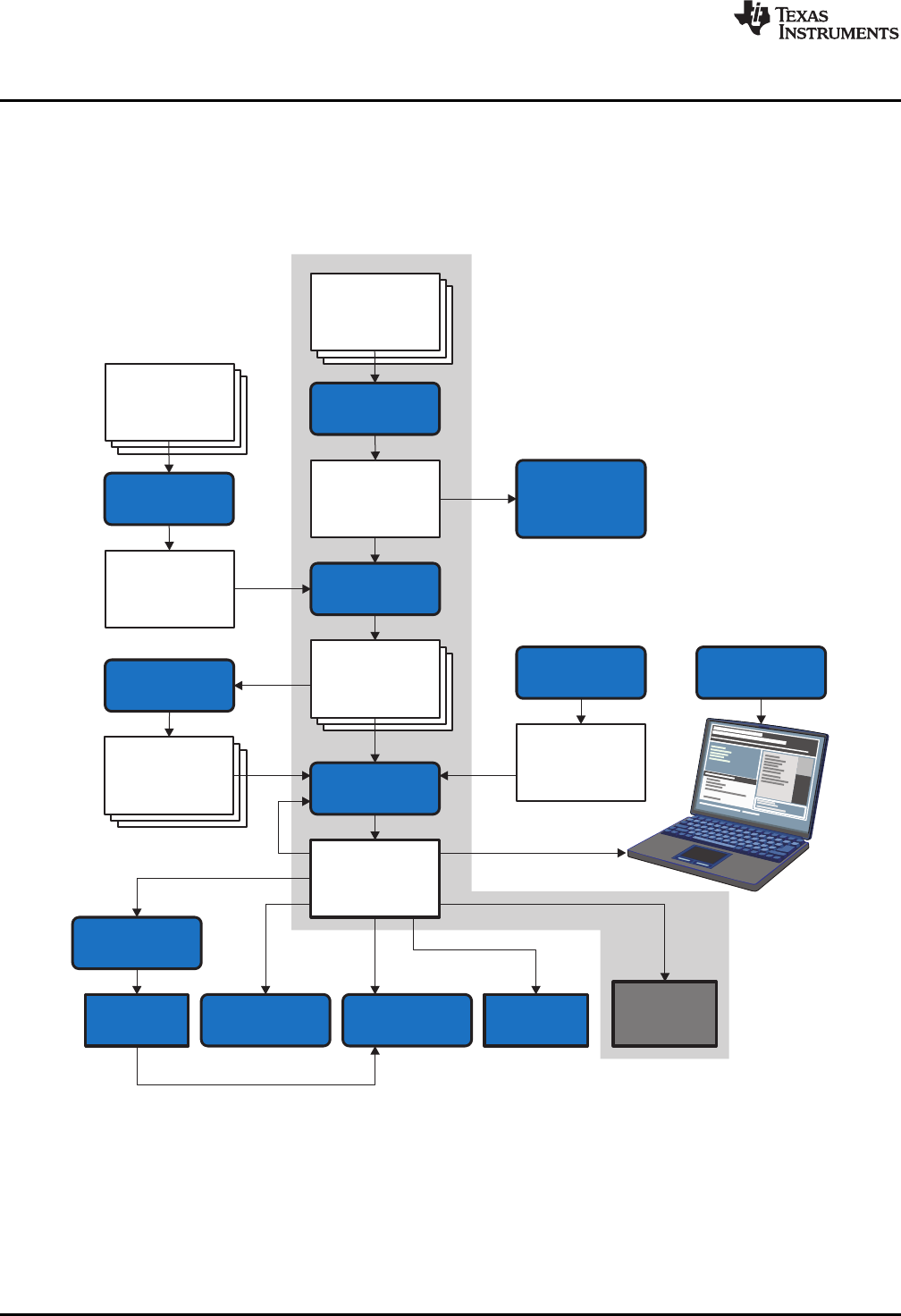

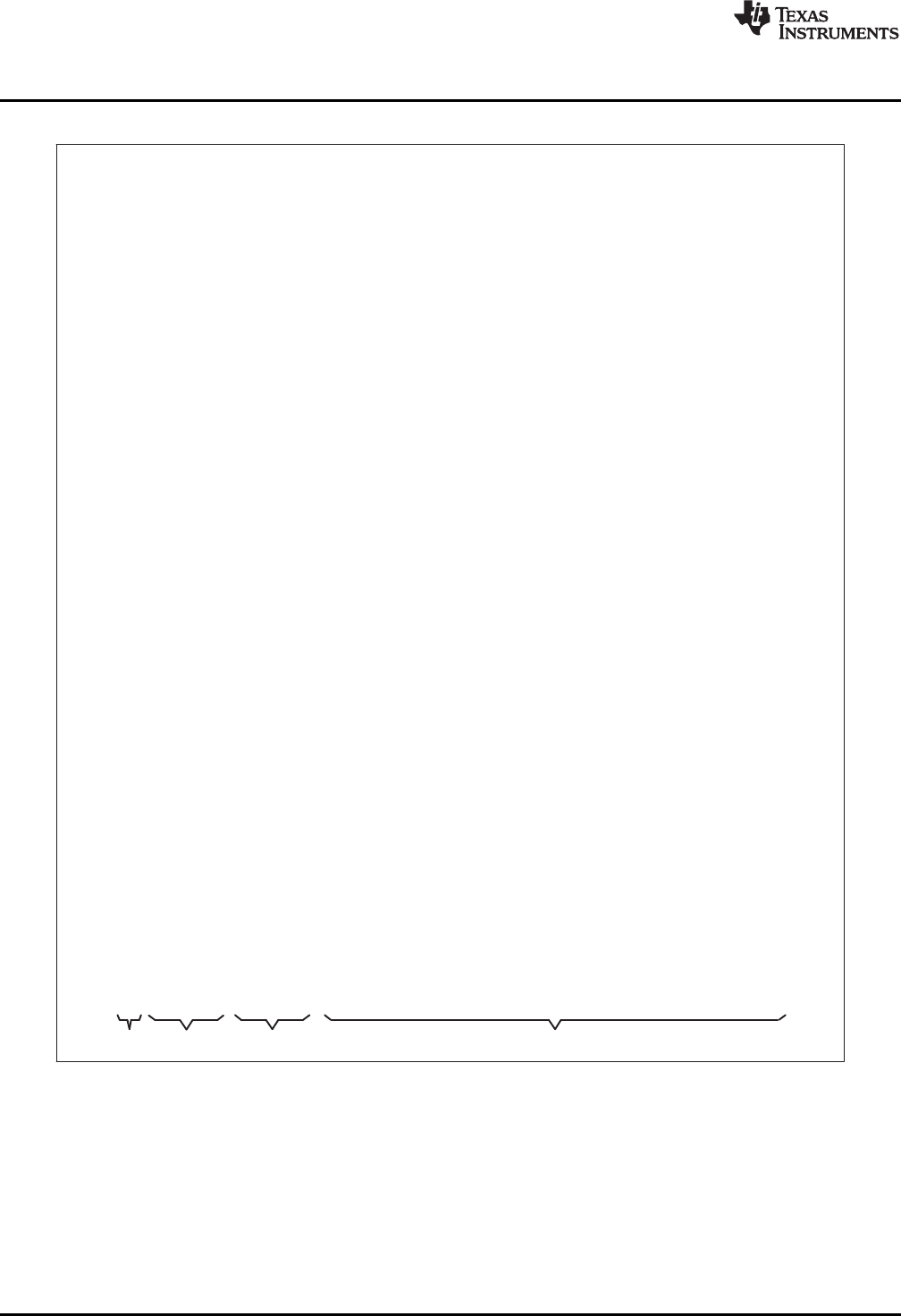

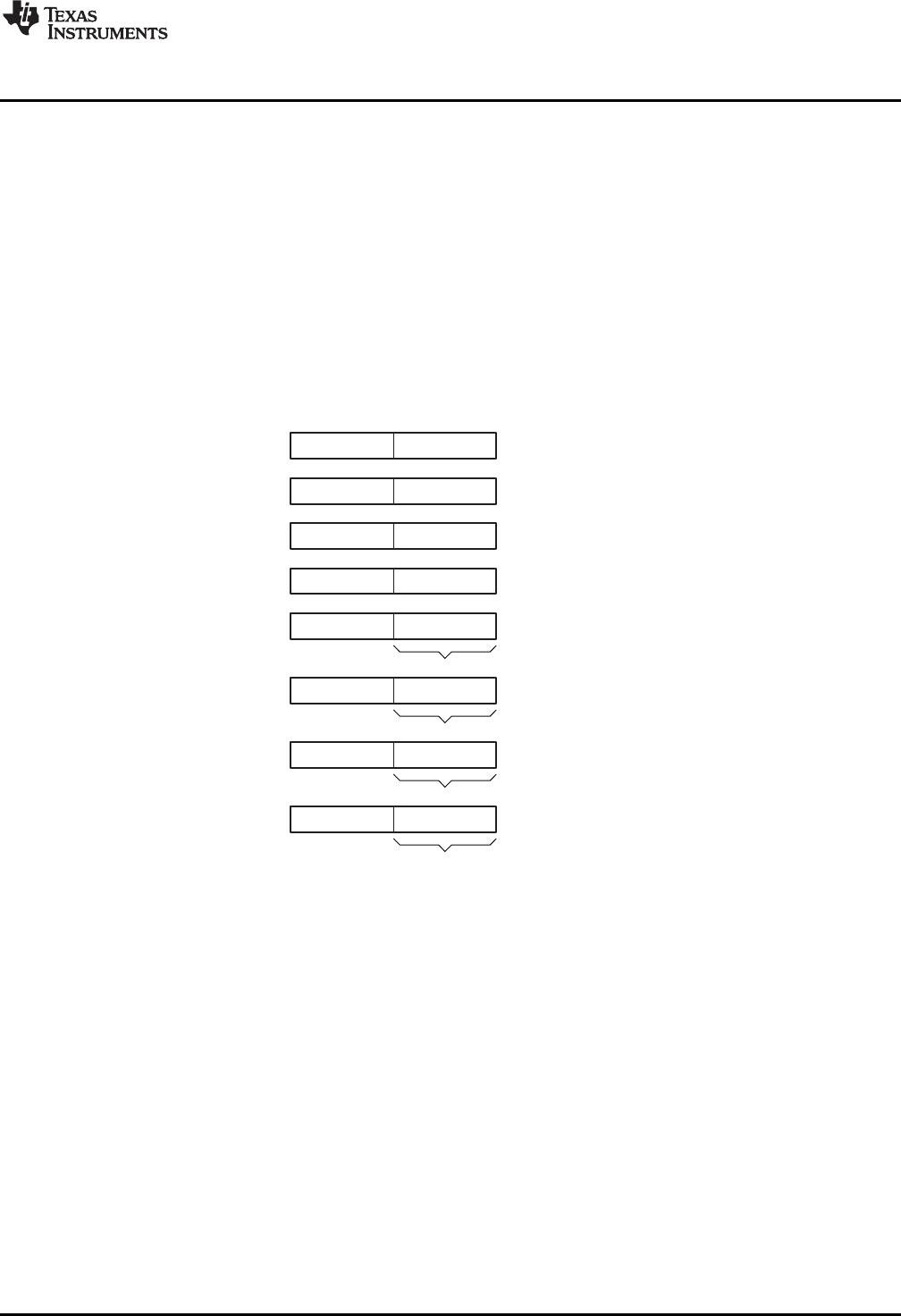

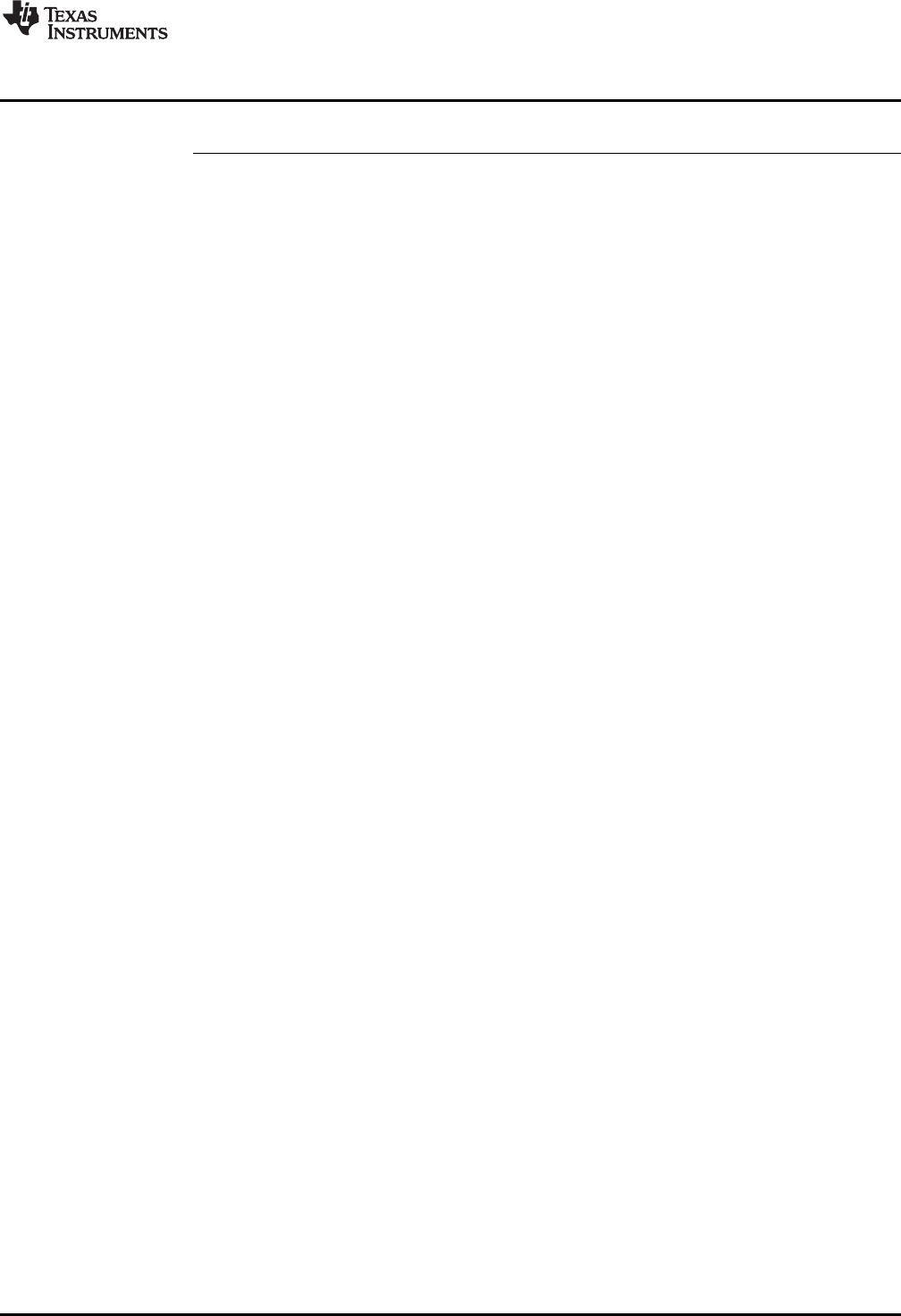

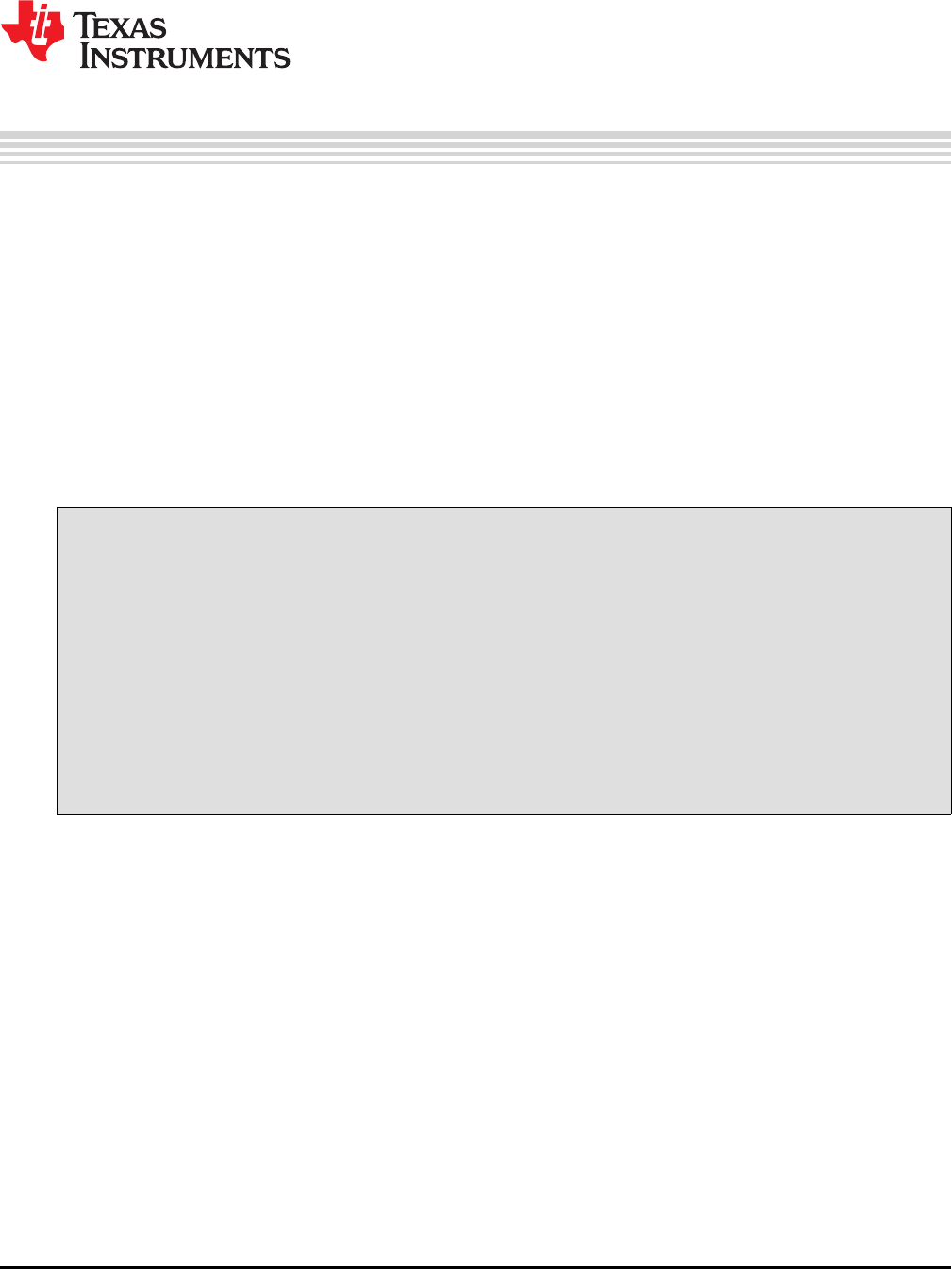

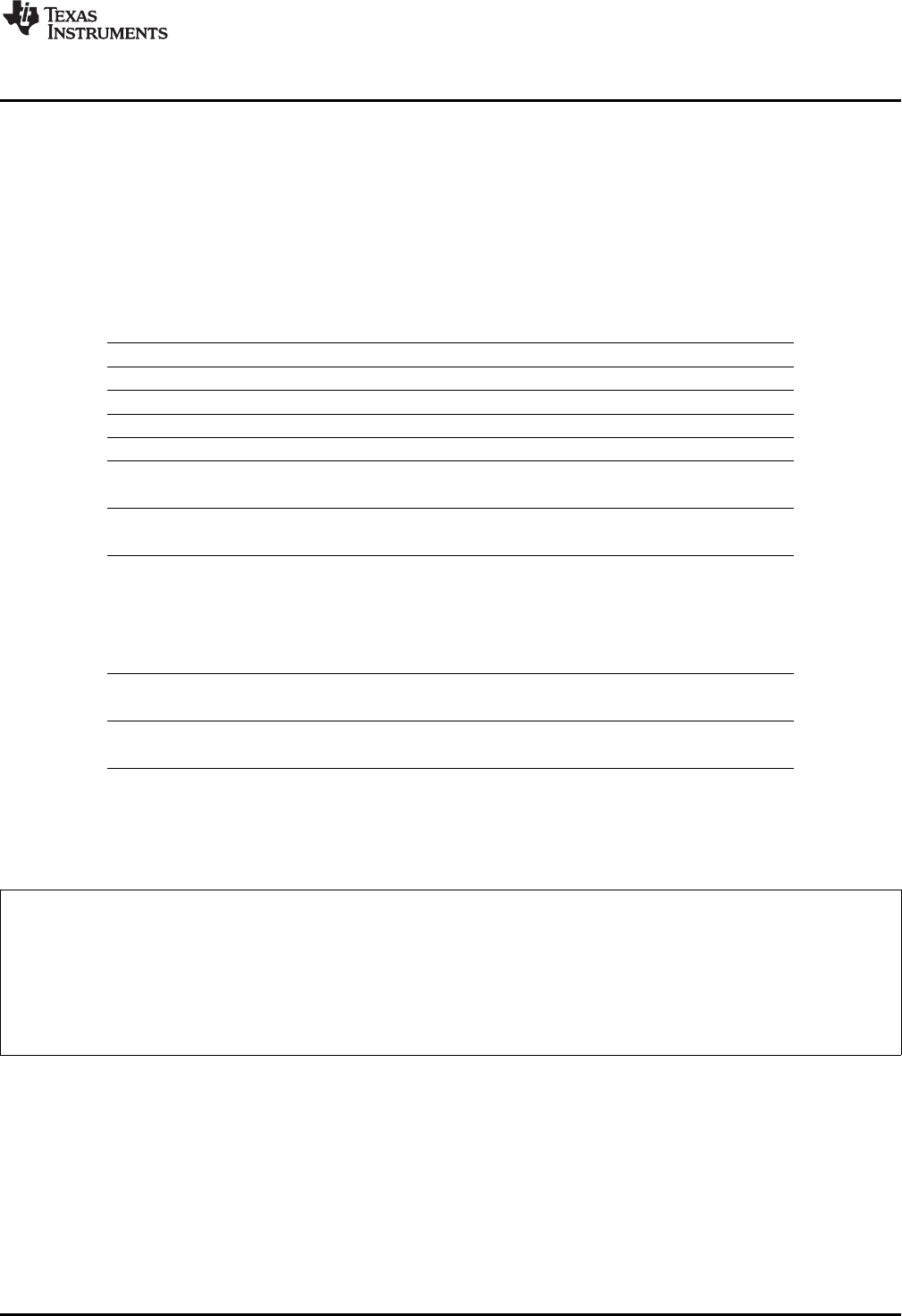

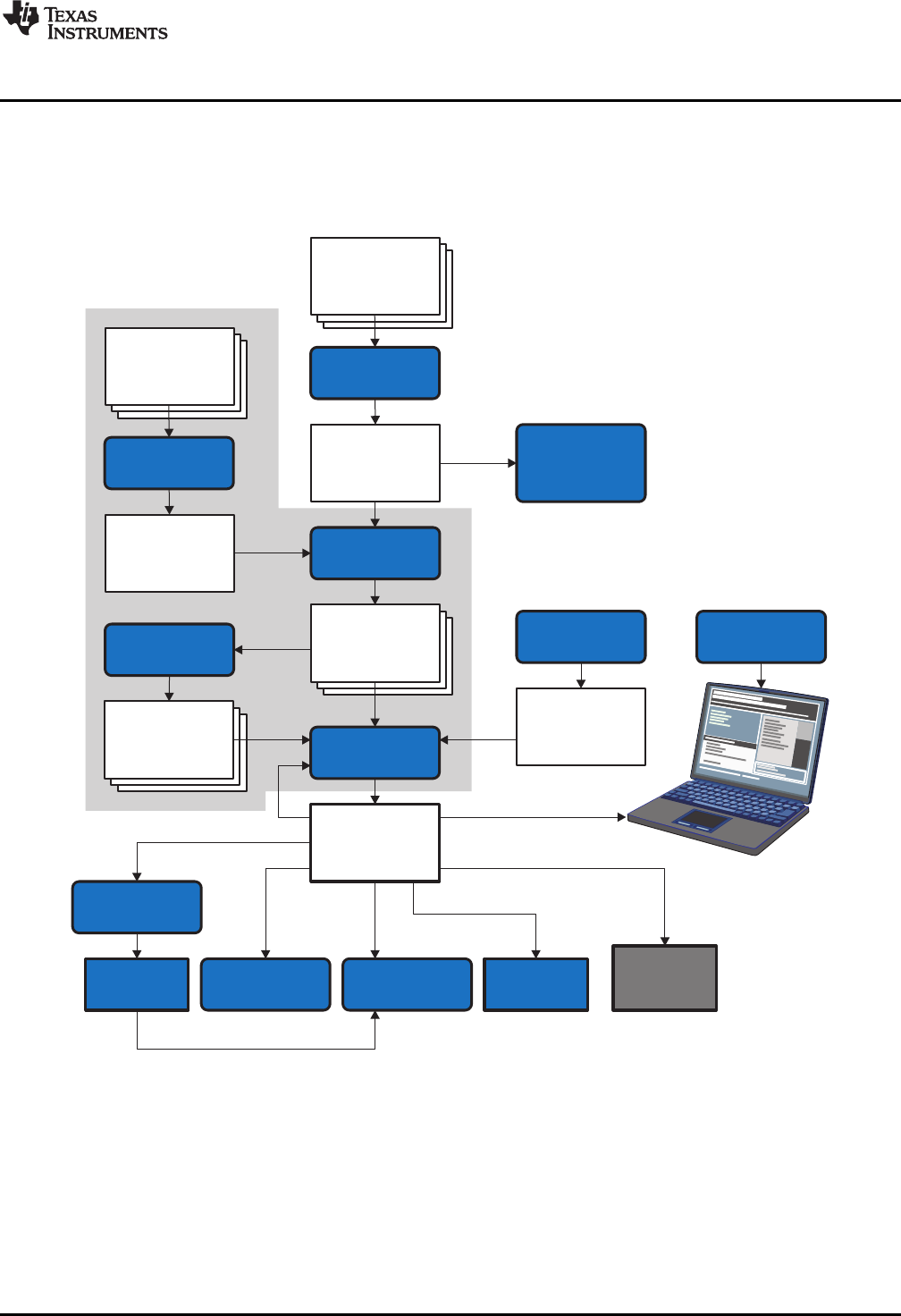

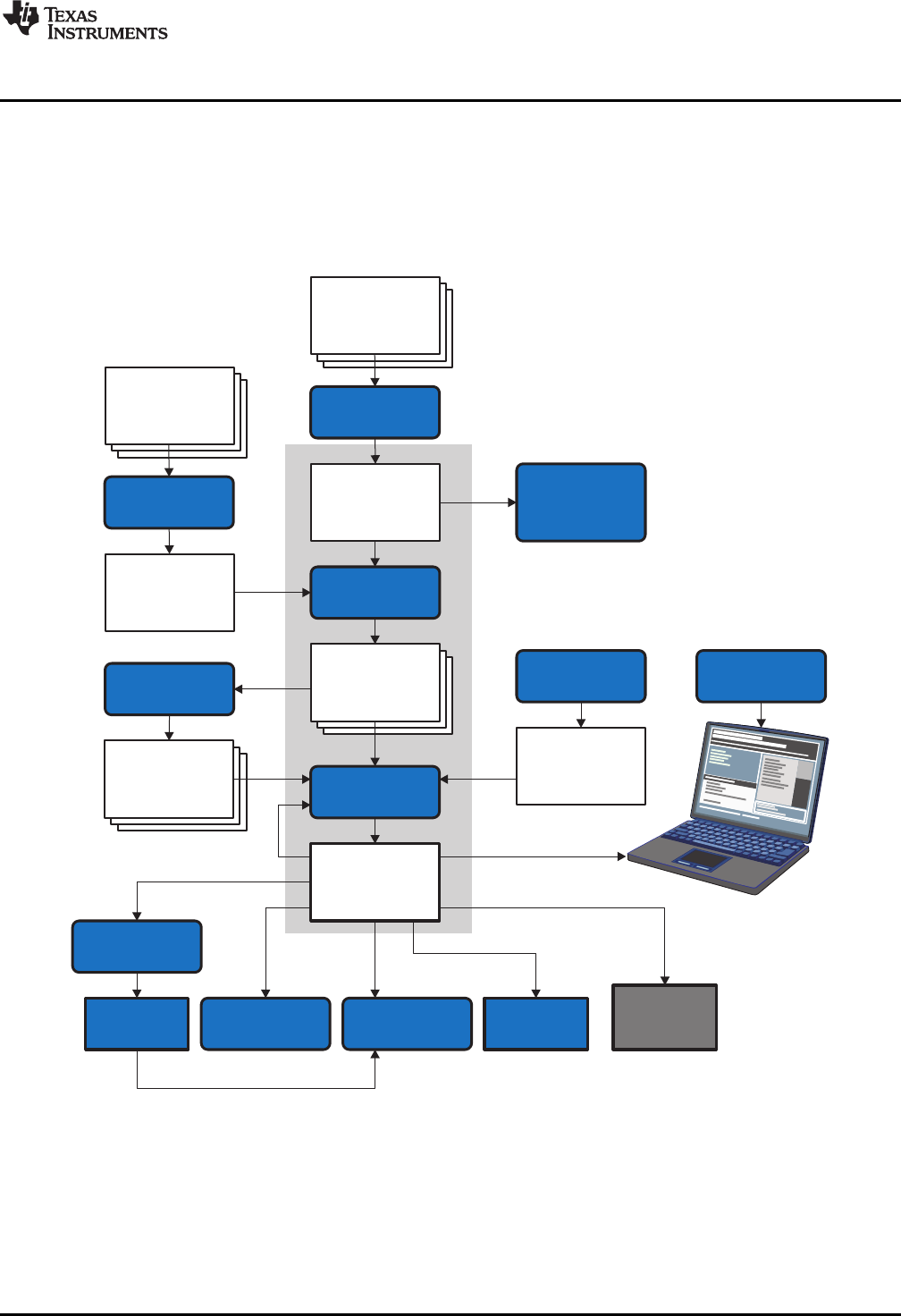

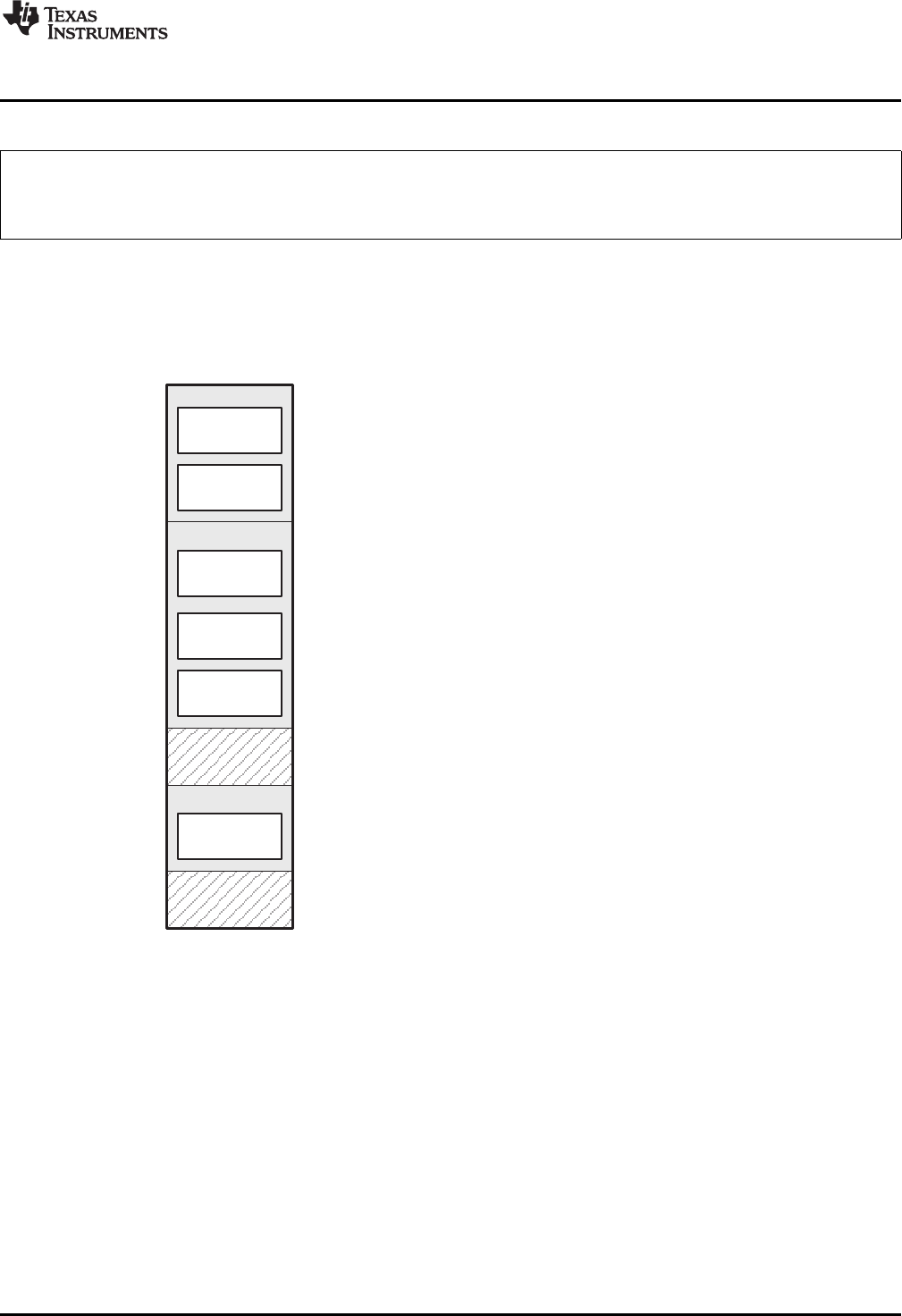

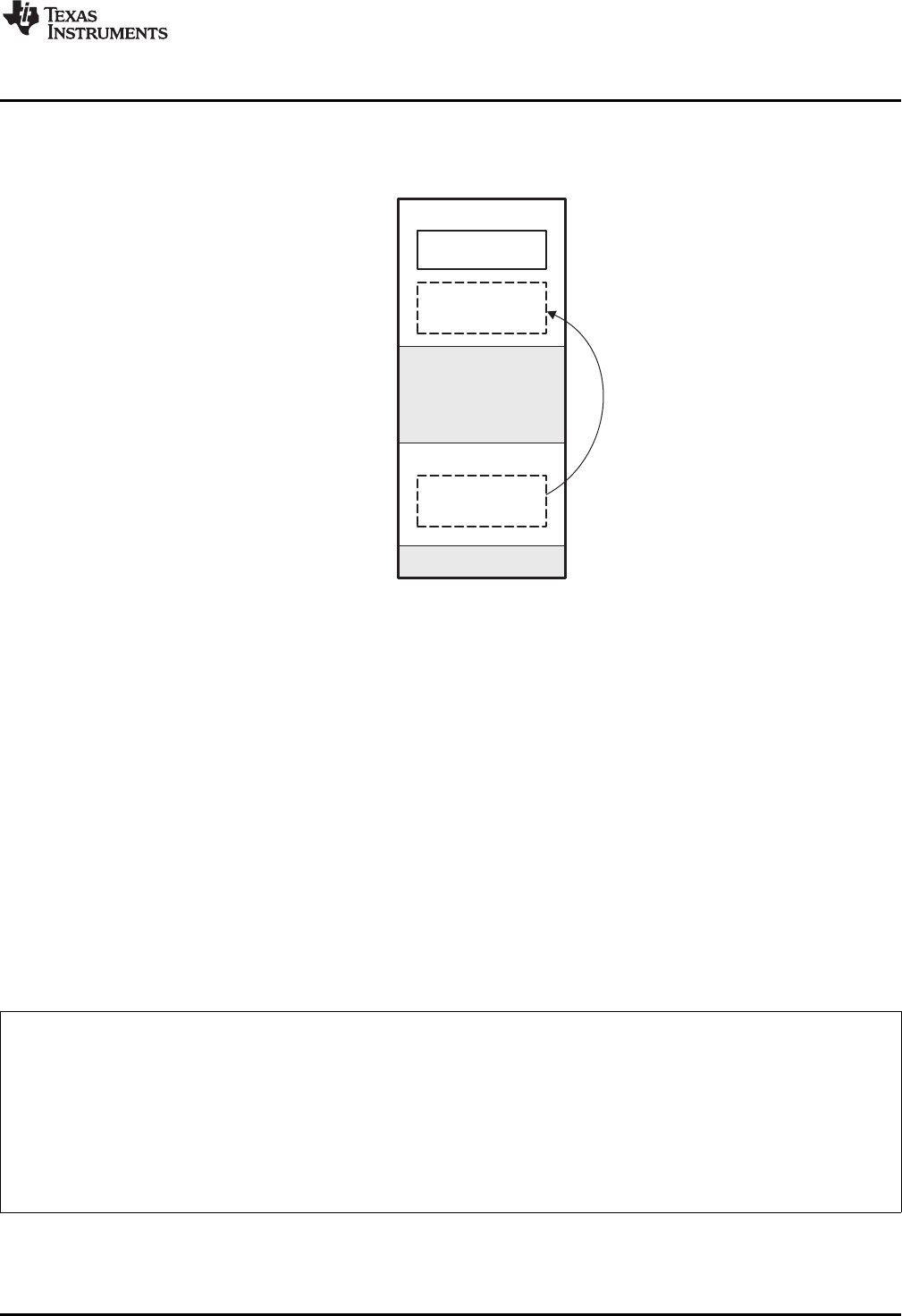

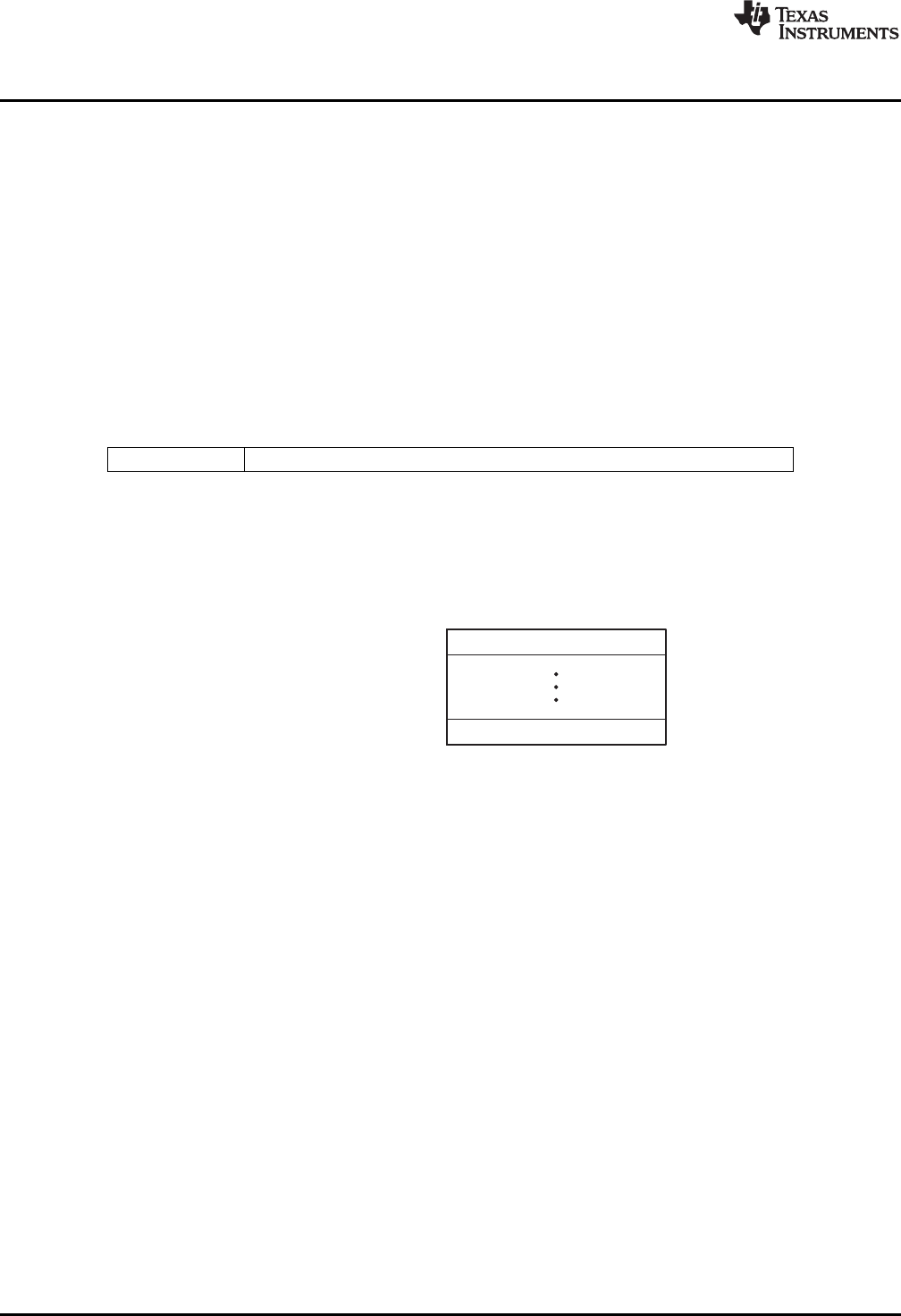

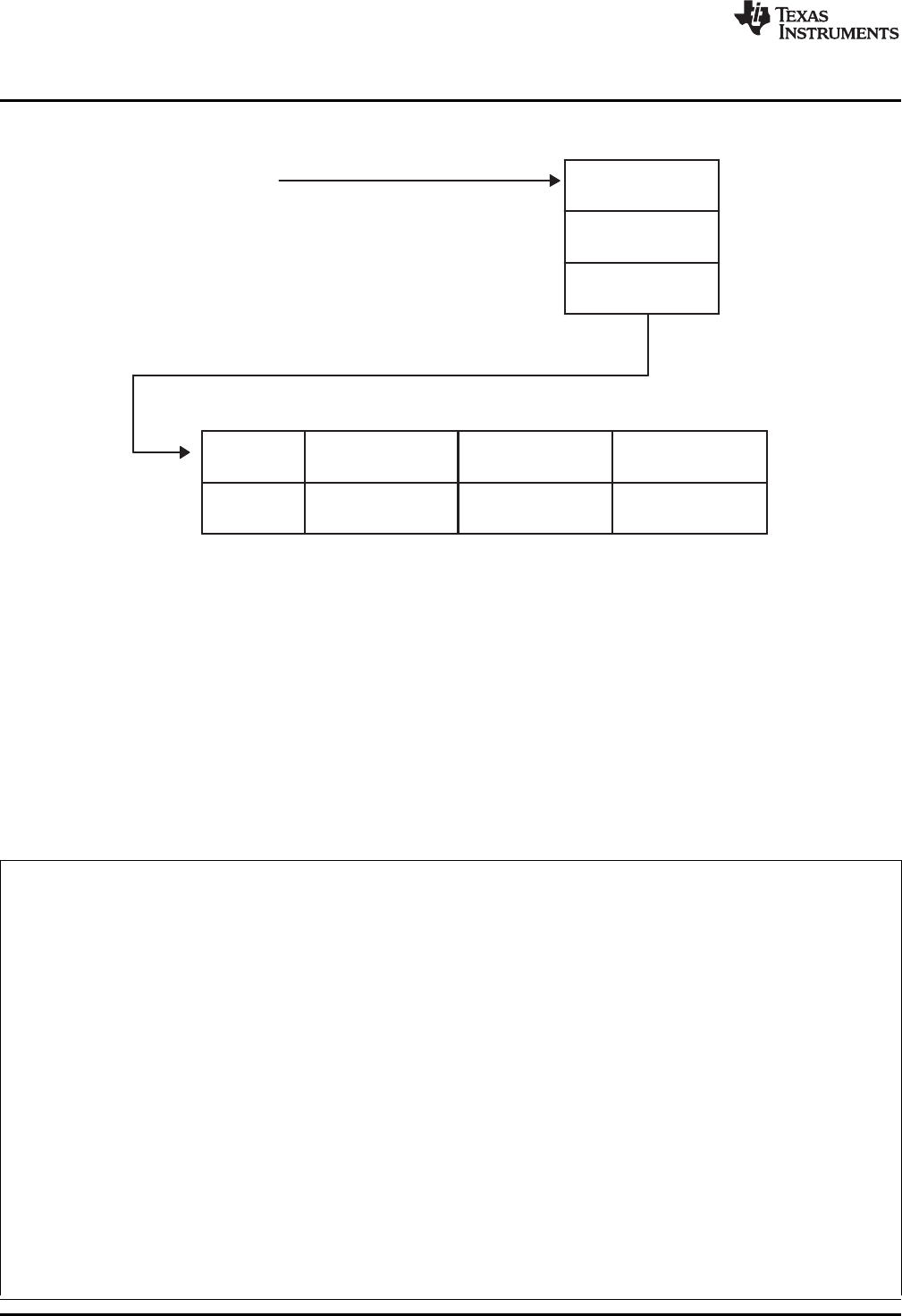

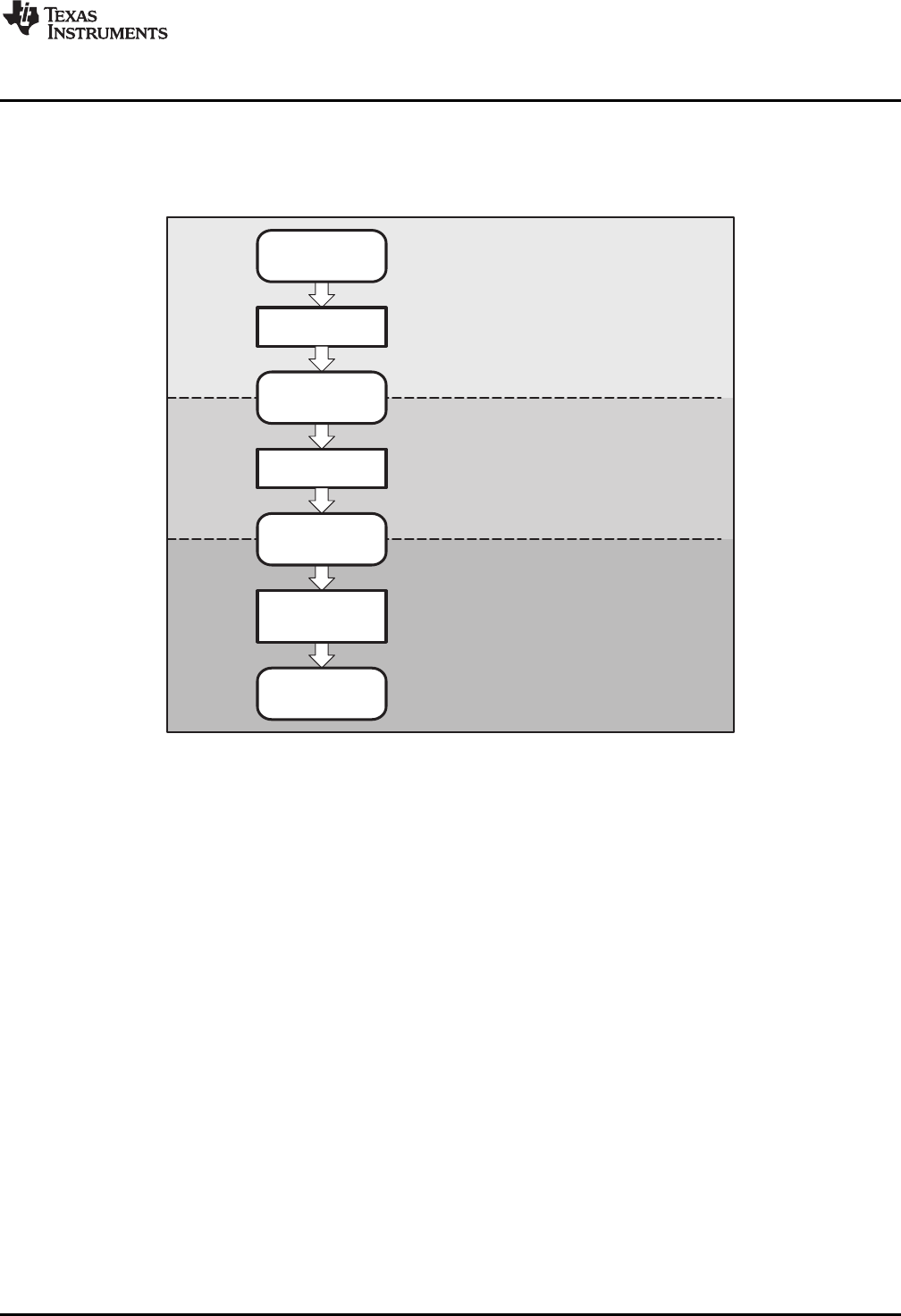

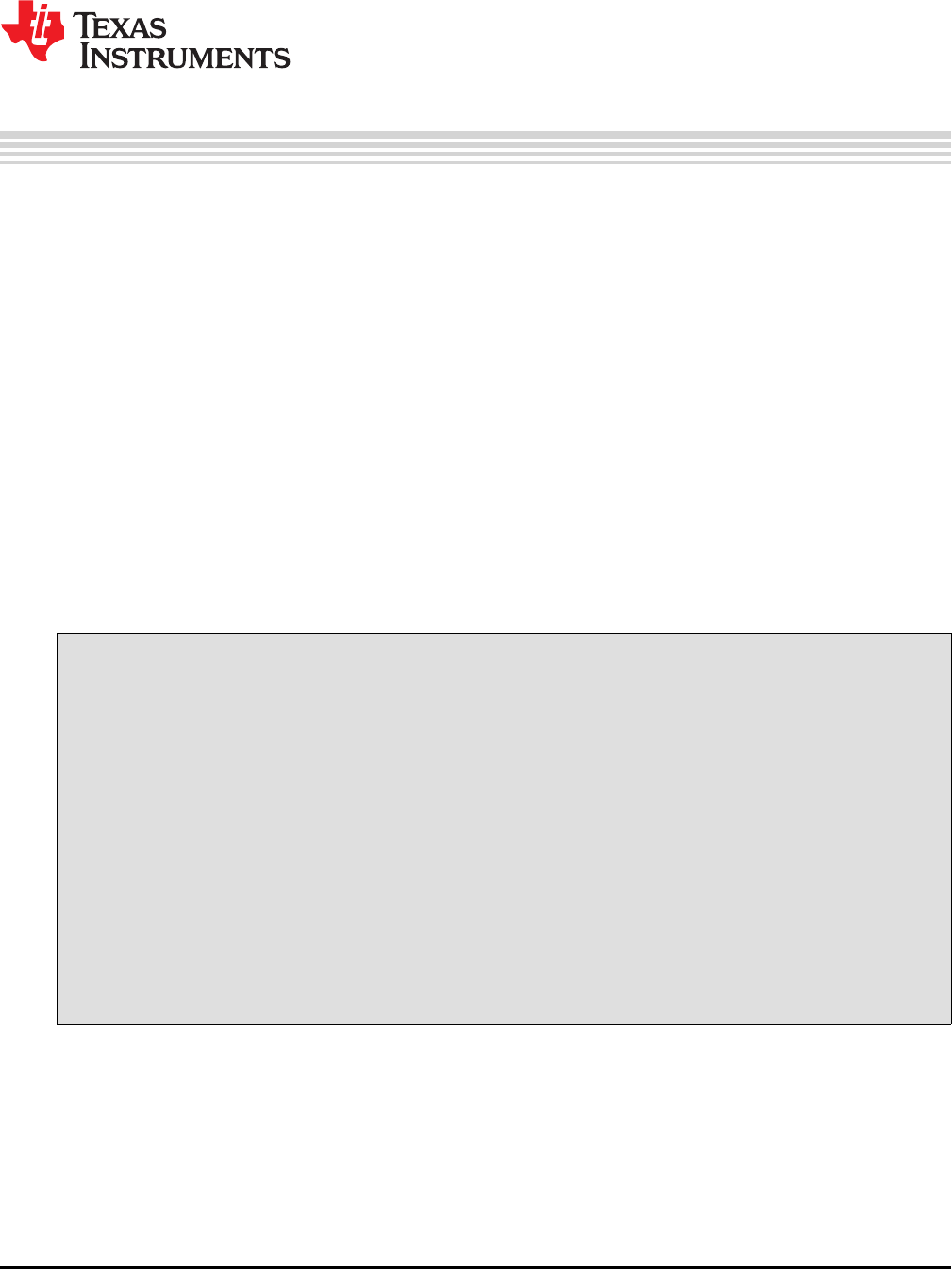

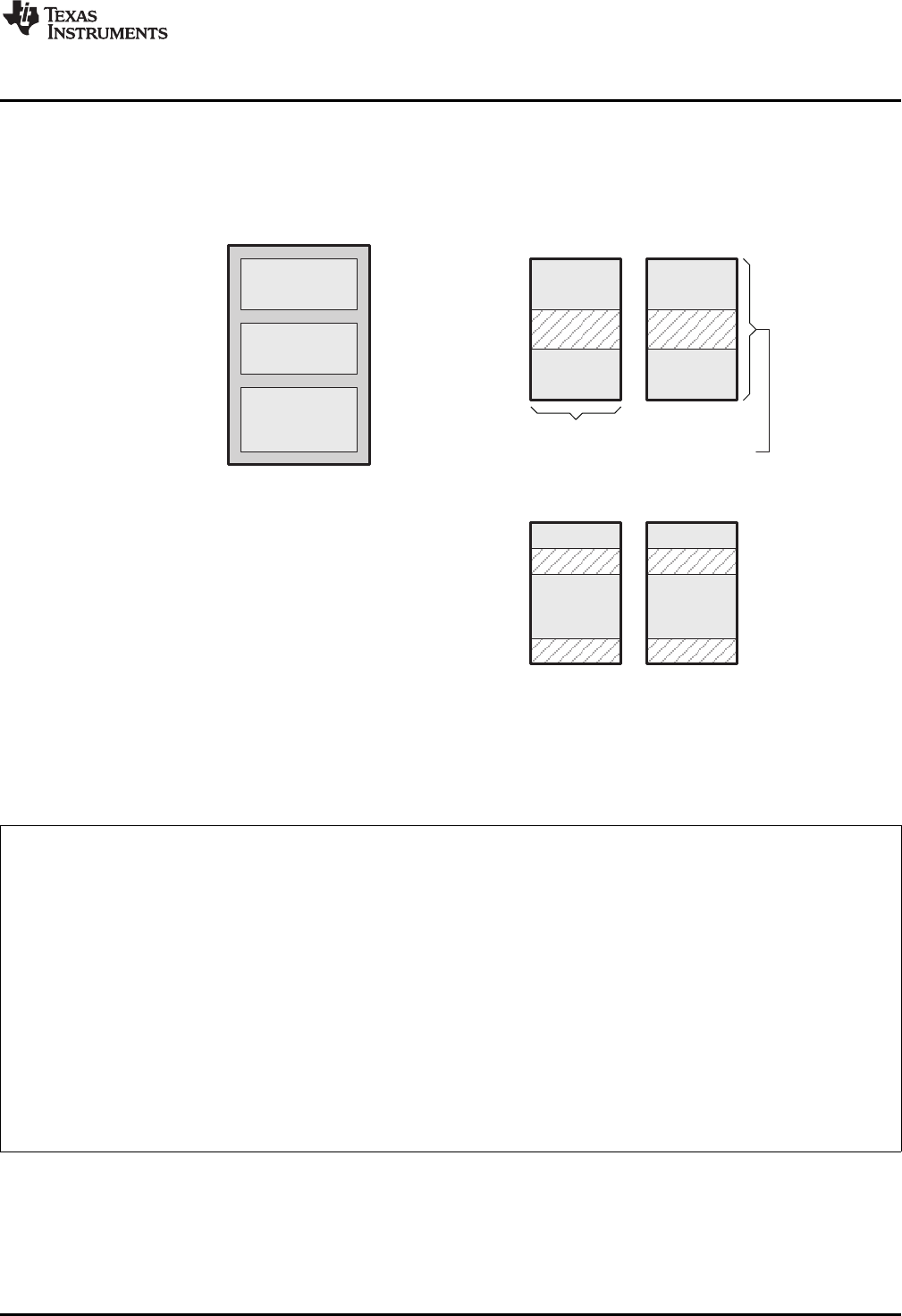

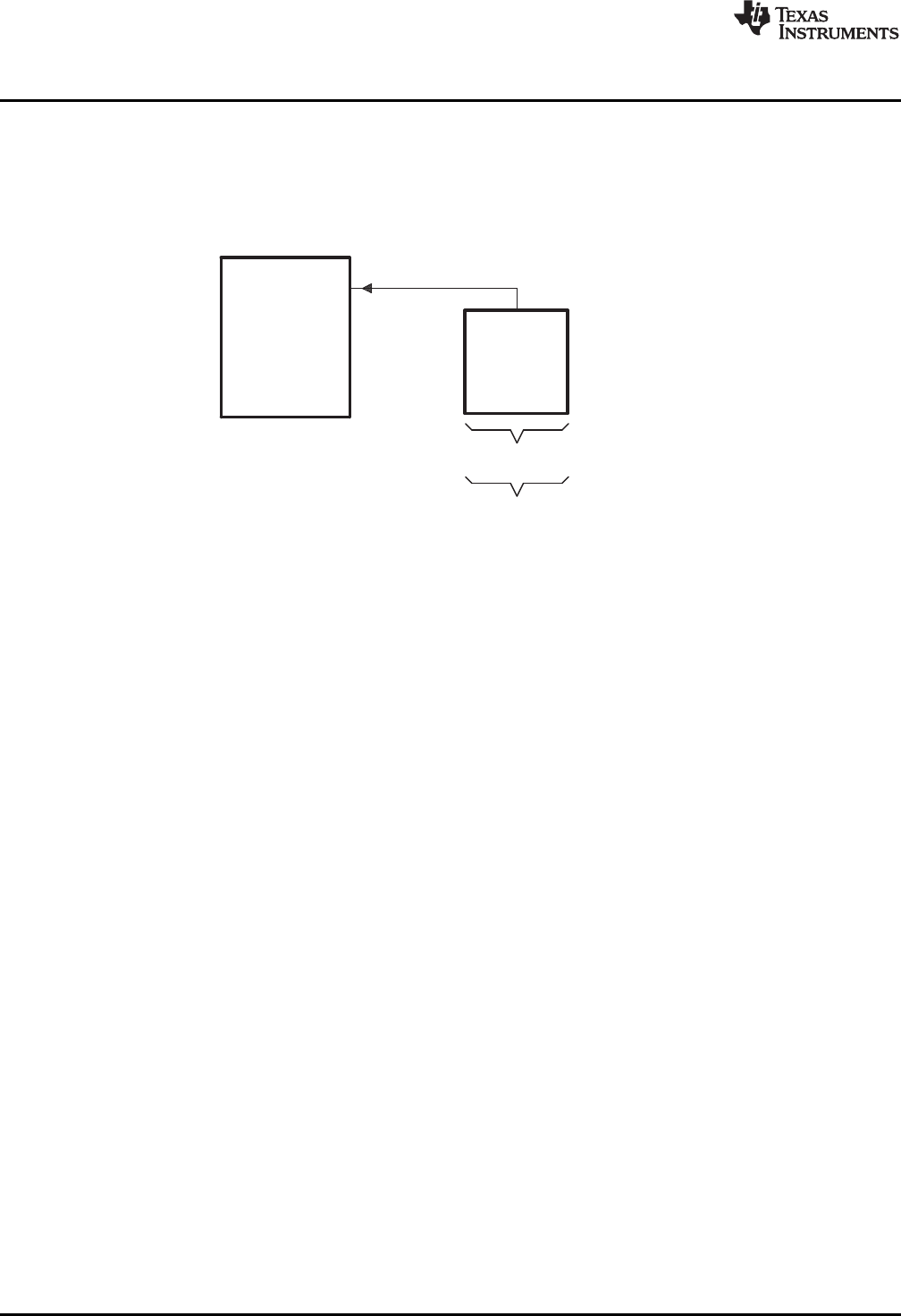

1.1 Software Development Tools Overview

Figure 1-1 shows the ARM device software development flow. The shaded portion highlights the most

common development path; the other portions are optional. The other portions are peripheral functions

that enhance the development process.

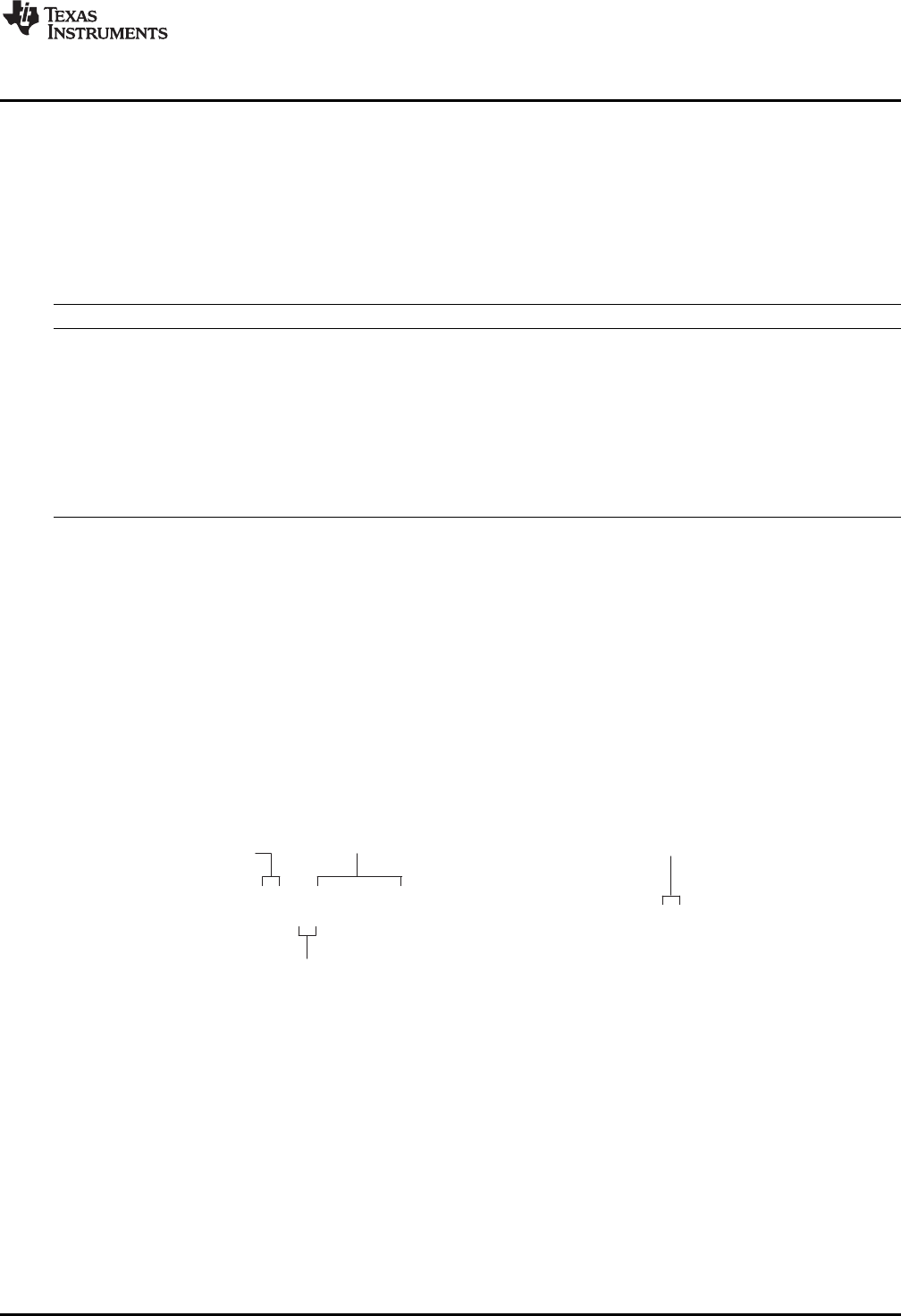

Figure 1-1. ARM Device Software Development Flow

14 Introduction to the Software Development Tools SPNU118K–August 2012

Submit Documentation Feedback

Copyright © 2012, Texas Instruments Incorporated

www.ti.com

Tools Descriptions

1.2 Tools Descriptions

The following list describes the tools that are shown in Figure 1-1:

• The C/C++ compiler accepts C/C++ source code and produces ARM machine code object modules. A

shell program, an optimizer, and an interlist utility are included in the compiler package:

– The shell program enables you to compile, assemble, and link source modules in one step.

– The optimizer modifies code to improve the efficiency of C/C++ programs.

– The interlist utility interlists C/C++ source statements with assembly language output to correlate

code produced by the compiler with your source code.

See the ARM Optimizing C/C++ Compiler User's Guide for more information.

• The assembler translates assembly language source files into machine language object modules.

Source files can contain instructions, assembler directives, and macro directives. You can use

assembler directives to control various aspects of the assembly process, such as the source listing

format, data alignment, and section content. See Chapter 3 through Chapter 5. See the TMS470R1x

User's Guide for detailed information on the assembly language instruction set.

• The linker combines object files into a single executable object module. It performs relocation and

resolves external references. The linker accepts relocatable object modules (created by the assembler)

as input. It also accepts archiver library members and output modules created by a previous linker run.

Link directives allow you to combine object file sections, bind sections or symbols to addresses or

within memory ranges, and define or redefine global symbols. See Chapter 7.

• The archiver allows you to collect a group of files into a single archive file, called a library. You can

also use the archiver to collect a group of object files into an object library. You can collect several

macros into a macro library. The assembler searches the library and uses the members that are called

as macros by the source file. The linker includes in the library the members that resolve external

references during the link. The archiver allows you to modify a library by deleting, replacing, extracting,

or adding members. See Section 6.1.

• The library information archiver allows you to create an index library of several object file library

variants, which is useful when several variants of a library with different options are available. Rather

than refer to a specific library, you can link against the index library, and the linker will choose the best

match from the indexed libraries. See Section 6.5.

• You can use the library-build utility to build your own customized run-time-support library. See the

ARM Optimizing C/C++ Compiler User's Guide for more information.

• The hex conversion utility converts object files to TI-Tagged, ASCII-Hex, Intel, Motorola-S, or

Tektronix object format. The converted file can be downloaded to an EPROM programmer. See

Chapter 11.

• The absolute lister uses linked object files to create .abs files. These files can be assembled to

produce a listing of the absolute addresses of object code. See Chapter 8.

• The cross-reference lister uses object files to produce a cross-reference listing showing symbols,

their definition, and their references in the linked source files. See Chapter 9.

• The main product of this development process is a executable object file that can be executed in a

ARM device. You can use one of several debugging tools to refine and correct your code. Available

products include:

– An instruction-accurate and clock-accurate software simulator

– An XDS emulator

In addition, the following utilities are provided:

• The object file display utility prints the contents of object files, executable files, and archive libraries

in either human readable or XML formats. See Section 10.1.

• The disassembler decodes object modules to show the assembly instructions that it represents. See

Section 10.2.

• The name utility prints a list of linknames of objects and functions defined or referenced in a object or

an executable file. See Section 10.3.

• The strip utility removes symbol table and debugging information from object and executable files.

See Section 10.4.

15

SPNU118K–August 2012 Introduction to the Software Development Tools

Submit Documentation Feedback Copyright © 2012, Texas Instruments Incorporated

Chapter 2

SPNU118K–August 2012

Introduction to Object Modules

The assembler creates object modules from assembly code, and the linker creates executable object files

from object modules. These executable object files can be executed by an ARM device.

Object modules make modular programming easier because they encourage you to think in terms of

blocks of code and data when you write an assembly language program. These blocks are known as

sections. Both the assembler and the linker provide directives that allow you to create and manipulate

sections.

This chapter focuses on the concept and use of sections in assembly language programs.

Topic ........................................................................................................................... Page

2.1 Sections ........................................................................................................... 17

2.2 How the Assembler Handles Sections ................................................................. 18

2.3 How the Linker Handles Sections ........................................................................ 23

2.4 Relocation ........................................................................................................ 25

2.5 Run-Time Relocation ......................................................................................... 26

2.6 Loading a Program ............................................................................................ 26

2.7 Symbols in an Object File ................................................................................... 27

2.8 Object File Format Specifications ........................................................................ 27

16 Introduction to Object Modules SPNU118K–August 2012

Submit Documentation Feedback

Copyright © 2012, Texas Instruments Incorporated

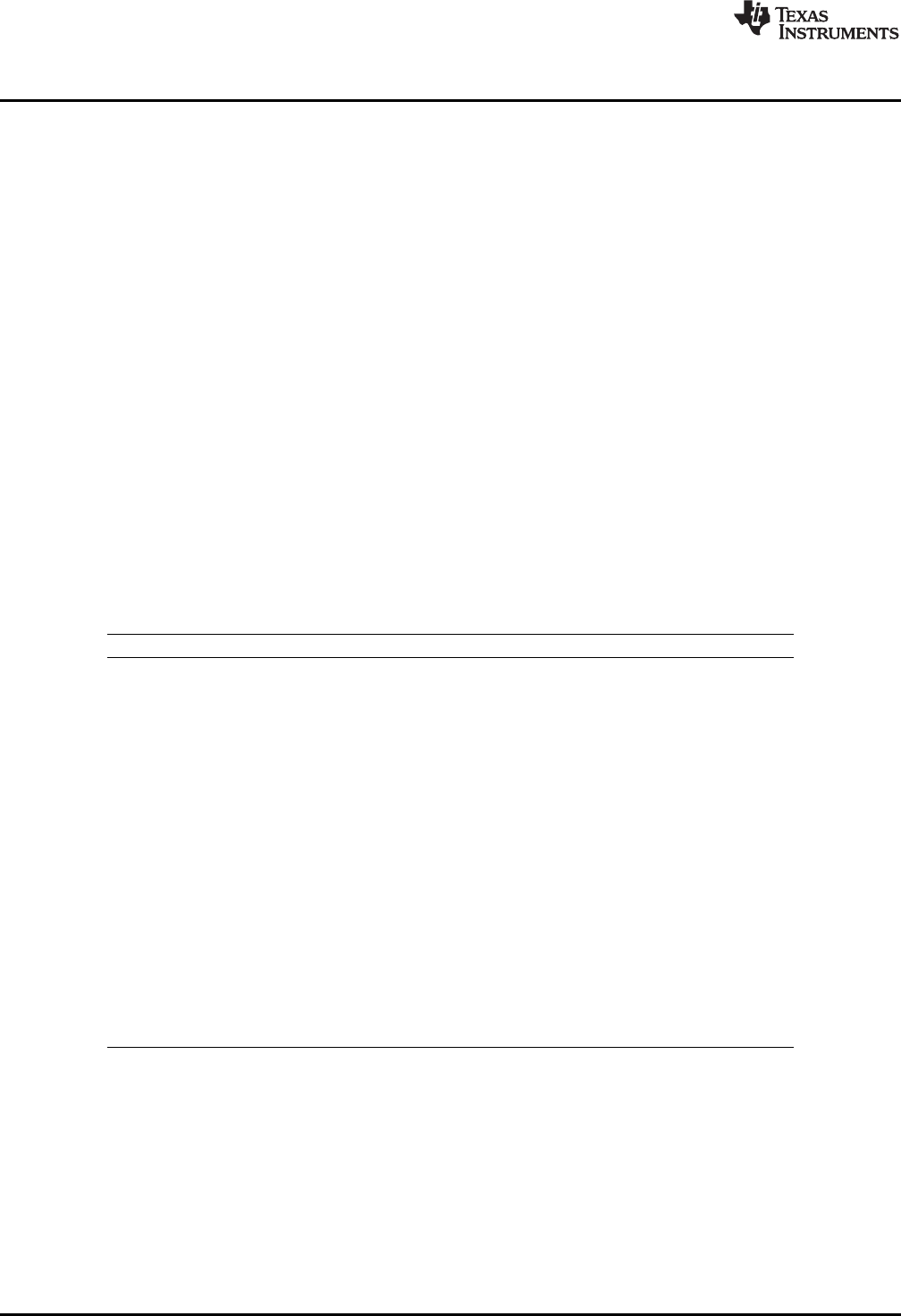

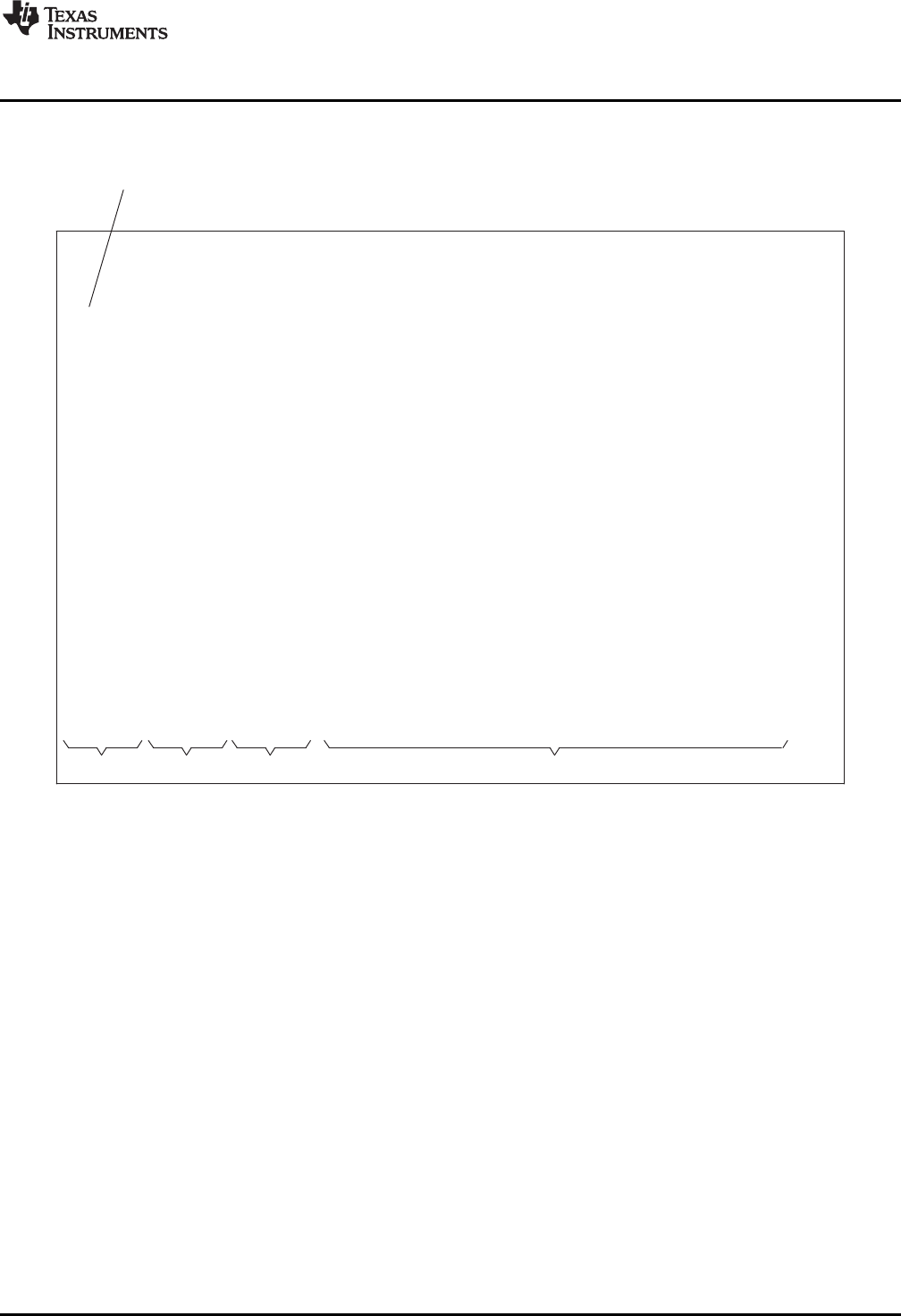

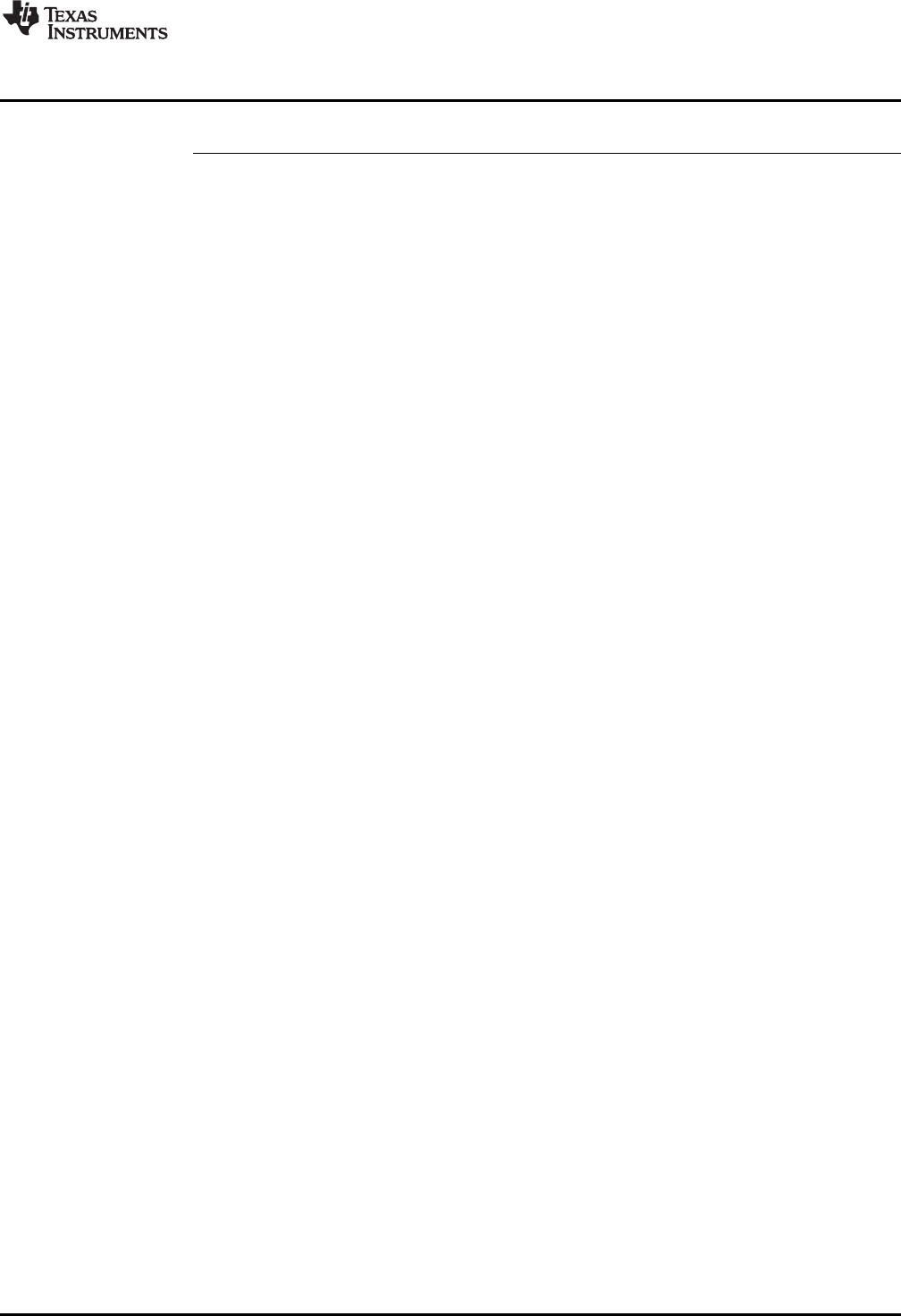

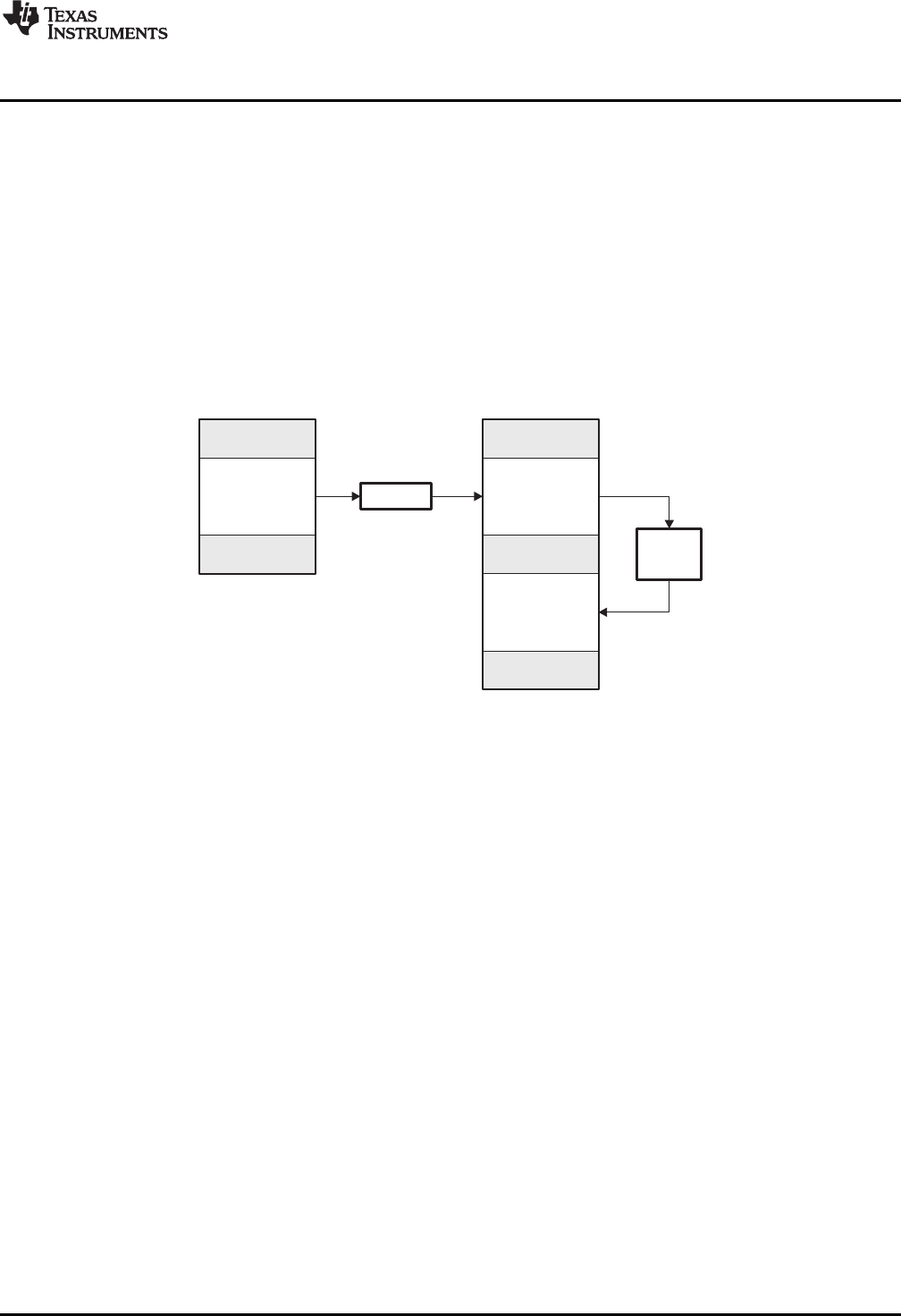

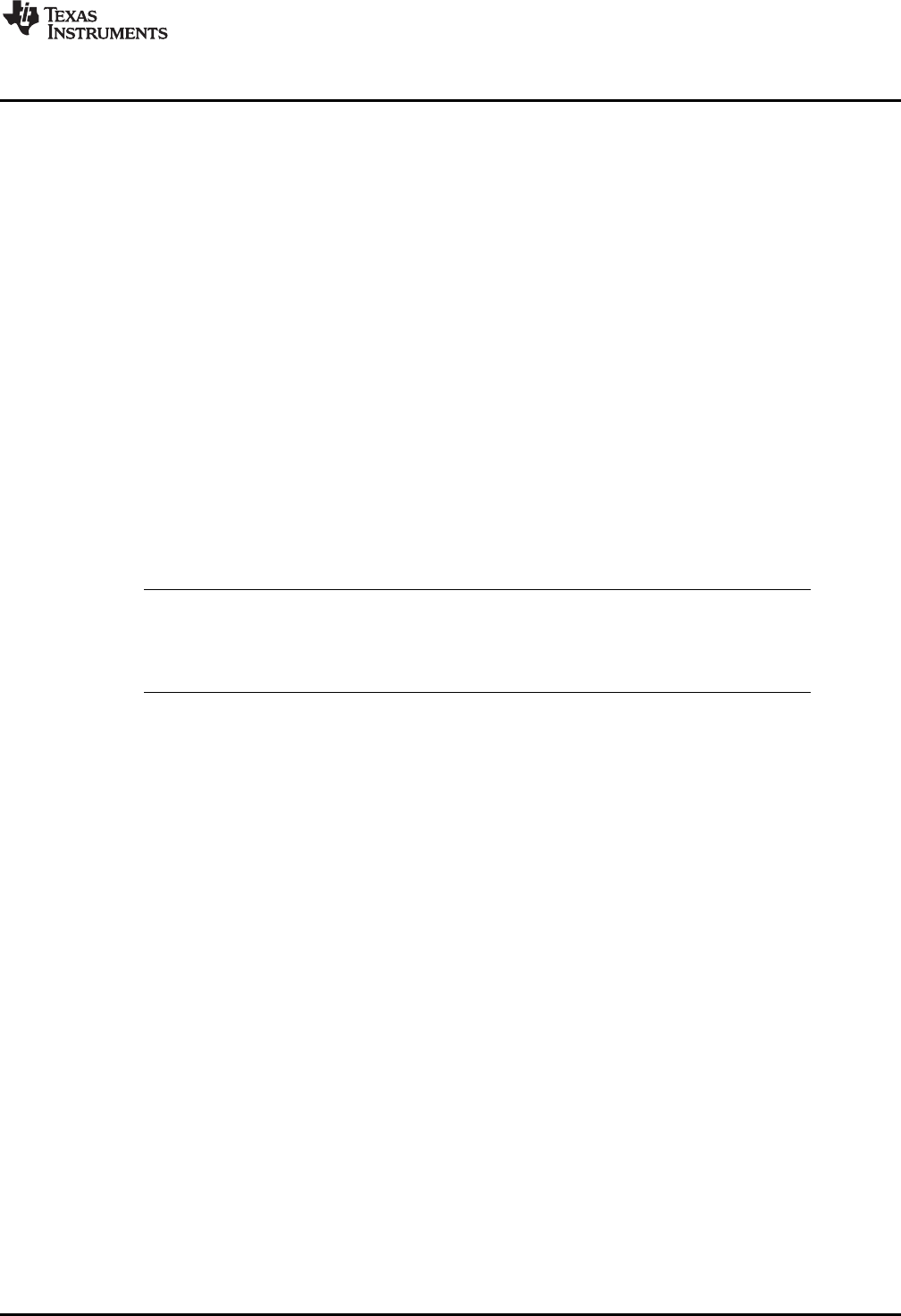

Objectfile

.bss

.data

.text

RAM

EEPROM

ROM

Targetmemory

www.ti.com

Sections

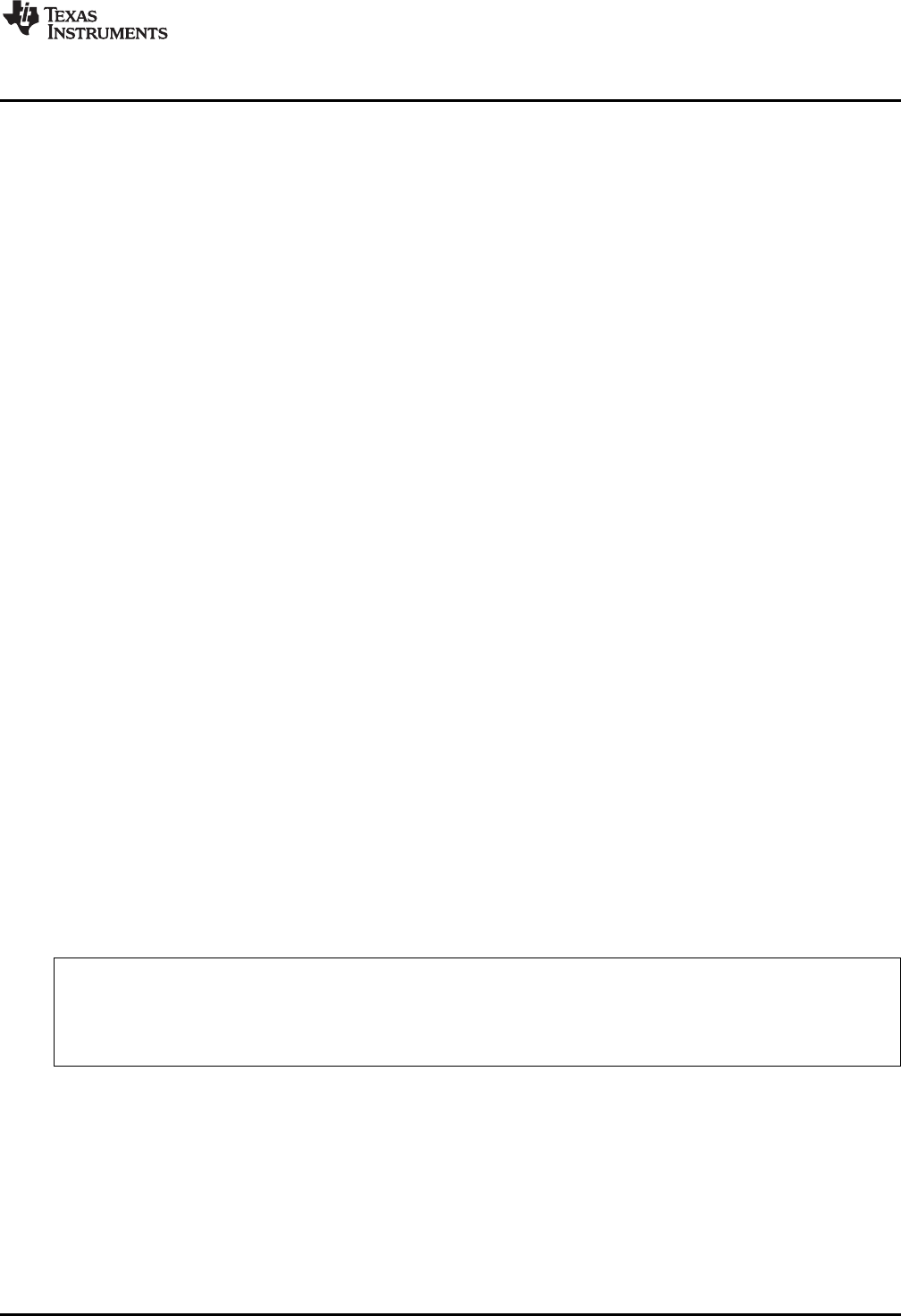

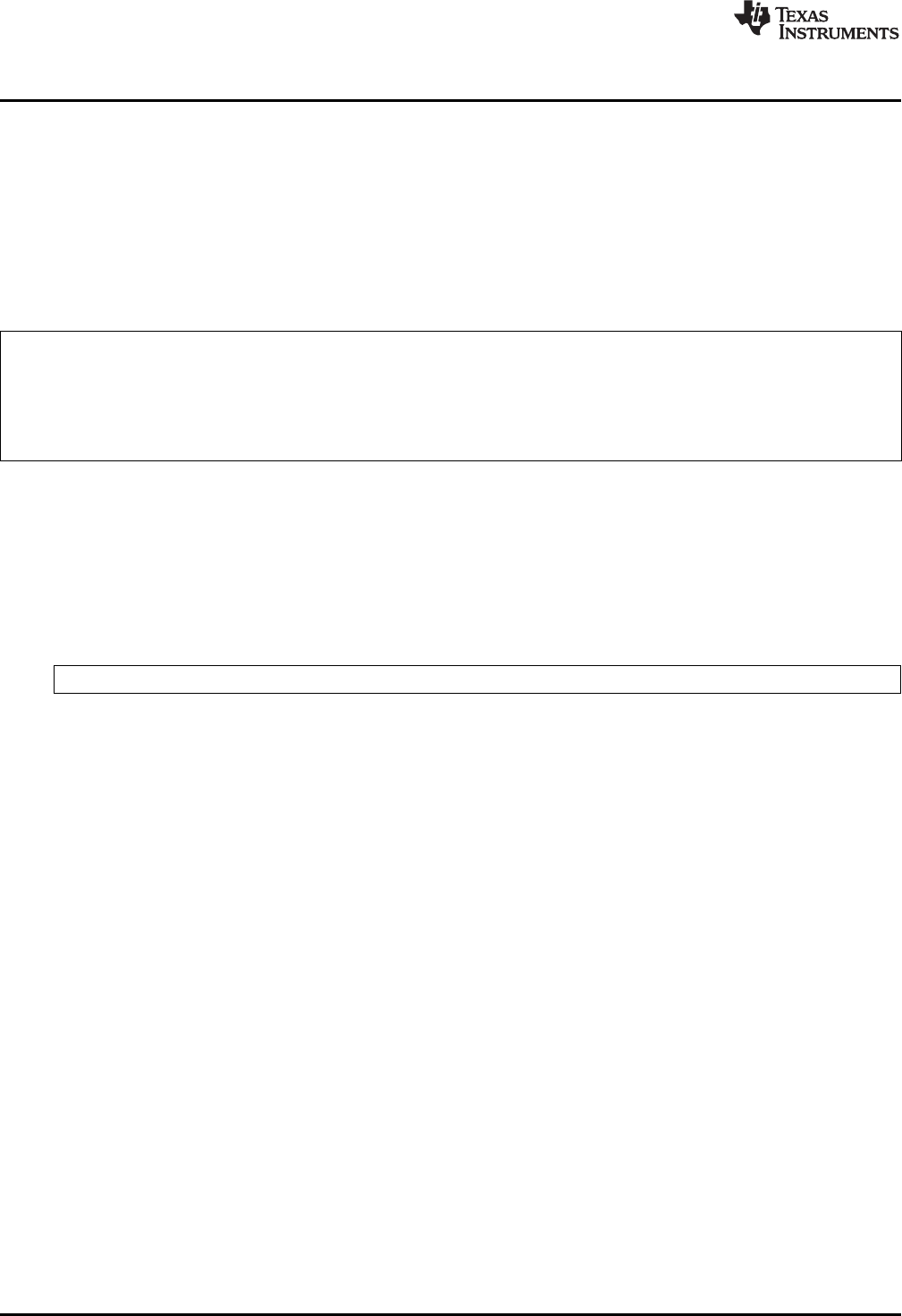

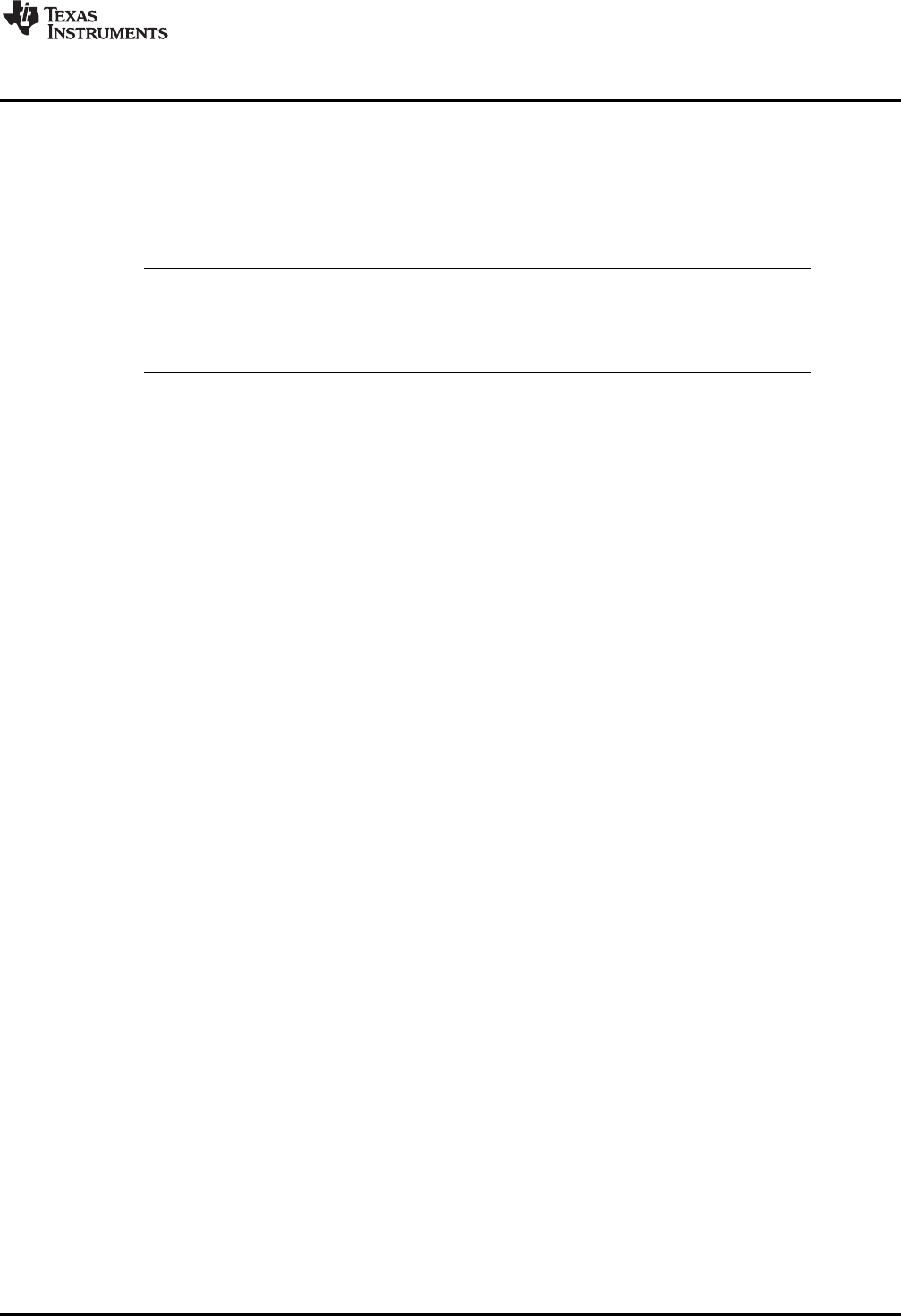

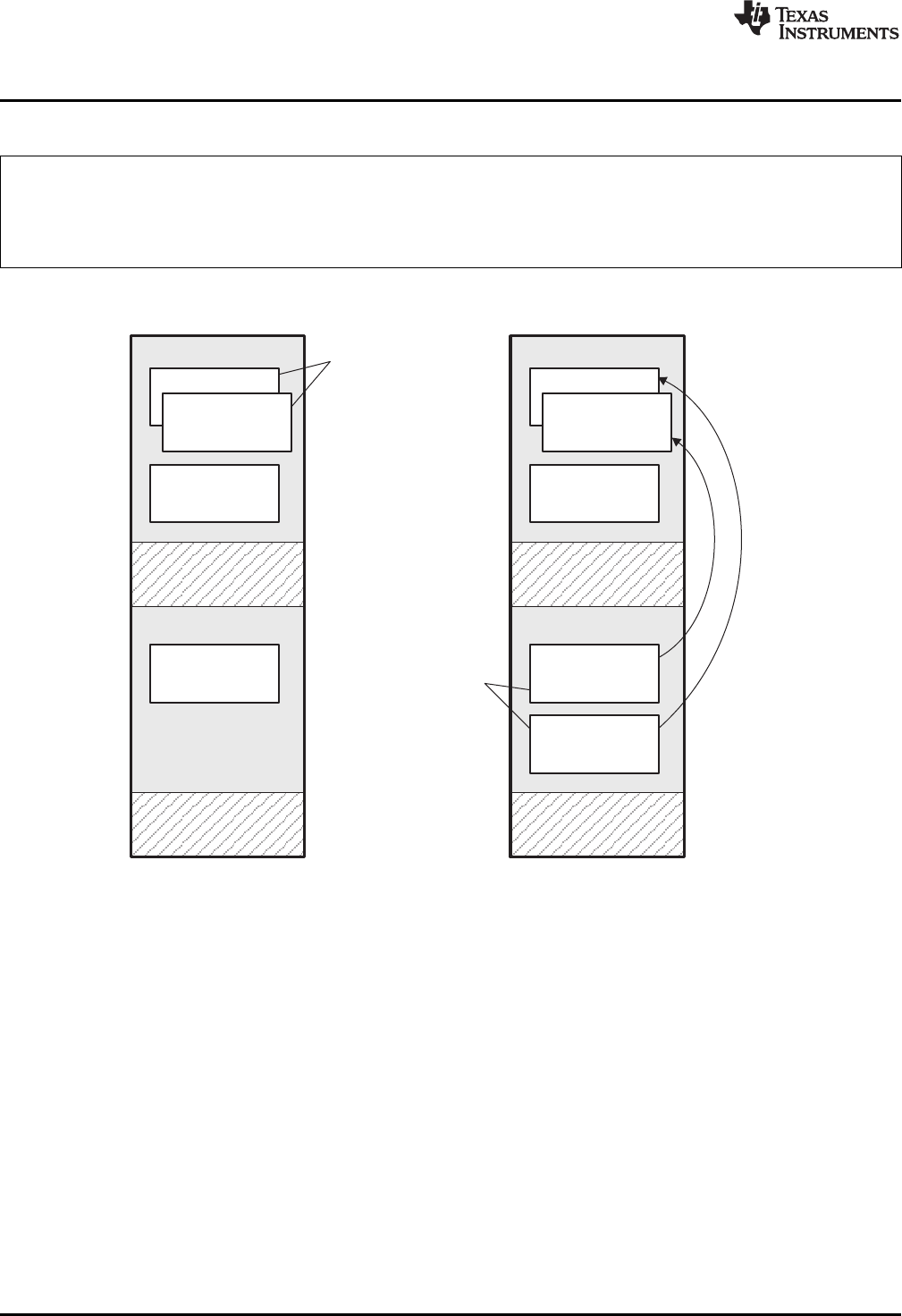

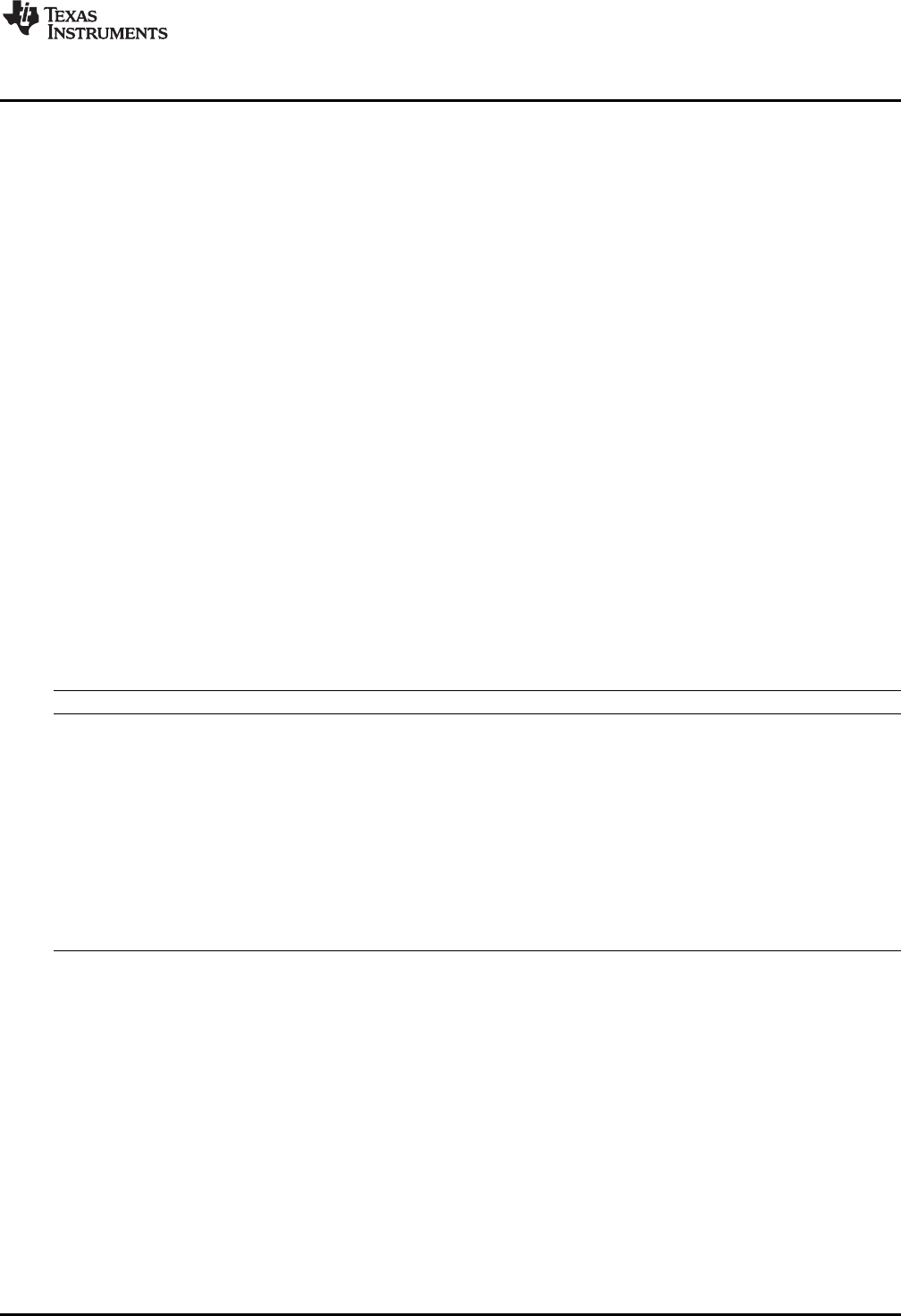

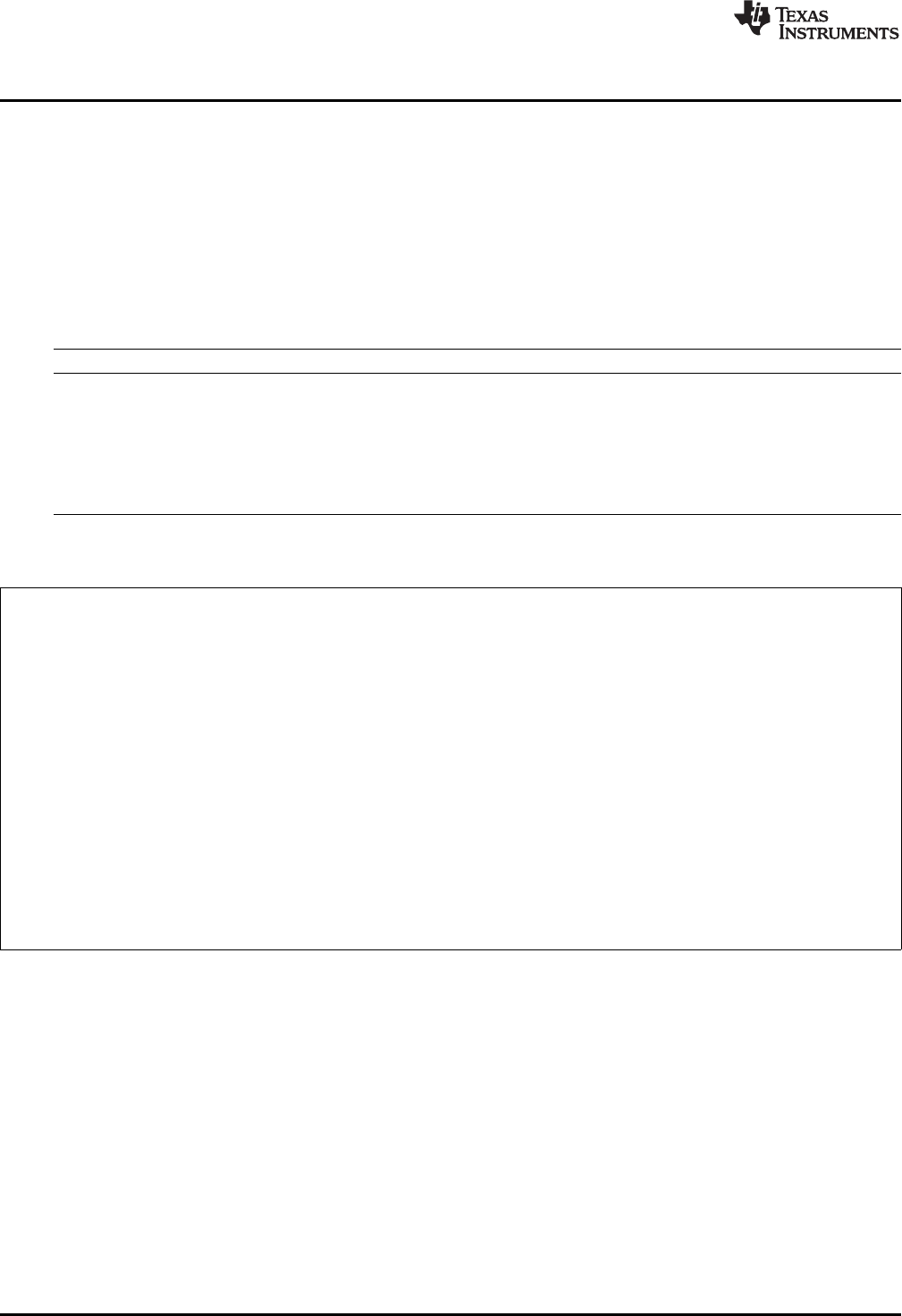

2.1 Sections

The smallest unit of an object file is a section. A section is a block of code or data that occupies

contiguous space in the memory map with other sections. Each section of an object file is separate and

distinct. Object files usually contain three default sections:

.text section contains executable code (1)

.data section usually contains initialized data

.bss section usually reserves space for uninitialized variables

(1) Some targets allow non-text in .text sections.

In addition, the assembler and linker allow you to create, name, and link named sections that are used like

the .data, .text, and .bss sections.

There are two basic types of sections:

Initialized sections contain data or code. The .text and .data sections are initialized; named

sections created with the .sect assembler directive are also initialized.

Uninitialized sections reserve space in the memory map for uninitialized data. The .bss section is

uninitialized; named sections created with the .usect assembler directive are

also uninitialized.

Several assembler directives allow you to associate various portions of code and data with the appropriate

sections. The assembler builds these sections during the assembly process, creating an object file

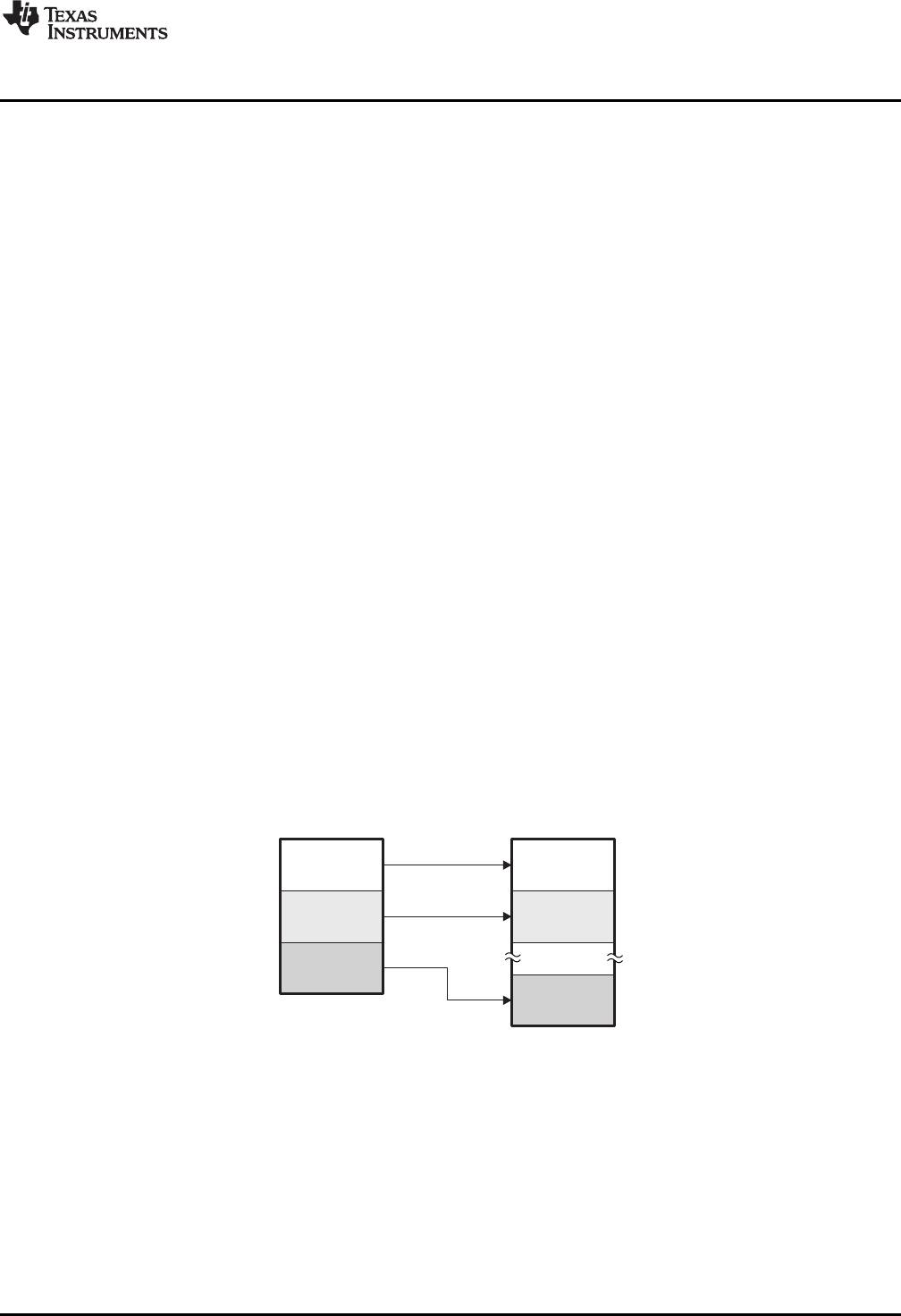

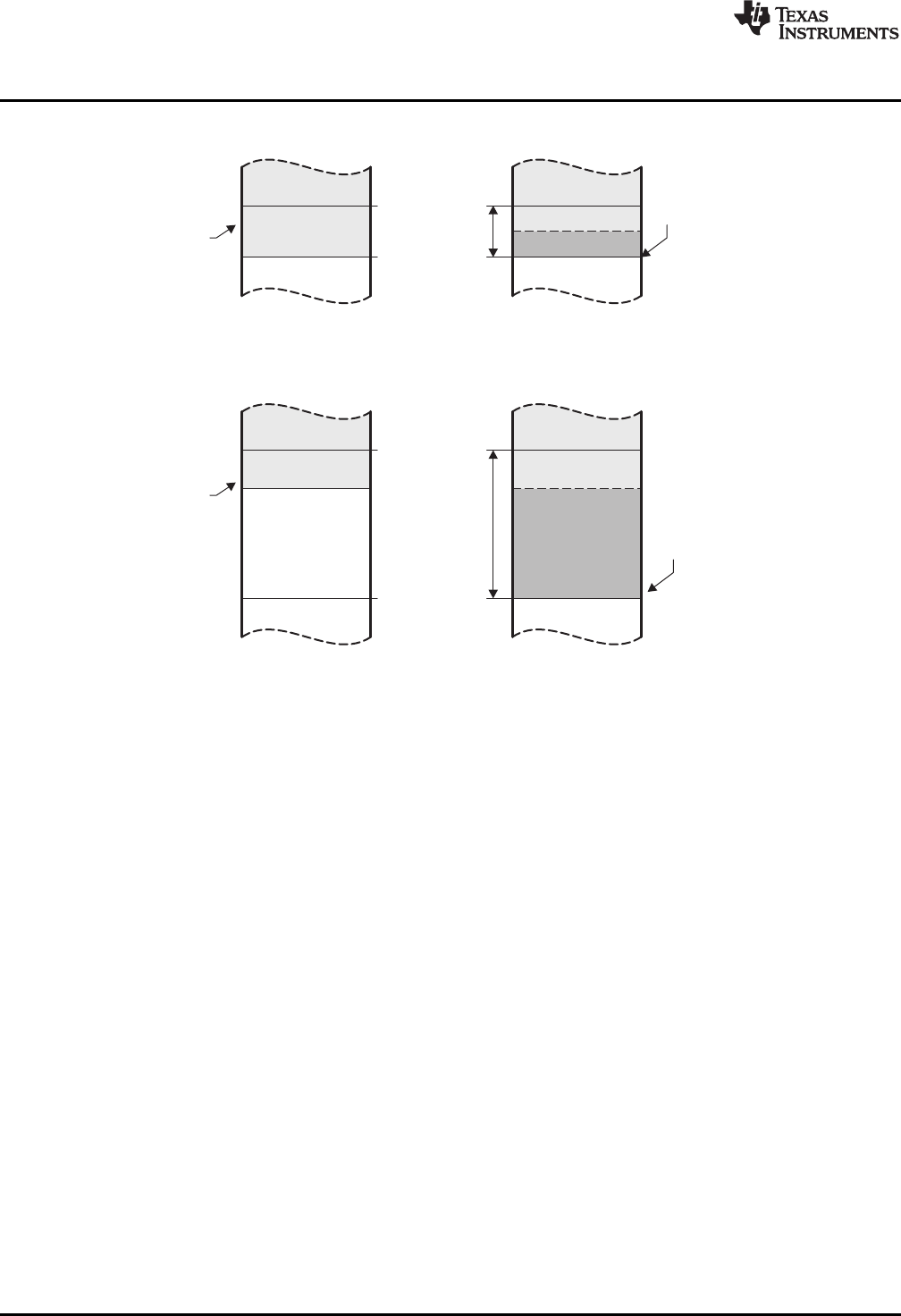

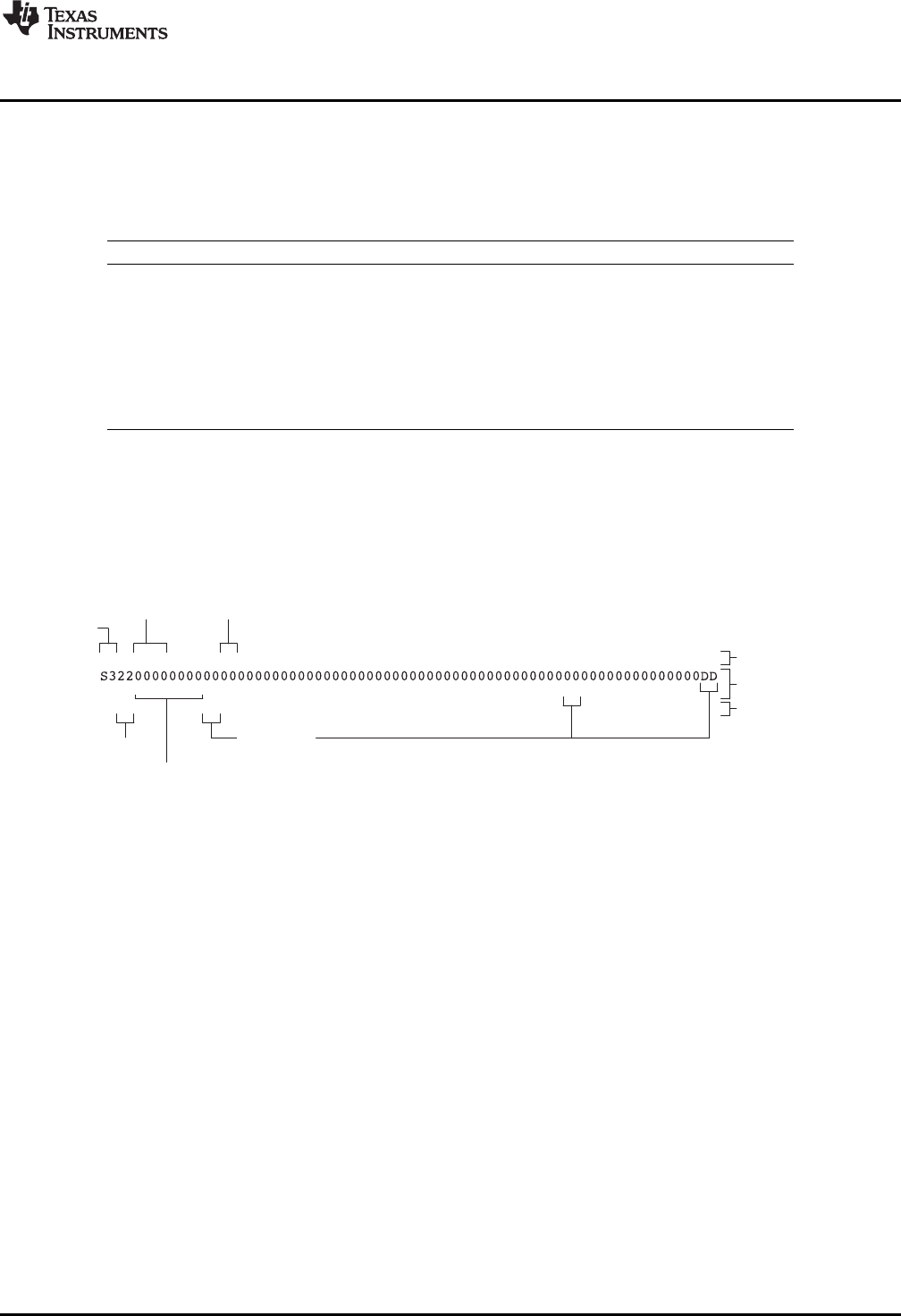

organized as shown in Figure 2-1.

One of the linker's functions is to relocate sections into the target system's memory map; this function is

called allocation. Because most systems contain several types of memory, using sections can help you

use target memory more efficiently. All sections are independently relocatable; you can place any section

into any allocated block of target memory. For example, you can define a section that contains an

initialization routine and then allocate the routine into a portion of the memory map that contains ROM.

Figure 2-1 shows the relationship between sections in an object file and a hypothetical target memory.

Figure 2-1. Partitioning Memory Into Logical Blocks

17

SPNU118K–August 2012 Introduction to Object Modules

Submit Documentation Feedback Copyright © 2012, Texas Instruments Incorporated

How the Assembler Handles Sections

www.ti.com

2.2 How the Assembler Handles Sections

The assembler identifies the portions of an assembly language program that belong in a given section.

The assembler has five directives that support this function:

• .bss

• .usect

• .text

• .data

• .sect

The .bss and .usect directives create uninitialized sections; the .text, .data, and .sect directives create

initialized sections.

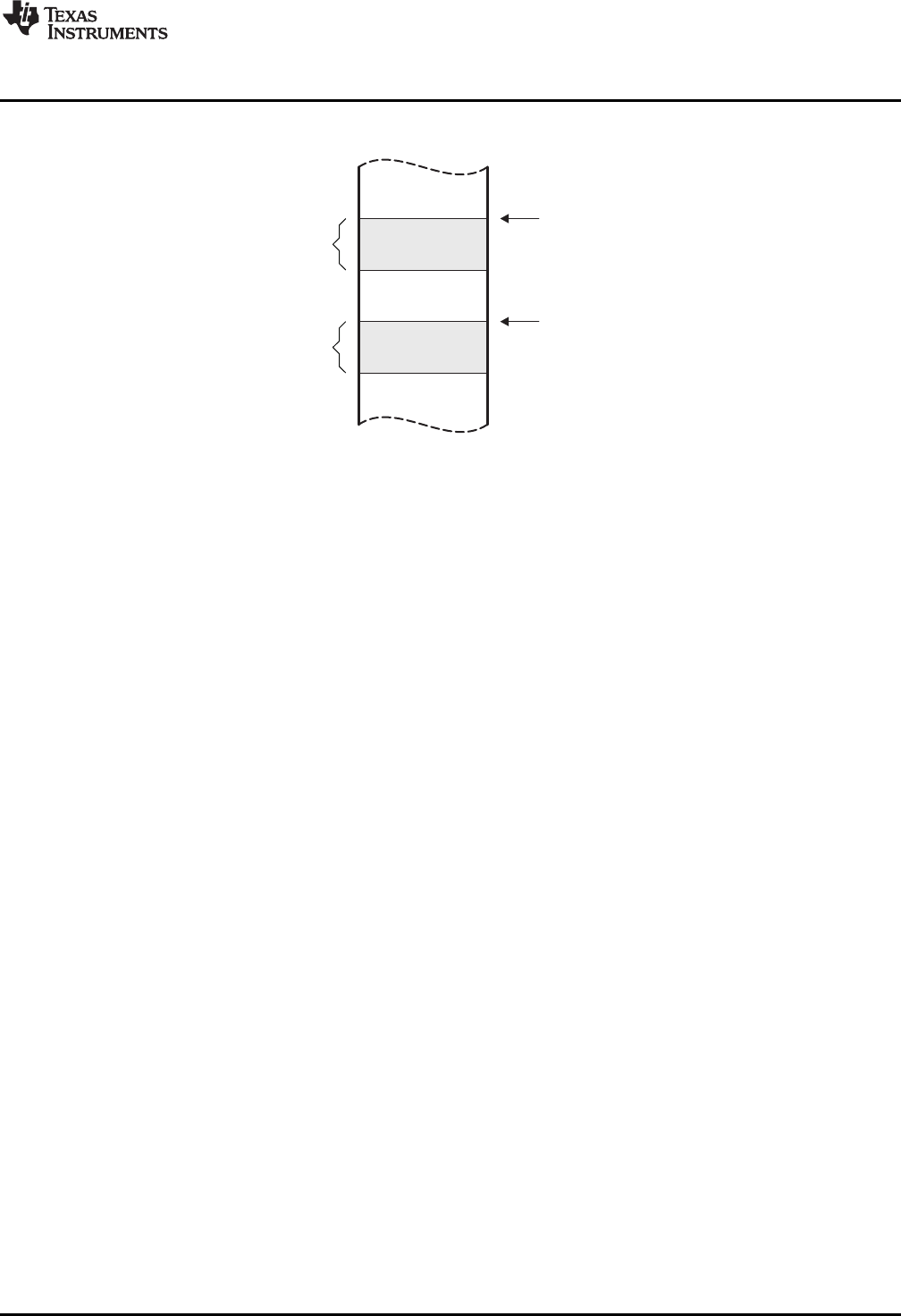

You can create subsections of any section to give you tighter control of the memory map. Subsections are

created using the .sect and .usect directives. Subsections are identified with the base section name and a

subsection name separated by a colon; see Section 2.2.4.

Default Sections Directive

NOTE: If you do not use any of the sections directives, the assembler assembles everything into the

.text section.

2.2.1 Uninitialized Sections

Uninitialized sections reserve space in ARM memory; they are usually allocated into RAM. These sections

have no actual contents in the object file; they simply reserve memory. A program can use this space at

run time for creating and storing variables.

Uninitialized data areas are built by using the .bss and .usect assembler directives.

• The .bss directive reserves space in the .bss section.

• The .usect directive reserves space in a specific uninitialized named section.

Each time you invoke the .bss or .usect directive, the assembler reserves additional space in the .bss or

the named section. The syntaxes for these directives are:

.bss symbol,size in bytes[,alignment [,bank offset] ]

symbol .usect "section name", size in bytes[,alignment[,bank offset] ]

symbol points to the first byte reserved by this invocation of the .bss or .usect directive. The

symbol corresponds to the name of the variable that you are reserving space for. It can

be referenced by any other section and can also be declared as a global symbol (with

the .global directive).