TM11_Manual TM11 Manual

TM11_Manual manual pdf -FilePursuit

TM11_Manual TM11_Manual

User Manual: TM11_Manual

Open the PDF directly: View PDF ![]() .

.

Page Count: 90

- 001

- 002

- 003

- 004

- 005

- 006

- 007

- 1-1

- 1-2

- 1-3

- 1-4

- 1-5

- 1-6

- 1-7

- 1-8

- 1-9

- 2-1

- 2-2

- 3-01

- 3-02

- 3-03

- 3-04

- 3-05

- 3-06

- 3-07

- 3-08

- 3-09

- 3-10

- 3-11

- 3-12

- 4-01

- 4-02

- 4-03

- 4-04

- 4-05

- 4-06

- 4-07

- 4-08

- 4-09

- 4-10

- 4-11

- 4-12

- 4-13

- 4-14

- 4-15

- 4-16

- 4-17

- 4-18

- 5-01

- 5-02

- 5-03

- 5-04

- 5-05

- 5-06

- 5-07

- 5-08

- 5-09

- 5-10

- 5-11

- 5-12

- 5-13

- 5-14

- 5-15

- 5-16

- 5-17

- 5-18

- 5-19

- 5-20

- 5-21

- 5-22

- 5-23

- 5-24

- 5-25

- 5-26

- 5-27

- 5-28

- 5-29

- 5-30

- 5-31

- 5-32

- 5-33

- 5-34

- 5-35

- 5-36

- 5-37

- 6-1

- 6-2

- a-1

- a-2

- x

DEC-I1-HTMAA-D-D

TM11

DECmagtape

system

.,

digital

equipment corporation · maynard, massachusetts

1 st Edition, August 1971

2nd Printing, March 1972

3rd Printing, May 1972

4th

Printing, October 1972

5th Printing, February 1973

6th

Printing (Rev), June 1973

7th Printing, July 1974

8th

Printing (Rev), August 1974

Copyright © 1971,

1972,1973,1974

by Digital Equipment Corporation

The material in this manual is for infonna-

tiona! purposes and

is

subject to change

without notice.

Print~d

in U.S.A.

The following are trademarks

of

Digital Equipment

Corporation, Maynard, Massachusetts:

DEC

FLIP CHIP

DIGITAL

UNIBUS

PDP

FOCAL

COMPUTER

LAB

CONTENTS Page

CHAPTER 1 INTRODUCTION

1.1

Introduction

1-1

1.2 Scope I-I

1.3 General Description

1-4

1.3.1

TUI0

DECmagtape Transport

1-4

1.3.2

TM

11

Controller

1-5

1.3.3 Magnetic Tape

1-6

1.4 Specifications

1-6

1.5

Engineering Drawings

1-6

1.6 Maintenance

1-9

CHAPTER 2 INSTALLATION

2.1

Scope

2-1

2.2 Configura tion

2-1

2.3 Unpacking

2-1

2.4 Inspection

2-1

2.5 Space Requirements 2-2

2.6 Power and Cable Requirements

2-2

2.7 Installation

2-2

2.8 Final Checkout 2-2

CHAPTER 3 OPERATION

3.1

Introduction

3-1

3.2 Controls and Indicators

3-1

3.2.1 TUIO DEC magtape Control Panel

3-1

3.2.2

TM

11

Controller Maintenance Panel 3-6

3.3 Operating Procedure

3-7

3.3.1 Mounting Tape

3-8

3.3.2 Off-Line Operation

3-9

3.3.3 On-Line Operation 3-10

3.3.4 Restart After Power Failure 3-10

3.3.5 Restart After Fail-Safe

3-11

3.3.6 Removing Tape

3-11

CHAPTER 4 PROGRAMMING INFORMATION

4.1

Scope

4-1

4.2 Device Registers

4-1

4.2.1 Status Register (MTS)

4-2

4.2.2 Command Register (MTC) 4-6

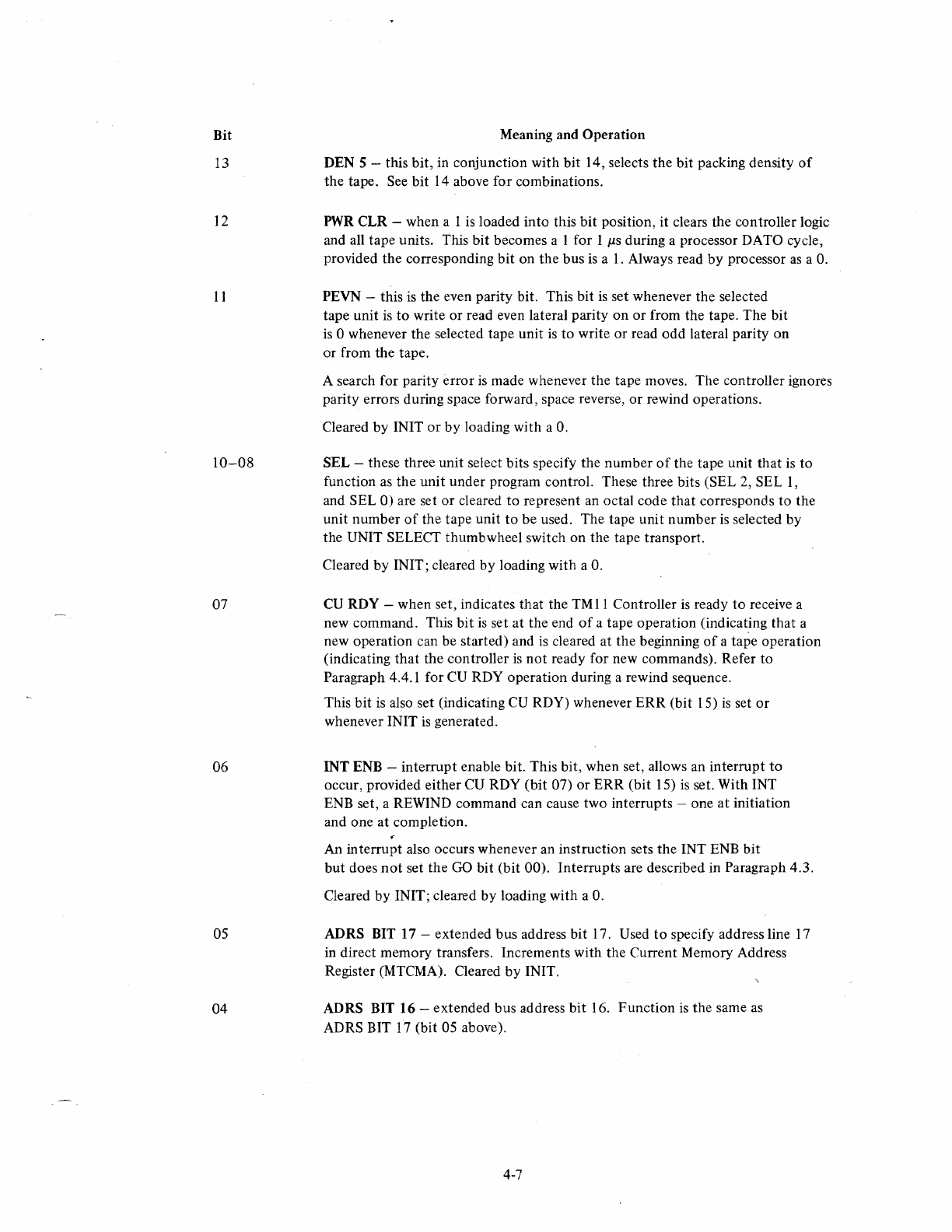

4.2.3 Byte Record Counter (MTBRC)

4-8

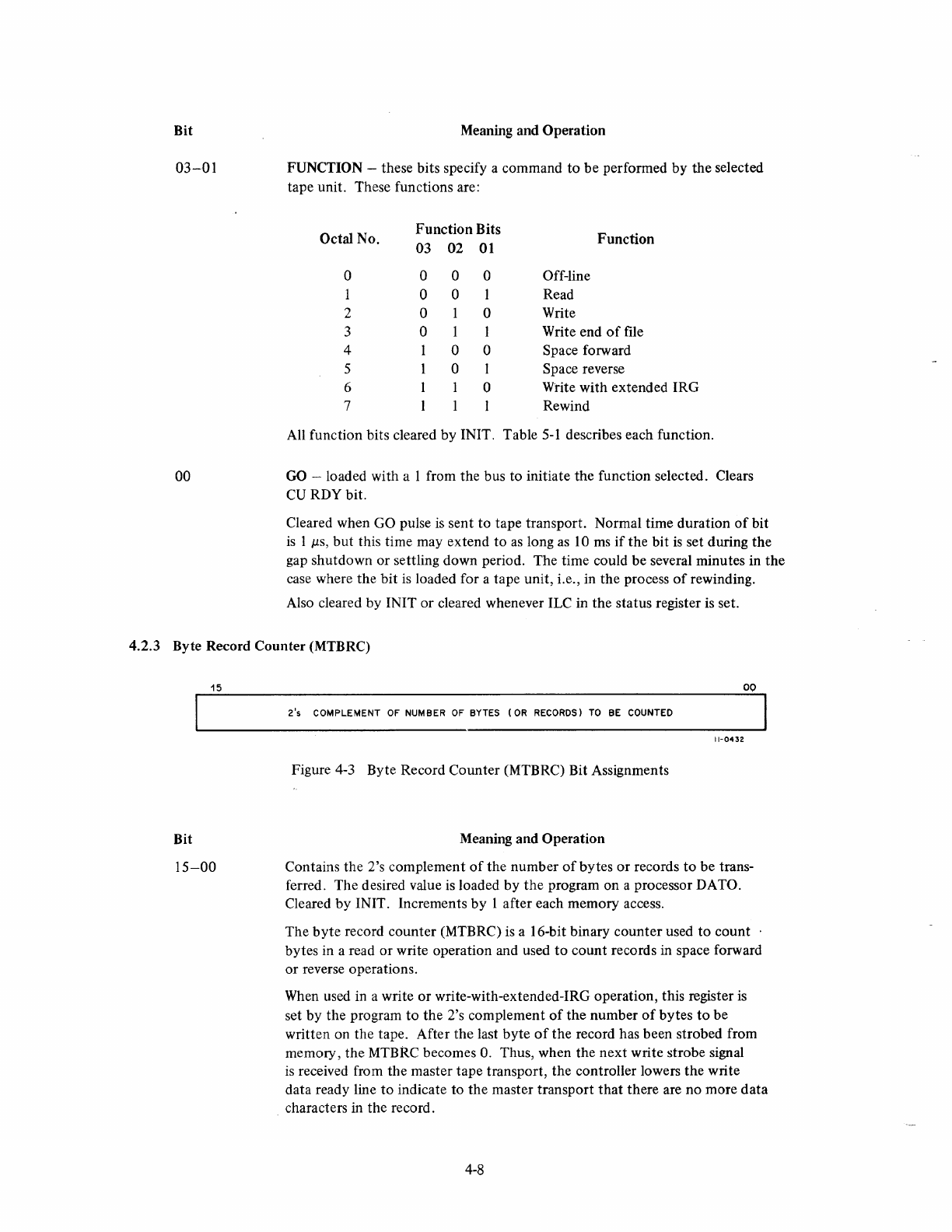

4.2.4 Current Memory Address Register (MTCMA) 4-9

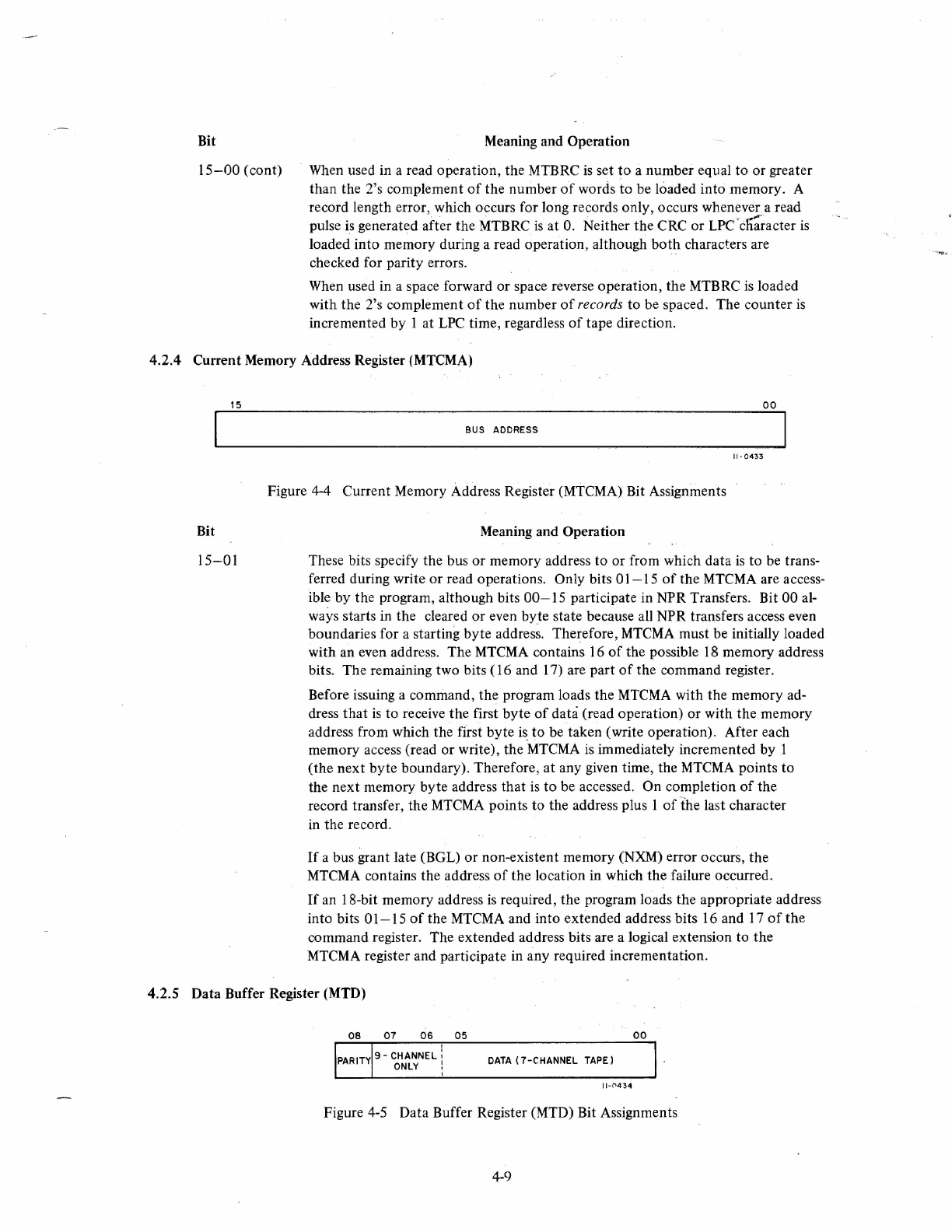

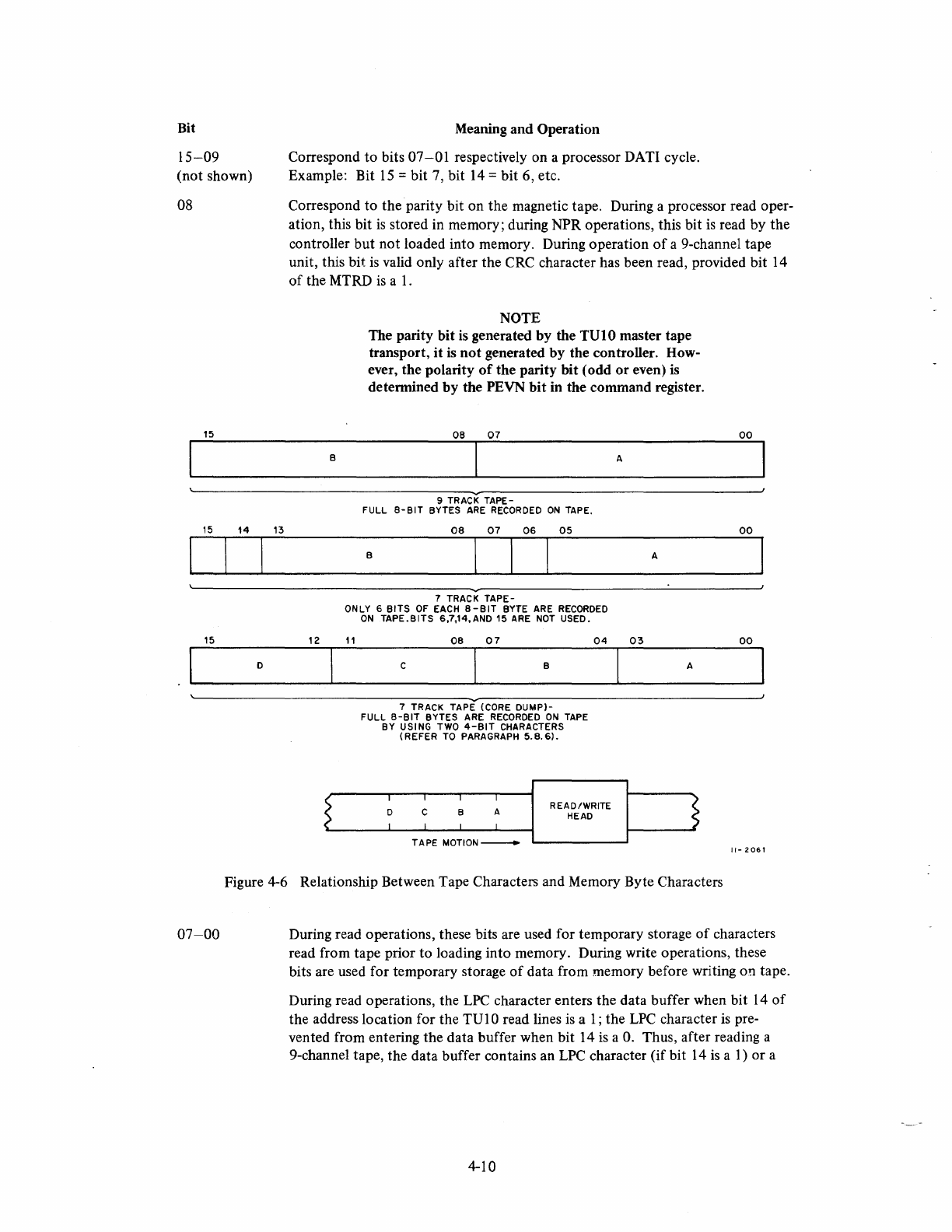

4.2.5 Data Buffer Register (MTD) 4-9

iii

CONTENTS (Cont)

Page

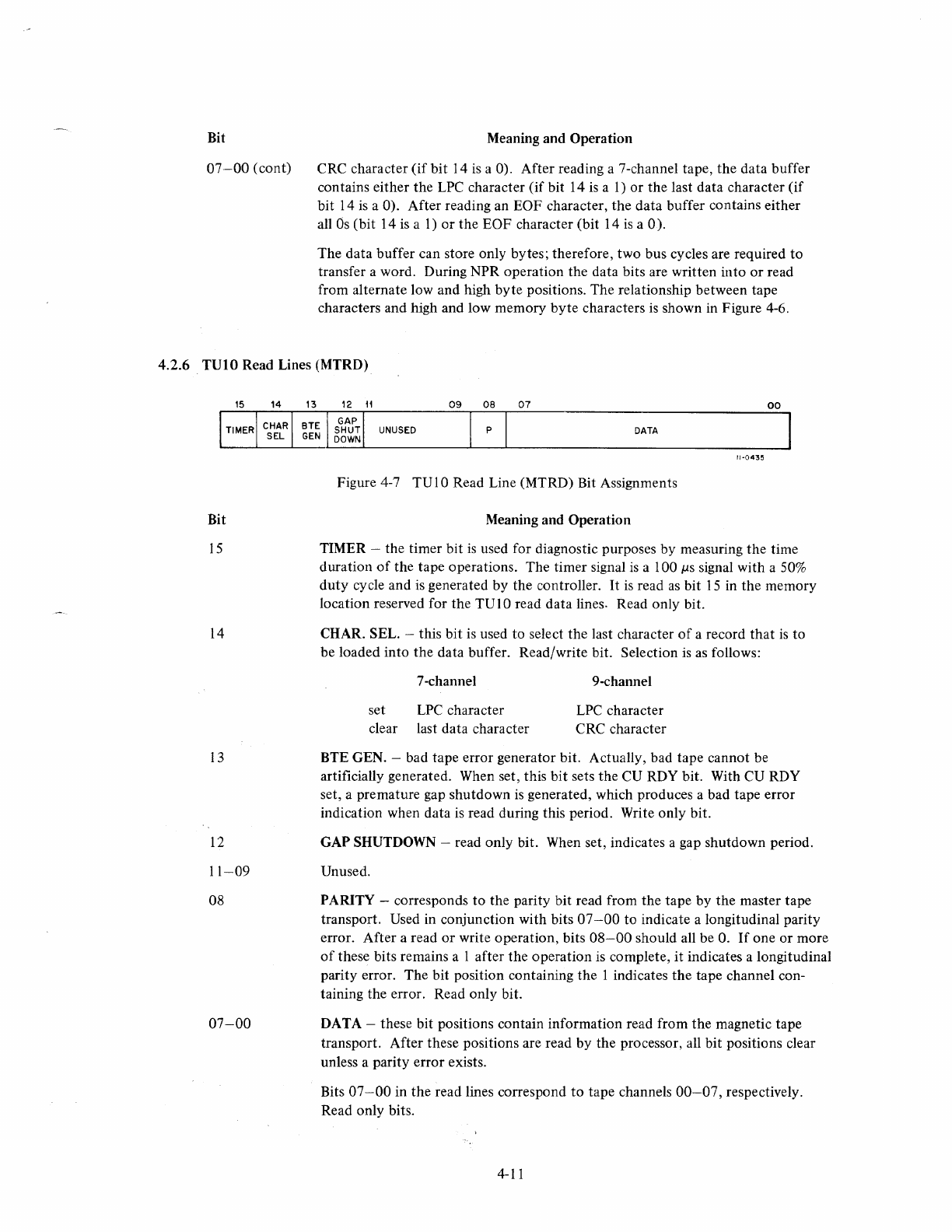

4.2.6 TUIO Read Lines (MTRD) 4-11

4.3 Interrupts 4-12

4.3.1 NPR Requests 4-12

4.3.2 BR Requests 4-12

4.4 Programming Notes 4-12

4.4.1 Rewind Operation 4-13

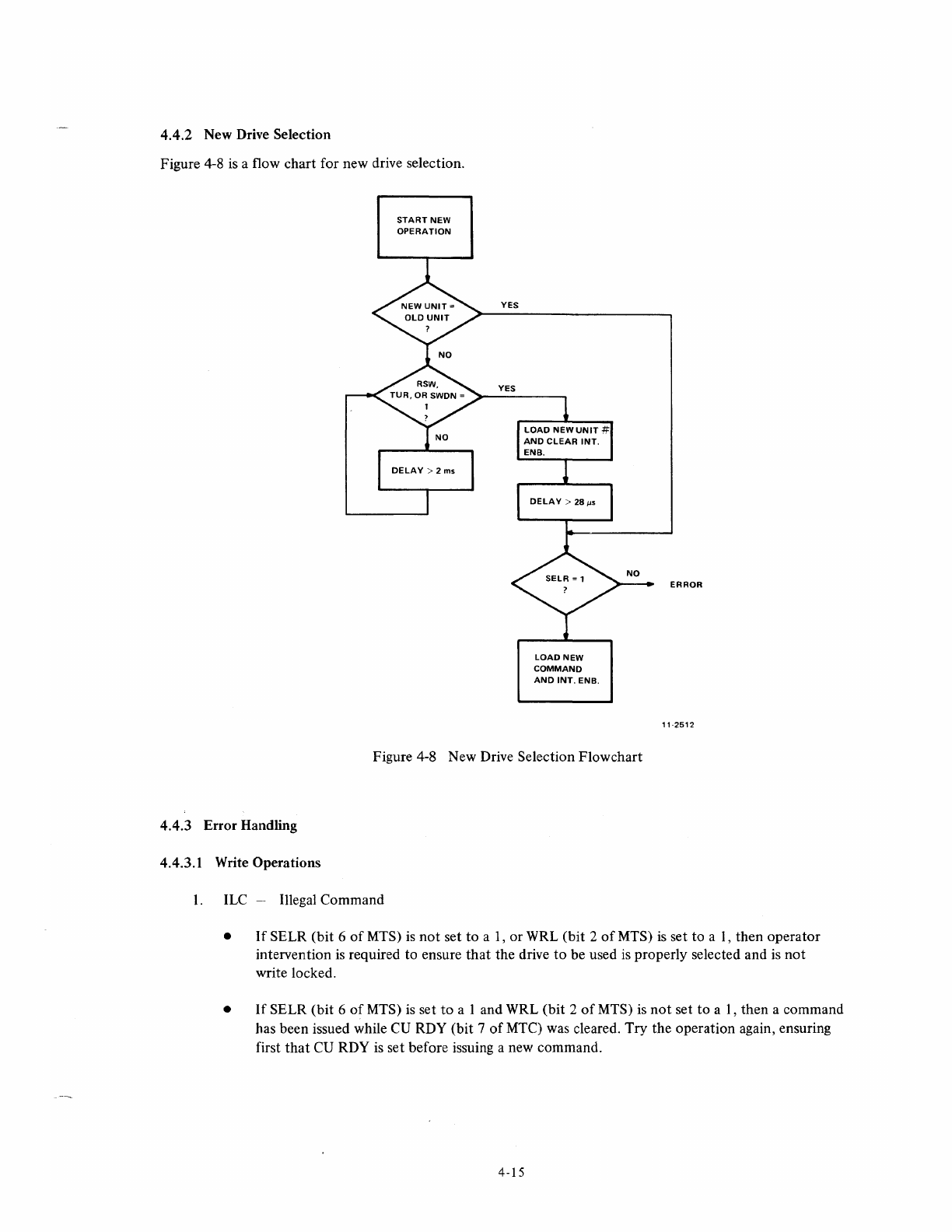

4.4.2 New Drive Selection 4-15

4.4.3 Error Handling 4-15

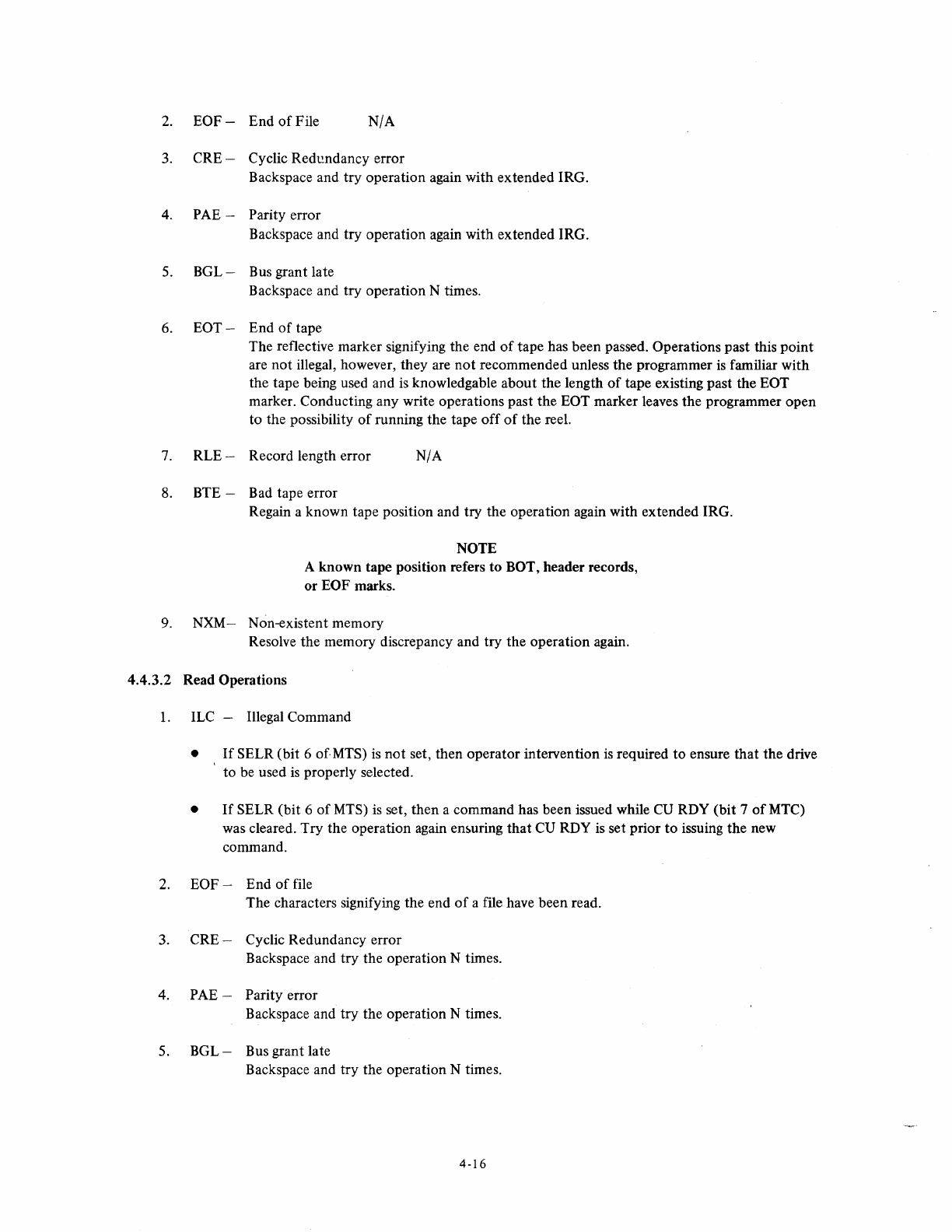

4.4.3.1 Write Operations 4-15

4.4.3.2 Read Operations 4-16

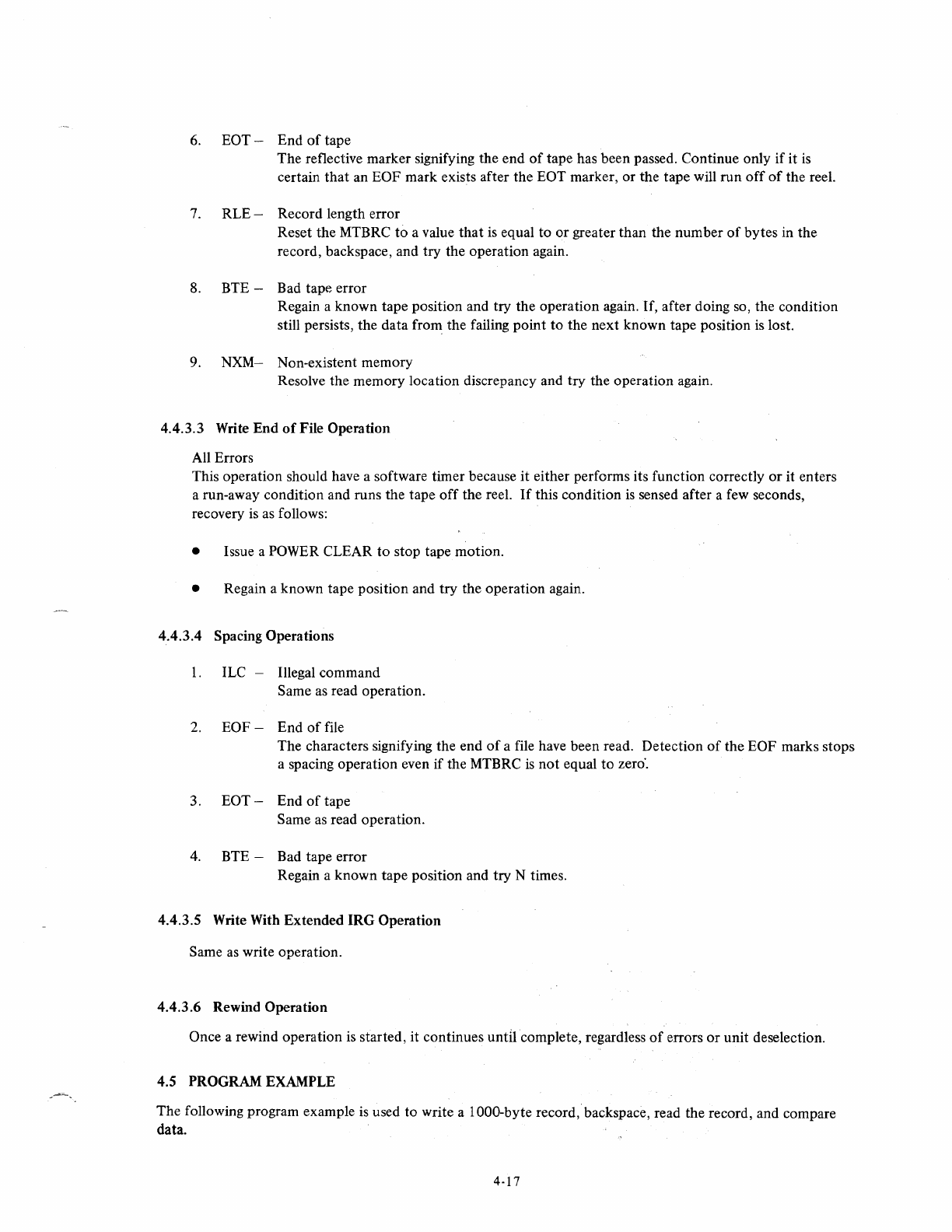

4.4.3.3 Write End

of

File Operation 4-17

4.4.3.4 Spacing Operations 4-17

4.4.3.5 Write With Extended IRG Operation 4-17

4.4.3.6 Rewind Operation 4-17

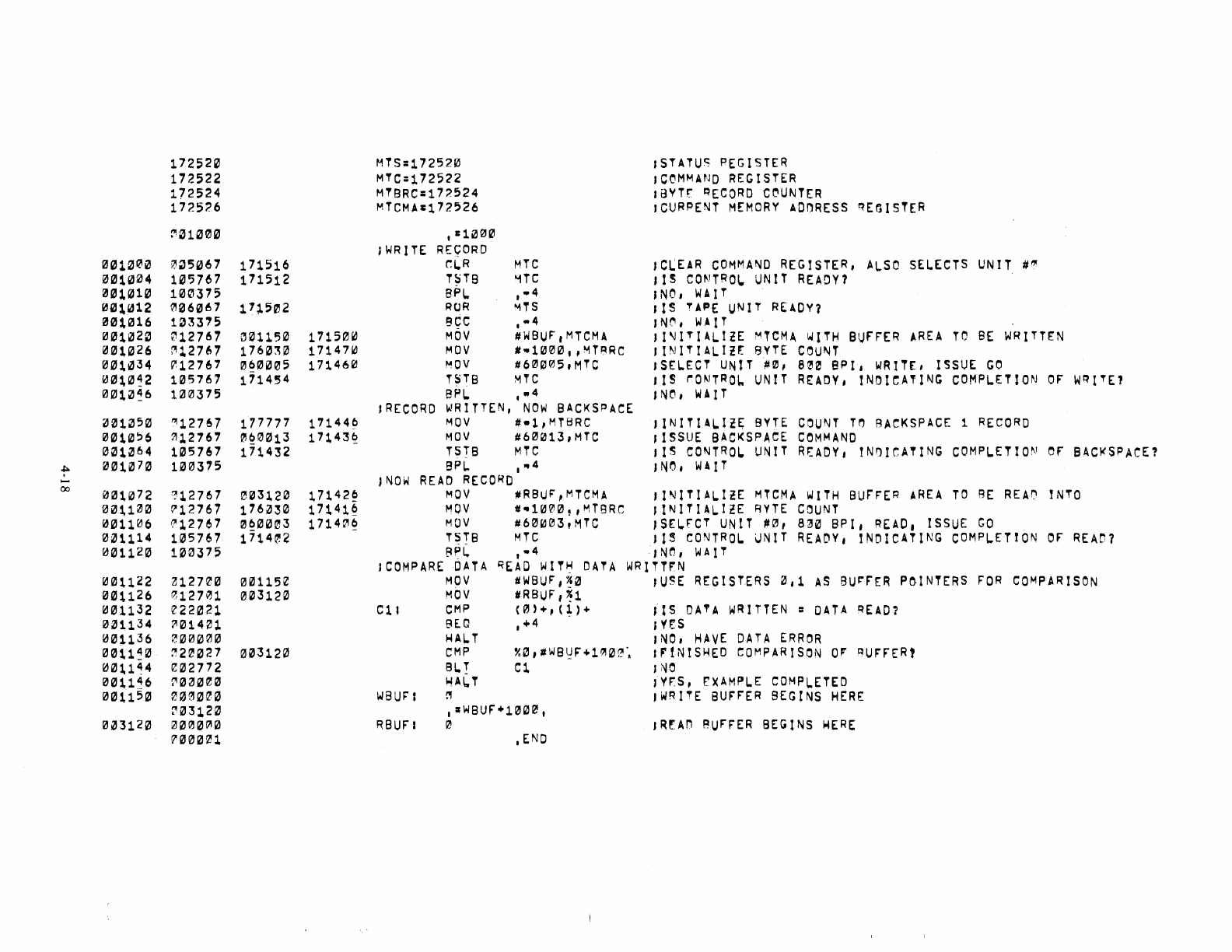

4.5 Program Example 4-17

CHAPTER 5 THEORY

OF

OPERATION

5.1

Introduction

5-1

5.2 Tape

Format

5-2

5.3 Functional Description

5-3

5.3.1 Parity 5-6

5.3.2 Gap Shutdown 5-7

5.3.3 Function Commands

5-7

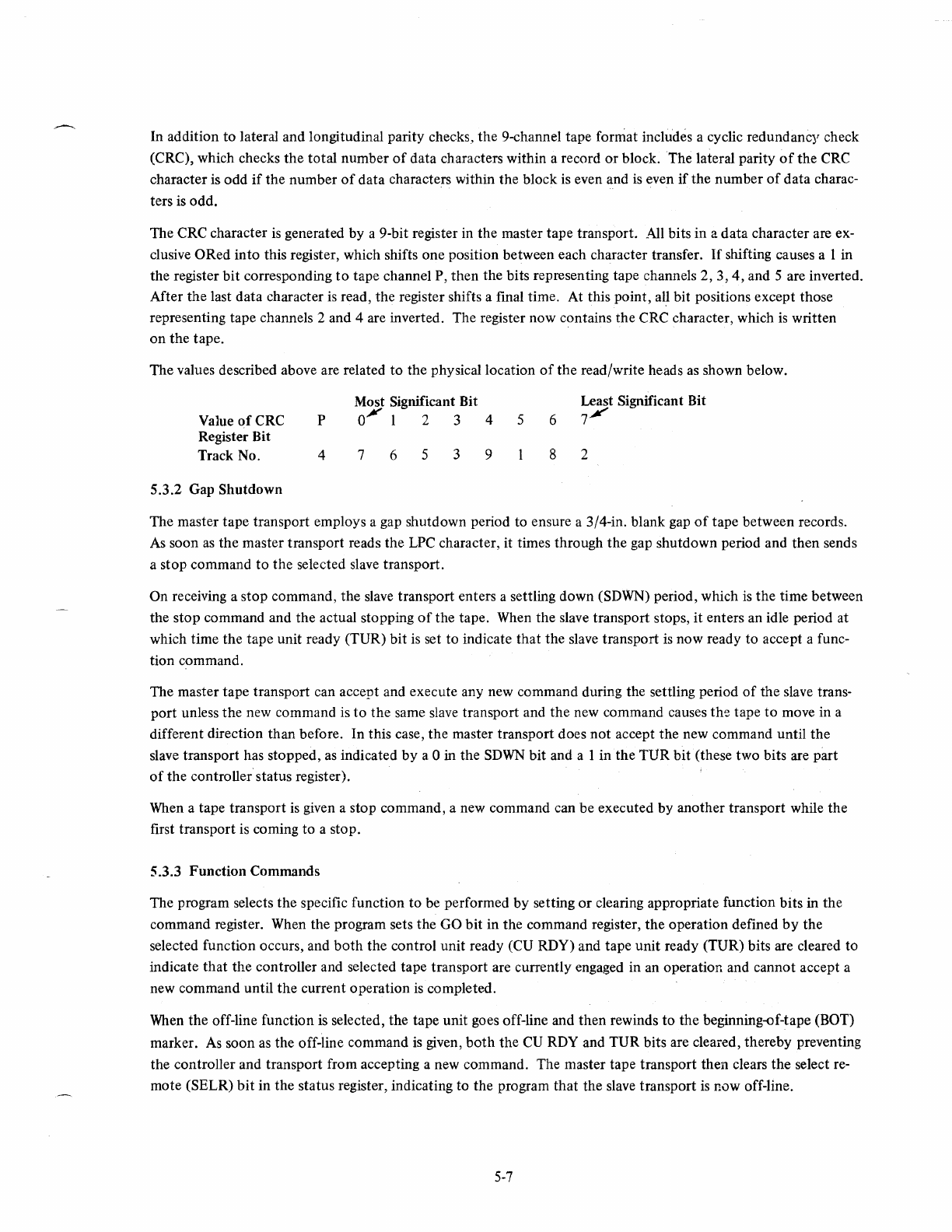

5.4 System Relationship 5-8

5.5 Address Selection 5-8

5.5.1 Address Selector Module 5-9

5.5.2 Register Select Logic 5-10

5.6 Bus Control 5-12

5.6.1 NPR Transfers 5-12

5.6.2

Interrupt

Request 5-14

5.6.3 Slave Response 5-15

5.7 Bus Drivers and Receivers 5-15

5.8 Registers 5-15

5.8.1 Initialize Logic 5-16

5.8.2 Command Register (MTC) 5-17

5.8.2.1 Error Bit (15) 5-17

5.8.2.2 Density Bits

(14

and 13) 5-18

5.8.2.3 Power Clear Bit (12) 5-19

5.8.2.4 Parity Bit

(11)

5-19

5.8.2.5 Unit Select Bits (10, 09, 08) 5-20

5.8.2.6 Control Unit Ready Bit (07) 5-20

5.8.2.7 Interrupt Enable Bit (06) 5-20

5.8.2.8 Extended Bus Address Bits

(OS

and 04) 5-21

5.8.2.9 Function Bits (03, 02, 01)

5-21

iv

CONTENTS (Cont)

5.8.2.10 Go Bit (00)

5-21

5.8.3 Status Register (MTS) 5-22

5.8.3.1 Illegal Command (15) 5-23

5.8.3.2 End-of-File Bit (14) 5-23

5.8.3.3 Cyclic Redundancy Error Bit (13) 5-23

5.8.3.4 Parity Error Bit (12) 5-24

5.8.3.5

Bus

Grant Late Error Bit (11) 5-24

5.8.3.6 End-of-Tape Bit (10) 5-24

5.8.3.7 Record Length Error Bit (09) 5-25

5.8.3.8

Bad

Tape Error Bit (08) 5-25

5.8.3.9 Non-Existent Memory Bit (07) 5-26

5.8.3.10 Select Remote Bit (06) 5-26

5.8.3.11 Beginning-of-Tape Bit (05) 5-26

5.8.3.12 7-Channel Bit (04) 5-26

5.8.3.13 Settle Down Bit (03) 5-26

5.8.3.14 Write Lock Bit (02) 5-26

5.8.3.15 Rewind Status Bit (01)

5:"27

5.8.3.16 Tape Unit Ready Bit (00) 5-27

5.8.4 Byte Record Counter (MTBRC) 5-27

5.8.5 Current Memory Address Register (MTCMA) 5-28

5.8.6 Data Buffer Register (MTD) 5-28

5.8.7 TUIO Read Lines (MTRD) 5-29

5.9 Tape Control 5-30

5.9.1 Unit Select 5-30

5.9.2 Function Control 5-30

5.9.3 Ready and Start Control

5-31

5.9.4 Tape Unit Motion Control

5-31

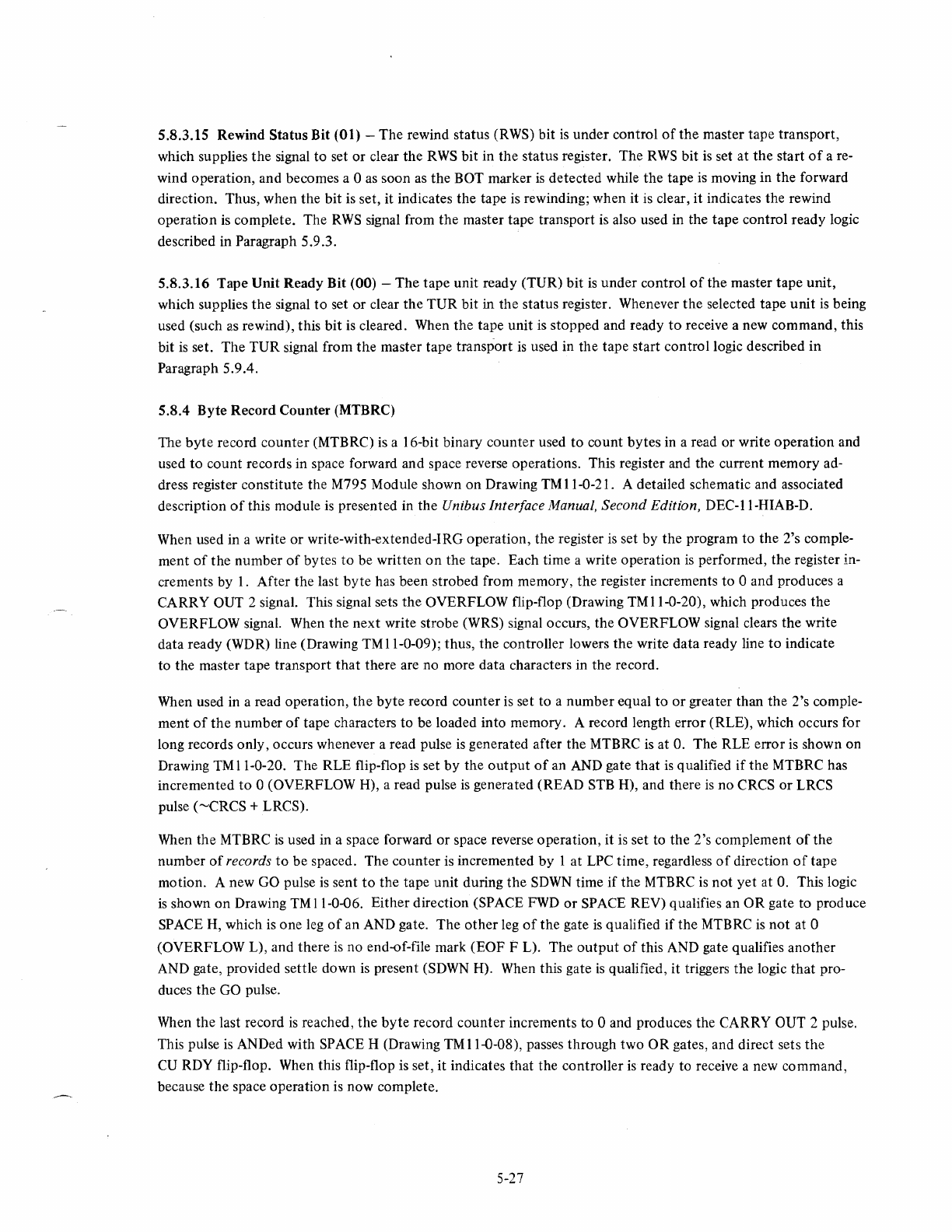

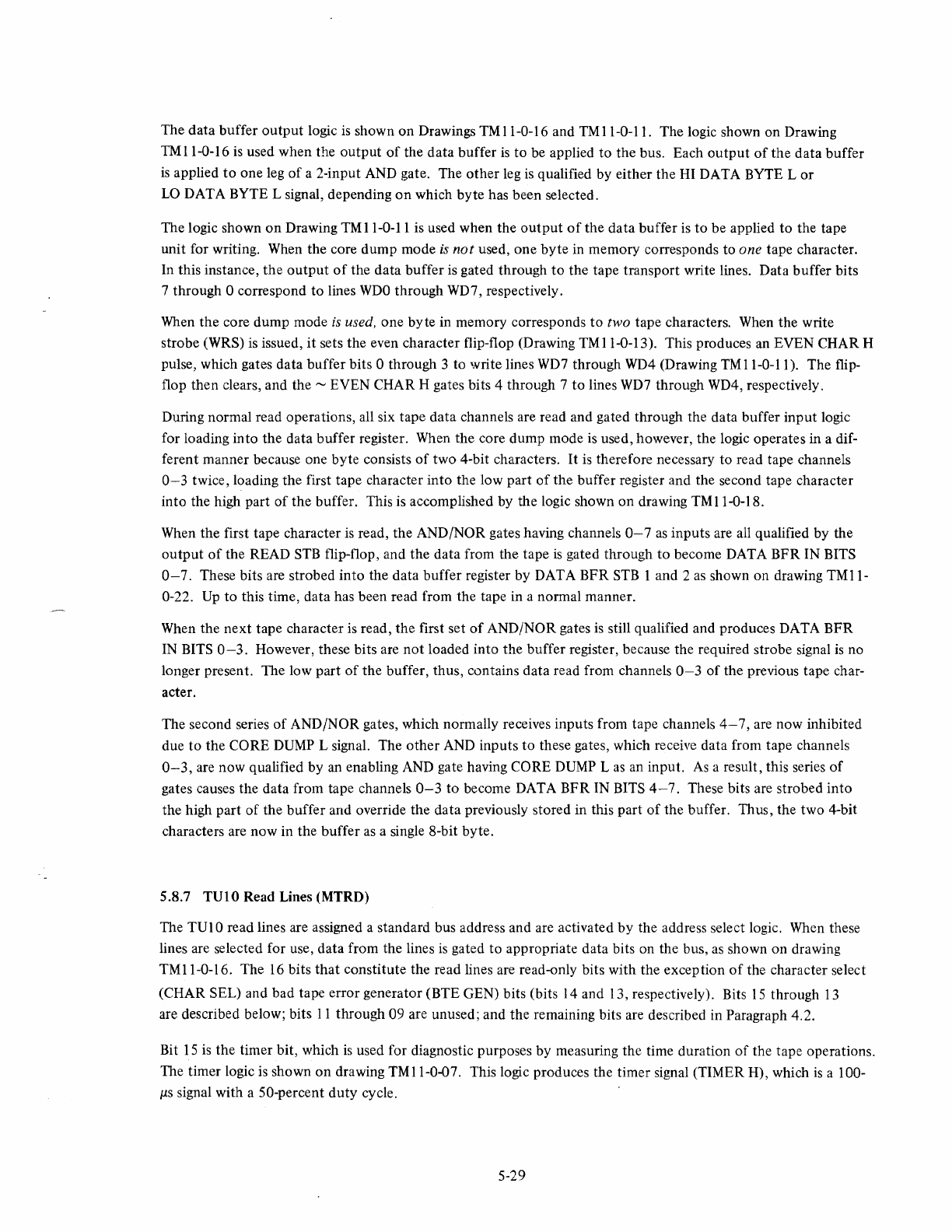

5.10 Timing Diagrams 5-32

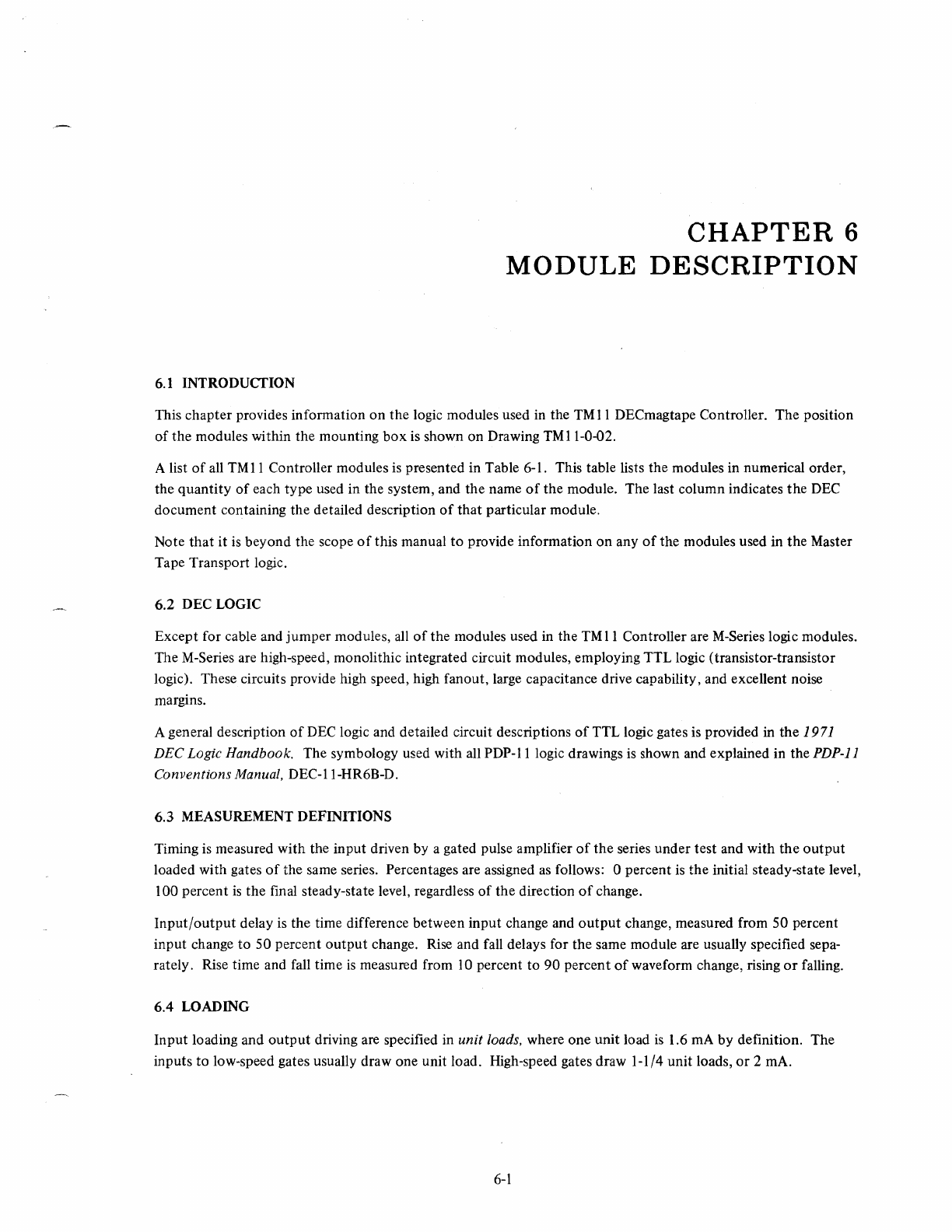

CHAPTER 6 MODULE DESCRIPTION

6.1

Introduction

6-1

6.2

DEC

Logic

6-1

6.3 Measurement Definitions

6-1

6.4 Loading

6-1

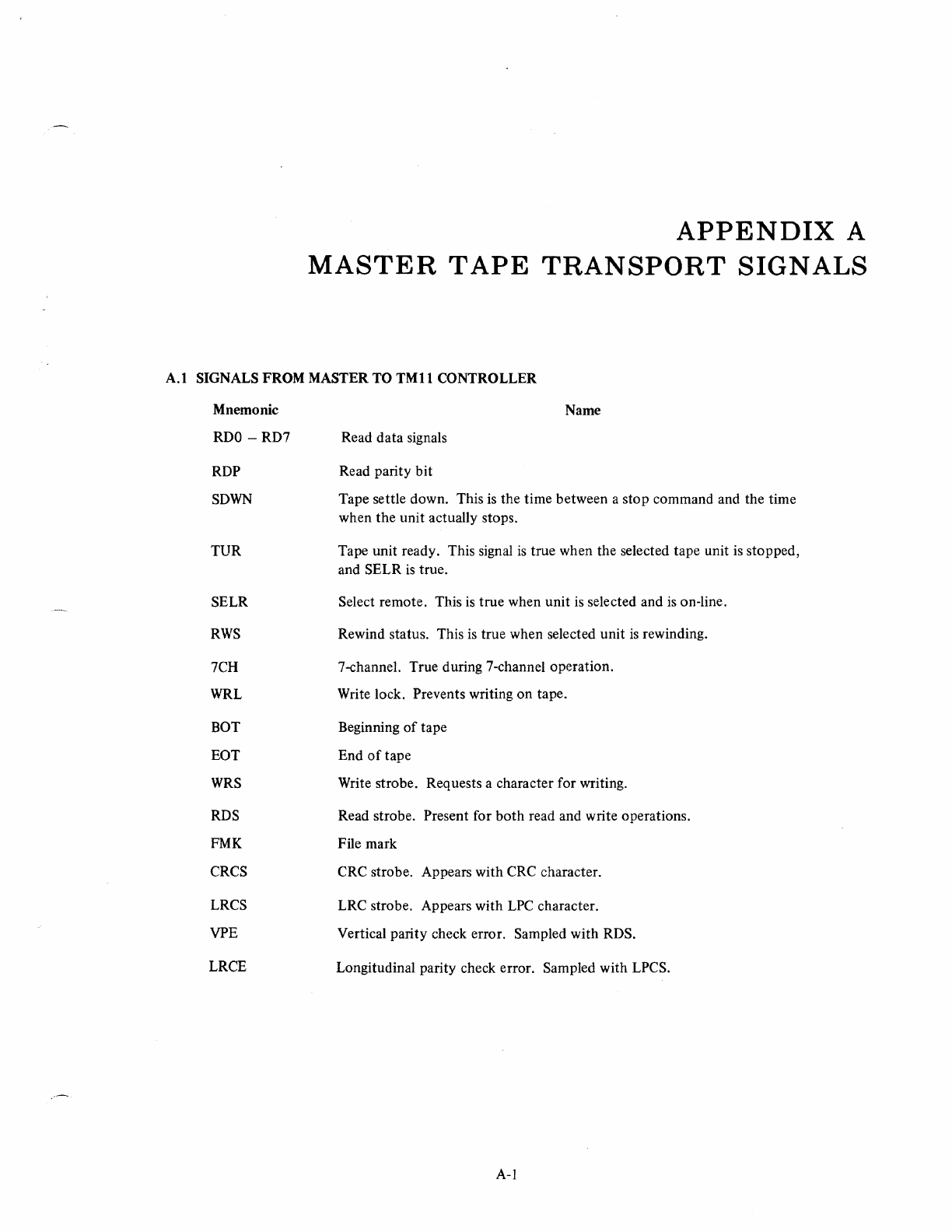

APPENDIX A MASTER TAPE TRANSPORT SIGNALS

A.I Signals from Master to

TMII

Controller A-I

A.2 Signals from

TM

11

Controller

to

Master

A-2

v

Figure No.

1-1

3-1

3-2

3-3

3-4

3-5

3-6

4-1

4-2

4-3

4-4

4-5

4-6

4-7

4-8

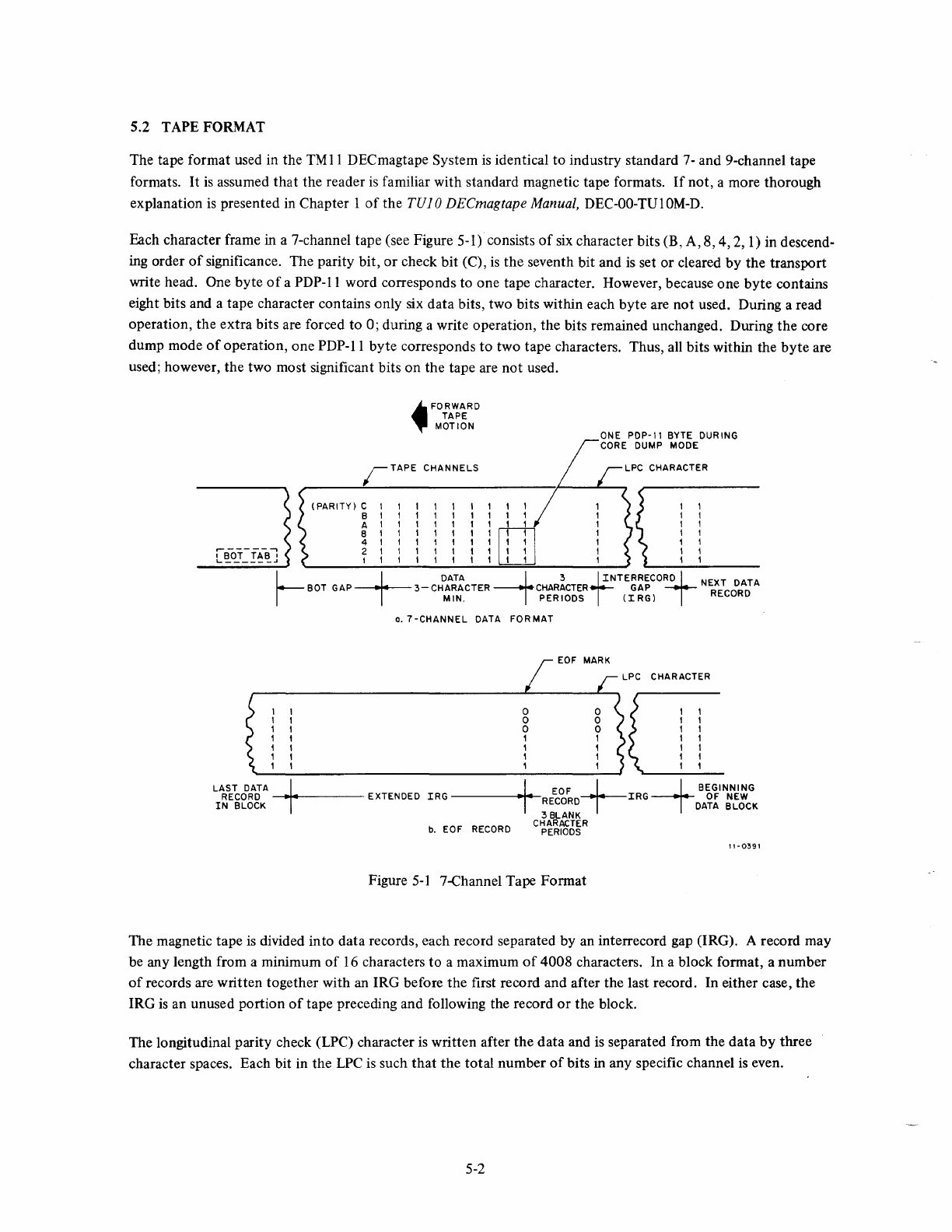

5-1

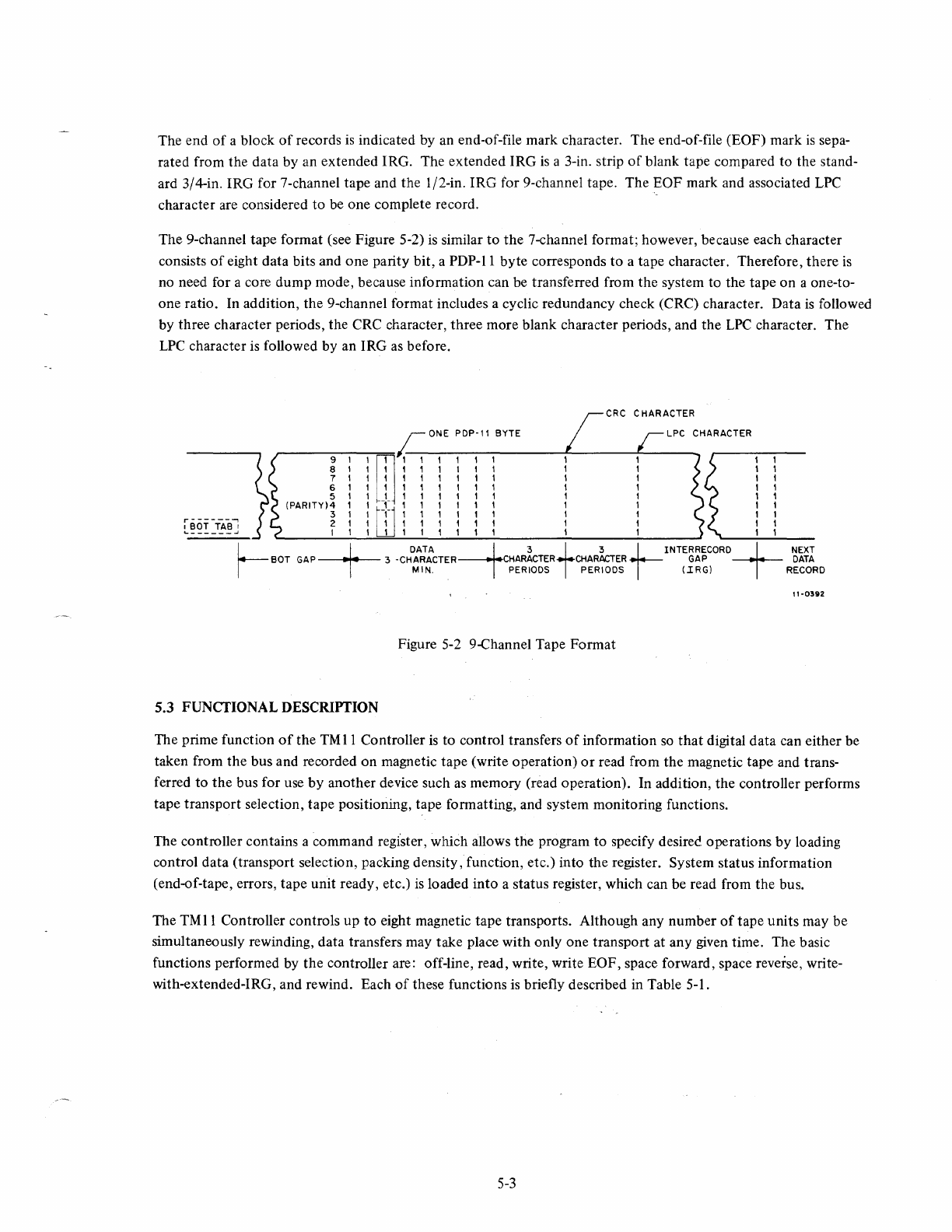

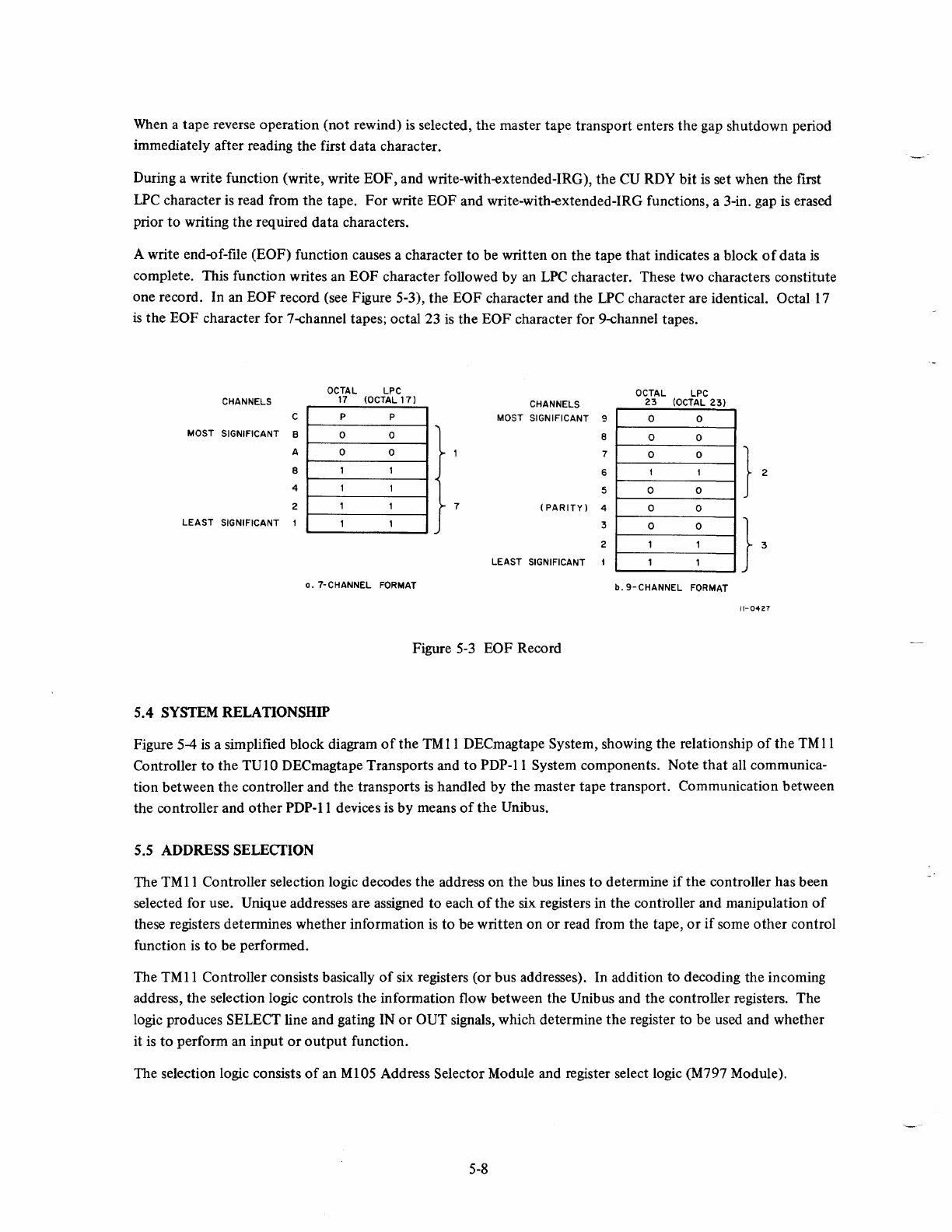

5-2

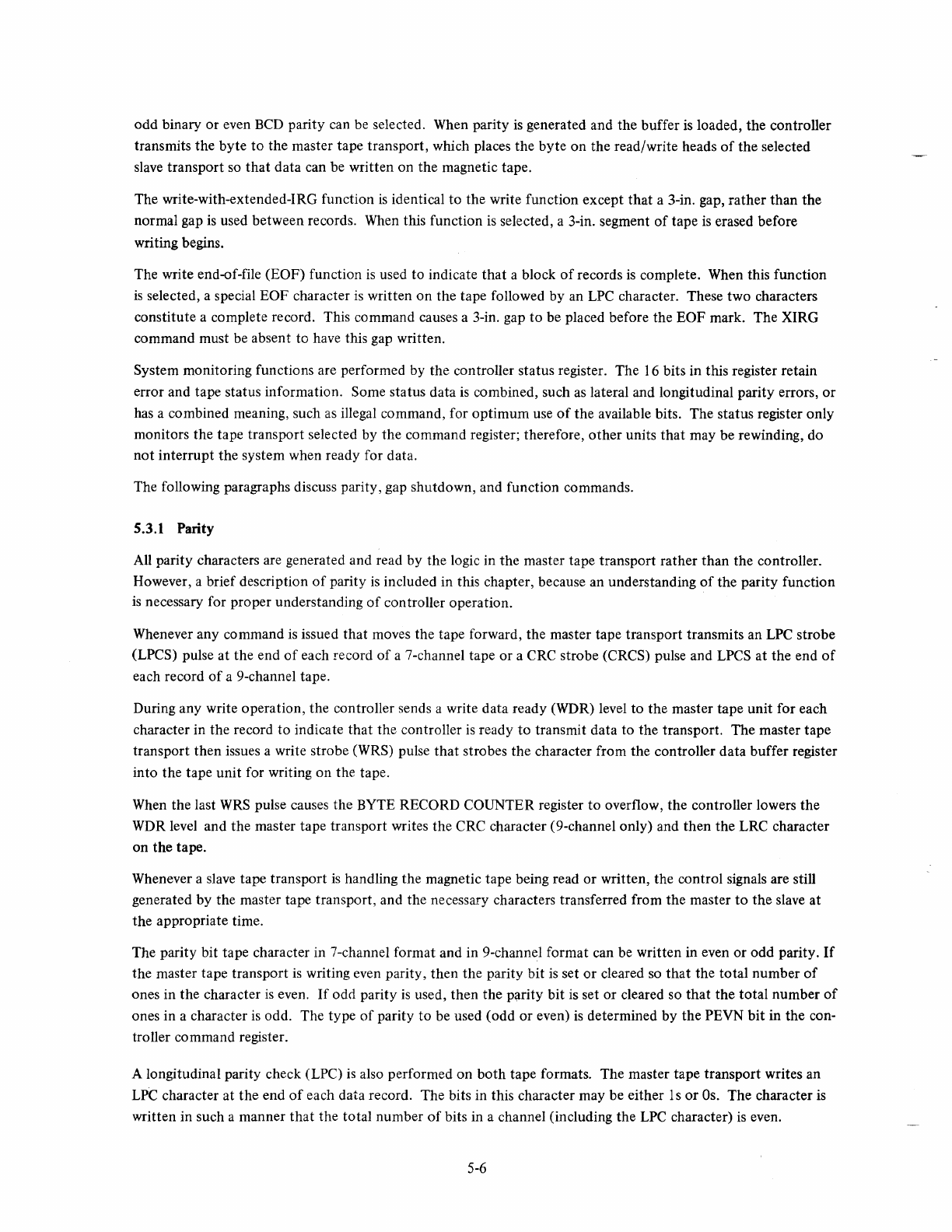

5-3

5-4

5-5

5-6

5-7

5-8

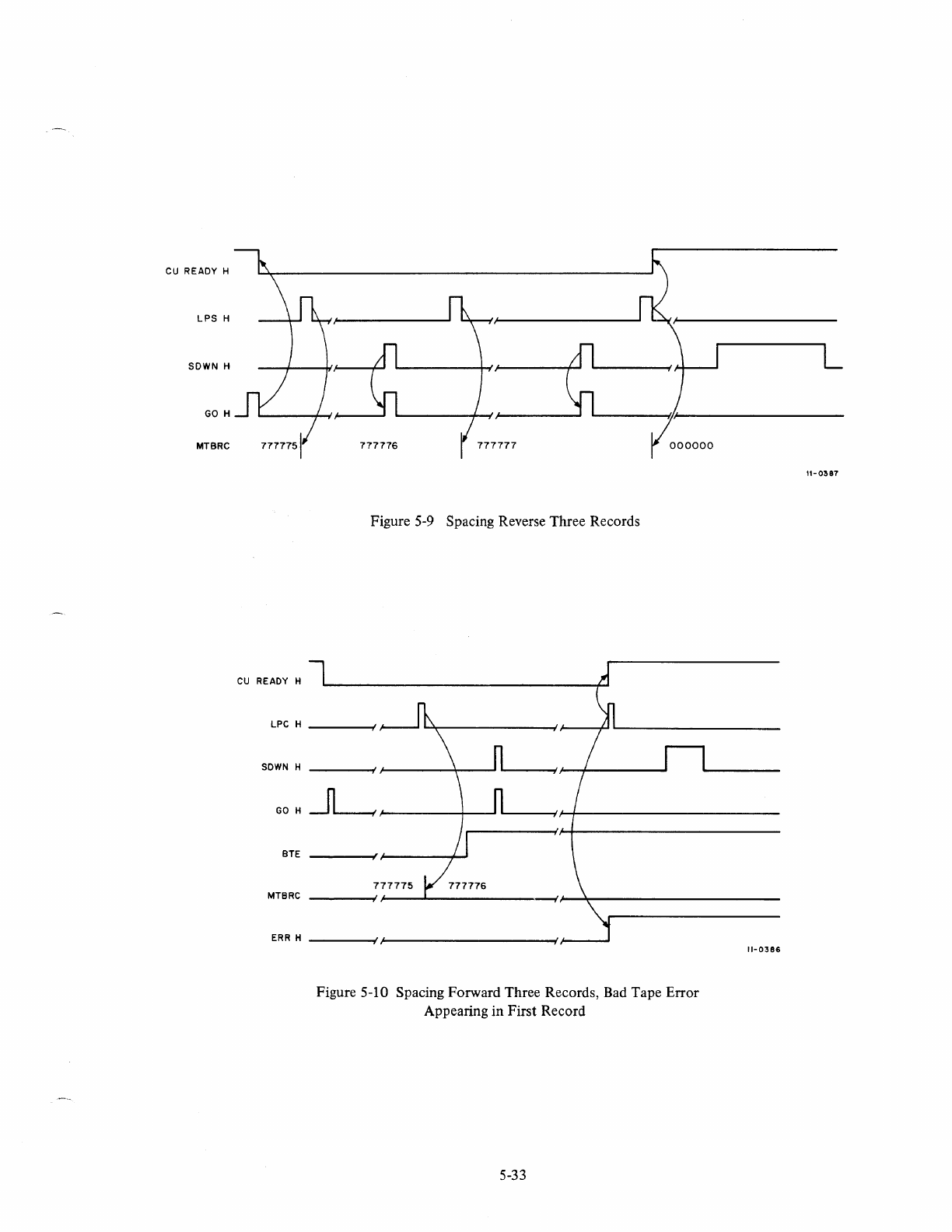

5-9

5-10

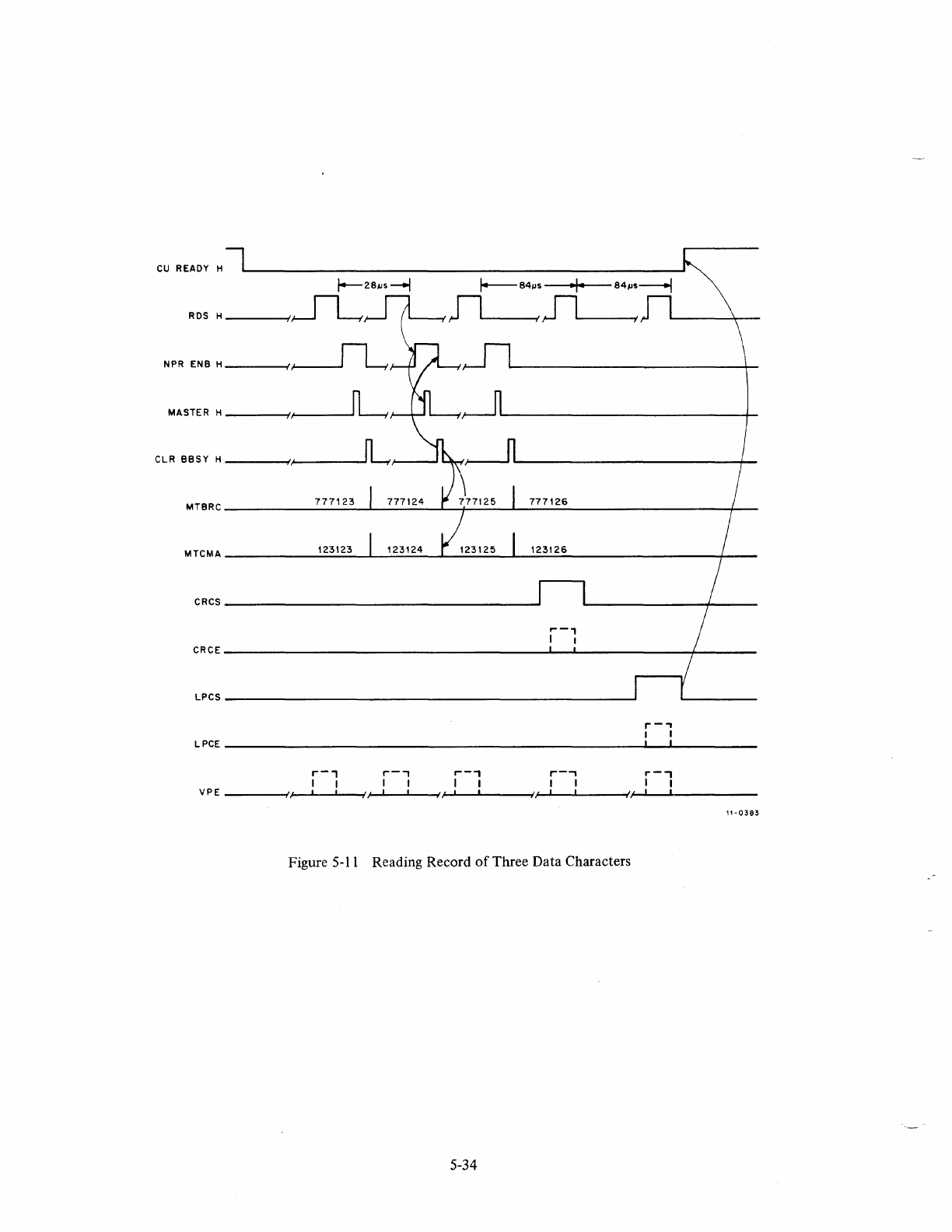

5-11

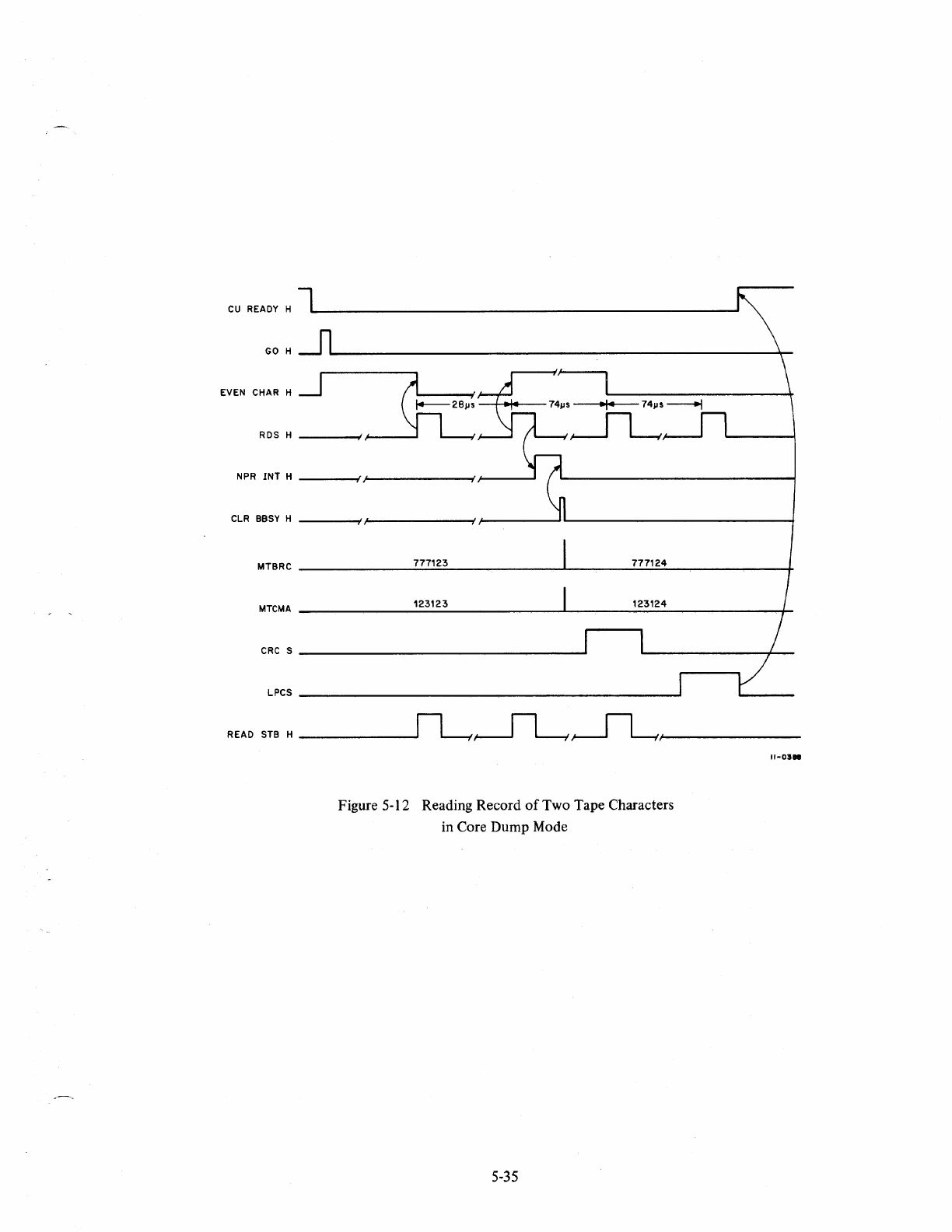

5-12

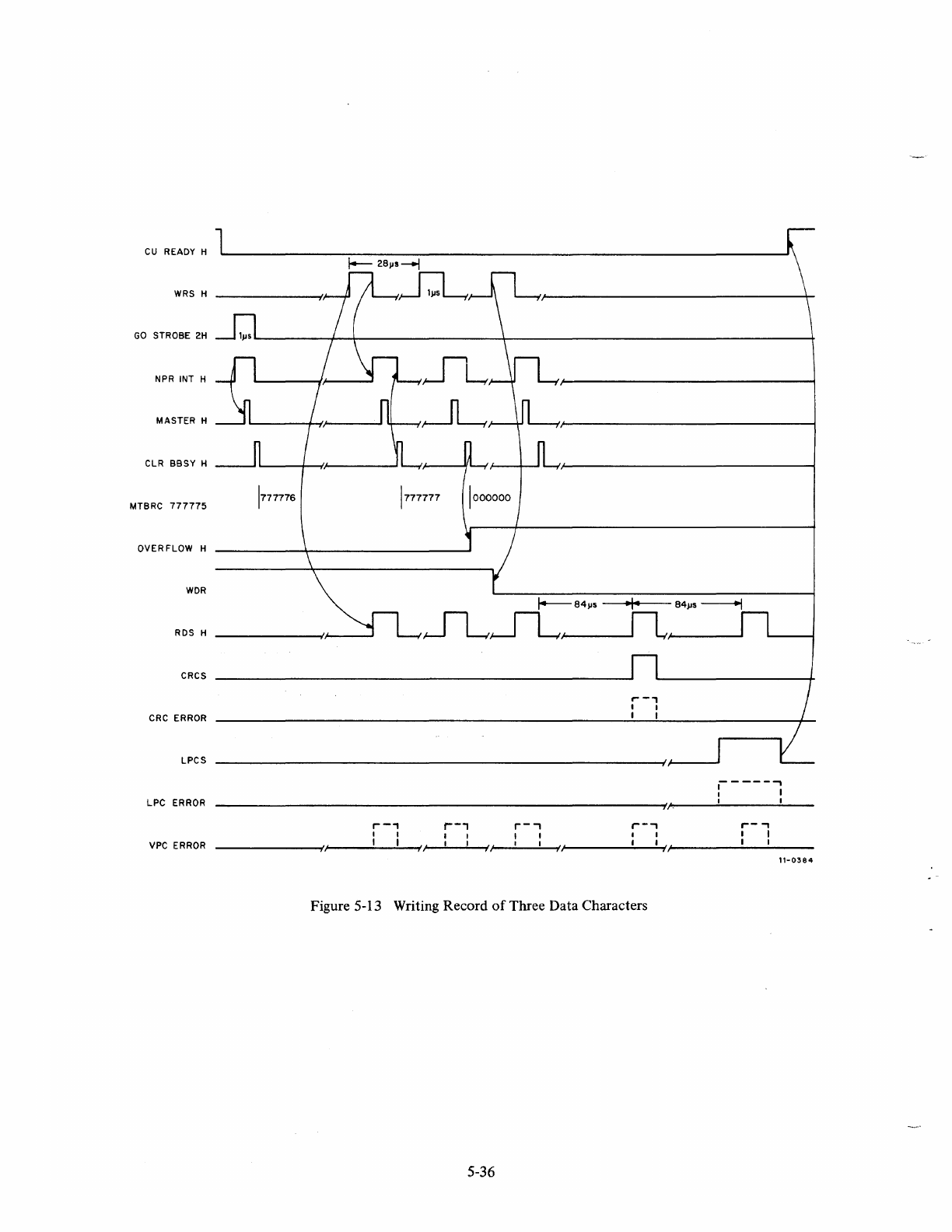

5-13

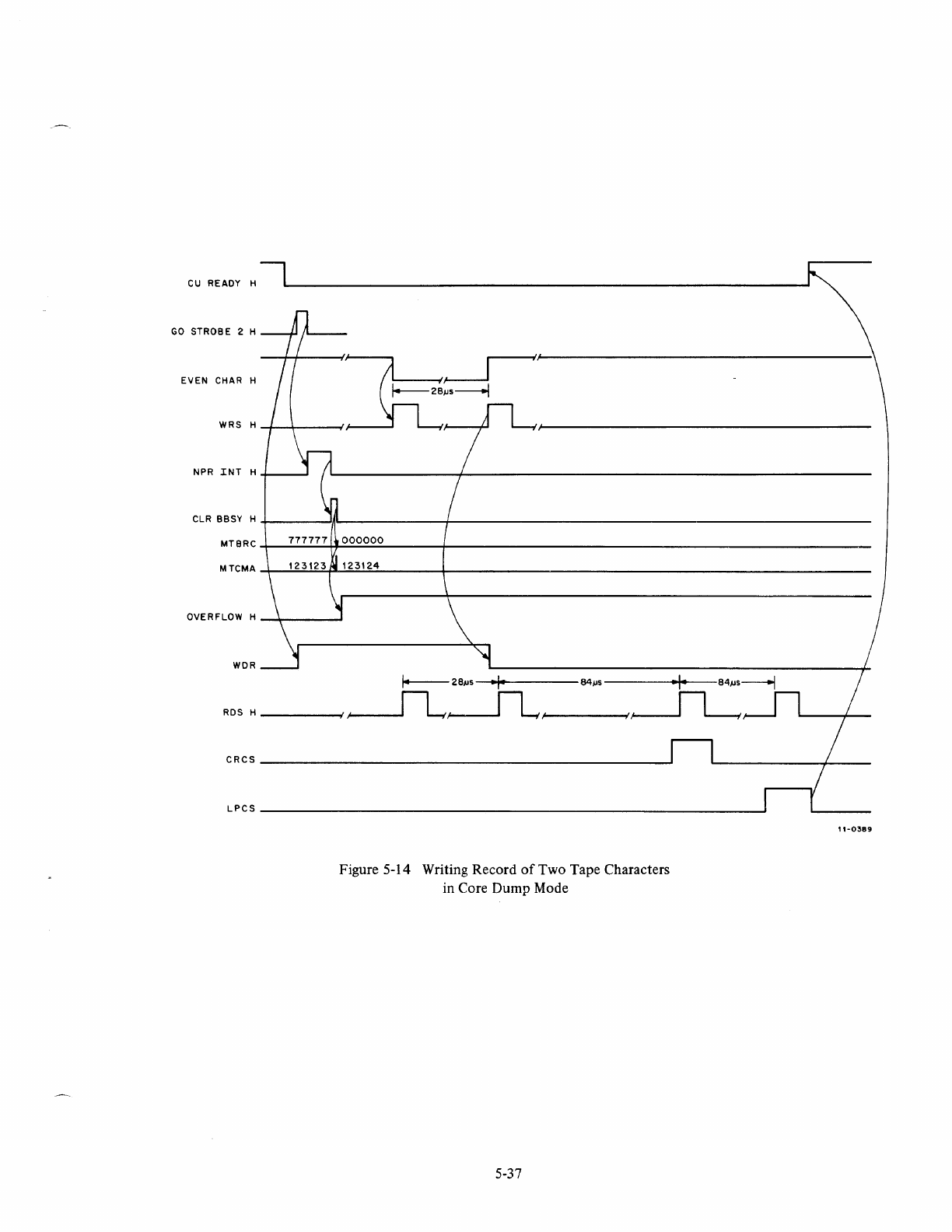

5-14

ILLUSTRATIONS

TM

11

DEC magtape System

TUI0

Control

Panel

Title

TM

II

Controller Maintenance Panel

Using

TMII

Maintenance Panel

Write-Enable Ring

Tape Threading

Tape

Loop

Limits

Status Register (MTS) Bit Assignments

Command Register (MTC) Bit Assignments

Byte Record

Counter

(MTBRC) Bit Assignments

Current Memory Address Register (MTCMA) Bit Assignments

Data Buffer Register (MTD) Bit Assignments

Relationship Between Tape Characters and Memory Byte Characters

TUI0

Read Line (MTRD) Bit Assignments

New Drive Selection Flowchart

7-Channel Tape

Format

9-Channel Tape

Format

EOF

Record

TM

II

System -Simplified Block Diagram

M 1

05 Address Decoding

Derivatives

of

GO Signal

Start

of

Tape Operation

Spacing Forward Three Records

Spacing Reverse Three Records

Page

1-2

3-1

3-6

3-6

3-9

3-10

3-11

4-2

4-6

4-8

4-9

4-9

4-10

4-11

4-15

5-2

5-3

5-8

5-9

5-10

5-22

5-32

5-32

5-33

Spacing

Forward

Three Records, Bad Tape

Error

Appearing in First Record 5-33

Reading Record

of

Three Data Characters 5-34

Reading Record

of

Two Tape Characters in Core

Dump

Mode

Writing Record

of

Three

Data

Characters

Writing Record

of

Two

Tape Characters

in

Core Dump Mode

vi

5-35

5-36

5-37

TABLES

Table No. Title Page

1-1

TM

11

System Manuals

1-3

1-2

Applicable Documents

1-3

1-3

TUIO Models

1-5

1-4

TM

II

DECmagtape System Specifications

1-8

2-1

Interconnecting Cables

2-2

3-1

TUIO DEC magtape Transport Controls

3-2

3-2

TUI0

DEC magtape Transport Indicators 3-4

3-3

Maintenance Panel Indicators

3-7

4-1

Standard Device Register Assignments 4-2

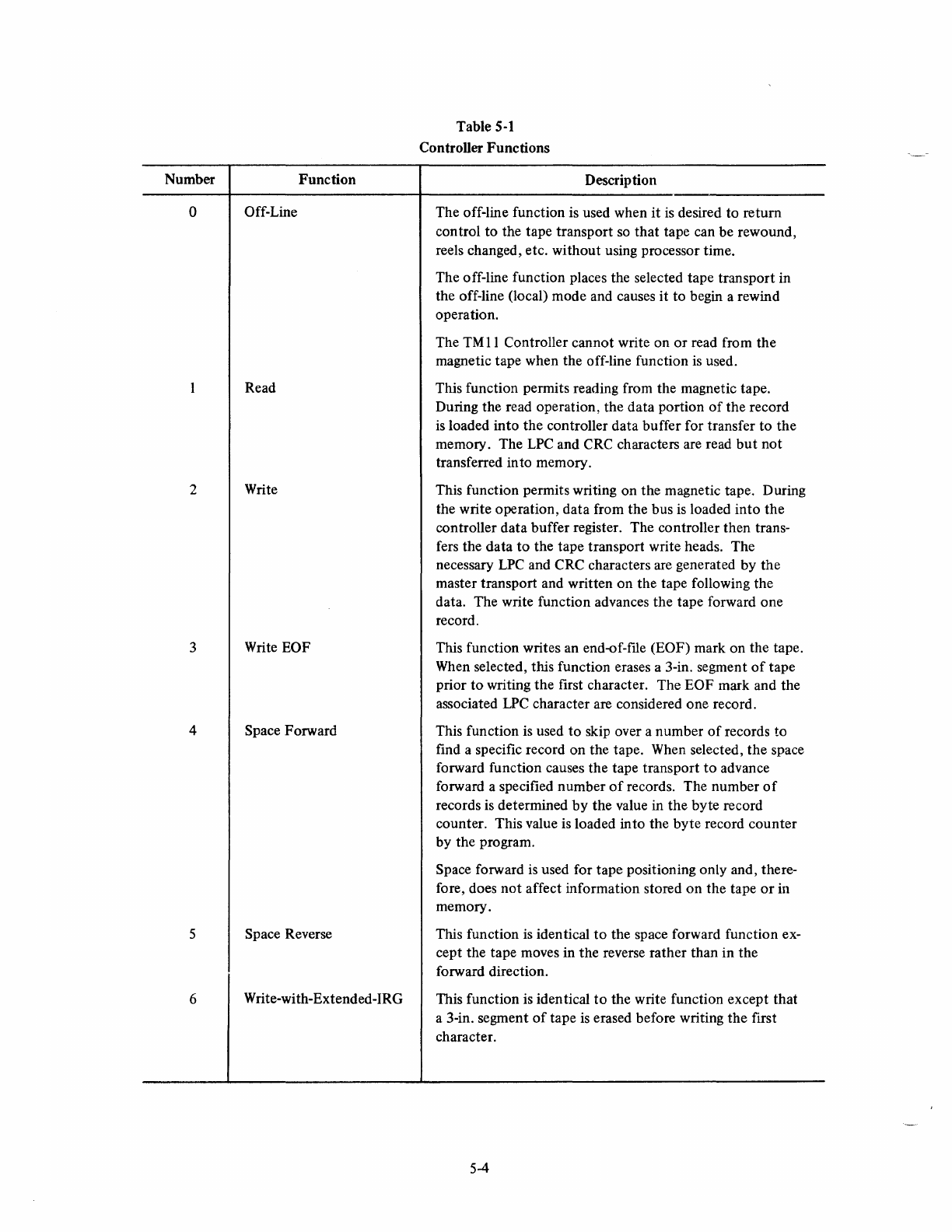

5-1

Controller Functions 5-4

5-2 M797 Decoder Selection

5-11

5-3

Gating and Select Line Signals

5-11

5-4 Bus Control Functions 5-12

5-5

Device Register Functions 5-16

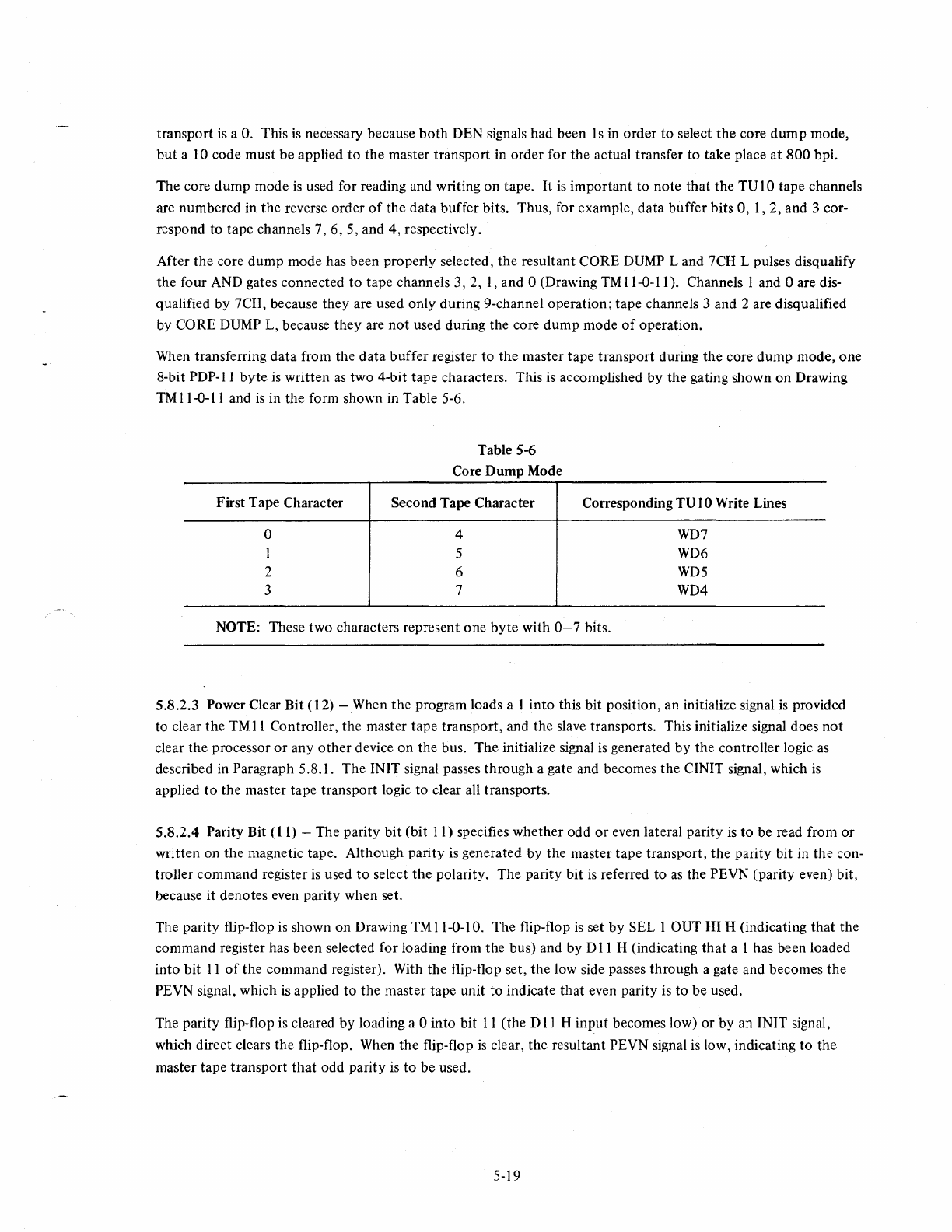

5-6 Core Dump Mode 5-19

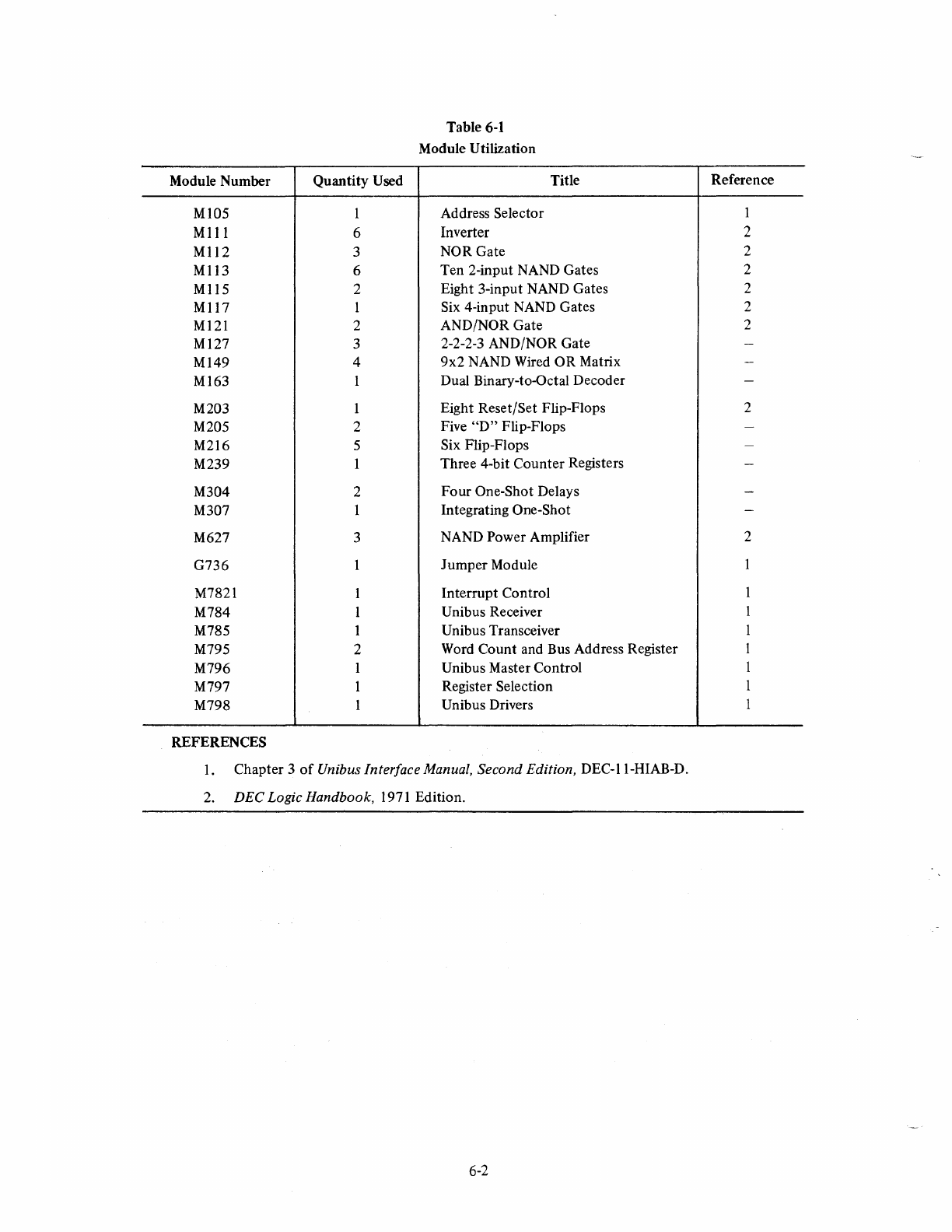

6-1

Module Utilization

6-2

vii

1.1

INTRODUCTION

CHAPTER

1

INTRODUCTION

The

TMll

DEC

magtape System (see Figure 1-1)

is

a magnetic tape handling system designed to interface with

the PDP-II family

of

processors and peripherals

to

provide storage for large amounts

of

digital information. This

system

is

ideally suited for writing, reading, and storing large volumes

of

data and programs in a serial manner:

Transfer

of

information can be made between the PDP-II and other computer systems, because the TM

11

System

reads and writes in industry-compatible formats.

The basic

TM

11

DECmagtape System consists

of

three distinct components:

TUI0

Tape Transport

TM

11

Controller

Magnetic Tape

1.2 SCOPE

A magnetic tape handling device

that

reads and/or writes information

on magnetic tape in either a 7-channel or 9-channel format. Includes

automatic parity checking and file protection.

Up

to eight TU10 transports may be used in one

TMII

System in

any combination

of

7-

or

9-channel versions. One transport always

functions

as

a master for the

other

system transports.

An

interface between the tape units and the PDP-II Unibus. Con-

trols information transfers between the transport and other devices

in a PDP-II System. One controller services up

to

eight TU

10

transports.

Also referred

to

as

"control unit", "interface", or "magtape control

unit (MTC)".

The recording medium used for data storage. Reel-mounted

mag-

netic tape that

is

formatted in either 7-channel or 9-channel

industry-compatible format.

Includes end-of-tape (EOT) and beginning-of-tape (BOT) reflective

markers, record gaps, lateral and longitudinal parity characters, and

file

marks. In addition, the 9-channel format includes a cyclic

red undancy check character.

Tape

is

I/2-in. wide with bit packing densities

of

200, 556, and

800 bpi for 7-channel; 800 bpi for 9-channel.

This manual provides the user with the information necessary

to

operate the

TM

11

DECmagtape System and

provides the theory

of

operation and logic diagrams necessary to understand and maintain the

TM

11

Controller.

1-1

Figure

1-1

TM

11

DECmagtape System

This manual and the TUlO DECmagtape Manual

(DEC-OO-TVIO-DA)

must be used together for a complete

understanding

of

the entire

TM

II

System. The prime subject matter

of

this manual

is

the

TM

11

Controller; the

prime subject matter

of

the

TV

1 0 manual

is

the tape transport and the magnetic tape. In addition, this manual

serves as an overall system operating guide.

Table

1-1

indicates the coverage in the two manuals, and Table

1-2

lists related PDP-II documents

that

are

applicable

to

the

TM

11

DECmagtape System.

1-2

Title

TMll

DECmagtape

System Manual

TU 10 DECmagtape

Transport Manual

TU10 DECmagtape

Master System

Manual

Title

TU10 DECmagtape

PDP-ll Processor and

Systems Manuals

PDP-ll

Processor

Handbook

PDP-ll

Peripherals

Handbook

Table

1-1

TMII

System Manuals

Number

DEC-II-HTMA-D

DEC-oO-TUIO-DA

DEC-oO-TUI0M-D

Coverage

Overall System -description, installation, operation,

programming.

TMII

Controller -detailed

theory

of

operation sup-

ported

by

logic diagrams in a second volume.

Tape Transport -description and installation; de-

tailed theory

of

operation; logic diagrams; mainten-

ance.

Magnetic Tape -detailed description

of

tape format.

Master

Tape

Transport -description, interface and

control, and

theory

of

operation.

Table 1-2

Applicable Documents

Number

DEC-OO-TU

I

O-DA

*

**

112-00973-2908

Coverage

Provides detailed theory, operation, maintenance,

and logic diagrams

for

the tape transport.

A series

of

maintenance and theory manuals

that

provide a detailed description

of

the basic

PDP-II

System.

A general

handbook

that

discusses system architec-

ture, addressing modes,

the

instruction set, pro-

gramming techniques, and software.

A

handbook

devoted

to

a discussion

of

the various

peripherals used with

PDP-II

systems.

It

also provides

detailed theory, flow, and logic descriptions

of

the

Unibus and external device logic;

methods

of

interface

construction; and examples

of

typical interfaces.

* Applicable manuals are furnished with the system at time

of

installation. The document number depends upon the specific

PDP-II family processor.

**Use the processor handbook unique to the actual

CPU.

1-3

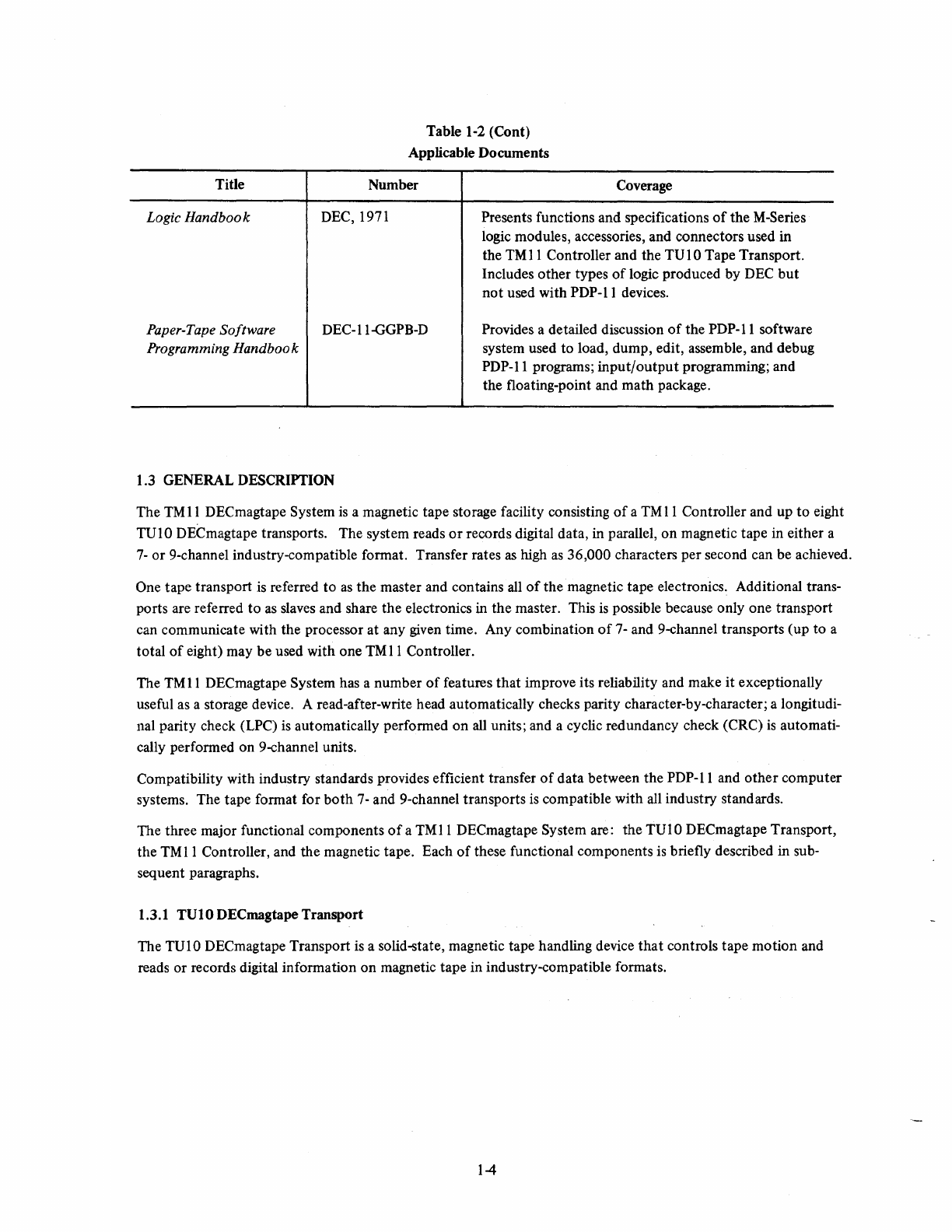

Table 1-2 (Cont)

Applicable Documents

Title Number

Logic

Handbook

DEC, 1971

Paper-Tape Software DEC-II-GGPB-D

Programming

Handbook

1.3 GENERAL DESCRIPTION

Coverage

Presents functions and specifications

of

the M-Series

logic modules, accessories, and connectors used in

the

TM

11

Controller and the TU 1 0 Tape Transport.

Includes other types

of

logic produced by

DEC

but

not used with PDP-II devices.

Provides a detailed discussion

of

the PDP-II software

system used to load, dump, edit, assemble, and debug

PDP-II programs; input/output programming; and

the floating-point and math package.

The

TM

11

DECmagtape System

is

a magnetic tape storage facility consisting

of

a

TM

11

Controller and up

to

eight

TUIO

DEC

magtape transports. The system reads

or

records digital data, in parallel,

on

magnetic tape in either a

7-

or 9-channel industry-compatible format. Transfer rates

as

high

as

36,000 characters per second can be achieved.

One tape transport is referred to

as

the master and contains

all

of

the magnetic tape electronics. Additional trans-

ports are referred to

as

slaves and share the electronics in the master. This

is

possible because only one transport

can communicate with the processor at any

given

time. Any combination

of

7-

and 9-channel transports (up to a

total

of

eight) may be used with one

TM

11

Controller.

The

TM

11

DECmagtape System has a number

of

features that improve its reliability and make it exceptionally

useful as a storage device. A read-after-write head automatically checks parity character-by-character; a longitUdi-

nal parity check (LPC)

is

automatically performed on

all

units; and a cyclic redundancy check (CRC)

is

automati-

cally performed on 9-channel units.

Compatibility with industry standards provides efficient transfer

of

data between the PDP-II and other computer

systems. The tape format for

both

7-

and 9-channel transports

is

compatible with all industry standards.

The three major functional components

of

a

TM

II

DECmagtape System are: the TUI 0 DECmagtape Transport,

the

TMll

Controller, and the magnetic tape. Each

of

these functional components

is

briefly described in sub-

sequent paragraphs.

1.3.1

TUI0

DECmagtape Transport

The

TUI0

DECmagtape Transport is a solid-state, magnetic tape handling device

that

controls tape motion and

reads or records digital information on magnetic tape in industry-compatible formats.

14

The TU lOuses vacuum columns and a servo-controlled single capstan

to

control tape motion. The only contact

with the oxide surface

is

the magnetic head and a rolling contact

on

one low-friction, low-inertja bearing. Dancer

arms and pinch rollers, which shorten tape life and can cause errors, are

not

used in the TUlO.

Tape transport commands can be issued manually from the TUI 0 control panel or remotely from the processor

by means

of

the

TMII

Controller. Indicators on

both

the transport and the controller indicate transport status.

Each tape transport (master or slave) consists

of

the TV 10 cabinet, reel and reel

motor

control, capstan drive, and

read/write components. In addition to these components, the master transport contains logic circuits that: start

and stop any tape unit, generate the read and write pulses, generate the required gaps, generate parity, and check

parity. These logic circuits are shared by all transports under control

of

the master and the

TM

II

Controller.

In addition

to

the parity checking features

of

the TUIO, the transport contains deskewing electronics to eliminate

static skew, and write-protect ring sensing.

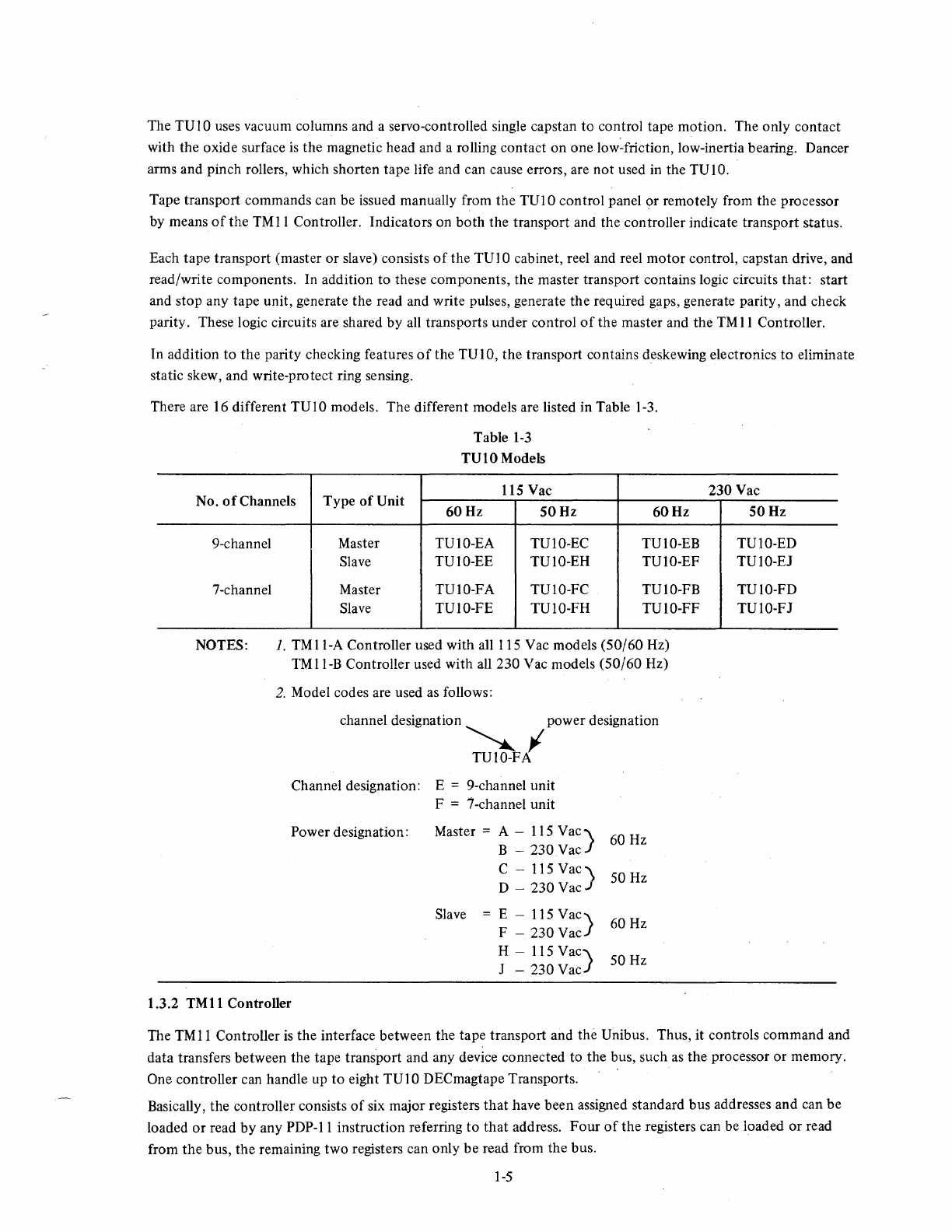

There are 16 different

TUI0

models. The different models are listed in Table 1-3.

Table

1-3

TUlOModels

115 Vac

No. 0 f Channels Type

of

Unit

60Hz

9-channel

7-channel

NOTES:

50Hz

60Hz

Master TUIO-EA TUIO-EC TUIO-EB

Slave TUIO-EE TUIO-EH TUIO-EF

Master TUIO-FA TUIO-FC TUIO-FB

Slave TUIO-FE TUIO-FH

TUI0-FF

1.

TMll-A

Controller used with all 115 Vac models (50/60 Hz)

TM

II-B Controller used with all 230 Vac models (50/60 Hz)

2.

Model codes are used

as

follows:

channel designation power designation

~I

Channel designation: E = 9-channel unit

F = 7 -channel unit

Power designation: Master =

A-lIS

Vac)

60 Hz

B - 230 Vac

Slave

C -115

Vac)

50 Hz

D - 230 Vac

E - 115

Vac)

60 Hz

F - 230 Vac

H - 115

Vac)

50

Hz

J - 230 Vac

1.3.2

TMII

Controller

230 Vac

50Hz

TUIO-ED

TUIO-EJ

TUIO-FD

TUIO-FJ

The

TM

11

Controller

is

the interface between the tape transport and the Unibus. Thus, it controls command and

data transfers between the tape trans'port and any device connected to the bus, such

as

the processor or memory.

One controller can handle up

to

eight TU 1 0 DECmagtape Transports.

Basically, the controller consists

of

six major registers

that

have been assigned standard bus addresses and can be

loaded

or

read by any PDP-II instruction referring to

that

address.

Four

of

the

registers can be loaded or read

from

the

bus, the remaining two registers can only be read from the bus.

1-5

The controller has three main functions: handling

data

transfers, issuing control commands, and monitoring

operation

of

the system.

During data transfer functions,

the

controller assembles the data word from

the

magnetic tape and places

it

on

the

bus (read operation),

or

assembles it from the bus and loads it

into

the

tape transport read/write heads (write

operation) for recording

on

magnetic tape. The commands necessary

to

perform

the

specified operation are gene-

rated

by

the

controller under program control.

Nonnal data word transfers are perfonned by direct memory access transactions

at

the NPR level.

If

the control-

ler

is

ready

to

begin a new function

or

if

an error condition exists, it issues an interrupt request

so

that

it

can be

serviced

by

the program.

In addition

to

the commands required for

data

transfers, the controller may issue

other

commands governing

tape unit selection, direction

of

tape

travel, rewind, space forward, space reverse, write end-of-file mark, etc.

The

controller also monitors various functions and provides an indication

of

error conditions.

The

status

of

the

monitored functions

is

stored in

one

of

the

controller registers.

A controller maintenance panel permits clearing

of

the

TM

11

System and includes 28 indicator lights

to

represent

error conditions and

the

status

of

selected functions.

1.3.3 Magnetic

Tape

The magnetic tape

is

the

recording medium used with the

TM

II

DECmagtape System.

The

tape is 1/2-in. oxide-

coated Mylar 8 . The tape includes reflective end-of-tape (EOT) and beginning-of-tape (BOT) markers and

is

stored

on

2400-ft reels.

Data

is

recorded in an industry-standard format.

The

7-channel format consists

of

six data channels

(I,

2, 4, 8, A,

and B) and a parity channel (C). Each

PDP-II

word

is

divided into

two

6-bit characters. Data

is

stored in variable-

length records separated

by

interrecord gaps

of

3/4

in. A longitudinally parity check (LPC) character

is

written at

the end

of

each record. Standard

fonnat

marks

(tape

mark, group mark, segment mark, etc.) may also be written

in a record along with

the

data. The 7-channel

fonnat

may be written in densities

of

200,556,

or

800

bpi.

The 9-channel format consists

of

eight data channels in

the

following order:

9,8,7,6,5,4,3,

2, and

1.

Channel

4 is used for parity.

In

addition, a cyclic redundancy check (CRC) character

is

written before

the

LPC character.

Data

is

stored in variable length records separated by interrecord gaps

of

one-half inch. Each

PDP-II

word con-

sists

of

two 8-bit characters. The 9-channel format always has a

bit

packing density

of

800

bpi.

Both formats are written

by

means

of

the

non-return-to-zero (NRZI) recording method. Although

the

tape has

two basic states

of

magnetization,

the

state does

not

determine

the

value

of

the

bit. A logical 1

is

represented

by

a change

of

magnetization in

either

direction. A logical 0

is

represented

by

a constant state

of

magnetization.

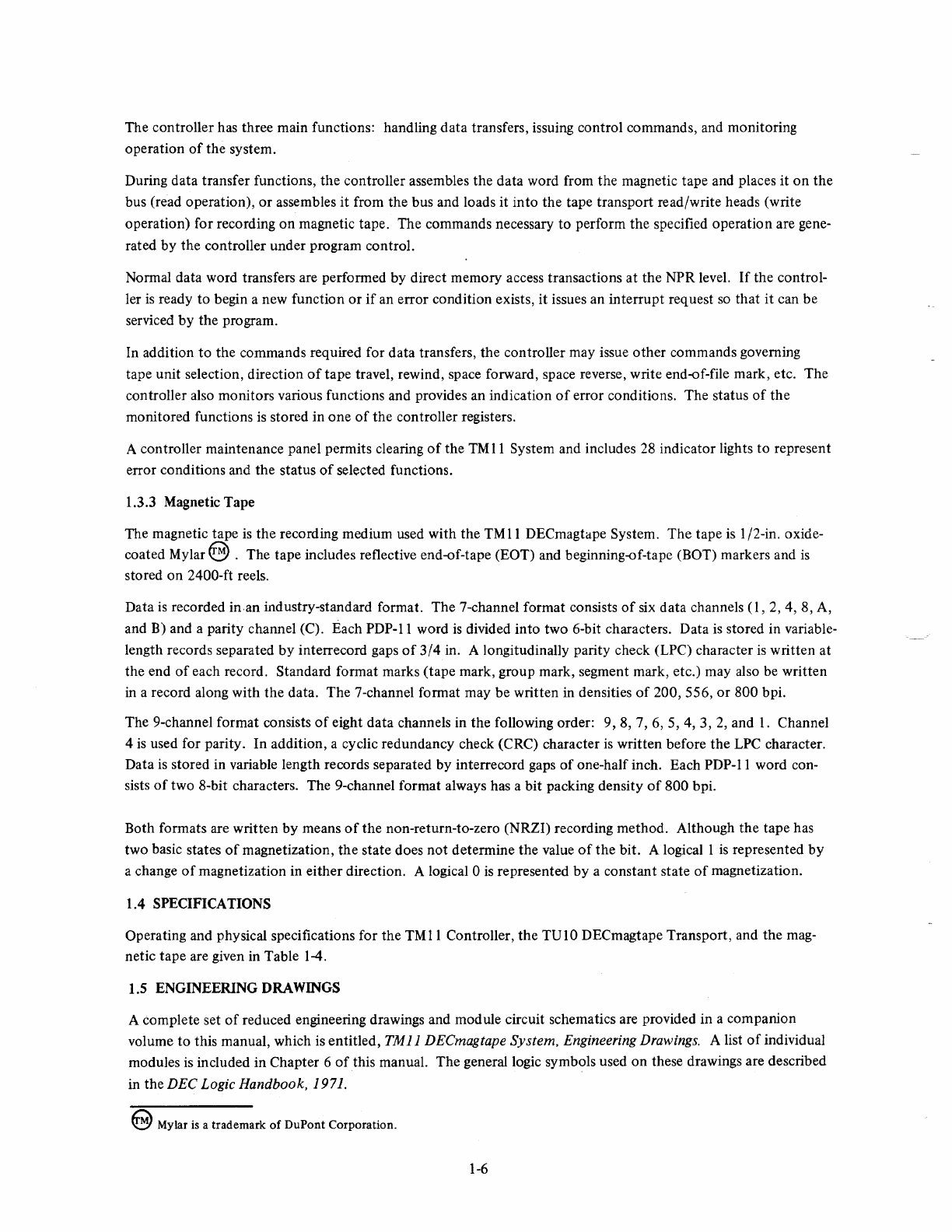

1.4 SPECIFICATIONS

Operating and physical specifications for the

TMII

Controller,

the

TUIO DECmagtape Transport, and

the

mag-

netic

tape

are given in Table 1-4.

1.5 ENGINEERING DRAWINGS

A complete set

of

reduced engineering drawings and module circuit schematics are provided in a companion

volume

to

this manual, which is entitled, TM11 DECmagtape System, Engineering Drawings. A list

of

individual

modules

is

included in Chapter 6

of

this manual. The general logic symbols used

on

these drawings are described

in

the

DEC Logic Handbook, 1971.

9 Mylar

is

a trademark

of

DuPont Corporation.

1-6

Table 1-4

TMtlDECmagtape

System Specifications

Tape Characteristics

Capacity:

Reel Diameter:

Tape Handling:

Tape Speed:

Rewind Speed:

Packing Density:

Data Recording and Transfer

Recording Mode:

Magnetic Head:

Data Transfers:

Transfer Rate:

BOT,

EaT

Detection:

Write Protection:

Data Checking:

Interrecord Gap:

Programmable Commands Accepted by

TUt

0

Rewind and

go

off-line

Read

Write

Write end-of-file (EOF) character

Space forward

Space reverse

Write with extended interrecord gap (IRG)

Rewind to beginning

of

tape (BOT)

Controller Register Addresses

Status Register (MTS):

Command Register (MTC):

Byte Record Counter (MTBRC):

2400 ft

of

I/2-in., industry standard, I-mil Mylar tape.

10-1/2 in. standard reels

Direct-drive reel motors; servo-controlled single capstan;

vacuum tape buffer chambers with constant tape winding

tension.

45

in. per second, reading and writing

150 in. per second (approximately 3-minute rewind time

for 2400-ft reel)

7-channel -200, 556, and 800 bpi, selectable under pro-

gram control

9-channel -800 bpi

NRZI, industry-compatible

Dual gap, read-after-write

Direct memory access (non-processor request)

36,000 characters per second, maximum

Photoelectric sensing

of

reflective strip, industry-

compatible.

Write-protect ring sensing

Read-after-write parity checking; longitudinal redundancy

check; cyclic redundancy check (9-channel only).

Reads tape with gap

of

0.48 in.

or

more; writes tape with

gap

of

0.52 in. or more (compatible with industry stan-

dard).

772520

772522

772524

1-7

(read only)

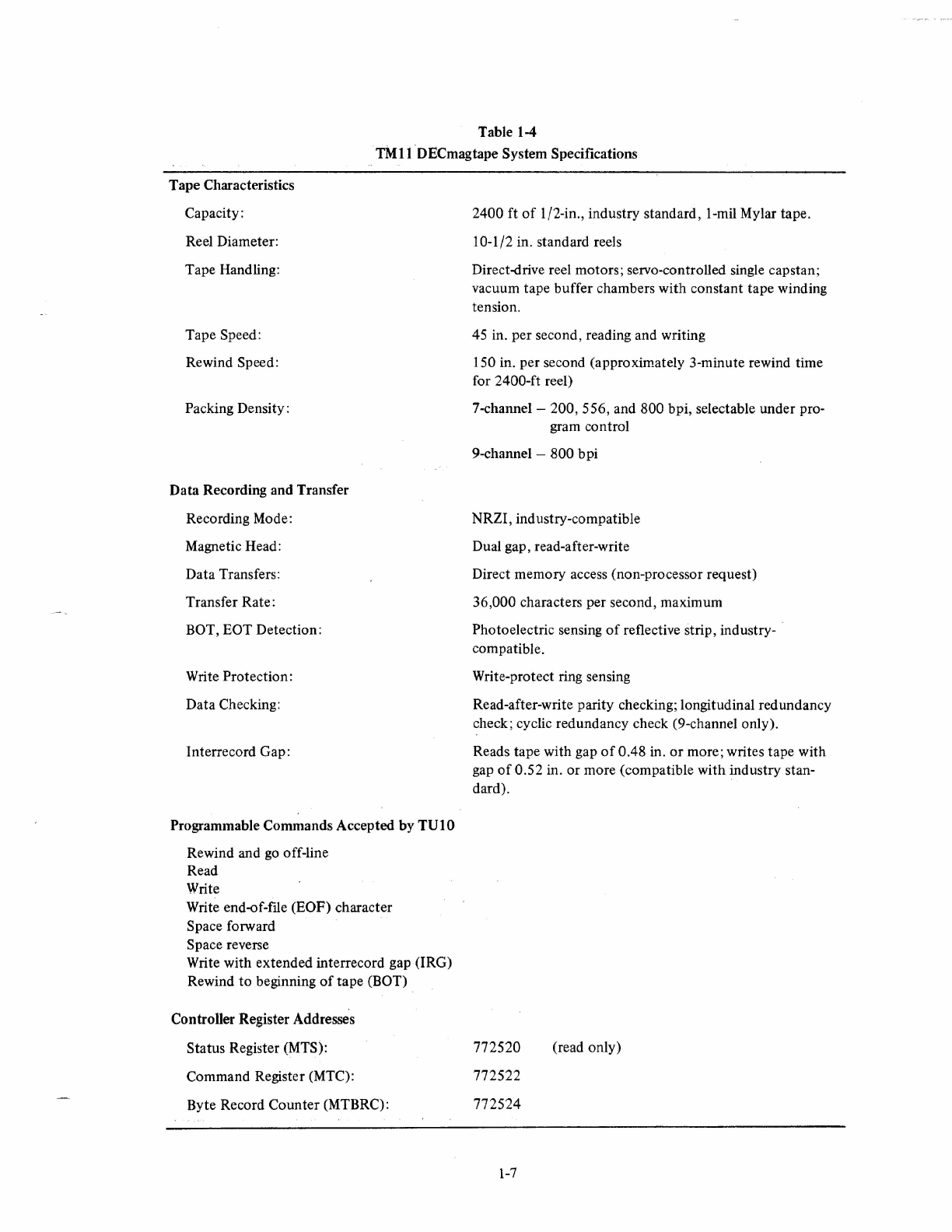

Table 1-4 (Cont)

TM

11

DECmagtape System Specifications

Controller Register Addresses (Cont)

Current Memory Address Register

(MTCMA):

Data Buffer Register (MTD) :

TUIO Read Lines (MTRD):

Interrupt

Priority Level:

Vector Address:

Local Transport Controls

PWR

ON/PWR

OFF

ON-LINE/OFF-LINE

START/STOP

LOAD/BR REL

UNIT SELECT

FWD/REW /REV

TUI0

DECmagtape Transport

Mounting:

Size:

Cooling:

Controls:

TM

11

Controller

Mounting:

Size:

Controls:

Environmental Conditions

Temperature:

Humidity:

772526

772530

772532

BR5

224

(read only)

power control switch

local or programmed operation

tape motion control

releases tape for loading

selects unit for program control

tape direction control

Mounts in standard H960C-A cabinet.

26 in. high,

19

in. wide, 25 in. deep

Internally-mounted fans

Front panel mounted

Mounts in standard 19-in. rack; normally mounted in

cabinet containing master tape transport.

10-1/2 in. high,

19

in. wide

On separate maintenance panel card that plugs into con-

troller; includes CLEAR switch and 28 indicators display-

ing status

of

selected system functions.

40°F

to 110°F for system

60°F to 80°F for magnetic tape

20%

to

95% (non-condensation) for system

40%

to

60% (non-condensation) for tape

1-8

Power

Input

Requirements

Controller:

TU I

O-EA,

EE, FA,

FE

TU 1 O-Ee,

EH,

FC, FH

TUIO-EB, EF, FB,

FF

TUIO-ED, EJ, FD,

FJ

Power and Cabling

TMII

Power:

TUIO Power:

Cabling:

1.6 MAINTENANCE

Table 1-4 (Cont)

TM11 DECmagtape System Specifications

either

lIS

Vac,

50/60

Hz at 6.25A (A model)

or 230 Vac, 50/60 Hz

at

6.25A

(B

model)

lIS

Vac, 60 Hz

115 Vac, 50 Hz

230 Vac, 60 Hz

230 Vac, 50 Hz

System power supplied by one H720 Power Supply

mounted at back

of

master cabinet. Provides +5V

at

16A and -15V at lOA for use

by

TMl1 and up

to

eight

TUI0s.

Tape transport power (reel motors and fans) provided by

internal power supply in each transport.

BC

ll-A

cable

to

connect controller

to

Unibus and

to

con-

nect command signals between controller and master

TUI

O.

M908 ribbon connector

to

connect master TU 10 to slave

TUIOs.

The basic maintenance philosophy

of

the

TM

II

DECmagtape System

is

to present the user with the information

necessary

to

understand normal operation

of

the

system. The user can utilize this information when analyzing

trouble symptoms to determine necessary corrective action.

It

is

beyond 'the scope

of

this manual

to

present de-

tailed troubleshooting information.

Detailed maintenance and troubleshooting information

of

the TUIO DECmagtape Transport

is

given in the TUIO

DECmagtape Manual, DEC-OO-TUIO-DA.

1-9

2.1

SCOPE

CHAPTER

2

INSTALLATION

This

chapter

covers general

infonnation

on

installation

of

the

TM

11

DECmagtape System. Detailed

information

on

installation

of

the

TVI

0 Tape Transport

is

presented in

the

TV]

0 DECmagtape Transport Manual,

DEC-OO-TVIO-DA.

Infonnation

on

various mounting cabinets

is

presented

in

the H720 Power Supply and

Mounting

Box

Manual, DEC-II-HRSB-D.

2.2 CONFIGURATION

Installation procedilres vary greatly, depending

on

the

system configuration.

For

example,

if

the

user has ordered

a complete

PDP-II

System,

the

TMII

DECmagtape System

is

shipped already installed in its appropriate rack

together with

the

required cables.

If

the

complete system

is

shipped,

the

interconnecting cables are already in-

stalled.

However,

if

only a part

of

the

system is shipped because the user already has a basic

PDP-II

System,

then

the

TM

11

DECmagtape System

is

shipped separately together with

the

appropriate cables. Installation procedures

may vary, depending on

whether

the unit

is

mounted

in a DEC-

or

customer-supplied cabinet,

the

number

of

tape

transports in the system, and

other

variable factors.

2.3 UNPACKING

The

equipment

should

be

unpacked

as

follows:

Step

2

3

2.4 INSPECTION

Procedure

Place

the

equipment package within the installation site

near

its final location.

Cut

the

shipping straps and carefully remove all packing material.

Remove

the

machine screws

that

hold

the

cabinet

to

the

shipping pallet. Slide

the

cabinet

off

the

pallet and move

it

to

its final location.

Remove any tape holding

the

modules in place within

the

mounting

panels and

any tape holding

the

power

and interconnecting cables to

the

floor

of

the

cabinet.

Inspect all

of

the

equipment

before installing

it,

checking each piece against

the

parts list.

Any

damage must

be

reported immediately

to

the

shipper and

to

the DEC representative.

2-1

2.5 SPACEREQUIREMENfS

No

special site preparation is required for installation

of

the

TM

11

DECmagtape System. However, when installing

the system, make certain

that

the front and rear

of

the cabinets are accessible

to

maintenance personnel.

If

the

cabinets are separated

by

long distances, consideration should be given

to

overhead trenching ducts

or

floor ducts

for

the

cabling.

2.6 POWER AND CABLE REQUIREMENTS

The

TM

11

Controller and associated

TUI0

transports operate from a line voltage

of

either 115 Vac

or

230 Vac

at

a frequency

of

either 50

or

60

Hz, depending

on

the model ordered

by

the customer. The maximum current

required

is

6.25A for the controller. The

TMII

Controller contains its own power supply, and each

TUI0

trans-

port has its own power supply. Power supply specifications are listed in Table 1-4. The interconnecting cables

are listed in Table 2-1.

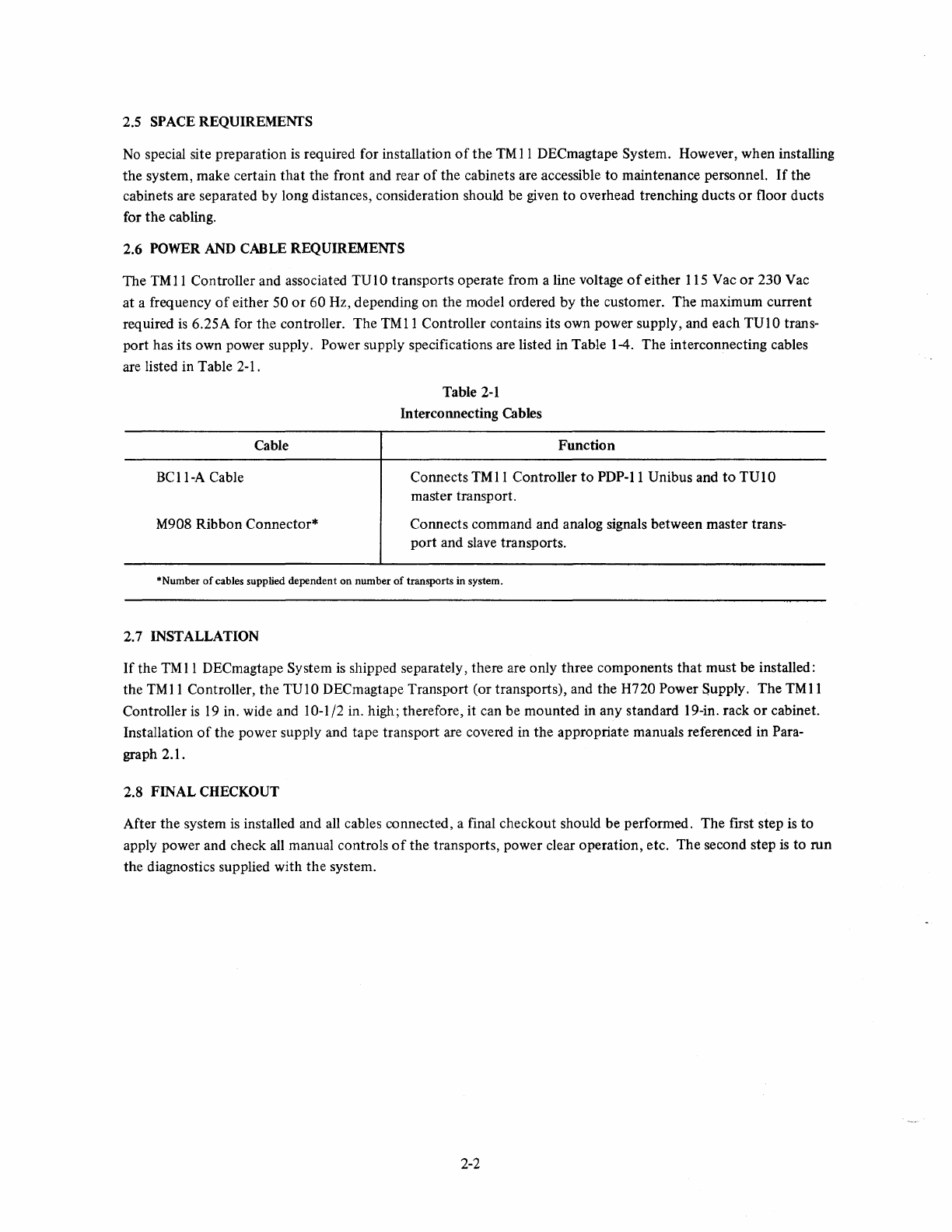

Cable

BC

II-A

Cable

M908 Ribbon Connector*

Table

2-1

Interconnecting Cables

Function

Connects

TMII

Controller

to

PDP-II Unibus and

to

TUIO

master transport.

Connects command and analog signals between master trans-

port

and slave transports.

*Number

of

cables supplied dependent on number

of

transports

in

system.

2.7 INSTALLATION

If

the

TM

II

DECmagtape System

is

shipped separately, there are only three components

that

must be installed:

the TMl1 Controller, the TUIO DECmagtape Transport (or transports), and the H720 Power Supply.

The

TMll

Controller

is

19

in. wide and 10-1/2 in. high; therefore, it can be mounted in any standard 19-in. rack

or

cabinet.

Installation

of

the power supply and tape transport are covered in the appropriate manuals referenced in Para-

graph 2.1.

2.8 FINAL CHECKOUT

After the system

is

installed and all cables connected, a final checkout should be performed. The fIrst step is

to

apply power and check all manual controls

of

the transports, power clear operation, etc. The second step is to run

the diagnostics supplied with

the

system.

2-2

3.1 INTRODUCTION

CHAPTER

3

OPERATION

This chapter provides the information necessary to operate the

TM

11

DECmagtape System. The description

is

divided into two major parts: controls and indicators, and operating procedures.

The description

of

the controls and indicators (refer to Paragraph 3.2)

is

in tabular form and provides the user

with the type and function

of

each operating switch and indicator on the

TVI

0 DECmagtape Transport and the

TM

11

Controller maintenance panel.

Step-by-step operating procedures for

both

on-line and off-line system operation are given in Paragraph 3.3.

Complete maintenance-type procedures and adjustments for the TVIO are beyond the scope

of

this manual and

are covered in the

TV

10 DECmagtape Manual.

3.2 CONTROLS AND INDICATORS

The controls and indicators used

to

operate the

TM

11

DECmagtape System are detailed in the following para-

graphs. These paragraphs describe the

TV

1 0 DECmagtape Transport control panel and the

TM

11

Controller

maintenance panel.

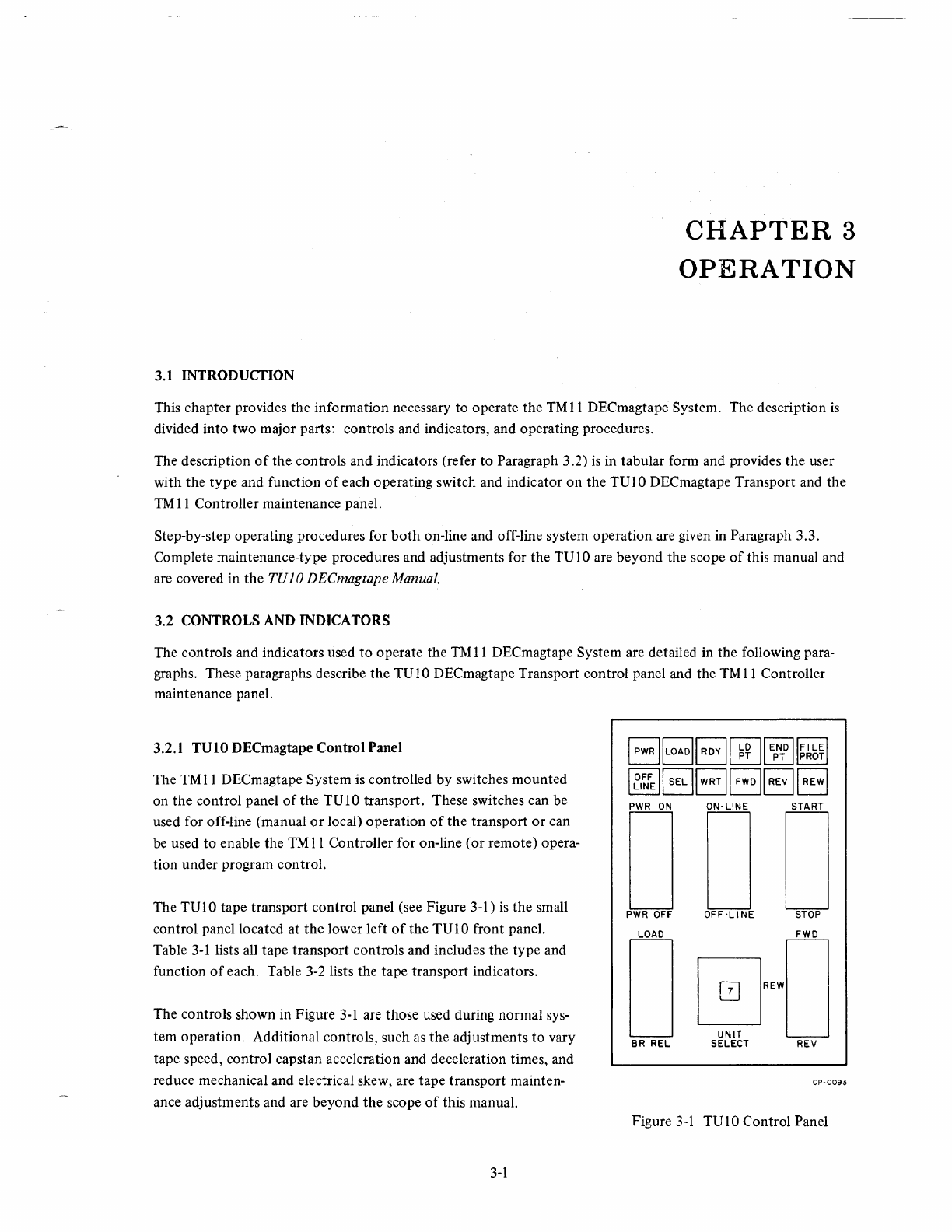

3.2.1 TVIO DECmagtape Control Panel

The

TM

11

DECmagtape System is controlled

by

switches mounted

on the control panel

of

the

TV

10 transport. These switches can be

used for off-line (manual

or

local) operation

of

the transport

or

can

be

used to enable the

TM

11

Controller for on-line (or remote) opera-

tion under program con trol.

The

TV

1 0 tape transport control panel (see Figure 3-1)

is

the small

control panel located at

the

lower left

of

the

TV

1 0 front panel.

Table

3-1

lists all tape transport controls and includes the type and

function

of

each. Table 3-2 lists the tape transport indicators.

The controls shown in Figure

3-1

are those used during normal sys-

tem operation. Additional controls, such as

the

adjustments

to

vary

tape speed, control capstan acceleration and deceleration times, and

reduce mechanical and electrical skew, are tape transport mainten-

ance adjustments and are beyond

the

scope

of

this manual.

3-1

I

PWR

IILOADII

ROY

liLDll

END

WI

LEI

~

PT

PROT

I~I~EIEJIWRTII

FWDIIREV IIREWI

PWR

ON

ON·

LINE

START

PWR

OFF

OFF'LINE

STOP

LOAD

FWD

0

REW

UNIT

BR

REL

SELECT

REV

CP-0093

Figure

3-1

TVIO

Control Panel

Table

3-1

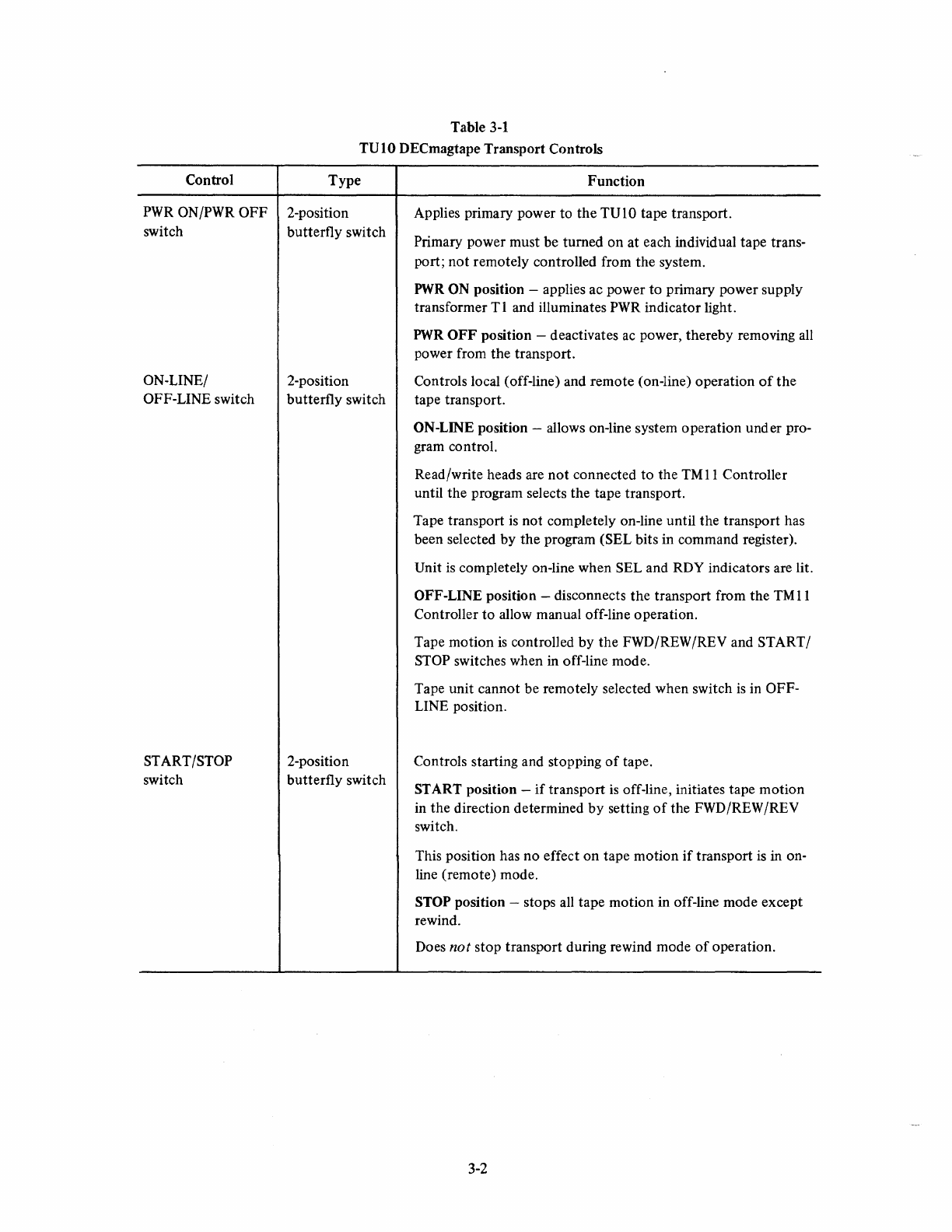

TU 10 DECmagtape Transport Controls

Control Type

PWR

ONjPWR

OFF

2-position

switch butterfly switch

ON-LINE/

OFF-LINE switch

START/STOP

switch

2-position

butterfly switch

2-position

butterfly switch

Function

Applies primary power to the TUIO tape transport.

Primary power must be turned on at each individual tape trans-

port;

not

remotely controlled from the system.

PWR

ON position -applies ac power to primary power supply

transformer T 1 and illuminates

PWR

indicator light.

PWR

OFF

position -deactivates

ac

power, thereby removing all

power from the transport.

Controls local (off-line) and remote (on-line) operation

of

the

tape transport.

ON-LINE position -allows on-line system operation under pro-

gram control.

Read/write heads are

not

connected to the

TM

II

Controller

until the program selects the tape transport.

Tape transport

is

not completely on-line until the transport has

been selected by the program (SEL bits in command register).

Unit

is

completely on-line when SEL and RDY indicators are lit.

OFF

-LINE position -disconnects the transport from the

TM

11

Controller to allow manual off-line operation.

Tape motion

is

controlled

by

the FWD/REW/REV and START/

STOP switches when in off-line mode.

Tape unit cannot be remotely selected when switch

is

in OFF-

LINE position.

Controls starting and stopping

of

tape.

START position -

if

transport

is

off-line, initiates tape motion

in the direction determined

by

setting

of

the FWD/REW fREY

switch.

This position has no effect on tape motion

if

transport

is

in on-

line (remote) mode.

STOP position -stops

all

tape motion in off-line mode except

rewind.

Does not stop transport during rewind mode

of

operation.

3-2

Control

LOAD/BR REL

switch

UNIT SELECT

switch

FWDjREW /REV

switch

Table

3-1

(Cont)

TUIO DECmagtape Transport Controls

Type

3-position

butterfly

switch

8-position

thumbwheel

switch

Each position has

corresponding in-

dicator number.

These are num-

bers 0 through 7.

3-position

butterfly switch

Function

LOAD position -energizes the vacuum system

to

place the

transport in a ready status

to

accept either on-line

or

off-line

commands. Tape is drawn into the

buffer

columns fonning

a tape loop between the vacuum switches.

Switch must always be in LOAD position when operating the

transport either locally (off-line)

or

remotely (on-line).

Lights LOAD indicator.

BR

REL

position -deenergizes the vacuum system and removes

the tape reel

motor

braking action. The tape reels can be man-

ually rotated, because there

is

no vacuum tension on the tape.

Used primarily for loading and removing tape from transport.

Center position -the vacuum system

is

deenergized and

the

brakes are locked.

Pennits remote selection

of

a tape transport

by

the program.

The tape transport

is

selected for use when the

TM

11

Control-

ler's selection code (SEL bits

in

the command register) corres-

ponds

to

the numeral on the UNIT SELECT switch.

When a tape transport is selected by the con troller and the

ON-LINE/OFF-LINE switch

is

set

to

ON-LINE, the ON-LINE

and SEL indicators light

to

indicate

that

the tape unit

is

fully

on-line.

When using more than one tape transport, make certain

that

each transport is dialed to a different number.

Moves tape in selected direction, depending on activation

of

the

START/STOP switch. Used during off-line (local) operation

of

the transport.

If

the tape

is

moving in one direction, moving this switch to a

different setting has

no

effect unless the tape is first stopped

by

START/STOP switch.

The

required sequence

is

given in

Paragraph 3.3.2.

FWD

position -tape

is

moved in the forward direction until the

EOT (end-of-tape) marker

is

sensed, at which time tape

motion

stops.

Causes

FWD

indicator

to

light.

3-3

Control

FWD/REW /REV

switch (cont)

Indicator

PWR

indicator

LOAD

indicator

RDY indicator

LD

PT (load point)

indicator

Table

3-1

(Cont)

TUI0

DECmagtape Transport Controls

Type Function

REW

position -tape

is

moved in the reverse direction, rewind-

ing it onto the feed reel until the BOT (beginning-of-tape) mark-

er

is

sensed, at which time tape motion stops.

After the BOT marker has been reached, depressing the switch

again causes the tape to continue to rewind until it

is

completely

rewound

onto

the feed reel

or

until the switch

is

deactivated.

Causes

REW

indicator to light. During this mode, tape moves

at a much faster speed than during the REV mode.

Tape rewinds to a point well beyond the BOT marker, then

stops, moves forward until the

BOT

marker

is

again sensed,

then comes to a complete stop.

REV position -tape

is

moved

in

the reverse direction until the

BOT

marker

is

sensed, at which time tape motion stops.

Causes REV indicator to light.

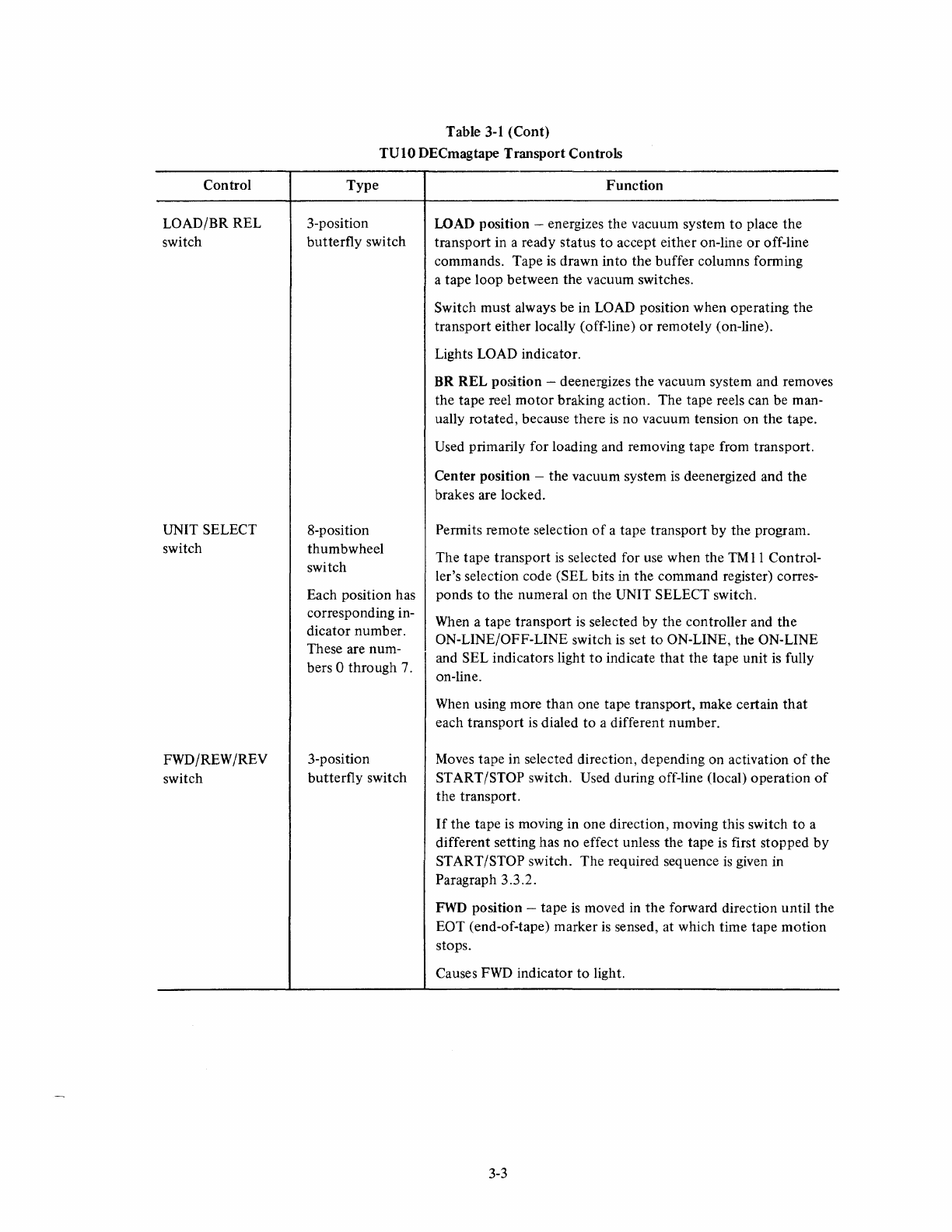

Table 3-2

TUI0

DECmagtape Transport Indicators

Type

single light

single light

single light

single light

Function

When

lit, indicates that primary power has been applied

to

the

TUIO transport.

Controlled by

PWR

ON/pWR

OFF

switch.

When

lit, indicates that the vacuum system has been enabled,

tape has been drawn into the buffer columns forming the re-

quired tape loop, and the transport

is

ready

to

accept either on-

line or off-line commands.

Controlled by LOAD/BR REL switch.

When

lit, indicates that

all

read/write circuits and

input/output

lines are enabled; thus, the transport can accept processor com-

mands provided the SEL indicator

is

also lit.

When

lit, indicates that the beginning-of-tape (BOT) marker has

been sensed, and the transport

is

ready for operation.

Tape motion stops when the BOT marker has been sensed.

When

LD

PT

is

lit, the transport does not accept a rewind

(REW) command

but

does accept forward (FWD) and reverse

(REV) commands.

34

Indicator

END PT (end point)

indicator

FILE PROT

(file protect)

indicator

OFF-LINE

indicator

SEL (select)

indicator

WRT (write)

indicator

FWD

(forward)

indicator

REV (reverse)

indicator

REW (rewind)

indicator

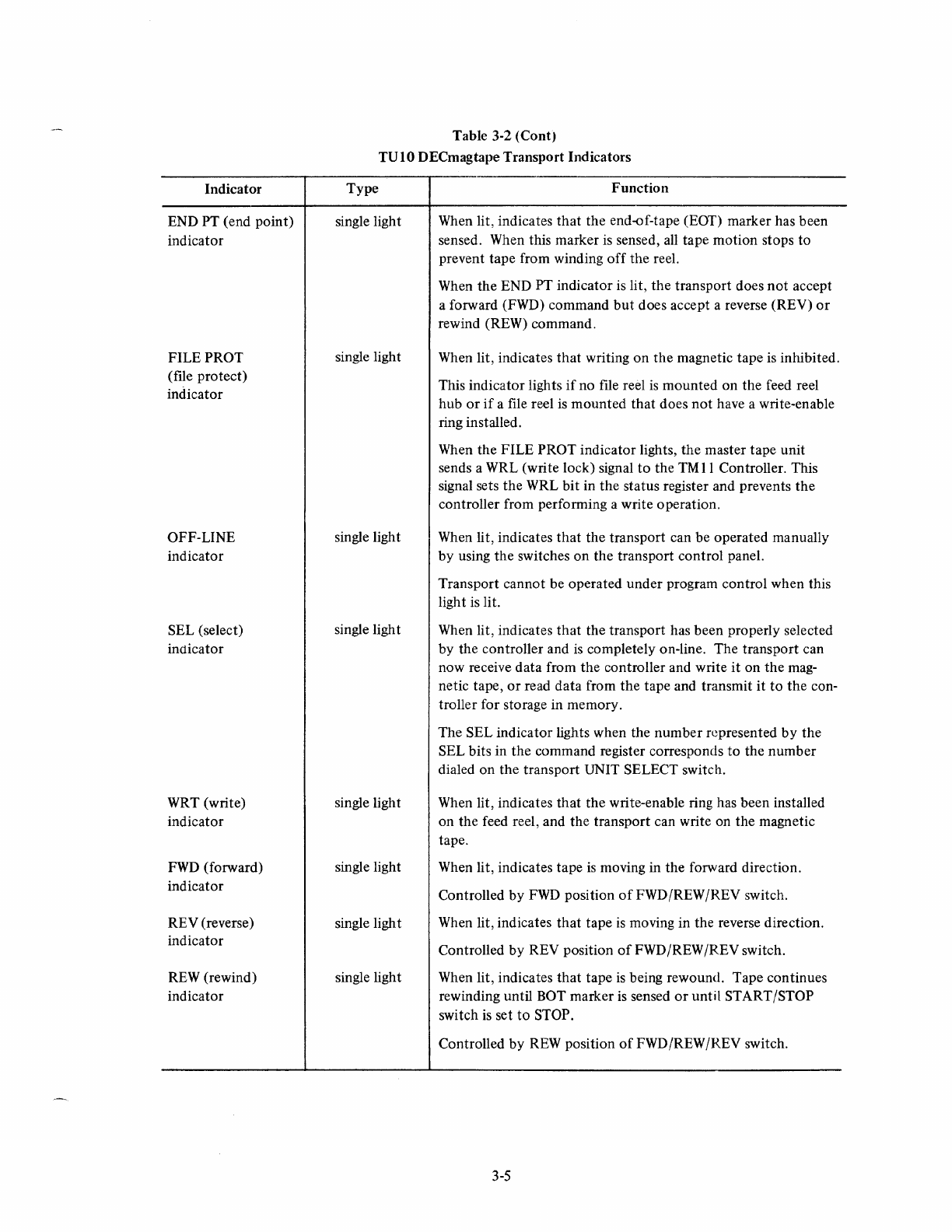

Table 3-2 (Cont)

TUIO

DECmagtape Transport Indicators

Type

single light

single light

single light

single ligh t

single light

single light

single light

single light

Function

When lit, indicates

that

the end-of-tape (EOT) marker has been

sensed. When this marker

is

sensed,

all

tape motion stops to

prevent tape from winding

off

the reel.

When the END PT indicator is lit, the transport does

not

accept

a forward (FWD) command

but

does accept a reverse (REV)

or

rewind (REW) command.

When lit, indicates

that

writing on the magnetic tape is inhibited.

This indicator lights

if

no file reel

is

mounted on the feed reel

hub

or

if

a file reel

is

mounted that does

not

have a write-enable

ring installed.

When the FILE PROT indicator lights, the master tape unit

sends a WRL (write lock) signal

to

the

TM

11

Controller. This

signal sets the WRL bit in

the

status register and prevents

the

controller from performing a write operation.

When lit, indicates

that

the transport can be operated manually

by

using the switches on the transport control panel.

Transport cannot be operated under program control when this

ligh t is

Ii

t.

When lit, indicates

that

the transport has been properly selected

by

the controller and

is

completely on-line. The transport can

now receive data from the controller and write

it

on the mag-

netic tape,

or

read data from

the

tape and transmit

it

to

the

con-

troller for storage in memory.

The SEL indicator lights when the

number

represented

by

the

SEL bits in the command register corresponds

to

the number

dialed on the transport UNIT SELECT switch.

When lit, indicates

that

the write-enable ring has been installed

on the feed reel, and the transport can write on the magnetic

tape.

When lit, indicates tape

is

moving in the forward direction.

Controlled

by

FWD

position

of

FWD/REW/REV switch.

When lit, indicates

that

tape

is

moving in the reverse direction.

Controlled

by

REV position

of

FWD/REW /REV switch.

When lit, indicates

that

tape

is

being rewound. Tape continues

rewinding until BOT marker is sensed

or

until START/STOP

switch

is

set

to

STOP.

Controlled by

REW

position

of

FWD/REW /REV switch.

3-5

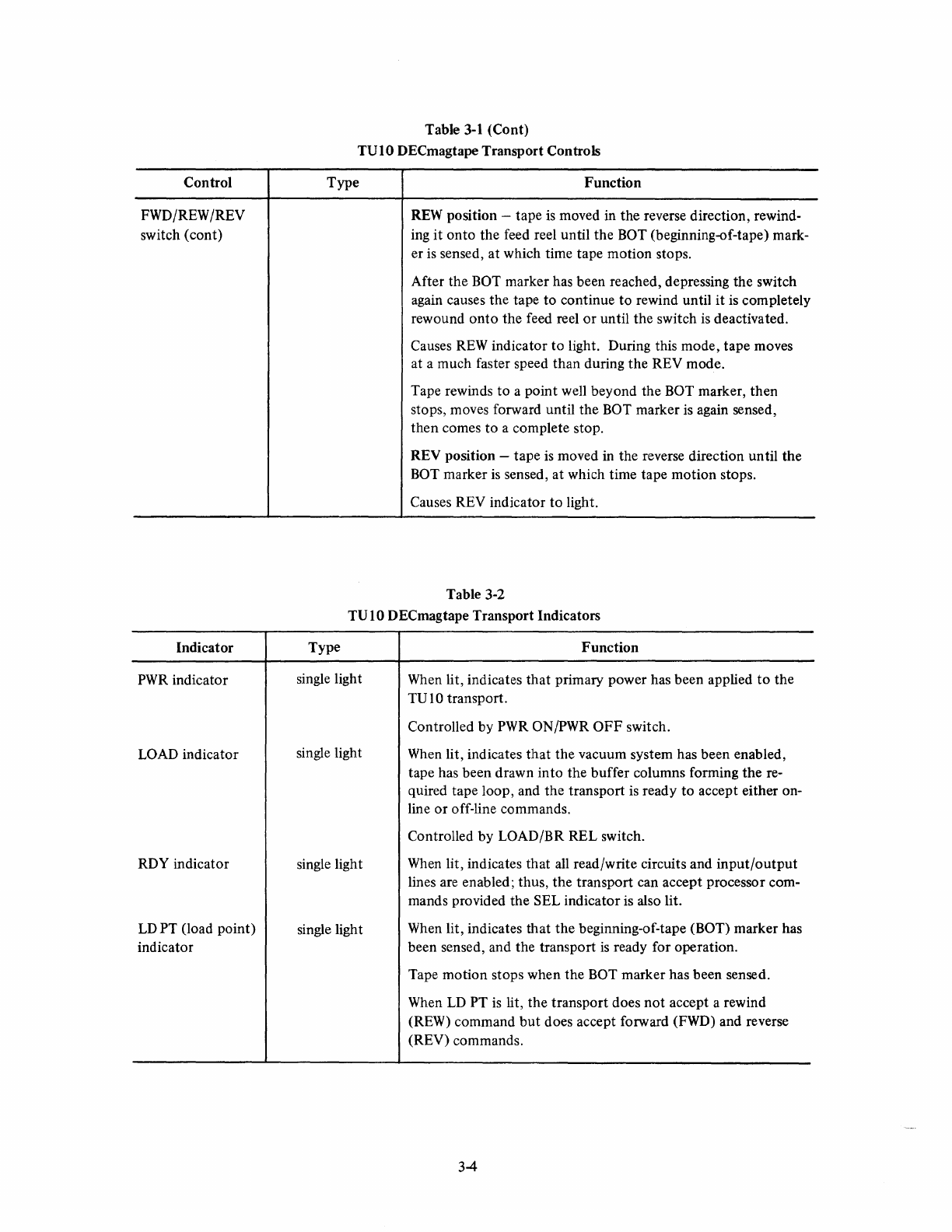

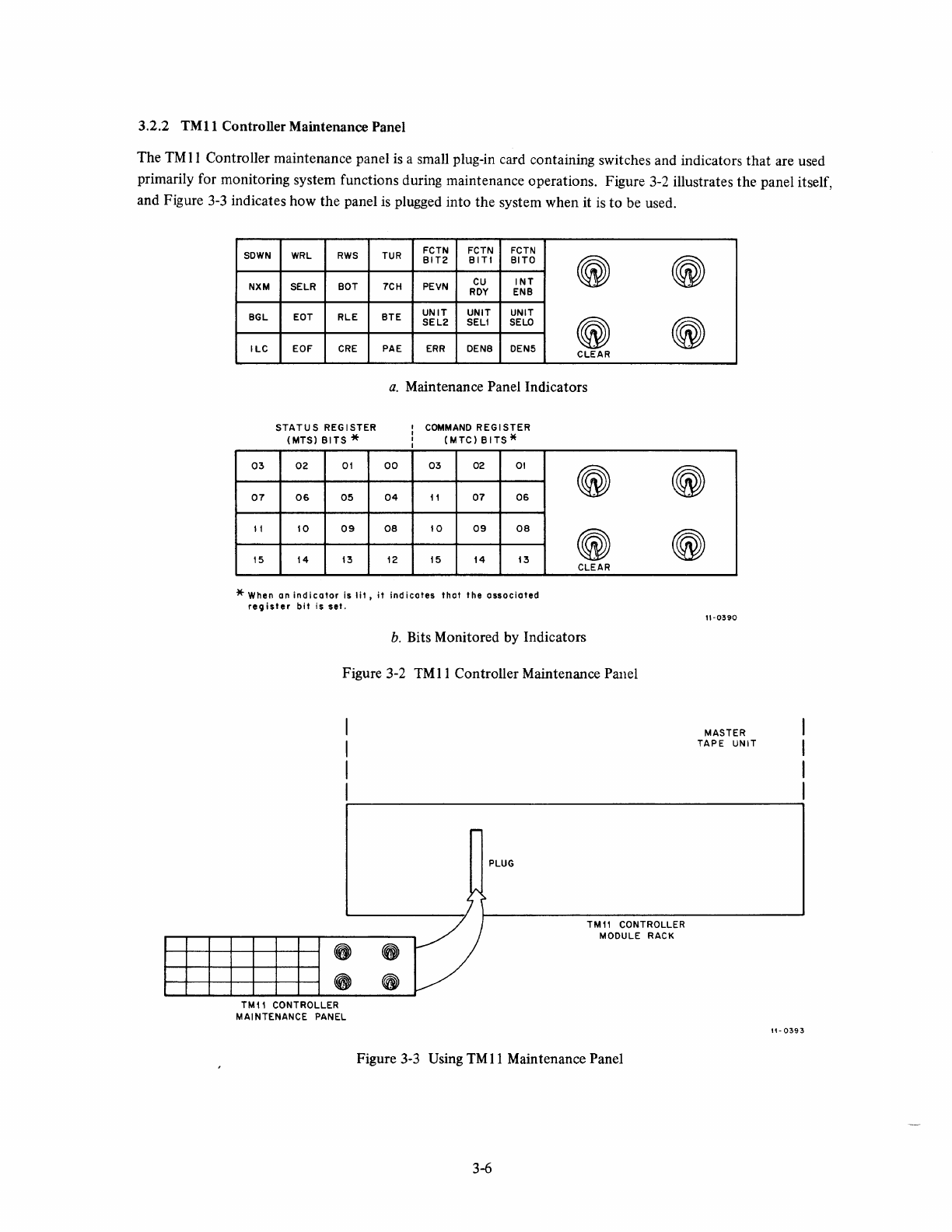

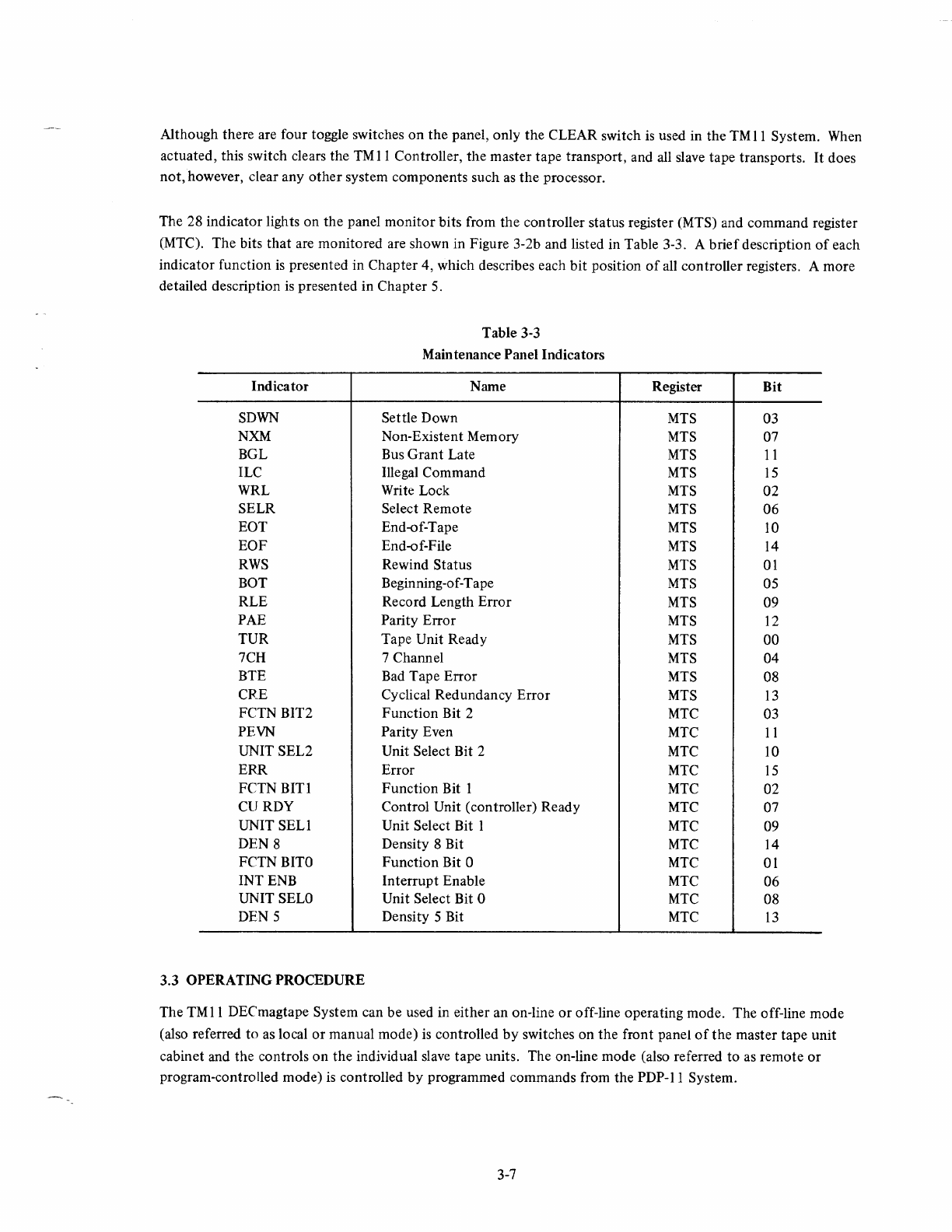

3.2.2

TMll

Controller Maintenance Panel

The

TM

11

Controller maintenance panel

is

a small plug-in card containing switches and indicators that are used

primarily for monitoring system functions during maintenance operations. Figure 3-2 illustrates the panel itself,

and Figure

3-3

indicates how the panel

is

plugged into the system when it

is

to be used.

SOWN

NXM

BGL

ILC

03

07

II

15

WRL

RWS

SELR BOT

EOT

RLE

EOF

CRE

STATUS

REGISTER

(MTS)

BITS

*

02

01

06

05

10

09

14

13

TUR FCTN FCTN

FCTN

BIT2

BITI

BITO

~

7CH PEVN

CU

INT

ROY

ENB

BTE

UNIT

UNIT UNIT

~

SEL2

SEll

SELO

PAE

ERR

DEN8 DEN5 CLEAR

a.

Maintenance Panel Indicators

00

04

08

12

COMMAND

REGI

STER

(MTC)

BITS*

03

02

01

11

07

06

10

09

08

15

14

13

~

~

CLEAR

* When an

indicator

is

lit.

it

indicates

that

the

associated

register

bit

is

set.

b.

Bits Monitored by Indicators

Figure 3-2

TM

11

Controller Maintenance Panel

I"'"

PLUG

II'-

,

J

~

~

~

~

11-0390

MASTER

TAPE UNIT

r/

TMI1

CONTROLLER

~

~

TMll

CONTROLLER

MAINTENANCE PANEL

MODULE RACK

~

~

Figure 3-3 Using

TM

11

Maintenance Panel

3-6

\1-0393

Although there are four toggle switches

on

the

panel, only

the

CLEAR switch

is

used in

the

TM

11

System. When

actuated, this switch clears

the

TM

II

Controller,

the

master tape transport, and all slave tape transports.

It

does

not,

however, clear any

other

system

components

such as

the

processor.

The 28 indicator lights on

the

panel

monitor

bits from

the

controller status register (MTS) and

command

register

(MTC).

The

bits

that

are monitored are shown in Figure 3-2b and listed in Table 3-3. A

brief

description

of

each

indicator function

is

presented in

Chapter

4, which describes each

bit

position

of

all controller registers. A more

detailed description

is

presented in

Chapter

5.

Indicator

SDWN

NXM

BGL

ILC

WRL

SELR

EDT

EOF

RWS

BOT

RLE

PAE

TUR

7CH

BTE

CRE

FCTN BIT2

PEVN

UNIT SEL2

ERR

FCTN

BITl

CURDY

UNIT

SELl

DEN 8

FCTN

BITO

INT ENB

UNIT SELO

DEN 5

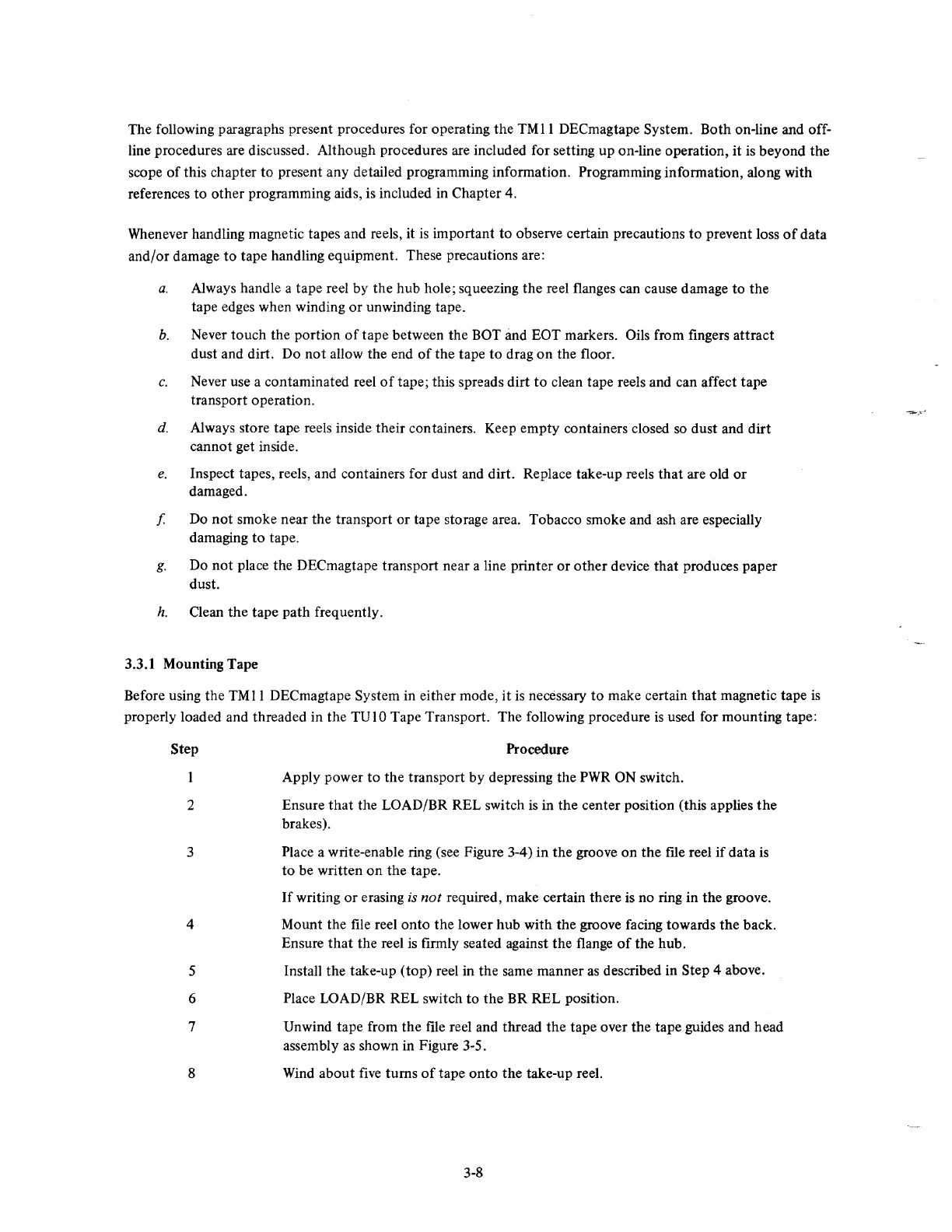

3.3 OPERATING PROCEDURE

Table 3-3

Maintenance Panel Indicators

Name

Settle Down

Non-Existent Memory

Bus

Grant

Late

Illegal Command

Write Lock

Select

Remote

End-of-Tape

End-of-File

Rewind Status

Beginning-of-Tape

Record Length

Error

Parity

Error

Tape Unit Ready

7 Channel

Bad

Tape

Error

Cyclical Redundancy

Error

Function

Bit 2

Parity Even

Unit Select Bit 2

Error

Function

Bit 1

Control Unit (controller) Ready

Unit Select Bit 1

Density 8 Bit

Function

Bit 0

Interrupt

Enable

Unit Select Bit 0

Density 5 Bit

Register

Bit

MTS 03

MTS 07

MTS

11

MTS

15

MTS

02

MTS

06

MTS 10

MTS 14

MTS

01

MTS 05

MTS

09

MTS

12

MTS

00

MTS

04

MTS

08

MTS

13

MTC 03

MTC

II

MTC 10

MTC

15

MTC

02

MTC 07

MTC 09

MTC

14

MTC 01

MTC

06

MTC

08

MTC

13

The

TMII

DEC magtape System can be used in either an on-line

or

off-line operating mode.

The

off-line

mode

(also referred

to

as local

or

manual

mode)

is

controlled

by

switches

on

the

front panel

of

the

master tape unit

cabinet and the controls

on

the

individual slave

tape

units. The on-line mode (also referred

to

as

remote

or

program-controlled mode)

is

controlled

by

programmed commands from the

PDP-II

System.

3-7

The following paragraphs present procedures for operating

the

TM

11

DECmagtape System. Both on-line and off-

line procedures are discussed. Although procedures are included for setting up on-line operation,

it

is beyond the

scope

of

this chapter

to

present any detailed programming information. Programming infonnation, along with

references

to

other

programming aids, is included in Chapter 4.

Whenever handling magnetic tapes and reels, it

is

important

to

observe certain precautions

to

prevent loss

of

data

and/or damage

to

tape handling equipment. These precautions are:

a.

Always handle a tape reel by the hub hole; squeezing the reel flanges can cause damage

to

the

tape edges when winding

or

unwinding tape.

b.

Never

touch

the portion

of

tape between the BOT and EOT markers. Oils from fingers

attract

dust and dirt. Do

not

allow the end

of

the tape

to

drag

on

the floor.

c.

Never use a contaminated reel

of

tape; this spreads dirt

to

clean tape reels and can affect tape

transport operation.

d.

Always store tape reels inside their containers. Keep empty containers closed so dust and

dirt

cannot get inside.

e.

Inspect tapes, reels, and containers for dust and dirt. Replace take-up reels

that

are old

or

damaged.

f Do

not

smoke near the transport

or

tape storage area. Tobacco smoke and ash are especially

damaging

to

tape.

g.

Do

not

place the DECmagtape transport near a line printer

or

other

device

that

produces paper

dust.

h.

Clean

the

tape path frequently.

3.3.1 Mounting Tape

Before using the

TMII

DECmagtape System in either mode,

it

is

necessary

to

make certain

that

magnetic tape

is

properly loaded and threaded

in

the TUIO Tape Transport. The following procedure

is

used for mounting tape:

Step

2

3

4

5

6

7

8

Procedure

Apply power

to

the transport

by

depressing the

PWR

ON switch.

Ensure

that

the LOAD/BR REL switch

is

in the center position (this applies

the

brakes).

Place a write-enable ring (see Figure 3-4)

in

the groove

on

the

file reel

if

data

is

to

be written

on

the tape.

If

writing

or

erasing is

not

required, make certain there is no ring in the groove.

Mount the file reel

onto

the lower

hub

with the groove facing towards the back.

Ensure

that

the reel is firmly seated against the flange

of

the hub.

Install the take-up

(top)

reel in the same manner

as

described in Step 4 above.

Place LOAD/BR REL switch to

the

BR REL position.

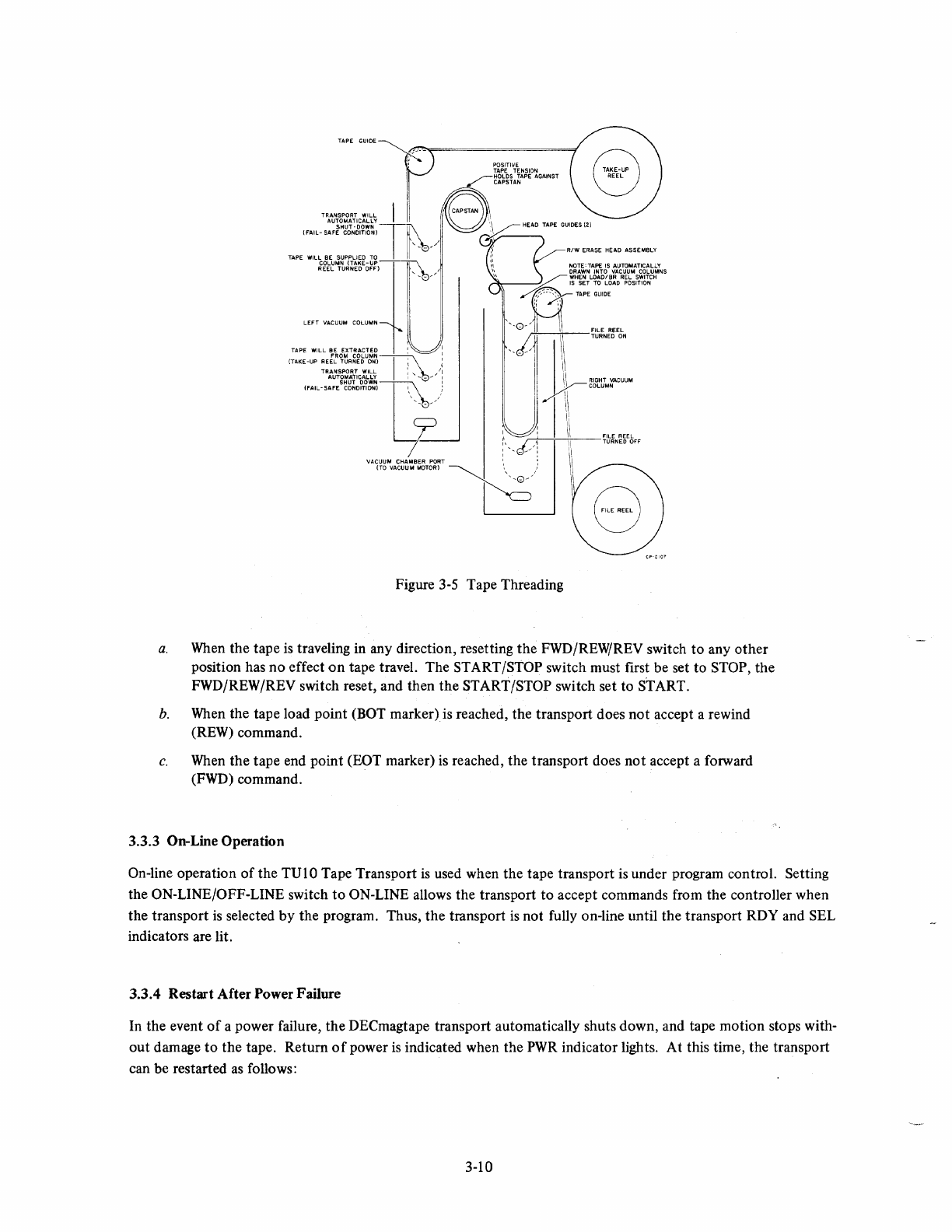

Unwind tape from the file reel and thread the tape over the tape guides and head

assembly

as

shown in Figure 3-5.

Wind

about

five

turns

of

tape

onto

the

take-up reel.

3-8

Step

9

10

Procedure

Set the LOAD/BR REL switch

to

the LOAD position to draw tape

into

the

vacuum columns.

Select

FWD

and depress the START switch

to

advance the tape

to

the load point.

When

the BOT marker is sensed, tape motion stops, the

FWD

indicator goes

out,

and the LOAD

PT

indicator comes on.

NOTE

If

tape

motion continues for more than 10 seconds,

depress STOP, select REV (reverse), and then depress

START. The

tape

should advance

to

the BOT marker

(load point) before stopping.

Figure 3-4 Write-Enable Ring

3.3.2 Oft-Line Operation

Off-line operation

of

the TU I 0 Tape Transport

is

used primarily for loading and unloading magnetic tape, for

positioning magnetic tape prior

to

on-line operation, and for controlling tape motion during maintenance. During

off-line operation, tape motion

is

controlled

by

the switches on the TUIO control panel.

Althouah there are no specific operating procedures for off-line operation (other than that the ON-LINE/OFF-

UNE

switch must be in OFF-LINE), the following switch restrictions should be noted:

3-9

TAPE

GUIDE~.~_

..============7'

POSITIVE

TAPE

TENSION

...----HOLDS

TAPE

AGAINST

"

CAPSTAN

TRANSPORT

WILL I '

AUTOMATICALLY 1

(FAIL-

SAF~H~JNg~r6~)

TR\I'

___

/

I

II'

-'8

RIW

ERASE

HEAD

ASSEMBLY

TAPE

WIL~;i:Hil~~~~O~~)+

[I"

\

__

,-' NOTE'TAPE

IS

AUTOMATICALLY

I "

.'

DRAWN

INTO

VACUUM

COLUMNS

--.J

~

WHEN

LOADI

BR

REL

SWITCH

/

H(--'~S

T:~:

:~,~:AD

POSITION

I:

/'::1

LEFT

VACUUM

COLUMN

"-8-'

1\

FILE REEL

i

~

'I

TURNED

ON

TAPE

WILL

BE

EXTRACTED : "

',

__

/1

II

FROM

COLUMNTh'

I

,.

(TAKE'UP REEL

TURNED

ON)

I \

~

I

'II

TRANSPORT WILL : ,

,/,

1"

AUT~~~i'bAcf~~

- - - : \ \

RIGHT

VACUUM

(FAIL-SAFE

CONDITION)

I '\\",; I

K\COLUMN

L? i,.': I

Ii

\~~":I'",

7-

~'-J':

VACUUM CHAMBER PORT

II:

(TO

VACUUM

MOTOR)

~

\-8-'

I~'

Figure

3-5

Tape Threading

a.

When

the tape

is

traveling in any direction, resetting the FWD/REW/REV switch

to

any other

position has no effect

on

tape travel. The START/STOP switch must first be set to STOP, the

FWD/REW/REV switch reset, and then the START/STOP switch set to START.

b.

When

the tape load point (BOT marker) is reached, the transport does not accept a rewind

(REW) command.

c.

When

the tape end point (EOT marker) is reached, the transport does

not

accept a forward

(FWD) command.

3.3.3 On-Line Operation

On-line operation

of

the TUIO Tape Transport

is

used when the tape transport

is

under program control. Setting

the ON-LINE/OFF-LINE switch

to

ON-LINE allows the transport

to

accept commands from the controller when

the transport

is

selected

by

the program. Thus, the transport

is

not fully on-line until the transport RDY and SEL

indicators are lit.

3.3.4 Restart After Power Failure

In the event

of

a power failure, the DECmagtape transport automatically shuts down, and tape motion stops with-

out damage

to

the tape. Return

of

power

is

indicated when the

PWR

indicator lights. At this time, the transport

can be restarted

as

follows:

3-10

Step

2

3

4

Procedure

Set LOAD/BR REL switch

to

BR

REL position

to

release the brakes.

Manually wind the reels

to

take up any tape slack.

Set the LOAD/BR REL switch to LOAD position

to

draw tape into the vacuum

columns.

Set ON-LINE/OFF-LINE switch

to

desired position and resume desired operation.

3.3.5 Restart After Fail-Safe

If

the tape loop in either buffer column exceeds the limits shown in Figure 3-6, the vacuum system automatically

shuts down, and tape motion stops without damage to the tape.

When

this fail-safe condition occurs, the tape

transport does not respond

to

either on-line or off-line commands. To restart the transport after fail-safe, perform

the same procedures

as

for restarting after power failure (refer to Paragraph 3.3.4).

3.3.6 Removing Tape

o

VACUUM I

SWITCHES

10

I

I I

NORMAL \

~./

OPERATING

,,_

....

LIMITS

NORMAL

OPERATING

LIMITS

SHORT

LOOP

(TRANSPORT

WILL SHUTDOWN)

BUFFER

COLUMN

LONG LOOP

~io"'"---(TRANSPORT

WILL SHUTDOWN

CP-0088

Figure 3-6 Tape Loop Limits

The following procedure describes the method for removing tape from the TUIO Tape Transport.

Step

2

3

4

Procedure

Make certain that ON-LINE/OFF-LINE switch

is

set

to

the OFF-LINE position.

Set START/STOP switch

to

STOP position.

Set FWD/REW /REV switch

to

REW

position.

Set START/STOP switch

to

START position. The tape should rewind until the

BOT marker

is

reached.

3-11

Step

5

6

7

Procedure

Set LOAD/BR REL switch

to

BR REL position

to

release the brakes.

Gently hand wind the file reel in a counterclockwise direction until all

of

the

tape

is

wound

onto

the reel.

CAUTION

When hand winding the tape,

do

not

jerk the reel. This may

stretch

or

compress

the

tape, which can cause irreparable

damage.

Remove the me reel from the hub assembly.

3-12

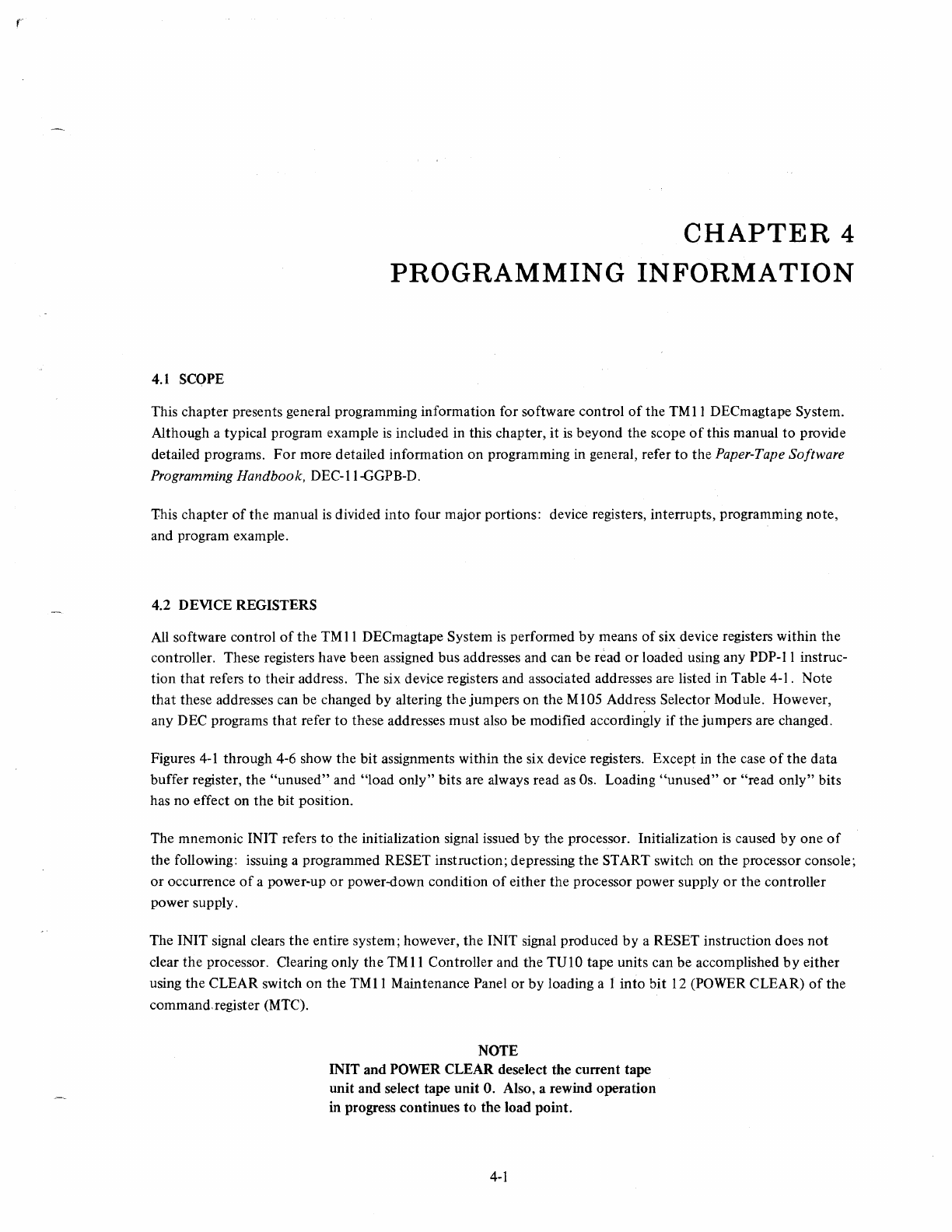

4.1 SCOPE

CHAPTER

4

PROGRAMMING

INFORMATION

This

chapter

presents general programming information for software control

of

the

TM

11

DECmagtape System.

Although a typical program example

is

included in this chapter, it is beyond the scope

of

this manual

to

provide

detailed programs.

For

more detailed information

on

programming in general, refer

to

the Paper-Tape Software

Programming Handbook, DEC-II-GGPB-D.

This

chapter

of

the

manual

is

divided

into

four major portions: device registers, interrupts, programming

note,

and program example.

4.2 DEVICE REGISTERS

All software control

of

the

TM

11

DECmagtape System

is

performed

by

means

of

six device registers within the

controller. These registers have been assigned bus addresses and can be read

or

loaded using any

PDP-II

instruc-

tion

that

refers to their address.

The

six device registers and associated addresses are listed in Table 4-1. Note

that

these addresses can be changed

by

altering

the

jumpers

on

the

M 1

05

Address Selector Module. However,

any DEC programs

that

refer

to

these addresses

must

also be modified accordingly

if

the jumpers are changed.

Figures

4-1

through 4-6 show

the

bit assignments within the six device registers. Except

in

the case

of

the

data

buffer register,

the

"unused"

and "load

only"

bits are always read

as

Os.

Loading

"unused"

or

"read

only"

bits

has no effect on

the

bit position.

The mnemonic INIT refers

to

the

initialization signal issued

by

the processor. Initialization

is

caused

by

one

of

the

following: issuing a programmed RESET instruction; depressing

the

START switch on

the

processor console;

or

occurrence

of

a power-up

or

power-down condition

of

either the processor power supply

or

the

controller

power supply.

The INIT signal clears

the

entire system; however,

the

INIT signal produced

by

a RESET instruction does

not

clear

the

processor. Clearing only

the

TMII

Controller and the TUIO tape units can

be

accomplished

by

either

using

the

CLEAR switch

on

the

TMll

Maintenance Panel

or

by

loading a 1

into

bit

12

(POWER CLEAR)

of

the

command.register (MTC).

NOTE

INIT

and

POWER CLEAR deselect

the

current tape

unit

and

select tape

unit

O.

Also, a rewind operation

in progress continues

to

the

load point.

4-1

Table

4-1

Standard Device Register Assignments

Register

Status Register

Command Register

Byte Record Counter

Current Memory Address Register

Data Buffer Register

TV

10 Read Lines

Mnemonic*

MTS

MTC

MTBRC

MTCMA

MTD

MTRD

Address

772520

772522

772524

772526

772530

772532

*First two letters

of

mnemonic (MT) refer

to

magnetic tape control; the remaining letters repre-

sent the mnemonic

of

a specific register.

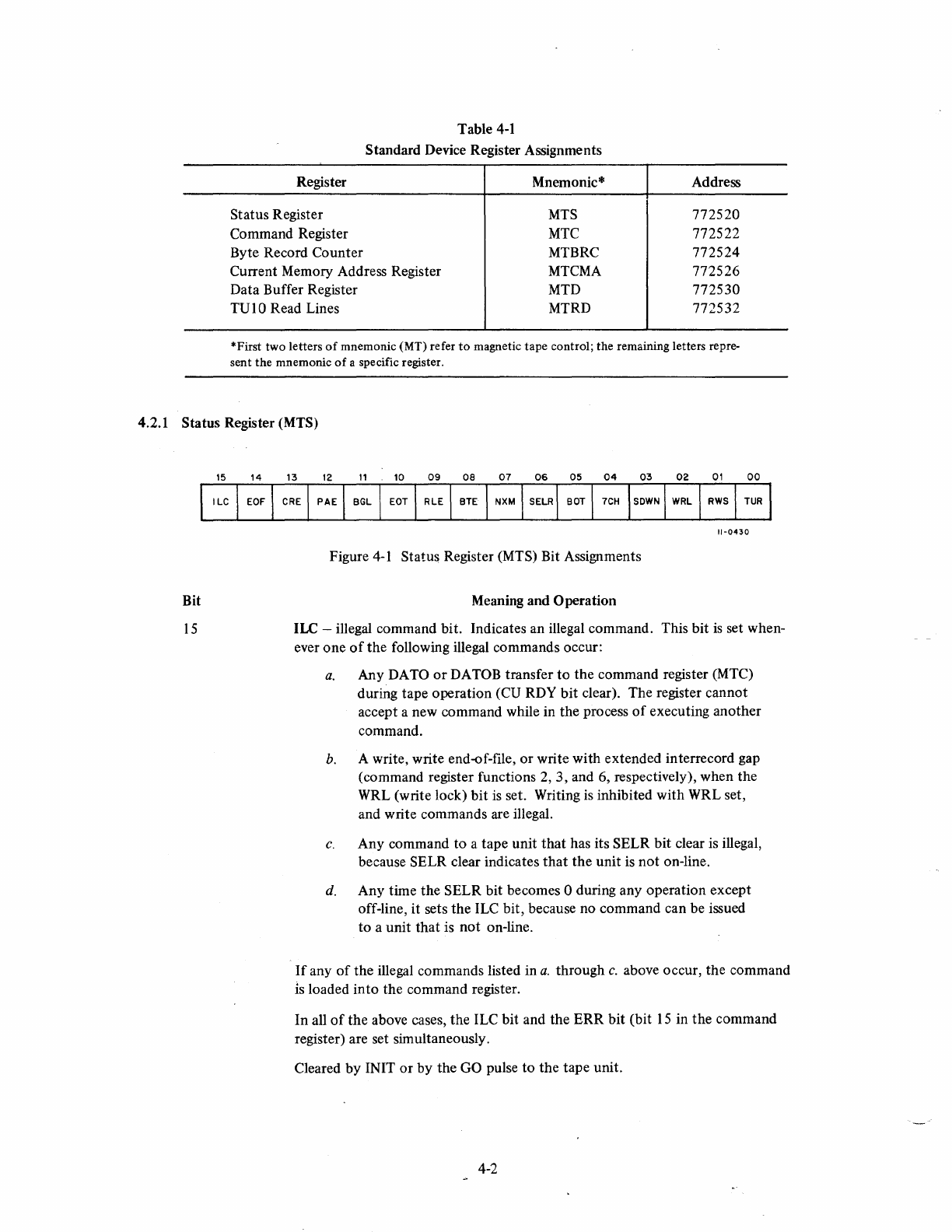

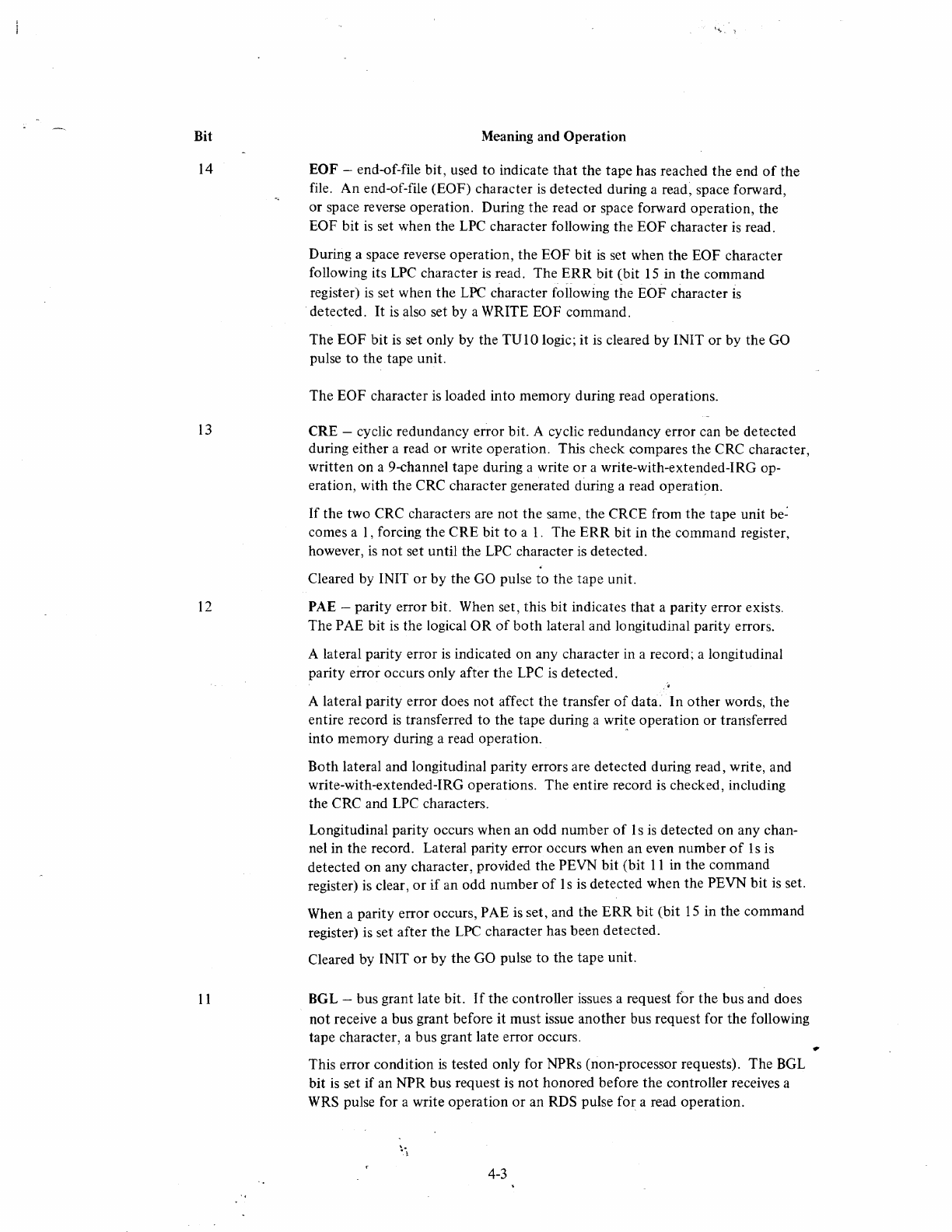

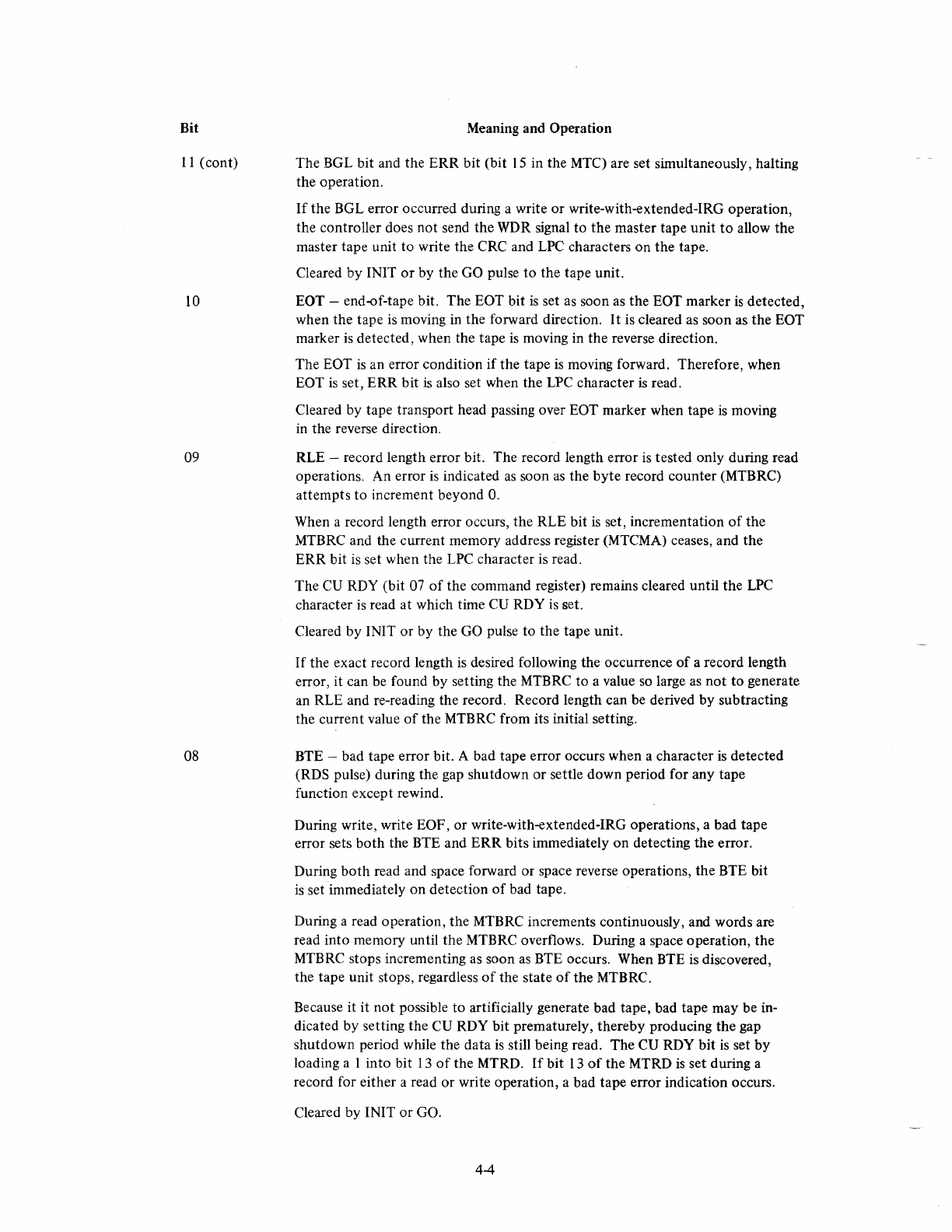

4.2.1 Status Register (MTS)

Bit

15

1/-0'130

Figure

4-1

Status Register (MTS) Bit Assignments

Meaning and Operation

ILC -illegal command bit. Indicates an illegal command. This bit

is

set when-

ever one

of

the following illegal commands occur:

a.

Any DATO

or

DATOB transfer

to

the command register (MTC)

during tape operation (CU RDY bit clear). The register cannot

accept a new command while in the process

of

executing another

command.

b.

A write, write end-of-file,

or

write with extended interrecord gap

(command register functions

2,

3, and 6, respectively), when the

WRL

(write lock) bit

is

set. Writing

is

inhibited with WRL set,

and write commands are illegal.

c.

Any command

to

a tape unit that has its SELR bit clear is illegal,

because SELR clear indicates

that

the unit

is

not on-line.

d.

Any time the SELR bit becomes 0 during any operation except

off-line,

it

sets the ILC bit, because no command can be issued

to

a unit that is not on-line.

If

any

of

the illegal commands listed in

a.

through

c.

above occur, the command

IS

loaded into the command register.

In all

of

the above cases, the ILC bit and the ERR bit (bit

15

in the command

register) are set simultaneously.

Cleared

by

IN

IT or by the

GO

pulse

to

the tape unit.

4-2

Bit

14

13

12

11

Meaning and Operation

EOF -end-of-file bit, used

to

indicate

that

the tape has reached the end

of

the

file. An end-of-file (EOF) character

is

detected during a read, space forward,

or

space reverse operation. During the read or space forward operation, the

EOF bit

is

set when the

LPC

character following the EOF character is read.

During a space reverse operation, the EOF bit

is

set when the EOF character

following its

LPC

character

is

read. The

ERR

bit (bit

15

in the command

register)

is

set when the

LPC

character following the EOF character

is

. detected. It is also set by a WRITE EOF command.

The EOF bit

is

set only by the TUIO logic; it

is

cleared

by

INIT

or

by the

GO

pulse

to

the tape unit.

The EOF character

is

loaded into memory during read operations.

eRE

-cyclic redundancy error bit. A cyclic redundancy error can be detected

during either a read or write operation. This check compares the CRC character,

written on a 9-channel tape during a write

or

a write-with-extended-IRG op-

eration, with the CRC character generated during a read operatis>n.

If the two CRC characters are

not

the same, the

CReE

from the tape unit

be~

comes a

I,

forcing the CRE bit

to

a

1.

The ERR bit in the command register,

however,

is

not

set until the LPC character

is

detected.

Cleared by INIT

or

by

the GO pulse to the tape unit.

PAE -parity error bit. When set, this bit indicates that a parity error exists.

The PAE bit

is

the logical

OR

of

both

lateral and longitudinal parity errors.

A lateral parity error

is

indicated on any character in a record; a longitudinal

parity error occurs only after the

LPC

is

detected.

.'

A lateral parity error does not affect the transfer

of

data.

In

other words, the

entire record

is

transferred

to

the tape during a

wri~e

operation or transferred

into memory during a read operation.

Both lateral and longitudinal parity errors are detected during read, write, and

write-with-extended-IRG operations. The entire record is checked, including

the CRC and

LPC

characters.

Longitudinal parity occurs when an odd number

of

I s

is

detected on any chan-

nel in the record. Lateral parity error occurs when an even number

of

I s is

detected

on

any character, provided the PEVN bit (bit

11

in the command

register)

is

clear,

or

if

an odd number

of

1 s is detected when the PEVN bit

is

set.

When a parity error occurs, PAE is set, and the

ERR

bit (bit

15

in the command

register) is set after the

LPC

character has been detected.

Cleared by INIT

or

by

the GO pulse

to

the

tape unit.

BGL -bus grant late bit.

If

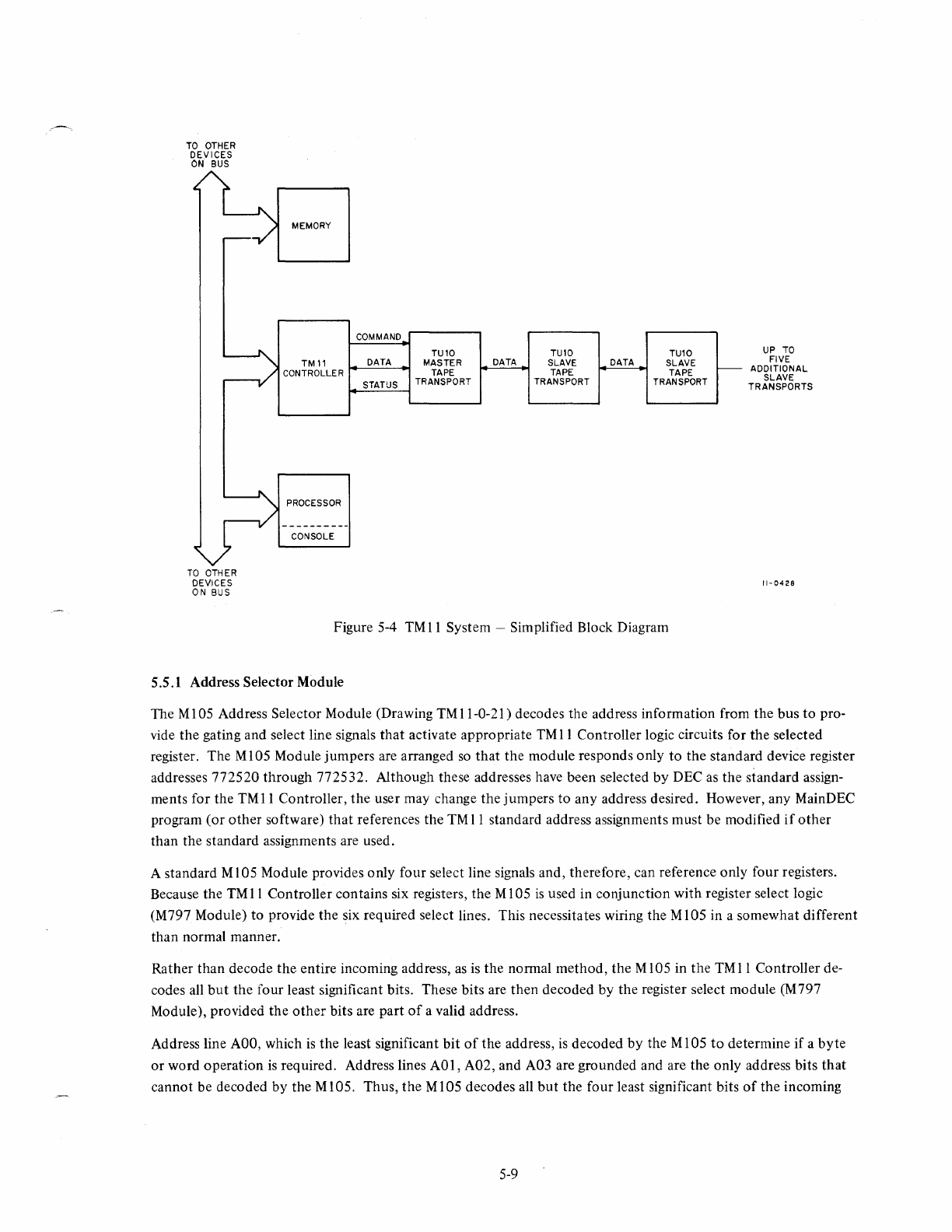

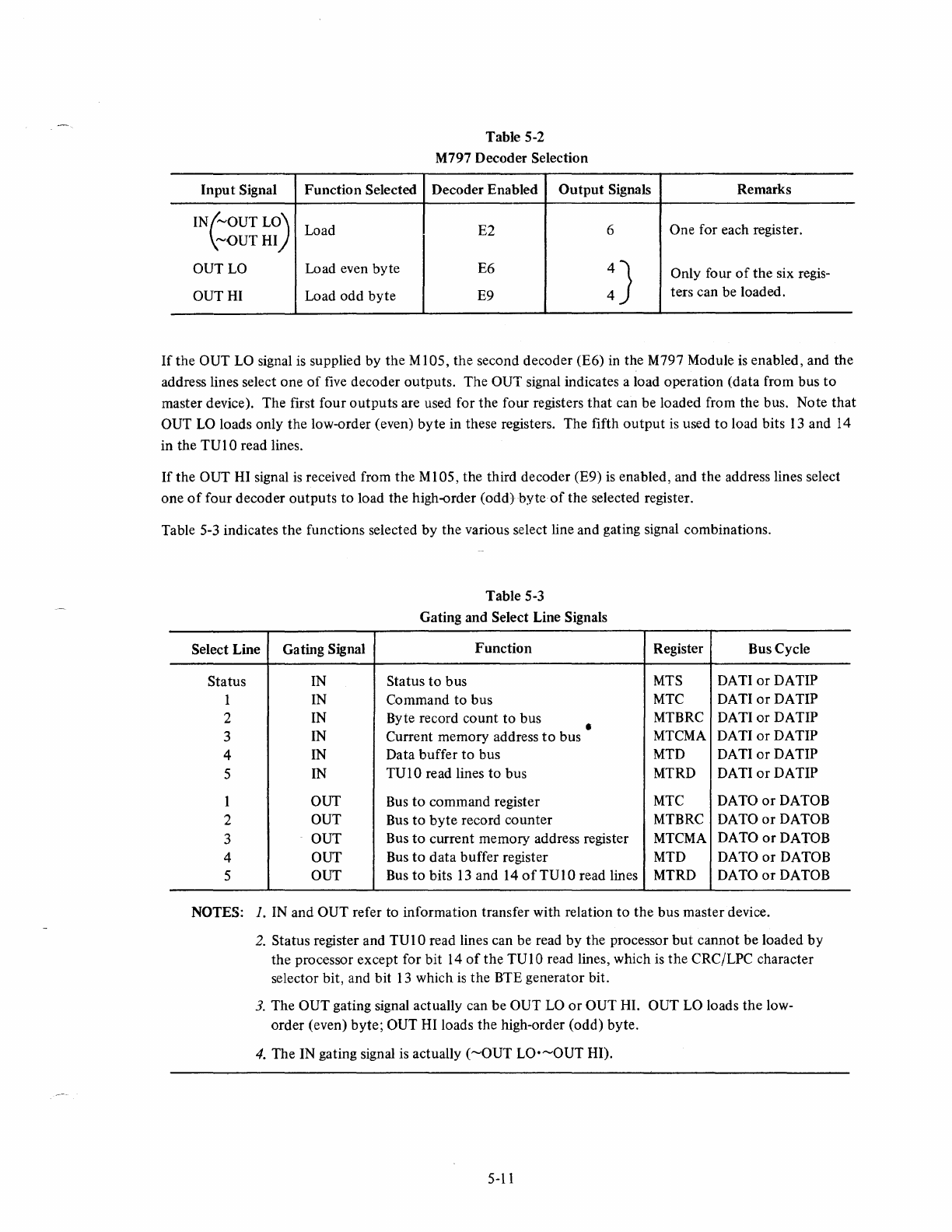

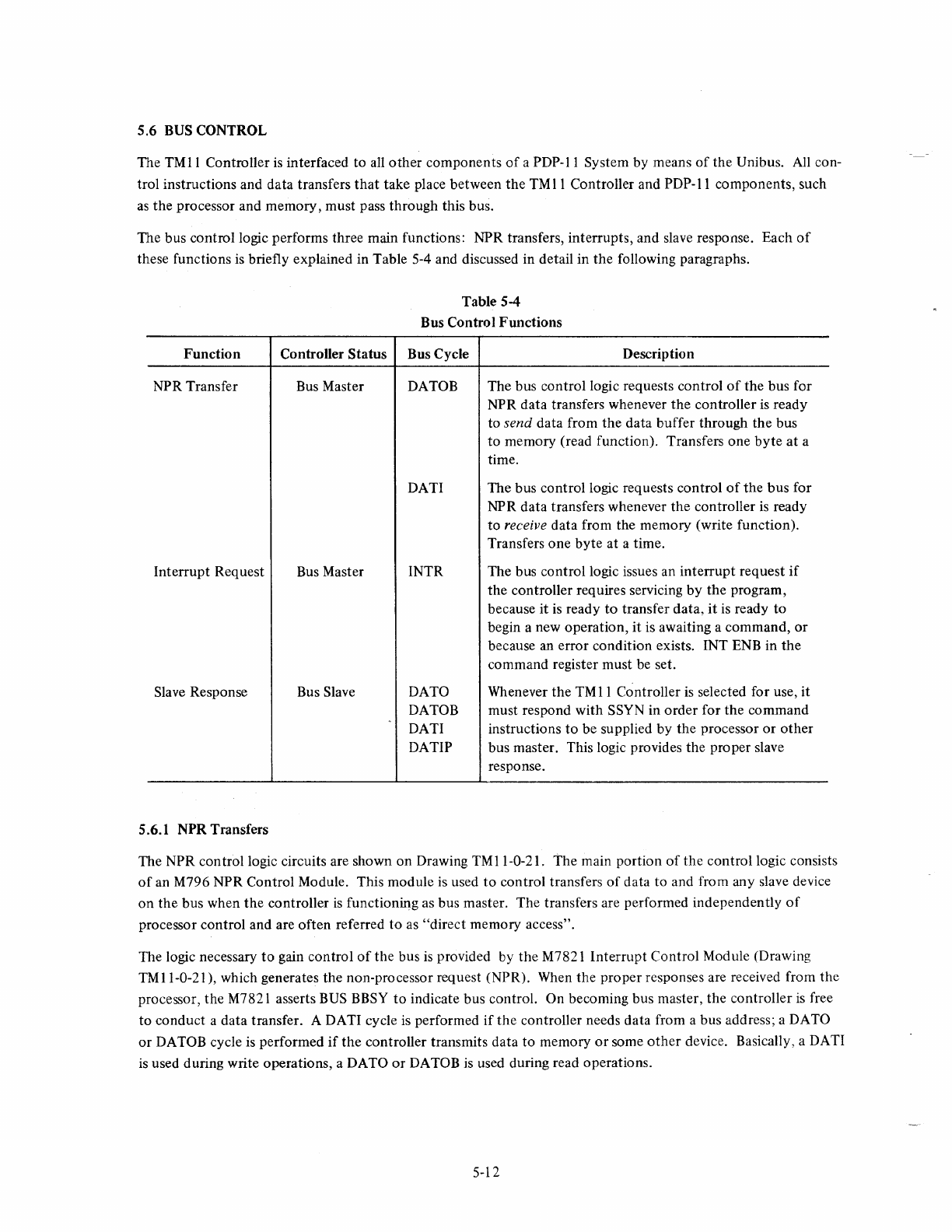

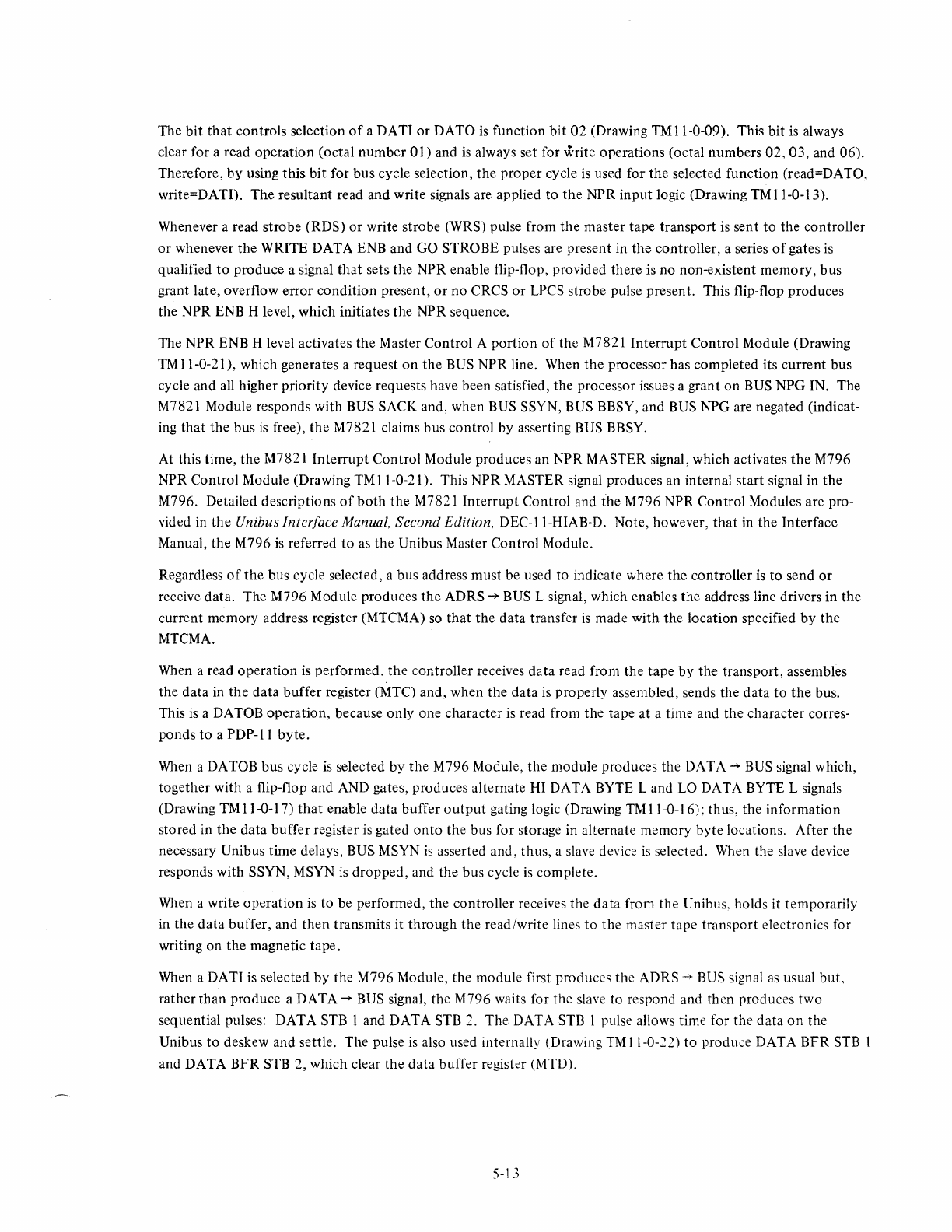

the controller issues a request for the bus and does