Systèmes Embarqués 1 & 2 Jeu D'instructions Du µP ARM A.11 Assembler Instructions Handout

User Manual:

Open the PDF directly: View PDF ![]() .

.

Page Count: 22

Systèmes Embarqués 1 & 2

a.11 - Jeu d’instrucons du µP ARM

Classes T-2/I-2 // 2018-2019

Daniel Gachet | HEIA-FR/TIC

a.11 | 16.11.2018

Contenu

■Les instrucons de transfert

Load and Store instrucon

■Les instrucons pour les opéraons arithméques et logiques

Arithmecal and logical instrucons

■Les instrucons pour des boucles et des branchements

Loop and branch instrucons

[Gac/a.11] T-2/I-2 // 16.11.2018 Systèmes Embarqués 1 & 2 - Jeu d’instrucons du µP ARM 2 / 22

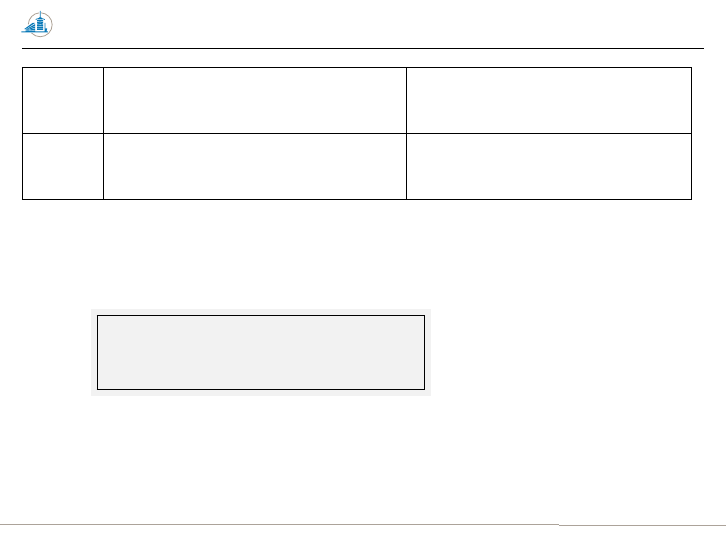

Instrucon de transfert

■On trouve 3 familles d’instrucons

▶Load pour les transferts de données de la mémoire vers le CPU

(registres Rx)

▶Move pour les transferts de données à l’intérieur du CPU (entre

registres Rx)

▶Store pour les transferts de données du CPU (registres Rx) vers la

mémoire

CPU Memory

I/O

ldr

(load)

mov

(move)

str

(store)

[Gac/a.11] T-2/I-2 // 16.11.2018 Systèmes Embarqués 1 & 2 - Jeu d’instrucons du µP ARM 3 / 22

MOV Instrucons

■MOV (move) place une donnée dans le registre desnaon. La

donnée peut être une valeur immédiate ou une donnée contenue

dans un autre registre. Elle peut être décalée (shied) avant d’être

stockée.

MOV{<cond>}{S} <Rd>, <shifter_operand>

■Ulisaon

▶copie d’une donnée d’un registre vers un autre

mov r1, r4 // copie de la donnée contenue dans le

// registre R4 dans le registre R1

▶décalage ou rotaon sur un registre

mov r1, r1, lsl #5 // décale sur la gauche de 5 bits la donnée

// contenue dans le registre R1

▶retour de sous-roune en copiant l’adresse de retour (LR/R14) dans

le compteur ordinal (PC/R15)

mov pc, lr // retour de sous-routine si l’adresse a été

// précédemment sauvée dans le registre LR

[Gac/a.11] T-2/I-2 // 16.11.2018 Systèmes Embarqués 1 & 2 - Jeu d’instrucons du µP ARM 4 / 22

”move”, d’autres instrucons…

MVN Copie le complément à 1 de la donnée

(inversion binaire de la valeur) MVN{<cond>}{S} <Rd>, <shier_operand>

MRS Copie la donnée d’un registre de statut

dans un registre général

MRS{<cond>} <Rd>, CPSR

MRS{<cond>} <Rd>, SPSR

MSR

Copie la donnée d’un registre général

dans les champs (c, x, s, f) d’un registre

de statut (CPSR current ou SPSR saved)

MSR{<cond>} CPSR_<fields>, #<immediate>

MSR{<cond>} CPSR_<fields>, <Rm>

MSR{<cond>} SPSR_<fields>, #<immediate>

MSR{<cond>} SPSR_<fields>, <Rm>

<fields> :

c = control (bits 0..7)

x = extended (bits 8..15)

s = status (bits 16..23)

f = flags (bits 24..31)

[Gac/a.11] T-2/I-2 // 16.11.2018 Systèmes Embarqués 1 & 2 - Jeu d’instrucons du µP ARM 5 / 22

MSR/MRS, un exemple…

■Instrucons forçant le processeur en mode user (bit 4 – bit 0) du

CPSR (0b10000)

mrs r0,cpsr // read CPSR

bic r0,r0,#0xf // modify by removing current mode

msr cpsr_c,r0 // write the result back to CPSR

[Gac/a.11] T-2/I-2 // 16.11.2018 Systèmes Embarqués 1 & 2 - Jeu d’instrucons du µP ARM 6 / 22

LDR Instrucon

■LDR (load) charge le contenue d’une cellule mémoire à une adresse

donnée dans un registre général du CPU

LDR{<cond>} <Rd>, <addressing_mode>

■Ulisaon

▶copie d’une constante dans un registre interne

ldr r0,=0x1201 // copie la constante 0x1201 dans le registre R0

▶copie d’une adresse dans un registre interne

ldr r4,=var // copie de la valeur de l’adresse de la

// variable var dans le registre R4

▶copie d’une donnée stockée en mémoire dans un registre général

ldr r1,[r4] // copie de la donnée stockée en mémoire à

// l’adresse contenue dans le registre R4 (var)

// dans le registre R1

[Gac/a.11] T-2/I-2 // 16.11.2018 Systèmes Embarqués 1 & 2 - Jeu d’instrucons du µP ARM 7 / 22

”load”, une autre instrucon…

LDM

Transferts mulples de la mémoire vers

les registres. Ulisé pour restaurer de

manière conguë le contenu de plu-

sieurs registres préalablement stocké en

mémoire.

LDM{<cond>}<addr_mode> <Rn>{ !}, <registers>

dest : .long 101,102,103,104,105,106

ldr r9,=dest

ldmia r9 !,{r1-r6}

Modes d’adressage :

IA → increment aer

IB → increment before

DA → decrement aer

DB → decrement before

! → Mise à jour du registre <Rn> après opéraon

[Gac/a.11] T-2/I-2 // 16.11.2018 Systèmes Embarqués 1 & 2 - Jeu d’instrucons du µP ARM 8 / 22

STR Instrucon

■STR (store) transfert le contenu d’un registre général du CPU vers

une cellule mémoire à une adresse donnée

STR{<cond>} <Rd>, <addressing_mode>

■Ulisaon

▶copie d’une donnée d’un registre général vers la mémoire

str r1,[r4] // copie de la donnée contenue dans le

// registre R1 vers l’adresse contenue

// dans le registre R4

▶stockage du PC (R15) comme adresse relave en mémoire

str pc,[r3] // copie l’adresse de PC, vers la position

// mémoire contenue dans le registre R3

[Gac/a.11] T-2/I-2 // 16.11.2018 Systèmes Embarqués 1 & 2 - Jeu d’instrucons du µP ARM 9 / 22

”store”, une autre instrucon…

STM

Transferts mulples des registres vers

la mémoire. Ulisée pour sauvegarder

de manière conguë le contenu de plu-

sieurs registres dans la mémoire.

STM{<cond>}<addr_mode> <Rn>{ !}, <registers>

dest : .space 16*4

ldr r1,=1

ldr r2,=2

ldr r3,=3

ldr r4,=4

ldr r9,=dest

stmia r9 !,{r1-r4}

Modes d’adressage :

IA → increment aer

IB → increment before

DA → decrement aer

DB → decrement before

! → Mise à jour du registre <Rn> après opéraon

[Gac/a.11] T-2/I-2 // 16.11.2018 Systèmes Embarqués 1 & 2 - Jeu d’instrucons du µP ARM 10 / 22

Instrucons arithméques et logiques

■Les instrucons arithméques et logiques sont groupées en

plusieurs familles disnctes

▶Les instrucons arithméques (addion, soustracon et

mulplicaon)

▶Les instrucons logiques ( ET, OU, OU exclusif, test)

▶Les instrucons de comparaison

■Format de ces opéraons

<opcode>{<cond>}{S} <Rd>, <Rn>, <shifter_operand>

▶<opcode>: opération (mov, add, sub,…)

▶{<cond>} : condition d’exécution, optionnel

▶{S} : mise à jour des fanions après exécution, optionnel

▶<Rd>: 1ère opérande -> registre de destination

▶<Rn>: 2ème opérande

▶<shifter_operand>: 3ème opérande

[Gac/a.11] T-2/I-2 // 16.11.2018 Systèmes Embarqués 1 & 2 - Jeu d’instrucons du µP ARM 11 / 22

Opéraons arithméques

ADD Addion de deux données

(Rd = Rn + shier_operand) ADD{<cond>}{S} <Rd>, <Rn>, <shier_operand>

ADC Addion de deux données en tenant

compte du carry ADC{<cond>}{S} <Rd>, <Rn>, <shier_operand>

SUB Soustracon de deux données

(Rd = Rn - shier_operand) SUB{<cond>}{S} <Rd>, <Rn>, <shier_operand>

SBC Soustracon de deux données en tenant

compte du carry SBC{<cond>}{S} <Rd>, <Rn>, <shier_operand>

RSB Soustracon inverse de deux données

(Rd = shier_operand - Rn) RSB{<cond>}{S} <Rd>, <Rn>, <shier_operand>

RSC Soustracon inverse de deux données

en tenant compte du carry RSC{<cond>}{S} <Rd>, <Rn>, <shier_operand>

ldr r0, =3583

ldr r1, =7620

add r2, r0, r1

→ R2 = R0 + R1 = 3583 + 7620

[Gac/a.11] T-2/I-2 // 16.11.2018 Systèmes Embarqués 1 & 2 - Jeu d’instrucons du µP ARM 12 / 22

Addion avec Carry

■Une addion avec carry permet de réaliser une addion sur 64 bits

R1 0x00000000 R0 0xffffffff

R3 0x00000000 R2 0x00000001

R5 0x00000001 R4 0x00000000

ldr r0,=0xffffffff

ldr r1,=0x0

ldr r2,=0x1

ldr r3,=0x0

adds r4,r0,r2

adc r5,r1,r3

[Gac/a.11] T-2/I-2 // 16.11.2018 Systèmes Embarqués 1 & 2 - Jeu d’instrucons du µP ARM 13 / 22

Soustracon et soustracon inverse

■L’opéraon de soustracon a un sens :

Rd = Rn – shier_operand

ldr r0, =50

ldr r1, =24

sub r2, r0, r1

→R2 = R0 – R1 = 50 – 24 = 26

■L’opéraon de soustracon inverse change le sens des opérandes :

Rd = shier_operand – Rn

ldr r0, =50

rsb r2, r0, #24 →R2 = 24 – R0 = 24 – 50 = -26

■La soustracon inverse permet d’obtenir le complément à 2 d’une

valeur contenue dans un registre

rsb r2, #0→R2 = 0 – R2 = -R2

[Gac/a.11] T-2/I-2 // 16.11.2018 Systèmes Embarqués 1 & 2 - Jeu d’instrucons du µP ARM 14 / 22

Opéraons de mulplicaon

MUL Mulplicaon

32 bits x 32 bits → 32 bits

MUL <Rd>, <Rm>, <Rs>

→Rd = Rm * Rs

MLA Mulplicaon avec un accumulateur

32 bits x 32 bits → 32 bits + acc

MLA <Rd>, <Rm>, <Rs>, <Rn>

→ Rd = Rm * Rs + Rn

SMULL

Mulplicaon en valeurs signées

32 bits signés x 32 bits signés

→ 64 bits signés

SMULL <RdLo>, <RdHi>, <Rm>, <Rs>

→ RdLo = lower (Rm * Rs) → bits 31-0

→ RdHi = upper (Rm * Rs) → bits 63-32

UMULL Mulplicaon en valeurs non-signés

32 bits x 32 bits → 64 bits

UMULL <RdLo>, <RdHi>, <Rm>, <Rs>

→ RdLo = lower (Rm * Rs) → bits 31-0

→ RdHi = upper (Rm * Rs) → bits 63-32

■Hormis ces quatre instrucons principales, le processeur

implémente également d’autres opéraons de mulplicaon

[Gac/a.11] T-2/I-2 // 16.11.2018 Systèmes Embarqués 1 & 2 - Jeu d’instrucons du µP ARM 15 / 22

Opéraons logiques / booléennes

AND Réalise une opéraon ET logique bit à bit

entre deux opérandes AND{<cond>}{S} <Rd>, <Rn>, <shier_operand>

EOR Réalise une opéraon OU-Exclusif lo-

gique bit à bit entre deux opérandes EOR{<cond>}{S} <Rd>, <Rn>, <shier_operand>

ORR Réalise une opéraon OU logique bit à

bit entre deux opérandes ORR{<cond>}{S} <Rd>, <Rn>, <shier_operand>

BIC

Réalise un ET logique bit à bit entre une

valeur et le complément à 1 de la se-

conde

BIC{<cond>}{S} <Rd>, <Rn>, <shier_operand>

ldr r0, =0x11

ldr r1, =0x22

ldr r2, =0x44

ldr r3, =0x88

and r0, r0, #0x0f

orr r1, r1, #0x88

eor r2, r2, #0xf0

bic r3, r3, #0xf0

[Gac/a.11] T-2/I-2 // 16.11.2018 Systèmes Embarqués 1 & 2 - Jeu d’instrucons du µP ARM 16 / 22

CMP Instrucon

■CMP (compare) compare deux données. La première donnée vient

d’un registre. La deuxième peut être une valeur immédiate, une

donnée contenue dans un registre ou le résultat d’un décalage

avant la comparaison. CMP met à jour les condion flags à parr

du résultat de la soustracon de la deuxième donnée à la première.

CMP{<cond>} <Rn>, <shifter_operand>

→<Rn> - <shifter_operand>

■Ulisaon

▶comparaison d’un registre avec une valeur immédiate

cmp r1, #35 // compare la donnée contenue dans le

// registre R1 avec la valeur 35

▶comparaison de deux données contenues dans deux registres

cmp r1, r3 // compare les données contenues dans les

// registres R1 et R3

[Gac/a.11] T-2/I-2 // 16.11.2018 Systèmes Embarqués 1 & 2 - Jeu d’instrucons du µP ARM 17 / 22

CMN Instrucon

■CMN (Compare Negave) compare une donnée avec le

complément à 2 d’une deuxième donnée. La première donnée

vient d’un registre. La seconde peut être une valeur immédiate, une

donnée contenue dans un registre ou le résultat d’un décalage

préalable. CMN met à jour les condion flags à parr du résultat de

l’addion des deux données.

CMN{<cond>} <Rn>, <shifter_operand>

→<Rn> - (0 - <shifter_operand>)

→<Rn> + <shifter_operand>

■Ulisaon

▶compare avec le complément à 2 d’une donnée

cmn r1, #35 // compare la donnée contenue dans le

// registre R1 avec la valeur -35

[Gac/a.11] T-2/I-2 // 16.11.2018 Systèmes Embarqués 1 & 2 - Jeu d’instrucons du µP ARM 18 / 22

Autres instrucons de comparaison…

TST

Compare deux données et met à jour les

flags sur la base d’une opéraon AND lo-

gique

TST{<cond>}{S} <Rn>, <shier_operand>

TEQ

Compare deux données et met à jour les

flags sur la base d’une opéraon EOR (ou

exclusif)

TEQ{<cond>}{S} <Rn>, <shier_operand>

■TST peut être ulisé afin de déterminer si au moins un bit contenu

dans une série est à un.

■Exemple

ldr r0, =0x53

ldr r1, =0x04

tst r0, r1

[Gac/a.11] T-2/I-2 // 16.11.2018 Systèmes Embarqués 1 & 2 - Jeu d’instrucons du µP ARM 19 / 22

Opéraons de branchement

B

Branchement par offset, valeur immé-

diate de 24 bits signés

→ PC = PC + offset « 2 + 8 → ±32MB

B <offset_24>

loop :

…

…

b loop

BX

Branchement direct par registre (p. ex.

pour le retour de sous-rounes)

→ PC = Rm & 0xffff’fffe

BX <Rm>

roune :

…

…

bx lr

BL

Branchement par offset et sauvetage de

l’adresse de la prochaine instrucon à

exécuter (adresse de retour), pour appel

de sous-rounes

→ LR = PC + 4

→ PC = PC + offset « 2 + 8 → ±32MB

BL <offset_24>

…

…

…

bl roune

BLX

Branchement et sauvetage de la pro-

chaine adresse à exécuter, pour appel in-

direct de sous-rounes

→ LR = PC + 4

→ PC = Rm & 0xffff’fffe

BLX <Rm>

ldr r1,=roune

…

…

blx r1

■Chaque branchement peut s’exécuter de manière condionnelle

[Gac/a.11] T-2/I-2 // 16.11.2018 Systèmes Embarqués 1 & 2 - Jeu d’instrucons du µP ARM 20 / 22

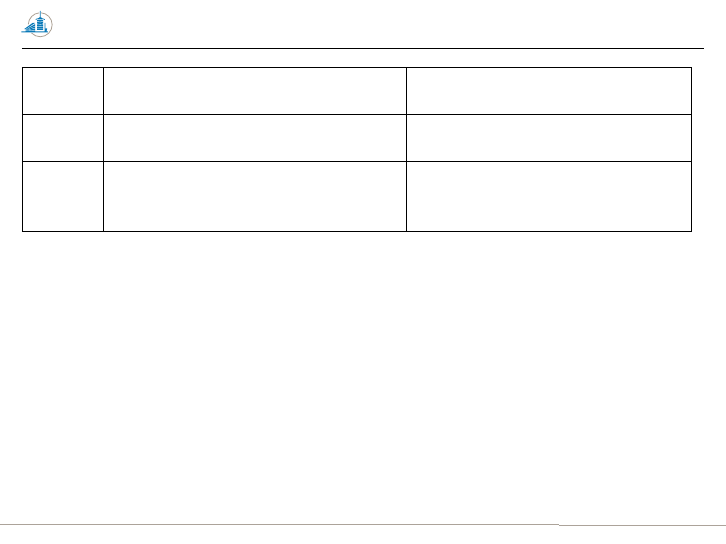

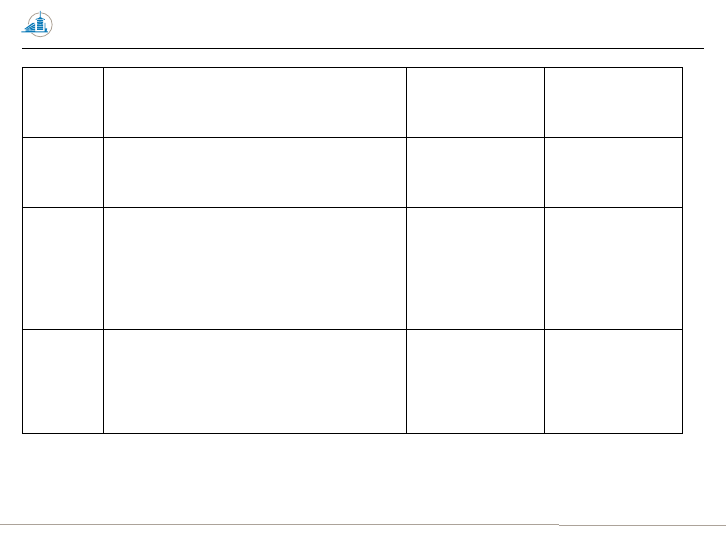

Branchements condionnels

■Pour effectuer un branchement condionnel, il suffit d’ajouter les 2

caractères de la condion à l’opéraon de branchement

B<cc> label ou BLX<cc> R1

Mnemonic Descripon

AL Always (AL normally omied)

EQ (Z==1) Equal

NE (Z==0) Not equal

CS (C==1) Carry Set

CC (C==0) Carry Clear

MI (N==1) Negave (minus)

PL (N==0) Posive or zero (plus)

VS (V==1) Overflow

VC (V==0) No overflow

Mnemonic Descripon

HI > Unsigned higher

HS >= Unsigned higher or same

LS <= Unsigned lower or same

LO < Unsigned lower

Mnemonic Descripon

GT > Signed greater than

GE >= Signed greater than or equal

LE <= Signed less than or equal

LT < Signed less than

[Gac/a.11] T-2/I-2 // 16.11.2018 Systèmes Embarqués 1 & 2 - Jeu d’instrucons du µP ARM 21 / 22

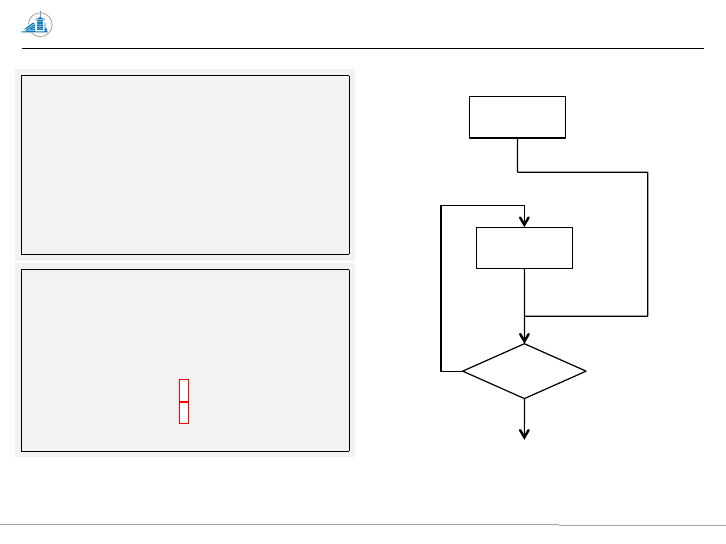

Exemple de boucle

// C-code

#define CONSTANT 10

int sum =CONSTANT ;

for (int i=0 ; i<CONSTANT ; i++) {

sum += i ;

}

// Assembler-code

ldr r3, =10

ldr r2, =0

b test

loop : add r3, r3, r2

add r2,#1

test : cmp r2,#10

blo loop

sum=10'

i'='0'

i'<'10'

sum'+='i'

i'++'

Yes

No

[Gac/a.11] T-2/I-2 // 16.11.2018 Systèmes Embarqués 1 & 2 - Jeu d’instrucons du µP ARM 22 / 22