Clevo M730TG Service Manual. Www.s Manuals.com. Manual

User Manual: Notebook Clevo M730TG - Service manuals and Schematics, Disassembly / Assembly. Free.

Open the PDF directly: View PDF ![]() .

.

Page Count: 91

- Manual

- Preface

- Chapter 1: Introduction

- Overview

- System Specifications

- External Locator - Top View with LCD Panel Open

- External Locator - Front & Right side Views

- External Locator - Left Side & Rear View

- External Locator - Bottom View

- Mainboard Overview - Top (Key Parts)

- Mainboard Overview - Bottom (Key Parts)

- Mainboard Overview - Top (Connectors)

- Mainboard Overview - Bottom (Connectors)

- Chapter 2: Disassembly

- Overview

- Maintenance Tools

- Connections

- Maintenance Precautions

- Disassembly Steps

- Removing the Battery

- Removing the Hard Disk Drive

- Removing the Optical (CD/DVD) Device

- Removing the System Memory (RAM)

- Removing the Inverter Board

- Removing the Processor

- Removing the Wireless LAN Module

- Removing the Bluetooth Module

- Removing the Keyboard

- Removing the Modem

- Appendix A: Part Lists

- Appendix B: Schematic Diagrams

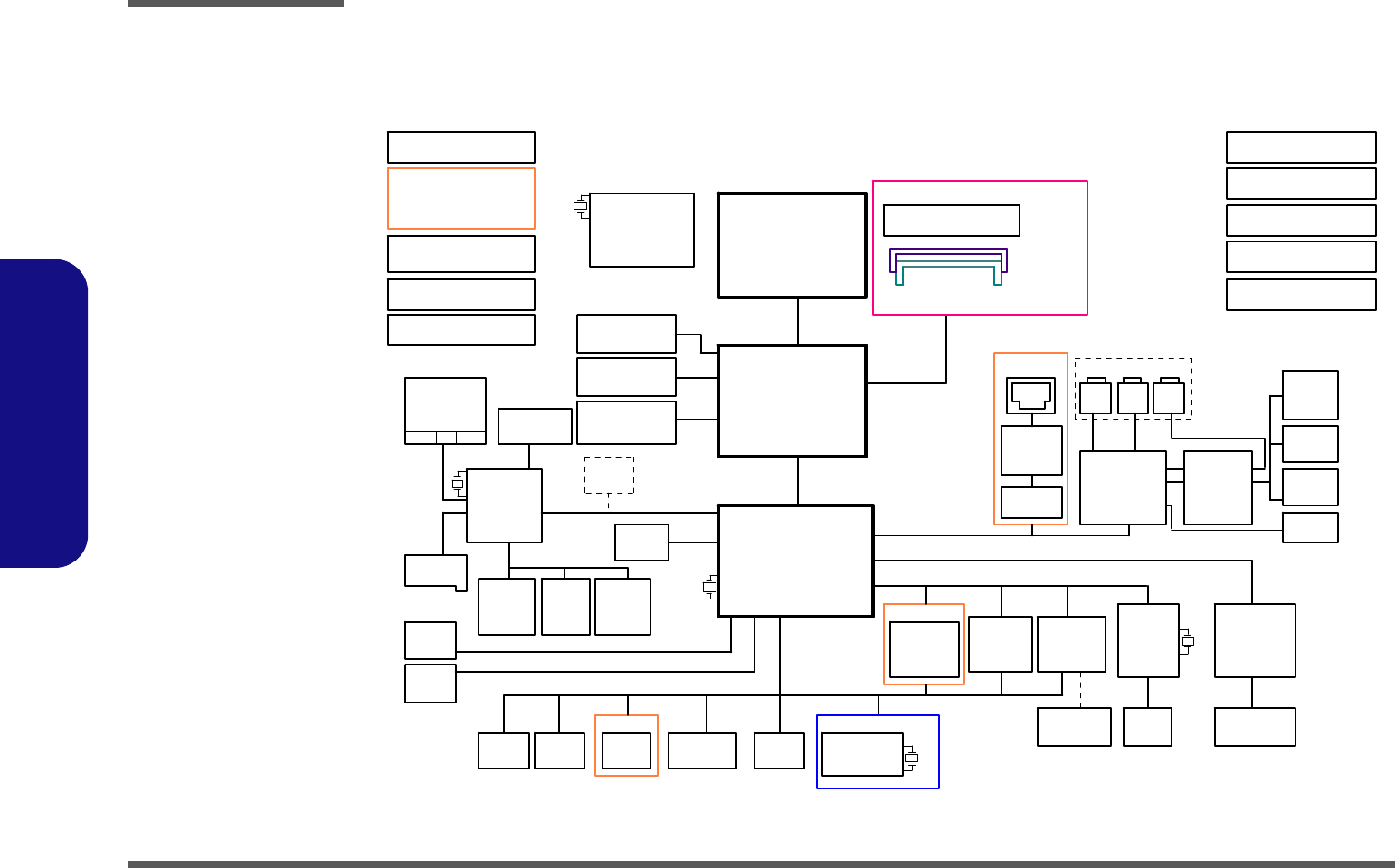

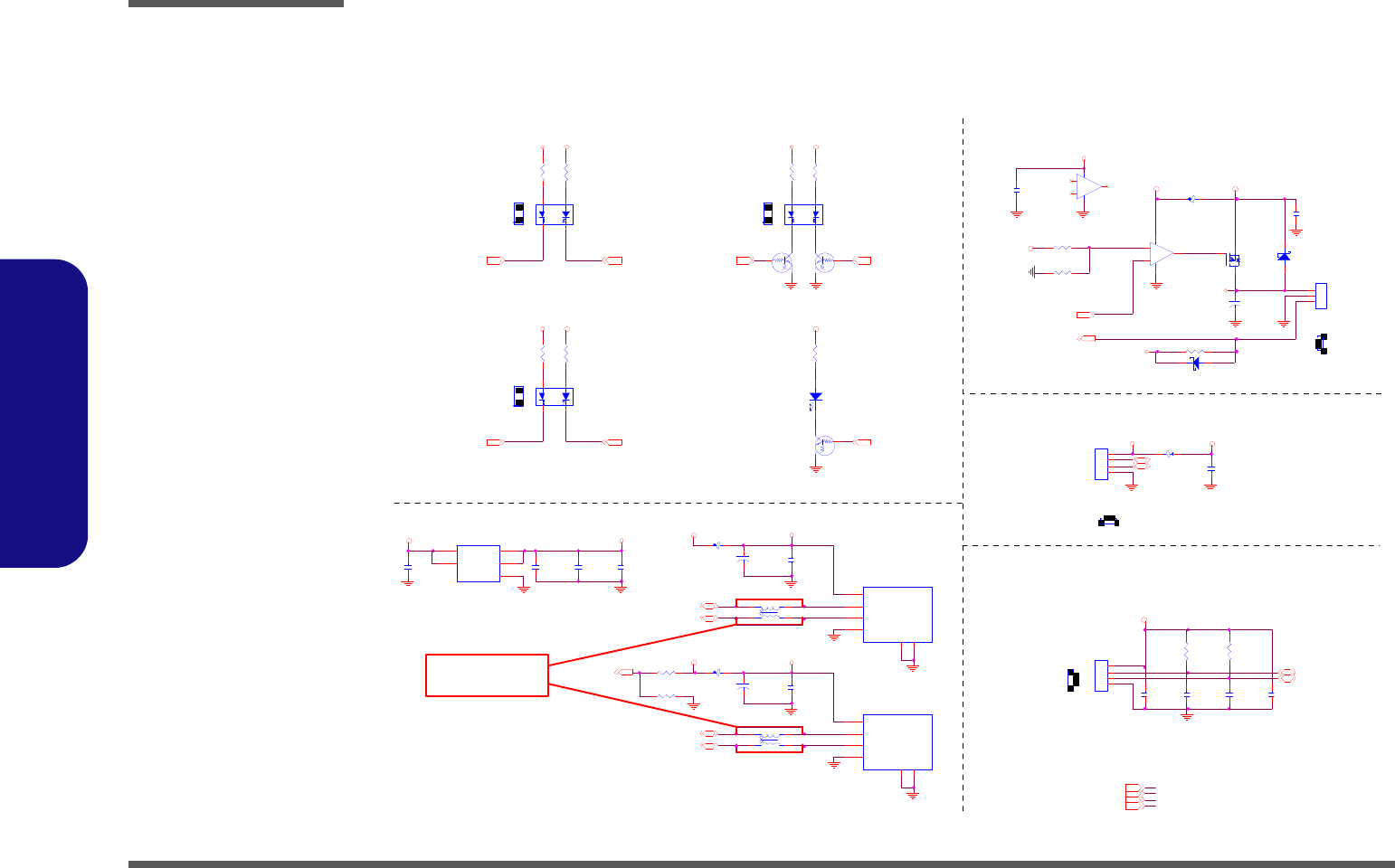

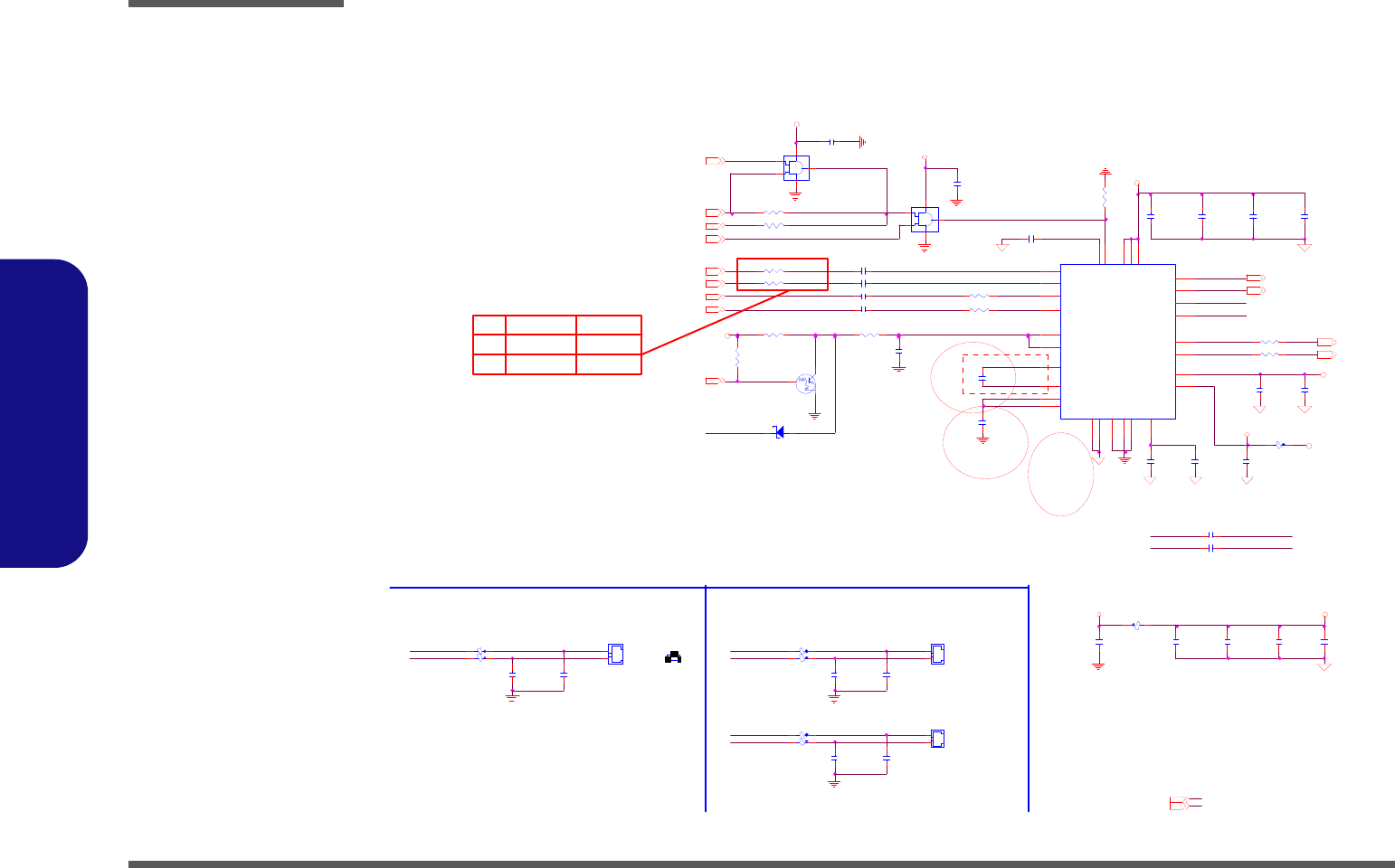

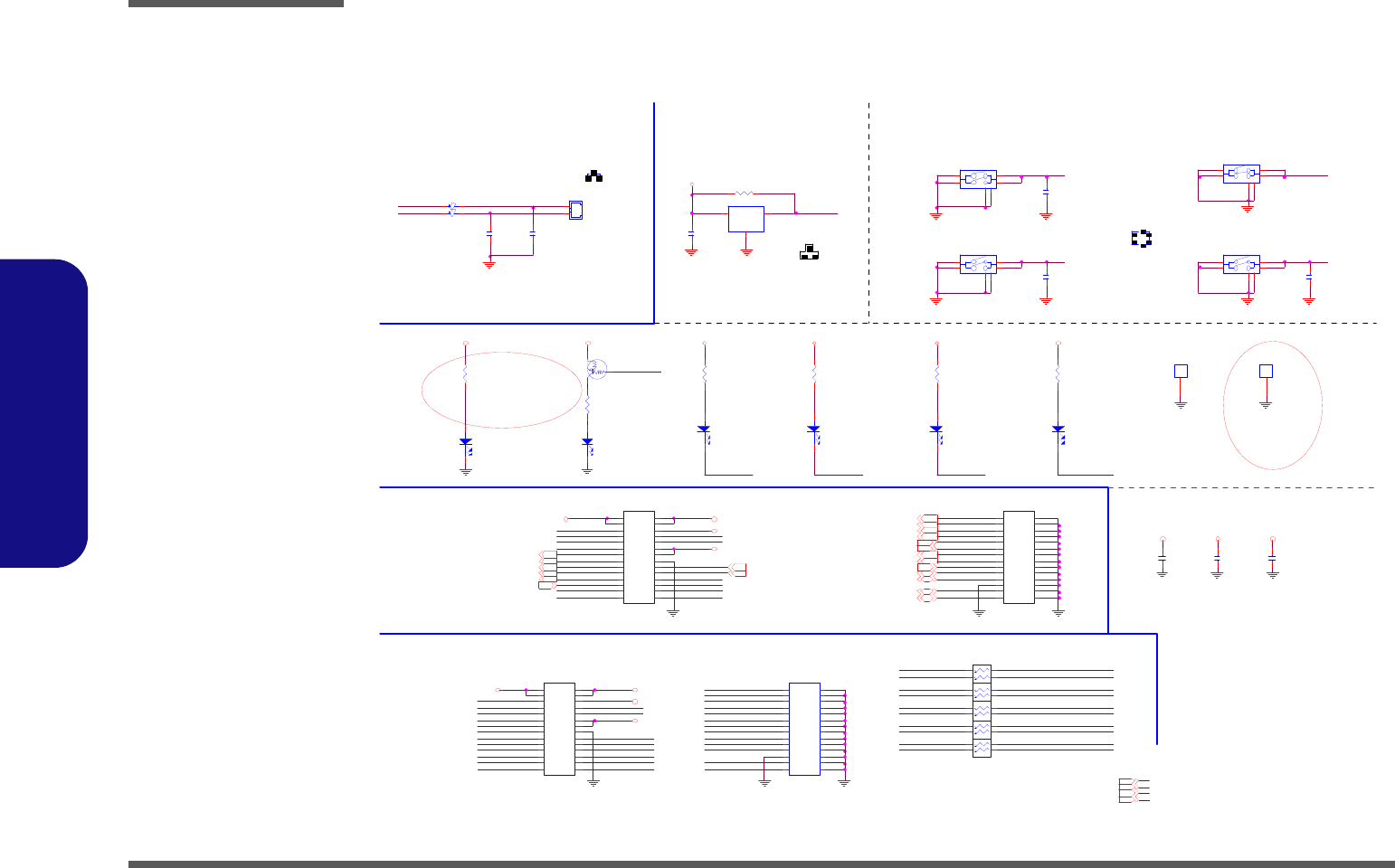

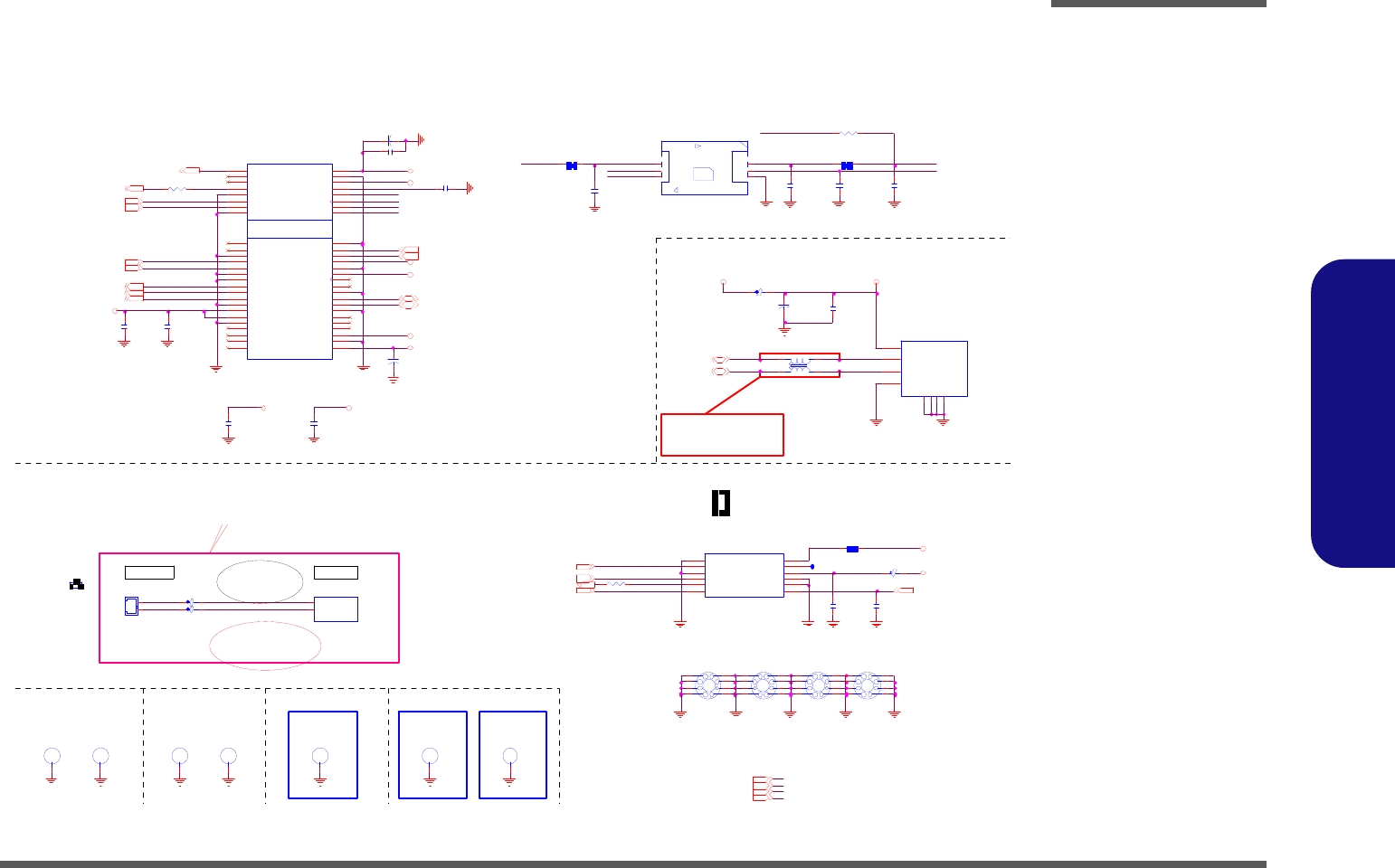

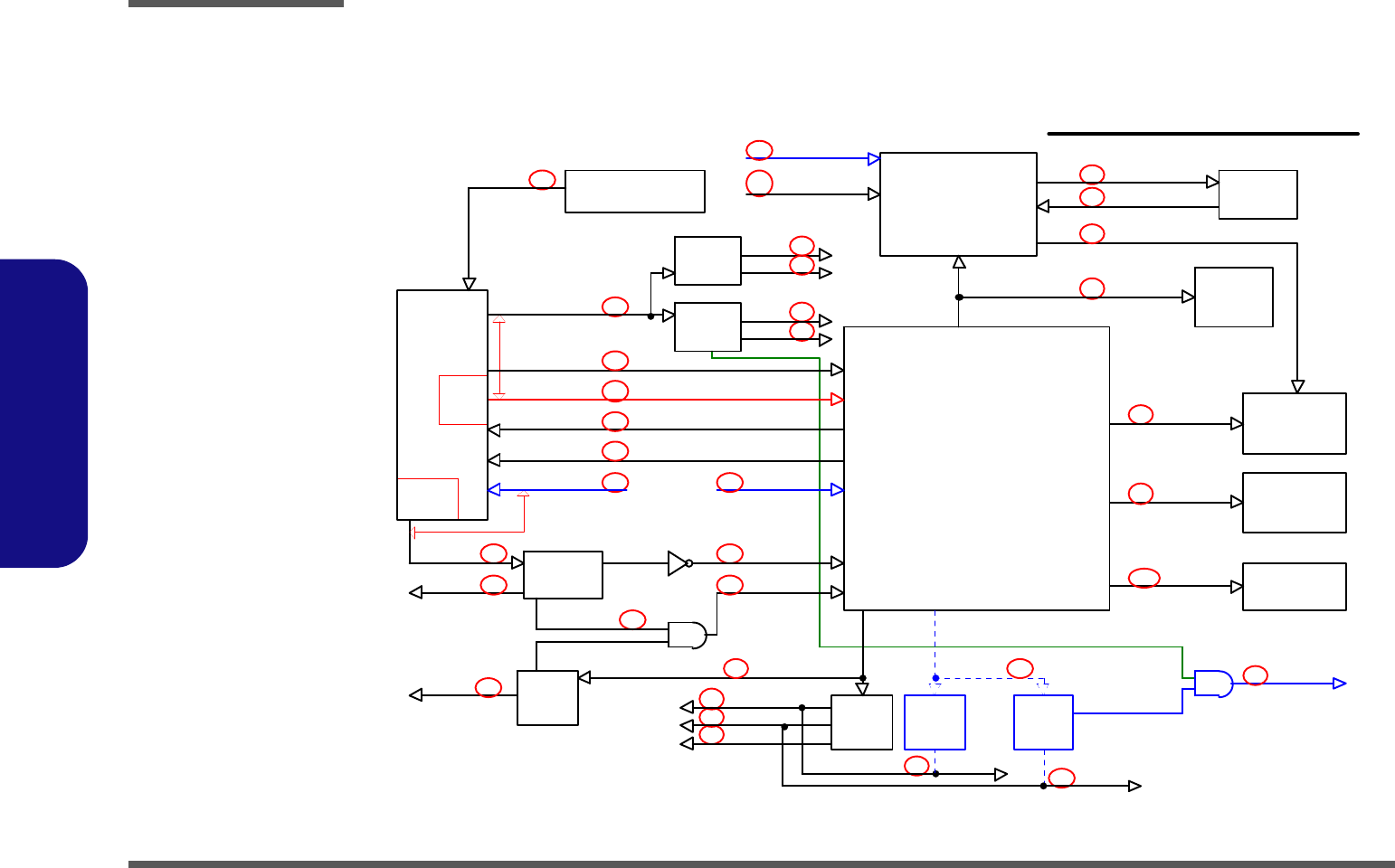

- System Block Diagram

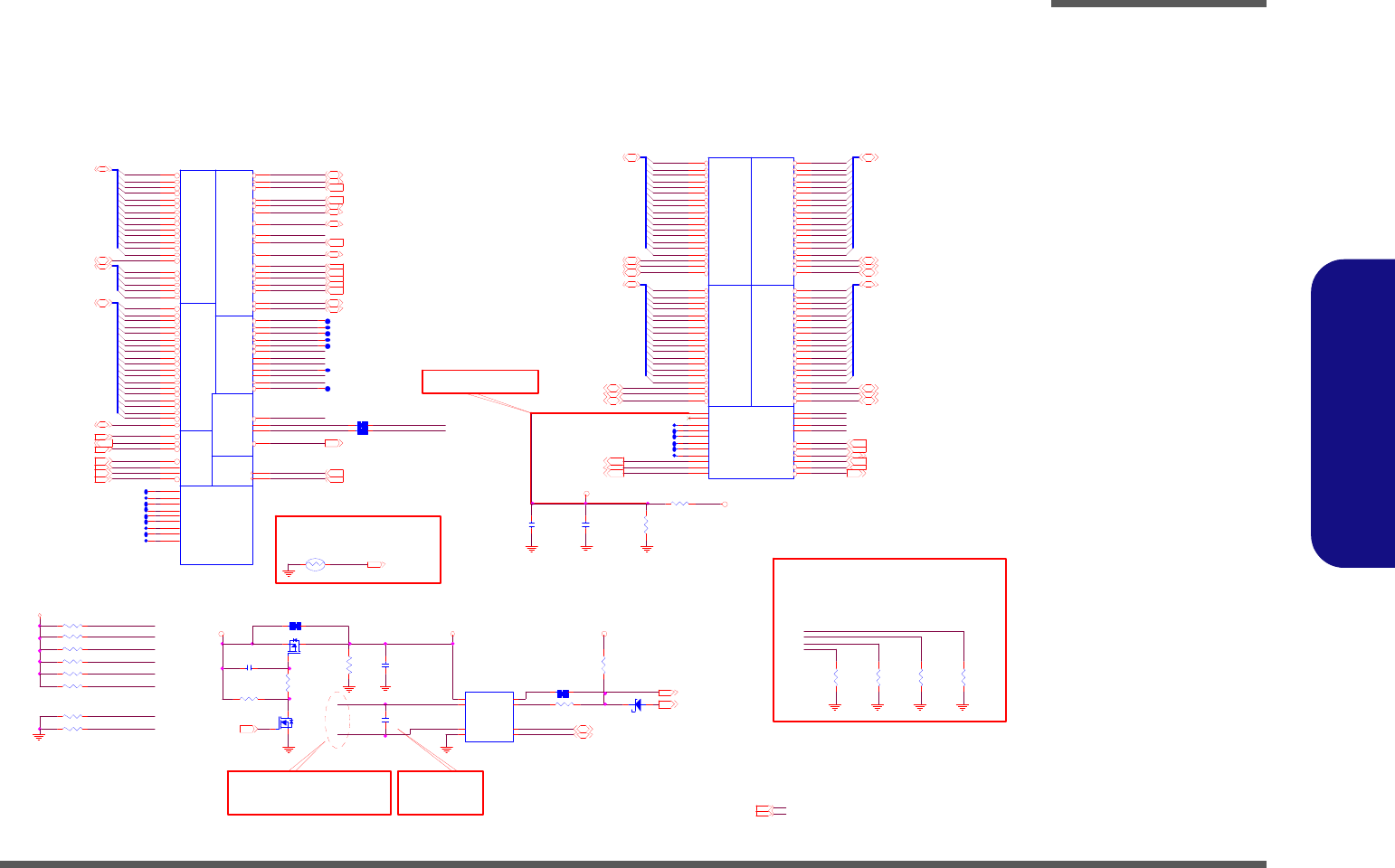

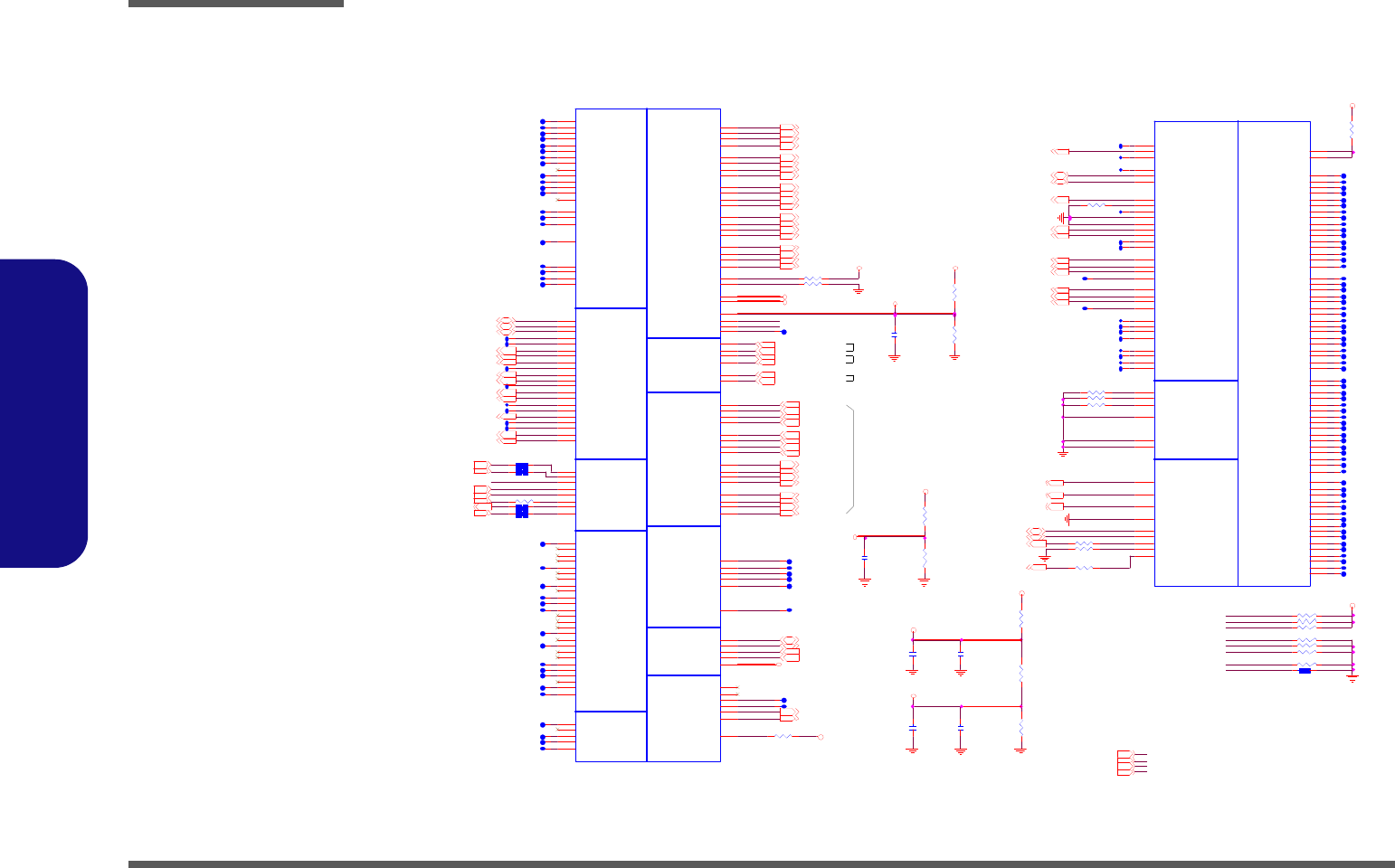

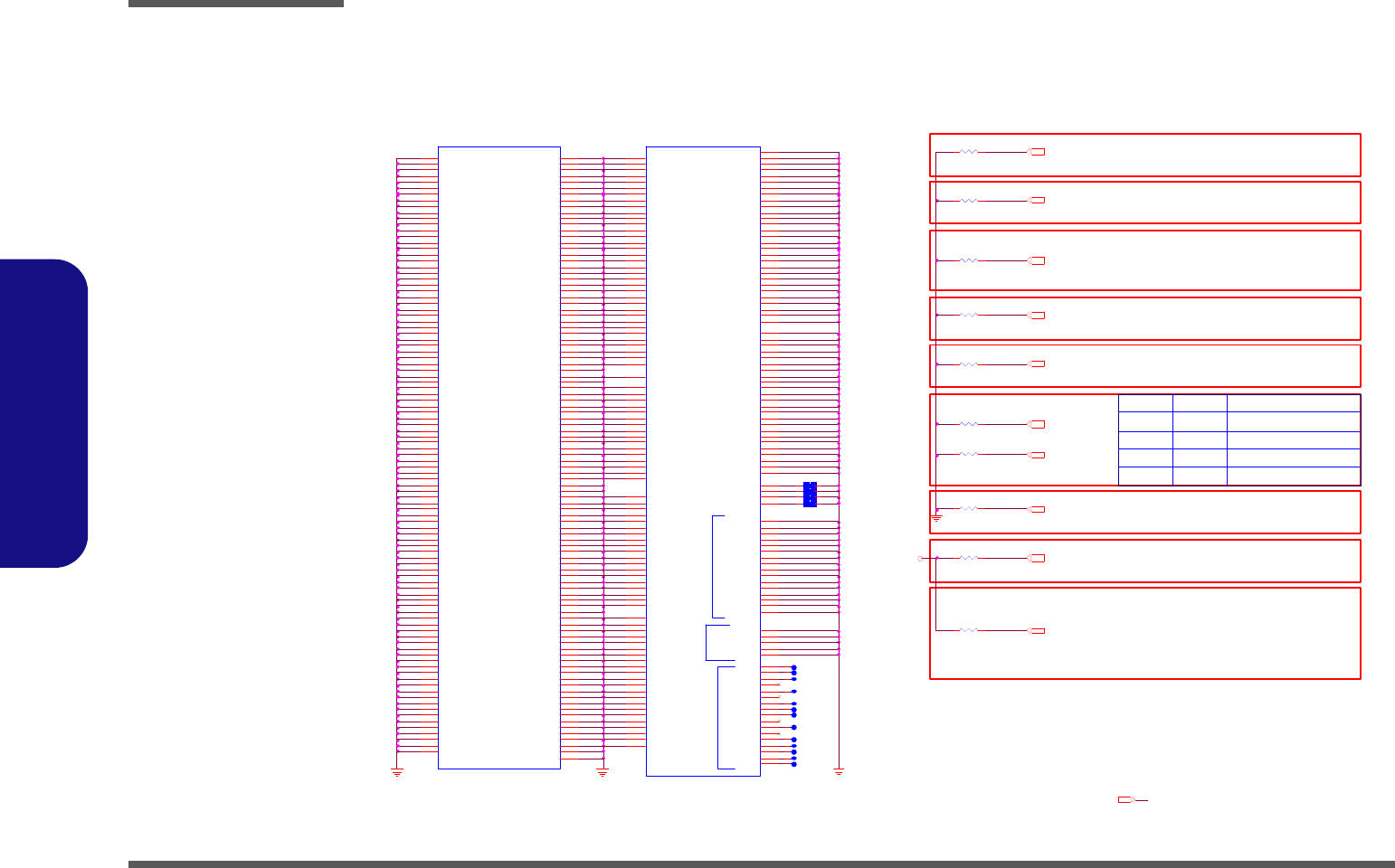

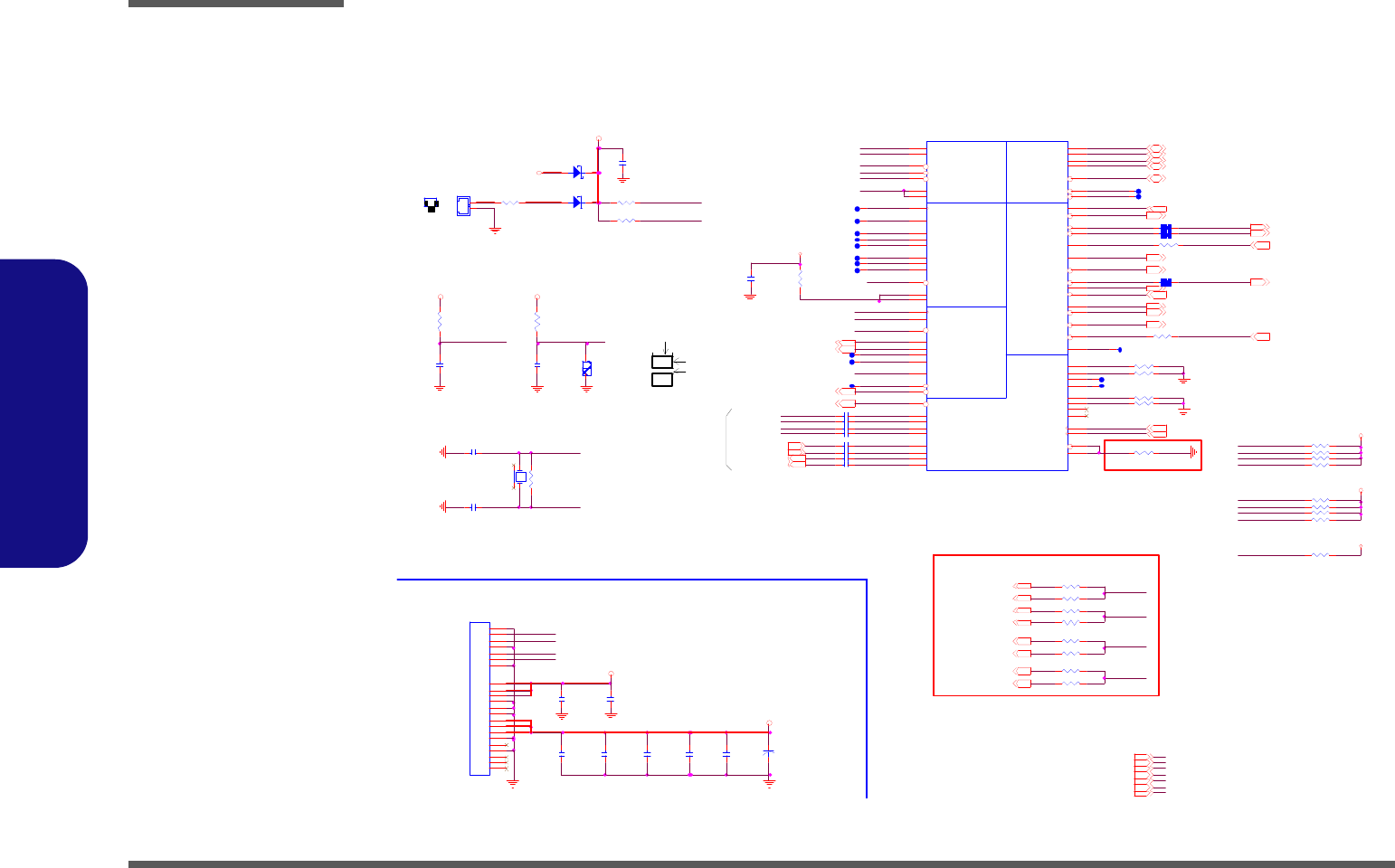

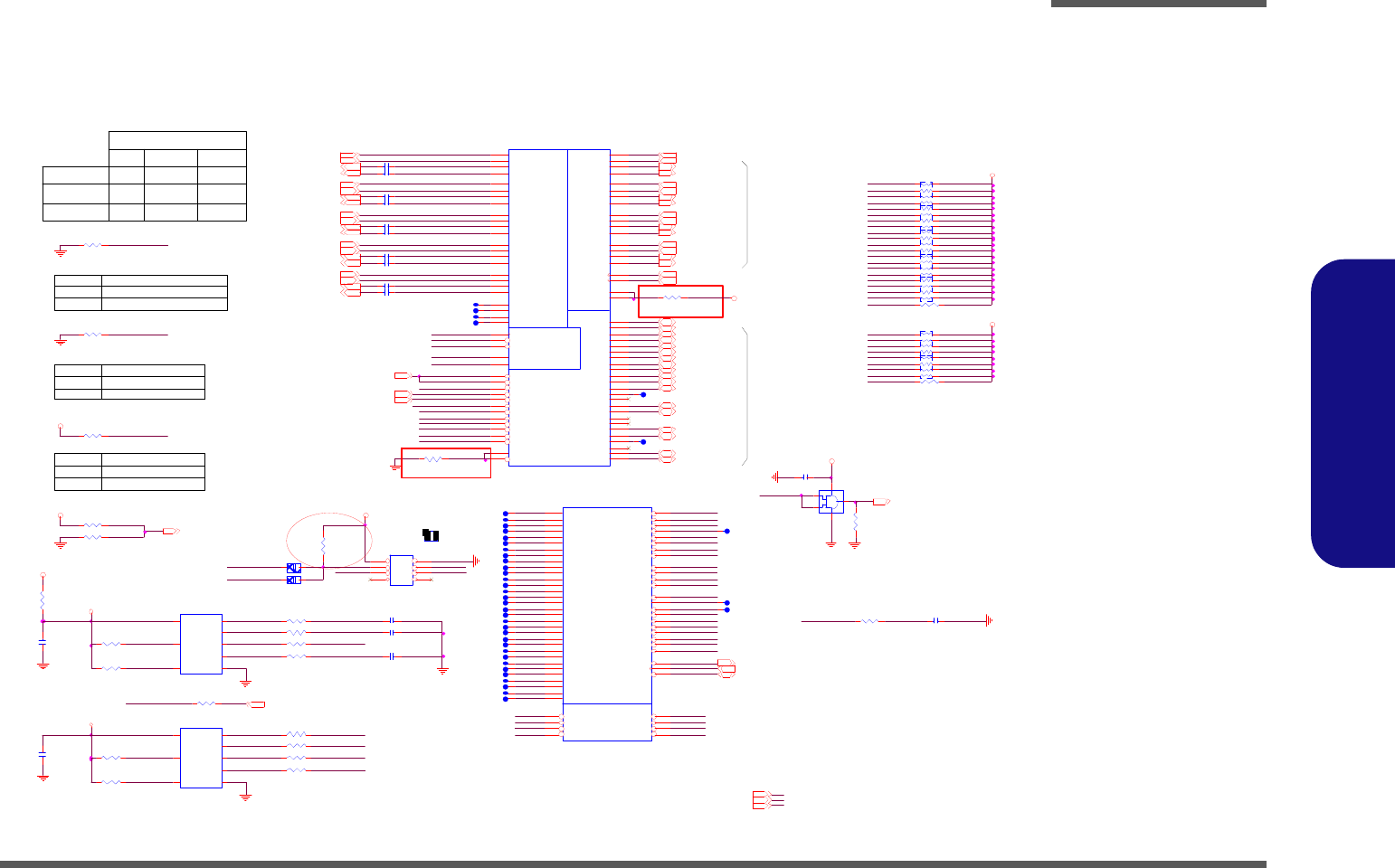

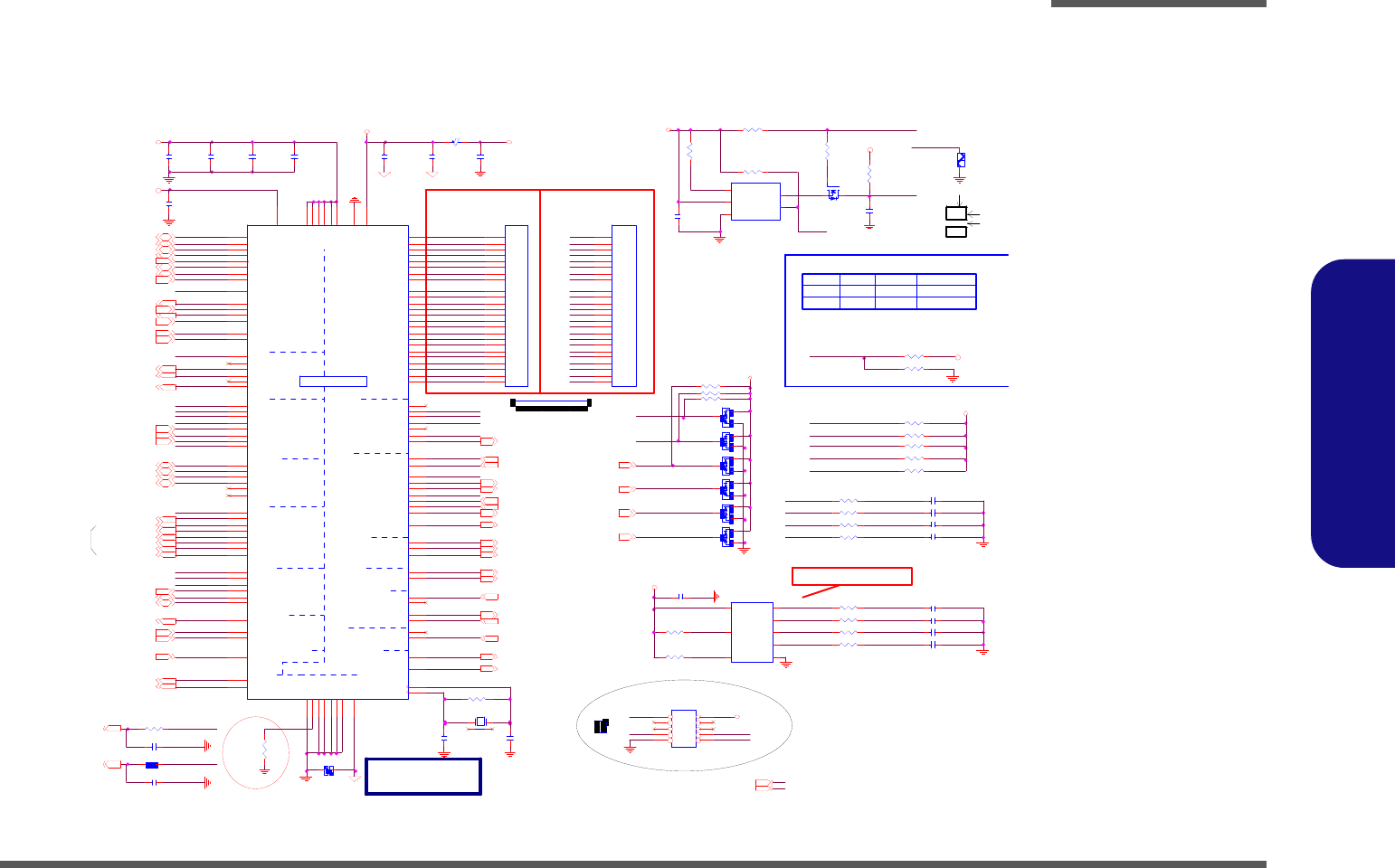

- Intel Penryn (Socket-P) 1/2

- Intel Penryn (Socket-P) 2/2

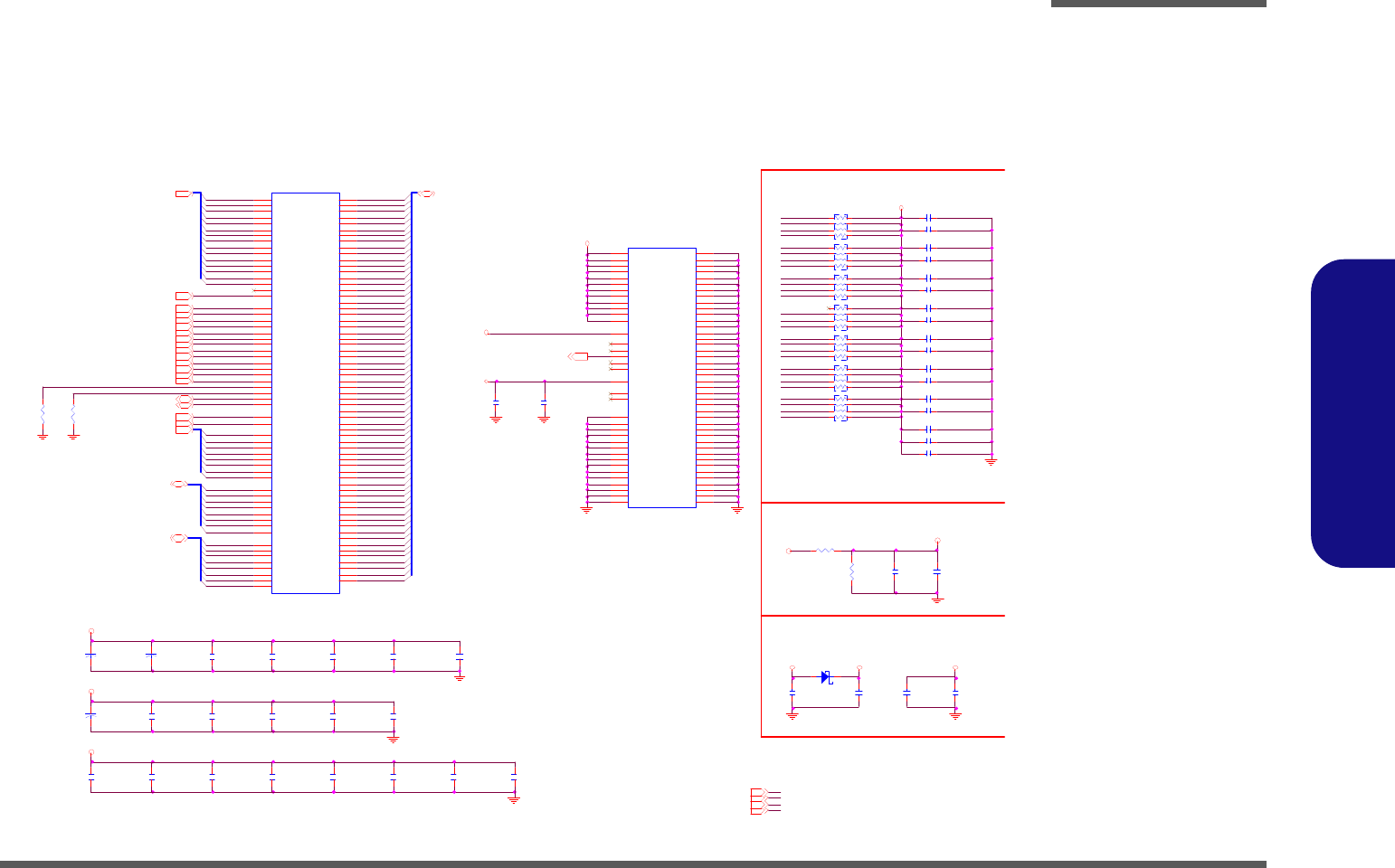

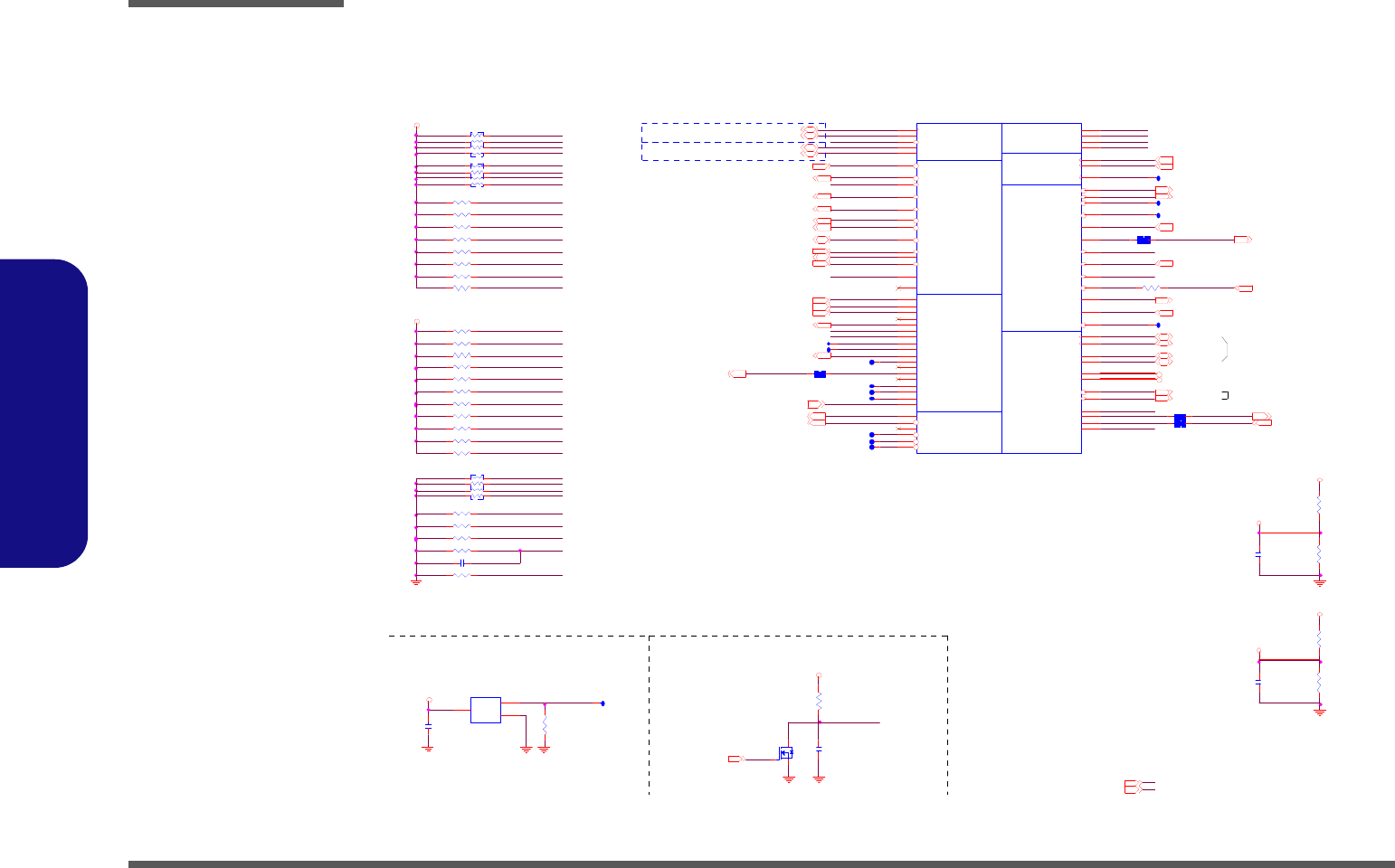

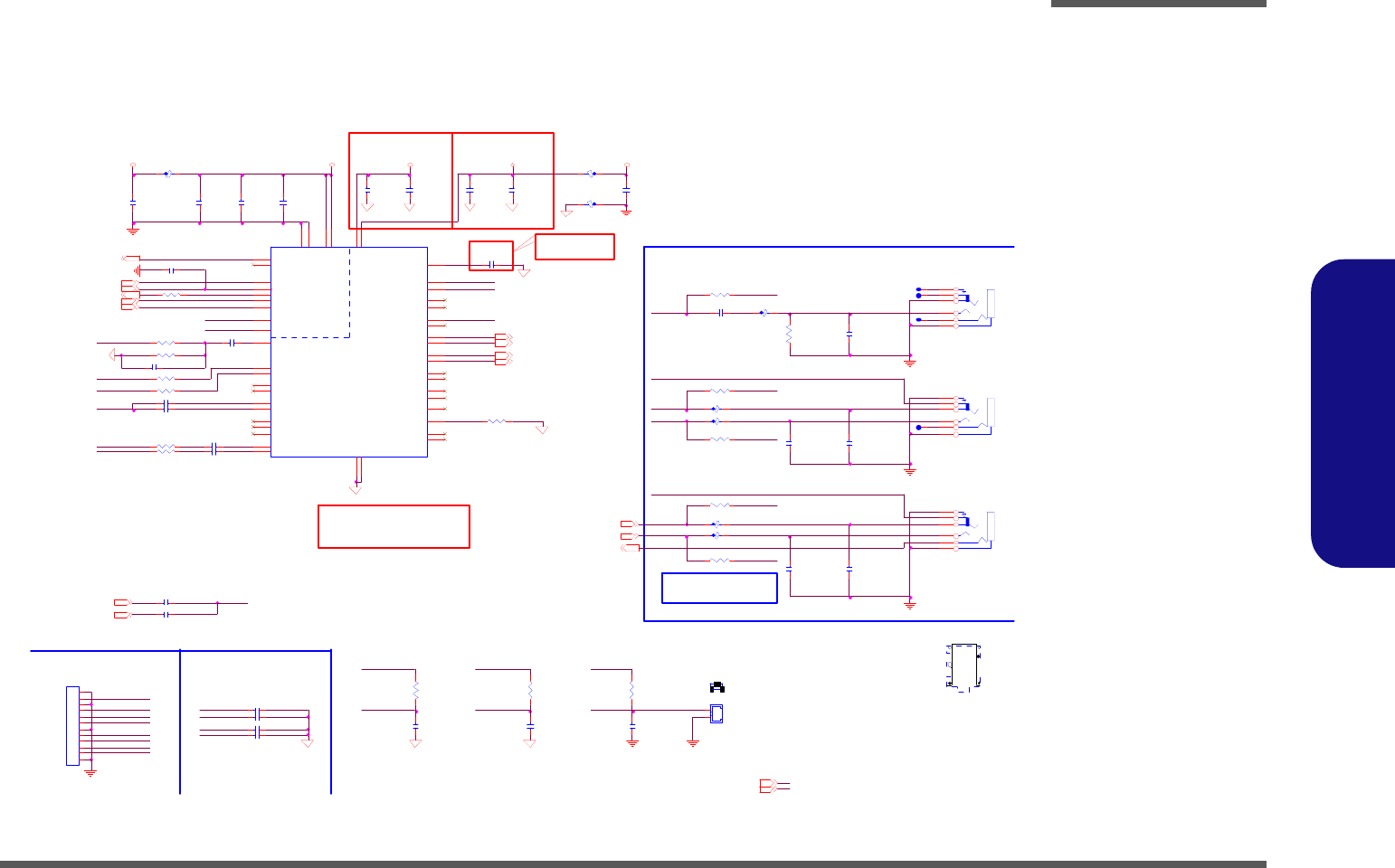

- Cantiga 1/6 - Host

- Cantiga 2/6 - VGA, CRT

- Cantiga 3/6 - DDR

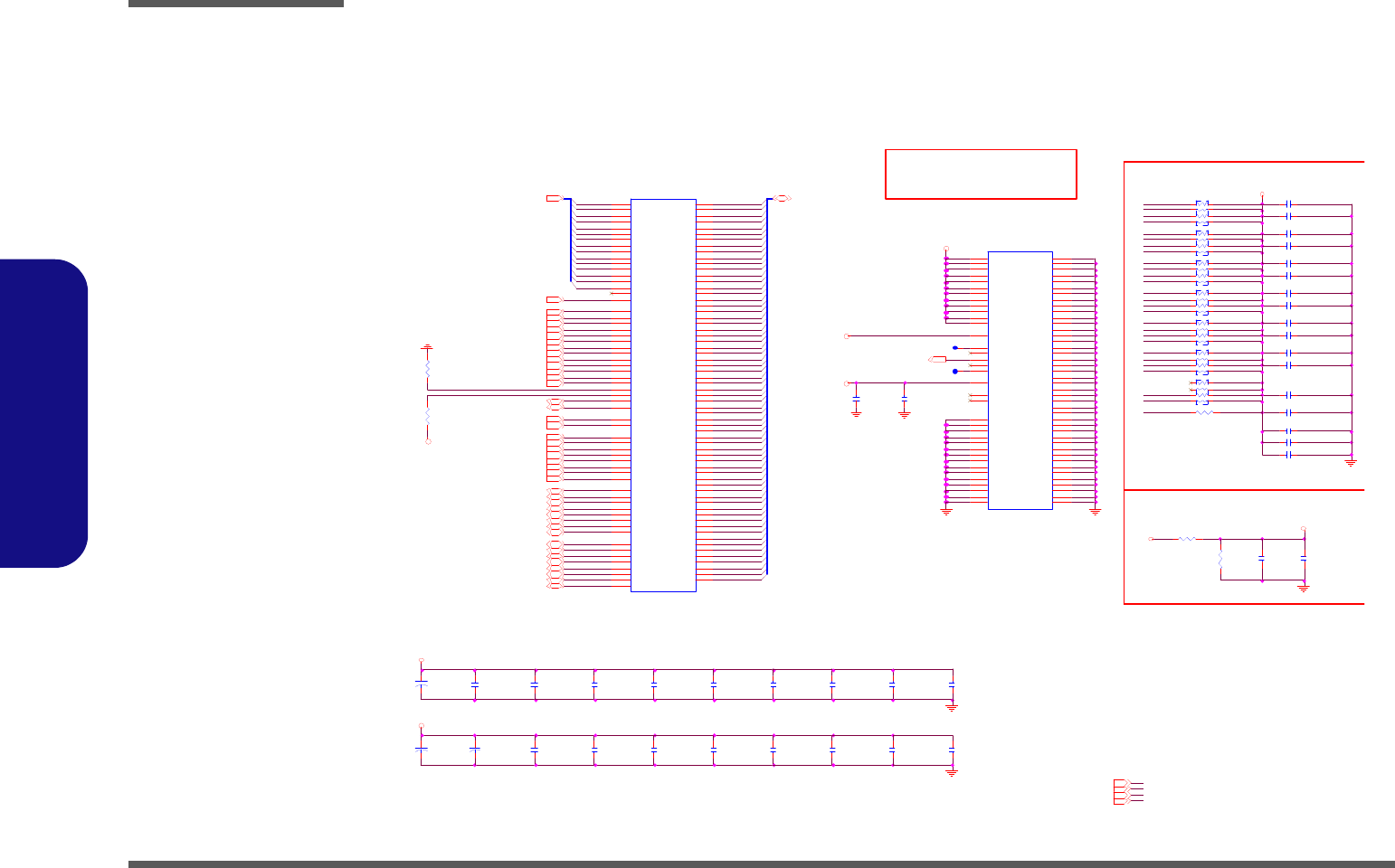

- Cantiga 4/6 - Power

- Cantiga 5/6 - Power

- Cantiga 6/6 - GND

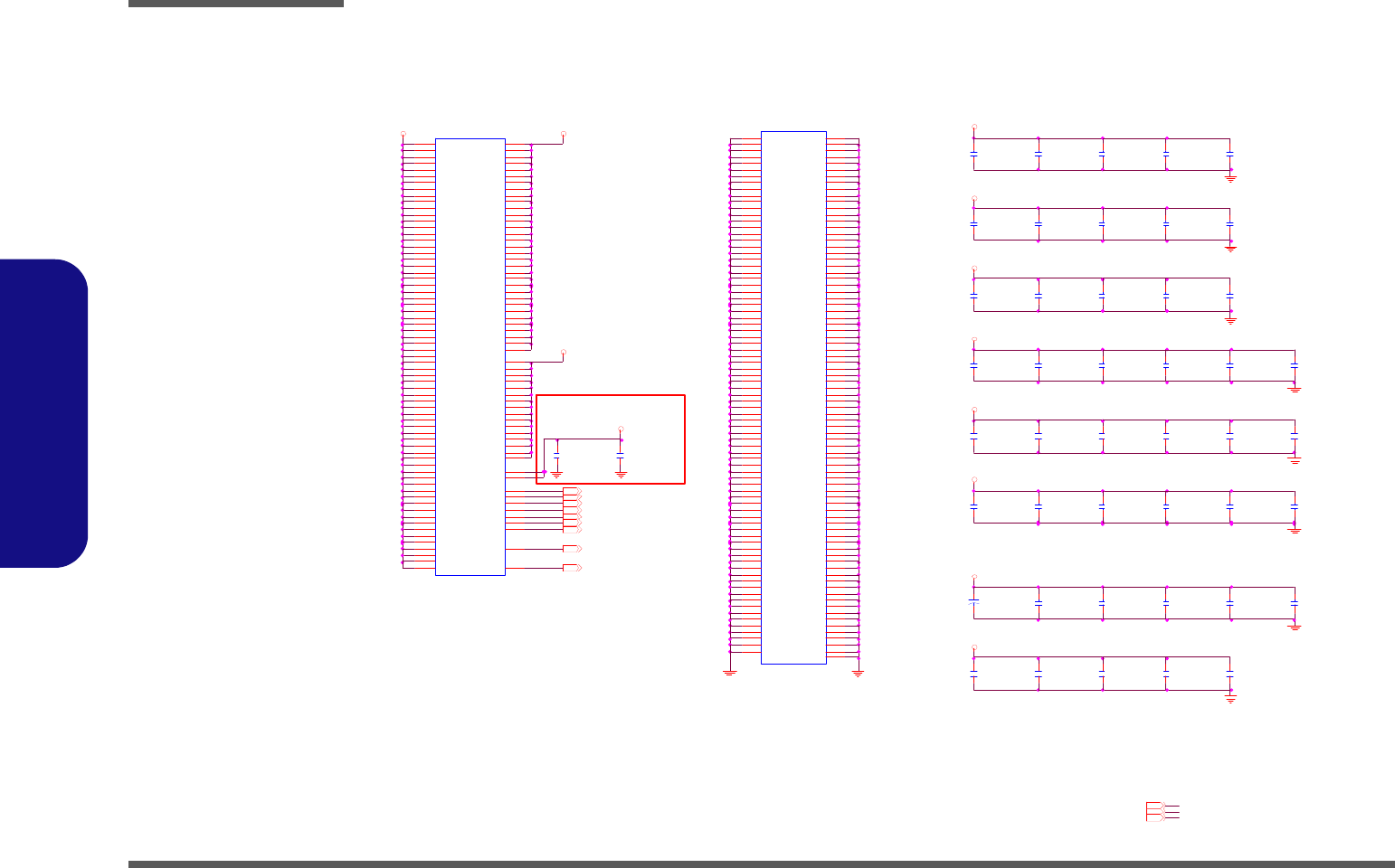

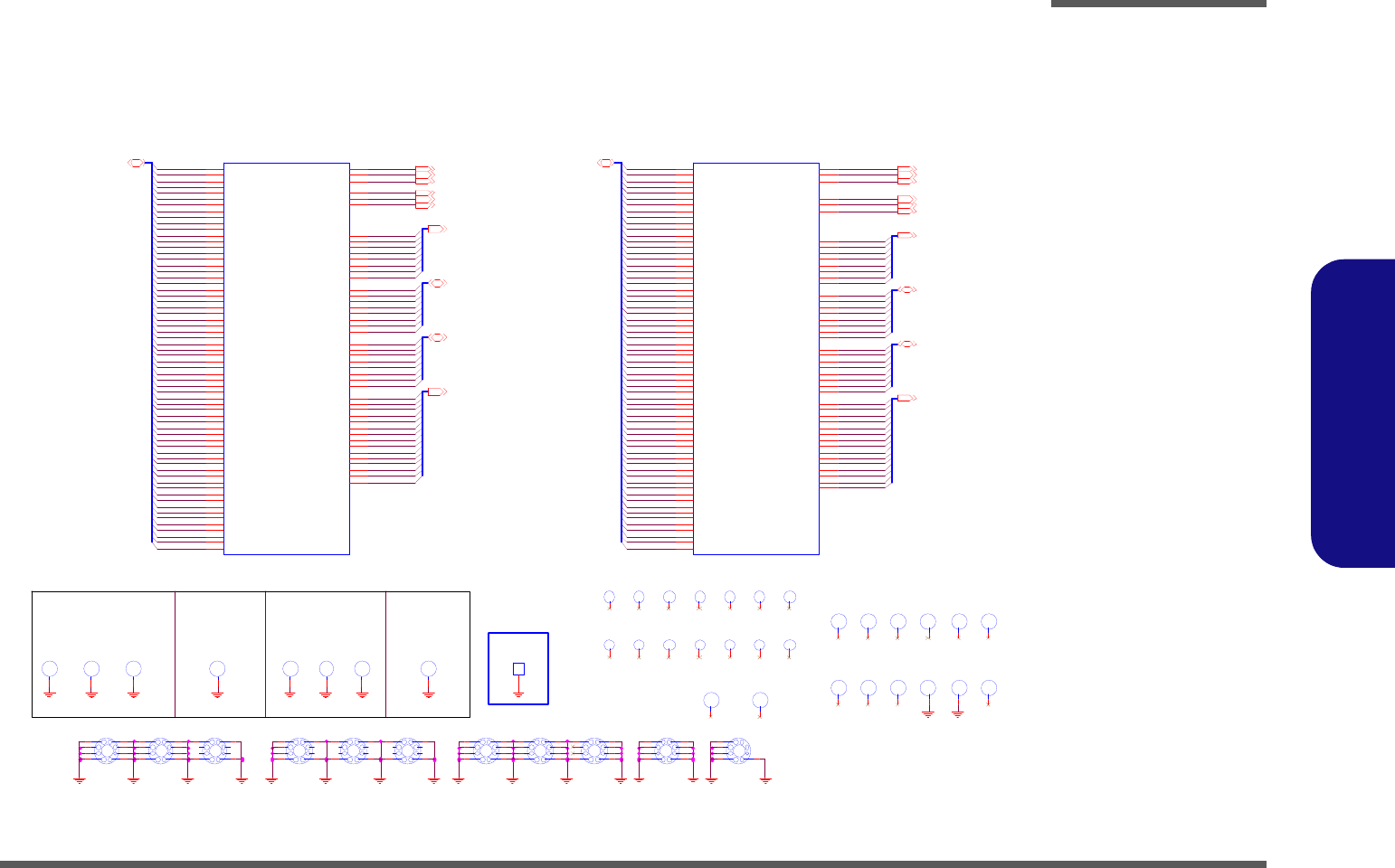

- DDRII CHANNEL A

- DDRII CHANNEL B

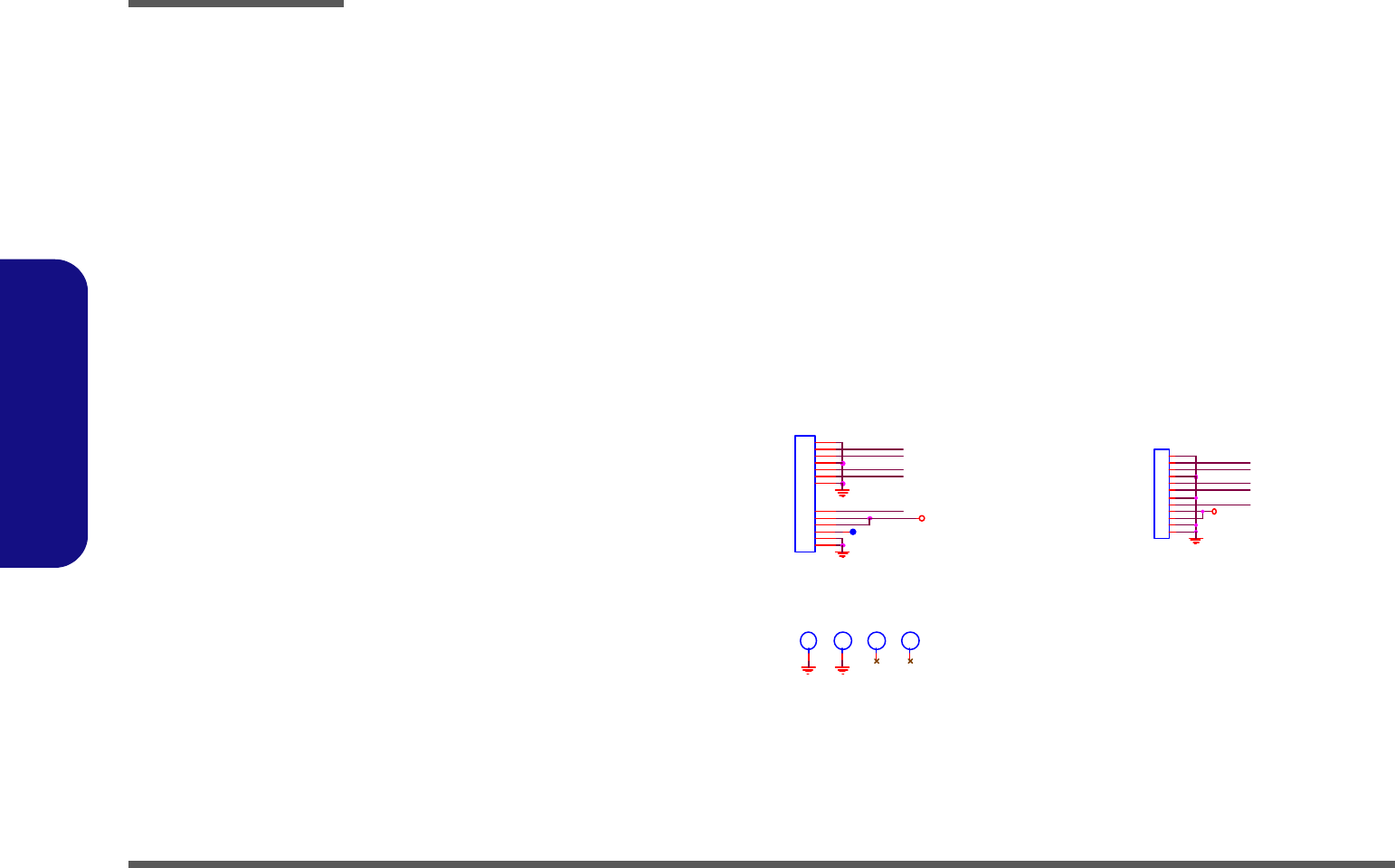

- Panel, Inverter, CRT

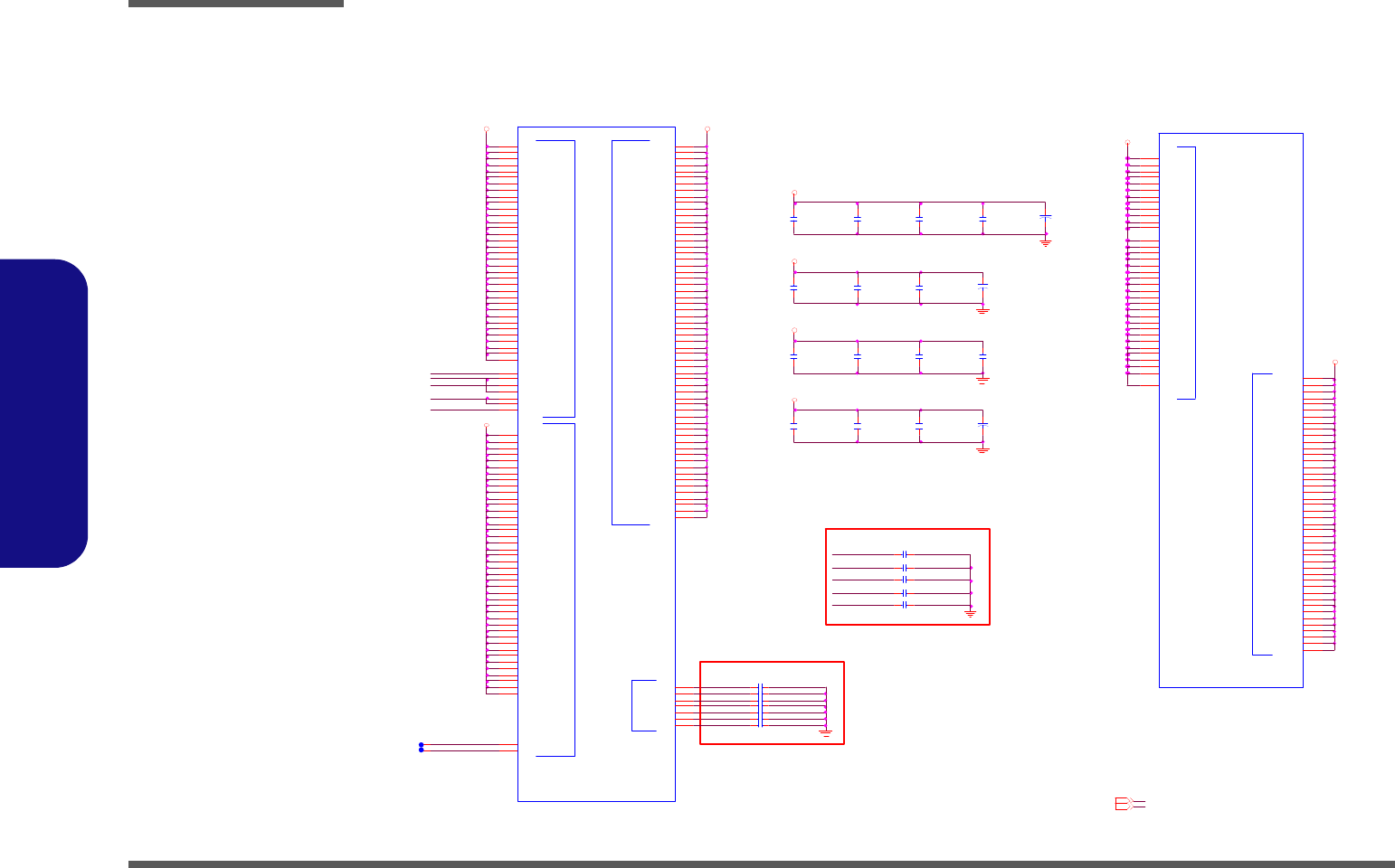

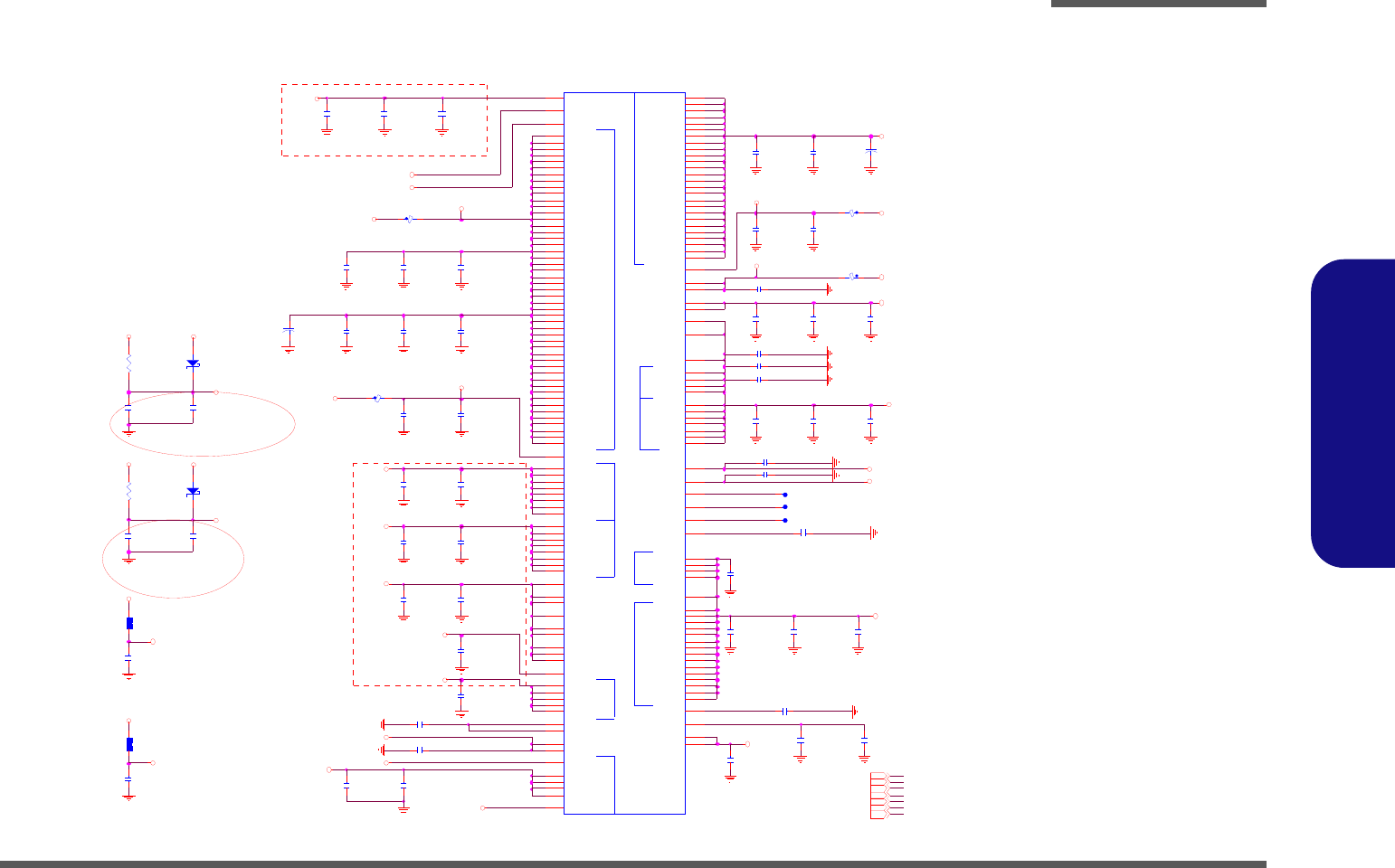

- ICH9-M 1/5 - SATA

- ICH9-M 2/5 - PCIE, PCI, USB

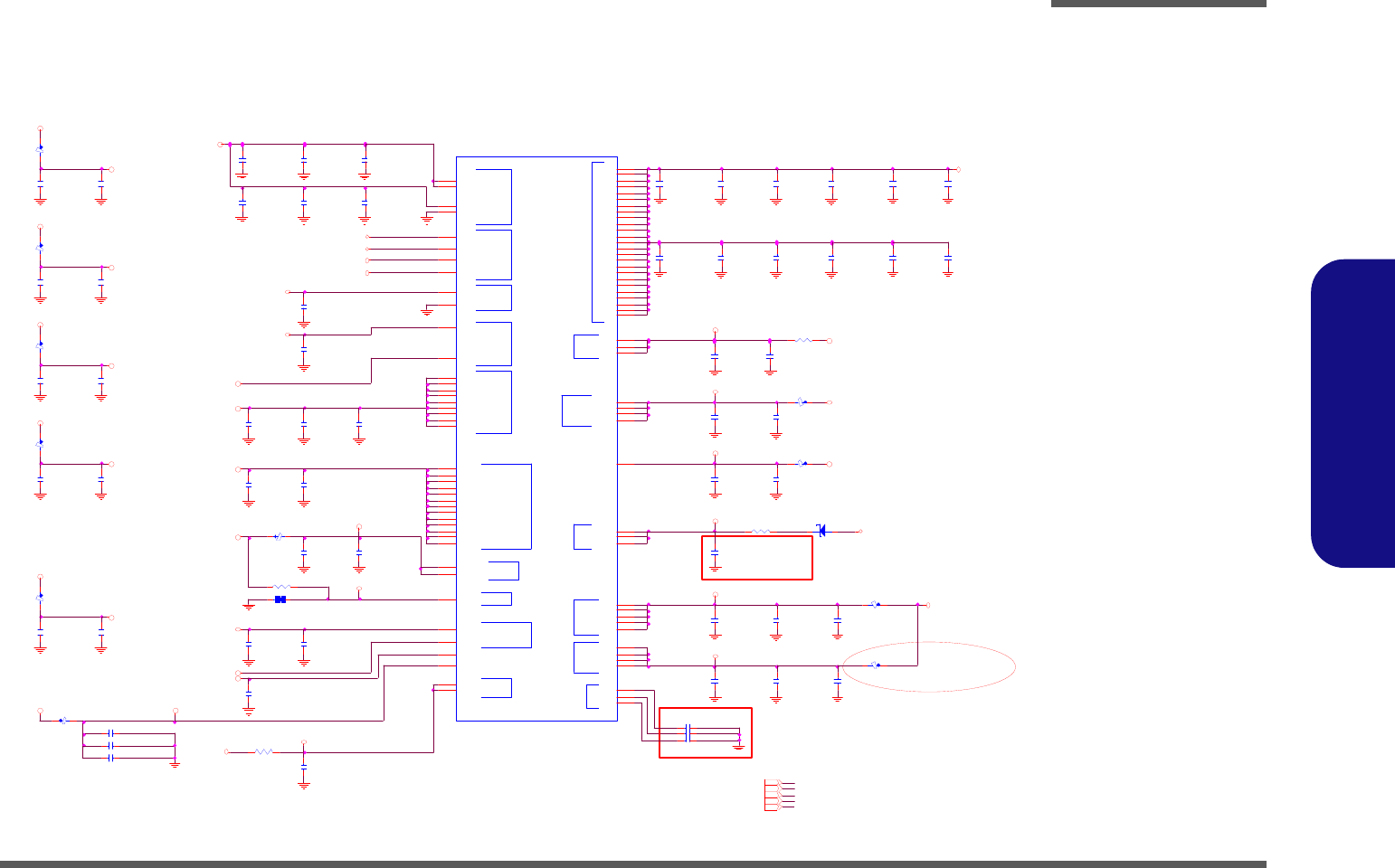

- ICH9-M 3/5 - GPIO, PWR Management

- ICH9-M 4/5 - Power

- ICH9-M 5/5 - GND

- Clock Generator

- Multi I/O, ODD, CCD, BT, TPM

- New Card, Mini PCIE

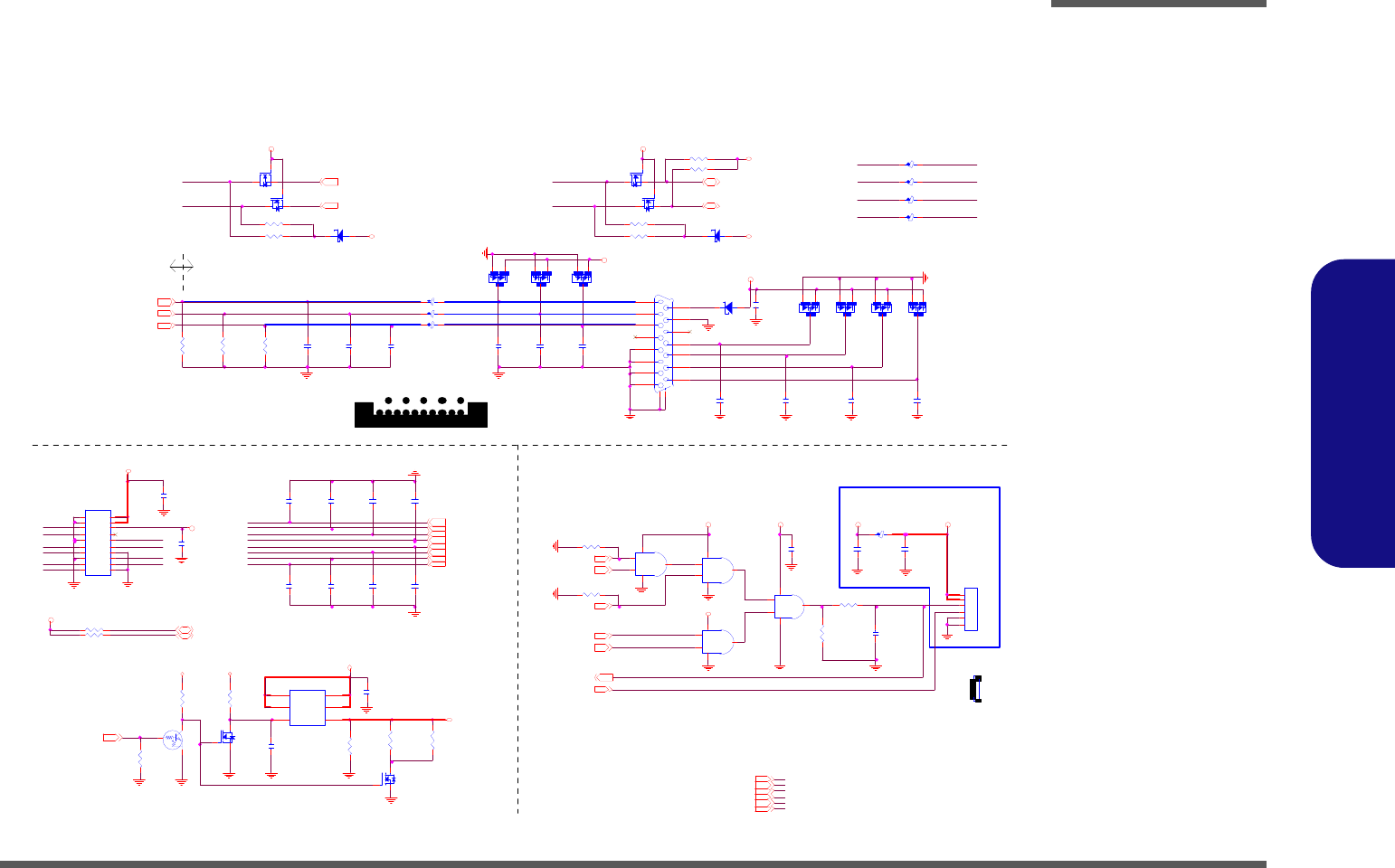

- LED, FAN, TP, FP, USB

- JMB385 Card Reader

- PCI-E LAN RTL8111C

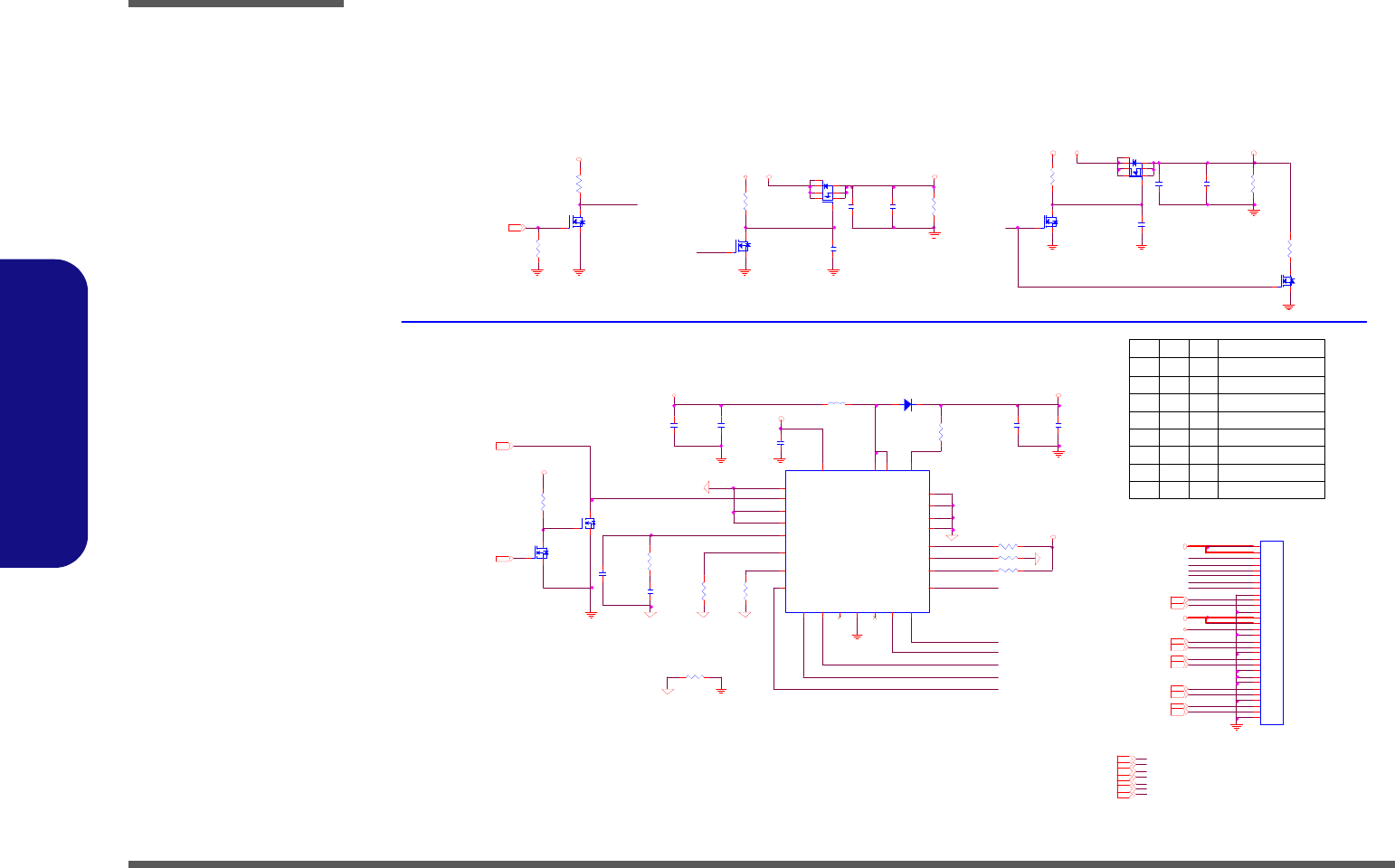

- Audio Codec ALC662

- Audio AMP2056

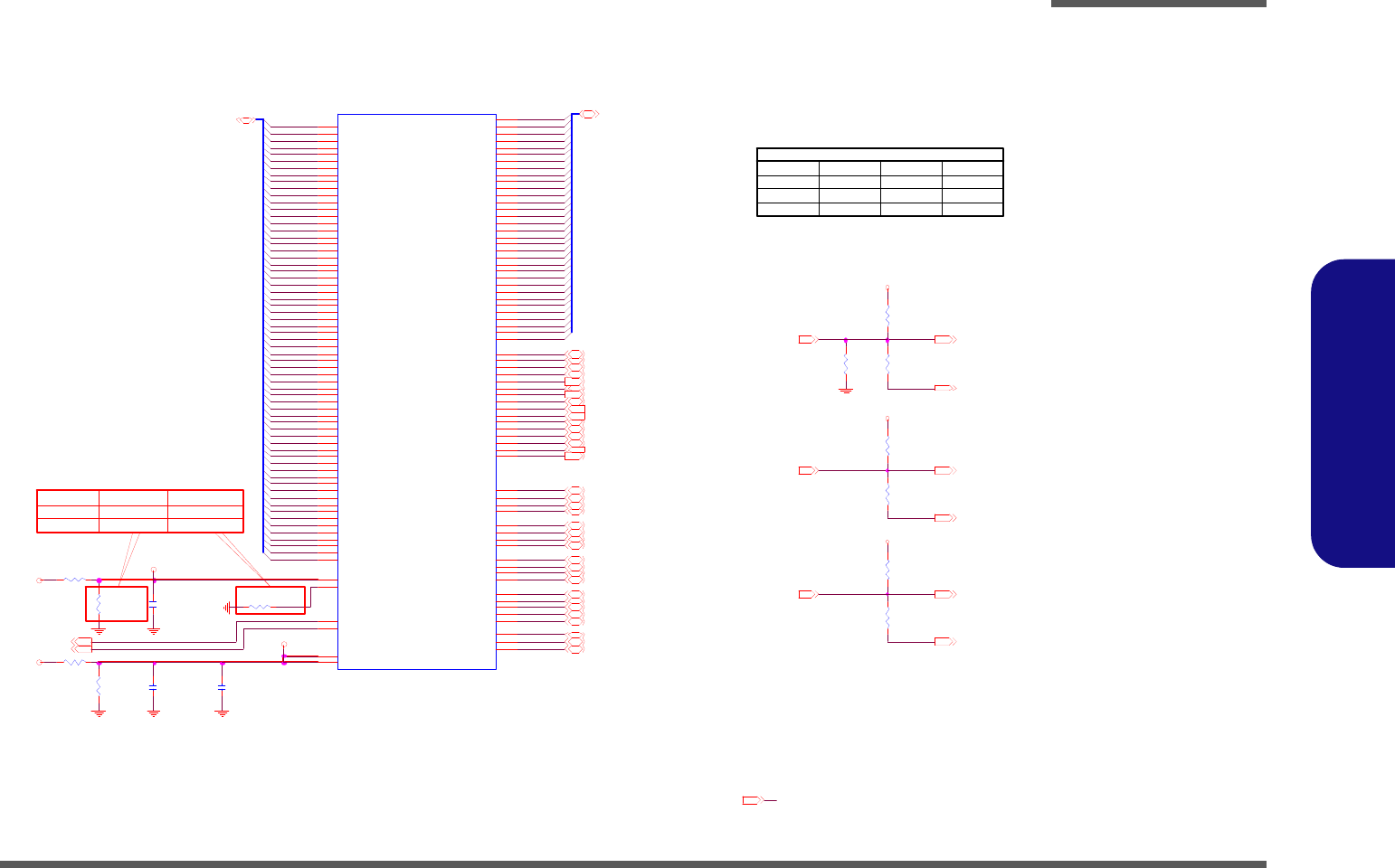

- KBC-ITE IT8512E

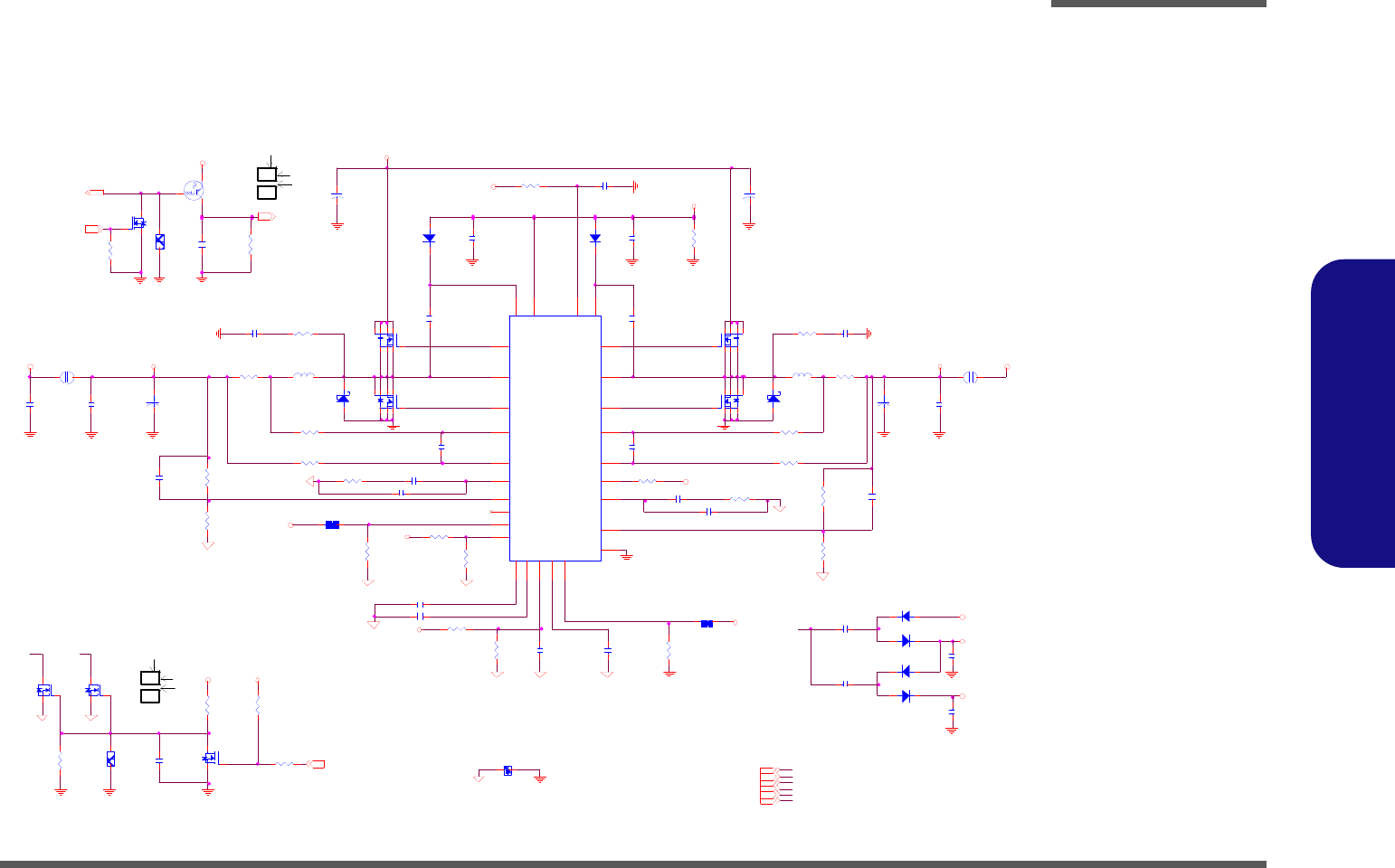

- System Power, LED BKLT

- Power VDD3, VDD5

- Power 1.5VS, 1.05VS, 3.3V, 5V

- Power 1.8V, 0.9VSM

- Power VCORE

- Power AC-IN, Charger

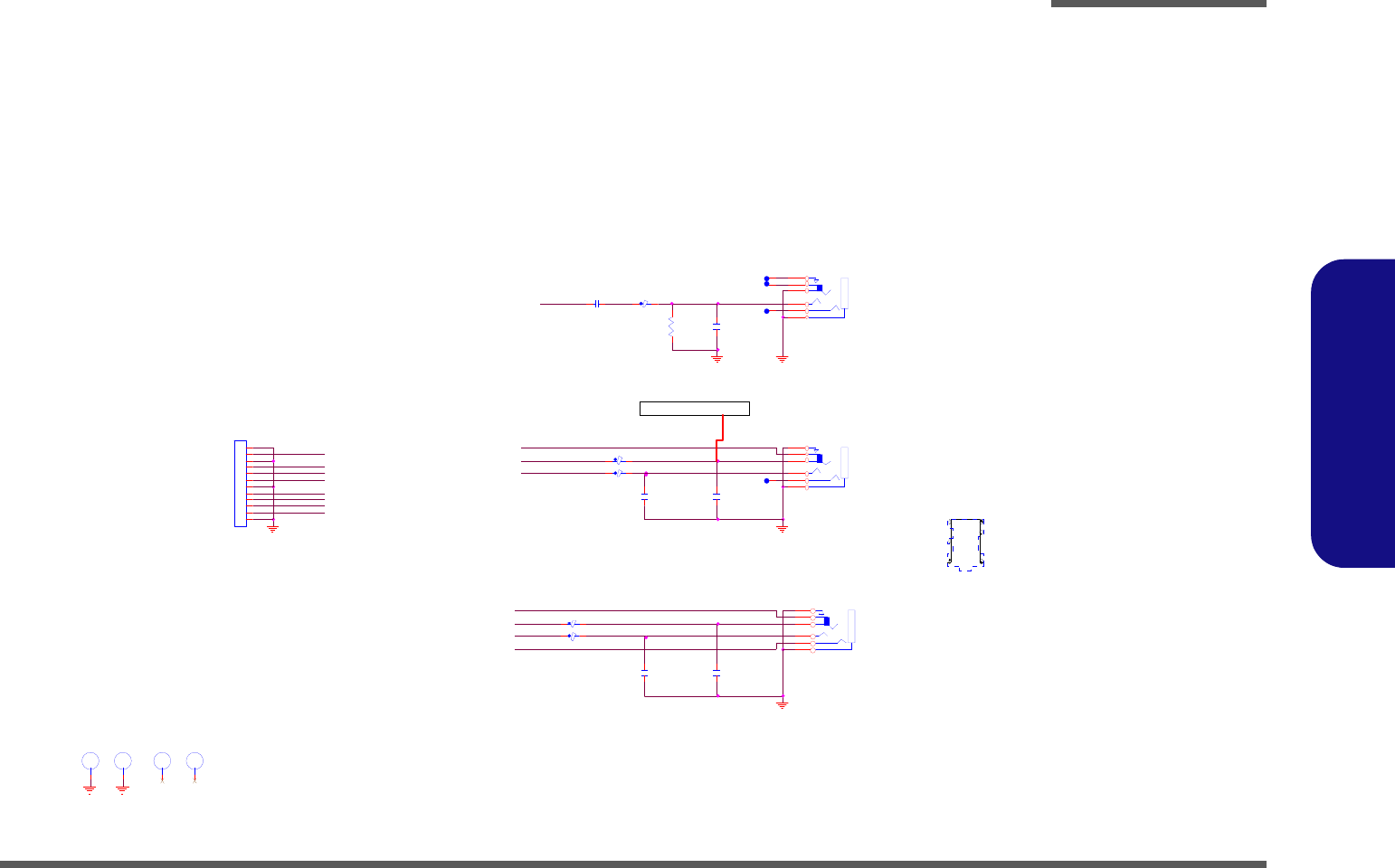

- Multi I/O Board 1/2

- Multi I/O Board 2/2

- Finger Printer Board

- Click Board

- M730T ODD Bridge Board

- M730T Audio Board

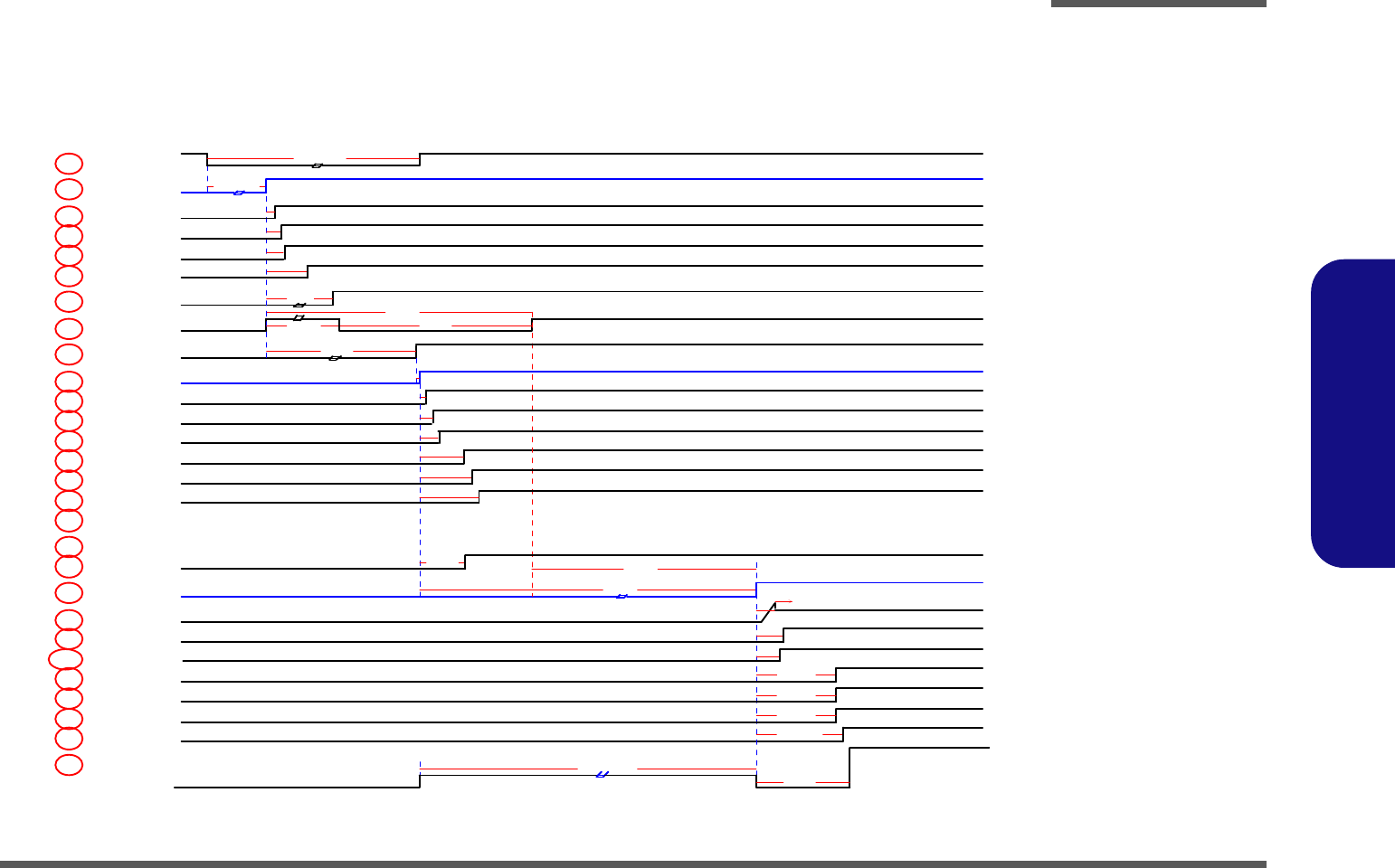

- Power Sequence Diagram

- Power Sequence v3.0

Preface

I

Preface

Notebook Computer

M730TG

Service Manual

Preface

II

Preface

Notice

The company reserves the right to revise this publication or to change its contents without notice. Information contained

herein is for reference only and does not constitute a commitment on the part of the manufacturer or any subsequent ven-

dor. They assume no responsibility or liability for any errors or inaccuracies that may appear in this publication nor are

they in anyway responsible for any loss or damage resulting from the use (or misuse) of this publication.

This publication and any accompanying software may not, in whole or in part, be reproduced, translated, transmitted or

reduced to any machine readable form without prior consent from the vendor, manufacturer or creators of this publica-

tion, except for copies kept by the user for backup purposes.

Brand and product names mentioned in this publication may or may not be copyrights and/or registered trademarks of

their respective companies. They are mentioned for identification purposes only and are not intended as an endorsement

of that product or its manufacturer.

Version 1.0

February 2010

Trademarks

Intel, Celeron and Intel Core are trademarks of Advanced Micro Devices, Inc.

Windows® is a registered trademark of Microsoft Corporation.

Other brand and product names are trademarks and./or registered trademarks of their respective companies.

Preface

III

Preface

About this Manual

This manual is intended for service personnel who have completed sufficient training to undertake the maintenance and

inspection of personal computers.

It is organized to allow you to look up basic information for servicing and/or upgrading components of the M730TG se-

ries notebook PC.

The following information is included:

Chapter 1, Introduction, provides general information about the location of system elements and their specifications.

Chapter 2, Disassembly, provides step-by-step instructions for disassembling parts and subsystems and how to upgrade

elements of the system.

Appendix A, Part Lists

Appendix B, Schematic Diagrams

Appendix C, Updating the FLASH ROM BIOS

Preface

IV

Preface

IMPORTANT SAFETY INSTRUCTIONS

Follow basic safety precautions, including those listed below, to reduce the risk of fire, electric shock and injury to per-

sons when using any electrical equipment:

1. Do not use this product near water, for example near a bath tub, wash bowl, kitchen sink or laundry tub, in a wet

basement or near a swimming pool.

2. Avoid using a telephone (other than a cordless type) during an electrical storm. There may be a remote risk of elec-

trical shock from lightning.

3. Do not use the telephone to report a gas leak in the vicinity of the leak.

4. Use only the power cord and batteries indicated in this manual. Do not dispose of batteries in a fire. They may

explode. Check with local codes for possible special disposal instructions.

5. This product is intended to be supplied by a Listed Power Unit (DC Output 19V, 3.42A OR 18.5V, 3.5A (65W) mini-

mum AC/DC Adapter).

CAUTION

Always disconnect all telephone lines from the wall outlet before servicing or disassembling this equipment.

TO REDUCE THE RISK OF FIRE, USE ONLY NO. 26 AWG OR LARGER,

TELECOMMUNICATION LINE CORD

This Computer’s Optical Device is a Laser Class 1 Product

Preface

V

Preface

Instructions for Care and Operation

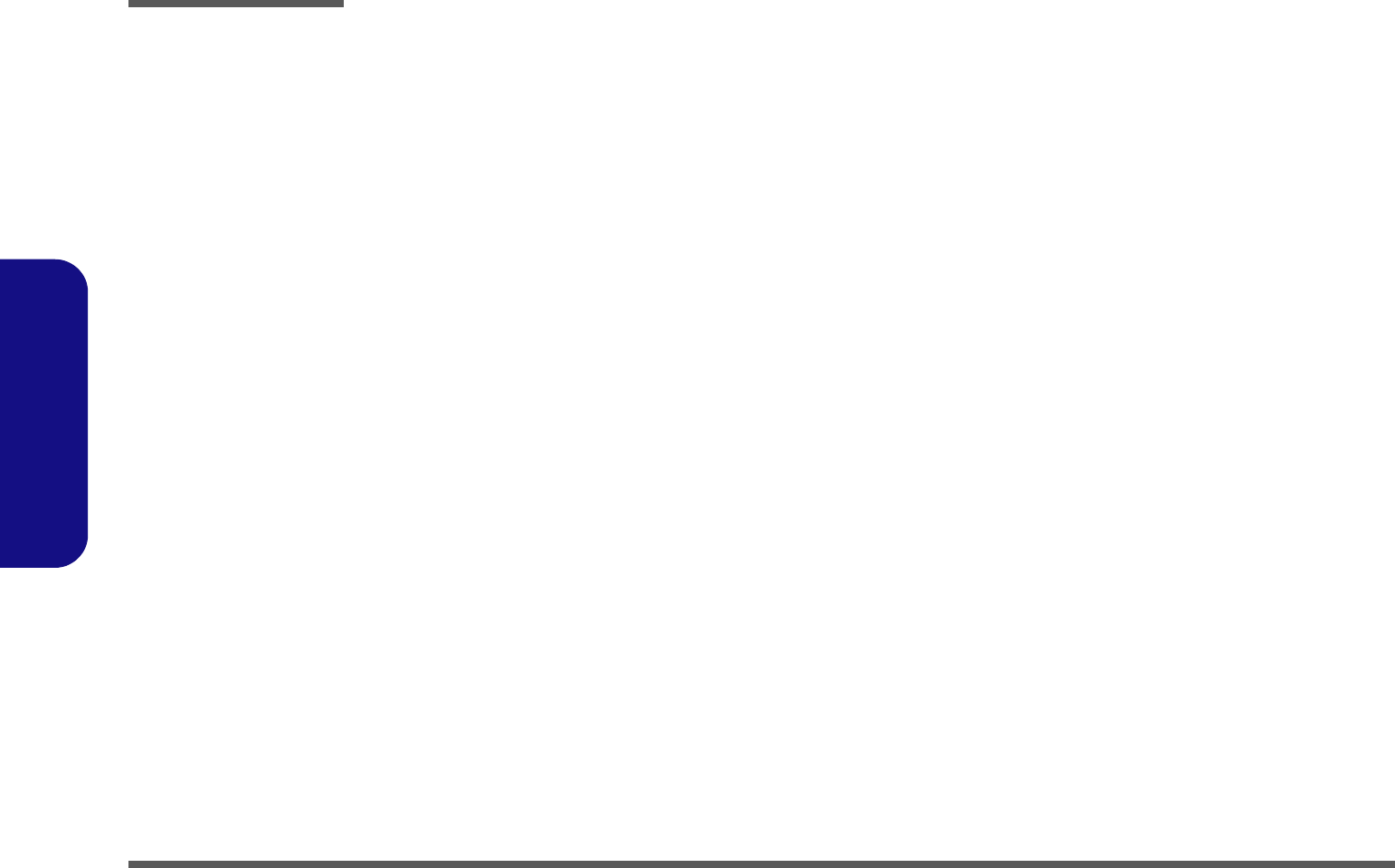

The notebook computer is quite rugged, but it can be damaged. To prevent this, follow these suggestions:

1. Don’t drop it, or expose it to shock. If the computer falls, the case and the components could be damaged.

2. Keep it dry, and don’t overheat it. Keep the computer and power supply away from any kind of heating element. This

is an electrical appliance. If water or any other liquid gets into it, the computer could be badly damaged.

3. Follow the proper working procedures for the computer. Shut the computer down properly and don’t forget to save

your work. Remember to periodically save your data as data may be lost if the battery is depleted.

Do not expose the computer

to any shock or vibration. Do not place it on an unstable

surface. Do not place anything heavy

on the computer.

Do not expose it to excessive

heat or direct sunlight. Do not leave it in a place

where foreign matter or mois-

ture may affect the system.

Don’t use or store the com-

puter in a humid environment. Do not place the computer on

any surface which will block

the vents.

Do not turn off the power

until you properly shut down

all programs.

Do not turn off any peripheral

devices when the computer is

on.

Do not disassemble the com-

puter by yourself. Perform routine maintenance

on your computer.

Preface

VI

Preface

4. Avoid interference. Keep the computer away from high capacity transformers, electric motors, and other strong mag-

netic fields. These can hinder proper performance and damage your data.

5. Take care when using peripheral devices.

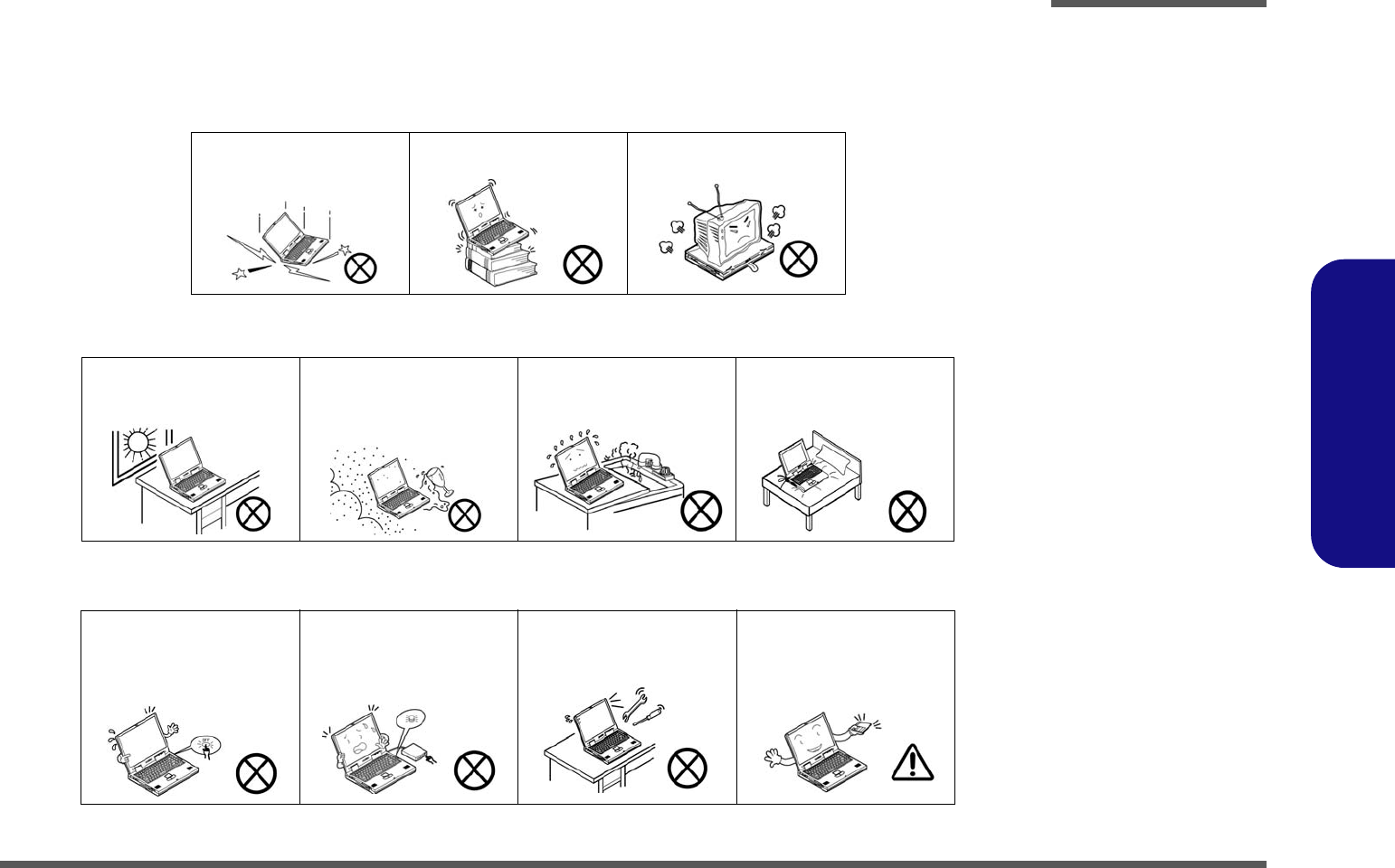

Power Safety

The computer has specific power requirements:

• Only use a power adapter approved for use with this computer.

• Your AC adapter may be designed for international travel but it still requires a steady, uninterrupted power supply. If you are

unsure of your local power specifications, consult your service representative or local power company.

• The power adapter may have either a 2-prong or a 3-prong grounded plug. The third prong is an important safety feature; do

not defeat its purpose. If you do not have access to a compatible outlet, have a qualified electrician install one.

• When you want to unplug the power cord, be sure to disconnect it by the plug head, not by its wire.

• Make sure the socket and any extension cord(s) you use can support the total current load of all the connected devices.

• Before cleaning the computer, make sure it is disconnected from any external power supplies.

Use only approved brands of

peripherals. Unplug the power cord before

attaching peripheral devices.

Do not plug in the power

cord if you are wet. Do not use the power cord if

it is broken. Do not place heavy objects

on the power cord.

Power Safety

Warning

Before you undertake

any upgrade proce-

dures, make sure that

you have turned off the

power, and discon-

nected all peripherals

and cables (including

telephone lines). It is

advisable to also re-

move your battery in

order to prevent acci-

dentally turning the

machine on.

Preface

VII

Preface

Battery Precautions

• Only use batteries designed for this computer. The wrong battery type may explode, leak or damage the computer.

• Do not continue to use a battery that has been dropped, or that appears damaged (e.g. bent or twisted) in any way. Even if the

computer continues to work with a damaged battery in place, it may cause circuit damage, which may possibly result in fire.

• Recharge the batteries using the notebook’s system. Incorrect recharging may make the battery explode.

• Do not try to repair a battery pack. Refer any battery pack repair or replacement to your service representative or qualified service

personnel.

• Keep children away from, and promptly dispose of a damaged battery. Always dispose of batteries carefully. Batteries may explode

or leak if exposed to fire, or improperly handled or discarded.

• Keep the battery away from metal appliances.

• Affix tape to the battery contacts before disposing of the battery.

• Do not touch the battery contacts with your hands or metal objects.

Battery Guidelines

The following can also apply to any backup batteries you may have.

• If you do not use the battery for an extended period, then remove the battery from the computer for storage.

• Before removing the battery for storage charge it to 60% - 70%.

• Check stored batteries at least every 3 months and charge them to 60% - 70%.

Battery Disposal

The product that you have purchased contains a rechargeable battery. The battery is recyclable. At the end of its useful life, under var-

ious state and local laws, it may be illegal to dispose of this battery into the municipal waste stream. Check with your local solid waste

officials for details in your area for recycling options or proper disposal.

Caution

Danger of explosion if battery is incorrectly replaced. Replace only with the same or equivalent type recommended by the manufacturer.

Discard used battery according to the manufacturer’s instructions.

Battery Level

Click the battery icon in the taskbar to see the current battery level and charge status. A battery that drops below a level of 10%

will not allow the computer to boot up. Make sure that any battery that drops below 10% is recharged within one week.

Preface

VIII

Preface

Related Documents

You may also need to consult the following manual for additional information:

User’s Manual on CD

This describes the notebook PC’s features and the procedures for operating the computer and its ROM-based setup pro-

gram. It also describes the installation and operation of the utility programs provided with the notebook PC.

Preface

IX

Preface

Contents

Introduction ..............................................1-1

Overview .........................................................................................1-1

System Specifications .....................................................................1-2

External Locator - Top View with LCD Panel Open ......................1-4

External Locator - Front & Right side Views .................................1-5

External Locator - Left Side & Rear View .....................................1-6

External Locator - Bottom View .....................................................1-7

Mainboard Overview - Top (Key Parts) .........................................1-8

Mainboard Overview - Bottom (Key Parts) ....................................1-9

Mainboard Overview - Top (Connectors) .....................................1-10

Mainboard Overview - Bottom (Connectors) ...............................1-11

Disassembly ...............................................2-1

Overview .........................................................................................2-1

Maintenance Tools ..........................................................................2-2

Connections .....................................................................................2-2

Maintenance Precautions .................................................................2-3

Disassembly Steps ...........................................................................2-4

Removing the Battery ......................................................................2-5

Removing the Hard Disk Drive .......................................................2-6

Removing the Optical (CD/DVD) Device ......................................2-8

Removing the System Memory (RAM) ..........................................2-9

Removing the Inverter Board ........................................................2-11

Removing the Processor ................................................................2-12

Removing the Wireless LAN Module ...........................................2-14

Removing the Bluetooth Module ..................................................2-15

Removing the Keyboard ................................................................2-16

Removing the Modem ...................................................................2-17

Part Lists ..................................................A-1

Part List Illustration Location ........................................................A-2

Top without Fingerprint ................................................................. A-3

Bottom ........................................................................................... A-4

LCD ............................................................................................... A-5

DVD-Dual Drive ............................................................................ A-6

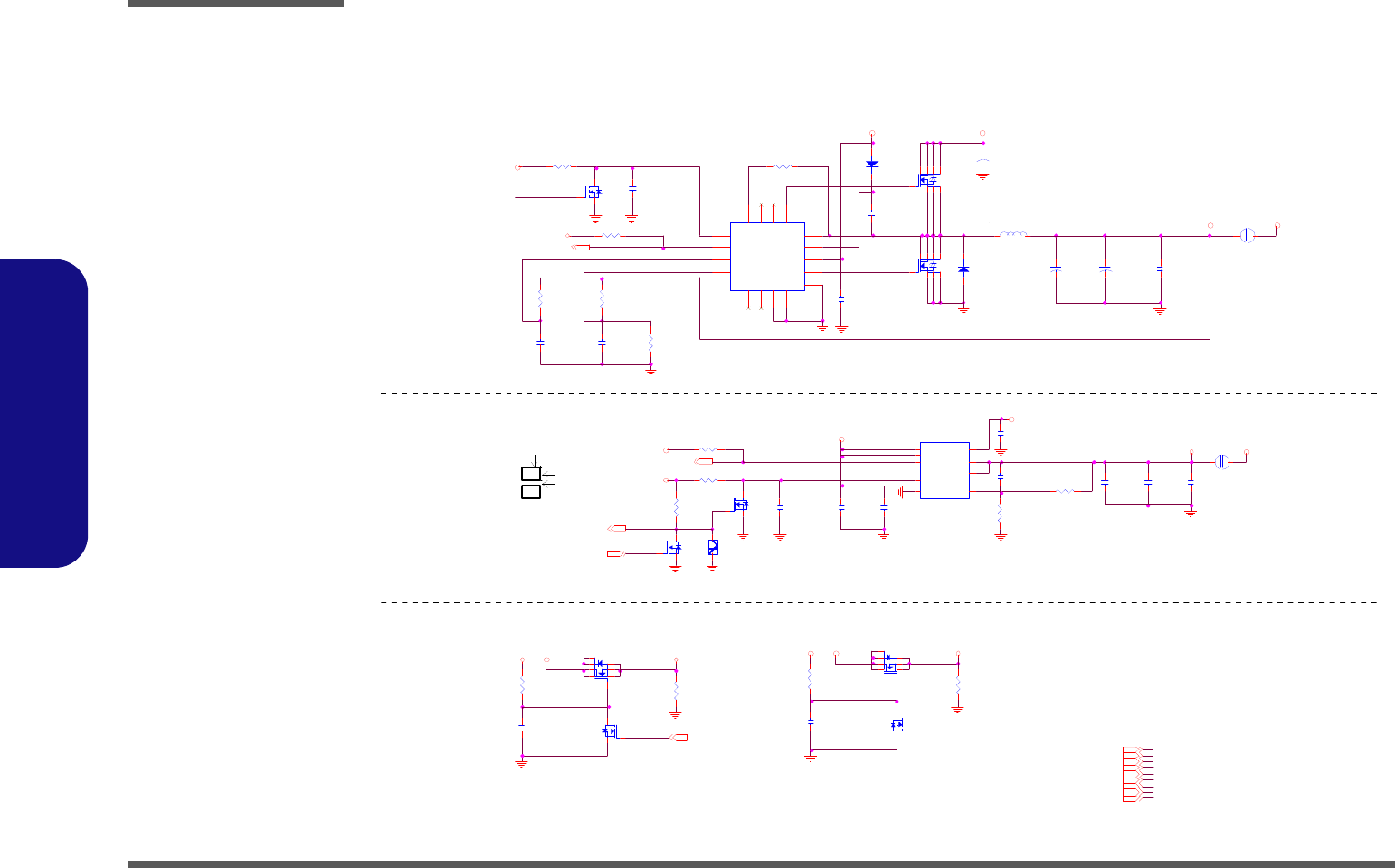

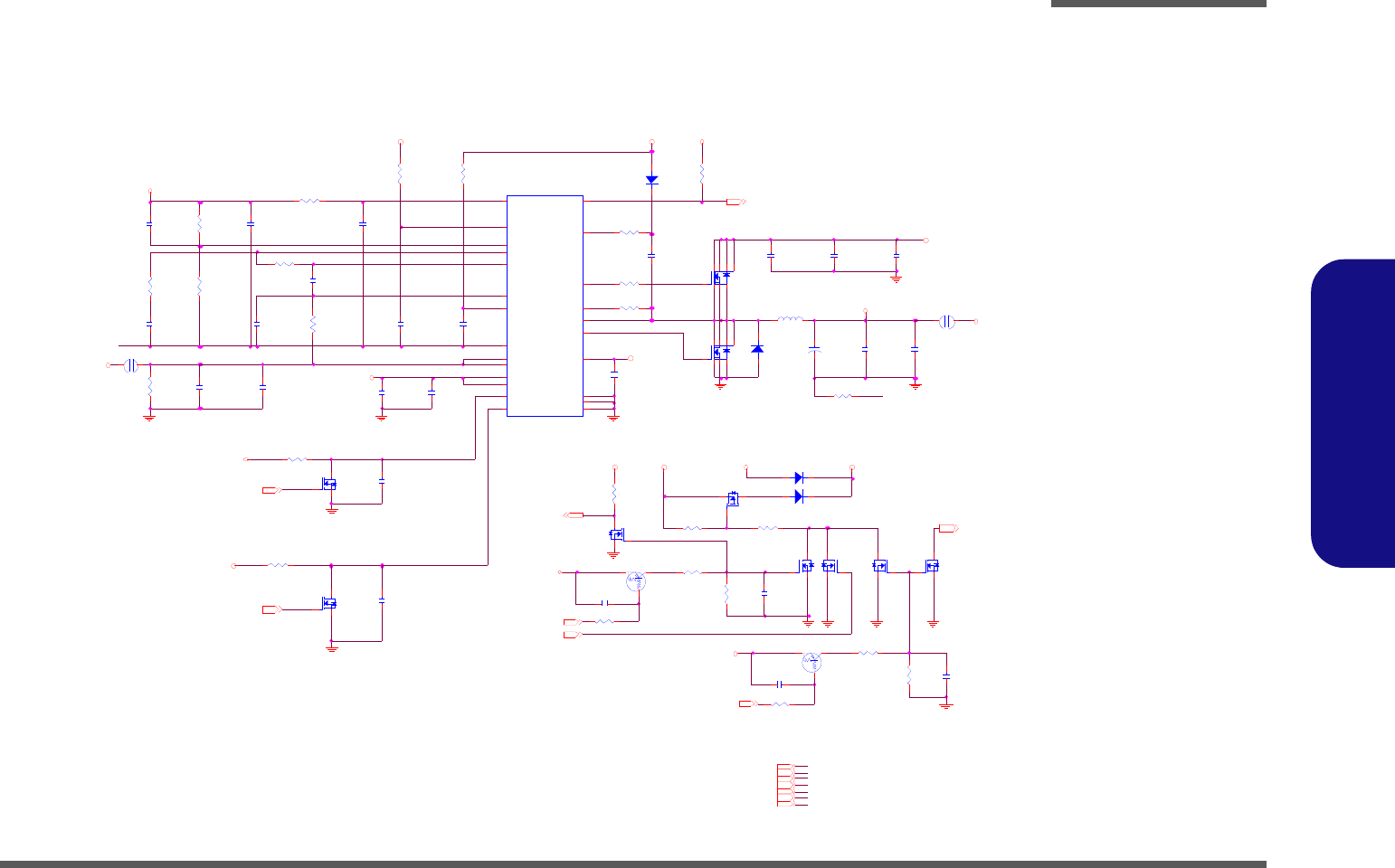

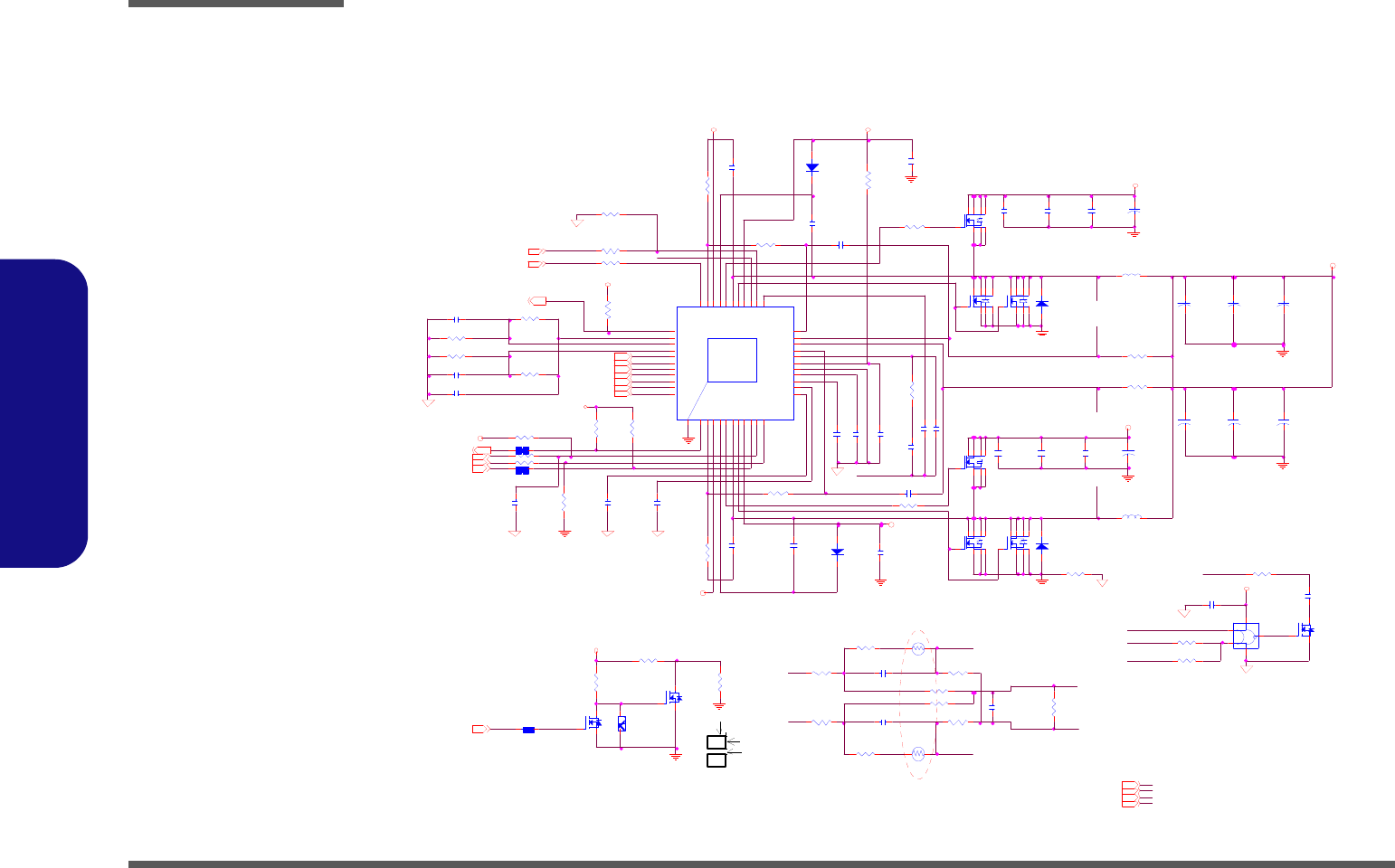

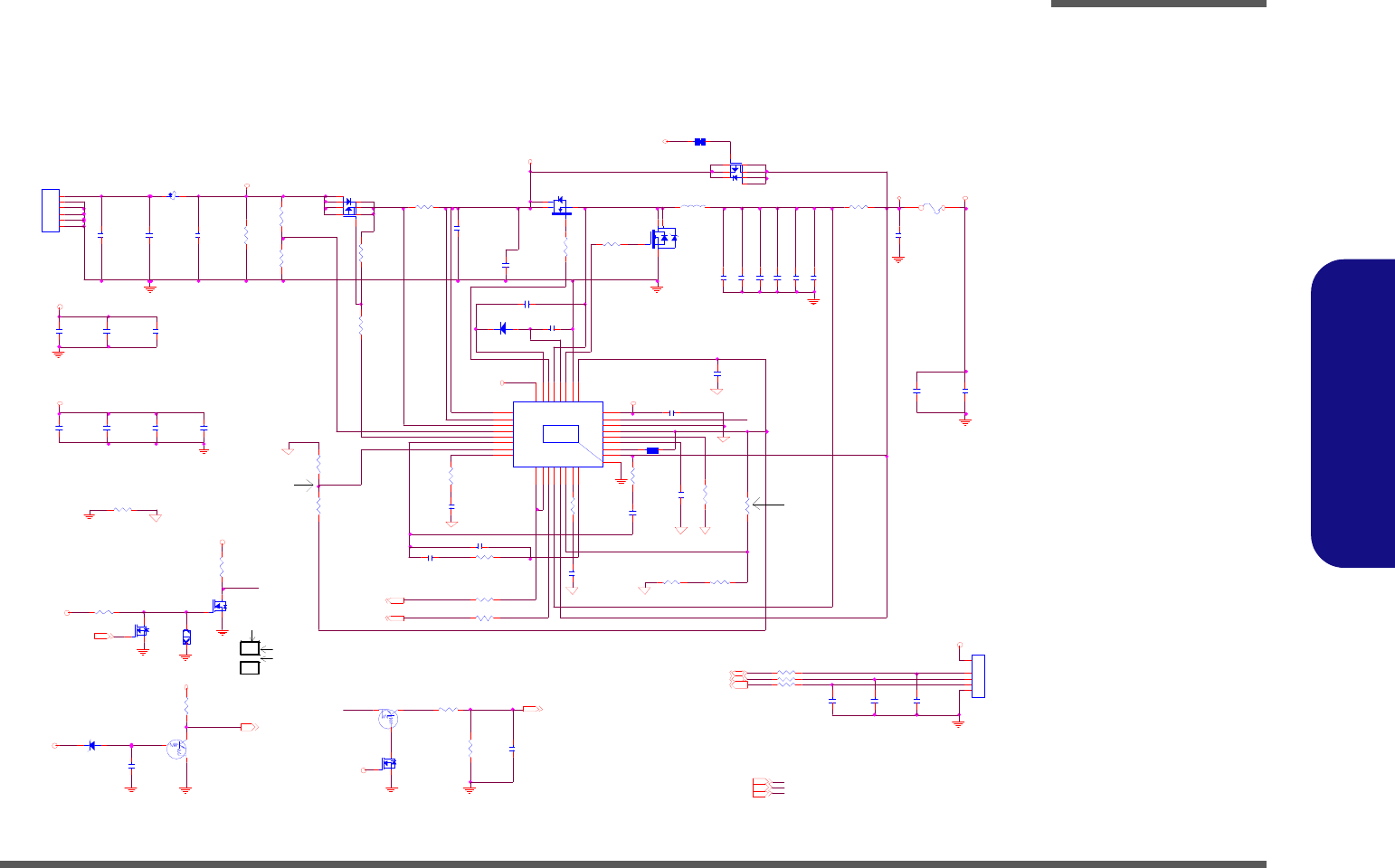

Schematic Diagrams.................................B-1

System Block Diagram ...................................................................B-2

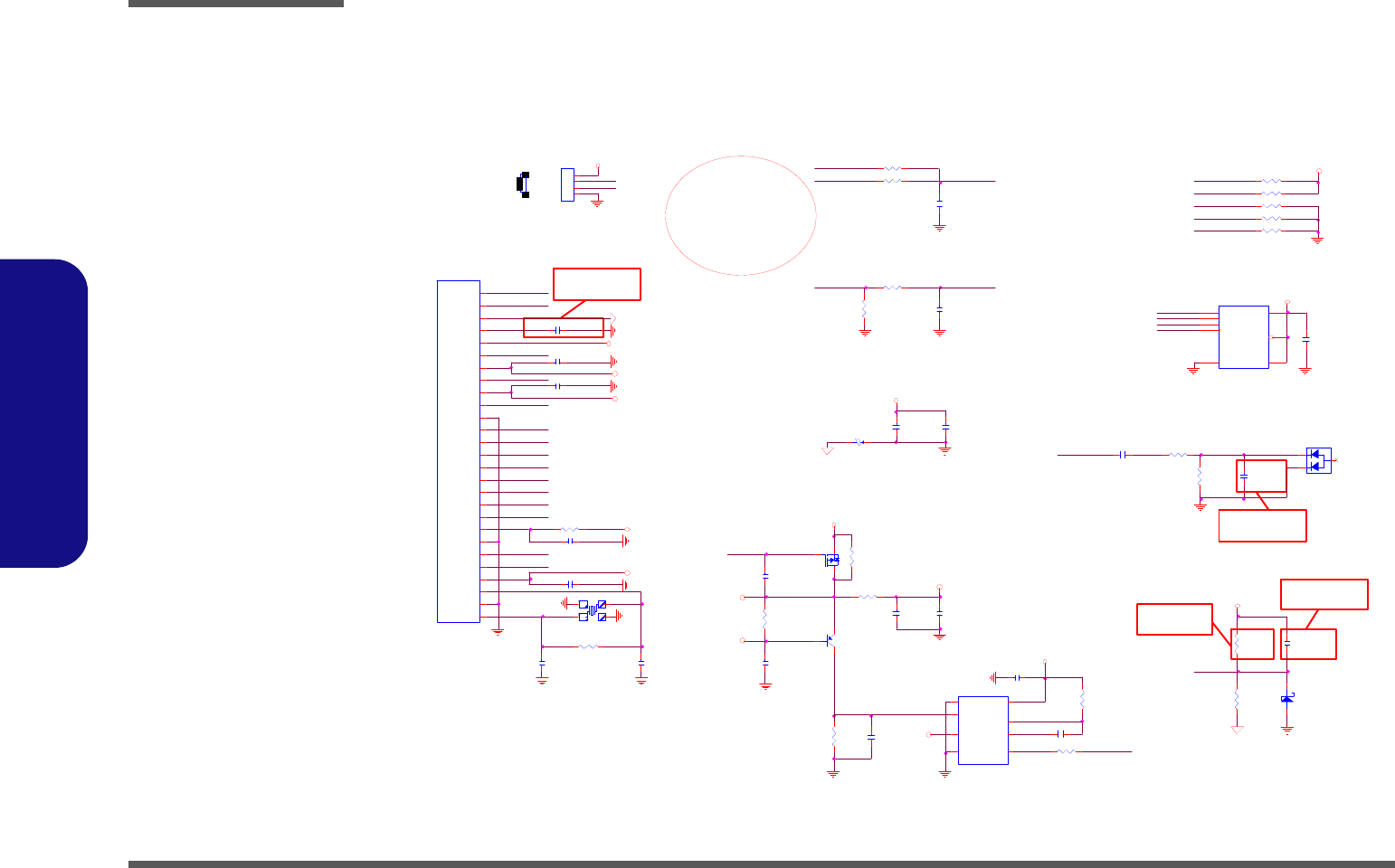

Intel Penryn (Socket-P) 1/2 ............................................................B-3

Intel Penryn (Socket-P) 2/2 ............................................................B-4

Cantiga 1/6 - Host ...........................................................................B-5

Cantiga 2/6 - VGA, CRT ................................................................B-6

Cantiga 3/6 - DDR ..........................................................................B-7

Cantiga 4/6 - Power ........................................................................B-8

Cantiga 5/6 - Power ........................................................................B-9

Cantiga 6/6 - GND ........................................................................B-10

DDRII CHANNEL A ...................................................................B-11

DDRII CHANNEL B ...................................................................B-12

Panel, Inverter, CRT .....................................................................B-13

ICH9-M 1/5 - SATA .....................................................................B-14

ICH9-M 2/5 - PCIE, PCI, USB ....................................................B-15

ICH9-M 3/5 - GPIO, PWR Management ....................................B-16

ICH9-M 4/5 - Power .....................................................................B-17

ICH9-M 5/5 - GND ......................................................................B-18

Clock Generator ............................................................................B-19

Multi I/O, ODD, CCD, BT, TPM .................................................B-20

New Card, Mini PCIE ...................................................................B-21

LED, FAN, TP, FP, USB ..............................................................B-22

JMB385 Card Reader ...................................................................B-23

PCI-E LAN RTL8111C ................................................................B-24

Audio Codec ALC662 ..................................................................B-25

Audio AMP2056 ...........................................................................B-26

Preface

X

Preface

KBC-ITE IT8512E ....................................................................... B-27

System Power, LED BKLT .......................................................... B-28

Power VDD3, VDD5 ................................................................... B-29

Power 1.5VS, 1.05VS, 3.3V, 5V .................................................. B-30

Power 1.8V, 0.9VSM ...................................................................B-31

Power VCORE .............................................................................B-32

Power AC-IN, Charger ................................................................. B-33

Multi I/O Board 1/2 ...................................................................... B-34

Multi I/O Board 2/2 ...................................................................... B-35

Finger Printer Board ..................................................................... B-36

Click Board ..................................................................................B-37

M730T ODD Bridge Board .......................................................... B-38

M730T Audio Board ....................................................................B-39

Power Sequence Diagram ............................................................ B-40

Power Sequence v3.0 ................................................................... B-41

Introduction

Overview 1 - 1

1.Introduction

Chapter 1: Introduction

Overview

This manual covers the information you need to service or upgrade the M730TG series notebook computer. Information

about operating the computer (e.g. getting started, and the Setup utility) is in the User’s Manual. Information about driv-

ers (e.g. video & audio) is also found in User’s Manual. That manual is shipped with the computer.

Operating systems (e.g. Windows XP, Windows Vista, Windows 7, etc.) have their own manuals as do application soft-

ware (e.g. word processing and database programs). If you have questions about those programs, you should consult

those manuals.

The M730TG series notebook is designed to be upgradeable. See Disassembly on page 2 - 1 for a detailed description

of the upgrade procedures for each specific component. Please note the warning and safety information indicated by the

“” symbol.

The balance of this chapter reviews the computer’s technical specifications and features.

Introduction

1 - 2 System Specifications

1.Introduction

System Specifications

Processor

Intel® Mobile Celeron Dual Core Processor:

T3100 (1.9GHz)

45nm (45 Nanometer) Process Technology, 1MB

L2 Cache & 800MHz FSB

(478-pin) Micro-FC-PGA Package - Socket-P

T3000 (1.8GHz)

45nm (45 Nanometer) Process Technology, 1MB

L2 Cache & 800MHz FSB

(478-pin) Micro-FC-PGA Package - Socket-P

T1700 (1.9GHz)

65nm (65 Nanometer) Process Technology, 1MB

L2 Cache & 667MHz FSB

(478-pin) Micro-FC-PGA Package - Socket-P

T1600 (1.83GHz)

65nm (65 Nanometer) Process Technology, 1MB

L2 Cache & 667MHz FSB

(478-pin) Micro-FC-PGA Package - Socket-P

Intel® Mobile Celeron Processor:

900 (2.2GHz)

45nm (45 Nanometer) Process Technology, 1MB

L2 Cache & 800MHz FSB

(478-pin) Micro-FC-PGA Package - Socket-P

Core Logic

Intel® GL40 + ICH9M Chipset

Display

13.3” WXGA (1280 * 800) TFT LCD

Memory

Dual Channel DDRII (DDR2)

Two 200 Pin SO-DIMM Sockets Supporting

DDRII (DDR2) 800MHz

Memory Expandable up to 4GB (Supporting

1GB/2GB Modules)

Video

Intel® GL40 Integrated Video

High Preference 3D/2D Graphic Accelerator

Shared Memory Architecture of up to 512M

Supports Microsoft DirectX 10

BIOS

One 16M SPI Flash ROM

Phoenix™ BIOS

Storage

One Changeable 12.7mm(h) Super Multi

Optical Device Drive - SATA interface

One Changeable 2.5" 9.5 mm (h) HDD OR

with SATA (Serial) Interface

Audio

High Definition Audio

Compliant with Microsoft UAA (Universal

Audio Architecture)

Direct Sound 3D™ Compatible

Built-In Microphone

2 * Built-In Speakers

Keyboard & Pointing Device

Full Size WinKey Keyboard

Built-in TouchPad

Interface

Three USB 2.0 Ports

One External Monitor Port

One Headphone-Out Jack

One Microphone-In Jack

One S/PDIF-Out Jack

One RJ-11 LAN Jack for Fax/Modem

One RJ-45 LAN Jack for LAN

One DC-In Jack

Card Reader

Embedded 7-in-1 Card Reader (MS/ MS Pro/

SD/ Mini SD/ MMC/ RS MMC/ MS Duo)

Note: MS Duo/ Mini SD/ RS MMC Cards

require a PC adapter

Slots

One ExpressCard/34/54 Slot

Two Mini-Card Slots with USB & PCIe

interface:

Slot 1 for Mini-Card WLAN Module with PCIe

Interface

Slot 2 for 3.75G Module with USB Interface

(

Factory Option

)

Introduction

System Specifications 1 - 3

1.Introduction

Communication

56K Fax/Modem V90/92 Compliant

10/100/100Mb Base-TX Ethernet LAN

Intel® WiFi Link 5300 Series (3*3 - 802.11a/g/

n) Wireless LAN Mini-Card Module with PCIe

interface (Option)

3rd Party 802.11b/g Wireless LAN Mini-Card

Module with USB interface (Option)

Bluetooth 2.1 + EDR (Enhanced Data Rate)

Module (Factory Option)

1.3M Pixel PC Camera Module with USB

interface (Factory Option)

3.75G Module:

UMTS/HSPDA-based 3.75G Module with

Mini-Card Interface (Factory Option)

Quad-band GSM/GPRS (850 MHz, 900 MHz,

1800 MHz, 1900 MHz)

UMTS WCDMA FDD (2100 MHz)

Note that UMTS modes CAN NOT be used

in North America

Power Management

Supports Wake on LAN

Supports Wake on Modem Ring

Power

Full Range AC/DC Adapter

AC input 100 - 240V, 50 - 60Hz,

DC Output 19V, 3.42A or 18.5V, 3.5A (65

Watts)

4 Cell Smart Lithium-Ion Battery Pack,

2400mAH

8 Cell Smart Lithium-Ion Battery Pack,

4400mAH (Option)

Security

Security (Kensington® Type) Lock Slot

BIOS Password

Operating System

Windows® Vista (with Service Pack 2)

Windows® XP (with Service Pack 3)

Environmental Spec

Temperature

Operating: 5°C - 35°C

Non-Operating: -20°C - 60°C

Relative Humidity

Operating: 20% - 80%

Non-Operating: 10% - 90%

Dimensions & Weight

310mm (w) * 233mm (d) * 30 - 36mm (h)

2.0 kg (with 4 Cell Battery and ODD)

Optional

Intel® WiFi Link 5300 Series (3*3 - 802.11a/g/

n) Wireless LAN Mini-Card Module with PCIe

interface

3rd Party 802.11b/g Wireless LAN Mini-Card

Module with USB interface

Bluetooth 2.1 + EDR (Enhanced Data Rate)

Module (Factory Option)

1.3M Pixel PC Camera Module with USB

interface (Factory Option)

UMTS/HSPDA-based 3.75G Module with

Mini-Card Interface (Factory Option)

8 Cell Smart Lithium-Ion Battery Pack,

4400mAH (Option)

Introduction

1 - 4 External Locator - Top View with LCD Panel Open

1.Introduction

External Locator - Top View with LCD Panel Open

Figure 1

Top View

1. Optional Built-In

PC Camera

2. LCD

3. Built-In

Microphone

4. Power Button

5. Hot Key Buttons

6. LED Status

Indicators

7. Keyboard

8. Touchpad &

Buttons

9. LED Power &

Communication

Indicators

10

2

5

1

7

8

4

6

9

6

5 4 Touchpad Buttons

(valid operation area)

3

Introduction

External Locator - Front & Right side Views 1 - 5

1.Introduction

External Locator - Front & Right side Views

Figure 2

Front Views

1. LED Power &

Communication

Indicators

2. 7-in-1 Card

Reader

3. S/PDIF-Out Jack

4. Microphone-In

Jack

5. Headphone-Out

Jack

Figure 3

Right Side Views

1. Optical Device

Drive Bay

2. USB 2.0 Port

3. RJ-11 Phone

Jack

4. Security Lock

Slot

1

43 5

2

1234

Introduction

1 - 6 External Locator - Left Side & Rear View

1.Introduction

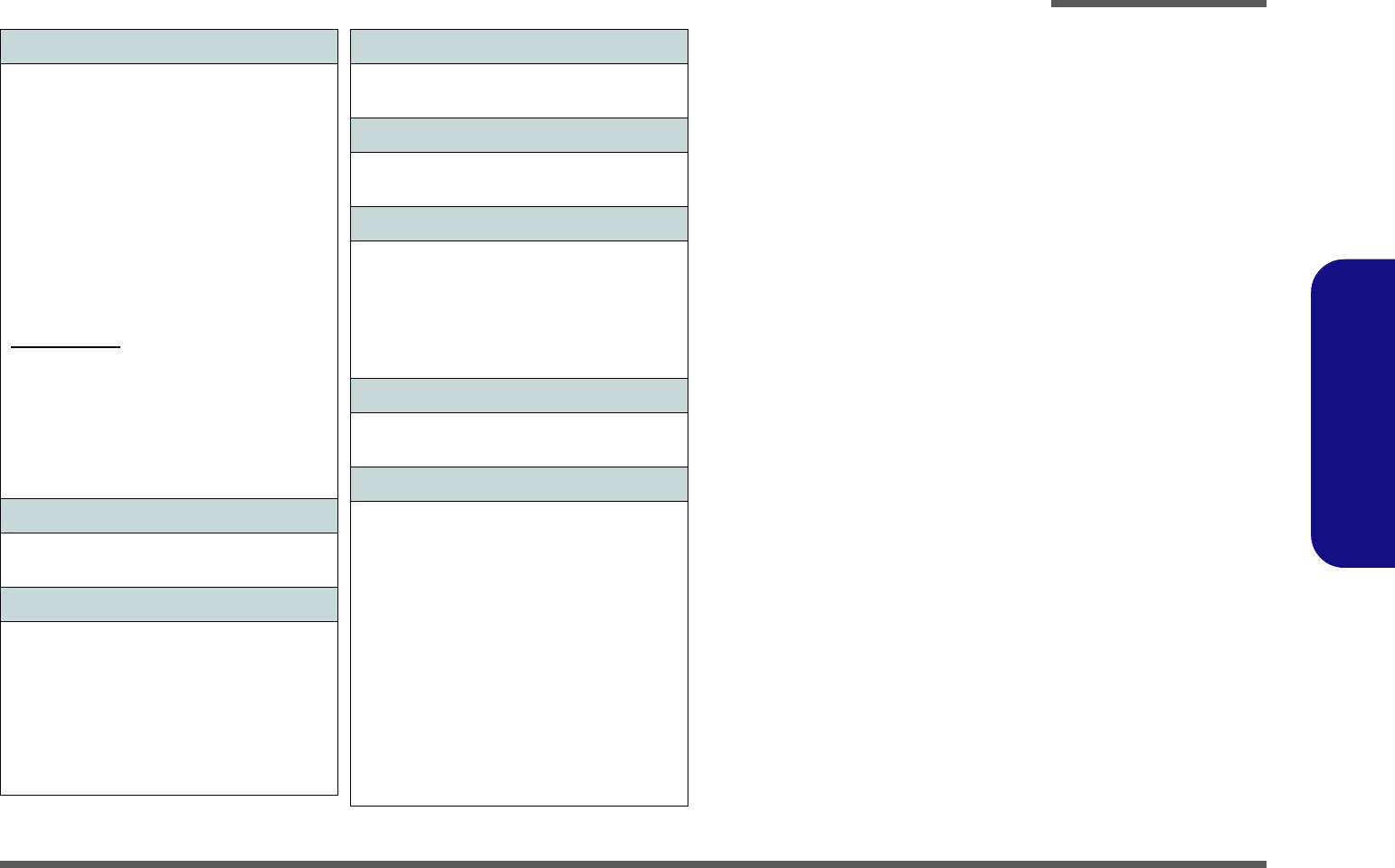

External Locator - Left Side & Rear View

Figure 4

Left Side View

1. DC-In Jack

2. RJ-45 LAN Jack

3. External Monitor

Port

4. Vent/Fan Intake/

Outlet

5. 2 * USB 2.0 Ports

6. ExpressCard Slot

4

12355

6

Figure 5

Rear View

1. Battery

1

Introduction

External Locator - Bottom View 1 - 7

1.Introduction

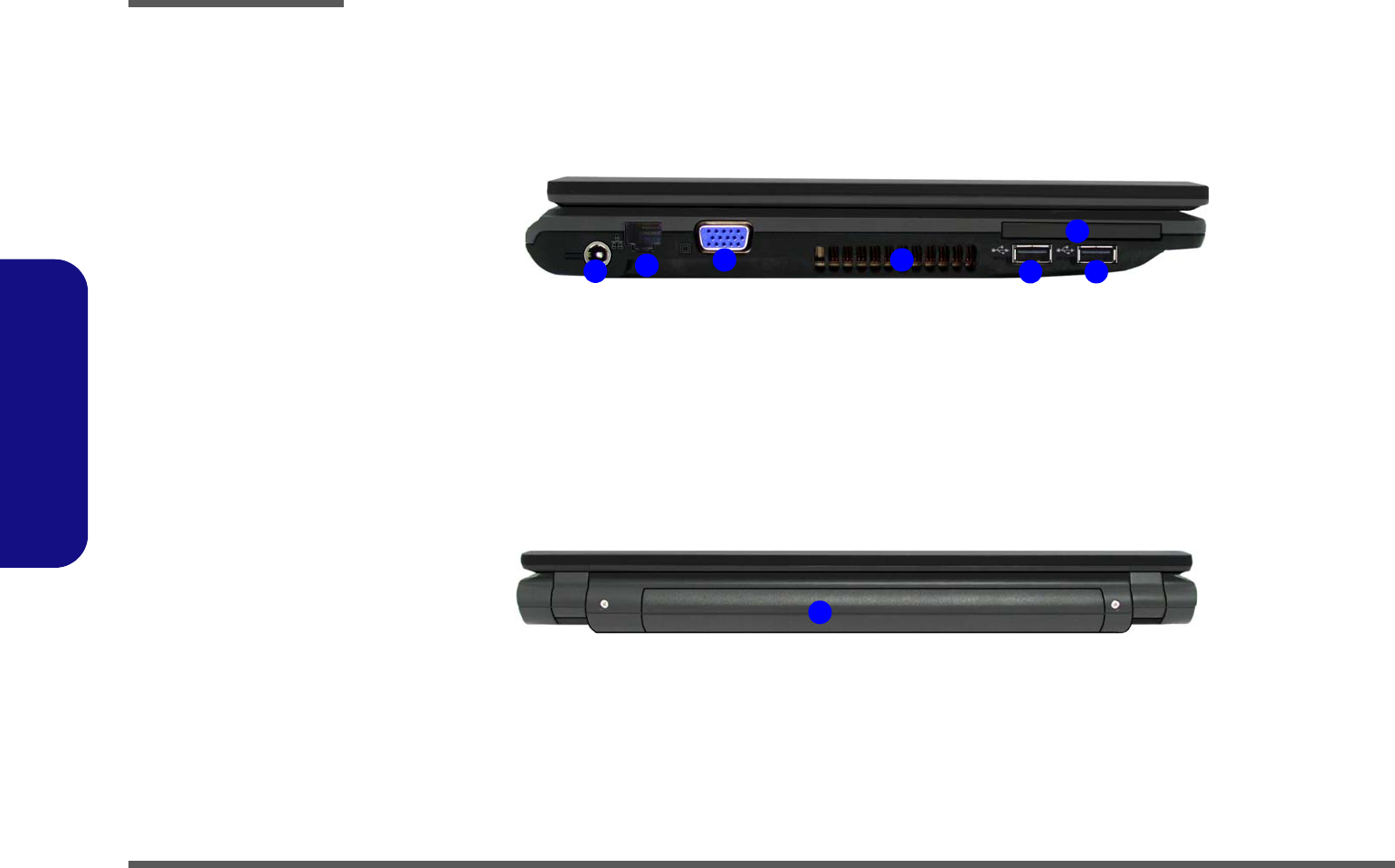

External Locator - Bottom View

Figure 6

Bottom View

1. Battery (4 Cell

Battery Pictured)

2. Hard Disk Bay

Cover

(3.5G Module

Location)

3. RAM & CPU Bay

Cover

4. Vent/Fan Intake/

Outlet

5. Speakers

Overheating

To prevent your com-

puter from overheating

make sure nothing

blocks the vent/fan in-

takes while the com-

puter is in use.

2

3

1

4

54

5

Introduction

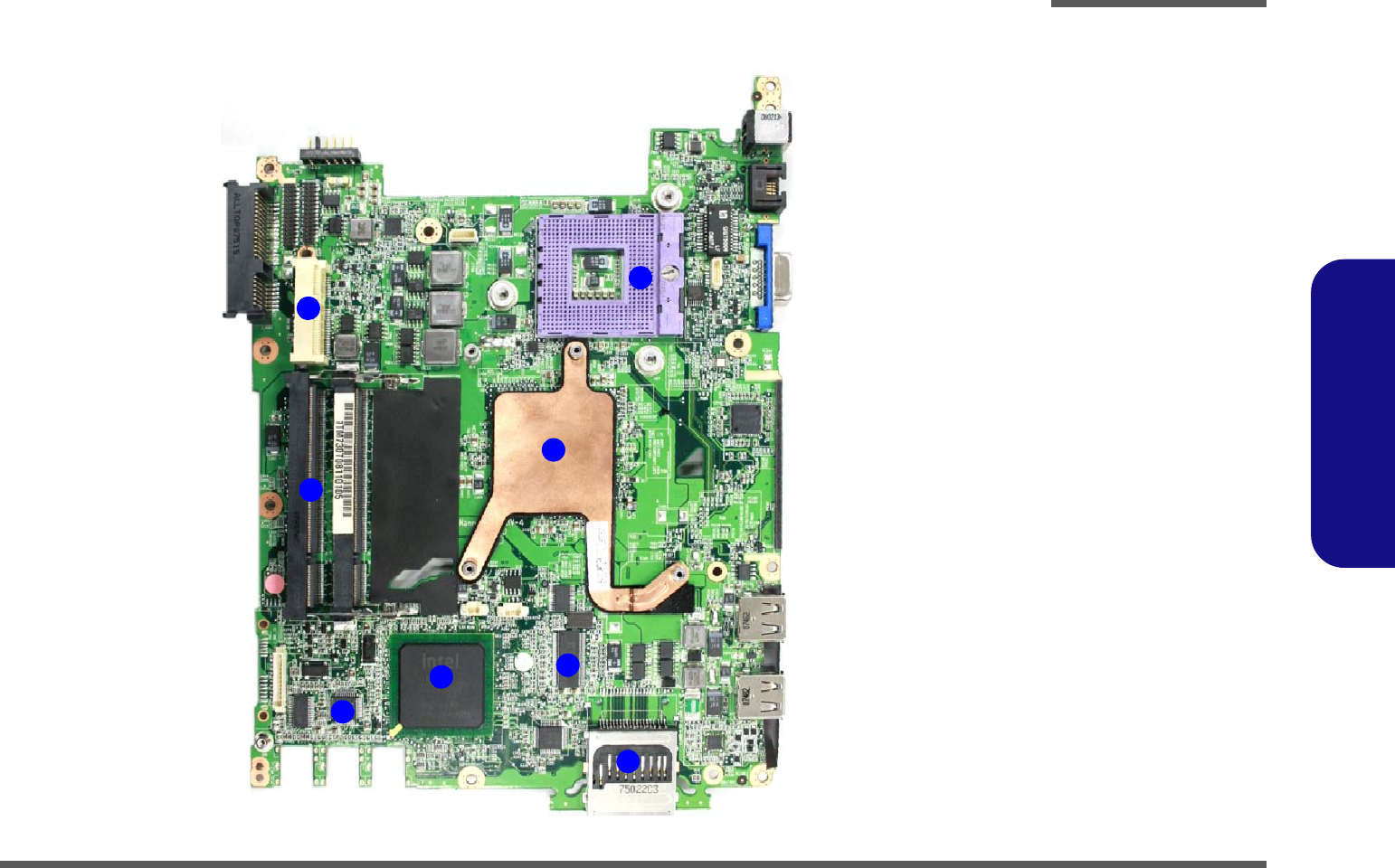

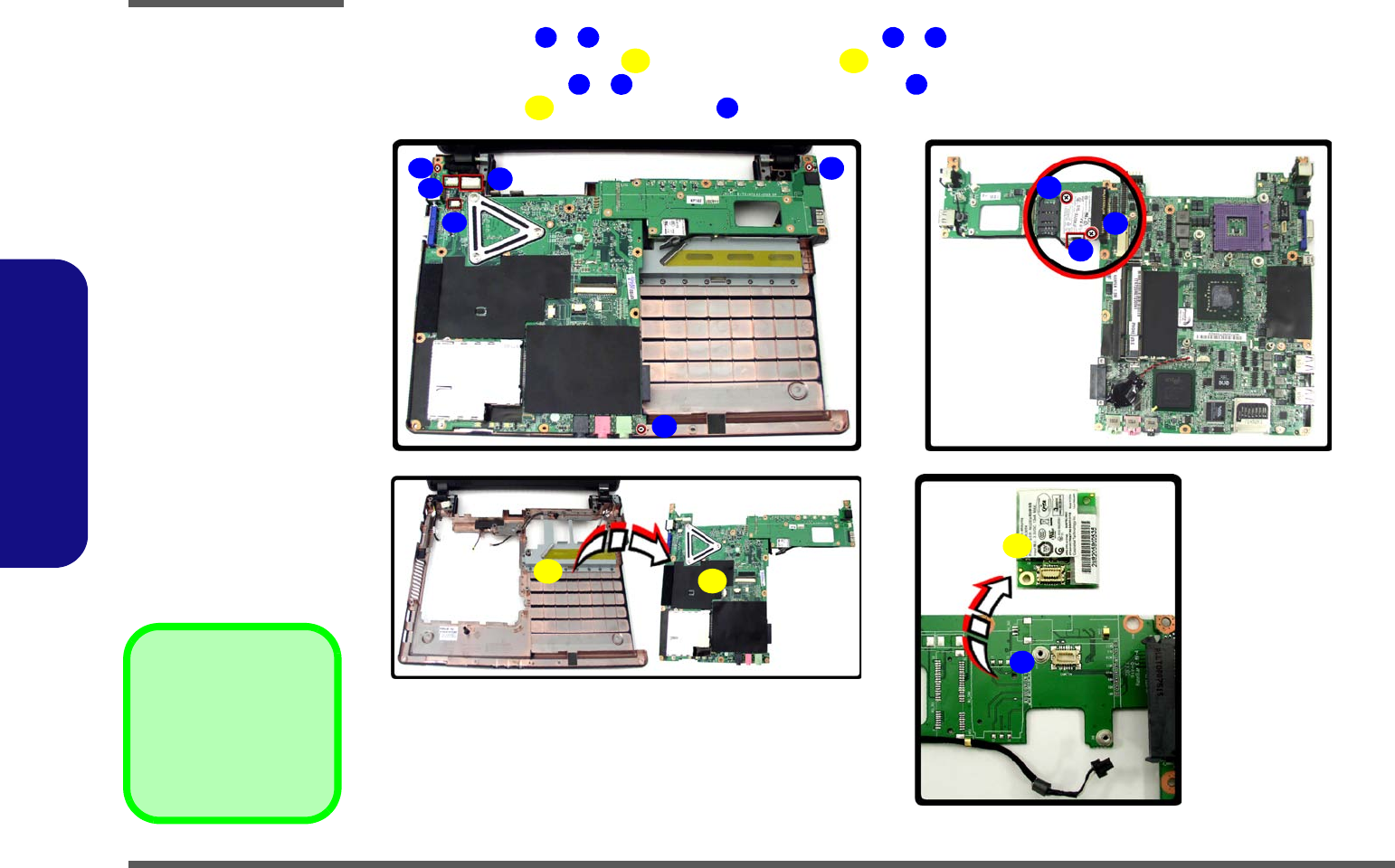

1 - 8 Mainboard Overview - Top (Key Parts)

1.Introduction

Mainboard Overview - Top (Key Parts)

Figure 7

Mainboard Top

Key Parts

1. Transformer

2. RTL6111C

3. ExpressCard

Connector

4. JMB385

5. KBC ITE IT8502E

1

2

3

4

5

Introduction

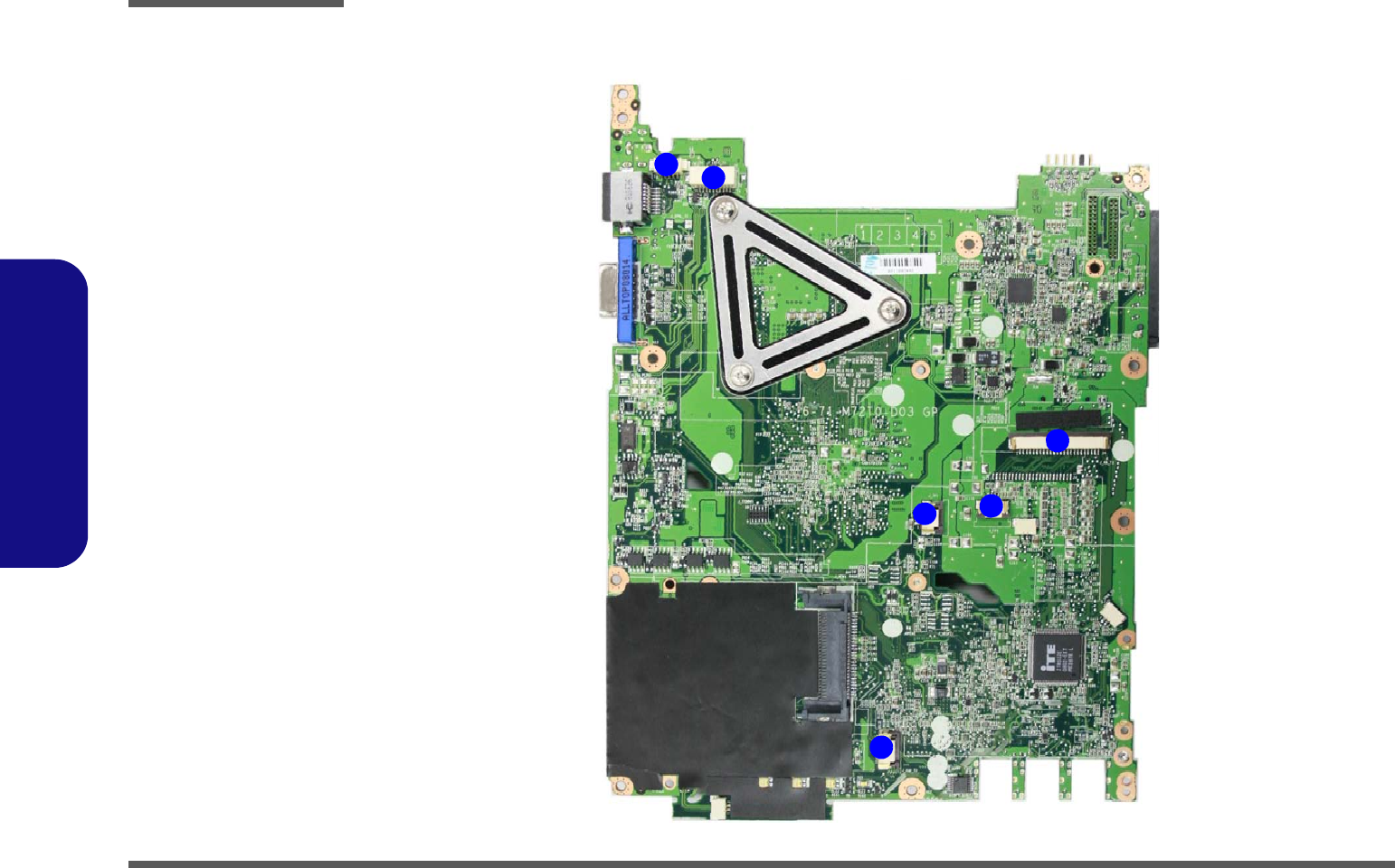

Mainboard Overview - Bottom (Key Parts) 1 - 9

1.Introduction

Mainboard Overview - Bottom (Key Parts)

1

2

3

4

5

6

7

8

Figure 8

Mainboard Bottom

Key Parts

1. CPU Socket (no

CPU installed)

2. Northbridge

3. Memory Slots

DDR2 SO-DIMM

4. ICS

5. Card Reader

Socket

6. Southbridge

7. Audio Codec

8. Mini-Card

Connector (WLAN

Module)

Introduction

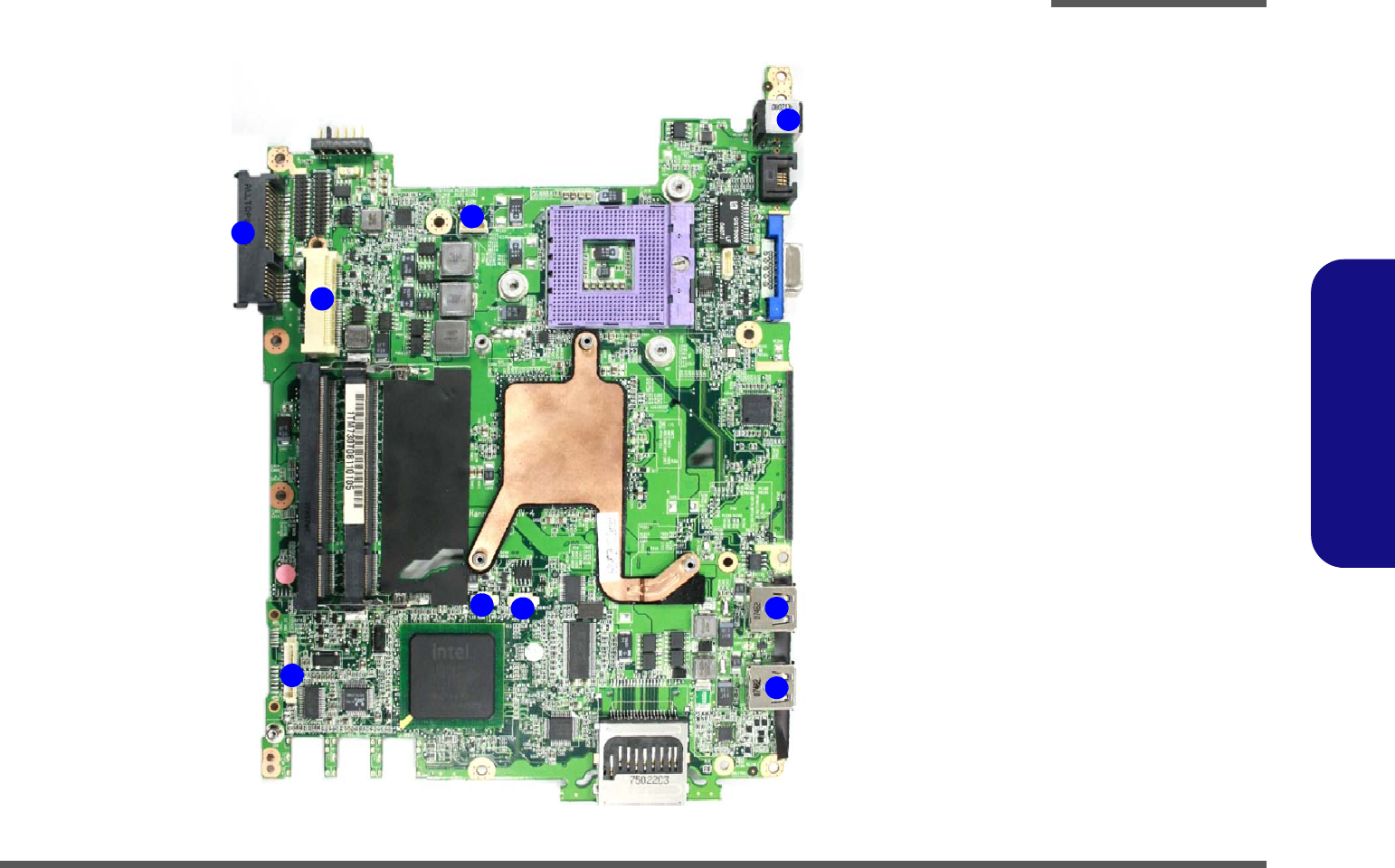

1 - 10 Mainboard Overview - Top (Connectors)

1.Introduction

Mainboard Overview - Top (Connectors)

Figure 9

Mainboard Top

Connectors

1. Hot-key

Connector

2. LCD Cable

Connector

3. Keyboard Cable

Connector

4. Audio Board

Connector

5. Microphone

Cable Connector

6. TouchPad Cable

Connector

65

1

4

2

3

Introduction

Mainboard Overview - Bottom (Connectors) 1 - 11

1.Introduction

Mainboard Overview - Bottom (Connectors)

Figure 10

Mainboard Bottom

Connectors

1. BT Cable

Connector

2. Multi Board

Connector

3. CD-ROM

Connector

4. HDD Connector

5. CMOS Bat.

Connector

6. CPU Fan Cable

Connector

7. DC-In Jack

8. USB Port

1

2

3

4

568

8

7

Introduction

1-12

1.Introduction

Disassembly

Overview 2 - 1

2.Disassembly

Chapter 2: Disassembly

Overview

This chapter provides step-by-step instructions for disassembling the M730TG series notebook’s parts and subsystems.

When it comes to reassembly, reverse the procedures (unless otherwise indicated).

We suggest you completely review any procedure before you take the computer apart.

Procedures such as upgrading/replacing the RAM, optical device and hard disk are included in the User’s Manual but are

repeated here for your convenience.

To make the disassembly process easier each section may have a box in the page margin. Information contained under

the figure # will give a synopsis of the sequence of procedures involved in the disassembly procedure. A box with a

lists the relevant parts you will have after the disassembly process is complete. Note: The parts listed will be for the dis-

assembly procedure listed ONLY, and not any previous disassembly step(s) required. Refer to the part list for the previ-

ous disassembly procedure. The amount of screws you should be left with will be listed here also.

A box with a will also provide any possible helpful information. A box with a contains warnings.

An example of these types of boxes are shown in the sidebar.

Information

Warning

Disassembly

2 - 2 Overview

2.Disassembly

NOTE: All disassembly procedures assume that the system is turned OFF, and disconnected from any power supply (the

battery is removed too).

Maintenance Tools

The following tools are recommended when working on the notebook PC:

• M3 Philips-head screwdriver

• M2.5 Philips-head screwdriver (magnetized)

• M2 Philips-head screwdriver

• Small flat-head screwdriver

• Pair of needle-nose pliers

• Anti-static wrist-strap

Connections

Connections within the computer are one of four types:

Locking collar sockets for ribbon connectors To release these connectors, use a small flat-head screwdriver to

gently pry the locking collar away from its base. When replac-

ing the connection, make sure the connector is oriented in the

same way. The pin1 side is usually not indicated.

Pressure sockets for multi-wire connectors To release this connector type, grasp it at its head and gently

rock it from side to side as you pull it out. Do not pull on the

wires themselves. When replacing the connection, do not try to

force it. The socket only fits one way.

Pressure sockets for ribbon connectors To release these connectors, use a small pair of needle-nose pli-

ers to gently lift the connector away from its socket. When re-

placing the connection, make sure the connector is oriented in

the same way. The pin1 side is usually not indicated.

Board-to-board or multi-pin sockets To separate the boards, gently rock them from side to side as

you pull them apart. If the connection is very tight, use a small

flat-head screwdriver - use just enough force to start.

Disassembly

Overview 2 - 3

2.Disassembly

Maintenance Precautions

The following precautions are a reminder. To avoid personal injury or damage to the computer while performing a re-

moval and/or replacement job, take the following precautions:

1. Don't drop it. Perform your repairs and/or upgrades on a stable surface. If the computer falls, the case and other

components could be damaged.

2. Don't overheat it. Note the proximity of any heating elements. Keep the computer out of direct sunlight.

3. Avoid interference. Note the proximity of any high capacity transformers, electric motors, and other strong mag-

netic fields. These can hinder proper performance and damage components and/or data. You should also monitor

the position of magnetized tools (i.e. screwdrivers).

4. Keep it dry. This is an electrical appliance. If water or any other liquid gets into it, the computer could be badly

damaged.

5. Be careful with power. Avoid accidental shocks, discharges or explosions.

•Before removing or servicing any part from the computer, turn the computer off and detach any power supplies.

•When you want to unplug the power cord or any cable/wire, be sure to disconnect it by the plug head. Do not pull on the wire.

6. Peripherals – Turn off and detach any peripherals.

7. Beware of static discharge. ICs, such as the CPU and main support chips, are vulnerable to static electricity.

Before handling any part in the computer, discharge any static electricity inside the computer. When handling a

printed circuit board, do not use gloves or other materials which allow static electricity buildup. We suggest that

you use an anti-static wrist strap instead.

8. Beware of corrosion. As you perform your job, avoid touching any connector leads. Even the cleanest hands pro-

duce oils which can attract corrosive elements.

9. Keep your work environment clean. Tobacco smoke, dust or other air-born particulate matter is often attracted

to charged surfaces, reducing performance.

10. Keep track of the components. When removing or replacing any part, be careful not to leave small parts, such as

screws, loose inside the computer.

Cleaning

Do not apply cleaner directly to the computer, use a soft clean cloth.

Do not use volatile (petroleum distillates) or abrasive cleaners on any part of the computer.

Power Safety

Warning

Before you undertake

any upgrade proce-

dures, make sure that

you have turned off the

power, and discon-

nected all peripherals

and cables (including

telephone lines). It is

advisable to also re-

move your battery in

order to prevent acci-

dentally turning the

machine on.

Disassembly

2 - 4 Disassembly Steps

2.Disassembly

Disassembly Steps

The following table lists the disassembly steps, and on which page to find the related information. PLEASE PERFORM

THE DISASSEMBLY STEPS IN THE ORDER INDICATED.

To remove the Battery:

1. Remove the battery page 2 - 5

To remove the HDD:

1. Remove the battery page 2 - 5

2. Remove the HDD page 2 - 6

To remove the Optical Device:

1. Remove the battery page 2 - 5

2. Remove the Optical device page 2 - 8

To remove the System Memory:

1. Remove the battery page 2 - 5

2. Remove the system memory page 2 - 9

To remove the Inverter Board:

1. Remove the battery page 2 - 5

2. Remove the inverter board page 2 - 11

To remove and install a Processor:

1. Remove the battery page 2 - 5

2. Remove the processor page 2 - 12

To remove the Wireless LAN Module:

1. Remove the battery page 2 - 5

2. Remove the wireless LAN page 2 - 14

To remove the Bluetooth Module:

1. Remove the battery page 2 - 5

2. Remove the Bluetooth page 2 - 15

To remove the Keyboard:

1. Remove the battery page 2 - 5

2. Remove the keyboard page 2 - 16

To remove the Modem:

1. Remove the battery page 2 - 5

2. Remove the HDD page 2 - 6

3. Remove the system memory page 2 - 9

4. Remove the Optical device page 2 - 8

5. Remove the processor page 2 - 12

6. Remove the keyboard page 2 - 16

7. Remove the modem page 2 - 17

Disassembly

Removing the Battery 2 - 5

2.Disassembly

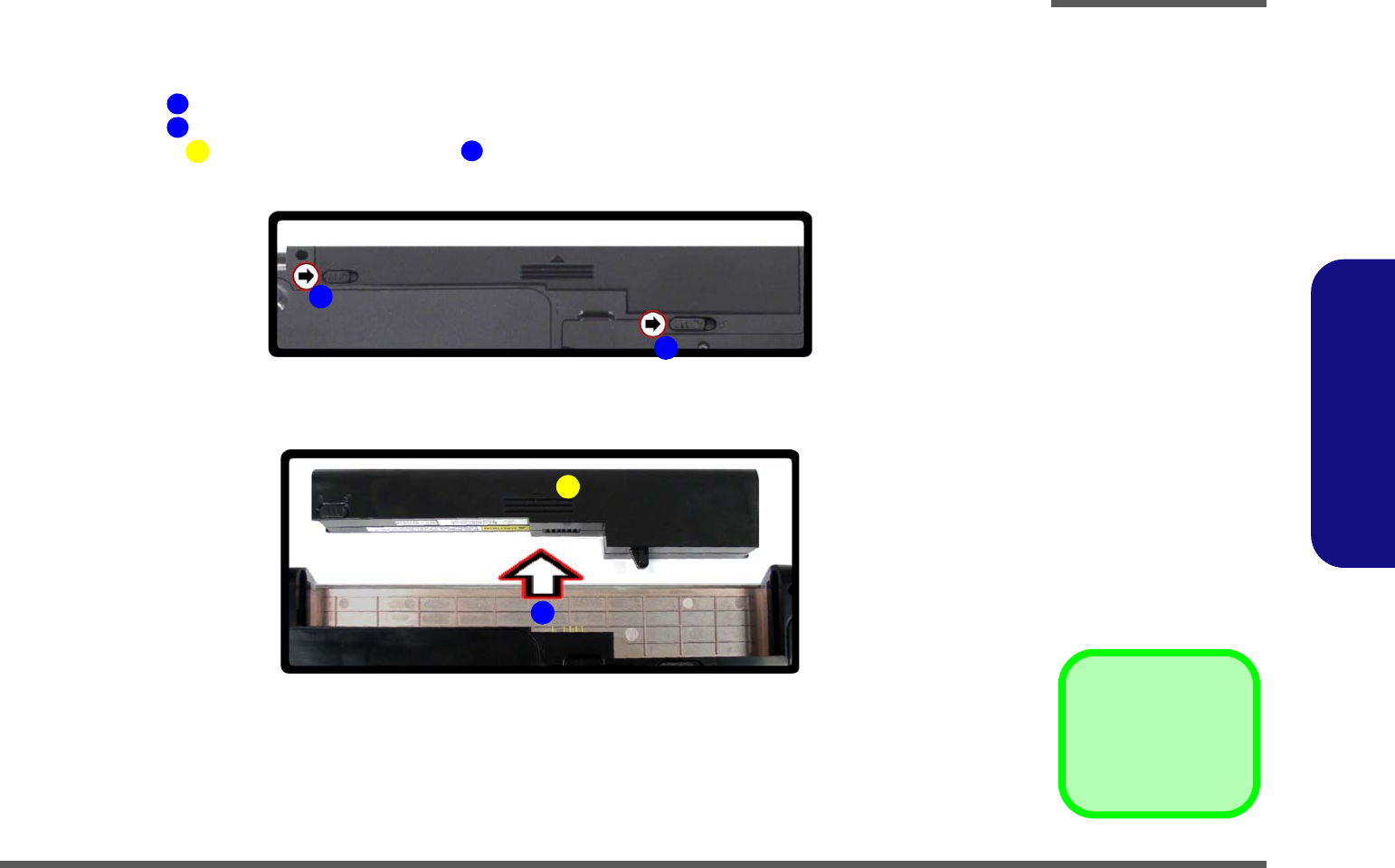

Removing the Battery

1. Turn the computer off, and turn it over.

2. Slide the latch in the direction of the arrow.

3. Slide the latch in the direction of the arrow, and hold it in place.

4. Slide the battery in the direction of the arrow .

3. Battery

1

2

6

3

4

a.

3

b.

2

4

1

Figure 1

Battery Removal

a. Slide the latch and hold

in place.

b. Slide the battery in the di-

rection of the arrow.

Disassembly

2 - 6 Removing the Hard Disk Drive

2.Disassembly

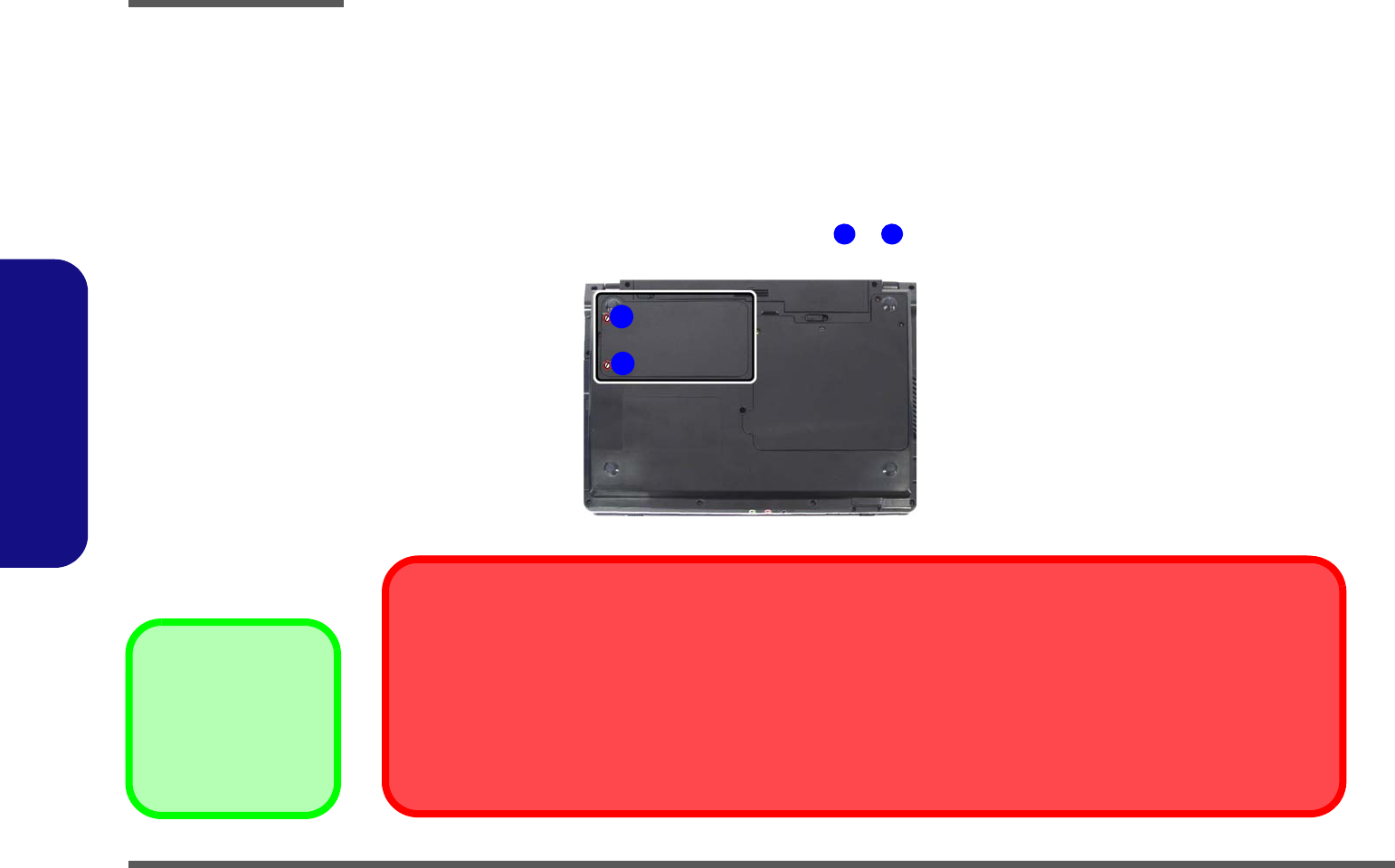

Removing the Hard Disk Drive

The hard disk drive can be taken out to accommodate other 2.5" serial (SATA) hard disk drives with a height of 9.5mm

(h). Follow your operating system’s installation instructions, and install all necessary drivers and utilities (as outlined in

Chapter 4 of the User’s Manual) when setting up a new hard disk.

Hard Disk Upgrade Process

1. Turn off the computer, and remove the battery (page 2 - 5).

2. Locate the hard disk bay cover and loosen screws & .

Figure 2

HDD Assembly

Removal

a. Locate the HDD bay

cover and loosen the

screw(s).

•2 Screws

1

2

a.

HDD System Warning

New HDD’s are blank. Before you begin make sure:

You have backed up any data you want to keep from your old HDD.

You have all the CD-ROMs and FDDs required to install your operating system and programs.

If you have access to the internet, download the latest application and hardware driver updates for the operating system you plan

to install. Copy these to a removable medium.

2

1Note:

Only one model is pictured

here, however the compo-

nent locations are the same

for both models.

Disassembly

Removing the Hard Disk Drive 2 - 7

2.Disassembly

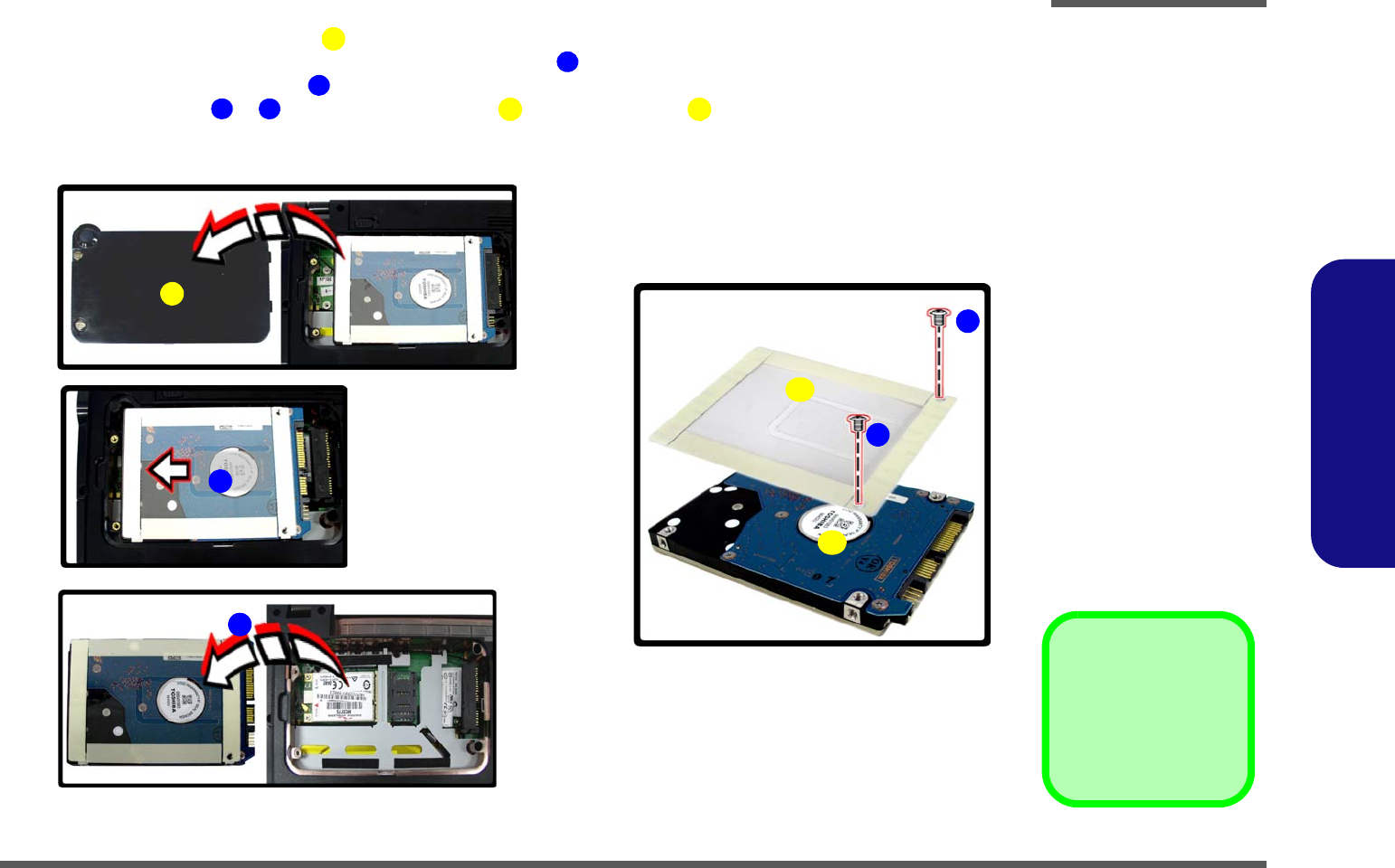

3. Remove the hard disk bay cover .

4. Grip the tab and slide the hard disk in the direction of arrow .

5. Lift the hard disk out of the bay .

6. Remove the screws & and the adhesive cover from the hard disk .

7. Reverse the process to install a new hard disk (do not forget to replace all the screws and covers).

6

3

4

5

6

7

6

8

6

9

4

b.

c.

e.

5

6

d.

3

8

9

7

3. HDD Bay Cover

8. Adhesive Cover

9. HDD

•2 Screws

Figure 3

HDD Assembly

Removal (cont’d.)

b. Remove the HDD bay

cover.

c. Grip the tab and slide the

HDD in the direction of

the arrow.

d. Lift the HDD assembly

out of the bay.

e. Remove the screw and

adhesive cover.

Disassembly

2 - 8 Removing the Optical (CD/DVD) Device

2.Disassembly

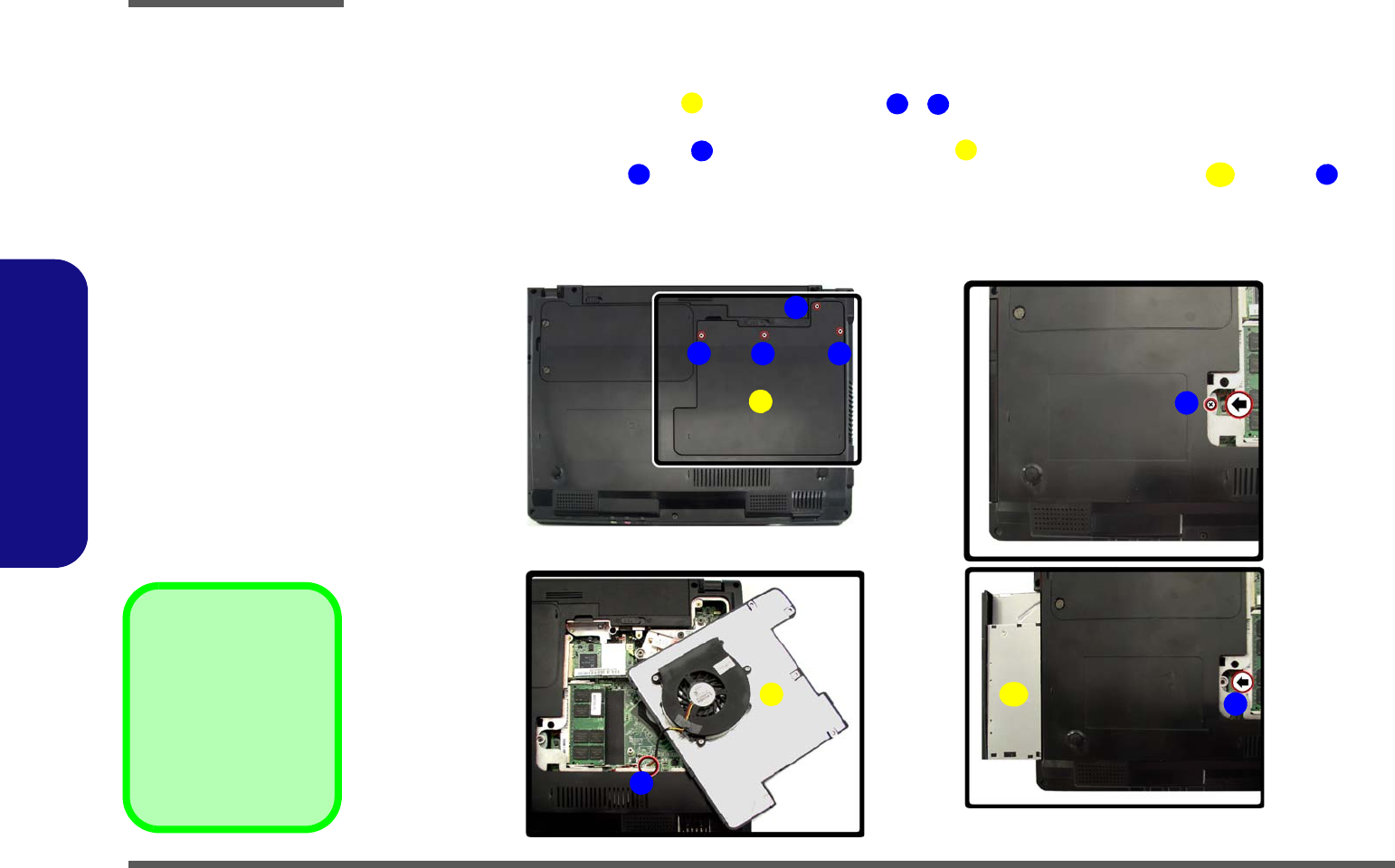

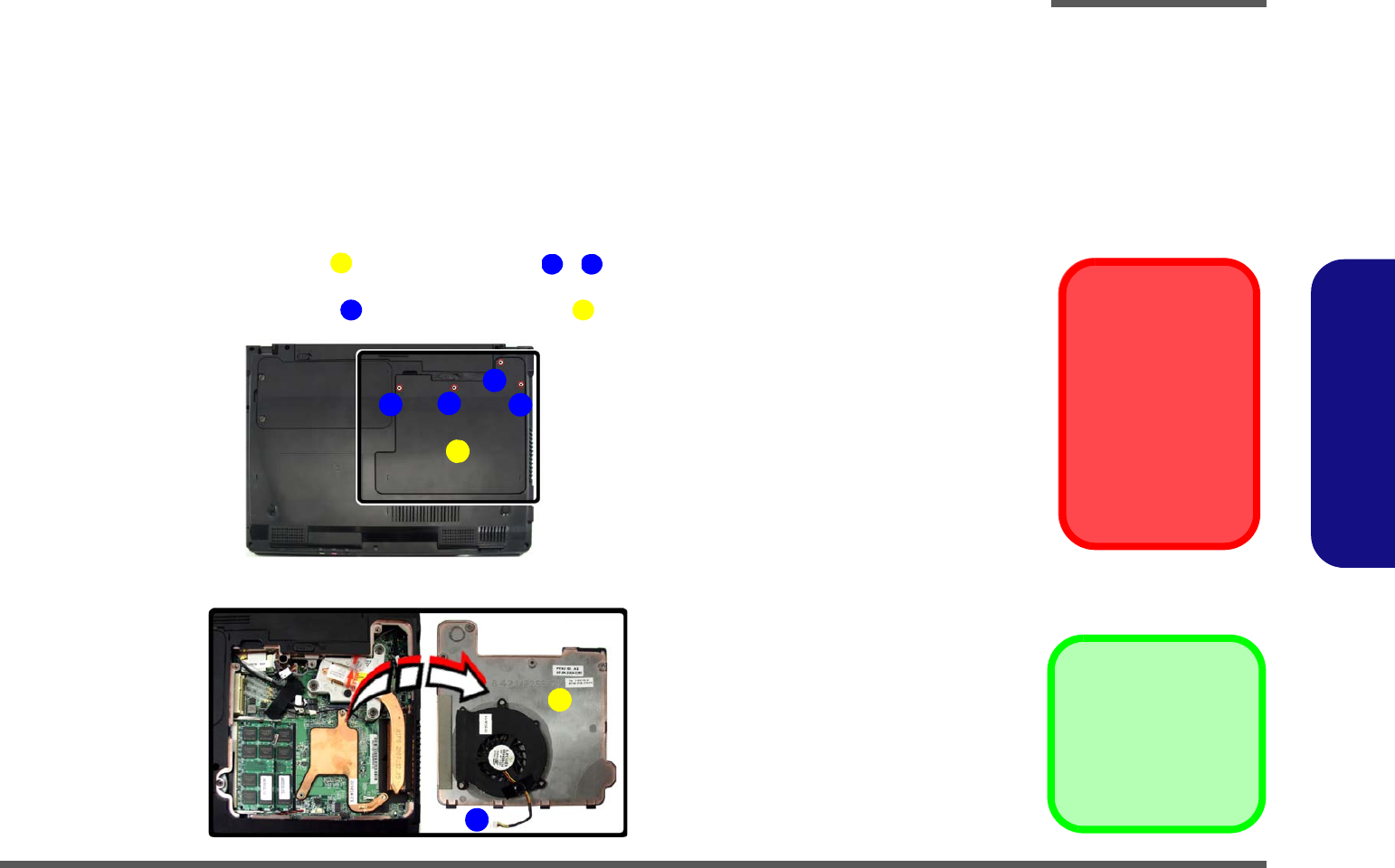

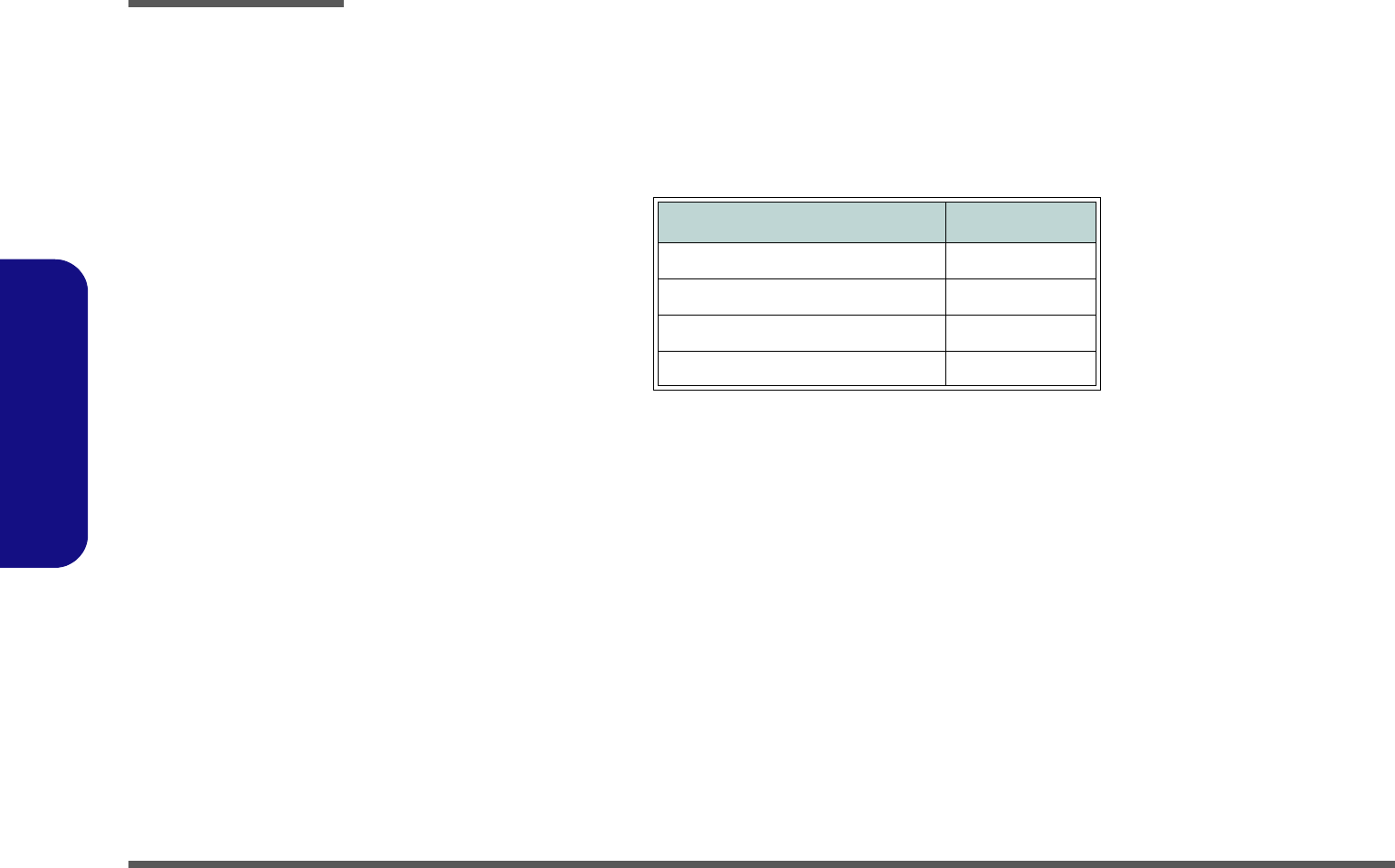

Removing the Optical (CD/DVD) Device

1. Turn off the computer, and remove the battery (page 2 - 5).

2. Locate the component bay cover and remove screws - .

3. Carefully (a fan and cable are attached to the under side of the cover) lift up the bay cover.

4. Carefully disconnect the fan cable and remove the bay cover .

5. Remove the screw at point , and use a screwdriver to carefully push out the optical device at point .

6. Insert the new device and carefully slide it into the computer (the device only fits one way. DO NOT FORCE IT; The

screw holes should line up).

7. Restart the computer to allow it to automatically detect the new device.

1

2

5

6

1

7

9

8

1. Component Bay Cover

9. Optical Device

•5 Screws

3

4

2

6

7

c.

d.

9

1

a.

b.

5

18

Figure 4

Optical Device

Removal

a. Remove the screws.

b. Disconnect the fan cable

and remove the cover.

c. Remove the screw.

d. Push the optical device

out off the computer at

point 8.

Disassembly

Removing the System Memory (RAM) 2 - 9

2.Disassembly

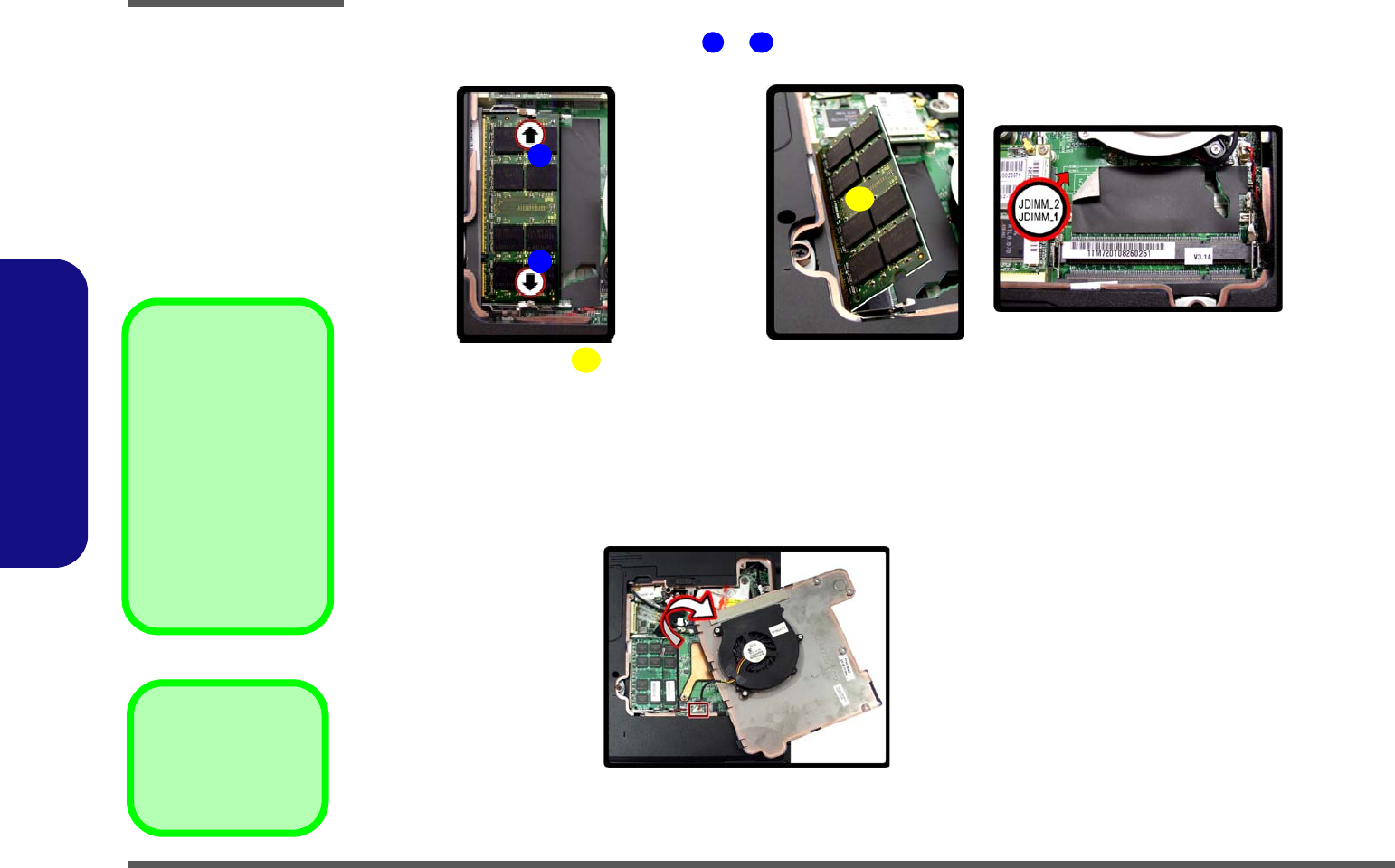

Removing the System Memory (RAM)

The computer has two memory sockets for 200 pin Small Outline Dual In-line Memory Modules (SO-DIMM) supporting

DDR2 800MHz. The main memory can be expanded up to 4GB. The SO-DIMM modules supported are 1024MB, and

2048MB and DDRII Modules. The total memory size is automatically detected by the POST routine once you turn on

your computer.

Memory Upgrade Process

1. Turn off the computer, remove the battery (page 2 - 5).

2. Locate the component bay cover , and remove screws - .

3. Carefully (a fan and cable are attached to the under side of the cover) lift up the bay cover.

4. Carefully disconnect the fan cable , and remove the cover .

Figure 5

RAM Module

Removal

a. Remove the screws.

b. Remove the cover.

Contact Warning

Be careful not to touch

the metal pins on the

module’s connecting

edge. Even the clean-

est hands have oils

which can attract parti-

cles, and degrade the

module’s perfor-

mance.

1

2

5

6

1

1. Component Bay

Cover

•4 Screws

a.

b.

6

1

Note:

Only one model is pictured

here, however the compo-

nent locations are the same

for both models.

34

2

1

5

Disassembly

2 - 10 Removing the System Memory (RAM)

2.Disassembly

5. Gently pull the two release latches ( & ) on the sides of the memory socket in the direction indicated by the

arrows (Figure 6c).

6. The RAM module(s) will pop-up (Figure 6d), and you can then remove it.

7. Pull the latches to release the second module if necessary.

8. Insert a new module holding it at about a 30° angle and fit the connectors firmly into the memory slot.

9. The module’s pin alignment will allow it to only fit one way. Make sure the module is seated as far into the slot as it

will go. DO NOT FORCE the module; it should fit without much pressure.

10. Press the module in and down towards the mainboard until the slot levers click into place to secure the module.

11. Replace the bay cover and screws (make sure you reconnect the fan cable before screwing down the bay

cover).

12. Restart the computer to allow the BIOS to register the new memory configuration as it starts up.

7

8

d.

9

7

8

c.

Figure 6

RAM Module

Removal (cont’d.)

c. Pull the release

latch(es).

d. Remove the module(s).

e. Replace the bay cover.

Single Memory

Module Installation

If your computer has a

single memory module,

then insert the module

into the Channel 0

(JDIMM_1) socket. In

this case, this is the up-

per memory socket (the

socket furthest to the

mainboard) as shown in

Figure 6d.

9. RAM Module(s)

9

e.

Note:

Only one model is pictured

here, however the compo-

nent locations are the same

for both models.

Disassembly

Removing the Inverter Board 2 - 11

2.Disassembly

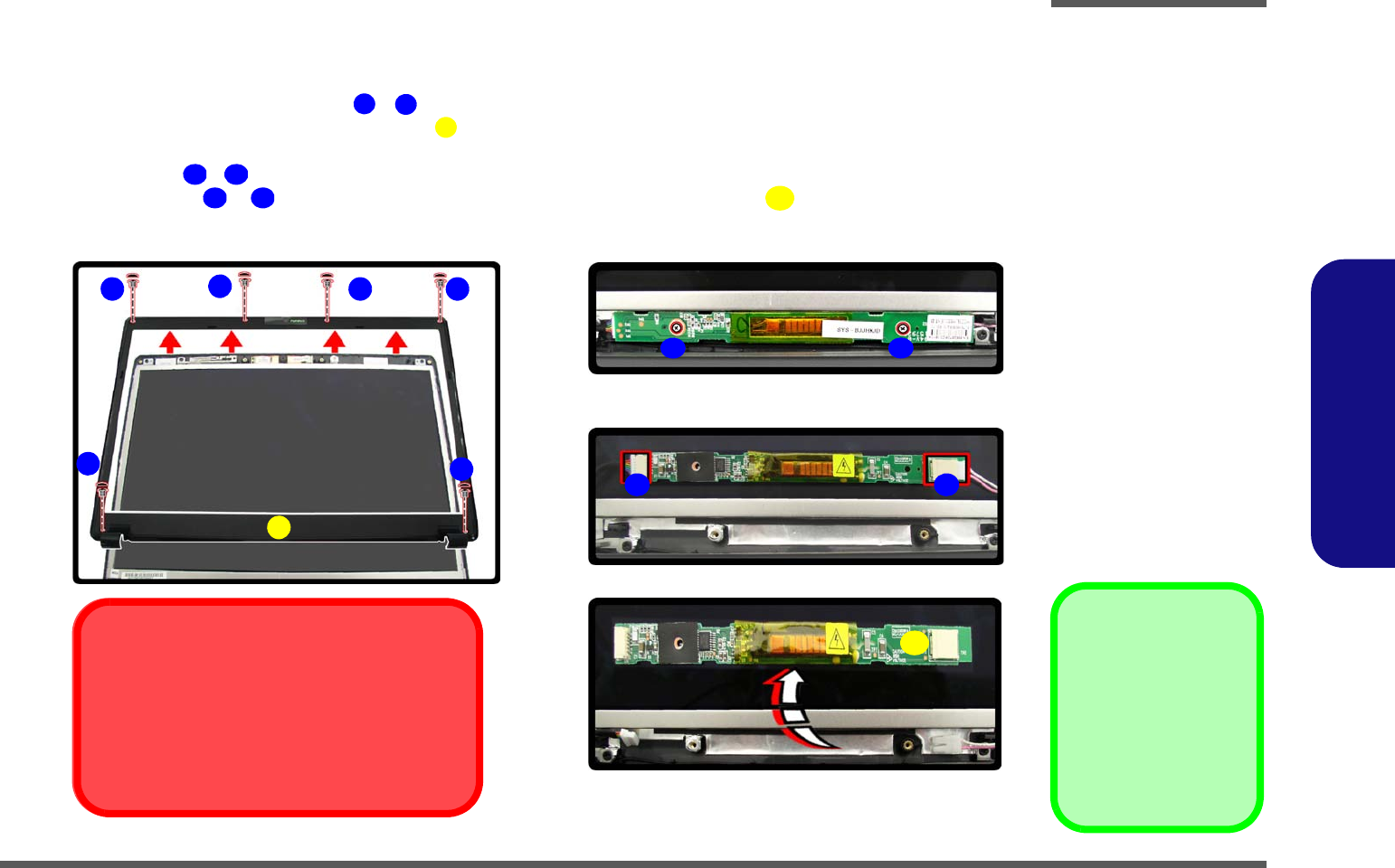

Removing the Inverter Board

1. Turn off the computer, and remove the battery (page 2 - 5).

2. Remove any rubber covers, screws - (Figure 7a), then run your finger around the middle of the frame to

carefully unsnap the LCD front panel module from the back.

3. Discharge the remaining system power (see Inverter Power Warning below).

4. Remove screws - (Figure 7b) from the inverter, and carefully lift the inverter board up slightly.

5. Disconnect cables & (Figure 7c) from the inverter, then remove the inverter (Figure 7d) from the top

case assembly.

Figure 7

Inverter Board

Removal

a. Remove the 6 screws

and unsnap the LCD

front panel module from

the back.

b. Remove the screw and

discharge the remaining

power from the inverter

board and lift the board

up slightly.

c. Disconnect the cables

from the inverter.

d. Remove the inverter.

1

6

7

8

9

10

11

12

7. LCD Front Panel

12. Inverter Board

• Screws

a. b.

Inverter Power Warning

In order to prevent a short circuit when removing

the inverter it is necessary to discharge any re-

maining system power. To do so, press the com-

puter’s power button for a few seconds before

disconnecting the inverter cable.

1

2 5

34

6

c.

d.

8

7

9

12

10 11

Disassembly

2 - 12 Removing the Processor

2.Disassembly

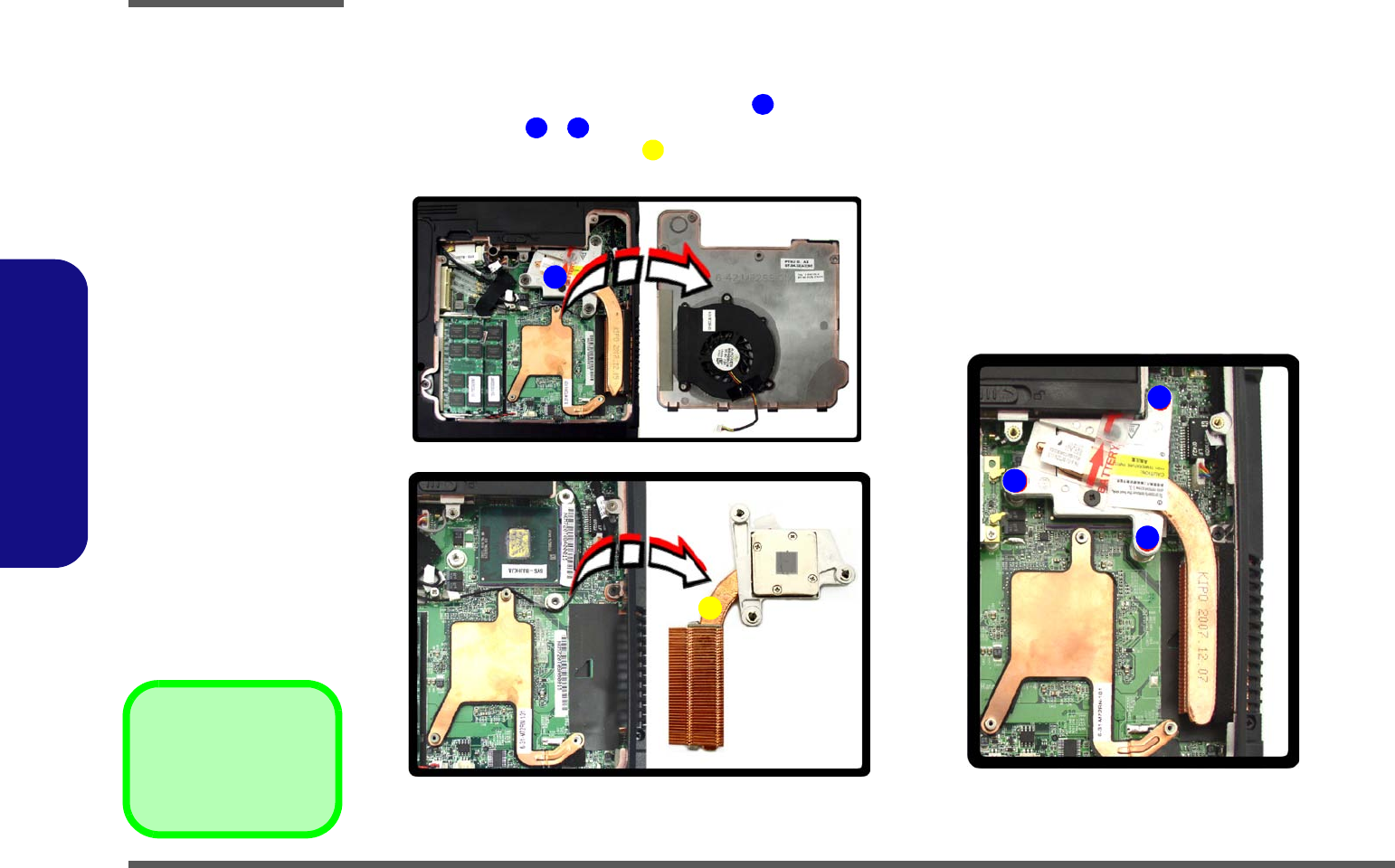

Removing the Processor

1. Turn off the computer, and remove the battery (page 2 - 5) and the CPU/RAM bay cover (page 2 - 9).

2. The CPU heat sink will be visible at point on the mainboard.

3. Loosen screws - from the heat sink in the order indicated.

4. Carefully lift up the heat sink (Figure c) off the computer.

1

2

4

5

Figure 8

Processor Removal

a. Remove the cover and

Iocate the heat sink.

b. Remove the 3 screws in

the order indicated.

c. Remove the heat sink.

5. Heat Sink

b.

5

1

4

a.

c.

3

2

Note:

Only one model is pictured

here, however the compo-

nent locations are the same

for both models.

Disassembly

Removing the Processor 2 - 13

2.Disassembly

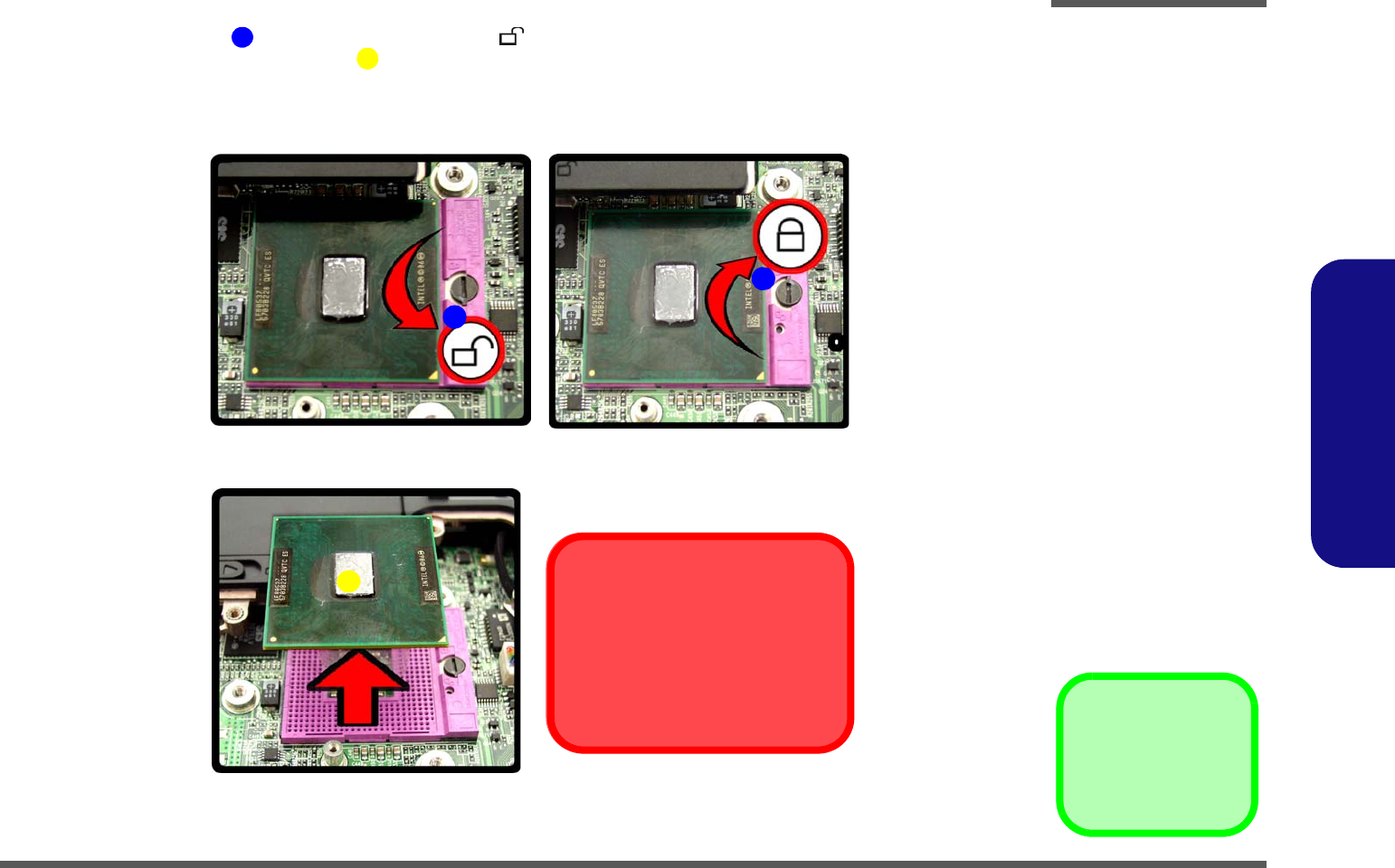

5. Turn the release latch towards the unlock symbol , to release the CPU (Figure d).

6. Carefully (it may be hot) lift the CPU up out of the socket (Figure e).

7. Reverse the process to install a new CPU.

8. When re-inserting the CPU, pay careful attention to the pin alignment, it will fit only one way (DO NOT FORCE IT!).

6

7

Figure 9

Processor Removal

Sequence

d. Turn the release latch to

unlock the CPU.

e. Lift the CPU out of the

socket.

d.

7

e.

Caution

The heat sink, and CPU area in

general, contains parts which are

subject to high temperatures. Allow

the area time to cool before remov-

ing these parts.

Unlock Lock

6

6

7. CPU

Disassembly

2 - 14 Removing the Wireless LAN Module

2.Disassembly

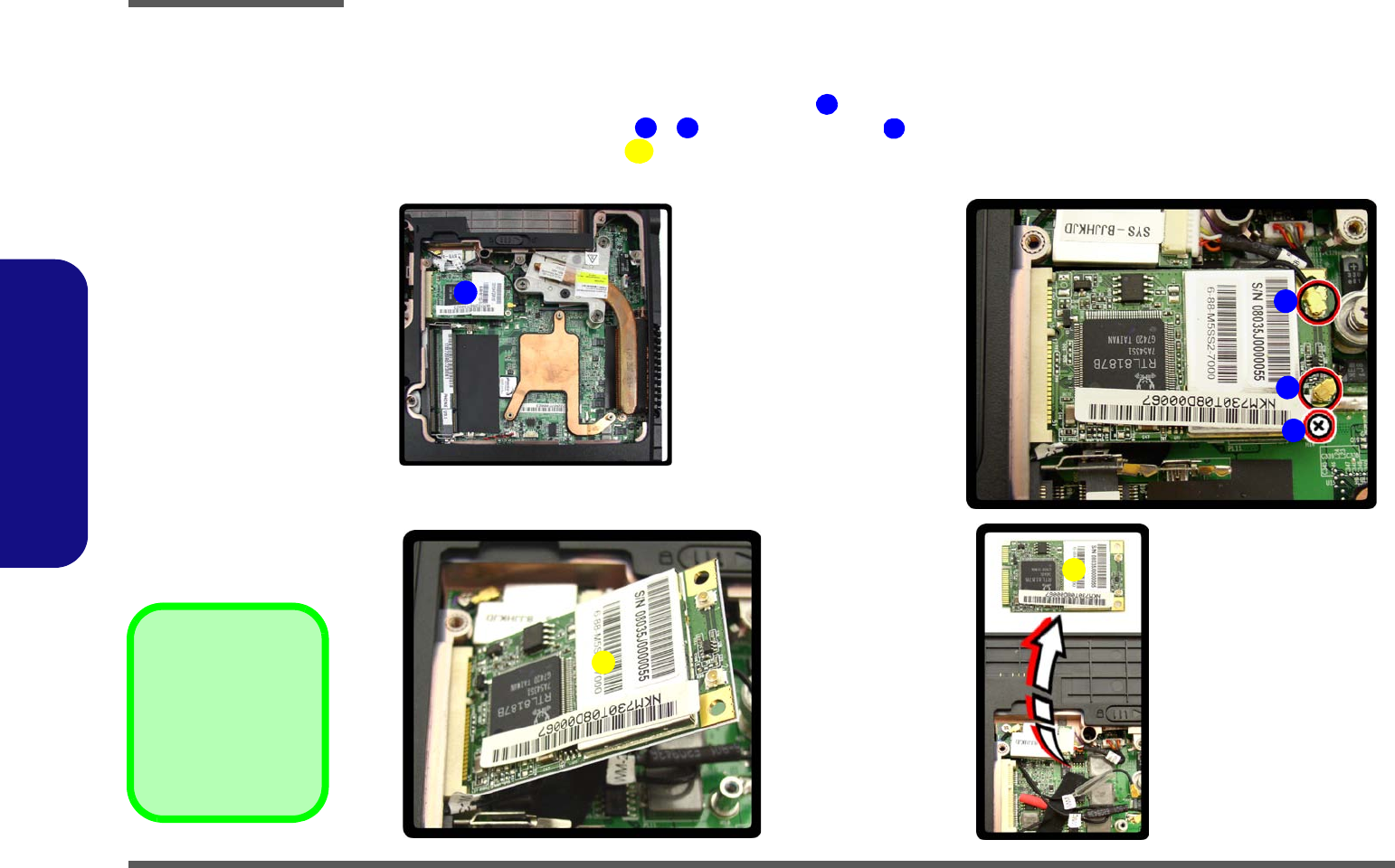

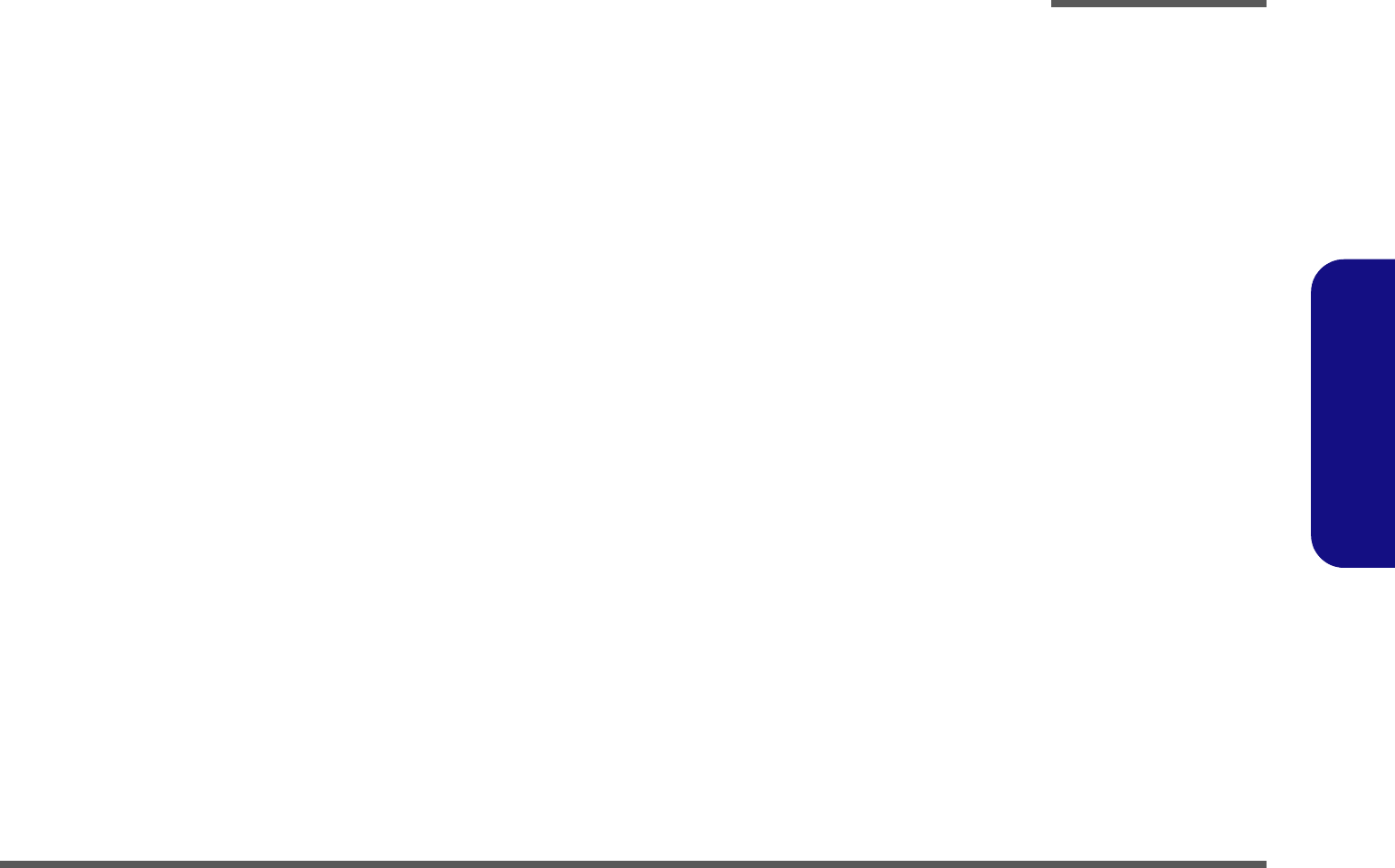

Removing the Wireless LAN Module

1. Turn off the computer, remove the battery (page 2 - 5) and the component bay cover (page 2 - 9).

2. The Wireless LAN module will be visible at point on the mainboard.

3. Carefully disconnect cables - , then remove screw from the module socket.

4. The Wireless LAN module will pop-up.

5. Lift the Wireless LAN module (Figure 10d) up and off the computer.

Figure 10

Wireless LAN

Module Removal

a. Remove the cover.

b. Disconnect the cables

and remove the screw.

c. The WLAN module will

pop up.

d. Lift the WLAN module

out.

Note: Make sure you

reconnect the antenna

cable to “1” + “2”

socket (Figure b).

1

2

3

4

5

5

b.

c.

a.

d.

2

3

1Note:

Only one model is pic-

tured here, however

the component loca-

tions are the same for

both models. 4

5

5. WLAN Module.

•1 Screw

Disassembly

Removing the Bluetooth Module 2 - 15

2.Disassembly

Removing the Bluetooth Module

1. Turn off the computer, remove the battery (page 2 - 5).

2. The Bluetooth module will be visible at point on the mainboard.

3. Remove screw and carefully disconnect the cable and separate the module from the connector .

4. Lift the Bluetooth module up and off the computer.

1

2

3

4

5

Figure 11

Bluetooth Removal

a. Remove the cover and

locate the Bluetooth

module.

b. Remove the screw and

disconnect the cable and

seperate the connector.

c. Lift the Bluetooth module

out.

a.

b.

34

1

2

c.

5

Note:

Only one model is pic-

tured here, however

the component loca-

tions are the same for

both models.

5. Bluetooth Module

•1 Screw

Disassembly

2 - 16 Removing the Keyboard

2.Disassembly

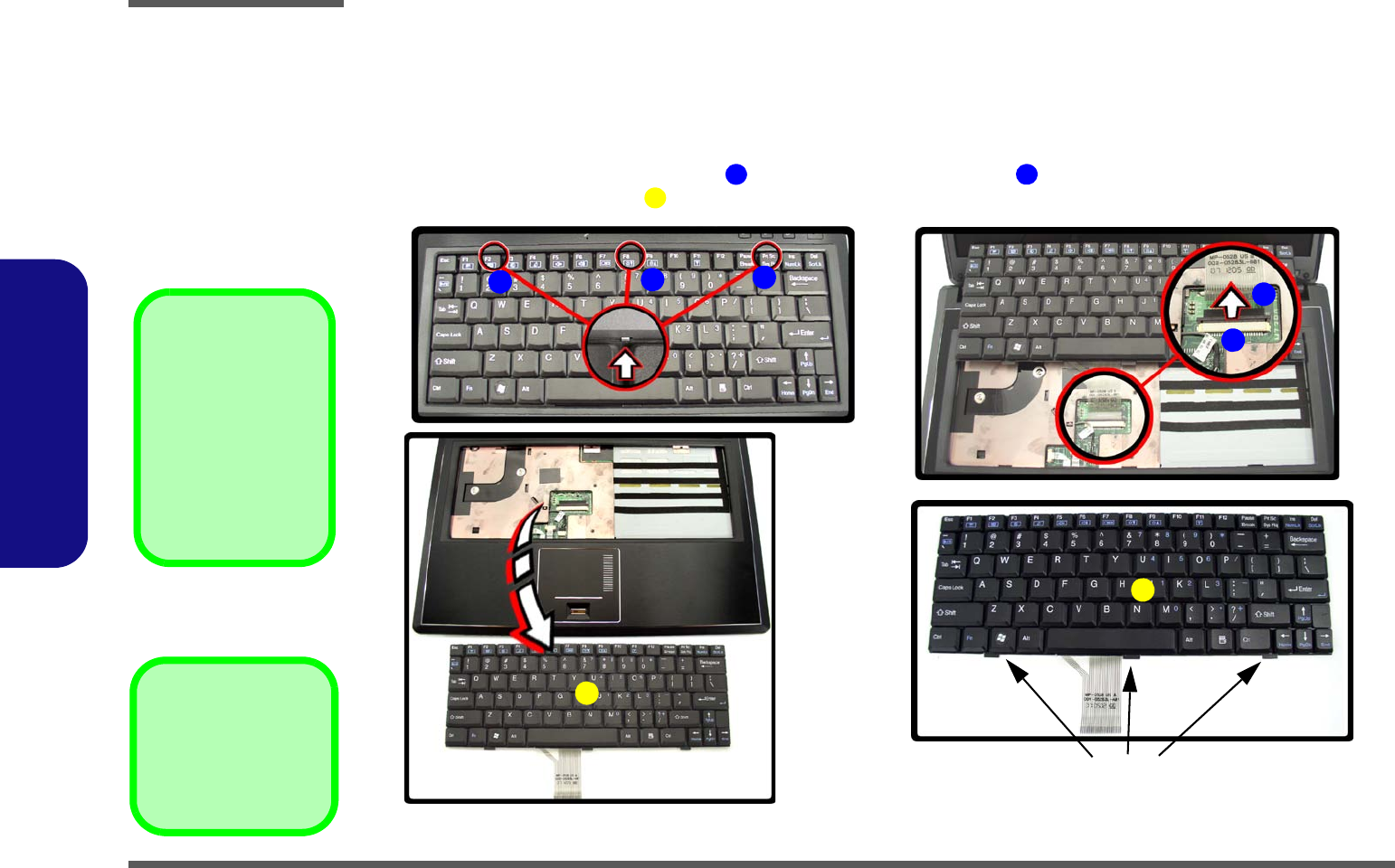

Removing the Keyboard

1. Turn off the computer, and remove the battery (page 2 - 5).

2. Press the three keyboard latches at the top of the keyboard to elevate the keyboard from its normal position (you

may need to use a small screwdriver to do this).

3. Carefully lift the keyboard up, being careful not to bend the keyboard ribbon cable (Figure 12b).

4. Disconnect the keyboard ribbon cable from the locking collar socket .

5. Carefully lift up the keyboard (Figure 12c) off the computer.

4

5

Figure 12

Keyboard Removal

a. Press the three latches

to release the keyboard.

b. Lift the keyboard up and

disconnect the cable

from the locking collar.

c. Remove the keyboard.

Re-Inserting the Key-

board

When re-inserting the

keyboard firstly align

the three keyboard

tabs at the bottom of

the keyboard with the

slots in the case.

6. Keyboard Module.

6

a. b.

5

4

6

Keyboard Tabs

c.

13

2

6

Disassembly

Removing the Modem 2 - 17

2.Disassembly

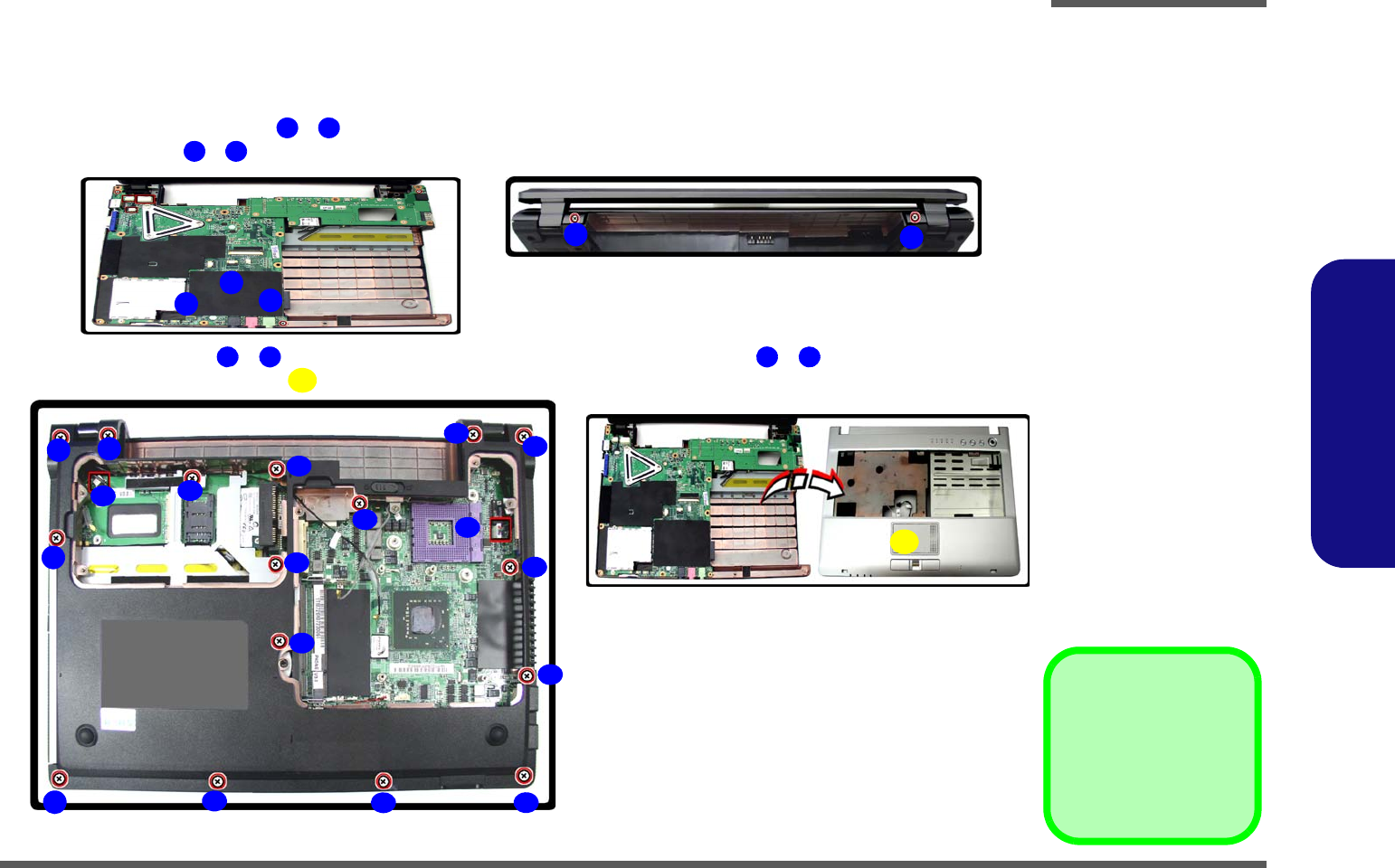

Removing the Modem

1. Turn off the computer, remove the battery (page 2 - 5), HDD (page 2 - 6), component bay cover (page 2 - 9), opti-

cal device (page 2 - 8), CPU (page 2 - 12), bluetooth (page 2 - 15) and keyboard (page 2 - 16).

2. Disconnect the connectors - from under the keyboard and turn it over.

3. Remove screws - from the rear of the computer.

4. Remove the screws - from the bottom case and disconnect the connectors - on the mainboard.

5. Carefully lift up the top case off the computer.

1

3

4

5

a. b.

13

2

5

4

Figure 13

Modem Removal

a. Disconnect the connec-

tors from under the key-

board.

b. Remove the screws.

c. Remove the screws and

disconnect the connec-

tors from the main-

board.

d. Remove the top case.

24. Top Case

•18 Screws

6

21

22

23

24

c.

9

76

8

10 11

13

12

14

15

16

23

17

20

18

19

21

22

d.

24

Disassembly

2 - 18 Removing the Modem

2.Disassembly

6. Remove screws - and disconnect the connectors - from the mainboard.

7. Separate the bottom case from the mainboard and turn it over.

8. Remove the screws - and disconnect the connector from the modem.

9. Lift the modem up off the socket .

25

27

28

30

Figure 14

Modem Removal

Sequence

e. Remove the screws and

and disconnect the con-

nectors.

f. Separate the bottom

case from the main-

board.

g. Remove the screws and

and disconnect the con-

nector.

h. Lift the modem up off

the socket.

31. Bottom Case

32. Mainboard

37. Modem

•5 Screws

31

32

33

34

35

37

36

e.

h.

g.

32

31

28

29

25 30 26

27

33

34

35

37

36

f.

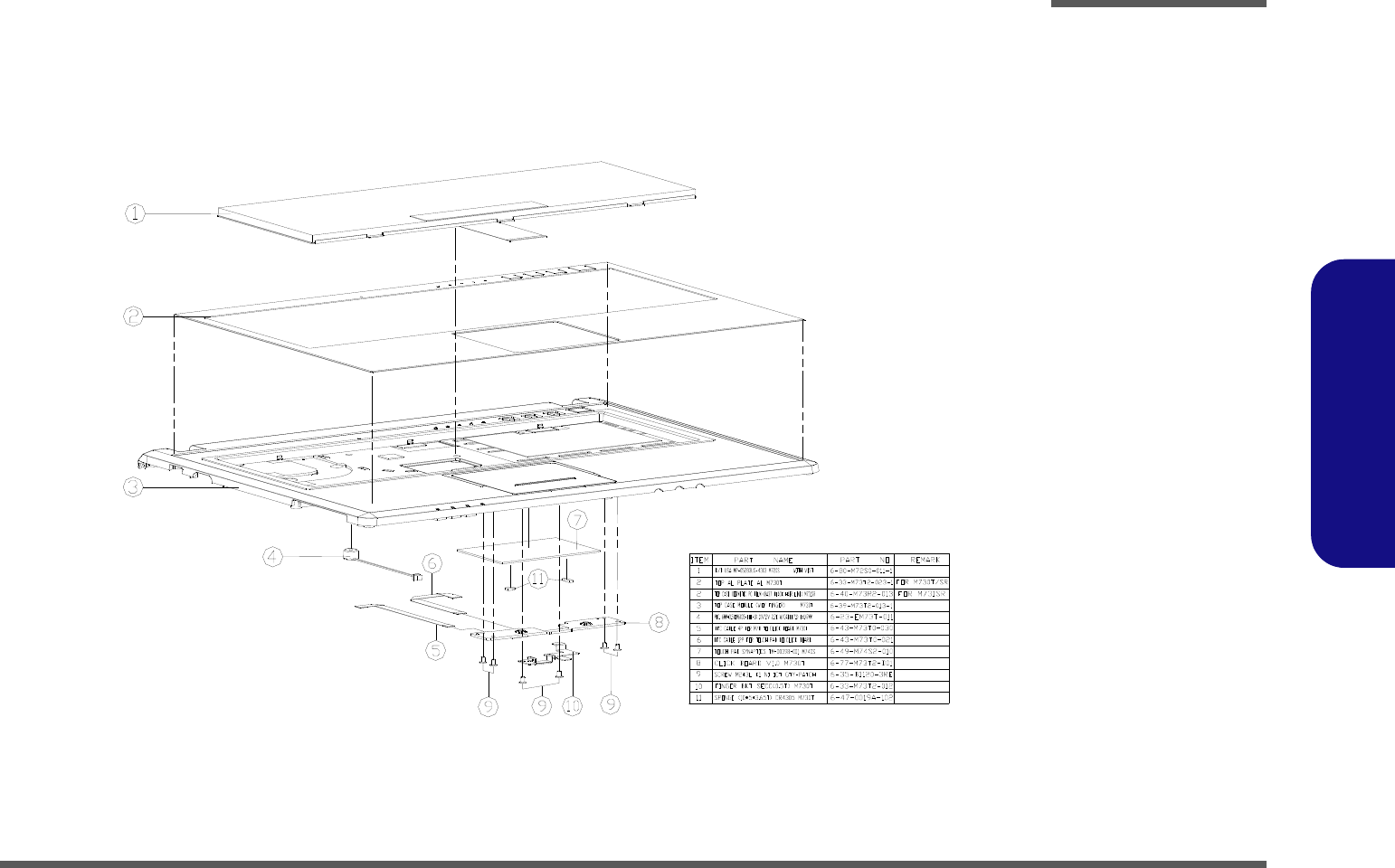

Part Lists

A-1

A.Part Lists

Appendix A: Part Lists

This appendix breaks down the M730TG series notebook’s construction into a series of illustrations. The component part

numbers are indicated in the tables opposite the drawings.

Note: This section indicates the manufacturer’s part numbers. Your organization may use a different system, so be sure

to cross-check any relevant documentation.

Note: Some assemblies may have parts in common (especially screws). However, the part lists DO NOT indicate the

total number of duplicated parts used.

Note: Be sure to check any update notices. The parts shown in these illustrations are appropriate for the system at the

time of publication. Over the product life, some parts may be improved or re-configured, resulting in new part numbers.

Part Lists

A - 2 Part List Illustration Location

A.Part Lists

Part List Illustration Location

The following table indicates where to find the appropriate part list illustration.

Table A- 1

Part List Illustration

Location

Parts M730T

Top without Fingerprint page A - 3

Bottom page A - 4

LCD page A - 5

DVD-Dual Drive page A - 6

Part Lists

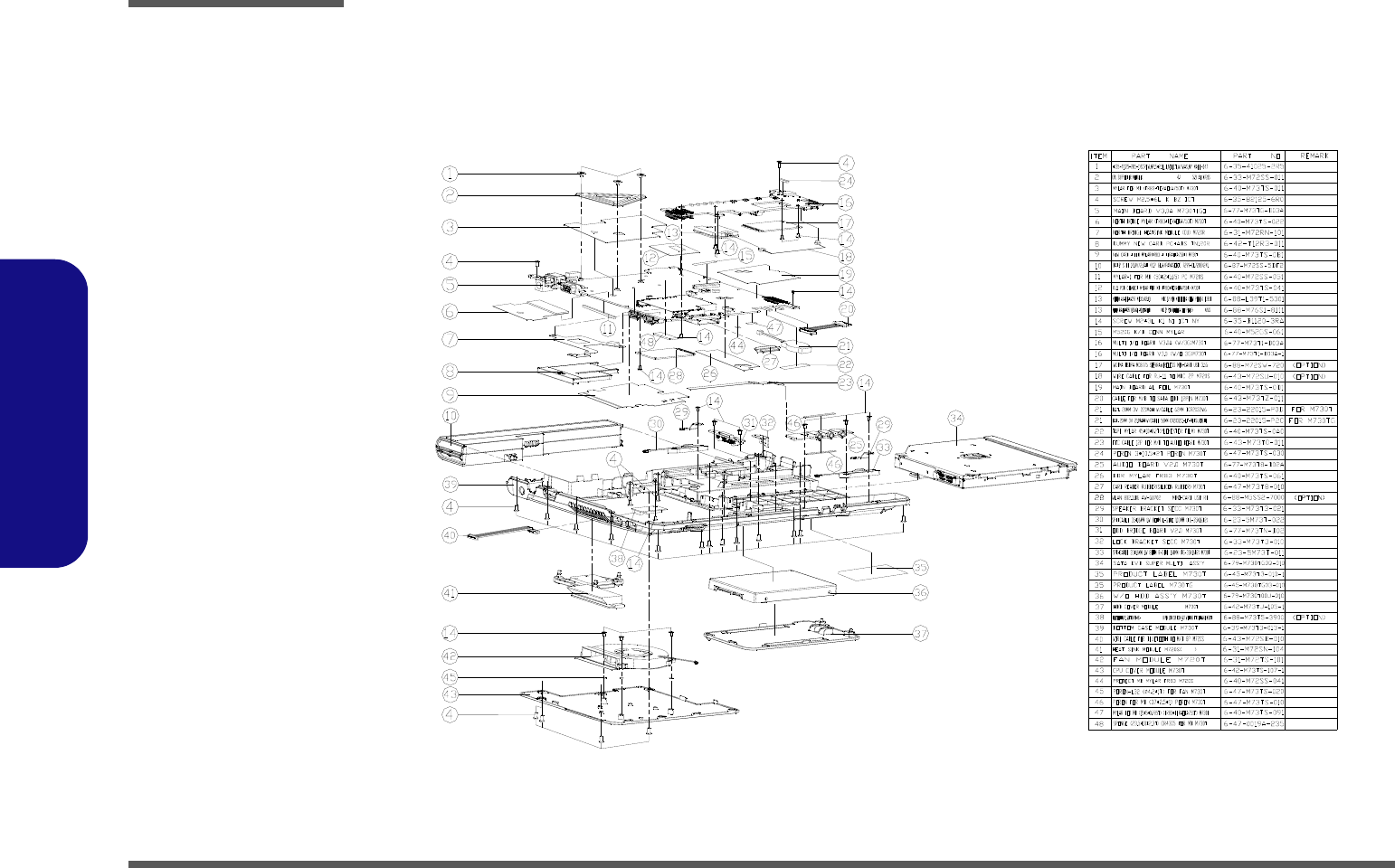

Top without Fingerprint A - 3

A.Part Lists

Top without Fingerprint

Figure A - 1

Top without

Fingerprint

Part Lists

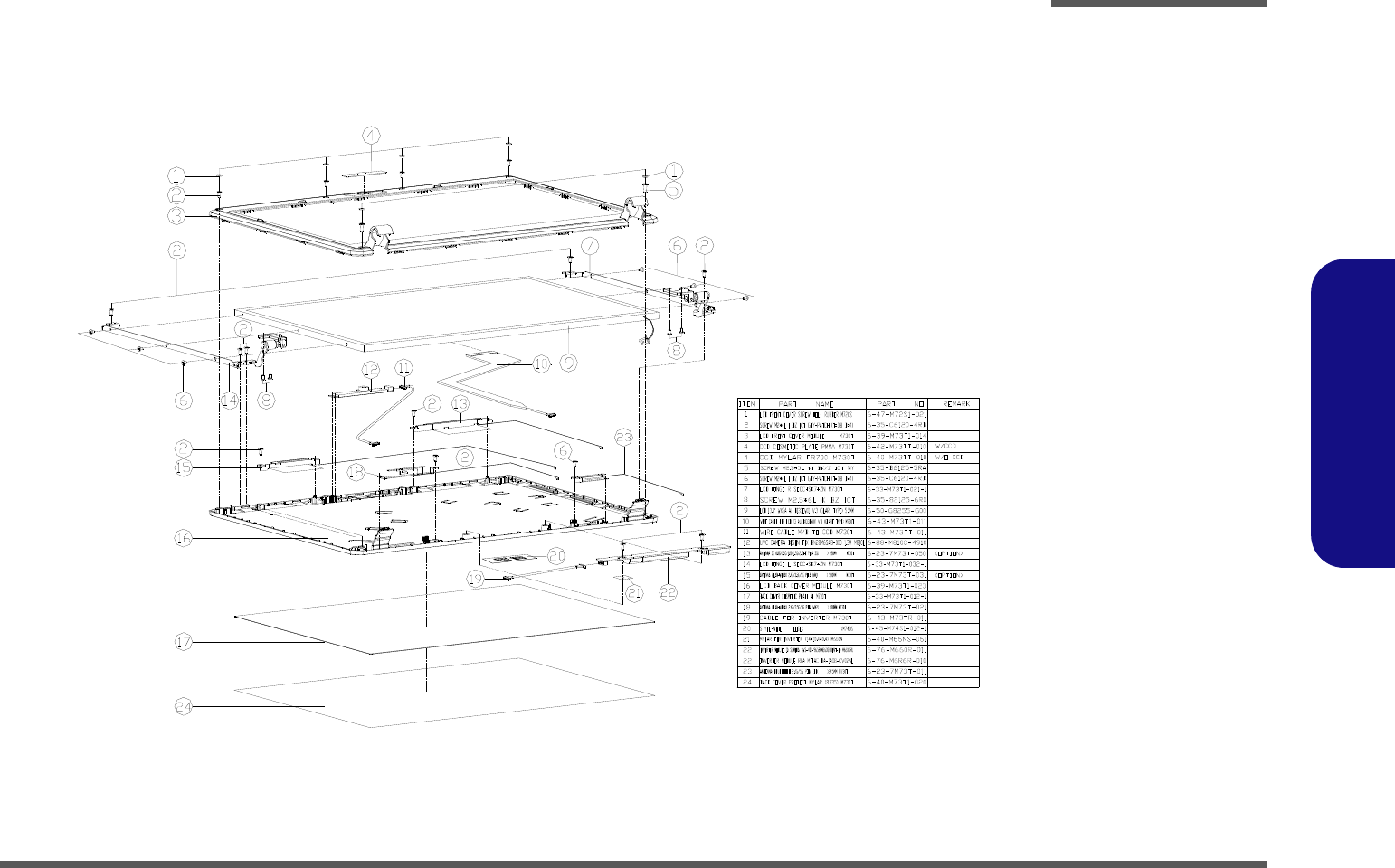

A - 4 Bottom

A.Part Lists

Bottom

Figure A - 2

Bottom

Part Lists

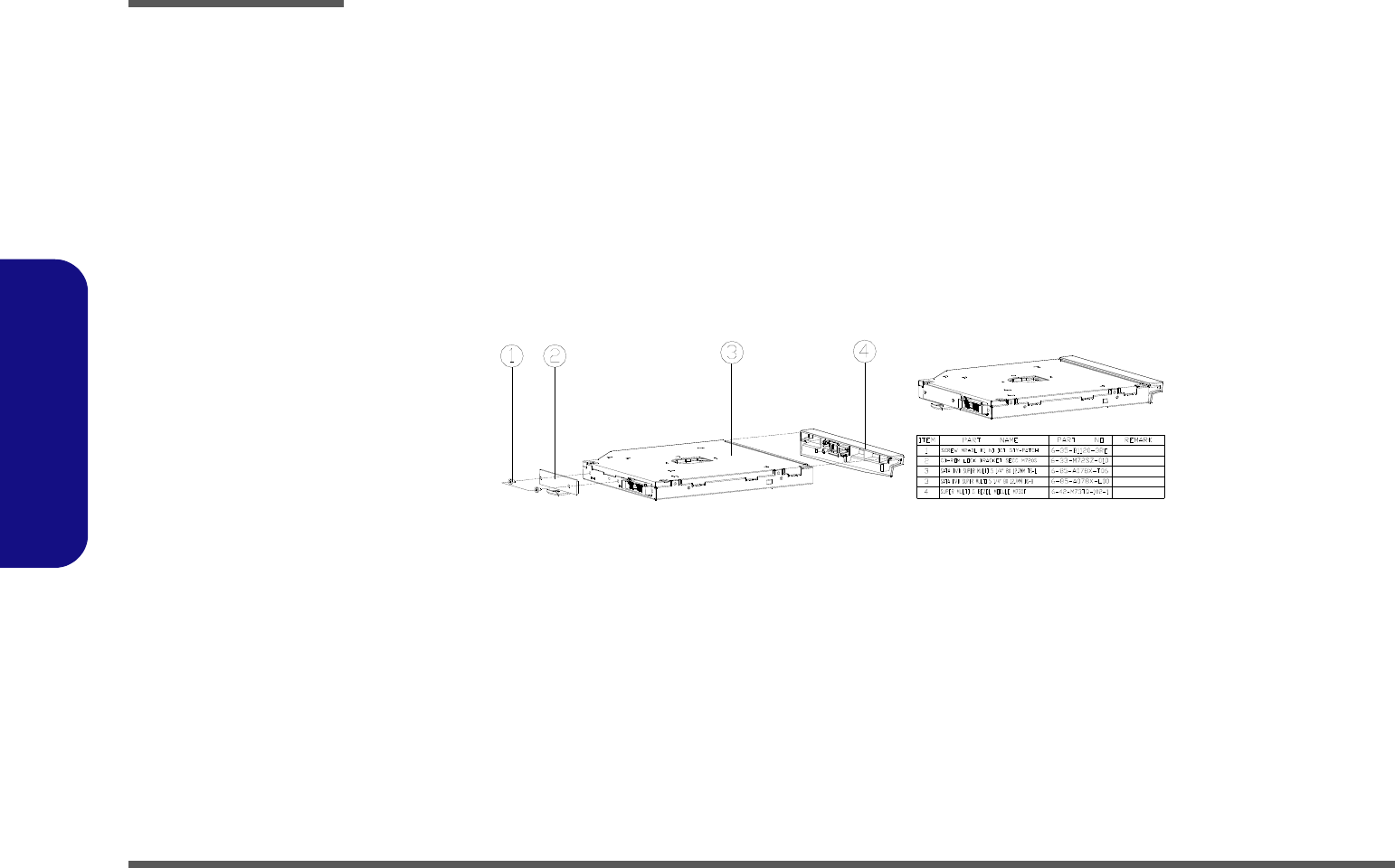

LCD A - 5

A.Part Lists

LCD

Figure A - 3

LCD

Part Lists

A - 6 DVD-Dual Drive

A.Part Lists

DVD-Dual Drive

Figure A - 4

DVD-Dual Drive

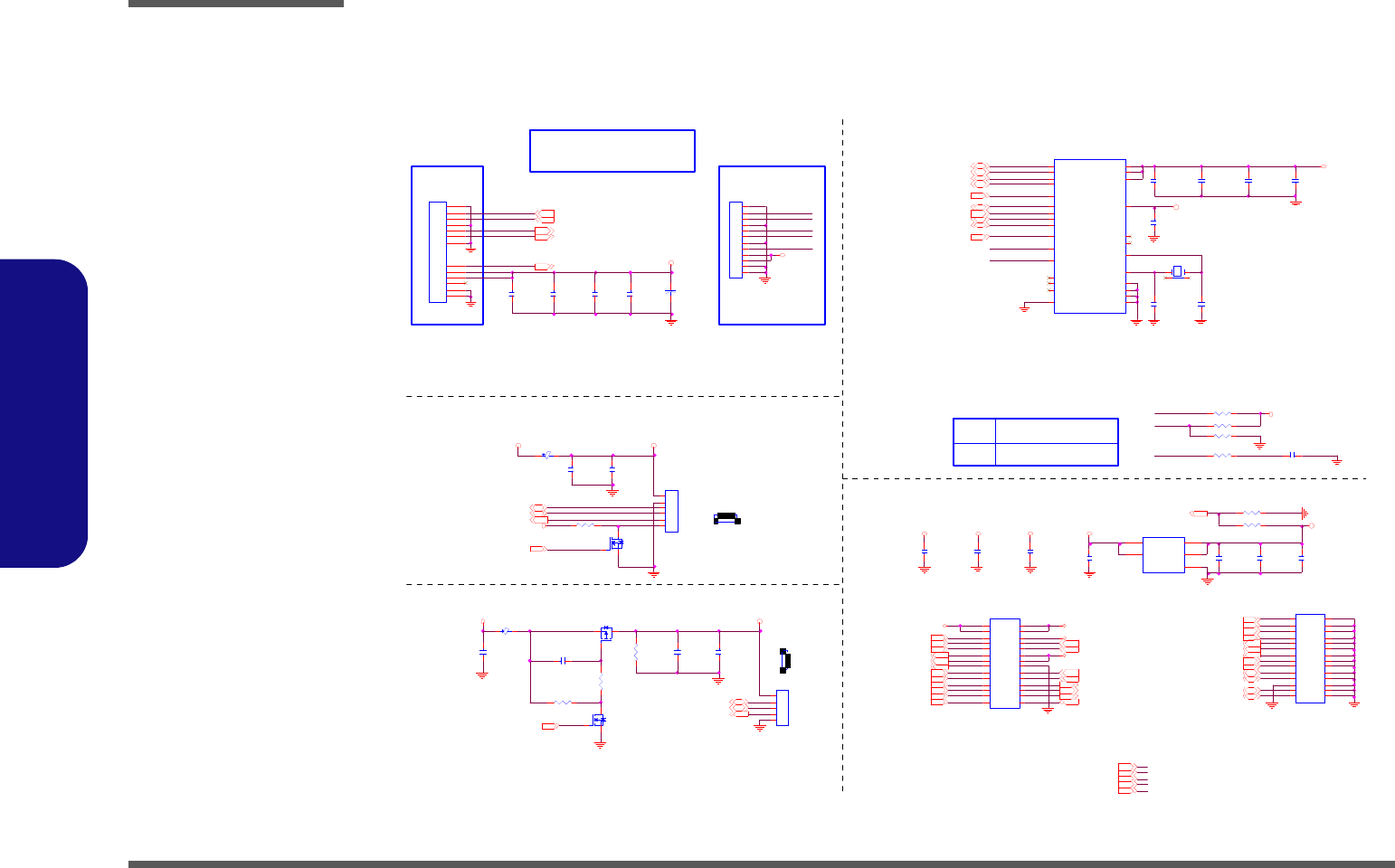

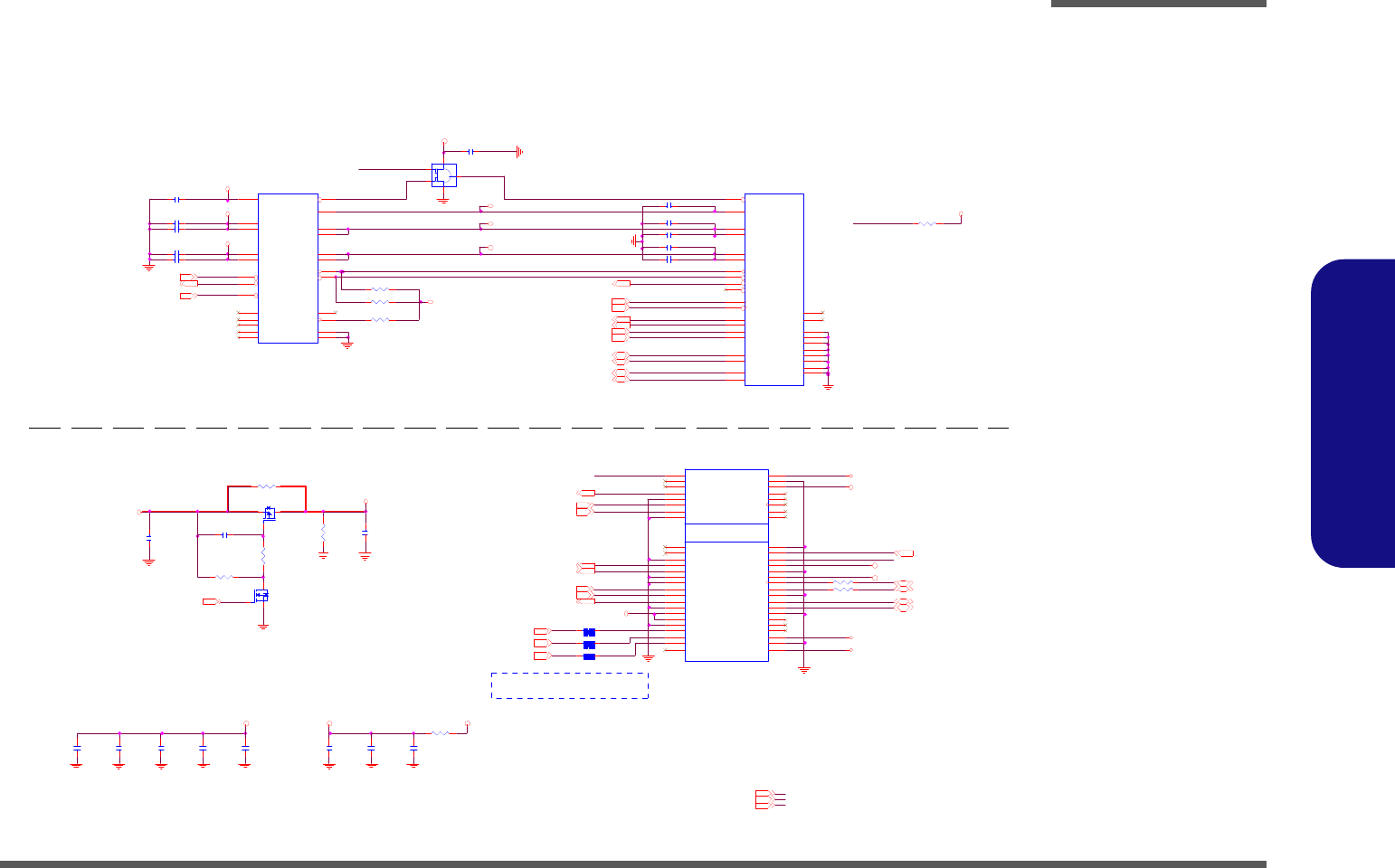

Schematic Diagrams

B-1

B.Schematic Diagrams

Appendix B: Schematic Diagrams

This appendix has circuit diagrams of the M730TG notebook’s PCB’s. The following table indicates where to find the

appropriate schematic diagram.

Diagram - Page Diagram - Page Diagram - Page

System Block Diagram - Page B - 2 ICH9-M 3/5 - GPIO, PWR Management - Page B - 16 Power 1.5VS, 1.05VS, 3.3V, 5V - Page B - 30

Intel Penryn (Socket-P) 1/2 - Page B - 3 ICH9-M 4/5 - Power - Page B - 17 Power 1.8V, 0.9VSM - Page B - 31

Intel Penryn (Socket-P) 2/2 - Page B - 4 ICH9-M 5/5 - GND - Page B - 18 Power VCORE - Page B - 32

Cantiga 1/6 - Host - Page B - 5 Clock Generator - Page B - 19 Power AC-IN, Charger - Page B - 33

Cantiga 2/6 - VGA, CRT - Page B - 6 Multi I/O, ODD, CCD, BT, TPM - Page B - 20 Multi I/O Board 1/2 - Page B - 34

Cantiga 3/6 - DDR - Page B - 7 New Card, Mini PCIE - Page B - 21 Multi I/O Board 2/2 - Page B - 35

Cantiga 4/6 - Power - Page B - 8 LED, FAN, TP, FP, USB - Page B - 22 Finger Printer Board - Page B - 36

Cantiga 5/6 - Power - Page B - 9 JMB385 Card Reader - Page B - 23 Click Board - Page B - 37

Cantiga 6/6 - GND - Page B - 10 PCI-E LAN RTL8111C - Page B - 24 M730T ODD Bridge Board - Page B - 38

DDRII CHANNEL A - Page B - 11 Audio Codec ALC662 - Page B - 25 M730T Audio Board - Page B - 39

DDRII CHANNEL B - Page B - 12 Audio AMP2056 - Page B - 26 Power Sequence Diagram - Page B - 40

Panel, Inverter, CRT - Page B - 13 KBC-ITE IT8512E - Page B - 27 Power Sequence v3.0 - Page B - 41

ICH9-M 1/5 - SATA - Page B - 14 System Power, LED BKLT - Page B - 28

ICH9-M 2/5 - PCIE, PCI, USB - Page B - 15 Power VDD3, VDD5 - Page B - 29

Table B - 1

Schematic

Diagrams

Version Note

The schematic dia-

grams in this chapter

are based upon ver-

sion 6-7P-M72T6-005.

If your mainboard (or

other boards) are a lat-

er version, please

check with the Service

Center for updated di-

agrams (if required).

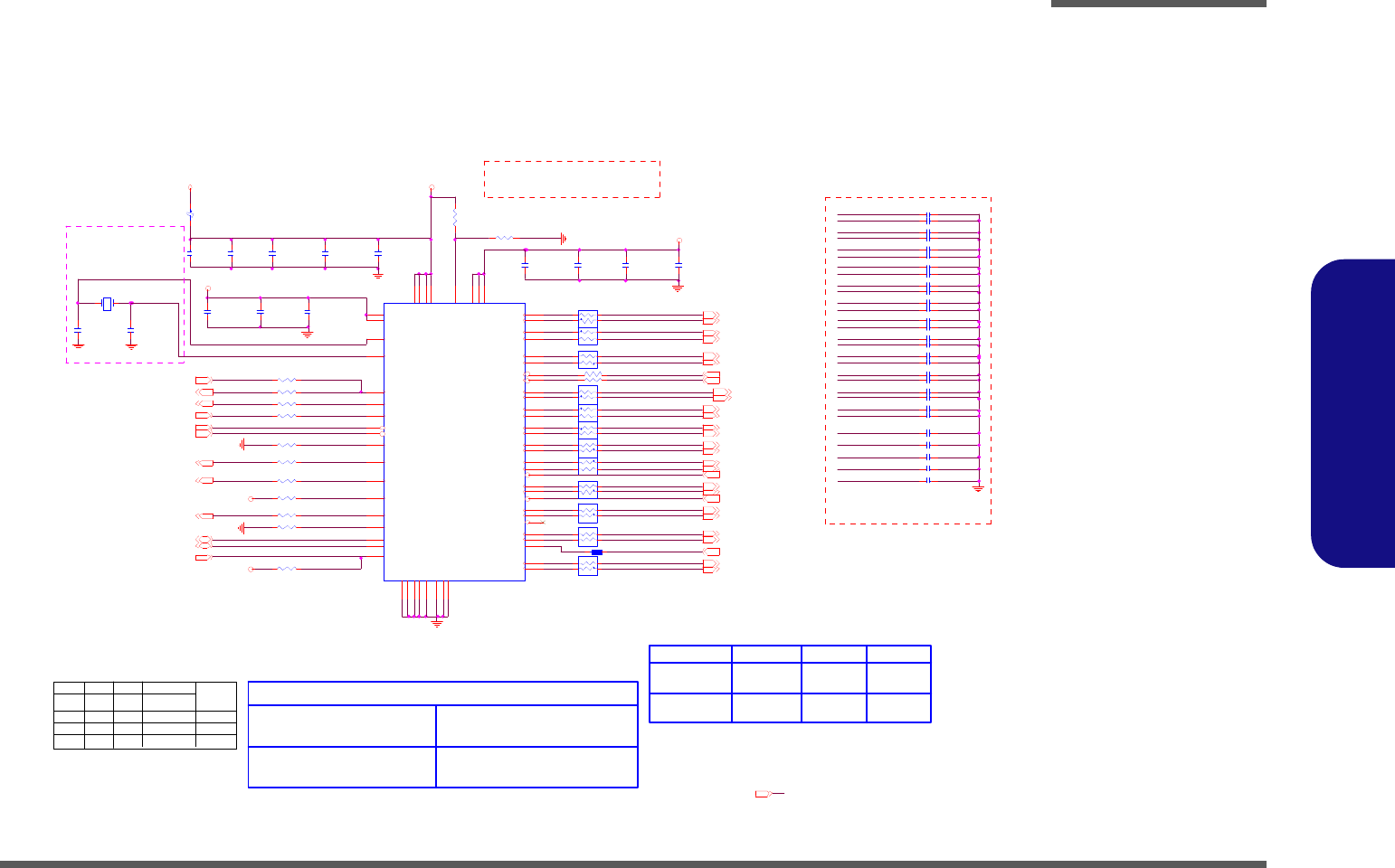

Schematic Diagrams

B - 2 System Block Diagram

B.Schematic Diagrams

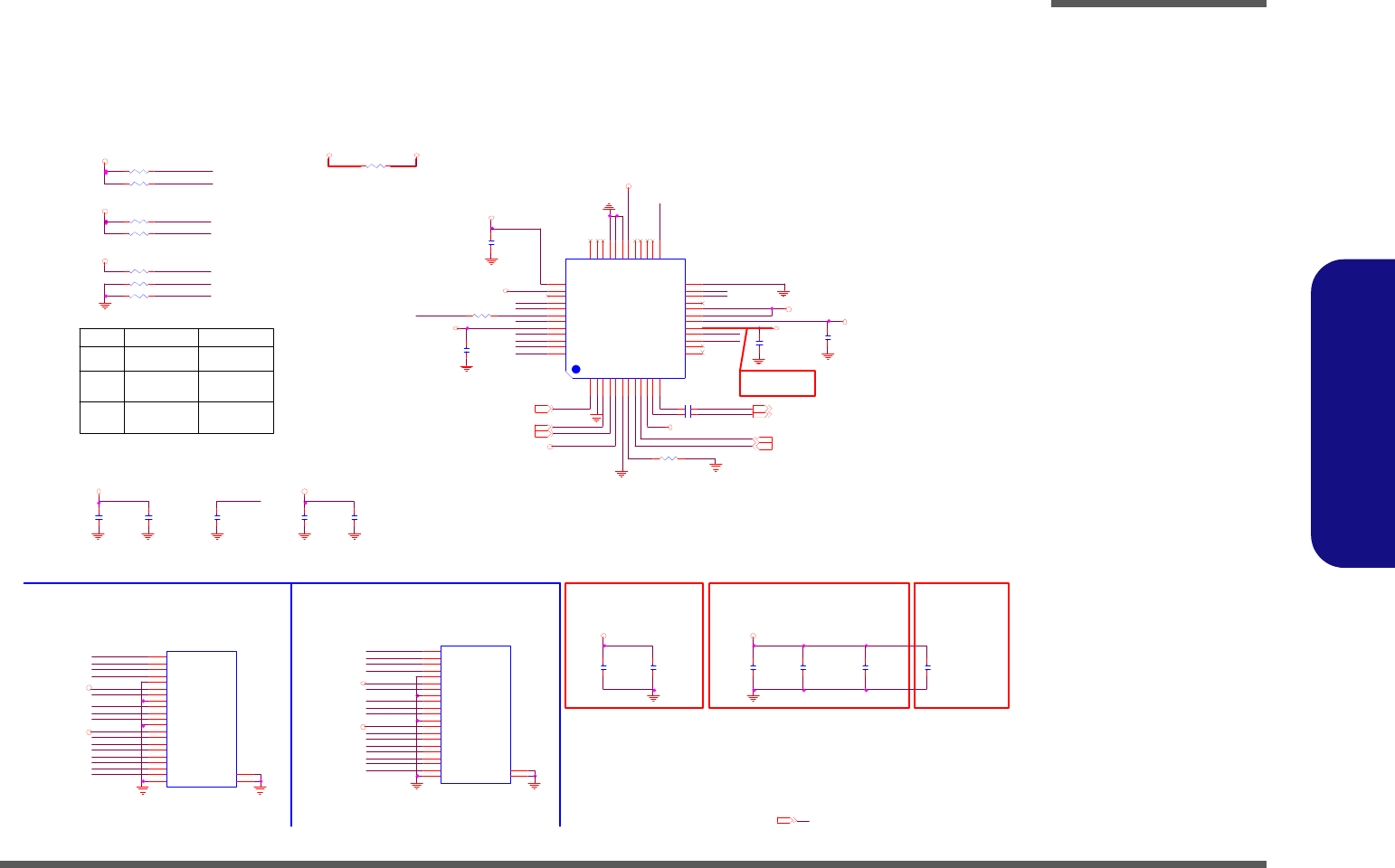

System Block Diagram

Sheet 1 of 40

System Block

Diagram

24 MHz

100 MHz

33 MHz

SPK_R, RJ-11, LED

PCI

128pins LQFP

IT 85 12E /E X

0. 1" ~1 3

M 73 0T OD D Bo ar d

Azalia Codec

LP C

Multi I/O

Board

128pins LQFP

14 *1 4*1. 6mm

0.5"~11"

( USB 5)

M720T

1. 05 VM, 1. 5V S

533/667/800 MHz

MD C

Co nn ec tor

(U SB 11)

9*9*1. 6mm

1"~16"

51 2K b

INT SPK L

667/800/1066 MHz

TP M1 .2

AL C66 2

Azalia

SA TA I /II 3 .0 Gb /s

12 MHz

<1 2"

<8"

M730T

Colck Generator

480 Mbps

LID, HOT KEY, USB, 3G

IN T MI C

EC S PI RO M

1" ~16 "

CRT Connector

M 72 0T /M7 30 T Cl ic k

Board

North Bridge

USB2.0

A PA2 05 6A

Sm ar t

Ba tt ery

Smart

FAN

478pins uFCPGA

13 29 FC BGA

Multi I/O

Board

3G Ca rd /

Ra bos on

<1 2"

USB0

SP D IF

OU T

A C- IN ,Ch ar ge r

<1 2"

PCIe

SO-DIMM1

LAN

32.768 KHz

To uc h Pad

Co nn ec tor

Cantiga GMCH

Re alt ek

M ul ti I/ O Bo ar d

16 Mb

VC OR E

SA TA I /II 3 .0 Gb /s

14 *1 4* 1. 4mm

DM I

AM P.

Th erm al

Se nso r

INT SPK R

ITE

Min i ca rd

Intel Penryn

Socket

9. 8* 6.4 * 1.2 mm

14.318 MHz

VD D3 ,VD D5

SO-DIMM0

25

MHz

(U SB 7)

FS B

M73 0T

LED B AC KLI GH T

DRI VE R

Ca rd Re ad er

EC

SA TA

HD D

DDR2

810602-1703

Socket

HP

OU T

Sy st em Powe r

Ne w Car d

32.768KHz

X4

RJ-11

INT K/B

REALTEK

M 73 0T Au di o Bo ar d

South Bridge

(USB9)

7 IN1

33 MHz

S PI RO M

RJ-45

ANP AC

CLEVO M720T System Block Diagram

IC S9 LPR 36 3EG LF

Memory Termination

EC S MBUS

64 p i ns T SS O P

31*31*2.5mm

(USB2)

Bl ue too th

SO CKE T

SA TA

OD D

CCD

Soket P

RTL8111C

28 p i ns T SS O P

DDR2

17. 1*8. 1*1. 2mm

25*21*2.05mm

676 mBGA

US B3

MIC

IN

ICH9-M

INT SPK R

<=8"

64pins QFN

Sy na pt ic

Min i PC Ie

US B1

ID T

System Me mory

<15"

FINGER PRINTER BOARD

JMB385

Az al ia

MD C

Mo du le

M720T

Proces sor

0 .5" ~5 .5 "

9*9*1.0mm

1. 8V ,0. 9V

Multi I/O

Board

FingerPrint

LC D Con ne ct or,

In ve rte r

JMicron

48pins LQFP

(USB4)

WiF i/ Wi Max

Ech o Pe ak

aS C75 25

INT SPK L

Schematic Diagrams

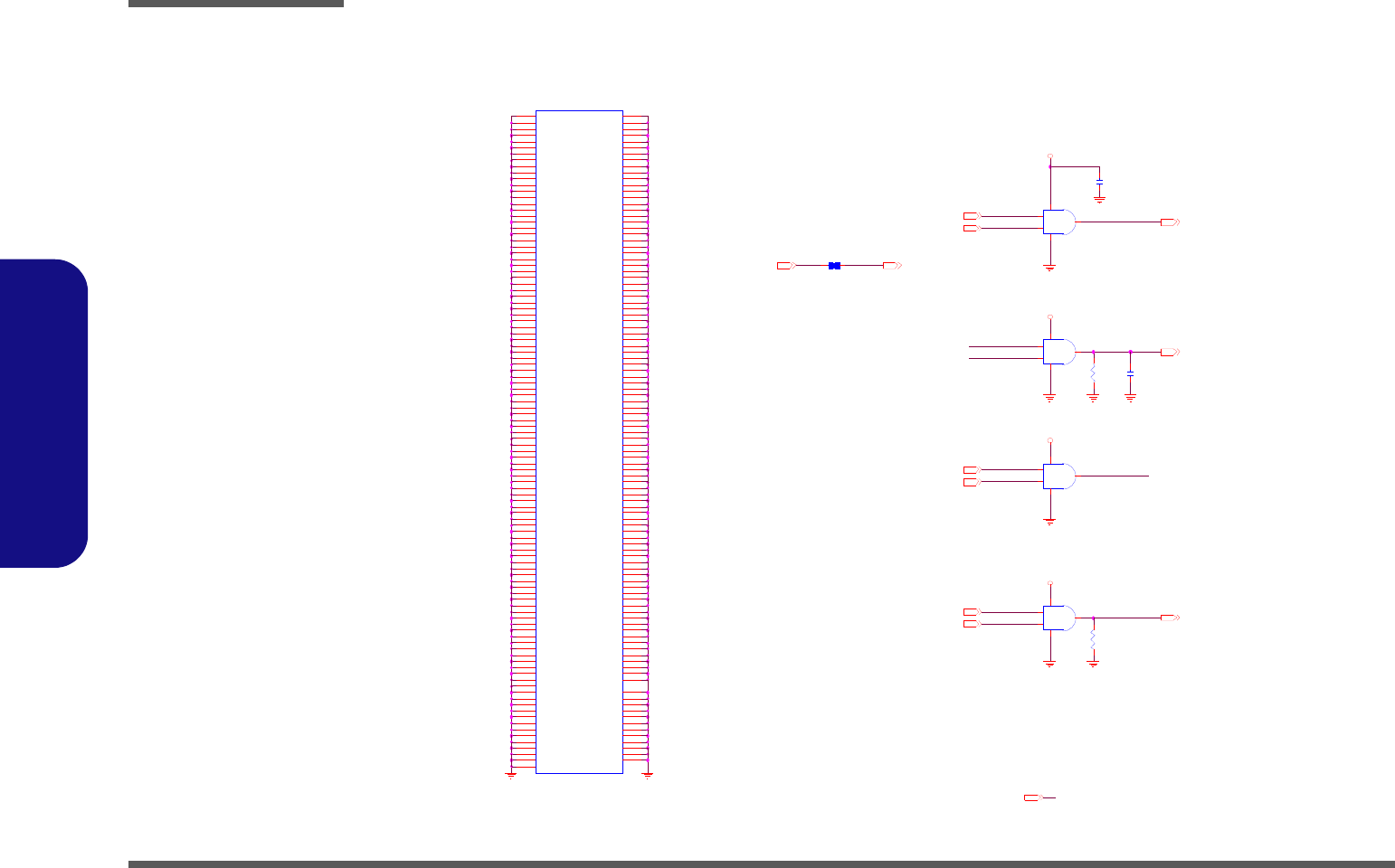

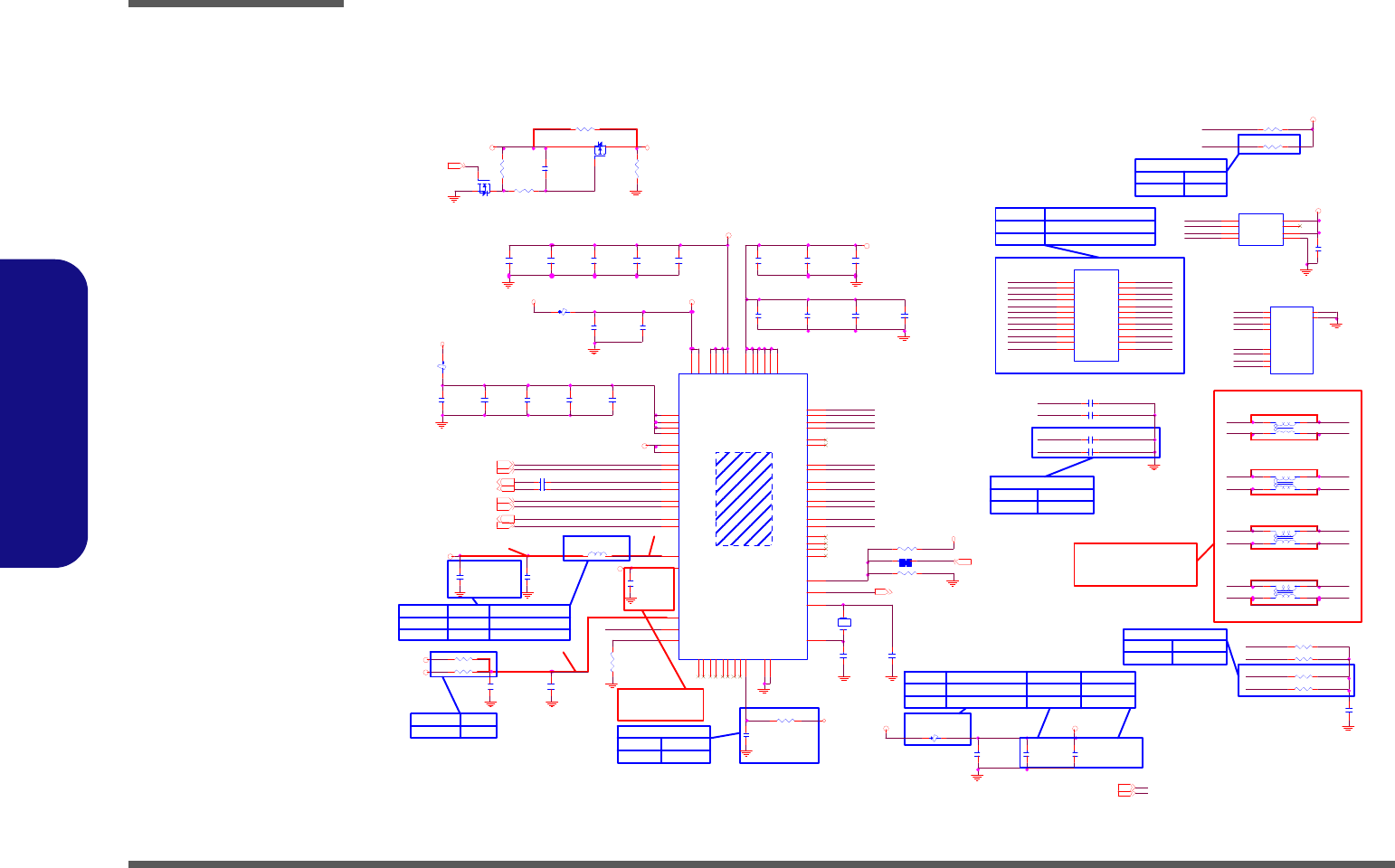

Intel Penryn (Socket-P) 1/2 B - 3

B.Schematic Diagrams

Intel Penryn (Socket-P) 1/2

Sheet 2 of 40

Intel Penryn

(Socket-P) 1/2

H_BNR # [4]

R5 1 K_ 1 %_ 0 4

H_A#4

H_D#63

V_TH RM

TR 1

* T S M 1A 1 0 3 H 3 4D 3R

CL K_ CPU_ BC LK# [18 ]

H_DSTBN#0[4 ]

H_NMI[13] C PU_BSEL1[4,18]

H_ D# 2 7

H_ DEF ER # [4 ]

H_A#26

R4

2K_1% _04

H_DSTBN#2 [4]

THER M_RST#[26 ]

H_ D# 2 5

H_A#9

H_A#18

H _A#[35:3][4 ]

H_ DBSY # [4 ]

H_HITM# [4]

H_A#7

H_A#34

H_PREQ#

H_ D# 2 8

C3 3 7

*0.01U _16V_X7R _04

1.05VS

C336

1U _6.3V_04

H_ TH E RM DA

H_ D# 2 1

H_ D# 6

H_ D# 1

H_D#41

H_D#44

H_ RS# 2 [4 ]

H_D#59

H_ D# 1 9

H_A#10

COMP2

H_ D# 2 3

R8

54.9_1%_04

R2 0 0

*100K_04

H_ D# 2 6

PM _THR M# [15]

COMP2

H_D#33

SM C_ CPU _T HE RM [26 ]

H_ D# 3 1

H_ D# 2 9

C7

*1U_6.3V_X5R_06

? ADT7421 Colay

PS I# [31 ]

H_D#57

R2 1 1

*330K_04

H_ RS# 1 [4 ]

H_A#25

H_REQ#2

R 7 54 . 9 _ 1% _ 04

H_ DIN V # 1[4]

R 197 56_04

H_ADS# [4]

H_DINV#3 [4]

H_A#12

H_ D# 3 0

H_REQ#4

H_D#53

H_A#14

R 173 54.9_1%_04

R2 09

*1 00 K _ 0 4

ADDR

GROUP_0 ADDR

GROUP_1

CONTROL

XD P /I TP S I GNALS

H C LK

THERM AL

RESERVED

ICH

U9 A

MOLEX_47430-6215

N3

P5

P2

L2

P4

P1

R1

Y2

U5

R3

W6

U4

Y5

U1

R4

T5

T3

W2

W5

Y4

J4

U2

V4

M4

N5

T2

V3

B2

D2

D22

L5

L4

K5

M3

N2

J1

A6

H1

M1

V1

D3

A22

A21

E2

AD 4

AD 3

AD 1

AC 4

G5

F1

C2 0

E1

H5

F21

A5

G6

E4

D2 0

C4

B3

C6

B4

H4

AC 2

AC 1

D2 1

K3

H2

K2

J3

L1

C1

F3

F4

G3

A3

D5

AC 5

AA6

AB3

C7

A24

B25

AB5

G2

AB6

W3

AA4

AB2

AA3

F6

A[10]#

A[11]#

A[12]#

A[13]#

A[14]#

A[15]#

A[16]#

A[17]#

A[18]#

A[19]#

A[20]#

A[21]#

A[22]#

A[23]#

A[24]#

A[25]#

A[26]#

A[27]#

A[28]#

A[29]#

A[3]#

A[30]#

A[31]#

RSVD[01]

RSVD[02]

RSVD[03]

RSVD[04]

RSVD[05]

RSVD[06]

RSVD[07]

A[4]#

A[5]#

A[6]#

A[7]#

A[8]#

A[9]#

A20M#

ADS#

AD STB [0]#

AD STB [1]#

RSVD[08]

BCLK[0]

BCLK[1]

BN R#

BPM[0]#

BPM[1]#

BPM[2]#

BPM[3]#

BPRI#

BR 0#

DBR#

D BSY#

DEFER#

DRD Y#

FER R#

HI T#

HITM#

IER R#

IG NNE #

INI T#

LINT0

LINT1

LO C K #

PRD Y#

PR EQ#

PROCHOT#

REQ[0]#

REQ[1]#

REQ[2]#

REQ[3]#

REQ[4]#

RESE T#

RS[0 ]#

RS[1 ]#

RS[2 ]#

SM I#

STPCLK#

TC K

TDI

TD O

THER MTRIP#

TH E R M D A

THER MD C

TM S

TRD Y#

TRS T#

A[32]#

A[33]#

A[34]#

A[35]#

RSVD[09]

H_A#31

H_ RS# 0 [4 ]

H_D#34

R195 *10mil_short

V_TH RM

SM D_ CPU _T HE RM [26 ]

PM_ T HRM T RIP# [5 ,1 3, 28 ]

COMP0, COMP2: 0.5" Max, Zo=27.4 Ohms

COMP1, COMP3: 0.5" Max, Zo=55 Ohms

Best estimate is 18 mils wide trace for outer

layers and 14 mils wide trace if on internal

layers.

Put it at central of

CPU socket

H_ HIT# [4 ]

H _DPRSTP# [5,13,31]

CPU ONLY SUPPORT TO 35W

CL K_ CPU_ BC LK [1 8]

H_DSTBN#1[4 ]

H_D#50

H_A#5

H_D#47

H_D#42

R1 9 3 * 0_ 0 4

3.3V

3. 3 V[12..17,19,20,23,29,30]

H_REQ#3

COMP3

H_ INIT# [1 3 ]

H_ D# [6 3:0 ][4 ]

H_D#38

H_A#13

H_ D# 2 2

R 171 649_1%_06

Q 18 *AO 3409

G

DS

Layout Note:

H_PREQ#

H_ D# 1 0

U1 3

aS C 75 2 5

1

2

3

4

5

6

7

8

VD D

D+

D-

THER M

GND

ALER T

SDA TA

SC LK

H_A#16

H_A#28

H_ D# 4

H_ D# 1 1

H_D#55

H_ TRDY # [4 ]

H_ DST BP# 1[4]

H_D#52

H_PROCHOT#

H_D#51

R6

27.4_1%_04

1.05VS[3..5,7,8,13,16,29]

CPU_ BSEL 0

C335

1000P_50V_X7R_04

H_ D# 1 7

H_ THE RM DC

H_BPRI# [4]

H_TDI

H_D#61

10mils

H_TMS

CPU_ BSEL 1

H_CPURST#

Route H_THERMDA and

H_THERMDC on same layer.

10 mil trace on 10 mil spacing.

1. 0 5 V S

H_A#6

H_A#17

H_A#32

H_TCK

COMP0

H_A#29

H_IERR#

THER M_AL ERT# [26]

H_AD STB#1[4 ]

R210 *10m il_short

H_D#45

R182

54.9_1%_04

12mils

H_INTR[13]

Layout Note:

H_ D# 3

H_A#11

H_ D# 1 2

COMP1

H_CPU RST# [4]

COMP0

H_D#46

H_ D# 1 6

H_TDI

H_ D# 2 0

H_PR OCH OT #

H_D#48

H_ D# 2 4

0.5" max, Zo= 55 Ohms

H_A#23

H_D#54

Near to Thermal

IC

H_D#62

H_DPSLP# [13]

R183

27.4_1%_04

COMP3

H_D#58

H_D#32

H_T HER MDC _ R

H_DINV#2 [4]

H_DSTBP#3 [4]

R196 *10mil_short

H_ ST PCL K#[13]

COMP1

CPU_ BSEL 2

H_REQ#1

H_A#21

H_A#30

H_TRST#

R194

10K_04

H_D#60

H_D#56

D15

ASD751V

AC

CPU TEMP [26]

H_ D# 8

H_IGNNE#[13 ]

H_A#15

H_ D# 1 8

H_DSTBP#2 [4]

H_A#8

H_TRST#

H_ D# 2

H_ REQ #[4 :0 ][4]

H_IERR#

H_ D# 5

H_D#39

R 19 *51_1% _04

H_DR DY# [4]

H_A#24

H_D#49

H _A#[35:3][4 ]

H_REQ#0

H_ D# 1 5

R 198 54.9_1%_04

Q1 9

*2N7002W

G

DS

Layout note:

H_ TH E RM DC

H_A#19

H_ D# 7

H_A#22

Layout Note:

H _A20M#[13 ]

DATA GRP 0 DATA GRP 1

DATA GRP 2DATA GRP 3

MIS C

U9B

MOLEX_47430-6215

R2 6

U2 6

AA1

Y1

E22

F24

J24

J23

H22

F26

K22

H23

N22

K25

P26

R23

E26

L23

M24

L22

M23

P25

P23

P22

T24

R24

L25

G22

T25

N25

Y22

AB2 4

V24

V26

V23

T22

U2 5

U2 3

F23

Y25

W22

Y23

W24

W25

AA2 3

AA2 4

AB2 5

AE2 4

AD24

G25

AA2 1

AB2 2

AB2 1

AC26

AD20

AE2 2

AF2 3

AC25

AE2 1

AD21

E25

AC22

AD23

AF2 2

AC23

E23

K24

G24

AF 1

H25

N24

U2 2

AC20

E5

B5

D2 4

J26

L26

Y26

AE2 5

H26

M26

AA2 6

AF2 4

AD 26

AE6

D6

D7

C24

B22

B23

C21

D25

AF2 6

A26

C23

C3

CO MP[0 ]

CO MP[1 ]

CO MP[2 ]

CO MP[3 ]

D[0]#

D[1]#

D[10]#

D[11]#

D[12]#

D[13]#

D[14]#

D[15]#

D[16]#

D[17]#

D[18]#

D[19]#

D[2]#

D[20]#

D[21]#

D[22]#

D[23]#

D[24]#

D[25]#

D[26]#

D[27]#

D[28]#

D[29]#

D[3]#

D[30]#

D[31]#

D[32]#

D[33]#

D[34]#

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[4]#

D[40]#

D[41]#

D[42]#

D[43]#

D[44]#

D[45]#

D[46]#

D[47]#

D[48]#

D[49]#

D[5]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

D[58]#

D[59]#

D[6]#

D[60]#

D[61]#

D[62]#

D[63]#

D[7]#

D[8]#

D[9]#

TEST5

D INV[0 ]#

D INV[1 ]#

DINV[2 ]#

DINV[3 ]#

DPRST P#

DPSL P #

DPWR#

DSTBN[0]#

DSTBN[1]#

DSTBN[2]#

DSTBN[3]#

DSTBP[0]#

DSTBP[1]#

DSTBP[2]#

DSTBP[3]#

GTLREF

PSI#

PW RG OO D

SLP#

TEST3

BSE L[0]

BSE L[1]

BSE L[2]

TEST2

TEST4

TEST6

TEST1

TEST7

H_ D# [6 3:0 ][4 ]

H_ THE RM DA

R192 *10mil_short

H_D#[63:0] [4]

H _PWRGD [13]

H_AD STB#0[4 ] H_ L OCK# [4]

Layout Note:

H_A#33

H_A#27

H_TMS

C PU_BSEL2[4,18]

H_A#35

H_D#36

H_ BREQ # [4 ]

H_DSTBN#3 [4]

H_A#3

R 181 54.9_1%_04

H _CPUSLP# [4]

H_D#40

CPU_GTLREF

H_F ERR #[1 3]

H_DINV#0[4 ]

H_ D# 9

H_D#43

R 174 54.9_1%_04

H_DSTBP#0[4]

H_ D# 1 4

H_SMI#[13]

H_D#[63:0] [4]

H_ D# 0

C PU_BSEL0[4,18] H_DPWR# [4]

H_D#35

H_D#37

H_ D# 1 3

CPU_GRFE=0.7V

H_A#20

H_TCK

H_T HER MDA_R

H_CPURST#

C8

0. 0 1 U _ 1 6V _ X 7R _ 04

Schematic Diagrams

B - 4 Intel Penryn (Socket-P) 2/2

B.Schematic Diagrams

Intel Penryn (Socket-P) 2/2

C311

0.1U_10V_X7R_04

C301

1U _6.3V_04

C 309

0.1U _10V _X7R _04

C283

10U_6.3V_X5R_08

H _V ID4 [31]

C3 3 0

22U _6.3V _X5R _08

C2 9 6

1U _6.3V_04

1.5VS[8,13,14,16,19,20, 29]

VCO R E

C332

1U_6.3V_04

1.05V S

C31

0.1U_10V_X7R_04

C38

22U_6.3V_X5R_08

C2 9 9

0. 01 U _ 16 V _X 7 R _0 4

1.05VS

H _V ID3 [31]

C PU_VS SSEN SE [31]

C 308

* 0.1U_1 0 V_X7R_04

C322

22U_6.3V_X5R_08

C291

0.01U _16V_X7R _04

C327

10U_6.3V_X5R_08

VC OR E[31 ]

C 321

10U _6.3V _X5R _08

C3 2 3

10U _6.3V _X5R _08

C 279

0.1U _10V_X7R_04

C 305

1U _6.3V _04

C334

1U _6.3V_04

C 316

0.1U _10V_X7R_04

U9 C

MO LEX_47430-6215

.

A7

A9

A10

A12

A13

A15

A17

A18

A20

B7

B9

B10

B12

B14

B15

B17

B18

B20

C9

C1 0

C1 2

C1 3

C1 5

C1 7

C1 8

D9

D1 0

D1 2

D1 4

D1 5

D1 7

D1 8

E7

E9

E10

E12

E13

E15

E17

E18

E20

F7

F9

F10

F12

F14

F15

F17

F18

F20

AA7

AA9

AA10

AA12

AA13

AA15

AA17

AA18

AA20

AB9

AC10

AB10

AB12

AB14

AB15

AB17

AB18

AB20

AB7

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF1 0

AF1 2

AF1 4

AF1 5

AF1 7

AF1 8

AF2 0

B26

J6

K6

M6

J2 1

K21

M2 1

N2 1

N6

R2 1

R6

T2 1

T6

V21

W21

AF7

AD6

AF5

AE5

AF4

AE3

AF3

AE2

AE7

C2 6

G2 1

V6

V CC [001]

V CC [002]

V CC [003]

V CC [004]

V CC [005]

V CC [006]

V CC [007]

V CC [008]

V CC [009]

V CC [010]

V CC [011]

V CC [012]

V CC [013]

V CC [014]

V CC [015]

V CC [016]

V CC [017]

V CC [018]

V CC [019]

V CC [020]

V CC [021]

V CC [022]

V CC [023]

V CC [024]

V CC [025]

V CC [026]

V CC [027]

V CC [028]

V CC [029]

V CC [030]

V CC [031]

V CC [032]

V CC [033]

V CC [034]

V CC [035]

V CC [036]

V CC [037]

V CC [038]

V CC [039]

V CC [040]

V CC [041]

V CC [042]

V CC [043]

V CC [044]

V CC [045]

V CC [046]

V CC [047]

V CC [048]

V CC [049]

V CC [050]

V CC [051]

V CC [052]

V CC [053]

V CC [054]

V CC [055]

V CC [056]

V CC [057]

V CC [058]

V CC [059]

V CC [060]

V CC [061]

V CC [062]

V CC [063]

V CC [064]

V CC [065]

V CC [066]

V CC [067]

VC C[ 068]

VC C[ 069]

VC C[ 070]

VC C[ 071]

VC C[ 072]

VC C[ 073]

VC C[ 074]

VC C[ 075]

VC C[ 076]

VC C[ 077]

VC C[ 078]

VC C[ 079]

VC C[ 080]

VC C[ 081]

VC C[ 082]

VC C[ 083]

VC C[ 084]

VC C[ 085]

VC C[ 086]

VC C[ 087]

VC C[ 088]

VC C[ 089]

VC C[ 090]

VC C[ 091]

VC C[ 092]

VC C[ 093]

VC C[ 094]

VC C[ 095]

VC C[ 096]

VC C[ 097]

VC C[ 098]

VC C[ 099]

VC C[ 100]

VC CA[01]

VC CP[03]

VC CP[04]

VC CP[05]

VC CP[06]

VC CP[07]

VC CP[08]

VC CP[09]

VC CP[10]

VC CP[11]

VC CP[12]

VC CP[13]

VC CP[14]

VC CP[15]

VC CP[16]

V CC SEN SE

VI D[0]

VI D[1]

VI D[2]

VI D[3]

VI D[4]

VI D[5]

VI D[6]

VS SSEN SE

VC CA[02]

VC CP[01]

VC CP[02]

C 320

22U _6.3V _X5R _08

C39

1U _6.3V _04

C 315

* 0.1U_10V_X7R _04

VCO R E

VC OR E

H _V ID1 [31]

H _V ID2 [31]

C 319

10U _6.3V_X5R_08

1. 05 V S[2 ,4 ,5 ,7, 8, 13 ,1 6 ,2 9 ]

C 281

22U _6.3V_X5R_08

C35

* 0. 1U _10V _X7R _04

C324

1U_6.3V_04

C3 1 3

150U_4V_B2

C 295

1U _6.3V _04

C304

0.1U_10V_X7R_04

H _V ID0 [31]

VCO R E

VCO R E

C 302

1U _6.3V _04

1.05VS

C2 8 0

22U _6.3V _X5R _08

Layout Note:

C36

22U_6.3V_X5R_08

C282

10U_6.3V_X5R_08

C333

22U_6.3V_X5R_08

0.5A

C362

0.1U_10V_X7R_04

C278

1U_6.3V_04

H _V ID6 [31]

47A

C1 7

0.1U_10V_X7R _04

C331

0.1U_10V_X7R_04

H _V ID5 [31]

C328

0.01U_16V_X7R_04

VCO R E

C 298

0.1U _10V _X7R _04

C3 2 9

1U _6.3V_04

2.5A

U9D

M O LE X_47430- 6215

.

P6

AE11

A8

A11

A14

A16

A19

A23

AF2

B6

B8

B11

B13

B16

B19

B21

B24

C5

C8

C1 1

C1 4

C1 6

C1 9

C2

C2 2

C2 5

D1

D4

D8

D1 1

D1 3

D1 6

D1 9

D2 3

D2 6

E3

E6

E8

E11

E14

E16

E19

E21

E24

F5

F8

F11

F13

F16

F19

F2

F22

F25

G4

G1

G2 3

G2 6

H3

H6

H2 1

H2 4

J2

J5

J22

J25

K1

K4

K23

K26

L3

L6

L21

L24

M2

M5

M2 2

M2 5

N1

N4

N2 3

N2 6

P3 A25

AF21

AF19

AF16

AF13

AF11

AF8

AF6

A2

AE26

AE23

AE19

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC 3

AC 6

AC 8

AC 11

AC 14

AC 16

AC 19

AC 21

AC 24

AD 2

AD 5

AD 8

AD 11

AD 13

AD 16

AD 19

AD 22

AD 25

AE1

AE4

Y6

A4

AE14

AE16

AE8

AF25

VSS [082]

VSS [148]

VS S[00 2]

VS S[00 3]

VS S[00 4]

VS S[00 5]

VS S[00 6]

VS S[00 7]

VS S[00 8]

VS S[00 9]

VS S[01 0]

VS S[01 1]

VS S[01 2]

VS S[01 3]

VS S[01 4]

VS S[01 5]

VS S[01 6]

VS S[01 7]

VS S[01 8]

VS S[01 9]

VS S[02 0]

VS S[02 1]

VS S[02 2]

VS S[02 3]

VS S[02 4]

VS S[02 5]

VS S[02 6]

VS S[02 7]

VS S[02 8]

VS S[02 9]

VS S[03 0]

VS S[03 1]

VS S[03 2]

VS S[03 3]

VS S[03 4]

VS S[03 5]

VS S[03 6]

VS S[03 7]

VS S[03 8]

VS S[03 9]

VS S[04 0]

VS S[04 1]

VS S[04 2]

VS S[04 3]

VS S[04 4]

VS S[04 5]

VS S[04 6]

VS S[04 7]

VS S[04 8]

VS S[04 9]

VS S[05 0]

VS S[05 1]

VS S[05 2]

VS S[05 3]

VS S[05 4]

VS S[05 5]

VS S[05 6]

VS S[05 7]

VS S[05 8]

VS S[05 9]

VS S[06 0]