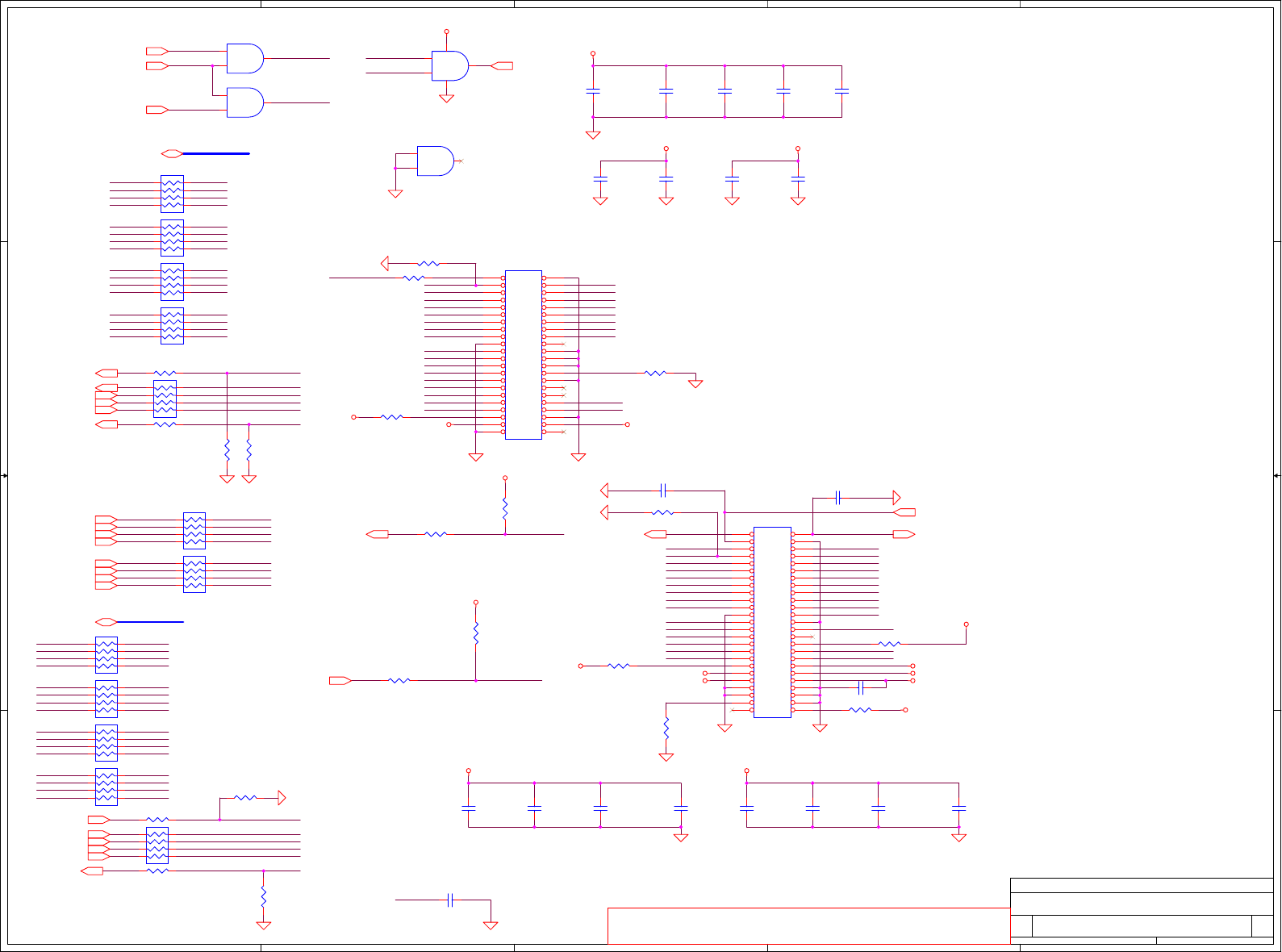

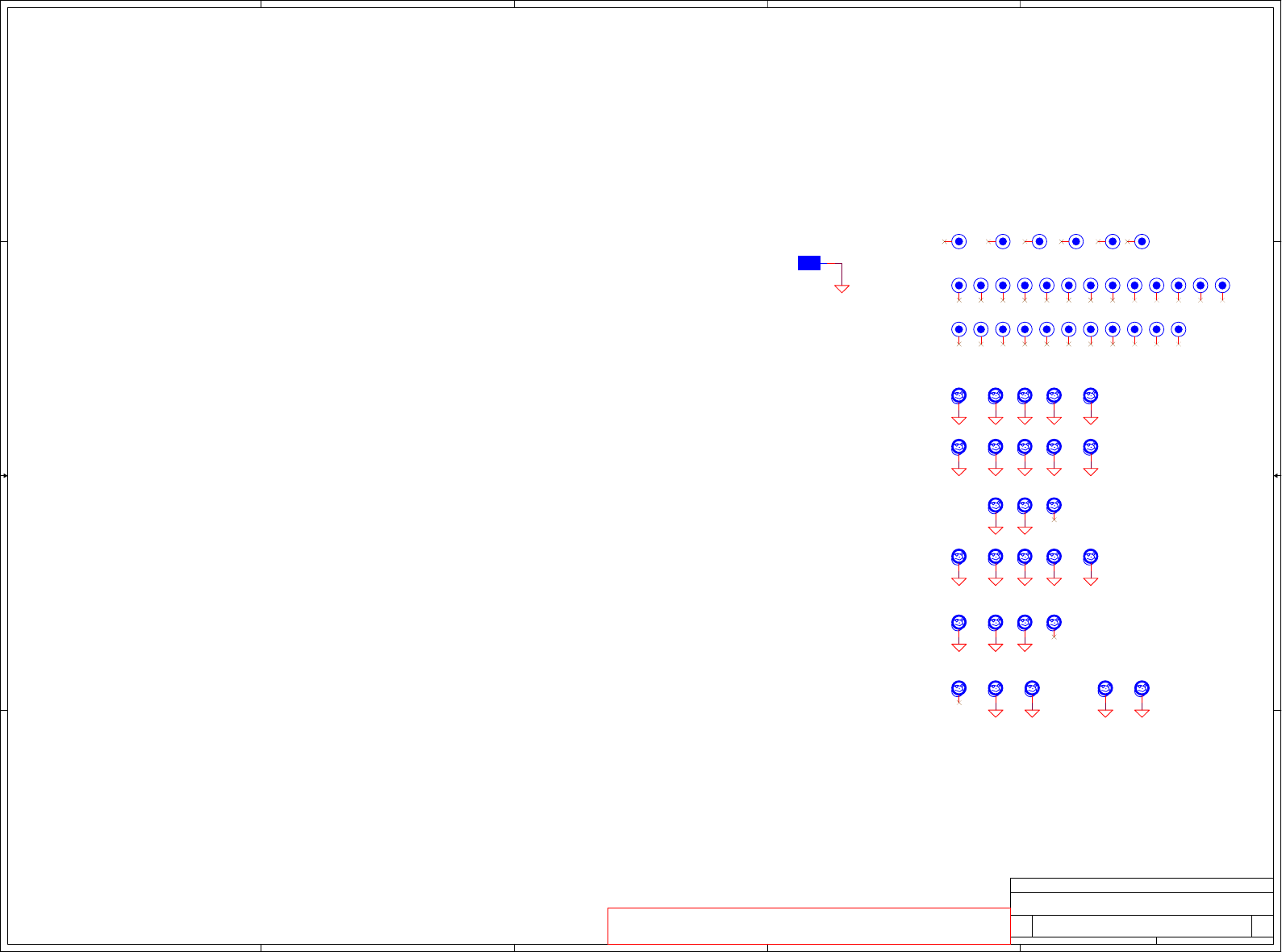

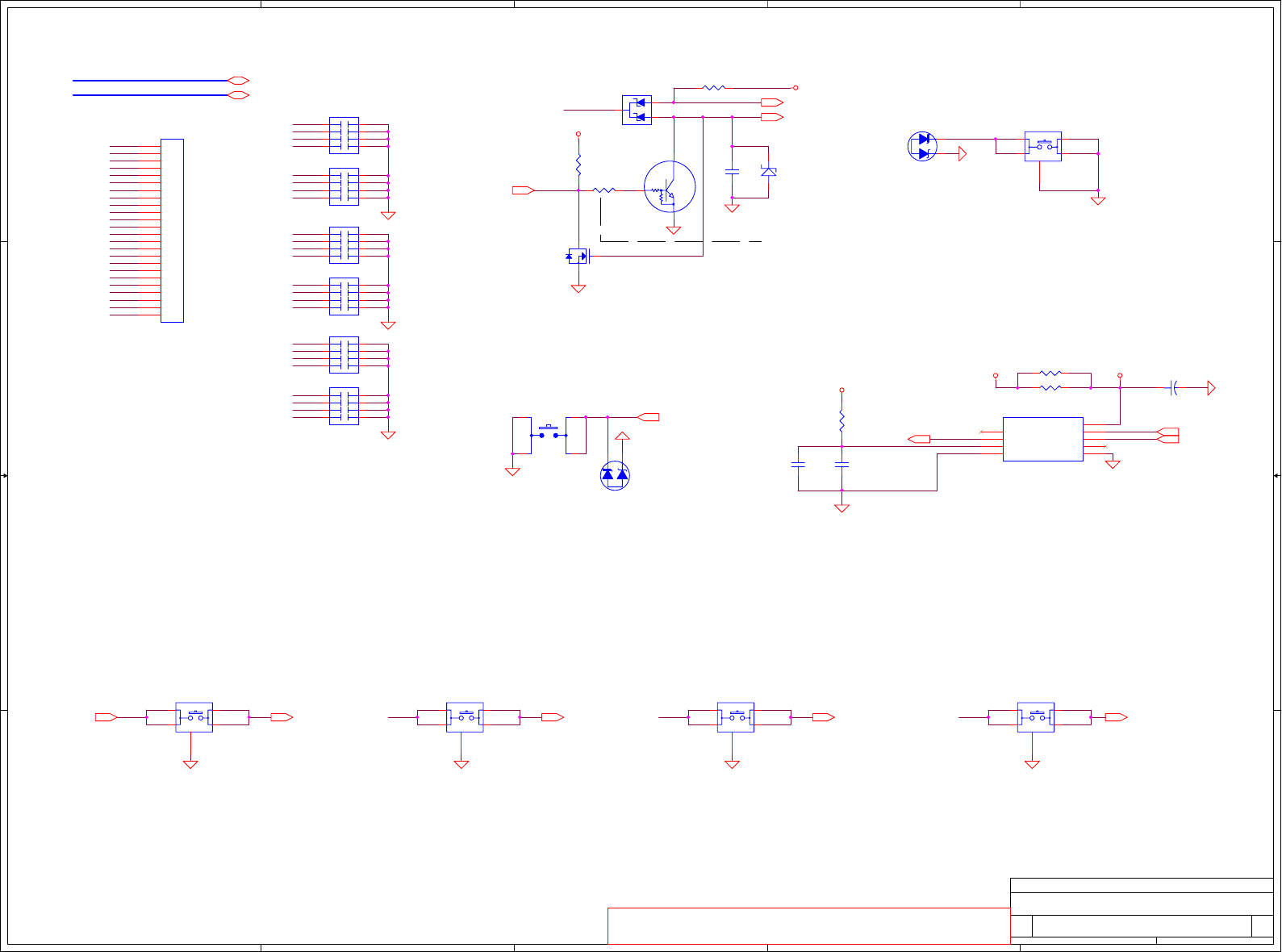

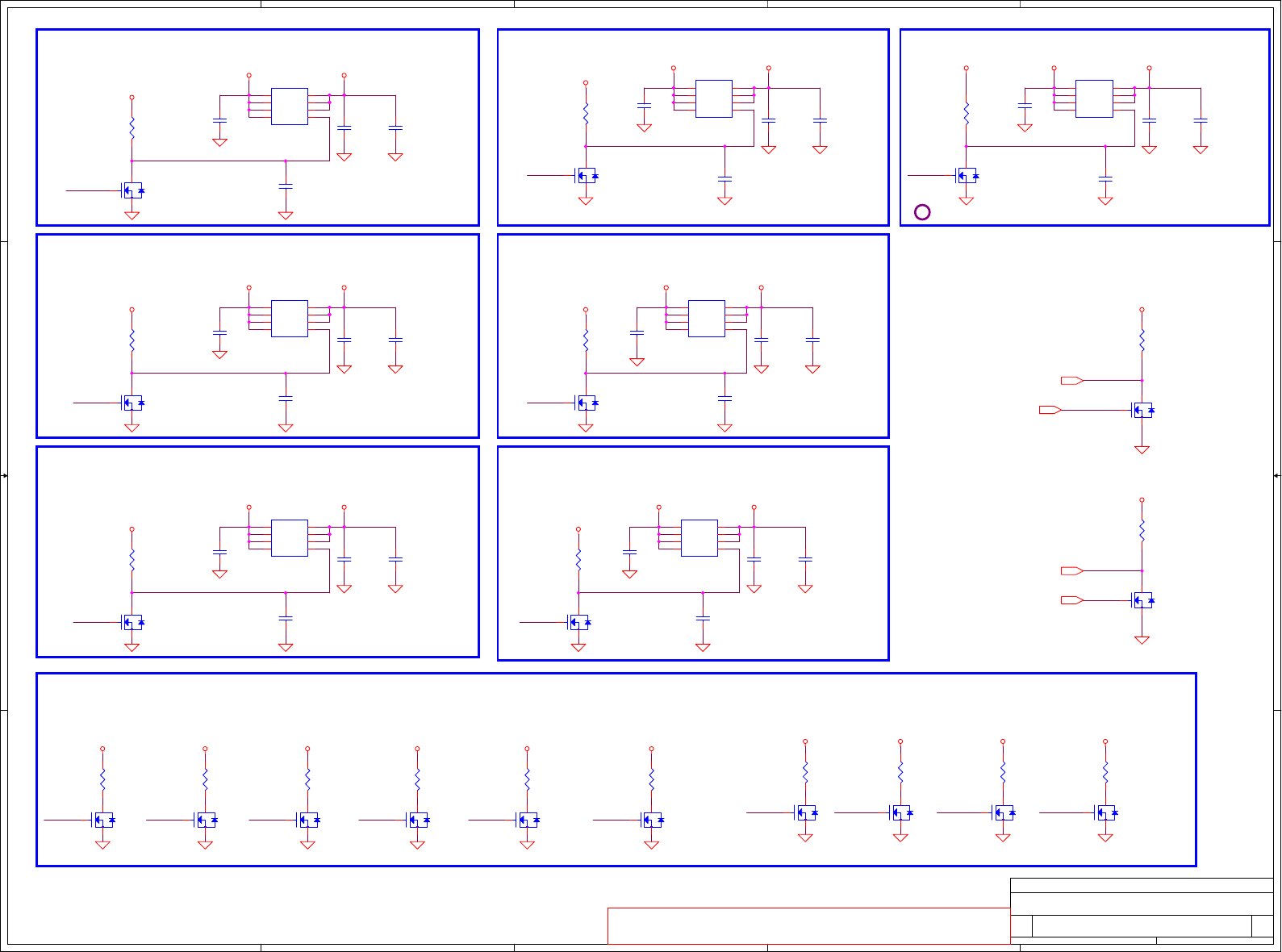

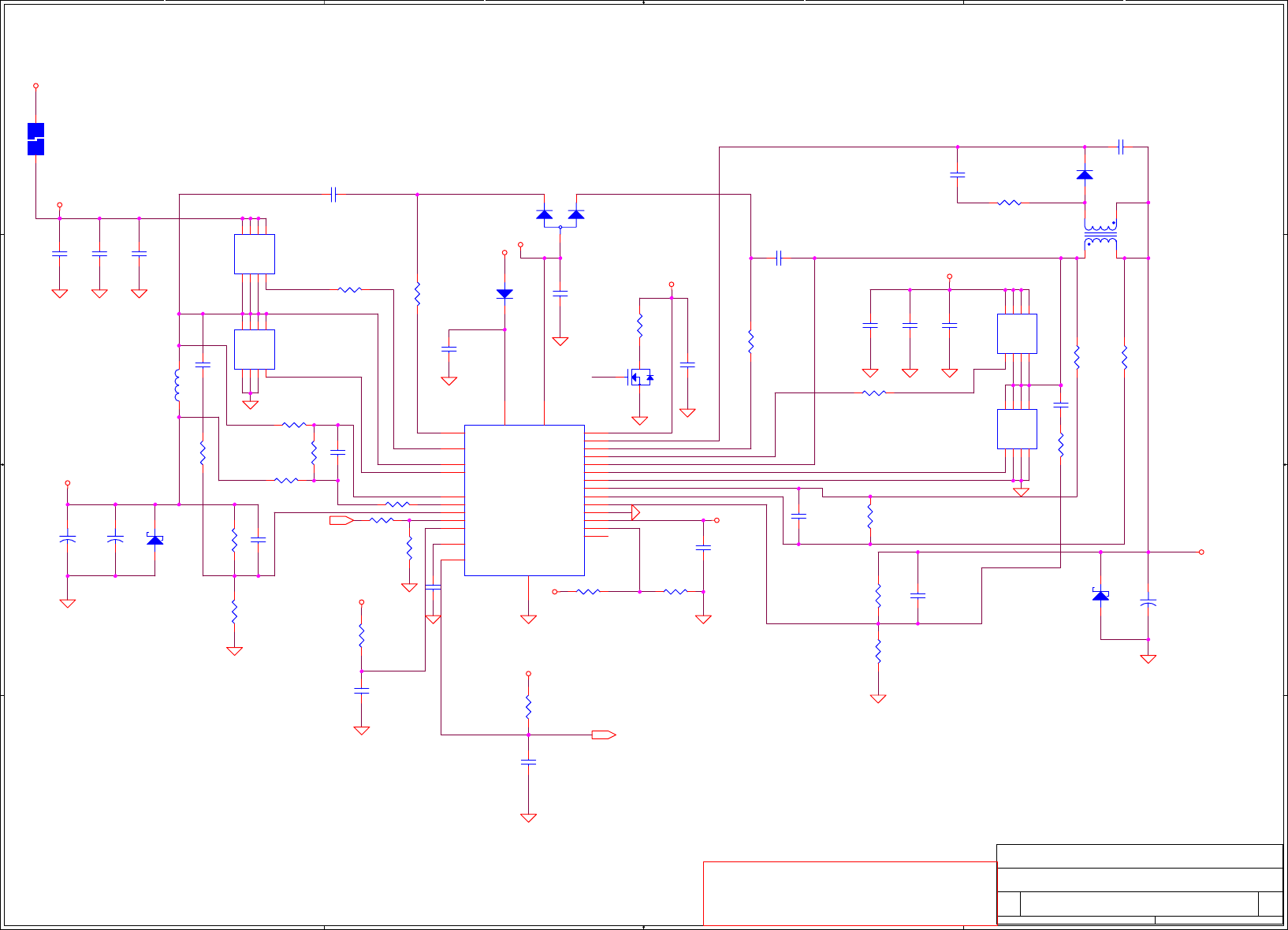

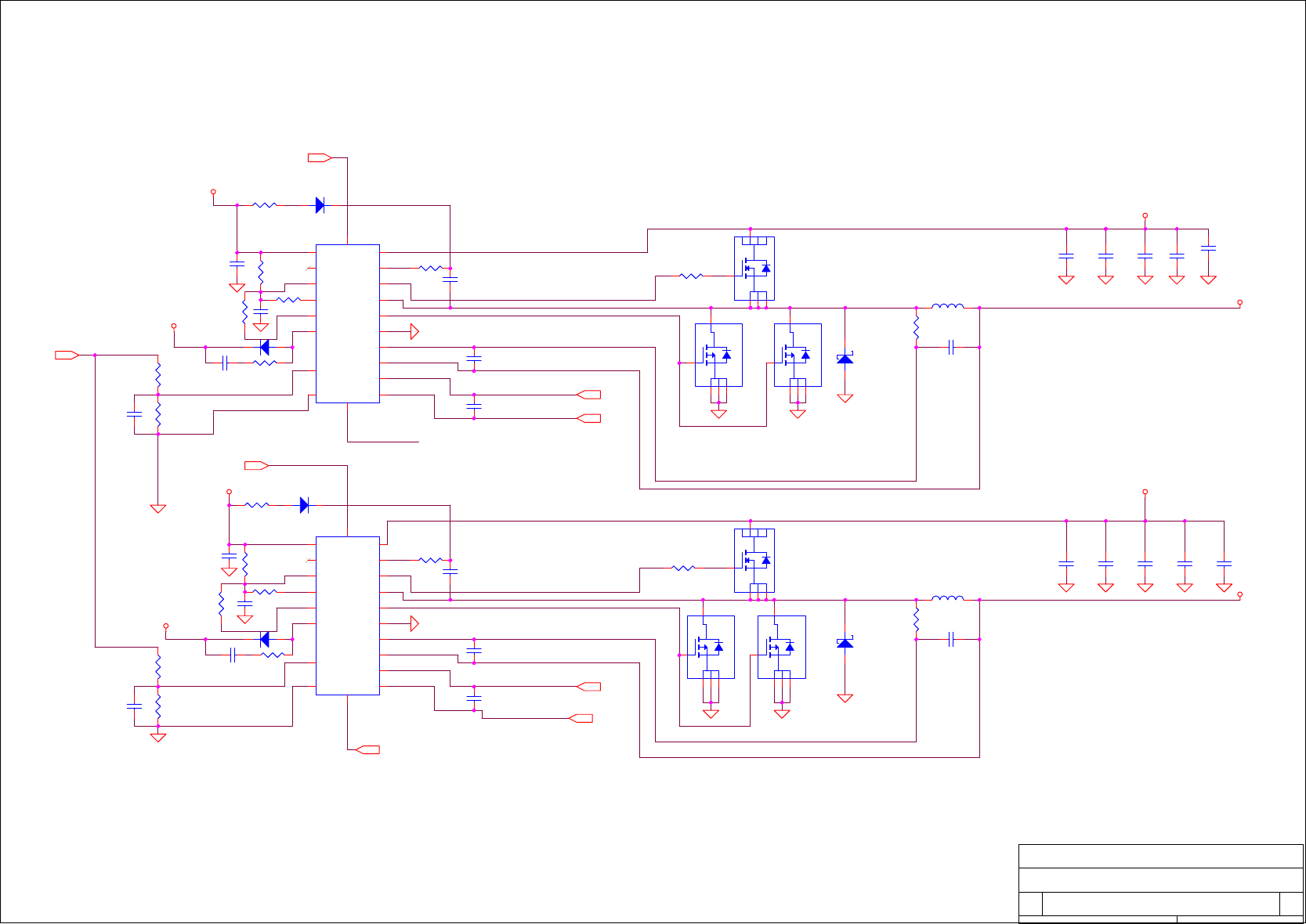

Compal LA 2411 Schematic. Www.s Manuals.com. R0.3 Schematics

User Manual: Compal LA-2411 - Schematics. Free.

Open the PDF directly: View PDF ![]() .

.

Page Count: 66

A

A

B

B

C

C

D

D

E

E

1 1

2 2

3 3

4 4

Title

Size Document Number Rev

Date: Sheet of

LA-2411

0.1

Cover Sheet

165, 07, 2004

星期三 七月

Compal Electronics, Inc.

Schematics Document

Compal confidential

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

2004-06-28

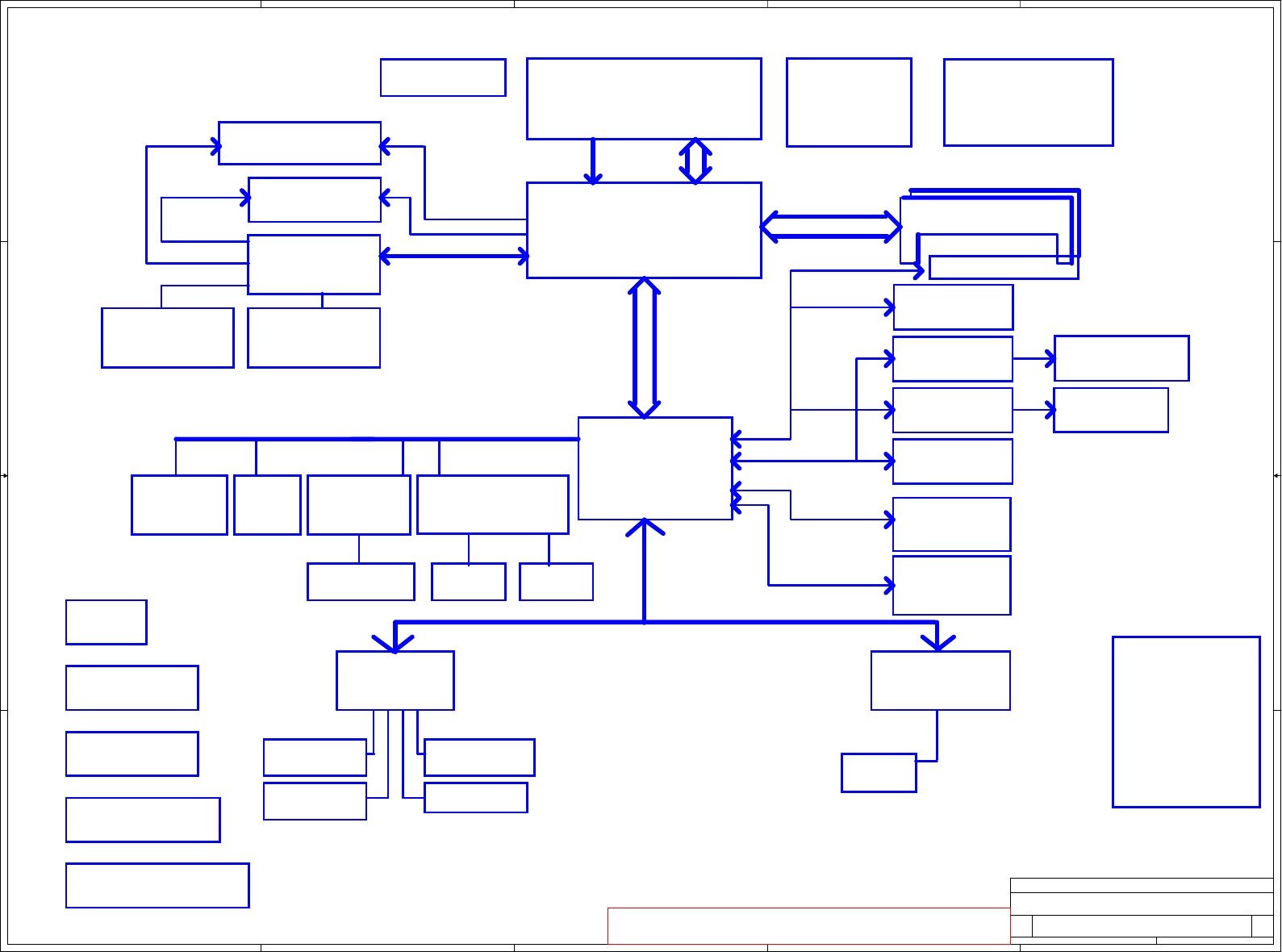

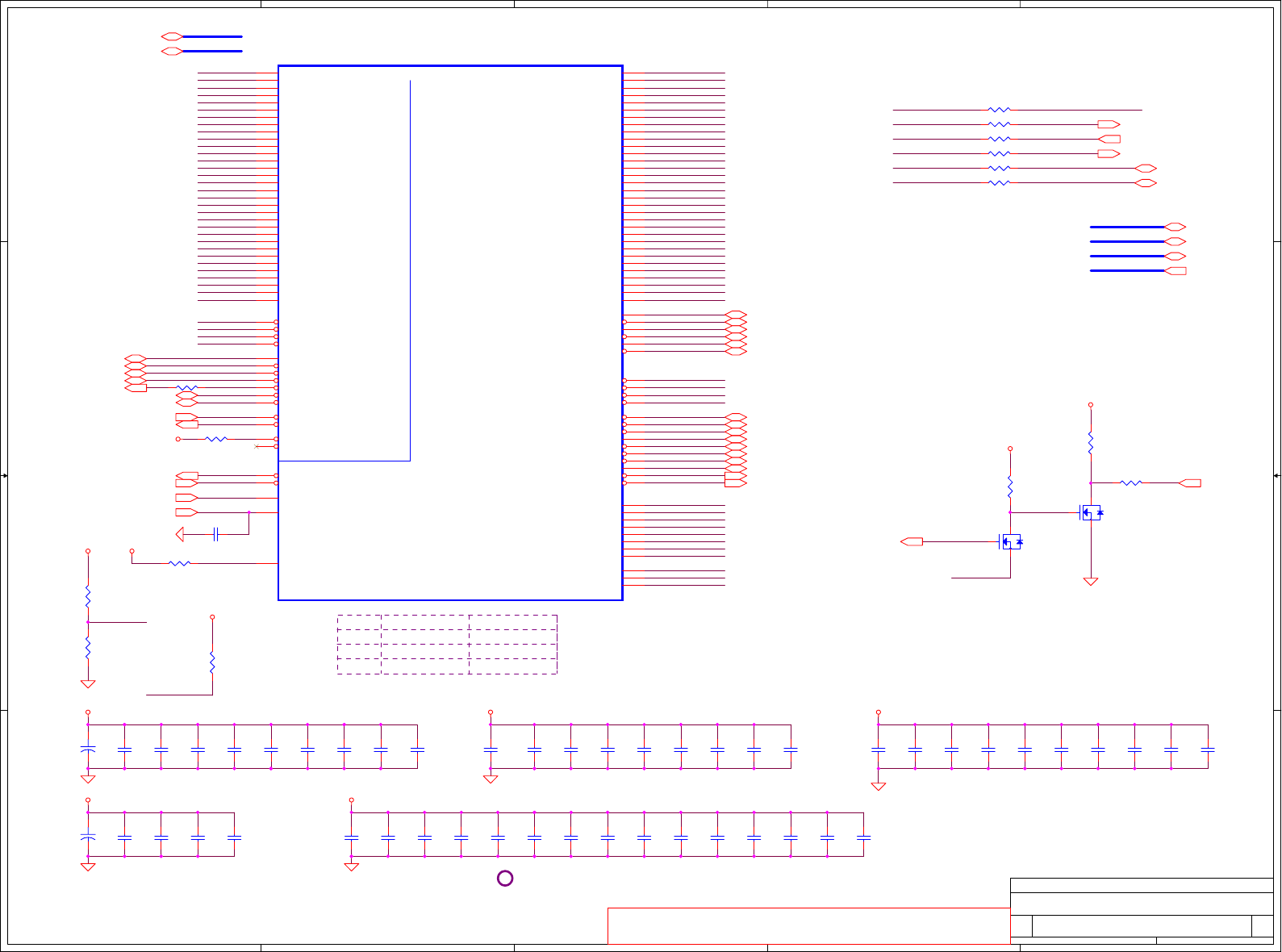

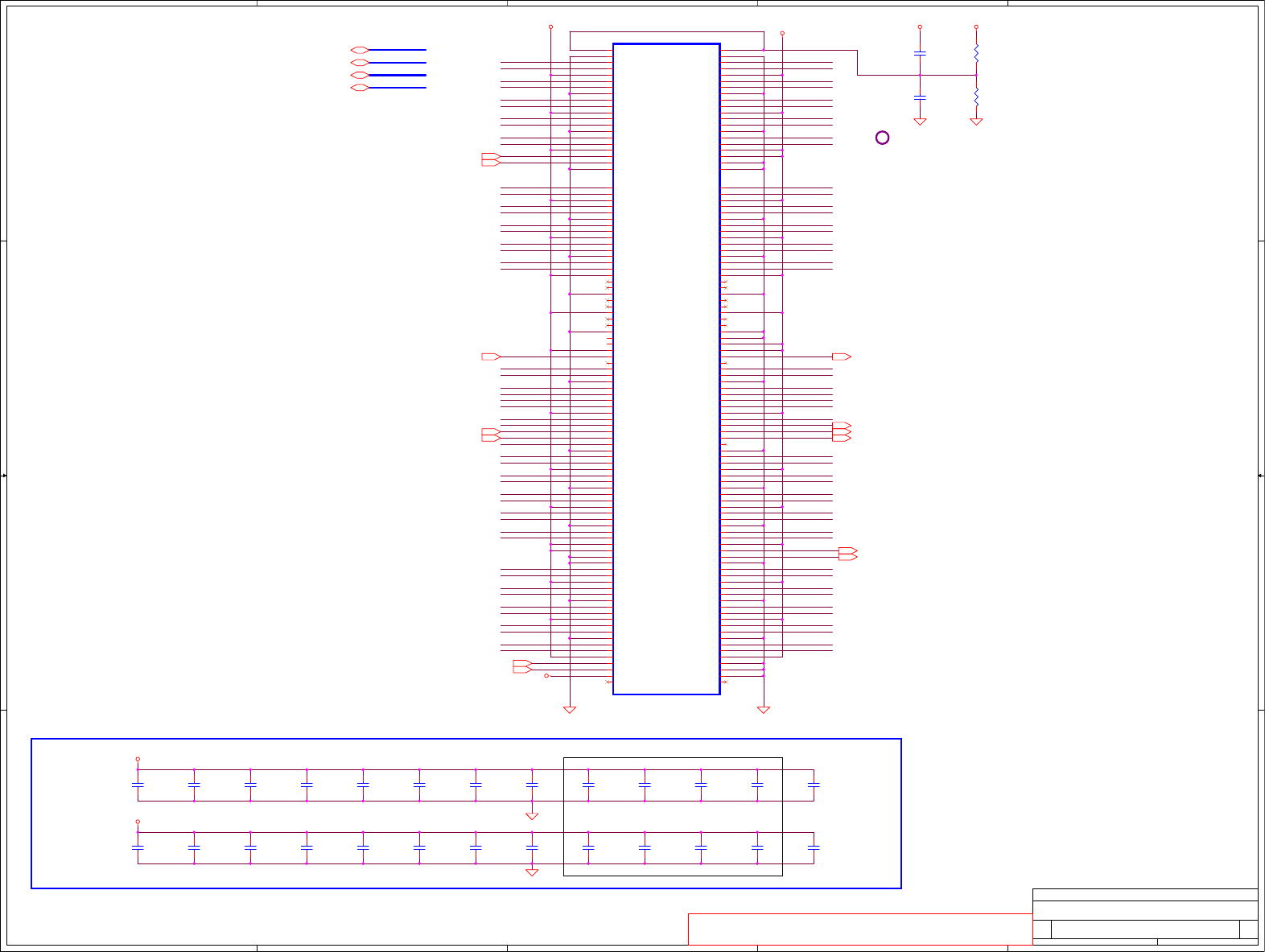

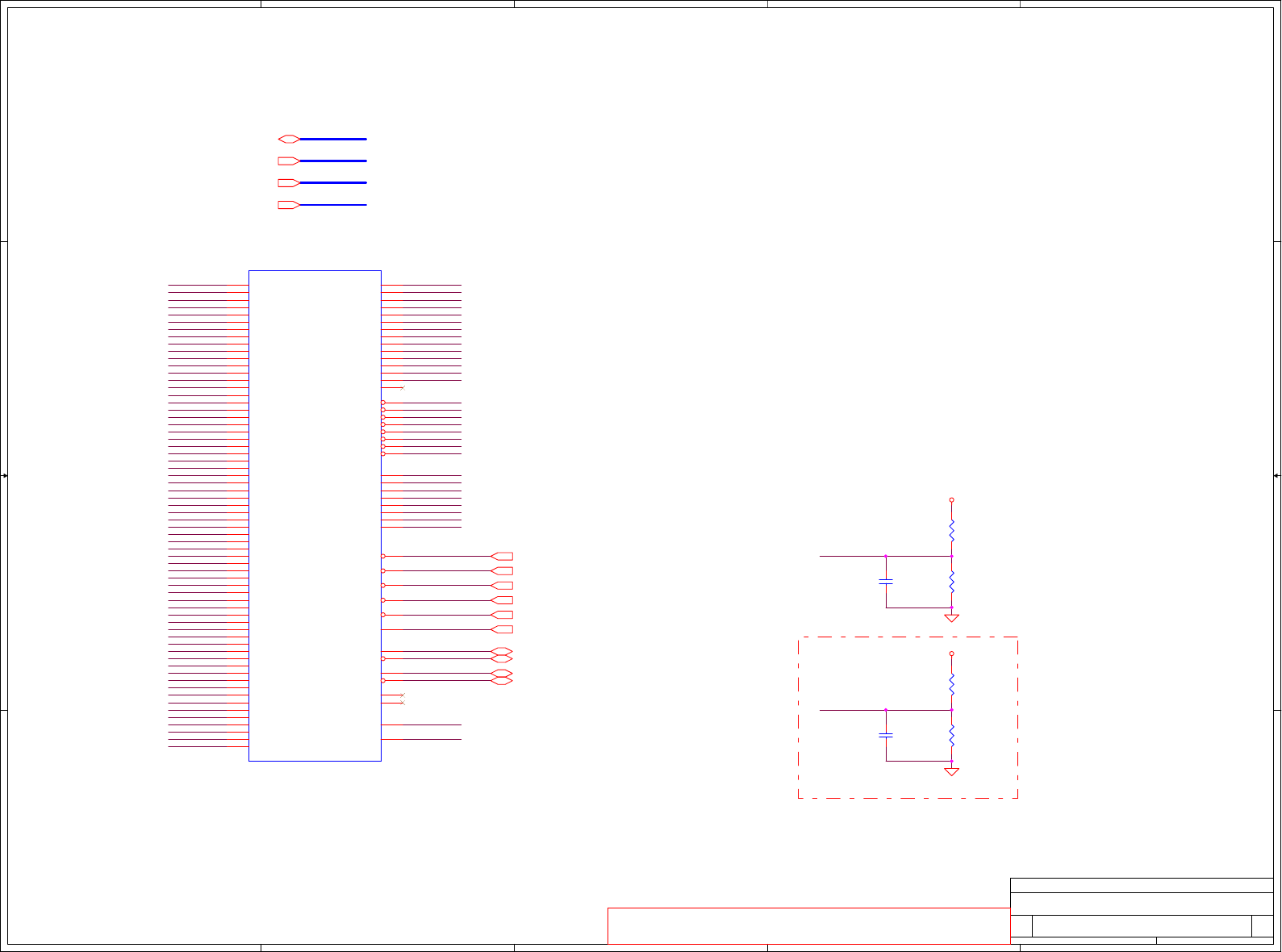

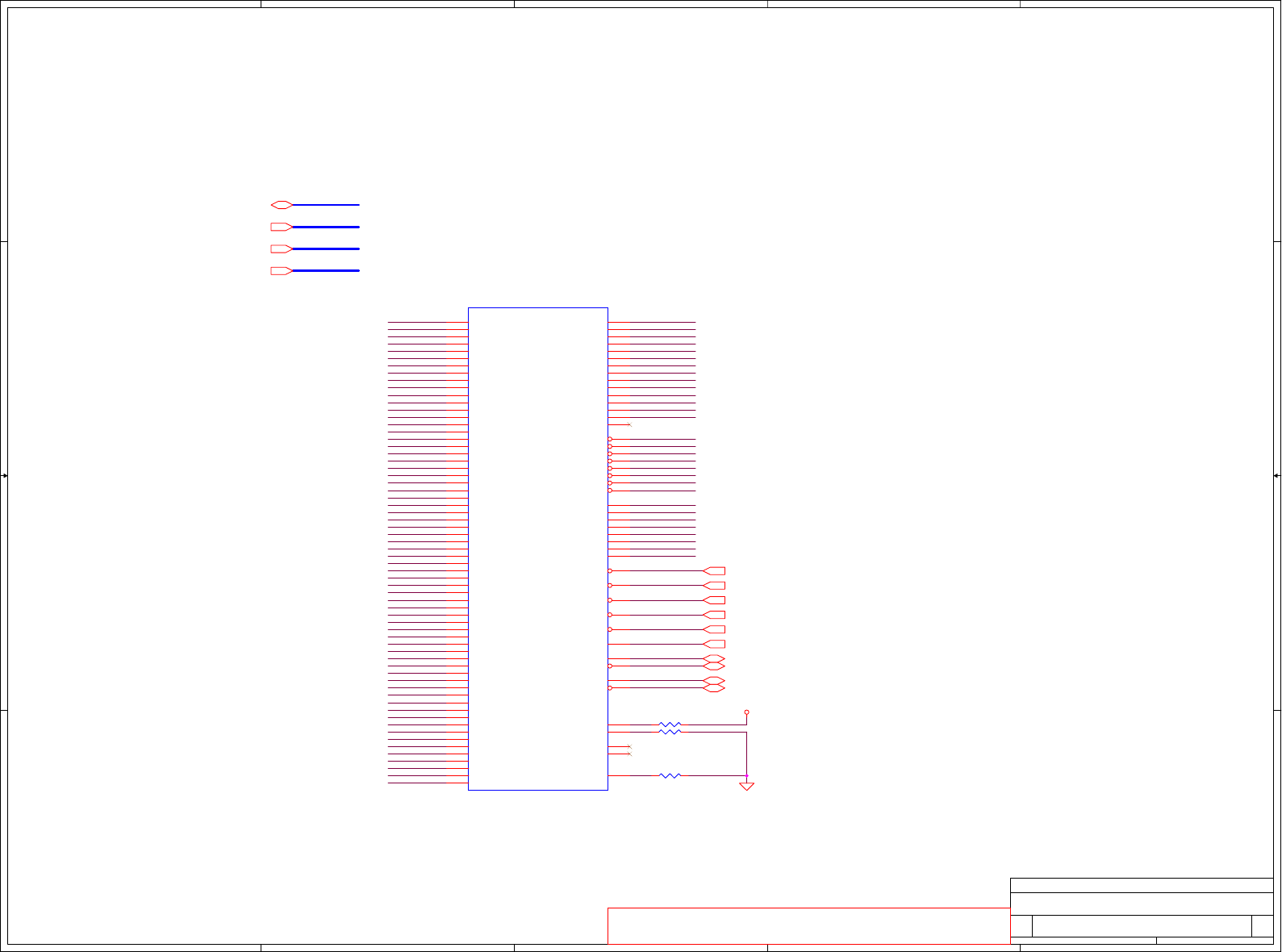

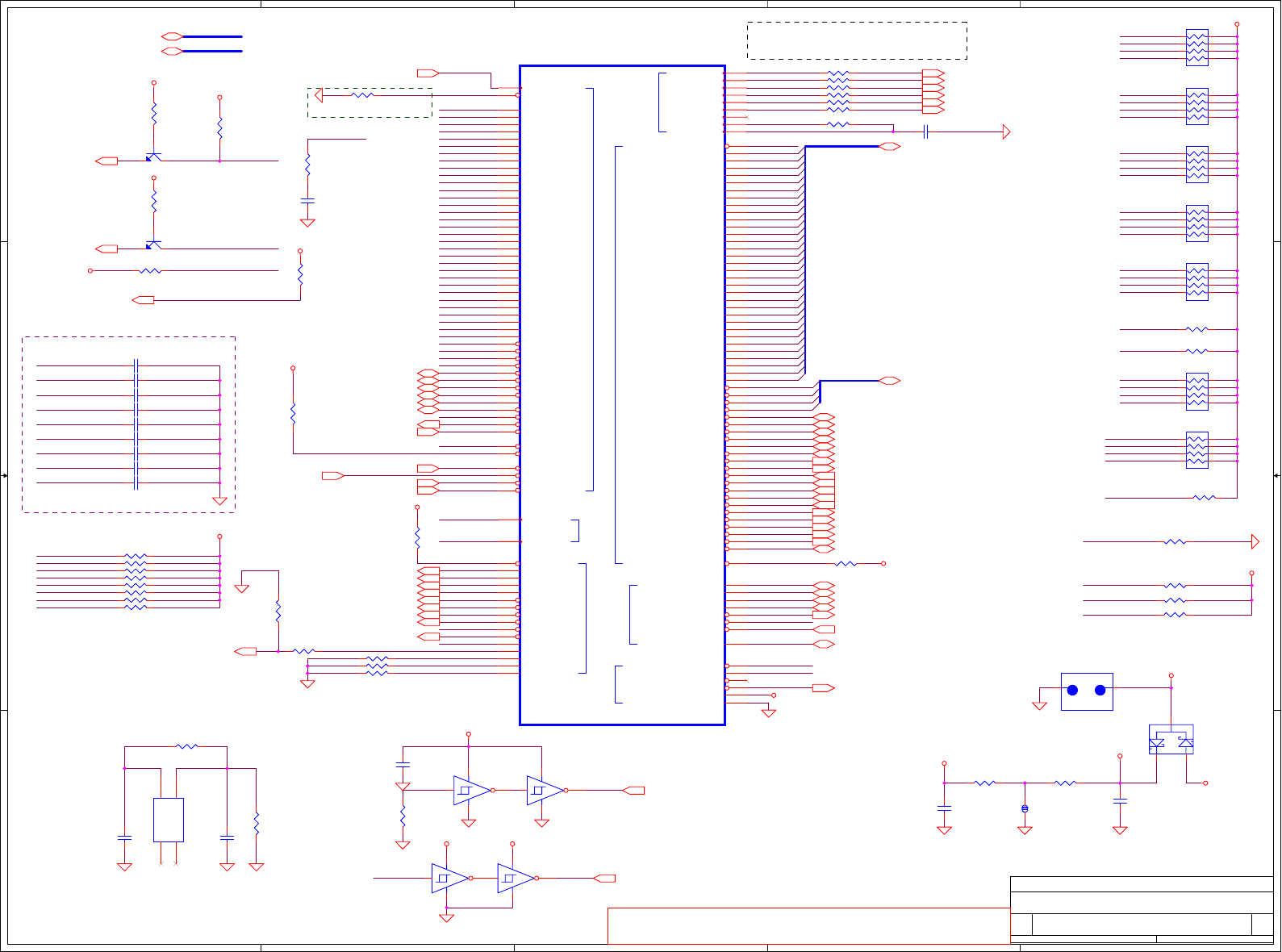

DT TRANSPORT or Prescott uFCPGA

with ATI-RC300M+SB200 core logic

LA-2411

REV:0.3

A

A

B

B

C

C

D

D

E

E

1 1

2 2

3 3

4 4

Title

Size Document Number Rev

Date: Sheet of

LA-2411

0.1

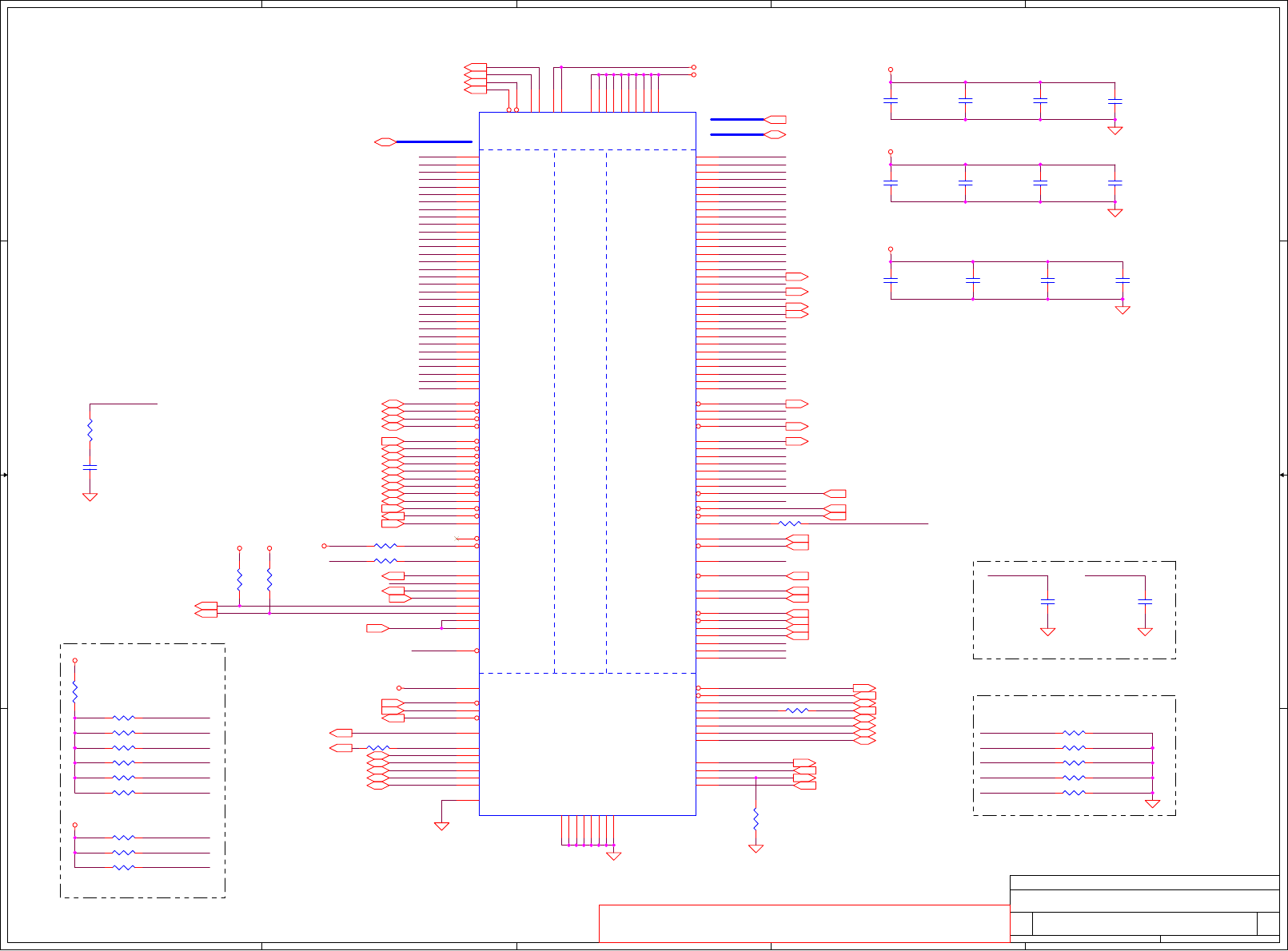

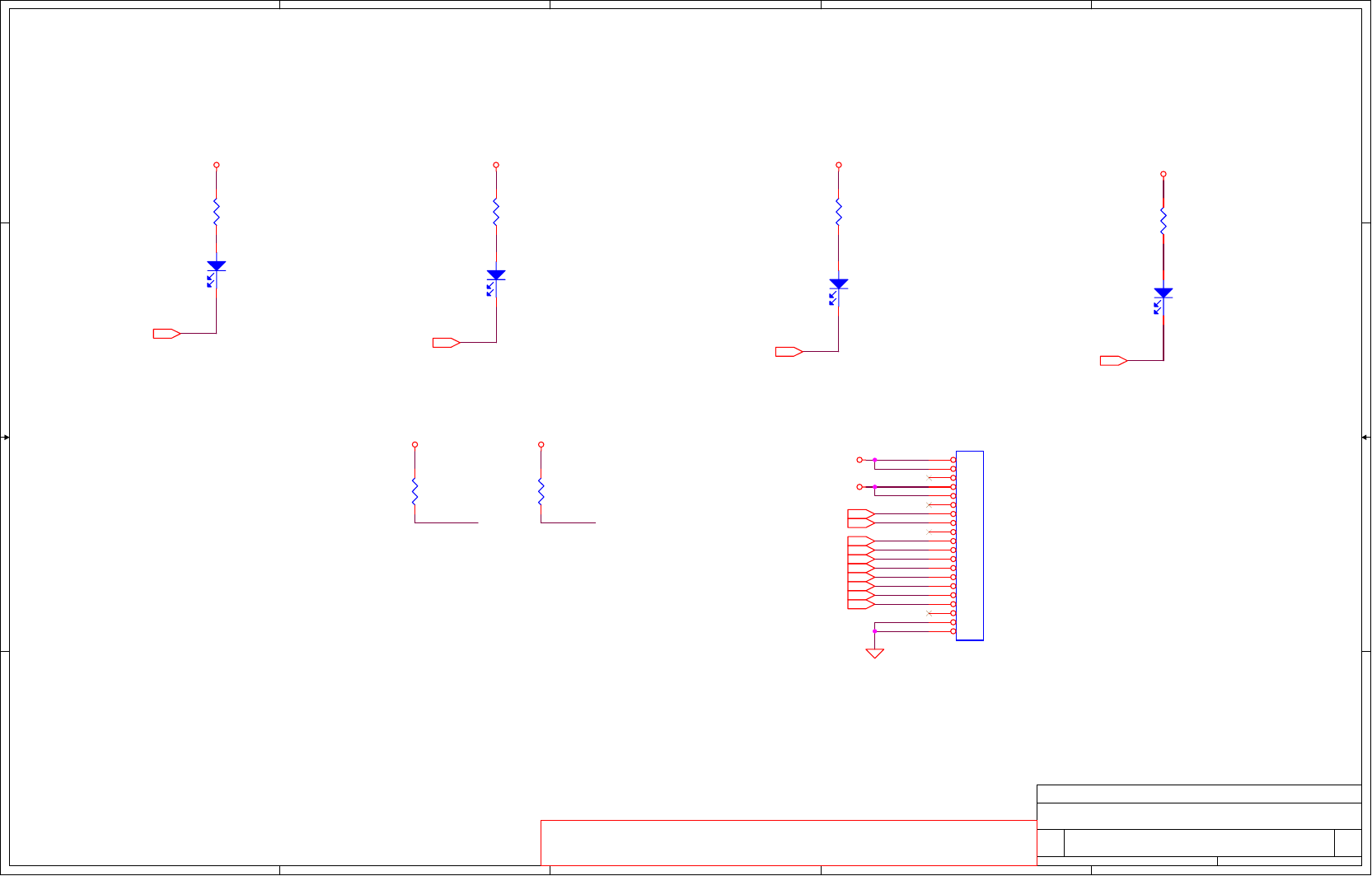

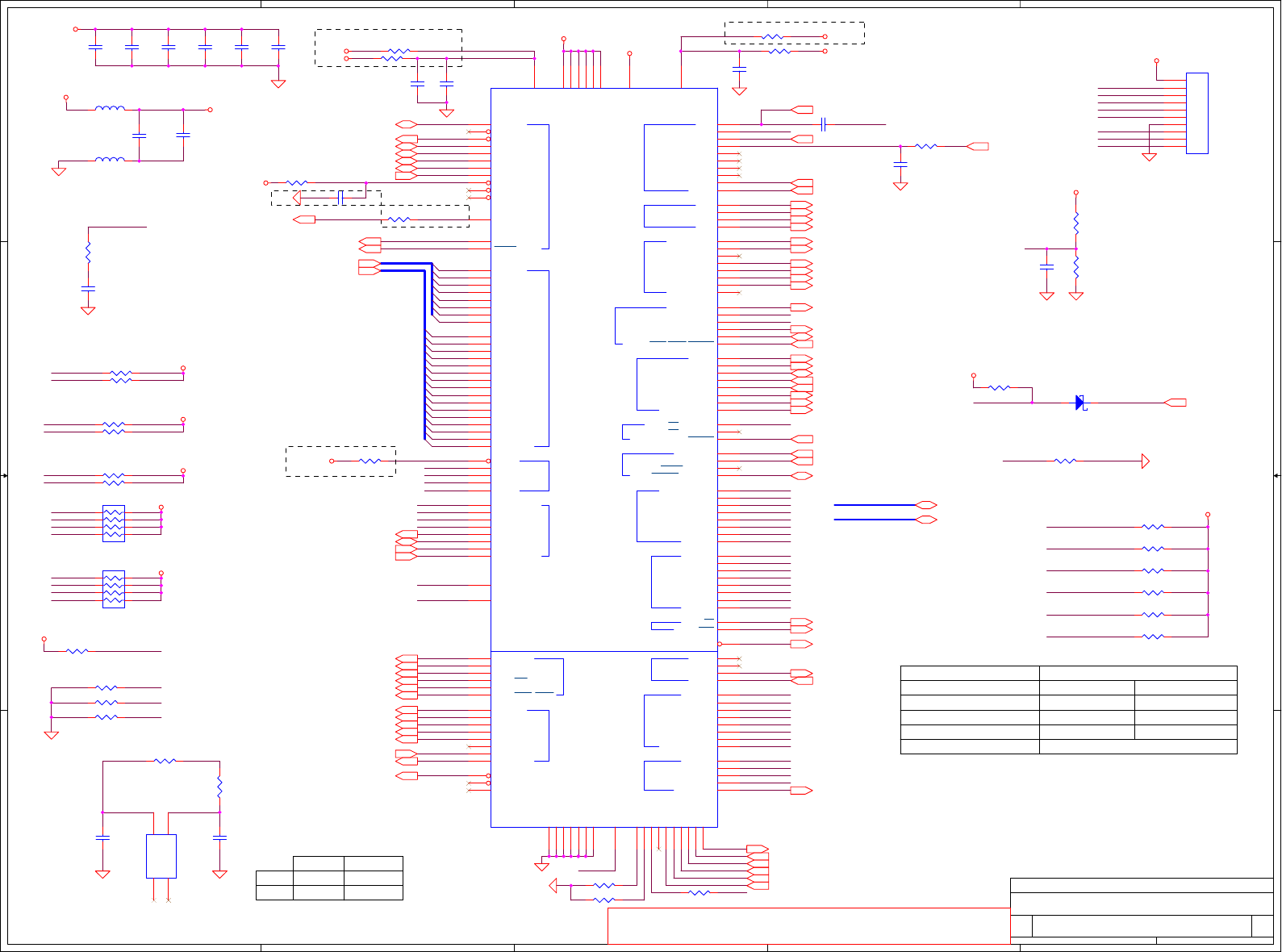

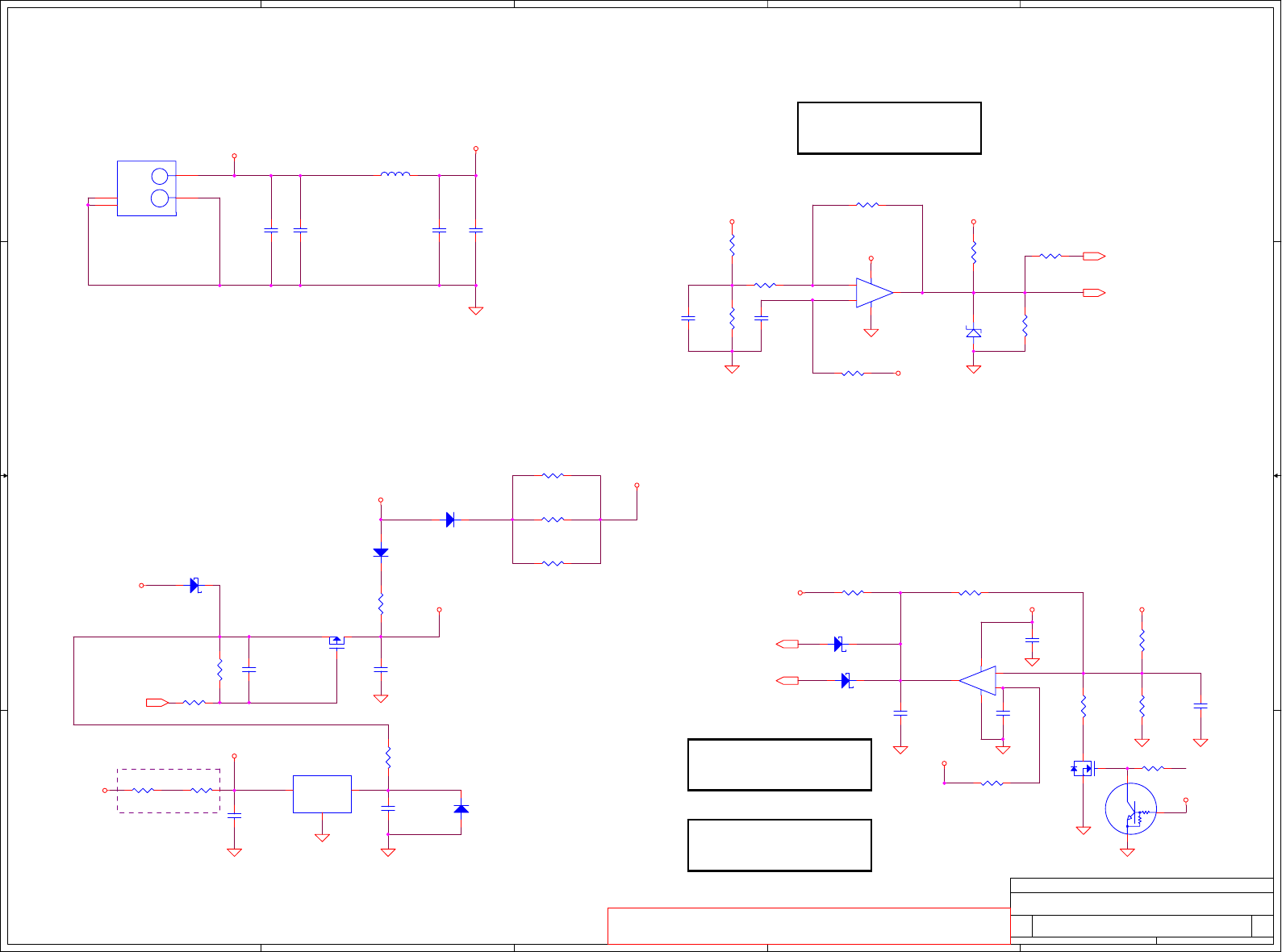

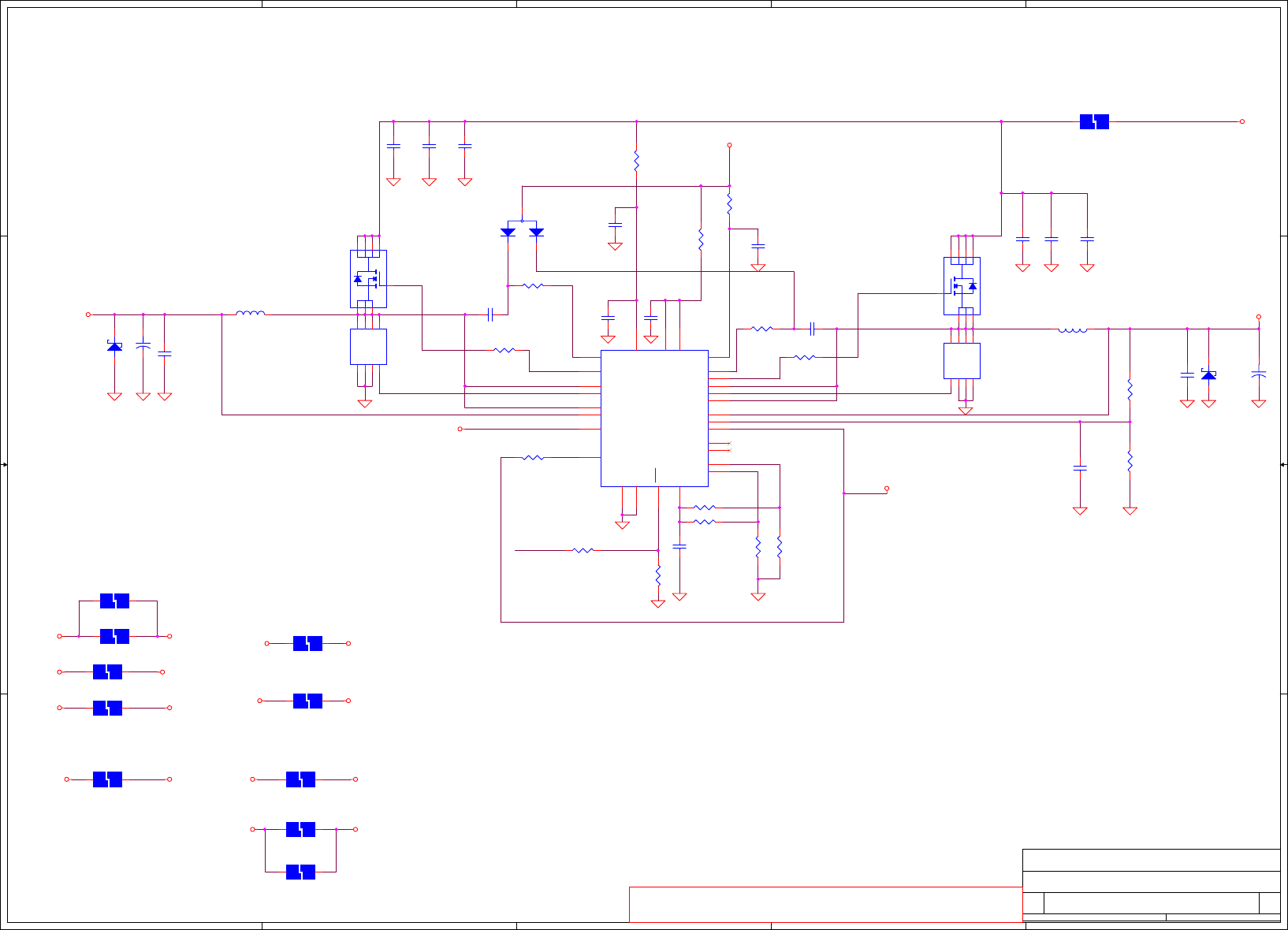

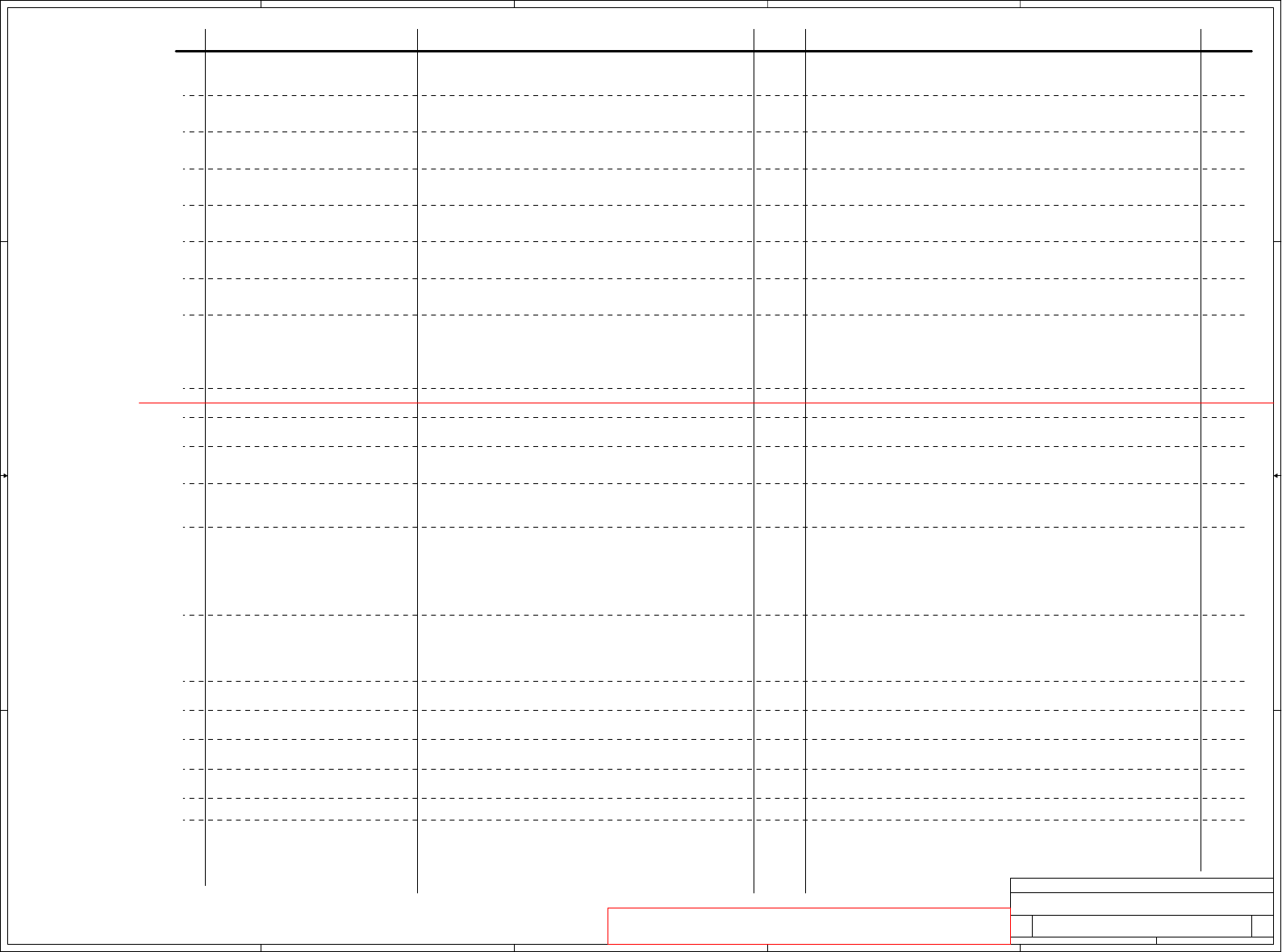

Block Diagram

265, 07, 2004

星期三 七月

Compal Electronics, Inc.

page 7

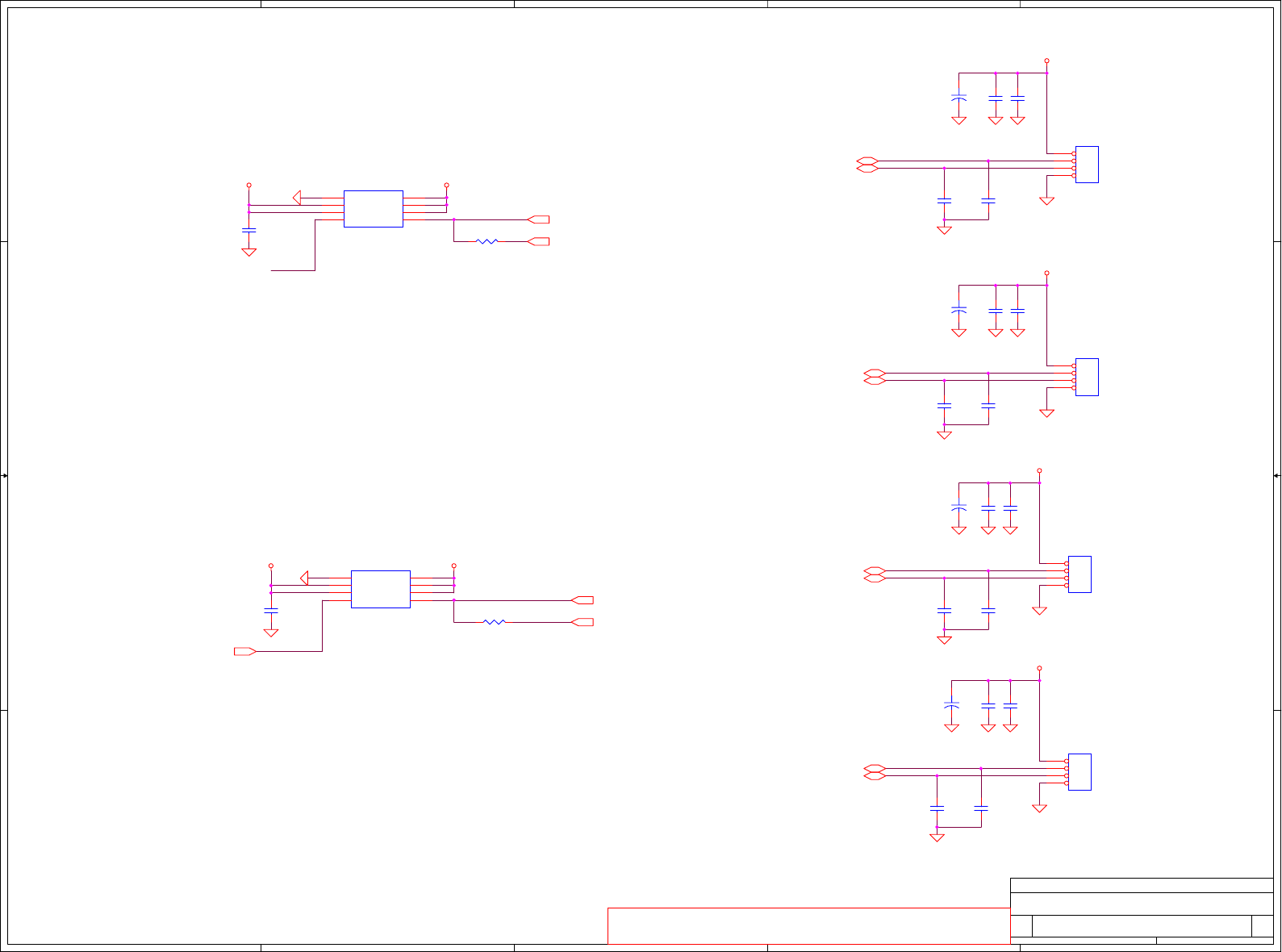

MDC & BT Conn

EC I/O Buffer

page 25

VGA DDR x2 CHB

page 38

page 41

HDD

Connector

page 31

Thermal Sensor

ADM1032AR

page 42

AC-LINK

page 43

LCD Conn

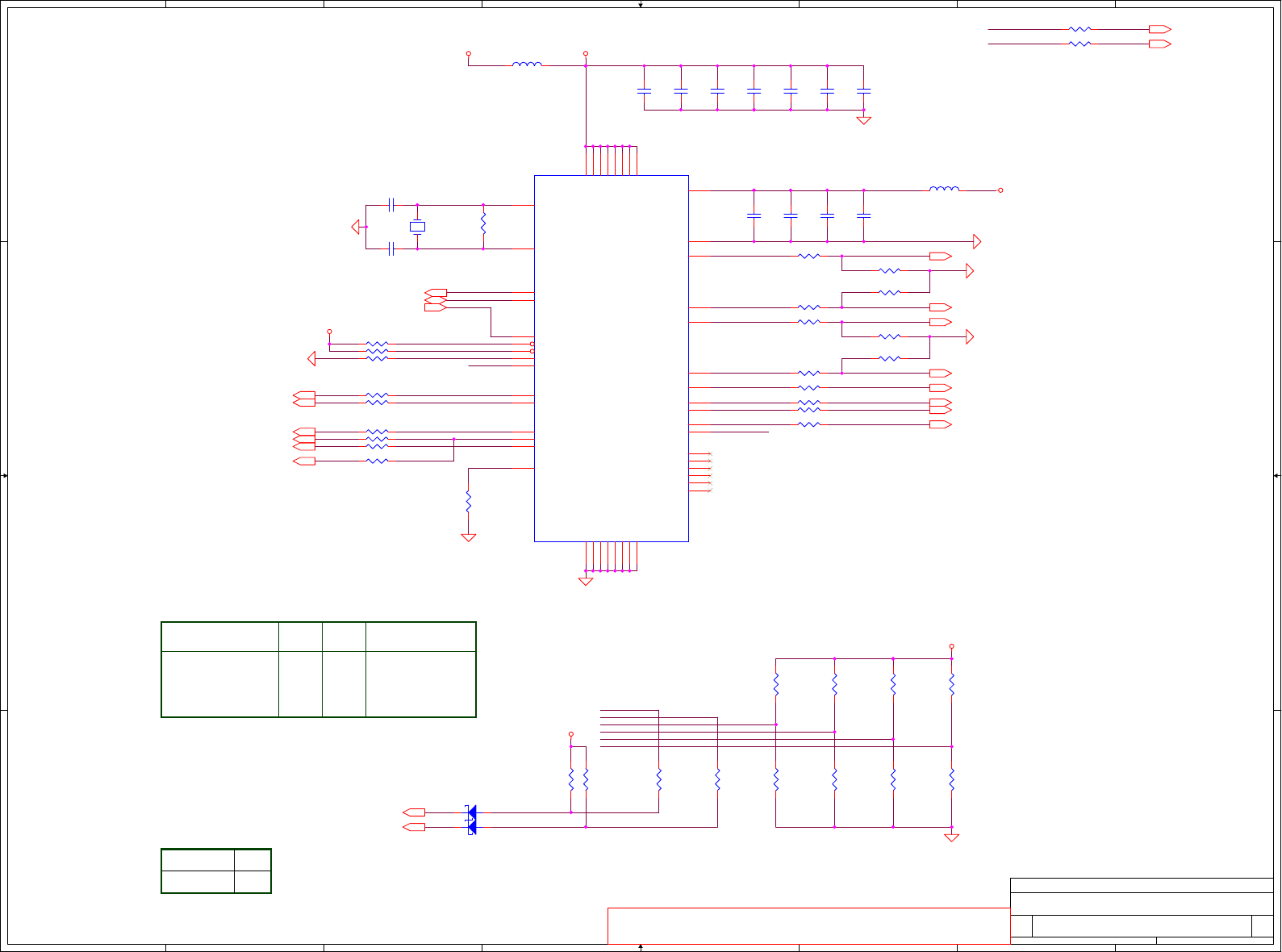

ATI-RC300M

SUPER I/O SMC 207

DC/DC Interface CKT.

page 25

page 45

CABLE CONN.

page 14,15,16

page 47

page 4,5,6

Audio Codec

ATI-M9+X/M10C

page 40

page 26,27,28,29

CDROM

Connector

IDSEL:AD20

(PIRQA,B#,GNT#2,REQ#2)

page 36

BGA 457 pin

page 44

CardBus Controller

868 pin u-BGA

Secondary IDE

ENE910

IDSEL:AD19

(PIRQD#,GNT#1,REQ#1)

page 41page 34

VGA DDR x2 CHA

IDSEL:AD18

(PIRQC#,GNT#3,REQ#3)

ALC 250

Primary IDE

Touch Pad

Mini PCI

socket

IEEE 1394

TI-TSB43AB22

Compal confidential

AGP BUS

page 30

USB2.0

page 33

page 50,51,52,53,54,55,56,57

page 33

page 43

ATI-SB200

H_A#(3..31)

PCI BUS

RTC CKT.

page 23

RJ45 CONN

LAN

Int.KBD

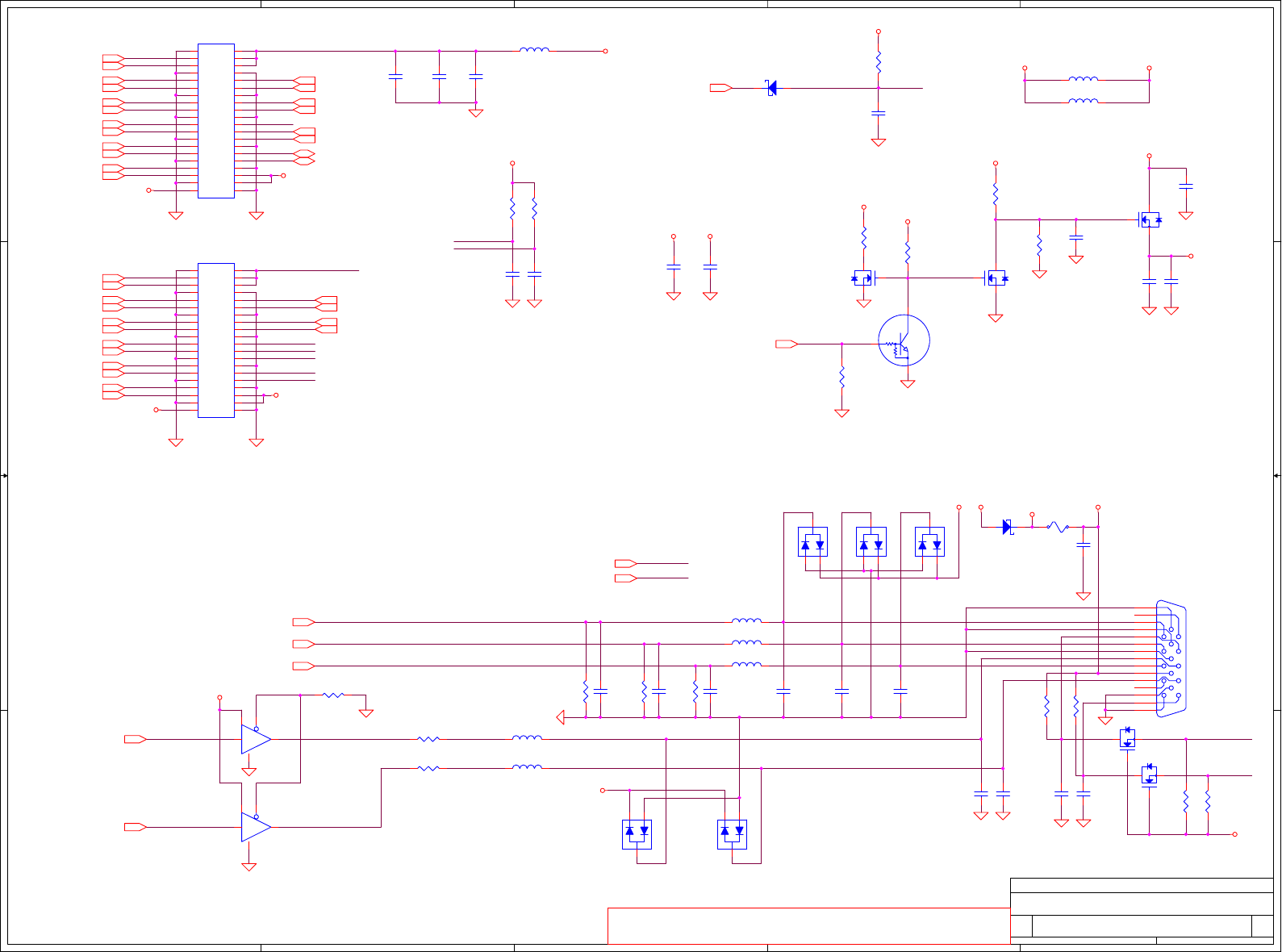

Power Circuit DC/DC

uFCBGA-479/uFCPGA-478 CPU

H_D#(0..63)

page 22

page 26

ATA-100

page 45

RJ11 CONN

IDSEL:AD16

(PIRQA#,GNT#0,REQ#0)

2.5V DDR- 200/266

BIOS

USB conn x4

A-Link

page 37

Power OK CKT.

ATA-100

page 7

PSB

Intel Northwood/Prescott Processor

page 41

page 46

Fan Control

page 42

Mini-PCI solt

LPC BUS

AMP & Audio Jack

RTL 81000CL

page 32

File Name :LA2411

W/EXT VGA CHIP

page 46

800MHz

DDR-SO-DIMM X2

Slot 0

page 17,18,19,20,21

3.3V 33 MHz

page 35

W/EXT VGA CHIP

Power On/Off CKT.

BANK 0, 1, 2, 3

Memory BUS(DDR)

FIR

W/O EXT VGA CHIP

page 8,9,10,11,12,13

CRT & TV-OUT Conn.

ENE 714/1410

VGA M9 Embeded

W/O EXT VGA CHIP

*RJ45 CONN

*LINE IN JACK

*DC JACK

*COM PORT

*USB CONN x1

*SPDIF

*5V INPUT

*VOLUME ADJUSTMENT KEY

+TV-OUT PORT

page 30

Card slot

BT

USB1.1

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

CLOCK GENERATOR

ICS951402AGT

page 24

page 32

page 42

A

A

1 1

Title

Size Document Number Rev

Date: Sheet of

LA-2411

0.1

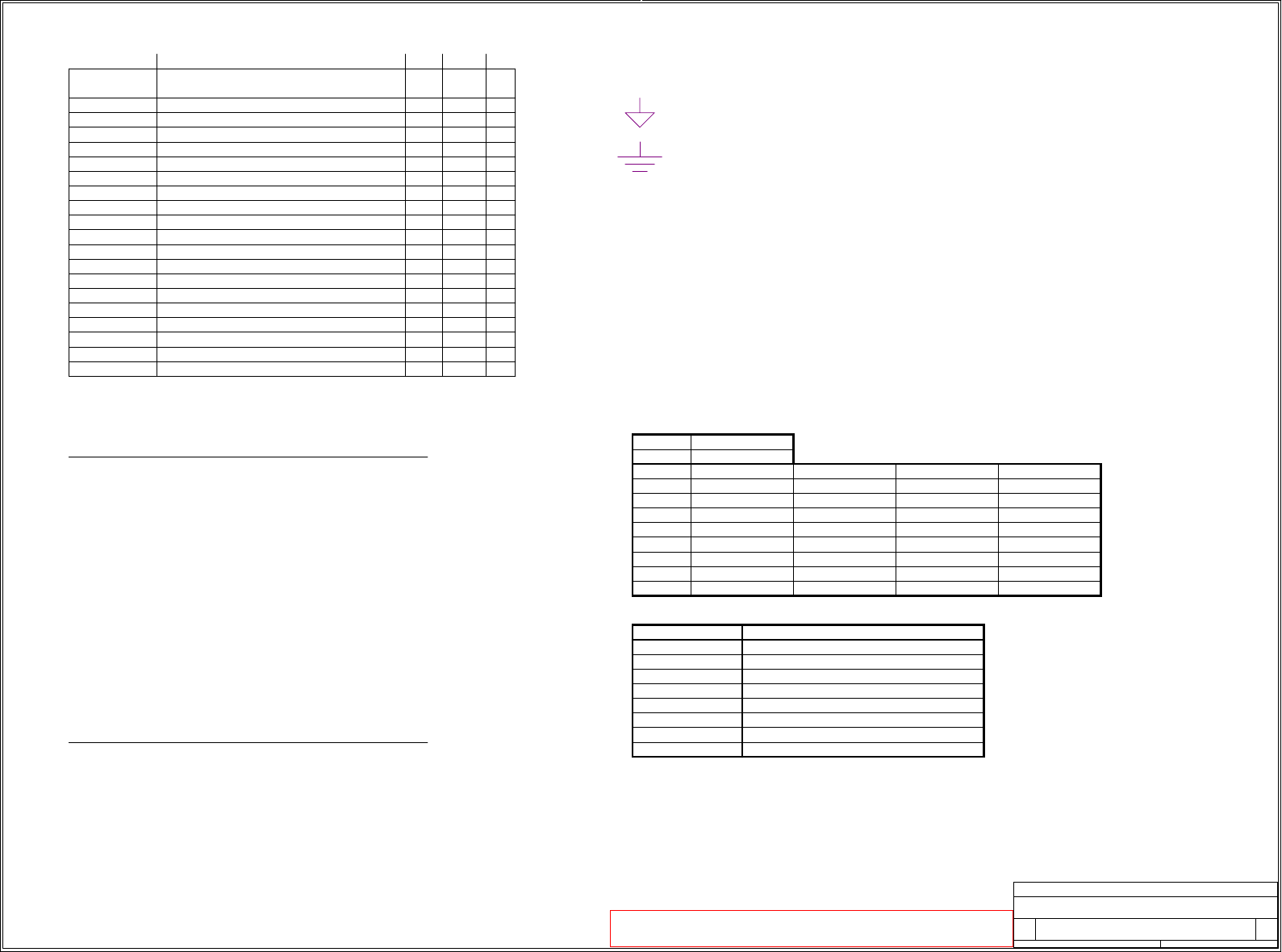

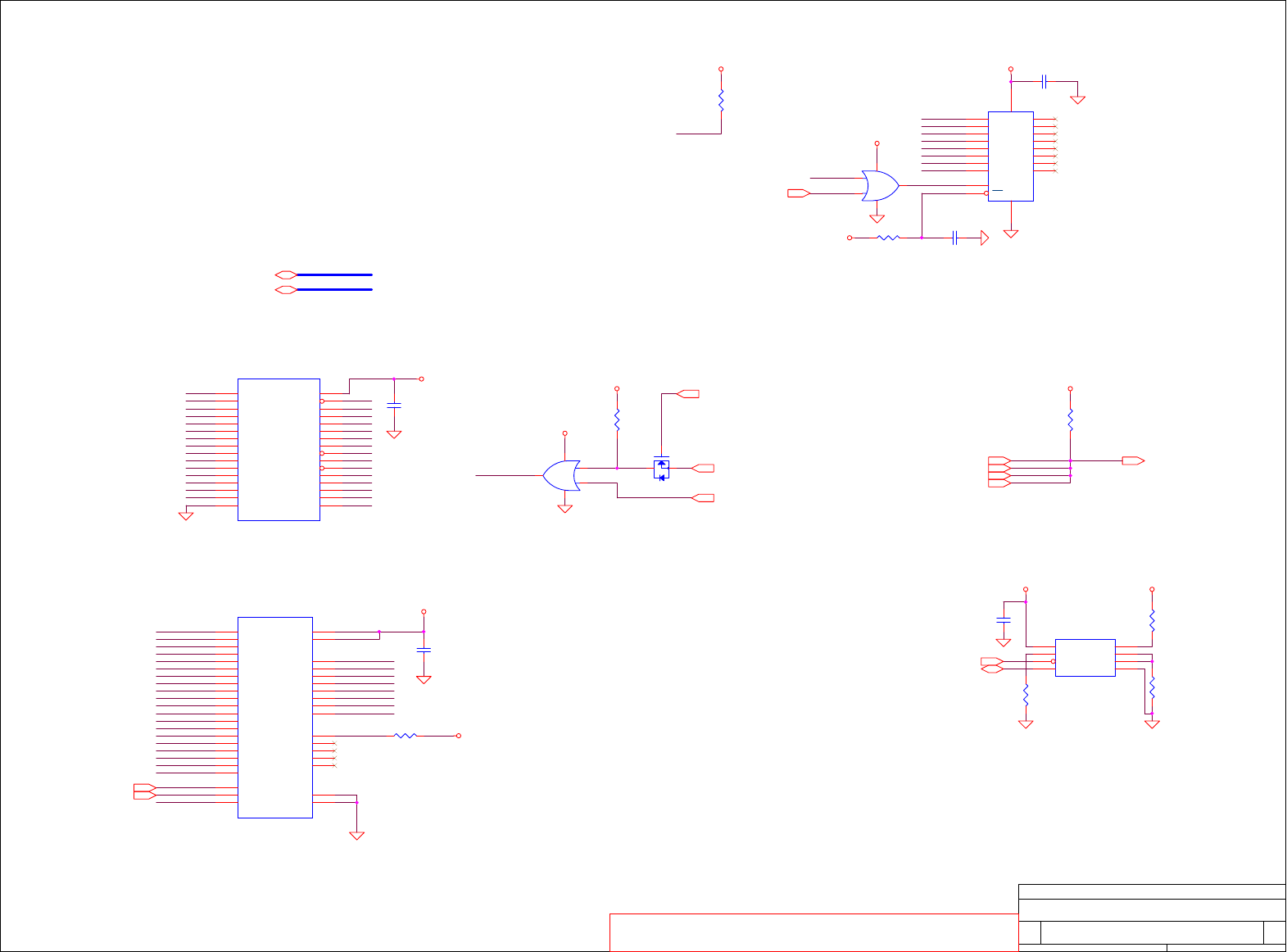

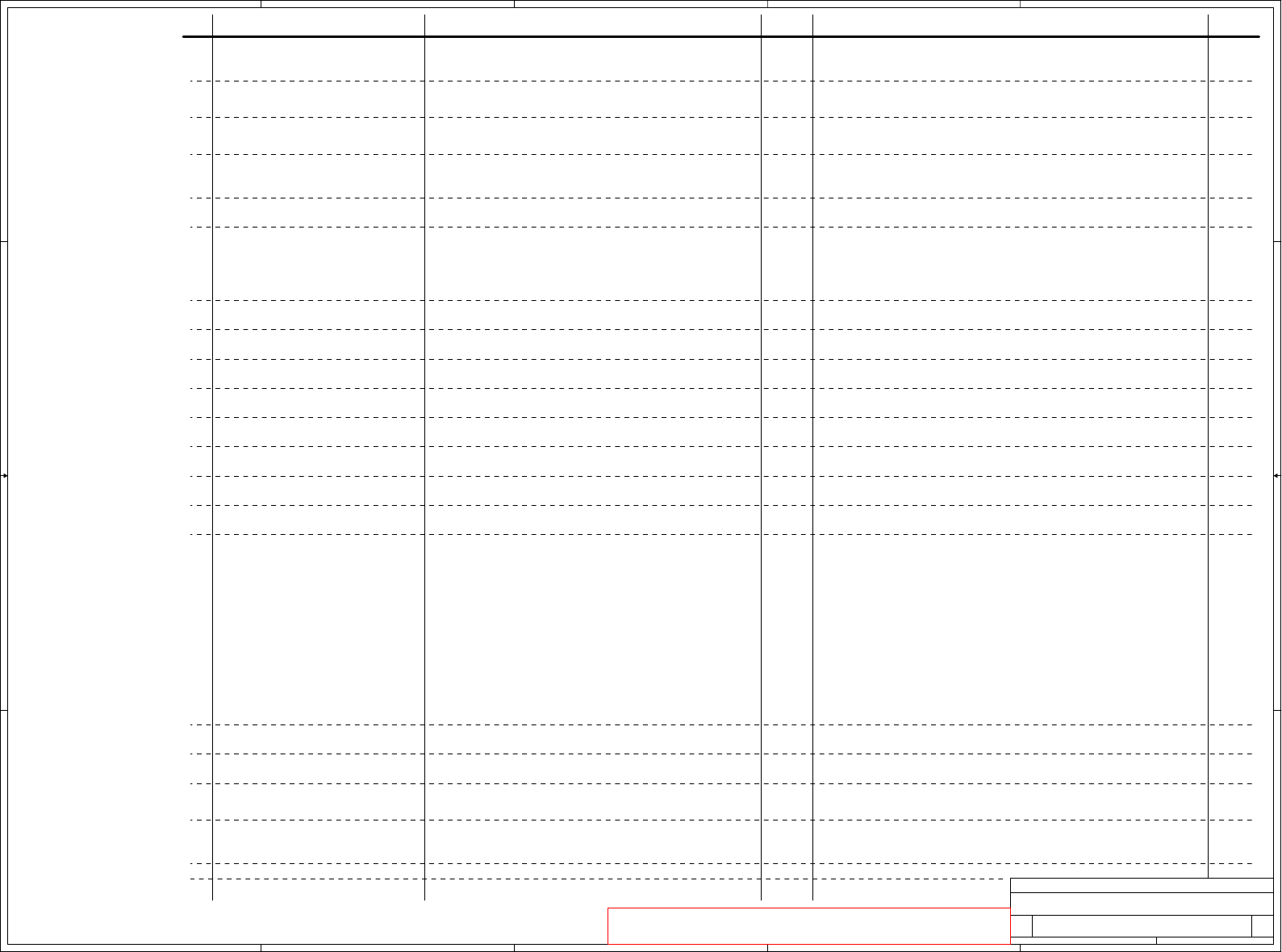

Notes List

365, 07, 2004

星期三 七月

Compal Electronics, Inc.

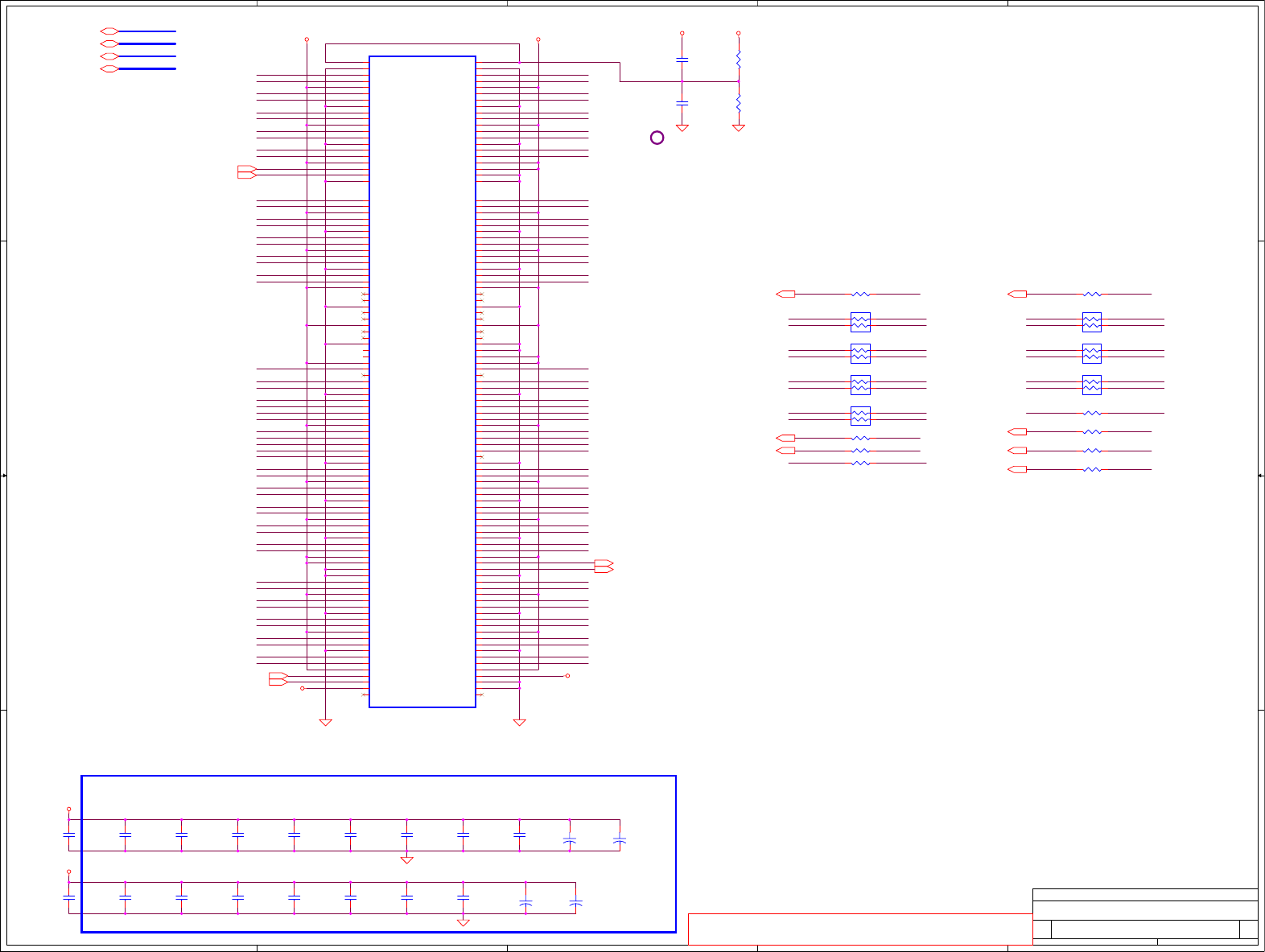

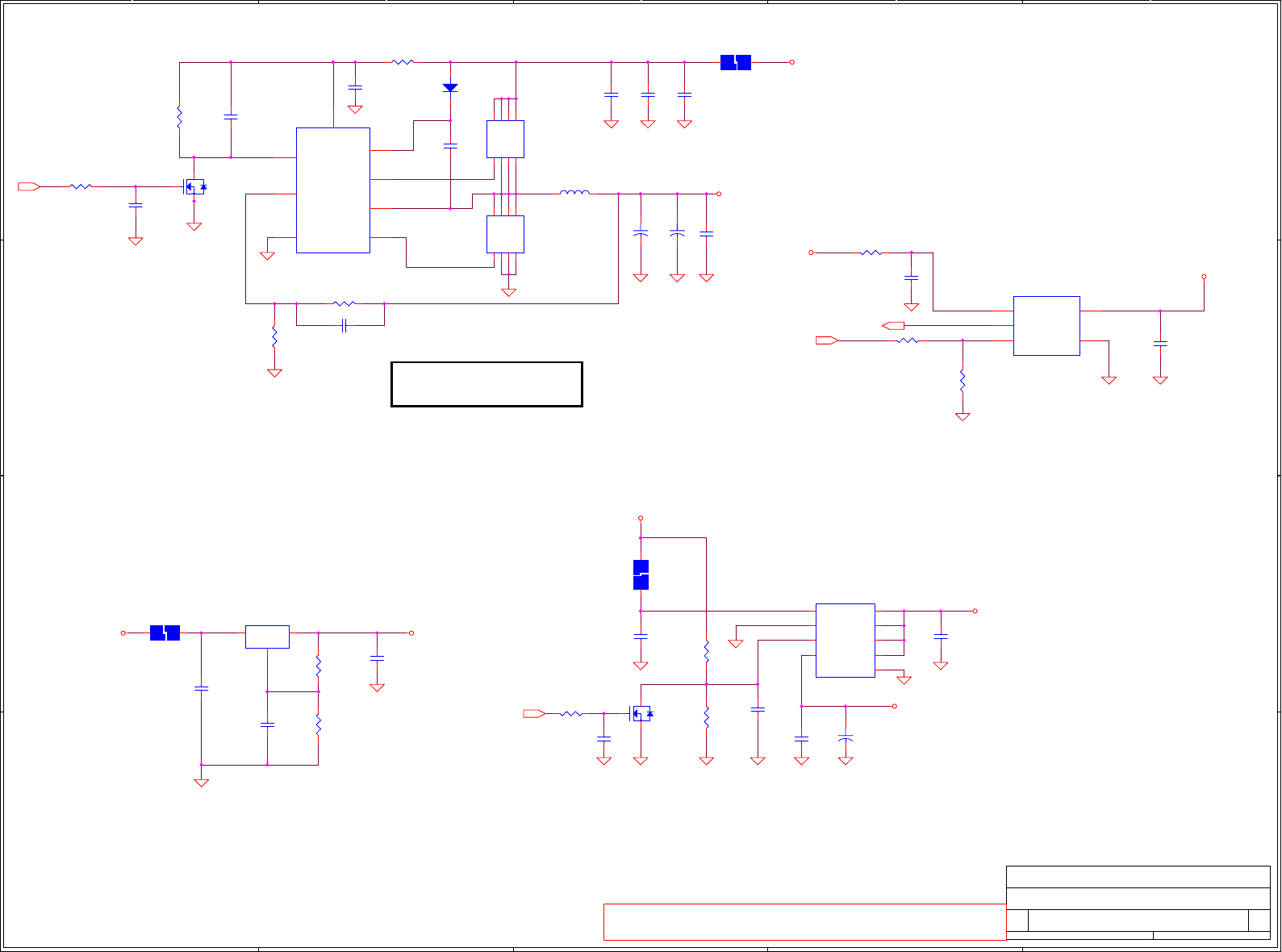

External PCI Devices

Voltage Rails

IDSEL # PIRQ

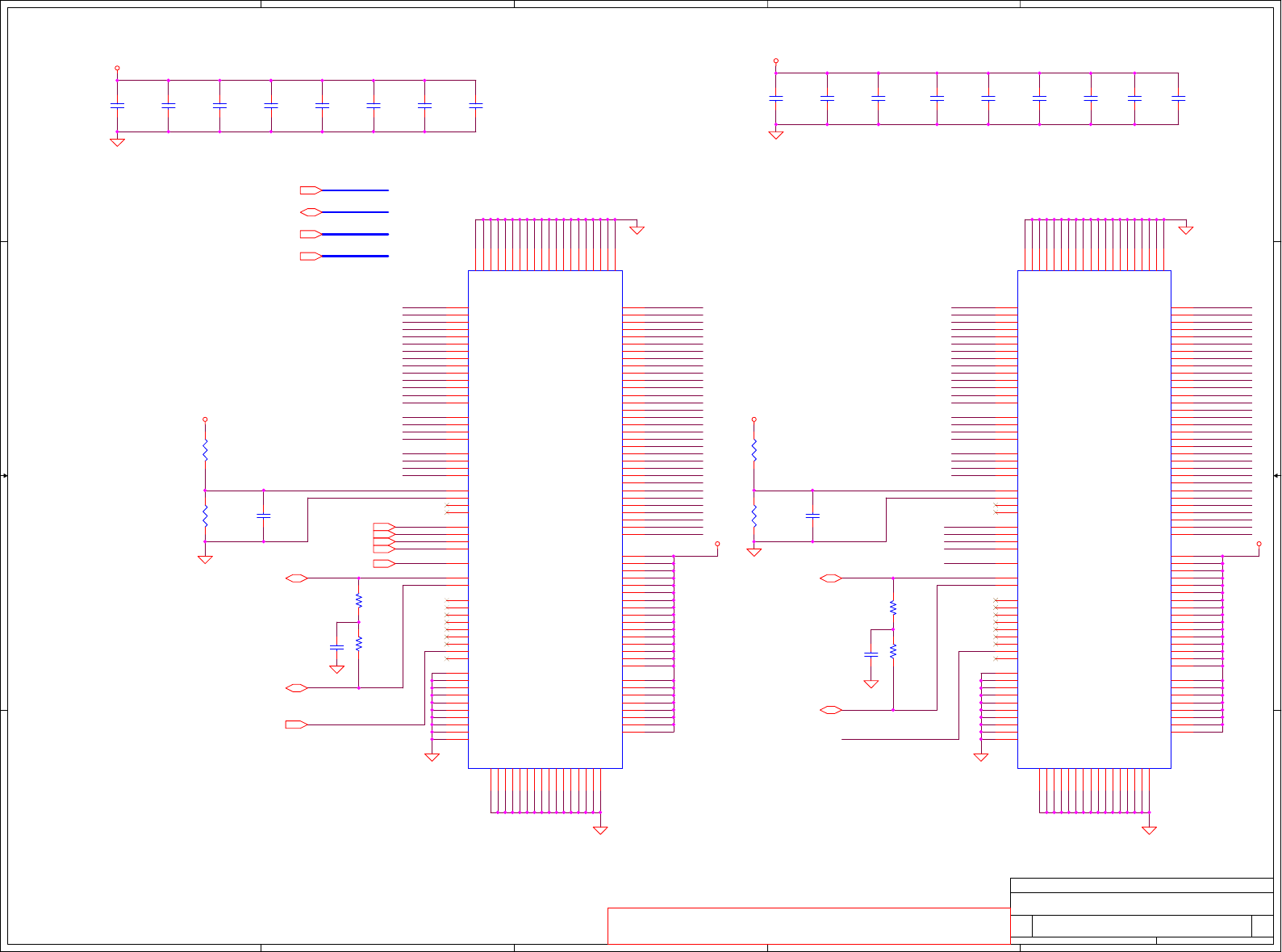

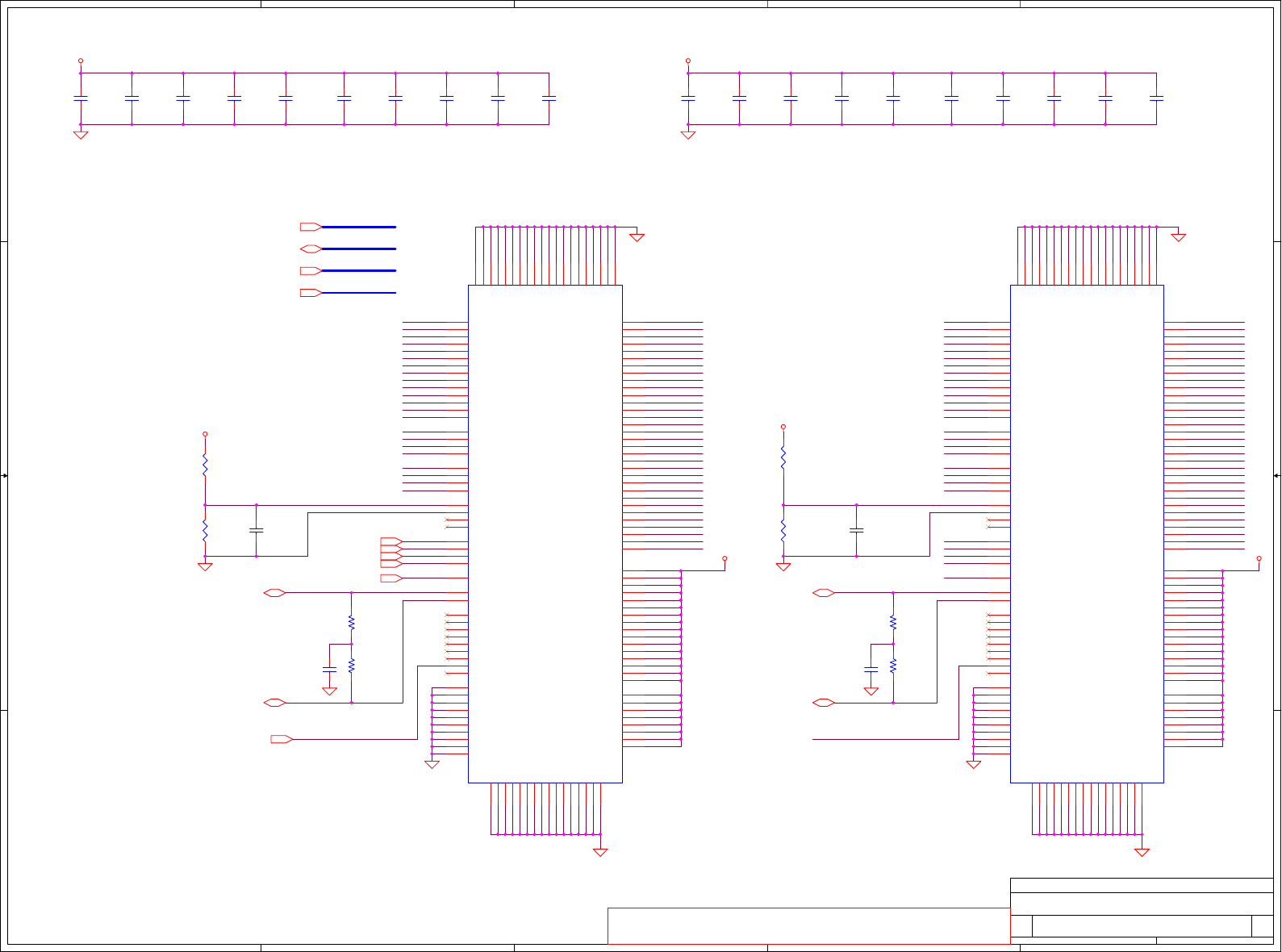

DDR SO-DIMM 0

REQ/GNT #DEVICE

NB Internal VGA

1 0 1 0 0 0 0 XA0

AGP BUS

SOUTHBRIDGE

USB

AC97

ATA 100

ETHERNET

1394

LAN

CARD BUS

Wireless LAN(MINI PCI)

N/A

AGP_DEVSEL

AD31 (INT.)

AD30 (INT.)

AD31 (INT.)

AD31 (INT.)

AD24(INT.)

AD16

AD19

AD20

AD18 2

N/A

3

0

1

N/A

N/A

N/A

N/A

N/A

N/A

N/A

A

A

D

B

C

A

A

A.B

C

D

I2C / SMBUS ADDRESSING

DEVICE HEX ADDRESS

DDR SO-DIMM 1

CLOCK GENERATOR (EXT.) A2

D2 1 0 1 0 0 0 1 X

1 1 0 1 0 0 1 X

Power Plane

B+

+1.25VS

Description

VIN

+VCC_CORE Core voltage for CPU

AC or battery power rail for power circuit.

1.25V switched power rail for DDR Vtt

The voltage for Processor VID select

Adapter power supply (19V)

+VCCVID

ON

N/A

N/A

S3

OFF

ON

S5

OFF

N/A

OFF

N/A

N/A

ON

N/A

OFF

OFF OFF

S0-S1

Symbol Note :

: means Digital Ground

: means Analog Ground

@ : means just reserve , no build

NAGP@ : means just build when no external AGP VGA chip build in (UMA).

OFF

OFF

ON

2.5V switched power rail

+3VS OFF

ON*

+2.5VS

3.3V switched power rail

ONON

2.5V system power rail for DDR

ON*

ON

OFF

+2.5VALW

+2.5V

ON

1.5V I/O power rail for ATI-RS300M/RC300M NB AGP.

OFF

2.5V always on power rail

+3VALW

ON

ON

OFF

ON

OFF

+1.5VS

3.3V always on power rail

+1.8VS

ON

1.8V switched power rail for ATI-RS300M/RC300M NB.

OFF

OFF

OFF

ON

ON

+1.2VS_VGA 1.2V I/O power rail for ATI-VGA M9+X/M10P. ON OFFOFF

12V always on power rail

+5VS

ON

ON

ON

OFF

ON

ON

ON

+12VALW

5V switched power rail OFF

RTC power

ON*

Note : ON* means that this power plane is ON only with AC power available, otherwise it is OFF.

ON

RTCVCC ON

ON*+5VALW 5V always on power rail

+3V 3.3V system power rail for SB,LAN,CardReader and HUB.

ON

ON

OFF

+5V 5V system power rail .

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

ON ON OFF

M10@ : means build VGA M10

M9@ : means build VGA M9+X

M9-M10@ : means build VGA M9 or M10

1520@ : means build Cardbus PCI1520

1620@ : means build Cardbus PCI1620

ATI@ : means build ATI SB USB2.0 related to turn on the function .

NEC@ : means build NEC USB2.0 related to turn on the function .

7

PCB Revision

0.1

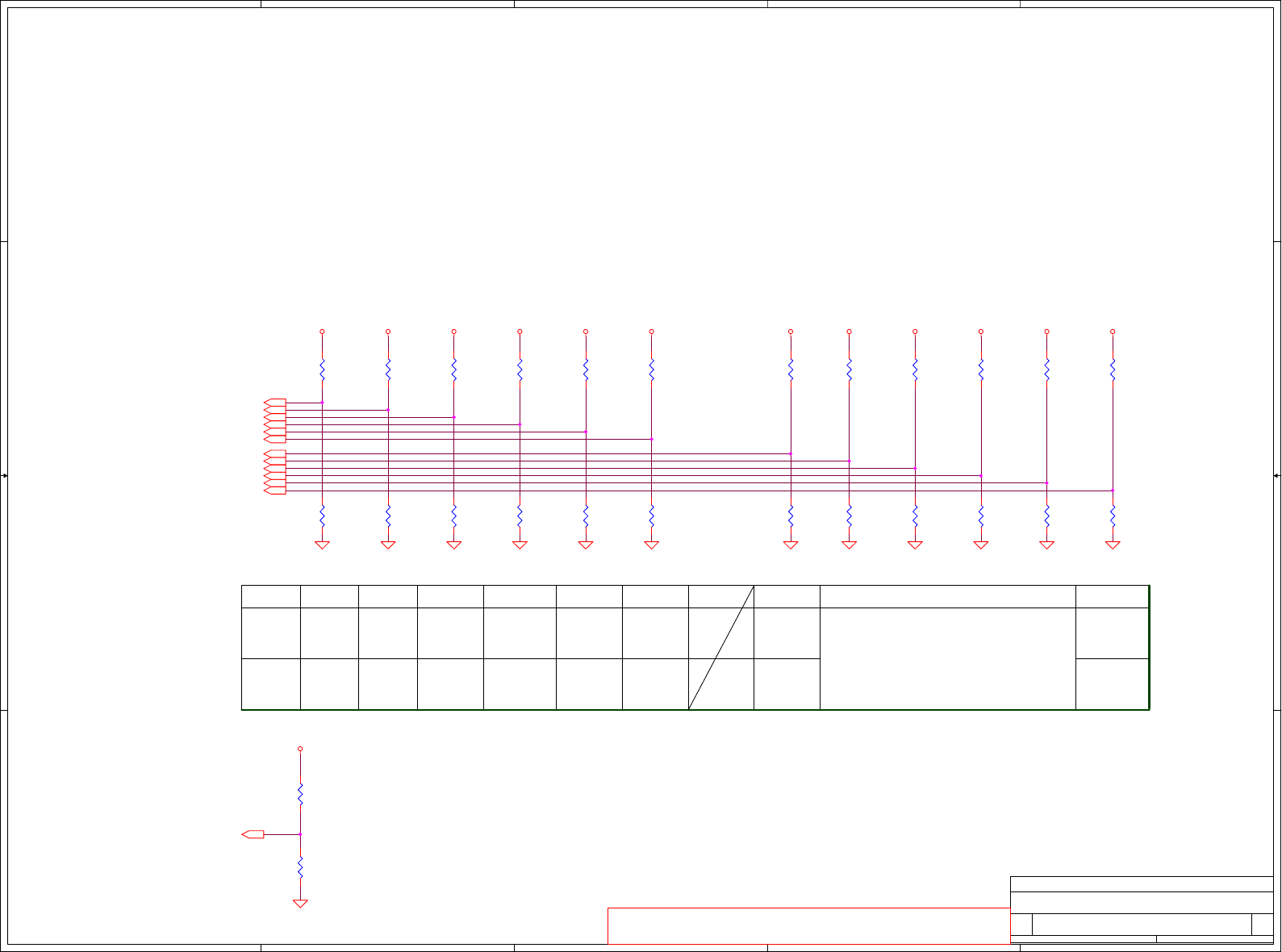

Board ID Table for AD channel

Vcc 3.3V +/- 5%

100K +/- 5%Ra

Board ID

Rb V min

0

1

2

3

0

8.2K +/- 5%

0 V

0.216 V 0.250 V 0.289 V

0.436 V

0.712 V

0.503 V

0.819 V

0.538 V

0.875 V

AD_BID

Vtyp

AD_BID

V

AD_BID

max

18K +/- 5%

33K +/- 5%

56K +/- 5%

100K +/- 5%

200K +/- 5%

3.300 V

0 V 0 V

4

5

6

7NC

1.036 V

1.453 V 1.650 V 1.759 V

1.935 V

2.500 V

2.200 V

3.300 V

2.341 V

1.185 V 1.264 V

Board ID

0

1

2

3

4

5

6

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

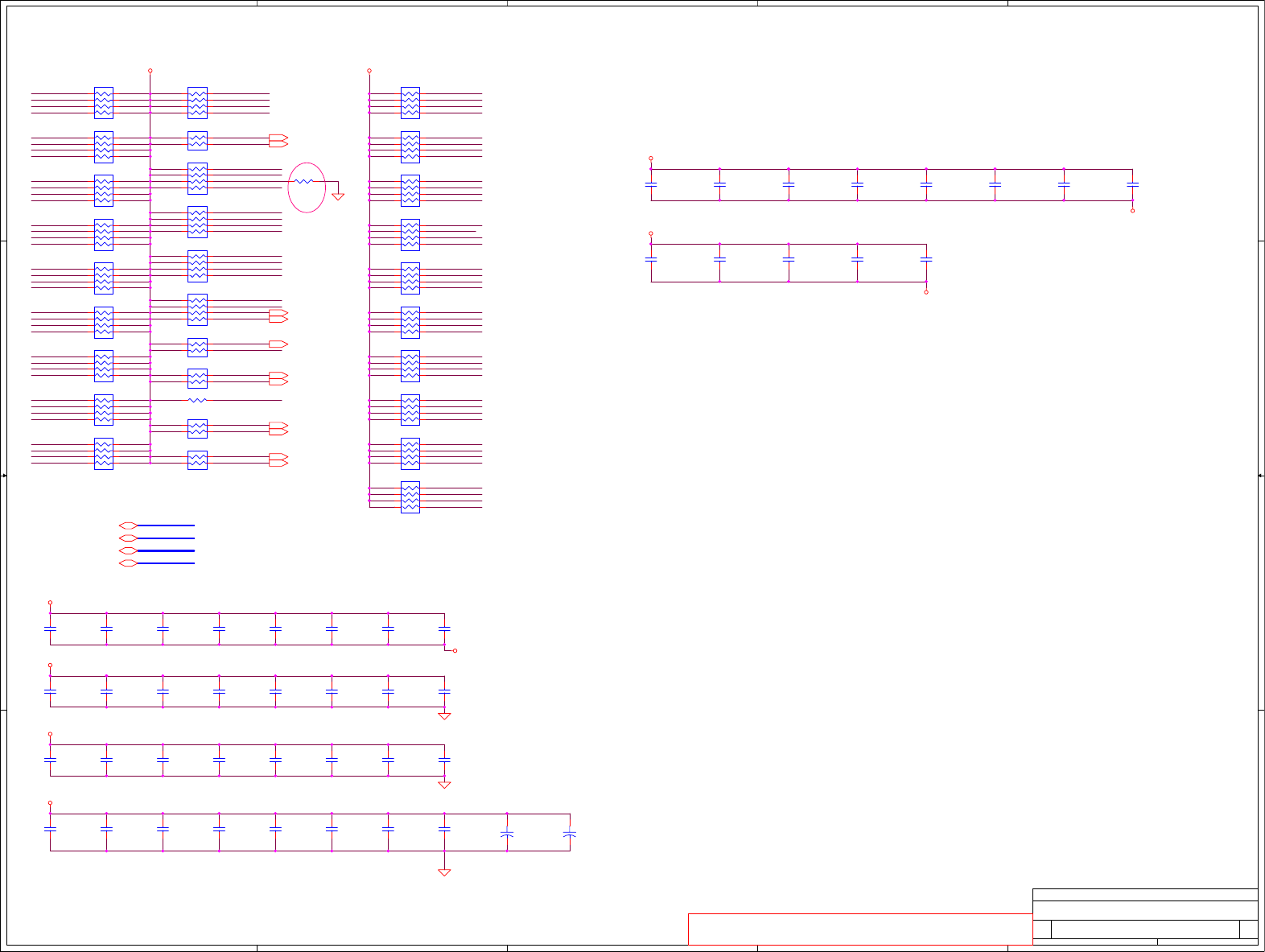

CK_BCLK#

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#31

H_A#29

H_A#30

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_IERR#

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

CK_BCLK

H_D#[0..63] <8>H_A#[3..31]<8>

H_REQ#[0..4]<8>

H_ADS#<8>

H_BR0#<8>

H_LOCK#<8>

CK_BCLK<24>CK_BCLK#<24>

H_HIT#<8>

H_HITM#<8>

H_DEFER#<8>

H_BOOTSELECT <54>

H_BNR#<8> H_BPRI#<8>

+VCC_CORE

+VCC_CORE

+VCC_CORE

+VCC_CORE

+5VS+5VS

Title

Size Document Number Re v

Date: Sheet of

LA-2411

0.1

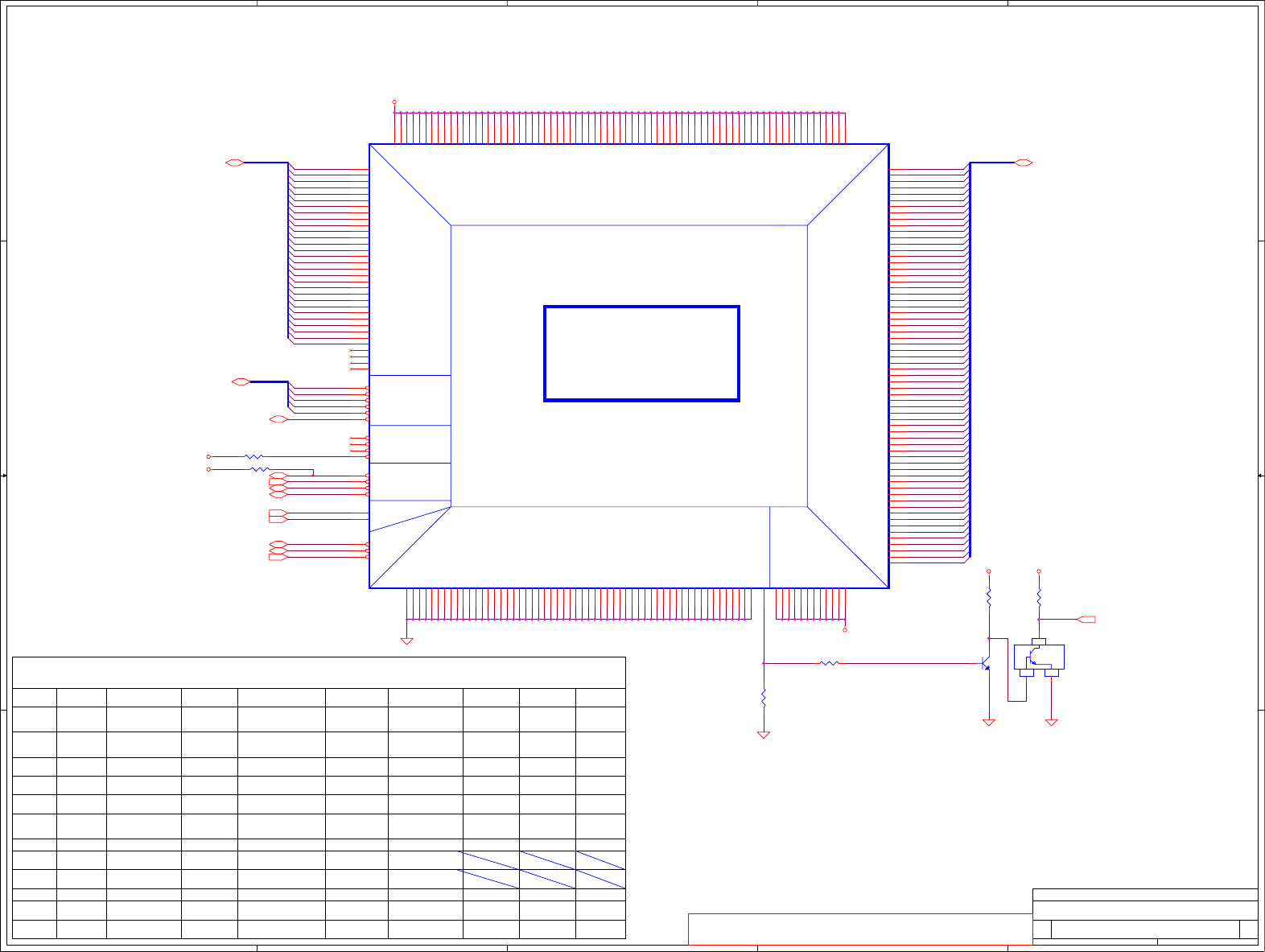

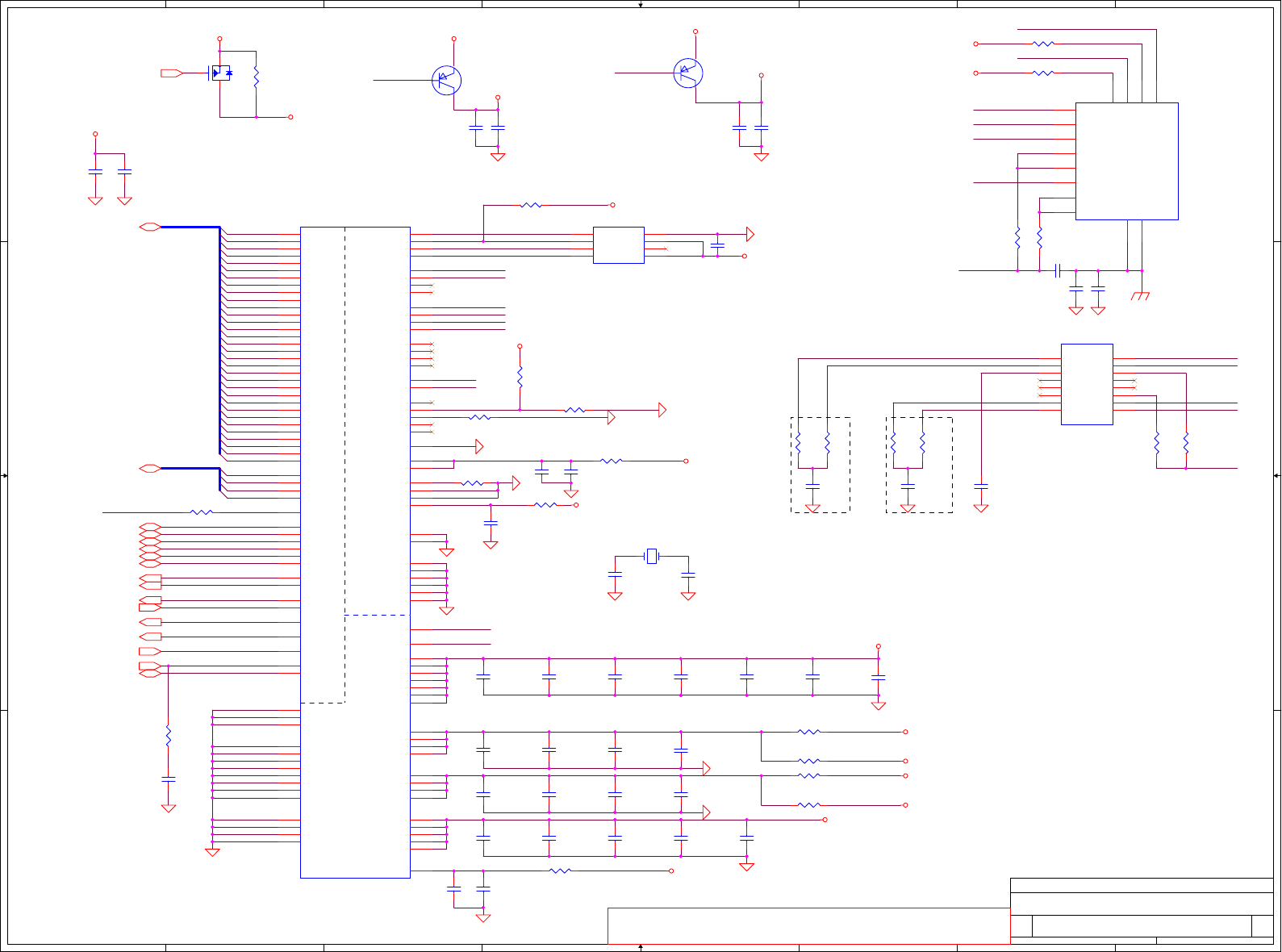

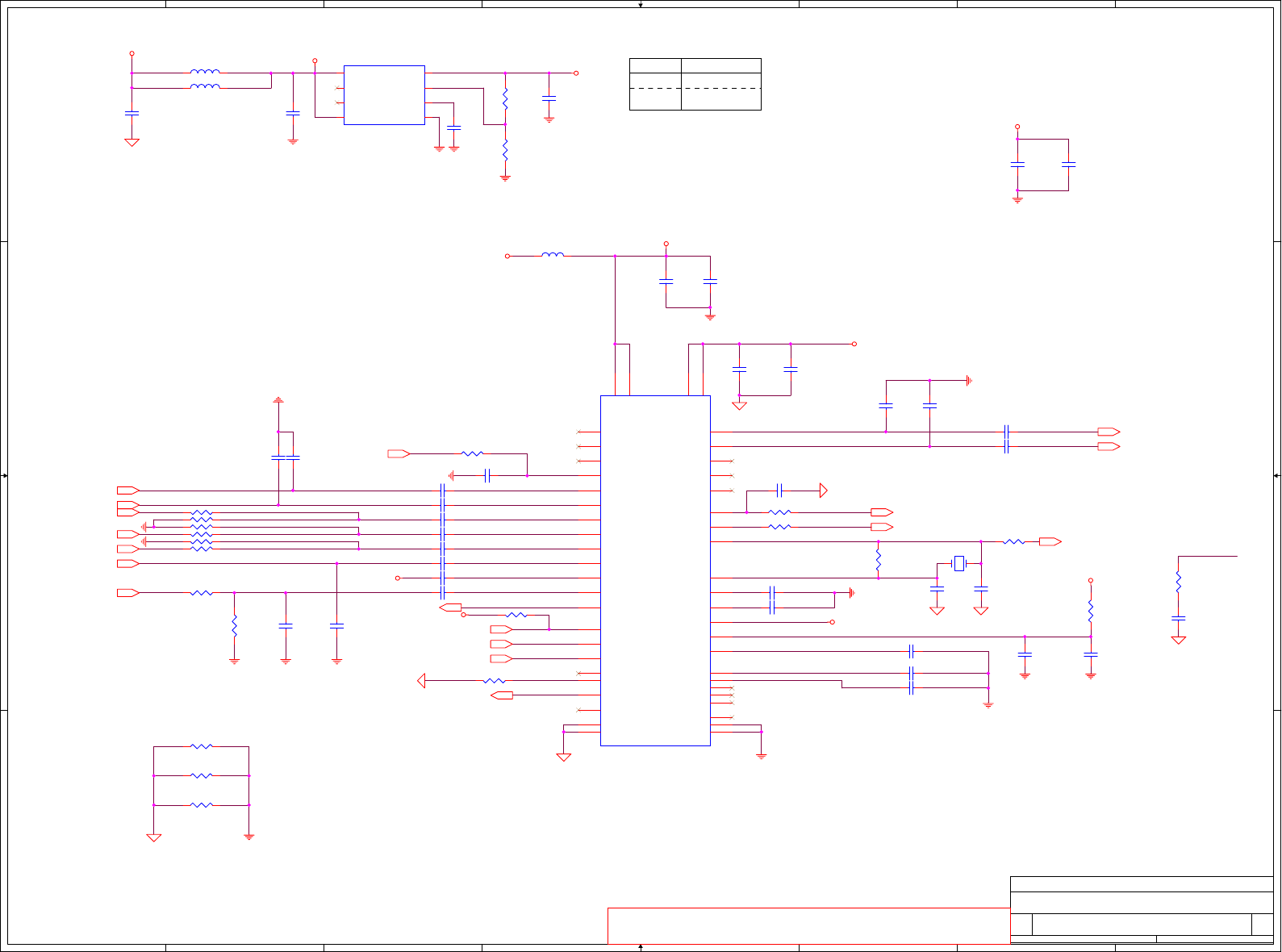

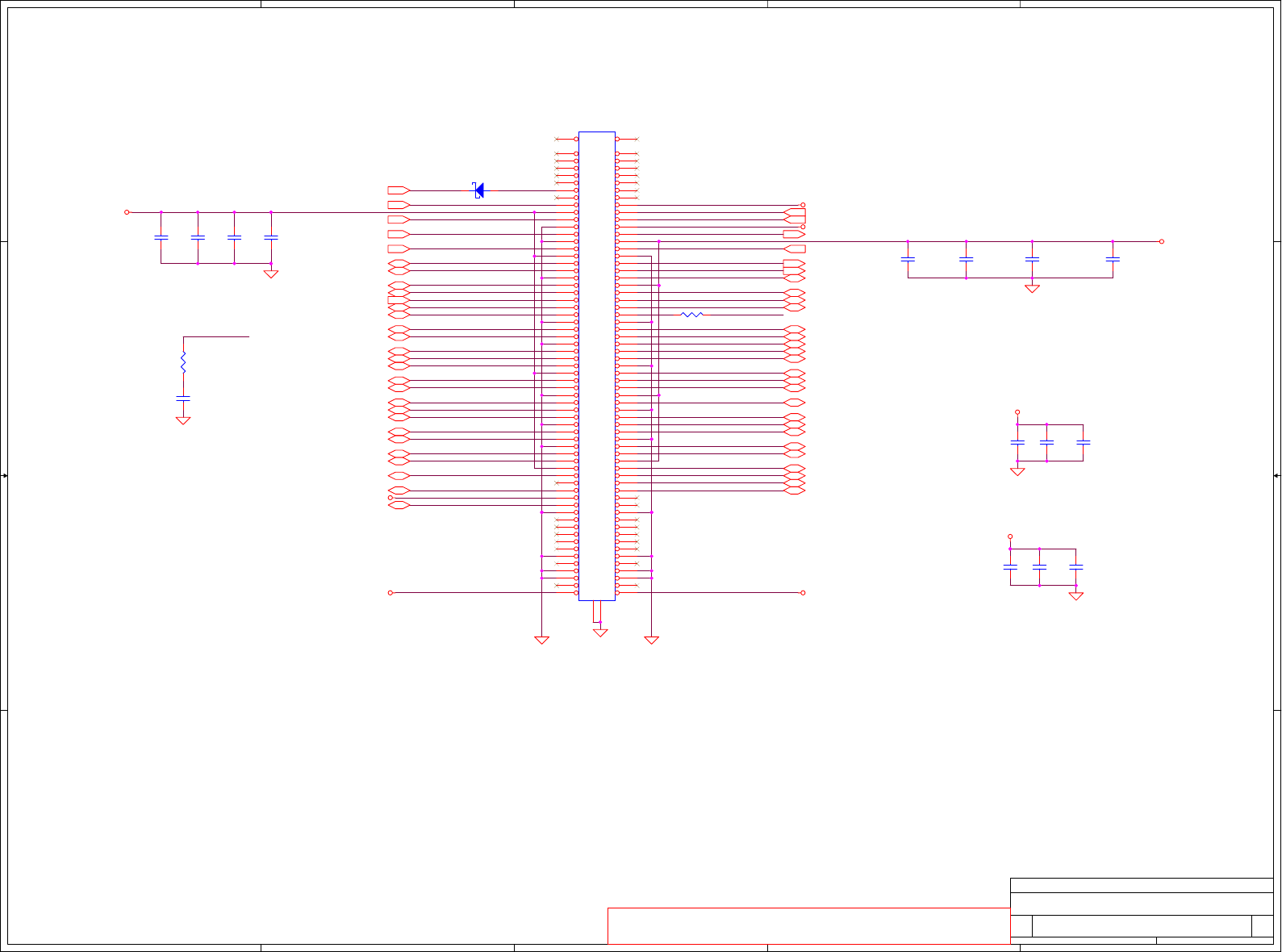

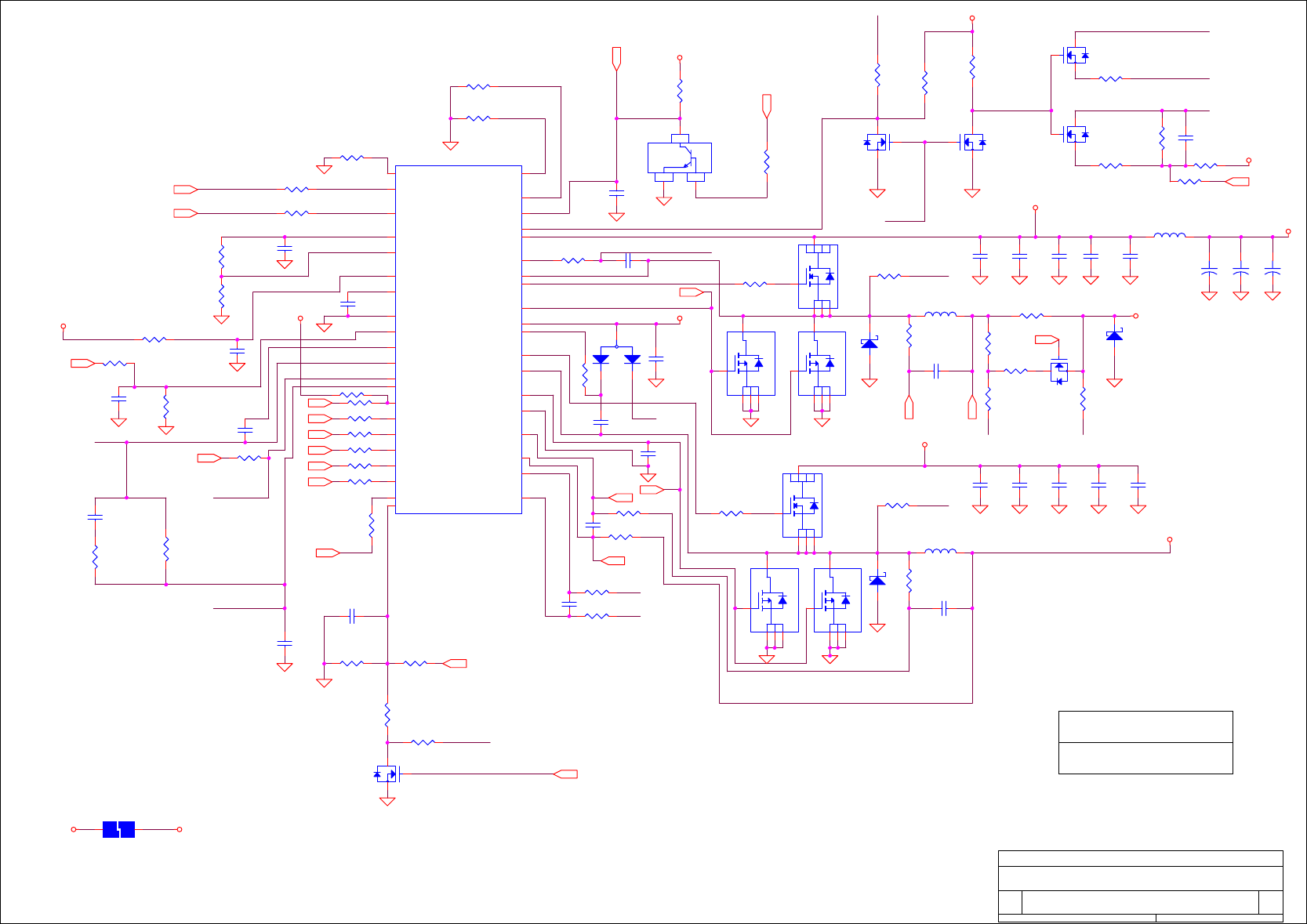

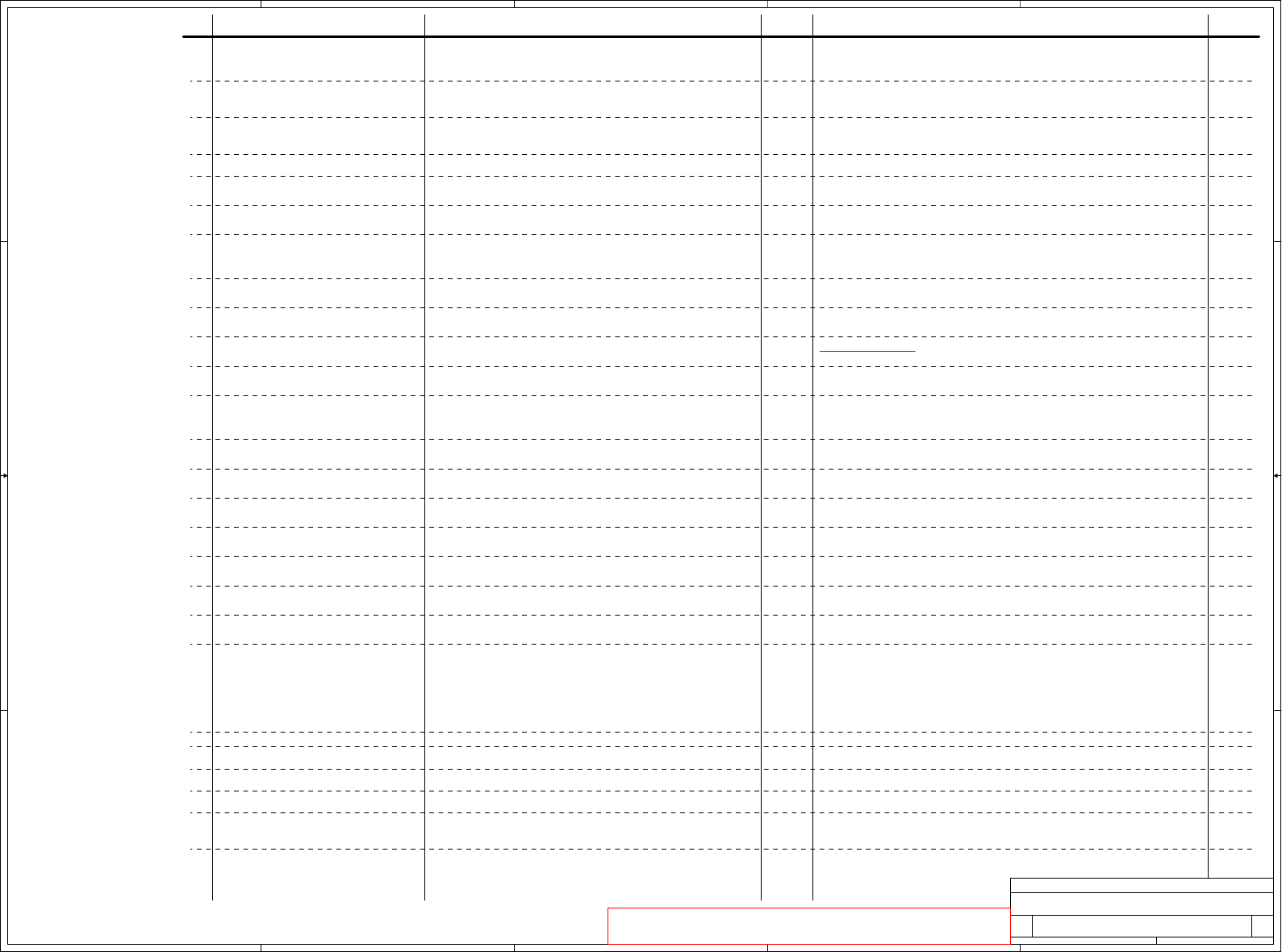

Prescott Processor in uFCPGA478

465, 07

星期三 七月

, 2004

Compal Electronics, Inc.

Pull-up56ohm

to +VCC_CORE

Pull-up 56ohm

to +VCC_CORE

Pull-up 62ohm

to +VCC_CORE

Prescott

B6 FERR# FERR#/PBE# Pull-up 62ohm

to +VCC_CORE

Pull-up 62ohm

to +VCC_CORE

Reference Intel document

Desktop P4 Spec.: 10988 P4 0.13u 512KB L2 EMTS Rev.2.0

Desktop Prescott Spec.: 11910 Prescott EMTS Rev.0.5

Pin number Northwood

Pin name Prescott

Pin name

Commend Commend

AA20 ITPCLKOUT0 Pull-up56ohm

to +VCC_CORE TESTHI6 Pull-up 62ohm

to +VCC_CORE

Pop

Pop

Pop

Pop

Pop

PopDepop

Pop

Pop

Depop

DepopPop

Pop

Northwood

Pop

Depop

Depop

AB22 ITPCLKOUT1 Pull-up 56ohm

to +VCC_CORE TESTHI7 Pull-up 62ohm

to +VCC_CORE

AD2 NC VIDPWRGD Pull-up 2.43K ohm

to +VCCVID

float

AD3 NC float VID5 Pull-up1Kohm to

+3VRUN & connect

to PWRIC

AF3 NC float VCCVIDLB Connect to +VCCVID

Northwood

MT

Northwood MT

Pin name

AD20

VCCA VCCIOPLLConnect to CPU

Filter

FERR#

ITPCLKOUT0

ITPCLKOUT1

Connect to CPU

Filter

AE23

Connect to CPU

Filter Connect to CPU

Filter

NC

NC

NC

VCCA

VSS

VCCIOPLL VCCA

AD1 VSS BOOTSELECT

VCCIOPLL

VSS

Connect to GND CPU determine

AE26 VSS Connect to GND OPTIMIZED/

COMPAT#

Commend

float

Pop

Pop

Pop

TESTHI12 TESTHI12AD25 DPSLP

Connect to CPU

Filter

Connect to CPU

Filter

Connect to GND

Connect to GND

Pop

Pop

float

float

float

Depop

Depop

Depop

Pull-up 62ohm

to +VCC_CORE Pop

Pull-up 200ohm

to +VCC_CORE Connect to PLD

through 0ohm Pop Pop

A6 TESTHI11 GHIPull-up 200ohm

to +VCC_CORE

Pull-up 62ohm

to +VCC_CORE Connect to PLD

CPUPREF through

0ohm PopPop Pop

TESTHI11

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

R230

51_0402_5%

1 2

R900

100K_0402_5%

12

R1099

47K_0402_5%

12

R1100

47K_0402_5%

12

R899 22K_0402_5%

1 2

Prescott

JP8A

AMP_3-1565030-1_Prescott

A#3

K2

A#4

K4

A#5

L6

A#6

K1

A#7

L3

A#8

M6

A#9

L2

A#10

M3

A#11

M4

A#12

N1

A#13

M1

A#14

N2

A#15

N4

A#16

N5

A#17

T1

A#18

R2

A#19

P3

A#20

P4

A#21

R3

A#22

T2

A#23

U1

A#24

P6

A#25

U3

A#26

T4

A#27

V2

A#28

R6

A#29

W1

A#30

T5

A#31

U4

A#32

V3

A#33

W2

A#34

Y1

A#35

AB1

REQ#0

J1

REQ#1

K5

REQ#2

J4

REQ#3

J3

REQ#4

H3

ADS#

G1

AP#0

AC1

AP#1

V5

BINIT#

AA3

IERR#

AC3

BNR#

G2 BPRI#

D2 BR0#

H6

LOCK#

G4

DEFER#

E2 HITM#

E3 HIT#

F3

D#0 B21

D#1 B22

D#2 A23

D#3 A25

D#4 C21

D#5 D22

D#6 B24

D#7 C23

D#8 C24

D#9 B25

D#10 G22

D#11 H21

D#12 C26

D#13 D23

D#14 J21

D#15 D25

D#16 H22

D#17 E24

D#18 G23

D#19 F23

D#20 F24

D#21 E25

D#22 F26

D#23 D26

D#24 L21

D#25 G26

D#26 H24

D#27 M21

D#28 L22

D#29 J24

D#30 K23

D#31 H25

D#32 M23

D#33 N22

D#34 P21

D#35 M24

D#36 N23

D#37 M26

D#38 N26

D#39 N25

D#40 R21

D#41 P24

D#42 R25

D#43 R24

D#44 T26

D#45 T25

D#46 T22

D#47 T23

D#48 U26

D#49 U24

D#50 U23

D#51 V25

D#52 U21

D#53 V22

D#54 V24

D#55 W26

D#56 Y26

D#57 W25

D#58 Y23

D#59 Y24

D#60 Y21

D#61 AA25

D#62 AA22

D#63 AA24

VCC_0 A10

VCC_1 A12

VCC_2 A14

VCC_3 A16

VCC_4 A18

VCC_5 A20

VCC_6 A8

VCC_7 AA10

VCC_8 AA12

VCC_9 AA14

VCC_10 AA16

VCC_11 AA18

VCC_12 AA8

VCC_13 AB11

VCC_14 AB13

VCC_15 AB15

VCC_16 AB17

VCC_17 AB19

VCC_18 AB7

VCC_19 AB9

VCC_20 AC10

VCC_21 AC12

VCC_22 AC14

VCC_23 AC16

VCC_24 AC18

VCC_25 AC8

VCC_26 AD11

VCC_27 AD13

VCC_28 AD15

VCC_29 AD17

VCC_30 AD19

VCC_31 AD7

VCC_32 AD9

VCC_33 AE10

VCC_34 AE12

VCC_35 AE14

VCC_36 AE16

VCC_37 AE18

VCC_38 AE20

VCC_39 AE6

VCC_40 AE8

VCC_41 AF11

VCC_42 AF13

VCC_43 AF15

VCC_44 AF17

VCC_45 AF19

VCC_46 AF2

VCC_47 AF21

VCC_48 AF5

VCC_49 AF7

VCC_50 AF9

VCC_51 B11

VCC_52 B13

VCC_53 B15

VCC_54 B17

VCC_55 B19

VCC_56 B7

VCC_57 B9

VCC_58 C10

VCC_59 C12

VCC_61 C14

VCC_62 C16

VCC_63 C18

VCC_64 C20

VCC_65 C8

VCC_66 D11

VCC_67 D13

VCC_68 D15

VCC_69 D17

VCC_70 D19

VCC_71 D7

VCC_72 D9

VCC_74

E12 VCC_75

E14 VCC_76

E16 VCC_77

E18 VCC_78

E20 VCC_79

E8 VCC_80

F11

VSS_0

H1

VSS_1

H4

VSS_2

H23

VSS_3

H26

VSS_4

A11

VSS_5

A13

VSS_6

A15

VSS_7

A17

VSS_8

A19

VSS_9

A21

VSS_10

A24

VSS_11

A26

VSS_12

A3

VSS_13

A9

VSS_14

AA1

VSS_15

AA11

VSS_16

AA13

VSS_17

AA15

VSS_18

AA17

VSS_19

AA19

VSS_20

AA23

VSS_21

AA26

VSS_22

AA4

VSS_23

AA7

VSS_24

AA9

VSS_25

AB10

VSS_26

AB12

VSS_27

AB14

VSS_28

AB16

VSS_29

AB18

VSS_30

AB20

VSS_31

AB21

VSS_32

AB24

VSS_33

AB3

VSS_34

AB6

VSS_35

AB8

VSS_36

AC11

VSS_37

AC13

VSS_38

AC15

VSS_39

AC17

VSS_40

AC19

VSS_41

AC2

VSS_42

AC22

VSS_43

AC25

VSS_44

AC5

VSS_45

AC7

VSS_46

AC9

BOOTSELECT

AD1

VSS_47

AD10

VSS_48

AD12

VSS_49

AD14

VSS_50

AD16

VSS_51

AD18

VSS_52

AD21

VSS_53

AD23

VSS_54

AD4

VSS_55

AD8

BCLK0

AF22

BCLK1

AF23

VCC_81

F13

VCC_82

F15

VCC_83

F17

VCC_84

F19

VCC_85

F9

VCC_73 E10

R231 51_0402_5%

1 2

Q106

2SC2411K_SC59

C1

E

3

B

2

Q107

MMBT3904_SOT23

2

3 1

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

ITP_TMS

ITP_TDI

ITP_TCK

ITP_TDO

H_TESTHI2_7

H_FERR#

H_THERMTRIP#

H_RESET#

H_PROCHOT#

H_PWRGOOD

CK_ITP

CK_ITP#

VID3

VID4

VID5

ITP_TRST#

H_TESTHI9

H_PWRGOOD

H_RS#0

ITP_BPM#3

ITP_TDI

ITP_TCK

H_RS#2

H_RESET#

ITP_BPM#0

H_RS#1

H_PROCHOT#

ITP_BPM#2

VID0

H_THERMTRIP#

ITP_DBRESET#

H_TESTHI0_1

COMP0

ITP_TDO

H_VCCA

ITP_BPM#1

COMP1

H_FERR#

H_TESTHI11

ITP_TRST#

ITP_BPM#5

ITP_BPM#4

H_TESTHI10

H_THERMDC

H_TESTHI8

ITP_TMS

H_THERMDA

H_DPSLP#

VID1

VID2

VID4

VID1

VID2

VID5

VID3

VID0

H_VID_PWRGD

ITP_DBRESET#

H_VSSA

CPU_STP#

CPU_STP#

H_VID_PWRGD

H_RS#[0..2]<8>

H_TRDY#<8>

H_A20M#<26> H_FERR#<26> H_IGNNE#<26> H_SMI#<26>

H_PWRGOOD<26> H_STPCLK#<26>

H_INTR<26> H_NMI<26>H_INIT#<26>

H_RESET#<8,26>

H_DBSY#<8> H_DRDY#<8>

H_THERMDA<7> H_THERMDC<7>

H_THERMTRIP#<7>

VCCSENSE<54> VSSSENSE<54>

H_DSTBN#0 <8>

H_DSTBN#1 <8>

H_DSTBN#2 <8>

H_DSTBN#3 <8>

H_DSTBP#0 <8>

H_DSTBP#1 <8>

H_DSTBP#2 <8>

H_DSTBP#3 <8>

H_ADSTB#0 <8>

H_ADSTB#1 <8>

H_DINV#0 <8>

H_DINV#1 <8>

H_DINV#2 <8>

H_PROCHOT# <49>

H_DINV#3 <8>

H_CPUSLP# <26>

VID4<54>

VID2<54> VID1<54>

VID5<54>

VID0<54>

VID3<54>

VID_PWRGD<53,54>

CK_ITP<24> CK_ITP#<24>

CPU_GHI# <27>

CPUCLK_STP#<11,26,54>

BSEL0<13,24> BSEL1<13,24>

+CPU_GTLREF

+CPU_GTLREF

+VCCVID

+VCC_CORE

+3VS

+VCC_CORE

+VCC_CORE

+VCC_CORE

+VCC_CORE

+3VS

+3VALW

+VCCVID

+VCCVID

+3VS

+VCC_CORE

Title

Size Document Number Re v

Date: Sheet of

LA-2411

0.1

Prescott Processor in uFCPGA478

565, 07

星期三 七月

, 2004

Compal Electronics, Inc.

Place near SB200 (U6)

Place near CPU

Close to the CPU

3. Place decoupling cap 220PF near CPU.

GTL Reference Voltage

2. Place R_A and R_B near CPU.

Layout note :

R_A

R_B

1. +CPU_GTLREF Trace wide

12mils(min),Space 15mils

1.Place cap within 600 mils of

the VCCA and VSSA pins.

Note: Please change to 10uH, DC current

of 100mA parts and close to cap

PLL Layout note :

2.H_VCCIOPLL,HVCCA,HVSSA trace wide

12 mils(min)

Close to the ITP

Between the CPU and ITP

H_TESTHI12

If CPU is P4 , Change the resistor

R546 value to 75_0603_1%

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

Pop: Northwood

Depop: Prescott

R_E

RE

Pop: Prescott

Depop: Northwood

51.1 Ohm for Northwood,

61.9 Ohm for Prescott

width= 10mil

W/O ITP

R1017->

Pop: Prescott

Depop: Northwood

for mobile CPU

R522 56_0402_5%

1 2

R545

4.7K_0402_5%

R521 56_0402_5%

1 2

R1125

12K_0402_5%

1 2

R559

1K_0402_5%

1 2

R550

1K_0402_5%

12

+

C854

33U_D2_8M_R35

1

2

G

D

S

Q45

2N7002 1N_SOT23

2

13

C546

1U_0603_10V4Z

1

2

RP137 56_0804_8P4R_5%

1 8

2 7

3 6

4 5

L37 LQG21F4R7N00_0805

1 2

Prescott

JP8B

AMP_3-1565030-1_Prescott

RS#0

F1

RS#1

G5

RS#2

F4

RSP#

AB2

TRDY#

J6

A20M#

C6

FERR#

B6

IGNNE#

B2

SMI#

B5

PWRGOOD

AB23

STPCLK#

Y4

TESTHI12 AD25

LINT0

D1

LINT1

E5

INIT#

W5

RESET#

AB25

DRDY#

H2 DBSY#

H5

THERMDC

C4 THERMDA

B3

TDI

C1 TCK

D4

TDO

D5

TMS

F7

TRST#

E6

COMP1

P1 COMP0

L24

DP#0 J26

DP#1 K25

DP#2 K26

DP#3 L25

VSS_57 AE11

VSS_58 AE13

VSS_59 AE15

VSS_60 AE17

VSS_61 AE19

VSS_62 AE22

VSS_63 AE24

OPTIMIZED/COMPAT# AE26

VSS_65 AE7

VSS_66 AE9

VSS_67 AF1

VSS_68 AF10

VSS_69 AF12

VSS_70 AF14

VSS_71 AF16

VSS_72 AF18

VSS_73 AF20

SKTOCC# AF26

VSS_75 AF6

VSS_76 AF8

VSS_77 B10

VSS_78 B12

VSS_79 B14

VSS_80 B16

VSS_81 B18

VSS_82 B20

VSS_83 B23

VSS_84 B26

VSS_85 B4

VSS_86 B8

VSS_87 C11

VSS_88 C13

VSS_89 C15

VSS_90 C17

VSS_91 C19

VSS_92 C2

VSS_93 C22

VSS_94 C25

VSS_95 C5

VSS_96 C7

VSS_97 C9

VSS_98 D10

VSS_99 D12

VSS_100 D14

VSS_101 D16

VSS_102 D18

VSS_103 D20

VSS_104 D21

VSS_105 D24

VSS_106 D3

VSS_107 D6

VSS_108 D8

VSS_109 E1

VSS_110 E11

VSS_111 E13

VSS_112 E15

VSS_113 E17

VSS_114 E19

VSS_115 E23

VSS_116 E26

VSS_117 E4

VSS_118 E7

VSS_119 E9

VSS_120 F10

VSS_121 F12

VSS_122 F14

VSS_123 F16

VSS_124 F18

VSS_125 F2

VSS_126 F22

VSS_127 F25

VSS_128 F5

VID0

AE5

VID1

AE4

VID2

AE3

VID3

AE2

VID4

AE1

GTLREF0 AA21

GTLREF1 AA6

GTLREF2 F20

GTLREF3 F6

NC1 A22

NC2 A7

TESTHI0 AD24

TESTHI1 AA2

TESTHI2 AC21

TESTHI3 AC20

TESTHI4 AC24

TESTHI5 AC23

TESTHI6 AA20

TESTHI7 AB22

TESTHI8 U6

TESTHI9 W4

TESTHI10 Y3

TESTHI11 A6

VSS_129

F8

VSS_130

G21

VSS_131

G24

VSS_132

G3

VSS_133

G6

VSS_134

J2

VSS_135

J22

VSS_136

J25

VSS_137

J5

VSS_138

K21

VSS_139

K24

VSS_140

K3

VSS_141

K6

VSS_142

L1

VSS_143

L23

VSS_144

L26

VSS_145

L4

VSS_146

M2

VSS_147

M22

VSS_148

M25

VSS_149

M5

VSS_150

N21

VSS_151

N24

VSS_152

N3

VSS_153

N6

VSS_154

P2

VSS_155

P22

VSS_156

P25

VSS_157

P5

VSS_158

R1

VSS_159

R23

VSS_160

R26

VSS_161

R4

VSS_162

T21

VSS_163

T24

VSS_164

T3

VSS_165

T6

VSS_166

U2

VSS_167

U22

VSS_168

U25

VSS_169

U5

VSS_170

V1

VSS_171

V23

VSS_172

V26

VSS_173

V4

VSS_174

W21

VSS_175

W24

VSS_176

W3

VSS_177

W6

VSS_178

Y2

VSS_179

Y22

VSS_180

Y25

VSS_181

Y5

BSEL0

AD6

BSEL1

AD5

BPM#0

AC6

BPM#1

AB5

BPM#2

AC4

BPM#3

Y6

BPM#4

AA5

BPM#5

AB4

DSTBN#0 E22

DSTBN#1 K22

DSTBN#2 R22

DSTBN#3 W22

DSTBP#0 F21

DSTBP#1 J23

DSTBP#2 P23

DSTBP#3 W23

ITP_CLK0

AC26

ITP_CLK1

AD26

ADSTB#0 L5

ADSTB#1 R5

DBI#0 E21

DBI#1 G25

DBI#2 P26

DBI#3 V21

DBR# AE25

VCCIOPLL

AD20

VCCSENSE

A5

VCCA

AE23

VCCVID

AF4

THERMTRIP#

A2

PROCHOT# C3

MCERR# V6

SLP# AB26

VSSA

AD22

VSSSENSE

A4

VIDPWRGD

AD2

VID5

AD3

NC5 AE21

NC4 AF24

NC3 AF25

VCCVIDLB

AF3

R547

@54.9_0603_1%

1 2

R530 56_0402_5%

1 2

L36 LQG21F4R7N00_0805

1 2

R529 56_0402_5%

1 2

R542 1K_0402_5%

1 2

R514

@0_0402_5%

1 2

C547

220P_0402_25V8K

1

2

RP136 56_0804_8P4R_5%

1 8

2 7

3 6

4 5

R520 @0_0402_5%

1 2

R527 56_0402_5%

1 2

R518 300_0402_5%

1 2

R552 1K_0402_5%

1 2

RP94 1K_1206_8P4R_5%

18 27 36 45

R519 56_0402_5%

1 2

R543 1K_0402_5%

1 2

+

C544

33U_D2_8M_R35

1

2

R539

61.9_0603_1%

12

R558

169_0402_1%

12

R1017 0_0402_5%

1 2

R546

@54.9_0603_1%

1 2

R556 1K_0402_5%

12

R515 56_0402_5%

1 2

R517 130_0402_5%

1 2

C932

0.1U_0402_10V6K

1

2

R541

680_0603_5%

1 2

Q95

MMBT3904_SOT23

2

3 1

R553

100_0402_1%

12

R513 56_0402_5%

1 2

R993

4.7K_0402_5%

12

R990 300_0402_5%

1 2

Q96

MMBT3904_SOT23

2

3 1

R540

61.9_0603_1%

12

U32A

SN74LVC14APWLE_TSSOP14

O2

I

1

P14

G

7

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

+VCC_CORE

+VCC_CORE

+VCC_CORE

+VCC_CORE

+VCC_CORE

+VCC_CORE

+VCC_CORE

+VCC_CORE

Title

Size Document Number Re v

Date: Sheet of

LA-2411

0.1

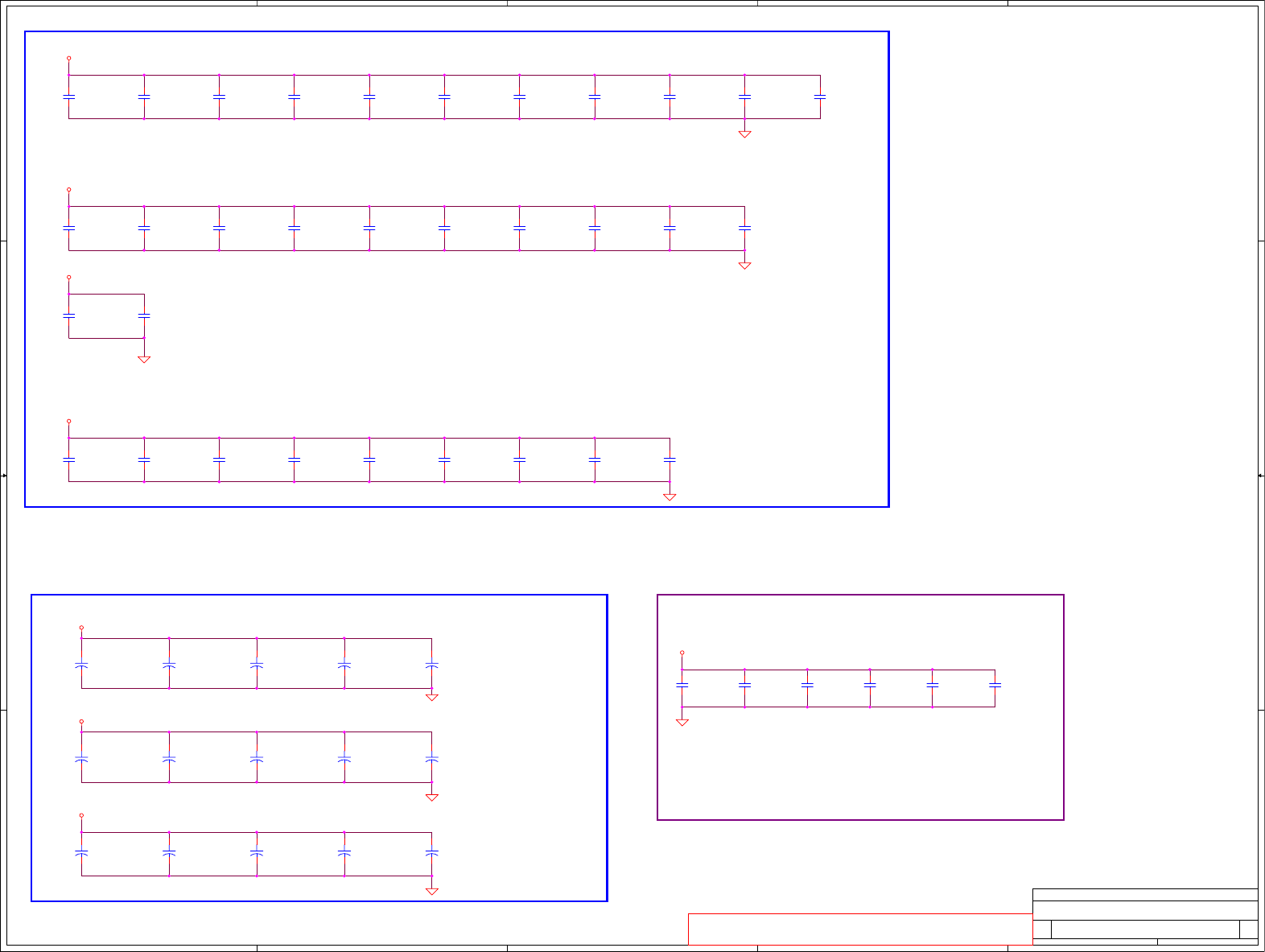

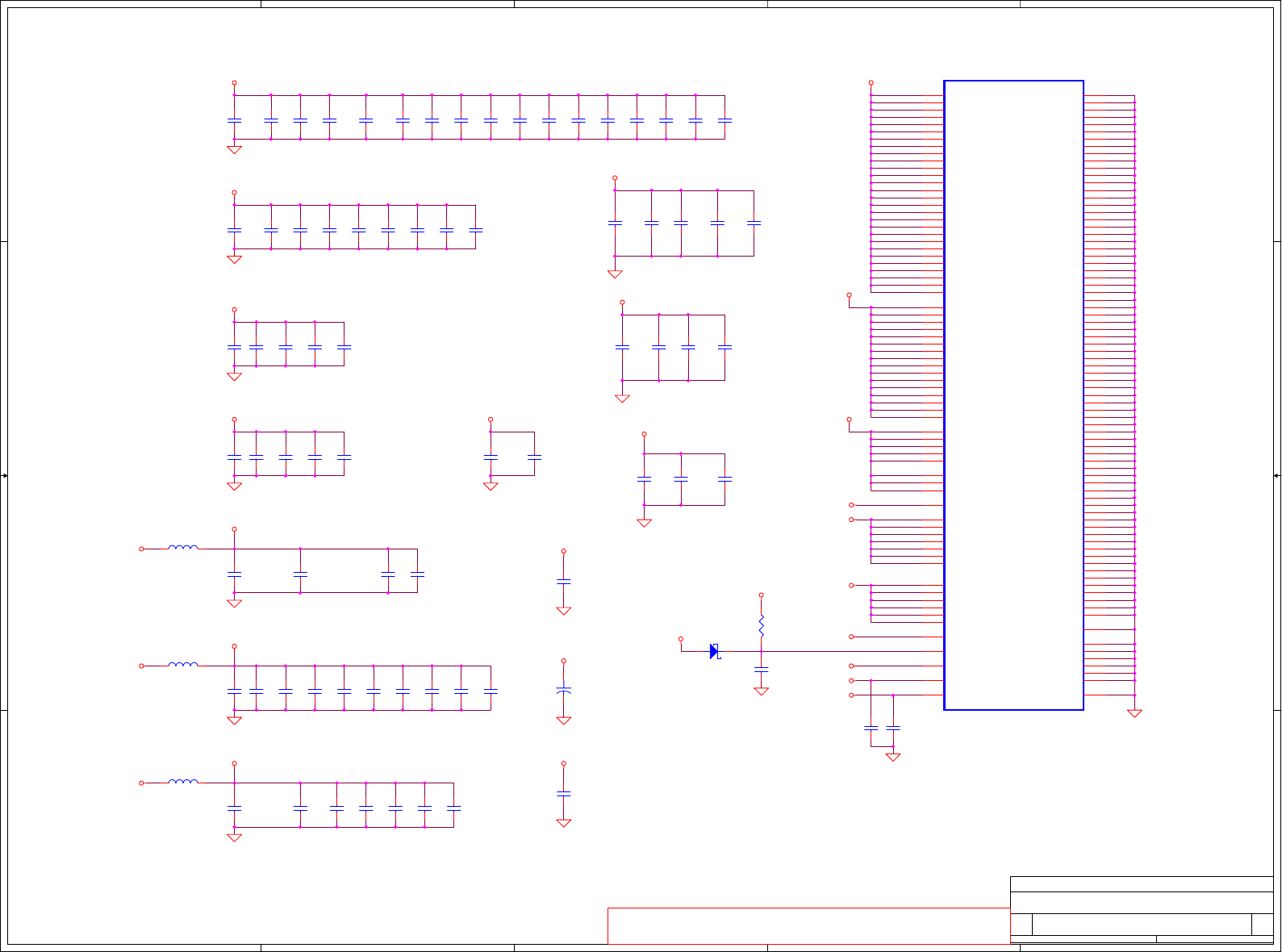

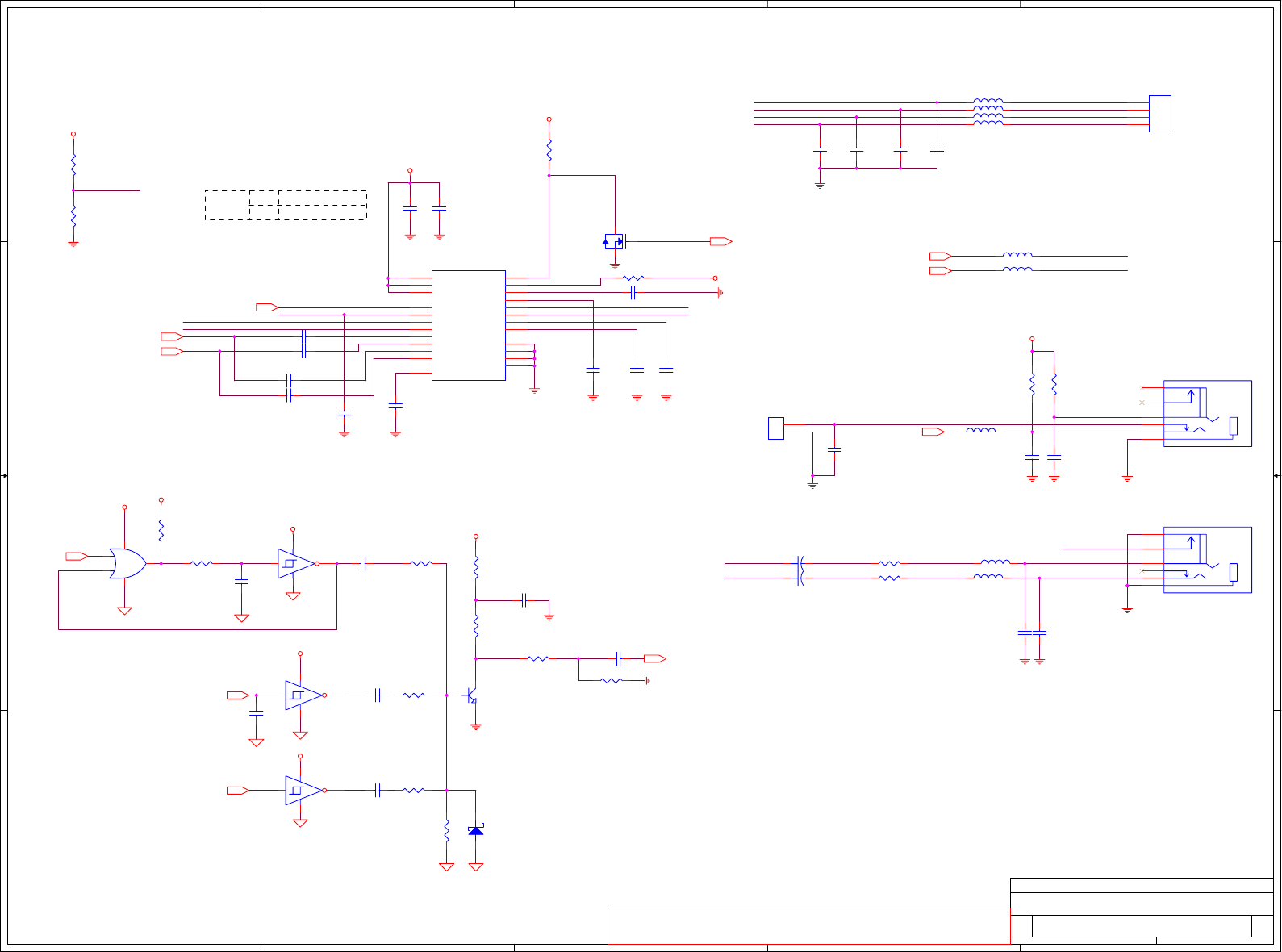

CPU Decoupling

665, 07

星期三 七月

, 2004

Compal Electronics, Inc.

Place 11 North of Socket(Stuff 6)

Place 12 Inside Socket(Stuff all)

Place 9 South of Socket(Unstuff all)

Place Inside Socket around the edge

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

SANYO OS-CON 820uF H:13*3 (C163,C164,C165)

SANYO OS-CON 820uF H:9*2 (C166,C167)

+

C178

@470U_D2_2.5VM

1

2

C159

22U_1206_16V4Z

1

2

C143

22U_1206_16V4Z

1

2

+

C180

470U_D2_2.5VM

1

2

C162

22U_1206_16V4Z

1

2

C172

0.22U_0603_10V7K

1

2

C132

22U_1206_16V4Z

1

2

C170

0.22U_0603_10V7K

1

2

C139

22U_1206_16V4Z

1

2

C168

0.22U_0603_10V7K

1

2

+

C163

820U_E9_2_5V_M_R7

1

2

+

C183

@470U_D2_2.5VM

1

2

C134

22U_1206_16V4Z

1

2

C154

22U_1206_16V4Z

1

2

C153

22U_1206_16V4Z

1

2

C151

22U_1206_16V4Z

1

2

C145

22U_1206_16V4Z

1

2

C135

22U_1206_16V4Z

1

2

C146

22U_1206_16V4Z

1

2

C173

0.22U_0603_10V7K

1

2

C156

22U_1206_16V4Z

1

2

+

C179

470U_D2_2.5VM

1

2

C141

22U_1206_16V4Z

1

2

C147

22U_1206_16V4Z

1

2

+

C166

820U_E9_2_5V_M_R7

1

2

C152

22U_1206_16V4Z

1

2

C155

22U_1206_16V4Z

1

2

C158

22U_1206_16V4Z

1

2

C138

22U_1206_16V4Z

1

2

C131

22U_1206_16V4Z

1

2

C171

0.22U_0603_10V7K

1

2

+

C176

@470U_D2_2.5VM

1

2

C142

22U_1206_16V4Z

1

2

C136

22U_1206_16V4Z

1

2

+

C164

820U_E9_2_5V_M_R7

1

2

C161

22U_1206_16V4Z

1

2

+

C182

470U_D2_2.5VM

1

2

C157

22U_1206_16V4Z

1

2

C150

22U_1206_16V4Z

1

2

C140

22U_1206_16V4Z

1

2

C149

22U_1206_16V4Z

1

2

C160

22U_1206_16V4Z

1

2

C133

22U_1206_16V4Z

1

2

C148

22U_1206_16V4Z

1

2

+

C174

470U_D2_2.5VM

1

2

+

C177

@470U_D2_2.5VM

1

2

C144

22U_1206_16V4Z

1

2

C137

22U_1206_16V4Z

1

2

+

C175

470U_D2_2.5VM

1

2

+

C165

820U_E9_2_5V_M_R7

1

2

+

C181

470U_D2_2.5VM

1

2

C169

0.22U_0603_10V7K

1

2

+

C167

820U_E9_2_5V_M_R7

1

2

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

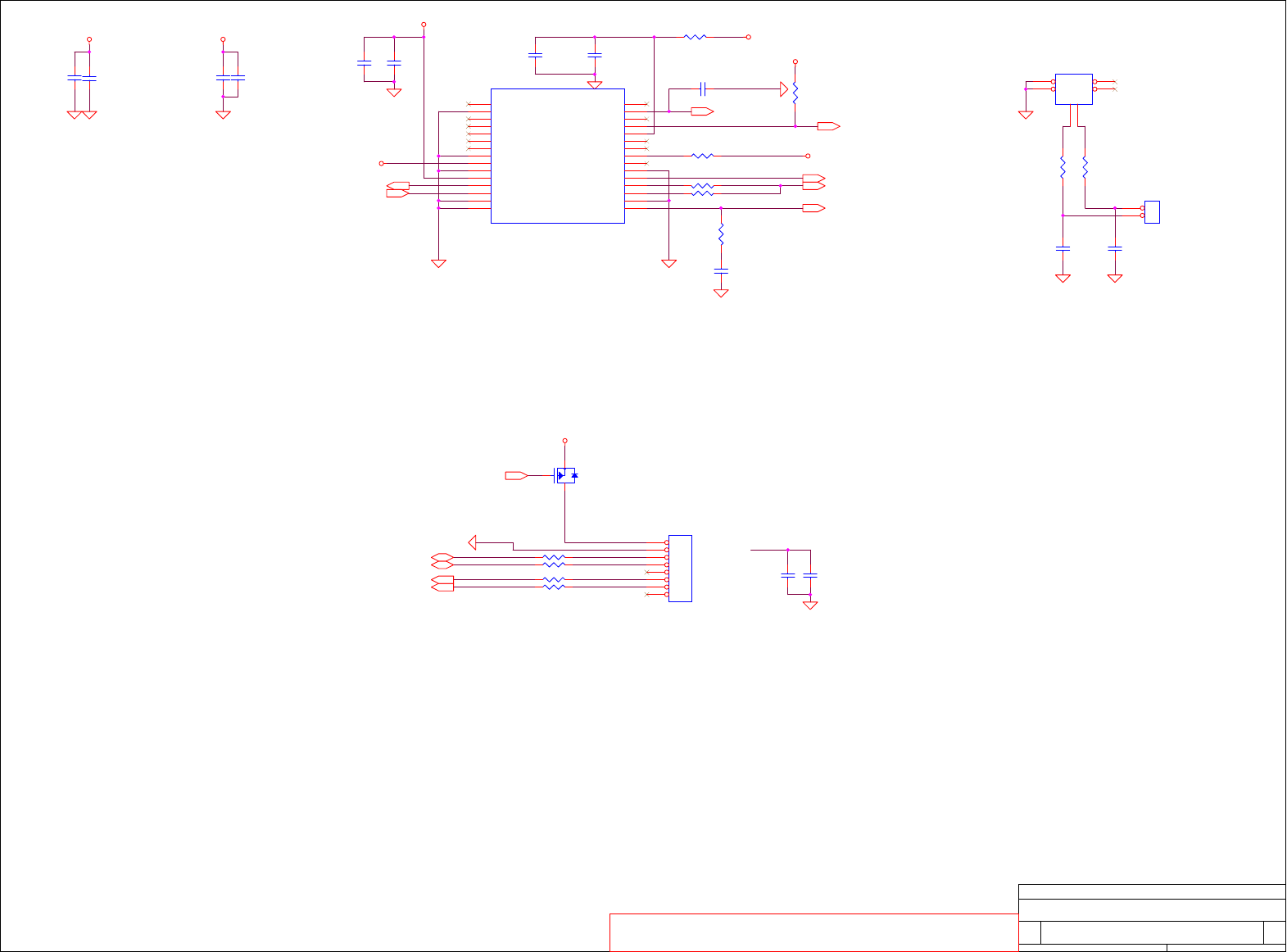

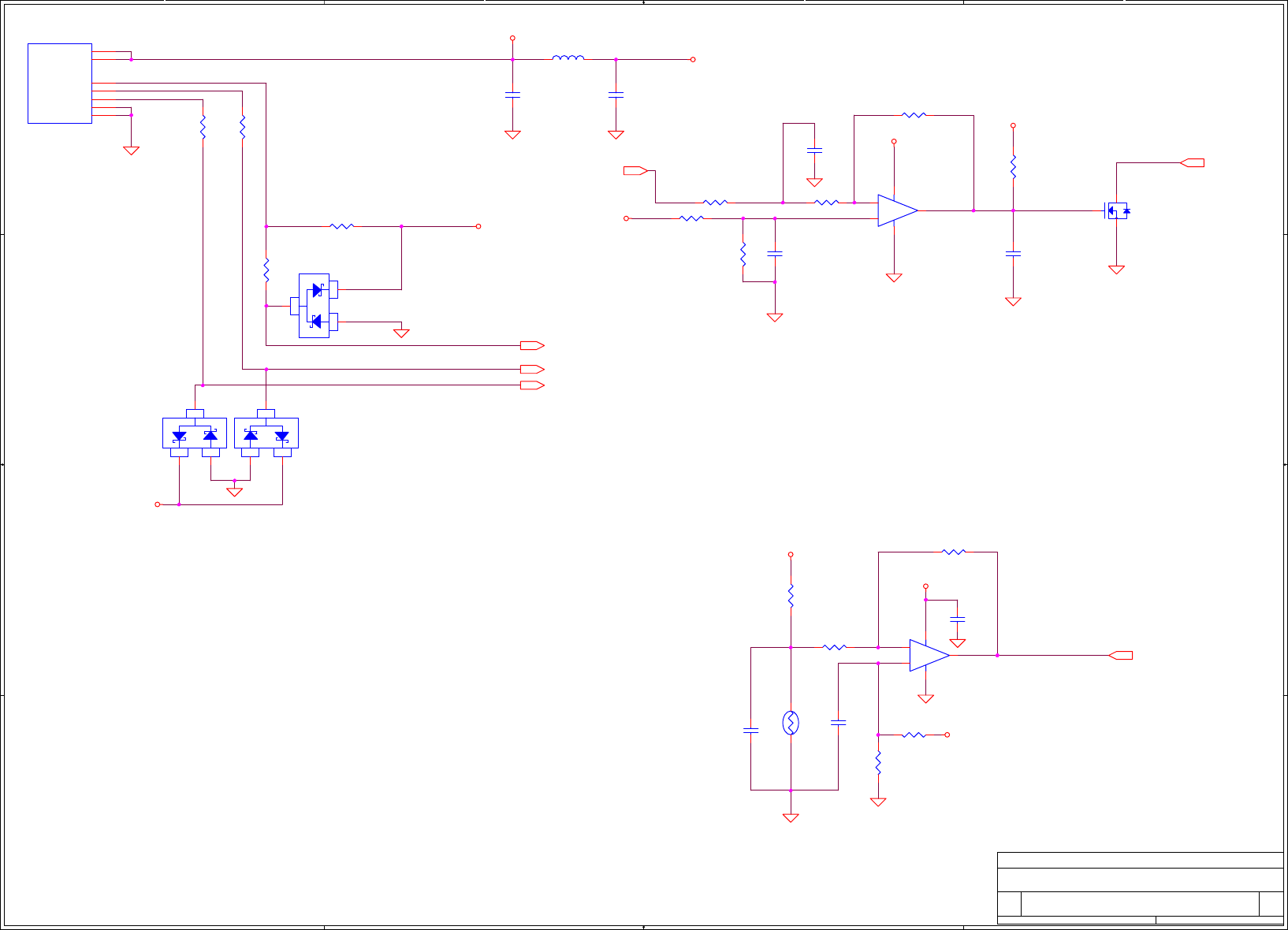

EN_FAN1 EN_FAN2

FAN1 FAN2

H_THERMTRIP#

H_THERMDA

H_THERMDC

H_THERMDA

H_THERMDC

EC_SMC_2 <44>

EC_SMD_2 <44>

H_THERMDA <5>

H_THERMDC <5>

EN_FAN1<44> EN_FAN2<44>

FANSPEED2<44>FANSPEED1<44>

H_THERMTRIP#<5>

MAINPWON <48,49,51>

+3VALW

+VCC_CORE

+5VS

+3VS

+5VS

+3VS

+12VALW

Title

Size Document Number Re v

Date: Sheet of

LA-2411

0.1

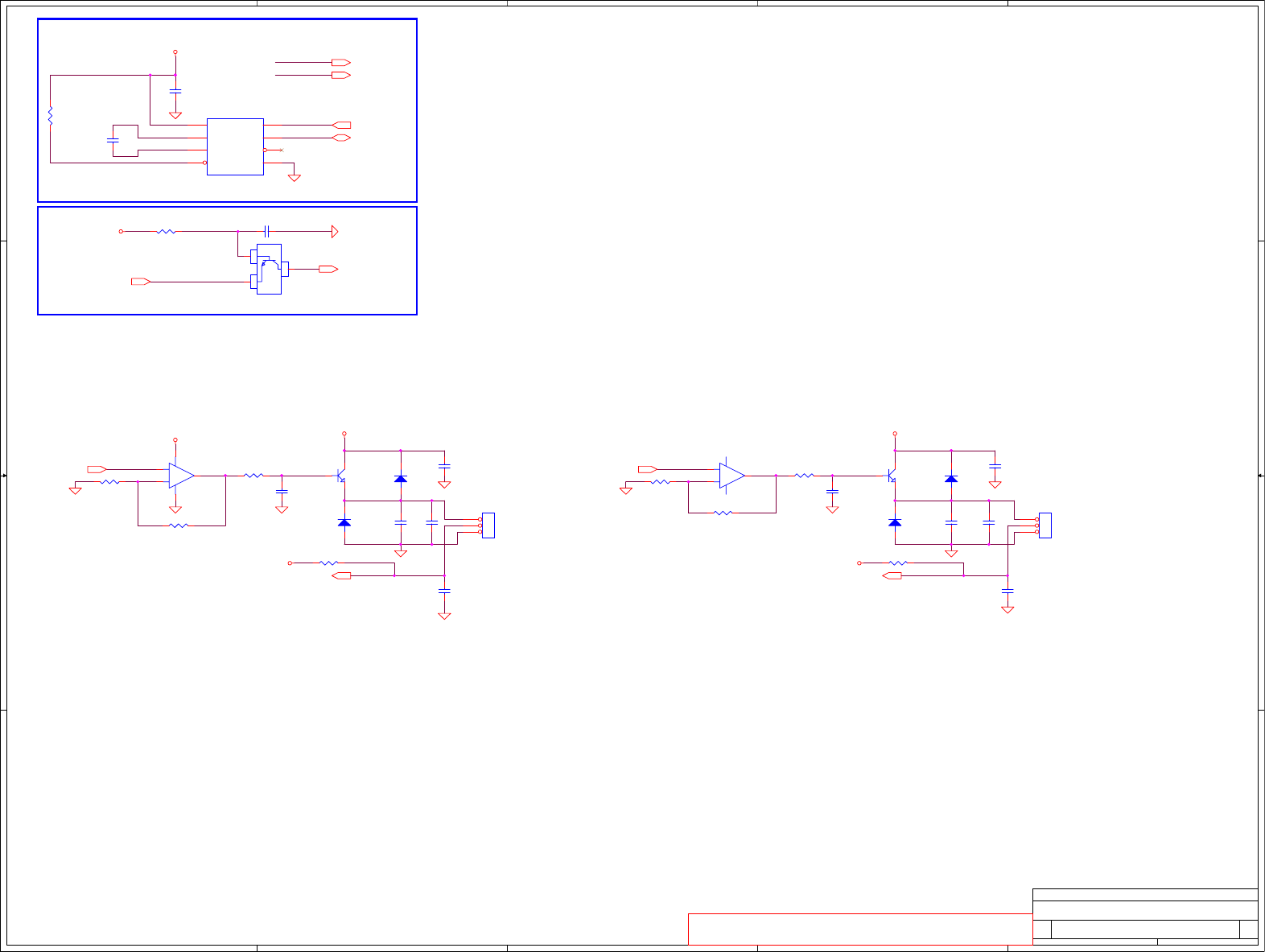

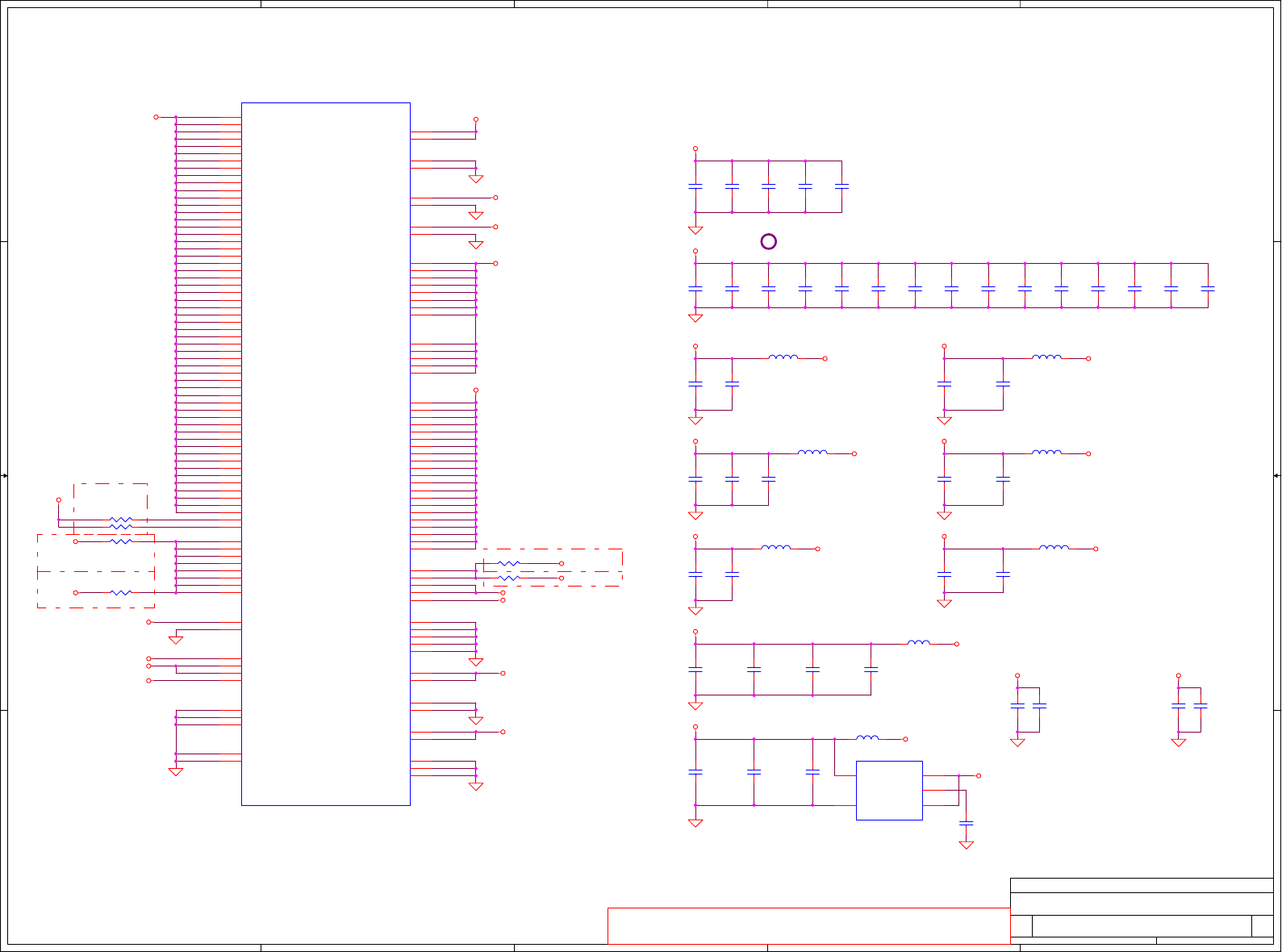

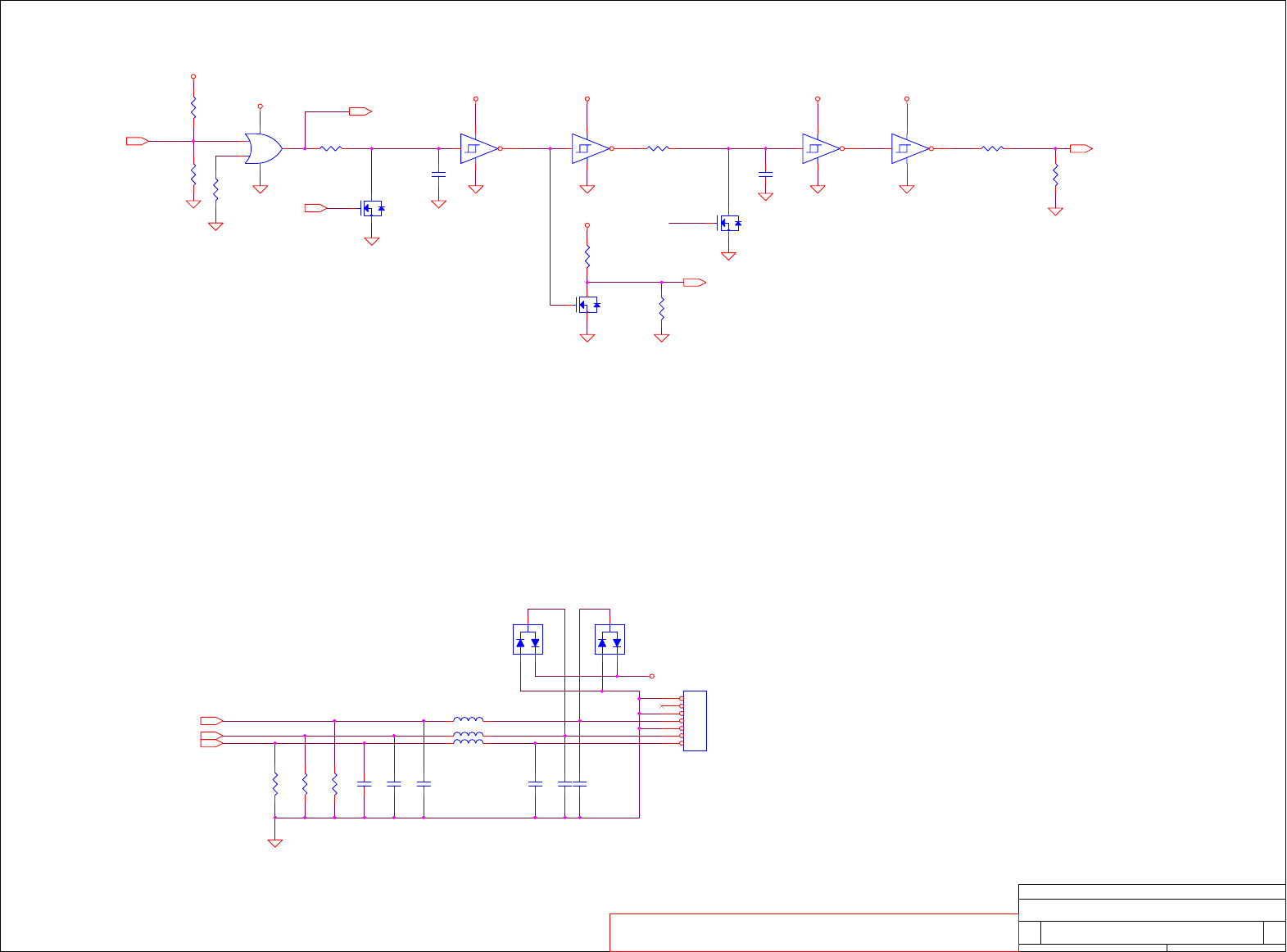

CPU Thermal Sensor&FAN CTRL

765, 07

星期三 七月

, 2004

Compal Electronics, Inc.

Thermal Sensor ADM1032AR

Address:1001_100X

W=15mil

FAN CONN.1 FAN CONN. 2

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

C265

10U_0805_10V4Z

1

2

R916

10K_0402_5%

12

R917 8.2K_0402_5%

1 2

C840

0.1U_0402_10V6K

1

2

R920 10K_0402_5%

1 2

R918 8.2K_0402_5%

1 2

JP11

ACES_85205-0300

1

2

3

C253

2200P_0402_25V7K

1

2

C

B

E

Q90

FMMT619_SOT23

1

2

3

JP10

ACES_85205-0300

1

2

3

U10A

LM358A_SO8

+IN

3

-IN

2OUT 1

P8

G

4

R283

@10K_0402_5%

12

C856

1000P_0402_16V7K

1

2

C855

1000P_0402_16V7K

1

2

C

B

E

Q91

FMMT619_SOT23

1

2

3

D25

1N4148_SOD80

12

C251

0.1U_0402_10V6K

1

2

C907

1000P_0402_16V7K

1

2

Q17

2SC2411K_SC59

C1

E

3

B

2

D68

1SS355_SOD323

12

R913 100_0402_5%

1 2

D67

1SS355_SOD323

12

C838

10U_0805_16V4Z

12

C266

10U_0805_10V4Z

1

2

R286 300_0402_5%

12

C256 @1U_0603_10V6K

12

R919 10K_0402_5%

1 2

C839

10U_0805_16V4Z

1

2

R915

10K_0402_5%

12

D26

1N4148_SOD80

12

U8

ADM1032AR_SOP8

VDD

1

ALERT# 6

THERM#

4GND 5

D+

2

D-

3

SCLK 8

SDATA 7

R914 100_0402_5%

1 2

C841

0.1U_0402_10V6K

1

2

C908

1000P_0402_16V7K

1

2

U10B

LM358A_SO8

+IN

5

-IN

6OUT 7

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

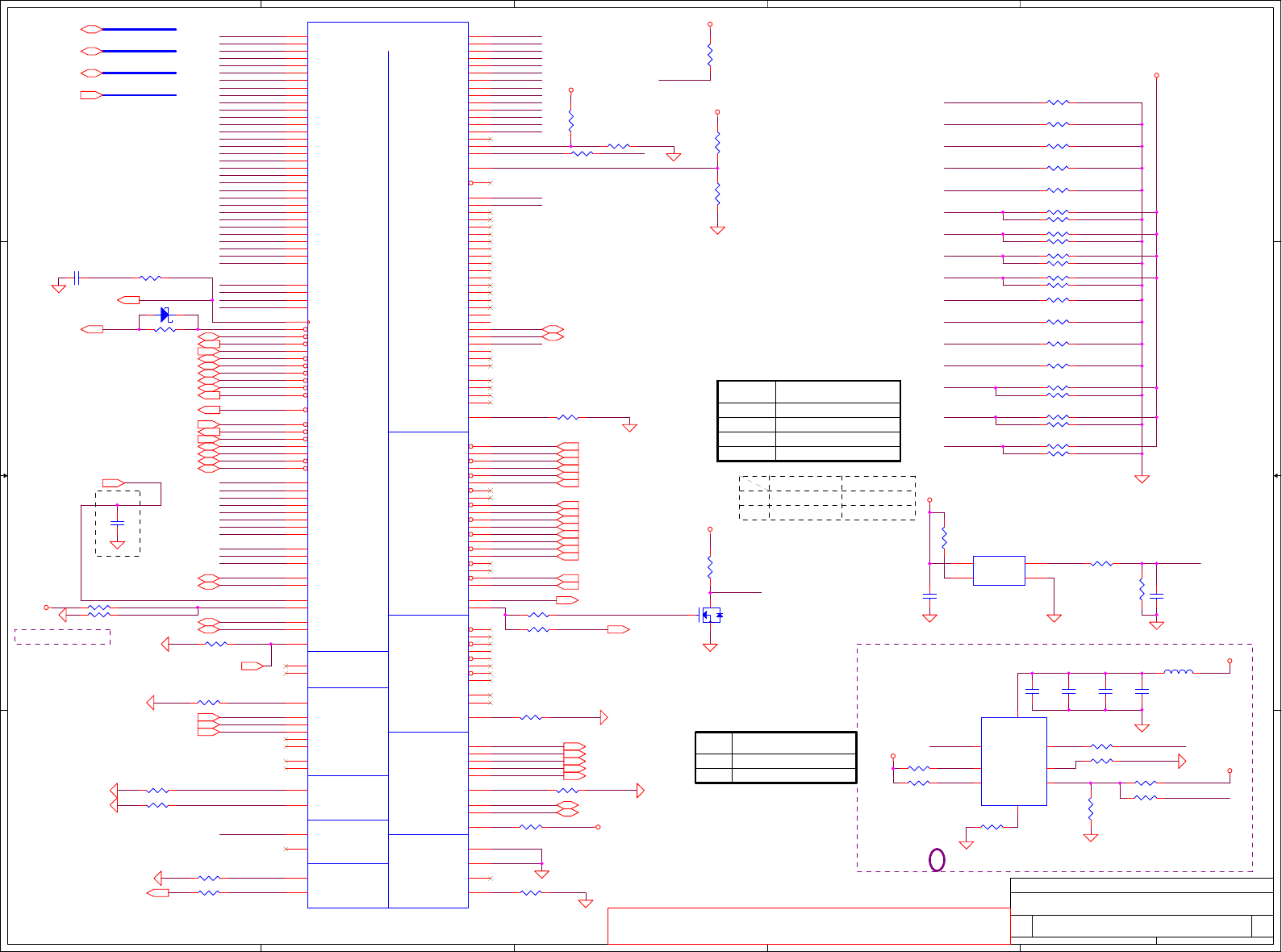

H_D#[0..63]

H_REQ#[0..4]

H_A#[3..31]

H_D#62

H_DSTBP#3

H_D#37

H_D#59

H_DINV#2

H_D#39

H_D#54

H_D#11

H_DSTBN#2

H_D#12

H_D#46

H_D#63

H_D#8

H_DSTBP#2

H_D#48

H_D#50

H_DSTBN#0

H_D#19

H_D#47

H_D#0

H_D#6

H_D#13

H_D#5

H_D#9

H_D#18

H_D#4

H_D#28

H_D#57

H_D#40

H_D#36

H_DSTBP#1

H_D#43

H_D#33

H_D#24

H_D#25

H_D#34

H_D#29

H_D#55

H_DSTBN#3

H_DINV#0

H_D#16

H_D#51

H_D#2

H_D#45

H_D#31

H_D#23

H_D#52

H_D#3

H_D#20

H_D#17

H_D#7

H_DINV#3

H_D#22

H_D#15

H_D#30

H_DSTBP#0

H_D#32

H_D#58

H_D#10

H_D#1

H_D#35

H_D#21

H_D#41

H_D#44

H_D#42

H_D#53

H_D#60

H_D#27

H_D#38

H_DSTBN#1

H_D#56

H_D#49

H_D#26

H_D#61

H_DINV#1

H_D#14

H_A#28

H_ADSTB#1

H_A#7

H_A#30

H_A#3

H_A#20

H_A#29

H_A#6

H_A#22

H_A#18

H_A#24

H_REQ#3

H_A#23

H_BNR#

H_A#9

H_A#8

H_A#25

H_A#11

H_DEFER#

H_A#10

H_ADSTB#0

H_A#4

H_DRDY#

H_LOCK#

H_A#17

H_TRDY#

H_A#27

H_A#16

H_A#13

H_HIT#

H_ADS#

H_RS#1

H_RESET#

H_DBSY#

H_A#5

COMP_P

H_A#15

H_A#14

H_A#26

H_A#31

H_HITM#

H_RS#2

H_BPRI#

H_REQ#1

H_A#19

H_REQ#2

NB_GTLREF

H_A#21

H_REQ#4

H_REQ#0

H_RS#0

H_A#12

H_BR0#

COMP_N

CPVSS

CPVDD

H_D#[0..63] <4>

H_A#[3..31] <4>

H_REQ#[0..4] <4>

H_DSTBP#0 <5>

H_DSTBN#3 <5>

H_DSTBN#0 <5>

H_DSTBP#3 <5>

H_DSTBP#2 <5>

H_DSTBN#2 <5>

H_DSTBP#1 <5>

H_DSTBN#1 <5>

H_TRDY#<5>

H_RS#1<5>

H_DEFER#<4>

H_HITM#<4> H_HIT#<4>

NB_PWRGD<10,46>

H_ADSTB#1<5>

H_DRDY#<5>

H_ADSTB#0<5>

H_RS#2<5>

H_LOCK#<4>

H_DBSY#<5>

H_BPRI#<4> H_BNR#<4>

H_RS#0<5>

H_RESET#<5,26>

NB_RST#<17,26>

H_ADS#<4>

H_BR0#<4>

H_DINV#3 <5>

H_DINV#0 <5>

H_DINV#2 <5>

H_DINV#1 <5>

NB_SUS_STAT#<27>

+VCC_CORE

+VCC_CORE +1.8VS

+VCC_CORE

Title

Size Document Number Rev

Date: Sheet of

LA-2411

0.1

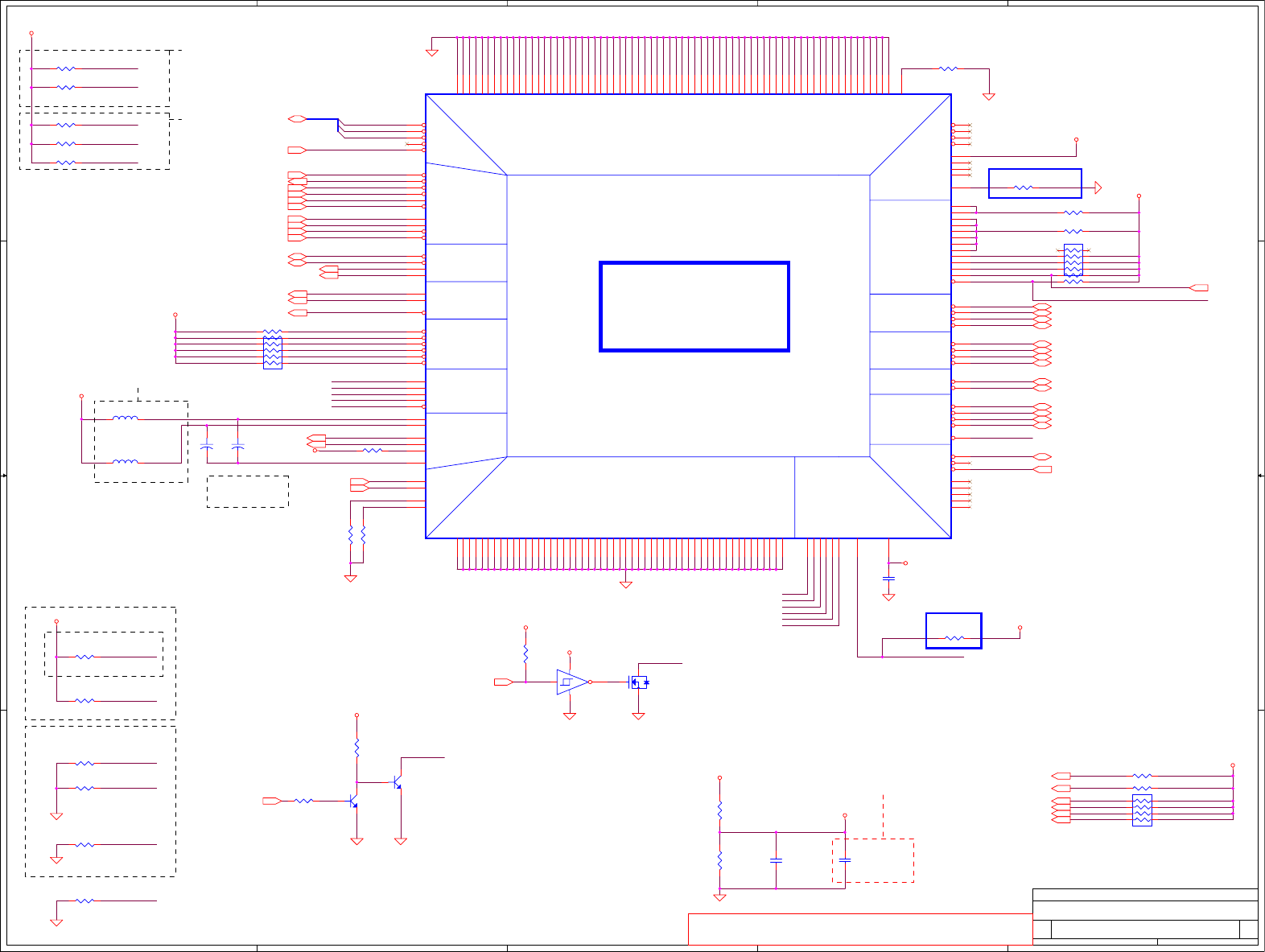

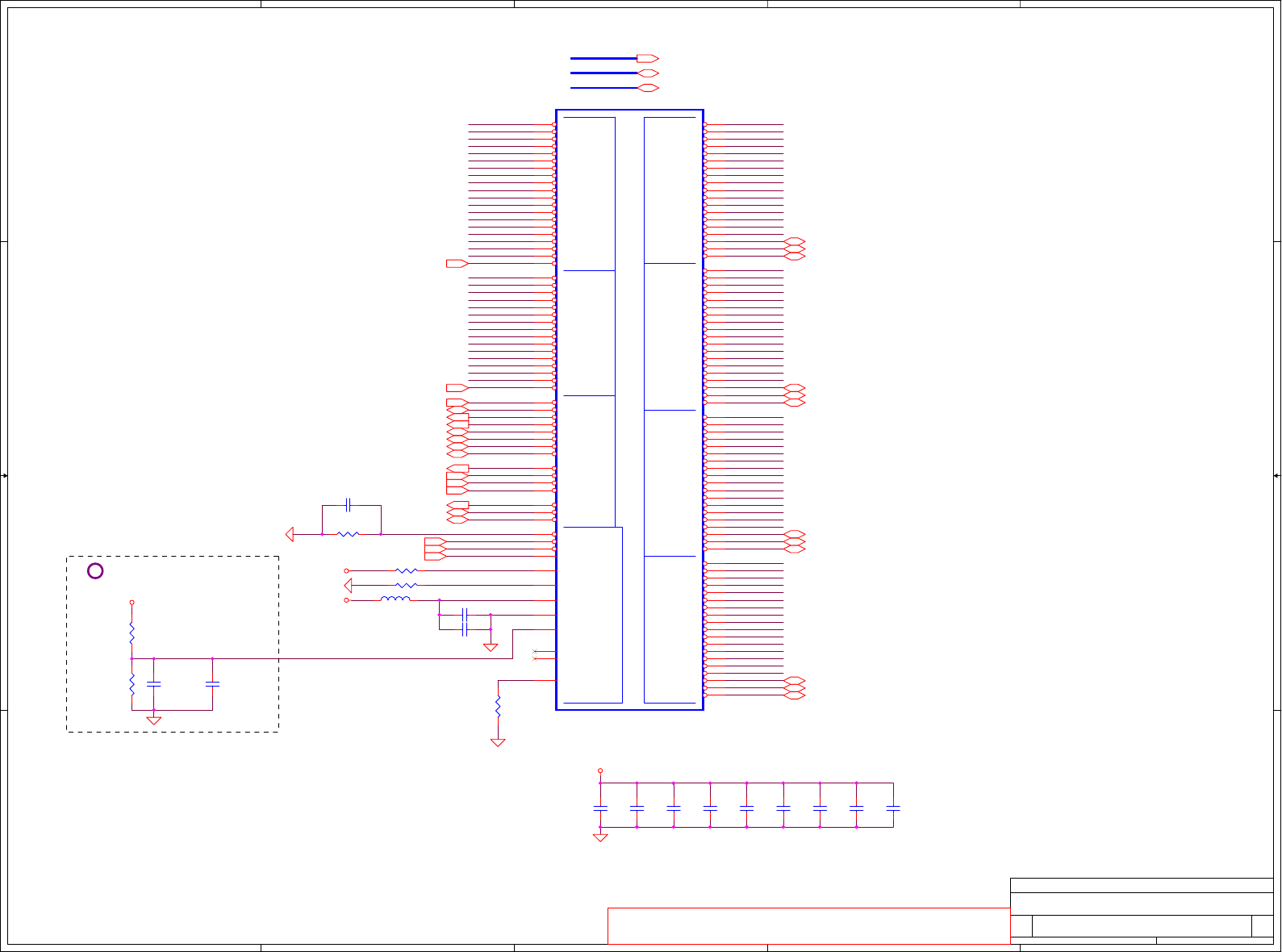

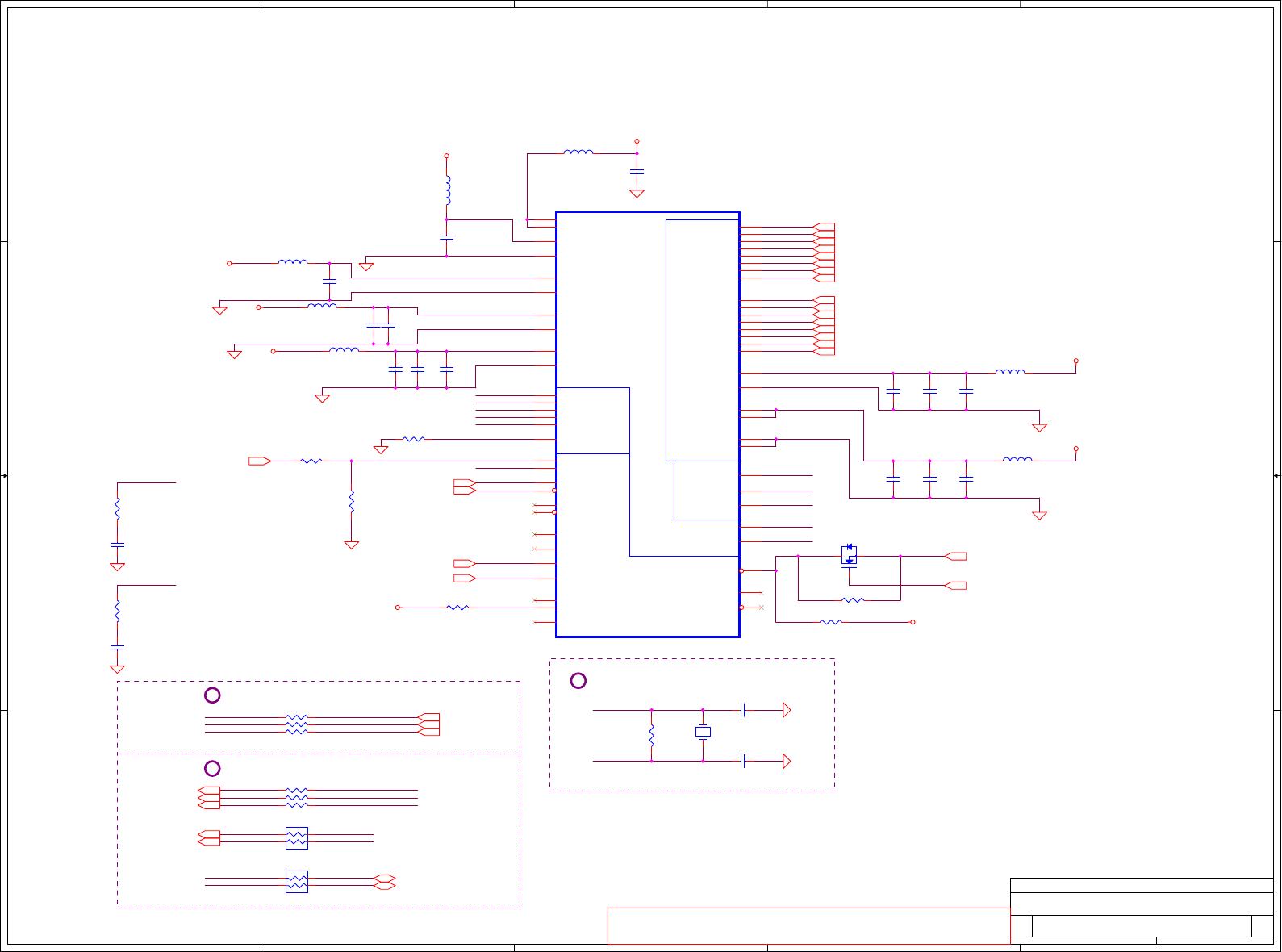

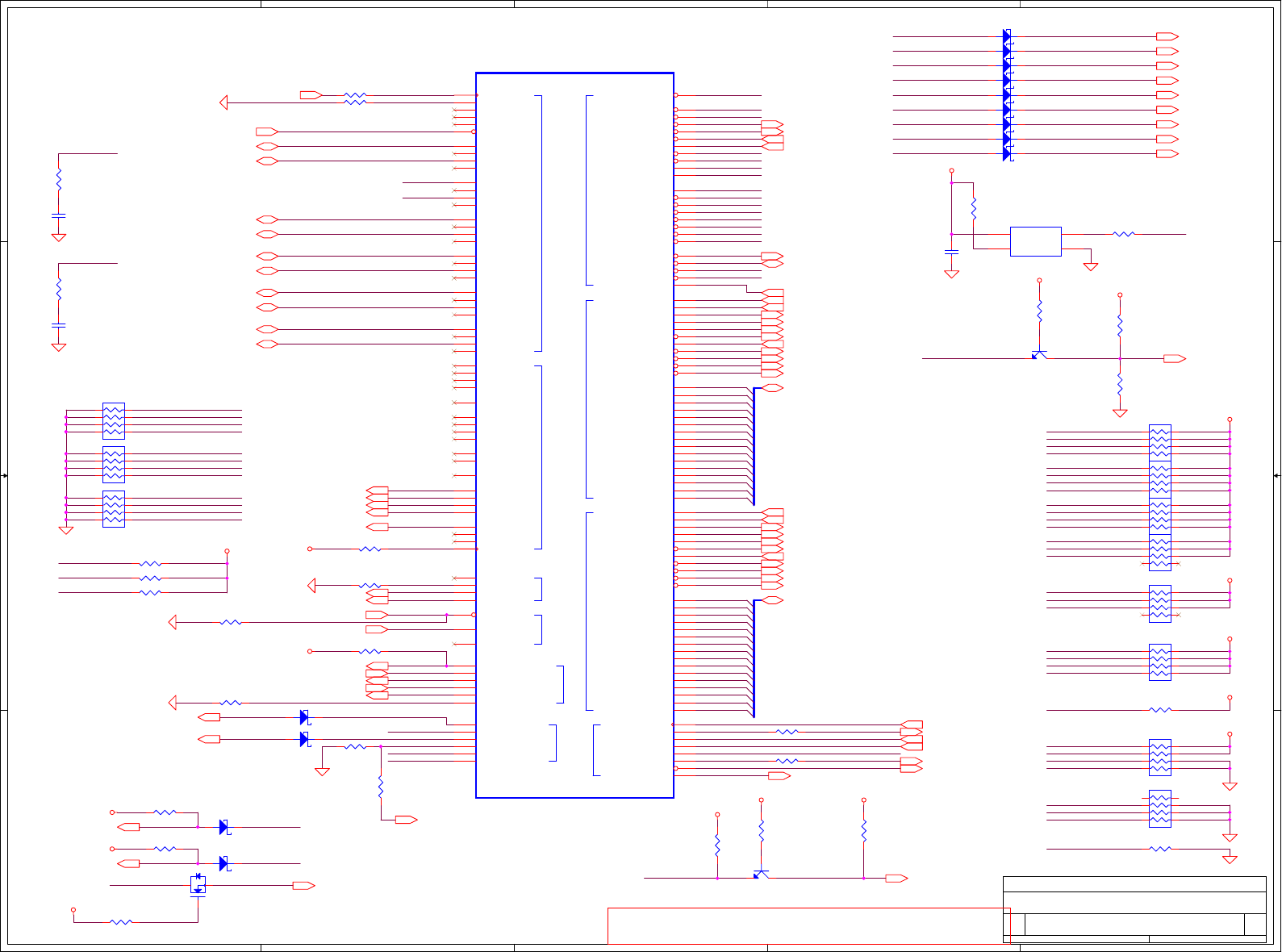

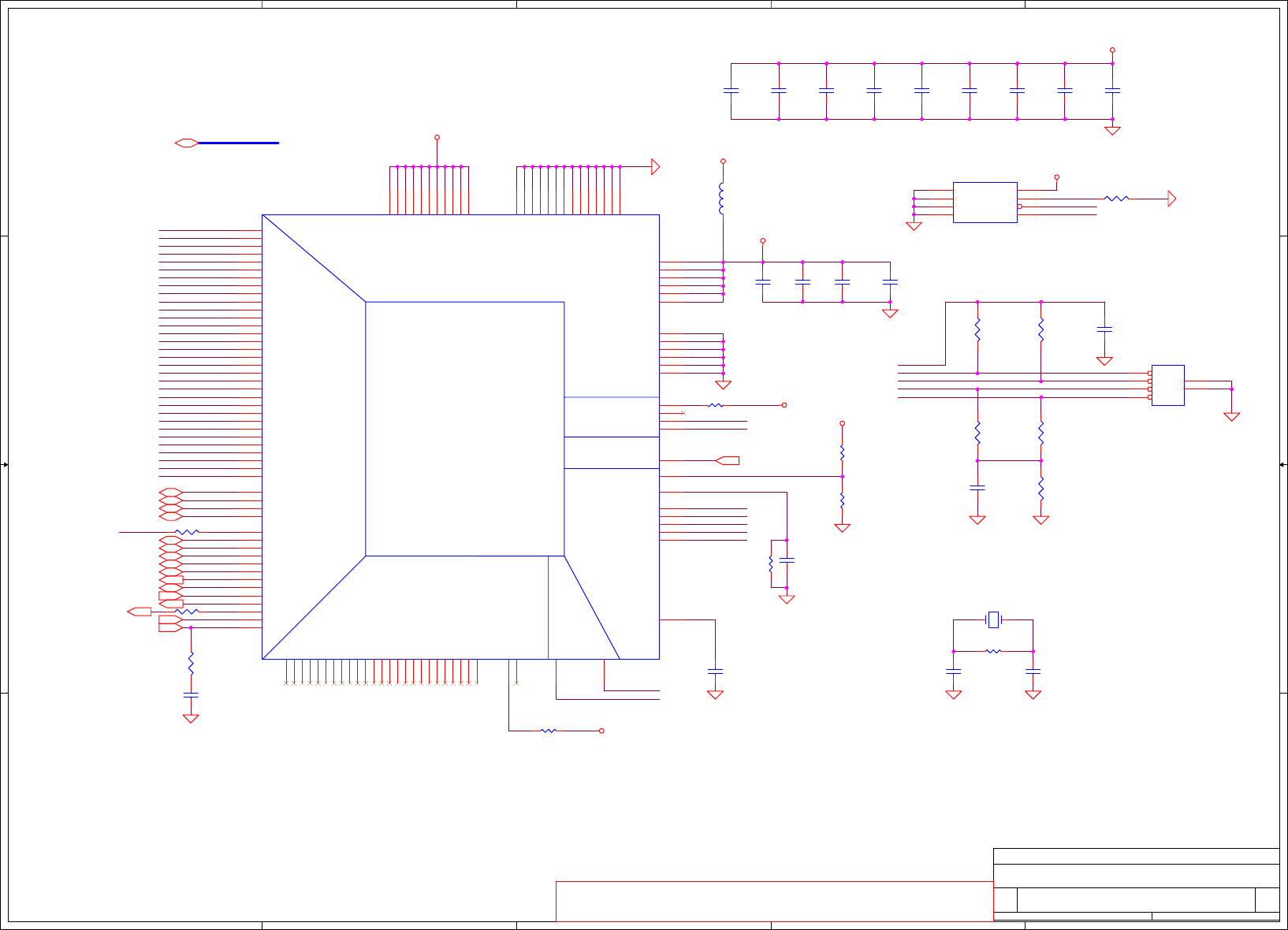

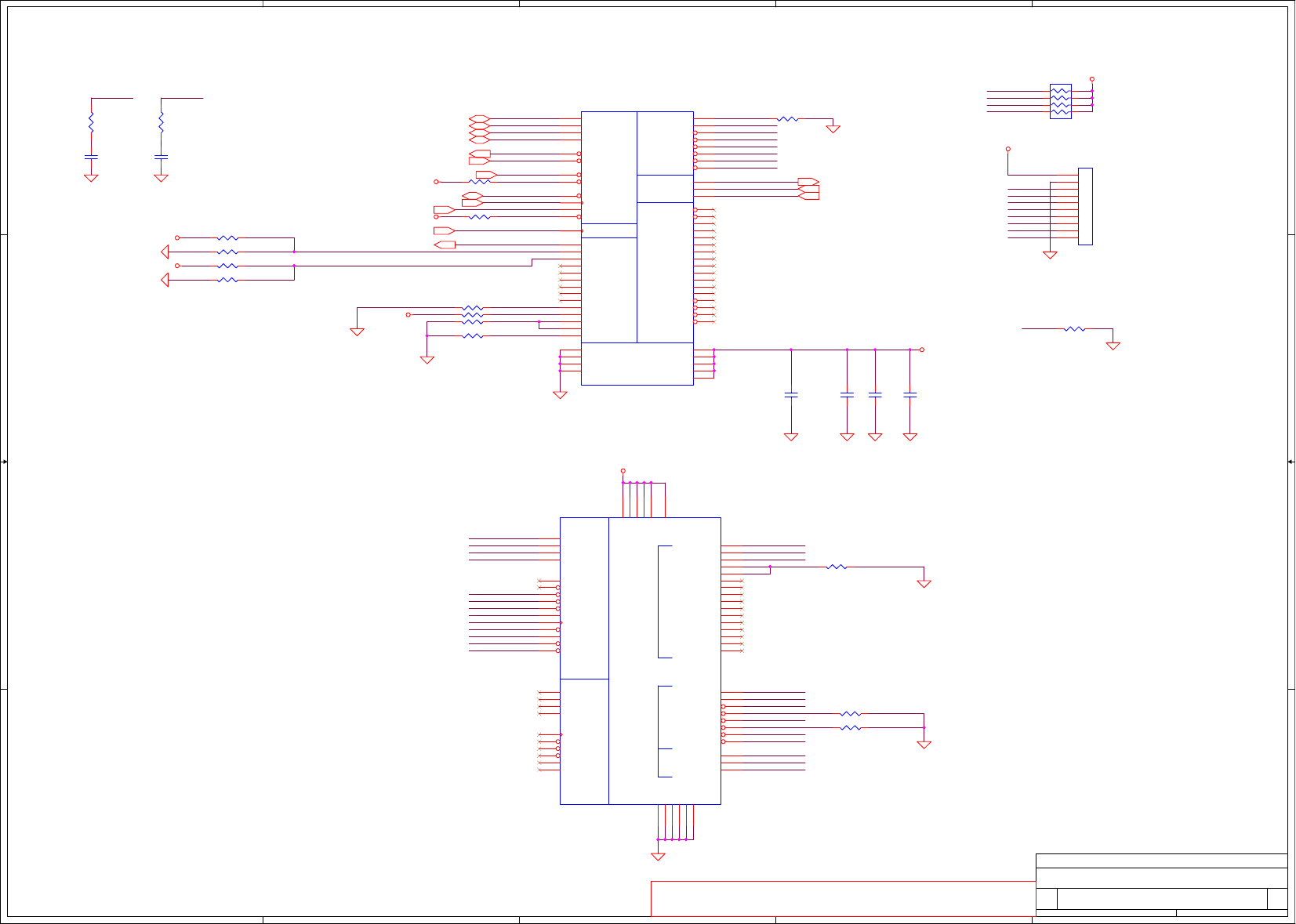

ATI RC300M-AGTL+

865, 07, 2004

星期三 七月

Compal Electronics, Inc.

C363 CLOSE

TO Ball W28

PLACE CLOSE TO U27 Ball

W28, USE 20/20

WIDTH/SPACE

Note: PLACE CLOSE TO RC300M,

USE 10/10 WIDTH/SPACE

L

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

--> 412_0402_1%

R383

100_0402_1%

1 2

C372

0.1U_0402_10V6K

1

2

R381 24.9_0402_1%

1 2

C366

0.1U_0402_10V6K

1

2

R384

169_0402_1%

12

C368

0.1U_0402_10V6K

1

2

C369

0.1U_0402_10V6K

1

2

C362

1U_0603_10V6K

1

2

L34

HB-1M2012-121JT03_0805

1 2

R382 49.9_0402_1%

1 2

C364

22U_1206_16V4Z_V1

1

2

C371

0.1U_0402_10V6K

1

2

C99610U_0805_10V4Z

1 2

C365

0.1U_0402_10V6K

1

2

R385

4.7K_0402_5%

12

C363

220P_0402_25V8K

1

2

C361

@1U_0603_10V6K

1 2

R380 330_0402_5%

1 2

C370

0.1U_0402_10V6K

1

2

C974

0.1U_0402_10V6K

12

C367

0.1U_0402_10V6K

1

2

PART 1 OF 6

PENTIUM

IV

ADDR. GROUP 1 ADDR. GROUP 0CONTROL

MISC.

DATA GROUP 0DATA GROUP 1DATA GROUP 2DATA GROUP 3

AGTL+ I/F

U27A

216RC300M_BGA_718

CPU_ADS#

L27

CPU_BNR#

K25

CPU_BPRI#

H26

CPU_D0# L30

CPU_D1# K29

CPU_D2# J29

CPU_D3# H28

CPU_D4# K28

CPU_D5# K30

CPU_D6# H29

CPU_D7# J28

CPU_D8# F28

CPU_D9# H30

CPU_D10# E30

CPU_D11# D29

CPU_D12# G28

CPU_D13# E29

CPU_D14# D30

CPU_D15# F29

CPU_D16# B26

CPU_D17# C30

CPU_D18# A27

CPU_D19# B29

CPU_D20# C28

CPU_D21# C29

CPU_D22# B28

CPU_D23# D28

CPU_D24# D26

CPU_D25# B27

CPU_D26# C26

CPU_D27# E25

CPU_D28# E26

CPU_D29# A26

CPU_D30# B25

CPU_D31# C25

CPU_D32# F24

CPU_D33# D24

CPU_D34# E23

CPU_D35# E24

CPU_D36# F23

CPU_D37# C24

CPU_D38# B24

CPU_D39# A24

CPU_D40# F21

CPU_D41# A23

CPU_D42# B23

CPU_D43# C22

CPU_D44# B22

CPU_D45# C21

CPU_D46# E21

CPU_D47# D22

CPU_D48# B21

CPU_D49# F20

CPU_D50# A21

CPU_D51# C20

CPU_D52# E20

CPU_D53# D20

CPU_A3#

M28

CPU_A4#

P25

CPU_D54# A20

CPU_D55# D19

CPU_D56# C18

CPU_D57# B20

CPU_D58# E18

CPU_D59# B19

CPU_D60# D18

CPU_D61# B18

CPU_D62# C17

CPU_D63# A18

CPU_ADSTB0#

R27

CPU_ADSTB1#

T29

CPU_BR0#

F25 CPU_DBSY#

G27

CPU_DEFER#

J27

CPU_DRDY#

L26

CPU_LOCK#

K26

CPU_TRDY#

F26

CPU_REQ0#

M29

CPU_REQ1#

N25

CPU_REQ2#

R26

CPU_REQ3#

L28

CPU_REQ4#

L29

CPU_HIT#

J26

CPU_HITM#

H25

CPU_RS0#

J25 CPU_RS1#

G26 CPU_RS2#

G25

CPU_DSTBN3# E19

CPU_DSTBN2# E22

CPU_DSTBN1# D27

CPU_DSTBN0# G30

CPU_DSTBP3# F18

CPU_DSTBP2# F22

CPU_DSTBP1# E27

CPU_DSTBP0# G29

CPU_DBI3# F19

CPU_DBI2# D23

CPU_DBI1# A28

CPU_DBI0# E28

CPU_CPURSET#

A17

CPU_COMP_P

W29

CPU_COMP_N

V28

CPVSS

J23

CPU_VREF

W28

THERMALDIODE_N

Y29

THERMALDIODE_P

Y28

TESTMODE

B17

CPVDD

H23

SYSRESET#

AG5

POWERGOOD

C7

CPU_A5#

M25

CPU_A6#

N29

CPU_A7#

N30

CPU_A8#

M26

CPU_A9#

N28

CPU_A10#

P29

CPU_A11#

P26

CPU_A12#

R29

CPU_A13#

P30

CPU_A14#

P28

CPU_A15#

N26

CPU_A16#

N27

CPU_A17#

U30

CPU_A18#

T30

CPU_A19#

R28

CPU_A20#

R25

CPU_A21#

U25

CPU_A22#

T28

CPU_A23#

V29

CPU_A24#

T26

CPU_A25#

U29

CPU_A26#

U26

CPU_A27#

V26

CPU_A28#

T25

CPU_A29#

V25

CPU_A30#

U27

CPU_A31#

U28

SUS_STAT#

AH5 CPU_RSET#

A9

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

MPVSS

DDRA_DQ44

DDRA_DQ48

DDRA_DQ49

DDRA_DQ54

DDRA_DQ59

DDRA_DM0

DDRA_DM3

DDRA_ADD15

DDRA_CLK3

MEN_COMP

DDRA_DQ3

DDRA_DQ33

DDRA_DQ52

DDRA_ADD4

DDRA_ADD8

DDRA_DM5

DDRA_CLK1

DDRA_DQ18

DDRA_DQ21

DDRA_DQ23

DDRA_ADD10

DDRA_DM6

DDRA_CLK4

DDRA_DQ6

DDRA_DQ13

DDRA_DQ38

DDRA_DQ42

DDRA_DQ43

DDRA_DQ47

DDRA_DQS1

DDRA_DQ57

DDRA_ADD12

DDRA_CLK0

DDRA_CLK1#

DDRA_DQ7

DDRA_DQ15

DDRA_DQ17

DDRA_DQ24

DDRA_DQ25

DDRA_DQ35

DDRA_DQ40

DDRA_DQ41

DDRA_DQ60

DDRA_DQ63

DDRA_ADD6

DDRA_ADD9

DDRA_RAS#

DDRA_CAS#

DDRA_DQS4

MPVDD

DDRA_CLK3#

DDRA_CLK4#

DDRA_DQ9

DDRA_DQ62

DDRA_ADD5

DDRA_DM4

DDRA_DQ4

DDRA_DQ32

DDRA_DQ34

DDRA_DQ53

DDRA_DQ56

DDRA_CKE_R0

DDRA_CKE_R1

DDRA_DQ11

DDRA_DQ14

DDRA_DQ16

DDRA_DQ37

DDRA_DQ55

DDRA_DQS5

DDRA_CLK0#

DDRA_DQ20

DDRA_DQ26

DDRA_DQ27

DDRA_DQ45

DDRA_ADD2

DDRA_ADD7

DDRA_DQ2

DDRA_DQ5

DDRA_DQ51

DDRA_DQ61

DDRA_ADD3

DDRA_ADD13

DDRA_DQS0

DDRA_DQ0

DDRA_DQ1

DDRA_DQ8

DDRA_DQ19

DDRA_DQ12

DDRA_DQ28

DDRA_DQ39

DDRA_DQ46

DDRA_ADD14

DDRA_DM2

DDRA_WE#

DDRA_DQS2

DDRA_DQ30

DDRA_DQ50

DDRA_DQ58

DDRA_ADD1

DDRA_ADD11

DDRA_DM7

DDRA_DQS6

DDRA_DQ10

DDRA_DQ22

DDRA_DQ29

DDRA_DQ36

DDRA_DM1

DDRA_DQS3

DDRA_DQ31

DDRA_ADD0

DDRA_DQS7

DDRA_CKE_R2

DDRA_CKE_R3

DDRA_CS#0

DDRA_CS#1

DDRA_CS#3

DDRA_CS#2

DDR_VREF

DDRA_DQ23

DDRA_SDQ22

DDRA_SDQ23

DDRA_DQ19

DDRA_DQ22 DDRA_SDQ18

DDRA_SDQ19

DDRA_DQ18

DDRA_ADD[0..15]

DDRA_SDQS[0..7]

DDRA_SDQ[0..63]

DDRA_SDQ0

DDRA_SDQ1

DDRA_SDQ4

DDRA_SDQ5DDRA_DQ5

DDRA_DQ1

DDRA_DQ4

DDRA_DQ0

DDRA_DQ30

DDRA_DQ29

DDRA_DQ25

DDRA_DQS3 DDRA_SDQS3

DDRA_DQ28

DDRA_DQ31

DDRA_SDQ30

DDRA_DQ27

DDRA_SDQ28

DDRA_SDQ31

DDRA_DQ24

DDRA_SDQ29

DDRA_DQ26

DDRA_SDQ24

DDRA_SDQ27

DDRA_SDQ26

DDRA_DM3 DDRA_SDM3

DDRA_SDQ25

DDRA_DM0

DDRA_DQS0 DDRA_SDQS0

DDRA_SDM0

DDRA_DQ9

DDRA_DQ10

DDRA_DQ15

DDRA_DQ11

DDRA_DQ8

DDRA_DQ12

DDRA_DQ14

DDRA_DQ13

DDRA_DM1

DDRA_DQS1

DDRA_SDM1

DDRA_SDQS1

DDRA_SDQ9

DDRA_SDQ8

DDRA_SDQ10

DDRA_SDQ11

DDRA_SDQ12

DDRA_SDQ13

DDRA_SDQ15

DDRA_SDQ14

DDRA_SDM[0..7]

DDRA_SDM5

DDRA_SDQS6DDRA_DQS6

DDRA_DM7

DDRA_DQ51

DDRA_DQ54

DDRA_SDQS7

DDRA_DQ50

DDRA_SDM7

DDRA_DQS5

DDRA_SDM4

DDRA_DQS7

DDRA_SDQS4

DDRA_SDQ50

DDRA_SDQS5

DDRA_SDQ54

DDRA_DM4

DDRA_SDQ51

DDRA_DQ55

DDRA_DM5

DDRA_SDQ55

DDRA_DQS4

DDRA_SDM6DDRA_DM6

DDRA_DQ49 DDRA_SDQ49

DDRA_SDQ53DDRA_DQ53

DDRA_SDQ48DDRA_DQ48

DDRA_DQ52 DDRA_SDQ52

DDRA_SDQ63DDRA_DQ63

DDRA_DQ59 DDRA_SDQ59

DDRA_SDQ62DDRA_DQ62

DDRA_DQ58 DDRA_SDQ58

DDRA_SDQ61DDRA_DQ61

DDRA_DQ57 DDRA_SDQ57

DDRA_SDQ56DDRA_DQ56

DDRA_DQ60 DDRA_SDQ60

DDRA_SDQ43

DDRA_SDQ47DDRA_DQ47

DDRA_DQ43

DDRA_SDQ46

DDRA_SDQ42

DDRA_DQ46

DDRA_DQ42

DDRA_DQ45

DDRA_DQ41 DDRA_SDQ45

DDRA_SDQ41

DDRA_SDQ40

DDRA_SDQ44DDRA_DQ44

DDRA_DQ40

DDRA_DQ39

DDRA_DQ35 DDRA_SDQ35

DDRA_SDQ39

DDRA_SDQ38

DDRA_SDQ34

DDRA_DQ38

DDRA_DQ34

DDRA_DQ33

DDRA_DQ37 DDRA_SDQ33

DDRA_SDQ37

DDRA_SDQ32

DDRA_SDQ36

DDRA_DQ32

DDRA_DQ36

DDRA_SDQ21

DDRA_SDQ17

DDRA_DQ21

DDRA_DQ17

DDRA_SDQ16

DDRA_SDQ20

DDRA_DQ16

DDRA_DQ20

DDRA_DM2 DDRA_SDM2

DDRA_SDQS2

DDRA_DQ2

DDRA_DQ3

DDRA_DQ6

DDRA_DQ7 DDRA_SDQ3

DDRA_SDQ7

DDRA_SDQ2

DDRA_SDQ6

DDRA_DQS2

DDRA_CLK0<14>

DDRA_CLK3<15>

DDRA_CLK1#<14>

DDRA_CLK4<15>

DDRA_CLK3#<15>

DDRA_CLK1<14>

DDRA_CLK4#<15>

DDRA_CLK0#<14>

DDRA_SDQ[0..63] <14,15,16>

DDRA_SDQS[0..7] <14,15,16>

DDRA_SDM[0..7] <14,15,16>

DDRA_ADD[0..15] <14,15,16>

DDRA_CKE_R0<14,16> DDRA_CKE_R1<14,16> DDRA_CKE_R2<15,16> DDRA_CKE_R3<15,16>

DDRA_CS#0<14,16> DDRA_CS#1<14,16> DDRA_CS#2<15,16> DDRA_CS#3<15,16>

DDRA_RAS#<14,15,16> DDRA_CAS#<14,15,16>

DDRA_WE#<14,15,16>

+2.5V

+1.8VS

+2.5V+2.5V

DDR_VREF

+2.5V

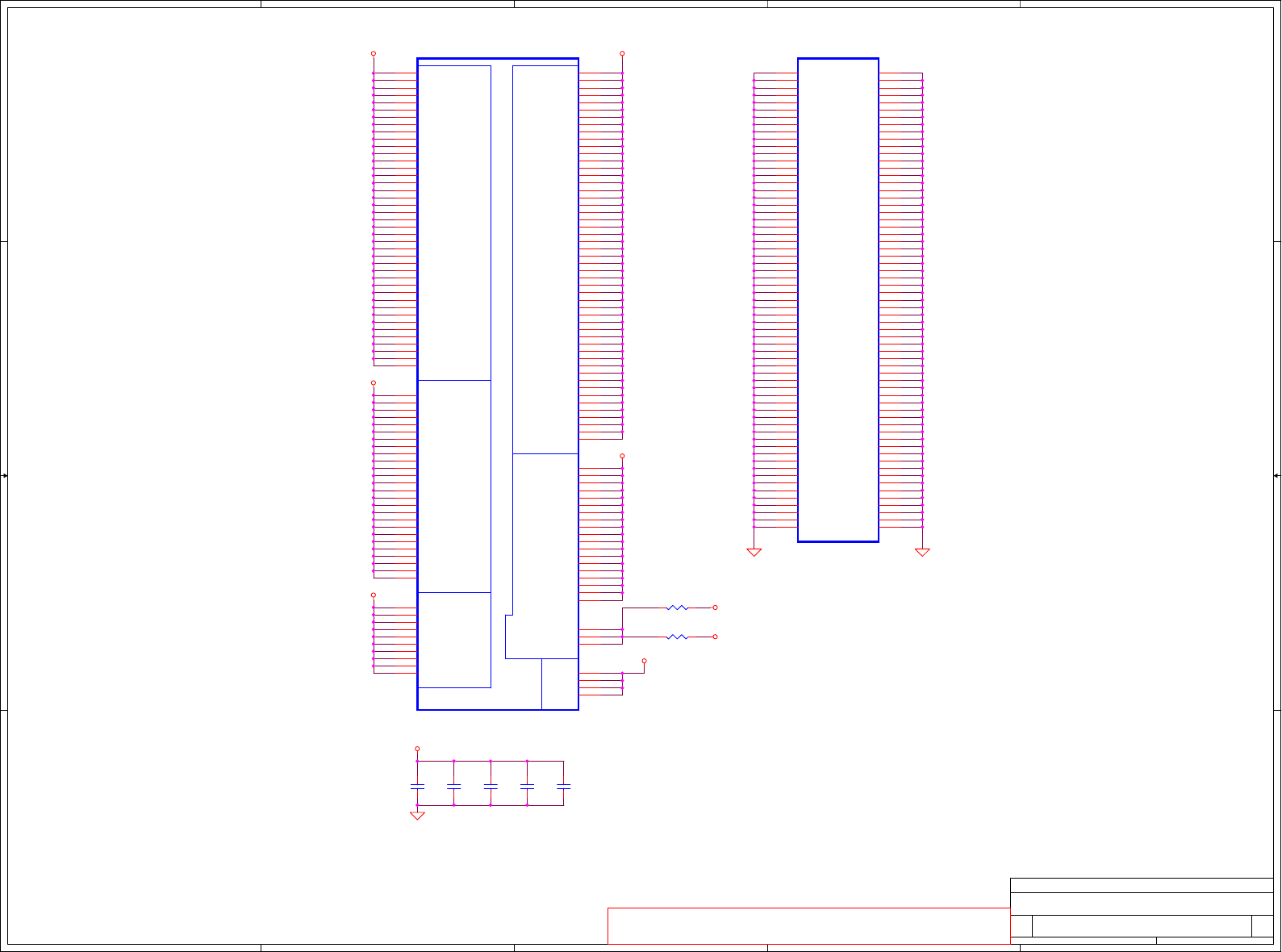

Title

Size Document Number Rev

Date: Sheet of

LA-2411

0.1

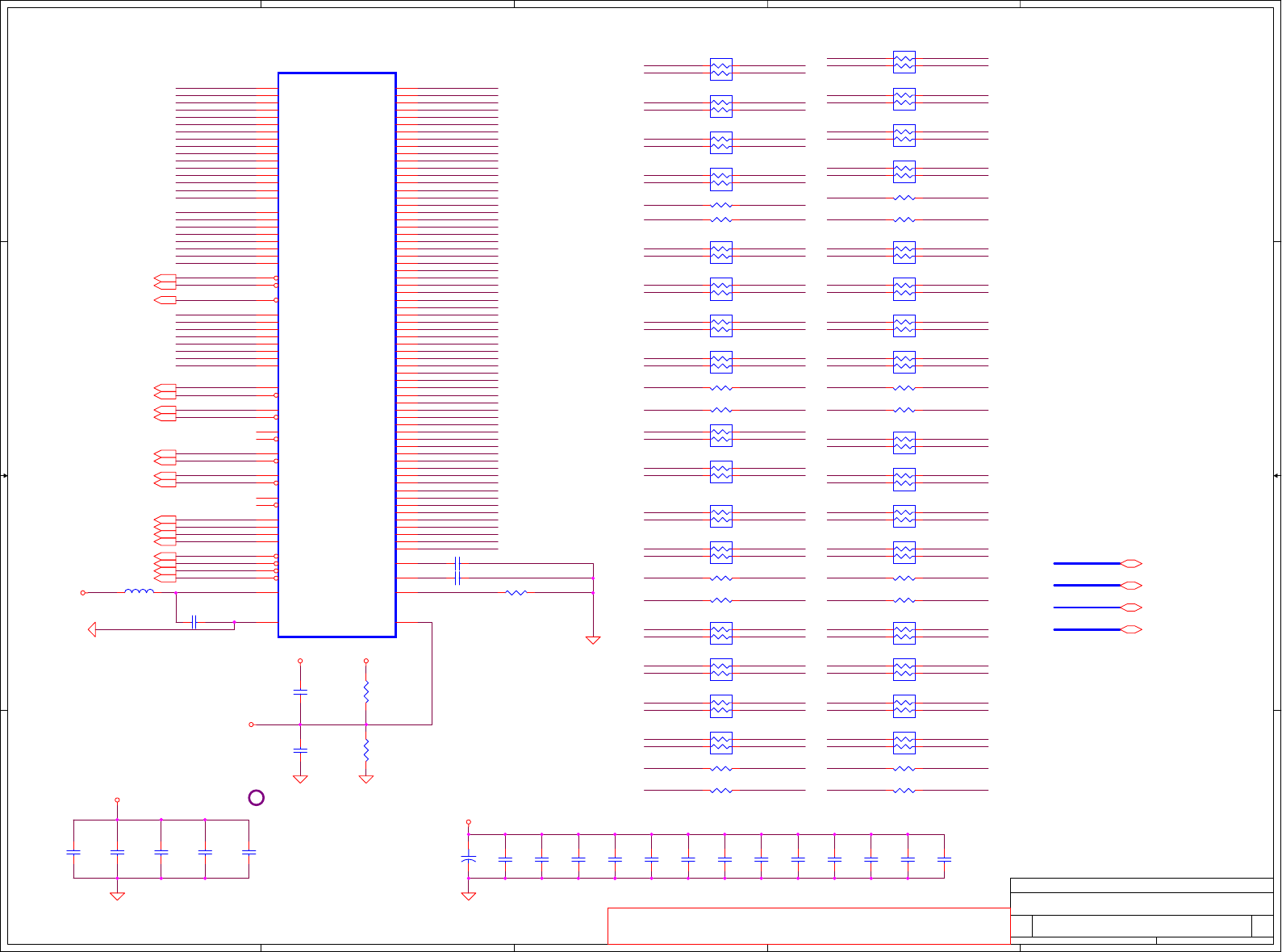

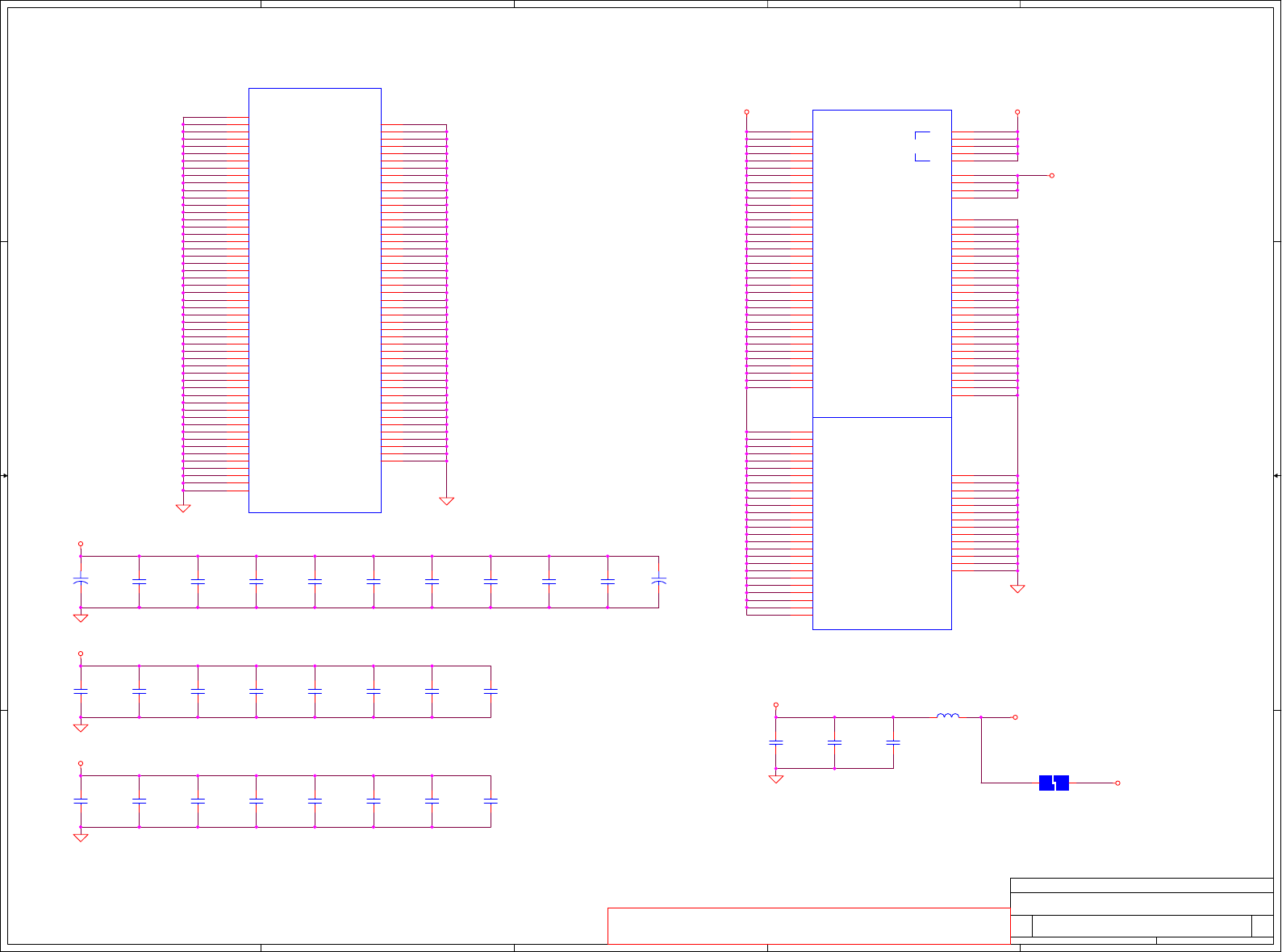

ATI RC300M-DDR I/F

965, 07, 2004

星期三 七月

Compal Electronics, Inc.

DDR_VREF trace width of

20mils and space

20mils(min)

L

Group 6 sweep Group 7

Place these resistor

closely DIMM0,

all trace length

Max=0.75"

Layout note

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

RP64

0_0404_4P2R_5%

1 4

2 3

C381

0.1U_0402_10V6K

1

2

RP46

0_0404_4P2R_5%

1 4

2 3

R405 49.9_0402_1%

1 2

RP31

0_0404_4P2R_5%

1 4

2 3

RP52

0_0404_4P2R_5%

1 4

2 3

RP61

0_0404_4P2R_5%

1 4

2 3

C376

0.1U_0402_10V6K 1

2

C384

0.1U_0402_10V6K

1

2

C385

0.1U_0402_10V6K

1

2

C374 0.47U_0603_16V7K

1 2

RP63

0_0404_4P2R_5%

1 4

2 3

C860

@0.1U_0402_10V6K

1

2

RP30

0_0404_4P2R_5%

1 4

2 3

RP47

0_0404_4P2R_5%

1 4

2 3

RP36

0_0404_4P2R_5%

1 4

2 3

RP33

0_0404_4P2R_5%

1 4

2 3

C380

0.1U_0402_10V6K

1

2

RP55

0_0404_4P2R_5%

1 4

2 3

C388

0.1U_0402_10V6K

1

2

R412 0_0402_5%

12

RP34

0_0404_4P2R_5%

1 4

2 3

R403 0_0402_5%

12

C386

0.1U_0402_10V6K

1

2

RP48

0_0404_4P2R_5%

1 4

2 3

RP51

0_0404_4P2R_5%

1 4

2 3

C382

0.1U_0402_10V6K

1

2

C859

@0.1U_0402_10V6K

1

2

R413 0_0402_5%

12

RP45

0_0404_4P2R_5%

1 4

2 3

R415 0_0402_5%

12

R395 0_0402_5%

12

RP37

0_0404_4P2R_5%

1 4

2 3

R387 0_0402_5%

12

+

C378

150U_D2_6.3VM

1

2

R404 0_0402_5%

12

R406 0_0402_5%

12

R409

1K_0603_1%

12

R408

1K_0603_1%

12

RP44

0_0404_4P2R_5%

1 4

2 3

R416 0_0402_5%

12

R394 0_0402_5%

12

R398 0_0402_5%

12

C858

@0.1U_0402_10V6K

1

2

C383

0.1U_0402_10V6K

1

2

RP62

0_0404_4P2R_5%

1 4

2 3

RP58

0_0404_4P2R_5%

1 4

2 3

RP54

0_0404_4P2R_5%

1 4

2 3

RP59

0_0404_4P2R_5%

1 4

2 3

RP40

0_0404_4P2R_5%

1 4

2 3

R389 0_0402_5%

12

RP43

0_0404_4P2R_5%

1 4

2 3

R386 0_0402_5%

12

MEM I/F

PART 2 OF 6

U27B

216RC300M_BGA_718

MEM_DQ0 AG6

MEM_DQ1 AJ7

MEM_DQ2 AJ9

MEM_DQ3 AJ10

MEM_DQ4 AJ6

MEM_DQ5 AH6

MEM_DQ6 AH8

MEM_DQ7 AH9

MEM_DQ8 AE7

MEM_DQ9 AE8

MEM_DQ10 AE12

MEM_DQ11 AF12

MEM_DQ12 AF7

MEM_DQ13 AF8

MEM_DQ14 AE11

MEM_DQ15 AF11

MEM_DQ16 AJ12

MEM_DQ17 AH12

MEM_DQ18 AH14

MEM_DQ19 AH15

MEM_DQ20 AH11

MEM_DQ21 AJ13

MEM_DQ22 AJ15

MEM_DQ23 AJ16

MEM_DQ24 AF18

MEM_DQ25 AG20

MEM_DQ26 AG21

MEM_DQ27 AF22

MEM_DQ28 AF19

MEM_DQ29 AF20

MEM_DQ30 AE22

MEM_DQ31 AF23

MEM_DQ32 AJ21

MEM_DQ33 AJ22

MEM_DQ34 AJ24

MEM_DQ35 AK25

MEM_DQ36 AH21

MEM_DQ37 AH22

MEM_DQ38 AH24

MEM_DQ39 AJ25

MEM_DQ40 AK26

MEM_DQ41 AK27

MEM_DQ42 AJ28

MEM_DQ43 AH29

MEM_DQ44 AH25

MEM_DQ45 AJ26

MEM_DQ46 AJ29

MEM_DQ47 AH30

MEM_DQ48 AF29

MEM_DQ49 AE29

MEM_DQ50 AB28

MEM_DQ51 AA28

MEM_DQ52 AE28

MEM_DQ53 AD28

MEM_DQ54 AC29

MEM_DQ55 AB29

MEM_DQ56 AC26

MEM_DQ57 AB25

MEM_DQ58 Y26

MEM_DQ59 W26

MEM_DQ60 AE26

MEM_DQ61 AD26

MEM_DQ62 AA26

MEM_DQ63 Y27

MEM_DDRVREF AK20

MEM_A0

AH19

MEM_A1

AJ17

MEM_A2

AK17

MEM_A3

AH16

MEM_A4

AK16

MEM_A5

AF17

MEM_A6

AE18

MEM_A7

AF16

MEM_A8

AE17

MEM_A9

AE16

MEM_A10

AJ20

MEM_A11

AG15

MEM_A12

AF15

MEM_A13

AE23

MEM_A14

AH20

MEM_DM0

AH7

MEM_DM1

AF10

MEM_DM2

AJ14

MEM_DM3

AF21

MEM_DM4

AH23

MEM_DM5

AK28

MEM_DM6

AD29

MEM_DM7

AB26

MEM_RAS#

AF24

MEM_CAS#

AF25

MEM_WE#

AE24

MEM_CKE0

AF13

MEM_DQS0

AJ8

MEM_DQS1

AF9

MEM_DQS2

AH13

MEM_DQS3

AE21

MEM_DQS4

AJ23

MEM_DQS5

AJ27

MEM_DQS6

AC28

MEM_DQS7

AA25

MEM_CK0#

AH10 MEM_CK0

AK10

MEM_CS#0

AH26

MEM_CS#1

AH27

MEM_CS#2

AF26

MEM_CS#3

AG27

MPVDD

AC18

MPVSS

AD18

MEM_A15

AE25

MEM_CKE1

AE13

MEM_CK1

AH18

MEM_CK1#

AJ19

MEM_CK2

AG30

MEM_CK2#

AG29

MEM_CK3

AK11

MEM_CK3#

AJ11

MEM_CK4

AH17

MEM_CK4#

AJ18

MEM_CK5

AF28

MEM_CK5#

AG28

MEM_CKE2

AG14

MEM_CKE3

AF14

MEM_CAP1 AF6

MEM_CAP2 AA29

MEM_COMP AK19

RP41

0_0404_4P2R_5%

1 4

2 3

RP49

0_0404_4P2R_5%

1 4

2 3

RP57

0_0404_4P2R_5%

1 4

2 3

L35

HB-1M2012-121JT03_0805

1 2

C391

0.1U_0402_10V6K

1

2

RP28

0_0404_4P2R_5%

1 4

2 3

RP50

0_0404_4P2R_5%

1 4

2 3

R388 0_0402_5%

12

C387

0.1U_0402_10V6K

1

2

RP56

0_0404_4P2R_5%

1 4

2 3

C375

2.2U_0805_10V4Z

1 2

C379

0.1U_0402_10V6K

1

2

C857

0.1U_0402_10V6K

1

2

C373 0.47U_0603_16V7K

1 2

R407 0_0402_5%

12

RP27

0_0404_4P2R_5%

1 4

2 3

R397 0_0402_5%

12

RP60

0_0404_4P2R_5%

1 4

2 3

C390

0.1U_0402_10V6K

1

2

C389

0.1U_0402_10V6K

1

2

C861

@0.1U_0402_10V6K

1

2

RP53

0_0404_4P2R_5%

1 4

2 3

C377

0.1U_0402_10V6K 1

2

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

A_AD[0..31]

A_CBE#[0..3]

AGP_AD2

AGP_SBA2

AGP_WBF#

AGP_AD27

AGP_AD18

AGP_AD4

AGP_SBSTB#

AGP_AD13

AGP_PAR

AGP_SBA6

AGP_SBA1

AGP_AD25

AGP_AD20

AGP_AD7

AGP_AD6

AGP_ST2

AGP_AD28

AGP_CBE#3

AGP_AD31

AGP_AD14

AGP_AD3

AGP_DBI_LO

AGP_RBF#

AGP_SBA4

AGP_AD12

AGP_AD1

AGP_DEVSEL#

AGP_ADSTB1

AGP_SBSTB

AGP_AD26

AGP_AD10

AGP_ST0

AGP_ADSTB1#

AGP_AD29

AGP_AD22

AGP_DBI_HI/PIPE#

AGP_STOP#

AGP_ADSTB0

AGP_AD19

AGP_AD9

AGP_ST1

AGP_SBA7

AGP_CBE#0

AGP_AD23

AGP_AD8

AGP_AD16

AGP_AD11

AGP_SBA5

AGP_SBA3

AGP_FRAME#

AGP_CBE#2

AGP_ADSTB0#

AGP_AD5

AGP_AD0

AGP_IRDY#

AGP_CBE#1

AGP_AD21

AGP_AD17

AGP_SBA0

AGP_TRDY#

AGP_AD30

AGP_AD24

AGP_AD15

A_AD11

A_AD17

A_AD20

A_END#

A_AD27

A_AD6

A_DEVSEL#

A_AD26

A_AD24

A_AD25

A_AD18

A_AD9

A_AD0

A_AD3

A_AD7

A_AD5

A_ACAT#

A_AD12

A_AD15

A_SBGNT#

A_AD1

A_AD13

A_AD16

A_AD30

A_AD22

A_AD29

AGP_GNT#

A_CBE#3

A_OFF#

A_AD31

A_AD8

A_SBREQ#

A_CBE#0

A_CBE#1

A_CBE#2

A_AD23

A_AD14

A_PAR

A_AD19

A_AD4

A_AD28

A_AD2

A_STROBE#

A_AD10

AGP_REQ#

A_AD21

AGP_SBA2

AGP_SBA3

ENBKL#

AGP_SBA4

AGP_SBA5

AGPREF_8X

AGP_COMP

AGP8X_DET#

DDC_DAT

DDC_CLK

AGP8X_DET#

AGPREF_8X

AGP_ST[0..2]

AGP_AD[0..31]

AGP_SBA[0..7]

AGP_CBE#[0..3]

AGP_SBA1

AGP_SBA0

ENBKL#

A_AD[0..31]<13,26>

A_CBE#[0..3]<13,26>

AGP_RBF# <17>

AGP_WBF# <17>

AGP_TRDY# <17>

AGP_IRDY# <17>

AGP_FRAME# <17>

AGP_ADSTB1# <17>

AGP_ADSTB0# <17>

AGP_STOP# <17>

AGP_SBSTB# <17>

AGP_SBSTB <17>

AGP_PAR <17>

AGP_ADSTB1 <17>

AGP_ADSTB0 <17>

AGP_DBI_HI/PIPE# <17>

AGP_DBI_LO <17>

AGP_DEVSEL# <17>

AGP_GNT#<17> AGP_REQ#<17>

VREF_8X_IN<17>

A_DEVSEL#<26>

A_SBGNT#<26>

A_OFF#<26>

A_END#<26>

A_SBREQ#<26>

A_ACAT#<26>

A_PAR<13,26>

A_STROBE#<26>

ENAVDD <17,25>

AGP_BUSY# <17,27>

AGP_STP# <17,27>

DDC_DAT <17,25>

DDC_CLK <17,25>

PCI_PIRQA#<17,26,31,34>

AGP8X_DET#<17>

AGP_AD[0..31] <17>

AGP_SBA[0..7] <17>

AGP_ST[0..2] <17>

AGP_CBE#[0..3] <17>

ENBKL <17,44>

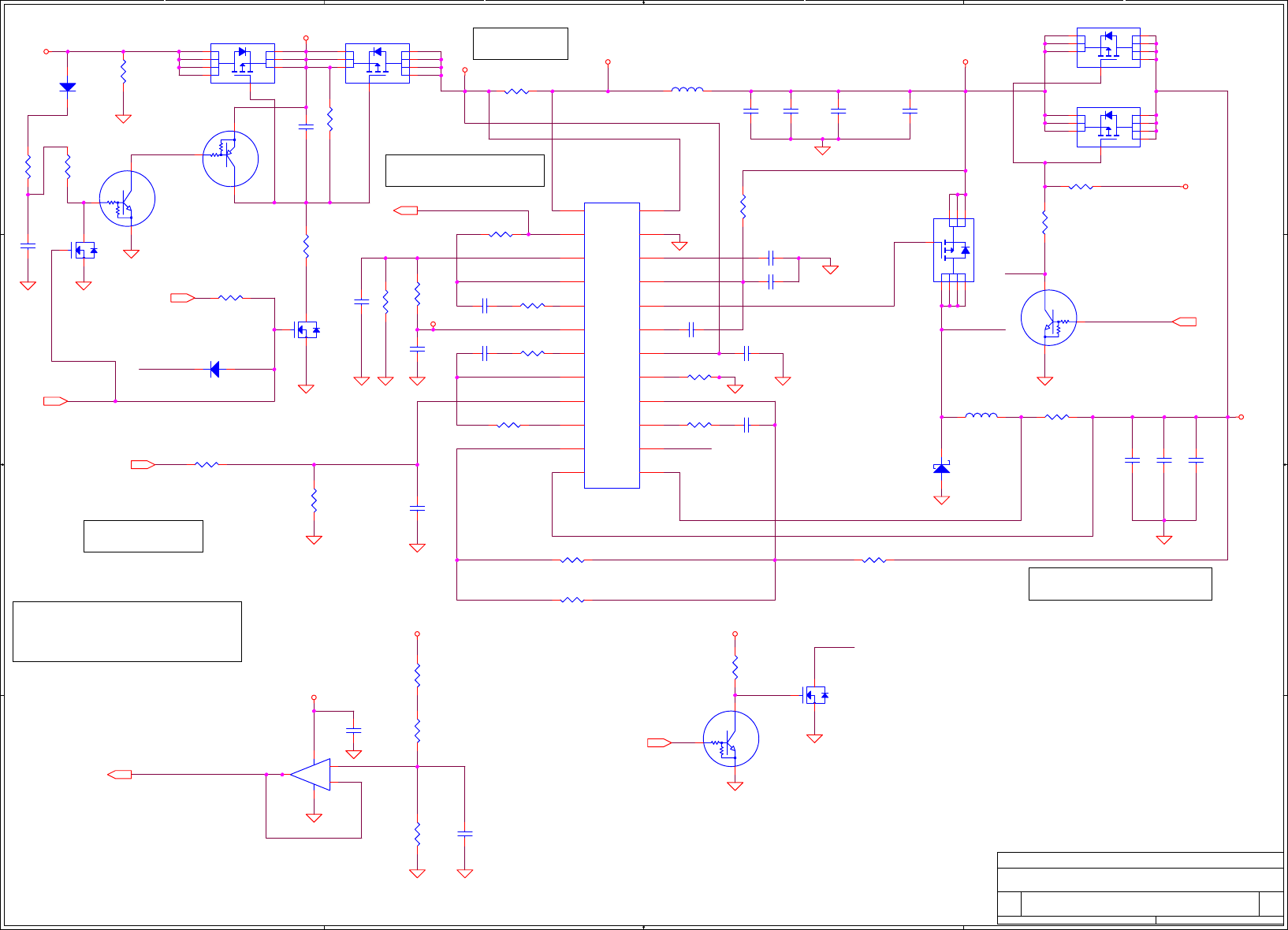

NB_PWRGD<8,46>

+1.5VS +3VS

+3VS

+3VS

+1.5VS

+1.5VS

+1.5VS+1.5VS

+1.5VS

+3VS

+3VS

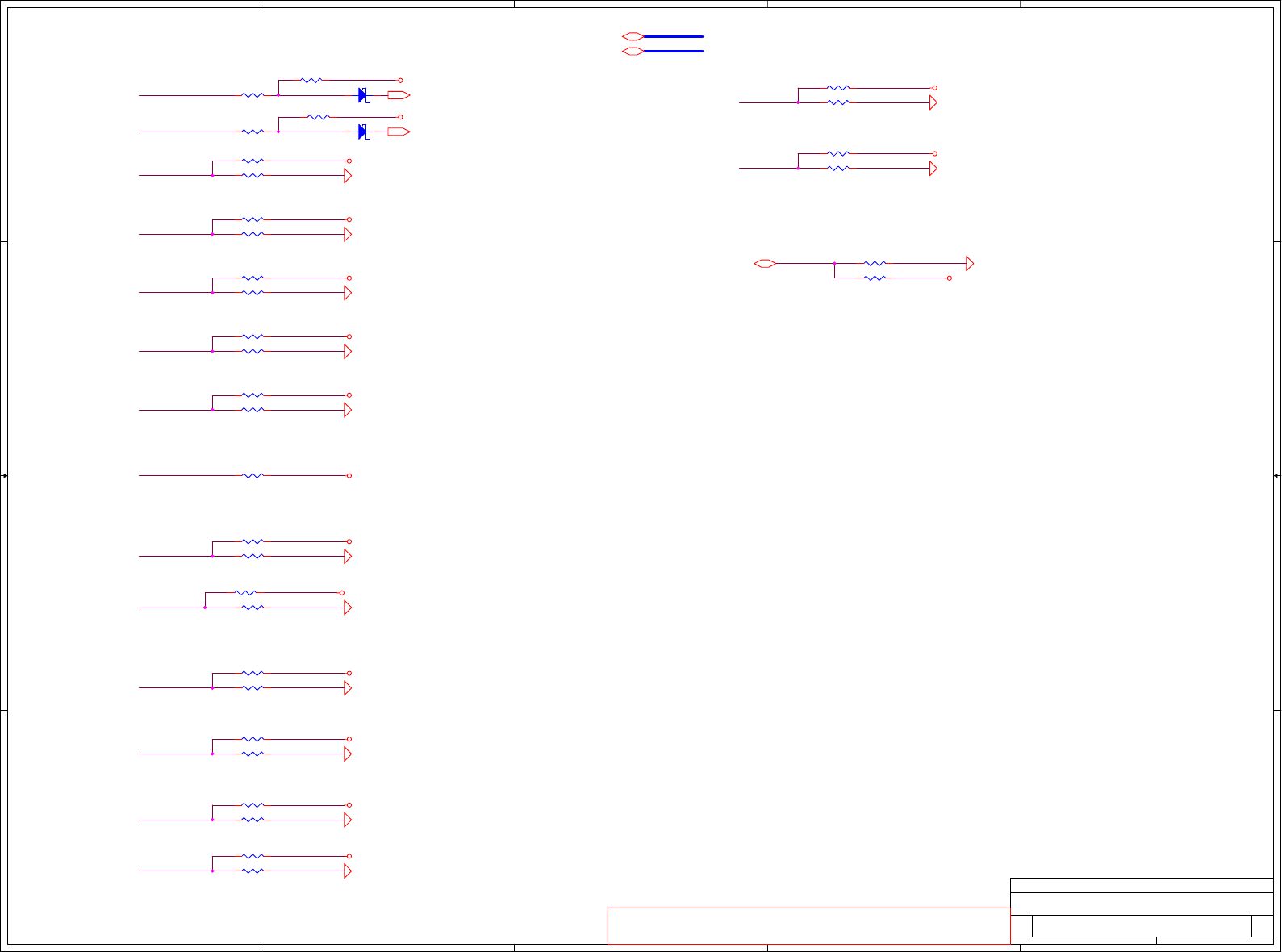

Title

Size Document Number Rev

Date: Sheet of

LA-2411

0.1

ATI RC300M-AGP, ALINK BUS

10 65, 07, 2004

星期三 七月

Compal Electronics, Inc.

AGPAND LVDS MUXED SIGNALS

?

PLACE CLOSE TO

CONNECTOR

8X(M9+M10@)

Ra

169_0402_1%

324_0402_1%

100_0402_1%

4X(NAGP@)

Rb

Rc

Ra

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

ATI request

1K_0402_1%

1K_0402_1%

Rb

Rc

Note: PLACE CLOSE TO U27 (NB RC300M)

L

Pop for internal AGP

Depop for M11P

Pop for internal AGP

Depop for M11P

Depop

C553

0.1U_0402_10V6K

1

2

C550

0.1U_0402_10V6K

1 2

R945

NAGP@47K_0402

1 2

G

D

S

Q1

NAGP@2N7002_SOT23

2

13

C557

0.1U_0402_10V6K

1

2

C573

0.1U_0402_10V6K

1

2

C943

0.1U_0402_10V6K

1

2

R560 NAPG@0_0402_5%

1 2

C556

0.1U_0402_10V6K

1

2

C935

0.01U_0402_16V7Z

1

2

C570

0.1U_0402_10V6K

1

2

C567

0.1U_0402_10V6K

1

2

C864

0.01U_0402_16V7Z

1

2

C572

0.1U_0402_10V6K

1

2

C560

0.1U_0402_10V6K

1

2

C951

0.01U_0402_16V7Z

1

2

R568

NAPG@10K_0402_5%

1 2

C938

0.1U_0402_10V6K

1

2

C950

0.01U_0402_16V7Z

1

2

C942

0.1U_0402_10V6K

1

2

C948

0.01U_0402_16V7Z

1

2

C574

0.1U_0402_10V6K

1

2

R576

324_0402_1%

1 2

C554

0.1U_0402_10V6K

1

2

R563 NAPG@0_0402_5%

1 2

C934

0.01U_0402_16V7Z

1

2

C578

0.1U_0402_10V6K

1

2

C947

0.01U_0402_16V7Z

1

2

C555

0.1U_0402_10V6K

1

2

R577

100_0402_1%

1 2

C939

0.1U_0402_10V6K

1

2

C945

0.1U_0402_10V6K

1

2

C568

0.1U_0402_10V6K

1

2

+

C551

47U_B_6.3VM

1

2

G

D

S

Q2

NAGP@2N7002_SOT23

2

13

C936

0.01U_0402_16V7Z

1

2

C562

0.1U_0402_10V6K

1

2

C940

0.1U_0402_10V6K

1

2

C946

0.1U_0402_10V6K

1

2

C577

0.1U_0402_10V6K

1

2

C569

0.1U_0402_10V6K

1

2

R570

8.2K_0402_5%

1 2

R569

NAGP@0_0402_5%

1 2

C563

0.1U_0402_10V6K

1

2

C561

0.1U_0402_10V6K

1

2

C564

0.1U_0402_10V6K

1

2

C566

0.1U_0402_10V6K

1

2

C576

0.1U_0402_10V6K

1

2

C571

0.1U_0402_10V6K

1

2

C559

0.1U_0402_10V6K

1

2

C632

10U_0805_10V4Z

1

2

C941

0.1U_0402_10V6K

1

2

C575

0.1U_0402_10V6K

1

2

R561 NAPG@0_0402_5%

1 2

R562 NAPG@0_0402_5%

1 2

R567

NAGP@10K_0402_5%

1 2

C933

0.01U_0402_16V7Z

1

2

C949

0.01U_0402_16V7Z

1

2

R994 NAPG@0_0402_5%

1 2

C558

0.1U_0402_10V6K

1

2

+

C552

47U_B_6.3VM

1

2

C944

0.1U_0402_10V6K

1

2

R575

169_0402_1%

1 2

R1005 0_0402_5%

1 2

C565

0.1U_0402_10V6K

1

2

C937

0.1U_0402_10V6K

1

2

PART 3 OF 6

PCI Bus 0 / A-Link I/F

PCI BUS 1 / AGP Bus (GPIO , TMDS , ZVPort)

U27C

216RC300M_BGA_718

ALINK_AD0

AK5

ALINK_AD1

AJ5

ALINK_AD2

AJ4

ALINK_AD3

AH4

ALINK_AD4

AJ3

ALINK_AD5

AJ2

ALINK_AD6

AH2

ALINK_AD7

AH1

ALINK_AD8

AG2

ALINK_AD9

AG1

ALINK_AD10

AG3

ALINK_AD11

AF3

ALINK_AD12

AF1

ALINK_AD13

AF2

ALINK_AD14

AF4

ALINK_AD15

AE3

ALINK_AD16

AE4

ALINK_AD17

AE5

ALINK_AD18

AE6

ALINK_AD19

AC2

ALINK_AD20

AC4

ALINK_AD21

AB3

ALINK_AD22

AB2

ALINK_AD23

AB5

ALINK_AD24

AB6

ALINK_AD25

AA2

ALINK_AD26

AA4

ALINK_AD27

AA5

ALINK_AD28

AA6

ALINK_AD29

Y3

ALINK_AD30

Y5

ALINK_AD31

Y6

ALINK_CBE#0

AG4

ALINK_CBE#1

AE2

ALINK_CBE#2

AC3

ALINK_CBE#3

AA3

PCI_PAR/ALINK_NC

AD5

PCI_FRAME#/ALINK_STROBE#

AC6

PCI_IRDY#/ALINK_ACAT#

AC5

PCI_TRDY#/ALINK_END#

AD2

INTA#

W4

ALINK_DEVSEL#

AD3

PCI_STOP#/ALINK_OFF#

AD6

ALINK_SBREQ#

W5

ALINK_SBGNT#

W6

PCI_REQ#0/ALINK_NC

V5

PCI_GNT#0/ALINK_NC

V6

AGP_AD0/TMD2_HSYNC Y2

AGP_AD1/TMD2_VSYNC W3

AGP_AD2/TMD2_D1 W2

AGP_AD3/TMD2_D0 V3

AGP_AD4/TMD2_D3 V2

AGP_AD5/TMD2_D2 V1

AGP_AD6/TMD2_D5 U1

AGP_AD7/TMD2_D4 U3

AGP_AD8/TMD2_D6 T2

AGP_AD9/TMD2_D9 R2

AGP_AD10/TMD2_D8 P3

AGP_AD11/TMD2_D11 P2

AGP_AD12/TMD2_D10 N3

AGP_AD13 N2

AGP_AD14 M3

AGP_AD15 M2

AGP_AD16/TMD1_VSYNC L1

AGP_AD17/TMD1_HSYNC L2

AGP_AD18/TMD1_DE K3

AGP_AD19/TMD1_D0 K2

AGP_AD20/TMD1_D1 J3

AGP_AD21/TMD1_D2 J2

AGP_AD22/TMD1_D3 J1

AGP_AD23/TMD1_D4 H3

AGP_AD24/TMD1_D7 F3

AGP_AD25/TMD1_D6 G2

AGP_AD26/TMD1_D9 F2

AGP_AD27/TMD1_D8 F1

AGP_AD28/TMD1_D11 E2

AGP_AD29/TMD1_D10 E1

AGP_AD30/TMDS_HPD D2

AGP_AD31 D1

AGP2_SBSTB/AGP3_SBSTBF/NC/LVDS_BLON E5

AGP2_SBSTB#/AGP3_SBSTBS/NC/ENA_BL E6

AGP2_ADSTB0/AGP3_ADSTBF0/TMD2_CLK# T3

AGP2_ADSTB0#/AGP3_ADSTBS0/TMD2_CLK U2

AGP2_ADSTB1/AGP3_ADSTBF1/TMD1_CLK# G3

AGP2_ADSTB1#/AGP3_ADSTBS1/TMD1_CLK H2

AGP2_CBE#0/AGP3_CBE0/TMD2_D7 R3

AGP2_CBE#1/AGP3_CBE1/TMD2_DE M1

AGP2_CBE#2/AGP3_CBE2 L3

AGP2_CBE#3/AGP3_CBE3/TMD1_D5 H1

AGP2_DEVSEL#/AGP3_DEVSEL/GPIO9/I2C_DATA R5

AGP2_FRAME#/AGP3_FRAME/TMDS_DVI_DATA P6

AGP2_IRDY#/AGP3_IRDY/GPIO8/I2C_CLK P5

AGP2_TRDY#/AGP3_TRDY/TMDS_DVI_CLK R6

AGP2_WBF#/AGP3_WBF N5

AGP2_SBA0/AGP3_SBA#0/GPIO0/VDDC_CNTL0 C3

AGP2_SBA1/AGP3_SBA#1/GPIO1/VDDC_CNTL1 C2

AGP2_SBA3/AGP3_SBA#3/GPIO3/LVDS_DIGON E4

AGP2_SBA5/AGP3_SBA#5/GPIO5/AGP_BUSY# F5

AGP2_SBA6/AGP3_SBA#6/GPIO6/LVDS_SSOUT G6

AGP2_SBA7/AGP3_SBA#7/GPIO7/LVDS_SSIN G5

AGP_ST0 L6

AGP_ST1 M6

AGP_ST2 L5

AGP8X_DET#

M5

AGP_VREF/TMDS_VREF

J6

AGP2_REQ#/AGP3_REQ

K6 AGP2_GNT#/AGP3_GNT

K5

AGP2_SBA2/AGP3_SBA#2/GPIO2/LVDS_BLON# D4

AGP2_SBA4/AGP3_SBA#4/GPIO4/STP_AGP# F6

AGP2_STOP#/AGP3_STOP/GPIO10/DDC_DATA T6

AGP_PAR T5

AGP2_RBF#/AGP3_RBF N6

AGP2_PIPE#/AGP3_DBI_HI C1

AGP2_NC/AGP3_DBI_LO D3

AGP_COMP

J5

R995 NAPG@0_0402_5%

1 2

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

RC300M_X2

RC300M_X1

CLK_AGP_66M

CLK_MEM_66M

CLK_AGP_66M

+1.8VS_LPVDD

+1.8VS_LVDDR

CRMA_R

COMPS_R

LUMA_R

HSYNC_R

GREEN_R

RED_R

BLUE_R

VSYNC_R

NB_RSET

CLK_NB_BCLK#

CLK_NB_BCLK

RC300M_X2

3VDDCCL

DDCDATA_R

DDCCLK_R

CRMA_R

3VDDCDA

DDCDATA_R

DDCCLK_R

CLK_MEM_66M

GREEN_RCRT_G

VSYNC_R

CRT_B BLUE_R

CRT_HSYNC

CRT_R

HSYNC_R

RED_R

CRT_VSYNC

RC300M_X1

TV_CRMA

LUMA_R TV_LUMA

TV_COMPSCOMPS_R

PLLVDD_18

+1.8VS_AVDDQ

+1.8VS_AVDDDI

CPUCLK_STP#

CLK_AGP_66M<24>

TXACLK-_NB <25>

TXA0+_NB <25>

TXB0+_NB <25>

TXB2+_NB <25>

TXBCLK-_NB <25>

TXB2-_NB <25>

TXA1-_NB <25>

TXBCLK+_NB <25>

TXA0-_NB <25>

TXB1+_NB <25>

TXB1-_NB <25>

TXA2-_NB <25>

TXACLK+_NB <25>

TXA2+_NB <25>

CLK_NB_BCLK#<24> CLK_NB_BCLK<24>

3VDDCCL <17,25>

TV_LUMA <17,46>

TV_COMPS <17,46>

TV_CRMA <17,46>

3VDDCDA <17,25>

CLK_MEM_66M<24>

CRT_HSYNC<17,25> CRT_VSYNC<17,25>

CRT_B<17,25>

CRT_R<17,25> CRT_G<17,25>

REFCLK1_NB<24>

TXB0-_NB <25>

TXA1+_NB <25>

PCI_RST# <26,30,31,33,34,38,41,44>

CPUCLK_STP# <5,26,54>

+1.8VS

+1.8VS

+3VS

+3VS

+1.8VS

+1.8VS

+1.8VS

+3VS

+2.5VS

Title

Size Document Number Rev

Date: Sheet of

LA-2411

0.1

ATI RC300M-VIDEO I/F

11 65, 07, 2004

星期三 七月

Compal Electronics, Inc.

Note: PLACE CLOSE TO U27 (NB CHIP)

L

Note: PLACE CLOSE TO U6 (VGA CHIP)

L

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

L

Note: PLACE CLOSE TO U27 (NB CHIP)

R595 NAPG@0_0402_5%

1 2

C600

10U_0805_16V4Z

1

2

R590 1K_0402_5%

R599 NAPG@0_0402_5%

1 2

C601

@15P_0402_50V8J

L58

FBM-11-160808-121-T_0603

1 2

C594

0.1U_0402_10V6K

1

2

L63

KC FBM-L11-201209-221LMAT_0805

1 2

R587

56_0402_5%

12

R596 NAPG@0_0402_5%

1 2

RP104

NAGP@0_4P2R_0402_5%

14 23

L59

KC FBM-L11-201209-221LMAT_0805

12

L61

KC FBM-L11-201209-221LMAT_0805

1 2

C587

0.1U_0402_10V6K

1

2

L62

KC FBM-L11-201209-221LMAT_0805

1 2

R592 10K_0402_5%

R597 NAPG@0_0402_5%

1 2

C605

@18P_0402_50V8K

C588

0.1U_0402_10V6K

1

2

Y4

@14.31818MHZ_20P_6X1430004201

12

R593

@1M_0402_1%

12

L60

KC FBM-L11-201209-221LMAT_0805

1 2

R589 @0_0402_5%

C598

0.1U_0402_10V6K

1

2

R591

@10_0402_5%

12

C592

0.1U_0402_10V6K

1

2

G

D

S

Q97

@2N7002 1N_SOT23

2

1 3

L64

KC FBM-L11-201209-221LMAT_0805

1 2

PART 4 OF 6

CRT

CLK. GEN.

SVID LVDS

U27D

216RC300M_BGA_718

TXOUT_U0N D12

TXOUT_U0P E12

TXOUT_U1N F11

TXOUT_U1P F12

TXOUT_U2N D13

TXOUT_U2P D14

TXCLK_UN E13

TXCLK_UP F13

TXOUT_L0N E10

TXOUT_L0P D10

TXOUT_L1N B9

TXOUT_L1P C9

TXOUT_L2N D11

TXOUT_L2P E11

TXCLK_LN B10

TXCLK_LP C10

LVDDR_18 B12

LPVSS A11

LVDDR_18 C12

LPVDD_18 A12

LVSSR B11

LVSSR C11

C_R E15

Y_G C15

COMP_B D15

DACSCL D6

DACSDA C6

CPUSTOP# D5

RED

F14

GREEN

F15

BLUE

E14

DACHSYNC

C8

DACVSYNC

D9

RSET

C14

VDDR3

H9

AVDDQ

A15

AVSSN

B13

AVDD_25

A14

AVDDDI_18

B14

AVSSDI

C13

AVSSQ

B15

PLLVDD_18

H11

PLLVSS

G11

VDDR3

G9

XTALIN

A4

XTALOUT

B4

EXT_MEM_CLK

A3

SYSCLK A8

SYSCLK# B8

AGPCLKIN

B3

HCLKIN#

B5

ALINK_CLK

D8

AGPCLKOUT

B2

USBCLK

D7

REF27

B7

SYS_FBCLKOUT

B6

OSC

C5

SYS_FBCLKOUT#

A6

HCLKIN

A5

C596

10U_0805_16V4Z

1

2

R594 NAPG@0_0402_5%

1 2

R584 715 _0402_1%

1 2

R598 NAPG@0_0402_5%

1 2

C590

0.1U_0402_10V6K

1

2

C591

10U_0805_16V4Z

1

2

C589

0.1U_0402_10V6K

1

2

C603

@15P_0402_50V8J

C586

0.1U_0402_10V6K

1

2

R588

@10_0402_5%

12

RP103

NAGP@0_4P2R_0402_5%

1 4

2 3

C599

0.1U_0402_10V6K

1

2

C593

0.1U_0402_10V6K

1

2

C604

@18P_0402_50V8K

R585 0_0402_5%

1 2

C595

0.1U_0402_10V6K

1

2

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

+1.5VS +2.5V

+VCC_CORE

+3VS

+3VS

+1.5VS

+1.8VS

+1.5VS

+1.8VS

Title

Size Document Number Rev

Date: Sheet of

LA-2411

0.1

ATI RC300M-POWER

12 65, 07, 2004

星期三 七月

Compal Electronics, Inc.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

Pop for M11P

Depop for internal AGP

Pop for internal AGP

Depop for M11P

C583

0.1U_0402_10V6K

1

2

C582

0.1U_0402_10V6K

1

2

C579

10U_0805_10V4Z

1

2

C580

0.1U_0402_10V6K

1

2

R418 M9-M10@0_0603_5%

1 2

C581

0.1U_0402_10V6K

1

2

PART 6 OF 6

GND

U27F

216RC300M_BGA_718

VSS

A29

VSS

AB23

VSS

AB24

VSS

AB27

VSS

AB4

VSS

AB8

VSS

AC1

VSS

AC11

VSS

AC14

VSS

AC16

VSS

AC20

VSS

AC30

VSS

AD11

VSS

AD14

VSS

AD16

VSS

AD20

VSS

AD4

VSS

AE27

VSS

AF30

VSS

AF5

VSS

AG10

VSS

AG13

VSS

AG16

VSS

AG19

VSS

AG22

VSS

AG25

VSS

AG7

VSS

AH28

VSS

AH3

VSS

AJ1

VSS

AK13

VSS

AK2

VSS

AK22

VSS

AK29

VSS

AK4

VSS

AK7

VSS

B1

VSS

B16

VSS

B30

VSS

C19

VSS

C23

VSS

C27

VSS

C4

VSS

D21

VSS

D25

VSS

E3

VSS

E8

VSS

E9

VSS

F27

VSS

F4

VSS

F8

VSS

G14

VSS

G15

VSS

G18

VSS

G20

VSS

H14

VSS

H15

VSS

H18

VSS

H20

VSS

H27

VSS

H4

VSS

H8

VSS

J7 VSS J8

VSS K27

VSS K4

VSS L23

VSS L24

VSS L25

VSS L7

VSS L8

VSS M15

VSS M16

VSS M27

VSS M4

VSS N15

VSS N16

VSS N23

VSS N24

VSS N8

VSS P15

VSS P16

VSS P27

VSS P4

VSS R1

VSS R12

VSS R13

VSS R14

VSS R15

VSS R16

VSS R17

VSS R18

VSS R19

VSS R23

VSS R7

VSS R8

VSS T12

VSS T13

VSS T14

VSS T15

VSS T16

VSS T17

VSS T18

VSS T19

VSS T27

VSS T4

VSS U15

VSS U16

VSS U7

VSS U8

VSS V15

VSS V16

VSS V27

VSS V4

VSS V7

VSS V8

VSS W15

VSS W16

VSS W27

VSS Y1

VSS Y23

VSS Y24

VSS Y30

VSS Y4

VSS Y7

VSS Y8

R419 NAGP@0_0603_5%

1 2

PART 5 OF 6

POWER

CORE PWR

AGP PWR

MEM I/F PWR

CPU I/F PWRALINK PWR

U27E

216RC300M_BGA_718

VDD_CORE

F10

VDD_CORE

F9

VDD_CORE

G12

VDD_CORE

H12

VDD_CORE

H13

VDD_CORE

M12

VDD_CORE

M13

VDD_CORE

M14

VDD_CORE

M17

VDD_CORE

M18

VDD_CORE

M19

VDD_CORE

N12

VDD_CORE

N13

VDD_CORE

N14

VDD_CORE

N17

VDD_CORE

N18

VDD_CORE

N19

VDD_CORE

P12

VDD_CORE

P13

VDD_CORE

P14

VDD_CORE

P17

VDD_CORE

P18

VDD_CORE

P19

VDD_CORE

U12

VDD_CORE

U13

VDD_CORE

U14

VDD_CORE

U17

VDD_CORE

U18

VDD_CORE

U19

VDD_CORE

V12

VDD_CORE

V13

VDD_CORE

V14

VDD_CORE

V17

VDD_CORE

V18

VDD_CORE

V19

VDD_CORE

W12

VDD_CORE

W13

VDD_CORE

W14

VDD_CORE

W17

VDD_CORE

W18

VDD_CORE

W19

VDD_18 H22

VDD_18 H10