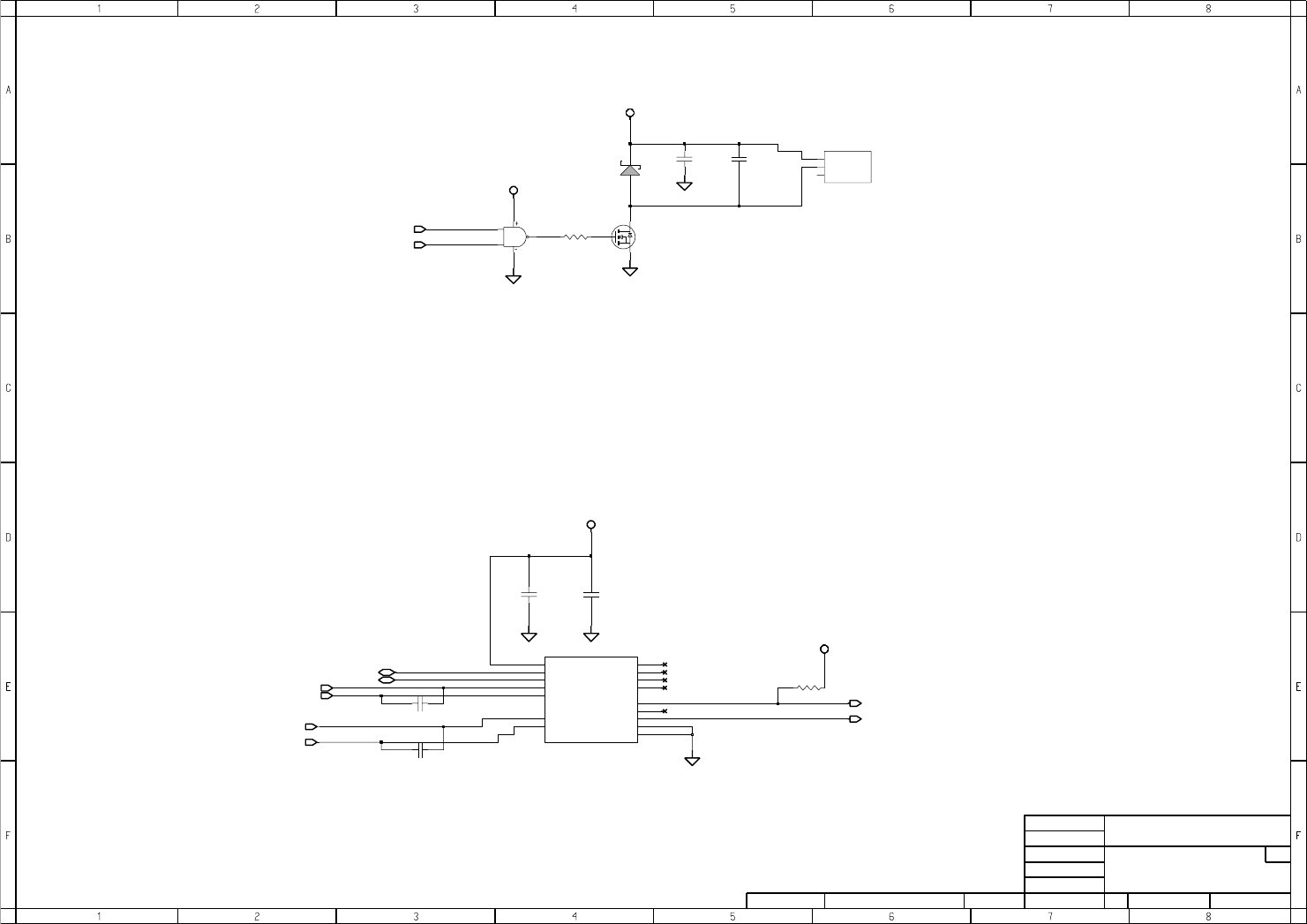

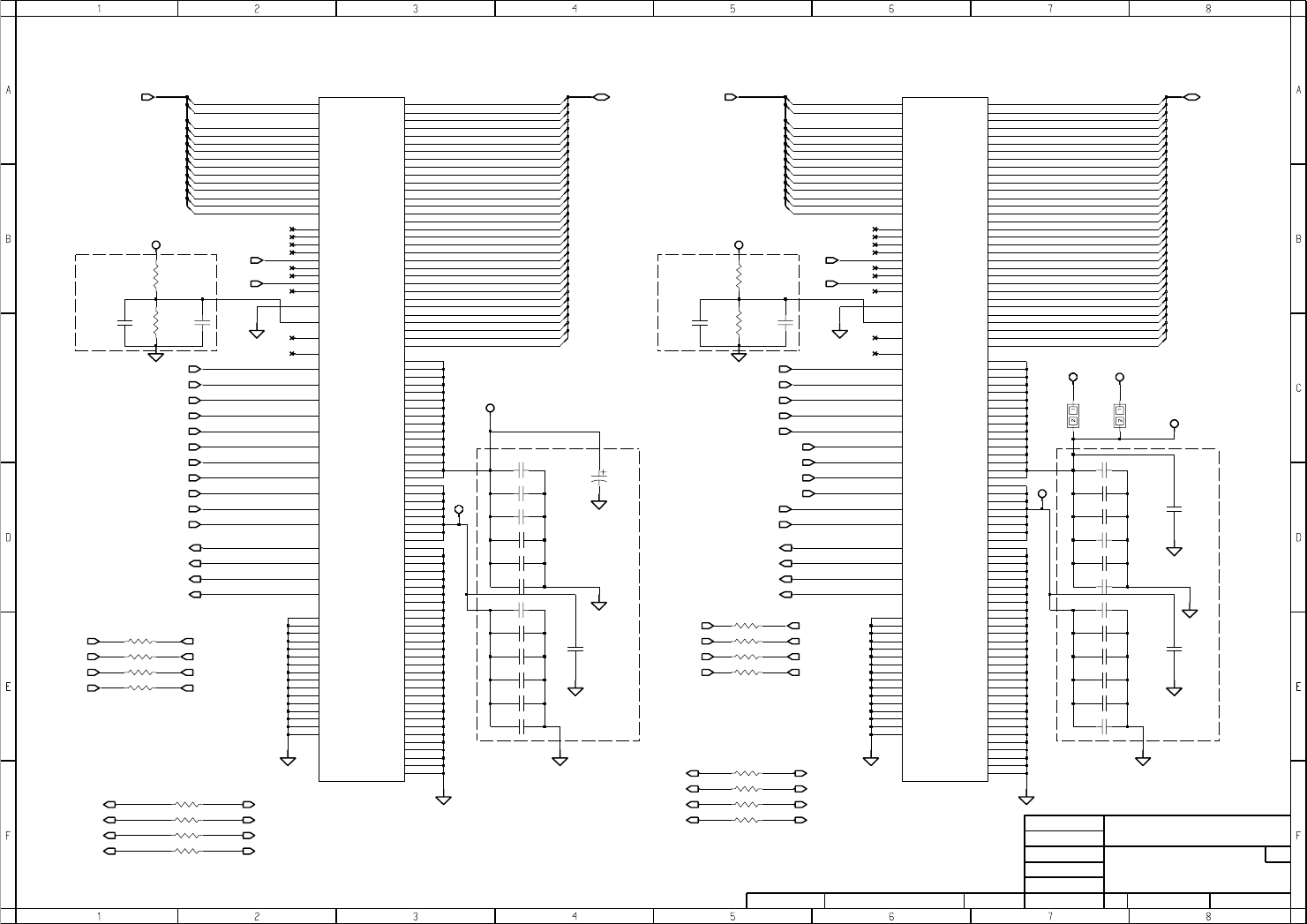

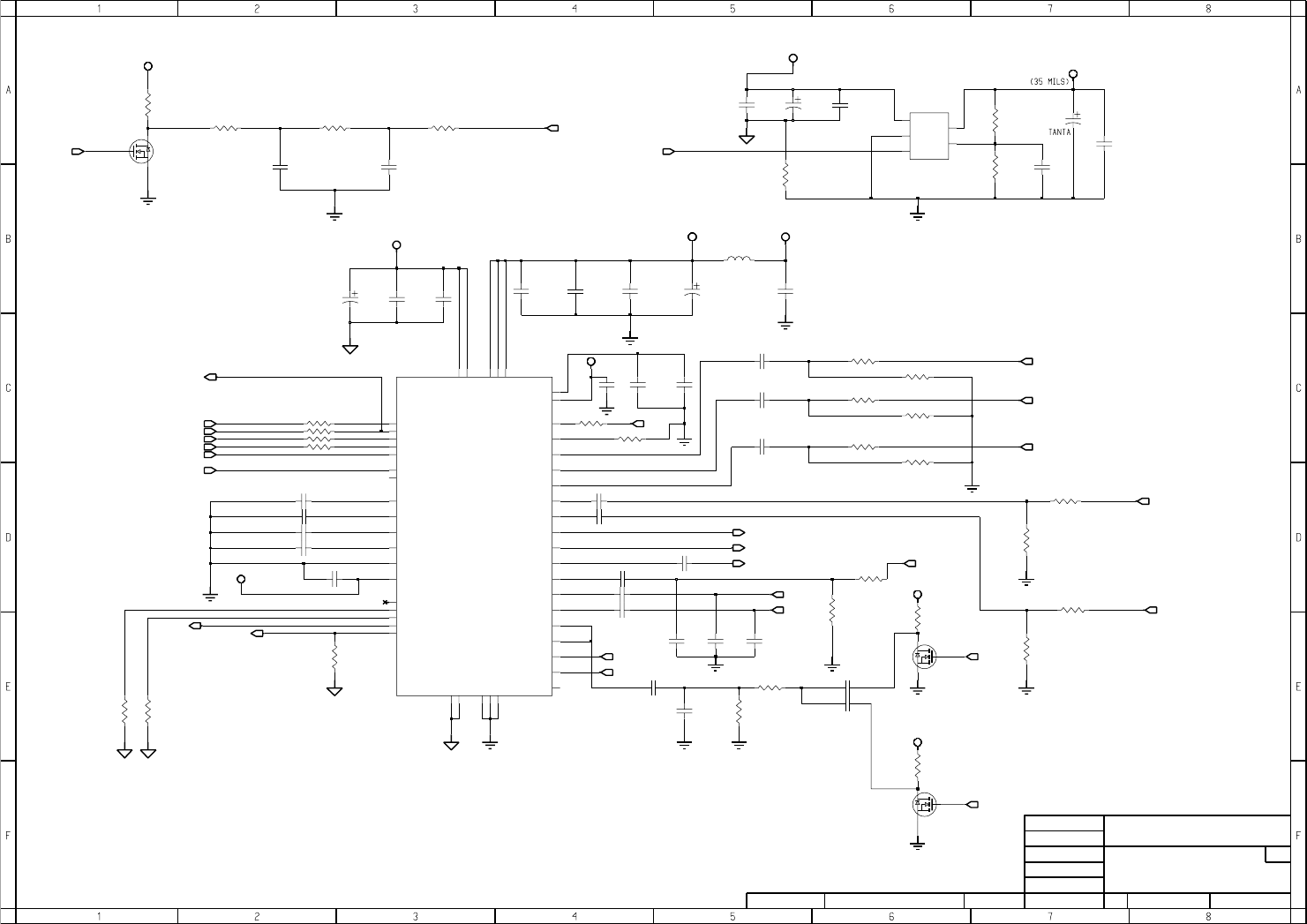

Inventec Diamond Schematics. Www.s Manuals.com. Ra02 Schematics

User Manual: Motherboard Inventec Diamond 6050A0032501 - Schematics. Free.

Open the PDF directly: View PDF ![]() .

.

Page Count: 68

VER

2008/08/21

MV B

Time Changed

Drawn by

Date Changed QA CHK

Size

TITLE

Engineer

R&D CHK

MFG ENGR CHK

FINAL

Model Number Sheet

Changed by

DOC CTRL CHK

EE2 Thursday, August 21, 2003 11:19:38 am

David Du

David Du

A02 PC8803 167

DIAMOND

A3

DIAMOND npubished dataOND

- BUILD

of

INVENTEC

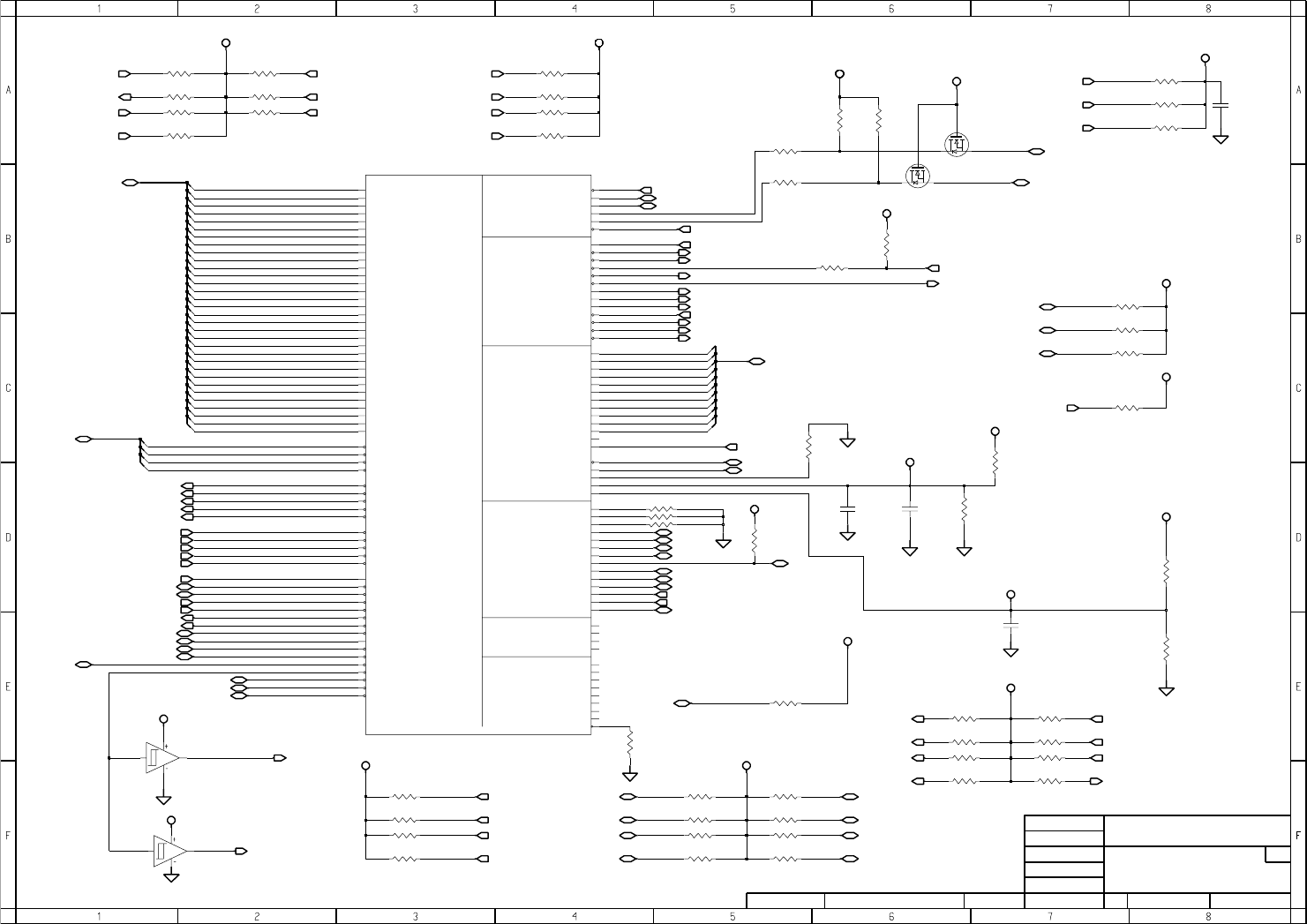

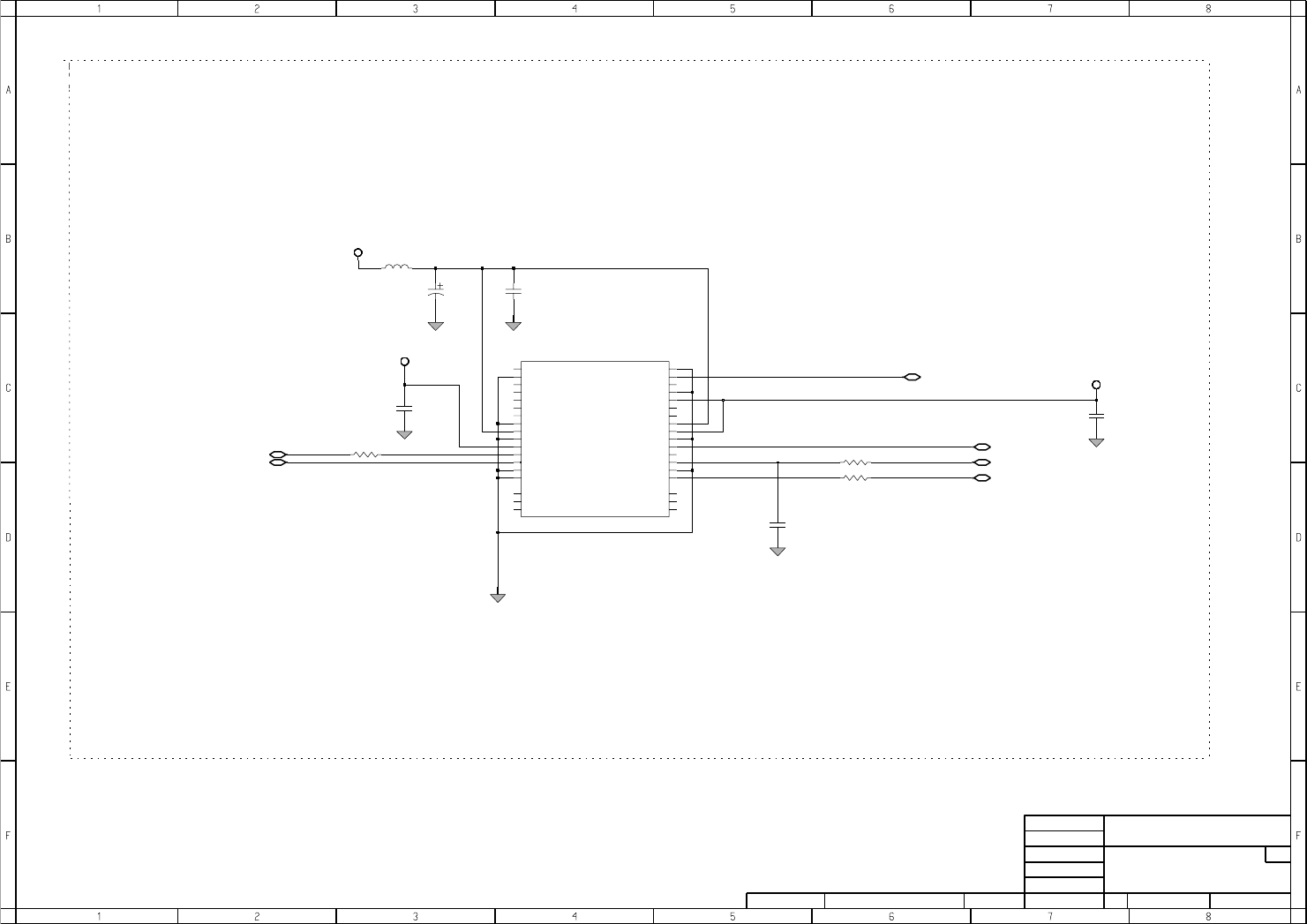

6- SELECT & BATTERY CONN

7- SYSTEM POWER(3V/5V/12V)

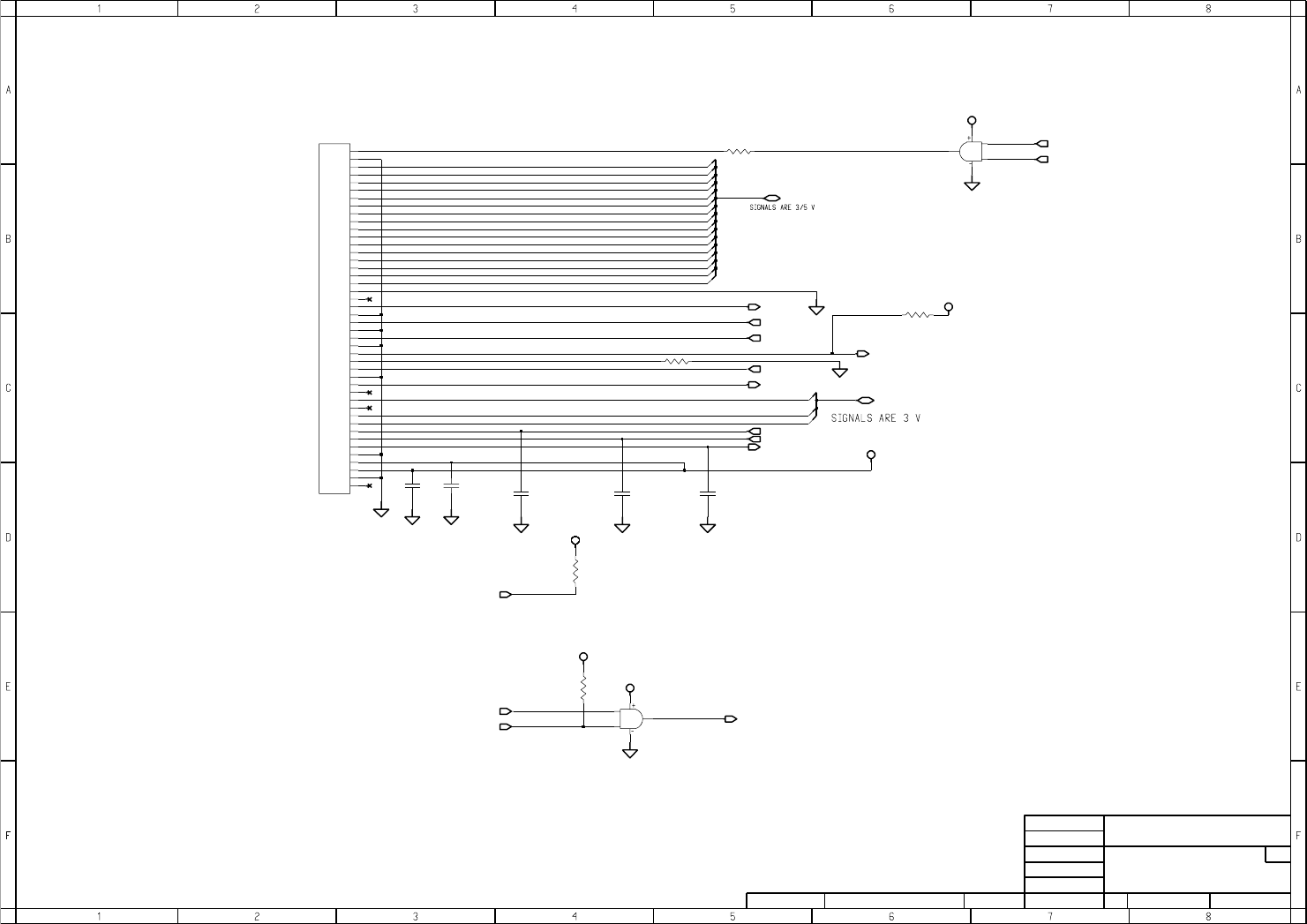

40- KBC

35- CRT& SVEDIO CONN

DOC CTRL CHK

37- ICH4-1

MFG ENGR CHK

51- CARDBUS CONTROLL

16- BANIAS-1

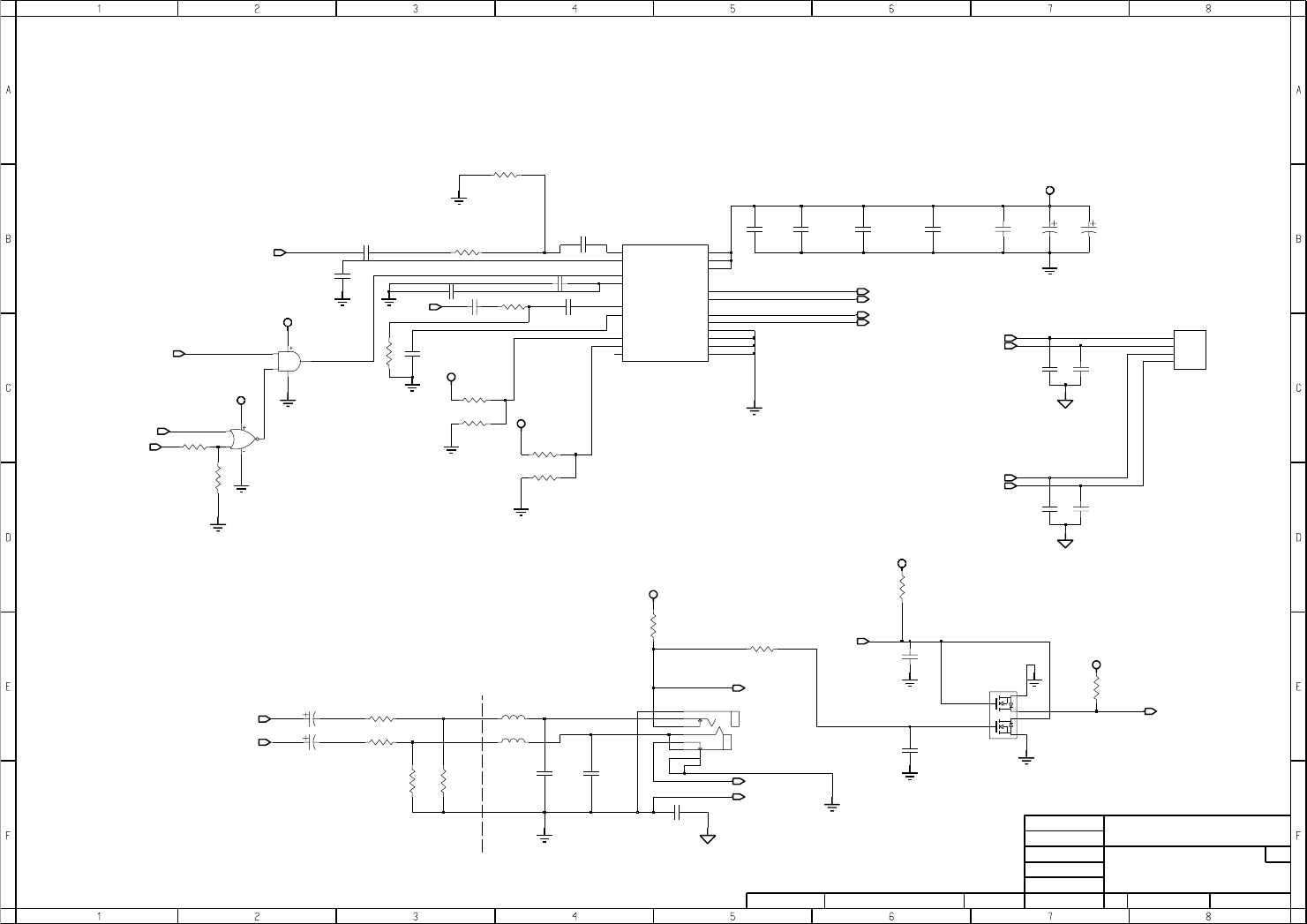

TITLE

36- LCD CONN

QA CHK

24- ODEM-4

15- CLOCK_GENEATOR

27- DDR-SDRAM-3

of

57- DOCKING CONN

26- DDR-SDRAM-2

43- SERIAL PORT

34- VIDEO RAM-2

30- ATI-M10-P-2

28- DDR-SDRAM-4

55- LAN INTERFACE-1

21- ODEM-1

25- DDR-SDRAM-1

44- PARALLER PORT

10- DAUGHTER SYSTEM POWER(2.5V/VGAVCC)

9- SYSTEM POWER(VCCP/1.2V)

38- ICH4-2 59- BOARD TO BOARD CONN & LID SWITCH

31- ATI-M10-P-3

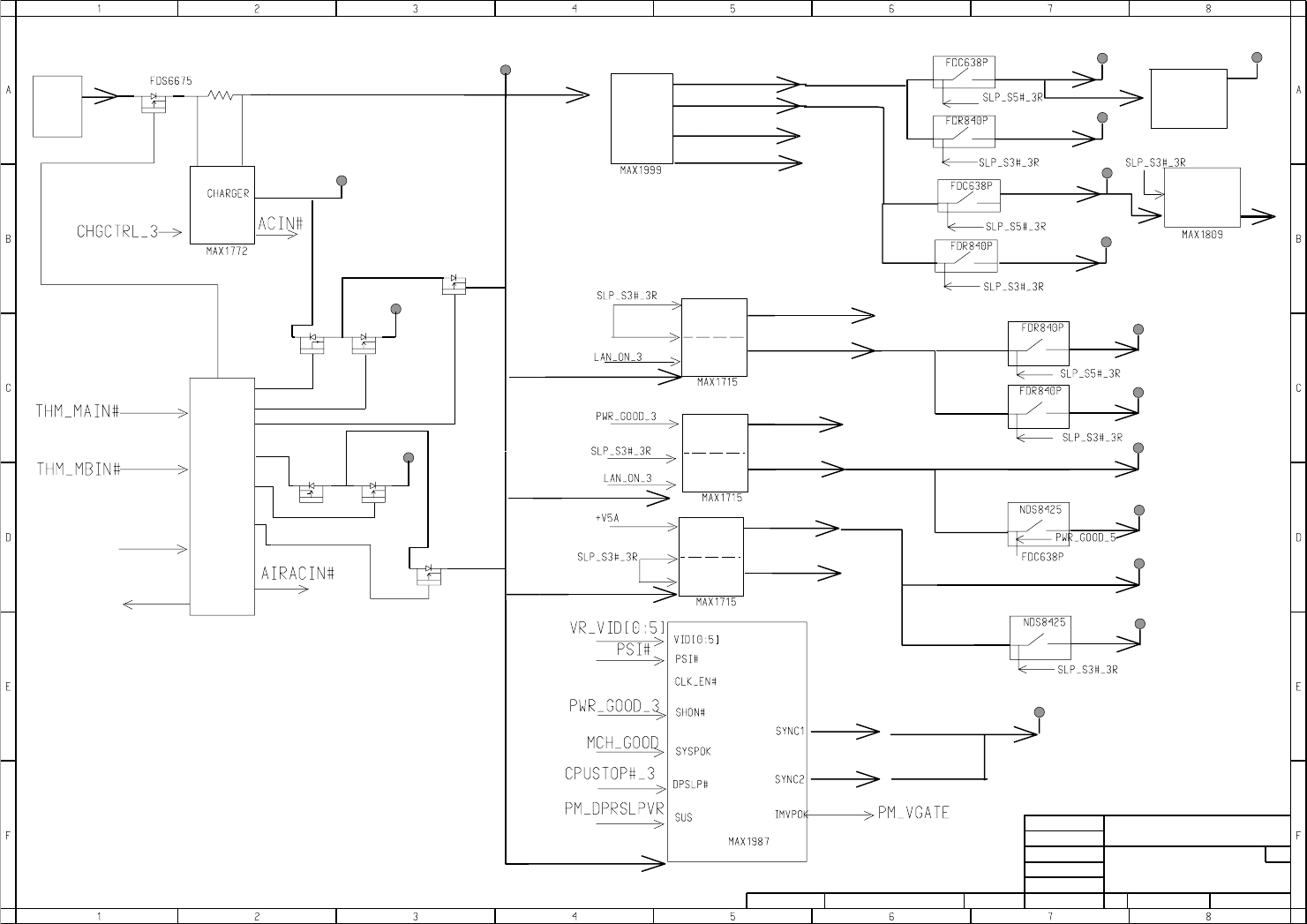

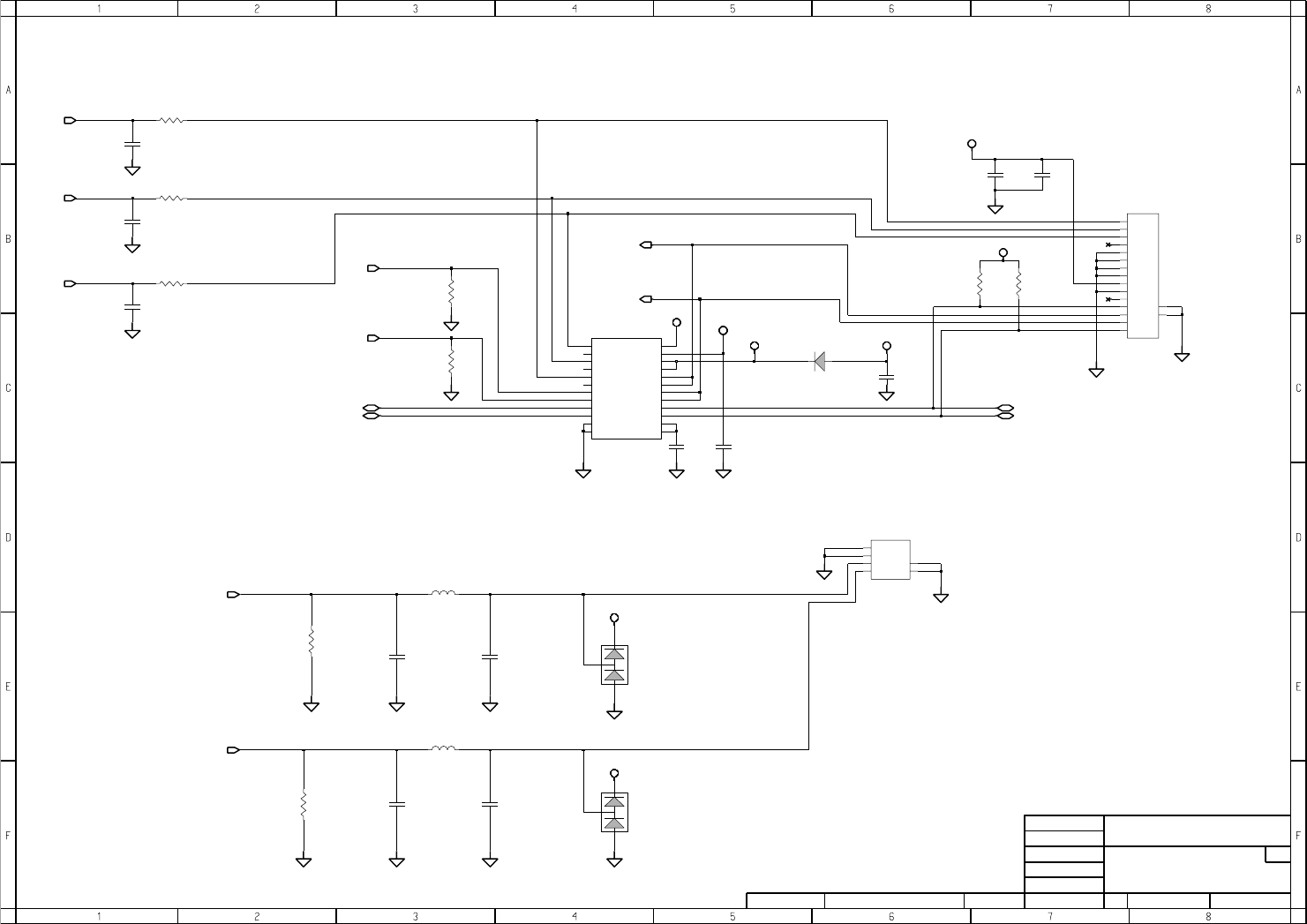

5- DC& BATTERY CHANGER

INVENTEC

52- PC CARD SLOT

54- MINIPCI CONN

56- LAN INTERFACE-2

VERChanged by

PAGE

19- BANIAS-4

18- BANIAS-3

8- DAUGHTER SYSTEM POWER(1.5V/1.8V)

41- INT.KBC/POINT DEVICES

29- ATI-M10-P-1

Drawn by

49- MULTIBAY CONN

17- BANIAS-2

42- SUPER I/O

39- ICH4-3

R&D CHK

62- DAUGTHER TCPA CONN

63- DAUGTHER CONN & SWITCH LED

64- DAUGTHER LED & VOL BUTTON

11- CPU POWER(VCC_CORE)

Model Number

23- ODEM-3

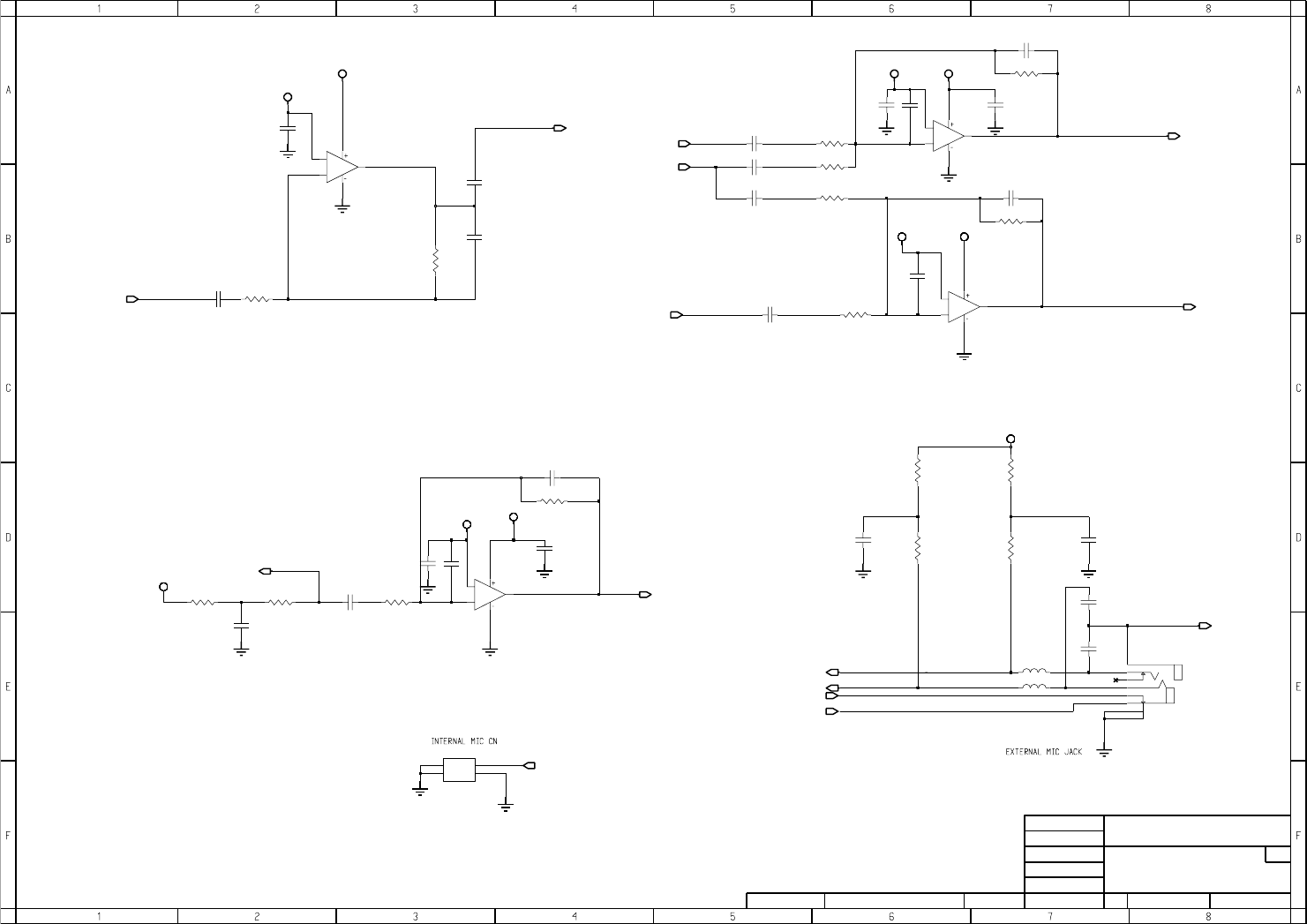

47- AUDIO AMP&HP JACK

46- EQ&MIC JACK

58- BLUETOOTH

Sheet

45- AC97 CODEC

60- DAUGHTER FHW

12- DDR_TERMINATION

61- DAUGTHER MDC CONN

20- THERMAL&FAN CONTROLLER

PAGE

Size

13- POWER(SLEEP)

33- VIDEO RAM DEPEND

22- ODEM-2

David Du

David Du

10:53:56 amThursday, July 31, 2003EE2 672

PC8803A02

DIAMOND

A3

Date Changed Time Changed

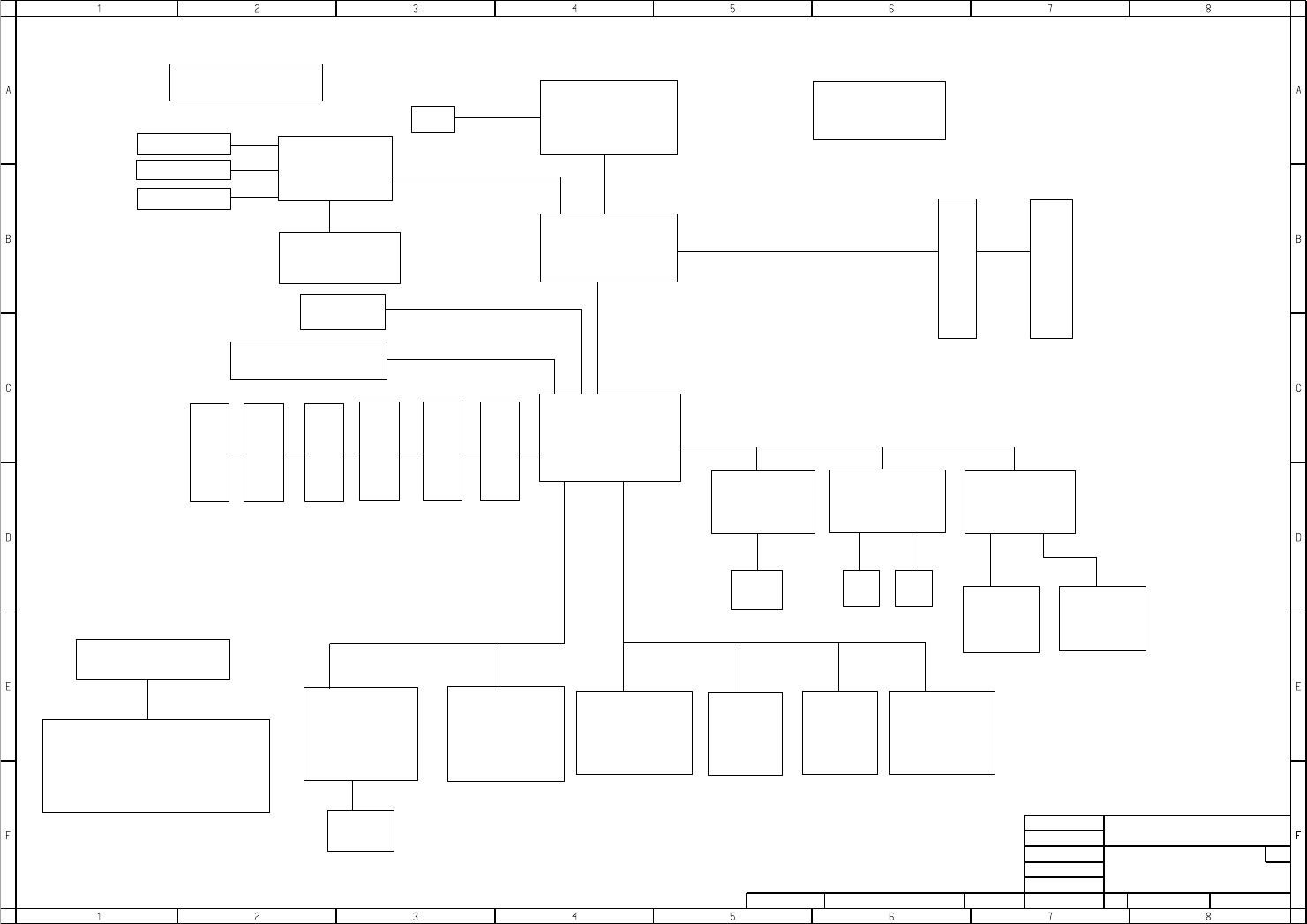

TABLE OF CONTENTS

32- ATI-M10-P-4

50- USB&IR CONN

48- HDD CONN

Engineer

PAGE

53- SD CARD CONN

14- POWER(SEQUENCE)

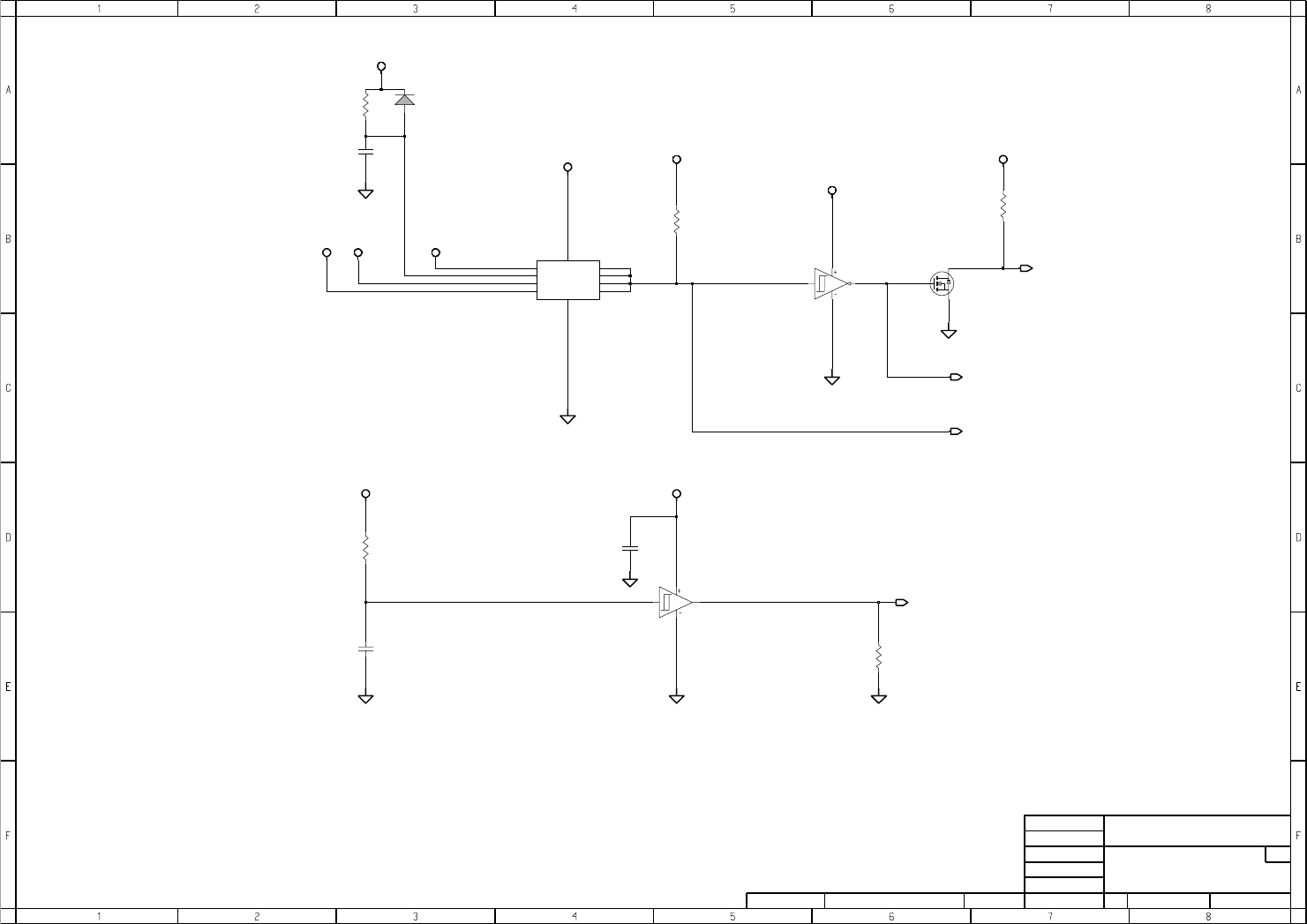

421 BGA

Primary_IDE

ATA 66/100

CONN B

USB2

Dock

USB3

Bluetooth

BATTERY

System Charger & AC97 Codec

PORT REPLICATOR

QA CHK VER Model Number

INVENTEC

Giga-bit LAN

ITP

RJ11

System BIOS TCPA

47N250

3.3V, AC97 LINK 3.3MHz 3.3V, LPC_Interface,33MHz

PSB, VCCP,400MHz

BANIAS

(Micro-FCPGA)

3.3V, PCI_Interface,33MHz

BCM 5705

ICH4-M

CK 408

Clock generator

CRT

ATI_M9-X

VGA Chip

Multi-bay/ Battery

Mini_PCI

Wireless LAN

O2_711M3B

CARD BUS

Odem MCH-M

Date Changed

RJ45 ANT ANT SD Card

Changed by Time Changed

MFG ENGR CHK

SLOT Cardbus

SLOT A/B

Module

Module 56K

AD_1981

Engineer

Drawn by

Super I/O

47N227

Kahuna Lite

1.5V,AGP 4X/8X_BUS,66MHz

R&D CHK

DOC CTRL CHK

Sheet of

1.8V, Hub Link, 66MHz

HDD

FWH

32MB/64MB

Size

TITLE

DDR RAM

S-video

LCM

593 BGA

David Du

David Du

10:54:58 amThursday, July 31, 2003EE2

673

PC8803A02

DIAMOND

A3

DDR _SODIMM0

DDR _SODIMM1

2.5V,DDR SDRAM200/266 Interface

Secondary_IDE

USB0

CONN A

USB1

Dock

USB4

USB5

DC/DC System power

MDC/Modem

COMA

CHGA

+VGAVCC

+V2.5L

1.8V

ACOK

MFG ENGR CHK

ICTL

DOC CTRL CHK

+VBATB

+V5

+VBATA

+V5S

+V1.2L

+V3S

+V3

+V1.5A

PDS

BATSTAT

0.0295

Time Changed

ON1

DISB

ADPT

ON1

+VBATR

ACPRES#

+VCC_CORE

ON2

+V12

5V

+V3L NS_LM2621MMX

1.2V

1.5V

+V2.5

2.5V

SKIP#

ON2

+V3A

of

TITLE

+V1.2_MCH

INVENTEC

Engineer

R&D CHK Size

+V1.2L

THMB

Sheet

DISA

Model Number

+V5A

SKIP#

+V1.5S

Drawn by

ON1

+V5L

SKIP#

+V3L

3V

+V2.5S

+V5L

BATSELB_A#

BATSTAT#

BATSEL

+VCCP

SKIP#

Changed by

+V1.5A

Date Changed

+V1.8S

+VBDC

EE2 Thursday, July 31, 2003 10:56:04 am

David Du

David Du

A02 PC8803 467

DIAMOND

A3

ON2

VERQA CHK

1.05V

+V1.25

COMB

THMA

+VGAVCC

CHGB

$V

Engineer

Time Changed

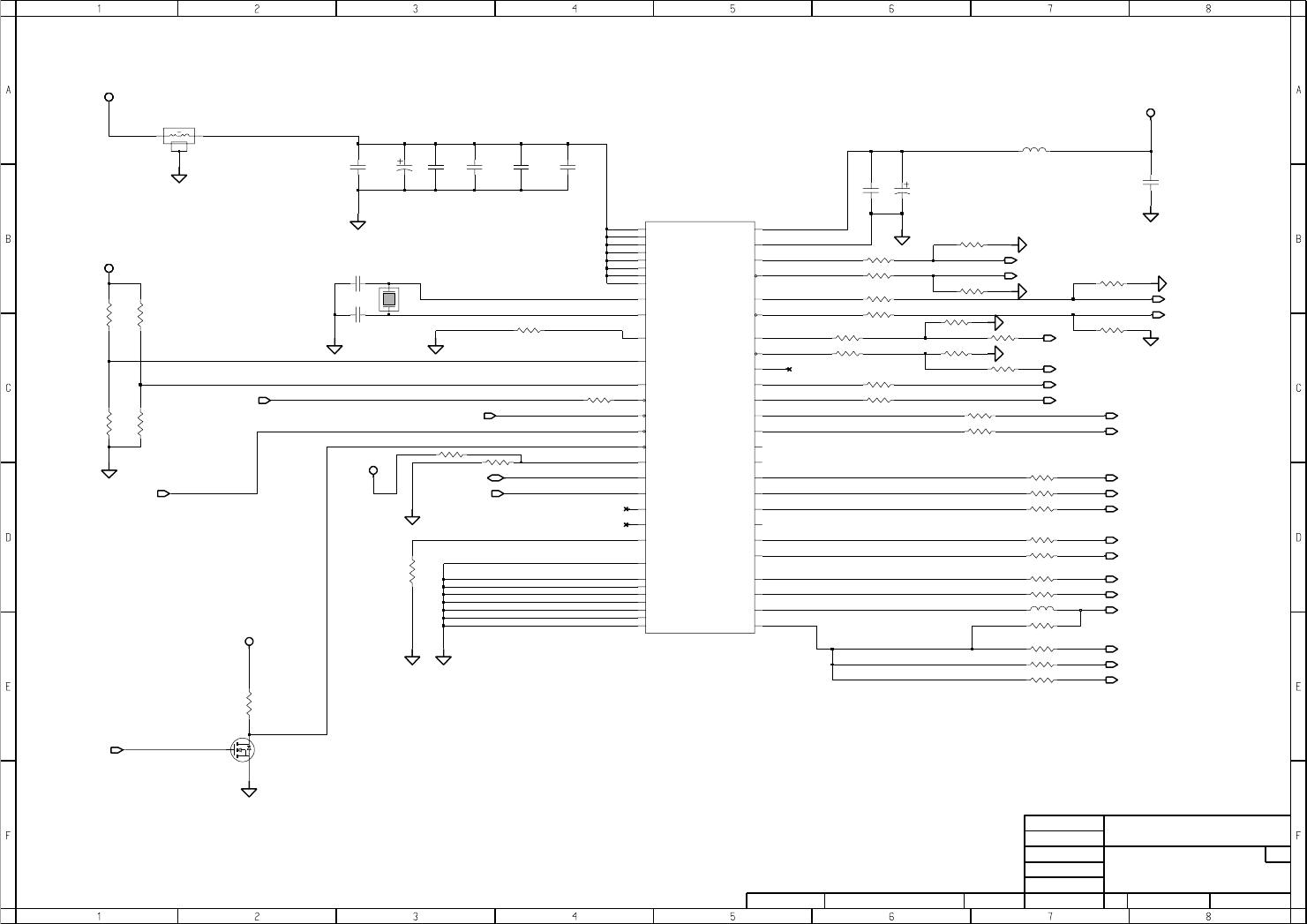

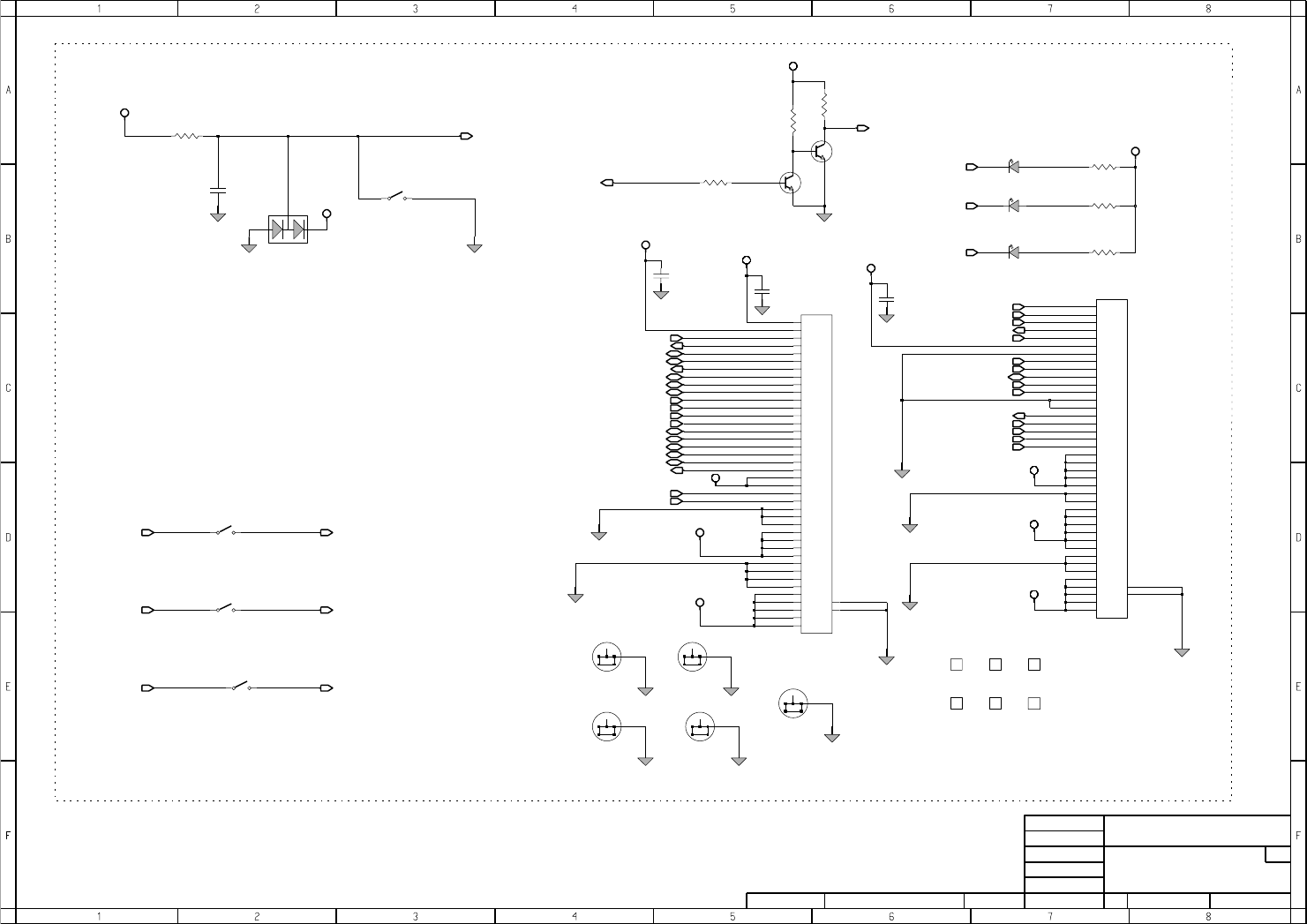

CELLSEL=1,Vcharger=12.6V

5.4V_15mil

Icharger=2.5A

Date Changed

DC JACK

Size

2.5A_100mil

15mil

VER

15mil

15mil

R&D CHK

Model Number Sheet

10mil

Changed by

$V

$V

Drawn by

15mil

15mil

15mil

Note:

high power trace

CELLSEL=0,Vcharger=16.8V

15mil

WAIT TO CHANGE 38.3K

QA CHK

MFG ENGR CHK

INVENTEC

+

++

+

+

TITLE

4.096V_10mil

Iadp=3.3A

11:22:36 amThursday, August 21, 2003EE2

675

PC8803A02

DC &BATTERY CHANGER

DIAMOND

A3

of

3.3A_150mil 3.3A_150mil

10mil

3.3A_150mil

DOC CTRL CHK

R16

3.3A_150mil

10mil

10mil

R1016 CHANGE TO 133K_1%

15mil

10mil

10mil

C

E

2

1772REF

R1035

0.018_1%_1W

12

David Du

David Du

3

10K_5%

R1053

1

2

Q1003

MMBT3906

B

1

3

FDS6680S

U1007

8

D

7

6

5

4

G

S

12

R1051

1K_5%

12

C1038

10UF_25V

1

2

1UF_10V

C10491

2

R1061

37.4K_1%

1

2

+VBDC

R1067

40.2K_1%

12

1UF_25V

C10151

2

499_1%

R6036

12

C6038

1UF_6.3V

1

2

1

2

+VBATR

R265

0.05_1W_1%

12

5-

C301

10PF

1

2

VADP1

0.01UF_16V

C1042

0.1UF_25V

12

1772LDO

C288

10UF_25V

1

2

+V3A

40-

40-,6- R1055

10K_5%

12

VADP C1051

R1588

OPEN

12

R1068

10.2K_1%

12

+V5S

57-,55-

3

2

4

5

4.7

R1048

12

OUT 8

0.1UF_25V

C3001

2

SINGA_2DC_S028I200

JACK3

1

52.3K_1%

1

2

U1002 LM324A

10 +

-

9

11

4

1

2

5-

2

R1064

1

2

R1052

12

4.7

R1049

1

2

10UF_25V

C1037

R1050

1

2

1UF_10V

C10441

2

C1053 0.1UF_16V

C1043

1

2

R1046

2.2_5%

12

52.3K_1%

1

NC

NC 2

ANODE

5

CATHODE 3

REF

4

+VBATR

+VADP2

0.01UF_16V

R1036

0.015_1W_1%

12

5-

+V3A

NS_LMV431ACM5X_SOT23_5P

U1000

5+

6-

11

4

7

OUT

133K_1%

R1016

1

2

37-,16-

C1033

0.47UF_25V

1

2

LM324A

U1002

OPEN

C6023

1

2

0.1UF_16V

C1040

1

2

VADP

C1052

1

2

10K_5%

R1037

1

2

1

2

2N7002

Q1005 3

D

2

G

S

1

0.1UF_16V

1UF_25V

1

2

0.1UF_25V

C2991

2

VADP1

10K_0.5%

R1006

2200PFC1000

12 100K_5%

R1019

12

C1034

R1039

237K_1%

12

R1062

47K_5%

1

2

47K_5%

R1063

12

10PF

C302

1

2

R1592

OPEN

1

2

OPEN

R1590

12 +V3A

1

0.1UF_25V

C1039

12

R1038

47K_5%

1

2

6-

1N4148

D1004

2

1

1N4148

D1006

2

R1015

100K_5%

12

0_5%

R6029

12 37-

3

+

2

-

11

4

1OUT

0_5%

R1022

1

2

1772LDO

12

R1021

0_5%

1

2

LM324A

U1002

2

R1065

1

2

1772LDO

L27

PLFC1055P_220A_22UH

12

-

13

11

4

OUT 14

7-

1772REF

100K_0.5%

R1001

12

2

10K_5%

R1040

1

2

U1002

LM324A

+

+V3A

100K_5%

R1071

1

2

D1000 BAT54S

1

3

R1020

4.7K

1

2R1011

10

1

2

54 G

S

1

2

3

40-

R1000

10K_1%

1

2

R1017

1

2

IRF7807V

Q1007

8

D7

6

OPEN

12

MMBT3906

Q1002

1

B

C

3

2

E

80.6K_1%

3

0.1UF_25V

C1050

12

R1591

R6043

0

12

R6044

OPEN

12

BAT54C

D6009

1

2

1

2

10K_5%

R1047

1

2

2

22UF_23V_METAL

C297

1

VADP

0.47UF_25V

C1041

Q1008

SST3904

2

B

3

C

E

1

C1046

0.1UF_16V

1

21

22

DL0V

10 ICHG

14 ICTL

IINP 28

2LD0

23

LX

PGND 20

REF

4

13 REFIN 15

VCTL

CCI

CCS

5

CCV

7

16

CELLS

CLS

3

CSIN 18

CSIP 19

26

CSSN

CSSP 27

DCIN

1

DHI 24

DL0

S2

U1008

MAX_MAX1772EEI_QSOP_28P

GND

8

GND

9

AC0K

12 ACIN

11 17

BATT

25

BST

6

2

5-

Q1004

NDC7002N

D1 6

D2 4

1G1

G2

3

S1 5

2

12

1UF_6.3V

C1045

1

2

R1059

100K_1%

1

12

R1054

100K_5%

1

2

33

R1041

C10031

2

R1066

49.9K_1%

1

2

0_5%

R1060

1.37K_1%

R1070

1

2

C1016

6800PF_25V

1

2

1UF_16V

NFM60R30T222

12

3

4

0.1UF_25V

C312

1

2

STBY_SWIN#_3

L26

H_STPCLK#

1772GND

1772GND

AIRACIN#

AIRACIN

MAX_LX5

CELLSEL

+VADPTR

1772GND

CHGCTRL_3

1772GND

ICHG

ACIN#

3.3A_150mil

10mil

+

INVENTEC

10mil

MAIN BATT

5A_200mil

VER

2.5A_100mil

2.5A_100mil

Sheet

5A_200mil

Date ChangedChanged by QA CHK

DOC CTRL CHK

10mil

TITLE

10mil

5A_200mil 5A_200mil

2.5A_100mil

2.5A_100mil

15mil

15mil

10mil 3.3V_10mil

10mil

15mil

15mil

DIAMOND

SELECT & BATTERY CONN

A3

3.3A_150mil

10mil

10mil

R&D CHK

of

2nd BATT

Size

+

10mil

10mil

MFG ENGR CHK

Time Changed Model Number

Engineer

Drawn by

5A_200mil

5A_200mil

47PF_50V

1

2

+V3A

57-,40-

EE2 Thursday, July 31, 2003 10:58:32 am

David Du

David Du

A02 PC8803 667

100K_5%

R1218

1

2

6-

40-,6-

C1245

DISA 17

DISB

8EXTLD

6GND

7MINV

9PDS

14

TCOMP

THMA

2THMB 19

15

VDD

ACDET

10 12

ACPRES#

BATA

120

BATB

13

BATSEL

BATSTAT 11

CHGA

3CHGB 18

COMA

5COMB 16

4

12

+V3A

UDZS5.6B

D1015

2

1

MAX_MAX1773EUP_TSSOP_20P

U12

R1216

12

100K_5%

R1214

12

100_5%

R1217

+VBATB

6-

40-

R1219

0_5%

12

0_5%

1

2

+V3A

40-

+V3A

57-,40-

+VBATB

40-,6-

12

C1291

0.022UF

1

2

2.2UF_25V

C204

SFPB74

21

2.2UF_25V

C12881

2

R1234

100_5%

R1244

100K_5%

12

100K_1%

R203

12

D1002

R1581

3.3K_1%

1

2

R202

0_5%

12

34

4

55

66

0.022UF

C1287

1

2

6-

1.8K_5%

1

2

AMP_C1470694_1_6P

CN1003

1

12

23

R1232

12

C1282

47PF_50V

1

2

+V3A

R1231

UDZS5.6B2

1

1N4148

D1003

2

1

100_5%

1

22

33

4

45

56

6

+VBATA

D1016

65

G

41

S

23

CN14

AMP_1470444_1_6P

1

65

4

G

S

123

Q1025

FDS4435

D

87

100K_1%

12

VADP

+VBATA

FDS4435

Q1032

D

87

1

210K

R1245

1

2

40-,6-

R205

3.3K_5%

R1252

12

D1014

1N4148

2

1

R1246

10K

R1251

470K_5%

1

2

+VADP2

+VBDC

5

4

G

S

123

2.7K_1%

R1215

1

2

65

G

41

S

23

Q1028

FDS4435

8

D

76

5

G

41

S

23

Q1029

FDS4435

D

87

0.1UF_25V

1

2

Q1001

FDS6675

D

876

10K

R1026

12

100K_5%

R1247

12

C1289

R1250

1

2

+VADP2

+VBDC

0.1UF_25V

C2031

2

1

R283

13.0K_1%

1

2

40-,5-

+VBDC

47K_5%

100K_1%

R204

1

2

VADP1

SST3904

Q1062

2

B

3

C

E

10K_1%

R1249

12

R1248

100K_5%

12

1

2

40-

40-

+V3A

390K_5%

R1589

1

2

C1290

1

2

100_5%

R1229

12

R1233

100K_5%

6-

40-,6- MMBT3906

Q1030

1

B

C

3

2

E

0.33UF_10V

Q1031

D1 7

8

6

D2

5

G1

2

4G2

S1 1

S2 3

+V3A

5-

2

1

R1230

1.8K_5%

1

2

FDS4935

CELLSEL

BAT6CELL#

D1017

UDZS5.6B2

1

D1064

UDZS5.6B

BATSELB_A#

AIRACIN#

SDA_MAIN

BAT6CELL#

SDA_MBAY

SCL_MBAY

SCL_MAIN

1773VDD

THM_MBAY#

THM_MBAY#THM_MAIN#

BATSTAT#

1773VDD

THM_MAIN#

MFG ENGR CHK

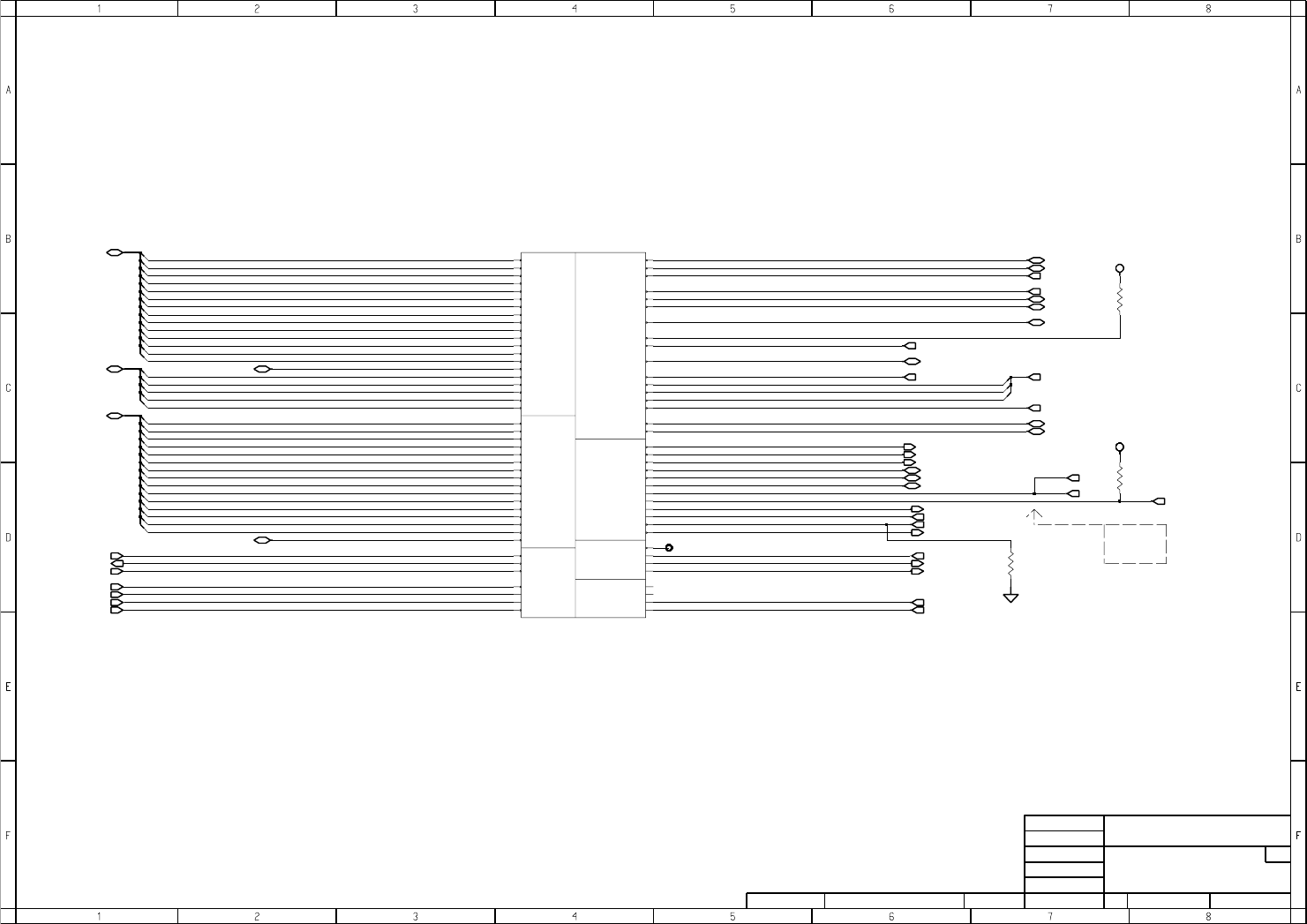

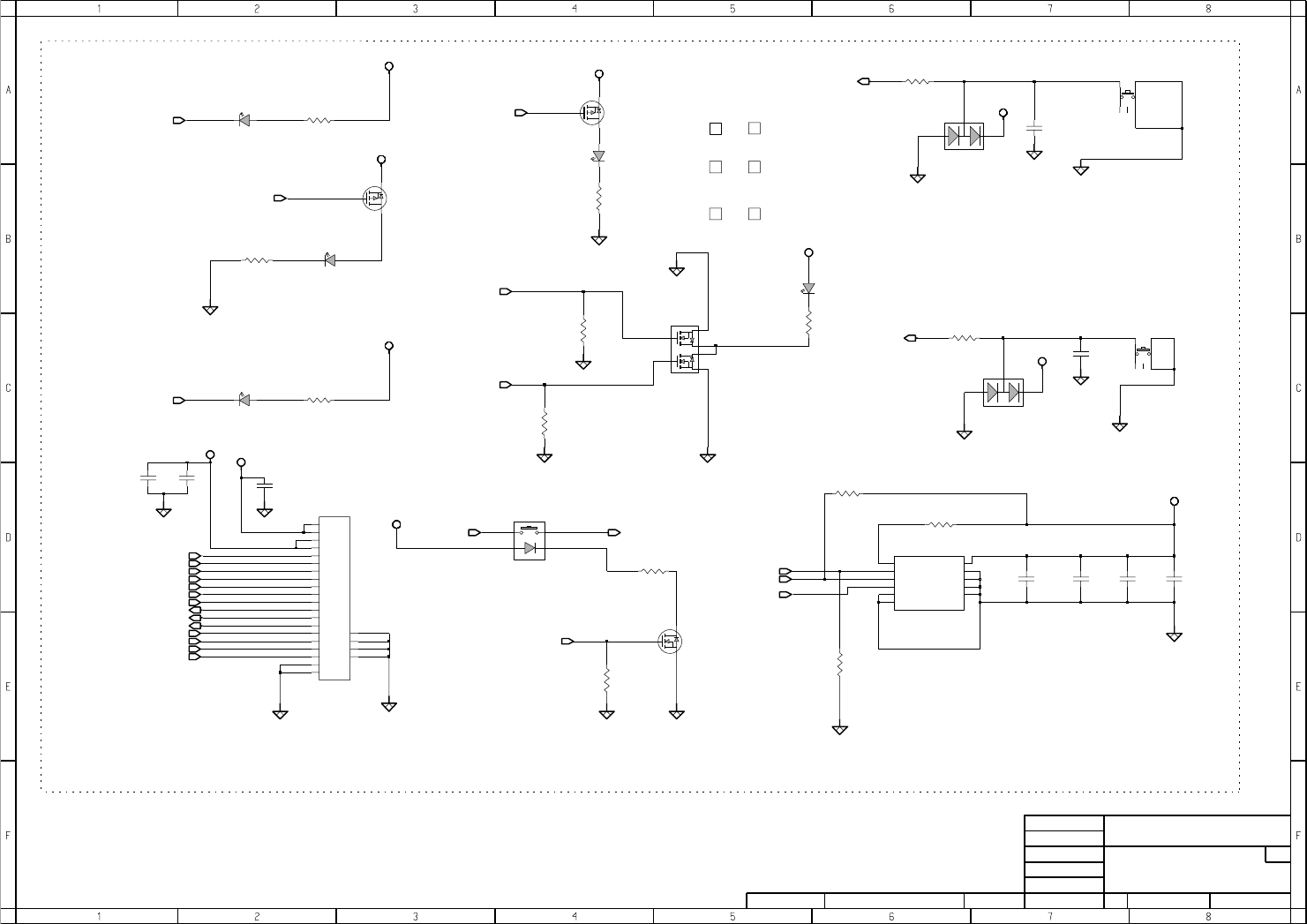

For power test

Sheet

4A_160mil

6A_250mil

4A_160mil

6A_250mil

2A_80mil

4A_160mil

20mil

20mil

15mil15mil

15mil

15mil

15mil

of

QA CHK

Size

Drawn by

120mA_30mil

15mil

15mil

15mil

15mil

15mil

120mA_30mil

15mil

15mil

20mil

15mil

10mil

10mil

15mil

A02 PC8803 767

DIAMOND

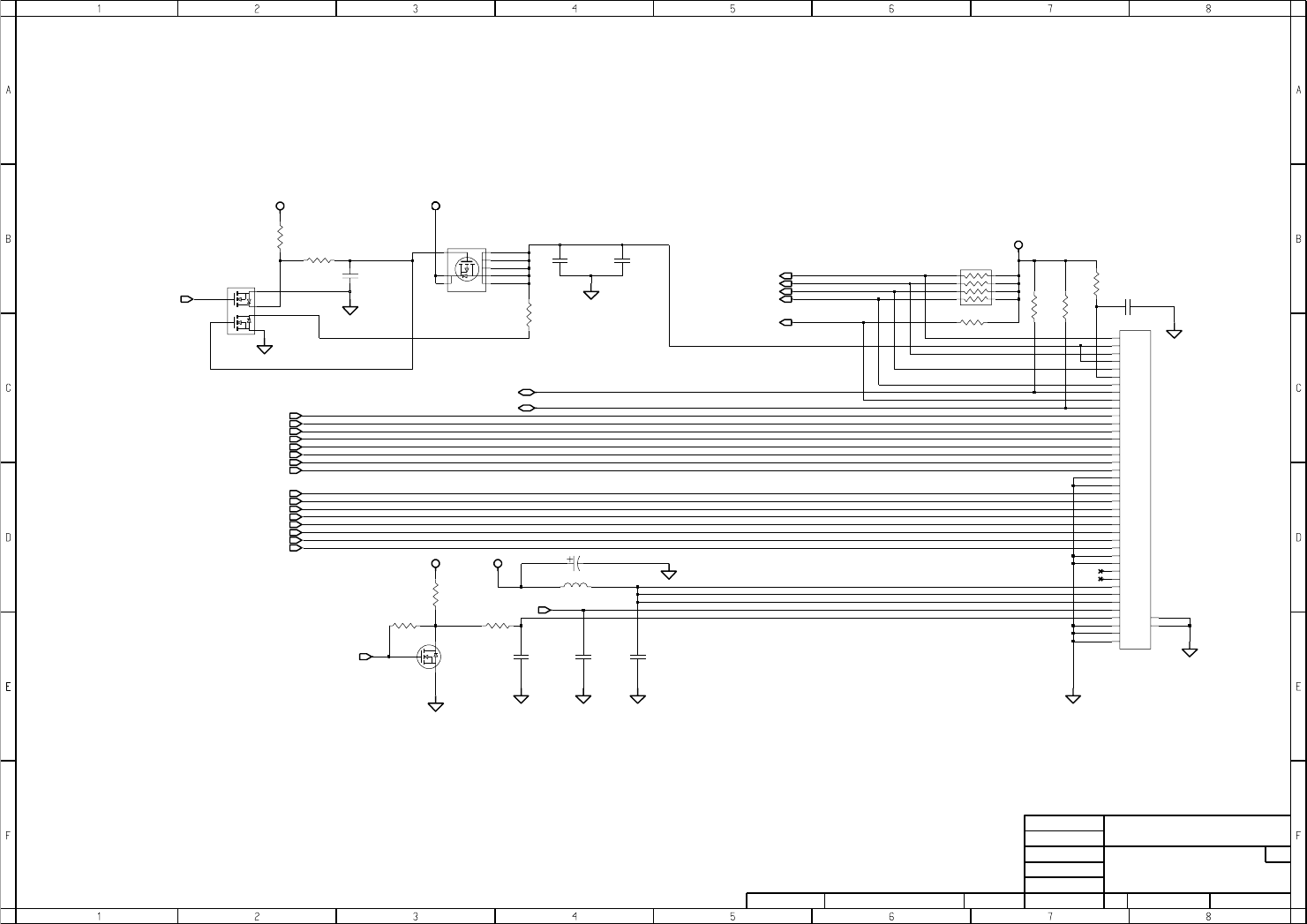

SYSTEM POWER(3V/5V/12V)

A3

15mil

30mil

20mil

10mil

5A_200mil

DOC CTRL CHK

Changed by Date Changed Time Changed

R&D CHK

Model Number

5A_200mil

VER

TITLE

INVENTEC

Engineer

10mil

10mil

0

R1241

12

EE2 Thursday, July 31, 2003 10:59:19 am

David Du

David Du

2

C182

220UF_6.3V_OSCON

1

47UF_20V

C1032

1

12

+V3L

7-

+V12

+VBATP

R1195

0

1

12

0_5%

R213 1

222

R1194

21

+V5

R1211

0_5%

1

2

R231

4.7_1206_1/4W

SIL520_6.8UH

L1000

12

1632GND

1632GND

D1005

EC10QS03L

59-,47-,45-,40-,38-,13-,12-,9-

0.022UF

C1244

1

2

+VBATP

324K_1%

R1209

1

2

0.1UF_25V

C226

1

2

+V5L

NS_LM2621MMX_MSO8_8P

U1006

BOOT 7

2EN

4FB

FREQ

3

PGND

1

5

SGND

8

SW

6

VDD

OPEN

C201

1

2

POWERPAD_4A

PAD1

1

2

3

4

1

2

C202

330UF_4V_OSCON

1

1632GND

1632GND

2

5-

C1222

10UF_25V

1

2 1UF_25V

C1223

2

C1221

0.1UF_25V

12

1632GND

C1219

0.1UF_10V

1

12

0

R1207

12C1242 0.1UF_25V

1

3

4

R1210

80.6K_1%

1

2

R216

10.2K_1%

R1213

12

7-

PAD4

POWERPAD_4A

1N4148

D1012

21

10UF_K_6.3V

C1981

2

OPEN

2

1UF_6.3V

C199

12

R232

220K_5%

1

2

C1048

0.1UF_16V

12

7-

R1044

0

1

1

2

+V5A

+V3A

MAX3V

+V5

10UF_K_6.3V

C1851

2

3

2.2PF_50V

C1035

1

2

22UF_10V

C1047

2FDS6680S

Q1024

8

D

7

6

5

4

G

S

12

S2

3

4.7UF_K_6.3V

C2001

2

143K_1%

R1242

1

2

FDS6982S

Q1022

D1

7

8

6

D2

5

G1

2

4

G2

1

S1

C225

4.7UF_K_25V

1

2

R1042

16.9K_1%

1

10UF_K_16V

C10361

2

147K_1%

R1043

12

+V5L

G

S

123

7-

0.22UF_K_10V

C1243

1

2

MAX5V L21

12

FDS6612A

Q1021

8

D

765

4

100UF_25V

C197

1

R1212

10K_5%

1

2

PLFC1055P_6R8A_6.8UH

C1218

10UF_25V

1

2

R1243

274K_1%

1

2

+VBATR

PAD2

1

2

3

4

470PF_50V

C1286

1

2

R1208

1

2

16K_1%

R214

12

POWERPAD_4A

C12171

2

SIQ127A_10UH

L19

12

+V5L

47K_5%

21

2PGOOD

10 PRO#

REF

8

SHDN#

6

SKIP#

12

TON

13

V+ 20

17

VCC

+V5L

10UF_25V

5ILIM3

11 ILIM5

25

LDO3

LDO5 18

LX3 27

LX5 15

1NC

3ON3

4ON5

22

OUT3

OUT5

U1012

MAX_MAX1999EEI_QSOP28_28P

28

BST3

BST5

14

26

DH3

DH5 16

DL3 24

DL5 19

7FB3

FB5

9

23

GND

12

3

+VBATP

C1220

4.7UF_K_6.3V

1

2

2

150K_1%

R1045

12

BAT54C

D1018

MAX5V

0

R217 12 R218

OPEN

1

+V3A

BAT54A

D10113

12

MAX_LX5

SLP_S3#_3R

M1999FB5

M1999FB5

M1999FB3

M1999FB3

15mil 15mil

10mil

SYSTEM POWER (1.5&1.8) ON BUTTON DAUGHTER BOARD

12mil

12mil

12mil

Drawn by

12mil

3A_100mil

3A_100mil

15mil

15mil

10mil

15mil

TITLE

of

Time ChangedChanged by

40mil

40mil

Engineer

Date Changed VER

15mil

QA CHK

15mil

12mil

12mil

15mil

INVENTEC

12mil

10mil

2

EE2 Thursday, July 31, 2003 10:59:26 am

David Du

David Du

A02 PC8803 867

DIAMOND

SYSTEM POWER(1.5V/1.8V)

A3

Size

DOC CTRL CHK

MFG ENGR CHK

R&D CHK

Model Number Sheet

12

PLFC0735P_6R8A

L4001

12

L4000

PLFC0735P_6R8A

1

22

7

PGOOD

REF

9

SKIP#

6

5TON

V+ 4

VCC

21

20

VDD

10

R4025

12 ILIM2

27

LX1

16

LX2

23 NC0

NC1

28

15

NC2

10 ON1

11 ON2

OUT1 1

OUT2 14

PGND

AGND

8

25

BST1

18

BST2

DH1 26

DH2 17

DL1 24

19

DL2

FB1 2

FB2 13

ILIM1

3

2

+VBATP_BN

C4003

0.1UF_16V

1

2

63-,10-

+VBATP_BN

U4000

MAX_MAX1715_QSOP_28P

C4001

1

2

+V1.5A_BN

15A18SGND

15A18SGND

R4004

20K_1%

1

G2

4

S11

3

S2

R4006

23.7K_1%

1

2

15A18SGND

0.1UF_25V

+VBATP_BN

+V1.8S_BN

Q4004

FDS6984S

7

D1 8

D2 6

5

2G1

1

2

220UF_2.5V_S18_METAL

C4004

1

180PF_50V

1

2

R4003

0_5%

12

C4005

220P_25V

BAT54A

3

12

15A18SGND

+V5A_BN

C4008

10UF_25V

C40111

2

220UF_2.5V_S18_METAL

C4010

1

D4004

3

C4002

0.1UF_25V

1

2

0.1UF_25V

C40211

2

2

FDS6984S

Q4000

D1 7

8

6

D2

5

G1

2

4G2

1

S1

S2

1

2

1UF_10V

C40201

2

C4009

0.1UF_16V

1

1

2

R4002

20K_1%

1

2

C4006

1UF_10V

10

1

2

0

R4008

12

R4001

10K_1%

10UF_25V

C4000

1

2

22

R4005

1

2

R4022

C4007

1UF_6.3V

1

2

0.1UF_25V

C4012

1

2

R4000

274K_1%

12

274K_1%

R4007

1

2

SLP_S3#_3R_BN

of

VGAVCC NOTES :

Engineer

R1582_5.49K_1%

Sheet

TITLE

INVENTEC

15mil

5A_200mil

OPEN

10mil

10mil

10mil

15mil

10mil

Size

Drawn by

R&D CHK

DOC CTRL CHK

Date Changed

4A_160mil

15mil

12mil

12mil

15mil

10mil

OPEN

VER Model Number

15mil

15mil

MFG ENGR CHK

QA CHK

60mil

15mil

USED M10 (1.0V/ 1.2V) USED M9(1.25V/ 1.5V)

12mil

Time Changed

R219_ 1K_1%

R220_20K_1%

15mil

R219_ 10.2K_1%

R220_40.2K_1%

R1582_40.2K_1%

Changed by

15mil 15mil

15mil

12

David Du

David Du

11:26:35 amThursday, August 21, 2003EE2

679

PC8803A02

SYSTEM POWER (2.5V/1.25V)

DIAMOND

A3

15mil

4A_160mil

4A_160mil

40mil

4

1S

2

3

OPEN

C1469

1

2

300K_1%

R221

12

VGA25LGND

Q1020

NDS8425

D8

7

6

5

G

R207

0

12

R223

200K_5%

TI_SN74LVC1G17DBVR_SOT_5P

U4005

2

3

5

4

PAD5

POWERPAD_2_0610

2

SSM3K17FU

Q1058 D

D

G

G

S

S

OPEN

R6019

1

2

PAD3

POWERPAD_2_0610

R1583

OPEN

1

220UF_4V_METAL

1

+VBATR

VGA25LGND

1UF_6.3V

C208

1

2

C231

1UF_10V

1

2

+VGAVCC

+V5A

C213

9.76K_1%

R225

1

2

220K_5%

R238

1

2

2

G1

G2

4

S11

3

S2

Q1019

NDS7002A

D

3

G

2

1

S

VGA25LGND

C212

1

2

Q12

FDS6982S

7

D1 8

D2 6

5

OUT2

22 PGND

PGOOD 7

9REF

SKIP#

6

TON

5

4

V+

21 VCC

VDD 20

VGA25LGND

0.1UF_25V

FB2

3ILIM1

ILIM2

12

LX1 27

LX2 16

NC0

23

28 NC1

NC2 15

ON1

10

ON2

11

1

OUT1 14

MAX_MAX1715_QSOP_28P

U13

8AGND

BST1 25

18

BST2

26

DH1

17

DH2

24

DL1

DL2 19

2

FB1

13

1

2

+V1.2_MCH

22

R1175

1

2

+VBATR

+VBATR

D

D

G

G

S

S

SIL104R_5R2

L20

12

1UF_10V

C209

1

2

220P_25V

C207

1

2

Q1057

SSM3K17FU

2

C186

0.1UF_25V

1

2

29-

R220

20K_1%

1

2

1UF_10V

C189

1

2

15K_1%

R226

1

0.1UF_25V

1

2

0.1UF_16V

C242

1

2

59-,47-,45-,40-,38-,13-,12-,7-

OPEN

C210

R236

10

12

OPEN

R1582

1

2

C232

1

2

1K_1%

R219

1

2

2

10

R235 1

2

59-,55-

+V3A

0.012UF_16V

C6016

10UF_25V

1

2

14-

+V3A

BAT54AD4

3

1

1

2

14-

68UF_6.3V_METAL

C1189

1

C205

6

5

G

41

S

23

470_5%

R1166

0.1UF_25V

C2061

2Q15

FDS6680S

D

87

5

4

G

S

123

+V1.2L

+V2.5L

C230

220UF_2.5V

1

SIL104R_7R0

L22

12

FDS6612A

Q7

8

D

76

300K_1%

R224

1

2

C211

10UF_25V

1

2

LAN_ON_3

PWRPLAY

SLP_S3#_3R

PWR_GOOD#_5

PWR_GOOD_5

15mil

15mil

15mil

15mil

10mil

R&D CHK Size

TITLE

of

15mil

3A_100mil

Sheet

SYSTEM POWER (VCCP&1.2) ON BUTTON DAUGHTER BOARD

15mil

10mil

10mil

40mil

40mil

15mil

DOC CTRL CHK

15mil

15mil

Date Changed Time Changed

15mil

Engineer

Drawn by

10mil

10mil

INVENTEC

MFG ENGR CHK

Model Number

15mil

15mil

VER

3A_100mil

15mil

Changed by

1

David Du

David Du

6:06:02 pmThursday, July 31, 2003EE2

6710

PC8803A02

SYSTEM POWER(VCCP/1.2V)

DIAMOND

A3

15mil

12mil

QA CHK

1

3

S2

C4040

0.1UF_25V

1

2

+V5A_BN

C4044

220UF_2.5V_S18_METAL

Q4006

FDS6984S

7

D1

8

D2

6

5

2G1

G2

4

S1

1

2

0.1UF_25V

C40351

2

+V1.2L_BN

C4026

1

2

PLFC0735P_6R8A

L4004

12

C4041

10UF_25V

1UF_6.3V

C4025

1

2

1.1K_1%

R4032

1

2220P_25V

VCCP12LGND

VCCP12LGND

R4050

100K_5%

1263-,10-

63-

2

1UF_10V

C4027

1

2

C4032

0.1UF_25V

1

2

1

2

0.1UF_16V

C4038

1

2

20K_1%

R4034

1

+VBATP_BN

R4042

22

1

2

VCCP12LGND

0.1UF_16V

C4043

0.1UF_25V

1

2

R4040

10

12

+VBATP_BN

220UF_2.5V_S18_METAL

1

R4029 0_5%

12

63-,8-

C4037

10UF_25V

1

2

L4003

PLFC0735P_6R8A

12

VCCP12LGND

C4039

10

R4041

1

2

1UF_10V

C40331

2

C4036

Q4007

FDS6984S

D1 7

8

6

D2

5

G1

2

4G2

1

S1

S2 3

2

100PF_50V

C4024

1

2

+VCCP_BN

63-,10-

+VBATP_BN

PGOOD 7

9REF

6SKIP#

TON

5

4

V+

21 VCC

VDD 20

R4028

274K_1%

1

12

LX1 27

LX2 16

NC0

23

28 NC1

NC2 15

ON1

10

ON2

11

1

OUT1 14

OUT2

22 PGND

U4003

8AGND

BST1 25

BST2 18

26

DH1

17

DH2

24

DL1

DL2 19

2

FB1

13

FB2

3ILIM1

ILIM2

63-

BAT54AD4005

3

12

MAX_MAX1715_QSOP_28P

3.92K_1%

R4027 1

2

R4030

0

12

MCH_GOOD_BN

18.7K_1%

R4026

1

2

274K_1%

R4031

1

2

SLP_S3#_3R_BN

PWR_GOOD_3_BN

LAN_ON_3_BN

PWR_GOOD_3_BN

Size

MFG ENGR CHK

C1780 C532 C531 PIN2 CONNECT TO Q16 , Q20 GND

TITLE

10mil

10mil

x3

10mil

of

10mil

x3

DOC CTRL CHK

R&D CHK

Date Changed

KENVEN SENSE

Time Changed Sheet

5A_200mil

25A

Drawn by

LAYOUT NOTES: C1779 C502 C503 PIN2 CONNECT TO Q14 , Q18 GND

10mil

10mil

10mil

10mil

10mil

KENVEN SENSE

VER

20mil

15mil

QA CHK

20mil

6711

PC8803A02

CPU POWER(VCC_CORE)

DIAMOND

A3

20mil

15mil

20mil

25mil

25mil

25mil

25mil

15mil

Changed by

10mil

Model Number

10mil

10mil

20mil

15mil

25mil

25mil

25mil

Engineer

INVENTEC

KENVEN SENSE

2

MAX1987GND

R272

3K_5%

1

2

David Du

David Du

10:53:10 amThursday, July 31, 2003EE2

C54

0.1UF_16V

1

2

100PF_50V

C1059 1

FAIR_NC7WZ17_SC70_6P

U1035

3

2

5

4

D1009

SSM34_3A40V2

1

MAX1987GND

+V3S

FAIR_NC7WZ17_SC70_6P

U1035

1

2

5

6

6

5

G

4

1S

2

3

10UF_25V

C10681

2

R1085

1

2

MAX1987GND

59-

Q1016FDS6694

D8

7

2

VCC_IN

C1107

220UF_2.5V

1

+VCC_CORE

0_5%

17- R2740_5%

12

S0

0_5%

R1082

1

Q1013FDS7764A

D8

7

6

5

G

4

1S

2

3

11-

0.1UF_25V

12

R10760_5%

12

+V5S

6

5

G

4

1S

2

3

59-,40-,30-,14-

15-

C1070

470PF_50V

12

+VCCP

S1

Q1012 FDS7764A

D8

7

2

11-

0.1UF_16V

C1402

1

2

11-

B2

38-

C1056

L24

12

S2

R1078

100K_5%

1

D8

7

6

5

G

4

1S

2

3

11-

HMU1050_0.6UH_17A

Q1011 8

D7

6

54 G

S

1

2

3

Q1010

FDS6694

0_5% R268

12

C11621

2

FDS6694

C291

1UF_6.3V

1

2

0.1UF_25V

C1067

12

12

R1092

4.7_5%

12

11-

R1079

1.1K_1%

1

2

R1094

750_1%

1

2

0_5%

R264

C11601

2

B0

470PF_50V

C1055

1

2

MAX1987GND

11-

OPEN

R273

1

2

+V3S

18-

S1

R1103

0_5% 12

1M_5%

R10811

2

2

R267

10

1

2

270PF_50VC1057

12

B1

S2 0.0015_5%_1W

R250

12

1K_1%

R1098

1

54 G

S

1

2

3

0_5% R1104

12

18-

R1101

0_5% 12

FDS7764AQ1014

8

D7

6

2

VCC_IN

11-

REF

SSM34_3A40V

D1008

2

1

B1

B2

R257

0.0015_5%_1W

12

100K_5%

R270

1

R1097

1K_1%

1

2

750_1%

R1095

1

2

11-

1000PF_50V_X7R

1

2

C1066

10UF_25V

1

2

11-

11-

R1404

200K_5%

12

C11611

2

C1123

R1077

28K_5%

12

0_5%

R1084

1

2

1

2

C263

220UF_2.5V

1

38-

MAX1987GND

MAX1987GND

12

0_5% R1102

12

C1058

4700PF_50V

2

L23

HMU1050_0.6UH_17A

12

18-

18-

4.7_5%

R1073

REF

R271

1.1K_1%

1

2

2.2UF_K_10V

C10691

R269

0_5%

12

C1054

0.22UF_K_10V

1

2

C10651

2

18-

MAX1987GND

OPEN

R1083

1

2

3

1

2

S0

0_5% R1075

12 SUS

43

SYSPOK

22

TH 49

TIME

1

TON

2

42

V+

12 VCC VDD 36

BAT54A

D1007

NEG

20

OAIN+

OAIN- 19

PGND 37

POS 15

PSI#

21

REF

10

6S0

S1

7

8S2

9SHDN#

34

DHS 39

35

DLM

38

DLS

44 DPSLP#

FB 18

13

GND

11 ILIM

IMVPOK

23

33

LXM

LXS 40

16

CMP 45

47

CSN

CSP 48

D0

30

29 D1

28 D2

D3

27

D4

26

25 D5

31 DDO#

DHM

MAX_MAX1987ETM_QFN48_48P

U1009

3B0

B1

4

B2

5

BSTM 32

41

BSTS

17

CCI

14 CCV

24 CLKEN#

CMN 46

1

B0

18-

C303

1UF_6.3V

1

21000PF_50V_X7R

C1064

1

2

11-

D1025 1N4148

2

FDS7764AQ1015

8

D7

6

54 G

S

1

2

3

REF

OPEN

C292

1

2

0_5% R1100

12

+VBATR

R1117

20_5%

1

2

OPEN

R1087

1

2

R1080

30.1K_1%

1

2

220UF_2.5V

C281

1

FDS6694

Q1017

8

D7

6

54 G

S

1

2

3

220UF_2.5V

C262

1

20_5%

R1159

1

2

R1086

0_5%

1

2

R1099

0_5% 12

11-

12

R1096

4.7K_5%

1

2

MAX1987GND

MAX1987GND

38-,15-

R1074

OPEN

MAX1987GND

PM_VGATE

SB_VGATE

MCH_GOOD

POWER_GROUND

LXM

PM_DPRSLPVR

CPUSTOP#_3

PSI#

PWR_GOOD_3

VR_VID2

VR_VID3

VR_VID4

VR_VID5

H_VID1

H_VID2

H_VID3

H_VID4

H_VID5

DLM

VR_VID2

VR_VID3

VR_VID4

VR_VID5

H_VID0 VR_VID0

VR_VID1

DHM

UGATE2

VR_VID0

VR_VID1

INVENTEC

R&D CHK

40mil

40mil

10mil

10mil

10mil

Drawn by

Engineer

3A_120mil

Changed by Date Changed

MFG ENGR CHK

Model NumberVERQA CHKTime Changed

DOC CTRL CHK

Sheet

2

EE2 Thursday, July 31, 2003 10:53:16 am

David Du

David Du

A02 PC8803 12 67

DIAMOND

VGA POWER(VDD_CORE)

A3

TITLE

of

Size

1

C298

0.01UF_16V

1

2

R266

68K_5%

1

2

10UF_K_6.3V

C11001

2

C290

330UF_2.5V_METAL

+V3

R1144 10

1

2

C1121

1UF_10V

1

GND 9

EXTREF

6

8FB

1SHDN#

SS

5

7TOFF

R1138

1K_1%

12

VCC 12

13

PGND 14

LX

PGND 15

16

LX

IN

2

3LX

4IN

1

2

+V1.25S

U1010

MAX_MAX1809EEE_QSOP_16P

10

REF 11

GND

1

2

R263

100

12

0.1UF_10V

C261

VCC

VEE

2

+V5

BAT54D6 13

C1099

10UF_K_6.3V

C1122

1UF_6.3V

1

2

59-,47-,45-,40-,38-,13-,9-,7-

MAX_MAX4322EUK_SOT23_5P

U1011

IN+

34

IN-

1OUT 5

0_5%

R1146

12

1UH

L25

12

1

2

+V2.5

26-,25-,21-

C1119

0.01UF_16V

1

2

1

2

10K_1%

R256

1

20.1UF_10V

C280

SM_VREF

10K_1%

R255

1

2

C1120

0.1UF_10V

SLP_S3#_3R

MAX1809_LXA

MA1809_V3

MA1809LX_FB

MFG ENGR CHK

R&D CHK

DOC CTRL CHK

QA CHK VER Model Number of

Size

INVENTEC

Drawn by

Date Changed

6

14

David Du

David Du

11:28:38 amThursday, August 21, 2003EE2

6713

PC8803A02

POWER(SLEEP)

DIAMOND

A3

Changed by Sheet

TITLE

Time Changed

Engineer

5

R78

220K

1

2

74ACT14MTC

U1038

7

5

FDR840P

Q1046 1

D2

3

6

74 G

S

8

47UF_6.3V_METAL

C1350

1

100K

R206

1

2

+V2.5L

+V5A

59-,47-,45-,40-,38-,12-,9-,7-

Q11

1

D2

3

6

74 G

S

8

5

C274

10UF_K_6.3V

1

2

49-,32-

FDR840P

+V5A

+V5

470_5%

R1345

1

2

+V1.5S

7

G

4

8

S

5

Q1039

NDS7002A

D

3

G

2

1

S

R1407

470_5%

1

2

Q10

FDR840P

D

1

2

3

6

R1344

470_5%

1

2

C1368

47UF_6.3V_METAL

1

S

5

C1369

OPEN

1

2

+V5A

+V1.5A

+V5A

+V2.5L

Q1041

FDR840P

D

1

2

3

6

7

G

4

8

470_5%

R1359

1

2

0.039UF_10V

C187

1

2

Q1042

FDC638P

D1

2

5

6

G

3

4S

NDS7002A

Q1033 3

D

2

G

S

1

+V2.5S

2

57-

+V3A

+V5A

C175

68UF_4V_METAL

1

470_5%

R1371

1

2

+V5A

+V2.5

220K

R1372

1

1

NDS7002A

Q1023 3

D

2

G

S

1

14

74ACT14MTC

U1038

7

34

14

68UF_4V_METAL

C188

C53

1

2

+V5A

74ACT14MTC

U1038

7

98

U1038

74ACT14MTC

7

11 10

14

0.1UF_16V

Q1043

NDS7002A

D

3

G

2

1

S

47UF_6.3V_METAL

C1351

1

+V3

NDS7002A

D

3

G

2

1

S

R1383

220K

1

2

7

6

54

G

S1

2

3

Q1047

1000PF_0402

C6024

1

2

NDS8425

Q6

8D

63 G

S

4

NDS7002A

Q1054 3

D

2

G

S

1

38-

R1373

330K

1

2

FDC638P

Q1035 1

D2

5

R1236

470_5%

1

2

0.1UF_16V

C52

1

2

Q1034

NDS7002A

D

3

G

2

1

S

+V3A

470_5%

R1382

1

2

2

R1204

220K

1

2

+V3S +V5S

2

14

47UF_6.3V_METAL

C1377

1

220K

R1343

1

74ACT14MTC

U1038

7

1

SLP_S3_5R

SLP_S3#_3R SLP_S3#_5R

SLP_S5#_3R SLP_S5#_5R

Time Changed

Changed by

MFG ENGR CHK

QA CHK

INVENTEC

of

Engineer

DOC CTRL CHK

Model Number Sheet

Size

Date Changed

+V5S

David Du

David Du

10:53:25 amThursday, July 31, 2003EE2

6714

PC8803A02

POWER(SEQUENCE)

DIAMOND

A3

Drawn by

VER

TITLE

R&D CHK

10K_5%

R1425

1

2

1N4148

D1029

2

1

1

2

Q1052

NDS7002A

D

3

G

2

1

S

59-,40-,30-,11-1

2IN2

3IN3

IN4

4

9

OUT1

OUT2 8

OUT3 7

6

OUT4

VCC

10

C1408

1UF_10V

U1032

2

3

5

4

U1036

MAX_MAX6338KUB_UMAX_10P

5

GND

IN1

C306

0.1UF_16V

1

2

+V1.5S

+V5A

TI_SN74LVC1G17DBVR_SOT_5P

180_0.5%

R1424

1

2

100K_5%

R278

1

2

1

2

R277

511K_1%

1

2

40-,38-

9-

9-

R1412

4.7K_5%

1

2

+V3S

+V3A+V3A

0.1UF_16V

C307

+V2.5S

+V5A

U1038

74ACT14MTC

7

13 12

14

VCC1_POR#_3

PWR_GOOD_5

+V1.8S

+V3S

PWR_GOOD#_5

PWR_GOOD_3

(10/5)

INVENTEC

Sheet

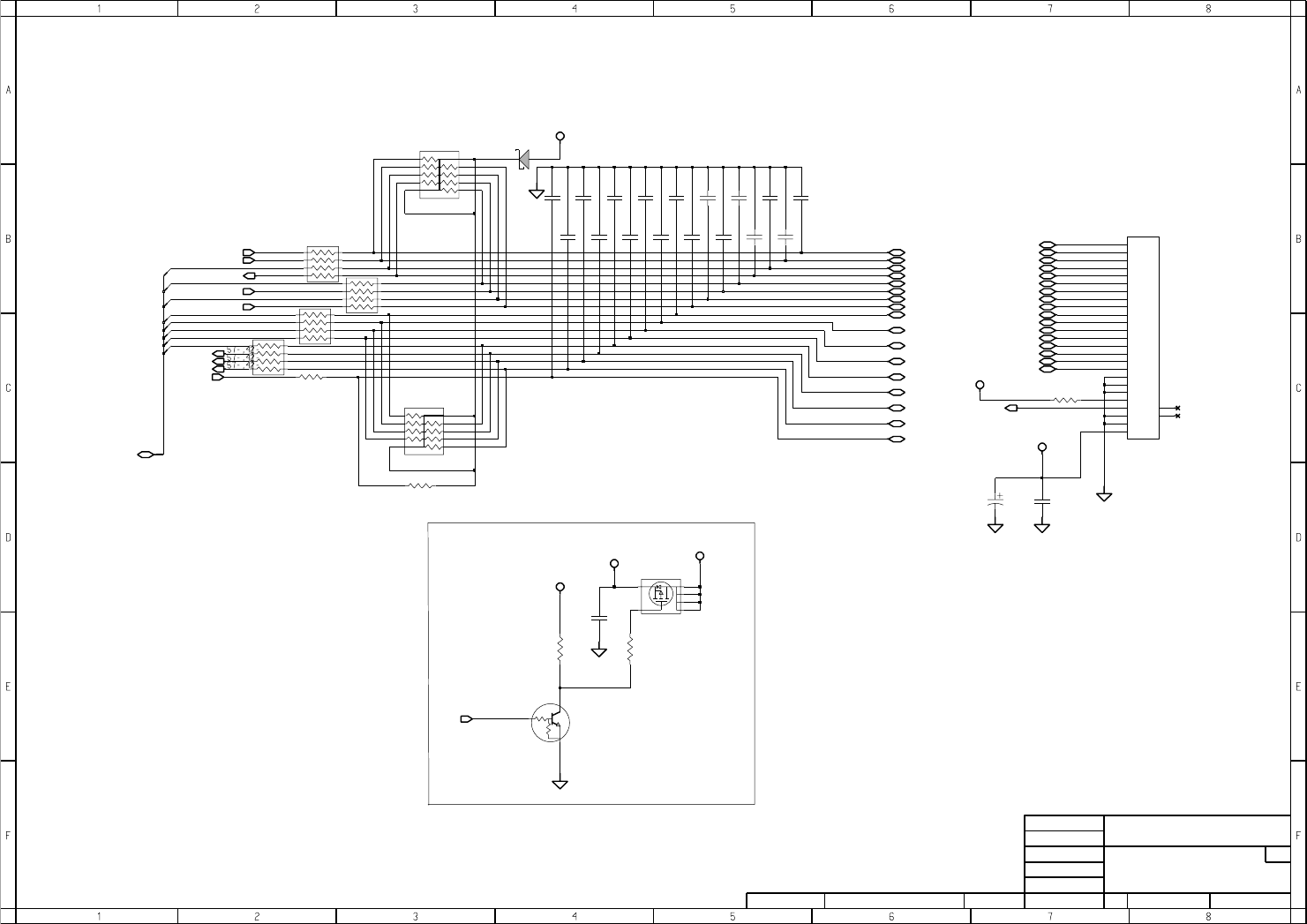

mils of CLK_TITAN

(15/5)

of

Size

TITLE

Engineer

Place crystal within 500

Date Changed Time Changed Model Number

R&D CHK

Drawn by

(10/5)

DOC CTRL CHK

MFG ENGR CHK

QA CHK VER

(10/5)

R1333 33_5%

12

EE2 Thursday, July 31, 2003 10:53:30 am

David Du

David Du

A02 PC8803 15 67

DIAMOND

CLOCK_GENEATOR

A3

Changed by

2

+V3S

38-

38-

40-

33_5%

R1340

12

2

33_5%

R1368

12

0.01UF_16V

C118

1

2

R1316

33_5% 12

37-

R1367 33_5%

1

1

2

R1313

OPEN

1

2

R1315

33_5% 1

1

2

49.9_1%R150

12

1K_5%

R1312 10PF

12

10PFC1339

12

R1366

10K_5%

OPEN 12

1K_5%

R1327

12

C1340

R147 49.9_1%

12

54-

16-

R1361

1

19-

22-

42-

45-

0.1UF_16V

C134

1

2

R1342

33_5% 12

NDS7002A

Q1040 3

D

2

G

S

29-

R1331 33_5%

12

49.9_1%R148

12

12

BLM11A221S

L1019

12

42-

C133

1

2

OPEN

R1329

12

+V3S

R1369 33_5%

2

R1341

33_5% 12

51-

16-

0.1UF_16V

R1334

33_5% 12

0_5%R1324

1

49.9_1%

R1308

12

0.01UF_16V

C1366 1

2

+V3S

1

33_5% R1338

12

19-

37-

R131733_5% 12

C1363

22UF_6.3V

X1001

14.318MHZ

1

2

0.1UF_16V

C132

1

2

0.1UF_16V

C135

1

2

33_5%

R1584

12

1

2

R1310 33_5%

12

11-

+V3S

37-,26-,25-,20-

12

R1311

1K_5%

1

2

R1335

475_1%

12

21-

R1314

OPEN

1

2

R1370

33_5%

NFM40P12C223

L1018

12

34

33_5%

R1332

1

2

49.9_1%R149

12

40-

33_5%

12

38-

49.9_1%

R1325

12

C1365

10UF_K_6.3V

0_5%

12

R1328 10K_5%

12

R1330

R133933_5% 12

59-

37-,26-,25-,20-

R1309

12

C1367

22UF_6.3V

1

55-

+V3S

38-,11-

20

VSS

31

VSS

36

VSS

47

28 VTT_PWRGD#

XTAL_IN

2

3XTAL_OUT

33_5%

R1326

37 VDD

46 VDD

50 VDD

27

VSSA

41 VSSIREF

VSS

4

VSS

9

VSS

15

VSS

55 SEL1

40 SEL2

39

USB

26

VDDA

1VDD

8VDD

14 VDD

19 VDD

32 VDD

17

PCI5

PCI6 18

5

PCIF0

PCIF1 6

7

PCIF2

34 PCI_STOP#

PWRDWN#

25

REF 56

30 SCLOCK

29 SDATA

SEL0

54

DOT 38

DRCG0

33

35 DRCG1_VCH

42 IREF

MULT0

43

PCI0 10

11

PCI1

PCI2 12

PCI3 13

16

PCI4

66BUF0

22

66BUF1

66BUF2 23

24

66INPUT

CPU0 52

CPU0# 51

49

CPU1

48

CPU1#

45

CPU2

CPU2# 44

CPU_STOP#

53

33_5% 12

38-

22-

ICS_950810_TSSOP_56P

U1020

21

PM_VGATE

CPUSTOP#_3

CLK_SIO14_3

33_5% R1337

12

R1336

CLK_ITP

CLK_MINIPCI_3R

ICH_SMDAT_3

ICH_SMCLK_3

SLP_S1#_3R

PCISTOP#_3

CLK_KBC14_3R

CLK_NICPCI_3

ADI48M

CLK_NICPCI_3R

ADI48M_3

CLK_ITP#

CLK_MCH66

CLK_MCH66_3

CLK_KBCPCI_3R

CLK_KBCPCI_3

CLK_ITP#_3

CLK_AGPCONN_3

CLK_ICHHUB_3

CLK_ICHPCI_3

CLK_CPU_BCLK

CLK_CPU_BCLK#

CLK_MCH_BCLK

CLK_MCH_BCLK#

CLK_MCH_BCLK#_3

CLK_AGPCONN

CLK_ICHHUB

CLK_ICHPCI_3R

CLK_CPU_BCLK_3

CLK_CPU_BCLK#_3

CLK_ITP_3

CLK_FWHPCI_3

CLK_SIOPCI_3R

CLK_SIOPCI_3

CLK_ICH48_3R

CLK_ICH48_3

CLK_SIO14_3R

CLK_ICH14_3R

CLK_MCH_BCLK_3

CLK_CBPCI_3R

CLK_CBPCI_3

CLK_MINIPCI_3

CLK_FWHPCI_3R

ADDR GROUP 0

ADDR GROUP 1

CONTROL

THERMH_CLK ITP SIGNALS

GTL4/8

POWER15/5

GTL4/8

GTL4/8

GTL4/8

GTL4/8

GTL4/8

GTL4/8

GTL4/8

GTL4/8

GTL4/8

GTL4/8

GTL4/8

GTL4/8

GTL4/8

GTL4/8

GTL4/8

AGP4/8

GTL4/8

GTL4/8

GTL4/8

GTL4/8

GTL4/8

GTL4/8

GTL4/8

GTL4/8

GTL4/8

GTL4/8

GTL4/8

GTL4/8

GTL4/8

GTL4/8

GTL4/8

GTL4/8

POWER15/5

CLK4/4_25A

CLK4/4_25A

GTL4/8

GTLDQS5/15-4/12

GTL4/8

GTL4/8

GTL4/8

GTL4/8

GTL4/8

GTL4/8

GTL4/8

GTLDQS5/15-4/12

GTL4/8

GTL4/8

GTL4/8

GTL4/8

GTL4/8

GTL4/8

GTL4/8

GTL4/8

GTL4/8

GTL4/8

THERM10/10

THERM10/10

GTL4/8

GTL4/8

GTL4/8

GTL4/8

GTL4/8

Time Changed

Engineer

Drawn by

R&D CHK

H_TCK FORKS

AT CPU PIN

Changed by Model NumberDate Changed Sheet of

Size

TITLE

DOC CTRL CHK

VER

INVENTEC

MFG ENGR CHK

QA CHK

GTL4/8

David Du

David Du

10:53:36 amThursday, July 31, 2003EE2

6716

PC8803A02

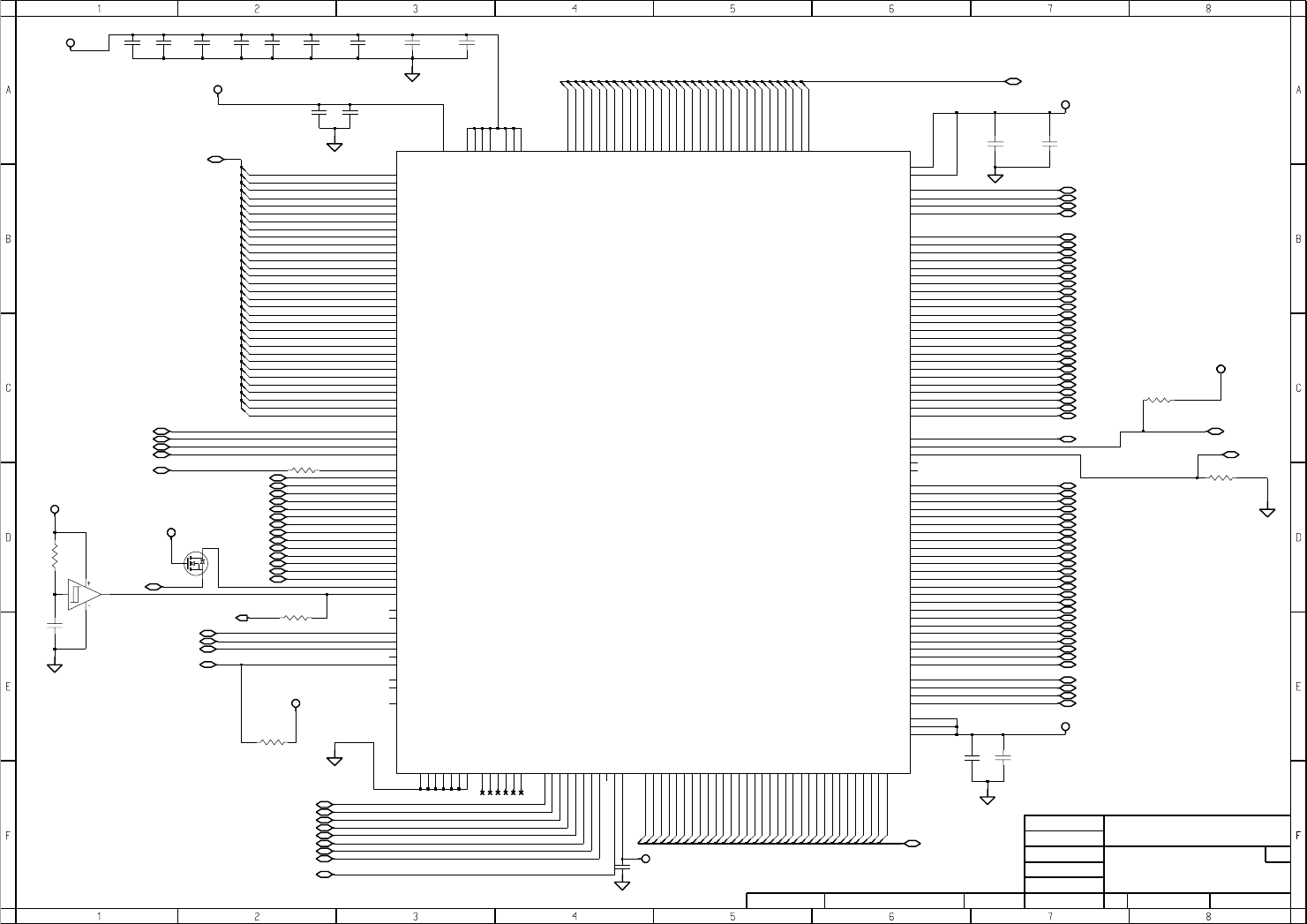

BANIAS-1

DIAMOND

A3

LAYOUT NOTES

23-

22-,19-

23-

37-

37-,5-

20-

22-

22-

23-

23-

23-

2

+VCCP

38-,19-

20-

38-

15-

15-

23-

22-

1

2

+VCCP

TP1

19-

56_5%

R261

1

680_5%

1

2

19-

19-

19-

R1140

150_5%

TCK A13

C12

TDI

TDO A12

B18

THERMDA

THERMDC A18

C17

THERMTRIP#

C11

TMS

M3

TRDY#

TRST# B13

R1120

R2

REQ1#

P3

REQ2#

T2

P1 REQ3#

T1 REQ4#

B11

RESET# H1

RS0#

RS1# K1

RS2# L2

B4 SMI#

C6 STPCLK#

A4

IGNNE#

A3

B5

INIT#

A16

ITP_CLK0

ITP_CLK1 A15

LINT0

D1

D4 LINT1

J2

LOCK#

A10

PRDY#

PREQ# B10

PROCHOT# B17

REQ0#

C9

BPM#3

J3

BPRI#

N4

BR0#

DBR# A7

M2

DBSY#

L4

DEFER#

DRDY# H2

D3 FERR#

HIT# K3

K4

HITM#

IERR#

W1

A9#

T4

N2

ADS#

U3 ADSTB#0

AE5 ADSTB#1

BCLK0 B15

B14

BCLK1

BNR# L1

C8

BPM#0

BPM#1 B8

BPM#2 A9

A26#

A27#

AE2

AD6 A28#

A29#

AF3

A3#

P4

A30#

AE1

AF1 A31#

U4 A4#

V3 A5#

A6#

R3

V2 A7#

A8#

A17#

AF4

A18#

AC4

AC7 A19#

A20#

AC3

A20M#

C2

AD3 A21#

AE4 A22#

A23#

AD2

A24#

AB4

AC6 A25#

AD5

19-

CN19

AMP_MPGA479M_C_1376756_479P_BANIAS

W2 A10#

Y4 A11#

A12#

Y1

A13#

U1

AA3 A14#

A15#

Y3

AA2 A16#

37-

19-

19-

19-

19-

19-

19-

19-

23-

23-

23-

37-

37-

37-

37-

22-

22-

23-

23-

23-

59-,37-

H_A#(13)

H_A#(14)

H_A#(15)

H_A#(16)

H_A#(5)

H_A#(6)

H_A#(7)

H_A#(8)

H_A#(9)

H_A#(10)

H_A#(11)

H_A#(12)

H_REQ#(2)

H_REQ#(3)

H_REQ#(4)

H_RS#(0)

H_RS#(1)

H_RS#(2)

H_A#(3)

H_A#(4)

H_A#(28)

H_A#(29)

H_A#(30)

H_A#(31)

H_BR0#

ITP_DBRESET#

H_REQ#(0)

H_REQ#(1)

H_A#(20)

H_A#(21)

H_A#(22)

H_A#(23)

H_A#(24)

H_A#(25)

H_A#(26)

H_A#(27)

TDI_FLEX

H_TDO

PM_THRMTRIP#

H_THERMDA

H_THERMDC

H_TMS

H_TRST#

H_BPM1_ITP#

H_BPM0_ITP#

H_A#(17)

H_A#(18)

H_A#(19)

CLK_CPU_BCLK#

H_BPM2_ITP#

H_BPM3_ITP#

H_BPM4_PRDY#

H_BPM5_PREQ#

H_FERR_S#

H_IGNNE#

H_INTR

H_NMI

H_SMI#

H_STPCLK#

H_TCK

H_TCK

H_HITM#

H_A#(3:16)

H_ADSTB#0H_REQ#(4:0)

H_A#(17:31)

H_LOCK#

H_INIT#

H_RS#(0:2)

H_TRDY#

H_CPURST#

H_A20M#

CLK_CPU_BCLK

H_ADS#

H_ADSTB#1

H_BNR#

H_BPRI#

H_DBSY#

H_DEFER#

H_DRDY#

H_HIT#

MISC

DATA GRP 0

DATA GRP 1

DATA GRP 2DATA GRP 3

Changed by Date Changed Sheet

R&D CHK

DOC CTRL CHK

MFG ENGR CHK

QA CHK VER Model Number

TITLE Size

DIAMOND

BANIAS-2

A3

LAYOUT NOTES : PLACE R1275 , R1276 CLOSE TO CN1008

of

INVENTEC

Time Changed

Engineer

Drawn by

22-

22-

22-

22-

22-

EE2 Thursday, July 31, 2003 10:53:41 am

David Du

David Du

A02 PC8803 17 67

R1118 330_5%

12

22-

22-

1K_1%

R242

1

2

21-

37-

1

2

TP570

TP571 27.4_1%R244 12

R241

2K_1%

27.4_1%R109312

PSI#

E4

PWRGOOD

C14 RSVD1

RSVD2

C3

AF7 RSVD3

A6

SLP#

TEST1 C5

F23

TEST2

C16 TEST3

DSTBN3#

DSTBP0#

C22

DSTBP1#

L24

DSTBP2# W24

AE25

DSTBP3#

GTLREF0

AD26

E26 GTLREF1

GTLREF2

G1 GTLREF3

AC1

NC0

A1

B2 NC1

E1

B24 D9#

D25 DINV0#

J26 DINV1#

T24

DINV2#

DINV3# AD20

DPSLP# B7

C19

DPWR#

DSTBN0#

C23

DSTBN1#

K24

DSTBN2# W25

AE24

AF23

AD24

D57# AF20

D58#

D59# AE21

A21 D6#

AD21

D60#

D61# AF25

D62# AF22

AF26

D63#

D7#

B20

D8#

C20

D46#

D47# Y25

AB25

D48#

D49# AC23

B26 D5#

D50# AB24

AC20

D51#

D52# AC22

D53# AC25

AD23

D54#

D55# AE22

D56#

D37# R24

D38# R26

R23

D39#

D4#

A24

AA23

D40#

D41# U26

D42# V24

D43# U25

D44# V26

Y23

D45# AA26

D27#

D28#

M25

H26 D29#

B21 D3#

N25 D30#

D31#

K25

D32# Y26

AA24

D33# T25

D34#

D35# U23

V23

D36#

D17#

L23 D18#

D19#

M26

D2#

A22

H24 D20#

D21#

F25

D22#

G24

J23 D23#

D24#

M23

D25#

J25

D26#

L26

N24

COMP3 AB1

A19 D0#

D1#

A25

D24 D10#

D11#

E24

C26 D12#

D13#

B23

E23 D14#

C25 D15#

D16#

H23

G25

22-

+VCCP

AMP_MPGA479M_C_1376756_479P_BANIAS

CN19

COMP0 P25

P26

COMP1 AB2

COMP2

22-

22-

22-

TP572

+VCCP

22-

R1088

12

11-

22-

22-

1

2

OPEN

R1141

1

2

0_5%

12

37-

R260

OPEN

12

R243 54.9_1%

37-,21-

22-

22-

R1091 54.9_1%

PSI#

R1147

OPEN

1

2

H_D#(9)

H_PWRGD

H_DPWR#

H_CPUSLP#

H_DPSLP#

H_D#(60)

H_D#(61)

H_D#(62)

H_D#(63)

H_D#(7)

H_D#(8)

H_D#(55)

H_D#(56)

H_D#(57)

H_D#(58)

H_D#(59)

H_D#(6)

H_D#(49)

H_D#(5)

H_D#(50)

H_D#(51)

H_D#(52)

H_D#(53)

H_D#(54)

H_D#(43)

H_D#(44)

H_D#(45)

H_D#(46)

H_D#(47)

H_D#(48)

H_D#(37)

H_D#(38)

H_D#(39)

H_D#(4)

H_D#(40)

H_D#(41)

H_D#(42)

H_D#(31)

H_D#(32)

H_D#(33)

H_D#(34)

H_D#(35)

H_D#(36)

H_D#(26)

H_D#(27)

H_D#(28)

H_D#(29)

H_D#(3)

H_D#(30)

H_D#(2)

H_D#(20)

H_D#(21)

H_D#(22)

H_D#(23)

H_D#(24)

H_D#(25)

H_D#(14)

H_D#(15)

H_D#(16)

H_D#(17)

H_D#(18)

H_D#(19)

H_D#(0)

H_D#(1)

H_D#(10)

H_D#(11)

H_D#(12)

H_D#(13)

H_D#(32:47)

H_DINV#2

H_DSTBN#2

H_DSTBP#2

H_D#(48:63)

H_DINV#3

H_DSTBN#3

H_DSTBP#3

H_D#(0:15)

H_DINV#0

H_DSTBN#0

H_DSTBP#0

H_D#(16:31)

H_DSTBP#1

H_DSTBN#1

H_DINV#1

Drawn by

R&D CHK

Changed by

Engineer

MFG ENGR CHK

QA CHK VERTime Changed

INVENTEC

DOC CTRL CHK

NOTES : INSTALL 54.9_1% FOR TESTING

Model Number Sheet of

Date Changed

Size

TITLE

0.1UF_16V

C1136

1

2

EE2 Thursday, July 31, 2003 10:53:46 am

David Du

David Du

A02 PC8803 18 67

DIAMOND

BANIAS-3

A3

10UF_K_6.3V

C11091

2

C265

10UF_K_6.3V

1

2

10UF_K_6.3V

C11141

2

C272

10UF_K_6.3V

1

2

10UF_K_6.3V

C2671

2

C284

10UF_K_6.3V

1

2

2

0.01UF_16V

C1071

1

2

0.01UF_16V

C1072

1

2

OPEN

R258

1

2

11-

0.01UF_16V

C293

1

0.1UF_16V

C1088

1

2

C1085

0.1UF_16V

1

2

0.1UF_16V

C1133

1

2

C1090

0.1UF_16V

1

2

VSSSENSE

0.1UF_16V

C1089

1

2

C1087

0.1UF_16V

1

2

VCCP8

VCCP9 F14

P23

VCCQ0

VCCQ1 W4

VCCSENSE AE7

E2

VID0 F2

VID1 F3

VID2

VID3 G3

VID4 G4

H4

VID5

AF6

VCCP20 R21

R5

VCCP21

VCCP22 T22

T6

VCCP23 U21

VCCP24

D16

VCCP3 E11

VCCP4 E13

VCCP5

VCCP6 E15

VCCP7 F10

F12

VCCP10 K6

VCCP11

VCCP12 L21

L5

VCCP13

VCCP14 M22

VCCP15 M6

VCCP16 N21

VCCP17 N5

P22

VCCP18 P6

VCCP19

D14

VCCP2

AA7

Y22

VCC70 Y6

VCC71

AA9 VCC8

AB10 VCC9

F26

VCCA0 B1

VCCA1

VCCA2 N1

VCCA3 AC26

D10

VCCP0

VCCP1 D12

F16

H22

VCC60

VCC61 H6

J21

VCC62 J5

VCC63 K22

VCC64 U5

VCC65 V22

VCC66

VCC67 V6

W21

VCC68

VCC69 W5

VCC7

E5

E7 VCC51

VCC52

E9

F18 VCC53

VCC54

F20

F22 VCC55

F6 VCC56

F8 VCC57

VCC58

G21

VCC59 G5

AA5 VCC6

VCC40

VCC41

AF8

VCC42

D18

D20 VCC43

D22 VCC44

D6 VCC45

D8 VCC46

VCC47

E17

E19 VCC48

E21 VCC49

VCC5

AA21

VCC50

VCC31

AE13

AE15 VCC32

AE17 VCC33

VCC34

AE19

VCC35

AE9

VCC36

AF10

AF12 VCC37

AF14 VCC38

VCC39

AF16

VCC4

AA19

AF18

AC17

AC19 VCC22

VCC23

AC9

AD10 VCC24

AD12 VCC25

VCC26

AD14

VCC27

AD16

VCC28

AD18

VCC29

AD8

AA17 VCC3

AE11 VCC30

VCC11

VCC12

AB16

VCC13

AB18

AB20 VCC14

VCC15

AB22

VCC16

AB6

AB8 VCC17

VCC18

AC11

AC13 VCC19

VCC2

AA15

VCC20

AC15

VCC21

0.01UF_16V

C243

1

2

+VCC_CORE

CN19

AMP_MPGA479M_C_1376756_479P_BANIAS

AA11 VCC0

AA13 VCC1

VCC10

AB12

AB14

10UF_K_6.3V

C10731

2

10UF_K_6.3V

C2941

2

10UF_K_6.3V

C2821

2

10UF_K_6.3V

C2451

2

10UF_K_6.3V

C2661

2

C1137

10UF_K_6.3V

1

2

2

C283

10UF_K_6.3V

1

210UF_K_6.3V

C11051

2

1

2

C264

10UF_K_6.3V

1

210UF_K_6.3V

C10931

+VCCP

11-

10UF_K_6.3V

C11311

2

C271

10UF_K_6.3V

1

2

C1138

10UF_K_6.3V

1

2

+VCC_CORE

+VCCA

0.1UF_16V

C1135

1

2

C1134

0.1UF_16V

1

2

C1084

10UF_K_6.3V

10UF_K_6.3V

C2951

2

C1132

0.1UF_16V

1

2

10UF_K_6.3V

C10921

2

C269

10UF_K_6.3V

1

2

11-

10UF_K_6.3V

C2731

2

C1091

10UF_K_6.3V

1

2

10UF_K_6.3V

C11061

2

C268

10UF_K_6.3V

1

2

2

C1110

10UF_K_6.3V

1

2

10UF_K_6.3V

C10831

2

1

2

C1113

10UF_K_6.3V

1

210UF_K_6.3V

C11281

1

2

+V1.5S

+V1.8S

11-

11-

11-

10UF_K_6.3V

C1129

1

2

R246

OPEN

1

2

R247

0

C2701

2

C1082

10UF_K_6.3V

1

2

10UF_K_6.3V

C1139

10UF_K_6.3V

C11111

2

C1112

10UF_K_6.3V

1

210UF_K_6.3V

10UF_K_6.3V

C2521

2

C1130

10UF_K_6.3V

1

2

C1108

100UF_2.5V_METAL

1C1086

100UF_2.5V_METAL

1

OPEN

R259

1

2

H_VID0

H_VID1

H_VID2

H_VID3

H_VID4

H_VID5

of

Size

TITLE

INVENTEC

LAYOUT NOTES : H_CPURST# PIN OF MCH_M FORK OUT INTO TWO BRANCHES ON CPU AND ITP CONNECTOR

POWER15/5

CLK4/4_25A

CLK4/4_25A

GTL4/8

POWER15/5

POWER15/5

19 67

DIAMOND

BANIAS-4

A3

In-Target Probe

Changed by Date Changed Time Changed

Engineer

Drawn by

R&D CHK

DOC CTRL CHK

MFG ENGR CHK

QA CHK VER Model Number Sheet

240_5%

R1106

1

2

EE2 Thursday, July 31, 2003 10:53:51 am

David Du

David Du

A02 PC8803

16-

16-

16-

16-

16-

38-,16-

C1074

0.1UF_16V

1

2

D5

D7 VSS94

VSS95

D9

D11 VSS96

D13

VSS97

VSS98 D15

D17

VSS99

+V3A

16-

VSS84

C4

C7 VSS85

C10 VSS86

VSS87

C13

C15 VSS88

VSS89

C18

VSS9

AA1

VSS90

C21

VSS91

C24

D2 VSS92

VSS93

AF24

B3 VSS75

VSS76

B6

B9 VSS77

B12 VSS78

VSS79

B16

A26 VSS8

VSS80

B19

VSS81

B22

VSS82

B25

C1 VSS83

VSS64

VSS65

AF2

VSS66

AF5

AF9 VSS67

VSS68

AF11

AF13 VSS69

A23 VSS7

AF15 VSS70

VSS71

AF17

AF19 VSS72

VSS73

AF21

VSS74

VSS55

AE6

AE8 VSS56

VSS57

AE10

VSS58

AE12

AE14 VSS59

VSS6

A20

VSS60

AE16

VSS61

AE18

AE20 VSS62

VSS63

AE23

AE26

VSS45

AD9 VSS46

VSS47

AD11

AD13 VSS48

VSS49

AD15

VSS5

A17

VSS50

AD17

VSS51

AD19

VSS52

AD22

AD25 VSS53

AE3 VSS54

AC8

AC10 VSS36

VSS37

AC12

VSS38

AC14

AC16 VSS39

A14 VSS4

AC18 VSS40

VSS41

AC21

VSS42

AC24

AD1 VSS43

VSS44

AD4

AD7

VSS26

AB13

AB15 VSS27

VSS28

AB17

AB19 VSS29

VSS3

A11

AB21 VSS30

VSS31

AB23

AB26 VSS32

AC2 VSS33

AC5 VSS34

VSS35

Y5

VSS19

AA22

Y21

VSS190

VSS191 Y24

A8 VSS2

AA25 VSS20

VSS21

AB3

AB5 VSS22

AB7 VSS23

AB9 VSS24

VSS25

AB11

V4

AA20 VSS18

V5

VSS180 V21

VSS181

VSS182 V25

W3

VSS183

VSS184 W6

VSS185 W22

W23

VSS186

VSS187 W26

Y2

VSS188

VSS189

AA18 VSS17

T5

VSS170

VSS171 T21

T23

VSS172 T26

VSS173

VSS174 U2

U6

VSS175 U22

VSS176

VSS177 U24

V1

VSS178

VSS179

AA16

VSS160 P2

VSS161 P5

P21

VSS162

VSS163 P24

R1

VSS164 R4

VSS165 R6

VSS166 R22

VSS167

VSS168 R25

VSS169 T3

AA14

VSS150 M1

M4

VSS151

VSS152 M5

VSS153 M21

M24

VSS154

VSS155 N3

N6

VSS156 N22

VSS157

VSS158 N23

N26

VSS159

VSS16

VSS140 J24

K2

VSS141

VSS142 K5

K21

VSS143

VSS144 K23

VSS145 K26

L3

VSS146 L6

VSS147 L22

VSS148 L25

VSS149

VSS15

G23

G26

VSS131

VSS132 H3

VSS133 H5

H21

VSS134

VSS135 H25

J1

VSS136

VSS137 J4

VSS138 J6

J22

VSS139

AA12 VSS14

VSS120 F13

VSS121

VSS122 F15

F17

VSS123

VSS124 F19

VSS125 F21

F24

VSS126

VSS127 G2

G6

VSS128 G22

VSS129

AA10 VSS13

VSS130

VSS111 E18

E20

VSS112 E22

VSS113

VSS114 E25

F1

VSS115

VSS116 F4

VSS117 F5

VSS118 F7

VSS119 F9

VSS12

AA8

F11

D21

D23

VSS102

VSS103 D26

E3

VSS104 E6

VSS105

VSS106 E8

E10

VSS107 E12

VSS108

VSS109 E14

AA6 VSS11

E16

VSS110

R1123

1

2

CN19

AMP_MPGA479M_C_1376756_479P_BANIAS

VSS0

A2

A5 VSS1

VSS10

AA4

VSS100 D19

VSS101

R112512

R1122 22.6_1%

12

39.2_1%

1

2

54.9_1%

R1105

1

2

+VCCP

22.6_1%

16-

15-

15-

27.4_1%

R1121

1

2

R1124

54.9_1%

55

6

6

77

88

9

9

16-

16-

16-

22-,16-

23

23

24

24

25 25

26

26

27

27

28 28

3

3

44

16

17

17

18

18

19 19

22

20

20

21 21

22 22

CN1002

MLX_52435_2891

11

10

10

11 11

12

12

13 13

14

14 15

15

16 H_BPM5_PREQ#

H_BPM4_PRDY#

H_BPM3_ITP#

H_BPM2_ITP#

H_BPM1_ITP#

H_BPM0_ITP#

ITP_DBRESET#

+VCCP+VCCP

16-

16-

H_TMS

H_TCK

H_TRST#

H_TDO

TDI_FLEX

H_CPURST#

H_TCK

CLK_ITP#

CLK_ITP

VER

Size

TITLE

LAYOUT NOTES: PUT THE THERMAL SENSOR CLOSE TO CPU

INVENTEC

Date ChangedChanged by

EE2 Wednesday, August 13, 2003 10:20:09 pm

David Du

David Du

A02 PC8803 20 67

DIAMOND

THERMAL&FAN CONTROLLER

A3

Time Changed

DOC CTRL CHK

Drawn by

R&D CHK

Sheet

MFG ENGR CHK

QA CHK of

Model Number

Engineer

8

GND 5

INT#_NTO 14

PWM_OUT1 1

3

PWM_OUT2

16 SCL

15 SDA

2

TACH1_AIN1

TACH2_AIN2 4

THERM# 7

VCC

6

2

+V3S

U15

ANLG_ADM1031ARQ_QSOP_16P

13

ADD

10 D+

D1-_NT1

9

D2+

12 D2-

11 FAN_FAULT#

2

0.1UF_16V

C285

1

2

+V5

R1435

2.2K_5%

1

NC7SZ00M5

U17

3

1

24

5

C111

0.1UF_16V

1

38-,20-

30-

30-

MLX_53398_0390_3P

CN20

GND

2

REFENCE

3

VCC

1

12

1K_5%

R262

12

+V3S

38-,20-

2

+V3S

2200PF_50V

C287

13

Q13

FDV303N

D

3

G

1

2

S

C296

1UF_10V

1

37-,26-,25-,15-

37-,26-,25-,15-

0.01UF_16V

C1060

1

2

D5

BAT54

C286

OPEN 12

40-

37-

16-

16-

ICH_SMDAT_3

ICH_SMCLK_3

THERM_SCI#

H_THERMDA

H_THERMDC

TEMP_WARN#_3

DMINUS

DPLUS

FAN_PWM_3

TEMP_WARN#_3

MEMORY

HUB

MEMORY

AGP

Drawn by

R&D CHK

Changed by

HUB_VREF_MCH

INVENTEC

Engineer

SM_VREF

TITLE

100MILS(+-5MILS)

QA CHKTime Changed

MCH_TEST#

Date Changed of

Size

DOC CTRL CHK

MFG ENGR CHK

VER Model Number Sheet

28-,26-

EE2 Thursday, July 31, 2003 10:54:07 am

David Du

David Du

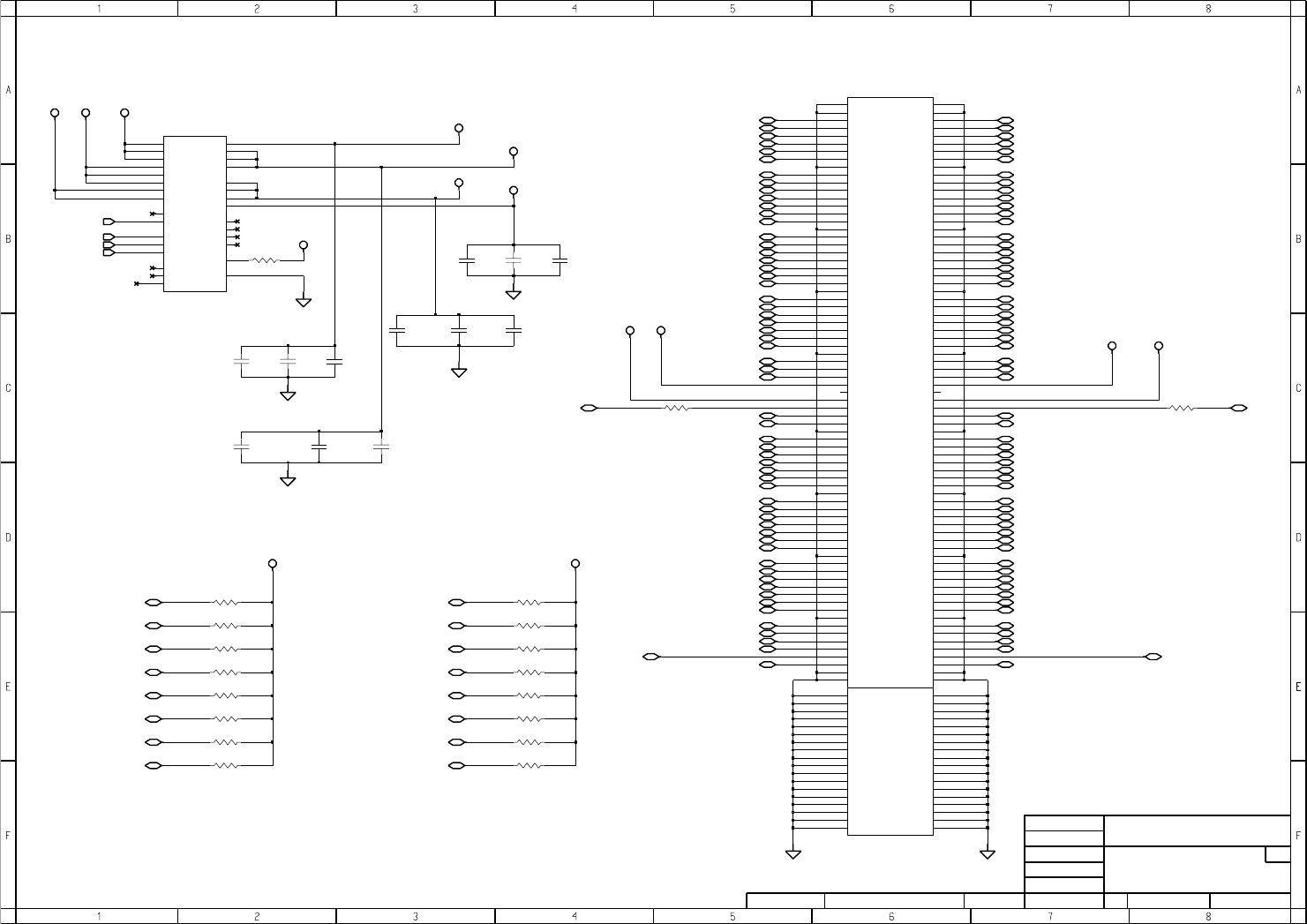

A02 PC8803 21 67

DIAMOND

ODEM-1

A3

TP544

28-,26-

29-

37-

28-,27-,26-

27-,28-,26-

TP540

AGPREF

+V1.8S

29-

28-,25-

29-

TP539

26-,25-,12-

0.1UF_16V

C1165

1

2

TP545

29- R253

0_5%

12

10_5%

12

37-

29-

29-

10_5%

12

55-,48-,37-,29-

R1143

ST2

SWE# G11

H26 TESTIN#

AE23 WBF#

+V1.25S

TP546

R1161

G18

SMA4

SMA5 E18

F19

SMA6 G20

SMA7

SMA8 G19

F21

SMA9

SMRCOMP

J28

SRAS# F11

AG25 ST0

ST1

AF24

AG26

E3

E15

SDQS8

SDREF0 J21

J9

SDREF1

E12

SMA0

SMA1 F17

SMA10 F13

SMA11 E20

SMA12 G21

SMA2 E16

G17

SMA3

C15

D14

SDQ71

E27

SDQ8

SDQ9 C27

F26

SDQS0 C26

SDQS1 C23

SDQS2

SDQS3 B19

D12

SDQS4

SDQS5 C8

C5

SDQS6

SDQS7

C2

SDQ61 E2

SDQ62

SDQ63 G4

SDQ64 C16

D16

SDQ65

SDQ66 B15

C14

SDQ67

SDQ68 B17

C17

SDQ69

SDQ7 B28

SDQ70

B3

E6

SDQ52

SDQ53 B5

C4

SDQ54 E4

SDQ55

SDQ56 C3

SDQ57 D3

SDQ58 F4

F3

SDQ59

SDQ6 F25

SDQ60 B2

SDQ41 D8

SDQ42

SDQ43 E8

SDQ44 E11

SDQ45 B9

B7

SDQ46 C7

SDQ47

SDQ48 C6

D6

SDQ49

SDQ5 G27

D4

SDQ50

SDQ51

E13

SDQ32

SDQ33 C12

SDQ34 B11

C10

SDQ35

SDQ36 B13

C13

SDQ37 C11

SDQ38

SDQ39 D10

H25

SDQ4

SDQ40 E10

C9

SDQ22

SDQ23 B21

SDQ24 C21

SDQ25 D20

C19

SDQ26 D18

SDQ27 C20

SDQ28

SDQ29 E19

SDQ3 E28

SDQ30 C18

E17

SDQ31

B27

D27

SDQ13 D26

SDQ14 E25

SDQ15 D24

SDQ16 E23

SDQ17

SDQ18 C22

E21

SDQ19

C28

SDQ2

SDQ20 C24

B23

SDQ21 D22

SCKE2

H23

SCKE3

F23

SCS#0

E9

SCS#1

F7

SCS#2

F9

E7 SCS#3

SDQ0 G28

F27

SDQ1

SDQ10 B25

C25

SDQ11

SDQ12

J24

SCK#4 G7

SCK#5 J23

J25

SCK0

SCK1 G5

SCK2 G24

G25

SCK3

G6

SCK4

K23

SCK5

SCKE0

G23

E22 SCKE1

AE25 SBA7

G12 SBS0

SBS1

G13

SB_STB

AF27

SB_STB#

AF26

G8

SCAS#

K25

SCK#0

F5

SCK#1

E24

SCK#2

SCK#3

RSVD1

RSVD2 G22

SBA0

AH28

AH27 SBA1

AG28 SBA2

SBA3

AG27

AE28 SBA4

SBA5

AE27

SBA6

AE24

HI_REF

HI_STB

N25

HI_STB#

N24

P27 HLRCOMP

AD26 NC0

AD27 NC1

AF22 PIPE#

RBF#

AE22

RCVENIN#

G15

RCVENOUT#

G14

RSTIN#

J27

H27

P24 HI_1

M24 HI_10

N27 HI_2

HI_3

P23

HI_4

M26

HI_5

M25

L28 HI_6

HI_7

L27

M27 HI_8

HI_9

N28

P26

AA23

GDEVSEL#

W28 GFRAME#

Y24

GGNT#

AH25

GIRDY#

W27

W25 GPAR

GRCOMP

AD25

AG24 GREQ#

GSTOP#

W23

W24 GTRDY#

HI_0

P25

T27

GAD6

U27

U28 GAD7

V26 GAD8

GAD9

V27

GCBE0#

V25

V23 GCBE1#

Y25 GCBE2#

GCBE3#

GAD26

GAD27

AB24

AC25 GAD28

GAD29

AC24

GAD3

R25

GAD30

AC22

AD24 GAD31

T26 GAD4

GAD5

GAD19

T25 GAD2

GAD20

AB27

AA27 GAD21

AB26 GAD22

GAD23

Y23

GAD24

AB23

AA24 GAD25

AA25

GAD11

GAD12

T24

U24 GAD13

U25 GAD14

GAD15

V24

Y27 GAD16

GAD17

Y26

GAD18

AA28

AB25

AD_STB0

R24

AD_STB1

AC27

AGPREF

AA21

DPSLP#

V8

Y8 DPWR#

GAD0

R27

R28 GAD1

GAD10

T23

U23

27-

17-

29-

U16

ITL_ODEM_BGA_593P

P22 66IN

AD_STB#0

R23

AC28 AD_STB#1

0_5%

R251

12

R254 0_5%

12

29-

29-

29-

25-

25-

TP547

28-,27-,26-

0.1UF_16V

C218

1

2

8.2K_1%

R237

1

2

0.01UF_16V

C1190 1

2

R1155 10_5%

12

R252

1

2

15-

28-,27-,26-

29-

29-

R1156 10_5%

12

26-

0_5%

29-

29-

+V1.5S

28-,27-,26-

R1169

150_1%

1

2

R1228

10_5%

12

29-

21-

29-

29-

29-

26-

28-,25-

29-

28-,25-

21-

25-

R1191 10_5%

12

29-

21-

C1191

0.1UF_16V

1

2

+V1.8S

29-

26-

R229

OPEN

12

21-

21-

28-,25-

R1205 10_5%

12

29-

26-

+V1.5S

37-,17-

28-,27-,26-

C1180

0.1UF_16V

1

2

37-

21-

1

2

28-,26-

40.2_1%R227

1

2

36.5_1%

1

2

21-

C1148

0.1UF_16V

28-,26-,25-

R1168

150_1%

1

2

R1167

12

28-,26-

30_1%

R228

12

M_CS1_R#

M_CS0_R#

M_CS3

M_CS2

M_CS1

M_CS0

21-

25-