MT6217 Datasheet. Www.s Manuals.com. R1.01 Mediatek

User Manual: Datasheets MT6217.

Open the PDF directly: View PDF ![]() .

.

Page Count: 350 [warning: Documents this large are best viewed by clicking the View PDF Link!]

MT6217 GSM/GPRS

Baseband Processor Data Sheet

Revision 1.01

Apr. 18, 2005

MT6217 GSM/GPRS Baseband Processor Data Sheet Revision 1.01

2/349 MediaTek Inc. Confidential

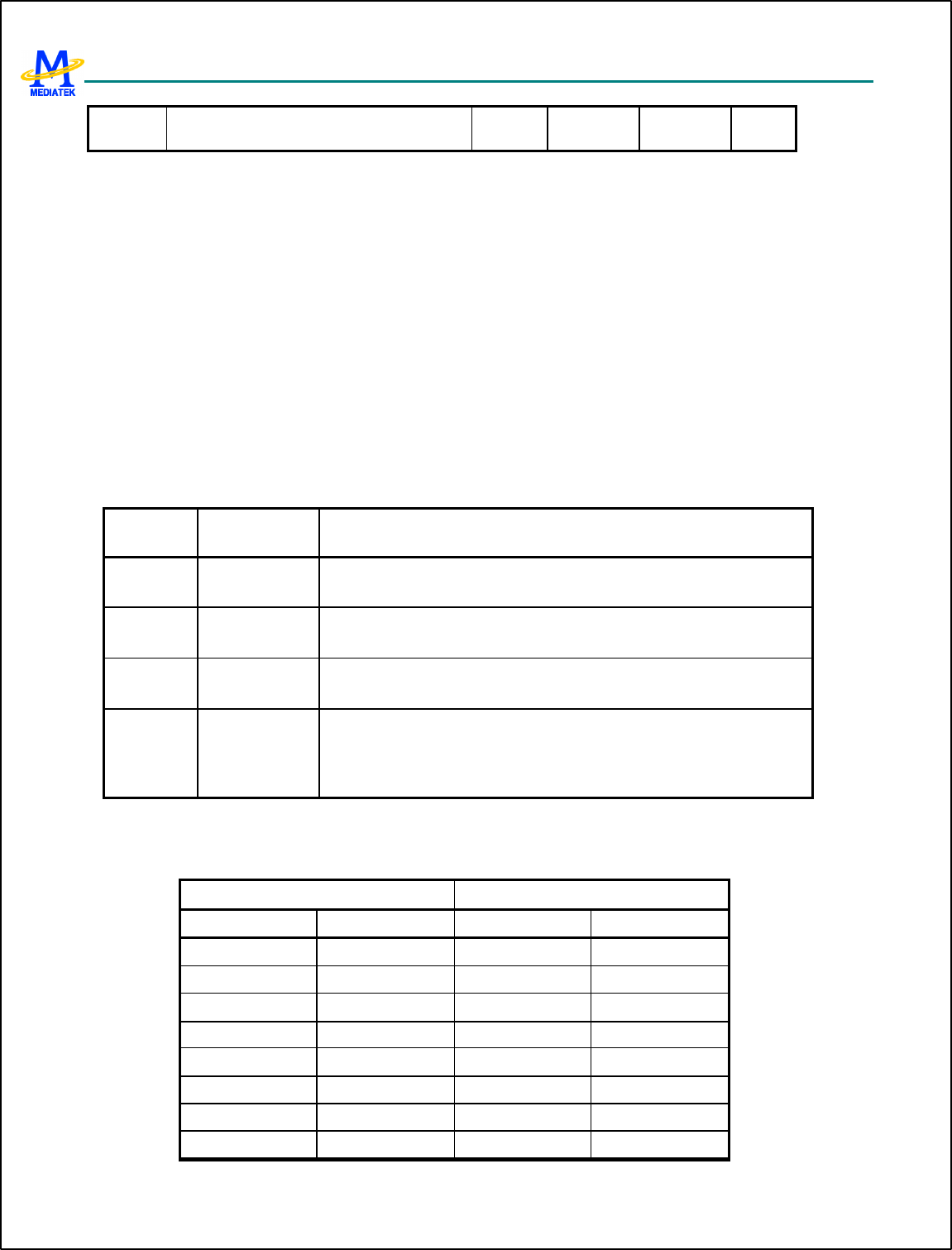

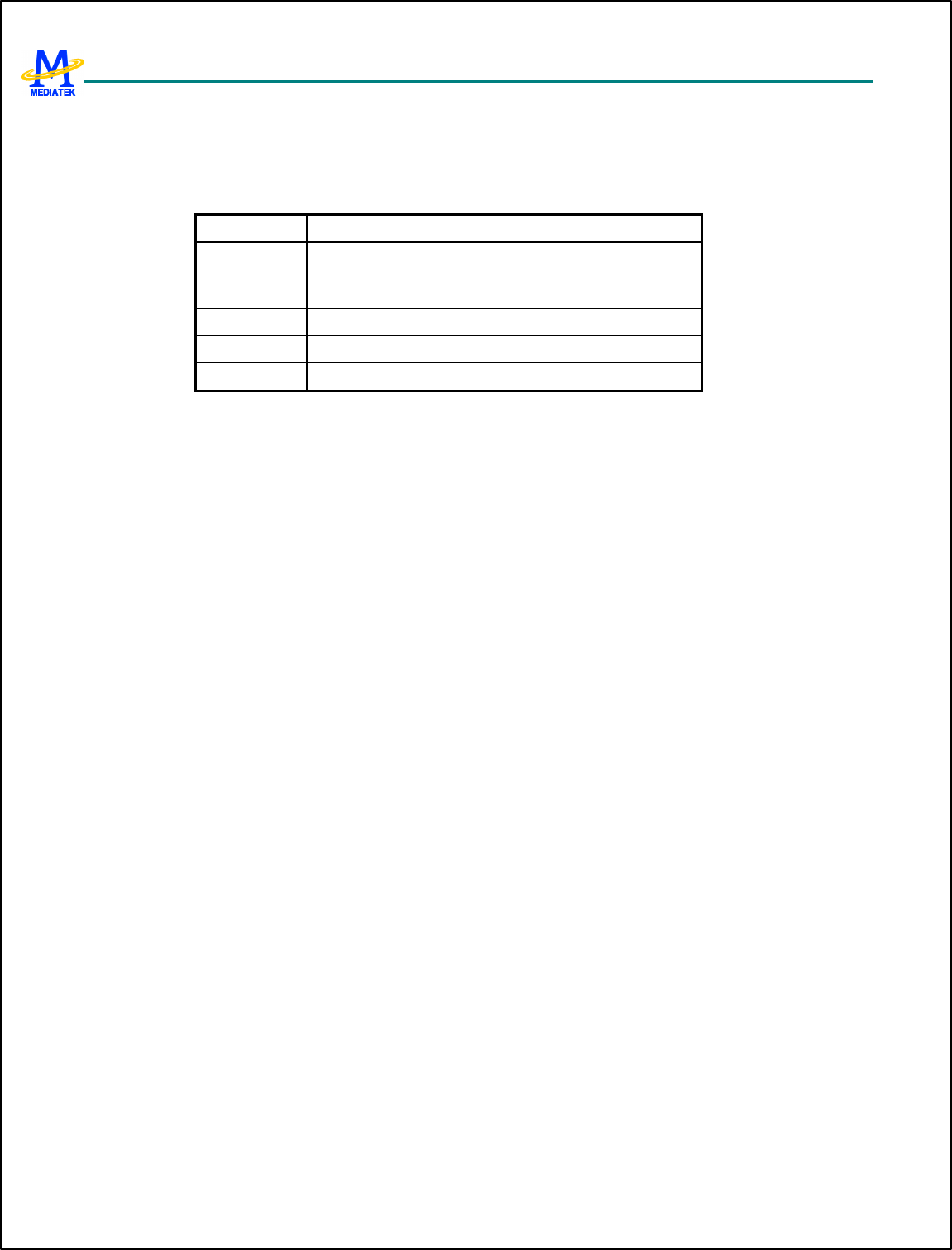

Revision History

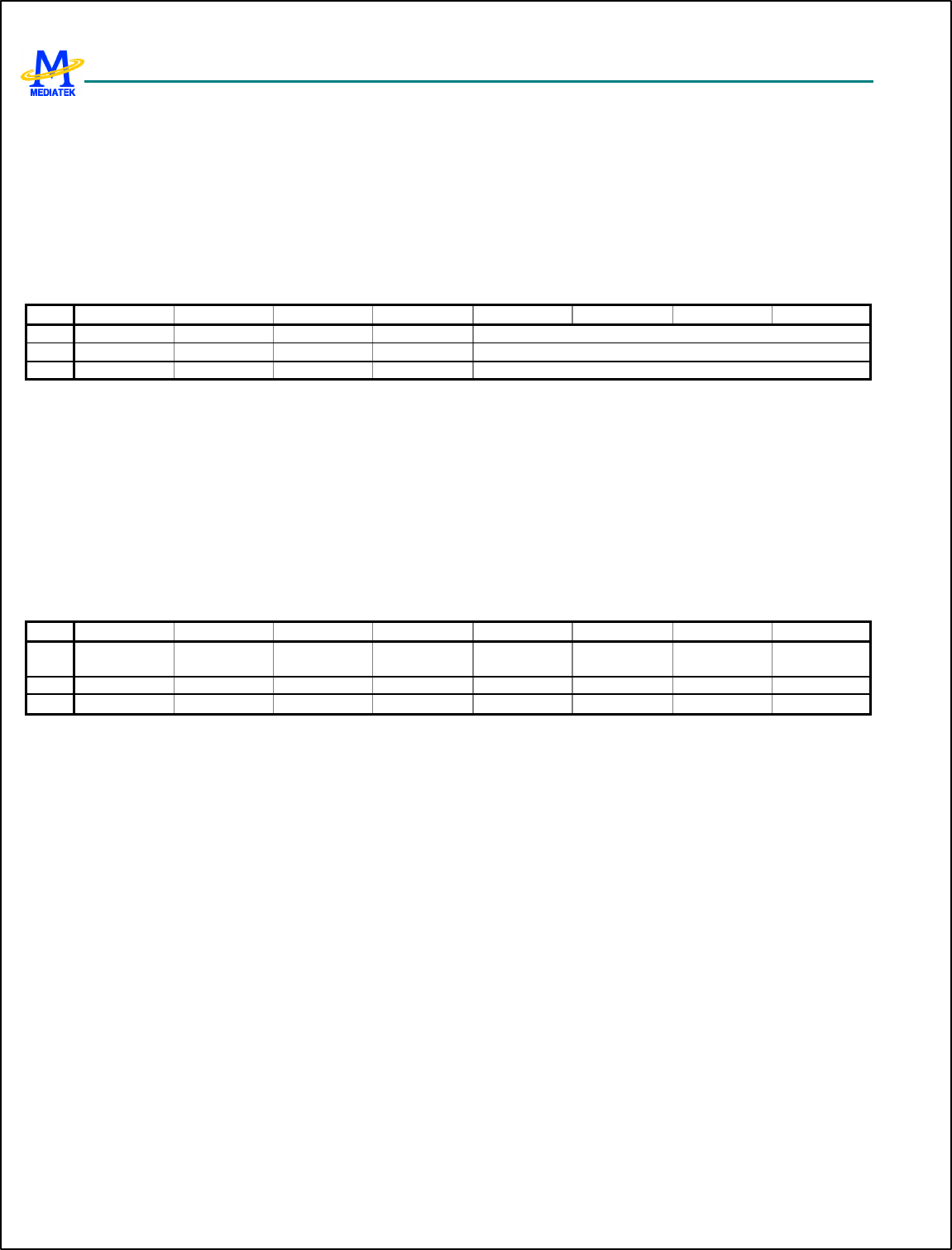

Revision Date Comments

1.00 Sep. 01, 2004 First Release

1.01 Apr. 18, 2005 1) Corrected interrupt source naming in MCU Subsystem > Interrupt Controller > Table 12.

GPI-FIQ -> MFIQ, GPI -> MIRQ

2) Corrected GPIO_MODE6 register description from nIRQ -> MIRQ and nFIQ -> MFIQ

3) Corrected LCD_SDAT0 and LCD_SDAT1 register address

4) Updated EMI_GEN register

5) Updated GPIO16, GPIO17, GPIO18 PU/PD control, and added GPIO40 in product

description

6) Updated GPIO_MODE2 register

7) Added NLD15~NLD8 digital pin characteristics

8) Updated driving strength in digital pin characteristics

MT6217 GSM/GPRS Baseband Processor Data Sheet Revision 1.01

3/349 MediaTek Inc. Confidential

TABLE OF CONTENTS

Revision History ......................................................................................................................................2

1. System Overview............................................................................................................................... 2

1.1 Features ........................................................................................................................................................................................... 2

1.2 General Description ...................................................................................................................................................................... 2

2 Product Description..........................................................................................................................2

2.1 Pin Outs........................................................................................................................................................................................... 2

2.2 Pin Description .............................................................................................................................................................................. 2

2.3 Power Description .........................................................................................................................................................................2

3 Micro-Controller Unit Subsystem................................................................................................... 2

3.1 Processor Core ............................................................................................................................................................................... 2

3.2 Memory Management .................................................................................................................................................................. 2

3.3 Bus System.....................................................................................................................................................................................2

3.4 Direct Memory Access.................................................................................................................................................................2

3.5 Interrupt Controller.......................................................................................................................................................................2

3.6 Internal Memory Controller ........................................................................................................................................................2

3.7 External Memory Interface..........................................................................................................................................................2

4 Microcontroller Peripherals ............................................................................................................ 2

4.1 Pulse-Width Modulation Outputs ............................................................................................................................................... 2

4.2 Alerter ............................................................................................................................................................................................. 2

4.3 SIM Interface ................................................................................................................................................................................. 2

4.4 Keypad Scanner.............................................................................................................................................................................2

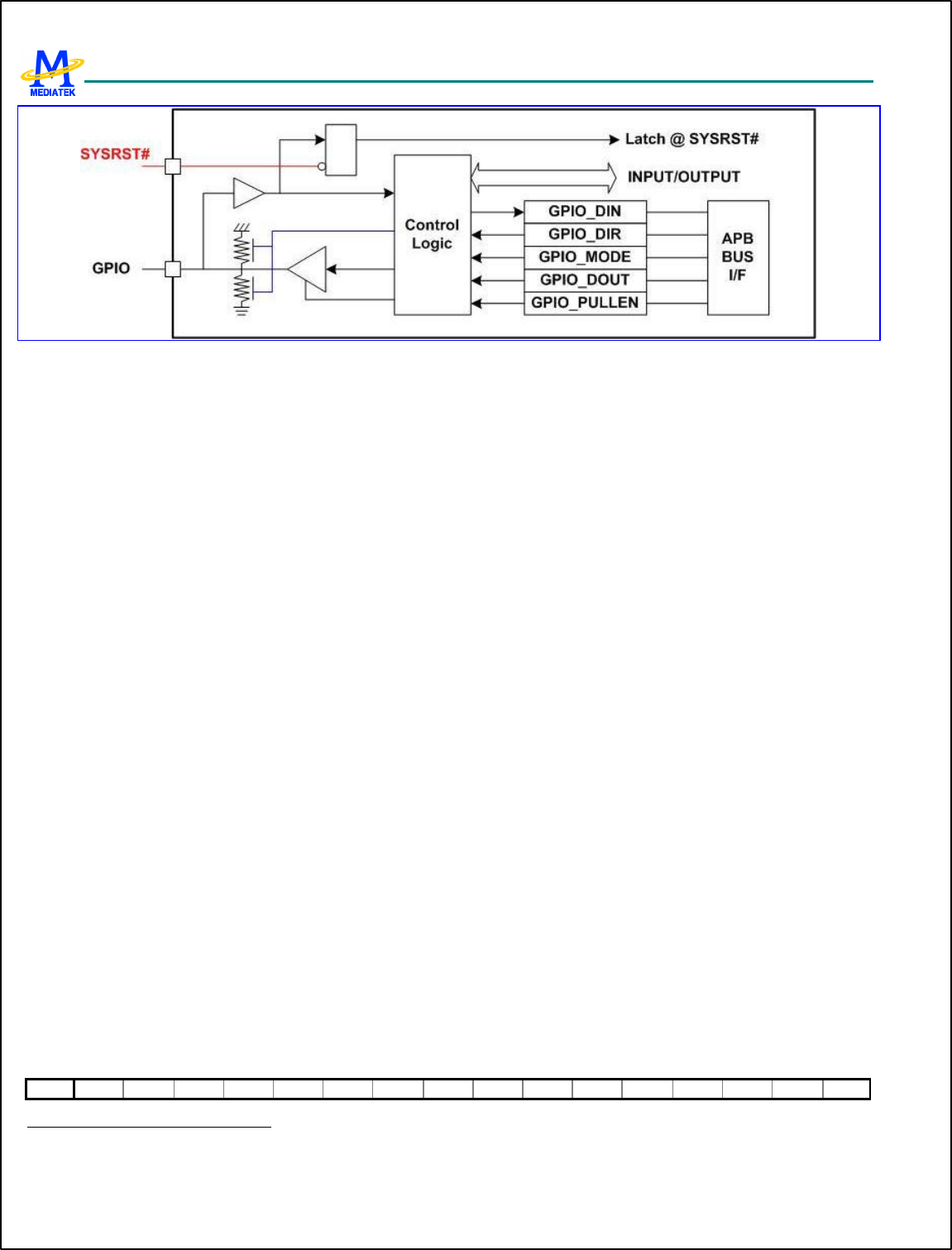

4.5 General Purpose Inputs/Outputs ................................................................................................................................................. 2

4.6 General Purpose Timer.................................................................................................................................................................2

4.7 UART .............................................................................................................................................................................................. 2

4.8 IrDA Framer................................................................................................................................................................................... 2

4.9 Real Time Clock ............................................................................................................................................................................2

4.10 Auxiliary ADC Unit ...................................................................................................................................................................... 2

5 Microcontroller Coprocessors .........................................................................................................2

5.1 GPRS Cipher Unit .........................................................................................................................................................................2

5.2 Divider ............................................................................................................................................................................................ 2

5.3 CSD Accelerator............................................................................................................................................................................2

5.4 FCS Codec......................................................................................................................................................................................2

6 Multi-Media Subsystem...................................................................................................................2

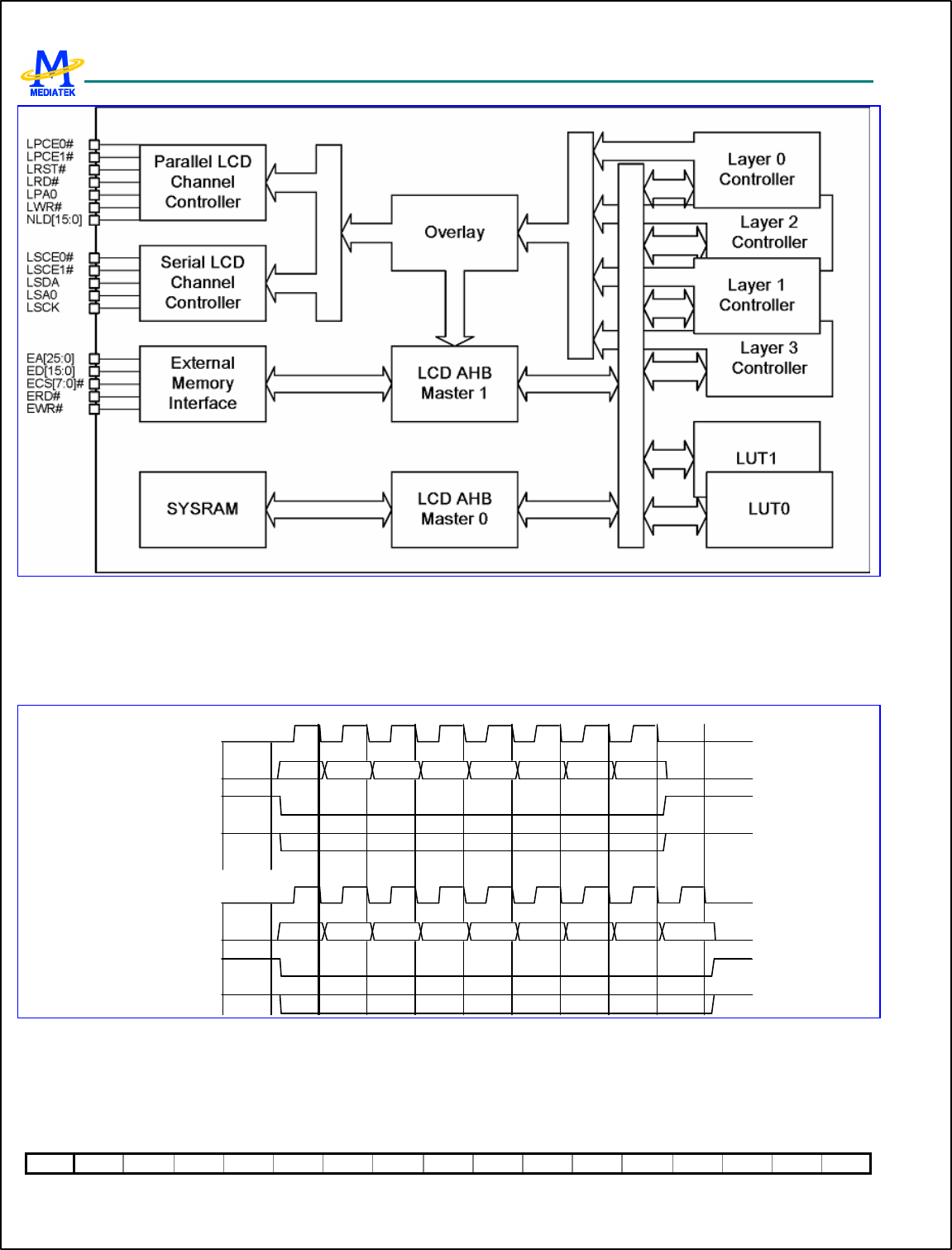

6.1 LCD Interface ................................................................................................................................................................................ 2

6.2 JPEG Decoder................................................................................................................................................................................ 2

6.3 Image Resizer................................................................................................................................................................................ 2

6.4 NAND FLASH interface ............................................................................................................................................................. 2

6.5 USB Device Controller ................................................................................................................................................................ 2

6.6 Memory Stick and SD Memory Card Controller.....................................................................................................................2

7 Audio Front-end................................................................................................................................ 2

7.1 General Description ...................................................................................................................................................................... 2

7.2 Register Definitions...................................................................................................................................................................... 2

7.3 Programming Guide...................................................................................................................................................................... 2

8 Radio Interface Control ...................................................................................................................2

8.1 Base-band Serial Interface........................................................................................................................................................... 2

8.2 Base-band Parallel Interface........................................................................................................................................................2

MT6217 GSM/GPRS Baseband Processor Data Sheet Revision 1.01

4/349 MediaTek Inc. Confidential

8.3 Automatic Power Control (APC) Unit ...................................................................................................................................... 2

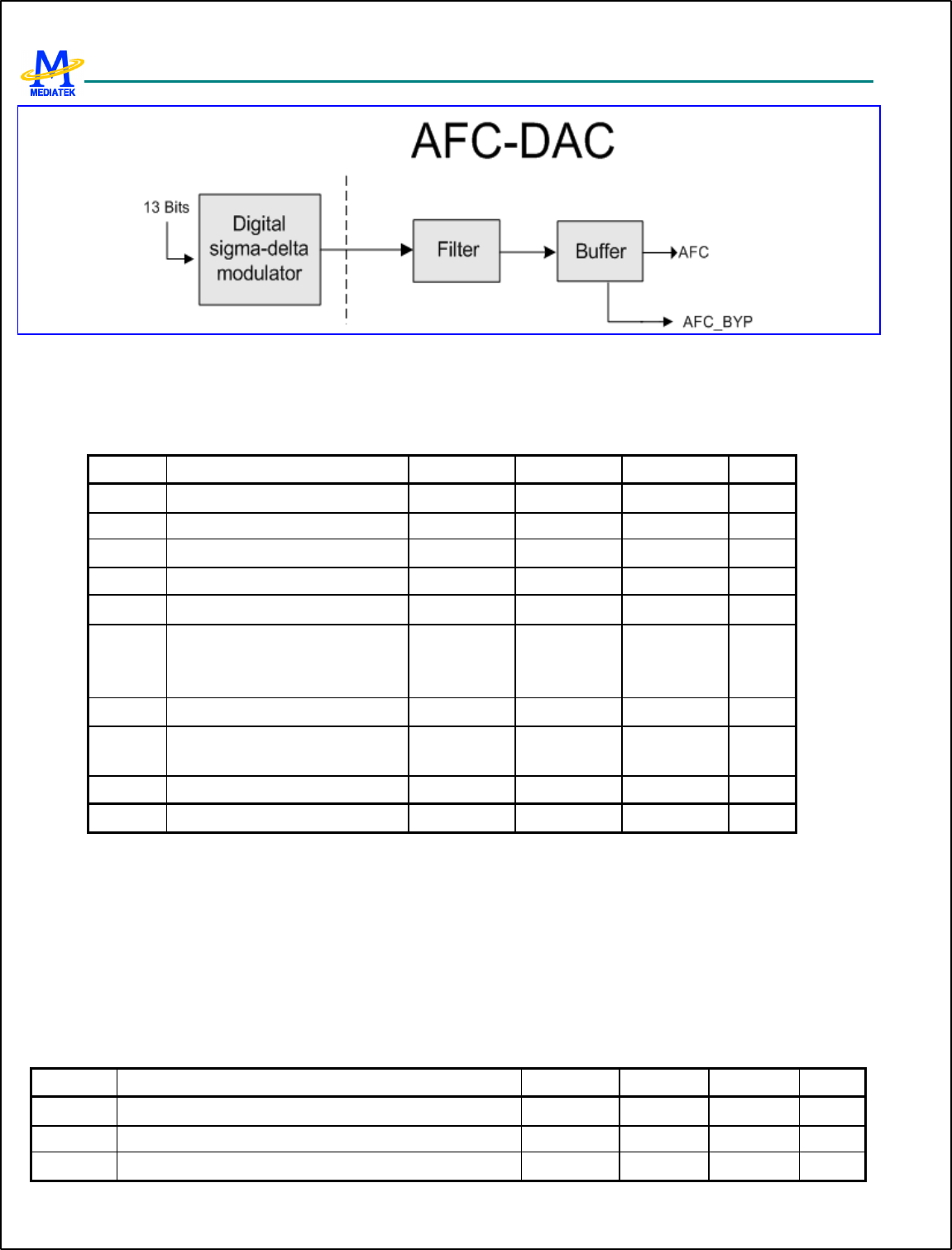

8.4 Automatic Frequency Control (AFC) Unit ............................................................................................................................... 2

9 Baseband Front End......................................................................................................................... 2

9.1 Baseband Serial Ports ................................................................................................................................................................... 2

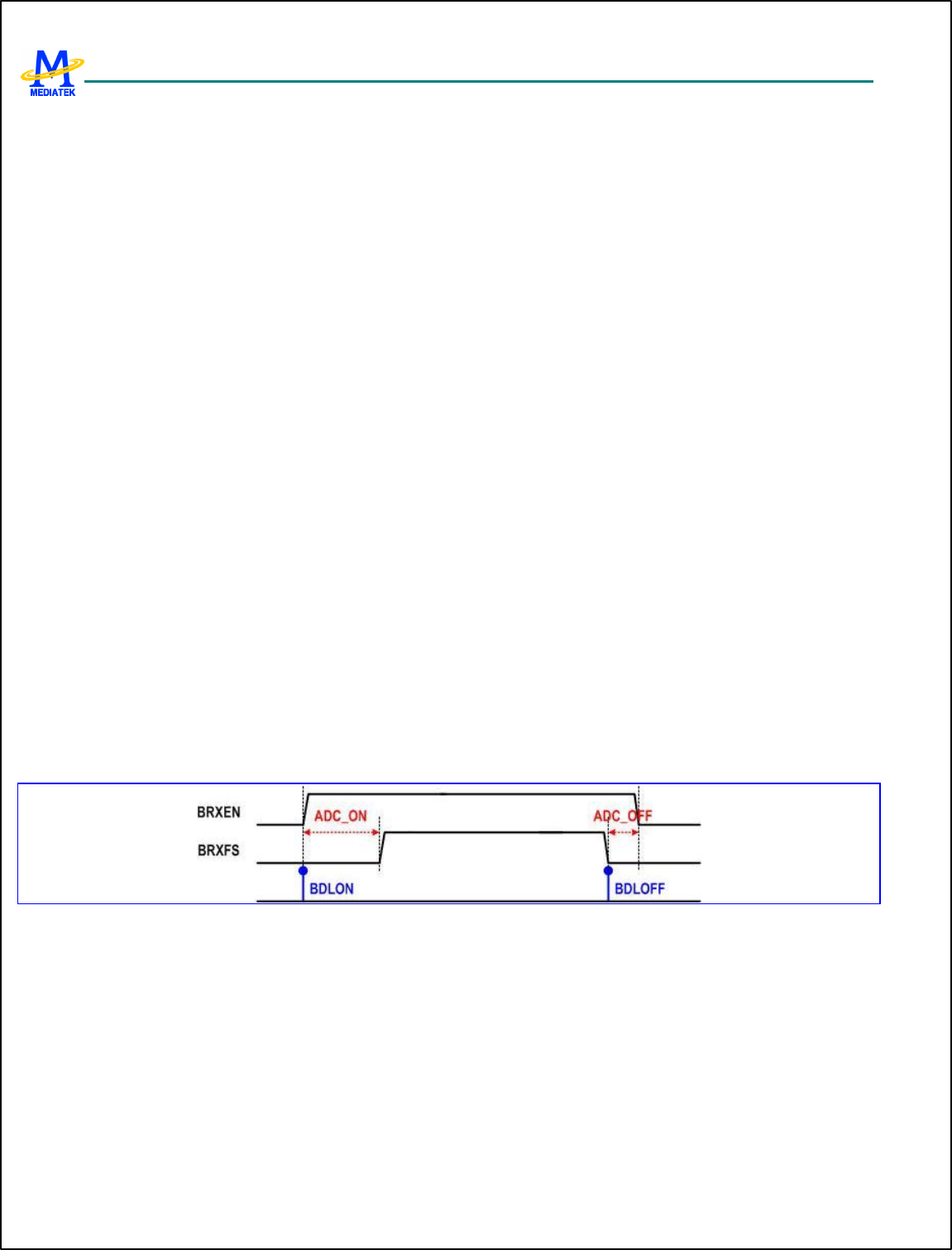

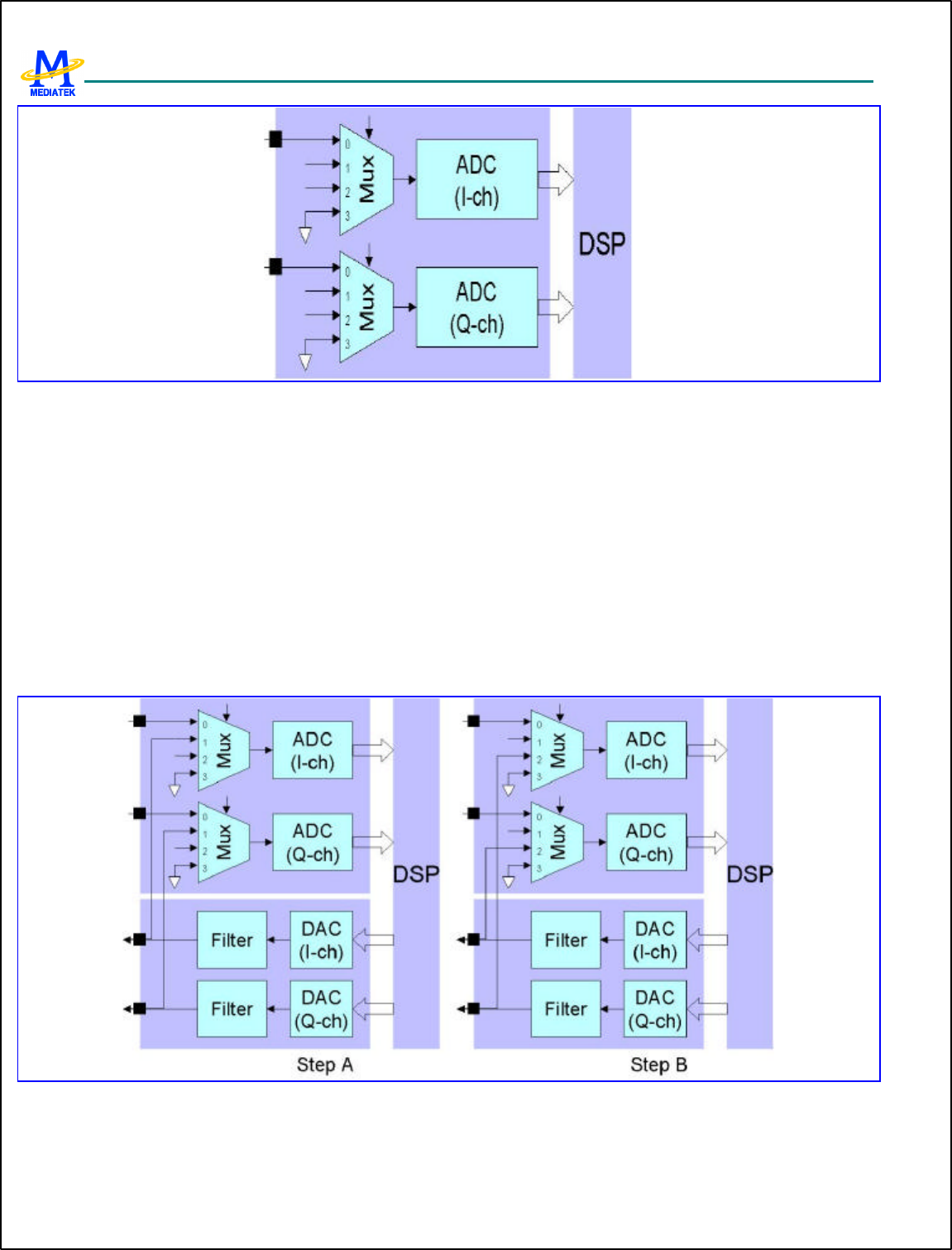

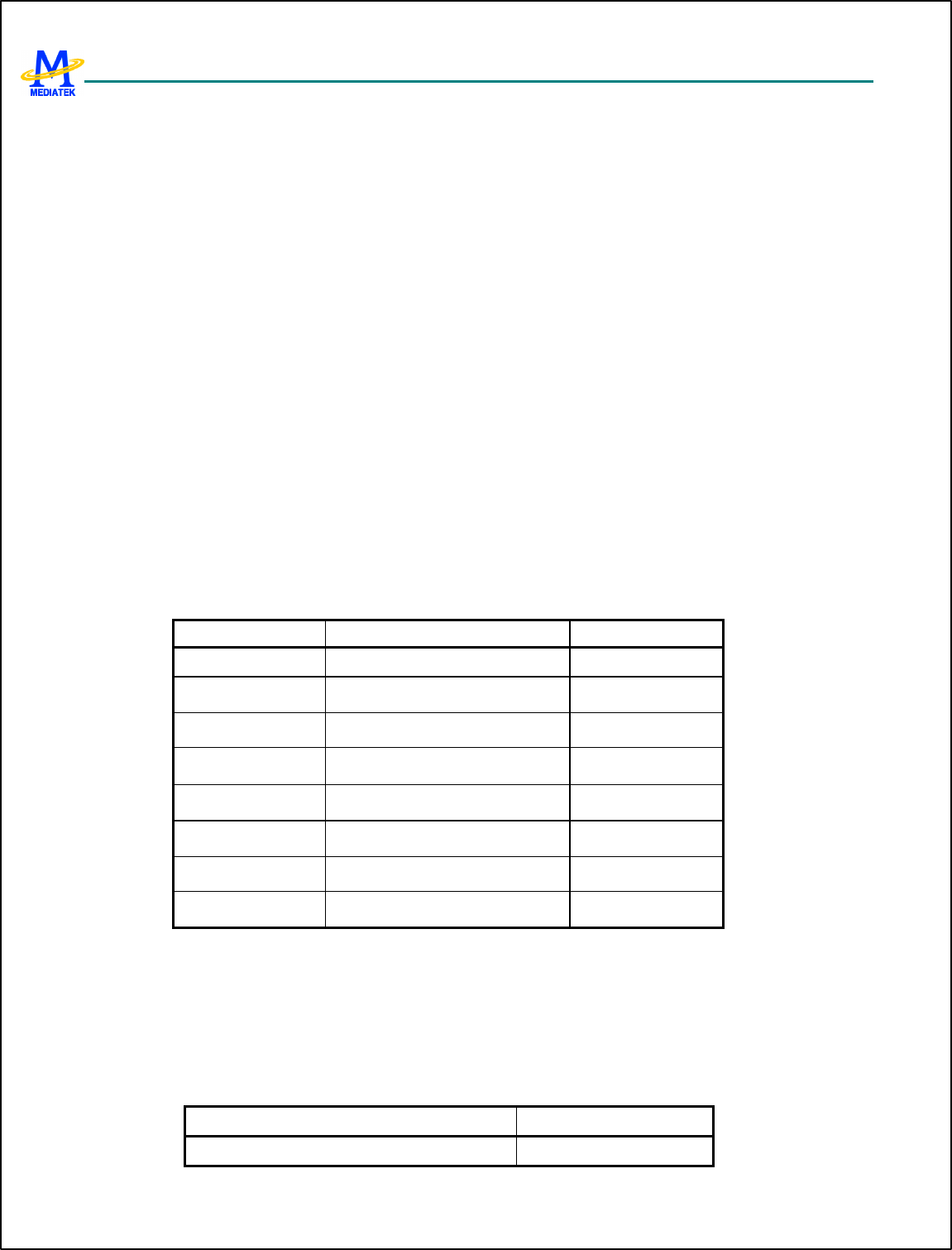

9.2 Downlink Path (RX Path) ............................................................................................................................................................ 2

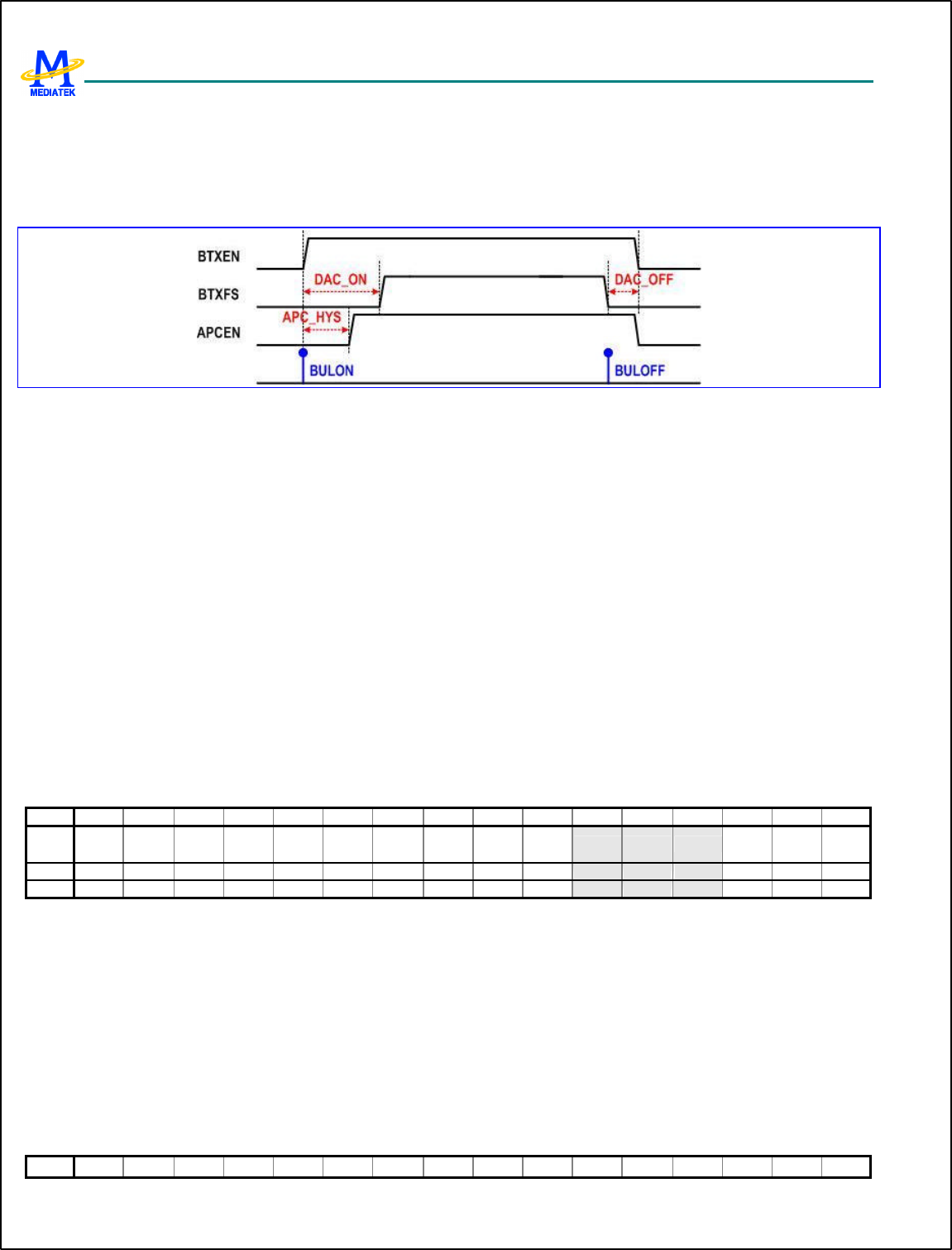

9.3 Uplink Path (TX Path).................................................................................................................................................................. 2

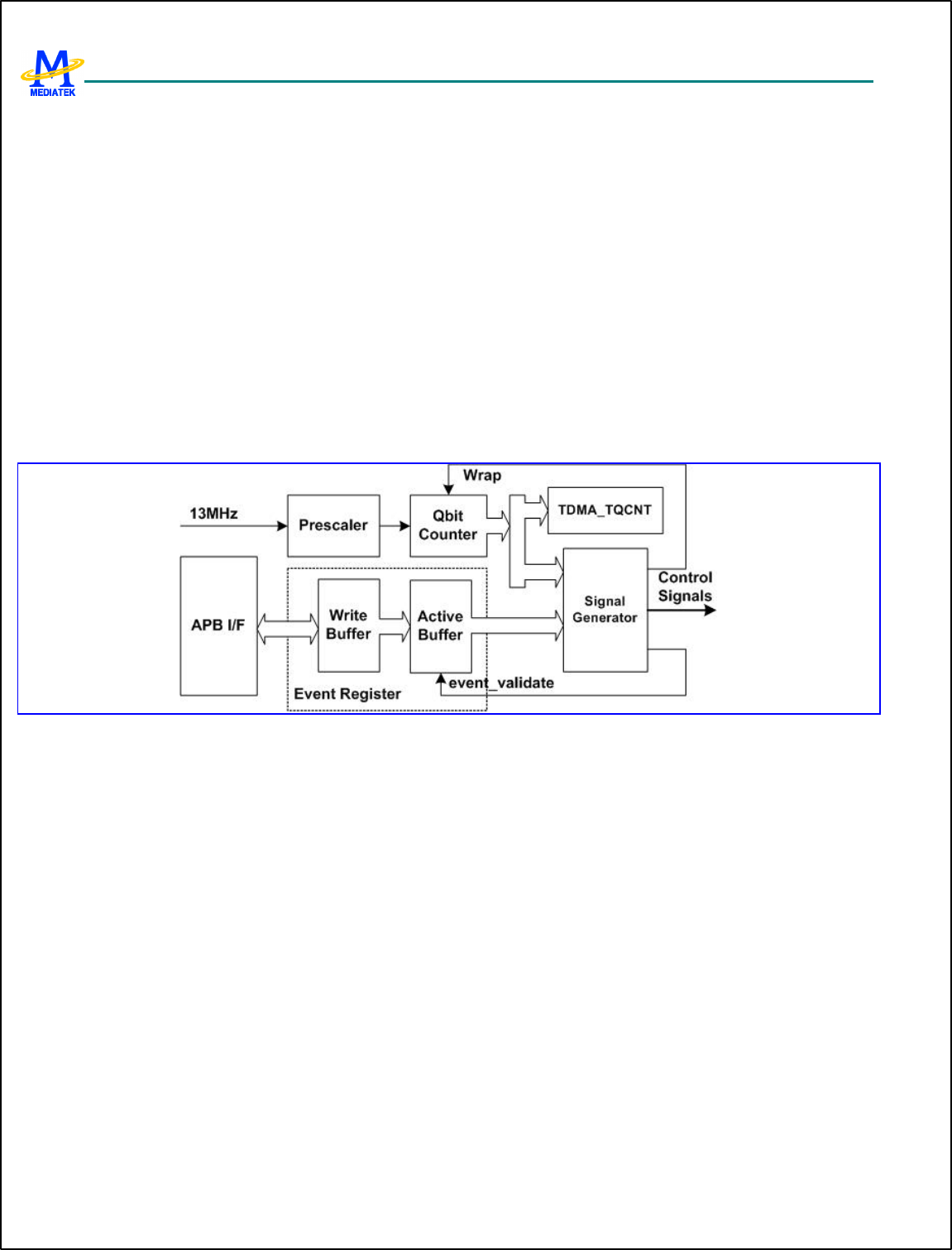

10 Timing Generator.............................................................................................................................2

10.1 TDMA timer................................................................................................................................................................................... 2

10.2 Slow Clocking Unit ...................................................................................................................................................................... 2

11 Power, Clocks and Reset...................................................................................................................2

11.1 Baseband to PMIC Serial Interface............................................................................................................................................2

11.2 Clocks.............................................................................................................................................................................................. 2

11.3 Reset Management........................................................................................................................................................................2

11.4 Software Power Down Control................................................................................................................................................... 2

12 Analog Front-end & Analog Blocks ................................................................................................ 2

12.1 General Description ...................................................................................................................................................................... 2

12.2 MCU Register Definitions........................................................................................................................................................... 2

12.3 Programming Guide...................................................................................................................................................................... 2

13 Digital Pin Electrical Characteristics.............................................................................................. 2

MT6217 GSM/GPRS Baseband Processor Data Sheet Revision 1.01

5/349 MediaTek Inc. Confidential

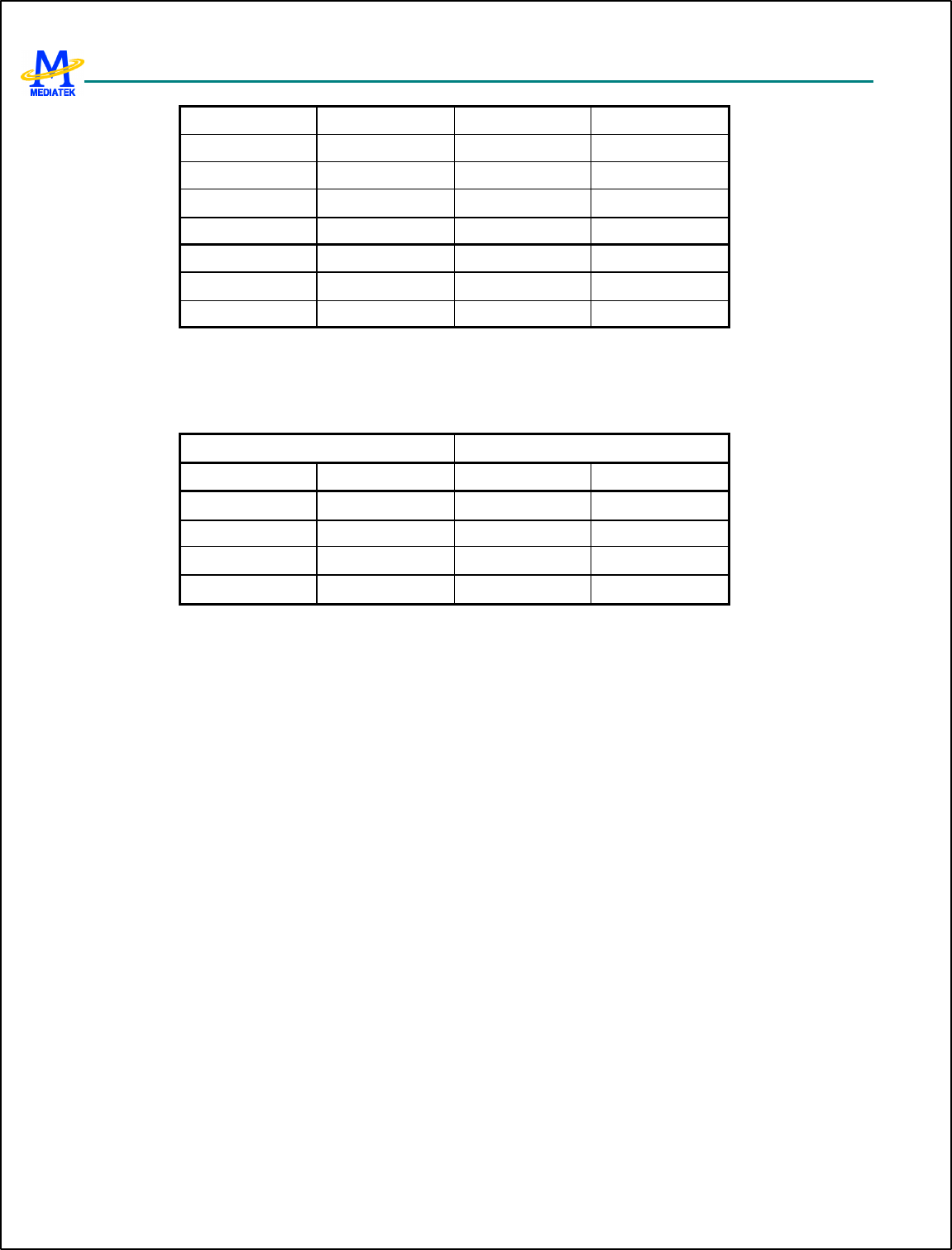

Preface

Acronym for Register Type

R/W Capable of both read and write access

RO Read only

RC Read only. After reading the register bank, each bit which is HIGH(1) will be cleared to LOW(0 )

automatically.

WO Write only

W1S Write only. When writing data bits to register bank, each bit which is HIGH(1) will cause the

corresponding bit to be set to 1. Data bits which are LOW(0) has no effect on the corresponding bit.

W1C Write only. When writing data bits to register bank, each bit which is HIGH(1) will cause the

corresponding bit to be cleared to 0. Data bits which are LOW(0) has no effect on the corresponding bit.

MT6217 GSM/GPRS Baseband Processor Data Sheet Revision 1.01

6/349 MediaTek Inc. Confidential

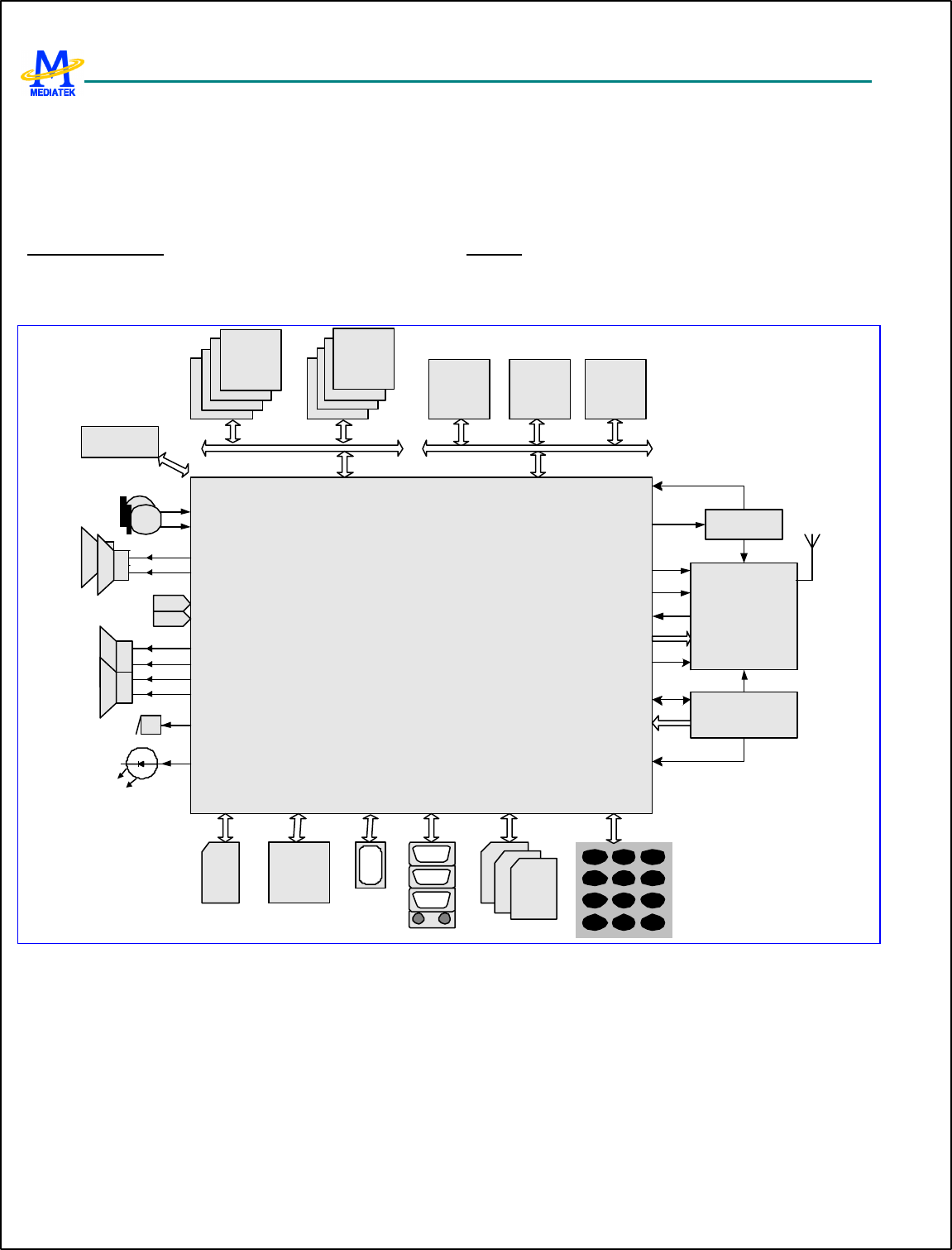

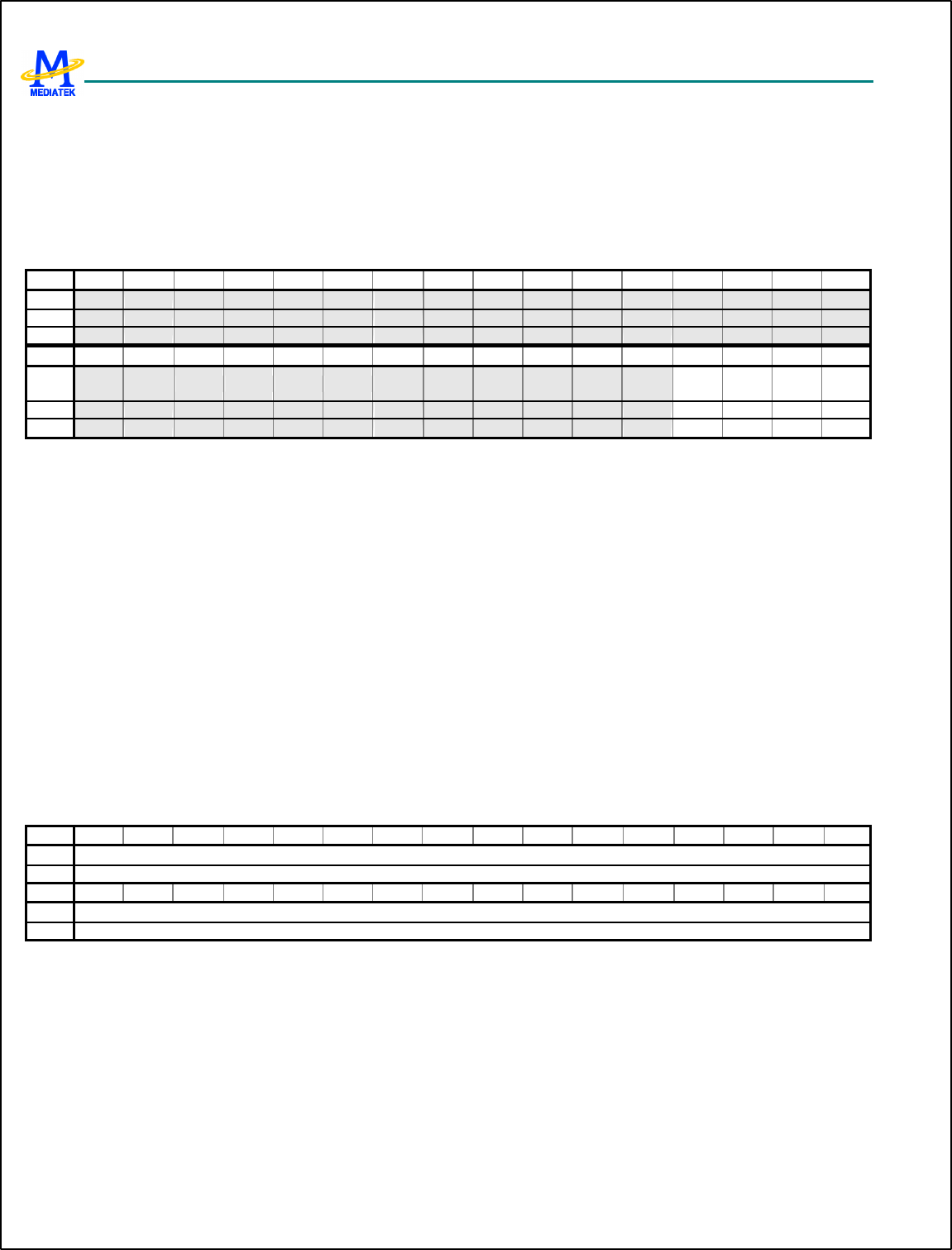

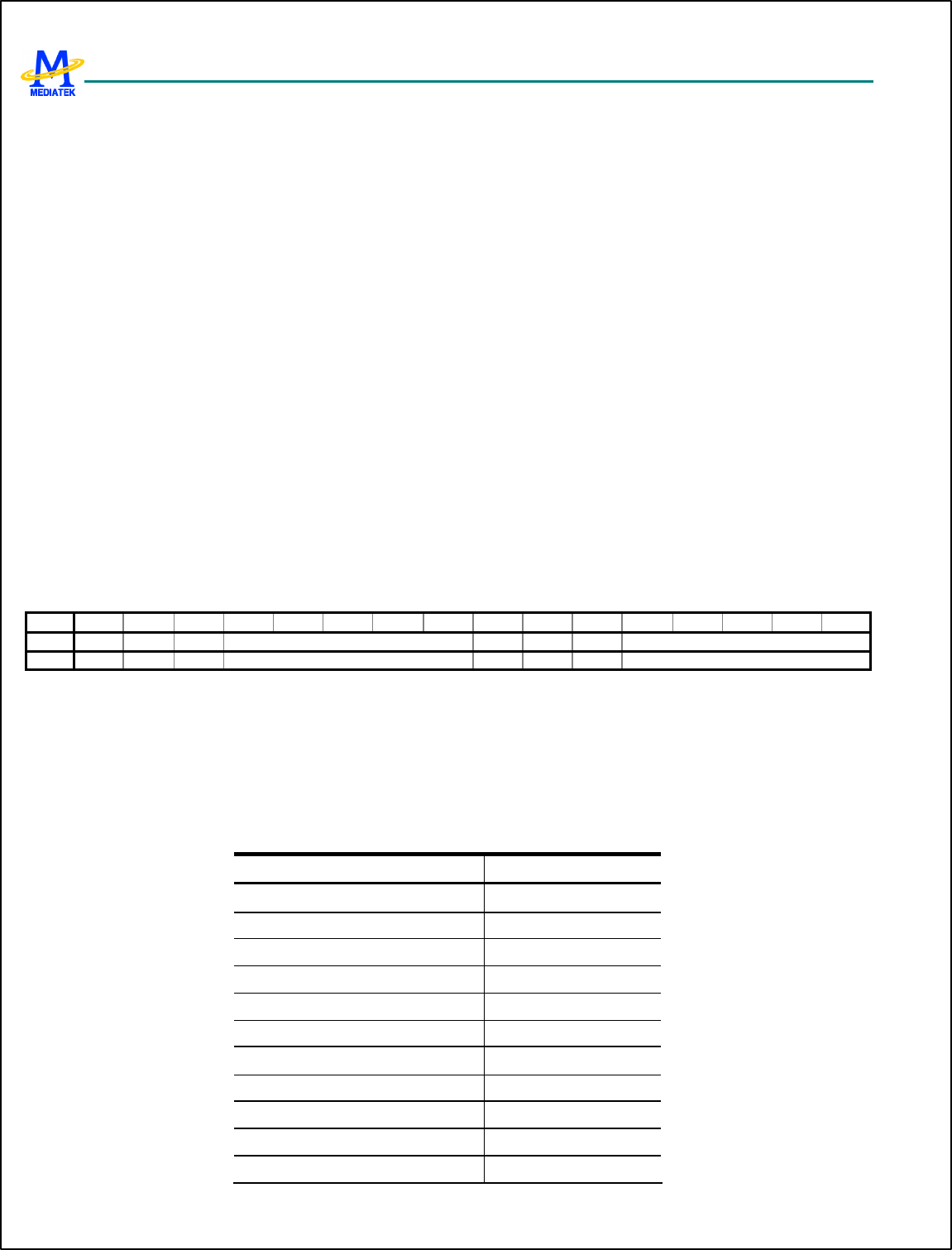

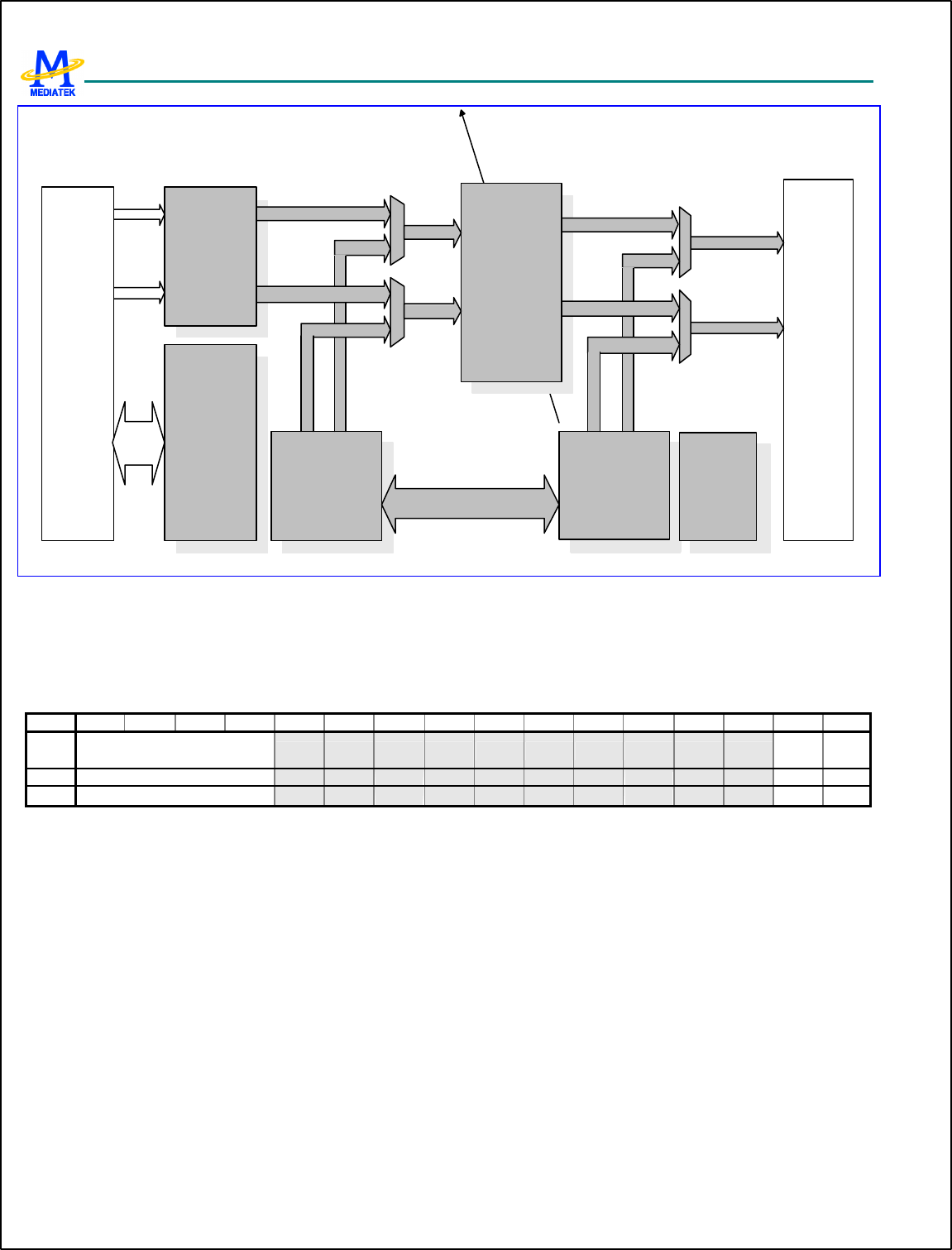

1. System Overview

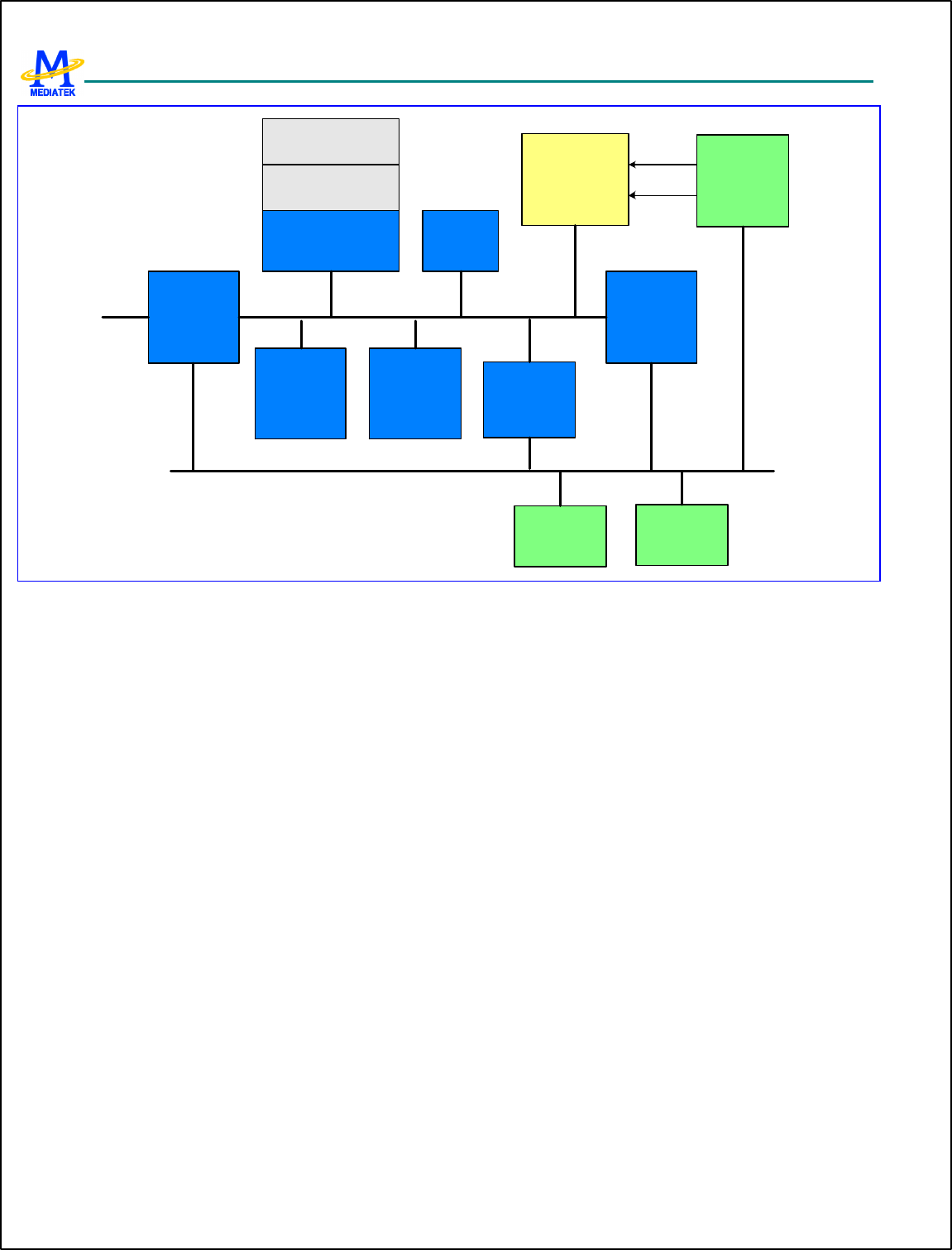

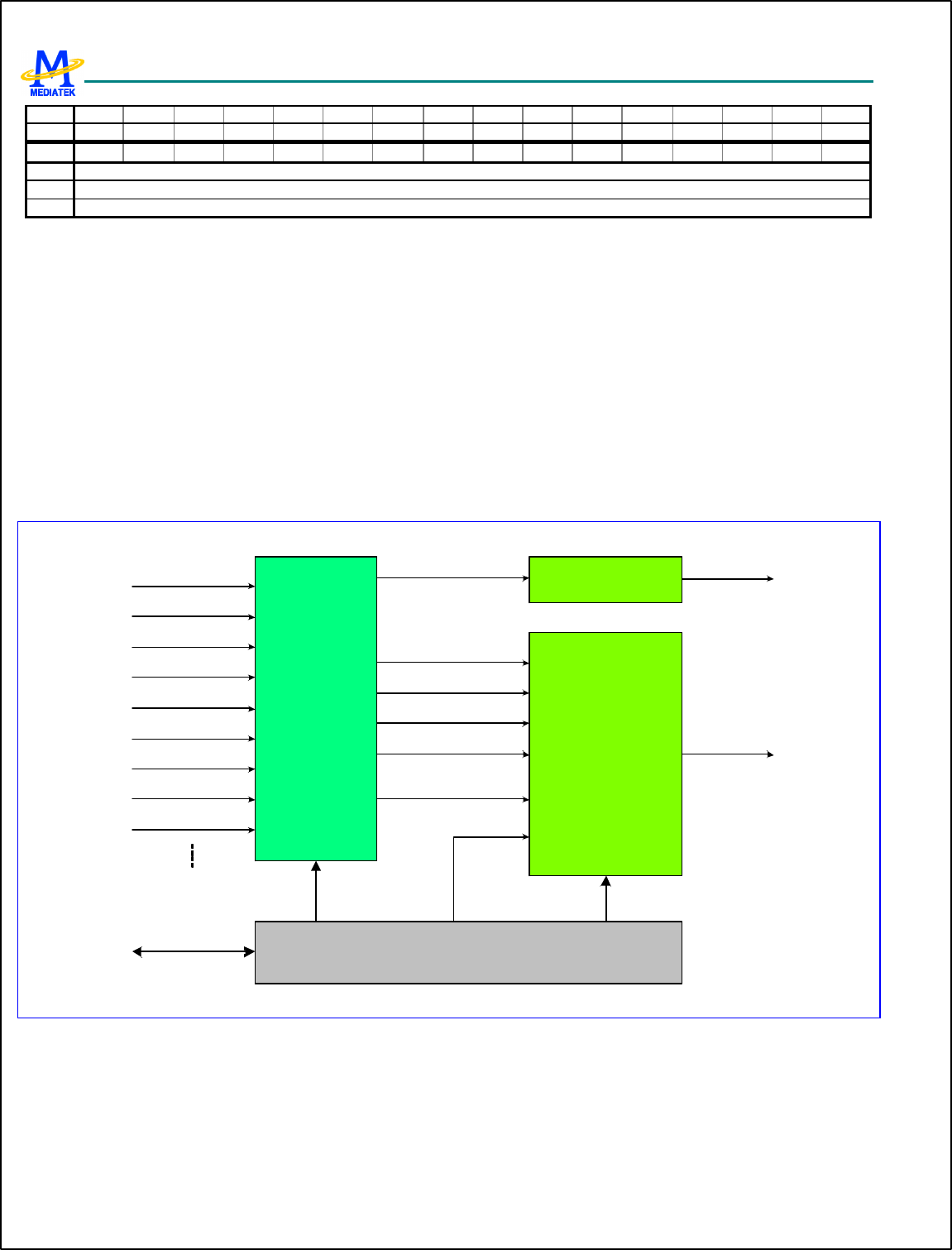

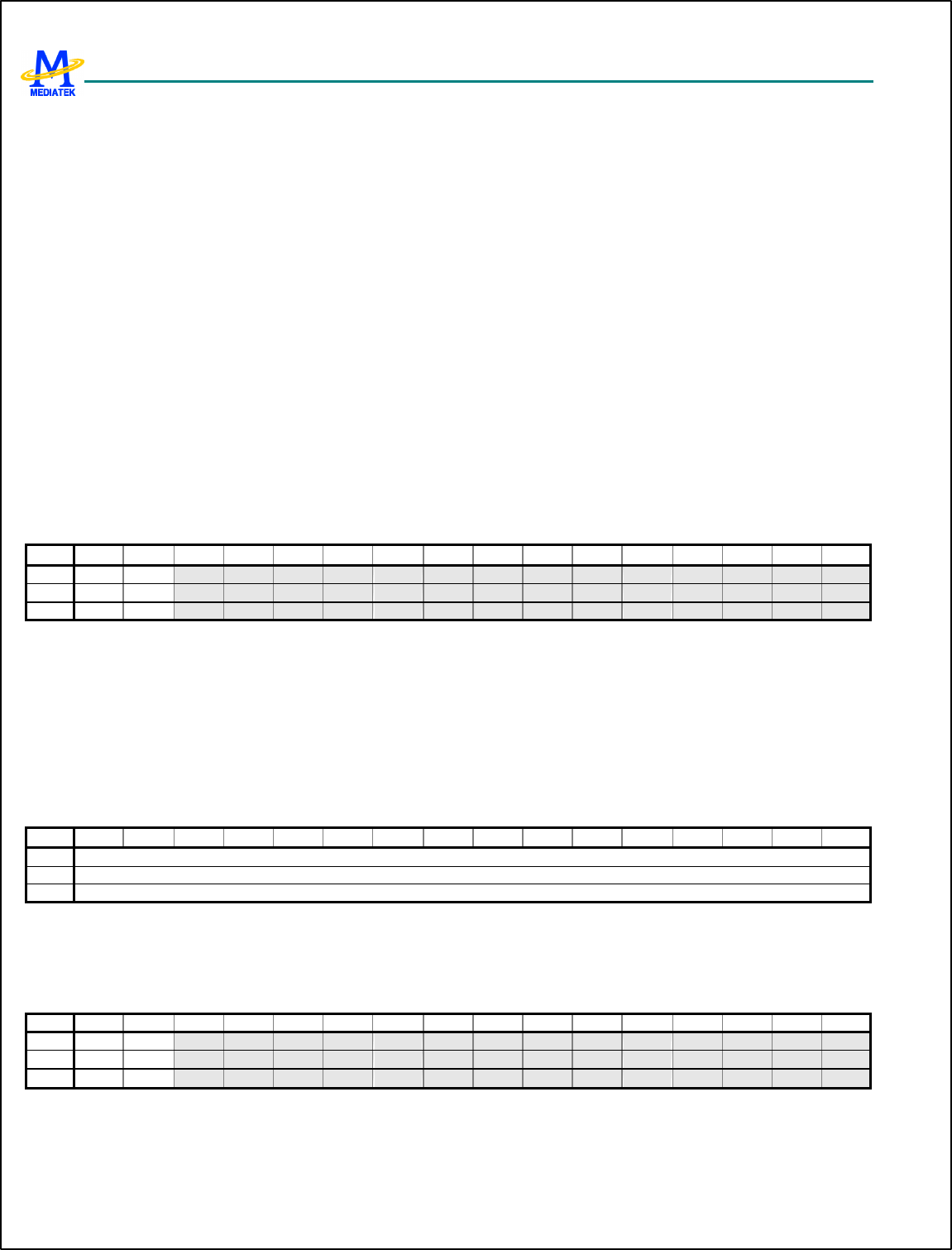

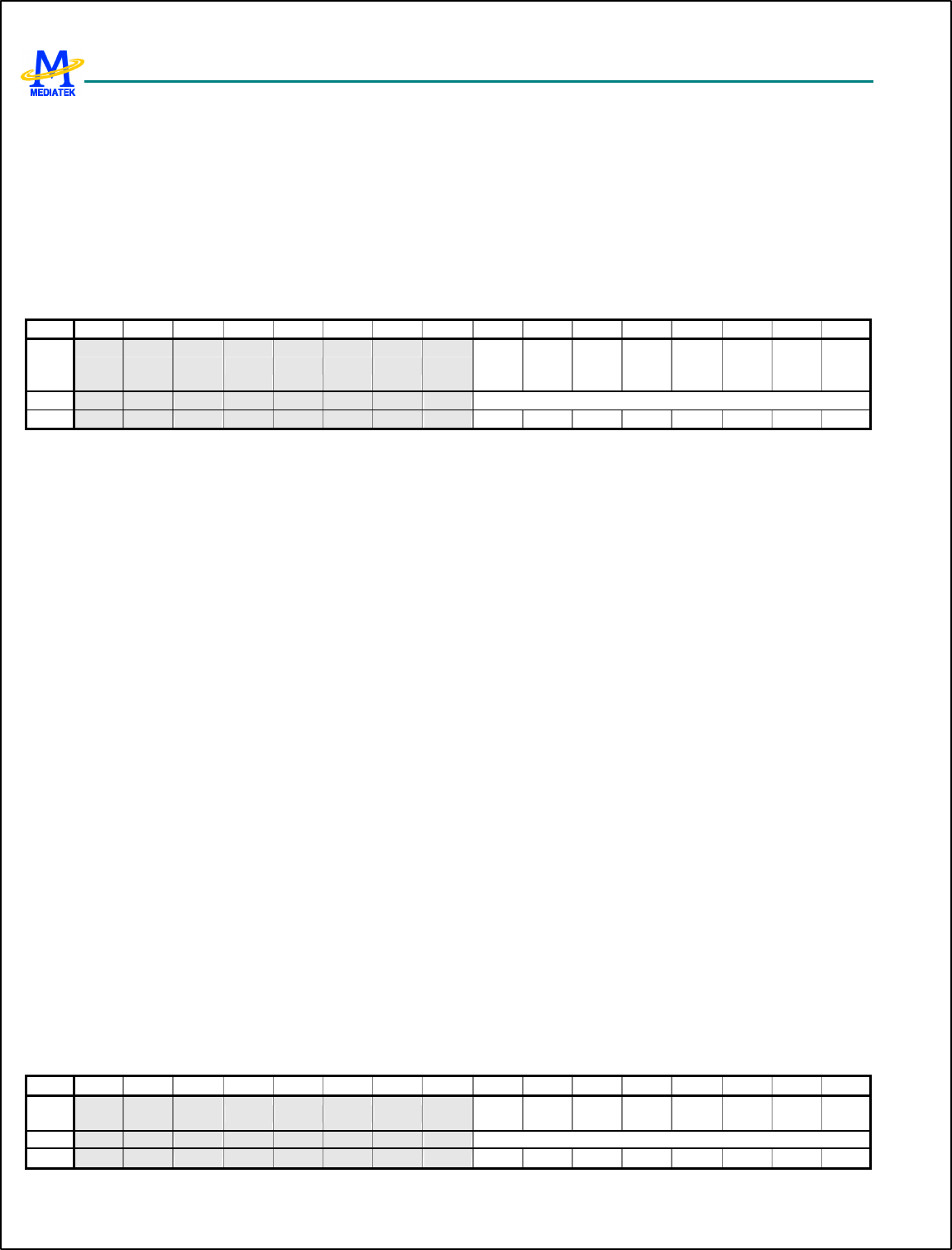

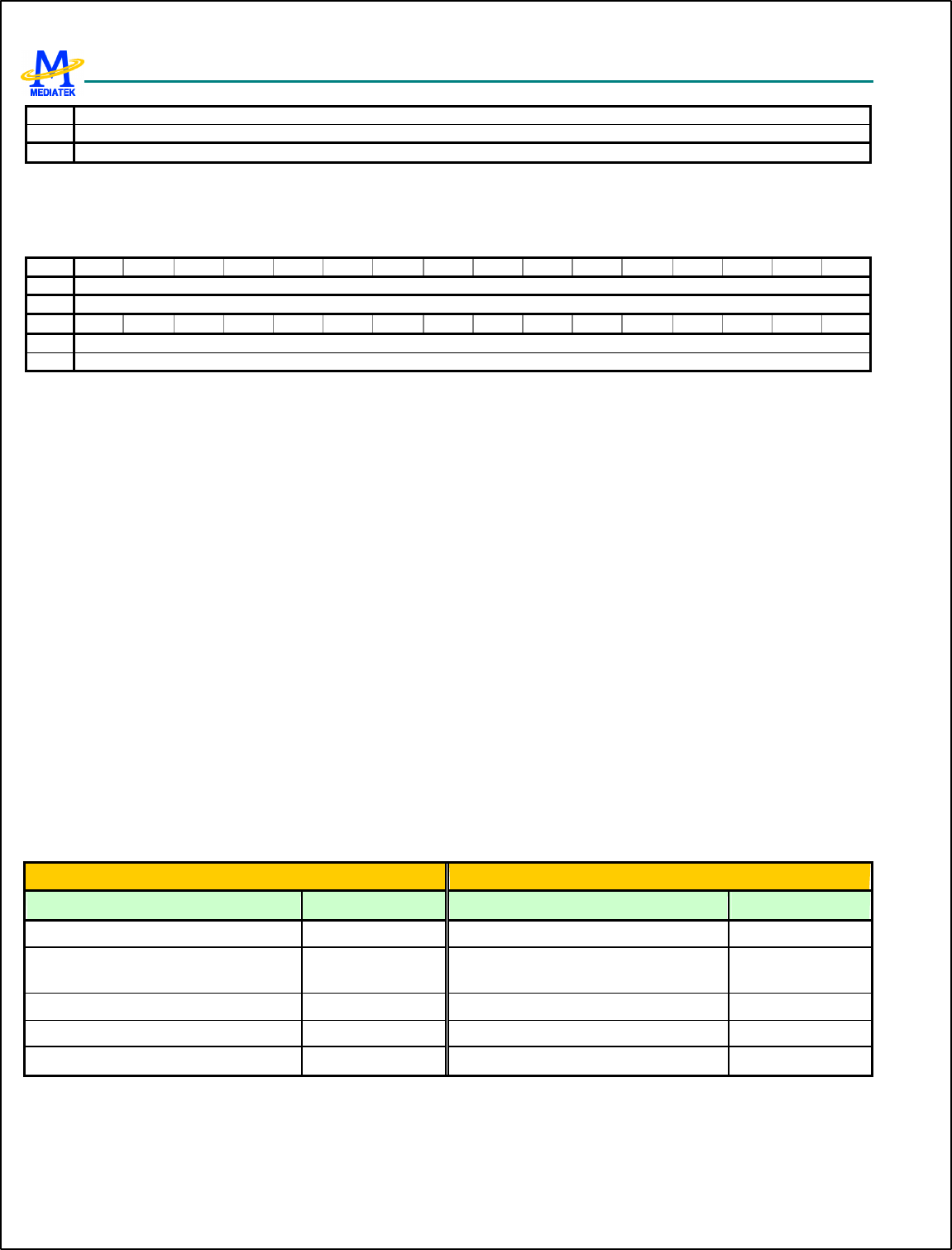

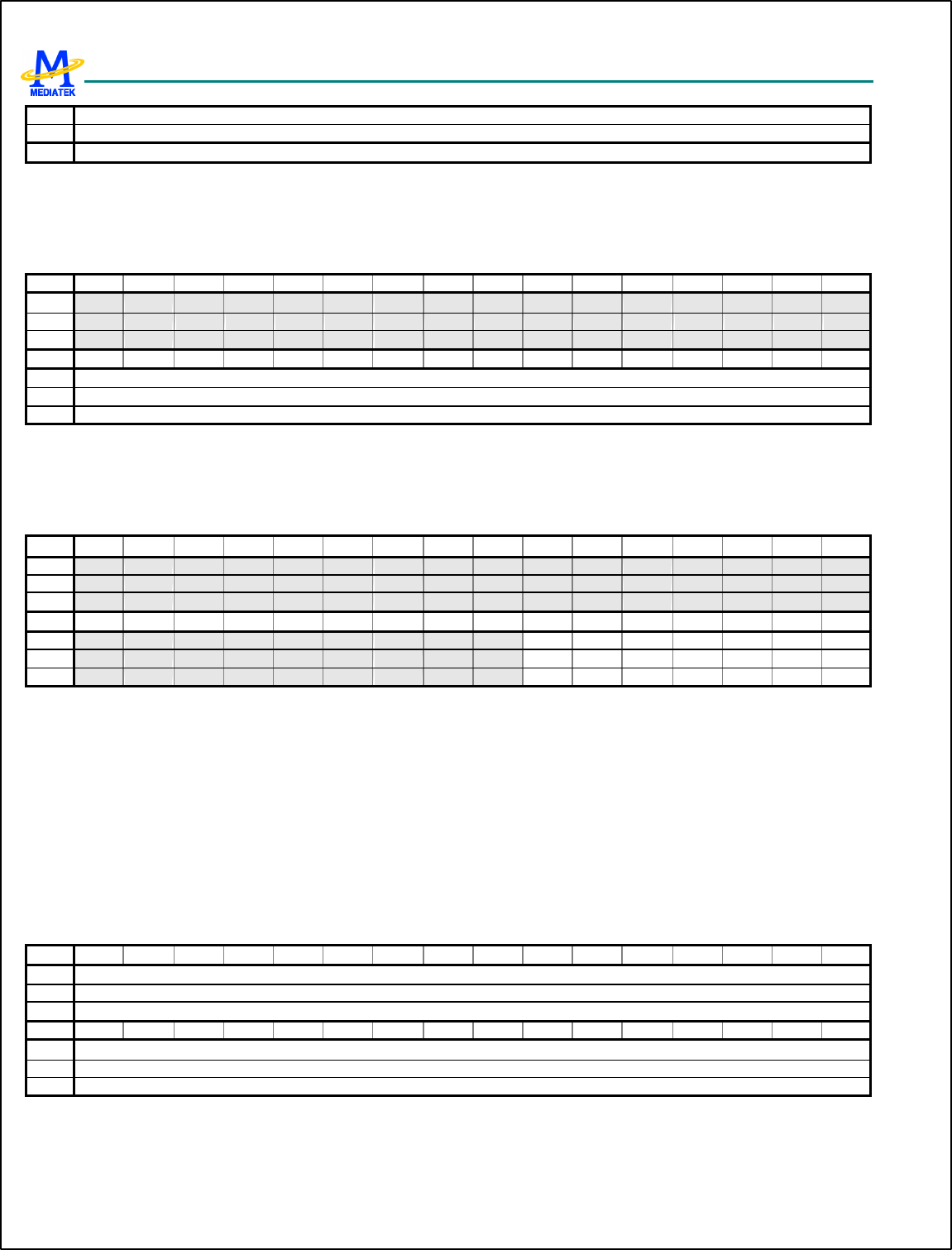

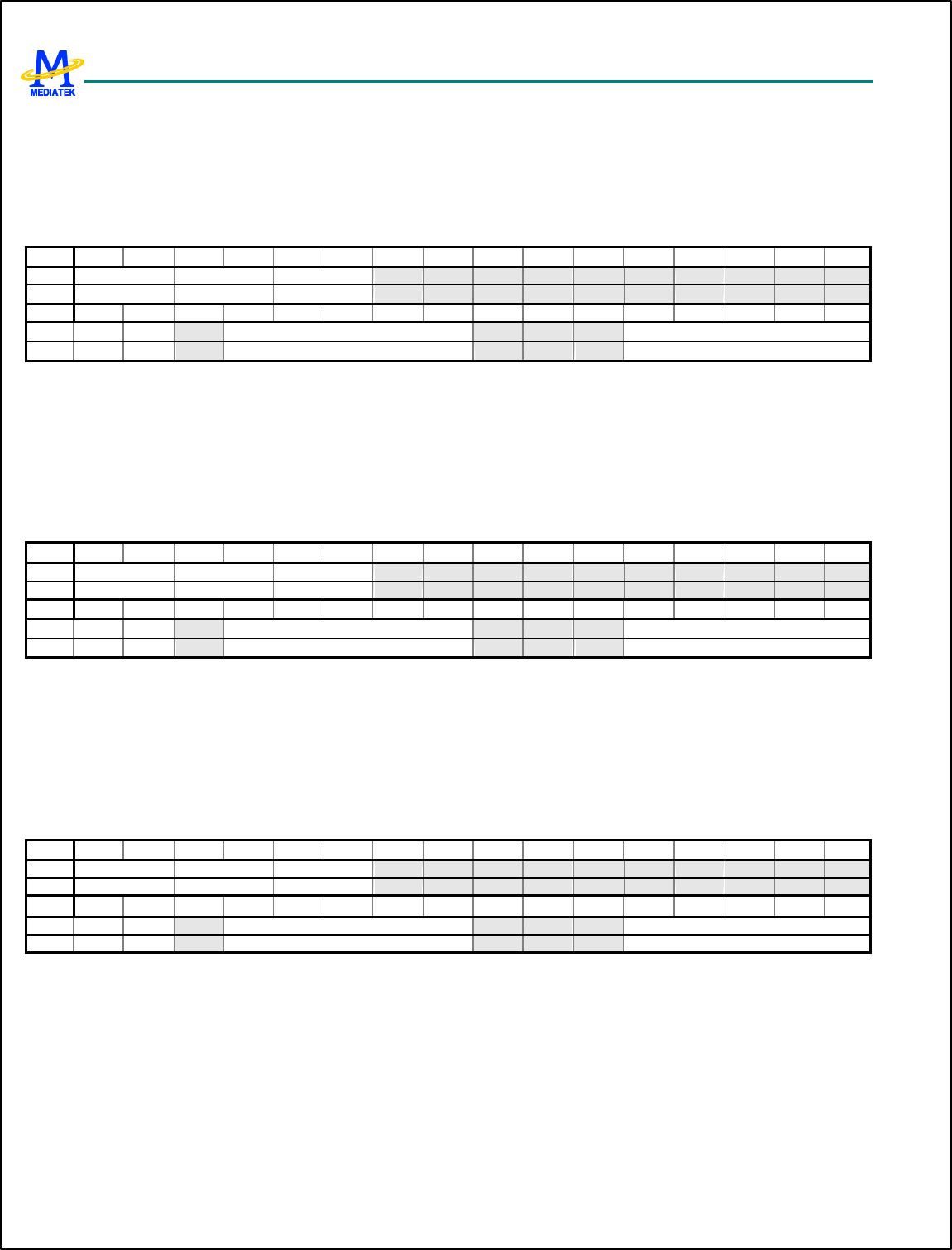

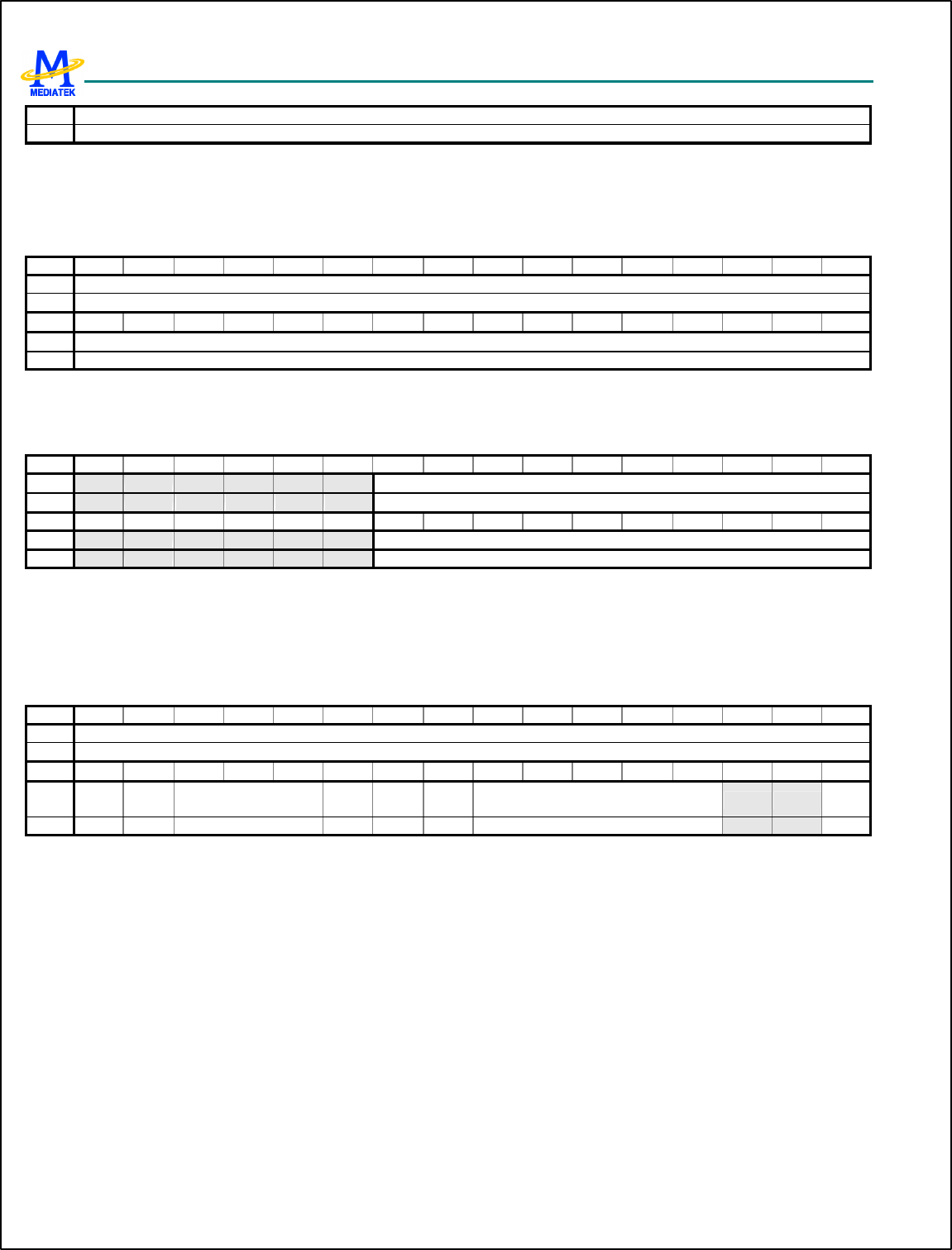

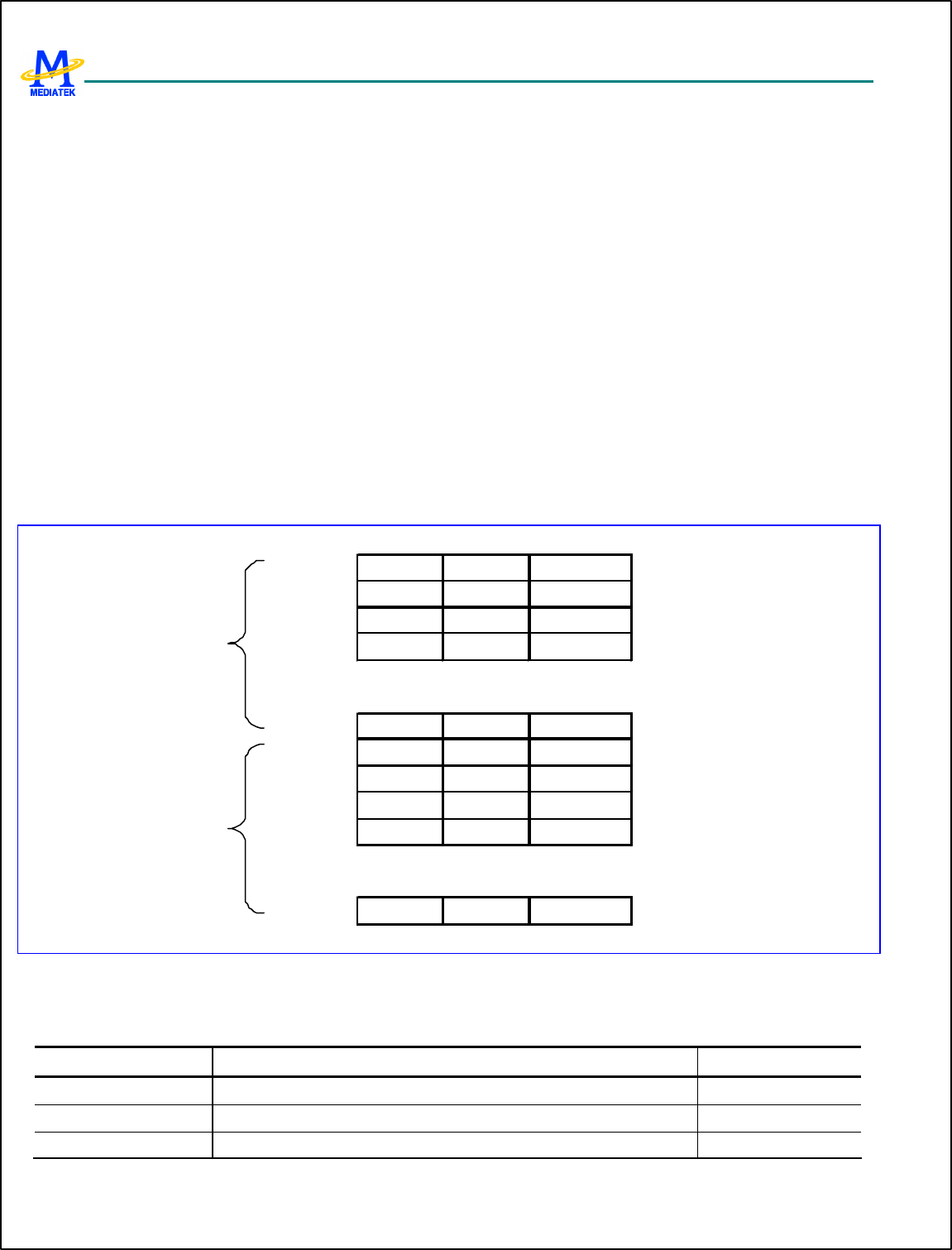

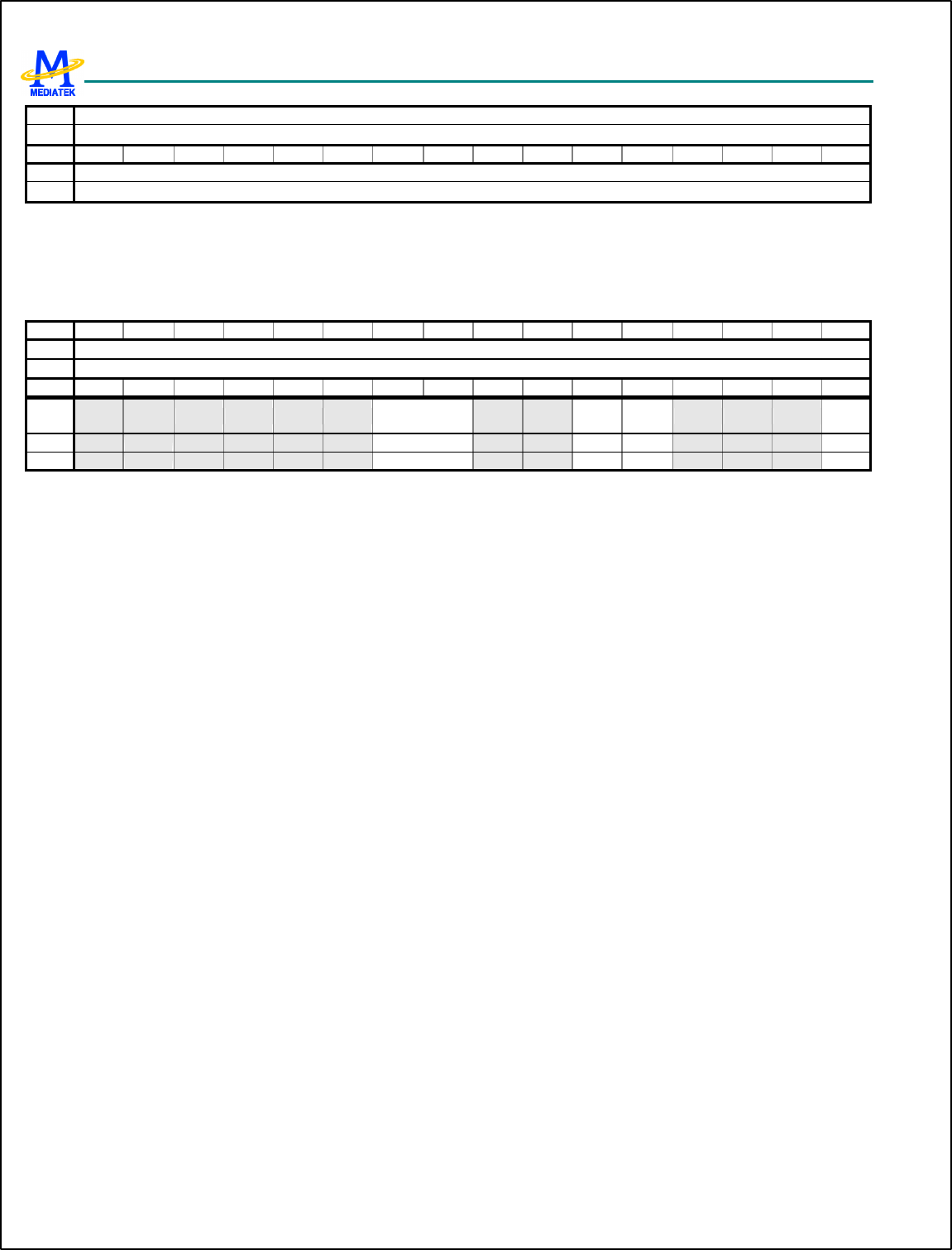

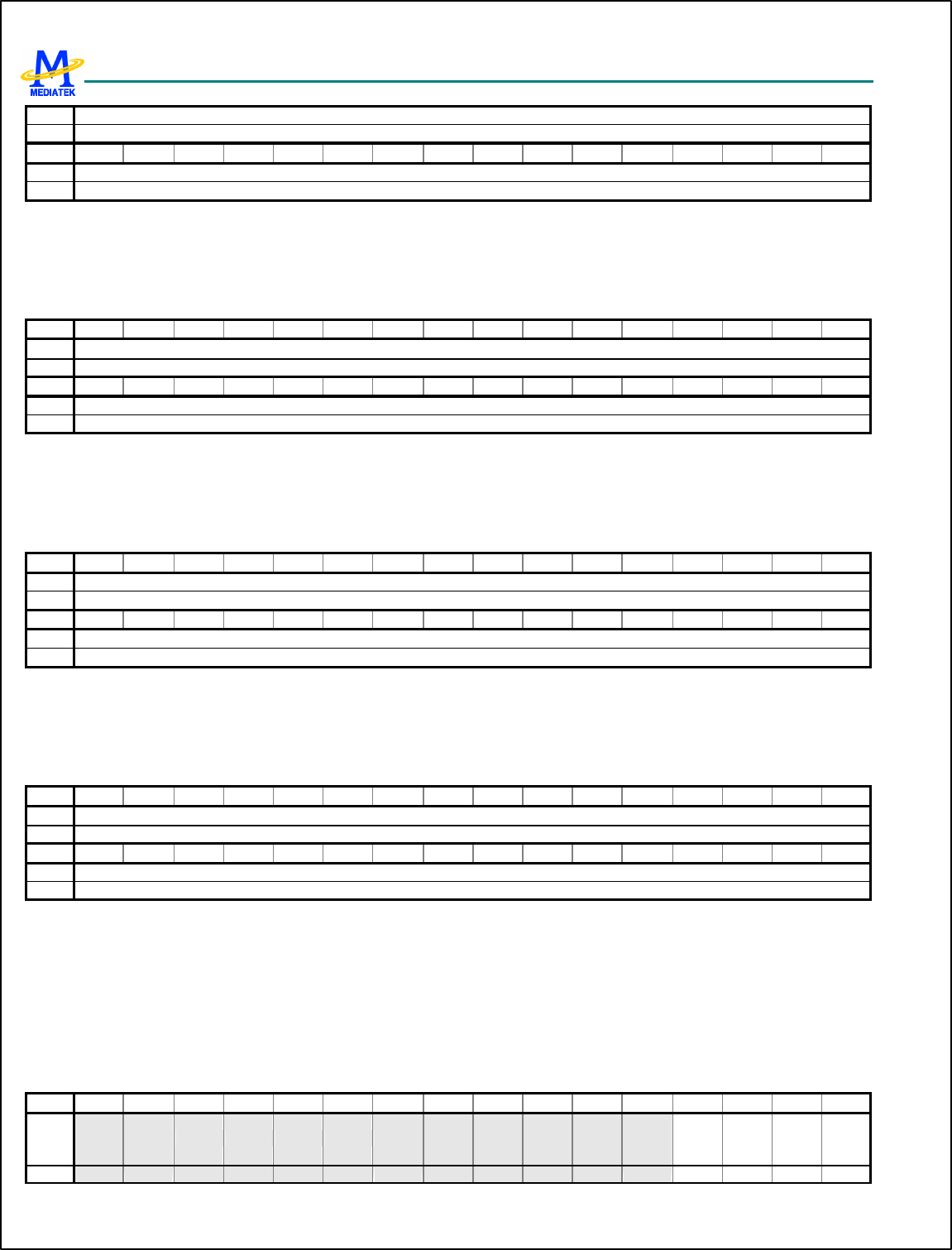

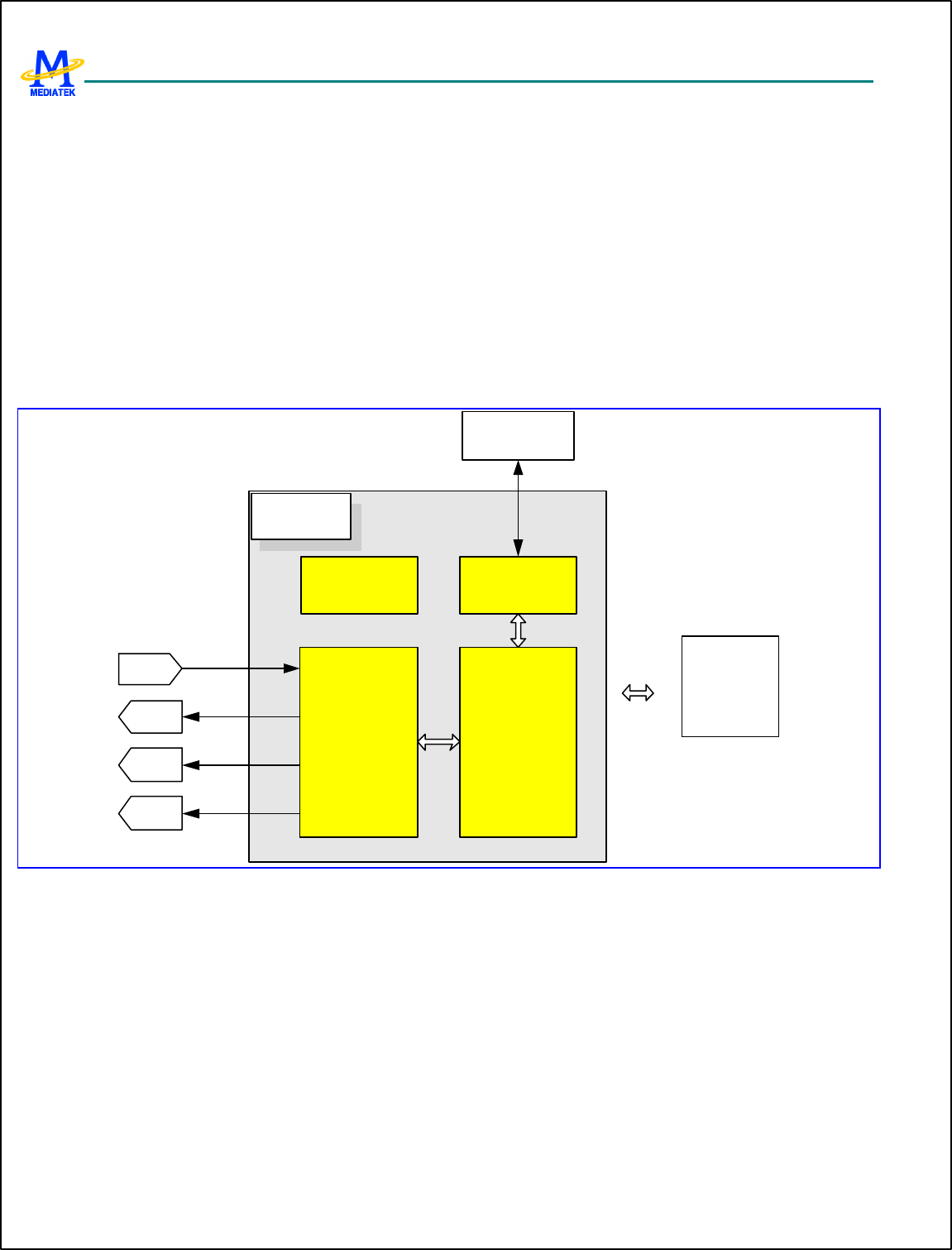

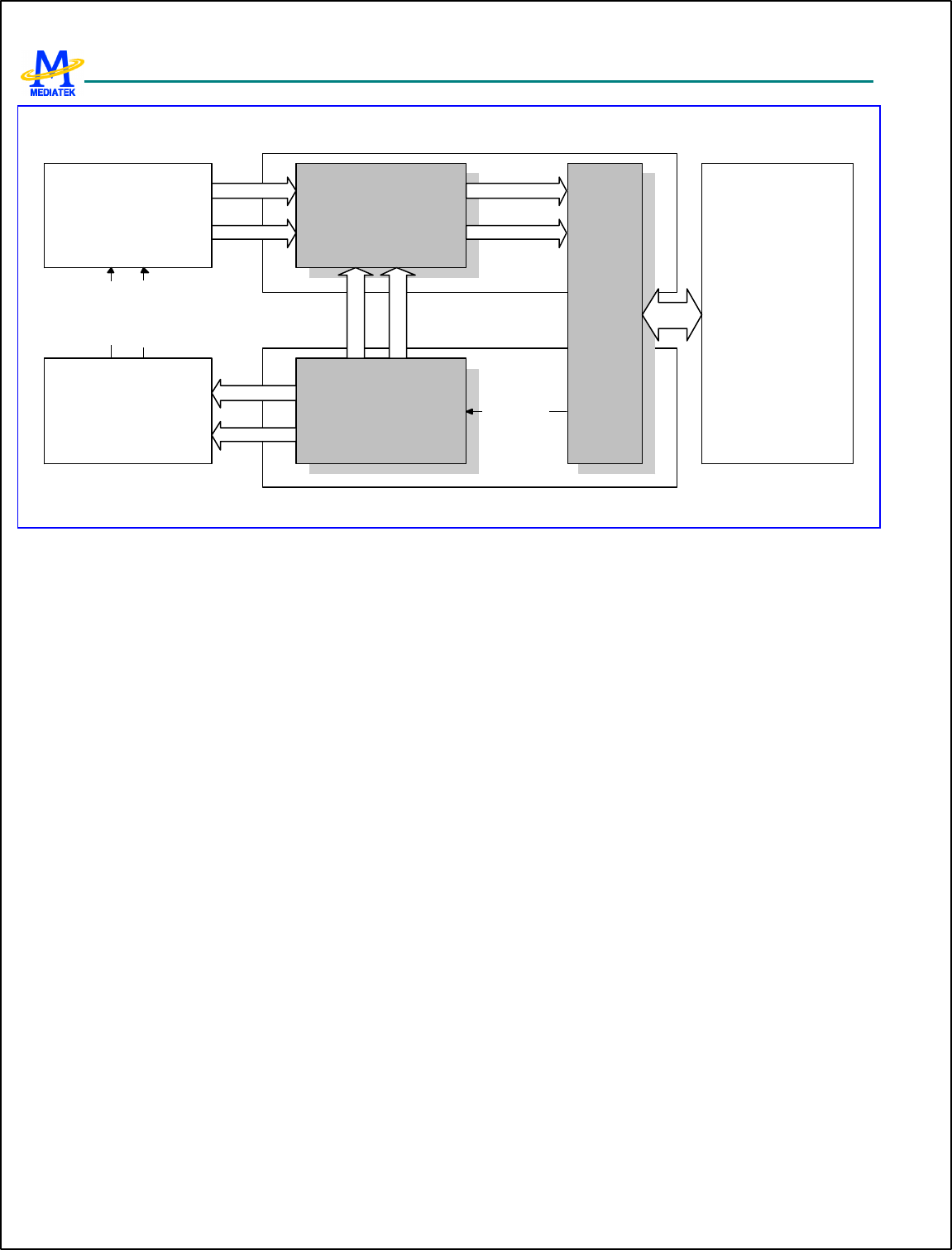

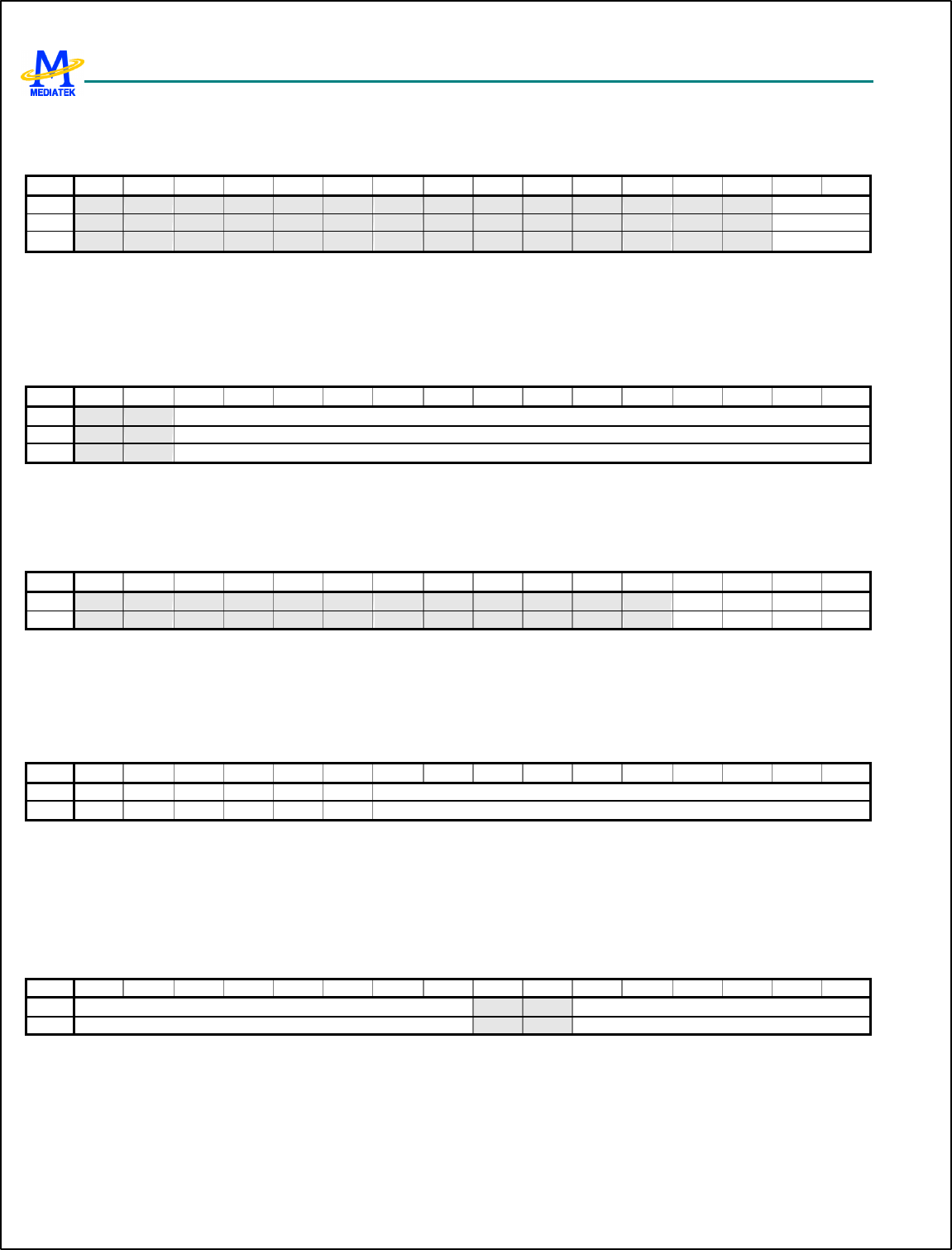

The MT6217 is a highly integrated single chip solution for

GSM/GPRS phone. Based on 32-bit ARM7EJ -STM RISC

processor, MT6217 features not only high performance

GPRS Class 12 MODEM but is also designed with support

for the wireless multi-media applications, such as

advanced display engine, hardware JPEG decoder,

synthesis audio with 64-tone polyphony, digital audio

playback, Java acceleration, MMS and etc. Additionally,

MT6217 provides varieties of advanced interfaces for

functionality extensions, like 8-port external memory

interface, 3-port 8/16-bit parallel interface, NAND Flash,

IrDA, USB and MMC/SD/MS/MS Pro. The typical

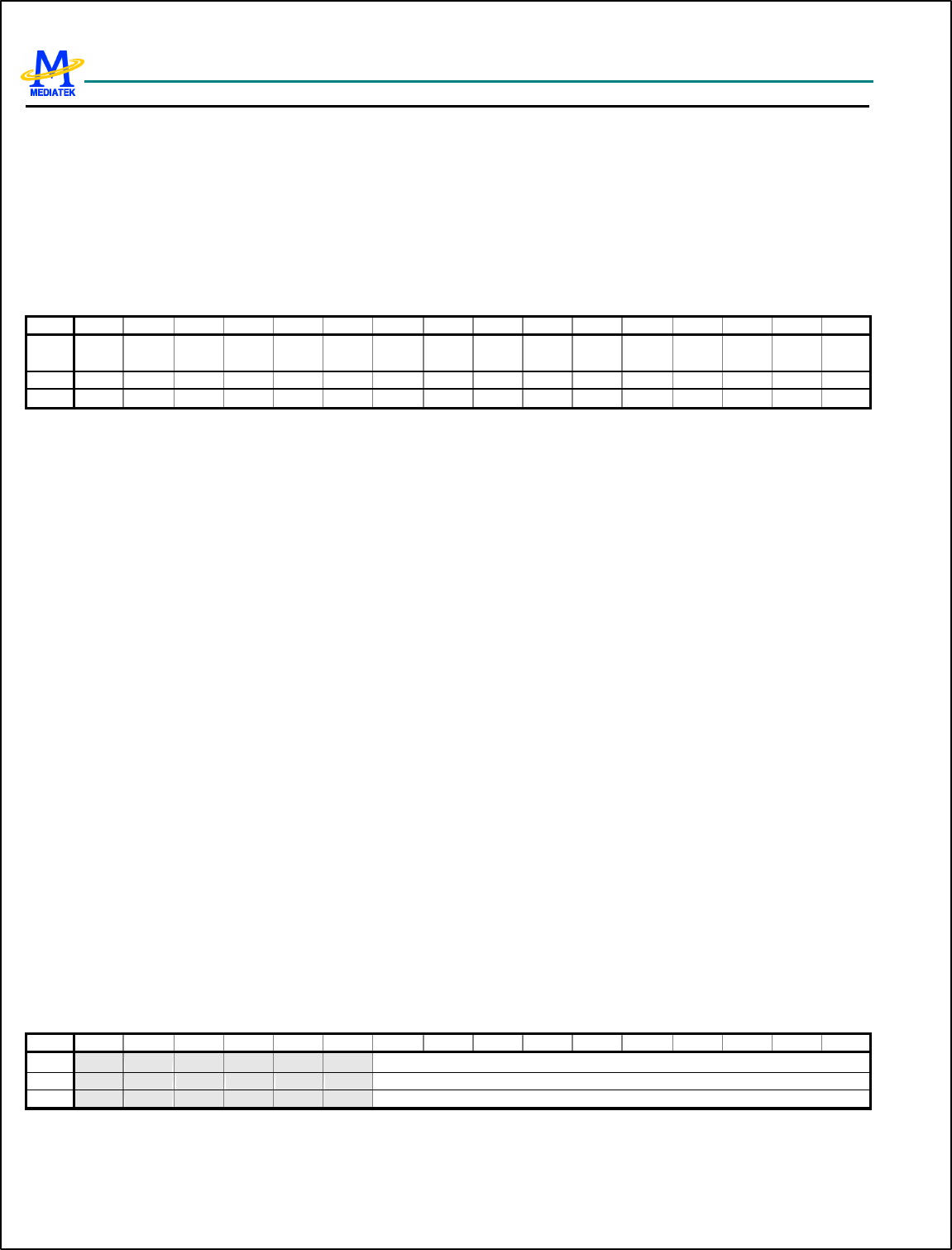

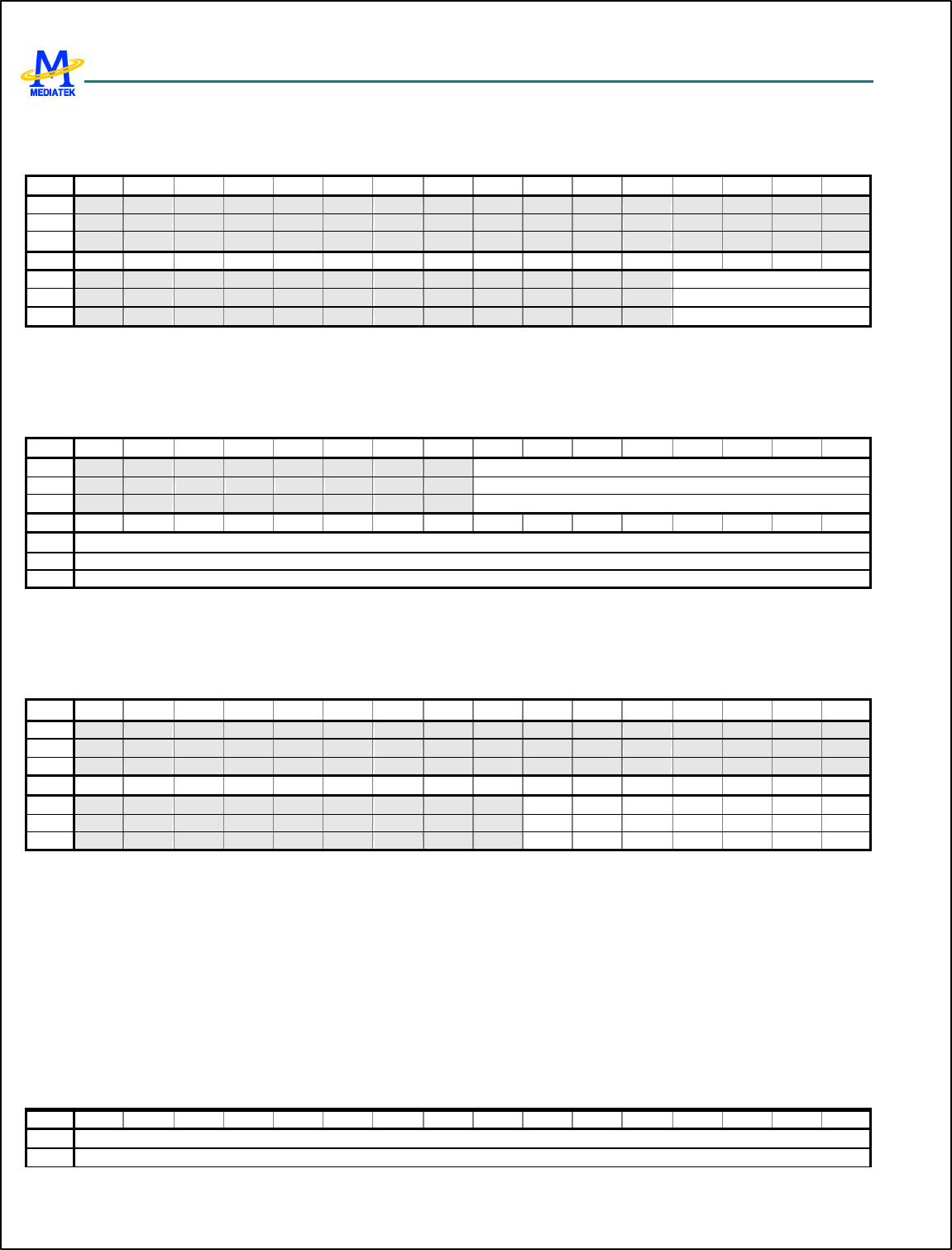

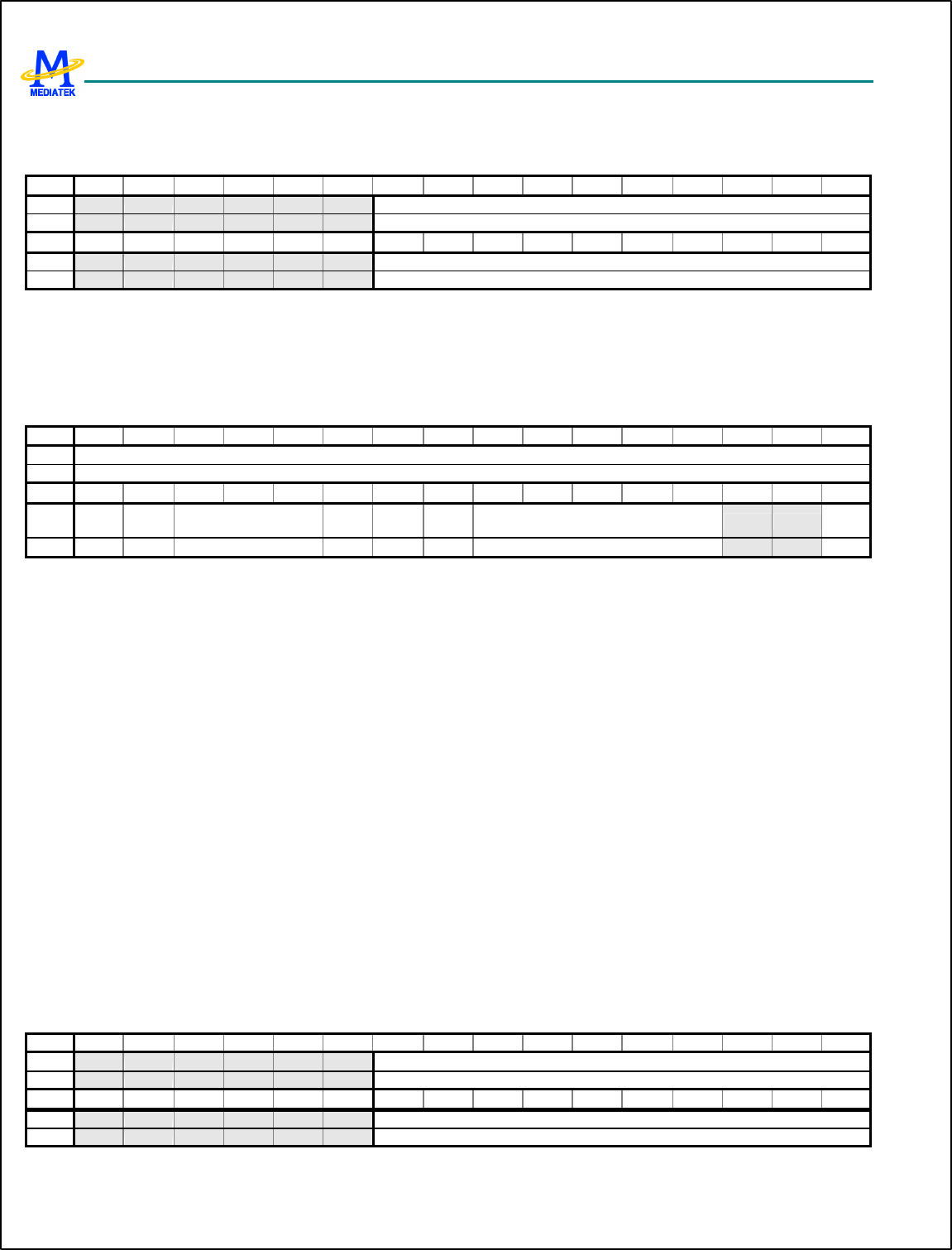

application can be shown as Figure 1.

External Memory Interface

Providing the greatest capacity for expansion, the MT6217

supports up to 8 state-of-the-art devices with SRAM-like

interface, including burst/page mode Flash, page mode

SRAM, Pseudo SRAM, Color/Parallel LCD, and

multi-media companion chip, like Camera and Melody

chips. Regarding the consideration of power consumption

and low noise, this interface is designed for flexible I/O

voltage and allows for lowering supply voltage down to

1.8V. In addition, the driving strength is configurable that

makes the signal integrity problem easy. Retention

technology is also specifically used on data bus to prevent

the bus from being floating during turn over.

Multi-media Subsystem

In order to provide more flexibility and bandwidth for

multi-media products, an additional 8/16 bit parallel

interface is incorporated. This interface is designed

specially for support with Camera companion chip as well

as LCD panel. Moreover, it can connect NAND flash

device to provide a solution for multi-media data storage.

For running multi-media application faster, MT6217

integrates also several hardware-based engines. With

hardware based JPEG decoder, the MT6217 easily handles

real-time playback of compressed image. With hardware

based Resizer and advanced display engine, it can display

and combine arbitrary size of images with up to 4 blending

layers.

User Interface

For user interactions, the MT6217 brings together all

necessary peripheral blocks for multi-media GSM/GPRS

phone. It comprises the Keypad Scanner with capability of

multiple key pressing, SIM Controller, Alerter, Real Time

Clock, PWM, Serial LCD Controller and General Purpose

Programmable I/Os. For connectivity and data storage, the

MT6217 consists of UART, IrDA, USB 1.1 Slave and

MMC/SD/MS/MS Pro. Besides, for large amount of data

transfer, high performance DMA (Direct Memory Access)

and hardware flow control are implemented, that greatly

enhances the performance and saves precious processing

power.

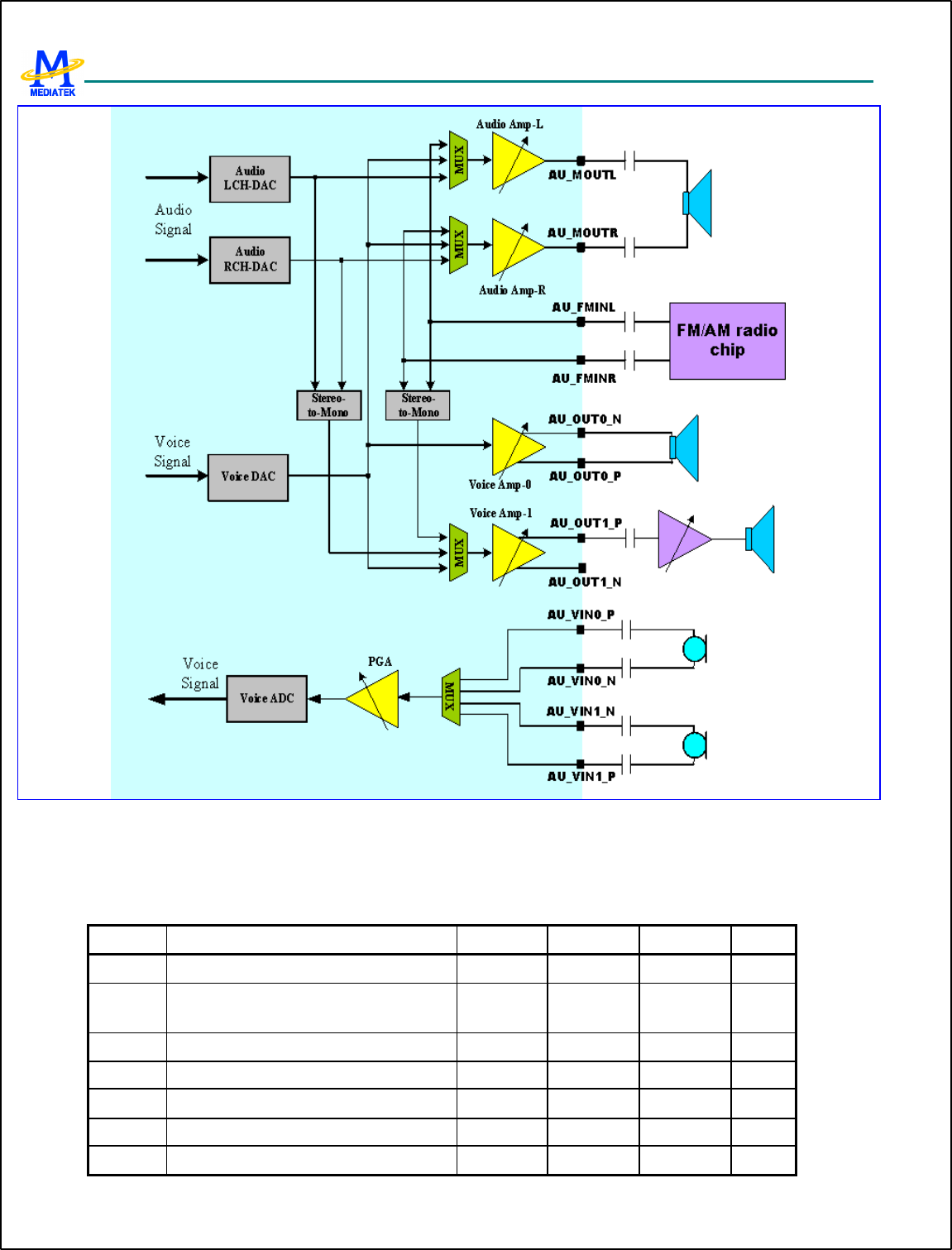

Audio Interface

With highly integrated mixed-signal Audio Front-End, the

MT6217 completes an architecture that allows for easy

audio interfacing with direct connection to the audio

transducers. Not only D/A and A/D Converters for Voice

Band, but also the high resolution Stereo D/A Converters

for Audio band are integrated. In addition, the MT6217

provides also Stereo Input and Analog Mixer. All of them

enable the MT6217 based terminal a rich platform for

multi-media applications.

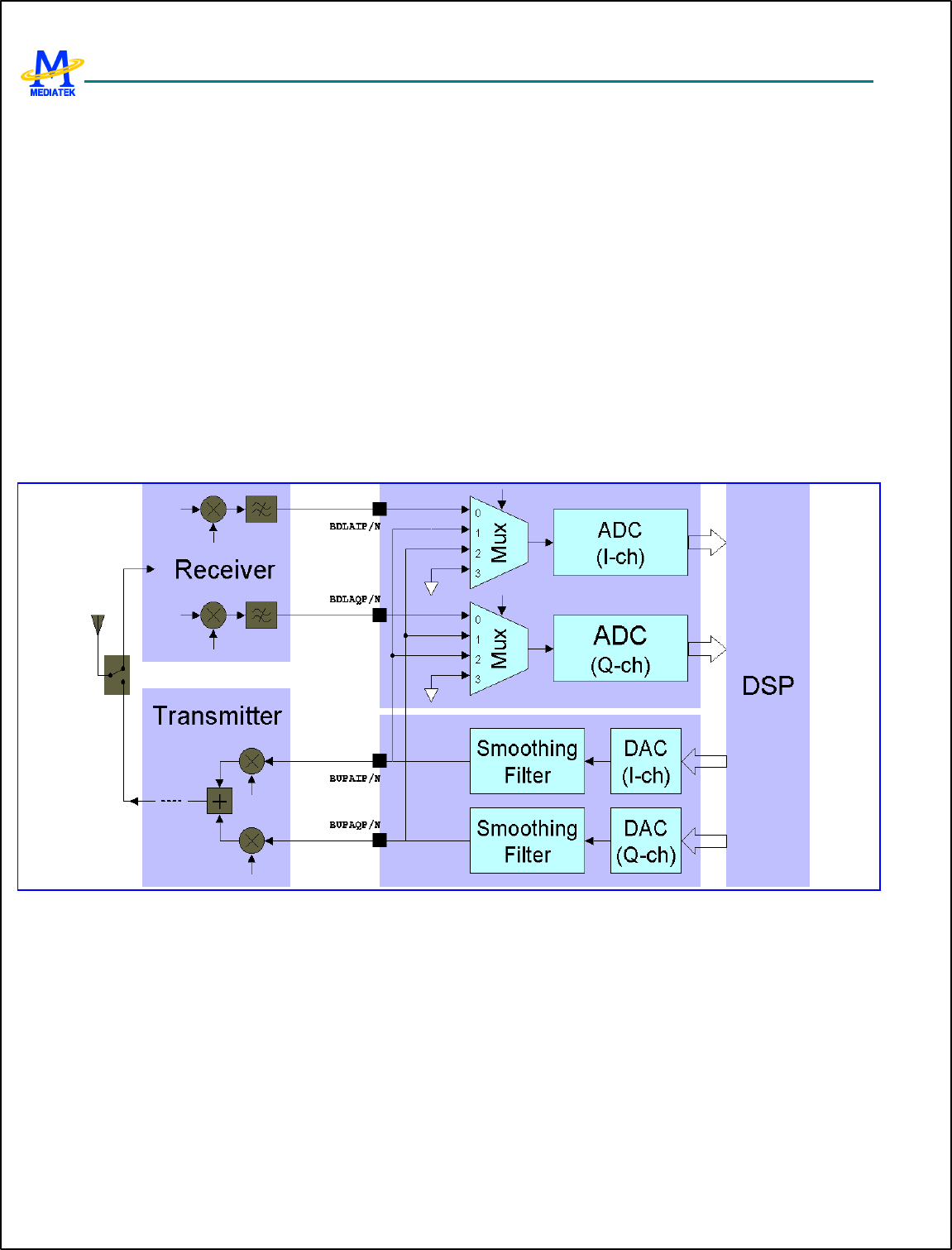

Radio Interface

Providing a well-organized radio interface with flexibility

for efficient customization, the MT6217 integrates

mixed-signal Baseband Front-End. It carries out gain and

offset calibration mechanisms and filters with

programmable coefficients for comprehensive

compatibility control on RF modules. The approach is also

combining a high resolution D/A Converter for controlling

VCXO or crystal instead of TCVCXO to reduce the

overall system cost. On the other hand, with 14-bit high

resolution A/D Converter for RF downlink path, MT6217

achieves great quality of MODEM performance. Besides,

to remove the necessary of external current-driving

component, the driving strength of some BPI outputs is

designed to be configurable.

Debug Function

MT6217 GSM/GPRS Baseband Processor Data Sheet Revision 1.01

7/349 MediaTek Inc. Confidential

The JTAG interface enables in-circuit debugging of

software program with the ARM7EJ -S core. With this

standardized debugger interface, the MT6217 provides

developers with a wide set of options for choosing ARM

development kits from supports of thirty parties.

Power Management

The MT6217 offers various low-power features helping

reduce system power consumption including Pause Mode

of 32KHz clocking at Standby State, Power Down Mode

for individual peripherals and Processor Sleep Mode.

Fabricated in low-power CMOS process, together with the

low-power features, the overall system can achieve ultra

low power consumption.

Package

The MT6217 device is offered in a 13mm×13mm, 282-ball,

0.65 mm pitch, TFBGA package.

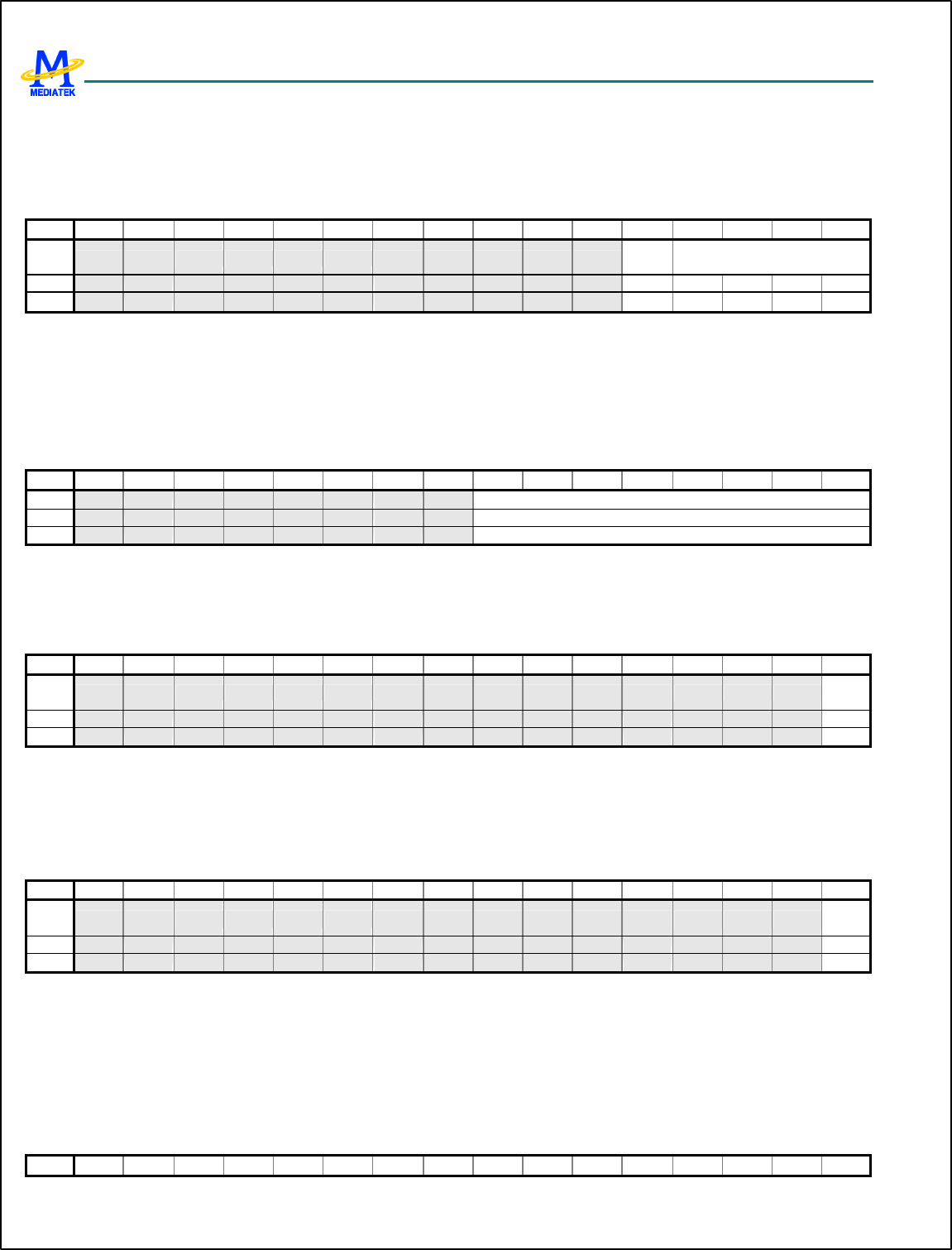

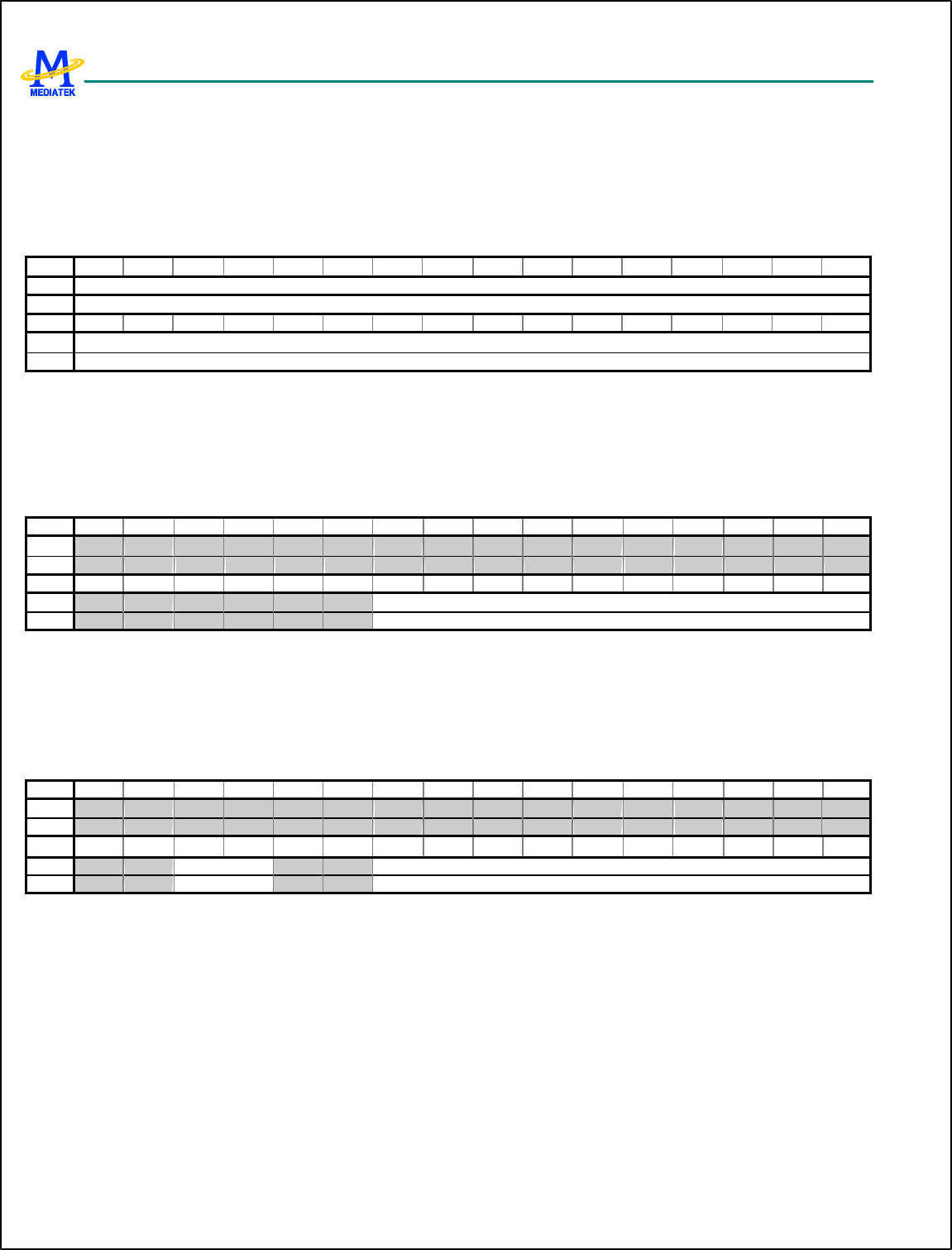

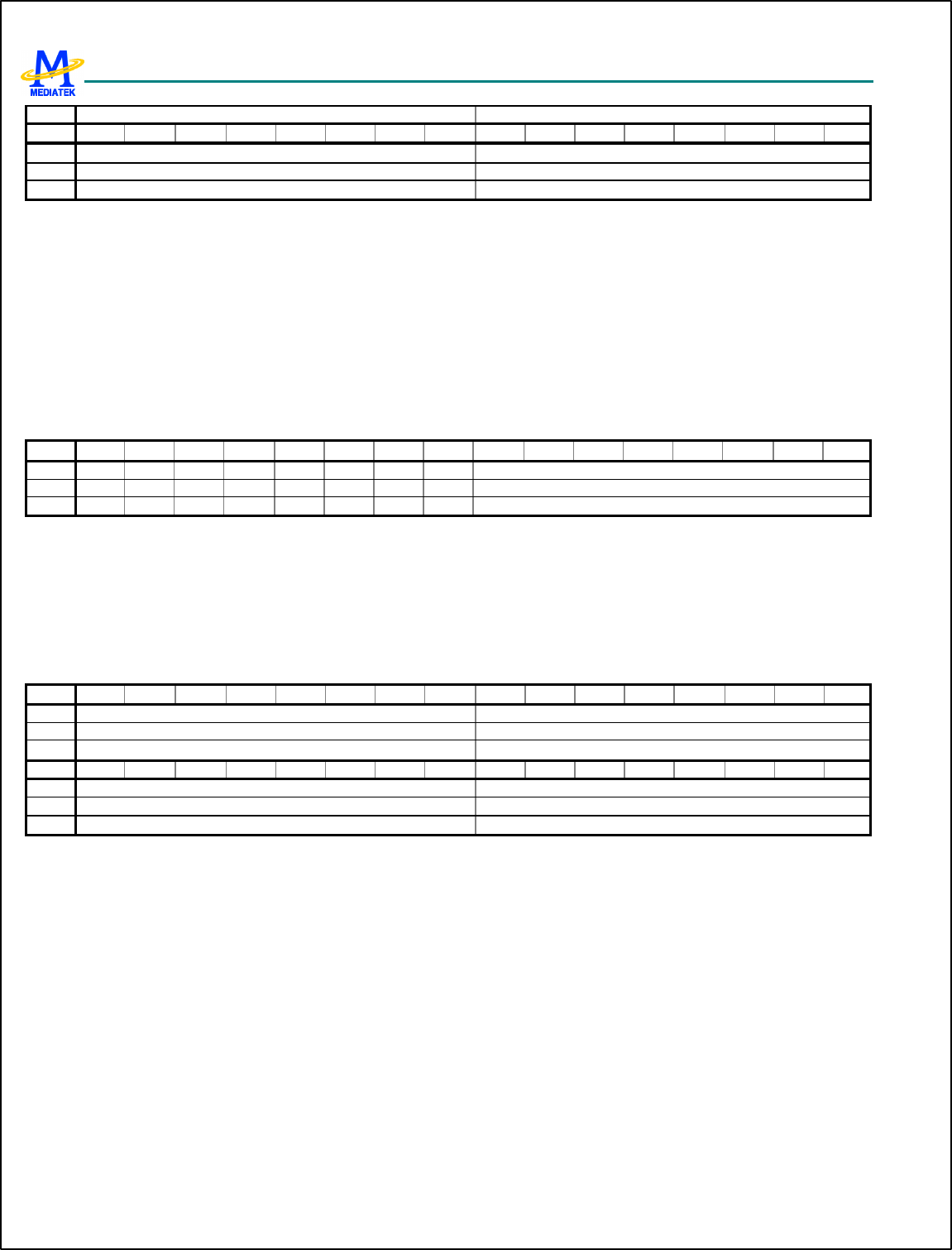

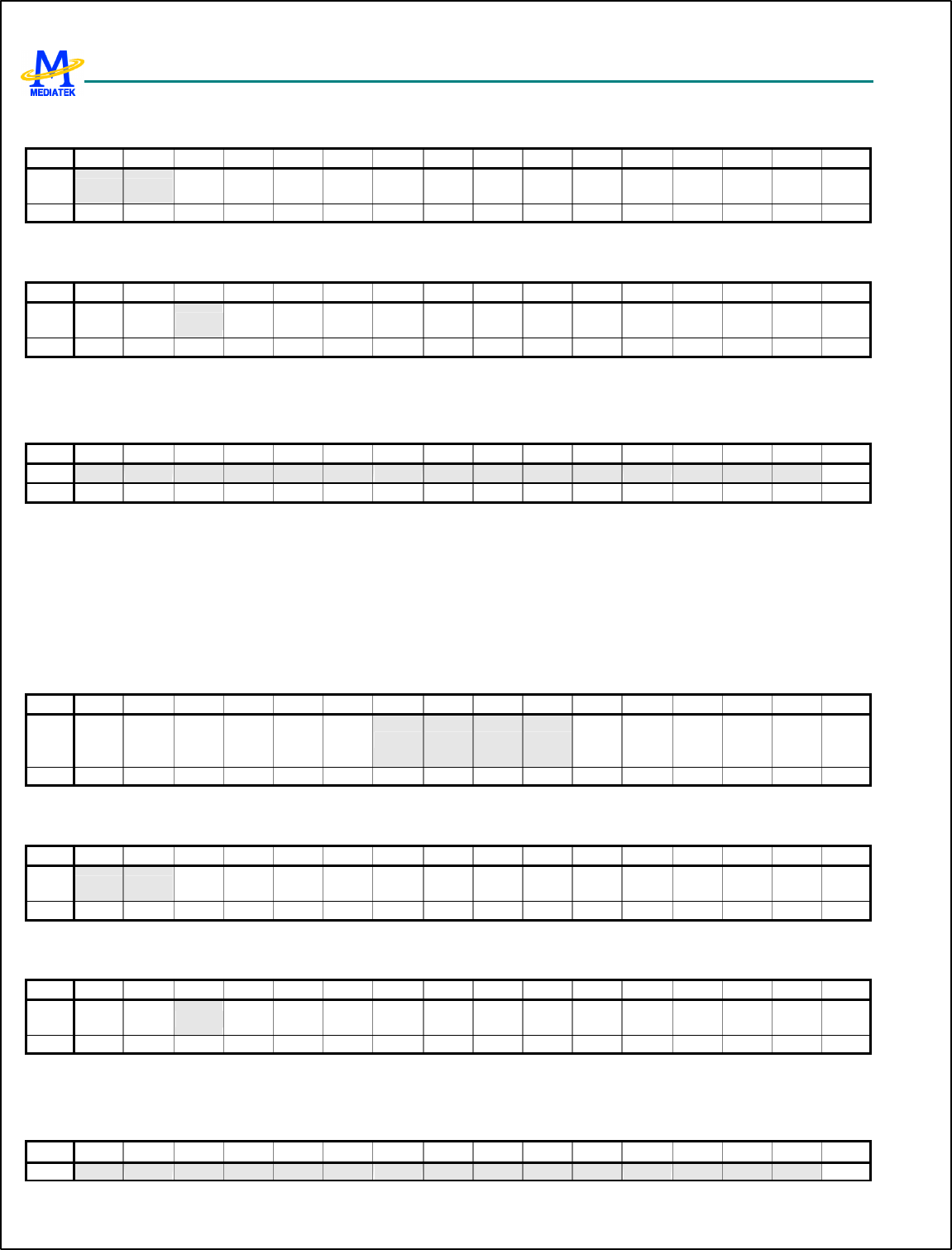

RF

Module

MT6217

Speech/Audio

Output

Speech/Audio

Input

Keypad

External Memory

Interface

Melody

LCD

TCVCXO

AFC

APC

TX I/Q

RX I/Q

BPI

BSI

Alerter

SIM

Supply Voltages

JTAG

UART

IrDA

Power

Management

Circuitry

Serial

LCD

SYSCLK

Serial

LCD

MMC/SD/MS/

MSPro

USB

B2PSI

AuxAD

C

1 2 3

4 5 6

7 8 9

*0 #

Camera

HiFi Stero

Output

FM Stereo

Radio Input

Debugger

PWM

NAND

Flash LCD

8/16-bit Parallel

Interface

Flash

SRAM

PSRAM

Figure 1 Typical application of MT6217

MT6217 GSM/GPRS Baseband Processor Data Sheet Revision 1.01

8/349 MediaTek Inc. Confidential

1.1 Features

n General

l Integrated voice-band, audio-band and base-band analog front ends

l TFBGA 13mm×13mm, 282-ball, 0.65 mm pitch package

n MCU Subsystem

l ARM7EJ -S 32-bit RISC processor

l Java hardware acceleration for faster Java-based games and other applets

l Operating frequency: 26/52 MHz

l 13 DMA channels

l 128K Bytes zero-wait-state on-chip SRAM

l On -chip boot ROM for Factory Flash Programming

l Watchdog timer for system crash recovery

l 2 sets of General Purpose Timer

l Circuit Switch Data and Division coprocessors

n External Memory Interface

l Support up to 8 external devices

l Support 8-bit or 16-bit memory components with size up to 64M Bytes each

l Support Flash and SRAM with Page Mode or Burst Mode

l Support Pseudo SRAM

l Industrial standard Parallel LCD Interface

l Built-in hardware acceleration function for color LCD panels

l Support multi-media companion chips with 8/16 bits data width

l Flexible I/O voltage of 1.8V ~ 3V for memory interface

l Configurable driving strength for memory interface

n Multi-media Subsystem

l Dedicated 8/16-bit Parallel Interface, support up to 3 external devices

l High speed hardware JPEG decoder, support both baseline sequential and progressive JPEG files

l High quality hardware Resizer capable of tailoring JPEG image to arbitrary size

l Support simultaneously equipping up to 2 parallel LCD and 1 serial LCD panels

l Support LCD panel maximum resolution up to 800x600 at 16bpp

MT6217 GSM/GPRS Baseband Processor Data Sheet Revision 1.01

9/349 MediaTek Inc. Confidential

l Capable of combining display memories with up to 4 blending layers

l NAND Flash Interface for mass storages

l Full-speed USB 1.1 Device

l Multi Media Card/Secure Digital Memory Card/Memory Stick/Memory Stick Pro controller

n Audio and Modem CODEC

l Wavetable synthesis with up to 64 notes

l Advanced wavetable synthesizer capable of generating simulated stereo

l Wavetable including GM full set of 128 instruments and 47 sets of percussion

l PCM Playback and Record

l Dial tone generation

l Voice Memo

l Noise Reduction

l Echo Suppression

l Advanced Sidetone Oscillation Reduction

l Digital sidetone generator with programmable gain

l Two programmable acoustic compensation filters

l GSM/GPRS quad vocoders for adaptive multirate (AMR), enhanced full rate (EFR), full rate (FR) and half rate (HR)

l GSM channel coding, equalization and A5/1 and A5/2 ciphering

l GPRS GEA and GEA2 ciphering

l Programmable GSM/GPRS Modem

l Packet Switched Data with CS1/CS2/CS3/CS4 coding schemes

l GSM Circuit Switch Data

l GPRS Class 12

n User Interfaces

l 6-row × 7-column keypad controller with hardware scanner

l Support multiple key press for gaming

l SIM Card Controller with hardware flow control

l 3 UARTs with hardware flow control and speed up to 921600 bps

l IrDA modulator/demodulator with hardware framer

l Real Time Clock (RTC) operating with a separate power supply

l Serial LCD Interface with 7 bytes TX FIFO

MT6217 GSM/GPRS Baseband Processor Data Sheet Revision 1.01

10/349 MediaTek Inc. Confidential

l General Purpose I/Os (GPIOs)

l 2 Sets of Pulse Width Modulation (PWM) Output

l Alerter Output with Enhanced PWM or PDM

l Six external interrupt lines

n Audio Interface and Audio Front End

l Two microphone inputs sharing one low noise amplifier with programmable gain

l Two Voice power amplifiers with programmable gain

l 2nd order Sigma-Delta A/D Converter for voice uplink path

l D/A Converter for voice downlink path

l High resolution D/A Converters for Stereo Audio playback

l Stereo analog input for stereo audio source

l Analog Multiplexer for Stereo Audio

l Stereo to Mono Conversion

l Support half-duplex hands-free operation

l Complying with GSM 03.50

n Radio Interface and Baseband Front End

l GMSK modulator with analog I and Q channel outputs

l 10 -bit D/A Converter for uplink baseband I and Q signals

l 14-bit high resolution A/D Converter for downlink baseband I and Q signals

l Calibration mechanism of offset and gain mismatch for baseband A/D Converter and D/A Converter

l 10 -bit D/A Converter for Automatic Power Control

l 13 -bit high resolution D/A Converter for Automatic Frequency Control

l Programmable Radio RX filter

l 2 Channels Baseband Serial Interface (BSI) with 3-wire control

l 10 -Pin Baseband Parallel Interface (BPI) with programmable driving strength

l Multi-band support

n Power Management

l Power Down Mode for analog and digital circuits

l Processor Sleep Mode

l Pause Mode of 32KHz clocking at Standby State

l 7-channel Auxiliary 10-bit A/D Converter for charger and battery monitoring

MT6217 GSM/GPRS Baseband Processor Data Sheet Revision 1.01

11/349 MediaTek Inc. Confidential

n Test and Debug

l Built-in digital and analog loop back modes for both Audio and Baseband Front-End

l DAI port complying with GSM Rec.11.10

l JTAG port for debugging embedded MCU

MT6217 GSM/GPRS Baseband Processor Data Sheet Revision 1.01

12/349 MediaTek Inc. Confidential

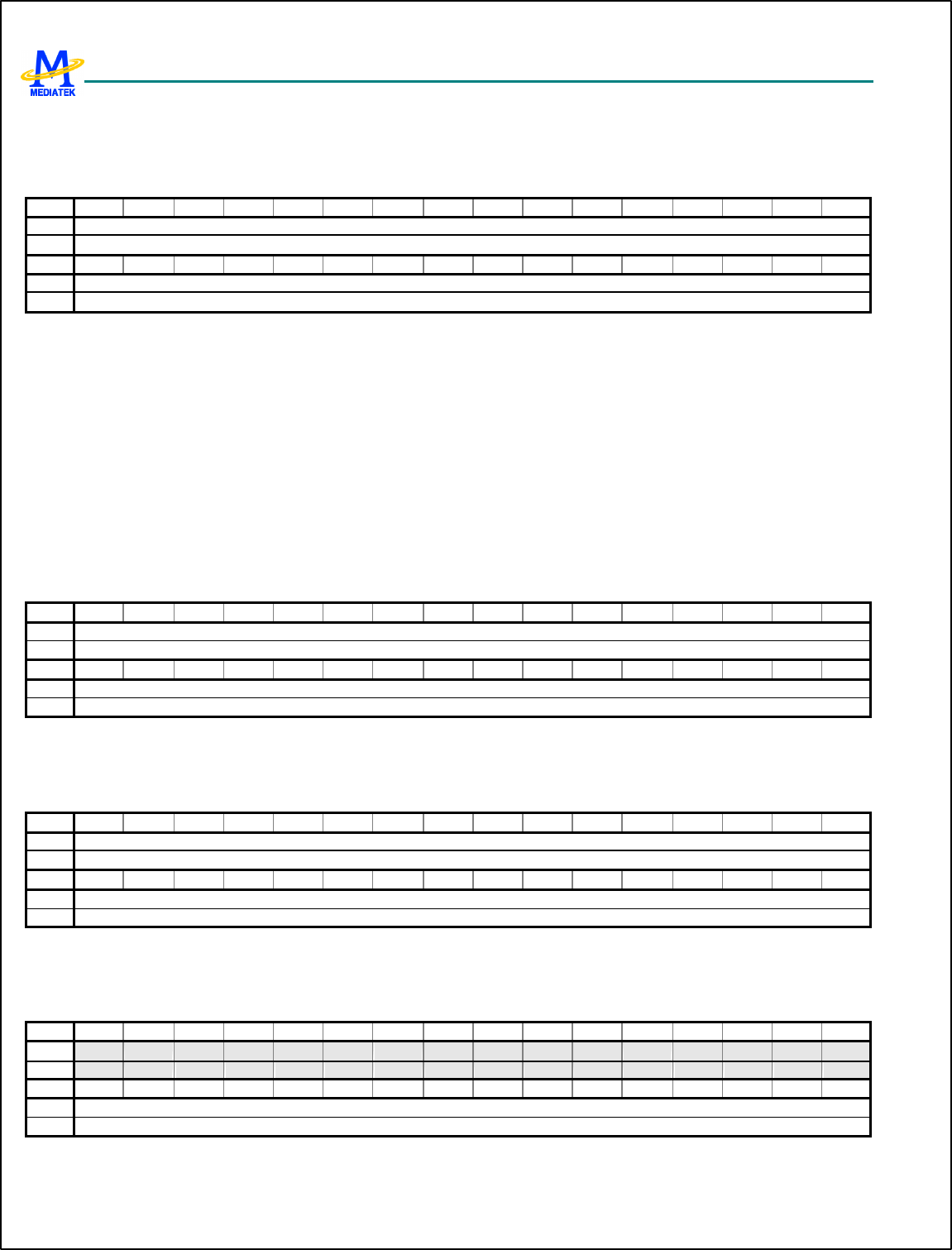

1.2 General Description

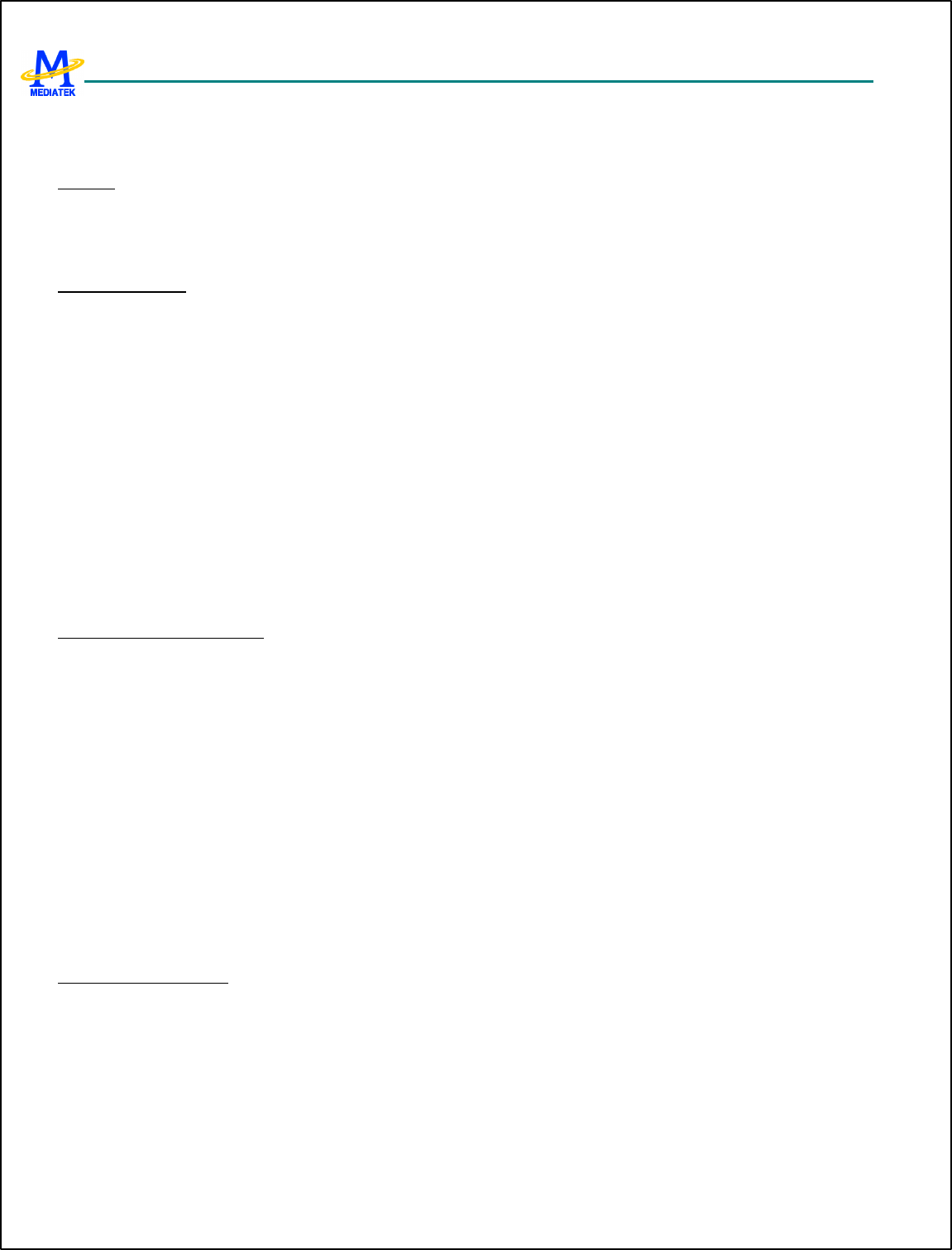

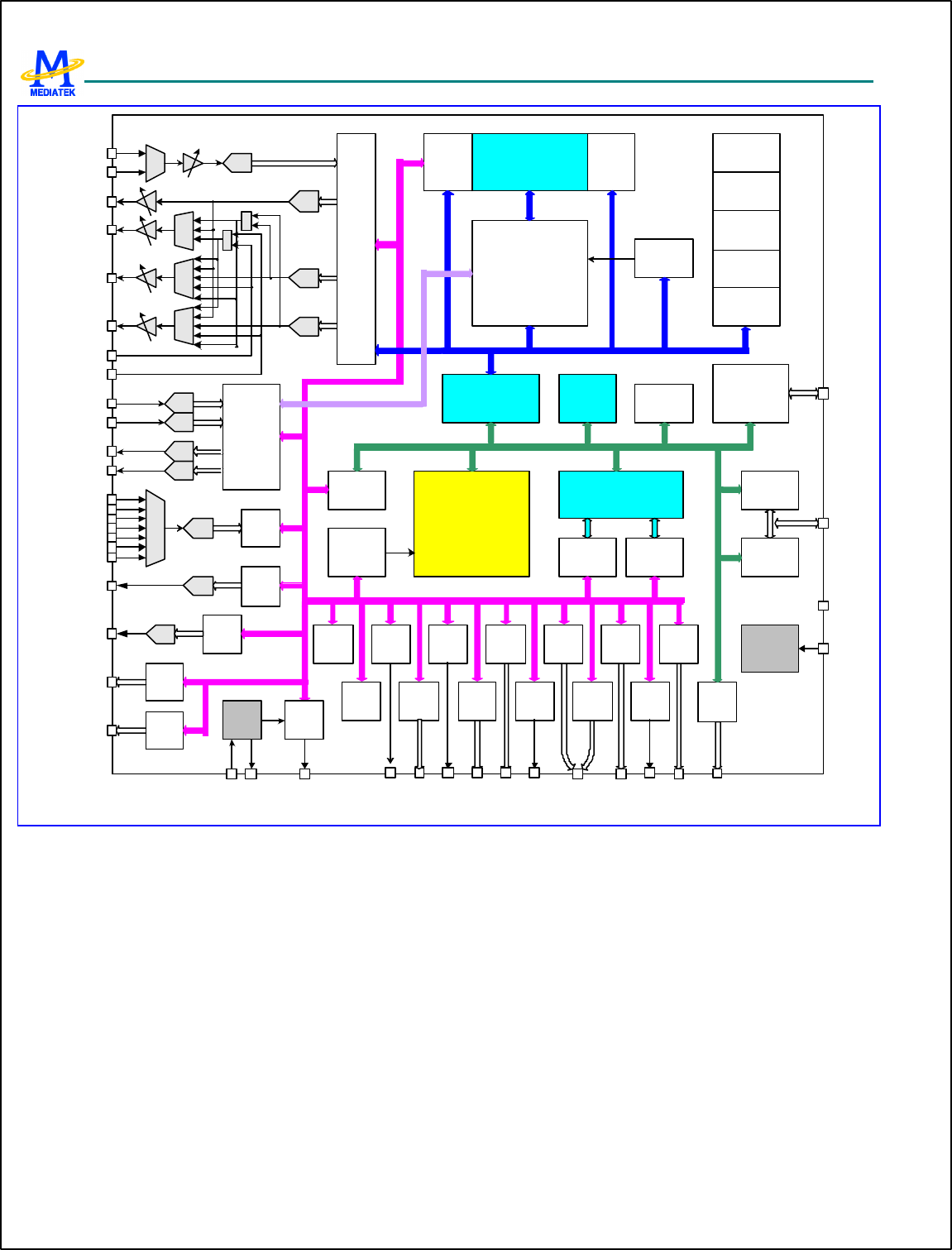

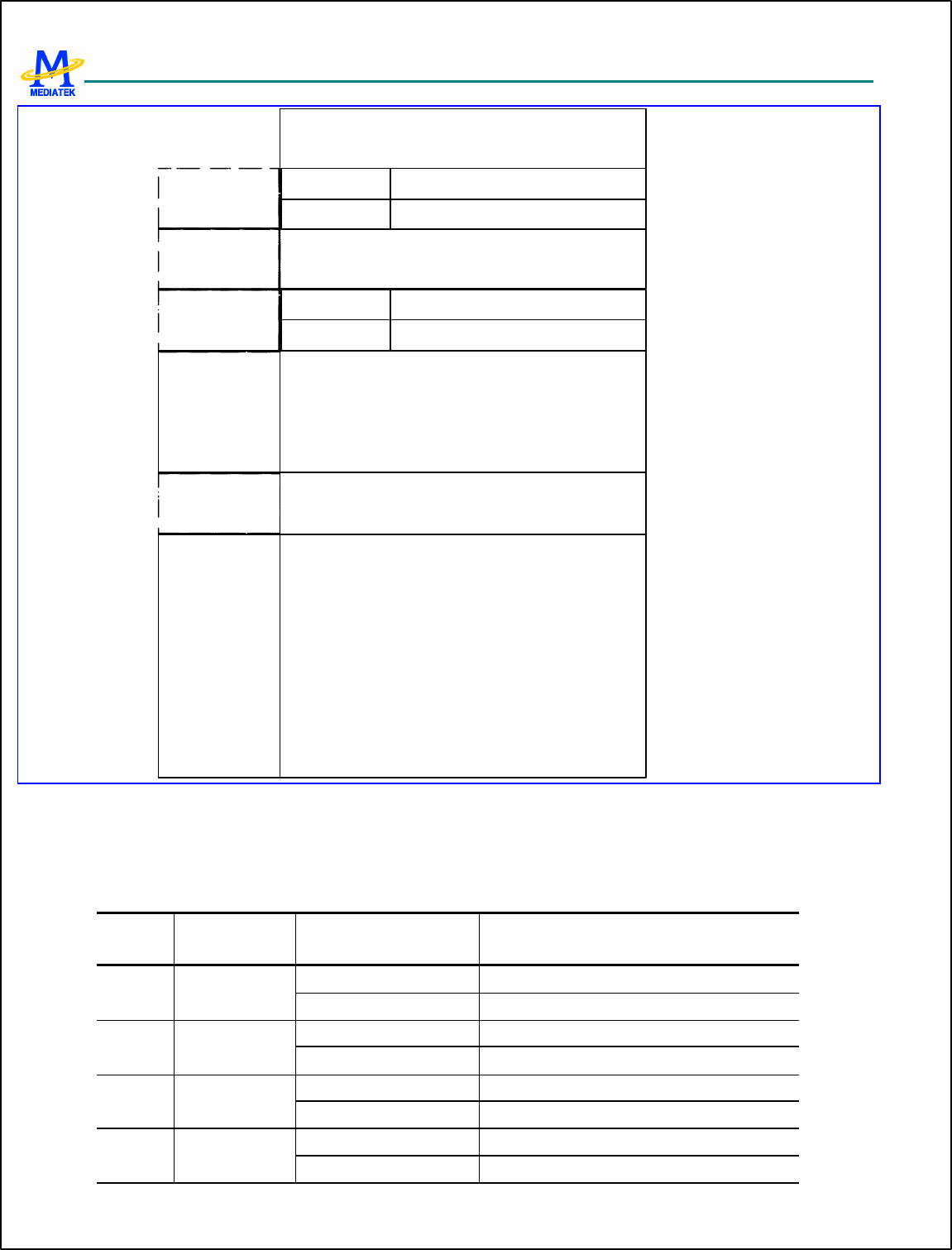

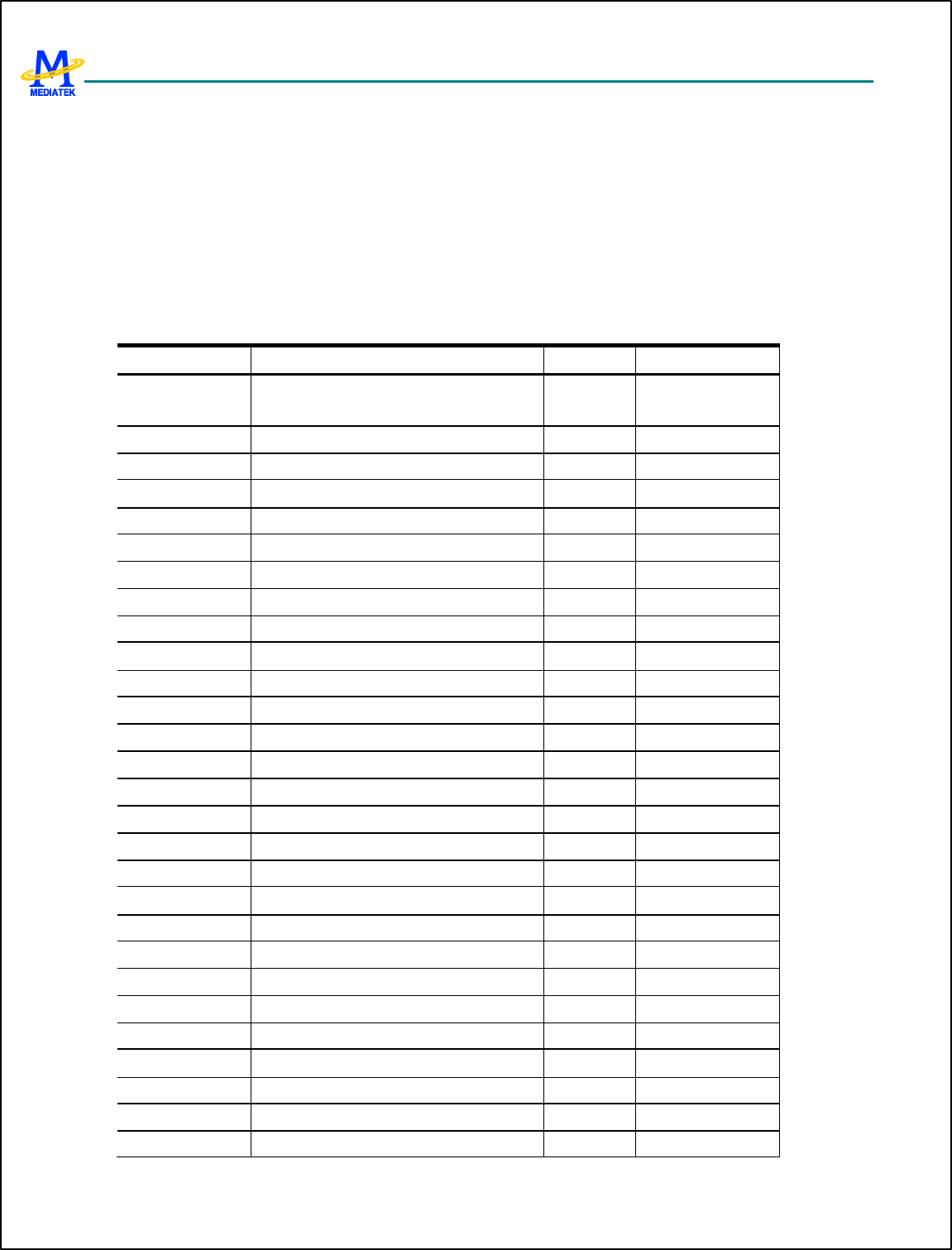

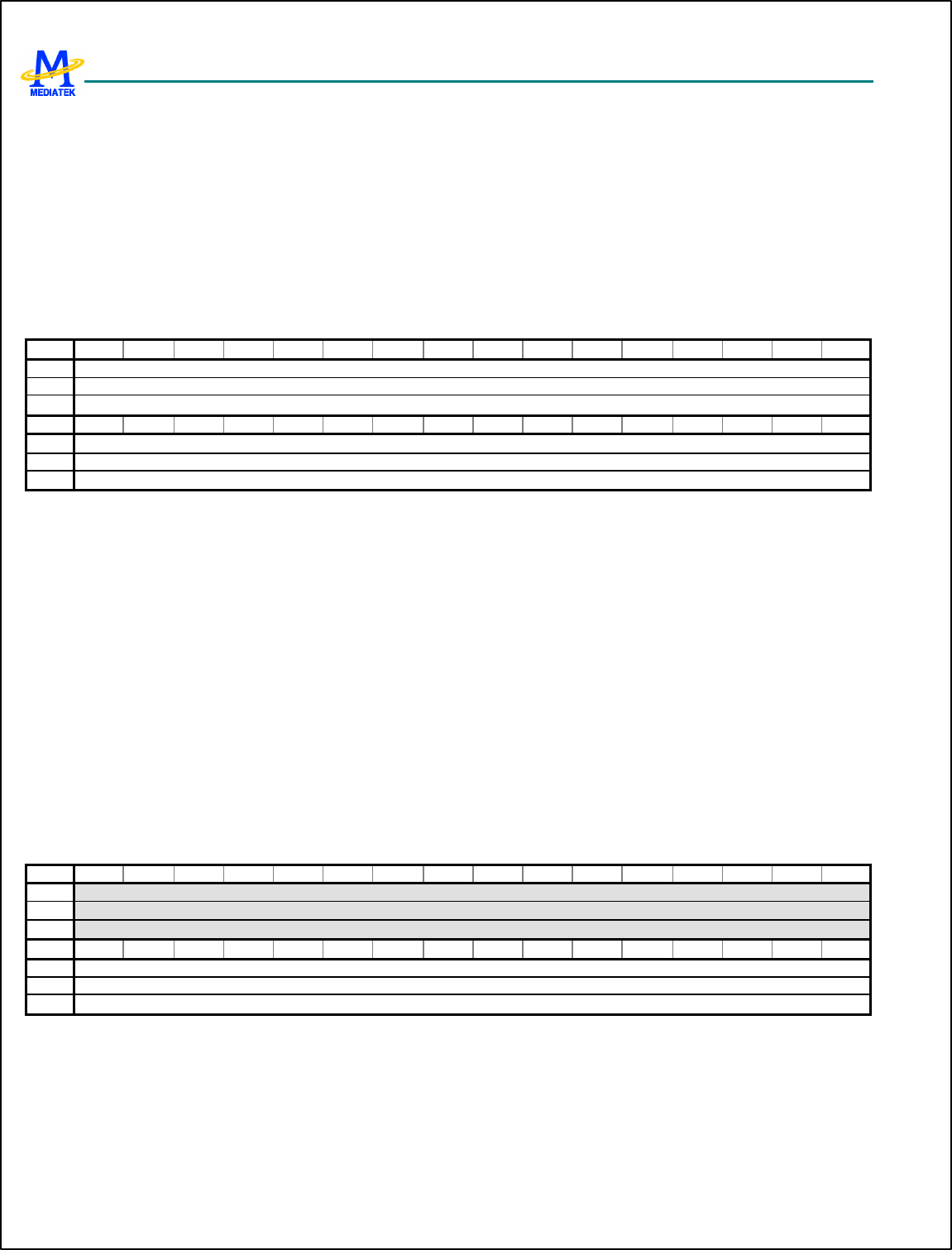

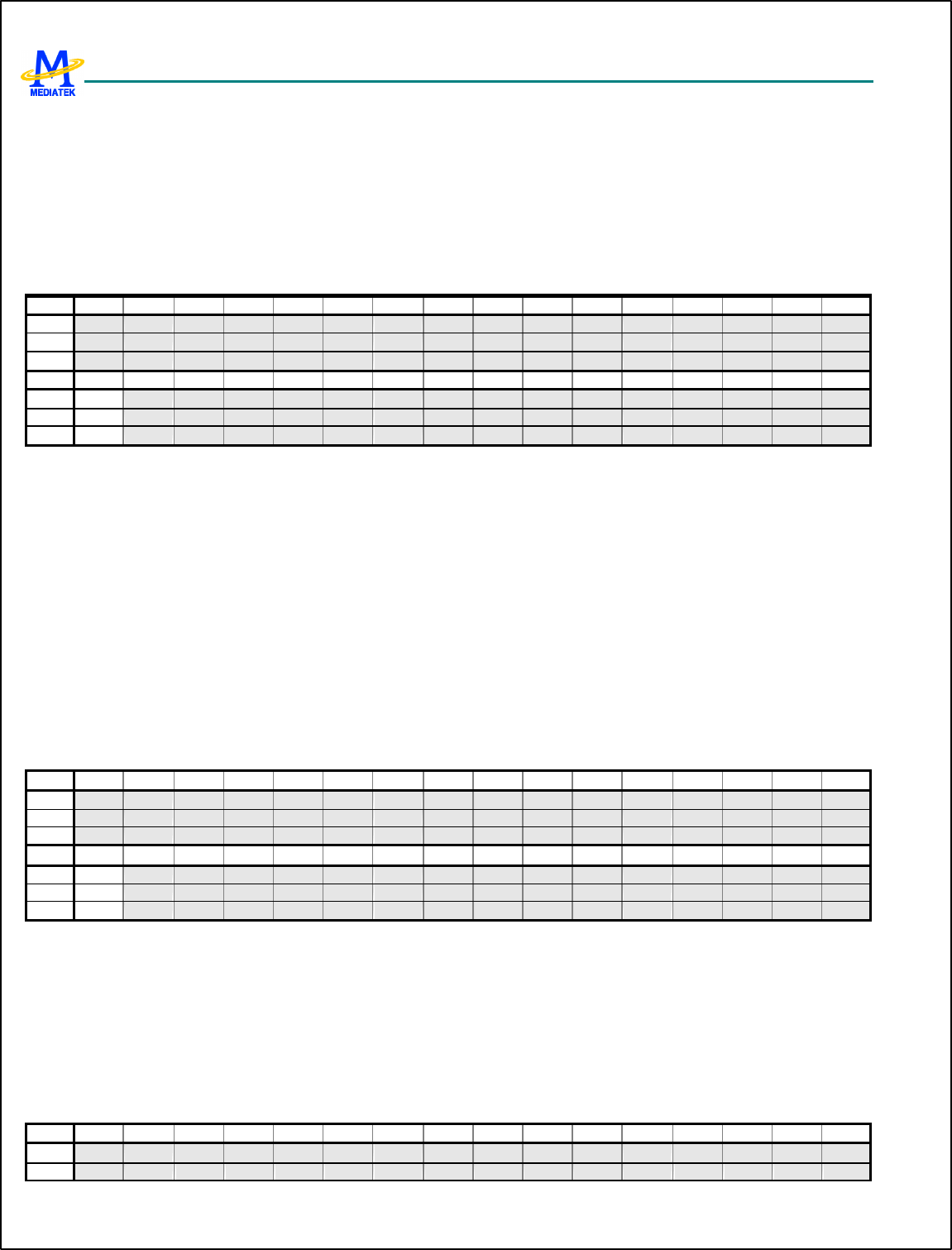

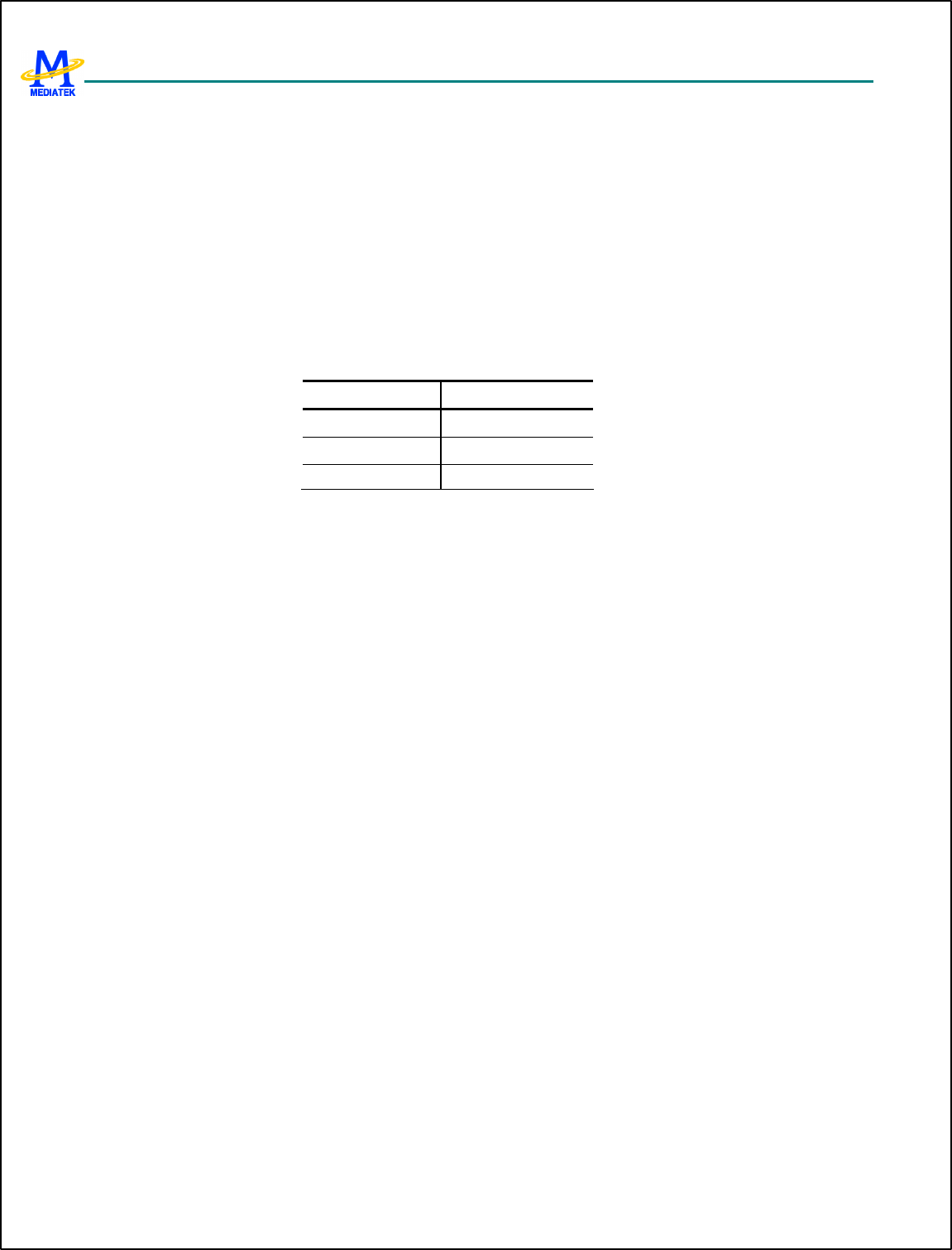

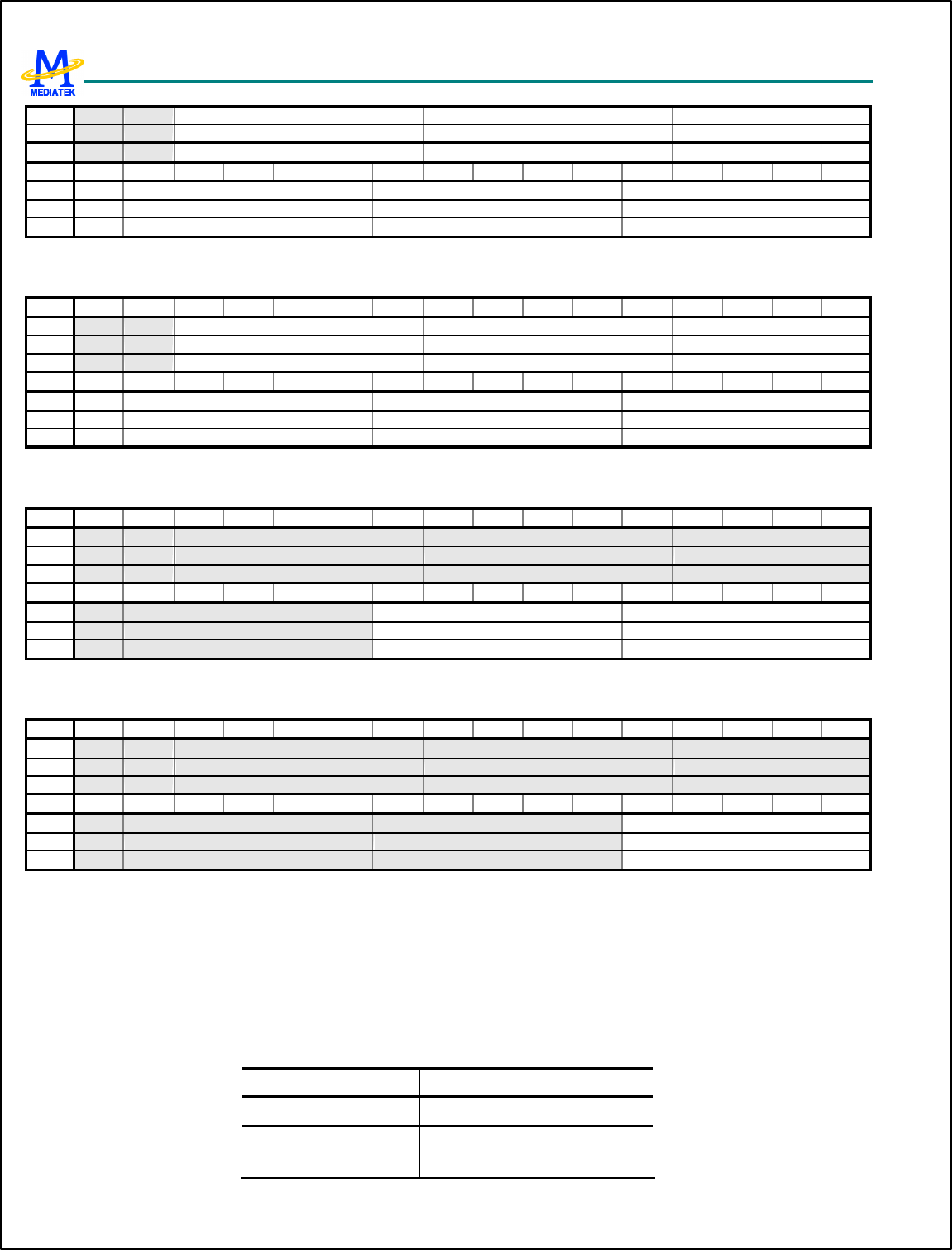

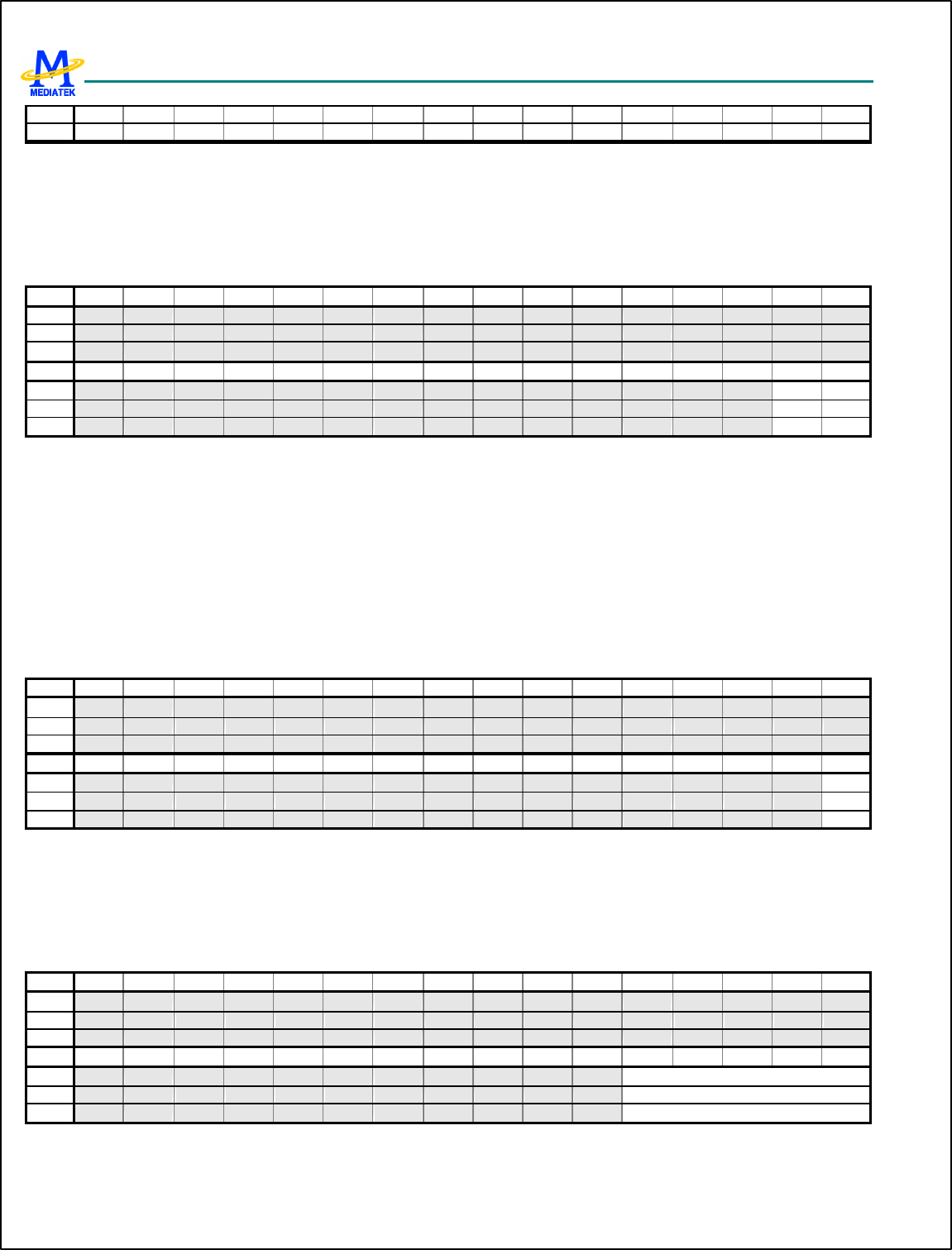

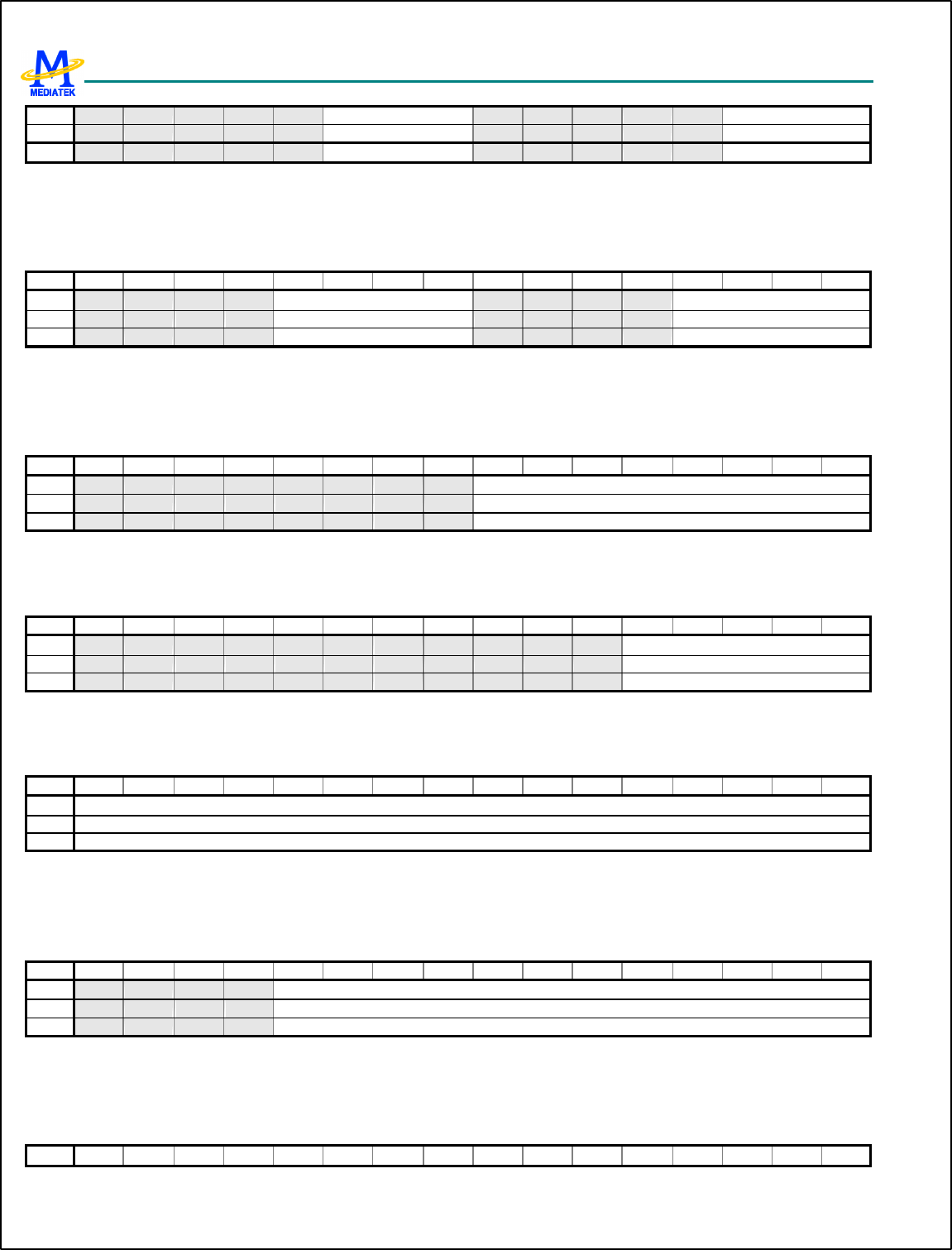

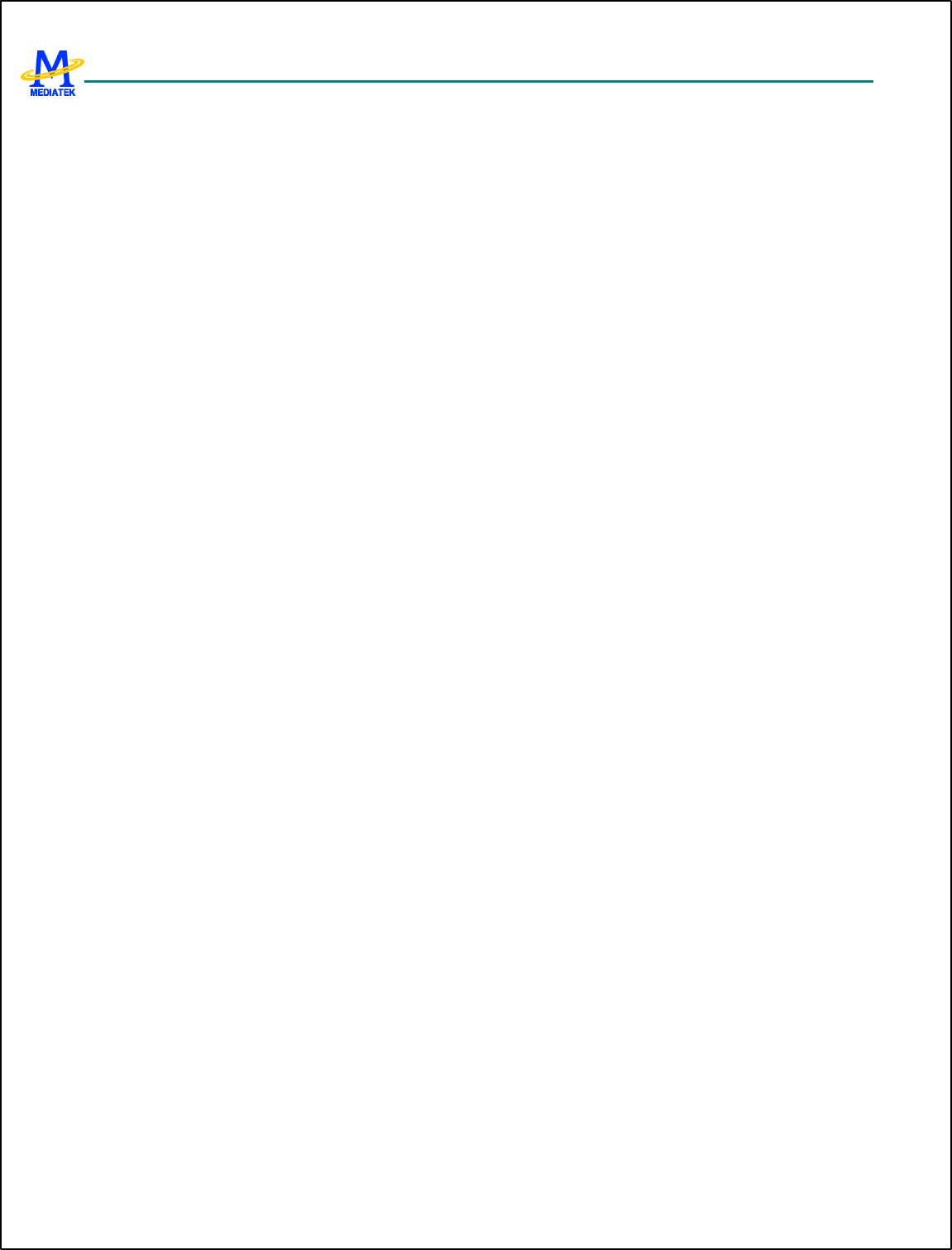

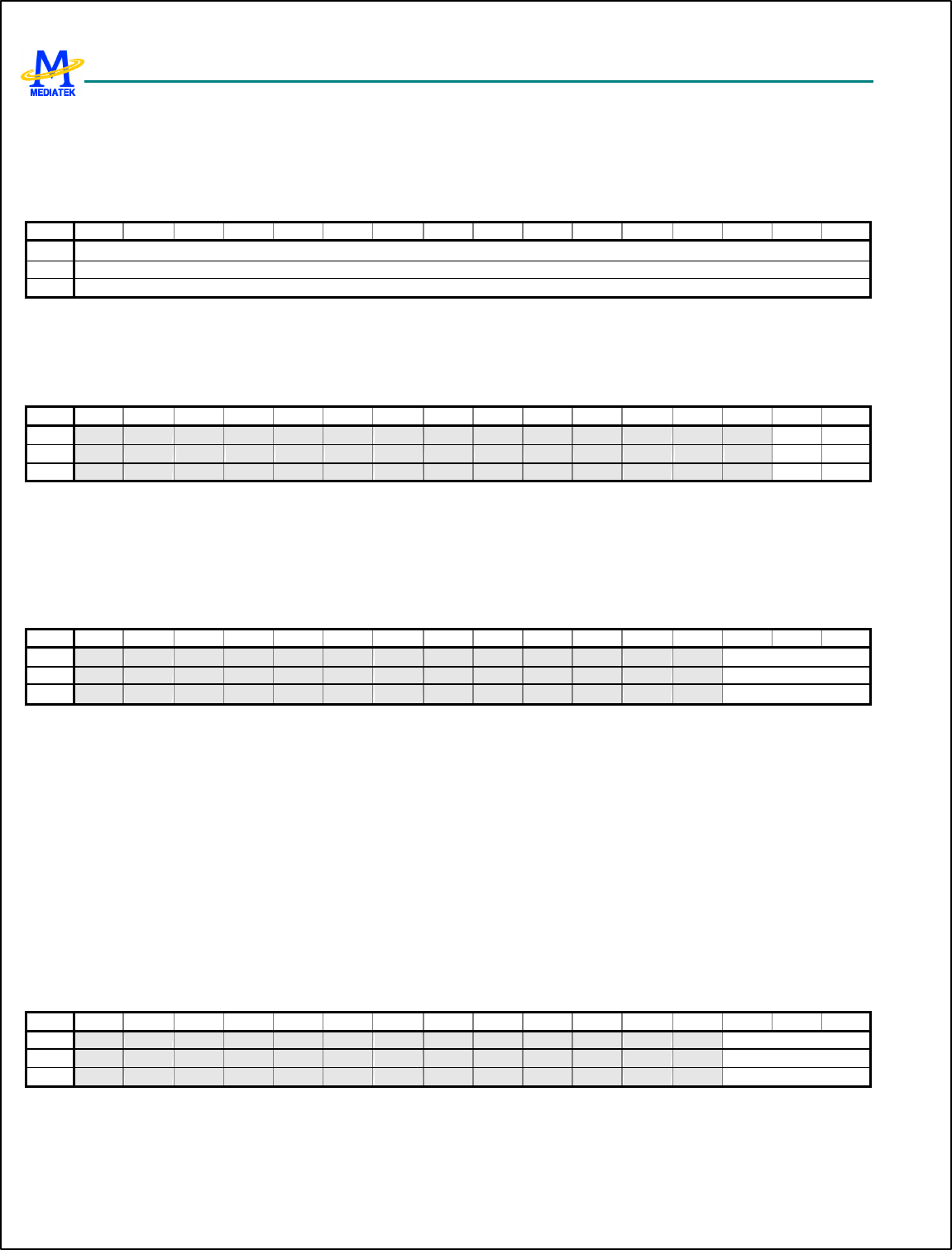

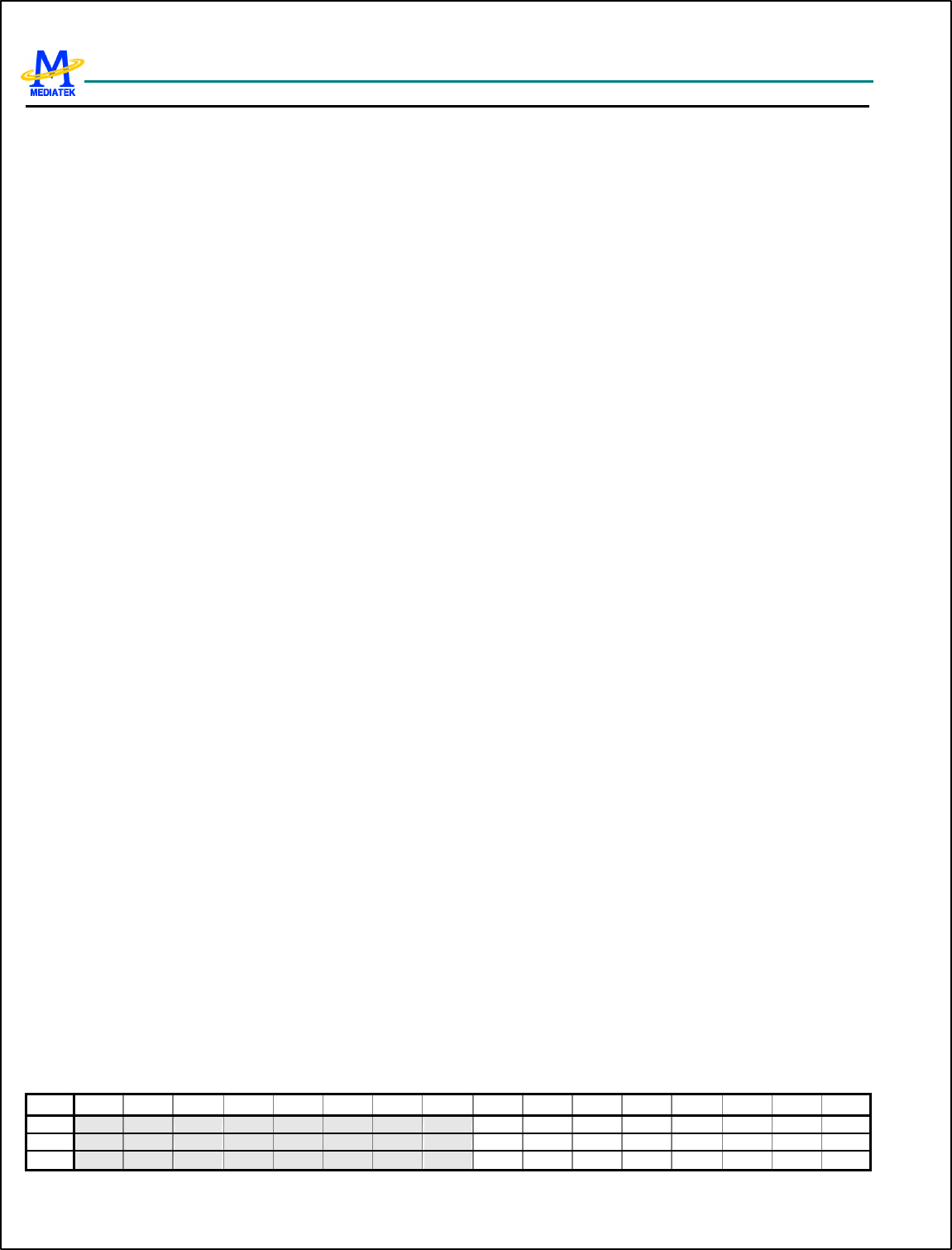

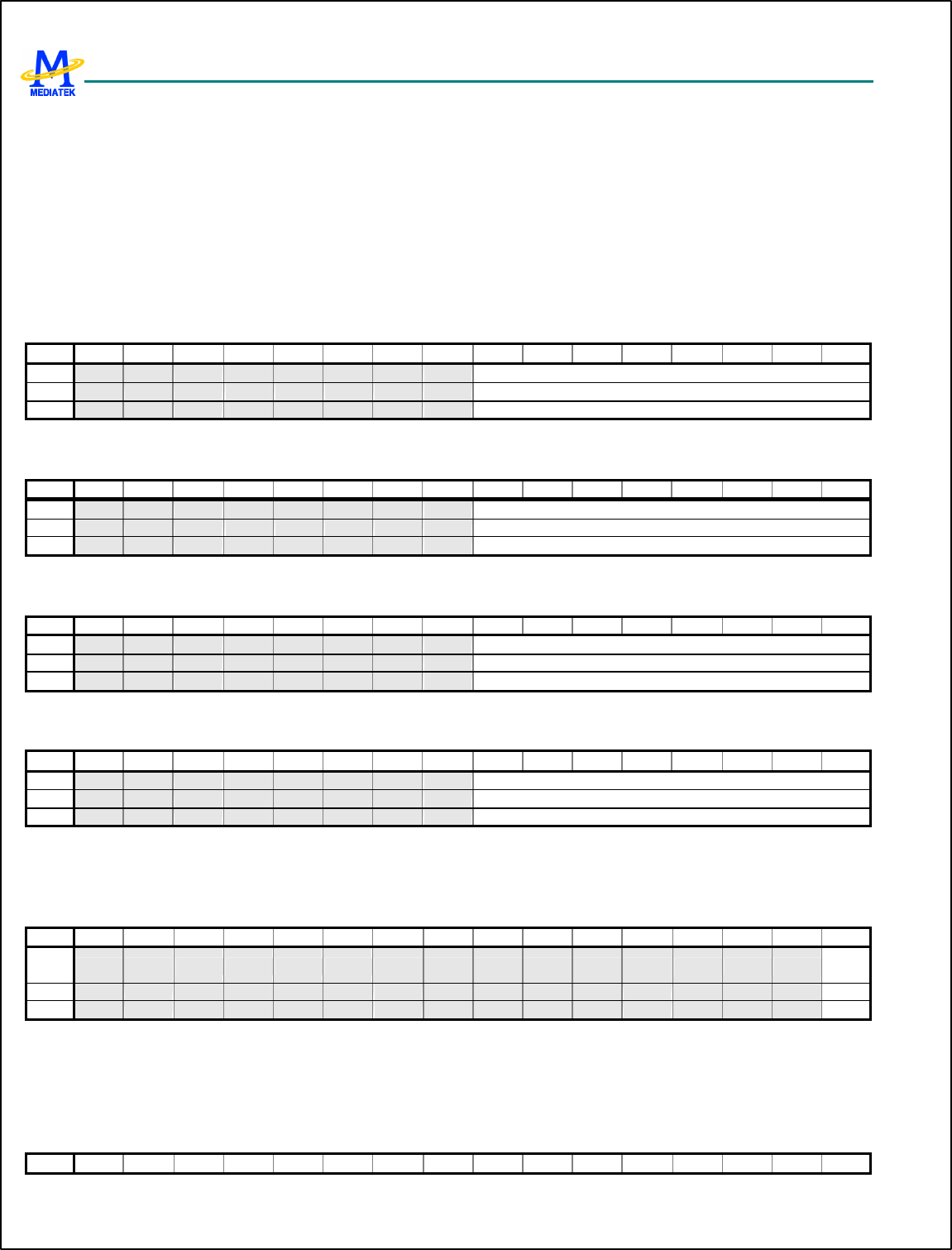

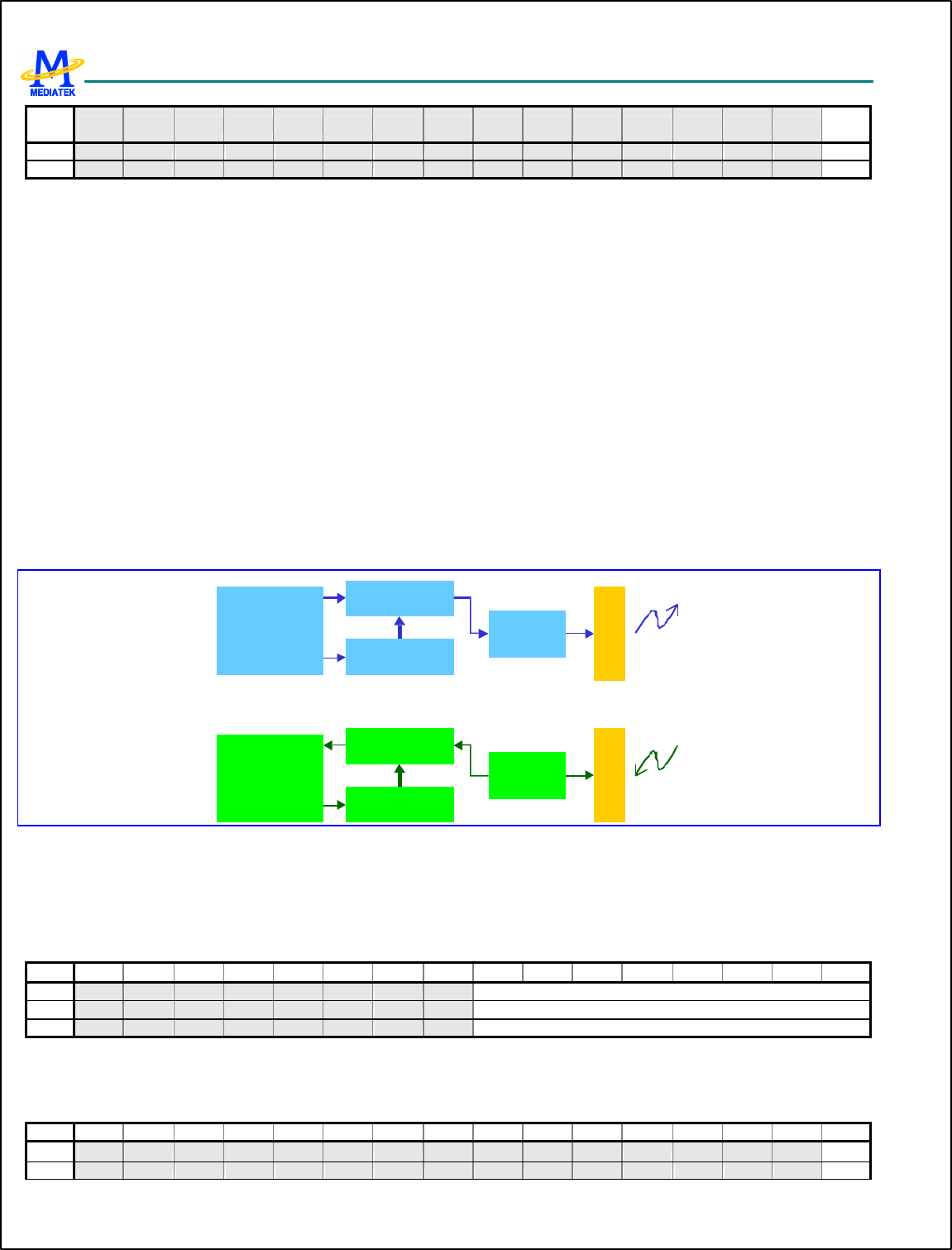

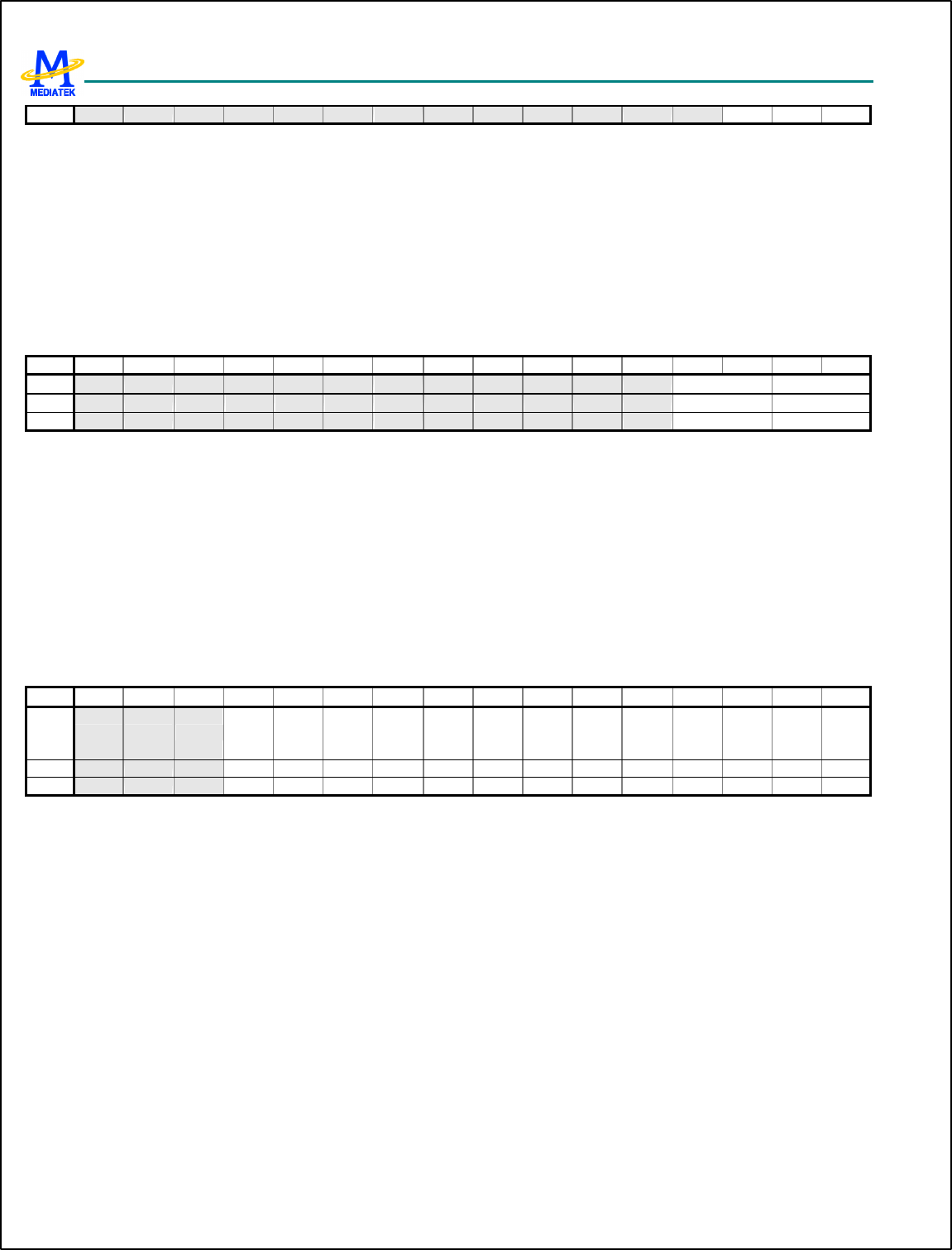

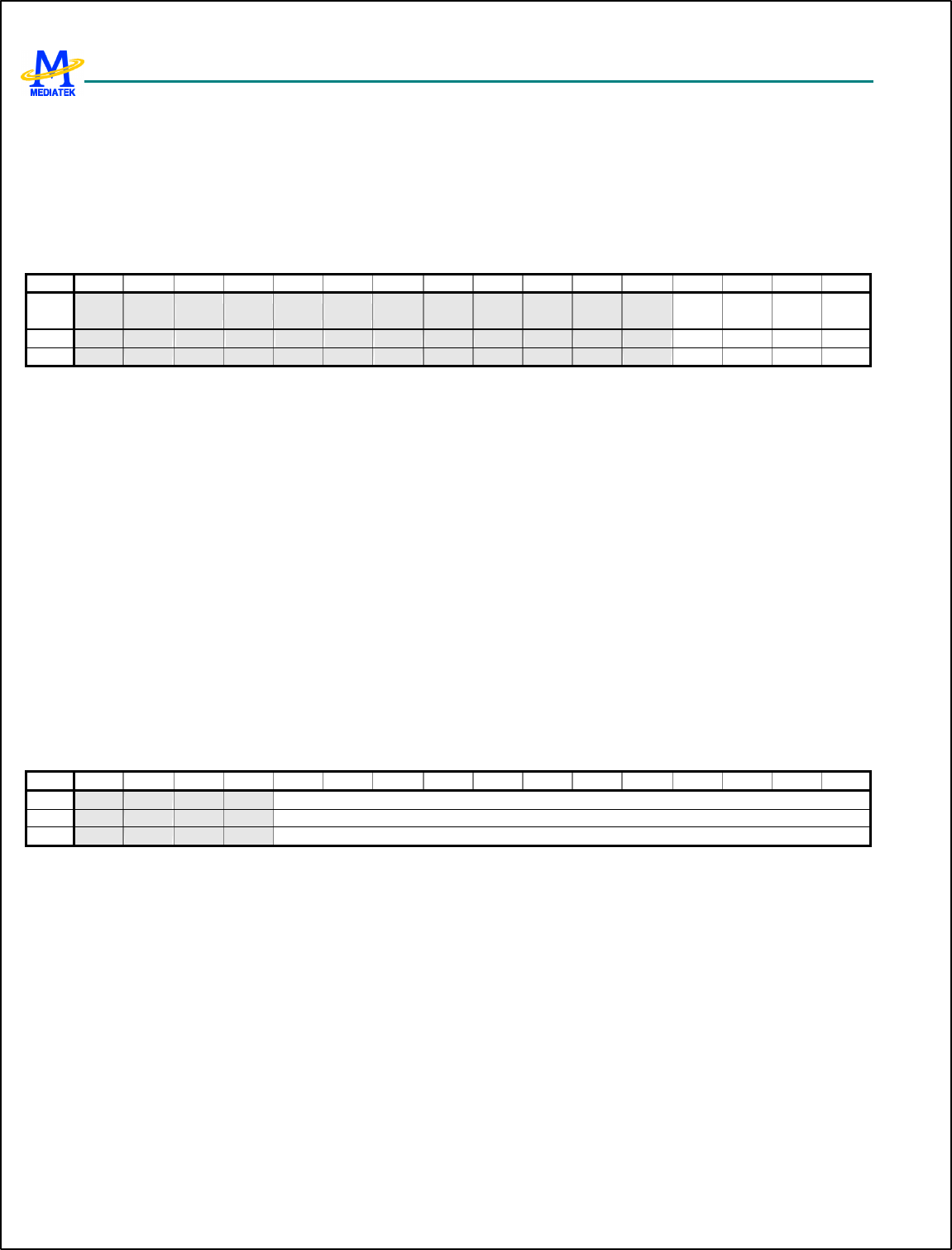

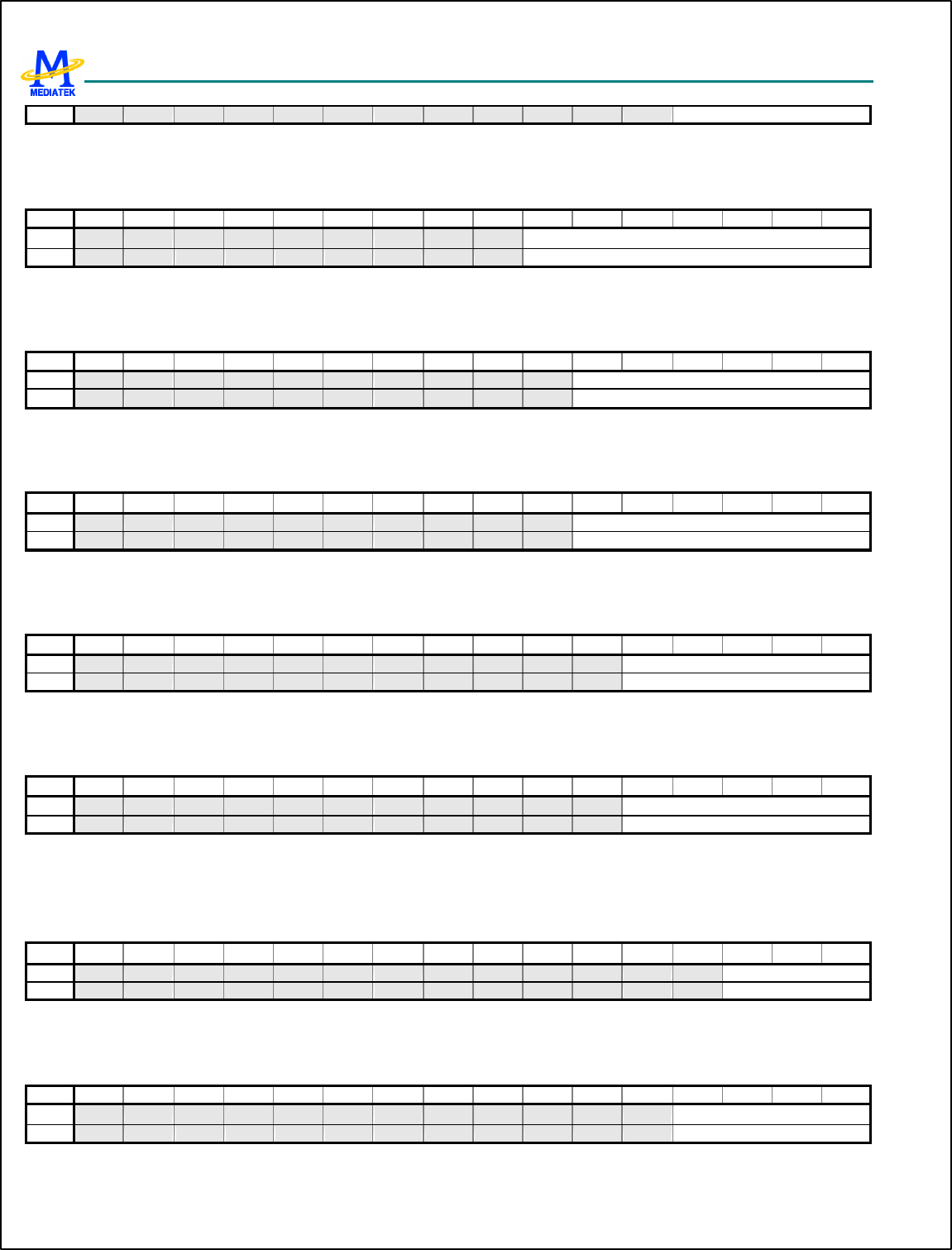

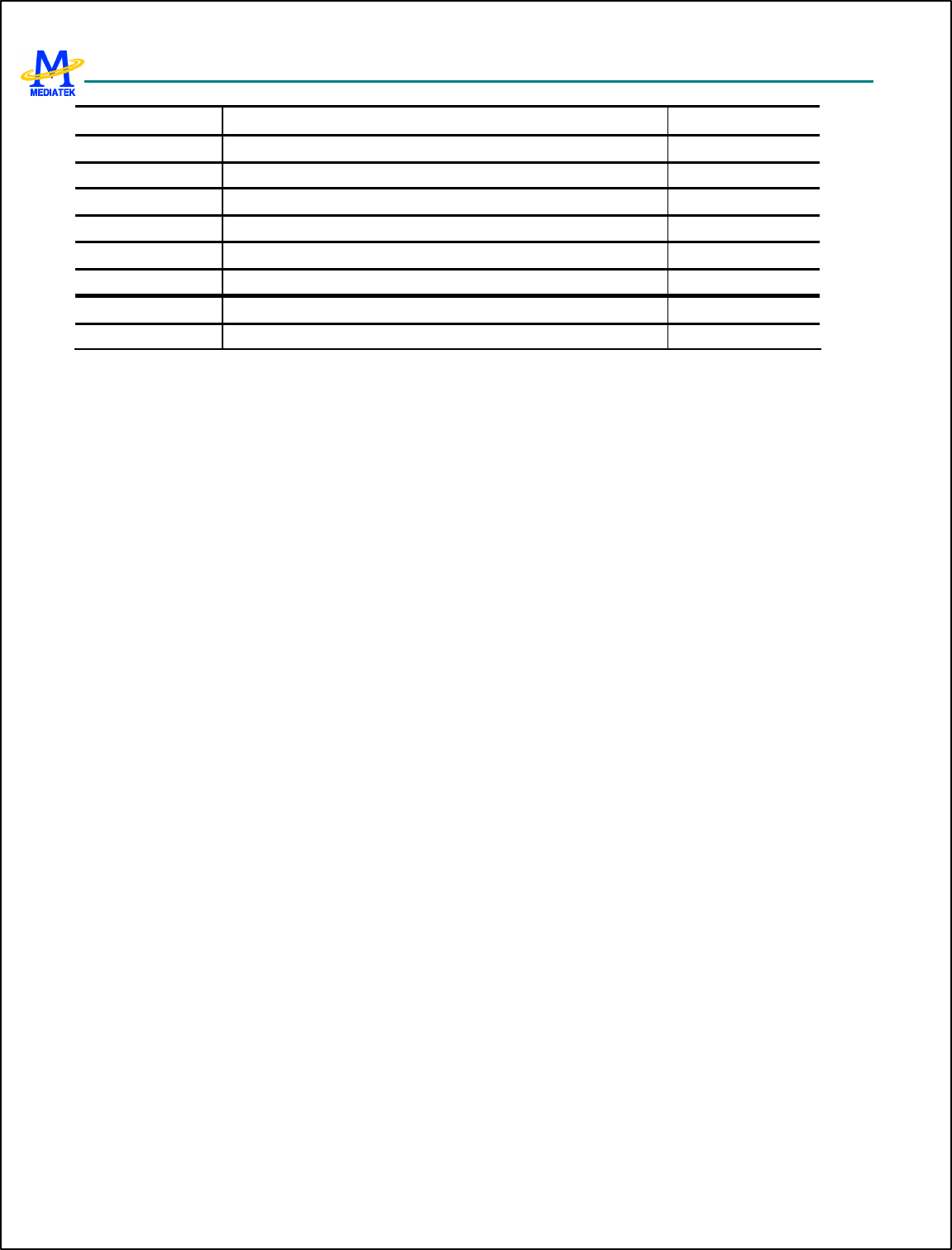

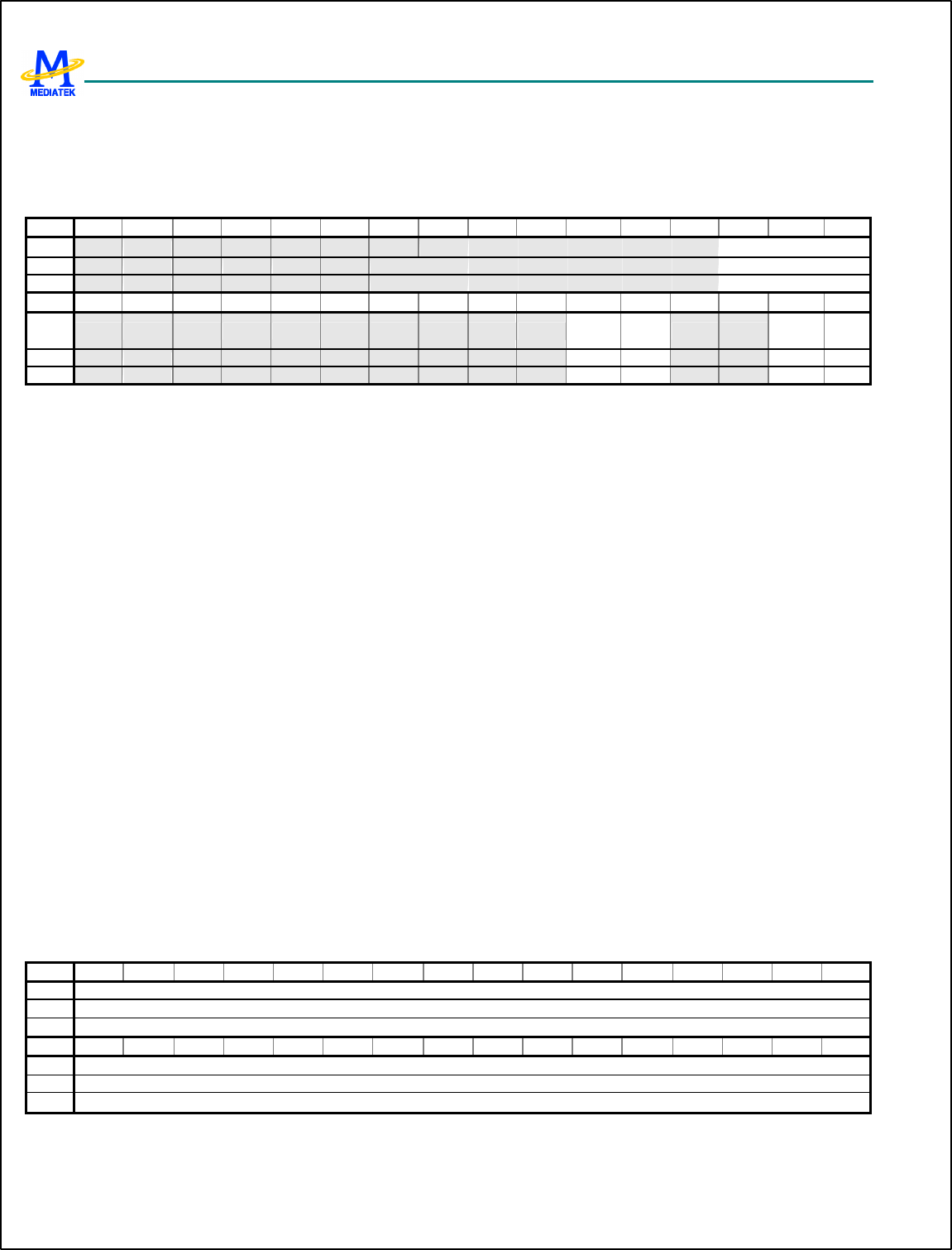

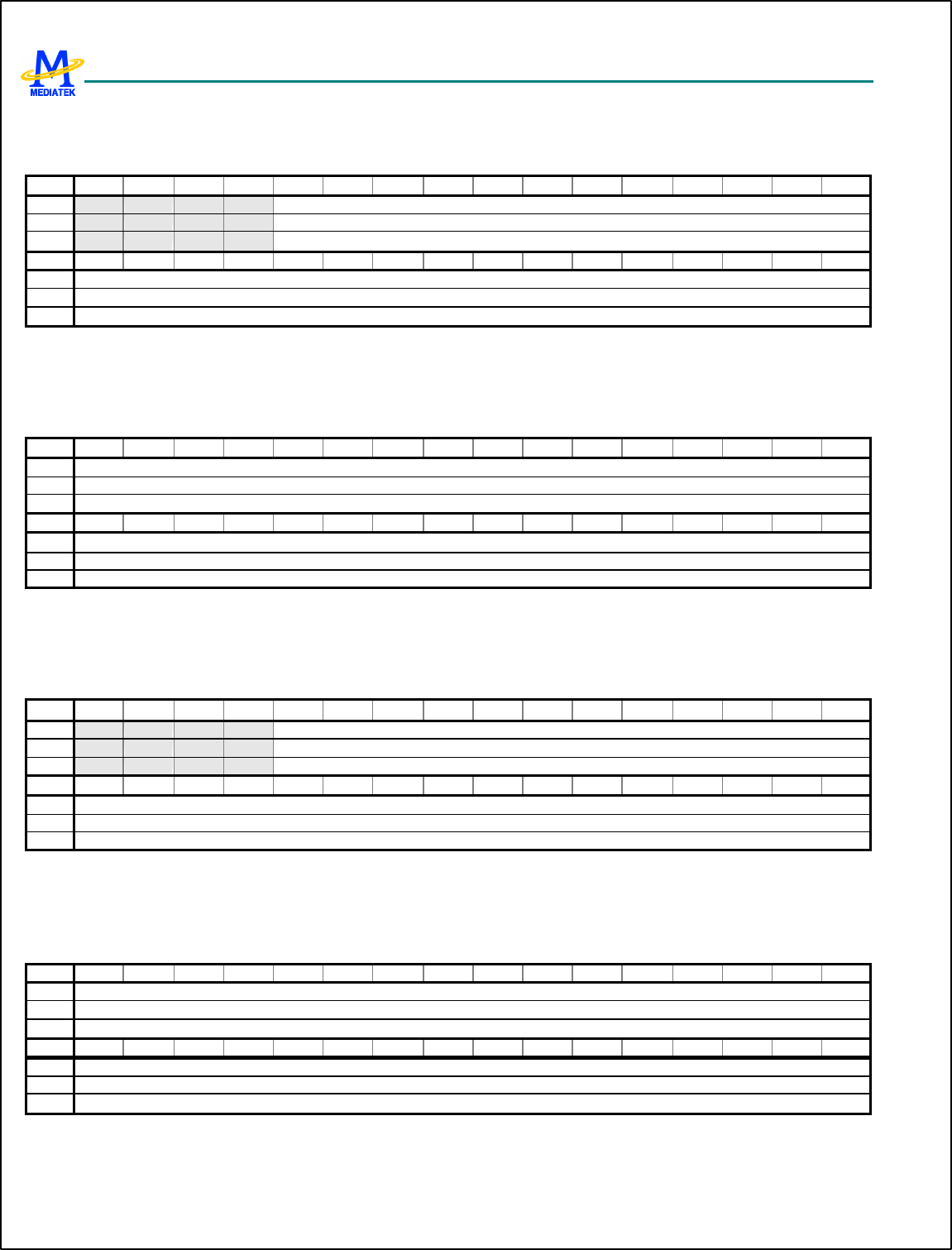

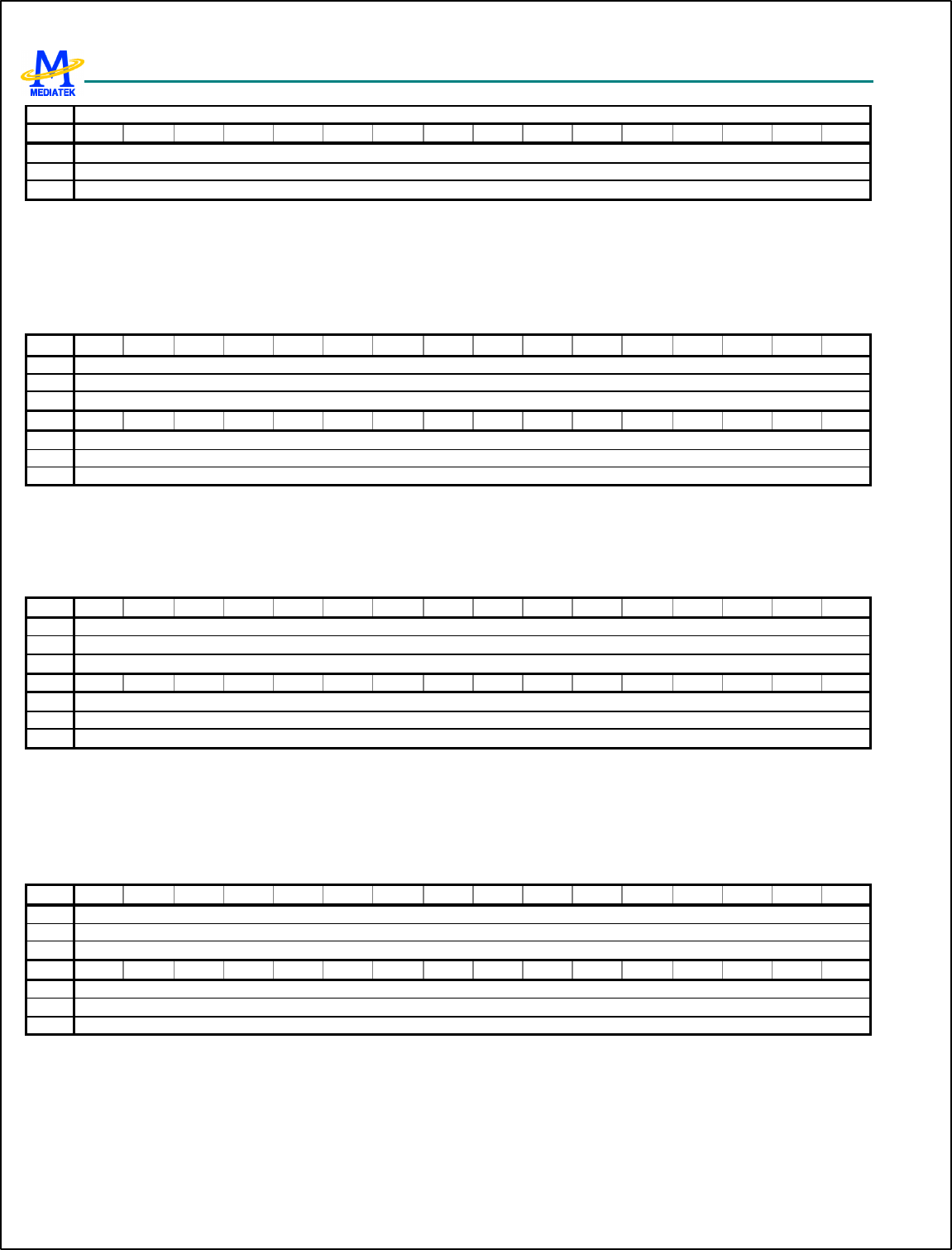

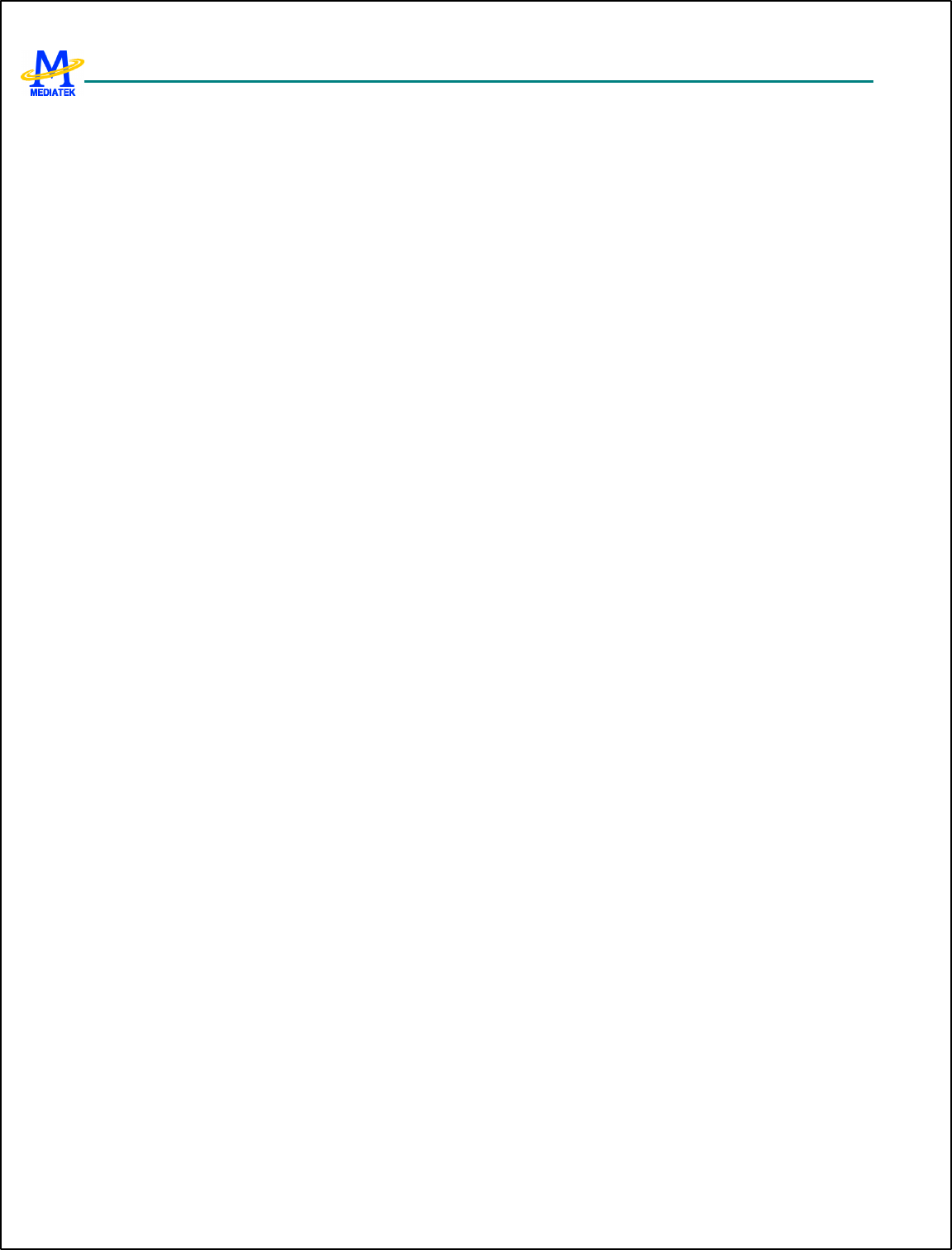

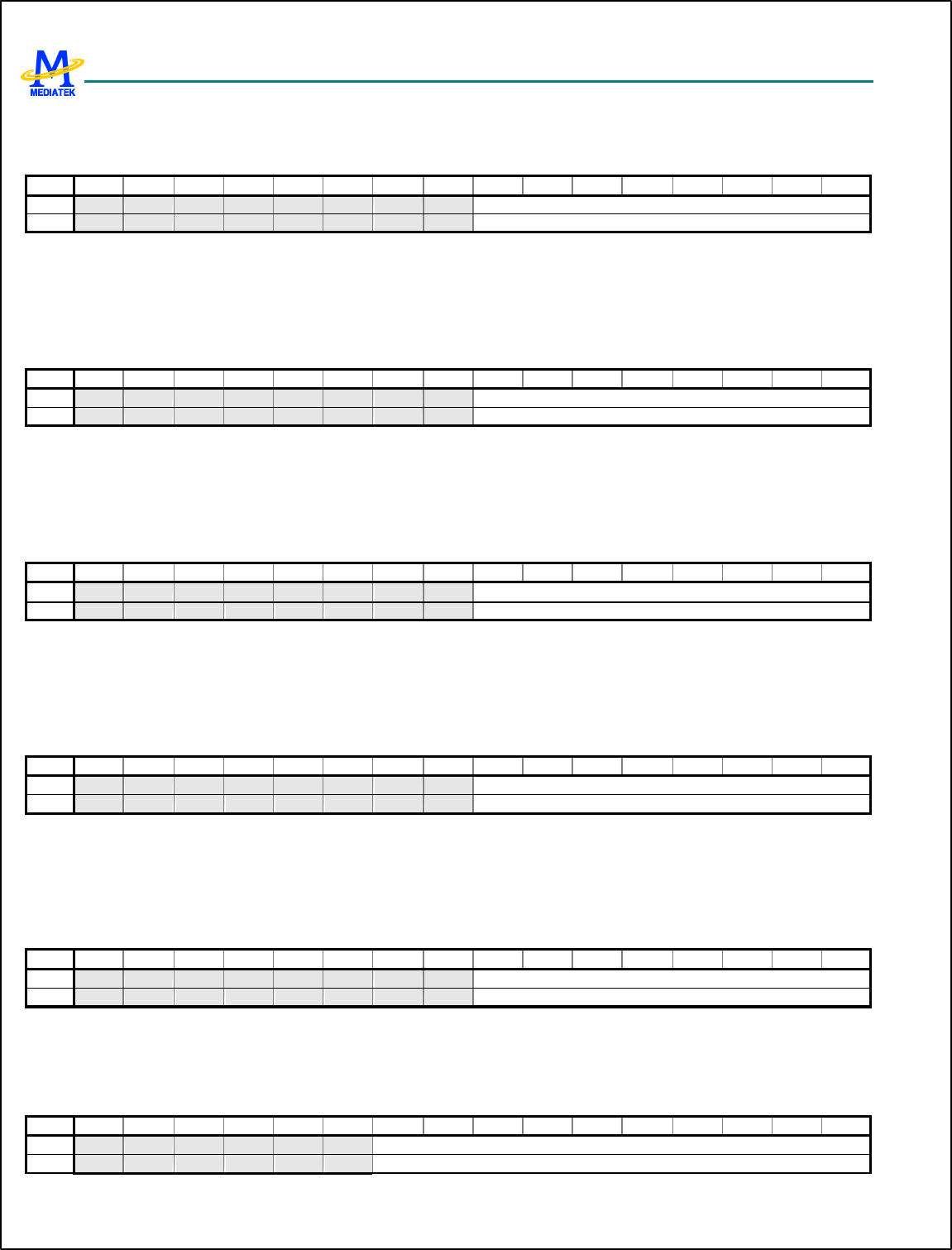

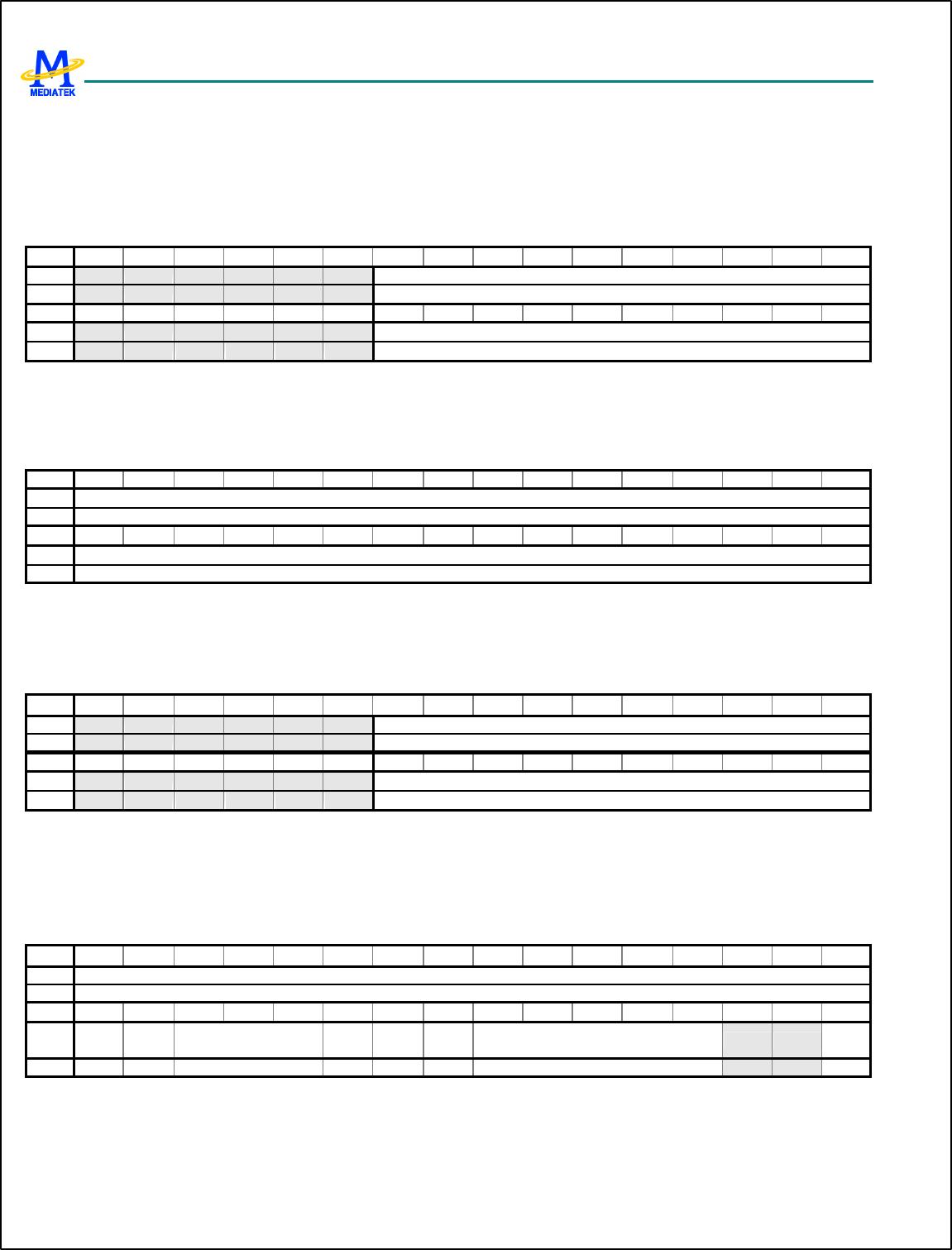

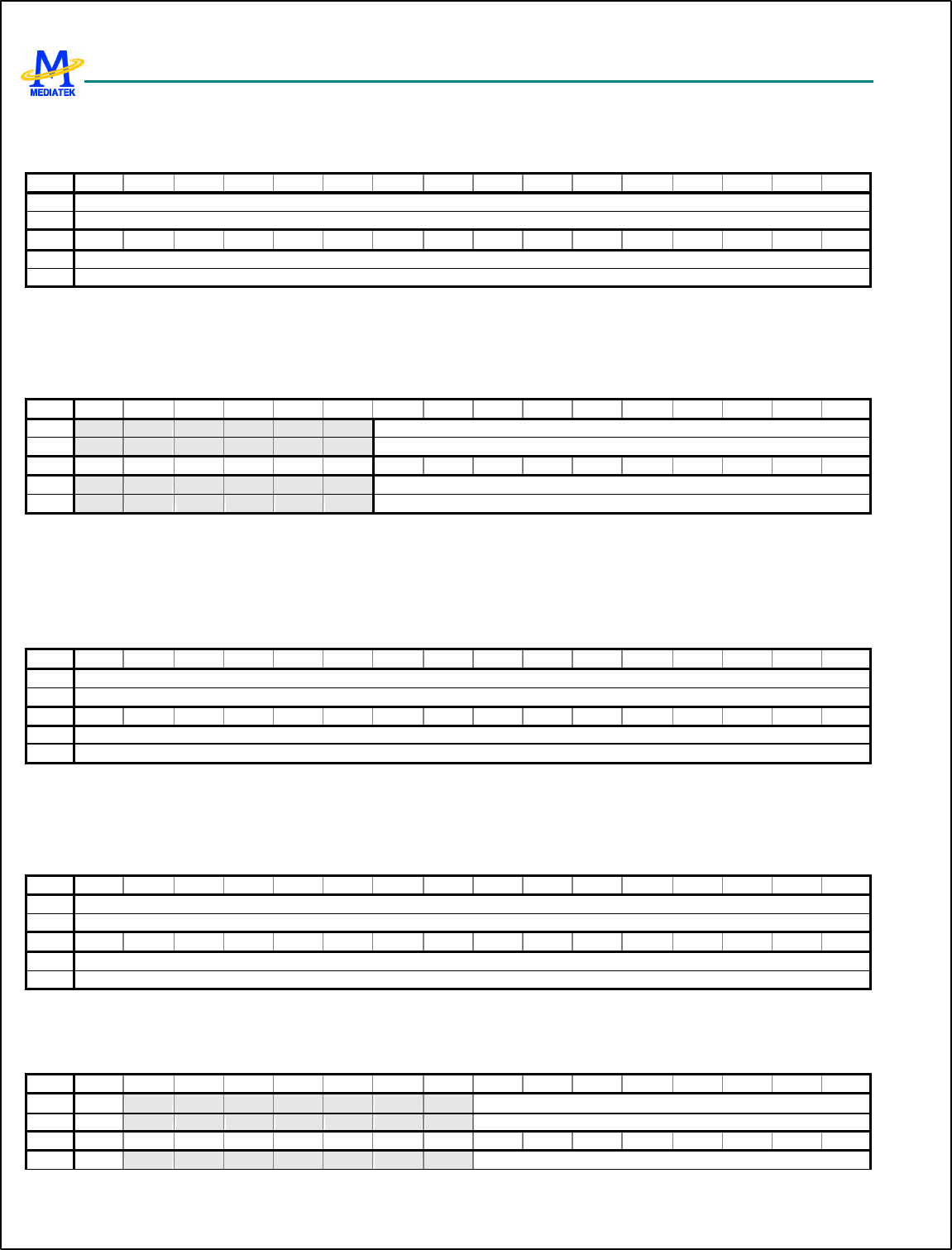

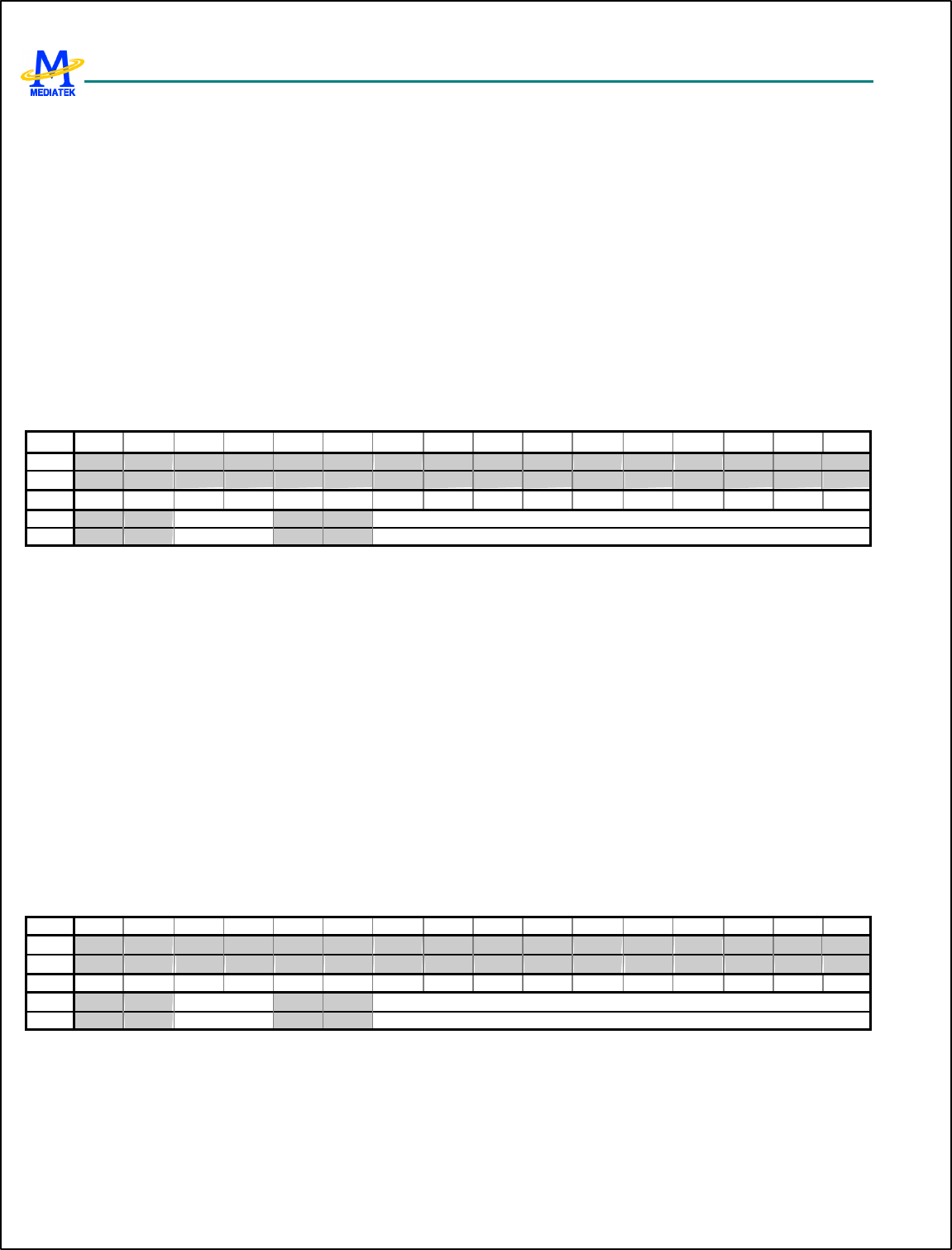

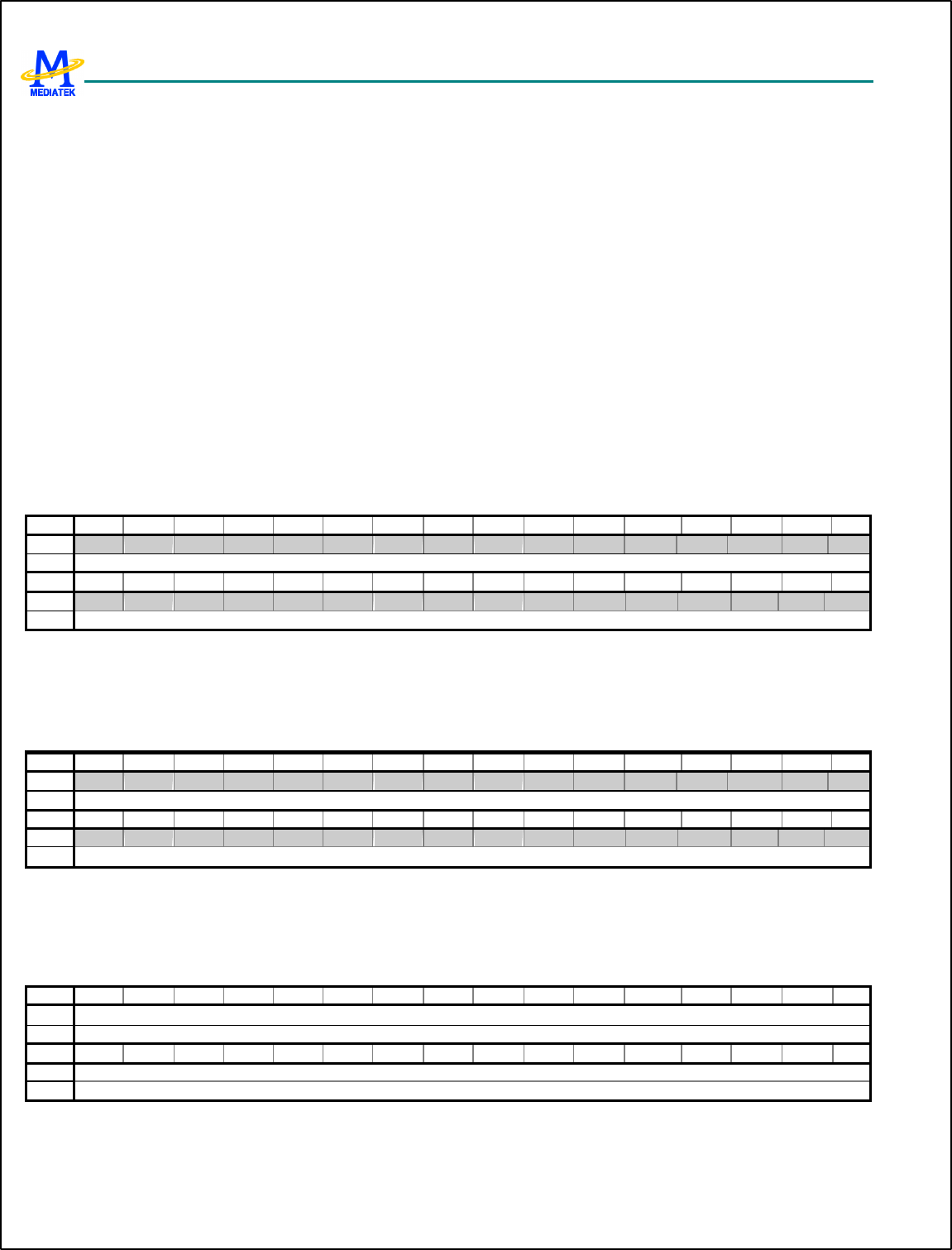

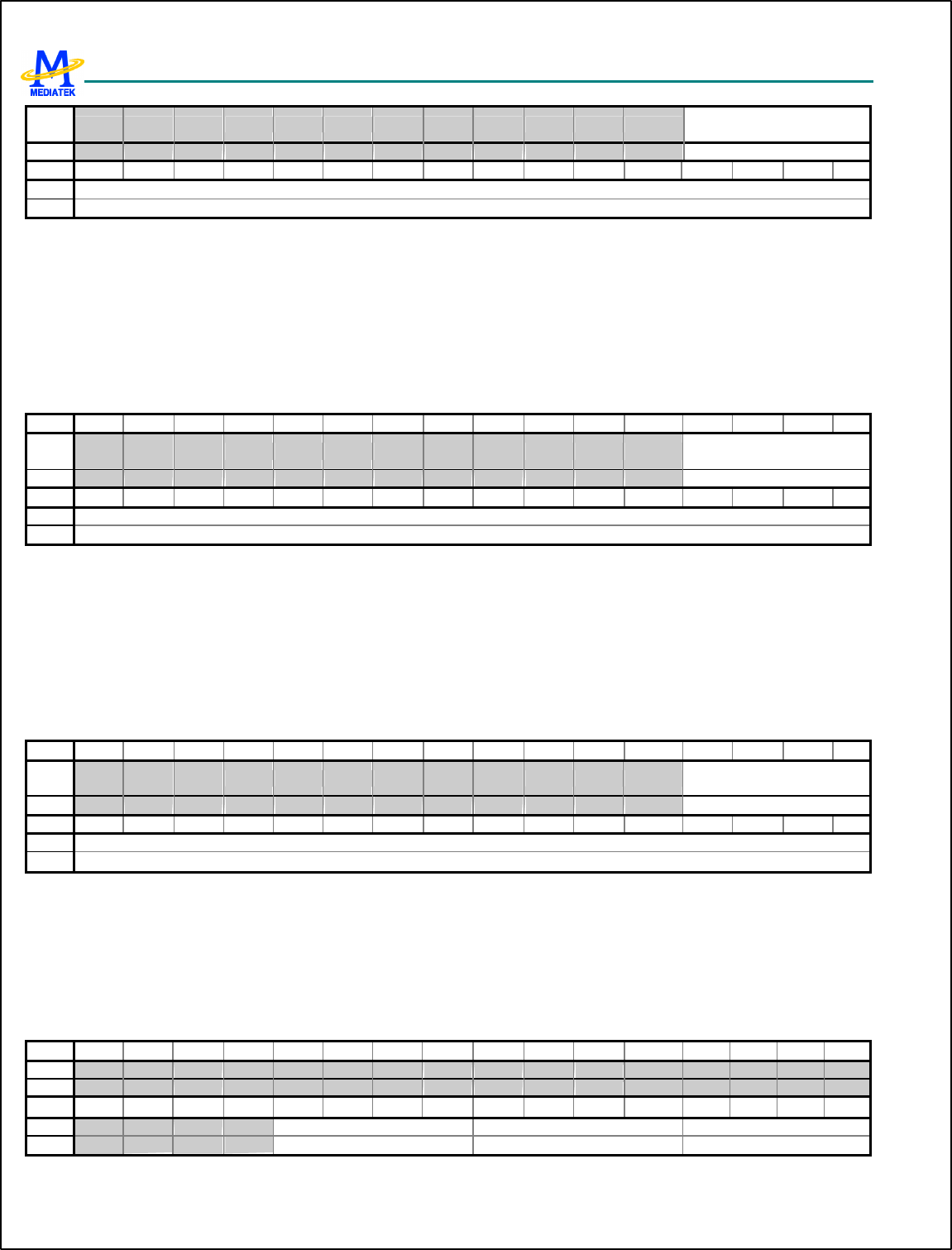

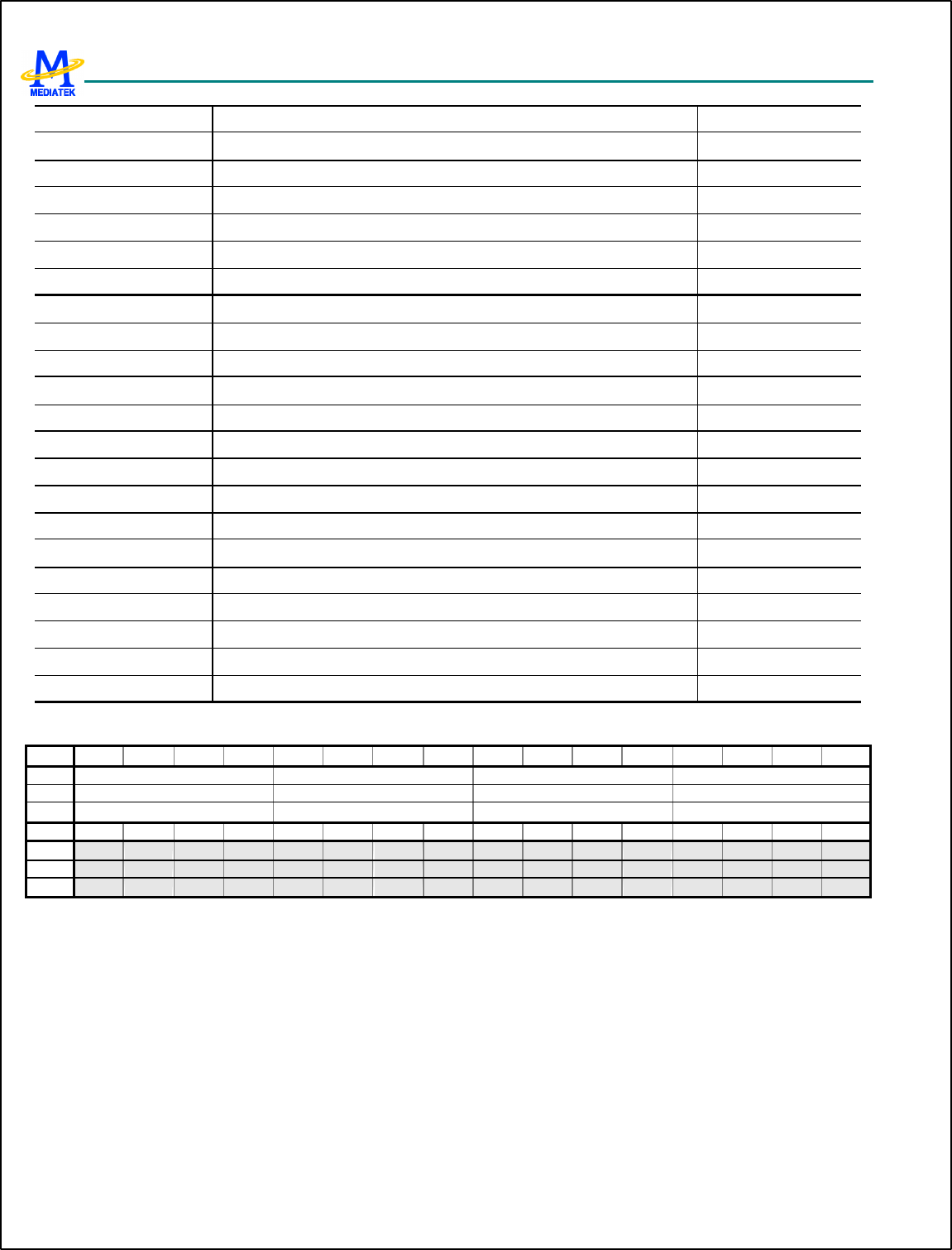

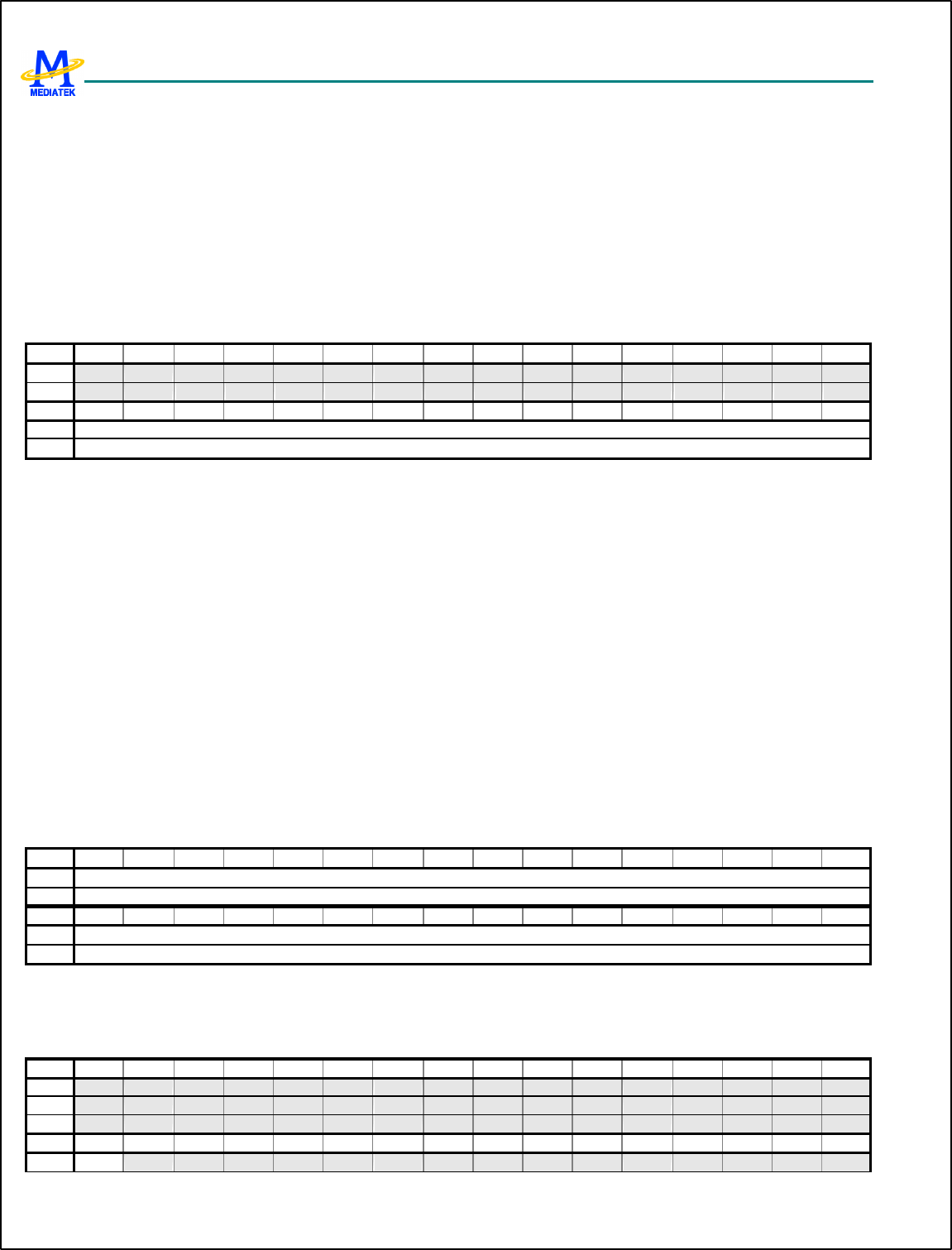

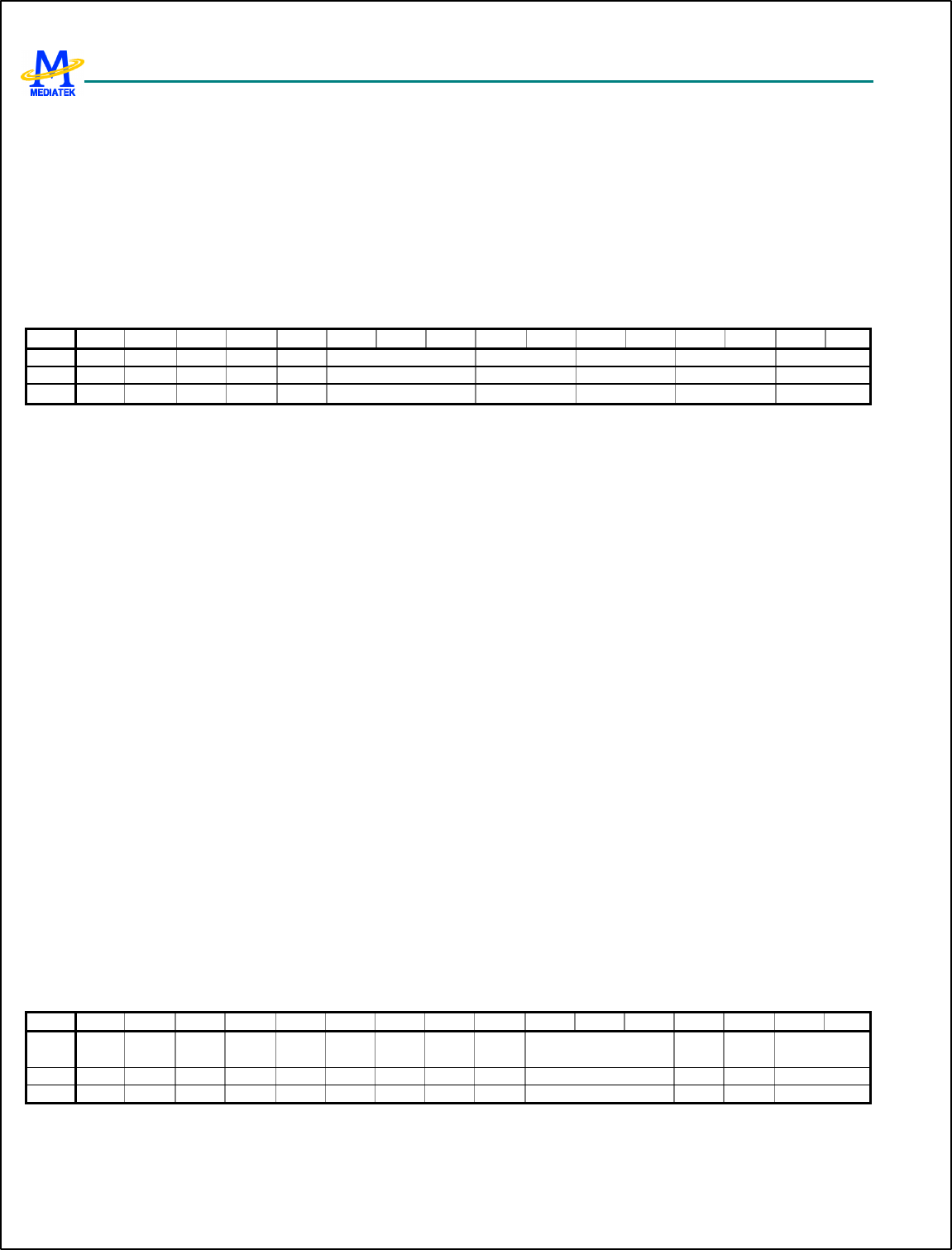

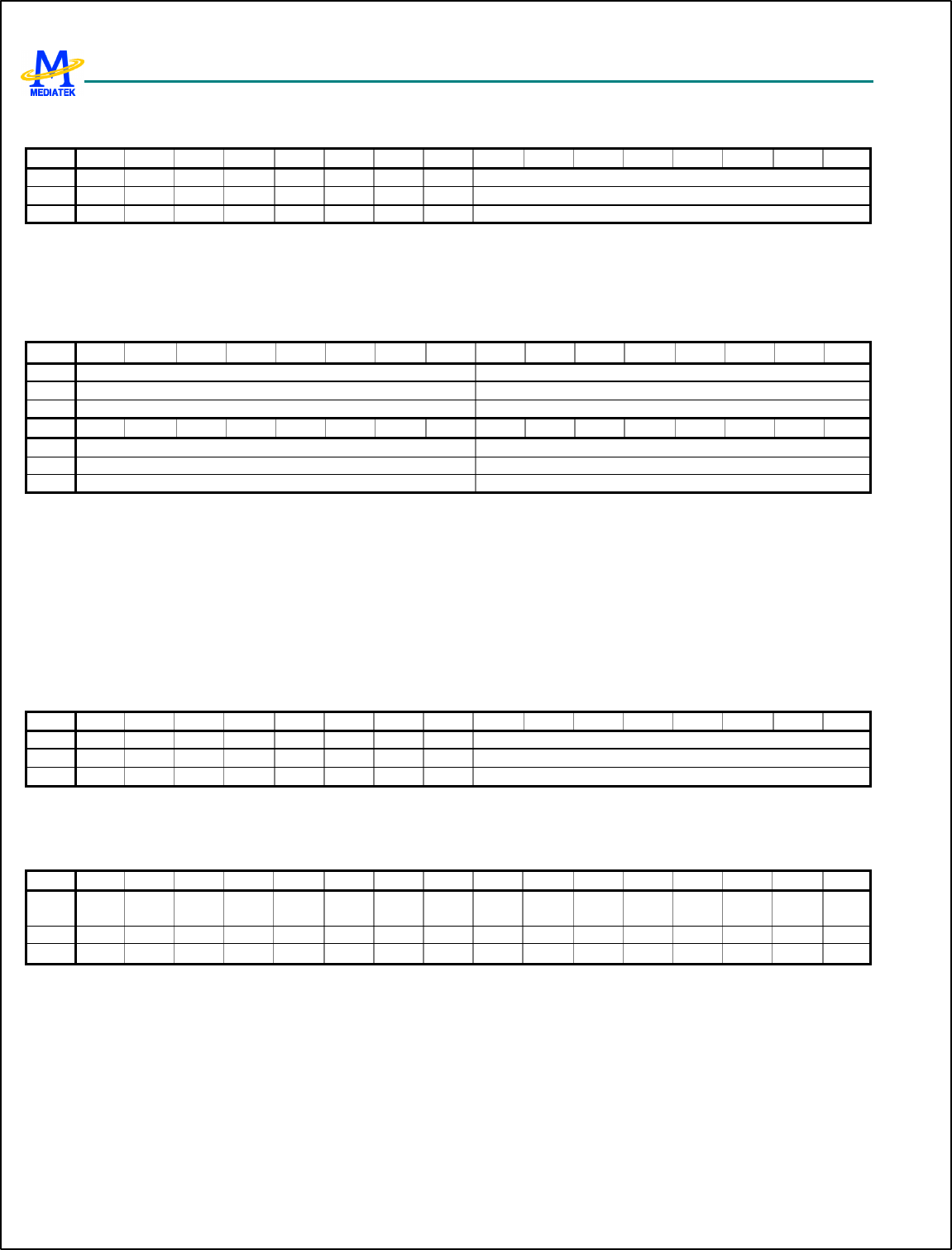

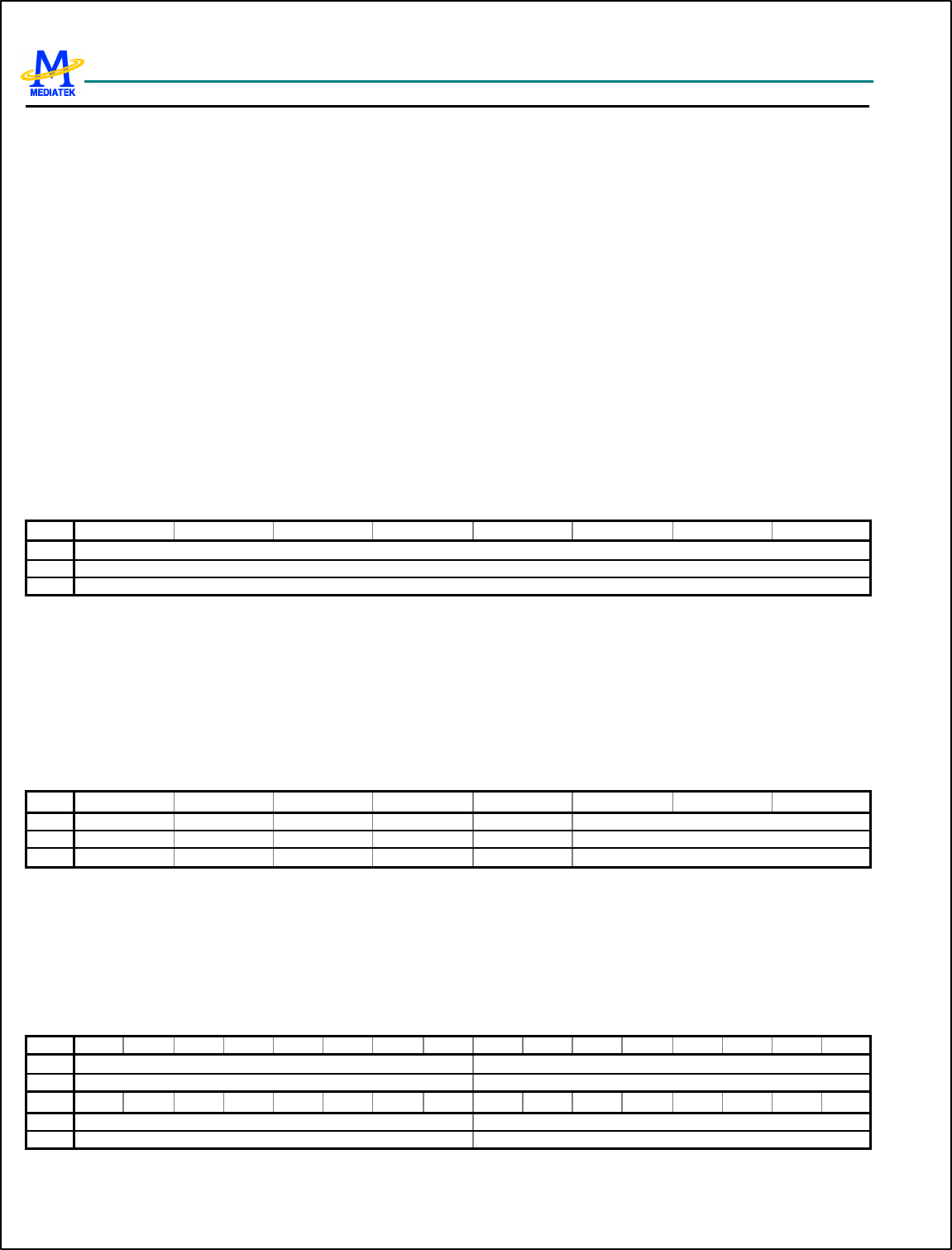

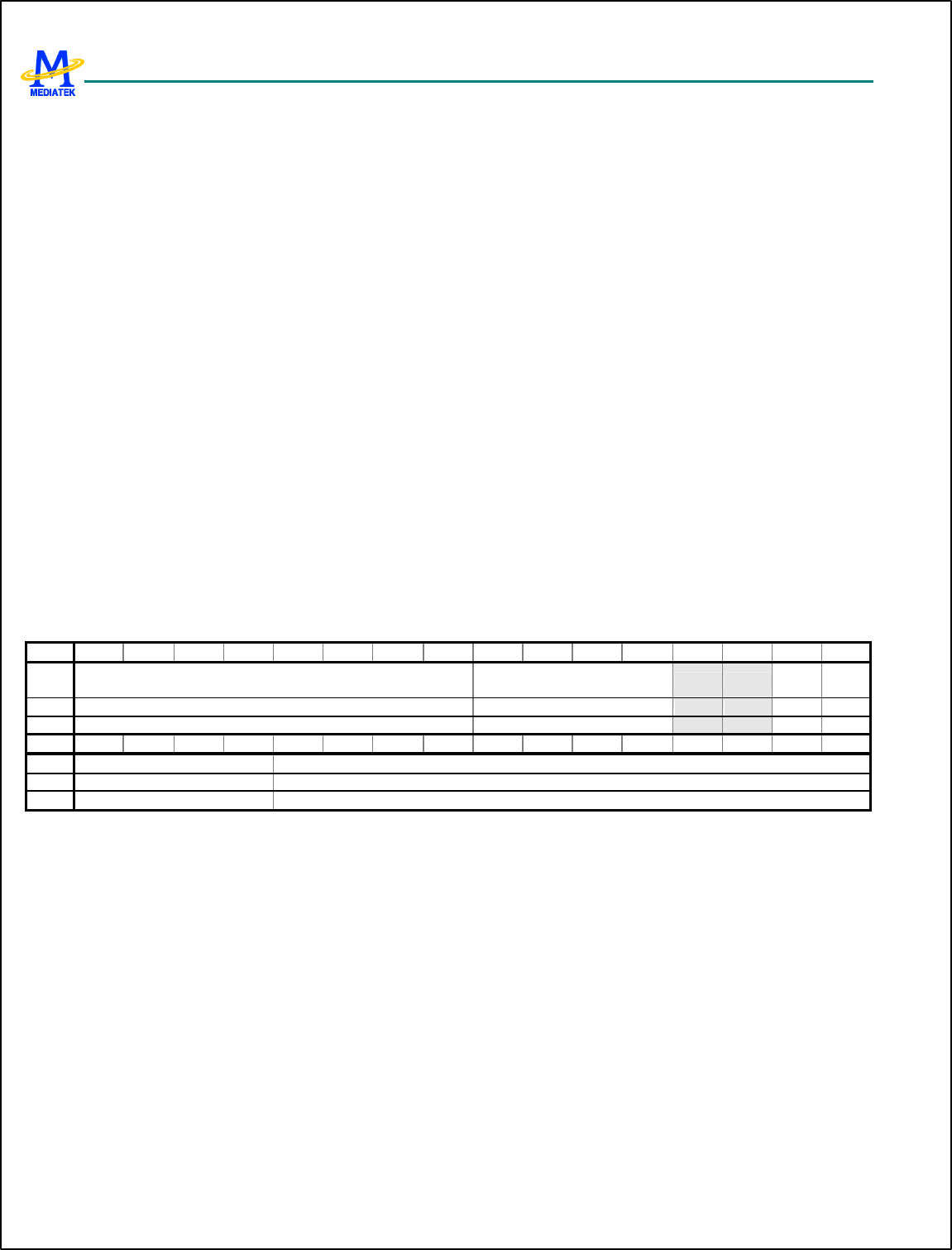

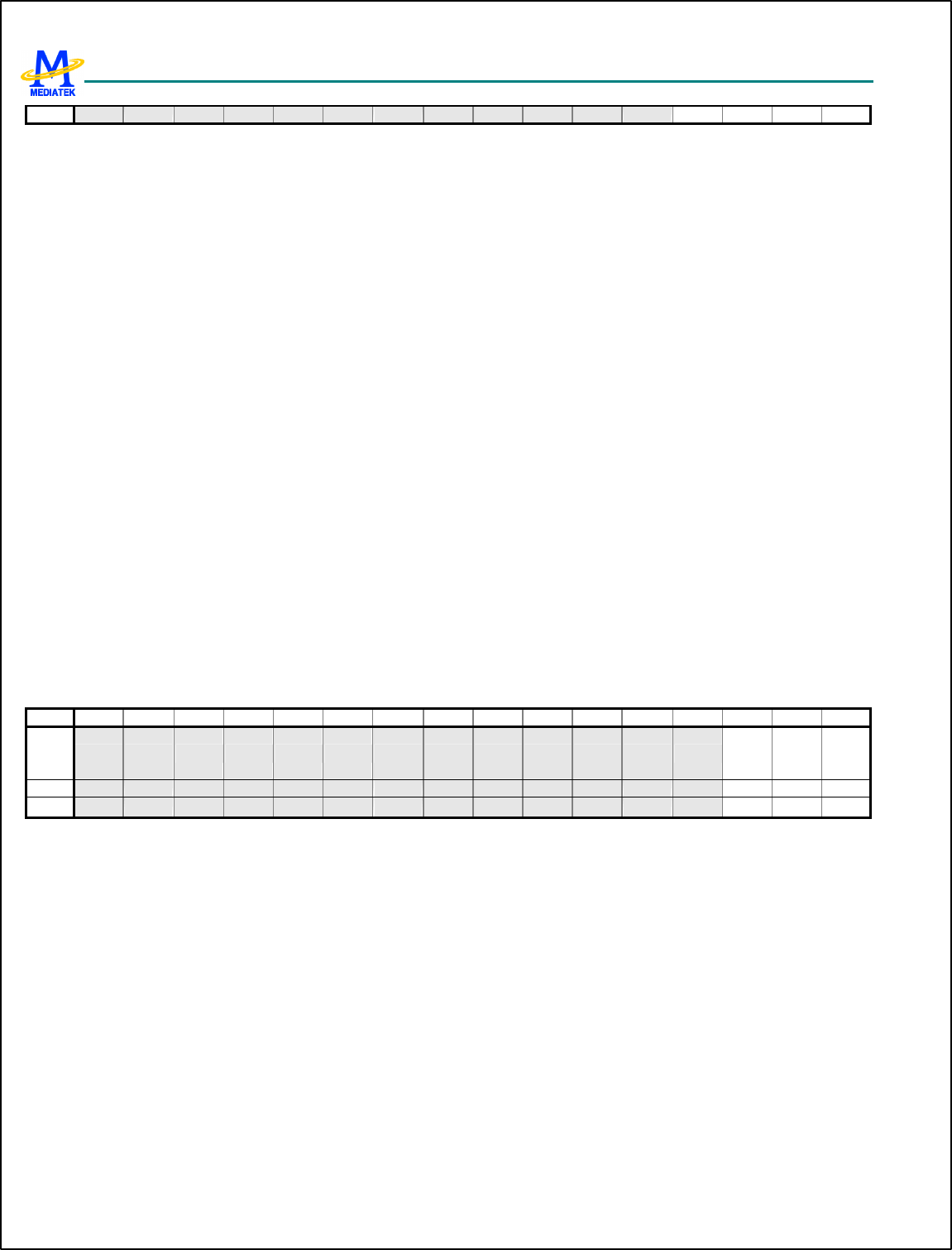

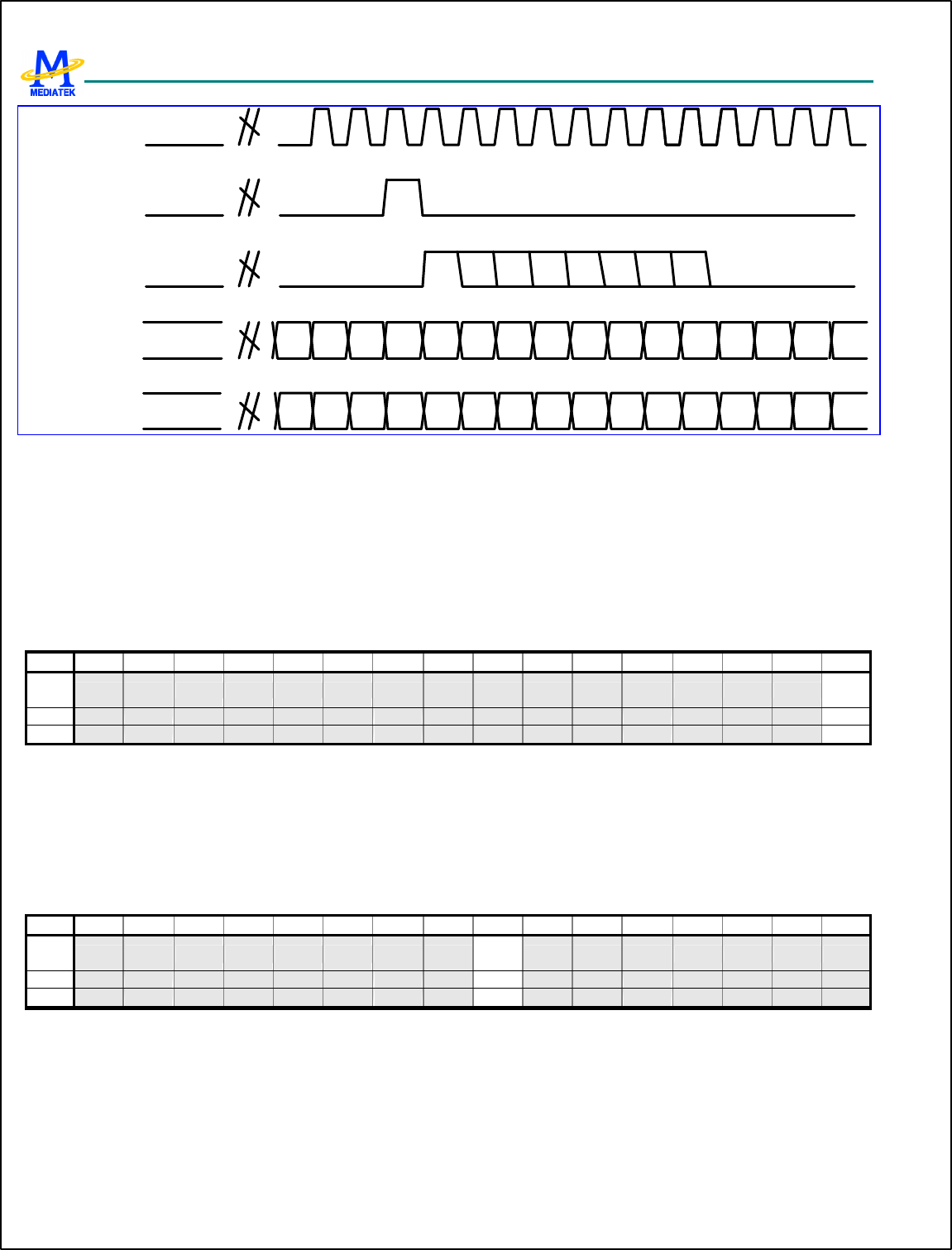

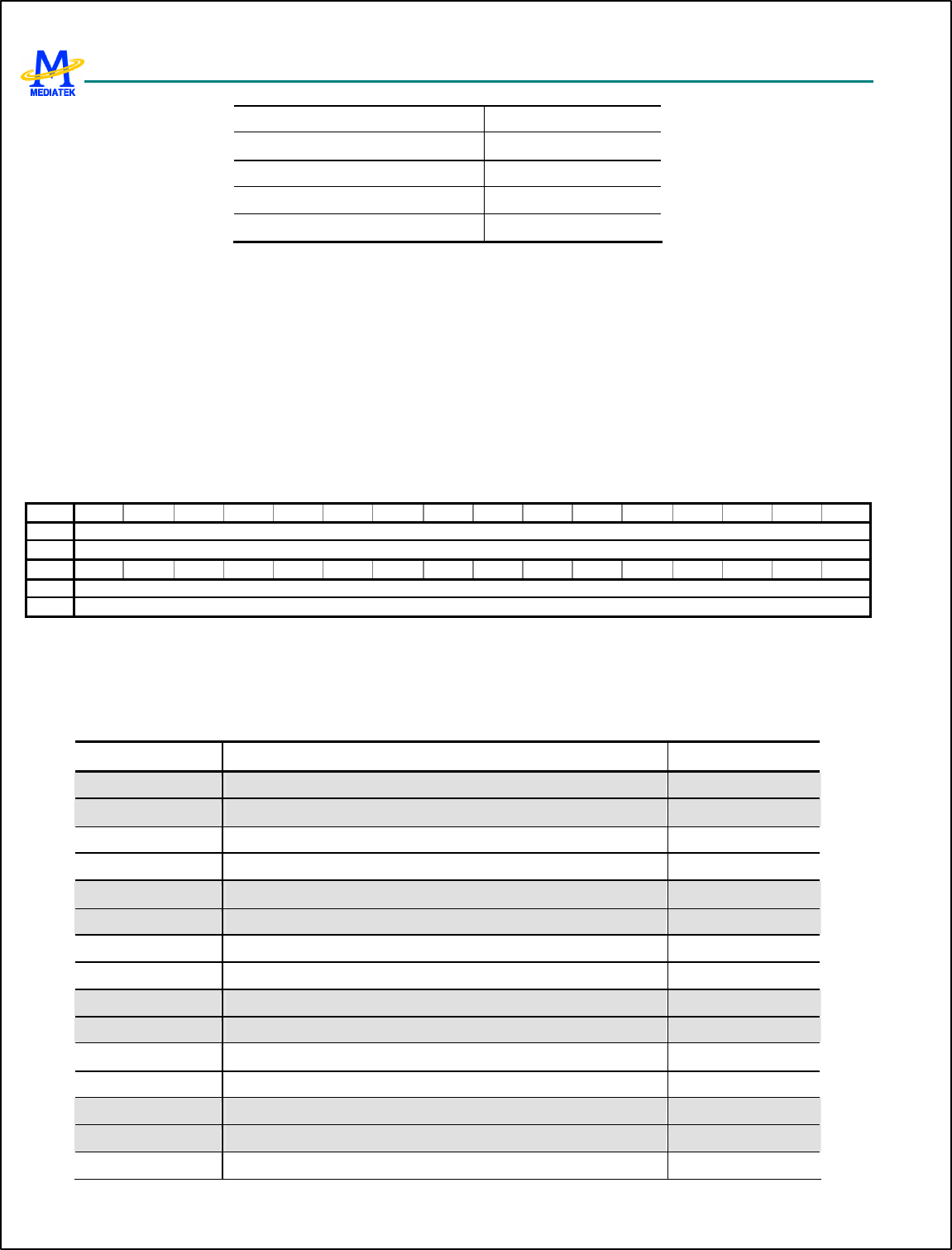

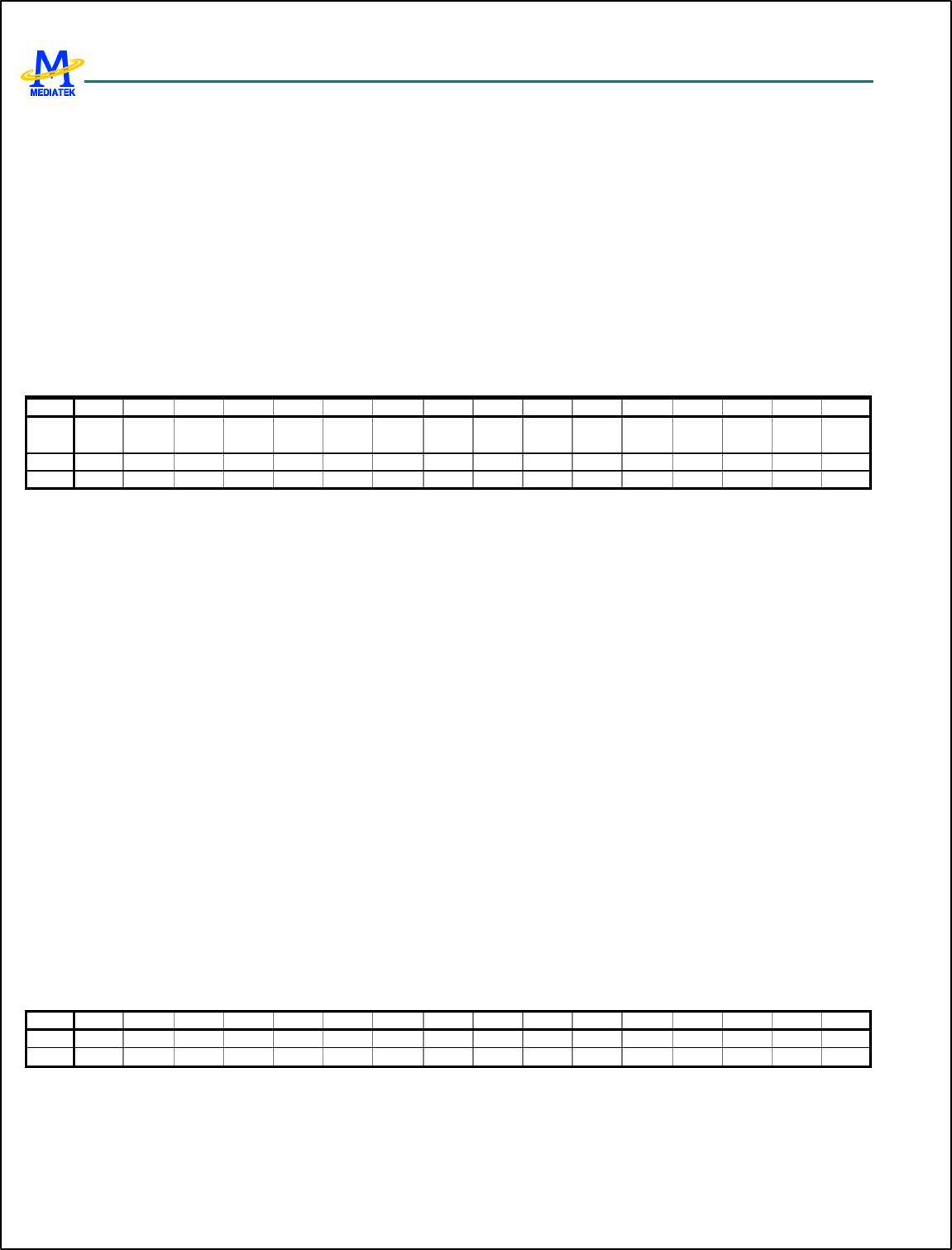

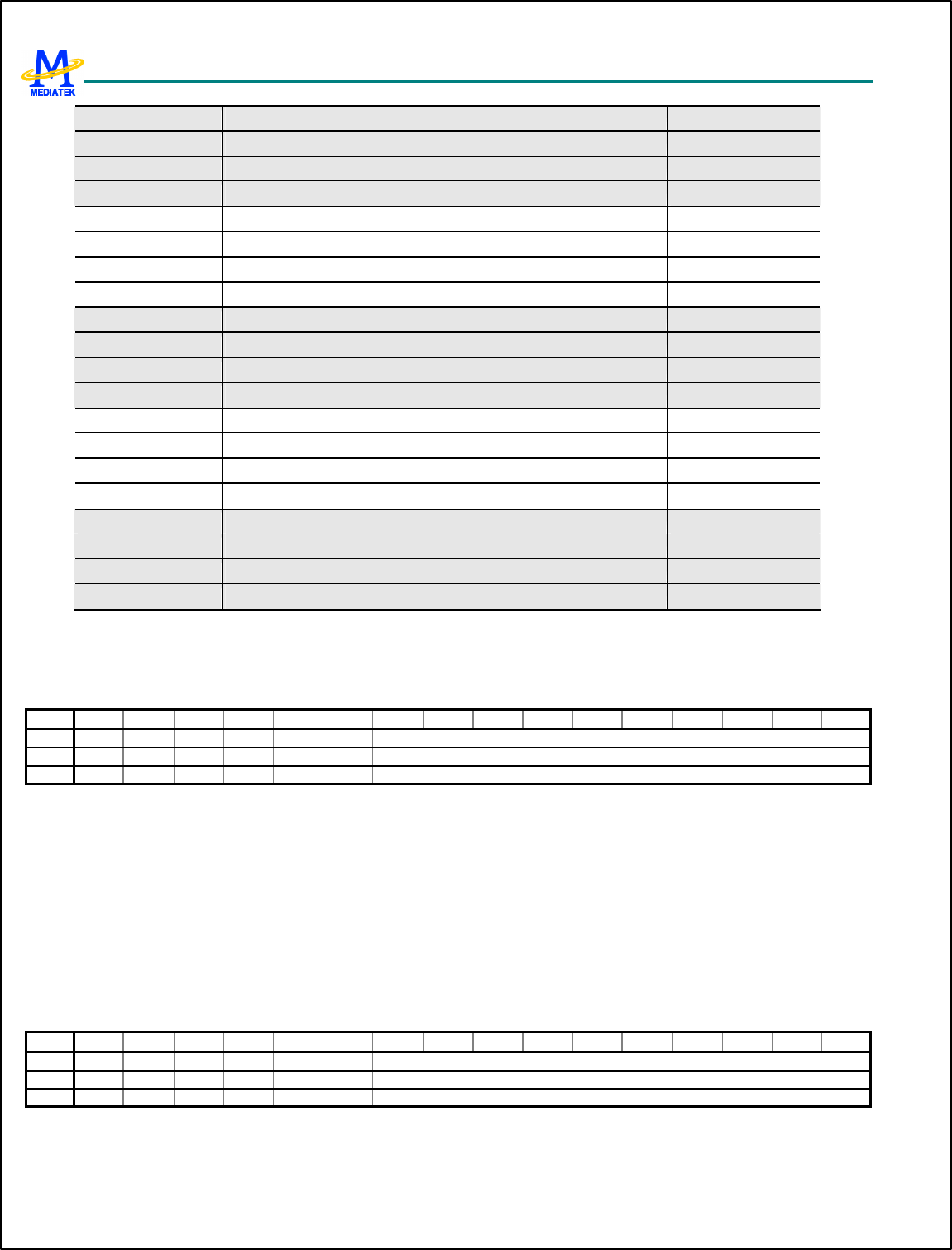

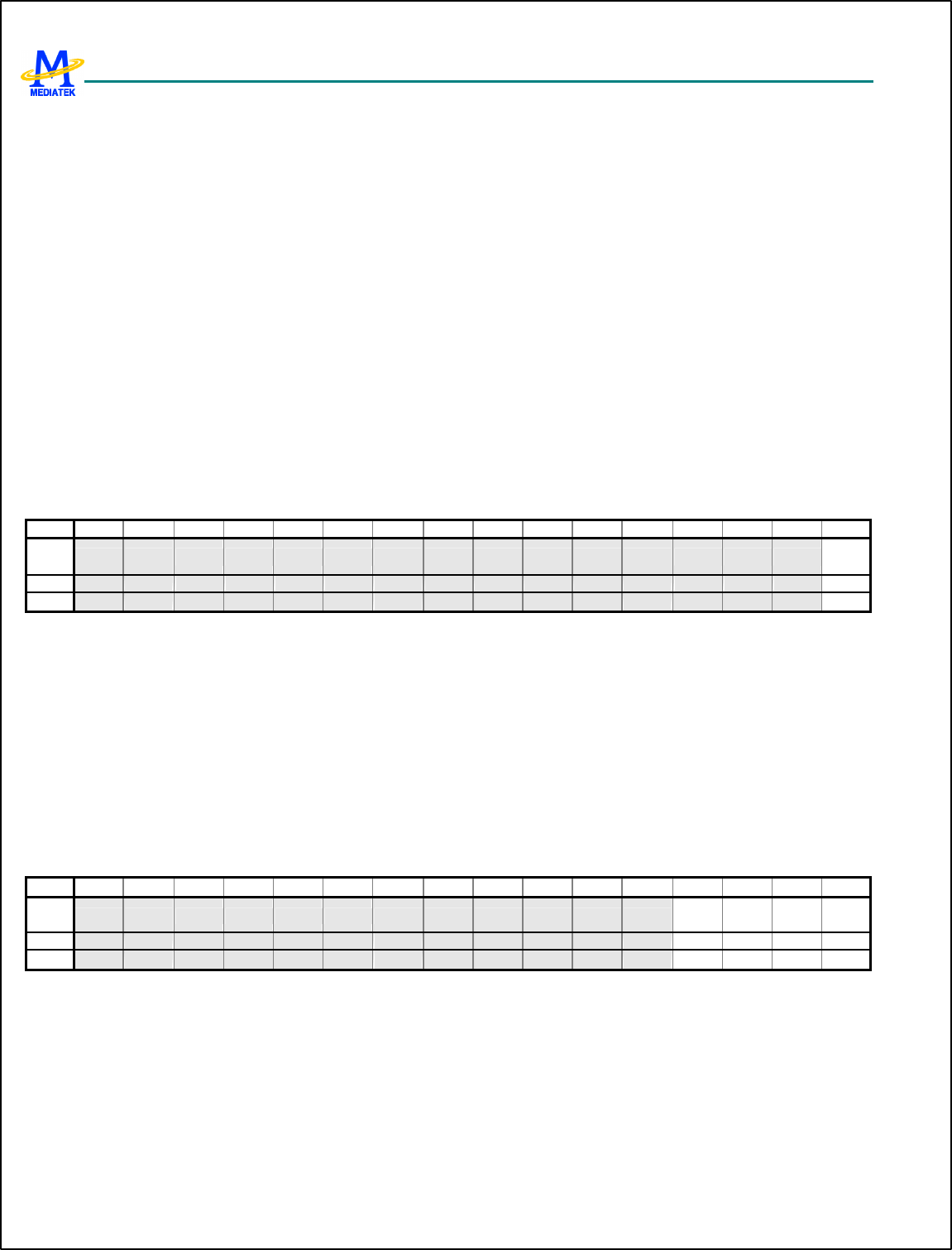

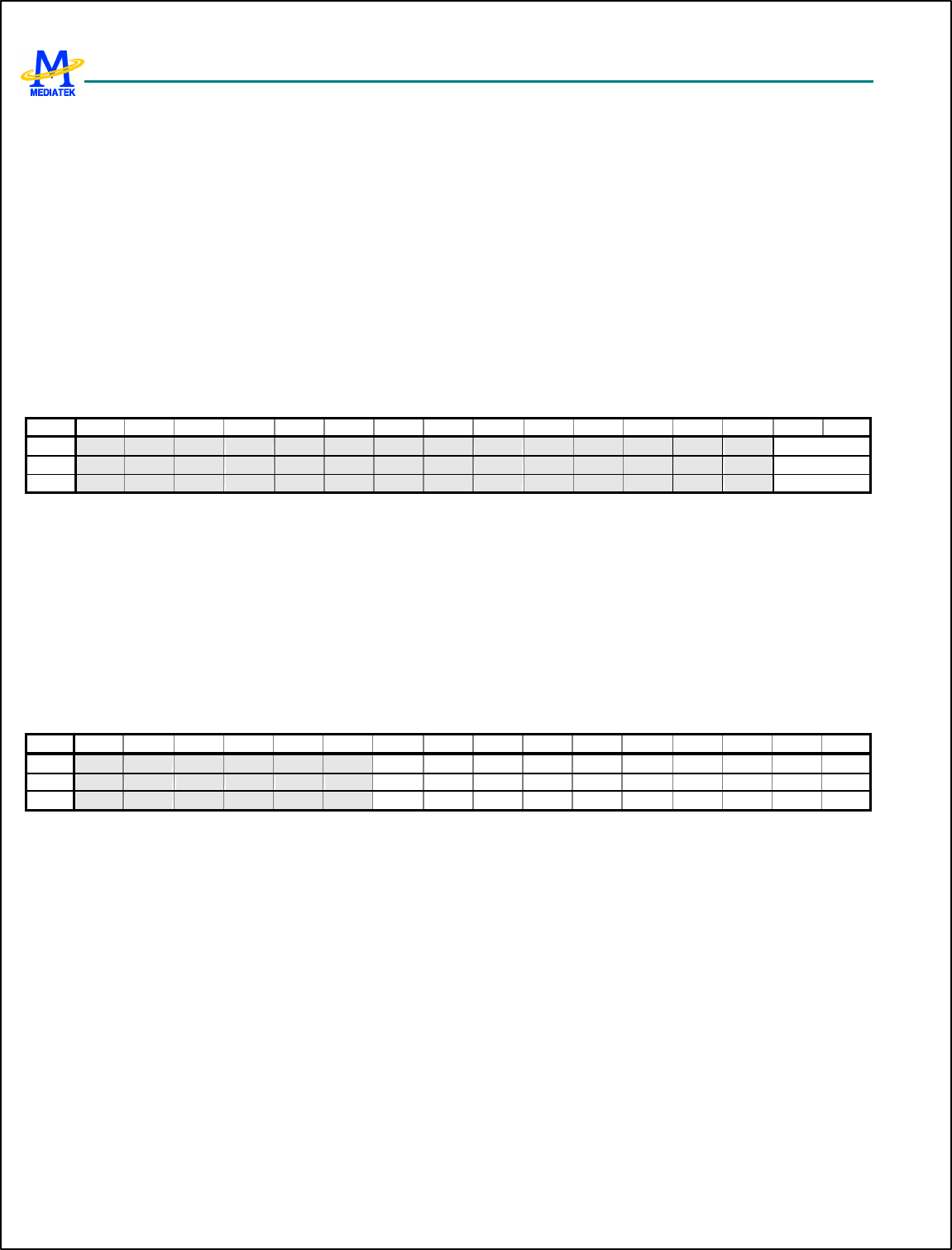

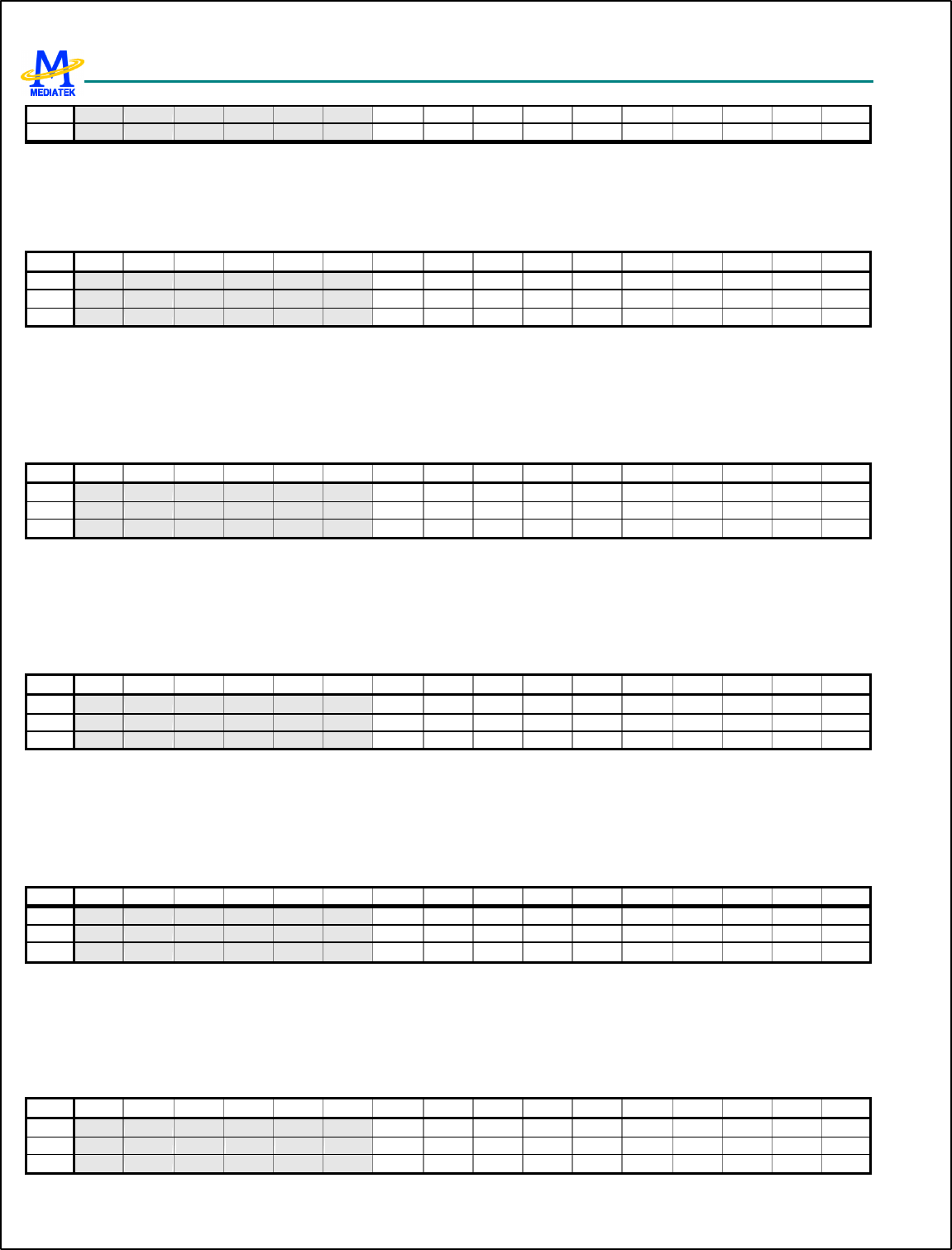

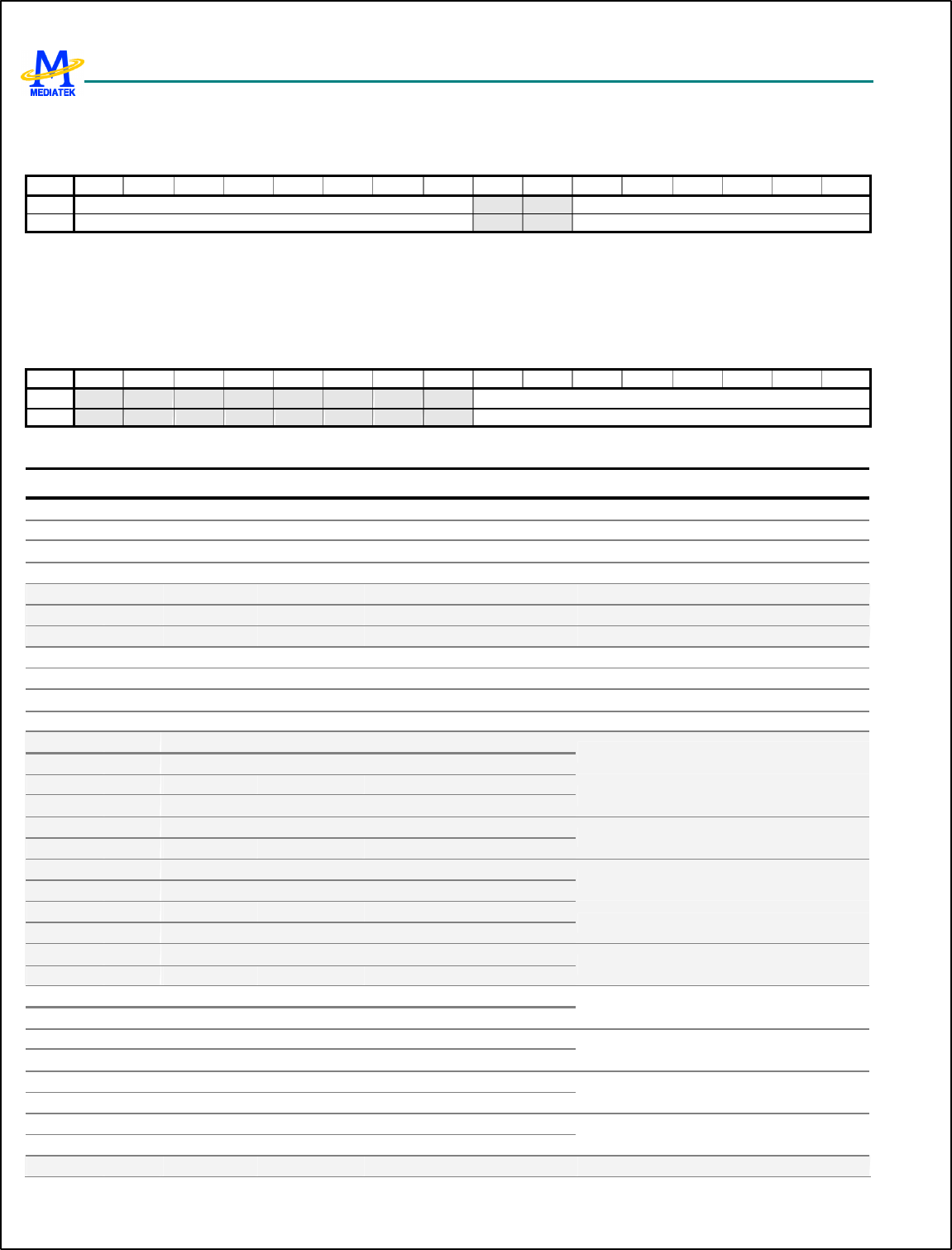

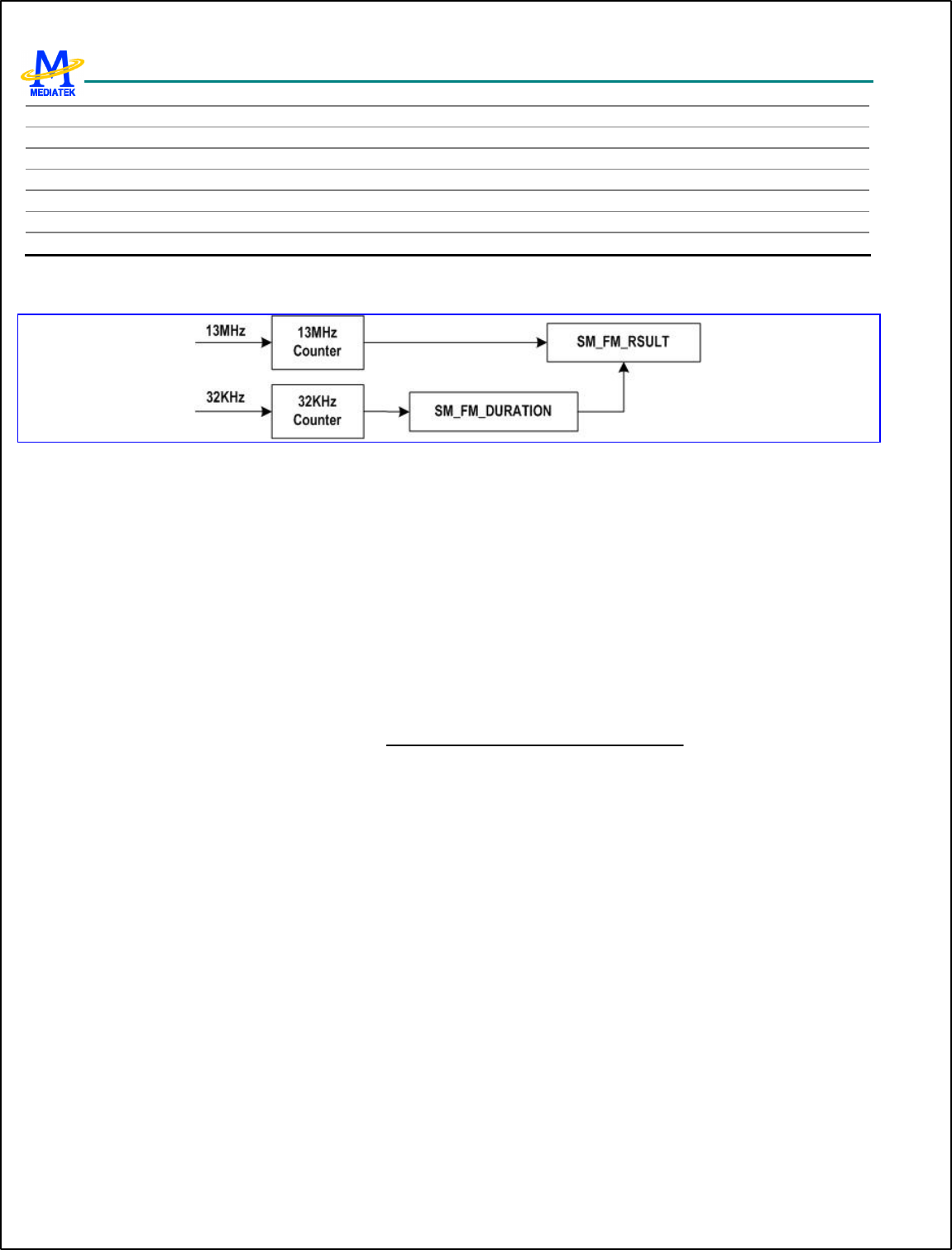

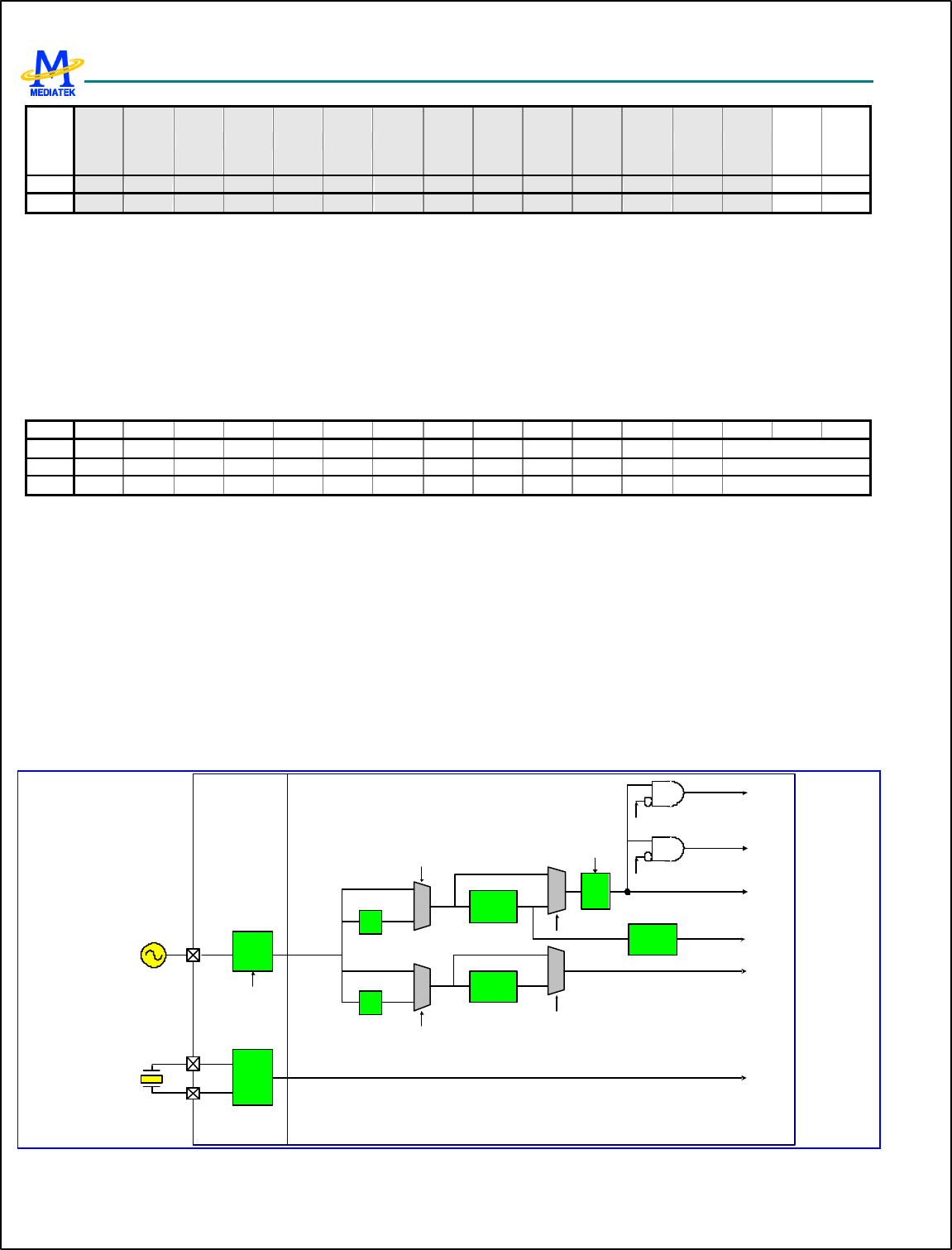

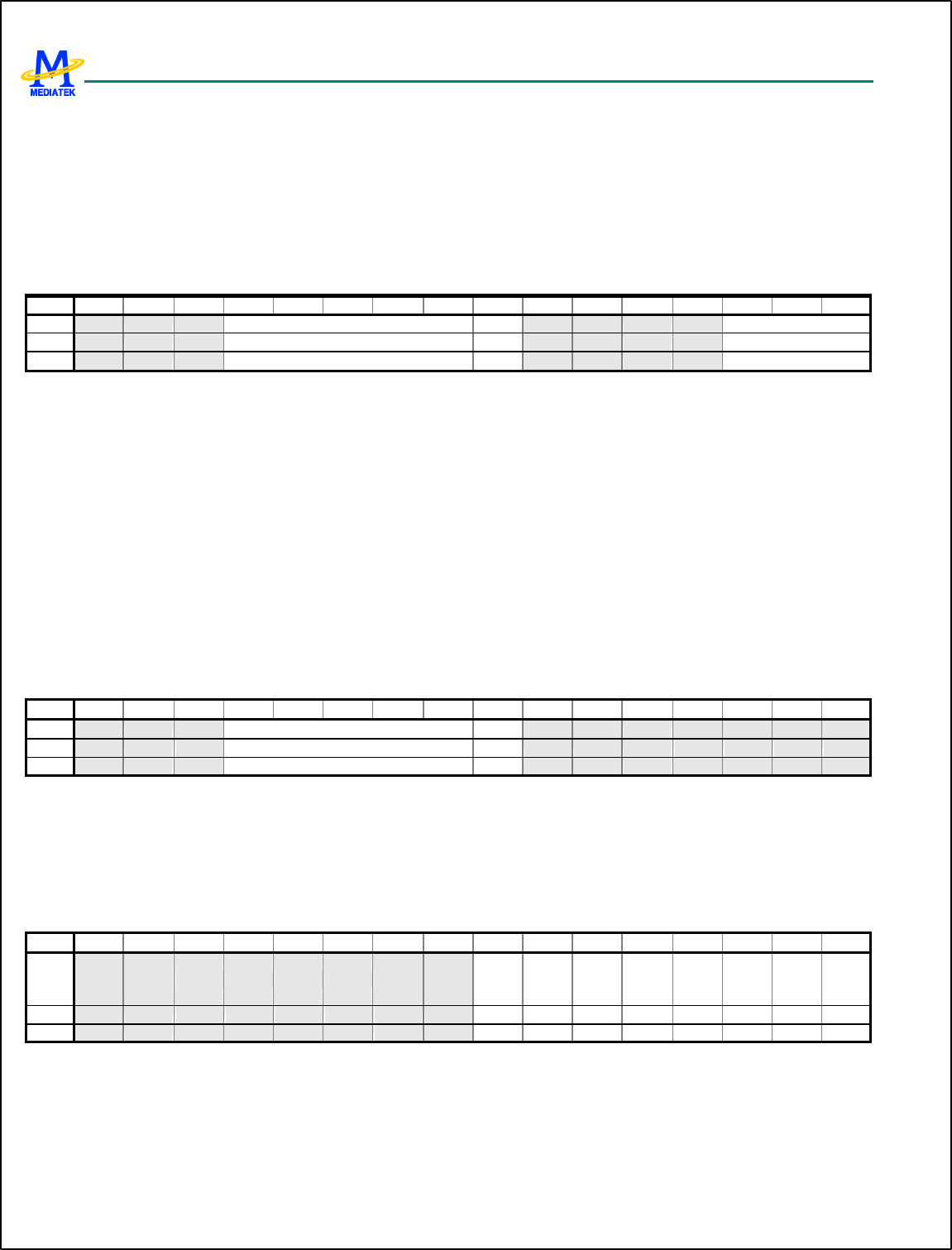

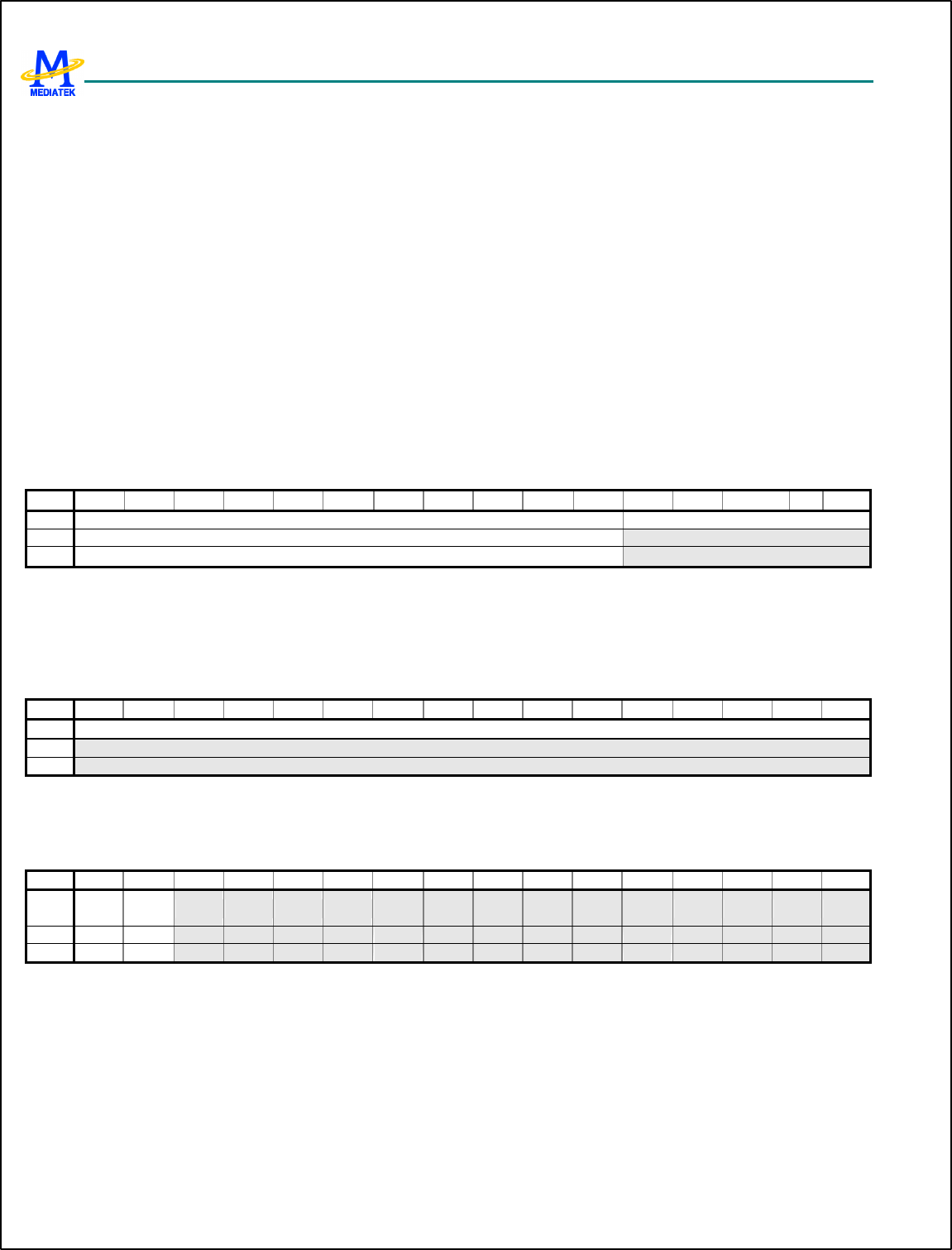

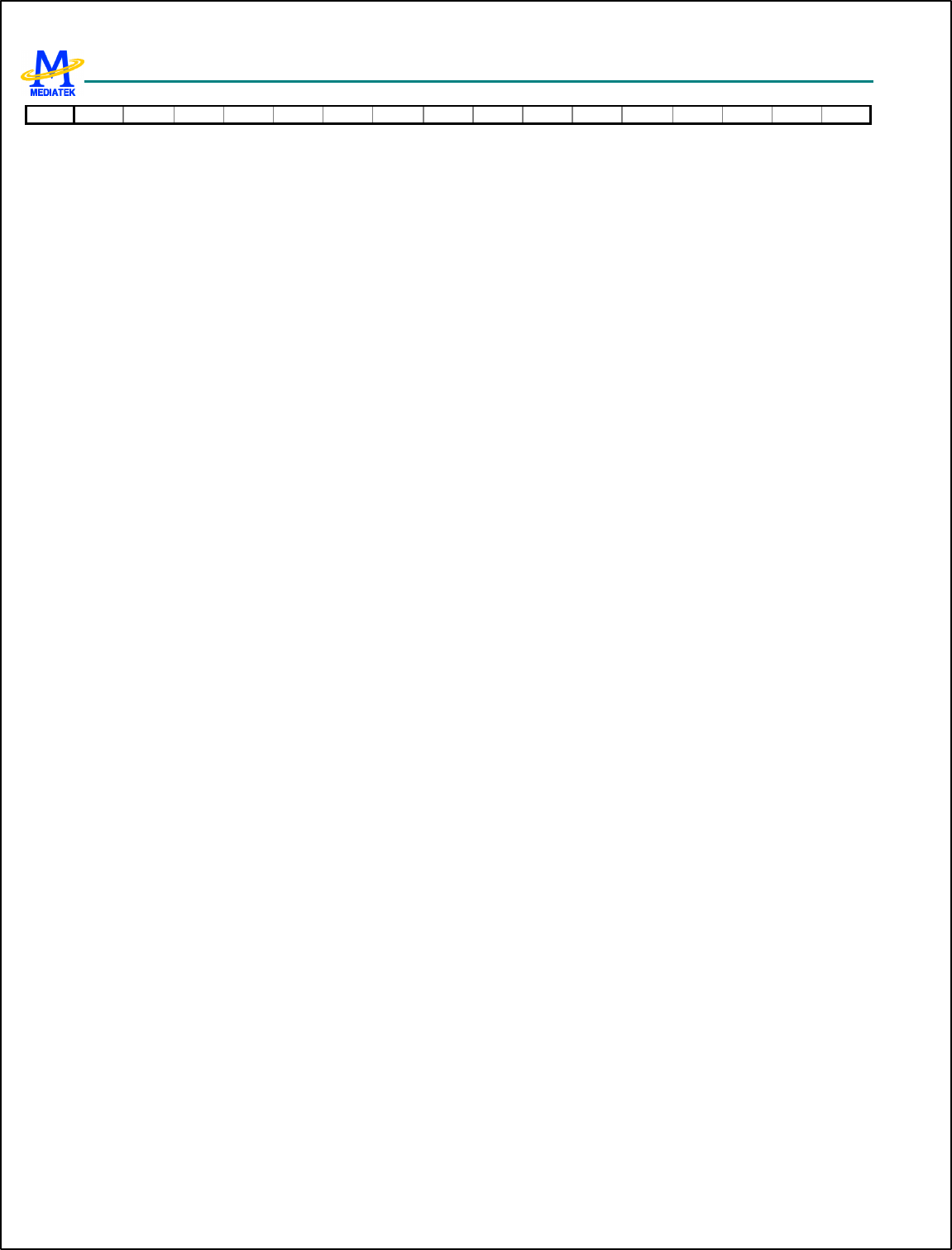

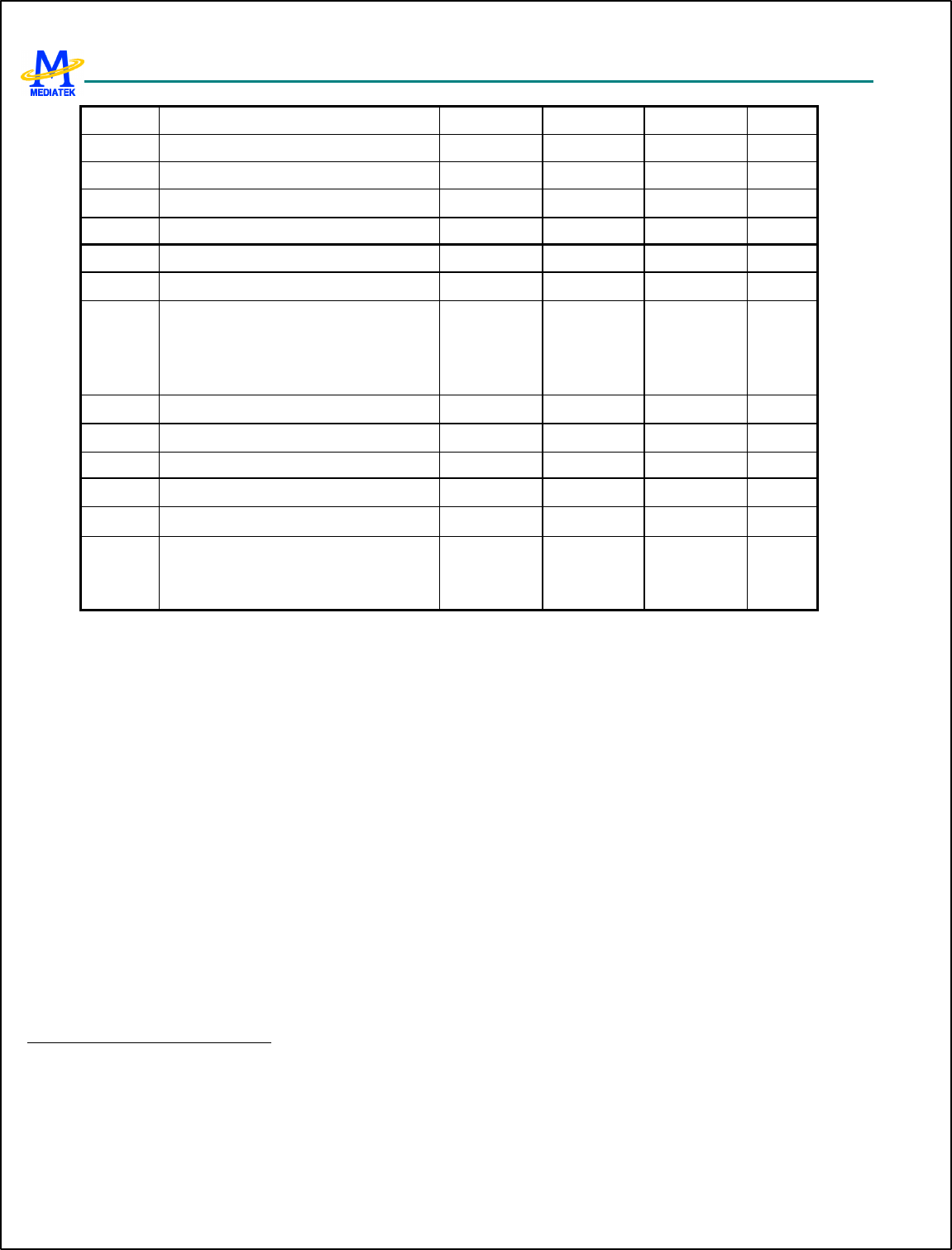

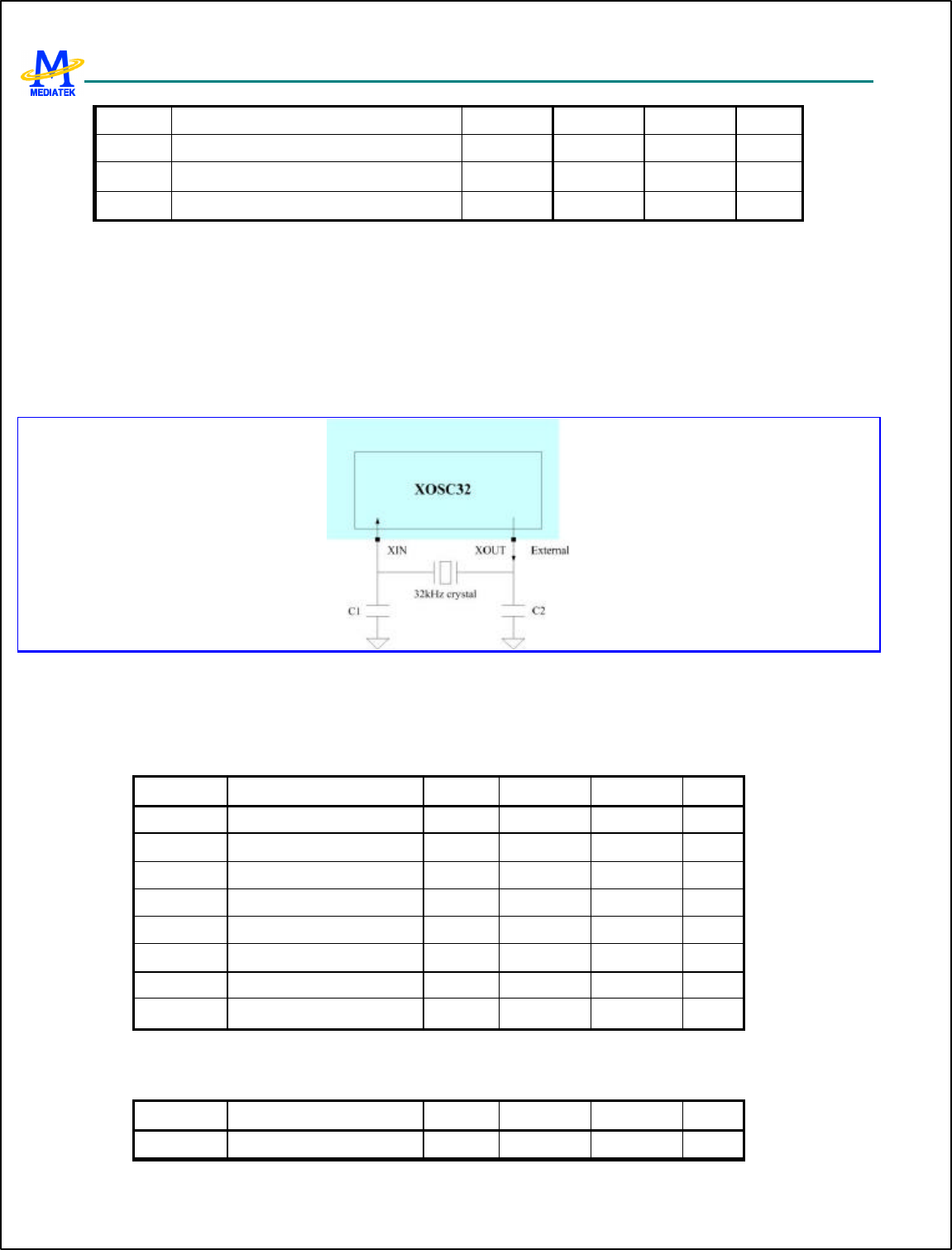

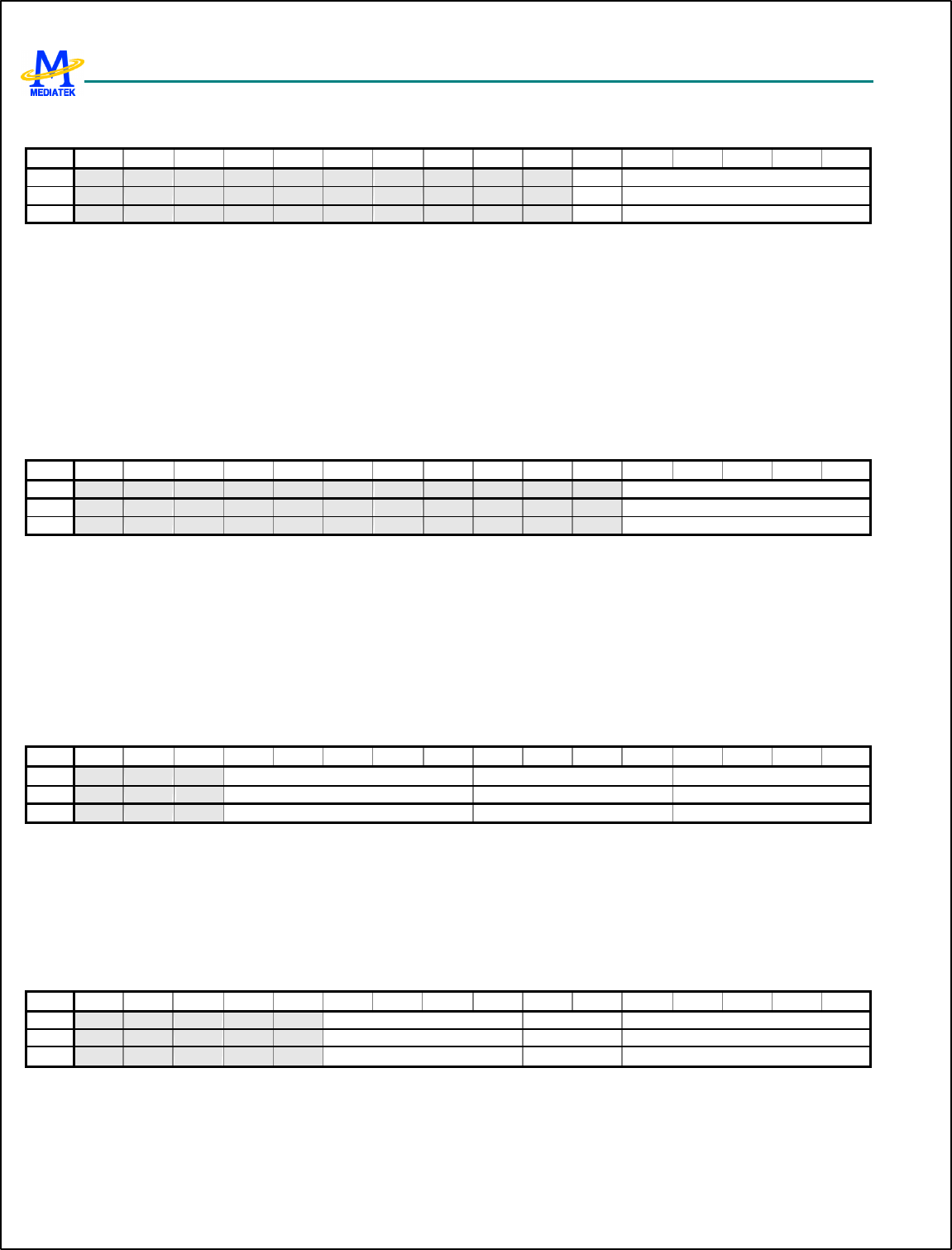

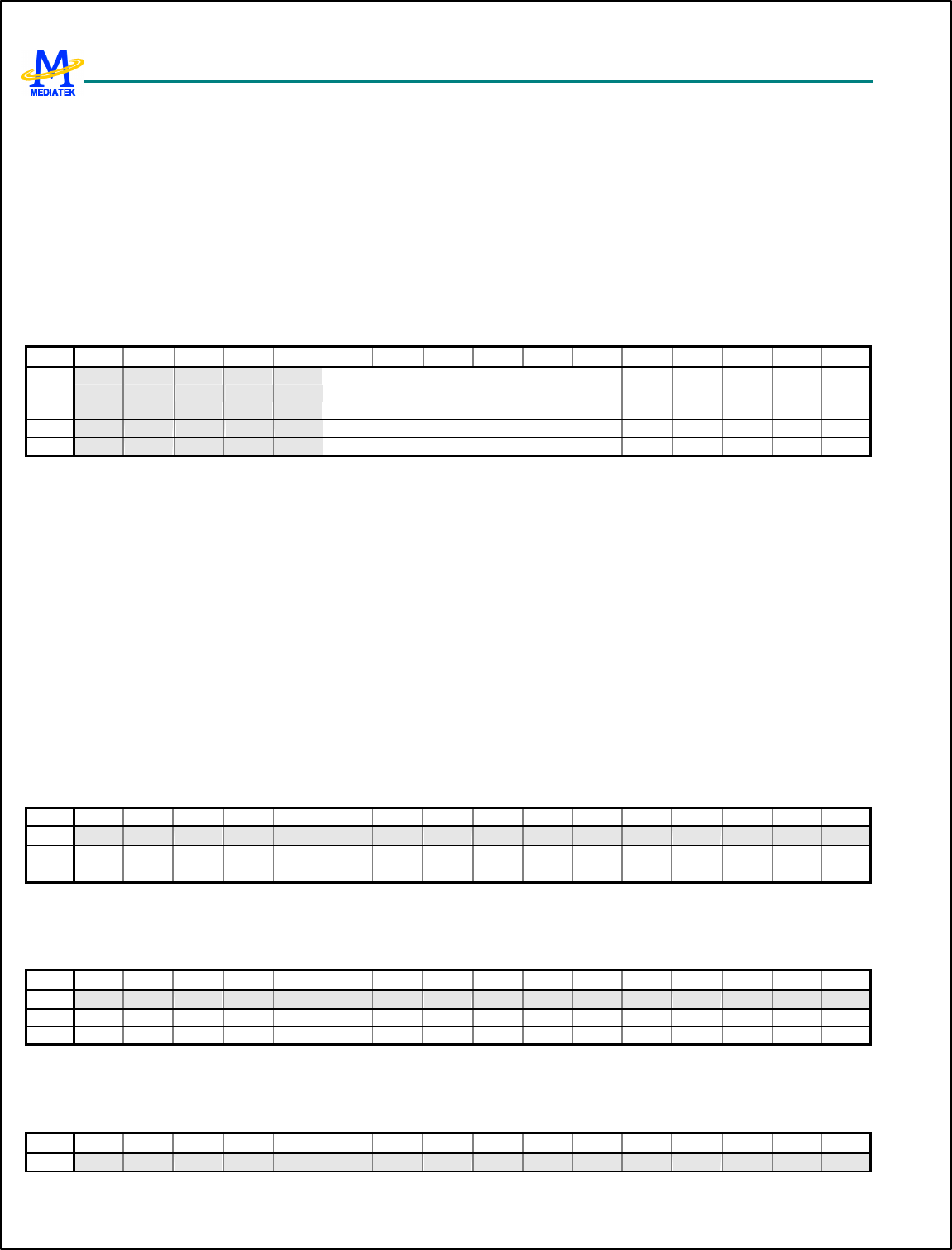

Figure 2 details the block diagram of MT6217. Based on dual-processor architecture, the major processor of MT6217 is

ARM7EJ -S, which mainly runs high-level GSM /GPRS protocol software as well as multi-media applications. With the

other one is a digital signal processor corresponding for handling the low-level MODEM as well as advanced audio

functions. Except for some mixed-signal circuitries, the other building blocks in MT6217 are connected to either the

microcontroller or the digital signal processor. Specifically, MT6217 consists of the following subsystems:

l Microcontroller Unit (MCU) Subsystem, including an ARM7EJ -S RISC processor and its accompanying memory

management and interrupt handling logics.

l Digital Signal Processor (DSP) Subsystem, including a DSP and its accompanying memory, memory controller,

and interrupt controller.

l MCU/DSP Interface, where the MCU and the DSP exchange hardware and software information.

l Microcontroller Peripherals, which includes all user interface modules and RF control interface modules.

l Microcontroller Coprocessors, which intends to run computing-intensive processes in place of Microcontroller.

l DSP Peripherals, which are hardware accelerators for GSM/GPRS channel codec.

l Multi-media Subsystem, which integrate several advanced accelerators to support multi-media applications.

l Voice Front End, the data path of conveying analog speech from and to digital speech.

l Audio Front End, also the data path of conveying stereo audio from stereo audio source

l Baseband Front End, the data path of conveying digital signal form and to analog signal of RF modules.

l Timing Generator, generating the control signals related to the TDMA frame timing.

l Power, Reset and Clock subsystem, managing the power, reset and clock distribution inside MT6217.

Details of the individual subsystems and blocks are described in following Chapters.

MT6217 GSM/GPRS Baseband Processor Data Sheet Revision 1.01

13/349 MediaTek Inc. Confidential

BSI

ARM7EJ-S

DSP

Interrupt

Controller

MCU/DSP

Interface

Memory

Patch

Unit

Trap

Unit

DSP

Coprocessor

Boot

ROM

On-Chip

SRAM

DMA

Controller

External

Memory

Interface

Interrupt

Controller

TDMA

Timer

DAC APC

DAC AFC

SIM GPIO

Keypad

Scanner

BPI

WDT

ADC Aux

ADC

Clock

Generator

MMC

SD/MS

MS Pro

Audio

Path

Baseband

Path

ADC

USBAlerter

MT6217

DSP

Coprocessor

DSP

Coprocessor

Serial RF

Control

Parallel RF

Control

APC

ADC

DAC

DAC

ADC

DAC

DAC

DAC

+

+

Bridge

DSP

Coprocessor

NAND Flash

Controller

DSP

Coprocessor

Aux

ADC

AFC

TX_Q

TX_I

RX_I

RX_Q

VOICE_0

VOICE_1

AUDIO_L

AUDIO_R

MIC_0

MIC_1

STEREO_L

STEREO_R

System

Clock

13/26MHz

32KHz

Crystal

JTAG

Flash

SRAM

LCD

Melody

Wake Up User InterfaceReset

GPT

LCD

Controller

Image

Resizer

JPEG

Decoder

NAND

Flash

LCD

Camera

B2PSI IrDA

PWM Serial

LCD

RTC

UART

32K

OSC

ConnectivitySerial Port

Figure 2 MT6217 block diagram.

MT6217 GSM/GPRS Baseband Processor Data Sheet Revision 1.01

14/349 MediaTek Inc. Confidential

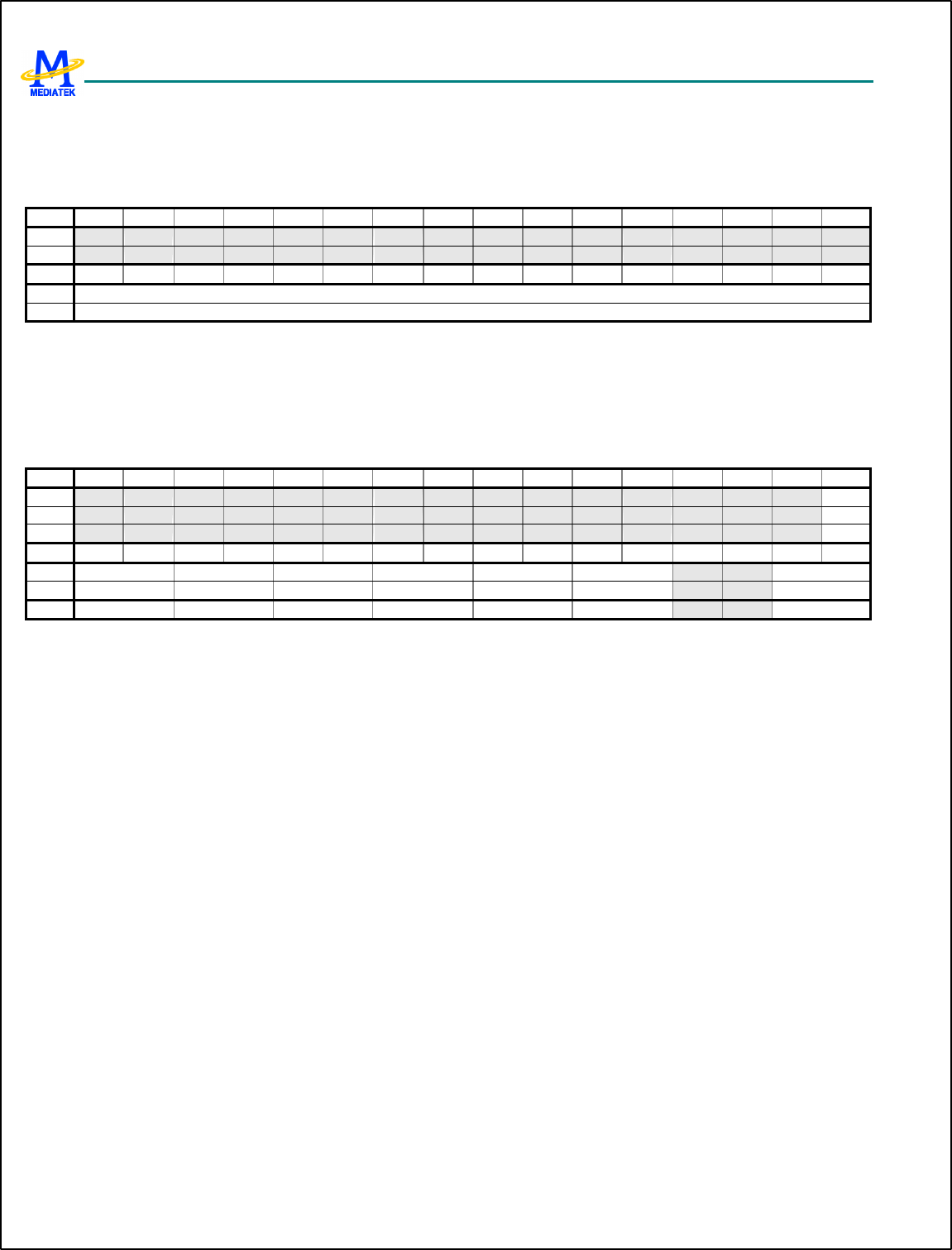

2 Product Description

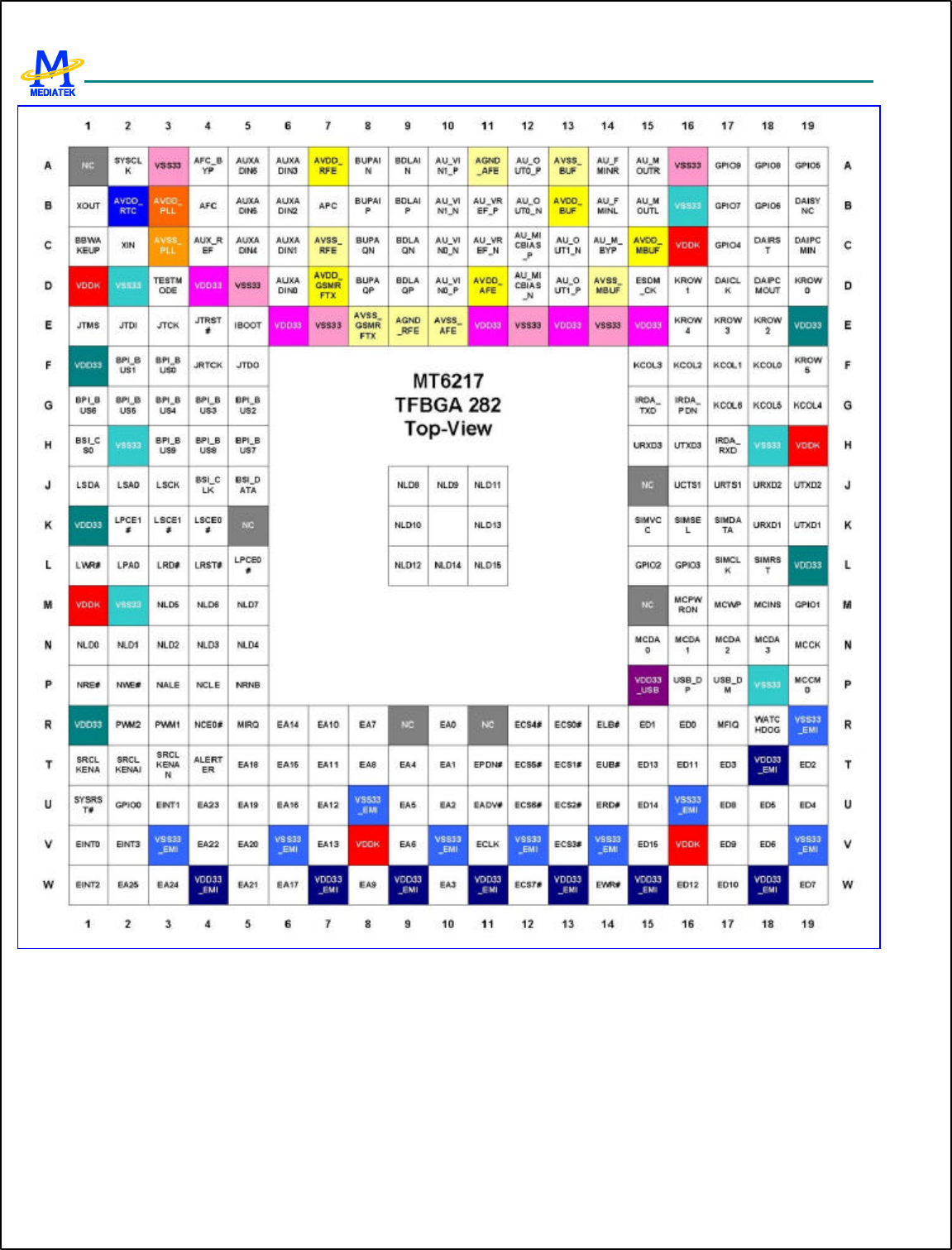

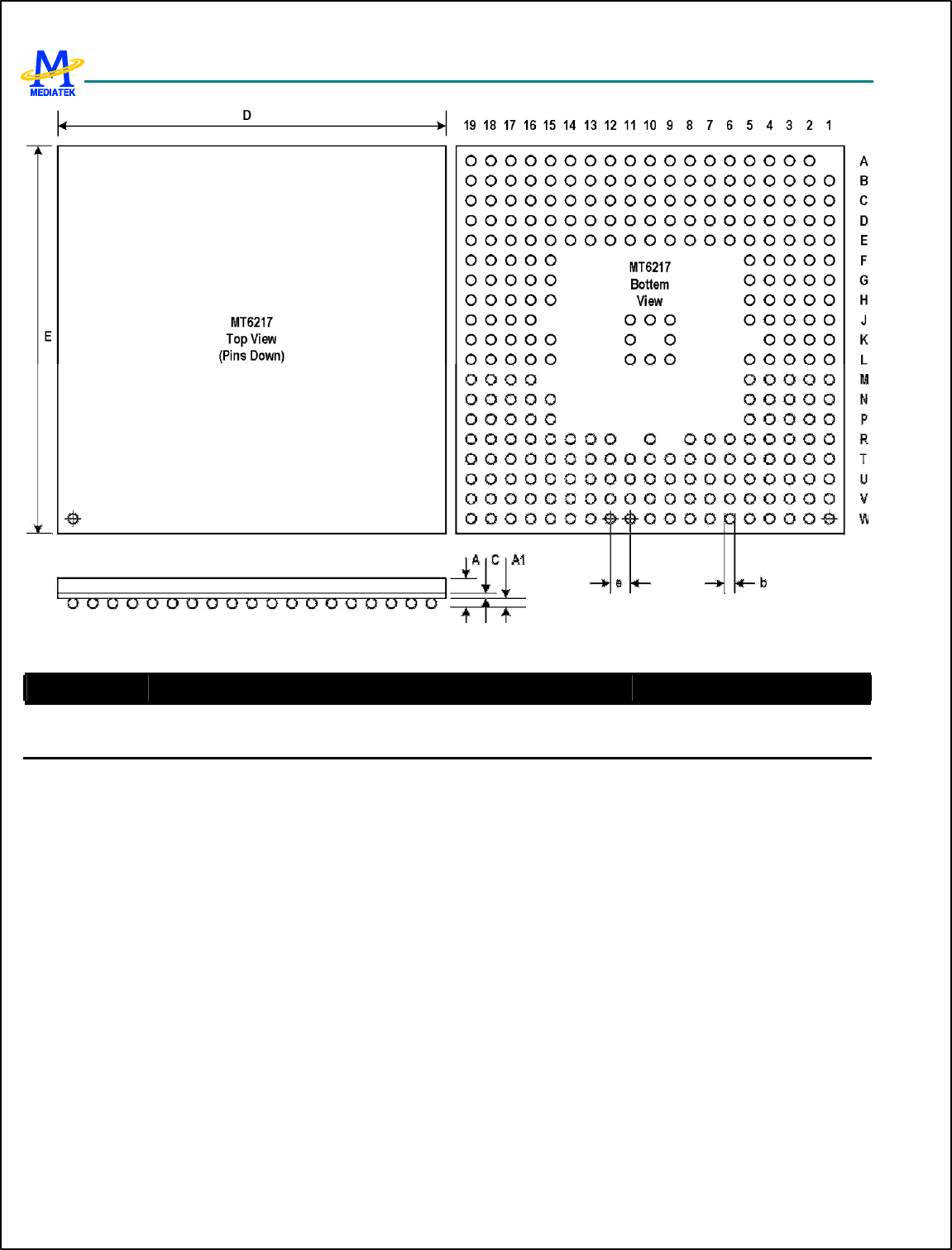

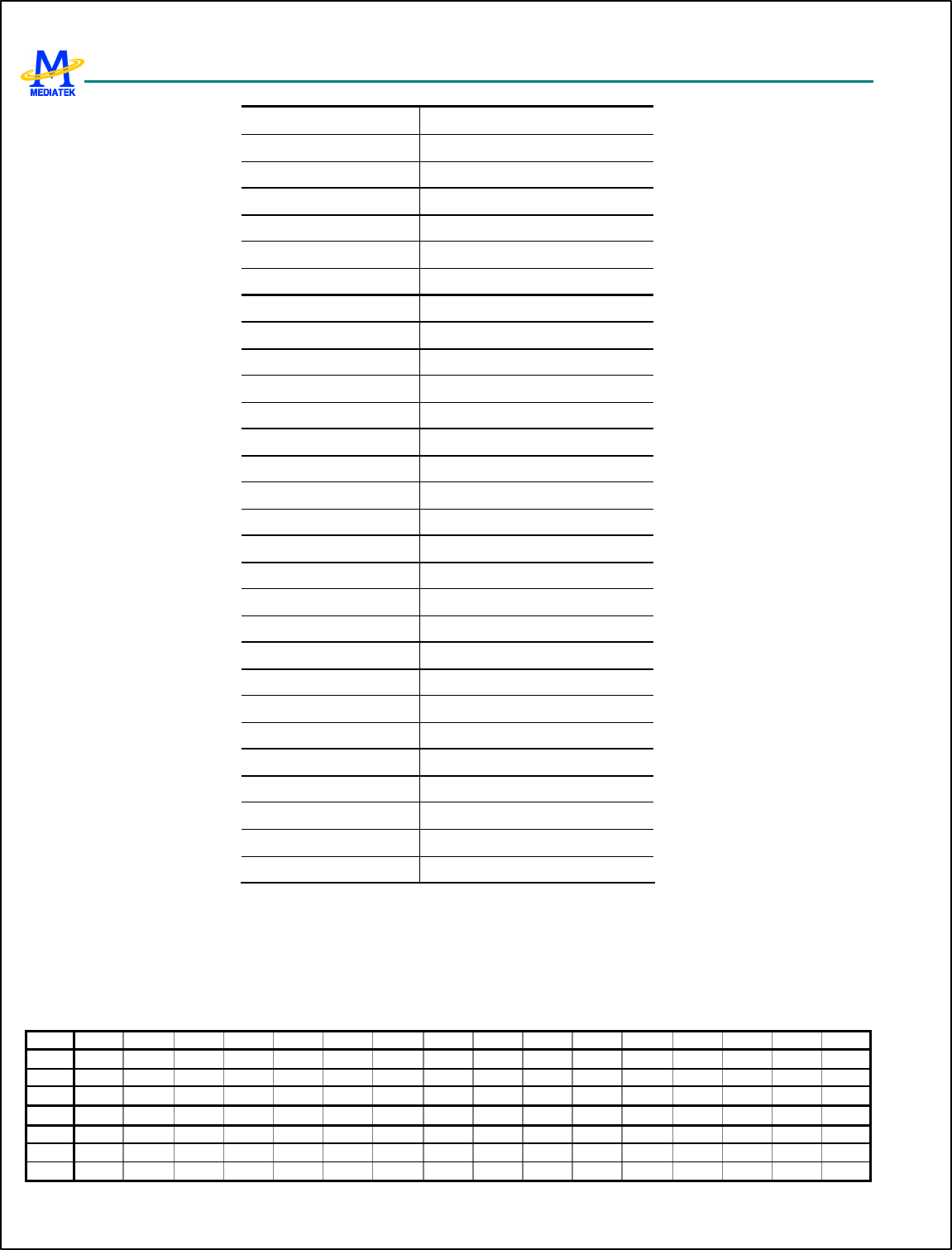

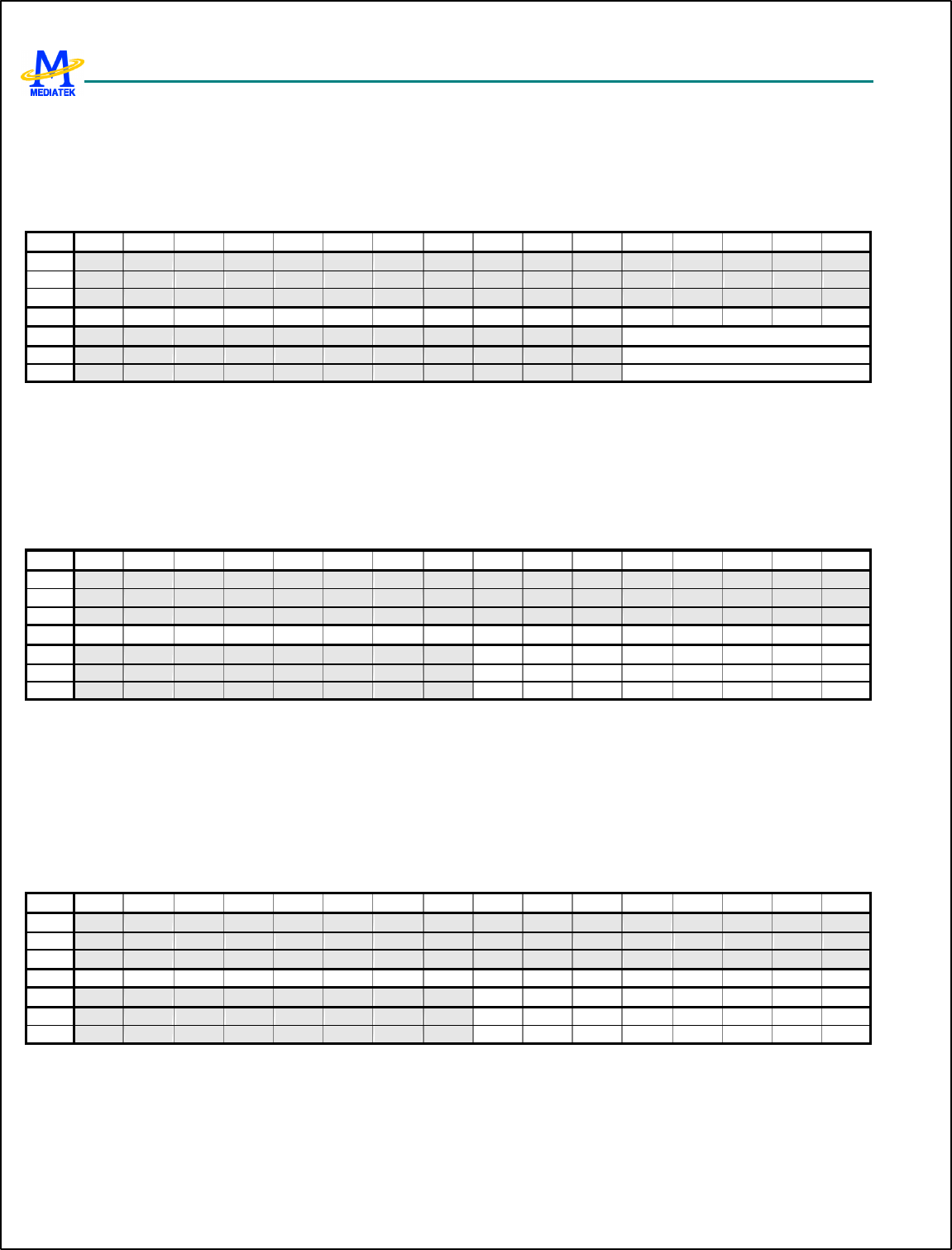

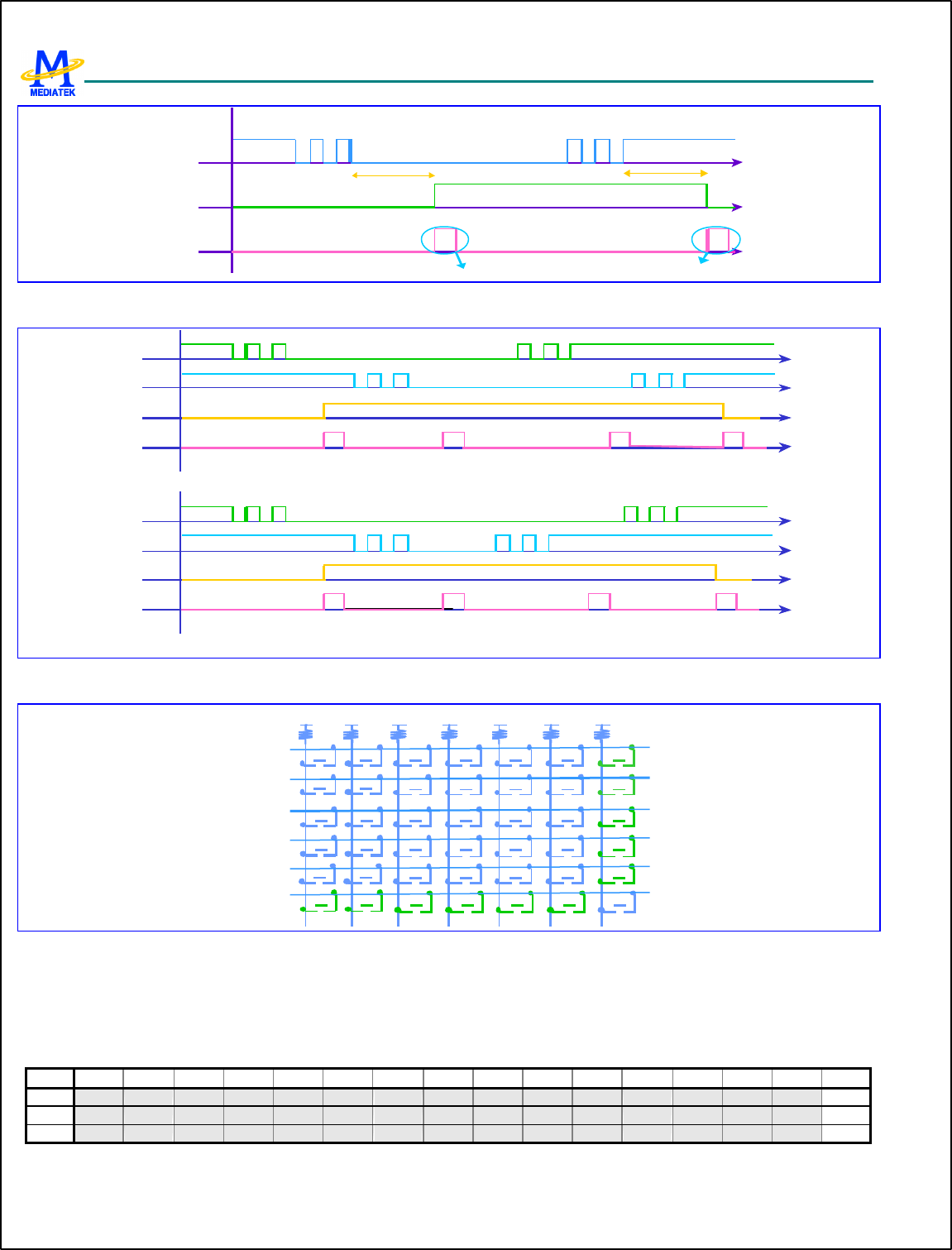

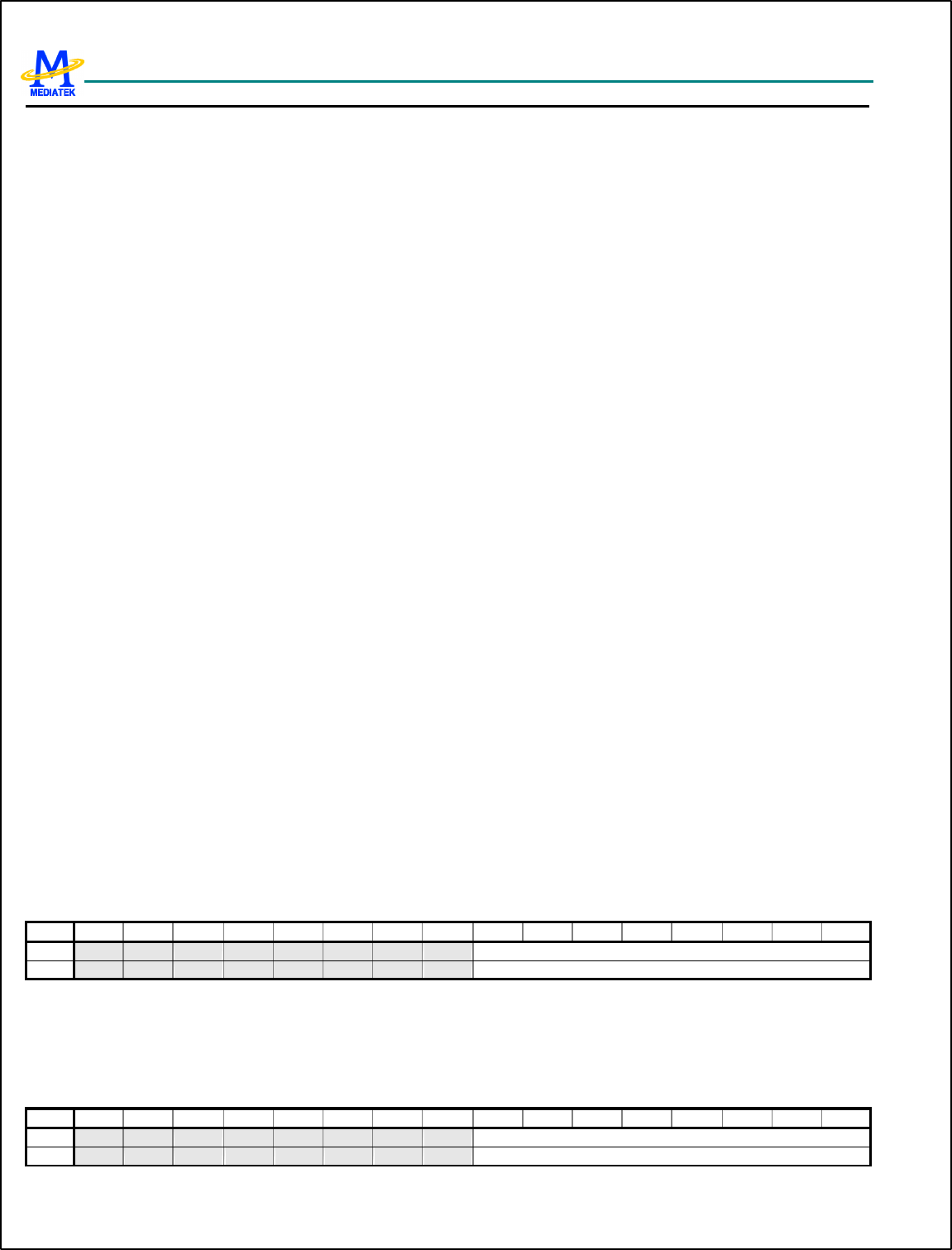

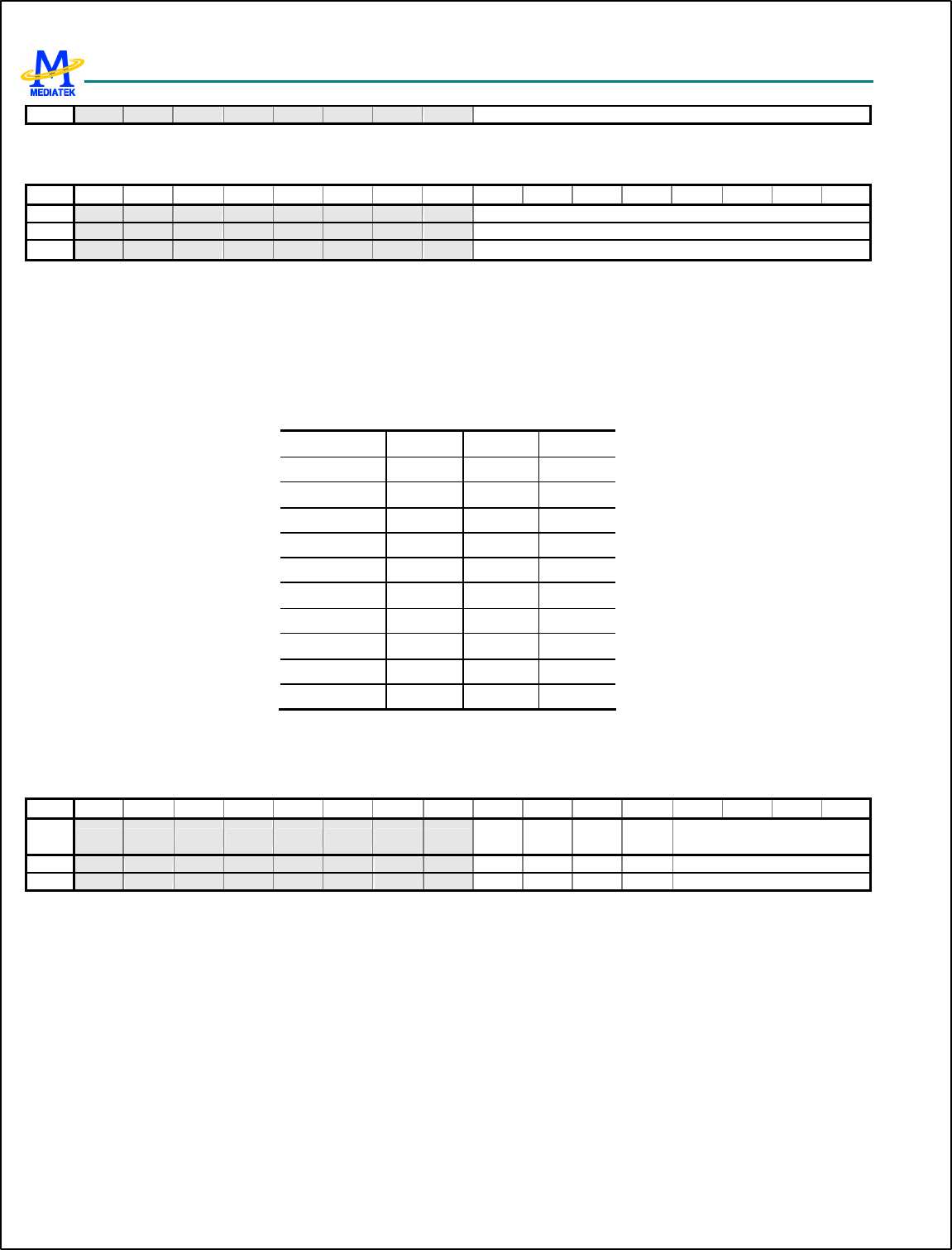

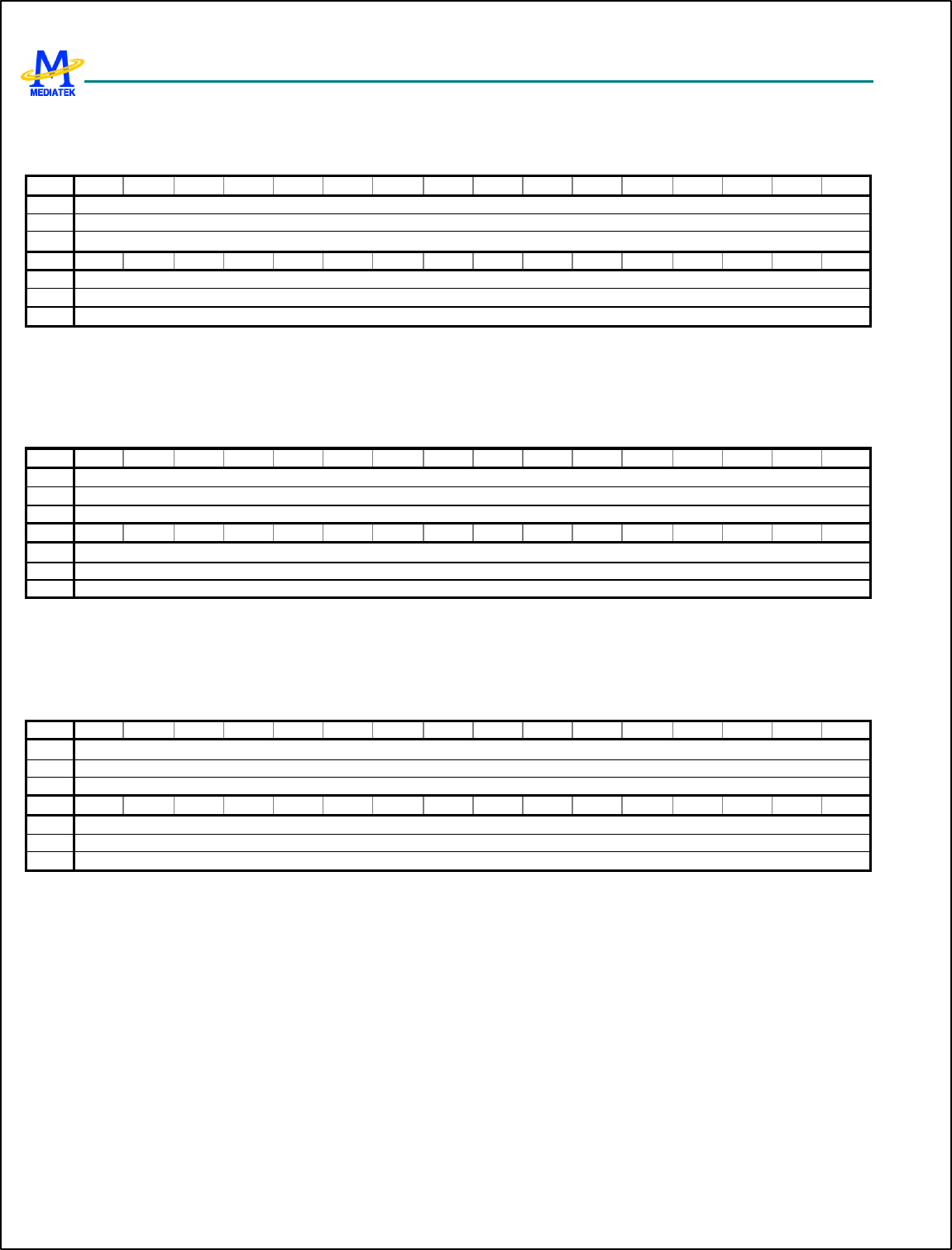

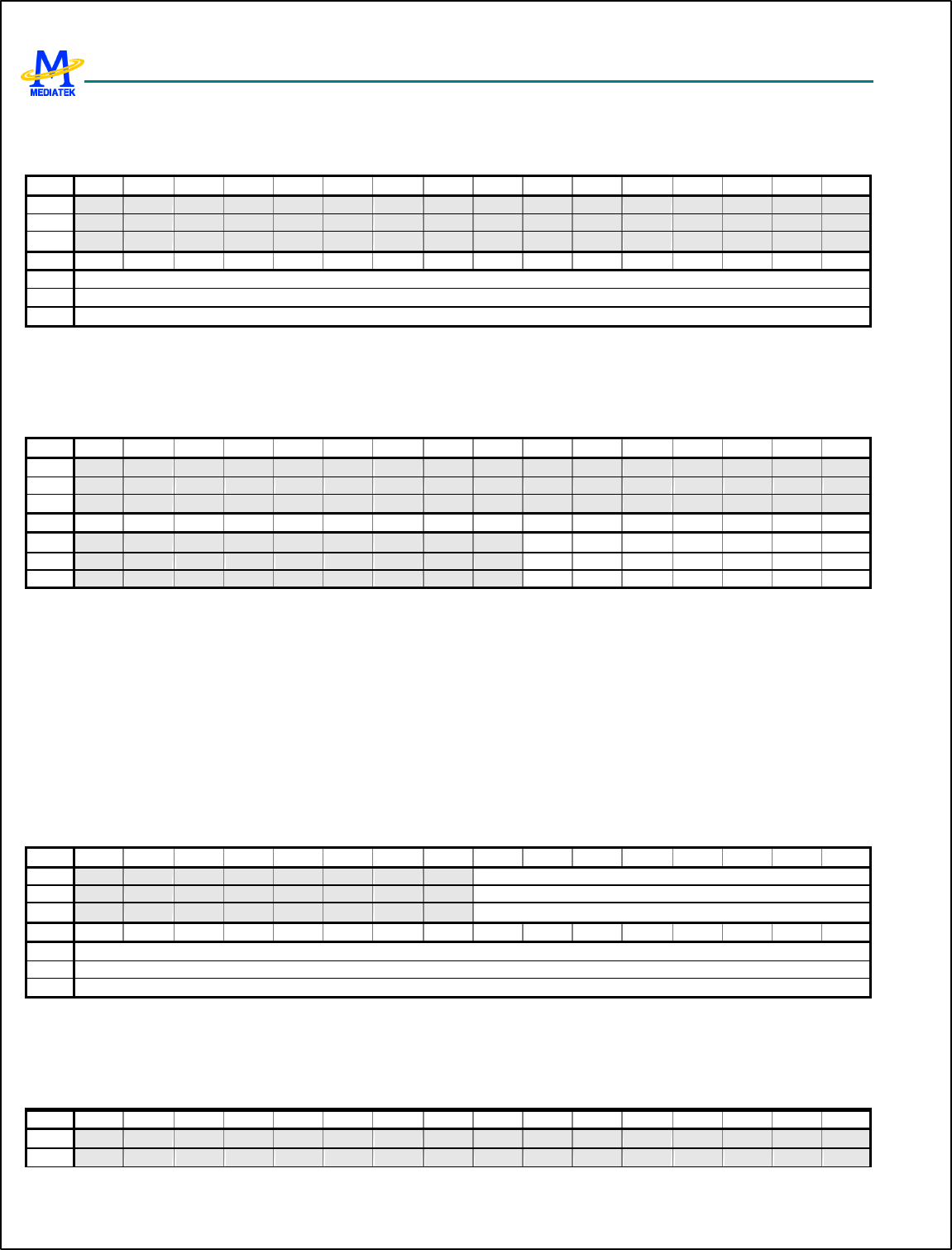

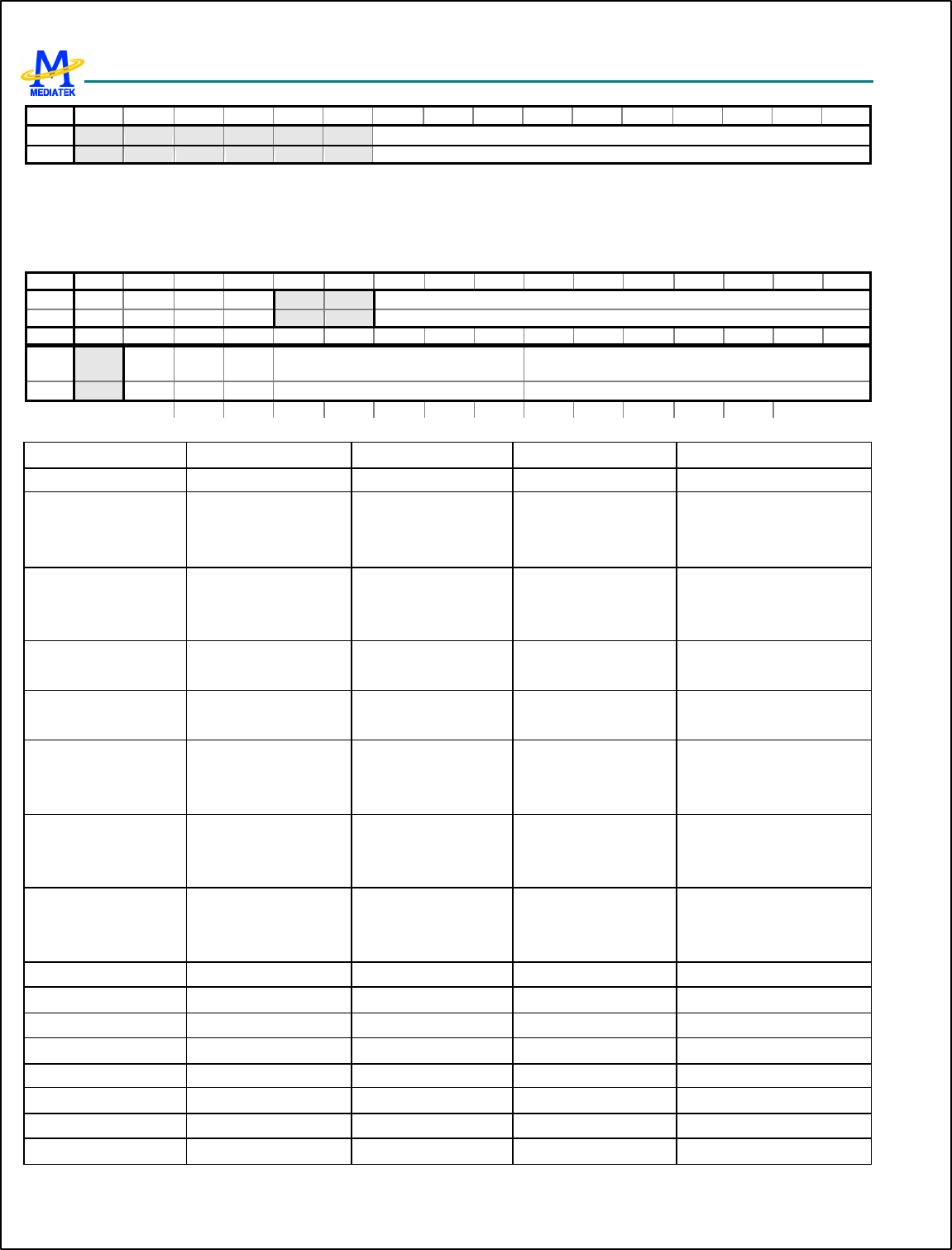

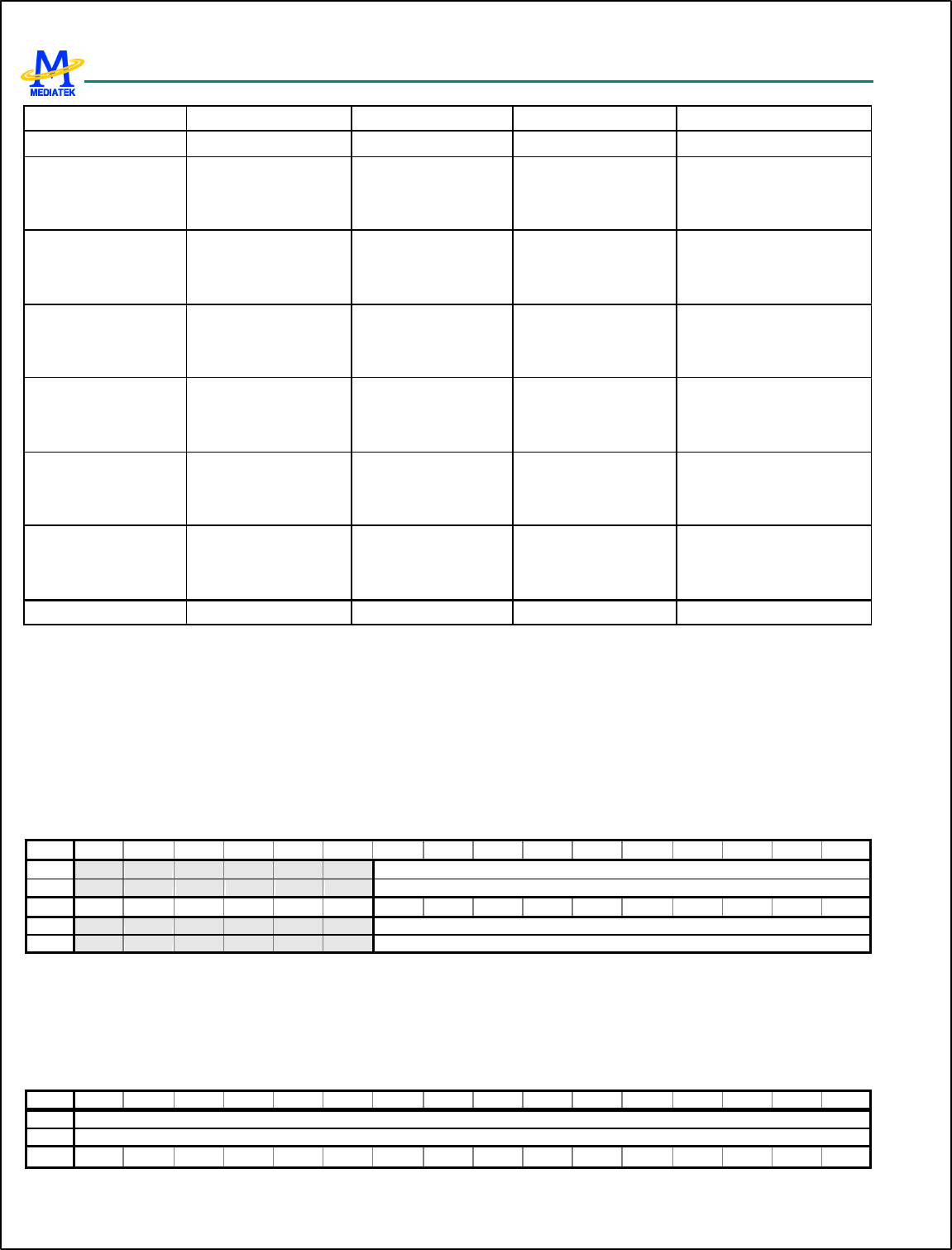

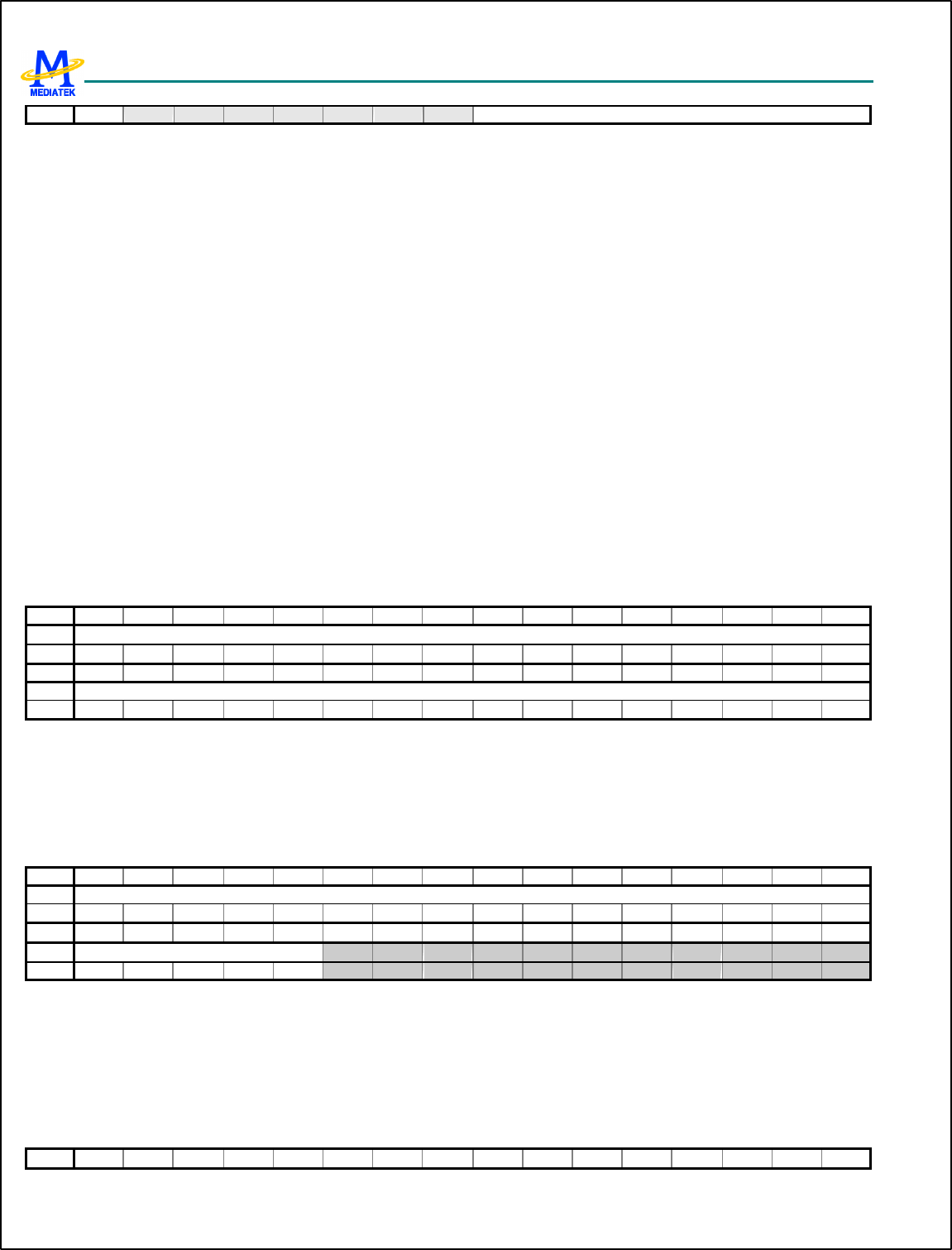

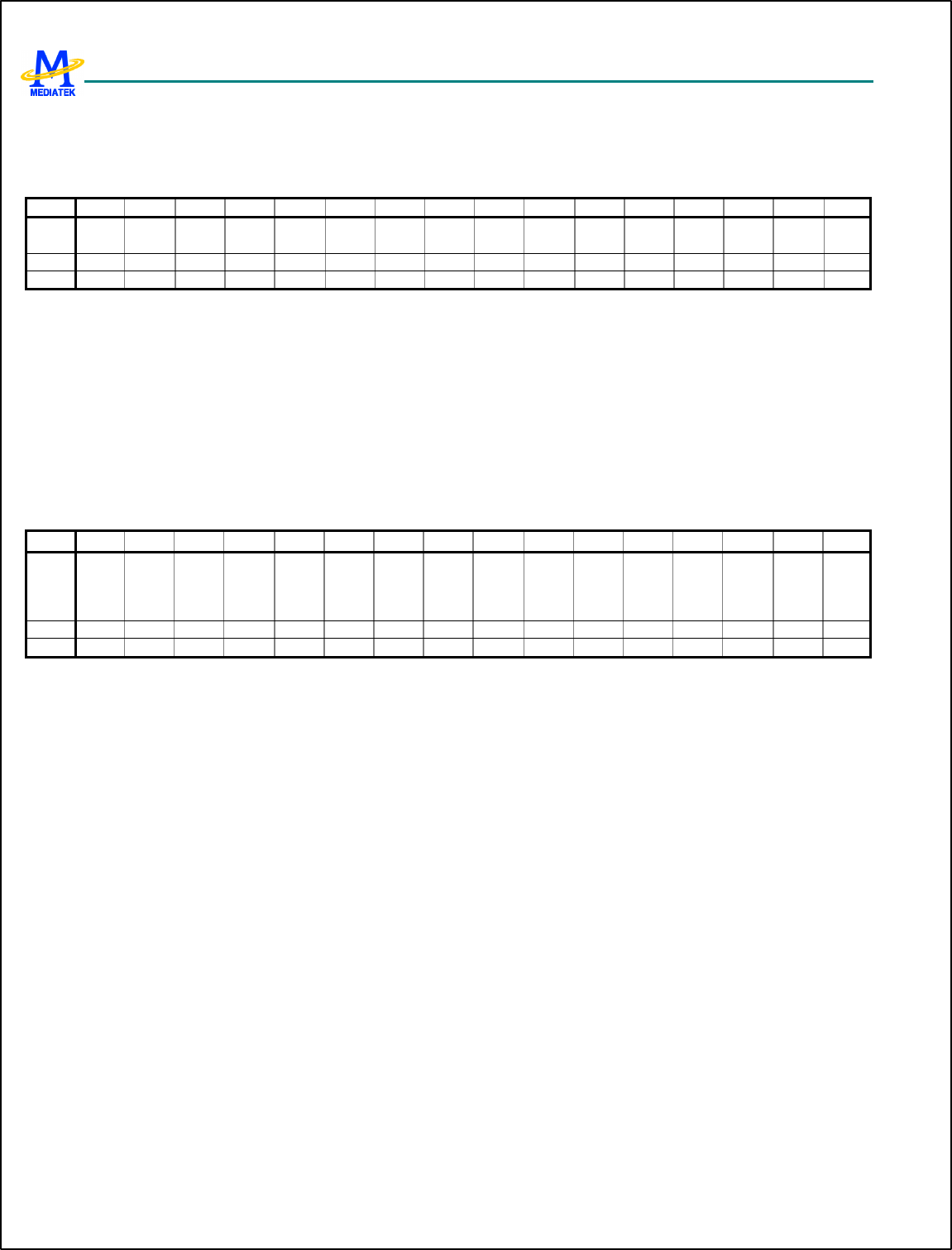

2.1 Pin Outs

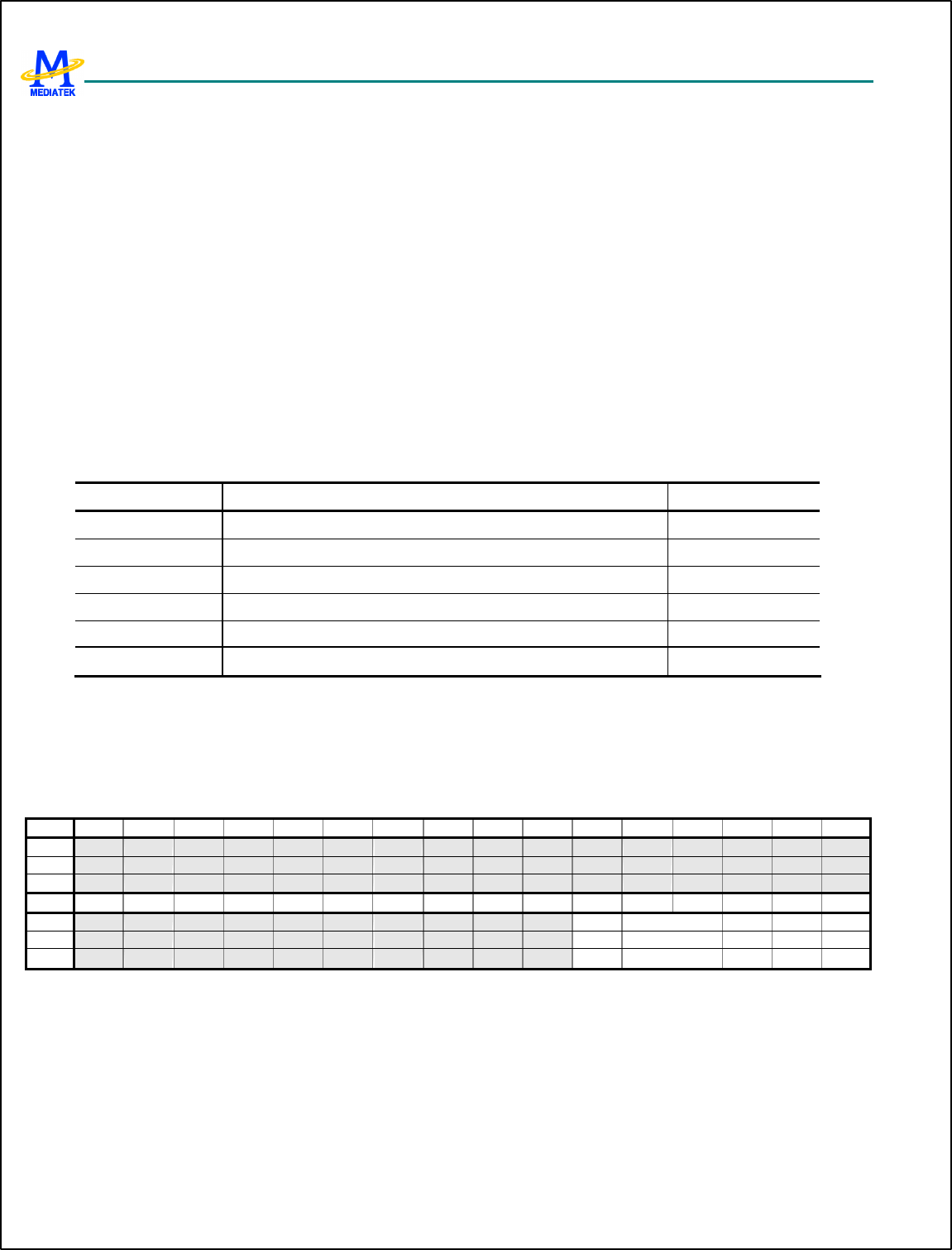

One type of package for this product, TFBGA 13mm*13mm, 282-ball, 0.65 mm pitch Package, is offered.

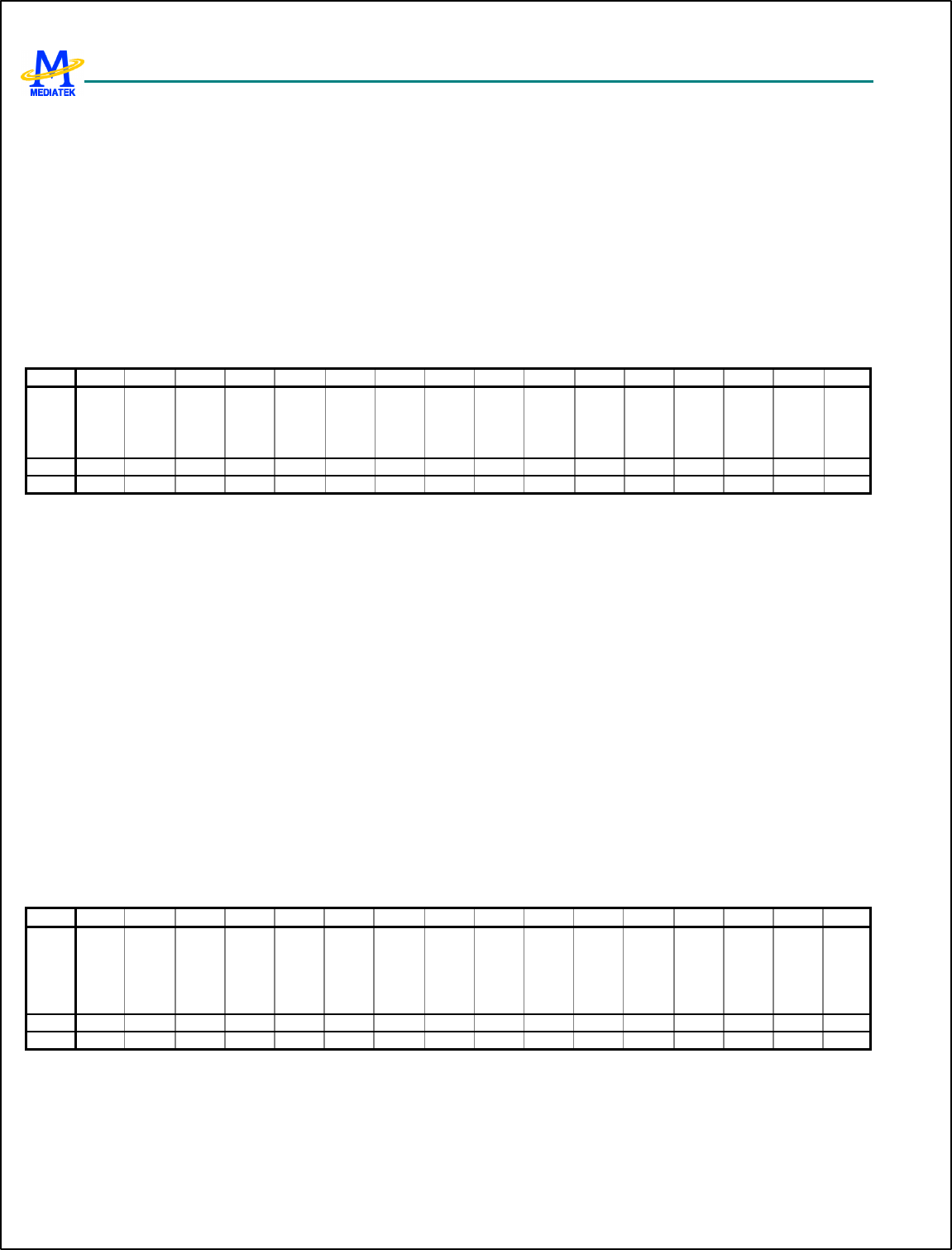

Pin outs and the top view are illustrated in Figure 3 for this package. Outline and dimension of package is illustrated in

Figure 4, while the definition of package is shown in Table 1.

MT6217 GSM/GPRS Baseband Processor Data Sheet Revision 1.01

15/349 MediaTek Inc. Confidential

Figure 3 Top View of MT6217 TFBGA 13mm*13mm, 282-ball, 0.65 mm pitch Package

MT6217 GSM/GPRS Baseband Processor Data Sheet Revision 1.01

16/349 MediaTek Inc. Confidential

Figure 4 Outlines and Dimension of TFBGA 13mm*13mm, 282-ball, 0.65 mm pitch Package

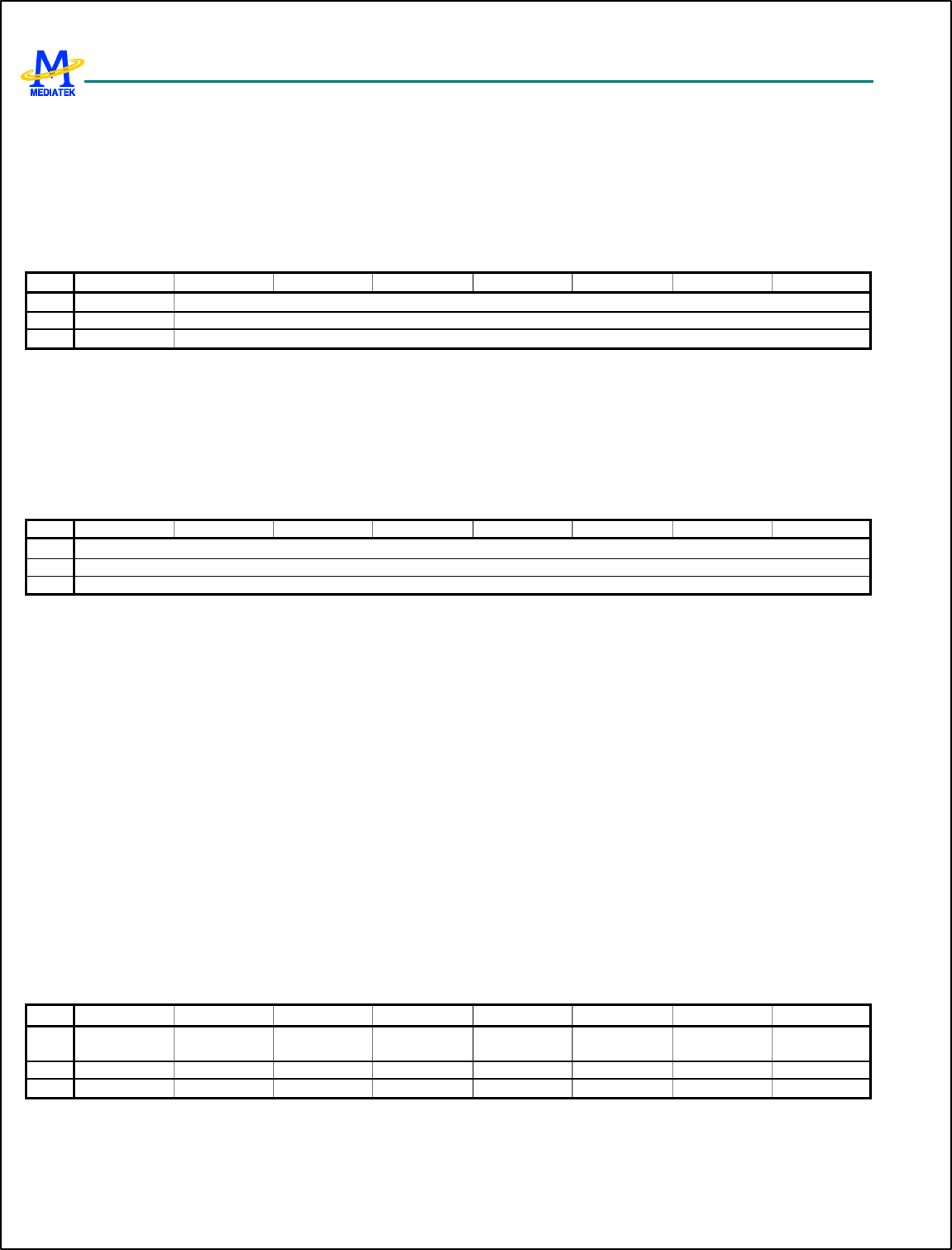

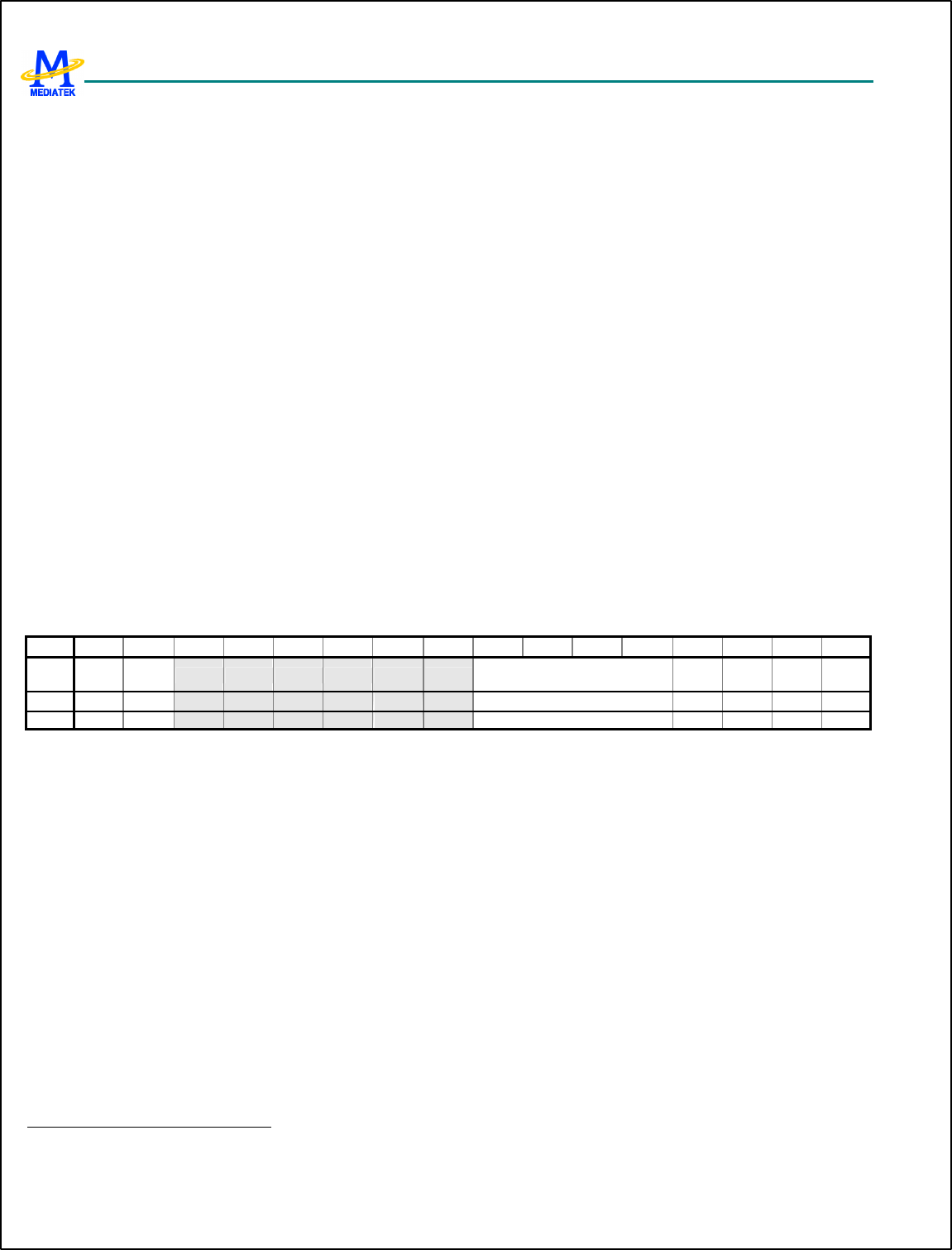

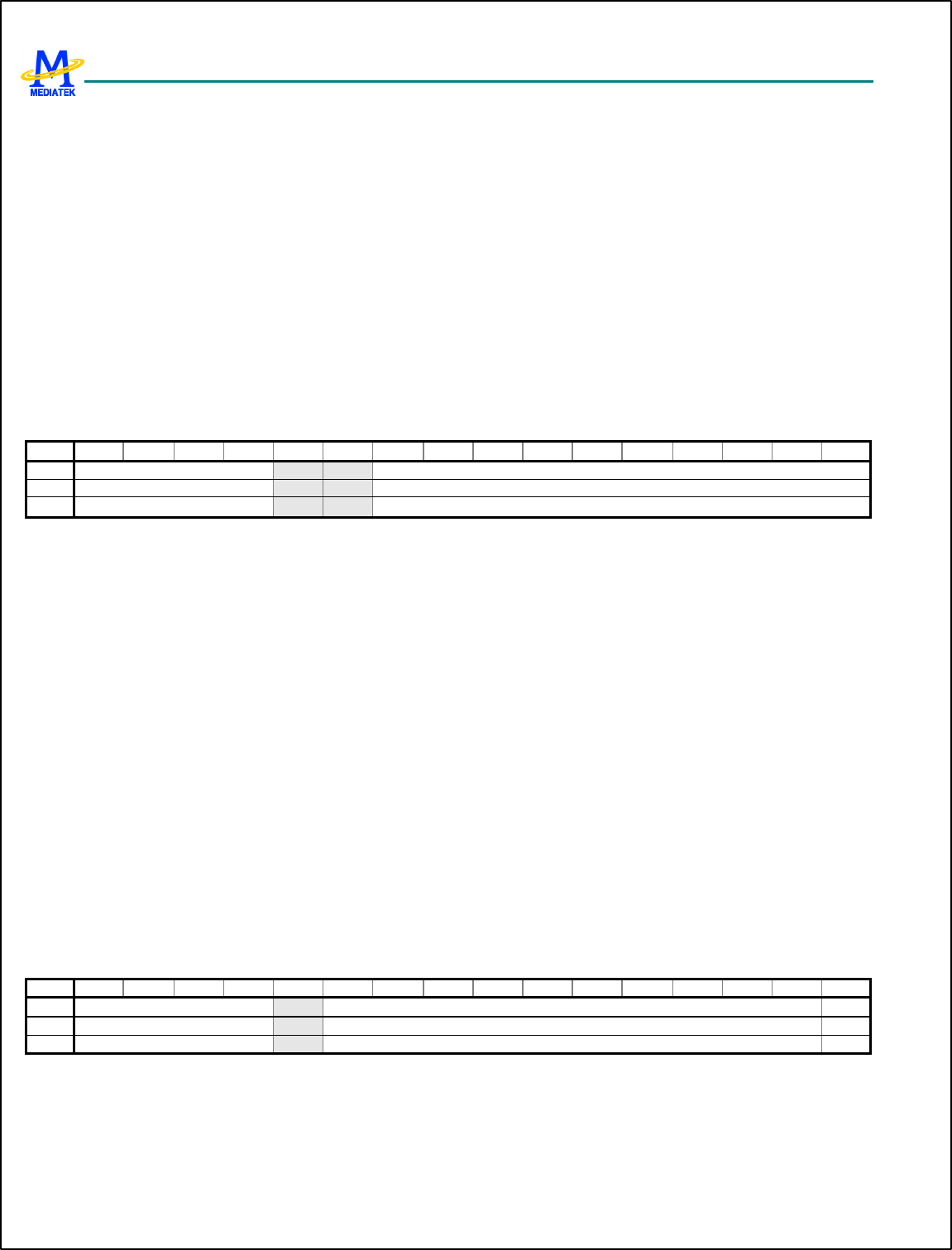

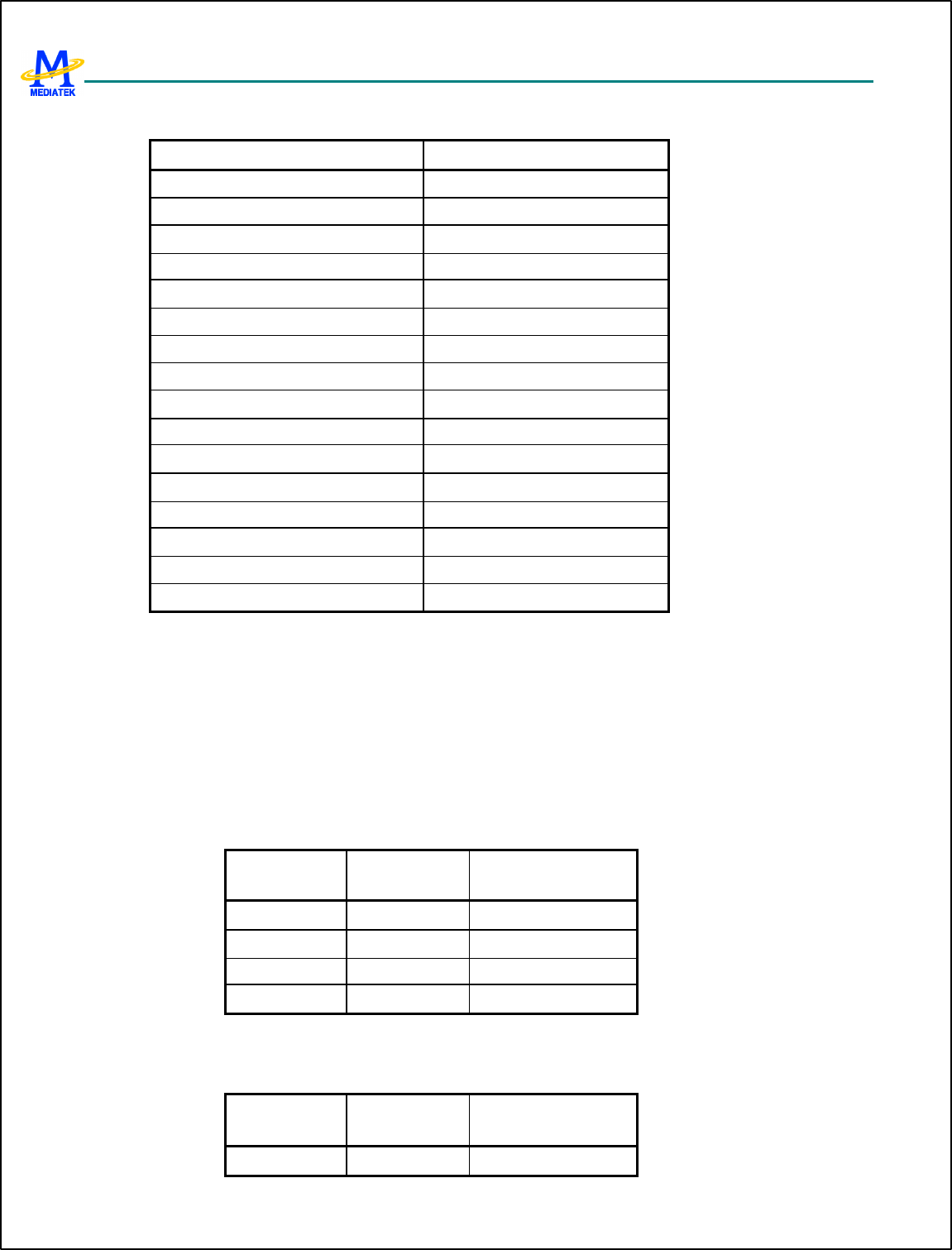

Body Size Ball Count Ball Pitch Ball Dia. Package Thk. Stand Off Substrate Thk.

D E N e b A (Max.) A1 C

13 13 282 0.65 0.3 1.4 0.3 0.36

Table 1 Definition of TFBGA 13mm*13mm, 282-ball, 0.65 mm pitch Package (Unit: mm)

MT6217 GSM/GPRS Baseband Processor Data Sheet Revision 1.01

17/349 MediaTek Inc. Confidential

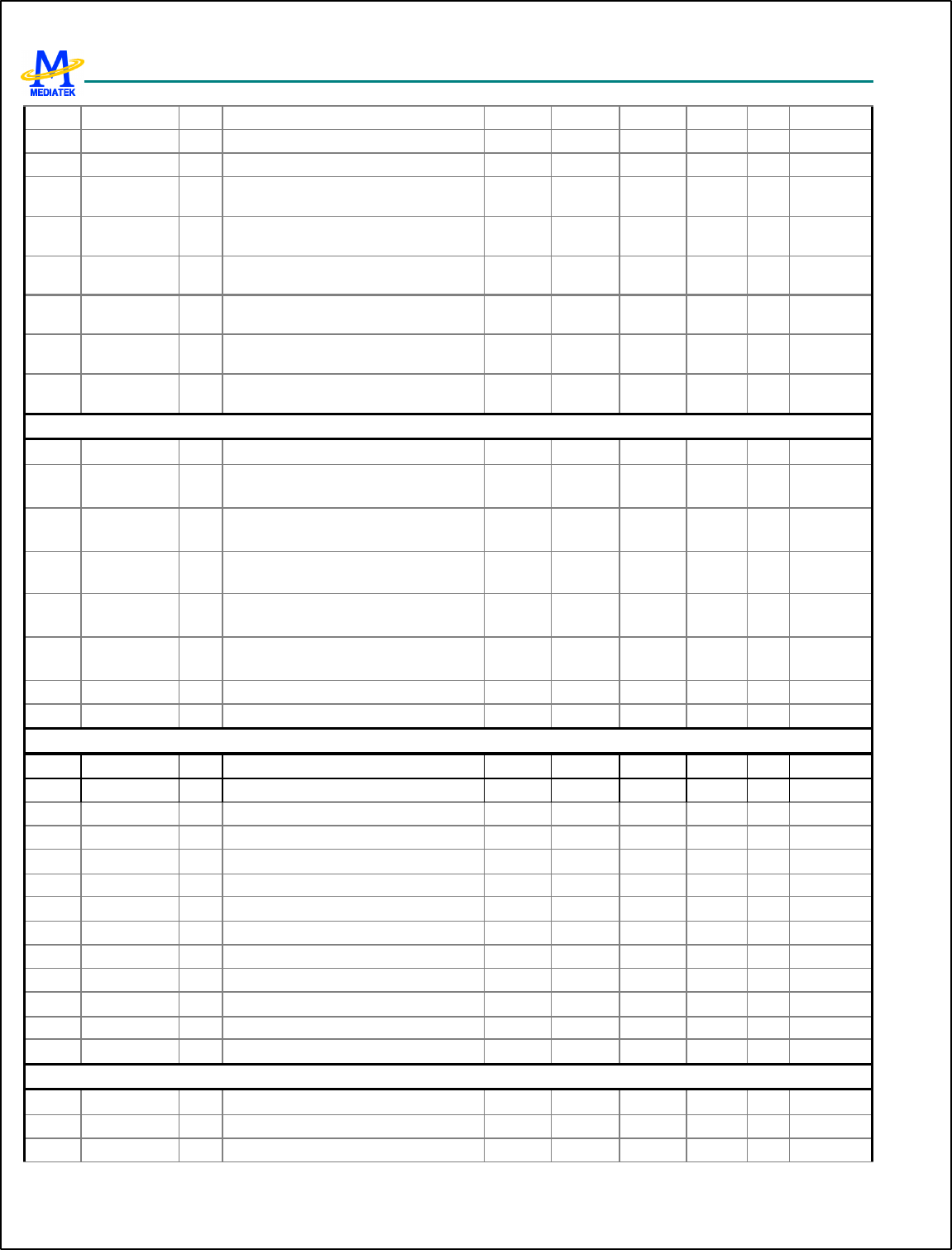

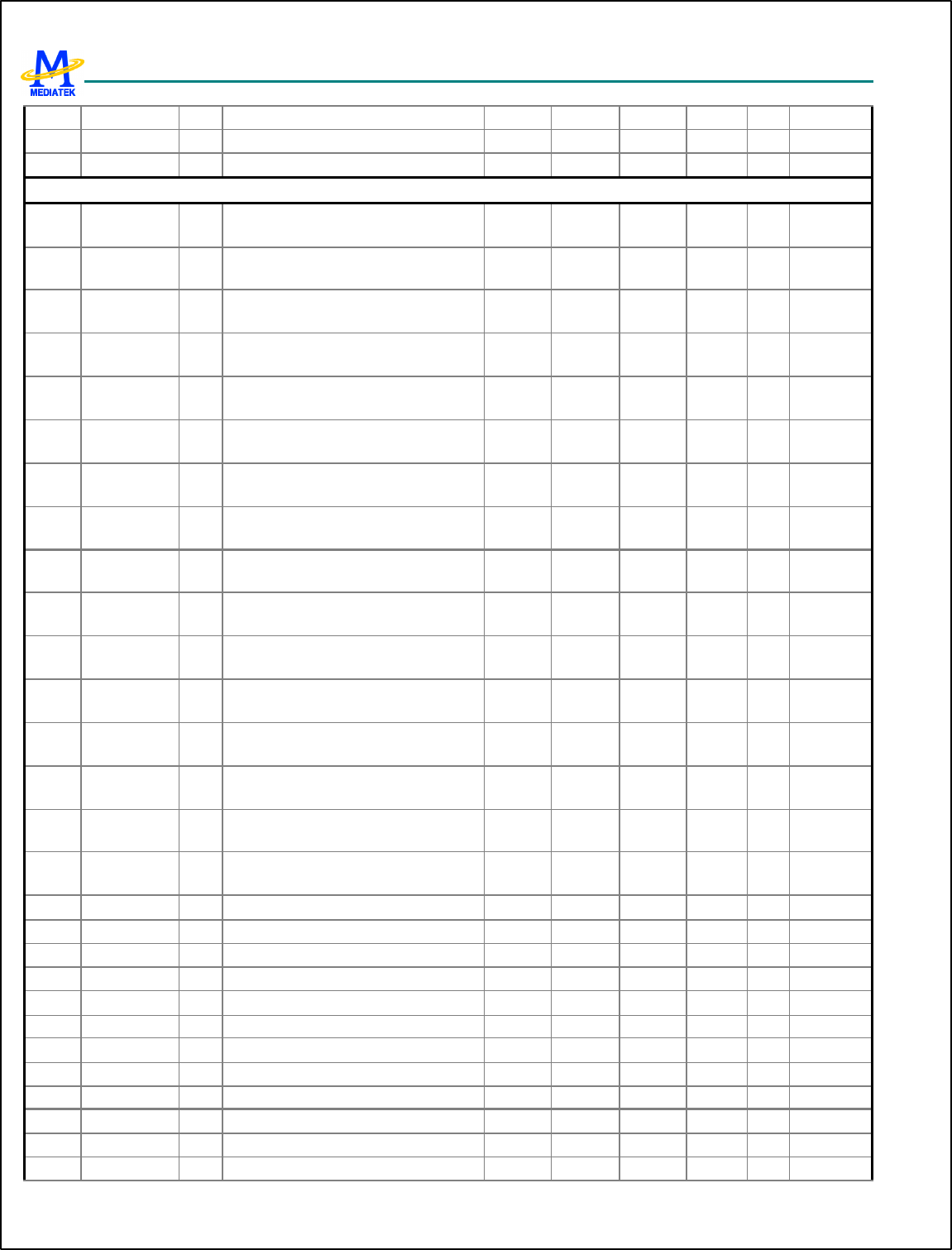

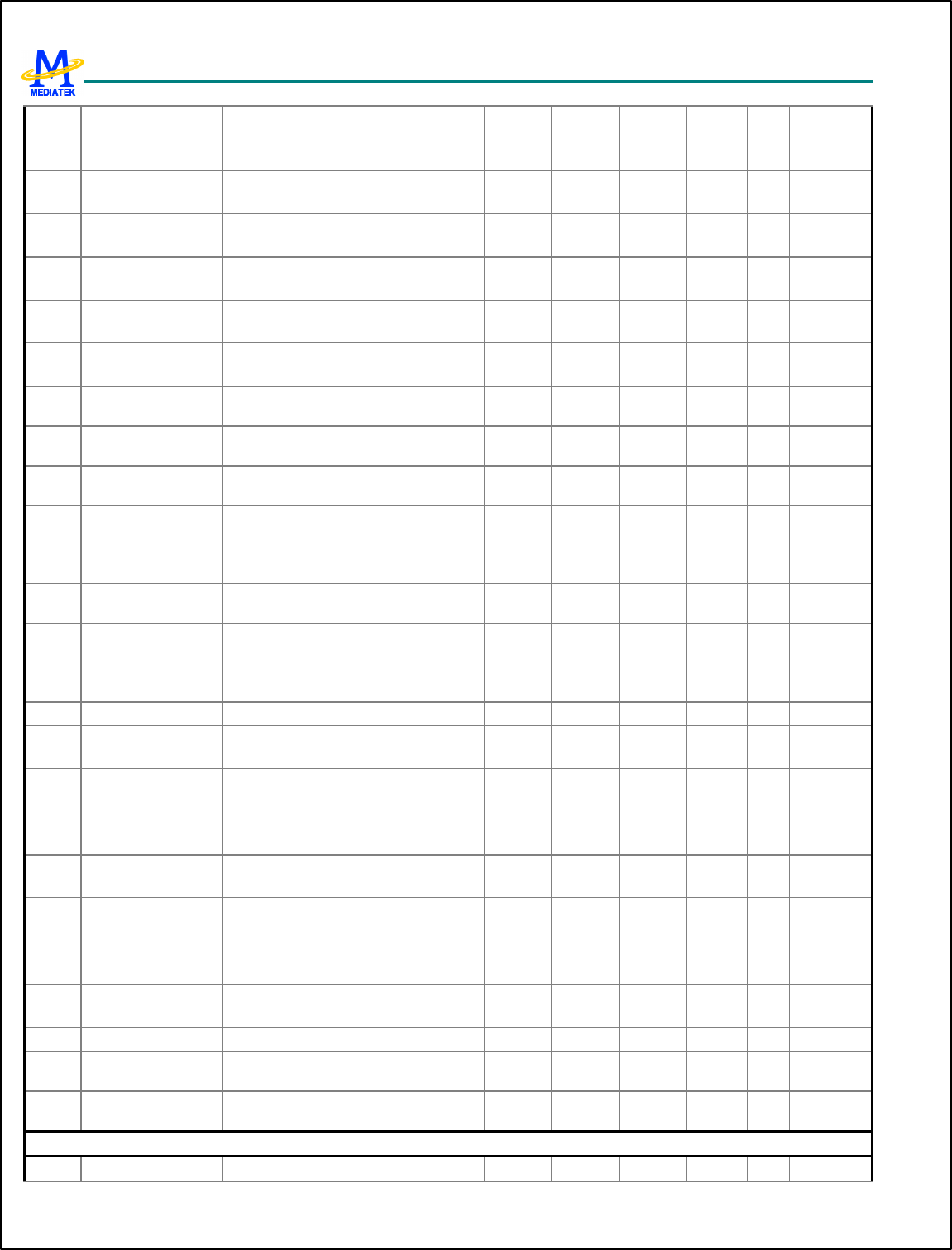

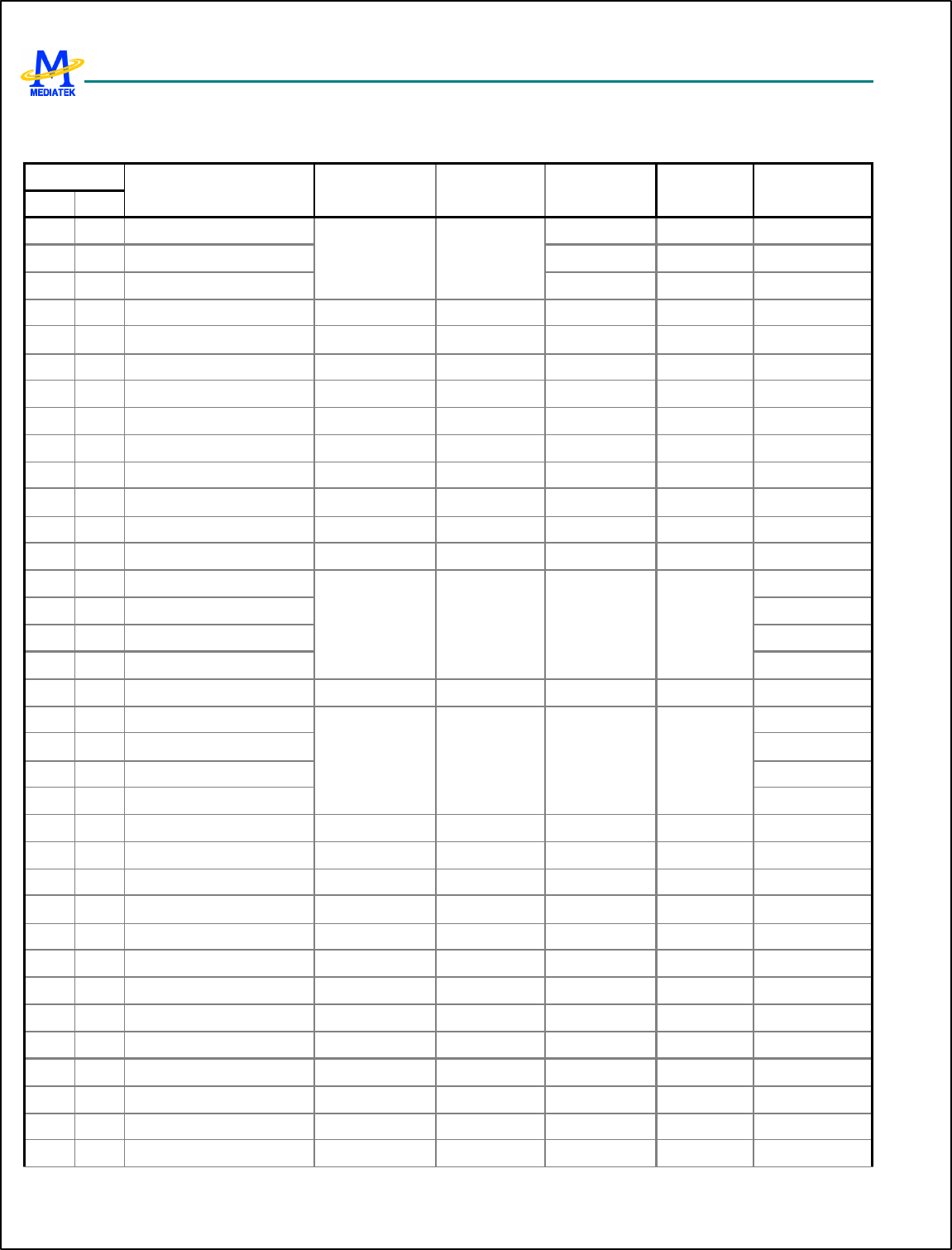

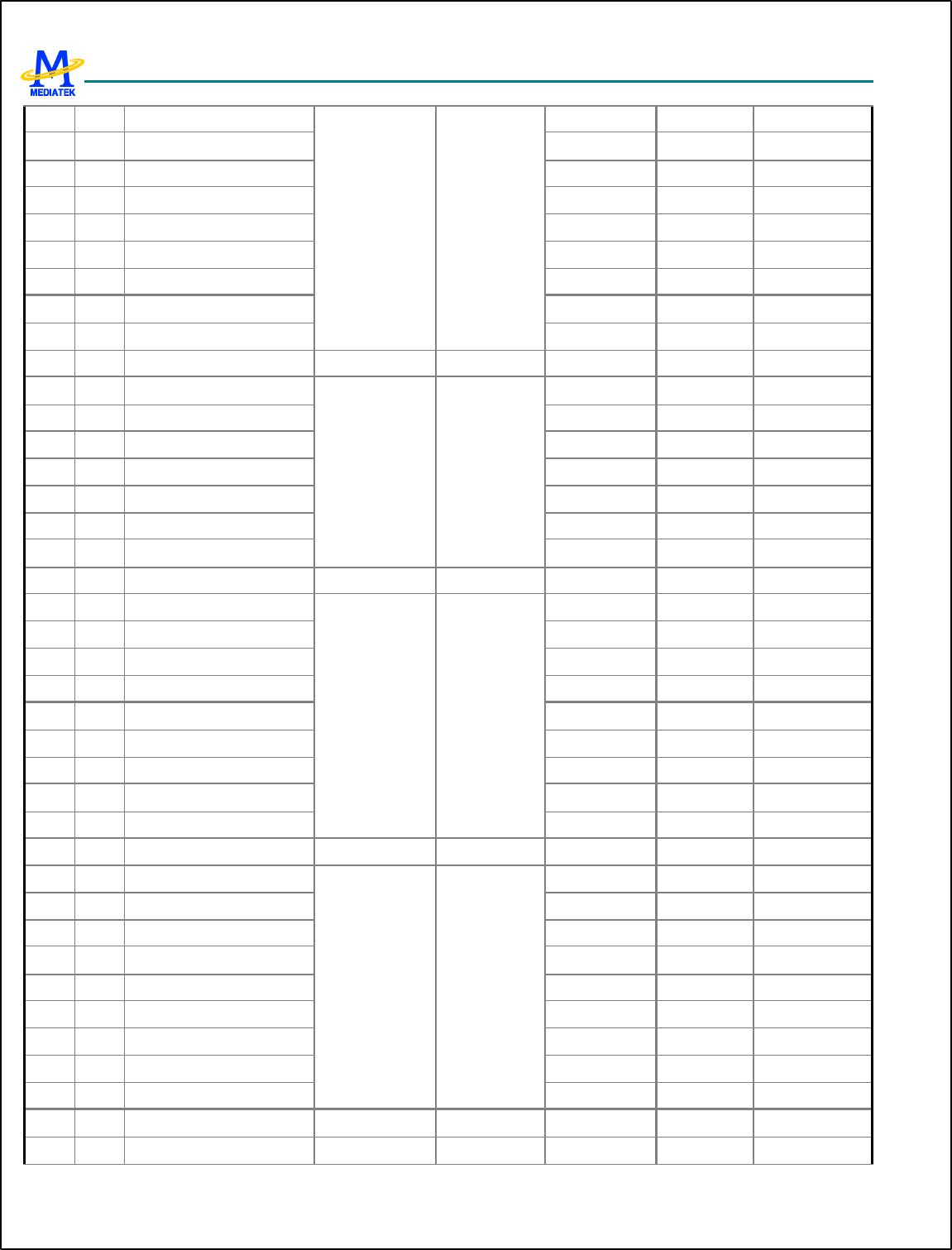

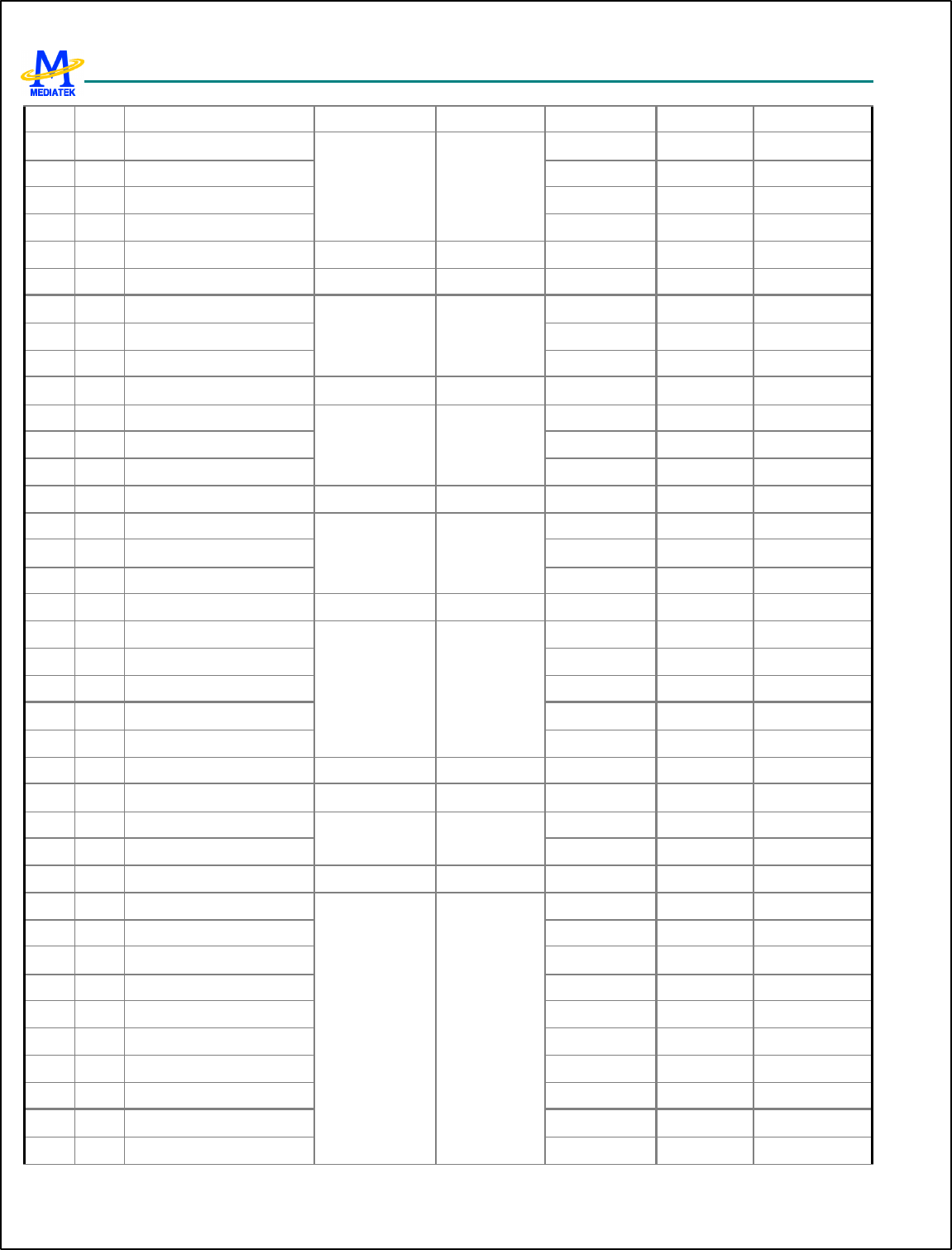

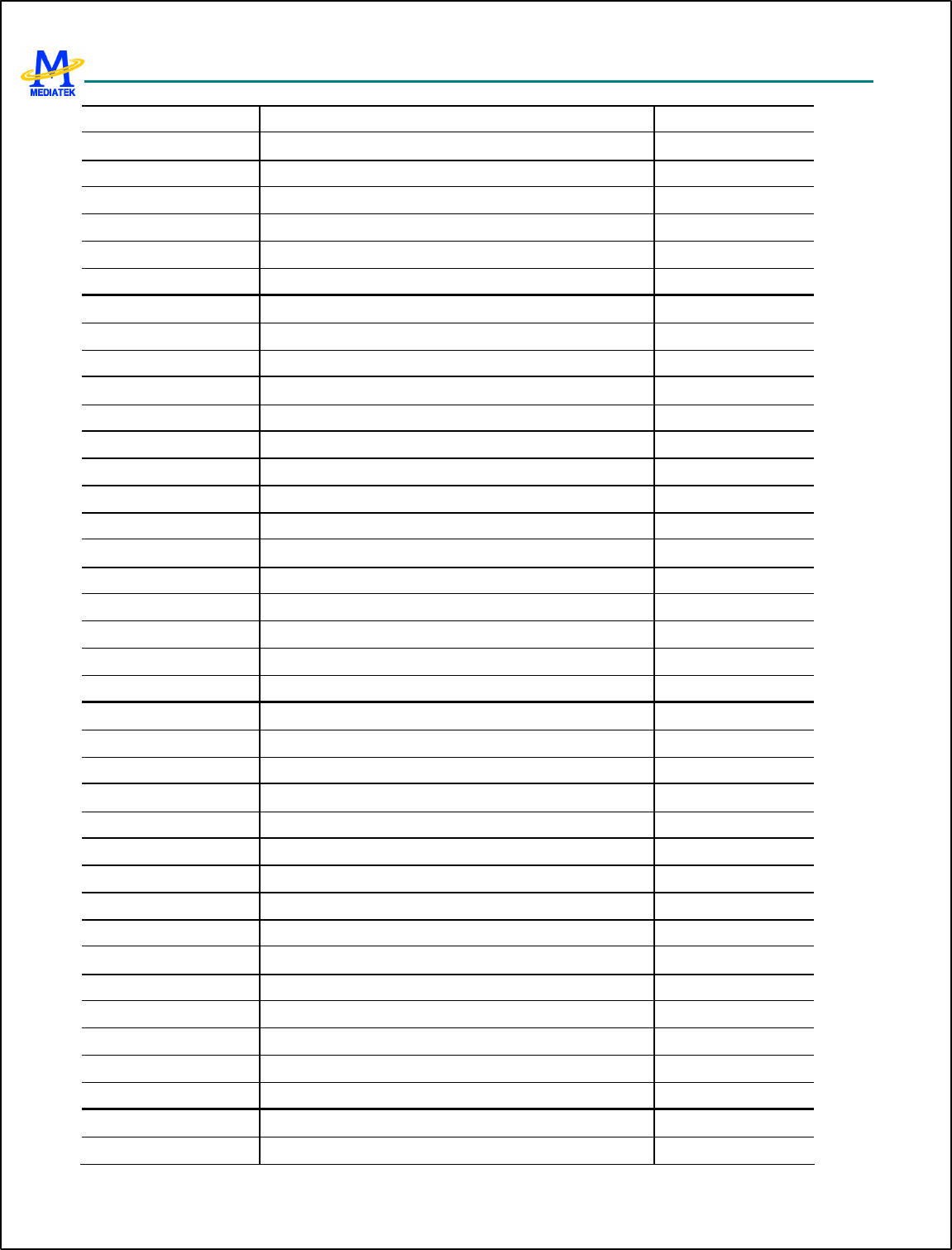

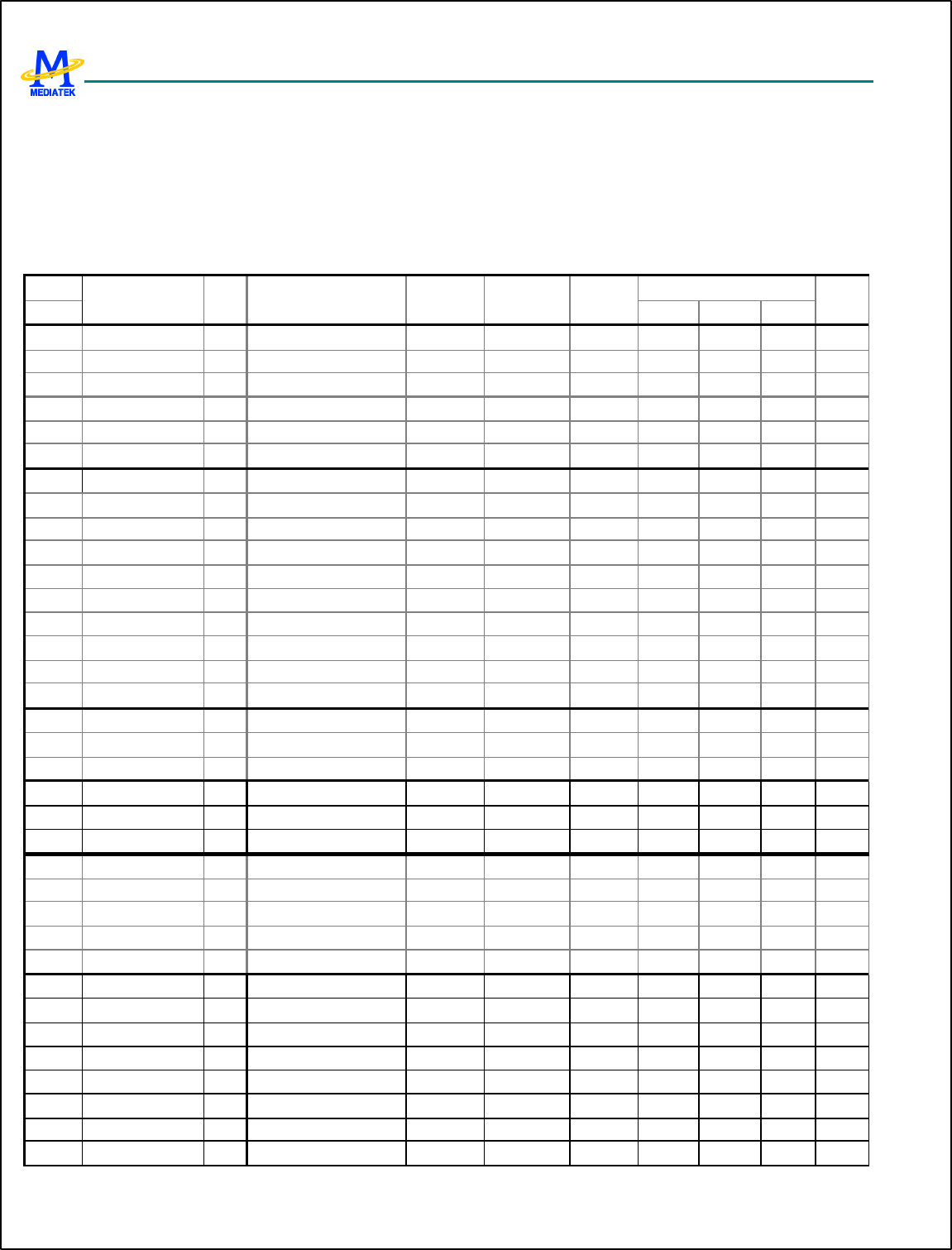

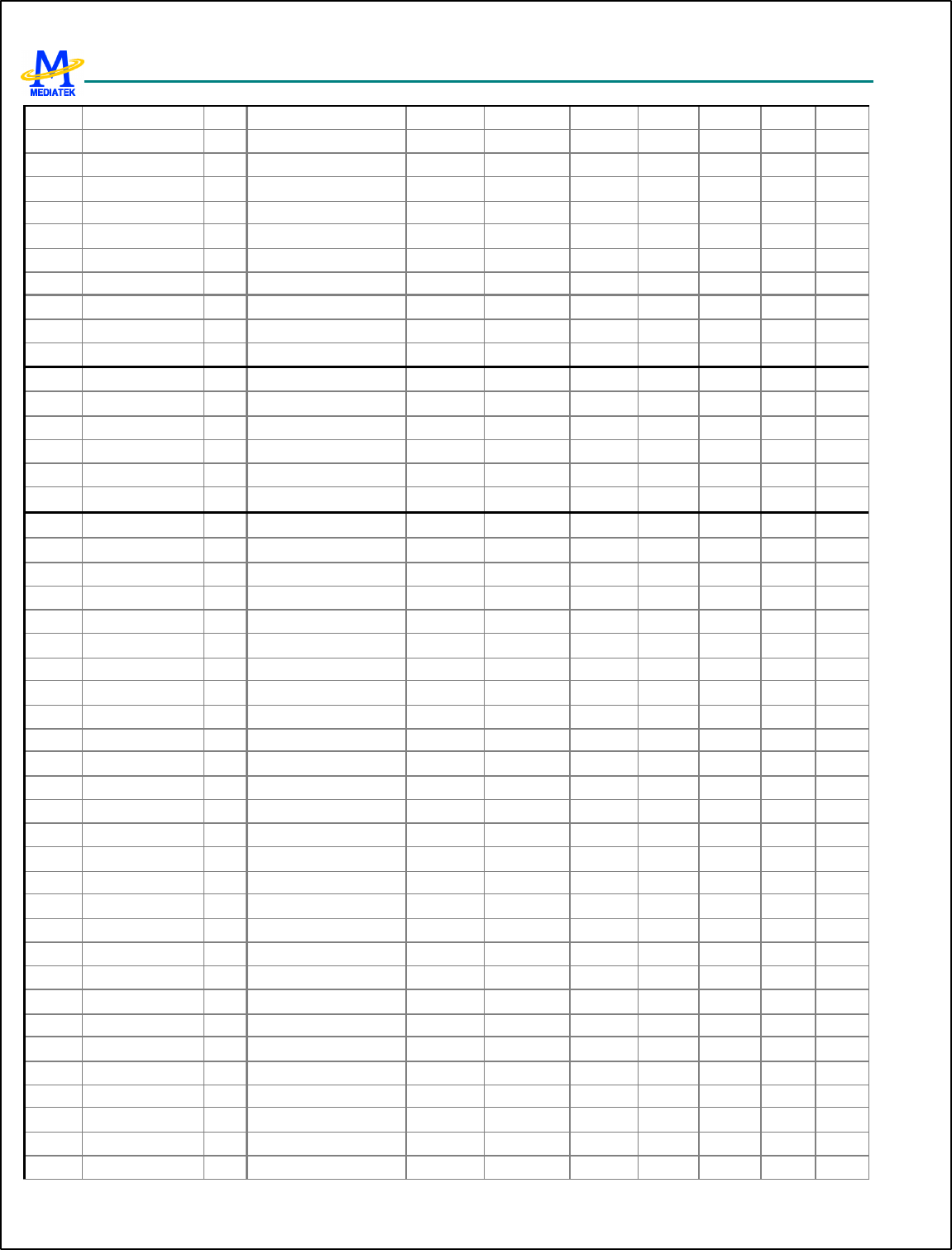

2.2 Pin Description

Ball

13X13 Name Dir Description Mode0 Mode1 Mode2 Mode3 Pull Reset

JTAG Port

E4 JTRST# I JTAG test port reset input PD Input

E3 JTCK I JTAG test port clock input PU Input

E2 JTDI I JTAG test port data input PU Input

E1 JTMS I JTAG test port mode switch PU Input

F5 JTDO O JTAG test port data output 0

F4 JRTCK O JTAG test port returned clock output 0

RF Parallel Control Unit

F3 BPI_BUS0 O RF hard-wire control bus 0 0

F2 BPI_BUS1 O RF hard-wire control bus 1 0

G5 BPI_BUS2 O RF hard-wire control bus 2 0

G4 BPI_BUS3 O RF hard-wire control bus 3 0

G3 BPI_BUS4 O RF hard-wire control bus 4 0

G2 BPI_BUS5 O RF hard-wire control bus 5 0

G1 BPI_BUS6 IO RF hard-wire control bus 6 GPIO10 BPI_BU

S6 PD Input

H5 BPI_BUS7 IO RF hard-wire control bus 7 GPIO11 BPI_BU

S7 6.5MHz 26MHz PD Input

H4 BPI_BUS8 IO RF hard-wire control bus 8 GPIO12 BPI_BU

S8

13MHz 26MHz PD Input

H3 BPI_BUS9 IO RF hard-wire control bus 9 GPIO13 BPI_BU

S9

BSI_CS

1

PD Input

RF Serial Control Unit

H1 BSI_CS0 O RF 3-wire interface chip select 0 0

J5 BSI_DATA O RF 3-wire interface data output 0

J4 BSI_CLK O RF 3-wire interface clock output 0

PWM Interface

R3 PWM1 IO Pulse width modulated signal 1 GPIO2

1

PWM1 DSP_G

PO0

TBTX

FS

PD Input

R2 PWM2 IO Pulse width modulated signal 2 GPIO2

2

PWM2 DSP_G

PO1

TBRX

EN

PD Input

T4 ALERTER IO Pulse width modulated signal for buzzer GPIO2

3

ALERT

ER

DSP_G

PO2

BTRX

FS

PD Input

Serial LCD/PM IC Interface

J3 LSCK IO Serial display interface data output GPIO16 LSCK TBTXE

N PU Input

J2 LSA0 IO Serial display interface address output GPIO17 LSA0 TDTIR

Q

PU Input

J1 LSDA IO Serial display interface clock output GPIO18 LSDA TCTIR

Q2 PU Input

K4 LSCE0# IO Serial display interface chip select 0

output GPIO19 LSCE0# DSP_TI

D0 TCTIR

Q1 PU Input

K3 LSCE1# IO Serial display interface chip select 1 GPIO20 LSCE1# LPCE2# TEVTV PU Input

MT6217 GSM/GPRS Baseband Processor Data Sheet Revision 1.01

18/349 MediaTek Inc. Confidential

output AL

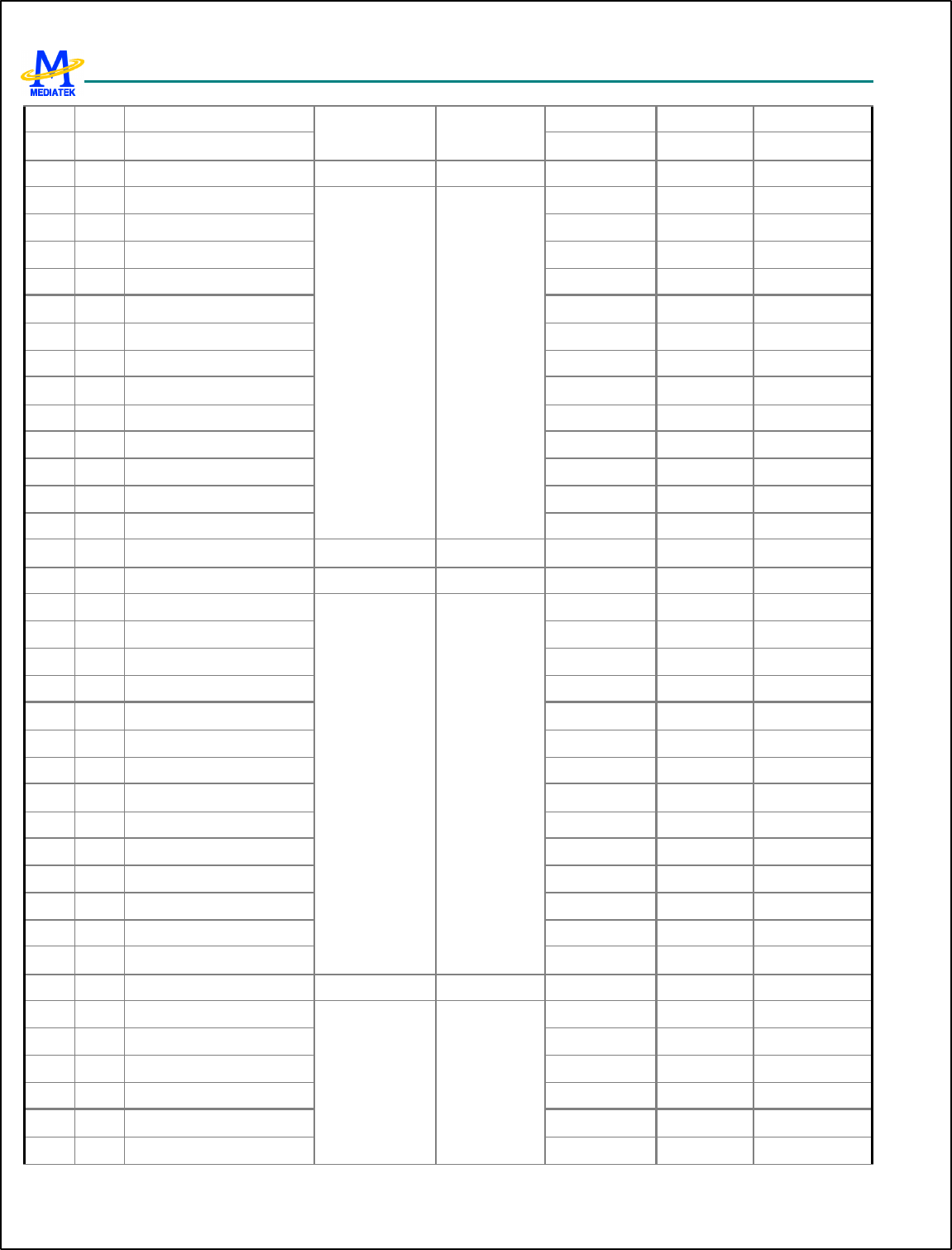

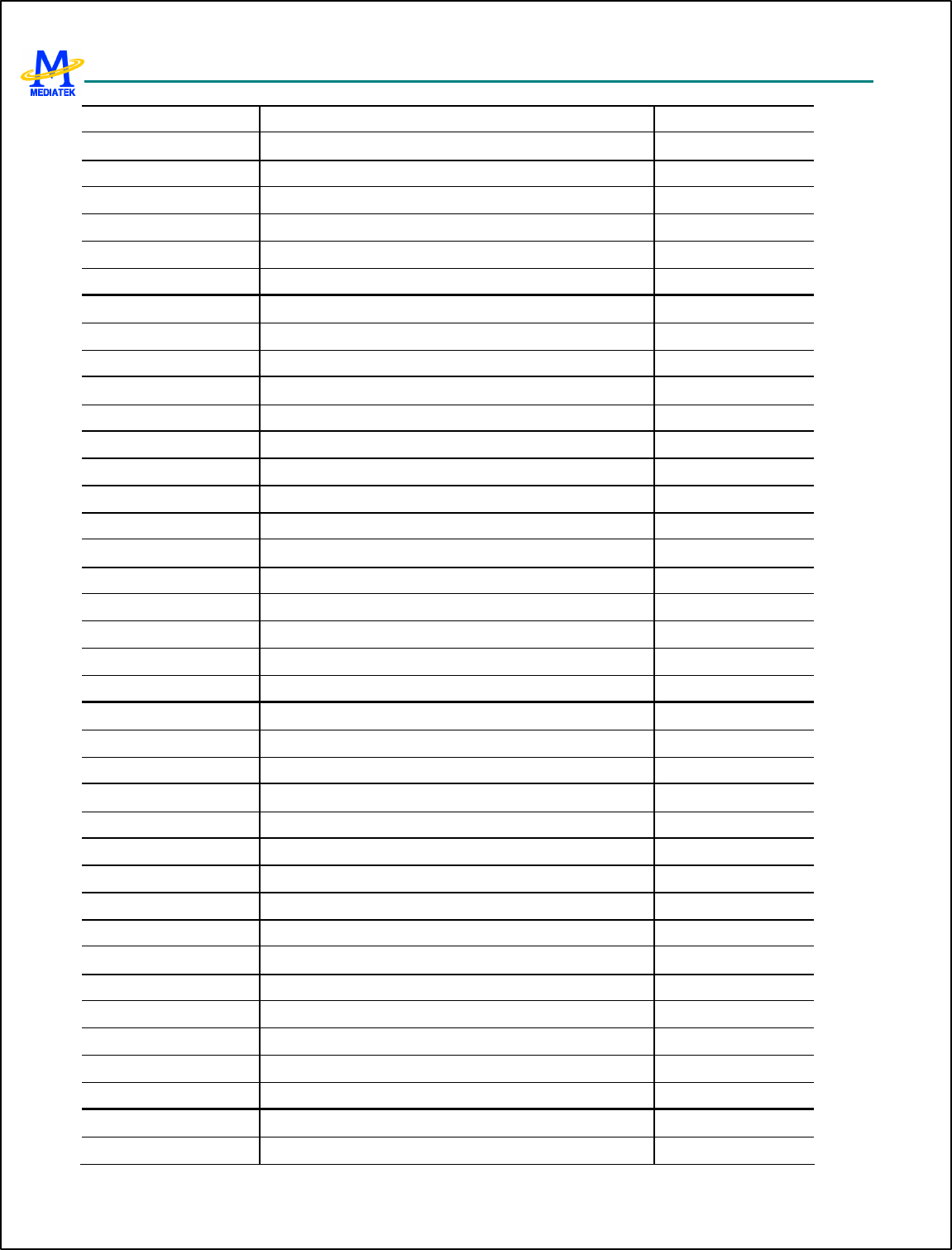

Parallel LCD/Nand-Flash Interface

K2 LPCE1# IO Parallel display interface chip select 1

output GPIO24 LPCE1# NCE1# MCU_

TD0 PU

L5 LPCE0# O Parallel display interface chip select 0

output

L4 LRST# O Parallel display interface Reset Signal

L3 LRD# O Parallel display interface Read Strobe

L2 LPA0 O Parallel display interface address output

L1 LWR# O Parallel display interface Write Strobe

L11 NLD15 IO Parallel LCD/NAND-Flash Data 15 PD

L10 NLD14 IO Parallel LCD/NAND-Flash Data 14 PD

K11 NLD13 IO Parallel LCD/NAND-Flash Data 13 PD

L9 NLD12 IO Parallel LCD/NAND-Flash Data 12 PD

J11 NLD11 IO Parallel LCD/NAND-Flash Data 11 PD

K9 NLD10 IO Parallel LCD/NAND-Flash Data 10 PD

J10 NLD9 IO Parallel LCD/NAND-Flash Data 9 PD

J9 NLD8 IO Parallel LCD/NAND-Flash Data 8 PD

M5 NLD7 IO Parallel LCD/NAND-Flash Data 7 PD

M4 NLD6 IO Parallel LCD/NAND-Flash Data 6 PD

M3 NLD5 IO Parallel LCD/NAND-Flash Data 5 PD

N5 NLD4 IO Parallel LCD/NAND-Flash Data 4 PD

N4 NLD3 IO Parallel LCD/NAND-Flash Data 3 PD

N3 NLD2 IO Parallel LCD/NAND-Flash Data 2 PD

N2 NLD1 IO Parallel LCD/NAND-Flash Data 1 PD

N1 NLD0 IO Parallel LCD/NAND-Flash Data 0 PD

P5 NRNB IO NAND-Flash Read/Busy Flag GPIO25 NRNB DSP_TI

D1 MCU_T

ID1 PU

P4 NCLE IO NAND-Flash Command Latch Signal GPIO26 NCLE DSP_TI

D2 MCU_

TID2 PD

P3 NALE IO NAND-Flash Address Latch Signal GPIO27 NALE DSP_TI

D3

MCU_

TID3 PD

P2 NWE# IO NAND-Flash Write Strobe GPIO28 NWE# DSP_TI

D4

MCU_

DID PU

P1 NRE# IO NAND-Flash Read Strobe GPIO29 NRE# DSP_TI

D5 MCU_

DFS PU

R4 NCE0# IO NAND-Flash Chip select output GPIO30 NCE0# DSP_TI

D6 MCU_

DCK PU

SIM Card Interface

L18 SIMRST O SIM card reset output 0

L17 SIMCLK O SIM card clock output 0

K15 SIMVCC O SIM card supply power control 0

K16 SIMSEL IO SIM card supply power select GPIO32 SIMSE

L

PD 0

K17 SIMDATA IO SIM card data input/output 0

Dedicated GPIO Interface

U2 GPIO0 IO General purpose input/output 0 GPIO0 DSP_GP

O3

PD Input

MT6217 GSM/GPRS Baseband Processor Data Sheet Revision 1.01

19/349 MediaTek Inc. Confidential

M19 GPIO1 IO General purpose input/output 1 GPIO1 DICK PD Input

L15 GPIO2 IO General purpose input/output 2 GPIO2 DID PD Input

L16 GPIO3 IO General purpose input/output 3 GPIO3 DIMS PD Input

C17 GPIO4 IO General purpose input/output 4 GPIO4 DSP_CK

L

DSPLC

K

TRASD

4 PD Input

A19 GPIO5 IO General purpose input/output 5 GPIO5 AHB_C

LK

DSPLD3 TRASD

3 PD Input

B18 GPIO6 IO General purpose input/output 6 GPIO6 ARM_C

LK DSPLD2 TRASD

2 PD Input

B17 GPIO7 IO General purpose input/output 7 GPIO7 SLOW_

CK DSPLD1 TRASD

1 PD Input

A18 GPIO8 IO General purpose input/output 19 GPIO8 F32K_C

K DSPLD0 TRASD

0 PD Input

A17 GPIO9 IO General purpose input/output 21 GPIO9 TRARS

YN C PD Input

Miscellaneous

U1 SYSRST# I System reset input active low Input

R18 WATCHD

OG# O Watchdog reset output 1

T3 SRCLKEN

AN O External TCXO enable output active low GPO1 SRCLK

ENAN 0

T1 SRCLKEN

A O External TCXO enable output active

high GPO0 SRCLK

ENA 1

T2 SRCLKEN

AI IO External TCXO enable input GPIO31 SRCLK

ENAI PD

D3 TESTMOD

E I Test Mode control input PD

D15 ESDM_CK O Internal monitor clock output N.C.

E5 IBOOT I Boot Device Configuration Input Input

Keypad Interface

G17 KCOL6 I Keypad column 6 PU Input

G18 KCOL5 I Keypad column 5 PU Input

G19 KCOL4 I Keypad column 4 PU Input

F15 KCOL3 I Keypad column 3 PU Input

F16 KCOL2 I Keypad column 2 PU Input

F17 KCOL1 I Keypad column 1 PU Input

F18 KCOL0 I Keypad column 0 PU Input

F19 KROW5 O Keypad row 5 0

E16 KROW4 O Keypad row 4 0

E17 KROW3 O Keypad row 3 0

E18 KROW2 O Keypad row 2 0

D16 KROW1 O Keypad row 1 0

D19 KROW0 O Keypad row 0 0

External Interrupt Interface

V1 EINT0 I External interrupt 0 PU Input

U3 EINT1 I External interrupt 1 PU Input

W1 EINT2 I External interrupt 2 PU Input

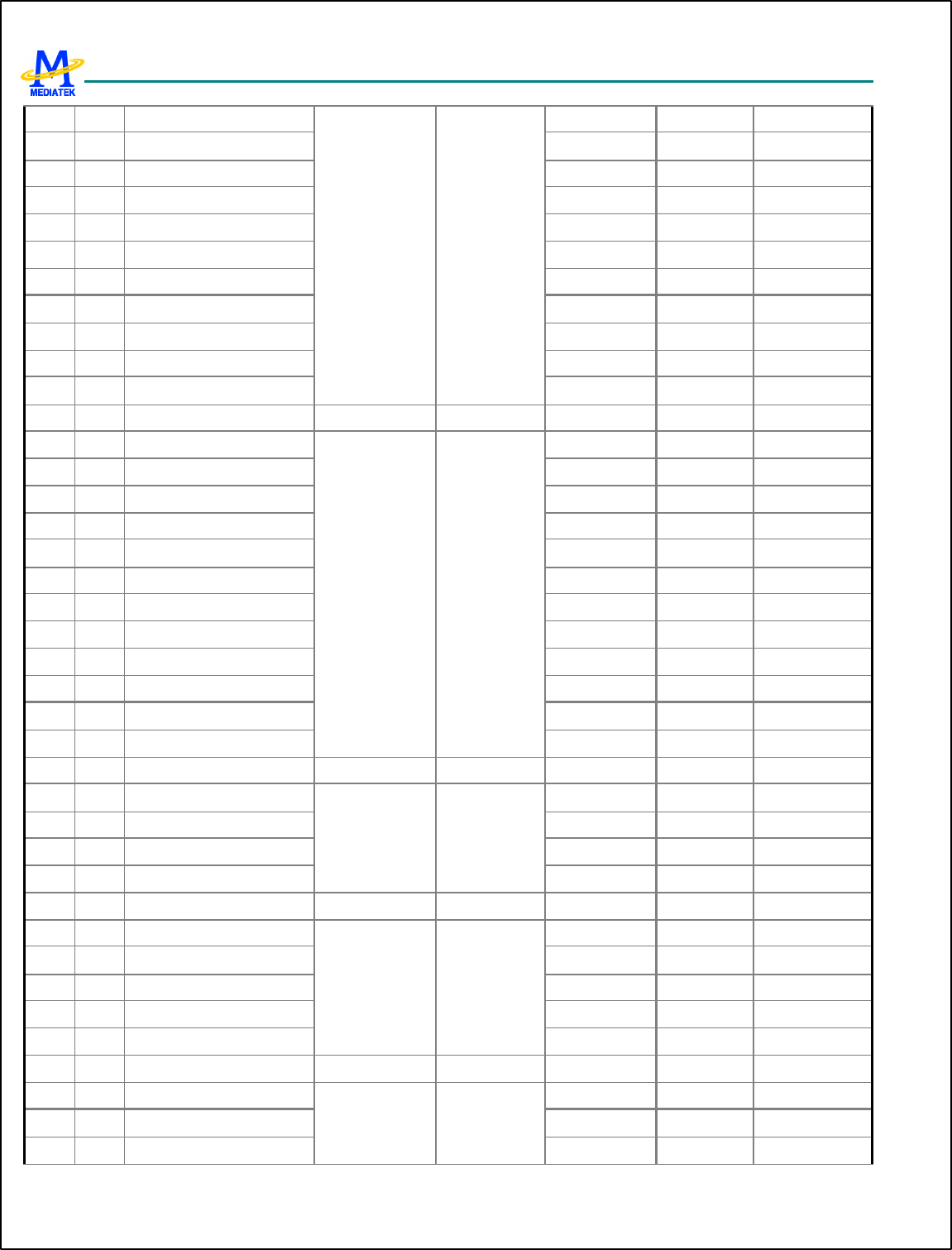

MT6217 GSM/GPRS Baseband Processor Data Sheet Revision 1.01

20/349 MediaTek Inc. Confidential

V2 EINT3 I External interrupt 3 PU Input

R5 MIRQ IO Interrupt to MCU GPIO41 MIRQ 13MHz 6.5MHz PU Input

R17 MFIQ IO Interrupt to MCU GPIO42 MFIQ PU Input

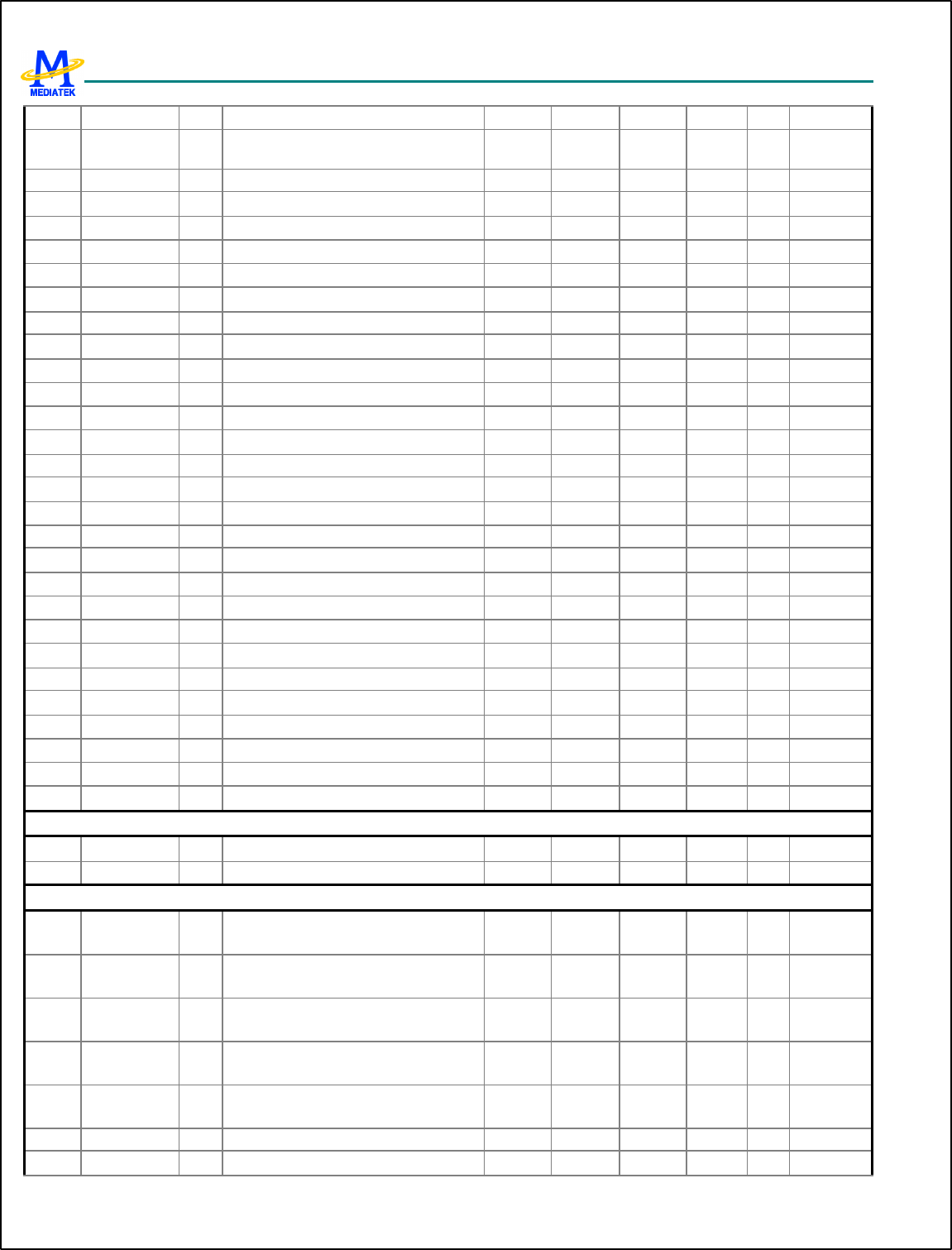

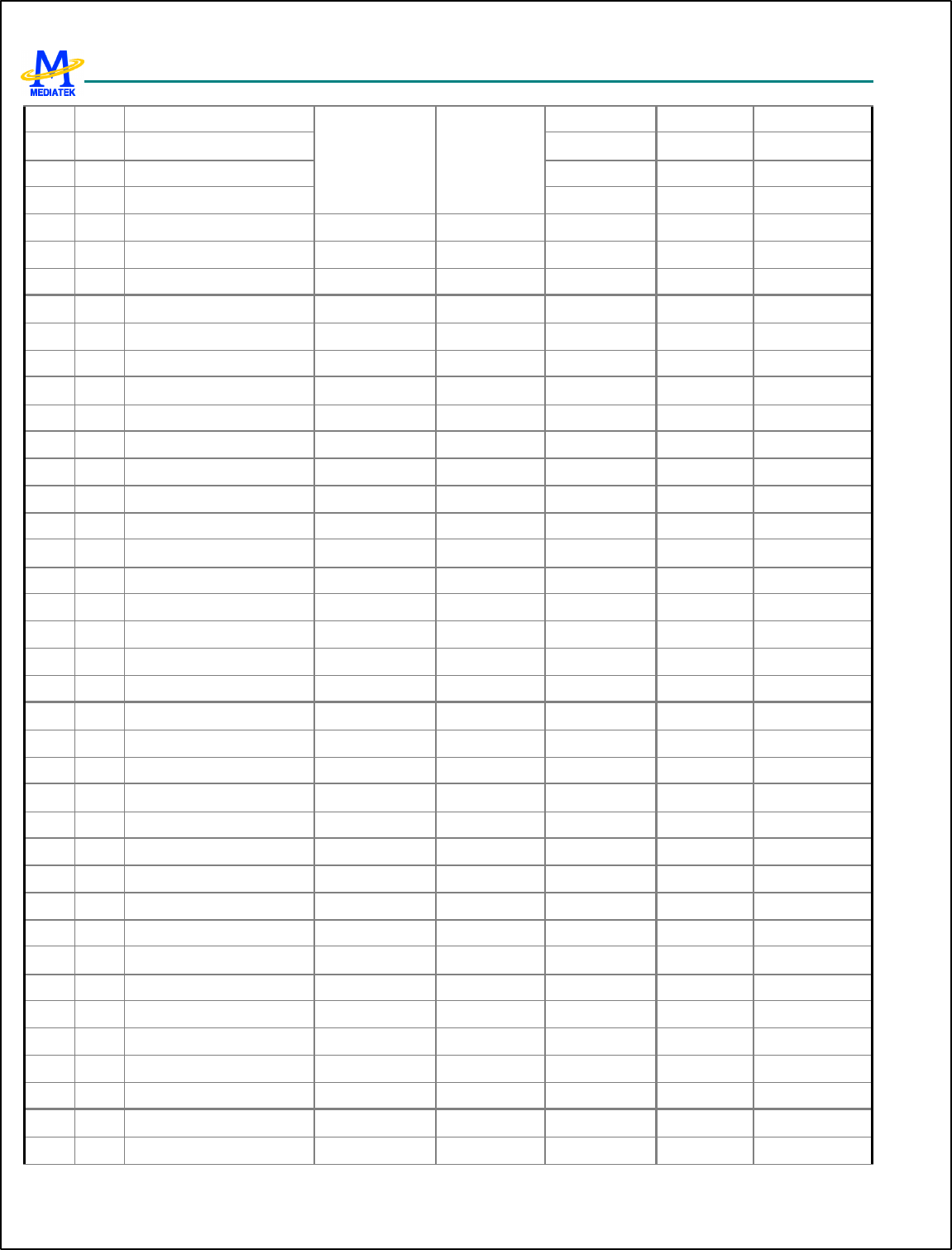

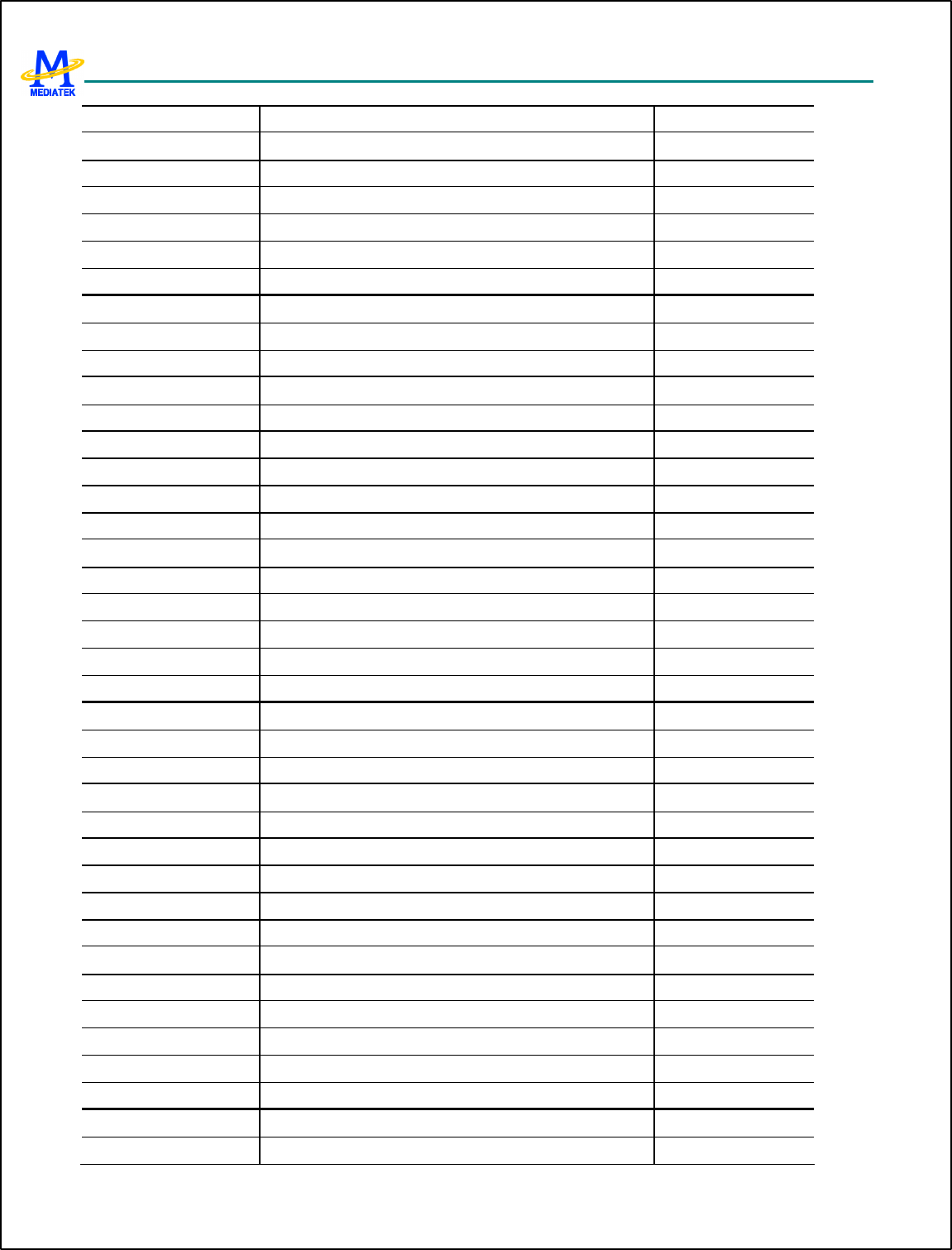

External Memory Interface

R16 ED0 IO External memory data bus 0 PU/

PD

Input

R15 ED1 IO External memory data bus 1 PU/

PD

Input

T19 ED2 IO External memory data bus 2 PU/

PD

Input

T17 ED3 IO External memory data bus 3 PU/

PD

Input

U19 ED4 IO External memory data bus 4 PU/

PD

Input

U18 ED5 IO External memory data bus 5 PU/

PD

Input

V18 ED6 IO External memory data bus 6 PU/

PD

Input

W19 ED7 IO External memory data bus 7 PU/

PD

Input

U17 ED8 IO External memory data bus 8 PU/

PD

Input

V17 ED9 IO External memory data bus 9 PU/

PD

Input

W17 ED10 IO External memory data bus 10 PU/

PD

Input

T16 ED11 IO External memory data bus 11 PU/

PD

Input

W16 ED12 IO External memory data bus 12 PU/

PD

Input

T15 ED13 IO External memory data bus 13 PU/

PD

Input

U15 ED14 IO External memory data bus 14 PU/

PD

Input

V15 ED15 IO External memory data bus 15 PU/

PD

Input

U14 ERD# O External memory read strobe 1

W14 EWR# O External memory write strobe 1

R13 ECS0# O External memory chip select 0 1

T13 ECS1# O External memory chip select 1 1

U13 ECS2# O External memory chip select 2 1

V13 ECS3# O External memory chip select 3 1

R12 ECS4# O External memory chip select 4 1

T12 ECS5# O External memory chip select 5 1

U12 ECS6# O External memory chip select 6 1

W12 ECS7# IO External memory chip select 7 GPIO40 ECS7# PU 1

R14 ELB# O External memory lower byte strobe 1

T14 EUB# O External memory upper byte strobe 1

MT6217 GSM/GPRS Baseband Processor Data Sheet Revision 1.01

21/349 MediaTek Inc. Confidential

T11 EPDN# O Power Down Control Signal for PSRAM GPO2 EPDN# 0

U11 EADV# O Address valid for burst mode flash

memory 1

V11 ECLK O Clock for flash memory 0

R10 EA0 O External memory address bus 0 0

T10 EA1 O External memory address bus 1 0

U10 EA2 O External memory address bus 2 0

W10 EA3 O External memory address bus 3 0

T9 EA4 O External memory address bus 4 0

U9 EA5 O External memory address bus 5 0

V9 EA6 O External memory address bus 6 0

R8 EA7 O External memory address bus 7 0

T8 EA8 O External memory address bus 8 0

W8 EA9 O External memory address bus 9 0

R7 EA10 O External memory address bus 10 0

T7 EA11 O External memory address bus 11 0

U7 EA12 O External memory address bus 12 0

V7 EA13 O External memory address bus 13 0

R6 EA14 O External memory address bus 14 0

T6 EA15 O External memory address bus 15 0

U6 EA16 O External memory address bus 16 0

W6 EA17 O External memory address bus 17 0

T5 EA18 O External memory address bus 18 0

U5 EA19 O External memory address bus 19 0

V5 EA20 O External memory address bus 20 0

W5 EA21 O External memory address bus 21 0

V4 EA22 O External memory address bus 22 0

U4 EA23 O External memory address bus 23 0

W3 EA24 O External memory address bus 24 0

W2 EA25 O External memory address bus 25 0

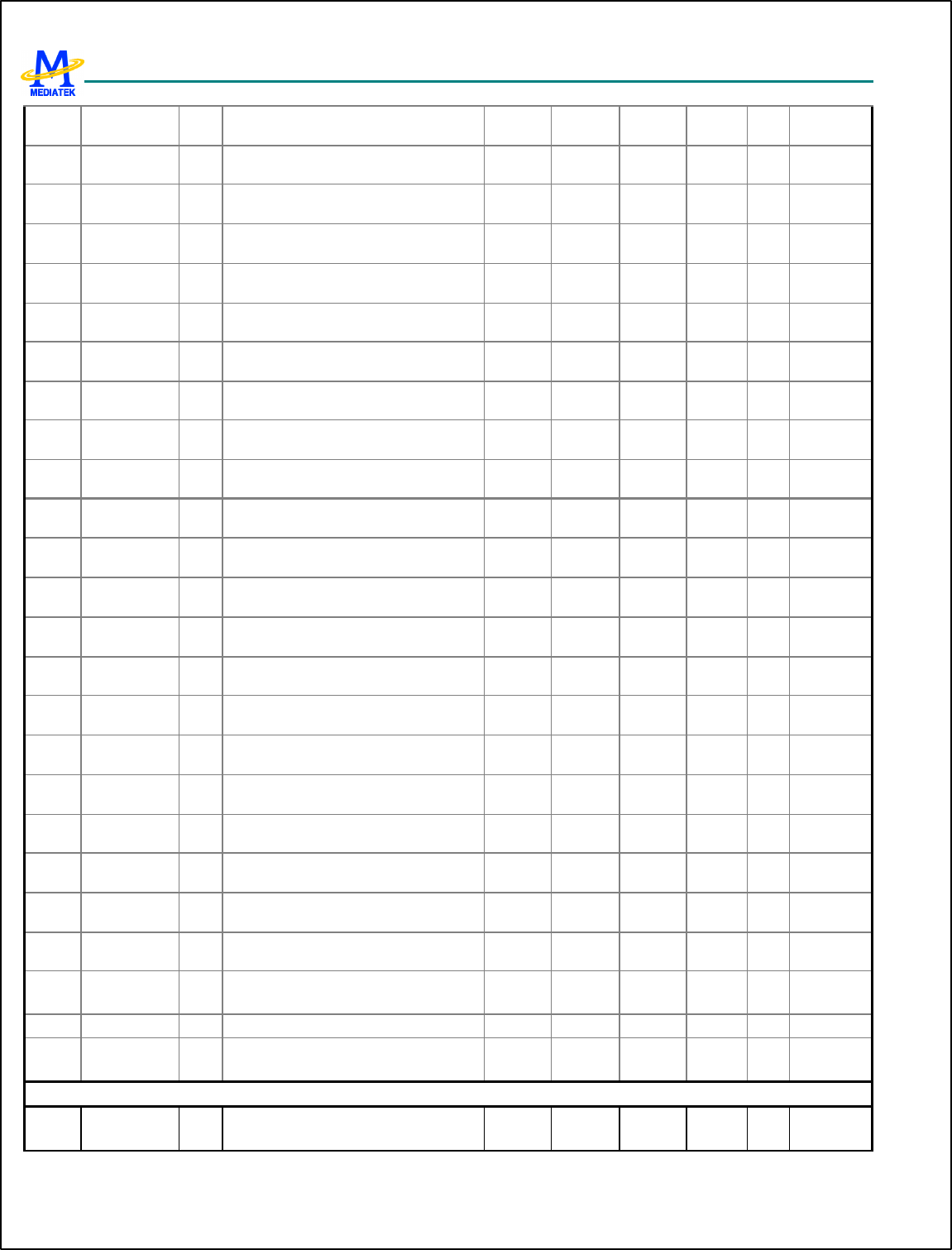

USB Interface

P16 USB_DP IO USB D+ Input/Output

P17 USB_DM IO USB D- Input/Output

Memory Card Interface

P19 MCCM0 IO SD Command/MS Bus State Output PU/

PD

N15 MCDA0 IO SD Serial Data IO 0/MS Serial Data IO PU/

PD

N16 MCDA1 IO SD Serial Data IO 1 PU/

PD

N17 MCDA2 IO SD Serial Data IO 2 PU/

PD

N18 MCDA3 IO SD Serial Data IO 3 PU/

PD

N19 MCCK O SD Serial Clock/MS Serial Clock Output

M16 MCPWRO O SD Power On Control Output

MT6217 GSM/GPRS Baseband Processor Data Sheet Revision 1.01

22/349 MediaTek Inc. Confidential

N

M17 MCWP I SD Write Protect Input GPIO15 MCWP PU

M18 MCINS I SD Card Detect Input GPIO14 MCINS PU

UART Interface

K18 URXD1 I UART 1 receive data PU Input

K19 UTXD1 O UART 1 transmit data 1

J16 UCTS1 I UART 1 clear to send PU Input

J17 URTS1 O UART 1 request to send 1

J18 URXD2 IO UART 2 receive data GPIO35 URXD2 UCTS3 PU Input

J19 UTXD2 IO UART 2 transmit data GPIO36 UTXD2 URTS3 PU Input

H15 URXD3 IO UART 3 receive data GPIO33 URXD3 PU Input

H16 UTXD3 IO UART 3 transmit data GPIO34 UTXD3 PU Input

H17 IRDA_RXD IO IrDA receive data GPIO37 IRDA_R

XD UCTS2 PU Input

G15 IRDA_TXD IO IrDA transmit data GPIO38 IRDA_T

XD

URTS2 PU Input

G16 IRDA_PDN IO IrDA Power Down Control GPIO39 IRDA_P

DN

PU Input

Digital Audio Interface

D17 DAICLK IO DAI clock output GPIO43 DAICLK TDMA_

CK TRACL

K PU Input

D18 DAIPCM O

UT

IO DAI pcm data out GPIO44 DAIPC

MOUT

TDMA_

D1

TRASY

NC

PD Input

C19 DAIPCMIN IO DAI pcm data input GPIO45 DAIPC

MIN

TDMA_

D2

TRASD

7

PU Input

C18 DAIRST IO DAI reset signal input GPIO47 DAIRST TDMA_

FS TRASD

6 PU Input

B19 DAISYNC IO DAI frame synchronization signal output GPIO46 DAISYN

C BFEPRB

O TRASD

5 PU Input

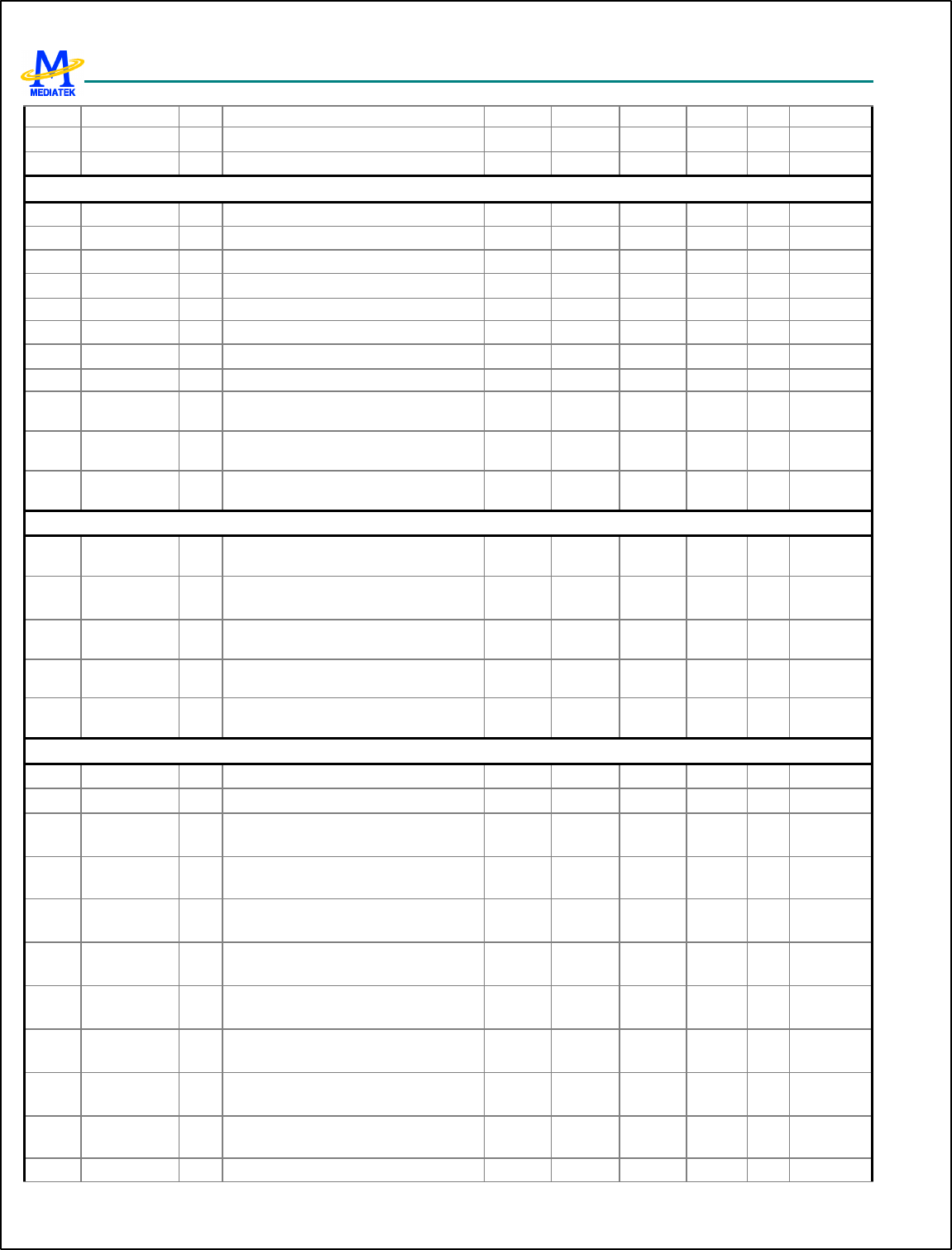

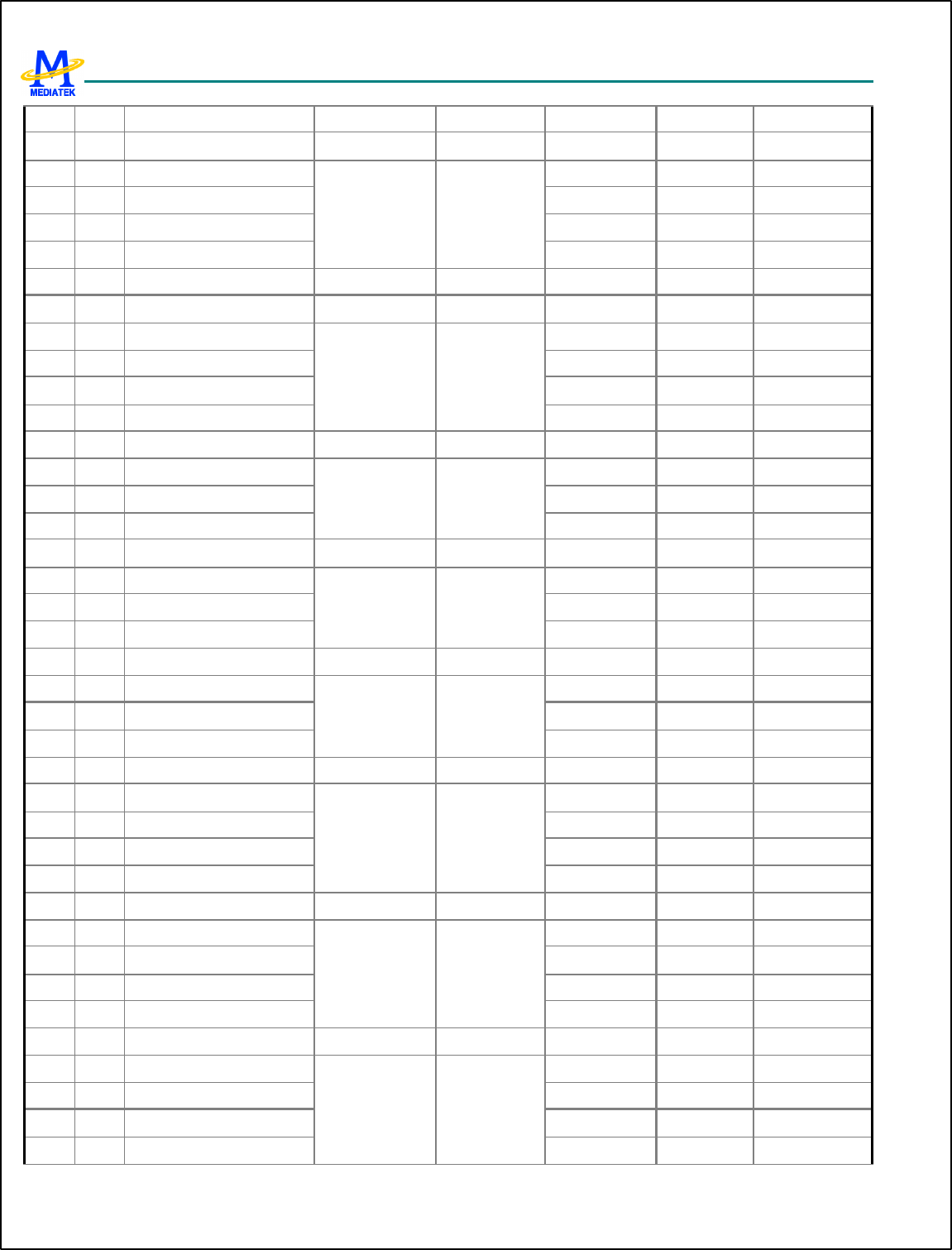

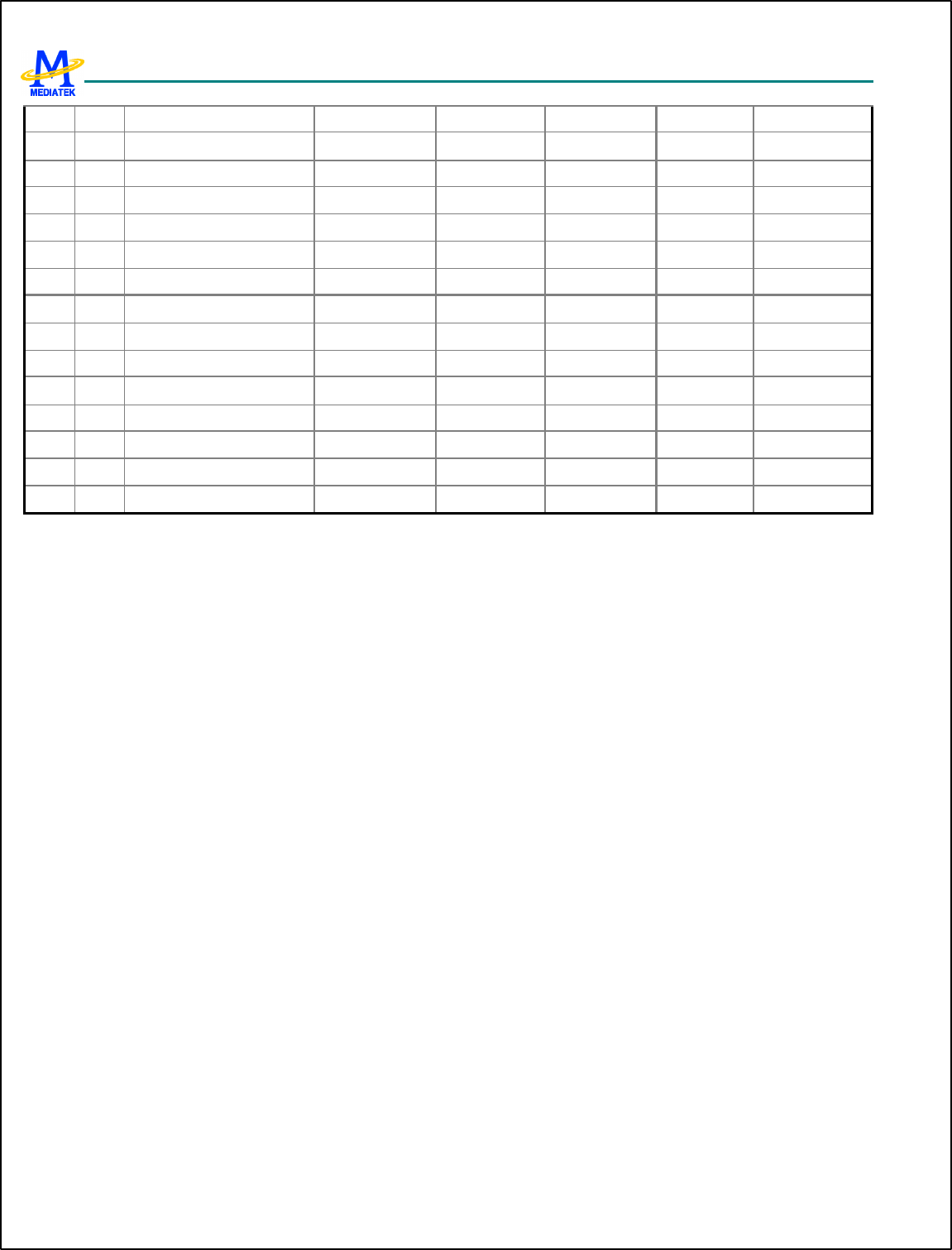

Analog Interface

B15 AU_MOUL Audio analog output left channel

A15 AU_MOUR Audio analog output right channel

C14 AU_M_BY

P Audio DAC bypass pin

B14 AU_FMIN

L FM radio analog input left channel

A14 AU_FMIN

R FM radio analog input right channel

D13 AU_OUT1_

P Earphone 1 amplifier output (+)

C13 AU_OUT1_

N Earphone 1 amplifier output (-)

B12 AU_OUT0_

N Earphone 0 amplifier output (-)

A12 AU_OUT0_

P Earphone 0 amplifier output (+)

C12 AU_MICBI

AS_P Microphone bias supply (+)

D12 AU_MICBI Microphone bias supply (-)

MT6217 GSM/GPRS Baseband Processor Data Sheet Revision 1.01

23/349 MediaTek Inc. Confidential

AS_N

C11 AU_VREF_

N Audio reference voltage (-)

B11 AU_VREF_

P

Audio reference voltage (+)

D10 AU_VIN0_

P

Microphone 0 amplifier input (+)

C10 AU_VIN0_

N Microphone 0 amplifier input (-)

B10 AU_VIN1_

N Microphone 1 amplifier input (-)

A10 AU_VIN1_

P Microphone 1 amplifier input (+)

D9 BDLAQP Quadrature input (Q+) baseband codec

downlink

C9 BDLAQN Quadrature input (Q -) baseband codec

downlink

A9 BDLAIN In-phase input (I+) baseband codec

downlink

B9 BDLAIP In-phase input (I-) baseband codec

downlink

B8 BUPAIP In-phase output (I+) baseband codec

uplink

A8 BUPAIN In-phase output (I-) baseband codec

uplink

C8 BUPAQN Quadrature output (Q+) baseband codec

uplink

D8 BUPAQP Quadrature output (Q-) baseband codec

uplink

B7 APC Automatic power control DAC output

D6 AUXADIN

0

Auxiliary ADC input 0

C6 AUXADIN

1

Auxiliary ADC input 1

B6 AUXADIN

2 Auxiliary ADC input 2

A6 AUXADIN

3 Auxiliary ADC input 3

C5 AUXADIN

4 Auxiliary ADC input 4

B5 AUXADIN

5 Auxiliary ADC input 5

A5 AUXADIN

6

Auxiliary ADC input 6

C4 AUX_REF Auxiliary ADC reference voltage input

B4 AFC Automatic frequency control DAC

output

A4 AFC_BYP Automatic frequency control DAC

bypass capacitance

VCXO Interface

A2 SYSCLK 13MHz or 26MHz system clock input

MT6217 GSM/GPRS Baseband Processor Data Sheet Revision 1.01

24/349 MediaTek Inc. Confidential

RTC Interface

C2 XIN 32.768 KHz crystal input

B1 XOUT 32.768 KHz crystal output

C1 BBWAKEU

P O Baseband power on/off control 1

Supply Voltages

D1 VDDK Supply voltage of internal logic

M1 VDDK Supply voltage of internal logic

V8 VDDK Supply voltage of internal logic

V16 VDDK Supply voltage of internal logic

H19 VDDK Supply voltage of internal logic

C16 VDDK Supply voltage of internal logic

W4 VDD33_E

MI

Supply voltage of memory interface

driver

W7 VDD33_E

MI

Supply voltage of memory interface

driver

W9 VDD33_E

MI

Supply voltage of memory interface

driver

W11 VDD33_E

MI

Supply voltage of memory interface

driver

W13 VDD33_E

MI

Supply voltage of memory interface

driver

W15 VDD33_E

MI

Supply voltage of memory interface

driver

W18 VDD33_E

MI

Supply voltage of memory interface

driver

T18 VDD33_E

MI

Supply voltage of memory interface

driver

V3 VSS33_EM

I

Ground of memory interface driver

V6 VSS33_EM

I

Ground of memory interface driver

U8 VSS33_EM

I

Ground of memory interface driver

V10 VSS33_EM

I

Ground of memory interface driver

V12 VSS33_EM

I

Ground of memory interface driver

V14 VSS33_EM

I

Ground of memory interface driver

U16 VSS33_EM

I

Ground of memory interface driver

V19 VSS33_EM

I

Ground of memory interface driver

R19 VSS33_EM

I

Ground of memory interface driver

P15 VDD33_US

B

Supply voltage of drivers for USB

MT6217 GSM/GPRS Baseband Processor Data Sheet Revision 1.01

25/349 MediaTek Inc. Confidential

D4 VDD33 Supply voltage of drivers except

memory interface and USB

F1 VDD33 Supply voltage of drivers except

memory interface and USB

K1 VDD33 Supply voltage of drivers except

memory interface and USB

R1 VDD33 Supply voltage of drivers except

memory interface and USB

L19 VDD33 Supply voltage of drivers except

memory interface and USB

E19 VDD33 Supply voltage of drivers except

memory interface and USB

E15 VDD33 Supply voltage of drivers except

memory interface and USB

E13 VDD33 Supply voltage of drivers except

memory interface and USB

E11 VDD33 Supply voltage of drivers except

memory interface and USB

E6 VDD33 Supply voltage of drivers except

memory interface and USB

A3 VSS33 Ground of drivers except memory

interface

D2 VSS33 Ground of drivers except memory

interface

D5 VSS33 Ground of drivers except memory

interface

H2 VSS33 Ground of drivers except memory

interface

M2 VSS33 Ground of drivers except memory

interface

P18 VSS33 Ground of drivers except memory

interface

H18 VSS33 Ground of drivers except memory

interface

A16 VSS33 Ground of drivers except memory

interface

B16 VSS33 Ground of drivers except memory

interface

E14 VSS33 Ground of drivers except memory

interface

E12 VSS33 Ground of drivers except memory

interface

E7 VSS33 Ground of drivers except memory

interface

B3 AVDD_PL

L

Supply voltage for PLL

C3 AVSS_PLL Ground for PLL supply

B2 AVDD_RT

C

Supply voltage for Real Time Clock

Analog Supplies

C15 AVDD_MB

UF Supply Voltage for Audio band section

MT6217 GSM/GPRS Baseband Processor Data Sheet Revision 1.01

26/349 MediaTek Inc. Confidential

D14 AVSS_MB

UF

GND for Audio band section

B13 AVDD_BU

F

Supply voltage for voice band transmit

section

A13 AVSS_BUF GND for voice band transmit section

D11 AVDD_AF

E

Supply voltage for voice band receive

section

A11 AGND_AF

E

GND reference voltage for voice band

section

E10 AVSS_AFE GND for voice band receive section

E9 AGND_RF

E

GND reference voltage for baseband

section, APC, AFC and AUXADC

E8 AVSS_GS

MRFTX

GND for baseband transmit section

D7 AVDD_GS

MRFTX

Supply voltage for baseband transmit

section

C7 AVSS_RFE GND for baseband receive section, APC,

AFC and AUXADC

A7 AVDD_RF

E Supply voltage for baseband receive

section, APC, AFC and AUXADC

Table 2 Pin Descriptions (Bolded types are functions at reset)

MT6217 GSM/GPRS Baseband Processor Data Sheet Revision 1.01

27/349 MediaTek Inc. Confidential

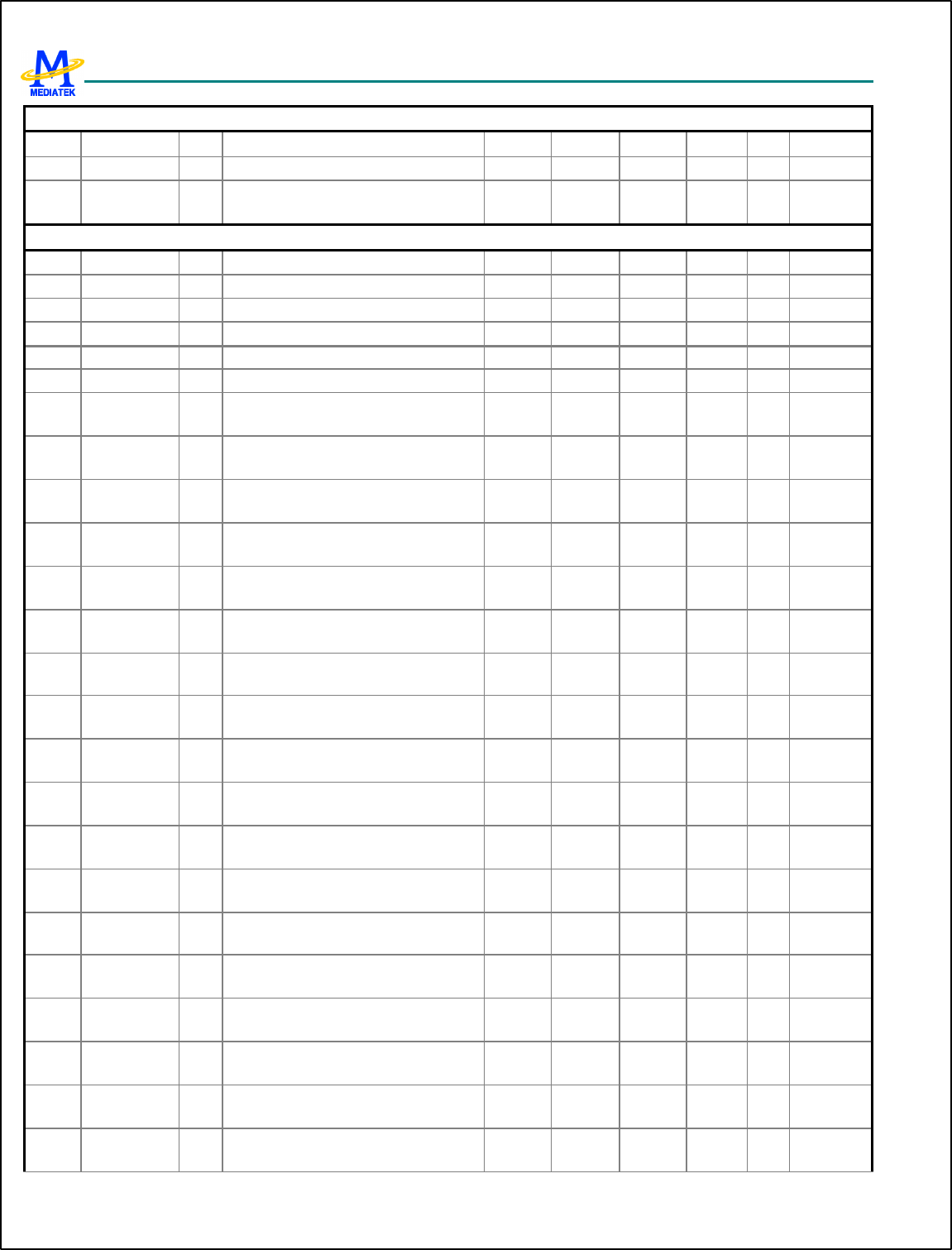

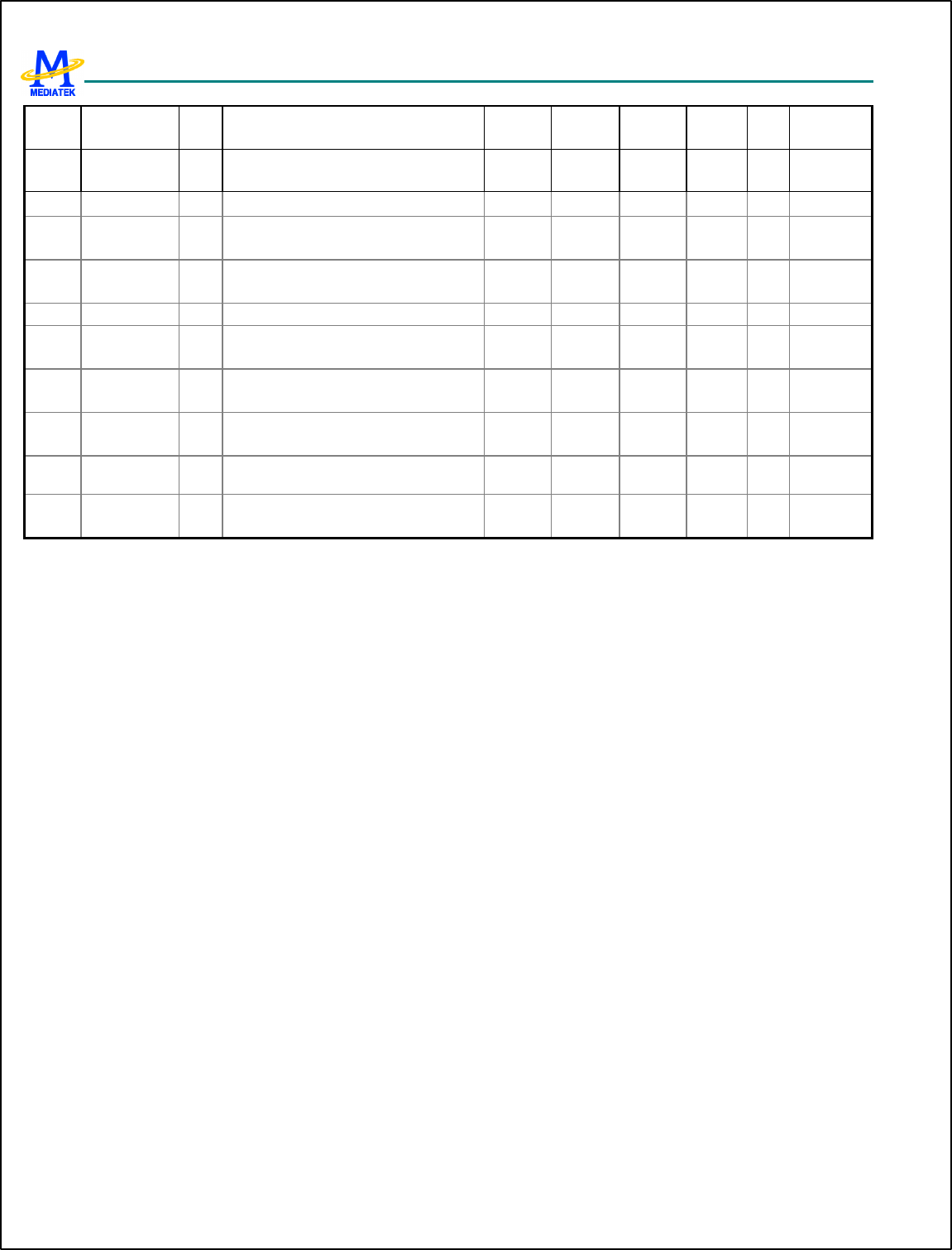

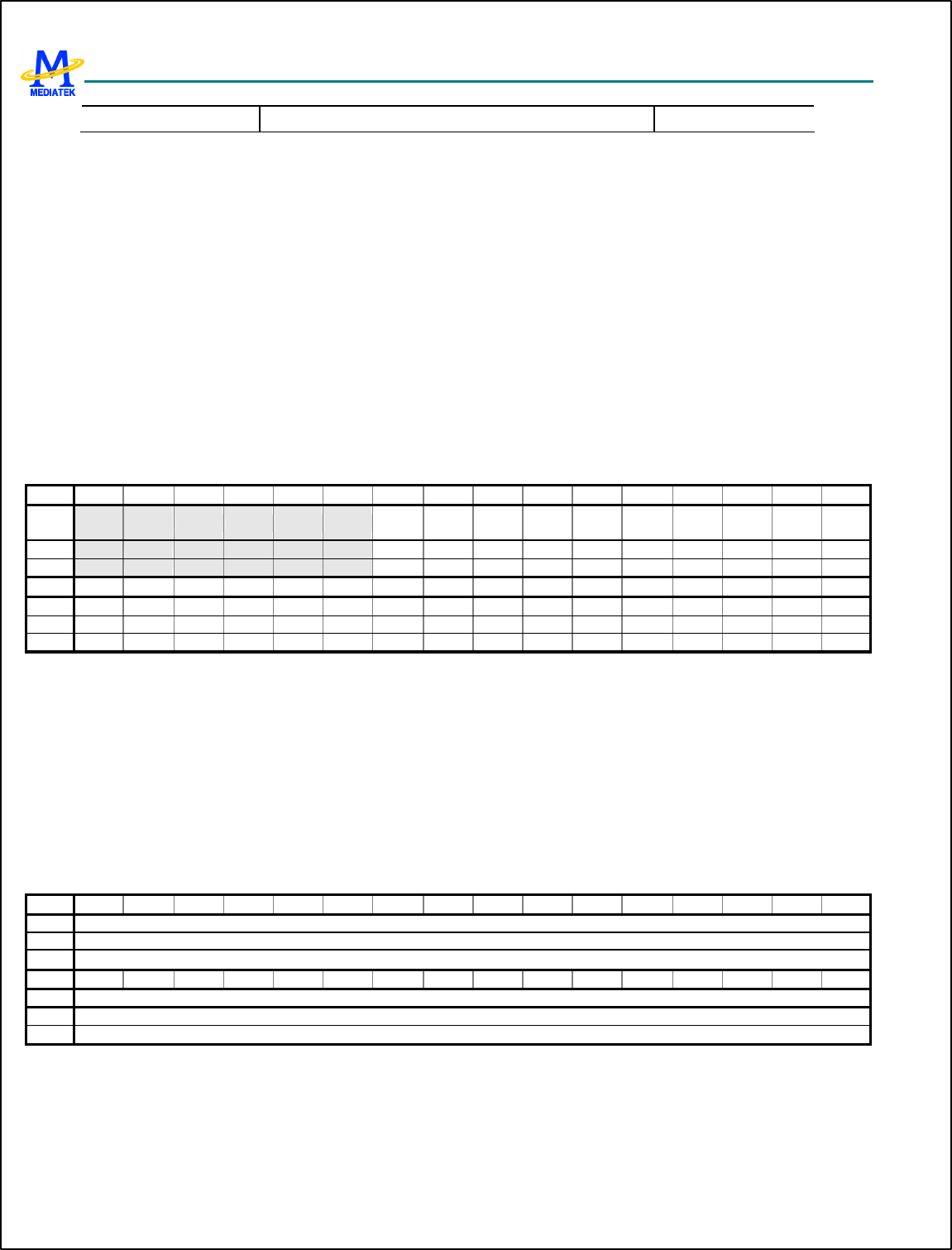

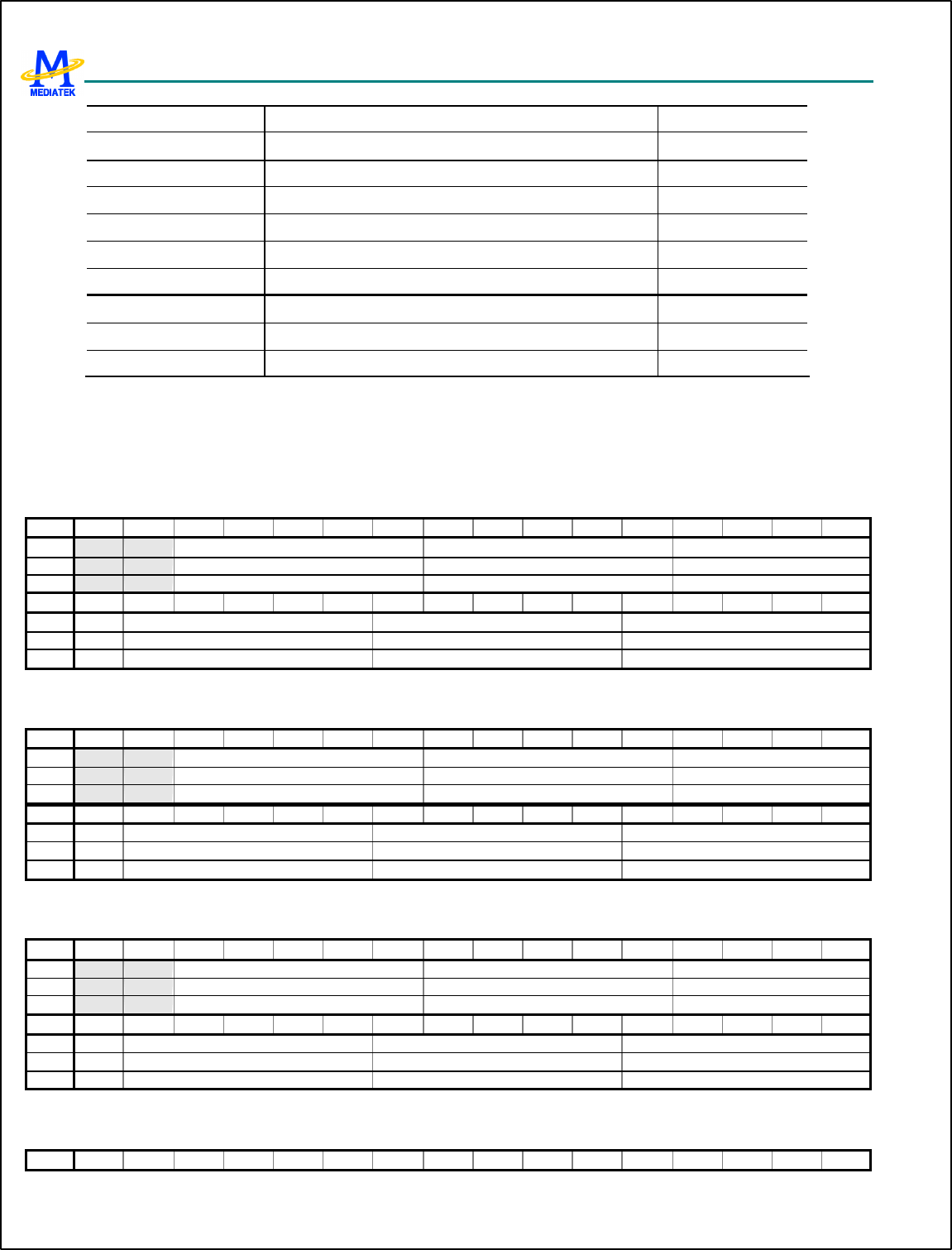

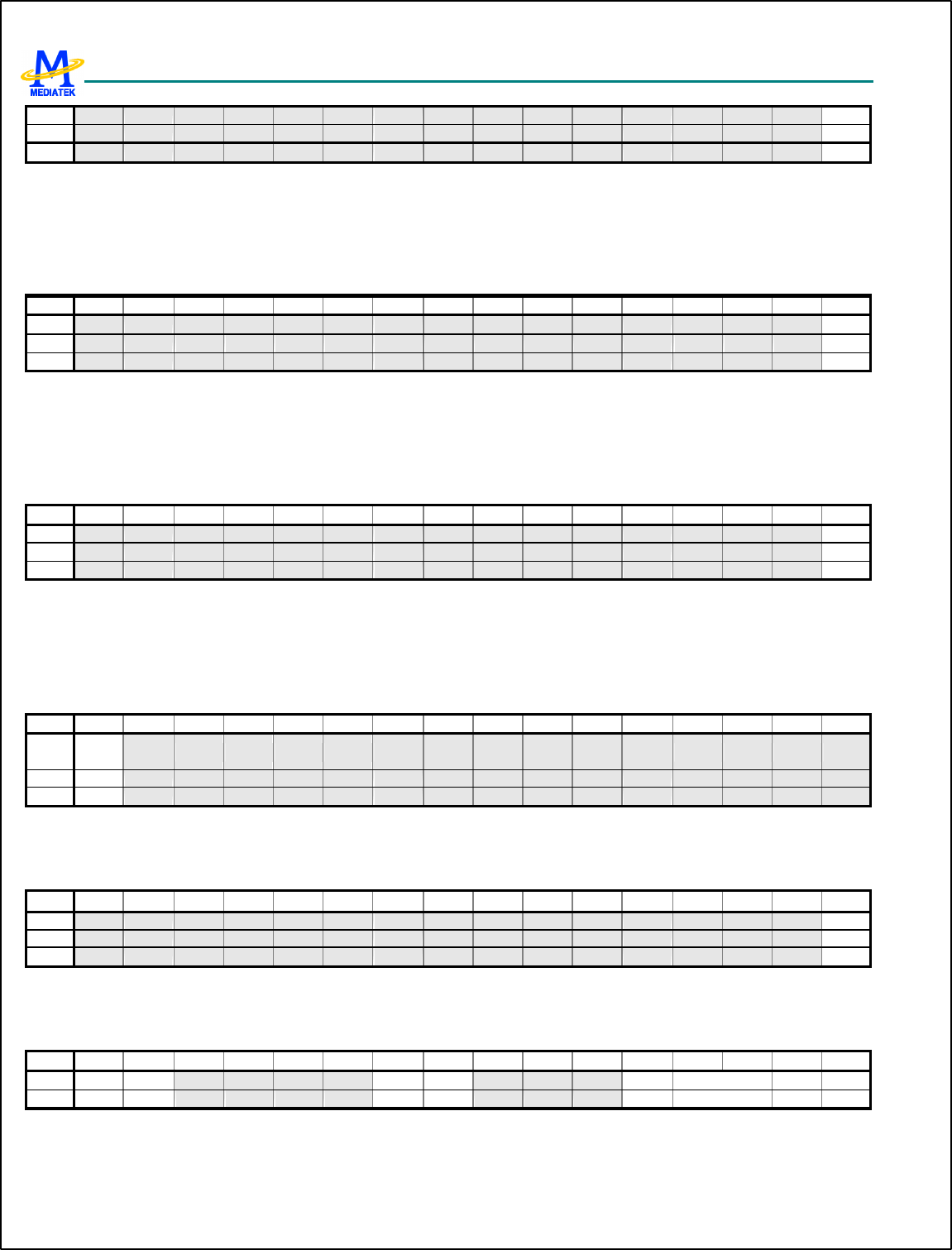

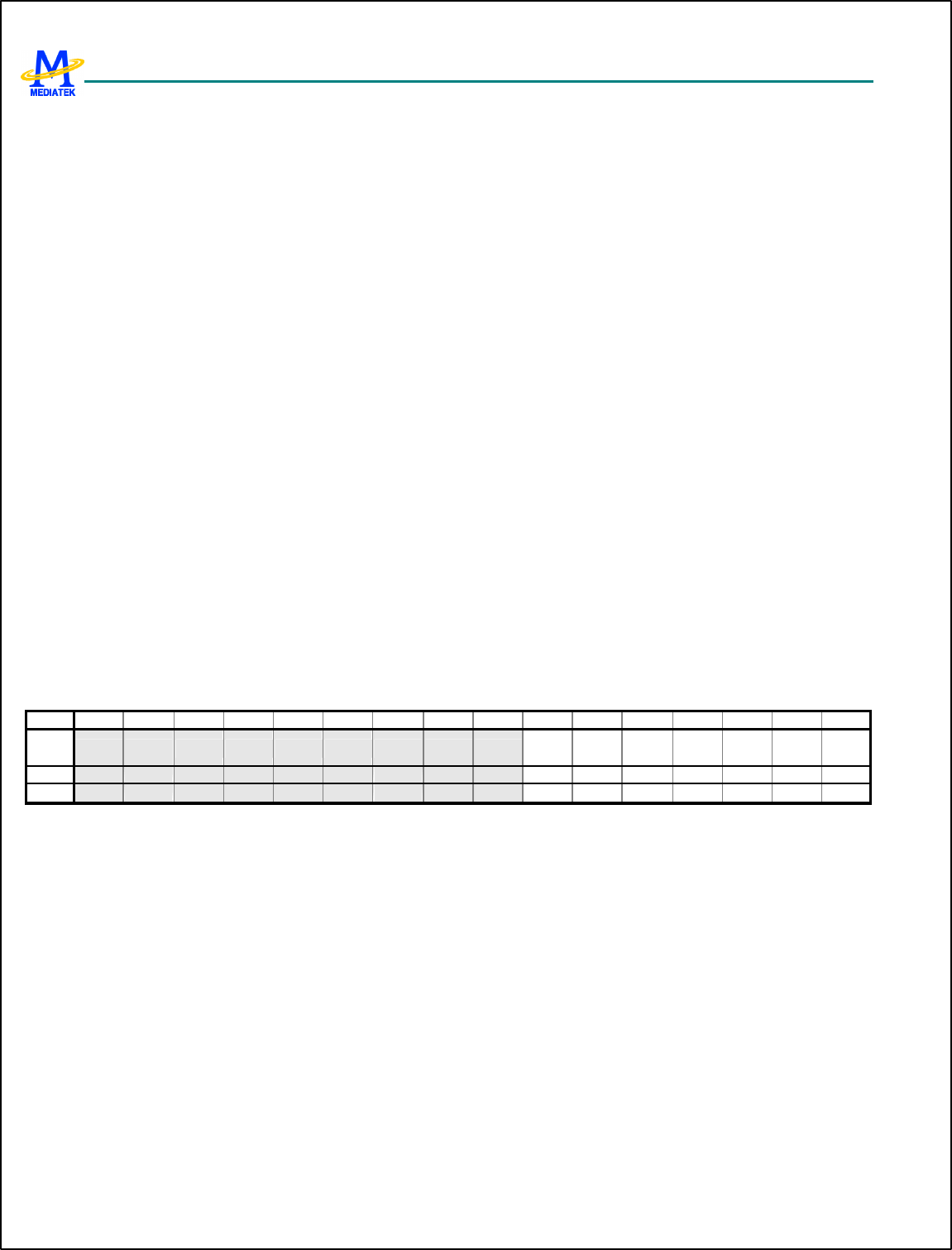

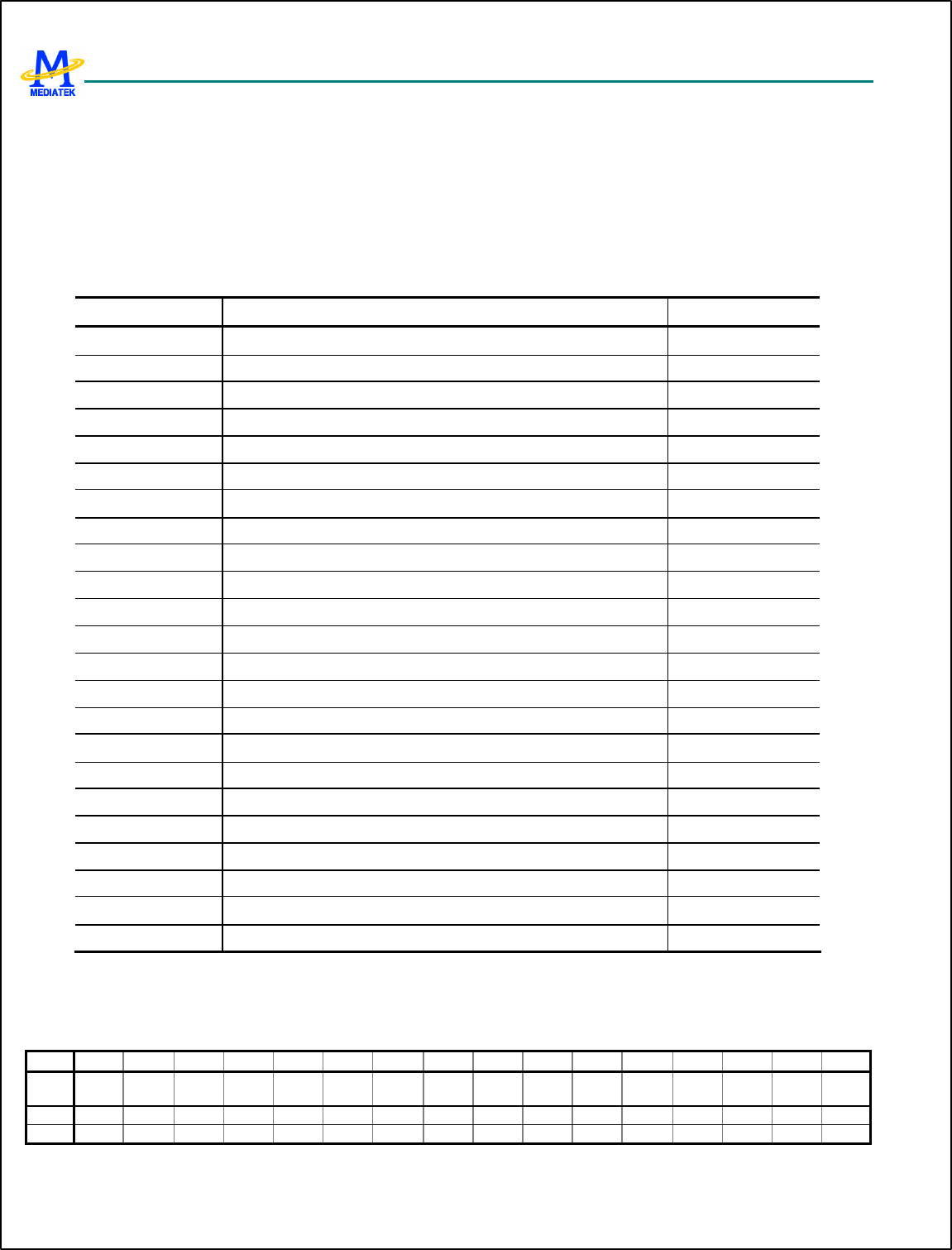

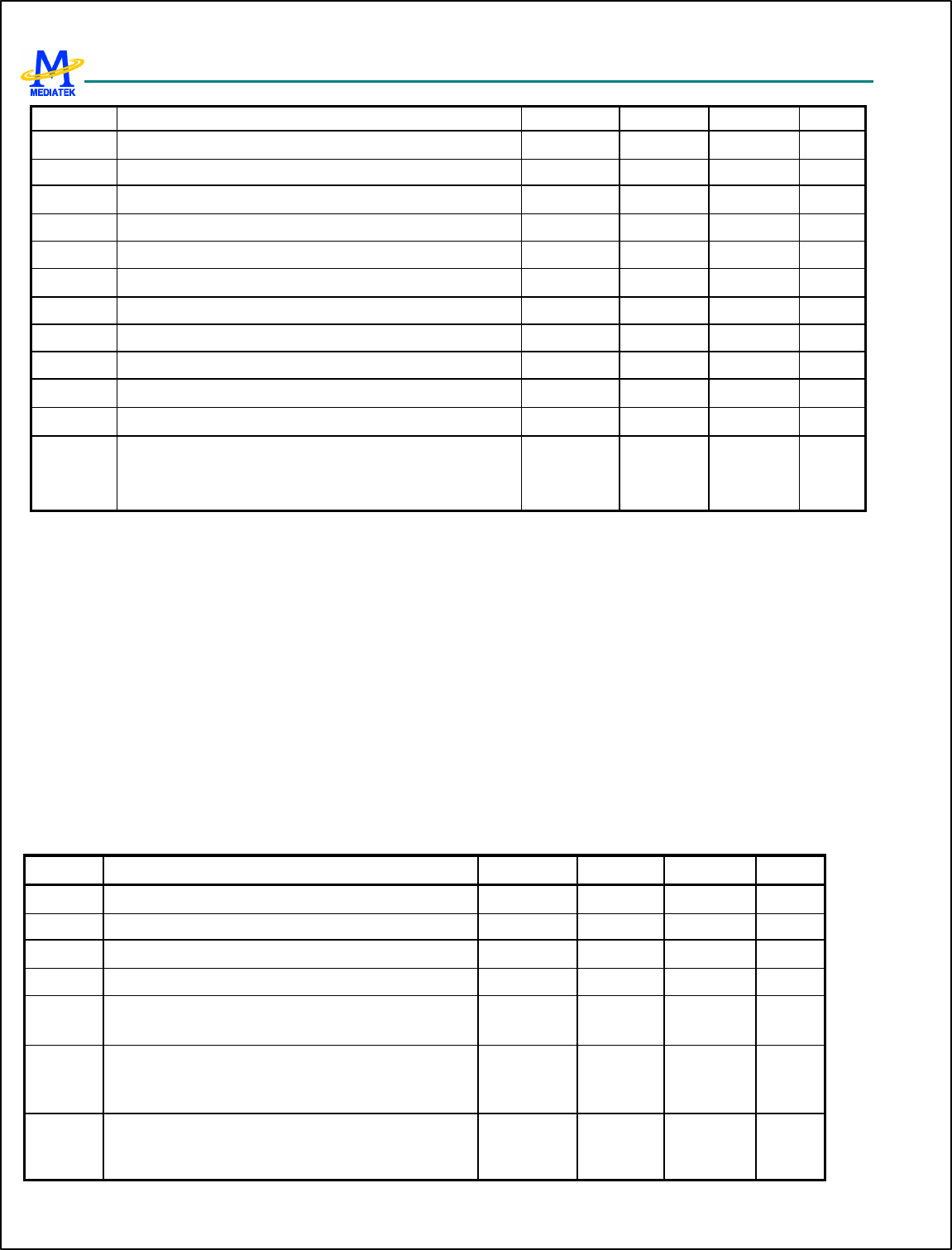

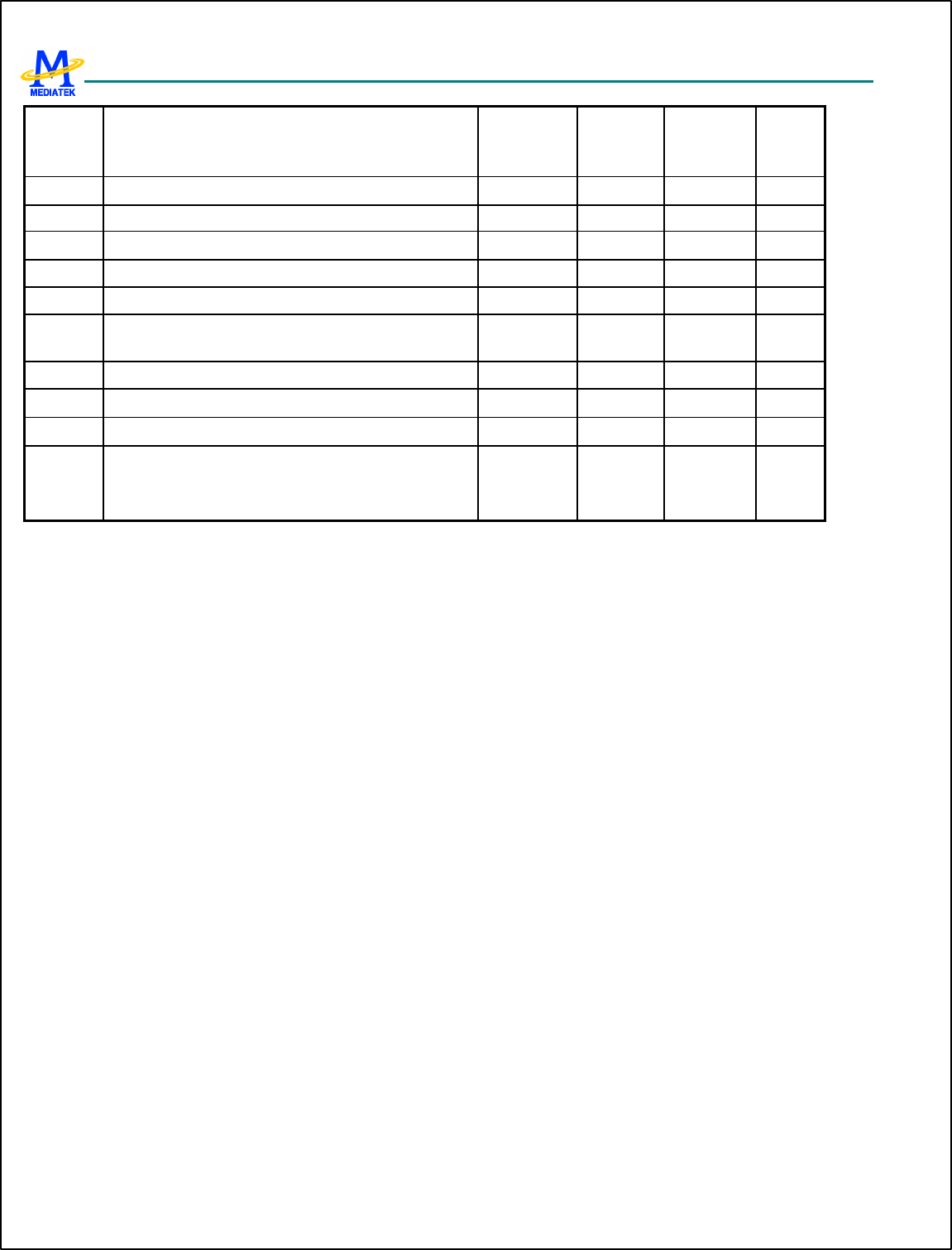

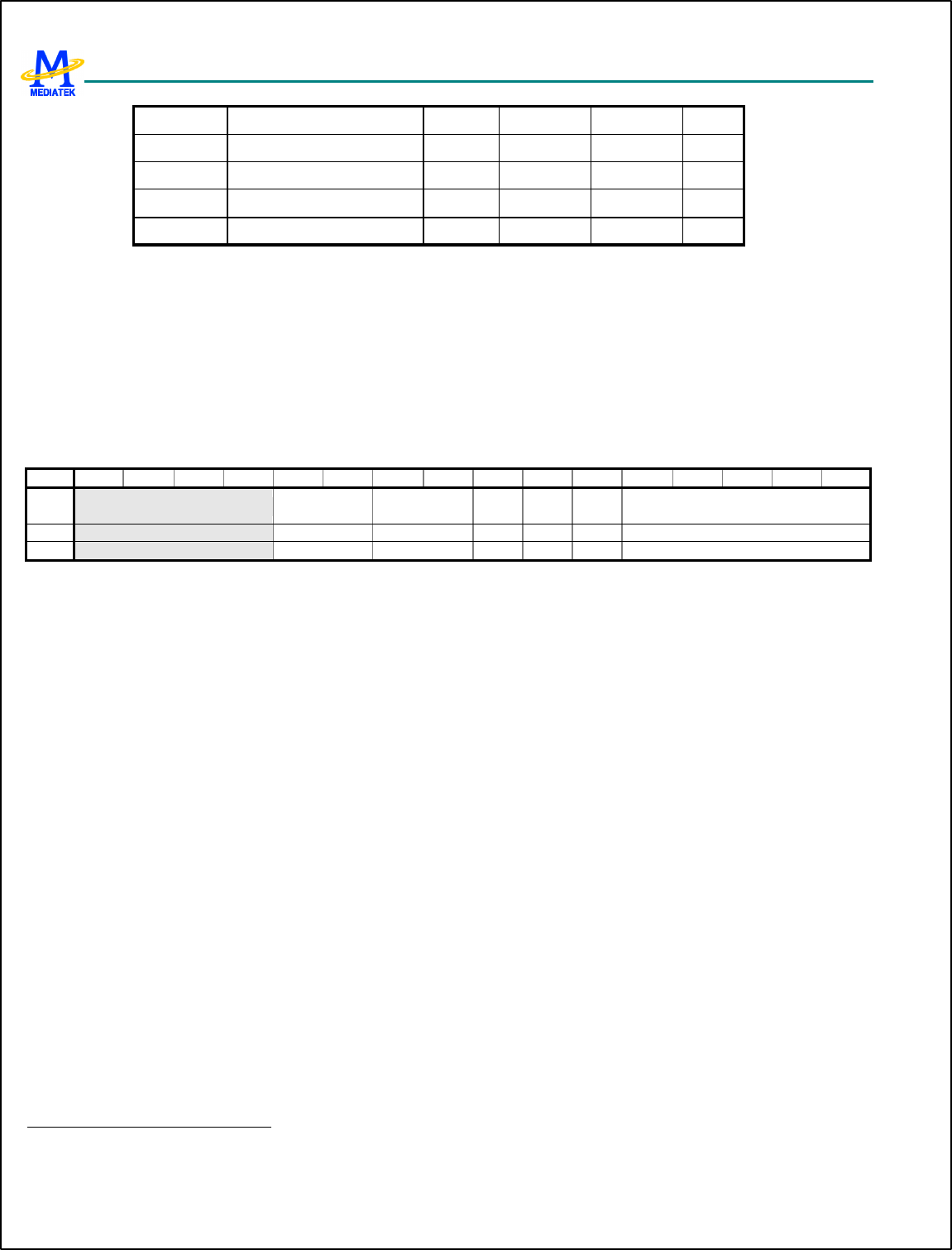

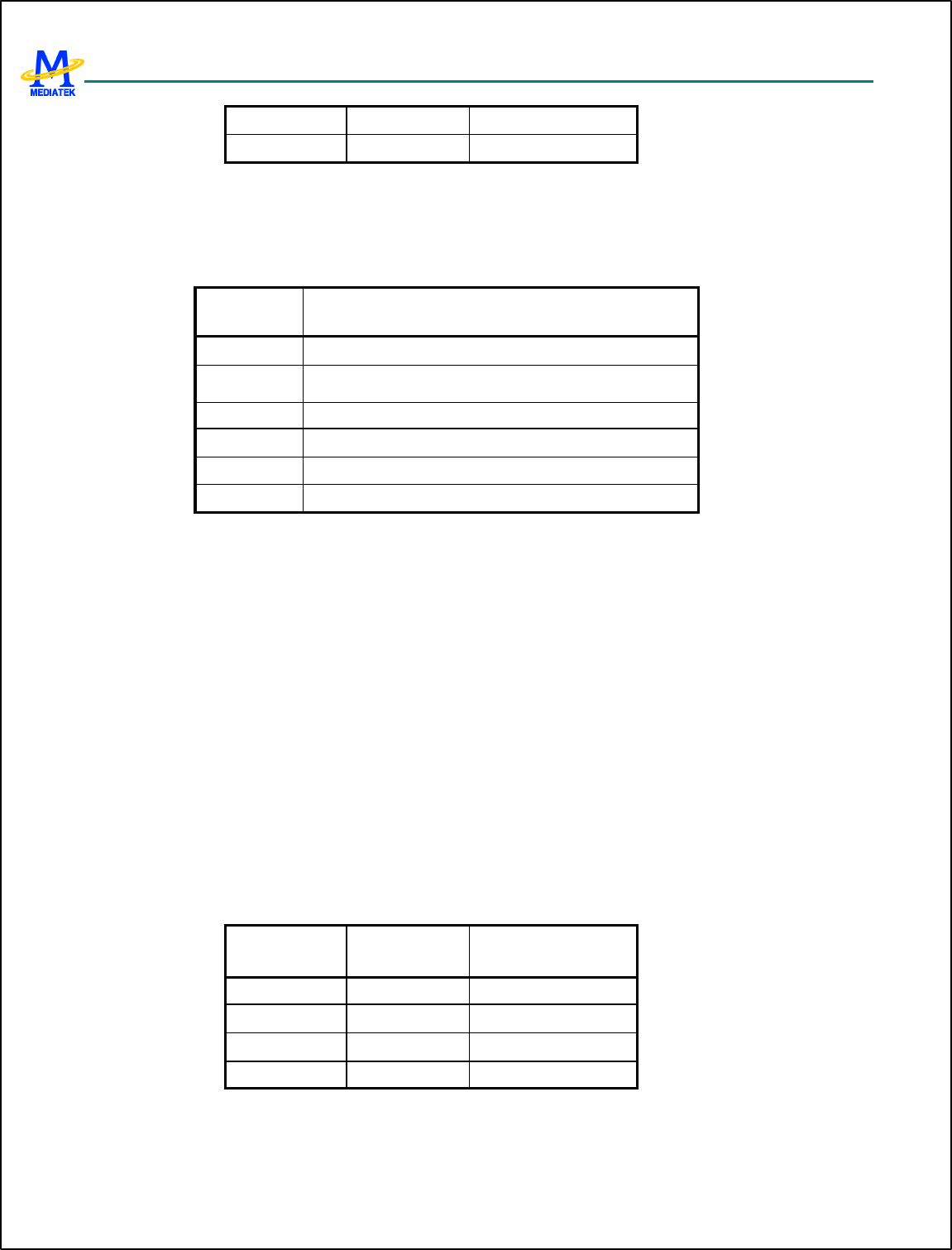

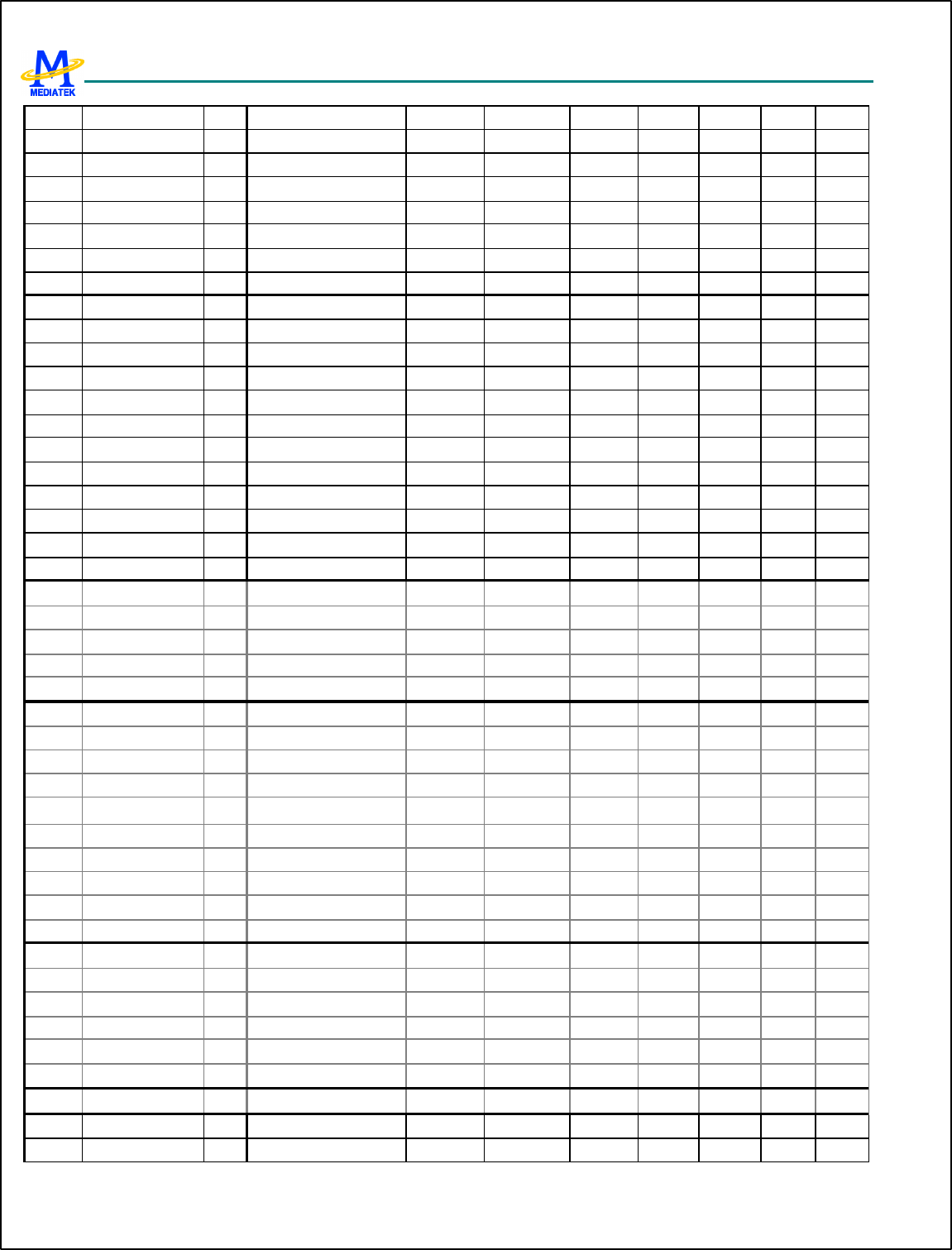

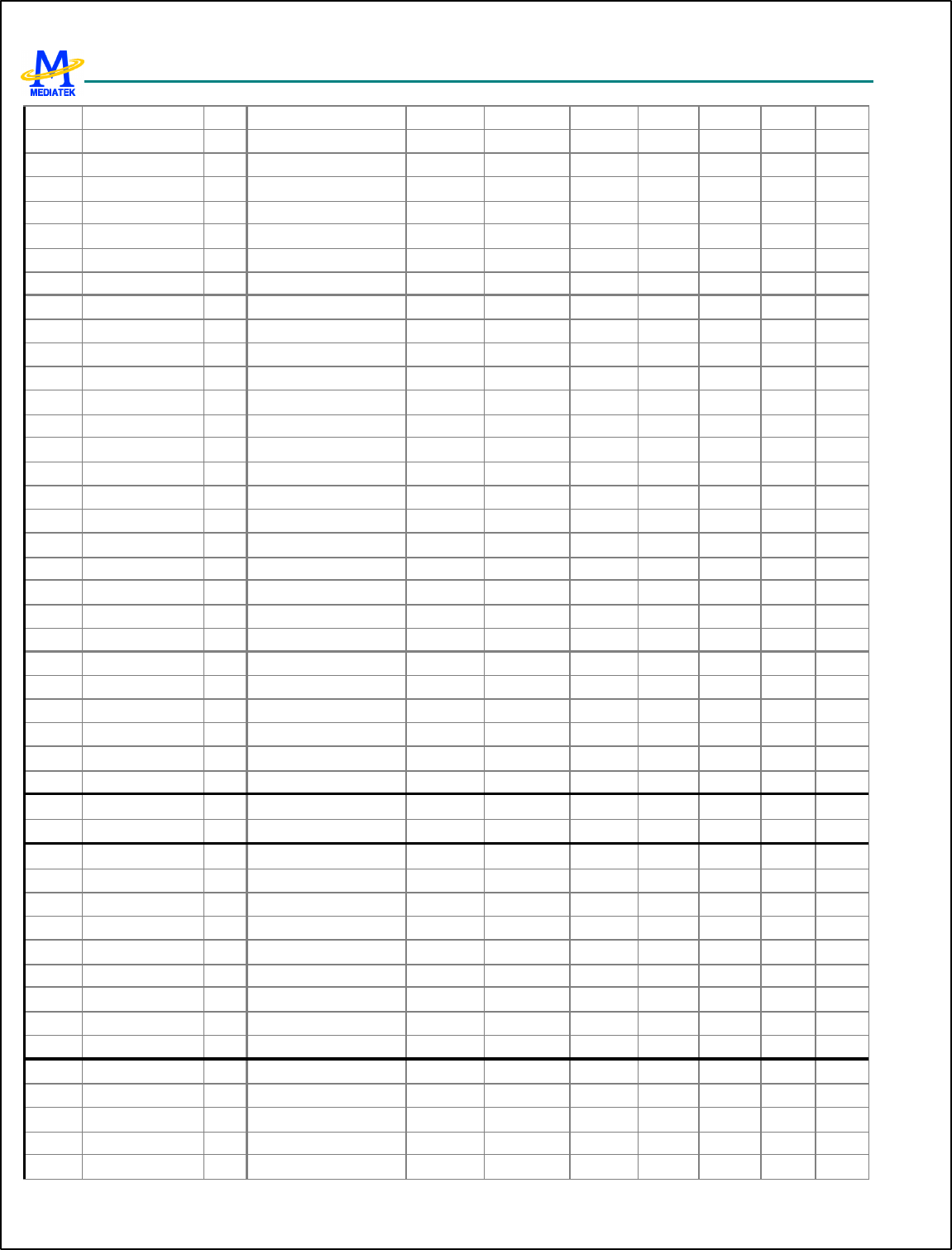

2.3 Power Description

Ball

13X13 Name IO Suppl y IO GND Core Supply Core GND Remark

B17 GPIO7 VDDK VSSK

A18 GPIO8 VDDK VSSK

A17 GPIO9

VDD33 VSS33

VDDK VSSK

B16 VSS33

A16 VSS33

C16 VDDK Typ. 1.8V

E15 VDD33 Typ. 2.8V

D15 ESDM_CK VDD33 VSS33 VDDK VSSK

E14 VSS33

E13 VDD33 Typ. 2.8V

E12 VSS33

E11 VDD33 Typ. 2.8V

E7 VSS33

J9 NLD8

J10 NLD9

K9 NLD10

J11 NLD11

VDD33 VSS33 VDDK VSSK

E6 VDD33 Typ. 2.8V

L9 NLD12

K11 NLD13

L10 NLD14

L11 NLD15

VDD33 VSS33 VDDK VSSK

D5 VSS33

D4 VDD33 Typ. 2.8V

A3 VSS33

B3 AVDD_PLL Typ. 2.8V

A2 SYSCLK AVDD_PLL AVSS_PLL AVDD_PLL AVSS_PLL

C3 AVSS_PLL

B2 AVDD_RTC Typ. 1.5V

B1 XOUT AVDD_RTC VSS33 AVDD_RTC VSS33

C2 XIN AVDD_RTC VSS33 AVDD_RTC VSS33

C1 BBWAKEUP AVDD_RTC VSS33 AVDD_RTC VSS33

D2 VSS33

D3 TESTMODE VDD33 VSS33 VDDK VSSK

D1 VDDK Typ. 1.8V

MT6217 GSM/GPRS Baseband Processor Data Sheet Revision 1.01

28/349 MediaTek Inc. Confidential

E5 IBOOT VDDK VSSK

E4 JTRST# VDDK VSSK

E3 JTCK VDDK VSSK

E2 JTDI VDDK VSSK

E1 JTMS VDDK VSSK

F5 JTDO VDDK VSSK

F4 JRTCK VDDK VSSK

F3 BPI_BUS0 VDDK VSSK

F2 BPI_BUS1

VDD33 VSS33

VDDK VSSK

F1 VDD33 Typ. 2.8V

G5 BPI_BUS2 VDDK VSSK

G4 BPI_BUS3 VDDK VSSK

G3 BPI_BUS4 VDDK VSSK

G2 BPI_BUS5 VDDK VSSK

G1 BPI_BUS6 VDDK VSSK

H5 BPI_BUS7 VDDK VSSK

H4 BPI_BUS8

VDD33 VSS33

VDDK VSSK

H2 VSS33

H3 BPI_BUS9 VDDK VSSK

H1 BSI_CS0 VDDK VSSK

J5 BSI_DATA VDDK VSSK

J4 BSI_CLK VDDK VSSK

J3 LSCK VDDK VSSK

J2 LSA0 VDDK VSSK

J1 LSDA VDDK VSSK

K4 LSCE0# VDDK VSSK

K3 LSCE1#

VDD33 VSS33

VDDK VSSK

K1 VDD33

K2 LPCE1# VDDK VSSK

L5 LPCE0# VDDK VSSK

L4 LRST# VDDK VSSK

L3 LRD# VDDK VSSK

L2 LPA0 VDDK VSSK

L1 LWR# VDDK VSSK

M5 NLD7 VDDK VSSK

M4 NLD6 VDDK VSSK

M3 NLD5

VDD33 VSS33

VDDK VSSK

M2 VSS33

M1 VDDK Typ. 1.8V

MT6217 GSM/GPRS Baseband Processor Data Sheet Revision 1.01

29/349 MediaTek Inc. Confidential

N5 NLD4 VDDK VSSK

N4 NLD3 VDDK VSSK

N3 NLD2 VDDK VSSK

N2 NLD1 VDDK VSSK

N1 NLD0 VDDK VSSK

P5 NRNB VDDK VSSK

P4 NCLE VDDK VSSK

P3 NALE VDDK VSSK

P2 NEW# VDDK VSSK

P1 NRE# VDDK VSSK

R4 NCE#

VDD33 VSS33

VDDK VSSK

R1 VDD33 Typ. 2.8V

R3 PWM1 VDDK VSSK

R2 PWM2 VDDK VSSK

T4 ALERTER VDDK VSSK

T1 SRCLKENA VDDK VSSK

T3 SRCLKENAN VDDK VSSK

T2 SRCLKENAI VDDK VSSK

U1 SYSRST# VDDK VSSK

U2 GPIO0 VDDK VSSK

V1 EINT0 VDDK VSSK

U3 EINT1 VDDK VSSK

W1 EINT2 VDDK VSSK

V2 EINT3

VDD33 VSS33

VDDK VSSK

V3 VSS33_EMI

W2 EA25 VDDK VSSK

W3 EA24 VDDK VSSK

U4 EA23 VDDK VSSK

V4 EA22

VDD33_EMI

VSS33_EMI

VDDK VSSK

W4 VDD33_EMI Typ. 1.8~2.8V

R5 MIRQ VDDK VSSK

W5 EA21 VDDK VSSK

V5 EA20 VDDK VSSK

U5 EA19 VDDK VSSK

T6 EA18

VDD33_EMI

VSS33_EMI

VDDK VSSK

V6 VSS33_EMI

W6 EA17 VDDK VSSK

U6 EA16 VDDK VSSK

T6 EA15

VDD33_EMI

VSS33_EMI

VDDK VSSK

MT6217 GSM/GPRS Baseband Processor Data Sheet Revision 1.01

30/349 MediaTek Inc. Confidential

R6 EA14 VDDK VSSK

W7 VDD33_EMI Typ. 1.8~2.8V

V7 EA13 VDDK VSSK

U7 EA12 VDDK VSSK

T7 EA11 VDDK VSSK

R7 EA10

VDD33_EMI VSS33_EMI

VDDK VSSK

V8 VDDK Typ. 1.8V

U8 VSS33_EMI

W8 EA9 VDDK VSSK

T8 EA8 VDDK VSSK

R8 EA7 VDDK VSSK

V9 EA6

VDD33_EMI

VSS33_EMI

VDDK VSSK

W9 VDD33_EMI Typ. 1.8~2.8V

U9 EA5 VDDK VSSK

T9 EA4 VDDK VSSK

W10 EA3

VDD33_EMI

VSS33_EMI

VDDK VSSK

V10 VSS33_EMI

U10 EA2 VDDK VSSK

T10 EA1 VDDK VSSK

R10 EA0

VDD33_EMI VSS33_EMI

VDDK VSSK

W11 VDD33_EMI Typ. 1.8~2.8V

U11 EADV# VDDK VSSK

V11 ECLK VDDK VSSK

T11 EPDN#

VDD33_EMI VSS33_EMI

VDDK VSSK

V12 VSS33_EMI

W12 ECS7# VDDK VSSK

U12 ECS6# VDDK VSSK

T12 ECS5# VDDK VSSK

R12 ECS4#

VDD33_EMI VSS33_EMI

VDDK VSSK

W13 VDD33_EMI Typ. 1.8~2.8V

V13 ECS3# VDDK VSSK

U13 ECS2# VDDK VSSK

T13 ECS1# VDDK VSSK

R13 ECS0#

VDD33_EMI

VSS33_EMI

VDDK VSSK

V14 VSS33_EMI

W14 EWR# VDDK VSSK

U14 ERD# VDDK VSSK

T14 EUB# VDDK VSSK

R14 ELB#

VDD33_EMI

VSS33_EMI

VDDK VSSK

MT6217 GSM/GPRS Baseband Processor Data Sheet Revision 1.01

31/349 MediaTek Inc. Confidential

W15 VDD33_EMI Typ. 1.8~2.8V

V15 ED15 VDDK VSSK

U15 ED14 VDDK VSSK

T15 ED13 VDDK VSSK

W16 ED12

VDD33_EMI VSS33_EMI

VDDK VSSK

V16 VDDK

U16 VSS33_EMI

T16 ED11 VDDK VSSK

W17 ED10 VDDK VSSK

V17 ED9

VDD33_EMI VSS33_EMI

VDDK VSSK

W18 VDD33_EMI Typ. 1.8~2.8V

U17 ED8 VDDK VSSK

W19 ED7 VDDK VSSK

V18 ED6

VDD33_EMI VSS33_EMI

VDDK VSSK

V19 VSS33_EMI

U18 ED5 VDDK VSSK

U19 ED4 VDDK VSSK

T17 ED3

VDD33_EMI VSS33_EMI

VDDK VSSK

T18 VDD33_EMI Typ. 1.8~2.8V

T19 ED2 VDDK VSSK

R15 ED1 VDDK VSSK

R16 ED0 VDDK VSSK

R17 MFIQ VDDK VSSK

R18 WATCHDOG

VDD33_EMI

VSS33_EMI

VDDK VSSK

R19 VSS33_EMI

P15 VDD33_USB Typ. 3.3V

P16 USB_DP VDDK VSSK

P17 USB_DM

VDD33_USB VSS33_USB

VDDK VSSK

P18 VSS33

P19 MCCM0 VDDK VSSK

N15 MCDA0 VDDK VSSK

N16 MCDA1 VDDK VSSK

N17 MCDA2 VDDK VSSK

N18 MCDA3 VDDK VSSK

N19 MCCK VDDK VSSK

M16 MCPWRON VDDK VSSK

M17 MCWP VDDK VSSK

M18 MCINS VDDK VSSK

M19 GPIO1

VDD33

VSS33

VDDK VSSK

MT6217 GSM/GPRS Baseband Processor Data Sheet Revision 1.01

32/349 MediaTek Inc. Confidential

L15 GPIO2 VDDK VSSK

L16 GPIO3 VDDK VSSK

L19 VDD33 Typ. 2.8V

L18 SIMRST VDDK VSSK

L17 SIMCLK VDDK VSSK

K15 SIMVCC VDDK VSSK

K16 SIMSEL VDDK VSSK

K17 SIMDATA VDDK VSSK

K18 URXD1 VDDK VSSK

K19 UTXD1 VDDK VSSK

J16 UCTS1 VDDK VSSK

J17 URTS1 VDDK VSSK

J18 URXD2 VDDK VSSK

J19 UTXD2 VDDK VSSK

H15 URXD3 VDDK VSSK

H16 UTXD3

VDD33

VSS33

VDDK VSSK

H19 VDDK VDDK VSSK Typ. 1.8V

H18 VSS33 VDDK VSSK

H17 IRDA_PDN VDDK VSSK

G15 IRDA_TXD VDDK VSSK

G16 IRDA_RXD VDDK VSSK

G17 KCOL6 VDDK VSSK

G18 KCOL5 VDDK VSSK

G19 KCOL4 VDDK VSSK

F15 KCOL3 VDDK VSSK

F16 KCOL2 VDDK VSSK

F17 KCOL1 VDDK VSSK

F18 KCOL0 VDDK VSSK

F19 KROW5 VDDK VSSK

E16 KROW4 VDDK VSSK

E17 KROW3 VDDK VSSK

E18 KROW2

VDD33

VSS33

VDDK VSSK

E19 VDD33 Typ. 2.8V

D16 KROW1 VDDK VSSK

D19 KROW0 VDDK VSSK

D17 DAICLK VDDK VSSK

D18 DAIPCMOUT VDDK VSSK

C19 DAIPCMIN VDDK VSSK

C18 DAIRST

VDD33 VSS33

VDDK VSSK

MT6217 GSM/GPRS Baseband Processor Data Sheet Revision 1.01

33/349 MediaTek Inc. Confidential

B19 DAISYNC VDDK VSSK

C17 GPIO4 VDDK VSSK

A19 GPIO5 VDDK VSSK

A18 GPIO6 VDDK VSSK

C15 AVDD_MBUF Typ. 2.8V

B15 AU_MOUTL

A15 AU_MOUTR

D14 AVSS_MBUF

C14 AU_M_BYP

B14 AU_FMINL

A14 AU_FMINR

D13 AU_OUT1_P

C13 AU_OUT1_N

B12 AU_OUT0_N

B13 AVDD_BUF Typ. 2.8V

A12 AU_OUT0_P

A13 AVSS_BUF

C12 AU_MICBIAS_P

D12 AU_MICBIAS_N

D11 AVDD_AFE Typ. 2.8V

C11 AU_VREF_N

B11 AU_VREF_P

A11 AGND_AFE

D10 AU_VIN0_P

C10 AU_VIN0_N

B10 AU_VIN1_N

A10 AU_VIN1_P

E10 AVSS_AFE

D9 BDLAQP

C9 BDLAQN

E9 AGND_RFE

A9 BDLAIN

B9 BDLAIP

E8 AVSS_GSMRFTX

B8 BUPAIP

A8 BUPAIN

D7 AVDD_GSMRFTX Typ. 2.8V

C8 BUPAQN

D8 BUPAQP

MT6217 GSM/GPRS Baseband Processor Data Sheet Revision 1.01

34/349 MediaTek Inc. Confidential

C7 AVSS_RFE

B7 APC

A7 AVDD_RFE Typ. 2.8V

D6 AUXADIN0

C6 AUXADIN1

B6 AUXADIN2

A6 AUXADIN3

C5 AUXADIN4

B5 AUXADIN5

A5 AUXADIN6

C4 AUX_REF

B4 AFC

A4 AFC_BYP

Table 3 Power Descriptions

MT6217 GSM/GPRS Baseband Processor Data Sheet Revision 1.01

35/349 MediaTek Inc. Confidential

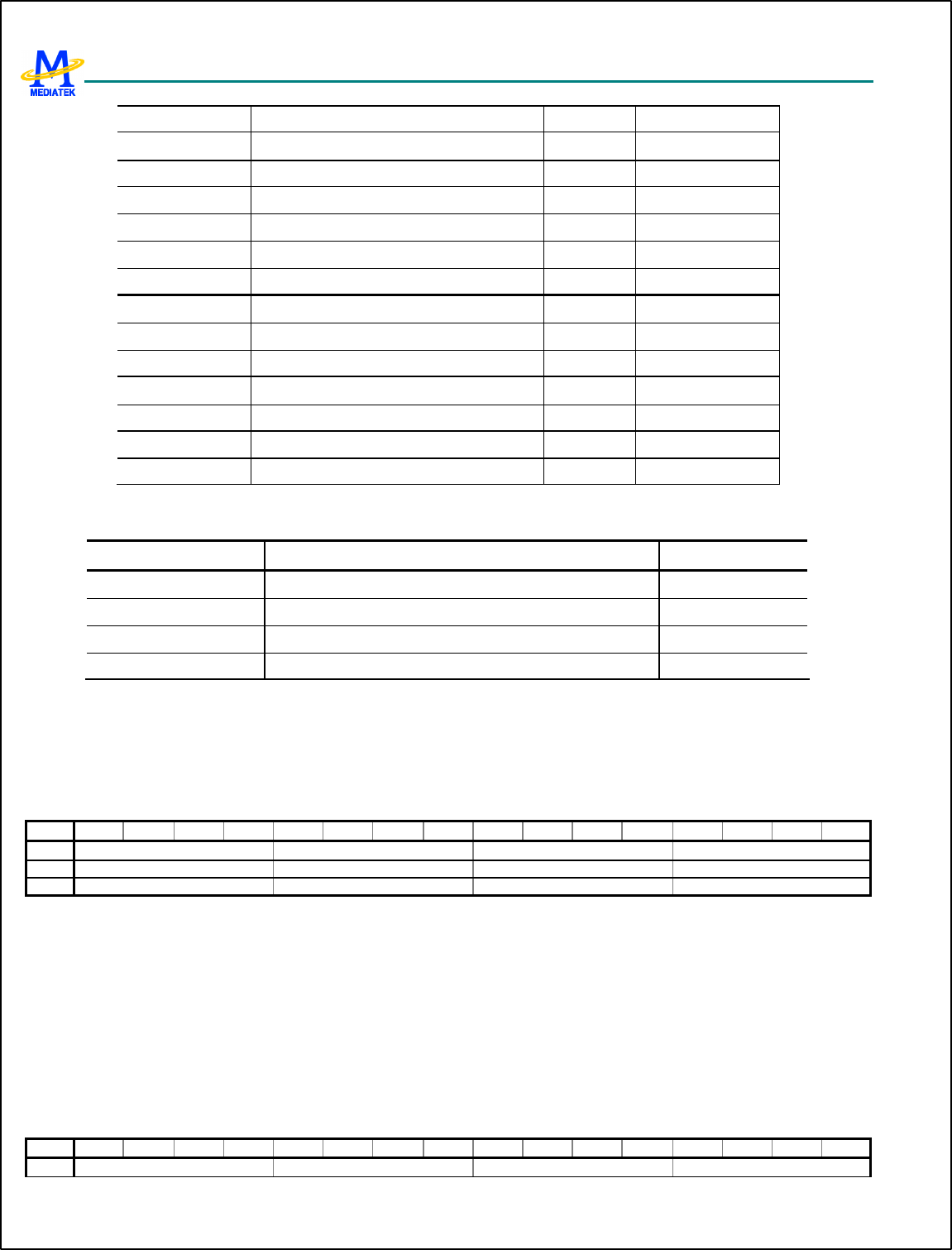

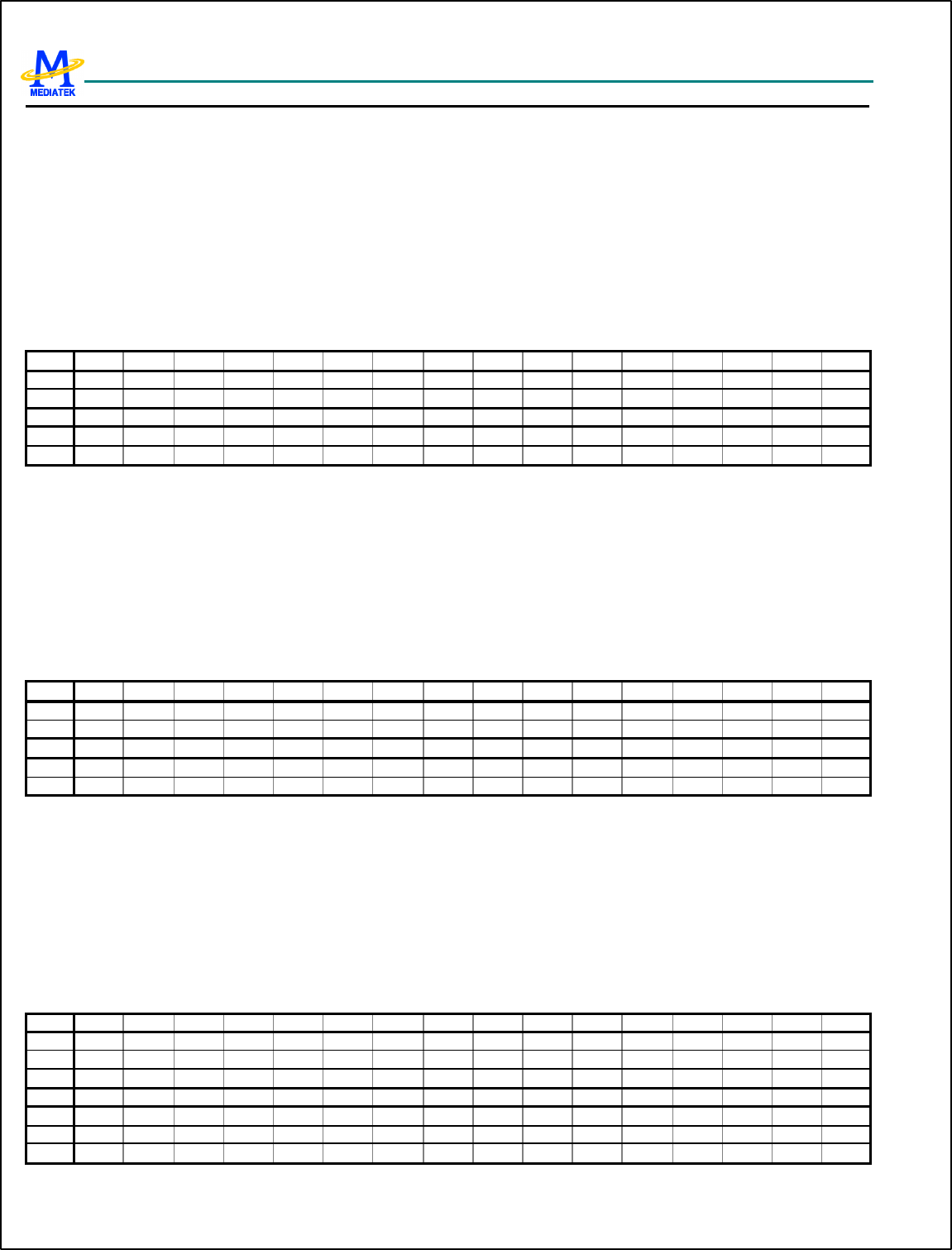

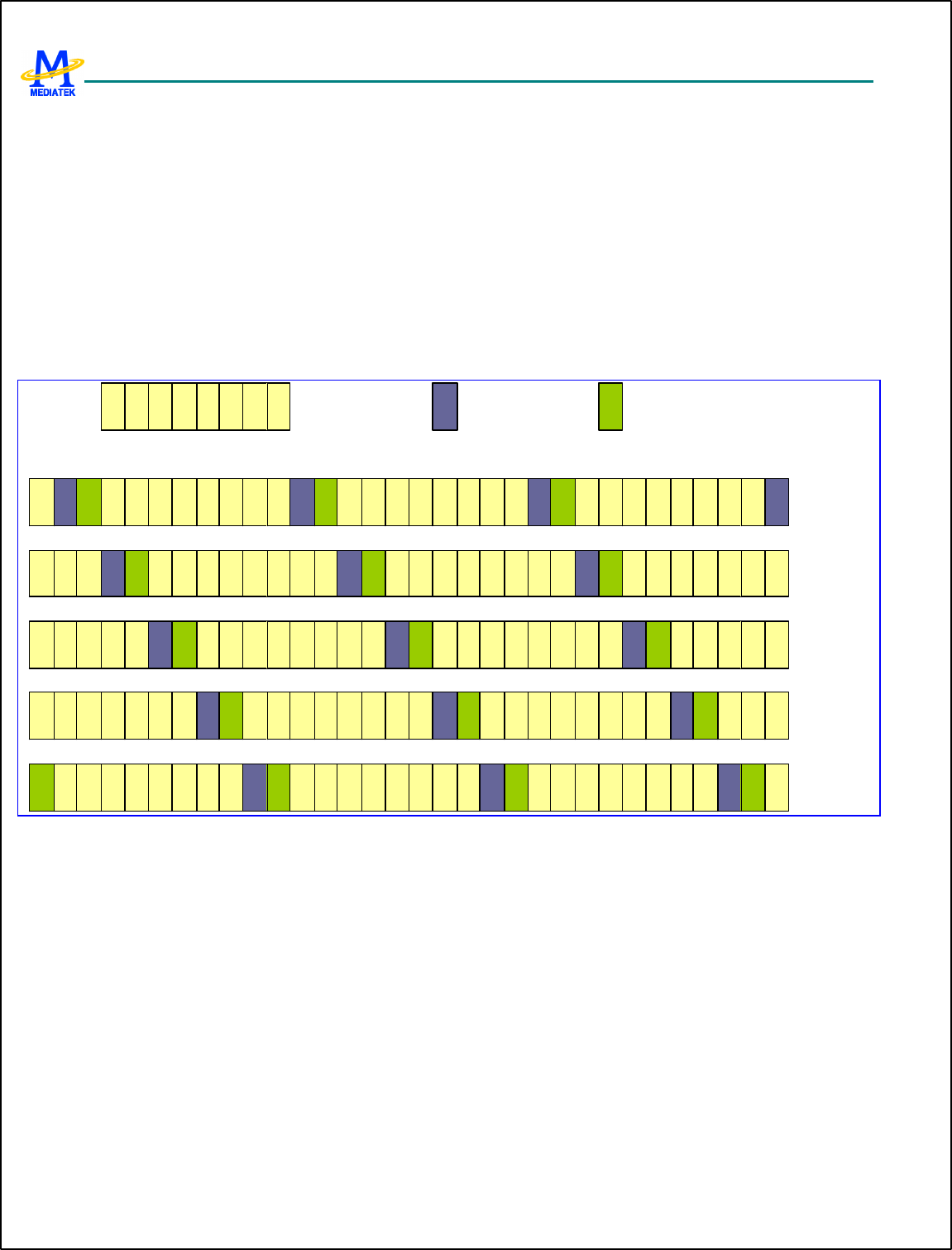

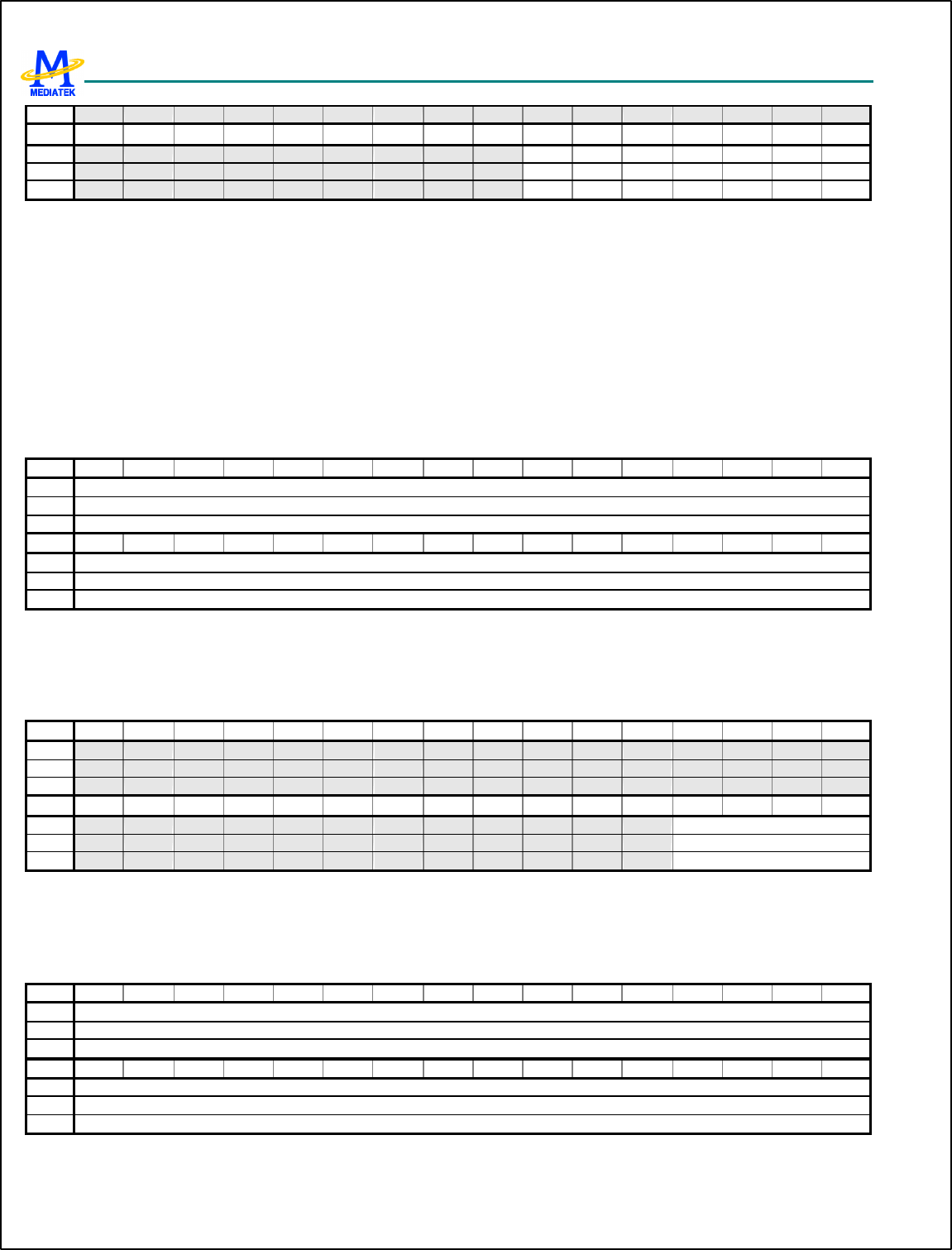

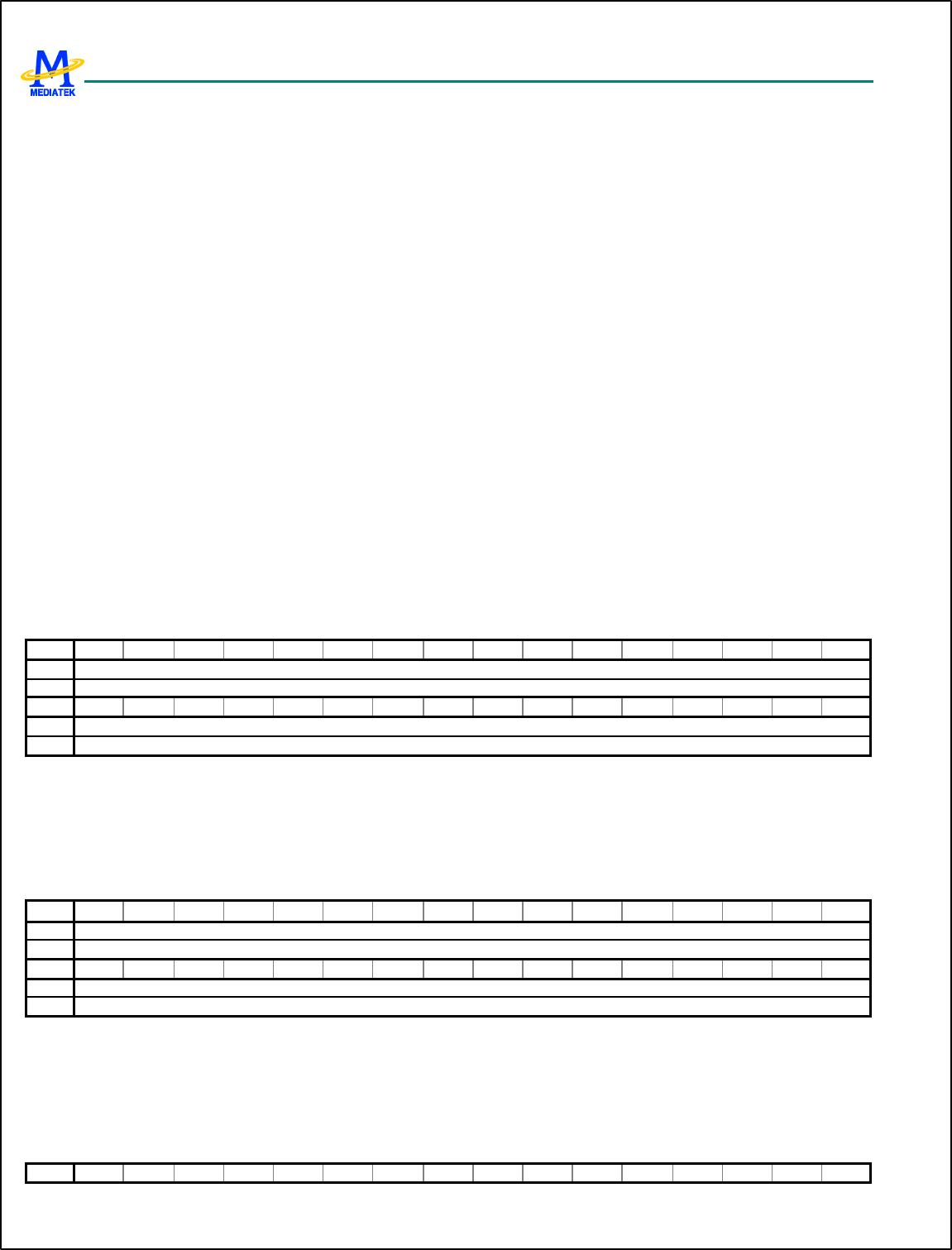

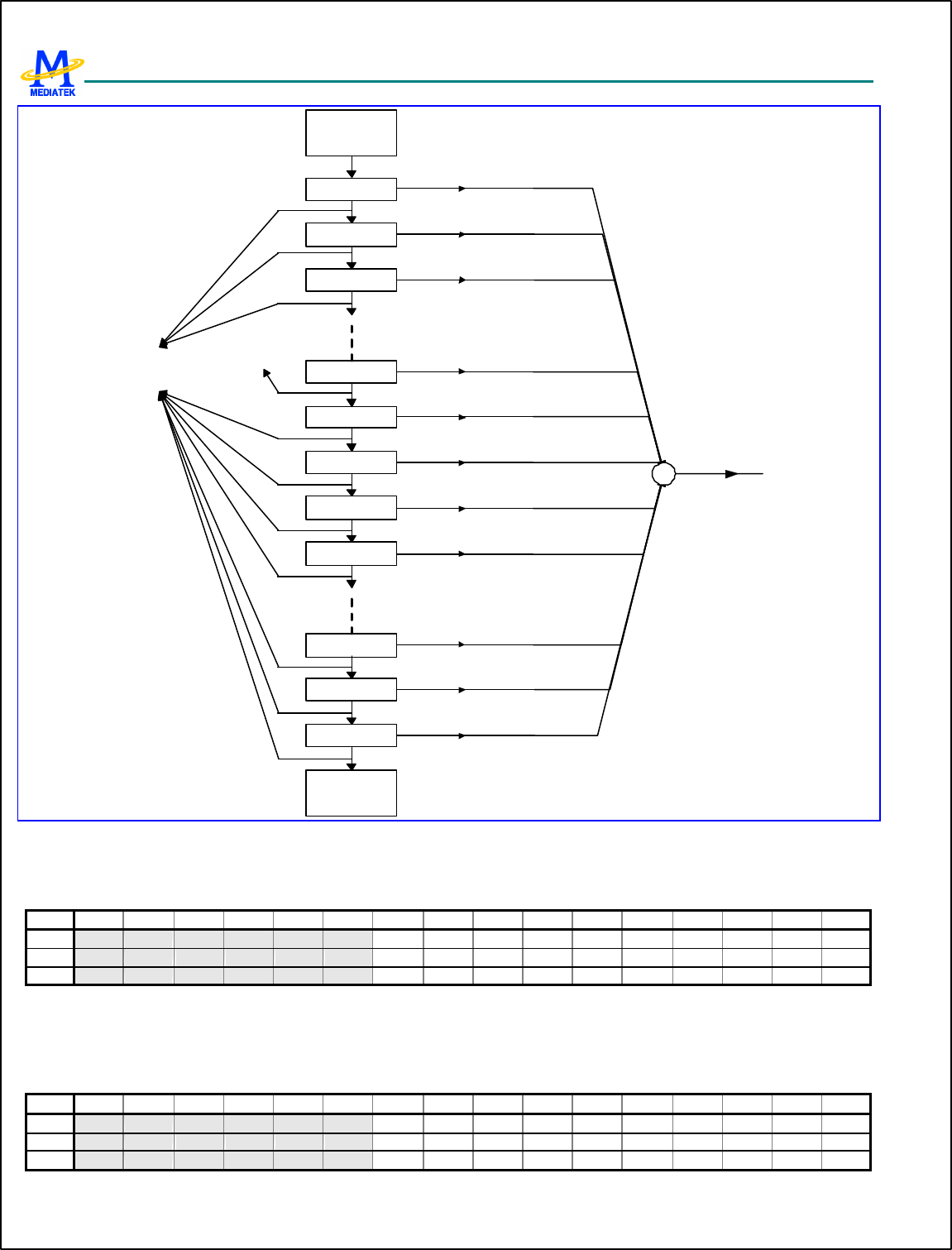

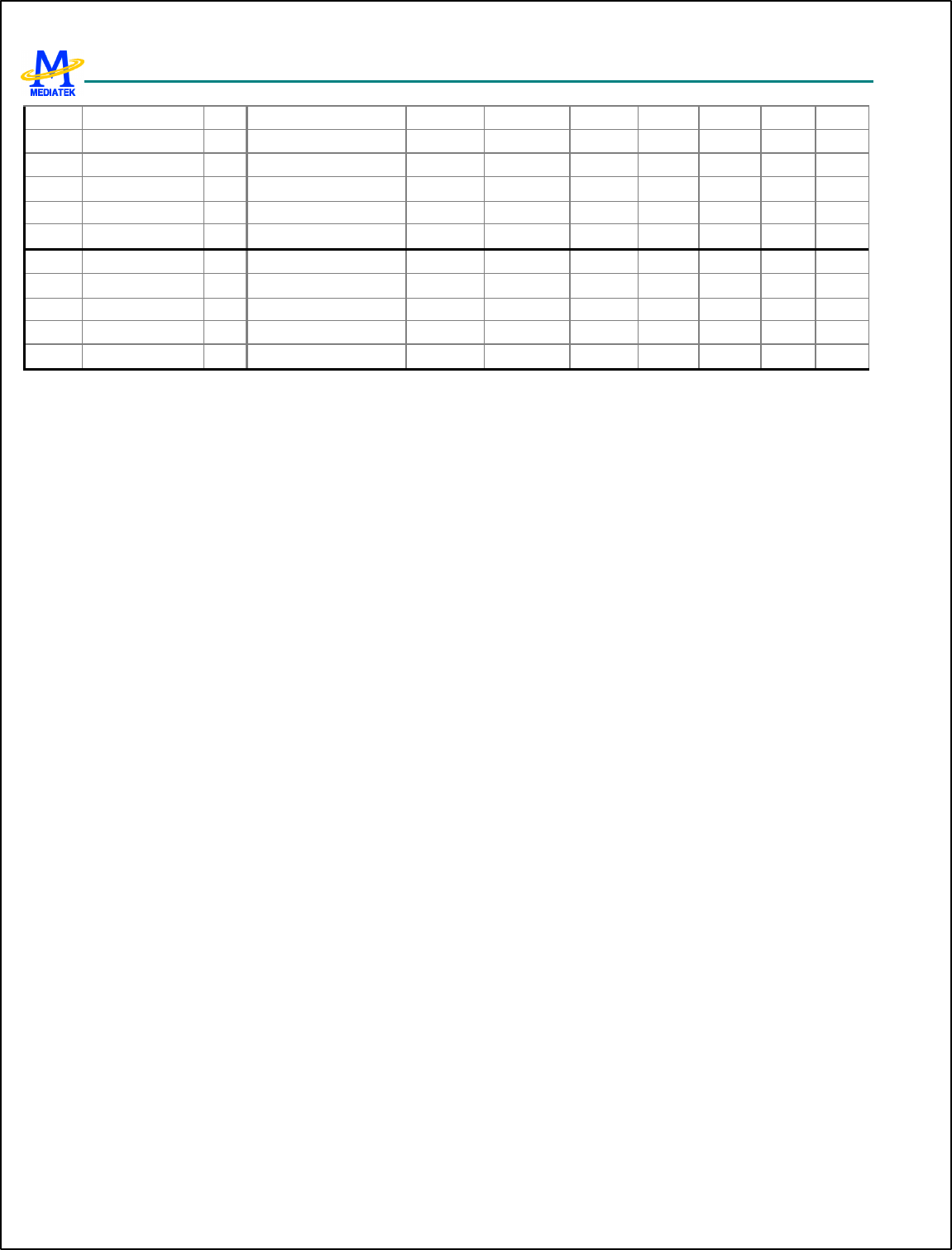

3 Micro-Controller Unit Subsystem

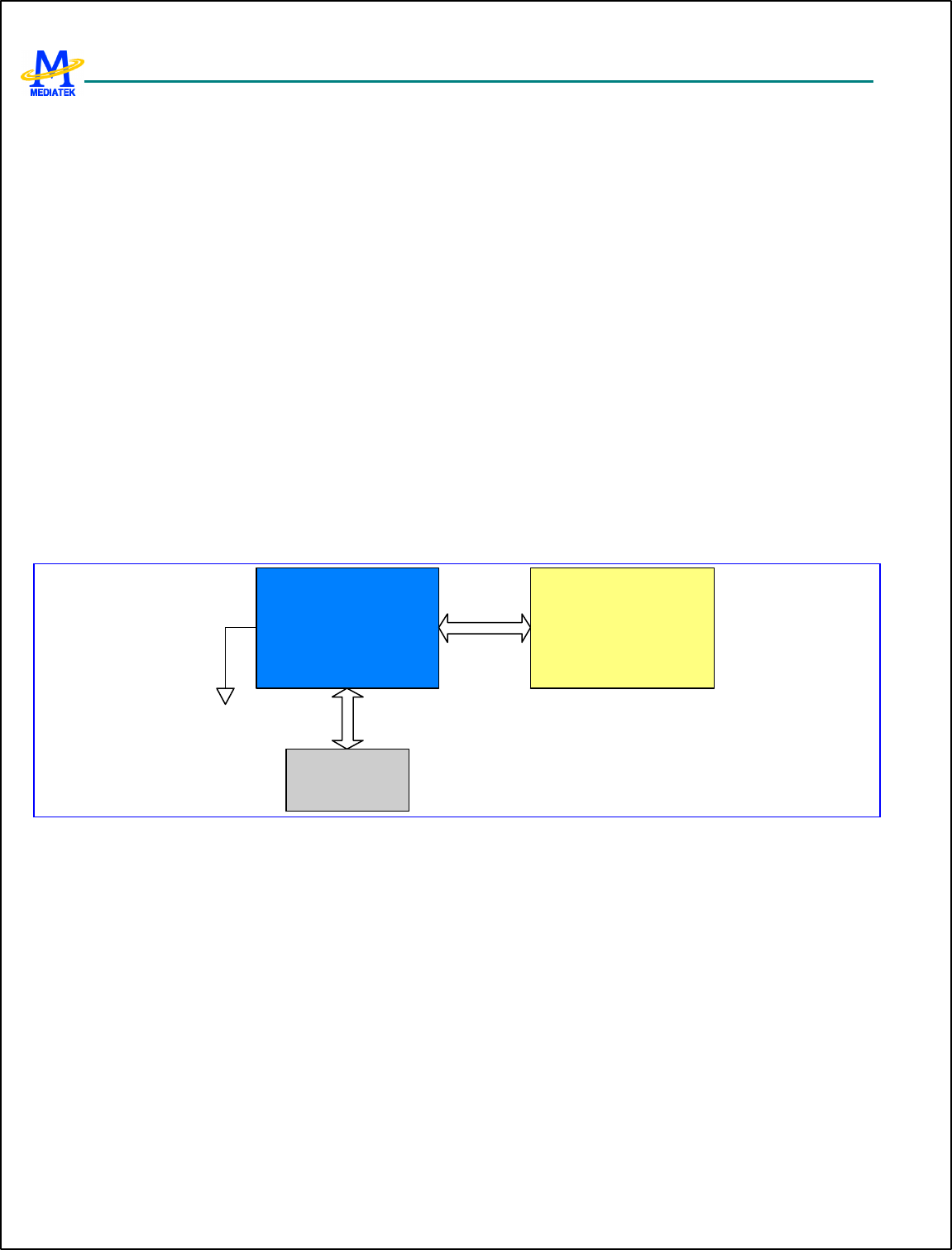

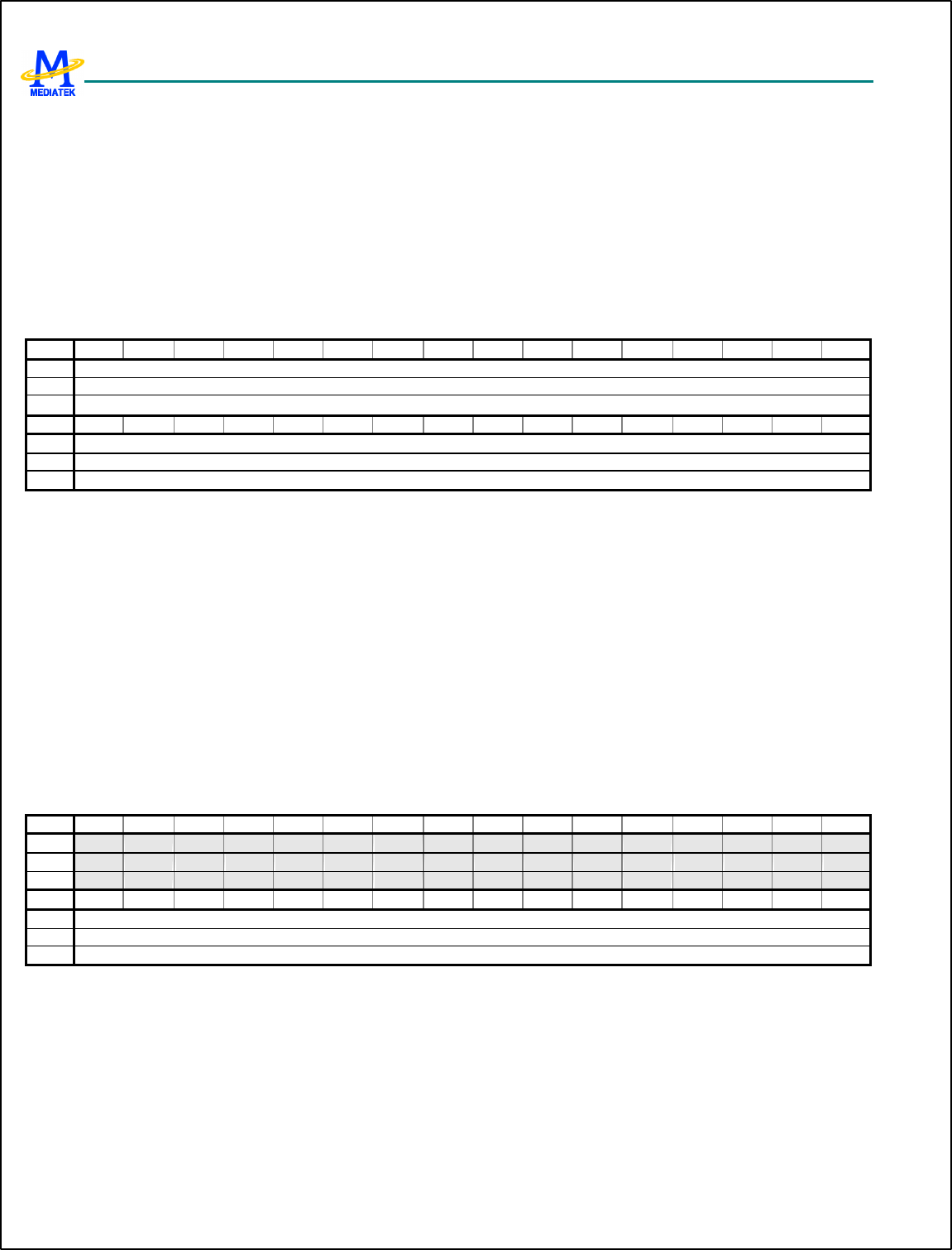

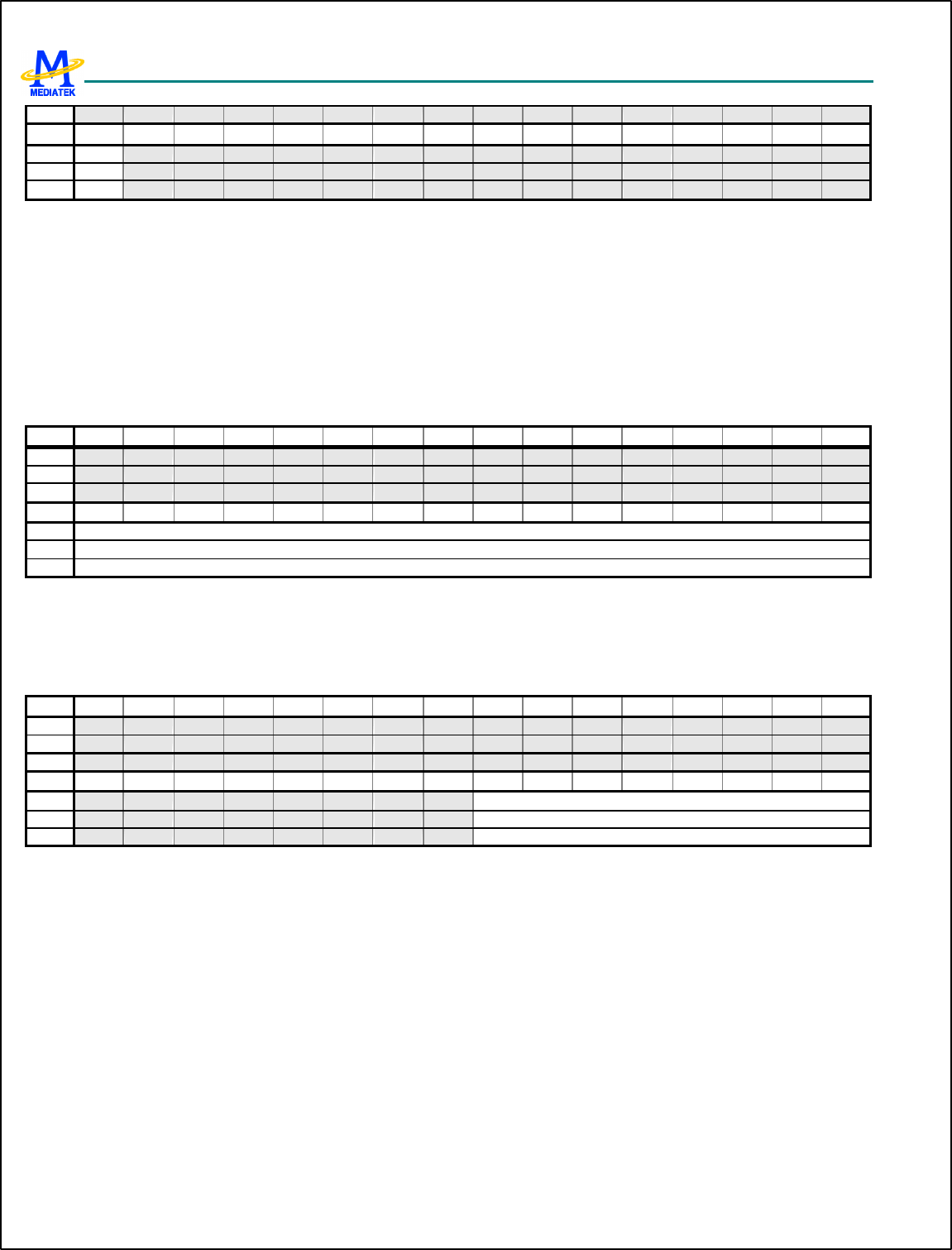

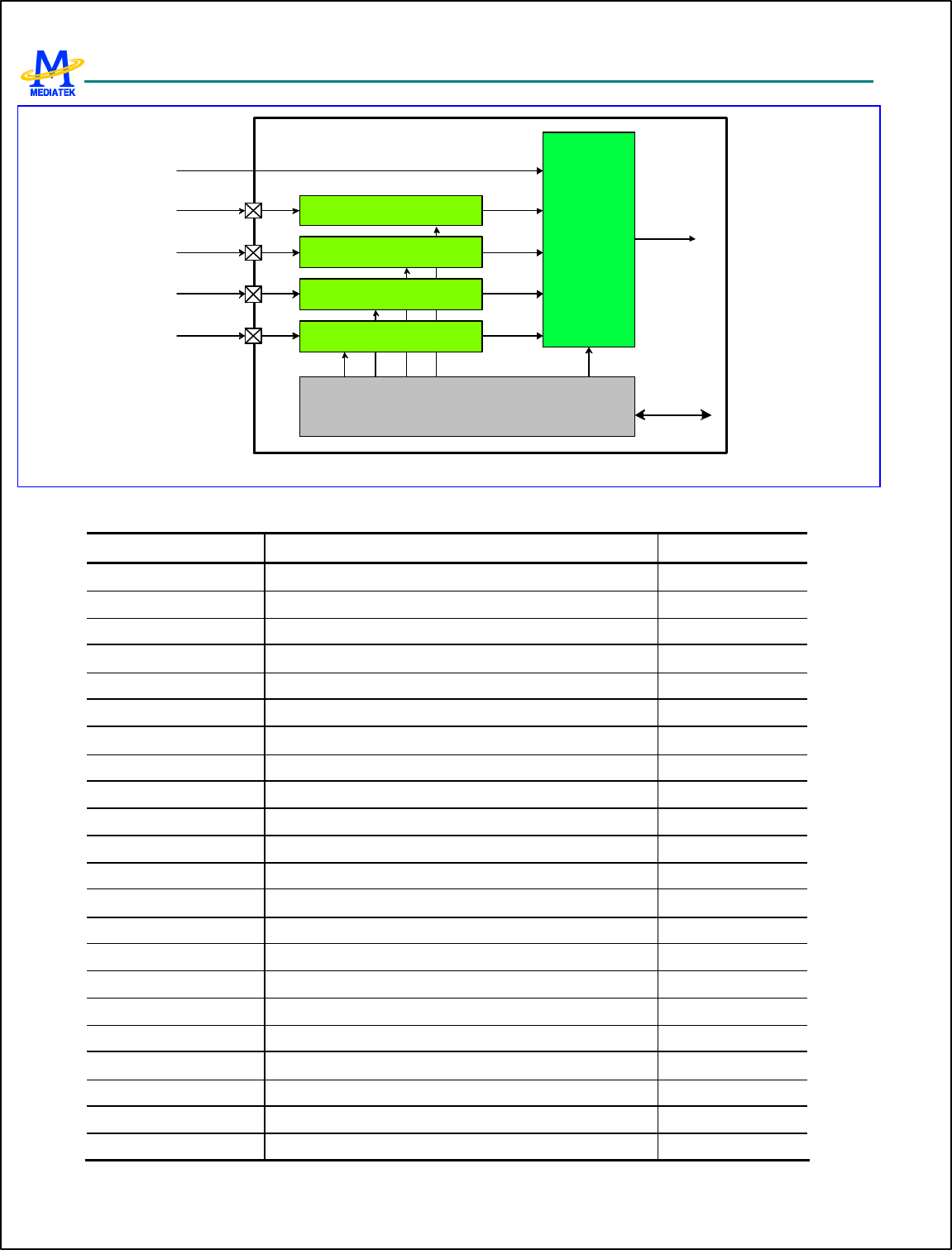

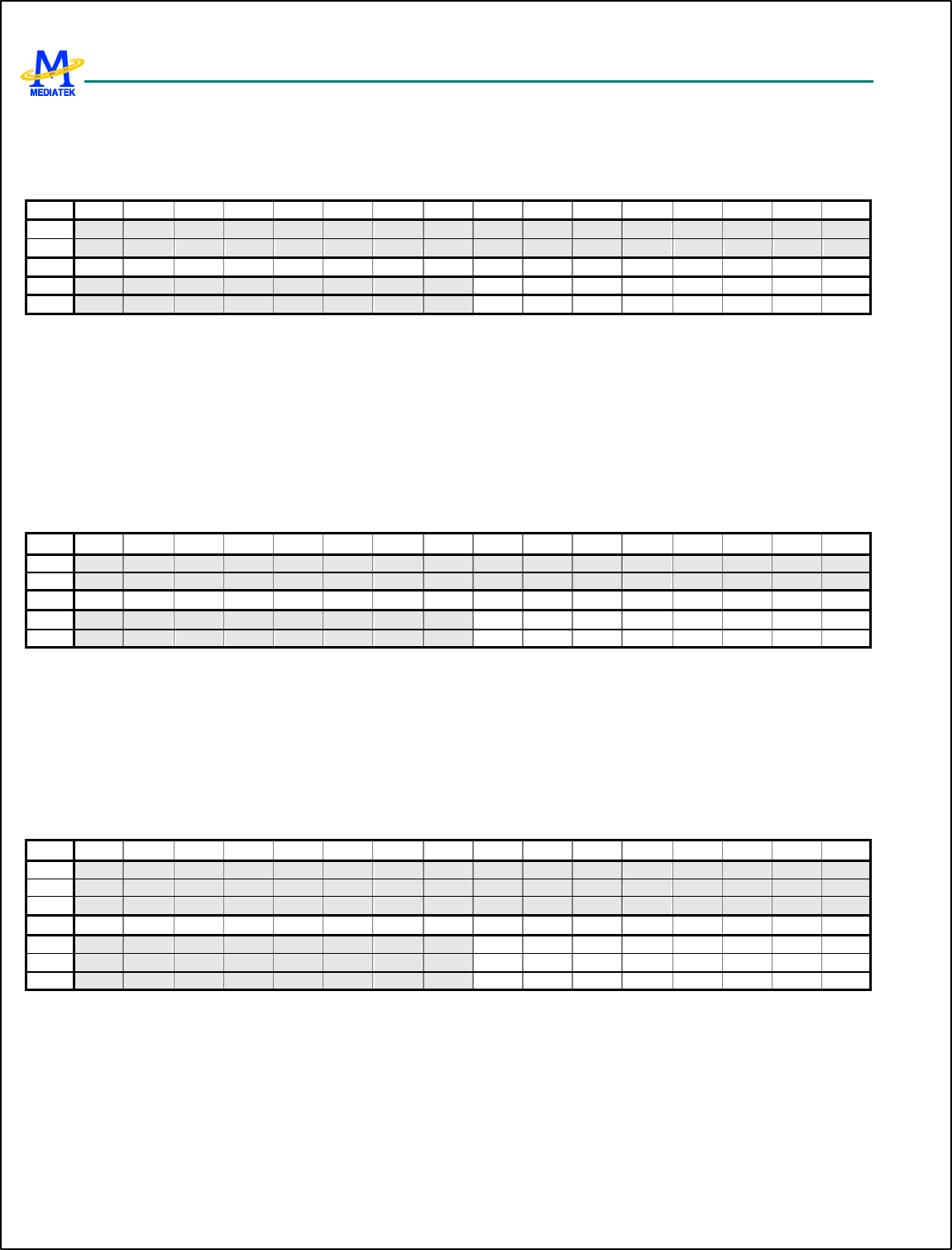

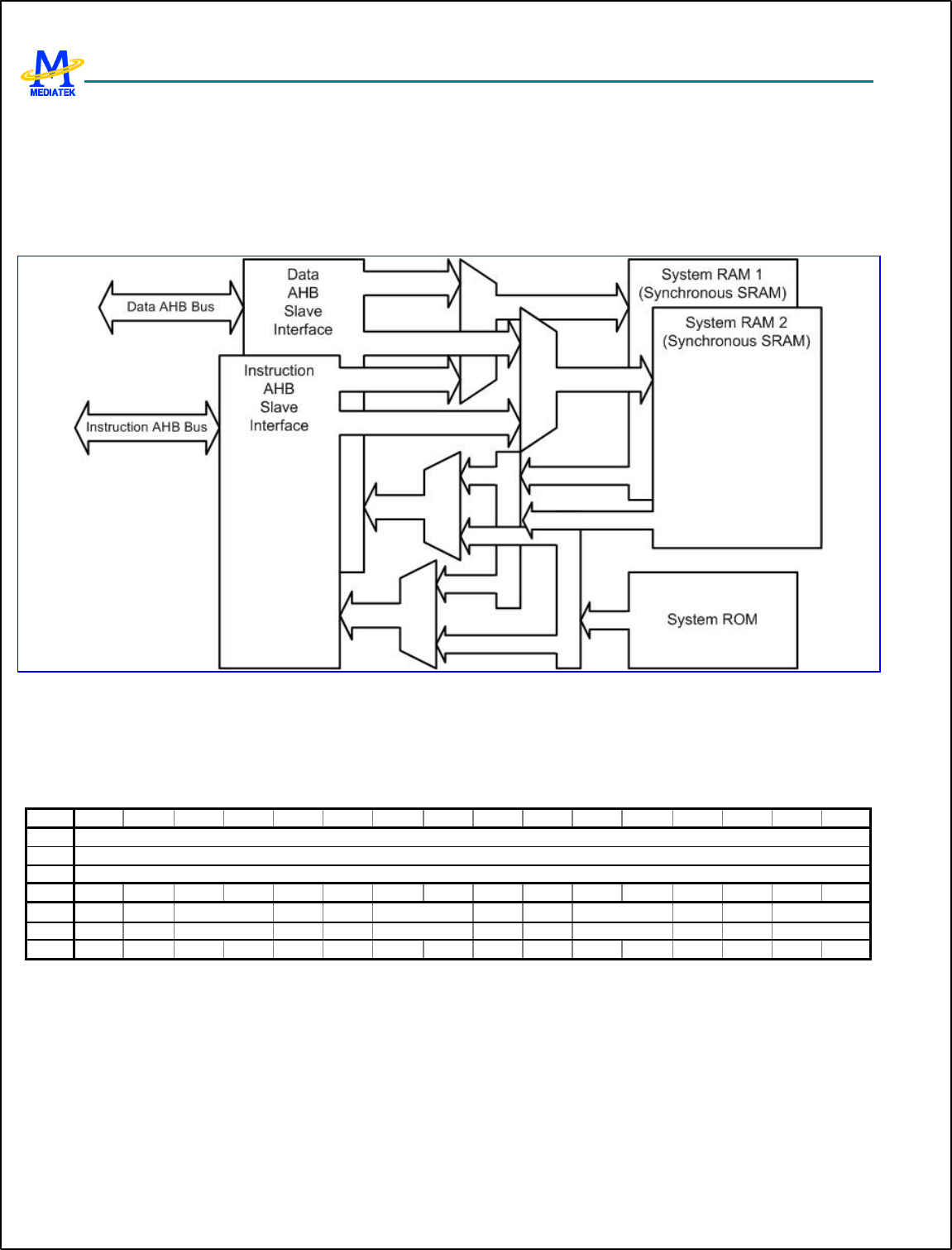

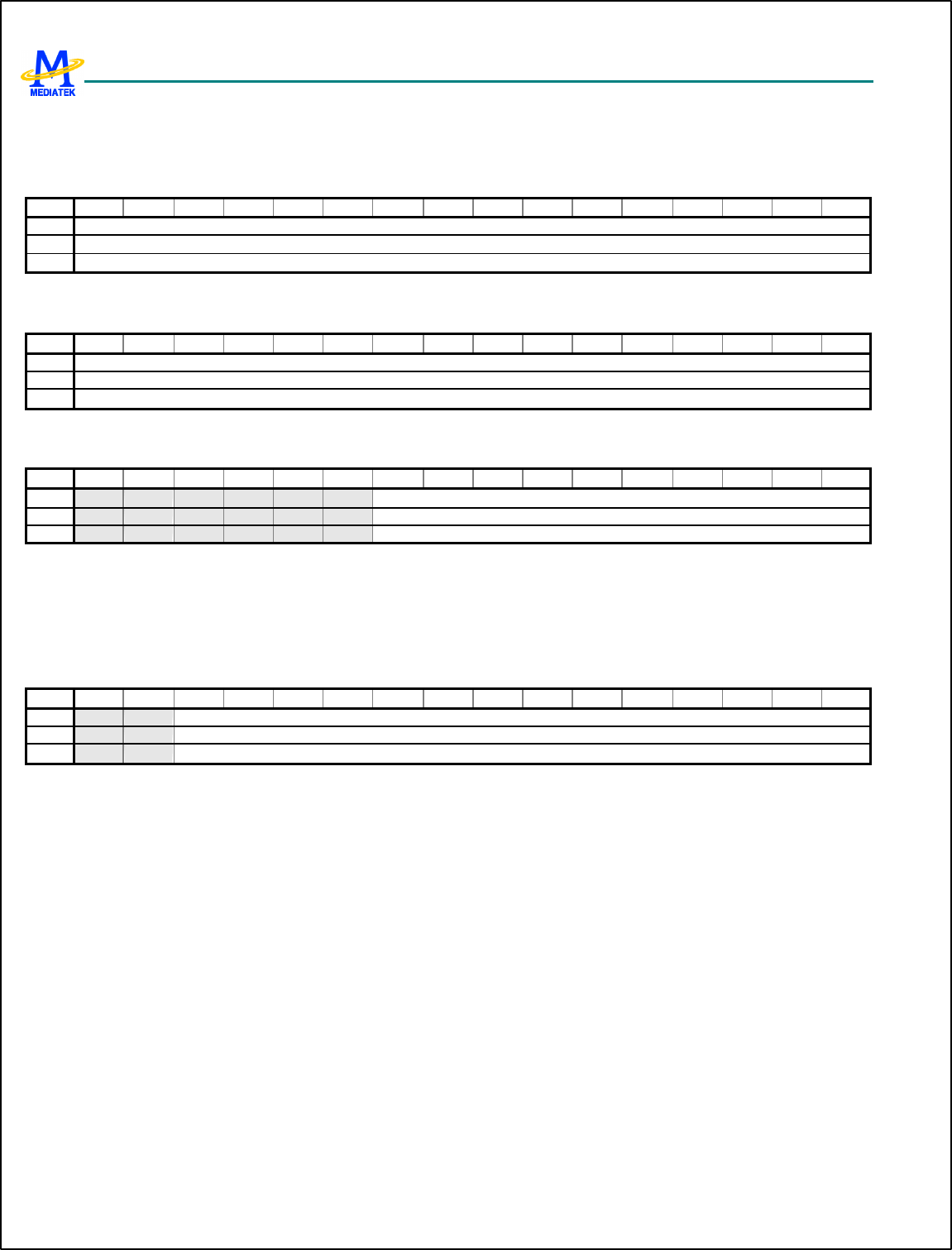

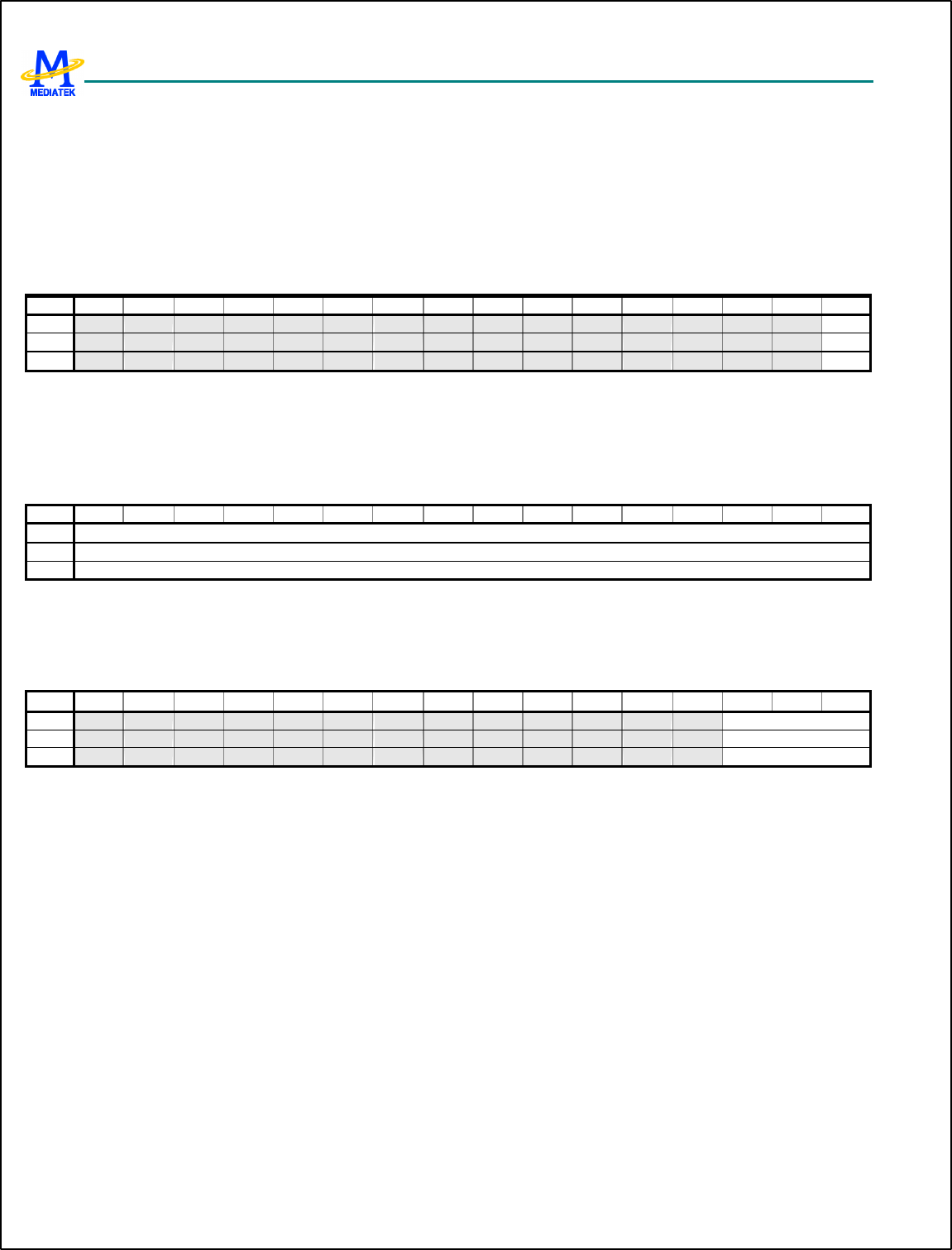

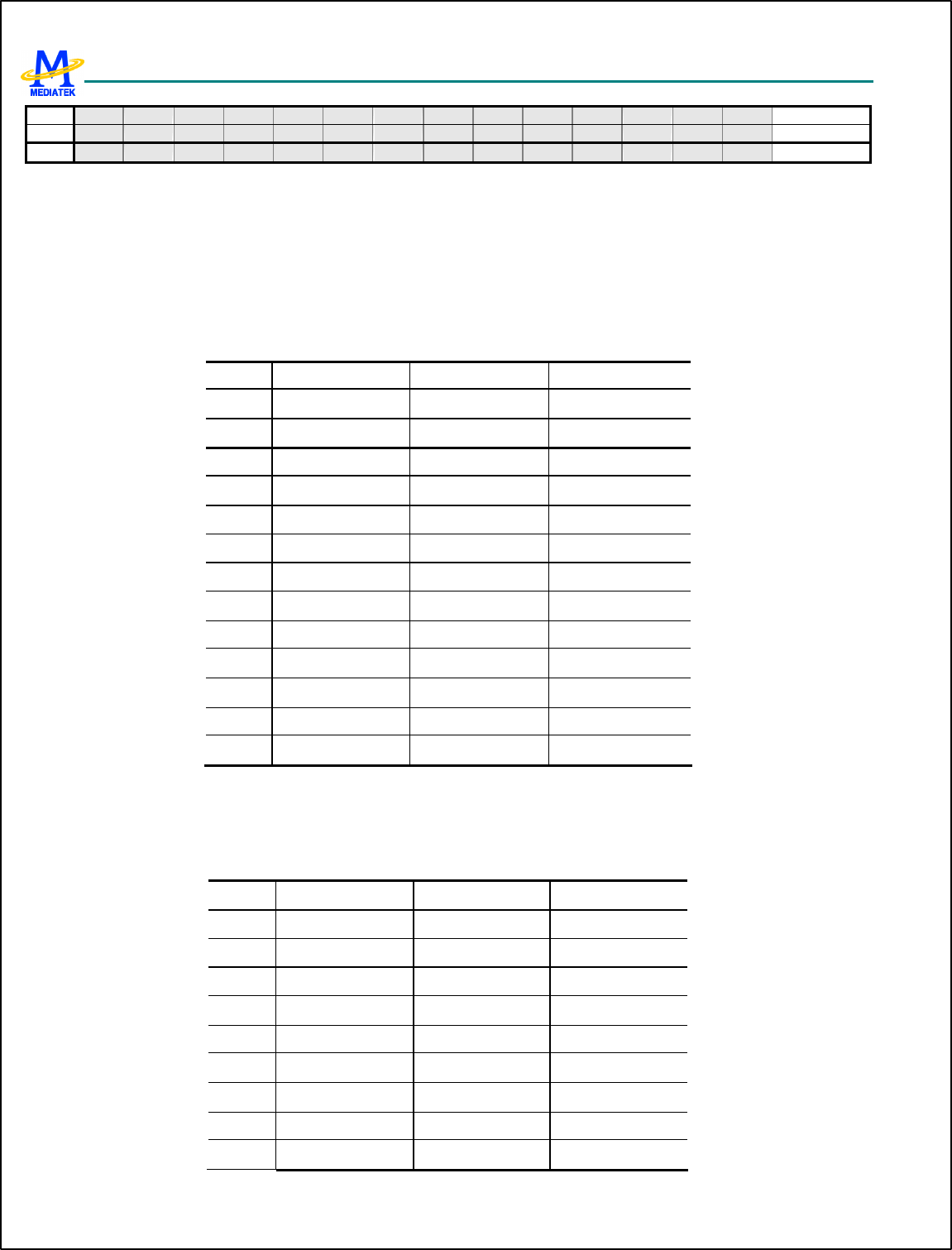

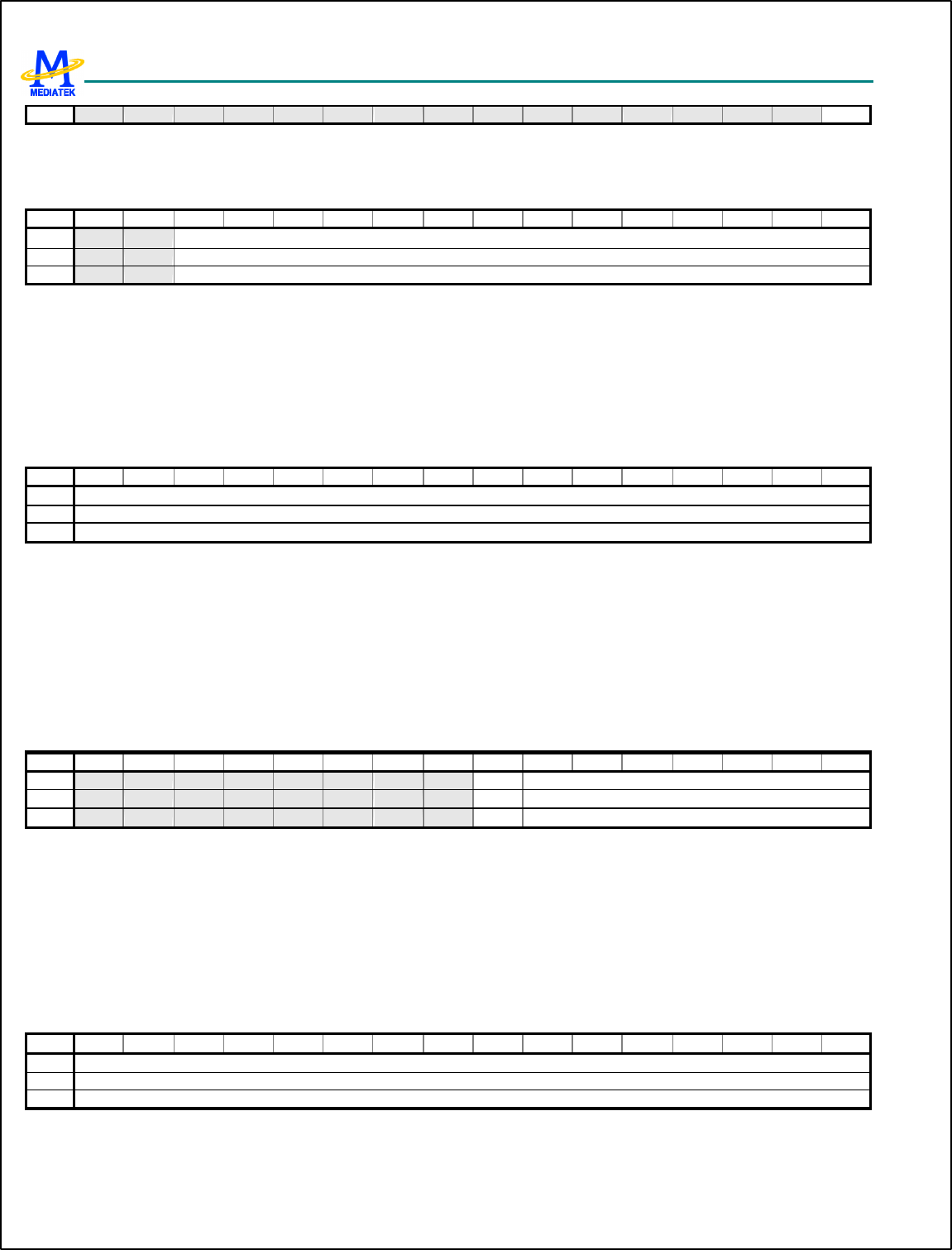

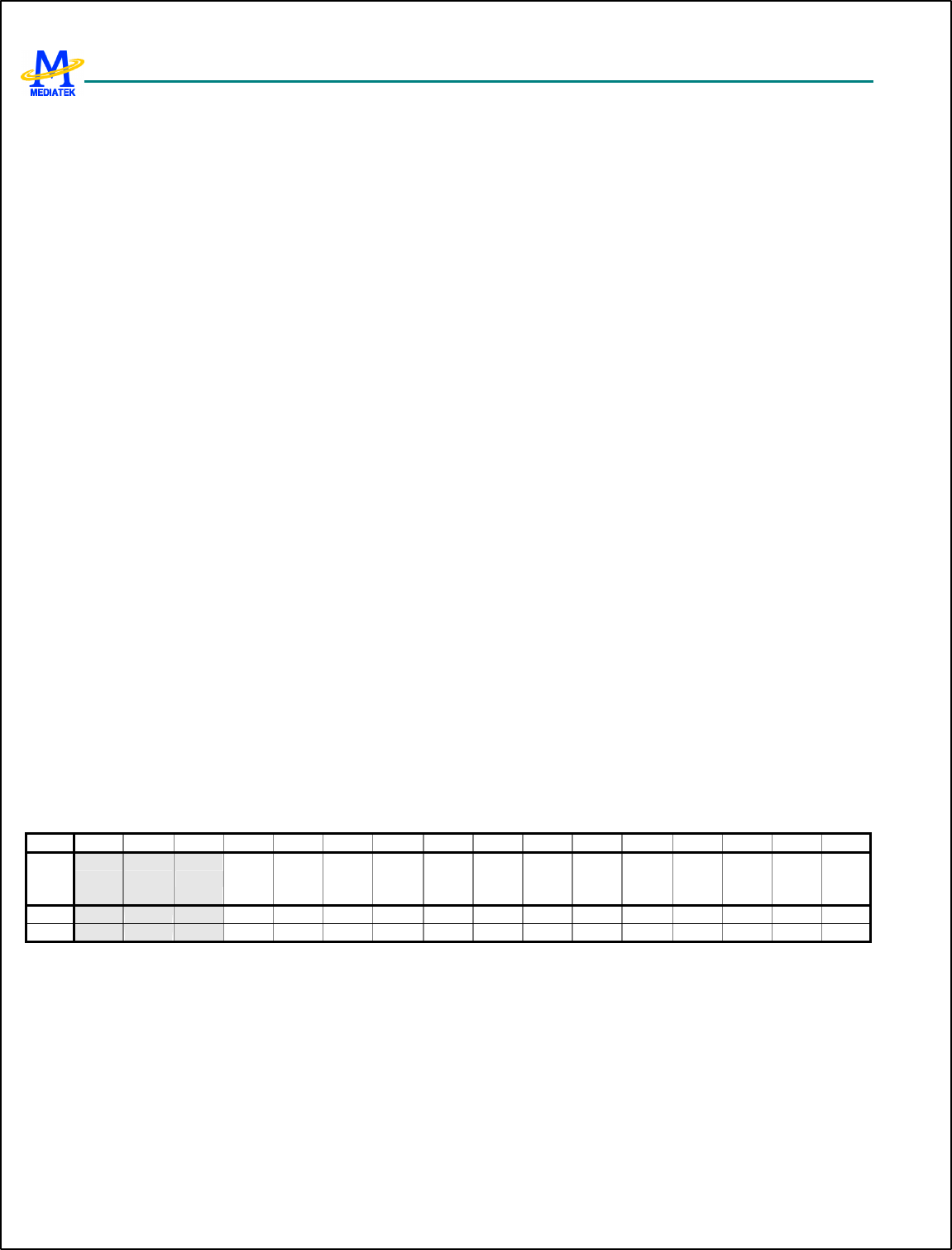

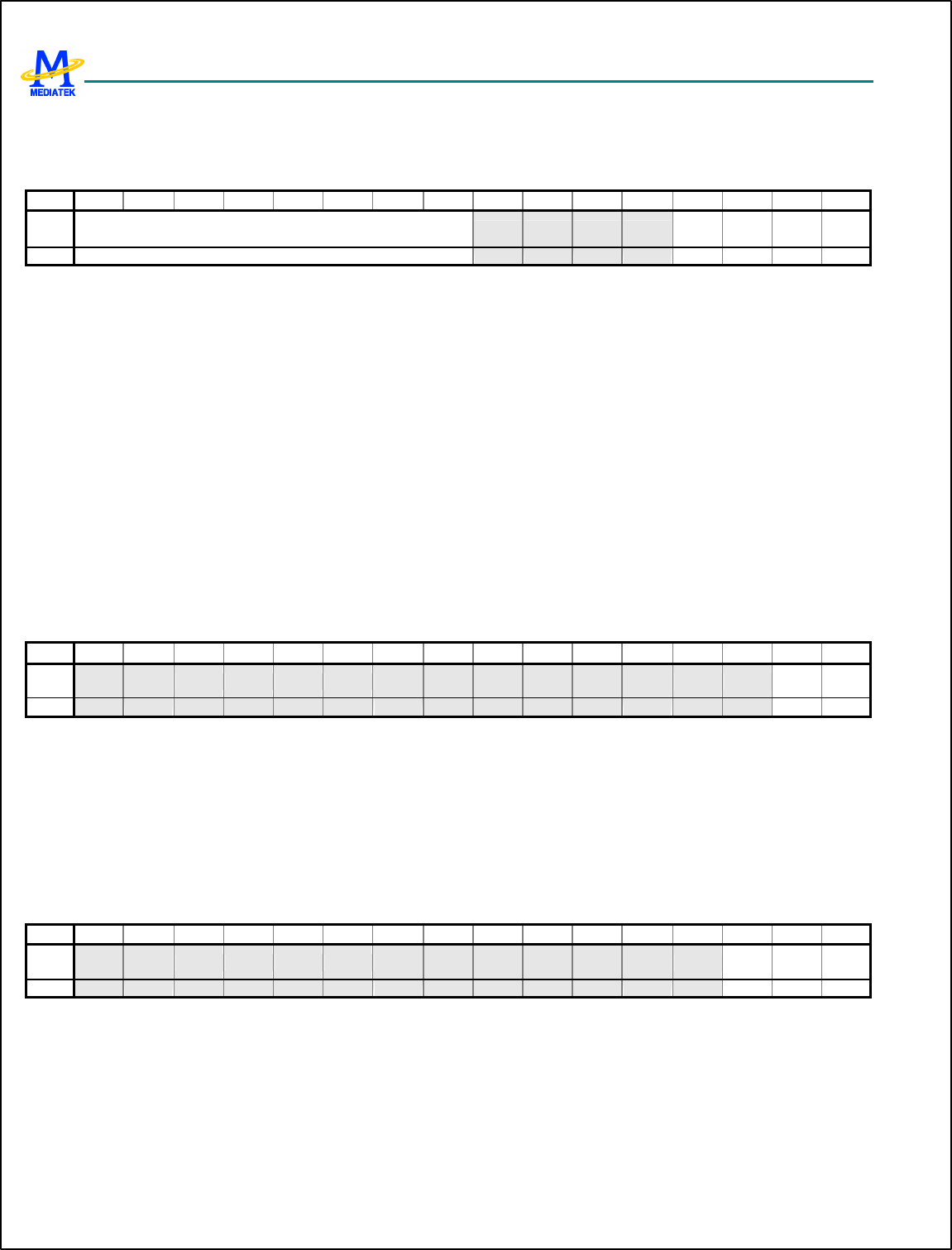

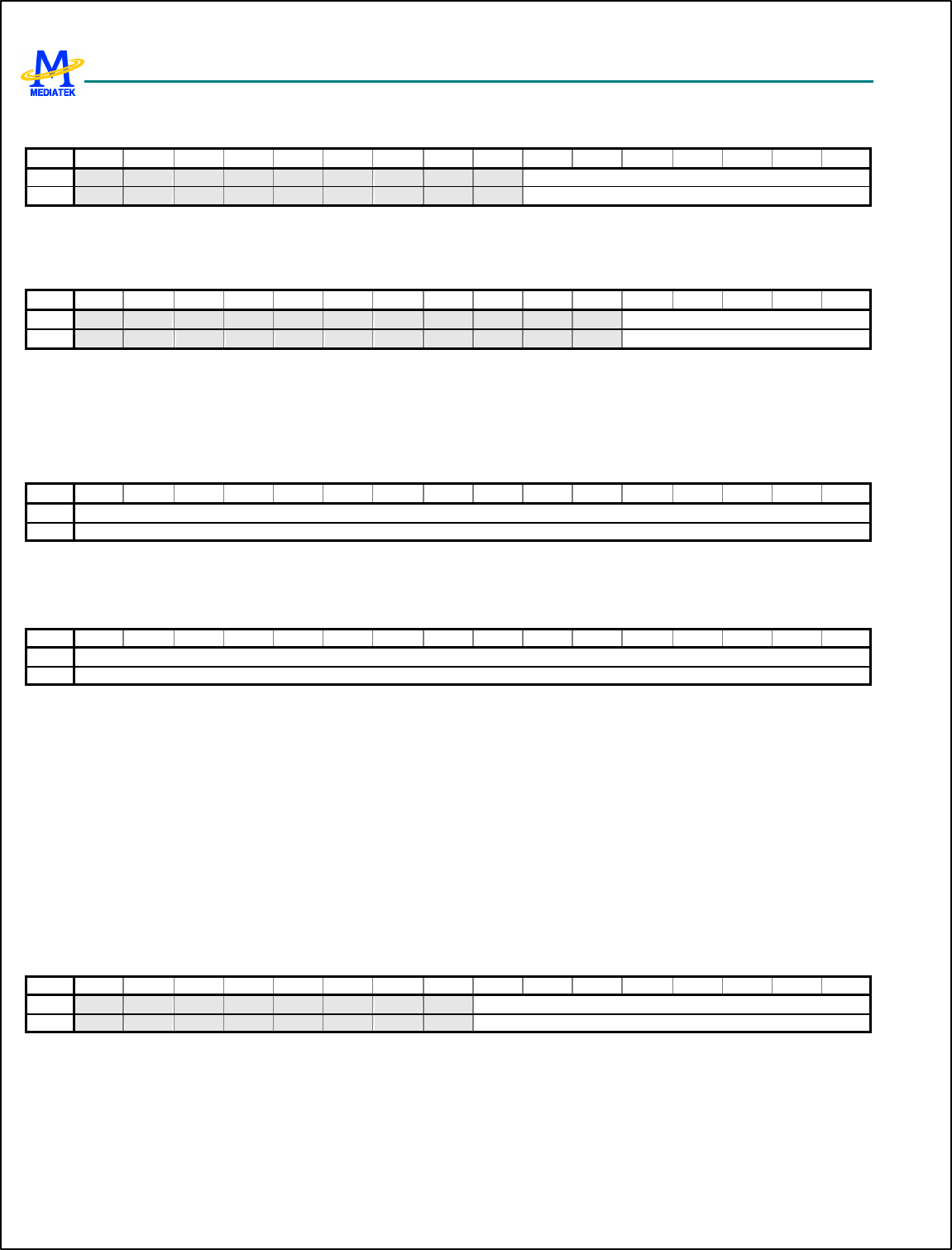

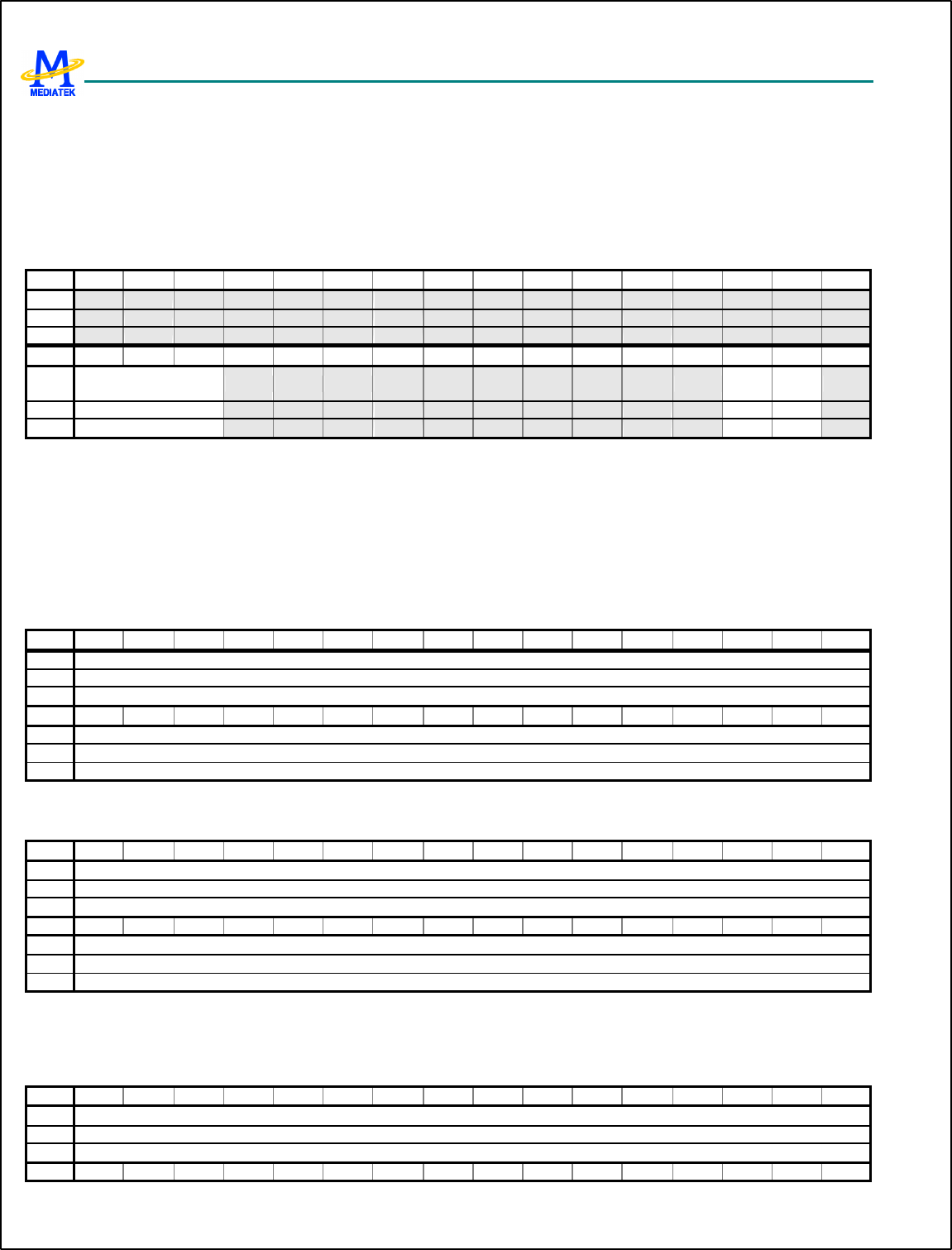

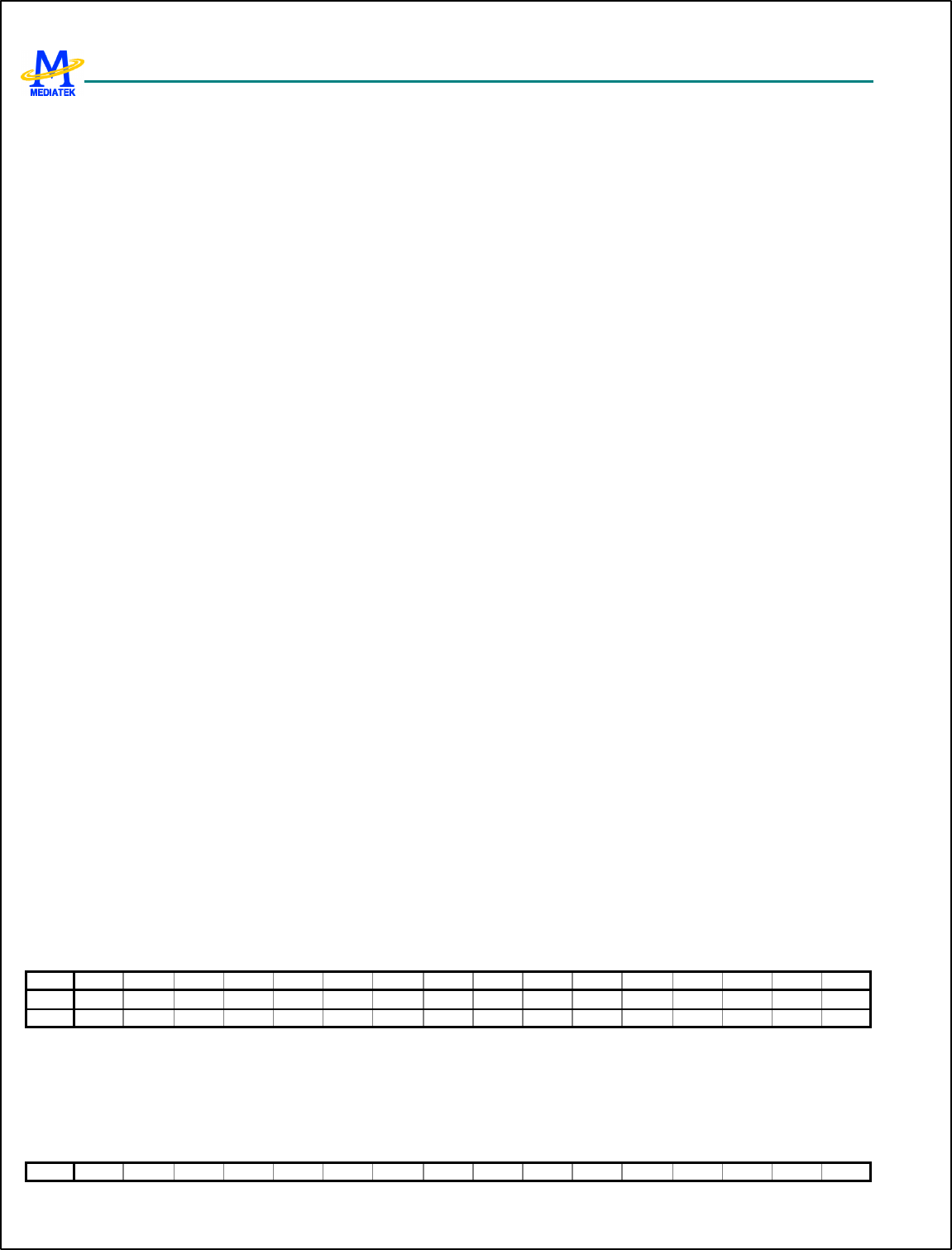

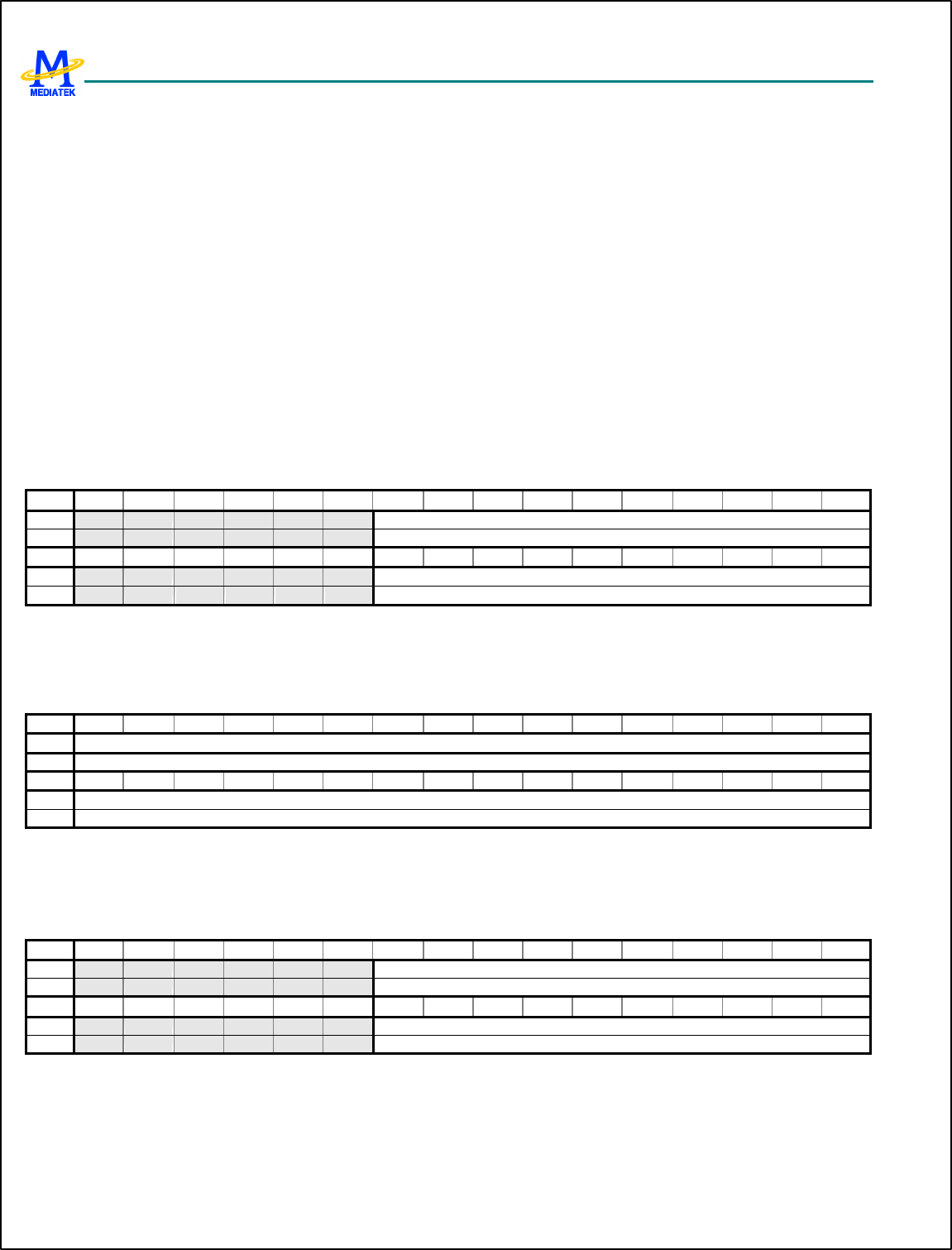

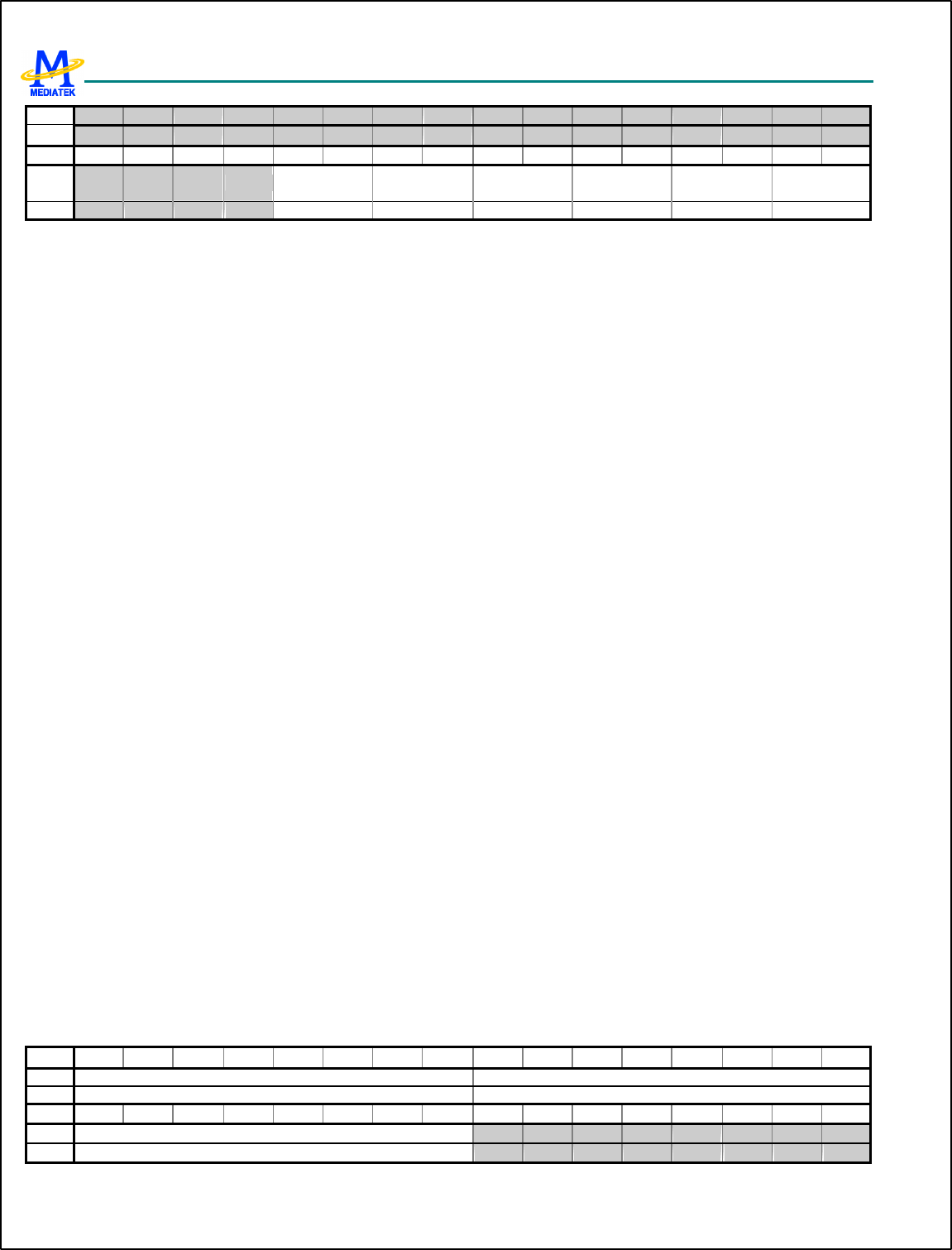

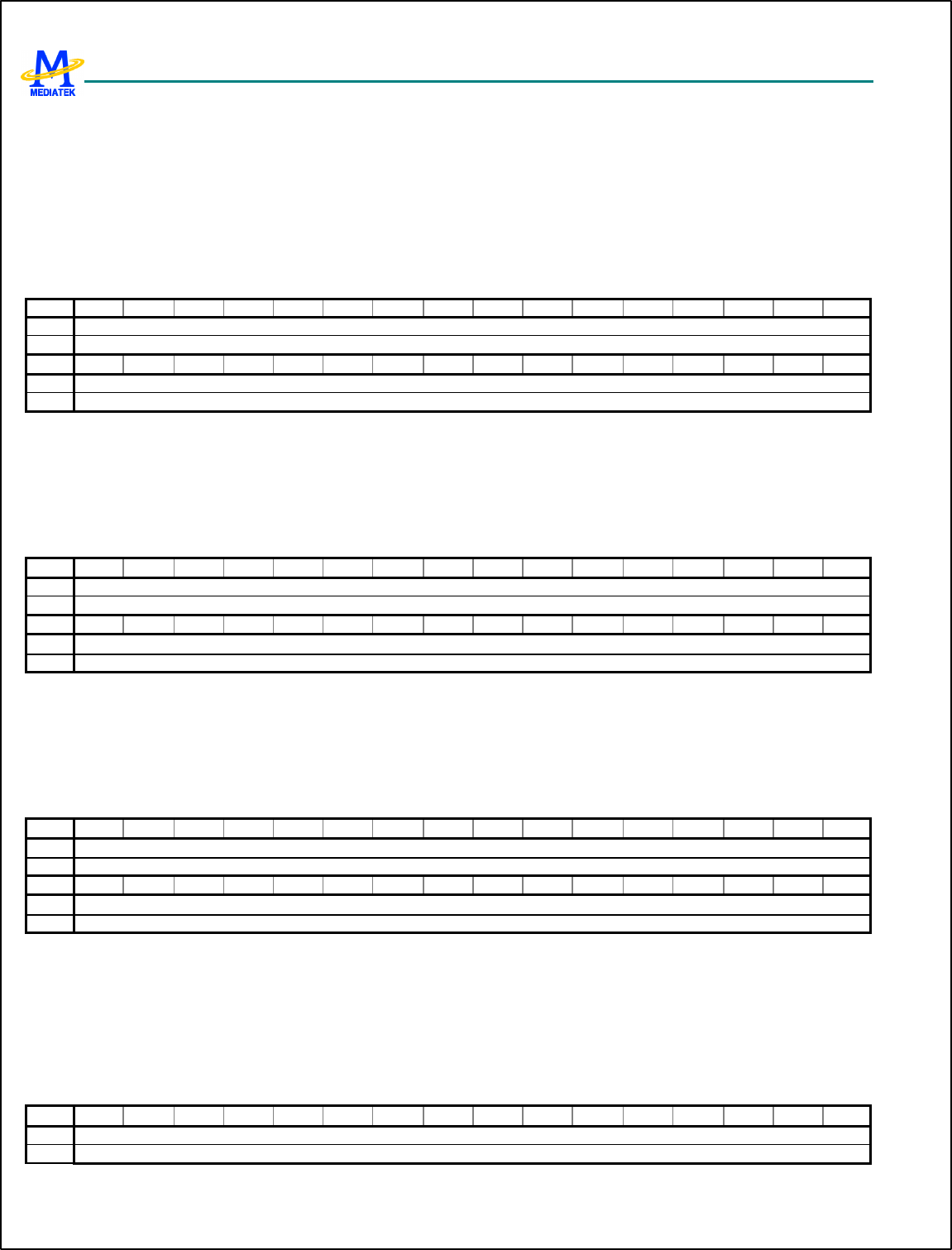

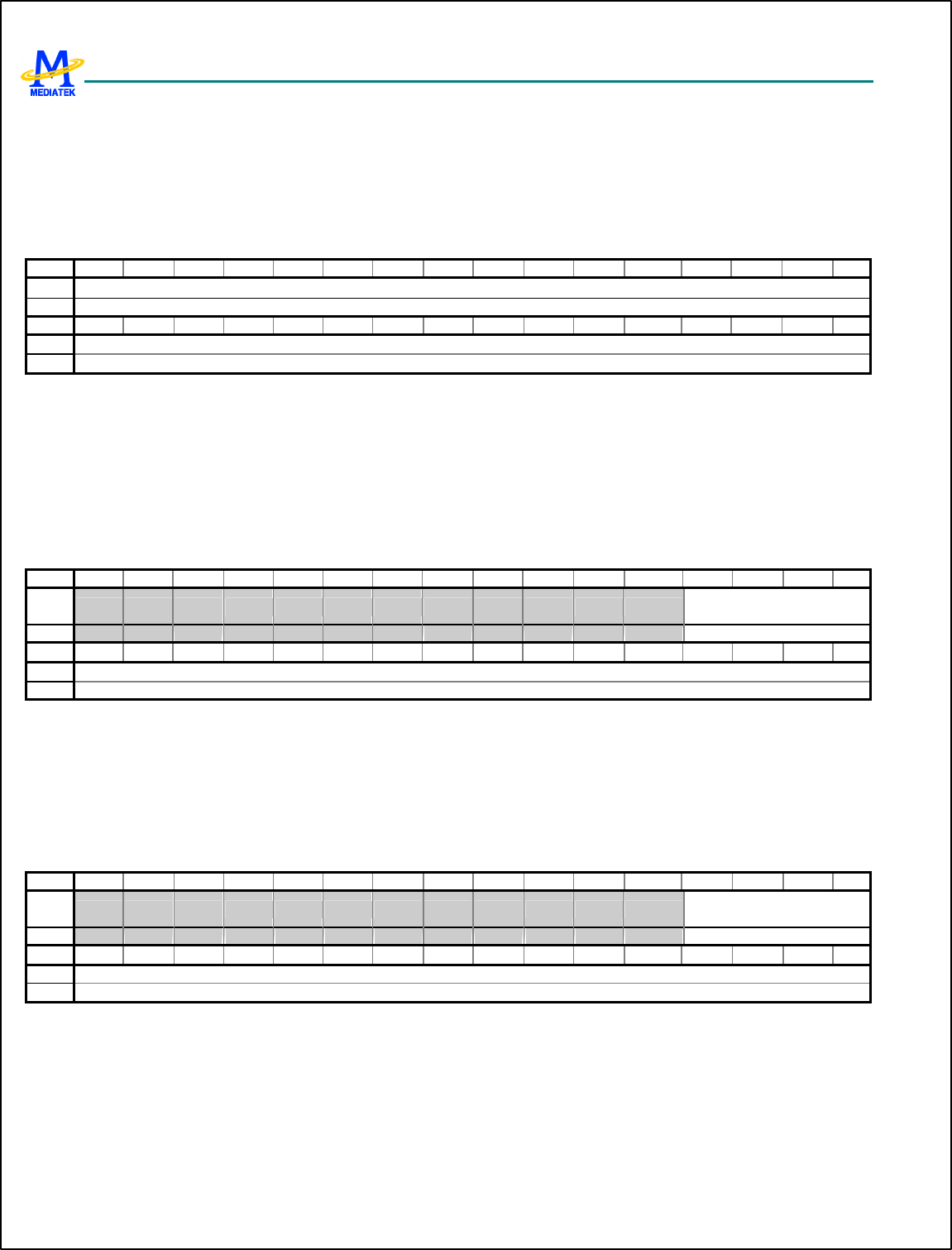

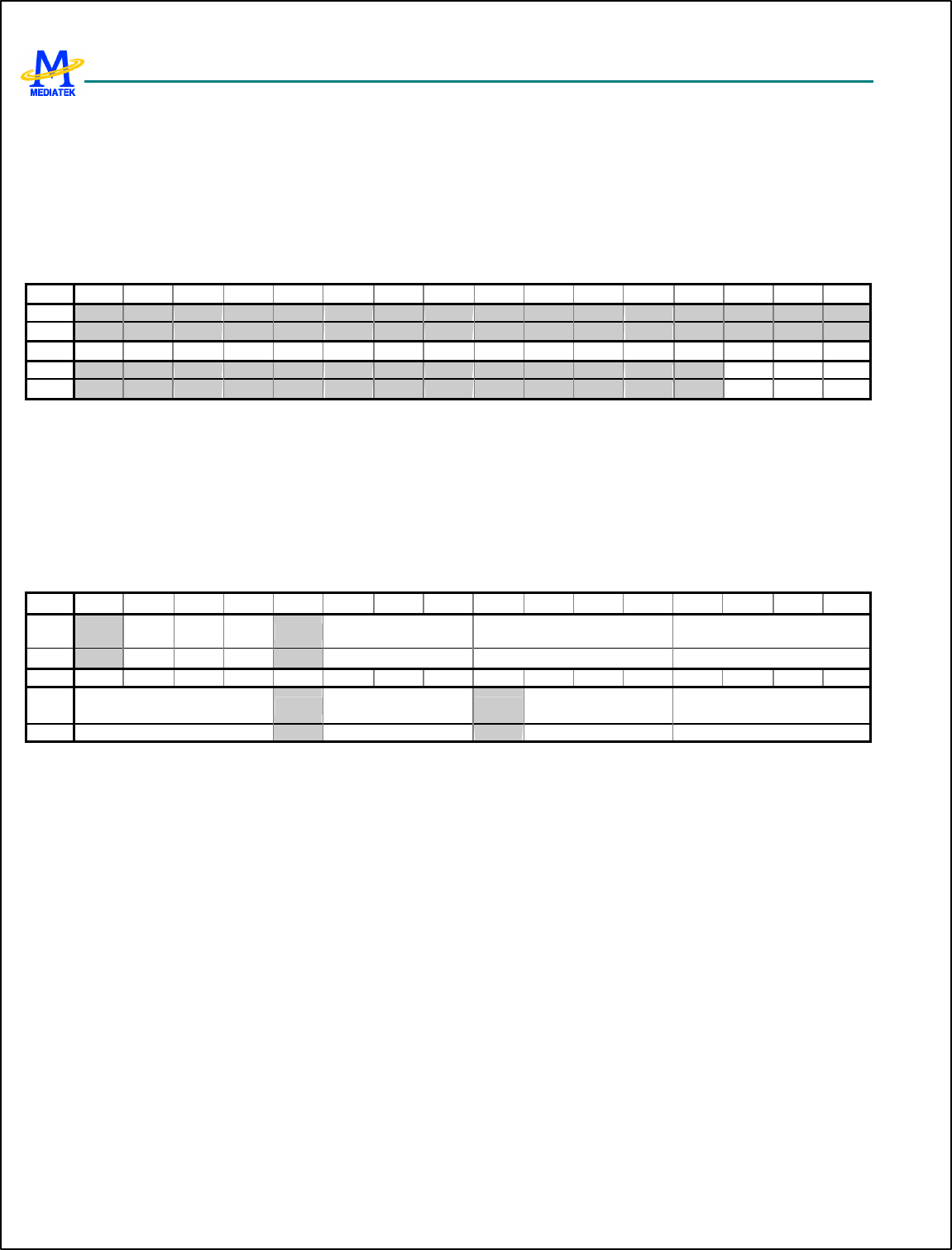

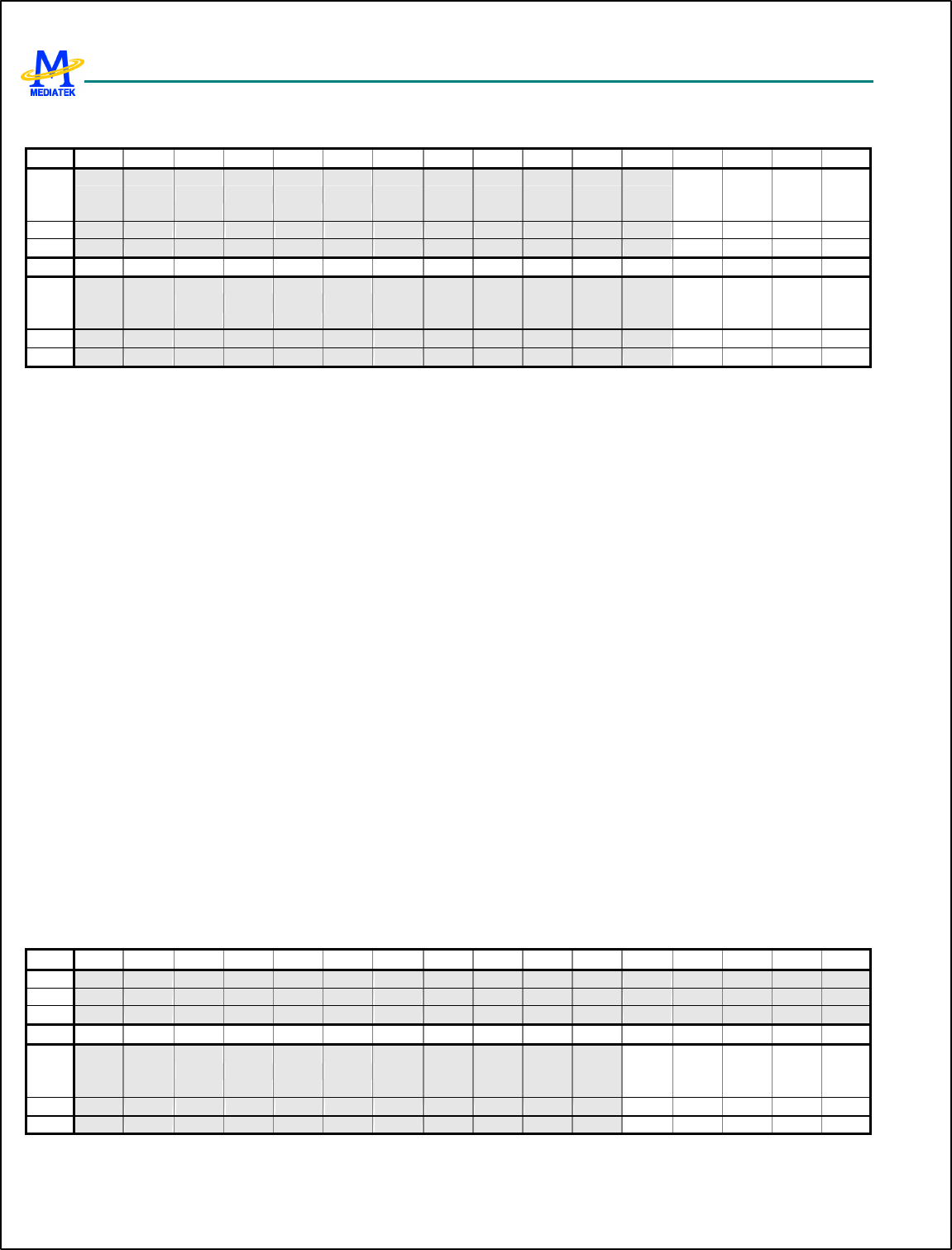

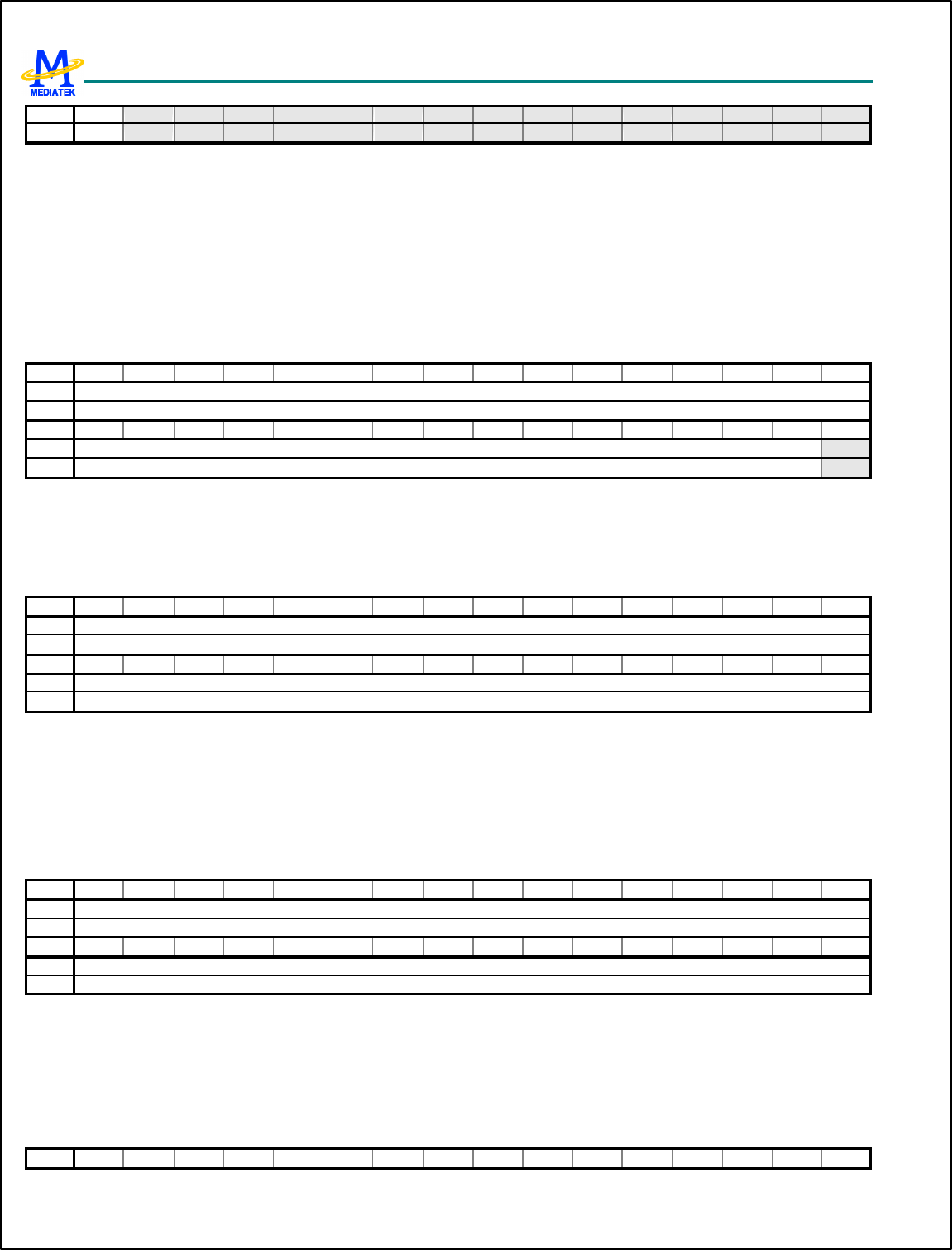

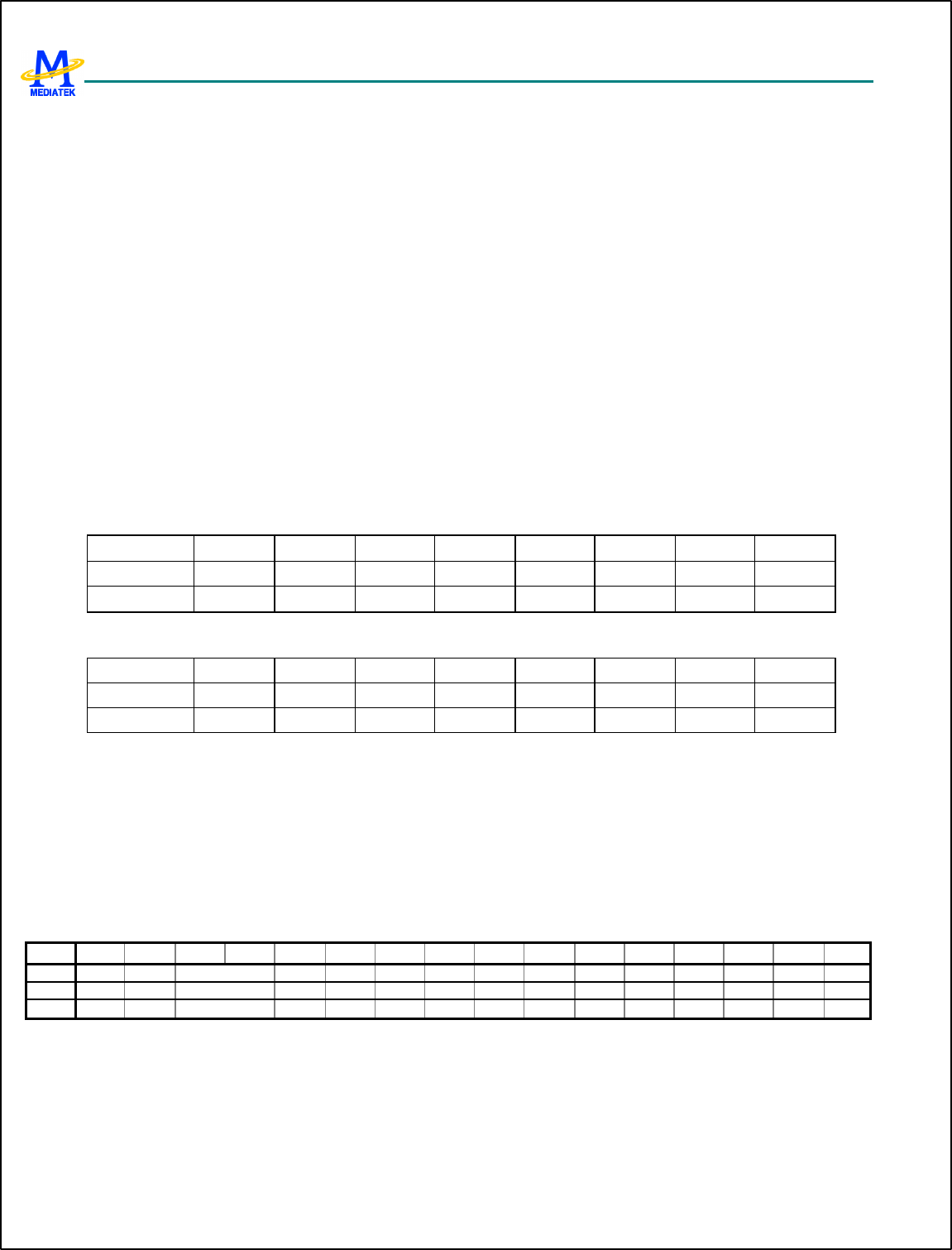

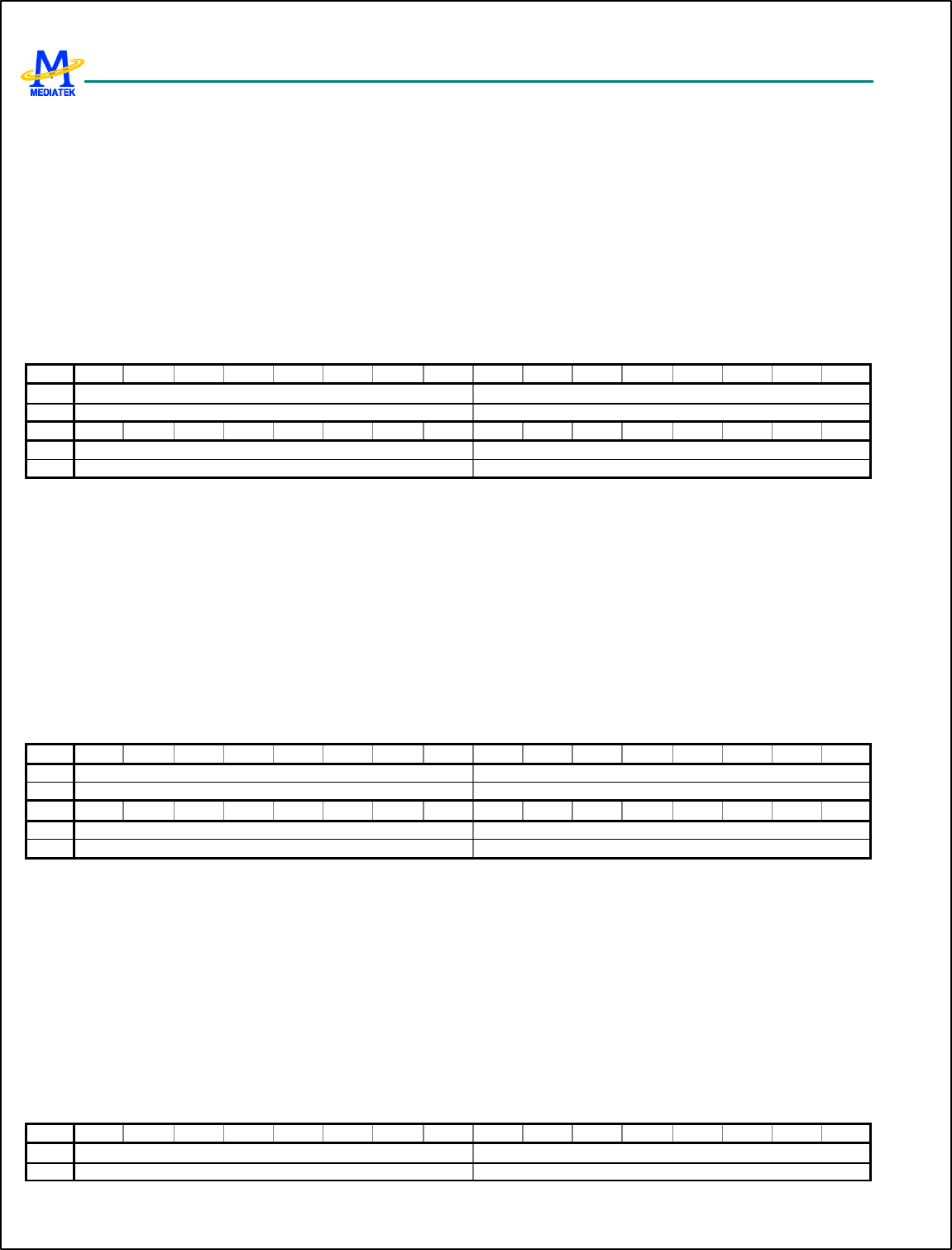

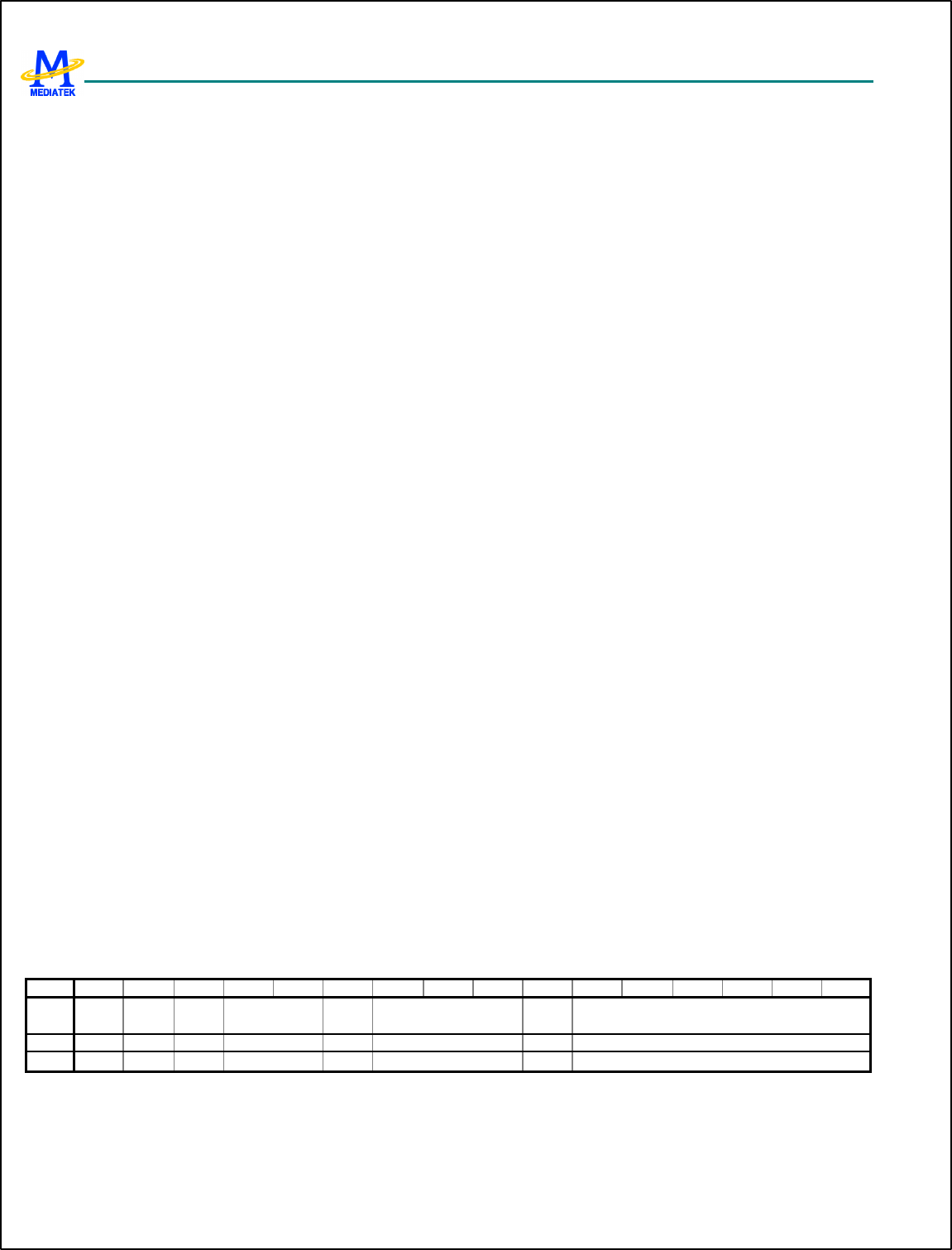

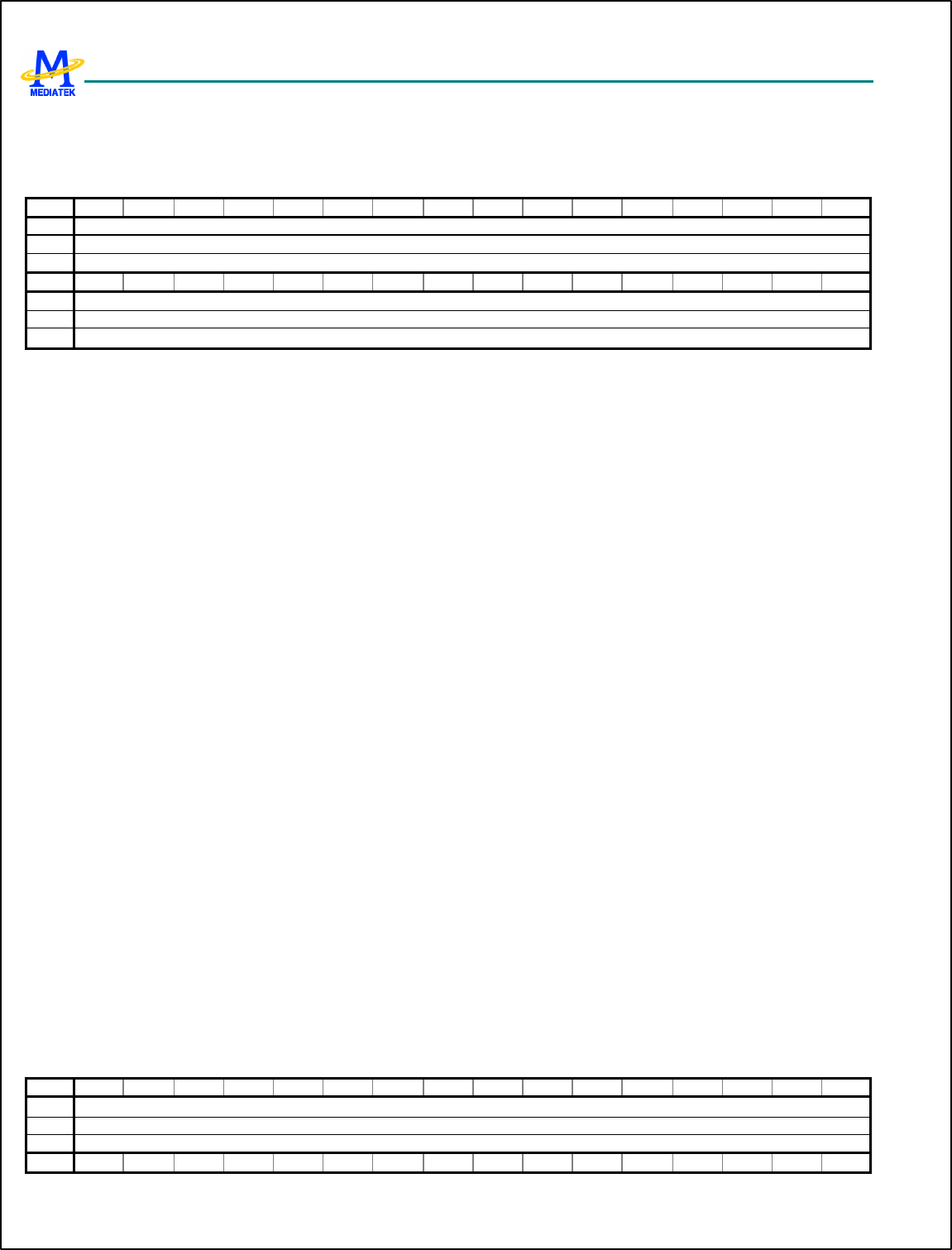

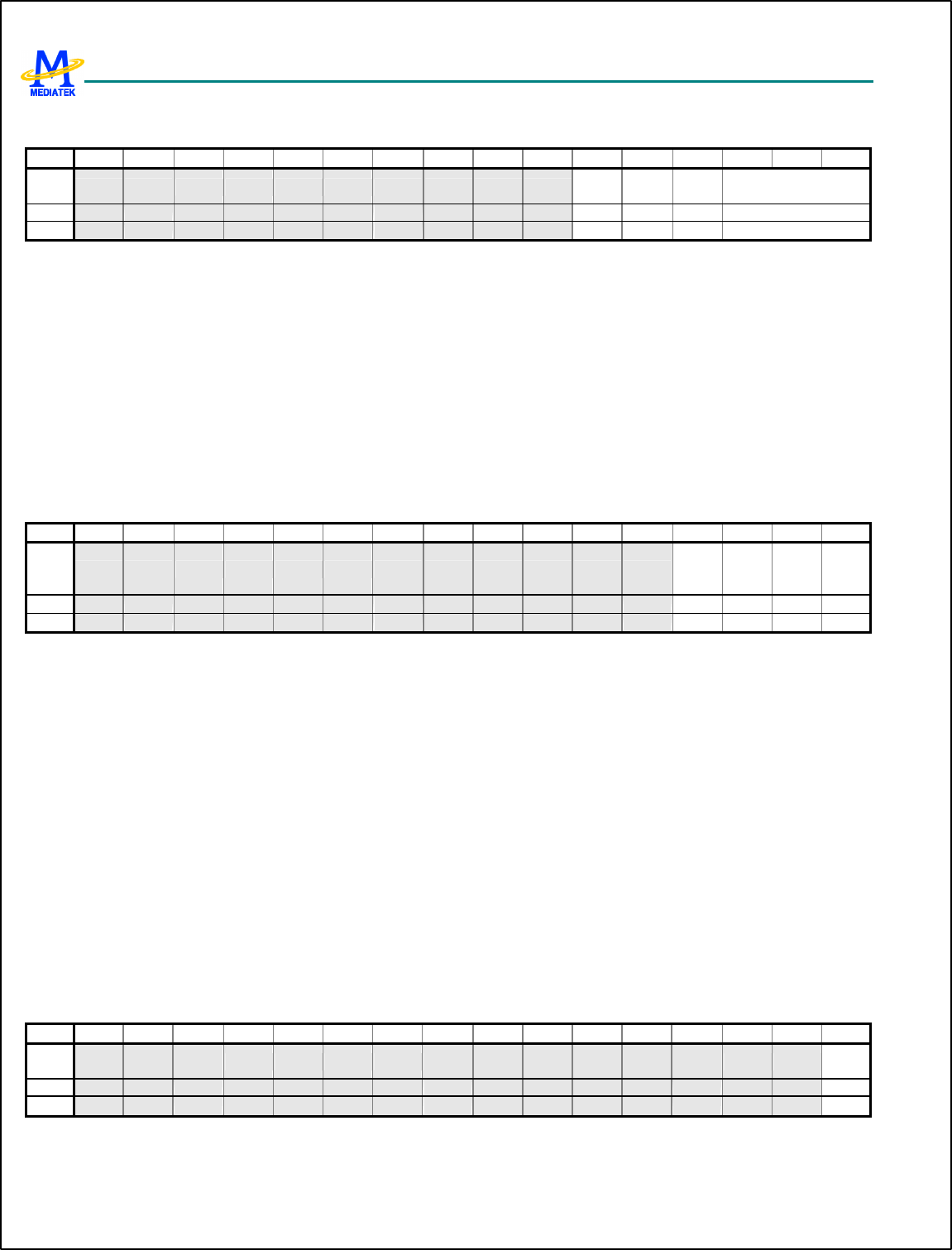

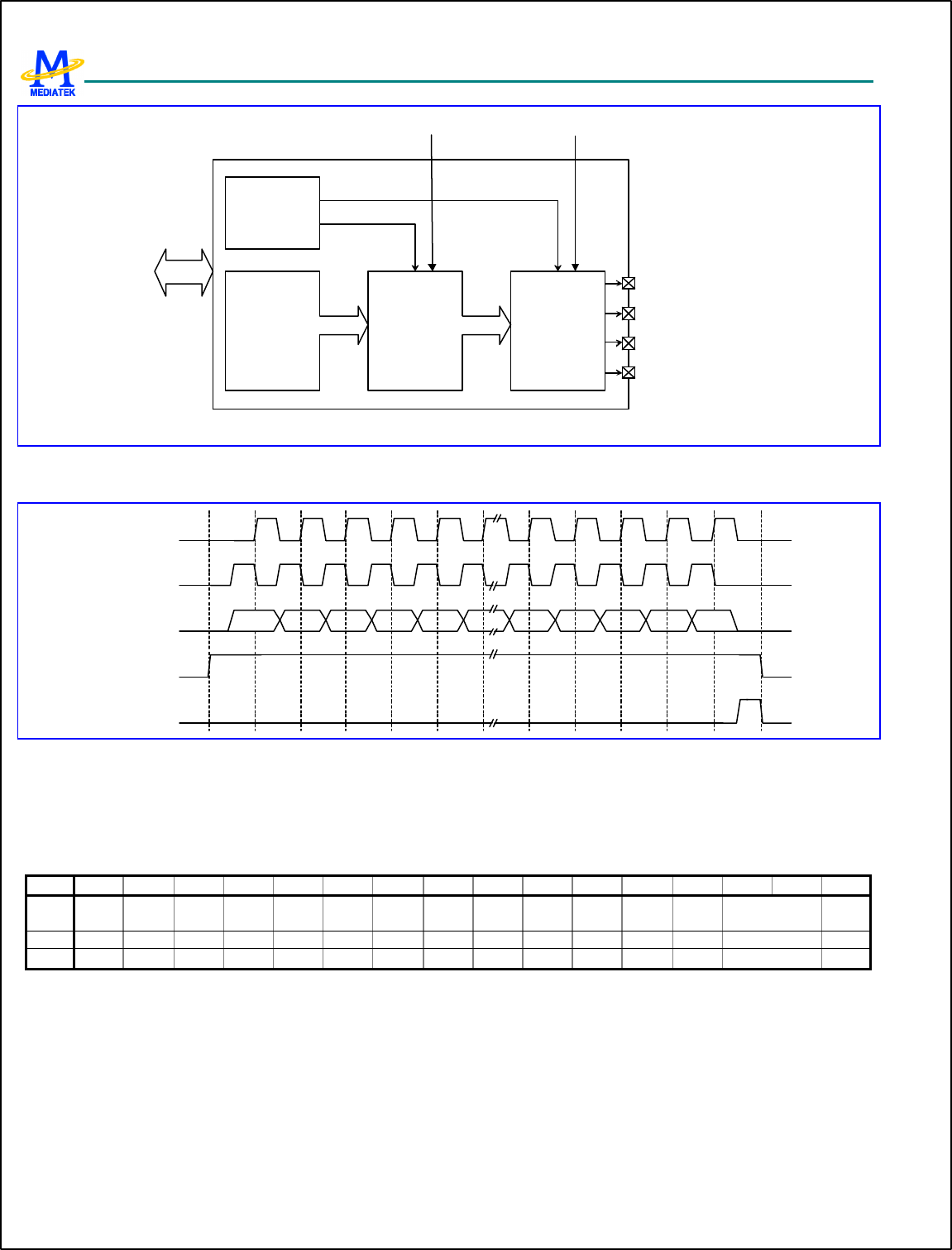

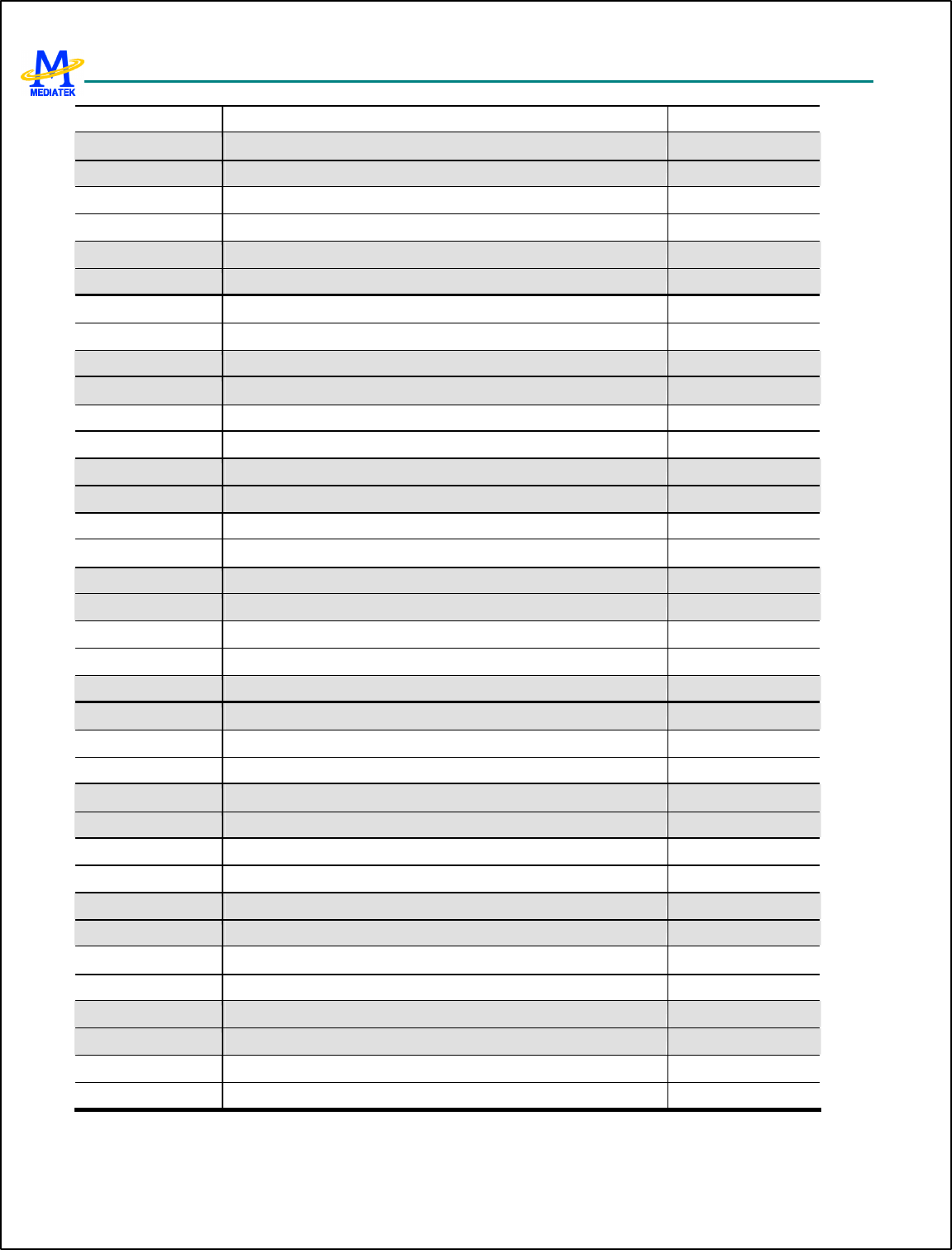

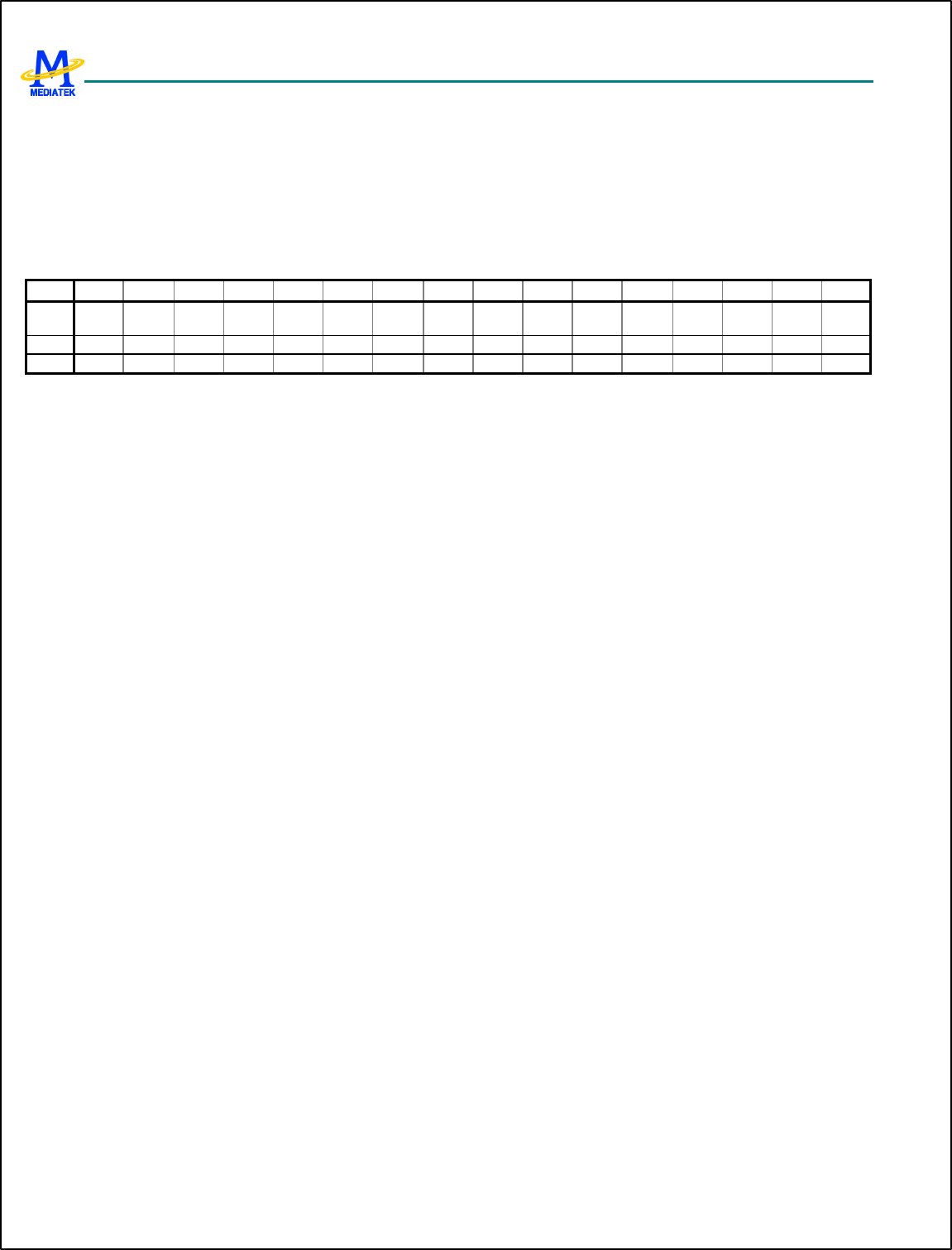

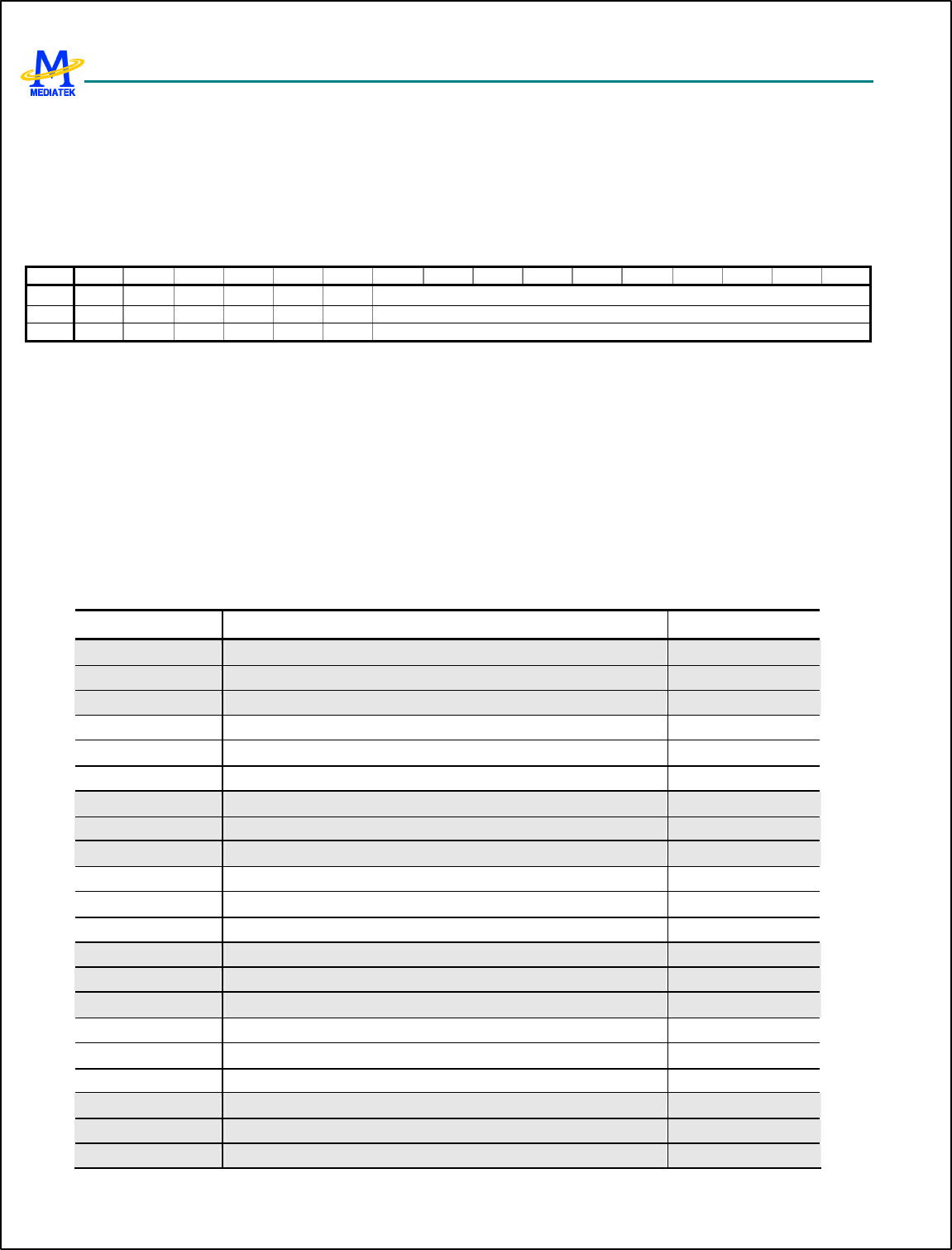

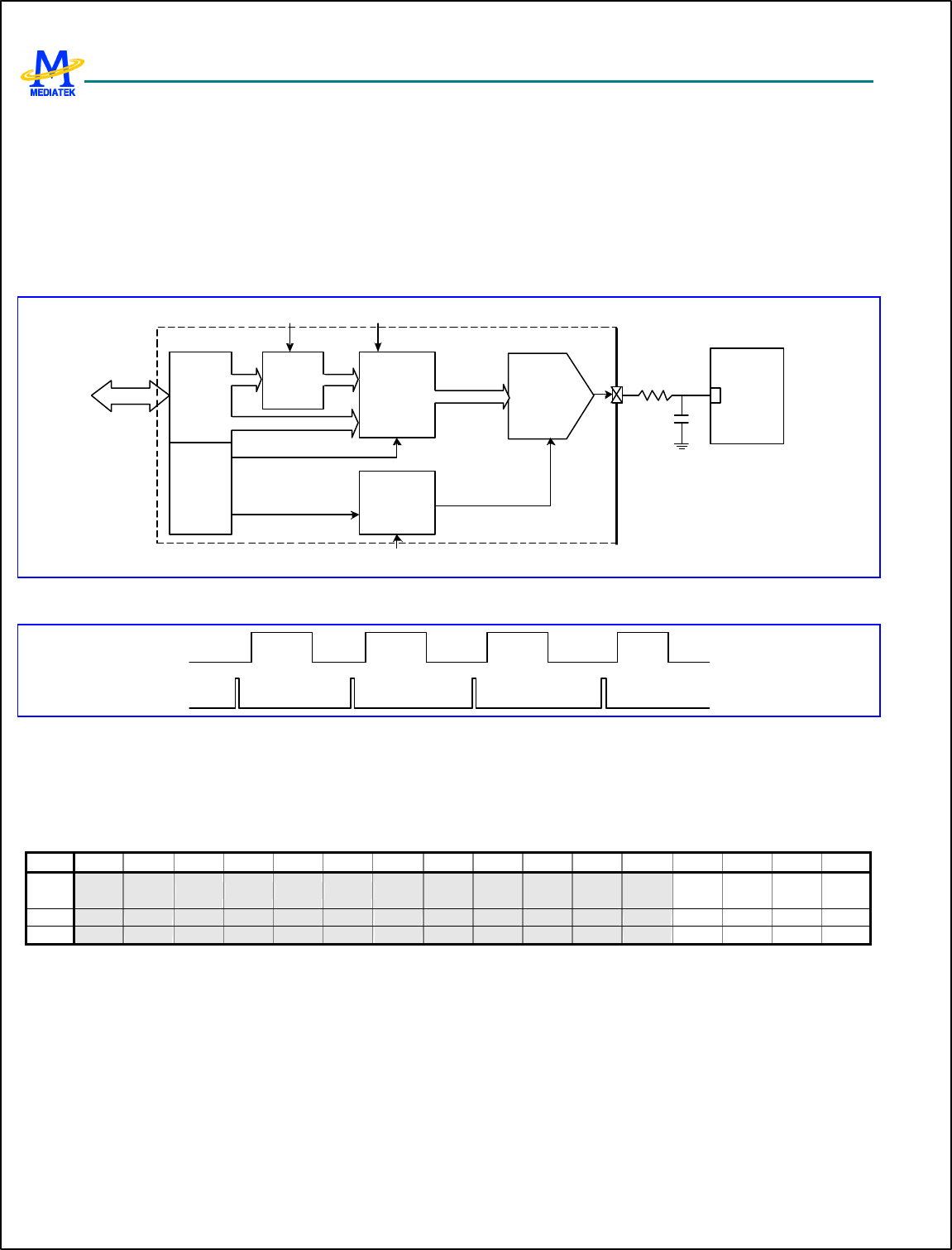

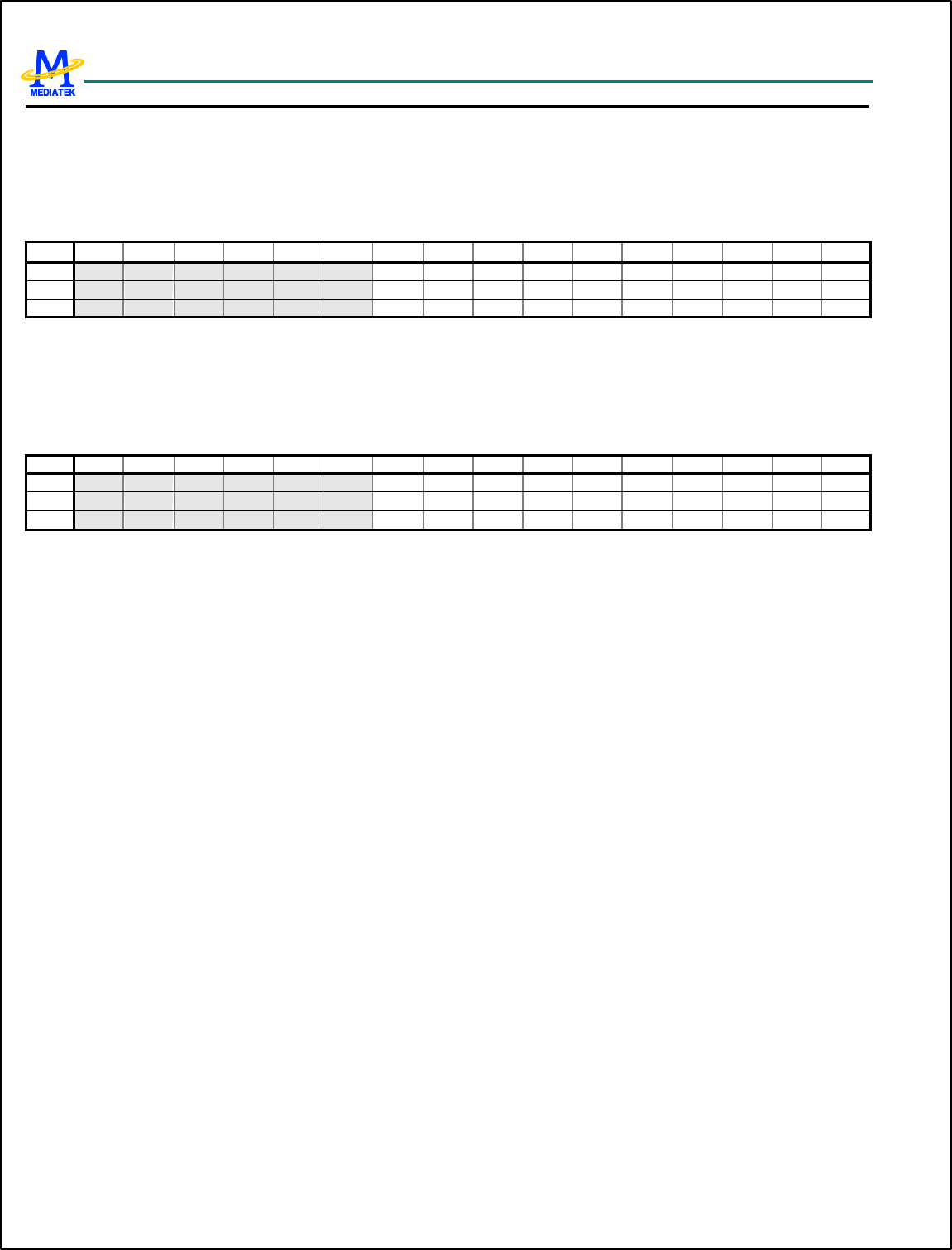

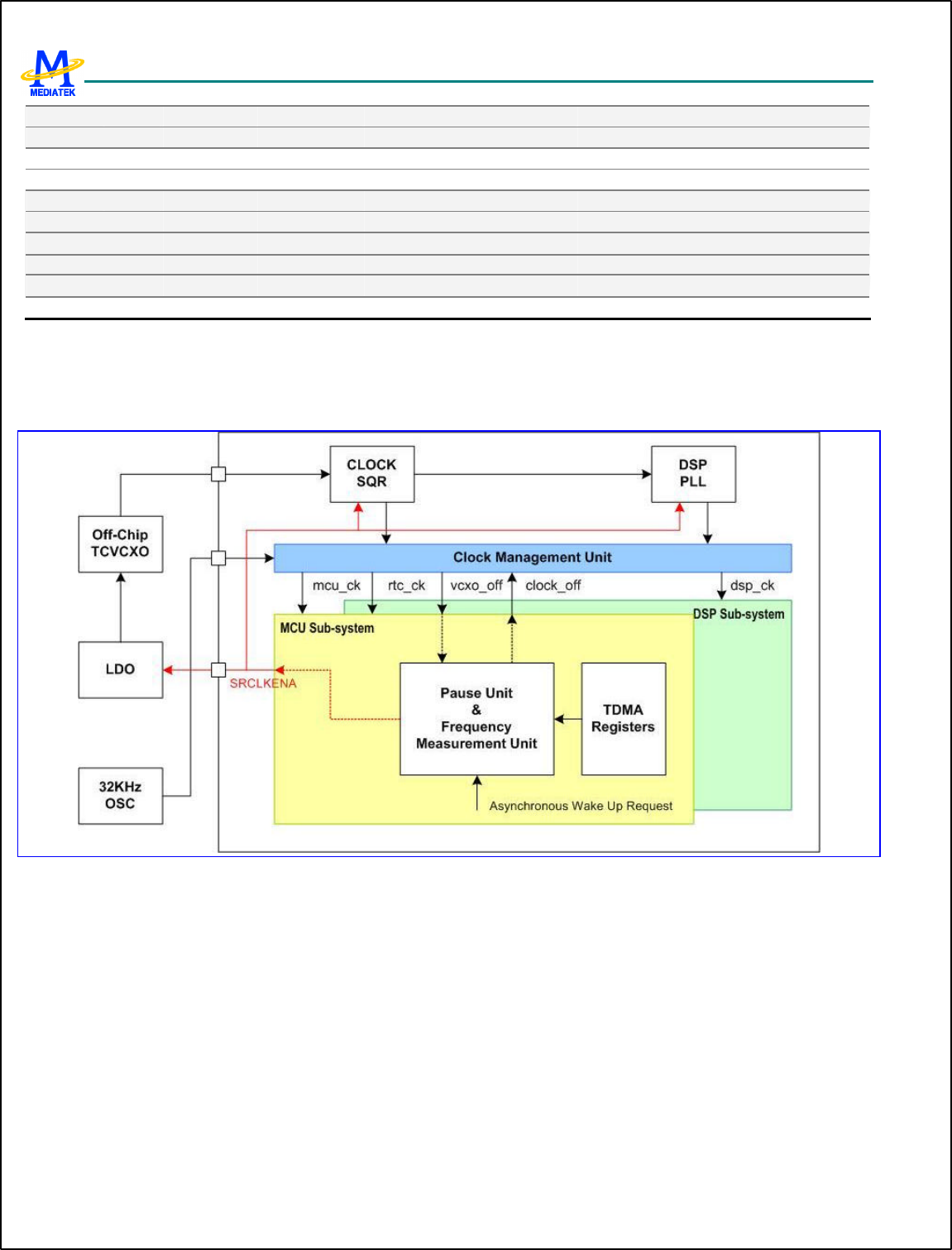

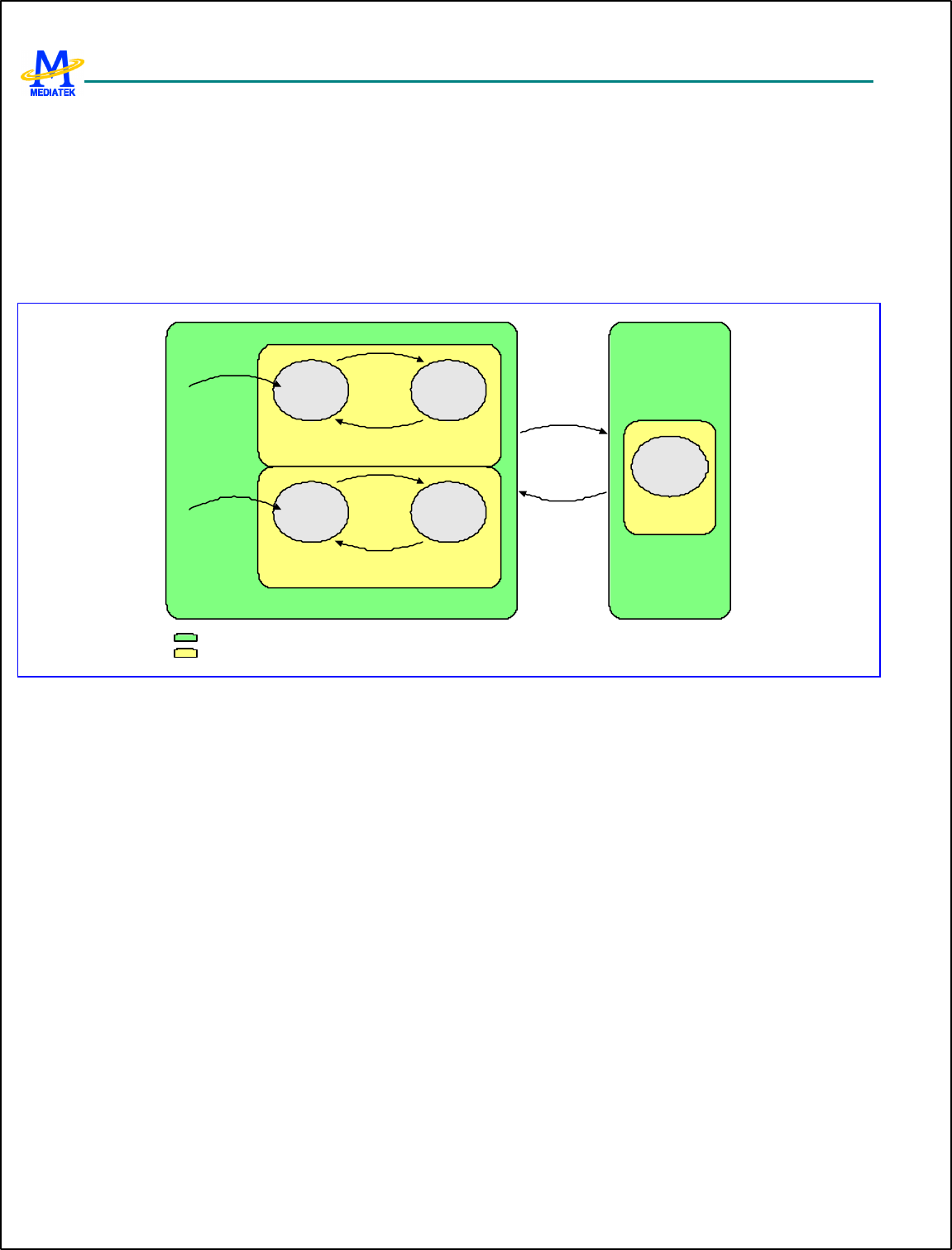

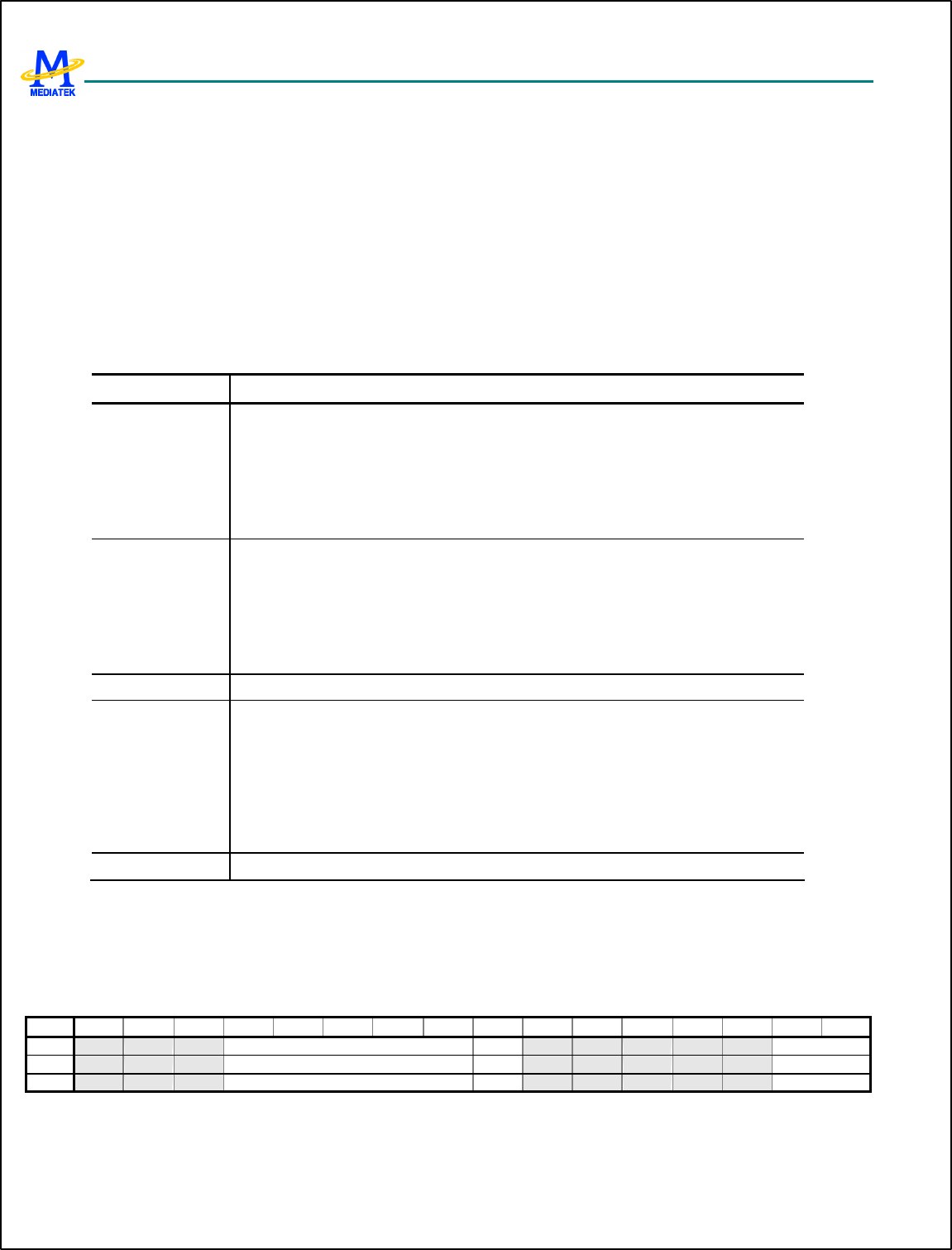

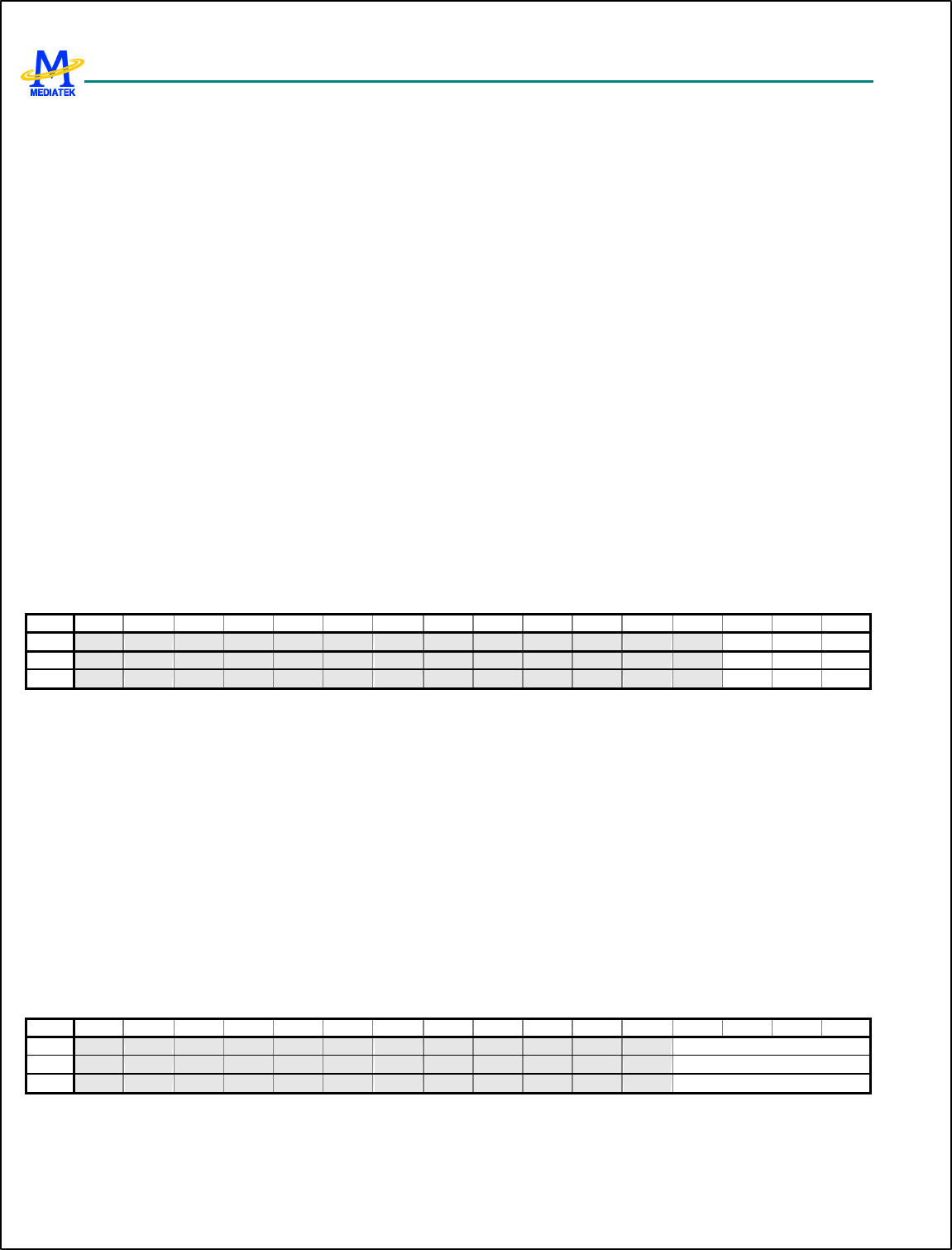

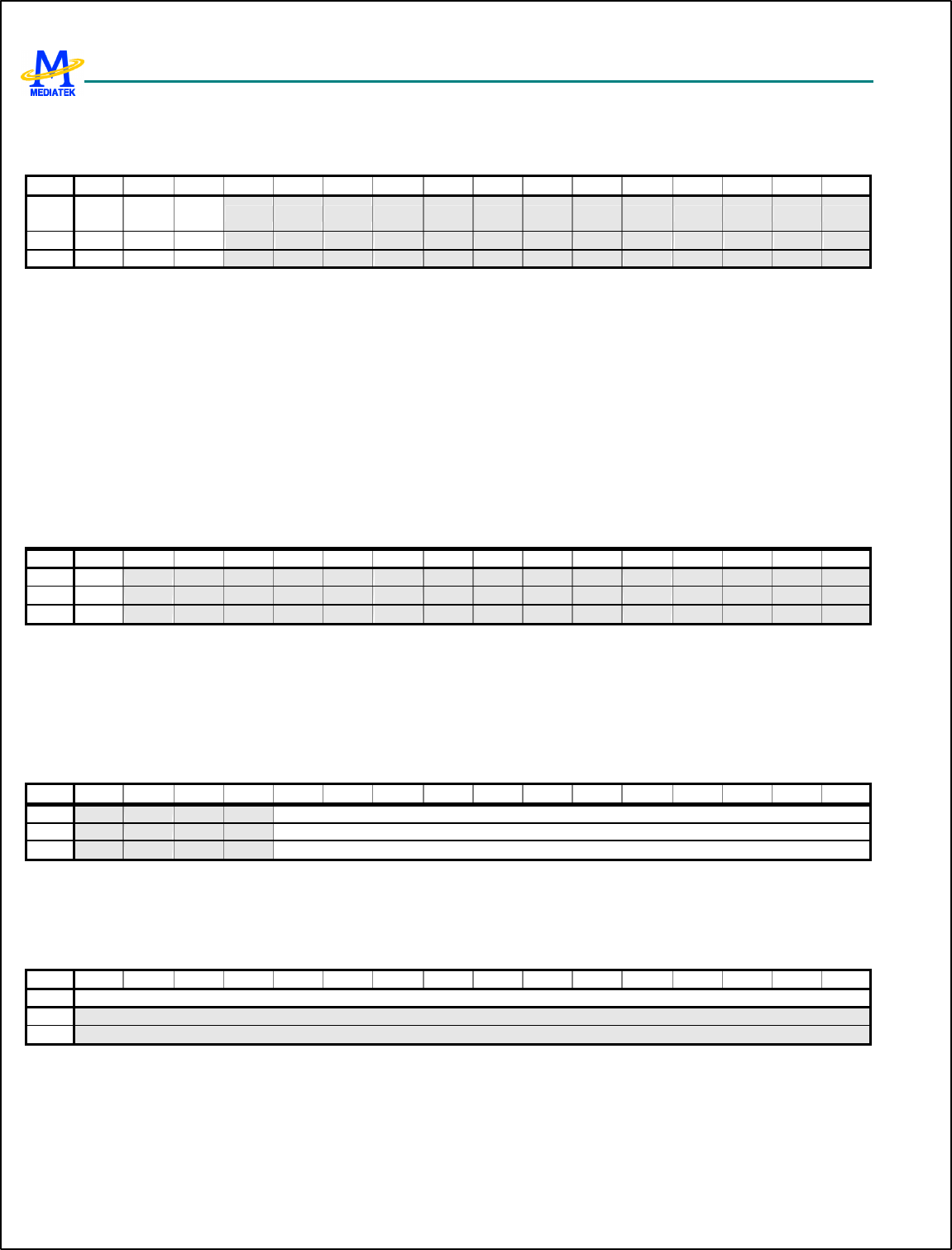

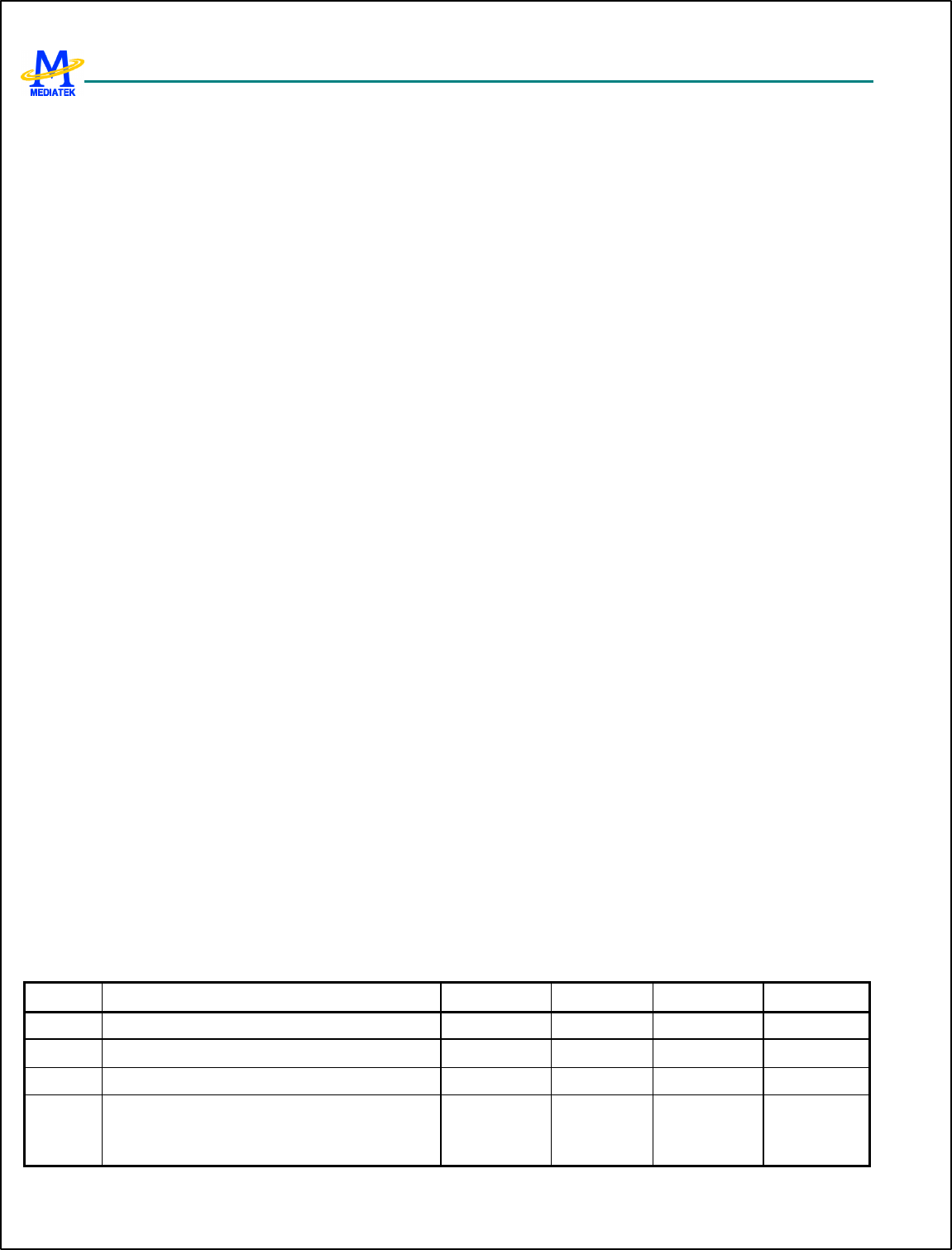

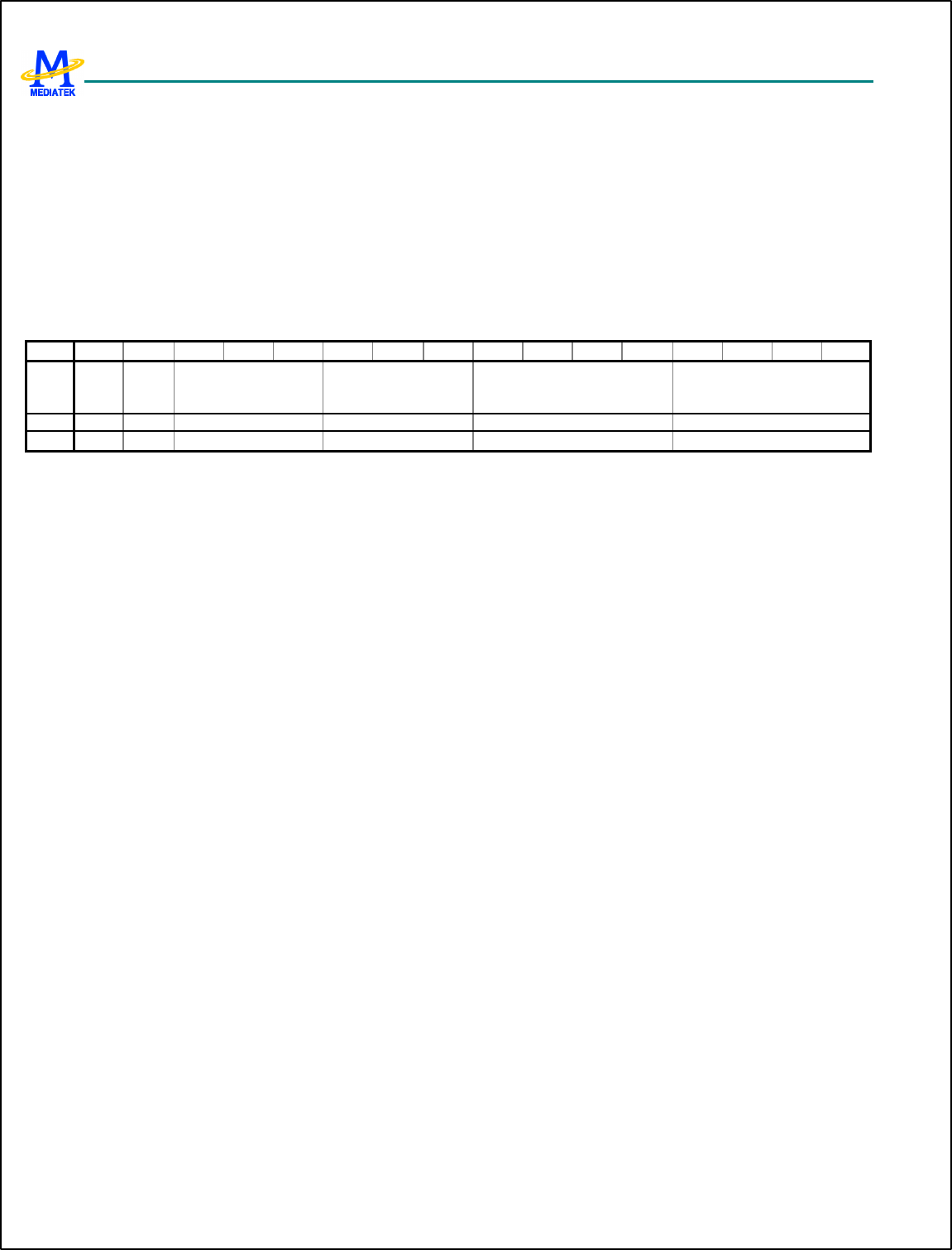

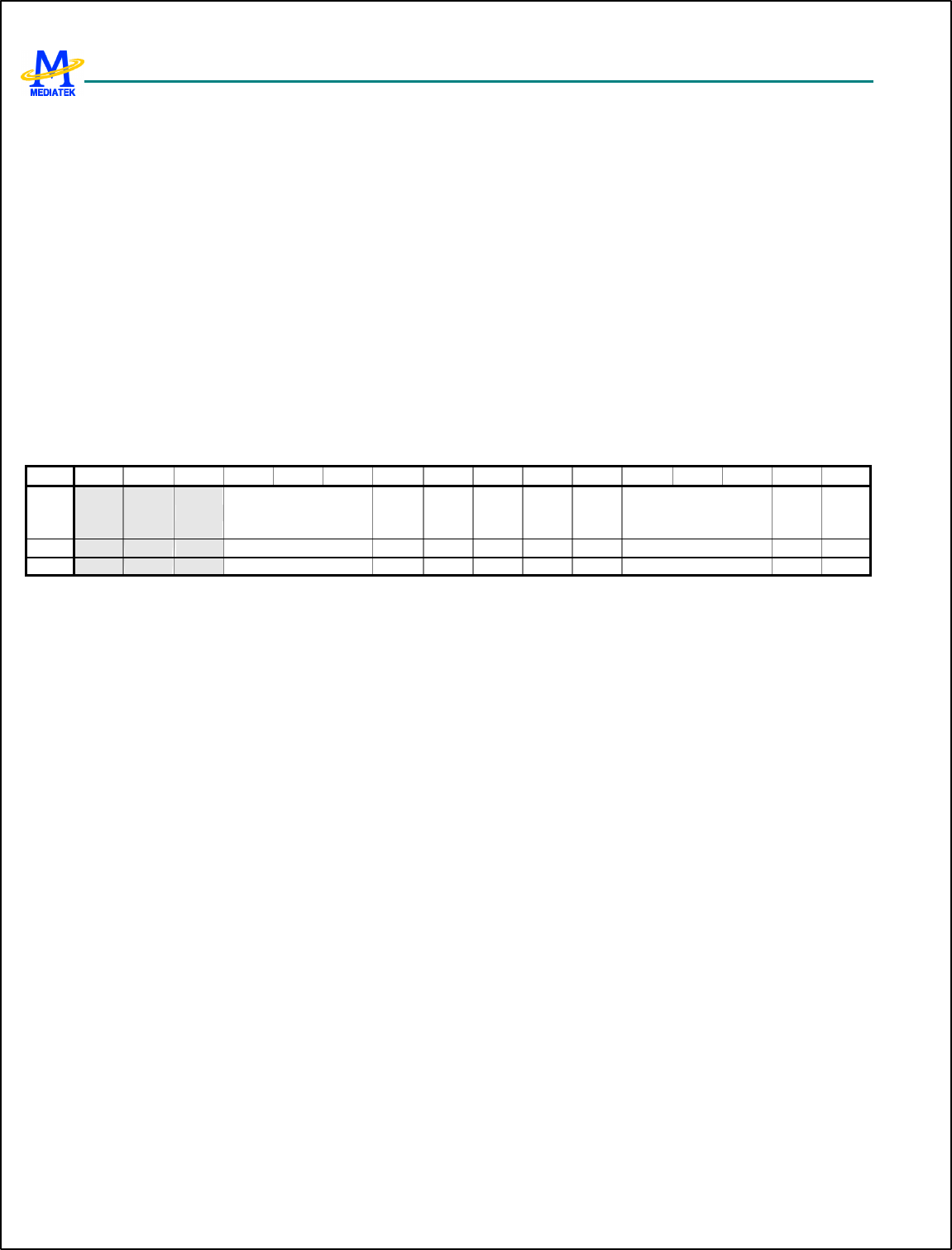

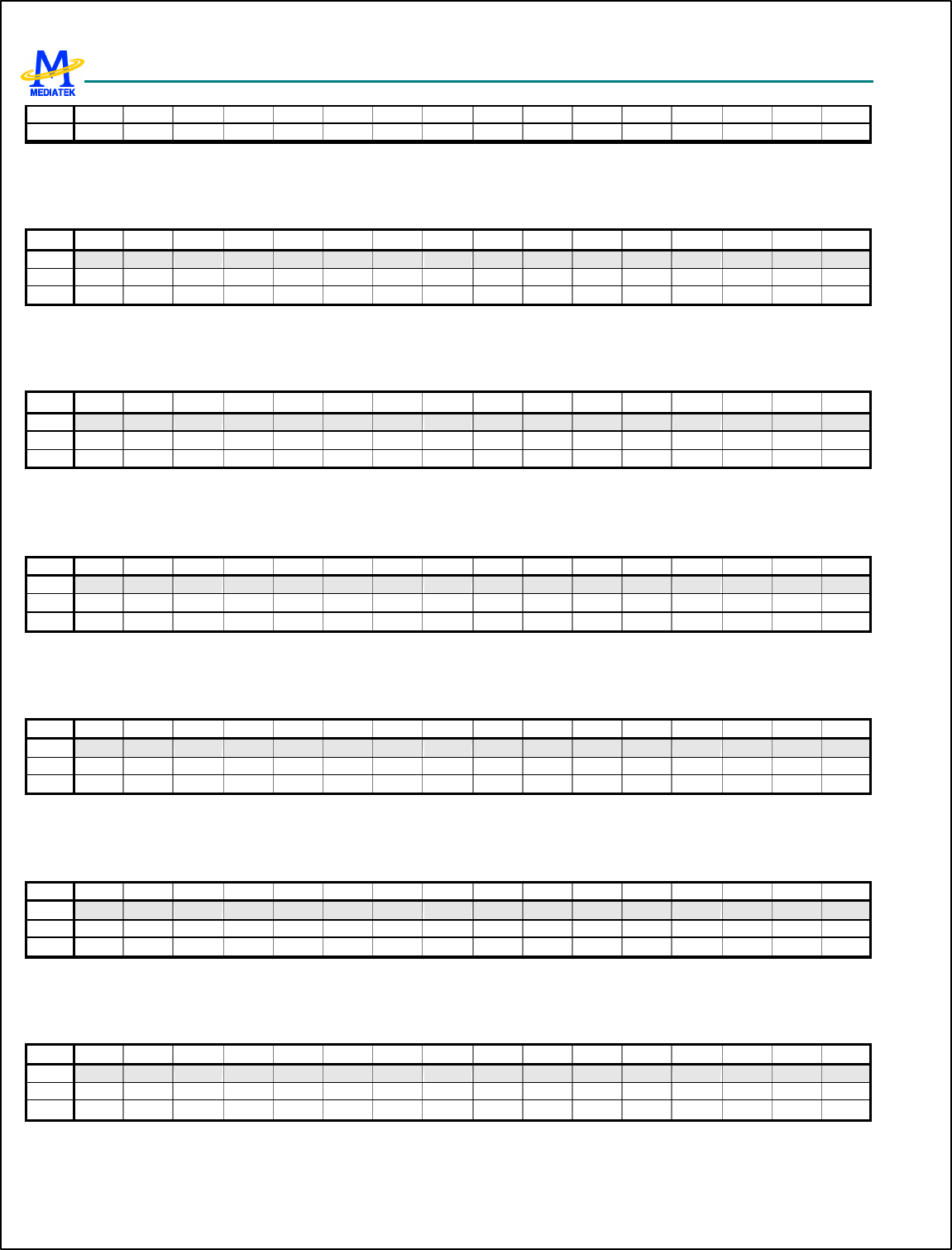

Figure 5 illustrates the block diagram of the Micro-Controller Unit Subsystem in MT 6217. A 32-bit RISC processor,

ARM7EJ -S, plays the role of the major bus master controlling the whole subsystem. Essentially, it communicates with all

the other on-chip modules by way of system buses: AHB Bus and APB Bus.

All bus transactions originate from bus masters, while slaves can only respond requests from bus masters. Prior to a data

transfer can be established, bus master must ask for bus ownership. This is accomplished by request-grant handshaking

protocol between masters and arbiters.

Two levels of bus hierarchy are designed to provide alternatives for different performance requirements, i.e. AHB Bus and

APB Bus for system back bone and peripheral buses, respectively. To have high performance and proper effic iency, the

AHB Bus provides 32-bit data path with multiplex scheme for bus interconnections.

For APB Bus, it supports 16-bit addressing and both 16-bit and 32-bit data paths. Since it is designated to reduce interface

complexity for lower data transfer rate, it is isolated from high bandwidth AHB Bus by APB Bridge. APB Bus is also

optimized for minimal power consumption by employing gated-clock scheme.

Whenever the target slave locates on AHB Bus, the transaction is conducted directly on AHB Bus. However, if the target

slave is a peripheral, the transaction should be further forwarded to APB Bus by APB Bridge.

Only memory addressing method is used in MT6217 based system. All components are mapped onto MCU 32-bit address

space. A Memory Management Unit is employed to have a central decode scheme. It generates certain selection signals for

each memory-addressed modules on AHB Bus.

In order to off-load the processor core, a DMA Controller is designated to act as a master and share the bus resources on

AHB Bus to do fast data movement between modules. This controller comprises thirteen DMA channels.

The Interrupt Controller provides a software interface to manipulate interrupt events. It can handle up to 32 interrupt

sources asserted at the same time. In general, it generates 2 levels of interrupt requests, FIQ and IRQ, to the processor.

A 256K Byte SRAM is provided for acting as system memory for high-speed data access. For factory programming

purpose, a Boot ROM module is used. These two modules use the same Internal Memory Controller to connect to AHB

Bus.

External Memory Interface supports both 8-bit and 16-bit devices. Since AHB Bus is 32-bit wide, all the data transfer will

be converted into several 8-bit or 16-bit cycles depending on the data width of target device. Note that, this interface is

specific to both synchronous and asynchronous components, like Flash, SRAM and parallel LCD. This interface supports

also page and burst mode type of Flash.

MT6217 GSM/GPRS Baseband Processor Data Sheet Revision 1.01

36/349 MediaTek Inc. Confidential

MCU-DSP

Interface

ARM7EJ-S

External

Memory

Interface

System RAM

DMA

Controller

APB

Bridge

System ROM

Peripheral

Peripheral

Interrupt

Controller

Internal Memory

Controller Arbiter

AHB Bus

APB Bus

Ext

Bus

USB

Figure 5 Block Diagram of the Micro-Controller Unit Subsystem in MT 6217

3.1 Processor Core

3.1.1 General Description

The Micro -Controller Unit Subsystem in MT6217 is built up with a 32-bit RISC core, ARM7EJ-S that is based on Von

Neumann architecture with a single 32-bit data bus carrying both instructions and data. The memory interface of

ARM7EJ -S is totally compliant to AMBA based bus system. Basically, it can be connected to AHB Bus directly.

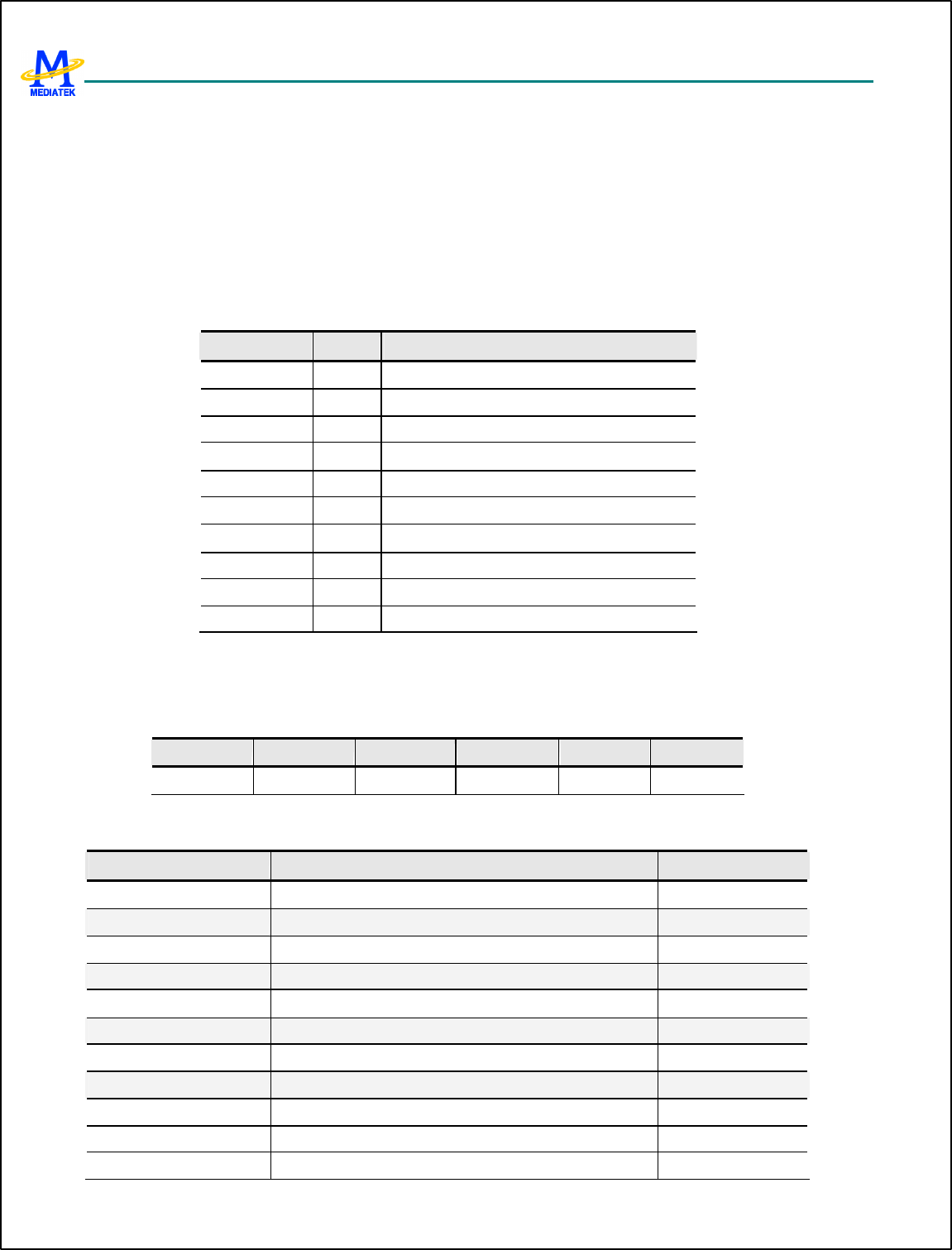

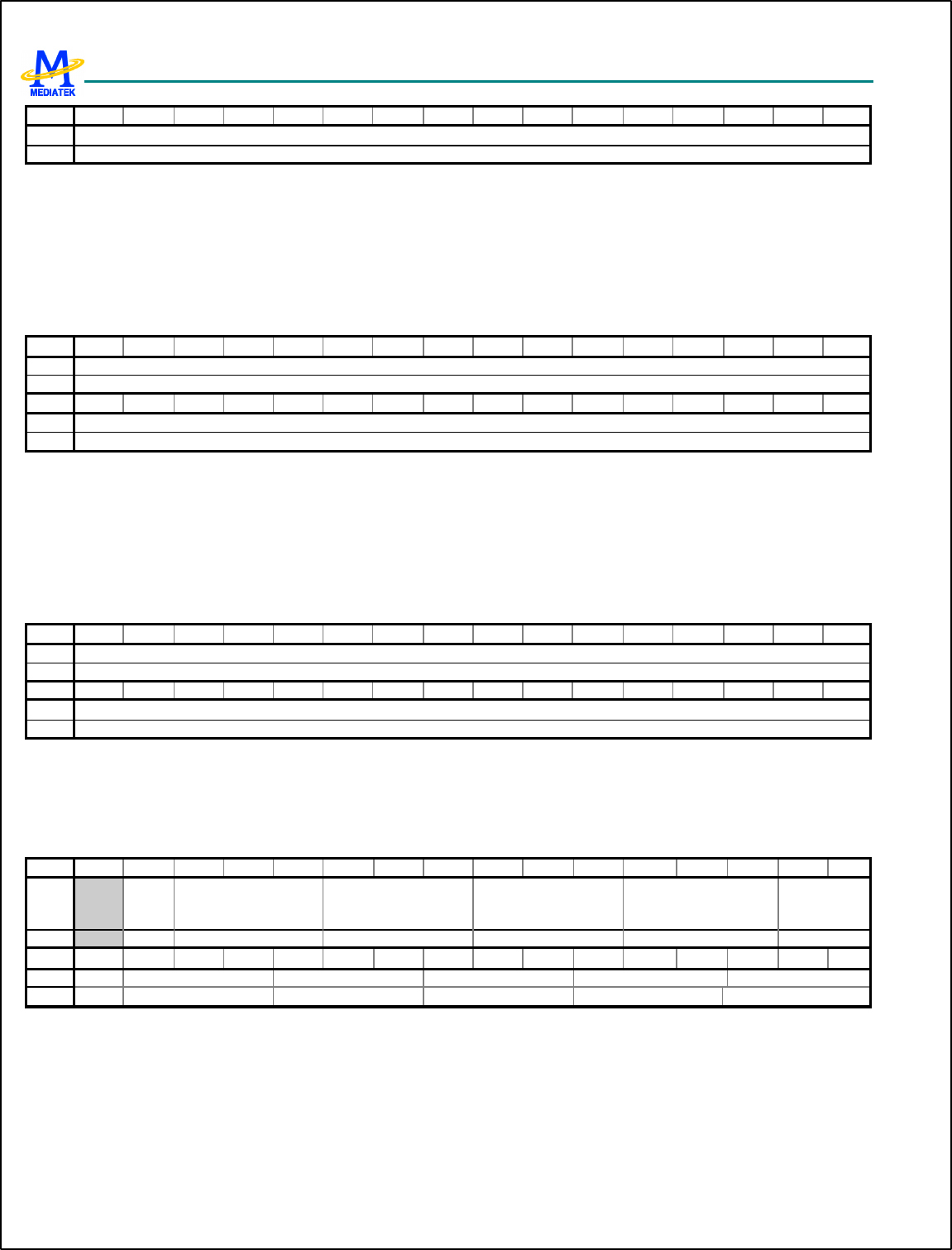

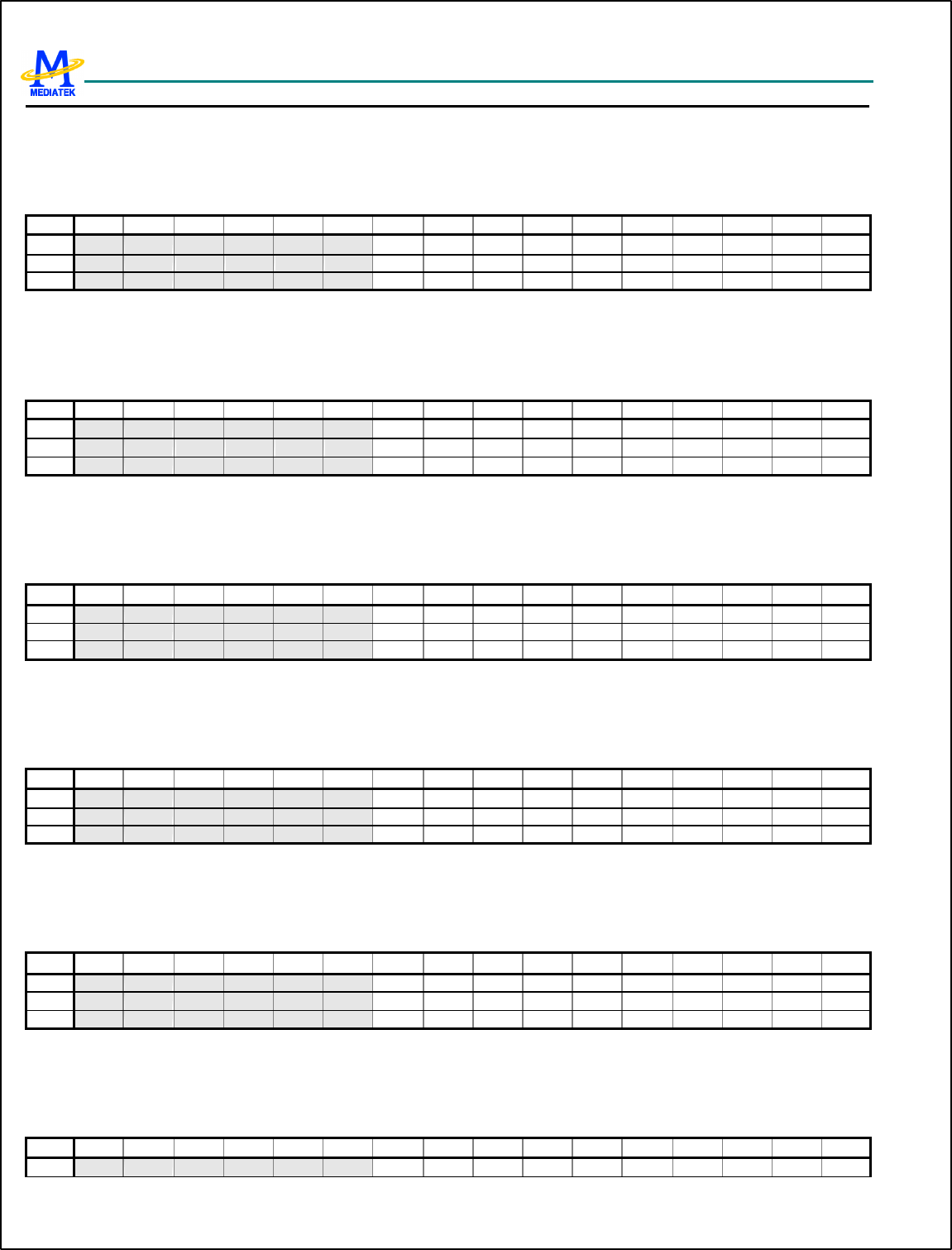

3.2 Memory Management

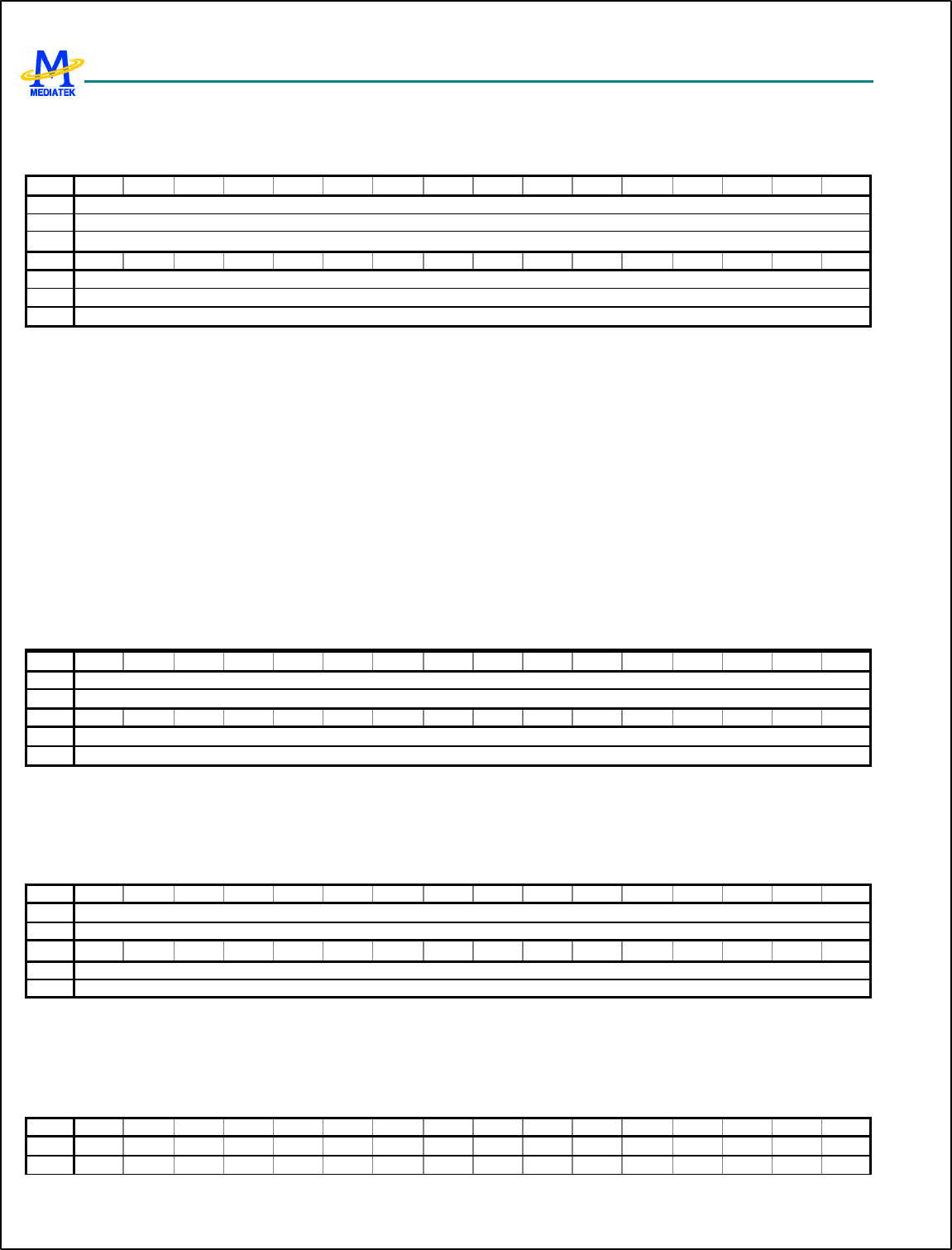

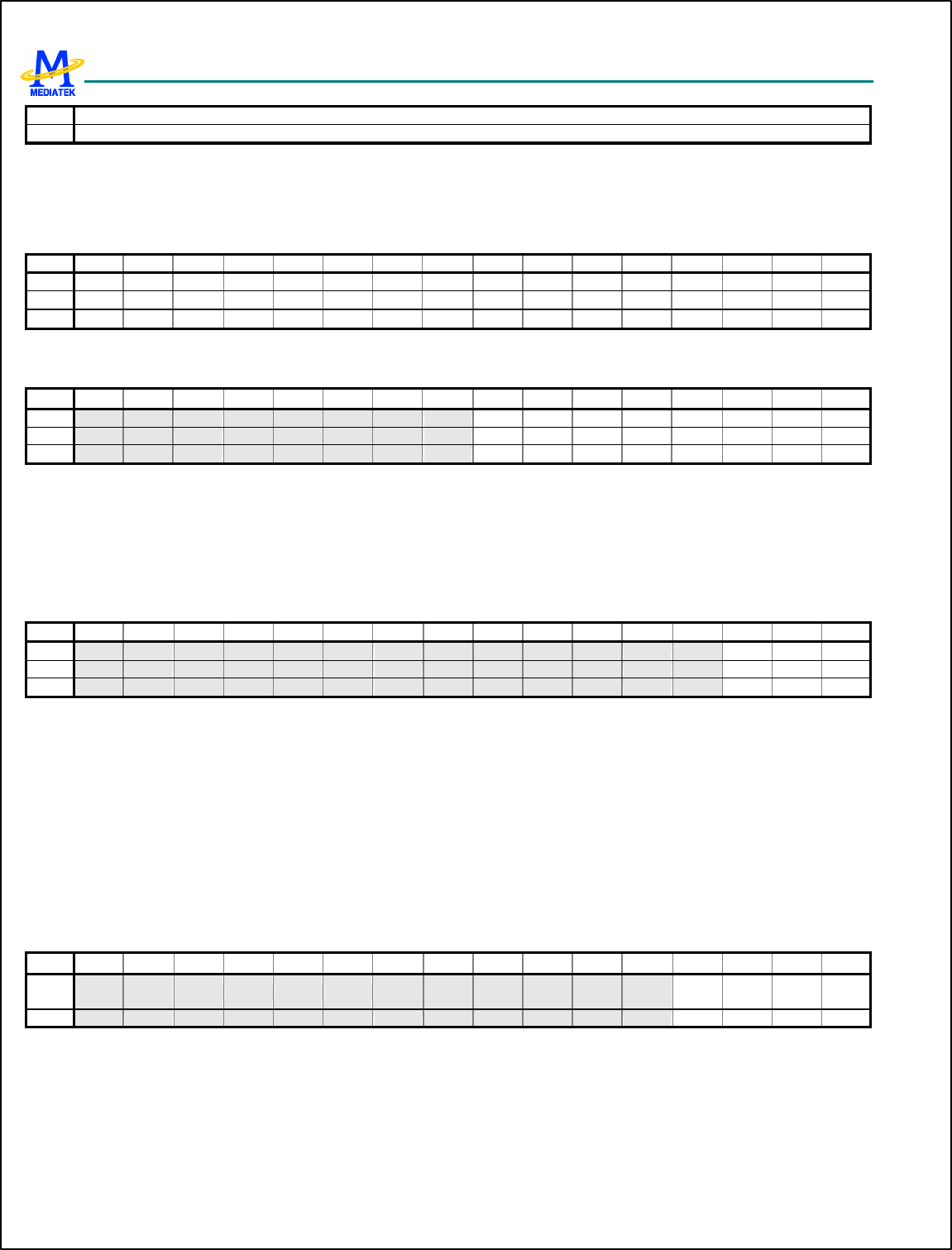

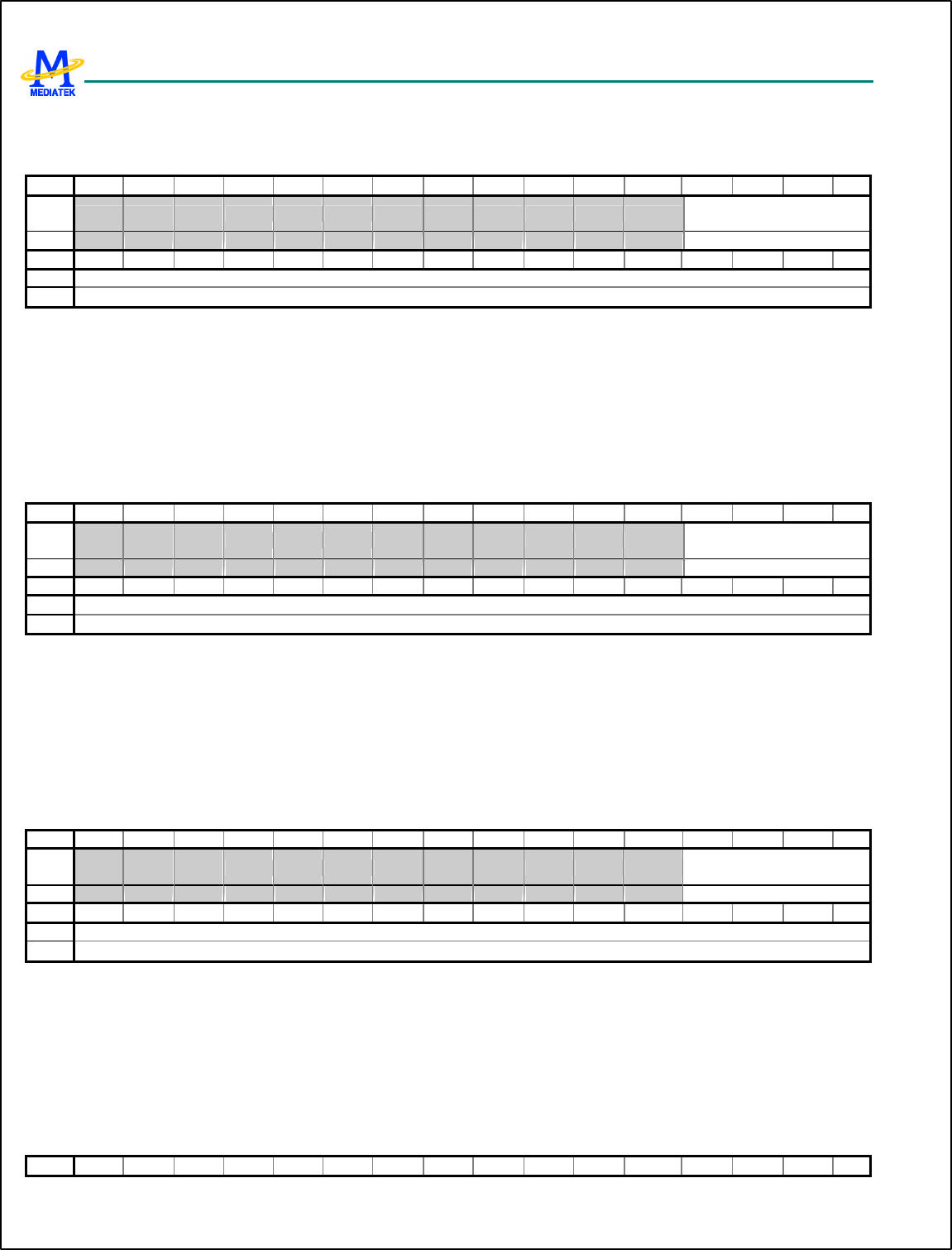

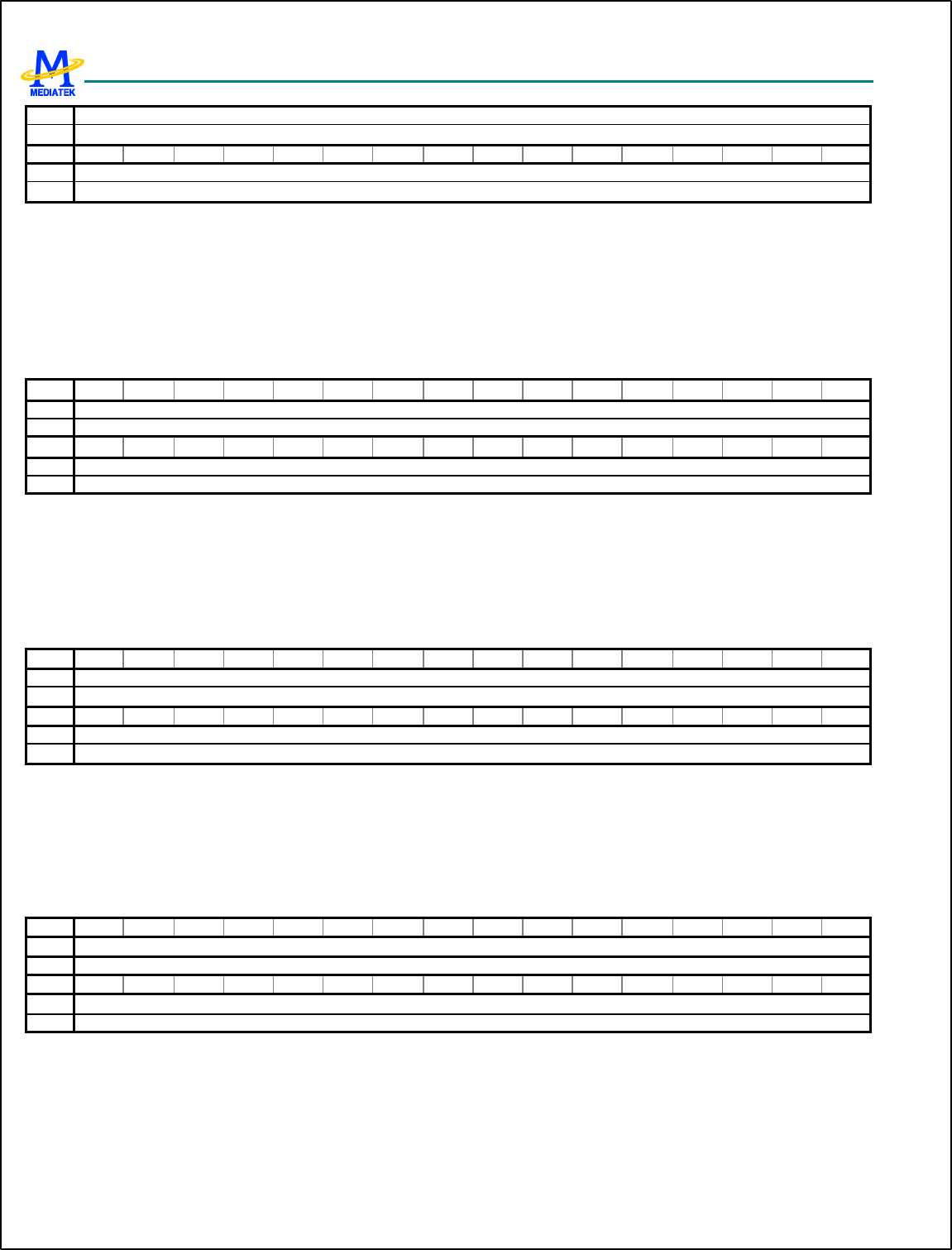

3.2.1 General Description

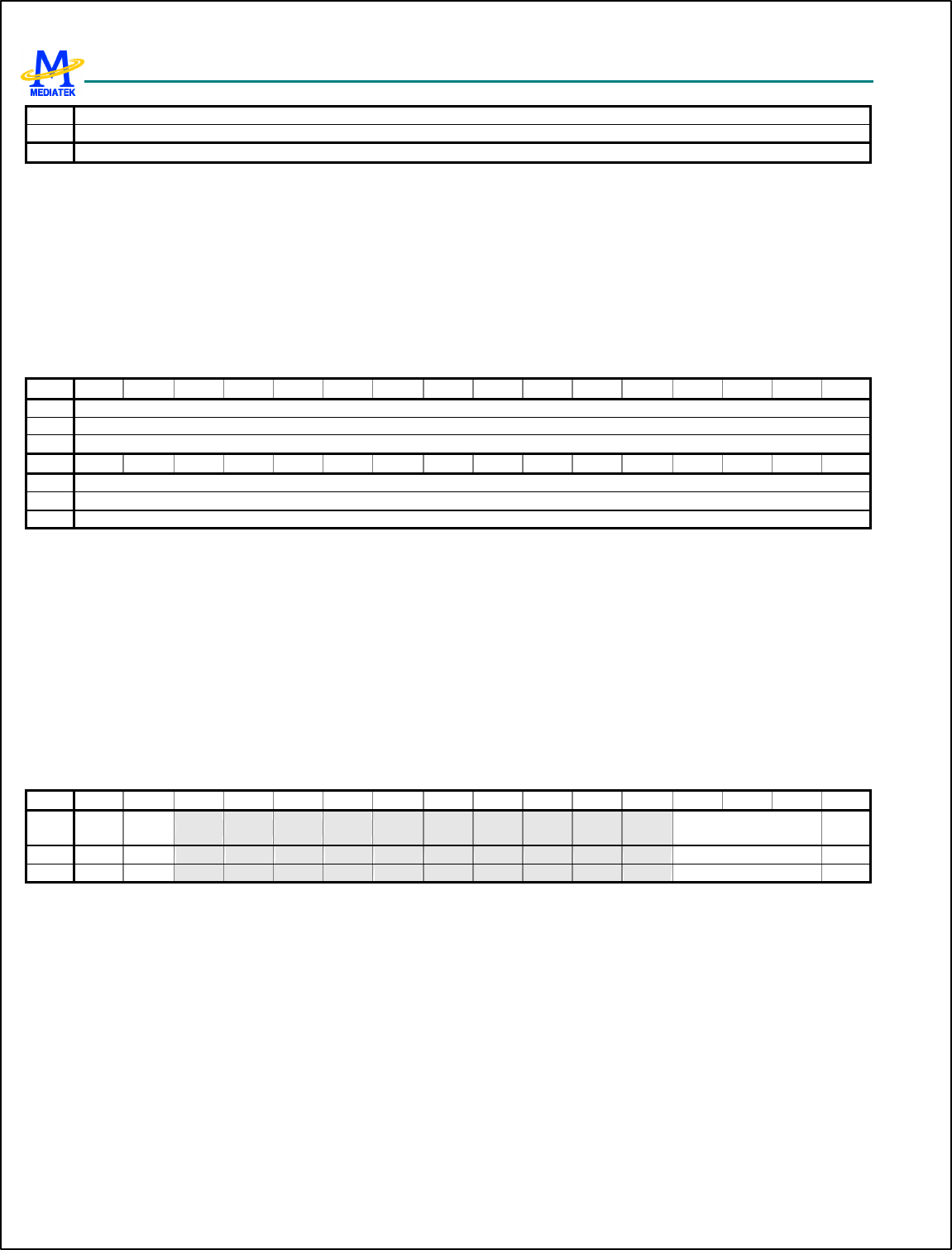

The processor core of MT6217, ARM7EJ -S, supports only memory addressing method for instruction fetch and data access.

It manages a 32-bit address space that has addressing capability up to 4GB. System RAM, System ROM, Registers, MCU

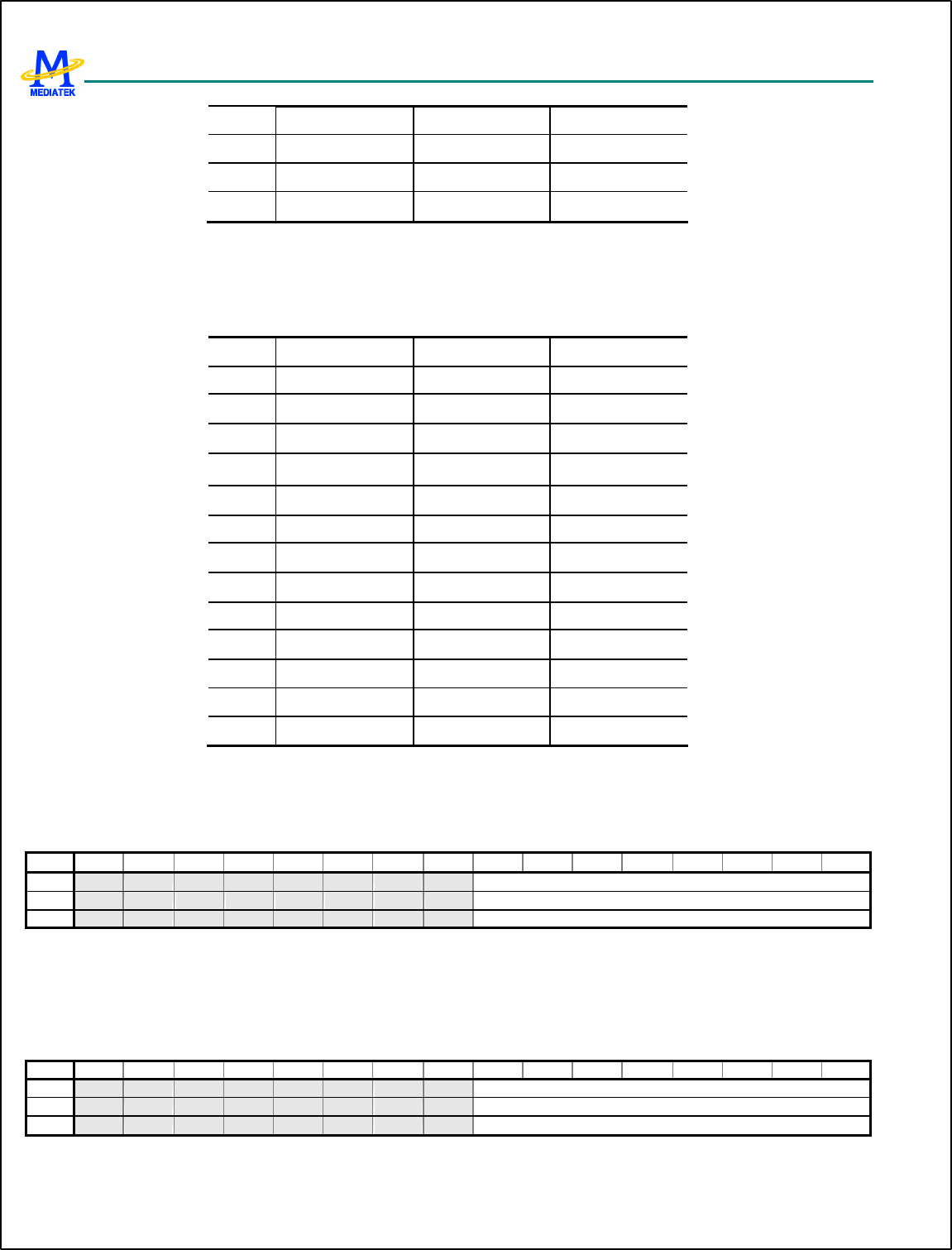

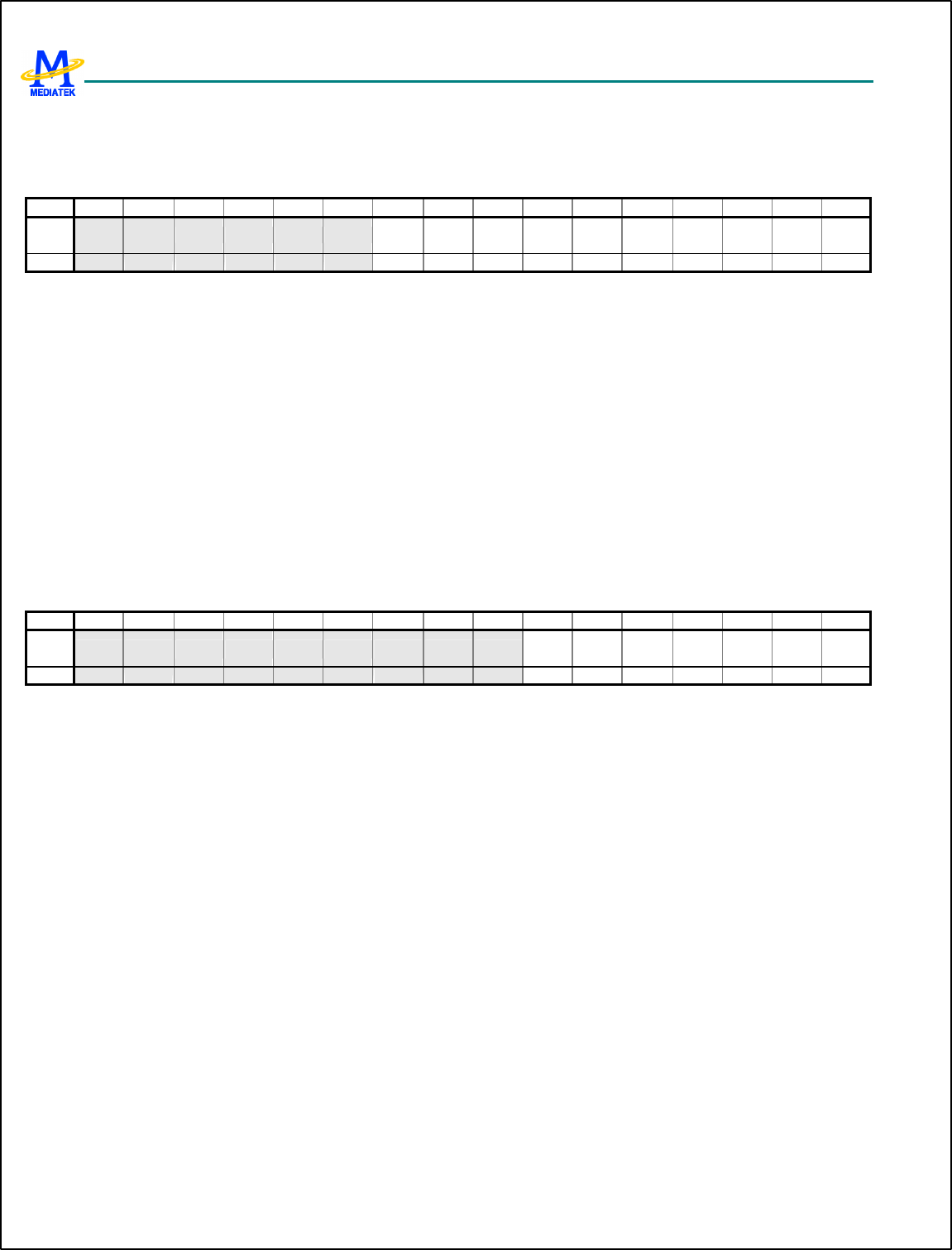

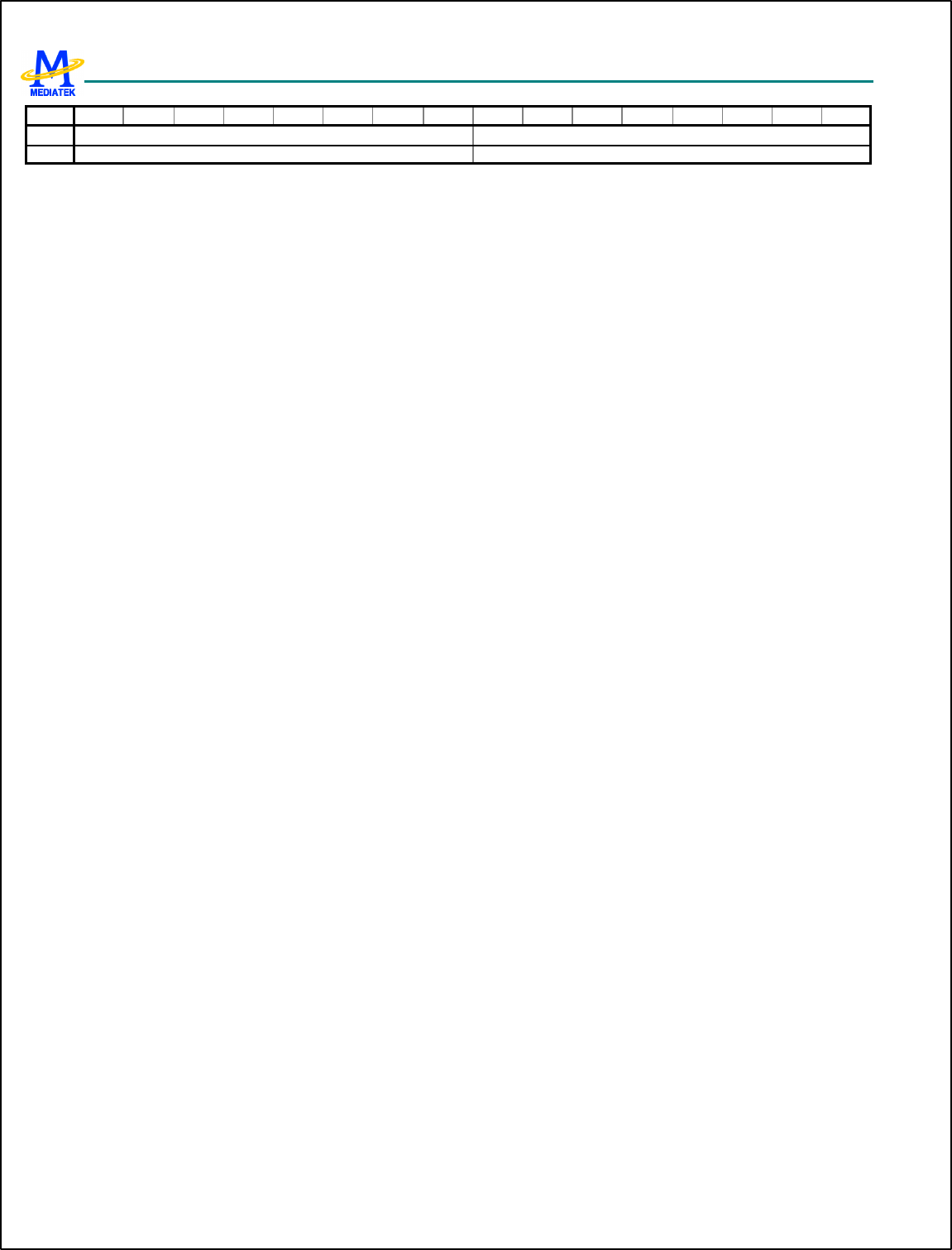

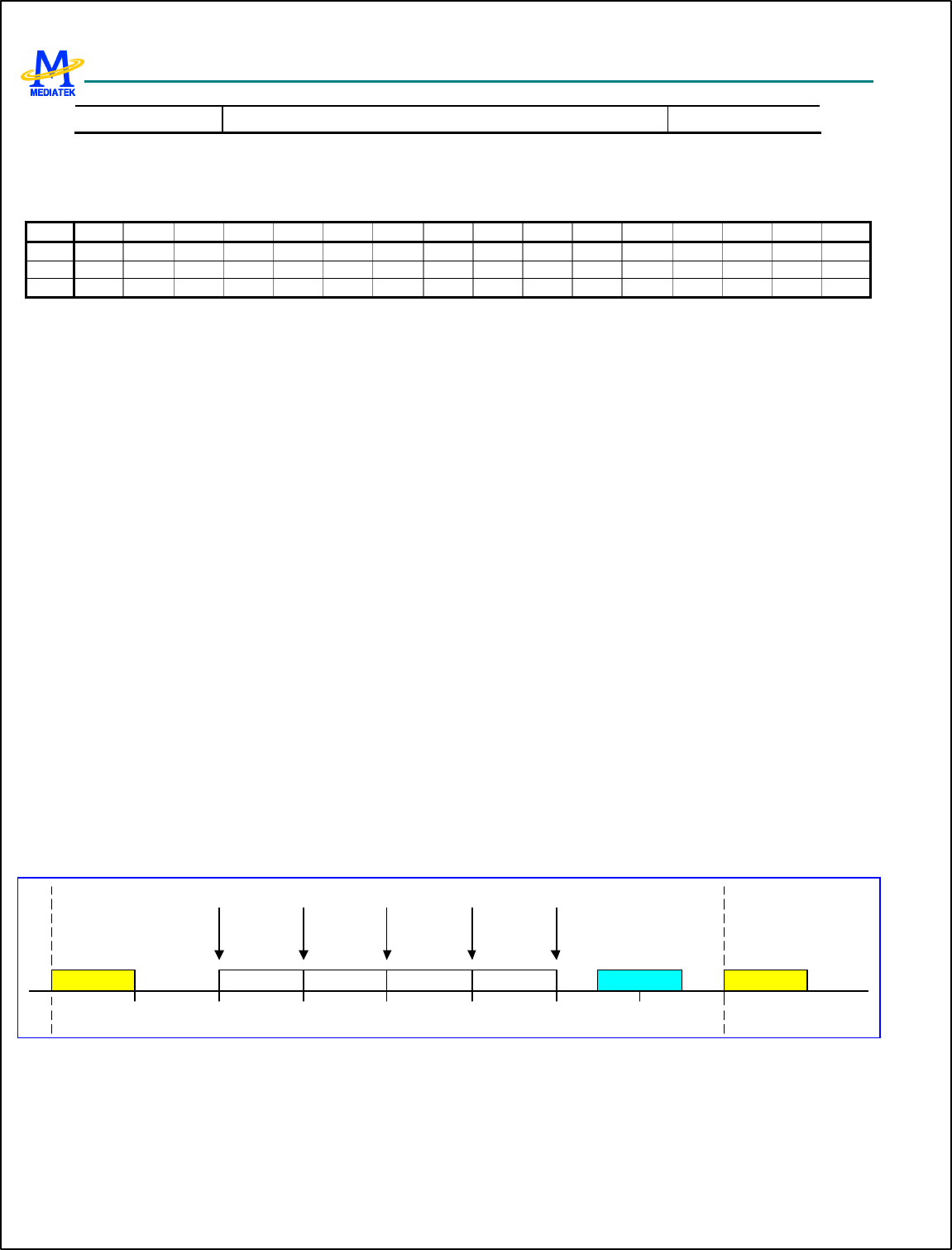

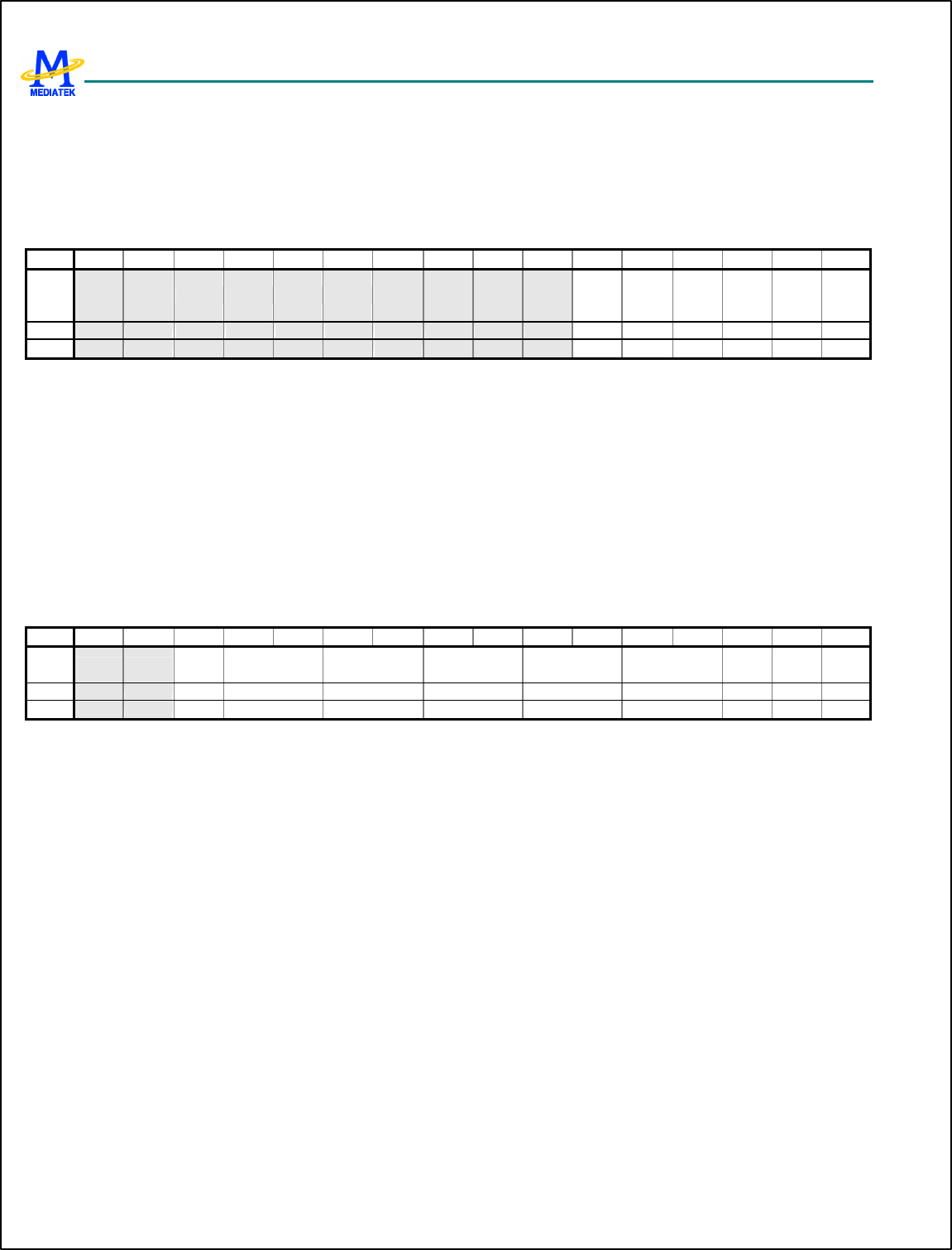

Peripherals and external components are all mapped onto such 32-bit address space, as depicted in Figure 6.

MT6217 GSM/GPRS Baseband Processor Data Sheet Revision 1.01

37/349 MediaTek Inc. Confidential

MCU 32-bit

Addressing

Space

EA[25:0]

Addressing

Space

APB Peripherals

MCU-DSP Interface

Reserved

8FFF_FFFFh

|

8000_0000h

7FFF_FFFFh

|

7000_0000h

6FFF_FFFFh

|

5000_0000h

4FFF_FFFFh

|

4000_0000h

3FFF_FFFFh

|

0000_0000h External Memroy

Internal Memory

7800_0000h

7000_0000h USB

Virtual FIFO

9FFF_FFFh

|

9000_0000h

9800_0000h

9000_0000h LCD

Reserved

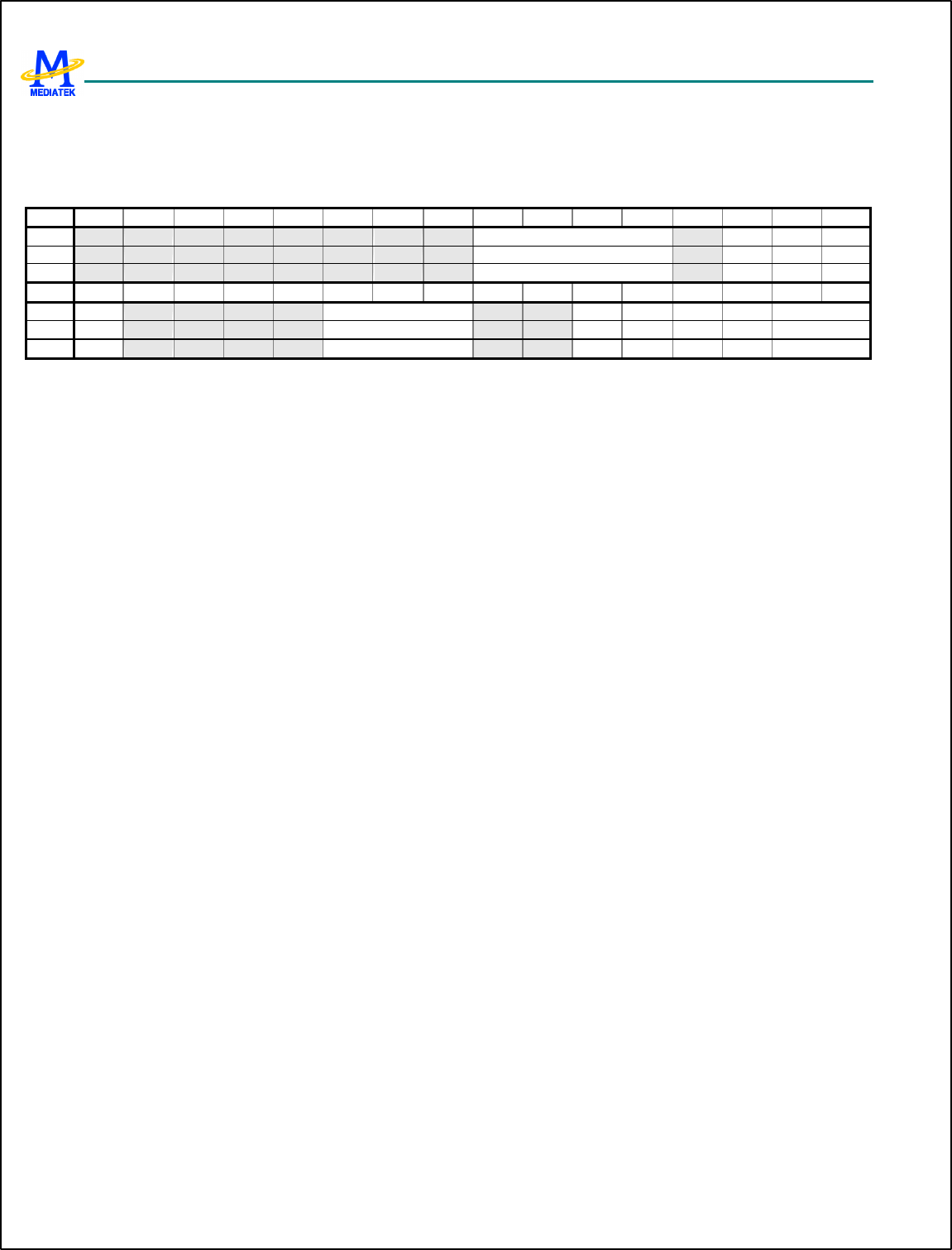

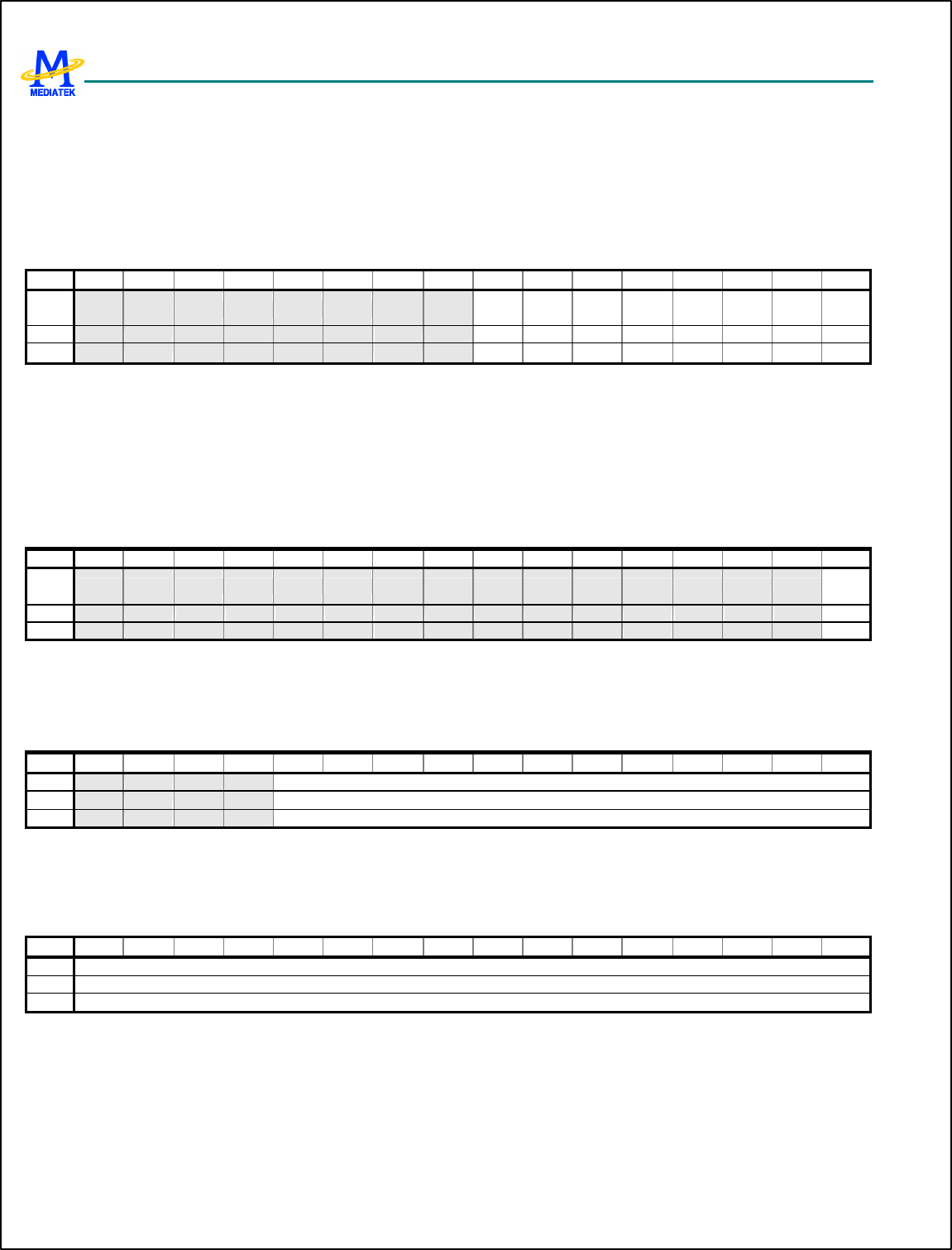

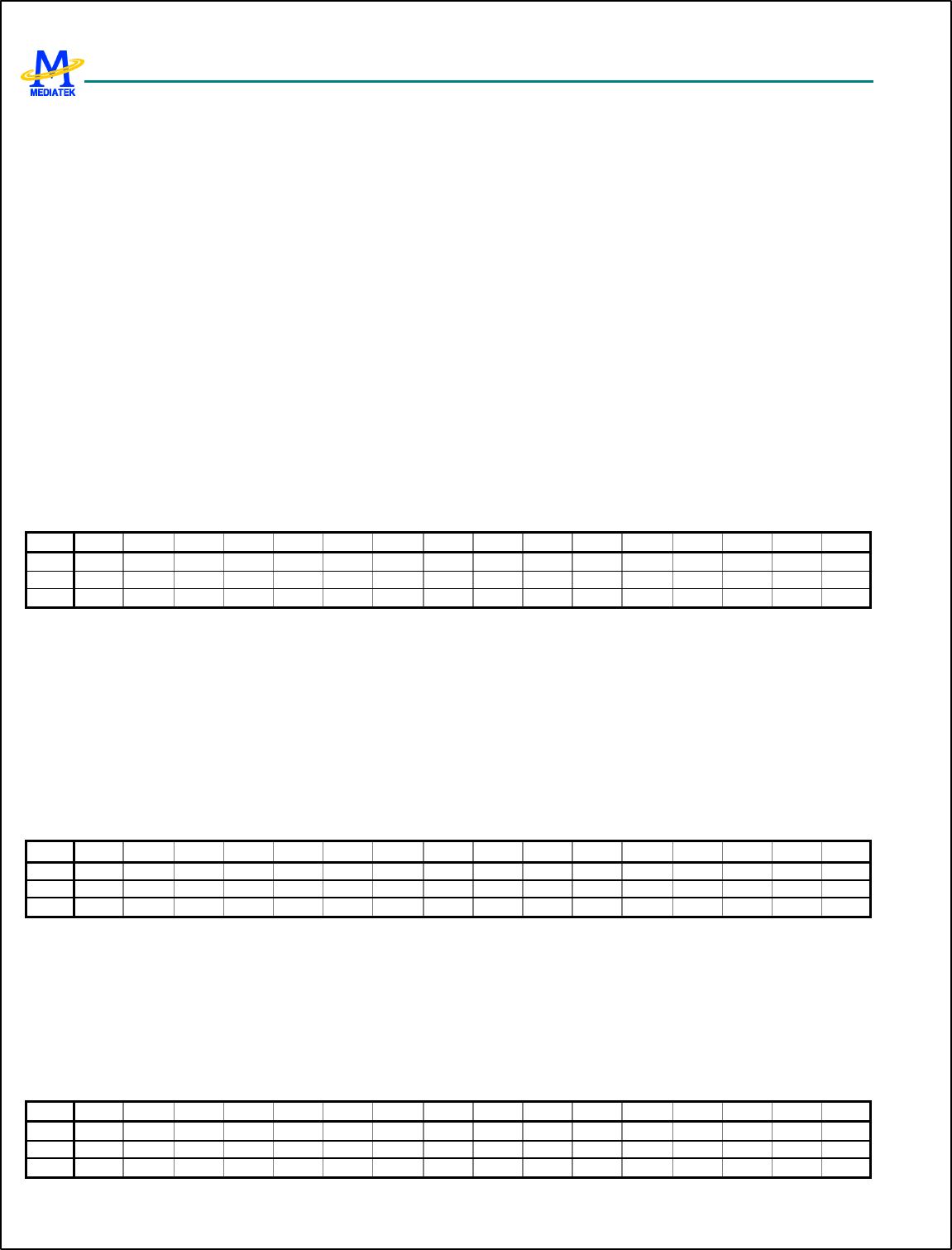

Figure 6 The Memory Layout of MT6217

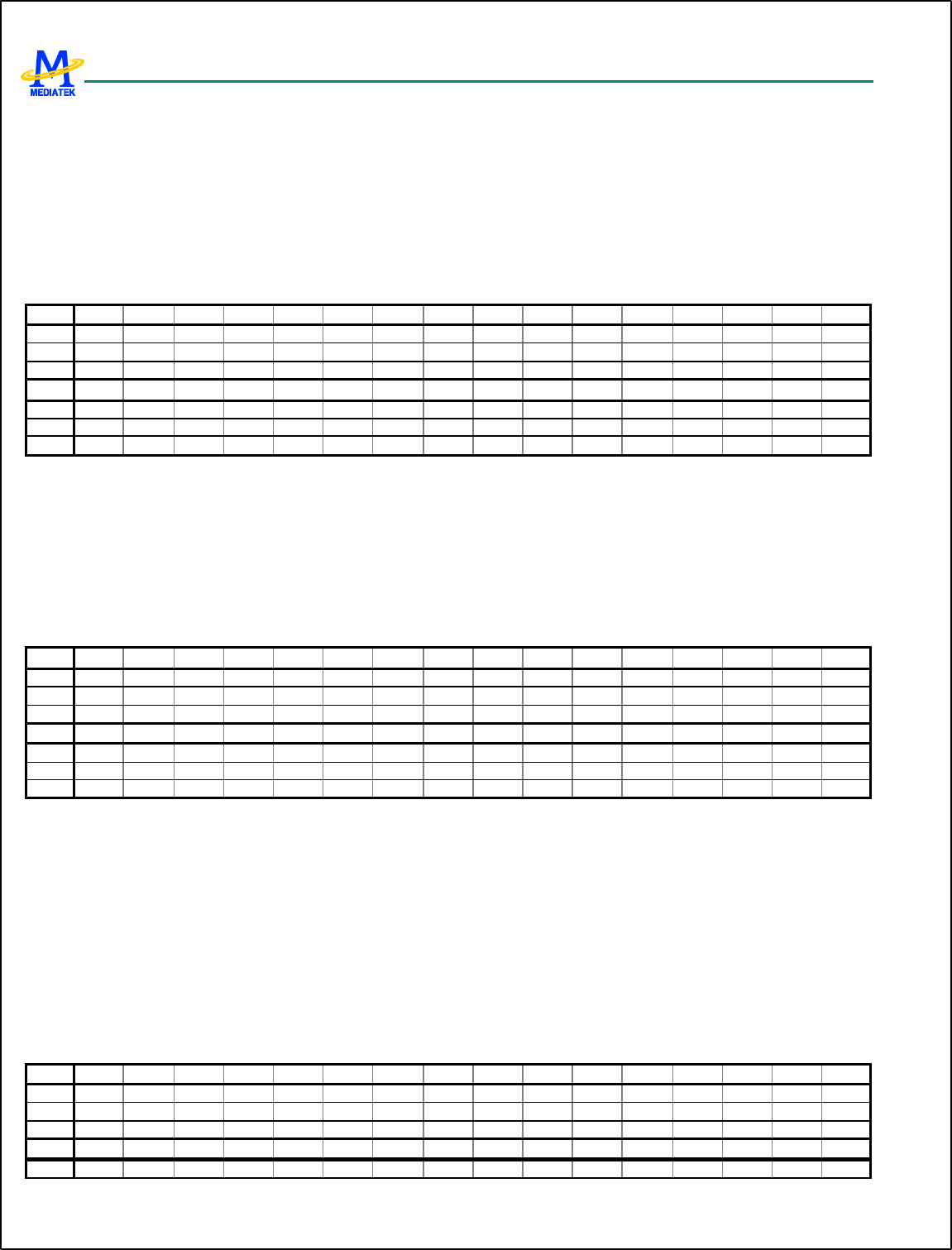

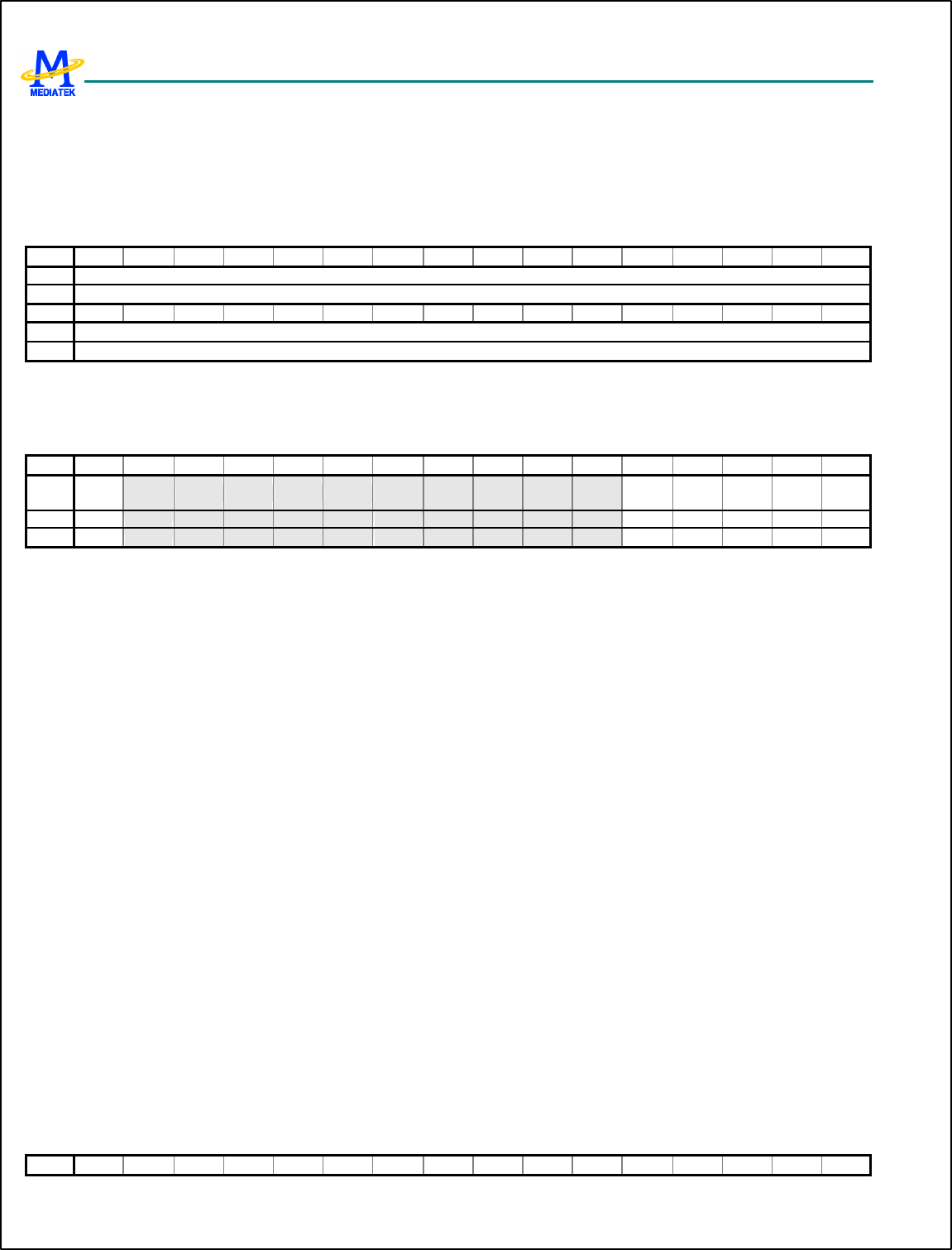

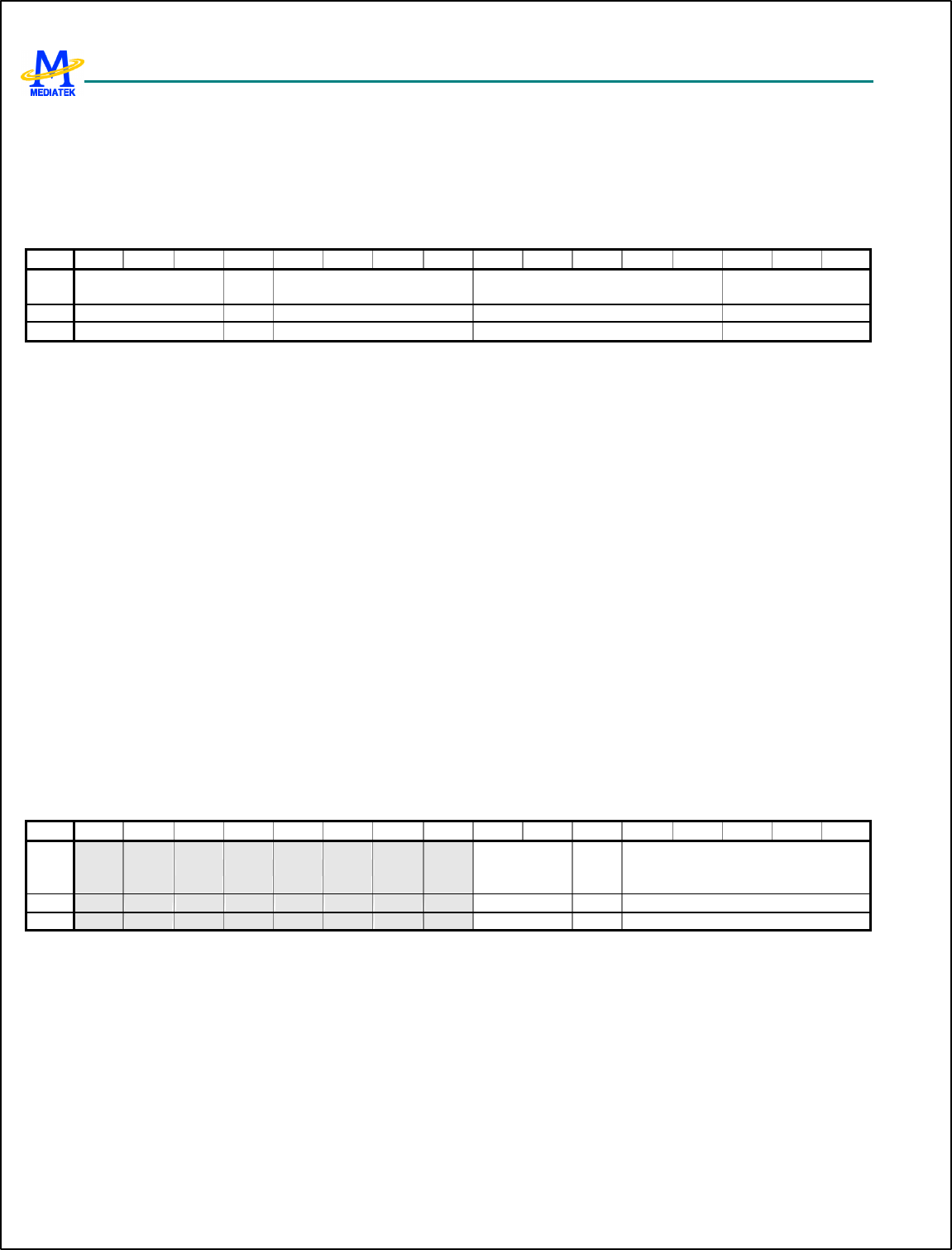

The address space is organized as basis of blocks with size of 256M By tes for each. Memory blocks MB0-MB9 are

determined and currently dedicated to specific functions, as shown in Table 4, while the others are reserved for future usage.

Essentially, the block number is uniquely selected by address line A31-A28 of internal system bus.

Memory

Block

Block Address

A31-A28 Address Range Description

00000000h-07FFFFFFh Boot Code, EXT SRAM or EXT Flash/MISC

MB0 0h 08000000h-0FFFFFFFh EXT SRAM or EXT Flash/MISC

10000000h-17FFFFFFh EXT SRAM or EXT Flash/MISC

MB1 1h 18000000h-1FFFFFFFh EXT SRAM or EXT Flash/MISC

20000000h-27FFFFFFh EXT SRAM or EXT Flash/MISC

MB2 2h 28000000h-2FFFFFFFh EXT SRAM or EXT Flash/MISC

30000000h-37FFFFFFh EXT SRAM or EXT Flash/MISC

MB3 3h 38000000h-3FFFFFFFh EXT SRAM or EXT Flash/MISC

MT6217 GSM/GPRS Baseband Processor Data Sheet Revision 1.01

38/349 MediaTek Inc. Confidential

40000000h-47FFFFFFh System RAM

MB4 4h 48000000h-4FFFFFFFh System ROM

MB5 5h 50000000h-5FFFFFFFh

MB6 6h 60000000h-6FFFFFFFh MCU-DSP Interface

70000000h-77FFFFFFh USB

MB7 7h 78000000h-7FFFFFFFh Virtual FIFO

MB8 8h 80000000h-8FFFFFFFh APB Slaves

90000000h-97FFFFFFh LCD

MB9 9h

Table 4 Definitions of Memory Blocks in MT6217

3.2.1.1 External Access

To have external access, the MT6217 outputs 26 bits (A25-A0) of address lines along with 8 selection signals that

correspond to associated memory blocks. That is, MT6217 can support at most 8 MCU addressable external components.

The data width of internal system bus is fixed as 32-bit wide, while the data width of the external components can be either

8 or 16 bit.

Since devices are usually available with variety operating grades, adaptive configurations for different applications are

needed. MT6217 provides software programmable registers to configure to adapt operating conditions in terms of different

wait-states.

3.2.1.2 Memory Re-mapping Mechanism

To permit system being configured with more flexible, a memory re-mapping mechanism is provided. It allows software

program to swap BANK0 (ECS0#) and BANK1 (ECS1#) dynamically. Whenever the bit valu e of RM0 in register

EMI_REMAP is changed, these two banks will be swapped accordingly. Besides, it also permits system being boot in

different sequence as detailed in 3.2.1.3 Boot Sequence.

3.2.1.3 Boot Sequence

Since the ARM7EJ -S core always starts to fetch instructions from the lowest memory address at 00000000h (MB0) after

system being reset. It is designed to have a dynamic mapping architecture capable of associating Boot Code, external Flash

or external SRAM with memory block MB0.

By default, the Boot Code is mapped onto MB0 while the state of IBOOT is “0”. But, this configuration can be changed by

altering the state of IBOOT before system reset or programming bit value of RM1 in register EMI_REMAP directly.

MT6217 system provides two kinds of boot up scheme:

l Start up system of running codes from Boot Code for factory programming

l Start up system of running codes from external FLASH or ROM device for normal operation

MT6217 GSM/GPRS Baseband Processor Data Sheet Revision 1.01

39/349 MediaTek Inc. Confidential

3.2.1.3.1 Boot Code

The Boot Code is placed together with Memory Re -Mapping Mechanism in External Memory Controller and comprises

just two words of instructions as shown below. It is quite obvious that there is a jump instruction that leads the processor to

run the code started at address of 48000000h wh ere the System ROM is placed.

ADDRESS BINARY CODE ASSEMBLY

00000000h E51FF004h LDR PC, 0x4

00000004h 48000000h (DATA)

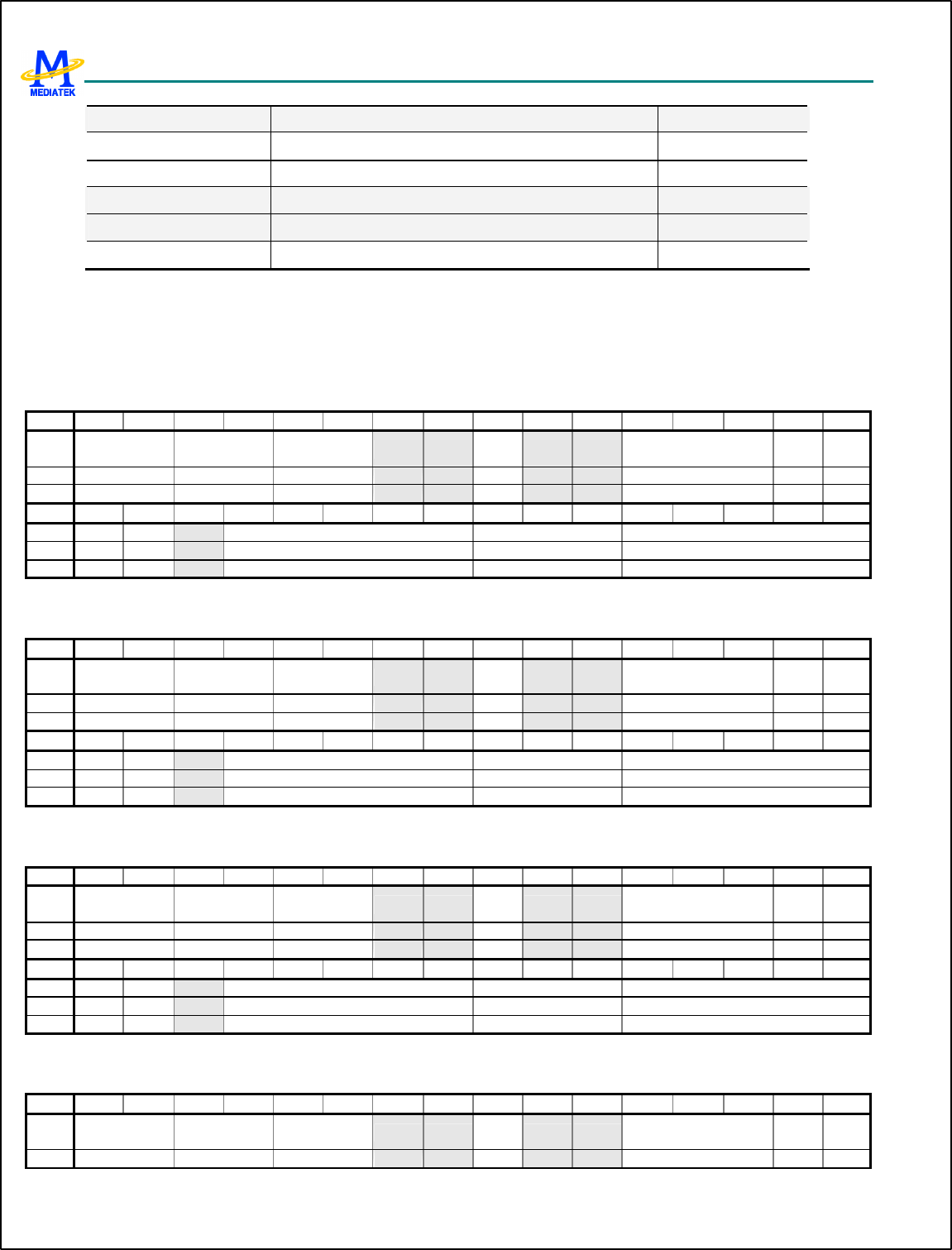

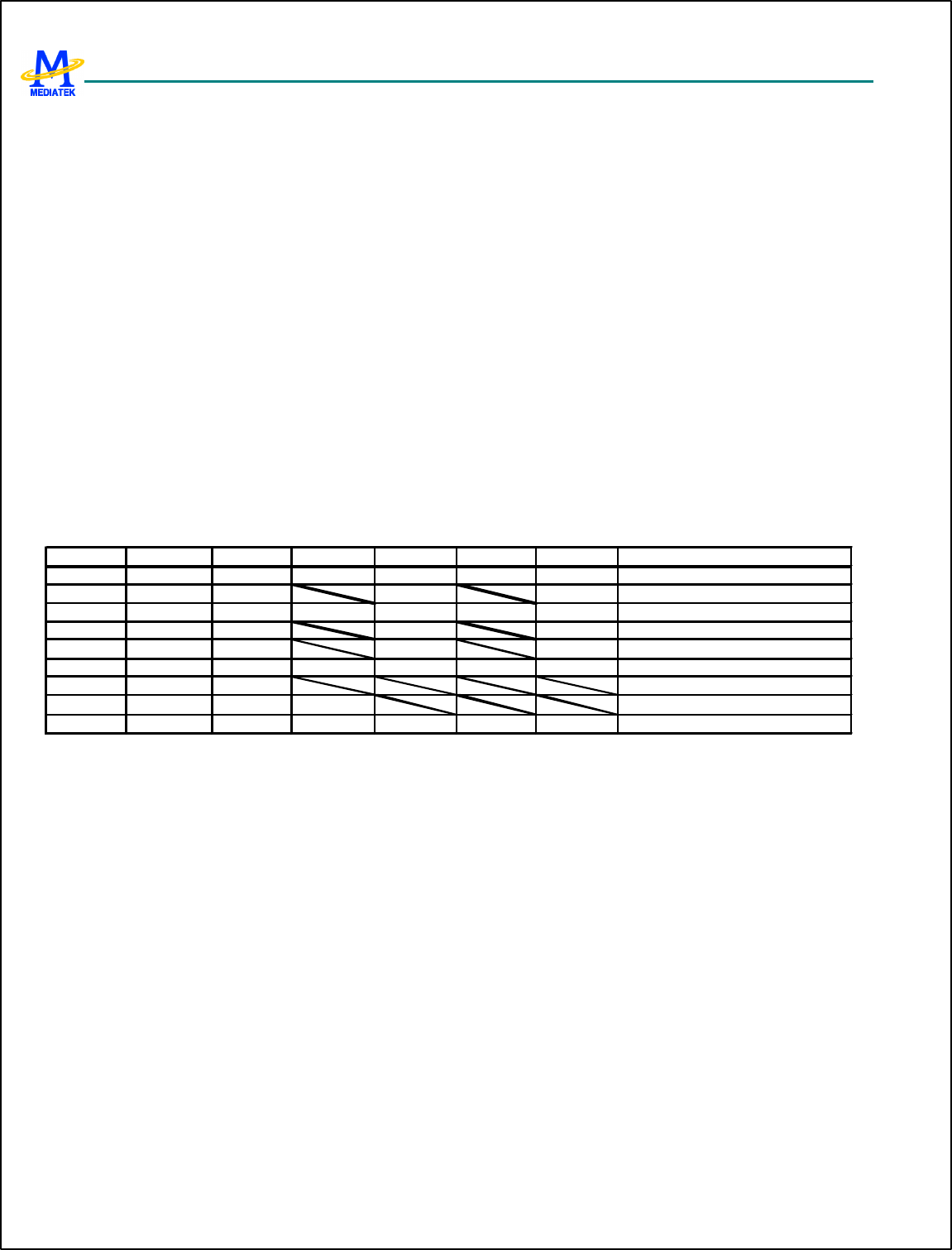

3.2.1.3.2 Factory Programming

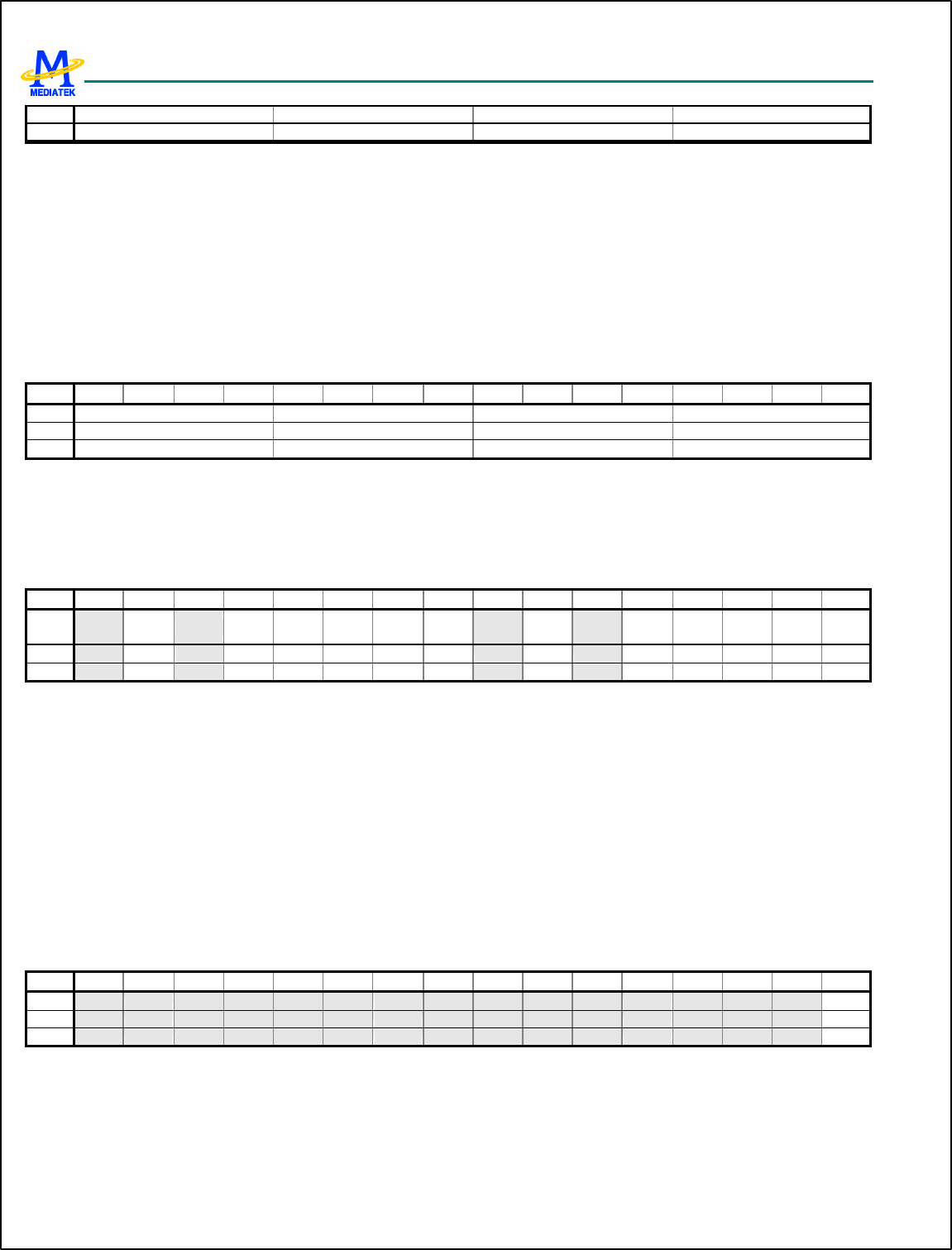

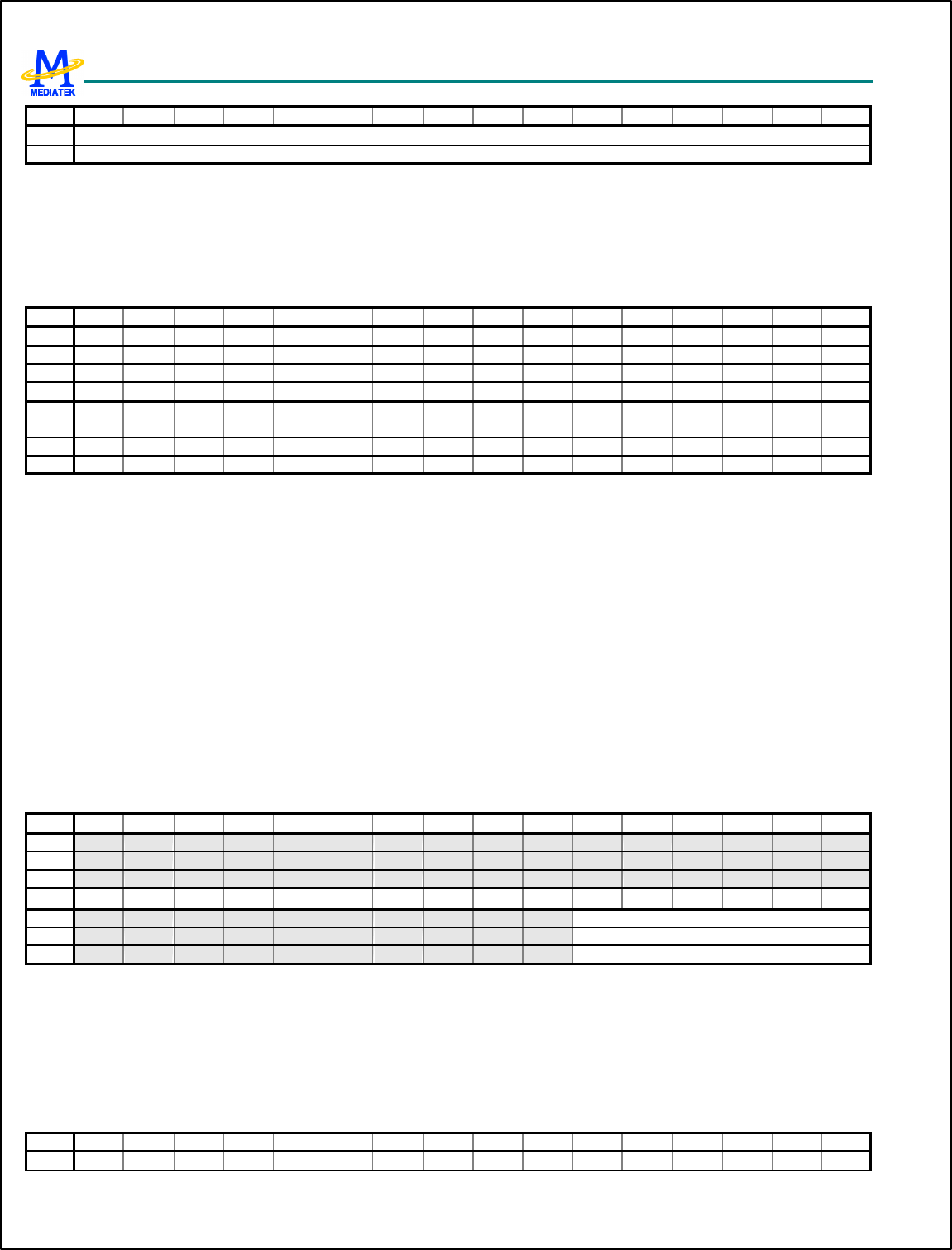

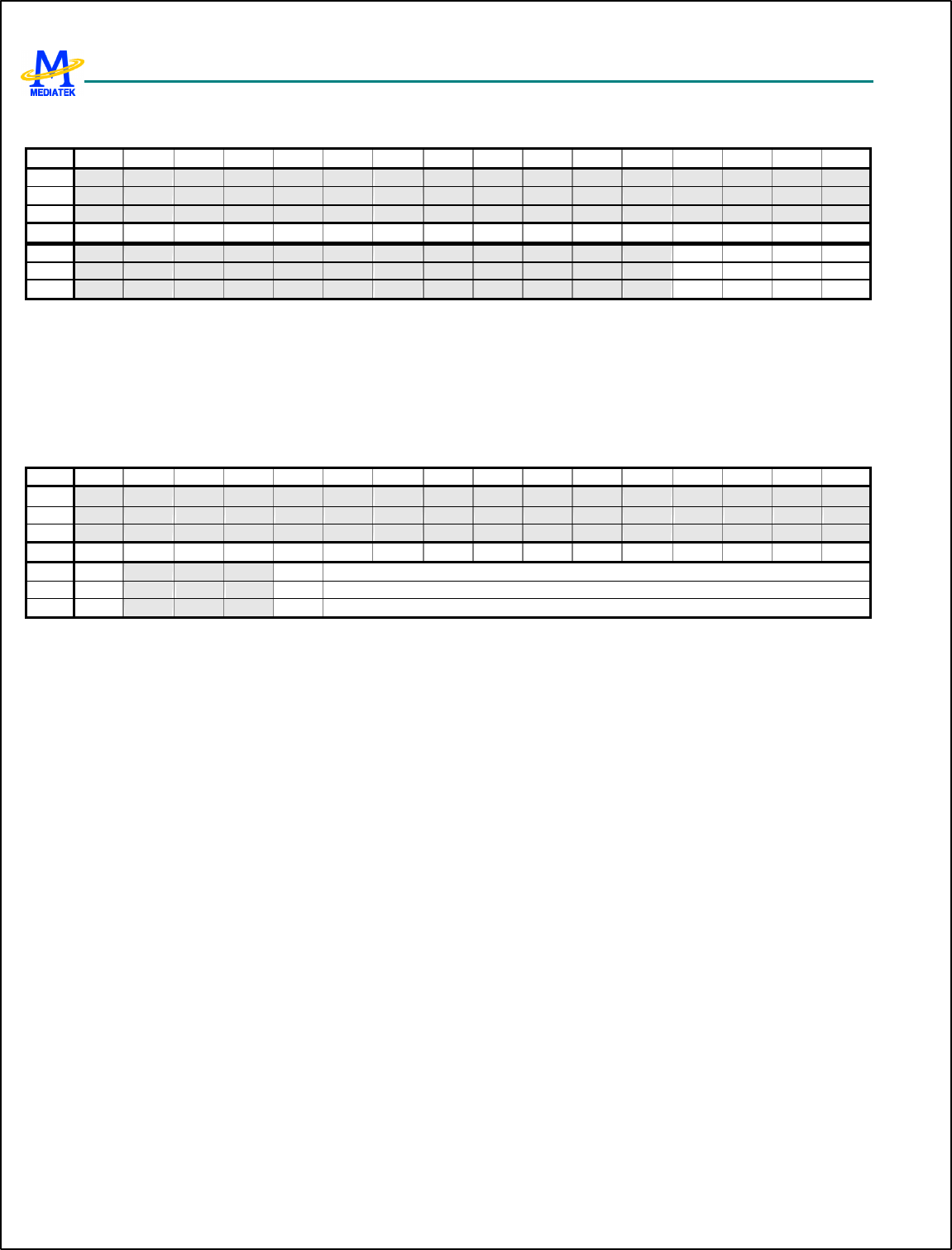

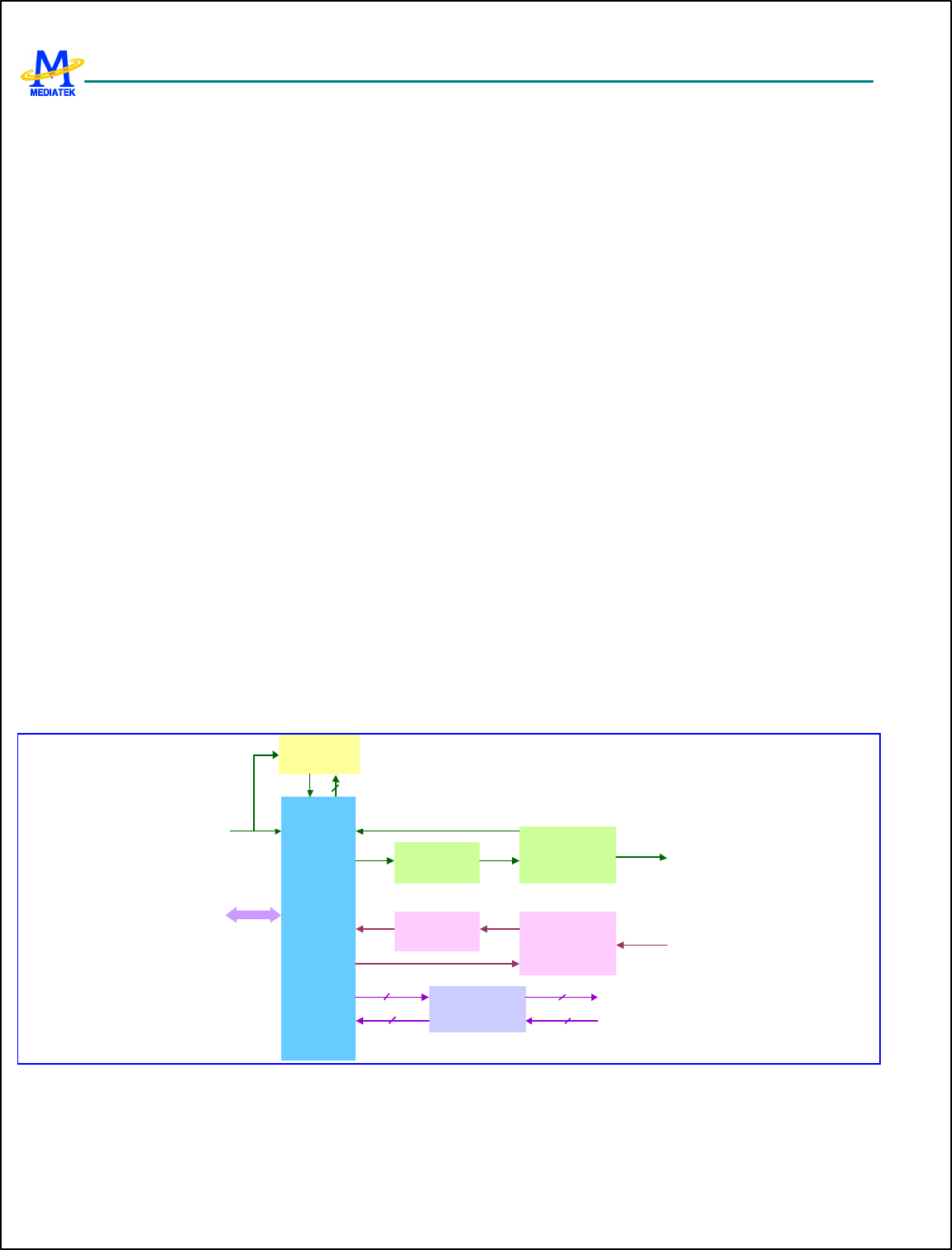

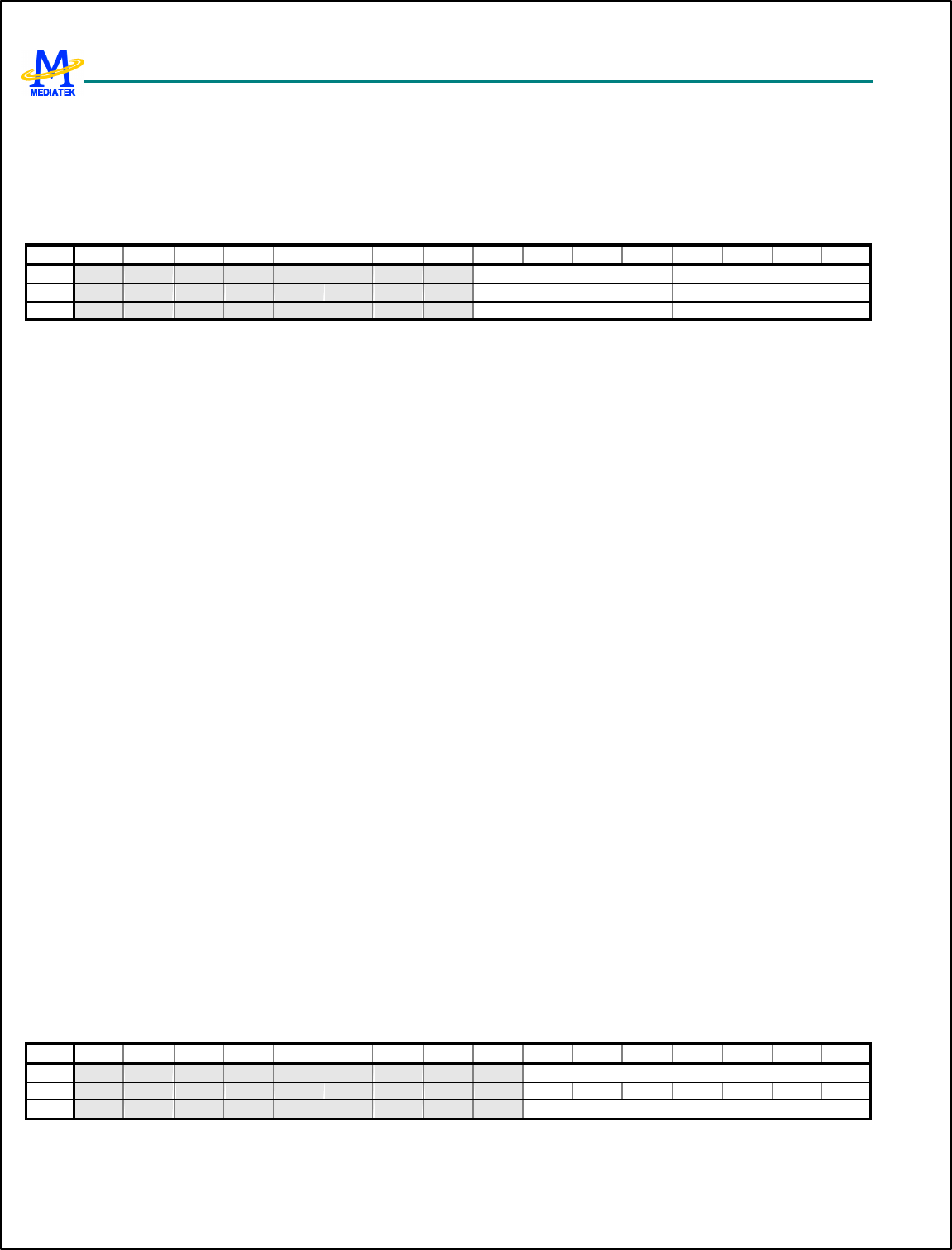

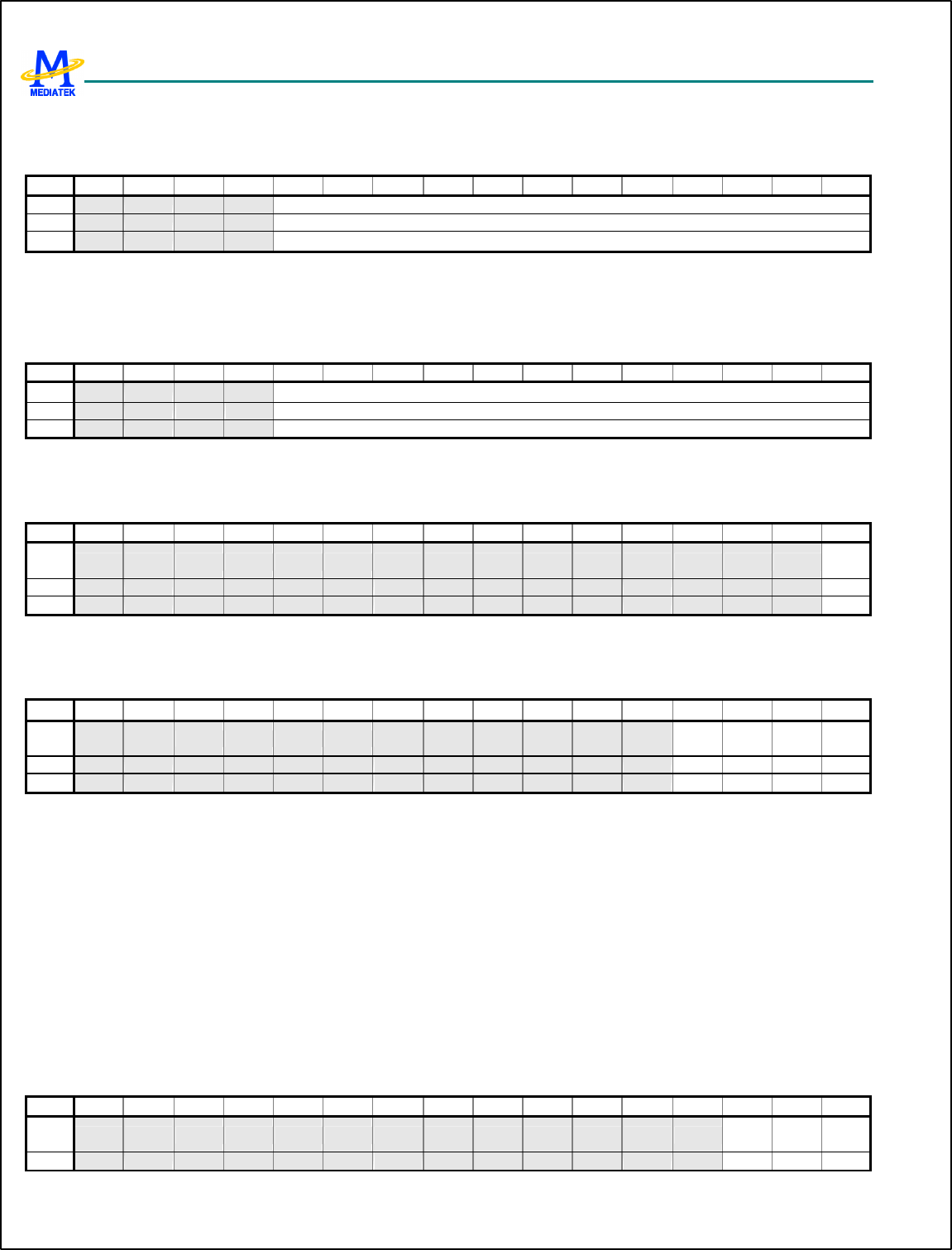

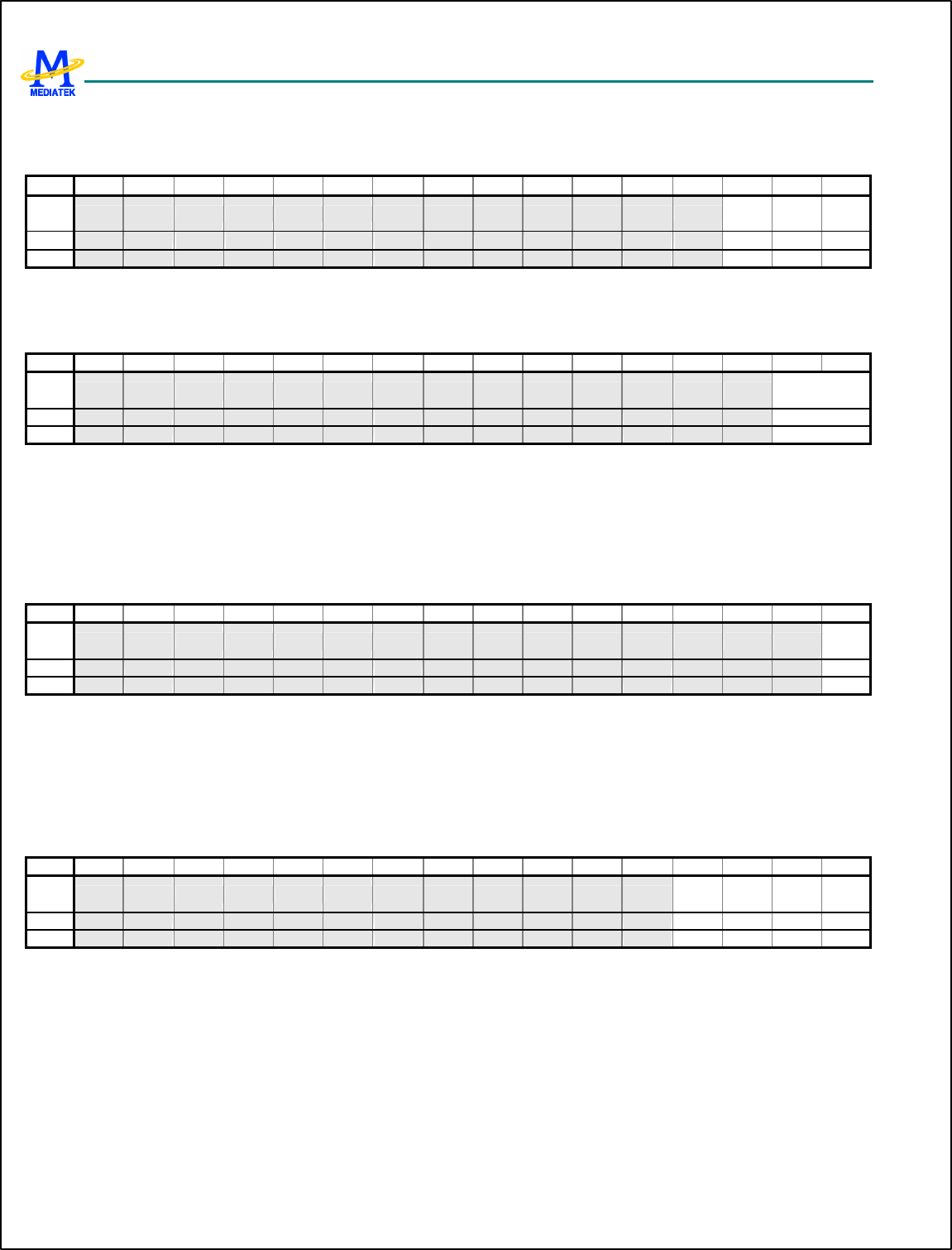

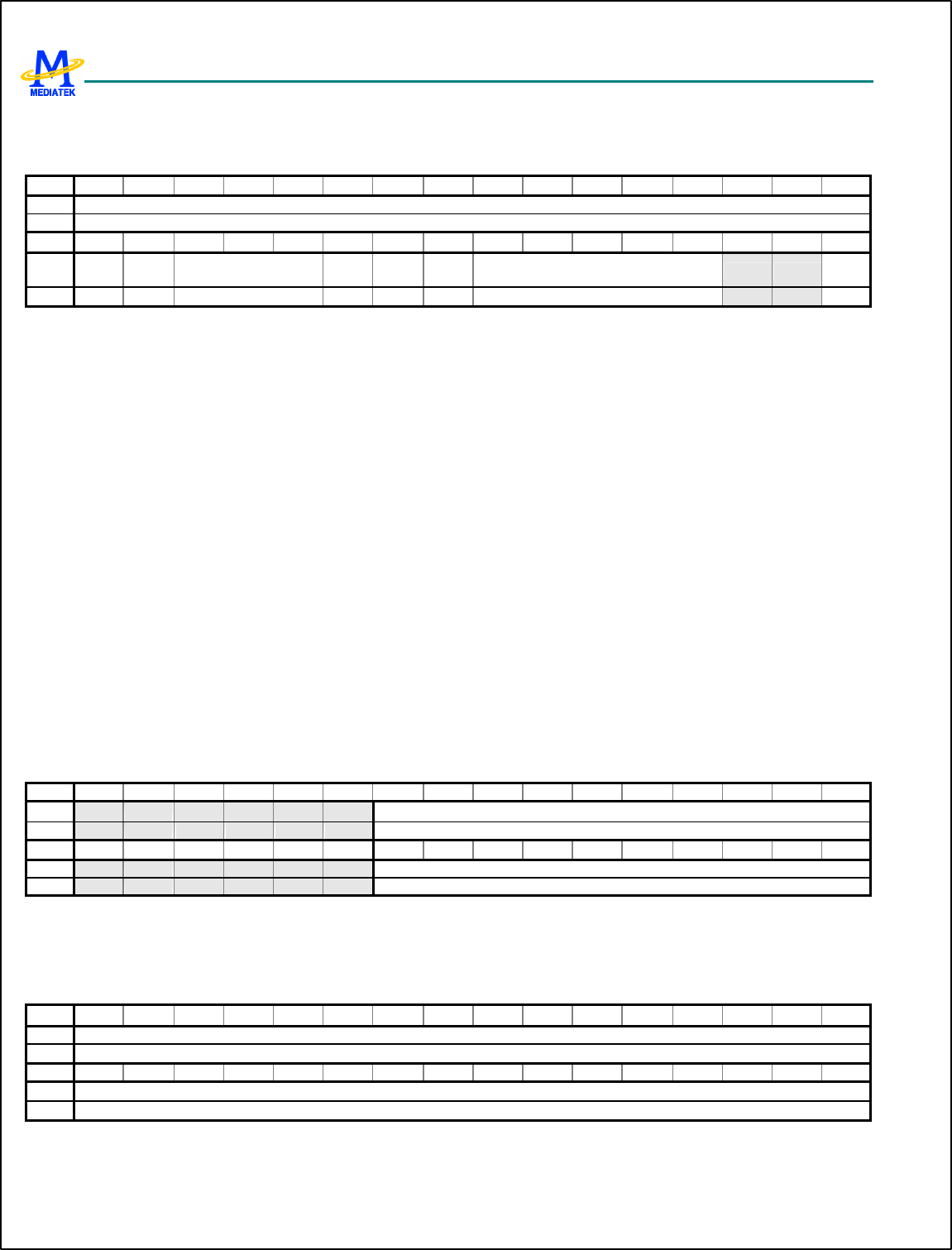

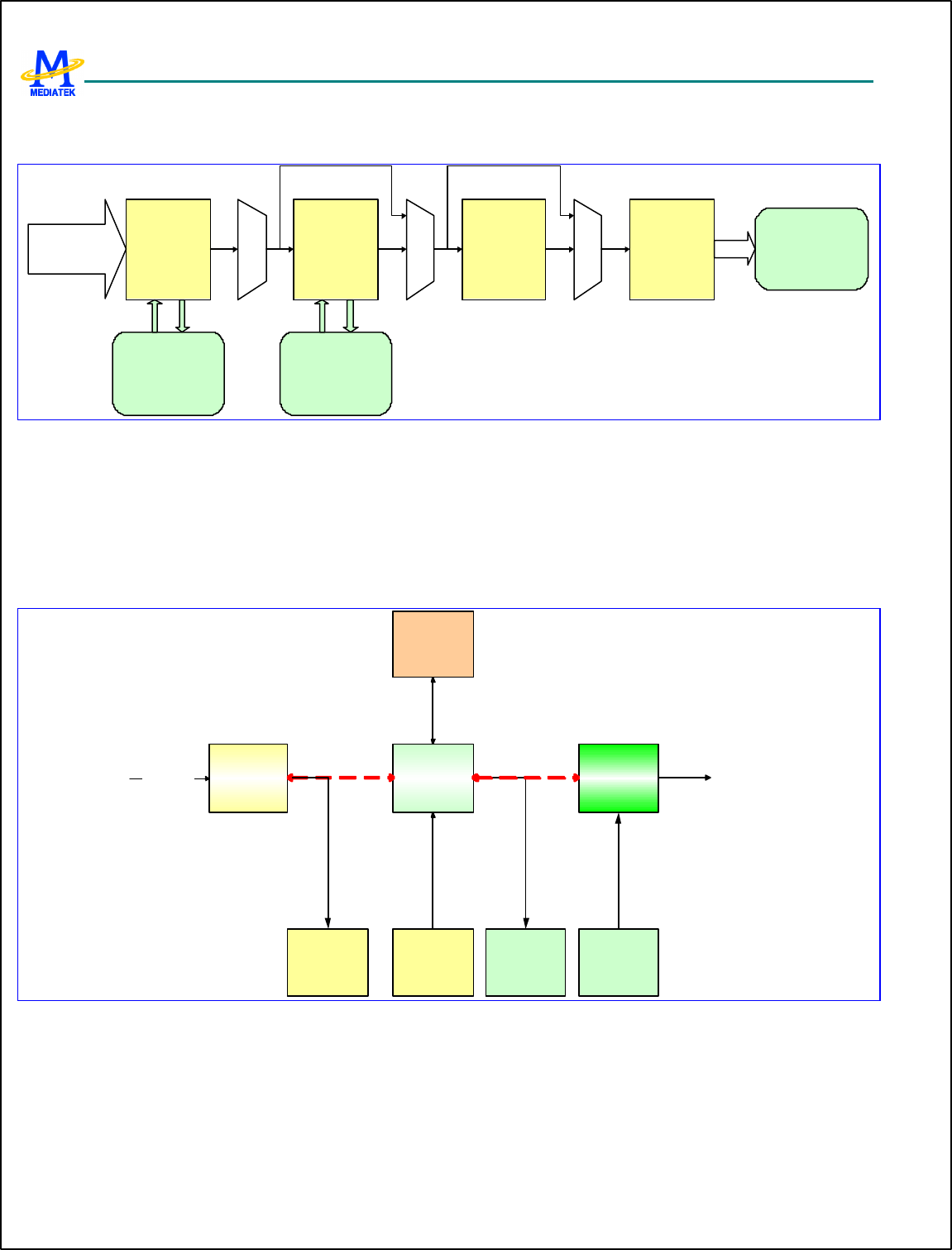

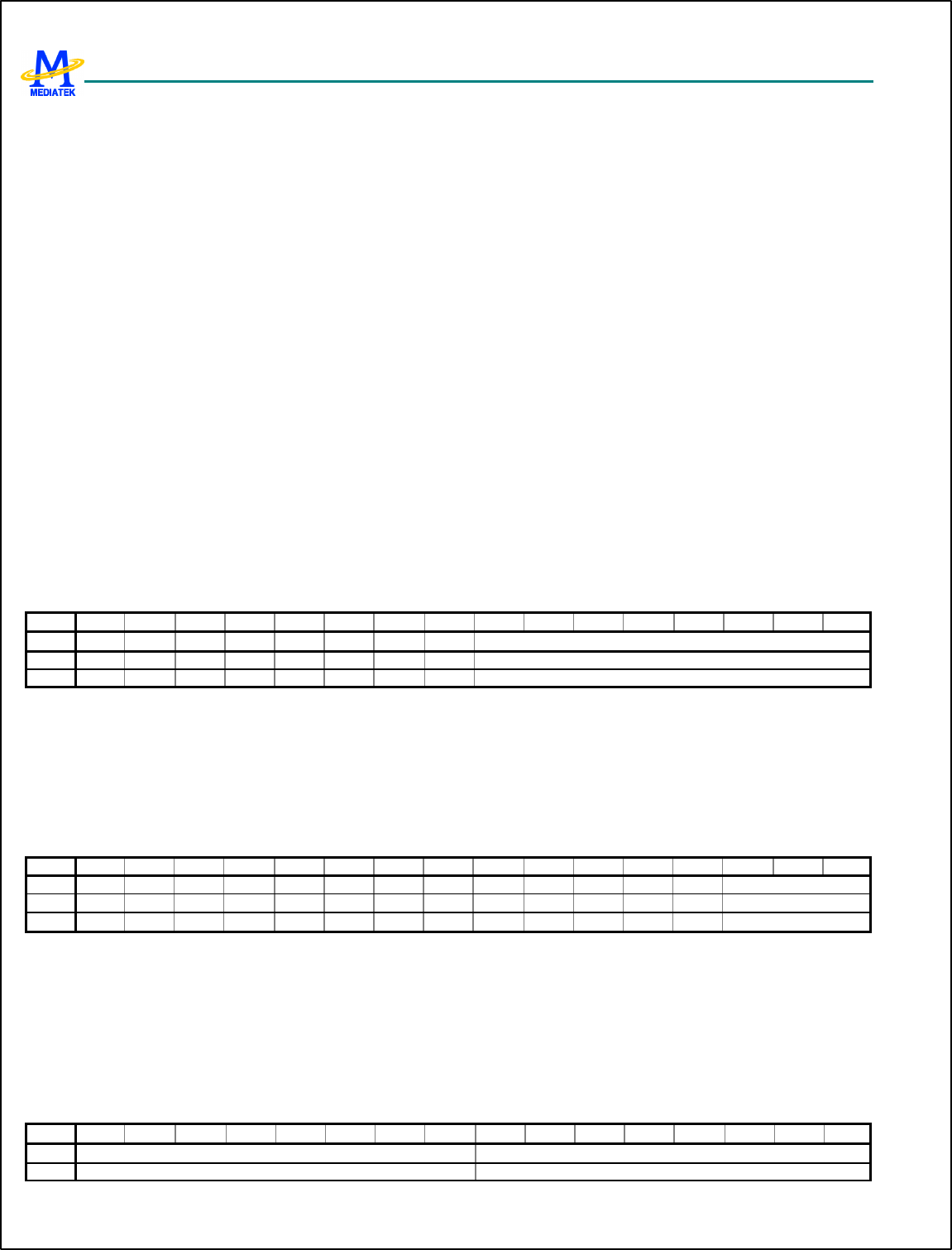

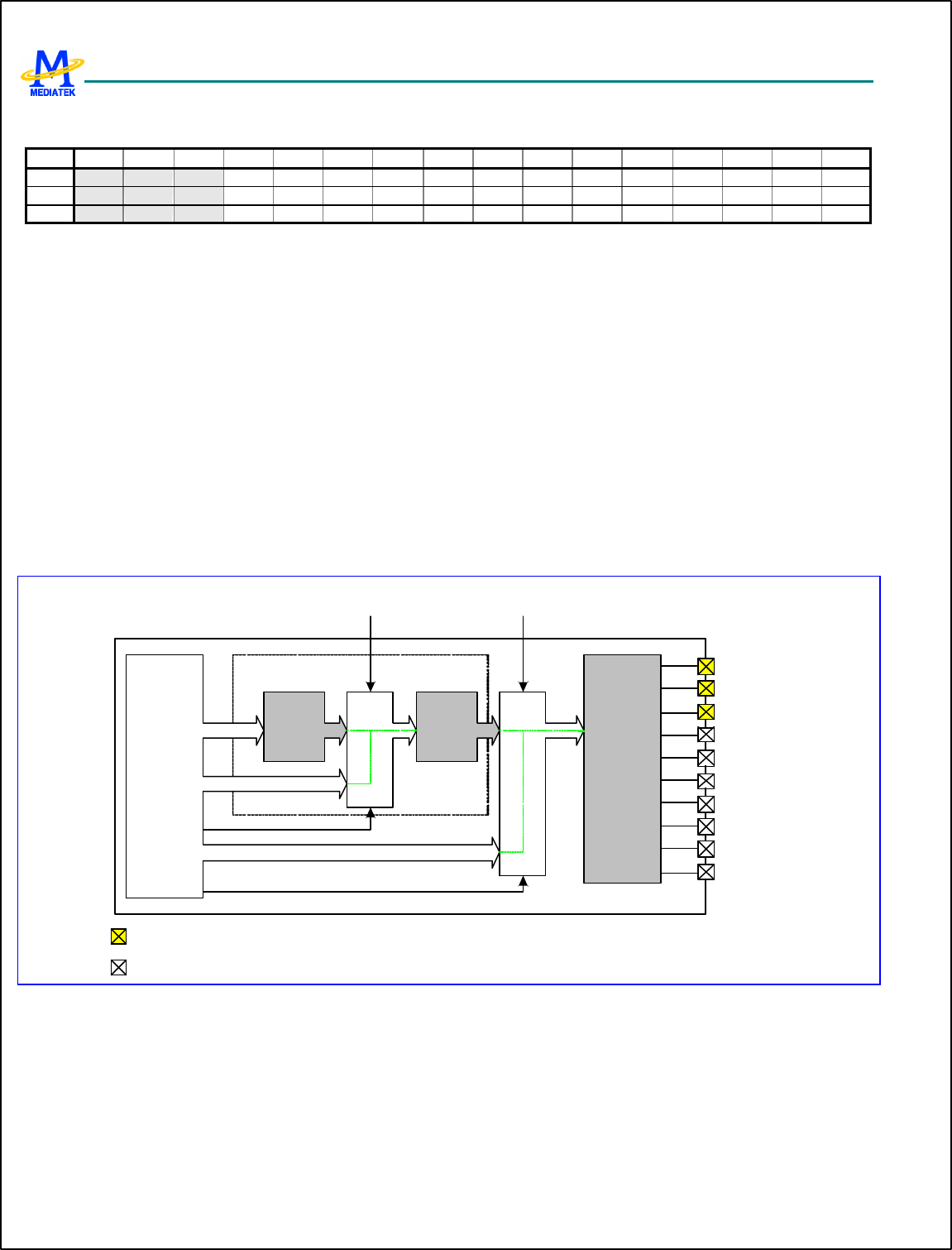

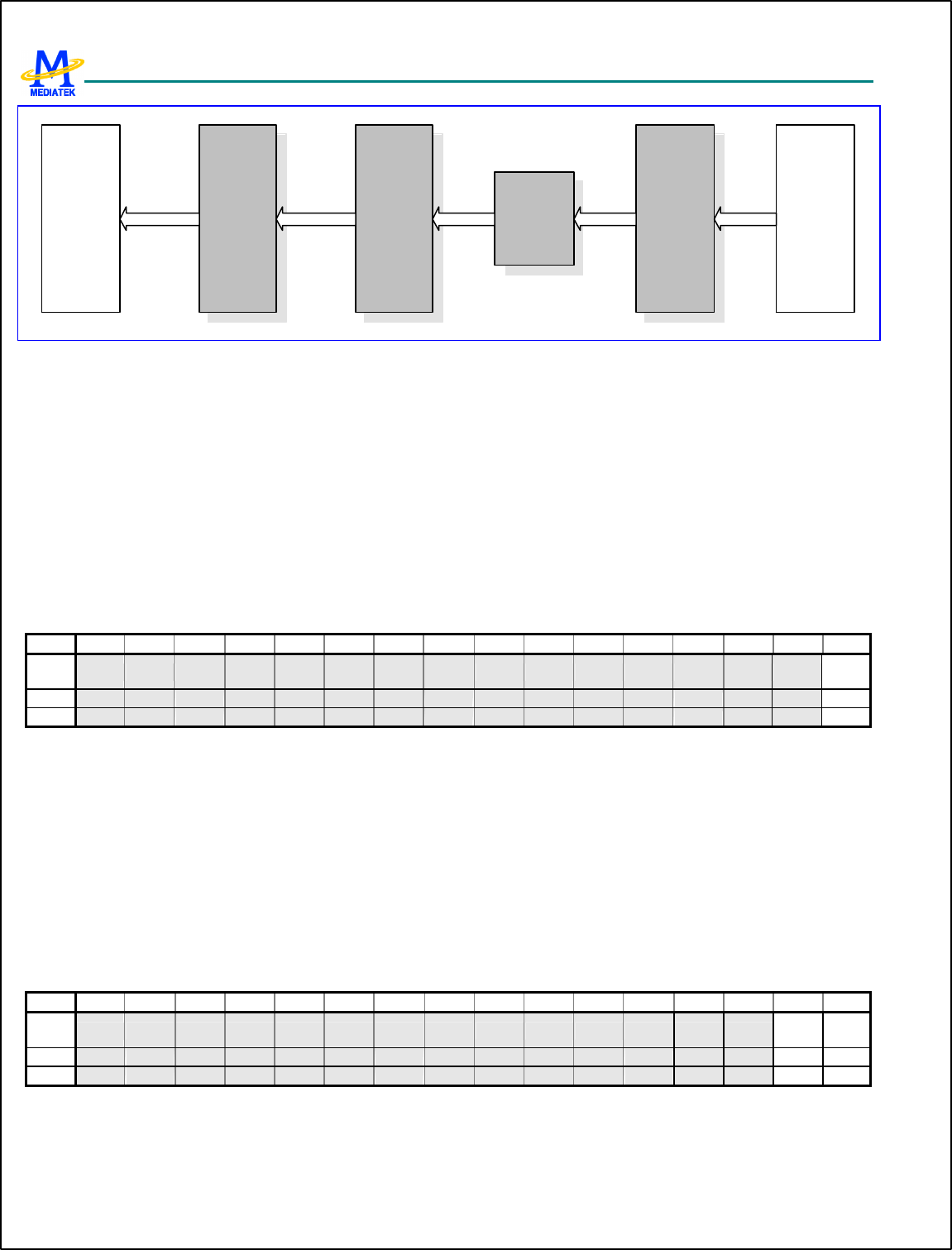

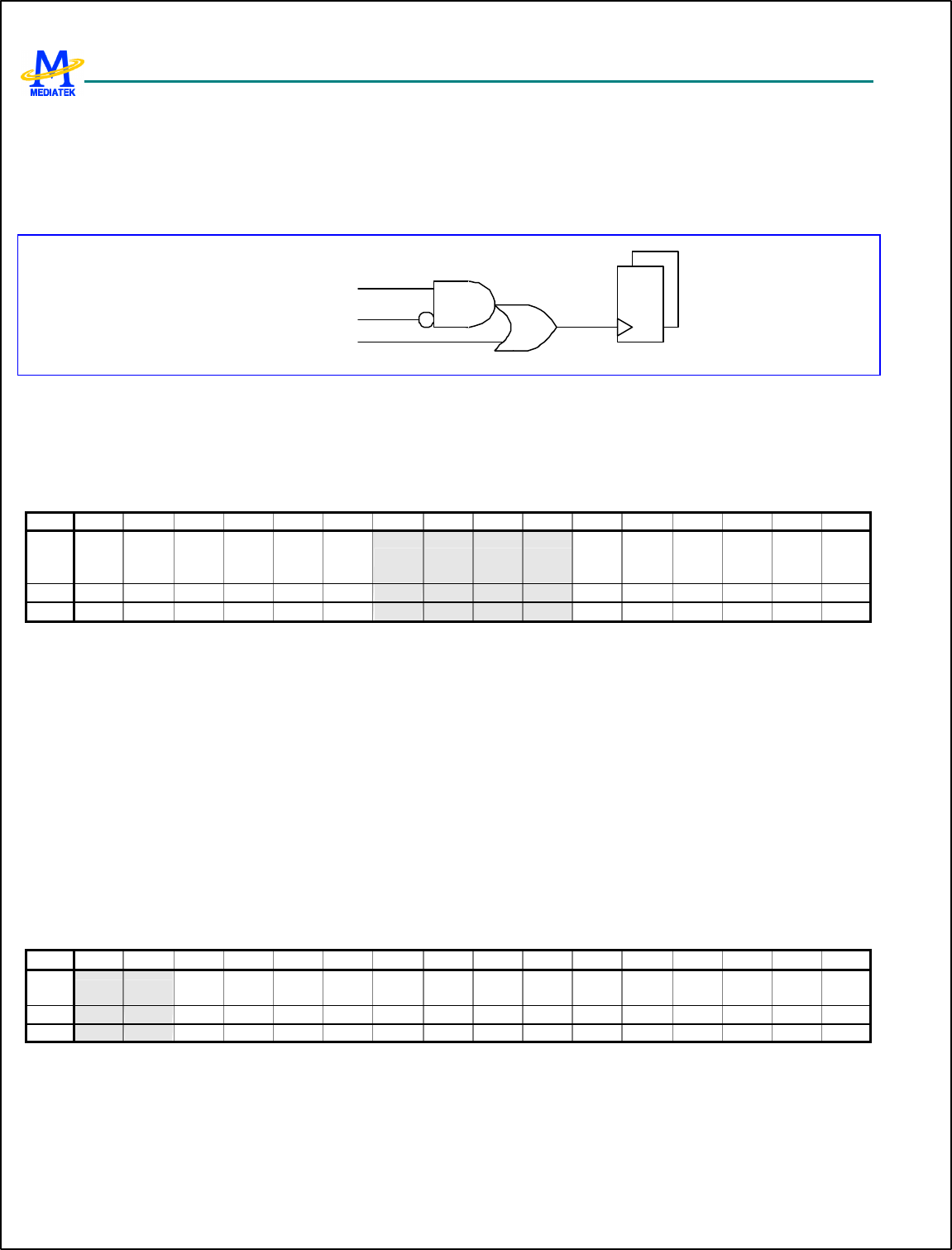

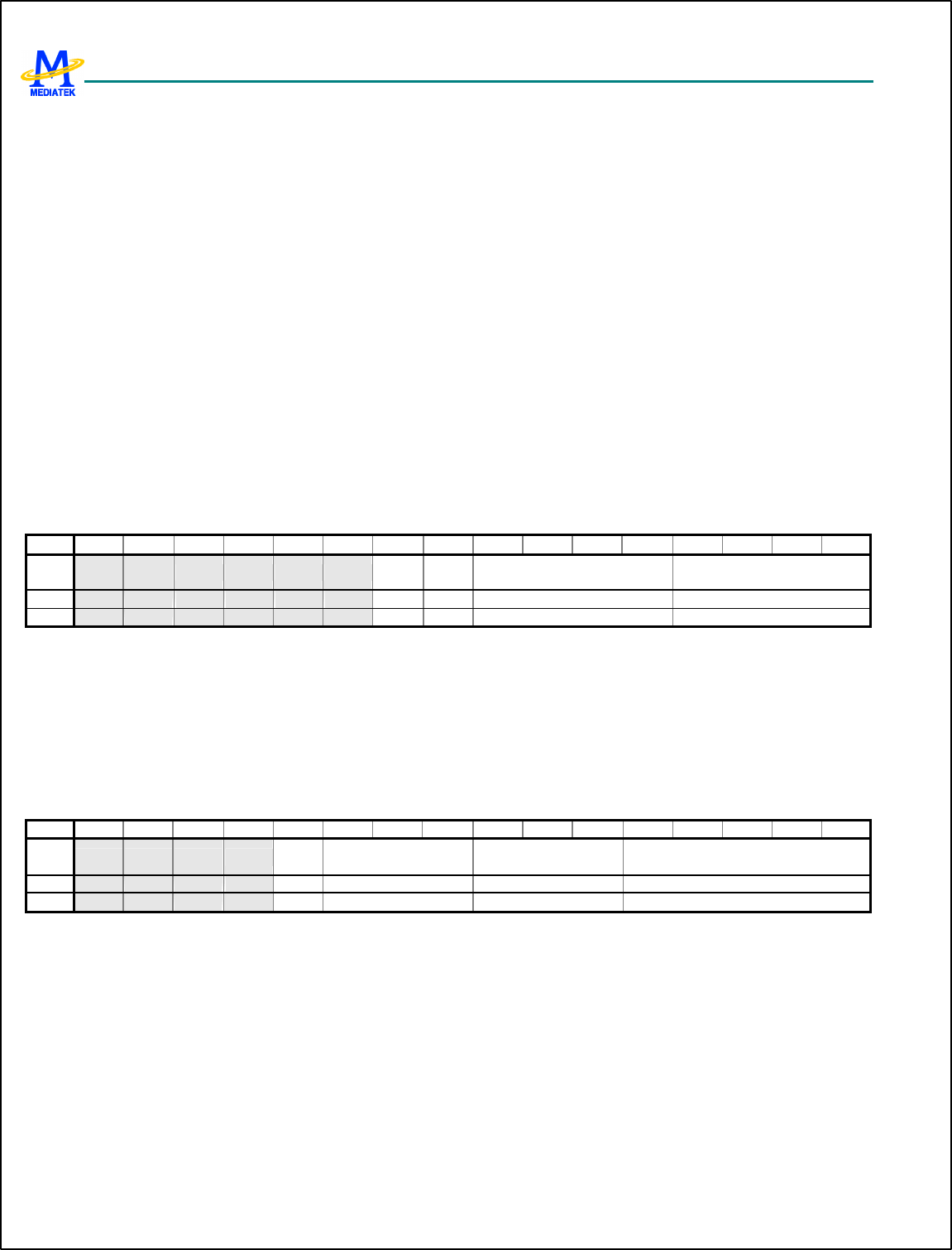

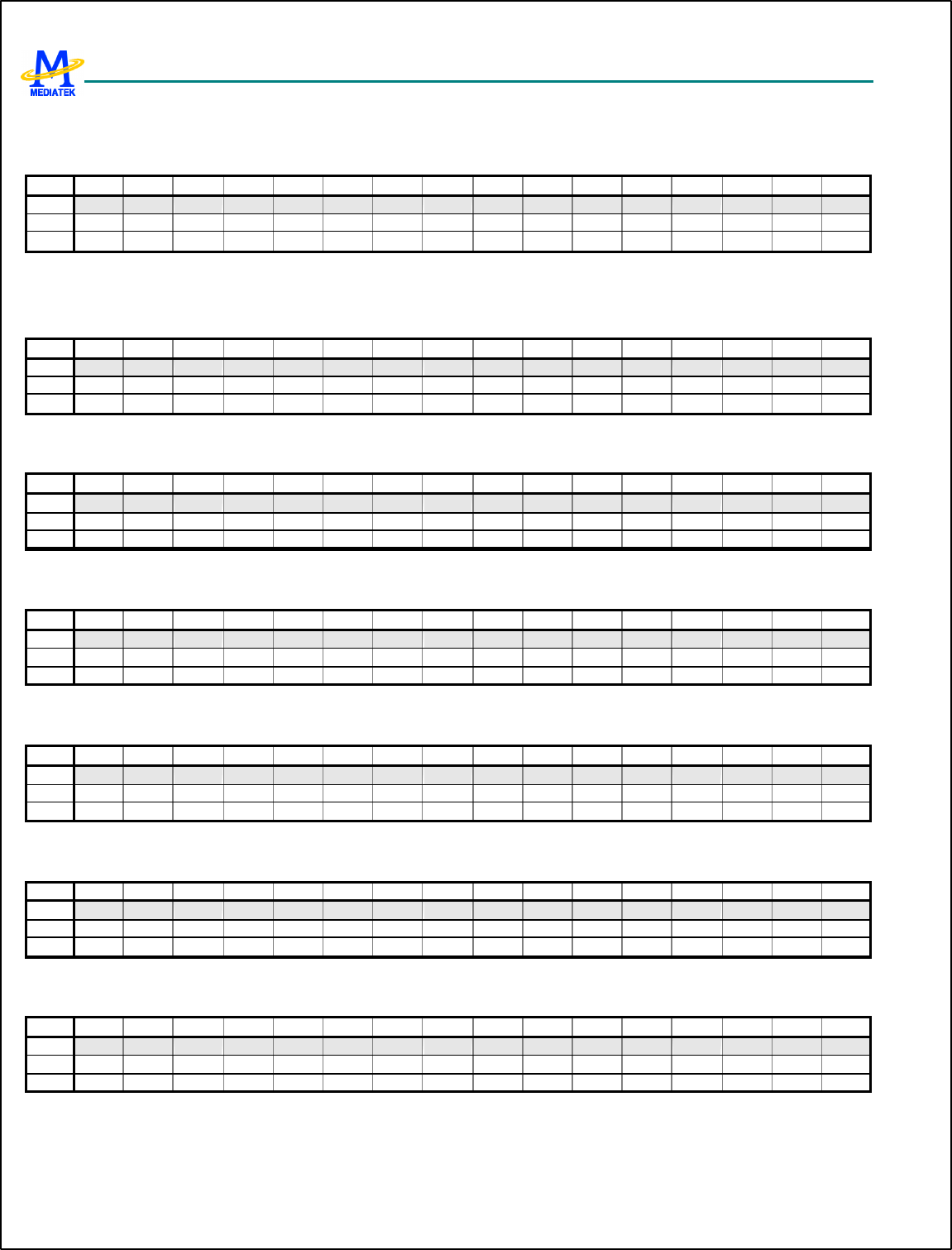

The configuration for factory programming is shown in Figure 7. Usually the Factory Programming Host connects with

MT6217 by way of UART interface. To have it works properly, the system should boot up from Boot Code. That is the

IBOOT should be tied to GND. The down load speed can be up to 921K bps while MCU is running at 26MHz.

After system being reset, the Boot Code will guide the processor to run the Factory Programming software placed in

System ROM. Then, MT6217 will start and continue to poll the UART1 port until valid information is detected. The first

information received on the UART1 will be used to configure the chip for factory programming. The Flash down loader

program is then transferred into System RAM or external SRAM.

Further information will be detailed in MT6217 Software Programming Specification.

MT6217 Factory

Programming

Host

FLASH

UART

External

Memory

Interface

IBOOT

Figure 7 System configuration required for factory programming

3.2.1.4 Little Endian Mode

The MT6217 system always treats 32-bit words of memory in Little Endian format. In Little Endian mode, the lowest

numbered byte in a word is stored in the least significant byte, and the highest numbered byte in the most significant

position. Byte 0 of the memory system is therefore connected to data lines 7 through 0.

3.3 Bus System

3.3.1 General Description

Two levels of bus hierarchy are employed in constructing the Micro-Controller Unit Subsystem of MT 6217. As depicted in

Figure 5, AHB Bus and APB Bus serve for system backbone and peripheral buses, while an APB bridge connects these two

buses. Both AHB and APB Buses operate at the same clock rate as processor core.

MT6217 GSM/GPRS Baseband Processor Data Sheet Revision 1.01

40/349 MediaTek Inc. Confidential

The APB Bridge is the only bus master resided on the APB bus. All APB slaves are mapped onto memory block MB8 in

MCU 32-bit addressing space. A central address decoder is implemented inside the bridge to generate those select signals

for individual peripheral. In addition, since the base address of each APB slave has been associated with select signals, the

address bus on APB will contains only the value of offset address.

The maximum address space that can be allocated to a single APB slave is 64KB, i.e. 16-bit address lines. The width of

data bus is mainly constrained to 16-bit to minimize the design complexity and power consumption while some of them

uses 32-bit data bus to accommodate more bandwidth. In the case where an APB slave needs large amount of transfers, the

device driver can also request a DMA resource or channel to conduct a burst of data transfer. The base address and data

width of each peripheral are listed in Table 5.

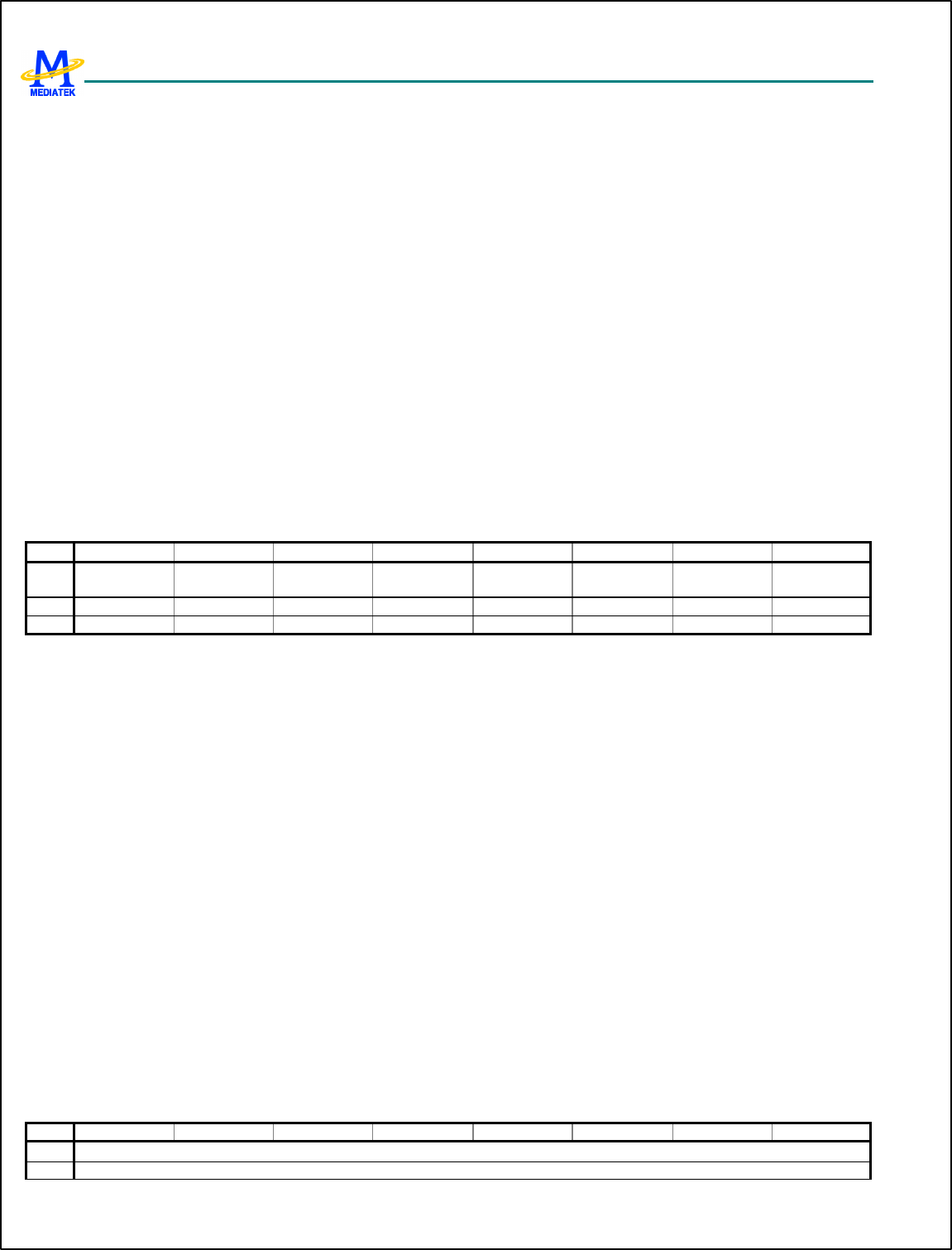

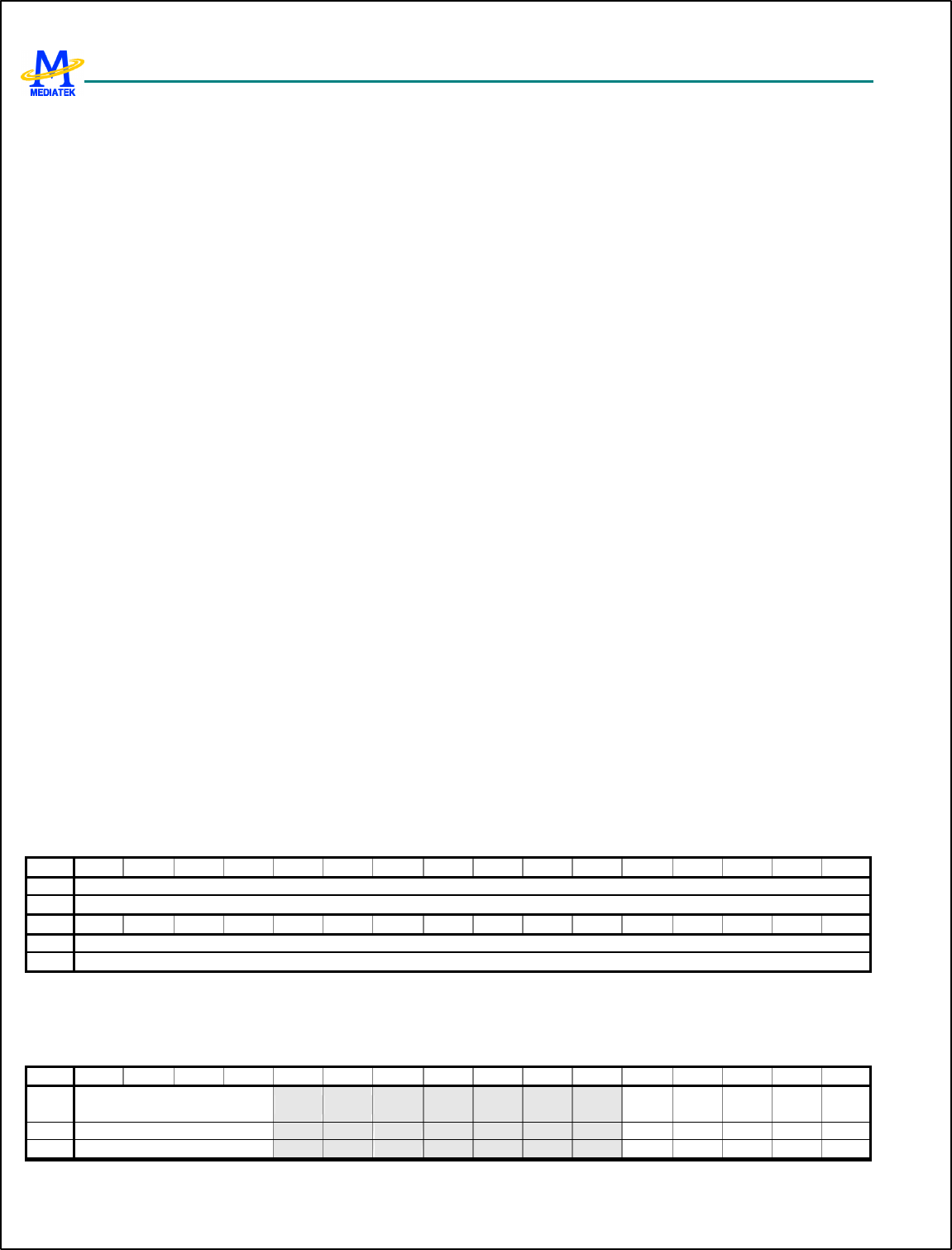

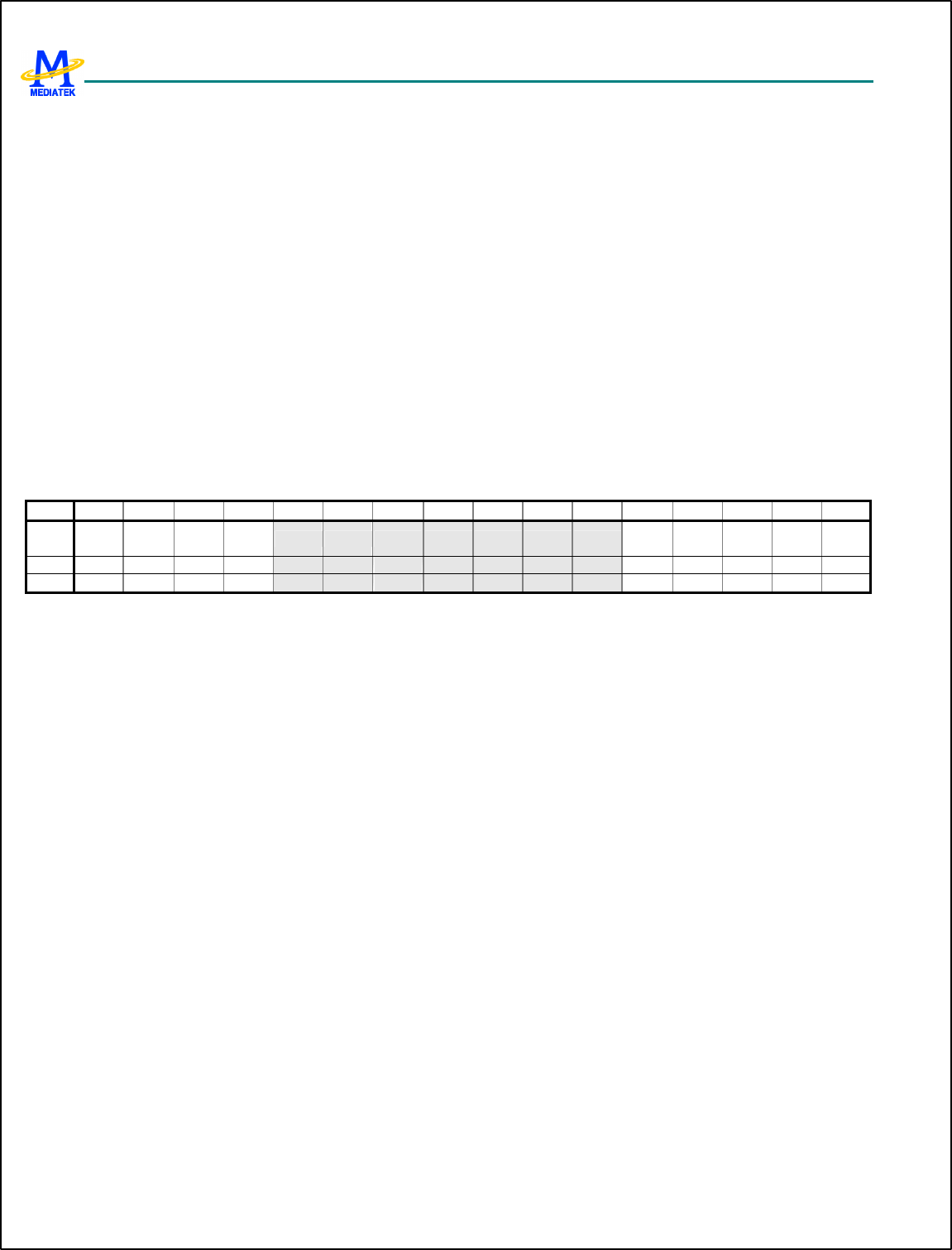

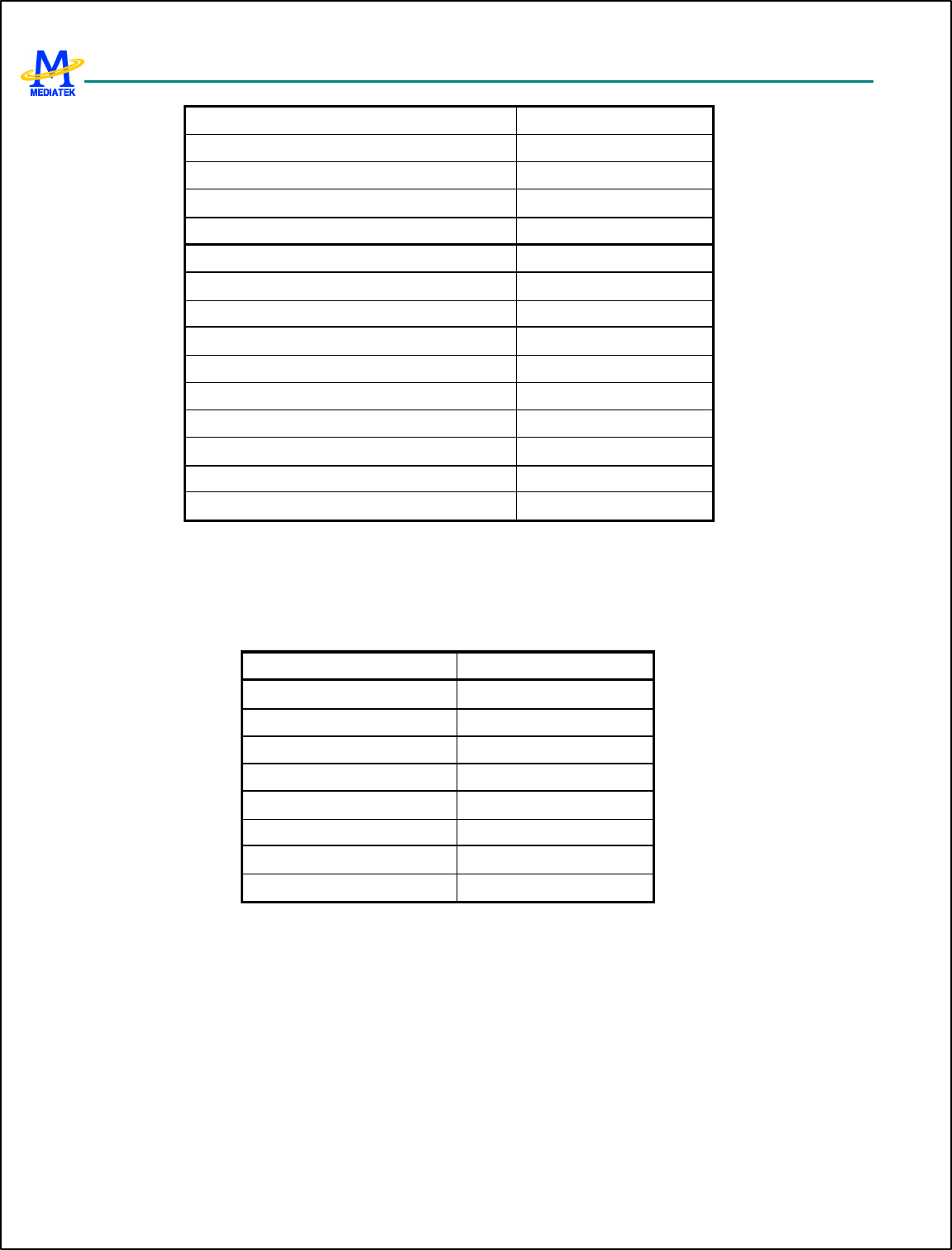

Base Address Description Data Width Software Base ID

8000_0000h Configuration Registers

(Clock, Power Down, Version and Reset) 16 CONFG Base

8001_0000h External Memory Interface 16 EMI Base

8002_0000h Interrupt Controller 32 CIRQ Base

8003_0000h DMA Controller 32 DMA Base

8004_0000h Reset Generation Unit 16 RGU Base

8005_0000h Reserved

8006_0000h GPRS Cipher Unit 32 GCU Base

8007_0000h Software Debug 16 SWDBG Base

8008_0000h MCU Tracer 32 TRC Base

8009_0000h NAND Flash Interface 32 NFI base

8010_0000h General Purpose Timer 16 GPT Base

8011_0000h Keypad Scanner 16 KP Base

8012_0000h General Purpose Inputs/Outputs 16 GPIO Base

8013_0000h UART 1 16 UART1 Base

8014_0000h SIM Interface 16 SIM Base

8015_0000h Pulse-Width Modulation Outputs 16 PWM Base

8016_0000h Alerter Interface 16 ALTER Base

8017_0000h Reserved

8018_0000h UART 2 16 UART2 Base

8019_0000h Reserved

801a_0000h IrDA 16 IRDA Base

801b_0000h UART 3 16 UART3 Ba se

801c_0000h Base-Band to PMIC Serial Interface 16 B2PSI Base

8020_0000h TDMA Timer 16 TDMA Base

8021_0000h Real Time Clock 16 RTC Base

8022_0000h Base-Band Serial Interface 32 BSI Base

8023_0000h Base-Band Parallel Interface 16 BPI Base

8024_0000h Automatic Frequency Control Unit 16 AFC Base

MT6217 GSM/GPRS Baseband Processor Data Sheet Revision 1.01

41/349 MediaTek Inc. Confidential

8025_0000h Automatic Power Control Unit 32 APC Base

8026_0000h Frame Check Sequence 16 FCS Base

8027_0000h Auxiliary ADC Unit 16 AUXADC Base

8028_0000h Divider/Modulus Coprocessor 32 DIVIDER Base

8029_0000h CSD Format Conversion Coprocessor 32 CSD_ACC Base

802a_0000h MS/SD Controller 32 MSDC Base

8030_0000h MCU-DSP Shared Register 16 SHARE Base

8031_0000h DSP Patch Unit 16 PATCH Base

8040_0000h Audio Front End 16 AFE Base

8041_0000h Base-Band Front End 16 BFE Base

8050_0000h Analog Chip Interface Controller 16 MIXED Base

8060_0000h JPEG Decoder 32 JPEG Base

8061_0000h Resizer 32 RESZ Base

Table 5 Register Base Addresses for MCU Peripherals

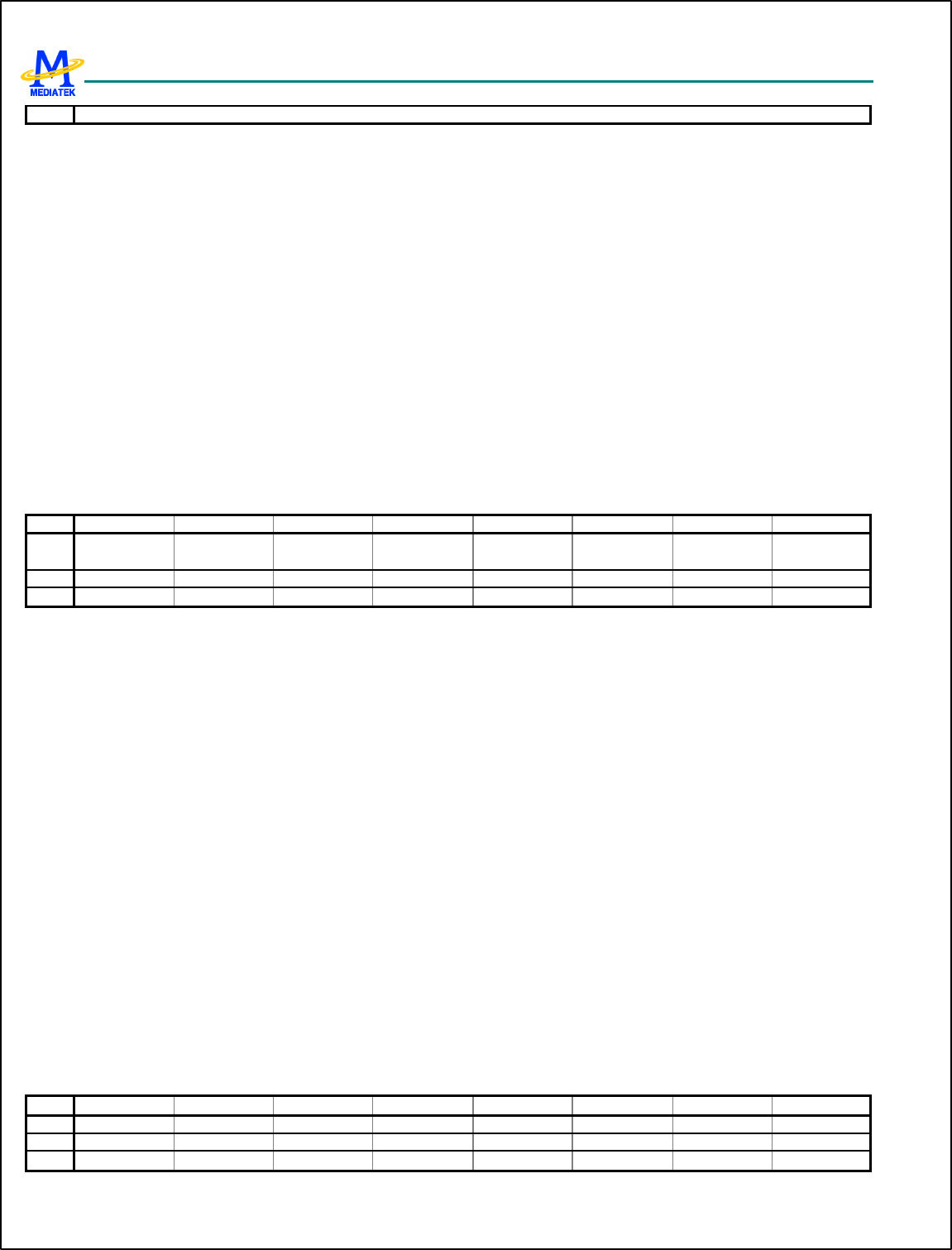

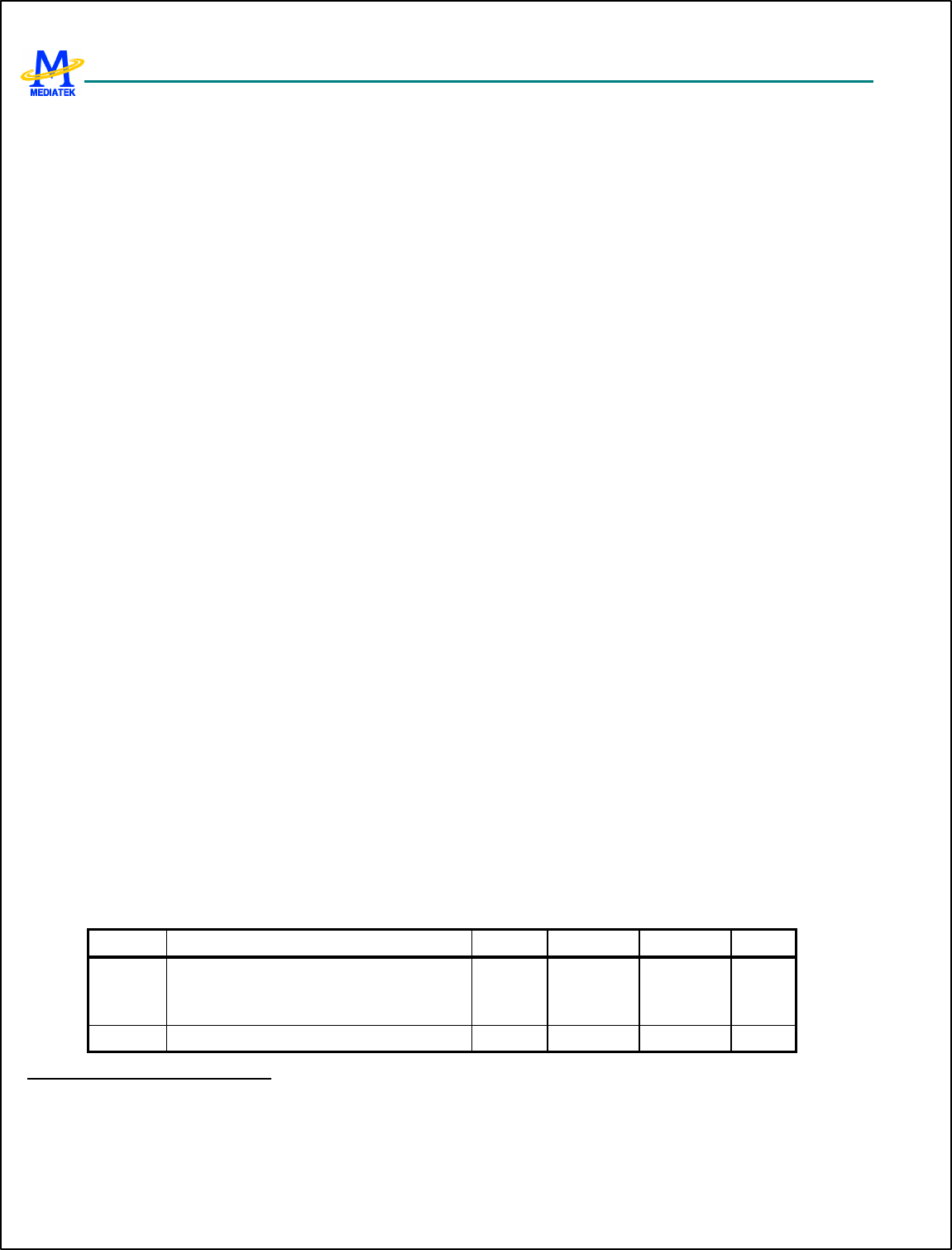

REGISTER ADDRESS REGISTER NAME SYNONYM

CONFG + 0000h Hardware Version Register HW_VER

CONFG + 0004h Firmware Version Register FW_VER

CONFG + 0008h Hardware Code Register HW_CODE

CONFG + 0404h APB Bus Control Register APB_CON

Table 6 APB Bridge Register Map

3.3.2 Register Definitions

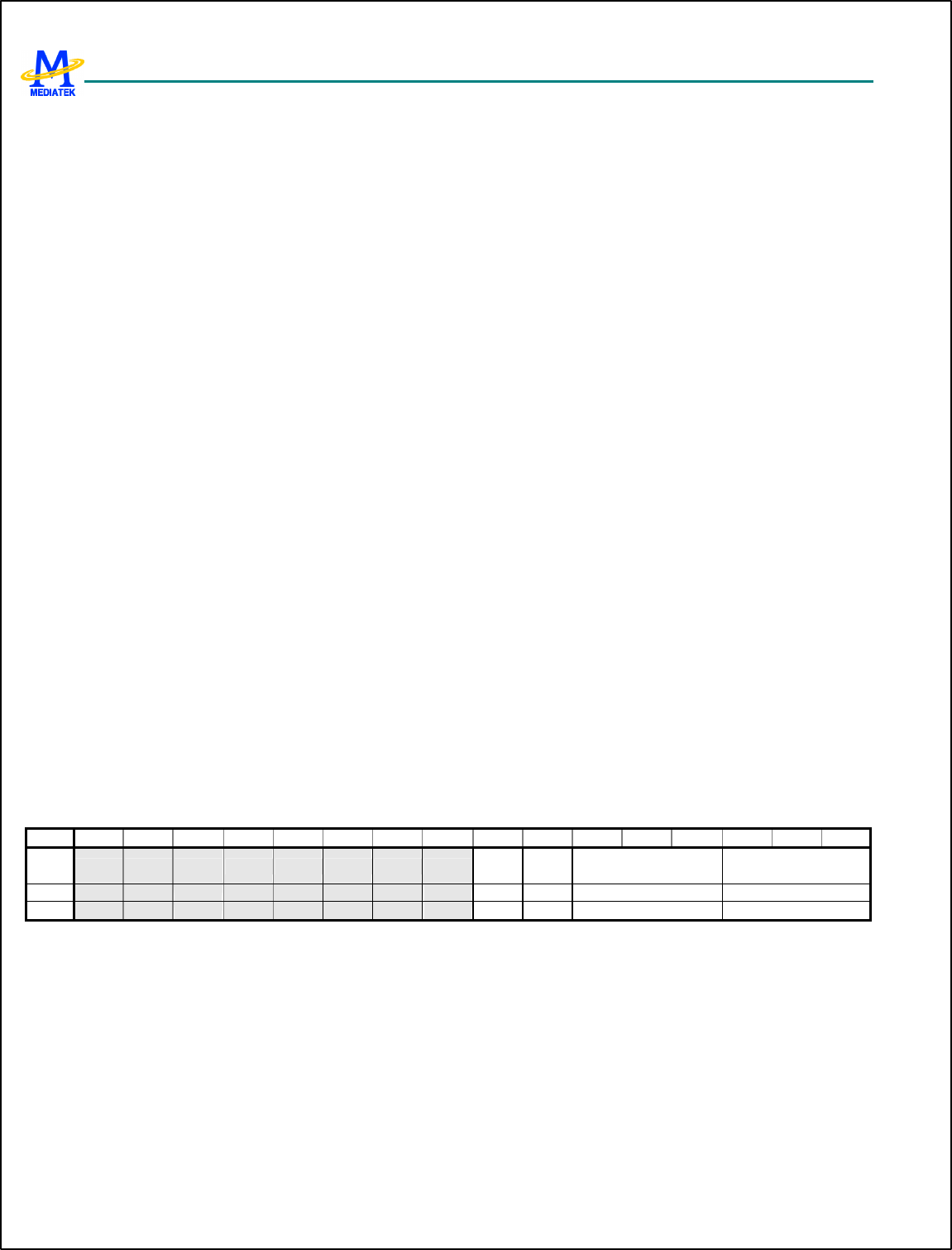

CONFG+0000h

Hardware Version Register HW_VERSION

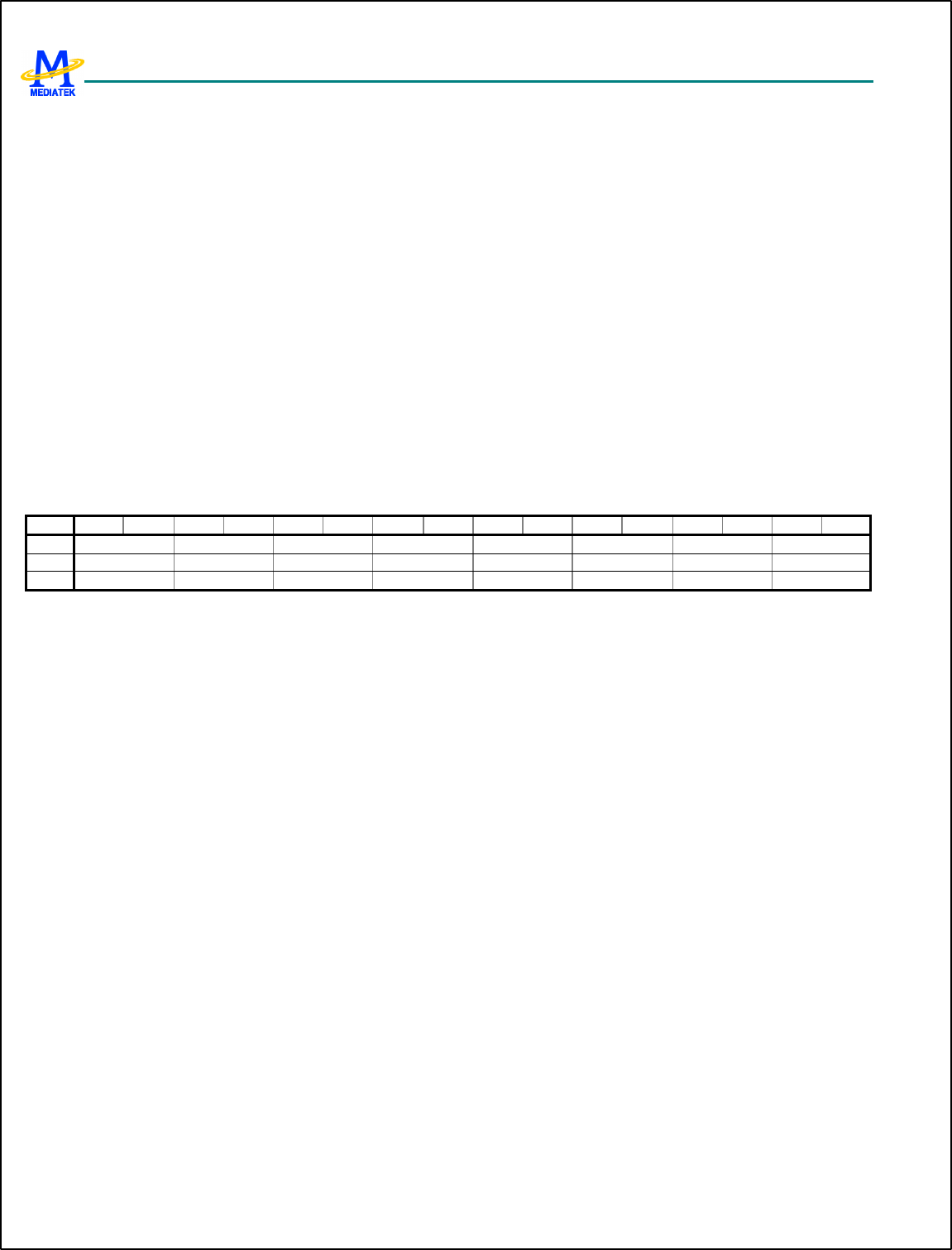

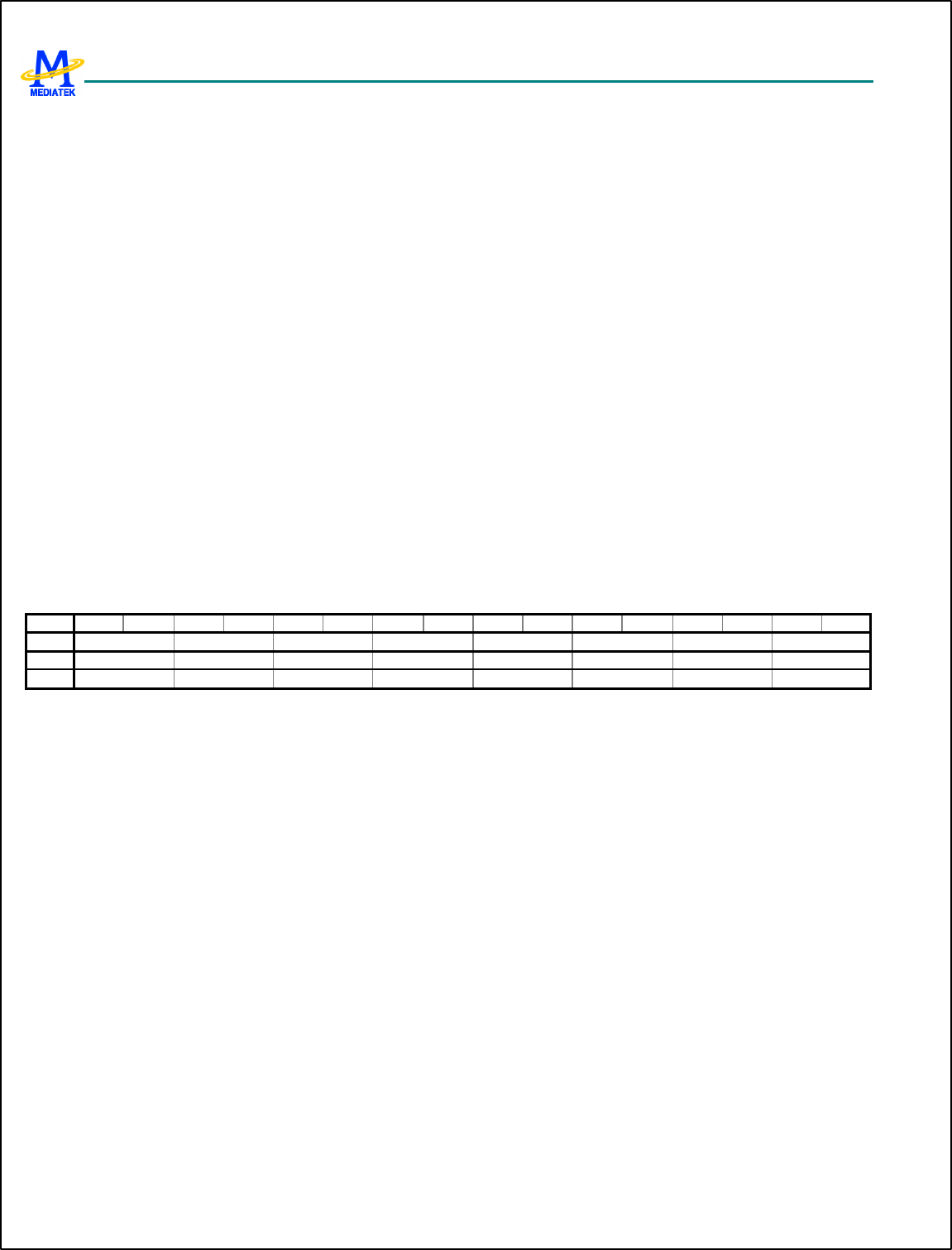

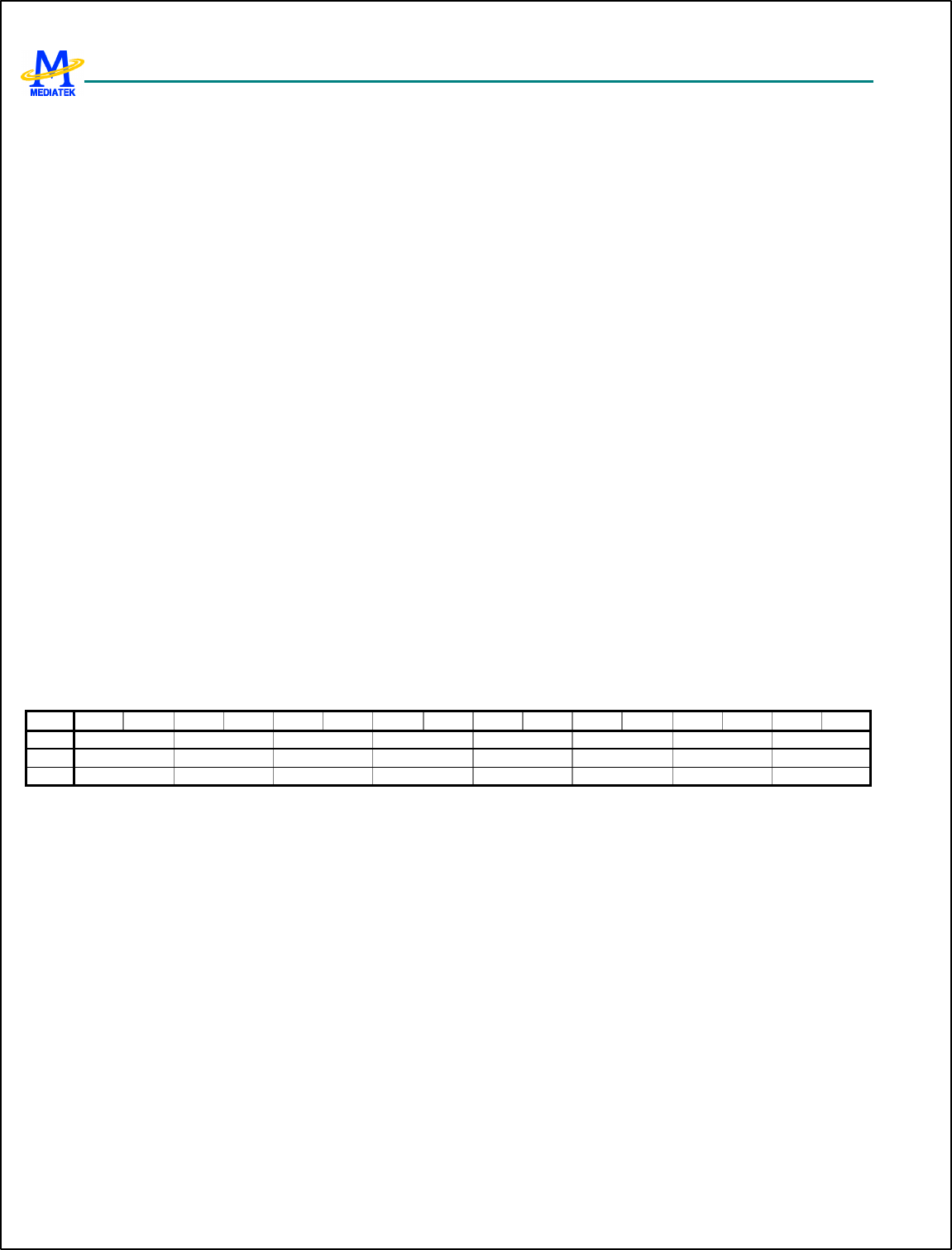

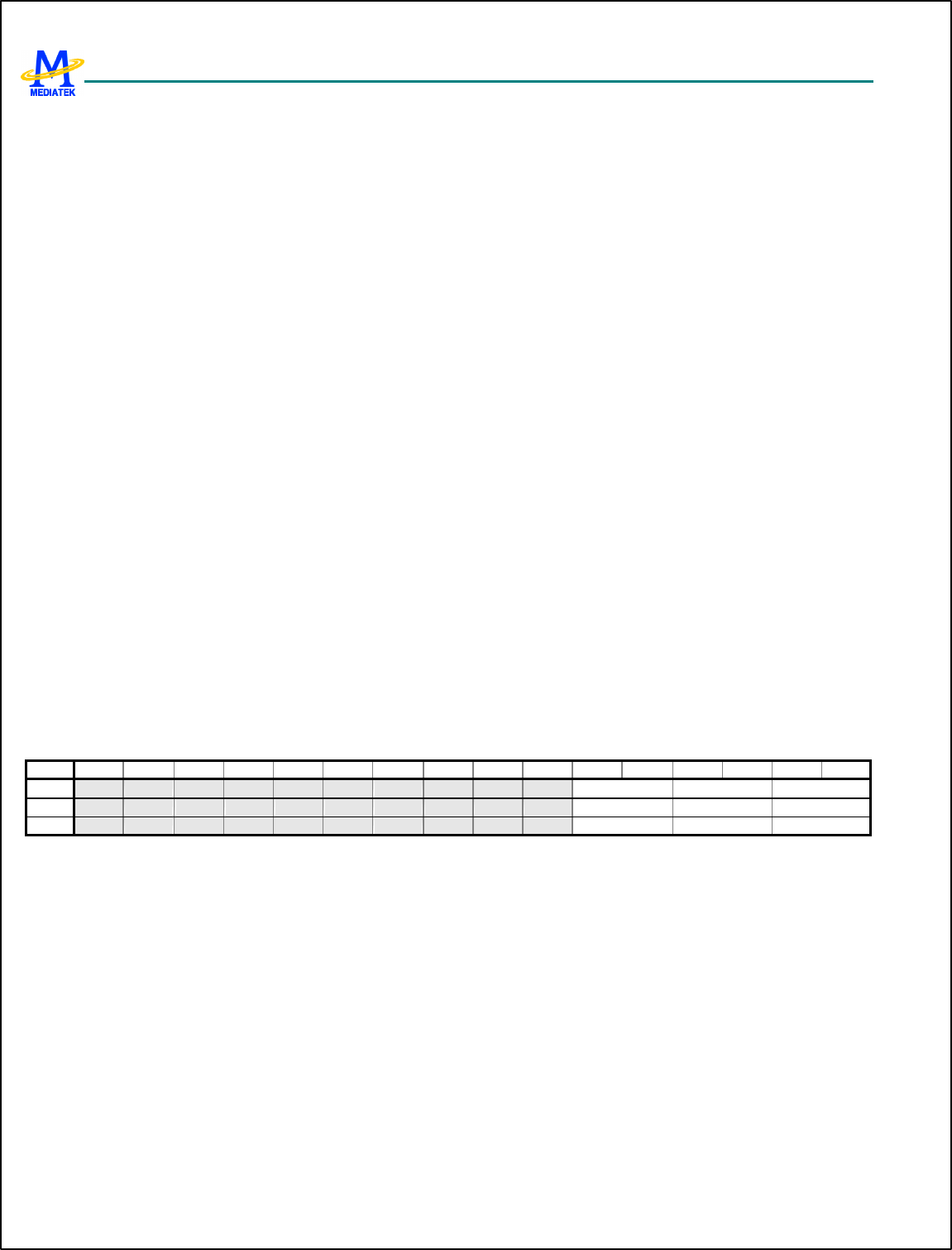

Bit 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Name

EXTP MAJREV MINREV HFIX

Type RO RO RO RO

Reset

8 A 0 0

This register is useful for software program to determine the hardware version of the chip. It will have a new value

whenever each metal fix or major step is performed. All these values are incremented by a step of 1.

HFIX Iteration to fix a hardware bug, in case of some layer mask fixed

MINREV Minor Revision of the chip, in case of all layer masks changed

MAJREV Major Revision of the chip

EXTP This field shows the existence of Hardware Code Register that presents the Hardware ID while the value is other

than zero.

CONFG+0004h

Firmware Version Register FW_VERSION

Bit 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Name

EXTP MAJREV MINREV FFIX

MT6217 GSM/GPRS Baseband Processor Data Sheet Revision 1.01

42/349 MediaTek Inc. Confidential

Type RO RO RO RO

Reset

8 A 0 0

This register is useful for software program to determine the Firmware ROM version that is included in this chip. All these

values are incremented by a step of 1.

FFIX Iteration to fix a firmware bug

MINREV Minor Revision of the firmware

MAJREV Major Revision of the firmware

EXTP This field shows the existence of Hardware Code Register that presents the Hardware ID when the value is other

than zero.

CONFG+0008h

Hardware Code Register HW_CODE

Bit 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Name

CODE3 CODE2 CODE1 CODE0

Type RO RO RO RO

Reset

6 2 1 7

This register presents the Hardware ID.

CODE This version of chip is coded as 6217h.

CONFG+0404h

APB Bus Control Register APB_CON

Bit 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Name

APBW

6 APBW

4 APBW

3 APBW

2 APBW

1 APBW

0 APBR

6 APBR

4 APBR

3 APBR

2 APBR

1 APBR

0

Type R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W

Reset

0 0 0 0 0 0 1 1 1 1 1 1

This register is used to control the timing of Read Cycle and Write Cycle on APB Bus. Note that APB Bridge 5 is different

from other bridges. The access time is varied, and access is not completed until acknowledge signal from APB slave is

asserted.

APBR0-APBR6 Read Access Time on APB Bus

0 1-Cycle Access

1 2-Cycle Access

APBW0-APBW6 Write Access Time on APB Bus

0 1-Cycle Access

1 2-Cycle Access

CONFG+0500h

AHB Bus Control Register AHB_CON

Bit 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Name

EMI

Type R/W

Reset

0

EMI Control the AHB-EMI interface

0 latch mode. In order to meet bus timing constraints, Additional stage of registers are inserted between AHB

and EMI. While running at 52MHz, AHB-EMI interface must be set as latch mode..

1 direct couple mode. AHB and EMI are directly coupled. While running

MT6217 GSM/GPRS Baseband Processor Data Sheet Revision 1.01

43/349 MediaTek Inc. Confidential

at 26MHz, AHB-EMI interface must be set as direct couple mode for better

bus efficiency.

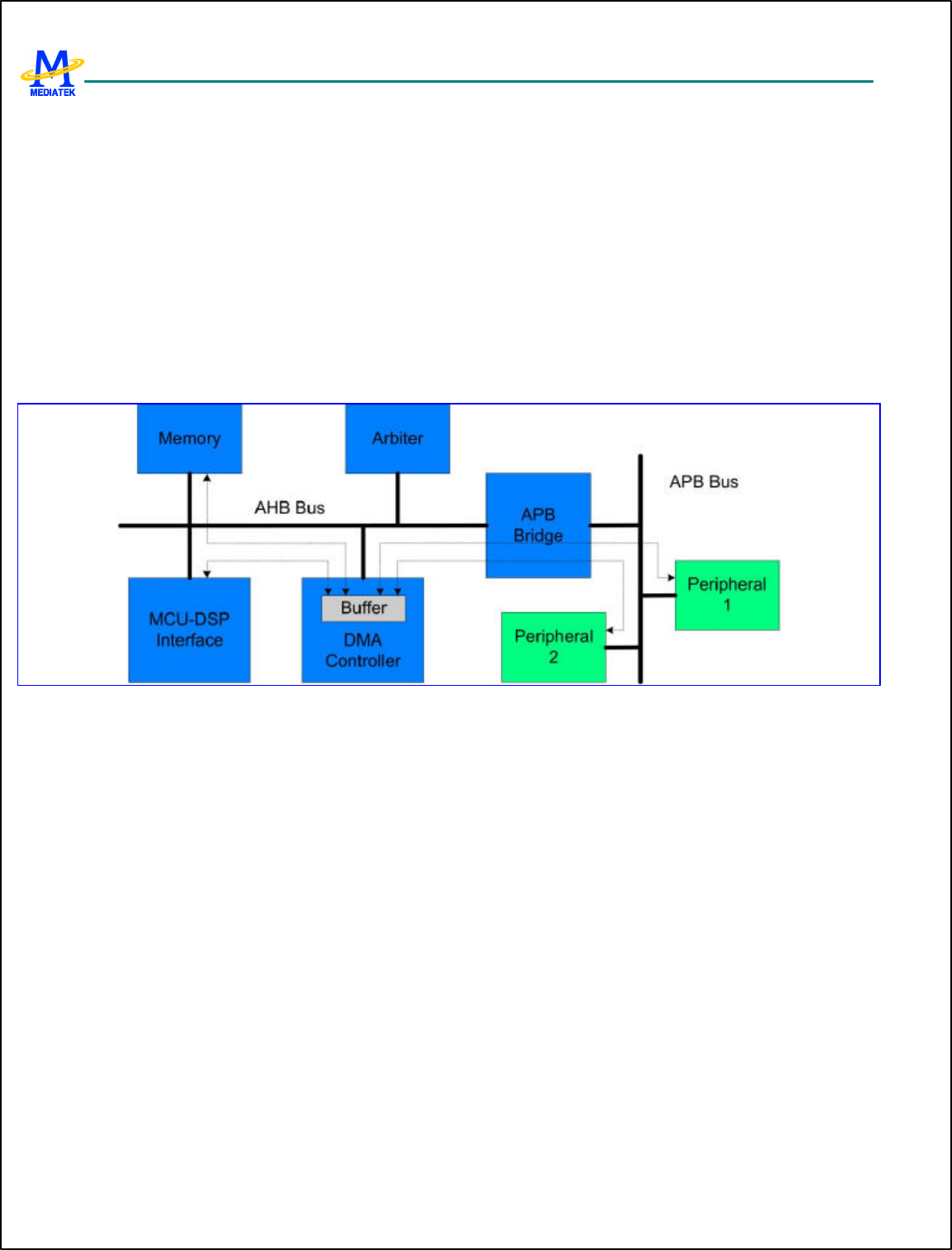

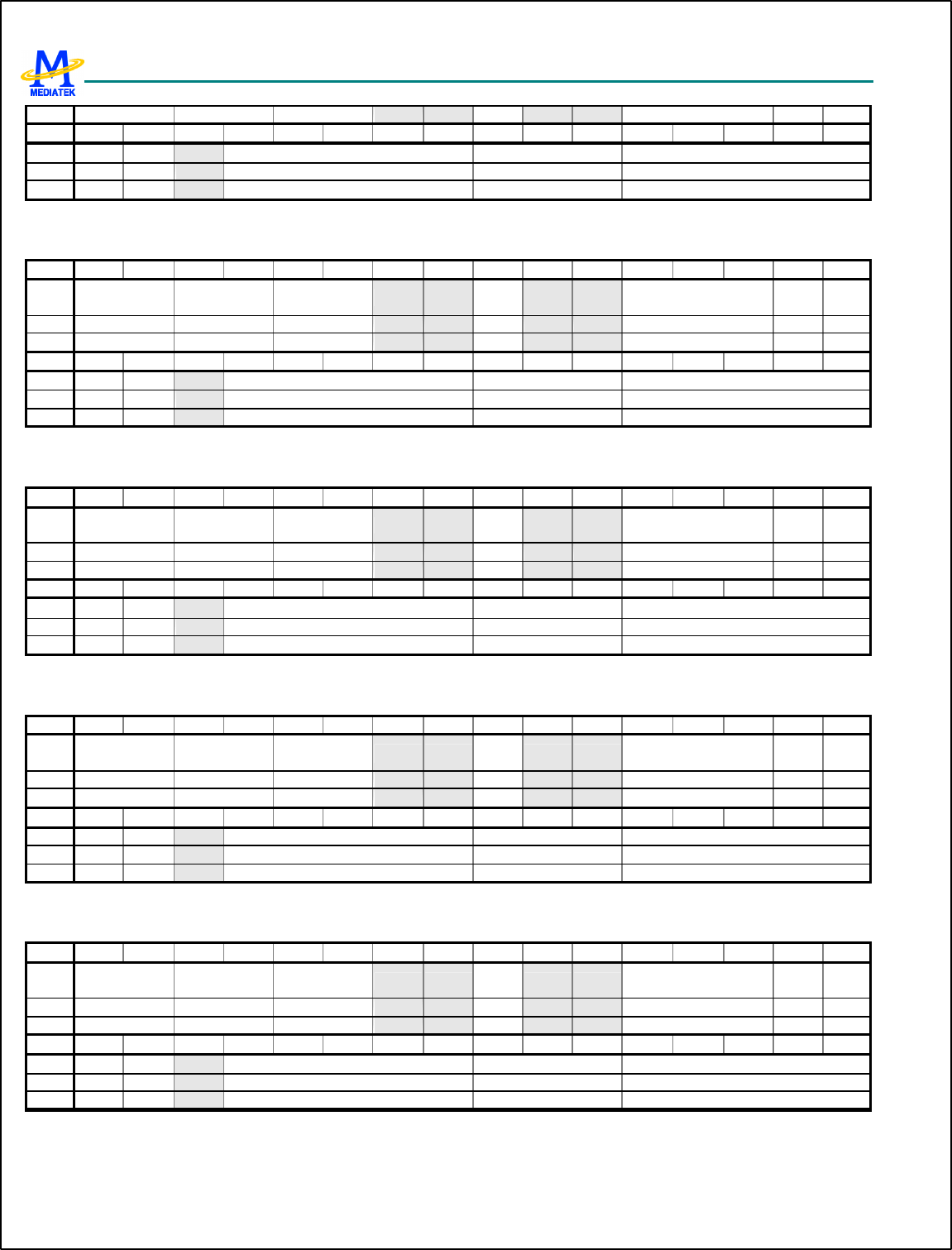

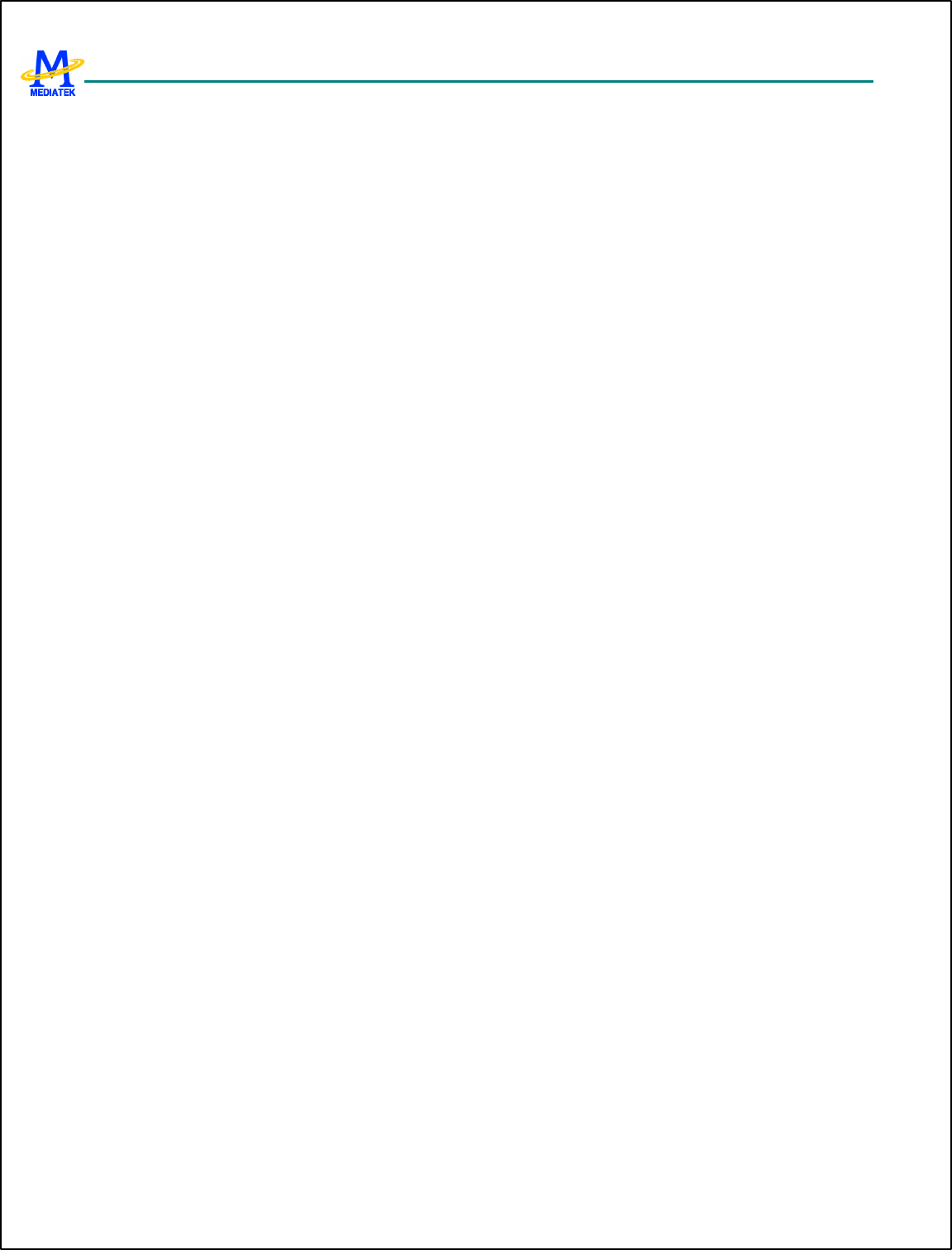

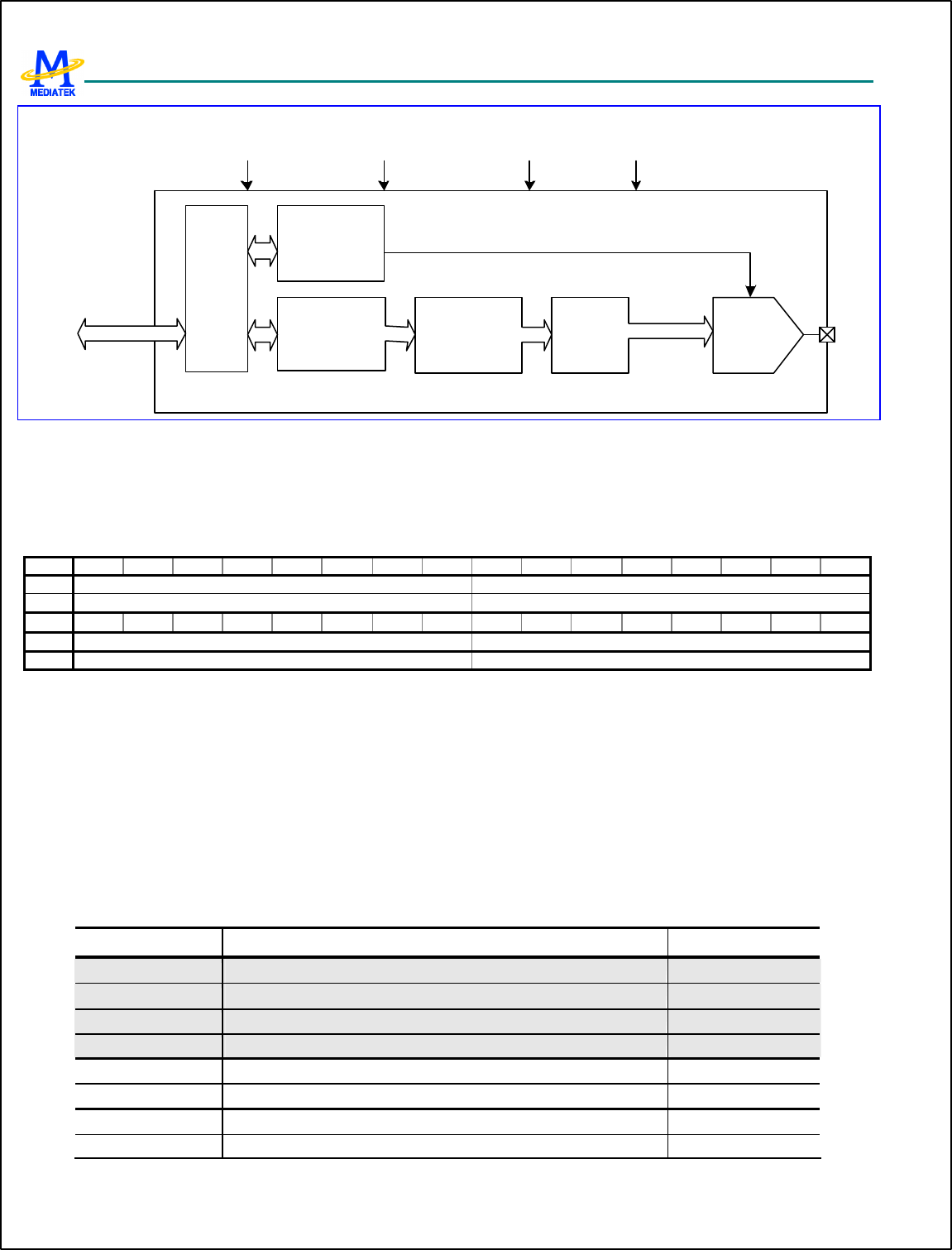

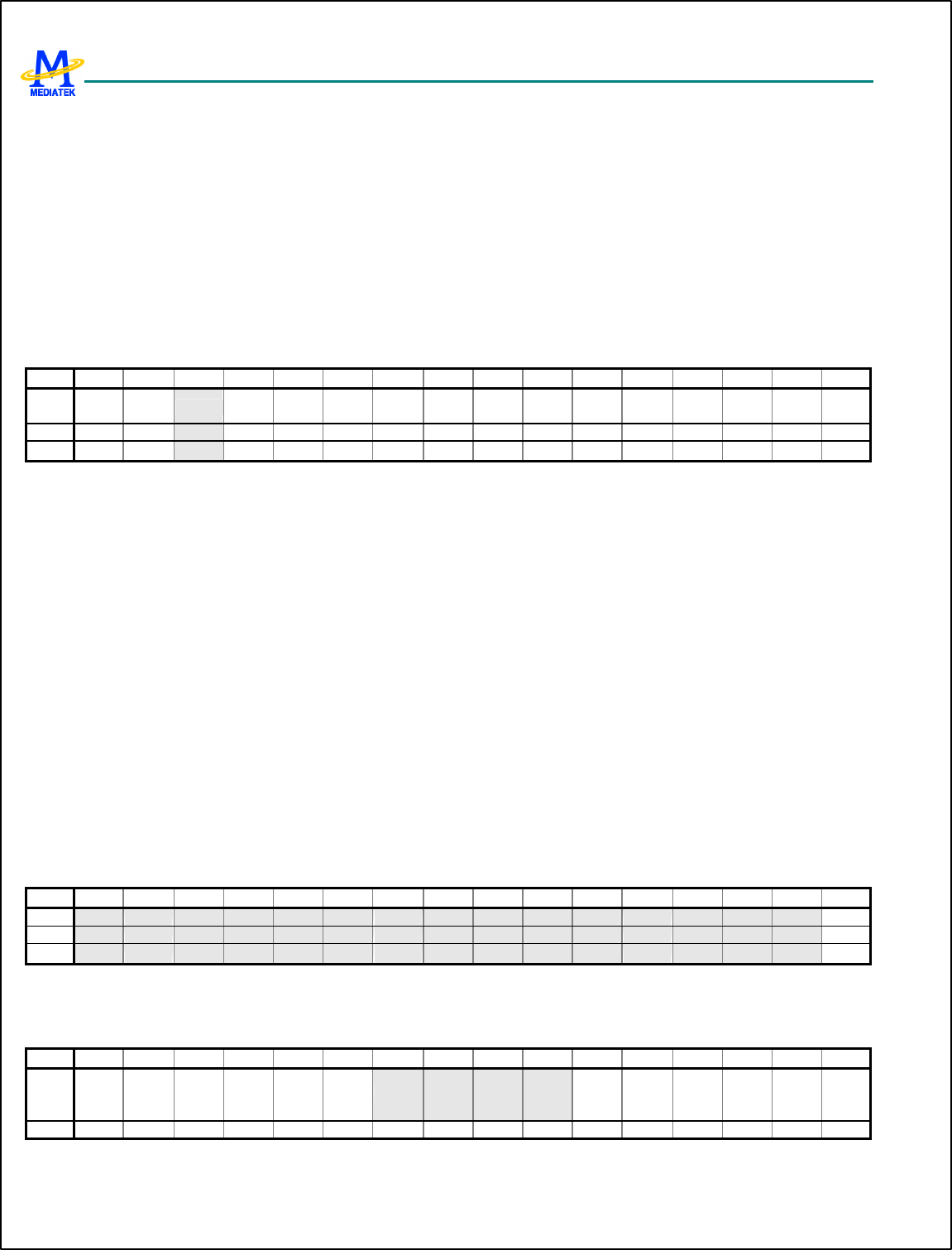

3.4 Direct Memory Access

3.4.1 General Description

A generic DMA Controller is placed on Layer 2 AHB Bus to support fast data transfers, and also to off-load the processor.

With this controller, specific devices on AHB or APB buses can benefit greatly from quickly completing data movement

from or to memory module, i.e. Internal System RAM or External SRAM. Such Generic DMA Controller can also be used

to connect any two devices other than memory module as long as they can be addressed in memory space.

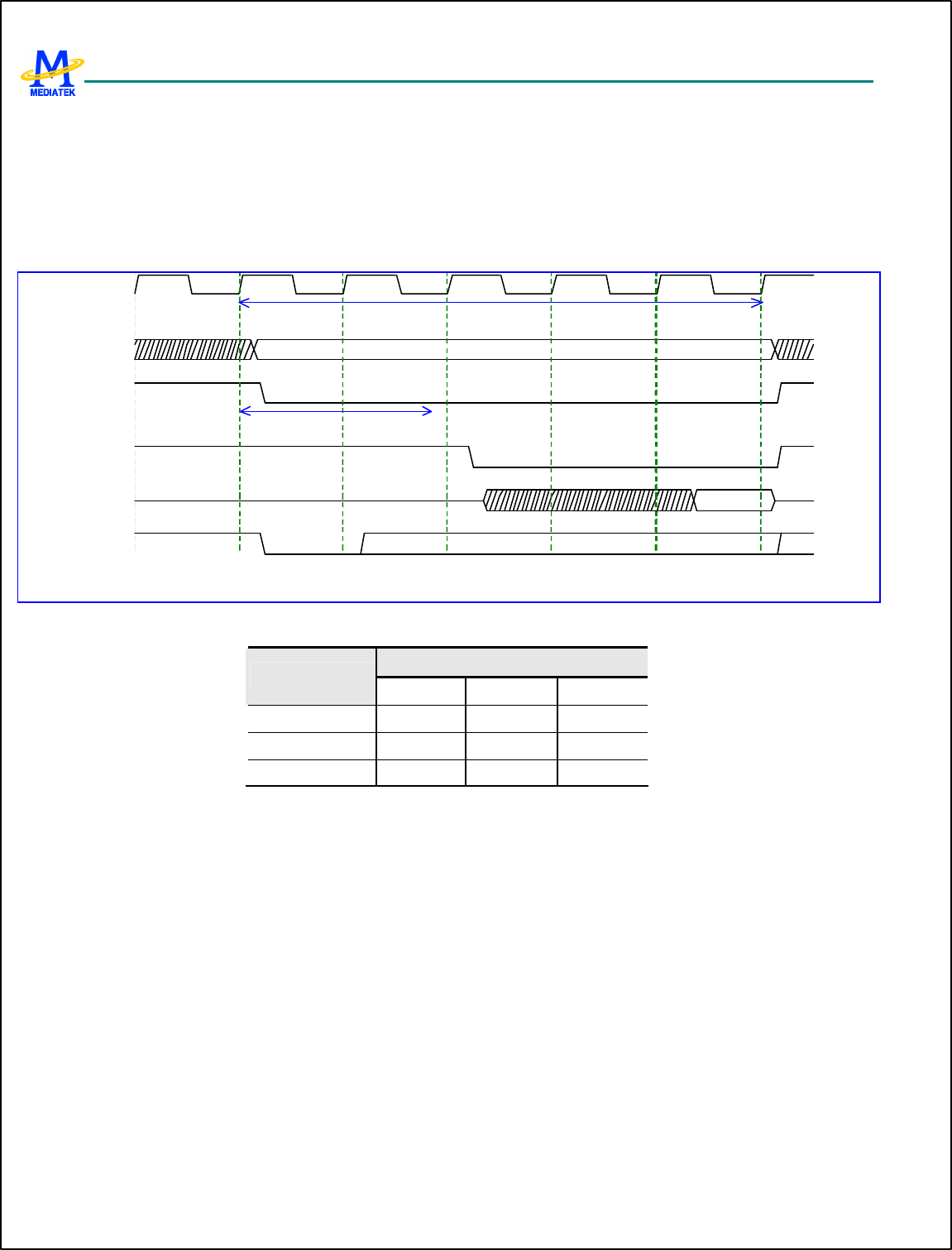

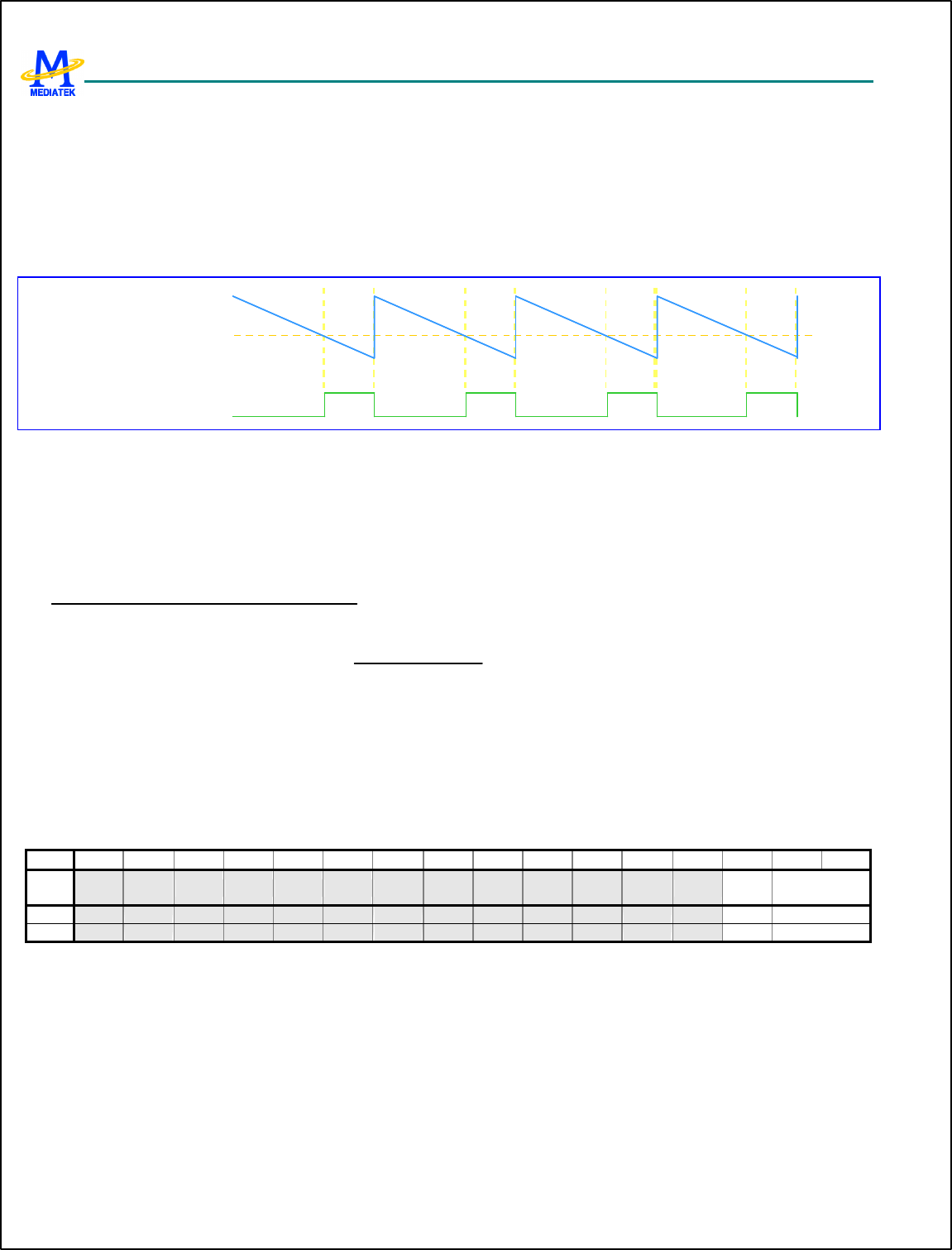

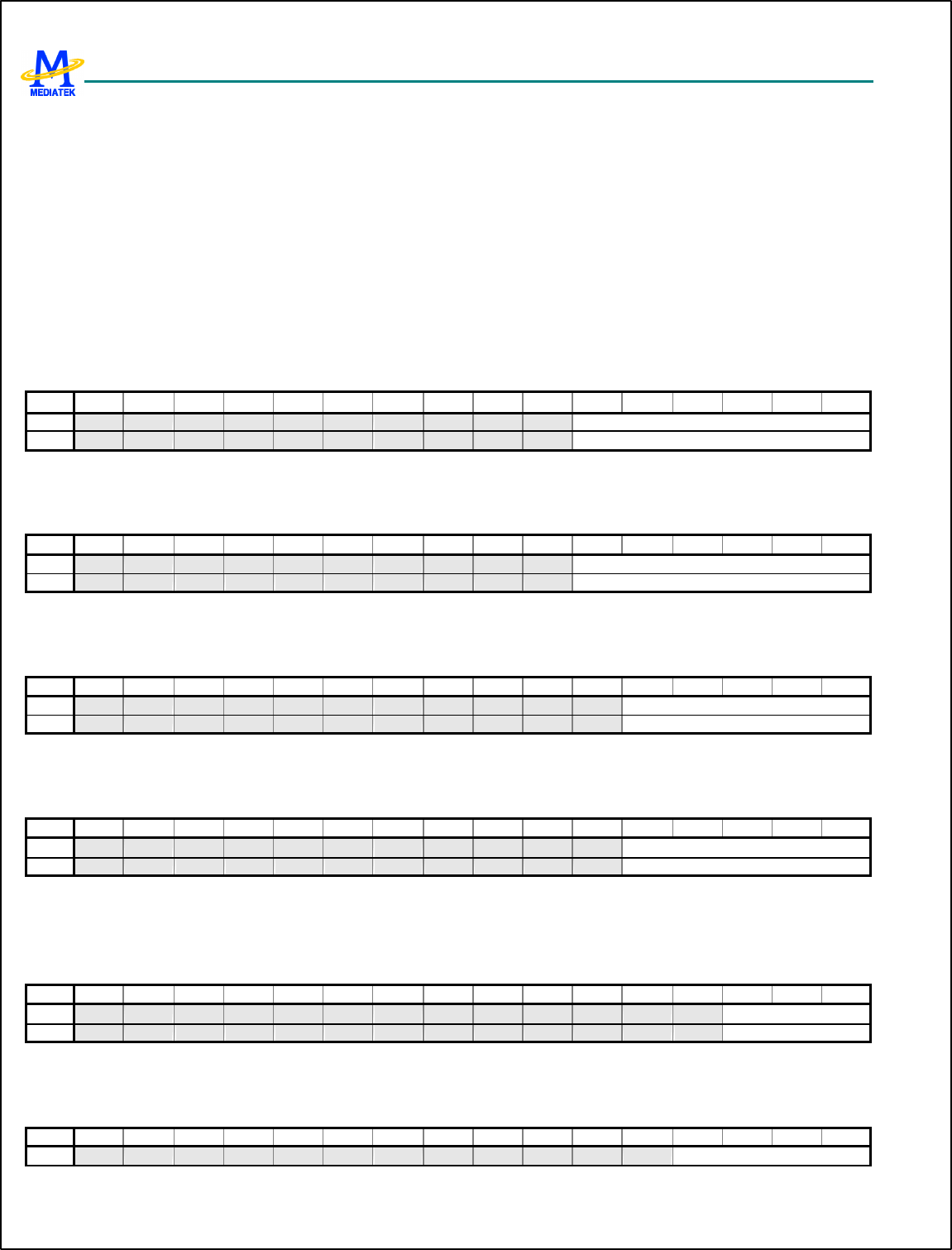

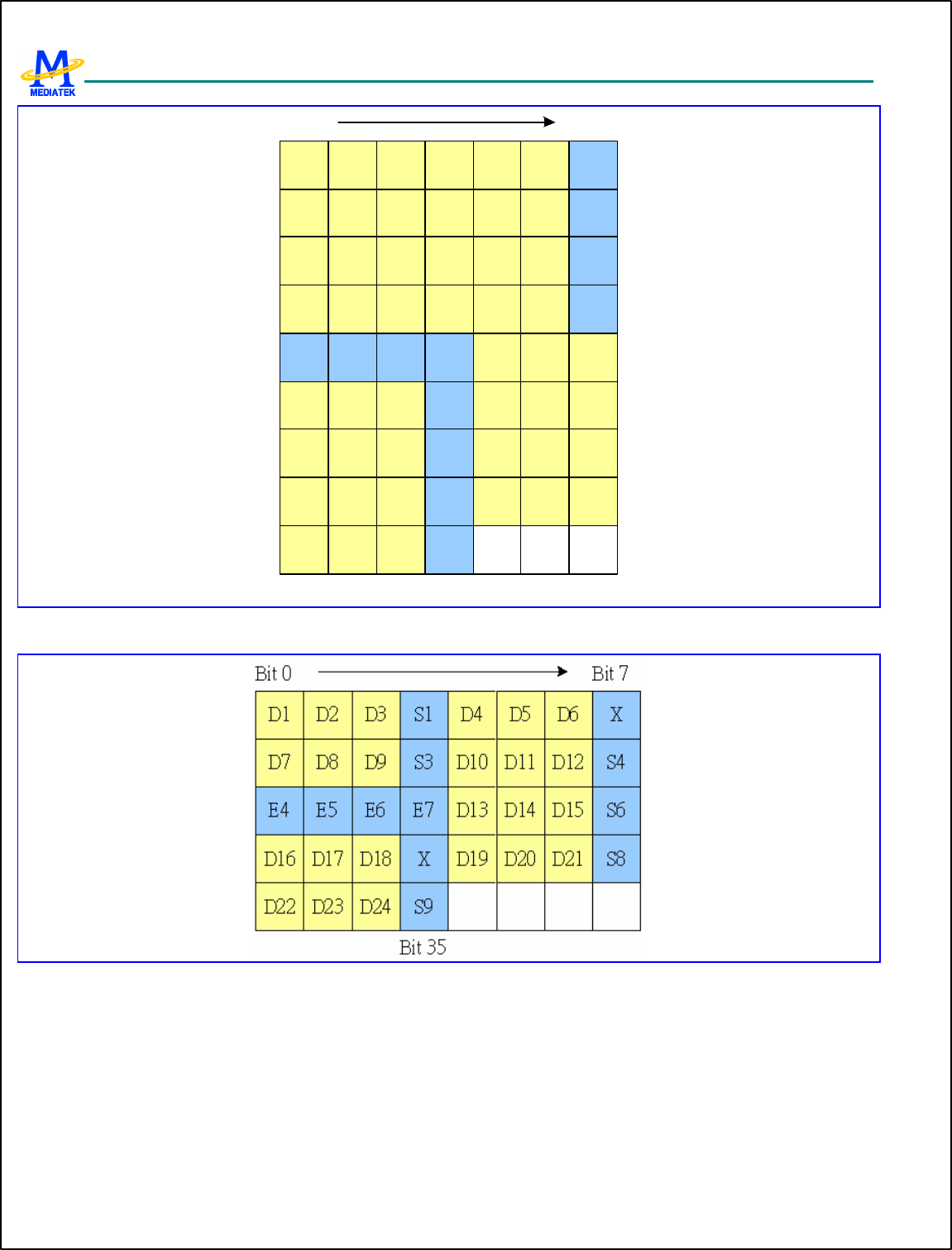

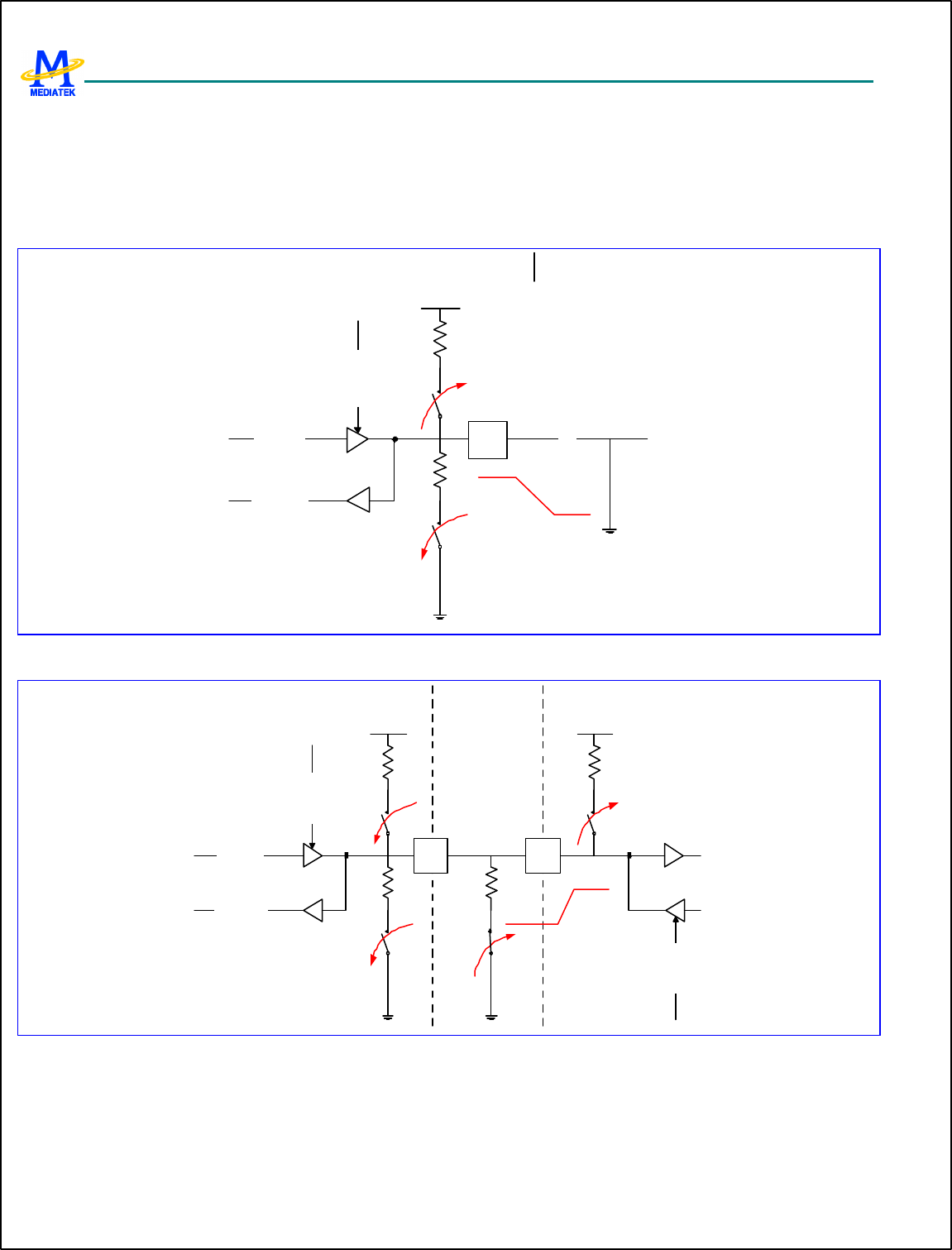

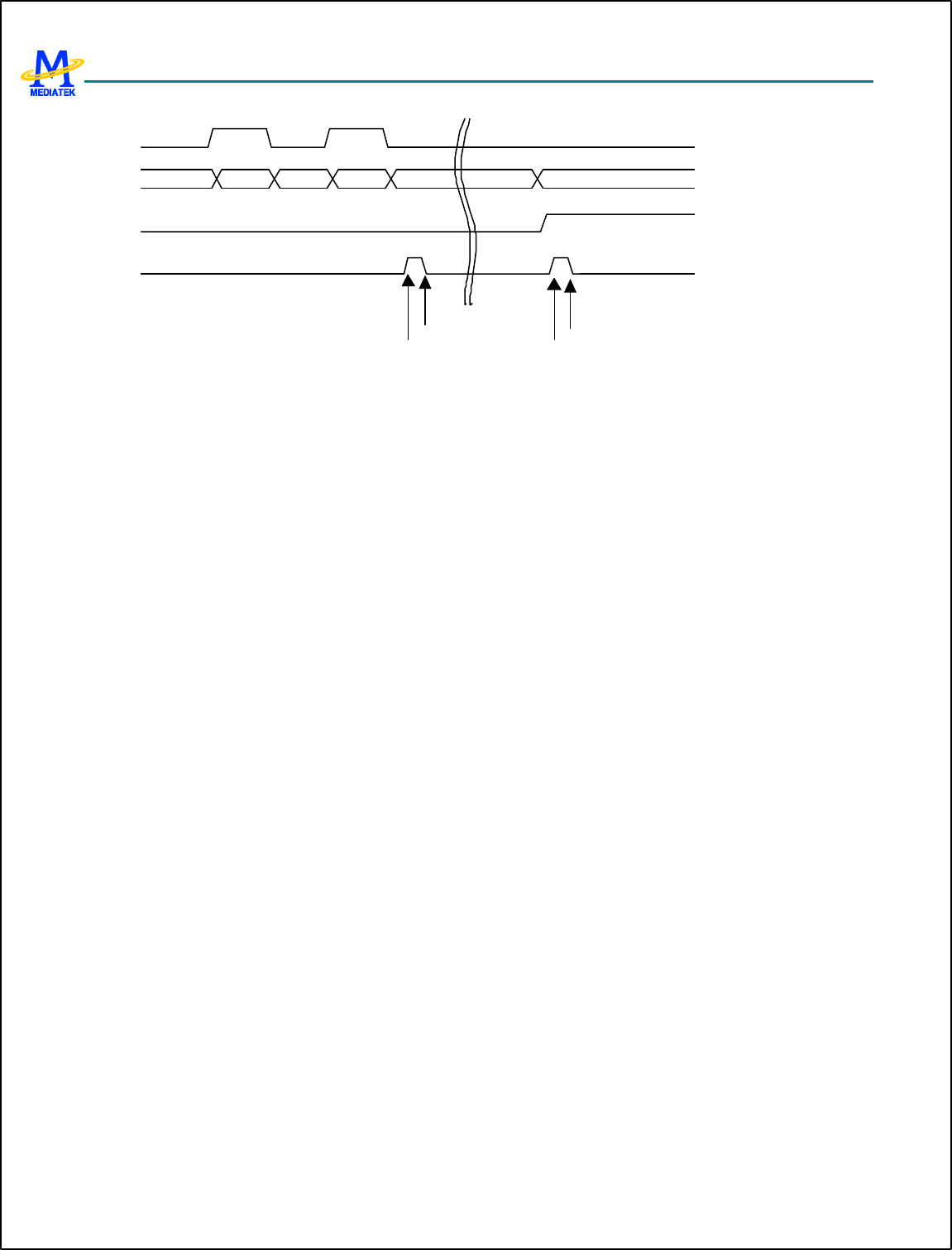

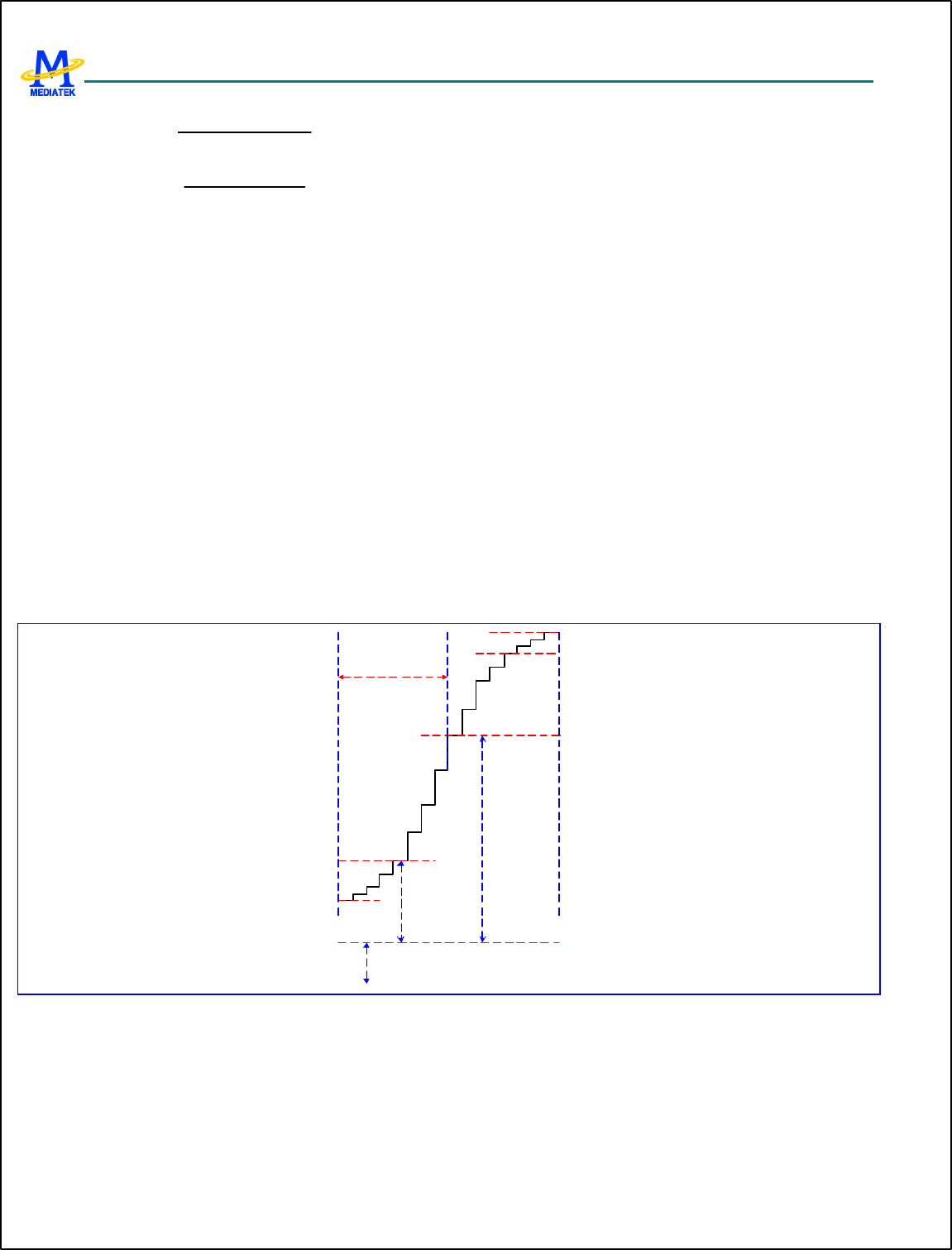

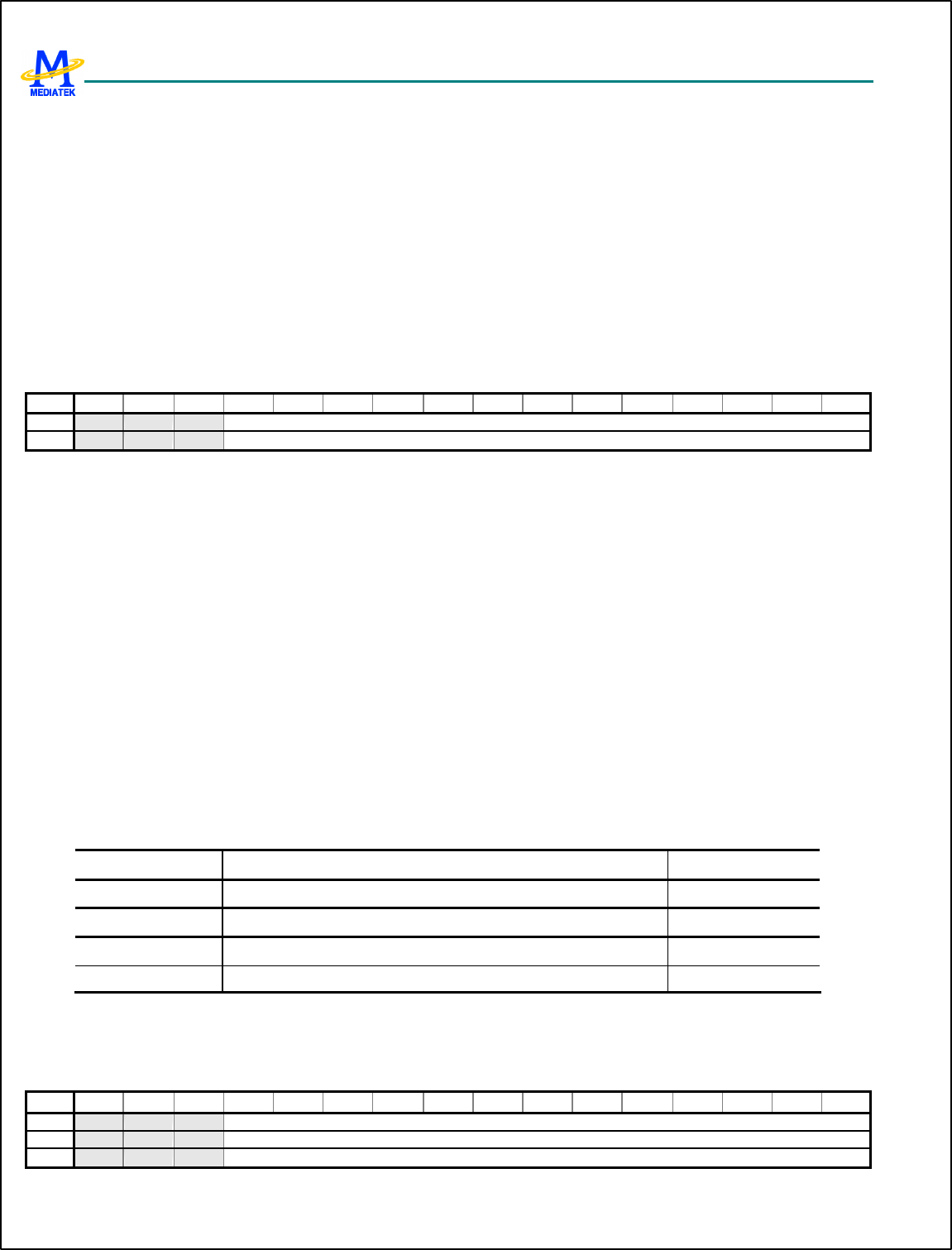

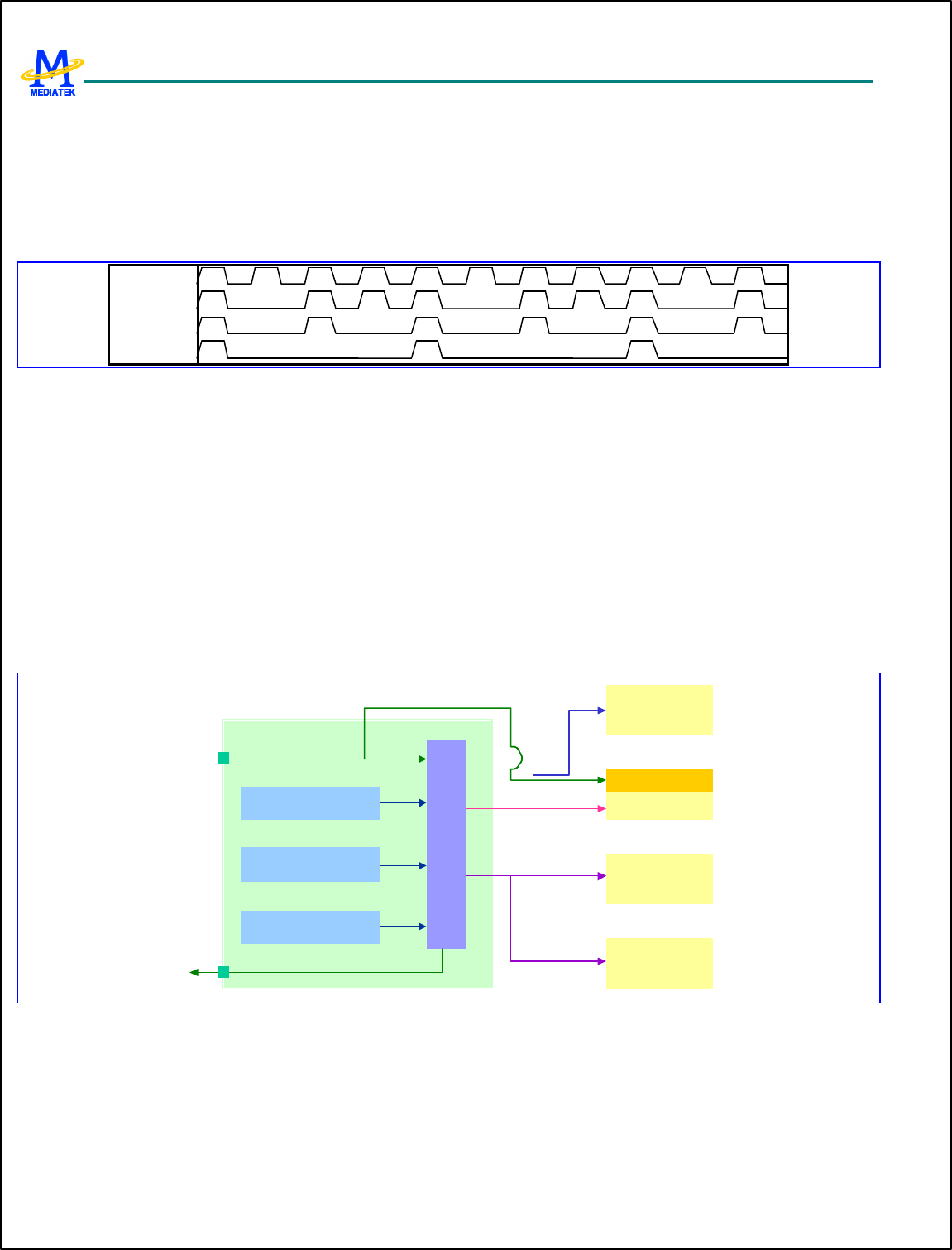

Figure 8 Variety Data Paths of DMA Transfers

Thirteen channels of data transfer are supported at one time. Each channel has a similar set of registers to be configured to

different scheme as desired. If more than thirteen devices are requesting the DMA resources at the same time, software

based arbitration should be employed. Once the service candidate is decided, the responsible device driver should configure

the Generic DMA Controller properly in order to conduct DMA transfers. Both Interrupt and Polling based schemes in

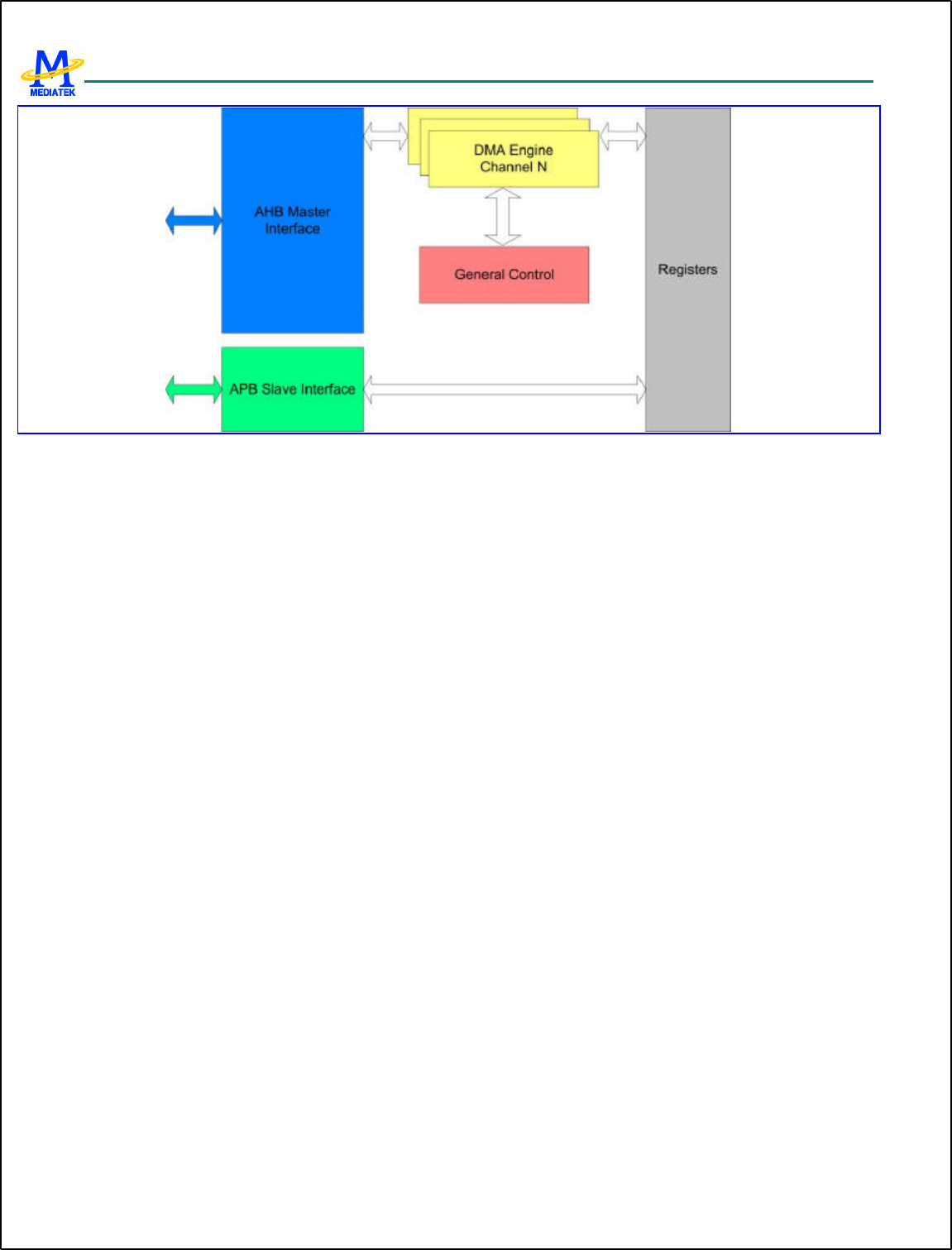

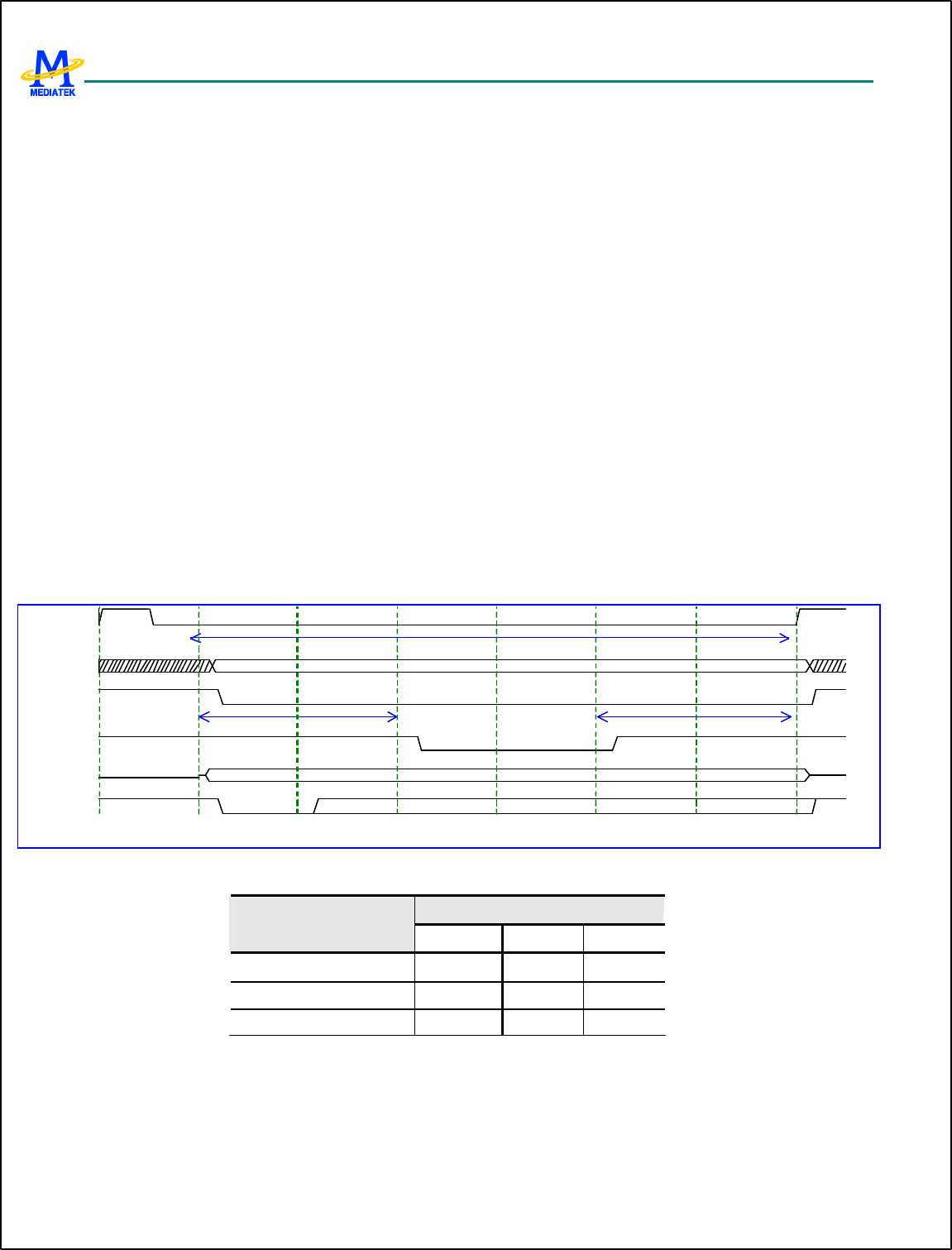

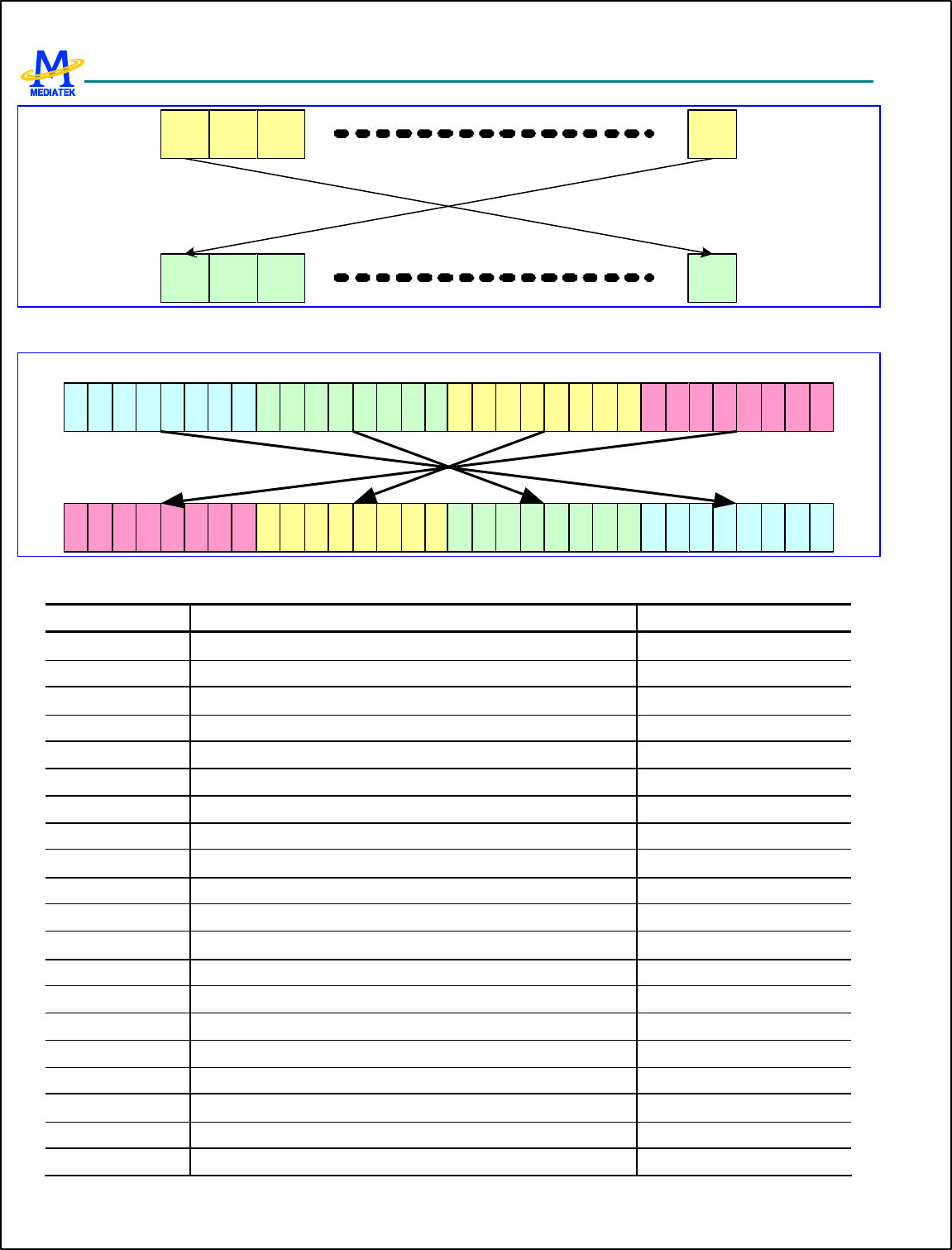

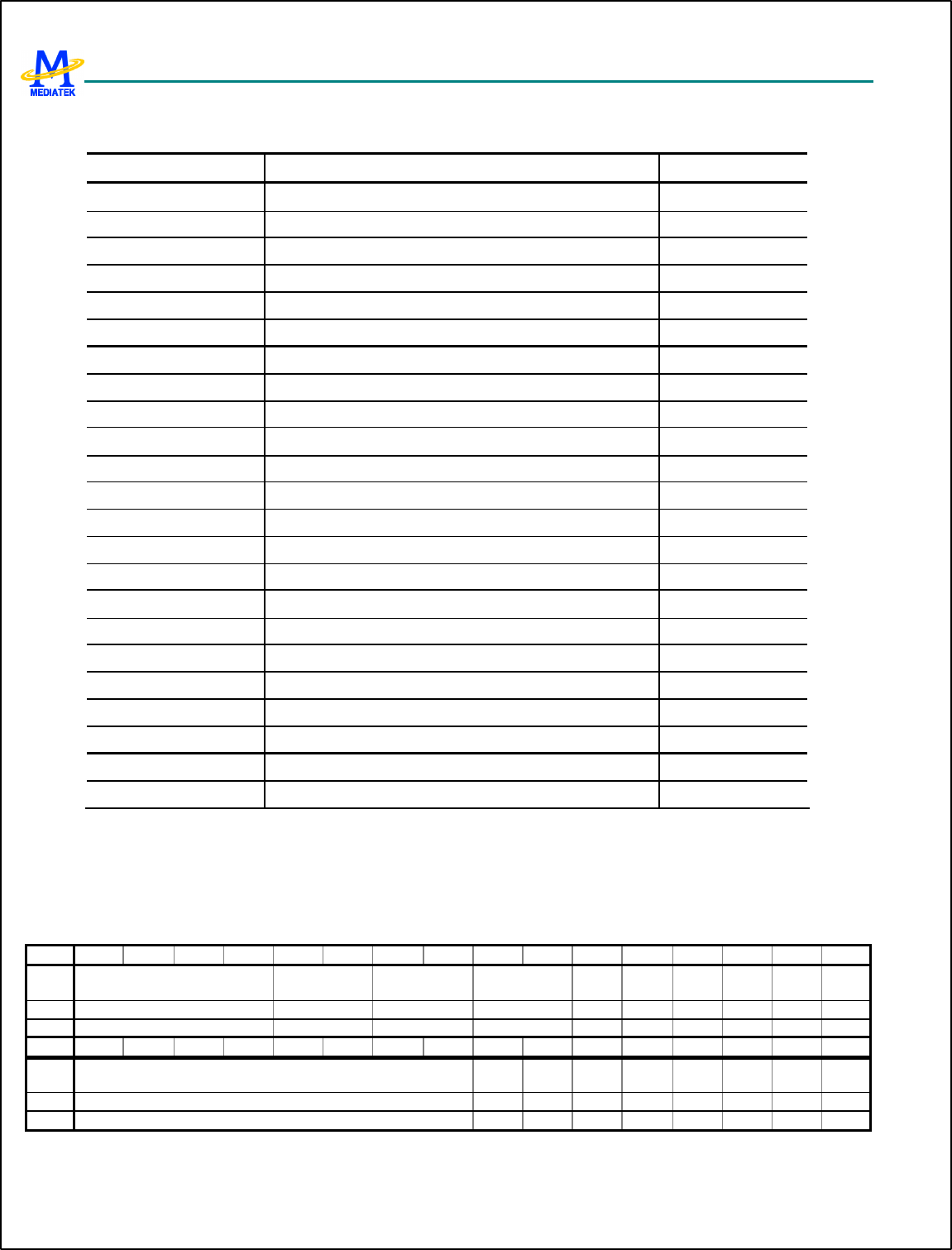

handling the completion event are supported. The block diagram of such generic DMA Controller is illustrated in Figure 9.

MT6217 GSM/GPRS Baseband Processor Data Sheet Revision 1.01

44/349 MediaTek Inc. Confidential

Figure 9 Block Diagram of Direct memory Access Module

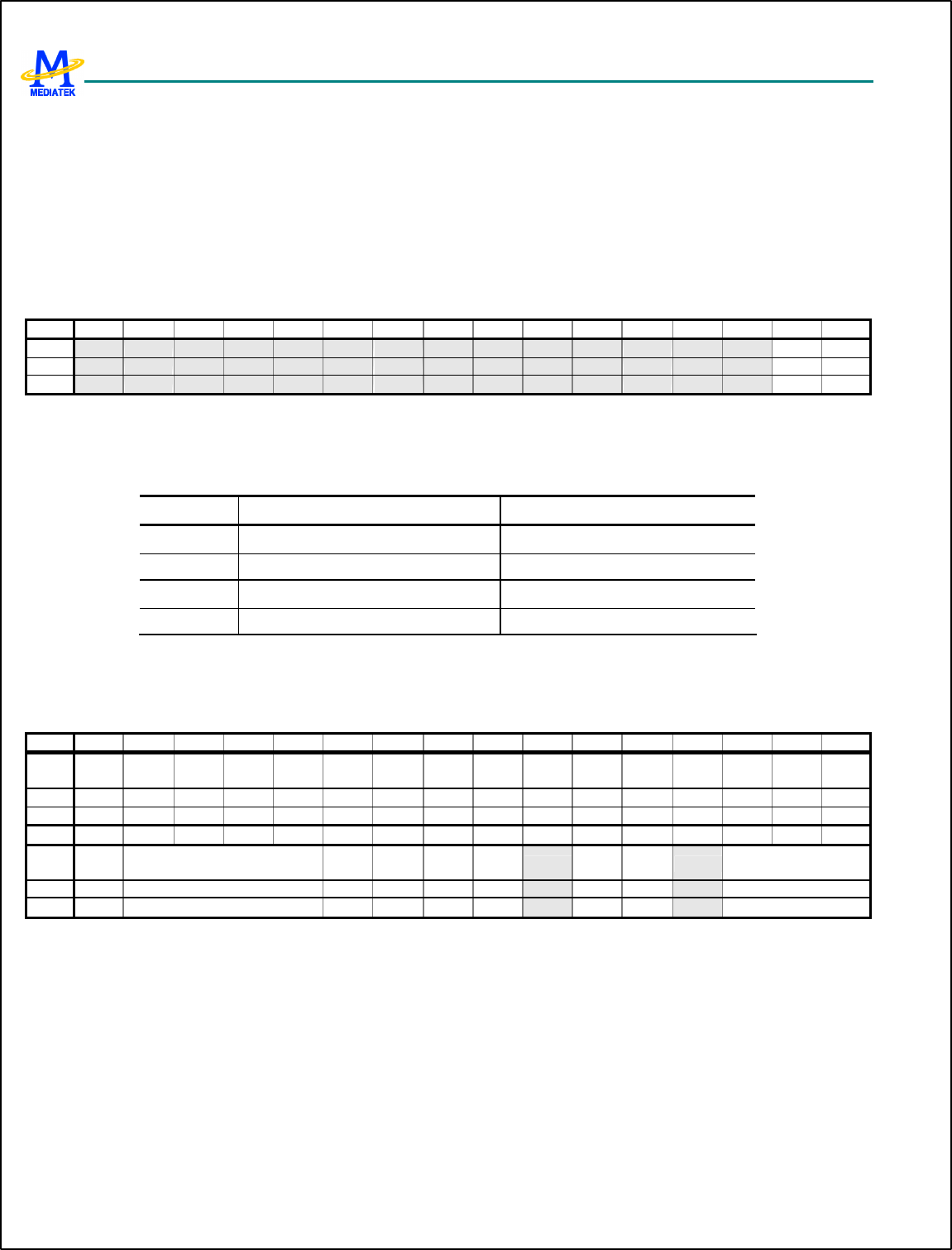

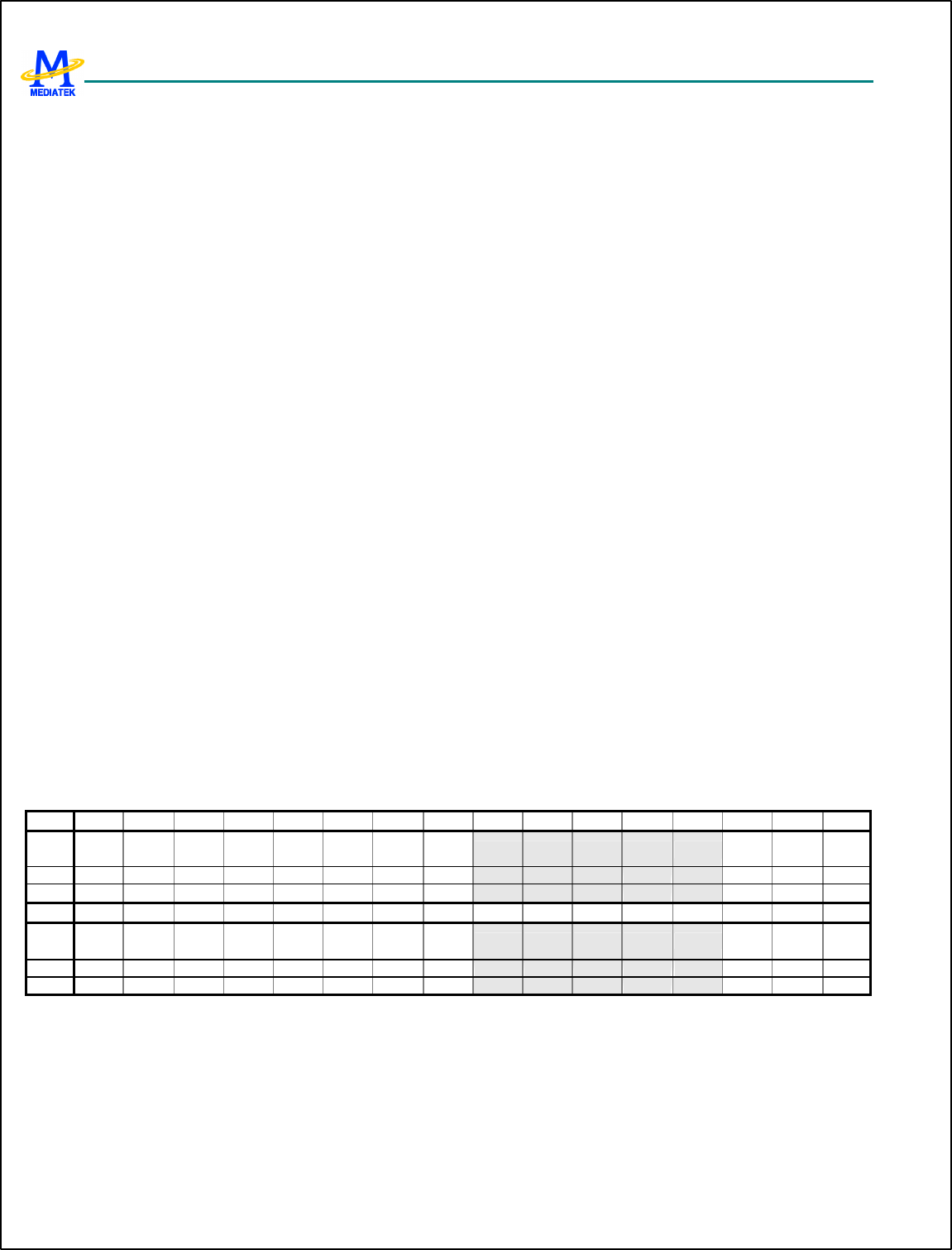

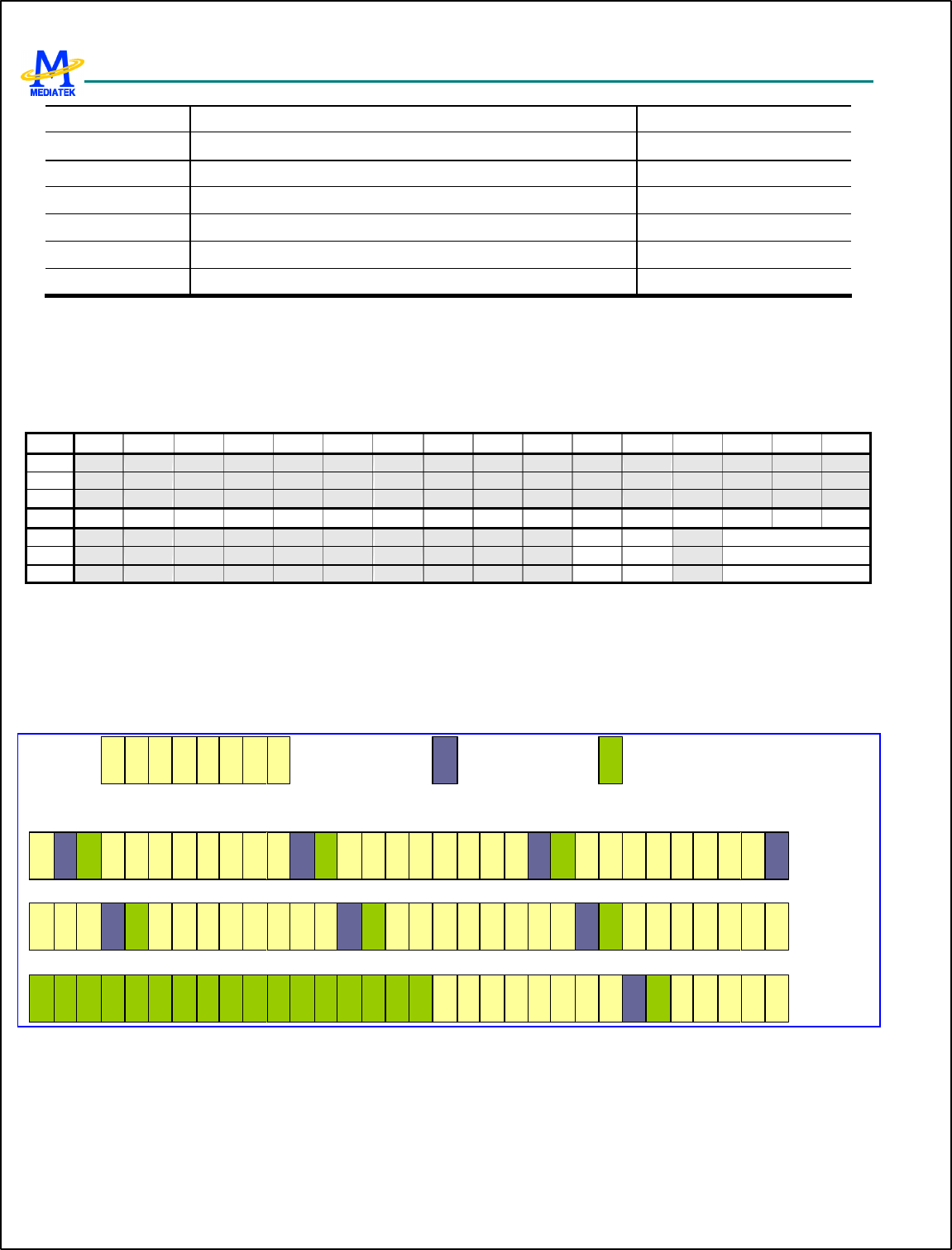

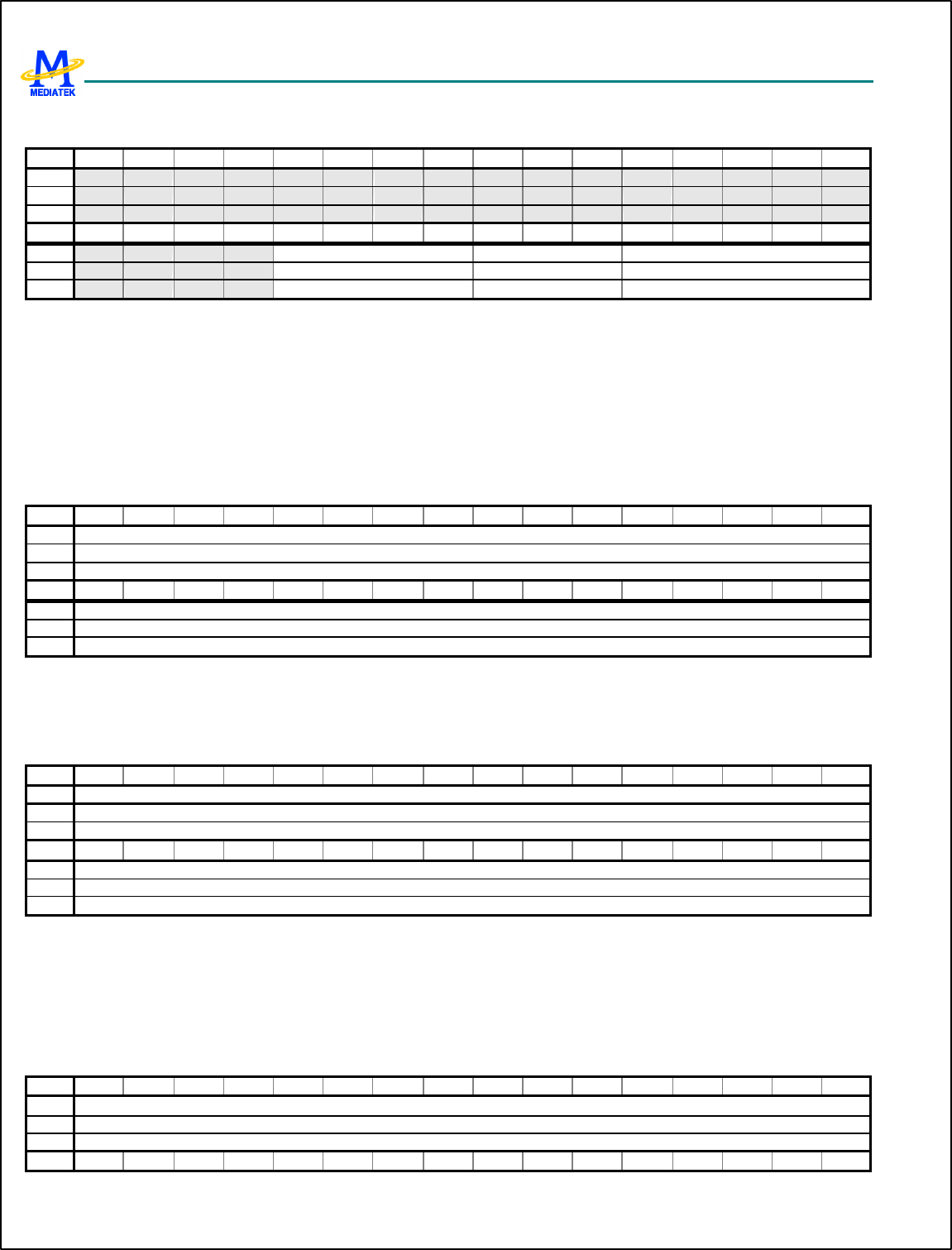

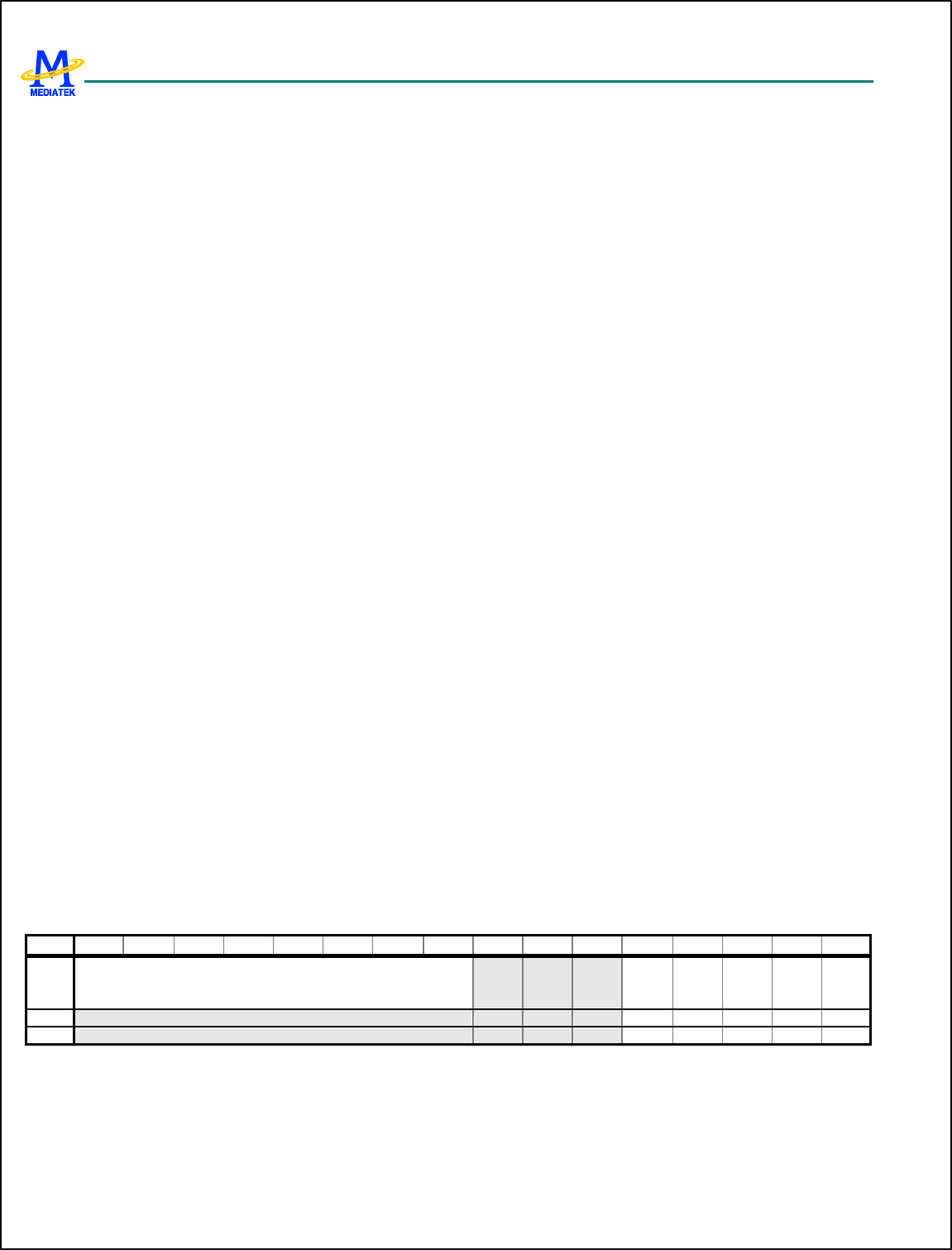

3.4.1.1 Full-Size & Half-Size DMA Channels

There are two types of DMA channels in the DMA controller. The first one is called full-size DMA channel, and the second

one is called half-size DMA channel. Channel 1 to 3 are full-size DMA channels, and channel 4 to 9 are half-size ones. The

difference between the two types of DMA channels is that both source and destination address are programmable in