R3000 Manual

User Manual:

Open the PDF directly: View PDF ![]() .

.

Page Count: 354 [warning: Documents this large are best viewed by clicking the View PDF Link!]

- IDT R30xx Family Software Reference Manual

- About IDT

- About This Manual

- Table of Contents

- INTRODUCTION CHAPTER 1

- MIPS-1 (R30xx) ARCHITECTURE CHAPTER 2

- SYSTEM CONTROL CO-PROCESSOR ARCHITECTURE CHAPTER 3

- EXCEPTION MANAGEMENT CHAPTER 4

- CACHE MANAGEMENT CHAPTER 5

- MEMORY MANAGEMENT AND THE TLB CHAPTER 6

- RESET INITIALIZATION CHAPTER 7

- FLOATING POINT CO-PROCESSOR CHAPTER 8

- ASSEMBLER LANGUAGE PROGRAMMING CHAPTER 9

- C PROGRAMMING CHAPTER 10

- PORTABILITY CONSIDERATIONS CHAPTER 11

- WRITING POWER-ON DIAGNOSTICS CHAPTER 12

- INSTRUCTION TIMING AND OPTIMIZATION CHAPTER 13

- SOFTWARE TOOLS FOR BOARD BRING-UP CHAPTER 14

- SOFTWARE DESIGN EXAMPLES CHAPTER 15

- ASSEMBLY LANGUAGE PROGRAMMING TIPS CHAPTER 16

- MACHINE INSTRUCTIONS REFERENCE APPENDIX A

- FPA INSTRUCTION REFERENCE APPENDIX B

- CP0 OPERATION REFERENCE APPENDIX C

- ASSEMBLER LANGUAGE SYNTAX APPENDIX D

- OBJECT CODE FORMATS APPENDIX E

- GLOSSARY OF COMMON "MIPS" TERMS APPENDIX F

Table of Contents

i–1

IDT R30xx Family

Software Reference Manual

Revision 1.0

1994 Integrated Device Technology, Inc.

Portions

1994 Algorithmics, Ltd.

Chapter 16 contains some material that is

1988 Prentice-Hall.

Appendices A & B contain material that is

1994 by Mips Technology, Inc.

Table of Contents

i–2

About IDT

Integrated Device Technology, Inc. has been a MIPS semiconductor

partner since 1988, and has led efforts to bring the high-performance

inherent in the MIPS architecture to embedded systems engineers. These

efforts include derivatives of MIPS R3xxx and R4xxx CPUs, development

tools, and applications support.

Additional information about IDT’s RISC family can be obtained from

your local sales representative. Alternately, IDT can be reached directly at:

Corporate Marketing (800) 345-7015

RISC Applications "Hotline" (408) 492-8208

RISC Applications FAX (408) 492-8469

RISC Applications Internet rischelp@idtinc.com

About Algorithmics

Much of this manual was written by Dominic Sweetman and Nigel

Stephens of Algorithmics Ltd in London, England, under contract to IDT.

Algorithmics were early enthusiasts for the MIPS architecture, designing

their first MIPS systems and system software in 1986/87. A small

engineering company, Algorithmics provide enabling technologies for

companies designing in both R30xx family CPUs and the 64-bit R4x00

architecture. This includes training, toolkits, GNU C support, and

evaluation boards. Dominic Sweetman can be reached at the following:.

Dominic Sweetman phone: +44 71 700 3301

Algorithmics Ltd fax: +44 71 700 3400

3 Drayton Park email: dom@algor.co.uk

London N5 1NU

ENGLAND.

Table of Contents

i–3

About This Manual

This manual is targeted to a systems programmer building an R30xx-

based system. It contains the architecture specific operations and

programming conventions relevant to such a programmer.

This manual is not intended to be a tutorial on structured programming,

real-time operating systems, any particular high-level programming

language, or any particular toolchain. Other references are better suited to

those topics.

This manual does contain specific code fragments and the most

common programming conventions that are specific to the IDT R30xx

RISController family. The manual was consciously limited to the R30xx

family; information relevant to the R4xxx family of processors may be

found, but the device specific programs (such as cache management,

exception handling, etc.) shown as examples are specific to the R30xx

family.

This manual contains references to the toolchains most commonly used

by the authors (IDT, Inc., and Algorithmics, Ltd.). Code fragments shown

are typically from software used by and/or provided by these companies,

includeing development tools such as IDT/c and software utilities (such as

IDT/kit, IDT/sim, and Micromonitor). A wide variety of other, 3rd party

products, are also available to support R30xx development, under the

Advantage-IDT program. The reader of this manual is encouraged to look

at all the available tools to determine which toolchains and utilities best fit

the system development requirements.

Additional information on the IDT family of RISC processors, and their

support tools, is available from your local IDT salesman.

Table of Contents

i–4

Integrated Device Technology, Inc. reserves the right to make changes to its products or specifications at

any time, without notice, in order to improve design or performance and to supply the best possible product.

IDT does not assume any responsibility for use of any circuitry described other than the circuitry embodied

in an IDT product. The Company makes no representations that circuitry described herein is free from patent

infringement or other rights of third parties which may result from its use. No license is granted by impli-

cation or otherwise under any patent, patent rights or other rights, of Integrated Device Technology, Inc.

LIFE SUPPORT POLICY

Integrated Device Technology's products are not authorized for use as critical components in life

support devices or systems unless a specific written agreement pertaining to such intended use is

executed between the manufacturer and an officer of IDT.

1. Life support devices or systems are devices or systems which (a) are intended for surgical implant

into the body or (b) support or sustain life and whose failure to perform, when properly used in

accordance with instructions for use provided in the labeling, can be reasonably expected to result in

a significant injury to the user.

2. A critical component is any components of a life support device or system whose failure to

perform can be reasonably expected to cause the failure of the life support device or system, or to

affect its safety or effectiveness.

The IDT logo is a registered trademark and BiCameral, BurstRAM, BUSMUX, CacheRAM, DECnet,

Double-Density, FASTX, Four-Port, FLEXI-CACHE, Flexi-PAK, Flow-thruEDC, IDT/c, IDTenvY, IDT/sae,

IDT/sim, IDT/ux, MacStation, MICROSLICE, Orion, PalatteDAC, REAL8, R3041, R3051, R3052, R3081,

R3721, R4600, RISCompiler, RISController, RISCore, RISC Subsystem, RISC Windows, SARAM, SmartLogic,

SyncFIFO, SyncBiFIFO, SPC, TargetSystem and WideBus are trademarks of Integrated Device Technology,

Inc.

MIPS is a registered trademark of MIPS Computer Systems, Inc

All others are trademarks of their respective companies..

Table of Contents

i–5

IDT R30xx Family

Software Reference Manual

Table of Contents

Introduction........................................................................................................................1

What is a RISC?......................................................................................................... 1-1

PIPELINES................................................................................................................ 1-2

The IDT R3xxx Family CPUs ................................................................................... 1-3

MIPS Architecture Levels.......................................................................................... 1-4

MIPS-1 Compared with CISC Archtectures.............................................................. 1-4

Unusual Instruction Encoding Features............................................................... 1-5

Addressing and Memory Accesses...................................................................... 1-5

Operations not Directly Supported ...................................................................... 1-6

Multiply and Divide Operations ................................................................................ 1-7

Programmer-visible Pipeline Effects......................................................................... 1-7

A Note on Machine and Assembler Language .......................................................... 1-8

MIPs-1 (R30xx) Architecture............................................................................................2

Programmer’s View of the Processor Archtecture.....................................................2-1

Registers..................................................................................................................... 2-1

Conventional Names and Uses of General-Purpose Registers .................................. 2-2

Notes on Conventional Register Names ............................................................. 2-2

Integer Multiply Unit and Registers .......................................................................... 2-3

Instruction Types ....................................................................................................... 2-4

Loading and Storing: Addressing Modes .................................................................. 2-5

Data types in Memory and Registers......................................................................... 2-6

Integer Data Types .............................................................................................. 2-6

Unaligned Loads and Stores ............................................................................... 2-6

Floating Point Data in Memory .......................................................................... 2-7

Basic Address Space.................................................................................................. 2-8

Summary of System Addressing................................................................................ 2-9

Kernel vs. User Mode .......................................................................................... 2-9

Memory map for CPUs without MMU Hardware............................................. 2-10

Subsegments in the R3041 – Memory Width Configuration ...................... 2-10

System Control Coprocessor Architecture......................................................................3

CPU Control Summary.............................................................................................. 3-1

CPU Control and ‘‘CO-PROCESSOR 0’’................................................................. 3-2

CPU Control Instructions..................................................................................... 3-2

Standard CPU control registers............................................................................ 3-3

PRId Register ................................................................................................ 3-4

SR Register .................................................................................................... 3-4

Cause Register ............................................................................................... 3-7

EPC Register ................................................................................................. 3-8

BadVaddr Register ........................................................................................ 3-8

R3041, R3071, and R3081 Specific Registers..................................................... 3-8

Table of Contents

i–6

Count and Compare Registers (R3041 only) .................................................3-8

Config Register (R3071 and R3081) .............................................................3-8

Config Register (R3041) ...............................................................................3-9

BusCtrl Register (R3041 only) ....................................................................3-10

PortSize Register (R3041 only) ...................................................................3-11

What registers are relevant when?......................................................................3-11

Exception Management.....................................................................................................4

Exceptions ..................................................................................................................4-1

Precise Exceptions................................................................................................4-1

When Exceptions Happen ....................................................................................4-2

Exception vectors .................................................................................................4-2

Exception Handling – Basics................................................................................4-3

Nesting Exceptions...............................................................................................4-4

An Exception Routine ..........................................................................................4-4

Interrupts...................................................................................................................4-12

Conventions and Examples ................................................................................4-14

Cache Management...........................................................................................................5

Caches and Cache Management.................................................................................5-1

Cache Isolation and Swapping .............................................................................5-3

Initializing and Sizing the Caches ........................................................................5-4

Invalidation...........................................................................................................5-6

Testing and Probing..............................................................................................5-8

Configuration (R3041/71/81 only).......................................................................5-8

Write Buffer................................................................................................................5-9

Implementing

wbflush()......................................................................................5-10

Memory Management and the TLB ................................................................................6

Memory Management and the TLB ...........................................................................6-1

MMU Registers Described...................................................................................6-3

EntryHi, EntryLo ...........................................................................................6-3

Index ..............................................................................................................6-4

Random ..........................................................................................................6-4

Context ...........................................................................................................6-4

MMU Control Instructions ...................................................................................6-5

Programming Interface to the TLB.......................................................................6-5

How Refill Happens ......................................................................................6-5

Using ASIDs ..................................................................................................6-6

The Random Register and Wired Entries ......................................................6-6

Memory Translation – Setup................................................................................6-6

TLB Exception Sample Code...............................................................................6-7

Basic Exception Handler ...............................................................................6-7

Fast kuseg Refill from Page Table ................................................................6-7

Simulating Dirty Bits............................................................................................6-8

Use of TLB in Debugging ..........................................................................................6-8

TLB Management Utilities.........................................................................................6-9

Reset Initialization.............................................................................................................7

Starting Up..................................................................................................................7-1

Probing and Recognizing the CPU .......................................................................7-4

Bootstrap Sequences.............................................................................................7-5

Starting Up an Application ...................................................................................7-5

Table of Contents

i–7

Floating Point Coprocessor...............................................................................................8

The IEEE754 Standard and its Background .............................................................. 8-1

What is Floating Point?.............................................................................................. 8-2

IEEE exponent field and bias............................................................................... 8-3

IEEE mantissa and normalization........................................................................ 8-3

Strange values use reserved exponent values ...................................................... 8-3

MIPS FP Data formats......................................................................................... 8-4

MIPS Implementation of IEEE754............................................................................ 8-5

Floating Point Registers............................................................................................. 8-6

Floating Point Eeceptions/Interrupts.......................................................................... 8-6

The Floating Point Control/Status Register............................................................... 8-6

Floating Point Implementation/Revision Register..................................................... 8-8

Guide to FP Instructions ............................................................................................ 8-8

Load/Store............................................................................................................ 8-8

Move Between Registers ..................................................................................... 8-9

3-Operand Arithmetic Operations........................................................................ 8-9

Unary (sign-changing) Operations..................................................................... 8-10

Conversion Operations....................................................................................... 8-10

Conditional Branch and Test Instructions.......................................................... 8-10

Instruction Timing Requirements ............................................................................ 8-12

Instruction Timing for Speed................................................................................... 8-12

Initialization and Enable On Demand...................................................................... 8-12

Floating Point Emulation......................................................................................... 8-13

Assembler Language Programming.................................................................................9

Syntax Overview........................................................................................................ 9-1

Key Points to Note............................................................................................... 9-1

Register-to-Register Instructions ............................................................................... 9-2

Immediate (Constant) Operands ................................................................................ 9-3

Multiply/Divide.......................................................................................................... 9-4

Load/Store Instructions.............................................................................................. 9-5

Unaligned Loads and Store.................................................................................. 9-5

Addressing Modes ..................................................................................................... 9-6

Gp-Relative Addressing....................................................................................... 9-6

Jumps, Subroutine Calls and Branches...................................................................... 9-8

Conditional Branches................................................................................................. 9-8

Co-processor Conditional Branches .................................................................... 9-9

Compare and Set........................................................................................................ 9-9

Coprocessor Transfers ............................................................................................... 9-9

Coprocessor Hazards ......................................................................................... 9-10

Assembler Directives............................................................................................... 9-10

Sections.............................................................................................................. 9-10

.text, .rdata, .data ......................................................................................... 9-10

.lit4, .lit8 ...................................................................................................... 9-10

Program Segments in Memory ................................................................... 9-11

.bss .............................................................................................................. 9-12

.sdata, .sbss .................................................................................................. 9-12

Stack and Heap ........................................................................................... 9-12

Special Symbols .......................................................................................... 9-12

Data Definition and Alignment.......................................................................... 9-12

Table of Contents

i–8

.byte, .half, .word ........................................................................................ 9-13

.float, .double .............................................................................................. 9-13

.ascii, .asciiz ................................................................................................ 9-13

.align ............................................................................................................ 9-13

.comm, .lcomm ........................................................................................... 9-13

.space ........................................................................................................... 9-14

Symbol Binding Attributes ................................................................................ 9-14

.globl ........................................................................................................... 9-14

.extern .......................................................................................................... 9-15

.weakext ...................................................................................................... 9-15

Function Directives............................................................................................ 9-15

.ent, .end ...................................................................................................... 9-15

.aent ............................................................................................................. 9-16

.frame, .mask, .fmask .................................................................................. 9-16

Assembler Control (.set).................................................................................... 9-17

.set noreorder/reorder .................................................................................. 9-17

.set volatile/novolatile ................................................................................. 9-17

.set noat/at ................................................................................................... 9-18

.set nomacro/macro ..................................................................................... 9-18

.set nobopt/bopt ........................................................................................... 9-18

The Complete Guide to Assembler Instructions...................................................... 9-18

Alphabetic List of Assembler Instructions .............................................................. 9-30

C Programming................................................................................................................10

The Stack, Subroutine Linkage, Parameter Passing ................................................ 10-1

Stack Argument Structure.................................................................................. 10-1

Which Arguments go in What Registers ........................................................... 10-1

Examples from the C Library ............................................................................ 10-2

Exotic Example; Passing Structures .................................................................. 10-2

How Printf() and Varargs Work ........................................................................ 10-3

Returning Value from a Function ...................................................................... 10-4

Macros for Prologues and Epilogues................................................................. 10-4

Stack-Frame Allocation ..................................................................................... 10-4

Leaf Functions ............................................................................................ 10-4

Non-Leaf Functions .................................................................................... 10-5

Functions Needing Run-Time Computed Stack Locations ........................ 10-7

Shared and Non-Shared Libraries............................................................................ 10-9

Sharing Code in Single-Address Space Systems............................................... 10-9

Sharing Code Across Address Spaces ............................................................. 10-10

An Introduction to Optimization............................................................................ 10-11

Common Optimizations................................................................................... 10-11

How to Prevent Unwanted Effects From Optimization................................... 10-14

Optimizer-Unfriendly Code and How to Avoid It........................................... 10-15

Portability Considerations ..............................................................................................11

Writing Portable C................................................................................................... 11-1

C Language Standards ...................................................................................... 11-1

C Library Functions and POSIX ....................................................................... 11-2

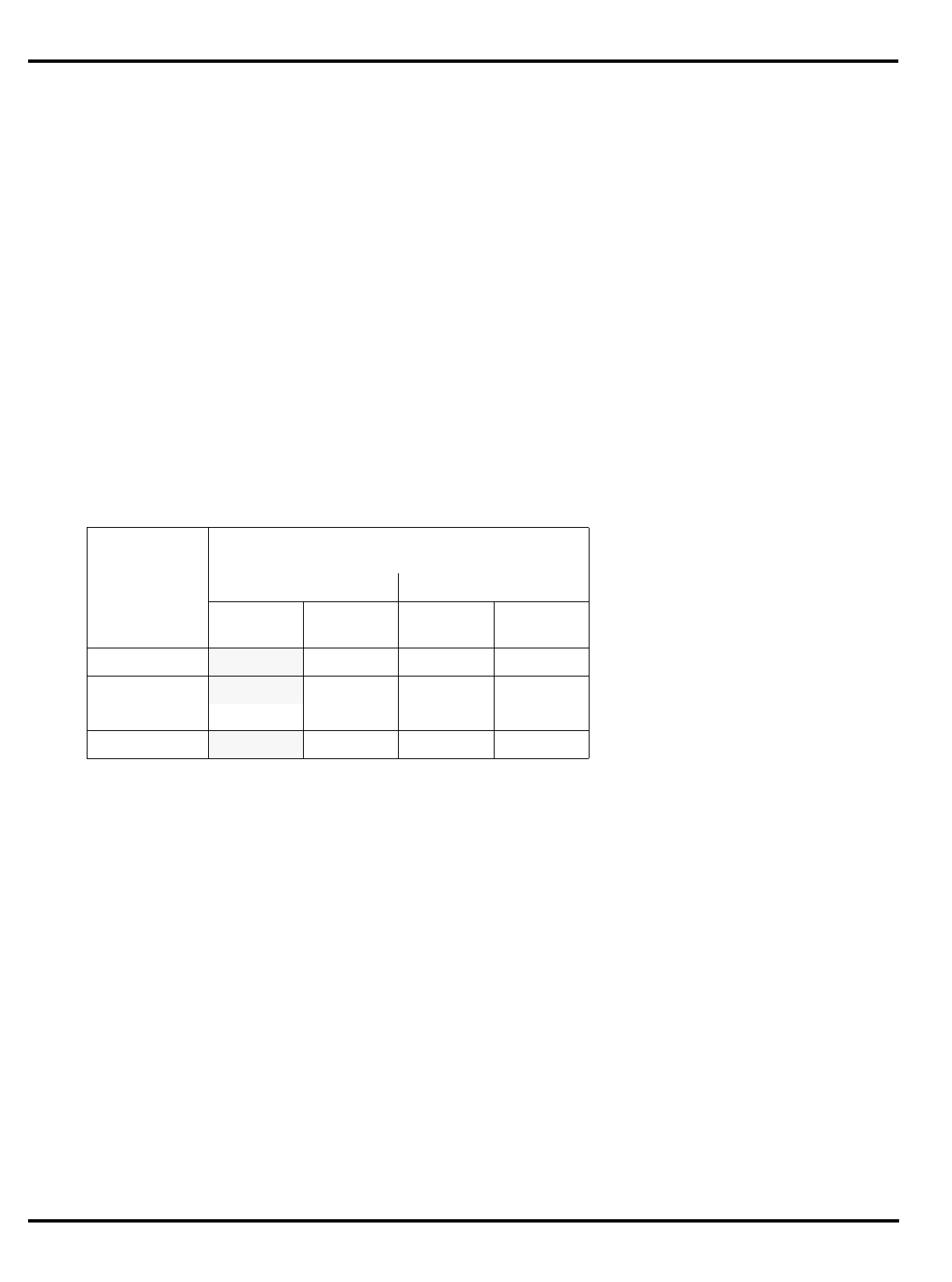

Data Representations and Alignment....................................................................... 11-3

Notes on Structure Layout and Padding ............................................................ 11-3

Isolating System Dependencies ............................................................................... 11-5

Table of Contents

i–9

Locating System Dependencies......................................................................... 11-5

Fixing Up Dependencies.................................................................................... 11-5

Isolating Non-Portable Code ....................................................................... 11-6

Using Assembler................................................................................................ 11-6

Endianness ............................................................................................................... 11-7

What It Means to the Programmer..................................................................... 11-8

Bitfield Layout and Endianness .................................................................. 11-9

Changing the Endianness of a MIPS CPU....................................................... 11-10

Designing and Specifying for Configurable Endianness................................. 11-10

Read-Only Instruction Memory ................................................................ 11-10

Writable (Volatile) Memory ..................................................................... 11-11

Byte-Lane Swapping ................................................................................. 11-11

Configurable IO Controllers ..................................................................... 11-12

Portability and Endianness-Independent Code................................................ 11-13

Endianness-Independent Code .................................................................. 11-13

Compatibility Within the R30XX Family.............................................................. 11-13

Porting to MIPS: Frequently Encountered Issues.................................................. 11-15

Considerations for Portability to Future Devices................................................... 11-16

Writing Power-On Diagnostics.......................................................................................12

Golden Rules for Diagnostics Programming........................................................... 12-1

What Should Tests Do? ........................................................................................... 12-2

How to Test the Diagnostic Tests? .......................................................................... 12-3

Overview of Algorithmics’ Power-On Selftest........................................................ 12-3

Starting Points.................................................................................................... 12-3

Control and Environment Variables .................................................................. 12-4

Reporting............................................................................................................ 12-4

Unexpected Exceptions During Test Sequence................................................. 12-5

Driving Test Output Devices ............................................................................. 12-5

Restarting the System ........................................................................................ 12-5

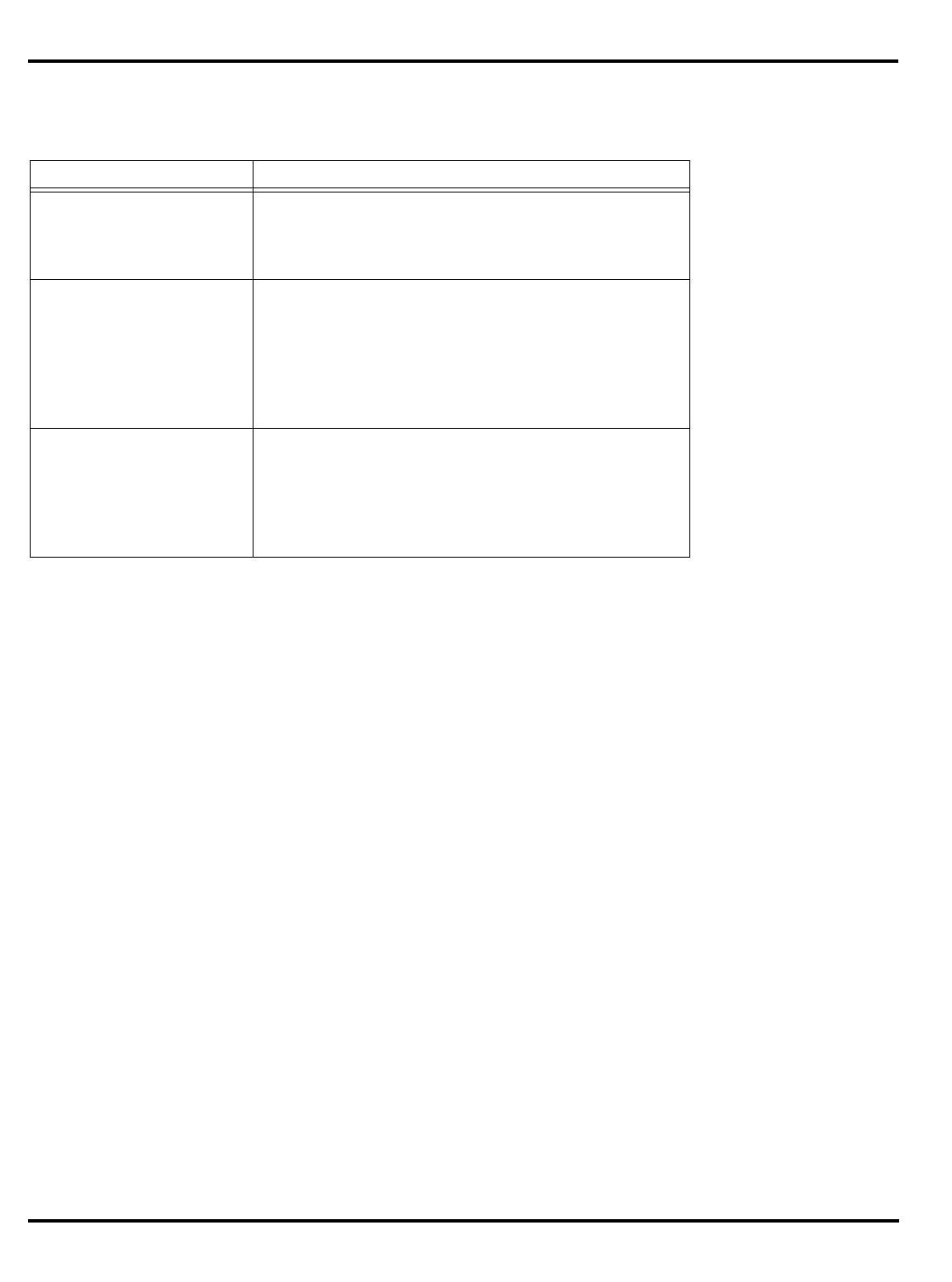

Standard Test Sequence..................................................................................... 12-5

Notes on the Test Sequence............................................................................... 12-6

Annotated Examples from the Test Code.......................................................... 12-9

Instruction Timing and Optimization............................................................................13

Notes and Examples........................................................................................... 13-1

Additional Hazards .................................................................................................. 13-2

Early Modification of HI and LO ...................................................................... 13-2

Bitfields in CPU Control Registers.................................................................... 13-3

Non-Obvious Hazards........................................................................................ 13-3

Software Tools for Board Bring-Up...............................................................................14

Tools Used in Debug ............................................................................................... 14-1

Initial Debugging ..................................................................................................... 14-2

Porting Micromonitor .............................................................................................. 14-2

Running Micromonitor ............................................................................................ 14-2

Initial IDT/SIM Activity.......................................................................................... 14-2

A Final Note on IDT/KIT ........................................................................................ 14-3

Software Design Examples..............................................................................................15

Application Software ............................................................................................... 15-1

Memory Map ..................................................................................................... 15-1

Starting Up......................................................................................................... 15-1

Table of Contents

i–10

C Library Functions........................................................................................... 15-2

Input and Output ......................................................................................... 15-3

Character Class Tests .................................................................................. 15-3

String Functions .......................................................................................... 15-3

Mathematical Functions .............................................................................. 15-3

Utility Functions ......................................................................................... 15-3

Diagnostics .................................................................................................. 15-4

Variable Argument Lists ............................................................................. 15-4

Non-Local Jumps ........................................................................................ 15-4

Signals ......................................................................................................... 15-4

Date and Time ............................................................................................. 15-4

Running the Program......................................................................................... 15-4

Debugging the Program..................................................................................... 15-5

Embedded System Software .................................................................................... 15-5

Memory Map ..................................................................................................... 15-6

Starting Up......................................................................................................... 15-6

Embedded System Library Functions................................................................ 15-7

Trap and Interrupt Handling ....................................................................... 15-8

Simple Interrupt Routines ........................................................................... 15-8

Floating-Point Traps and Interrupts ............................................................ 15-9

Emulating Floating Point Instructions ...................................................... 15-10

Debugging........................................................................................................ 15-10

Unix-Like System S/W.......................................................................................... 15-11

Terminology..................................................................................................... 15-11

Components of a Process................................................................................. 15-12

System Calls and Protection ............................................................................ 15-13

What the Kernel Does...................................................................................... 15-13

Virtual Memory Implementation for MIPS..................................................... 15-14

Interrupt Handling for MIPS............................................................................ 15-15

How it Works ............................................................................................ 15-16

Assembly Language Programming Tips........................................................................16

32-bit Address or Constant Values .................................................................... 16-1

Use of “Set” Instructions ................................................................................... 16-1

Use of “Set” with Complex Branch Operations ......................................... 16-2

Carry, Borrow, Overflow, and Multi-Precision Math ................................. 16-2

Machine Instructions Reference (Appendix A)..............................................................A

CPU Instruction Overview.................................................................................. A-1

Instruction Classes .............................................................................................. A-1

Instruction Formats............................................................................................. A-2

Instruction Notation Conventions....................................................................... A-2

Instruction Notation Examples ..................................................................... A-3

Load and Store Instructions ................................................................................ A-4

Jump and Branch Instructions............................................................................. A-5

Coprocessor Instructions..................................................................................... A-5

System Control Coprocessor (CP0) Instructions................................................ A-6

Instruct Set Details.............................................................................................. A-6

Instruction Summary......................................................................................... A-79

FPA Instruction Reference (Appendix B).......................................................................B

FPU Instruction Set Details .................................................................................B-1

Table of Contents

i–11

FPU Instructions ...........................................................................................B-1

Floating-Point Data Transfer ........................................................................B-1

Floating-Point Conversions ..........................................................................B-1

Floating-Point Arithmetic .............................................................................B-2

Floating-Point Register-to-Register Move ....................................................B-2

Floating-Point Branch ...................................................................................B-2

FP Computational Instructions and Valid Operands ...........................................B-2

FP Compare and Condition values ......................................................................B-3

FPU Register Specifiers.......................................................................................B-3

32-bit CP1 registers..............................................................................................B-4

FPU Register Access for 32-bit CP1 Registers..............................................B-5

Instruction Notation Conventions ..................................................................B-5

Load and Store Memory ......................................................................................B-6

Instruction Descriptions.......................................................................................B-6

FPA Instruction Set Summary ...........................................................................B-27

CP0 Operation Reference (Appendix C) ........................................................................C

CP0 Operation Details .........................................................................................C-1

MMU Operations.................................................................................................C-1

Exception Operations...........................................................................................C-1

Dand Register Movement Operations............................................................C-1

Operation Descriptions ........................................................................................C-1

Assembler Language Syntax (Appendix D)....................................................................D

Object Code Formats (Appendix E)................................................................................E

Sections and Segments...............................................................................................E-1

ECOFF Object File Format (RISC/OS).....................................................................E-1

File Header...........................................................................................................E-2

Optional a.out Header..........................................................................................E-2

Example Loader...................................................................................................E-3

Further Reading ...................................................................................................E-4

ELF (MIPS ABI)........................................................................................................E-4

File Header...........................................................................................................E-4

Program Header ...................................................................................................E-5

Example Loader...................................................................................................E-6

Further Reading ...................................................................................................E-7

Object Code Tools .....................................................................................................E-7

Glossary of Common "MIPS" Terms.............................................................................F

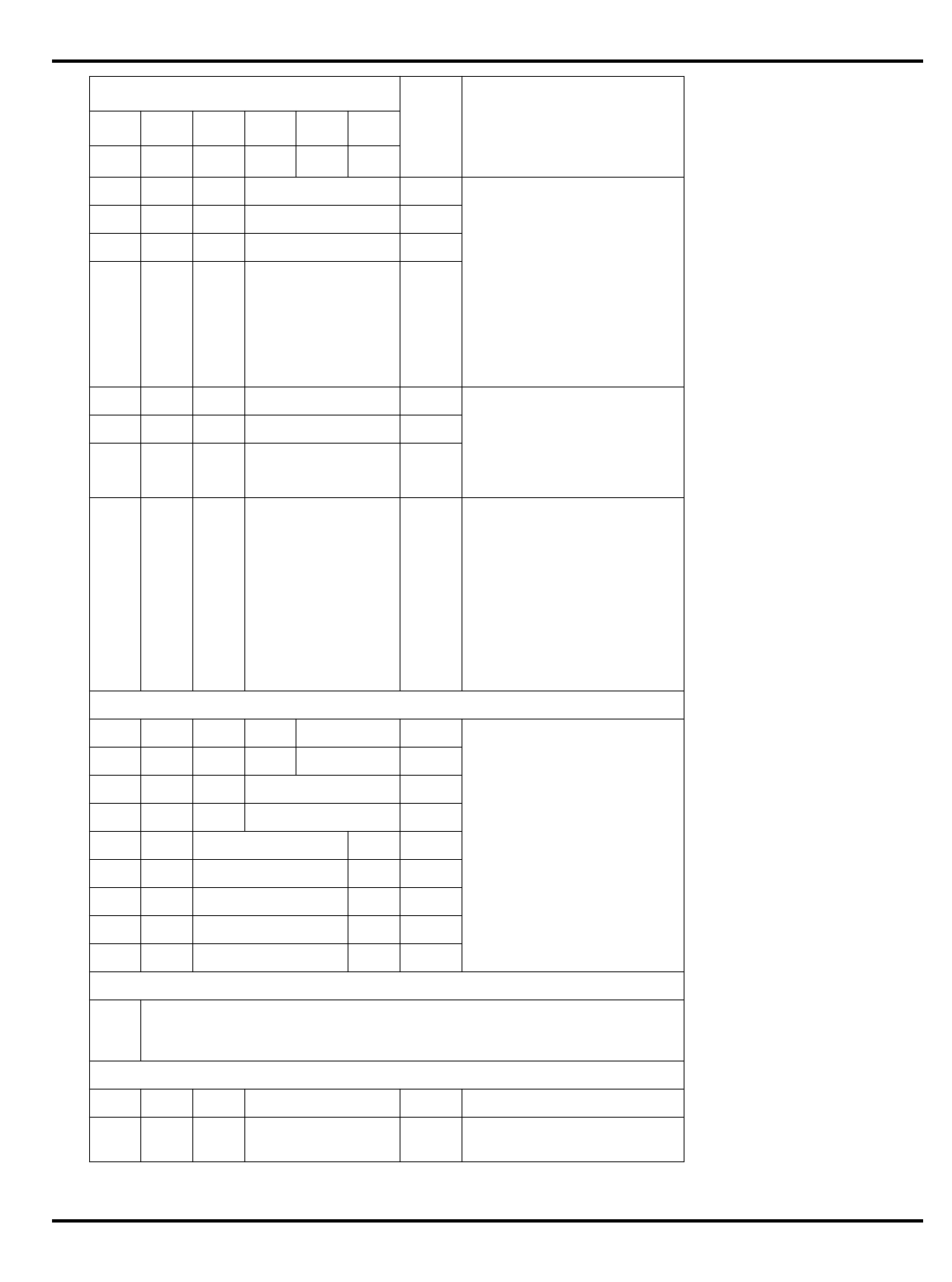

DRAWINGS

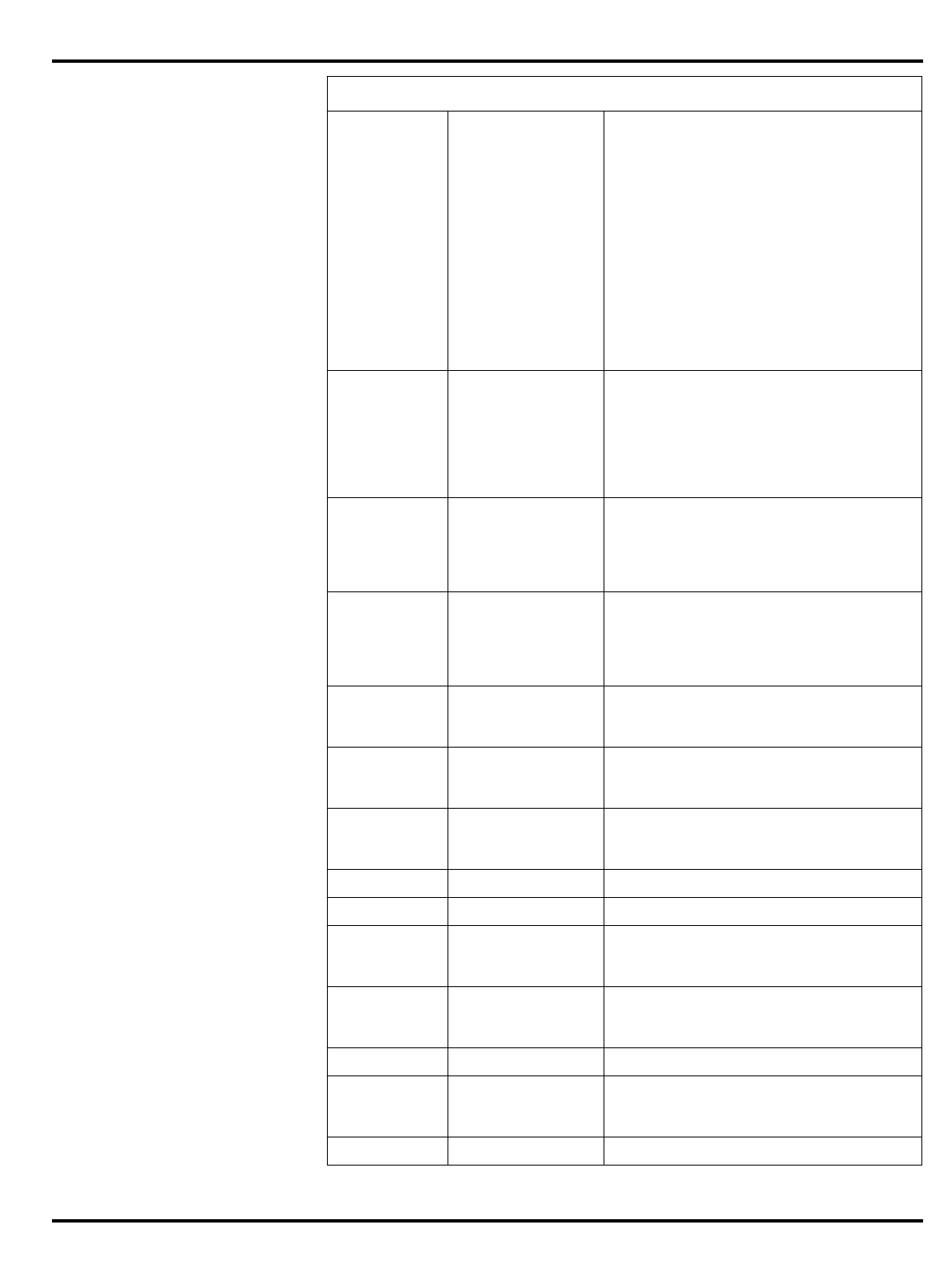

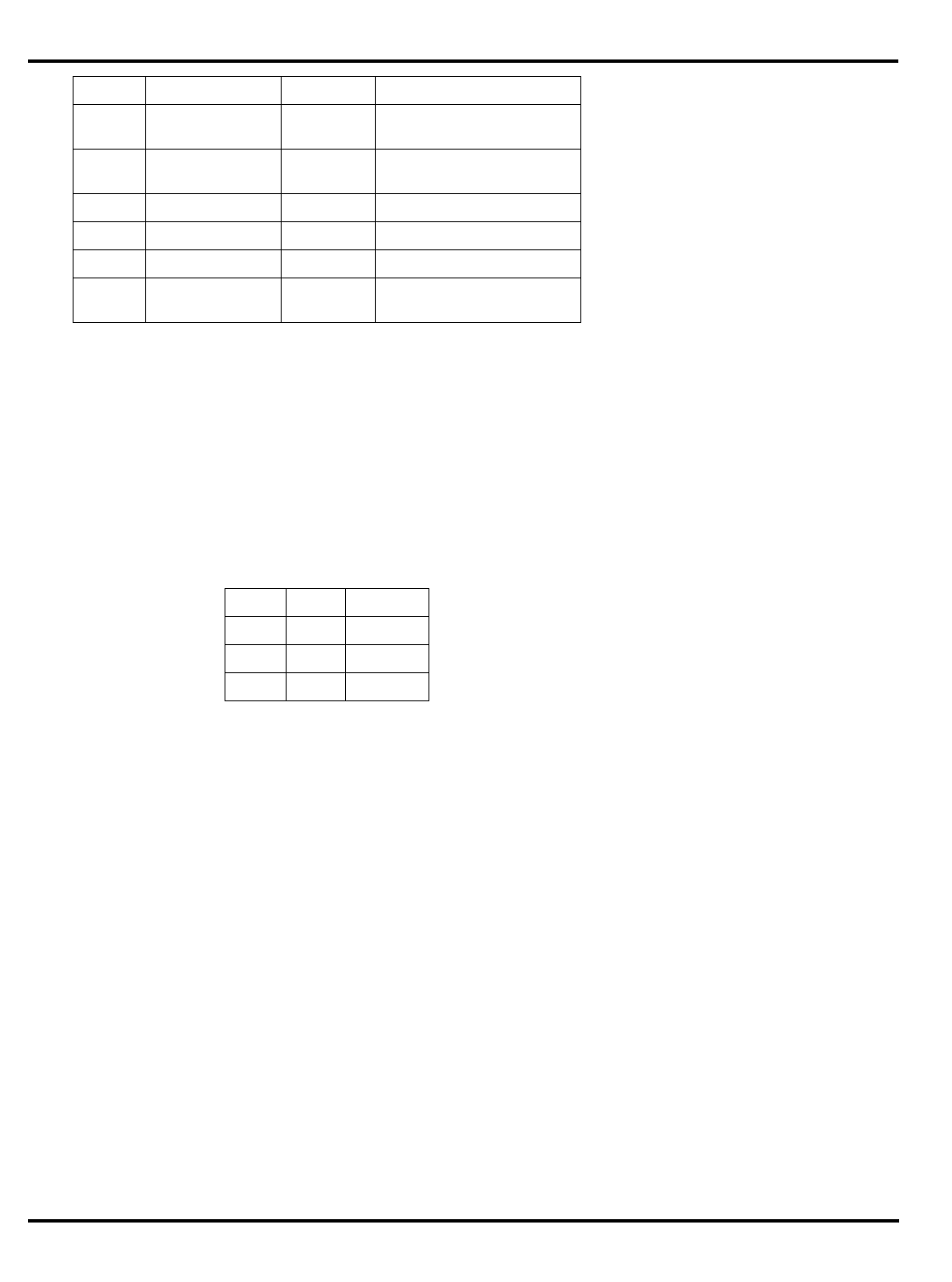

1.1 MIPS 5-Stage Pipeline..........................................................................................1.2

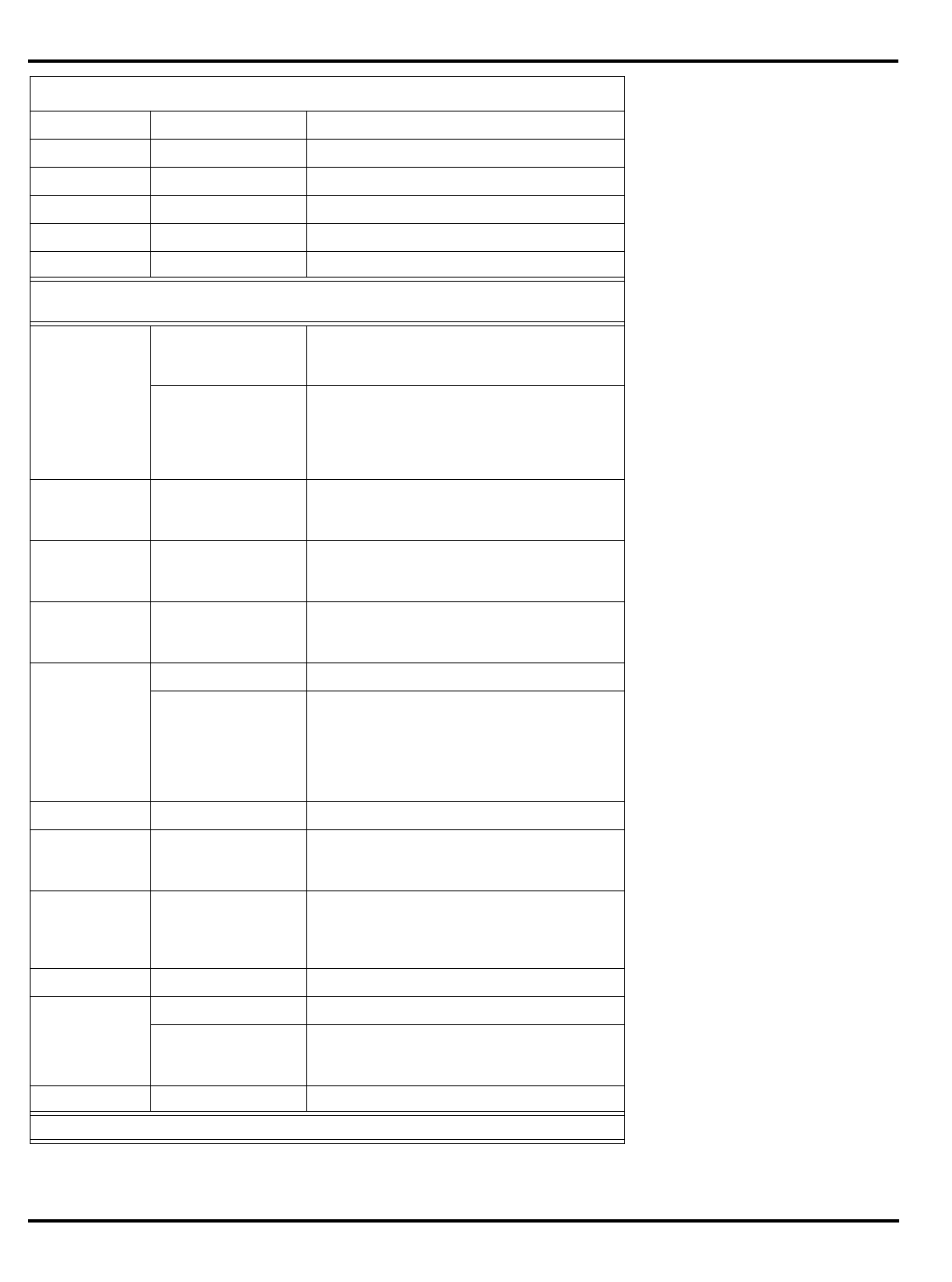

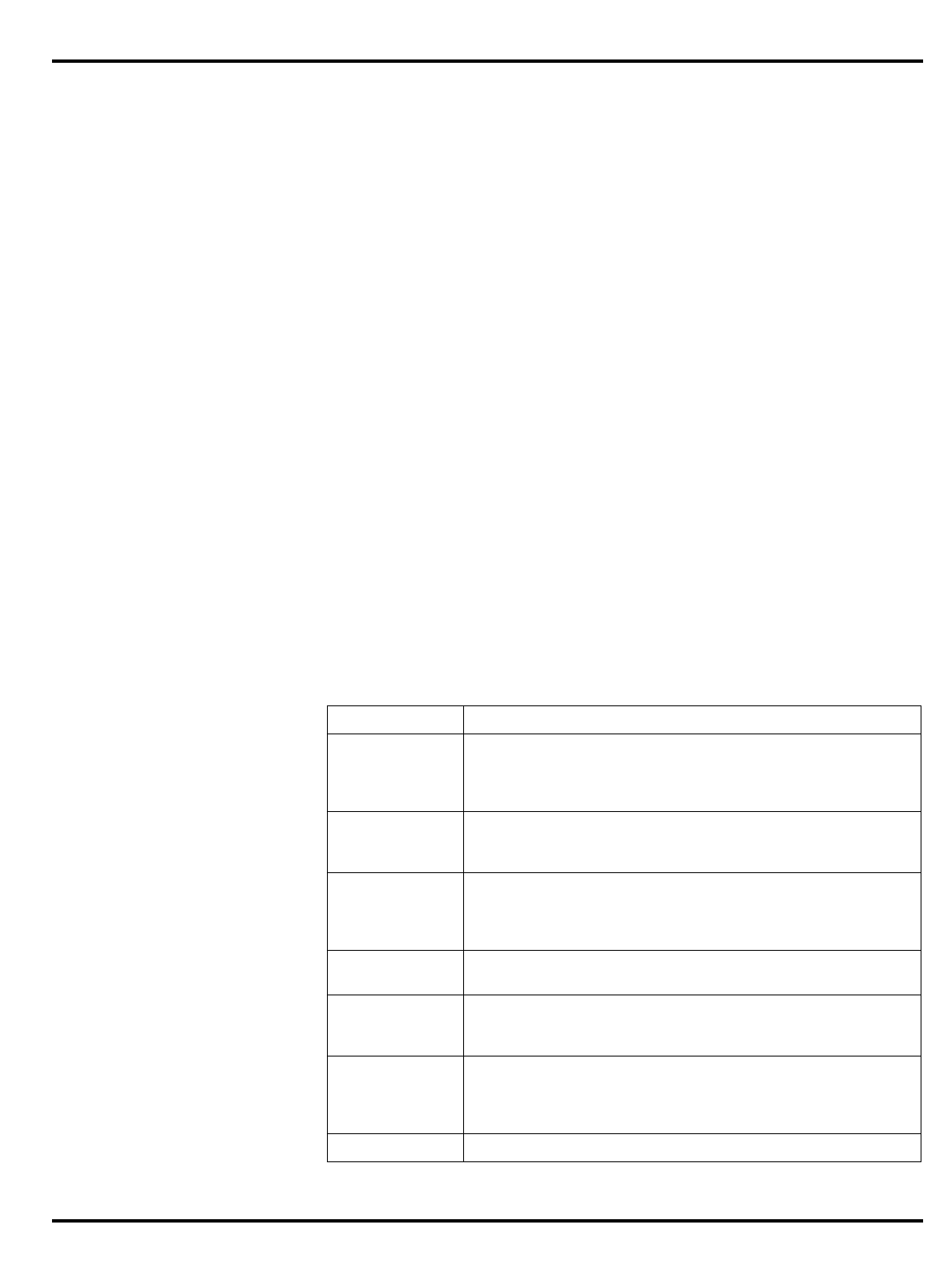

1.2 The Pipeline and Branch Delays.......................................................................... 1-7

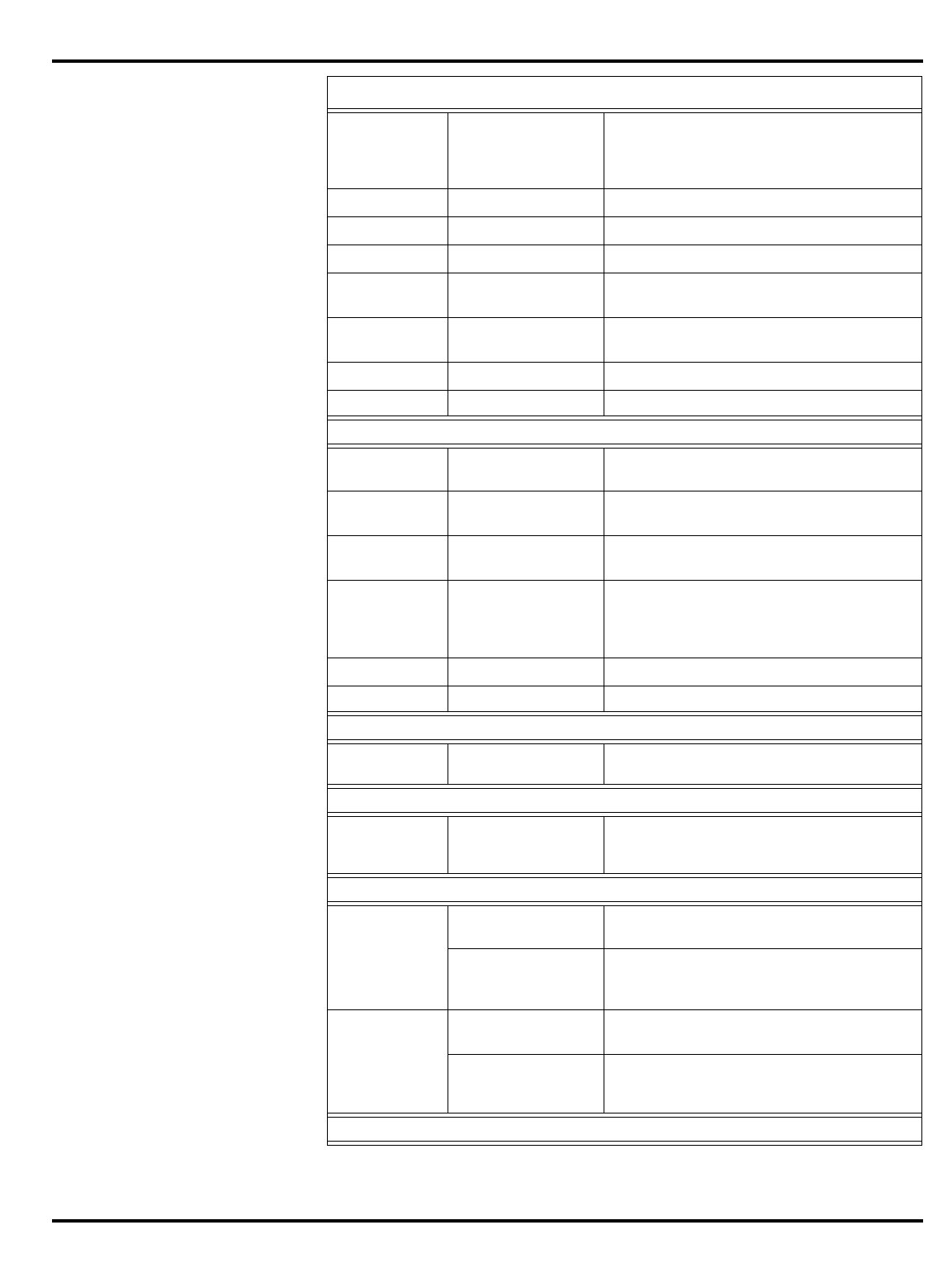

1.3 The Pipeline and Load Delays............................................................................. 1-8

3.1 PRId Register Fields ............................................................................................ 3-4

3.2 Fields in Status Register....................................................................................... 3-4

3.3 Fields in the Cause Register................................................................................. 3-7

3.4 Fields in the R3071/81 Config Register............................................................... 3-8

3.5 Fields in the R3041 Config (Cache Configuration)Register................................ 3-9

3.6 Fields in the R3041 Bus Control (BusCtrl) Register ......................................... 3-10

5.1 Direct Mapped Cache .......................................................................................... 5-1

6.1 EntryHi and EntryLo Register Fields .................................................................. 6-3

Table of Contents

i–12

6.2 EntryHi and EntryLo Register Fields .................................................................. 6-3

6.3 Fields in the Index Register ................................................................................. 6-4

6.4 Fields in the Random Register............................................................................. 6-4

6.5 Fields in the Context Register.............................................................................. 6-4

8.1 FPA Control/Status Register Fields..................................................................... 8-6

8.2 FPA Implementation/Revision Register .............................................................. 8-8

9.1 Program Segments in Memory .......................................................................... 9-11

10.1 Stackframe for a Non-Leaf Function................................................................. 10-5

11.1 Structure Layout and Padding in Memory......................................................... 11-3

11.2 Data Representation with #pragma Pack(1) ......................................................11-4

11.3 Data Representation with #pragma Pack(2) ......................................................11-5

11.4 Typical Big-Endians Picture.............................................................................. 11-8

11.5 Little Endians Picture......................................................................................... 11-8

11.6 Bitfields and Big-Endian.................................................................................... 11-9

11.7 Bitfields and Little-Endian............................................................................... 11-10

11.8 Garbled String Storage when Mixing Modes .................................................. 11-11

11.9 Byte-Lane Swapper.......................................................................................... 11-12

15.1 Memory Layout of a BSD Process .................................................................. 15-12

A.1 CPU Instruction Formats .................................................................................... A-2

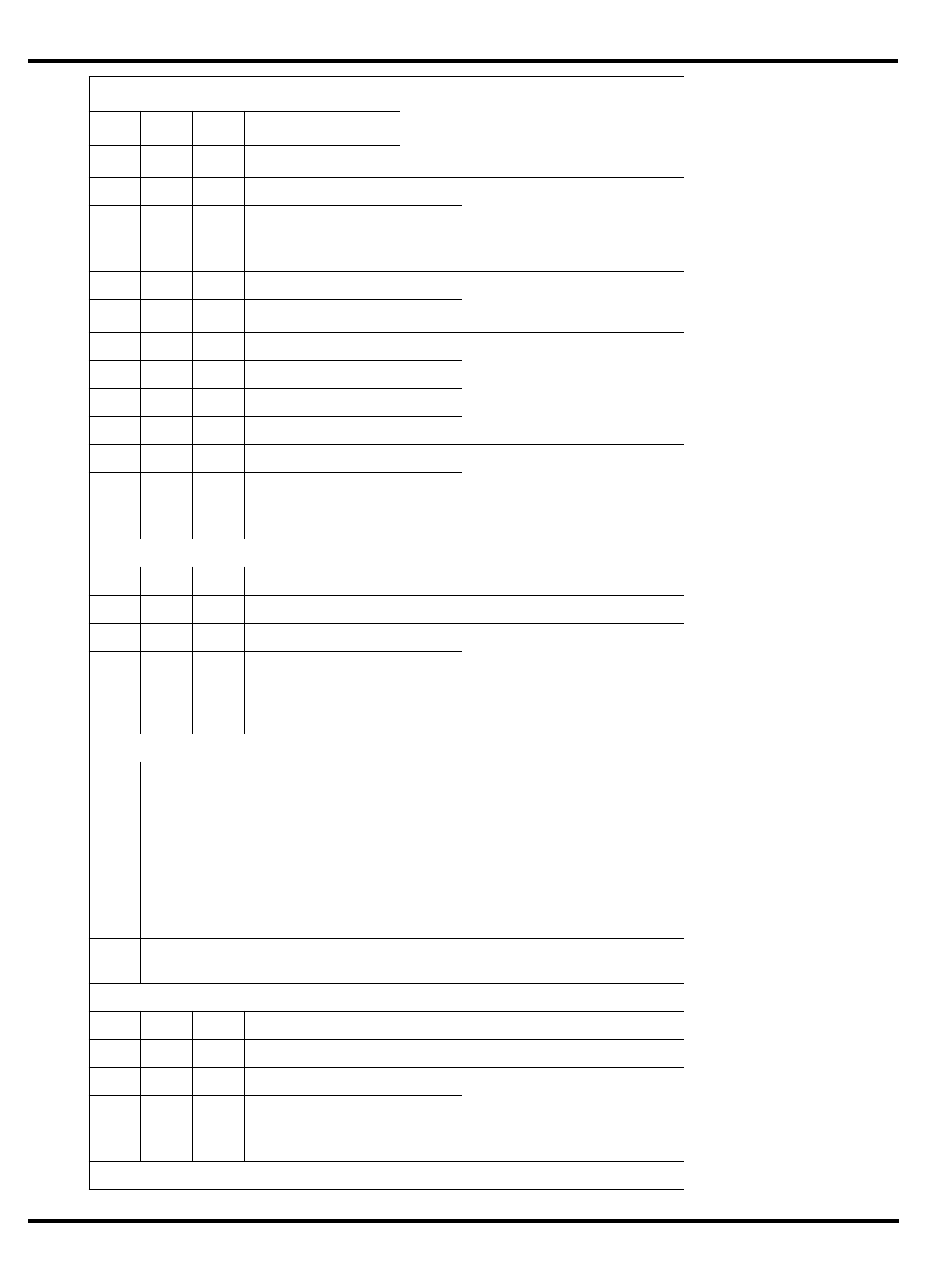

TABLES

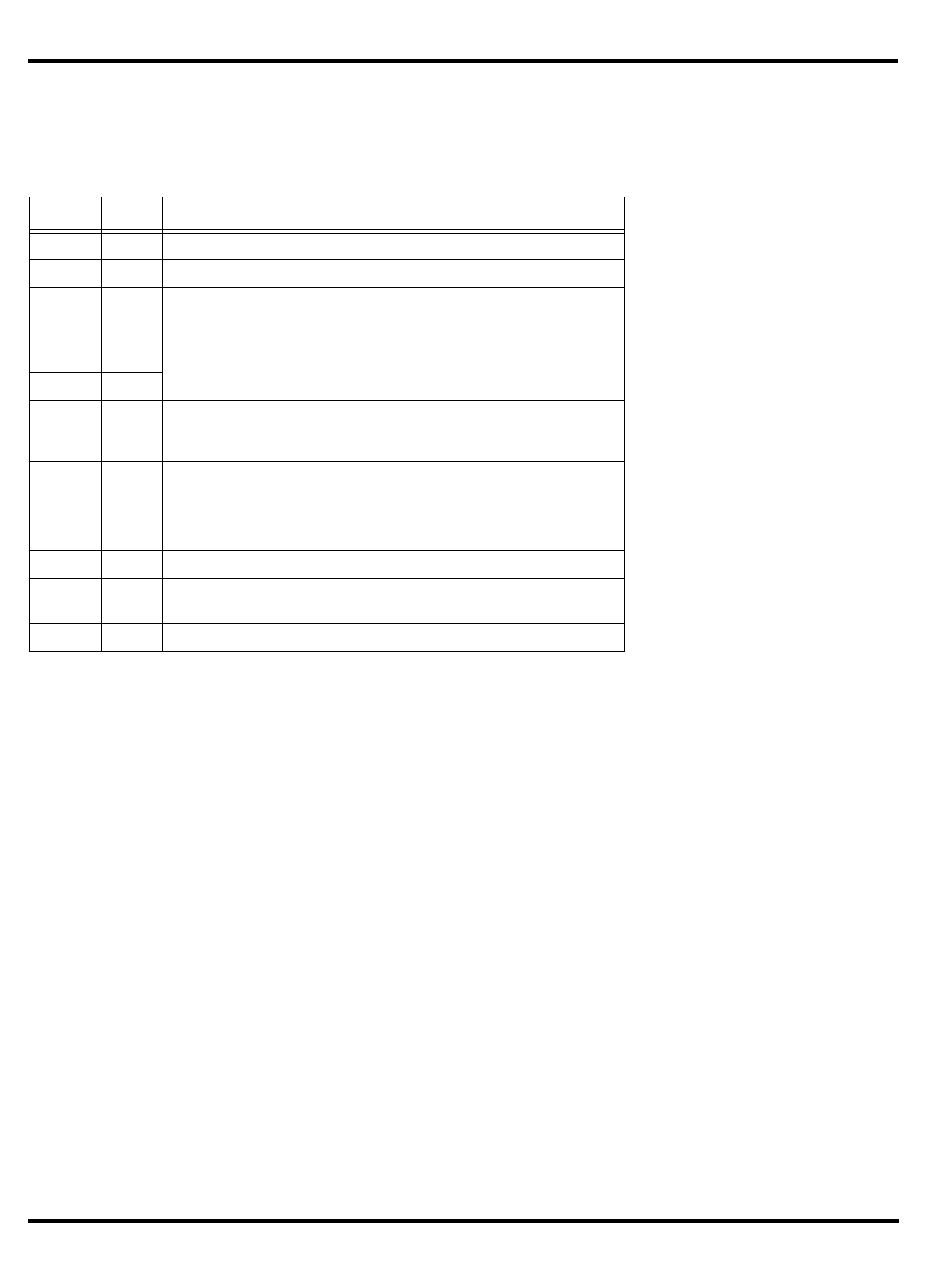

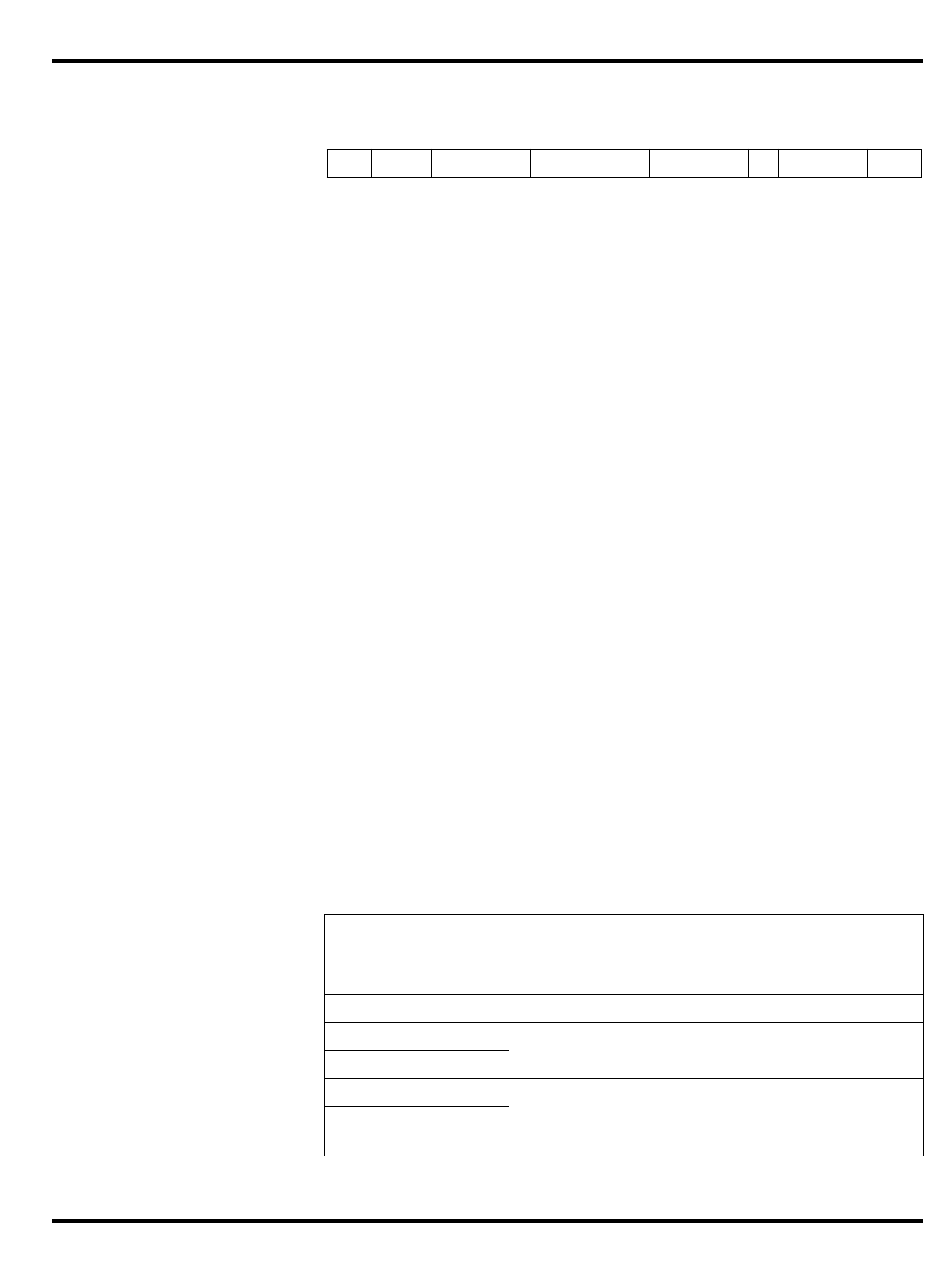

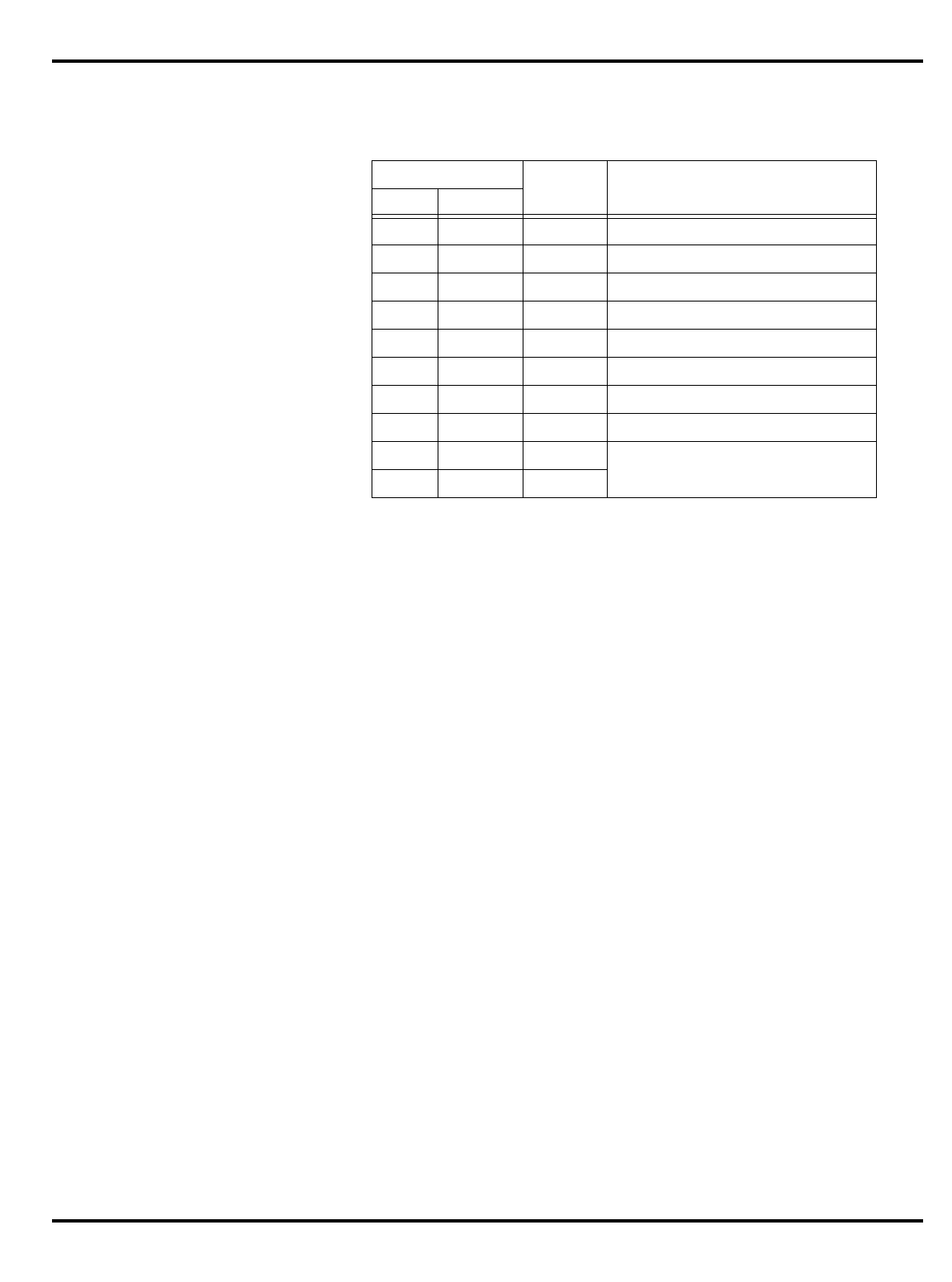

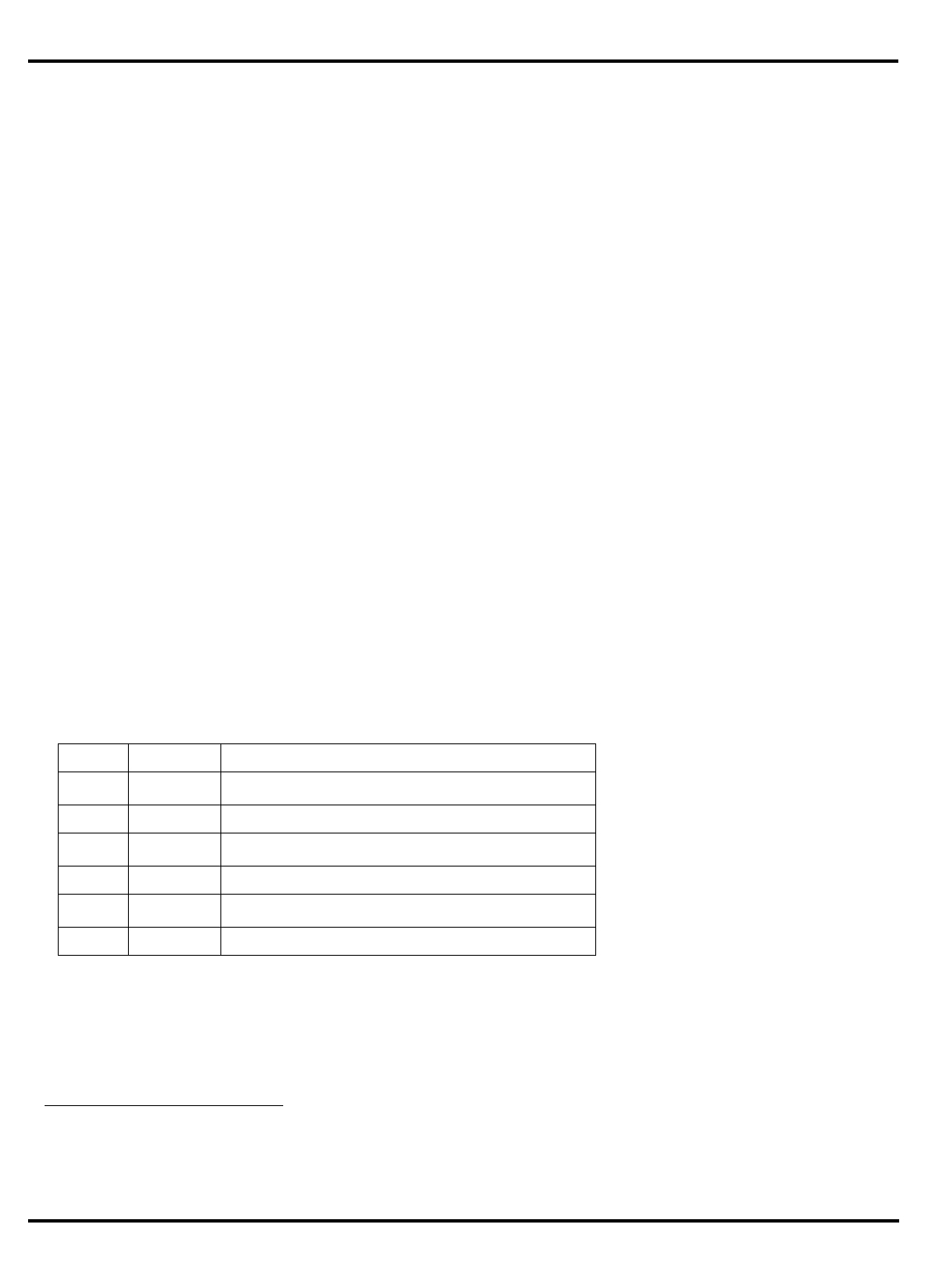

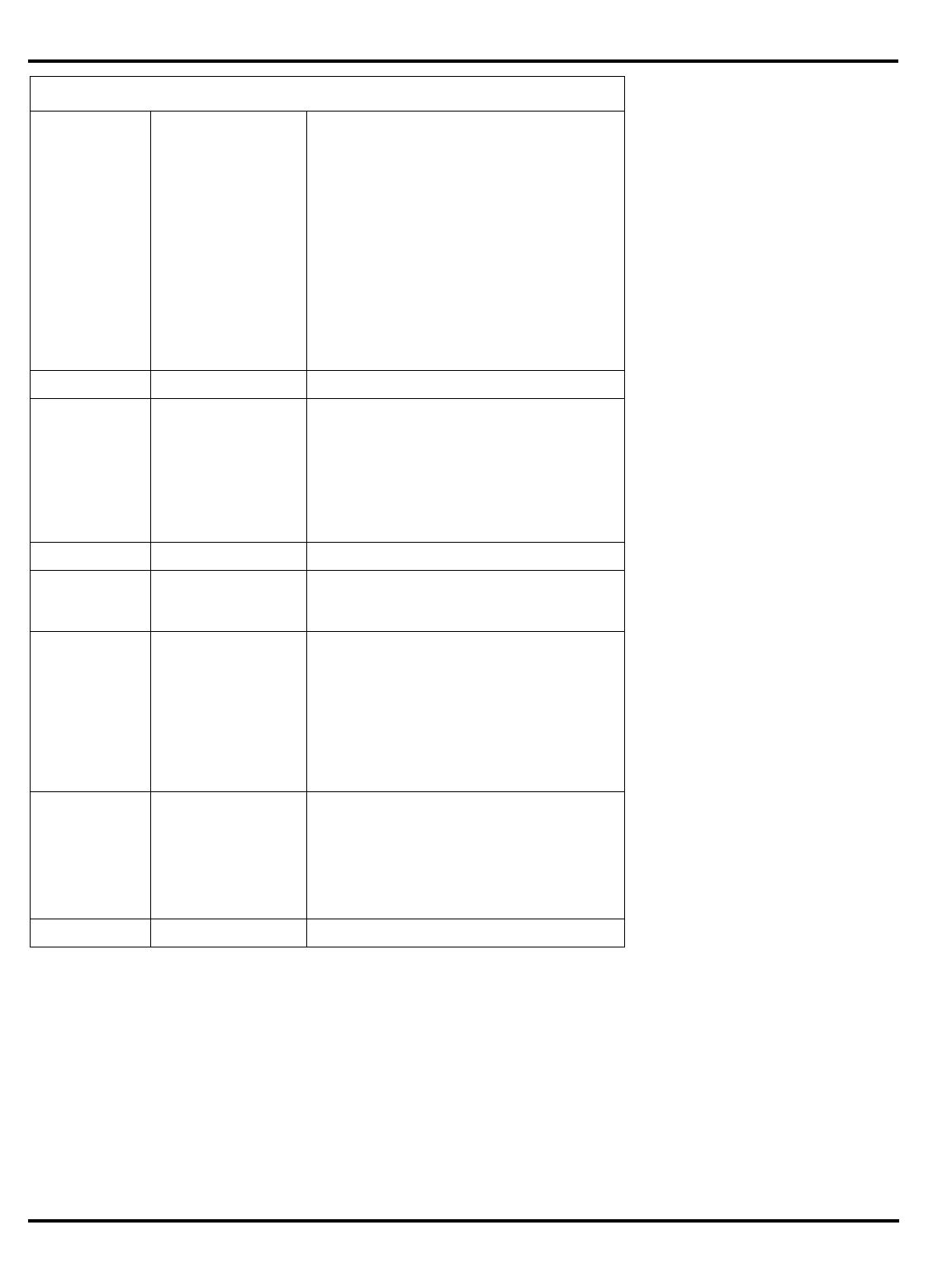

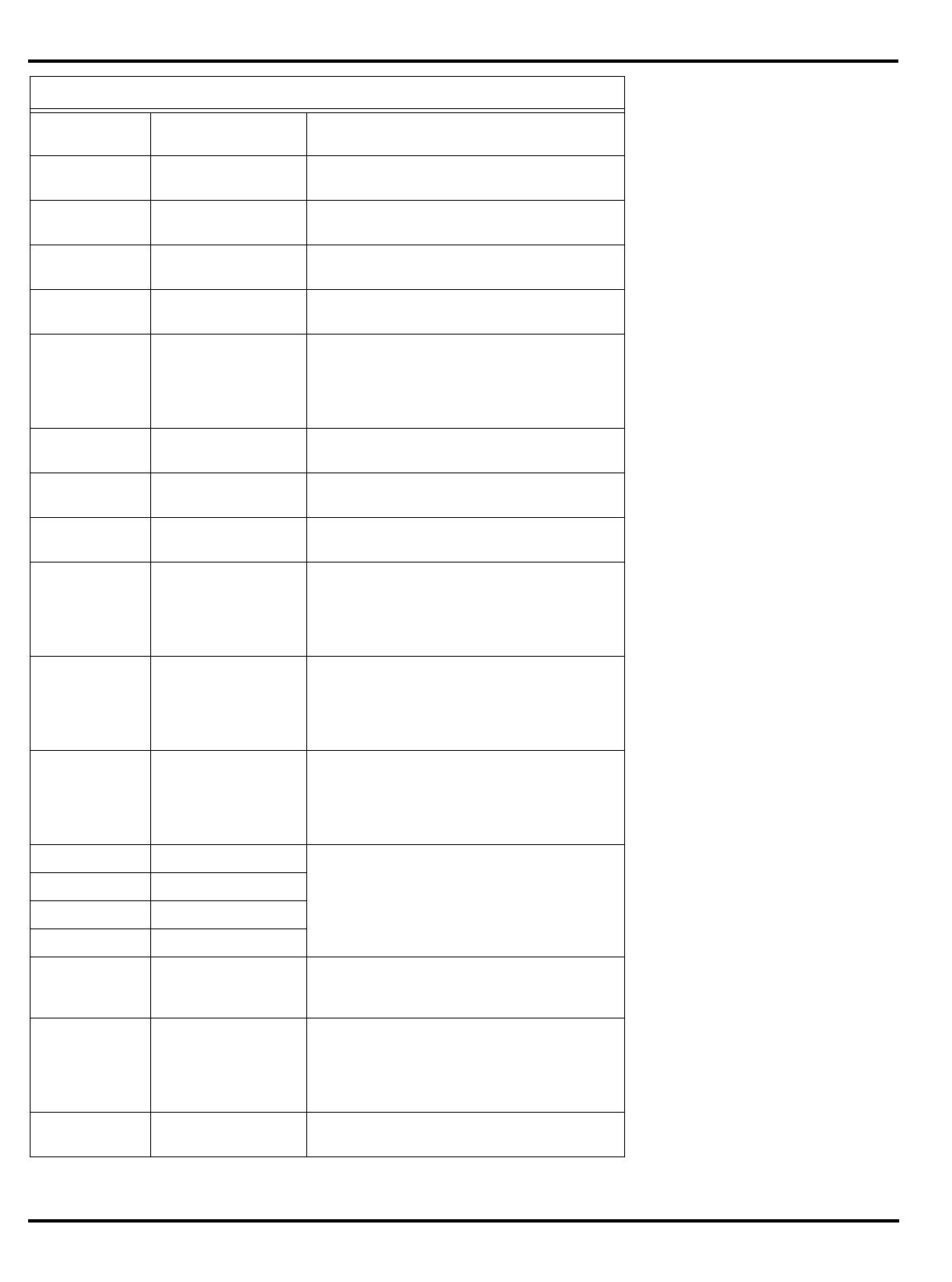

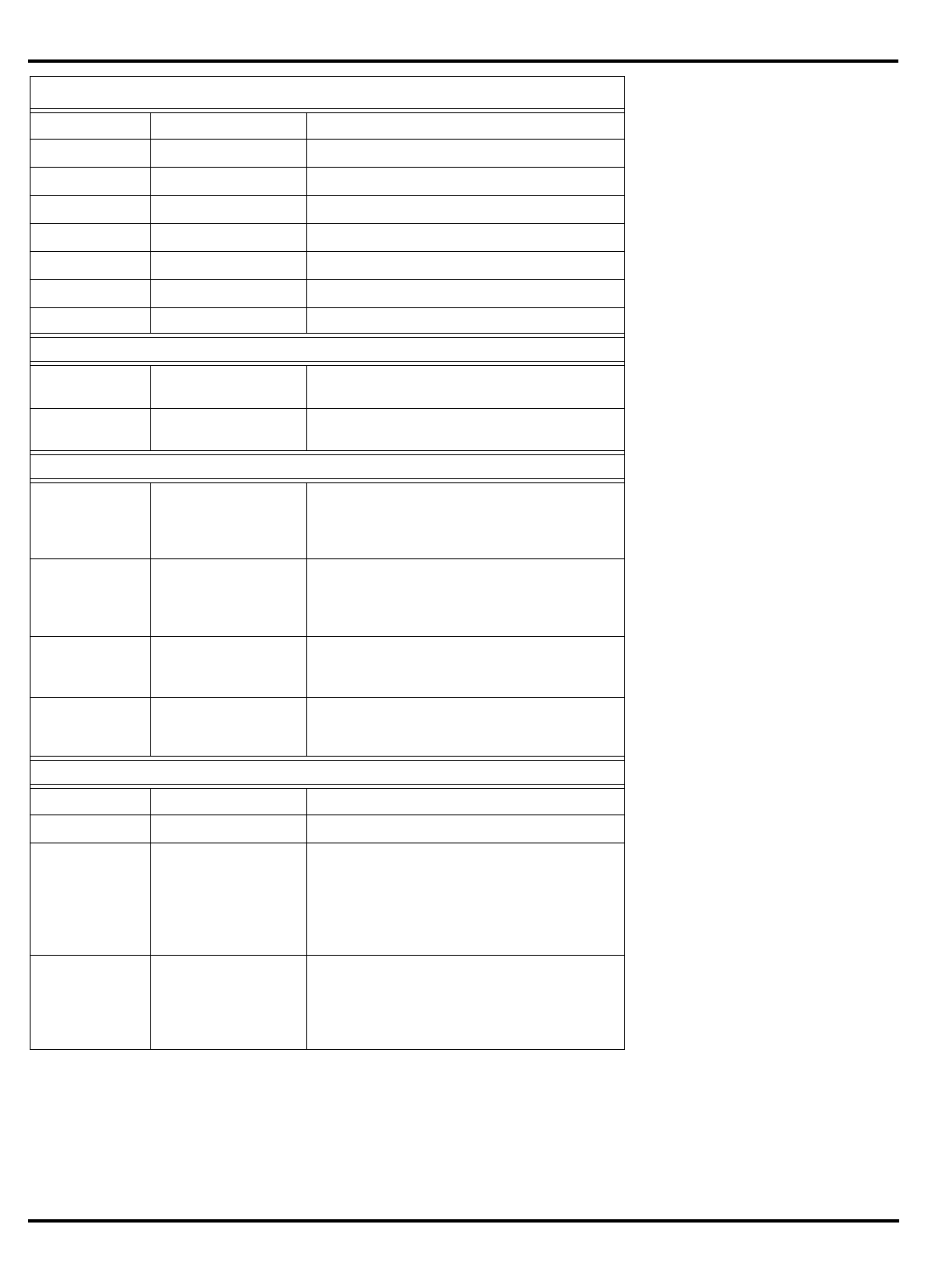

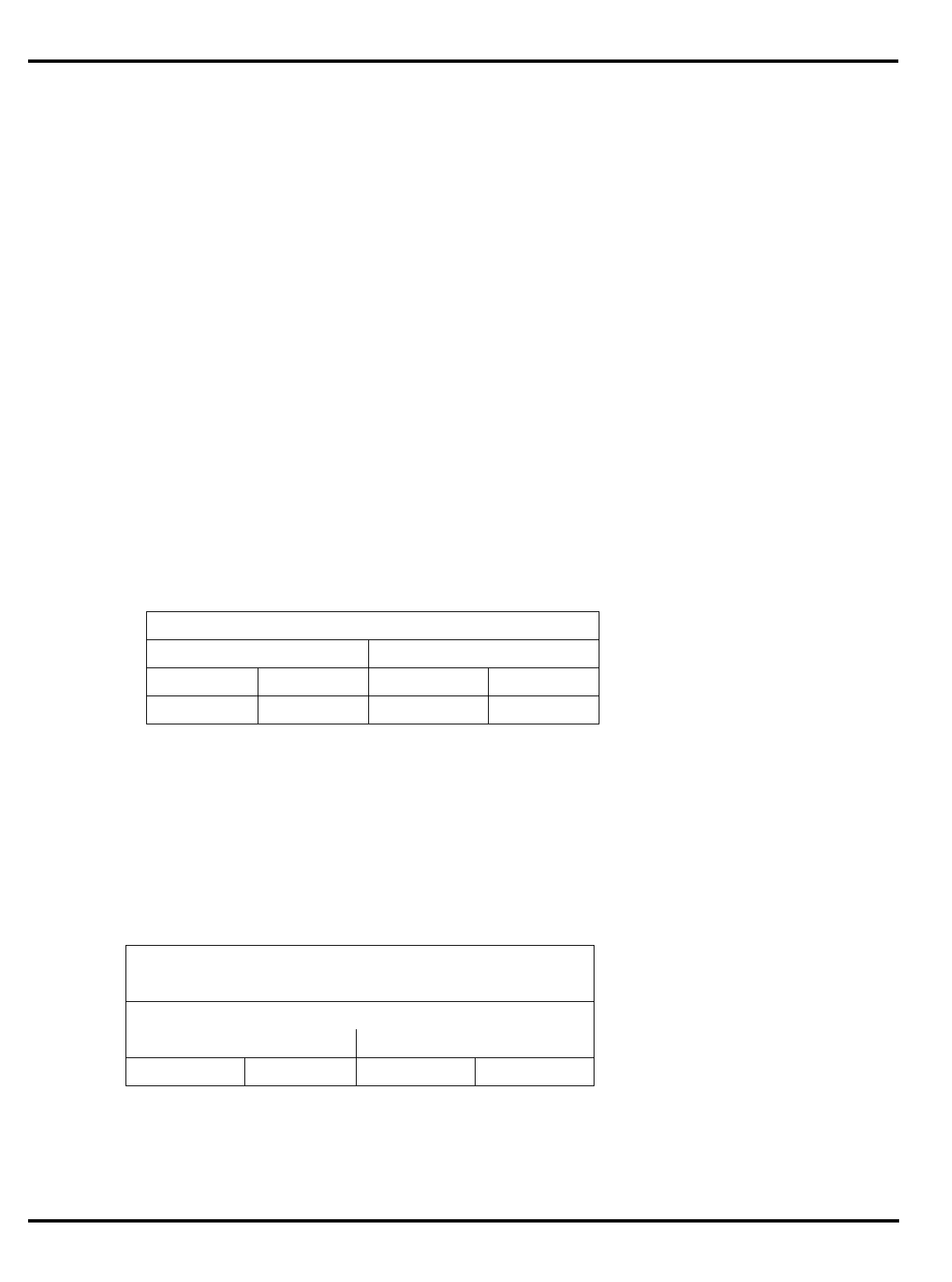

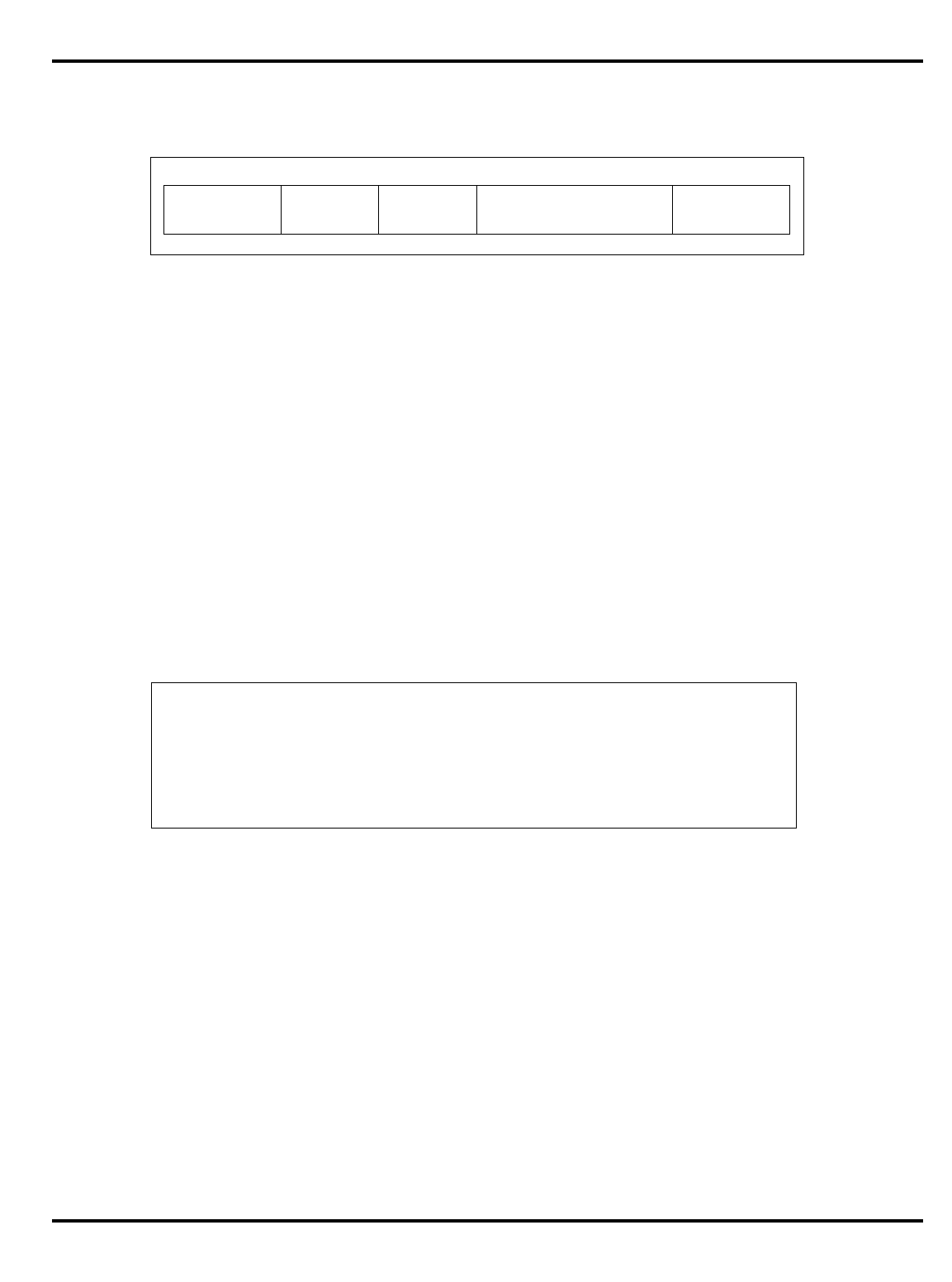

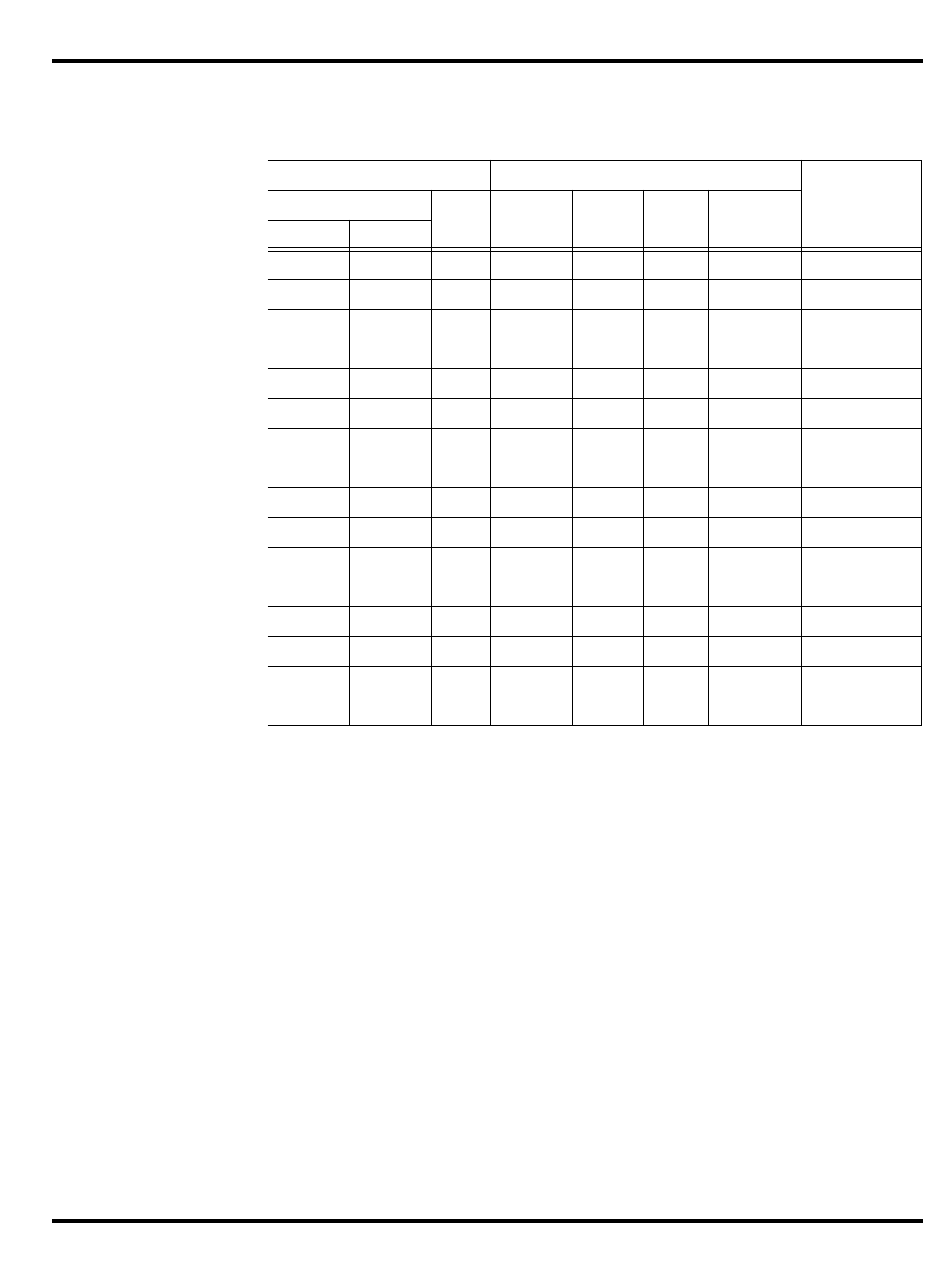

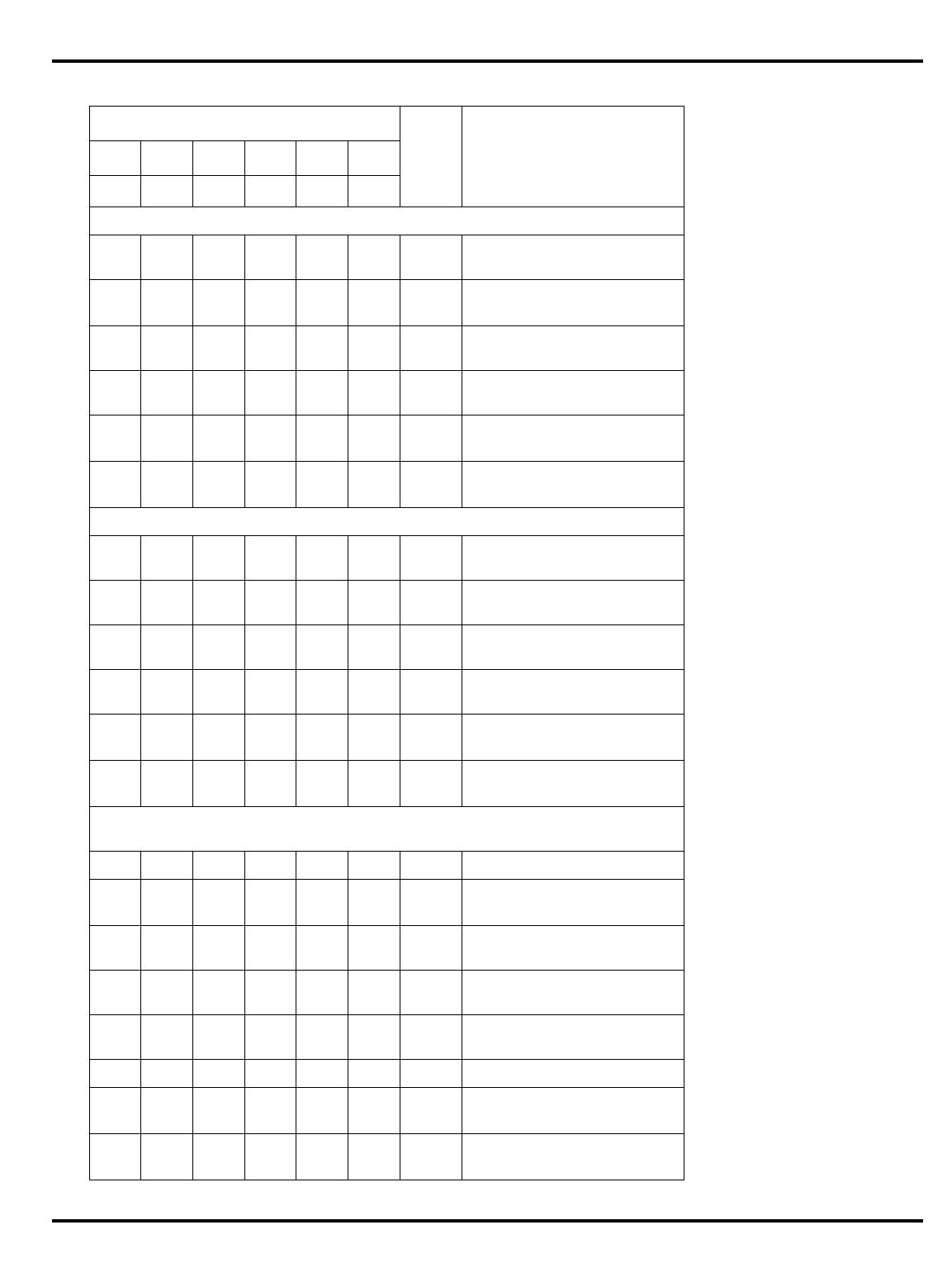

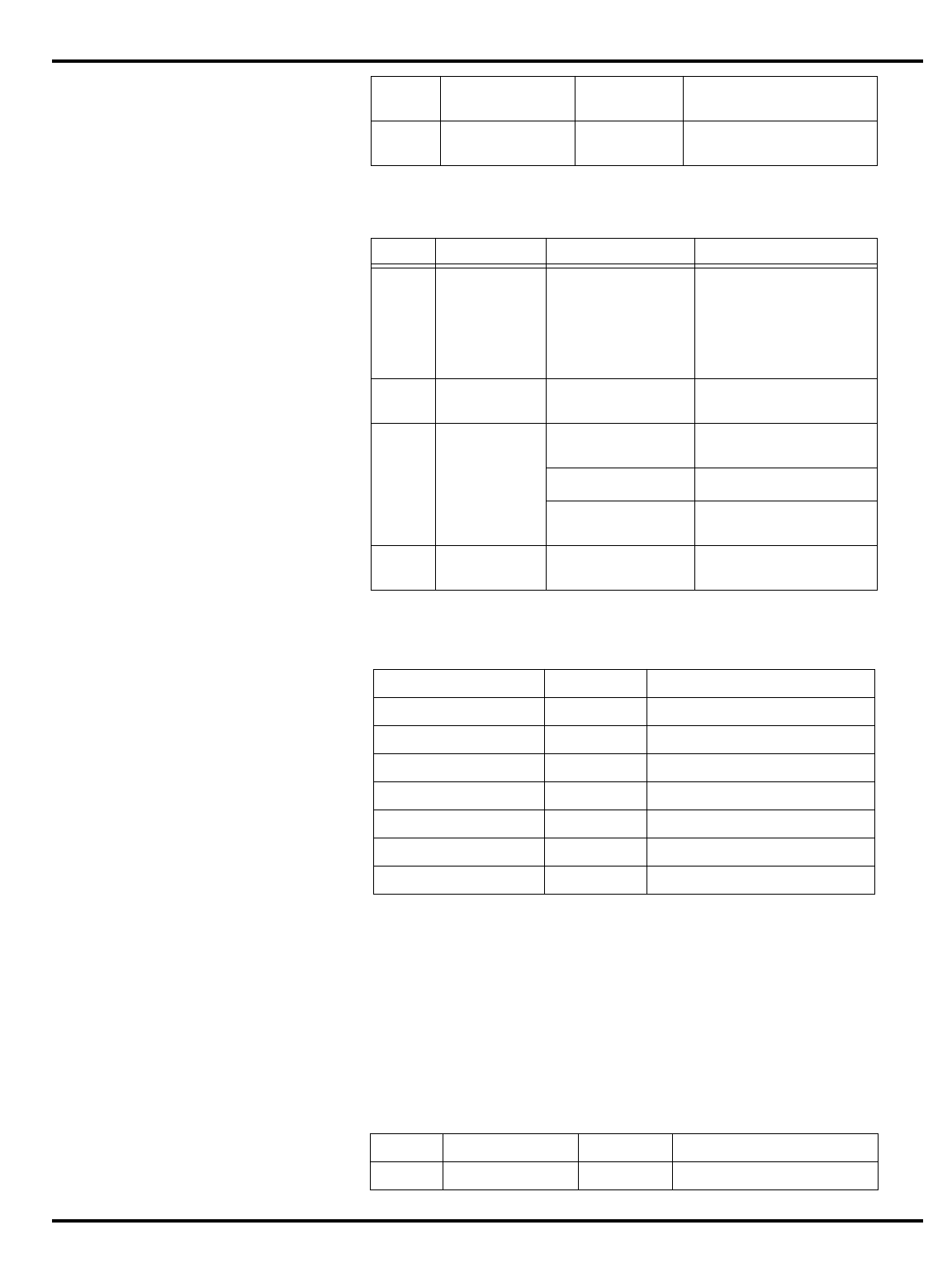

1.1 R30xx Family Members Compared..................................................................... 1-4

2.1 Conventional Names of Registers with Usage Mnemonics................................. 2-2

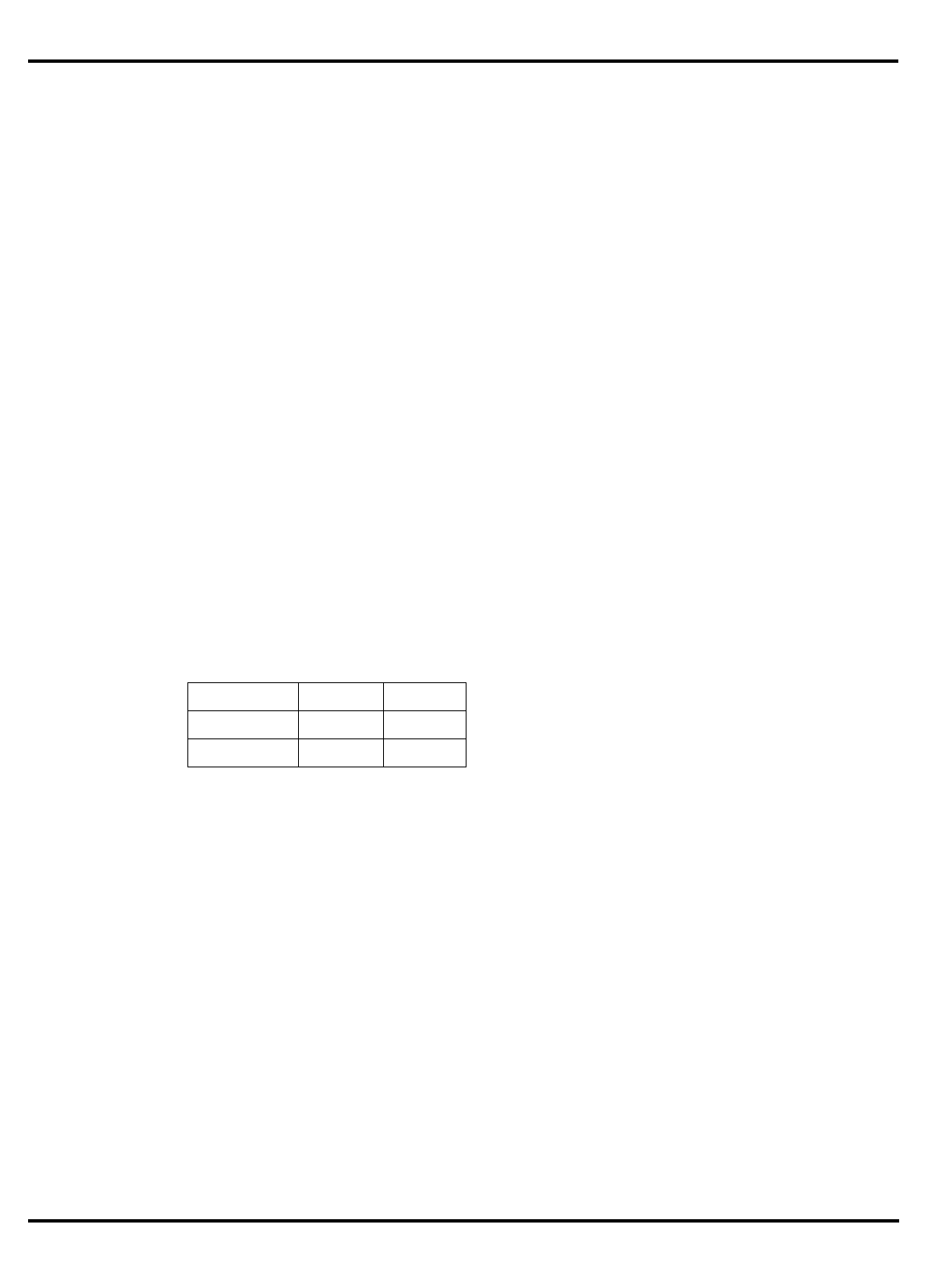

3.1 Summary of CPU Control Registers (Not MMU)............................................... 3-3

3.2 ExcCode Values: Different kinds of Exceptions ................................................. 3-7

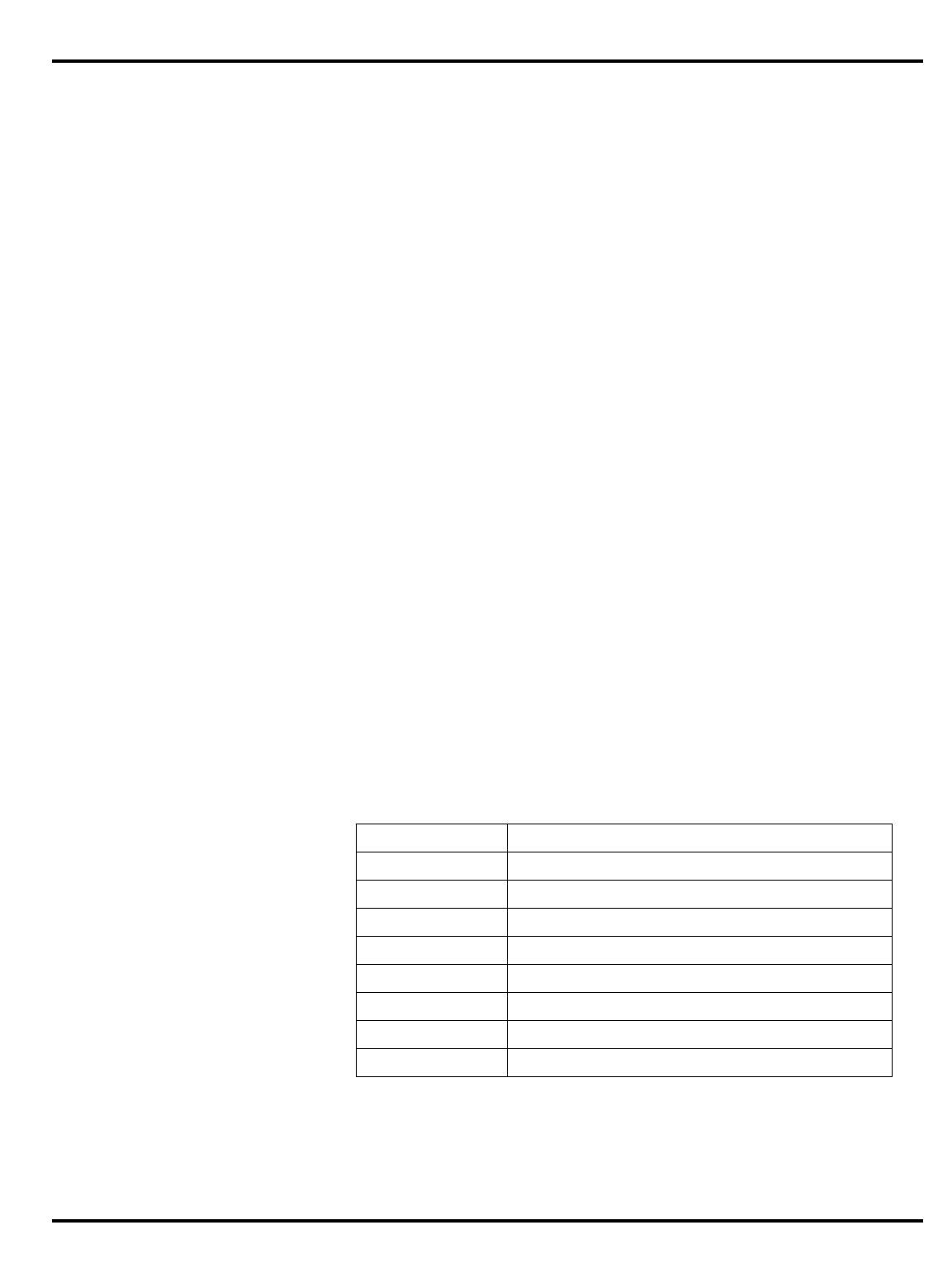

4.1 Reset and Exception Entry Points (Vectors) for R30xx Family.......................... 4-3

4.2 Interrupt Bitfields and Interrup Pins .................................................................. 4-13

6.1 CPU Control Registers for Memory Management .............................................. 6-3

8.1 Floating Point Data Formats................................................................................ 8-4

8.2 Rounding Modes Encoded in FP Control/Status Register................................... 8-7

8.4 FP Move Instructions........................................................................................... 8-9

8.5 FPA 3-Operand Arithmetic................................................................................ 8-10

8.6 FPA Sign-Changing Operators .......................................................................... 8-10

8.7 FPA Data Conversion Operations...................................................................... 8-10

8.8 FP Test Instructions ........................................................................................... 8-11

9.1 Assembler Register and Identifier Conventions ................................................ 9-20

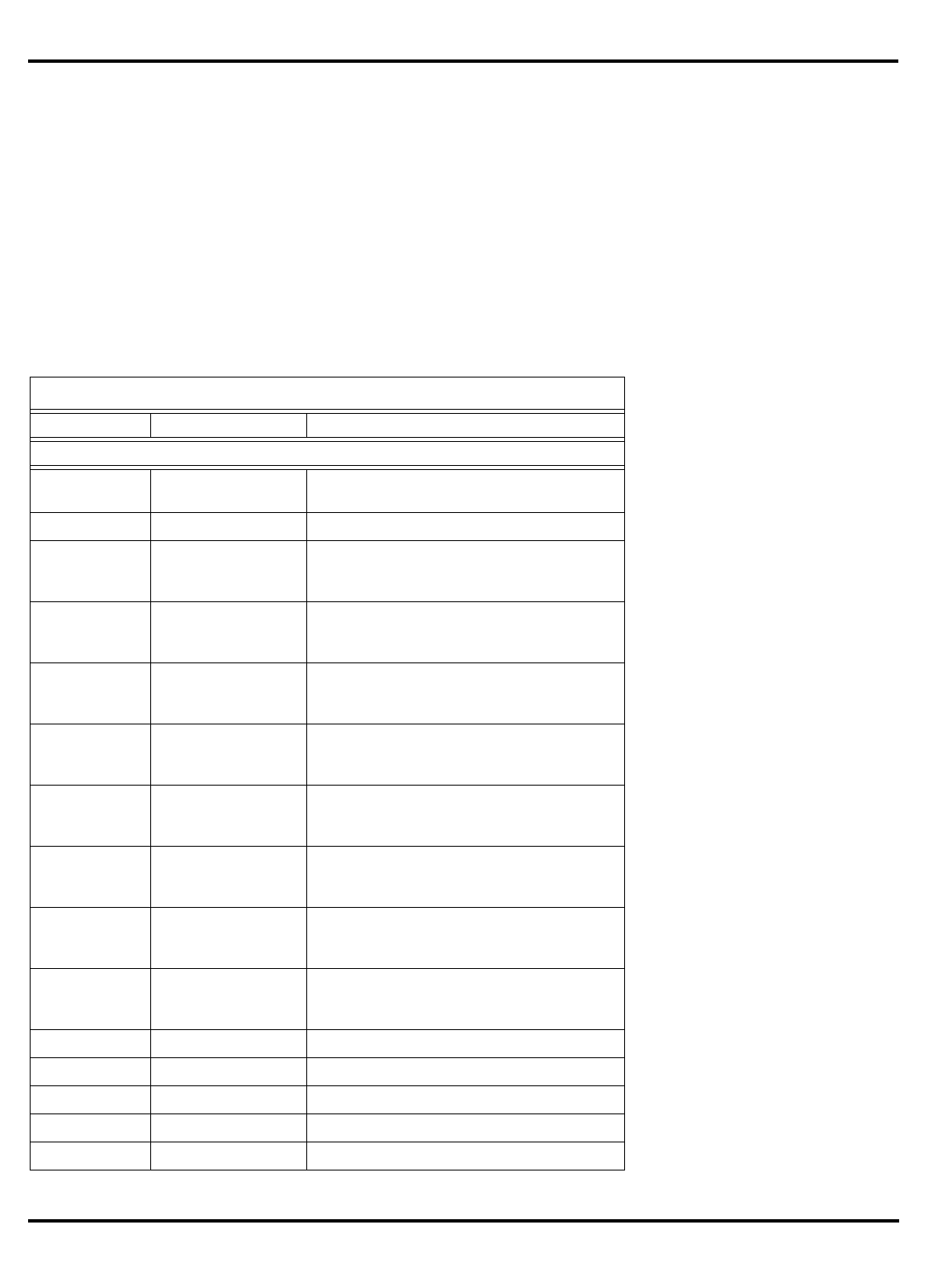

9.2 Assembler Instructions....................................................................................... 9-20

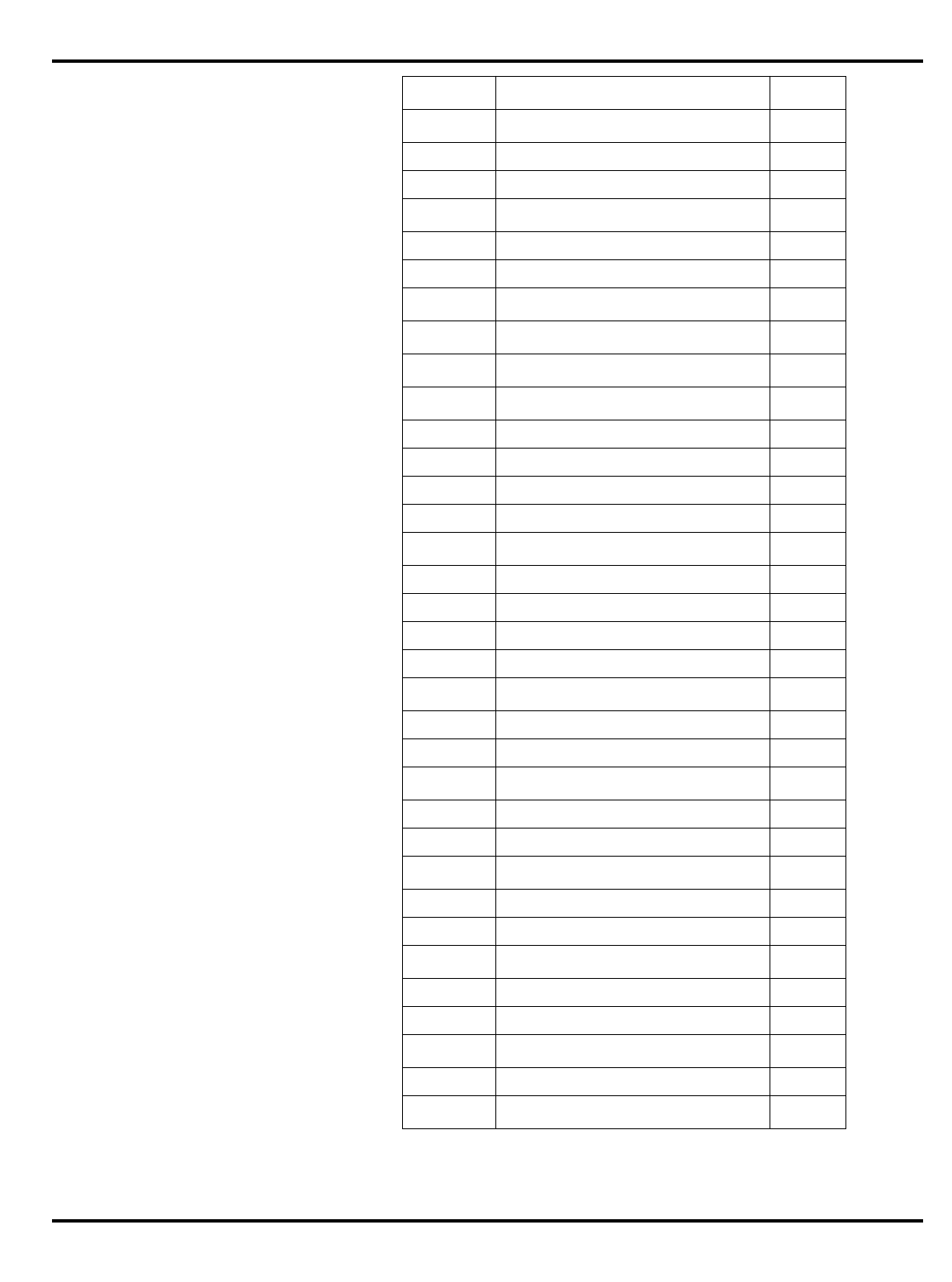

12.1 Test Sequence in Brief....................................................................................... 12-5

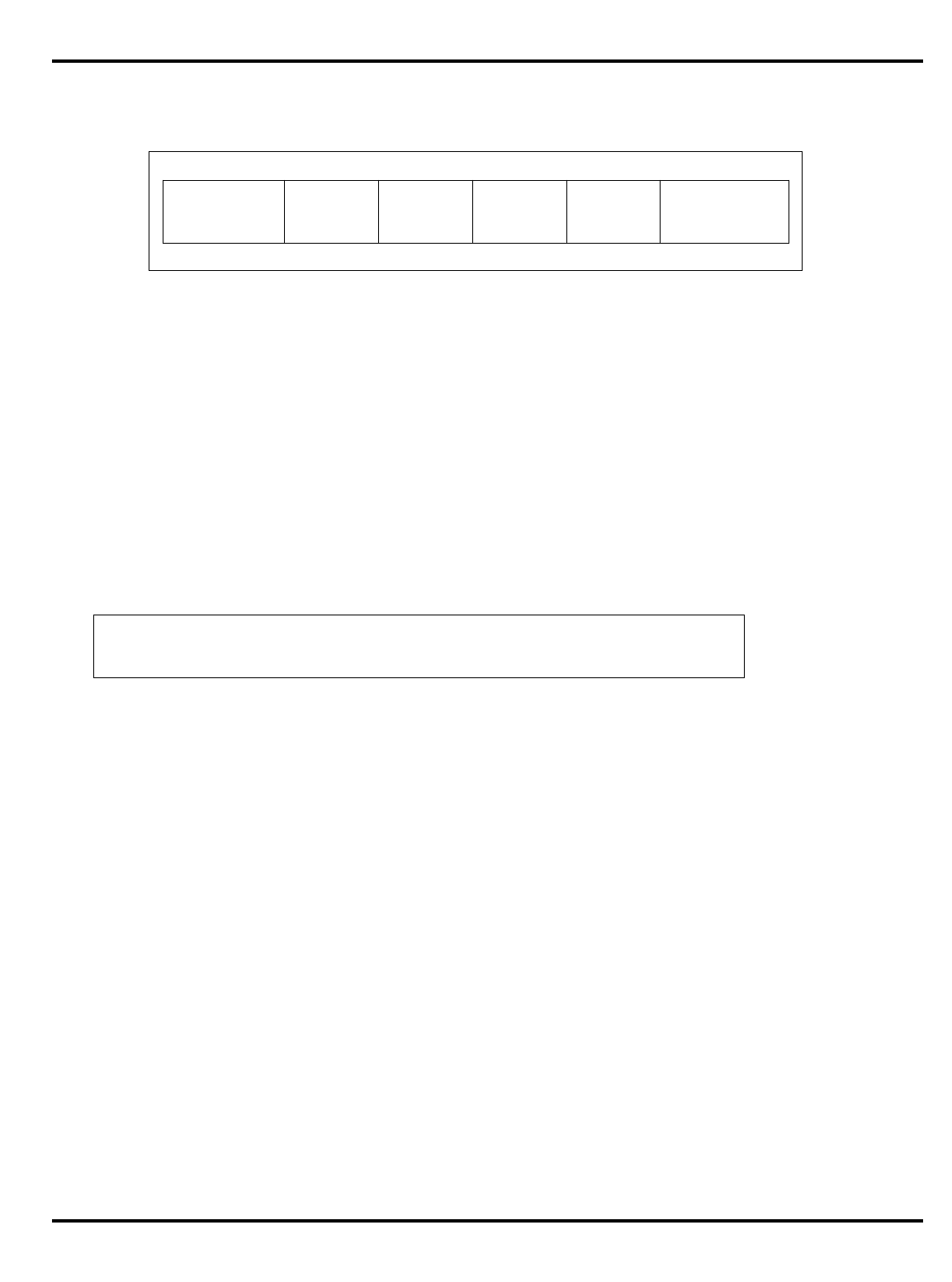

16.1 32-bit Immediate Values.................................................................................... 16-1

16.2 Add-With-Carry................................................................................................. 16-2

16.3 Subtract-with-Borrow Operation ....................................................................... 16-3

A.1 CPU Instruction Operation Notations................................................................. A-3

A.2 Load and Store Common Function..................................................................... A-4

A.3 Access Type Specifications for Load/Store........................................................ A-5

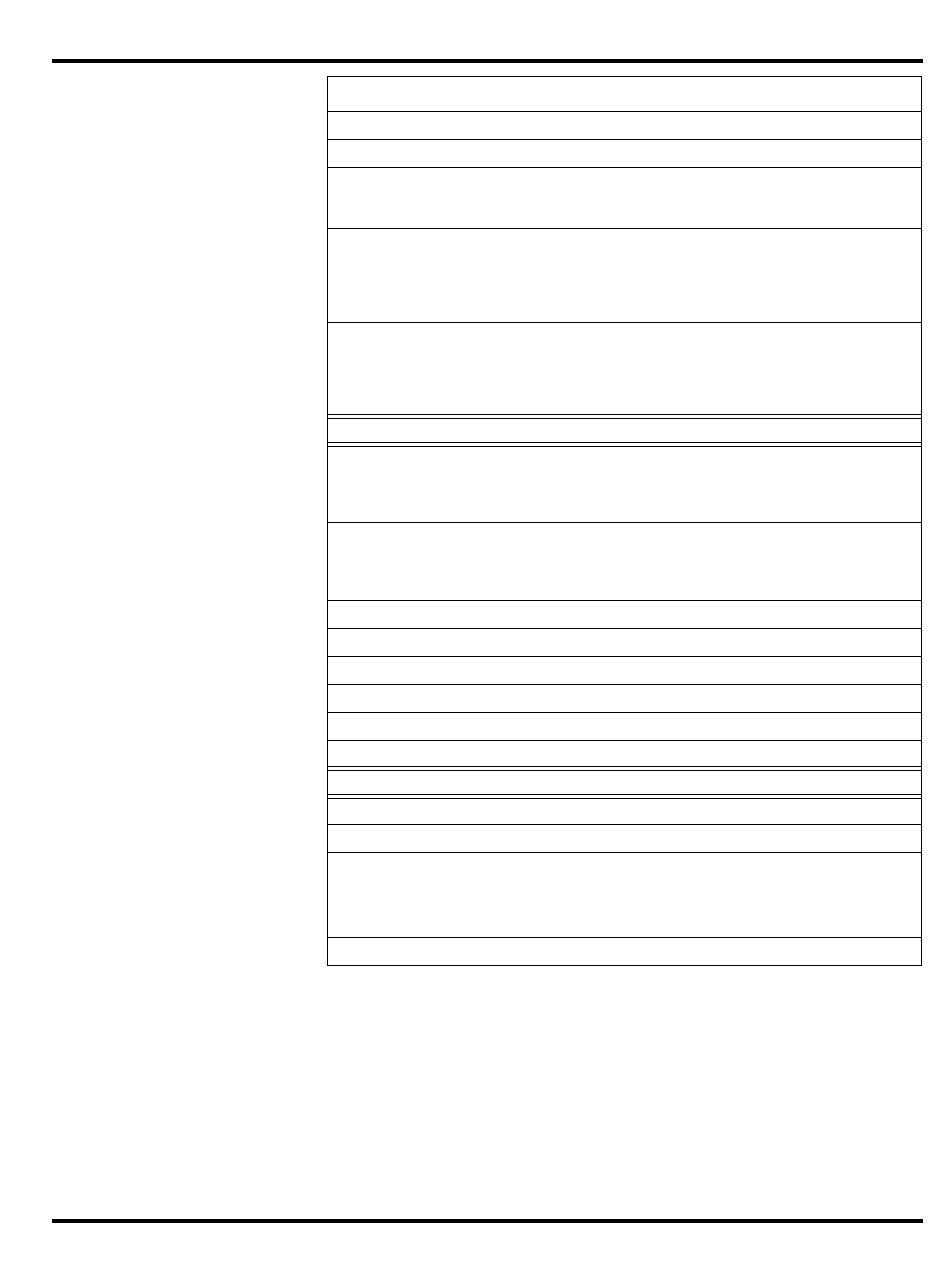

B.1 Format Field Decoding ........................................................................................B-2

B.2 Logical Negation of Predicates by Condition True/False....................................B-3

B.3 Valid FP Operand Specifiers with 32-bit Coprocessor 1 Registers.....................B-4

B.4 Load and Store Common Functions ....................................................................B-6

1–1

INTRODUCTION

®

Integrated Device Technology, Inc.

CHAPTER 1

IDT’s R30xx family of RISC microcontrollers family includes the R3051,

R3052, R3071, R3081 and R3041 processors. The different members of

the family offer different price/performance trade-offs, but are all basically

integrated versions of the MIPS R3000A CPU. The R3000A CPU is well

known for the high-performance Unix systems implemented around it; less

publicized but equally impressive is the performance it has brought to a

wide variety of embedded applications.

IDT’s RISController family also includes devices built around MIPS

R4000 64-bit microprocessor technology. These devices, such as the IDT

R4600 Orion microprocessor, offer even higher levels of performance than

the R3000A derivative family. However, these devices also feature slightly

different OS models, and allow 64-bit kernels and applications. Thus, they

are sufficiently different from the R30xx family that this manual is focused

exclusively on the R30xx family.

This manual is aimed at the programmer dealing with the IDT R30xx

family components. Although most programming occurs using a high-level

language (usually “C”), and with little awareness of the underlying system

or processor architecture, certain operations require the programmer to

use assembly programming, and/or be aware of the underlying system or

processor structure. This manual is designed to be consulted when

addressing these types of issues.

WHAT IS A RISC?

The MIPS CPU is one of the “RISC’’ CPUs, born out of a particularly

fertile period of academic research and development. RISC CPUs

(‘‘Reduced Instruction Set Computer’’) share a number of architectural

attributes to facilitate the implementation of high-performance processors.

Most new architectures (as opposed to implementations) since 1986 owe

their remarkable performance to features developed a few years earlier by

a couple of seminal research projects. Someone commented that ‘‘a RISC

is any computer architecture defined after 1984’’; although meant as a jibe

at the industry’s use of the acronym, the comment’s truth also derives

from the widespread acceptance of the conclusions of that research.

One of these was the ‘‘MIPS’’ project at Stanford University. The project

name MIPS puns the familiar ‘‘millions of instructions per second’’ by

taking its name from the key phrase ‘‘Microcomputer without Interlocked

Pipeline Stages’’. The Stanford group’s work showed that pipelining, a well-

known technique for speeding up computers, had been under-exploited by

earlier architectures.

1

CHAPTER 1 INTRODUCTION

1–2

PIPELINES

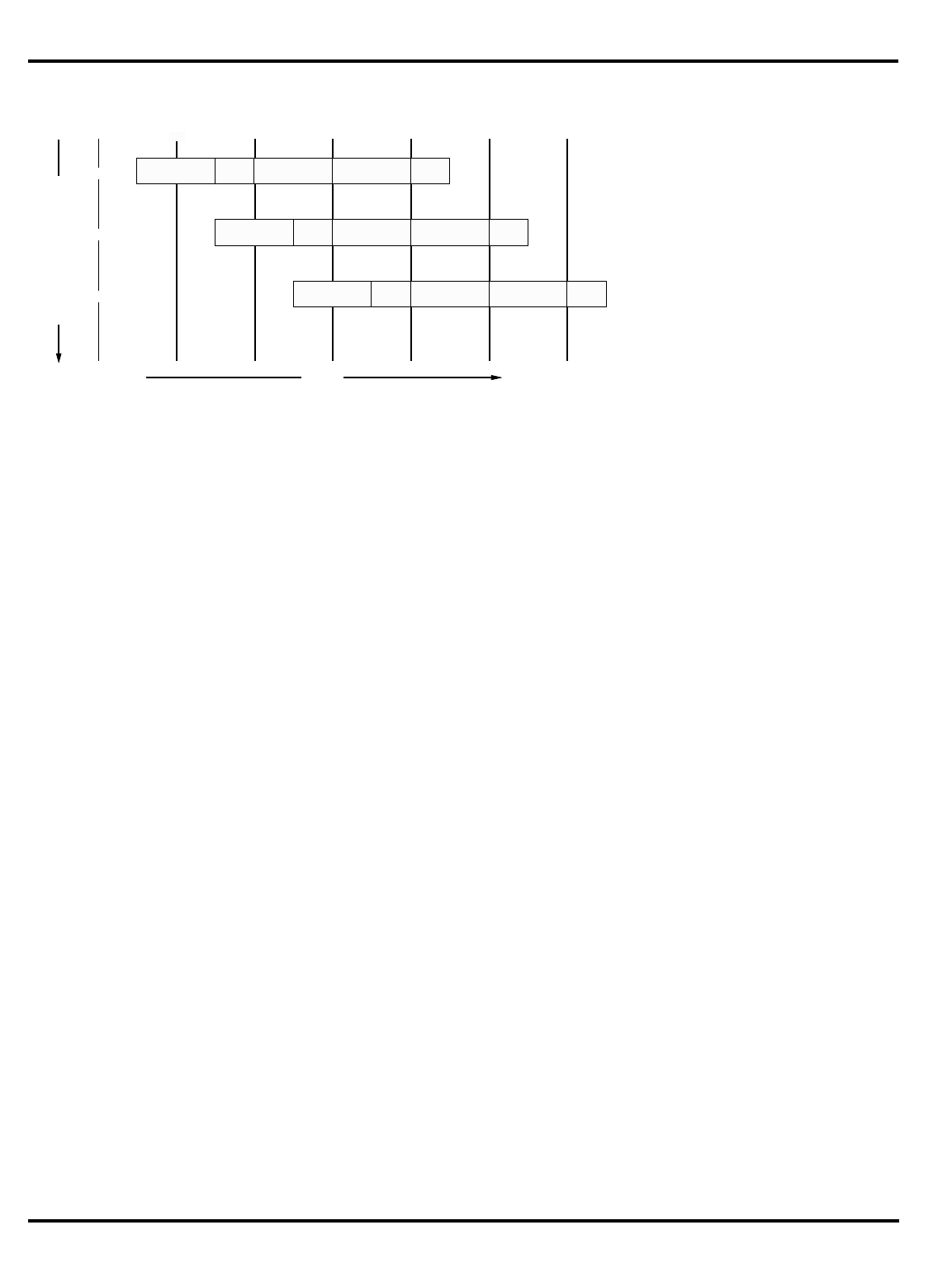

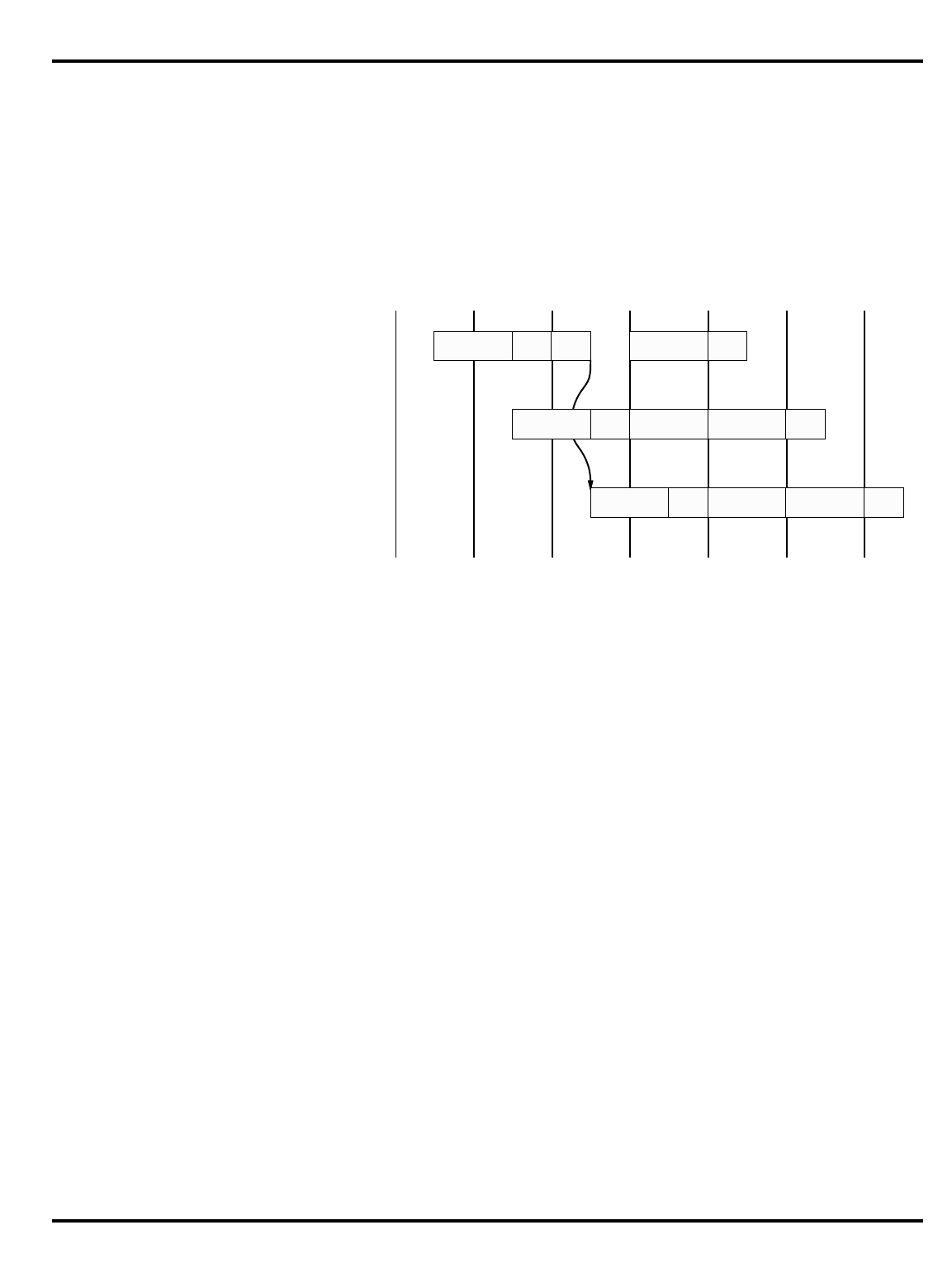

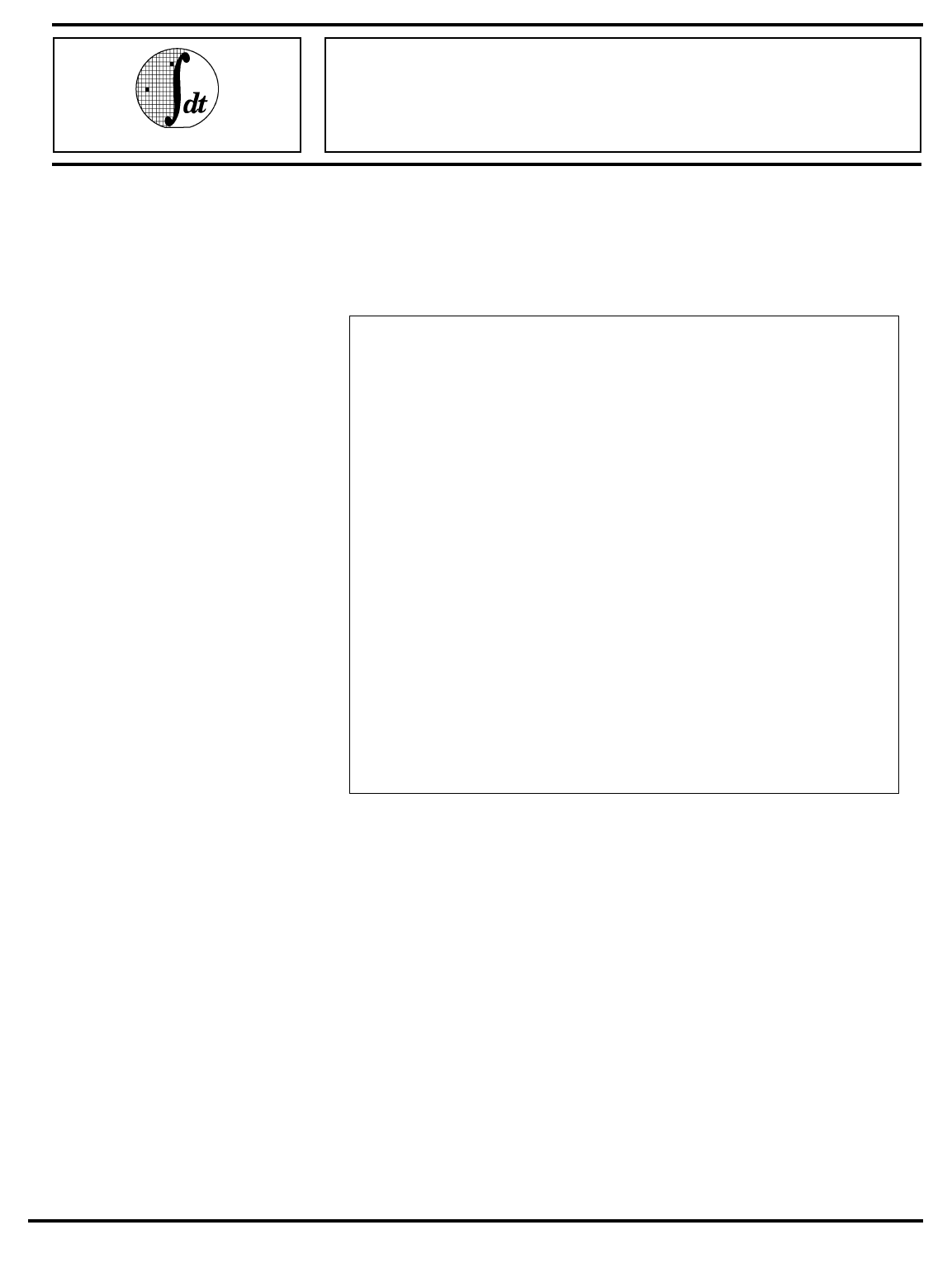

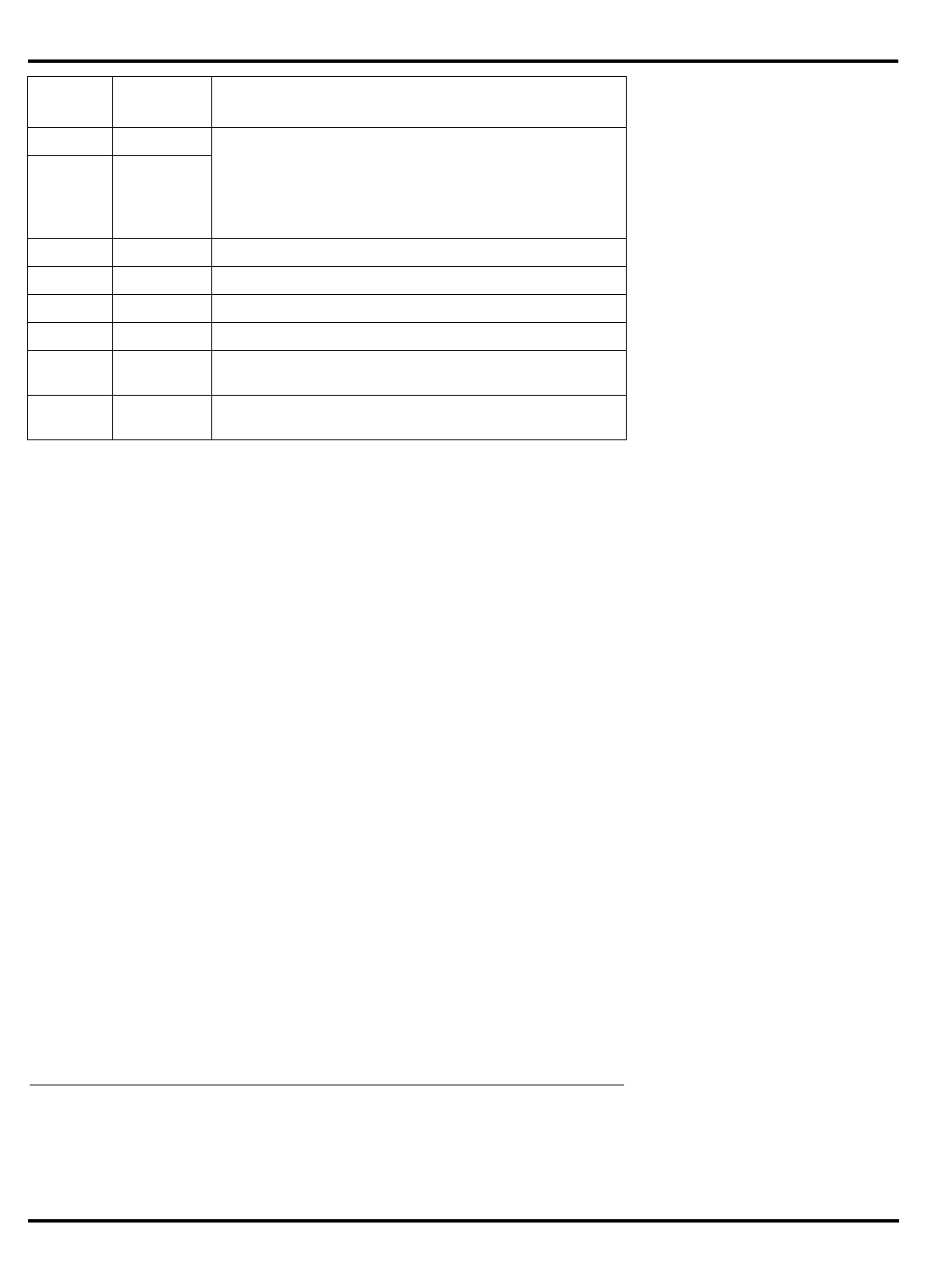

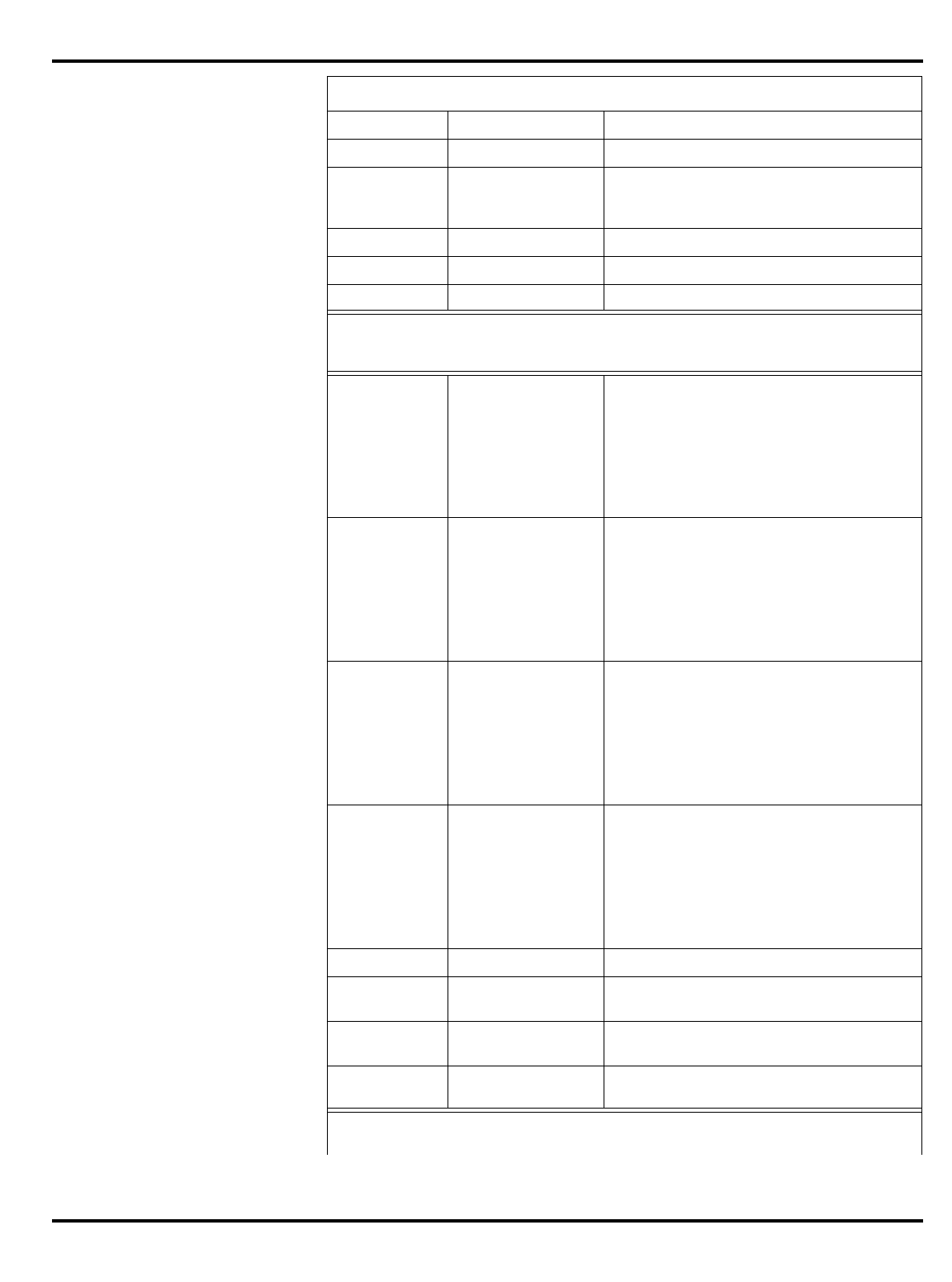

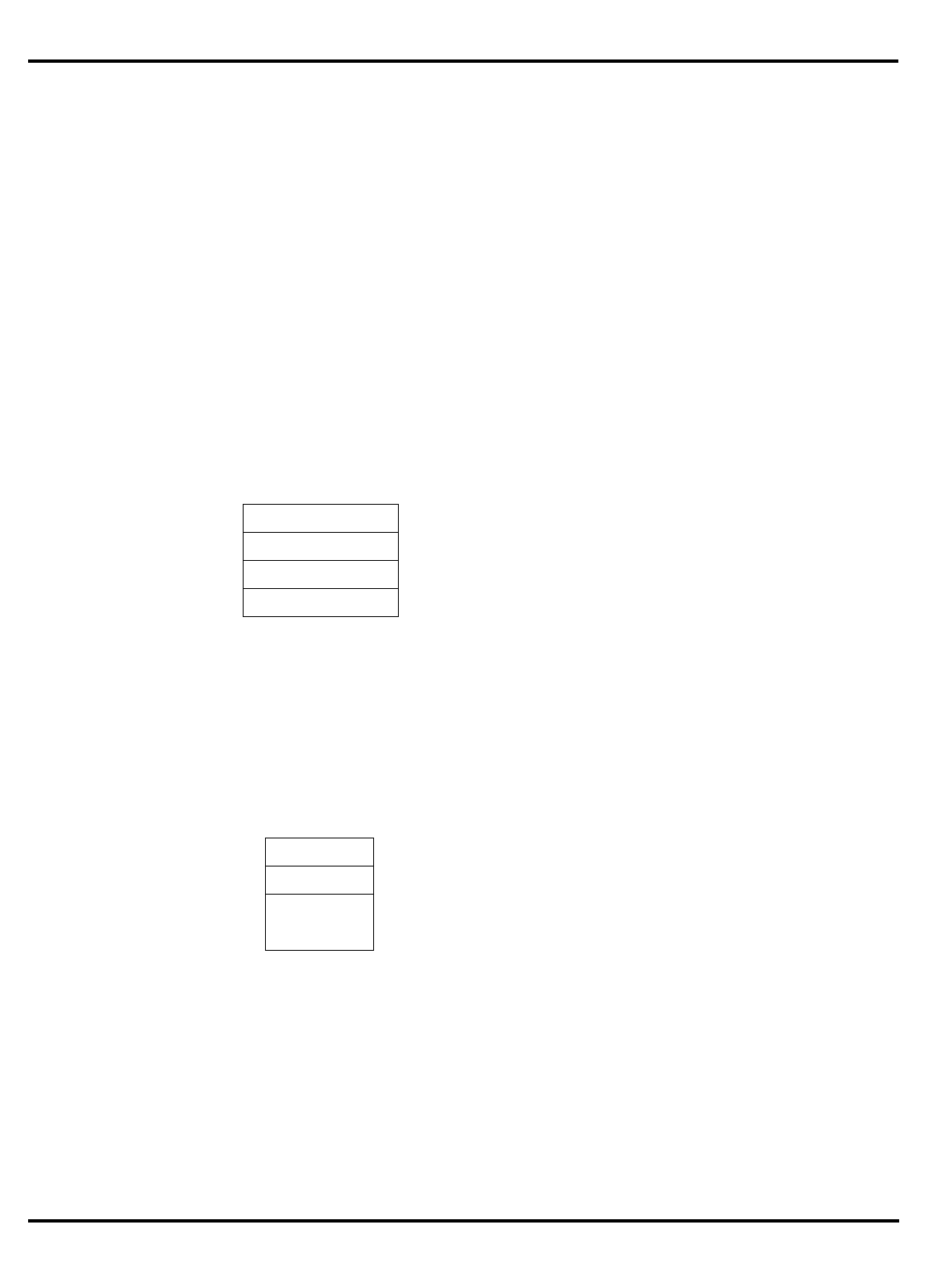

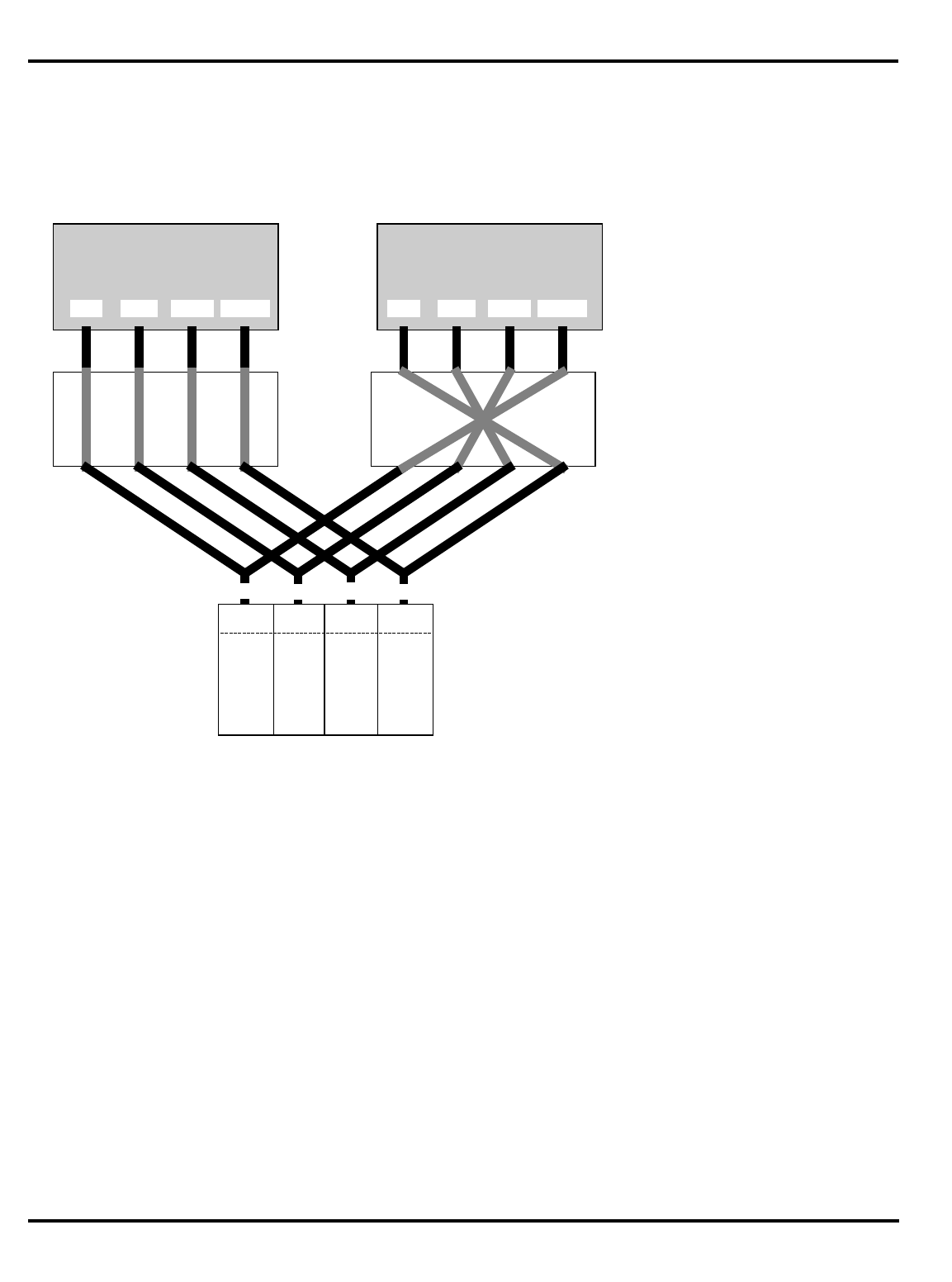

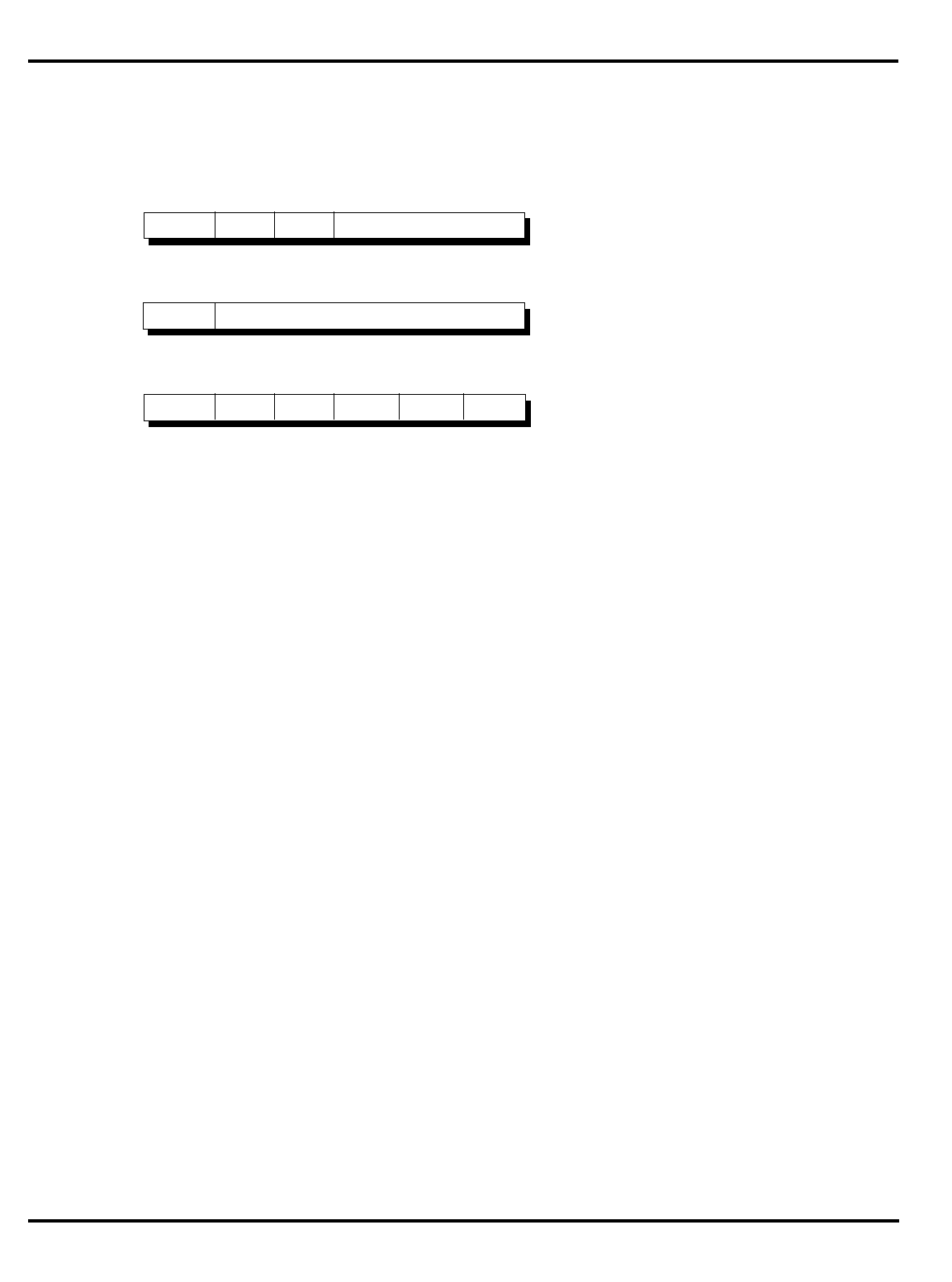

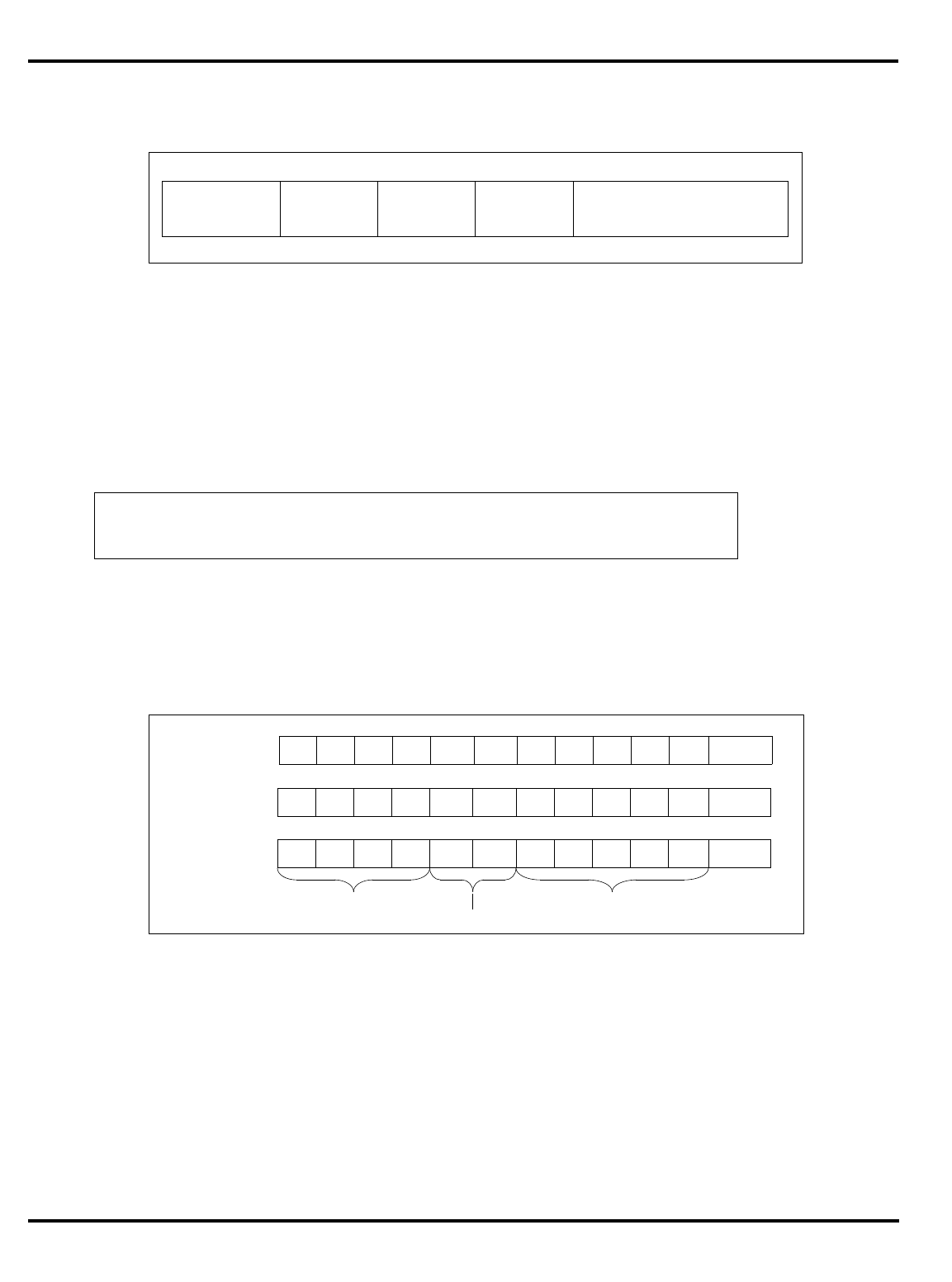

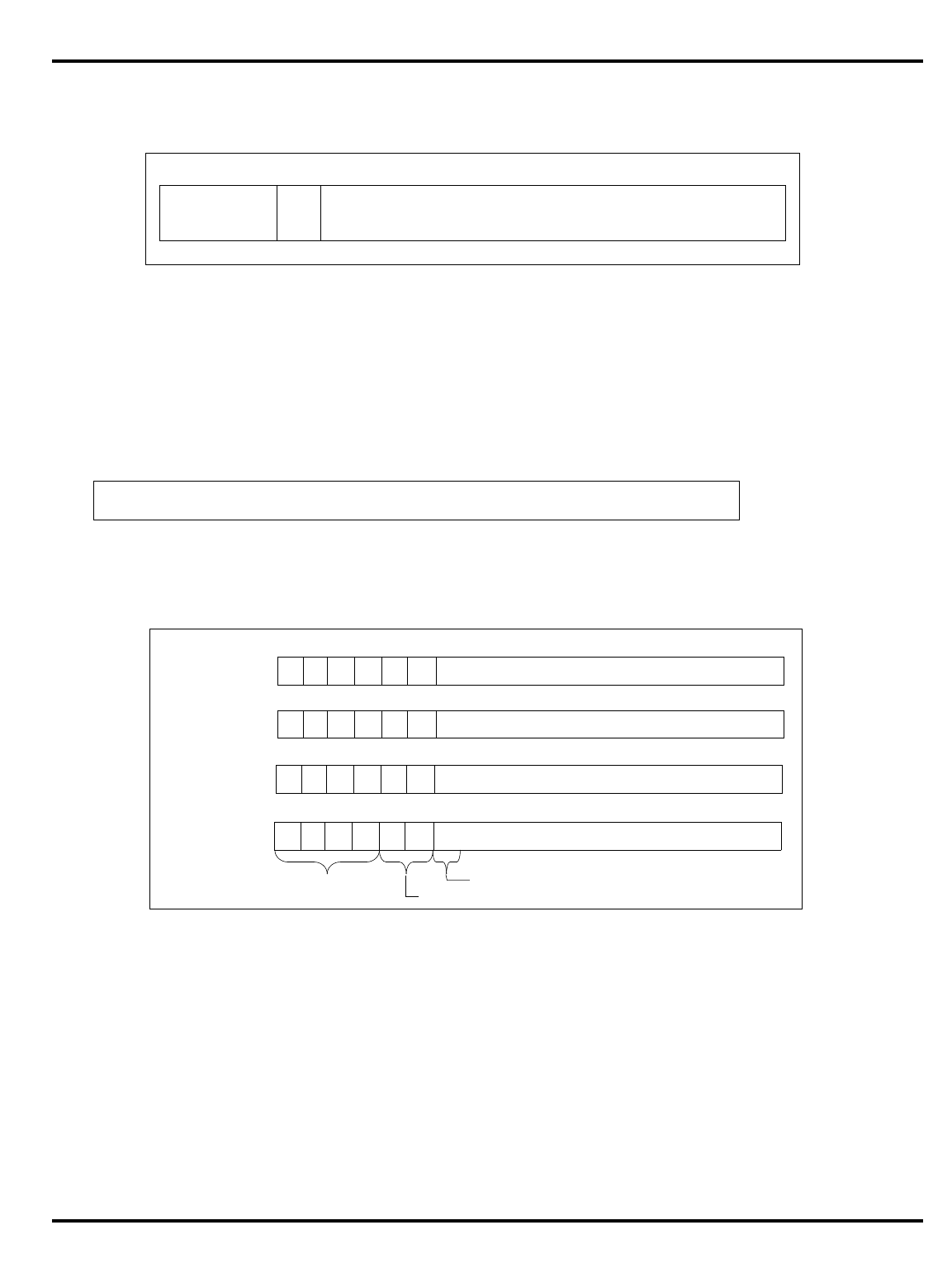

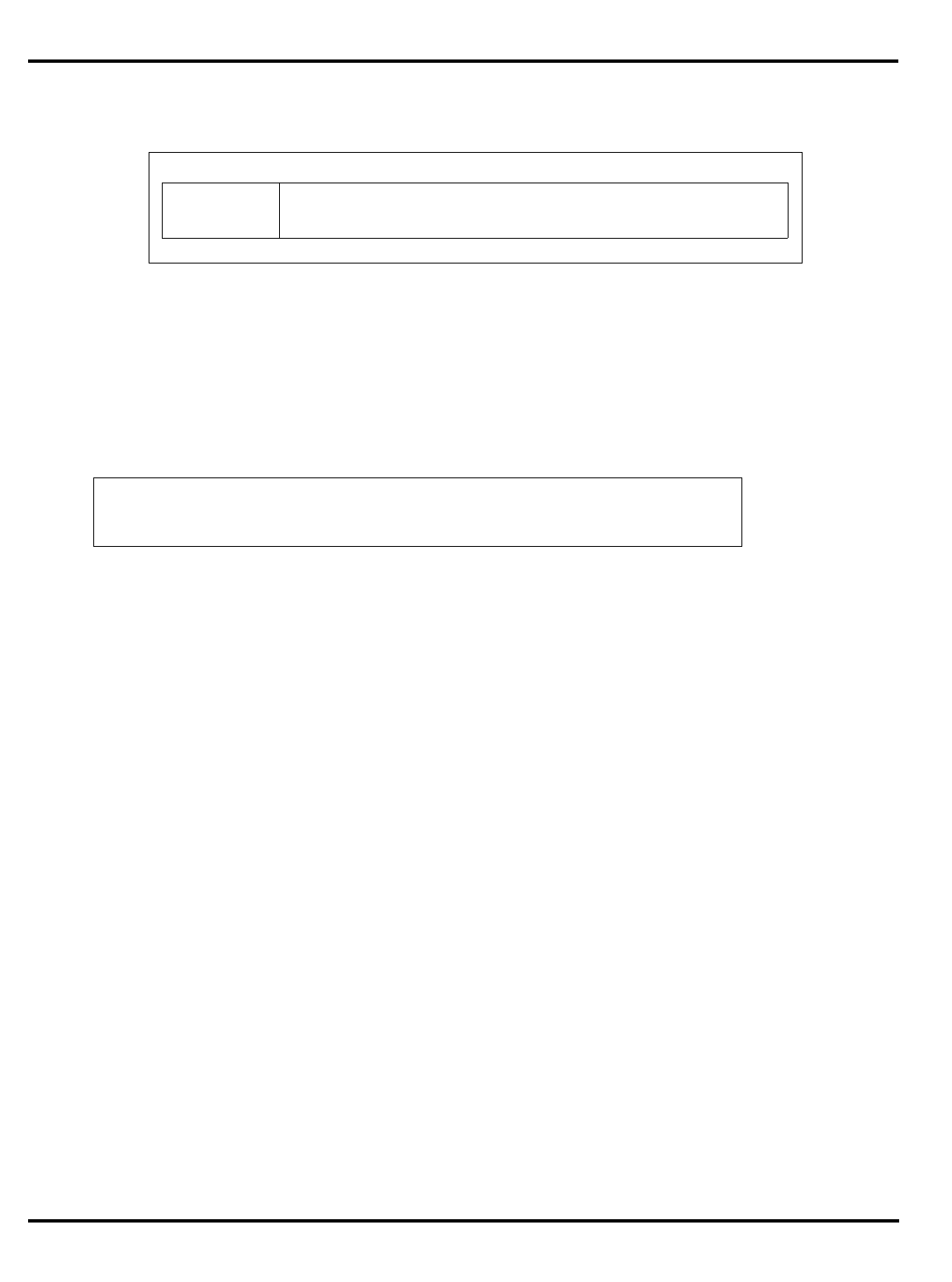

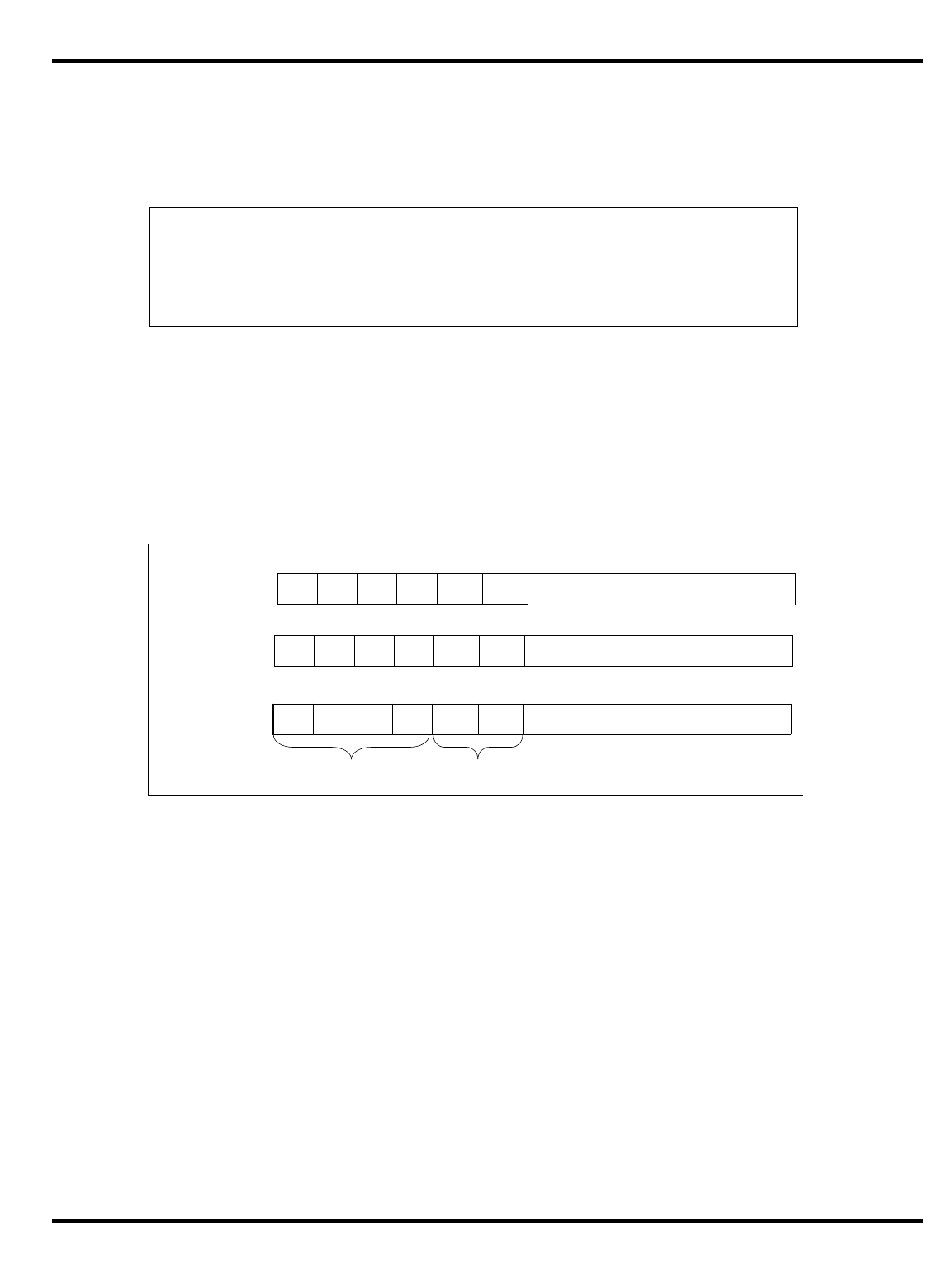

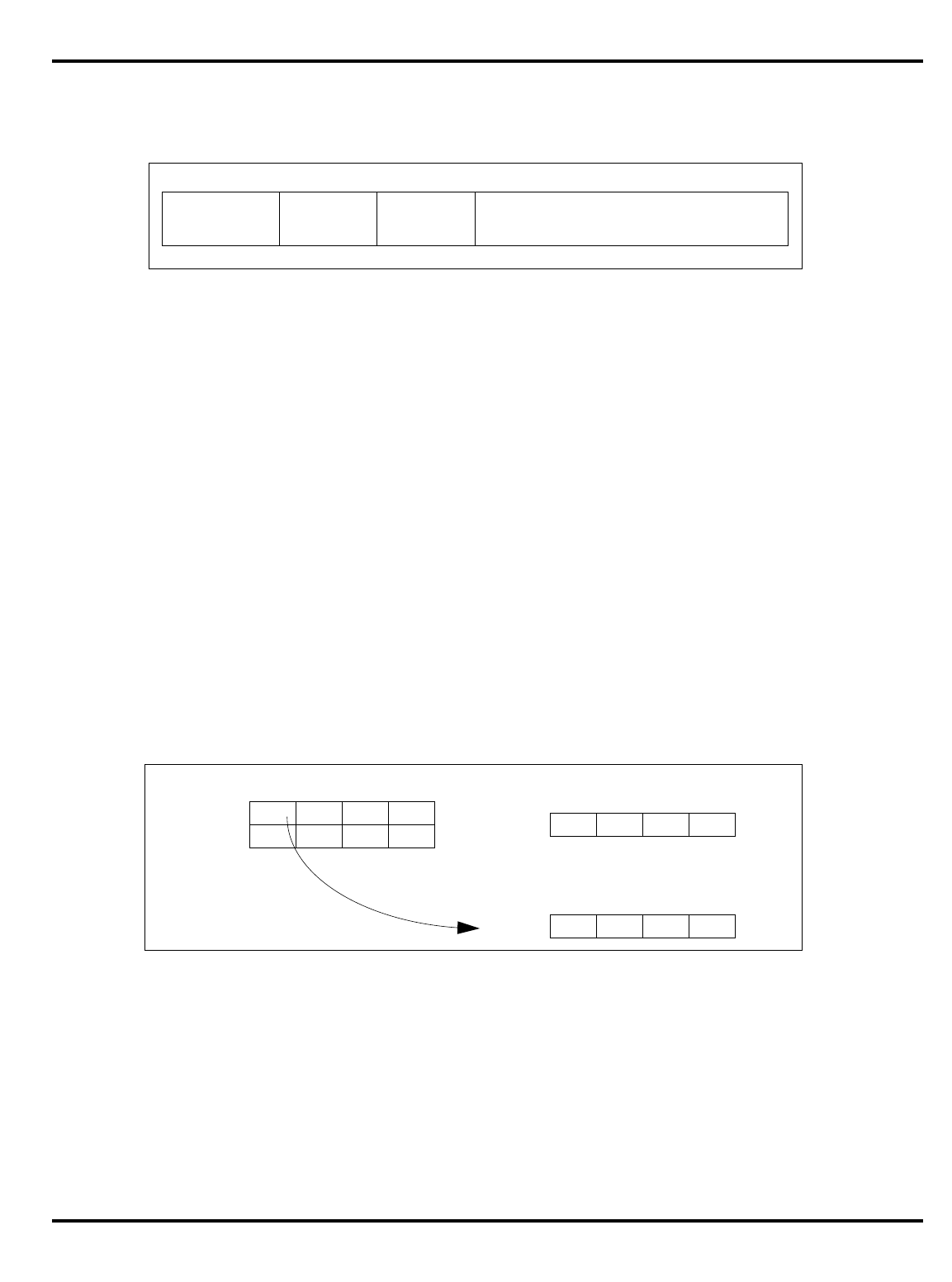

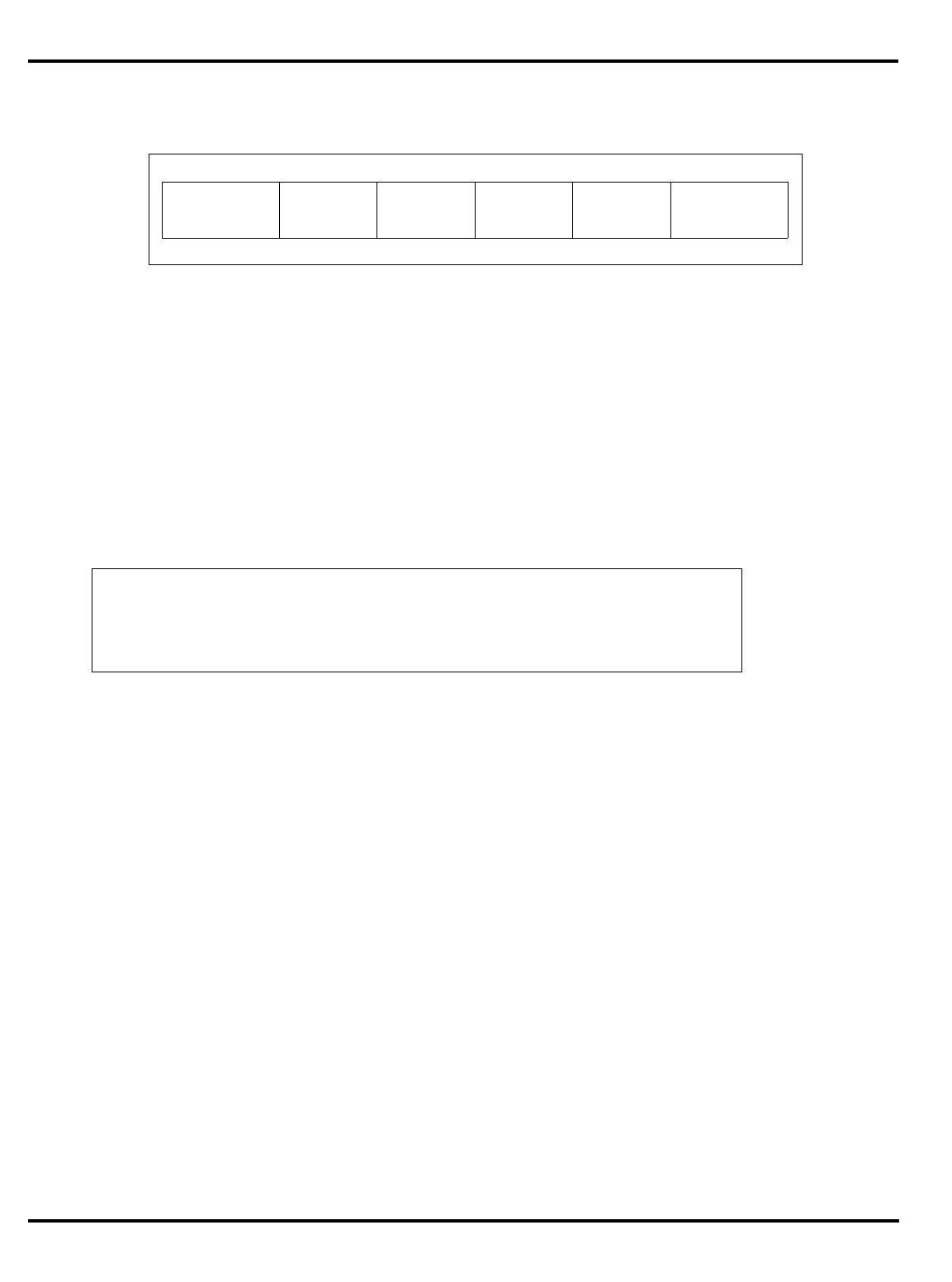

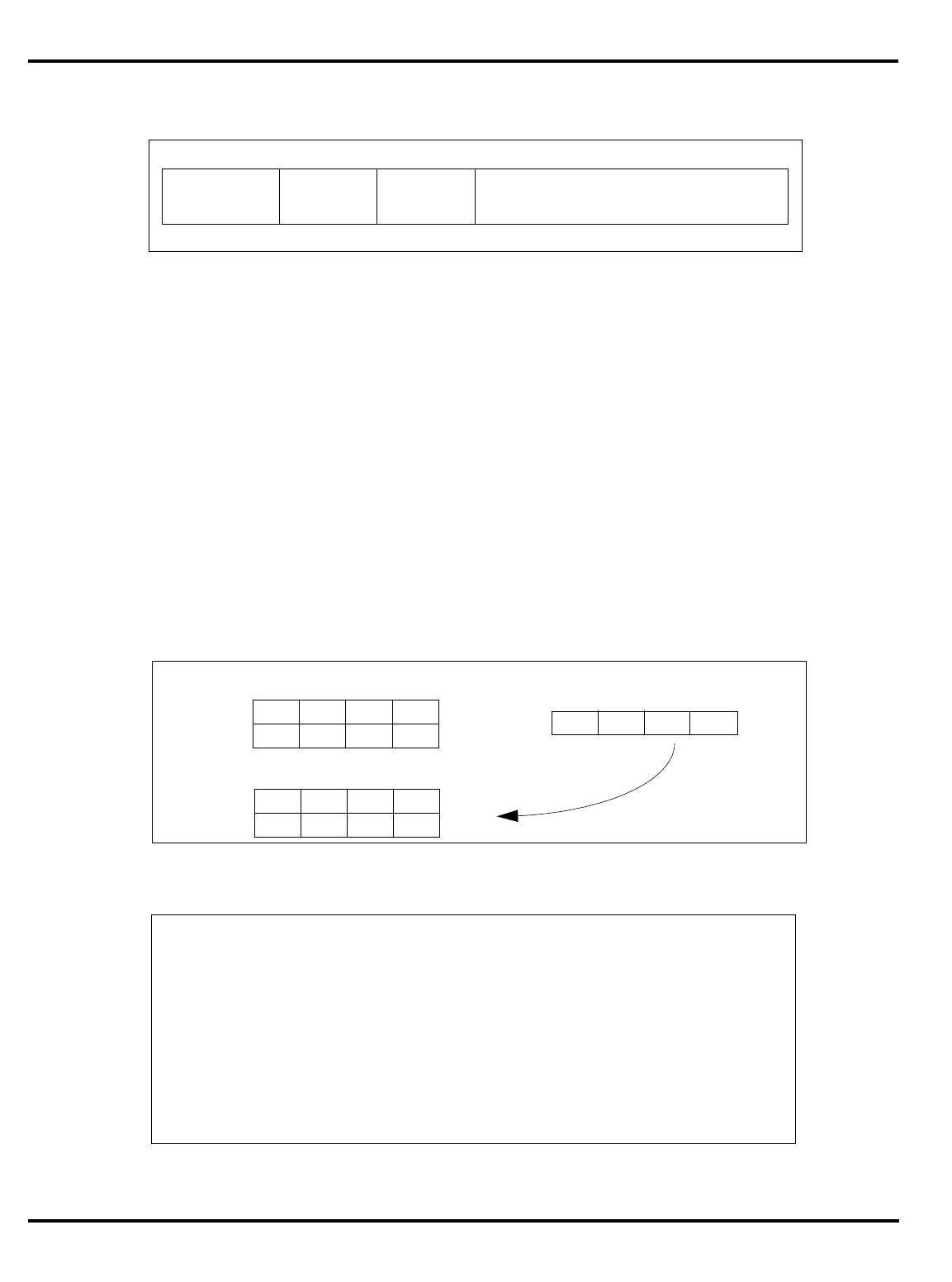

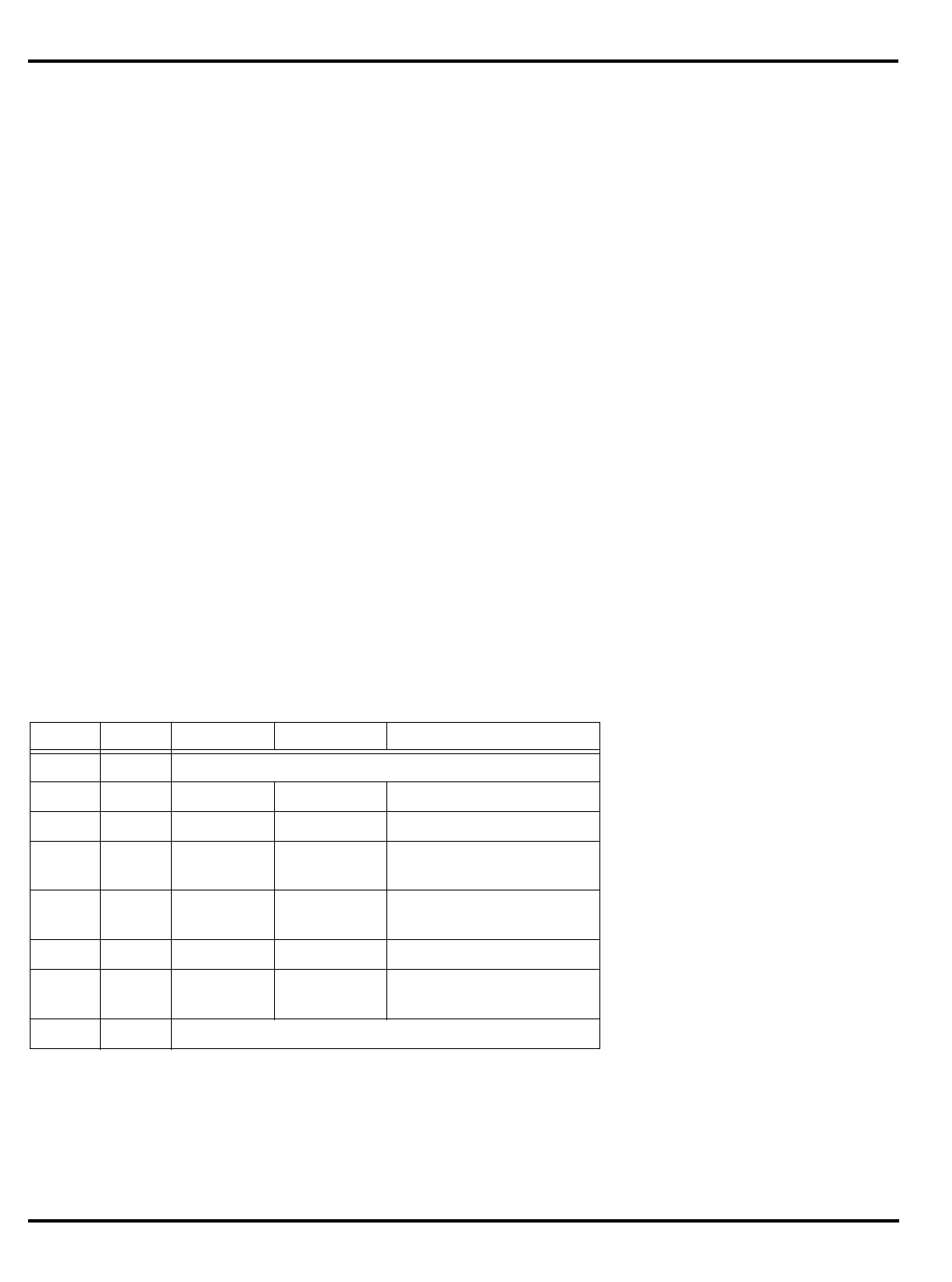

Figure 1.1. MIPS 5-stage pipeline

Pipelined processors operate by breaking instruction execution into

multiple small independent “stages”; since the stages are independent,

multiple instructions can be in varying states of completion at any one

time. Also, this organization tends to facilitate higher frequencies of

operation, since very complex activities can be broken down into “bite-

sized” chunks. The result is that multiple instructions are executing at any

one time, and that instructions are initiated (and completed) at very high

frequency. MIPS has consistently been among the most aggressive in the

utilization of these techniques.

Pipelining depends for its success on another technique; using

caches

to reduce the amount of time spent waiting for memory. The MIPS R3000A

architecture uses separate instruction and data caches, so it can fetch an

instruction and read or write a memory variable in the same clock phase.

By mating high-frequency operation to high memory-bandwidth, very

high-performance is achieved.

In CISC architectures, caches are often seen as part of memory. A RISC

architecture makes more sense if the dual caches are regarded as very

much part of the CPU; in fact, the pipelines of virtually all RISC processors

require caches to maintain execution. The CPU normally runs from cache

and a cache miss (where data or instructions have to be fetched from

memory) is seen as an exceptional event.

For the R3000A and its derivatives, instruction execution is divided into

five phases (called

pipestages

), with each pipestage taking a fixed amount

of time (see “MIPS 5-stage pipeline” on page 1-2). Again, note that this

model assumes that instruction fetches and data accesses can be satisfied

from the processor caches at the processor operation frequency. All

instructions are rigidly defined to follow the same sequence of pipestages,

even where the instruction does nothing at some stage.

The net result is that, so long as it keeps hitting the cache, the CPU

starts an instruction every clock.

"Figure 1.1. MIPS 5-stage pipeline”, illustrates this operation.

Instruction execution activity can be described as occurring in the

individual pipestages:

•

IF

: (‘‘instruction fetch’’) gets the next instruction from the instruction

cache (

I-cache

).

•

RD

: (‘‘read registers’’) decodes the instruction and fetches the

contents of any CPU registers it uses.

•

ALU

: (‘‘arithmetic/logic unit’’) performs an arithmetic or logical

operation in one clock (floating point math and integer multiply/

divide can’t be done in one clock and are done differently; this is

described later).

instr 1

instr 2

instr 3

ALU

I-cache D-cache

register

file register

file

RDIF ALU MEM WB

RDIF ALU MEM WB

RDIF ALU MEM WB

Time

Instruction sequence

INTRODUCTION CHAPTER 1

1–3

•

MEM

: the stage where the instruction can read/write memory

variables in the data cache (

D-cache

). Note that for typical programs,

three out of four instructions do nothing in this stage; but allocating

the stage to each instruction ensures that the processor never has

two instructions wanting the data cache at the same time.

•

WB

: (‘‘write back’’) store the value obtained from an operation back to

the register file.

A rigid pipeline does limit the kinds of things instructions can do; in

particular:

•

Instruction length

: ALL instructions are 32 bits (exactly one machine

‘‘word’’) long, so that they can be fetched in a constant time. This itself

discourages complexity; there are not enough bits in the instruction

to encode really complicated addressing modes, for example.

•

No arithmetic on memory variables

: data from cache or memory is

obtained only in stage 4, which is much too late to be available to the

ALU. Memory accesses occur only as simple load or store instructions

which move the data to or from registers (this is described as a ‘‘load/

store architecture’’).

However, the MIPS project architects also attended to the best thinking

of the time about what makes a CPU an easy target for efficient optimizing

compilers. So MIPS CPUs have 32 general purpose registers, 3-operand

arithmetical/logical instructions and eschew complex special-purpose

instructions which compilers can’t usually generate.

THE IDT R3xxx FAMILY CPUS

MIPS Corporation was formed in 1984 to make a commercial version of

the Stanford MIPS CPU. The commercial CPU was enhanced with memory

management hardware, first appearing late in 1985 as the R2000. An

ambitious external floating point math co-processor (the R2010 FPA) first

shipped in mid-87. The R3000, shipped in 1988, is almost identical from

the programmer’s viewpoint (although small hardware enhancements

combined to give a substantial boost to performance). The R3000A was

done in 1989, to improve the frequency of operation over the original

R3000 (other minor enhancements were added, such as the ability for user

tasks to operate with the opposite “endianness” from the kernel).

The R2000/R3000 chips include a cache controller – the

implementation of external caches merely required a few industry

standard SRAMs and some address latches. The math co-processor shares

the cache buses to interpret instructions (in parallel with the integer CPU)

and transfer operands and results between the FPA and memory or the

integer CPU.

The division of function was ingenious, practical and workable, allowing

the R2000/3000 generation to be built without extravagant ultra-high pin-

count packages. However, as clock speeds increased the very high-speed

signals in the cache interface increased design complexity and limited

operational frequency. In addition, overall chip count for the basic

execution core proved to be a limitation for area and power sensitive

embedded systems.

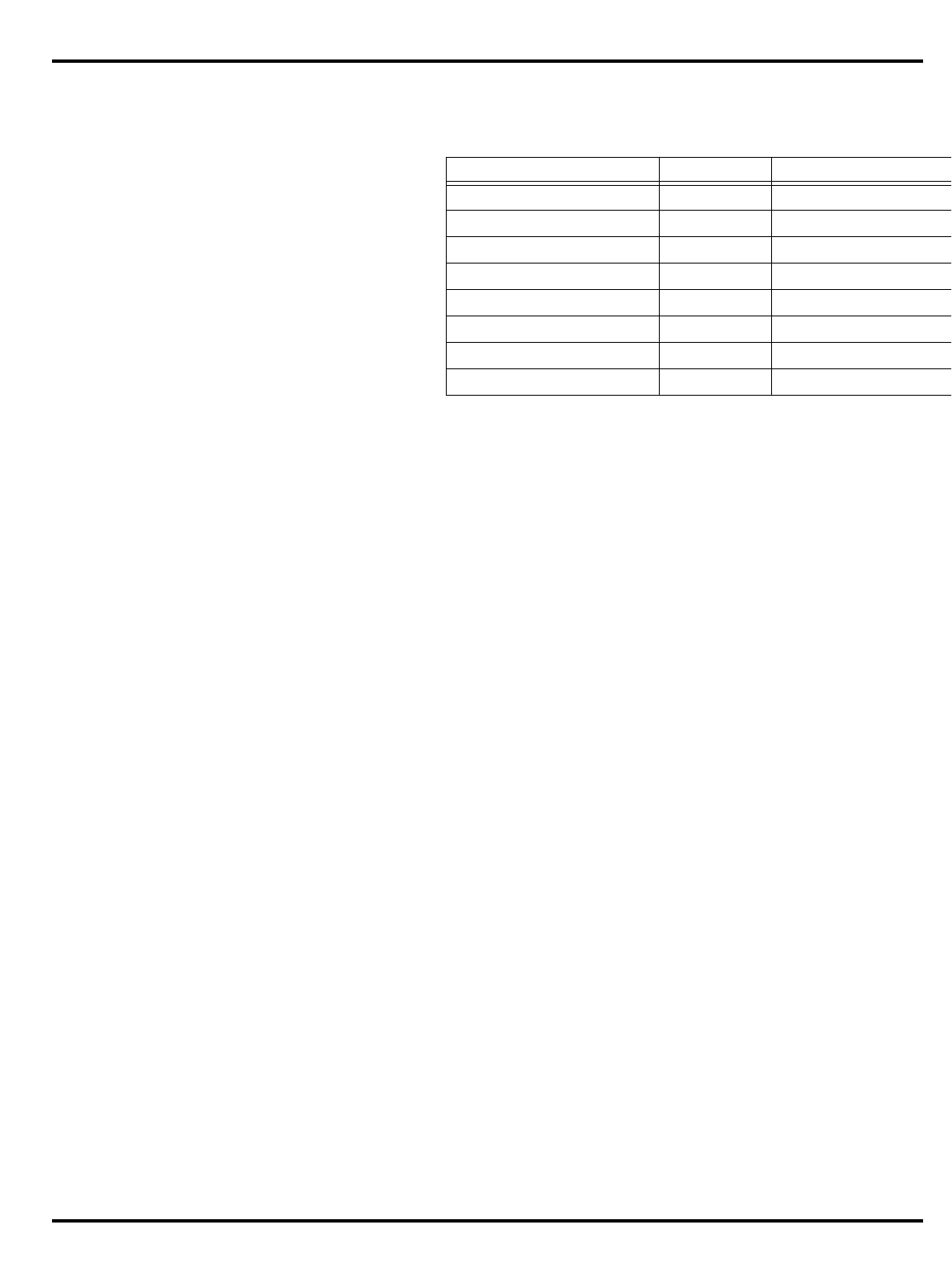

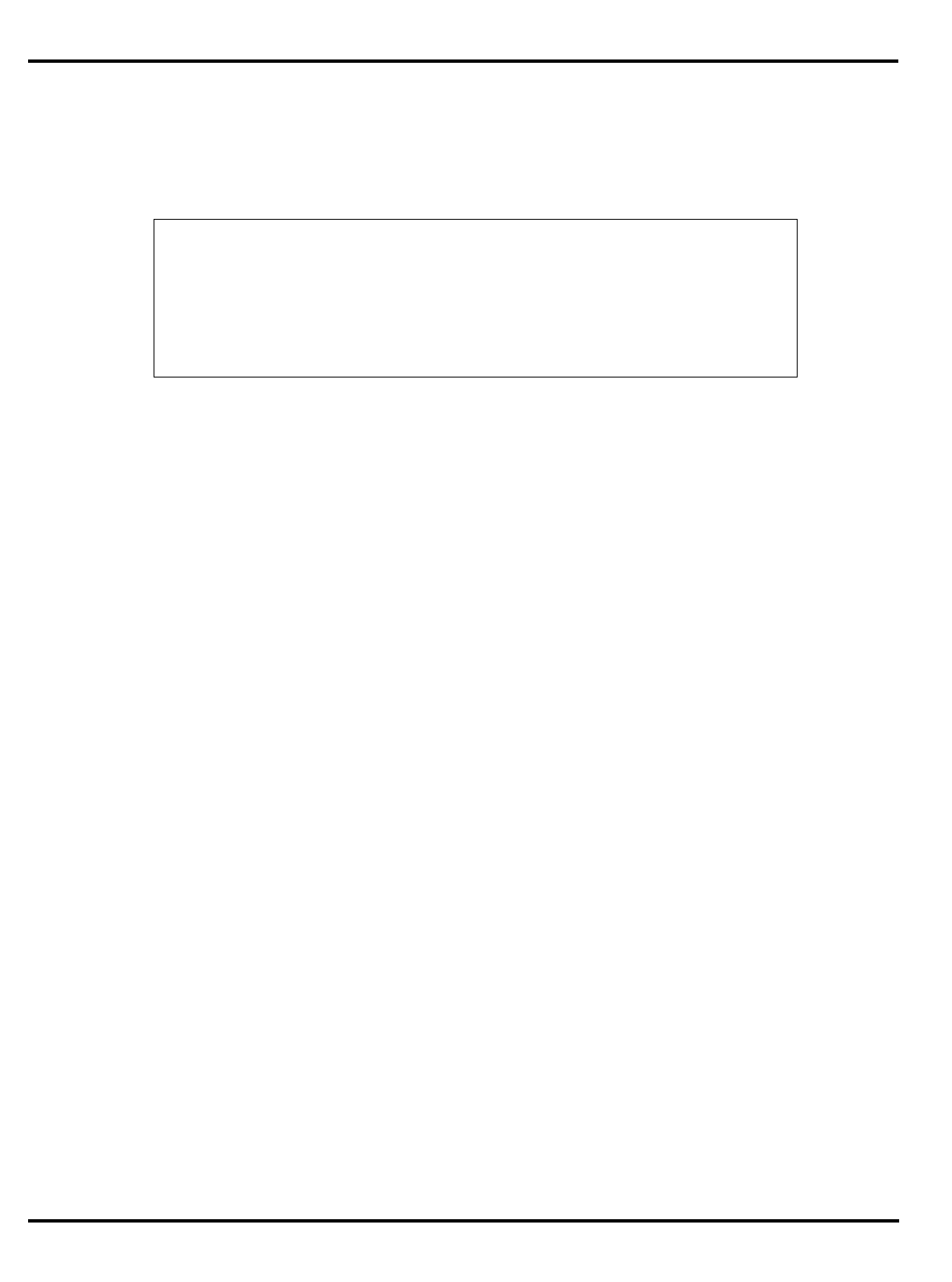

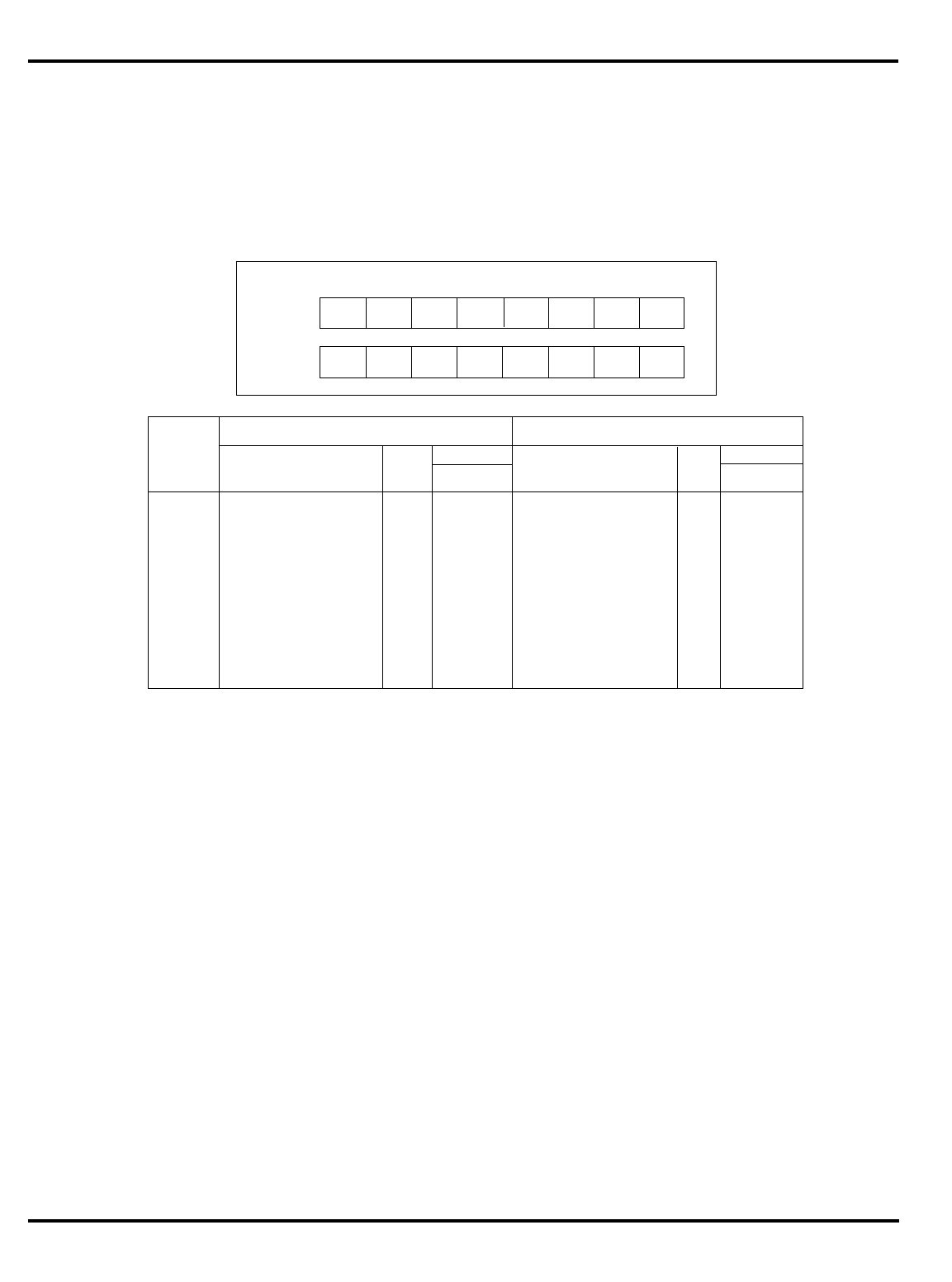

The R3051, R3052, R3071, R3081 and R3041 are the members (so far)

of a family of products defined, designed, and manufactured by IDT. The

chips integrate the functions of the R3000A CPU, cache memory and

(R3081 only) math co-processor. This means that all the fastest logic is on

chip; so the integrated chips are not only cheaper and smaller than the

original implementation, but also much easier to use.

The parts differ in their cache sizes, whether they include onchip MMU

and/or FPA, clock rates and packaging options. In addition, although all

parts can be used pin-compatibly, certain products feature optional

enhancements in their bus-interface that may serve to reduce system cost

or complexity, and other subtle enhancements for cost or performance.

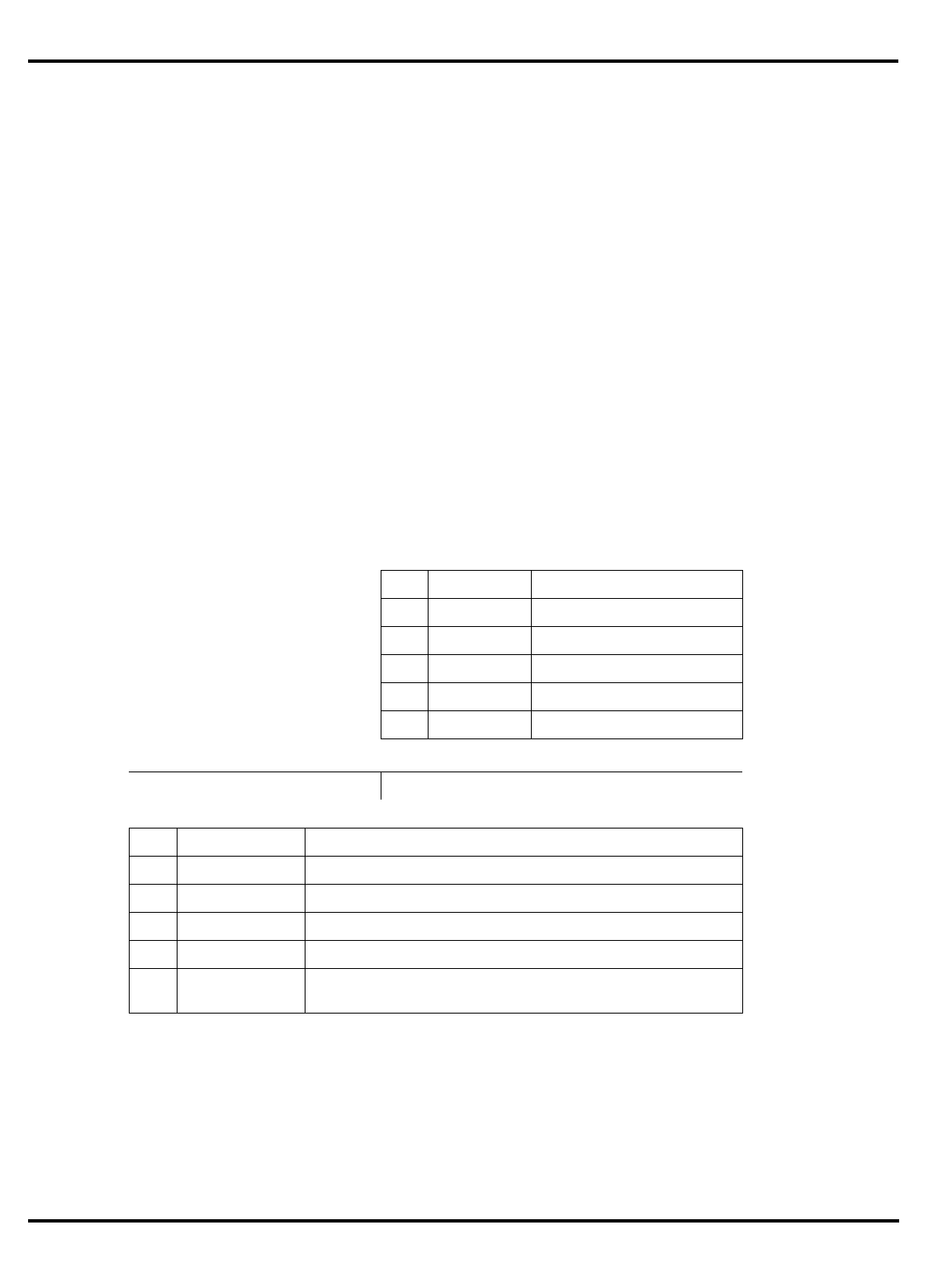

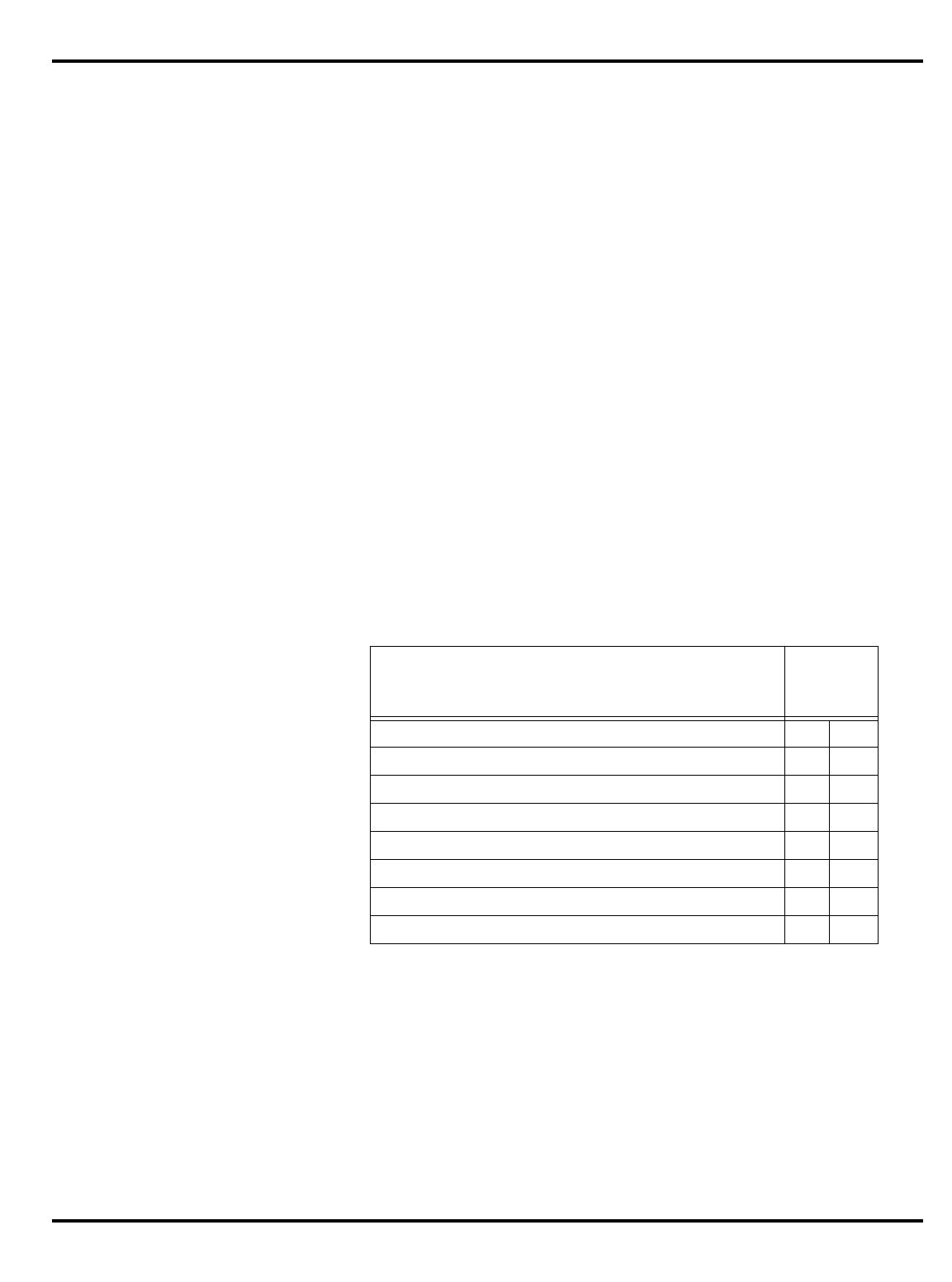

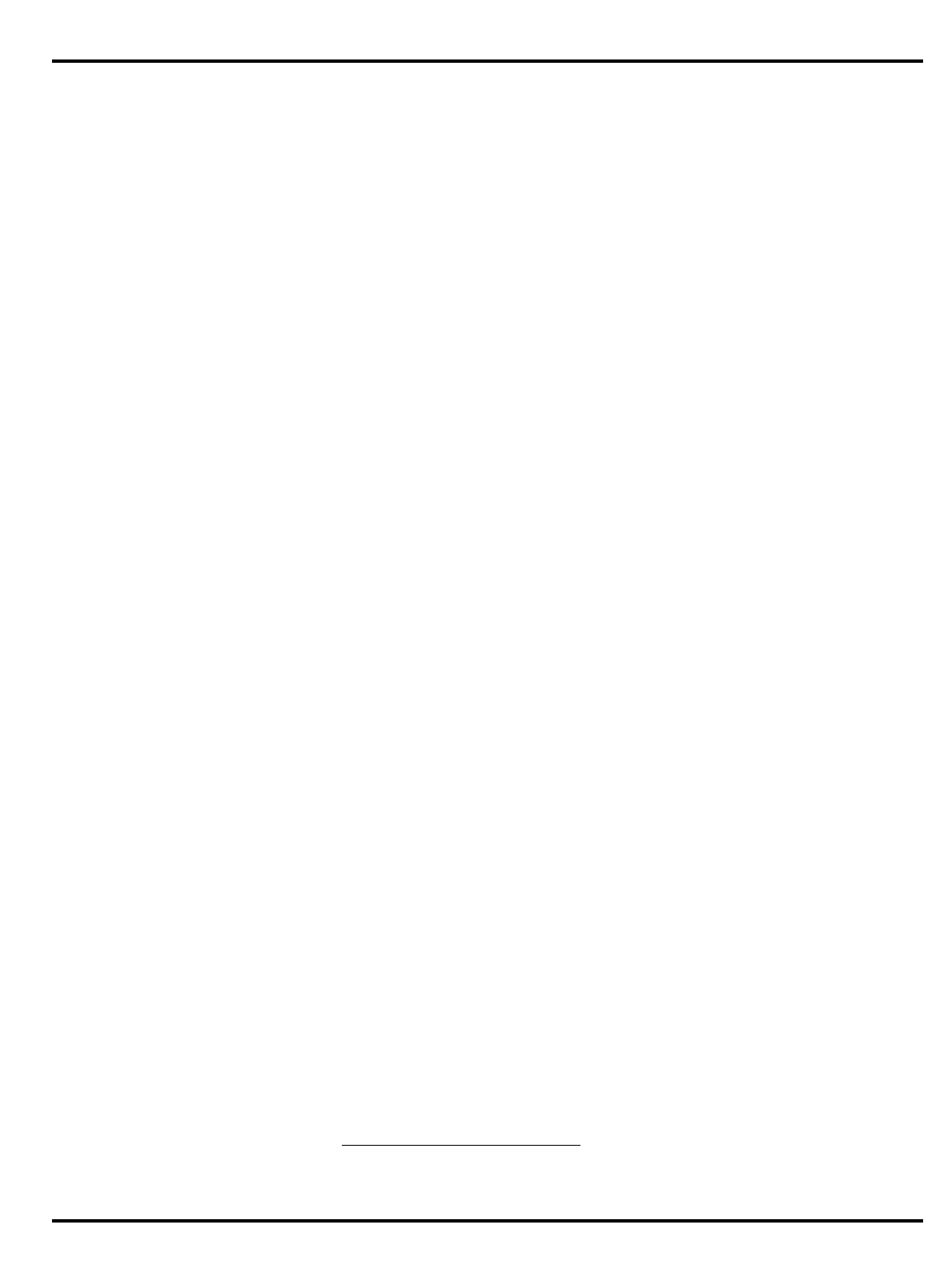

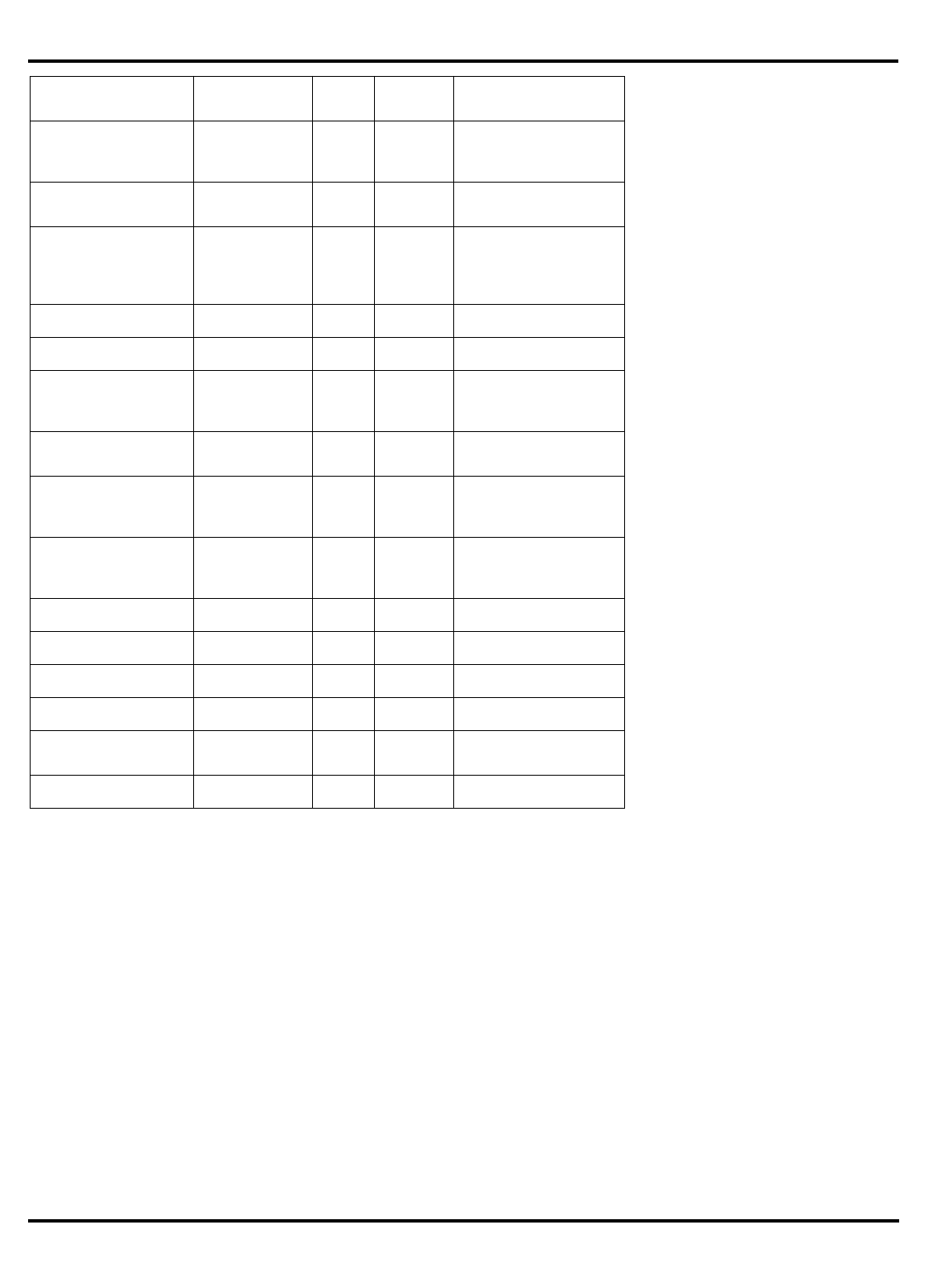

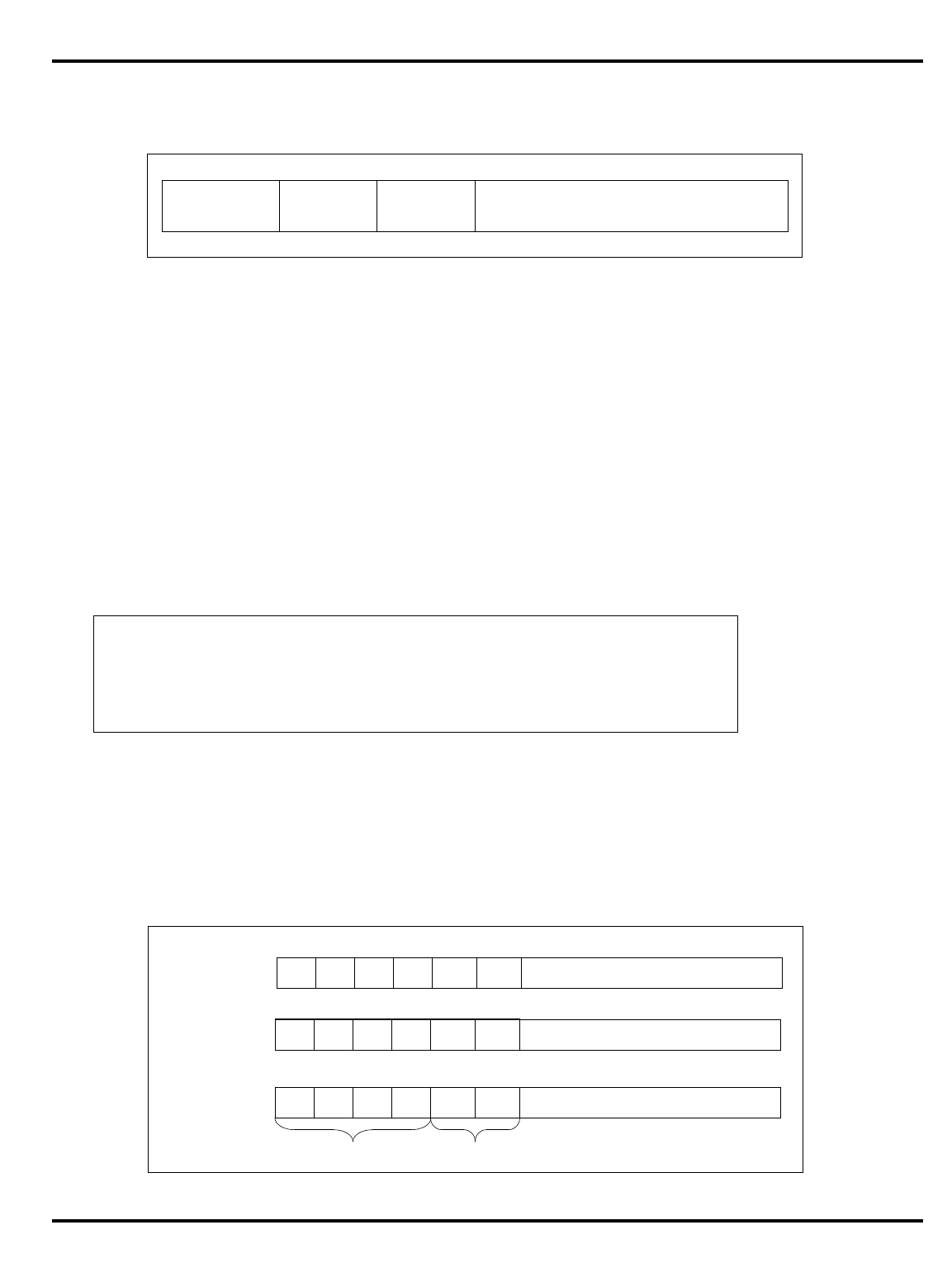

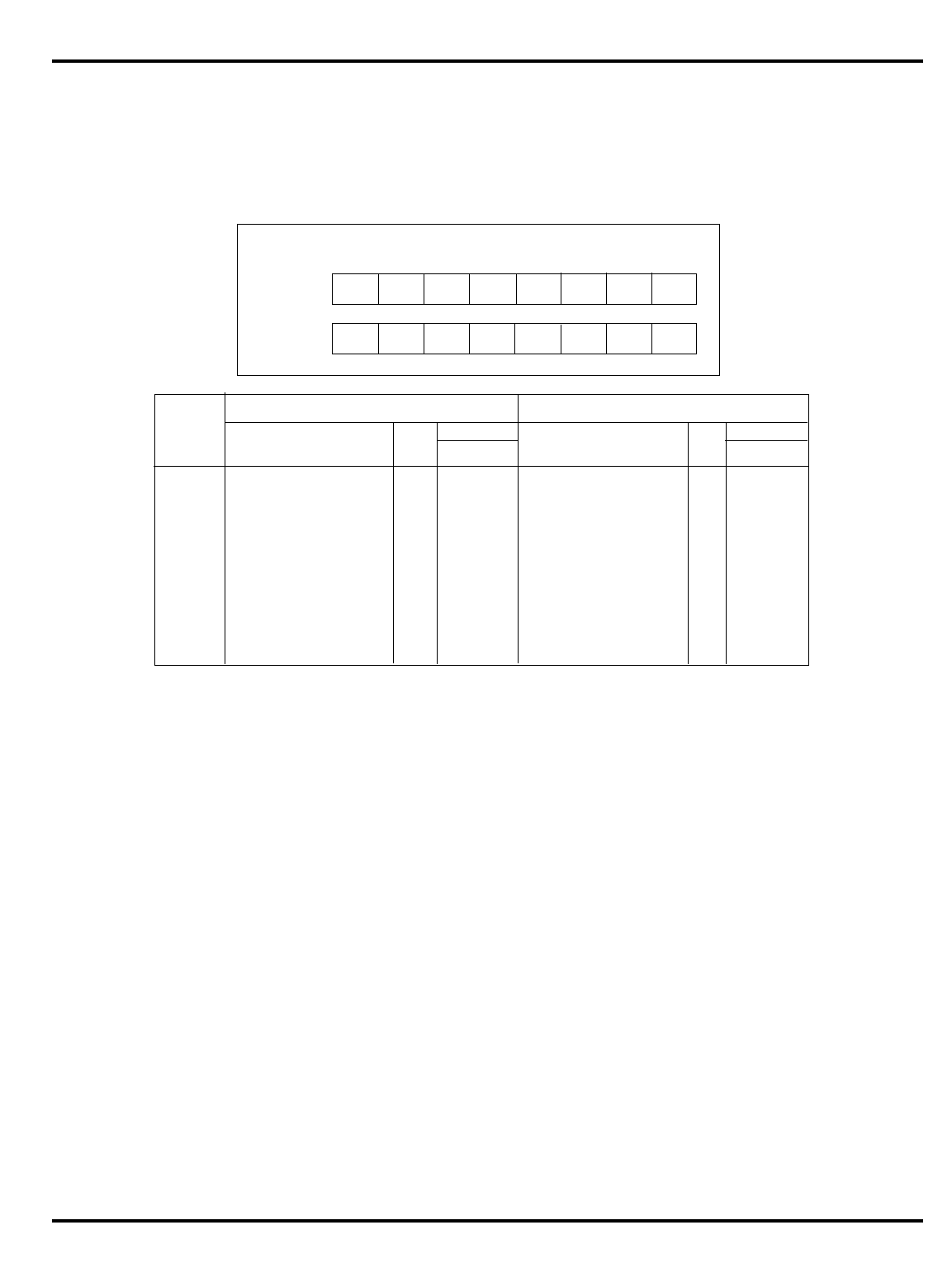

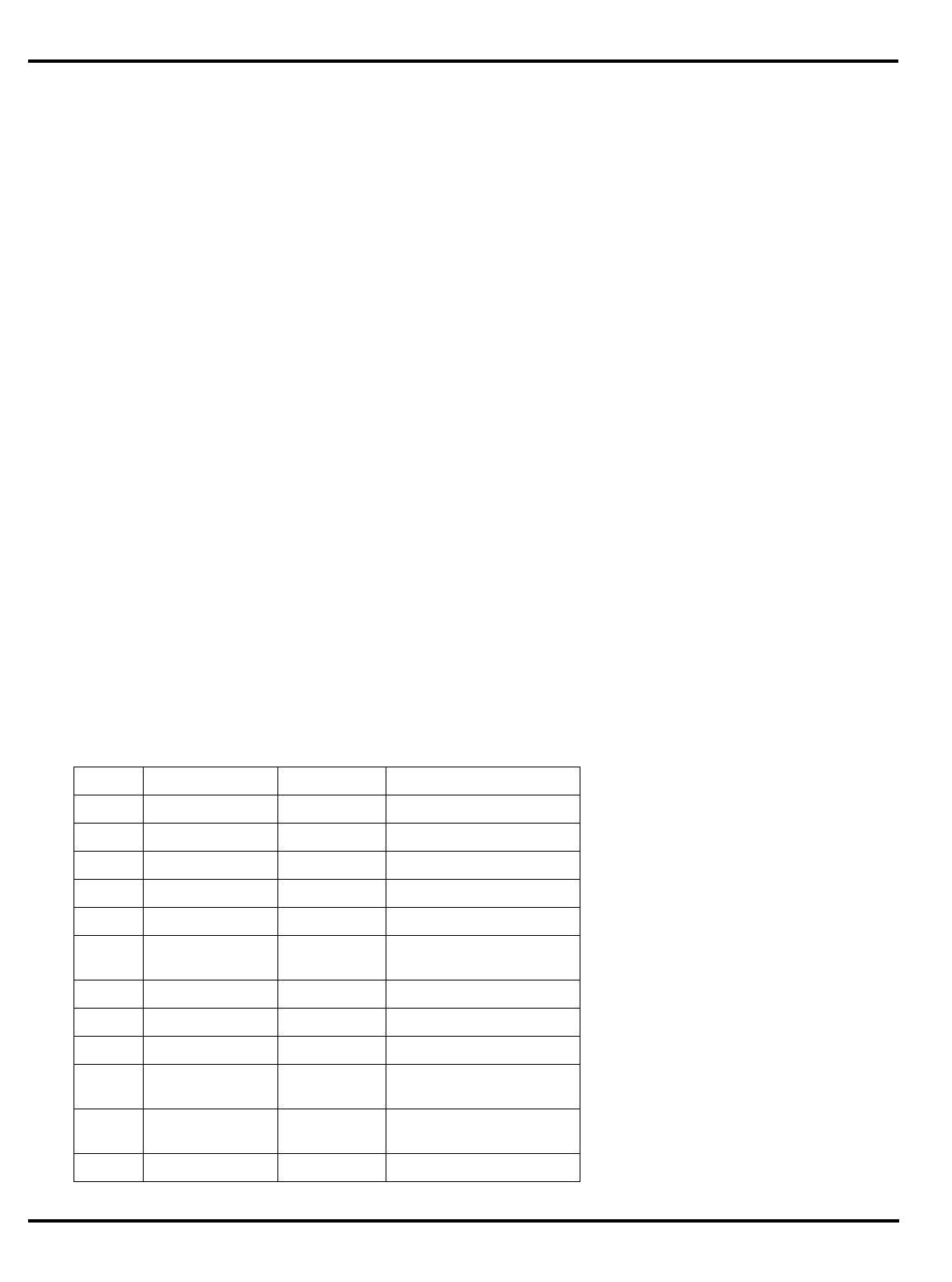

The major differences are summarized in "Table 1.1. R30xx family

members compared”.

CHAPTER 1 INTRODUCTION

1–4

MIPS ARCHITECTURE LEVELS

There are multiple generations of the MIPS architecture. The most

commonly discussed are the MIPS-1, MIPS-2, and MIPS-3 architectures.

MIPS-1 is the ISA found in the R2000 and R3000 generation CPUs. It is

a 32-bit ISA, and defines the basic instruction set. Any application written

with the MIPS-1 instruction set will operate correctly on all generations of

the architecture.

The MIPS-2 ISA is also 32-bit. It adds some instructions to speed up

floating point data movement, branch-likely instructions, and other minor

enhancements. This was first implemented in the MIPS R6000 ECL

microprocessor.

The MIPS-3 ISA is a 64-bit ISA. In addition to supporting all MIPS-1 and

MIPS-2 instructions, the MIPS-3 ISA contains 64-bit equivalents of certain

earlier instructions that are sensitive to operand size (e.g. load double and

load word are both supported), including doubleword (64-bit) data

movement and arithmetic. This ISA was first implemented in the R4000 as

a clean (“seamless”) transition from the existing 32-bit architecture.

Note that these ISA levels do not necessarily imply a particular structure

for the MMU, caches, exception model, or other kernel specific resources.

Thus, different implementations of ISA compatible chips may require

different kernels.

In the case of the R30xx family, all devices implement the MIPS-1 ISA.

Many devices are also kernel compatible with the R3000A, but some

devices (most notably those without an MMU) may require small kernel

changes or different boot modules†.

MIPS-1 COMPARED WITH CISC ARCHITECTURES

Although the MIPS architecture is fairly straight-forward, there are a few

features, visible only to assembly programmers, which may at first appear

surprising. In addition, operations familiar to CISC architectures are

† Historically, many embedded MIPS applications have run

exclusively out of the “kseg0 and kseg1” memory regions

(described later in the book). For these applications, the presence

or absence of the MMU is largely irrelevant.

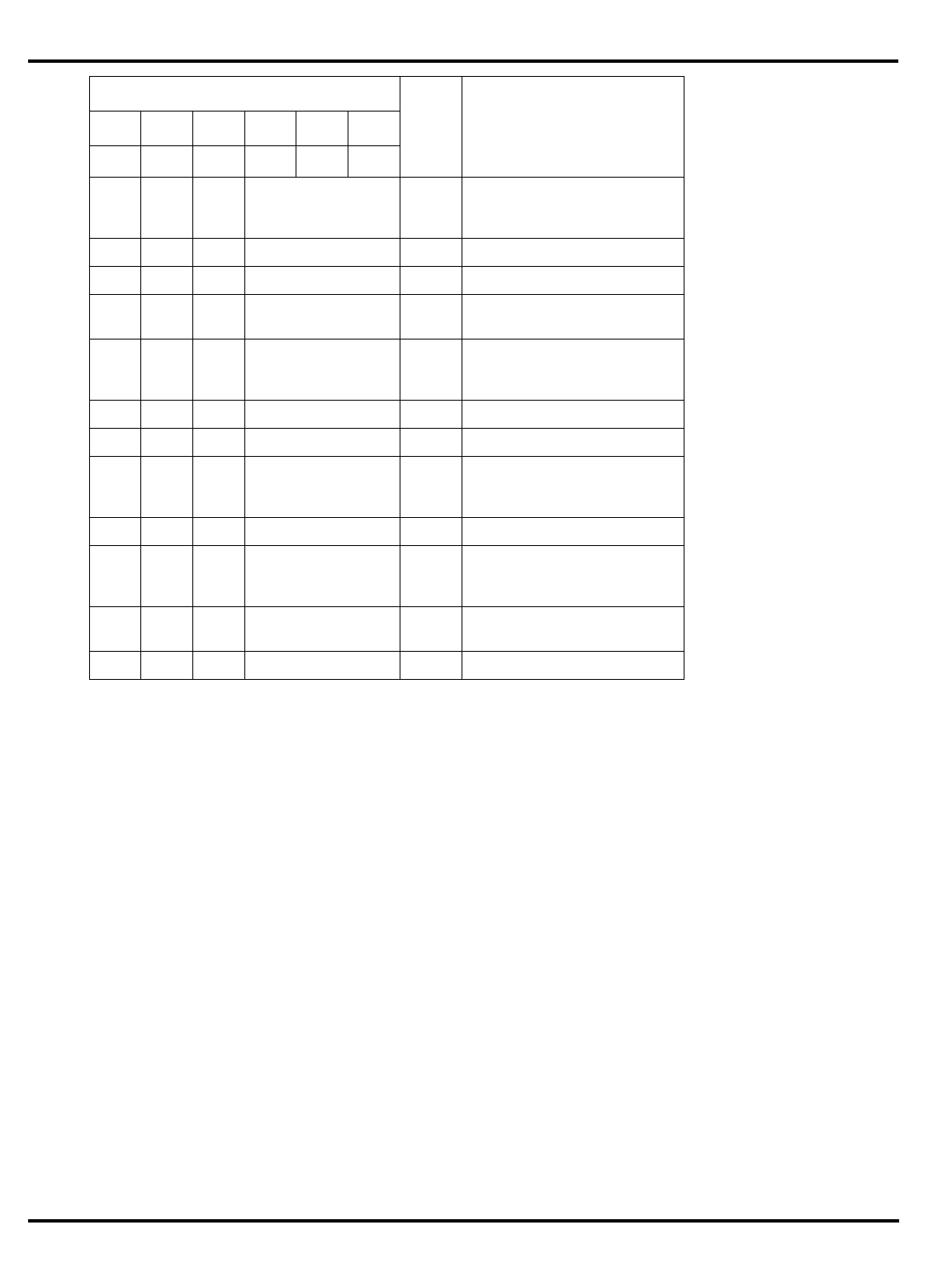

Part Cache

I + D MMU FPA Clock

(MHz) Package

Options System Interface

3051 4K + 1K – – 20-40 PLCC 32-bit MUX’ed A/D

3051E

×

3052 8K + 2K – – 20-40 PLCC 32-bit MUX’ed A/D

3052E

×

3081 16K+4K/

8K+8K –

×

20-50 PLCC Optional 1/2 frequency

bus operation

Optional 1x Clock Input

3081E 16K+4K/

8K+8K

×

3071 16K+4K/

8K+8K – – 33-50 PLCC 1/2 frequency bus

operation

1x Clock Input

3071E 16K+4K/

8K+8K

×

3041 2K + 0.5K – – 16-25 PLCC

TQFP Variable port width

interface.

Table 1.1. R30xx family members compared

INTRODUCTION CHAPTER 1

1–5

irrelevant to the MIPS architecture. For example, the MIPS architecture

does not mandate a stack pointer or stack usage; thus, programmers may

be surprised to find that push/pop instructions do not exist directly.

The most notable of these features are summarized here.

Unusual instruction encoding features

•

All instructions are 32-bits long

: as mentioned above. This means, for

example, that it is impossible to incorporate a 32-bit constant into a

single instruction (there would be no instruction bits left to encode

the operation and the registers!). A ‘‘load immediate’’ instruction is

limited to a 16-bit value; a special ‘‘load upper immediate’’ must be

followed by an ‘‘or immediate’’ to put a 32-bit constant value into a

register.

•

Instruction actions must fit the pipeline

: actions can only be carried out

in the designated pipeline phase, and must be complete in one clock.

For example, the register writeback phase provides for just one value

to be stored in the register file, so instructions can only change one

register.

•

3-operand instructions

: arithmetic/logical operations don’t have to

specify memory locations, so there are plenty of instruction bits to

define two independent source and one destination register.

Compilers love 3-operand instructions, which give optimizers more

scope to improve the code which handles complex expressions.

•

32 registers

: the choice of 32 has become universal; compilers like a

large (but not necessarily too large) number of registers, but there is

a cost in context-saving and in encoding the registers to be used by

an instruction. Register $0 always returns zero, to give a compact

encoding of that useful constant.

•

No condition codes

: the MIPS architecture does not provide condition

code flags implicitly set by arithmetical operations. The motivation is

to make sure that execution state is stored in one place – the register

file. Conditional branches (in MIPS) test a single register for sign/zero,

or a pair of registers for equality.

Addressing and memory accesses

•

Memory references are always register loads and stores

: arithmetic on

memory variables upsets the pipeline, so is not done. Memory

references only occur due to explicit load or store instructions. The

large register file allows multiple variables to be “on-chip”

simultaneously.

•

Only one data addressing mode

: all loads and stores define the

memory location with a single base register value modified by a 16-bit

signed displacement. Note that the assembler/compiler tools can use

the $0 register, along with the immediate value, to synthesize

additional addressing modes from this one directly supported mode.

•

Byte-addressed

: the instruction set includes load/store operations

for 8- and 16-bit variables (referred to as

byte

and

halfword

). Partial-

word load instructions come in two flavors – sign-extend and zero-

extend.

•

Loads/stores must be address-aligned

: memory word operations can

only load or store data from a single 4-byte aligned word; halfword

operations must be aligned on half-word addresses. Many CISC

microprocessors will load/store a multi-byte item from any byte

address (although unaligned transfers always take longer).

Techniques to generate code which will handle unaligned data

efficiently will be explained later.

•

Jump instructions

: The smallest op-code field in a MIPS instruction is

6 bits; leaving 26 bits to define the target of a jump. Since all

instructions are 4-byte aligned in memory the two least-significant

CHAPTER 1 INTRODUCTION

1–6

address bits need not be stored, allowing an address range of 2

28

=

256Mbytes. Rather than make this branch PC-relative, this is

interpreted as an absolute address within a 256Mbyte ‘‘segment’’. In

theory, this could impose a limit on the size of a single program; in

reality, it hasn’t been a problem.

Branches out of segment can be achieved by using a

jr

instruction,

which uses the contents of a register as the target.

Conditional branches have only a 16-bit displacement field (2

18

byte

range since instructions are 4-byte aligned) which is interpreted as a

signed PC-relative displacement. Compilers can only code a simple

conditional branch instruction if they know that the target will be

within 128Kbytes of the instruction following the branch.

Operations not directly supported

•

No byte or halfword arithmetic

: all arithmetical and logical operations

are performed on 32-bit quantities. Byte and/or halfword arithmetic

would require significant extra resources, many more op-codes, and

is an understandable omission. Most C programmers will use the

int

data type for most arithmetic, and for MIPS an

int

is 32 bits and such

arithmetic will be efficient. C’s rules are to perform arithmetic in

int

whenever any source or destination variable is as long as

int

.

However, where a program explicitly does arithmetic as

short

the

compiler must insert extra code to make sure that wraparound and

overflows have the appropriate effect.

•

No special stack support

: conventional MIPS assembler usage does

define a

sp

register, but the hardware treats

sp

just like any other

register. There is a recommended format for the stack frame layout of

subroutines, so that programs can mix modules from different

languages and compilers; it is recommended that programmers stick

to these conventions, but they have no relationship to the hardware.

•

Minimal subroutine overhead

: there is one special feature; jump

instructions have a ‘‘jump and link’’ option which stores the return

address into a register. $31 is the default, so for convenience and by

convention $31 becomes the ‘‘return address’’ register.

•

Minimal interrupt overhead

: The MIPS architecture makes very few

presumptions about system exception handling, allowing fast

response and a wide variety of software models. In the R30xx family,

the CPU stashes away the restart location in the special register

EPC,

modifies the machine state just enough to signal why the trap

happened and to disallow further interrupts; then it jumps to a single

predefined location† in low memory. Everything else is up to the

software.

Just to emphasize this: on an interrupt or trap a MIPS CPU

does not

store anything on a stack, or write memory, or preserve any registers

by itself.

By convention, two registers ($k0, $k1; register conventions are

explained in chapter 2) are reserved so that interrupt/trap routines

can ‘‘bootstrap’’ themselves – it is impossible to do anything on a MIPS

CPU without using some registers. For a program running in any

system which takes interrupts or traps, the values of these registers

may change at any time, and thus should not be used.

† One particular kind of trap (a TLB miss on an address in the

user-privilege address space) has a different dedicated entry point.

INTRODUCTION CHAPTER 1

1–7

Multiply and divide operations

The MIPS CPU does have an integer multiply/divide unit; worth

mentioning because many RISC machines don’t have multiply hardware.

The multiply unit is relatively independent of the rest of the CPU, with its

own special output registers.

Programmer-visible pipeline effects

In addition to the discussion above, programmers of R3xxx architecture

CPUs also must be aware of certain effects of the MIPS pipeline.

Specifically, the results of certain operations may not be available in the

immediately subsequent instruction; the programmer may need to be

explicitly aware of such cases.

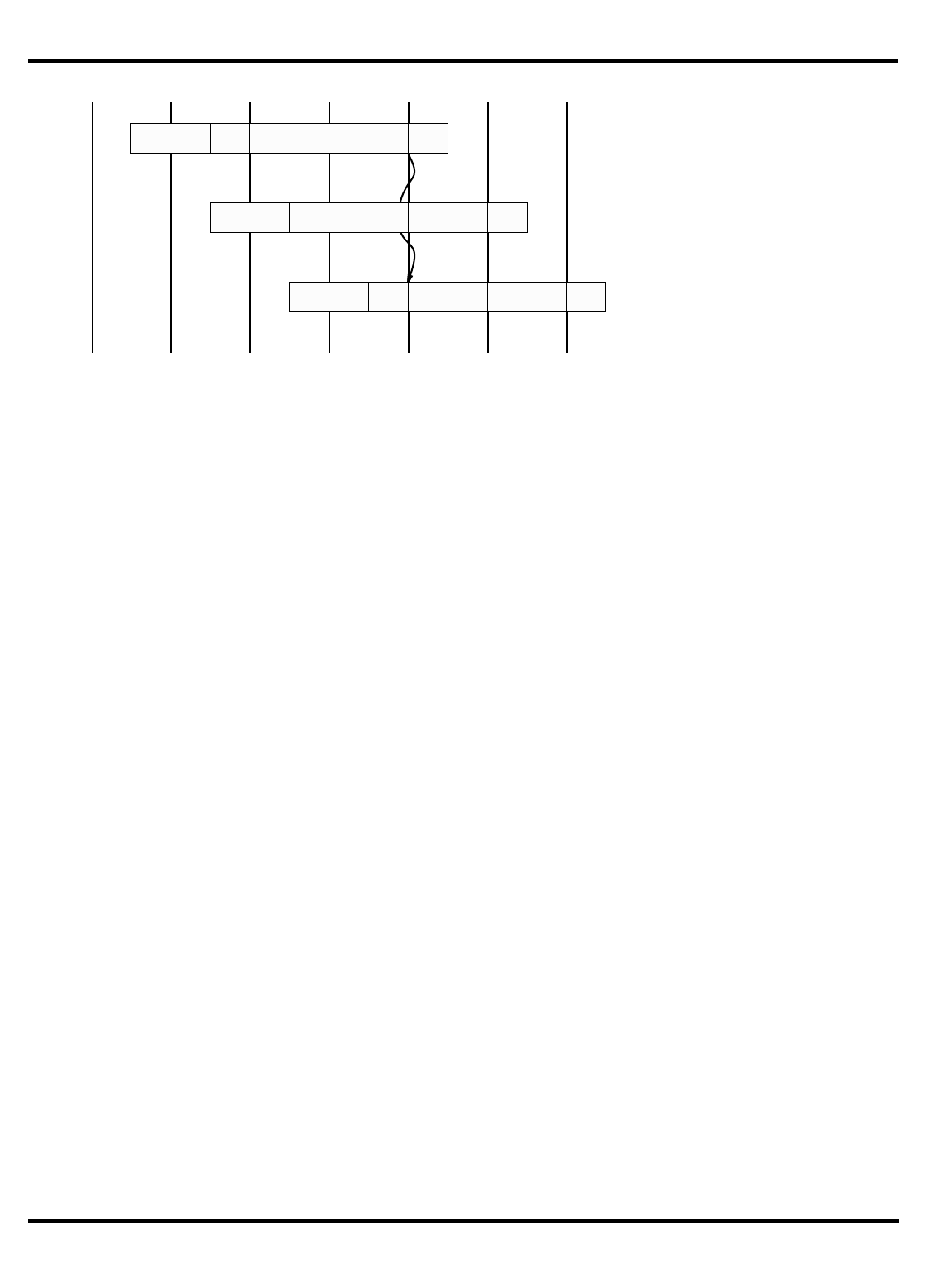

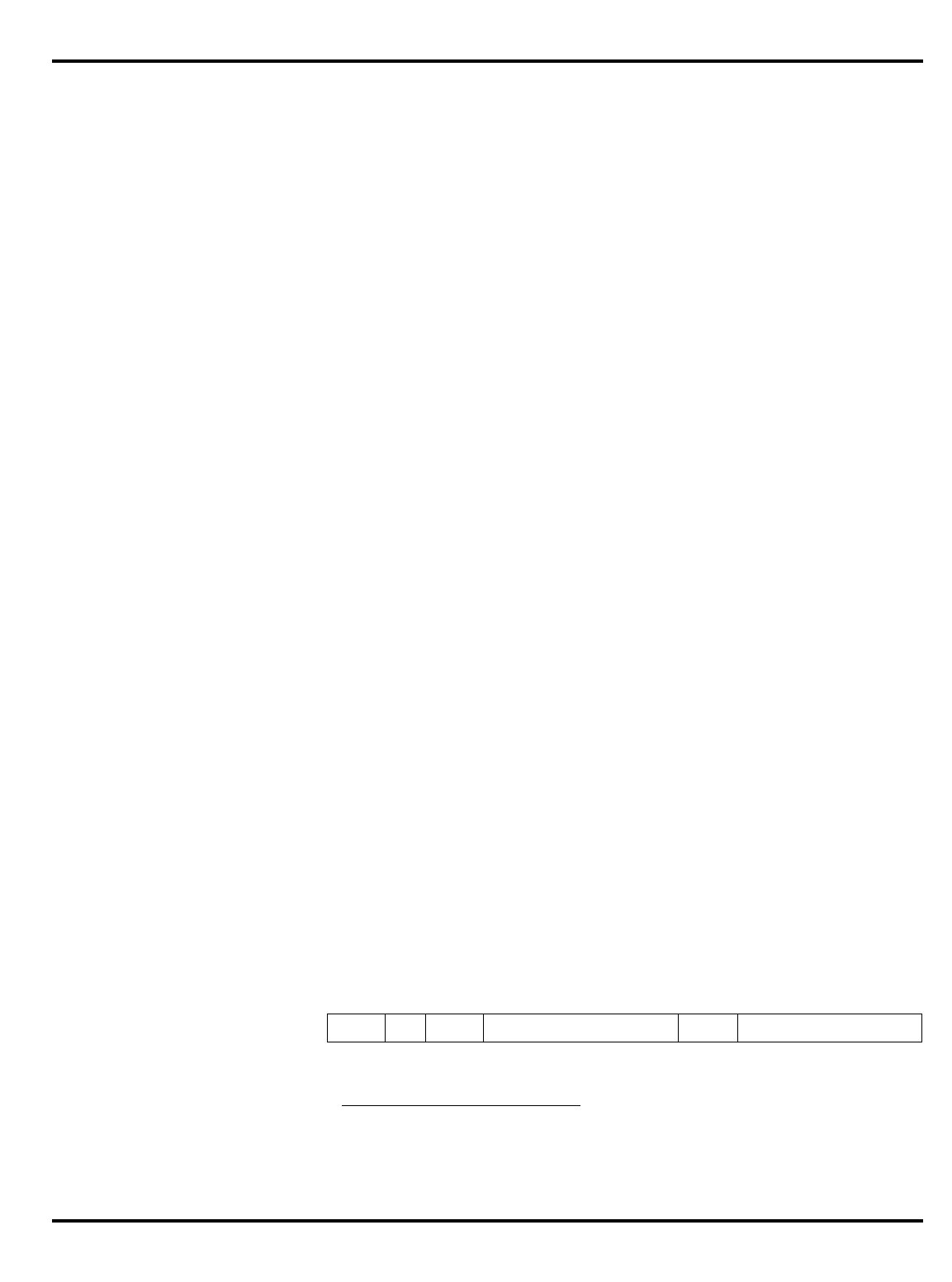

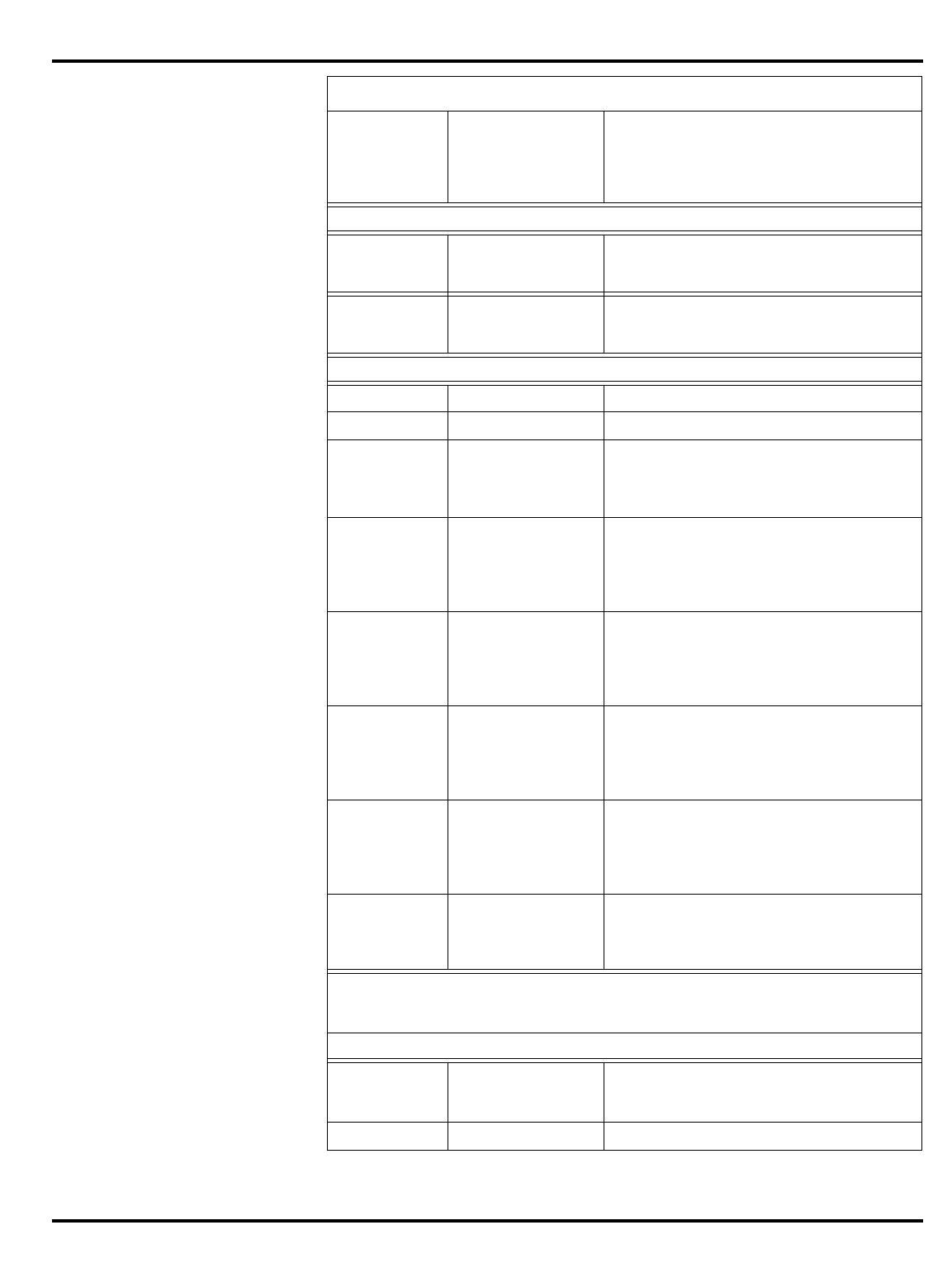

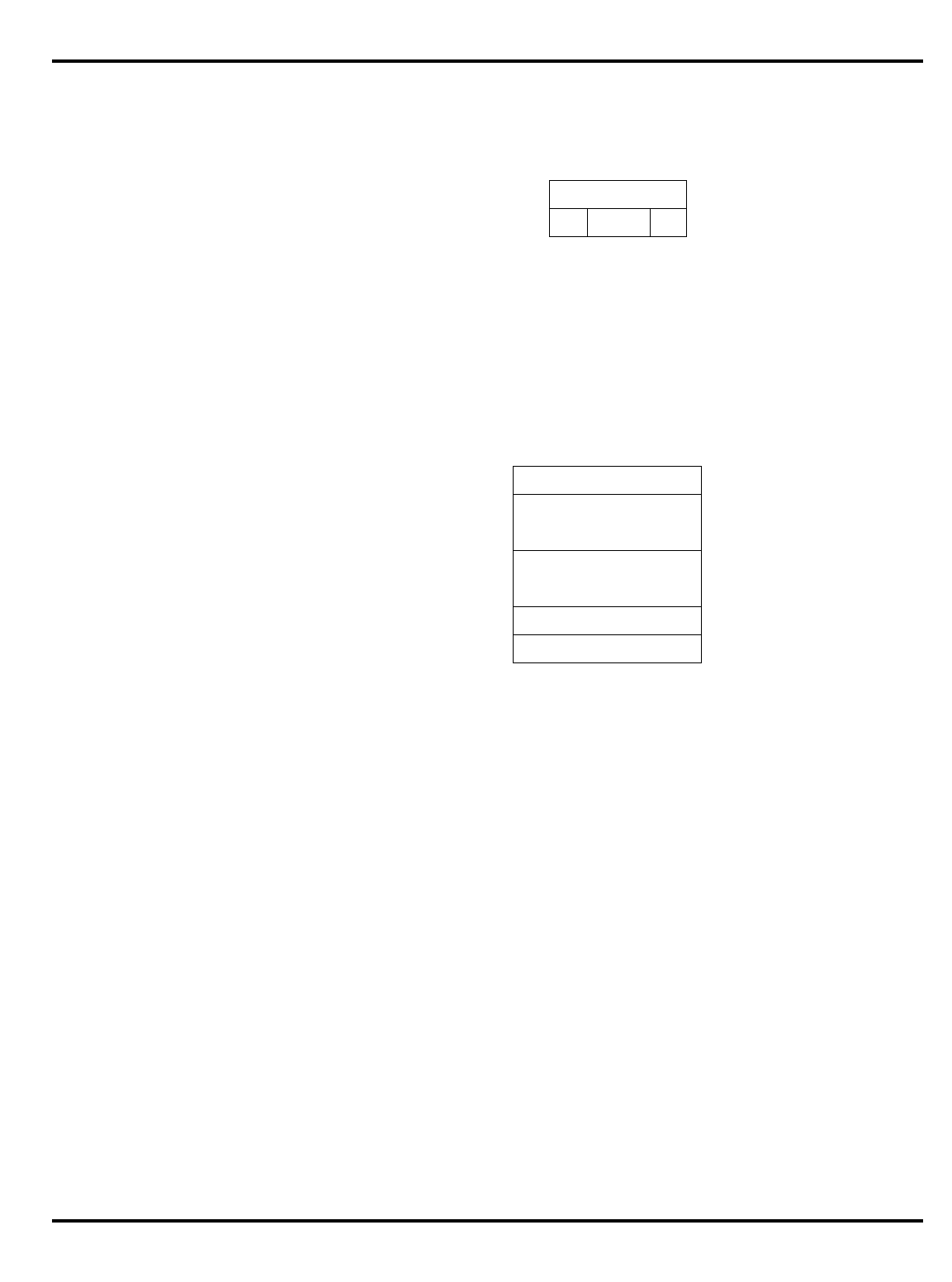

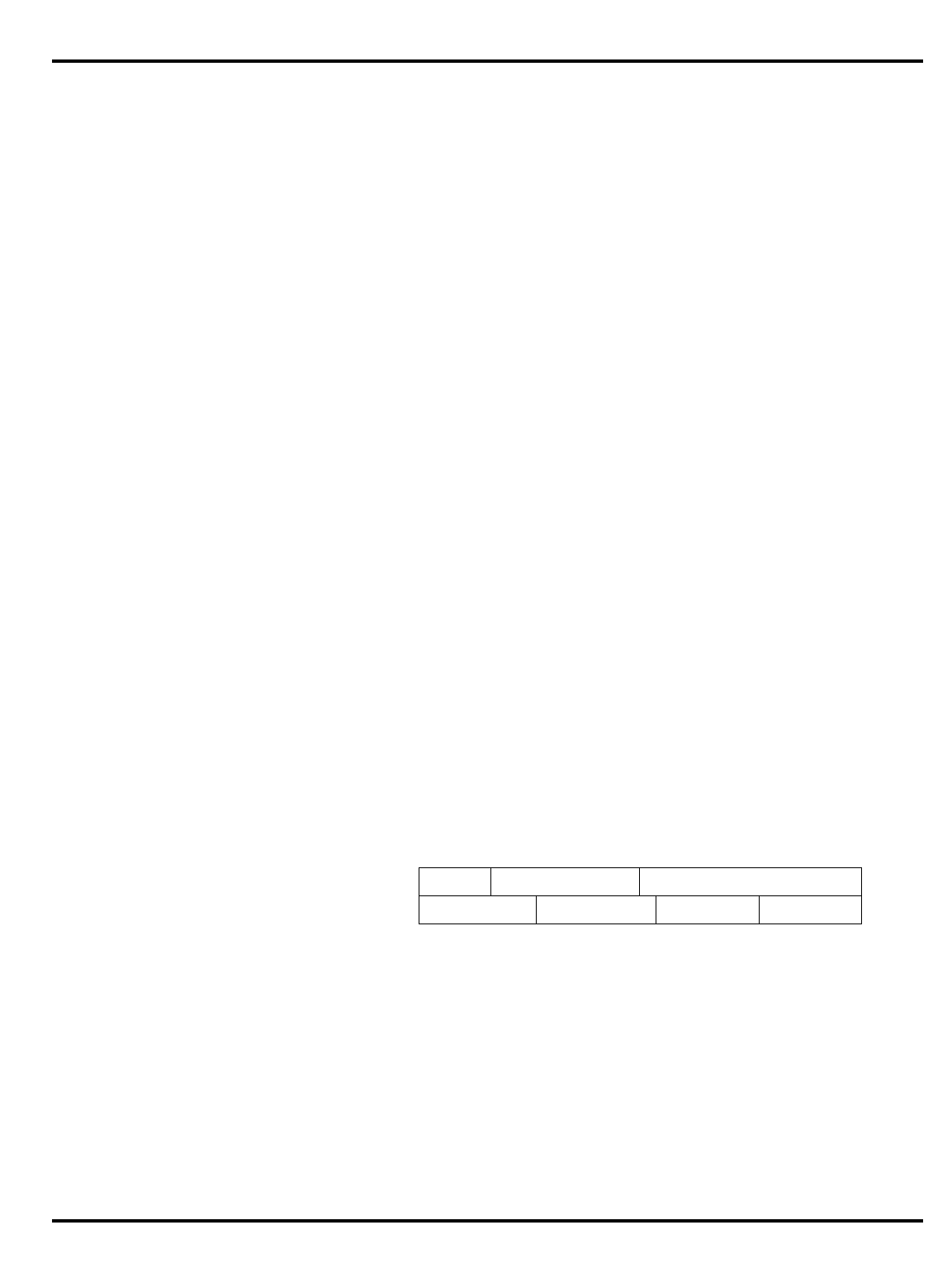

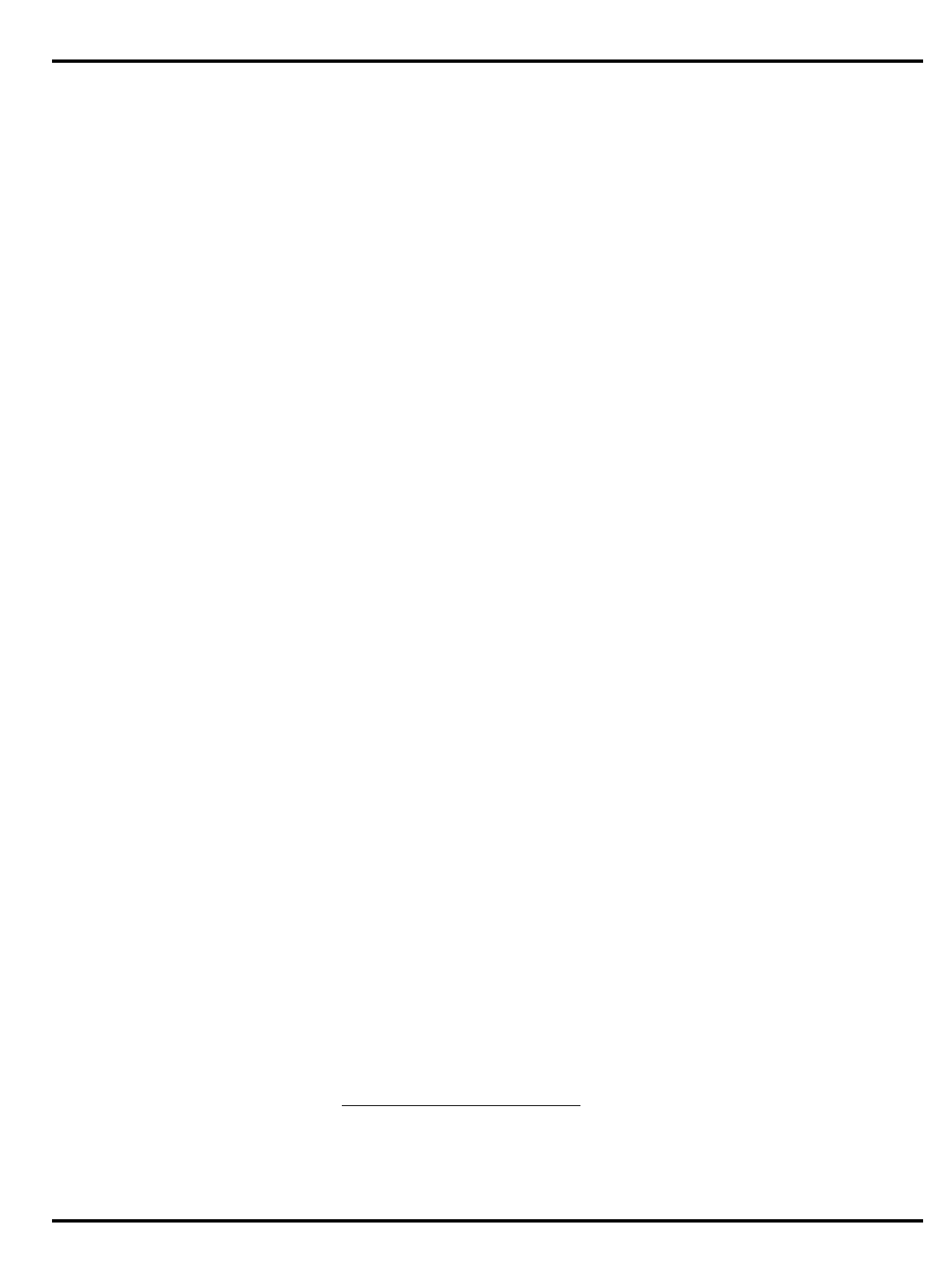

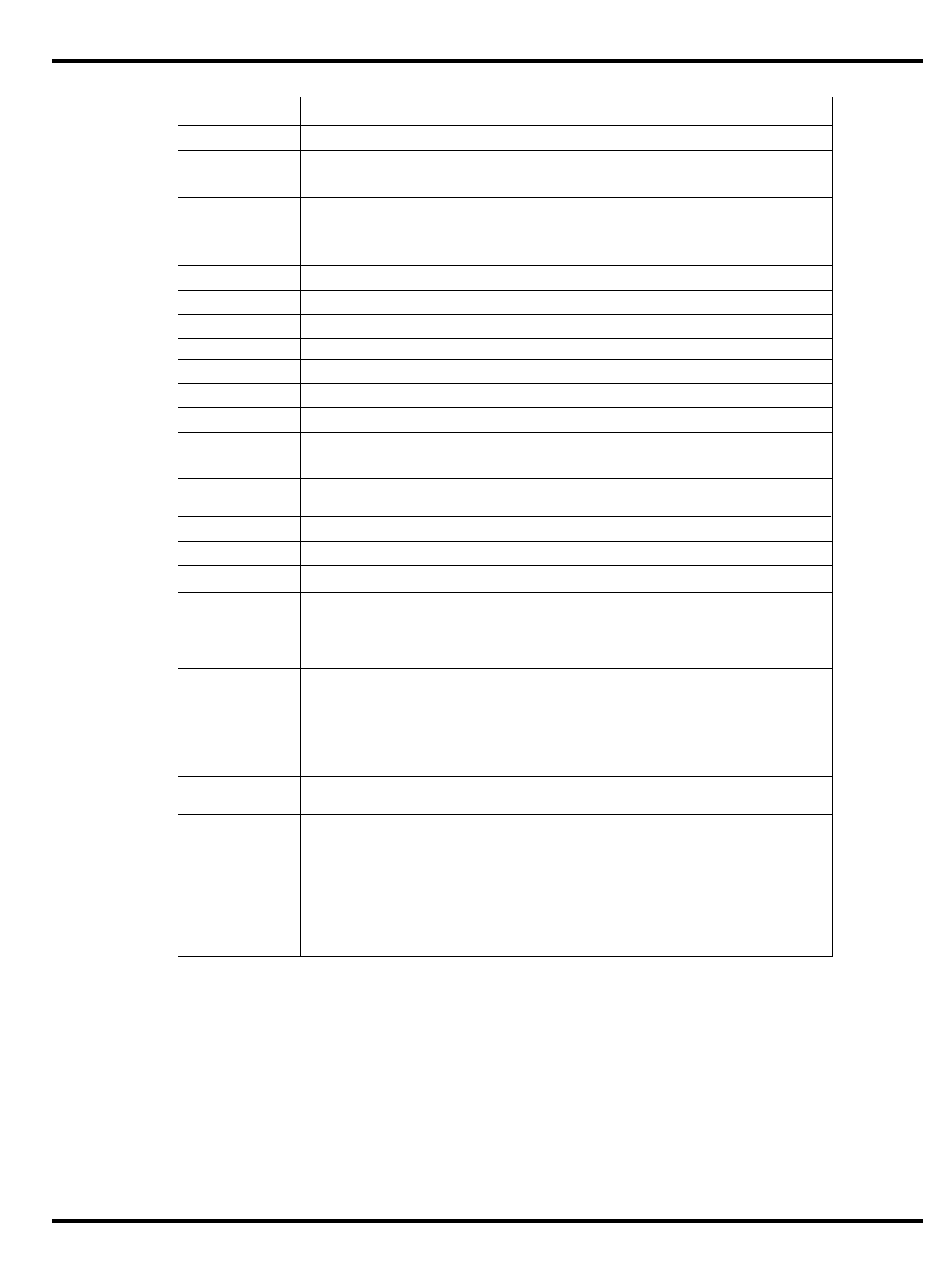

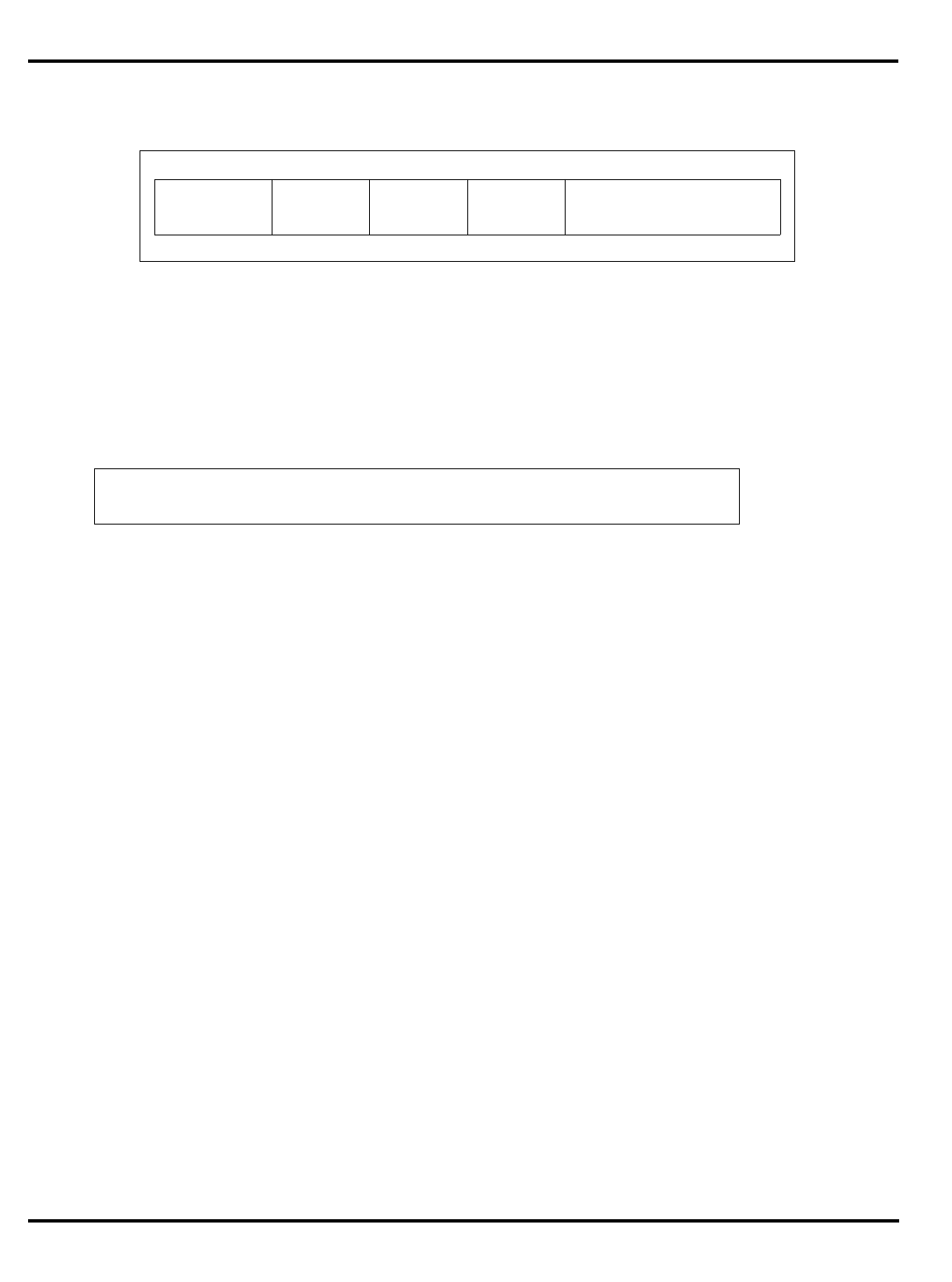

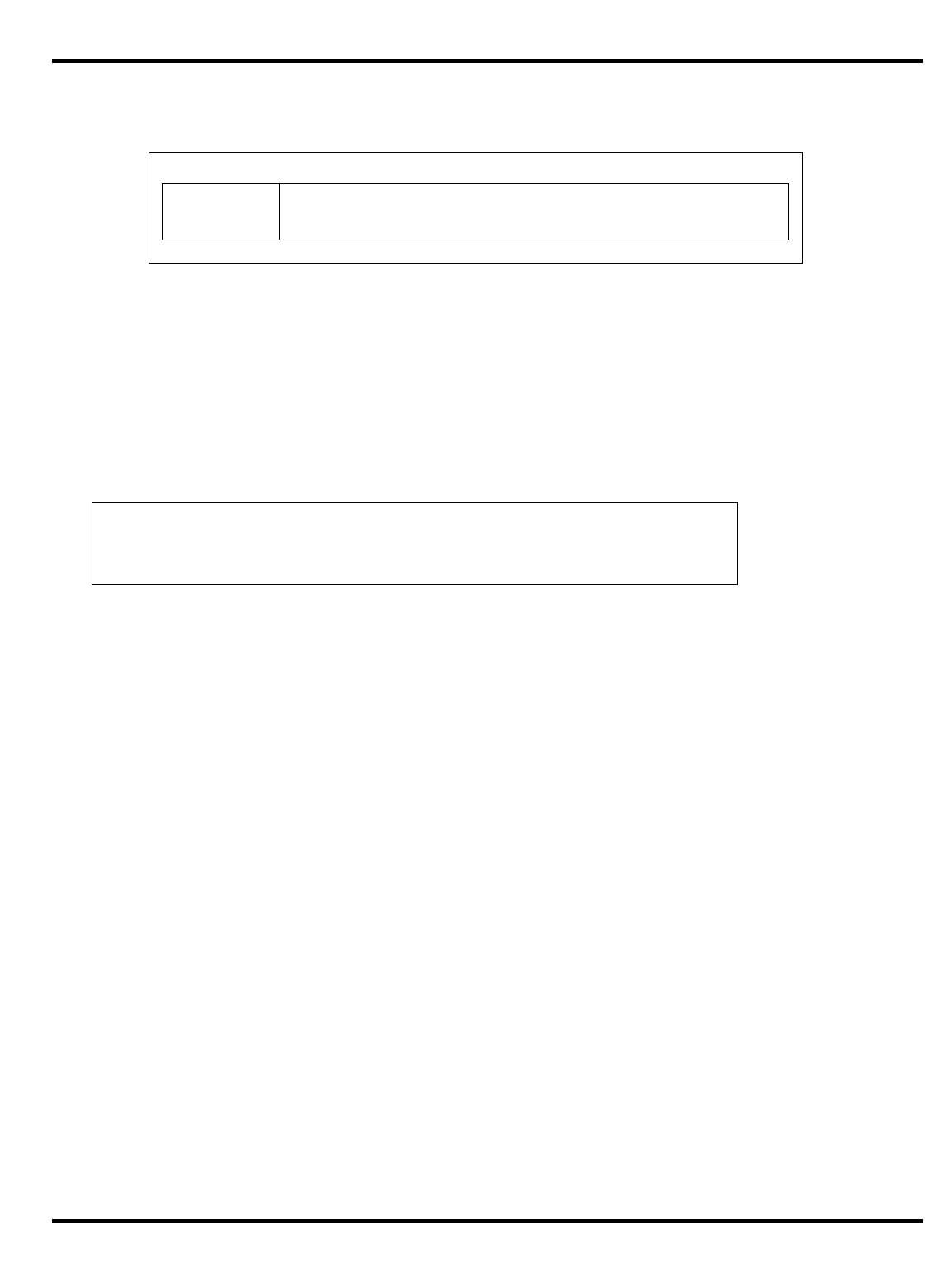

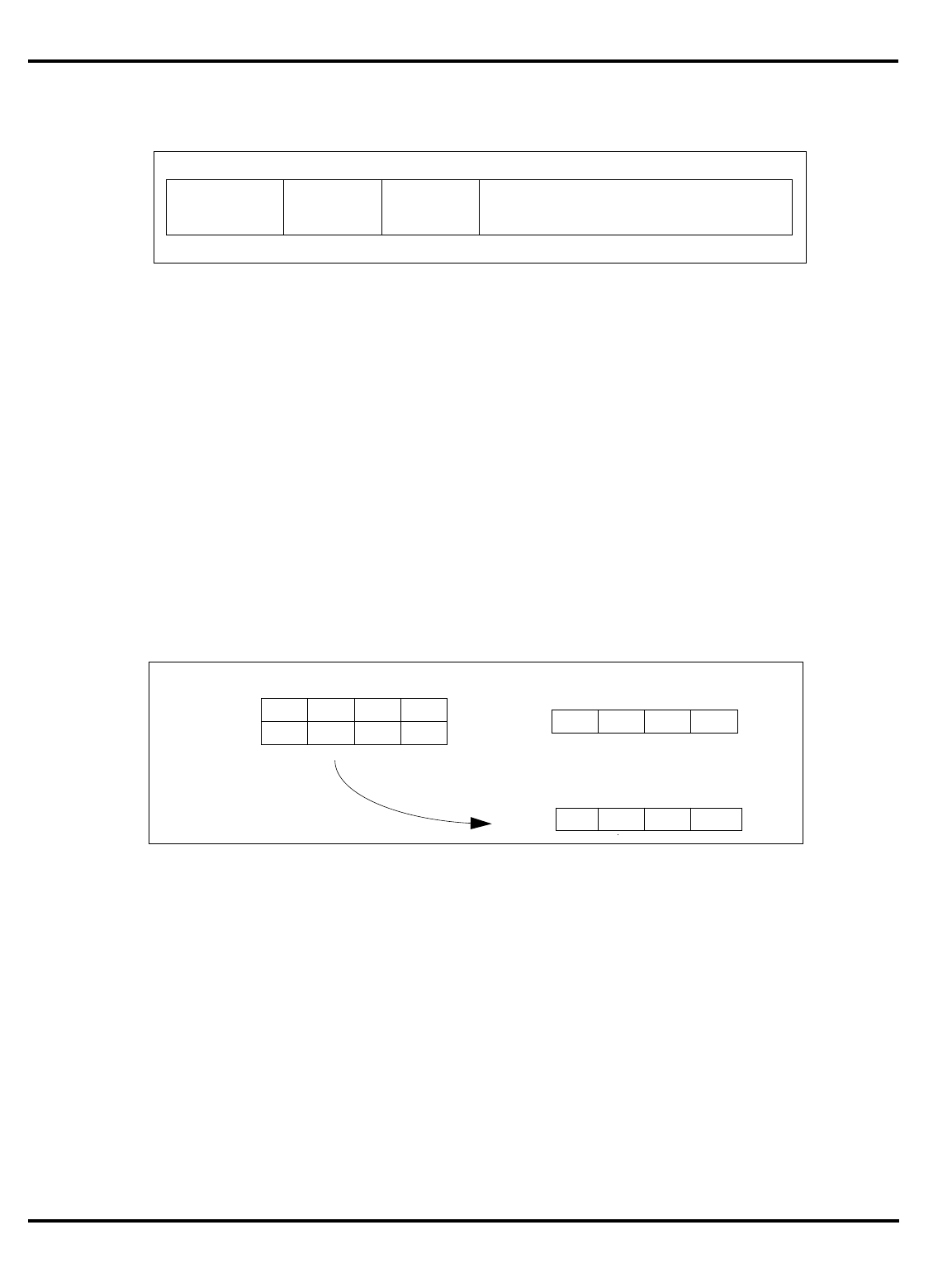

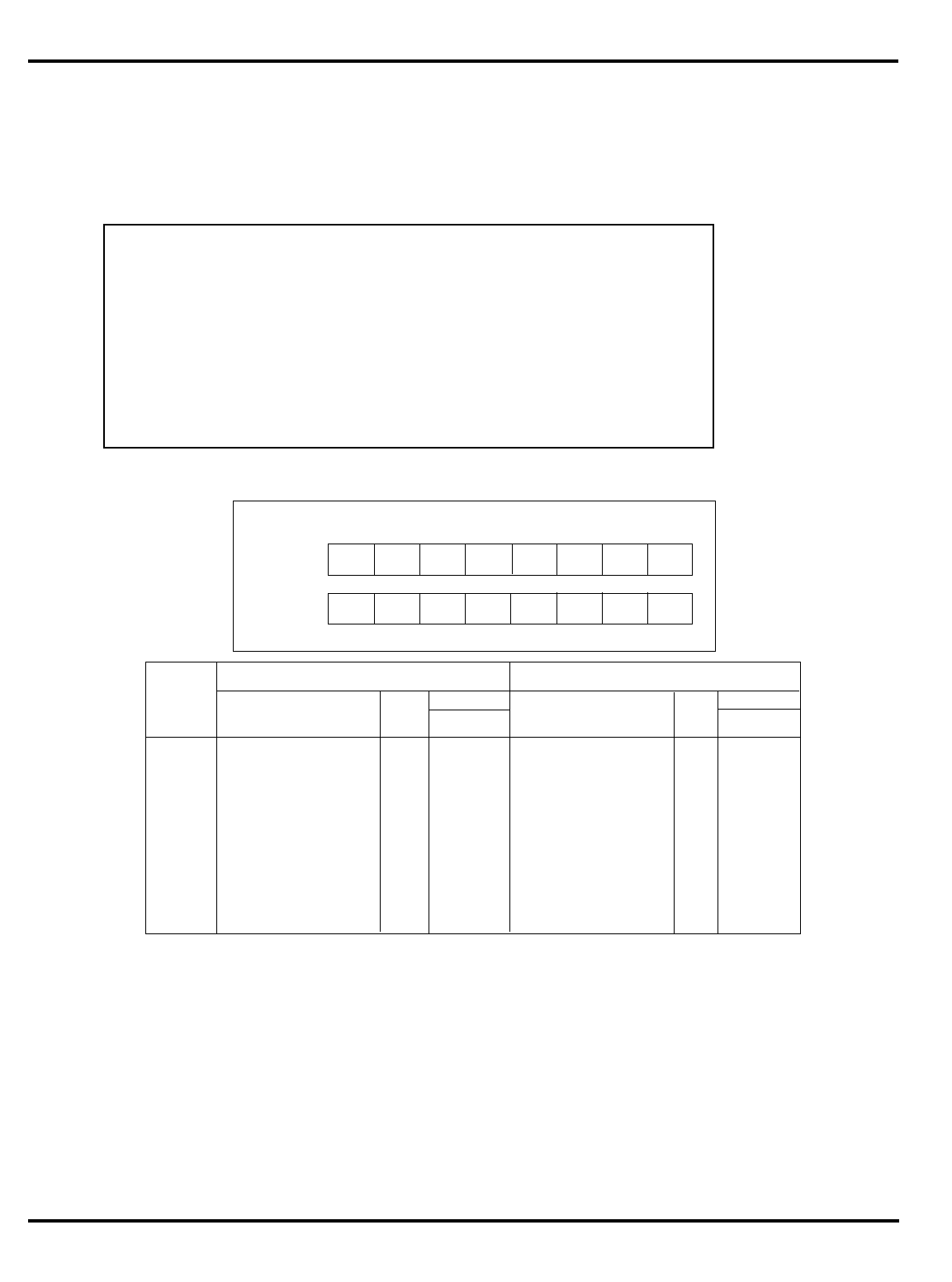

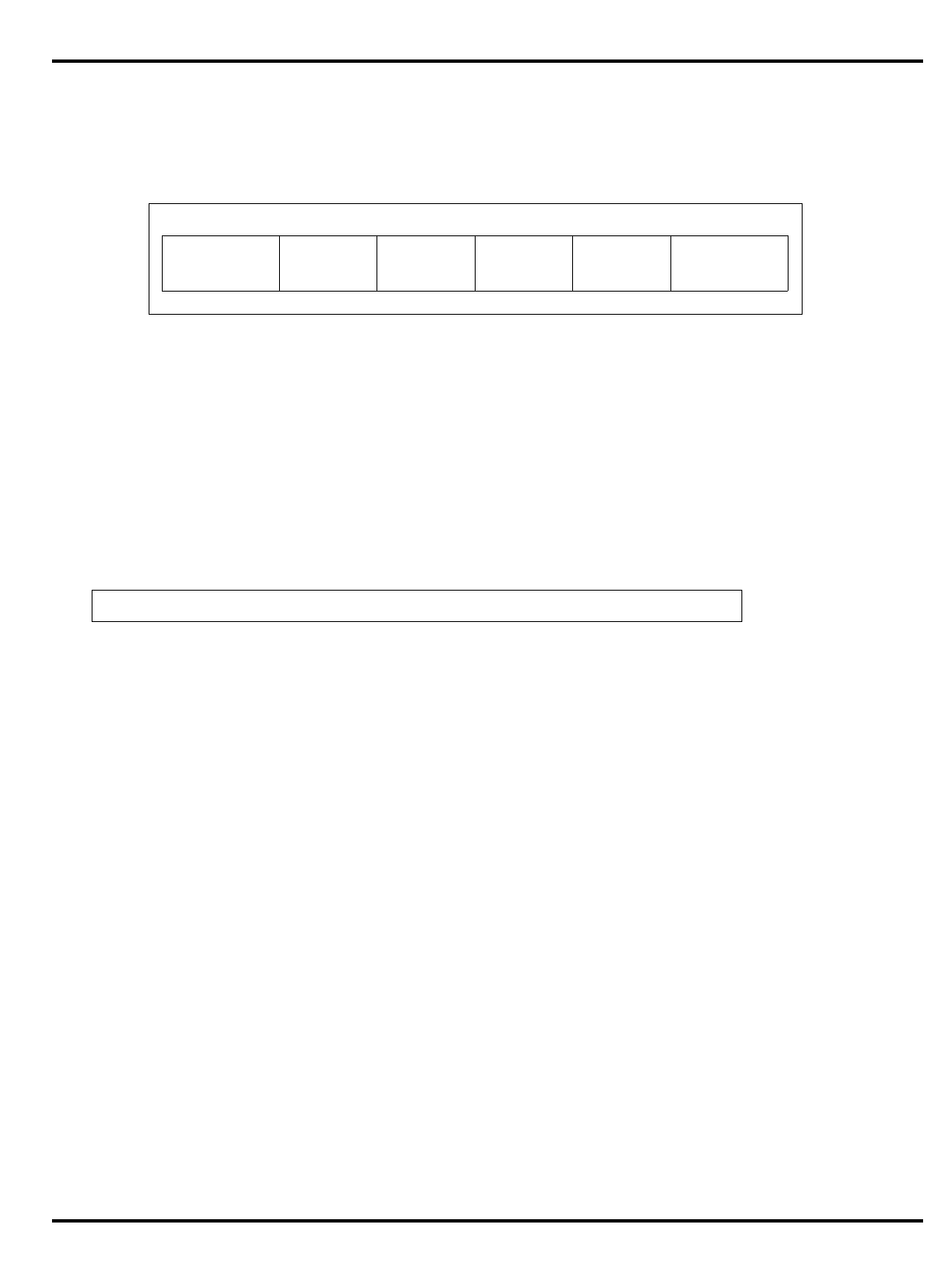

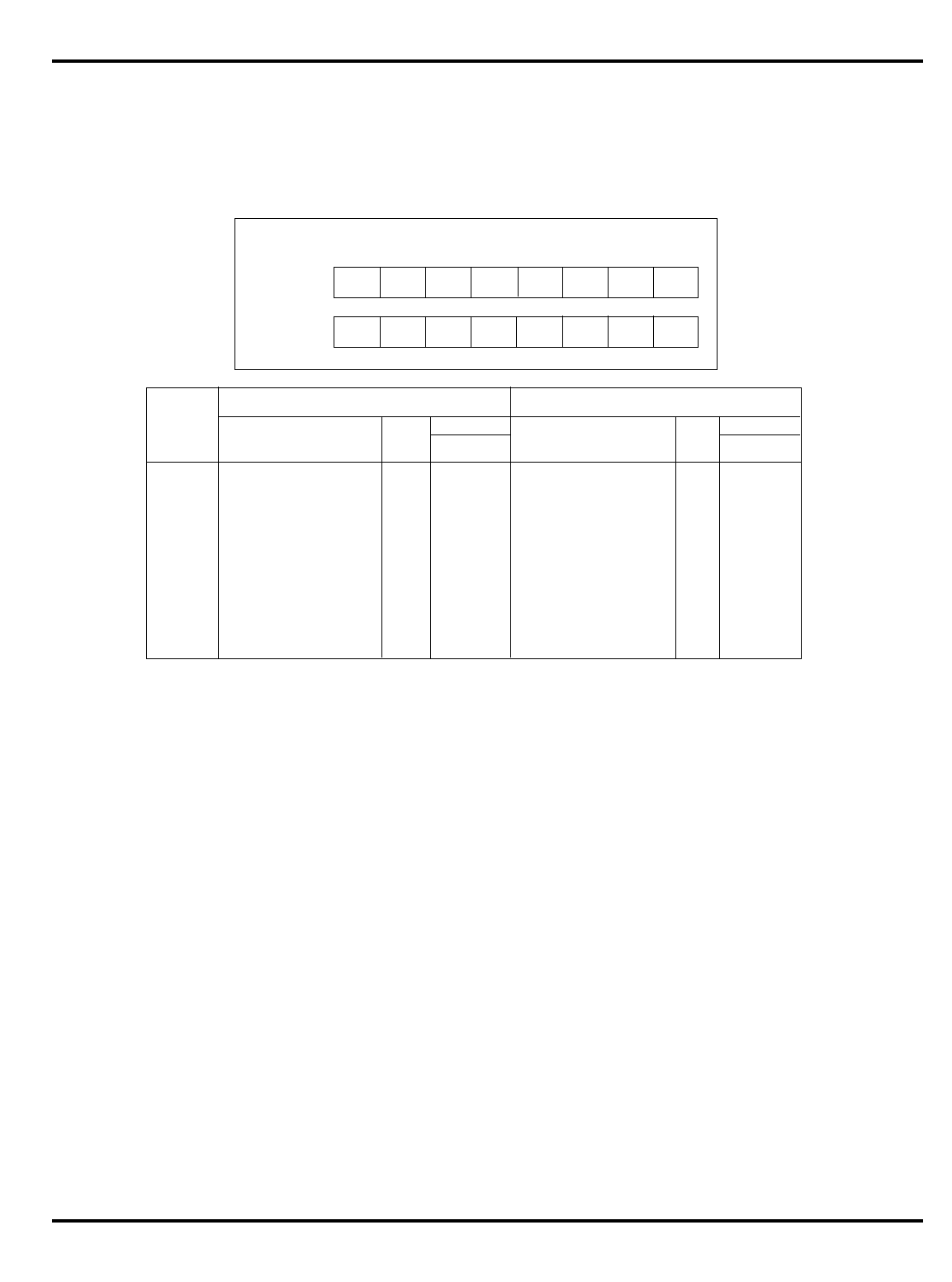

Figure 1.2. The pipeline and branch delays

•

Delayed branches

: the pipeline structure of the MIPS CPU (see "Figure

1.2. The pipeline and branch delays”) means that when a jump

instruction reaches the ‘‘execute’’ phase and a new program counter

is generated, the instruction after the jump will already have been

decoded. Rather than discard this potentially useful work, the

architecture rules state that the

instruction after a branch is always

executed before the instruction at the target of the branch

.

"Figure 1.2. The pipeline and branch delays” show that a special path

is provided through the ALU to make the branch address available a

half-clock early, ensuring that there is only a one cycle delay before

the outcome of the branch is determined and the appropriate

instruction flow (branch taken or not taken) is initiated.

It is the responsibility of the compiler system or the assembler-

programmer to allow for and even to exploit this “branch delay slot”;

it turns out that it is usually possible to arrange code such that the

instruction in the ‘‘delay slot’’ does useful work. Quite often, the

instruction which would otherwise have been placed before the

branch can be moved into the delay slot.

This can be a bit tricky on a conditional branch, where the branch

delay instruction must be (at least) harmless on the path where it isn’t

wanted. Where nothing useful can be done the delay slot is filled with

a ‘‘

nop

’’ (no-op, or no-operation) instruction.

Many MIPS assemblers will hide this feature from the programmer

unless explicitly told not to, as described later.

•

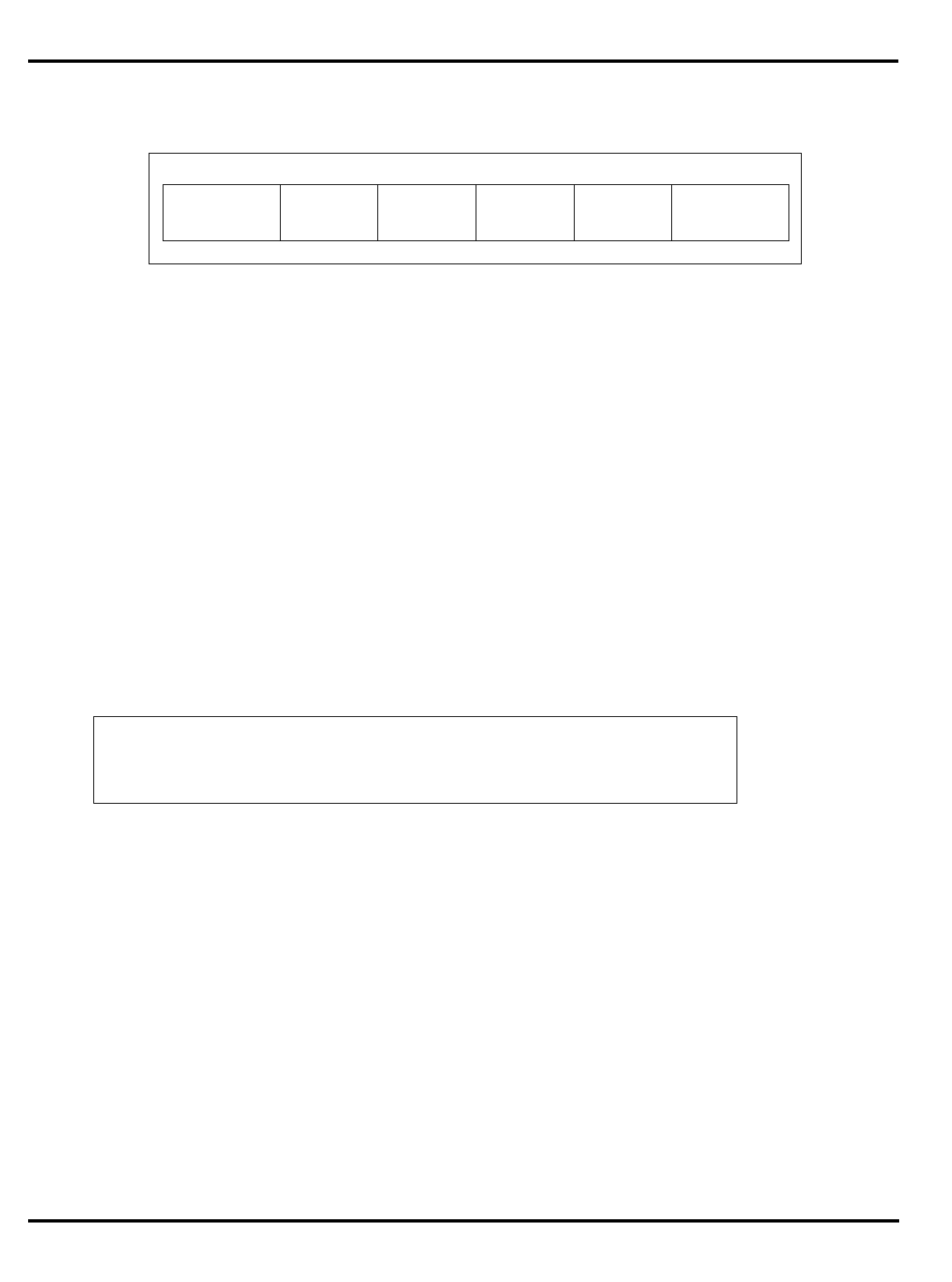

Load data not available to next instruction

: another consequence of

the pipeline is that a load instruction’s data arrives from the cache/

memory system AFTER the

next

instruction’s ALU phase starts – so it

is not possible to use the data from a load in the following instruction.

See "Figure 1.3. The pipeline and load delays” for how this works. On

the MIPS-1 architecture, the programmer must insure that this rule

is not violated

branch

branch

delay

branch

target

IF RF MEM WBALU

IF RF MEM WBALU

branch

addr

IF RF MEM WB

CHAPTER 1 INTRODUCTION

1–8

•.

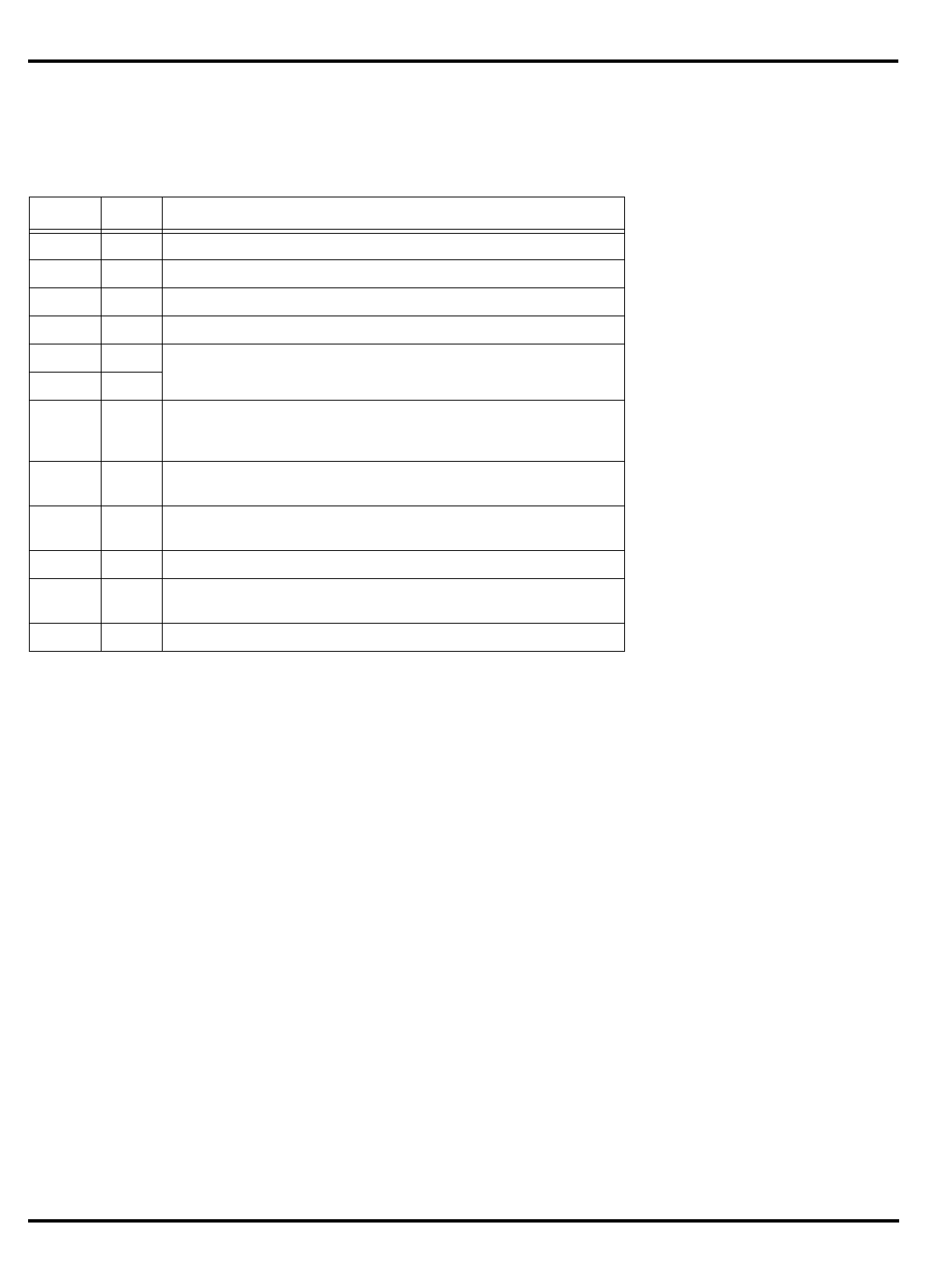

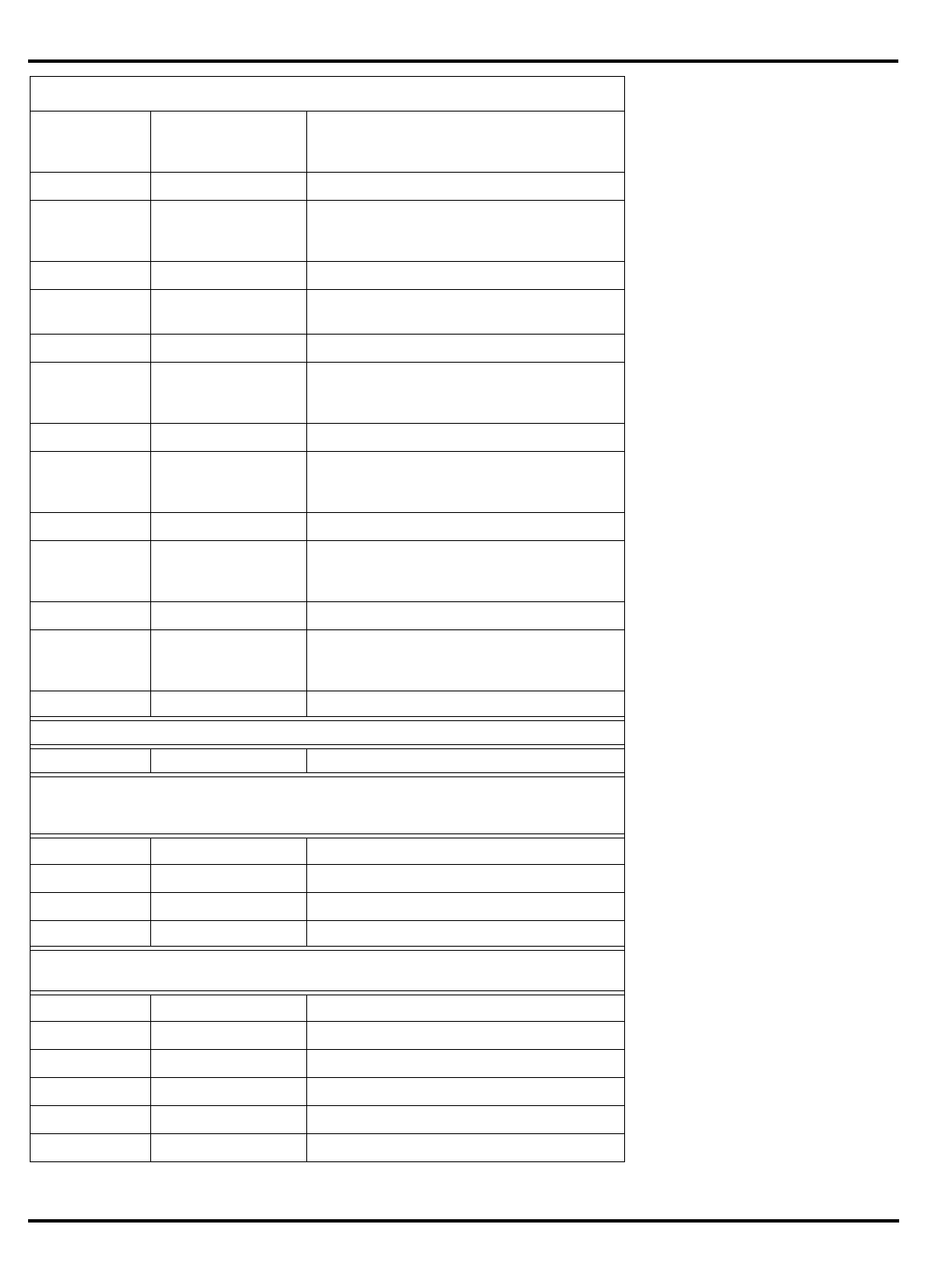

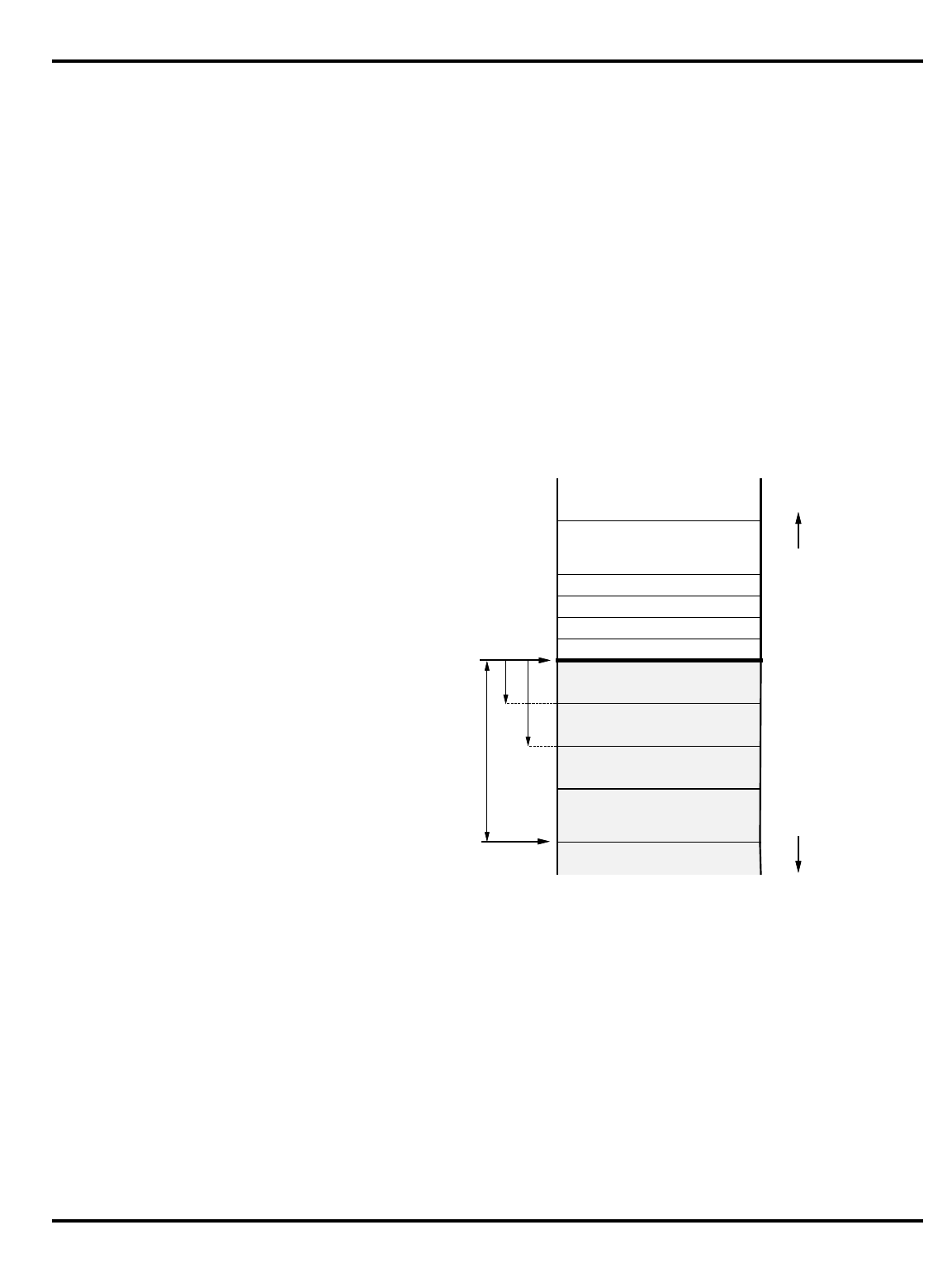

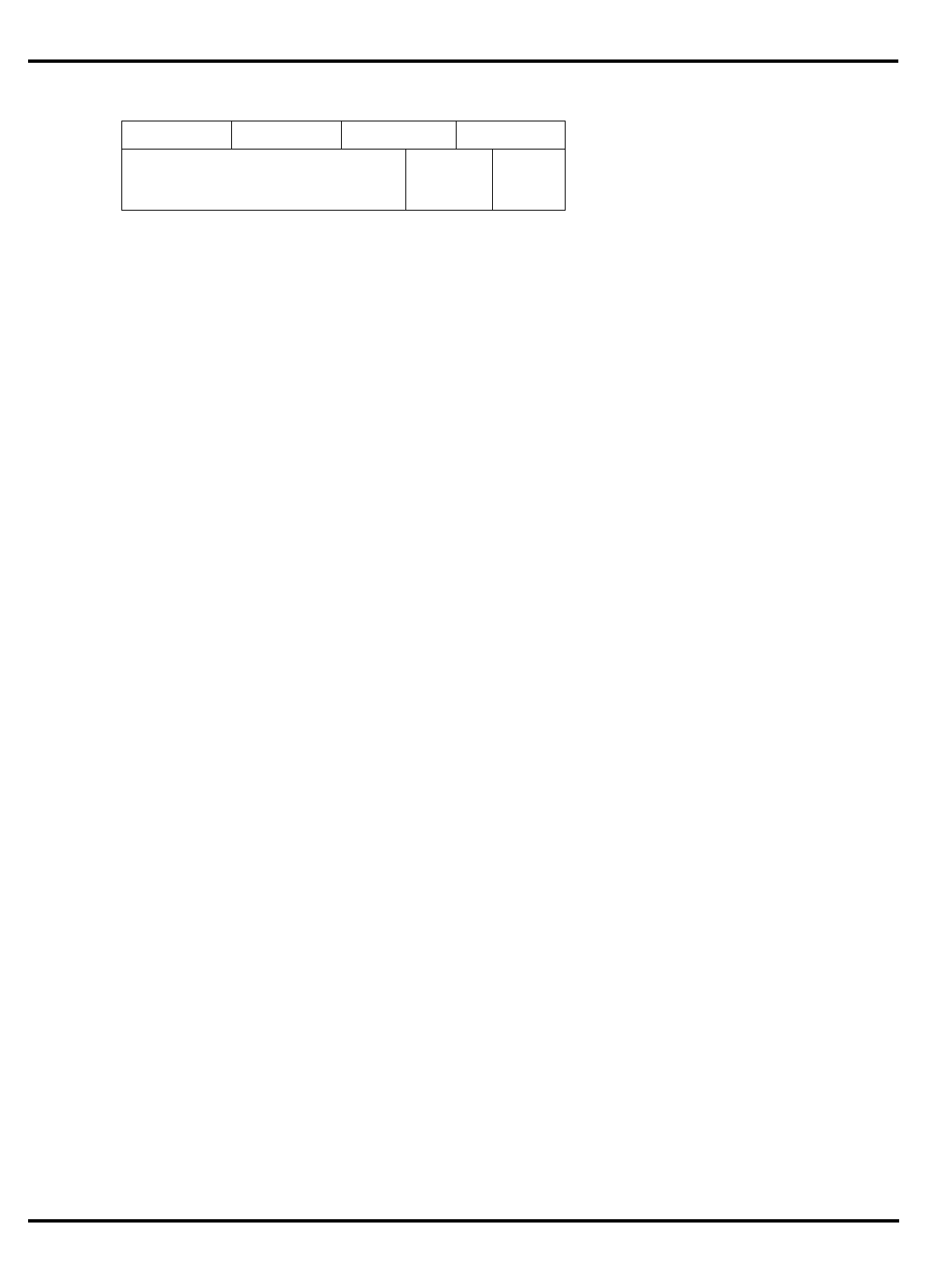

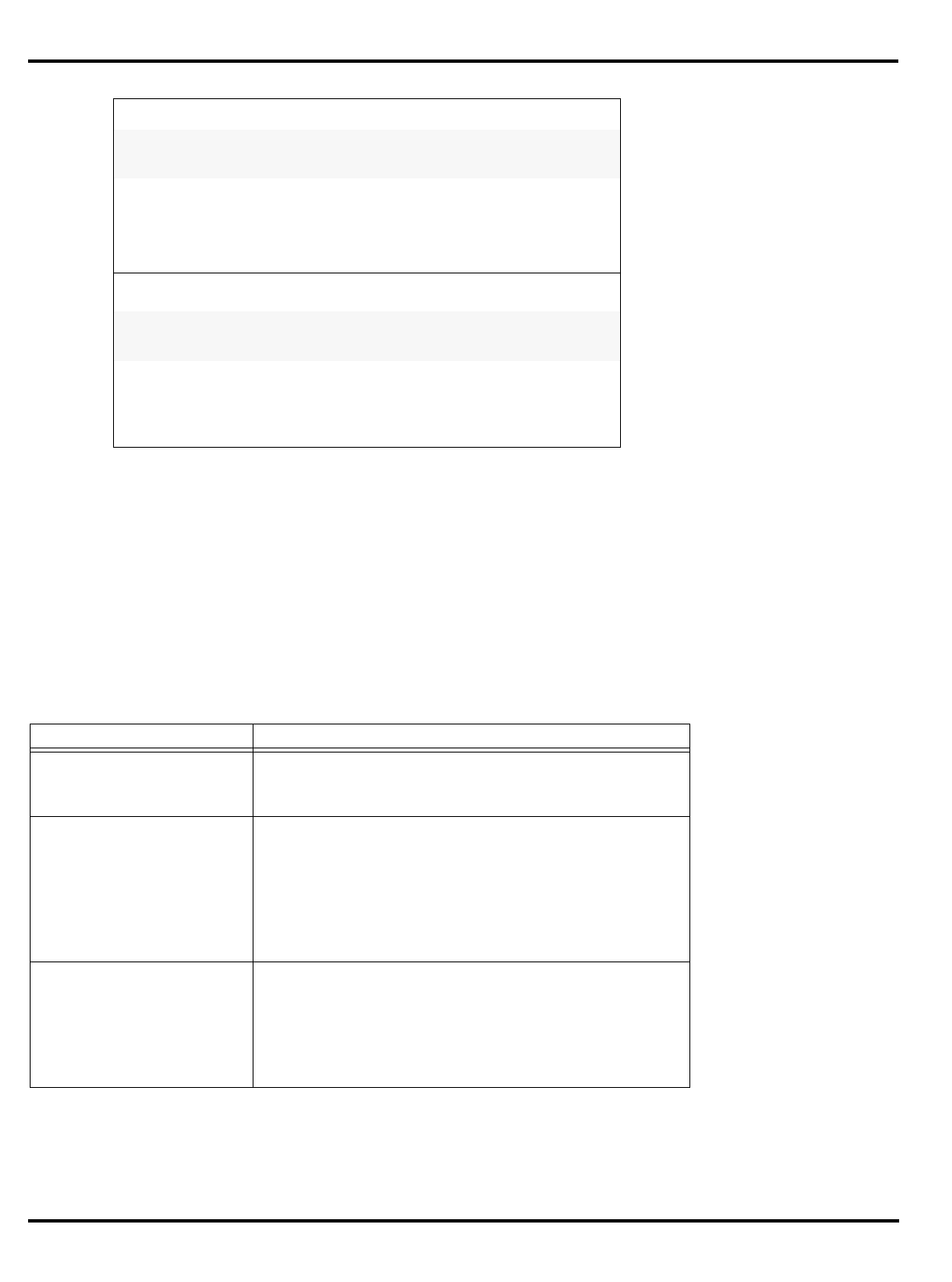

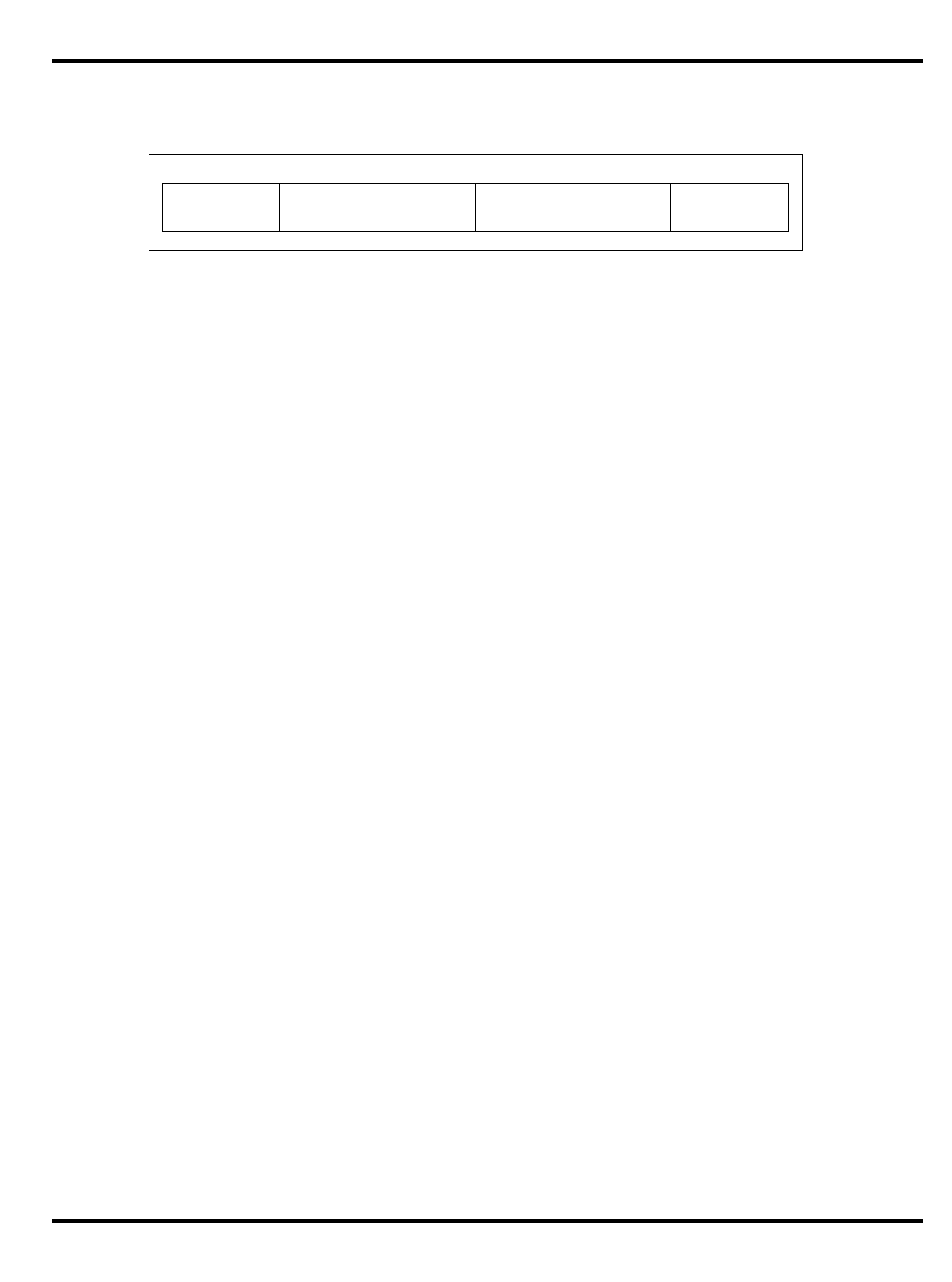

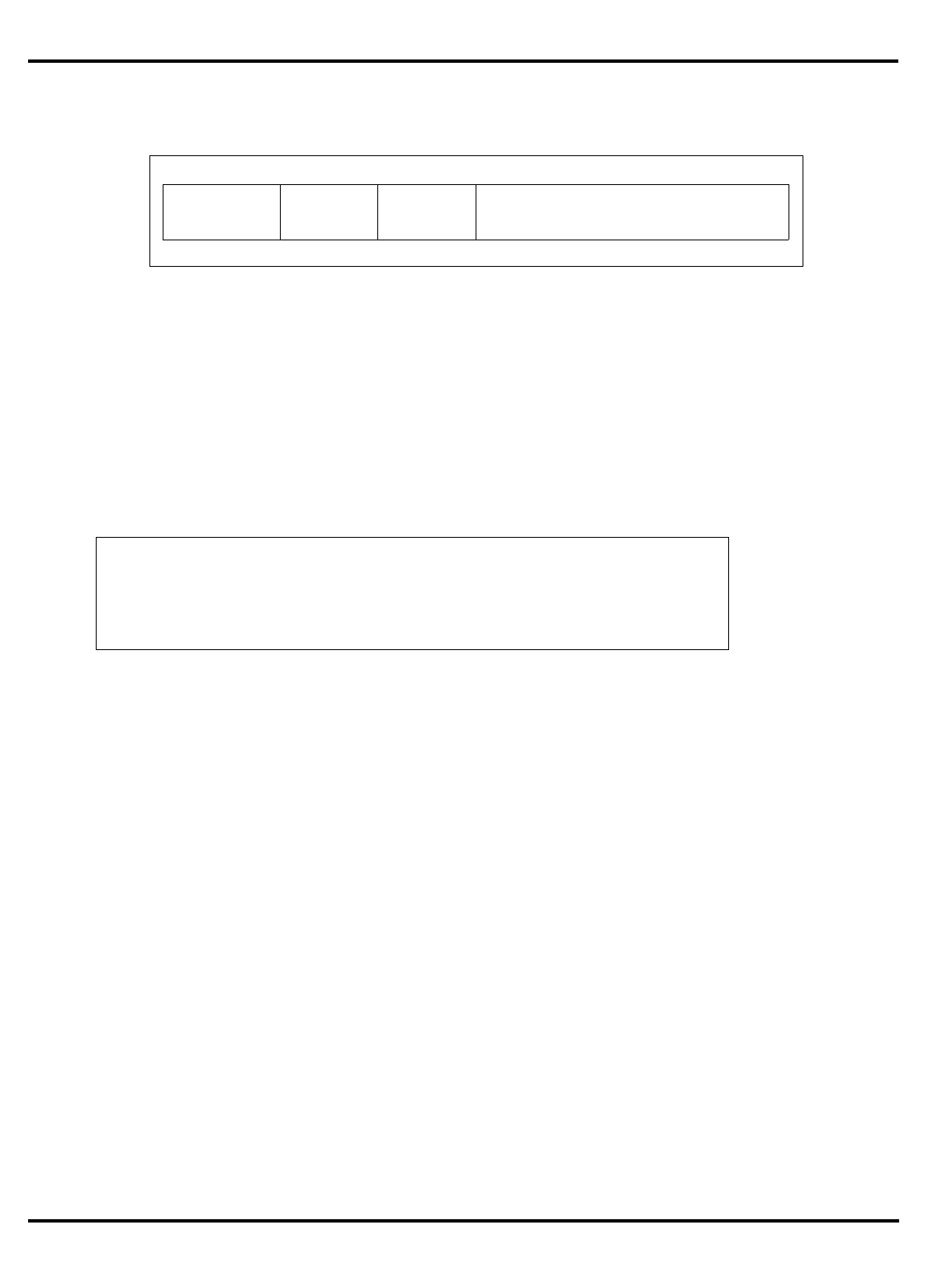

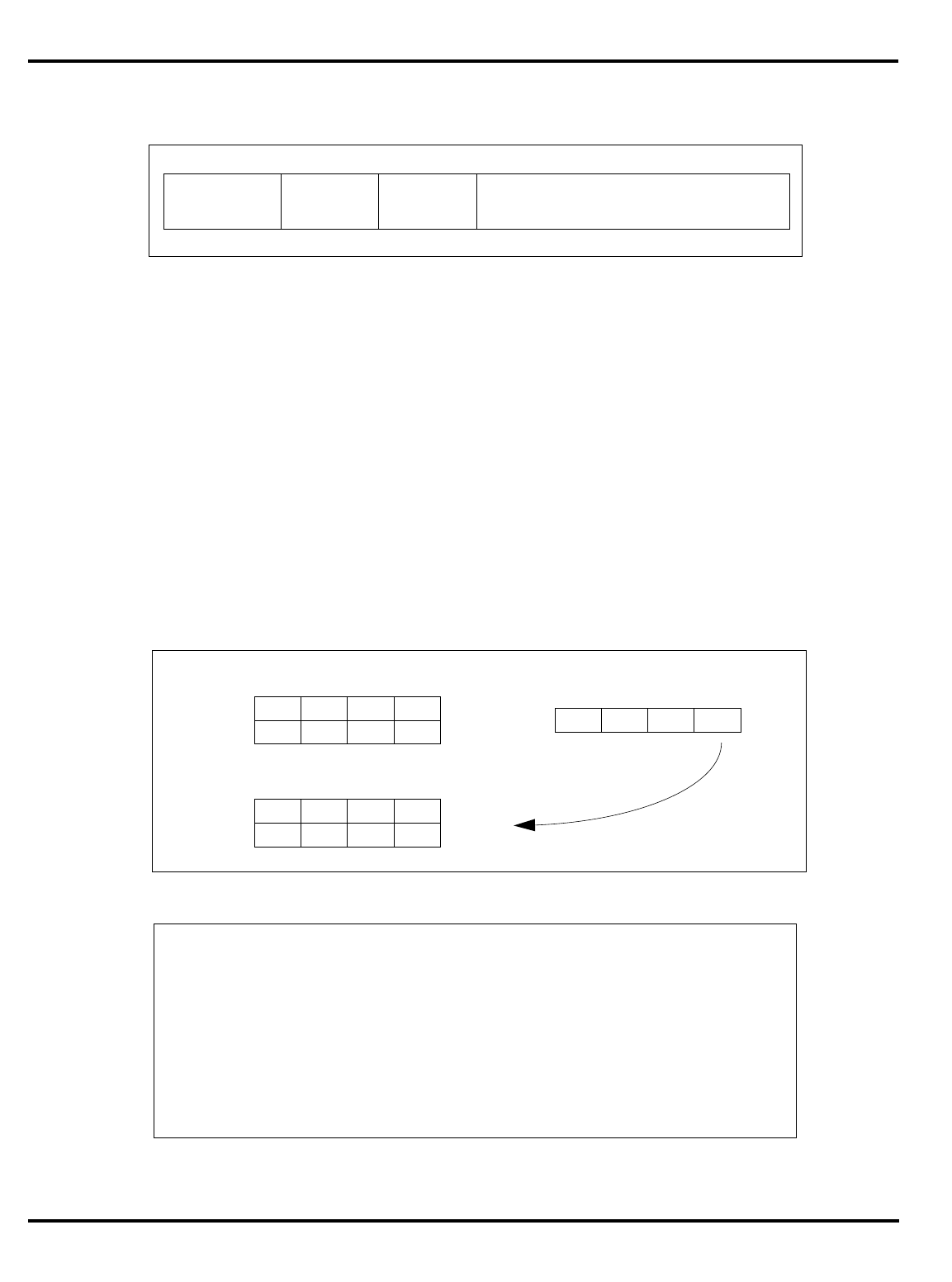

Figure 1.3. The pipeline and load delays

Again, most assemblers will hide this if they can. Frequently, the

assembler can move an instruction which is independent of the load

into the load delay slot; in the worst case, it can insert a

NOP

to insure

proper program execution.

A NOTE ON MACHINE AND ASSEMBLER LANGUAGE

To simplify assembly level programming, the MIPS Corp’s assembler

(and many other MIPS assemblers) provides a set of “synthetic”

instructions. Typically, a synthetic instruction is a common assembly level

operation that the assembler will map into one or more true instructions.

This mapping can be more intelligent than a mere macro expansion. For

example, an immediate load may map into one instruction if the datum is

small enough, or multiple instructions if the datum is larger. However,

these instructions can dramatically simplify assembly level programming.

For example, the programmer just writes a ‘‘load immediate’’ instruction

and the assembler will figure out whether it needs to generate multiple

machine instructions or can get by with just one (in this example,

depending on the size of the immediate datum).

This is obviously useful, but can be confusing. This manual will try to

use synthetic instructions sparingly, and indicate when it happens.

Moreover, the instruction tables below will consistently distinguish

between synthetic and machine instructions.

These features are there to help human programmers; most compilers

generate instructions which are one-for-one with machine code. However,

some compilers will in fact generate synthetic instructions.

Helpful things the assembler does:

•

32-bit load immediates

: The programmer can code a load with any

value (including a memory location which will be computed at link

time), and the assembler will break it down into two instructions to

load the high and low half of the value.

•

Load from memory location

: The programmer can code a load from a

memory-resident variable. The assembler will normally replace this

by loading a temporary register with the high-order half of the

variable’s address, followed by a load whose displacement is the low-

order half of the address.

Of course, this does not apply to variables defined inside C functions,

which are implemented either in registers or on the stack.

•

Efficient access to memory variables

: some C programs contain many

references to

static

or

extern

variables, and a two-instruction

sequence to load/store any of them is expensive. Some compilation

systems, with run-time support, get around this. Certain variables

are selected at compile/assemble time (by default MIPS Corp’s

assembler selects variables which occupy 8 or less bytes of storage)

D-cache rd

load

load

delay

use

data

RDIF ALU MEM WB

RDIF ALU MEM WB

RDIF ALU MEM WB

INTRODUCTION CHAPTER 1

1–9

and kept together in a single section of memory which must end up

smaller than 64Kbytes. The run-time system then initializes one

register ($28 or

gp

(global pointer) by convention) to point to the

middle of this section.