U PD72120 Users Manual Dec86

uPD72120_Users_Manual_Dec86 uPD72120_Users_Manual_Dec86

User Manual: manual pdf -FilePursuit

Open the PDF directly: View PDF ![]() .

.

Page Count: 118 [warning: Documents this large are best viewed by clicking the View PDF Link!]

" "

NEe

Electronics

Inc.

NEe

ADVANCE

PRODUCT

INFORMATION

December

1886

pPD72120

Advanced Graphics Display Controller

User's Manual

The information contained in this

document

is being iIIued

in

adYance

of

the

produCtiOn cycle

for

the

device. The

parameters

for

the

device may change before final production

or

NEe

Electronics Inc

.•

~

It

its

own

discretion.

may

withdraw the ctevice prior

to

production.

The information in this document is subject

to

change without

notice.

NEe

Electronics Inc. assumes

no

responsibility

for

any errors

or

omissions that may appear

in

this document. Devices sold

by

NEe

ElectroniCS Inc.

are covered

by

the warranty and patent indemnification provisions appearing in

NEe

illectronics

Inc~

Terms and

Conditions of Sale only.

NEe

Electronics Inc. makes

no

warranty. express, ltatutory, implied,

or

by

desCription.

regarding the information

.t

forth herein

or

regarding

the

freedom

of

the

deSCribed devices from patent

infringement. NEC Electronics Inc. makes

no

warranty

of

merchantability

or

fitness

for

any purpose.

NEe

Electronics Inc. makes

no

commitment

to

update

or

to

keep current

the

information contained in this document.

No

pert

of

this document may

be

copied

or

reproduced in any form

or

by

any means

without

the

prior written

~nsent

of

NEC Electronics Inc.

..

Advanced

Graphic Display Controller

Preliminary Product Informat:ion

1.

OVerview

•••••••••••••••••••••••••••••••••••••••••••••••••••••••••

Features

•••••••••••••••••••••••••••••••••••••••••••••••••••••••

Pin

Configurations

•••••••••••••••••••••••••••••••••••••••••••••

Pin Configuration

(Flat

package)

••••••••••••••••••••••••••

Pin Configuration

(PLCC

package)

••••••••••••••••••••••••••

Block

Diagram

••••••••••••••••••••••••••••••••••••••••••••••••••

Pin

Functions

••••••••••••••••••••••••••••••••••••••••••••••••••

Clock Pins

••••••••••••••••••••••••••••••••••••••••••••••••

system

Bus

Control Pins

•••••••••••••••••••••••••••••••••••

Dis~ay

Memo~

Control Pins

•••••••••••••••••••••••••••••••

Video

Timing

Signal Helated Pins

••••••••••••••••••••••••••

Display Signal Belated Pins

•••••••••••••••••••••••••••••••

Power

SUpply

and

Ground

Pins

••••••••••••••••••••••••••••••

SmlTery

••••••••••••••••••••••••••••••••••••••••••••••••••••••••

2.

Function Description

•••••••••••••••••••••••••••••••••••••••••••••

2.1

Features

••••••••••••••••••••••••••••••••••••••••••••••••••••••••

High

Speed

Graphics

Drawing

••••••••••••••••••••••••••••••••••••

Video

Timing

Signal Generation

•••••••••••••••••••••••••••••••••

Large capacity Display

Memo~

COntrol

••••••••••••••••••••••••••

CPtJ

Interface

••••••••••••••••••••••••••••••••••••••••••••••••••

2 .2 Corrmand/Paranete r

Exchange

Between

the

CPU

and A(;x'

••••••••••••

2.3 Beset and Abort Operation

••••••••••••••••••••••••••••••••••••••

3.

A~

C>}?eration

•••••••••••••••••••••••••••••••••••••••••••••••••••

3.1

How

to

Use

the

Internal

~ister

••••••••••••••••••••••••••••••••

3.2

AGDC

Control

~isters

••••••••••••••••••••••••••••••••••••••••••

S'm'ltlS (

Status)

••••••••••••••••••••••••••••••••••••••••••••••••

BANK

(Bank)

••••••••••••••••••••••••••••••••••••••••••••••••••••

C'l'RI., (Control)

•••••••••••••••••••••••••••••••••••••••••••••••••

3.3 Display

~lated

~isters

•••••••••••••••••••••••••••••••••••••••

DI~Y

FLAGS

(Display Flags)

••••••••••••••••••••••••••••••••••

DISPLAT

PITCH

(Display Pitch)

••••••••••••••••••••••••••••••••••

AC

(Address Control)

•••••••••••••••••••••••••••••••••••••••••••

DAD

(Display Address)

••••••••••••••••••••••••••••••••••••••••••

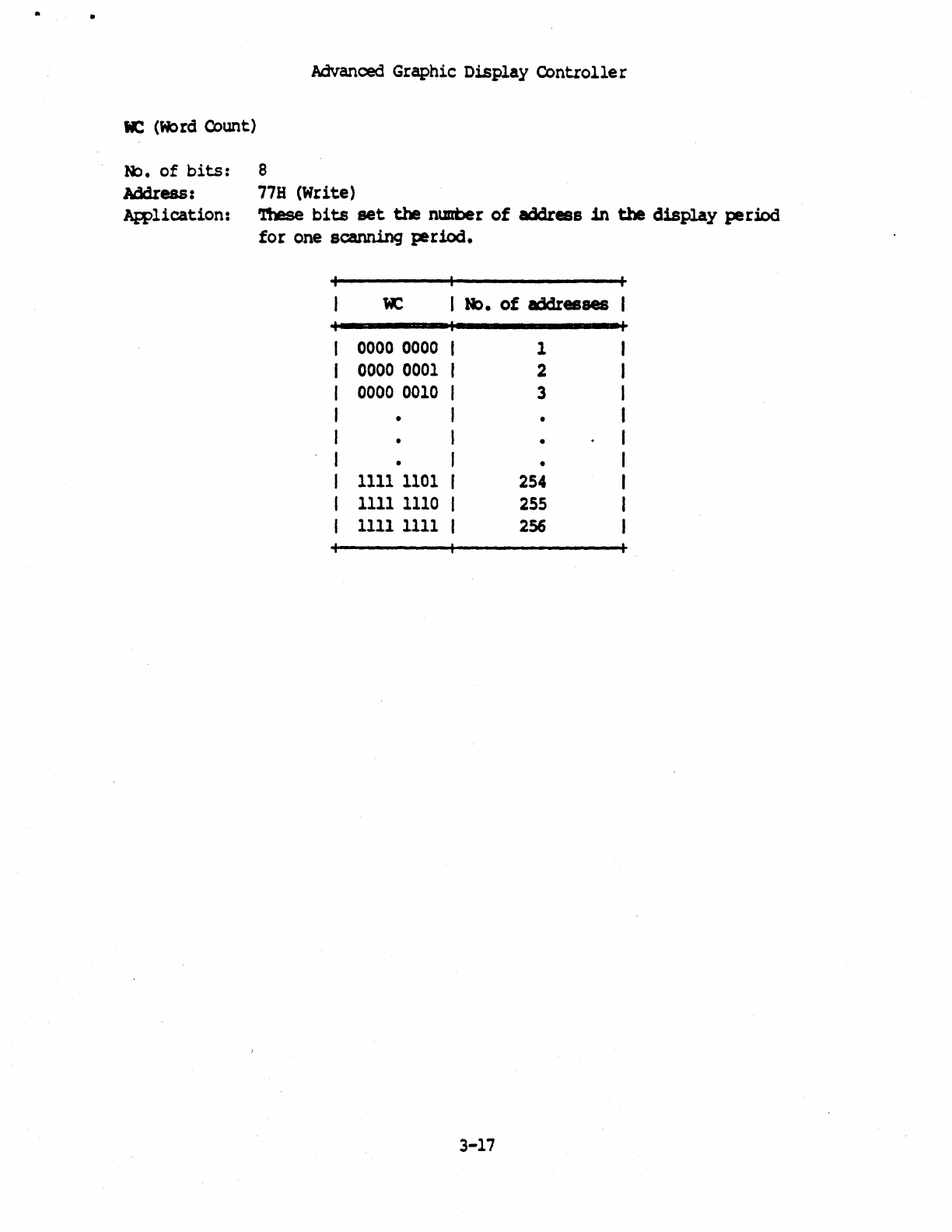

~

(~rd

Count)

••••••••••••••••••••••••••••••••••••••••••••••••

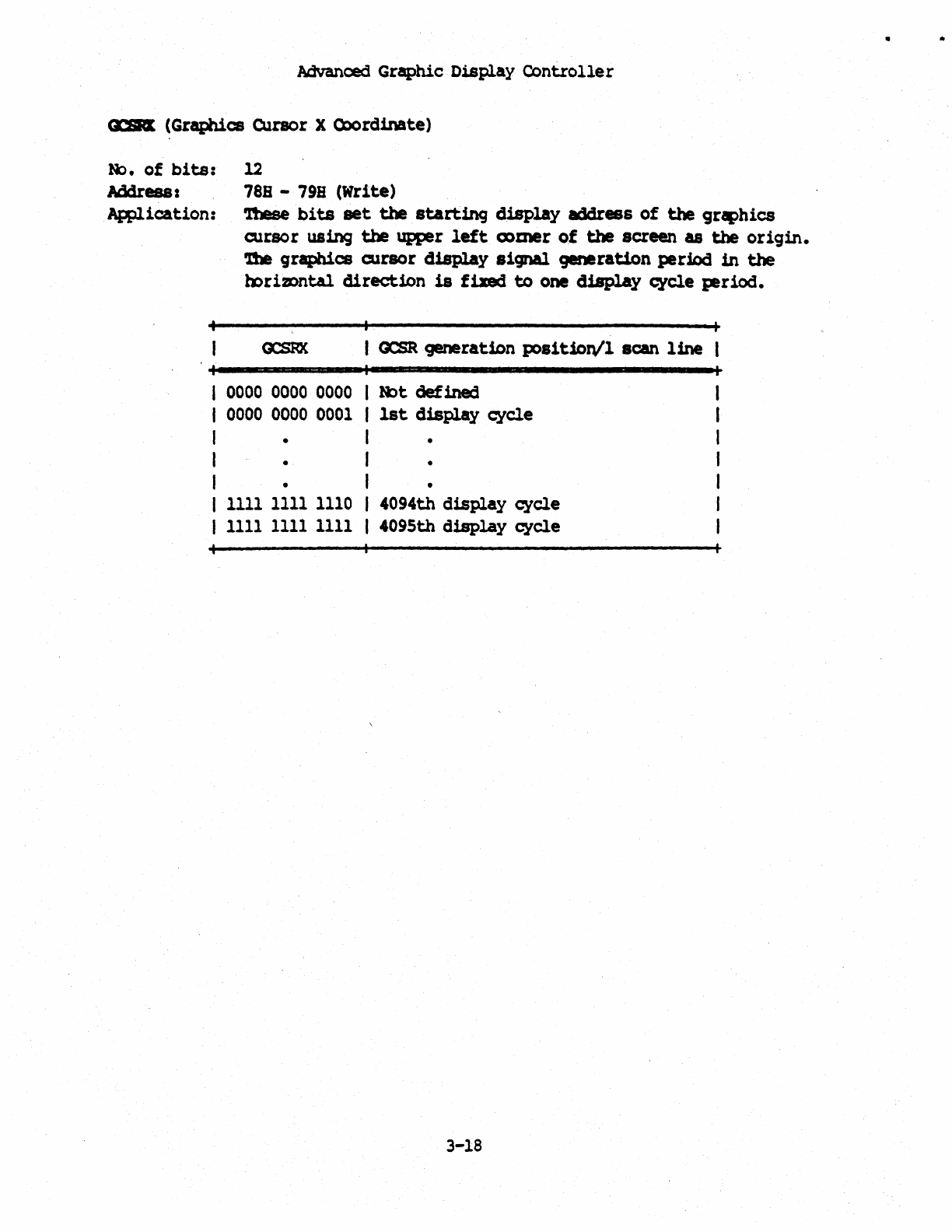

GCSRX

(Graphics Cursor X Coordinate)

•••••••••••••••••••••••••••

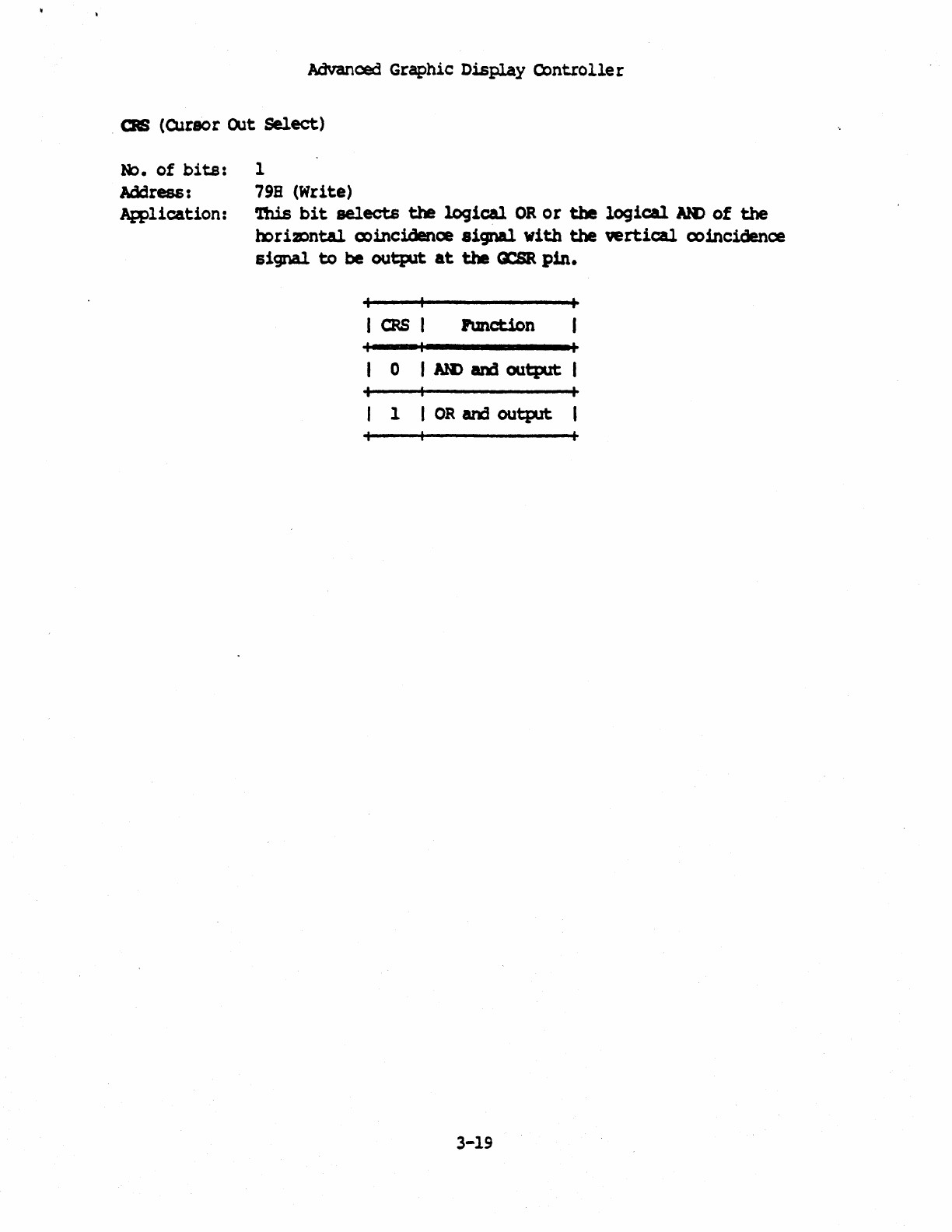

CRS

(OJrsor

()Ut

Select)

••••••••••••••••••••••••••••••••••••••••

i

1-1

1-1

1-2

1-3

1-4

1-5

1~

l~

1-6

1-8

1-9

1-9

1-9

1-10

2-1

2-1

2-1

2-3

2-3

2-3

2-5

2-9

3-1

3-1

3-3

3-3

3-5

3~

3-7

3-6

3-14

3-15

3-16

3-17

3-18

3-19

Advanced

Graphic Display

Controller

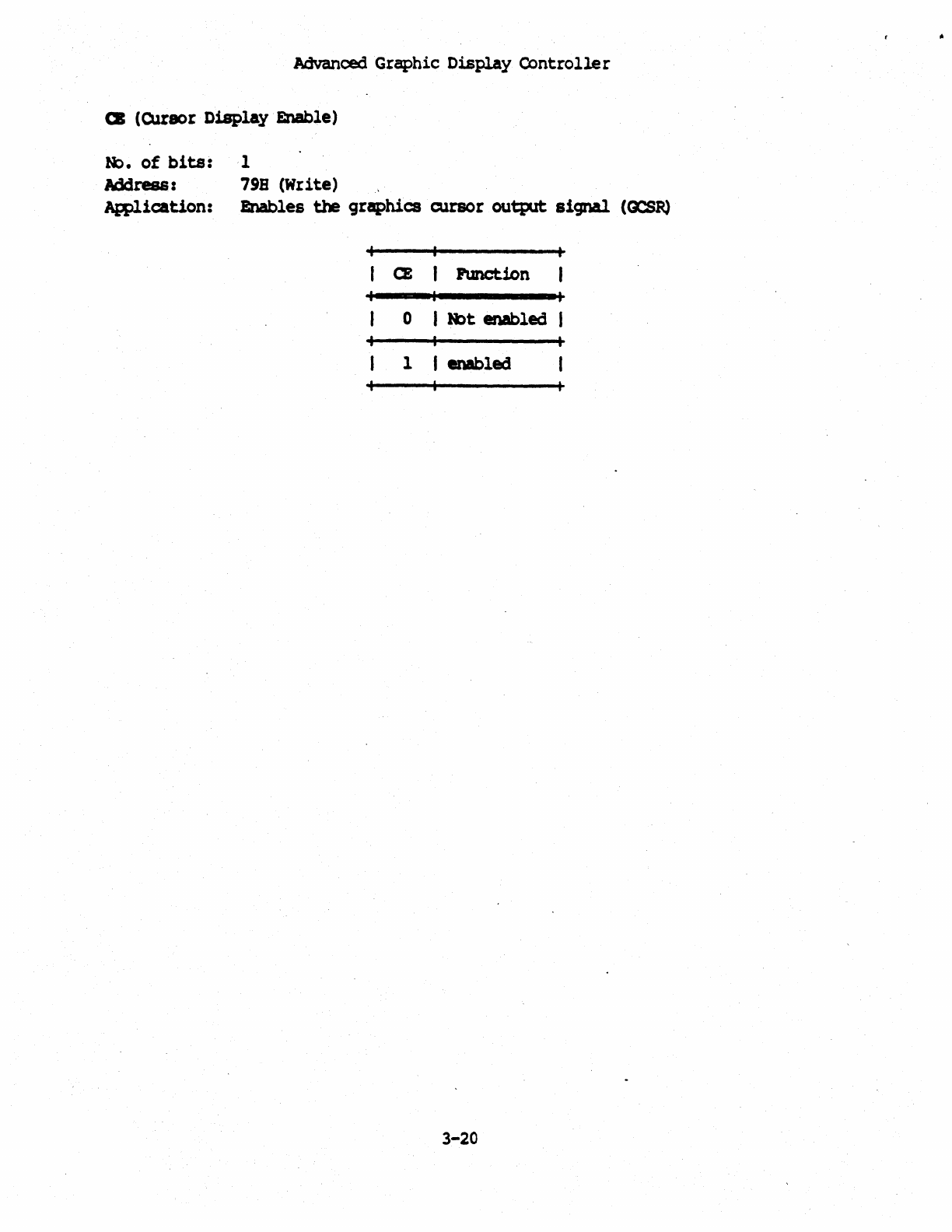

CE

(CUrsor

D~lay

Enable)

•••••••••••••••••••••••••••••••••••••

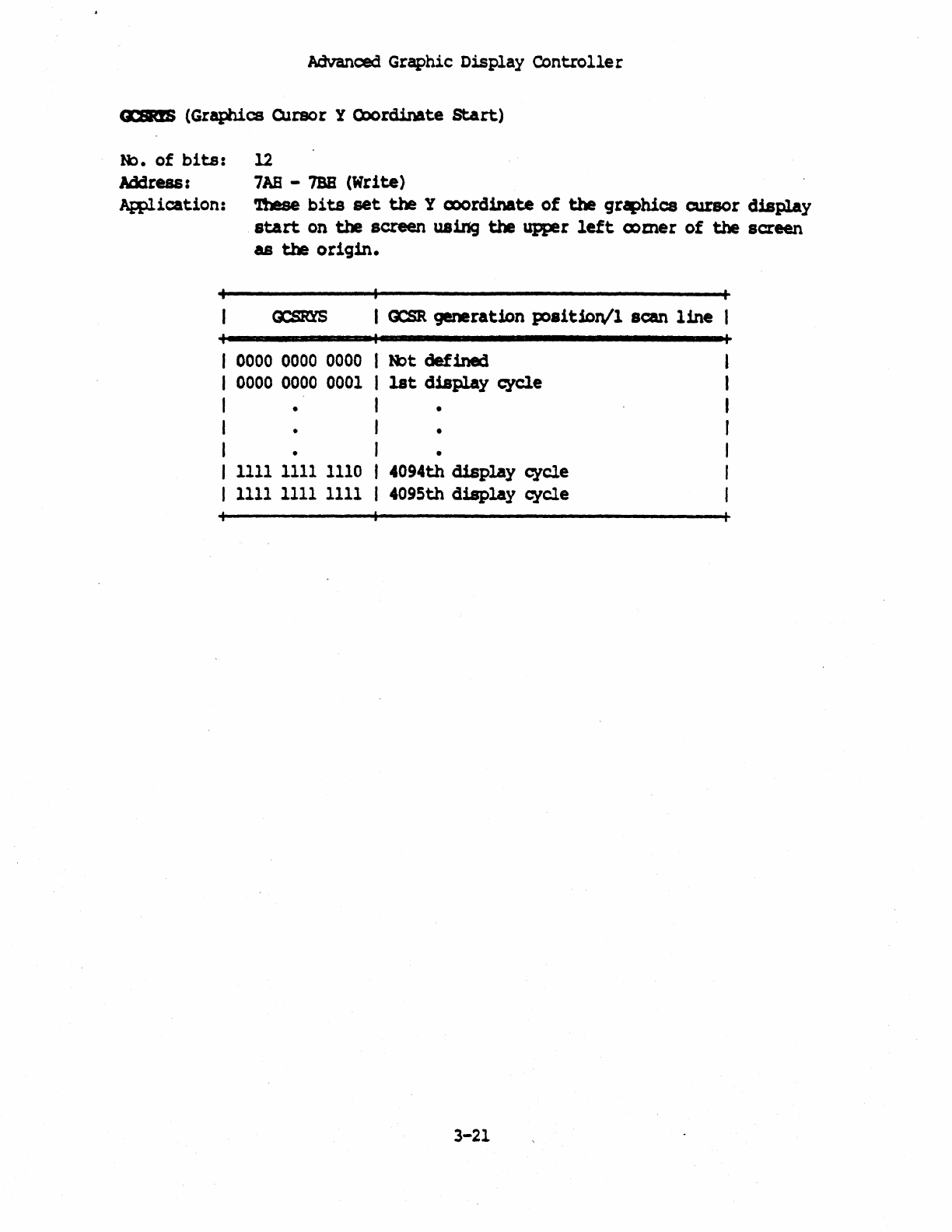

OCSRYS

(Graphics Cursor Y COOrdinate

Start)

••••••••••••••••••••

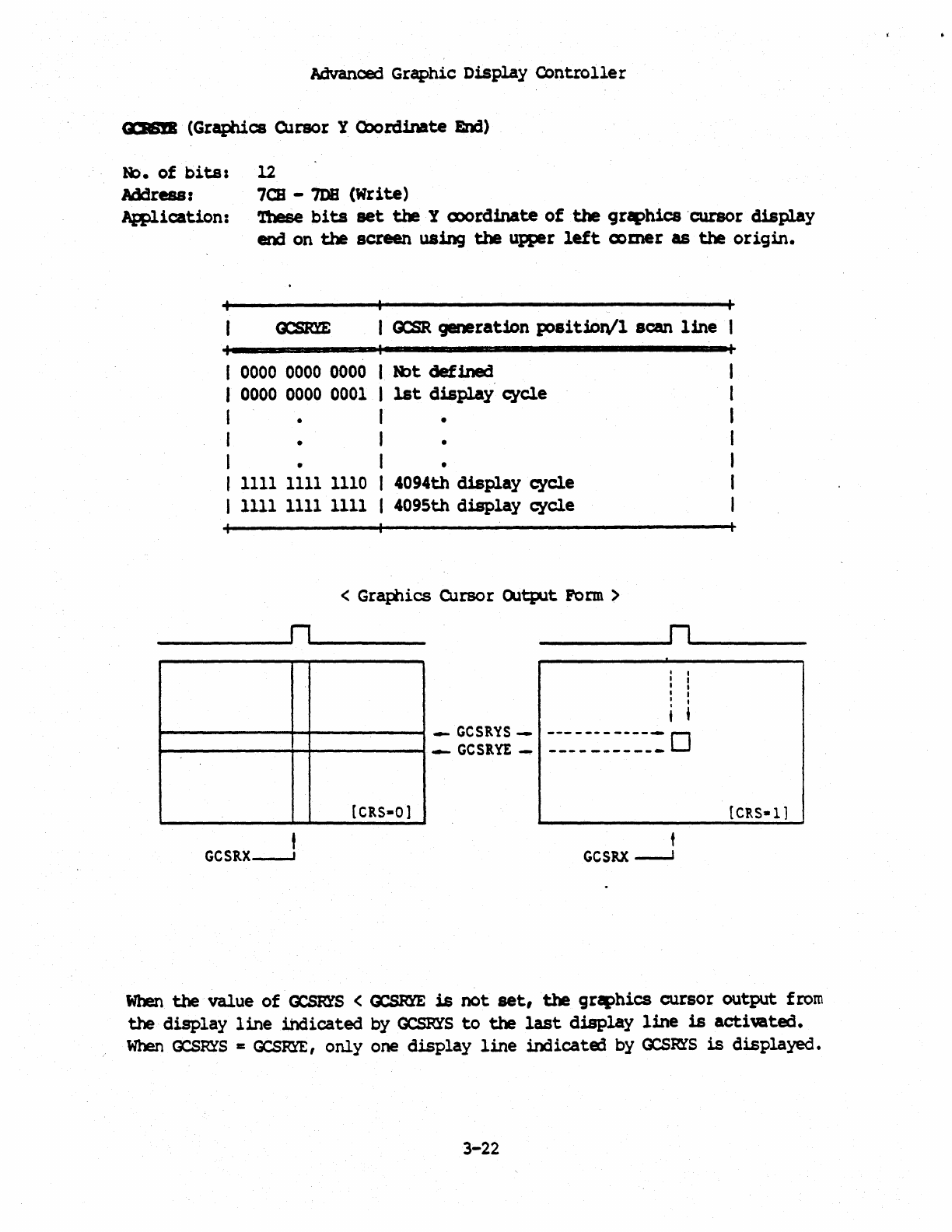

G:RSl'E (Graphics CUrsor Y OX>rdinate

End)

••••••••••••••••••••••

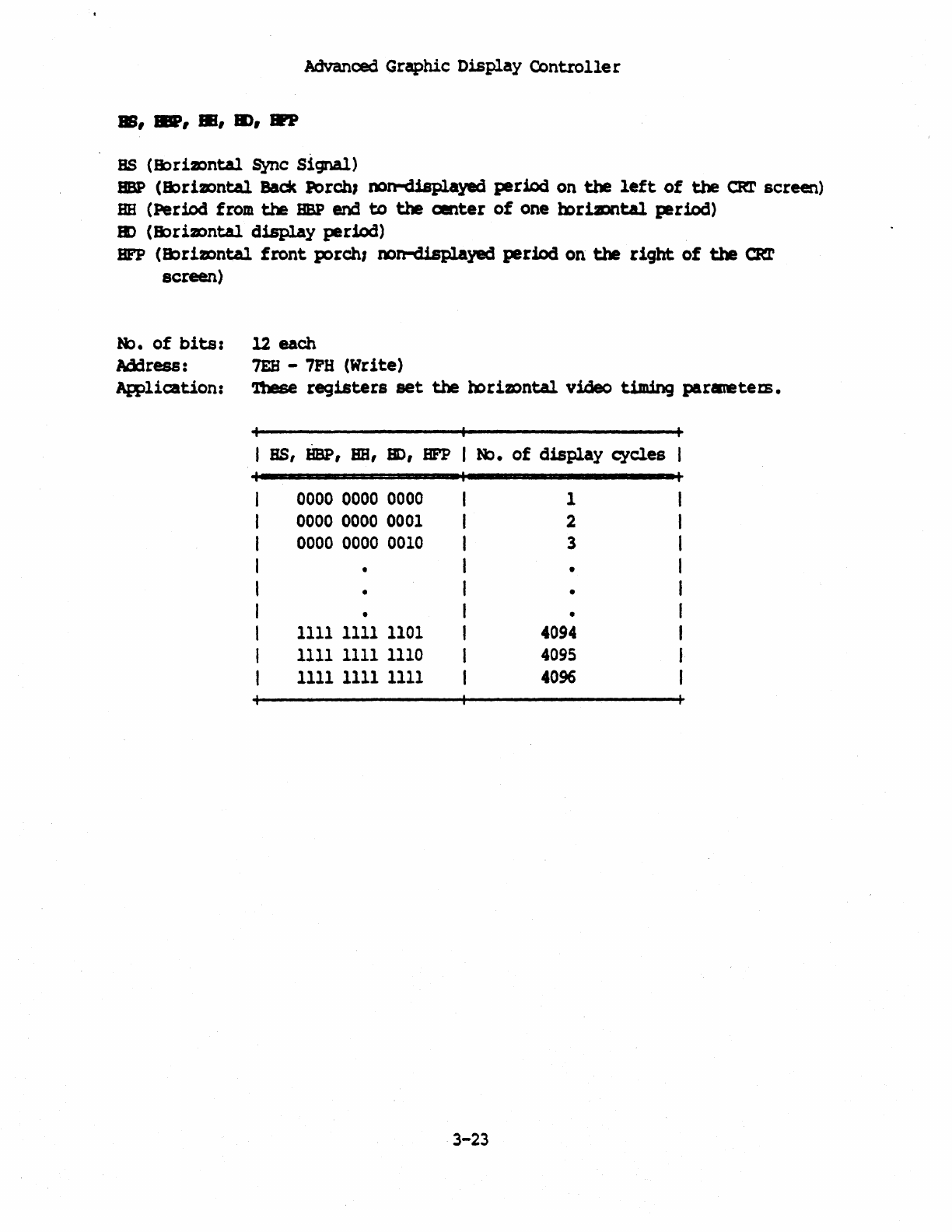

BS,

BBP,

BH, BO,

BFP

•••••••••••••••••••••••••••••••••••••••••••

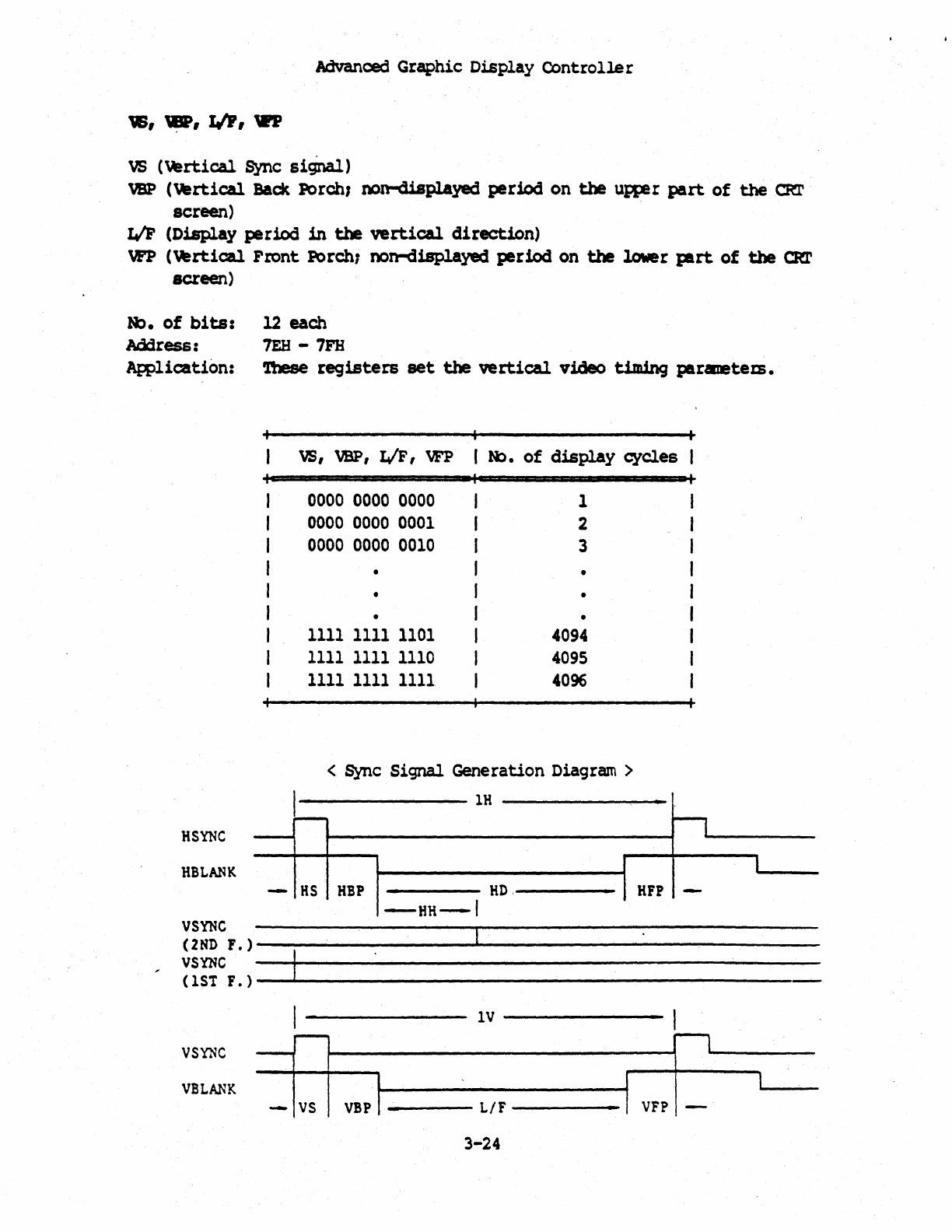

VS,

VBP,

LlF,

VFP

••••••••••••••••••••••••••••••••••••••••••••••

3.4

Inter.nal

Register

~le

•••••••••••••••••••••••••••••••••••••••••

3-20

3-21

3-22

3-23

3-24

3-25

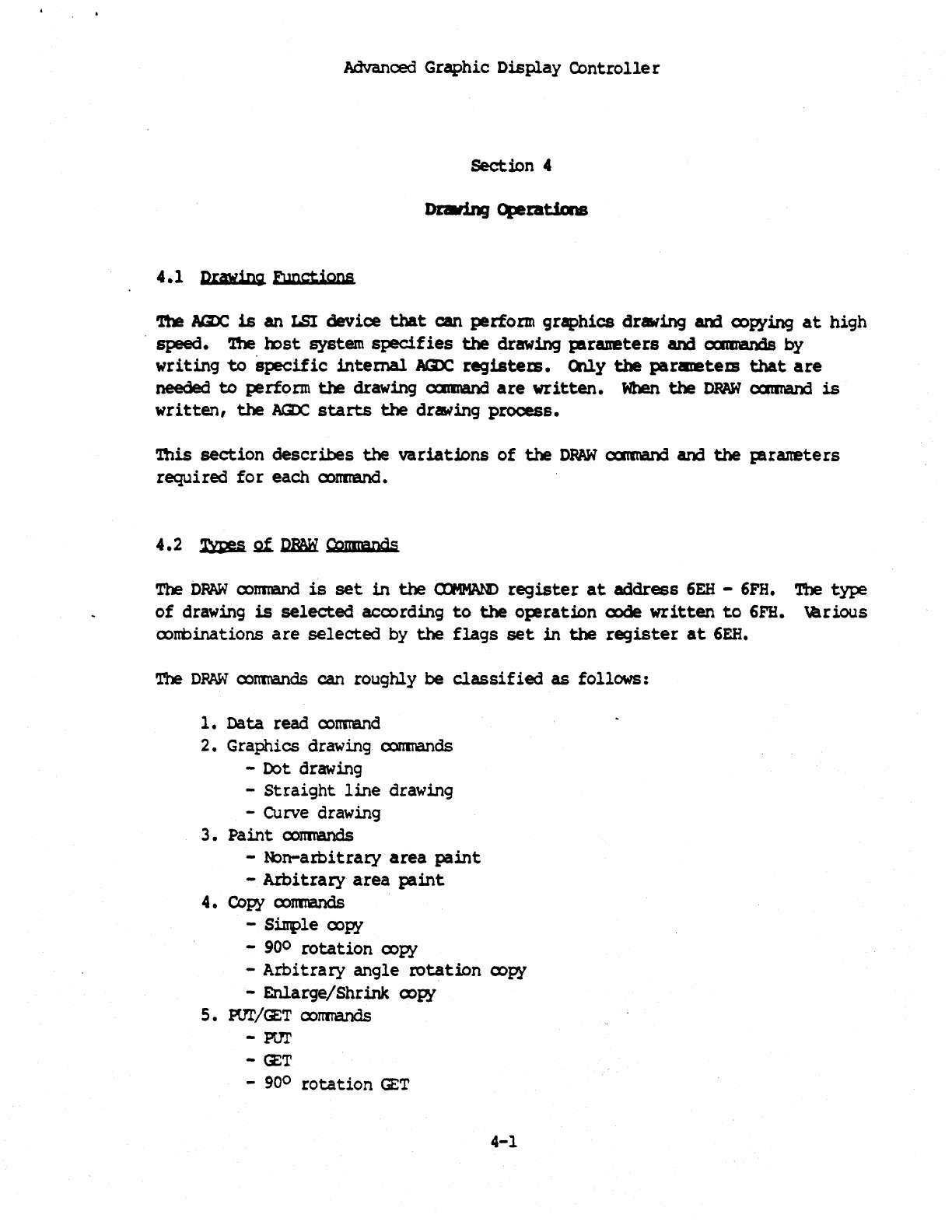

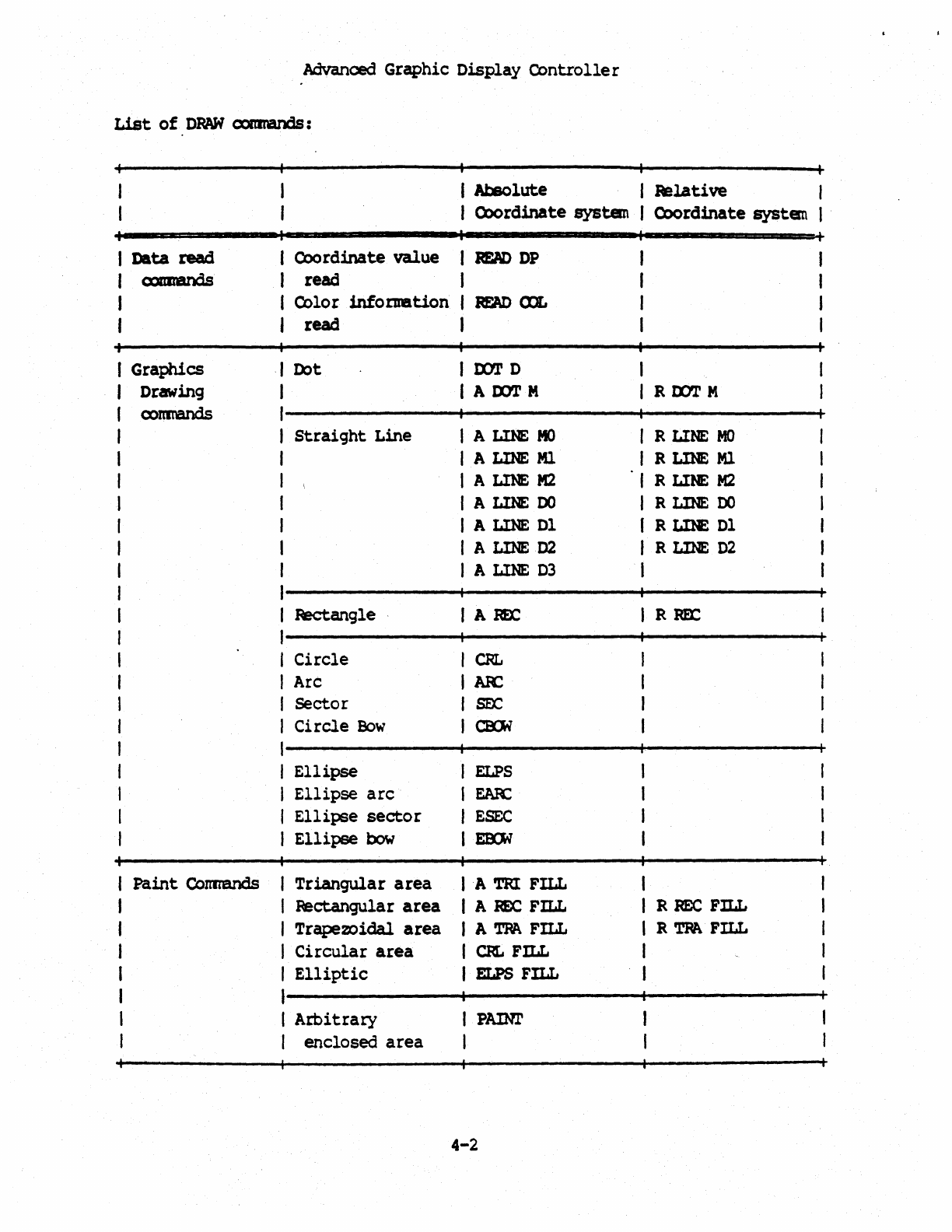

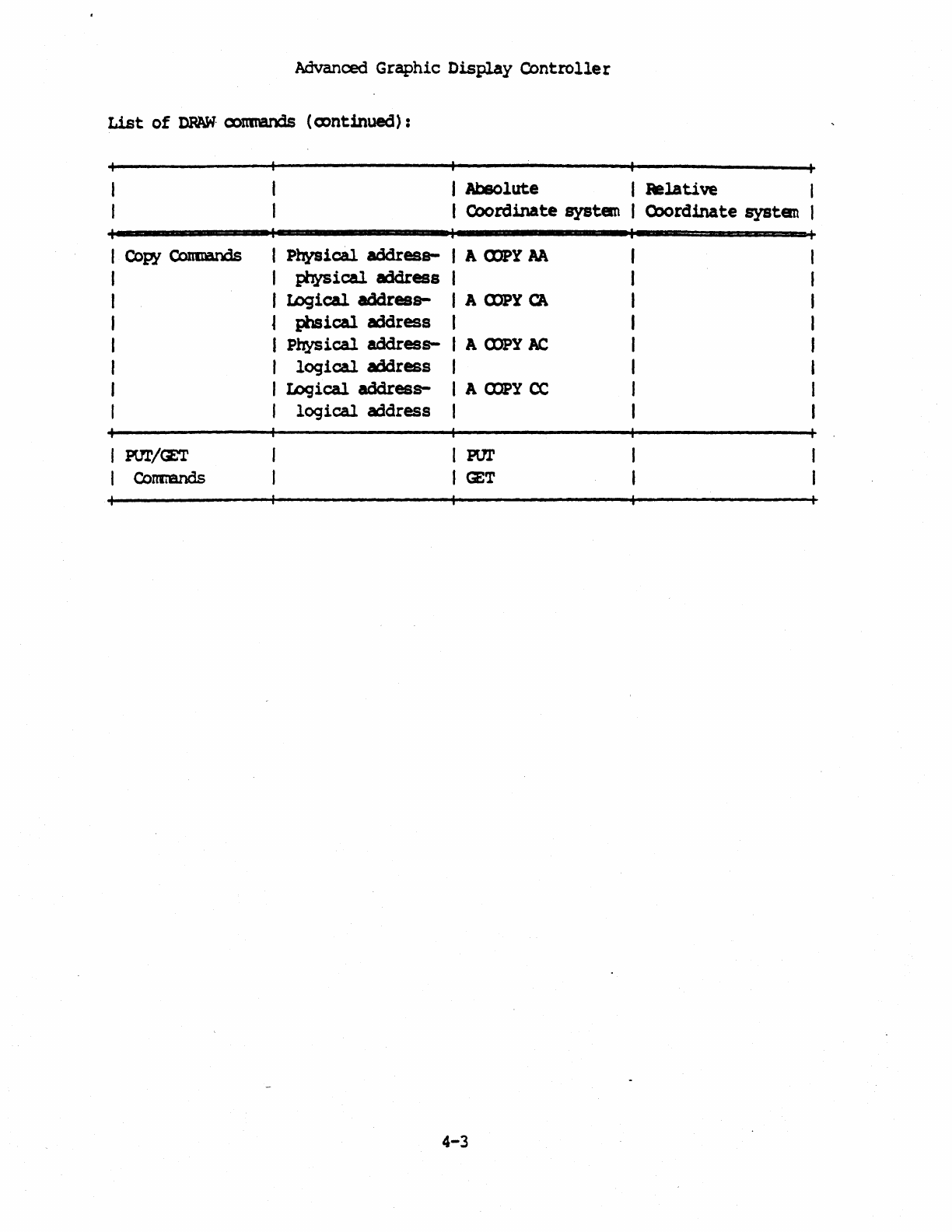

4.

Drawing

Operations

•••••••••••••••••••••••••••••••••••••••••••••••

4-1

4.1

Drawing

Functions

•••••••••••••••••••••••••••••••••••••••••••••••

4-1

4.2

~

of

DRAW

Commands

••••••••••••••••••••••••••••••••••••••••••

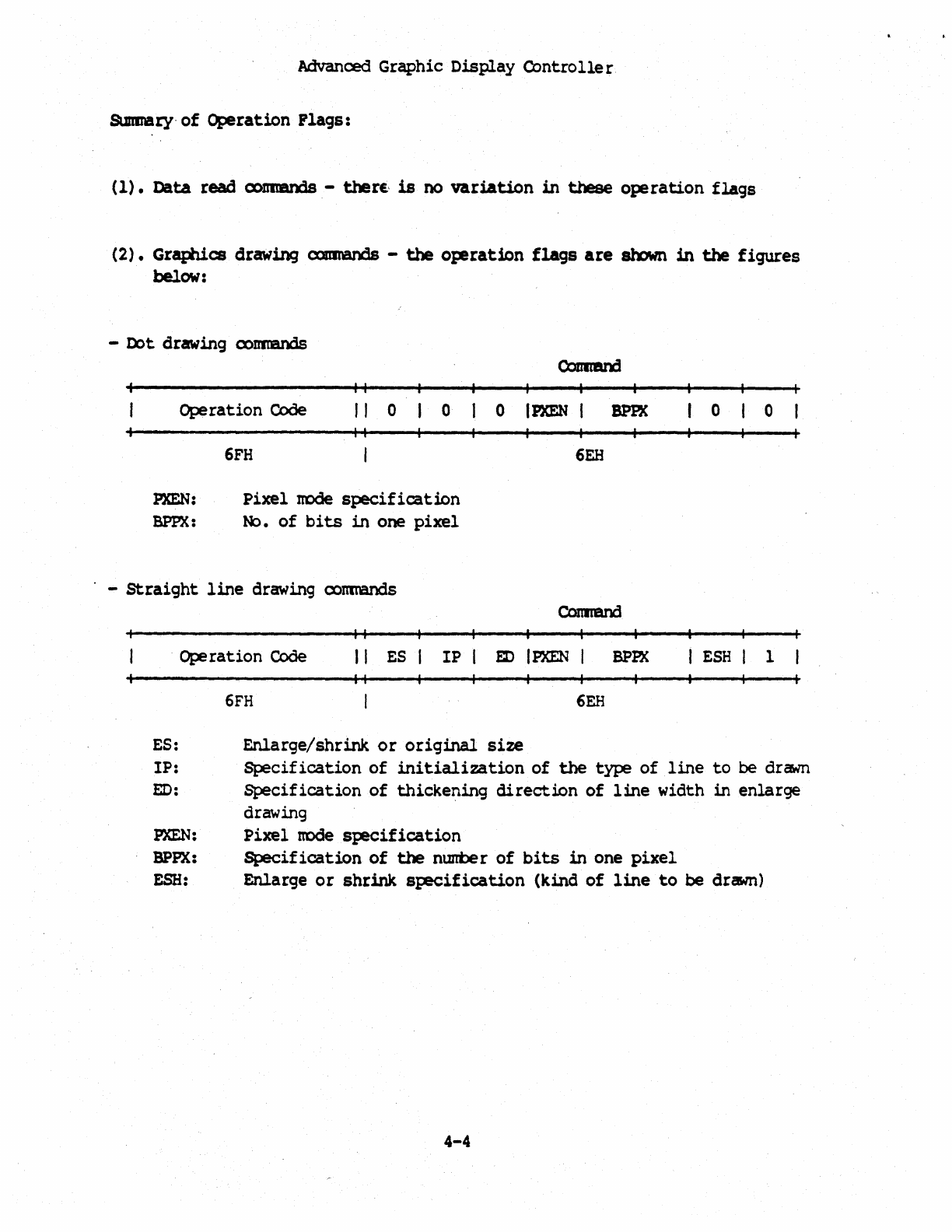

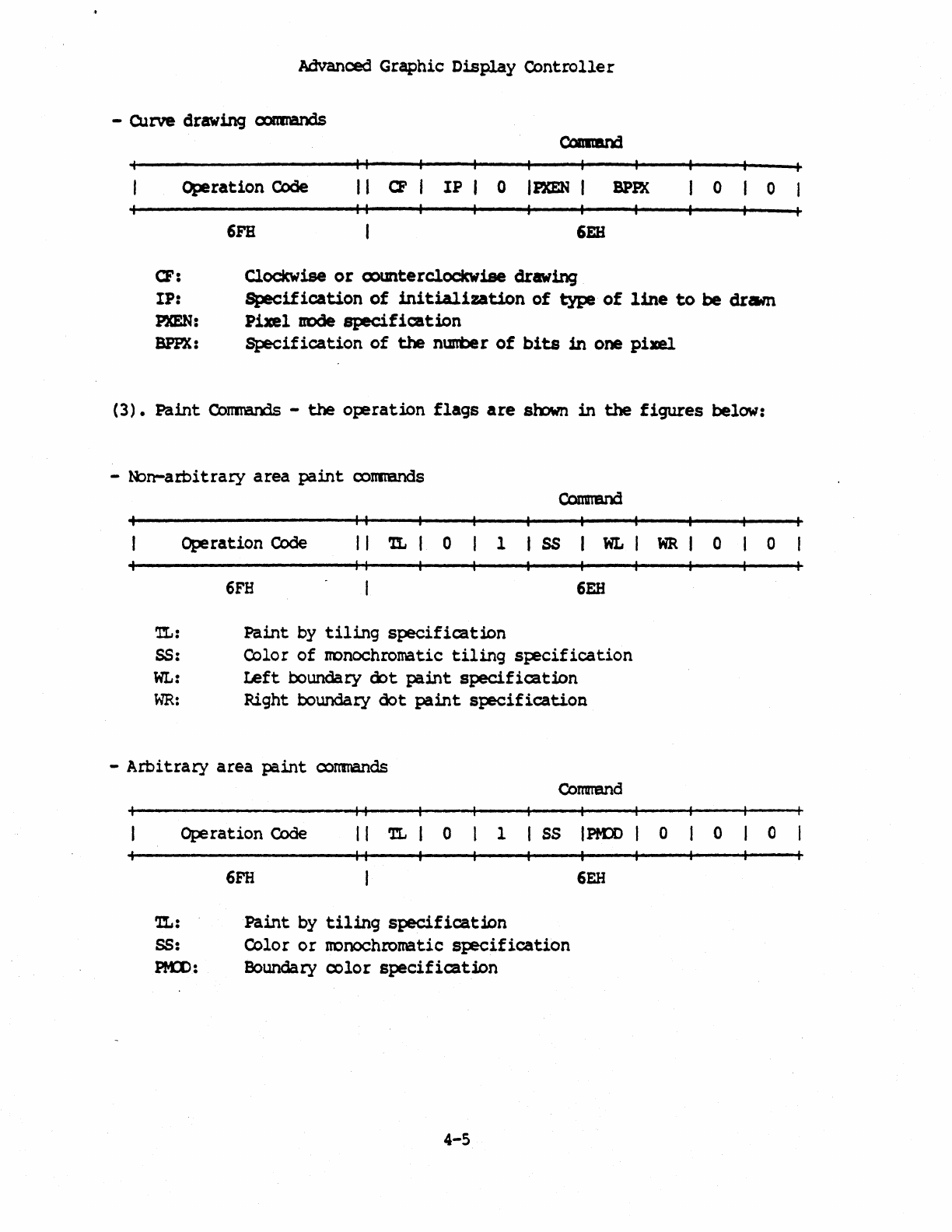

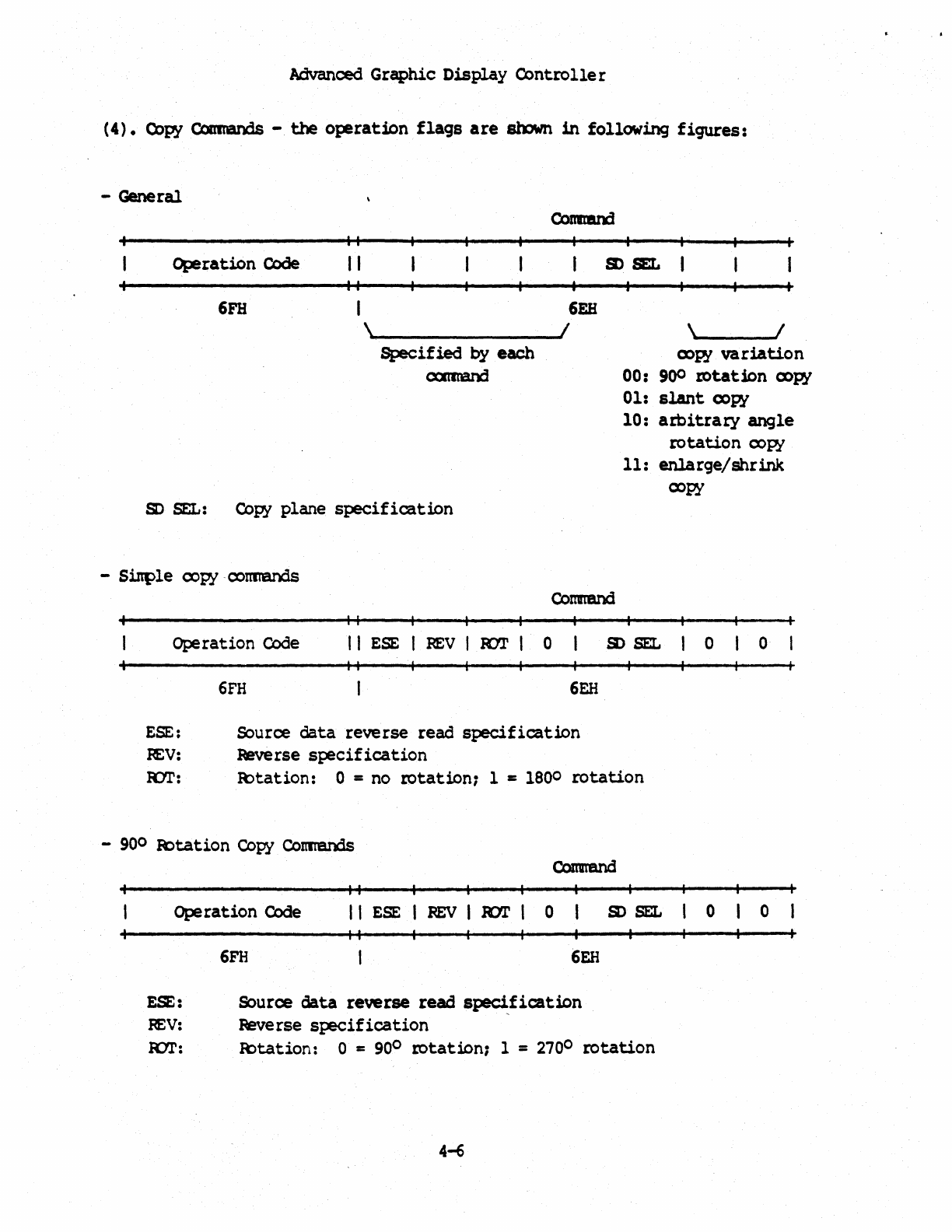

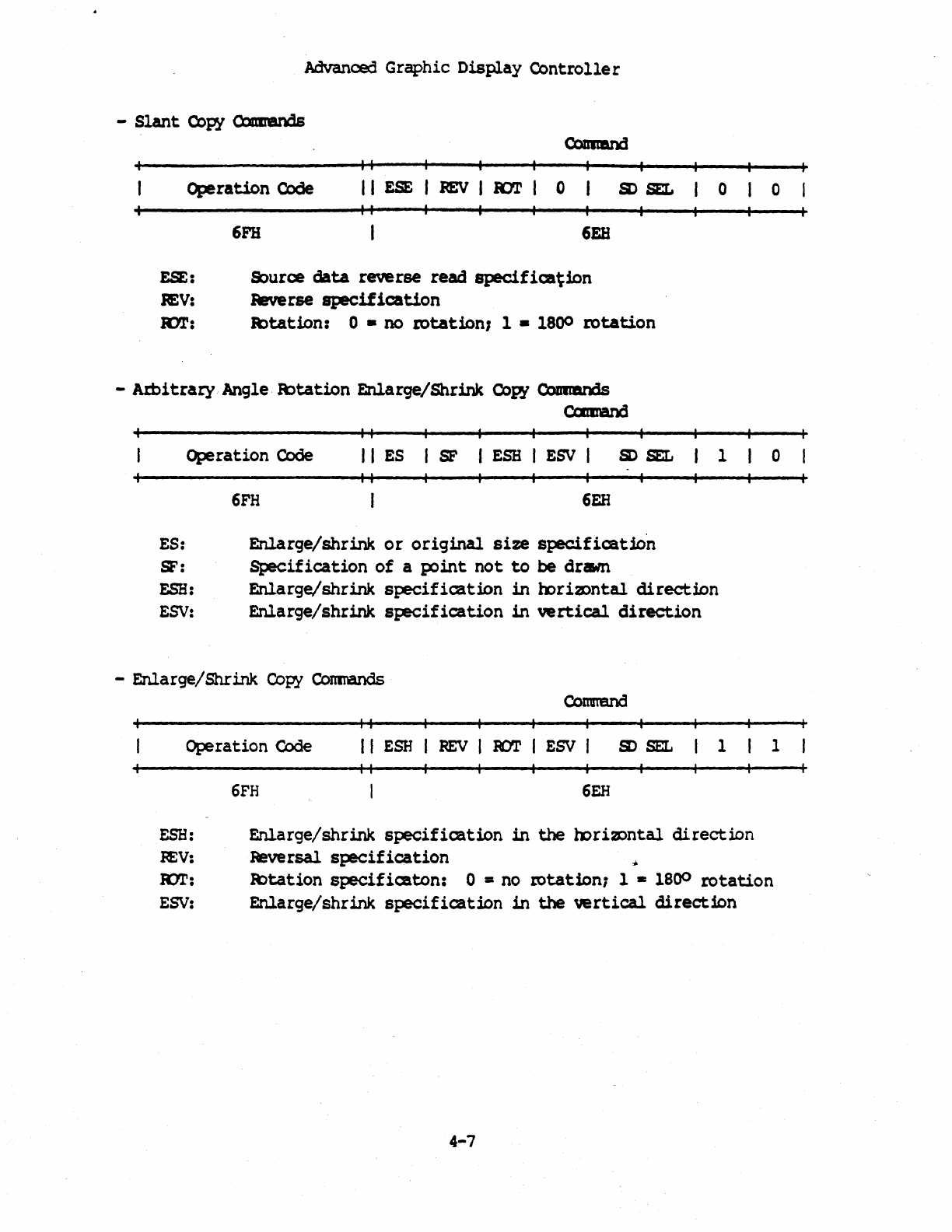

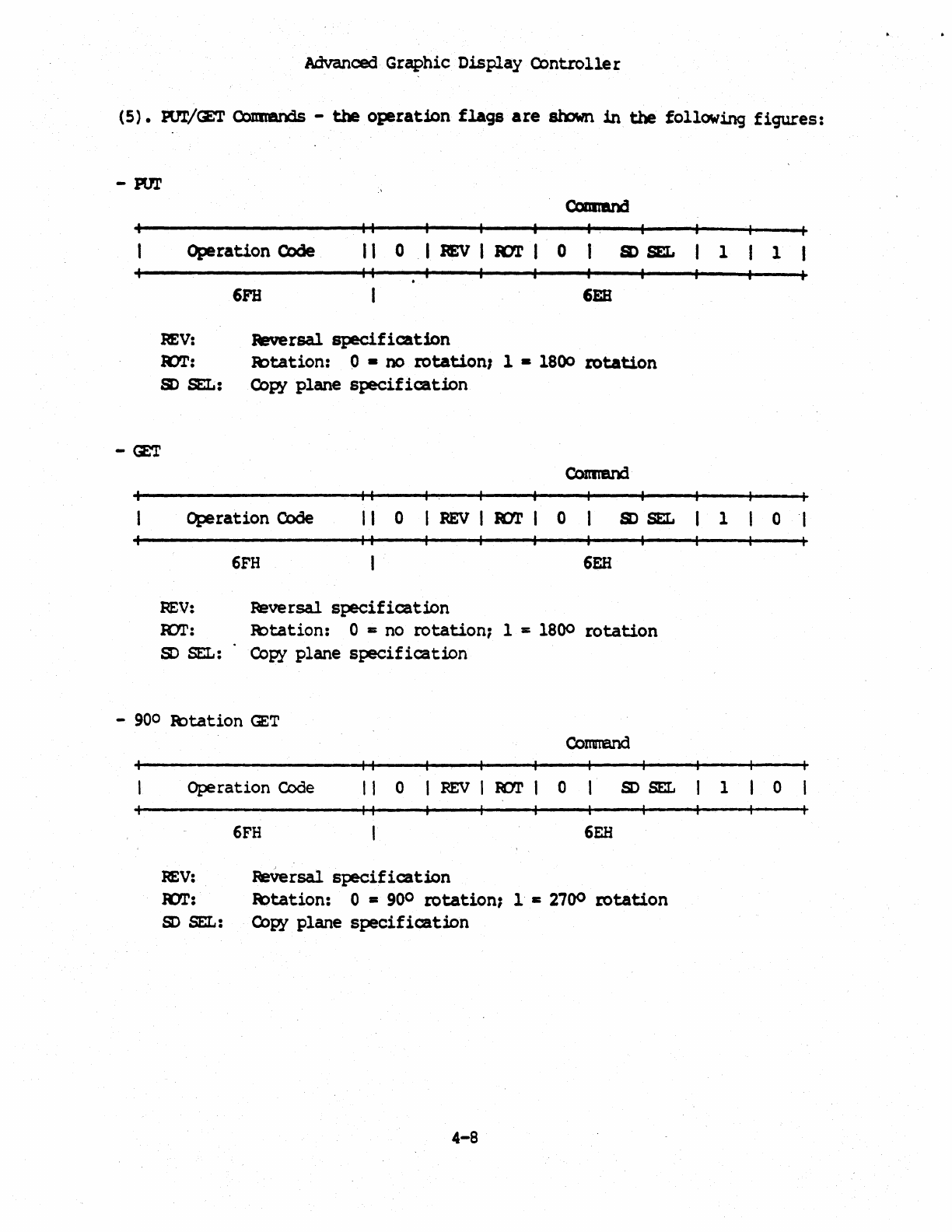

SUmma~

of

Operation Flags

•••••••••••••••••••••••••••••••••••••

4.3

Detailed

Description

of

DRAW

Commands

•••••••••••••••••••••••••••

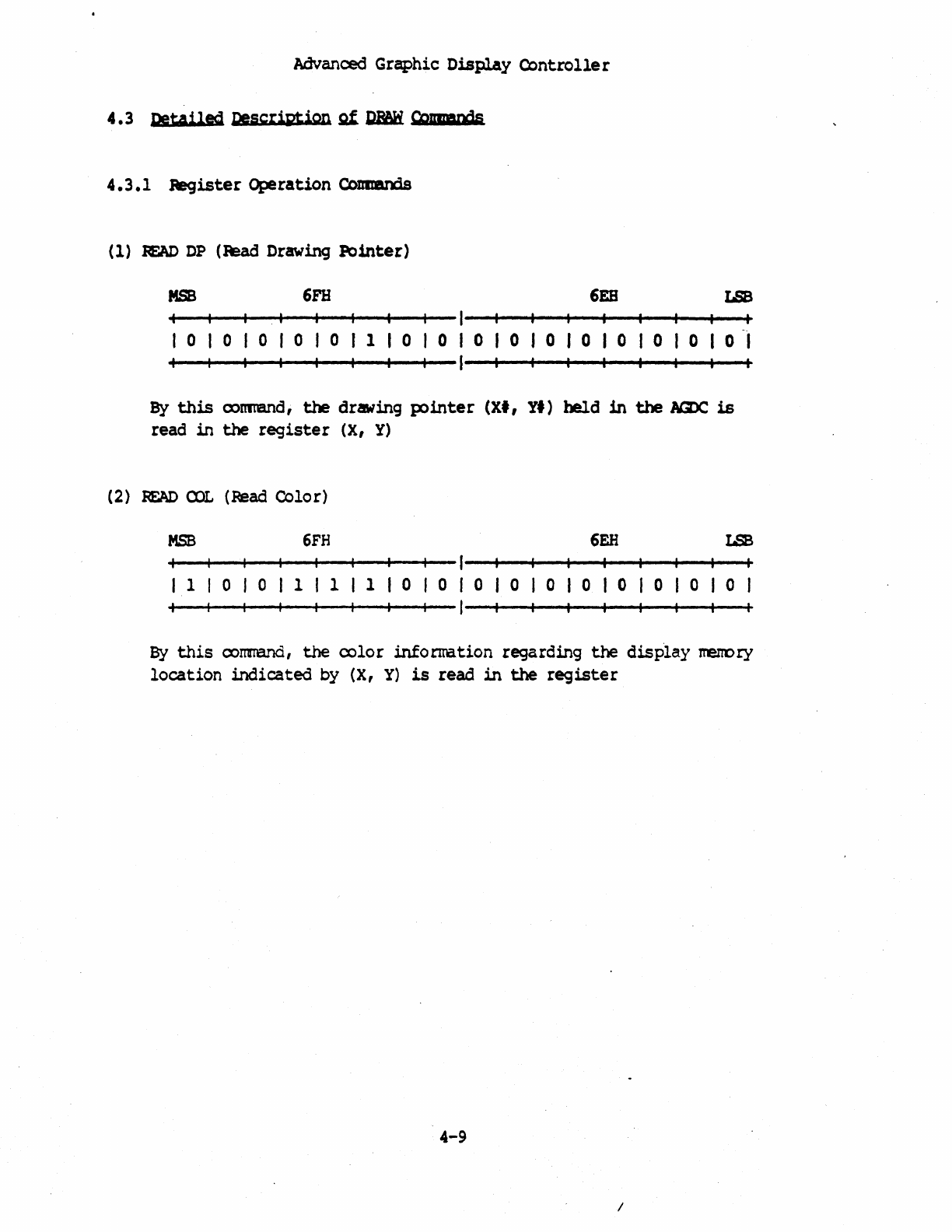

4.3.1

Register Operation

COmmands

•••••••••••••••••••••••••••••

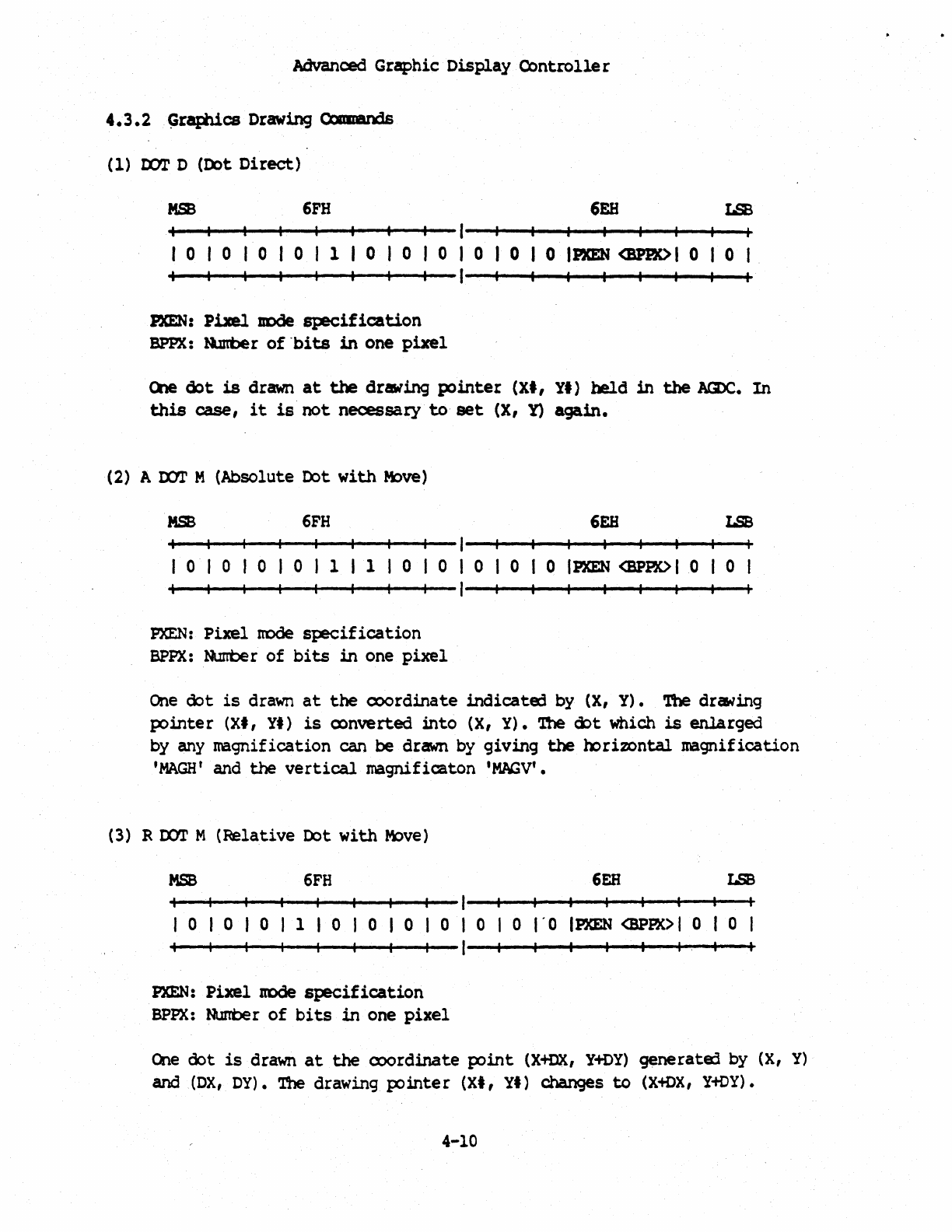

4.3.2

Graphics

Drawing

Commands

•••••••••••••••••••••••••••••••

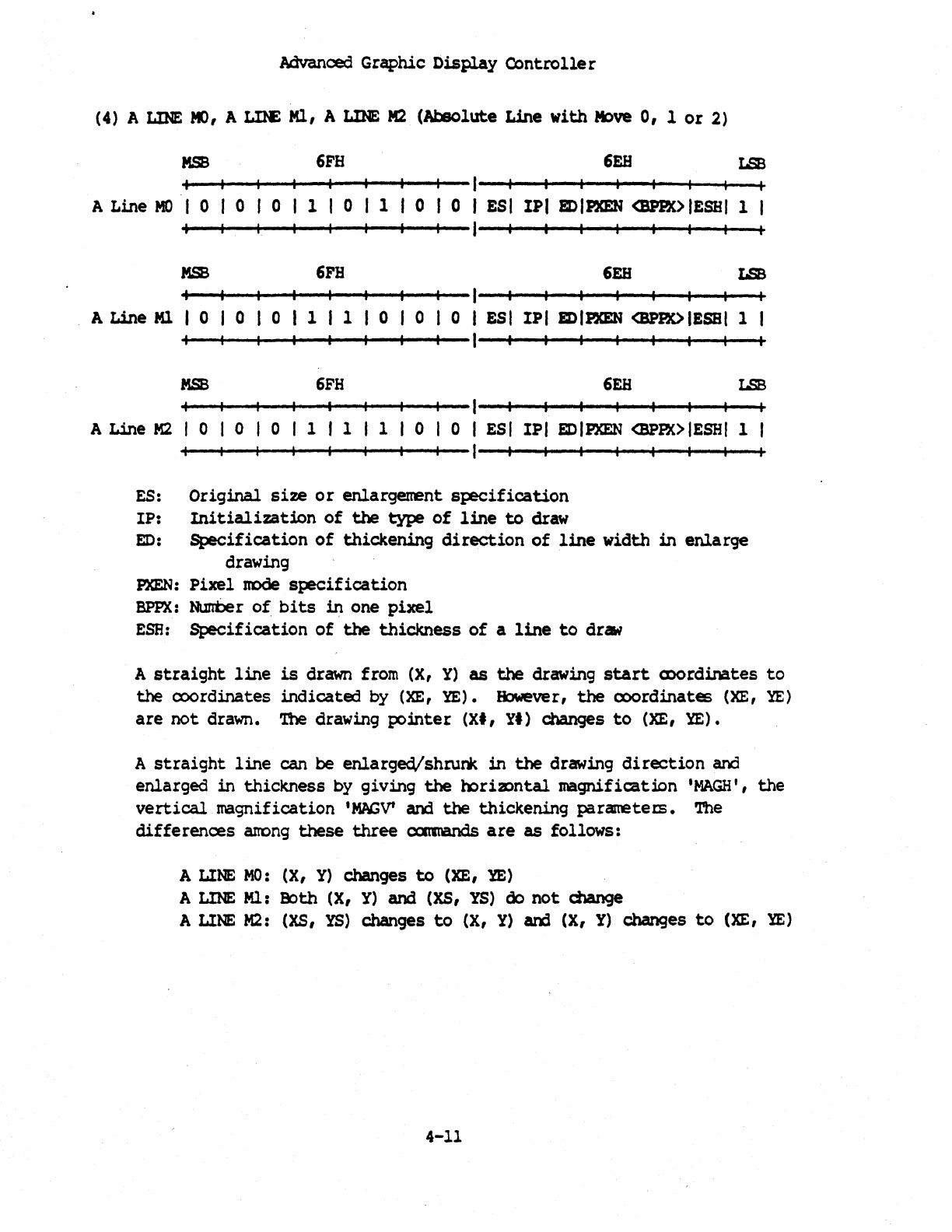

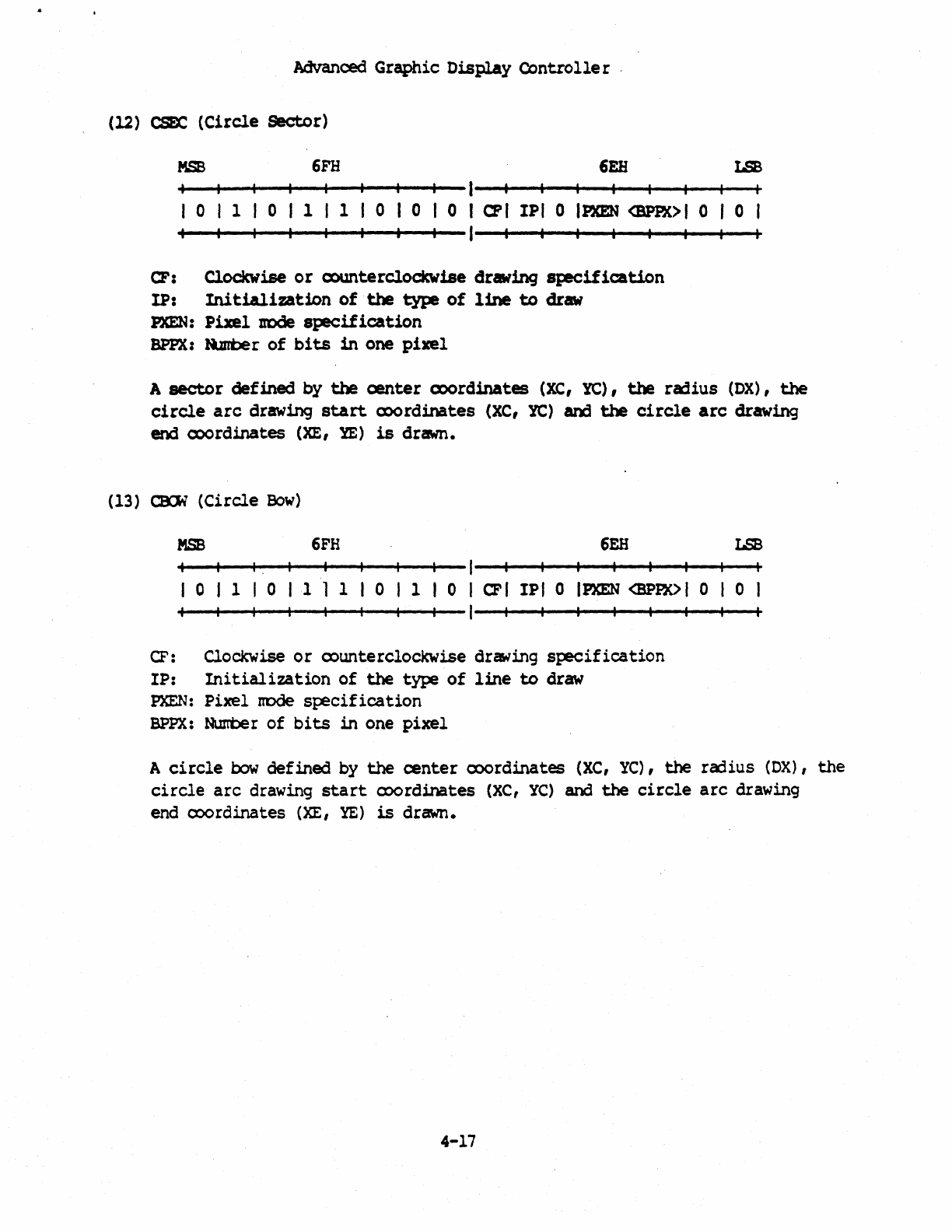

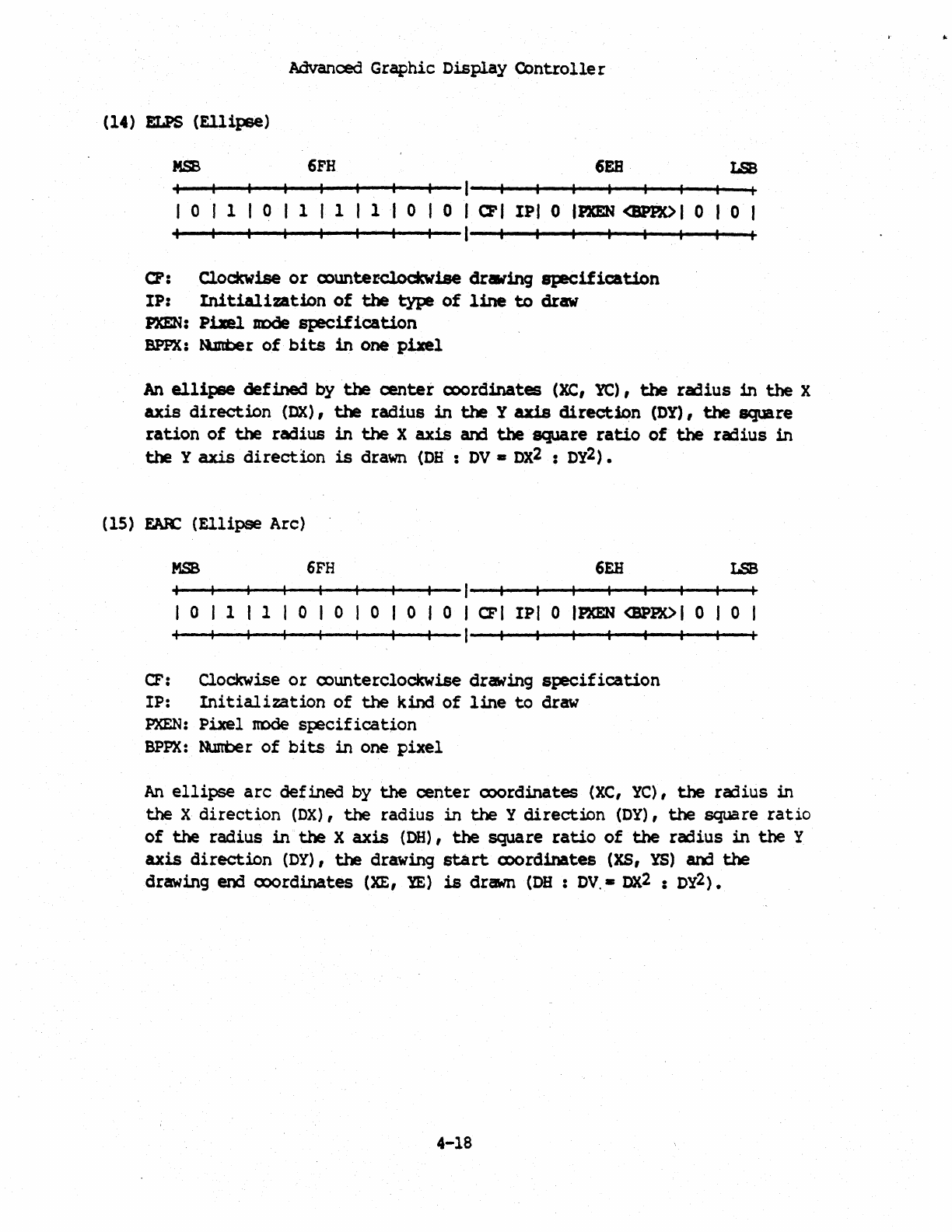

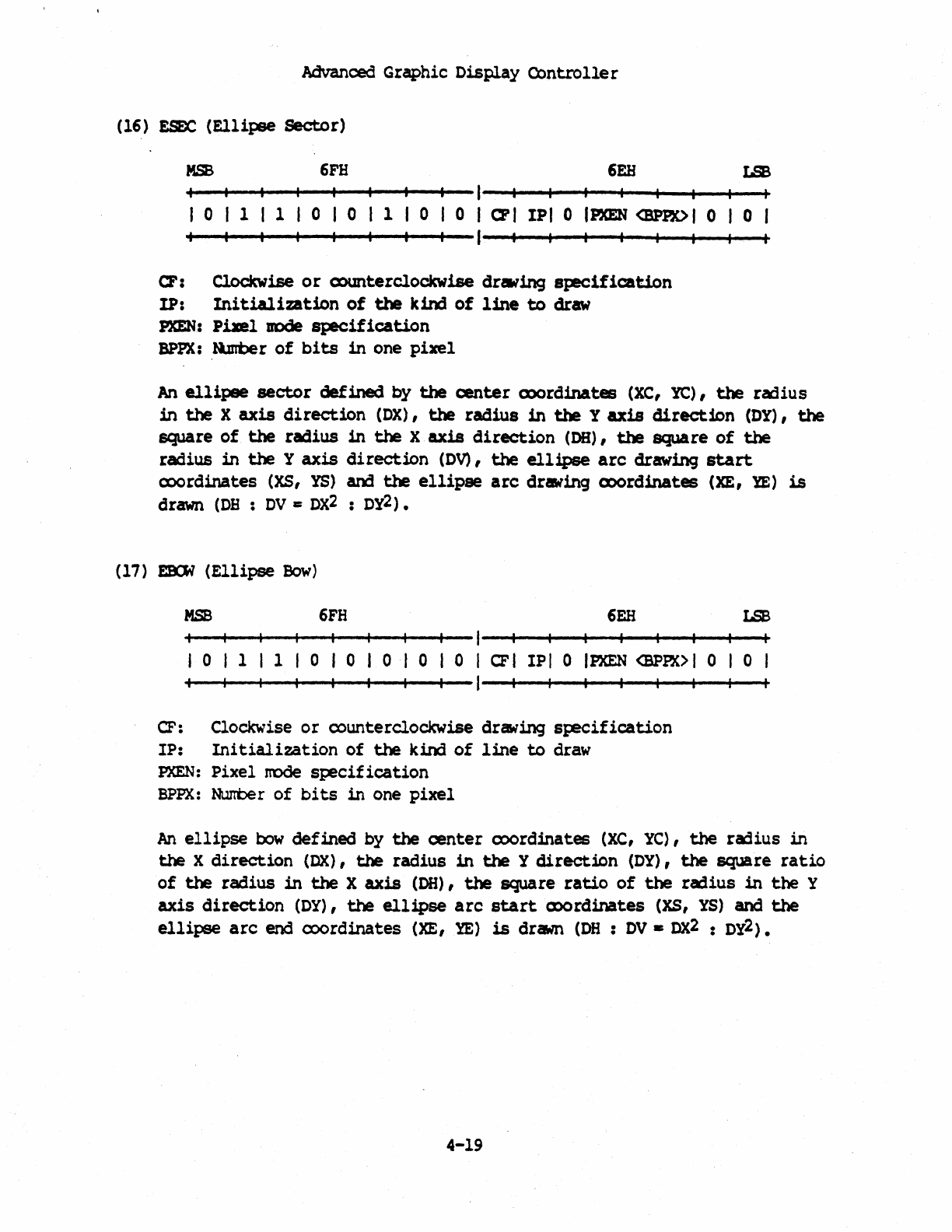

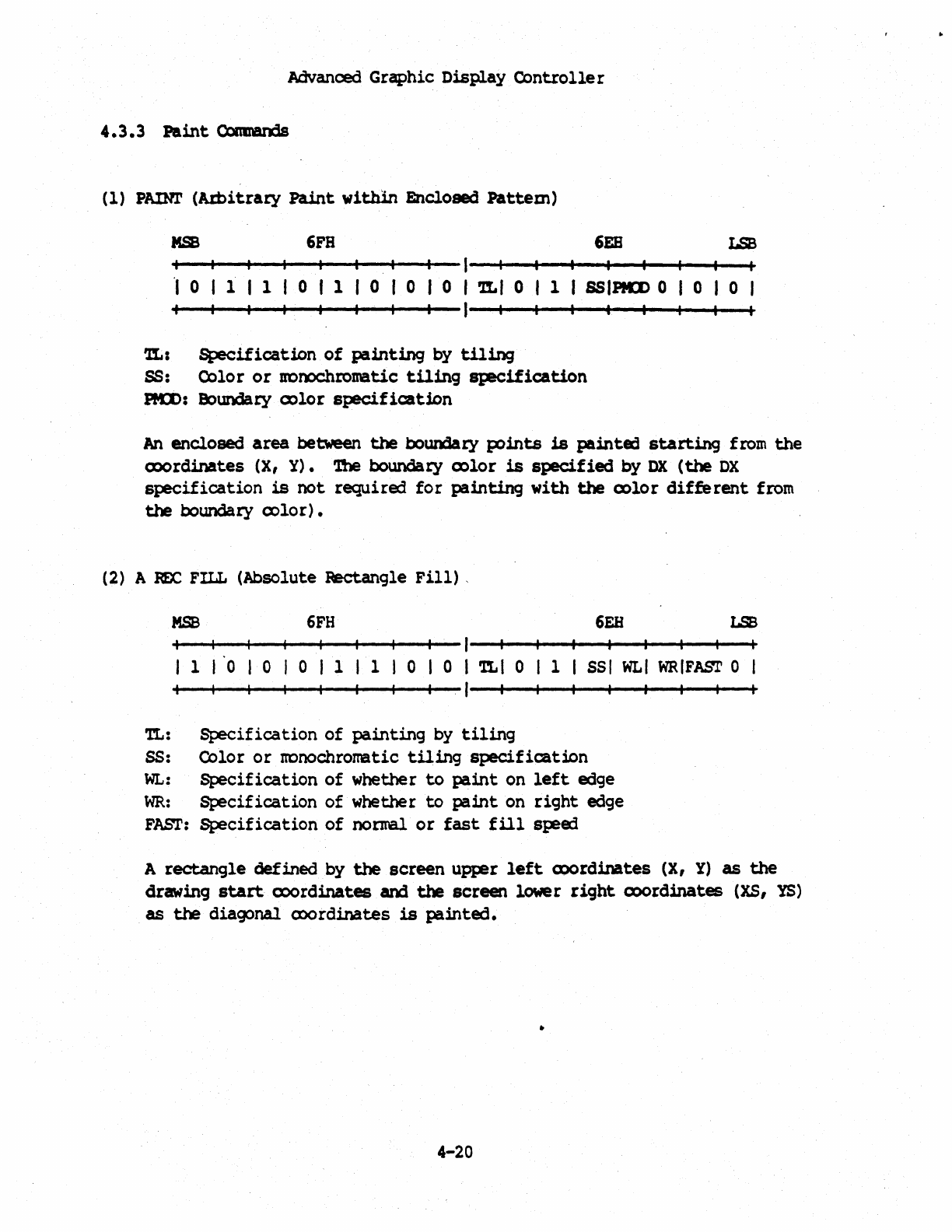

4.3.3

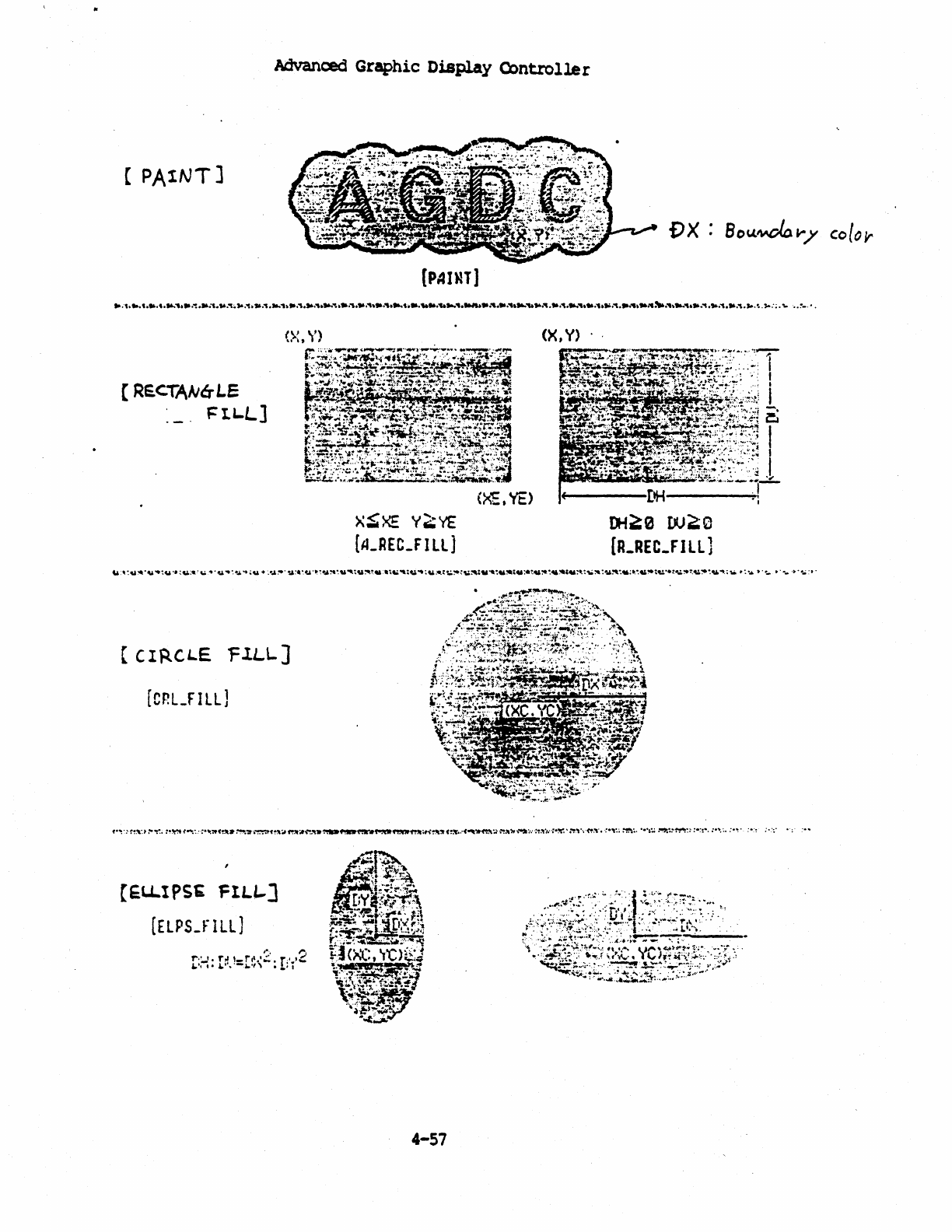

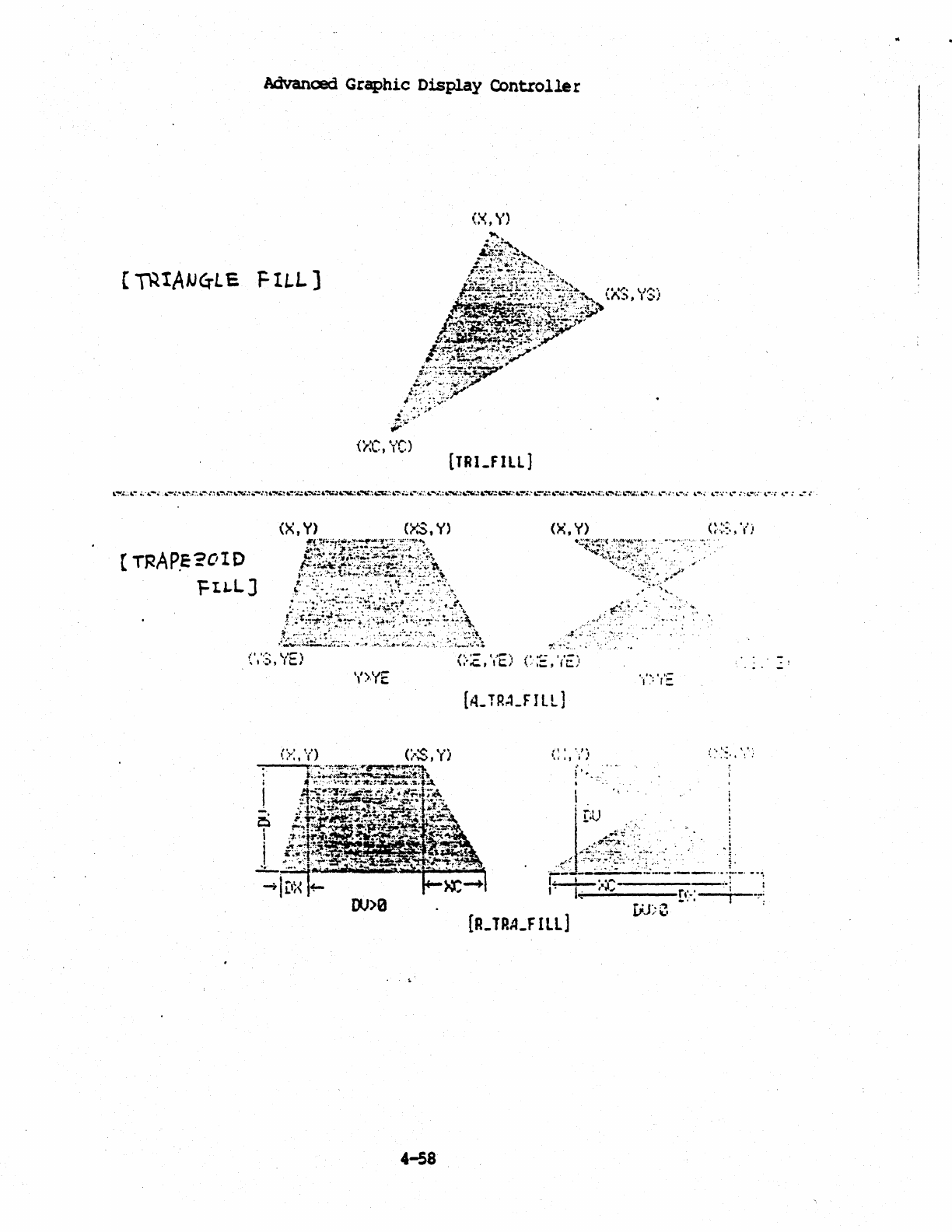

Paint

Commands

••••••••••••••••••••••••••••••••••••••••••

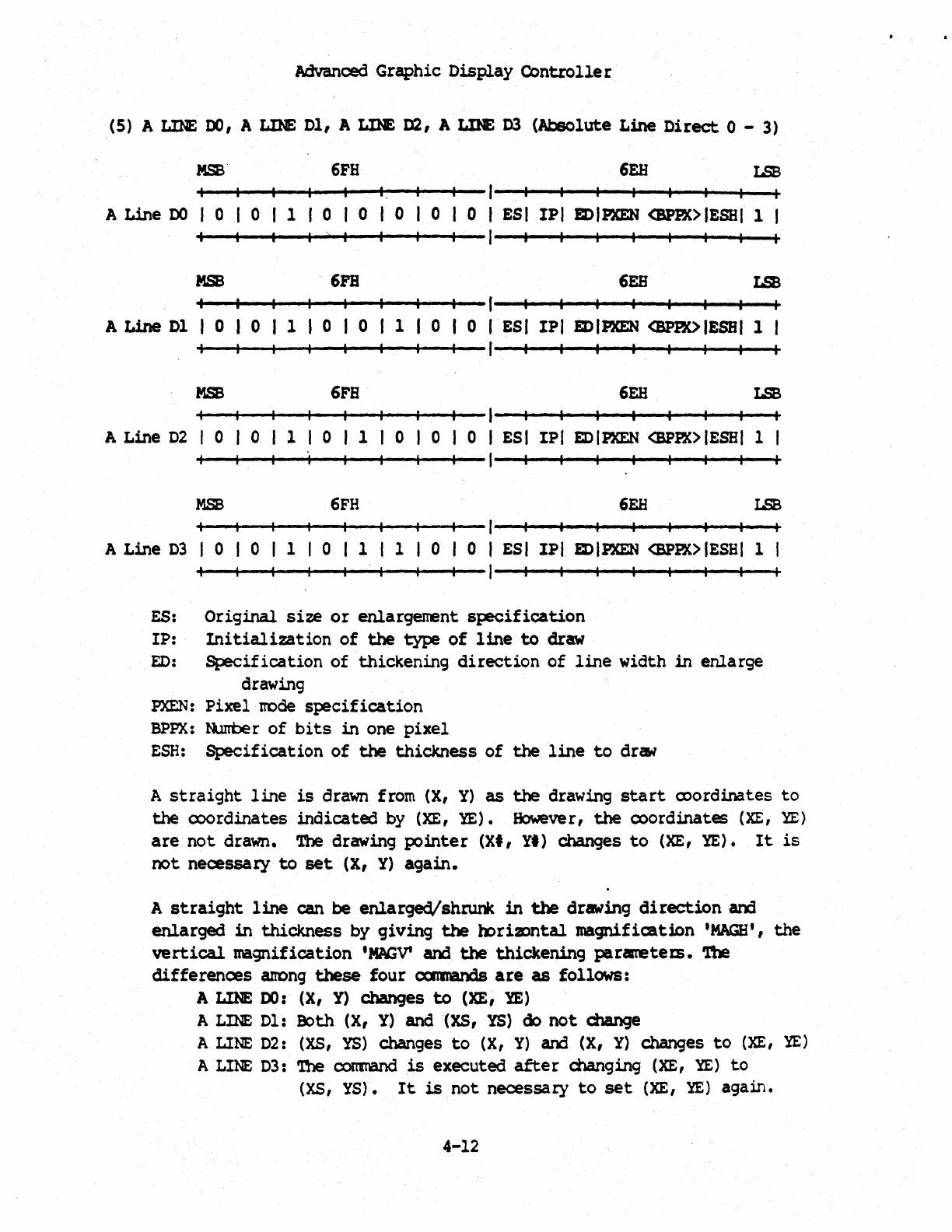

4.3.4

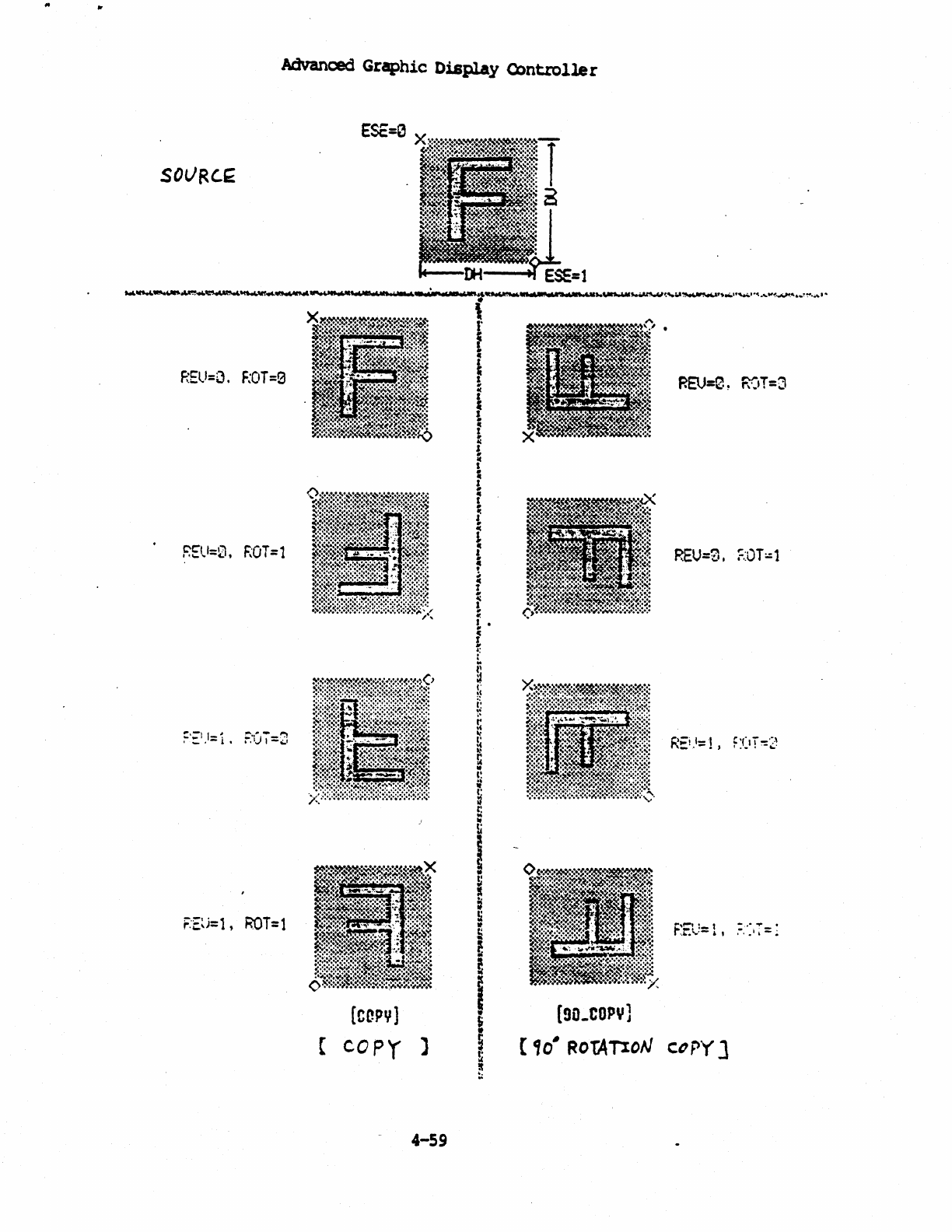

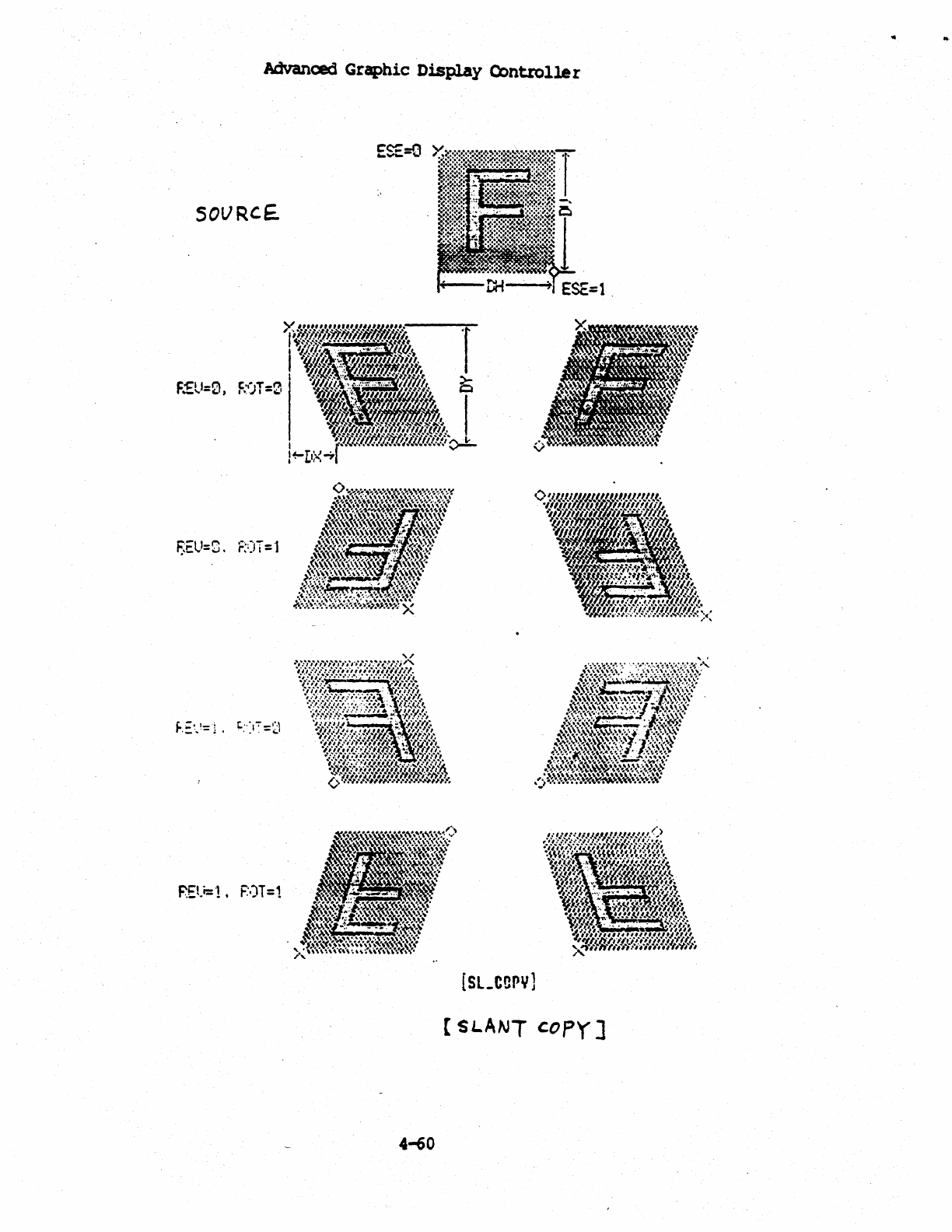

CDPY

Commands

•••••••••••••••••••••••••••••••••••••••••••

4.3.

5

PUT/~T

COrmands

4.4

How

to

Use

the

Flag

Bits

••••••••••••••••••••••••••••••••••••••••

••••••••••••••••••••••••••••••••••••••••

4.5

Painting

Pattern

~ferenoe

Examples

•••••••••••••••••••••••••••••

4.6

Inter-plane

Data Transfers

••••••••••••••••••••••••••••••••••••••

4.7 Drawing

~lated

~isters

•••••••••••••••••••••••••••••••••••••••

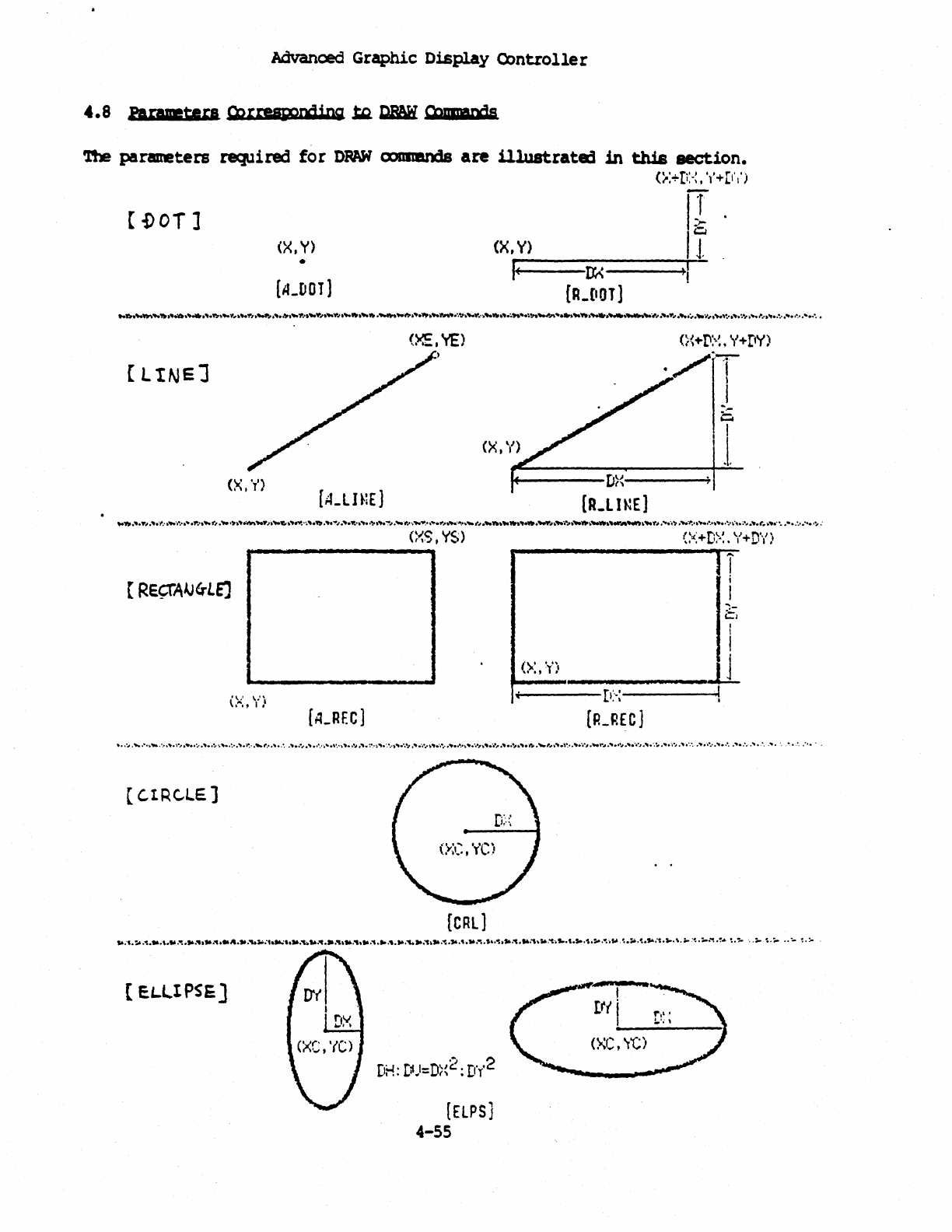

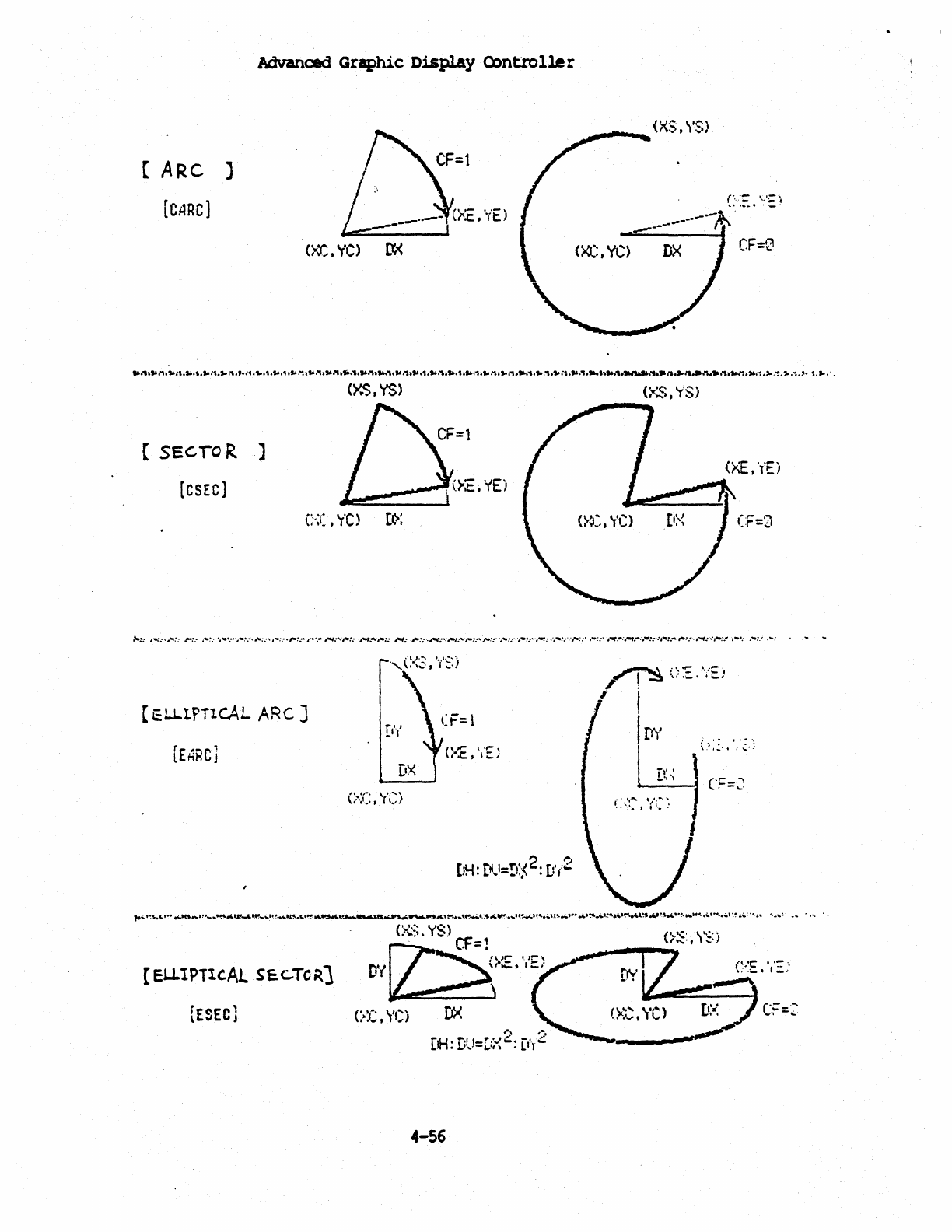

4.8 Parameters Corresponding

to

DFAW

Commands

•••••••••••••••••••••••

ii

4-1

4-4

4-9

4-9

4-10

4-20

4-25

4-30

4-32

4-43

4-46

4-47

4-55

Advanced

Graphic

Display

COntrolle

r

Section

1

'n1e

uP072120 Advanced

Gratilic

Display

Olntroller

(HDC)

displays

characters

and

graphics

on

a

raster

scan

CRr

aC(X)rding

to

coummds and pararretez:s received

from a h:>st processor

or

CPO.

It

has

high

speed

graPlic

drawing

capabilities,

video

timing

signal

generation,

large

capacity

display

IDeDDtY

ex>ntml

(including

Video

RAMs)

and a

versatile

CPO

interface.

'!hese

are

sene

of

the

features

that

allow

the

ACZX:,

to

ex>ntrol

graphics

dr_ing

and

display

of

bit

~

systems.

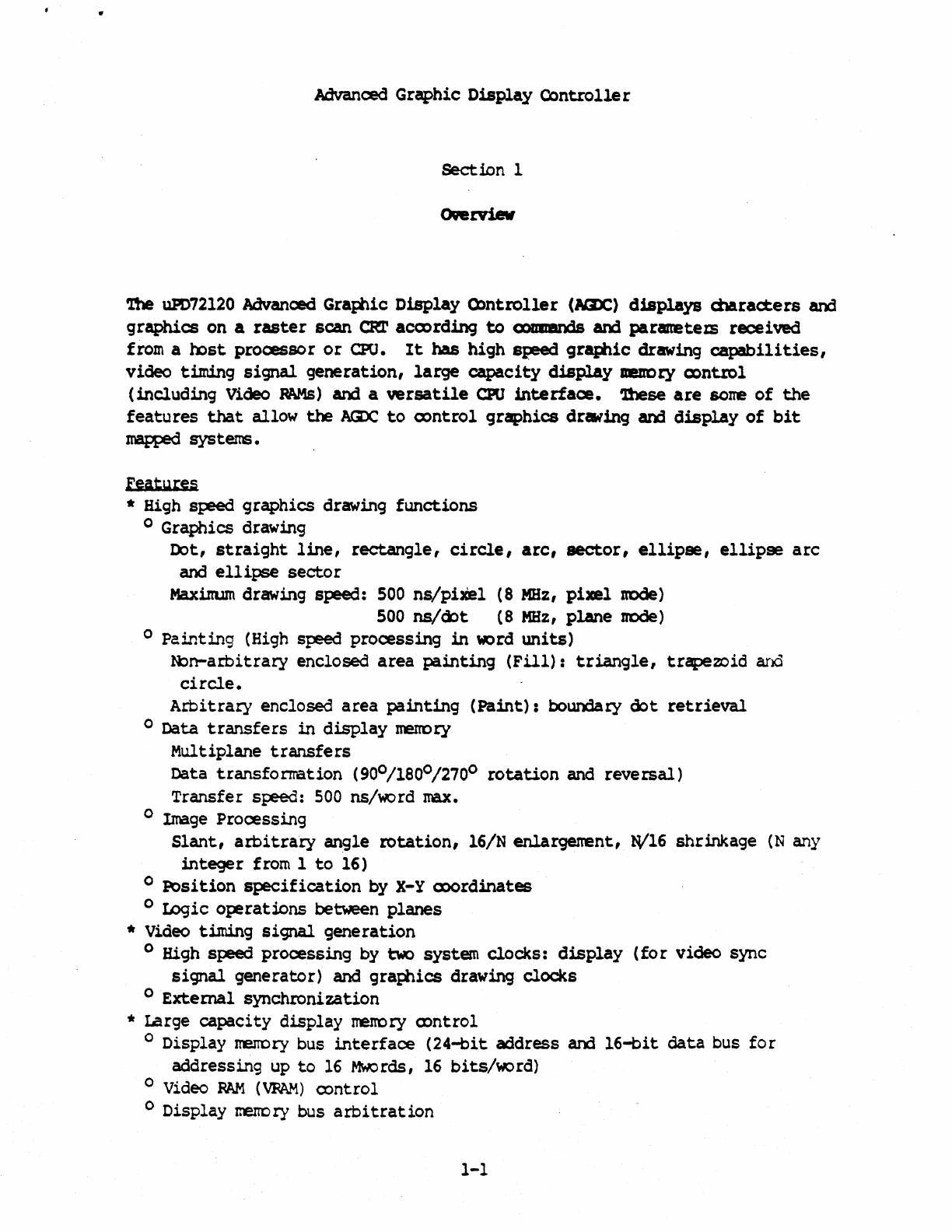

Features

* High

speed

graphics

drawing

functions

o

Graphics

drawing

!:bt,

straight

line,

rectangle,

circle,

are,

sector,

ellipse,

ellipse

arc

and

ellipse

sector

Maxirrum

drawing speed:

500

ns/piXel

(8

MHz,

pixel

node)

500

ns/d:>t

(8

MHz,

plane DDde)

o

Painting

(High speed

processing

in

word

units)

N:>n-arbitrary

enclosed

area

painting

(Fill):

triangle,

trapezoid

and

circle.

Arbitrary

enclosed

area

painting

(Paint):

boundary

&:>t

retrieval

o

Data

transfers

in

display

menory

Multiplane

transfers

Data

transfomation

(90°/180°/270°

rotation

and

reversal)

Transfer

speed:

500

ns/word

max.

° Image

Processing

Slant,

arbitrary

angle

rotation,

16/N

enlargenent,

W16

shrinkage

(N

any

integer

from 1

to

16)

o

Position

specification

by

X-Y

coordinates

o

IDgic

operations

between

planes

*

Video

timing

signal

generation

o High

speed

processing by two system

clocks:

display

(fo

r

video

sync

signal

generator)

and

gratilics

drawing

clocks

o

External

synchronization

* Large capacity

display

memo~

control

o

Display

menory bus

interface

(24-bit

address

and

16-bit

data

bus

fo

r

addressing

up

to

16

Mwords,

16

bits/word)

° Video

RAM

(VPAM)

oontrol

o

Display

memory

bus

arbitration

1-1

Advanced

Gr~hic

Display

Controller

*

IiJst

Processor

(CPU)

Interface

o System

bus

interface

-

-2o-bit

address

bus,

8

or

16

bit

data

bus

o

SYStem

ueItOry <->

display

nenory

data

transfer

with

extemal

IJ.1A

Controller

From

system

merrory

to

display

DeltCry (PU!')

From

display

uencry

to

system

meItDry

tCET)

o

Sigh

speed

pipeline

processing

with

preprocessor

before

drawing

processor

o

CPO

DerlDry

or

I/O

mapping

of

internal

registers

and

display

menory -

efficient

~stem

interface

* 8

MHz

System

Clock

*

CHJS

Technoloqy

*

Single

+5

V

Power

SJpply

* SO-pin

flat

package (uPD72l2DG)

or

84-pin

PICe

(uPD72l2OL)

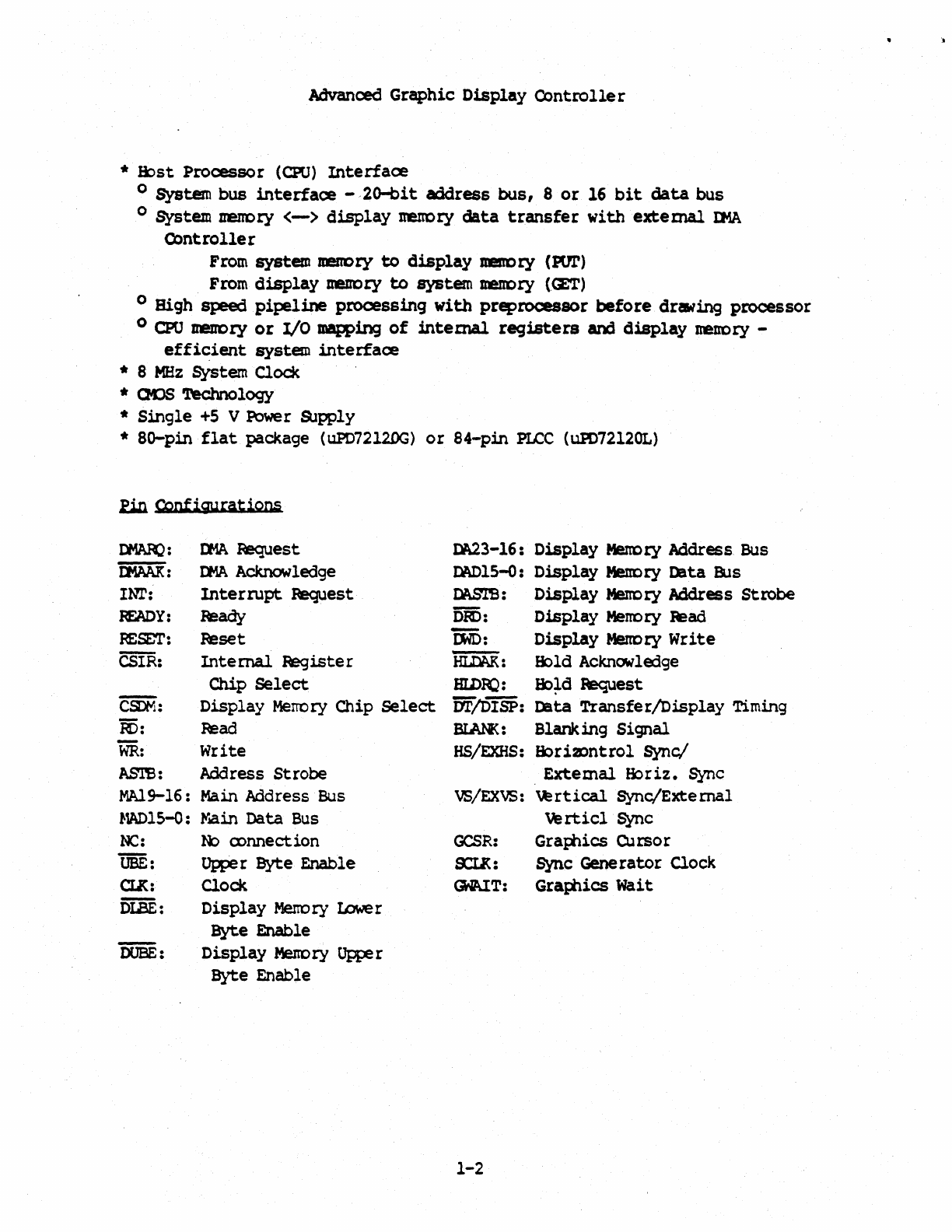

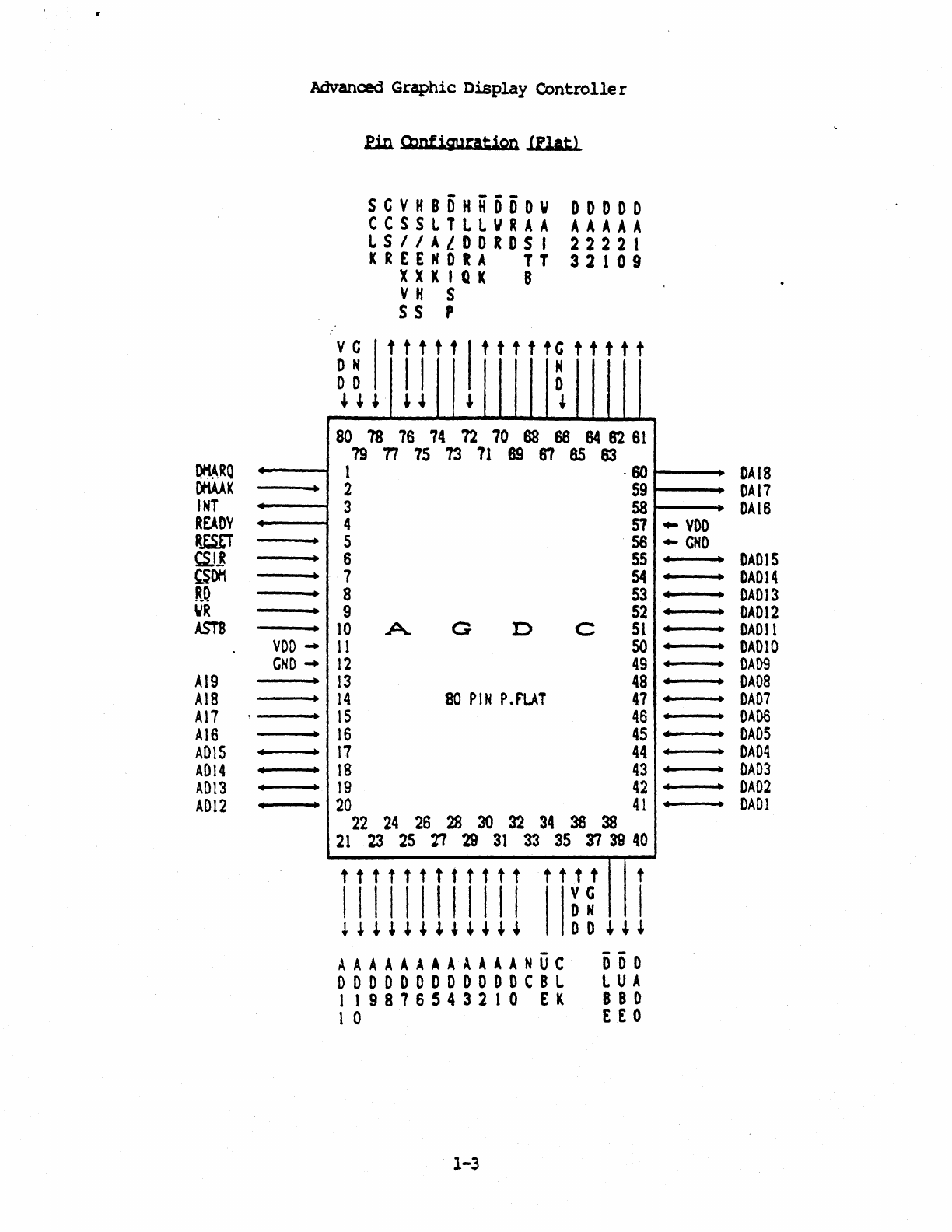

Ein

Configurations

~:

II1A

lequest

IJt\AAK:

II-1A

Acknowledge

INT:

Interrupt

~est

R'.ADY:

leady

RESET:

~set

CSIR:

Internal

~ister

Chip

Select

CS5M:

Display

Menory

Chip

select

R):

Read

WR:

Write

ASl'B: Address Strobe

MAl9-l6:

Main Address

Bus

l-1AD1S-o:

flain

Data

Bus

NC:

R:>

ex>nnection

USE:

Oppe r

Byte

Enable

CI.K:

Clock

DfBE:

-

DUBE:

Display

Memory

Lower

Byte

Enable

Display

Memory

Upper

Byte

Enable

W3-l6:

Display

Ment>ry

Address. Bus

IW>l5-o:

Display

Mem:>ry

Data

Bls

D.l\Sm:

Display

Memory

Address Strobe

~:

Display

MeIIOry

lead

'00:

Display

MenDry

Write

~:

9;)ld

Acknowle:lge

BLD~:

9;)ld

~est

DT/I5ISP:

D:lta

Transfer/Display

Timing

~:

Blanking

Signal

HS/EXHS:

9;)ri2Dntrol

Sync!

.

Exte

mal

Ii:>

r

iz.

Sync

VS/EXVS:

~rtical

Sync/External

va

rticl

Sync

GCSR:

Gratilics

CUrsor

s:LK: Sync Generator

Clock

~T:

Graphics

wait

1-2

~~

Ot1AAK

INT

READV

Jt£S£T

CSJ]

C.SDM

RO

WR

ASTB

A19

Al8

At7

Ale

AOtS

•

AOl4

..

ADt3

•

A012

•

Advanced Graphic

Display

Controlle

r

~

•

•

~

•

..

•

VOO

....

GND

....

..

•

•

•

II

•

II

II

E1D.

Cbnfiguration

(Plat)

SCVHBDHHODOV

CCSSl.TLLWRAA

LSIIAI.DORDS

I

K R £ £

NOR

A T T

XXKICk

B

V H S

SSP

00000

A A A A A

22221

3 2 1 0 9

vc

ttttt

tttftcttttt

~

~

II

~

~

~

~

,~~

~

80

78

76

74

72

70

88

68 64

82

61

79

T1

75

73

71

69 67

as

63

1 -60

2

59

3

58

4

51

5

56

6

55

7

54

8

53

9

52

10

A.

G D C

51

11

50

12

49

13

48

14

80

PIN

P.f'l.AT

47

15

46

16

45

17

44

18

43

19

42

20

41

22

24

26

28

30 32

34

38

38

21

23

25 27

29

31

33

35

37

39

40

, t t t t , t t t t t t t t t t t

I I I I I I I I I I I I

VG

I

o N

+ + + + + + + +

~

+

~

~

o 0

~ ~

+

A A A A A A A A A A A A N U C D D 0

o 0 0 0

DOD

0

DOD

0 C 8 L L U A

1 1

987

654

3 2 1 0 £ K B B 0

1 0 E E 0

1-3

OAI8

OAl7

DAI6

..

VOD

..

eND

•

~

DADtS

• Ii

OAD14

4

~

DADI3

• Ii

DAD12

• Ii

DADlt

4

Ii

DADlO

•

II

OAD9

•

II

DADa

•

II

DAD7

• •

DADS

• •

DADS

• •

OAD4

•

II

DAD3

• •

OA02

• •

DADl

fljAtQ

DMAAK

tNT

READY

&ES.ET

CSJ.&

CS~

&0

WR

AST8

A19

AlB

A17

AIS

AOlS

A014

AOl3

AD12

Advanced

Graphic

Display

Q)ntrolle

r

tin

Q:mfiguration

(PTa'l

sevHsDHiiooov

00000

CCSSLTLLWRAA

AAA.AA.

LSI

I

A.

l 0 0 R 0 S I

222

2 1

K R E £ N D

RAT

T

321

0 9

XXKIQK

B

V H S

ss·p

vee

ttttt

tttttcttttt

~~~

:

II

~

~

~ ~ ~ ~

~,

,

84

82 80

18

76

74 72

70

68

66 64

83

81

79

77

75 73

71

69 67

6S

1

631---

..

----..

2

62

1-----.

3

61~--"

4

~

~voo

----..

5

59

~

eND

----..

6

58

~

eND

----..

7

57

..

•

----..

8

~

~.--~

•

-----..

9 M

~

..

--~

•

----..

10

A.

G D C

54

~.-~

•

VDD

-.

11

53

+-.-~

•

eND

-.

12

52

+-.-~

•

•

eND....

13

51

~

..

-~

•

14

84

PIN

PLCC

50

~

..

-~

•

----..

15

49

~

..

-~

•

----..

16

48

....

-

....

•

----+.

11

47

~.-~

•

• •

18

46

~.-

....

•

• •

19

45

....

-~

I

•

..

•

20

44

..

4-

....

•

..

•

21

43

"'4-~

23

2S

2'7

29

31

33

35

37

39

41

22

24

26 28

30

32

34

36 38

40 42

t t t t t t t t t t t t t t t t f t

II

t

II1III111

~

~

~

I

~~~~,+".~,.

DOD'~~

AAAAA.AA.AAAAA

UC

DOD

o

DOD

0

DOD

0

DOD

B L L U A

1 1

987

654

321

0 £ k B B 0

ION

£ E 0

C

1-4

OAI8

DA17

DAIS

OADIS

DAD14

OAD13

OAD12

DAD1!

DADI0

OAD9

DADS

DAD?

DADS

DADS

DAD4

DAD3

DAD2

DADI

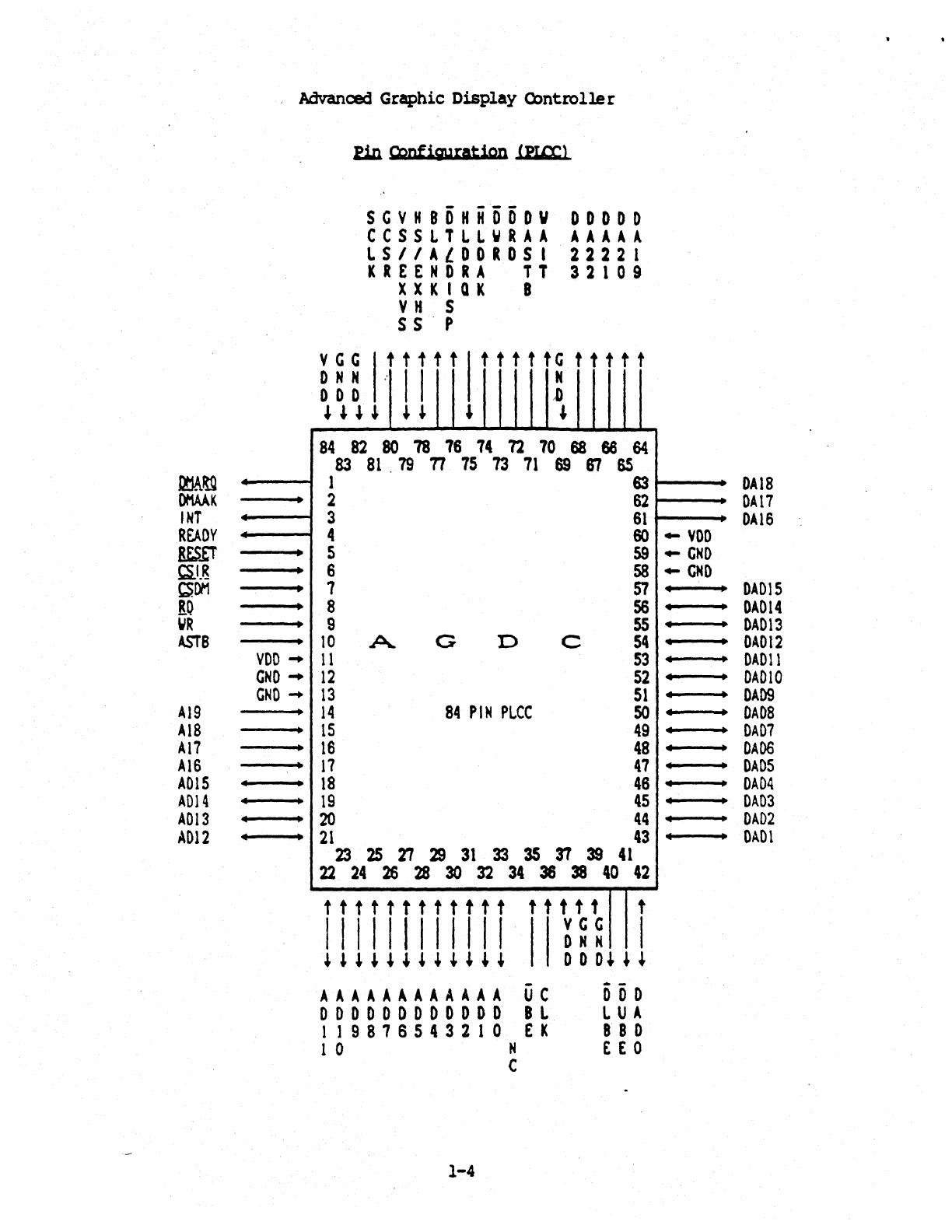

f-t

eLK

RESET

Vdd

GND

OMARa

OMAAK

NT

J,

READ'

CSIR

CSOM

RD

WR

ASTI

UBE

MA19-1

.

MAD15

CPU

INTERFACE

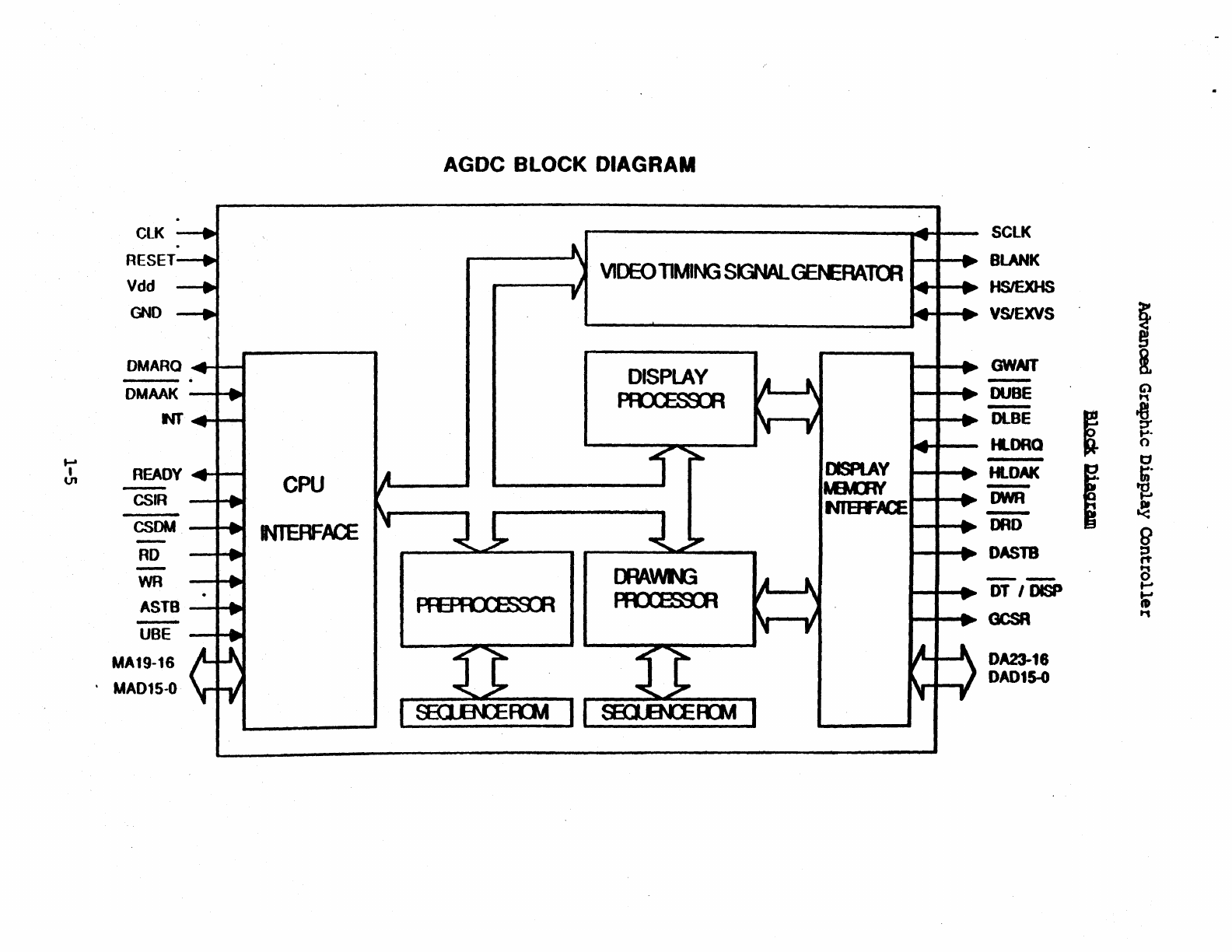

AGDC BLOCK DIAGRAM

VIDEO

TIMING

SGW.GBERA~

DISPLAY

~

DISPlAY

t.IMRf

NTEFFACE

00AVVN2

~

~

SClK

BLANK

HSIEXHS

VSlEXVS

I

GWNT

~

DUDE

G)

t1

DlBE

E t

....

HlDRQ

0

I c

HLDAK

In·

-

~

own

~

DAD

g

DASTB

~

--

a

OT

I

DISP

....

to

GCSR

..,

0m.18

DAD15-0

Advanced

Gr~hic

DisplayOont~ller

i.in

Functions

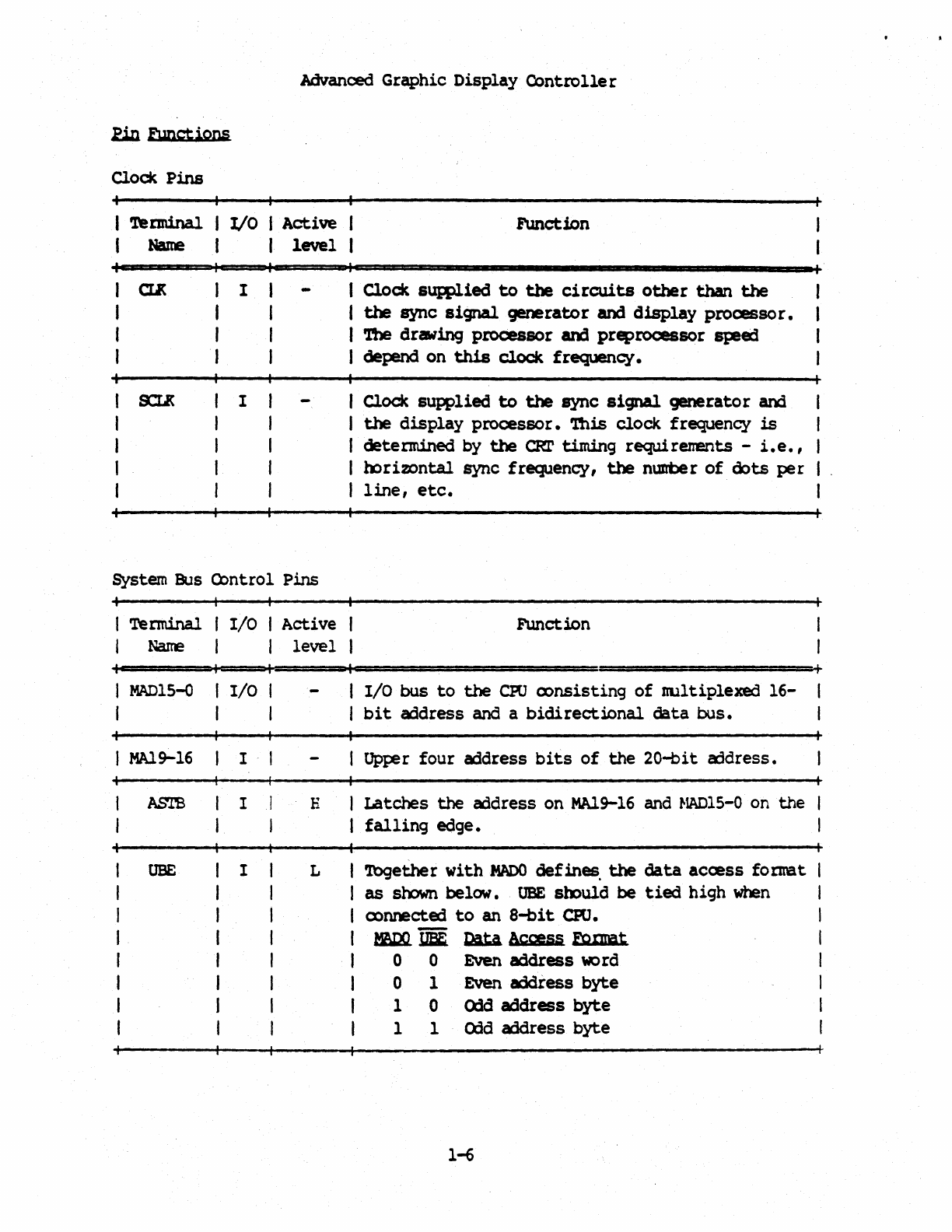

Clock

Pins

I TeDninal I

I/O

I

Active

I

Name

I I

level

I

I

System

Bus

Cbntrol

Pins

I Terminal

I

Narre

I/O

I

Active

I

level

I MADlS-o I

I/O

I

I I I

I MAl9-16 I

I·

I

Function

I Clock

sut¢ied

to

the

circuits

other

than

the

I

the

sync

signal

generator

and

display

processor.

I

'1'he

drawing

processor

am

preprocessor

speed

I depend on

this

clock

frequency.

I Clock

supplied

to

the

sync

signal

generator

and I

I

the

display

processor.

'.this

clock

frequency

is

I

I

determined

by

the

eRr

timing

requirenents

-

i.e.,

I

I

b:>rizontal

sync

frequency,

the

nUll'ber

of

dots

per

I .

I

line,

etc.

I

Function

I/O

bus

to

the

cro

ex>nsisting

of

nultiplexed

16-

I

bit

address

and a

bidirectional

data

bus.

I upper

four

address

bits

of

the

20-bit

address.

+

ASTB

I I

I

E I

Latches

the

address

on

MAl9-16

and

l-1AD1S-O

on

the

I

falling

edge.

USE

I I

I

I

I

I

I

I

I

L I

'lbgether

with

JW)()

defines.

the

data

acoess

fotltBt

I

as

shown

below.

tlBE

smuld

be

tied

high

when

I oonnected

to

an

8-bit

CPO.

I

~

tlBE

Di.tA

ACa!ss

Fonna

t

I 0 0 Even

address

word

I 0 1 Even

address

byte

I 1 0

~d

address

byte

I 1 1

Odd

address

byte

1-6

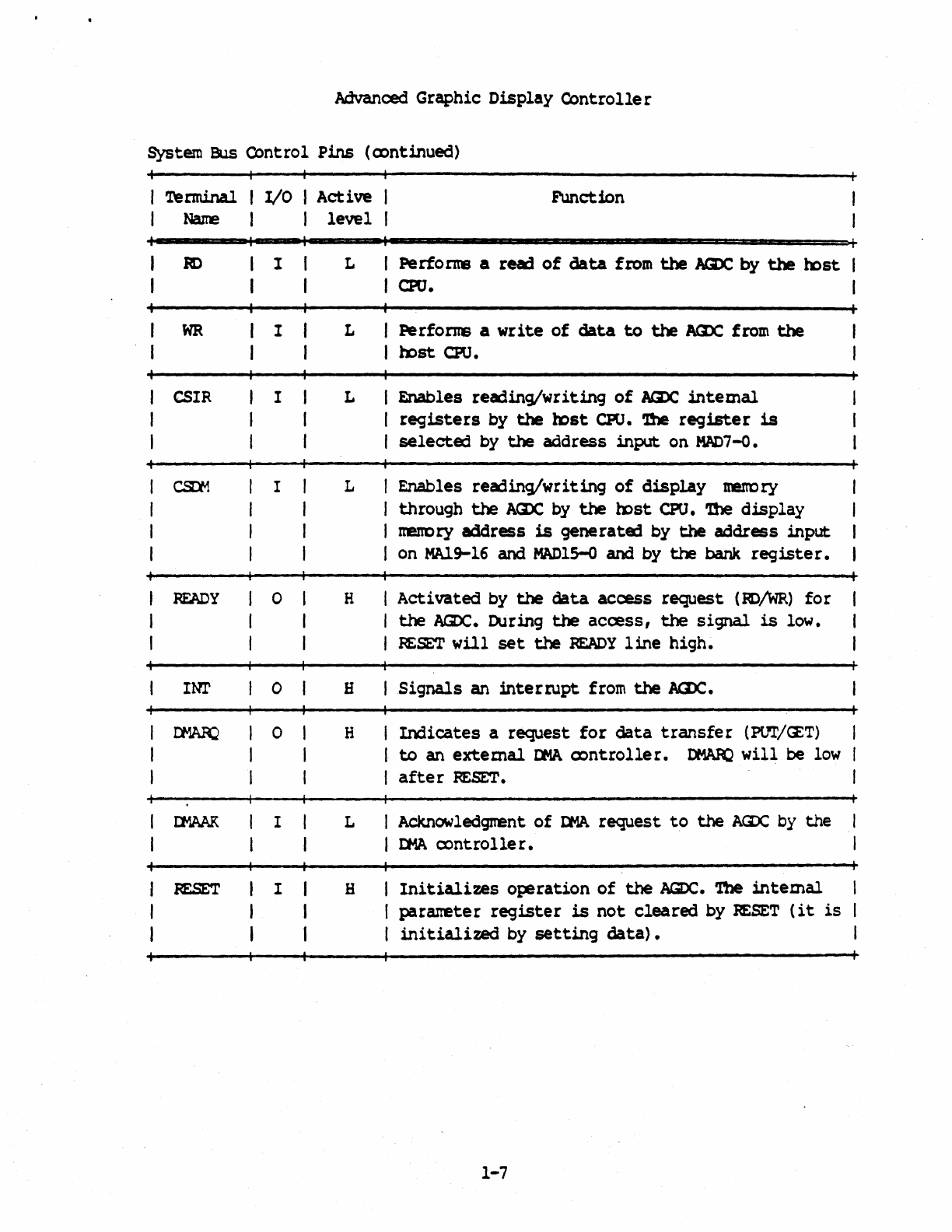

Advanced

Graphic

Display

Controller

System Bus

Control

pins

(oontinued)

'n!rmina.l I I/O I

Active

Function

Name

I I

level

RD

I L I

PerfOnt8

a read

of

data

from

the

NZY:, by

the

~st

I

CPO.

WR

I L

Perforns

a

write

of

data

to

the

ACDC

from

the

mst

CPU.

CSIR I L I Enables

reading/writing

of

laX:.

intemal

I

registers

by

the

mst

CPO.

'Dle

register

is

I

selected

by

the

address

input

on

MNl7-o.

CSl1

I L I Enables

reading/writing

of

display

uenory

I

through

the

Ar:D:

by·

the

mst

CPU.

'l'he

display

I rrerrcry

address

is

generated

by

the

address

input

I on

MAl9-16

and

MADl5-0

and by

the

bank

register.

RFADY

0 H I

Activated

by

the

data

access

request

(R>/WR)

for

I

the

AaX:.. During

the

access,

the

signal.

is

low.

I

~$T

will

set

the

READY

line

high.

IN!' 0 H

Signals

an

interrupt

from

the

AaX:..

~

0 H

Indicates

a

request

for

data

transfer

(PUT/GET)

to

an

extemal

~

ex>ntroller.

DMARO

will

be

low

afte

r

RESET.

Il1AAK

I L I Acknowledgnent

of

tt-1A

request

to

the

AGX

by

the

I

DMA

controller.

!£SET I H I

Initializes

operation

of

the

AGOC..

The

intemal

I

paraneter

register

is

not

cleared

by

H:SET

(it

is

I

initialized

by

setting

data).

1-7

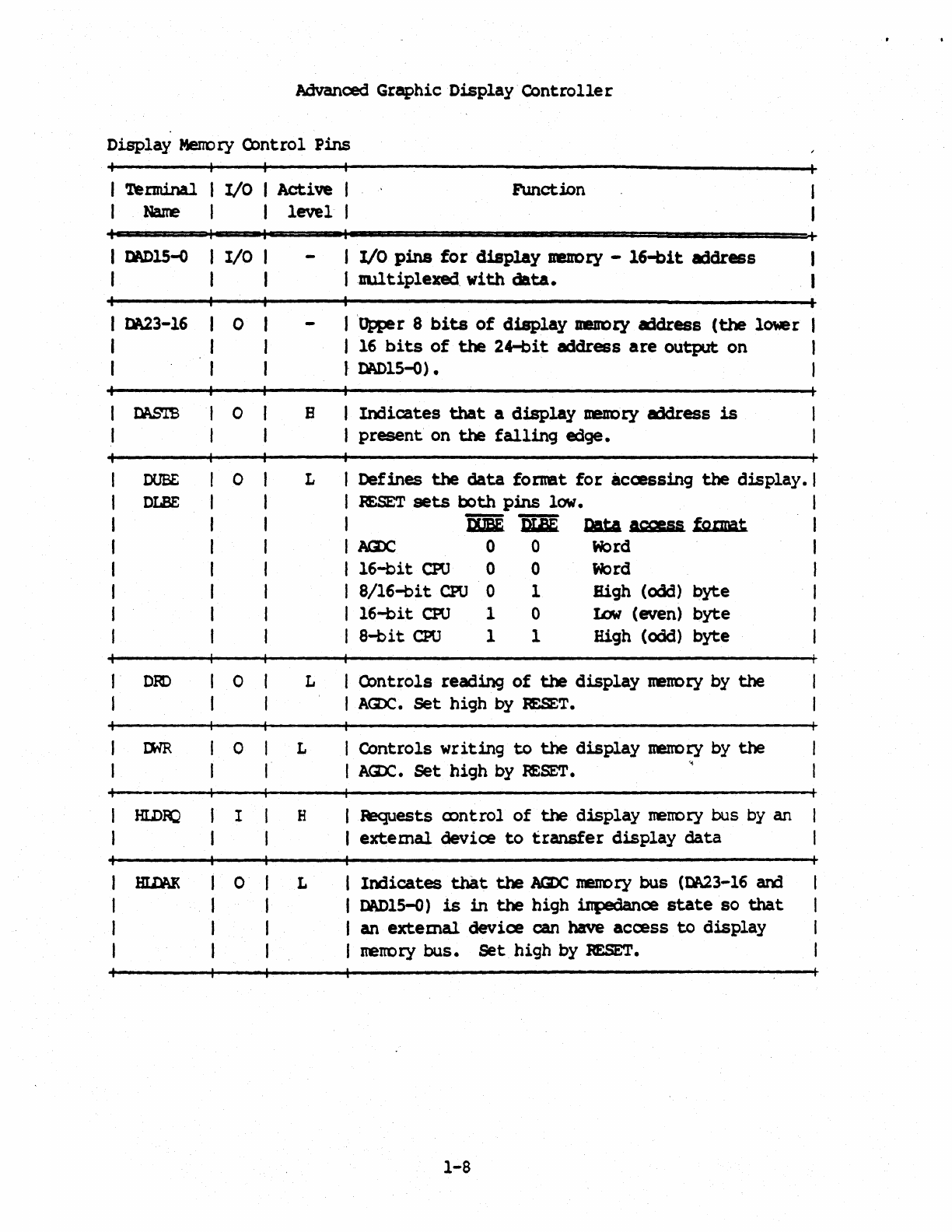

Advanced

Graphic

Display

Controller

Display

MeIrory

O:>ntrol

Pins

I

'1eminal

I

I/O

I

Active

I

I

Name

I I

level

I

Function

I

J:W)lS~

I

I/O

I

I I I

I

DA23-16

I

I

DUBE

DLBE

DR)

o

o

0

o

o

I

I/O

pins

for

display

DeDDty -

16-bit

mdress

luultiplexed.

with

data.

I 'Opper 8

bits

of

display

DeDOty

Iddress

(the

lower

I 16

bits

of

the

24-bit

address

are

output

on

I

IW>lS-o).

B I

Indicates

that

a

display

DeltDty

address

is

I

present

on

the

falling

edge.

L I Defines

the

data

fornat

for

accessing

the

display.

I

I

:RESET

sets

Ix>th

pins

low.

I

iiii

iim

JatI.

eme

ss

fQgnat

I /IGX:, 0 0

Word

I

16-bit

CPO

0 0

Word

I

8/16-bit

CPU

0 1 High

(odd)

byte

I

16-bit

CPO

1 0 Low

(even)

byte

I

8-bit

CPU

1 1 High

(odd)

byte

L I

O:>n

trols

reading

of

the

display

meoo

ry

by

the

I

AG:X:,.

Set

high

by

m:sET.

L I

Controls

writing

to

the

display

nenory

by

the

"

I AGX,.

Set

high

by

RESET.

+-------~---+------~------------------------------------~

HIDKJ

I H

o L

I

aequests

control

of

the

display

menory bus by an

I

extemal

device

to

transfer

display

data

I

Indicates

that

the

NZX:,

mem:>ry

bus

(W3-16

arx1

I [w)15-0)

is

in

the

high

iJrpedanoe

state

so

that

I an

extemal

device

can have

access

to

display

I nenory

bus.

Set

high

by

RESET.

1-8

Advanced Graphic

Display

Centrolle

r

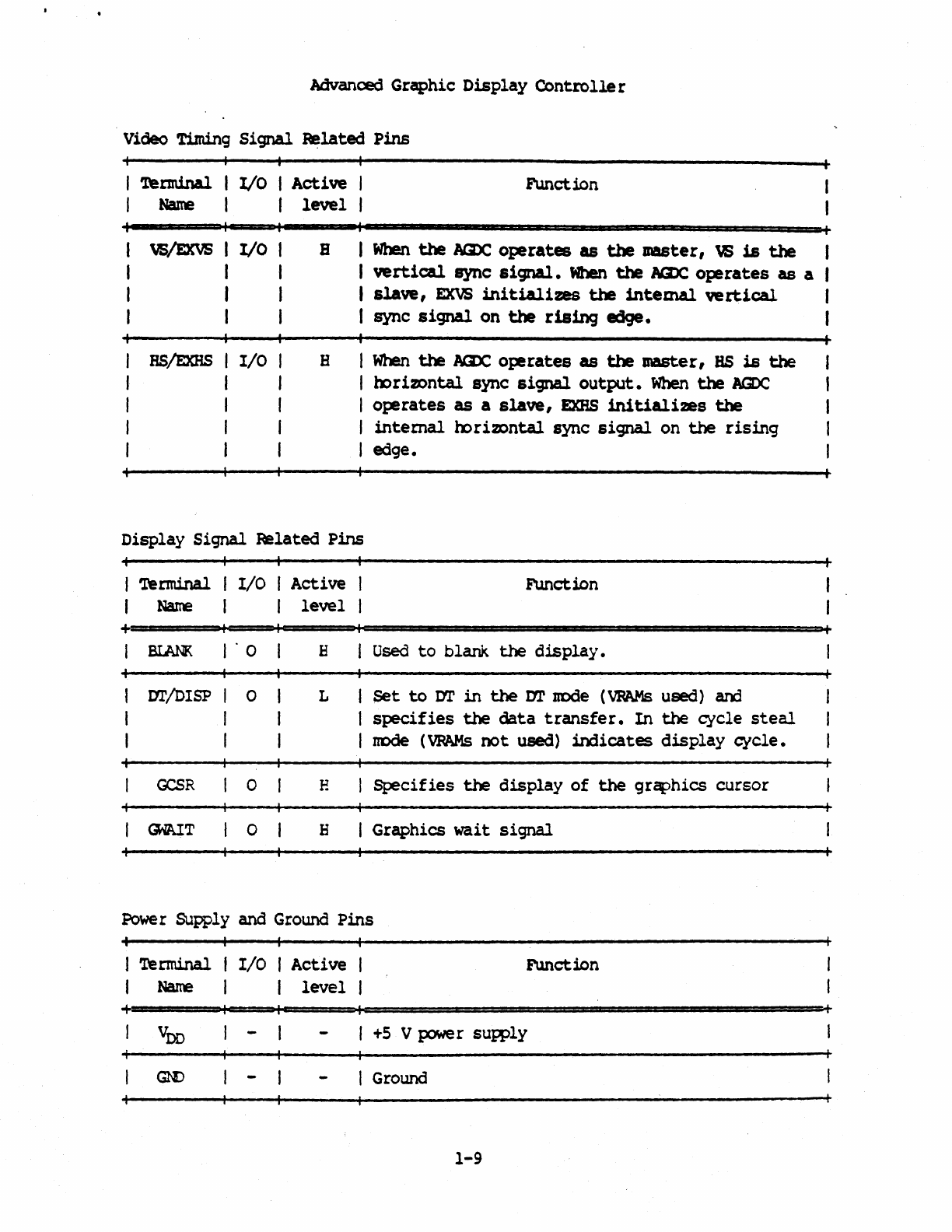

Video Timing Signal.

~latec1

Pins

I 'l'enninal I

I/o

I Active I

I

Name

I f

level

I

Function

vs/EXVS

I I/O I

I I

I I

I I

HS/EXHS

I

I/O

I

I I

I I

I I

I I

B I

When

the

laX;

operates

as

the

master,

VS

is

the

I

vertical

sync

signal.

When

the

NZJC

oparates

as

a

I

slave,

EXVS

initializes

the

intemal

vertical

I sync signal. on

the

rising

edge.

H I

When

the

AaX;

oparatee

as

the

master,

as

is

the

I

mrizontal

sync

signal

output.

When

the

AGDC

I

operates

as

a

slave,

EXHS

initialias

the

I

intemal

mrimntal

sync

signal

on

the

rising

I edge.

Display

Signal

Related

Pins

I 'l'e

rminal

I

I/O

I

Active

I

Name

I I

level

Function

+,======~~==*======+=====-==========-======================+

B.I.Mi(

I'

0

M/DISP I 0

I

I

GCSR

0

GlAIT 0

H

Used

to

blank

the

display.

L

Set

to

M

in

the

DT

nDde

(VPAMs

used)

aM

specifies

the

data

transfer.

In

the

cycle

steal

I

ItDde

(VPAMs

not

used)

indicates

display

Cjcle.

E I

Specifies

the

display

of

the

graphics

cursor

H I

Graphics

wait

signal

Power SUpply and Ground

Pins

J

Terminal

I

I/O

I

Active

I

Name

I I

level

+

I -

I -

Function

I

+5

V

powe

r

supply

I Ground

1-9

Advanced.

Graphic

Display

Controlle

r

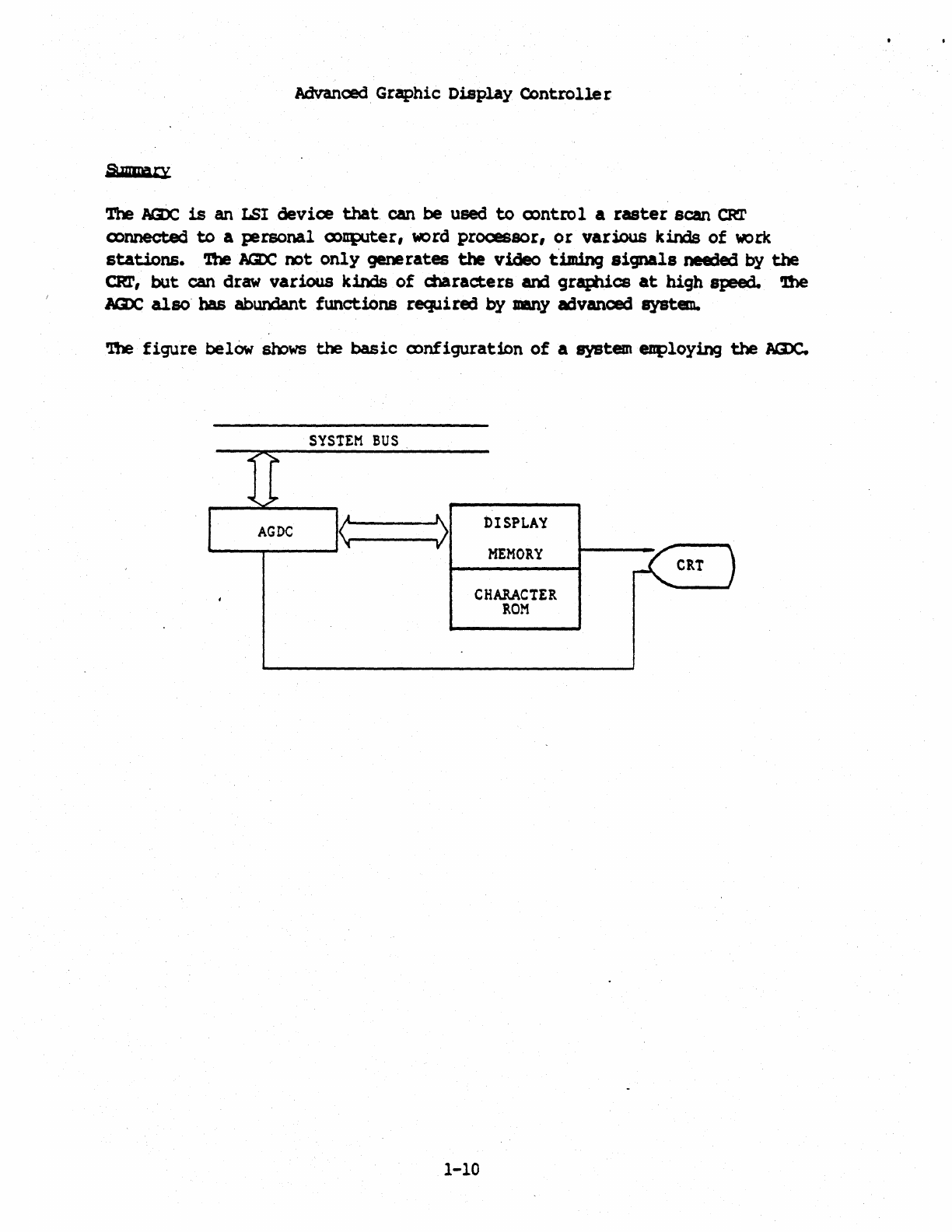

The

AGX.

is

an LSI device

that

can

be

used

to

(X)ntro

1 a

raster

scan

CRT

(X)nnecteQ

to

a personal

(X)lIp-lter,

word

processor,

or

various kinds

of

work

stations.

'1'be

AGOC,

not

only

generates

the

video t'iming

signals

needed

by

the

CRr,

but

can

draw

various kinds

of

maracters

and gratXUcs

at

high speed. '!be

lax:

also

bas

abundant

functions

required

by

many

advanced

system.

'!be

figure

below

sb:>ws

the

basic

ex>nfiguration

of

a system euploying

the

AGX.

SYSTEM

BUS

......

_..,..----'

<~>

DISPLAY

MEMORY

CHARACTER

ROM

1-10

Advanced Graphic Display

Centrolle

r

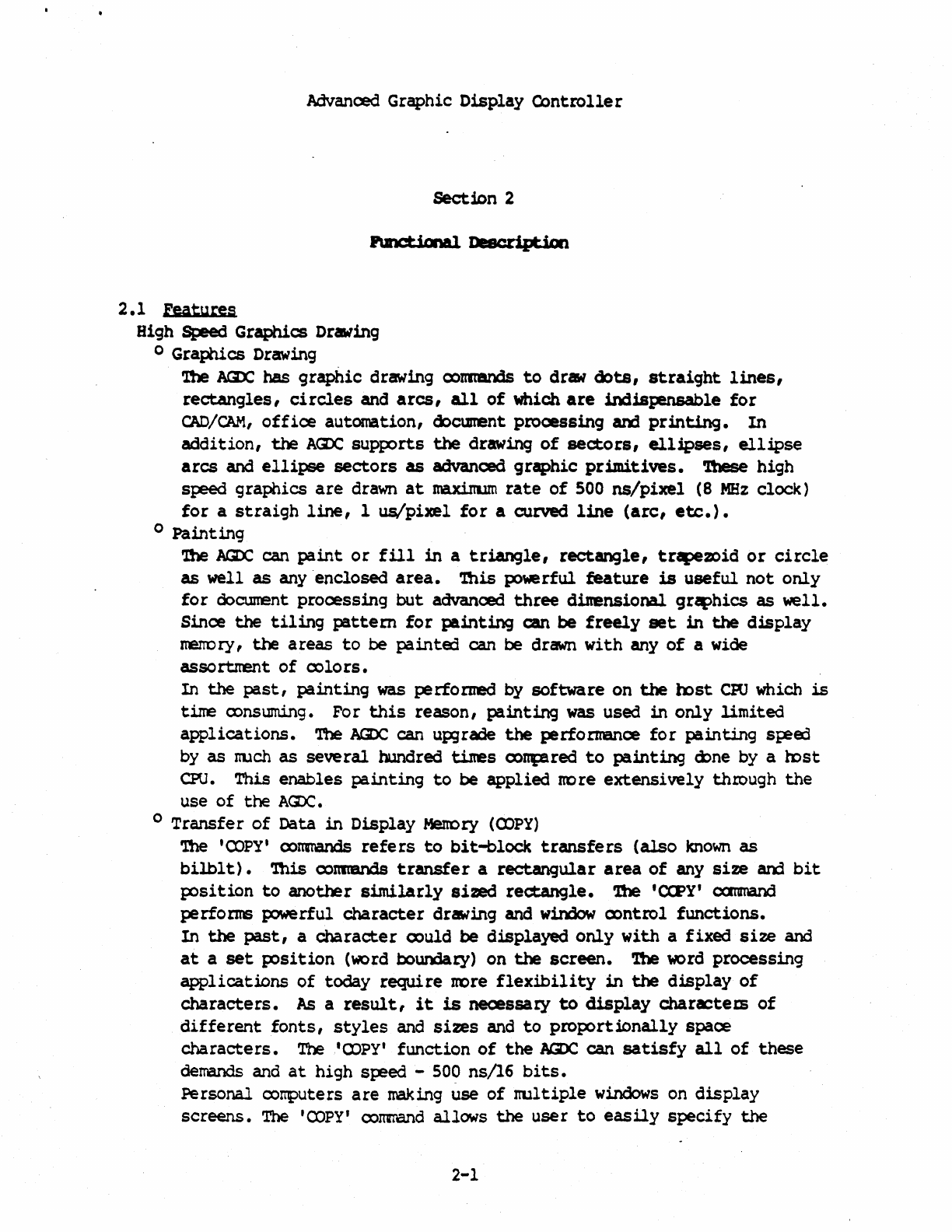

section

2

2.1

Features

High

Speed

Graphics Drawing

o Graphics Drawing

'!be

AaX

has

graphic

drawing

oormands

to

draw

oots,

straight

lines,

rectangles,

circles

and

arcs,

all

of

which

are

indispensable

for

CAD/CAM,

office

autonation,

cX>current

processing

am

printing.

In

addition,

the

At;zX;

supports

the

drawing

of

sectors,

ellipses,

ellipse

arcs

and

ellipse

sectors

as advanced

graphic

primitives.

'1hese

high

speed

graphics

are

drawn

at

maxirtum

rate

of

SOO

ns/pixel

(8

MHz

clock)

for

a

straigh

line,

1

us/pixel

for

a curved

line

(are,

etc.).

o

Painting

'!be

AaX,

can

paint

or

fill

in

a

triangle,

rectangle,

trapezoid

or

circle

as

well

as

any

enclosed

area.

'!his

powerful

feature

is

useful

not

only

for

docunent

processing

but

advanced

three

dinensional

graphics

as

well.

Since

the

tiling

pattern

for

painting

can

be

freely

set

in

the

display

merrory,

the

areas

to

be

painted

can

be

drawn

with

any

of

a wide

assortnent

of

oolors.

In

the

past,

painting

was

perfomed

by

software

on

the

mst

au

which

is

time oonsuming. For

this

reason,

painting

was

used

in

only

limited

applications.

The

AaX:,

can upgrade

the

performance

for

painting

sp?eO

by as nuch as

several

hundred

tines

oonpared

to

painting

c:bne

by a

mst

CPU.

This

enables

painting

to

be

applied

nore

extensively

through

the

use

of

the

AGDC.

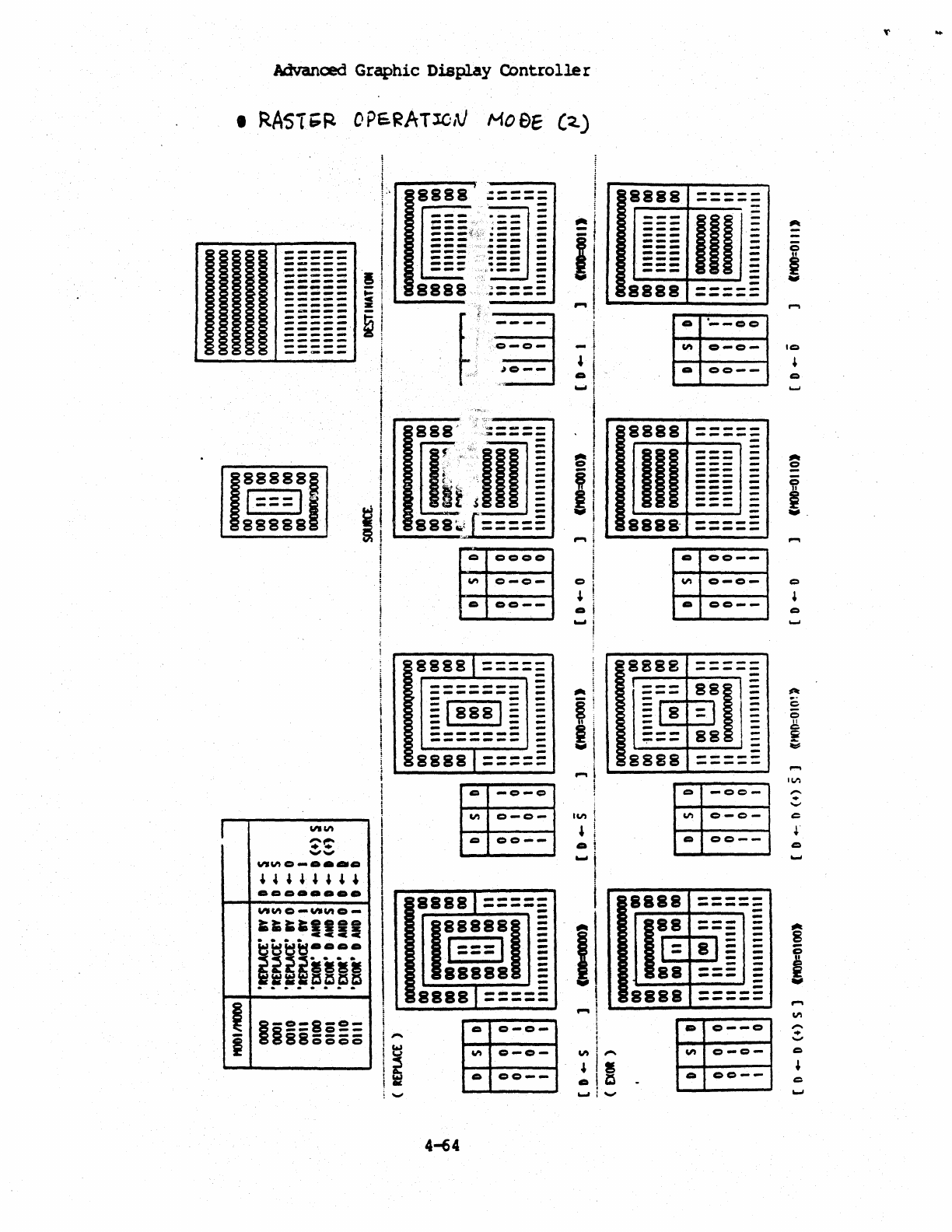

o

Transfer

of

Data

in

Display

Merrory

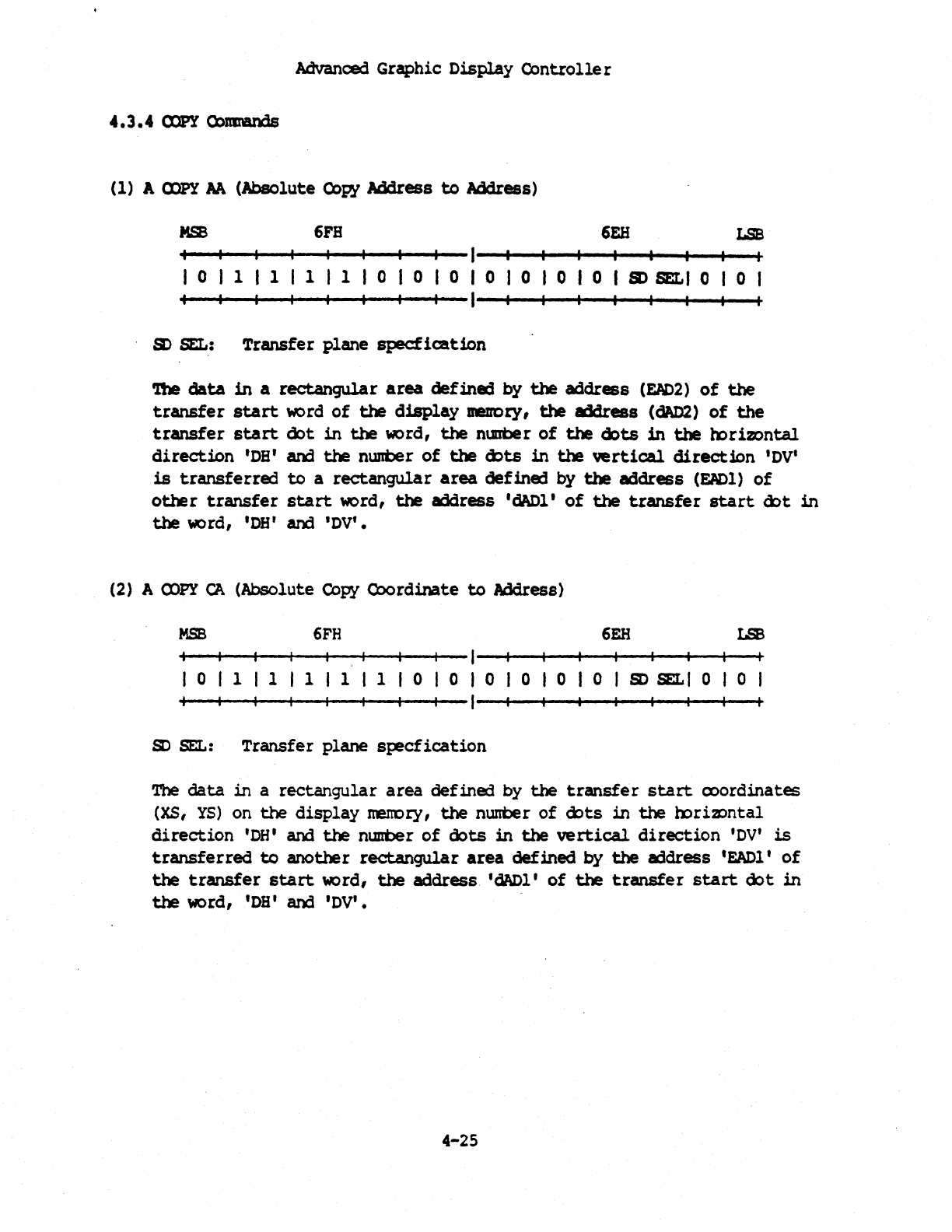

(CDPY)

'!be

'cx)PY'

oorrmands

refers

to

bit-block

transfers

(also

known

as

bilblt).

'!his

CX)rmands

transfer

a

rectangular

area

of

any

size

arxl

bit

position

to

another

similarly

siEd

rectangle.

1be

'CCPY'

canmand

performs powerful

character

drawing and

window

oontrol

functions.

In

the

past,

a

character

oould be

displayed

only

with

a

fixed

size

and

at

a

set

p:>sition (word

boundaty)

on

the

screen.

1be

word

processing

applications

of

today

require

!rore

flexibility

in

the

display

of

characters.

As

a

result,

it

is

neoessaty

to

display

charactecs

of

different

fonts,

styles

and

sizes

and

to

proportionally

space

characters.

The

'CDPY'

function

of

the

AGX

can

satisfy

all

of

these

demands

and

at

high

s~ed

-500 ns/16

bits.

Personal computers

are

making use

of

multiple

windows

on

display

screens.

The

'ropy'

oorrrnand

allows

the

user

to

easily

specify

the

2-1

Advanced

Graphic

Display

Q:)ntrolle r

nUJtbe

r,

shape

and

size

of

IEUltiple

windows.

Purthe

r,

the

'Qpy'

oanmand

of

the

ND:

can perform

various

logical

operations

between source

an::1

destination

planes.

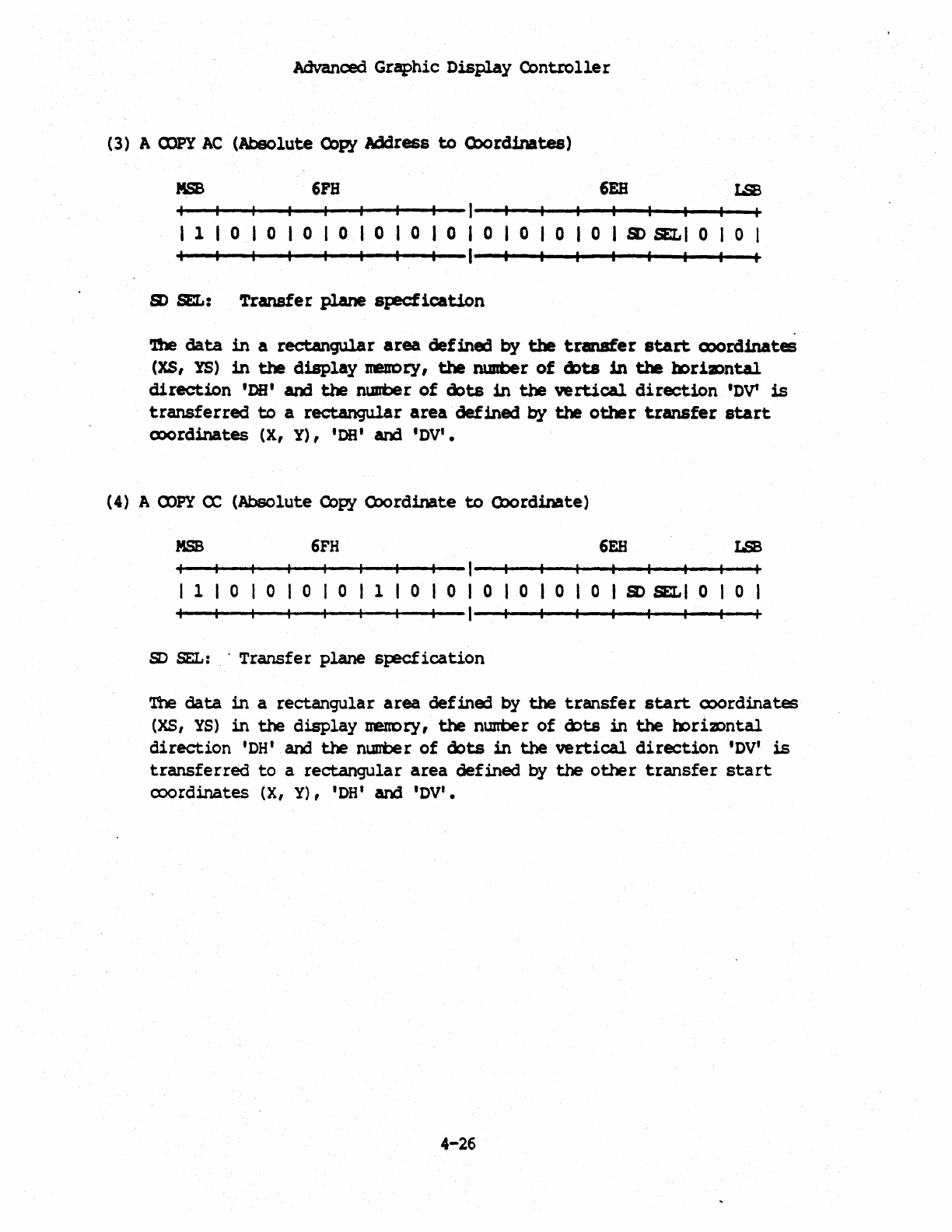

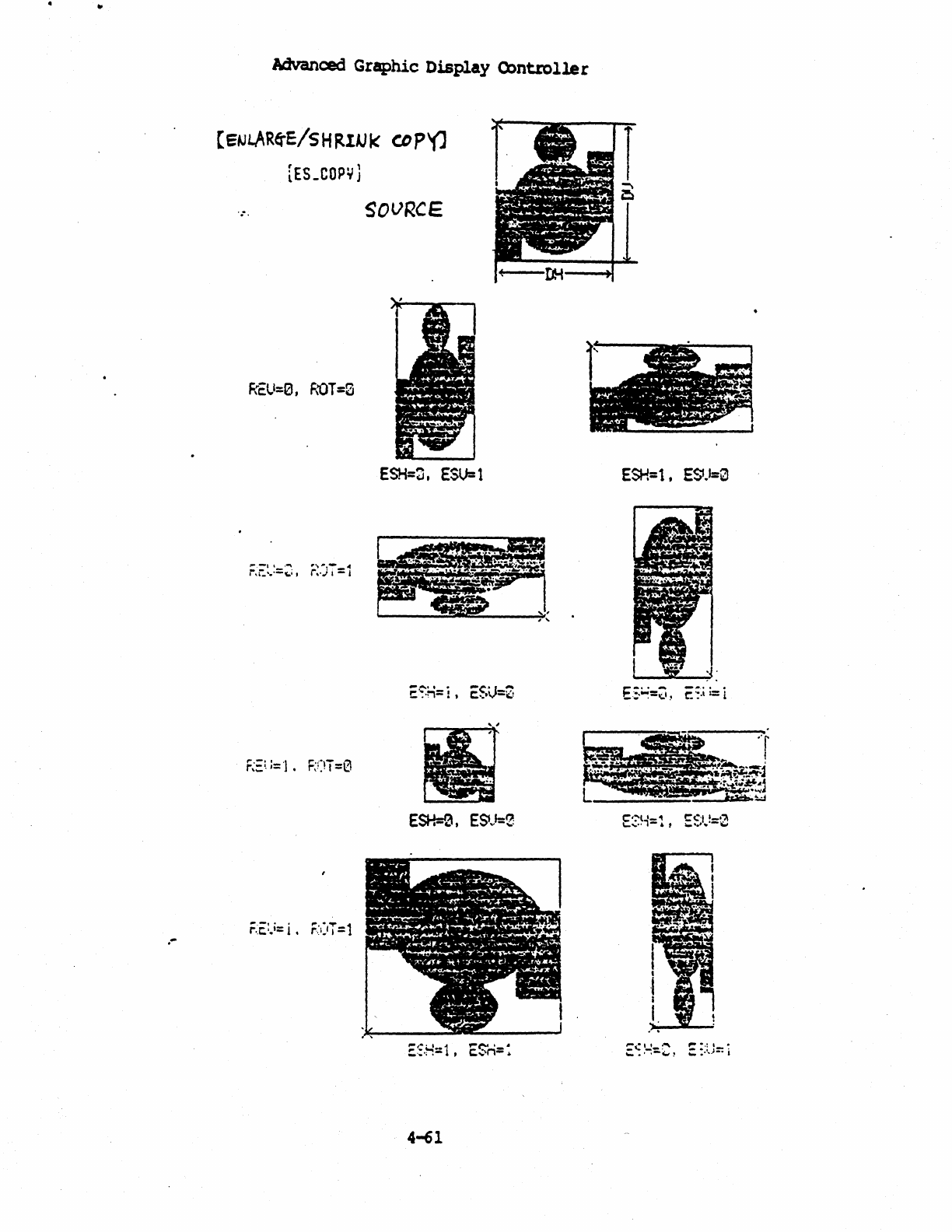

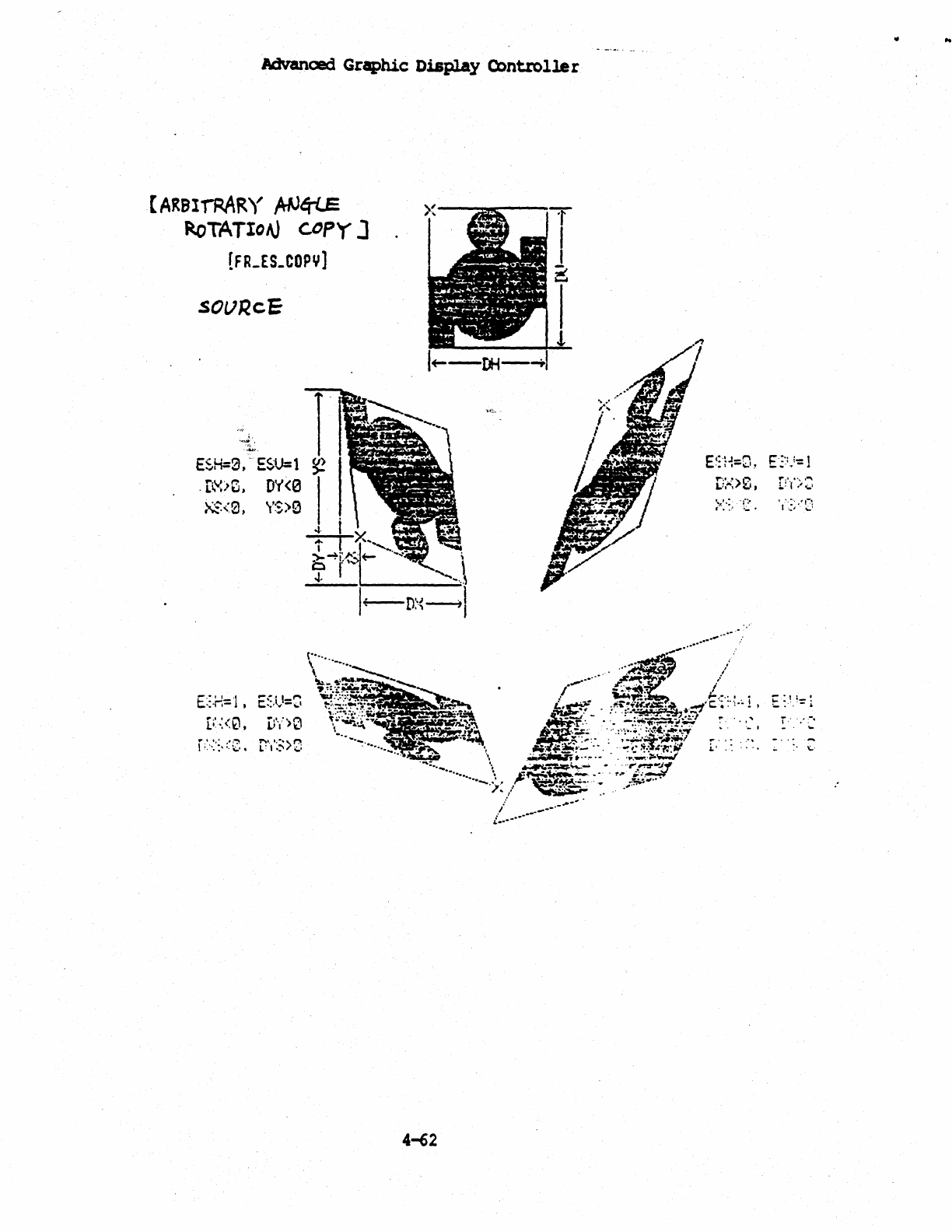

o

Image

Prooessing

'!be

NZ1:.

is

able

to

do

mre

than

just

copy

data.

It

can

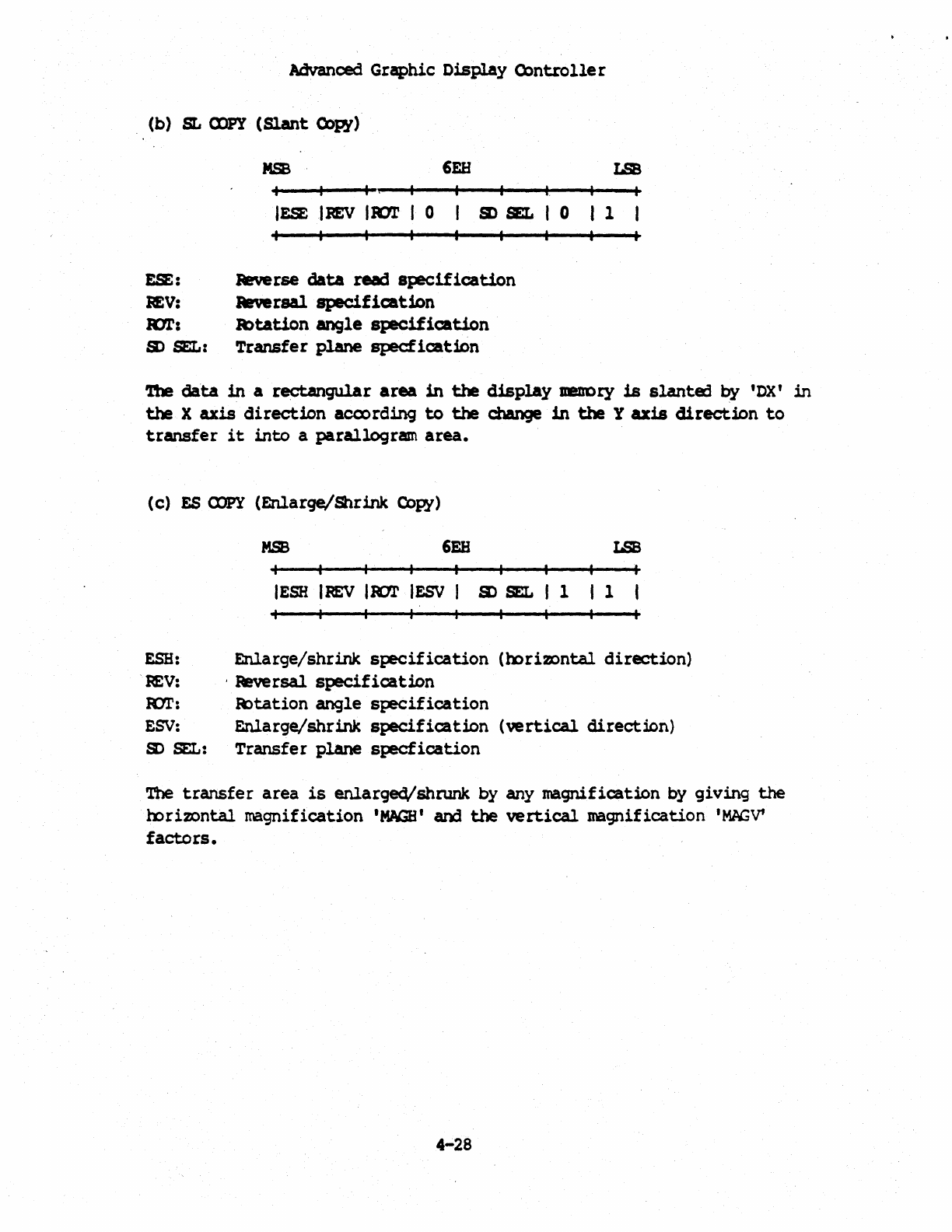

slant

oopy,

arbitrary

angle

rotation

CDPY,

16/n

enlargeuent

cx>py

or

n/16

shrink

CX)py

(n

any'

integer

from 1

to

16).

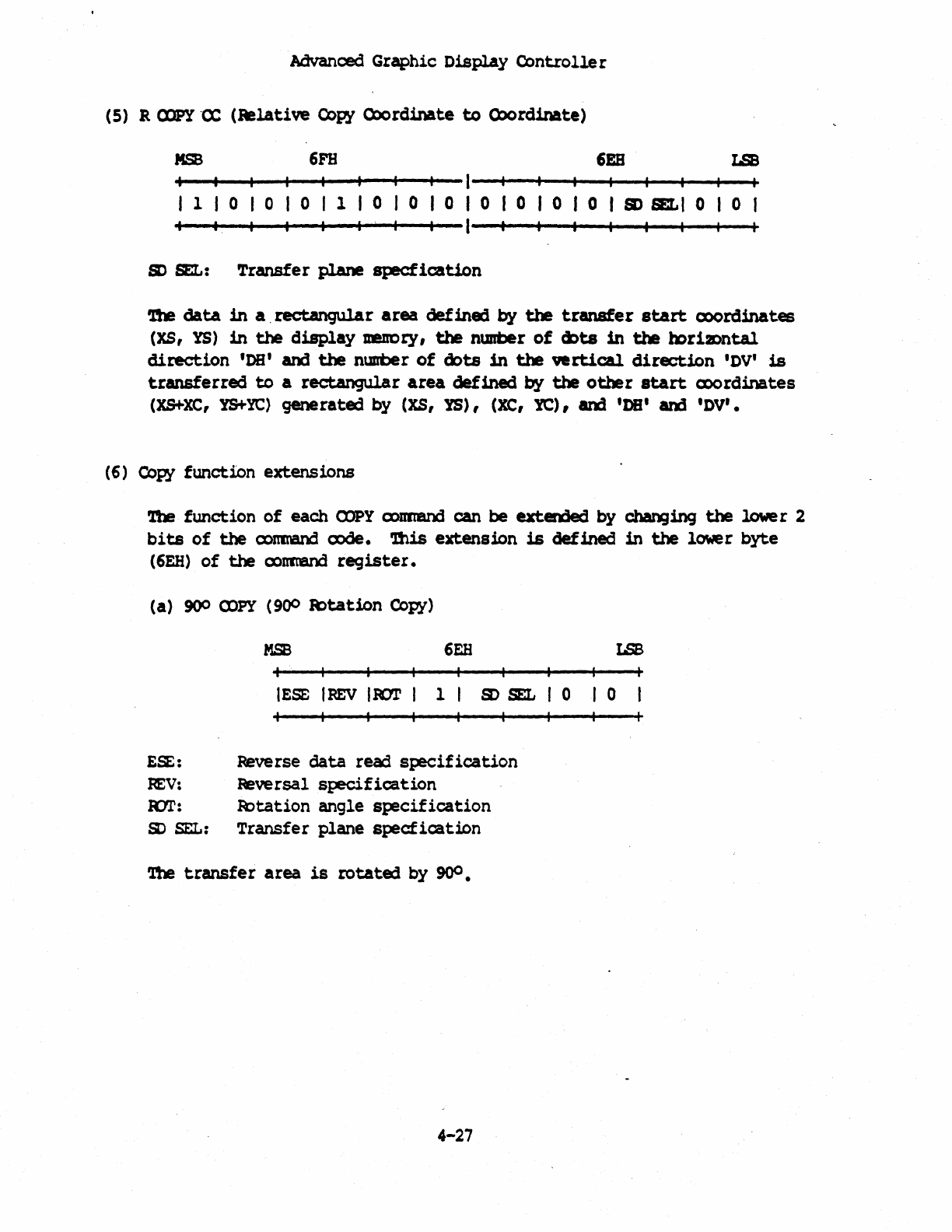

ihese

copies

transfer

data

from a

rectangular

source

area

to

a non-rec::tangW.ar

destination.

n.

slant

Q)PY

can be used

for

drawing

italic

cbaractem.

'!be

atbitraty

angle

rotation

oopy

is

useful

for

doctment

preparation

beca1se

it

can

rotate

characters,

graphics,

imsges,

etc.

1be

enlarge and

shrink

oopies

are

effective

for

editing

and

patching

doclments.

'lbese

AGX:,

ootrltBOOs

relieve

the

mst

CPO

of

what

was

a

software

intensive

function.

'!be

laX:,

can

quickly

acoorrplish

these

image

processing

tasks

and

for

a lower

cost.

o

Position

Specification

by

X-Y

Q)ordinates

'nle

graphics

drawing and oopy

paranetem

can be

given

as

X-Y

ooordinates

thereby

relieving

the

mst

CPU

of

the

address

calculation

requirenents.

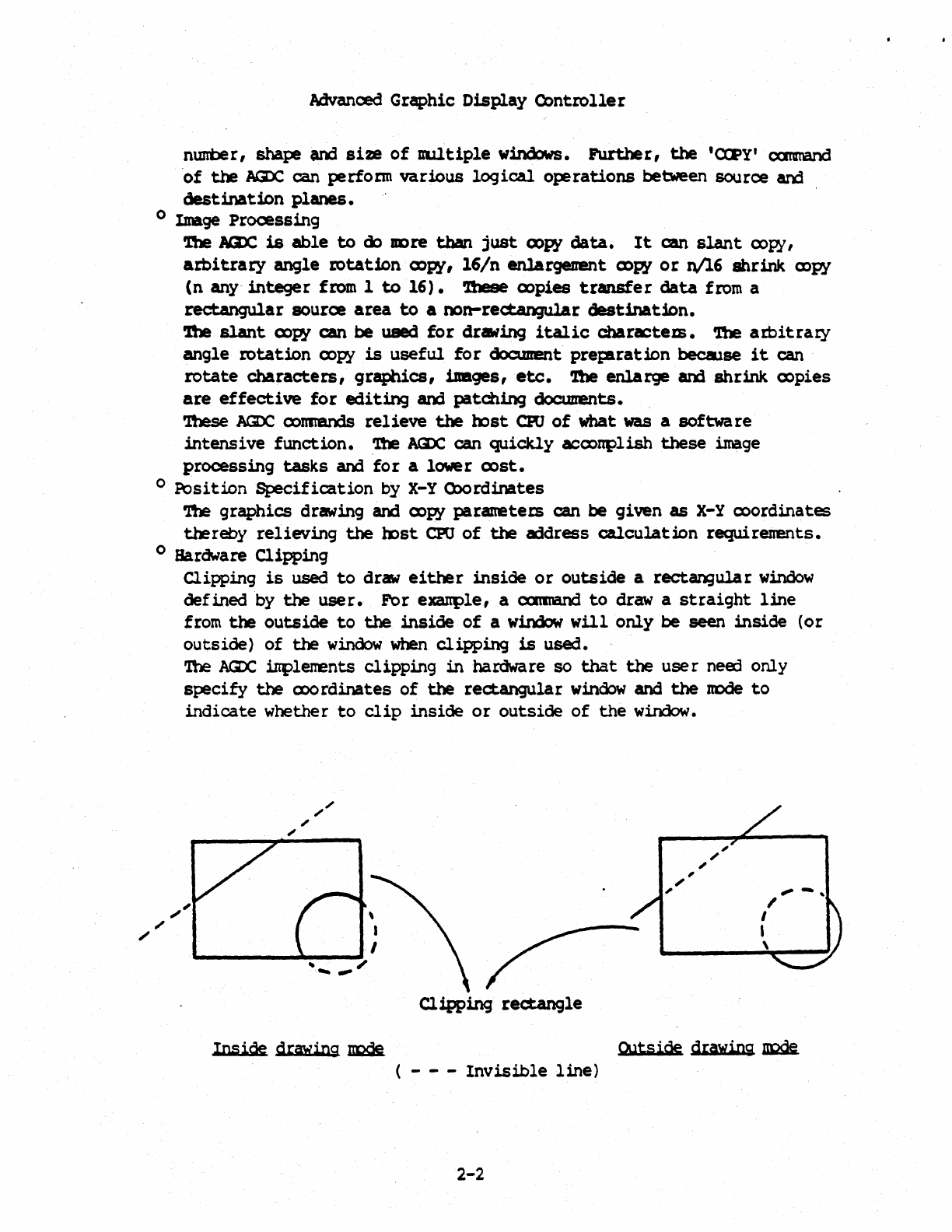

o Hardware

Clipping

Clipping

is

used

to

draw

either

inside

or

outside

a

rectangular

window

defined

by

the

user.

For

exanple,

a

cxm.nand

to

draw a

straight

line

from

the

outside

to

the

inside

of

a wirWw

wlllonly

be

seen

inside

(or

outside)

of

the

window

when

clipping

is

used.

'!be Aax:. inplements

clipping

in

hardware so

that

the

user

need only

specify

the

cx>ordinates

of

the

rectangular

winoow

and

the

mde

to

indicate

whether

to

clip

inside

or

outside

of

the

window.

Clipping

rectangle

Inside

drawing

~

( - - -

Invisible

line)

2-2

I

,

,

\

~

-,

OUtside

drawing

~

Advanced Graphic

Display

Controlle

r

Video Timing

Signal.

Generation

o High

Speed

Processing

by

Dual System

Clocks

Dual system

clocks

can

be

input

to

the

NZX':.

-

the

drawing

clock and

the

display

clock.

In

a

graphics

system,

the

display

rate

depends

on

the

resolution

of

the

CRr,

the

clock

frequency

of

the

display

mntrolle

r

depends on

the

display

rate.

In

the

past,

only

a

single

clock

was

used

for

the

display

a>ntroller.

It

was

often

necessary

to

limit

the

clock

to

5

MHz

even

trough

the

capacity

of

the

display

ex>ntrolle r

was

8

MHz.

'lberefore,

the

AaX:,

was

designed

to

have

the

display

clock

independent

of

the

drawing clock

so

that

drawing can

be

perforned

at

the

highest

tx>ssible

speed.

o

External

Sync

Inplt

In

systems

that

incx>rporate a

separate

circuit

to

generate

the

video

timing

signals

and use an

Aczx,

only

to

draw

gra];ilics,

or

in

systems

that

use

JIUltiple

AGDCs

to

achieve

higher

perfoanance,

it

is

necessar:y

to

synchronize

the

ACD:.

with

the

extemal

Circuitry

or

the

AiD:

with

other

AGDCs.

'1berefore,

the

1Q.X,

has

extemal

sync

input

capability

to

synchronize

its

operatlons

with

other

A£J)Cs

or

with

extemal

circuitry.

Large

capacity

Display

Menory

Control

o

~isplay

Mem:ay

Bus

Interface

With

its

24-bit

addressing

and

16-bit

data,

16

Mwords

of

16

bits/word

display

nerrory can

be

cx>nfigured

with

the

ACDC.

'!his

neans

that

up

to

64

planes

of

2048 x 2048

dots

can

be

cx>nnected.

o

Video

MM

(VRAM)

Q)ntrol

VPAMs

are

dual-p:>rted

DRAMs

with

intemal

line

buffer

shift

registers

(i.e.,

uPD41264). '!be

VMMs

provide

a

sep!lrate

port

for

display

data

so

that

when

drawing, JIel'Il)ry

access

tine

is

greatly

reduC2d. As a

result,

nost

of

the

entire

rreItDry

cycle

can

be

used

as

the

drawing

cycle

to

inprove system

throughput.

'nle

AGDC

supplies

the

signals

neEded

to

oontrol

VRAMs.

o

DisplayMemo~

Bus

Ar.bitration

In

a

basic

system,

the

display

ment>ry

is

accessed

by

the

AQ)C

only.

However,

in

a

nore

advanced system,

the

display

menory

may

be

accessed

by

other

processors.

In

other

words, a

local

bus

is

established

between

the

display

nen:cry and

the

Ja)C

or

other

processors.

In

this

case,

it

is

necessary

for

the

AaX:,

to

periodically

provide

refresh

am

display

cx>ntrol and

thus

act

as

the

local

bus

master.

Other

processors

on

the

.

display

nenory bus

(i.e.,

an

inage

processor)

are

slaves

ard

nust

request

use

of

the

bus from

the

AQJC.

'nle

Amc

oontrols

the

display

nerrory bus and can

grant

the

use

of

the

bus

to

other

processors.

'nle

ACXI:,

inoorporates

display

I11!rrory

bus

arbitration

logic

enabling

higher

performance

systens

to

be

oonstructed

for

a lower

oost.

2-3

Advanced

Gr~hic

Display

Cont~ller

CPU

interface

.

o Systen

MeIIO

ry

Bus

Inte

rface

o

CPO

Mapping

of

Internal

Registers

and

Display

Melrory

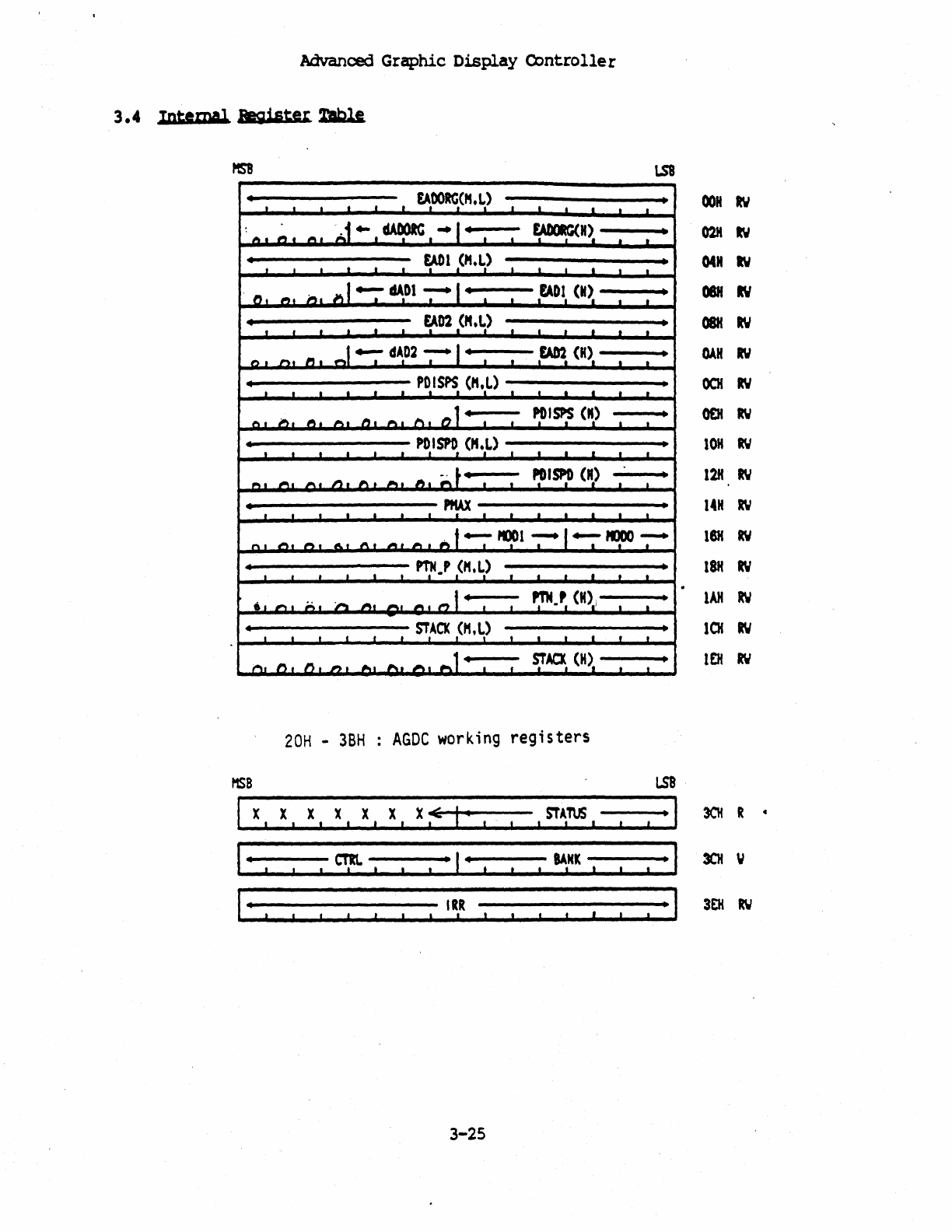

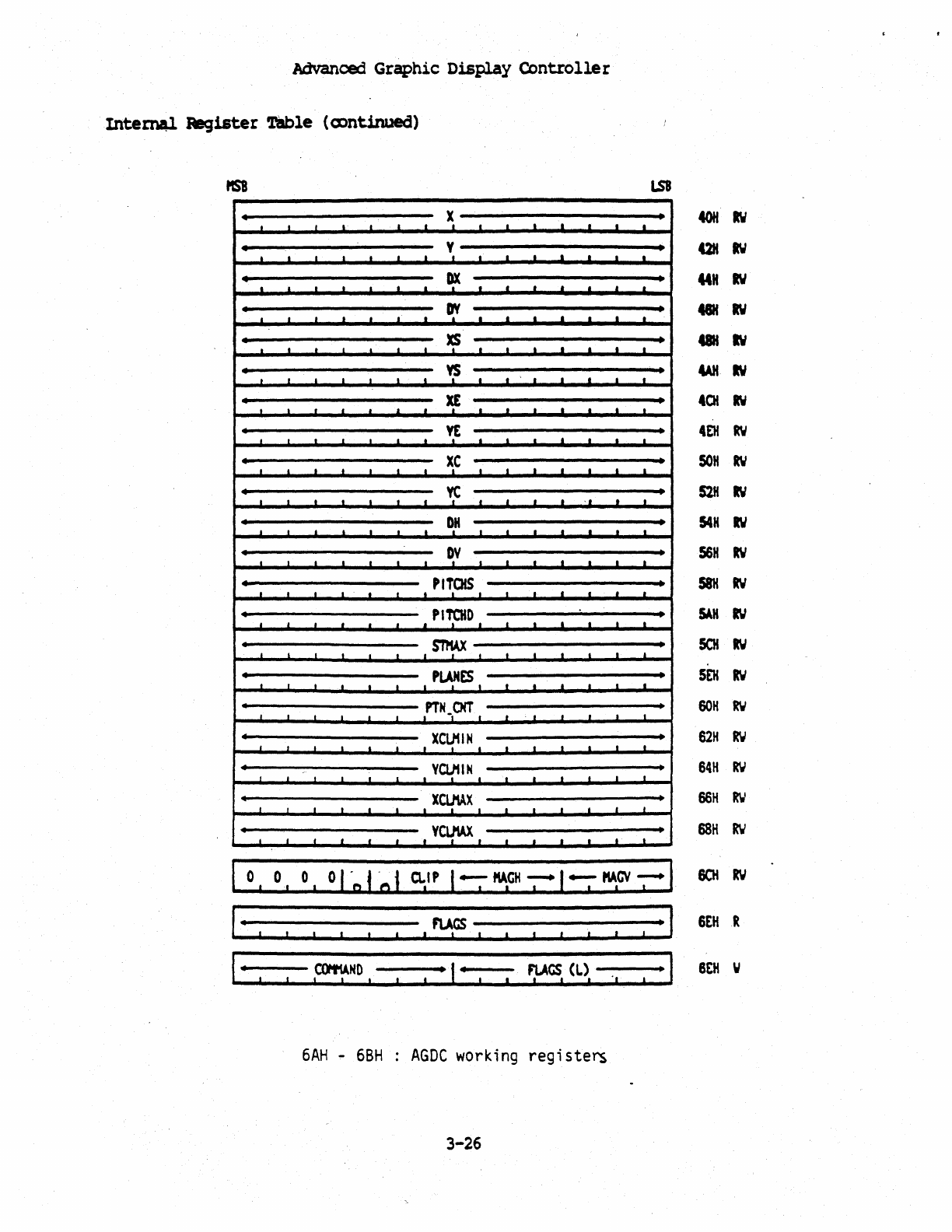

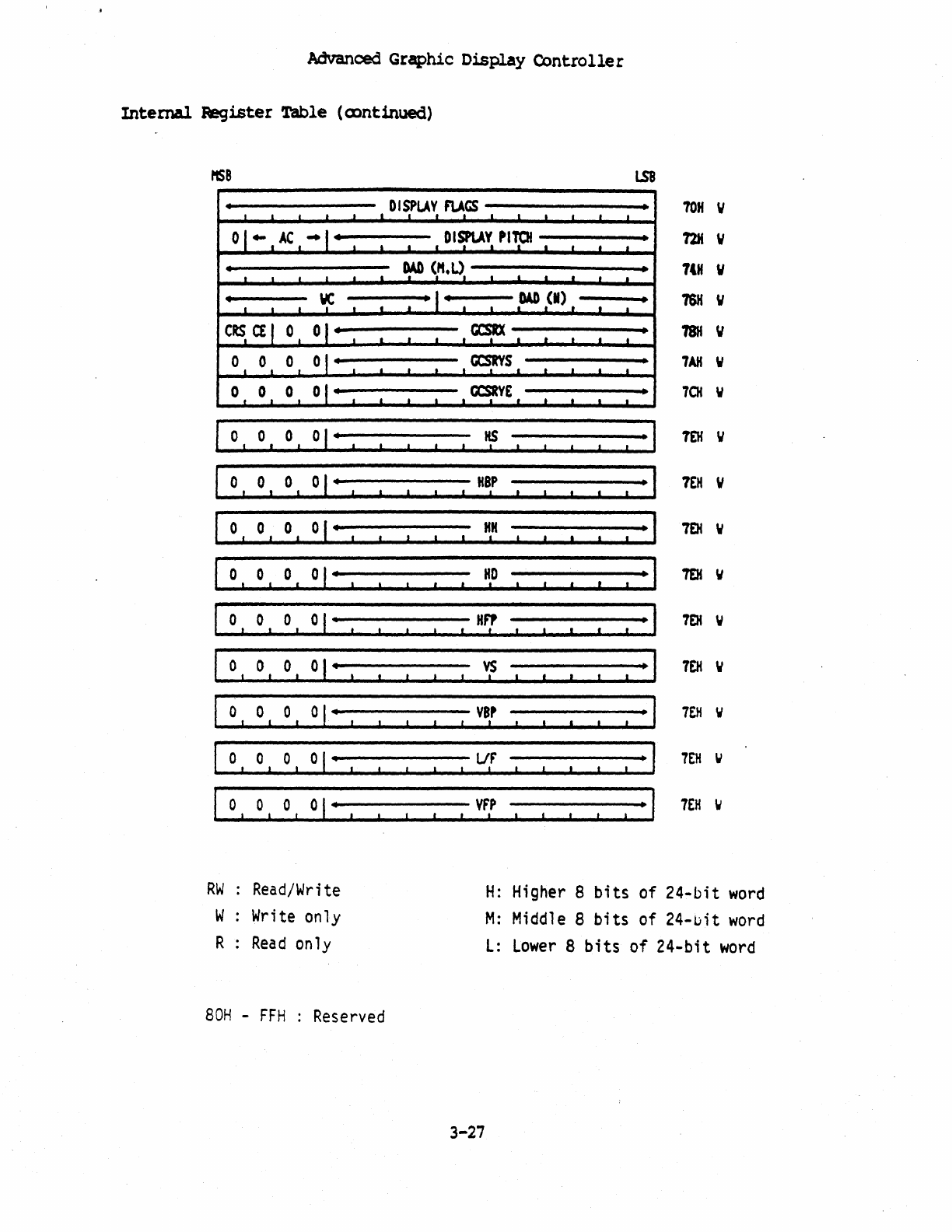

'!he Jta:£ system nenory

bus

interface

to

the

mst

CPO

is

indepen3ent

of

the

display

JleDDry

bus.

'!be

width

of

the

a:idress

mich

the

CPU

can

inPolt

to

the

AaX:.

is

20

bits

am

the

data

width

is

8

or

16

bits.

'!be

2o-bit

address

is

used

when

the

display

plraneters,

drawing

lBraneters

and

oonmmds

are

set

and

the

CPU

accesses

the

display

neDD

ry

directly.

ihe

intemal

AGX:,

registers

and

the

display

JDeDDry

can

be mapped

in

the

CPU

rrenory

or

I/O

space.

'1bi.s Allows

the

CPO

to

efficiently

execute

special

drawing

p~cessing

directly

in

the

display

JDeDDIy.

!be

mapping

of

AGX:,

registers

in

the

CPU

uerroty

space

provides

for

quick

access

of

inforrration

to

and from

the

Aa:C.

o System

Mem:>ry

<-> Display Menory

Data

Transfer

As

described

above,

it

is

p>ssible

to

map

,the

display

neuory

in

the

CPU

nenory

space.

It

is

also

possible

to

execute

PUlICE'!'

c:annands -

to

transfer

the

data

between

the

system uenory and

the

display

neIIOty

at

high

speed

th~ugh

the

use

of

an

exte

mal

IJt1A

oontrolle

r •

Pt1l'

is

the

oonrnand

to

transfer

data

from'

the

system

nem:>ry

to

the

display

nenory.

CET

is

the

comnand

to

transfer

data

from

the

display

nenory

to

the

system menory.

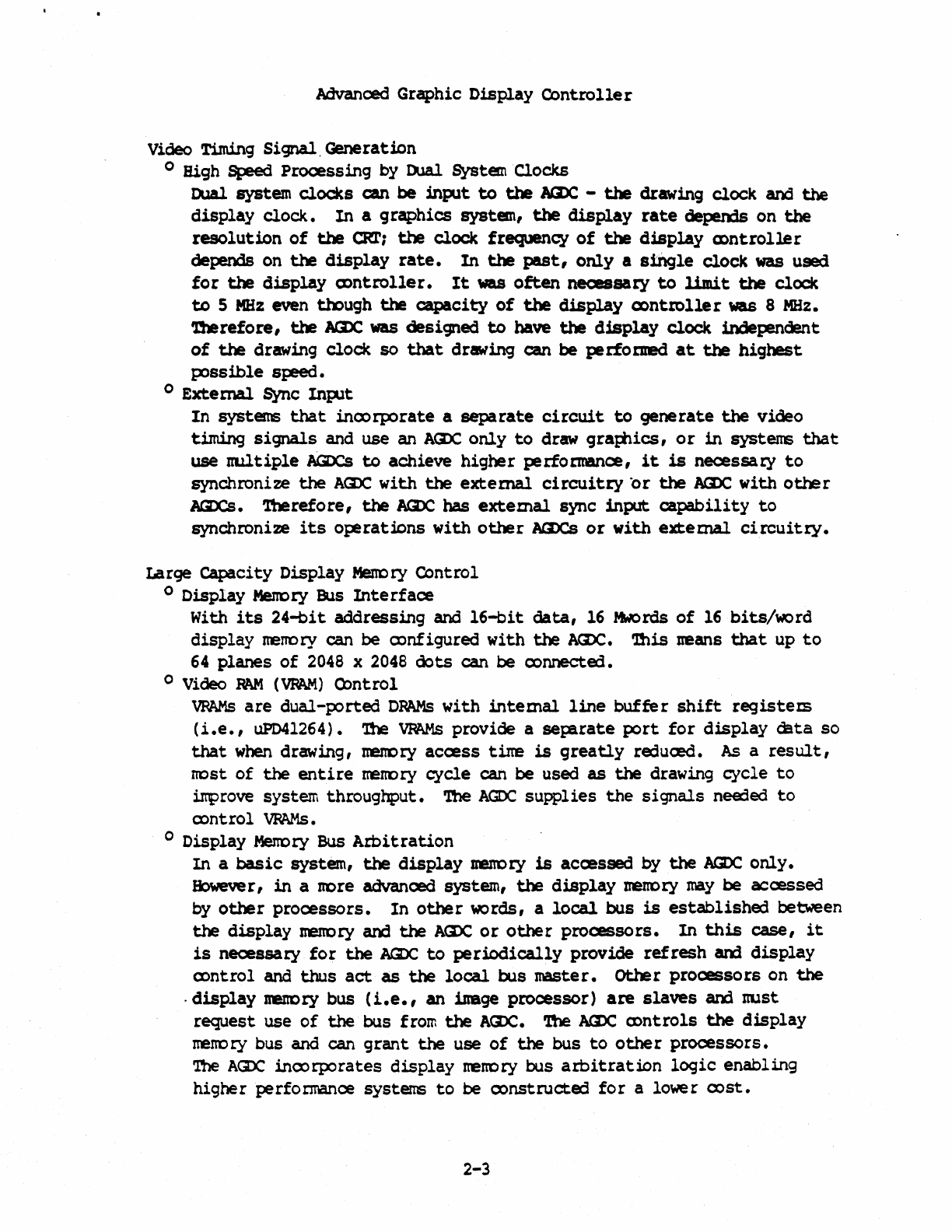

o High Speed

Pipeline

Drawing

P~cessing

The

paraneters

given by

the

CPU

to

the

ACJX;

are

greatly

reduced by using

X-y

ooordinates.

However,

it

is

necessary

for

the

Aa>C

to

calculate

physical

nenory

addresses

for

the

drawing

processor.

'!be

process

to

oonvert

the

X-Y (X)()rdinates from

the

CPU

into

physical

addresses

is

done

by

the

drawing

preprocessor.

'!be drawing

processor

executes

the

actual

drawing

ooImBnds

independent

of

the

preprocessor.

'1herefore

the

drcwing

processor and

preprocessor

can

oJ:erate

ooncurrently.

As srown

in

the

figure

below,

the

throughput

of

the

system

is

improved by

the

use

of

the

drawing

preprocessor

and

the

drawing

processor

in

a

pipeline.

Paranete

r

Input

(CPU

Interface)

~~p~ro~sor

__

~<

___

~~~

______

~)~~~<

____

_

Drawing Processor

tine

2-4

Advanced Graphic Display

Controller

2.2

Q:mmond/Pargete r Exc;hange

Between

.tl:&

a!l

.IDd

~

It

is

necessary

for

the

CPU

to

set

various parametem

and

ooammds

to

operate

the

drawing

and

display

oontrol

functions

of

the

AaX..

'lb

set

these

plraneters

and

Q)nm:mds,

the

CPO

writes

them

directly

to

the

NZJC

intemal

registers.

'nle

internal

registers

of

the

ND:

can

be

classified

into

registers

the

CPU

can

read and

write

directly

and

registers

in

which

reaiing

or

writing

is

prohibited.

'nle

registers

which can

be

read

and

written

are

assigned

unique

addresses.

'1tley

are

mapped

in

the

CPU

nent>ry

or

I/O

Splce and

referred

to

as

the

'(X)rrmand/paraneter

table'.

'lbese

registers

are

selected

by

the

lower 8

bits

(OOB

-

FFH)

of

the

address

input

on

MADO

-

MNJ7

to

the

AaX:,

when

CSIR

is

low. '!be

data

to

be

read

or

written

can be

sent

through

the

data

bus

in

the

sane

address

cycle

providing

high speed

comrcand

or

parameter exchange.

The

Ar:D::.

inoorporates

a

preprocessor

for

drawing

preprocessing

and

a drawing

processor

for

the

actual

drawing. '!be drawing

preprocessor

calculates

the

effective

(physical)

address

from

X-Y

cx>ordinates

(logical

address) given

by

the

CPU

and

generates

the

parameters

of

the

micro-level

CX>des

intetpretErl

by

the

drawing

processor.

'!be drawing

preprocessor

decodes

CXI'IItlaMs

and performs

the

drawing

preprocessing

necessary

to

execute

ex>nmmds

in

the

cx>mmmd/

paraneter'table.

It

is

not

necessary

to

write

all

the

paraneters

in

the

oorrm:md/parameter

table.

Cnl.y

the

required

paranetets

for

the

particular

command

need be

written.

Of

the

addresses

OOH

-

FFH

in

the

intemal

register

space,

80H

-

FFH

are

not

presently

used. These

are

reserved

for

future

use.

'!be

register

addresses

OOH-7FH

can be grouped

into

four

categories

as

shown

in

the

following

table.

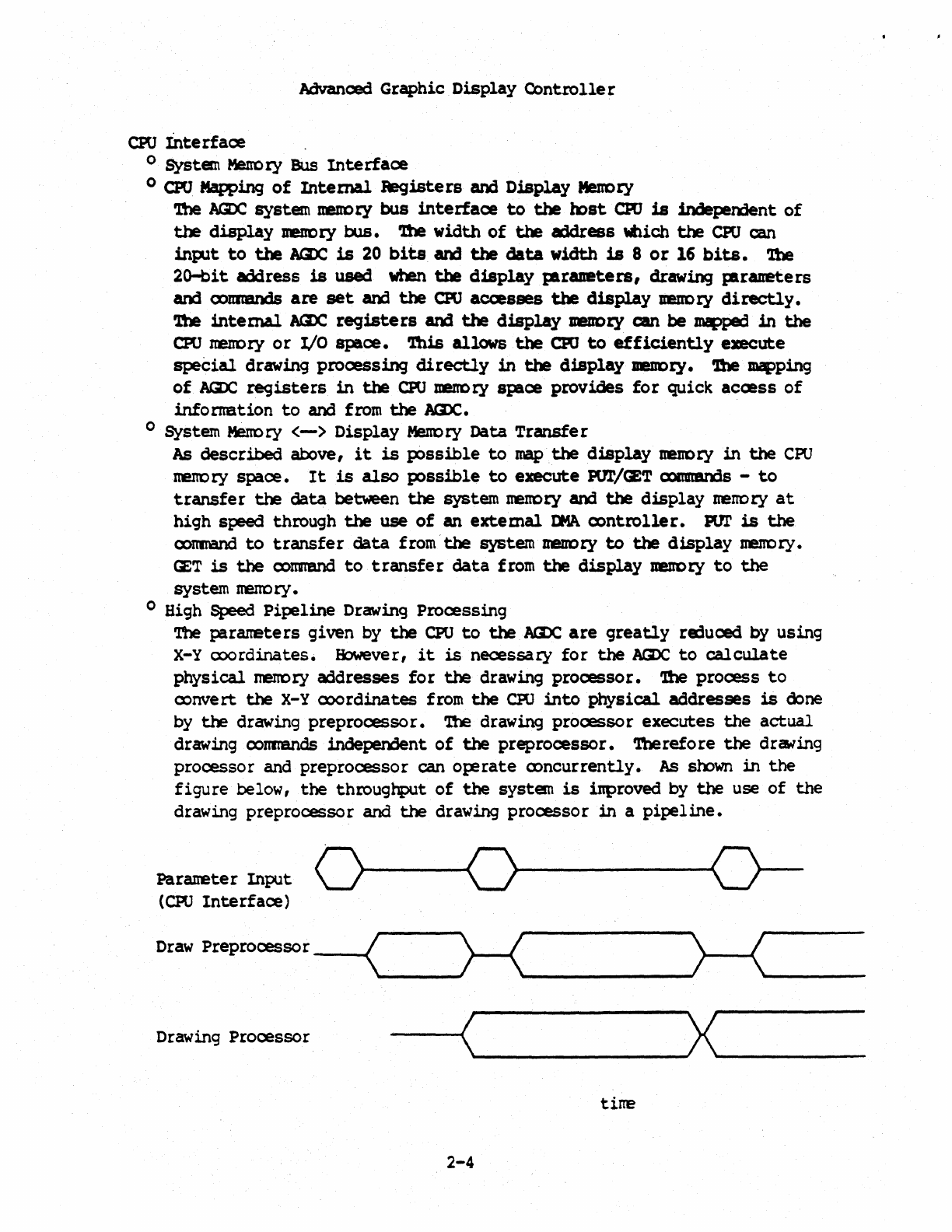

2-5

Advanced Graphic

Display

Controller

I

Classification

Register

Name

Address

CPO

Access

1(1)

1GX:,

oontrol

I

STA'lUS

(Read) I 301 -

30B

I

Read

-

at

any

tine

I I

Cl'RL,

IWt{

(Wr

ite)

I

3aI

-

3DB

I

Write

-

at

any

tine

I (2)

Display

I

DISPLAY

FIAGS

I 708 -

7PH

I R!ad -

inhibited

I

related

I

DISPIAY

PI'lCB I I

Write

at

any time

I

registers

. I

IW>,

le,

AC

I r

I I

OCSRK,GCSRlS

,GCSRVE

I I

I I

CRS,

CE

I I

I I

BS,HBP

,HH,BD,HFP

I I

I I

VS,VBP,I/F,VFP

I I

I (3) Drawing I FAro:£(;, dAIX)R:; I

OOB

-

lFB

Raad

at

any

tim:

related

I tADl,

dADl

I

40B

-

6FH

I

Write

- 3 types

of

registers

I

EAD2,

dAD2

I

hanlshaking

selectable

I PDISPS,

PDISPD

J A.

status

flag

I PI'1':HS,

PlroID

J B. ready

signal

I

PMAX,

MDl

,ftD)()

I C. IN.I'

signal

I

PIANES

I

I

PmP,

P.LN:NI'

I

J

STACK,

S'IMAX

I

I CLIP I

I

XCIlUN,XCI.MAX

I

f

YCl.MIN,

YCIl-W{

I

I

MACH

,l-lAGV

I

I

X,DX,XS,XE,XC,DH

I

I y,DY,yS,YE,yC,OV I

I

CDMMAID

I

I (4)

Data

port

I IlWORr

(during

3EH

-

3FH

I

I I

PUl'/CET

execution)

I I

I I

OX

(during

W.AD

I

44H

-

4sH

I

I I DP/lEAD

CX>L

I I

J I

execution)

I I

N:>te:

The

OX

register

is

used

as

the

logical

address

(.CX)()rdinate)

setting

register

and

at

the

same time

as

the

data

port

during

execution

of

the

READ

OP/WAD

CDL

oorme.nd.

2-6

I

I

I .

I

I

Advanced Graphic Display

Controller

1be

'registers

in

the

first

classification

-srA'lUS,

Cl'RL

and

BAR(

-

are

assigned

address

3CH

-

3DH.

'l!le

oontents

of

the

STA'lUS

register

can

be

reeD

at

any

tine.

'!be

Cl'R[,

and

BARt

registers

can

be

written

to

by

the

CPU

at

any ,

tine.

'!be

registers

in

the

seCX)m

group -

display

related

registem

-

are

assigned

addresses

in

the

range

70B

-7Fa. '!he CDntents

of

these

registers

cannot be

read.

Data

can be

written

to

these

registem

at

any

tine.

Ibweve~,

writing

to

these

registers

can

disturb

the

CRl'

display.

To

prevent

this,

the

display

can

be blanked

while

writing

to

these

registers.

First

set

the

S)

bit

in

the

DISPIAY FlAGS

register

(address 70B-7lB)

to

'1'.

Sea:>nd,

write

the

data

into

the

display

related

register

group.

'!bird,

set

the

SJ

bit

from

'1'

back

to

'0' •

Follow

these

procedures

to

write

data

(SYH:

parametets) such

as

SS,

HBP,

HE,

HO,

HFP,

VS,

VBP

and

!IF

on

the

registers

at

"address

7EH

-

7FB:

1.

Set

the

SYN:

bit

in

the

DISPIAY

FIAGS

register

(70H

-7lH)

to

'1'

2.

Write,

in

the

order

listed,

SS,

BBP,

HH, HO,

BFP,

VS,

VBP,

I/F

AN)

VFP

(address

7EH

-7FH).

3.

Set

the

SYNC

bit

to

'0'

The

registers

in

the

drawing

related

group

are

assigna:i

addresses

from

OOH

to

lFE and

40H

to

6FH.

The

preprocessor

resides

in

this

register

group. '!he

read/write

option

of

these

registers

are:

-aead

The

CPU

can read

the

contents

of

these

reg

is

te

IS

at

any

tine.

The

preprocessor

stops

for

one

clock

while

the

contents

of

a

register

are

read.

-Write

One

of

three

writing

procedures can be used:

1.

Check

the

STA'IUS

register

PPBSY

flag

(~dress

3CH)

2.

Use

the

READY

signal.

3.

Use

the

IN!'

pin

to

signal

an

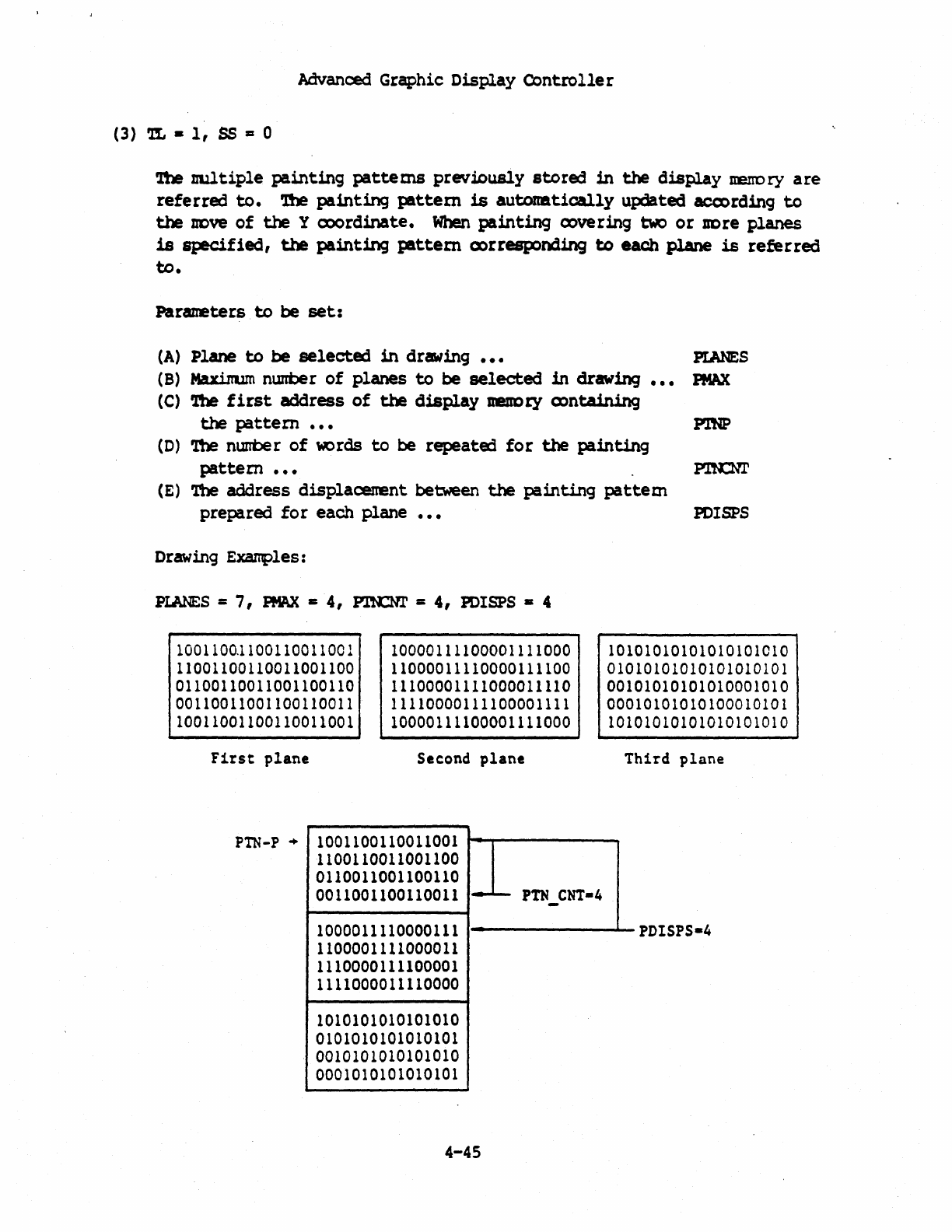

interrupt.

to

the

au

The method

described

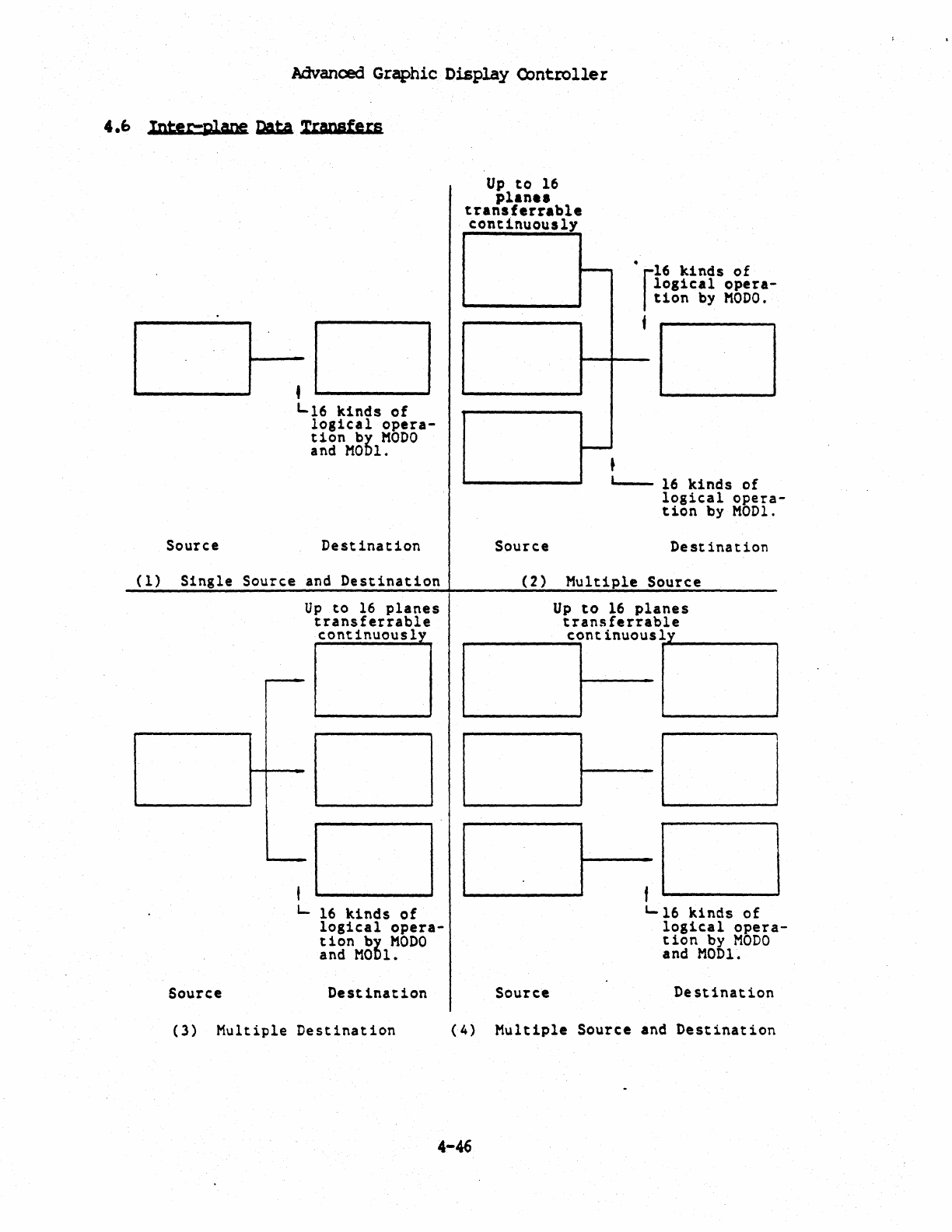

by (1)

is

the

general

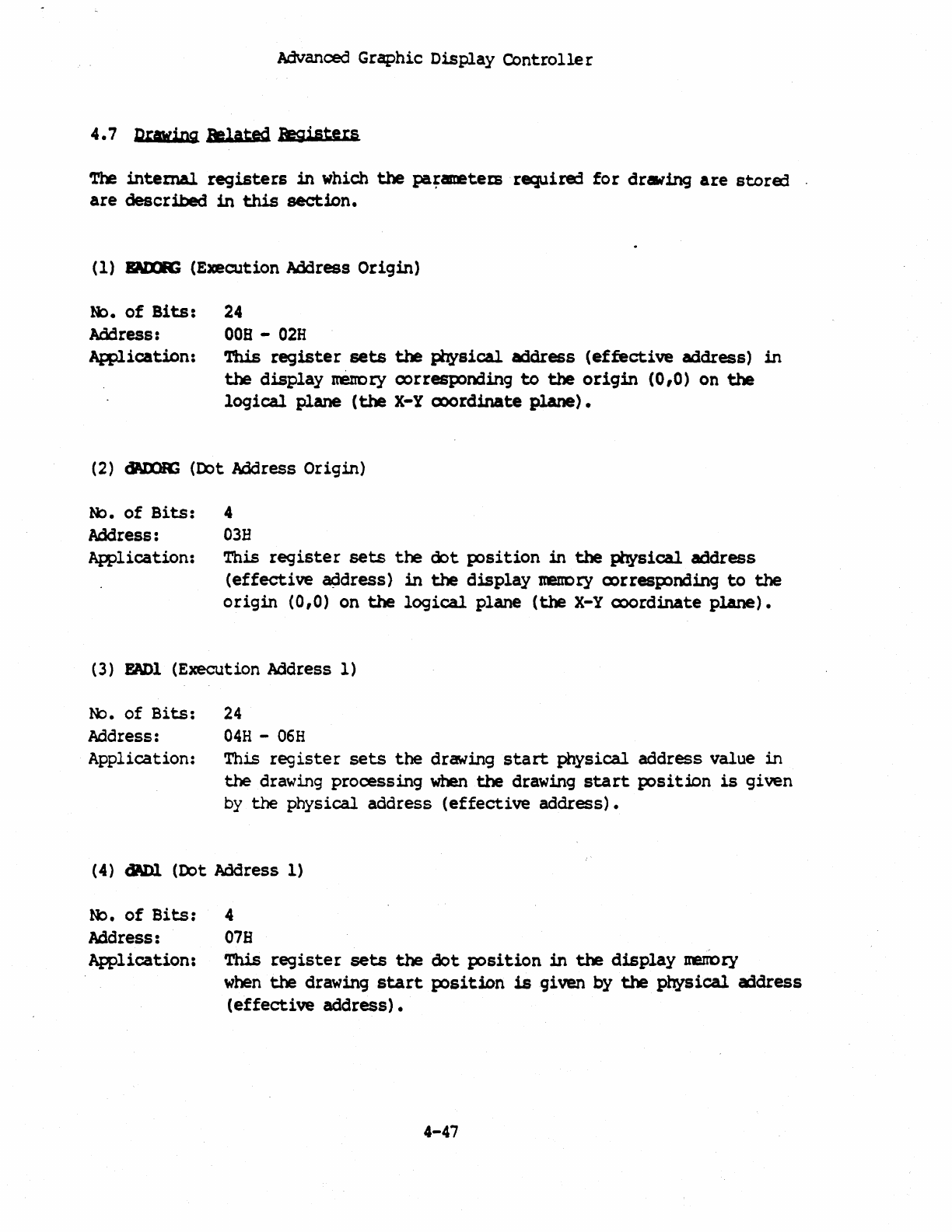

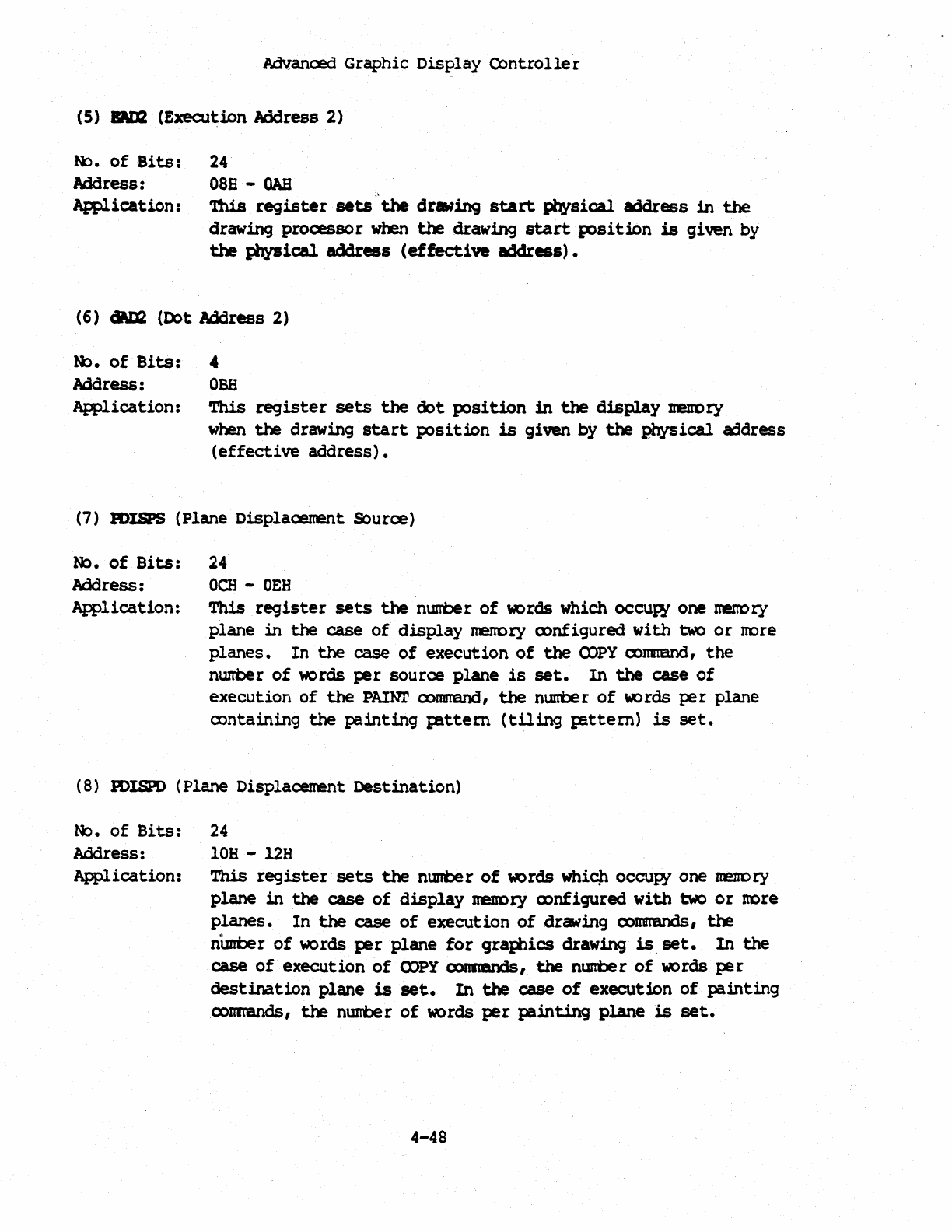

nettOO.

'!he

contents

of

the

status

flag

are

read

to

check

that

the

preprocessor

is

not

in

operation.

If

the

preprocessor

is

not

busy,

then

data

can be

written

to

the

CCIt1lti1!ld/plrarreter

table.

In

the

method

described

by

(2),

the

au

is

tied

to

the

A(])c's

READY

line.

If

the

preprocessor

is

busy,

the

CPU

cannot

write

the

data

until

the

preprocessor

is

finished

and

the

READY

line

goes

high.

This procedure

enables

the

exmmand/pararreter

data

to

be

sent

at

a

higher

speed.

2-7

Advanced Graphic

Display

Controlle

r

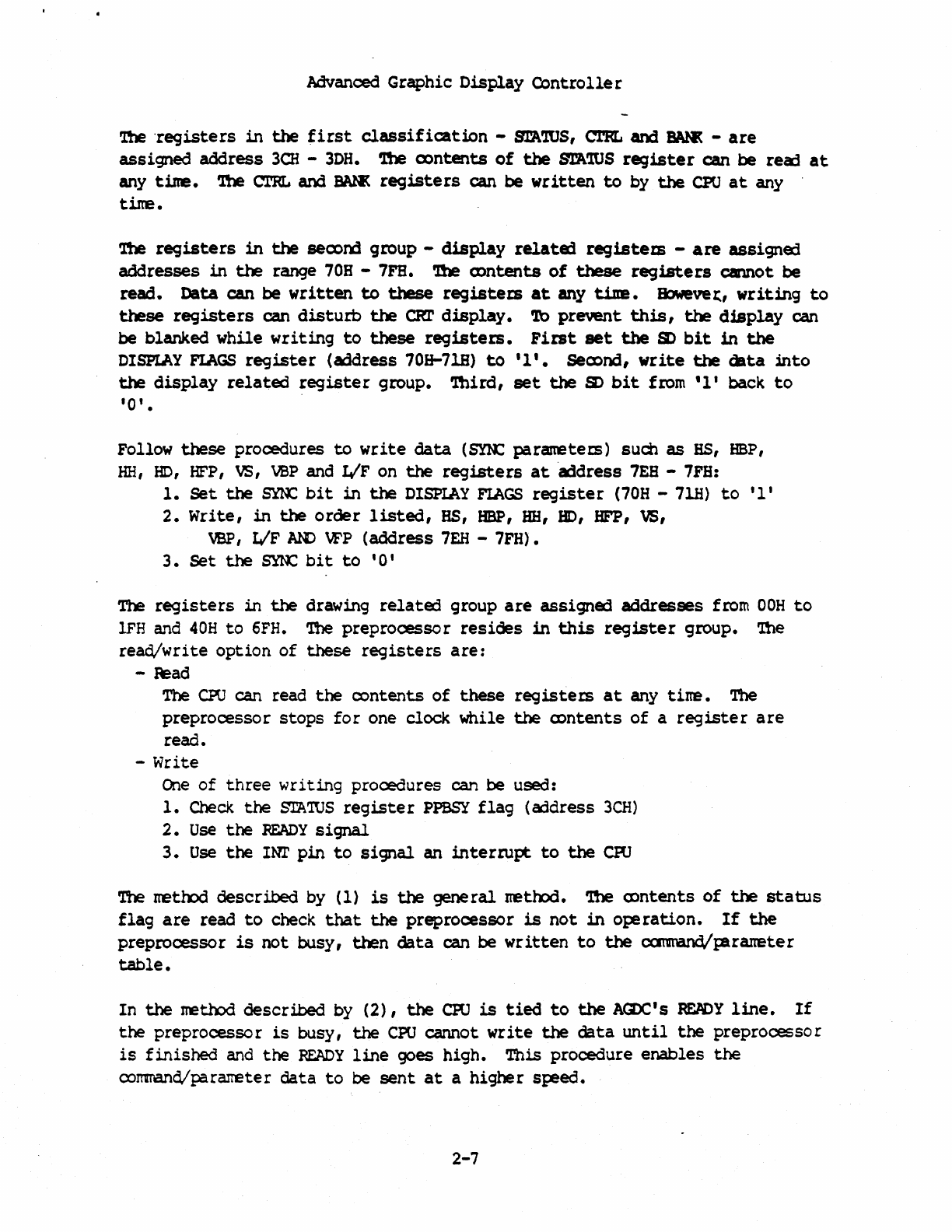

In

the

netb:>d

described

by

(3),

the

CPO

is

interNpted

,by

the

&CDC

when

the

preprocessor

is

available.

'!be

AaX:.,

through

its

IN!'

line,

inforns

the

au

to

send

cxmnand/paraneter

data.

The

CPU

interrupt

routine

srould

send a

CXIr1rt\aOO

and parameters

to

the

NZlC.

'!be'

INl"

line

is

enabled

or

disabled

by

a

flag

in

the

CTRL

register

(address

3OB).

'!be

three

write

meth:>ds

are

lllustrated

below.

Procedure

(A)

•••

Handshake by

the

busy

flag

Procedure

(I)

•••

-Handshake by

the

llEADY

Signal

I

Parameter

I

I

I

para~eter

I

I

YES

The

CPU

is

in

wait

cycle

during

the

execution

of

the

draw1nlpre-process1ng.

Command

Procedure

(C)

••

Handshake by

the

IN!

signal

Main

routine

!he

dra~ing

preprocessing

end

is

informed.

-------,t

r - - - - - - -

Interrupti?n

pl'ocessing

rout

ine

I I

I I

Parameter

I :

I

Parametel'

I :

I

I

Parameter

I

: I

Command

I :

_----L--------------'1 - - - - - - -

.J

MalT;

routine

2-8

Advanced Graphic

Display

Controlle

r

'nle

data

port

register,

~Rr,

is

at

address

3Ea

-3F8. '!he drawing

processor

uses

this

register

during

execution

of

the

drawing

preprocessing.

'1berefore,

to

read/write

this

register,

follow

the

uetb:>d

for

reading

or

writing

the

drawing

prep~ssor.

2.3

BIBt

ADd.

6tQ.G Qgeratioo

The

AfZX:,

resets

0 r

abo

rts

processing

by any

of

the

following

procedures:

-Reset Operation

1.

Set

the

RESET

input

signal

(pin

5)

to

a high

level

(hamware

reset)

2.

Set

the

~SET

flag

in

the

am:,

register

to

'1'

(sofbBre

reset).

-Abort

Operation

3.

Set

the

~RI'.

flag

in

the

CTR[.,

register

to

'1'.

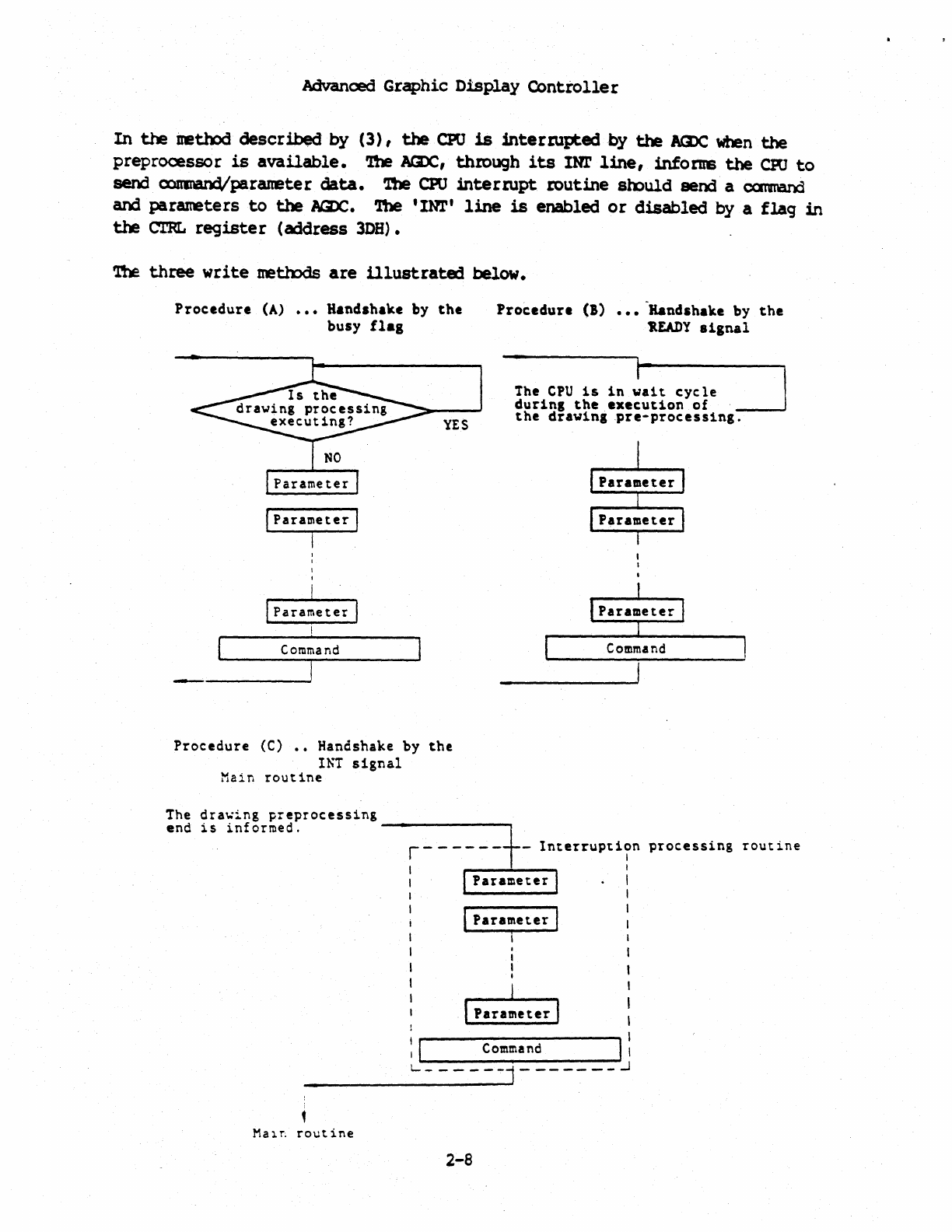

Reset/Abort

Operation

1(1)

Hardware

~set

I

I

I

I

I

I

1(2)

Software

~set

1

I

I

I

(3)

Abort

I

Operation

-

sets

the

display

stop

flag

S)

in

the

DISPIAY

FIAGS

register

(70R -

71B)

to

'1'

-

sets

all

bits

in

the

~

register

(3DH)

to

'0'

-

all

other

registers

maintain

the

same

status

-

stops

the

preprocessor

and

the

drawing

processor

-

initializes

the

video timing

signals

-

stops

the

l.nege nenory

direct

access

-

same

as

the

hardware

reset

but

Cbes

not

set

the

display

stop

flag

in

the

DISPIAY

FLAGS

register

(70H -71H)

to

'1'

and Cbes

not

initialize

the

video timing

signals

I -

all

registers

mintain

their

status

I -

stops

the

preprocessor

and drawing

processor

Advanced

Graphic Display

Controller

2-10

Advanced

Graphic Display Controller

Section

3

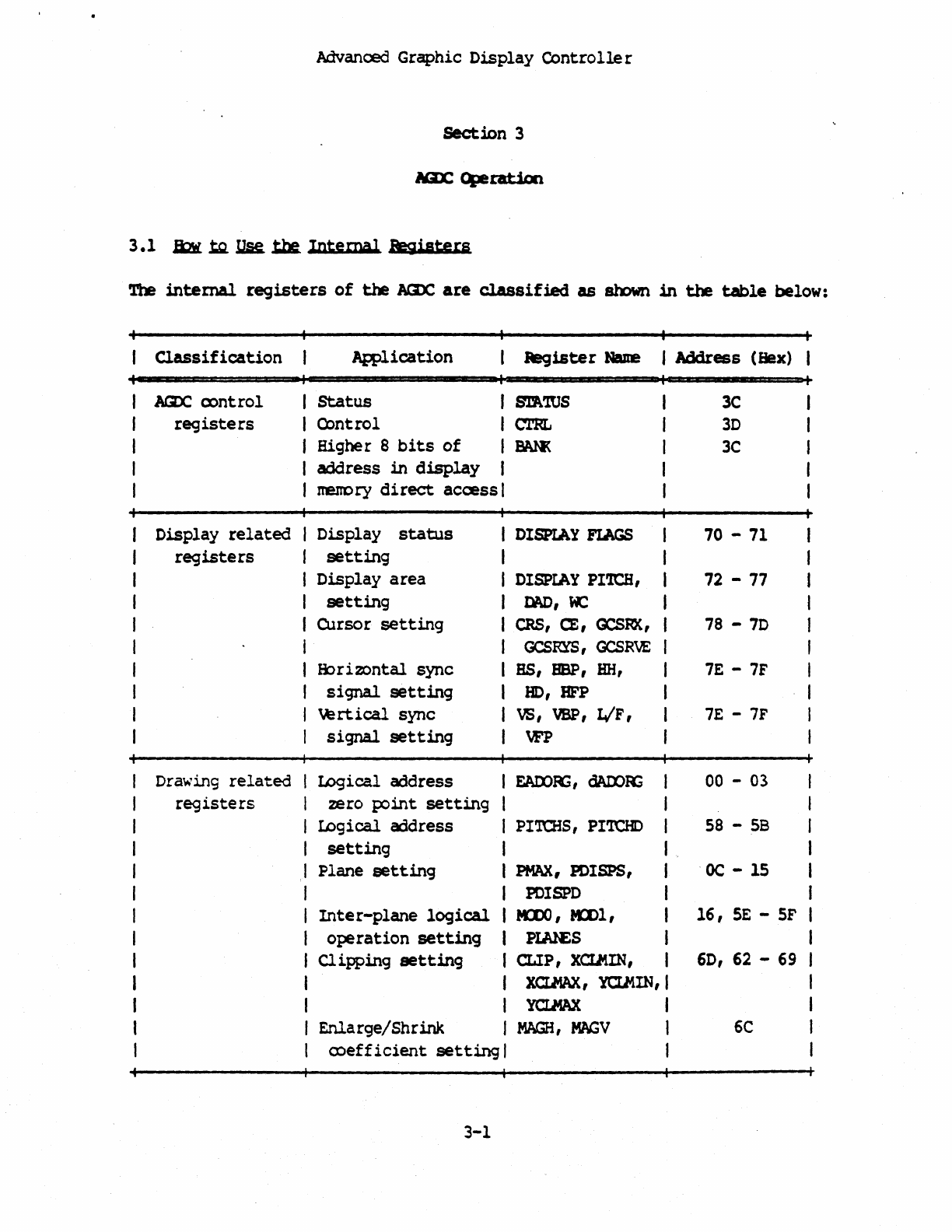

3.1

B14

m

12K

tbl

Intemal

Resisters

The

internal

registers

of

the

laX:

are

classified

as

smwn

in

the

table

below:

Classification

ItfZ'£

c:x>ntrol

registers

Display

related

registers

Dra~'ing

related

registers

AWlication Register

Nue

I Address (Hex)

~t~

I

~~S

I Q)ntrol I

CTRL

I Higher 8

bits

of I

BAR<

I address

in

dis,play I

I

memory

direct

access I

I Display

status

DISPIAY

FlAGS

I

setting

I Display area

DISPIAY

PI'lCH,

I

setting

Dt\D,

lC

I Cursor

setting

CRS,

CE,

GCSRX,

I

GCS~,

GCSRVE

I B:>rizontal sync BS,

BBP,

HH,

I

signal

setting

HO,

BFP

I

~rtical

sync

VS,

VBP,

L/F,

I

signal

setting

VFP

IDgical address I

EAIX)R:2,

dAlX)R:;

zero point

setting

I

wgical

address I

PITCHS,

PITCHD

setting

I

Plane

setting

I

PMAX,

PDISPS,

I

PDISPD

Inter-plane

logical

I KDO,

KDl,

operation

setting

I

PWES

Cl

ipping

setting

I

CLIP,

XCU'lIN,

I

XQIU\X,

YQlt1IN,

I

YCI.HAX

Enlarge/Shr ink I

MAGS,

MAGV

coefficient

setting

I

3-1

3C

3D

3C

70

-

71

72

-

77

78

-

7D

7E

-

7F

7E

-

7F

00 -03

58

-

5B

OC

-

lS

16,

SE

-

SF

6D,

62

-

69

6C

Advanced

Graphic

Display

Controlle

r

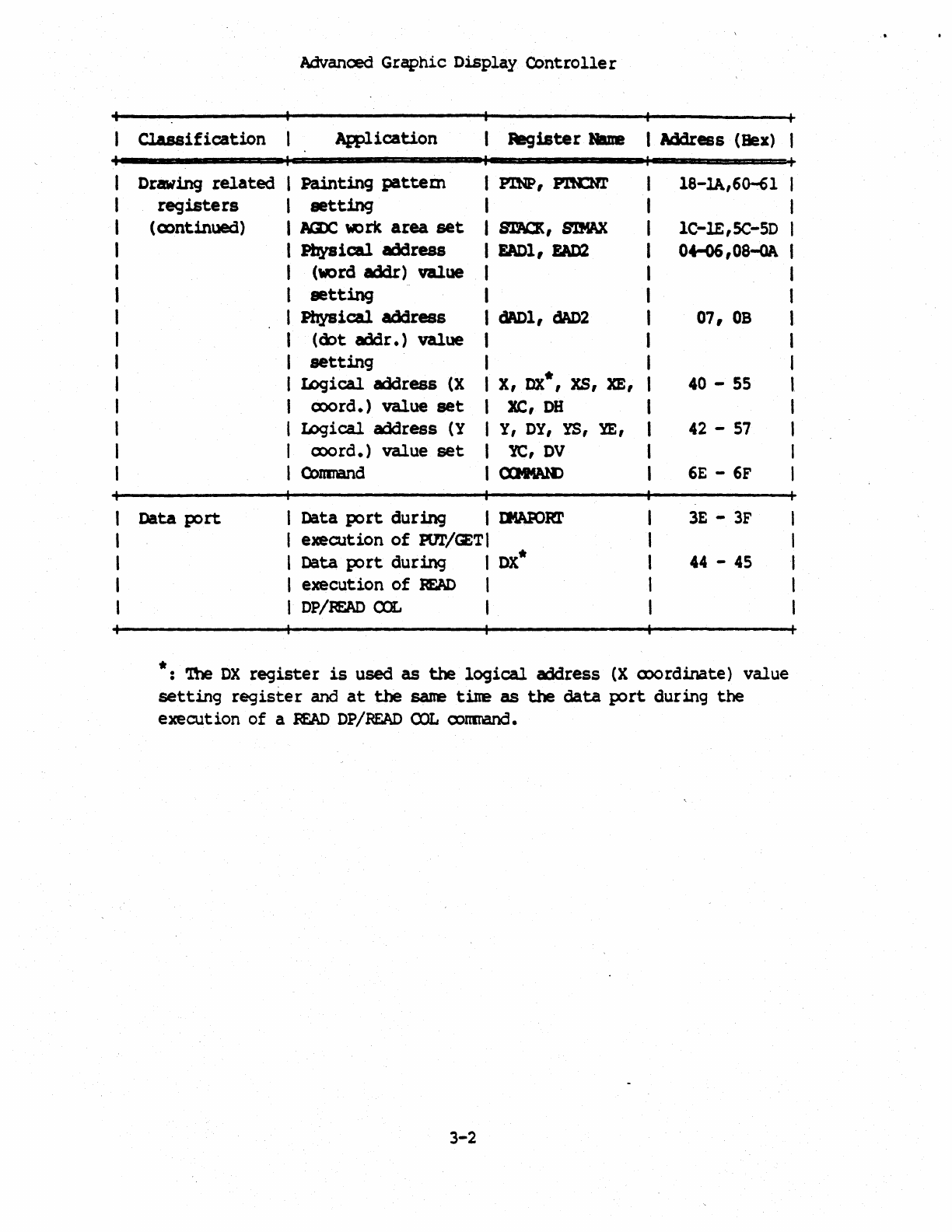

Classification

AJ;plication

Register

NIUIe

I Address (Hex)

Drawing

related

Painting

pattem

I PlNP, PnCN.r 18-lA,6G-61

registers

setting

(

mntinued)

JaY:,

work

area

set

sma,

S'l'MAX

le-lE,SC-50

Pbysical

address

IADl,

EAD2

04-06,OS-oA

(word

addr)

value

setting

Physical

address

dADl,

dAD2

07,

OB

(mt

addr.)

value

setting

IDgical

address

(X

*

X,

DX

, XS,

D,

40

-

S5

coord.)

value

set

XC,

DB

IDgica.l

address

(Y

Y,

DY,

YS,

YE,

42

-

57

cx>ord.)

value

set

!C,

DV

Conrnand

CD1MAN)

6E

-

6F

I

Data

port

I Data

port

during

IIJWORl'

3E

-

3F

I

execution

of

Pt1l'/GET

I

I

Data

port

during

IOX*

44

-

45

I

execution

of

READ

I

I

OP/H:.AD

CXL

I

*:

'!be

DX

register

is

used as

the

logical

address

(X

coordinate)

value

setting

register

and

at

the

saIre

tine

as

the

data

port

during

the

execution

of

a

m'AD

OP/READ

CXlL

oonrrand.

3-2

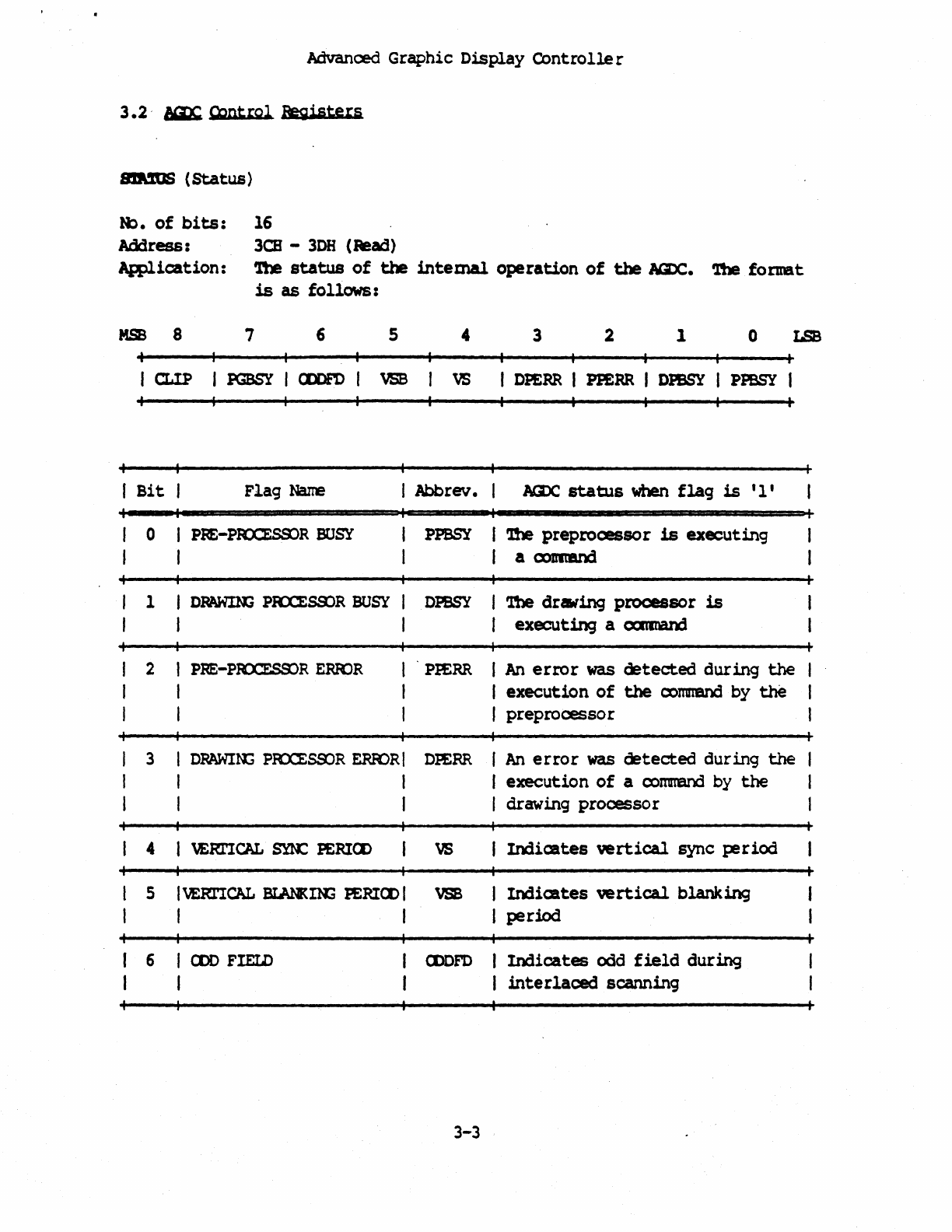

Advanced

Graphic

Dis~ay

Controller

3.2-

~

Qlntrol

Registers

BJUUS

(Status)

H:>.

of

bits:

16

Address:

3CB

-

30B

(Read)

ARUication:

'lhe

status

of

the

intemal

operation

of

the

1aX:,.

'!be format

is

as

follows:

MSB

8 7 6 5 4 3 2 1 o

LSB

I

CUP

I

PGBSY

I cmFD I

VSB

vs

I

DPERR

I

PPERR

I

DPBSY

I

PPBSY

I

I

Bit

Flag

Narre

I Abbrev. AmC

status

when

flag

is

'l'

0 I PF£-PR:Q8&)R

BOSY

PPBSY

I

1M

preprocessor

is

executing

I I a

COJIItIU'X3

1 I

DRAWm:;

PRXESS:>R

BUSY

I

OPBSY

I

1be

drwing

processor

is

I I I

executing

a

CX'IIIDal'd

2 I

PRE-PlO:!ES&:>R

ERR:>R

PI£RR I

An

error

was

detected

during

the

I I

execution

of

the

oomnand

by

the

I I preprooesso r

3 I

OPAWIN3

PRX'ESSOR

ERK>RI

DI£RR I

An

error

was

detected

during

the

I I I

execution

of

a

co~

by

the

I I I drawing

processor

4 I

VERI'ICAL

sm: PERIa>

VS

Indicates

vertical

sync

period

5 I

VERl'ICAL

BIAtl{nt;

PERICD

I

VSB

I

Indicates

vertical

blanking

I I I period

6 I

CDD

FIEID

CDDFD

Indicates

odd

field

during

I

interlaced

scanning

3-3

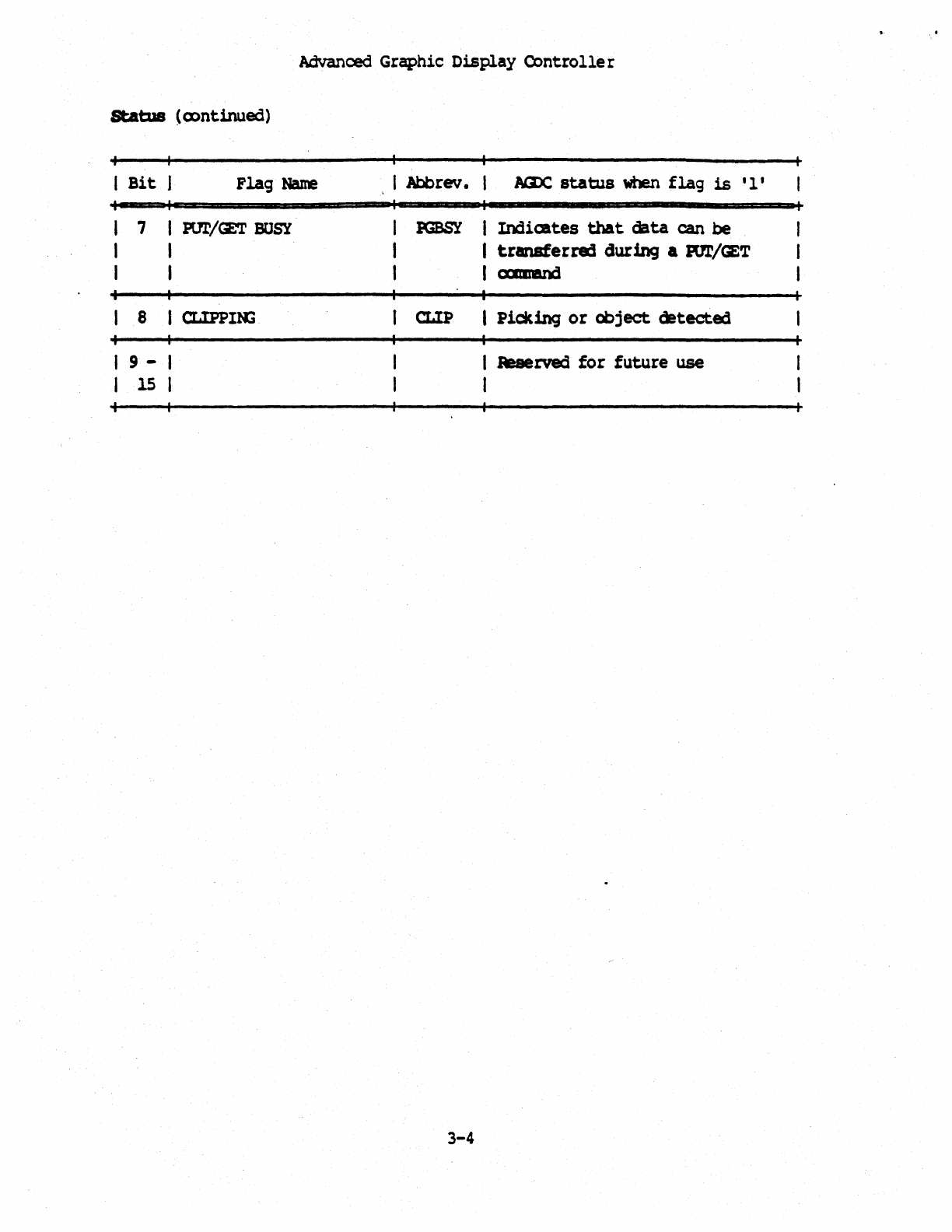

Advanced

Gr~hic

Dis~ay

Controller

Status

(cx:>ntinued)

1

Bit

J

Flag

Name

7 I PUr/GET

BUSY

I

I

8 1 CUPPIK;

19-1

I lS I

I

Abbrev.

NZX:.

status

when

flag

is

'1'

PGBSY

I

Indicates

that

data

can

be

I

transferra:i

during a

POT/CZT

I

CDIIIBnd

CUP

I

Picking

or

object

detected

3-4

I Reserved

for

future

use

I

, .

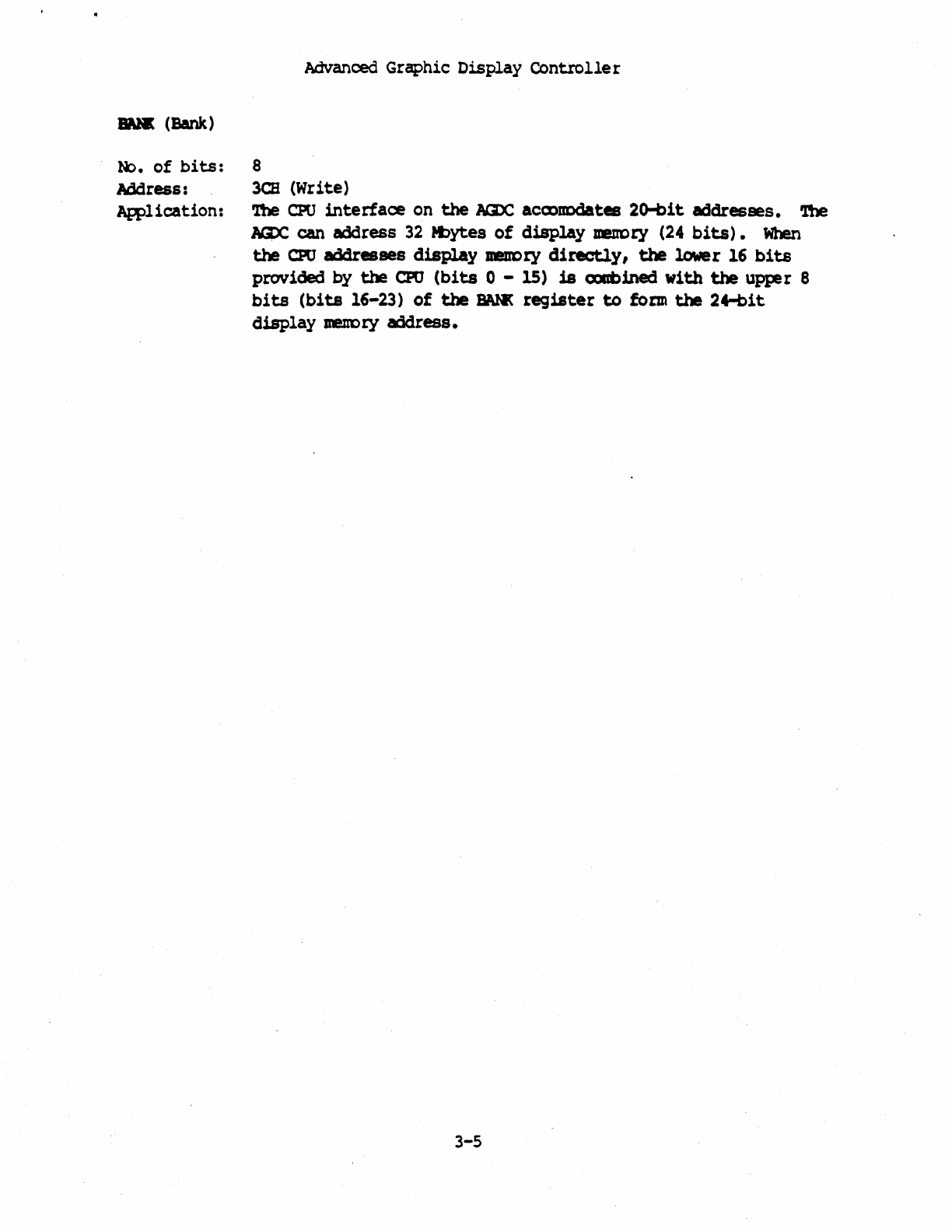

..

(Bank)

1t>.

of

bits:

Address:

AWlication:

Advanced Graphic

Display

Control

Ie

r

8

3CB

(Write)

'!be

CPU

interface on

the

AaX: acmDDdates

2o-bit

addresses.

'!be

~

can address 32

!bytes

of

display

meuDty (24

bits).

When

the

CPO

addresses

display

Jl8Dl)ty

directly,

the

lower 16

bits

provided

by

the

CPO

(bits

0 - 15)

is

CDlbJ.ned

with

the

upper

8

bits

(bits

16-23)

of

the

IW«

register

to

form

the

2..oit

display

JDeltDty address.

3-5

Advanced Graphic Display

Controlle

r

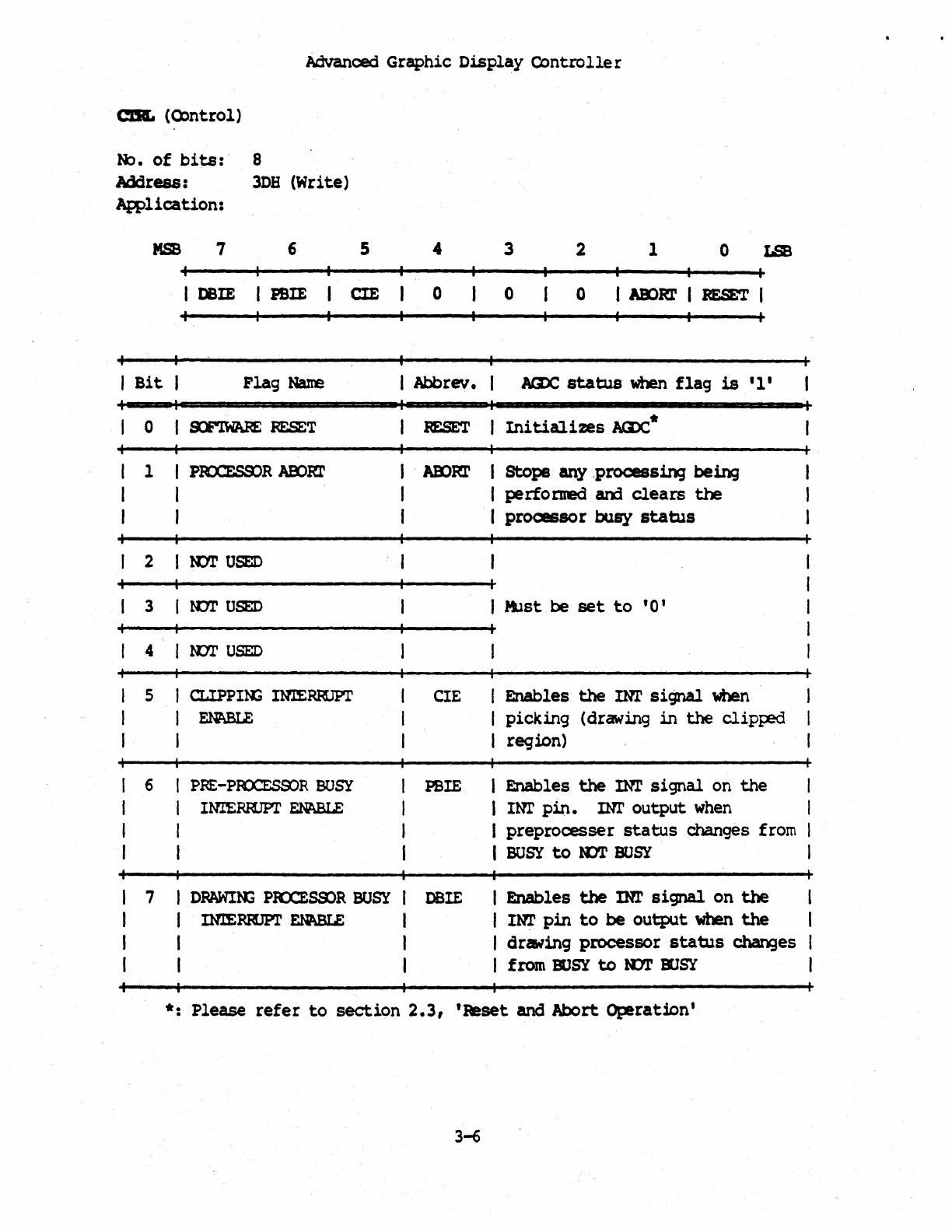

am. (OJntrol)

N::>.

of

bits:·

8

Address:

3DB

(Write)

AWlication:

MSB

7 6 5 3 2 1 o

LSB

I

DBlE

I PSIE

em

o o o I

ABlR1'

I

RESET

I

I

Bit

I

Flag

Na%re

I

Abbrev.

laX:.

status

when

flag

is

'1'

o I

s:FlWARE

RESET

1 I

P~R

AB:>Rl'

I

I

2 I N:n'

USED

3 I

N:Yr

USED

4 I

KYl'

USED

5 J CLIPPIt{'; INlERRJPr

I

EN1\BLE

I

6

PRE-PRXESOOR

BUSY

INrERRJPL'

EN1\BLE

Initializes

~*

AEDRl'

I Stope any ,processing

being

I performed

am

clears

the

I

processor

busy

status

I MJst

be

set

to

'0'

CIE I Enables

the

INI'

signal

trilen

I

picking

(drawing

in

the

clip~

I region)

PBIE I

Enables

the

INI'

signal

on

the

I IN!'

pin.

IN!'

output

when

I

preprocesser

status

changes from I

I

BUSY

to

RJI'

BUSY

I

7 I

DRAWIN:;

PRX:ESSOR

BUSY

I

OBIE

I Enables

the

IN!'

signal

on

the

I

Im'

pin

to

be

output

when

the

I INlERRJPr

EN1\BLE

I

I I

I I I drlWing

processor

status

chan3es

I from

BOSY

to

lCl'

ElJSY

*:

Please

refer

to

section

2.3,

'Reset

and Abort

Operation'

3-6

Advanced Graphic Display

Controlle

r

,

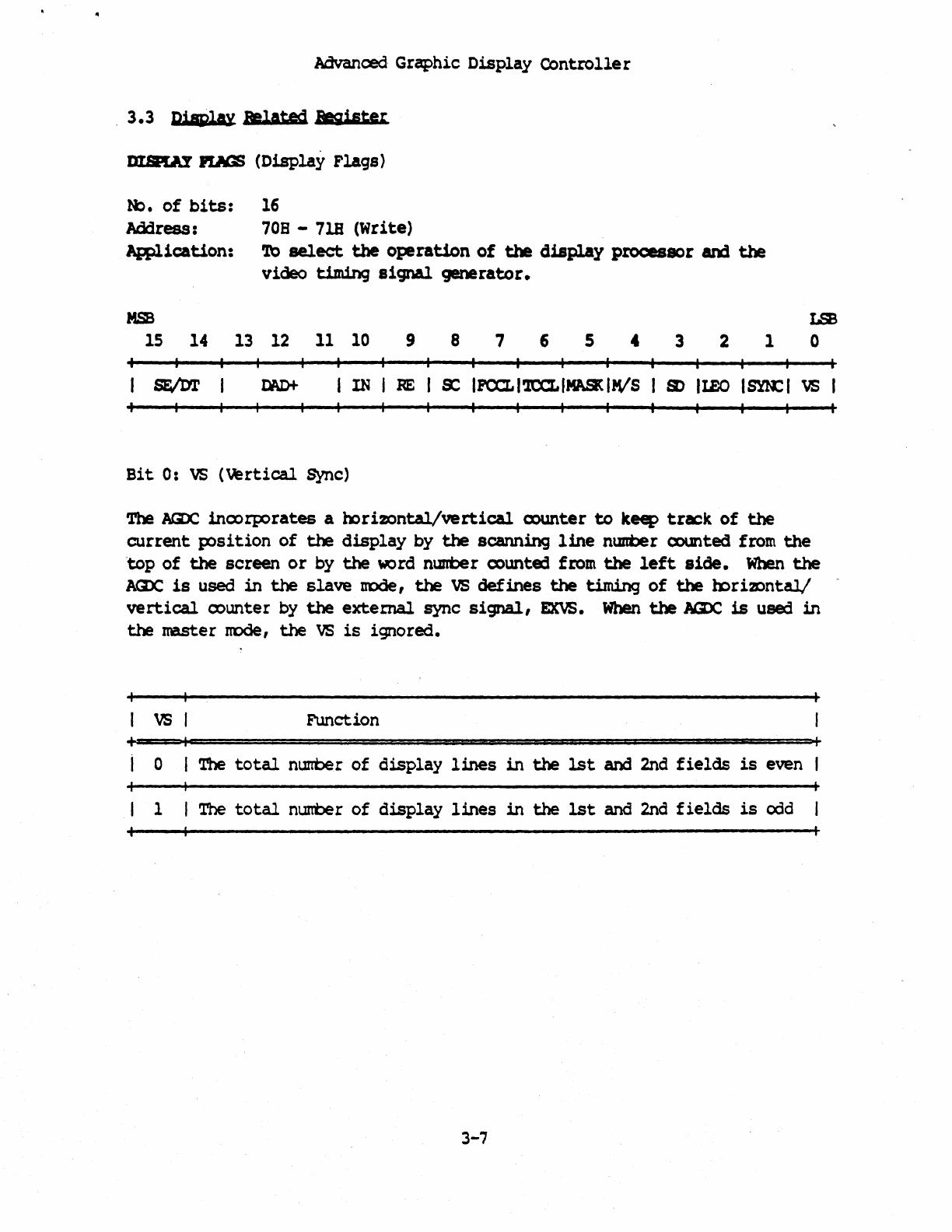

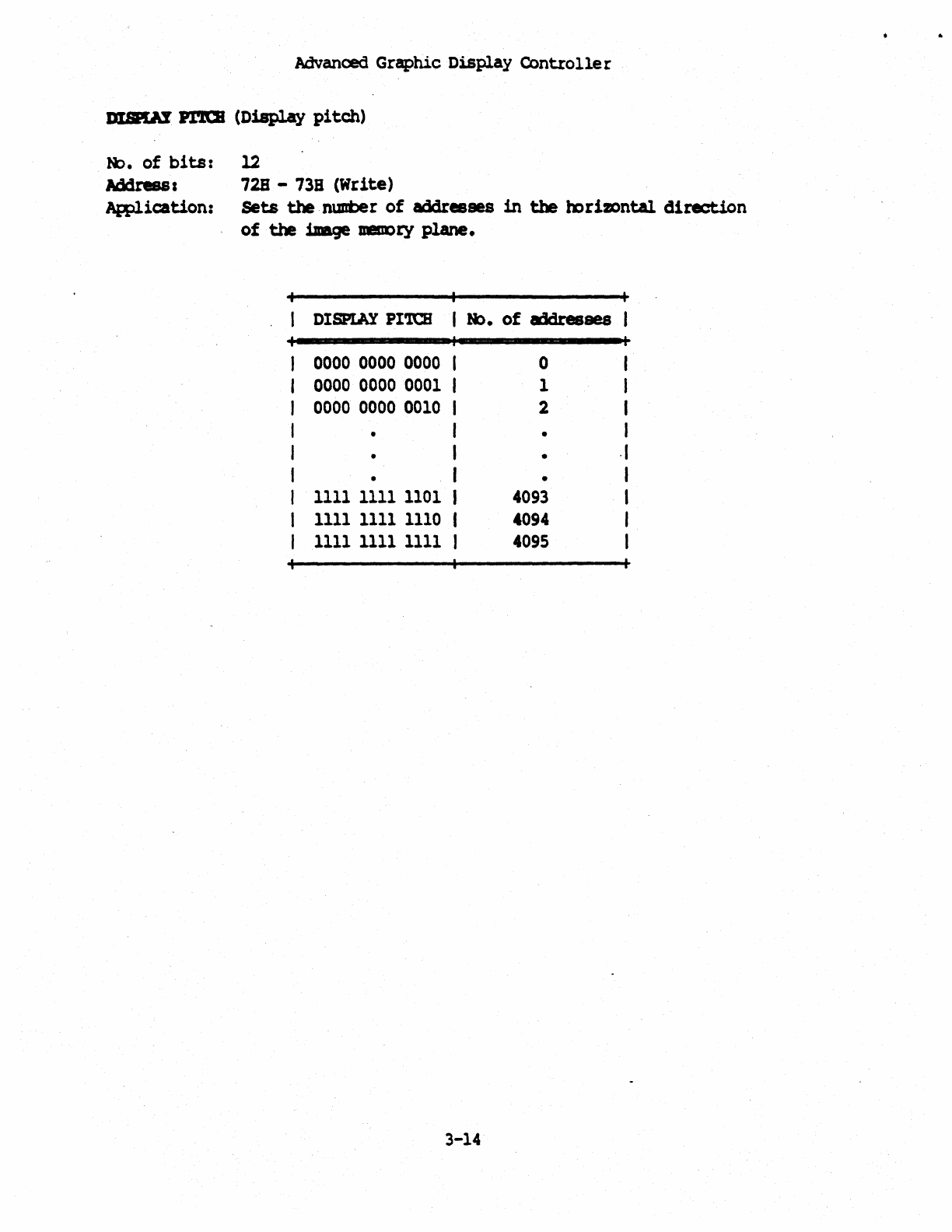

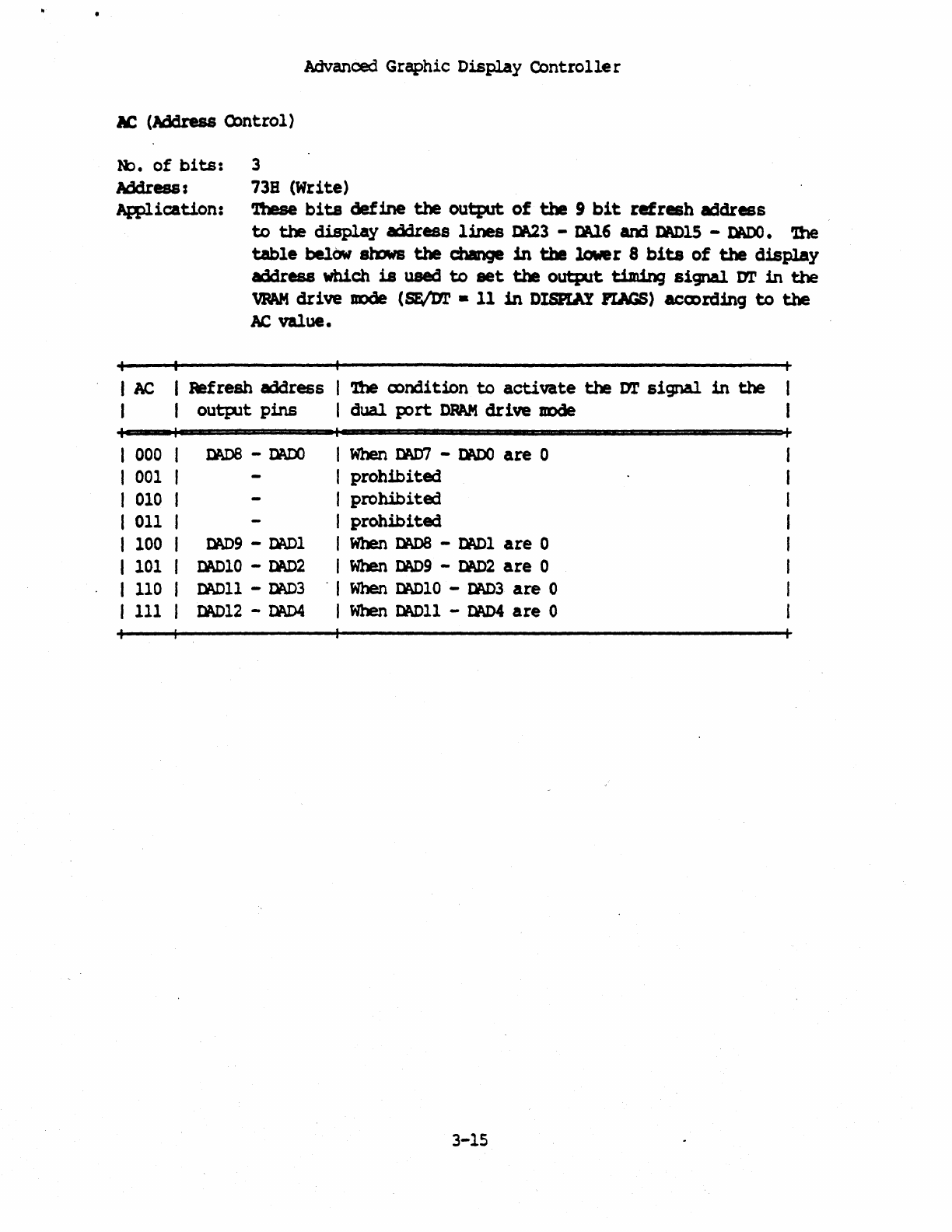

3.3

D!§glay

Belated

legiste

r

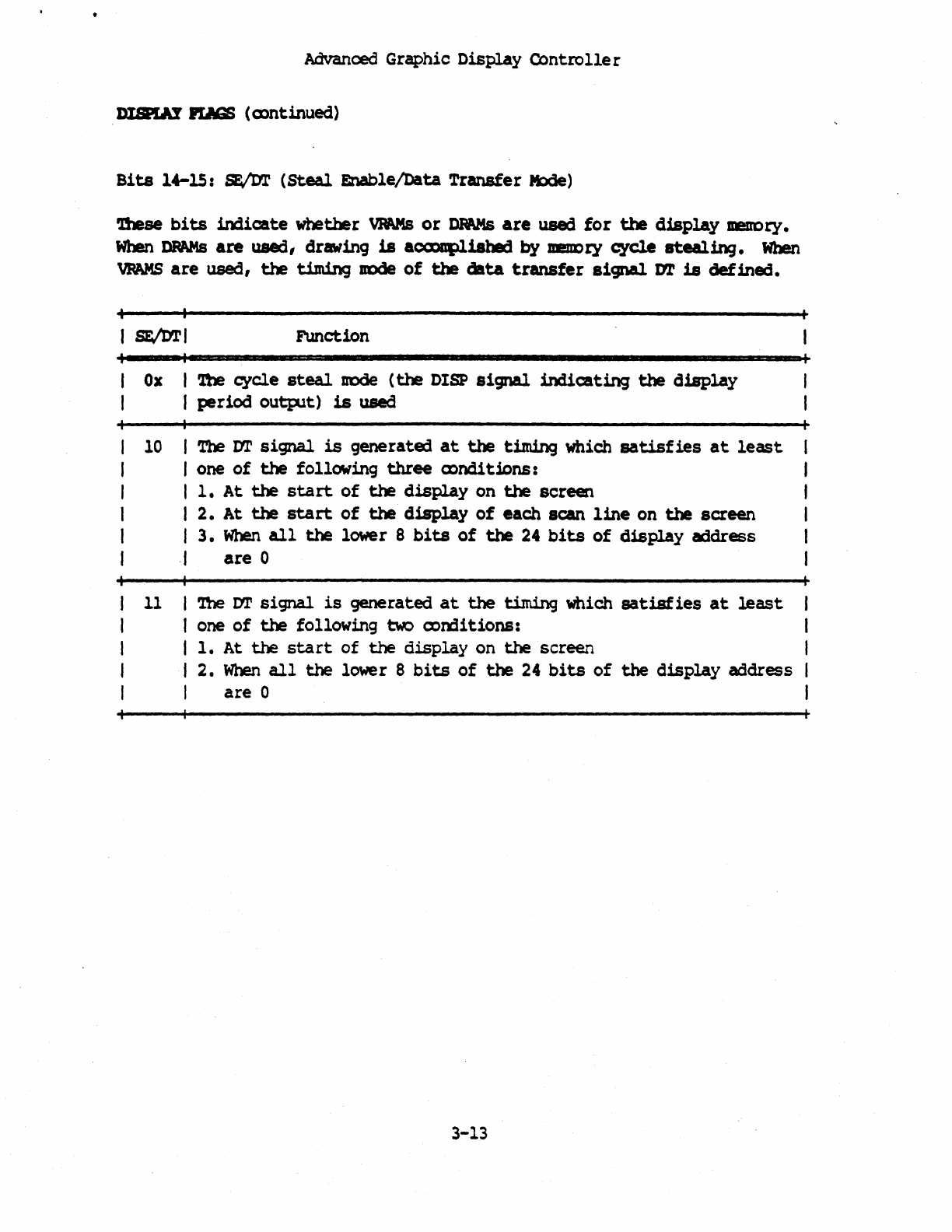

DISRAY

PUtGS

(Display

Flags>

~.

of

bits:

16

Address:

70B

-7lB (Write)

Application:

'1b

select

the

operation

of

the

display

processor

am

the

video

timing

signal

generator.

MSB

IS

14

13

12

11

10

9 8 7 6 5 4 3 2 1

LSB

o

I

SF/M

I IN

RE

s:

IPO:LI'ltCLIMASKlrvs

I

S)

IIEO

Ism:

I

VS

Bit

0:

VS

(vertical

Sync)

The

laX,

inoorporates

a

horizontal/vertical

CX)Ul\ter

to

keep

track

of

the

current

position

of

the

display

by

the

scanning

line

nlmber

ex>unted

from

the

'top

of

the

screen

or

by

the

word nurrber oounted from

the

left

side.

When

the

Aax:.

is

used

in

the

slave

node,

the

VS

defines

the

timing

of

the

h::>ri2Dntal/

vertical

oounter

by

the

external

sync

signal,

EKVS.

When

the

AGX:,

is

used

in

the

master

node,

the

VS

is

ignored.

vs

Function

+ o I

The

total

nurrber

of

display

lines

in

the

1st

and 2nd

fields

is

even

1 I

The

total

nurrber

of

display

lines

in

the

1st

and 2nd

fields

is

odd

3-7

Advanced

Graphic

Display

Controlle

r

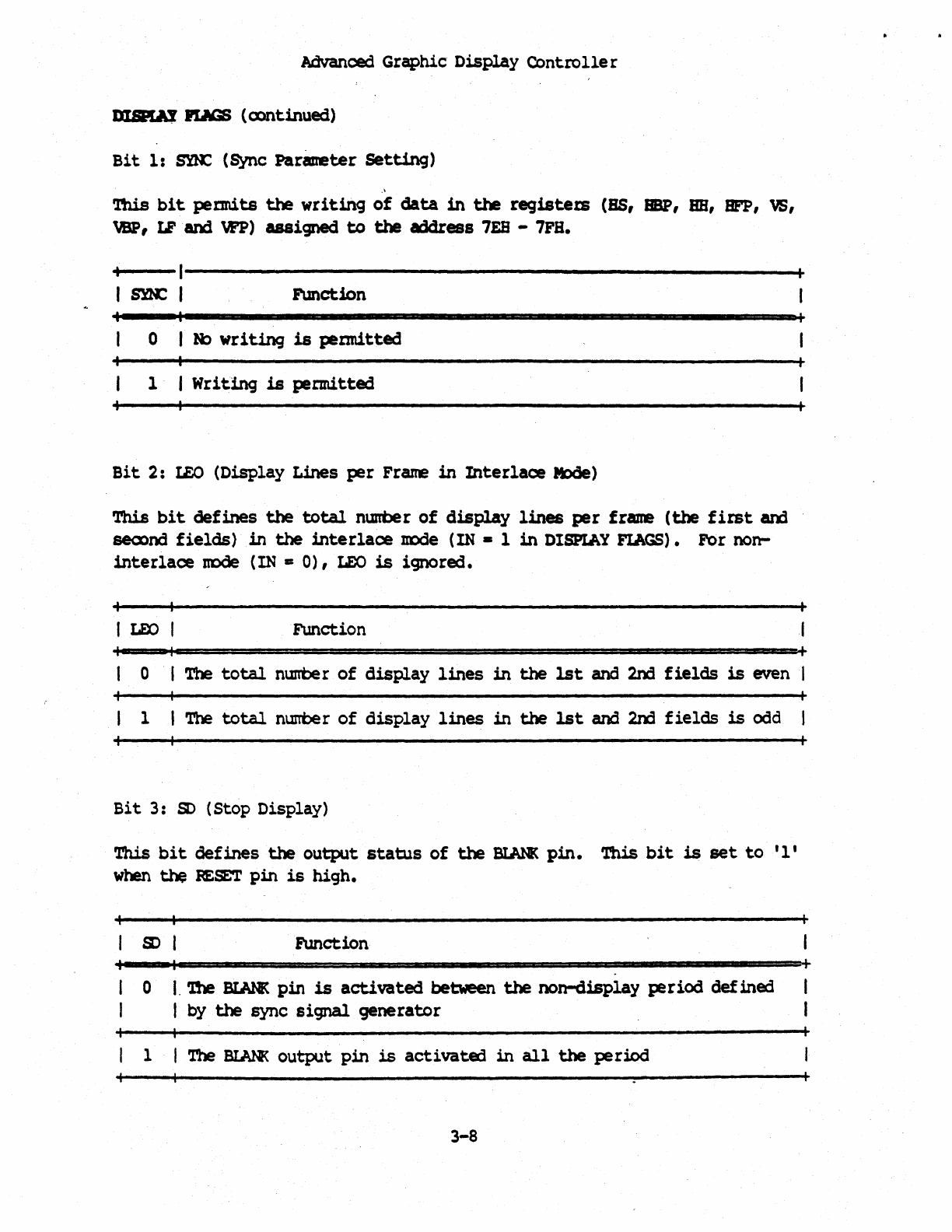

IJISIIAl

IUIGS

(CX)Ot1nued)

Bit

1:

sm: (Sync

Par_ter

Setting)

,\

'Ibis

bit

permits

the

writing

of

data

in

the

registem

(SS,

BBP,

RB,

BFP,

VS,

VBP,

LF

'and

VPP)

assigned

to

the

address

7EB

-

7FH.

+----1----------------------------------------------------+

I~I

Function

o

l!b

writing

is

pennitted

1 I Writ.ing

is

permitted

Bit

2:

LEO

(Display

Lines

per

Frame

in

Interlace

It>de)

This

bit

defines

the

total

nurrber

of

display

lines

per

frame

(the

first

arx1

seoond

fields)

in

the

interlace

DDde

(IN • 1

in

DISPIAY FlAGS). For non-

interlace

node

(IN

=

0),

LEO

is

ignored.

I

LEX>

I Function

o I The

total

nurrbe r

of

display

lines

in

the

1st

and 2nd

fields

is

even

1 I

The

total

nurrbe r

of

display

lines

in

the

1st

and 200

fields

is

cx1d

Bit

3:

SO

(Stop Display)

This

bit

defines

the

output

status

of

the

BlANK

pin.

'1'his

bit

is

set

to

'1'

when

the

~SET

pin

is

high.

Function

o

I.

'lb!

BlANK

pin

is

activated

between

the

non-display

period

defined

I

by

the

sync signal.

generator

1 I The BI.MI<

output

pin

is

activated

in

all

the

period

3-8

Advanced Graphic

Display

Controller

DUHAY

JUGS

(continued)

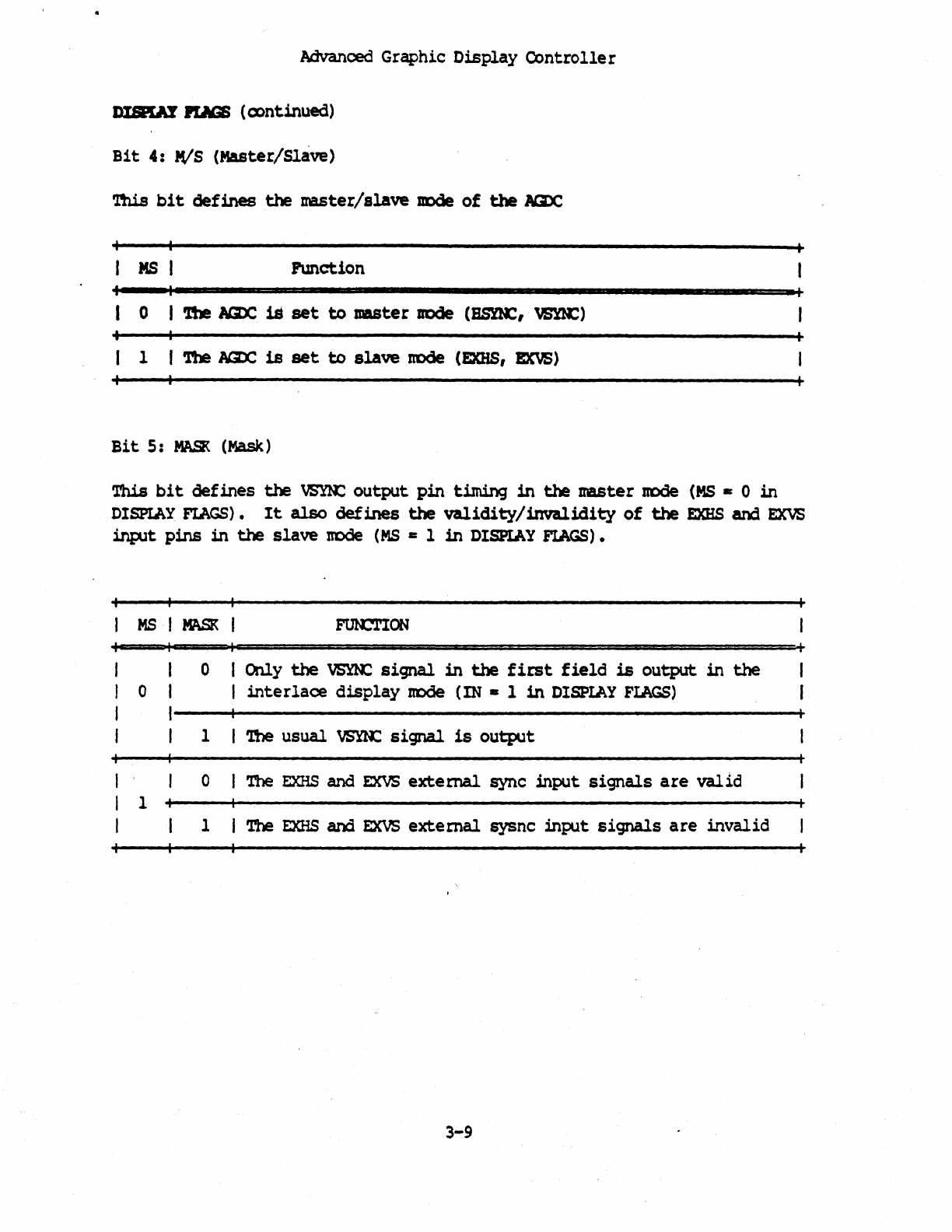

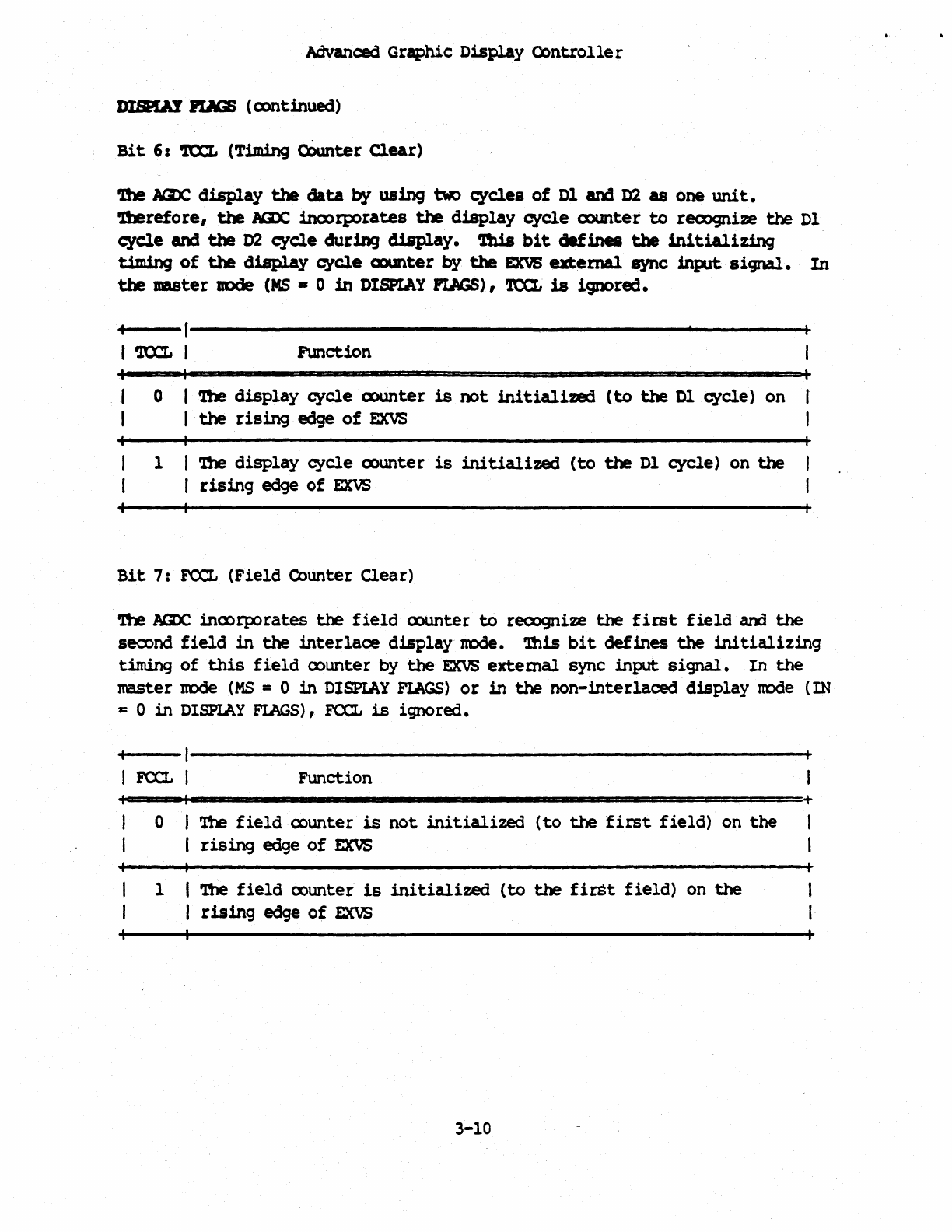

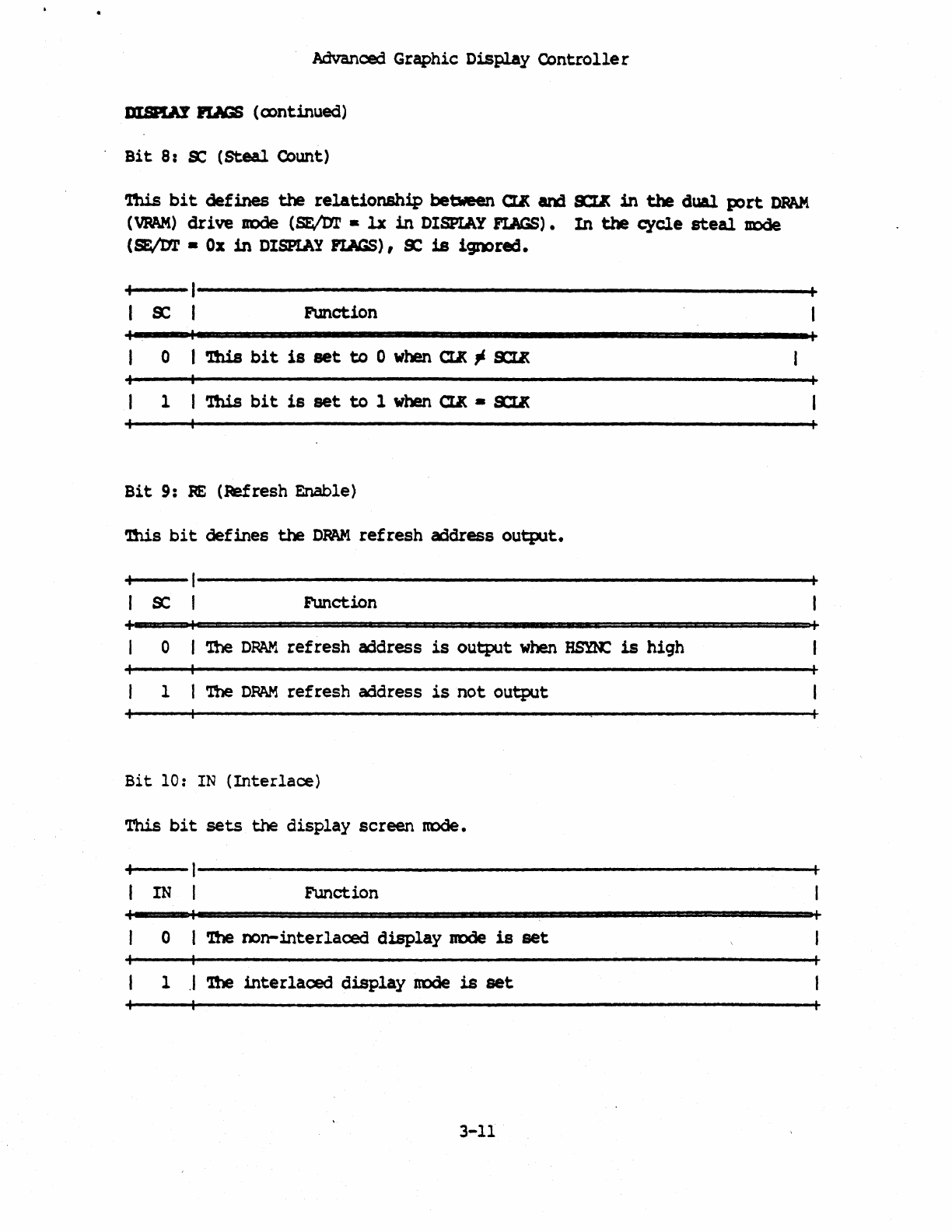

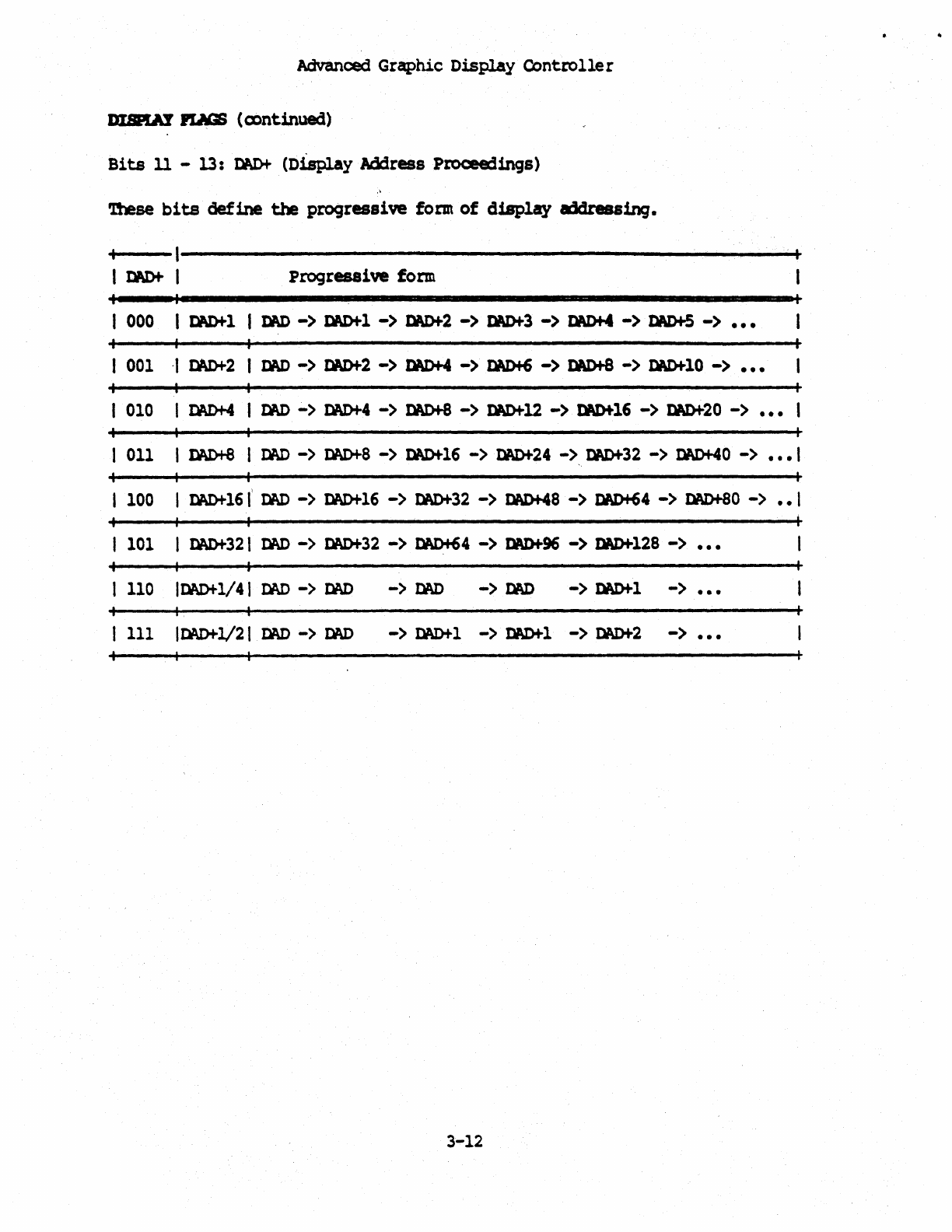

Bit

4:

MIS

(Master/Slave)

'l'his

bit

defines

the

master/slave

DDde

of

the

AGX

MS

Fwlction

o I

1be

NZJ;

is