Mentor Fastscan And Flex V8 6 4 Users Manual Reference

v8.6_4 to the manual 23e67613-2cad-48a6-9421-b3f3bb35edef

2015-02-09

: Mentor Mentor-Fastscan-And-Flex-V8-6-4-Users-Manual-554915 mentor-fastscan-and-flex-v8-6-4-users-manual-554915 mentor pdf

Open the PDF directly: View PDF ![]() .

.

Page Count: 831 [warning: Documents this large are best viewed by clicking the View PDF Link!]

- Bookcase

- TABLE OF CONTENTS

- LIST OF FIGURES

- LIST OF TABLES

- About This Manual

- Chapter 1 Introduction

- Chapter 2 Command Dictionary

- Command Summary

- Command Descriptions

- Abort Interrupted Process

- Add Ambiguous Paths

- Add Atpg Constraints

- Add Atpg Functions

- Add Capture Handling

- Add Cell Constraints

- Add Cell Library

- Add Clocks

- Add Cone Blocks

- Add Control Points

- Add Display Instances

- Add Display Loop

- Add Display Path

- Add Display Scanpath

- Add Faults

- Add Iddq Constraints

- Add Initial States

- Add LFSR Connections

- Add LFSR Taps

- Add LFSRs

- Add Lists

- Add Mos Direction

- Add Net Property

- Add Nofaults

- Add Nonscan Handling

- Add Notest Points

- Add Observe Points

- Add Output Masks

- Add Pin Constraints

- Add Pin Equivalences

- Add Pin Strobes

- Add Primary Inputs

- Add Primary Outputs

- Add Random Weights

- Add Read Controls

- Add Scan Chains

- Add Scan Groups

- Add Scan Instances

- Add Scan Models

- Add Slow Pad

- Add Tied Signals

- Add Write Controls

- Analyze Atpg Constraints

- Analyze Bus

- Analyze Control

- Analyze Control Signals

- Analyze Drc Violation

- Analyze Fault

- Analyze Observe

- Analyze Race

- Analyze Restrictions

- Close Schematic Viewer

- Compress Patterns

- Create Initialization Patterns

- Create Patterns

- Delete Atpg Constraints

- Delete Atpg Functions

- Delete Capture Handling

- Delete Cell Constraints

- Delete Clocks

- Delete Cone Blocks

- Delete Control Points

- Delete Display Instances

- Delete Faults

- Delete Iddq Constraints

- Delete Initial States

- Delete LFSR Connections

- Delete LFSR Taps

- Delete LFSRs

- Delete Lists

- Delete Mos Direction

- Delete Net Property

- Delete Nofaults

- Delete Nonscan Handling

- Delete Notest Points

- Delete Observe Points

- Delete Output Masks

- Delete Paths

- Delete Pin Constraints

- Delete Pin Equivalences

- Delete Pin Strobes

- Delete Primary Inputs

- Delete Primary Outputs

- Delete Random Weights

- Delete Read Controls

- Delete Scan Chains

- Delete Scan Groups

- Delete Scan Instances

- Delete Scan Models

- Delete Slow Pad

- Delete Tied Signals

- Delete Write Controls

- Diagnose Failures

- Dofile

- Exit

- Extract Subckts

- Flatten Model

- Flatten Subckt

- Help

- Insert Testability

- Load Faults

- Load Paths

- Macrotest

- Mark

- Open Schematic Viewer

- Read Modelfile

- Read Procfile

- Read Subckts Library

- Redo Display

- Report Aborted Faults

- Report Atpg Constraints

- Report Atpg Functions

- Report AU Faults

- Report Bus Data

- Report Capture Handling

- Report Cell Constraints

- Report Clocks

- Report Cone Blocks

- Report Control Data

- Report Control Points

- Report Core Memory

- Report Display Instances

- Report Drc Rules

- Report Environment

- Report Failures

- Report Faults

- Report Feedback Paths

- Report Flatten Rules

- Report Gates

- Report Hosts

- Report Id Stamp

- Report Iddq Constraints

- Report Initial States

- Report LFSR Connections

- Report LFSRs

- Report Lists

- Report Loops

- Report Mos Direction

- Report Net Properties

- Report Nofaults

- Report Nonscan Cells

- Report Nonscan Handling

- Report Notest Points

- Report Observe Data

- Report Observe Points

- Report Output Masks

- Report Paths

- Report Pin Constraints

- Report Pin Equivalences

- Report Pin Strobes

- Report Primary Inputs

- Report Primary Outputs

- Report Procedure

- Report Pulse Generators

- Report Random Weights

- Report Read Controls

- Report Scan Cells

- Report Scan Chains

- Report Scan Groups

- Report Scan Instances

- Report Scan Models

- Report Seq_transparent Procedures

- Report Slow Pads

- Report Statistics

- Report Test Stimulus

- Report Testability Data

- Report Tied Signals

- Report Timeplate

- Report Version Data

- Report Write Controls

- Reset Au Faults

- Reset State

- Resume Interrupted Process

- Run

- Save Flattened Model

- Save Patterns

- Save Schematic

- Select Iddq Patterns

- Select Object

- Set Abort Limit

- Set Atpg Compression

- Set Atpg Limits

- Set Atpg Window

- Set AU Analysis

- Set Bist Initialization

- Set Bus Handling

- Set Bus Simulation

- Set Capture Clock

- Set Capture Handling

- Set Capture Limit

- Set Checkpoint

- Set Clock Restriction

- Set Clock_off Simulation

- Set Clockpo Patterns

- Set Contention Check

- Set Control Threshold

- Set Decision Order

- Set Dofile Abort

- Set Drc Handling

- Set Driver Restriction

- Set Fails Report

- Set Fault Mode

- Set Fault Sampling

- Set Fault Type

- Set Flatten Handling

- Set Gate Level

- Set Gate Report

- Set Hypertrophic Limit

- Set Iddq Checks

- Set Iddq Strobe

- Set Instancename Visibility

- Set Instruction Atpg

- Set Internal Fault

- Set Internal Name

- Set Interrupt Handling

- Set IO Mask

- Set Learn Report

- Set List File

- Set Logfile Handling

- Set Loop Handling

- Set Multiple Load

- Set Net Dominance

- Set Net Resolution

- Set Nonscan Model

- Set Number Shifts

- Set Observation Point

- Set Observe Threshold

- Set Output Comparison

- Set Output Mask

- Set Pathdelay Holdpi

- Set Pattern Source

- Set Possible Credit

- Set Procedure Cycle_checking

- Set Pulse Generators

- Set Race Data

- Set Rail Strength

- Set Ram Initialization

- Set Ram Test

- Set Random Atpg

- Set Random Clocks

- Set Random Patterns

- Set Random Weights

- Set Redundancy Identification

- Set Schematic Display

- Set Screen Display

- Set Self Initialization

- Set Sensitization Checking

- Set Sequential Learning

- Set Shadow Check

- Set Simulation Mode

- Set Skewed Load

- Set Split Capture_cycle

- Set Stability Check

- Set Static Learning

- Set Stg Extraction

- Set System Mode

- Set Test Cycle

- Set Trace Report

- Set Transition Holdpi

- Set Unused Net

- Set Workspace Size

- Set Xclock Handling

- Set Z Handling

- Set Zhold Behavior

- Set Zoom Factor

- Setup Checkpoint

- Setup LFSRs

- Setup Pin Constraints

- Setup Pin Strobes

- Setup Tied Signals

- Step

- System

- Undo Display

- Unmark

- Unselect Object

- Update Implication Detections

- View

- View Area

- Write Core Memory

- Write Environment

- Write Failures

- Write Faults

- Write Initial States

- Write Library_verification Setup

- Write Loops

- Write Modelfile

- Write Netlist

- Write Paths

- Write Primary Inputs

- Write Primary Outputs

- Write Procfile

- Write Statistics

- Write Timeplate

- Zoom In

- Zoom Out

- Chapter 3 Shell Commands

- Chapter 4 Test Pattern File Formats

- Chapter 5 Distributed FlexTest

- Appendix A Timing Command Dictionary

- Appendix B FlexTest WDB Translation Support

- INDEX

- Send us feedback

FastScan and FlexTest

Reference Manual

Software Version V8.6_4

Copyright Mentor Graphics Corporation 1991—1999. All rights reserved.

This document contains information that is proprietary to Mentor Graphics Corporation and may be

duplicated in whole or in part by the original recipient for internal business purposes only, provided that this

entire notice appears in all copies. In accepting this document, the recipient agrees to make every

reasonable effort to prevent the unauthorized use of this information.

This document is for information and instruction purposes. Mentor Graphics reserves the right to make

changes in specifications and other information contained in this publication without prior notice, and the

reader should, in all cases, consult Mentor Graphics to determine whether any changes have been

made.

The terms and conditions governing the sale and licensing of Mentor Graphics products are set forth in

written agreements between Mentor Graphics and its customers. No representation or other affirmation

of fact contained in this publication shall be deemed to be a warranty or give rise to any liability of Mentor

Graphics whatsoever.

MENTOR GRAPHICS MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THIS MATERIAL

INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OR MERCHANTABILITY AND

FITNESS FOR A PARTICULAR PURPOSE.

MENTOR GRAPHICS SHALL NOT BE LIABLE FOR ANY INCIDENTAL, INDIRECT, SPECIAL, OR

CONSEQUENTIAL DAMAGES WHATSOEVER (INCLUDING BUT NOT LIMITED TO LOST PROFITS)

ARISING OUT OF OR RELATED TO THIS PUBLICATION OR THE INFORMATION CONTAINED IN IT,

EVEN IF MENTOR GRAPHICS CORPORATION HAS BEEN ADVISED OF THE POSSIBILITY OF

SUCH DAMAGES.

RESTRICTED RIGHTS LEGEND 03/97

U.S. Government Restricted Rights. The SOFTWARE and documentation have been developed

entirely at private expense and are commercial computer software provided with restricted rights. Use,

duplication or disclosure by the U.S. Government or a U.S. Government subcontractor is subject to the

restrictions set forth in the license agreement provided with the software pursuant to DFARS 227.7202-

3(a) or as set forth in subparagraph (c)(1) and (2) of the Commercial Computer Software - Restricted

Rights clause at FAR 52.227-19, as applicable.

Contractor/manufacturer is:

Mentor Graphics Corporation

8005 S.W. Boeckman Road, Wilsonville, Oregon 97070-7777.

A complete list of trademark names appears in a separate “Trademark Information” document.

This is an unpublished work of Mentor Graphics Corporation.

Table of Contents

FastScan and FlexTest Reference Manual, V8.6_4 iii

About This Manual .............................................................................................xvii

Overview.............................................................................................................xvii

Related Publications ............................................................................................xix

Mentor Graphics Documentation......................................................................xix

Acronyms Used in This Manual..........................................................................xxi

Command Line Syntax Conventions................................................................ xxiii

Chapter 1

Introduction ......................................................................................................... 1-1

Features............................................................................................................... 1-1

Inputs and Outputs.............................................................................................. 1-2

Chapter 2

Command Dictionary.......................................................................................... 2-1

Command Summary ........................................................................................... 2-1

Command Descriptions .................................................................................... 2-27

Abort Interrupted Process .............................................................................. 2-28

Add Ambiguous Paths.................................................................................... 2-29

Add Atpg Constraints..................................................................................... 2-31

Add Atpg Functions ....................................................................................... 2-36

Add Capture Handling ................................................................................... 2-40

Add Cell Constraints...................................................................................... 2-43

Add Cell Library ............................................................................................ 2-46

Add Clocks..................................................................................................... 2-47

Add Cone Blocks ........................................................................................... 2-49

Add Control Points......................................................................................... 2-51

Add Display Instances.................................................................................... 2-53

Add Display Loop.......................................................................................... 2-57

Add Display Path ........................................................................................... 2-60

Add Display Scanpath.................................................................................... 2-63

Add Faults ...................................................................................................... 2-66

Add Iddq Constraints ..................................................................................... 2-68

Add Initial States............................................................................................ 2-70

TABLE OF CONTENTS

TABLE OF CONTENTS [continued]

Table of Contents

FastScan and FlexTest Reference Manual, V8.6_4

iv

Add LFSR Connections ................................................................................. 2-72

Add LFSR Taps.............................................................................................. 2-74

Add LFSRs..................................................................................................... 2-76

Add Lists ........................................................................................................ 2-79

Add Mos Direction......................................................................................... 2-81

Add Net Property ........................................................................................... 2-83

Add Nofaults .................................................................................................. 2-84

Add Nonscan Handling.................................................................................. 2-87

Add Notest Points .......................................................................................... 2-89

Add Observe Points........................................................................................ 2-90

Add Output Masks ......................................................................................... 2-92

Add Pin Constraints ....................................................................................... 2-93

Add Pin Equivalences .................................................................................... 2-98

Add Pin Strobes............................................................................................ 2-101

Add Primary Inputs...................................................................................... 2-103

Add Primary Outputs ................................................................................... 2-105

Add Random Weights.................................................................................. 2-106

Add Read Controls....................................................................................... 2-108

Add Scan Chains.......................................................................................... 2-110

Add Scan Groups ......................................................................................... 2-112

Add Scan Instances ...................................................................................... 2-114

Add Scan Models ......................................................................................... 2-115

Add Slow Pad............................................................................................... 2-116

Add Tied Signals.......................................................................................... 2-117

Add Write Controls...................................................................................... 2-119

Analyze Atpg Constraints ............................................................................ 2-120

Analyze Bus ................................................................................................. 2-123

Analyze Control ........................................................................................... 2-126

Analyze Control Signals .............................................................................. 2-128

Analyze Drc Violation ................................................................................. 2-131

Analyze Fault ............................................................................................... 2-137

Analyze Observe .......................................................................................... 2-143

Analyze Race ............................................................................................... 2-145

Analyze Restrictions .................................................................................... 2-147

Close Schematic Viewer .............................................................................. 2-148

TABLE OF CONTENTS [continued]

Table of Contents

FastScan and FlexTest Reference Manual, V8.6_4 v

Compress Patterns........................................................................................ 2-149

Create Initialization Patterns........................................................................ 2-152

Create Patterns ............................................................................................. 2-154

Delete Atpg Constraints ............................................................................... 2-156

Delete Atpg Functions.................................................................................. 2-158

Delete Capture Handling.............................................................................. 2-160

Delete Cell Constraints ................................................................................ 2-162

Delete Clocks ............................................................................................... 2-164

Delete Cone Blocks...................................................................................... 2-165

Delete Control Points ................................................................................... 2-167

Delete Display Instances.............................................................................. 2-169

Delete Faults................................................................................................. 2-171

Delete Iddq Constraints................................................................................ 2-174

Delete Initial States ...................................................................................... 2-176

Delete LFSR Connections............................................................................ 2-177

Delete LFSR Taps........................................................................................ 2-179

Delete LFSRs ............................................................................................... 2-181

Delete Lists................................................................................................... 2-183

Delete Mos Direction ................................................................................... 2-184

Delete Net Property...................................................................................... 2-185

Delete Nofaults............................................................................................. 2-186

Delete Nonscan Handling ............................................................................ 2-189

Delete Notest Points..................................................................................... 2-191

Delete Observe Points.................................................................................. 2-193

Delete Output Masks.................................................................................... 2-195

Delete Paths.................................................................................................. 2-197

Delete Pin Constraints.................................................................................. 2-199

Delete Pin Equivalences............................................................................... 2-201

Delete Pin Strobes........................................................................................ 2-202

Delete Primary Inputs .................................................................................. 2-204

Delete Primary Outputs................................................................................ 2-206

Delete Random Weights .............................................................................. 2-208

Delete Read Controls ................................................................................... 2-210

Delete Scan Chains ...................................................................................... 2-211

Delete Scan Groups...................................................................................... 2-212

TABLE OF CONTENTS [continued]

Table of Contents

FastScan and FlexTest Reference Manual, V8.6_4

vi

Delete Scan Instances................................................................................... 2-214

Delete Scan Models...................................................................................... 2-215

Delete Slow Pad ........................................................................................... 2-216

Delete Tied Signals ...................................................................................... 2-217

Delete Write Controls .................................................................................. 2-219

Diagnose Failures......................................................................................... 2-220

Dofile............................................................................................................ 2-224

Exit ............................................................................................................... 2-226

Extract Subckts............................................................................................. 2-227

Flatten Model ............................................................................................... 2-228

Flatten Subckt............................................................................................... 2-229

Help.............................................................................................................. 2-230

Insert Testability........................................................................................... 2-232

Load Faults................................................................................................... 2-234

Load Paths.................................................................................................... 2-238

Macrotest...................................................................................................... 2-242

Mark ............................................................................................................. 2-248

Open Schematic Viewer............................................................................... 2-250

Read Modelfile............................................................................................. 2-252

Read Procfile................................................................................................ 2-255

Read Subckts Library................................................................................... 2-256

Redo Display................................................................................................ 2-257

Report Aborted Faults.................................................................................. 2-259

Report Atpg Constraints............................................................................... 2-262

Report Atpg Functions ................................................................................. 2-263

Report AU Faults ......................................................................................... 2-264

Report Bus Data ........................................................................................... 2-268

Report Capture Handling ............................................................................. 2-272

Report Cell Constraints................................................................................ 2-274

Report Clocks............................................................................................... 2-276

Report Cone Blocks ..................................................................................... 2-277

Report Control Data ..................................................................................... 2-278

Report Control Points................................................................................... 2-280

Report Core Memory ................................................................................... 2-281

Report Display Instances.............................................................................. 2-282

TABLE OF CONTENTS [continued]

Table of Contents

FastScan and FlexTest Reference Manual, V8.6_4 vii

Report Drc Rules.......................................................................................... 2-285

Report Environment..................................................................................... 2-293

Report Failures............................................................................................. 2-295

Report Faults ................................................................................................ 2-298

Report Feedback Paths................................................................................. 2-303

Report Flatten Rules..................................................................................... 2-305

Report Gates................................................................................................. 2-309

Report Hosts................................................................................................. 2-326

Report Id Stamp ........................................................................................... 2-327

Report Iddq Constraints ............................................................................... 2-329

Report Initial States...................................................................................... 2-331

Report LFSR Connections ........................................................................... 2-333

Report LFSRs............................................................................................... 2-334

Report Lists .................................................................................................. 2-335

Report Loops................................................................................................ 2-336

Report Mos Direction................................................................................... 2-337

Report Net Properties................................................................................... 2-338

Report Nofaults ............................................................................................ 2-339

Report Nonscan Cells................................................................................... 2-341

Report Nonscan Handling............................................................................ 2-345

Report Notest Points .................................................................................... 2-346

Report Observe Data.................................................................................... 2-347

Report Observe Points.................................................................................. 2-349

Report Output Masks ................................................................................... 2-350

Report Paths ................................................................................................. 2-351

Report Pin Constraints ................................................................................. 2-353

Report Pin Equivalences .............................................................................. 2-355

Report Pin Strobes........................................................................................ 2-356

Report Primary Inputs.................................................................................. 2-357

Report Primary Outputs ............................................................................... 2-359

Report Procedure.......................................................................................... 2-361

Report Pulse Generators............................................................................... 2-362

Report Random Weights.............................................................................. 2-363

Report Read Controls................................................................................... 2-364

Report Scan Cells......................................................................................... 2-365

TABLE OF CONTENTS [continued]

Table of Contents

FastScan and FlexTest Reference Manual, V8.6_4

viii

Report Scan Chains...................................................................................... 2-368

Report Scan Groups ..................................................................................... 2-369

Report Scan Instances .................................................................................. 2-370

Report Scan Models ..................................................................................... 2-371

Report Seq_transparent Procedures ............................................................. 2-372

Report Slow Pads ......................................................................................... 2-374

Report Statistics ........................................................................................... 2-375

Report Test Stimulus.................................................................................... 2-380

Report Testability Data ................................................................................ 2-386

Report Tied Signals...................................................................................... 2-389

Report Timeplate.......................................................................................... 2-391

Report Version Data..................................................................................... 2-392

Report Write Controls.................................................................................. 2-393

Reset Au Faults ............................................................................................ 2-394

Reset State.................................................................................................... 2-396

Resume Interrupted Process......................................................................... 2-397

Run ............................................................................................................... 2-399

Save Flattened Model................................................................................... 2-403

Save Patterns ................................................................................................ 2-405

Save Schematic ............................................................................................ 2-416

Select Iddq Patterns...................................................................................... 2-417

Select Object ................................................................................................ 2-422

Set Abort Limit ............................................................................................ 2-424

Set Atpg Compression.................................................................................. 2-427

Set Atpg Limits ............................................................................................ 2-430

Set Atpg Window......................................................................................... 2-433

Set AU Analysis........................................................................................... 2-434

Set Bist Initialization.................................................................................... 2-436

Set Bus Handling.......................................................................................... 2-438

Set Bus Simulation....................................................................................... 2-440

Set Capture Clock ........................................................................................ 2-441

Set Capture Handling ................................................................................... 2-444

Set Capture Limit ......................................................................................... 2-447

Set Checkpoint ............................................................................................. 2-449

Set Clock Restriction.................................................................................... 2-451

TABLE OF CONTENTS [continued]

Table of Contents

FastScan and FlexTest Reference Manual, V8.6_4 ix

Set Clock_off Simulation............................................................................. 2-454

Set Clockpo Patterns .................................................................................... 2-455

Set Contention Check................................................................................... 2-456

Set Control Threshold .................................................................................. 2-461

Set Decision Order ....................................................................................... 2-462

Set Dofile Abort ........................................................................................... 2-464

Set Drc Handling.......................................................................................... 2-465

Set Driver Restriction................................................................................... 2-475

Set Fails Report............................................................................................ 2-477

Set Fault Mode ............................................................................................. 2-478

Set Fault Sampling ....................................................................................... 2-480

Set Fault Type .............................................................................................. 2-482

Set Flatten Handling..................................................................................... 2-484

Set Gate Level.............................................................................................. 2-489

Set Gate Report ............................................................................................ 2-491

Set Hypertrophic Limit ................................................................................ 2-500

Set Iddq Checks............................................................................................ 2-502

Set Iddq Strobe............................................................................................. 2-506

Set Instancename Visibility.......................................................................... 2-508

Set Instruction Atpg ..................................................................................... 2-511

Set Internal Fault.......................................................................................... 2-513

Set Internal Name......................................................................................... 2-514

Set Interrupt Handling.................................................................................. 2-515

Set IO Mask.................................................................................................. 2-517

Set Learn Report .......................................................................................... 2-518

Set List File .................................................................................................. 2-520

Set Logfile Handling.................................................................................... 2-522

Set Loop Handling ....................................................................................... 2-524

Set Multiple Load......................................................................................... 2-527

Set Net Dominance ...................................................................................... 2-529

Set Net Resolution........................................................................................ 2-531

Set Nonscan Model ...................................................................................... 2-533

Set Number Shifts ........................................................................................ 2-536

Set Observation Point................................................................................... 2-537

Set Observe Threshold ................................................................................. 2-539

TABLE OF CONTENTS [continued]

Table of Contents

FastScan and FlexTest Reference Manual, V8.6_4

x

Set Output Comparison................................................................................ 2-541

Set Output Mask........................................................................................... 2-543

Set Pathdelay Holdpi.................................................................................... 2-545

Set Pattern Source ........................................................................................ 2-546

Set Possible Credit ....................................................................................... 2-550

Set Procedure Cycle_checking..................................................................... 2-551

Set Pulse Generators .................................................................................... 2-552

Set Race Data ............................................................................................... 2-553

Set Rail Strength .......................................................................................... 2-554

Set Ram Initialization................................................................................... 2-555

Set Ram Test ................................................................................................ 2-557

Set Random Atpg ......................................................................................... 2-559

Set Random Clocks...................................................................................... 2-560

Set Random Patterns .................................................................................... 2-562

Set Random Weights.................................................................................... 2-563

Set Redundancy Identification ..................................................................... 2-565

Set Schematic Display.................................................................................. 2-566

Set Screen Display ....................................................................................... 2-569

Set Self Initialization.................................................................................... 2-570

Set Sensitization Checking........................................................................... 2-572

Set Sequential Learning ............................................................................... 2-573

Set Shadow Check........................................................................................ 2-575

Set Simulation Mode.................................................................................... 2-576

Set Skewed Load.......................................................................................... 2-581

Set Split Capture_cycle................................................................................ 2-583

Set Stability Check....................................................................................... 2-584

Set Static Learning ....................................................................................... 2-586

Set Stg Extraction......................................................................................... 2-588

Set System Mode.......................................................................................... 2-589

Set Test Cycle .............................................................................................. 2-592

Set Trace Report........................................................................................... 2-593

Set Transition Holdpi ................................................................................... 2-594

Set Unused Net............................................................................................. 2-595

Set Workspace Size...................................................................................... 2-597

Set Xclock Handling .................................................................................... 2-598

TABLE OF CONTENTS [continued]

Table of Contents

FastScan and FlexTest Reference Manual, V8.6_4 xi

Set Z Handling ............................................................................................. 2-599

Set Zhold Behavior ...................................................................................... 2-601

Set Zoom Factor........................................................................................... 2-603

Setup Checkpoint ......................................................................................... 2-604

Setup LFSRs................................................................................................. 2-607

Setup Pin Constraints ................................................................................... 2-609

Setup Pin Strobes ......................................................................................... 2-612

Setup Tied Signals........................................................................................ 2-613

Step............................................................................................................... 2-615

System.......................................................................................................... 2-616

Undo Display ............................................................................................... 2-617

Unmark......................................................................................................... 2-619

Unselect Object ............................................................................................ 2-621

Update Implication Detections..................................................................... 2-623

View ............................................................................................................. 2-625

View Area .................................................................................................... 2-627

Write Core Memory ..................................................................................... 2-629

Write Environment....................................................................................... 2-631

Write Failures............................................................................................... 2-634

Write Faults.................................................................................................. 2-638

Write Initial States........................................................................................ 2-642

Write Library_verification Setup ................................................................. 2-644

Write Loops.................................................................................................. 2-646

Write Modelfile............................................................................................ 2-647

Write Netlist................................................................................................. 2-649

Write Paths................................................................................................... 2-651

Write Primary Inputs.................................................................................... 2-653

Write Primary Outputs ................................................................................. 2-655

Write Procfile............................................................................................... 2-657

Write Statistics ............................................................................................. 2-658

Write Timeplate ........................................................................................... 2-661

Zoom In........................................................................................................ 2-663

Zoom Out ..................................................................................................... 2-664

TABLE OF CONTENTS [continued]

Table of Contents

FastScan and FlexTest Reference Manual, V8.6_4

xii

Chapter 3

Shell Commands.................................................................................................. 3-1

Shell Command Descriptions ............................................................................. 3-1

fastscan............................................................................................................. 3-2

flextest.............................................................................................................. 3-7

Chapter 4

Test Pattern File Formats ................................................................................... 4-1

FastScan Test Pattern File Format...................................................................... 4-1

Header_Data..................................................................................................... 4-1

Setup_Data ....................................................................................................... 4-2

Functional_Chain_Test .................................................................................... 4-5

Scan_Test ......................................................................................................... 4-8

Scan_Cell ....................................................................................................... 4-11

FlexTest Test Pattern File Format .................................................................... 4-12

ASCII Pattern Format .................................................................................... 4-12

Table Pattern Format...................................................................................... 4-20

VCD Support Using VCD Plus...................................................................... 4-27

Chapter 5

Distributed FlexTest............................................................................................ 5-1

Environment Setup........................................................................................... 5-4

Host File Setup................................................................................................. 5-4

Appendix A

Timing Command Dictionary ............................................................................A-1

Timing Command Summary ..............................................................................A-1

FastScan Timing Commands..............................................................................A-3

SET END_MEASURE_CYCLE TIME ..........................................................A-4

SET PROCEDURE FILE ................................................................................A-8

SET SINGLE_CYCLE TIME........................................................................A-10

SET SPLIT_BIDI_CYCLE TIME.................................................................A-12

SET SPLIT_MEASURE_CYCLE TIME......................................................A-15

TABLE OF CONTENTS [continued]

Table of Contents

FastScan and FlexTest Reference Manual, V8.6_4 xiii

SET STROBE_WINDOW TIME..................................................................A-20

SET TIME SCALE ........................................................................................A-22

TIMEPLATE..................................................................................................A-23

FlexTest Timing Commands ............................................................................A-32

SET BIDI_FORCE TIME..............................................................................A-33

SET CYCLE...................................................................................................A-35

SET END_MEASURE_CYCLE TIME ........................................................A-38

SET FIRST_FORCE TIME ...........................................................................A-41

SET FORCE TIME........................................................................................A-42

SET MEASURE TIME..................................................................................A-45

SET PROCEDURE FILE ..............................................................................A-47

SET SINGLE_CYCLE TIME........................................................................A-49

SET SKEW_FORCE TIME...........................................................................A-52

SET SPLIT_BIDI_CYCLE TIME.................................................................A-54

SET SPLIT_MEASURE_CYCLE TIME......................................................A-57

SET STROBE_WINDOW TIME..................................................................A-60

SET TIME SCALE ........................................................................................A-62

Appendix B

FlexTest WDB Translation Support ..................................................................B-1

Invoking wdb2flex..............................................................................................B-1

Control File.........................................................................................................B-2

Example ..............................................................................................................B-4

Using wdb2flex Effectively................................................................................B-6

Index

Table of Contents

FastScan and FlexTest Reference Manual, V8.6_4

xiv

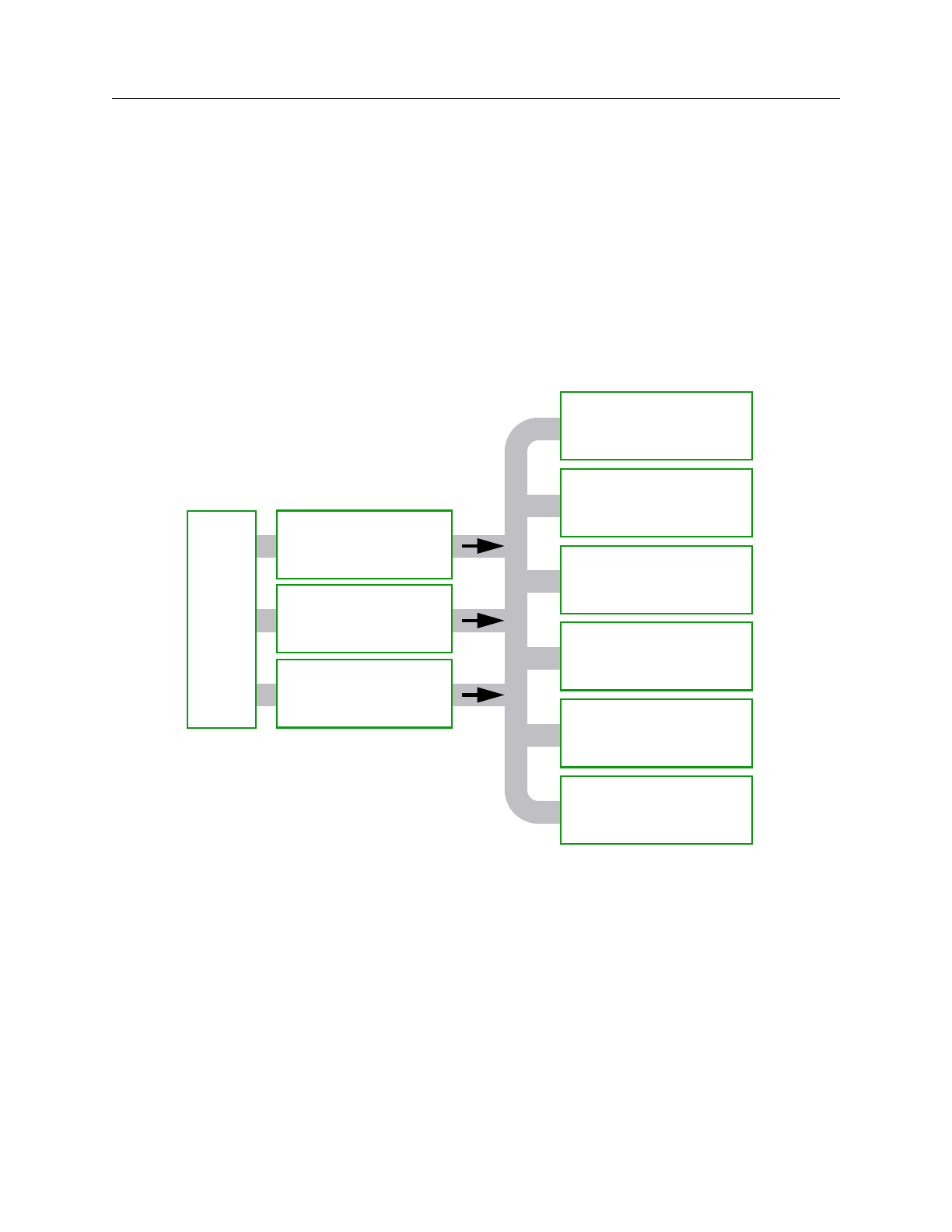

Figure 1. DFT Documentation Roadmap ...........................................................xix

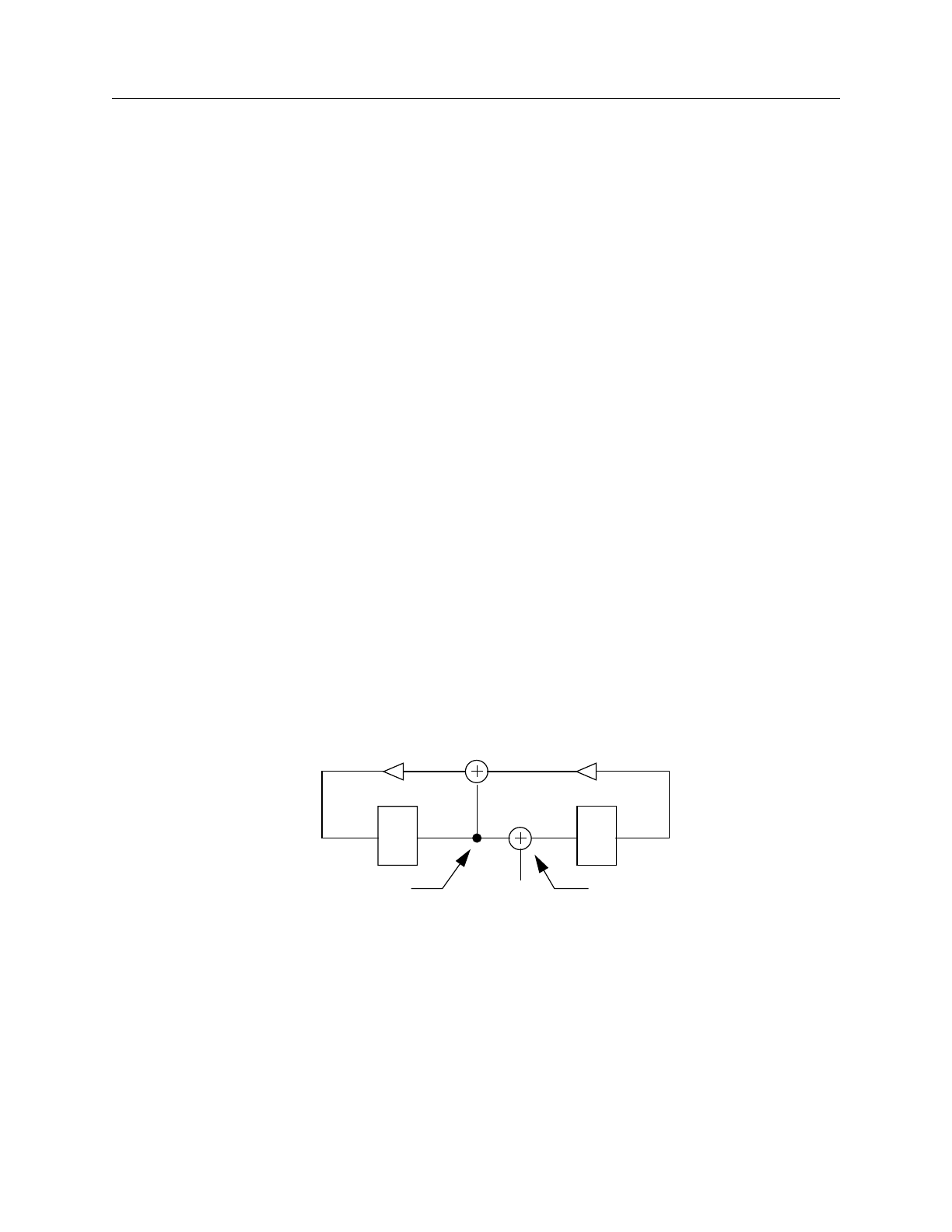

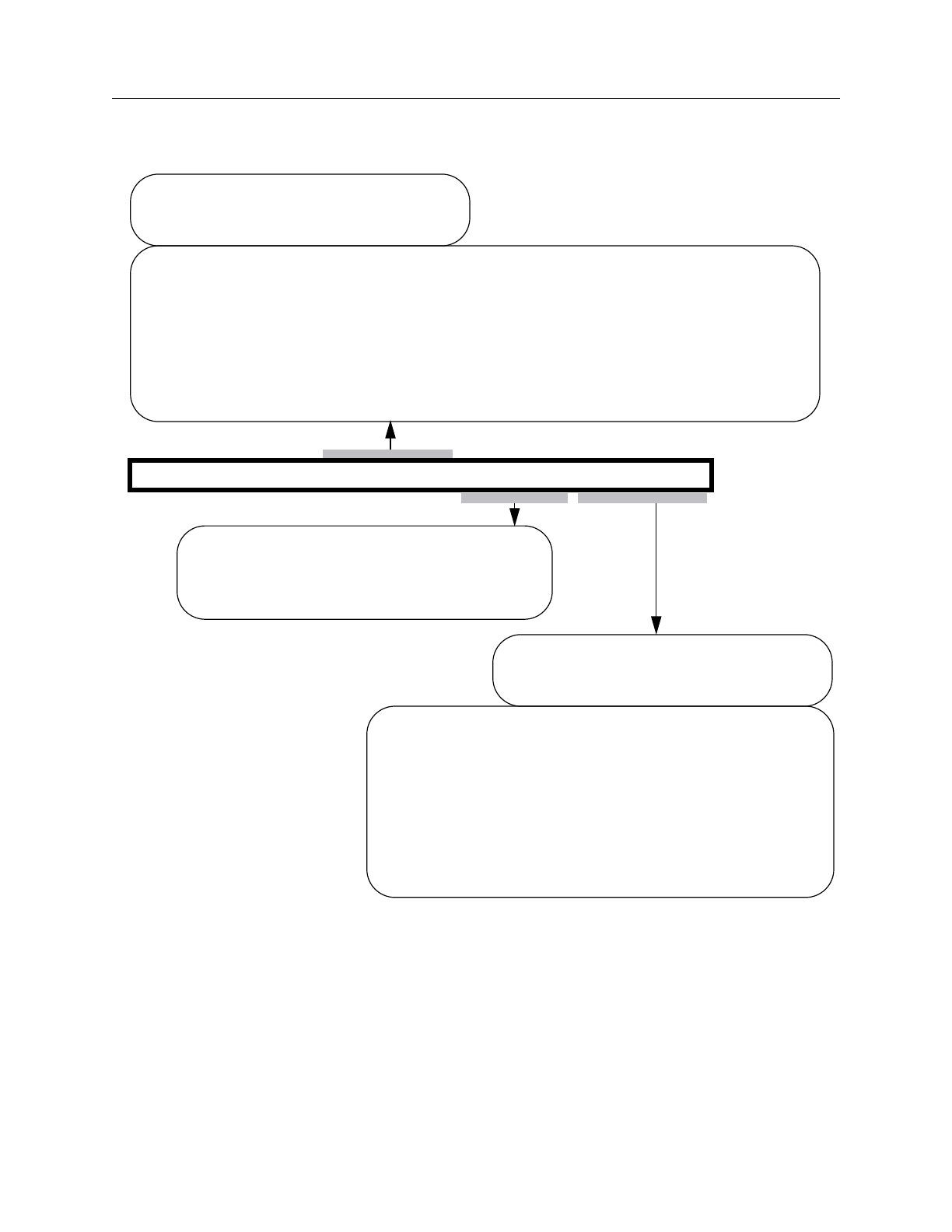

Figure 2-1. MISR placement ........................................................................... 2-72

Figure 5-1. Master and Slave Workstations ...................................................... 5-2

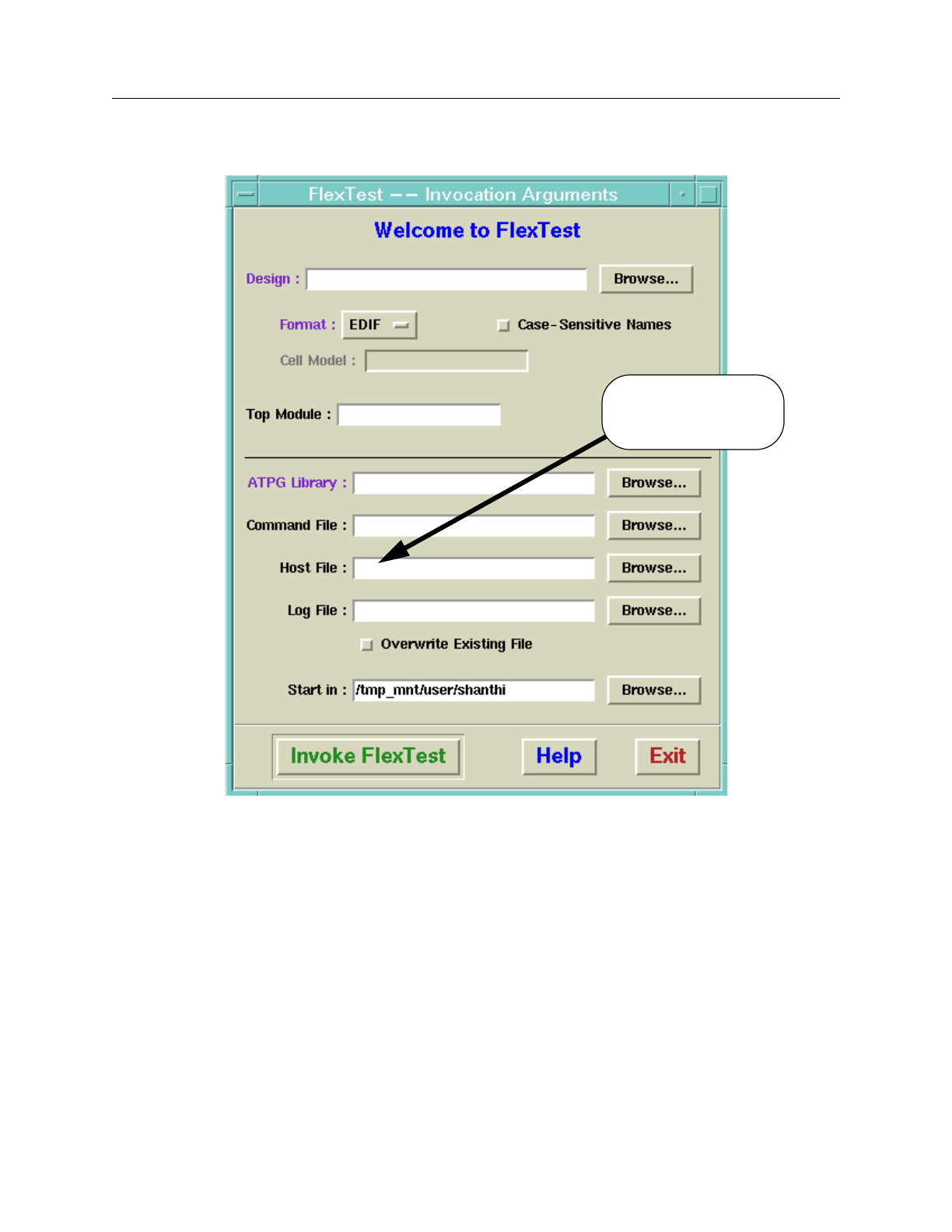

Figure 5-2. FlexTest Invocation Arguments Dialog Box .................................. 5-5

Figure A-1. Scan Event Timing for SET END_MEASURE_CYCLE TIME...A-4

Figure A-2. Scan Event Timing for SET SPLIT_MEASURE_CYCLE TIME ......

A-15

Figure A-3. SET SPLIT_MEASURE_CYCLE TIME Non-scan Event Timing

Diagram ............................................................................................................A-19

Figure A-4. SET STROBE_WINDOW Timing Diagram...............................A-21

Figure A-5. Template Timing for Example 1..................................................A-28

Figure A-6. SET BIDI_FORCE Timing Example ..........................................A-34

Figure A-7. SET CYCLE Timing Example ....................................................A-36

Figure A-8. SET FORCE Timing Example.....................................................A-43

Figure A-9. SET MEASURE Timing Example ..............................................A-46

Figure A-10. SET SKEW_FORCE Timing Example .....................................A-53

Figure A-11. SET STROBE_WINDOW Timing Diagram.............................A-61

Figure B-1. Example WDB2FLEX Circuit Timing Example ...........................B-4

Figure B-2. Detailed Pin Timing .......................................................................B-9

LIST OF FIGURES

Table of Contents

FastScan and FlexTest Reference Manual, V8.6_4 xv

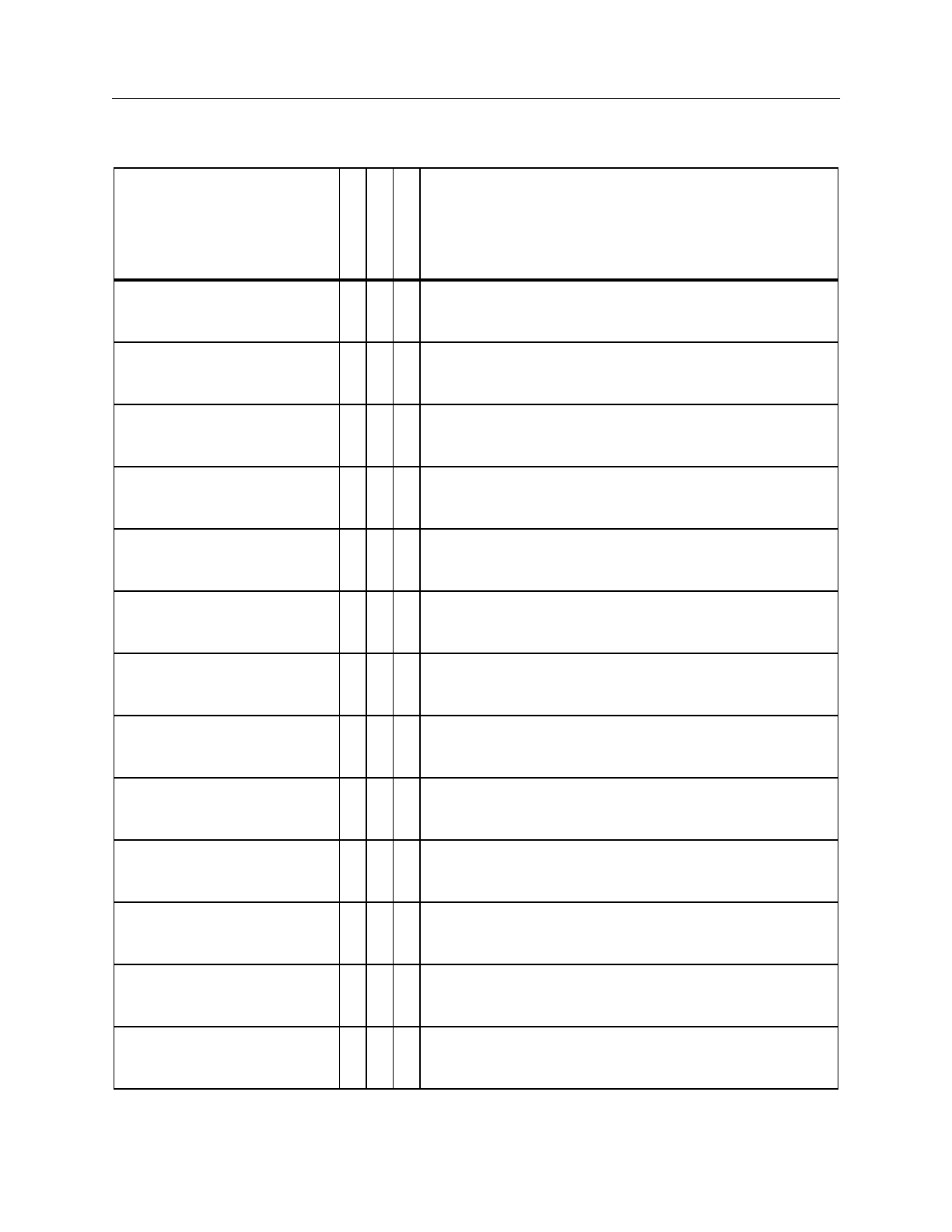

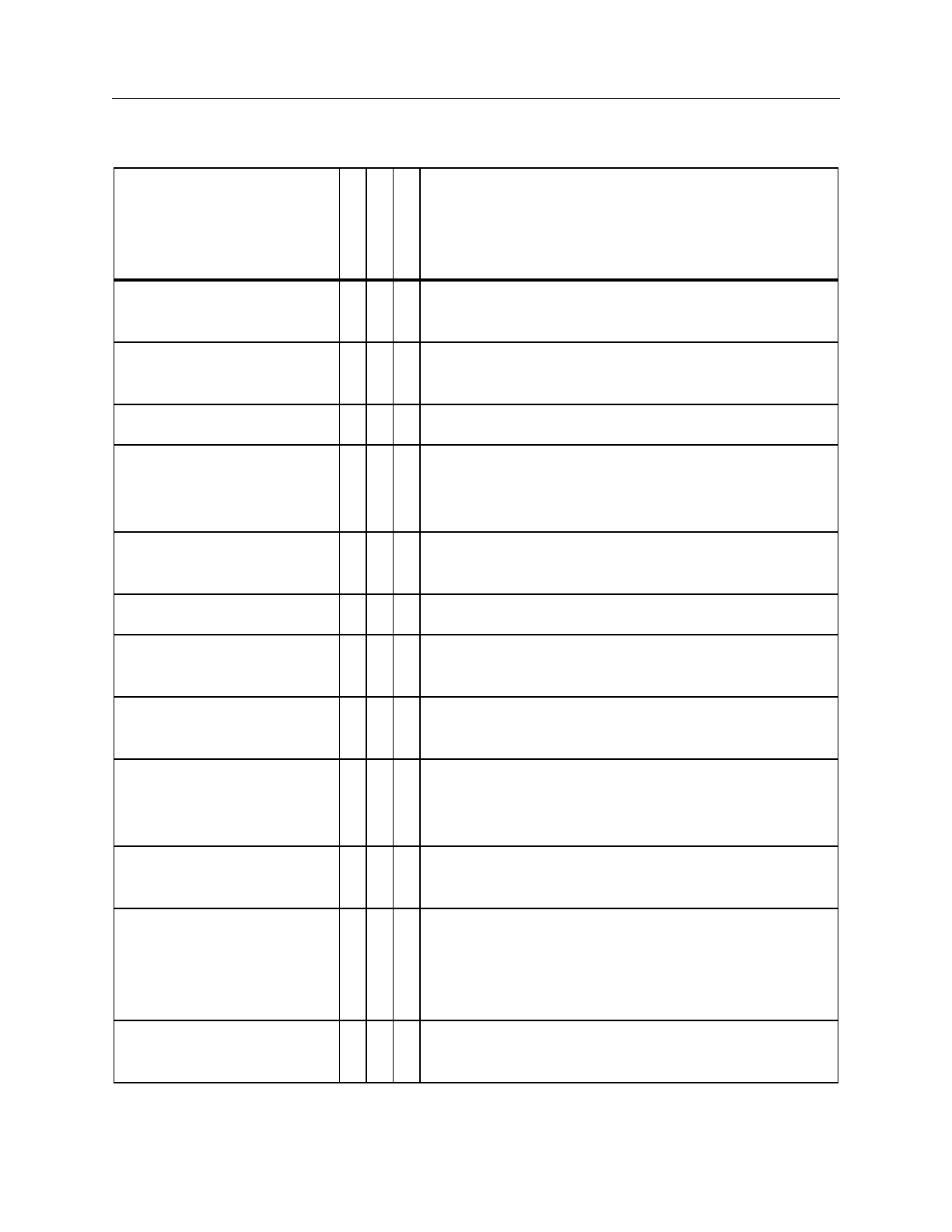

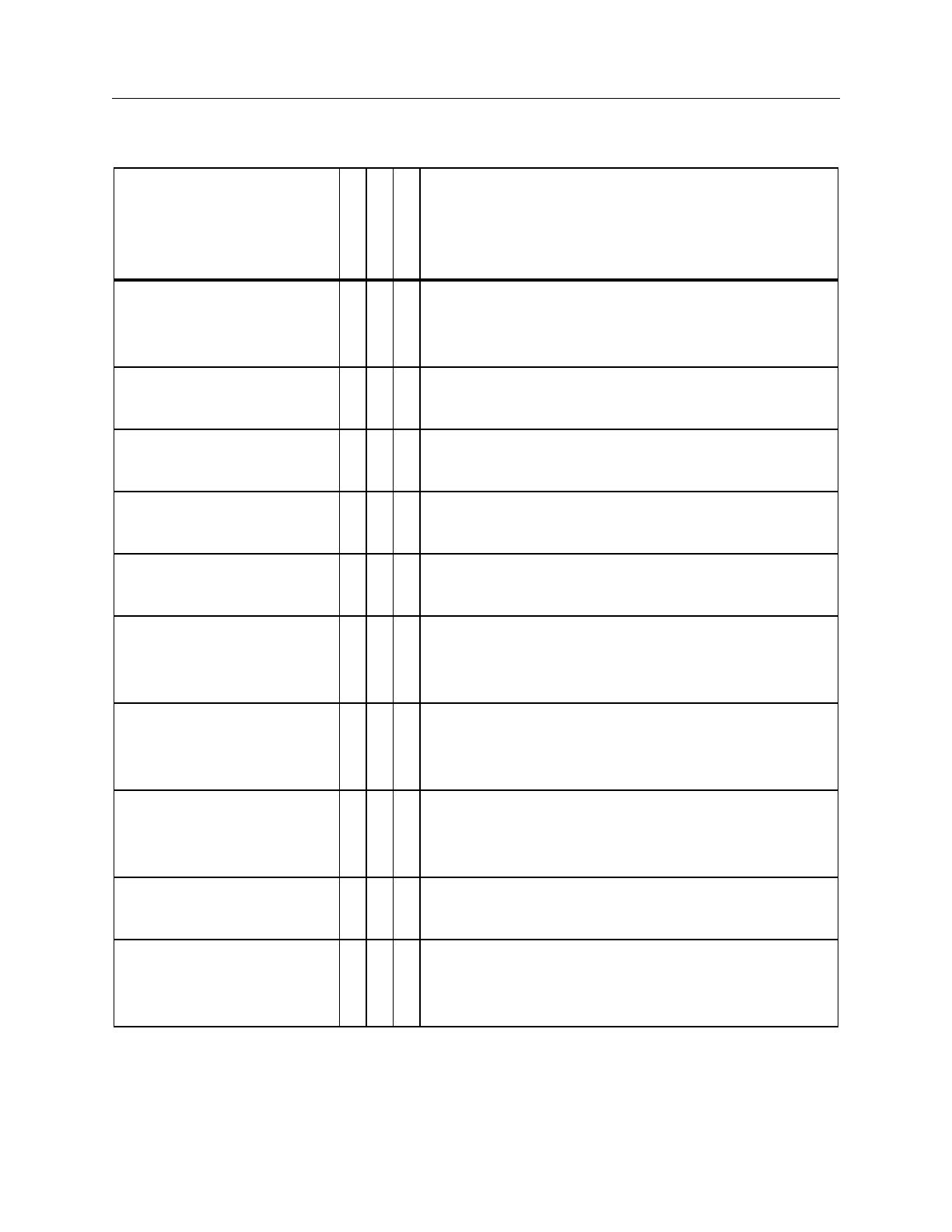

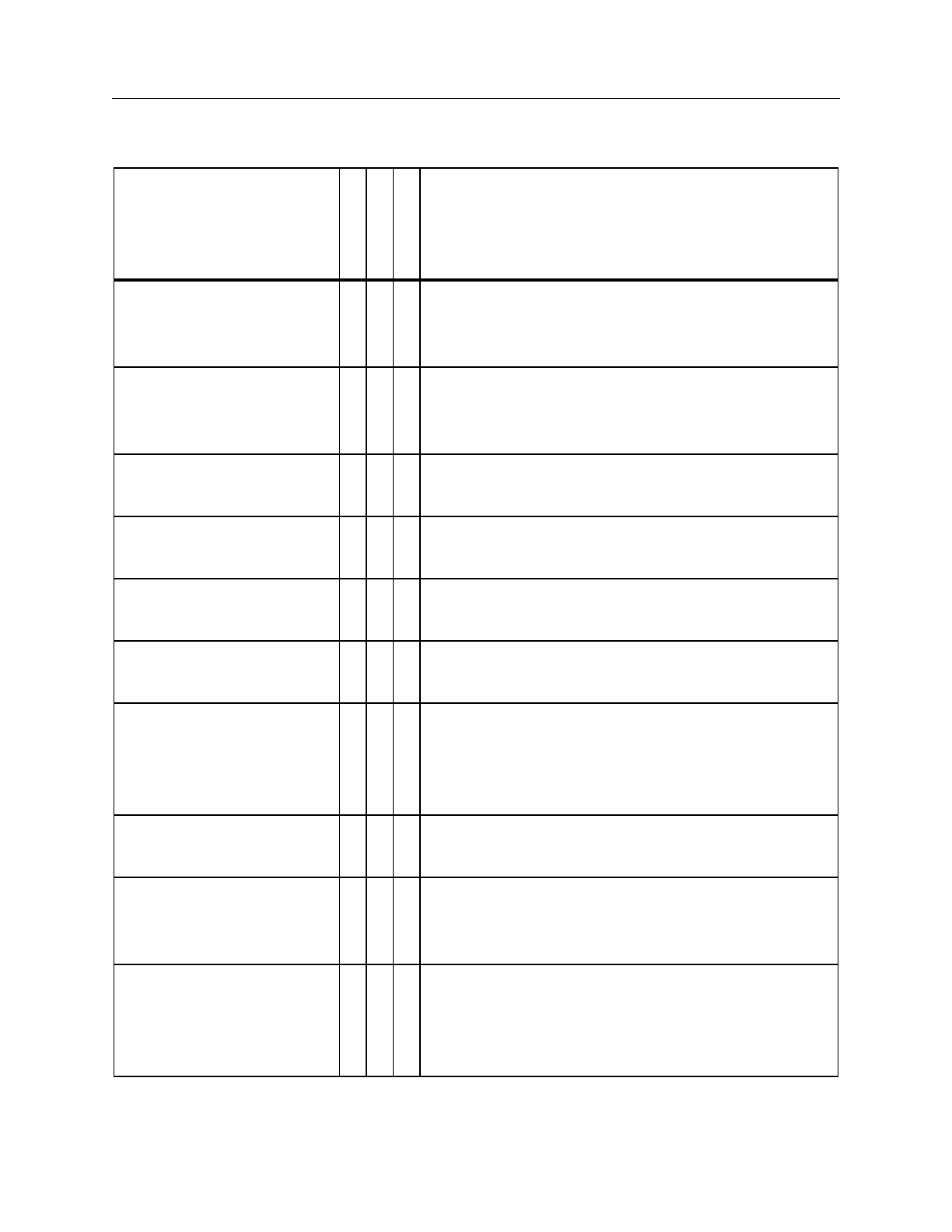

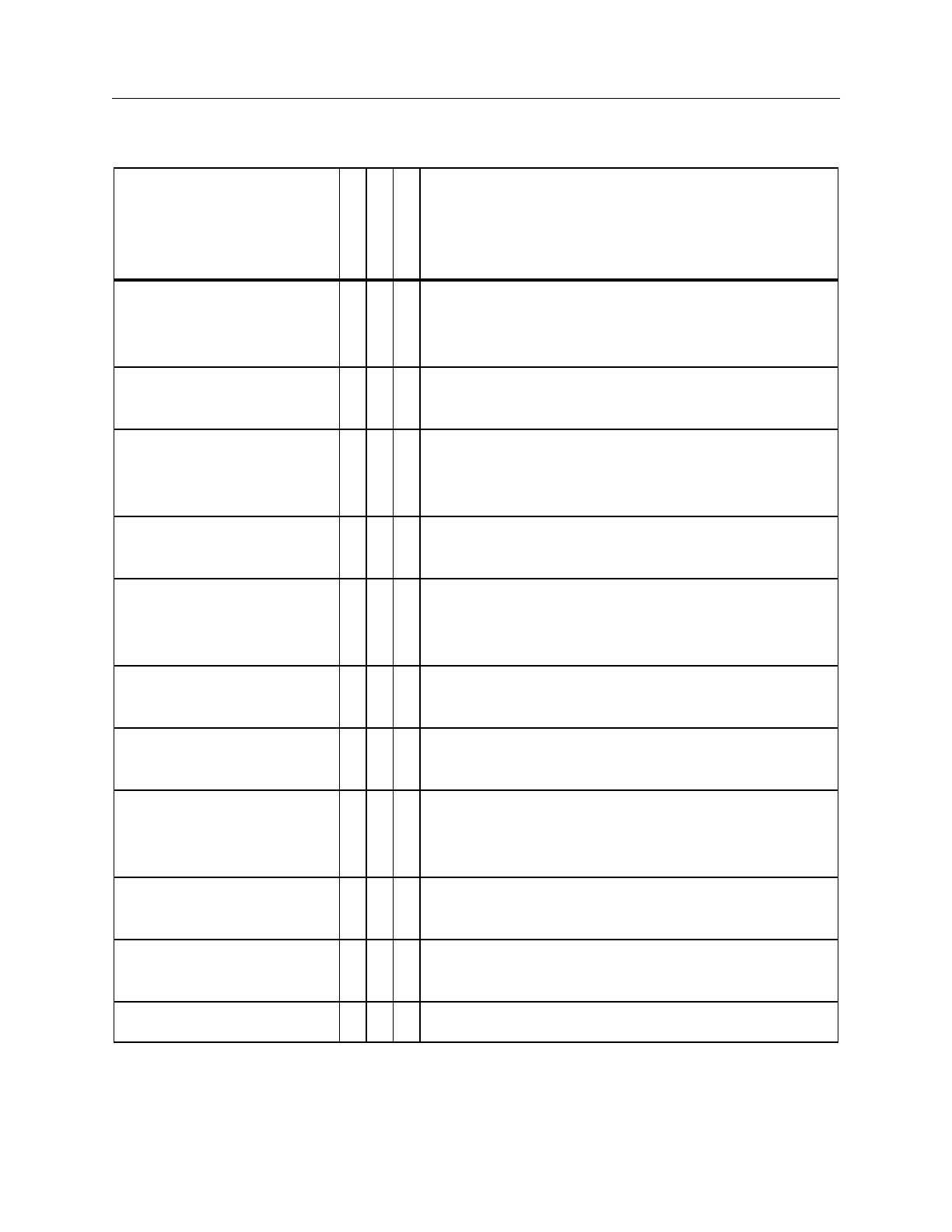

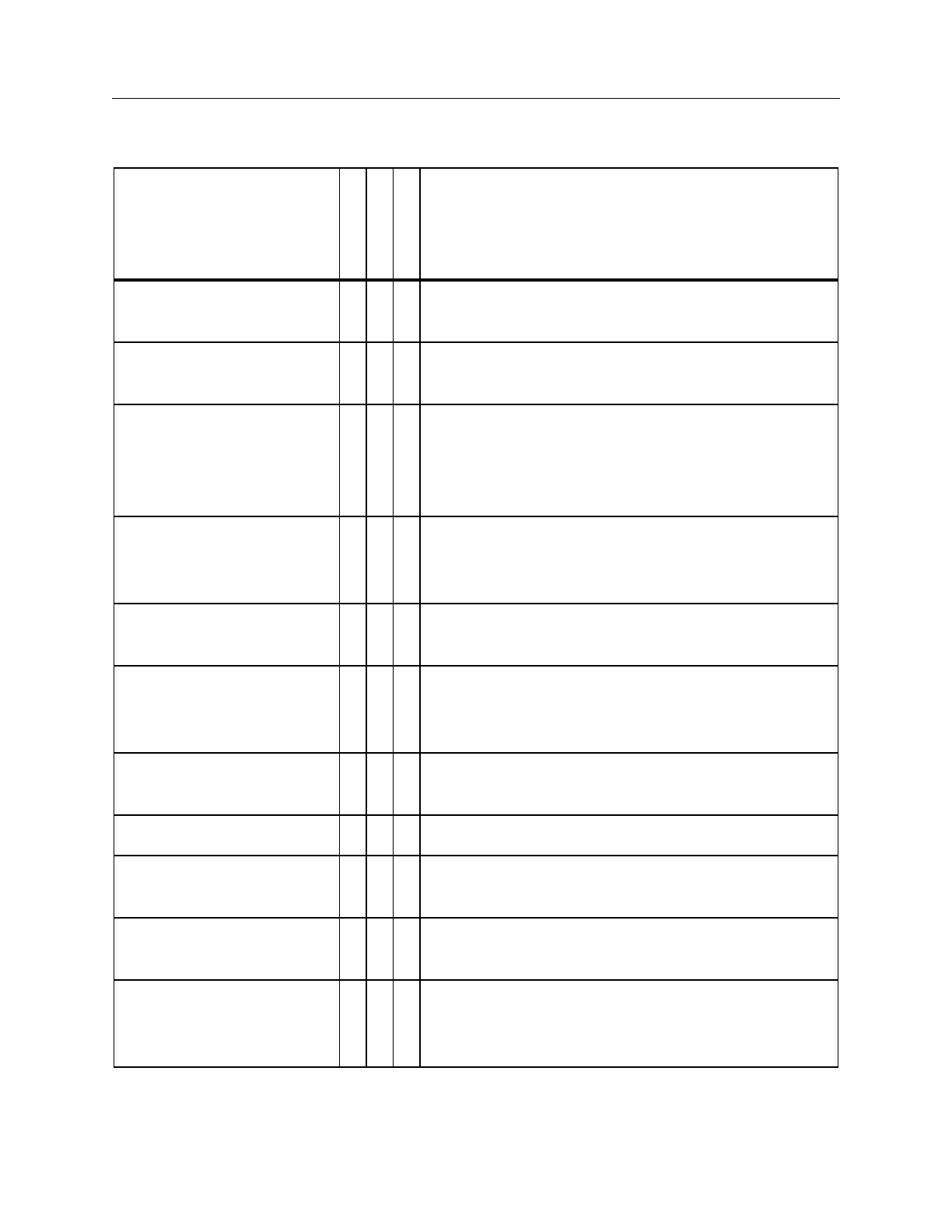

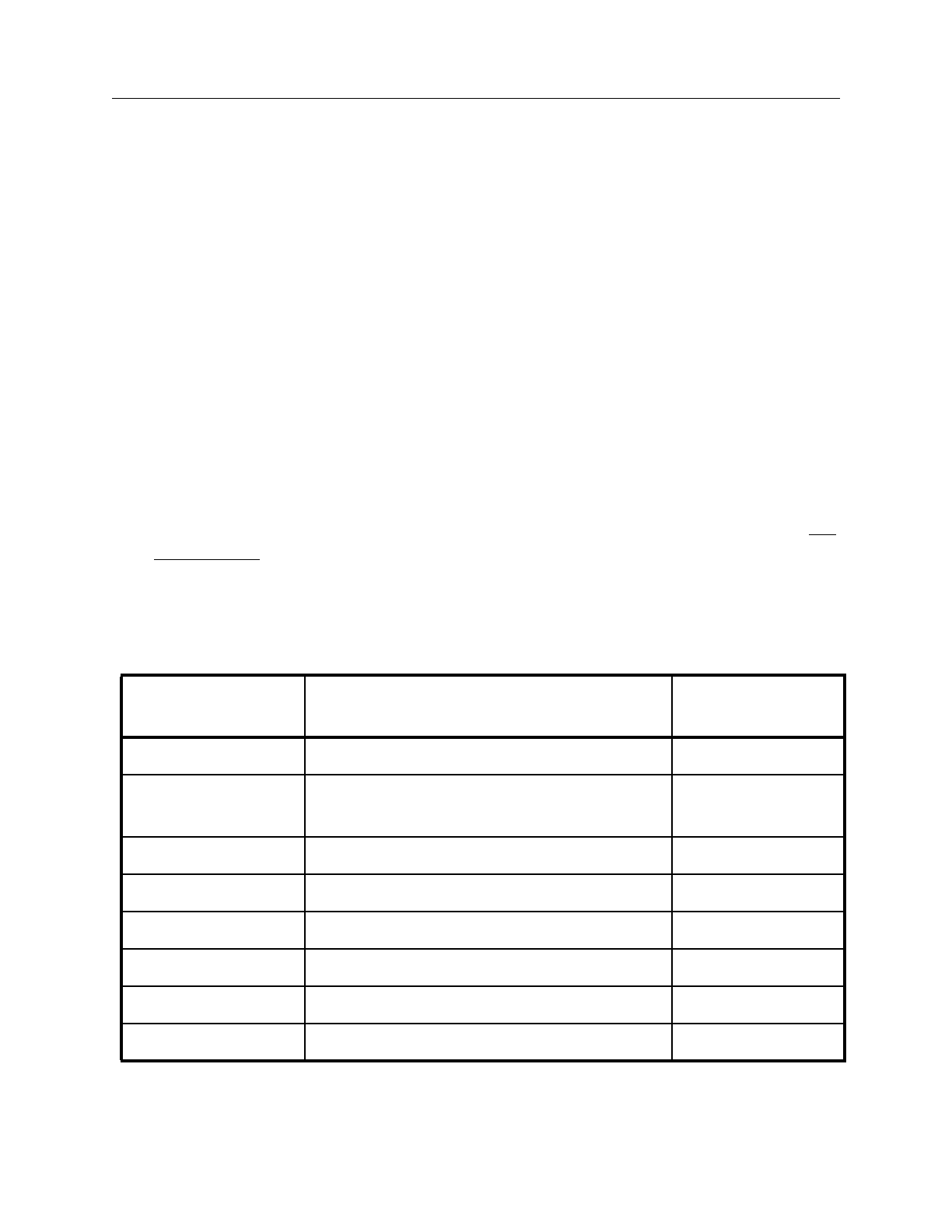

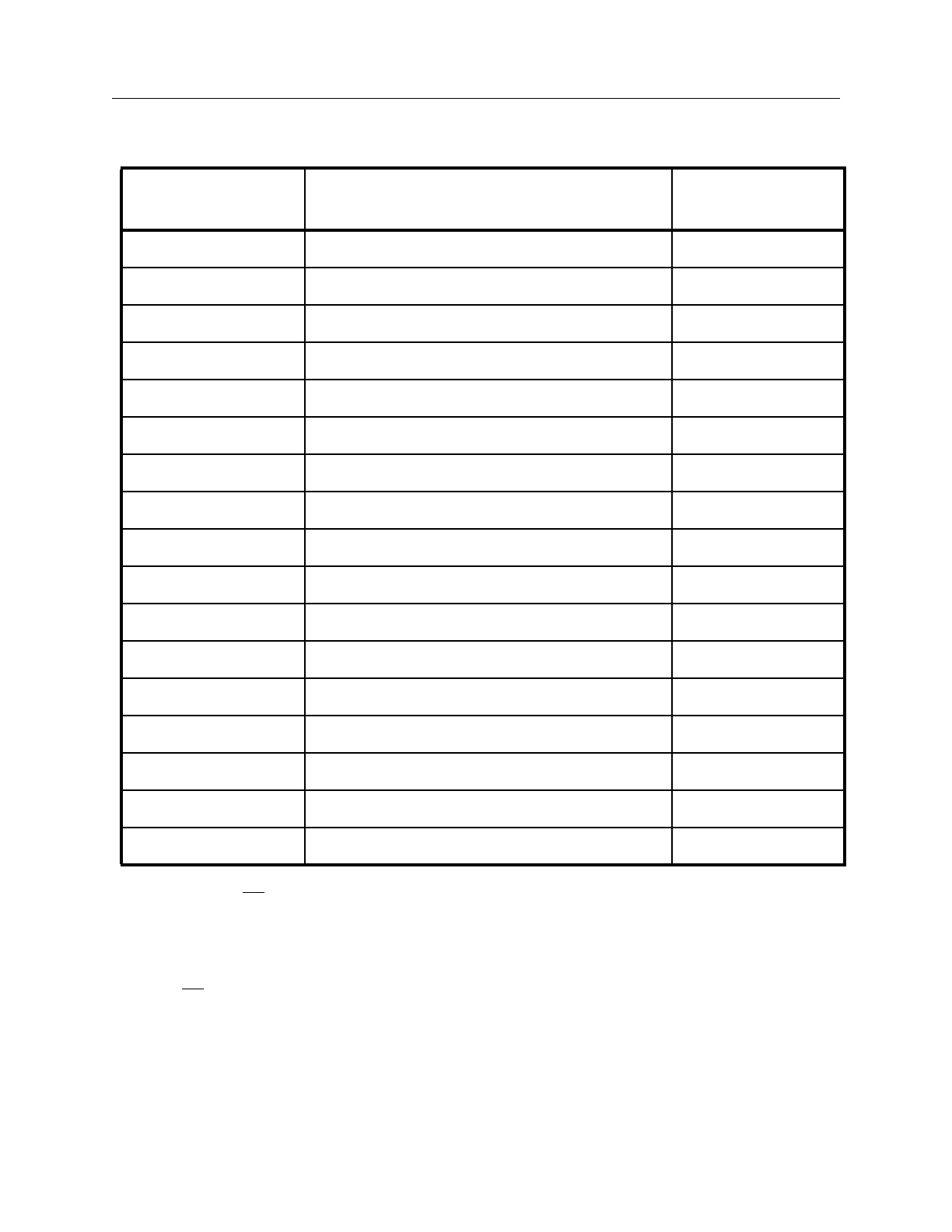

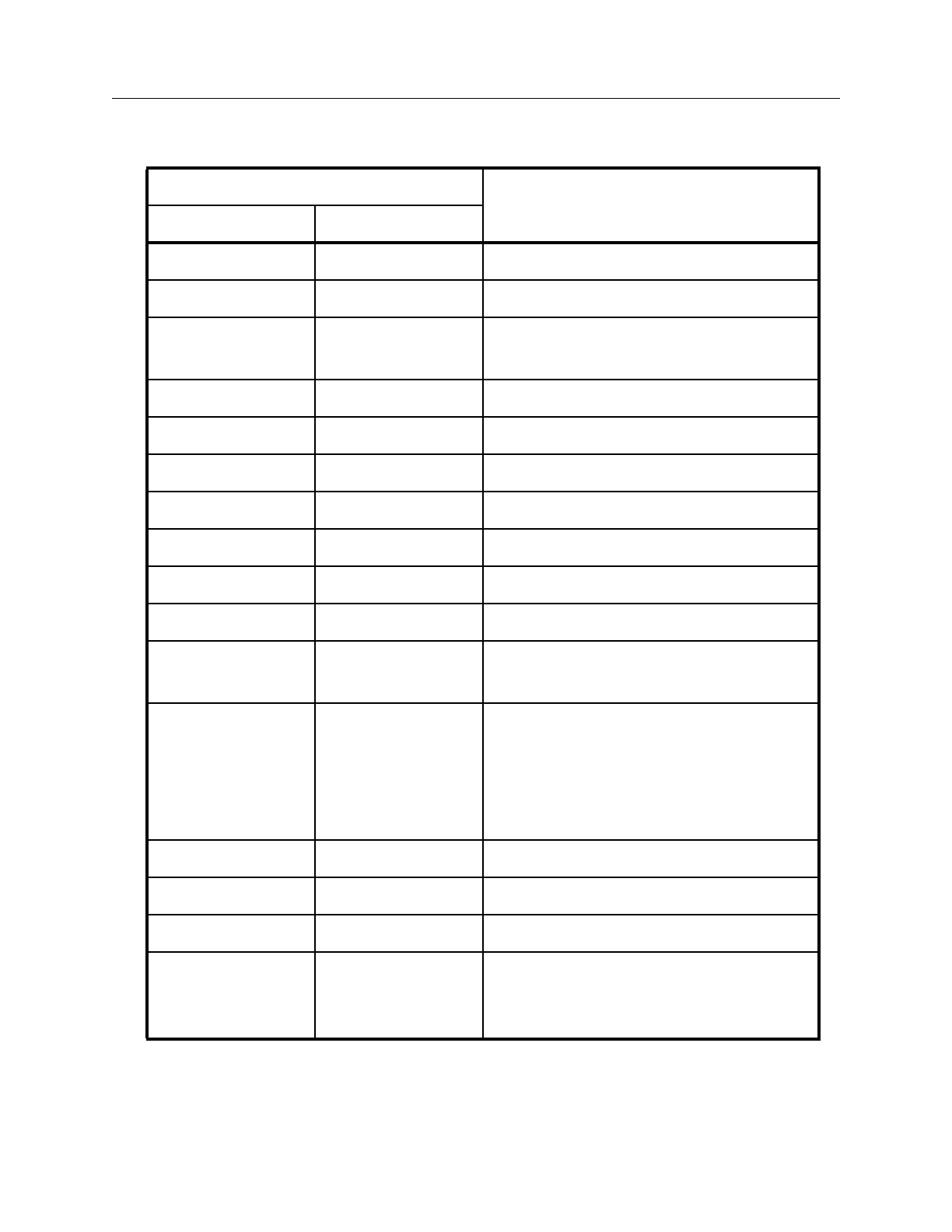

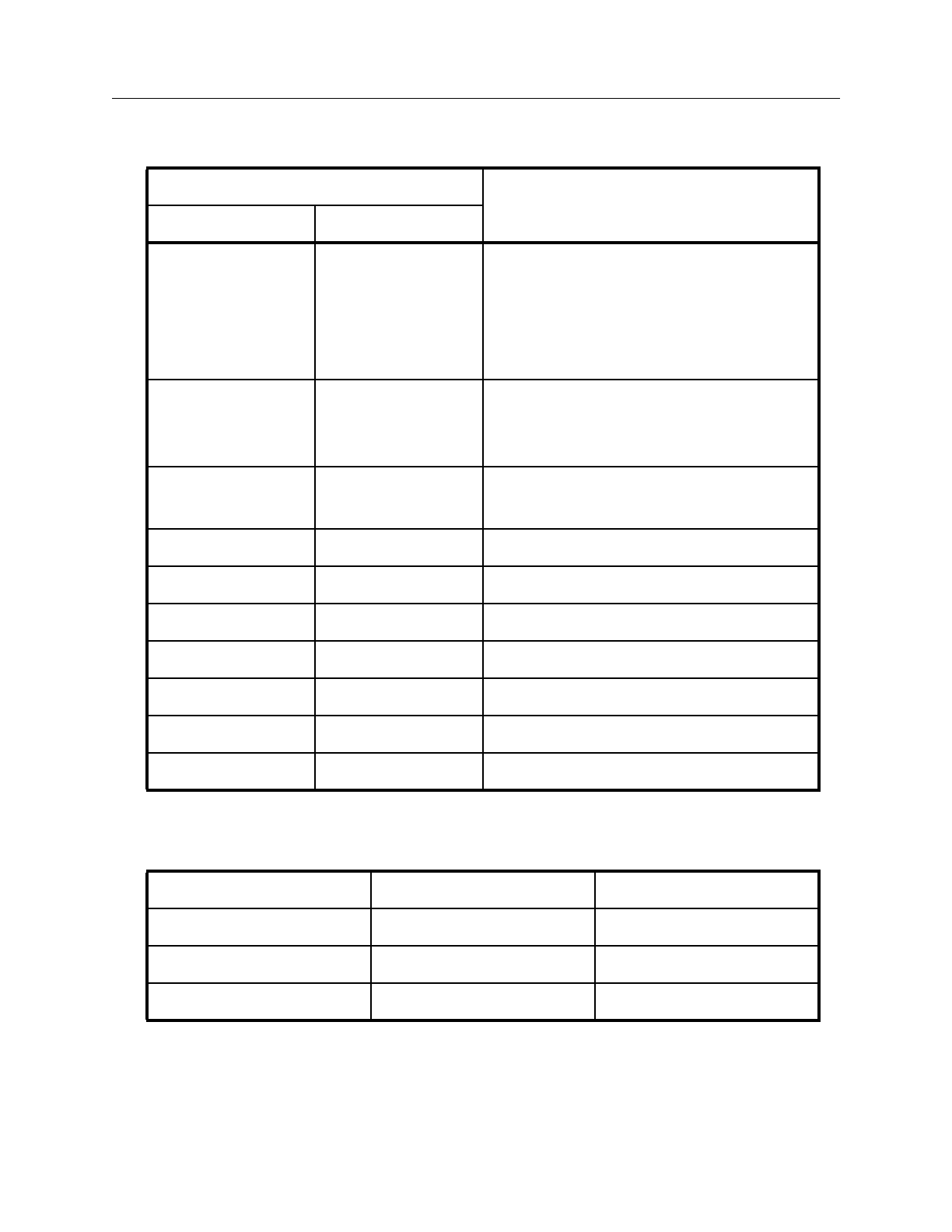

Table 2-1. Command Summary ......................................................................... 2-1

Table 2-2. Fault Class Codes and Names ...................................................... 2-299

Table 2-3. Reportable Gate Types ................................................................ 2-321

Table 2-4. FlexTest Learned Gate Types ...................................................... 2-323

Table 2-5. FastScan Clock Port Categories ................................................... 2-324

Table 2-6. WIRE Bus Contention Truth Table .............................................. 2-529

Table 2-7. AND Bus Contention Truth Table ............................................... 2-529

Table 2-8. OR Bus Contention Truth Table .................................................. 2-530

Table 2-9. DRC Non-scan Cell Classifications ............................................. 2-534

Table A-1. Timing Command Summary ...........................................................A-2

LIST OF TABLES

LIST OF TABLES [continued]

Table of Contents

FastScan and FlexTest Reference Manual, V8.6_4

xvi

About This Manual Overview

FastScan and FlexTest Reference Manual, V8.6_4 xvii

About This Manual

Overview

FastScan and FlexTest are Mentor Graphics ATPG tools which are an integral

part of the Mentor Graphics Design-For-Test solution.

FastScan is a comprehensive combinational Automatic Test Pattern Generation

(ATPG) system optimized for full scan designs. It offers the highest speed and

accurately measured high test coverage to guarantee your product quality and

reliability.

FlexTest is a high performance sequential Automatic Test Pattern Generation

(ATPG) system that allows you to create a set of test patterns that achieves a high,

accurately measured test coverage for your cycle-based circuits.

Optionally available with FastScan and FlexTest is Mentor Graphics DFTInsight

which can translate a specified portion of a netlist-based design to schematic form.

DFTInsight adds the ability to graphically investigate and interact with designs,

thus facilitating testability debugging efforts.

This manual contains information on each of the FastScan, FlexTest, and

DFTInsight application commands. Additionally, the manual contains reference

information specific to each of these applications. For procedural information on

how to use FastScan, FlexTest, or DFTInsight in the ASIC/IC design

environment, refer to the Scan and ATPG Process Guide.

This manual is divided into the sections and appendices that follow:

•Chapter 1 — Introduction - briefly describes the inputs, outputs, and

features of FastScan, FlexTest, and DFTInsight.

•Chapter 2 — Command Dictionary - lists the detailed information for

each command.

FastScan and FlexTest Reference Manual, V8.6_4

xviii

Overview About This Manual

•Chapter 3 — Shell Commands - lists the detailed information on the

FastScan, FlexTest, and DFTInsight invocation commands.

•Chapter 4 —Test Pattern File Formats - describes the test pattern file

format.

•Chapter 5 —Distributed FlexTest - describes how to divide ATPG

processes into smaller sets and run these sets simultaneously on multiple

workstations.

•Appendix A —Timing Command Dictionary - describes how to create a

timing file and apply it to the test pattern set.

•Appendix B —FlexTest WDB Translation Support - describes

FlexTest’s usage of the “wdb2flex” utility to translate Waveform Databases

to FlexTest Table Format Patterns.

The DFT applications use Adobe Acrobat Exchange as their online

documentation and help viewer. Online help requires installing the Mentor

Graphics-supplied Acrobat Exchange program with Mentor Graphics-specific

plugins and also requires setting an environment variable. For more information,

refer to the section, “Setting Up Online Manuals and Help” in Using Mentor

Graphics Documentation with Acrobat Exchange.

About This Manual Related Publications

FastScan and FlexTest Reference Manual, V8.6_4 xix

Related Publications

This section gives references to both Mentor Graphics product documentation and

industry DFT documentation.

Mentor Graphics Documentation

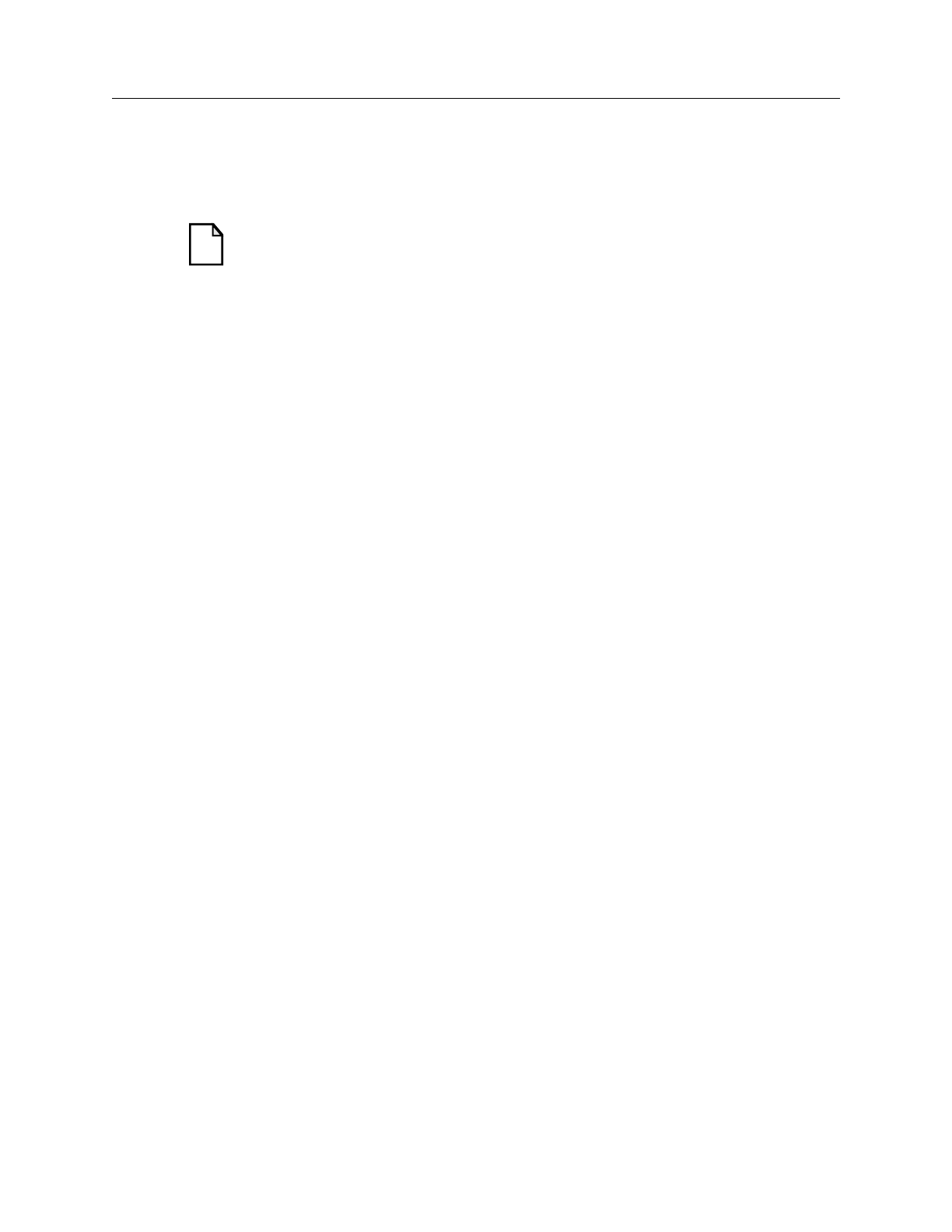

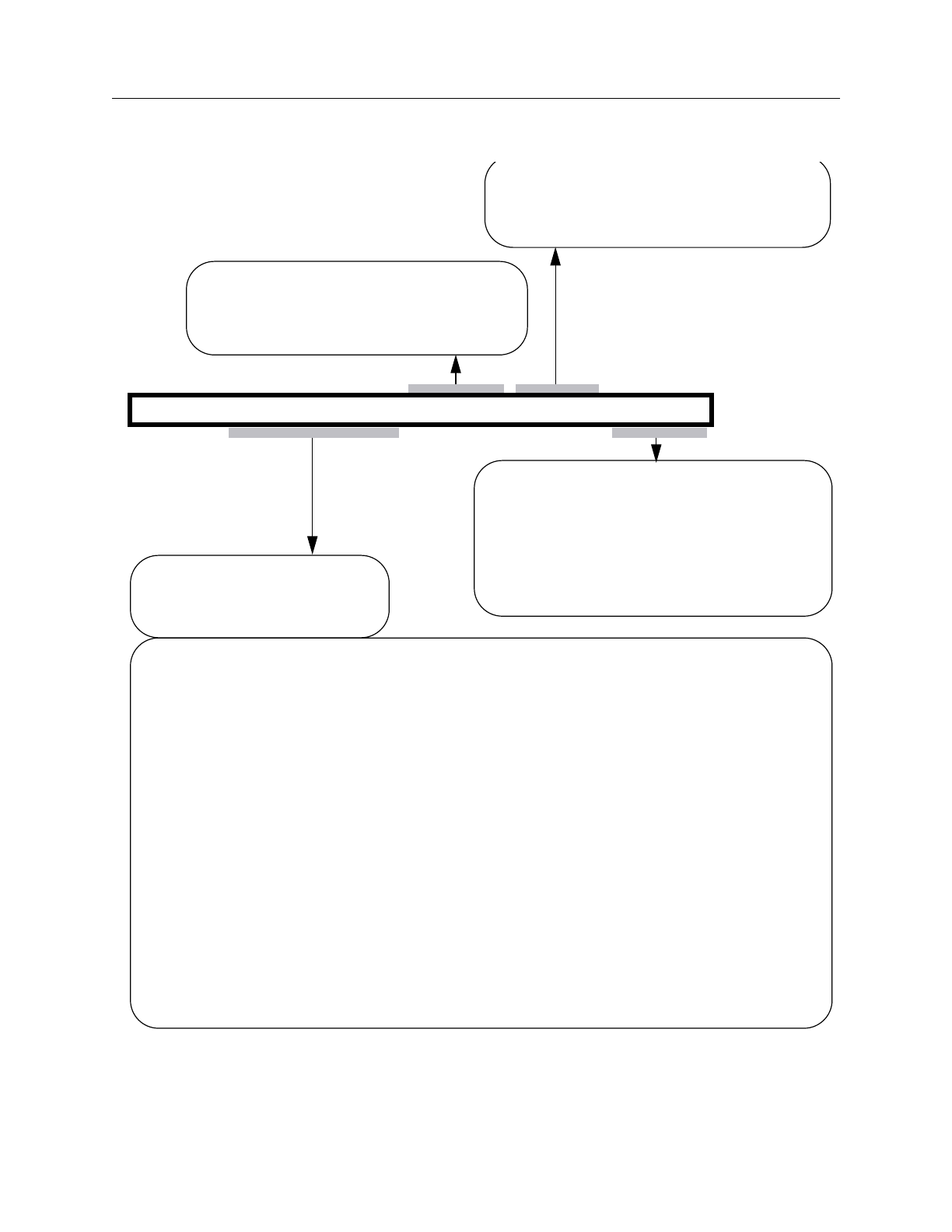

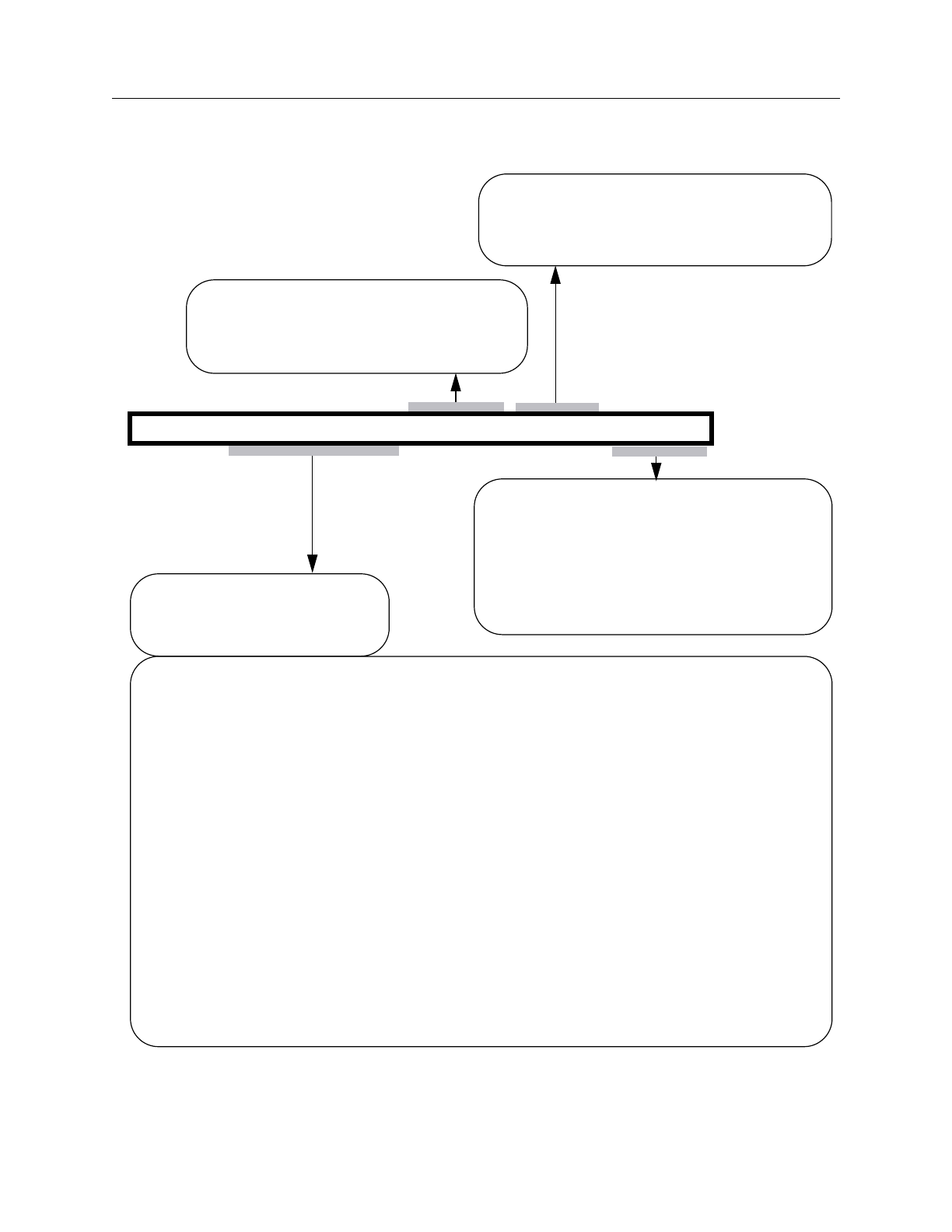

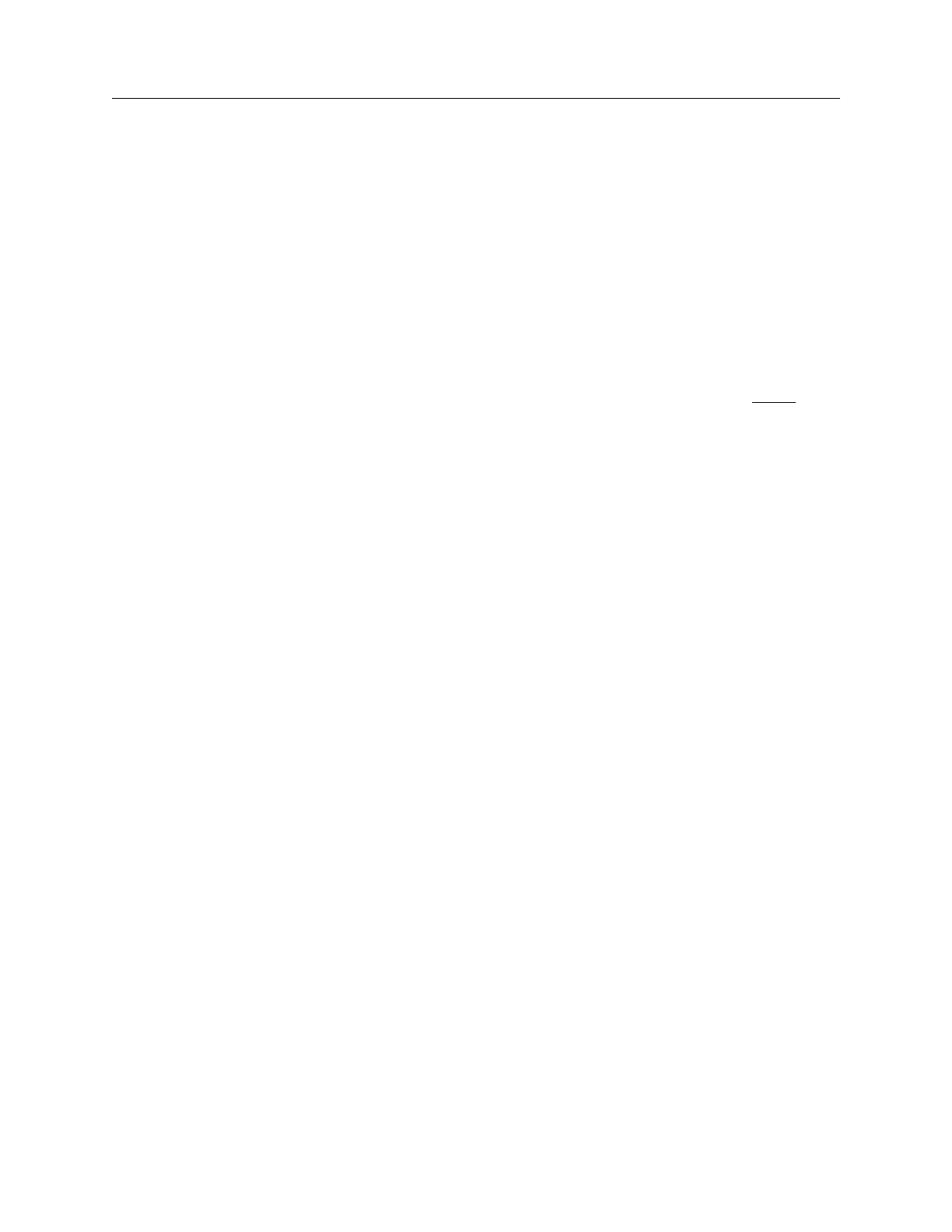

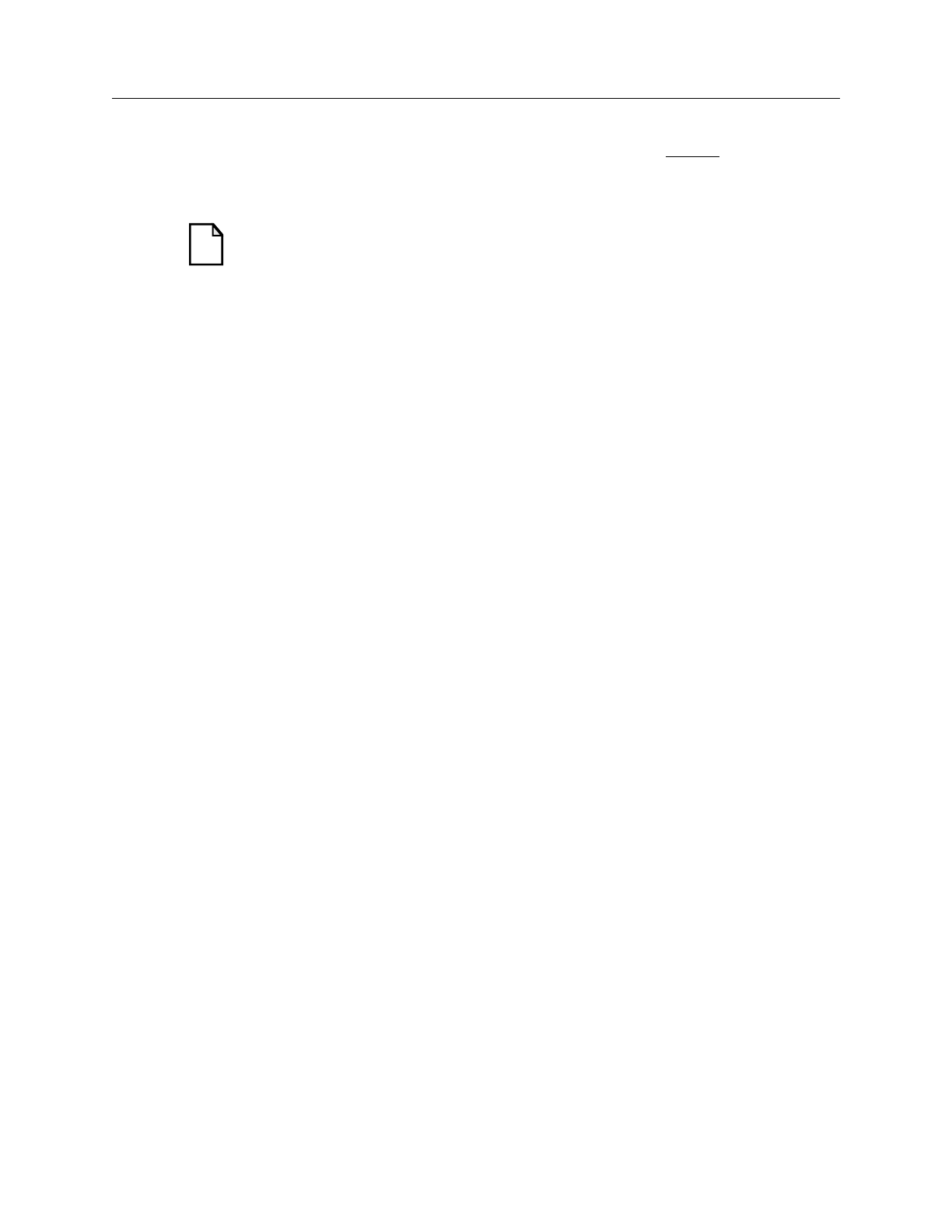

Figure 1 shows the Mentor Graphics DFT manuals and their relationship to each

other and is followed by a list of descriptions for these documents.

Figure 1. DFT Documentation Roadmap

Boundary Scan Process Guide — provides process, concept, and procedure

information for the boundary scan product, BSDArchitect. It also includes

information on how to integrate boundary scan with the other DFT

technologies.

BSDArchitect Reference Manual — provides reference information for

BSDArchitect, the boundary scan product.

DFTAdvisor

Reference Manual

FastScan & FlexTest

Reference Manual

Design-for-Test

Manual

Common Resources

Design-for-Test

Release Notes

LBISTArchitect

Reference Manual

MBISTArchitect

Reference Manual

Scan and ATPG

Process Guide

Built-in Self-Test

Process Guide

BSDArchitect

Reference Manual

Boundary Scan

Process Guide

FastScan and FlexTest Reference Manual, V8.6_4

xx

Related Publications About This Manual

Built-in Self-Test Process Guide — provides process, concept, and

procedure information for using MBISTArchitect, LBISTArchitect, and

other Mentor Graphics tools in the context of your BIST design process.

Design-for-Test Common Resources Manual — contains information

common to many of the DFT tools: design rule checks (DRC), DFTInsight

(the schematic viewer), library creation, VHDL support, Verilog support,

Spice support, and test procedure file format.

Design-for-Test Release Notes — provides release information that reflects

changes to the DFT products for the software version release.

DFTAdvisor Reference Manual — provides reference information for

DFTAdvisor (internal scan insertion) and DFTInsight (schematic viewer)

products.

FastScan and FlexTest Reference Manual — provides reference

information for FastScan (full-scan ATPG), FlexTest (non- to partial-scan

ATPG), and DFTInsight (schematic viewer) products.

LBISTArchitect Reference Manual — provides reference information for

LBISTArchitect, the logic built-in self-test product.

MBISTArchitect Reference Manual — provides reference information for

MBISTArchitect, the memory built-in self-test product.

Scan and ATPG Process Guide — provides process, concept, and

procedure information for using DFTAdvisor, FastScan, and FlexTest in

the context of your DFT design process.

Using Mentor Graphics Documentation with Acrobat Exchange —

describes how to set up and use the Mentor Graphics-supplied Acrobat

Exchange with enhancement plugins for online viewing of Mentor

Graphics PDF-based documentation and help. The manual contains

procedures for using Mentor Graphics documentation, including setting up

online manuals and help, opening documents, and using full-text searches.

Also included are tips on using Exchange.

About This Manual Acronyms Used in This Manual

FastScan and FlexTest Reference Manual, V8.6_4 xxi

Acronyms Used in This Manual

Below is an alphabetical listing of the acronyms used in this manual:

ASIC - Application Specific IC

ATE - Automatic Test Equipment

ATPG - Automatic Test Pattern Generation

AU - ATPG_Untestable fault

AVI - ASIC Vector Interfaces

BIST - Built-In Self Test

BSDA - Boundary Scan Design Architect

BSDL - Boundary Scan Design Language

CUT - Circuit Under Test

DFT - Design For Test

DFTA - DFTAdvisor

DFTI - DFTInsight

DRC - Design Rules Check

DUT - Device Under Test

EDDM - Electronic Design Data Model

EDIF - Electronic Design Interchange Format

FS - FastScan

FT - FlexTest

FastScan and FlexTest Reference Manual, V8.6_4

xxii

Acronyms Used in This Manual About This Manual

GENIE - General Interpreted Environment

IDDQ - Quiescent Drain Current

I/O - Input/Output

JTAG - Joint Test Action Group

LFSR - Linear Feedback Shift Register

LSSD - Level Sensitive Scan Design

MCM - Multi-Chip Module

MISR - Multiple Input Signature Register

PGS - Pulse Generator Sink

PI - Primary Input

PRPG - Pseudo-Random Pattern Generator

PO - Primary Output

PU - Posdet_Untestable fault

SFP - Single Fault Propagation

TDL - TEGAS Design Language

UI - User Interface

VHDL - VHSIC Hardware Description Language

VHSIC - Very High Speed IC

WDB - Waveform DataBase

About This Manual Command Line Syntax Conventions

FastScan and FlexTest Reference Manual, V8.6_4 xxiii

Command Line Syntax Conventions

Each point-tool manual will include the following notation conventions section in

the ATM chapter. For more information on Mentor Graphics documentation

conventions, see the “Mentor Graphics Learning Products Style Guide”

The notational elements for command line syntax are as follows:

Bold A bold font indicates a required argument.

[ ] Square brackets enclose optional arguments (in command line

syntax only). Do not enter the brackets.

UPPercase Required command letters are in uppercase; in most cases, you

may omit lowercase letters when entering commands or literal

arguments and you need not use uppercase. Command names and

options are normally case insensitive, but for some tools the initial

command name is case sensitive and must be lowercase.

Commands usually follow the 3-2-1 rule: the first three letters of

the first word, the first two letters of the second word, and the first

letter of the third, fourth, etc. words.

Italic An italic font indicates a user-supplied argument.

An underlined item indicates either the default argument or the

default value of an argument.

{ } Braces enclose arguments to show grouping. Do not enter the

braces.

| The vertical bar indicates an either/or choice between items. Do

not include the bar in the command.

… An ellipsis follows an argument that may appear more than once.

Do not include the ellipsis in commands.

You should enter literal text (that which is not in italics) exactly as shown.

FastScan and FlexTest Reference Manual, V8.6_4

xxiv

Command Line Syntax Conventions About This Manual

FastScan and FlexTest Reference Manual, V8.6_4 1-1

Chapter 1

Introduction

FastScan and FlexTest are Mentor Graphics high-performance Automatic Test

Pattern Generation (ATPG) tools. FastScan performs full-scan and scan-

sequential ATPG, while FlexTest performs sequential ATPG. These are two of

several tools in the Mentor Graphics Design-for-Test (DFT) tool suite. The

following subsections list the features and inputs/outputs of the tools. For

information on using FastScan or FlexTest in the context of a DFT flow, refer to

the “Generating Test Patterns” chapter in the Scan and ATPG Process Guide.

Features

FastScan and FlexTest share numerous features, including the following:

•You can use them within a Mentor Graphics flow or as a point tool within

other design flows.

•Contain an internal high-speed fault simulator.

•Read most standard gate-level netlists.

•Produce a number of standard test pattern data formats.

•Contain a powerful design rules checker.

FastScan-specific features include the following:

•Produces very high coverage test pattern sets for full-scan and scan-

sequential designs. Scan-sequential designs contain well-behaved

sequential scan circuitry, including non-scan latches, sequential memories,

and limited sequential depth.

FastScan and FlexTest Reference Manual, V8.6_4

1-2

Inputs and Outputs Introduction

•Contains functionality for handling embedded RAM and ROM.

•Contains functionality for simulating and generating test pattern sets for

BIST circuitry.

FlexTest-specific features include the following:

•Supports a wide range of DFT structures.

•Can display a wide variety of useful information—from design and

debugging information to statistical reports for the generated test set.

Inputs and Outputs

FastScan and FlexTest utilize the following inputs:

•Design - The supported netlist formats are EDDM, EDIF, GENIE, Verilog,

VHDL, SPICE and TDL.

•Test Procedure File - This file defines the operation of the scan circuitry in

your design. You can generate the file by hand or using the Write ATPG

Setup command in DFTAdvisor. For more information on test procedure

files, refer to “Test Procedure Files” in the Scan and ATPG Process Guide.

•Library - This file contains model descriptions for all library cells used in

your design.

•Fault List - This is an external fault list that you can use as a source of faults

for the internal fault list of FlexTest.

•Test Patterns - This is a set of externally-generated test patterns that you can

use as the pattern source for simulation.

Introduction Inputs and Outputs

FastScan and FlexTest Reference Manual, V8.6_4 1-3

FastScan and FlexTest produce the following outputs:

•Test Patterns - This file set contains test patterns in one or more of the

supported simulator or ASIC vendor pattern formats. For more information

on the available test pattern formats, refer to the Save Patterns command

reference page within this manual, or the “Saving the Patterns” section in

the Scan and ATPG Process Guide.

•ATPG Information Files - These files contain session information that you

can save using various FlexTest commands.

•Fault List - This is an ASCII file containing internal fault information in the

standard Mentor Graphics fault format.

FastScan and FlexTest Reference Manual, V8.6_4

1-4

Inputs and Outputs Introduction

FastScan and FlexTest Reference Manual, V8.6_4 2-1

Chapter 2

Command Dictionary

This chapter contains descriptions of the FastScan, FlexTest, and DFTInsight

commands. The subsections are named for the command they describe. For quick

reference, the commands appear alphabetically with each beginning on a separate

page.

Command Summary

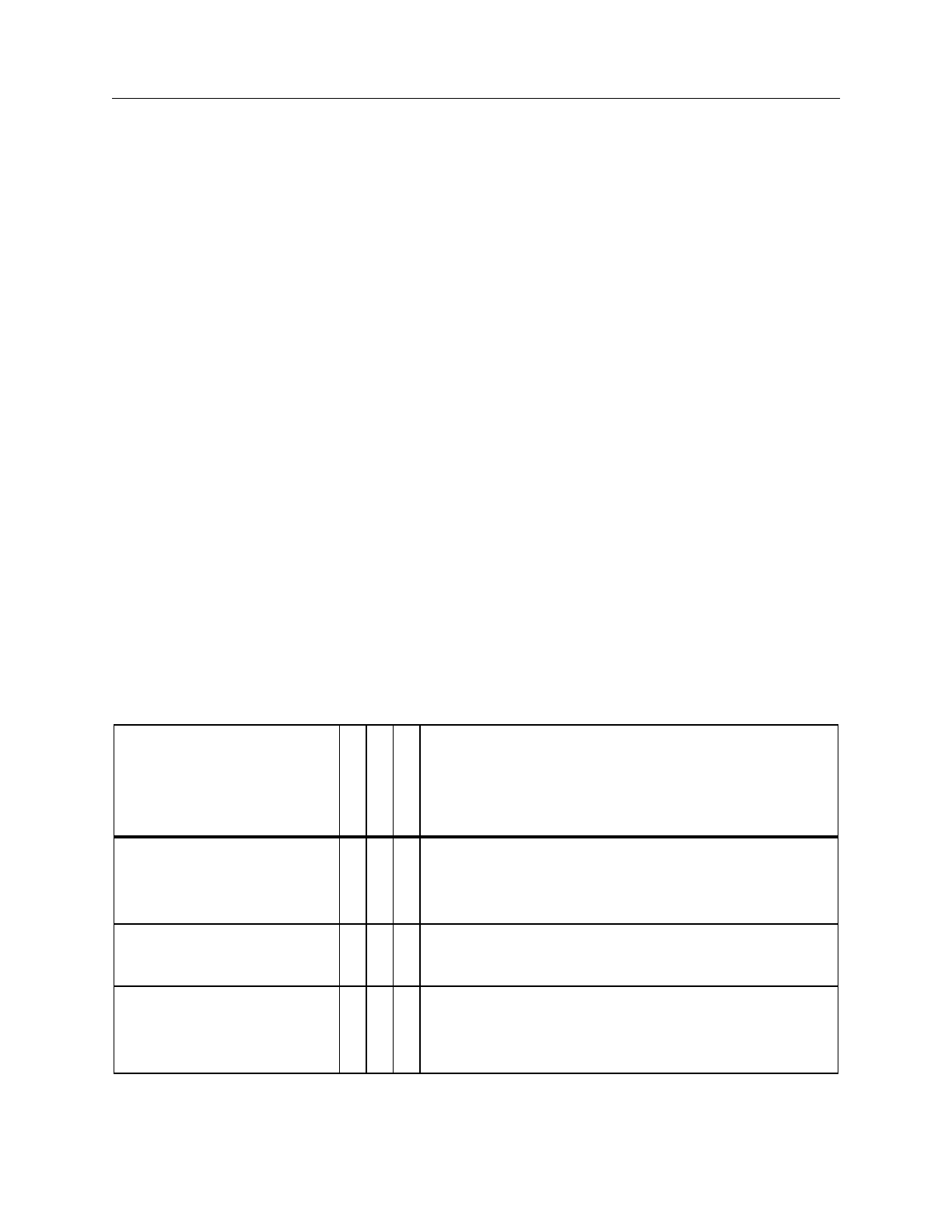

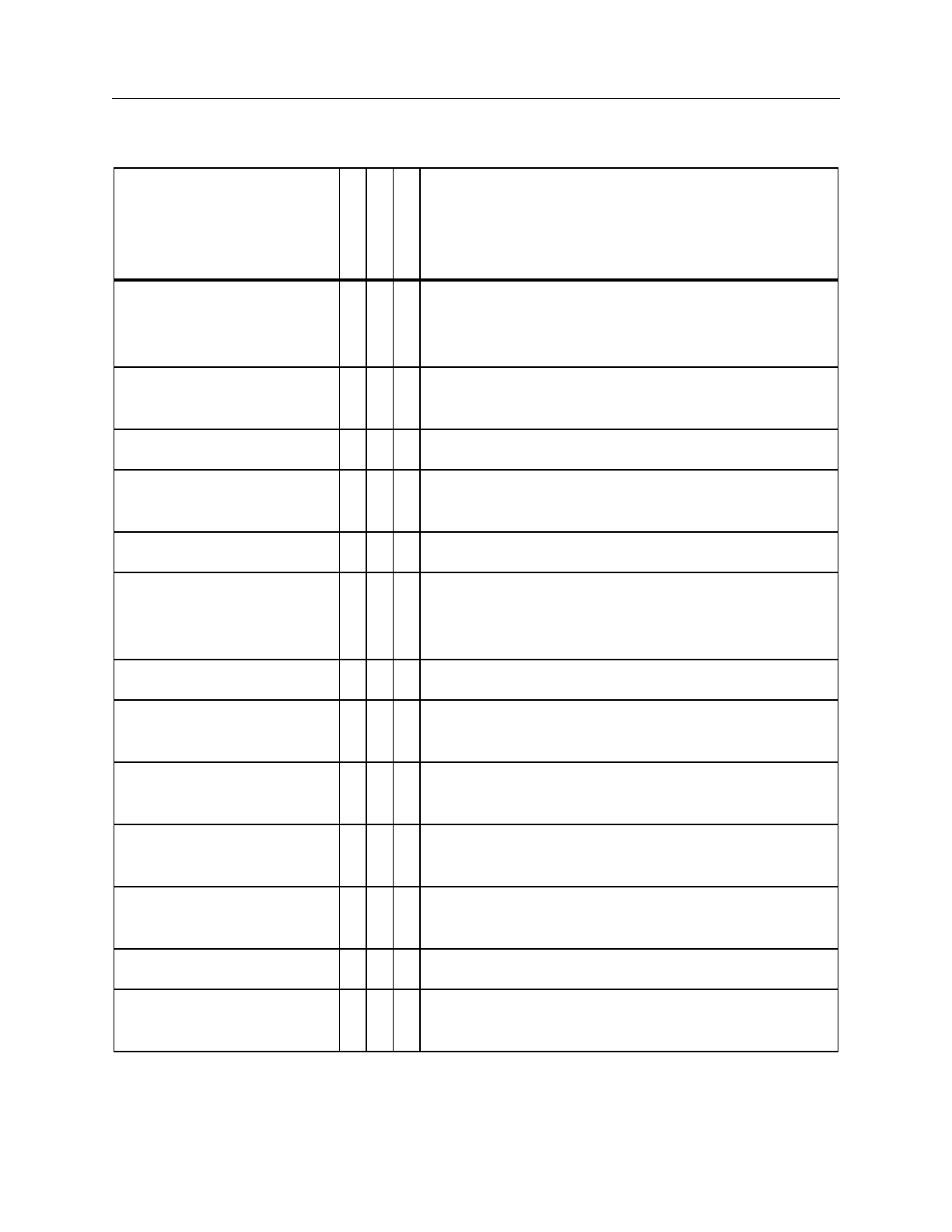

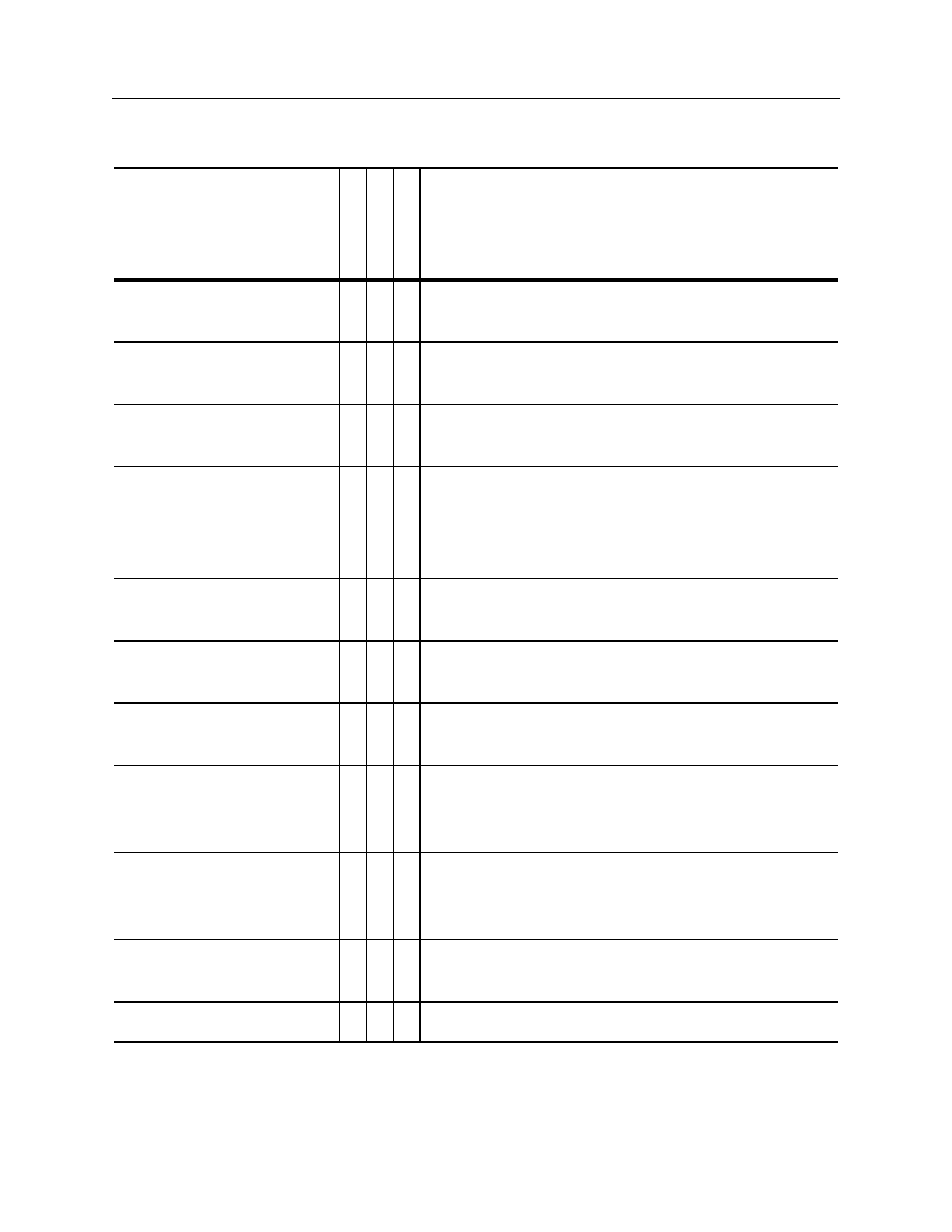

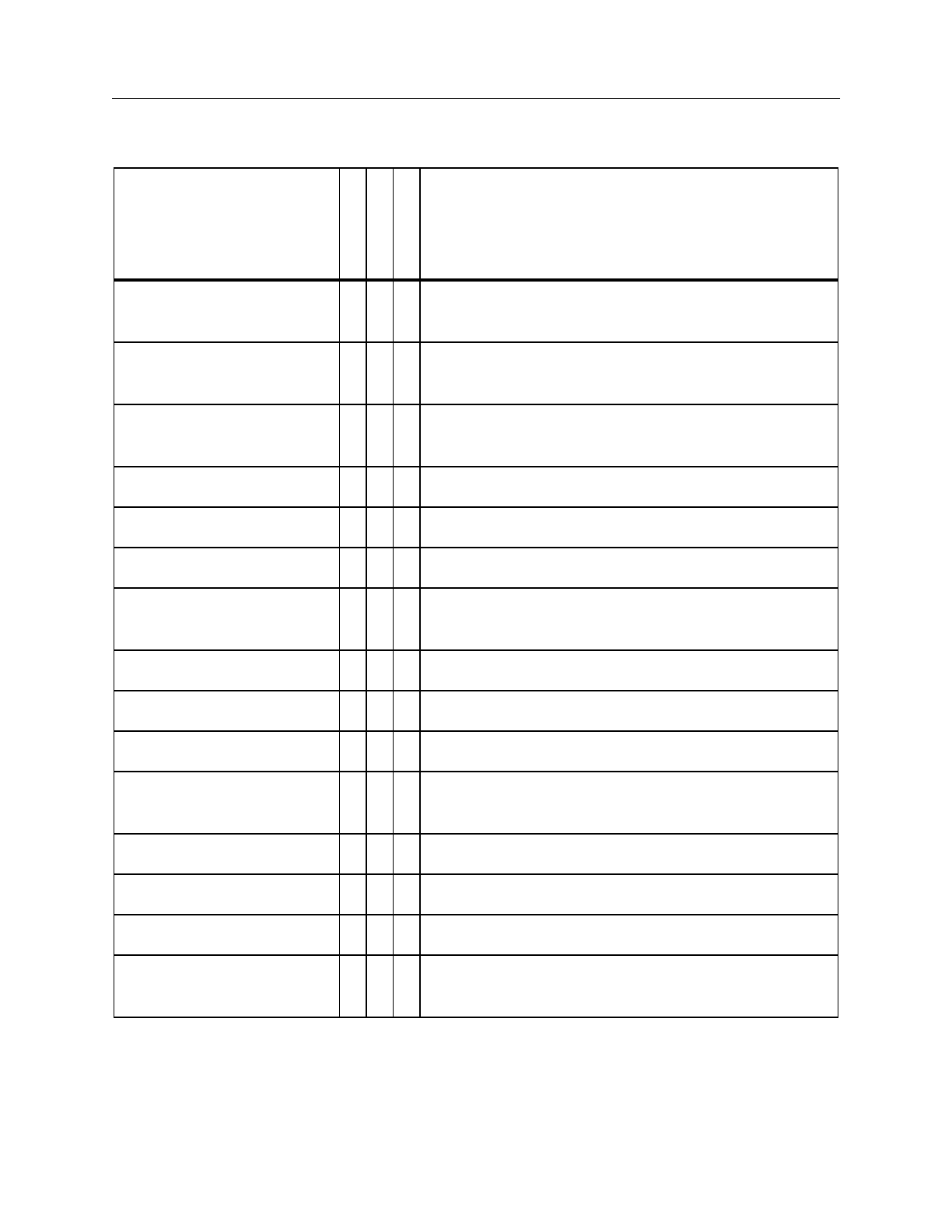

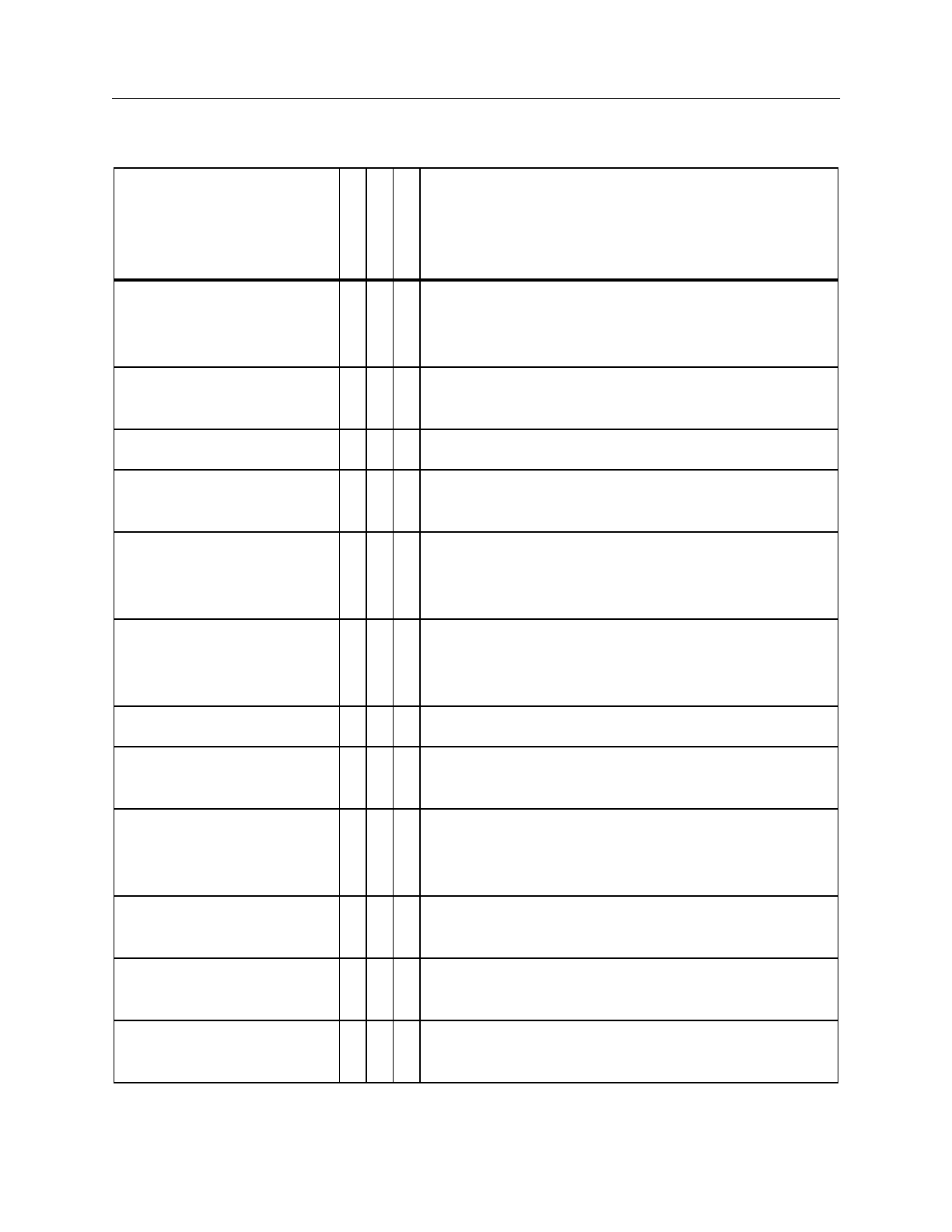

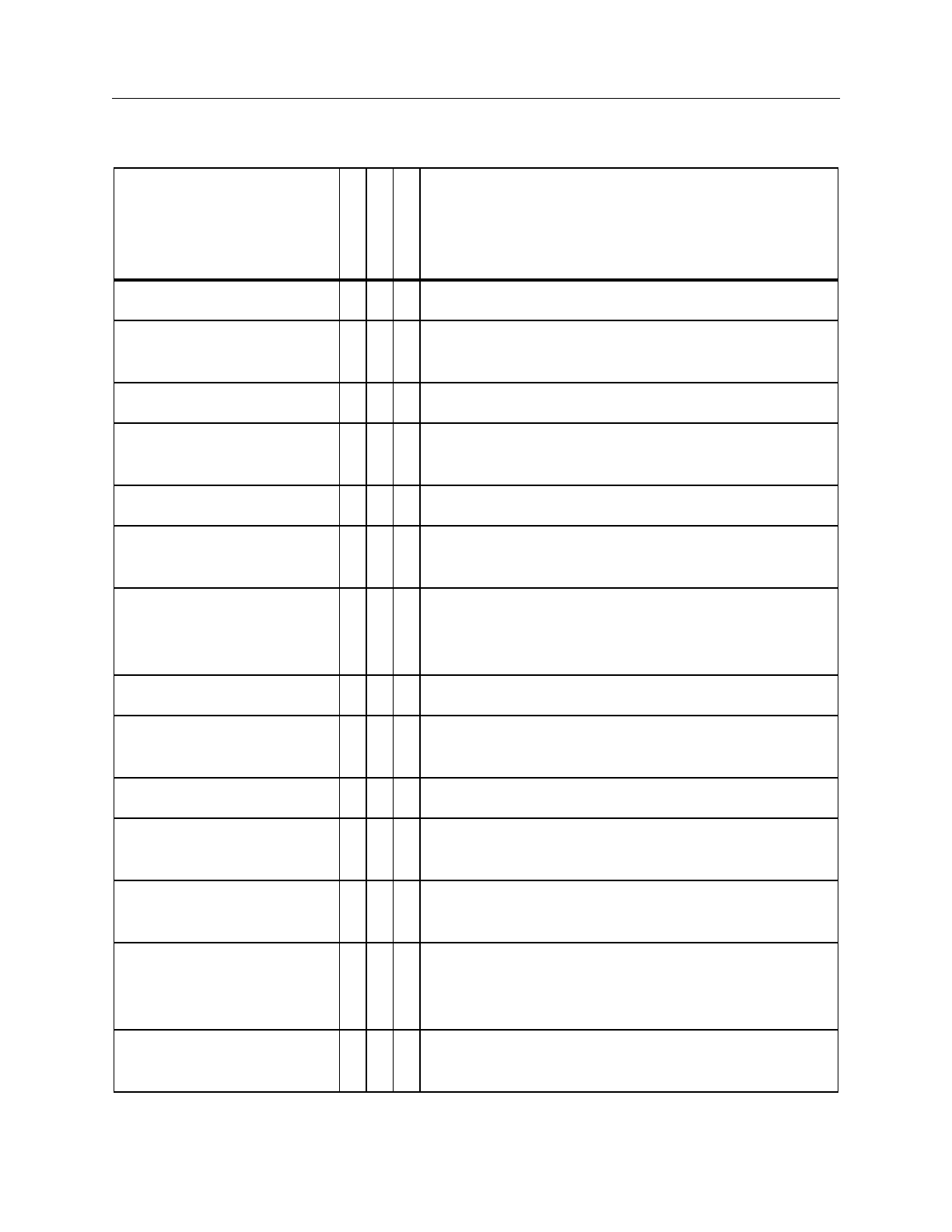

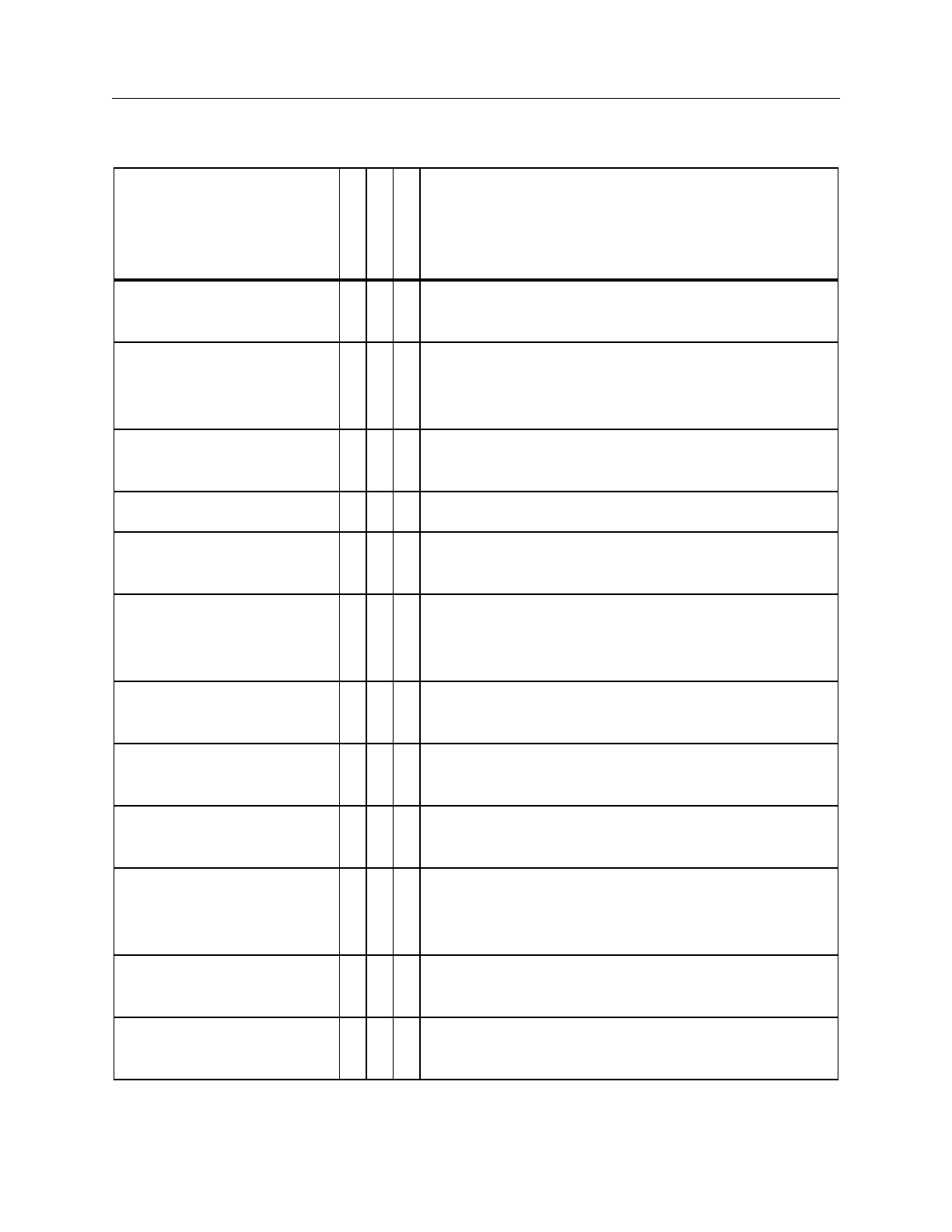

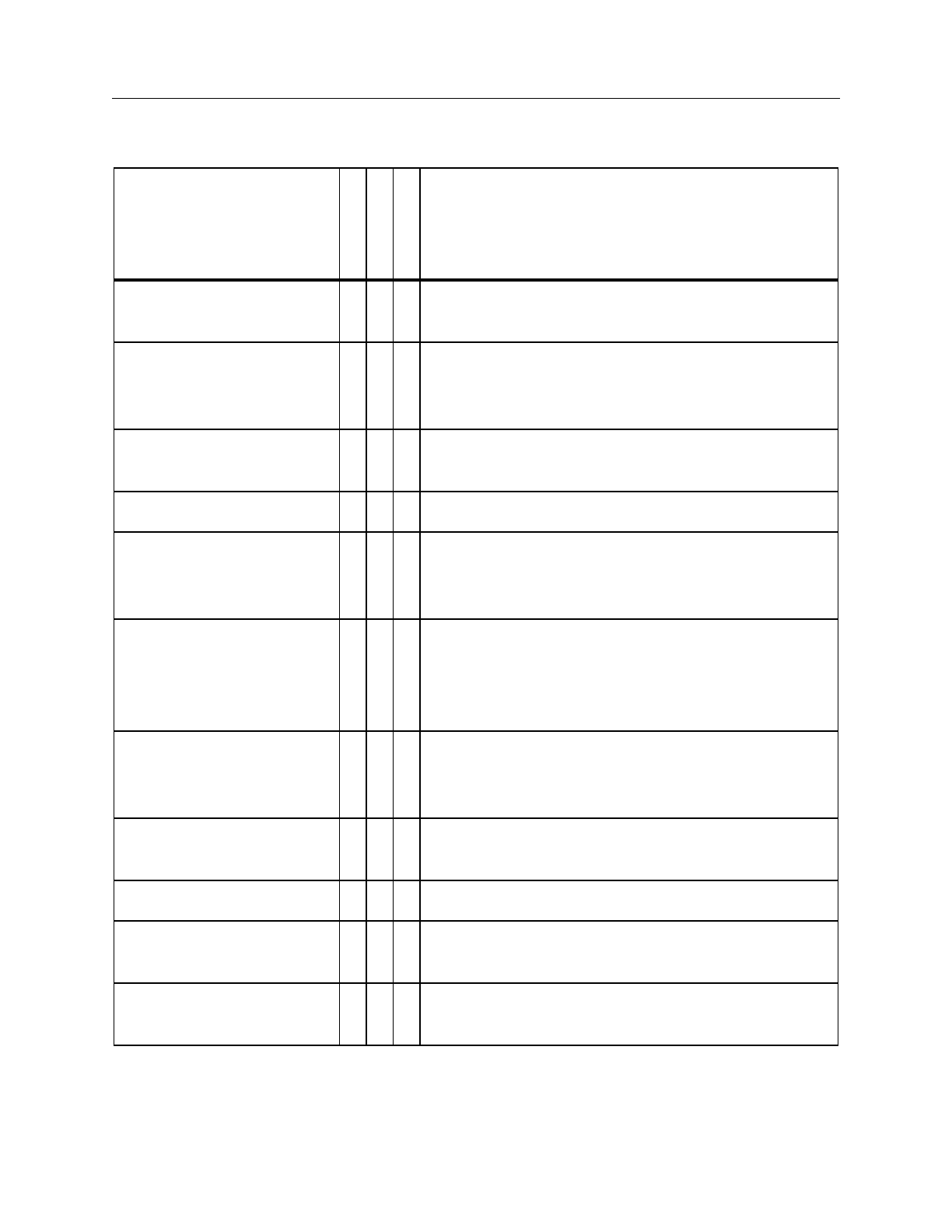

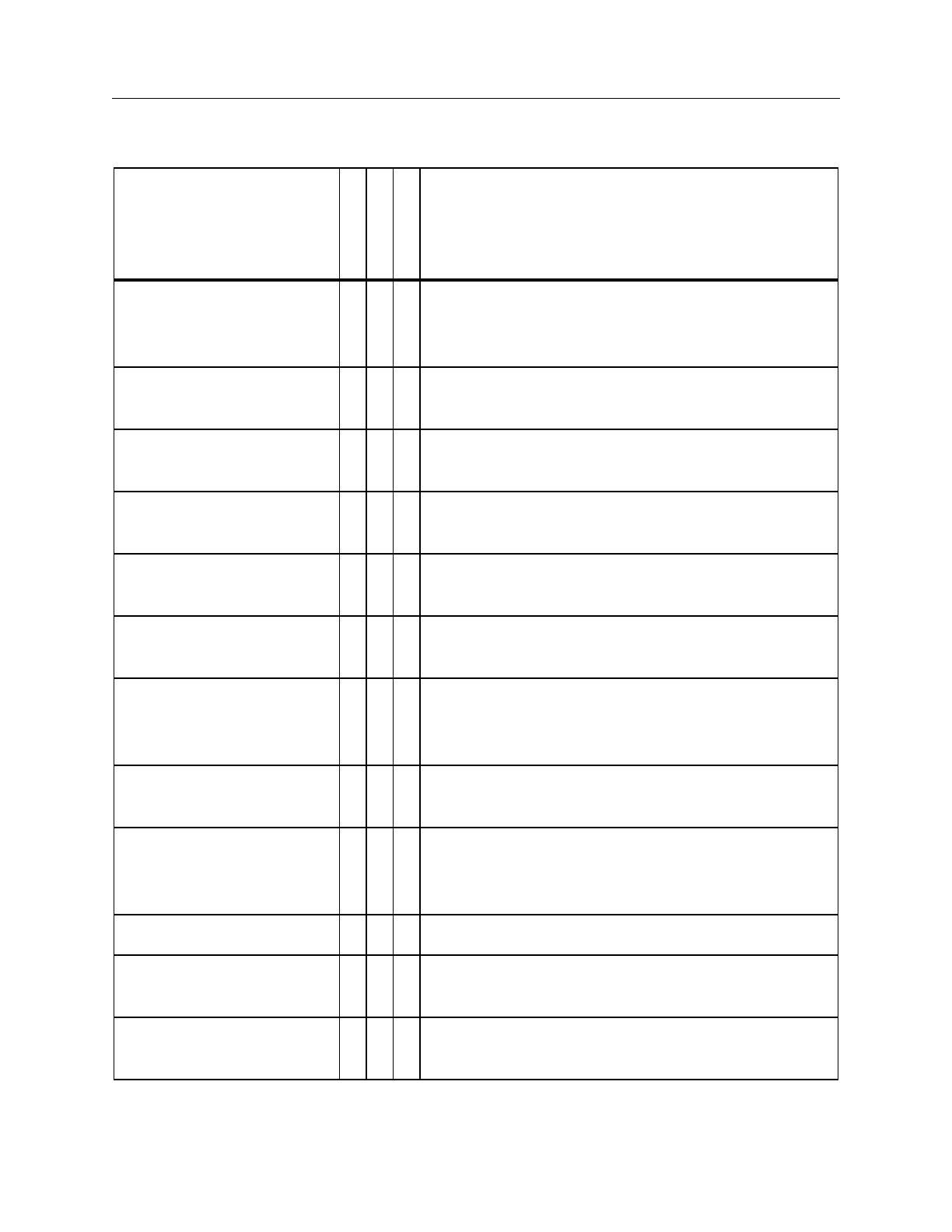

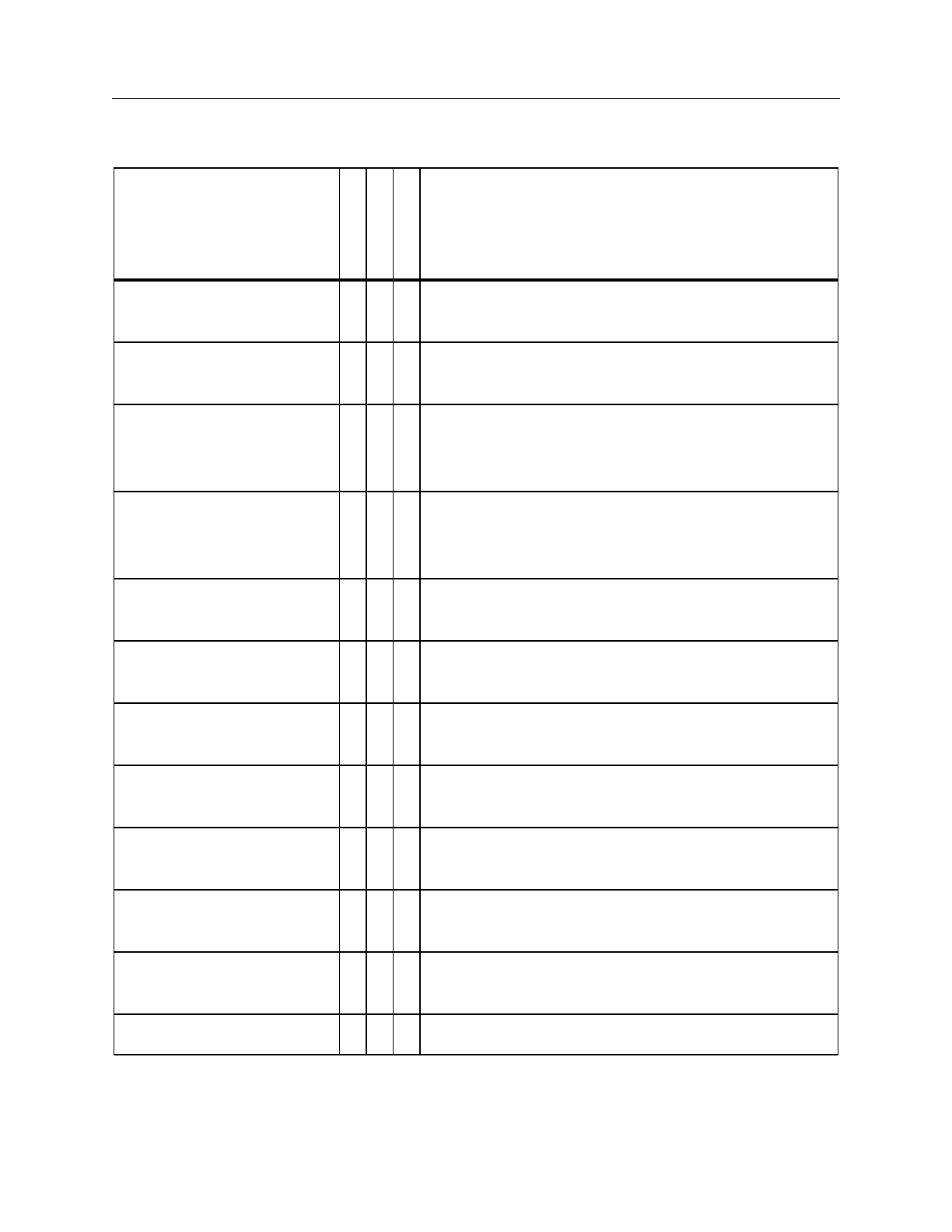

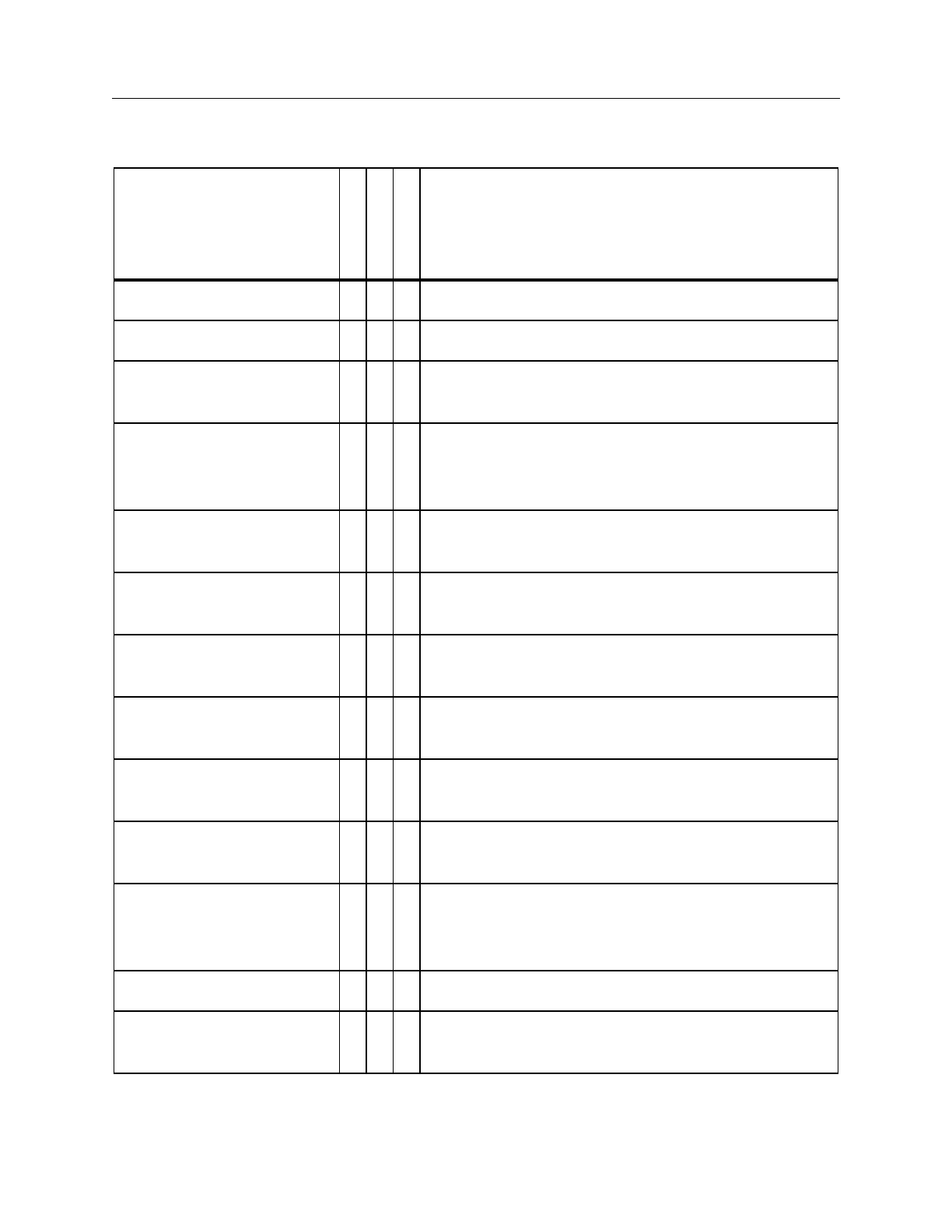

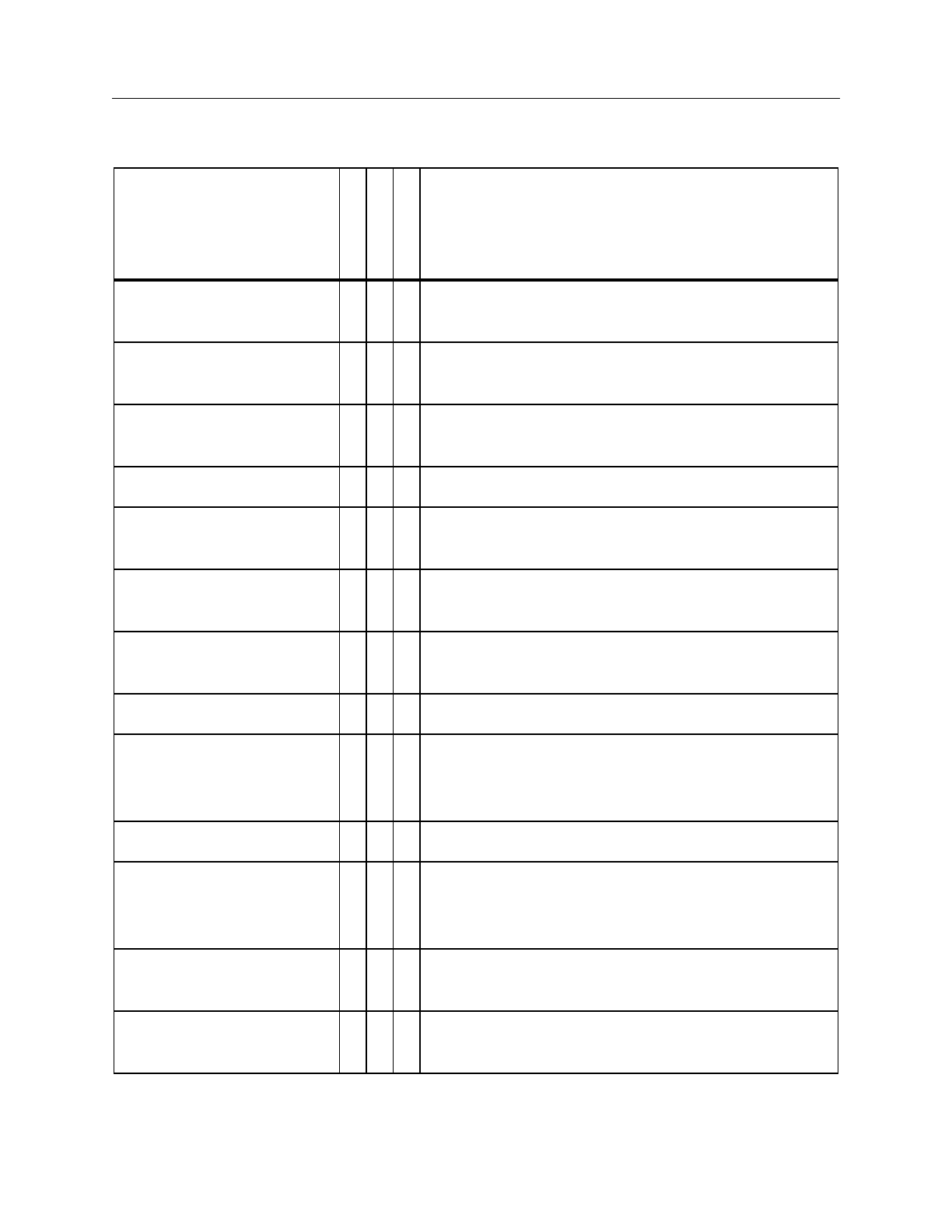

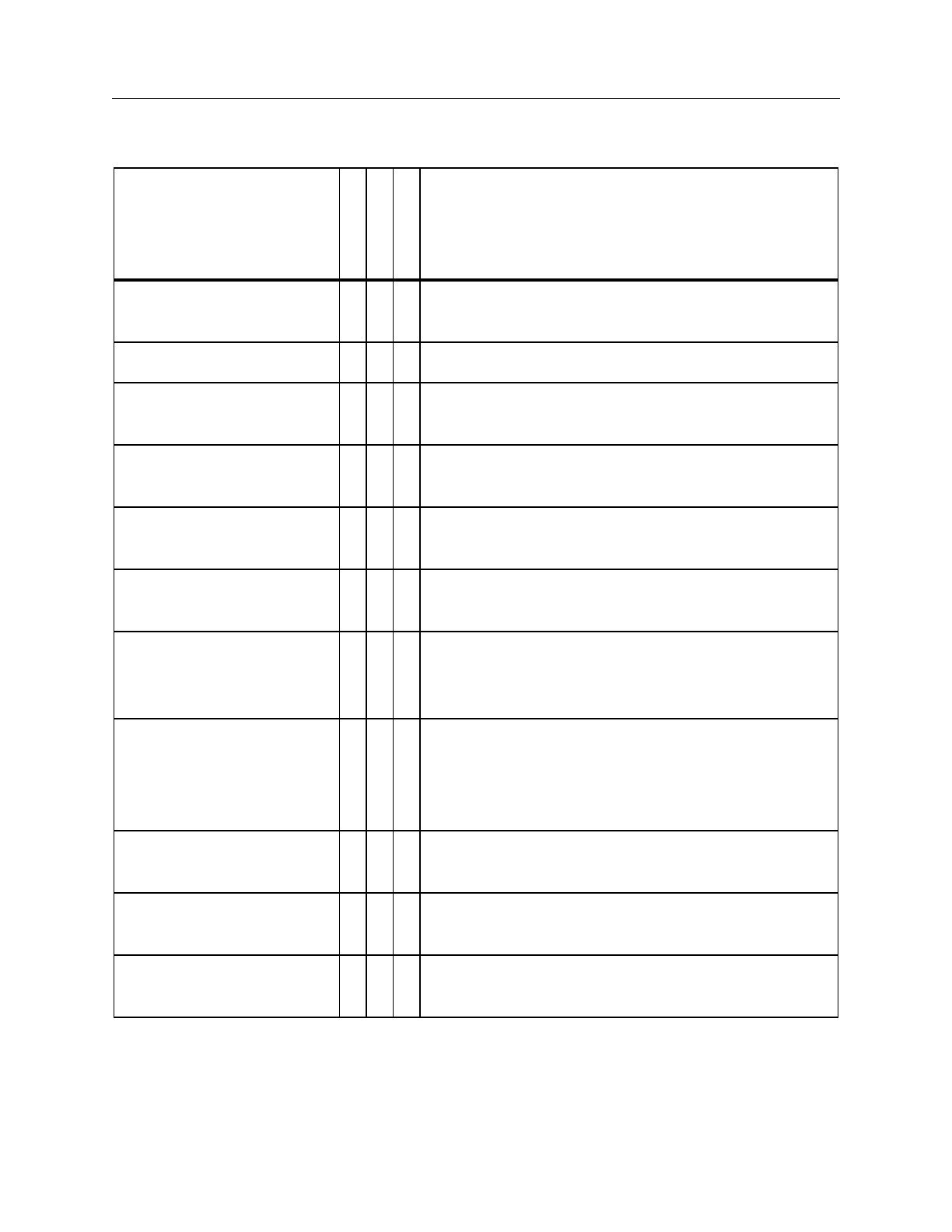

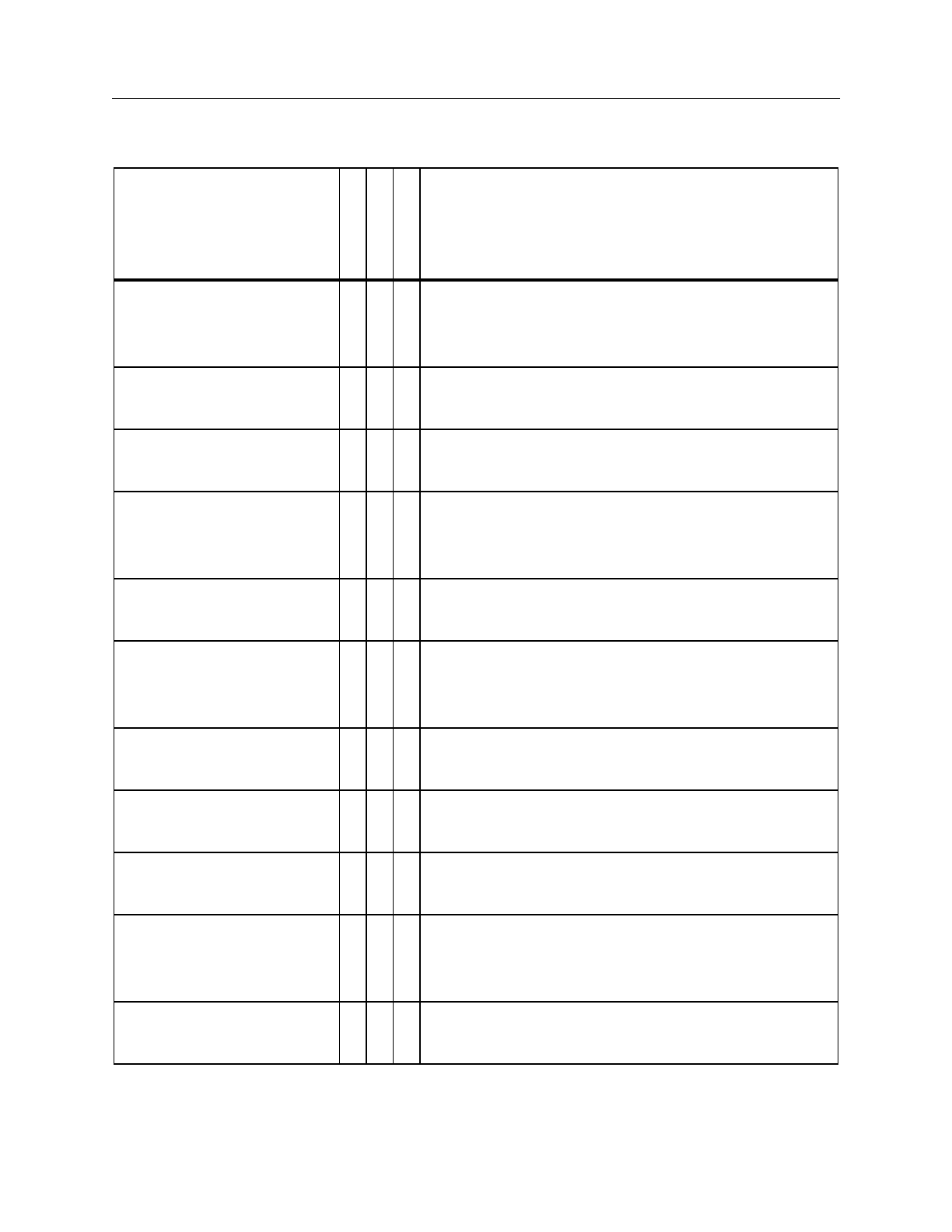

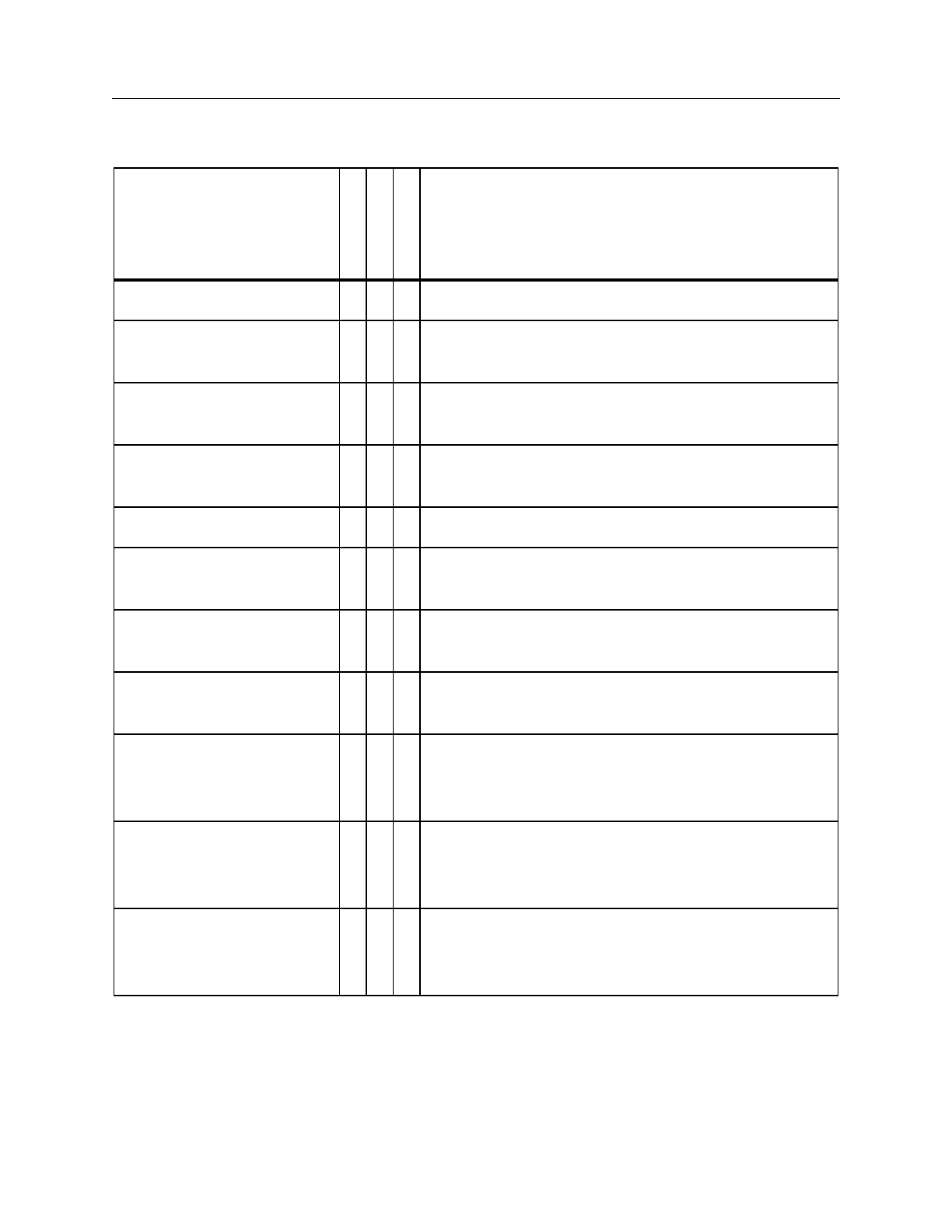

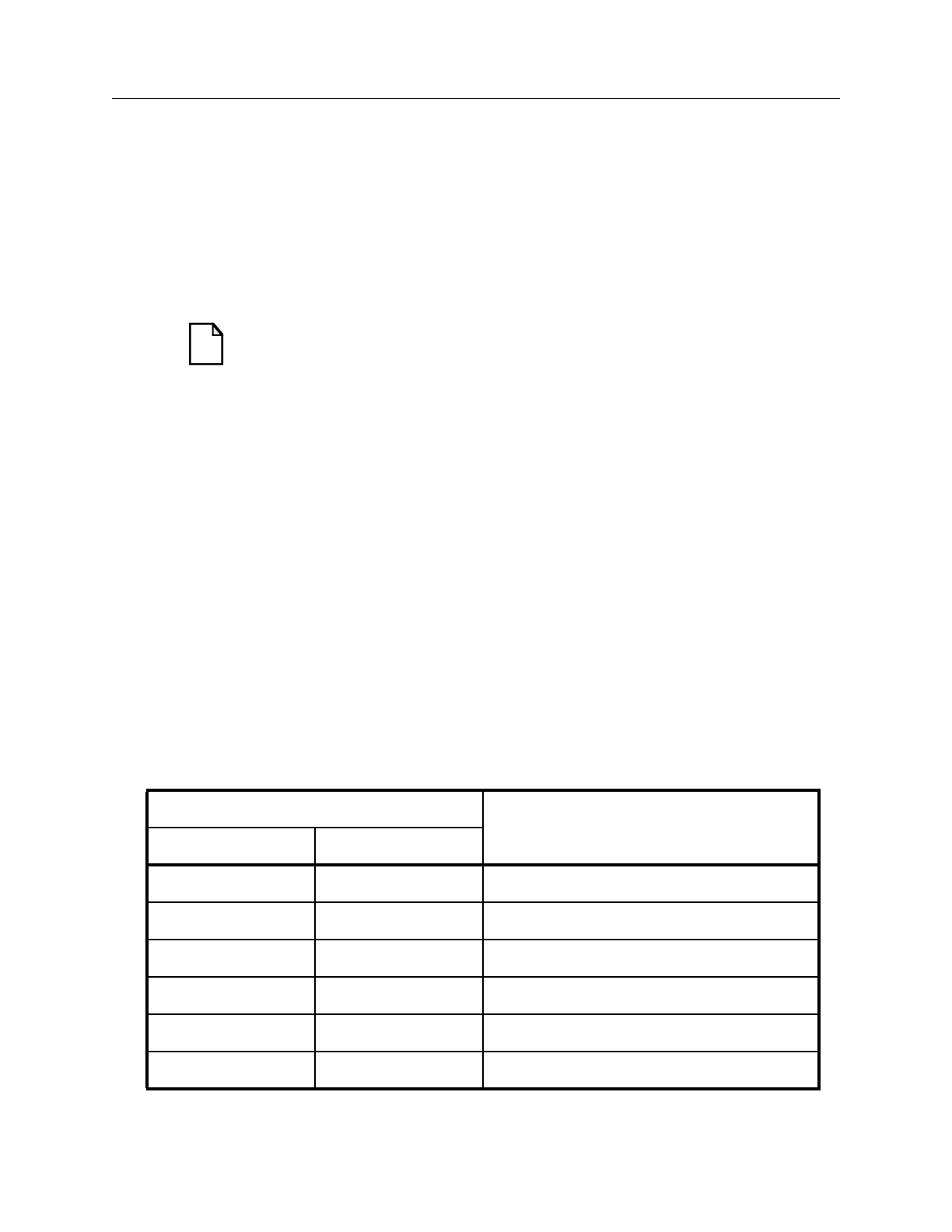

Table 2-1 contains a summary of the commands described in this manual. The

three columns that separate the command name and the description indicate the

tools in which you can use the commands. The following tool acronyms are used

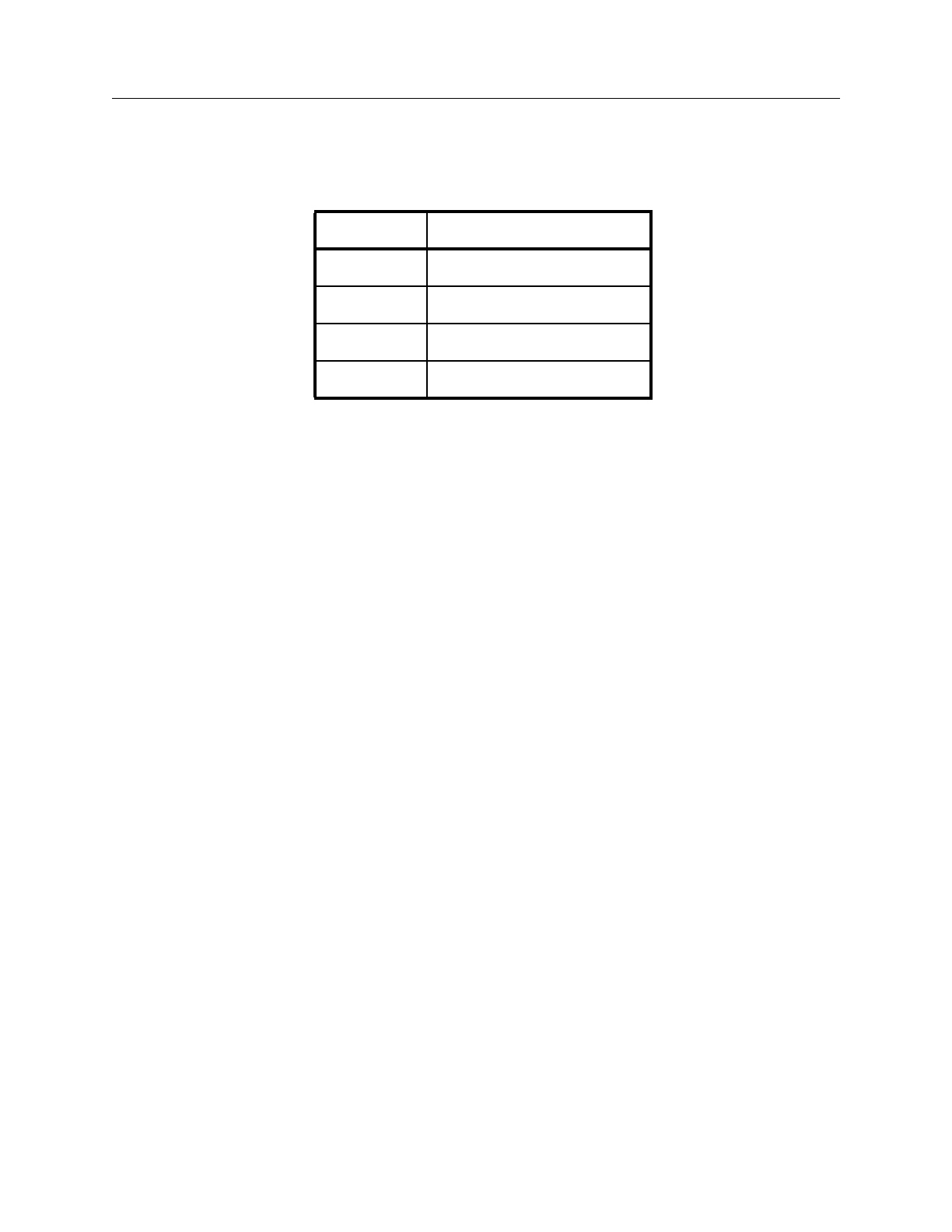

in the table:

DFTI DFTInsight FS FastScan FT FlexTest

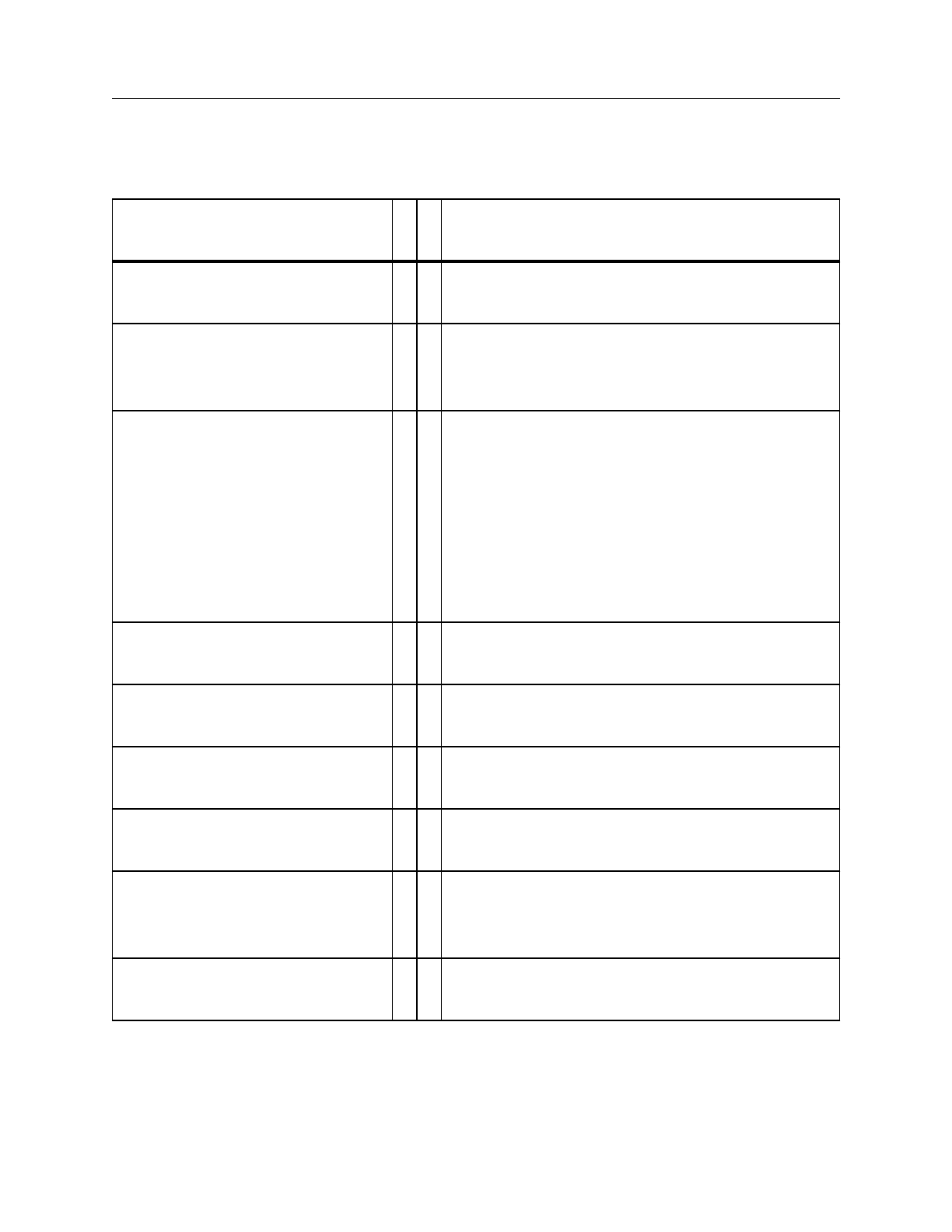

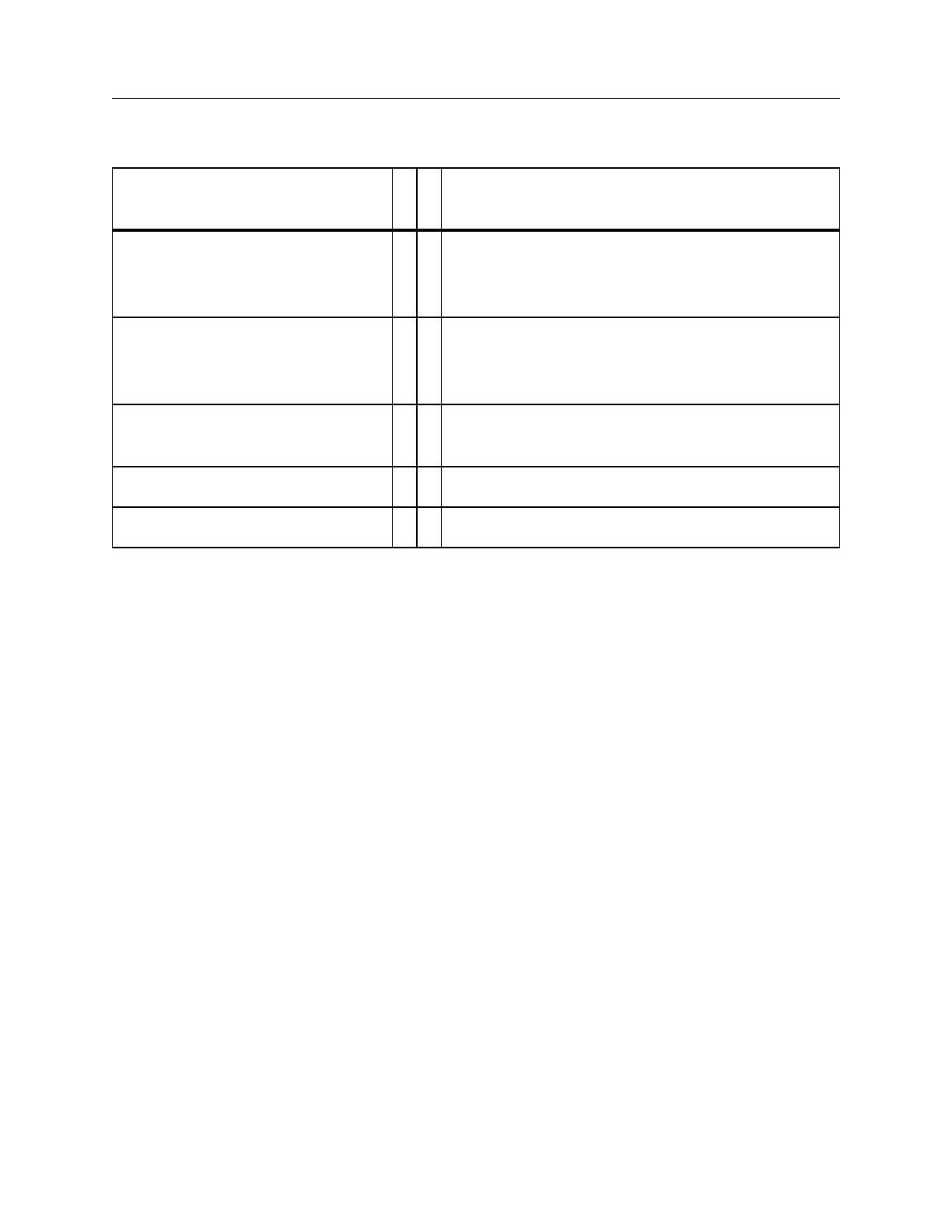

Table 2-1. Command Summary

Command

D

F

T

IF

SF

TDescription

Abort Interrupted

Process •Aborts a command placed in suspended state

by a Control-C interrupt while the Set

Interrupt Handling command is on.

Add Ambiguous Paths •Specifies for FastScan to select multiple paths

when there is path ambiguity.

Add Atpg Constraints ••Specifies that the tool restrict all patterns it

places into the internal pattern set according

to the user-defined constraints.

FastScan and FlexTest Reference Manual, V8.6_4

2-2

Command Summary Command Dictionary

Add Atpg Functions ••Creates an ATPG function that you can then

use when generating user-defined ATPG

constraints.

Add Capture Handling •Specifies the data capturing behavior for the

given state element.

Add Cell Constraints ••Constrains scan cells to be at a constant value.

Add Cell Library ••Specifies the EDIF library in which to place

all or specified library models.

Add Clocks ••Adds clock primary inputs to the clock list.

Add Cone Blocks ••Specifies the blockage points that you want

the tool to use during the calculation of the

clock and effect cones.

Add Control Points •Adds control points to output pins.

Add Display Instances •••Adds the specified instances to the netlist for

display.

Add Display Loop •••Displays all the gates in a specified feedback

path.

Add Display Path •••Displays all the gates associated with the

specified path.

Add Display Scanpath •••Displays all the associated gates between two

positions in a scan chain.

Add Faults ••Adds faults into the current fault list.

Add Iddq Constraints ••Sets constraints for generation or selection of

IDDQ patterns.

Table 2-1. Command Summary [continued]

Command

D

F

T

IF

SF

TDescription

Command Dictionary Command Summary

FastScan and FlexTest Reference Manual, V8.6_4 2-3

Add Initial States •Specifies an initial state for the selected

sequential instance.

Add LFSR Connections •Connects an external pin to a Linear Feedback

Shift Register (LFSR).

Add LFSR Taps •Adds the tap configuration to a Linear

Feedback Shift Register (LFSR).

Add LFSRs •Adds Linear Feedback Shift Registers

(LFSRs) for use as Pseudo-Random Pattern

Generators (PRPGs) or Multiple Input

Signature Registers (MISRs).

Add Lists ••Adds pins to the list of pins on which to

report.

Add Mos Direction ••Assigns the direction of a bi-directional MOS

transistor.

Add Net Property ••Defines the net in the Spice design and library

as VDD or GND.

Add Nofaults ••Places nofault settings either on pin

pathnames, pin names of specified instances,

or modules.

Add Nonscan Handling •Overrides behavior classification of non-scan

elements that FlexTest learns during the

design rules checking process.

Add Notest Points •Adds circuit points to list for exclusion from

testability insertion.

Add Observe Points •Adds observe points to output pins.

Table 2-1. Command Summary [continued]

Command

D

F

T

IF

SF

TDescription

FastScan and FlexTest Reference Manual, V8.6_4

2-4

Command Summary Command Dictionary

Add Output Masks ••Ignores any fault effects that propagate to the

primary output pins you name.

Add Pin Constraints ••Adds pin constraints to primary inputs and

input channel to I/O pins.

Add Pin Equivalences ••Adds restrictions to primary inputs such that

they have equal or inverted values.

Add Pin Strobes •Adds strobe time to the primary outputs.

Add Primary Inputs ••Adds primary inputs.

Add Primary Outputs ••Adds primary outputs.

Add Random Weights •Specifies the random pattern weighting

factors for primary inputs.

Add Read Controls ••Adds an off-state value to read control lines.

Add Scan Chains ••Adds a scan chain to a scan group.

Add Scan Groups ••Adds a scan chain group to the system.

Add Scan Instances •Adds sequential instances to the scan instance

list.

Add Scan Models •Adds sequential models to the scan model list.

Add Slow Pad •Sets the specified I/O pin as a slow pad.

Add Tied Signals ••Adds a value to floating signals or pins.

Add Write Controls ••Adds an off-state value to specified write

control lines.

Table 2-1. Command Summary [continued]

Command

D

F

T

IF

SF

TDescription

Command Dictionary Command Summary

FastScan and FlexTest Reference Manual, V8.6_4 2-5

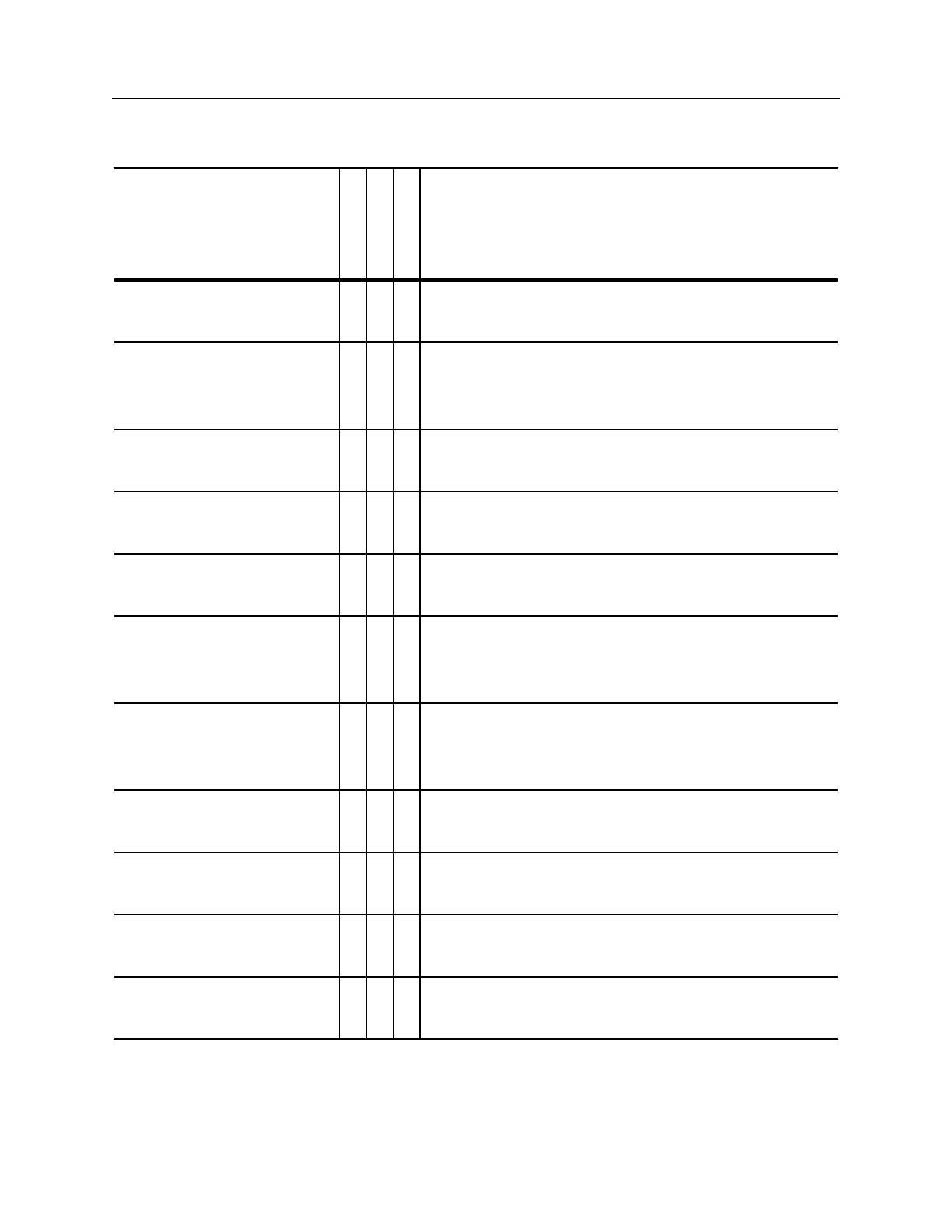

Analyze Atpg

Constraints ••Specifies for FastScan or FlexTest to check

the ATPG constraints you’ve created for their

satisfiability or for their mutual exclusivity.

Analyze Bus ••Causes the tool to analyze the specified bus

gates for contention problems.

Analyze Control •Calculates zero and one-state controllability.

Analyze Control

Signals ••Identifies the primary inputs of control

signals.

Analyze Drc Violation •••Generates a netlist of the portion of the design

involved with the specified rule violation

number.

Analyze Fault ••Performs an analysis to identify why a fault is

not detected and optionally displays the

relevant circuitry in DFTInsight.

Analyze Observe •Calculates observability coverage.

Analyze Race •Checks for race conditions between the clock

and data signals.

Analyze Restrictions •Performs an analysis to automatically

determine the source of the problems from a

failed ATPG run.

Close Schematic

Viewer •••Terminates the optional schematic viewing

application (DFTInsight).

Compress Patterns ••Compresses patterns in the current test pattern

set.

Create Initialization

Patterns •Creates RAM initialization patterns and

places them in the internal pattern set.

Table 2-1. Command Summary [continued]

Command

D

F

T

IF

SF

TDescription

FastScan and FlexTest Reference Manual, V8.6_4

2-6

Command Summary Command Dictionary

Create Patterns •Automates good ATPG compression flow.

Delete Atpg Constraints ••Removes the state restrictions from the

specified objects.

Delete Atpg Functions ••Removes the specified function definitions.

Delete Capture

Handling •Removes the special data capture handling for

the specified objects.

Delete Cell Constraints ••Removes constraints placed on scan cells.

Delete Clocks ••Removes primary input pins from the clock

list.

Delete Cone Blocks ••Removes the specified output pin names from

the user-created list which the tool uses to

calculate the clock and effect cones.

Delete Control Points •Removes previously specified control points.

Delete Display

Instances •••Removes the specified objects from the

display in DFTInsight.

Delete Faults ••Removes faults from the current fault list.

Delete Iddq Constraints ••Removes the IDDQ restrictions from the

specified pins.

Delete Initial States •Removes the initial state settings for the

specified instance names.

Delete LFSR

Connections •Removes connections between the specified

primary pins and Linear Feedback Shift