Mitac 8399 Users Manual

8399 to the manual 0564b034-38d1-4de1-a565-e2322c508721

2015-02-09

: Mitac Mitac-8399-Users-Manual-556373 mitac-8399-users-manual-556373 mitac pdf

Open the PDF directly: View PDF ![]() .

.

Page Count: 174 [warning: Documents this large are best viewed by clicking the View PDF Link!]

BY: Grass

Grass Ren

Ren

Repair Technology Research Department /EDVD

Repair Technology Research Department /EDVD

Aug.2004

SERVICE MANUAL FOR

8399

83998399

8399

SERVICE MANUAL FOR

SERVICE MANUAL FOR

8399

83998399

8399

8399

83998399

8399

8399

8399 N/B Maintenance

N/B Maintenance

1

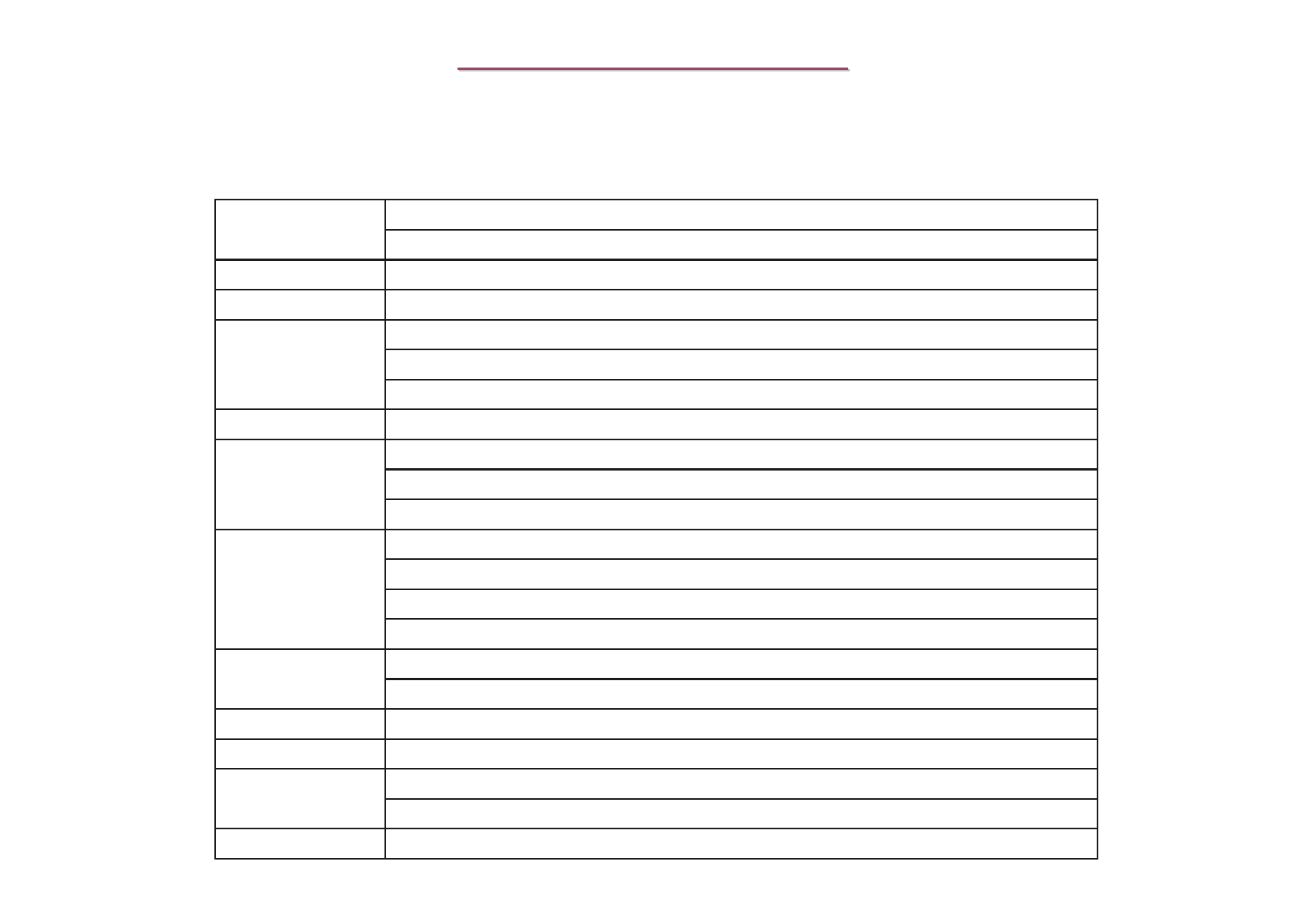

1. Hardware Engineering Specification …………………………………………………………………..

1.1 Introduction ……………………………………………………………………………………………

1.2 Hardware Specification …………………………………………………………………………………

1.3 System Hardware Parts …………………………………………………………………………………

1.4 Other Functions …………………………………………………………………………………….….

2. System View & Disassembly…………………………………………………………………………….

2.1 System View…………………………………………………………………………………….………

2.2 System Disassembly …………………………………………………………………………………….

3. Definition & Location of Connectors / Switches Setting ………………………………………………

4. Definition & Location of Major Component …………………………………………………………..

5. Pin Description of Major Component…………………………………………………………………..

5.1 AMD Mobile Athlon 64 (ClawHammer) Processor ……………………………………………………….

5.2 VIA K8N800 North Bridge ………………………………………………………………….…………..

5.3 VIA VT8235CD South Bridge …………………………………………………………………………...

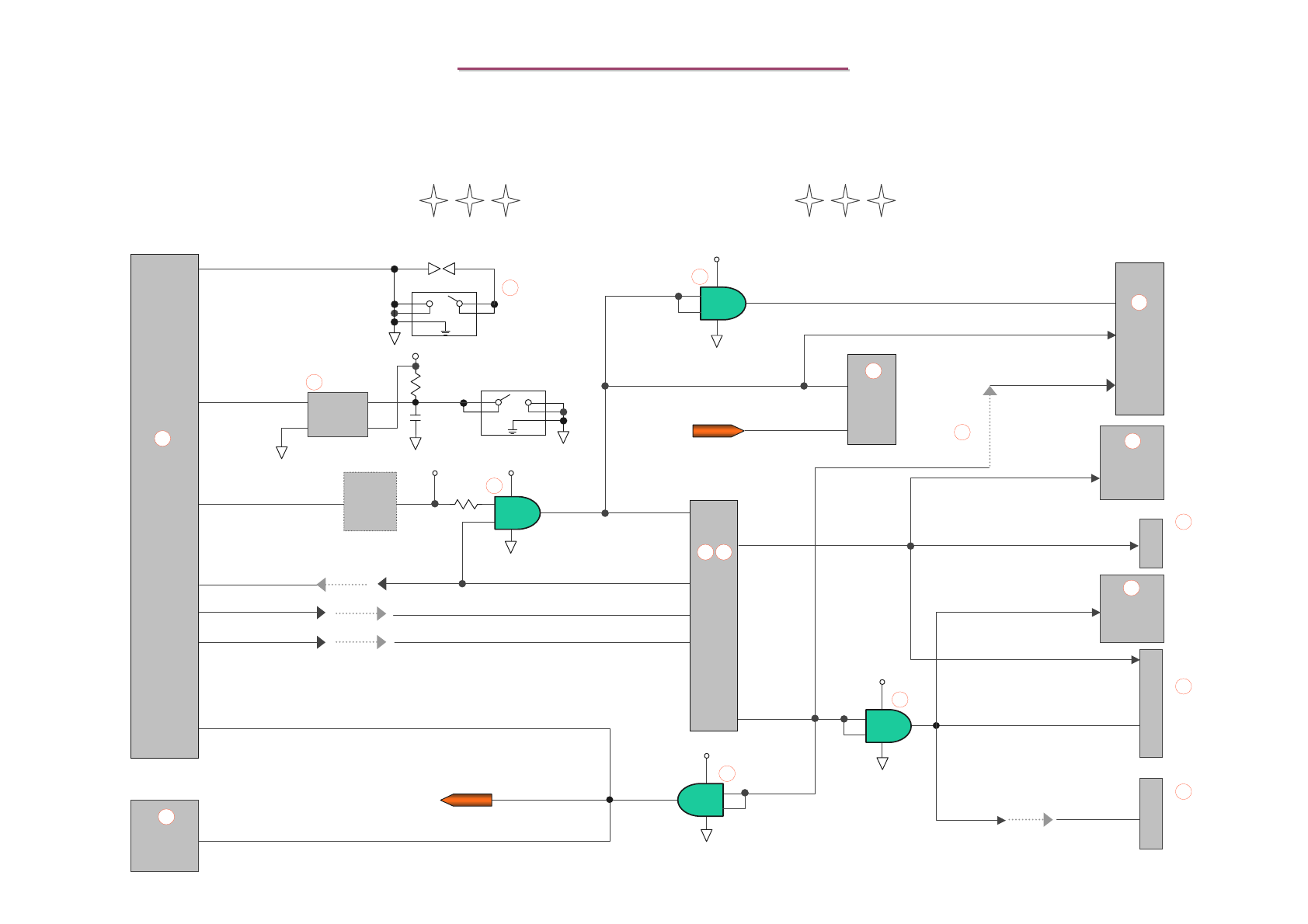

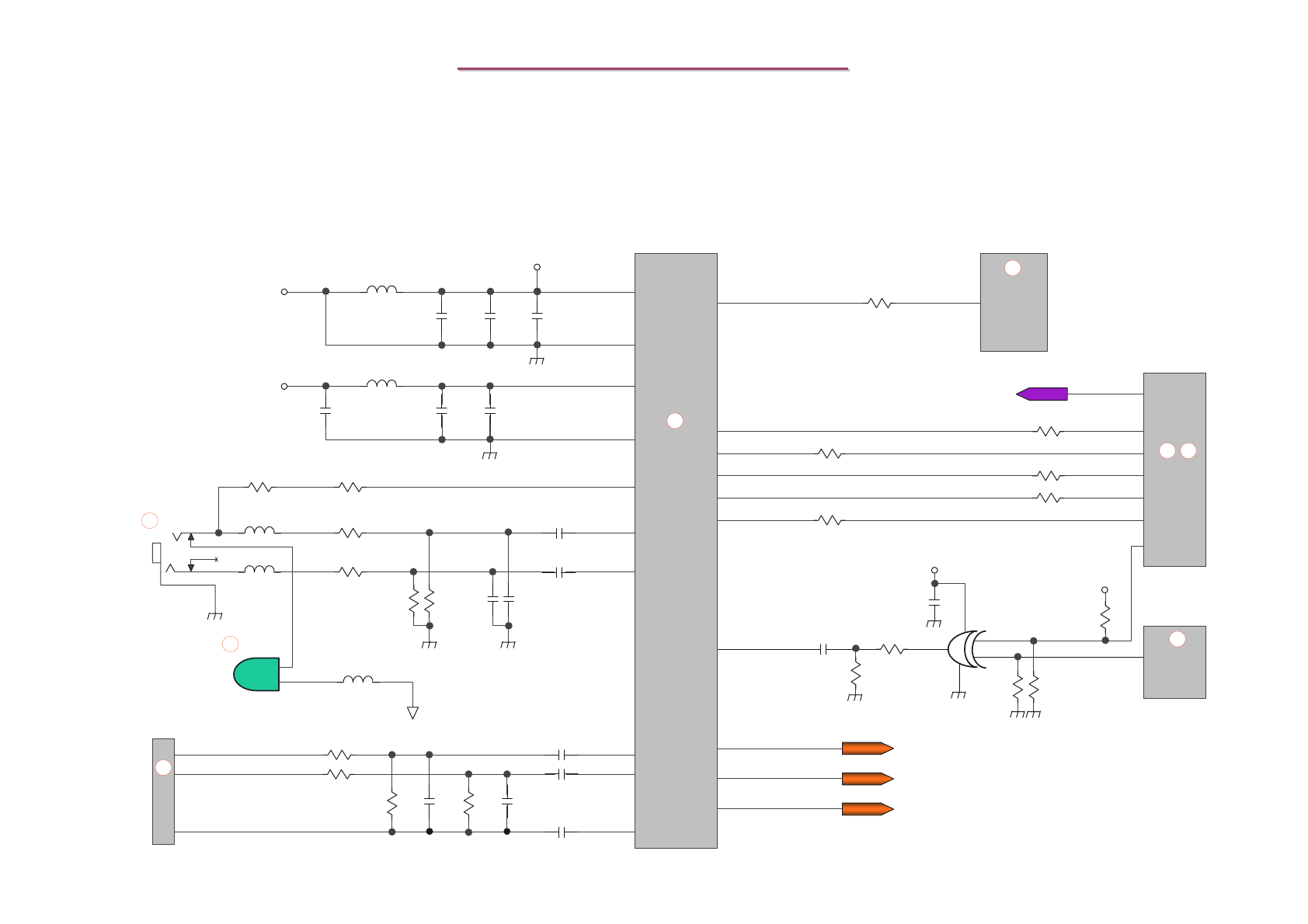

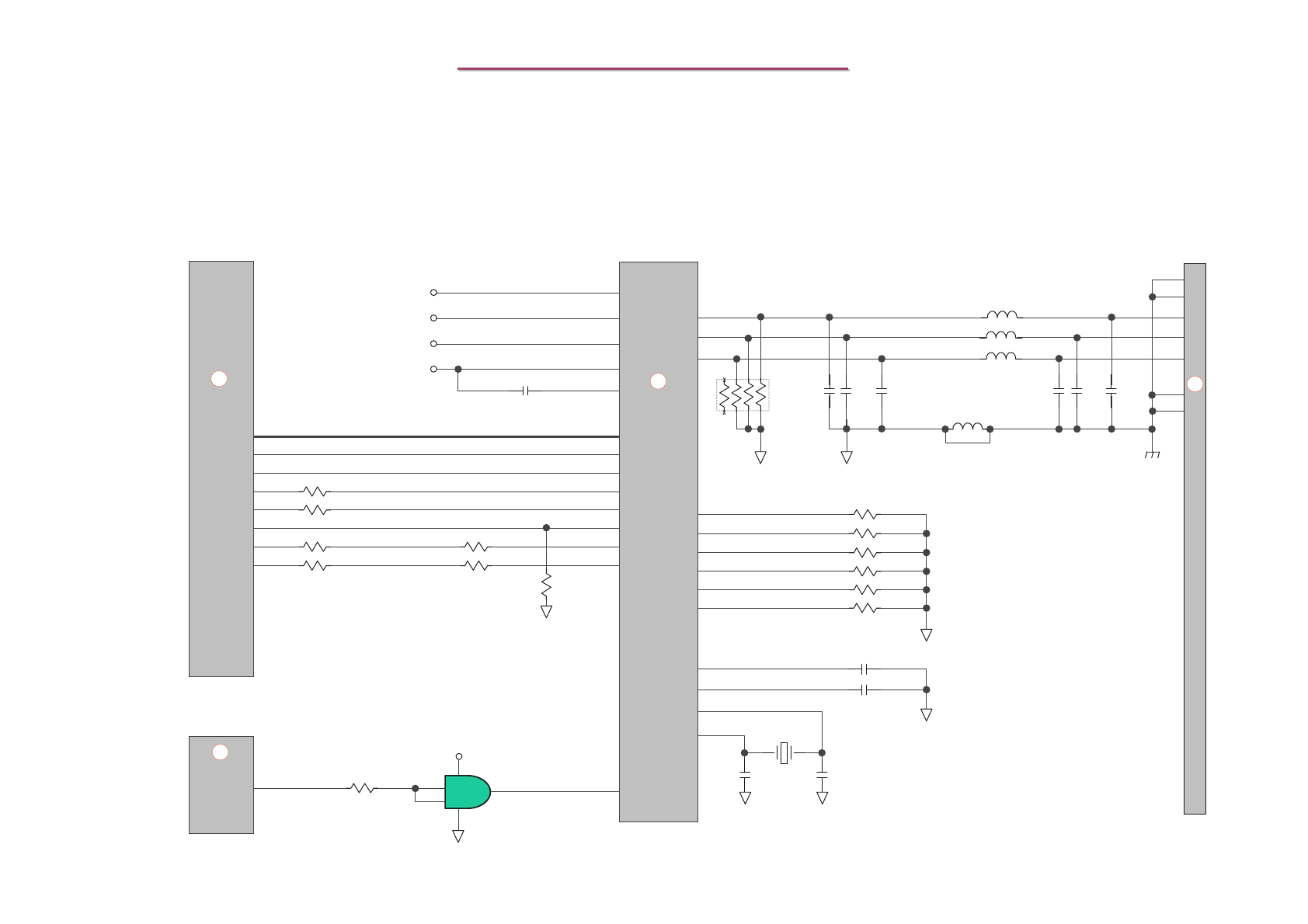

6. System Block Diagram ……………………………………………………….……………………….....

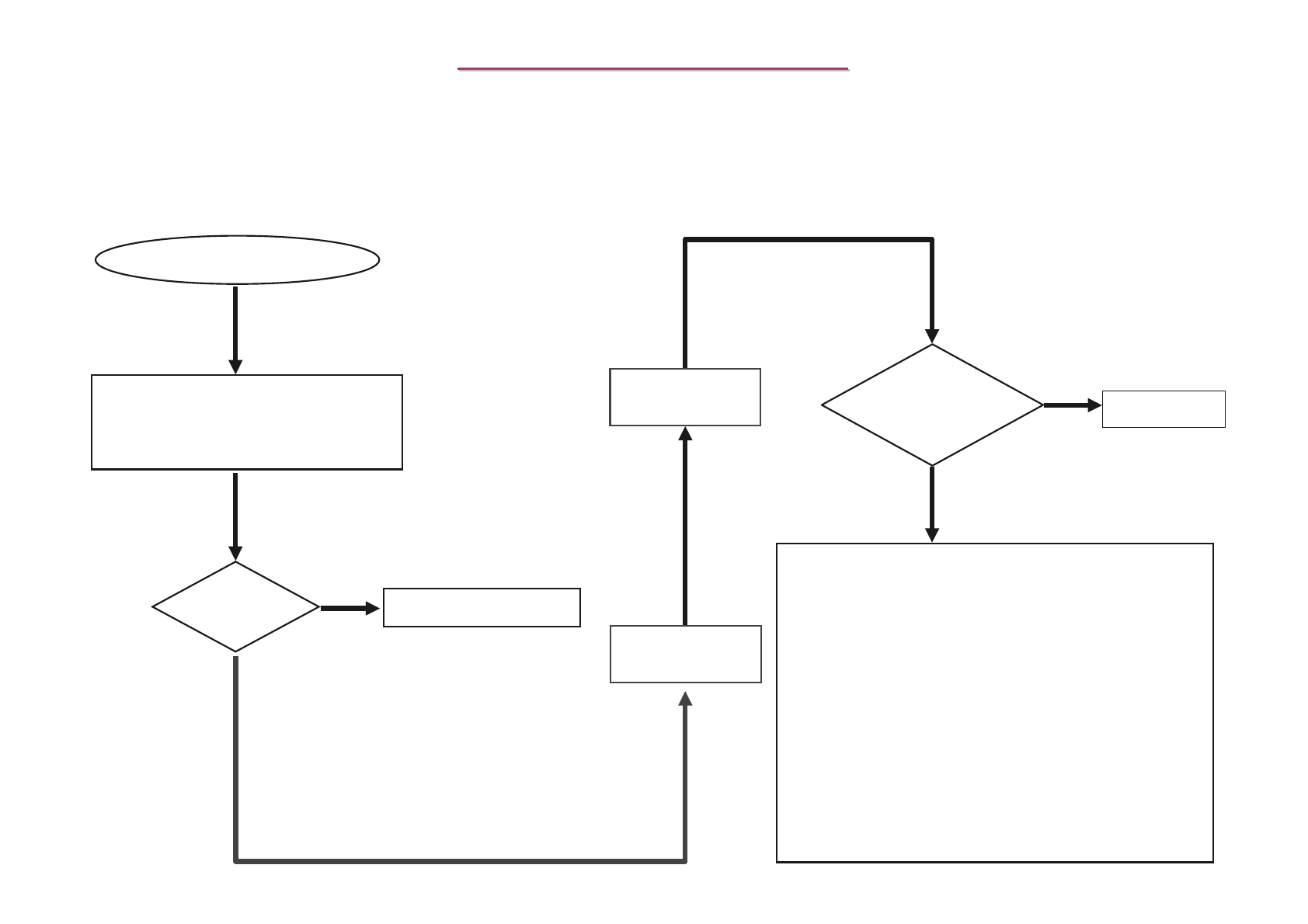

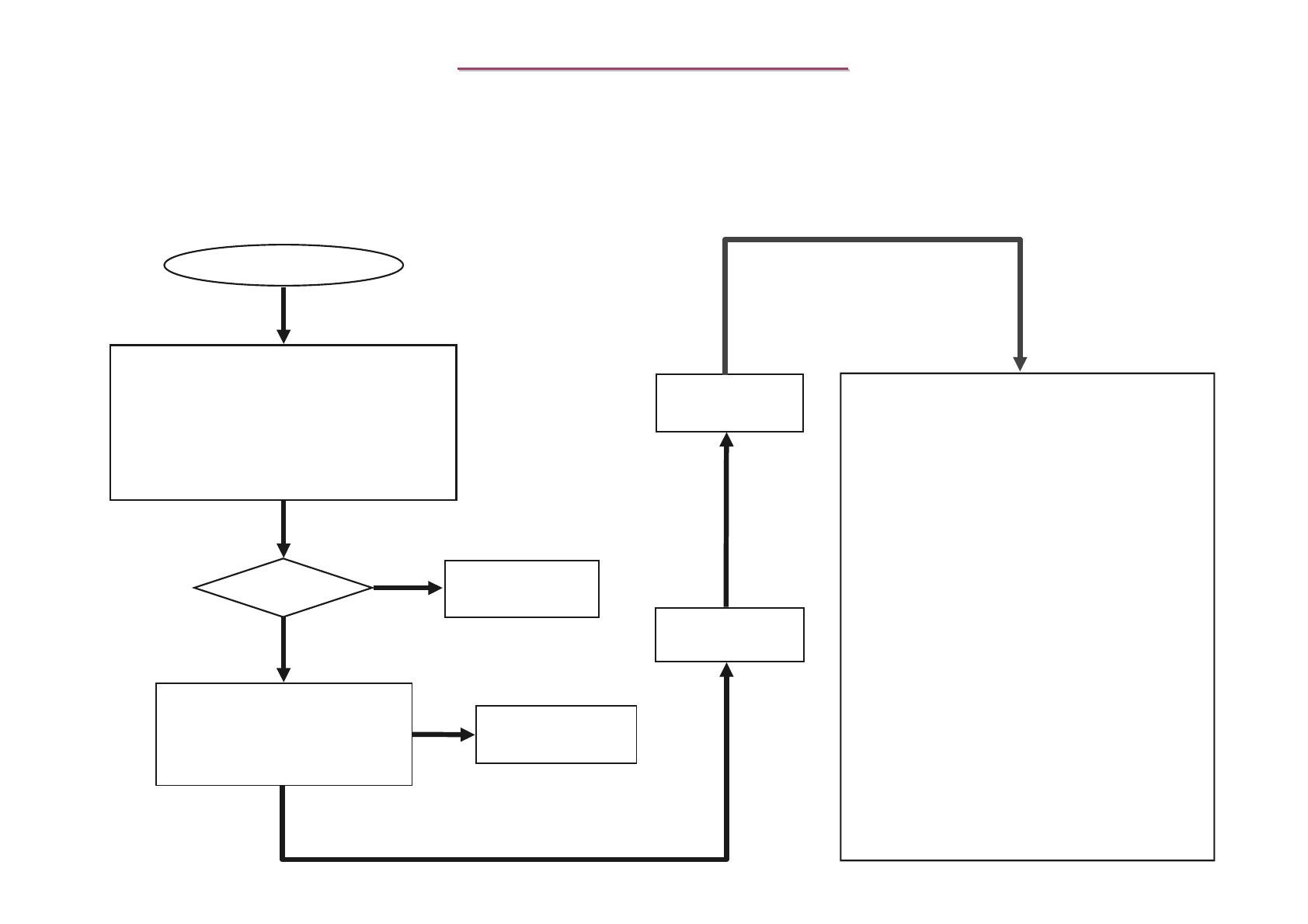

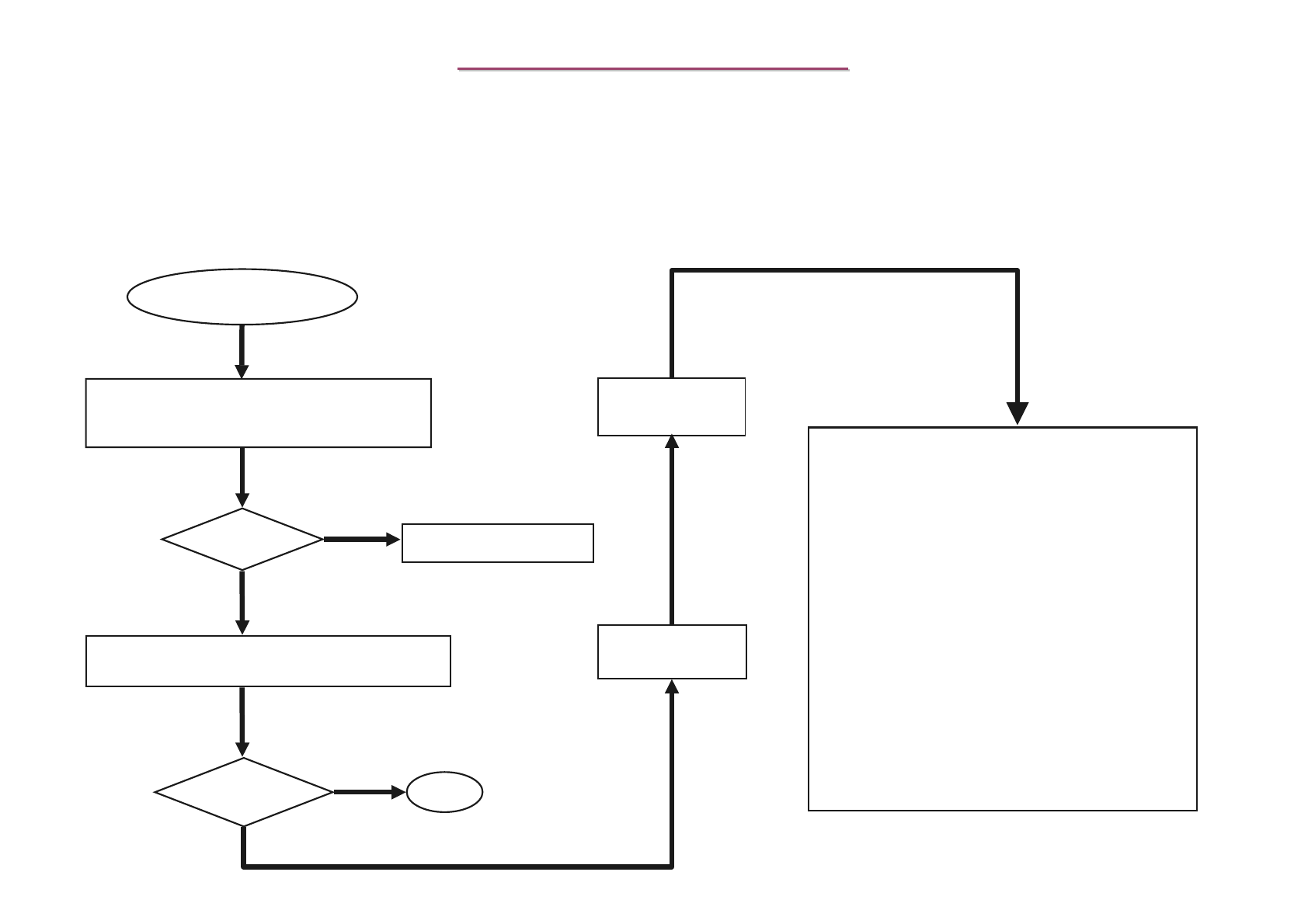

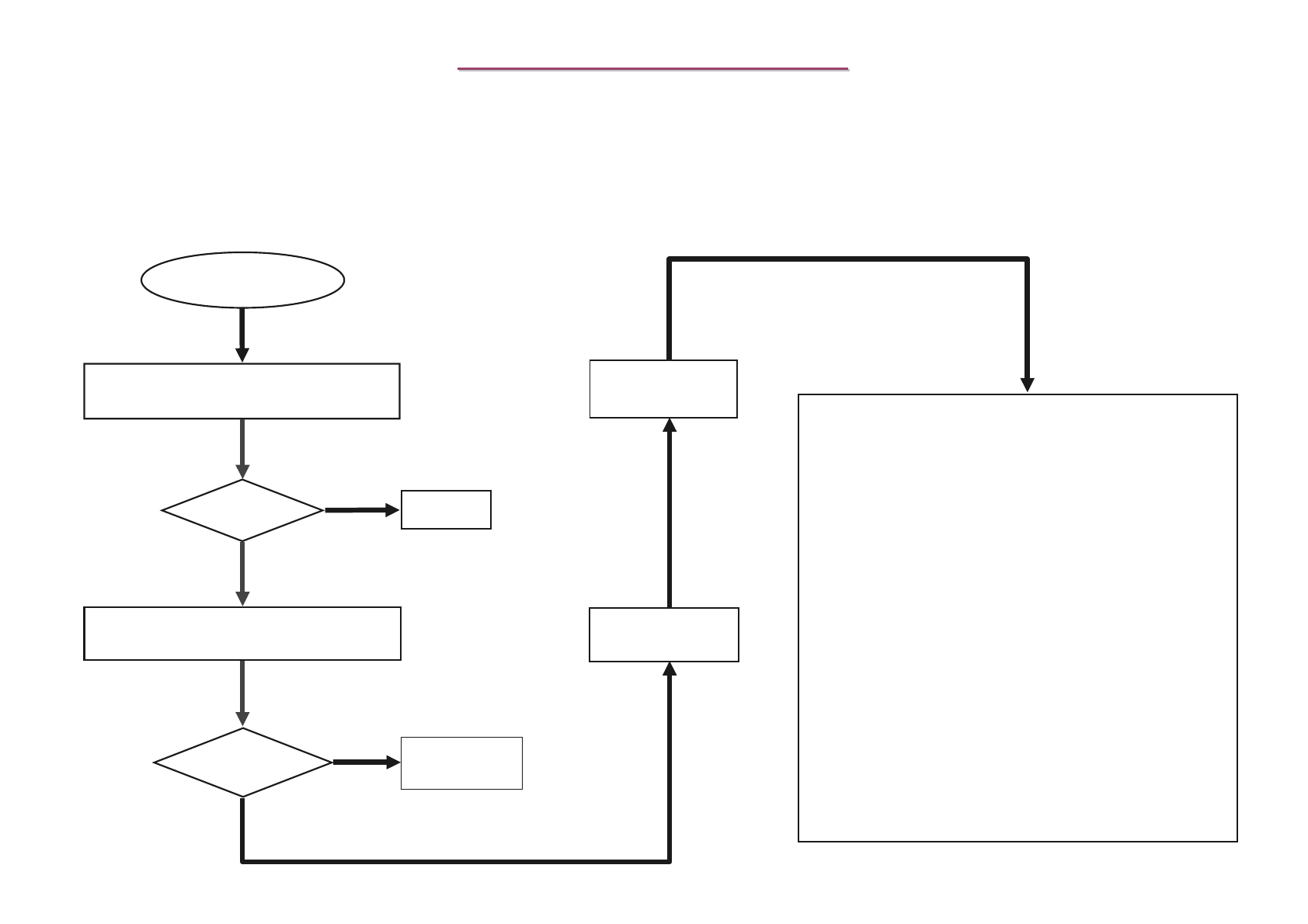

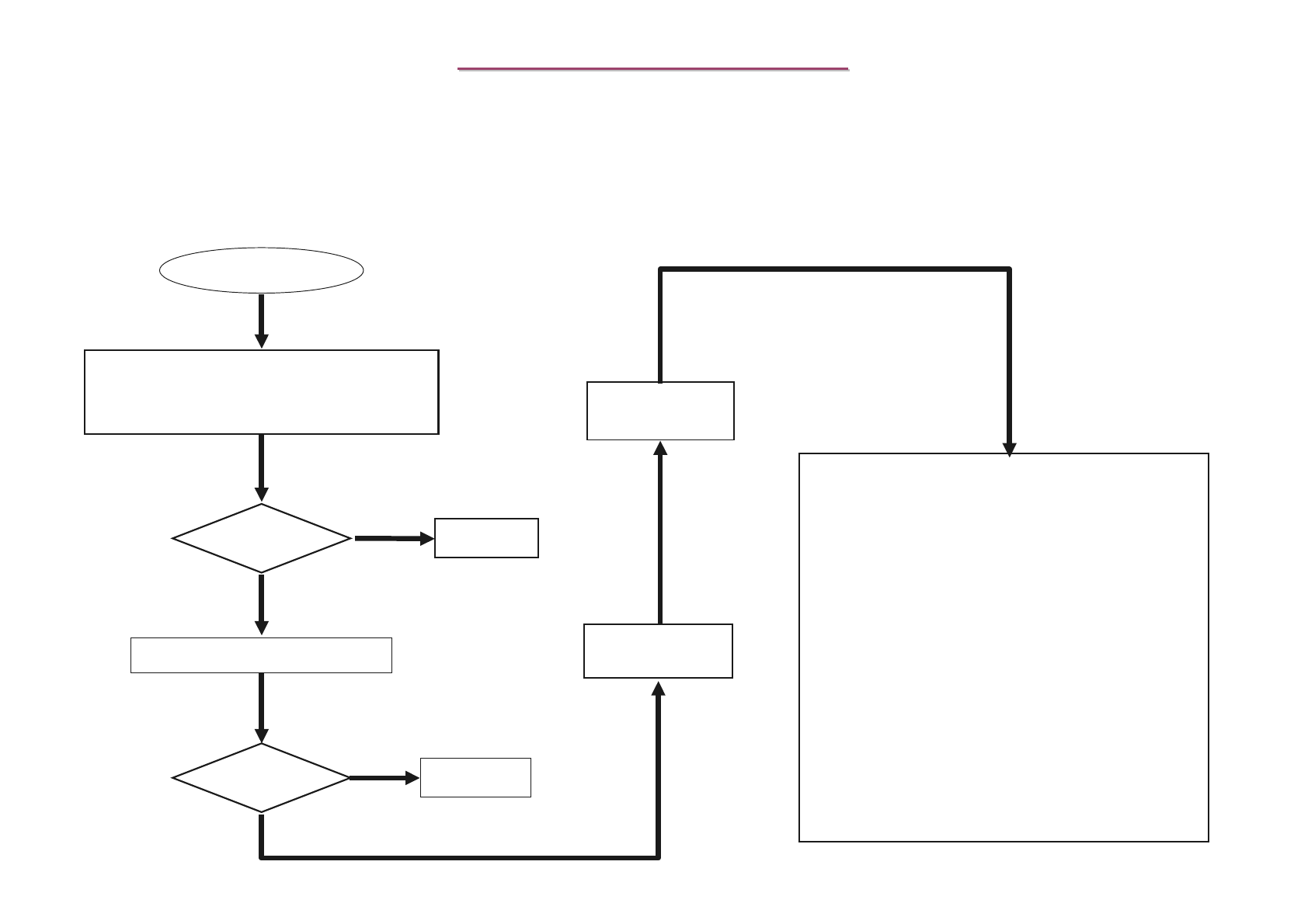

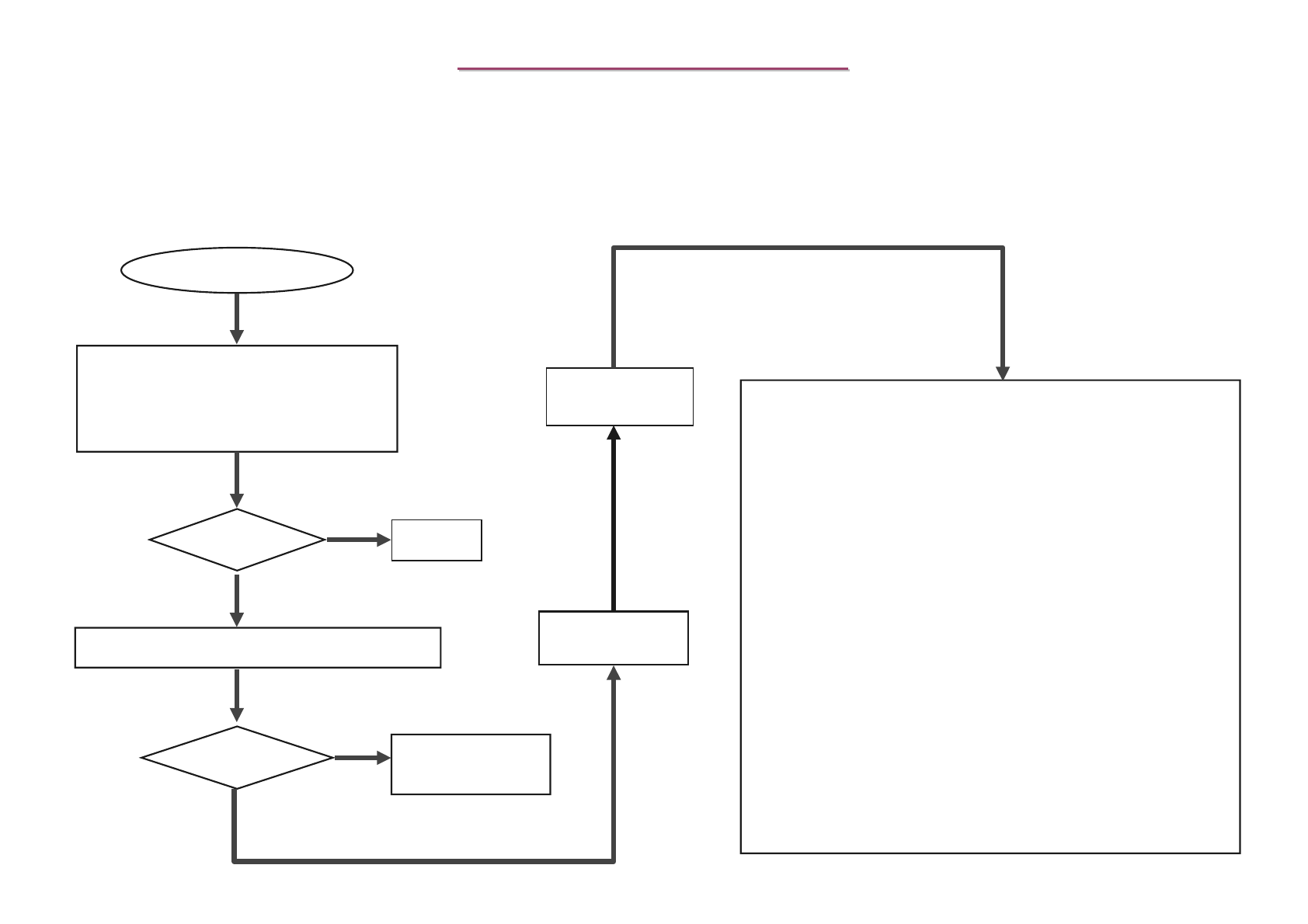

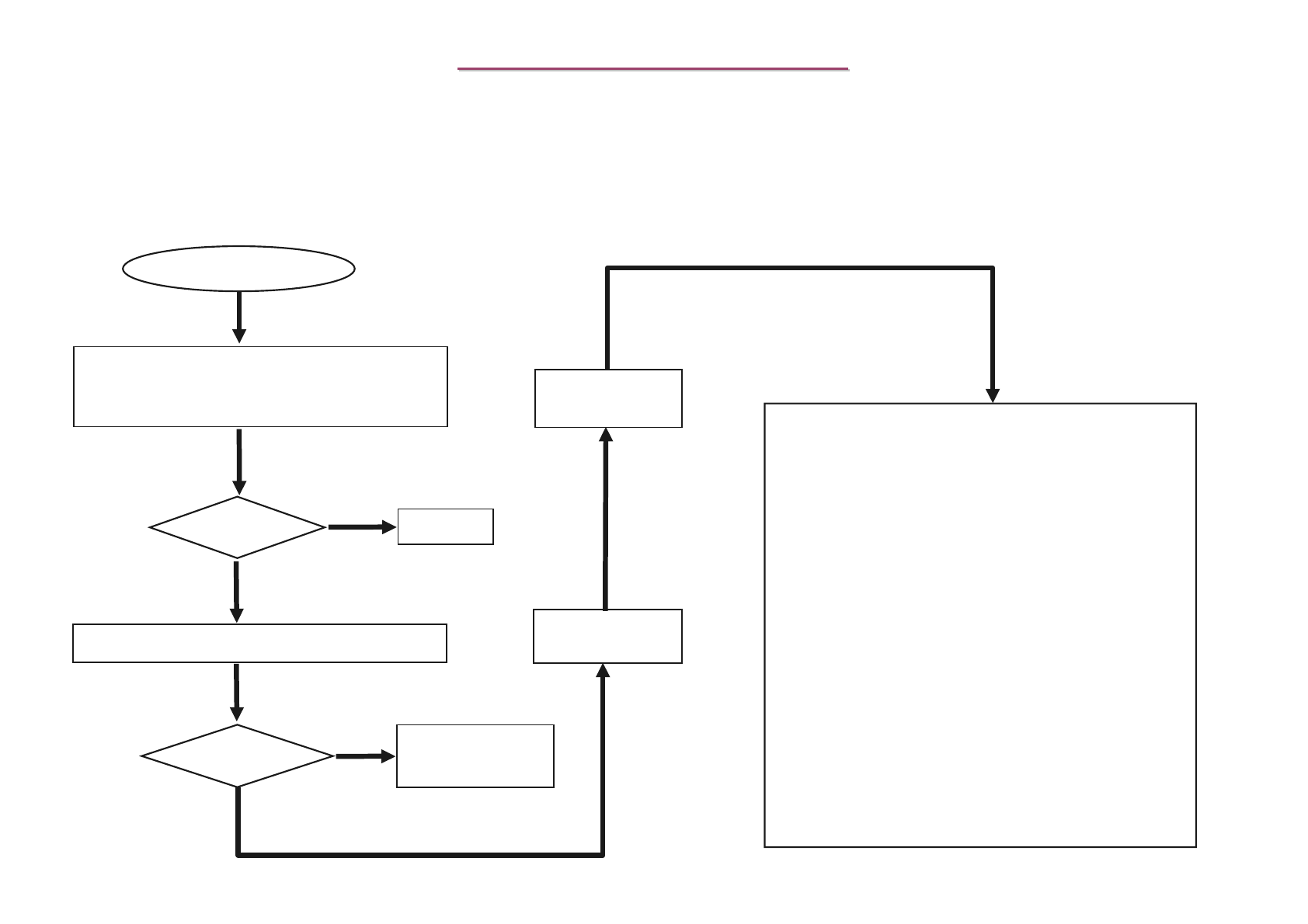

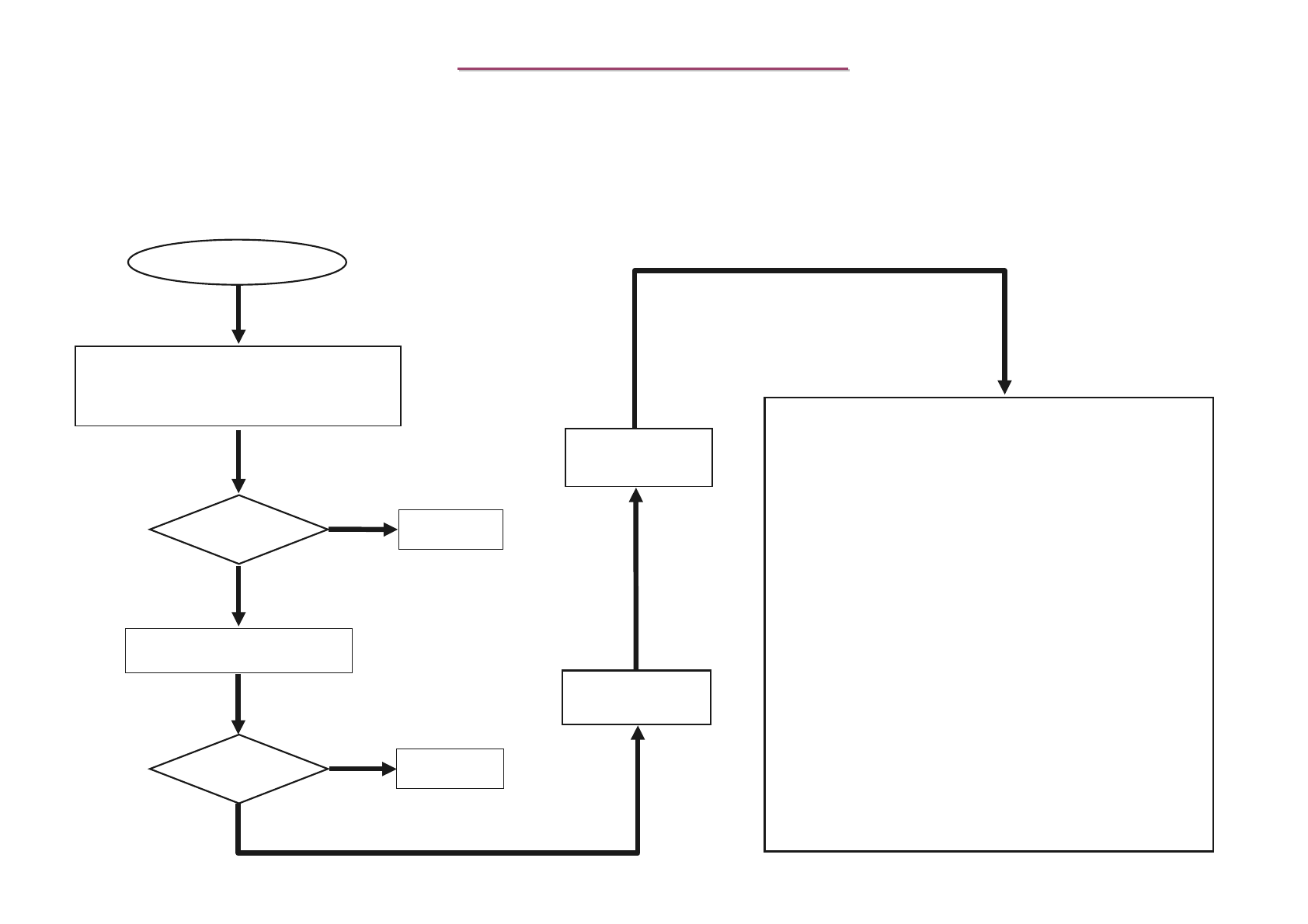

7. Maintenance Diagnostics ………………………………………………………………………………..

7.1 Introduction ……………………………………………………………………………………………

7.2 Diagnostic Tool for Mini PCI Slot ………………………………………………………………………

7.3 Error code……………………………………………………………………………………….……..

3

3

5

7

45

45

48

67

70

71

73

90

91

93

92

40

71

80

91

Contents

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

2

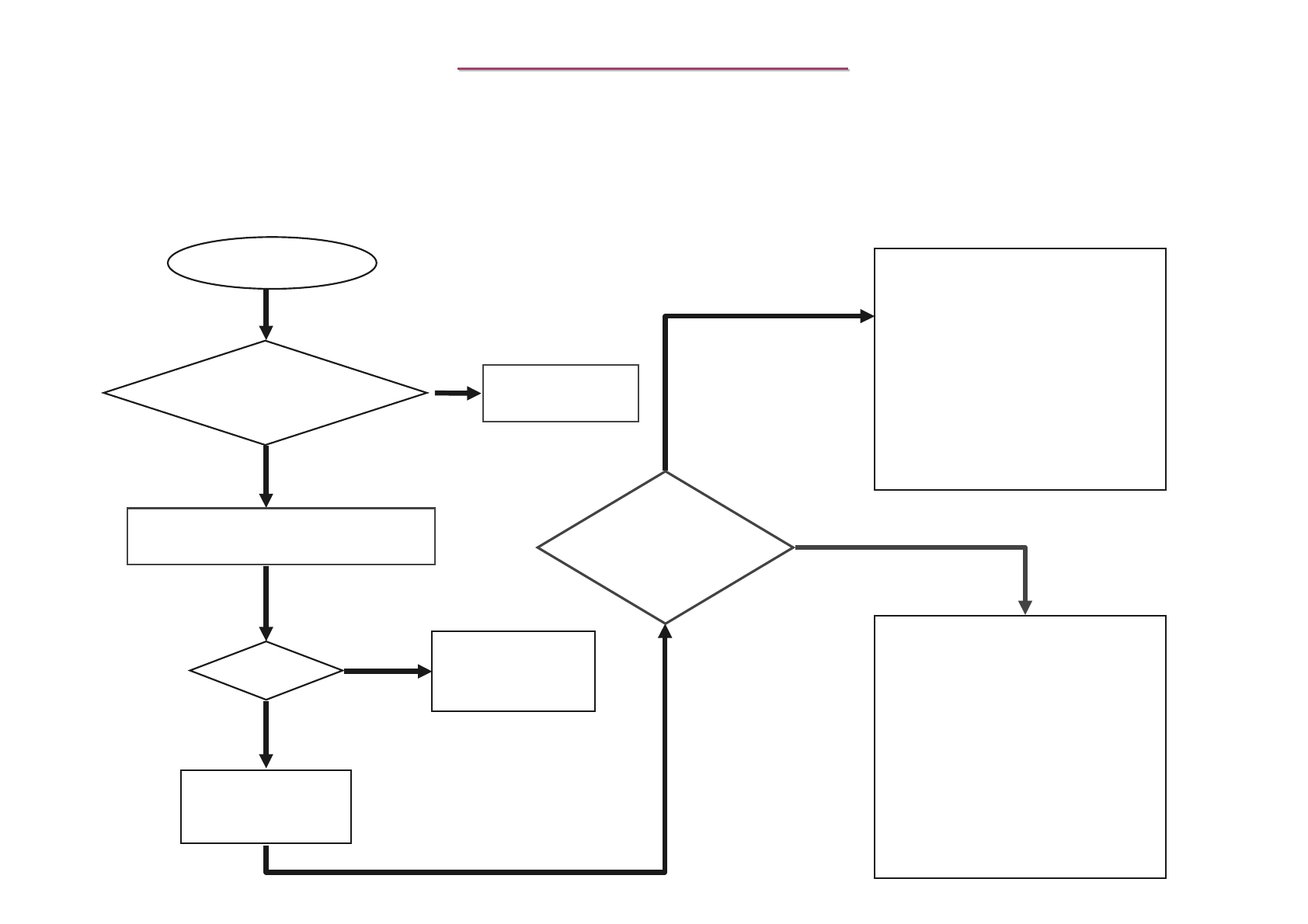

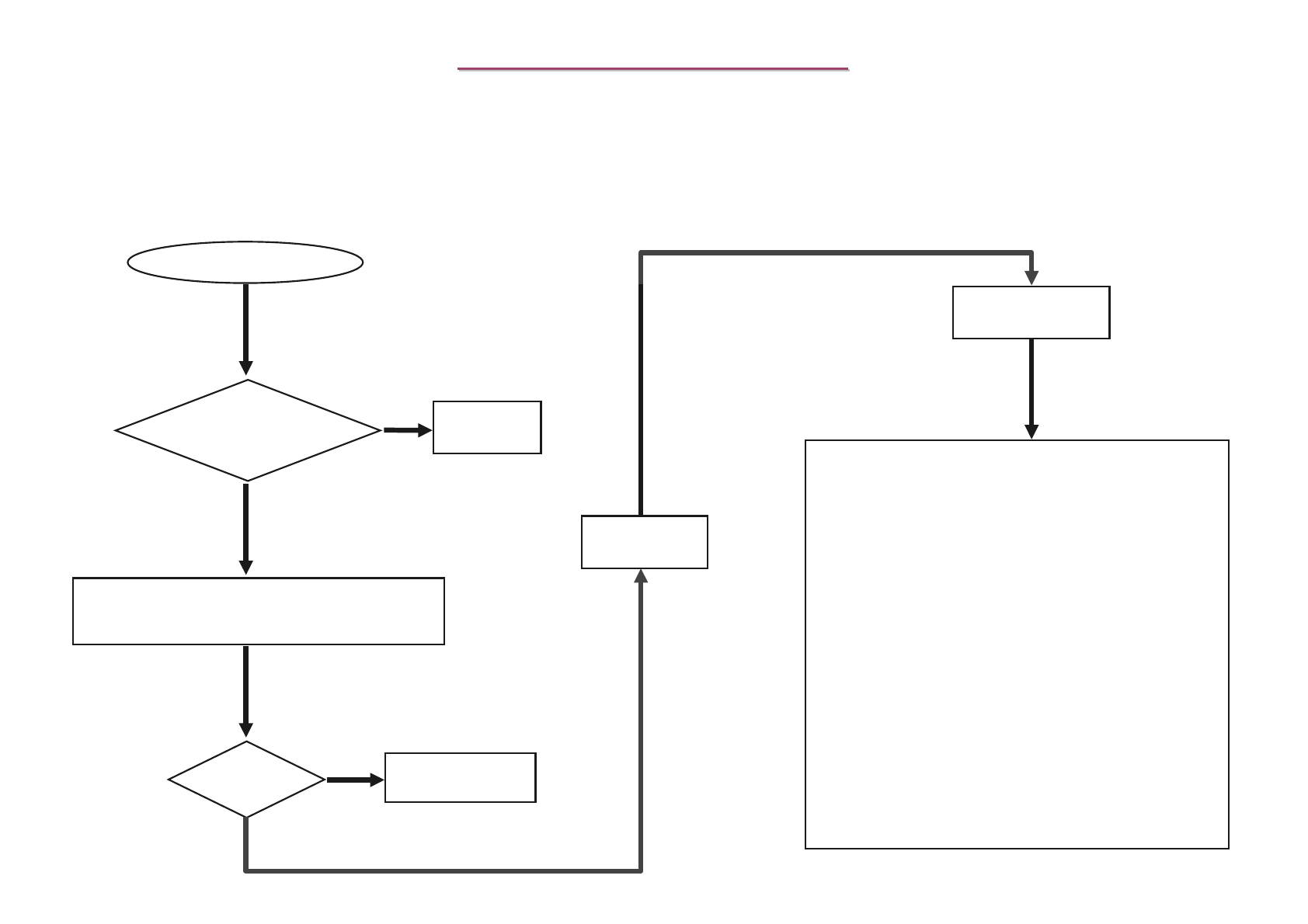

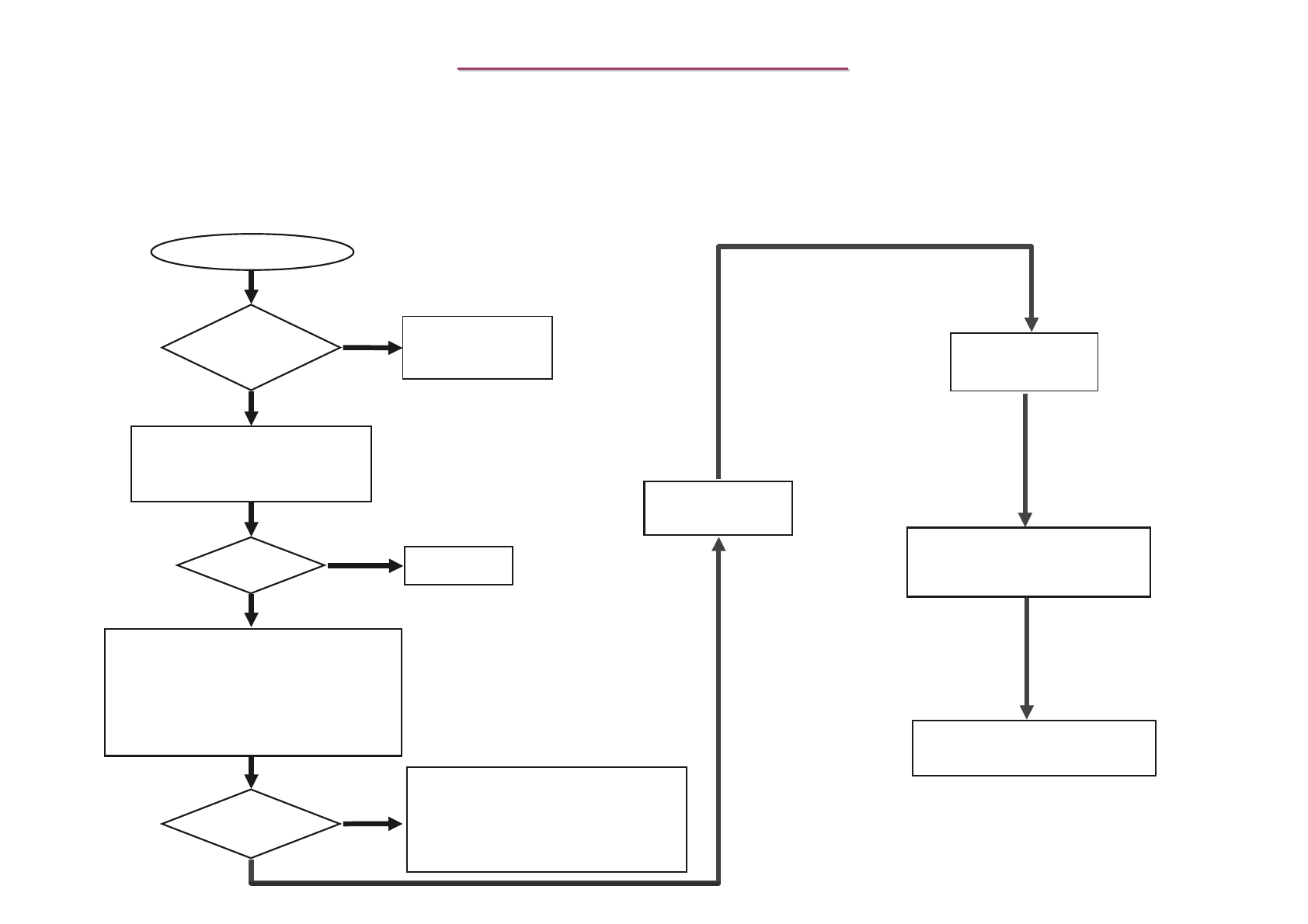

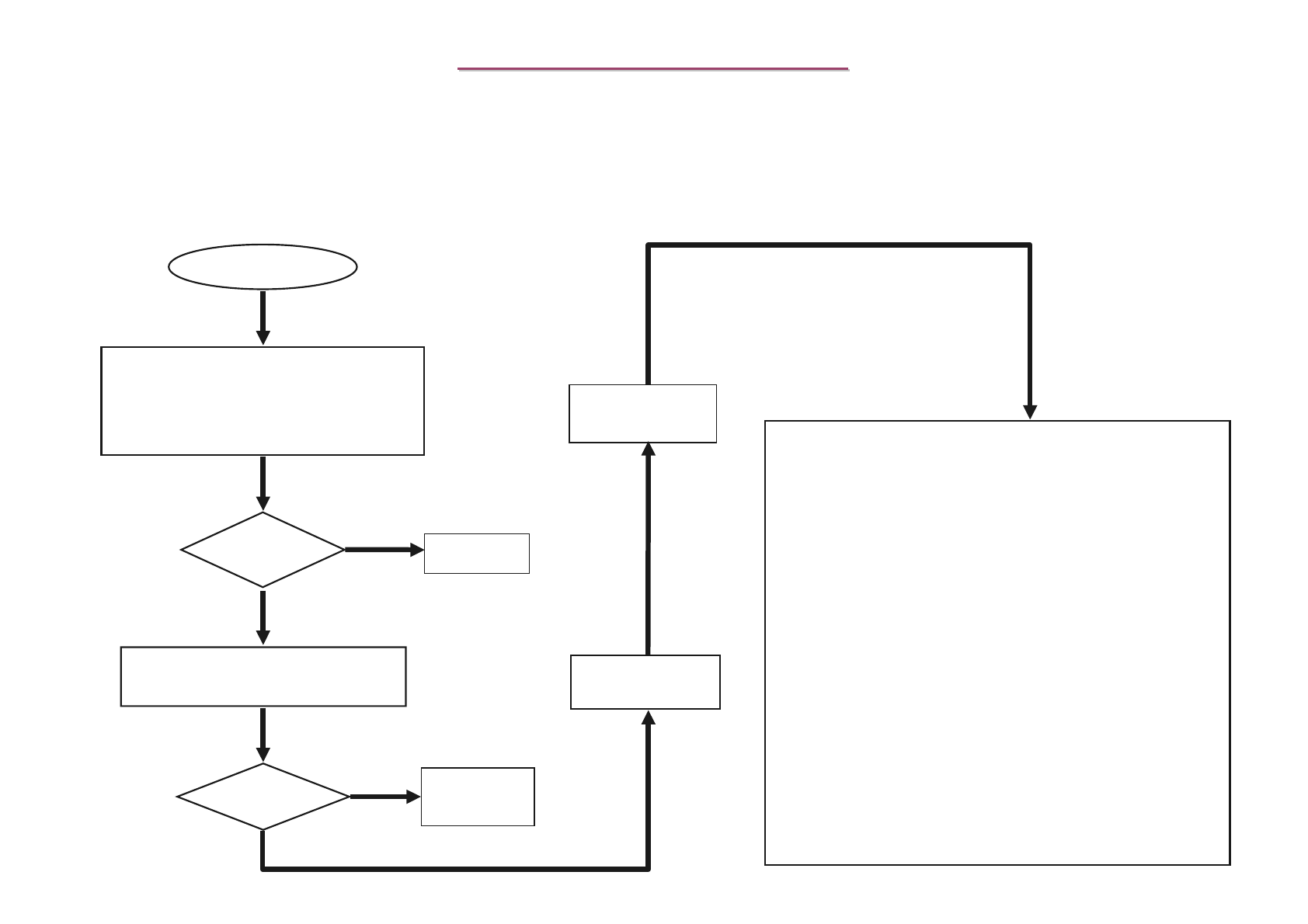

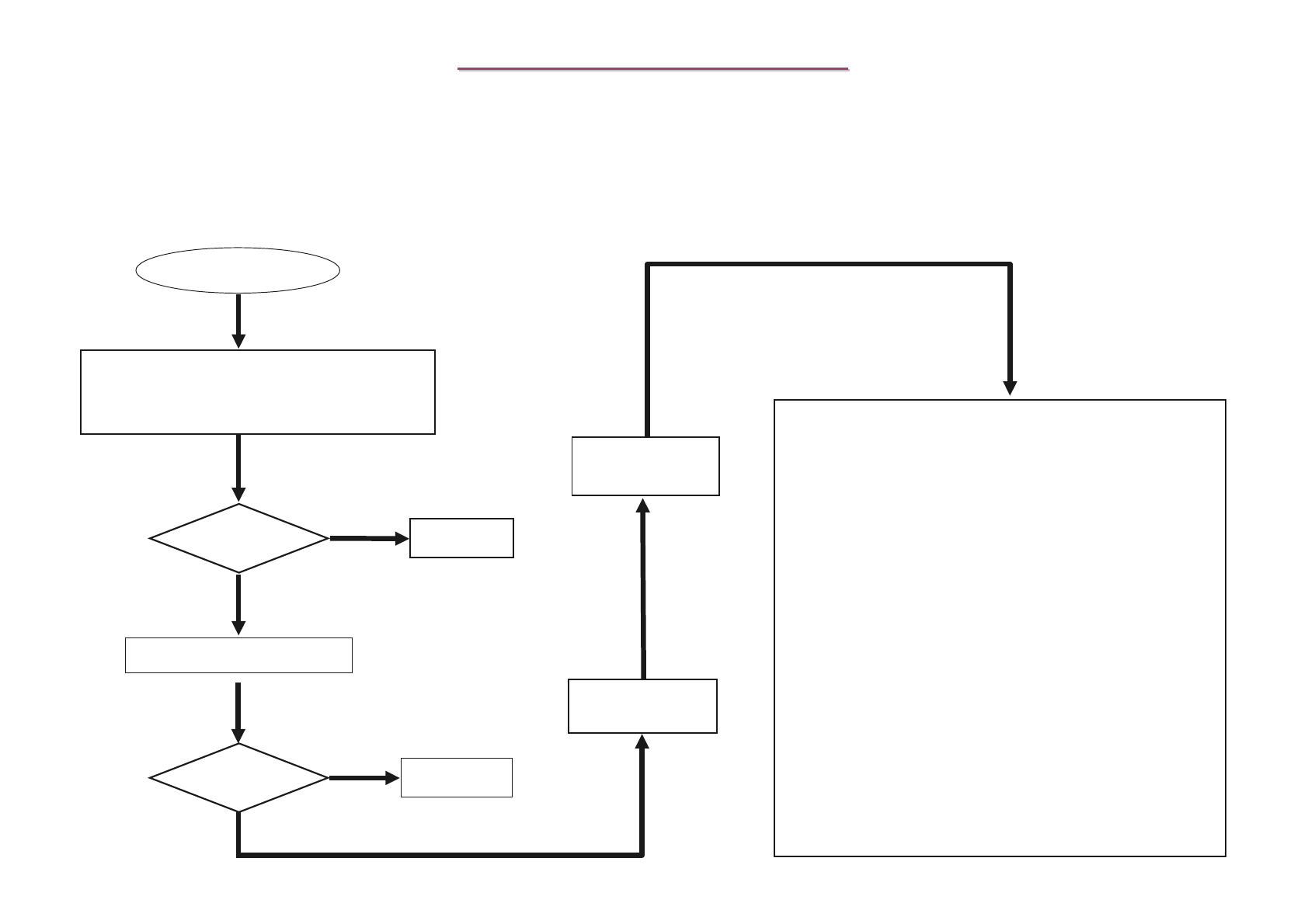

8. Trouble Shooting ……………………………………………………………………………………..….

8.1 Base Work Condition ……………………………………………………………………………………

8.2 No Power ……………………………………………………………………………………………….

8.3 Battery Can not Be Charged ……………………………………………………………………………..

8.4 No Display ………………………………… …………………………………………………………...

8.5 External Monitor No Display …………………………………………………………………………….

8.6 Memory Test Error ……………………………………………………………………………………..

8.7 Keyboard/Touch-pad Test Error ………………………………………………………………………...

8.8 USB Port Test error……………………………………………………………………………………...

8.9 Hard Disk Drive Test Error………………………………………………………………………………

8.10 CD-ROM Test Error …………………………………………………………………………………..

8.11 Audio Test Failure………………………………………………………………………………..….…

8.12 LAN Test Error ………………………………………………………………………………………..

8.13 Modem Test Error…………… …………………………………………………………………..……

8.14 Mini-PCI Test Error……….. ……… ………………………………………………………………....

8.15 Card Bus&Reader Test Error…………………………………………………………………………...

8.16 TV Encoder Test Error …………………………………………………………………………………

9. Spare Parts List ………………………………………………………………………………….…..…...

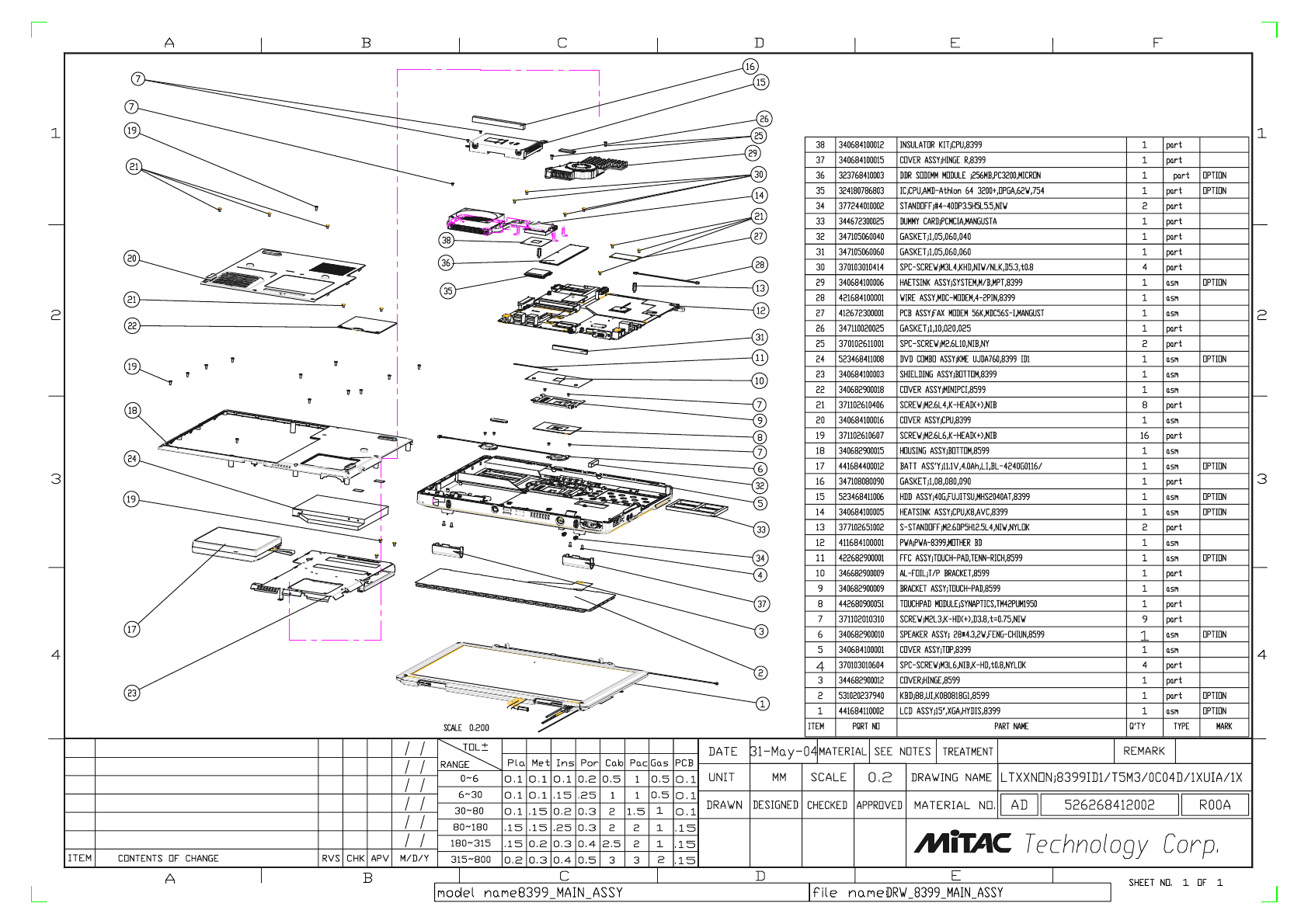

10. System Exploded View ……………………………………………………………………………...…..

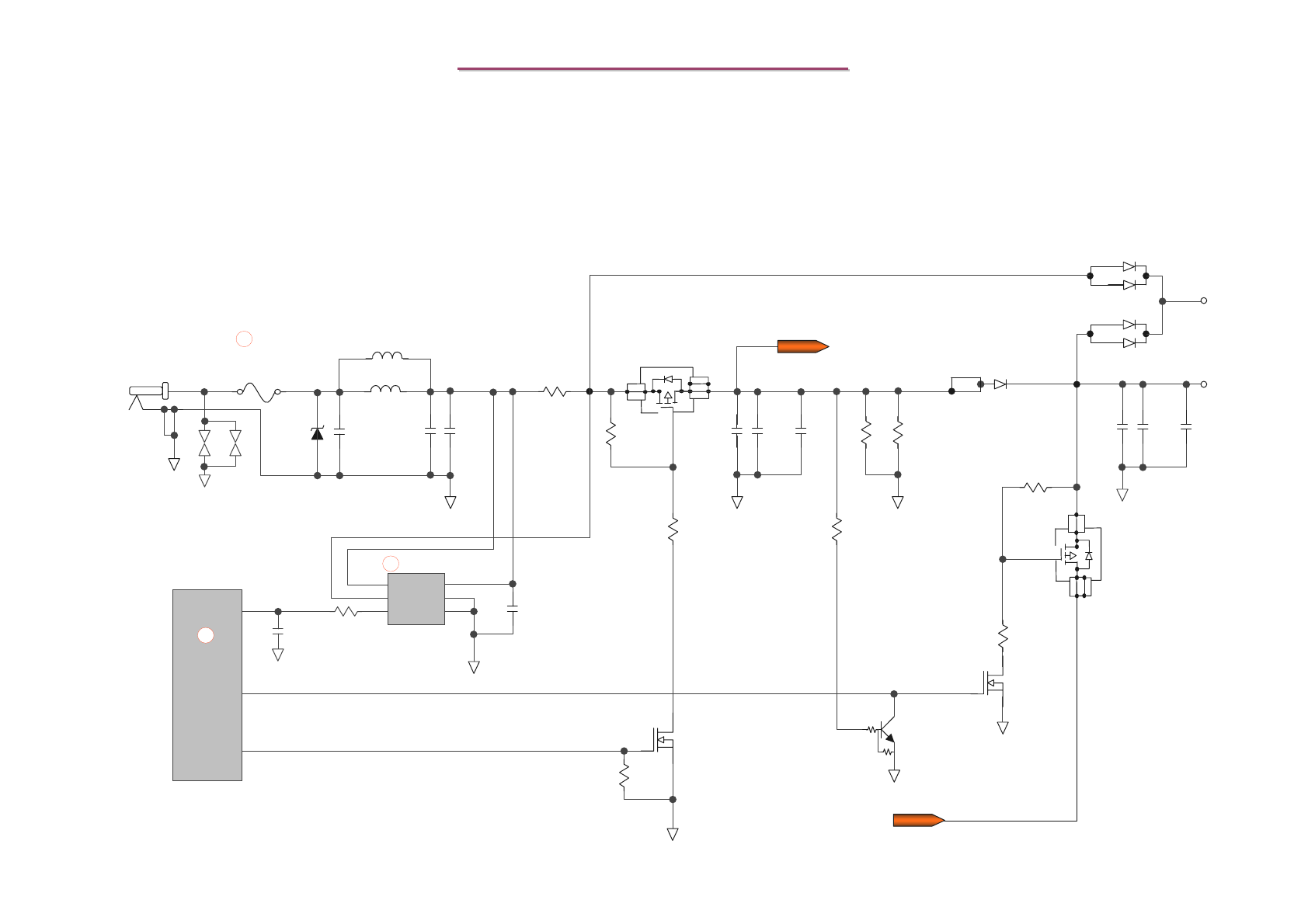

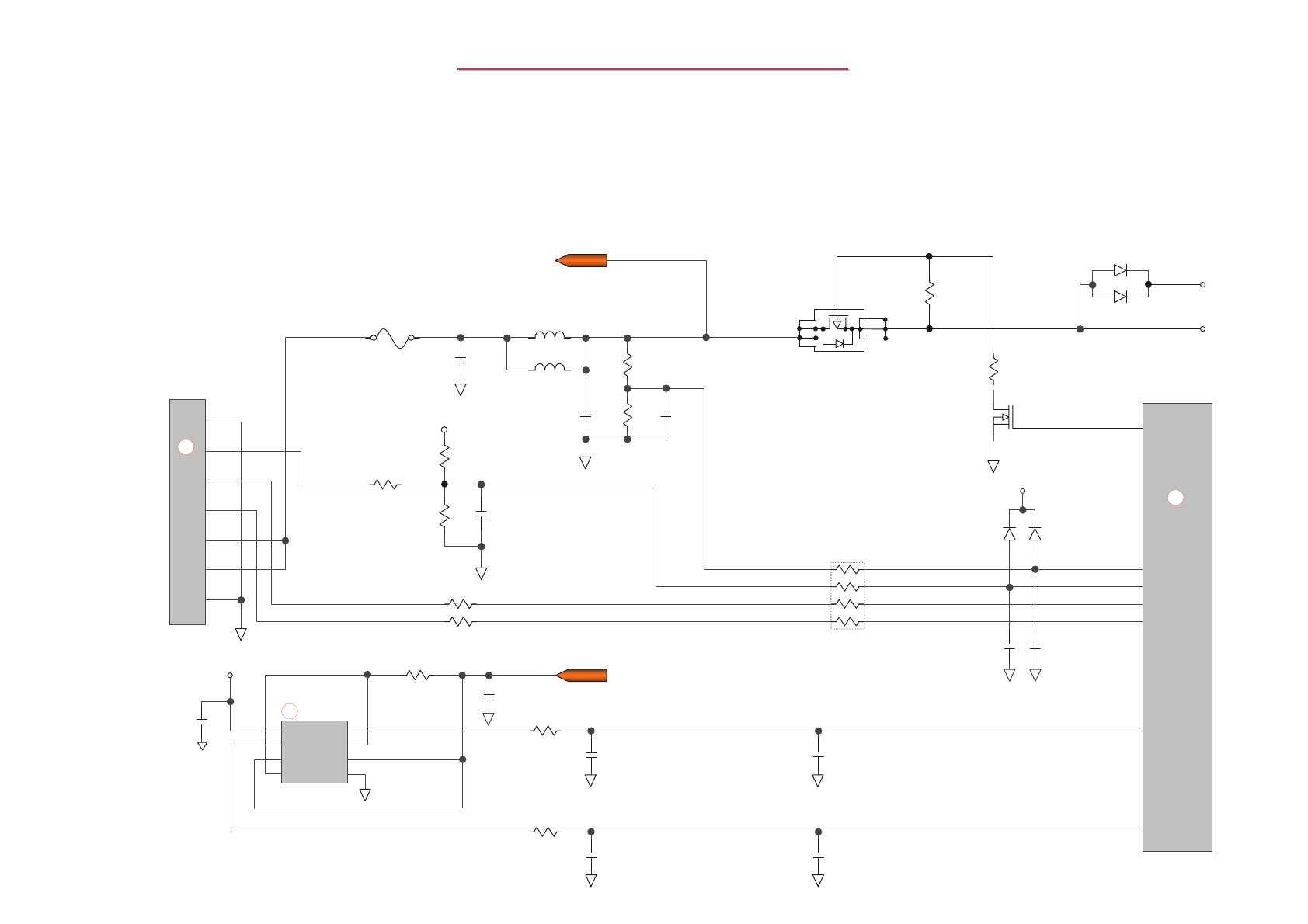

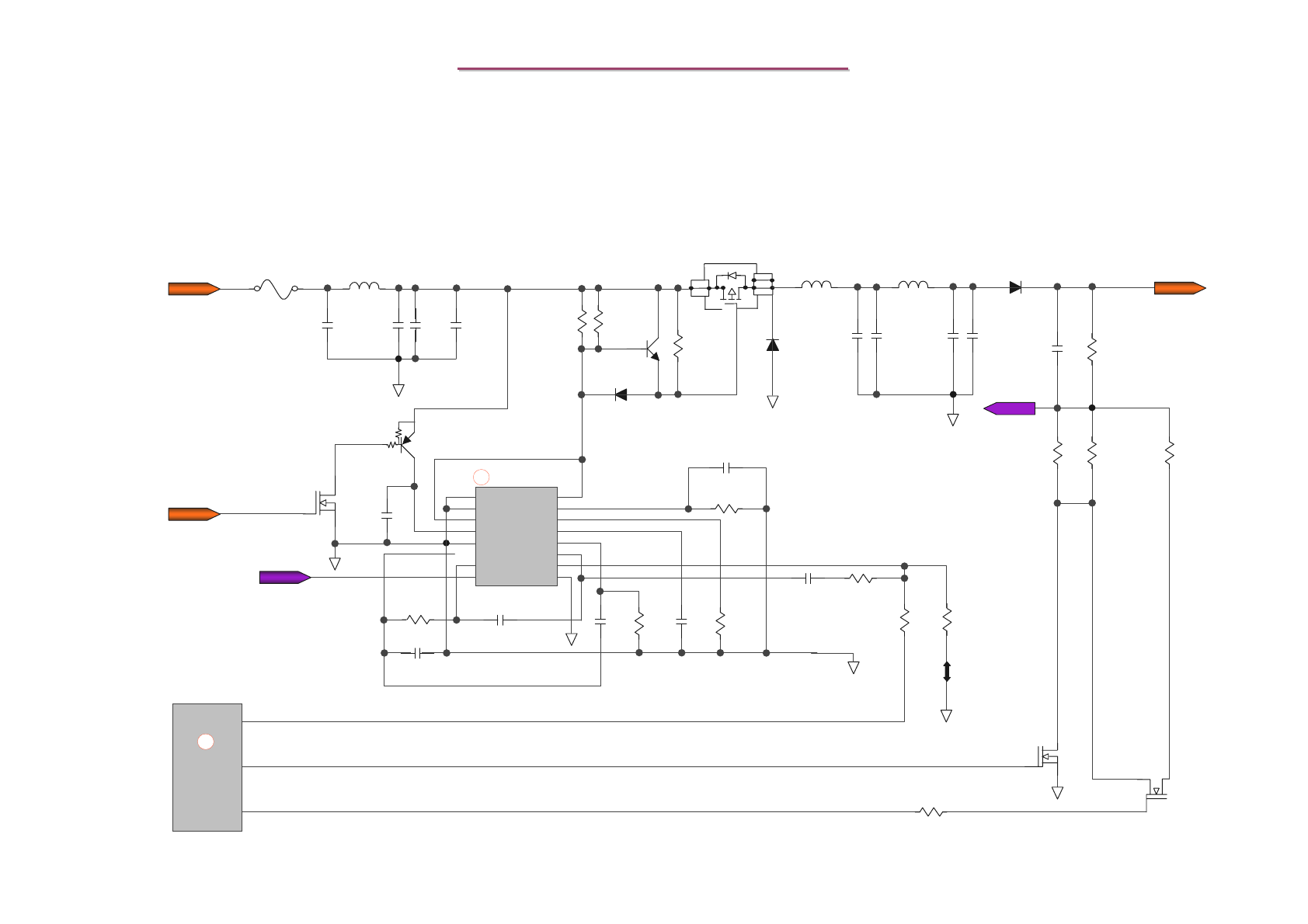

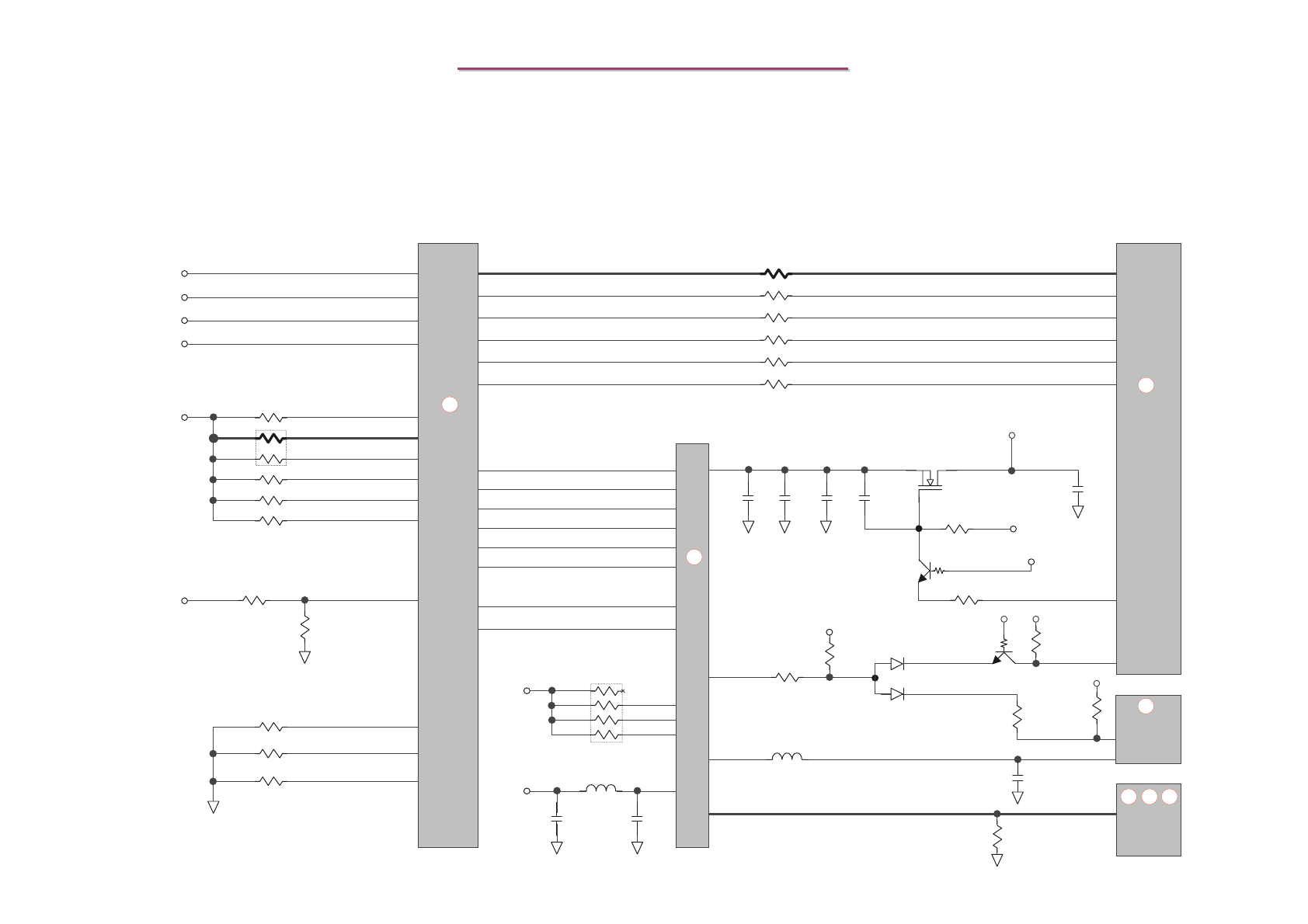

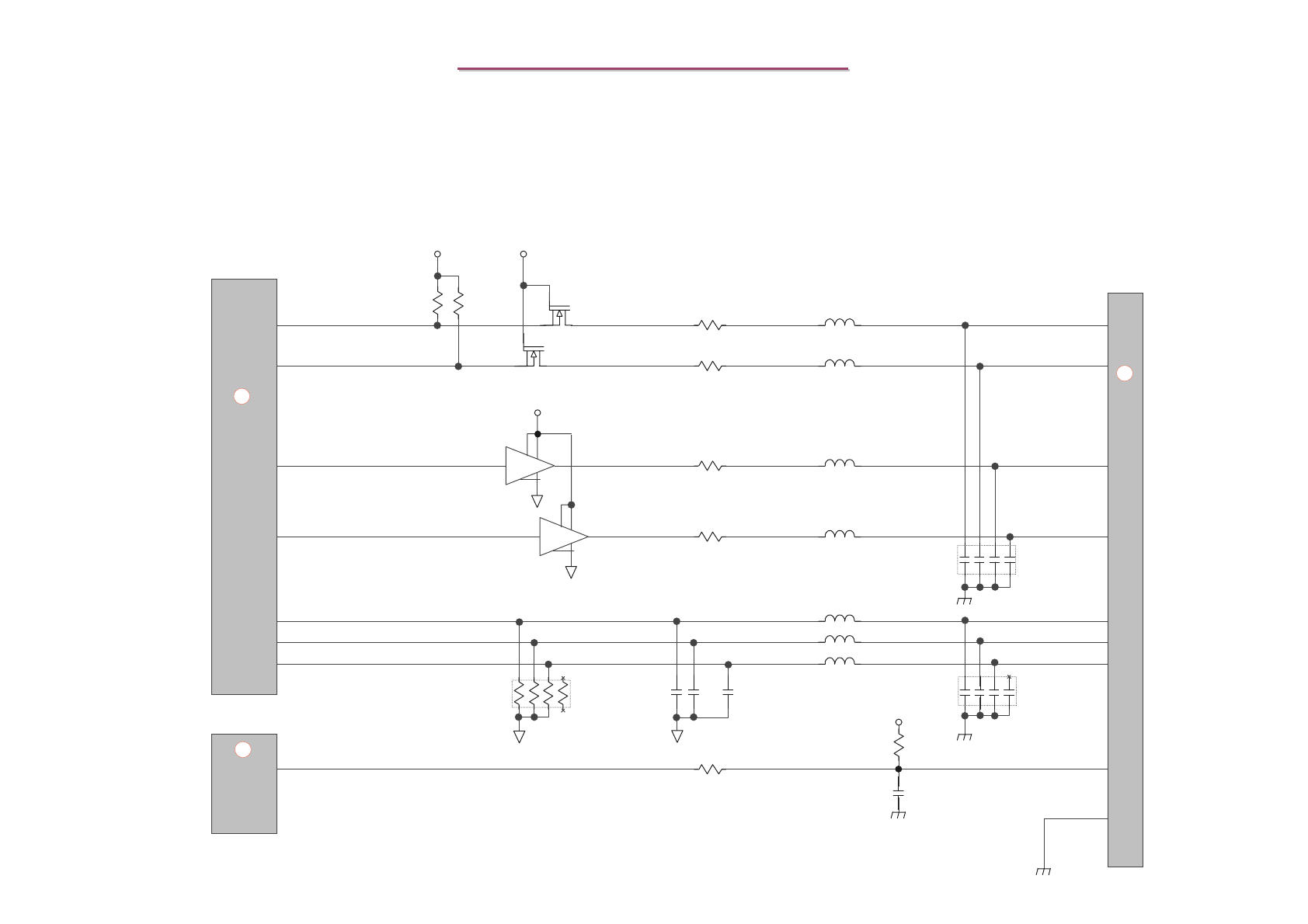

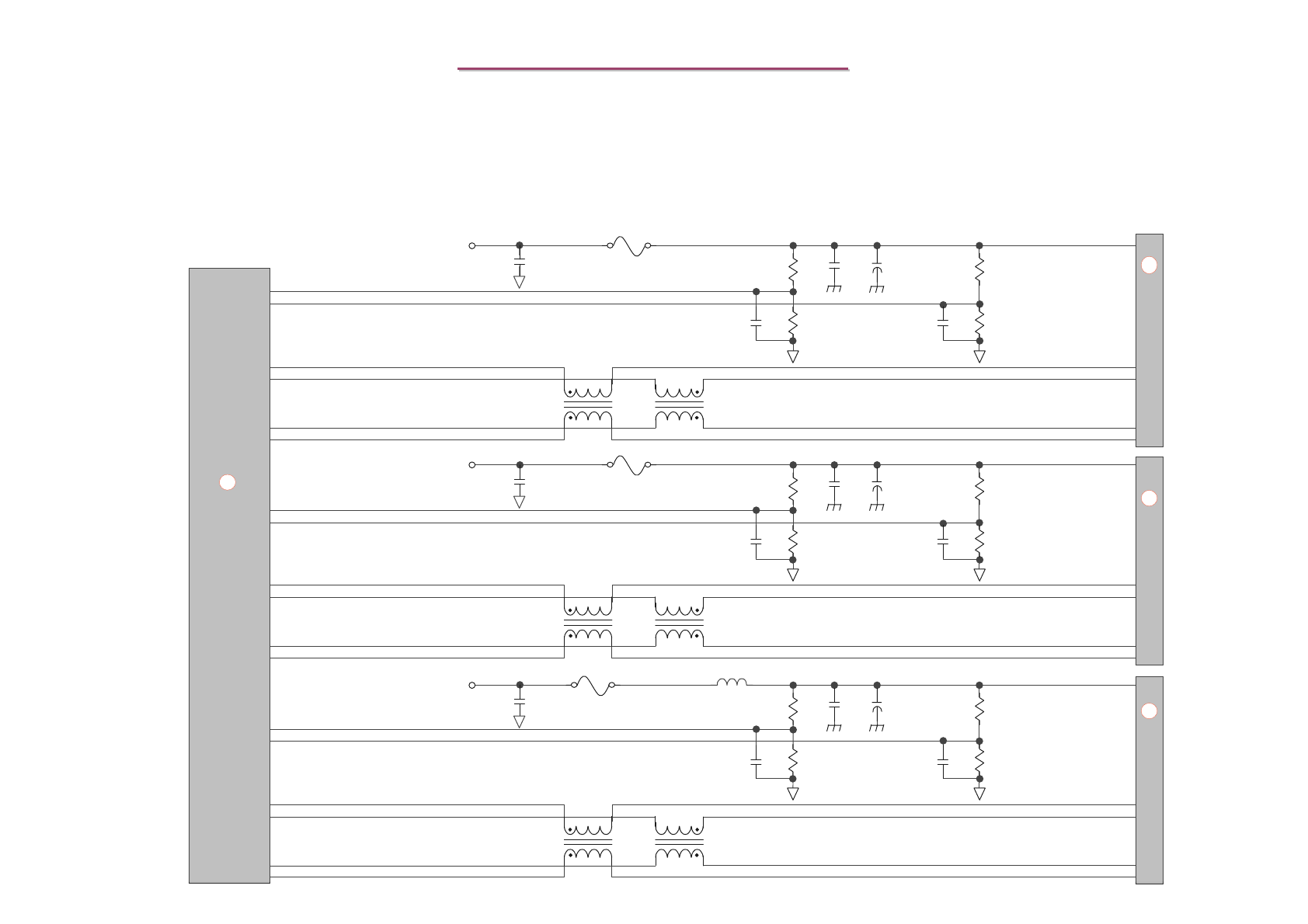

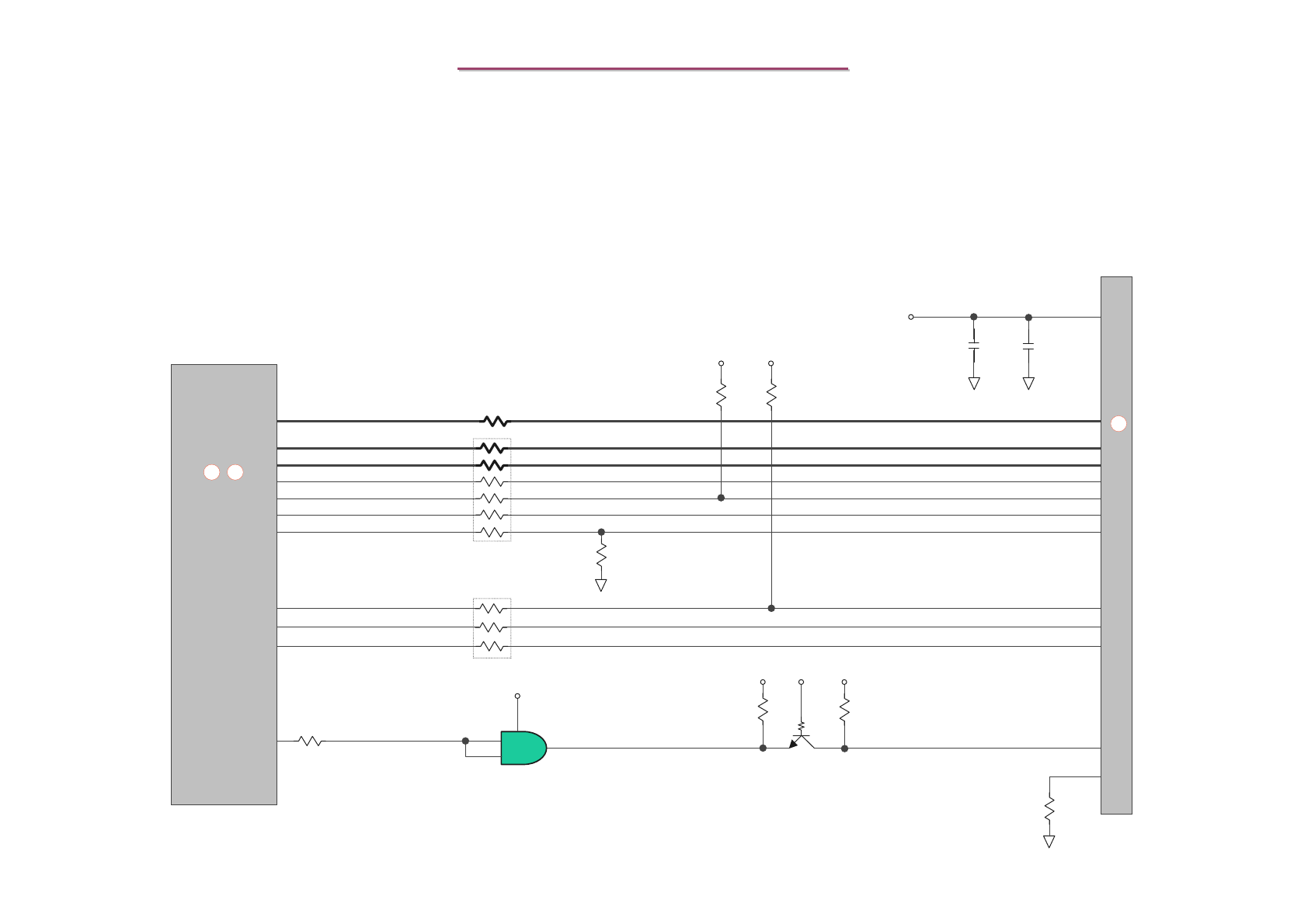

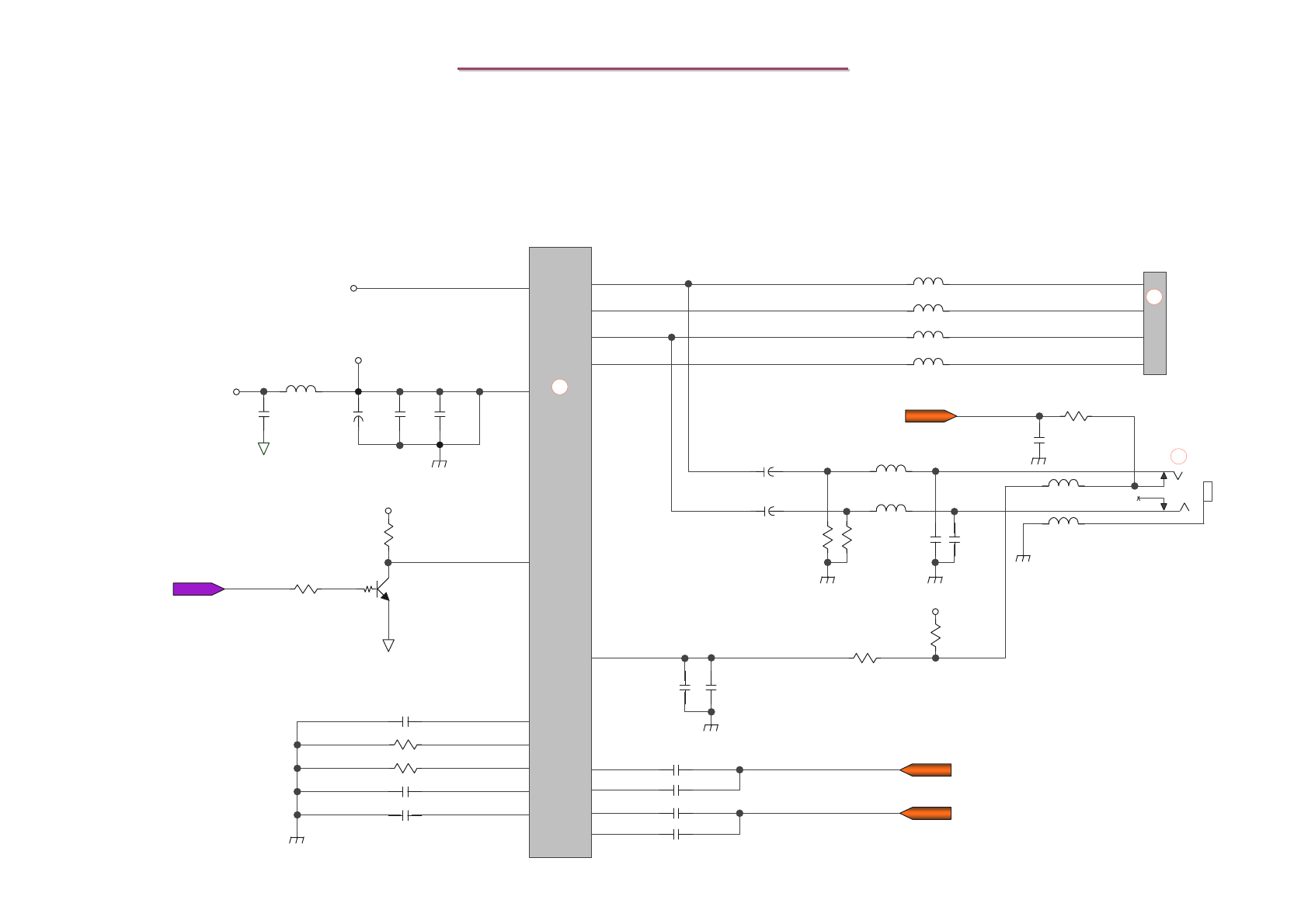

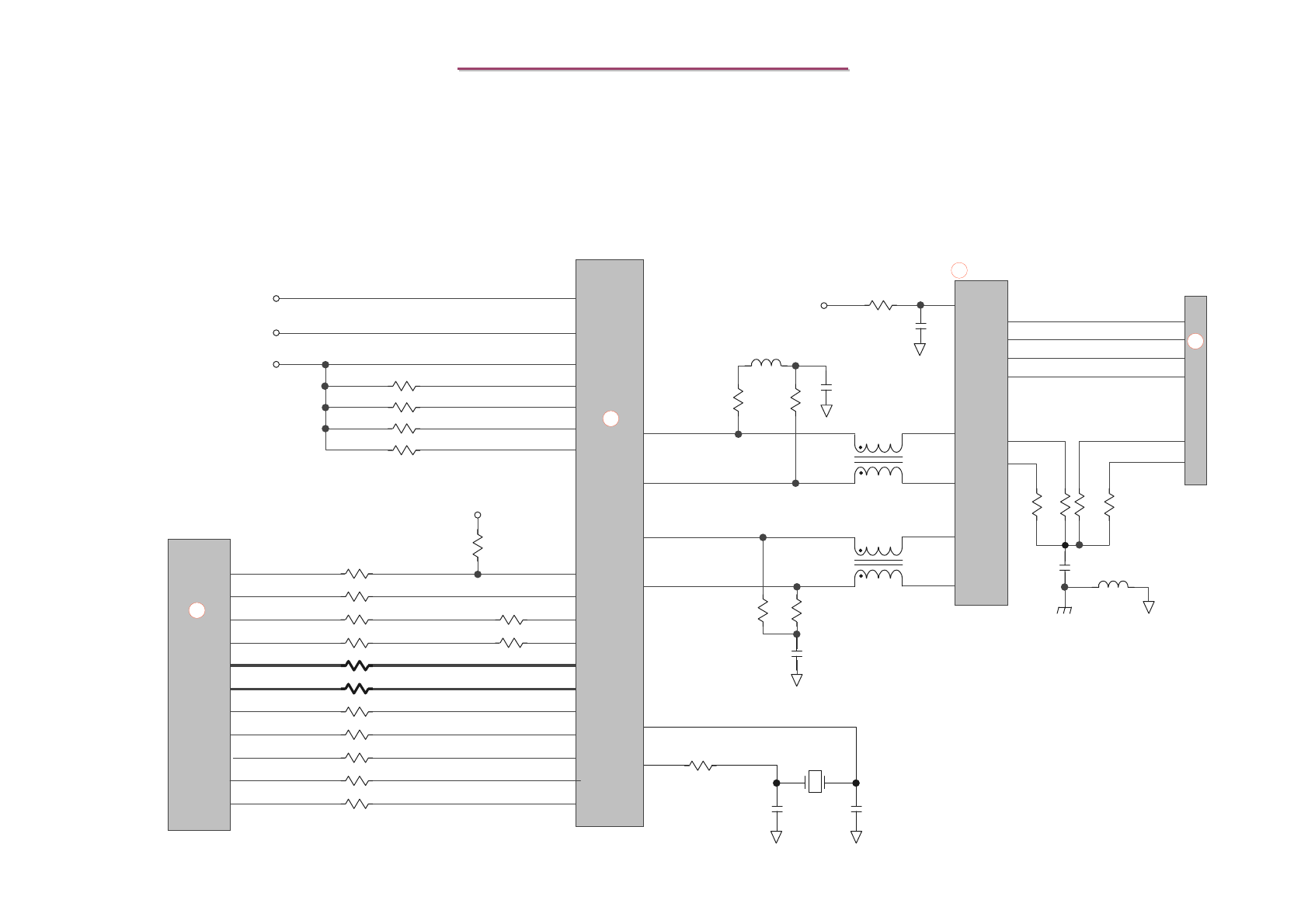

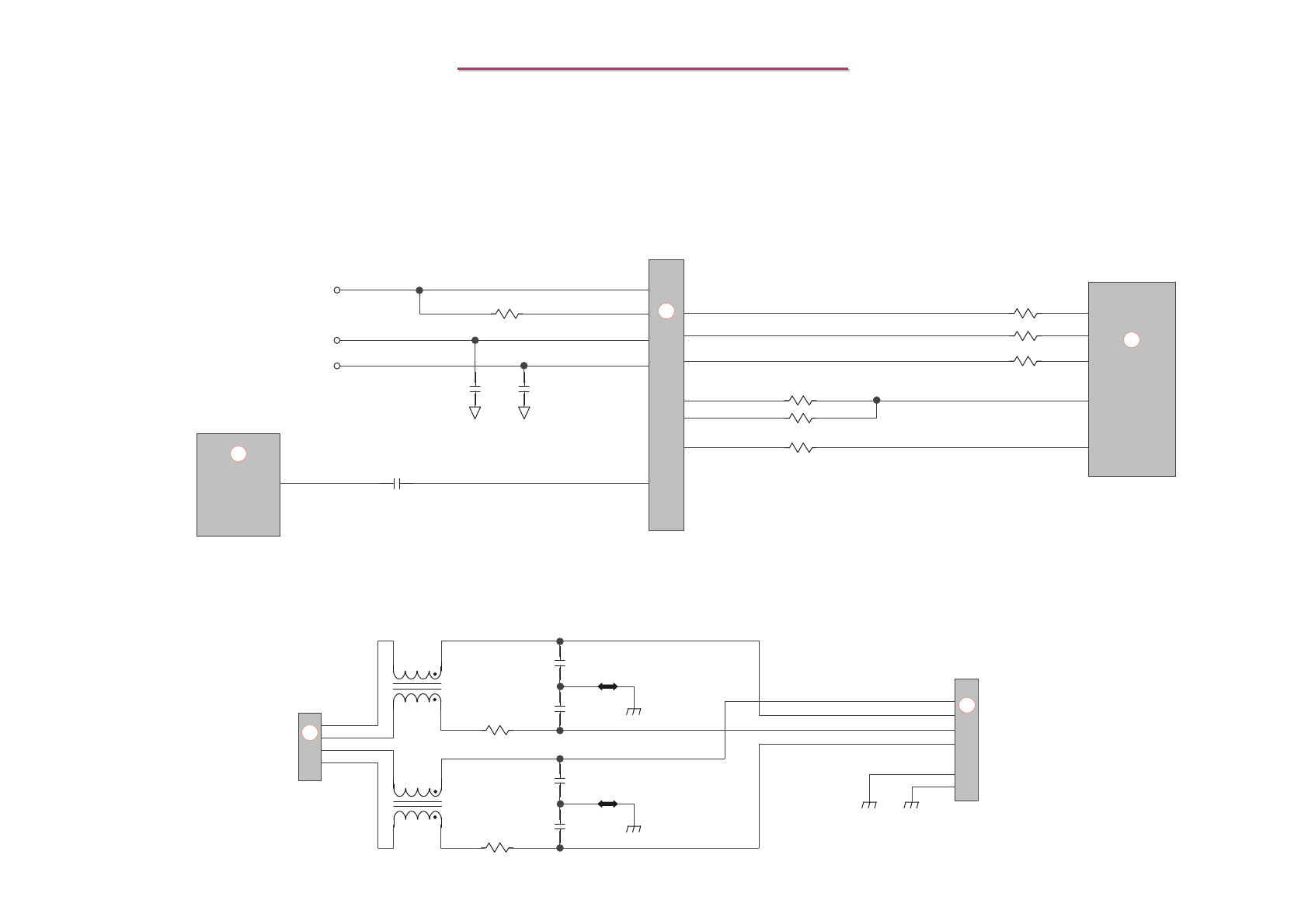

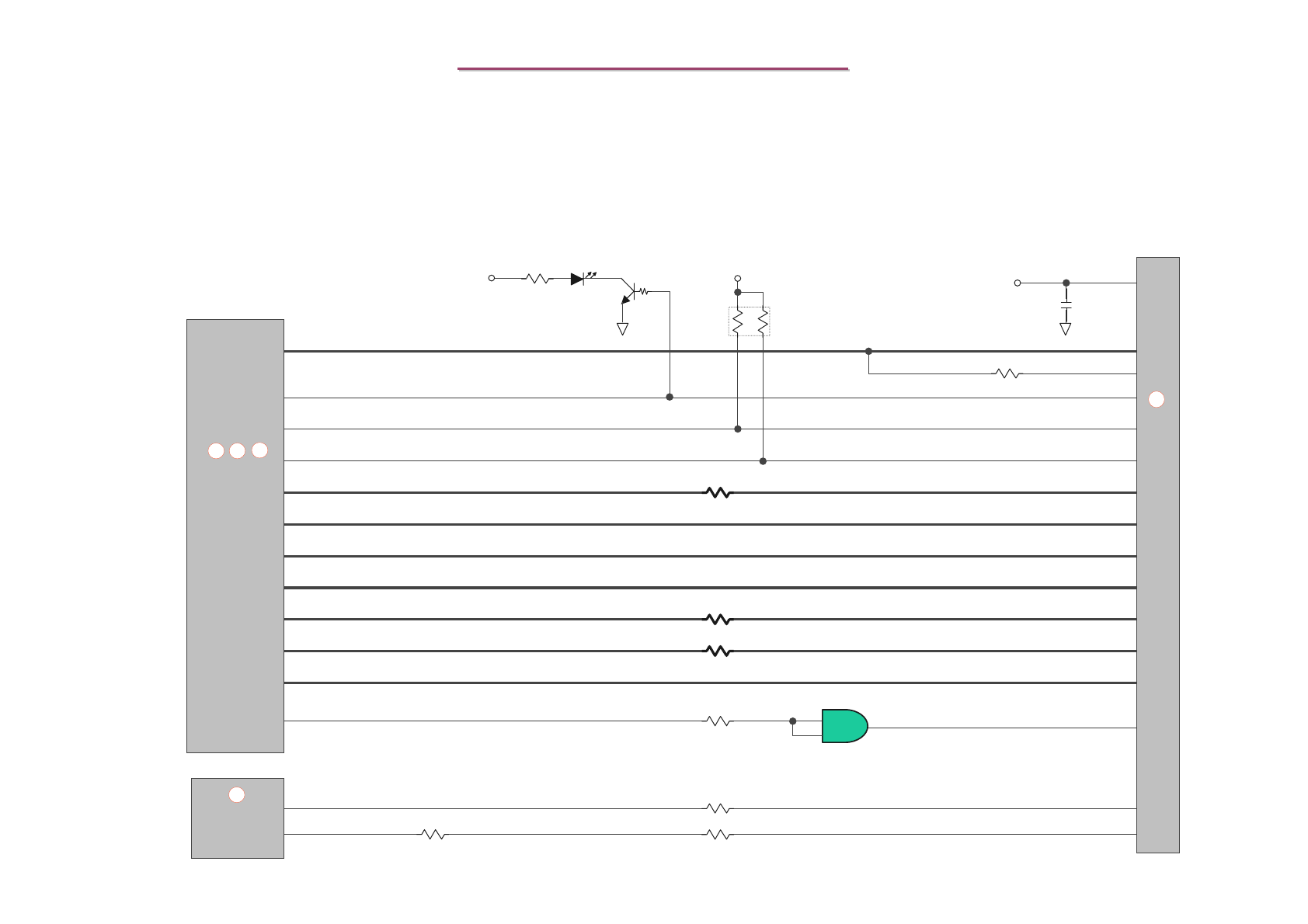

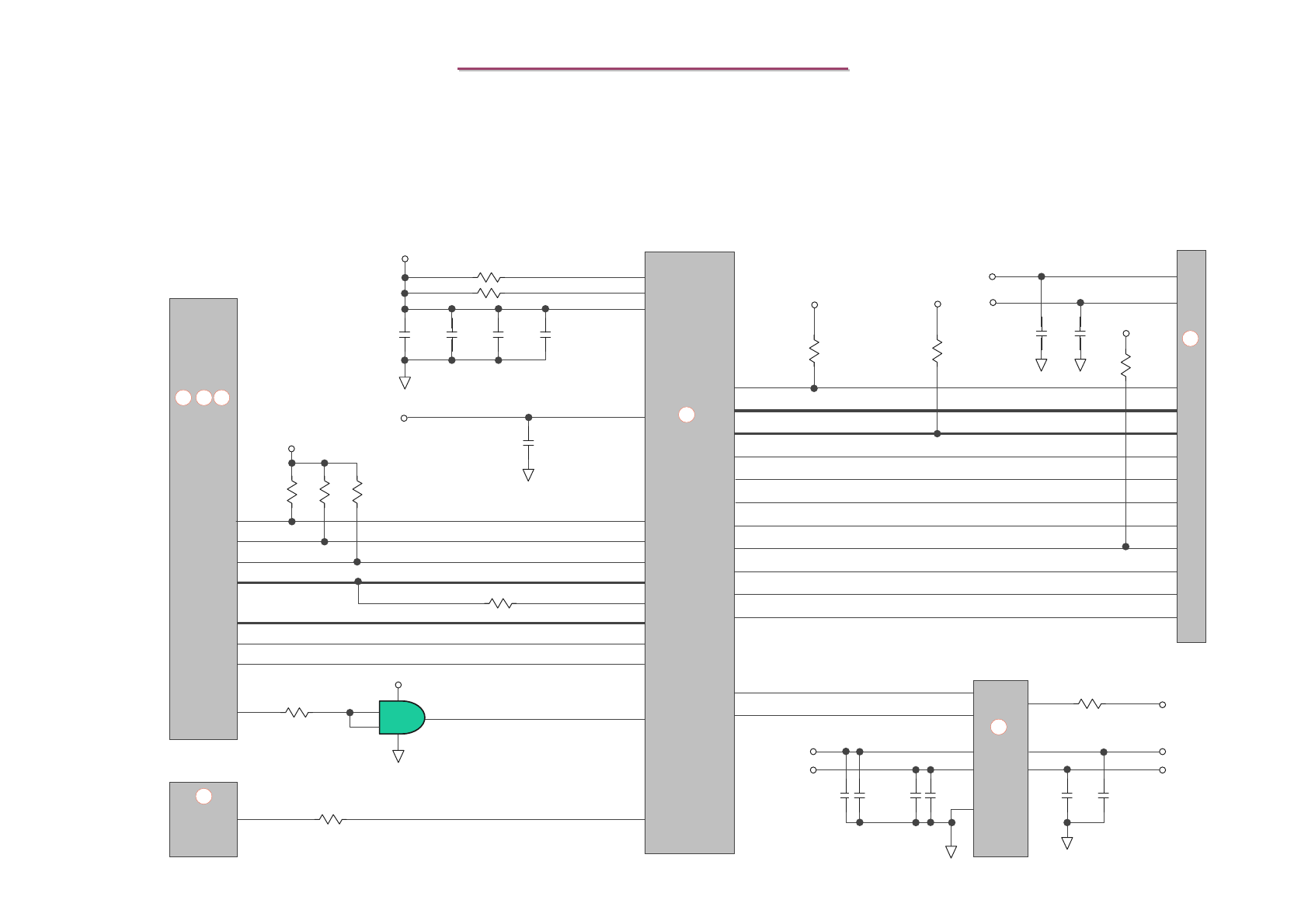

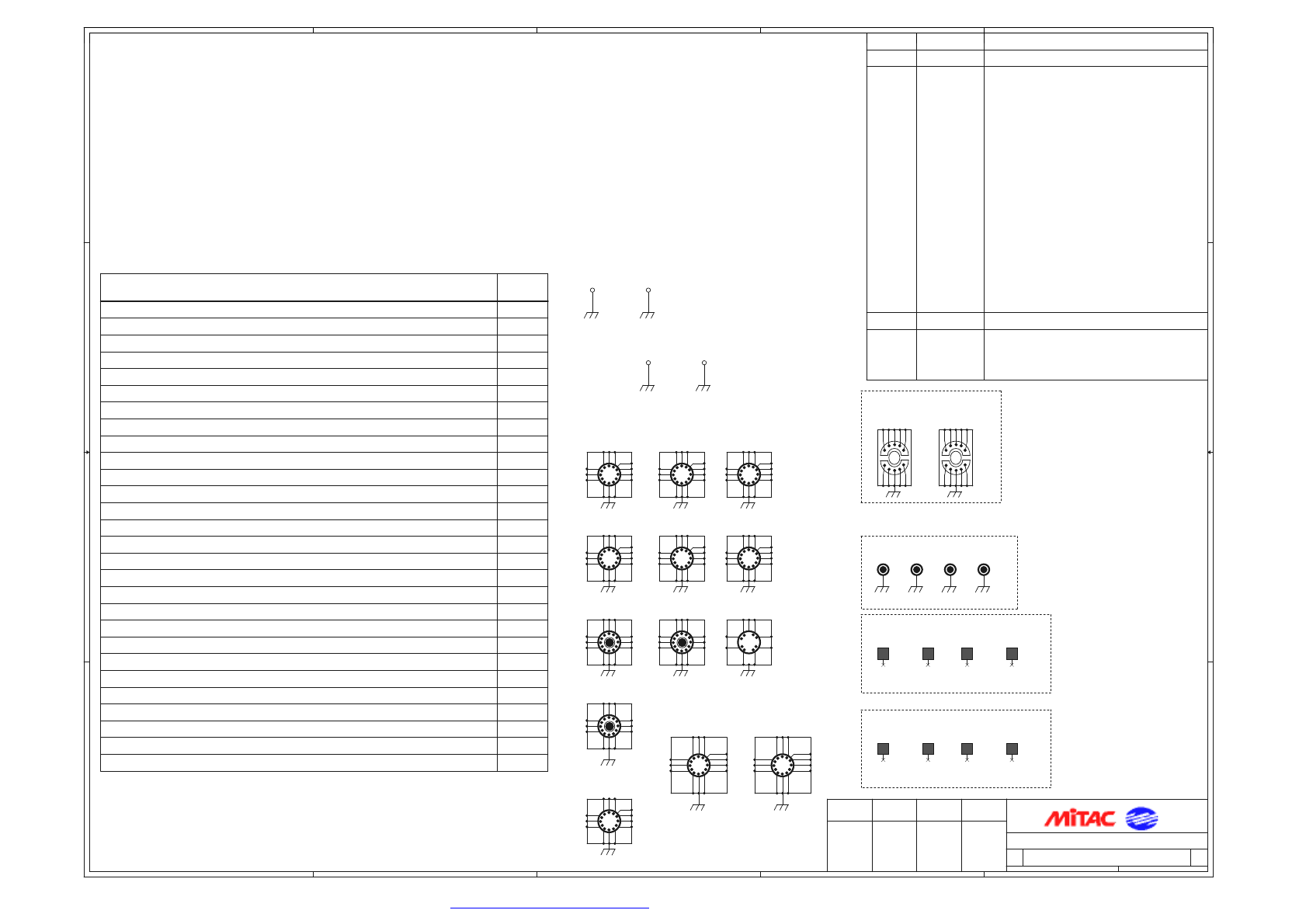

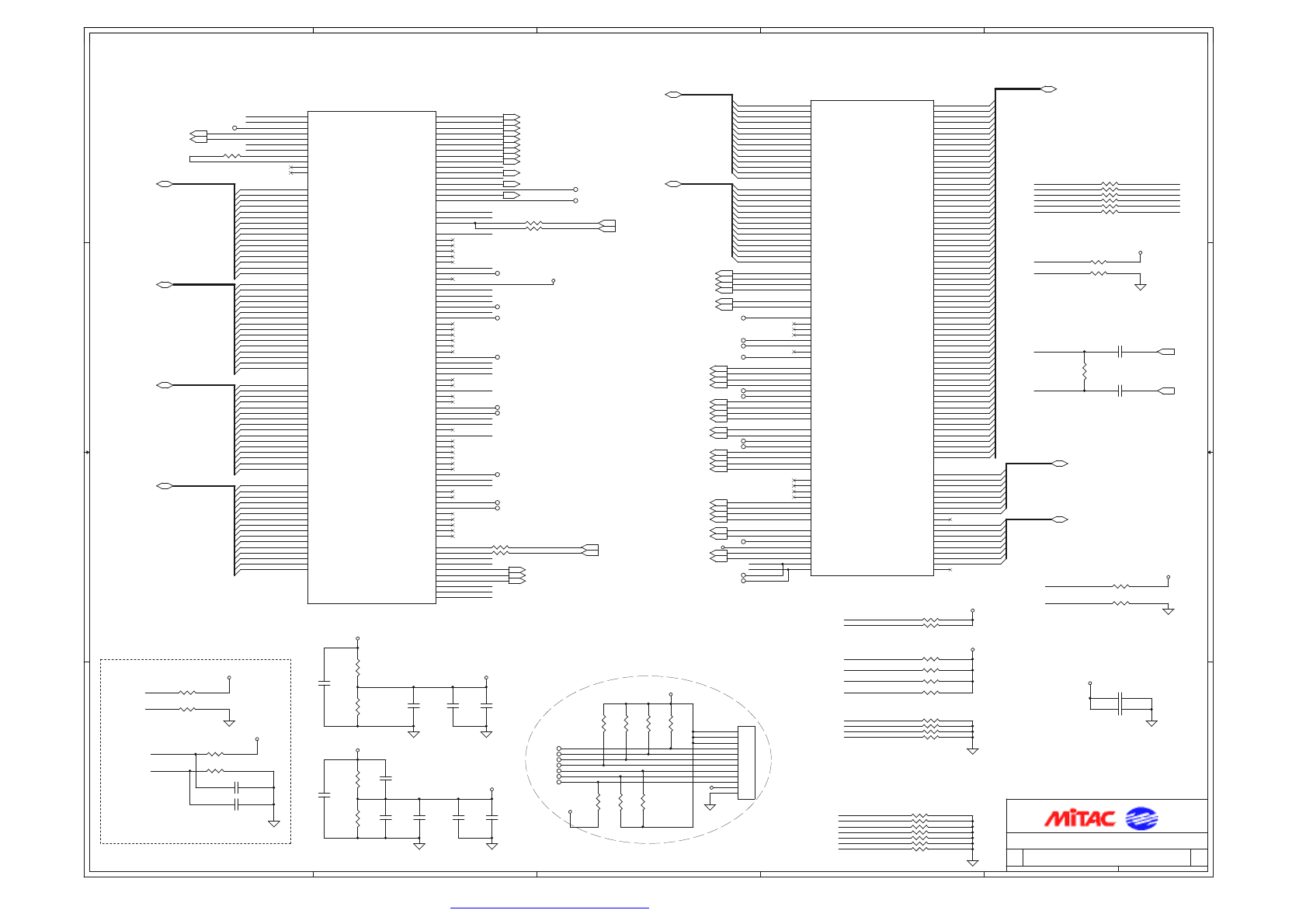

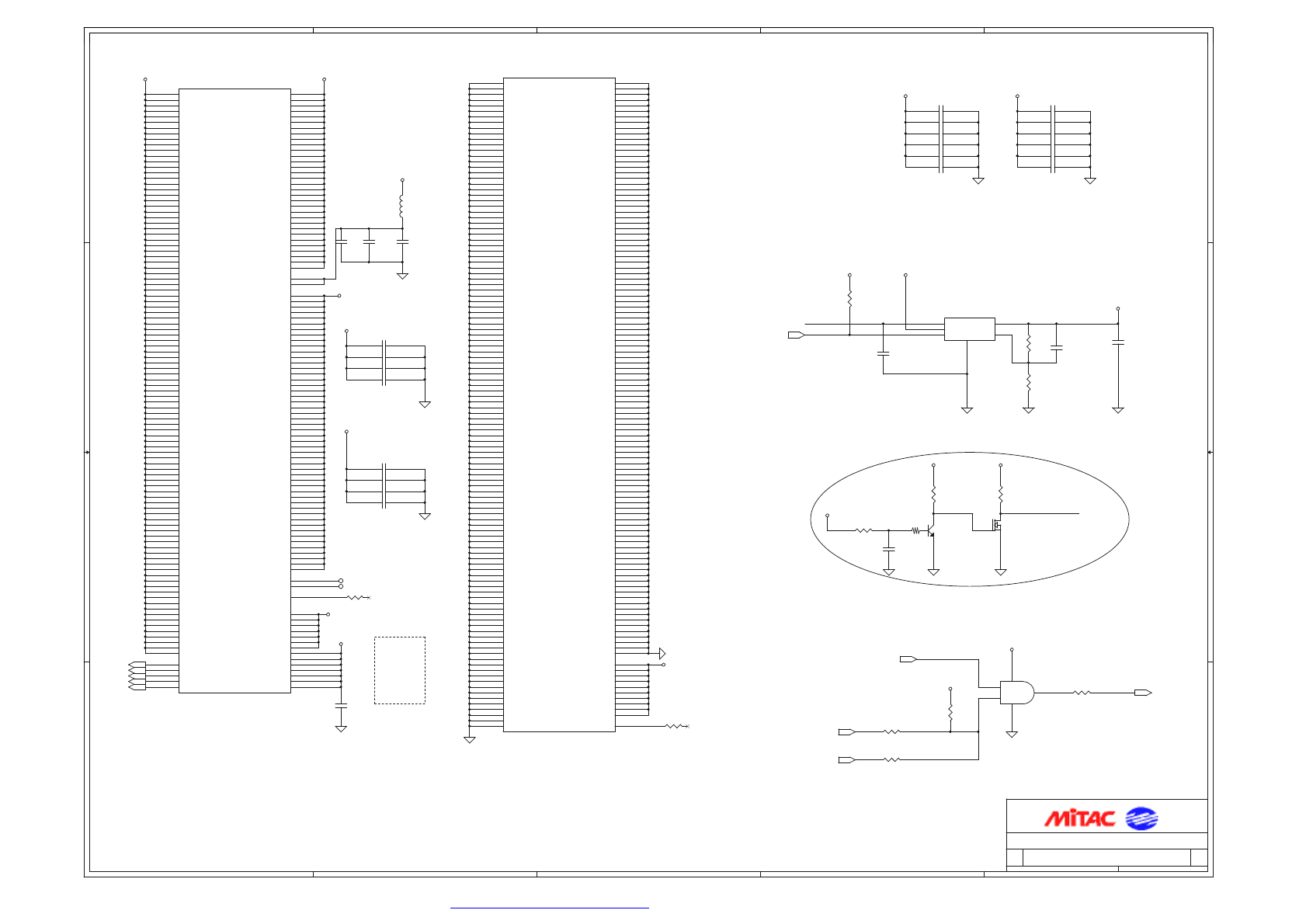

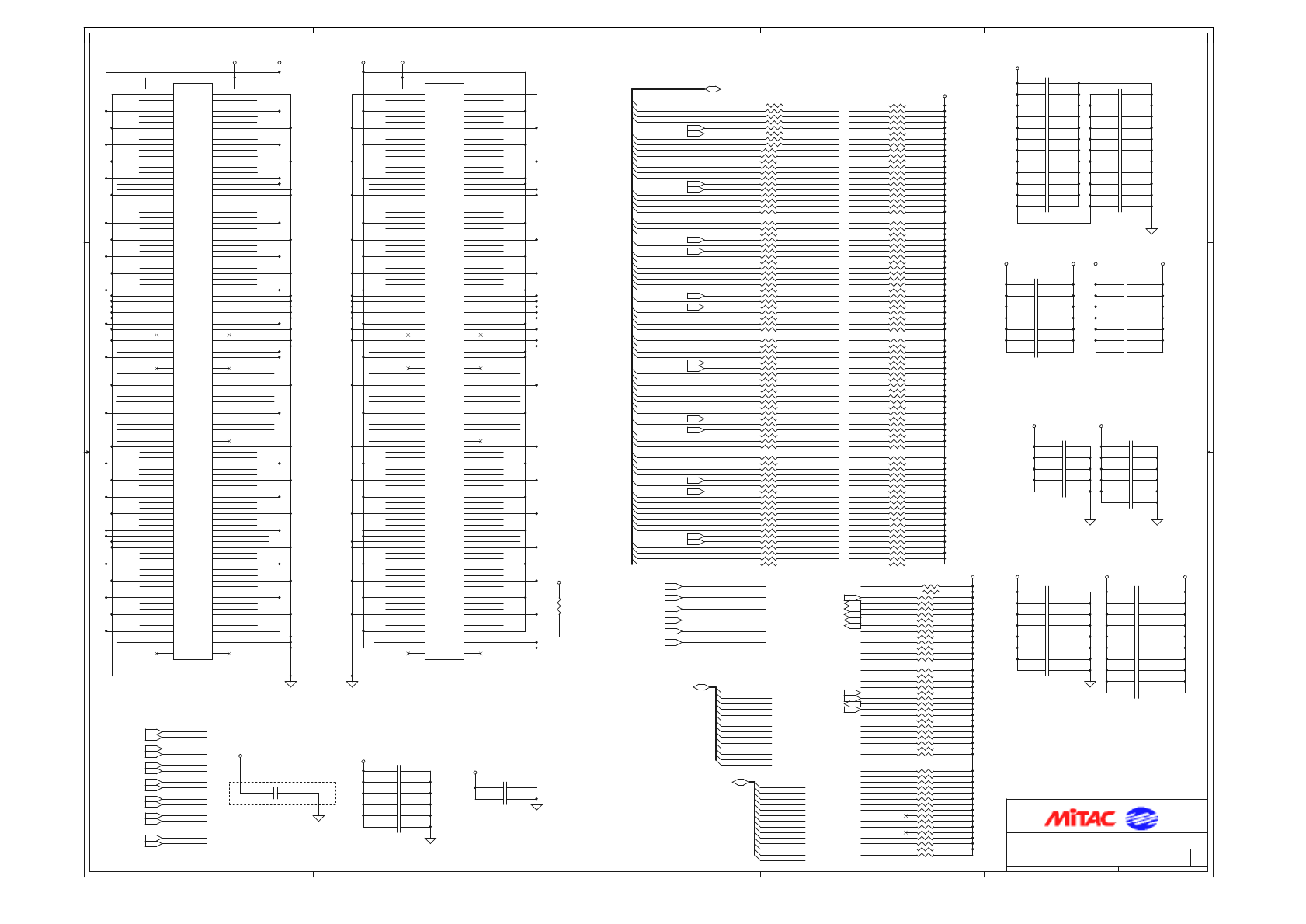

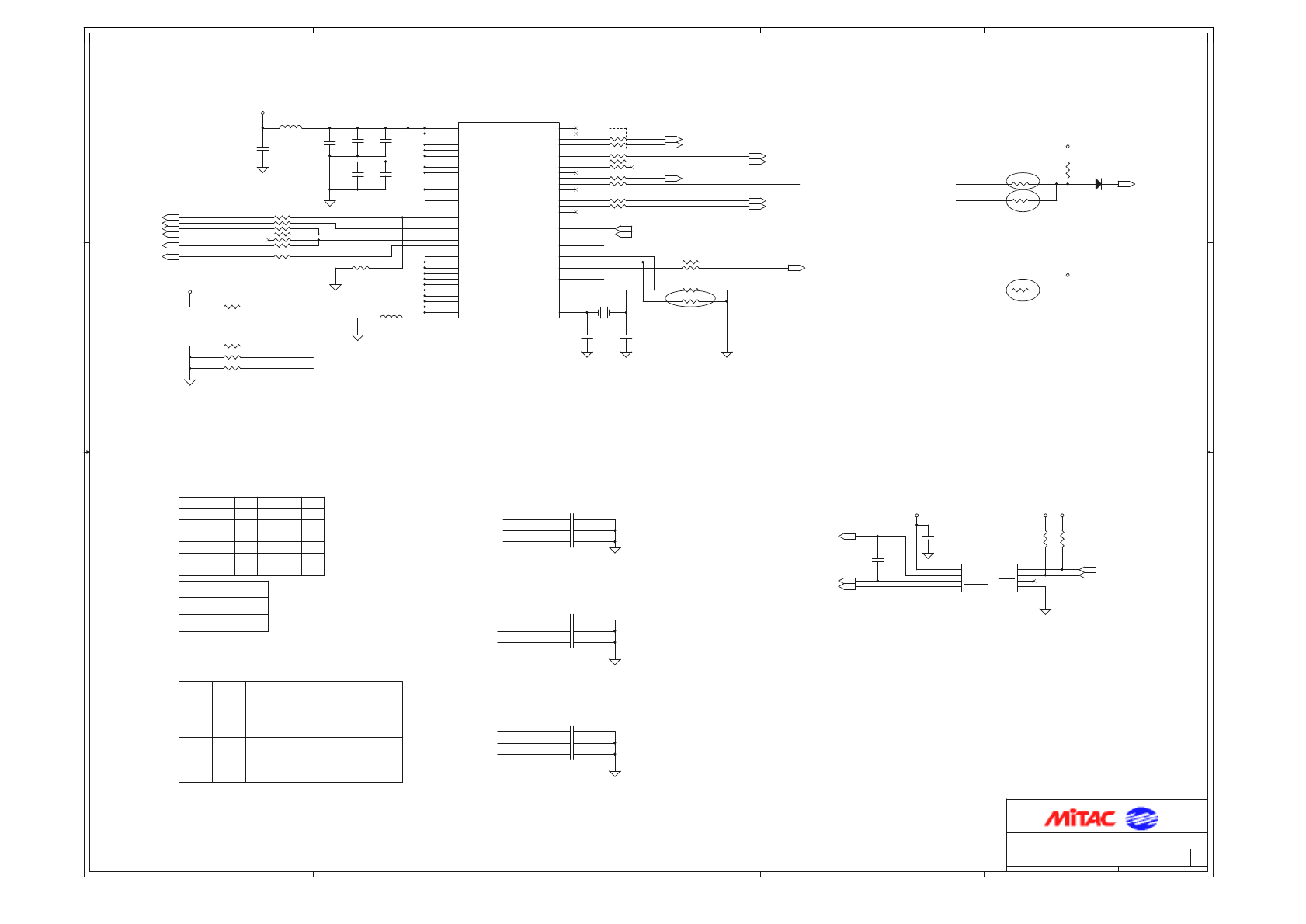

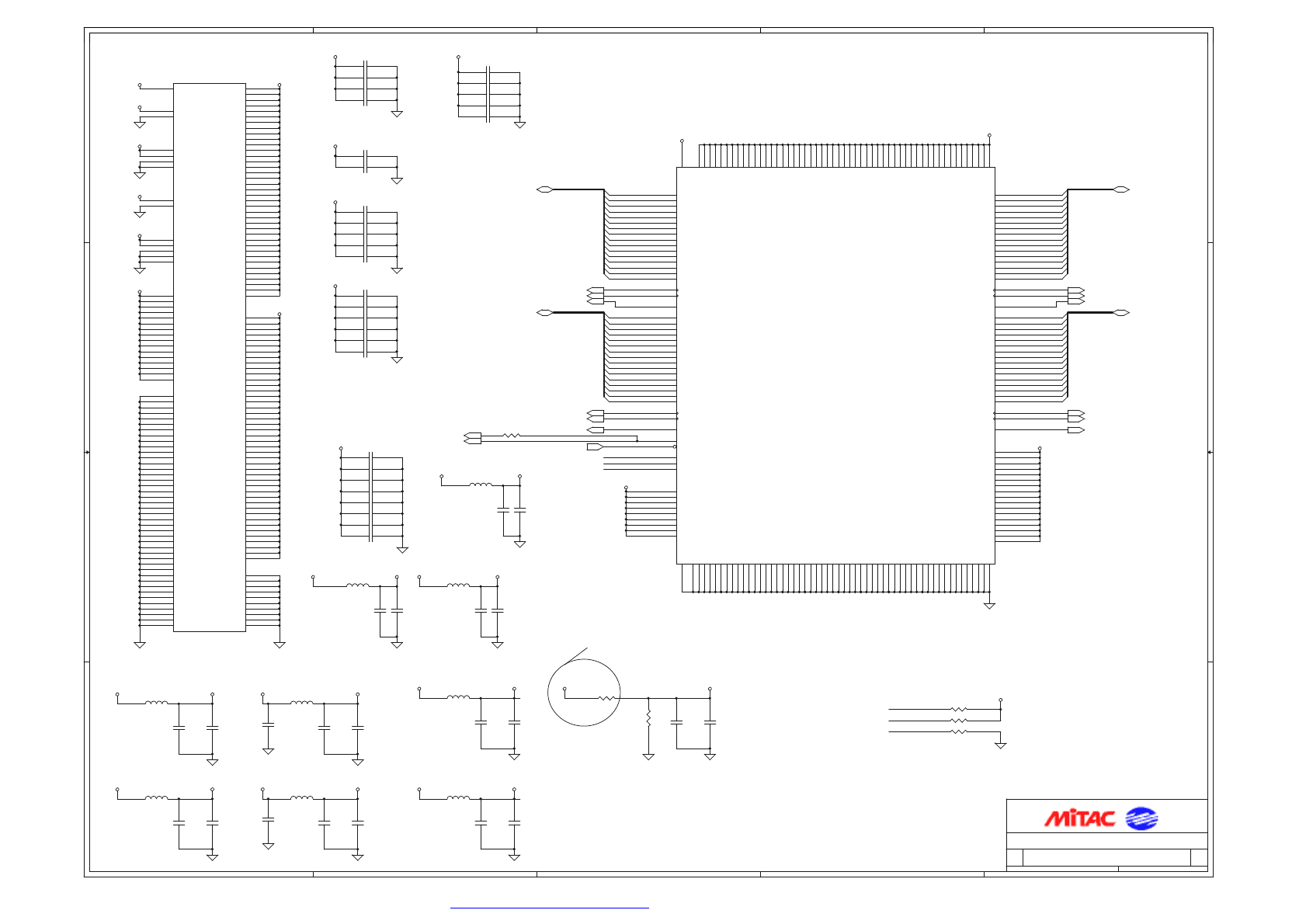

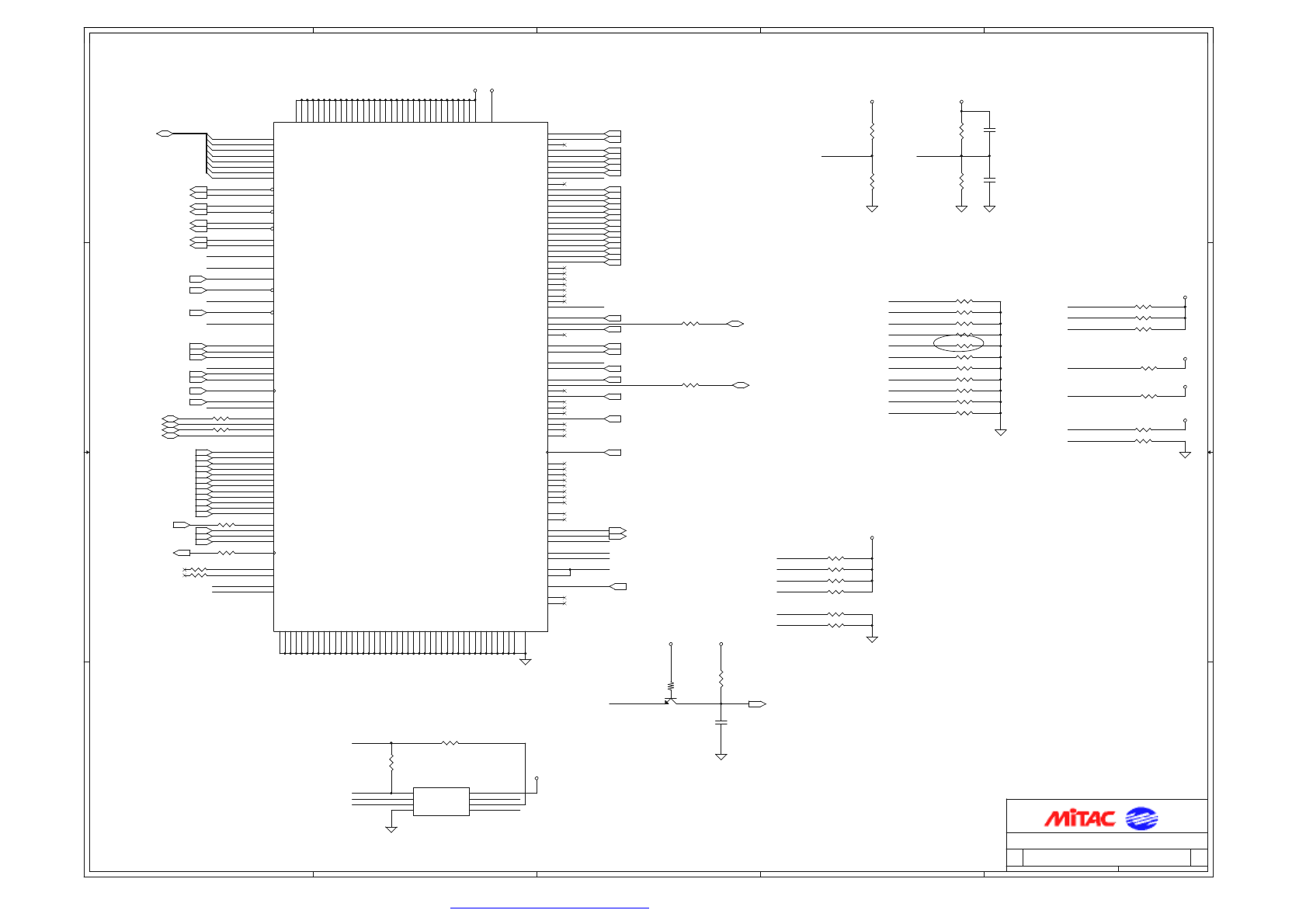

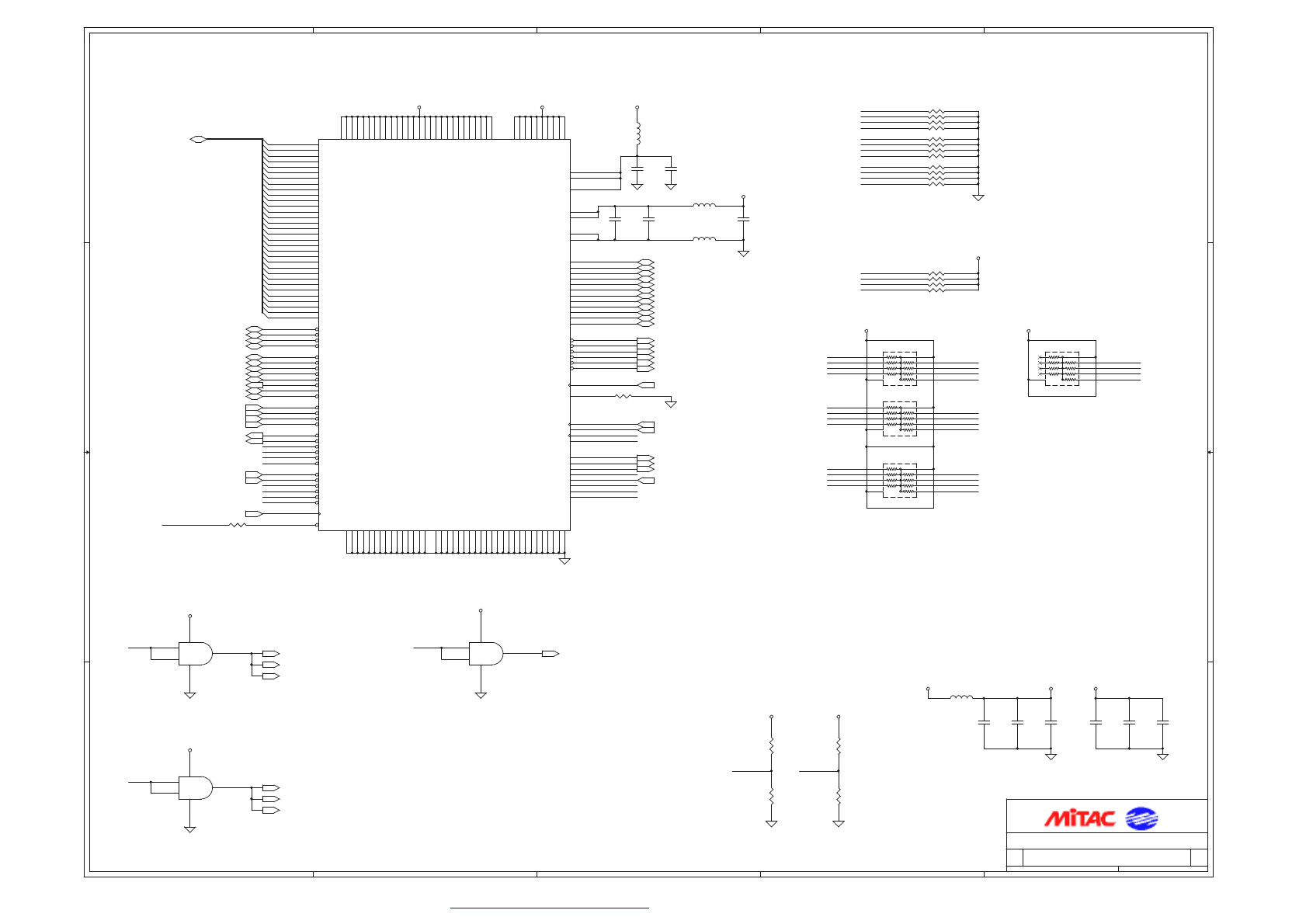

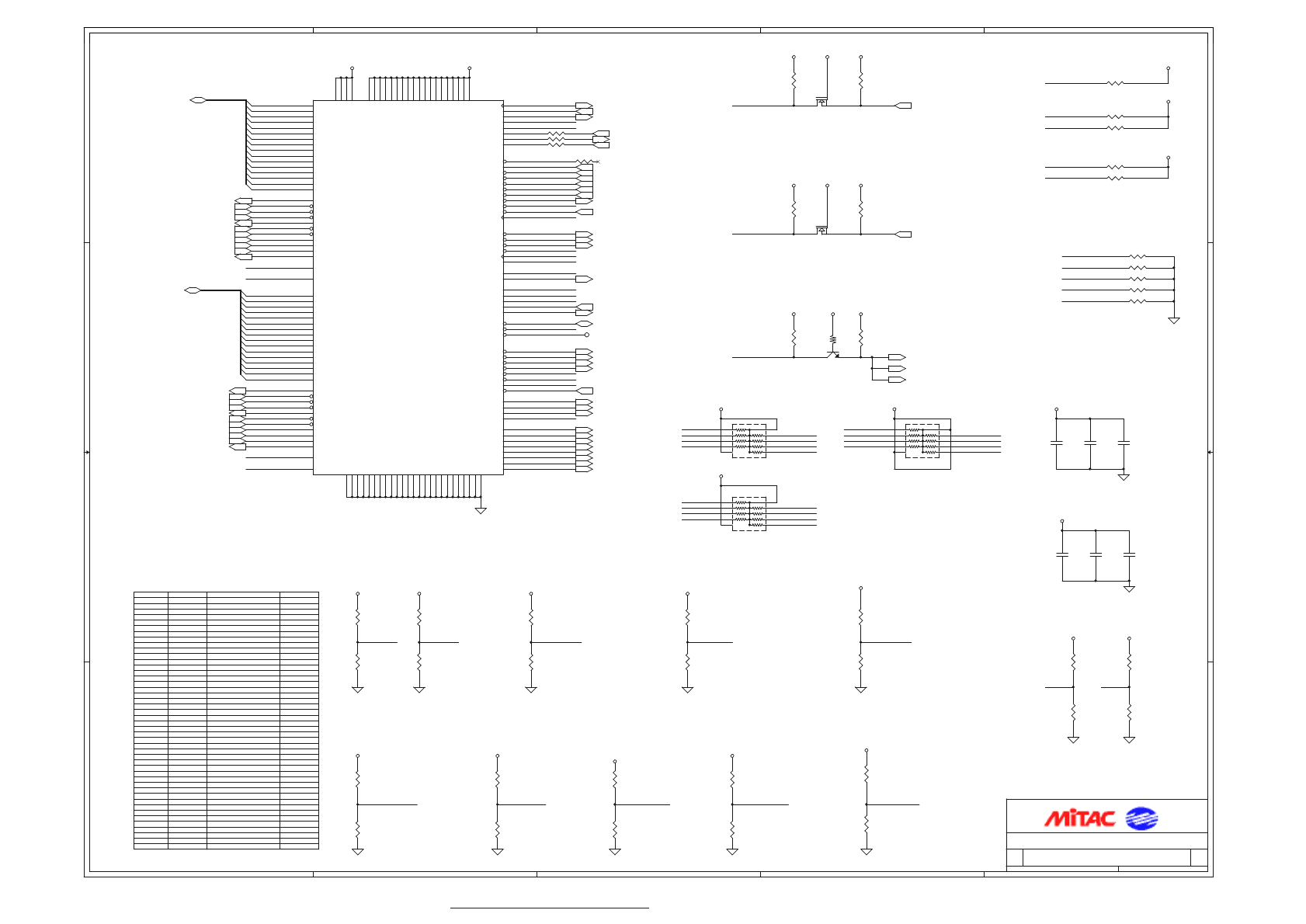

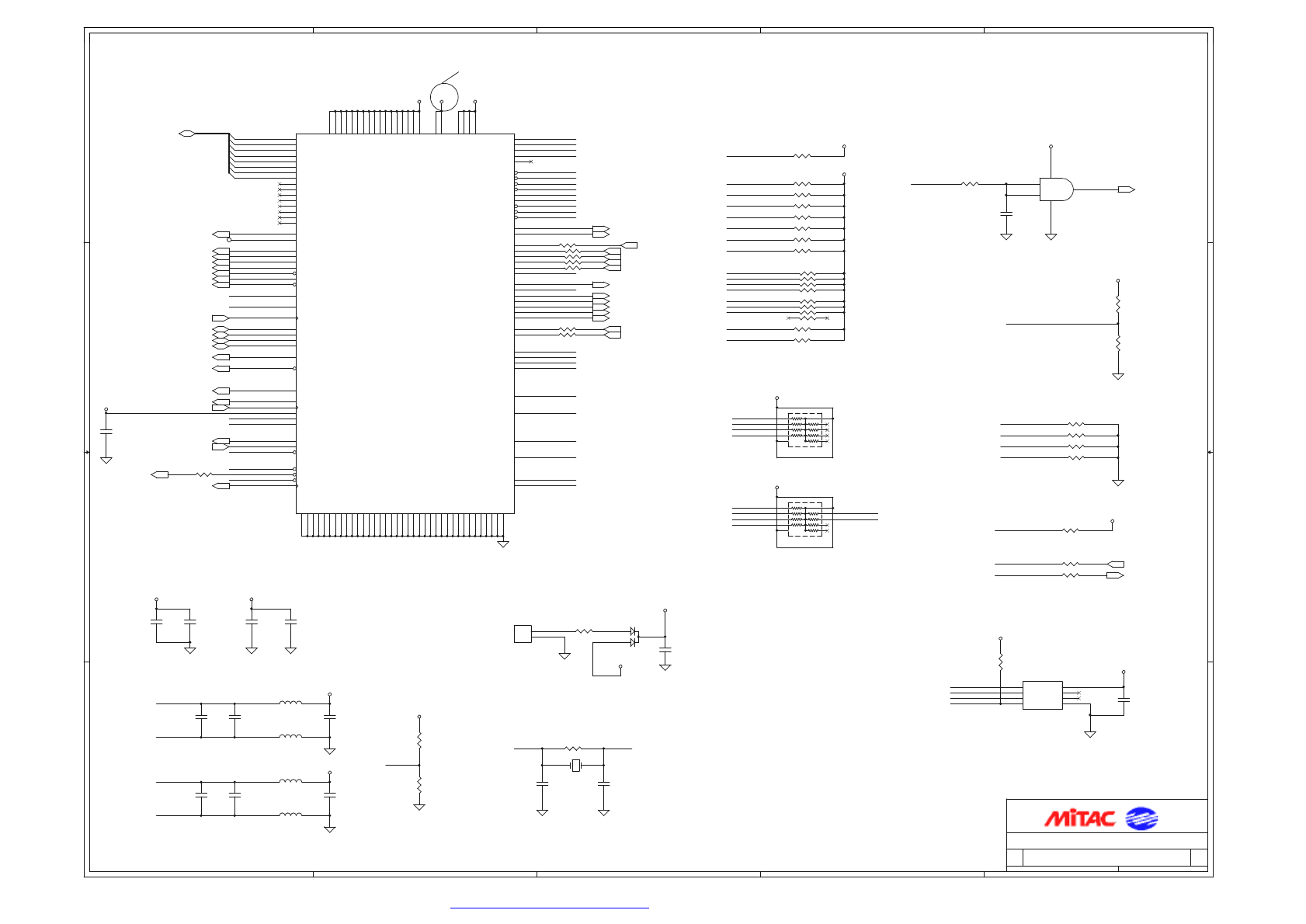

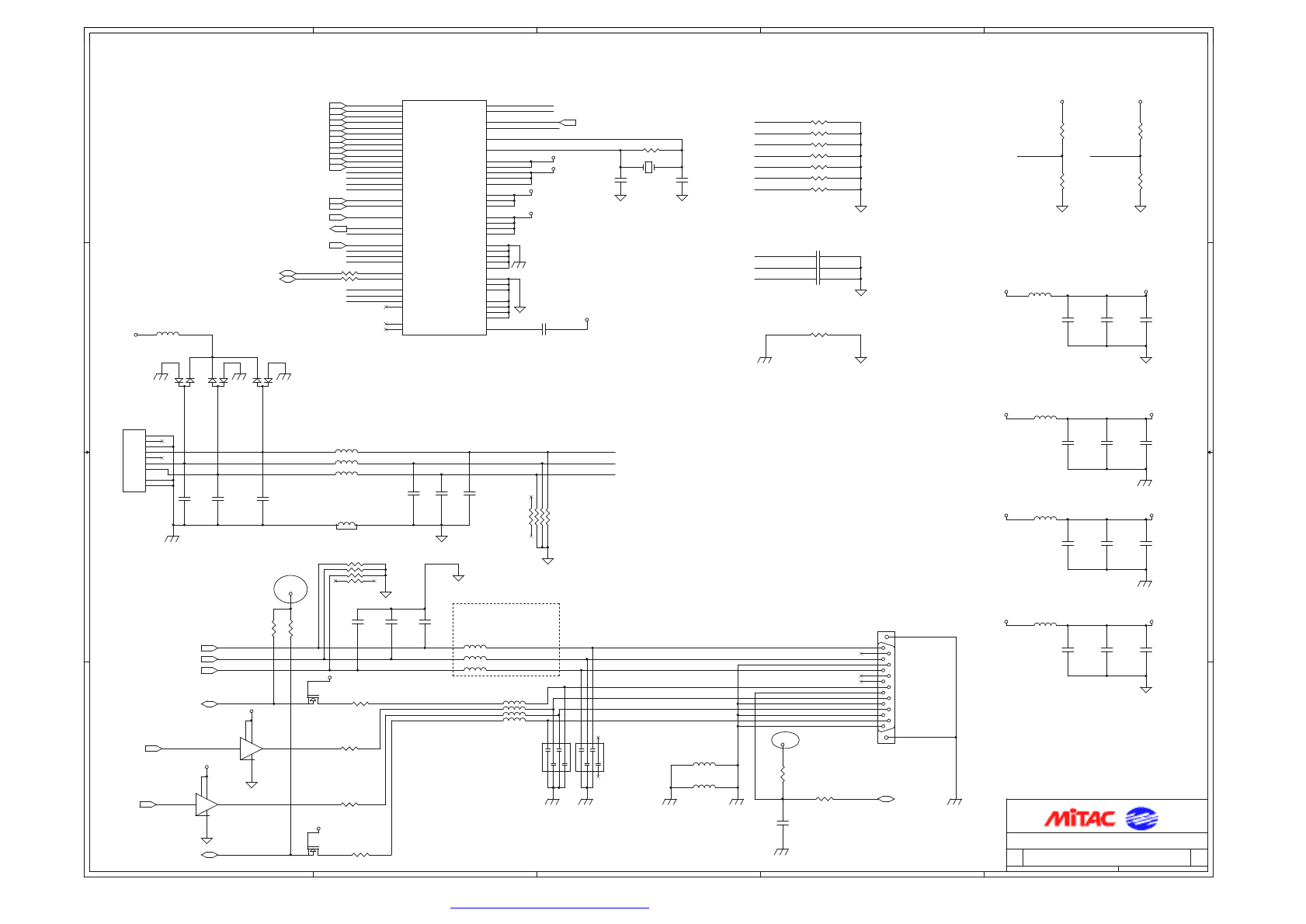

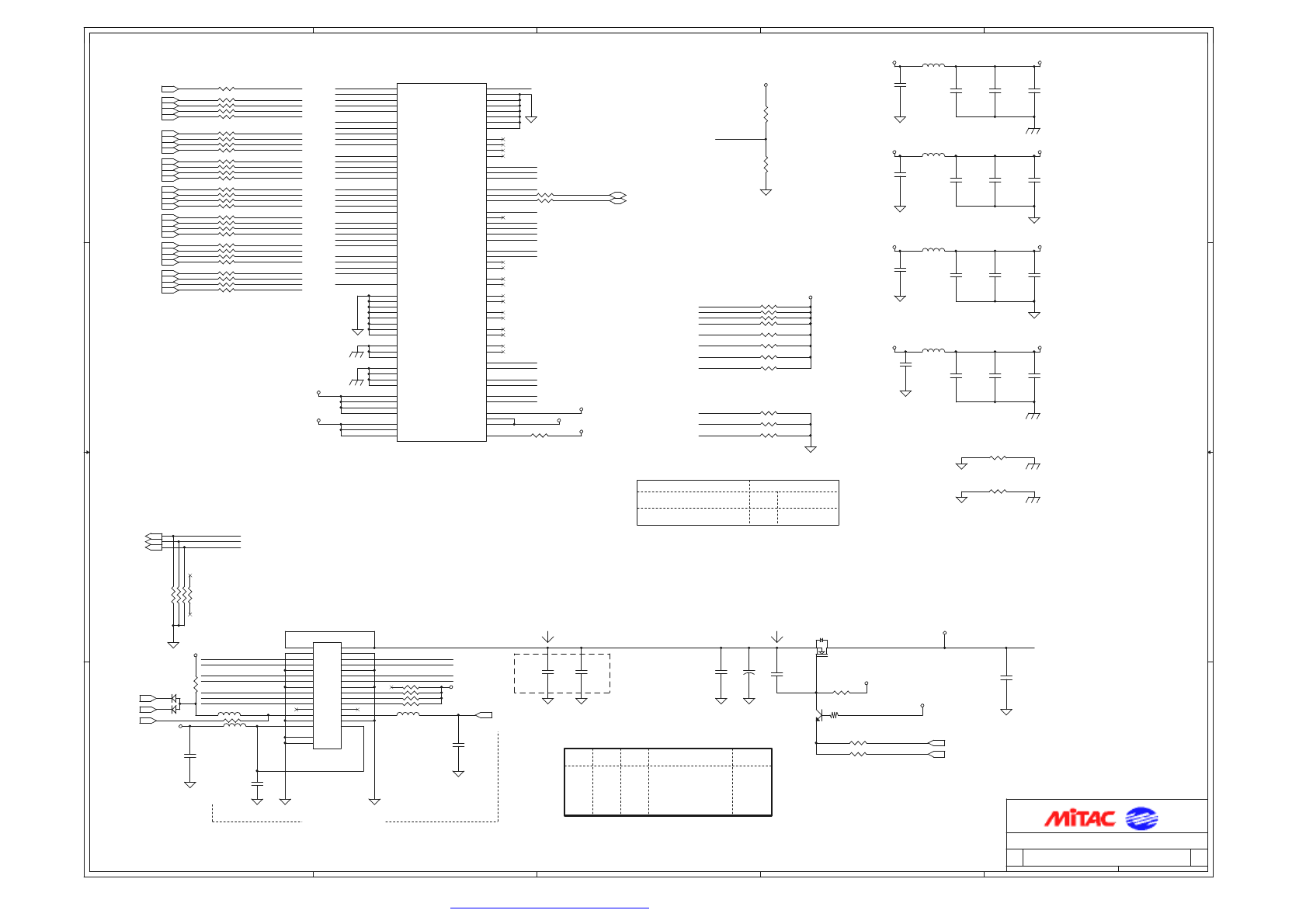

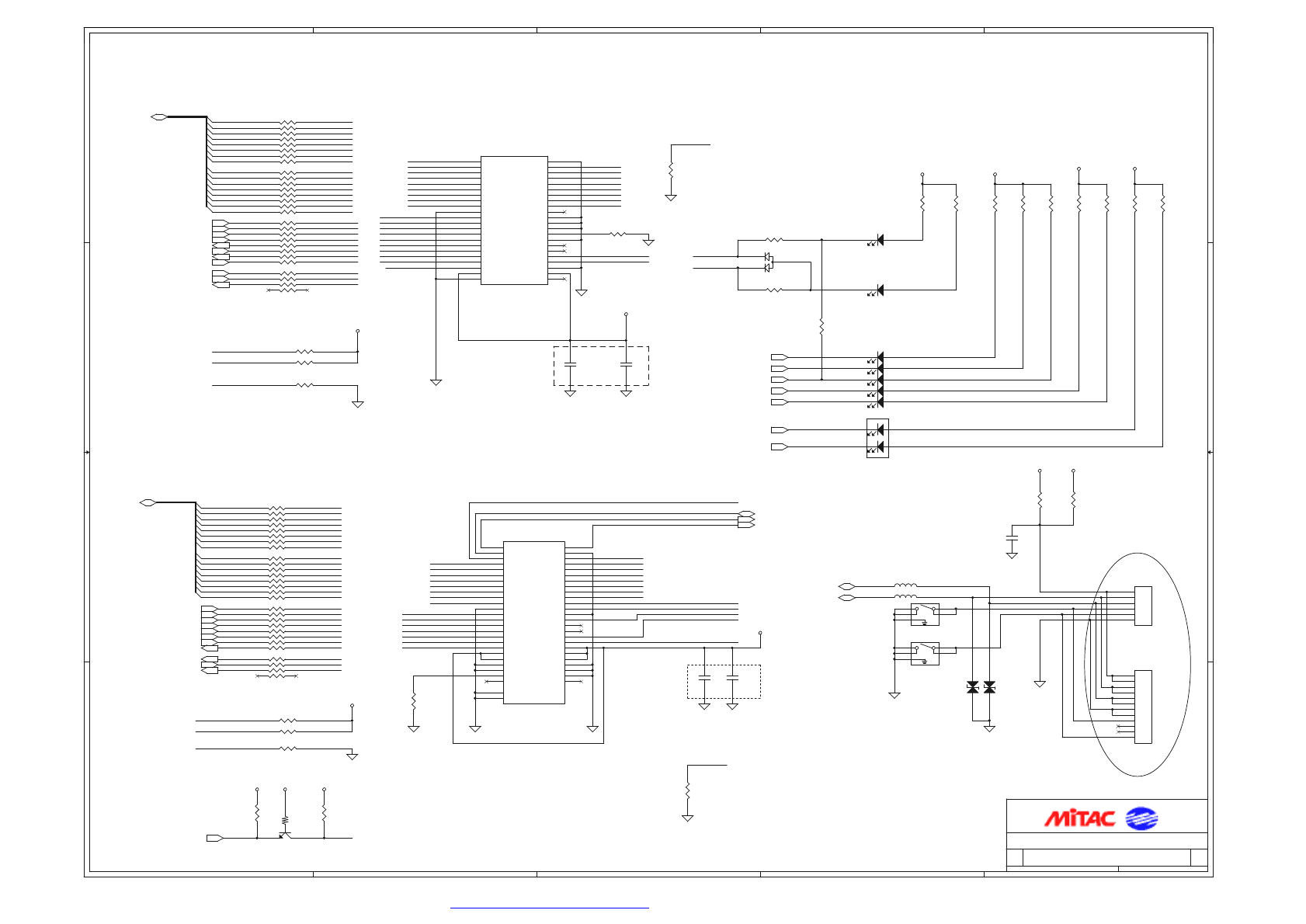

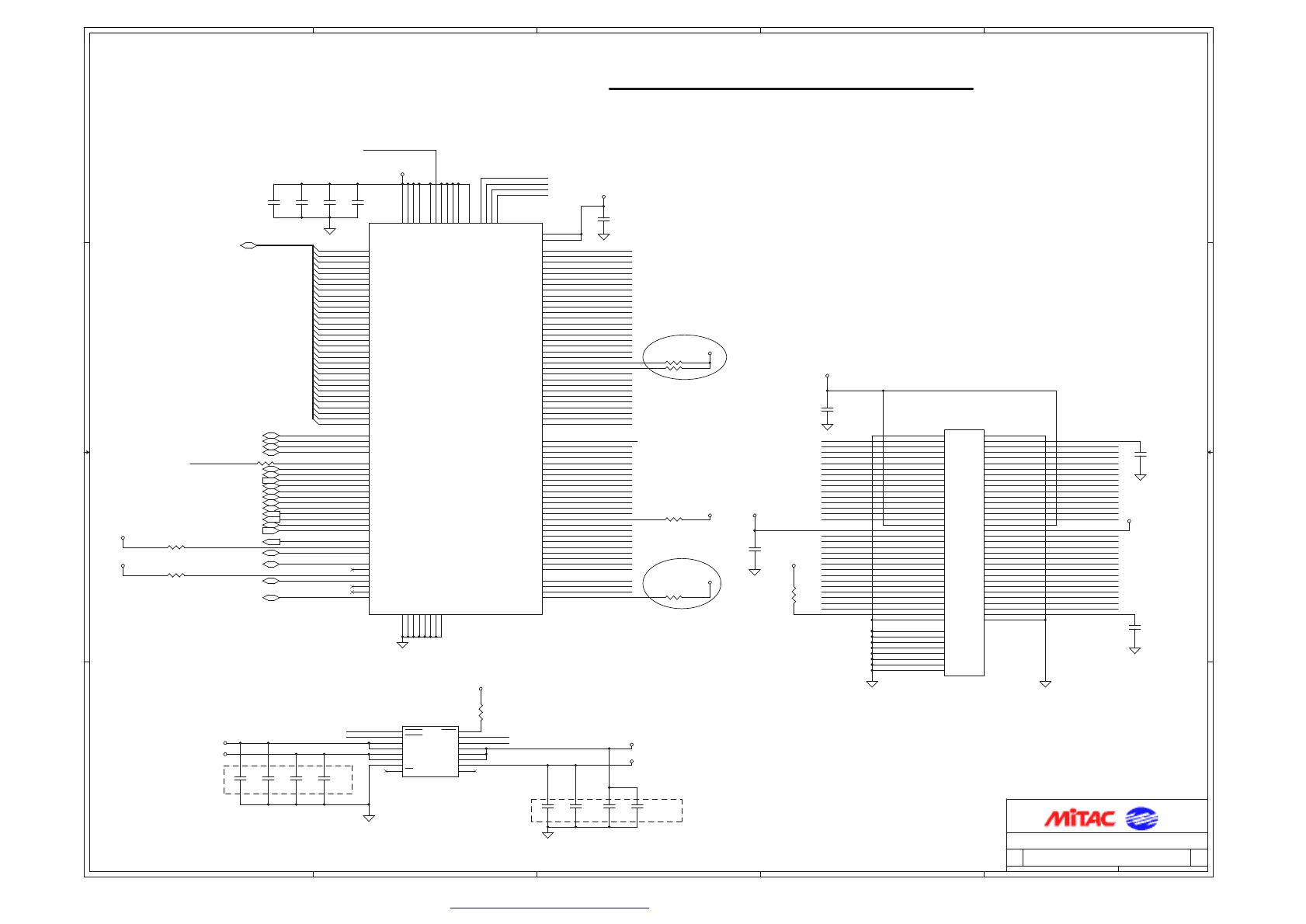

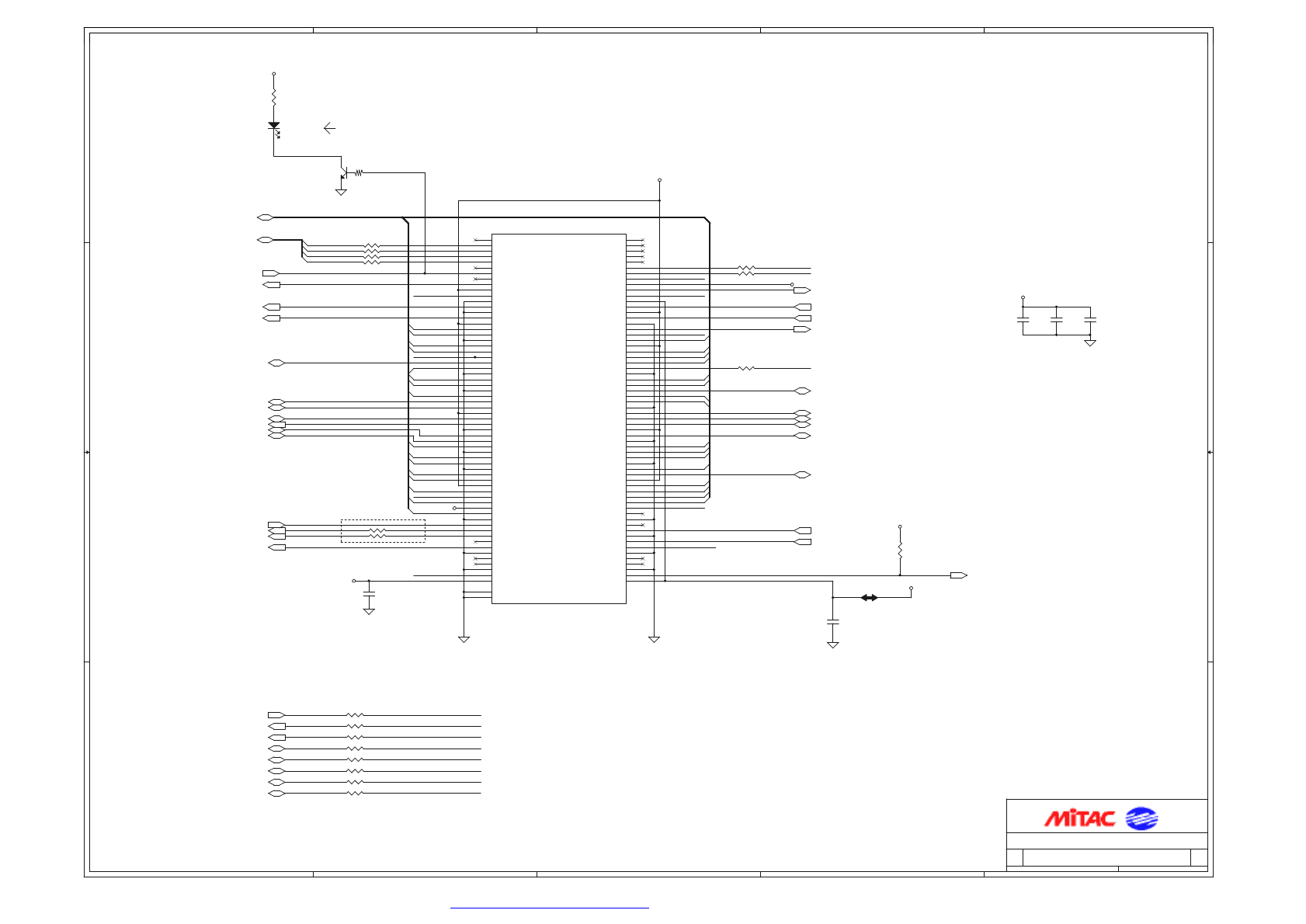

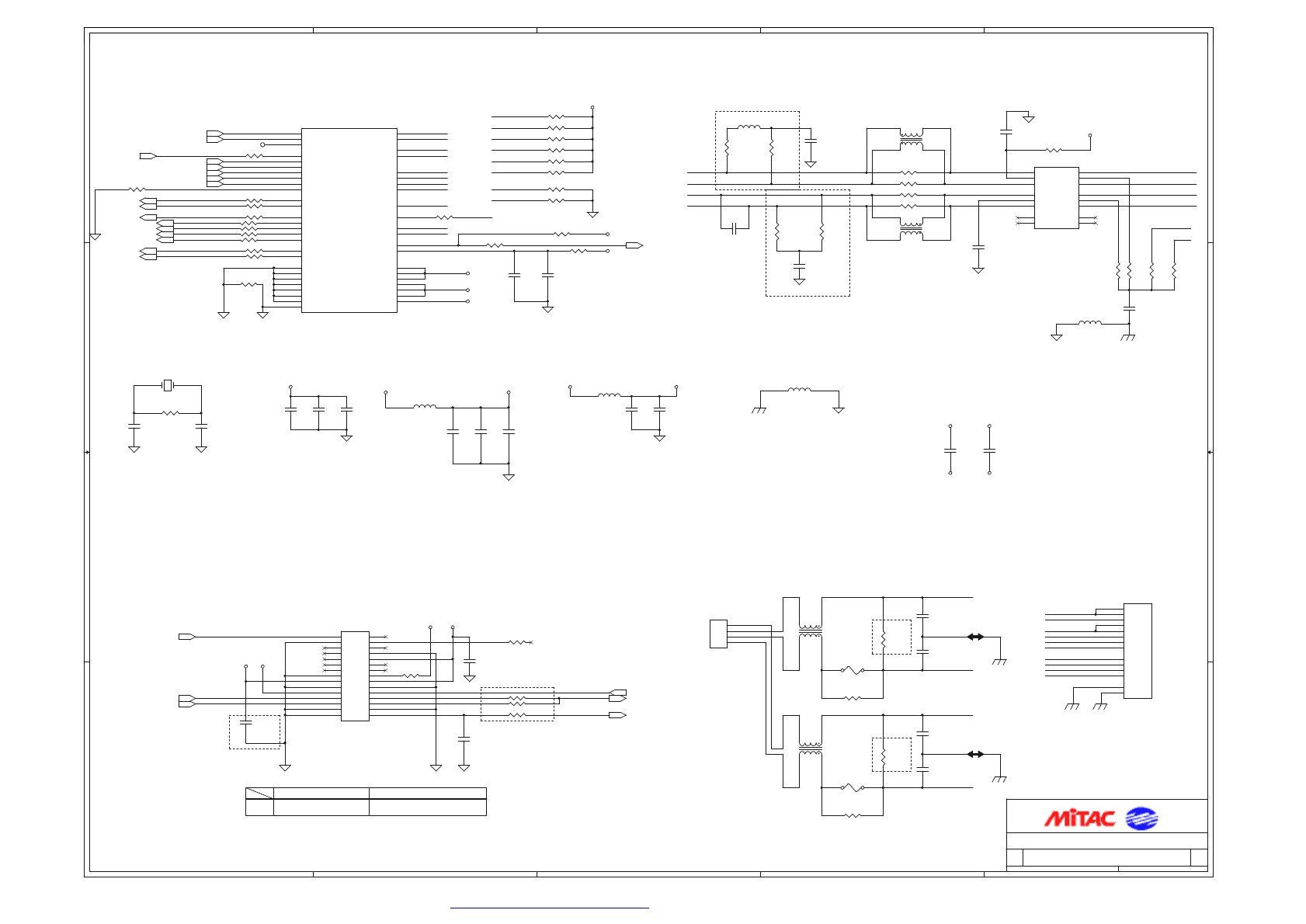

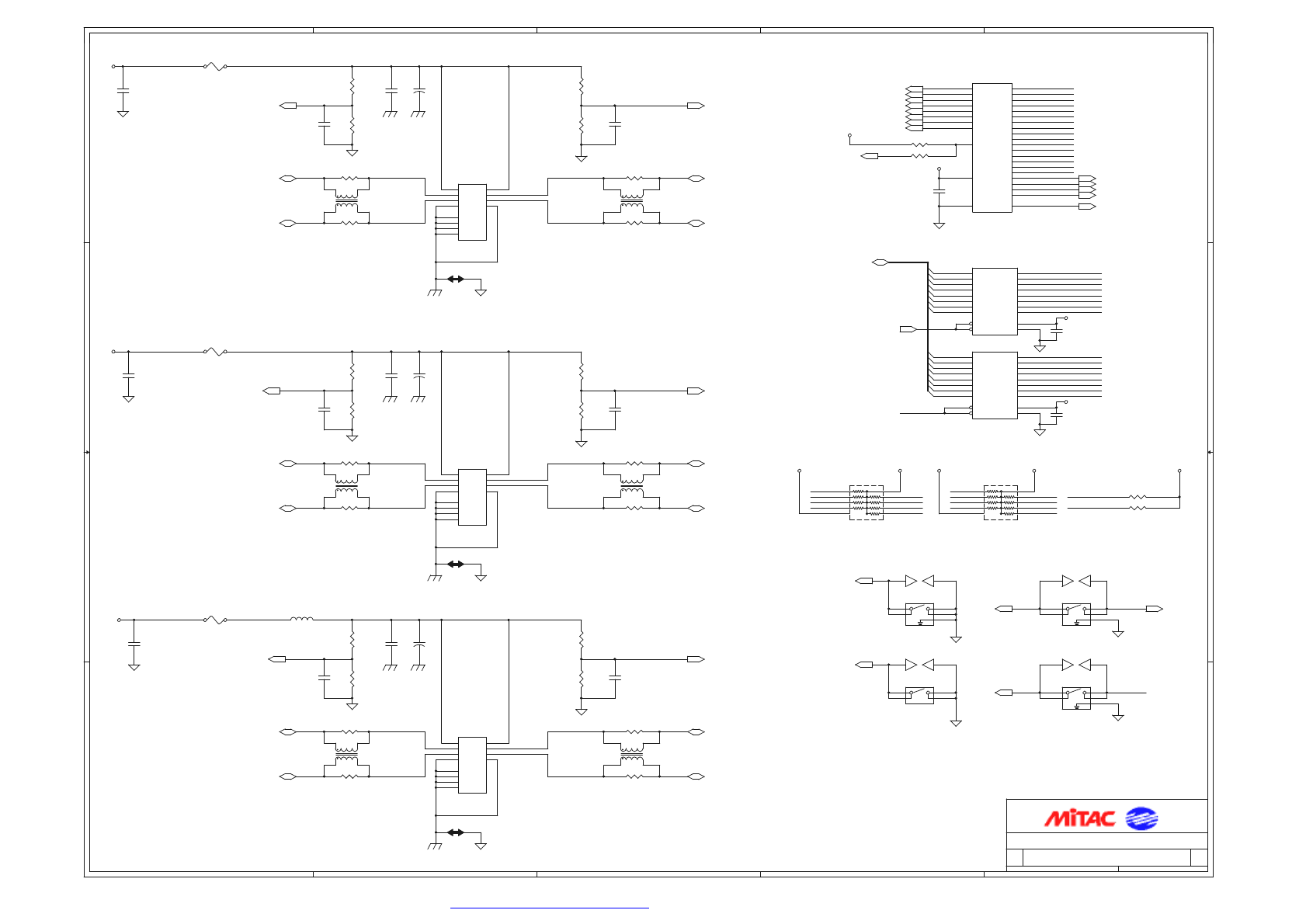

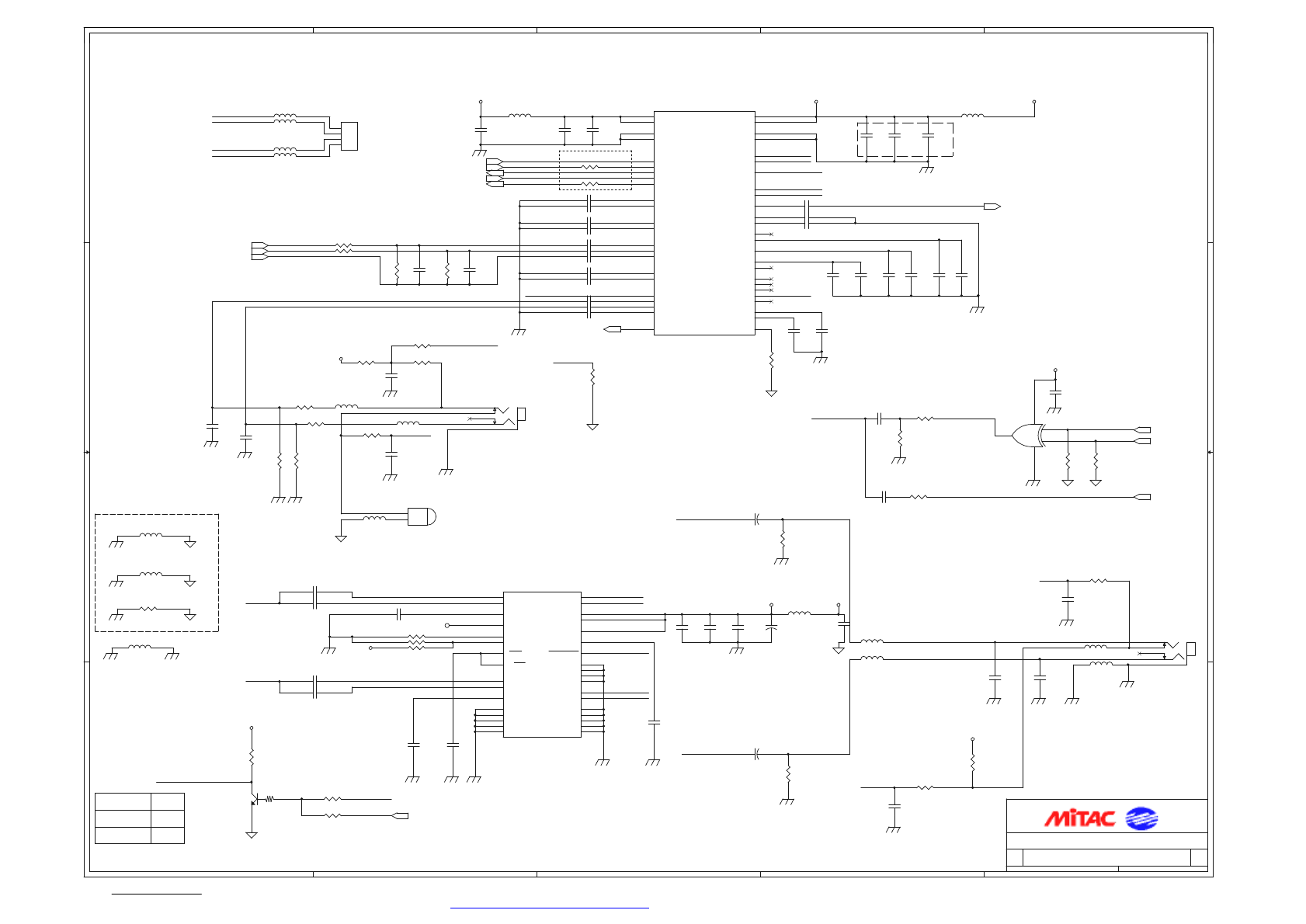

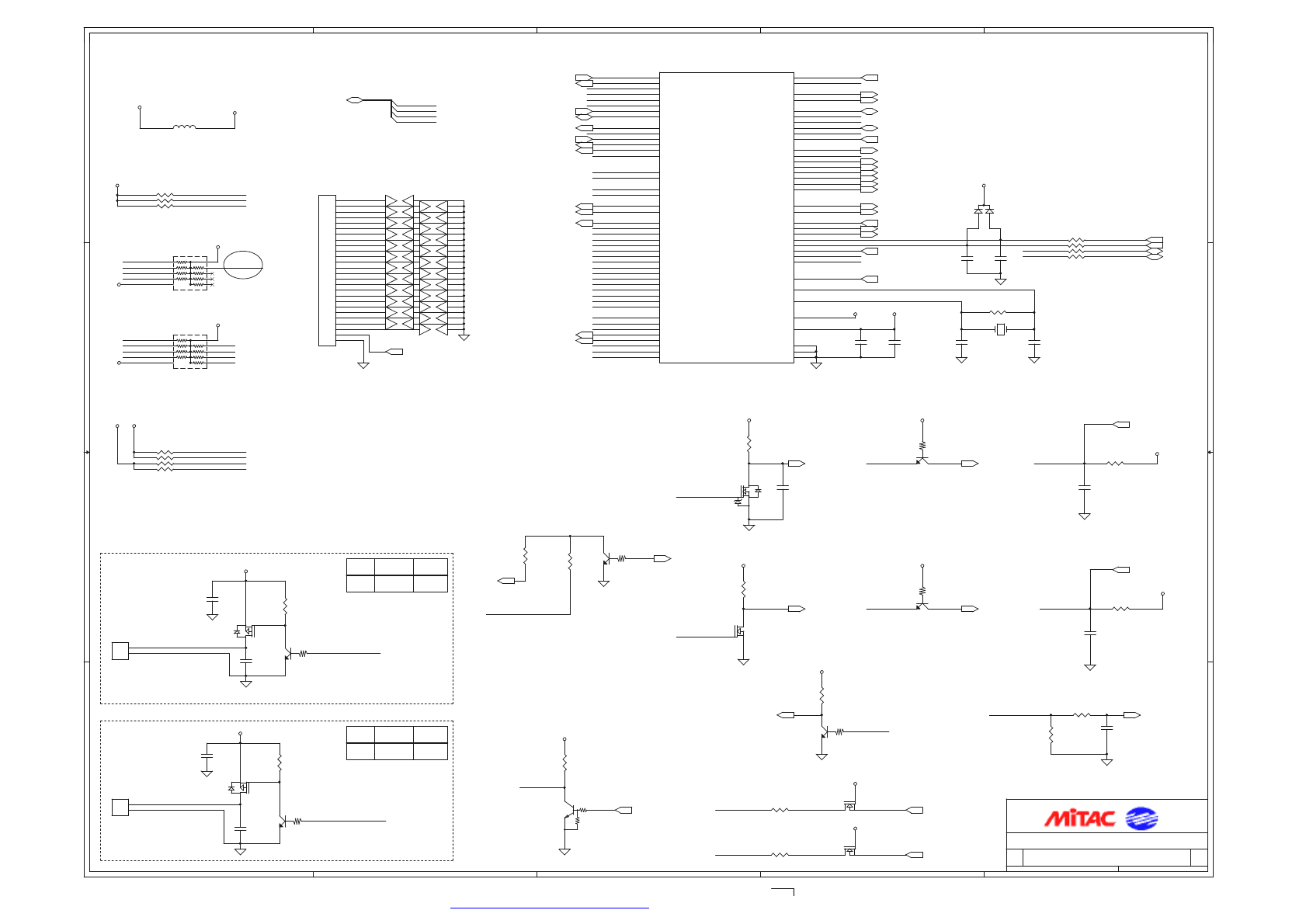

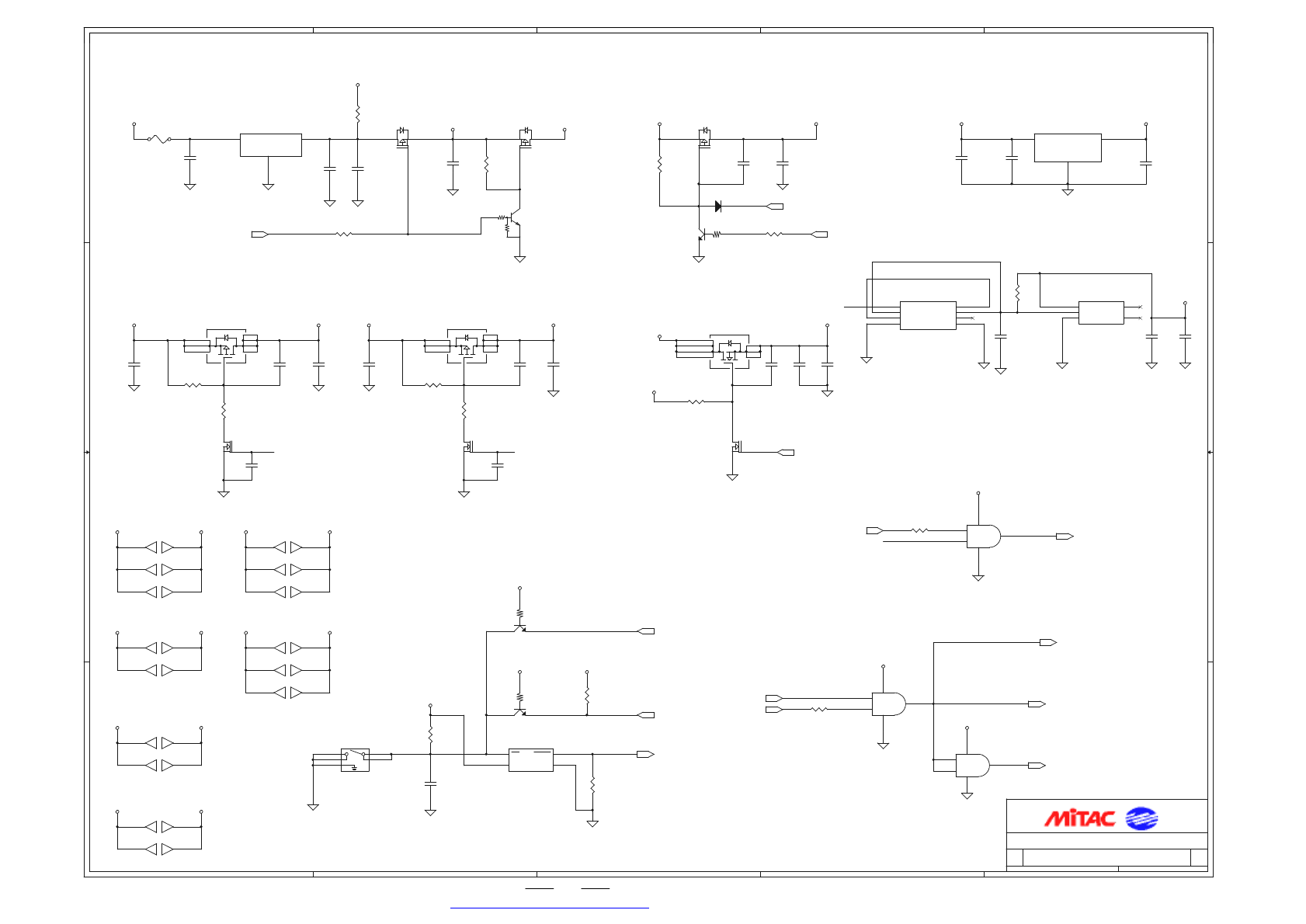

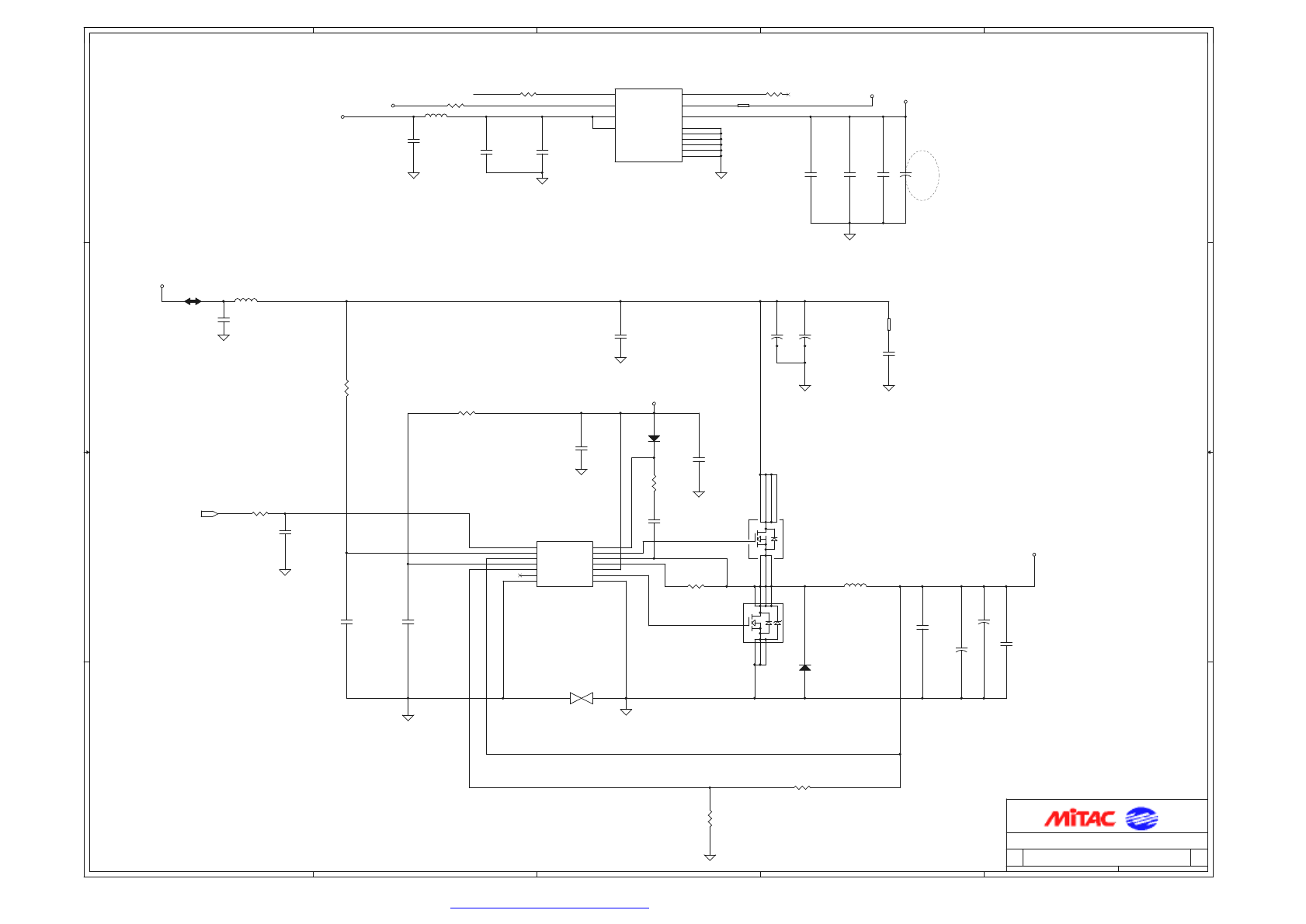

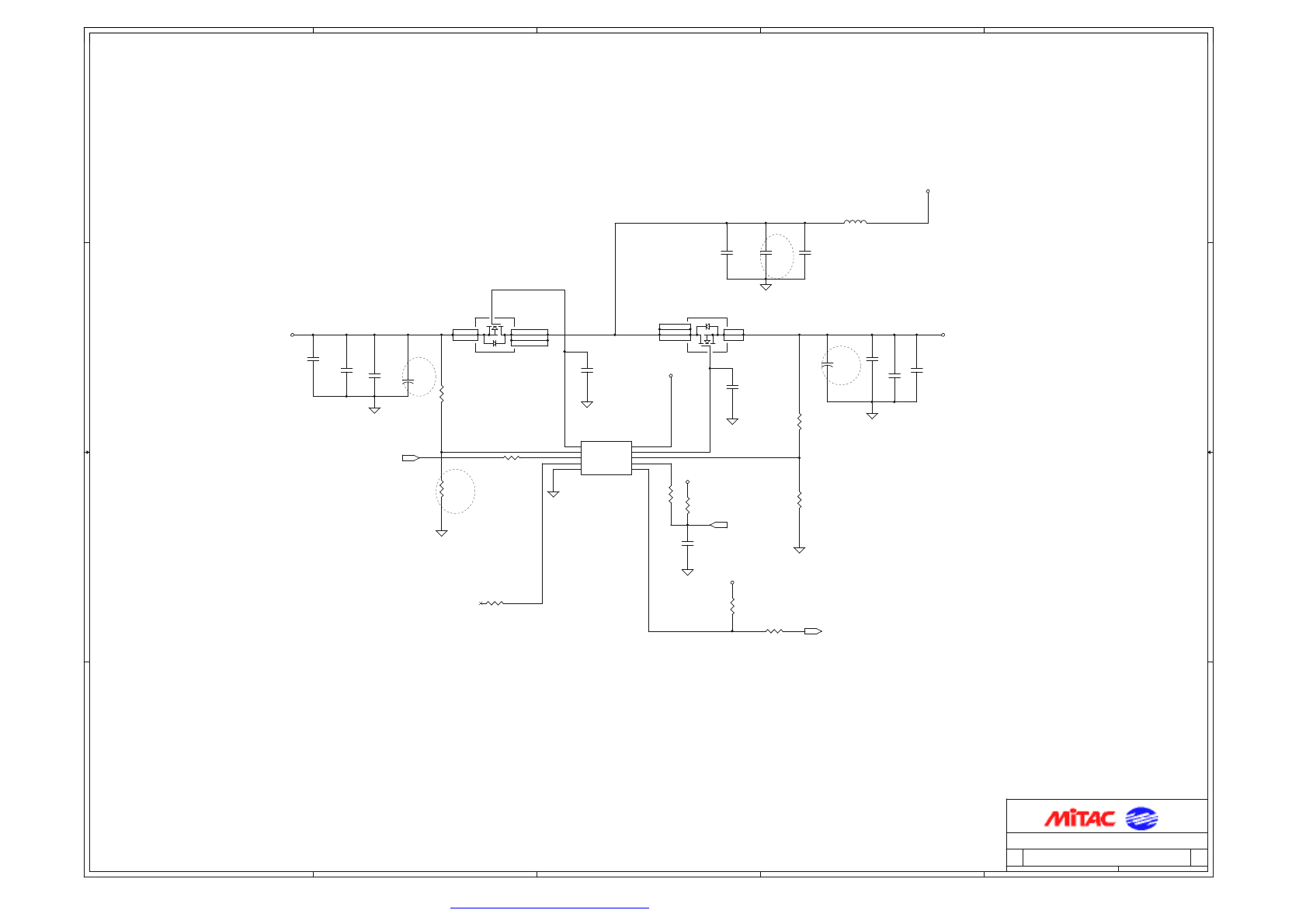

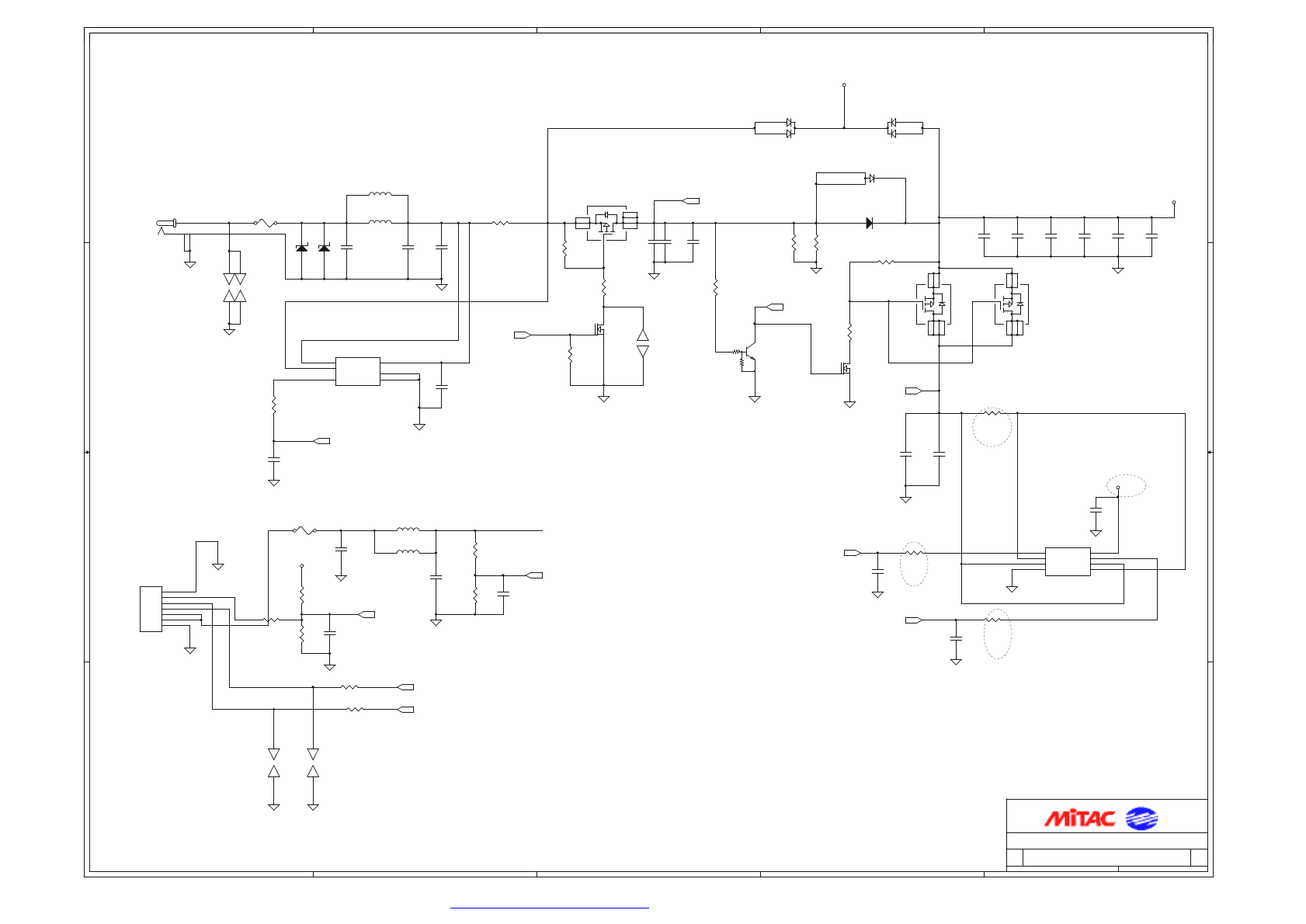

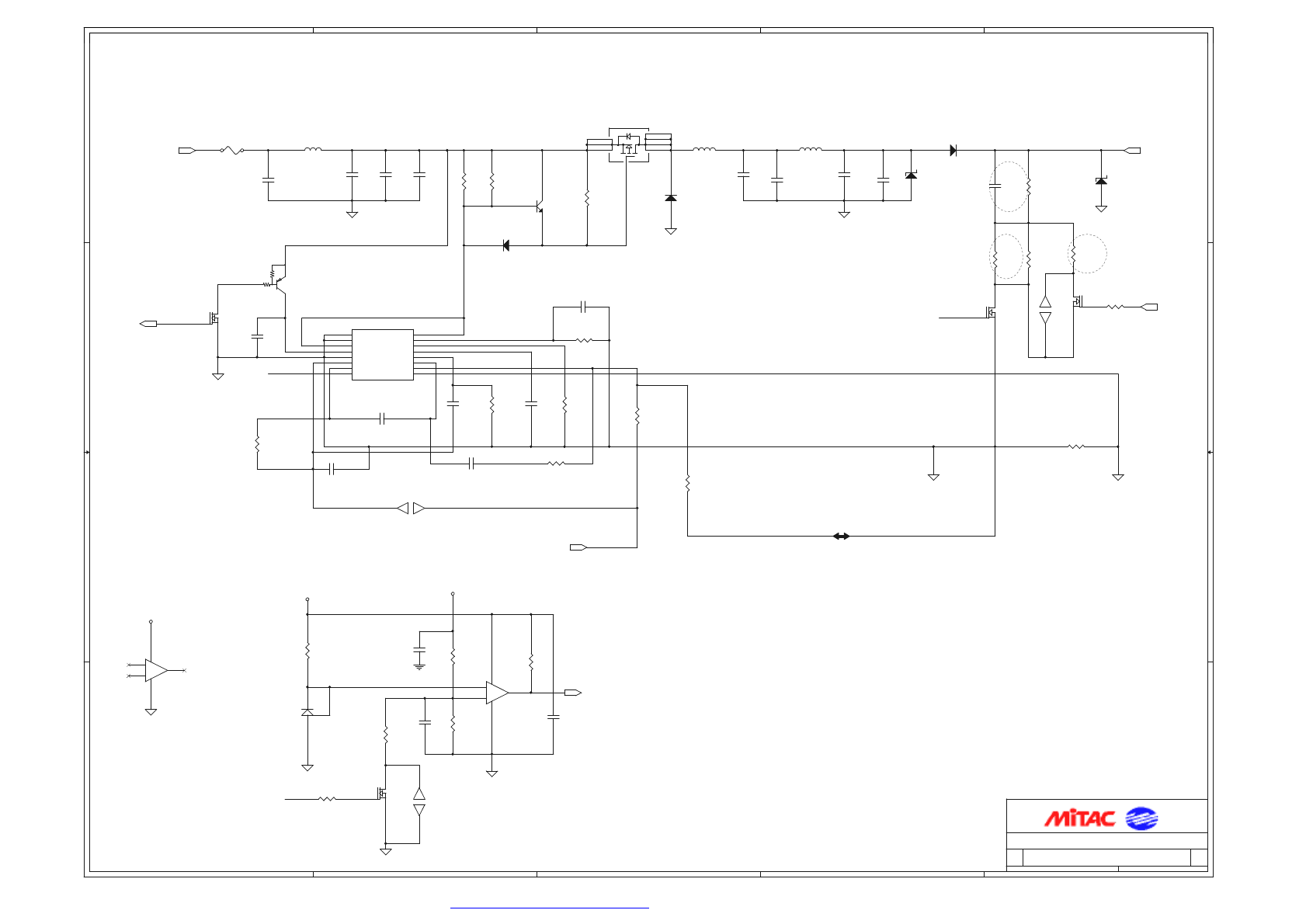

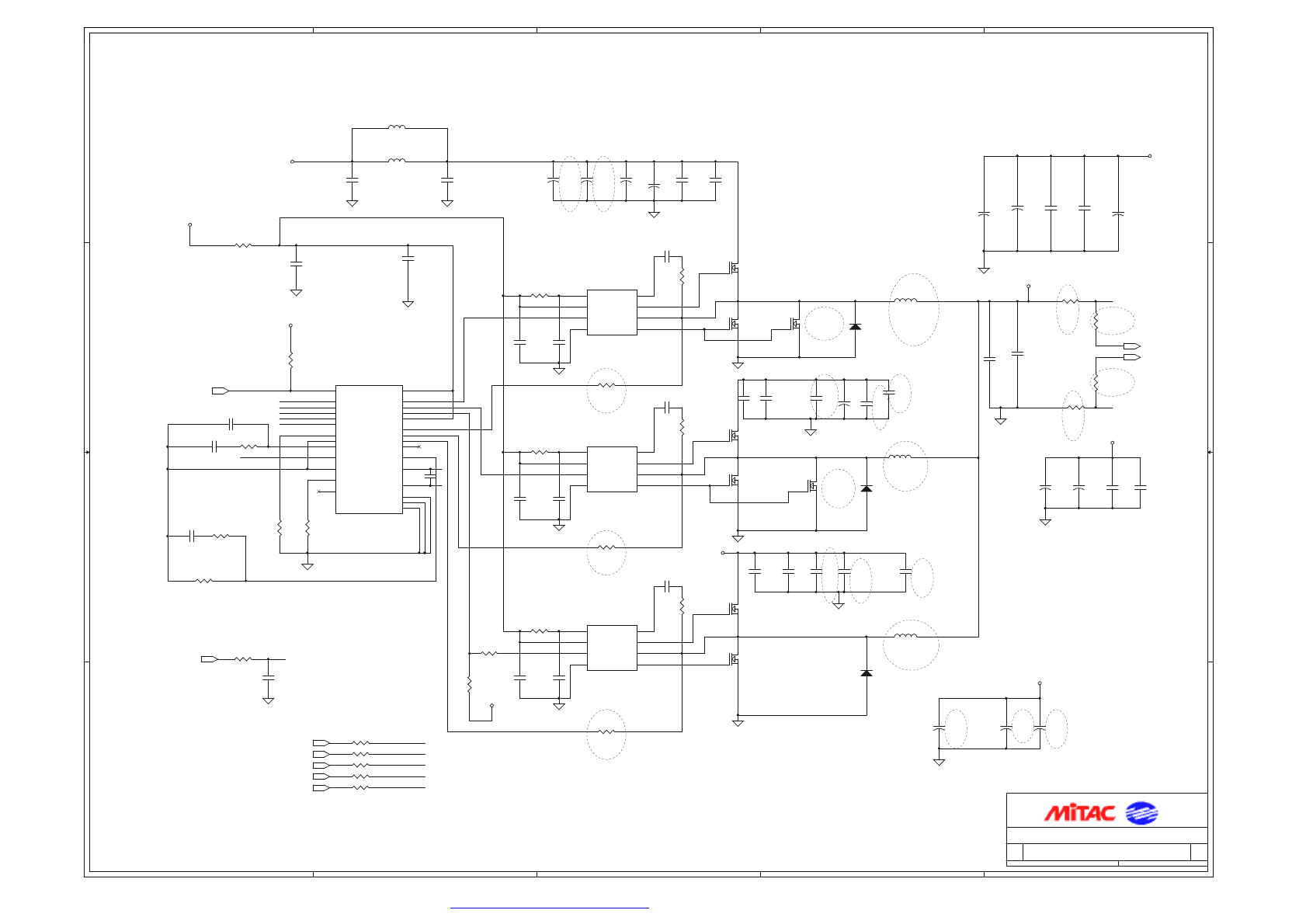

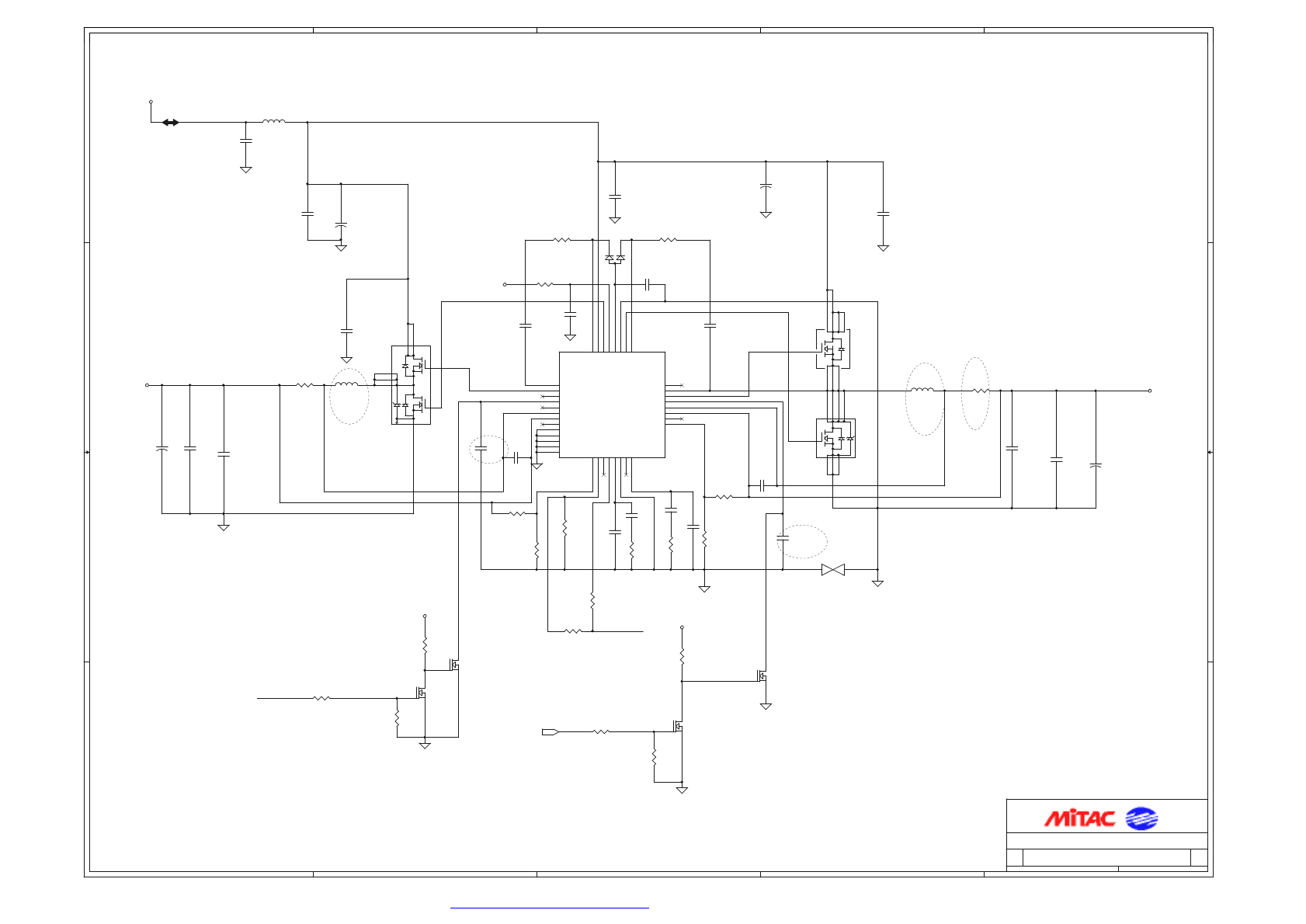

11. Circuit Diagram ………………………………………………………………………………………....

12. Reference Material …………………………………………………………………………………..….

Contents

120

123

125

127

129

133

145

146

172

95

96

101

104

108

110

114

116

118

106

112

131

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

3

1.1 Introduction

1. Engineer Hardware Specification

The 8399 motherboard would support the AMD K8 62W Dublin (32 bit) with 256KB L2 cache/ Hammer (64 bit)

with 1MB L2 cache with uPGA Package. This system is based on PCI architecture, which have standard hardware

peripheral interface. The power management complies with Advanced Configuration and Power Interface (ACPI)

1.0b. It also provides easy configuration through CMOS setup, which is built in system BIOS software and can be

pop-up by pressing F2 at system start up or warm reset. System also provides icon LEDs to display system status,

such as AC/Battery Power, Battery, WIRELESS LAN status, CD-ROM, HDD, NUM LOCK, CAP LOCK, and

SCROLL LOCK status. It also equipped 6 USB2.0 ports.

The memory subsystem supports 0MB on board; Expandable up to 1024MB Expandable with combination of

optional 128/256/512 MB memory 200-pin DDR 266/333/400 DRAM Memory Module x2, PC-2100/2700/3200

specification.

The “K8N800”chipset is a high performance, cost-effective and energy efficient solution for the implementation of

desktop personal computer systems with 8 / 16-bit 800 / 600 / 400 / 200MHz HyperTransport. CPU host interface

based on AMD K8 / ClawHammer. Processors. The K8N800 north bridge supports a high speed 8-bit 8x66 Mhz

Quad Data Transfer interconnect (V-Link) to the VT8235 South Bridge. These chips also contain a built-in bus-to-

bus bridge to allow simultaneous concurrent operations on each bus. Five levels (double words) of post write buffers

are included to allow for concurrent CPU and V-Link operation. For V-Link Host operation, forty-eight levels

(double words) of post write buffers and sixteen levels (double words) of prefetch buffers are included for

concurrent V-Link bus and DRAM / cache accesses. When combined, the V-Link host / Client controllers realize a

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

4

Complete PCI sub-system and support enhanced PCI bus commands such as “ Master-Read-Line”, “memory-Read-

Multiple” and “Memory-Write-Invalid” commands to minimize snoop overhead. In addition, advanced features are

supported such as snoop ahead, snoop filtering, L1 write-back forward to PCI master, and L1 write-back merged

with PCI post write buffers to minimize PCI master read latency and DRAM utilization. Delay transaction and read

caching mechanisms are also implemented for further improvement of overall system performance.

The VT8235CD “V-Link Client Controller” is a highly integrated PCI /LPC controller. Its internal bus structure is

based on a 66 MHz PCI bus that provides 2x bandwidth compared to previous generation PCI bridge chips. The

VT8235CD also provides a 533 MB/sec bandwidth Host / Client V-Link interface with V-Link-PCI and V-Link-

LPC controllers. It supports six PCI slots of arbitration and decoding for all integrated functions and LPC bus.

To provide for the increasing number of multimedia applications, the AC97 CODEC VT1617/1617A is integrated

onto the motherboard

A full set of software drivers and utilities are available to allow advanced operating systems such as Windows XP

and Windows 2000 to take full advantage of the hardware capabilities such as bus mastering IDE, Plug & Play, and

Advance configuration and power interface(ACPI).

Following chapters will have more detail description for each individual sub-systems and functions.

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

5

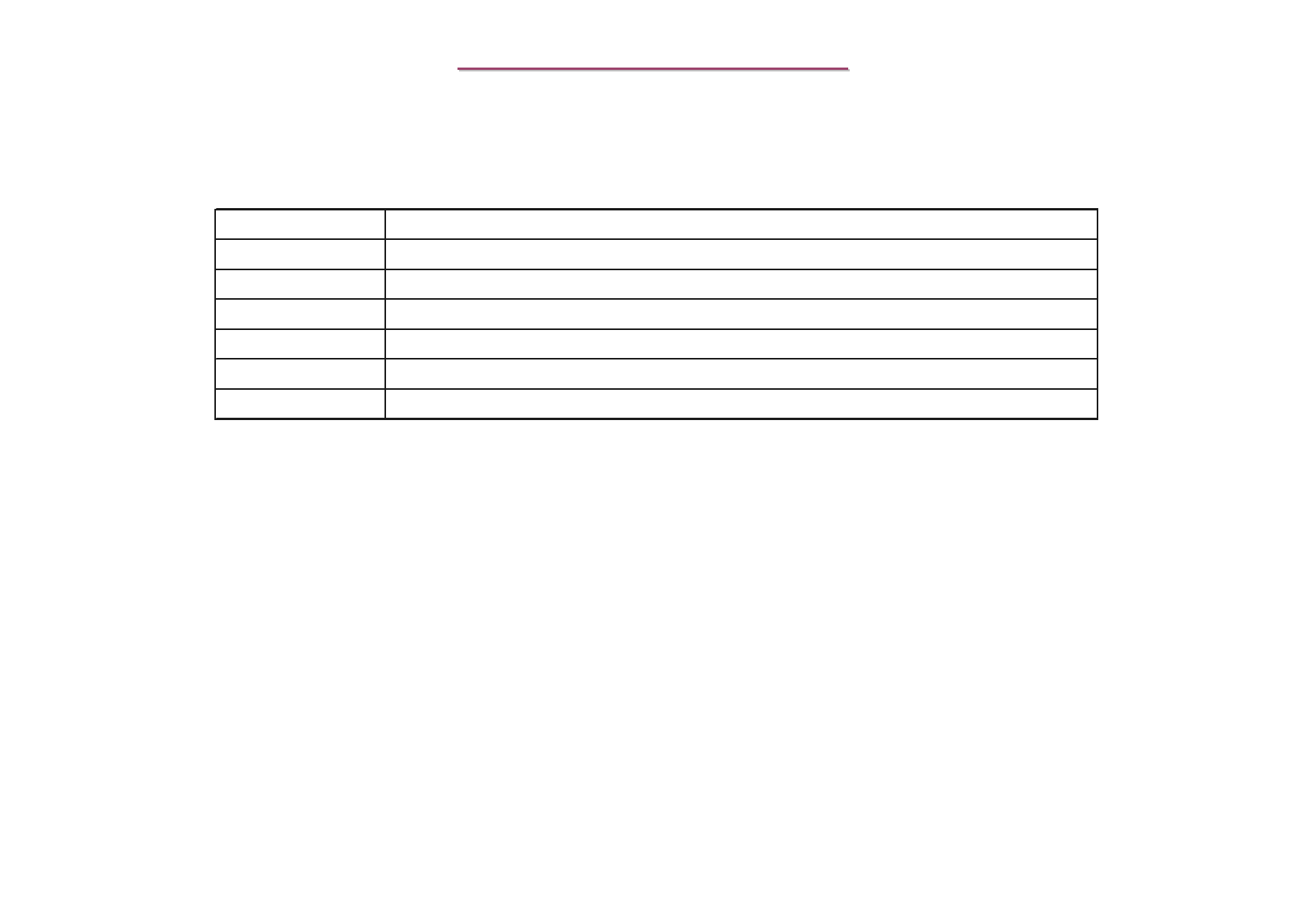

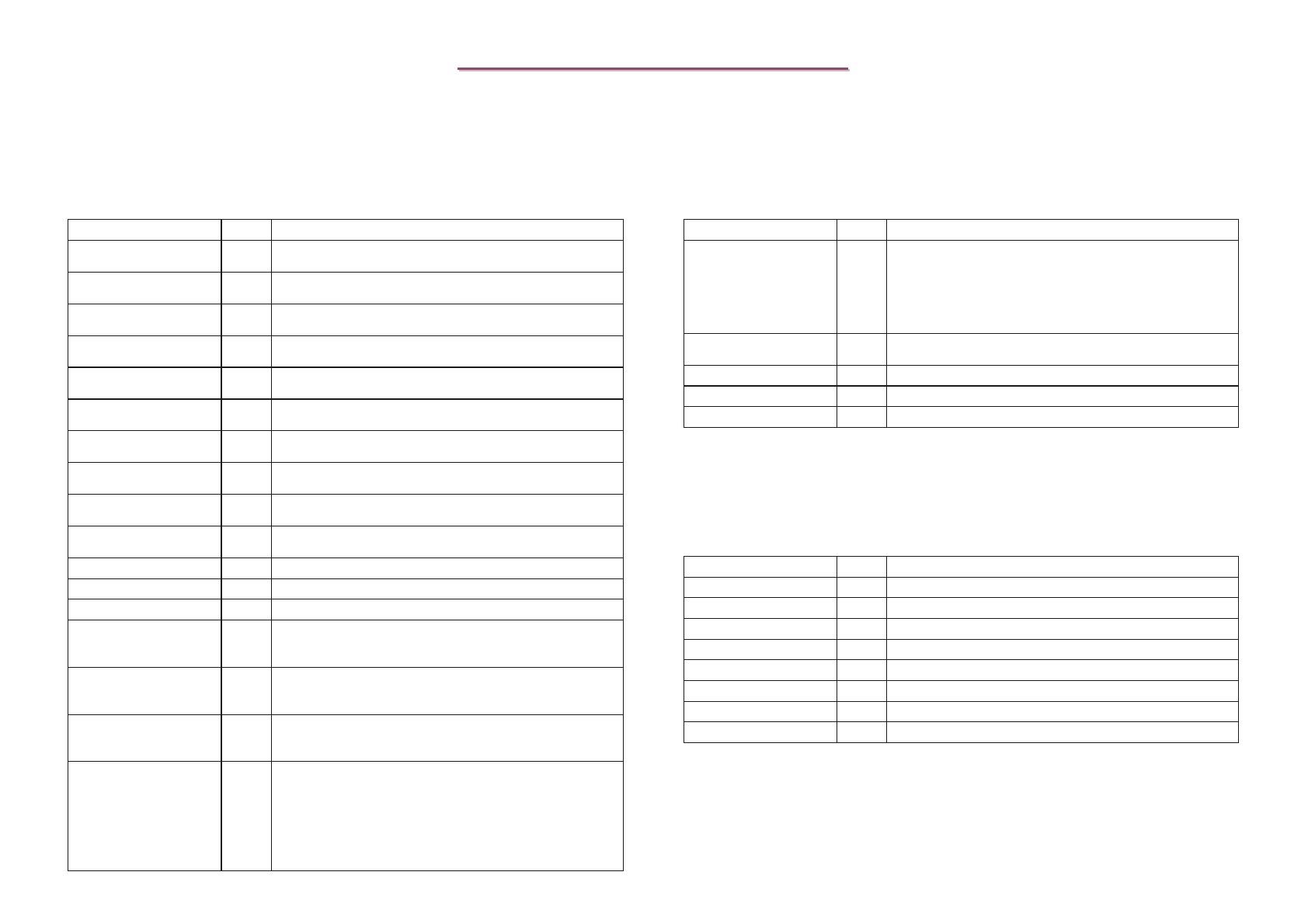

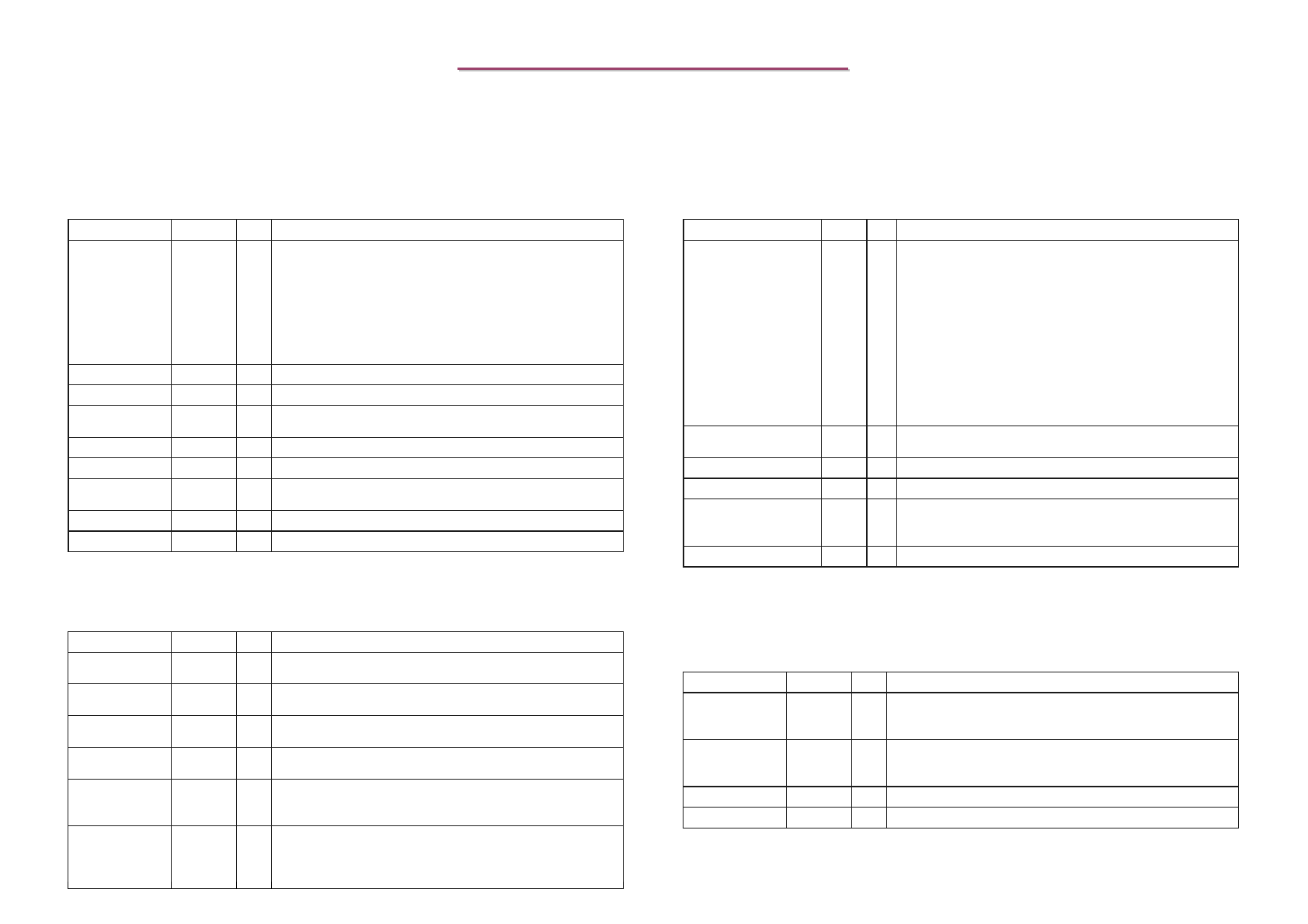

CPU AMD K8 62W Dublin (32 bit)/Hammer (64 bit) with uPGA Package

Thermal Ceiling 62W TDP

Core Logic VIA K8N800 + VT8235CD

L2 Cache 256KB for Dublin / 1MB for Hammer

System BIOS Inside 256 KB Flash EPROM (Include System BIOS and VGA BIOS)

ACPI 1.0b; DMI 2.3.1 compliant

Plug & Play capability

OSD Audio Volume Up/Down status, Brightness status, RF Antenna On/Off status, Display Status

Memory 0MB on board; Expandable up to 1024MB

Expandable with combination of optional 128/256/512 MB memory

200-pin DDR 333/400 DRAM Memory Module x2, PC-2700/3200 specification

ROM Driver 12.7mm Height

CD / DVD Rom Drive

Combo Drive

Super Combo Drive

HDD 2.5” (9.5 mm height): 40/60/80 GB; ATA 100/133 Support

Removable for Distributor

Display 15” XGA TFT Display; Resolution: 1024X768

Video Controller VIA K8N800 integrated(64MB SMA)

Keyboard 19mm key pitch/ 3.0mm key stroke/ 307mm length

Windows Logo Key x 1; Application Key x 1

Pointing Device Glide pad with 2x buttons and 2 direction scroll button

1.2 Hardware Specification(1)

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

6

PCMCIA Cardbus Controller: ENE CB1410

one type II slots CardBus / no ZV port support/ no wakeup from S3

Power switch: ENE CP-2211

Indicator 3 LEDs for Power/Battery/Charge status

1 LED for Radio wave status Power LED (BTO: Wireless LAN only )

5 LEDs for HDD Access, ODD Access , Num lock, Cap lock and Scroll Lock

Audio System Sound Blaster Pro compatible

AC97 V2.2 Codec

Built-in Mono Microphone

2X 2W Speakers

I/O Port USB port (2.0, backward compatible with USB1.1) x 6

RJ-11 port x 1

RJ-45 port x 1

DC input x 1

VGA monitor port x1

Audio-out x 1

Mic-in x 1

S/W Volume Control

7-Pin S Video TV-Out x 1 (NTSC/PAL)

Communication Built-in 56Kbps V.90 modem support ISN standard

Built-in 10/100 M based-T LAN

One Mini PCI slot and antenna reserved for wireless LAN

1.2 Hardware Specification(2)

Continue to previous page

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

7

AC Adapter Universal AC adapter 90W ; Input: 100-240V, 50/60Hz AC (support power on charge)

Battery 6/8 cell (2000/2200mAH,3.7V) Li-ion smart battery

Dimensions 335*280*30(min) , 335x280x42 (max)

Weight 3.5kg (P)

Accessories Power Cord, AC Adapter, RJ-11 Phone Cable (p),System Driver CD-Title

Architecture Microsoft WHQL Designed for Windows XP

Options 128/256/512MB DDR RAM, AC Adapter w/o Power Cord, Battery, Notebook Carry Bag

1.3 System Hardware Parts

1.3.1 Processor

The AMD K8 Hammer processor family is designed to support performance desktop and workstation applications. It

provides a high-performance HyperTransport. link to I/O, as well as a single 64-bit high-performance DDR memory

controller.

Compatible with Existing 32-bit Code Base

Including support for SSE, SSE2, MMXTM, 3DNow!TM, technology and all legacy x86 instructions

Runs existing operating systems and drivers

Local APIC on-chip

1.2 Hardware Specification(3)

Continue to previous page

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

8

AMD x86-64 Technology

AMD.s 64-bit x86 instruction set extensions

64-bit integer registers, 48-bit virtual addresses, 40-bit physical addresses

Eight new 64-bit integer registers (16 total)

Eight new 128-bit SSE/SSE2 registers (16 total)

Integrated Memory Controller

Low-latency, high-bandwidth

72-bit DDR at 100, 133, 166 and 200MHz

HyperTransport. Technology to I/O Devices

Two 8-bit links each support 1600 mega-transfers (MT) per second or 1.6 Gbytes/s in each direction

Can be configured as single 16-bit link supporting 1600 MT/s or 3.2 Gbytes/s in each direction

64-Kbyte 2-way Associative ECC-Protected L1 Data Cache

Two 64-bit operations per cycle, 3-cycle latency

64-Kbyte 2-way Associative Parity-Protected L1 Instruction Cache

With advanced branch prediction

16-way Associative ECC-Protected L2 Cache

Exclusive cache architecture.storage in addition to L1 caches

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

9

256 KB, 512 KB, and 1 MB options

Machine Check Architecture

Includes hardware scrubbing of major ECC-protected arrays

Power Management

Multiple low-power states

System Management Mode (SMM)

ACPI 2.0 compliant, including support for processor performance states

Electrical Interfaces

HyperTransport. Technology: LVDS-like differential, unidirectional

DDR: SSTL_2 per JEDEC DDR specification

Clock, reset, and test signals also use DDR-like electrical specifications

Packaging

754-pin lidded micro PGA

1.27-mm pin pitch

29x29 row pin array

40mm x 40mm organic substrate

Organic C4 die attach

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

10

1.3.2 K8N800 North Bridge

The “K8N800”chipset is a high performance, cost-effective and energy efficient solution for the implementation of

mobile personal computer systems with 8 / 16-bit 800 / 600 / 400 / 200 MHz HyperTransport. CPU host interface

based on AMD K8 / Claw Hammer processors.

Defines Highly Integrated Solutions for Performance PC Desktop Designs

High performance North Bridge with HyperTransport. interface to AMD K8 CPU plus AGP 8x external bus

to external Graphics Controller plus high-speed V-Link interface to South Bridge.

Combines with VIA VT8235CD V-Link South Bridge for integrated LAN, Audio, ATA133 IDE, and 6

USB 2.0 ports

587 Ball Grid Array package with 35 x 35 mm body size, 1.27mm ball pitch

1.5V core, 0.15 u process

High Performance HyperTransport CPU Interface

Chipset support for AMD. K8 / ClawHammer. Processor

Processor interface via HyperTransport. Bus

Separate “transmit” and “receive” buses for no lost “bus turnaround” cycles

All transmit and receive signals use 2 pin low-voltage-swing differential signalling for high-reliability and

high speed

8 or 16-bit control / address / data transfer both directions

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

11

800 / 600 / 400 / 200 MHz clock rates with “Double Data Rate”-style operation for 1600/1200/800/400

MT/s in both directions simultaneously (total 6.4GB/sec using 16-bit transfer mode)

Default 8-bit / 200 MHz operation on startup for high reliability with speedup to dual 16-bit, 800 MHz

operation (6.4 GB/sec total bandwidth) under software control (transmit and receive may be different widths

and / or speeds)

Full Featured Accelerated Graphics Port (AGP) 8x Controller

Supports 533 MHz 8x, 266 MHz 4x, and 133 MHz 2x transfer modes for AD and SBA signaling

AGP v3.0 compliant with 8x transfer mode

Pseudo-synchronous with the host CPU bus with optimal skew control

Supports SideBand Addressing (SBA) mode (non-multiplexed address / data)

AGP pipelined split-transaction long-burst transfers up to 1GB/sec

Eight level read request queue

Four level posted-write request queue

Thirty-two level (quadwords) read data FIFO (256 bytes)

Sixteen level (quadwords) write data FIFO (128 bytes)

Intelligent request reordering for maximum AGP bus utilization

Supports Flush/Fence commands

Graphics Address Relocation Table (GART)

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

12

One level TLB structure

Sixteen entry fully associative page table

LRU replacement scheme

Independent GART lookup control for host / AGP / PCI master accesses

Windows 95 OSR-2 VXD and integrated Windows 98 / 2000 / XP mini port driver support

High Bandwidth 533 MB / Sec 8-bit V-Link Host Controller South Bridge Interface

Supports 66 MHz V-Link Host interface with total bandwidth of 533 MB/sec

Operates in 2x, 4x, and 8x modes

Full duplex commands with separate command / strobe for 4x / 2x mode, half-duplex for 8x mode

Request / Data split transaction

Configurable outstanding transaction queue for Host to V-Link Client accesses

Supports Defer / Defer-Reply transactions

Transaction assurance for V-Link Host to Client access eliminates V-Link Host-Client Retry cycles

Intelligent V-Link transaction protocol to eliminate data wait-state / throttle transfer Latency

All V-Link transactions for both Host and Client have a consistent view of transaction data depth and buffer

size to avoid data overflow

Highly efficient V-Link arbitration with minimum overhead

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

13

All V-Link transactions have predictable cycle length with known command / data duration

Integrated Graphics / Video Accelerator

Optimized Share Memory Architecture (SMA)

16 / 32 / 64 MB frame buffers using system memory

Internal AGP 8x equivalent performance

Separate 128-bit data paths between north bridge and graphics core for pixel data flow and texture/command

access

Graphics engine clock up to 200MHz decoupled form memory clock

High quality DVD video playback

Internal hardware VGA controller with true-color / high-color sprite for hardware cursor implementation

128-bit 2D graphics engine

128-bit 3D graphics engine

Floating point triangle setup engine

Microsoft DirectX texture compression

4.5M triangles/second setup engine

400M texels/second bilinear fill rate

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

14

CRT display interface with 24-bit true-color RAMDAC up to 300MHz pixel rate with gamma correction

capability

DFP” flat panel interface supporting single-channel or dual-channel LVDS encoders

DVI” Flat Panel Monitor 12-bit DVI 1.0-compatible interface designed for use with external TMDS encoder

AGP 8x / 4x functions muxed on DFP/DVI pins for optional external graphics controller upgrade module

Dedicated 12-bit interface to TV Encoder for NTSC or PAL TV display (may be optionally configured as

12-bit DVI 1.0 interface to external TMDS encoder for driving a Flat Panel Monitor)

DuoView+ Dual Image Capability

Direct Win98, WinME and WinXP multi-monitor, extended desktop support

Independent resolution and color depth for secondary desktop

Improved display flexibility with simultaneous LCD/CRT, CRT/DVI, CRT/TV, LCD/TV, DVI/TV

operation capability

CRT, LCD or TV refresh rates are independently programmable to allow optimum image quality

Enables different images on different displays simultaneously for true multitasking

Full Media capabilities on all displays

Support for CRT resolutions up to 1920x1440 and panel resolutions up to 1600x1200

Automatic panel power sequencing and VESA DPMS CRT power-down

Extensive Display Support

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

15

Built-in reference voltage generator and monitor sense circuits

I2C Serial Bus and DDC Monitor Communications for CRT Plug-and-Play configuration

Video Support

High quality 5-tap horizontal and 5-tap vertical scaler (up or down) for both horizontal and vertical scaling

(linear interpolation for horizontal and vertical p-scaling filtering for horizontal and vertical down-scaling)

Color space conversion

Color enhancement (contrast, hue, saturation, brightness, and gamma correction)

Color and chroma key support

Hardware sub-picture blending

Bob / weave de-interlacing mode and advanced de-interlacing to improve video quality

Video gamma correction

PAL / NTSC TV output capability using external TV encoder

Support CCIR601 standard

MPEG-2/1 Video Decoder

MPEG-2 hardware slice layer, iDCT, and motion compensation for full speed DVD playback

2-D Hardware Acceleration Features

BitBLT 9bit block transfer) functions including alpha blts

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

16

Text function

Bresenham line drawing / style line function

ROP3, 256 operation

Color expansion

Source and destination color keys

Transparency mode

Window clipping

8, 16, and 32 bpp mode acceleration

3-D Hardware Acceleration Features

Microsoft DirectX 7.0 and 8.0 compatible

OpenGL driver available

Floating-point setup engine

Triangle rate up to 4.5-million triangles per second and Pixel rate up to 400 million pixels per second for 2

texture, depth test and alpha blending

8K Texture Cache

Microsoft DirectX Texture Compression (S3TC)

Flat and Gouraud shading

Hardware back-face culling

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

17

16-bit, 32-bit Z test, and 24+8 Z+ Stencil test support

Z-Bias support

Stipple Test, Line-Pattern test, Text re-Transparence test, Alpha test support

Edge anti-aliasing support

Two textures per pass

Tremendous Texture Format: 16/32 bpp ARGB, 1/2/4/8 bpp Luminance, 1/2/4/8 bpp Intensity, 1/2/4/8 bpp

Paletized (ARGB) , YUV 422/420 format

Texture sizes up to 2048x2048

High quality texture filter modes: Nearest, Linear, Bi-linear, Tri-linear, Anisotropic

LOD-Bias support

Vertex Fog and Fog Talbe

Specular Lighting

Alpha Blending

Bump mapping

High quality dithering

ROP2 support

Internal full 32-bit ARGB format for high rendering quality

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

18

System balance to achieve high performance

Advanced System Power Management

Power down of SDRAM (CKE)

Independent clock stop controls for CPU, DDR SDRAM, VLINK interface, graphics engine (2D,3D, video,

display) and on-chip AGP bus

Suspend power plane for preservation of memory data

Suspend-to-DRAM and self-refresh power down

Low-leakage I/O pads

ACPI 1.0B and PCI Bus Power Management 1.1 compliant

Full Software Support

Drivers for major operating system and APIs (windows 9x, Windows NT, Windows2000,Windows XP,

Direct3D, DirectDraw and DirectShow, OpenGL ICD for Windows 9x, NT, 2000, and XP)

Chipset and Video BIOS support (including all standard VESZA CRT display modes)

1.3.3 VIA VT8235CD BGA PCI-LPC/ISA South Bridge

The VT8235CD South Bridge is a high integration, high performance, power-efficient, and high compatibility

device that supports Intel and non-Intel based processor to V-Link bus bridge functionality to make a complete

Microsoft PC2001-compliant PCI/LPC system. The VT8235CD includes standard intelligent peripheral controllers:

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

19

IEEE 802.3 compliant 10 / 100 Mbps PCI bus master Ethernet MAC with standard MII interface to external

PHYceiver.

Master mode enhanced IDE controller with dual channel DMA engine and interlaced dual channel

commands. Dedicated FIFO coupled with scatter and gather master mode operation allows high

performance transfers between PCI and IDE devices. In addition to standard PIO and DMA mode operation,

the VT8235CD also supports the UltraDMA-133, 100, 66, and 33 standards to allow reliable data transfer at

rates up to 133 MB/sec. The IDE controller is SFF-8038i v1.0 and Microsoft Windows-family compliant.

Universal Serial Bus controller that is USB v2.0 / 1.1 and Universal HCI v2.0 / 1.1 compliant. The

VT8235CD includes three root hubs with six function ports with integrated physical layer transceivers. The

USB controller allows hot plug and play and isochronous peripherals to be inserted into the system with

universal driver support. The controller also implements legacy keyboard and mouse support so that legacy

software can run transparently in a non-USB-aware operating system environment.

Keyboard controller with PS2 mouse support.

Real Time Clock with 256 byte extended CMOS. In addition to the standard ISA RTC functionality, the

integrated RTC also includes the date alarm, century field, and other enhancements for compatibility with

the ACPI standard.

Notebook-class power management functionality compliant with ACPI and legacy APM requirements.

Multiple sleep states (power-on suspend, suspend-to-DRAM, and suspend-to-Disk) are supported with

hardware automatic wake-up. Additional functionality includes event monitoring, CPU clock throttling and

stop (Intel processor protocol), PCI bus clock stop control, modular power, clock and leakage control,

hardware-based and software-based event handling, general purpose I/O, chip select and external SMI.

Full System Management Bus (SMBus) interface.

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

20

Integrated bus-mastering dual full-duplex direct-sound AC97-link-compatible sound system.

Plug and Play controller that allows complete steer ability of all PCI interrupts and internal interrupts / DMA

channels to any interrupt channel. One additional steerable interrupt channel is provided to allow plug and

play and reconfigure ability of onboard peripherals for Windows family compliance.

The VT8235CD also enhances the functionality of the standard ISA peripherals. The integrated interrupt controller

supports both edge and level triggered interrupts channel by channel. The integrated DMA controller supports type F

DMA in addition to standard ISADMA modes. Compliant with the PCI-2.2 specification, the VT8235CD supports

delayed transactions and remote power management so that slower ISA peripherals do not block the traffic of the

PCI bus. Special circuitry is built in to allow concurrent operation without causing dead lock even in a PCI-to-PCI

bridge environment. The chip also includes eight levels (double words) of line buffers from the PCI bus to the ISA

bus to further enhance overall system performance.

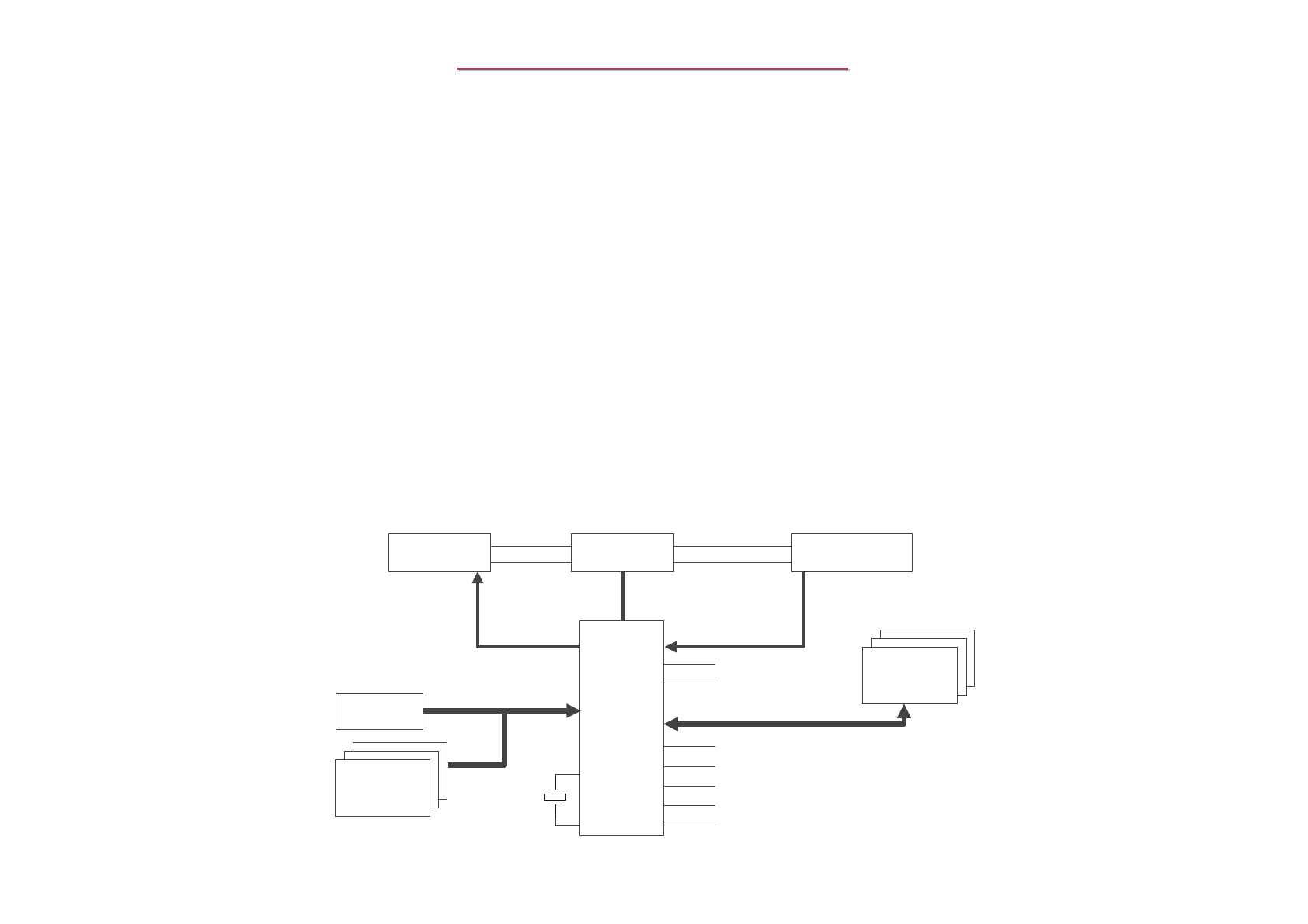

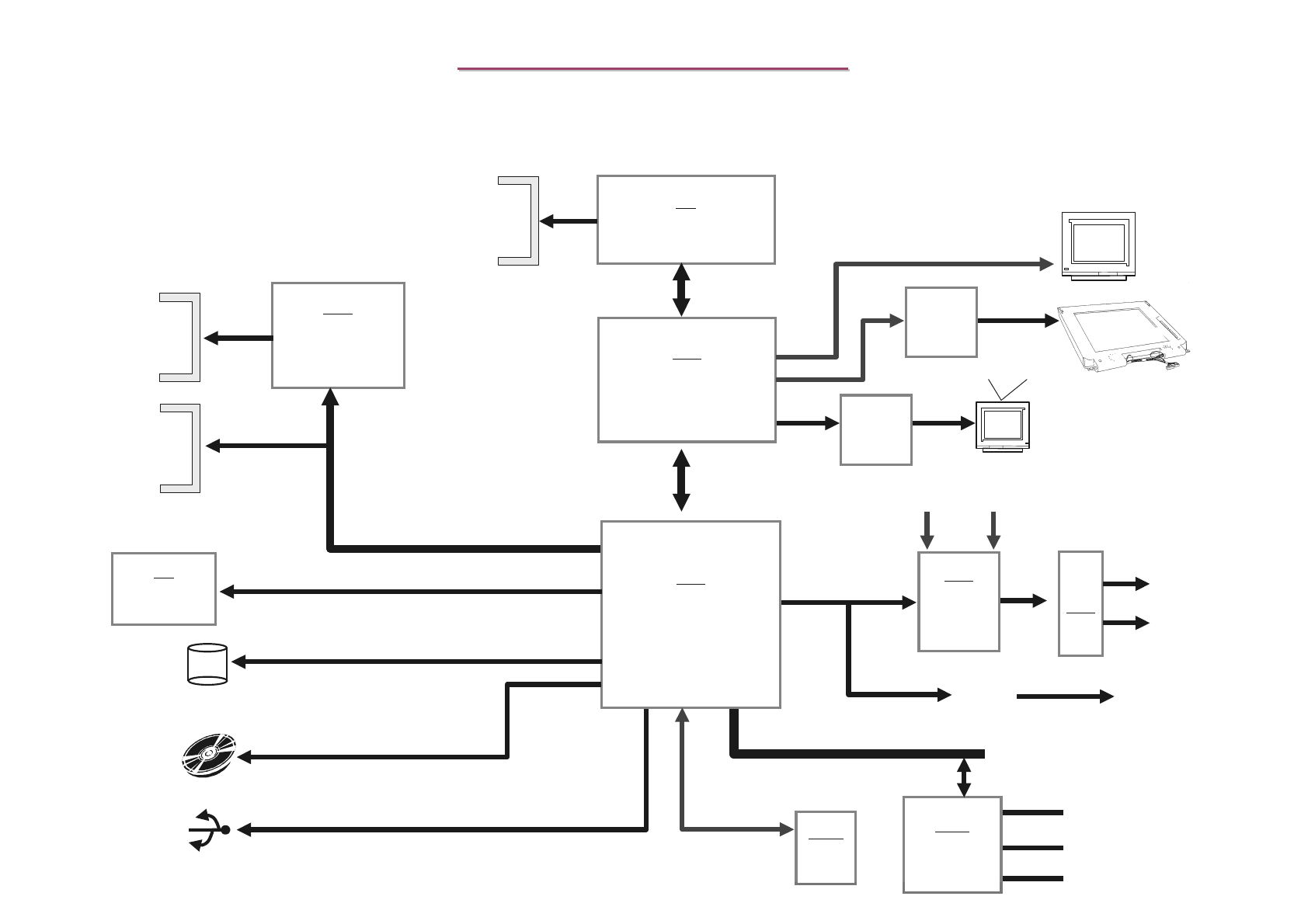

CPU/Cache North Bridge System Memory

VT8235

487 BGA

Expansion

Cards

On board

LPC I/O

Vlink

Interface

DIMM Module ID

SMB

RTC

Crystal

Boot Rom

USB 2.0 Ports 0~5

Keyboard/Mouse

IDE Primary and Secondary

AC97 Link

MII Fast Ethernet Interface

APLC

CA

CD

MA/Command

MD

GPIO, Power Control, Reset

Figure 1. PC System Configuration Using the VT8233

LPC PCI

Sideband Signals

Init/A20M#

INIR/NMI

SMI/Stop CLK

FERR/IGNNE Sleep

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

21

Inter-operable with VIA Host-to-V-Link Host Controller

Combine with VT8754 (Apollo P4X333) for a complete 533 / 400 MHz FSB Pentium 4 system

Combine with VT8377 (Apollo KX400) for a complete 266 / 200 MHz FSB Athlon Socket-A system

May be used interchangeably with the VT8235CDLSout h Bridge in most board designs

High Bandwidth 533 MB/s 8-bit V-Link Client Controller

Supports 66 MHz V-Link Client interface with peak bandwidth of 533 MB/sec

V-Link operates in 2x, 4x, and 8x modes

Full duplex commands with separate Strobe / Command

Request / Data split transaction

Configurable outstanding transaction queue for V-Link Client accesses

Auto Client Retry to eliminate V-Link Host-Client Retry cycles

Intelligent V-Link transaction protocol to eliminate data wait-state / throttle transfer latency; all V-Link

transactions for both Host and Client have a consistent view of transaction data depth and buffer size to

avoid data overflow.

Highly efficient V-Link arbitration with minimum overhead; all V-Link transactions have predictable cycle

length with known Command / Data duration

Auto connect / reconnect capability and dynamic stop for minimum power consumption

Parity checking to insure correct data transfers

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

22

Integrated Peripheral Controllers

Integrated Fast Ethernet Controller with 1 / 10 / 100 Mbit capability

Integrated USB 2.0 Controller with three root hubs and six function ports

Dual channel UltraDMA-133 / 100 / 66 / 33 master mode EIDE controller

AC-link interface for AC-97 audio codec and modem codec

HSP modem support

Integrated DirectSound compatible digital audio controller

LPC interface for Low Pin Count interface to Super-I/O or ROM

Integrated Legacy Functions

Integrated Keyboard Controller with PS2 mouse support

Integrated DS12885-style Real Time Clock with extended 256 byte CMOS RAM and Day/Month Alarm for

ACPI

Integrated DMA, timer, and interrupt controller

Serial IRQ for docking and non-docking applications

Fast reset and Gate A20 operation

Concurrent PCI Bus Controller

33 MHz operation

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

23

Supports up to six PCI masters

Peer concurrency

Concurrent multiple PCI master transactions; i.e., allow PCI masters from both PCI buses active at the same

time

Zero wait state PCI master and slave burst transfer rate

PCI to system memory data streaming up to 132Mbyte/sec (data sent to north bridge via high speed V-Link

Interface)

PCI master snoop ahead and snoop filtering

Eight DW of CPU to PCI posted write buffers

Byte merging in the write buffers to reduce the number of PCI cycles and to create further PCI bursting

possibilities

Enhanced PCI command optimization (MRL, MRM, MWI, etc.)

Four lines of post write buffers from PCI masters to DRAM

Sixteen levels (double-words) of prefetch buffers from DRAM for access by PCI masters

Delay transaction from PCI master accessing DRAM

Transaction timer for fair arbitration between PCI masters (granularity of two PCI clocks)

Symmetric arbitration between Host/PCI bus for optimized system performance

Complete steerable PCI interrupts

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

24

PCI-2.2 compliant, 32 bit 3.3V PCI interface with 5V tolerant inputs

Fast Ethernet Controller

High performance PCI master interface with scatter / gather and bursting capability

Standard MII interface to external PHYceiver

1 / 10 / 100 MHz full and half duplex operation

Independent 2K byte FIFOs for receive and transmit

Flexible dynamically loadable EEPROM algorithm

Physical, Broadcast, and Multicast address filtering using hashing function

Magic packet and wake-on-address filtering

Software controllable power down

UltraDMA- 133/ 100 / 66 / 33 Master Mode EIDE Controller

Dual channel master mode hard disk controller supporting four Enhanced IDE devices

Transfer rate up to 133MB/sec to cover PIO mode 4, multi-word DMA mode 2 drives, and UltraDMA-133

interface

Increased reliability using UltraDMA-133/100/66 transfer protocols Thirty-two levels (double words) of

prefetch and write buffers

Dual DMA engine for concurrent dual channel operation

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

25

Direct Sound Ready AC97 Digital Audio Controller

AC-Link access to 4 CODECs (AC97 + AMC97 + MC97)

Multi channel Audio

Bus Master Scatter / Gather DMA

Dedicated read and write channels supporting simultaneous stereo playback and record

Dedicated read and write channels supporting simultaneous modem receive and transmit

1 stereo DirectSound channel with source / volume control / mixer

1 shared FM / SPDIF PCM read channel

1 dedicated channel supporting multi-channel audio

32-byte line-buffers for each SGD channel

Programmable 8bit / 16bit mono / stereo PCM data format support

AC97 2.1 compliant

Bus master programming interface for SFF-8038i rev.1.0 and Windows-95 compliant

Full scatter gather capability

Support ATAPI compliant devices including DVD devices

Support PCI native and ATA compatibility modes

Complete software driver support

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

26

System Management Bus Interface

Host interface for processor communications

Slave interface for external SMBus masters

Universal Serial Bus Controller

USB v2.0 and Enhanced Host Controller Interface (EHCI) v1.0 compatible

USB v1.1 and Universal Host Controller Interface (UHCI) v1.1 compatible

Eighteen level (double words) data FIFO with full scatter and gather capability

Three root hubs and six function ports

Integrated physical layer transceivers with optional over-current detection status on USB inputs

Legacy keyboard and PS/2 mouse support

Sophisticated PC2001-Compatible Mobile Power Management

Supports both ACPI (Advanced Configuration and Power Interface) and legacy (APM) power management

ACPI v1.0 Compliant

APM v1.2 Compliant

CPU clock throttling and clock stop control for complete ACPI C0 to C3 state support

PCI bus clock run, Power Management Enable (PME) control, and PCI/CPU clock generator stop control

Supports multiple system suspend types: power-on suspends with flexible CPU/PCI bus reset options,

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

27

suspend to DRAM, and suspend to disk (soft-off), all with hardware automatic wake-up

Multiple suspend power plane controls and suspend status indicators

One idle timer, one peripheral timer and one general purpose timer, plus 24/32-bit ACPI compliant timer

Normal, doze, sleep, suspend and conserve modes

Global and local device power control

System event monitoring with two event classes

Primary and secondary interrupt differentiation for individual channels

Dedicated input pins for power and sleep buttons, external modem ring indicator, and notebook lid

open/close for system wake-up

32 general purpose input ports and 32 output ports

Multiple internal and external SMI sources for flexible power management models

Enhanced integrated real time clock (RTC) with date alarm, month alarm, and century field

Thermal alarm on external temperature sensing circuit

I/O pad leakage control

Plug and Play Controller

PCI interrupts steerable to any interrupt channel

Steerable interrupts for integrated peripheral controllers: USB, floppy, serial, parallel, and audio

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

28

Microsoft Windows XPTM, Windows NTTM, Windows 2000TM, Windows 98TM and plug and play BIOS

compliant

Built-in NAND-tree pin scan test capability

0.22um, 2.5V, low power CMOS process

Single chip 27 x 27 mm, 1.0 mm ball pitch, 487 pin BGA

1.3.4 System Frequency Synthesizer and DDR-SDRAM Buffer: ICS950403

The ICS950403 is a system clock synthesizer chip for AMD K8 based notebook systems with AMD, VIA or Ali

chipset. This provides all clocks required for such a system. The ICS950403 employs a proprietary closed loop

design, which tightly controls the percentage of spreading over process and temperature variations. Serial

programming I 2 C interface allows changing functions, stop clock programming and frequency selection.

Output Features

2 - Differential pair push-pull CPU clocks @ 3.3V

8 - PCICLK (Including 1 free running) @ 3.3 V

3 - Selectable PCICLK/HTTCLK @ 3.3V

1 - HTTCLK @ 3.3V

1 - 48MHz @ 3.3V fixed

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

29

Features/Benefits

Programmable output frequency

Programmable output divider ratios

Programmable output rise/fall time

Programmable output skew

Programmable spread percentage for EMI control

Watchdog timer technology and RESET# output to reset system if system malfunction

Programmable watch dog safe frequency

Support I2C index read/write and block read/write operations

Uses external 14.318MHz crystal

Support Hyper Transport Technology (HTTCLK)

48-Pin 300mil SSOP

1 - 24_48MHz @ 3.3V

3 - REF @ 3.3V, 14.318MHz

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

30

1.3.5 PC Card Interface Controller: ENE CB1410

The ENE CB1410 is a high-performance PCI-to-PC Card controller that supports a single PC Card socket compliant

with the 1997 PC Card Standard. The ENE CB1410 provides features that make it the best choice for bridging

between PCI and PC Cards in both notebook and desktop computers. The 1997 PC Card Standard retains the 16-bit

PC Card specification defined in PCI Local Bus Specification and defines the new 32-bit PC Card, CardBus, capable

of full 32-bit data transfers at 33 MHz. The ENE CB1410 supports both 16-bit and CardBus PC Cards, powered at 5

V or 3.3 V, as required.

The ENE CB1410 is compliant with the PCI Local Bus Specification, and its PCI interface can act as either a PCI

master device or a PCI slave device. The PCI bus mastering is initiated during 16-bit PC Card DMA transfers or

CardBus PC Card bridging transactions. The ENE CB1410 is also compliant with the latest PCI Bus Power

Management Interface Specification and PCI Bus Power Management Interface Specification for PCI to CardBus

Bridges.

All card signals are internally buffered to allow hot insertion and removal without external buffering. The ENE

CB1410 internal data path logic allows the host to access 8-, 16-, and 32-bit cards using full 32-bit PCI cycles for

maximum performance. Independent buffering and a pipeline architecture provide an unsurpassed performance level

with sustained bursting. The ENE CB1410 can also be programmed to accept fast posted writes to improve system-

bus utilization.

Multiple system-interrupt signaling options are provided, including: parallel PCI, parallel ISA, serialized ISA, and

serialized PCI. Furthermore, general-purpose inputs and outputs are provided for the board designer to implement

sideband functions. Many other features designed into the ENE CB1410, such as socket activity light-emitting diode

(LED) outputs, are discussed in detail throughout the design specification.

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

31

An advanced complementary metal-oxide semiconductor (CMOS) process achieves low system power consumption

while operating at PCI clock rates up to 33MHz. Several low-power modes enable the host power management

system to further reduce power consumption.

The CB1410 Supports the Following Features

3V operation with 5V tolerant

144-pin LQFP or 144-ball LFBGA package for CB1410 single slot Cardbus controller

Compliant with

PCI Local Bus Specification, Revision 2.2

PCI Bus Power Management Interface Specification, Revision 1.1

PCI Mobile Design Guide, Version 1.1

Advanced Configuration and Power Interface Specification, Revision 1.0

PC99 System Design Guide

PC Card Standard 8.0

Interrupt Configuration

Support parallel PCI interrupts

Support parallel IRQ and parallel PCI interrupts

Support serialized IRQ and parallel PCI interrupts

Support serialized IRQ and PCI interrupts

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

32

Power Management Control Logic

Support CLKRUN# protocol

Supports SUSPEND#

Support PCI PME# from D3, D2, D1 and D0

Support PCI PME# from D3 cold

Supports D3STATE#

Power Switch Interface

Supports parallel 4 wire power switch interface.

Misc Control Logic

Support CLKRUN# protocol

Support serial EEPROM interface

Support socket activity LED

Support 5 GPIOs and GPE#

Support standard Zoomed Video Port

Support SPKOUT, CAUDIO and RIOUT#

Support PCI LOCK

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

33

1.3.6 One-Slot PC Card Power Interface Switch: ENE CP-2211

CP-2211 is single Slot PCMCIA and CardBus power switch. It integrates control logic, low switching resistance

MOSFET, over current alarm and over temperature auto shutdown circuits. It can deliver 3.3V or 5V to PC Card

VCCOUT and 3.3V, 5V or 12V to PC Card VPPOUT. The output current is up to 1A for VCCOUT and 250mA for

VPPOUT.

Low Switching Resistance (100mΩfor VCC Switch)

Over temperature auto shutdown

1A output current for VCCOUT

150mA output current for VPPOUT

Only 3.3V is required for chip normal operation

12V is not required for 3.3V or 5V Output

Break-Before-Make Switching

16-Pin SSOP Package

1.3.7 AC’97 Audio System: VIA VT1617/1617A

The VT1617/1617A is a high performance audio codec which complies with the AC’97 revision 2.3. It integrates

Sample Rate Converters on all channels and can be adjusted in 1Hz increments. This chip supports 96KHz sampling

rates, high-quality 96KHz S/PDIF output, stereo digital playback.

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

34

The 20bit, ΣΔADCs VT1617/1617A implements stereo recording and white noise removal to ensure the best

quality of recording. It features 8-channel hardware-expansion for flexible 7.1-channel applications. It also contains

a hardware down-mixing feature that allows the end users enjoy 6-channel audio with 2-channel or 4-channel

speakers. The analog mixer circuitry integrates a stereo enhancement to provide a pleasing 3D surround sound effect

for stereo media. The VT1617/1617A has a built-in quality headphone amplifier and a high-accuracy PLL for cost

saving. This codec is designed with aggressive power management to achieve low power consumption; when used

with a 3.3V analog supply, the owner consumption is further reduced.

AC’97 V2.3 Audio Codec

Fully compliant with AC’97 Revision 2.3

High Audio Quality

Support sampling rates up to 96KHz

Independent 20-bit ADC and 20-bit DAC

SNR (Signal to Noise Ratio) exceeds 95dB

Built-in 1Hz resolution VSR converter

Various Output Format

Support 8-channel outputs

Hardware down-mixed 6-channel to 2-channel or 4-channel

Center and LFE channel swapping

Alternative Line-Level outputs at surround output

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

35

96KHz S/PDIF output

Direct CD input to S/PDIF output

Added-on Functions

Integrates headphone amplifier with mute

Dual microphones supporting Karaoke mixing

Extension Control

4-bit 3D depth control

Support EAPD control

Supports GPIO pins control

Selectable clock sources

Driver support Magic 5.1

Convenient Design

Flexible Jack-detect design

Built-in accurate PLL for saving an external crystal

Built-in Smart 5.1.

Power

Low power consumption mode

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

36

3.3V or 5V analog, 3.3V digital power supply

2M bit Flash memory

Flashed by 5V only

User can upgrade the system BIOS in the future just running flash program.

48-Pin LQFP Package

1.3.8 System Flash Memory (BIOS)

1.3.9 Memory System

JEDEC-standard 200-pin, small-outline, dual in-line memory module (SODIMM)

Utilizes 333Mb/s and 400Mb/s DDR SDRAM components

64MB (8 Meg x 64 [H]); 128MB (16 Meg x 64, [H] and [HD]); 256MB (32 Meg x 64 [HD]); 512MB (64

Meg x 64 [HD])

VDD= VDDQ= +2.5V ±0.2V

Package

64MB, 128MB, 256MB, 512MB (x64) 200-Pin DDR SDRAM SODIMMs

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

37

VDDSPD = +2.2V to +5.5V

2.5V I/O (SSTL_2 compatible)

Commands entered on each positive CK edge

DQS edge-aligned with data for READs; center-aligned with data for WRITEs

Internal, pipelined double data rate (DDR) architecture; two data accesses per clock cycle

Bidirectional data strobe (DQS) transmitted/received with data—i.e.,source-synchronous data capture

Differential clock inputs (CK and CK# - can be multiple clocks, CK0/CK0#, CK1/CK1#, etc.)

Four internal device banks for concurrent operation

Selectable burst lengths: 2, 4, or 8

Auto precharge option

Auto Refresh and Self Refresh Modes

15.6μs (MT4VDDT864H, MT8VDDT1664HD), 7.8125μs (MT4VDDT1664H, MT8VDDT3264HD,

MT8VDDT6464HD) maximum average periodic refresh interval

Serial Presence Detect (SPD) with EEPROM

Fast data transfer rates PC2700, PC2100 or PC1600

Selectable READ CAS latency for maximum compatibility

Gold-plated edge contacts

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

38

1.3.10 LAN: VT6103L 10Base-T/100Base-TX Ethernet PHY

The VT6103L is a Physical Layer device for Ethernet 10BASE-T and 100BASE-TX using category 5 Unshielded,

Type 1 Shielded, and Fiber Optic cables. This VLSI device is designed for easy implementation of 10 / 100 Mb/s

Fast Ethernet LANs. It interfaces to a MAC through an MII interface ensuring interoperability between products

from different vendors.

Single Chip 100Base-TX/10Base-T Physical Layer solution

Dual Speed – 100/10 Mbps

Half And Full Duplex

MII Interface to Ethernet Controller

MII Interface to Configuration & Status

Optional Repeater Interface

Auto Negotiation : 10/100, Full/Half Duplex

Meet All Applicable IEEE 802.3, 10Base-T and 100Base-Tx Standards

On Chip Wave Shaping – No External Filters Required

Adaptive Equalizer

Baseline Wander Correction

LED Outputs

Product Features

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

39

Link Status

Duplex status

Speed Status

Collision

48 Pin SSOP Package

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

40

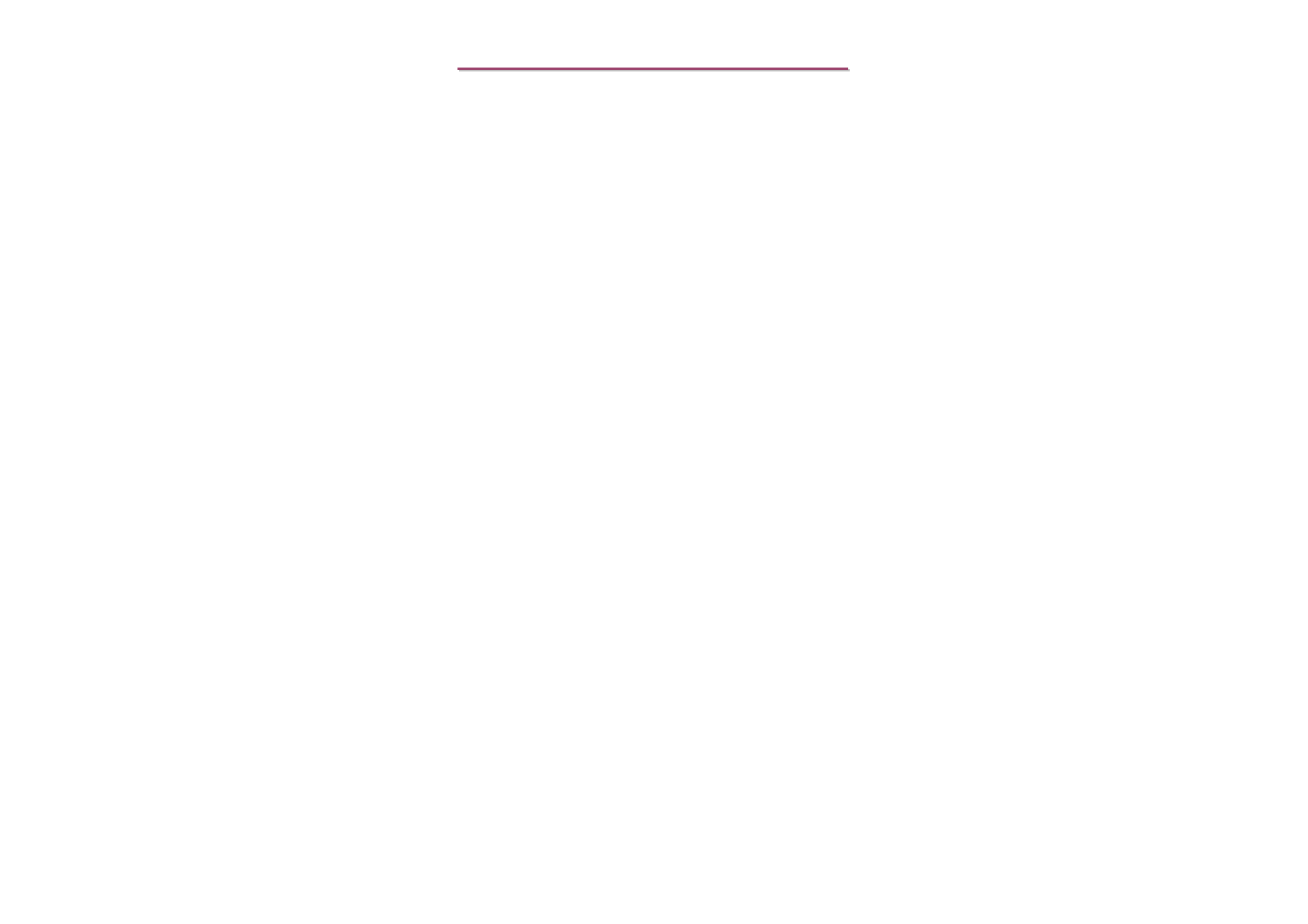

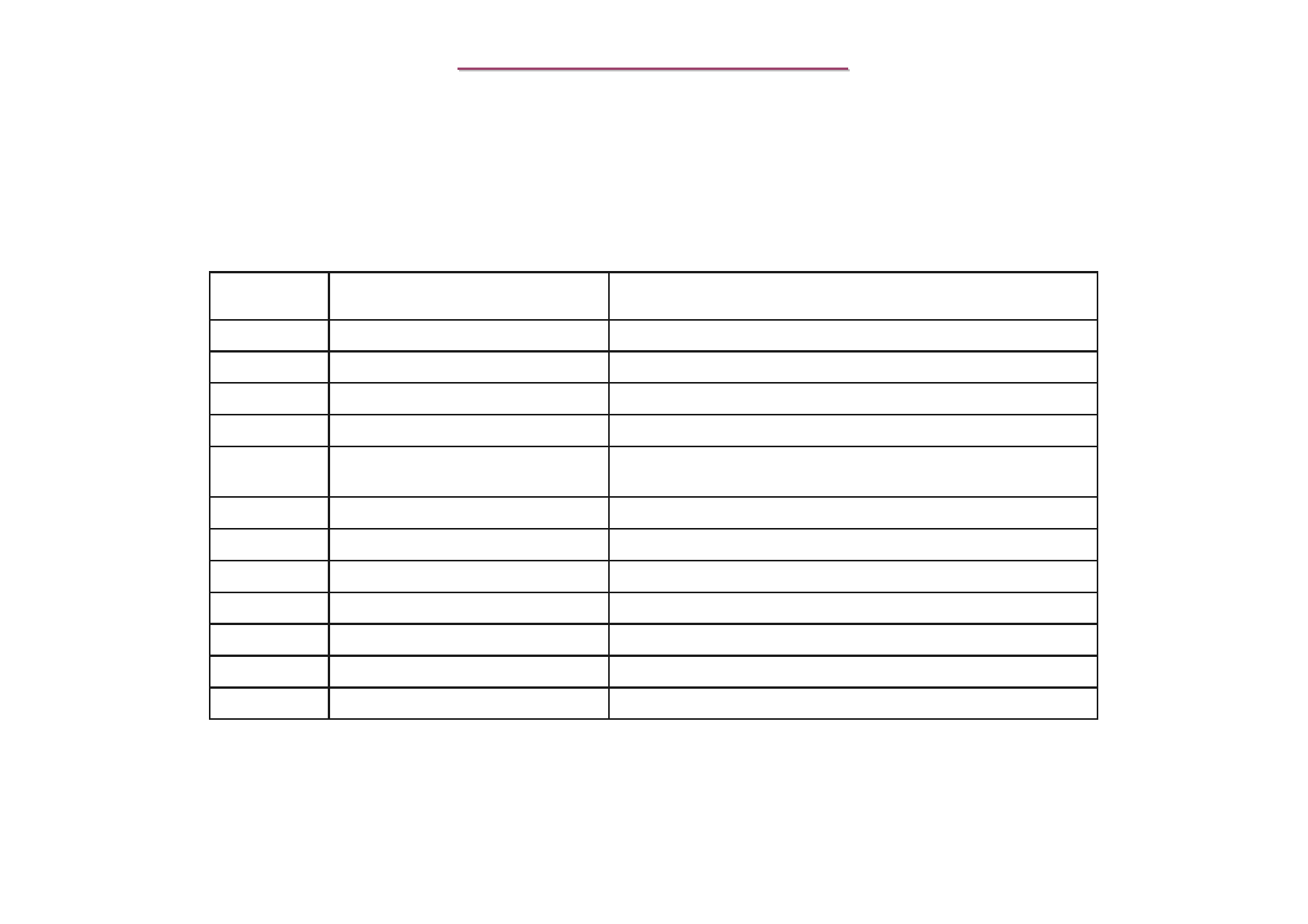

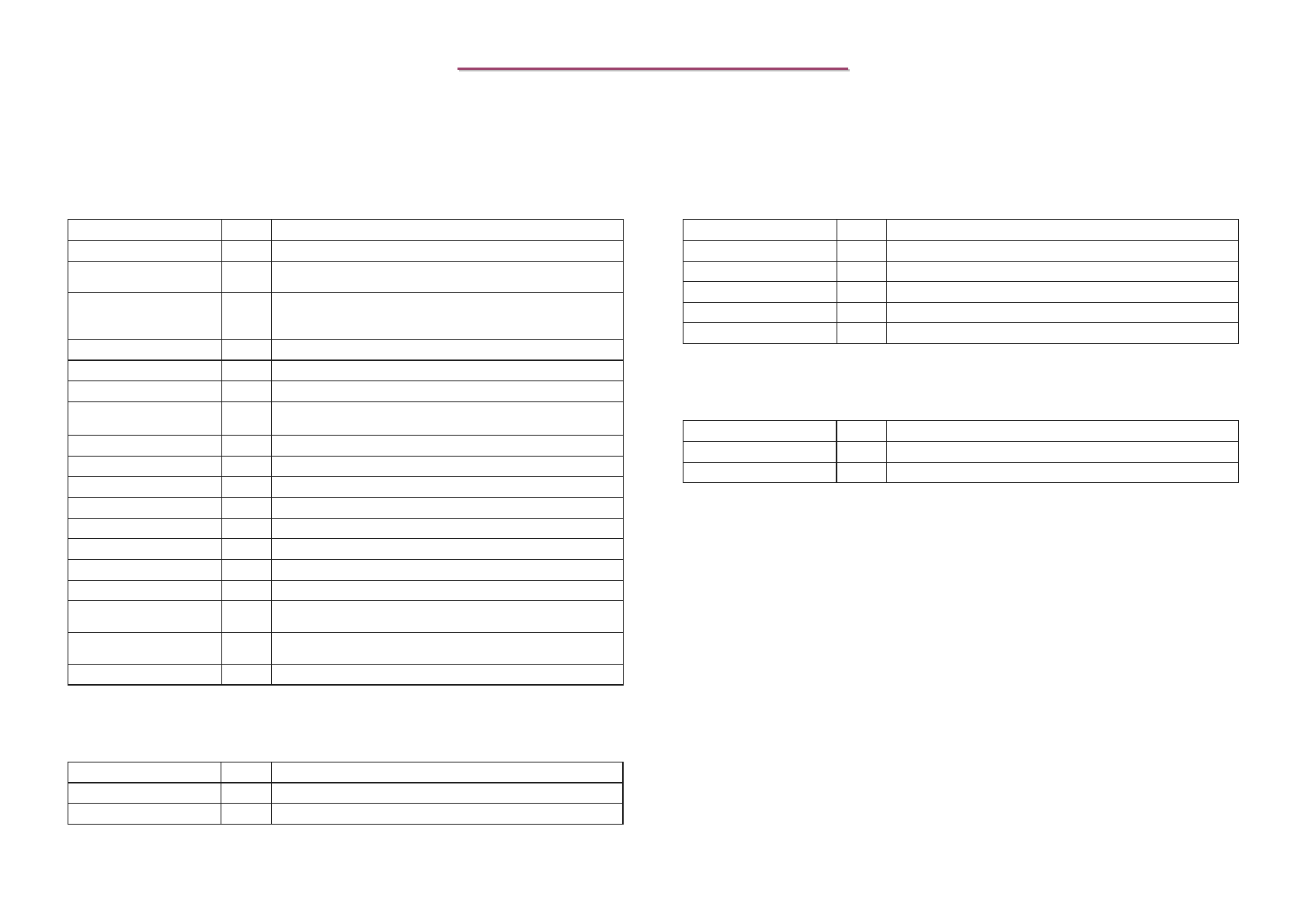

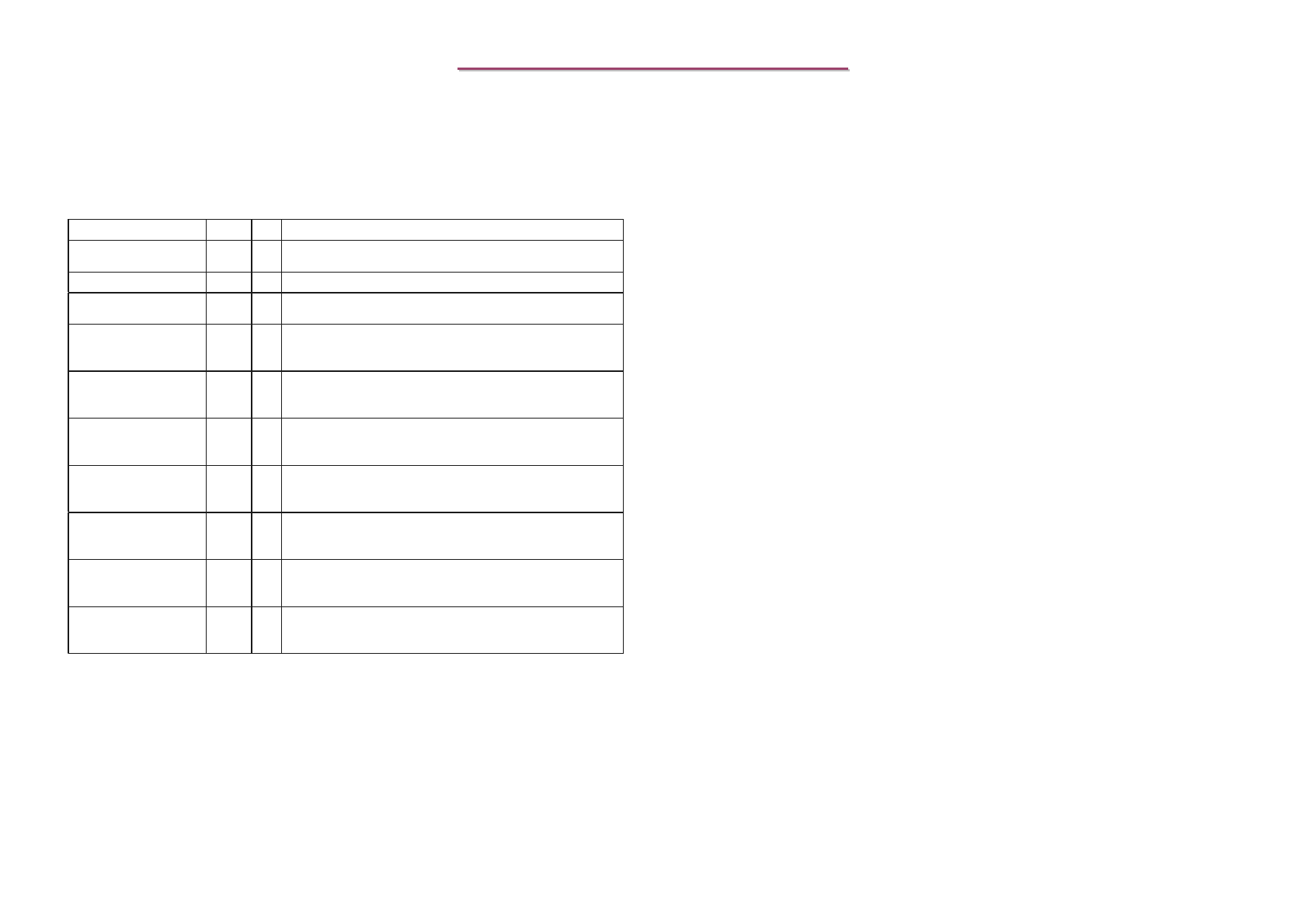

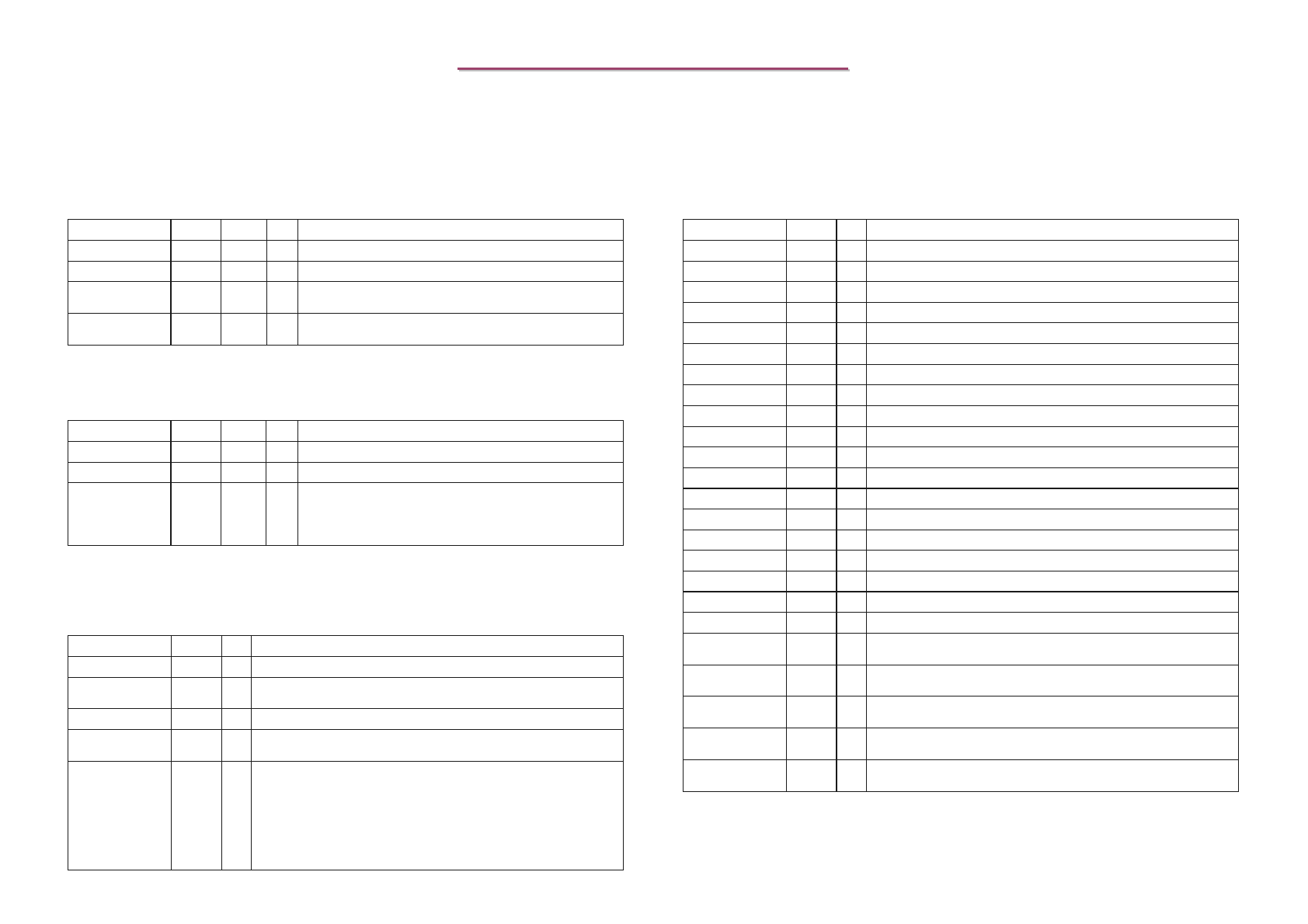

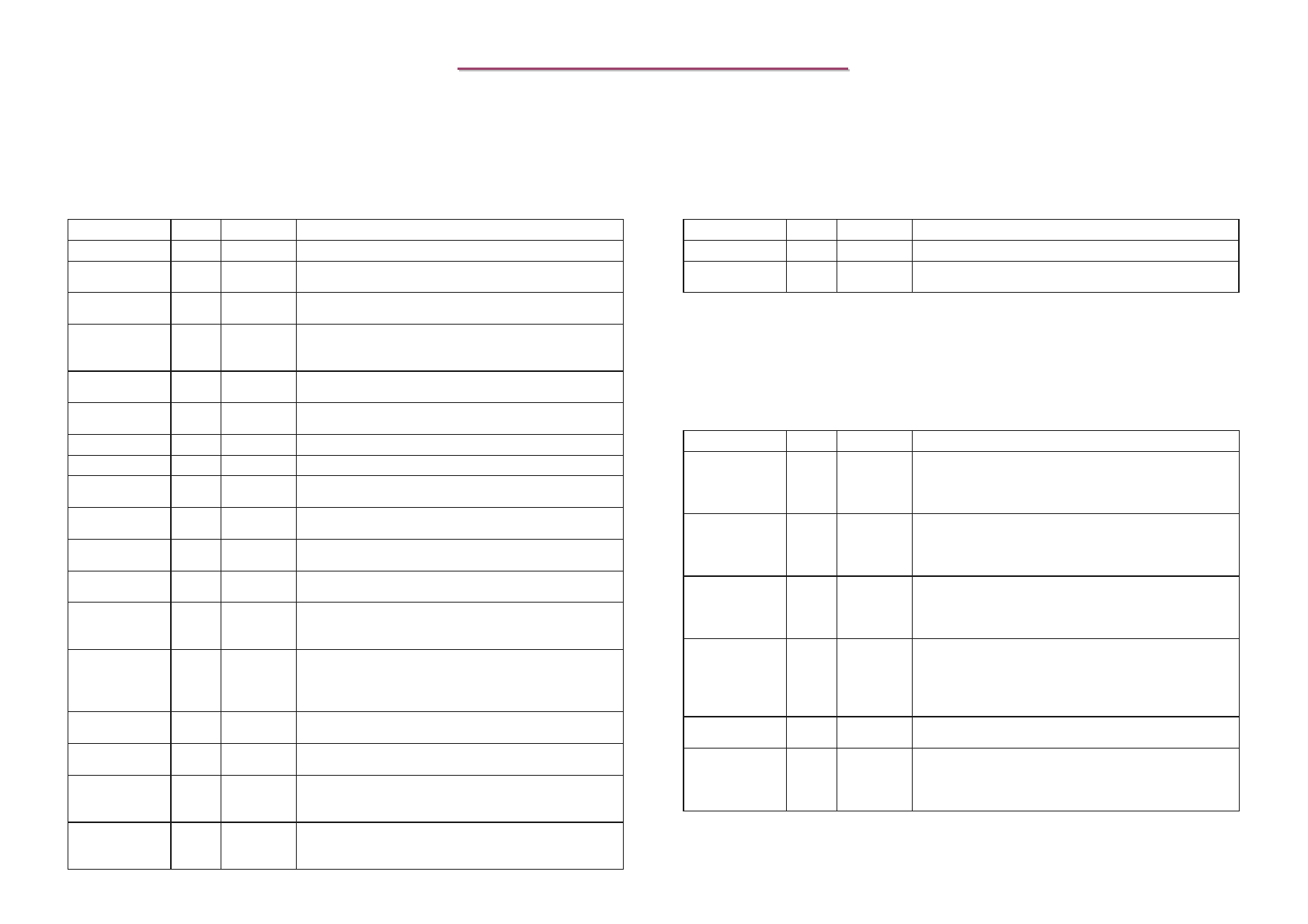

1.4.1 Hot Key Function

Keys Feature Meaning

Combination

Fn + F1 Wireless lan on/off Wireless Lan on ->off

Fn + F2 Reserve

Fn + F3 Volume down Adjust Audio volume down

Fn + F4 Volume up Adjust Audio volume up

Fn + F5 Display switch LCD->CRT->LCD&CRT, TV-out will be not TV present.

TV->CRT->TV&CRT, TV-out is connected.

Fn + F6 Brightness down Adjust LCD panel backlight darkness.

Fn + F7 Brightness up Adjust LCD panel backlight lightness.

Fn + F8 MAX brightness toggle Toggle LCD brightness maximum or user setting

Fn + F9 Reserved

Fn + F10 Battery Low warning beep toggle Toggle to enable/mute the “Battery Low Warning” beep sound

Fn + F11 LCD panel toggle on/off Toggle LCD panel on or off.

Fn + F12 System sleep System sleep button function.

1.4 Other Functions

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

41

1.4.2 Power on/off/Suspend/Resume Button

1.4.2.1 APM Mode

At APM mode, Power button is on/off system power.

1.4.2.2 ACPI Mode

At ACPI mode, power button behavior was set by windows power management control panel. You could set

“standby” or “power off” to power button function. Continue pushing power button over 4 seconds will force

system off at ACPI mode. There is no sleep button on this machine.

1.4.3 Lid Switch

System automatically provides a Keyboard cover state through PS2 to relative application when user closes the

Keyboard cover.

1.4.4 LED Indicators

System has some status LED indicators to display system activity,.

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

42

1.4.4.1 Three LED Indicators on Display Housing/Cover:

From left to right that indicates, AC Power/Battery Power and Battery Charger

AC Power:

This LED lights green when AC powers to the notebook, and flash (on 1 second, off 1 second) when

Suspend to DRAM is active using AC power. The LED is off when the notebook is off or powered by

batteries.

Battery Power:

This LED lights green when Battery powers to the notebook, and flash (on 1second, off 1 second) when

Suspend to DRAM is active using Battery power. The LED is off when the notebook is off or powered by

AC power.

Battery Charge Status:

During normal operation, this LED stays off as long as the battery is charged. When the battery charge

drops to 10% of capacity, the LED lights red, flashes per 1 second and beeps per 2 second. When AC is

connected, this indicator glows green if the battery pack is fully charged or orange (amber) if the battery is

being charged. When battery charging error, it will flash orange light.

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

43

WLAN RF Status (BTO: Wireless LAN only):

This LED indicates WLAN RF module power status. User could use Fn+F1 to enable or disable RF.

1.4.4.2 Five LED Indicators above Front Side Housing:

From left to right that indicates CD, HDD, NUM LOCK, CAPS LOCK and SCROLL LOCK.

1.4.5 Fan Power on/off Management

l FAN is controlled by Embedded Controller Winbond W83L950D. Thermal with hardware monitor to sense CPU

temperature and EC control fan on/off.

1.4.6 CMOS Battery

CR2032 3V 220mAh lithium battery

When AC in or system main battery inside, CMOS battery will consume no power

AC or main battery not exists, CMOS battery life is at lest 10 years

Battery was put in battery holder, can be replaced.

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

44

1.4.7 I/O Port

One 3 pins AC power socket

One CRT monitor

One S-Video TV out (PAL/NTSC)

Six USB 2.0 ports for all USB devices

One MODEM RJ-11 phone jack for PSTN line

One RJ-45 for LAN

Headphone out Jack

Microphone Input Jack

One Cardbus Sockets for one type II PC card extension

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

45

2.1 System View

2.1.1 Front View

2.1.2 Left-side View

Top Cover Latch

1

1

Lock

Ventilation Openings

1

2

12

2. System View and Disassembly

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

46

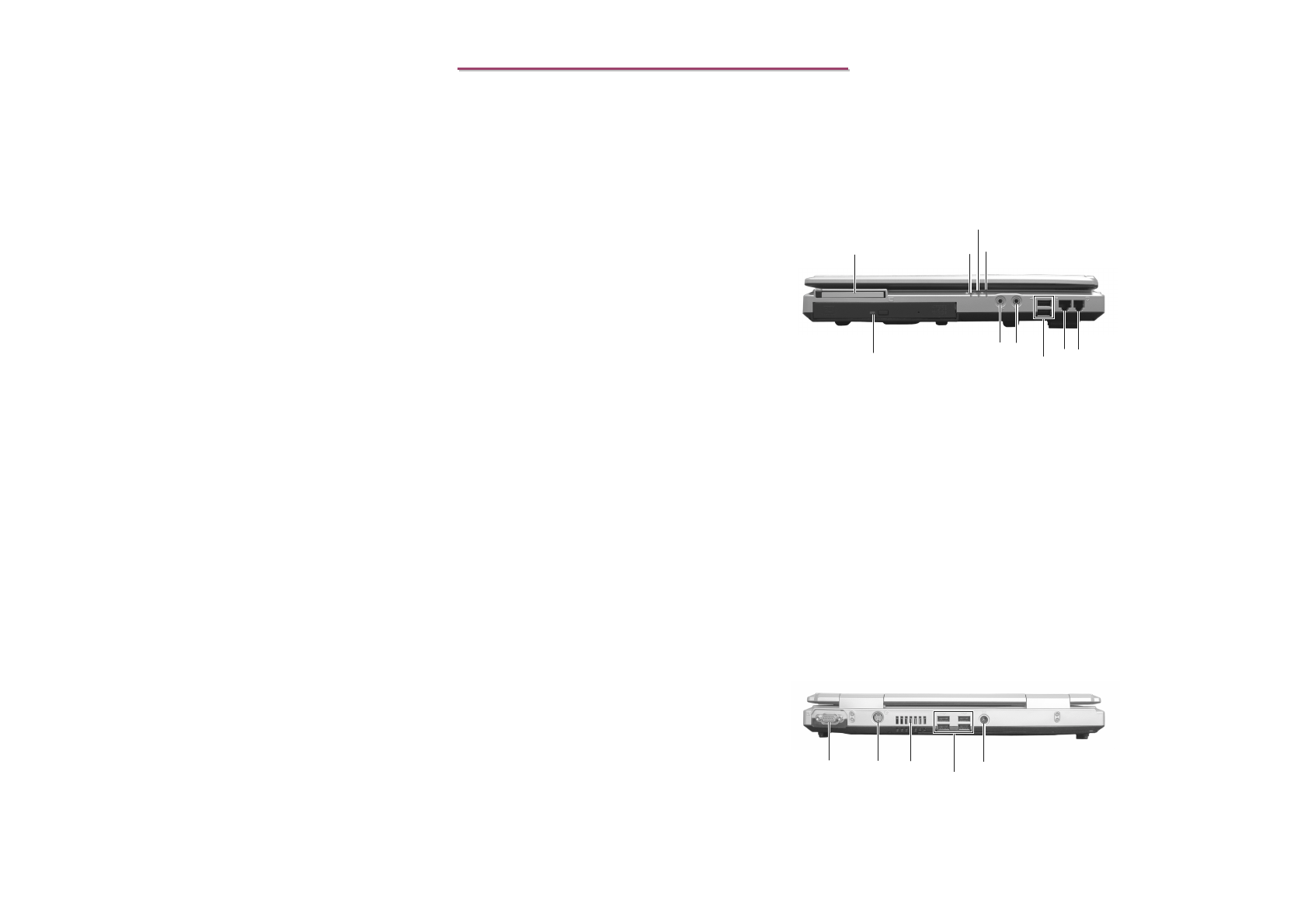

2.1.3 Right-side View

2.1.4 Rear View

10 9

8

7

6

5

4

3

2

1

CD/DVD driver

Line out jack

MIC in jack

USB port *2

RJ-45 connector

RJ-11 connector

AC Power Indicator

Battery Power Indicator

Battery Charge Indicator

PC Card slot

1

2

3

4

5

6

7

8

9

10

12345

VGA port

S-Video output connector

Ventilation Openings

USB port *4

Power connector

1

2

3

4

5

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

47

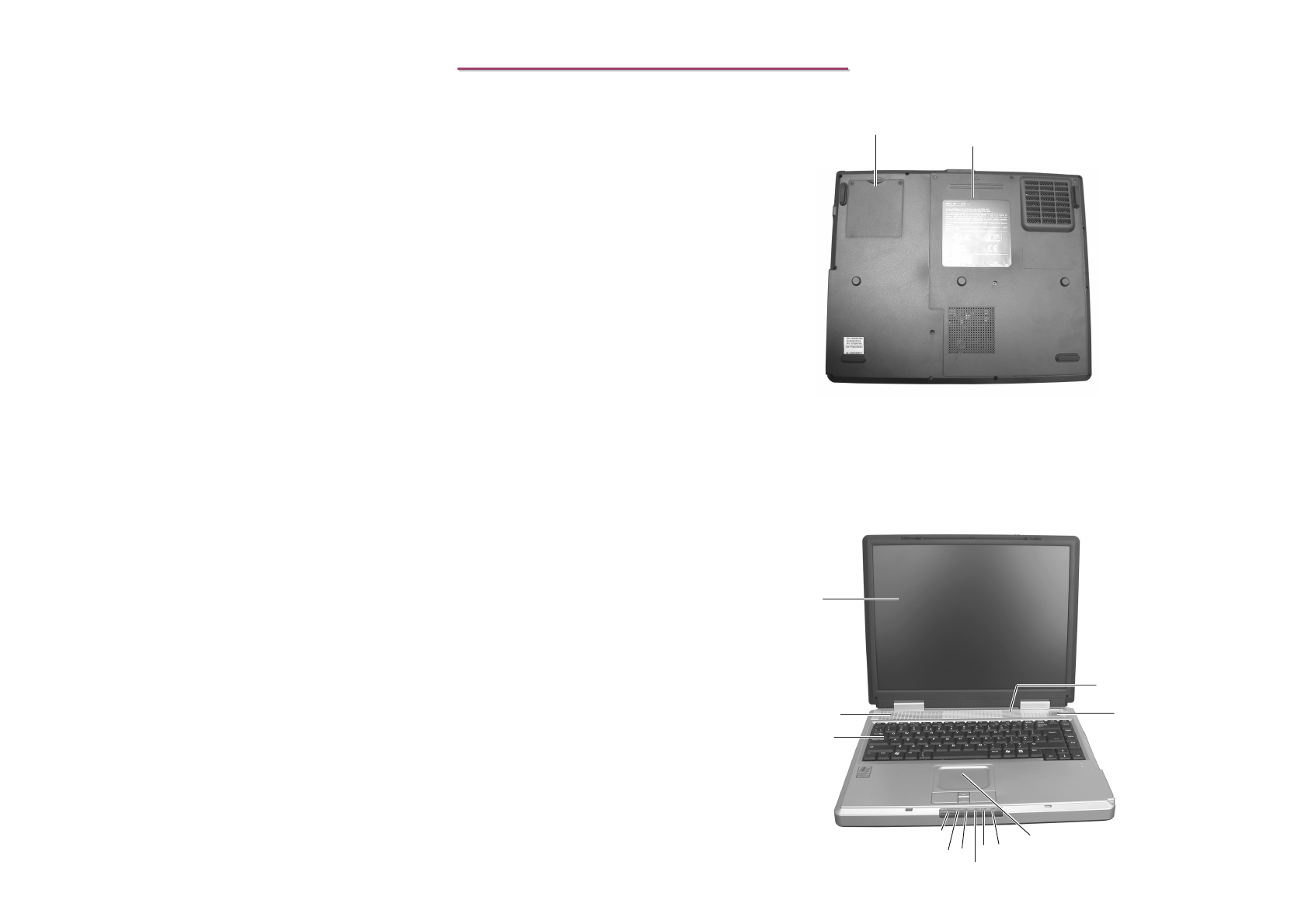

2.1.5 Bottom View

1

Wireless Card cover

CPU

1

2

1

2

3

456

7

89

10

11

2

2.1.6 Top-open View

LCD Screen

Stereo set

Keyboard

Caps Lock

Wireless Card Indicator

CD/DVD-Rom Indicator

HDD Indicator

Num Lock

Caps Lock

Scroll Lock

Power Button

1

2

3

4

5

6

7

8

9

10

11

2

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

48

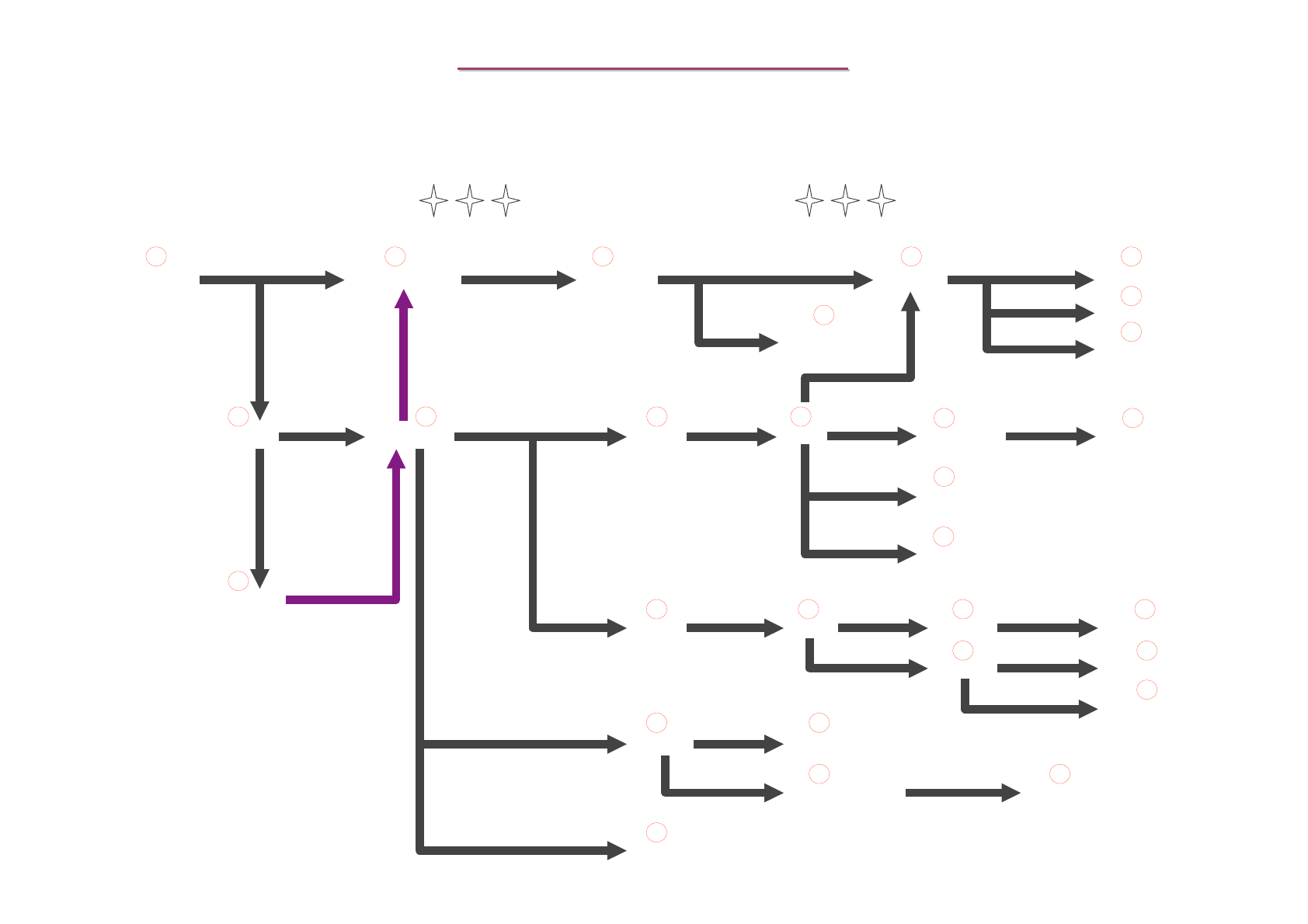

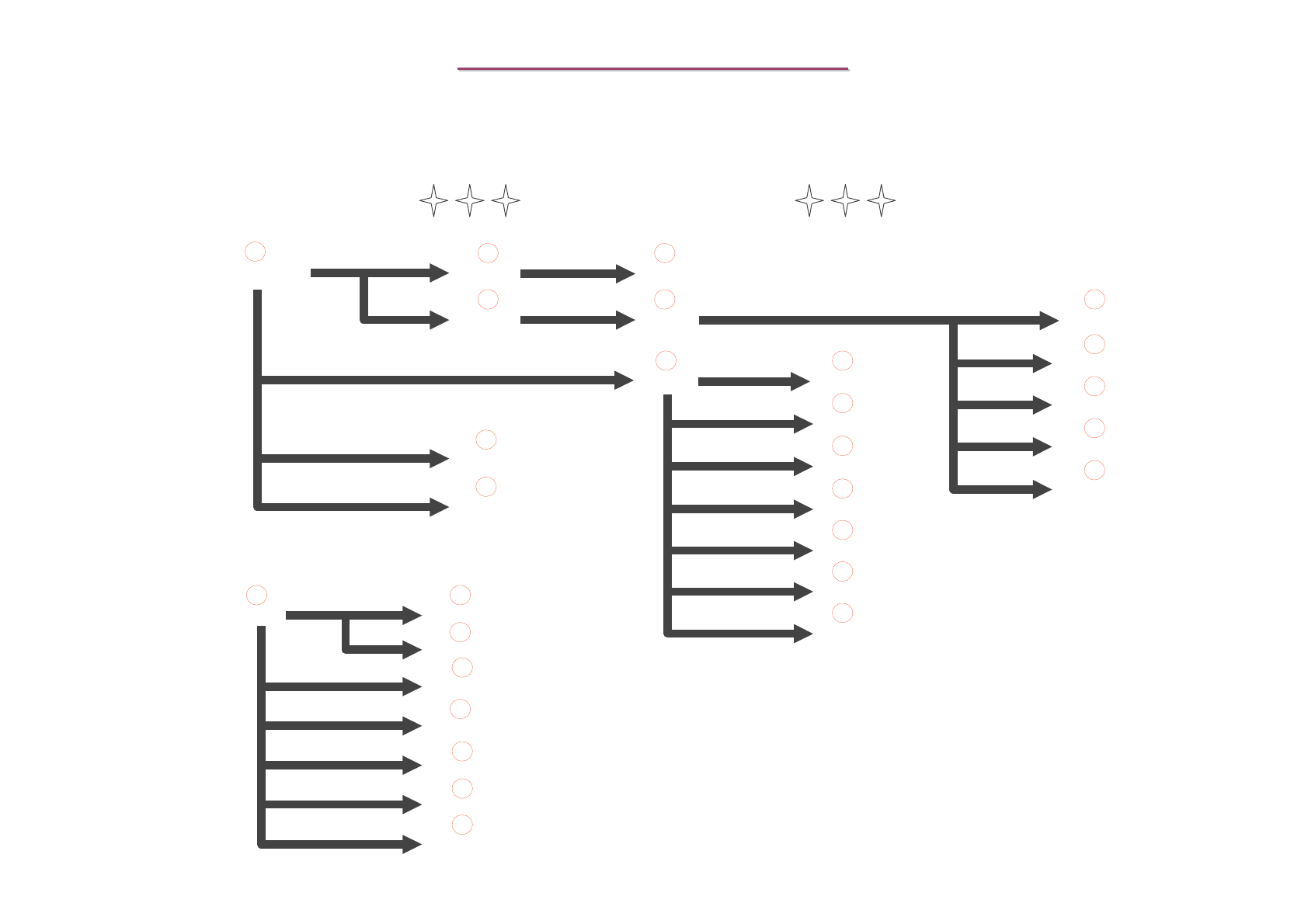

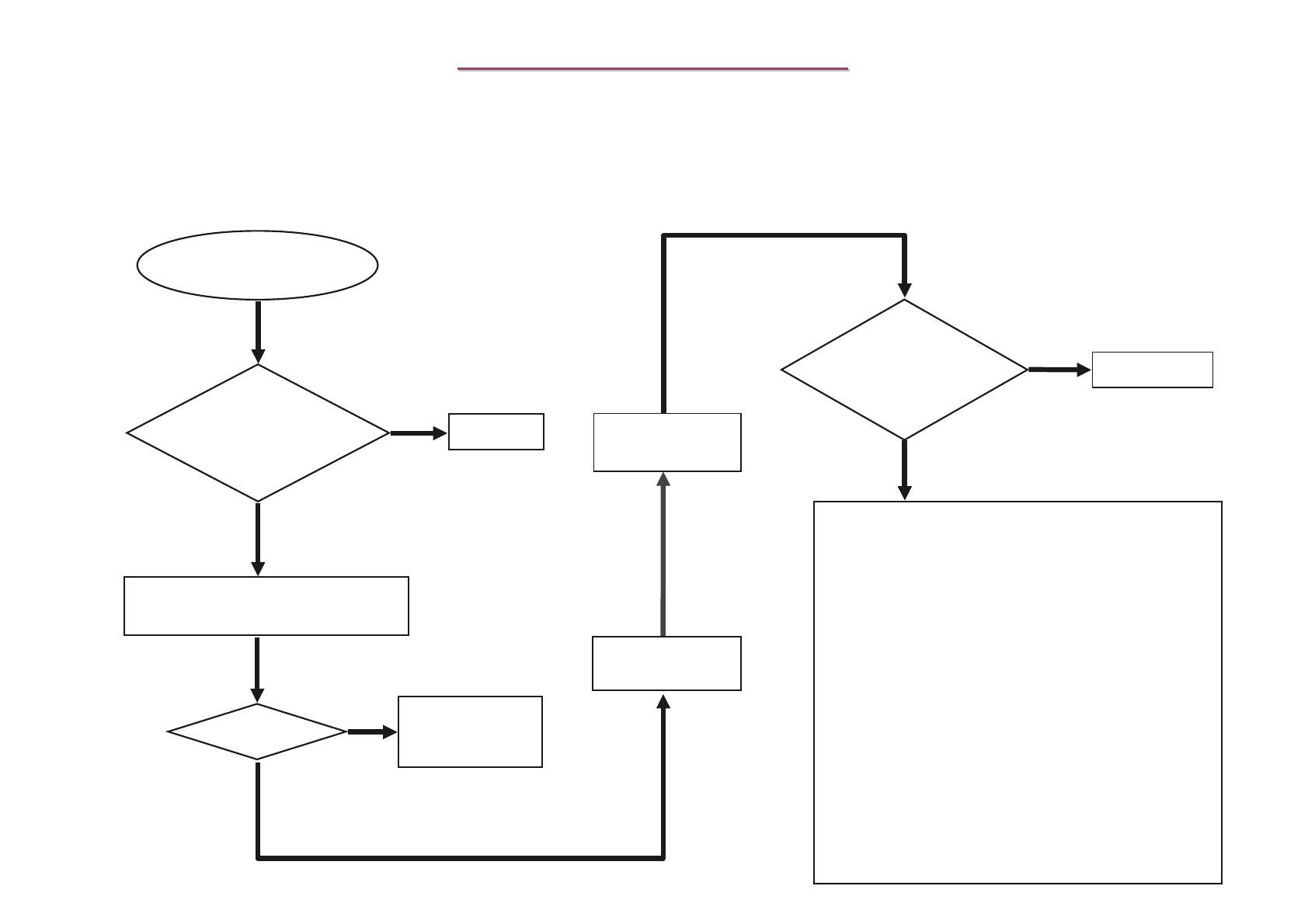

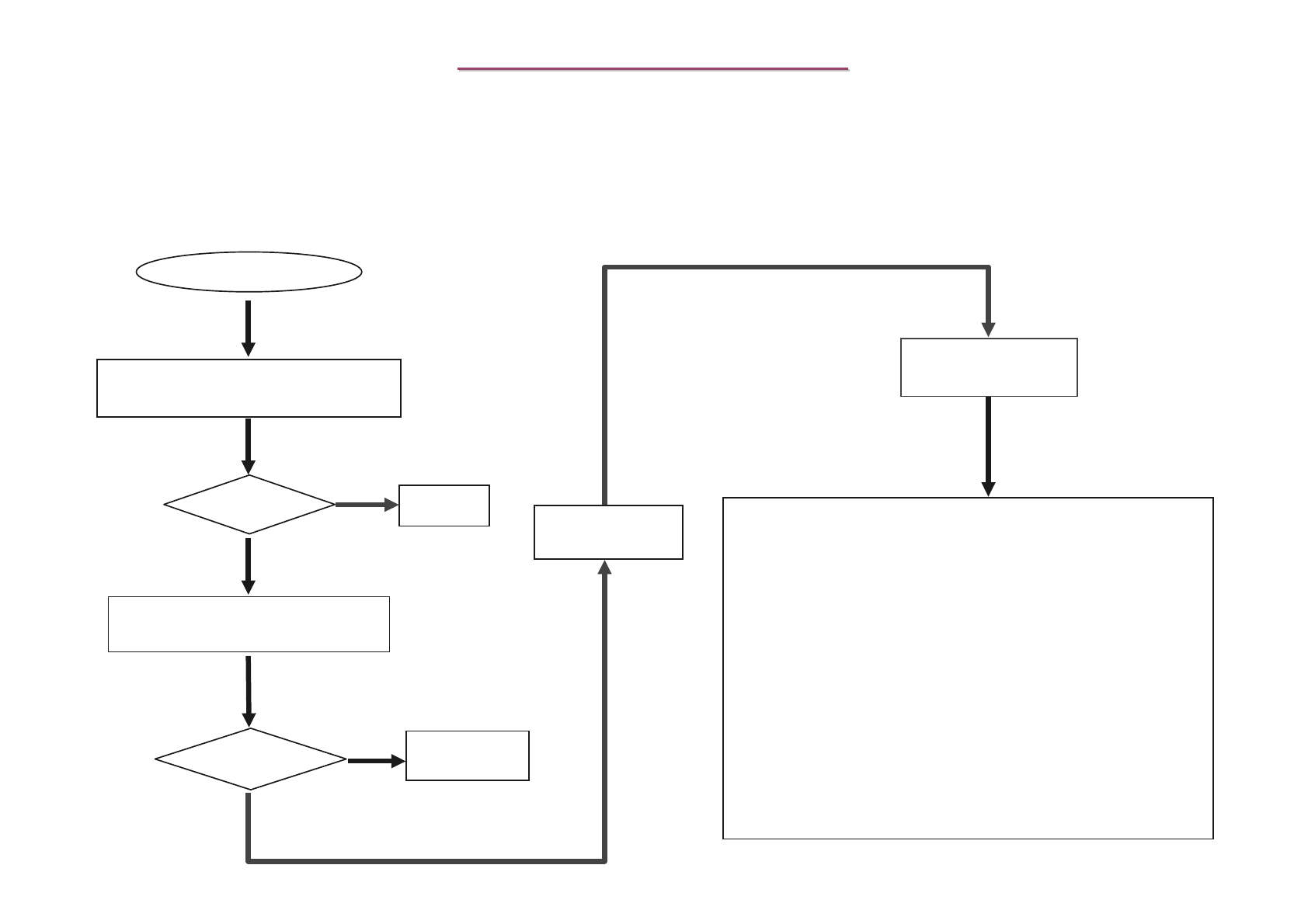

The section discusses at length each major component for disassembly/reassembly and show corresponding

illustrations. Use the chart below to determine the disassembly sequence for removing components from the

notebook.

2.2 System Disassembly

NOTE: Before you start to install/replace these modules, disconnect all peripheral devices and make sure the

notebook is not turned on or connected to AC power.

Modular Components

LCD Assembly Components

Base Unit Components

NOTEBOOK

2.2.1 Battery Pack

2.2.2 Keyboard

2.2.3 CPU

2.2.4 HDD Module

2.2.5 DVD-ROM Drive

2.2.6 DDR-SDRAM

2.2.7 Modem Card

2.2.8 LCD Assembly

2.2.9 Inverter Board

2.2.10 LCD Panel

2.2.11 System Board

2.2.12 Touch Pad

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

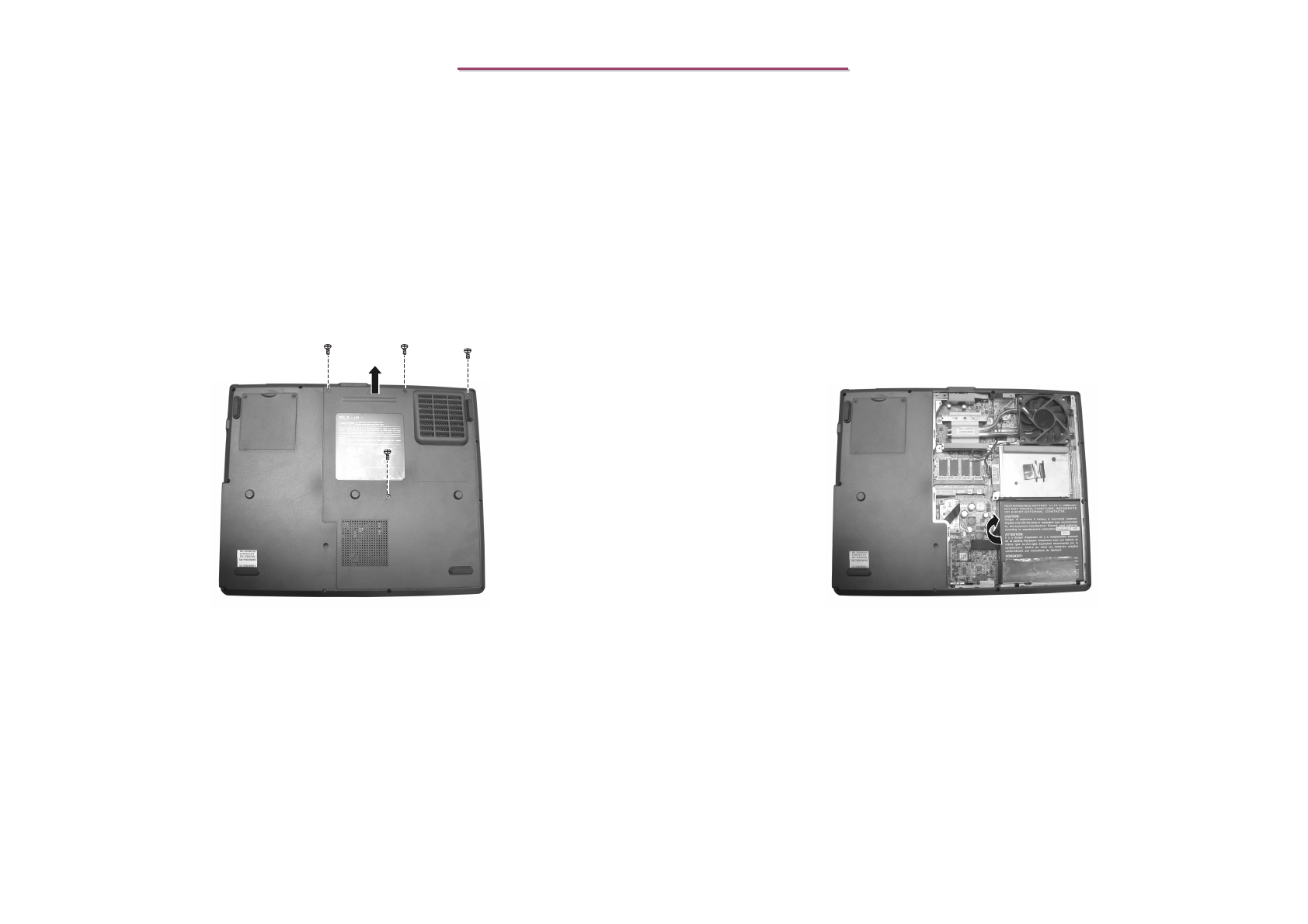

49

1. Replace the battery pack into the compartment. The battery pack should be correctly connected when you hear a

clicking sound.

2. Replace the CPU cover and secure the four screws.

2.2.1 Battery Pack

Disassembly

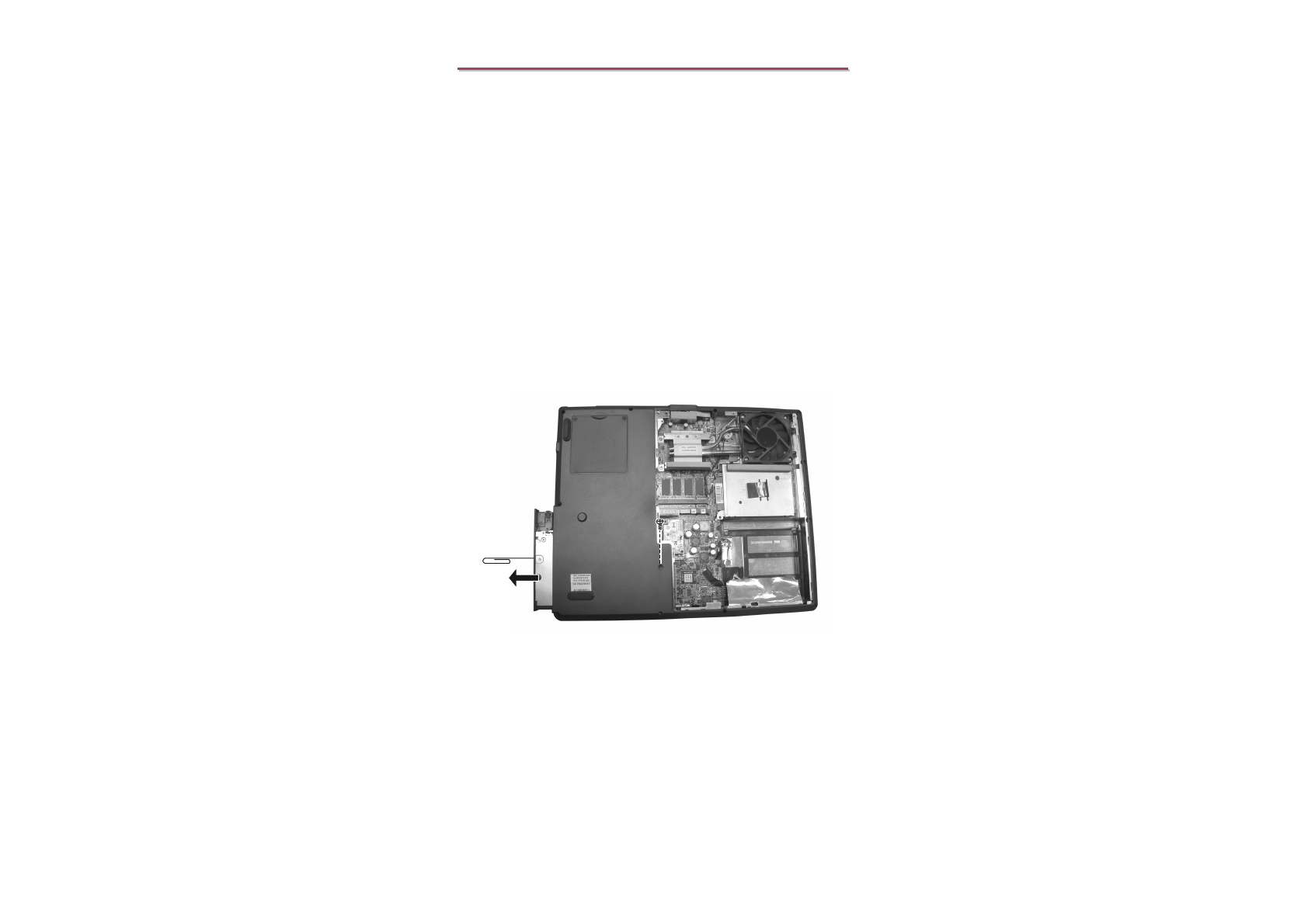

1. Carefully put the notebook upside down.

2. Remove the four screws, then remove the CPU cover. (Figure 2-1)

3. Put up the battery pack, then free the battery pack. (Figure 2-2)

Figure 2-2 Remove the battery pack

Reassembly

Figure 2-1 Remove the four screws

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

50

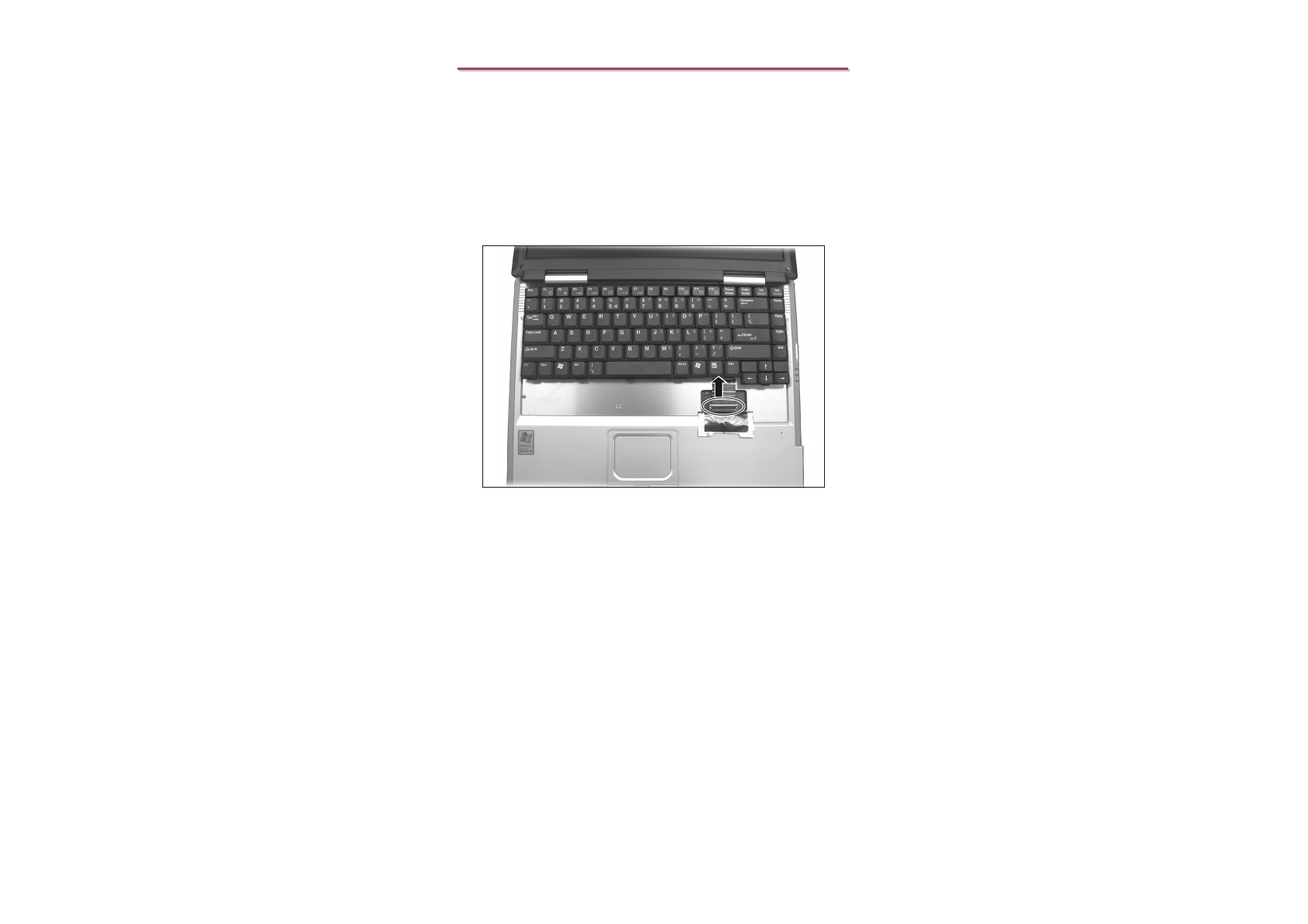

2.2.2 Keyboard

Disassembly

1. Remove the battery pack. (Refer to section 2.2.1 Disassembly)

2. Open the top cover.

3. Loosen the five latches locking the keyboard. (Figure 2-3)

Figure 2-3 Loosen the five latches

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

51

Reassembly

1. Reconnect the keyboard cable and fit the keyboard back.

2. Replace the keyboard into place and fasten the five latches.

3. Replace the battery pack. (Refer to section 2.2.1 reassembly)

4. Slightly lift up the keyboard and disconnect the cable from the mother board, then separate the keyboard.

(Figure 2-4)

Figure 2-4 Lift up the keyboard and disconnect the cable

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

52

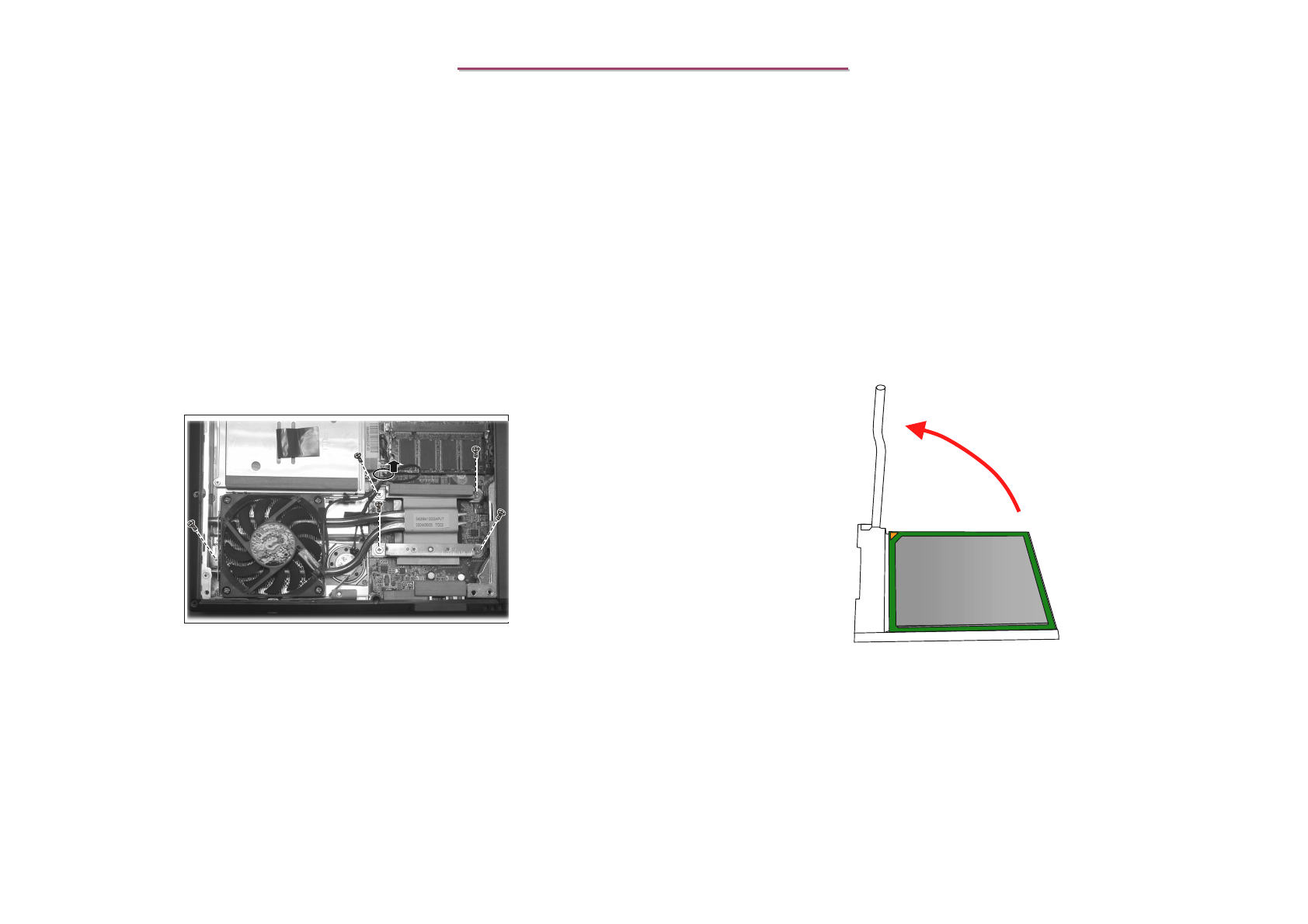

1. Remove the battery pack. (Refer to section 2.2.1 Disassembly)

2. Disconnect the fan’s power cord from system board and remove five screws that secure the heatsink upon the

CPU, Then free the heatsink. (Figure 2-5)

3. To remove the existing CPU, lift the socket arm up to the vertical position. (Figure 2-6)

2.2.3 CPU

Disassembly

Figure 2-5 Free the heatsink Figure 2-6 Disconnect the cable

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

53

CPU socket stopper

1. Carefully, align the arrowhead corner of the CPU with the beveled corner of the socket, then insert CPU pins into

the holes. Place the lever back to the horizontal position and push the lever to the left.

2. Reconnect the fan’s power cord to the system board, fit the heatsink onto the top of the CPU and secure with five

screws.

3. Replace the battery pack. (See section 2.2.1 reassembly)

Reassembly

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

54

2.2.4 HDD Module

Disassembly

1. Carefully put the notebook upside down. Remove the battery pack. (Refer to section 2.2.1 Disassembly)

2. Remove two screws fastening the HDD module and slightly lift up HDD module. (Figure 2-7)

3. Remove four screws to separate the hard disk drive from the bracket, free the hard disk driver. (Figure 2-8)

Figure 2-8 Free the HDD driverFigure 2-7 Remove HDD module

Reassembly

1. Attach the bracket to hard disk drive and secure with four screws.

2. Slide the HDD module into the compartment and secure with two screws.

3. Replace the battery pack. (Refer to section 2.2.1 reassembly)

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

55

2.2.5 CD/DVD-ROM Drive

DisassemblyDisassembly

Reassembly

1. Push the CD/DVD-ROM drive into the compartment and secure with one screw.

2. Replace the battery pack. (Refer to section 2.2.1 reassembly)

Figure 2-9 Remove the CD/DVD-

ROM drive

1. Carefully put the notebook upside down. Remove the battery pack. (Refer to section 2.2.1 Disassembly)

2. Remove one screw fastening the CD/DVD-ROM drive. (Figure 2-9)

3. Insert a small rod, such as a straightened paper clip, into CD/DVD-ROM drive’s manual eject hole () and push

firmly to release the tray. Then gently pull out the CD/DVD-ROM drive by holding the tray that pops out().

(Figure 2-9)

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

56

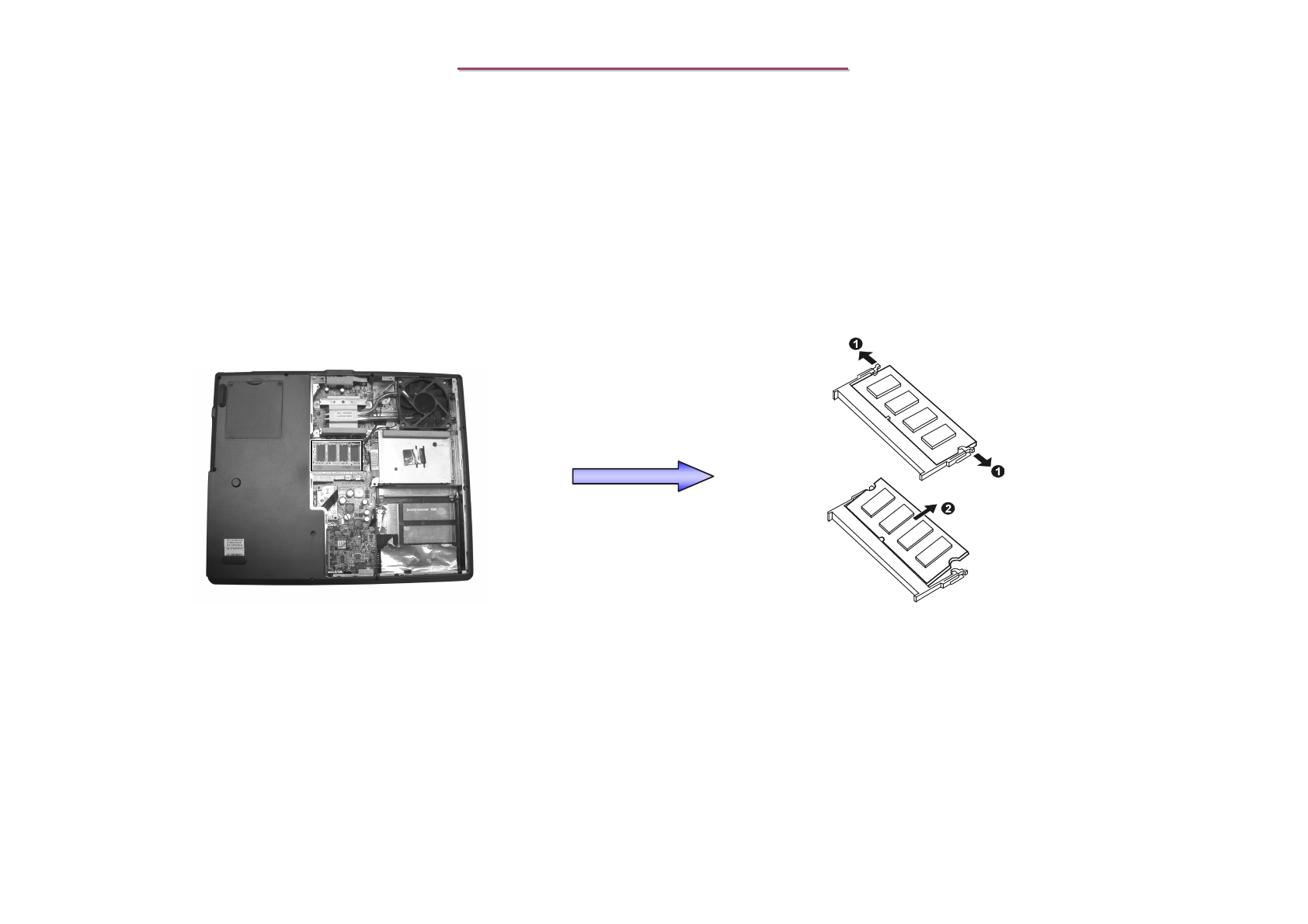

2.2.6 DDR-SDRAM

DisassemblyDisassembly

Reassembly

1. To install the DDR, match the DDR's notched part with the socket's projected part and firmly insert the DDR into

the socket at 20-degree angle. Then push down until the retaining clips lock the DDR into position.

2. Replace the battery pack. (Refer to section 2.2.1 reassembly)

Figure 2-10 Remove the DDR-SDRAM

1. Carefully put the notebook upside down. Remove the battery pack. (Refer to section 2.2.1 Disassembly)

2. Pull the retaining clips outwards () and remove the DDR-SDRAM (). (Figure 2-10)

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

57

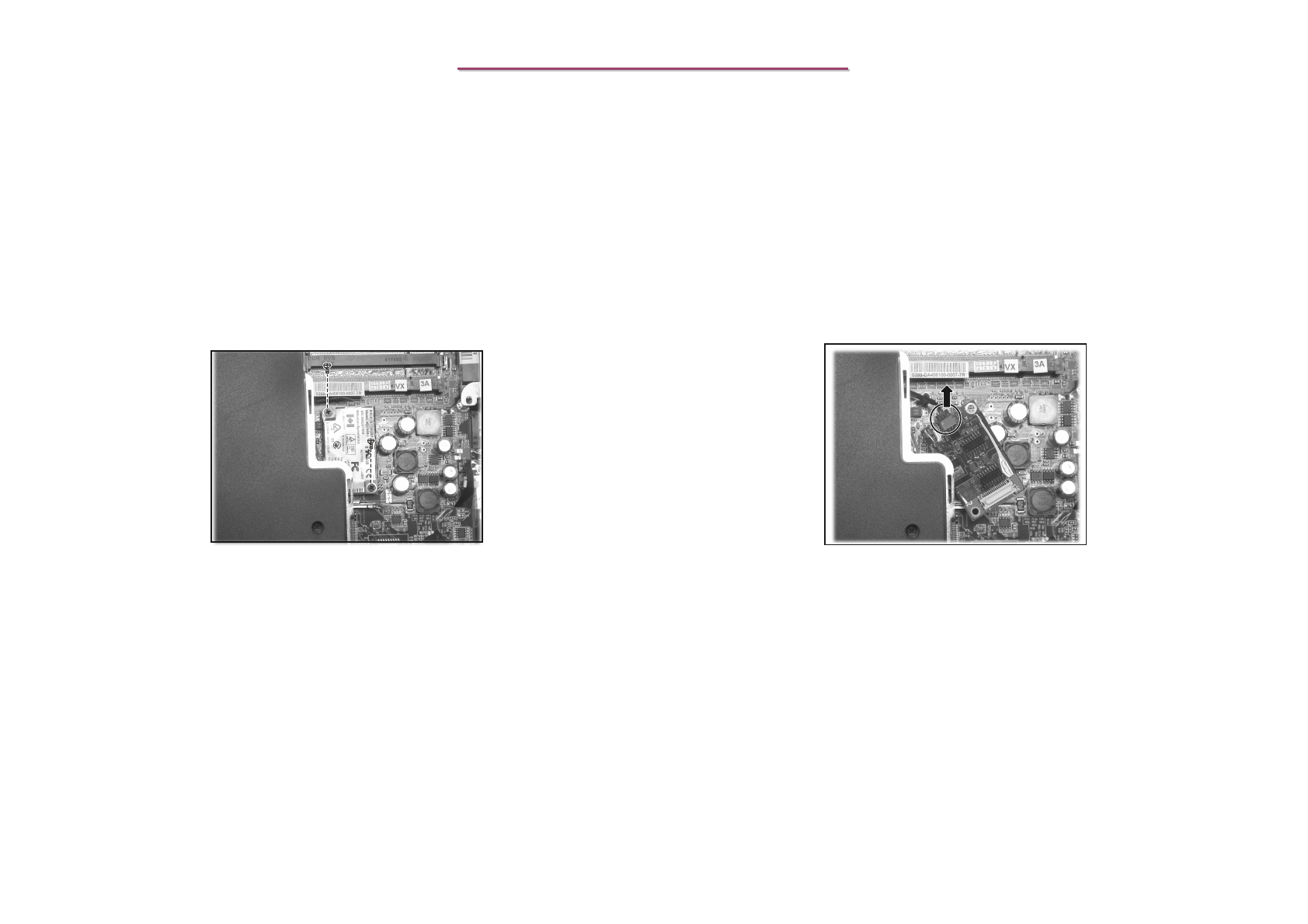

2.2.7 Modem Card

DisassemblyDisassembly

Reassembly

1. Fit the modem card, Then reconnect the cable and secure with two screws.

2. Replace the battery pack. (Refer to section 2.2.1 reassembly)

Figure 2-12 Disconnect the cable

1. Carefully put the notebook upside down. Remove the battery pack. (Refer to section 2.2.1 Disassembly)

2. Remove the two screws. (Figure 2-11)

3. Disconnect the cable from the system board, Then free the modem card. (Figure 2-12)

Figure 2-11 Remove the two screws

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

58

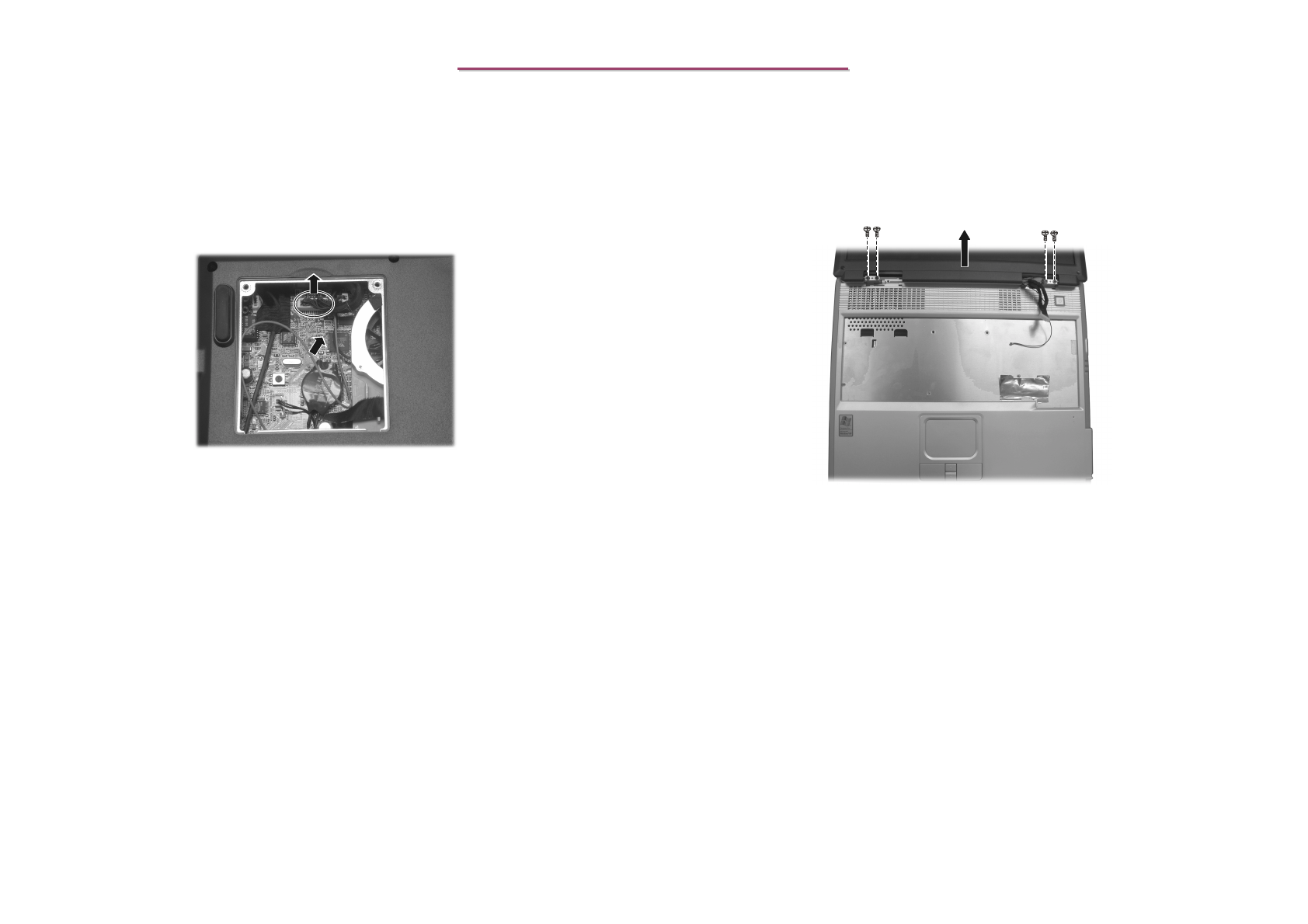

2.2.8 LCD ASSY

Disassembly

Figure 2-14 Remove the two screws

1. Remove the battery pack and keyboard. (See sections 2.2.1 and 2.2.2 Disassembly)

2. Remove two hinge covers. (Figure 2-13)

3. Carefully put the notebook upside down. Remove the two screws fastening the wireless cover. (Figure 2-14)

Figure 2-13 Remove two hinge covers

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

59

4. Disconnect the LCD cable from the system board and detach the antenna. (Figure 2-15)

5. Remove the four screws and put up the LCD assembly, then free the LCD assembly. (Figure 2-16)

Figure 2-16 Free the LCD assembly

1. Attach the LCD assembly to the base unit and secure with four screws, then fit the antenna.

2. Reconnect the one cable to the system board, Then replace the wireless cover and secure two screws.

3. Replace the two hinge covers.

4. Replace the keyboard and battery pack. (Refer to sections 2.2.2 and 2.2.1 Reassembly)

Reassembly

Figure 2-15 Disconnect the LCD cable

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

60

2.2.9 Inverter Board

Disassembly

1. Remove the battery, keyboard and LCD assembly. (Refer to section 2.2.1, 2.2.2 and 2.2.8 Disassembly)

2. Remove two screws and rubbers on the corners of the LCD panel. (Figure 2-17)

3. Insert a flat screwdriver to the lower part of the LCD cover and gently pry the frame out. Repeat the process until

the cover is completely separated from the housing.

4. Remove the one screw fastening the inverter board. (Figure 2-18)

Figure 2-18 Remove the one screwFigure 2-17 Remove LCD cover

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

61

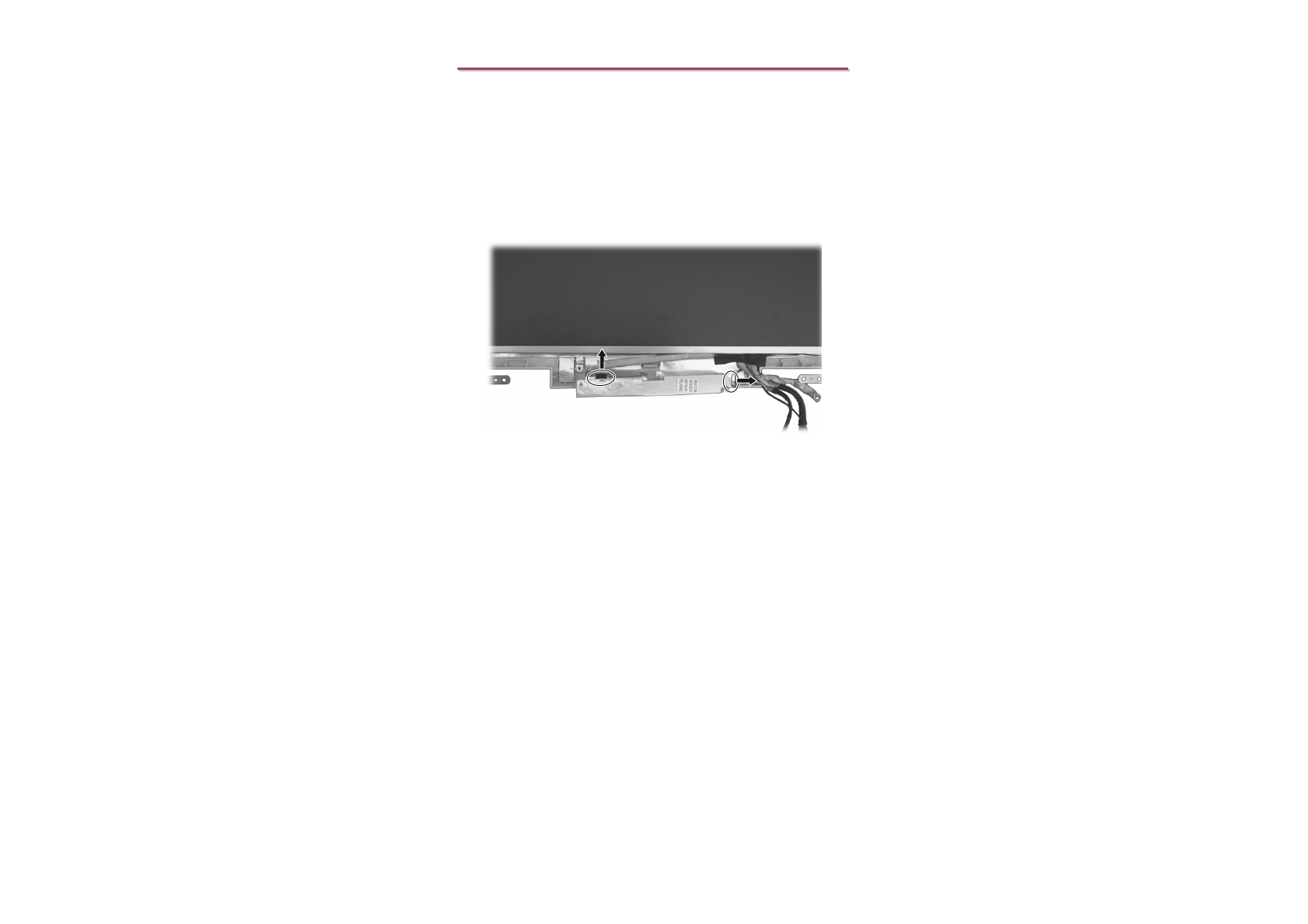

5. To remove the inverter board on the lower part of the LCD housing , disconnect two cables. (Figure 2-19)

Reassembly

1. Reconnect the two cables. Fit the inverter board back into place and secure with one screw.

2. Replace the LCD cover and secure with two screws and rubbers.

3. Replace the LCD assembly. (Refer to section 2.2.8 Reassembly)

4. Replace the keyboard and battery pack. (Refer to sections 2.2.2 and 2.2.1 Reassembly)

Figure 2-19 Remove the inverter board

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

62

2.2.10 LCD Panel

Disassembly

1. Remove the battery, keyboard and LCD assembly. (Refer to sections 2.2.1, 2.2.2 and 2.2.8 Disassembly)

2. Remove the LCD cover. (Refer for two steps 2,3 of section 2.2.9 Disassembly)

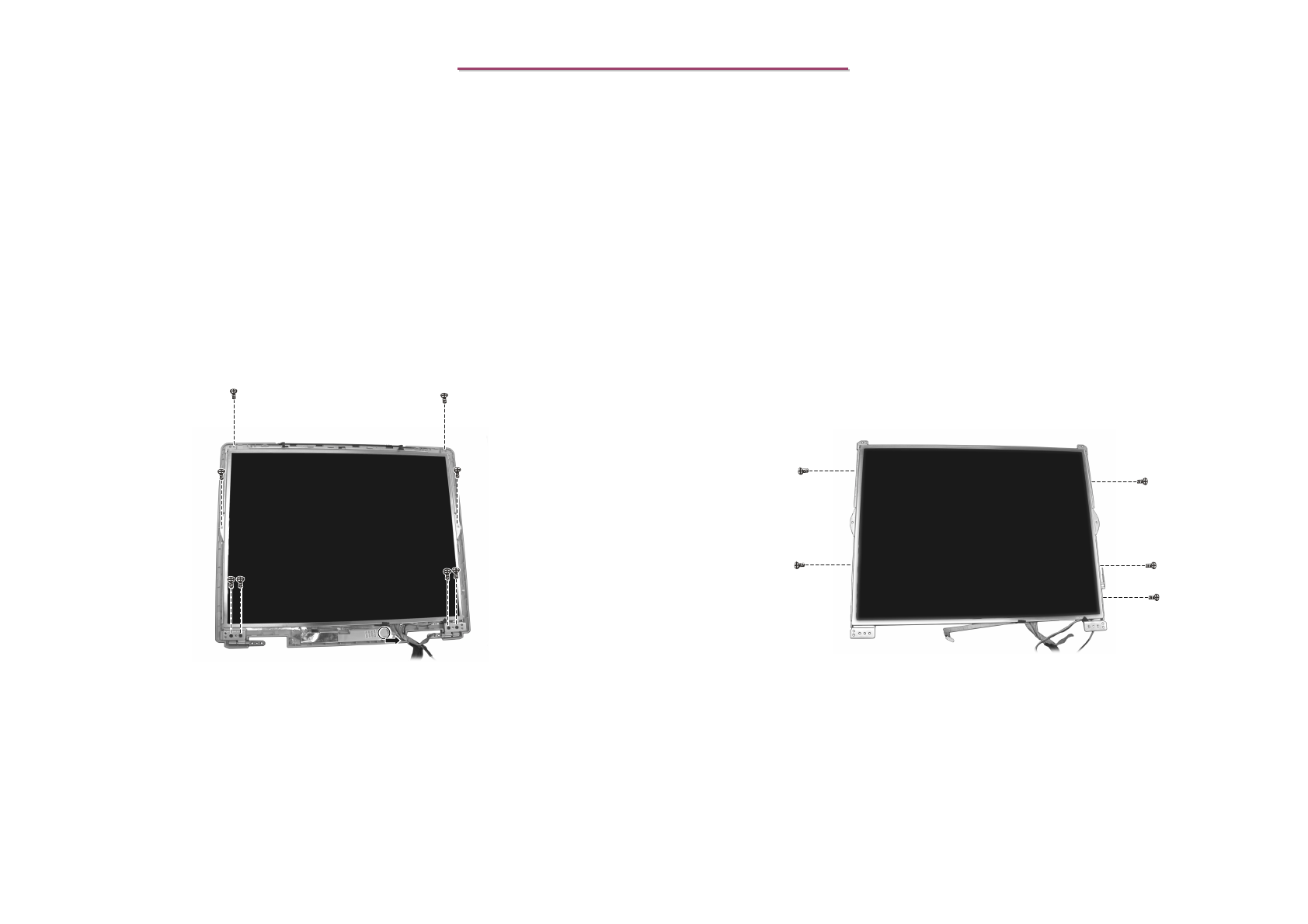

3. Remove the eight screws fastening the LCD panel and detach the cable, Then lift it up. (Figure 2-20)

4. Remove the five screws fastening the LCD brackets. (Figure 2-21)

Figure 2-20 Remove the eight screws

and detach the cable

Figure 2-21 Remove the five screws

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

63

5. Disconnect the cable and free the LCD panel. (Figure 2-22)

Reassembly

1. Reconnect the cable, then replace the LCD brackets and secure with five screws.

2. Fit the LCD panel back into place and secure with eight screws, then reconnect the cable to the inverter board.

3. Replace the LCD cover and secure with two screws and rubbers. (Refer to section 2.2.9 Reassembly)

4. Replace the LCD assembly. (Refer to section 2.2.8 Reassembly)

5. Replace the keyboard and battery pack. (Refer to sections 2.2.2 and 2.2.1 Reassembly)

Figure 2-22 Free the LCD panel

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

64

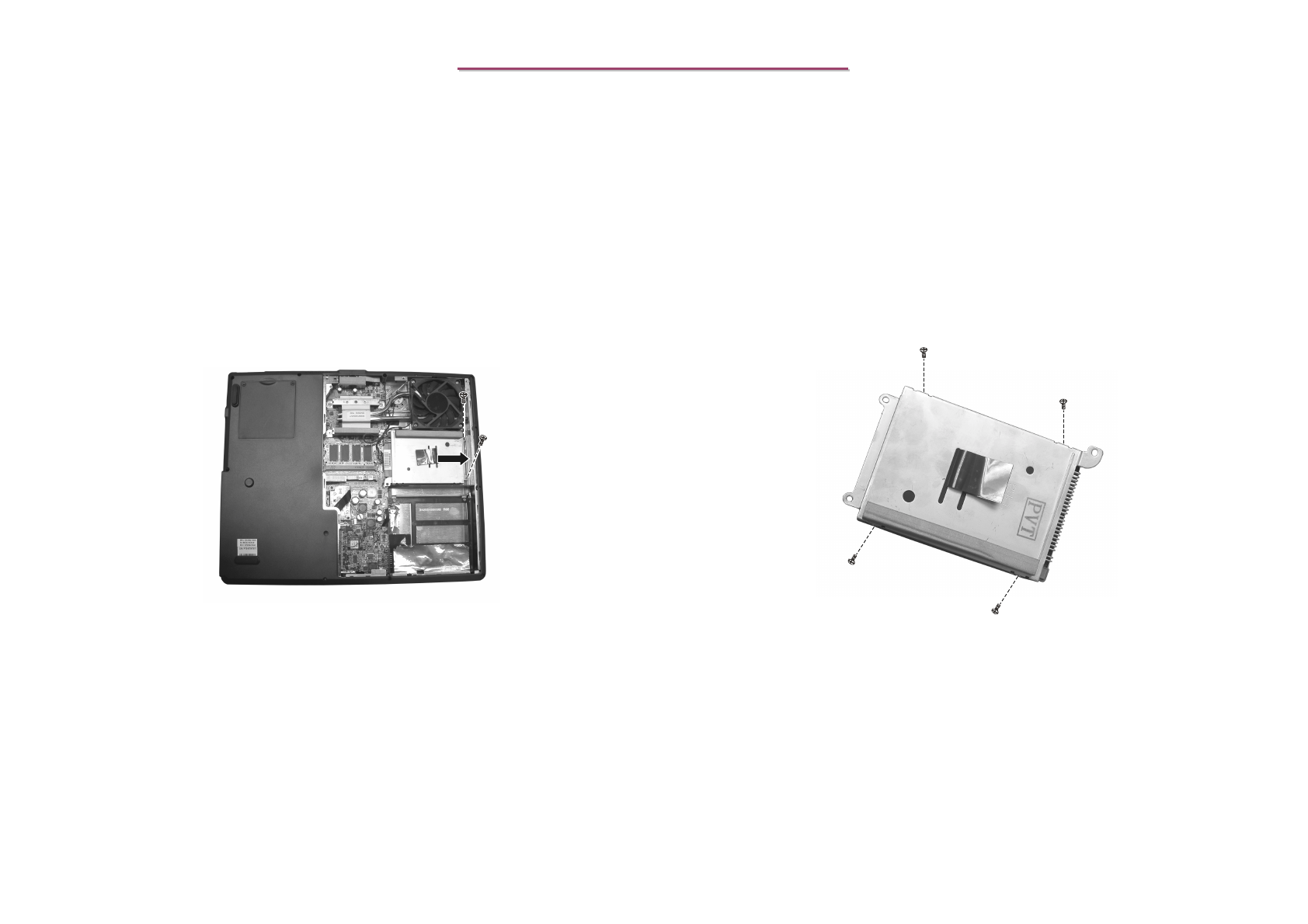

2.2.11 System Board

Disassembly

1. Remove the battery, keyboard, CPU, hard disk drive, CD/DVD-ROM drive, DDR-SDRAM, modem card and

LCD assembly. (Refer to sections 2.2.1, 2.2.2, 2.2.3, 2.2.4, 2.2.5, 2.2.6, 2.2.7 and 2.2.8 Disassembly)

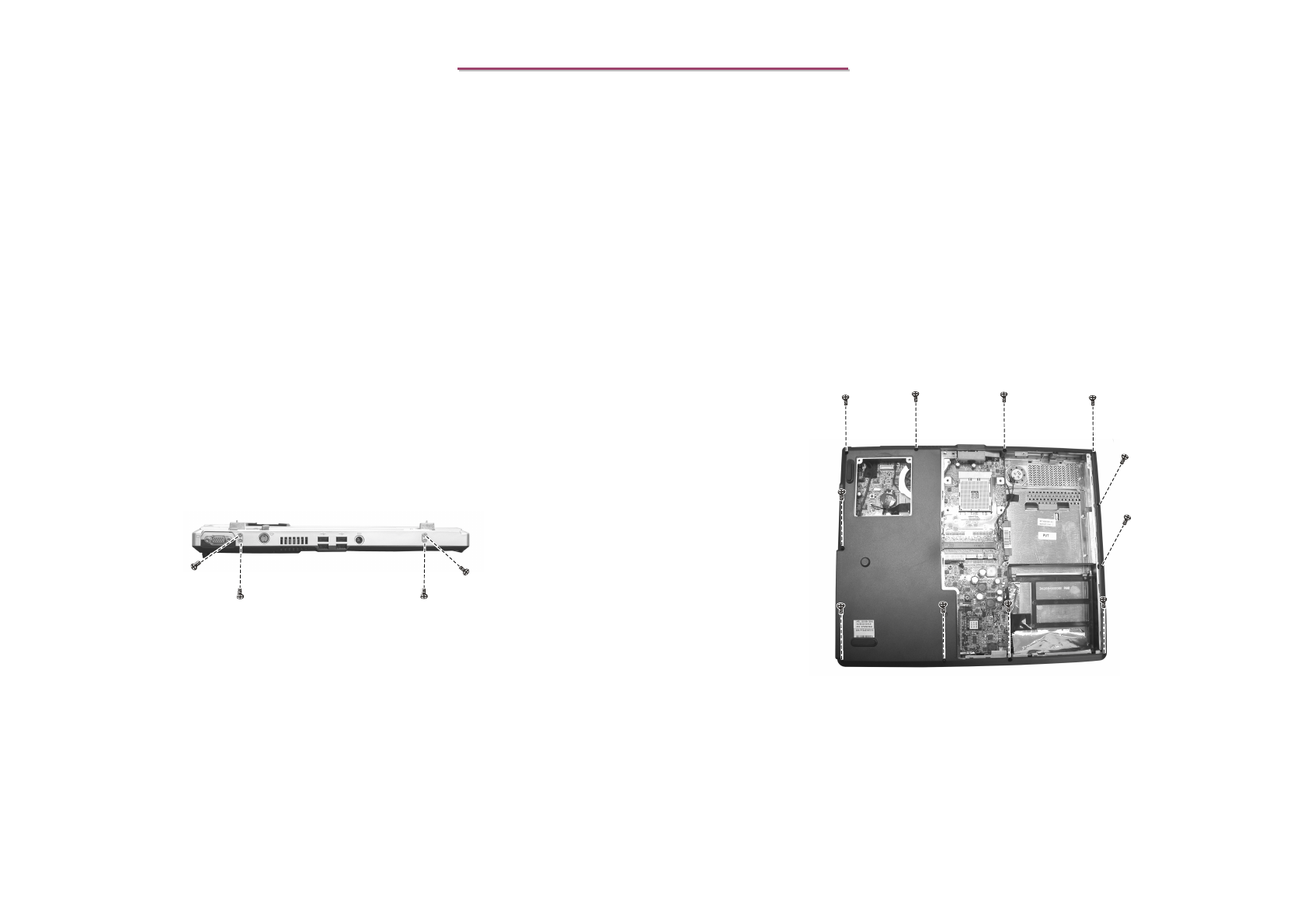

2. Remove the four screws. (Figure 2-23)

3. Remove the eleven screws and free the housing. (Figure 2-24)

Figure 2-24 Remove the eleven screwsFigure 2-23 Remove the four screws

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

65

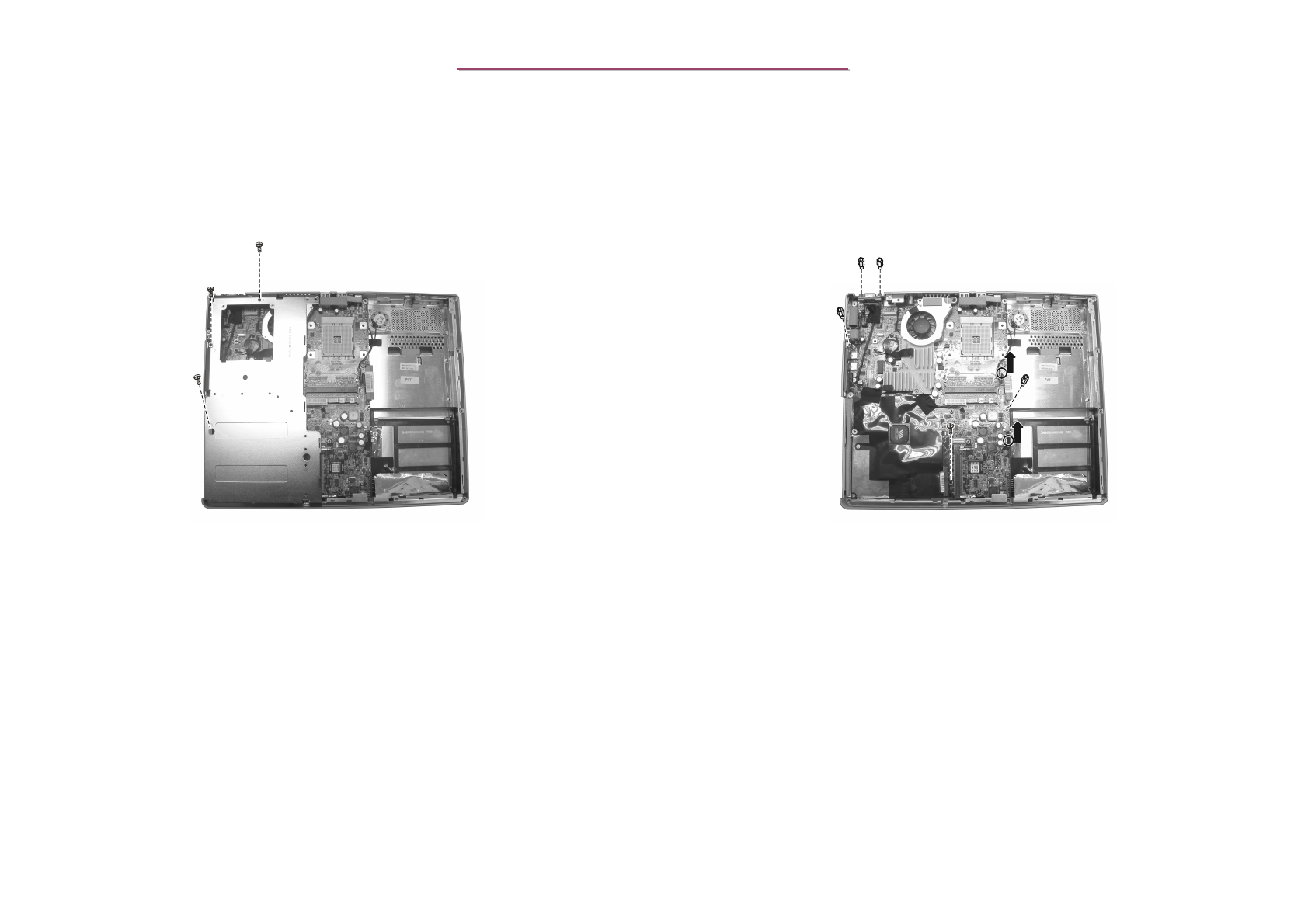

4. Remove the three screws and lift up the housing’s shielding. (Figure 2-25)

5. Disconnect the speaker’s cable and the touch pad’s cable, Then remove the one screw and four hex nuts. Now

you can lift up the system board. (Figure 2-26)

Figure 2-25 Remove the three screws Figure 2-26 Free the system board

Reassembly

1. Replace the system board into the top cover and secure with one screw and four hex nuts.

2. Reconnect the touch pad’s cable, the speaker’s cable.

3. Replace the housing’s shielding and secure with three screws.

4. Replace the housing and secure with fifteen screws.

5. Replace the LCD assembly, modem card, DDR-SDRAM, CD/DVD-ROM, HDD, CPU, keyboard and battery

pack. (See sections 2.2.8, 2.2.6, 2.2.5, 2.2.4, 2.2.3, 2.2.2 and 2.2.1 Reassembly)

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

66

2.2.12 Touch Pad

Disassembly

1. Remove the system board. (See section 2.2.11 Disassembly)

2. Remove the two screws and disconnect the cable, then free the touch pad. (Figure 2-27)

Reassembly

1. Replace the touch pad and reconnect the cable.

2. Replace the touch pad shielding and secure with two screws.

3. Reassemble the notebook. (See the previous sections Reassembly)

Figure 2-27 Free the touch pad

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

67

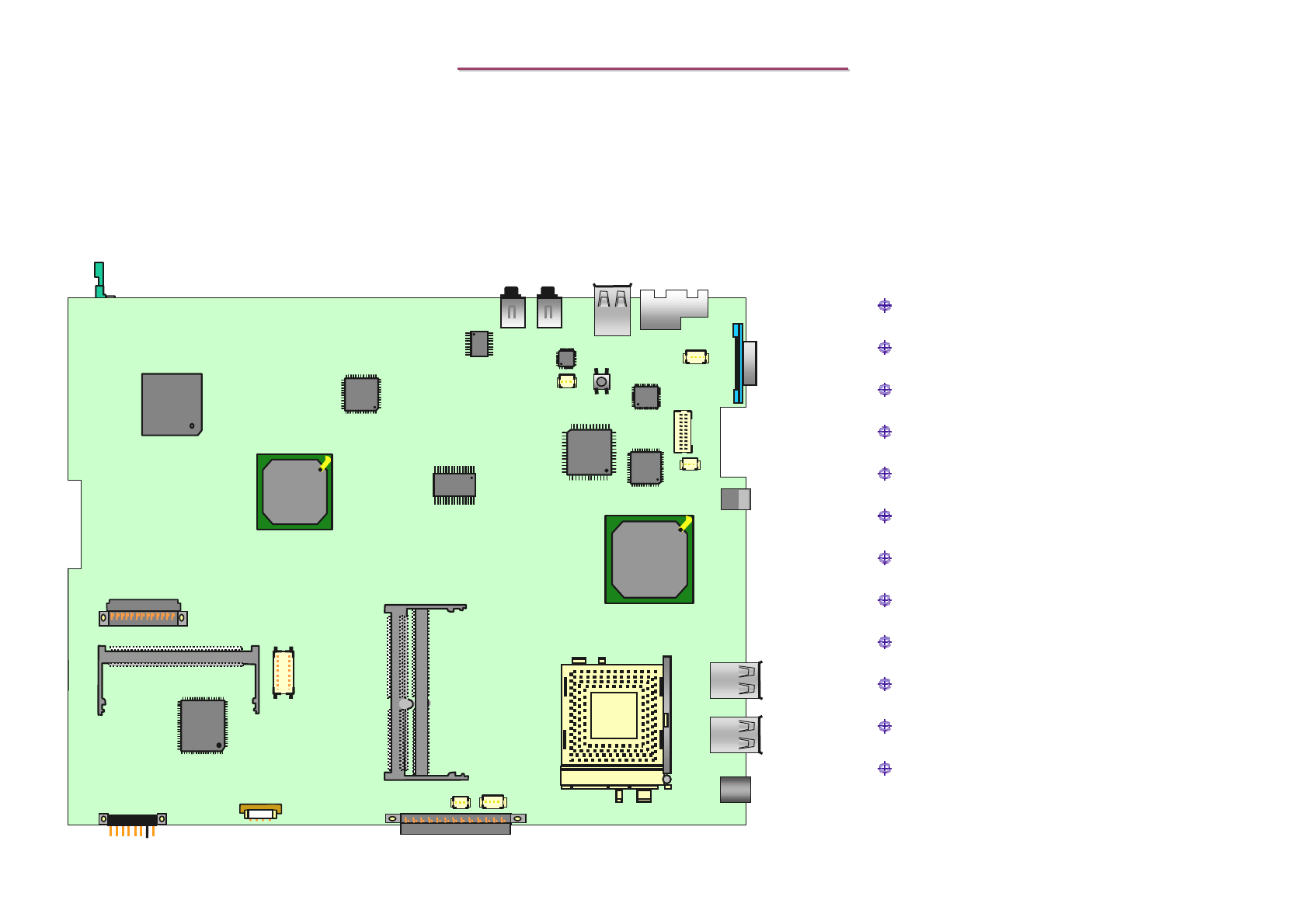

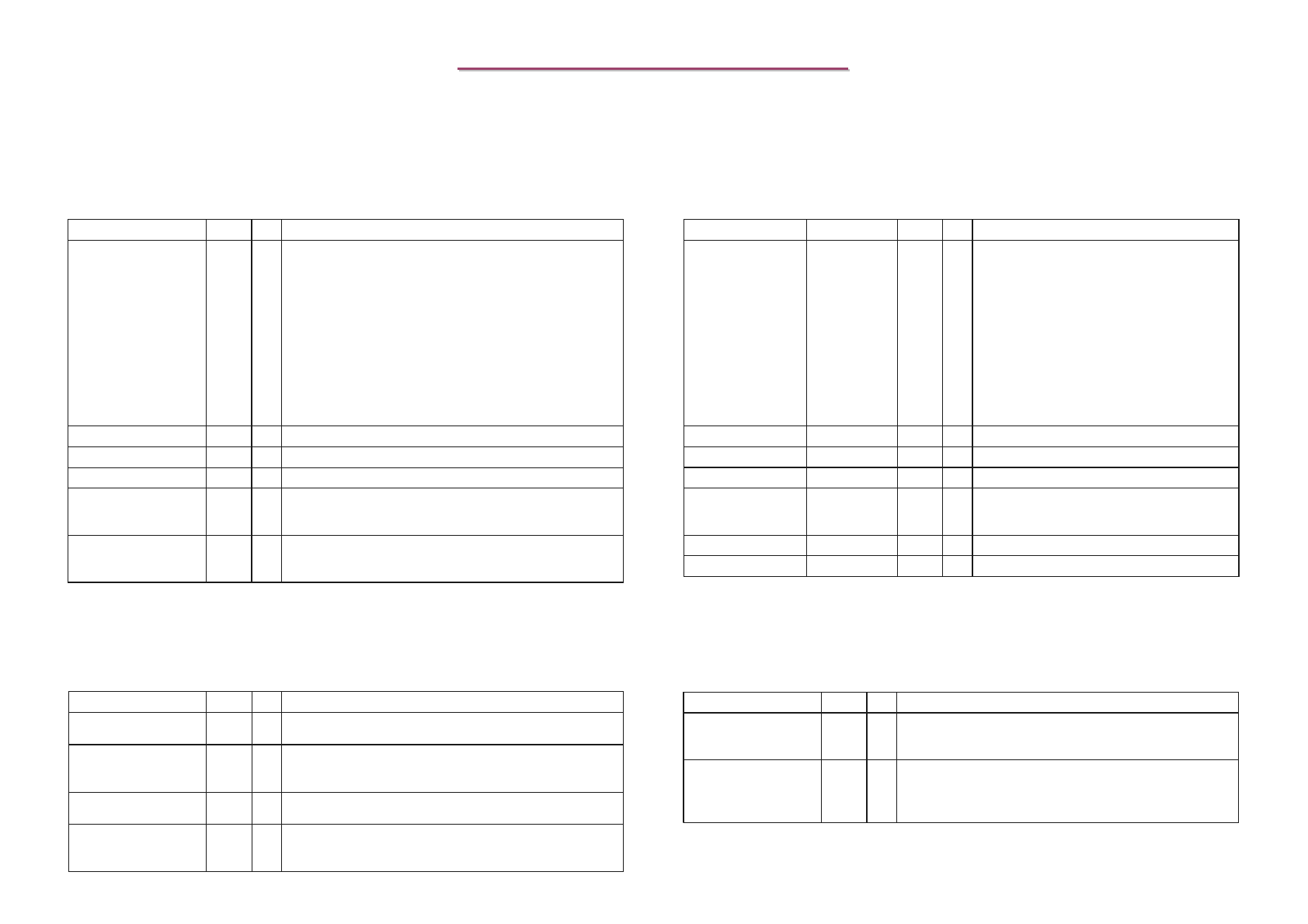

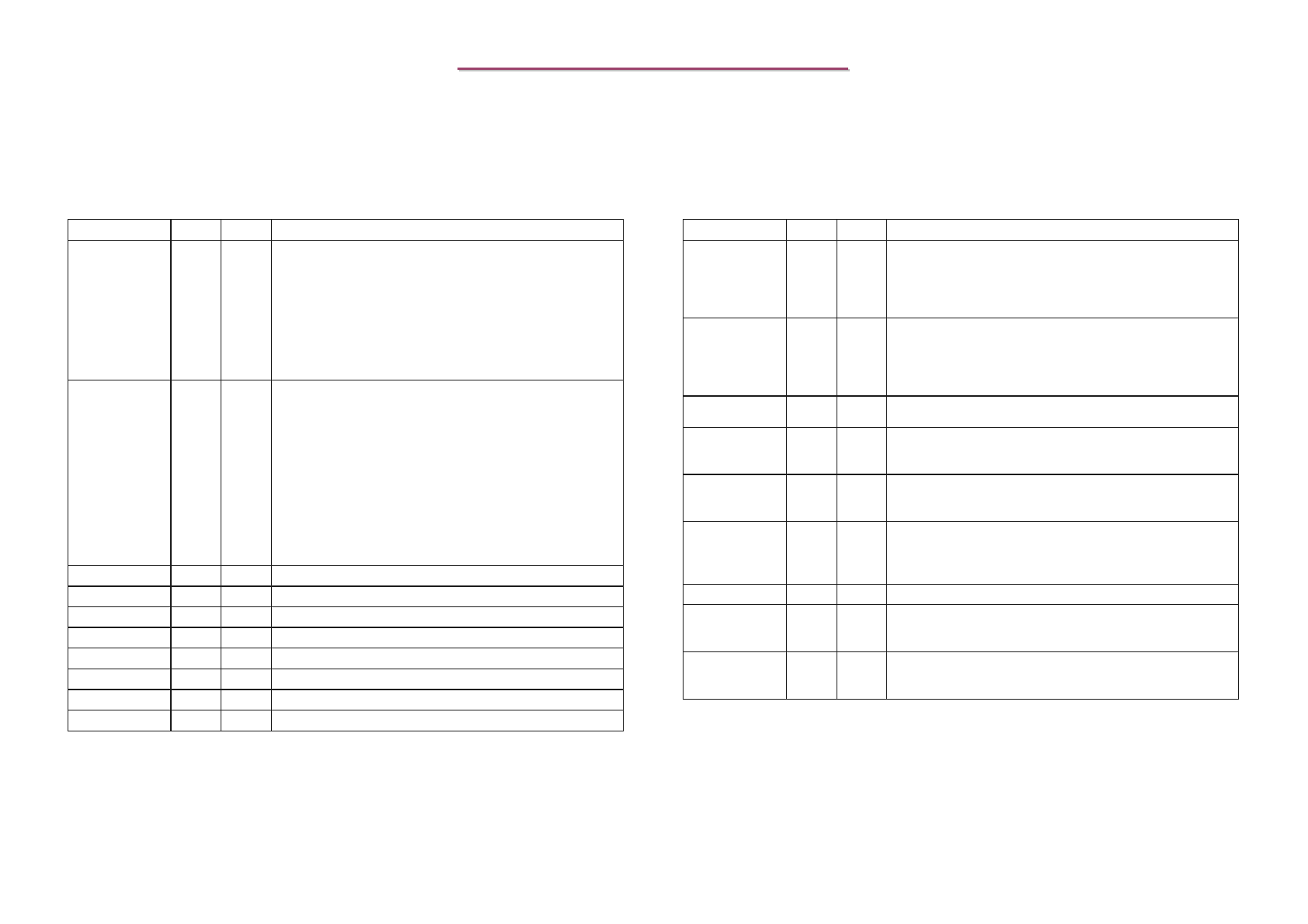

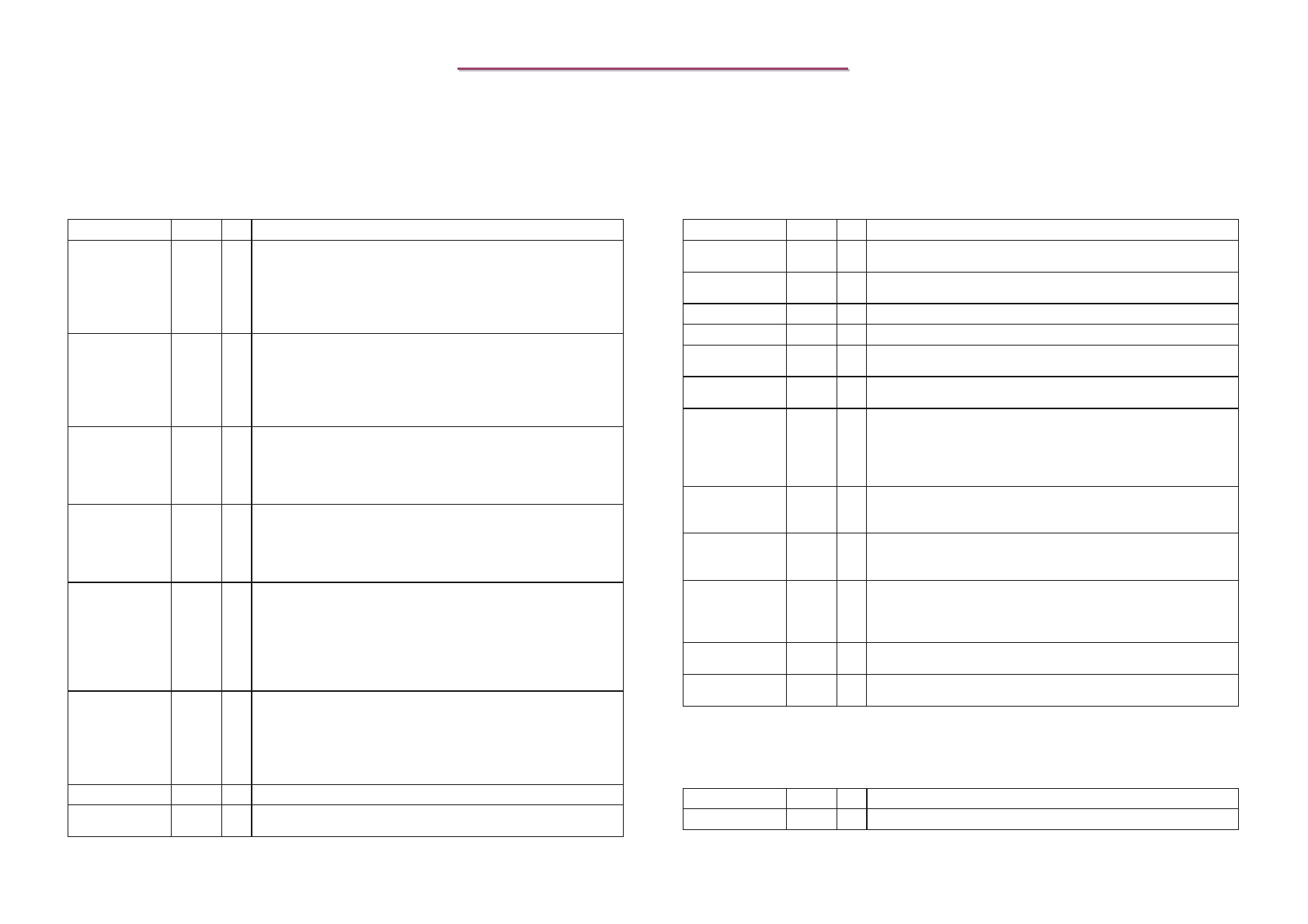

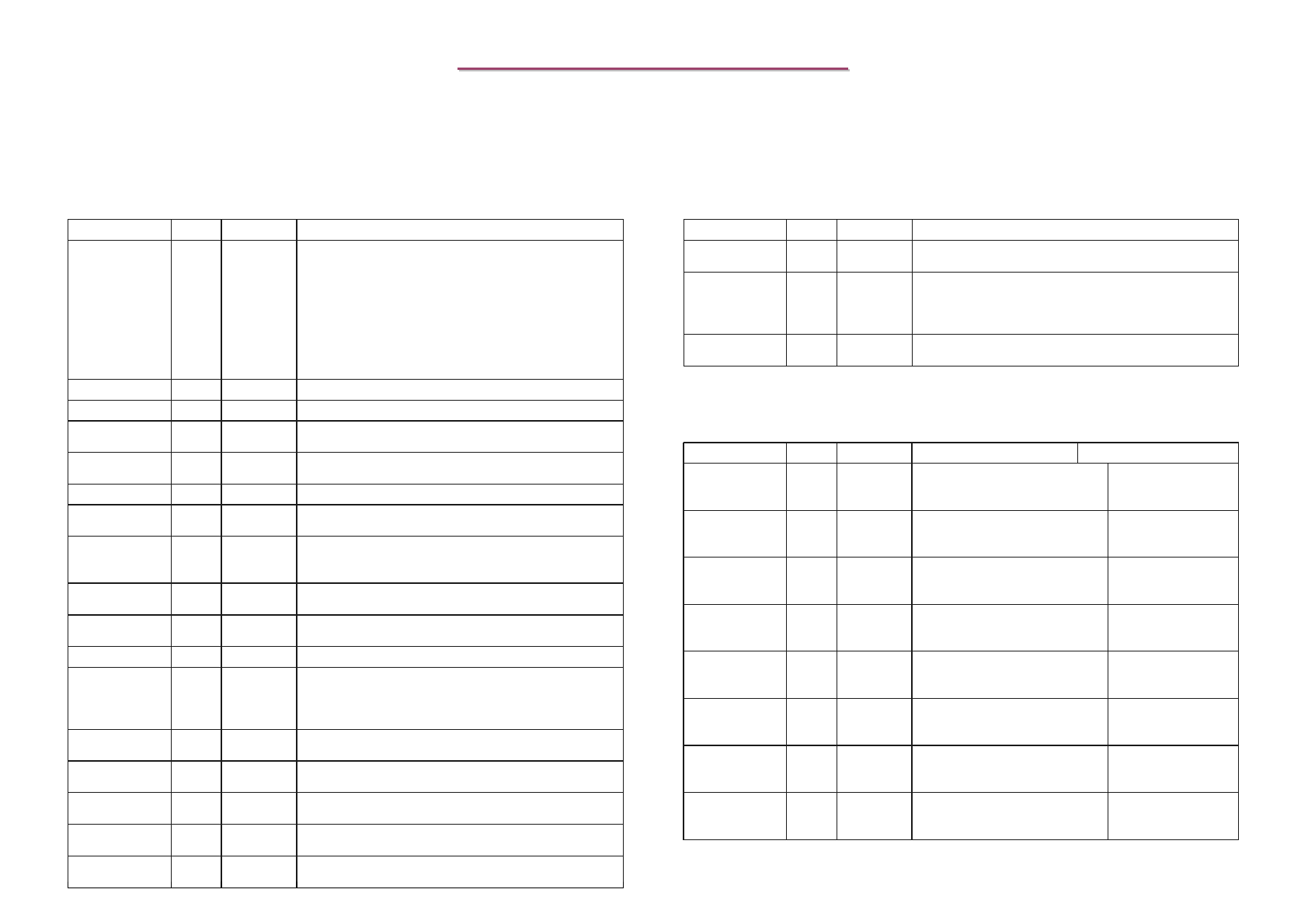

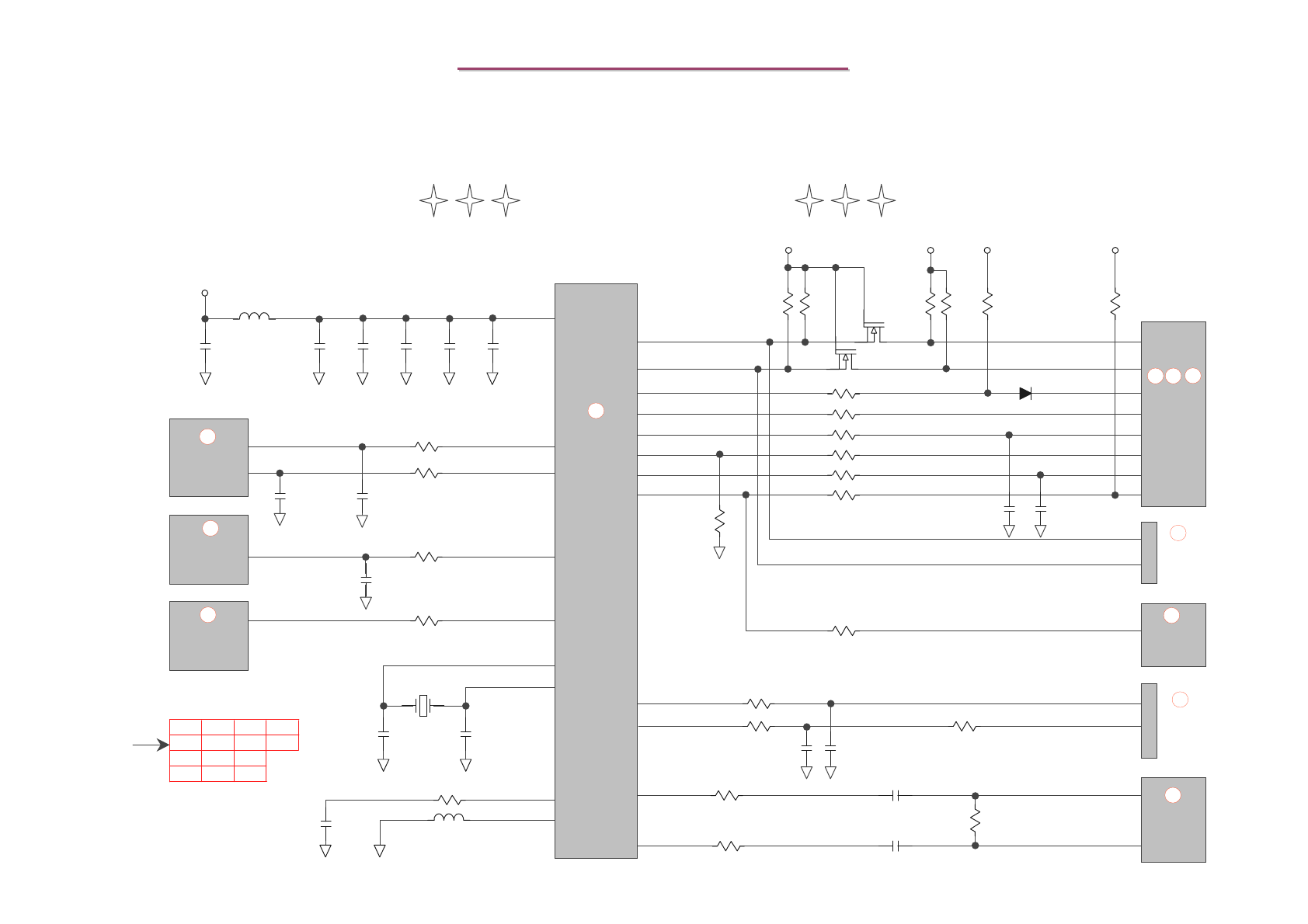

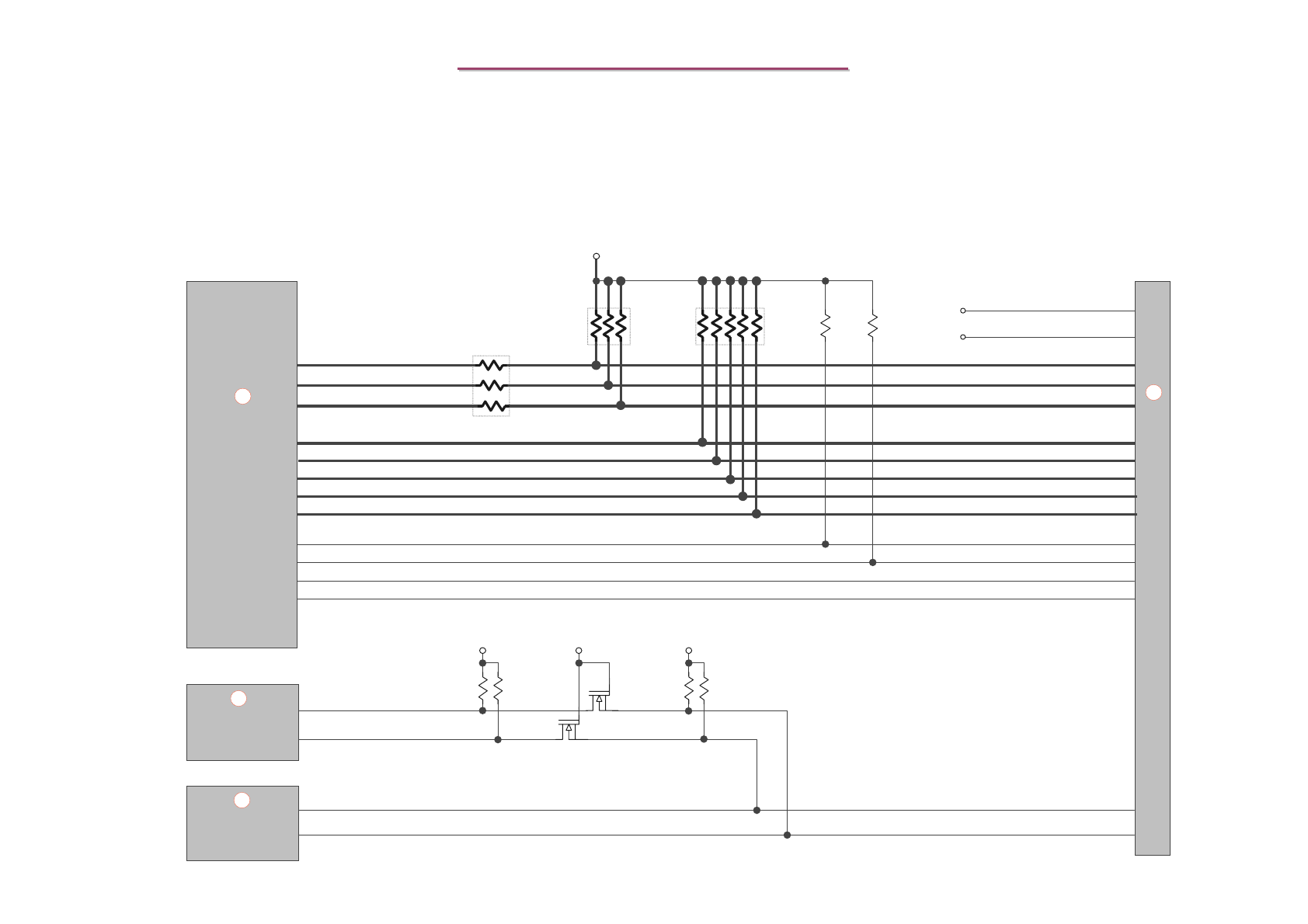

3.1 Mother Board – A(1)

PJ1 : AC Power Jack

PJ2 : Battery Connector

J1 : S-Video Port

J2 : External VGA Connector

J3, J4, J9 : USB Port Connector

J5 : RJ11 & RJ45 Connector

J6 : North Bridge Fan Connector

J7 : MDC Jump Wire Connector

J8 : LCD Connector

J10 : Microphone Jack

J11 : CPU Fan Connector

J12 : Line Out Jack

------ To next page ------

J509

PJ2

J9 J5

J7

J8

J1

J3

J4

PJ1

J2

J11

J6

J10 J12

3. Definition & Location of Connectors / Switches

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

68

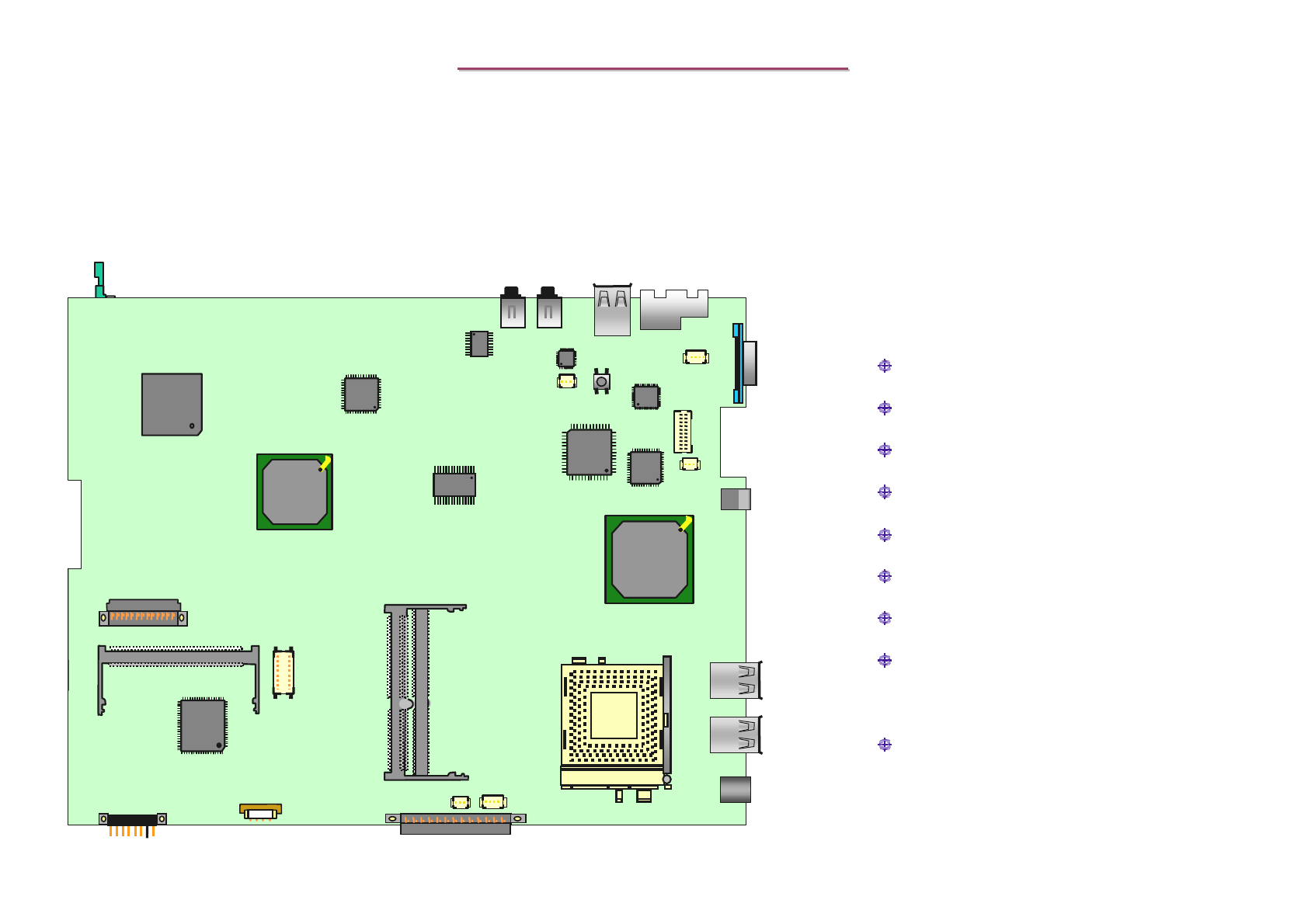

3.1 Mother Board – A(2)

------ Continue to previous page ------

J13 : Internal Speaker Connector

J14 : Primary EIDE Connector

J15 : MDC Board Connector

J16,J17 : Extend DDR SDRAM Socket

J18 : Touch-Pad Connector

J20 : RTC Battery Connector

J21 : Secondary IDE Connector

J22 : Mini-PCI Socket

SW1 : H8 Reset Button

J509

J13

J16

J21

J22

J18

J20 SW1

J15

J17

J14

3. Definition & Location of Connectors / Switches

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

69

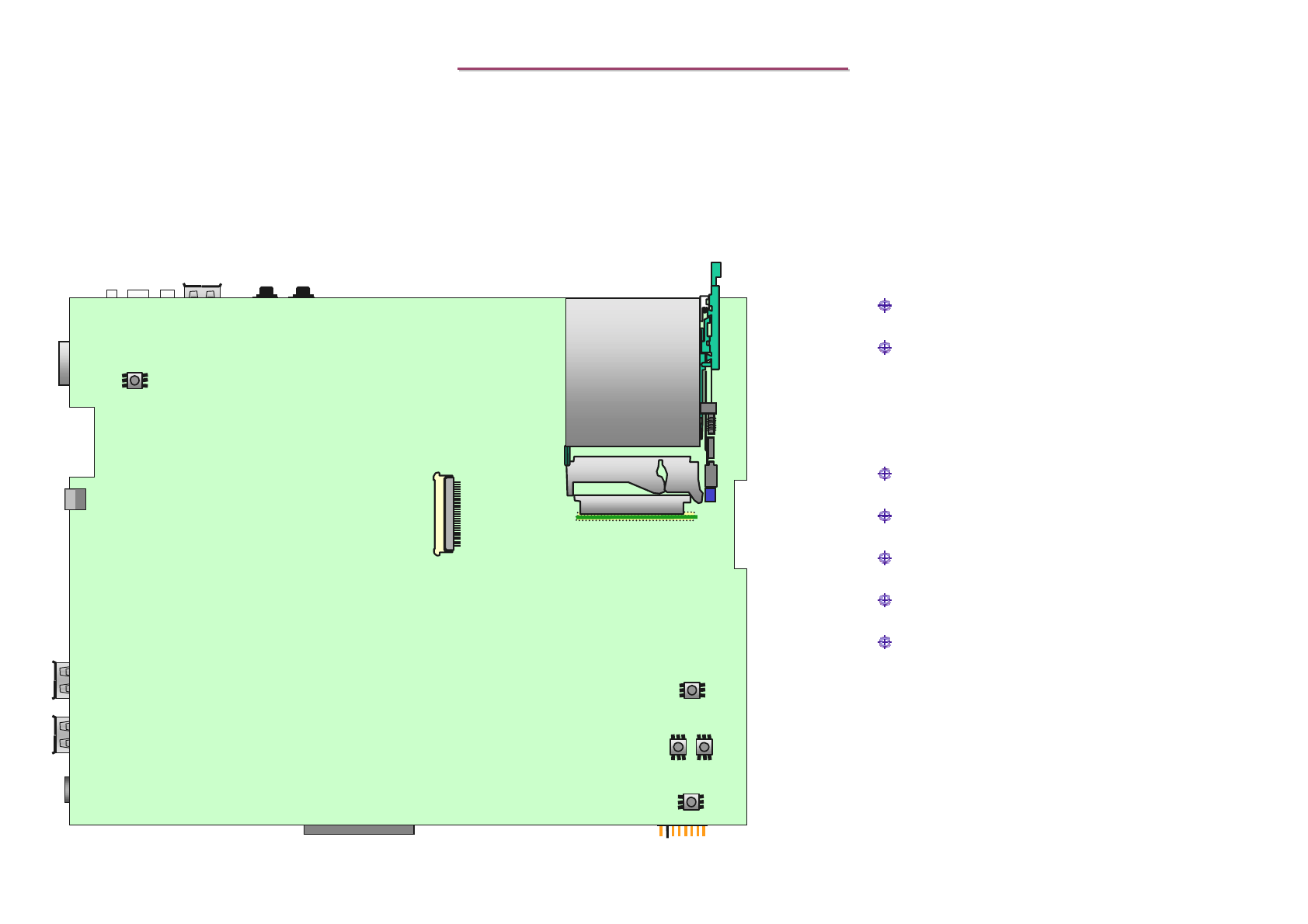

3.2 Mother Board - B

J501 : Internal Keyboard Connector

J502 : PCMCIA Card Socket

SW501 : Power Button

SW502 : Touch-Pad Up Button

SW503 : Touch-Pad Right Button

SW504 : Touch-Pad Left Button

SW505 : Touch-Pad Down Button

J509

J501

SW501

SW503

SW502

SW505

J502

SW504

3. Definition & Location of Connectors / Switches

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

70

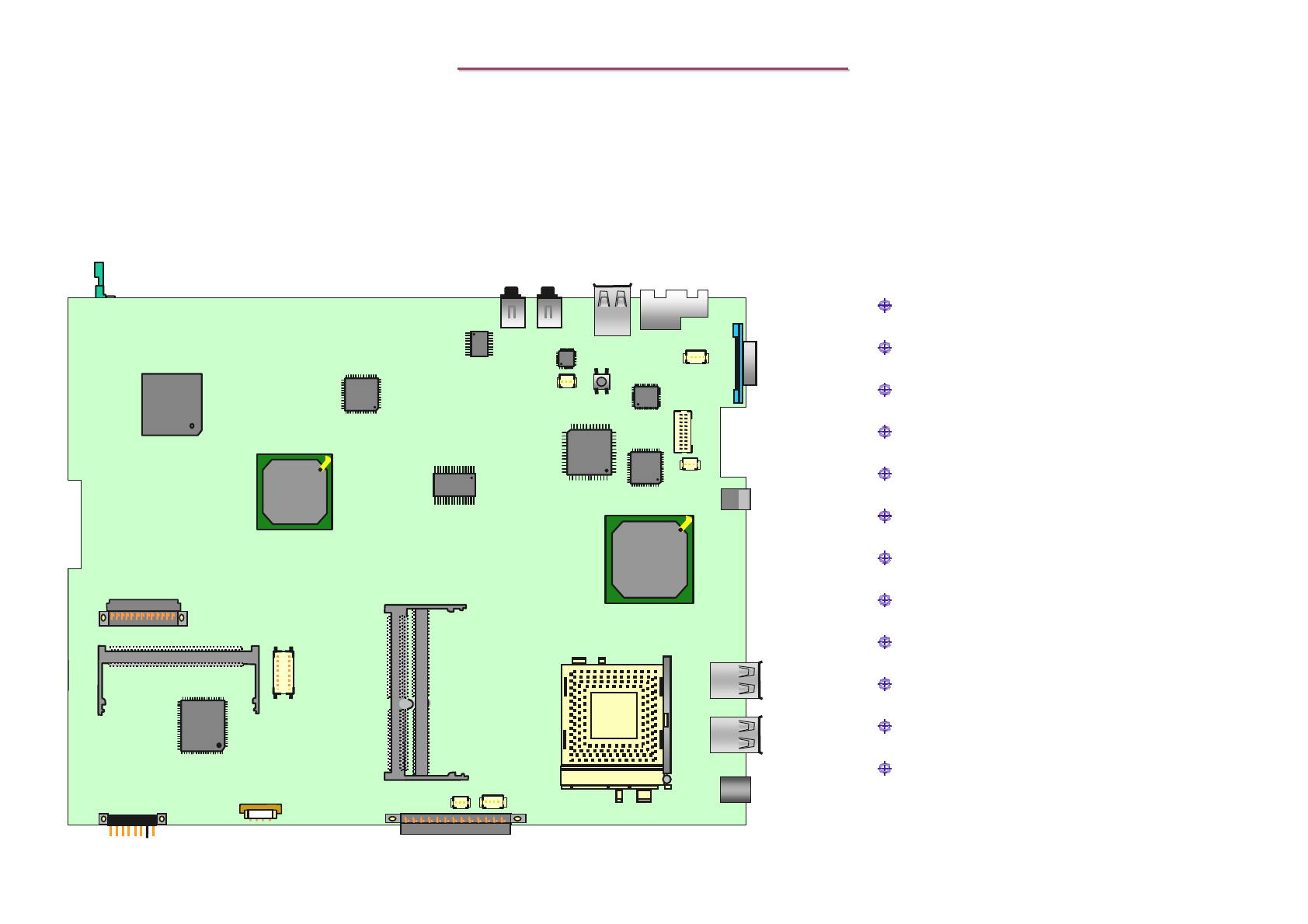

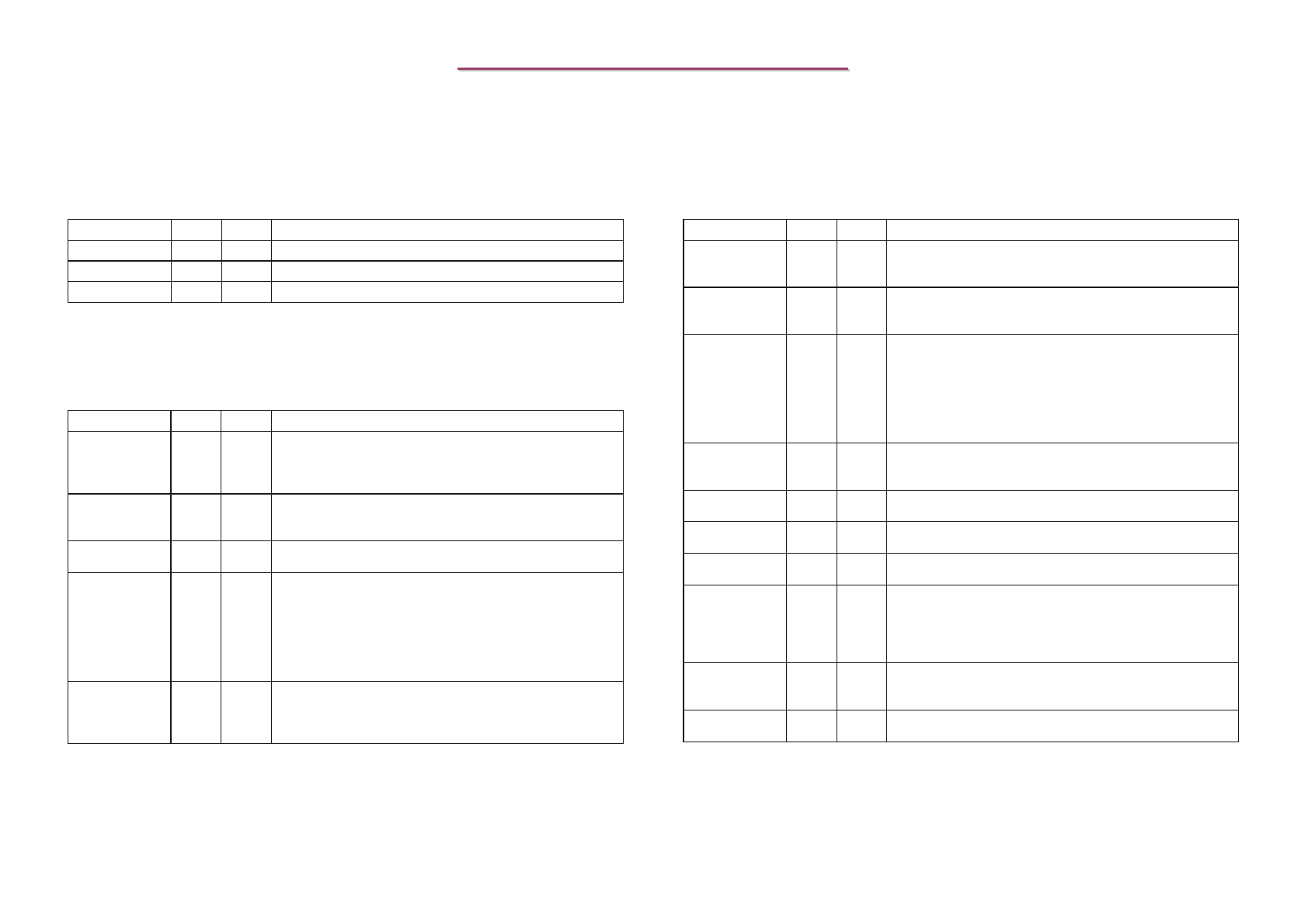

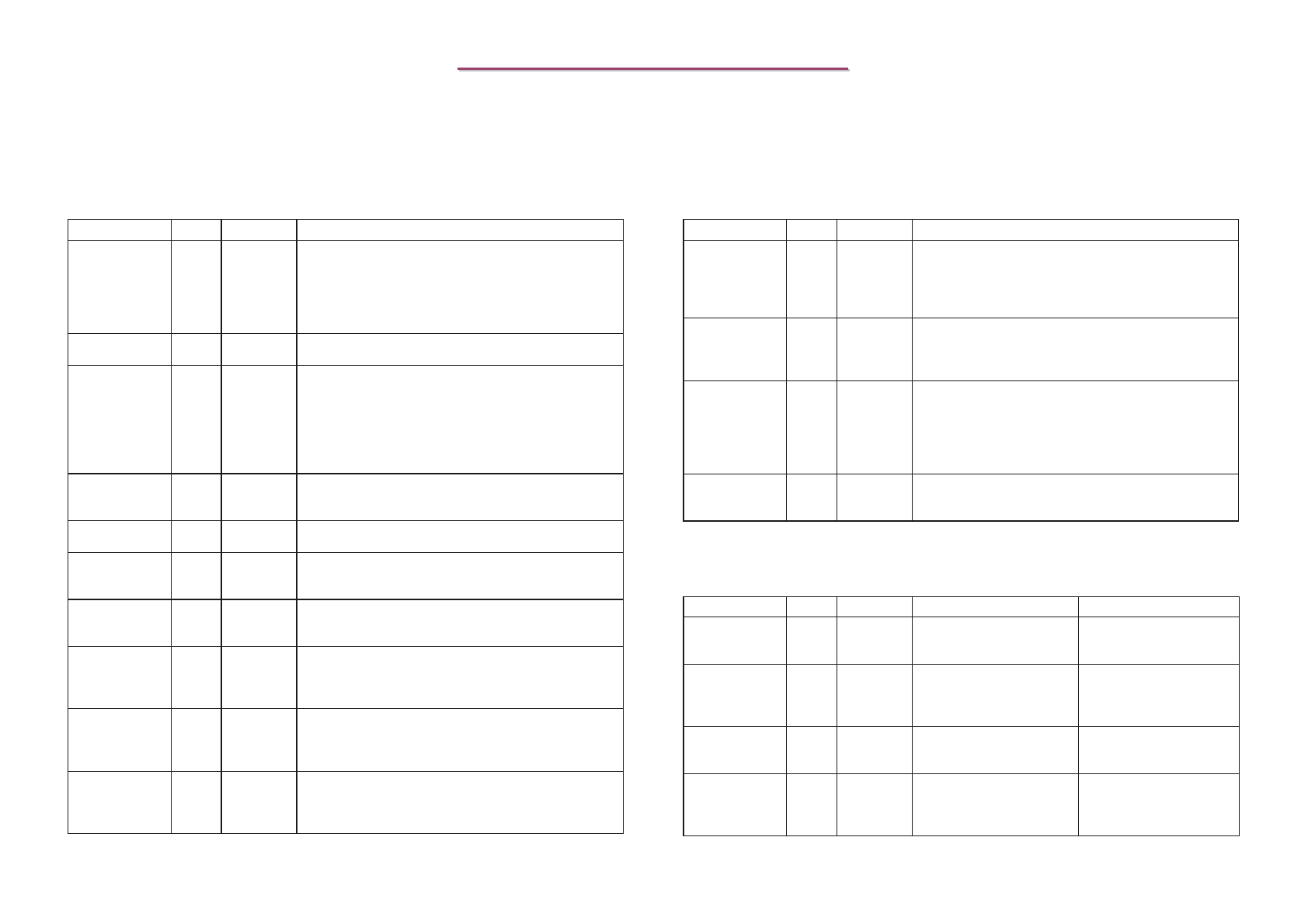

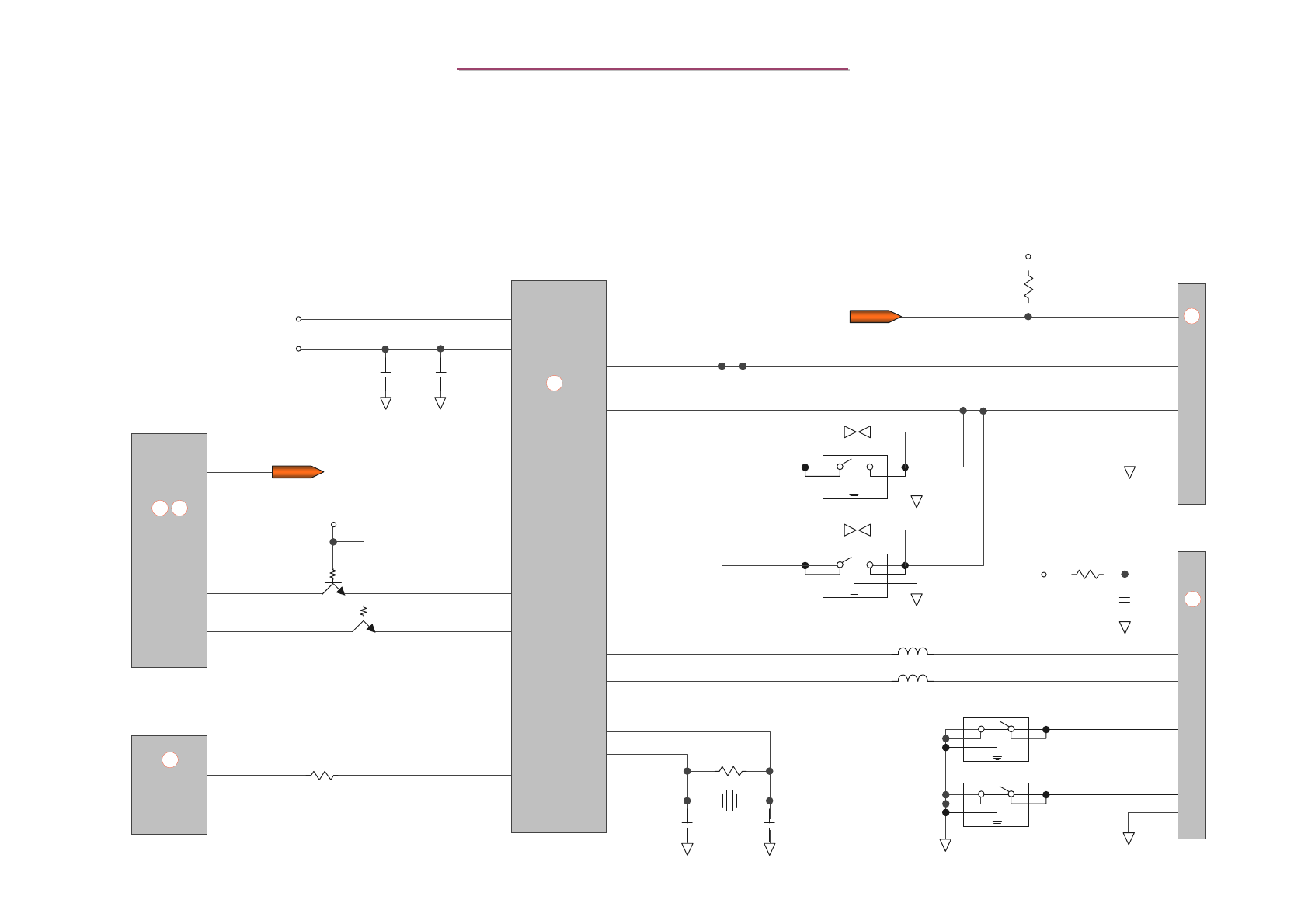

4.1 Mother Board - A

U2 : VT6103L LAN Controller

U3 : TV Encoder(VIA_VT1622)

U6 : AMD CPU Socket

U9 : LVDS Encoder(VIA_VT1634)

U10 : VT1617A Audio Codec

U12 : VIA_K8N800 North Bridge

U13 : G1428 Sounder Amplifier

U14 : ICS950403 Clock Generator

U16 : KBC (W83L950D)

U20 : VIA_VT8235CD South Bridge

U25 : LPC BIOS ROM

U26 : CB1410 PCMCIA Controller

J509

U26

U20

U16

U25

U9

U2

U12

U3

U6

U14

U13

U10

4. Definition & Location of Major Components

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

71

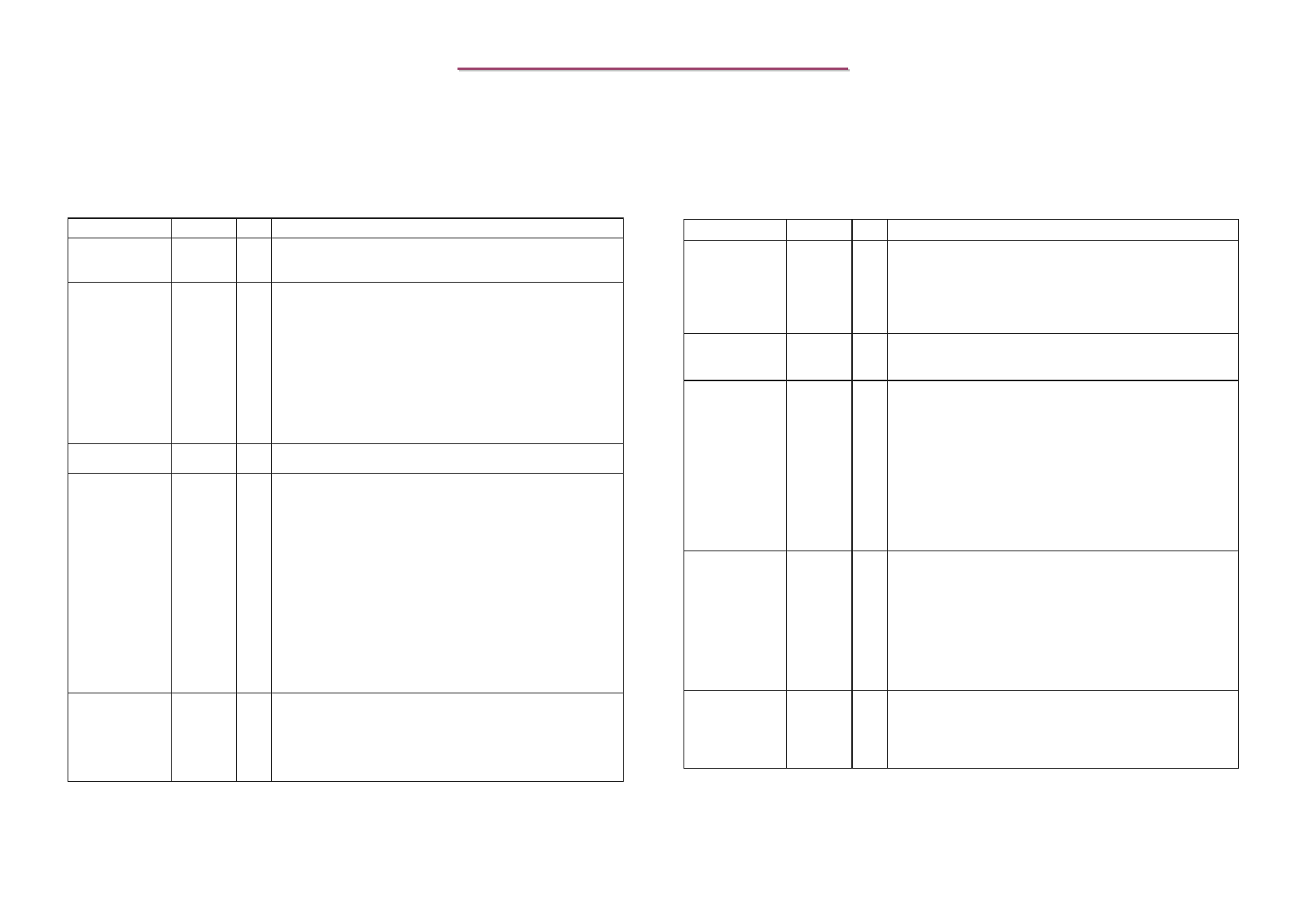

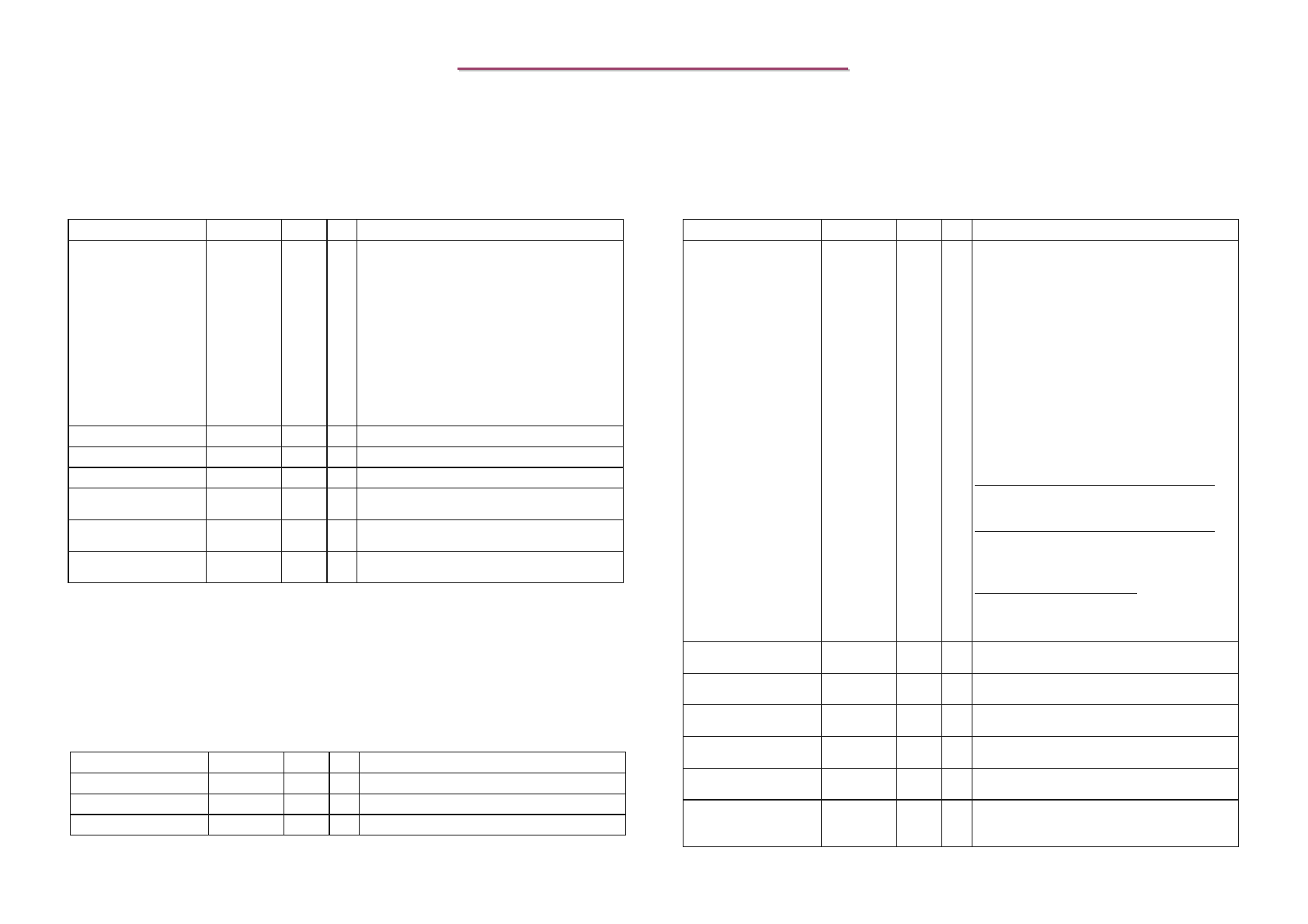

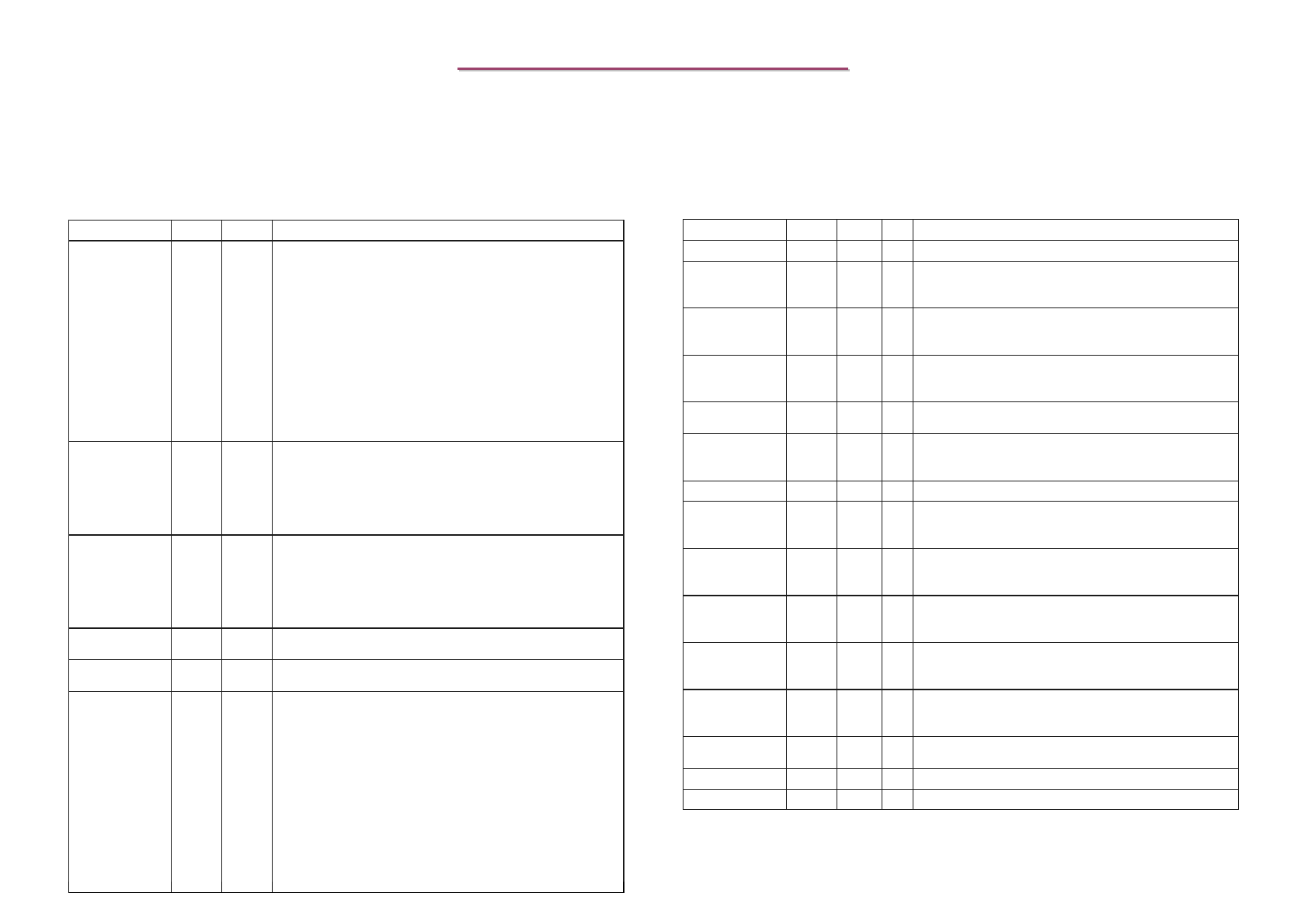

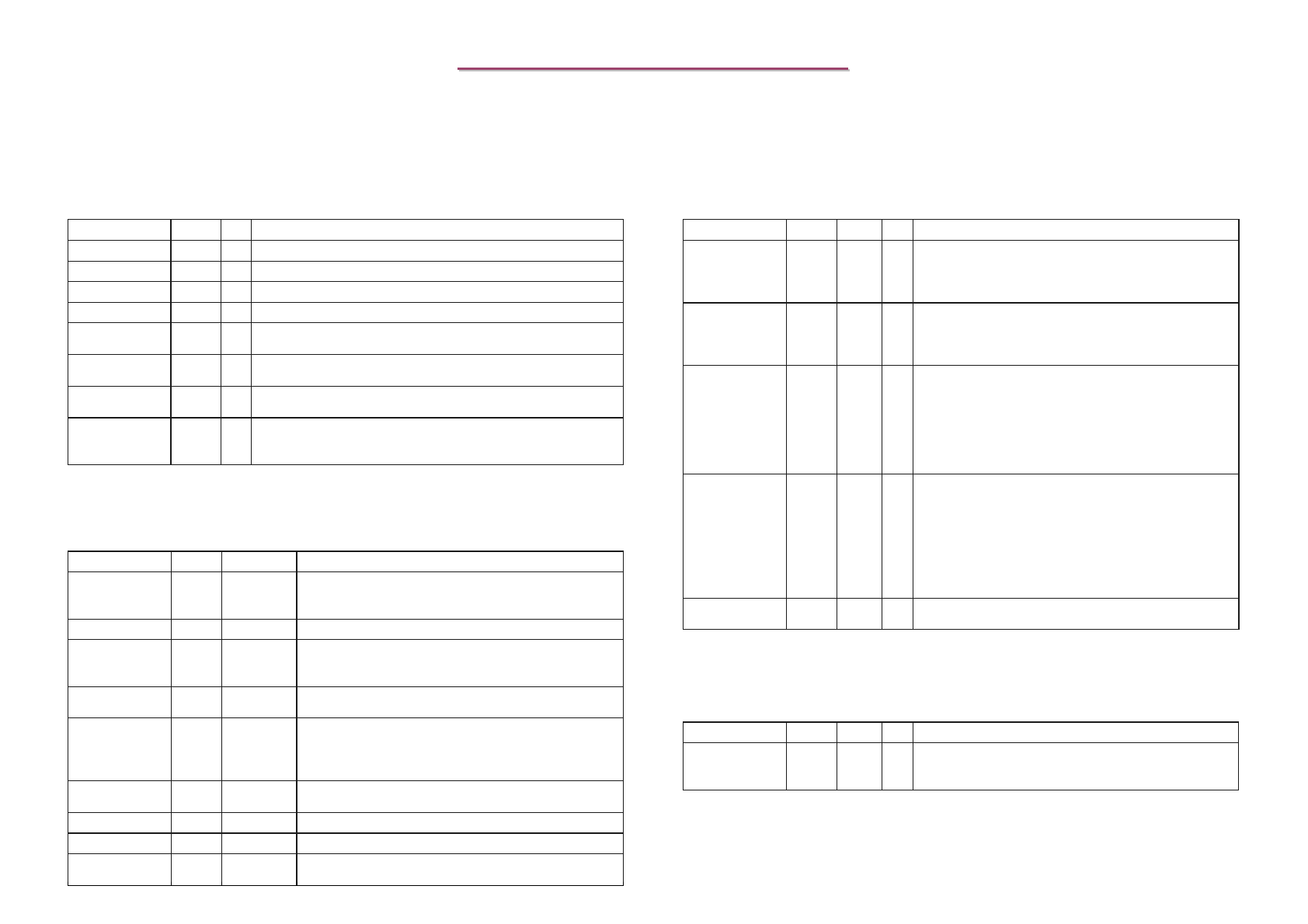

DDR SDRAM Memory Interface Pins

Signal Name Type Description

MEMCLK_H/L[7] O-IOD Differential DDR SDRAM clock to the top of DIMM 0 for

unbuffered DIMMs.1

MEMCLK_H/L[6] O-IOD Differential DDR SDRAM clock to the top of DIMM 1 for

unbuffered DIMMs.1

MEMCLK_H/L[5] O-IOD Differential DDR SDRAM clock to the bottom of DIMM 0 for

unbuffered DIMMs.1

MEMCLK_H/L[4] O-IOD Differential DDR SDRAM clock to the bottom of DIMM 1 for

unbuffered DIMMs.1

MEMCLK_H/L[3] O-IOD Differential DDR SDRAM clock to DIMM 3 for registered

DIMMs.1

MEMCLK_H/L[2] O-IOD Differential DDRS DRAM clock to DIMM 2 for registered

DIMMs.1

MEMCLK_H/L[1] O-IOD Differential DDR SDRAM clock to the middle of DIMM 1 for

unbuffered DIMMs, or DIMM 1 for registered DIMMs.1

MEMCLK_H/L[0] O-IOD Differential DDR SDRAM clock to the middle of DIMM 0 for

unbuffered DIMMs, or DIMM 0 for registered DIMMs.1

MEMCKEA

MEMCKEB

O-IOS Clock Enables to DIMMs. Used to gate clocks for power

management functionality.1

MEMDQS[17:0] B-IOS DRAM Data Strobes synchronous with MEMDATA and

MEMCHECK during DRAM read and writes.1

MEMDATA[63:0] B-IOS DRAM Interface Data Bus

MEMCHECK[7:0] B-IOS DRAM Interface ECC Check Bits

MEMCS_L[7:0] O-IOS DRAM Chip Selects 1

MEMRASA_L

MEMRASB_L

O-IOS DRAM Row Address Select. MEMRASA_L and

MEMRASB_L are functionally identical. Two copies are

provided to accommodate the loading of unbuffered DIMMs.1

MEMCASA_L

MEMCASB_L

O-IOS DRAM Column Address Select. MEMCASA_L and

MEMCASB_L are functionally identical. Two copies are

provided to accommodate the loading of unbuffered DIMMs.1

MEMWEA_L

MEMWEB_L

O-IOS DRAM Write Enable. MEMWEA_L and MEMWEB_L are

functionally identical. Two copies are provided to accommodate

the loading of unbuffered DIMMs.1

MEMADDA[13:0]

MEMADDB[13:0]

O-IOS DRAM Column/Row Address. Two copies are provided to

accommodate the loading of unbuffered DIMMs. During

precharges, activates, reads, and writes, the two copies are

inverted from each other (except A[10] which is used for

auto-precharge) to minimize switching noise. The signals are

inverted only when the bus is used to carry address

information.1

DDR SDRAM Memory Interface Pins (Continued)

Signal Name Type Description

MEMBANKA[1:0]

MEMBANKB[1:0]

O-IOS DRAM Bank Address. Two copies are provided to

accommodate the loading of unbuffered DIMMs. During

precharges, activates, reads, and writes the two copies are

inverted from each other to minimize switching noise. The

signals are inverted only when the bus is used to carry address

information.1

MEMRESET_L O-IOS DRAM Reset pin for Suspend-to-RAM power management

mode. This pin is required for registered DIMMs only.

MEMVREF VREF DRAM Interface Voltage Reference 1

MEMZP A Compensation Resistor tied to VSS 1

MEMZN A Compensation Resistor tied to 2.5 V 1

Note: For connection details and proper resistor values, see the AMD Athlon™ 64 Processor

Motherboard Design Guide, order# 24665.

HyperTransport™ Technology Pin Descriptions

Note: 1.These pins are used in an alternating fashion to compensate R TT by internal comparison to 3/4

VLDT and 1/4 VLDTand compensate R ON by comparison to each other around 1/2 VLDT.

For proper resistor value, see theAMD Athlon™ 64 Processor Motherboard Design Guide, order#

24665.

2.The unused L0_CTLIN_H/L[1] pins must be properly terminated such that the true pin is pulled

High and thecomplement is pulled Low. Refer to the AMD Athlon™ 64 Processor Motherboard

Design Guide, order# 24665, for details.

Signal Name Type Description

L0_CLKIN_H/L[1:0] I-HT Link 0 Clock Input

L0_CTLIN_H/L[1:0] I-HT Link 0 Control Input 2

L0_CADIN_H/L[15:0] I-HT Link 0 Command/Address/Data Input

L0_CLKOUT_H/L[1:0] O-HT Link 0 Clock Outputs

L0_CTLOUT_H/L[1:0] O-HT Link 0 Control Output

L0_CADOUT_H/L[15:0] O-HT Link 0 Command/Address/Data Outputs

L0_REF1 A Compensation Resistor to VLDT 1

L0_REF0 A Compensation Resistor to VSS 1

5.1 AMD Mobile Athlon 64(ClawHammer) Processor(1)

5. Pin Descriptions of Major Components

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

72

Miscellaneous Pin Descriptions

Signal Name Type Description

RESET_L I-IOS System Reset

PWROK I-IOS Indicates that voltages and clocks have reached specified

operation

LDTSTOP_L I-IOS HyperTransport™ Technology Stop Control Input. Used for

power management and for changing HyperTransport link width

and frequency.

VID[4:0] O-IOS Voltage ID to the regulator

THERMDA A Anode (+) of the thermal diode

THERMDC A Cathode (–) of the thermal diode

THERMTRIP_L O-IO-O

D

Thermal Sensor Trip output, asserted at nominal temperature of

125 ℃.

COREFB_H/L A Differential feedback for VDD Power Supply

VDDIOFB_H/L A Differential feedback for VDDIO Power Supply

CORE_SENSE A VDD voltage monitor pin

VDDA S Filtered PLL Supply Voltage

VTT_SENSE A VTT voltage monitor pin

VDDIO_SENSE A VDDIO voltage monitor pin

VDD S Core power supply

VDDIO S DDR SDRAM I/O ring power supply

VLDT_A

VLDT_B S HyperTransport™ I/O ring power supply for side A and side B

of the package

VTT_A

VTT_B

S VTT regulator voltage for side A and side B of the die

VSS S Ground

JTAG Pin Descriptions

Signal Name Type Description

TCK I-IOS JTAG Clock

TMS I-IOS JTAG Mode Select

TRST_L I-IOS JTAG Reset

TDI I-IOS JTAG Data Input

TDO O-IOS JTAG Data Output

Debug Pin Descriptions

Signal Name Type Description

DBREQ_L I-IOS Debug Request

DBRDY O-IOS Debug Ready

Clock Pin Descriptions

Signal Name Type Description

CLKIN_H/L I-IOD 200-MHz PLL Reference Clock

FBCLKOUT_H/L O-IOD Core Clock PLL 200-MHz Feedback Clock

5.1 AMD Mobile Athlon 64(ClawHammer) Processor(2)

MiTac Secret

Confidential Document

8399

8399 N/B Maintenance

N/B Maintenance

73

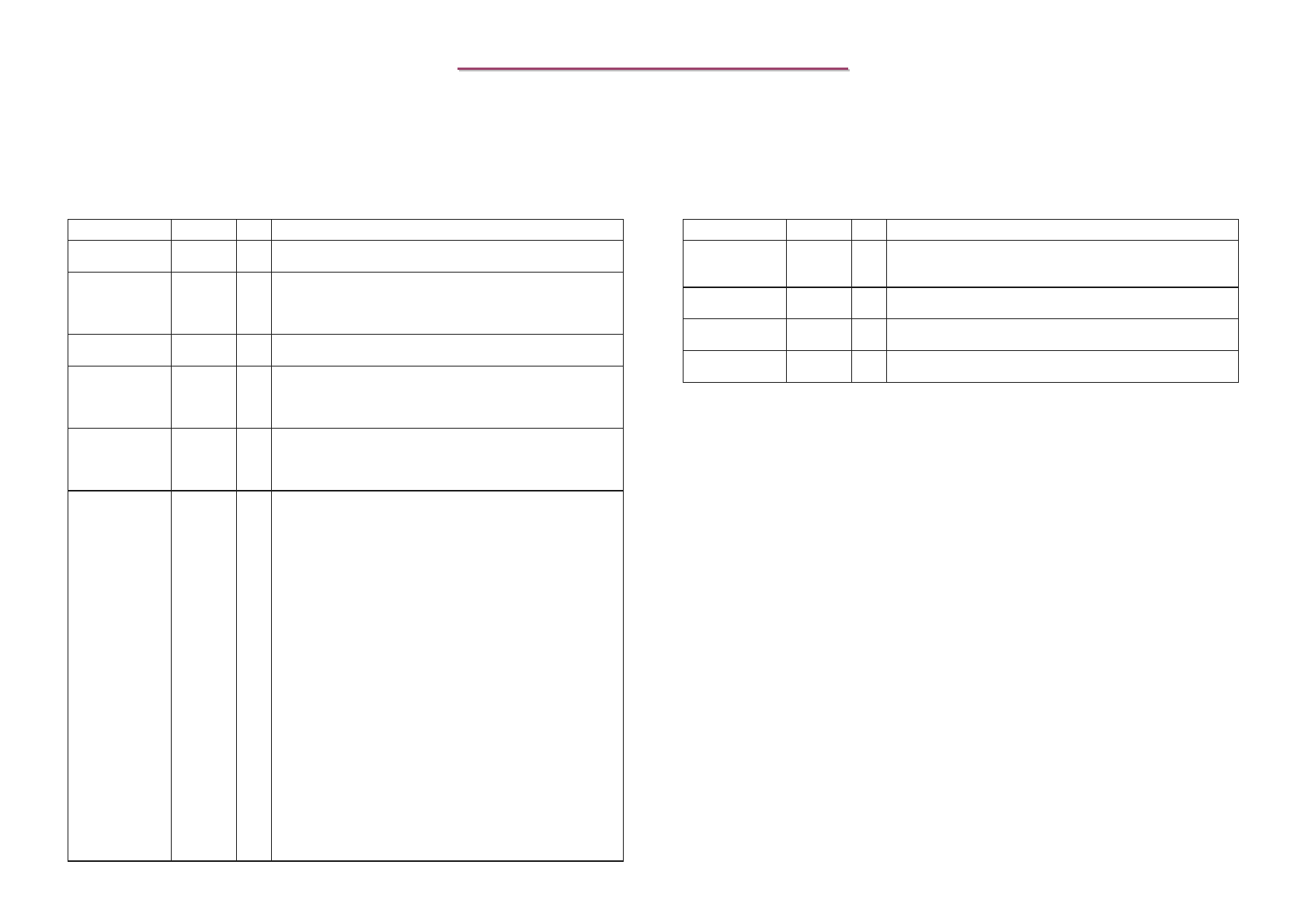

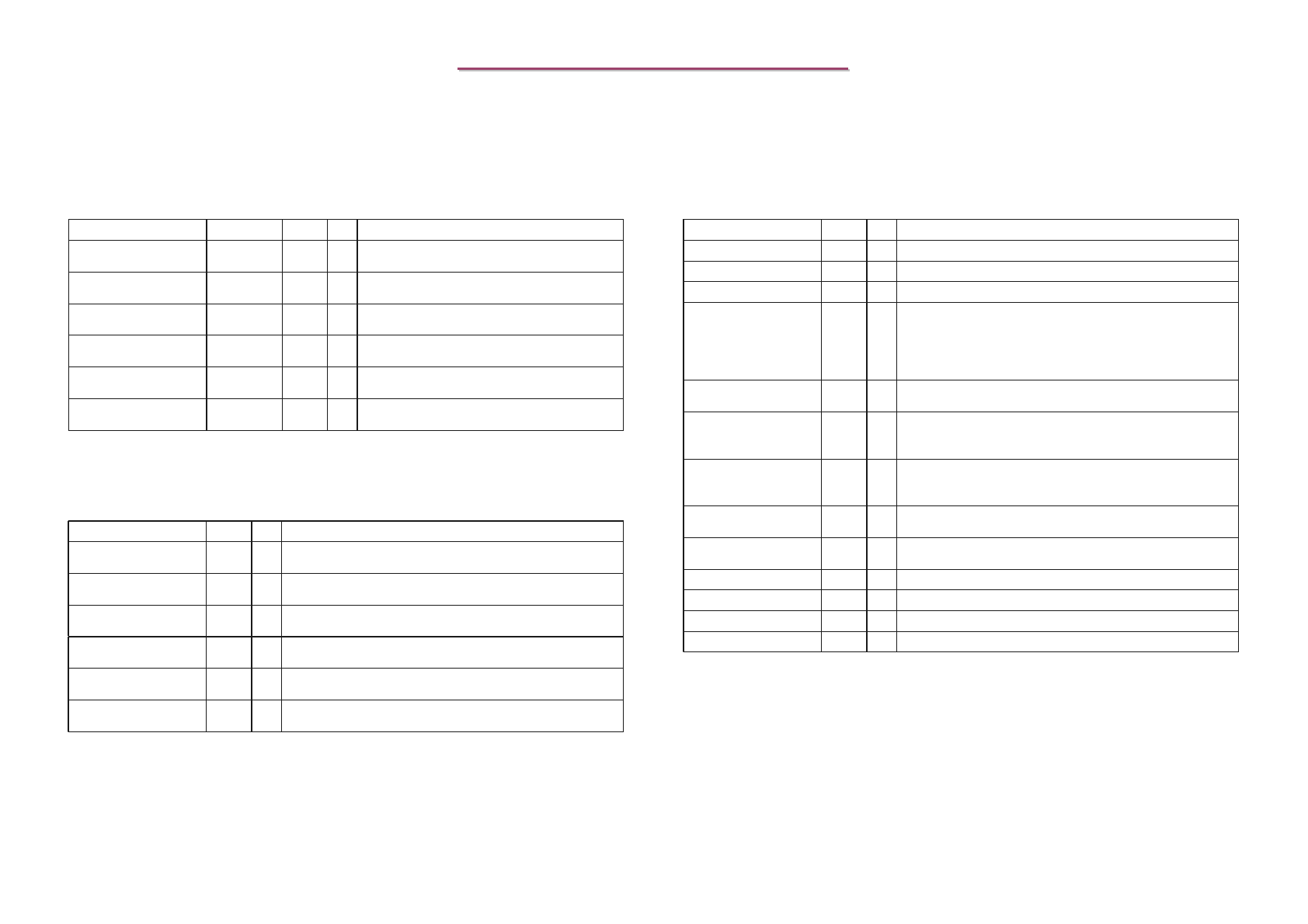

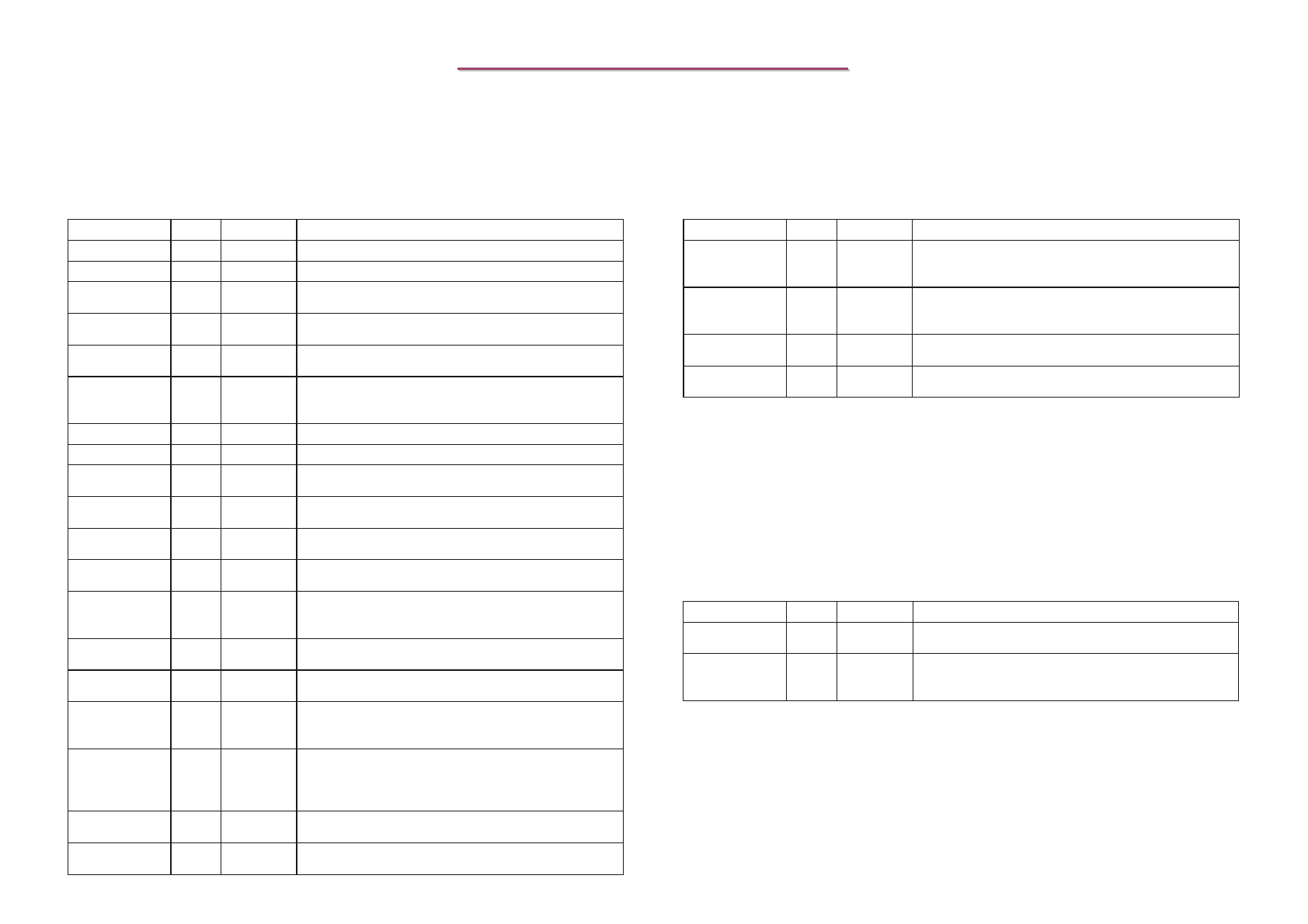

AGP Bus Interface

Signal Name Pin # I/O Signal Description

GD[31:0] (see pin

list)

IO Address / Data Bus. Address is driven with GDS assertion for

AGP-style transfers and with GFARME# assertion for PCI-style

transfers.

GC#BE[3:0]

(GCBE[3:0]# for

4x mode)

AC7

AD11

AF11

AD15

IO Command / Byte Enable. (Interpreted as GC/BE# for AGP

2x/4x and GC#/BE for 8x). For AGP cycles these pins provide

command information (different commands than for PCI) driven

by the master (graphics controller) when requests are being

enqueued using GPIPE# (2x/4x only as GPIPE# isn™t used in

8x mode). These pins provide valid byte information during

AGP write transactions and are driven by the master. The target

(this chip) drives these lines to io0000lt during the return of

AGP read data. For PCI cycles, commands are driven with

GFARME# assertion. Byte enables corresponding to supplied or

requested data are driven on following clocks.

GPAR AC16 IO AGP Parity. A single parity bit is provided over GD[31:0] and

GC#BE[3:0].

GDBIH /

GPIPE#GDBIL

AC5

AC4

IO Dynamic Bus Inversion High / Low. AGP 8x transfer mode

only. Driven by the source to indicate whether the

corresponding data bit group (GDBIH for GD[31:16] and

GDBIL for GD[15:0]) needs to be inverted on the receiving end

(1 on GDBIx indicates that the corresponding data bit group

should be inverted). Used to limit the number of simultaneously

switching outputs to 8 for each 16-pin group.

Pipelined Request. Not used by AGP 8x. Asserted by the

master (external graphics controller) to indicate that a full-width

request is to be enqueued by the target (North Bridge). The

master enqueues one request each rising edge of GCLK while

GPIPE# is asserted. When GPIPE# is deasserted no new

requests are enqueued across the AD bus.

Note: See RxAE[1] for GPIPE# / GDBIH pin function

selection.

GADSTB0F(GA

DSTB0 for 4x),

GADSTB0S(GA

DSTB0# for 4x)

AE15

AF15

IO Bus Strobe 0. Source synchronous strobes for GD[15:0] (the

agent that is providing the data drives these signals). GDS0

provides timing for 2x data transfer mode; GDS0 and GDS0#

provide timing for 4x mode. For 8x transfer mode, GDS0 is

interpreted as GDS0F (i1Firstl. strobe) and GDS0# as GDS0S

(iSSecondl. strobe).

AGP Bus Interface (Continued)

Signal Name Pin # I/O Signal Description

GADSTB1F(GA

DSTB1 for 4x),

GADSTB1S(GA

DSTB1# for 4x)

AE7

AF7

IO Bus Strobe 1. Source synchronous strobes for GD[31:16] (i.e.,

the agent that is providing the data drives these signals). GDS1

provides timing for 2x data transfer mode; GDS1 and GDS1#