Mitsubishi Electronics Digital Home Theater Server Qnucpu Users Manual User's (Function Explanation, Program Fundamentals)

QnUCPU to the manual 5f0c62ae-3154-4750-b924-eaffe9077da0

2015-02-09

: Mitsubishi-Electronics Mitsubishi-Electronics-Mitsubishi-Digital-Electronics-Home-Theater-Server-Qnucpu-Users-Manual-556715 mitsubishi-electronics-mitsubishi-digital-electronics-home-theater-server-qnucpu-users-manual-556715 mitsubishi-electronics pdf

Open the PDF directly: View PDF ![]() .

.

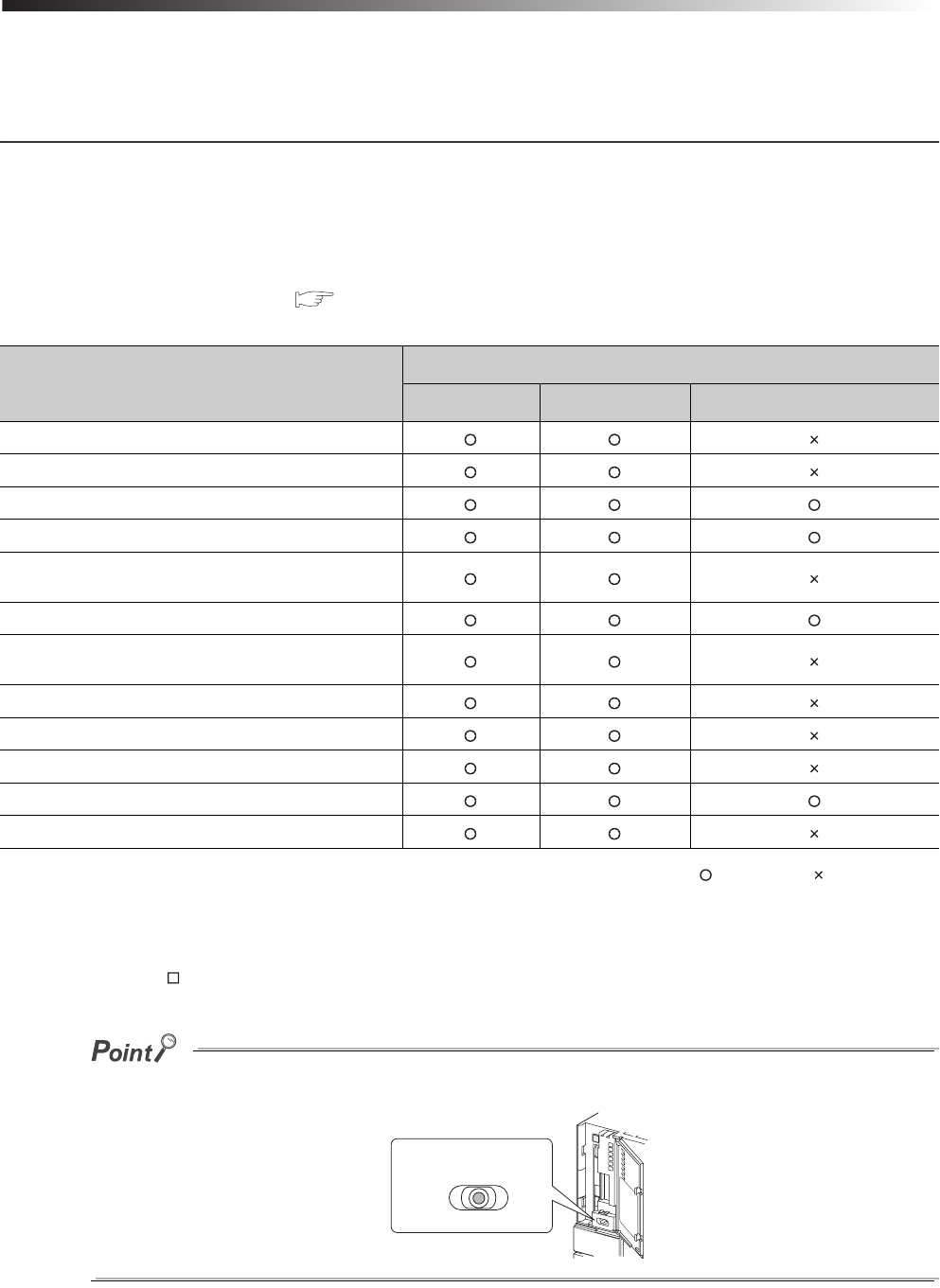

Page Count: 630 [warning: Documents this large are best viewed by clicking the View PDF Link!]

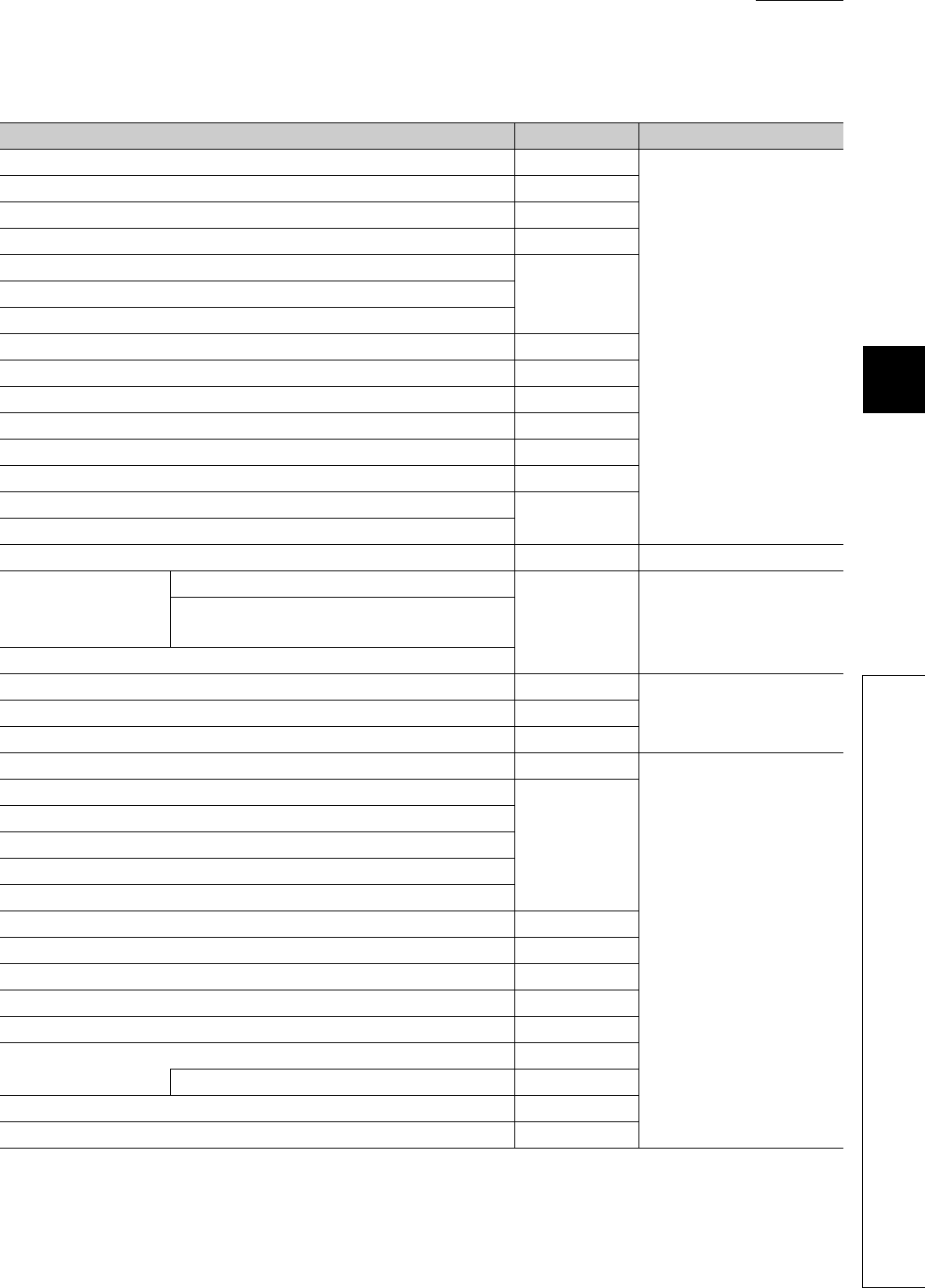

- SAFETY PRECAUTIONS

- CONDITIONS OF USE FOR THE PRODUCT

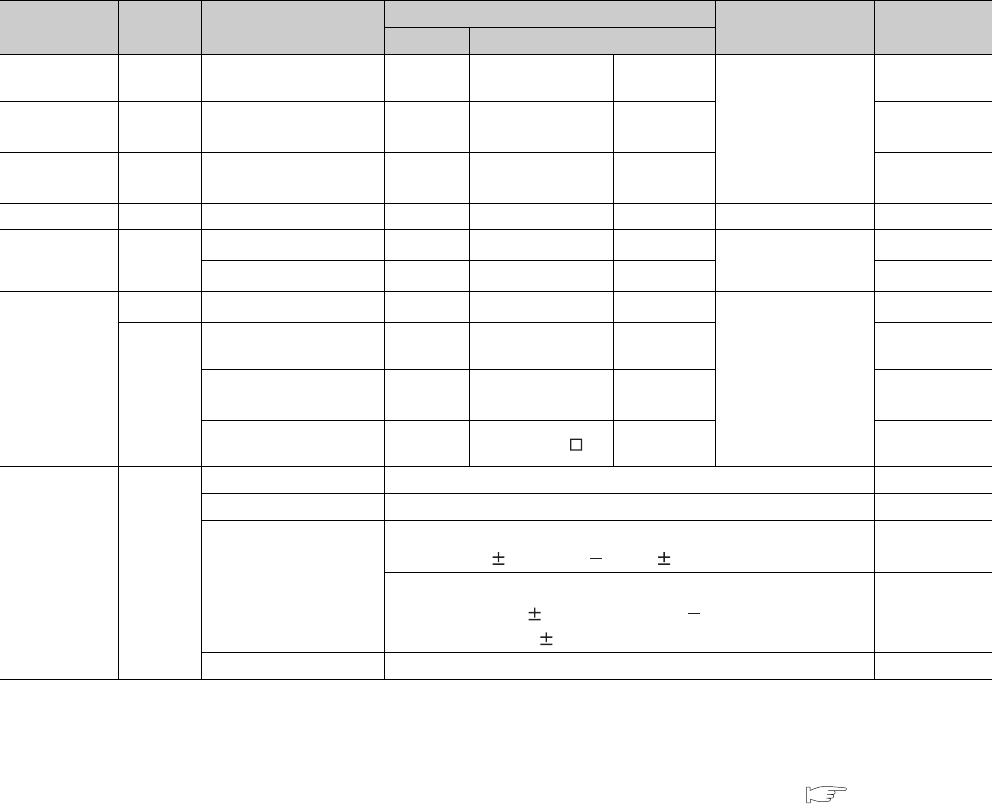

- REVISIONS

- INTRODUCTION

- CONTENTS

- MANUALS

- MANUAL PAGE ORGANIZATION

- GENERIC TERMS AND ABBREVIATIONS

- CHAPTER1 OVERVIEW

- CHAPTER2 SEQUENCE PROGRAMS

- CHAPTER3 CPU MODULE OPERATION

- CHAPTER4 ASSIGNMENT OF BASE UNIT AND I/O NUMBER

- CHAPTER5 MEMORIES AND FILES USED FOR CPU MODULE

- 5.1 Memories Used for CPU Module

- 5.1.1 Memory composition and storable data

- 5.1.2 Program memory

- 5.1.3 Program cache memory

- 5.1.4 Standard ROM

- 5.1.5 Standard RAM

- 5.1.6 Memory card

- 5.1.7 Writing to the Flash card by GX Developer

- 5.1.8 Operating the program in the memory card (boot operation)

- 5.1.9 Details of written files

- 5.1.10 Specifying valid parameters (parameter-valid drive setting)

- 5.2 Program File Structure

- 5.3 File Operations by GX Developer and Handling Precautions

- 5.1 Memories Used for CPU Module

- CHAPTER6 FUNCTIONS

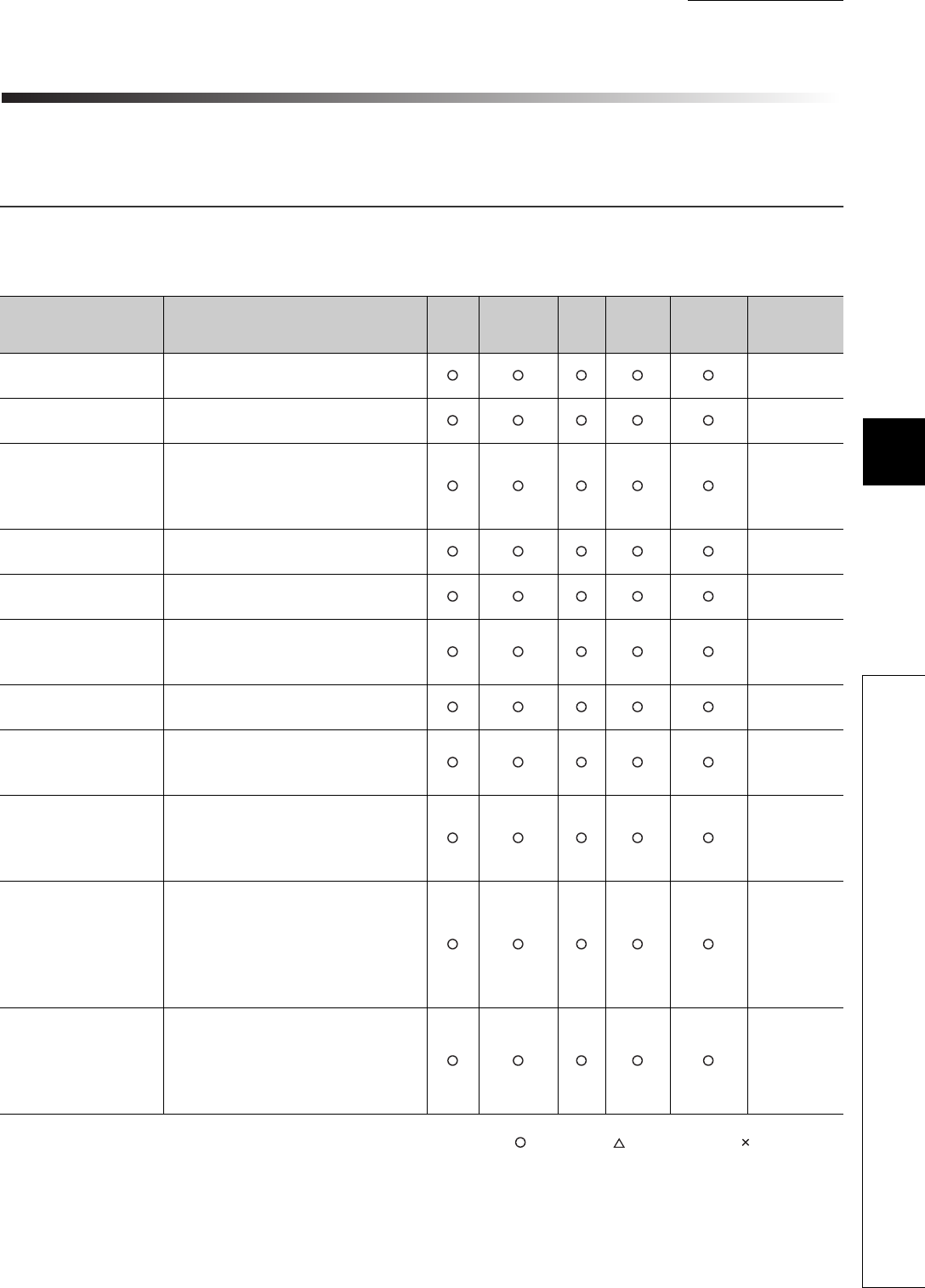

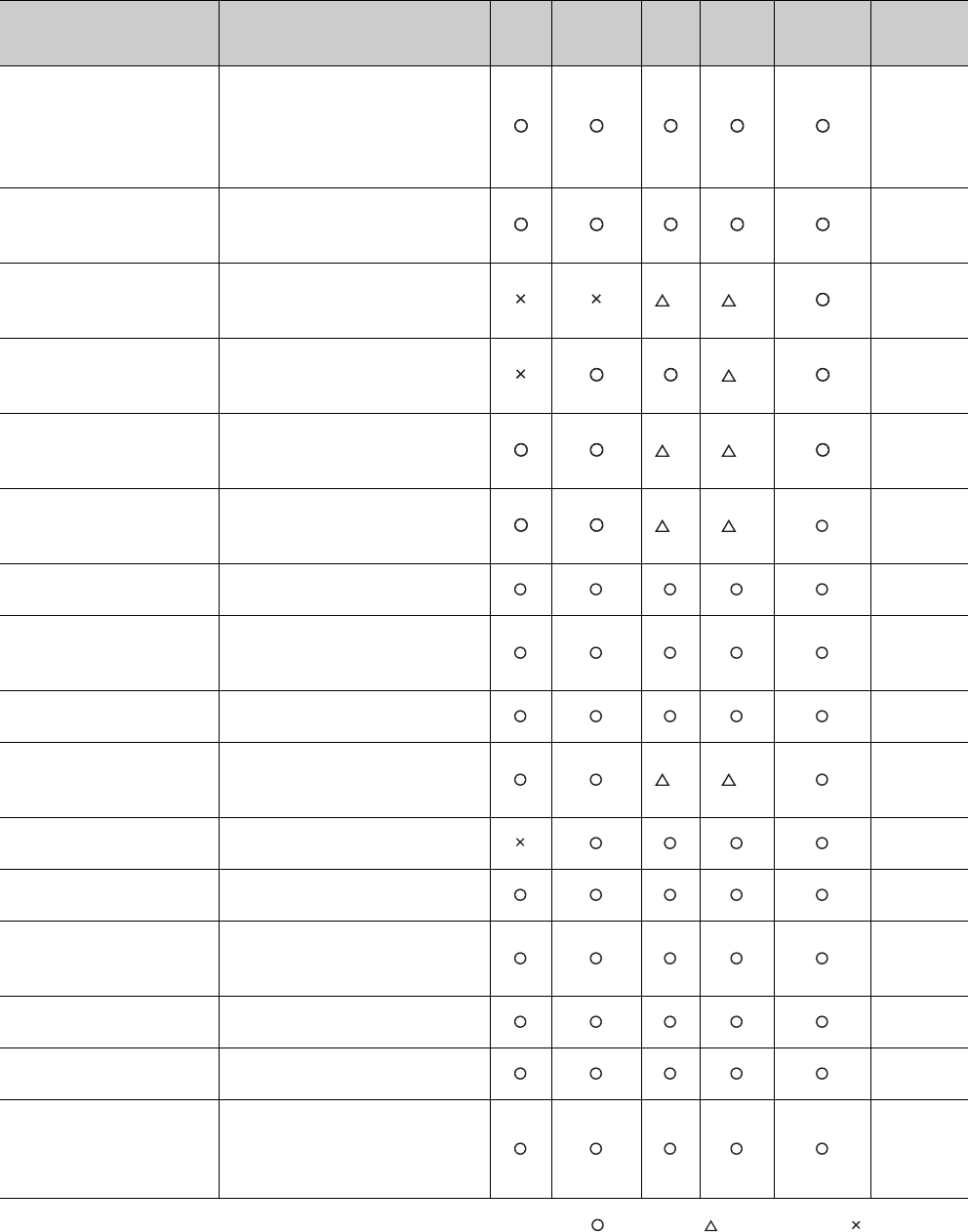

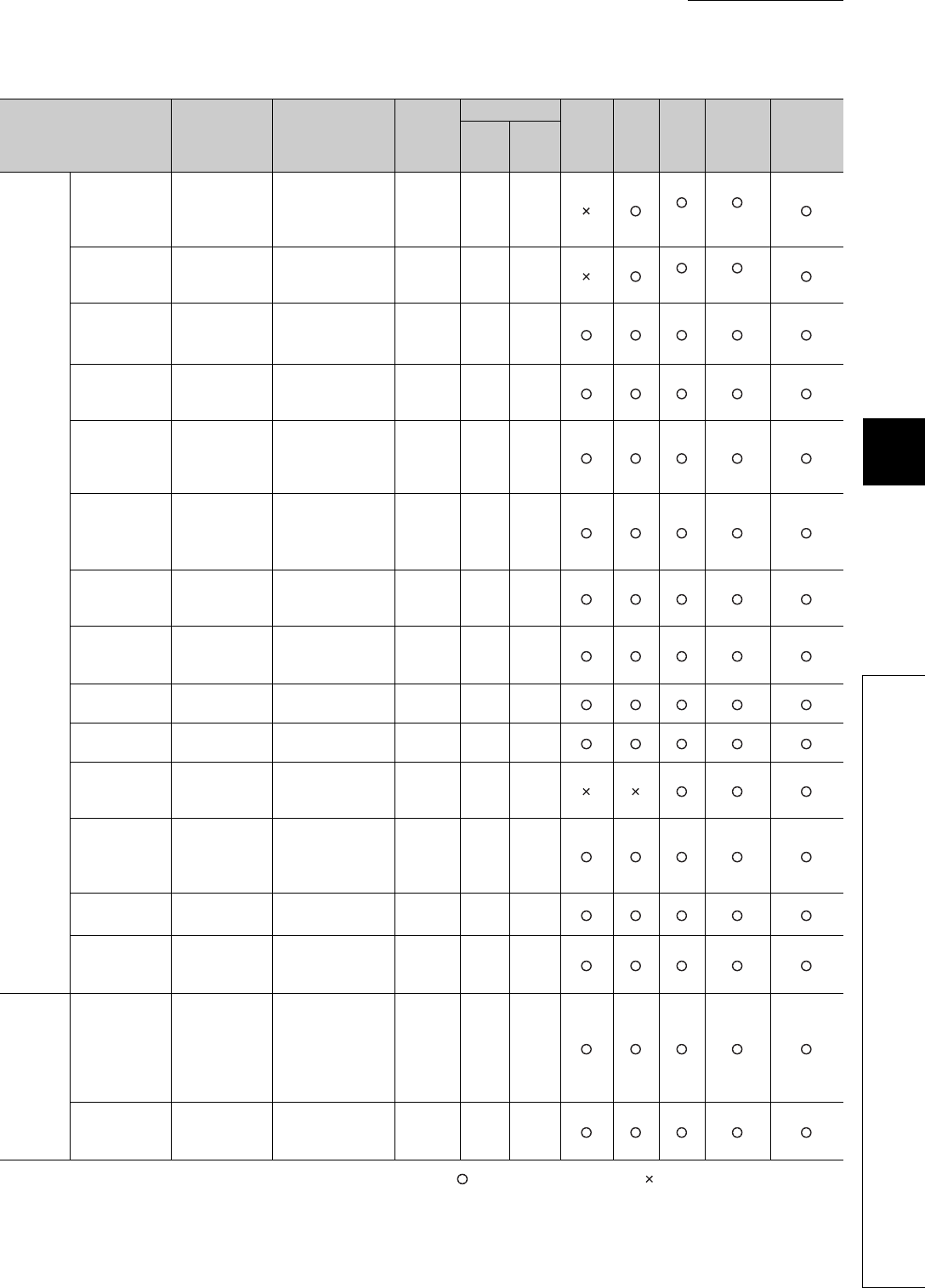

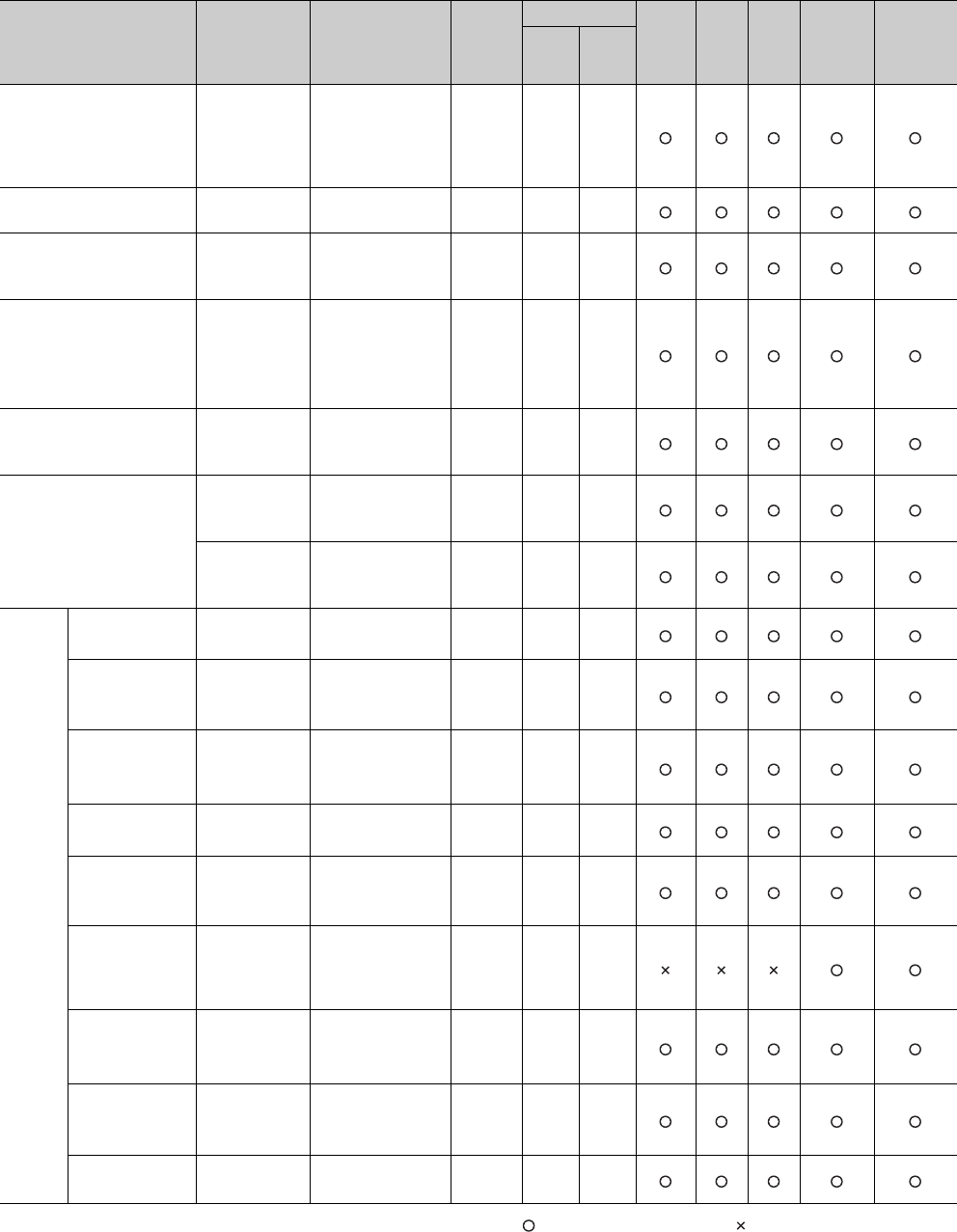

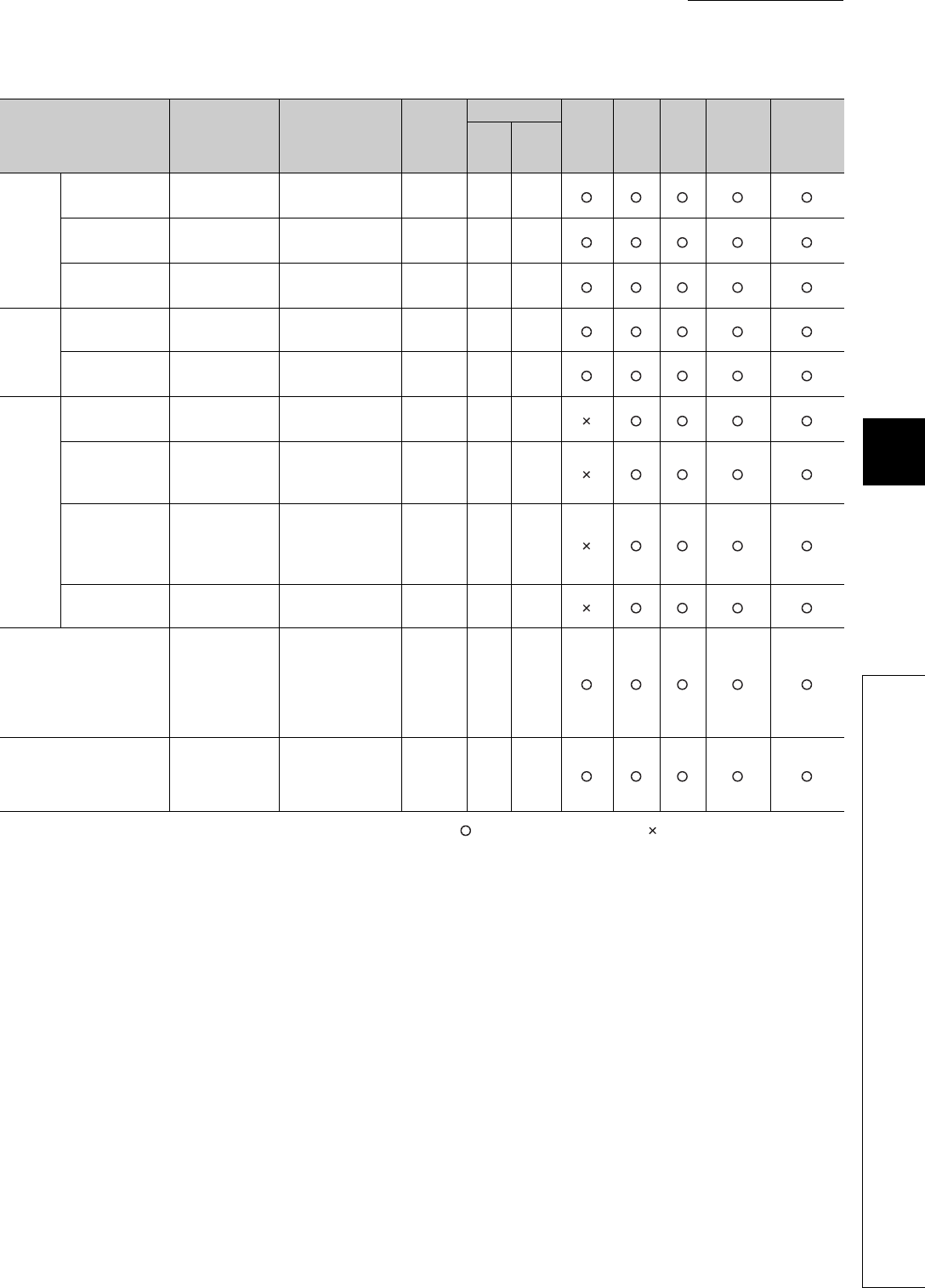

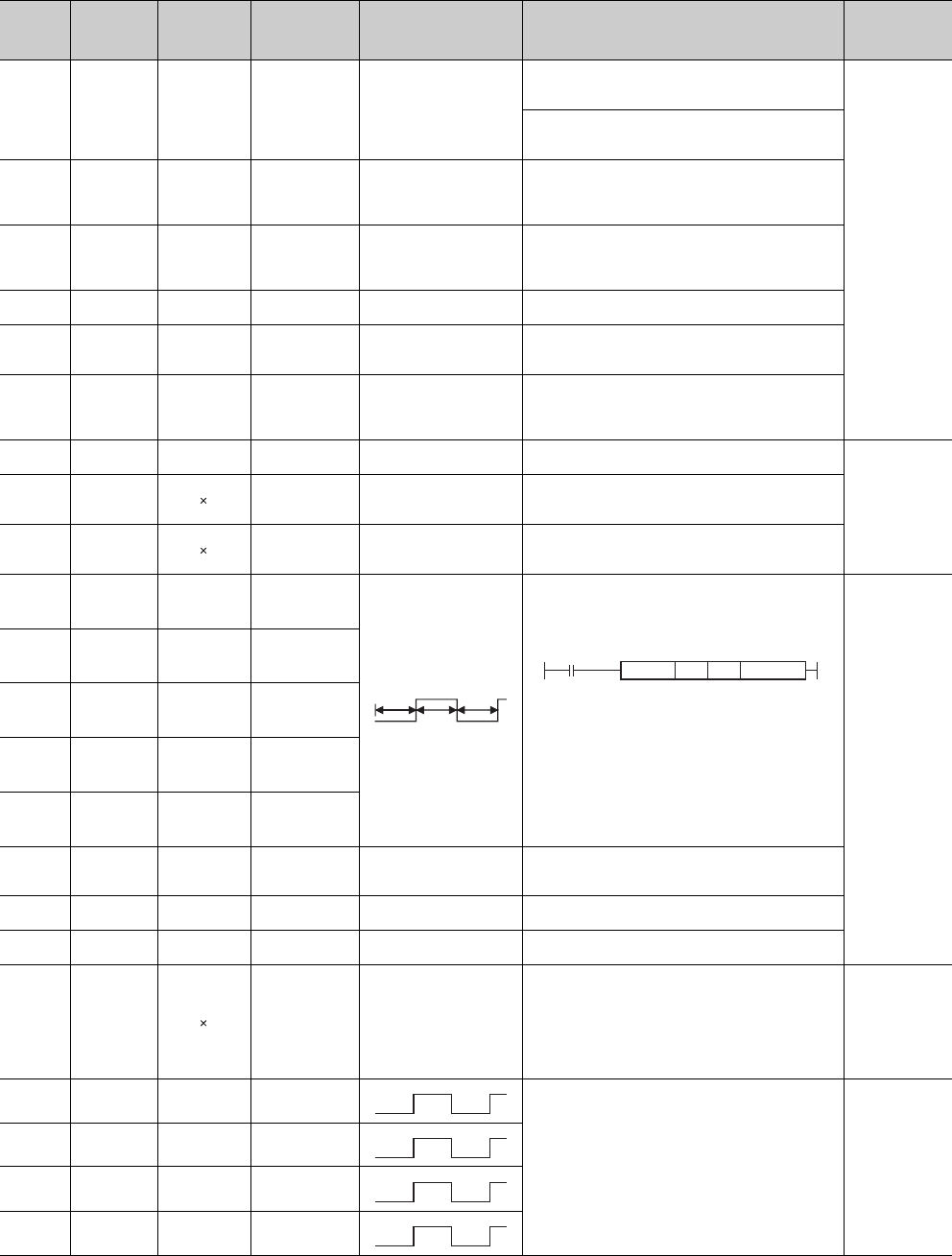

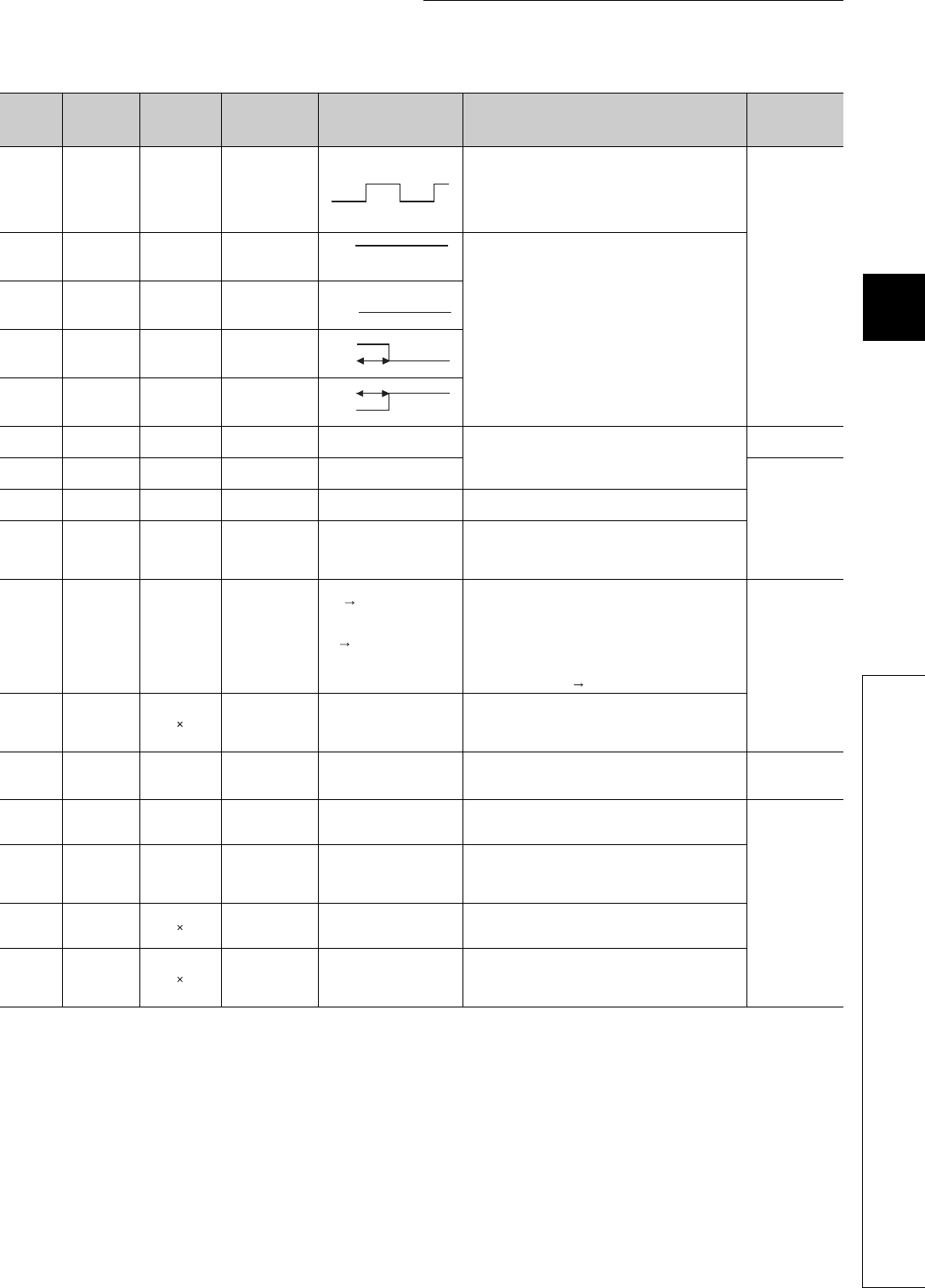

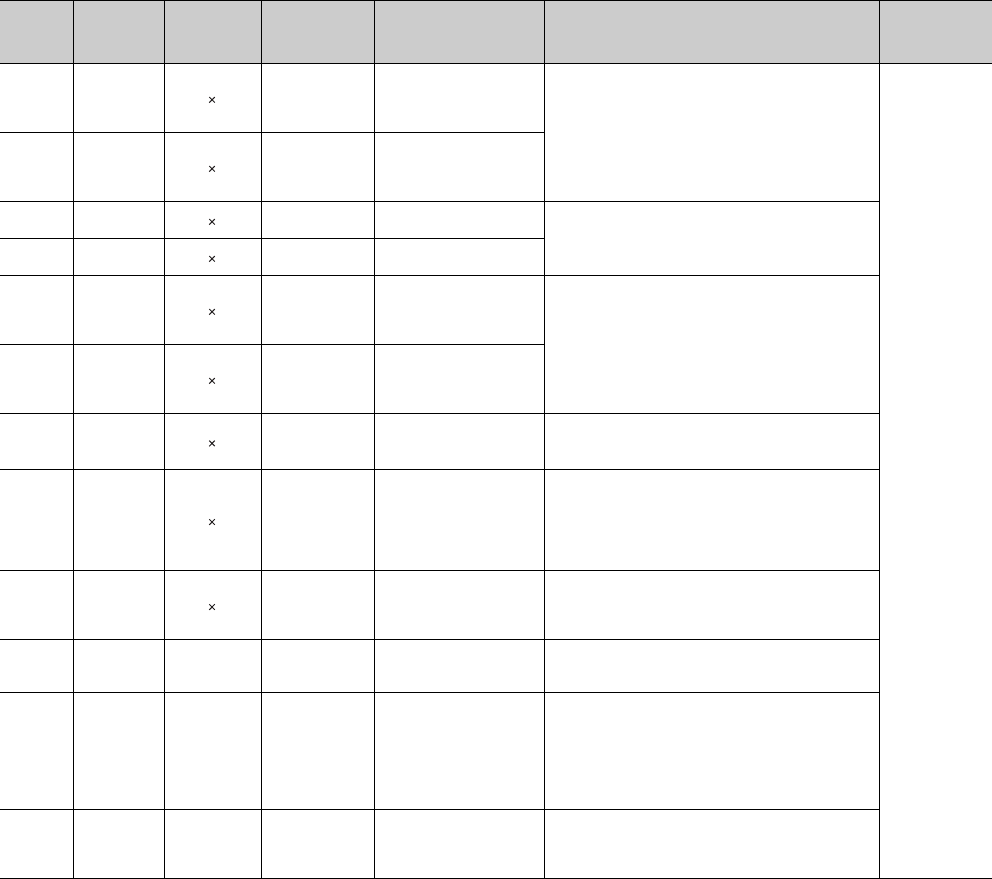

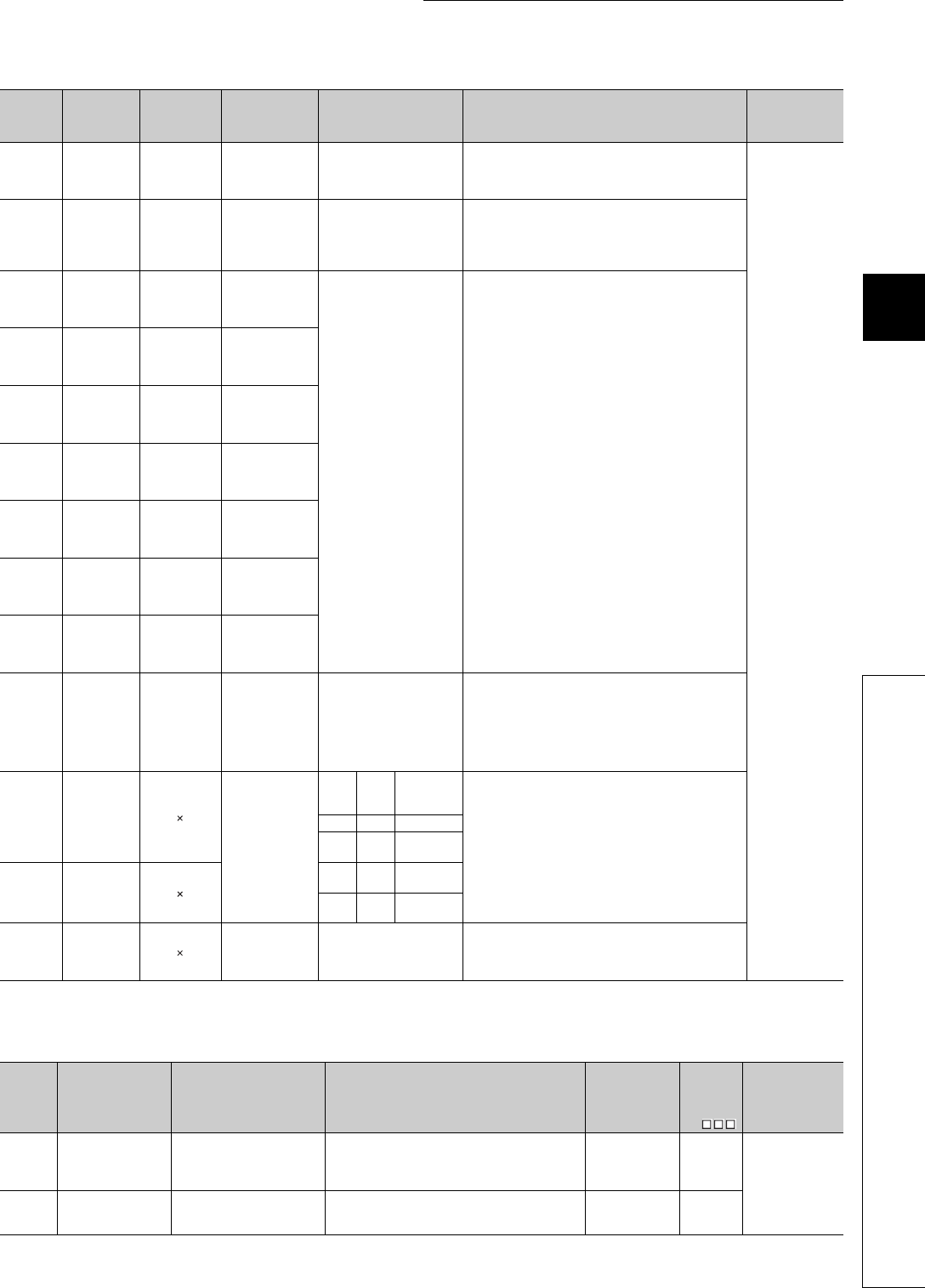

- 6.1 Function List

- 6.2 Constant Scan

- 6.3 Latch Function

- 6.4 Output Mode at Operating Status Change (STOP to RUN)

- 6.5 Clock Function

- 6.6 Remote Operation

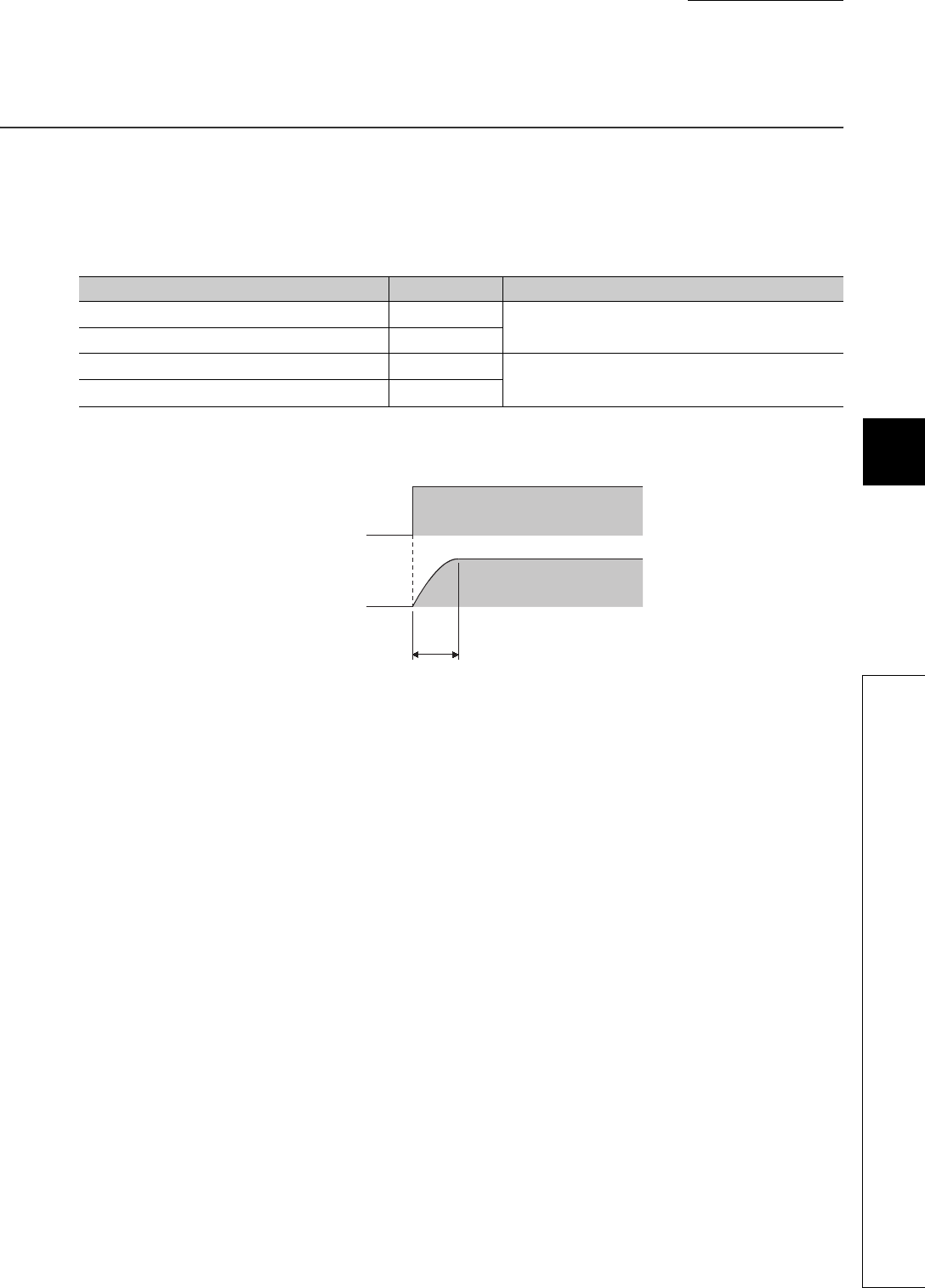

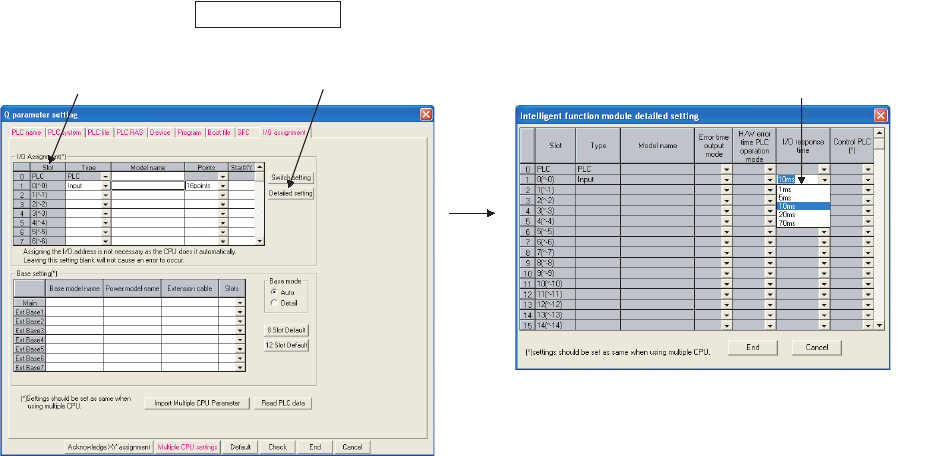

- 6.7 Q Series-compatible Module Input Response Time Selection (I/O Response Time)

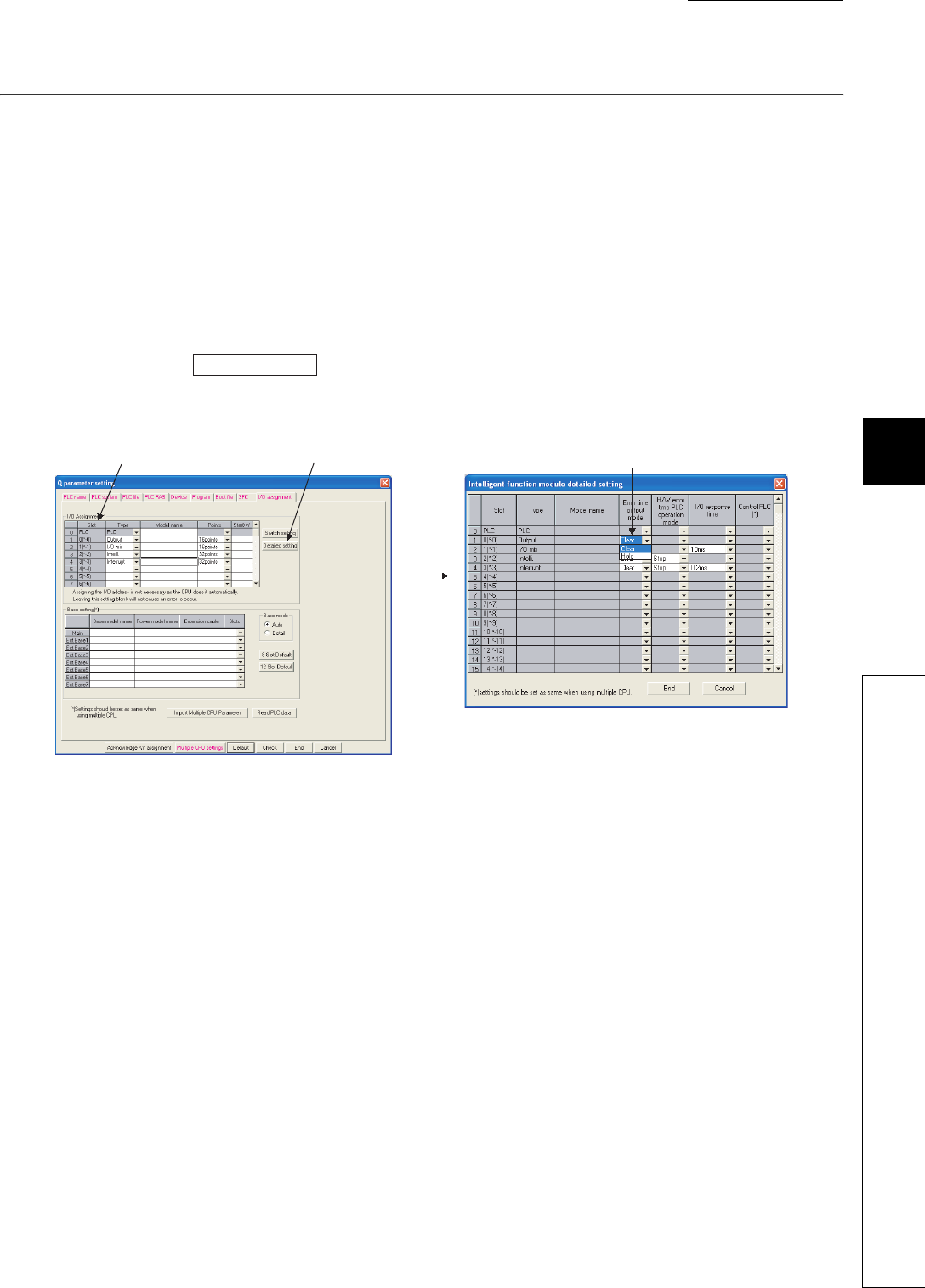

- 6.8 Error Time Output Mode Setting

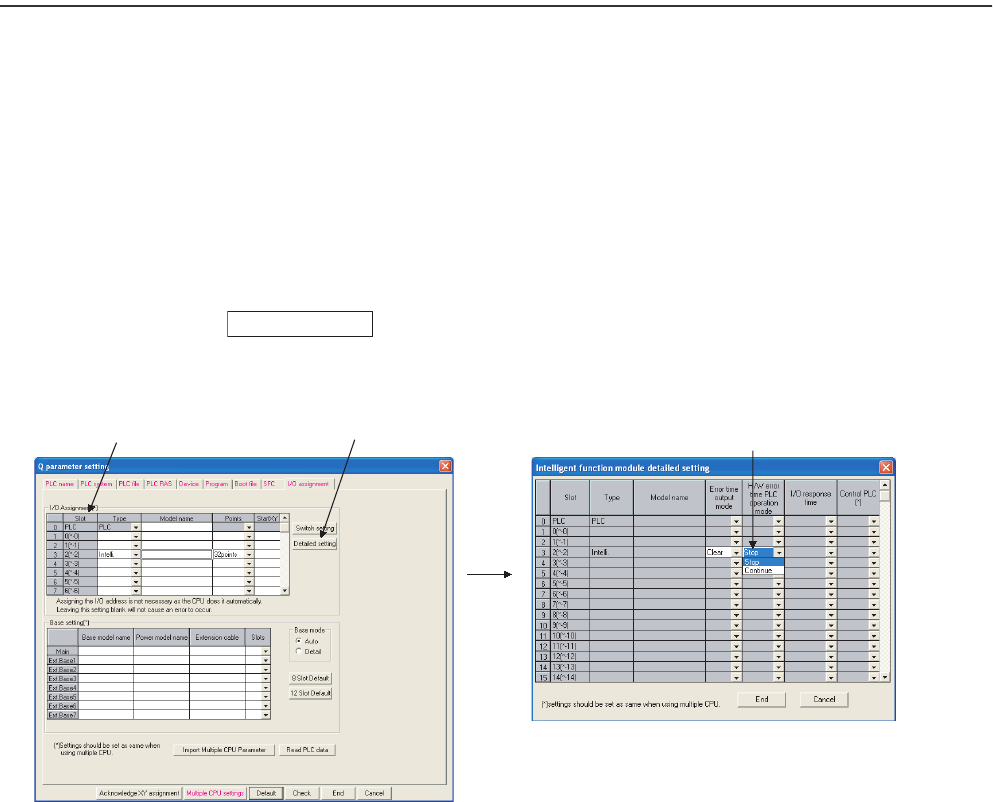

- 6.9 H/W Error Time PLC Operation Mode Setting

- 6.10 Intelligent Function Module Switch Setting

- 6.11 Monitor Function

- 6.12 Writing Programs While CPU Module is in RUN Status

- 6.13 Execution Time Measurement

- 6.14 Sampling Trace Function

- 6.15 Debug Function from Multiple GX Developers

- 6.16 Watchdog Timer (WDT)

- 6.17 Self-diagnostic Function

- 6.18 Error History

- 6.19 System Protection

- 6.20 System Display of CPU Module with GX Developer

- 6.21 LED Indication

- 6.22 Interrupt from Intelligent Function Module

- 6.23 Serial Communication Function

- 6.24 Service Processing

- 6.25 Initial Device Value

- 6.26 Battery Life-prolonging Function

- 6.27 Memory Check Function

- 6.28 Latch Data Backup to Standard ROM Function

- 6.29 Writing/Reading Device Data to/from Standard ROM

- 6.30 CPU Module Change Function with Memory Card

- 6.31 Module model name read

- 6.32 Module error collection

- CHAPTER7 COMMUNICATIONS WITH INTELLIGENT FUNCTION MODULE

- 7.1 Communications between CPU Module and Intelligent Function Module

- 7.1.1 Initial setting and auto refresh setting by GX Configurator

- 7.1.2 Initial setting by initial device value

- 7.1.3 Communications with the FROM and TO instructions

- 7.1.4 Communications using the intelligent function module device

- 7.1.5 Communications using the intelligent function module dedicated instruction

- 7.1 Communications between CPU Module and Intelligent Function Module

- CHAPTER8 PARAMETERS

- CHAPTER9 DEVICES

- 9.1 Device List

- 9.2 Internal User Device

- 9.2.1 Input (X)

- 9.2.2 Output (Y)

- 9.2.3 Internal relay (M)

- 9.2.4 Latch relay (L)

- 9.2.5 Annunciator (F)

- 9.2.6 Edge relay (V)

- 9.2.7 Link relay (B)

- 9.2.8 Link special relay (SB)

- 9.2.9 Step relay (S)

- 9.2.10 Timer (T)

- 9.2.11 Counter (C)

- 9.2.12 Data register (D)

- 9.2.13 Link register (W)

- 9.2.14 Link special register (SW)

- 9.3 Internal System Devices

- 9.4 Link Direct Device (J\)

- 9.5 Module Access Devices

- 9.6 Index Register (Z)/Standard Device Resister (Z)

- 9.7 File Register (R)

- 9.8 Extended Data Register (D) and Extended Link Register (W)

- 9.9 Nesting (N)

- 9.10 Pointer (P)

- 9.11 Interrupt Pointer(I)

- 9.12 Other Devices

- 9.13 Constants

- 9.14 Convenient Usage of Devices

- CHAPTER10 CPU MODULE PROCESSING TIME

- CHAPTER11 PROCEDURES FOR WRITING PROGRAM TO CPU MODULE

- CHAPTER12 SPECIAL RELAY LIST AND SPECIAL REGISTER LIST

- APPENDICES

- Appendix 1 List of Parameter Numbers

- Appendix 2 Functions Added or Changed by Version Upgrade

- Appendix 3 Method of Replacing Basic Model QCPU or High Performance Model QCPU with Universal Model QCPU

- Appendix 3.1 Replacement Precautions

- Appendix 3.2 Applicable devices and software

- Appendix 3.3 Instructions

- Appendix 3.4 Functions

- Appendix 3.4.1 Floating-point operation instructions

- Appendix 3.4.2 Error check processing for floating-point data comparison instructions

- Appendix 3.4.3 Range check processing for index-modified devices

- Appendix 3.4.4 Device latch function

- Appendix 3.4.5 File usability setting

- Appendix 3.4.6 Parameter-valid drive and boot file setting

- Appendix 3.4.7 External input/output forced on/off function

- Appendix 3.5 Special Relay and Special Register

- Appendix 4 Device Point Assignment Sheet

- INDEX

- Warranty

A - 1

SAFETY PRECAUTIONS

(Read these precautions before using this product.)

Before using this product, please read this manual and the relevant manuals carefully and pay full attention

to safety to handle the product correctly.

In this manual, the safety precautions are classified into two levels: " WARNING" and " CAUTION".

Under some circumstances, failure to observe the precautions given under " CAUTION" may lead to

serious consequences.

Make sure that the end users read this manual and then keep the manual in a safe place for future

reference.

WARNING

CAUTION

Indicates that incorrect handling may cause hazardous conditions,

resulting in death or severe injury.

Indicates that incorrect handling may cause hazardous conditions,

resulting in minor or moderate injury or property damage.

A - 2

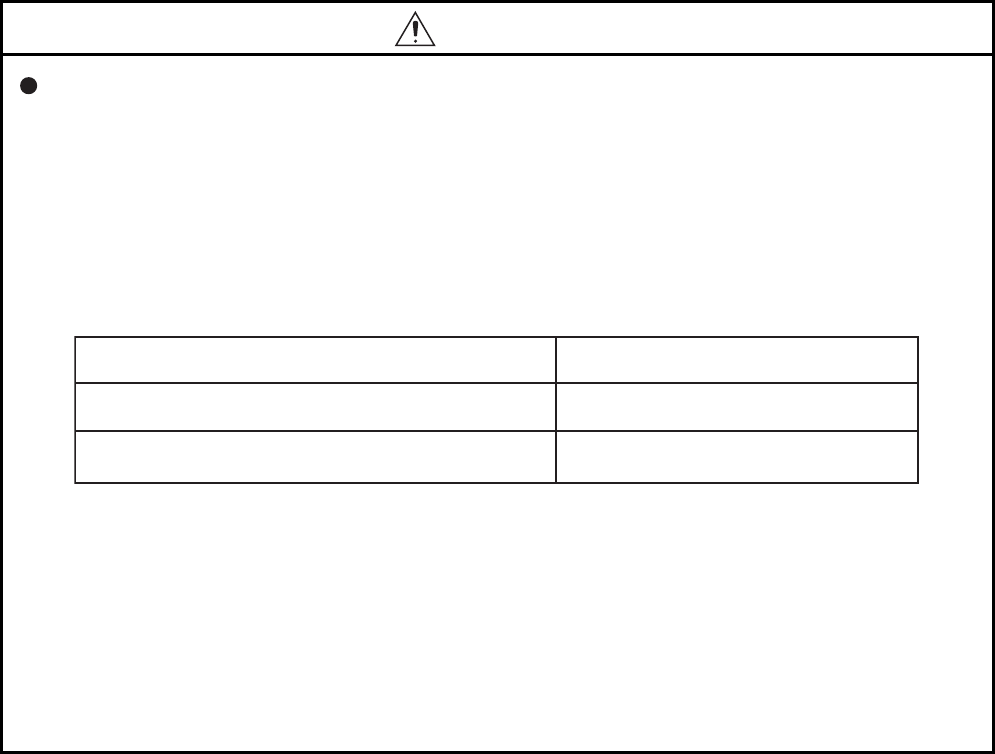

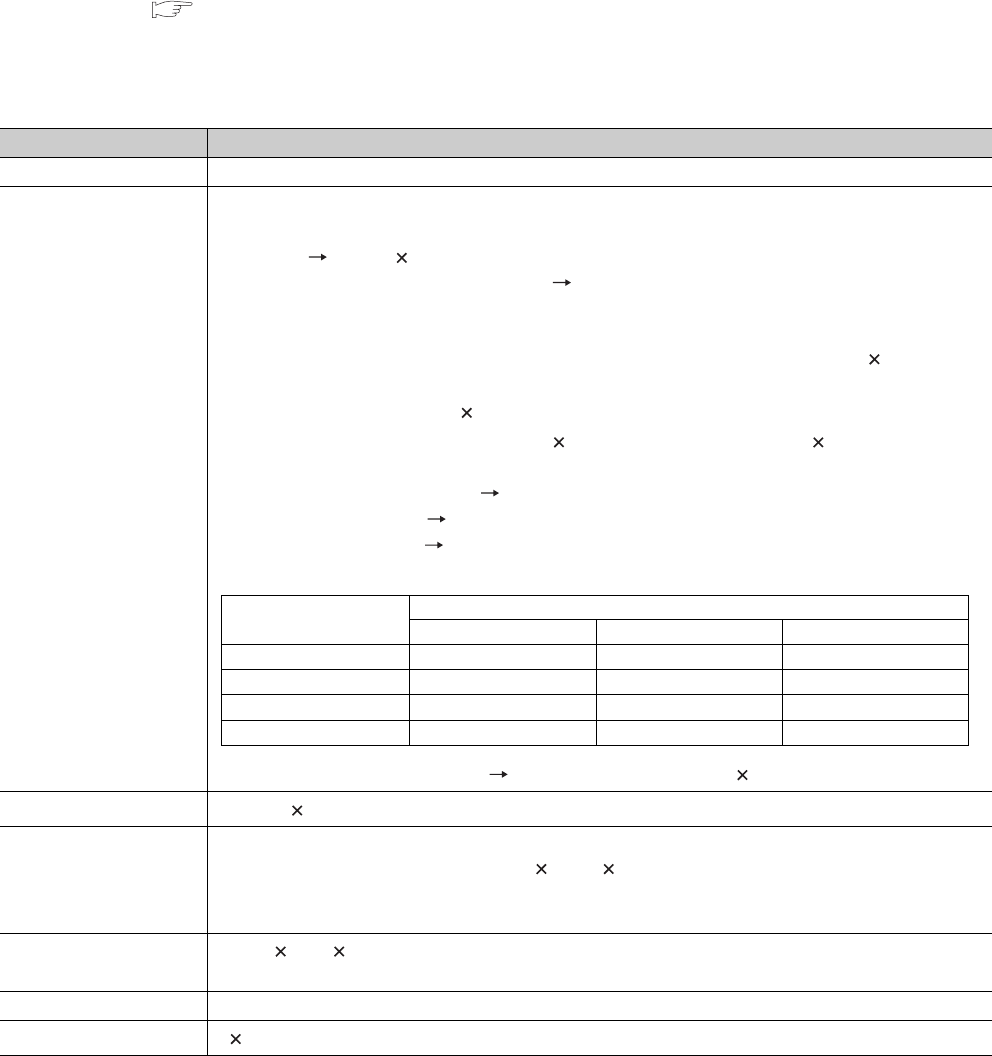

[Design Precautions]

WARNING

Configure safety circuits external to the programmable controller to ensure that the entire system

operates safely even when a fault occurs in the external power supply or the programmable

controller. Failure to do so may result in an accident due to an incorrect output or malfunction.

(1) Configure external safety circuits, such as an emergency stop circuit, protection circuit, and

protective interlock circuit for forward/reverse operation or upper/lower limit positioning.

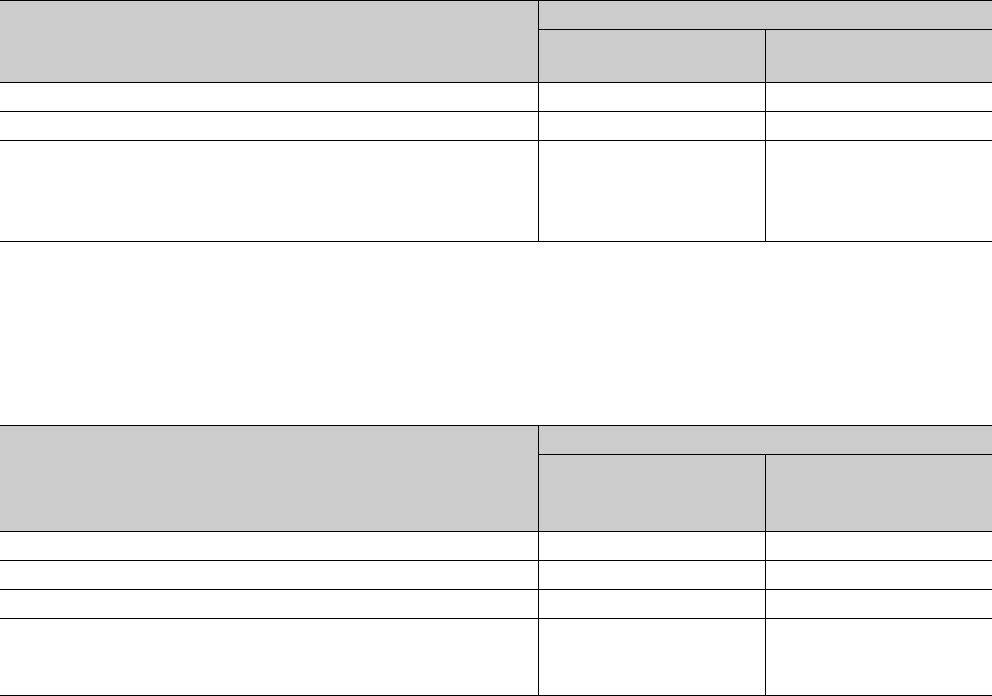

(2) The programmable controller stops its operation upon detection of the following status, and the

output status of the system will be as shown below.

All outputs may turn on when an error occurs in the part, such as I/O control part, where the CPU

module cannot detect any error. To ensure safety operation in such a case, provide a safety

mechanism or a fail-safe circuit external to the programmable controller. For a fail-safe circuit

example, refer to Chapter 10 LOADING AND INSTALLATION in the QCPU User's Manual

(Hardware Design, Maintenance and Inspection).

(3) Outputs may remain on or off due to a failure of an output module relay or transistor. Configure

an external circuit for monitoring output signals that could cause a serious accident.

Output

All outputs are turned off.

All outputs are held or turned off according to

the parameter setting.

Overcurrent or overvoltage protection of the power supply module

is activated.

The CPU module detects an error such as a watchdog timer error

by the self-diagnostic function.

Status

A - 3

[Design Precautions]

WARNING

In an output module, when a load current exceeding the rated current or an overcurrent caused by a

load short-circuit flows for a long time, it may cause smoke and fire. To prevent this, configure an

external safety circuit, such as a fuse.

Configure a circuit so that the programmable controller is turned on first and then the external power

supply.

If the external power supply is turned on first, an accident may occur due to an incorrect output or

malfunction.

For the operating status of each station after a communication failure, refer to relevant manuals for

the network.

Incorrect output or malfunction due to a communication failure may result in an accident.

When changing data of the running programmable controller from a peripheral connected to the

CPU module or from a personal computer connected to an intelligent function module, configure an

interlock circuit in the sequence program to ensure that the entire system will always operate safely.

For program modification and operating status change, read relevant manuals carefully and ensure

the safety before operation.

Especially, in the case of a control from an external device to a remote programmable controller,

immediate action cannot be taken for a problem on the programmable controller due to a

communication failure.

To prevent this, configure an interlock circuit in the sequence program, and determine corrective

actions to be taken between the external device and CPU module in case of a communication

failure.

CAUTION

Do not install the control lines or communication cables together with the main circuit lines or power

cables.

Keep a distance of 100mm (3.94 inches) or more between them.

Failure to do so may result in malfunction due to noise.

When a device such as a lamp, heater, or solenoid valve is controlled through an output module, a

large current (approximately ten times greater than normal) may flow when the output is turned from

off to on.

Take measures such as replacing the module with one having a sufficient current rating.

A - 4

[Installation Precautions]

CAUTION

Use the programmable controller in an environment that meets the general specifications in the

QCPU User's Manual (Hardware Design, Maintenance and Inspection).

Failure to do so may result in electric shock, fire, malfunction, or damage to or deterioration of the

product.

To mount the module, while pressing the module mounting lever located in the lower part of the

module, fully insert the module fixing projection(s) into the hole(s) in the base unit and press the

module until it snaps into place.

Incorrect mounting may cause malfunction, failure or drop of the module.

When using the programmable controller in an environment of frequent vibrations, fix the module

with a screw.

Tighten the screw within the specified torque range.

Undertightening can cause drop of the screw, short circuit or malfunction.

Overtightening can damage the screw and/or module, resulting in drop, short circuit, or malfunction.

When using an extension cable, connect it to the extension cable connector of the base unit securely.

Check the connection for looseness.

Poor contact may cause incorrect input or output.

When using a memory card, fully insert it into the memory card slot.

Check that it is inserted completely.

Poor contact may cause malfunction.

Shut off the external power supply for the system in all phases before mounting or removing the

module. Failure to do so may result in damage to the product.

A module can be replaced online (while power is on) on any MELSECNET/H remote I/O station or in

the system where a CPU module supporting the online module change function is used.

Note that there are restrictions on the modules that can be replaced online, and each module has its

predetermined replacement procedure.

For details, refer to the relevant sections in the QCPU User's Manual (Hardware Design,

Maintenance and Inspection) and in the manual for the corresponding module.

Do not directly touch any conductive part of the module.

Doing so can cause malfunction or failure of the module.

When using a Motion CPU module and modules designed for motion control, check that the

combinations of these modules are correct before applying power.

The modules may be damaged if the combination is incorrect.

For details, refer to the user's manual for the Motion CPU module.

A - 5

[Wiring Precautions]

WARNING

Shut off the external power supply for the system in all phases before wiring.

Failure to do so may result in electric shock or damage to the product.

After wiring, attach the included terminal cover to the module before turning it on for operation.

Failure to do so may result in electric shock.

CAUTION

Ground the FG and LG terminals to the protective ground conductor dedicated to the programmable

controller.

Failure to do so may result in electric shock or malfunction.

Use applicable solderless terminals and tighten them within the specified torque range. If any spade

solderless terminal is used, it may be disconnected when the terminal screw comes loose, resulting

in failure.

Check the rated voltage and terminal layout before wiring to the module, and connect the cables

correctly.

Connecting a power supply with a different voltage rating or incorrect wiring may cause a fire or

failure.

Connectors for external connection must be crimped or pressed with the tool specified by the

manufacturer, or must be correctly soldered.

Incomplete connections could result in short circuit, fire, or malfunction.

Tighten the terminal screw within the specified torque range.

Undertightening can cause short circuit, fire, or malfunction.

Overtightening can damage the screw and/or module, resulting in drop, short circuit, or malfunction.

Prevent foreign matter such as dust or wire chips from entering the module.

Such foreign matter can cause a fire, failure, or malfunction.

A - 6

[Wiring Precautions]

[Startup and Maintenance Precautions]

WARNING

A protective film is attached to the top of the module to prevent foreign matter, such as wire chips,

from entering the module during wiring.

Do not remove the film during wiring.

Remove it for heat dissipation before system operation.

Mitsubishi programmable controllers must be installed in control panels.

Connect the main power supply to the power supply module in the control panel through a relay

terminal block.

Wiring and replacement of a power supply module must be performed by maintenance personnel

who is familiar with protection against electric shock. (For wiring methods, refer to the QCPU User's

Manual (Hardware Design, Maintenance and Inspection)).

WARNING

Do not touch any terminal while power is on.

Doing so will cause electric shock.

Correctly connect the battery connector.

Do not charge, disassemble, heat, short-circuit, solder, or throw the battery into the fire.

Doing so will cause the battery to produce heat, explode, or ignite, resulting in injury and fire.

Shut off the external power supply for the system in all phases before cleaning the module or

retightening the terminal screws or module fixing screws.

Failure to do so may result in electric shock.

Undertightening the terminal screws can cause short circuit or malfunction.

Overtightening can damage the screw and/or module, resulting in drop, short circuit, or malfunction.

A - 7

[Startup and Maintenance Precautions]

CAUTION

Before performing online operations (especially, program modification, forced output, and operation

status change) for the running CPU module from the peripheral connected, read relevant manuals

carefully and ensure the safety.

Improper operation may damage machines or cause accidents.

Do not disassemble or modify the modules.

Doing so may cause failure, malfunction, injury, or a fire.

Use any radio communication device such as a cellular phone or PHS (Personal Handy-phone

System) more than 25cm (9.85 inches) away in all directions from the programmable controller.

Failure to do so may cause malfunction.

Shut off the external power supply for the system in all phases before mounting or removing the

module. Failure to do so may cause the module to fail or malfunction.

A module can be replaced online (while power is on) on any MELSECNET/H remote I/O station or in

the system where a CPU module supporting the online module change function is used.

Note that there are restrictions on the modules that can be replaced online, and each module has its

predetermined replacement procedure.

For details, refer to the relevant sections in the QCPU User's Manual (Hardware Design,

Maintenance and Inspection) and in the manual for the corresponding module.

After the first use of the product, do not mount/remove the module to/from the base unit, and the

terminal block to/from the module more than 50 times (IEC 61131-2 compliant) respectively.

Exceeding the limit of 50 times may cause malfunction.

Do not drop or apply shock to the battery to be installed in the module.

Doing so may damage the battery, causing the battery fluid to leak inside the battery.

If the battery is dropped or any shock is applied to it, dispose of it without using.

Before handling the module, touch a grounded metal object to discharge the static electricity from

the human body.

Failure to do so may cause the module to fail or malfunction.

A - 8

[Disposal Precautions]

[Transportation Precautions]

CAUTION

When disposing of this product, treat it as industrial waste.

When disposing of batteries, separate them from other wastes according to the local regulations.

(For details of the battery directive in EU member states, refer to the QCPU User's Manual

(Hardware Design, Maintenance and Inspection).)

CAUTION

When transporting lithium batteries, follow the transportation regulations.

(For details of the regulated models, refer to the QCPU User's Manual (Hardware Design,

Maintenance and Inspection).)

A - 9

CONDITIONS OF USE FOR THE PRODUCT

(1) Mitsubishi programmable controller ("the PRODUCT") shall be used in conditions;

i) where any problem, fault or failure occurring in the PRODUCT, if any, shall not lead to any major

or serious accident; and

ii) where the backup and fail-safe function are systematically or automatically provided outside of

the PRODUCT for the case of any problem, fault or failure occurring in the PRODUCT.

(2) The PRODUCT has been designed and manufactured for the purpose of being used in general

industries.

MITSUBISHI SHALL HAVE NO RESPONSIBILITY OR LIABILITY (INCLUDING, BUT NOT

LIMITED TO ANY AND ALL RESPONSIBILITY OR LIABILITY BASED ON CONTRACT,

WARRANTY, TORT, PRODUCT LIABILITY) FOR ANY INJURY OR DEATH TO PERSONS OR

LOSS OR DAMAGE TO PROPERTY CAUSED BY the PRODUCT THAT ARE OPERATED OR

USED IN APPLICATION NOT INTENDED OR EXCLUDED BY INSTRUCTIONS, PRECAUTIONS,

OR WARNING CONTAINED IN MITSUBISHI'S USER, INSTRUCTION AND/OR SAFETY

MANUALS, TECHNICAL BULLETINS AND GUIDELINES FOR the PRODUCT.

("Prohibited Application")

Prohibited Applications include, but not limited to, the use of the PRODUCT in;

• Nuclear Power Plants and any other power plants operated by Power companies, and/or any

other cases in which the public could be affected if any problem or fault occurs in the PRODUCT.

• Railway companies or Public service purposes, and/or any other cases in which establishment of

a special quality assurance system is required by the Purchaser or End User.

• Aircraft or Aerospace, Medical applications, Train equipment, transport equipment such as

Elevator and Escalator, Incineration and Fuel devices, Vehicles, Manned transportation,

Equipment for Recreation and Amusement, and Safety devices, handling of Nuclear or

Hazardous Materials or Chemicals, Mining and Drilling, and/or other applications where there is a

significant risk of injury to the public or property.

Notwithstanding the above, restrictions Mitsubishi may in its sole discretion, authorize use of the

PRODUCT in one or more of the Prohibited Applications, provided that the usage of the PRODUCT

is limited only for the specific applications agreed to by Mitsubishi and provided further that no

special quality assurance or fail-safe, redundant or other safety features which exceed the general

specifications of the PRODUCTs are required. For details, please contact the Mitsubishi

representative in your region.

A - 10

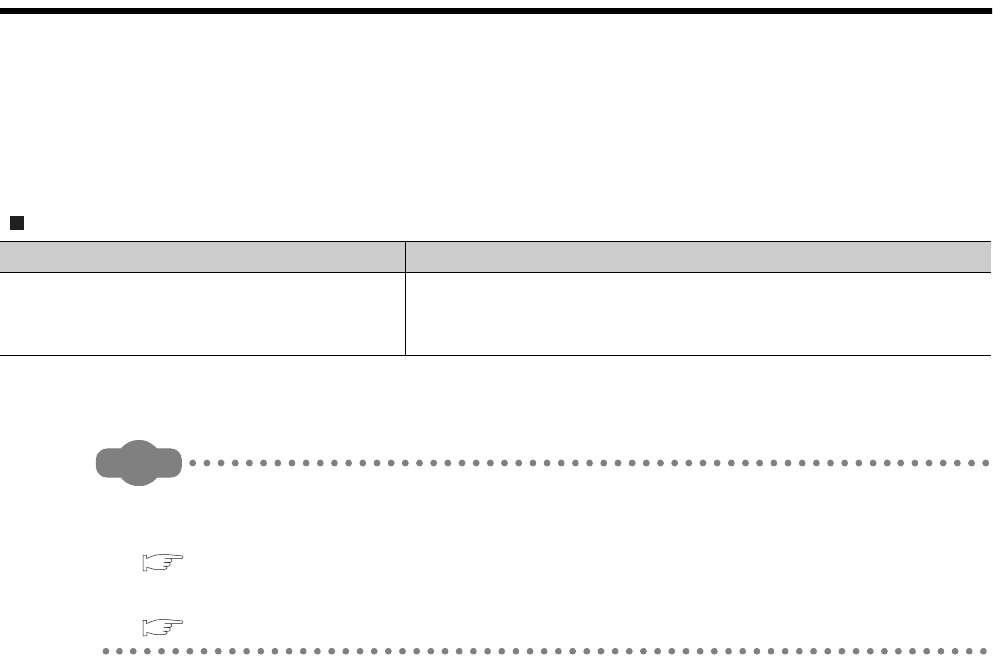

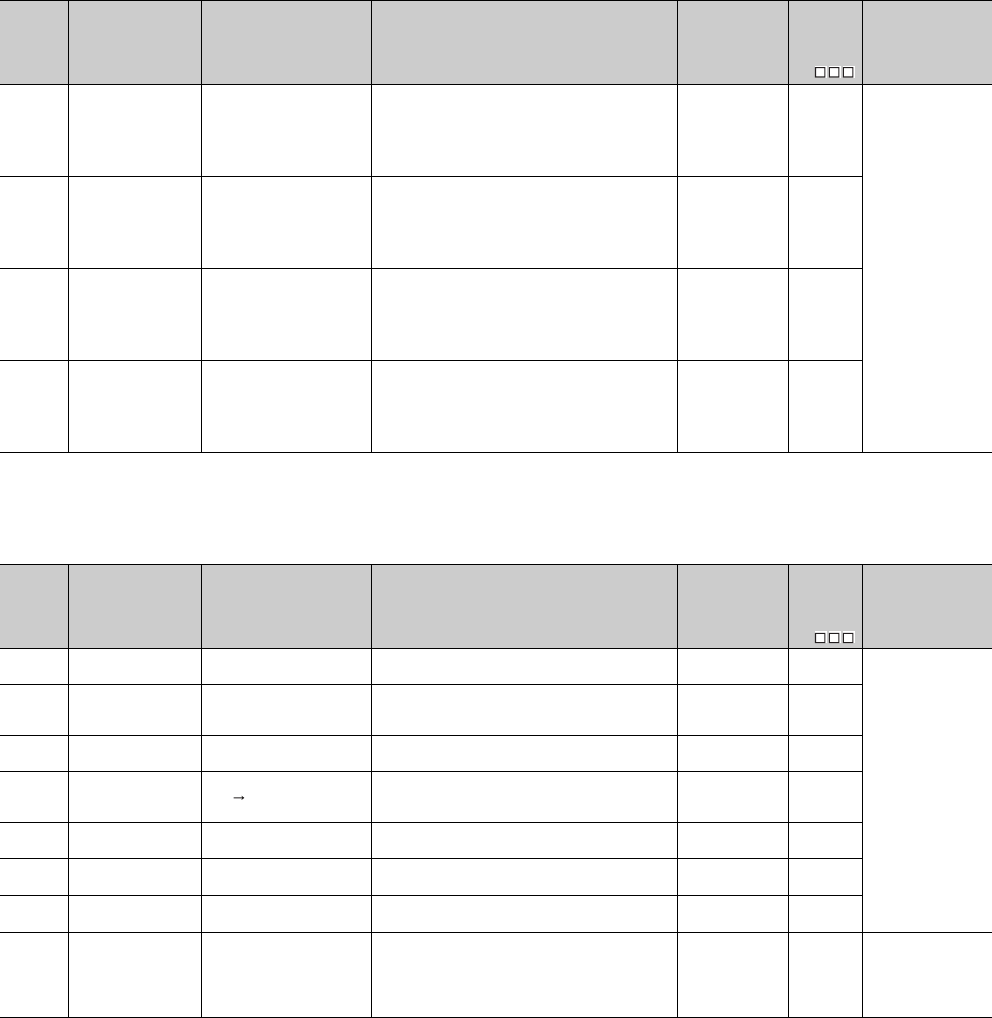

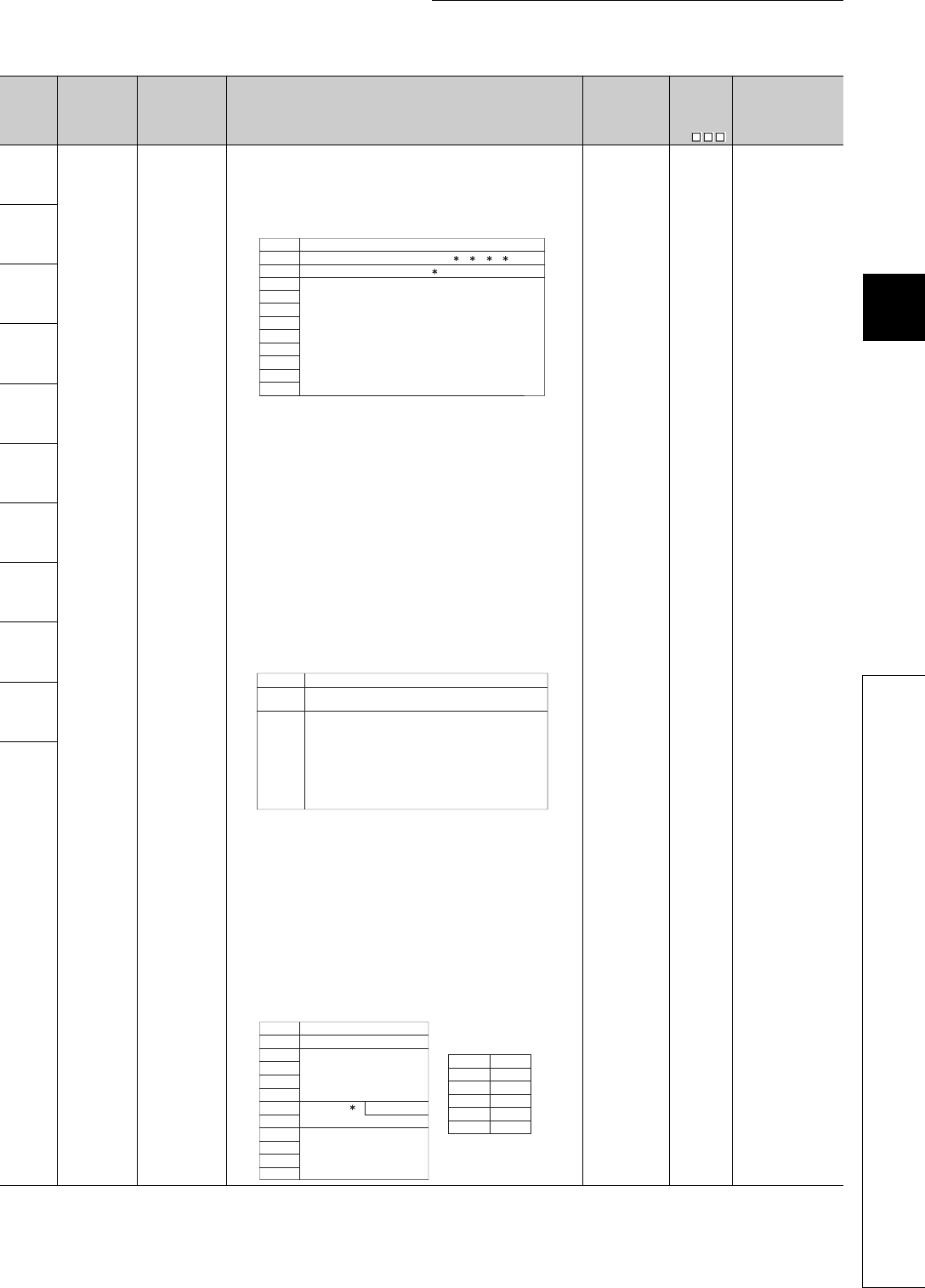

REVISIONS

*The manual number is given on the bottom left of the back cover.

Japanese manual version SH-080802-D

2008 MITSUBISHI ELECTRIC CORPORATION

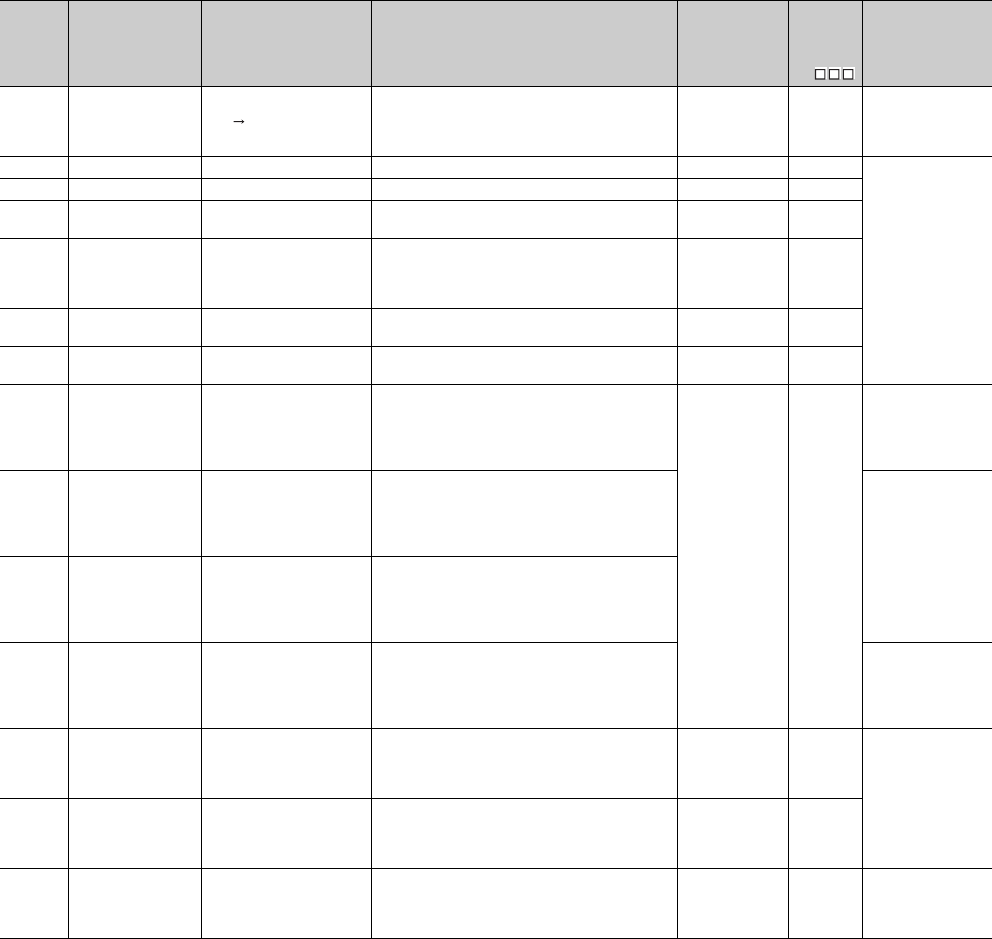

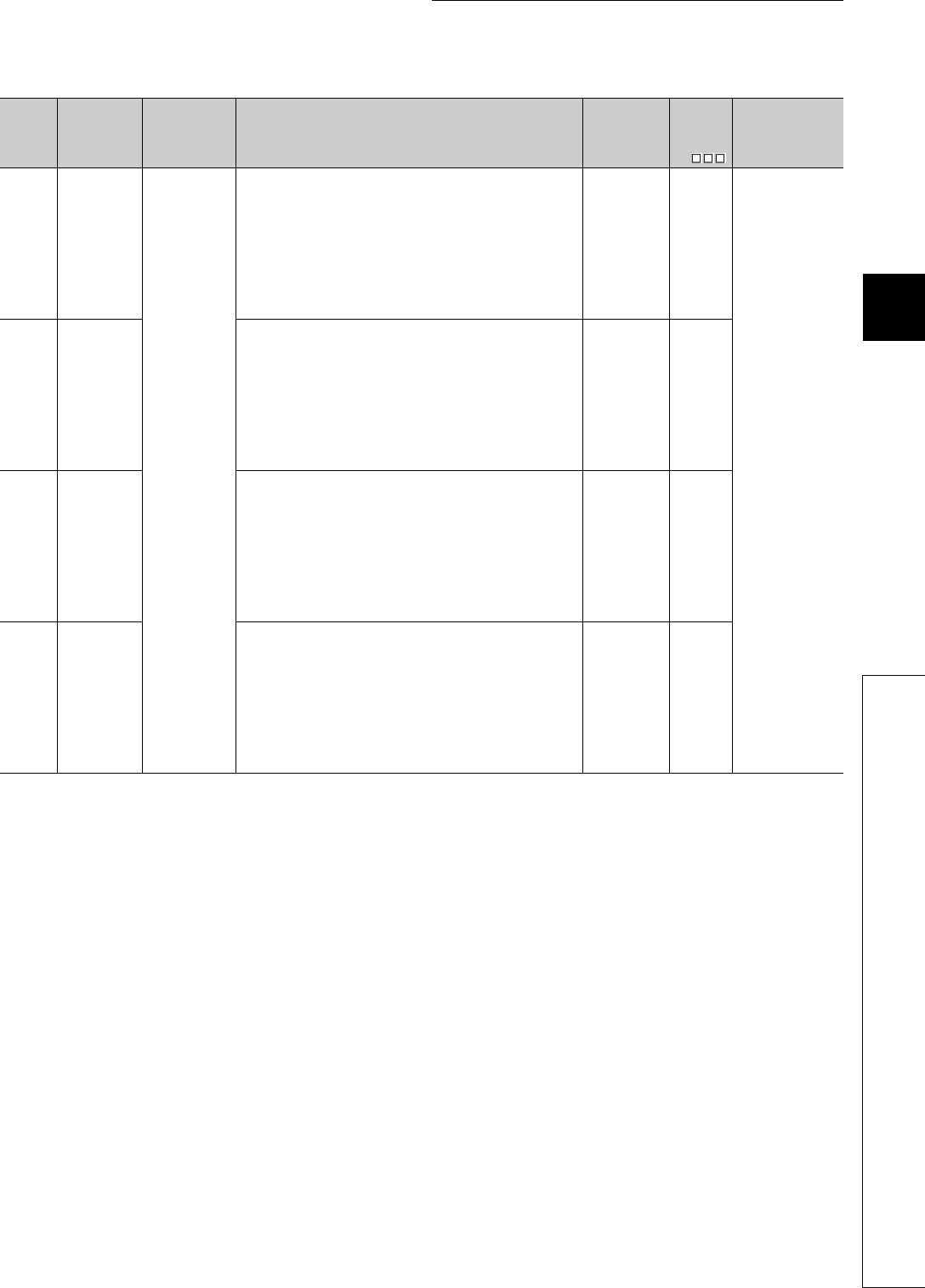

Print date Manual number Revision

Dec., 2008 SH(NA)-080807ENG-A First edition

Mar., 2009 SH(NA)-080807ENG-B Revision because of function addition to Built-in Ethernet port QCPU (first five

digits of the serial number is "11012" or later)

Partial correction

SAFETY PRECAUTIONS, INTRODUCTION, MANUALS, MANUAL PAGE

ORGANIZATION, GENERIC TERMS AND ABBREVIATIONS, Section 1.3, 1.6,

2.2.2, 2.2.3, 2.3, 2.3.3, 2.3.4, 2.4, CHAPTER 3, Section 3.3, CHAPTER 4, Sec-

tion 4.1.2, 4.2.2, 4.2.3, 5.1.1, 5.1.3, 5.1.6, 5.1.7, 5.1.8, 5.1.10, 6.1, 6.3, 6.4, 6.5,

6.6.1, 6.6.5, 6.11.1, 6.11.3, 6.11.4, 6.12.1, 6.13.3, 6.14, 6.15, 6.15.1, 6.15.2,

6.16, 6.17, 6.18, 6.20, 6.28, 6.30, 7.1.2, 8.2, 8.3, 9.2, 9.2.5, 9.2.11, 9.7.4, 9.11,

9.14.2, 11.5, Appendix 1, Appendix 2, Appendix 3.1, Appendix 3.3.2, Appendix 4

Addition

Appendix 3.4.2

Jul., 2009 SH(NA)-080807ENG-C Revision because of function addition to the Universal model QCPU (first five

digits of the serial number is "11043" or later)

Partial correction

Section 5.1.1, 5.1.5, 5.3.3, 6.1, 6.18, 6.21.2, 6.28, 8.1, 9.2.10, 9.6.1, 10.1.3, 12.2,

Appendix 1, Appendix 2, Appendix 3.1.2, Appendix 3.2

Addition

Section 6.31, 6.32

Nov., 2009 SH(NA)-080807ENG-D Partial correction

SAFETY PRECAUTIONS, Section 4.2.2, 9.6.1, 9.7.4, Appendix 3.1.1,

Appendix 3.1.2

Addition

CONDITIONS OF USE FOR THE PRODUCT

This manual confers no industrial property rights or any rights of any other kind, nor does it confer any patent licenses. Mit-

subishi Electric Corporation cannot be held responsible for any problems involving industrial property rights which may occur

as a result of using the contents noted in this manual.

C

A - 11

INTRODUCTION

This manual describes the memory maps, functions, programs, I/O number assignment, and devices of the Universal model

QCPU.

Before using this product, please read this manual and the relevant manuals carefully and develop familiarity with the

functions and performance of the Q series programmable controller to handle the product correctly.

Relevant CPU module

Remark

This manual does not describe the specifications of the power supply modules, base units, extension cables, memory

cards, and batteries.

For details, refer to the following.

QCPU User's Manual (Hardware Design, Maintenance and Inspection)

For multiple CPU systems, refer to the following.

QCPU User's Manual (Multiple CPU System)

CPU module Model

Universal model QCPU

Q00UJCPU, Q00UCPU, Q01UCPU, Q02UCPU, Q03UD(E)CPU,

Q04UD(E)HCPU, Q06UD(E)HCPU, Q10UD(E)HCPU,

Q13UD(E)HCPU, Q20UD(E)HCPU, Q26UD(E)HCPU

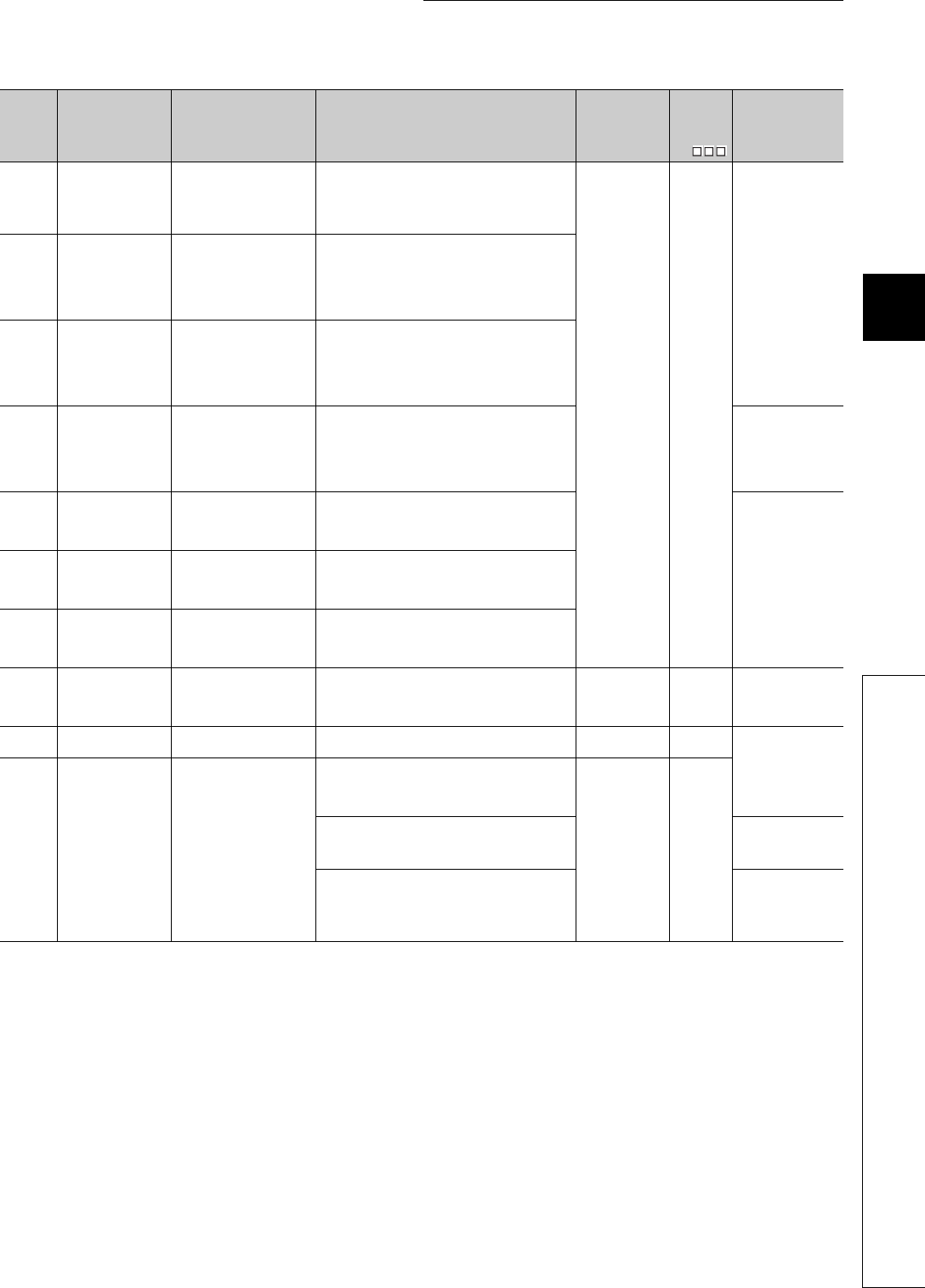

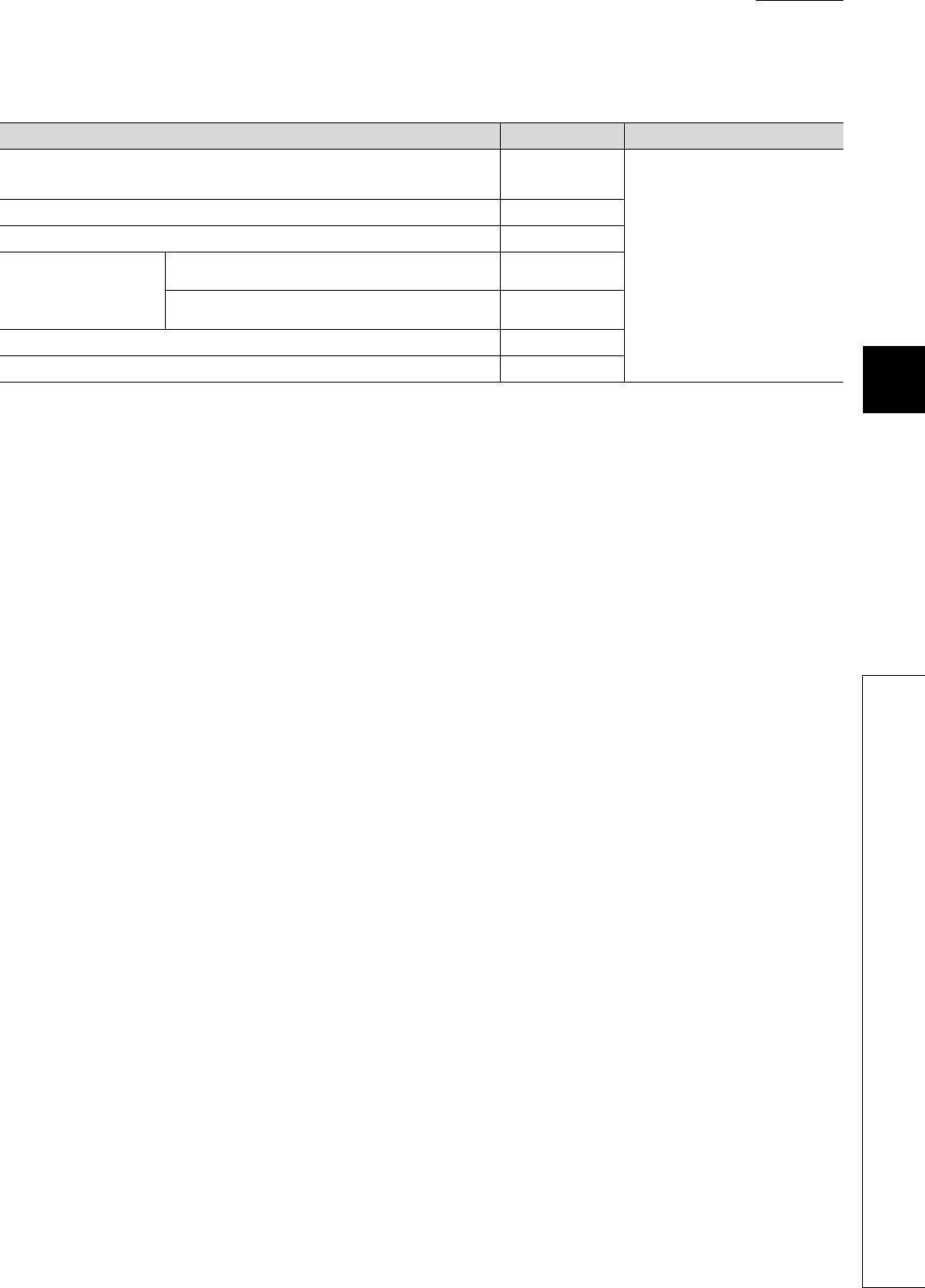

CONTENTS

A - 12

CONTENTS

SAFETY PRECAUTIONS......................................................................................................................A - 1

CONDITIONS OF USE FOR THE PRODUCT ......................................................................................A - 9

REVISIONS ...........................................................................................................................................A - 10

INTRODUCTION ...................................................................................................................................A - 11

MANUALS .............................................................................................................................................A - 18

MANUAL PAGE ORGANIZATION.........................................................................................................A - 20

GENERIC TERMS AND ABBREVIATIONS ..........................................................................................A - 21

CHAPTER1 OVERVIEW 1-1 to 1-14

1.1 Processing Order in the CPU Module....................................................................................1 - 1

1.2 Storing and Executing Programs ...........................................................................................1 - 2

1.3 Structured Programming........................................................................................................1 - 3

1.4 Devices and Instructions Useful for Programming................................................................. 1 - 6

1.5 Features................................................................................................................................. 1 - 11

1.6 Checking Serial Number and Function Version ..................................................................... 1 - 13

CHAPTER2 SEQUENCE PROGRAMS 2-1 to 2-43

2.1 Sequence Program Overview................................................................................................2 - 1

2.2 Sequence Program Configuration..........................................................................................2 - 3

2.2.1 Main routine program ........................................................................................................2 - 4

2.2.2 Subroutine program ..........................................................................................................2 - 5

2.2.3 Interrupt program ..............................................................................................................2 - 6

2.3 Settings When Program is Divided ........................................................................................2 - 13

2.3.1 Initial execution type program ...........................................................................................2 - 17

2.3.2 Scan execution type program ...........................................................................................2 - 20

2.3.3 Stand-by type program......................................................................................................2 - 21

2.3.4 Fixed scan execution type program ..................................................................................2 - 26

2.3.5 Changing the program execution type ..............................................................................2 - 30

2.4 Data Used in Sequence Programs ........................................................................................2 - 32

2.4.1 BIN (Binary Code) .............................................................................................................2 - 35

2.4.2 HEX (Hexadecimal)...........................................................................................................2 - 37

2.4.3 BCD (Binary-coded Decimal) ............................................................................................2 - 38

2.4.4 Real number (Floating-point data).....................................................................................2 - 39

2.4.5 Character string data.........................................................................................................2 - 43

CHAPTER3 CPU MODULE OPERATION 3-1 to 3-14

3.1 Initial Processing.................................................................................................................... 3 - 1

3.2 I/O Refresh (Refresh Processing with Input/Output Modules)...............................................3 - 2

3.3 Program Operation ................................................................................................................ 3 - 2

3.4 END Processing..................................................................................................................... 3 - 2

3.5 Operation Processing in the RUN,STOP, or PAUSE Status .................................................. 3 - 3

3.6 Operation Processing during Momentary Power Failure ....................................................... 3 - 5

3.7 Data Clear Processing........................................................................................................... 3 - 6

A - 13

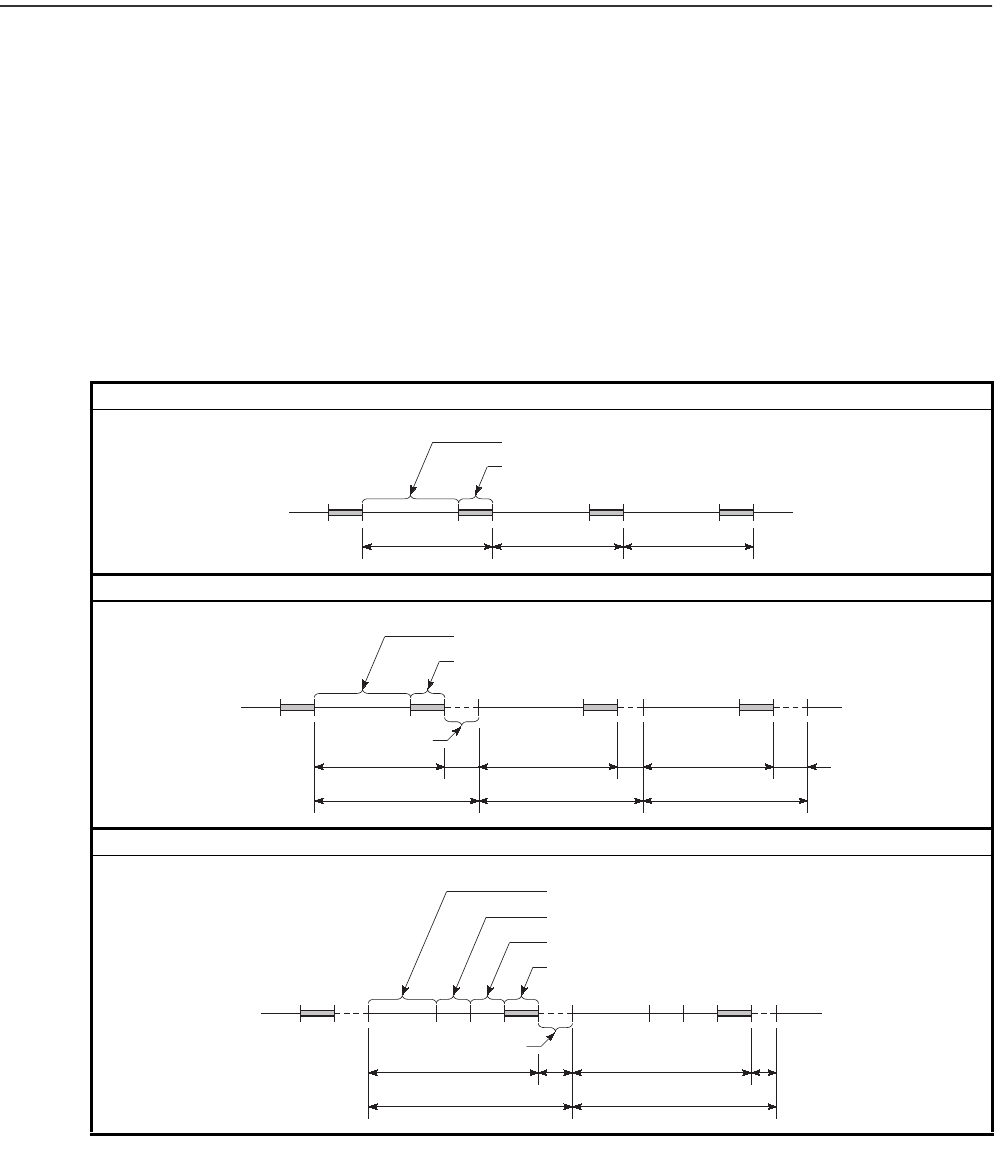

3.8 I/O Processing and Response Delay.....................................................................................3 - 8

3.8.1 Refresh mode....................................................................................................................3 - 9

3.8.2 Direct mode.......................................................................................................................3 - 12

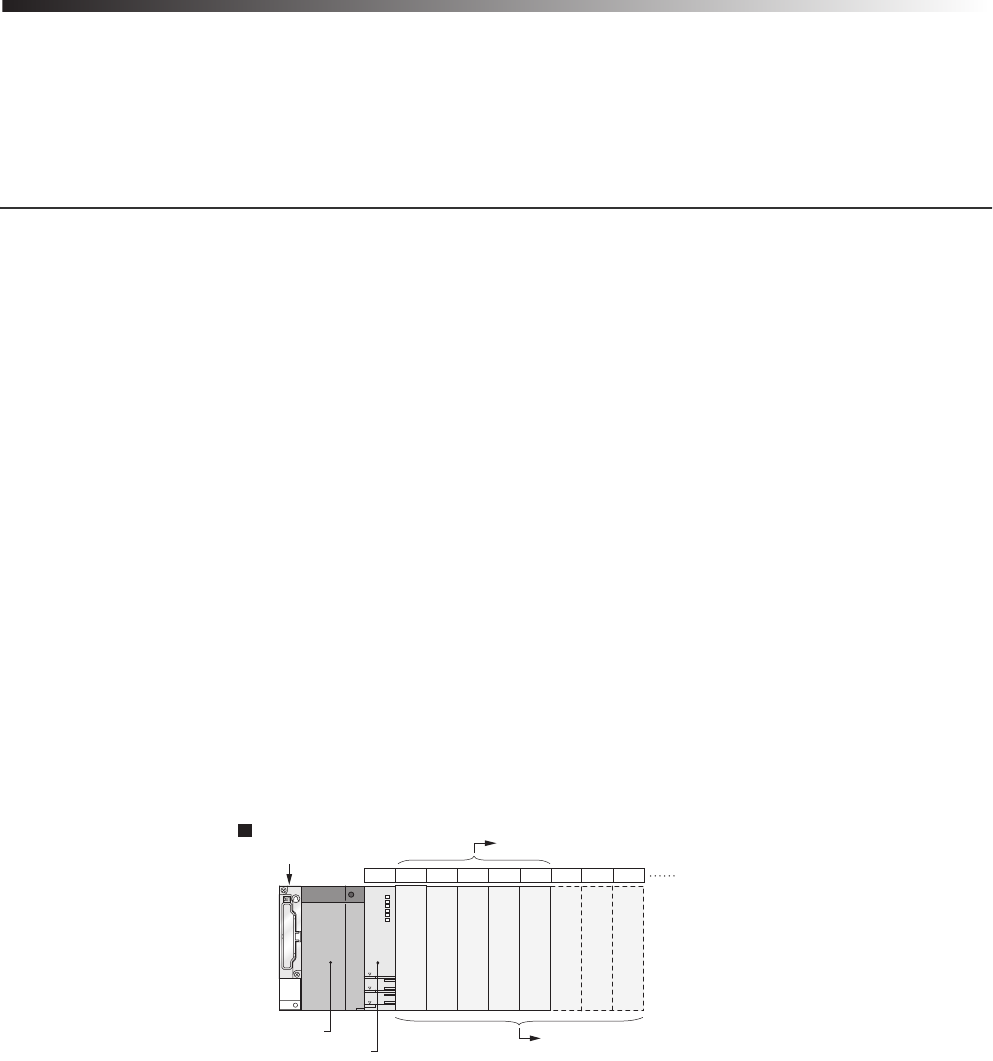

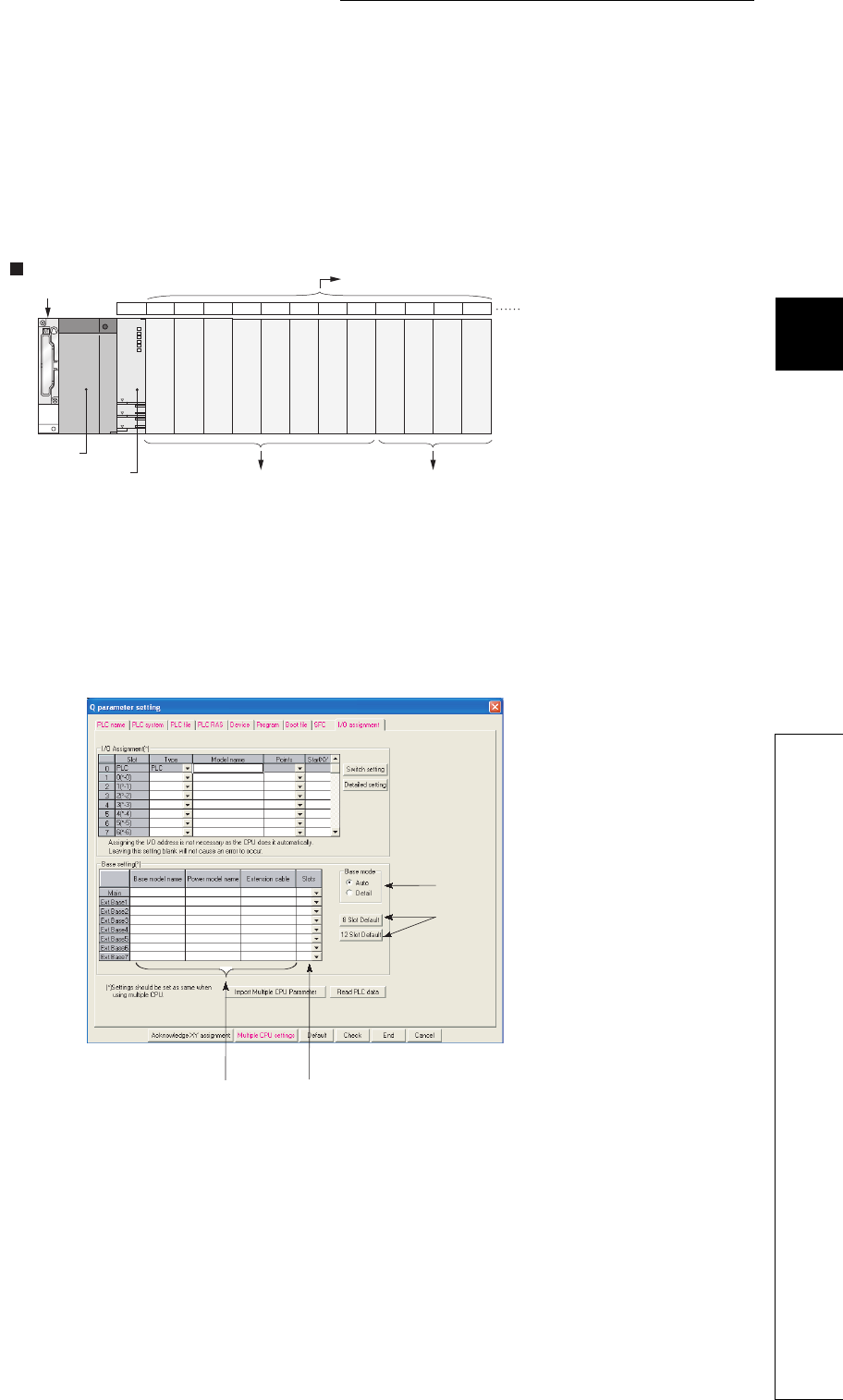

CHAPTER4 ASSIGNMENT OF BASE UNIT AND I/O NUMBER 4-1 to 4-17

4.1 Base Unit Assignment............................................................................................................4 - 1

4.1.1 Base mode ........................................................................................................................4 - 1

4.1.2 Base unit assignment setting ............................................................................................4 - 2

4.2 I/O Number Assignment.........................................................................................................4 - 4

4.2.1 Concept of I/O number assignment ..................................................................................4 - 5

4.2.2 Setting I/O numbers ..........................................................................................................4 - 8

4.2.3 I/O number setting example ..............................................................................................4 - 13

4.2.4 Checking I/O numbers ......................................................................................................4 - 17

CHAPTER5 MEMORIES AND FILES USED FOR CPU MODULE 5-1 to 5-38

5.1 Memories Used for CPU Module ...........................................................................................5 - 1

5.1.1 Memory composition and storable data ............................................................................5 - 1

5.1.2 Program memory ..............................................................................................................5 - 5

5.1.3 Program cache memory....................................................................................................5 - 8

5.1.4 Standard ROM ..................................................................................................................5 - 11

5.1.5 Standard RAM ...................................................................................................................5 - 12

5.1.6 Memory card .....................................................................................................................5 - 14

5.1.7 Writing to the Flash card by GX Developer .......................................................................5 - 18

5.1.8 Operating the program in the memory card (boot operation)............................................5 - 23

5.1.9 Details of written files ........................................................................................................5 - 27

5.1.10 Specifying valid parameters (parameter-valid drive setting)..............................................5 - 28

5.2 Program File Structure........................................................................................................... 5 - 30

5.3 File Operations by GX Developer and Handling Precautions................................................5 - 32

5.3.1 File operations...................................................................................................................5 - 32

5.3.2 Precautions for handling files ............................................................................................5 - 33

5.3.3 File size .............................................................................................................................5 - 34

5.3.4 Units of file sizes ...............................................................................................................5 - 36

CHAPTER6 FUNCTIONS 6-1 to 6-165

6.1 Function List........................................................................................................................... 6 - 1

6.2 Constant Scan ....................................................................................................................... 6 - 4

6.3 Latch Function ....................................................................................................................... 6 - 7

6.4 Output Mode at Operating Status Change (STOP to RUN)................................................... 6 - 10

6.5 Clock Function ....................................................................................................................... 6 - 13

6.6 Remote Operation.................................................................................................................. 6 - 18

6.6.1 Remote RUN/STOP ..........................................................................................................6 - 18

6.6.2 Remote PAUSE.................................................................................................................6 - 21

6.6.3 Remote RESET.................................................................................................................6 - 23

A - 14

6.6.4 Remote latch clear ............................................................................................................6 - 25

6.6.5 Relationship between remote operation and RUN/STOP status of the CPU module .......6 - 26

6.7 Q Series-compatible Module Input Response Time Selection (I/O Response Time) ............ 6 - 27

6.8 Error Time Output Mode Setting ............................................................................................6 - 29

6.9 H/W Error Time PLC Operation Mode Setting .......................................................................6 - 30

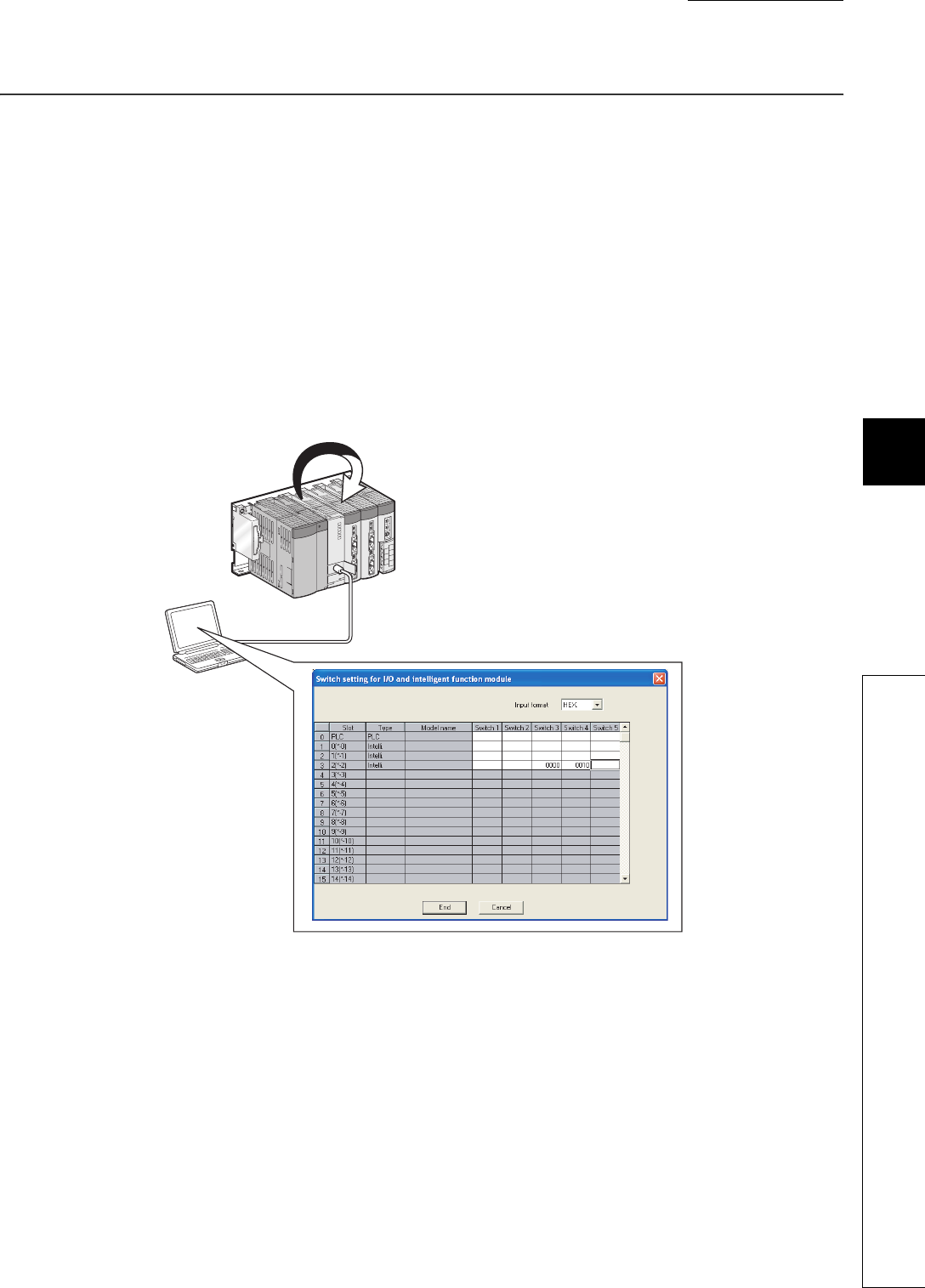

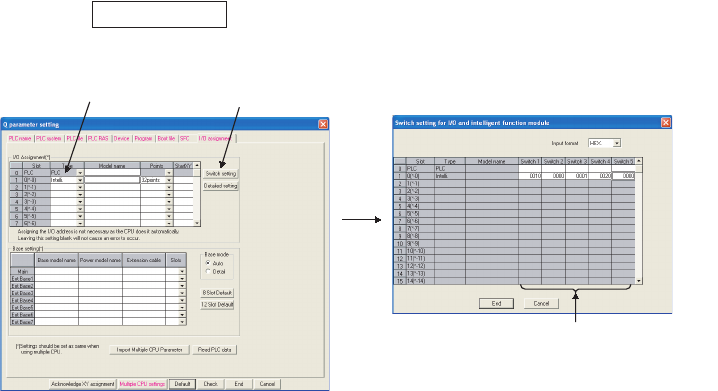

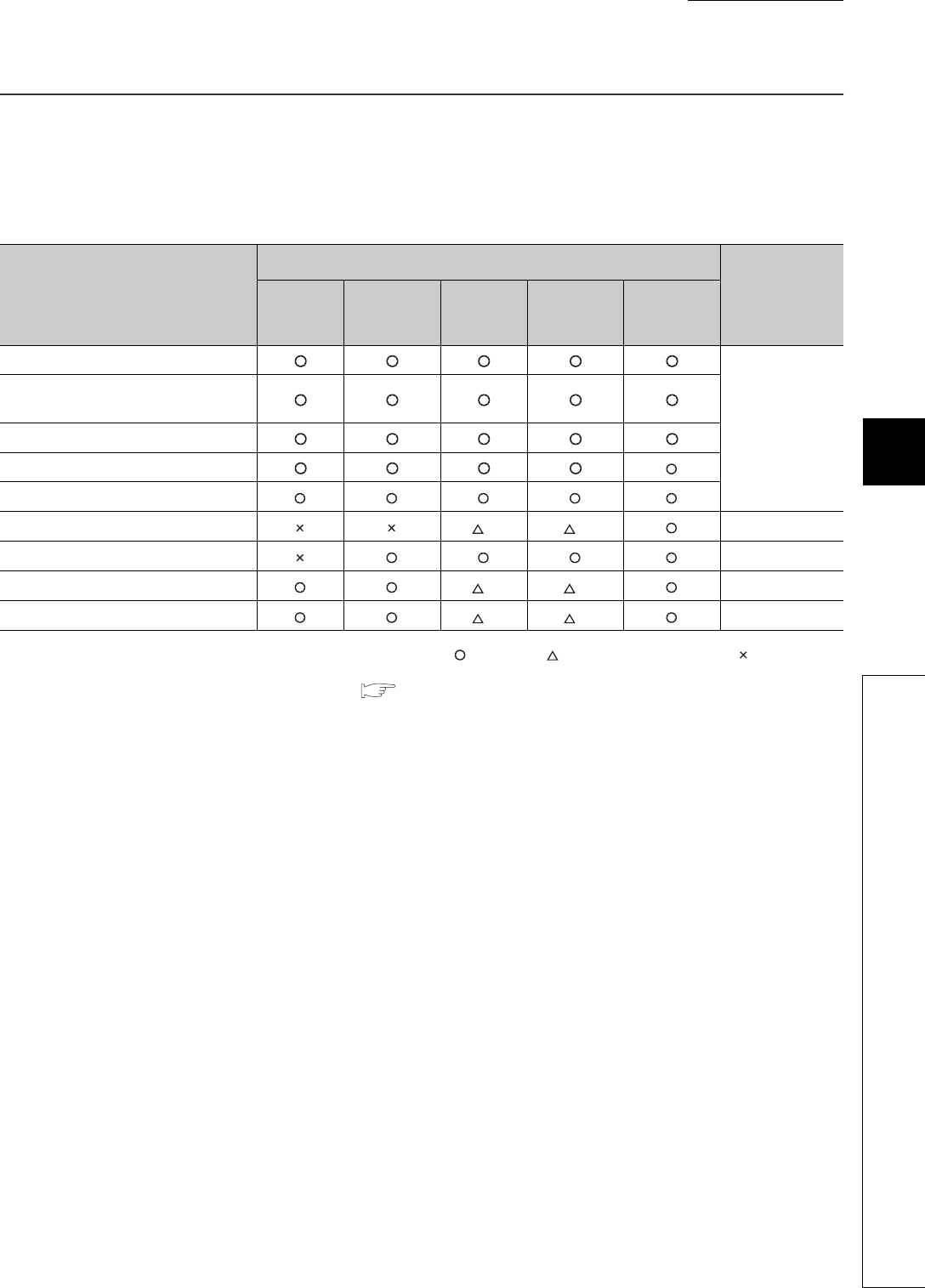

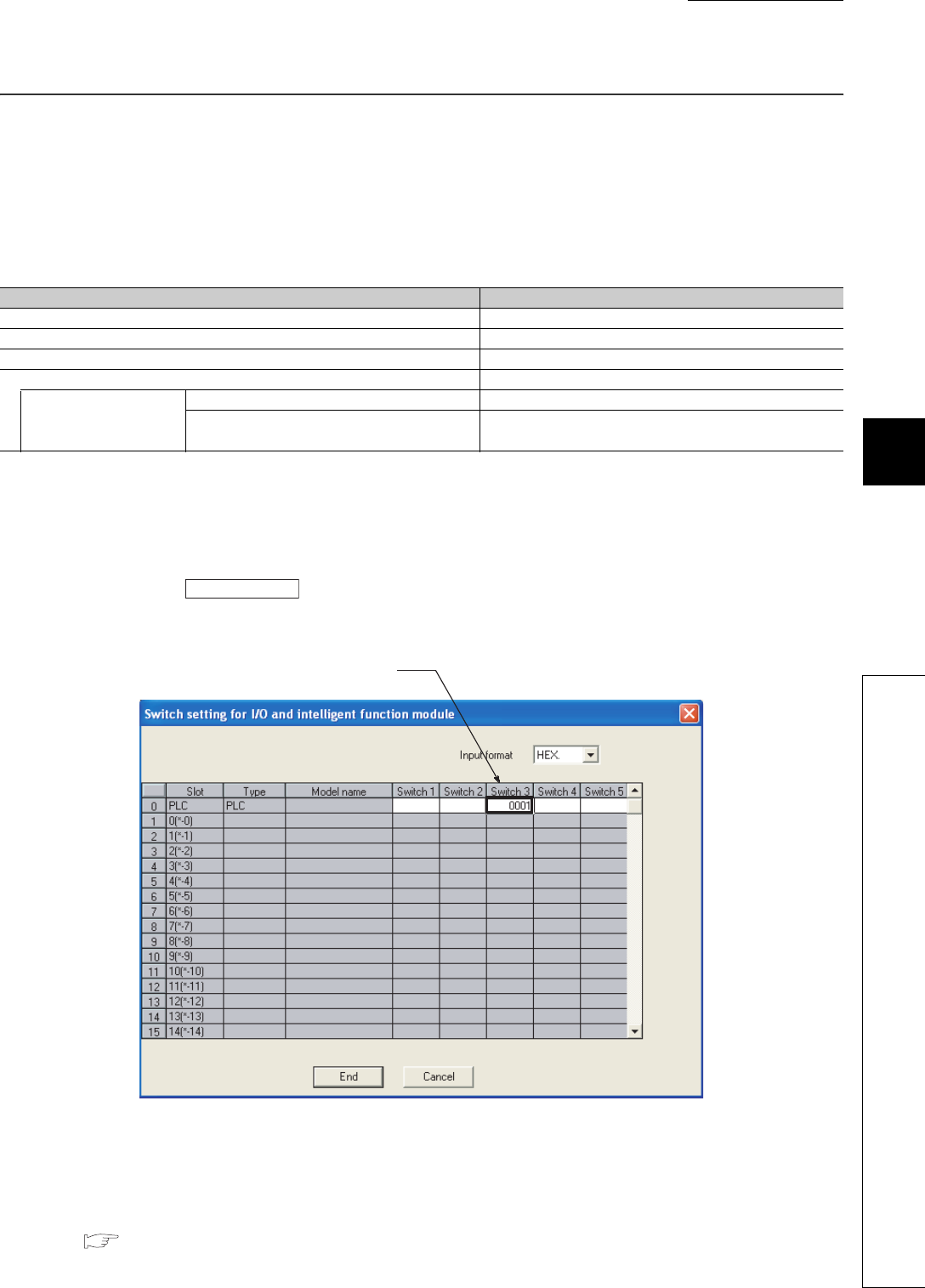

6.10 Intelligent Function Module Switch Setting ............................................................................ 6 - 31

6.11 Monitor Function .................................................................................................................... 6 - 33

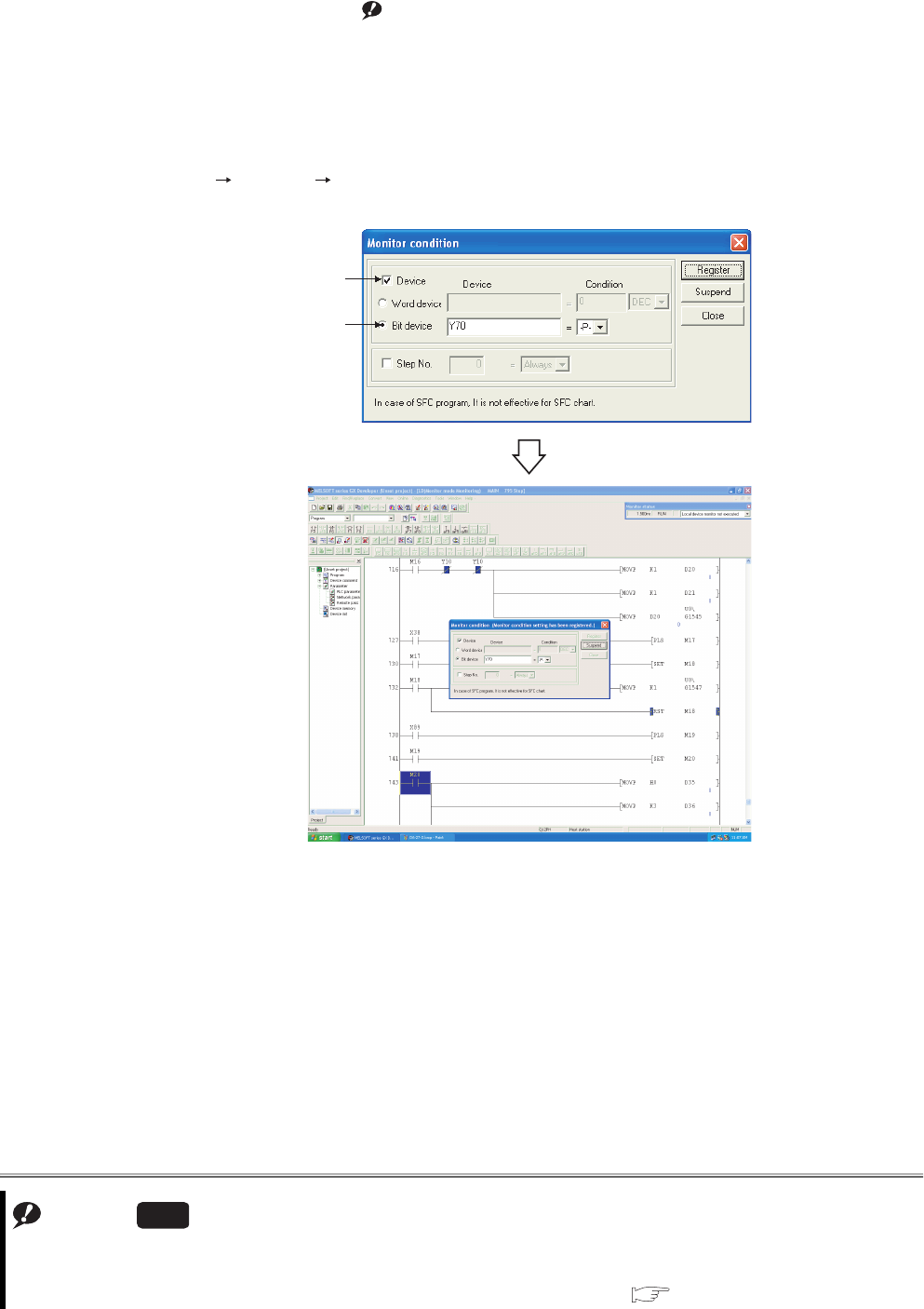

6.11.1 Monitor condition setting ...................................................................................................6 - 34

6.11.2 Local device monitor/test ..................................................................................................6 - 40

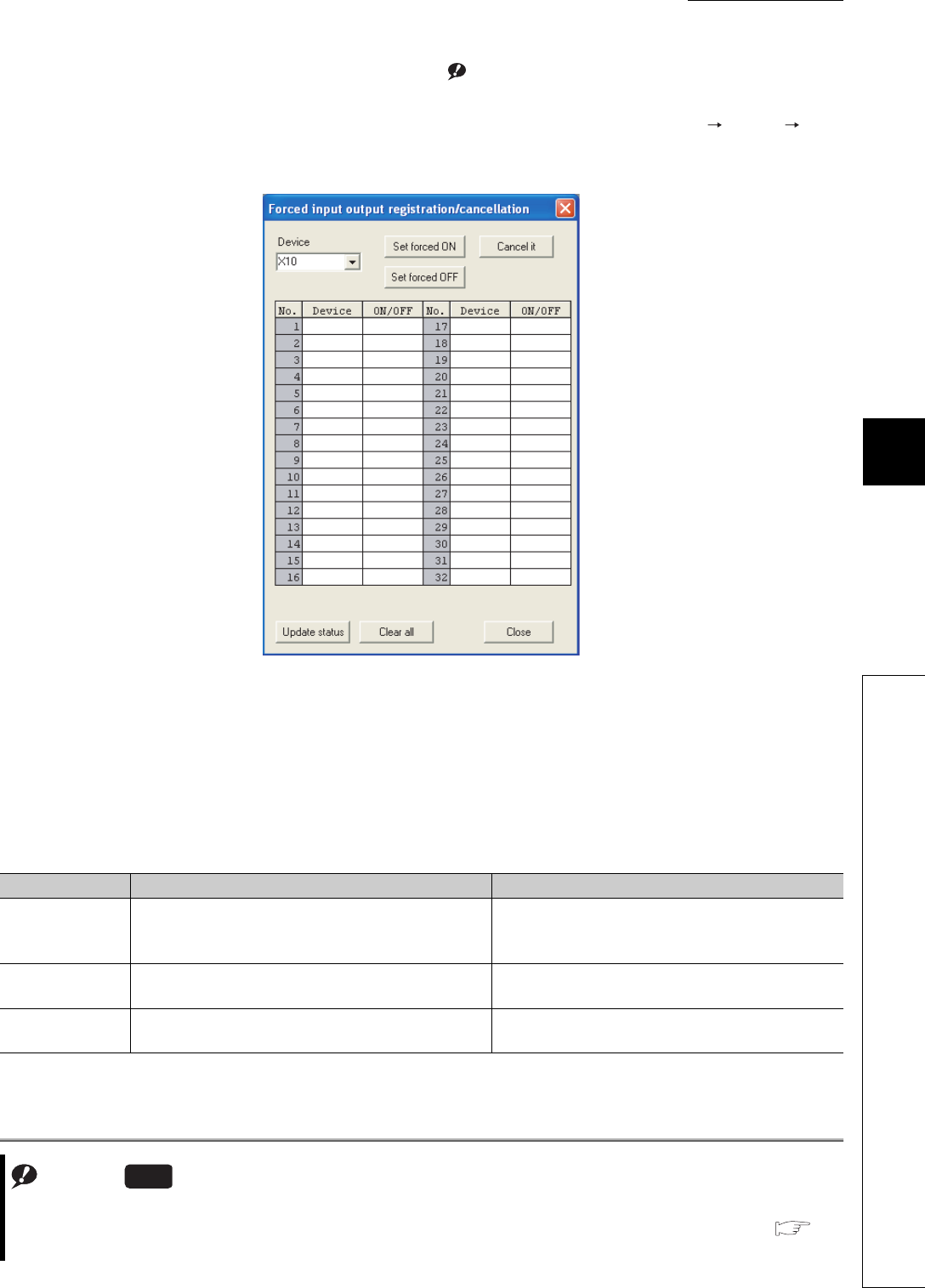

6.11.3 External input/output forced on/off ....................................................................................6 - 43

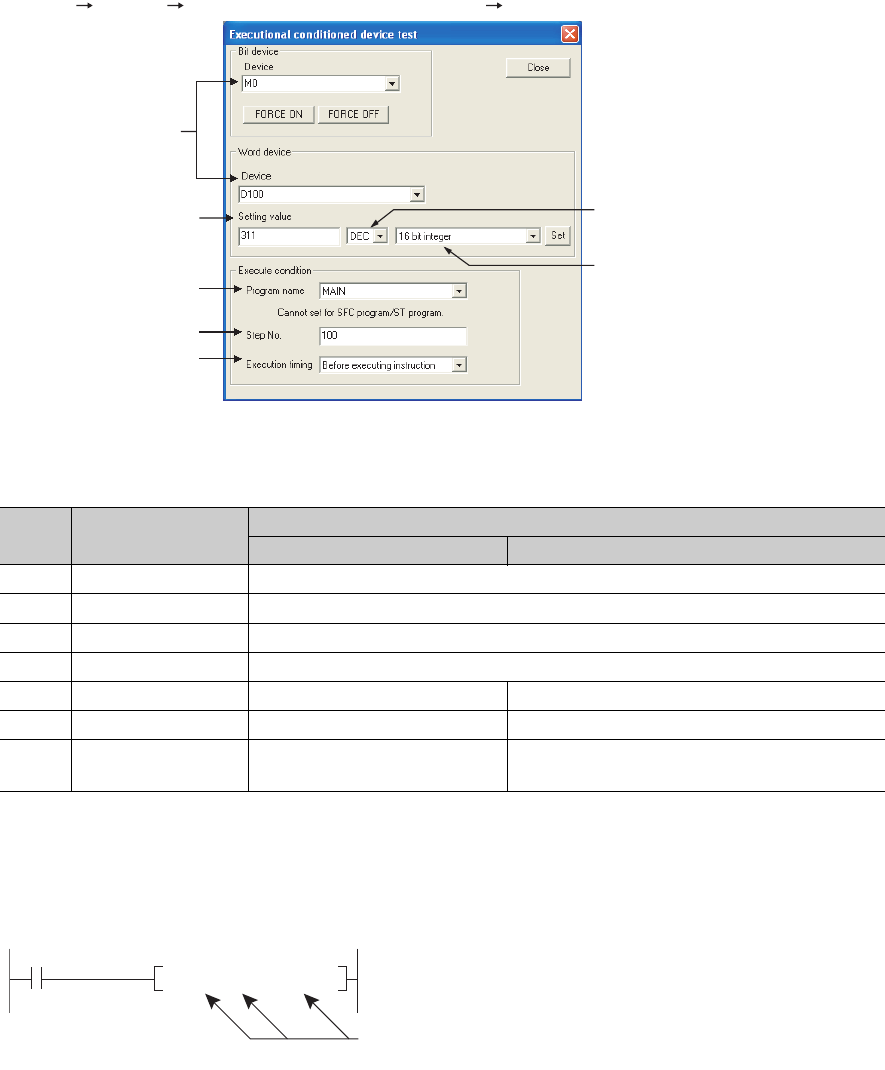

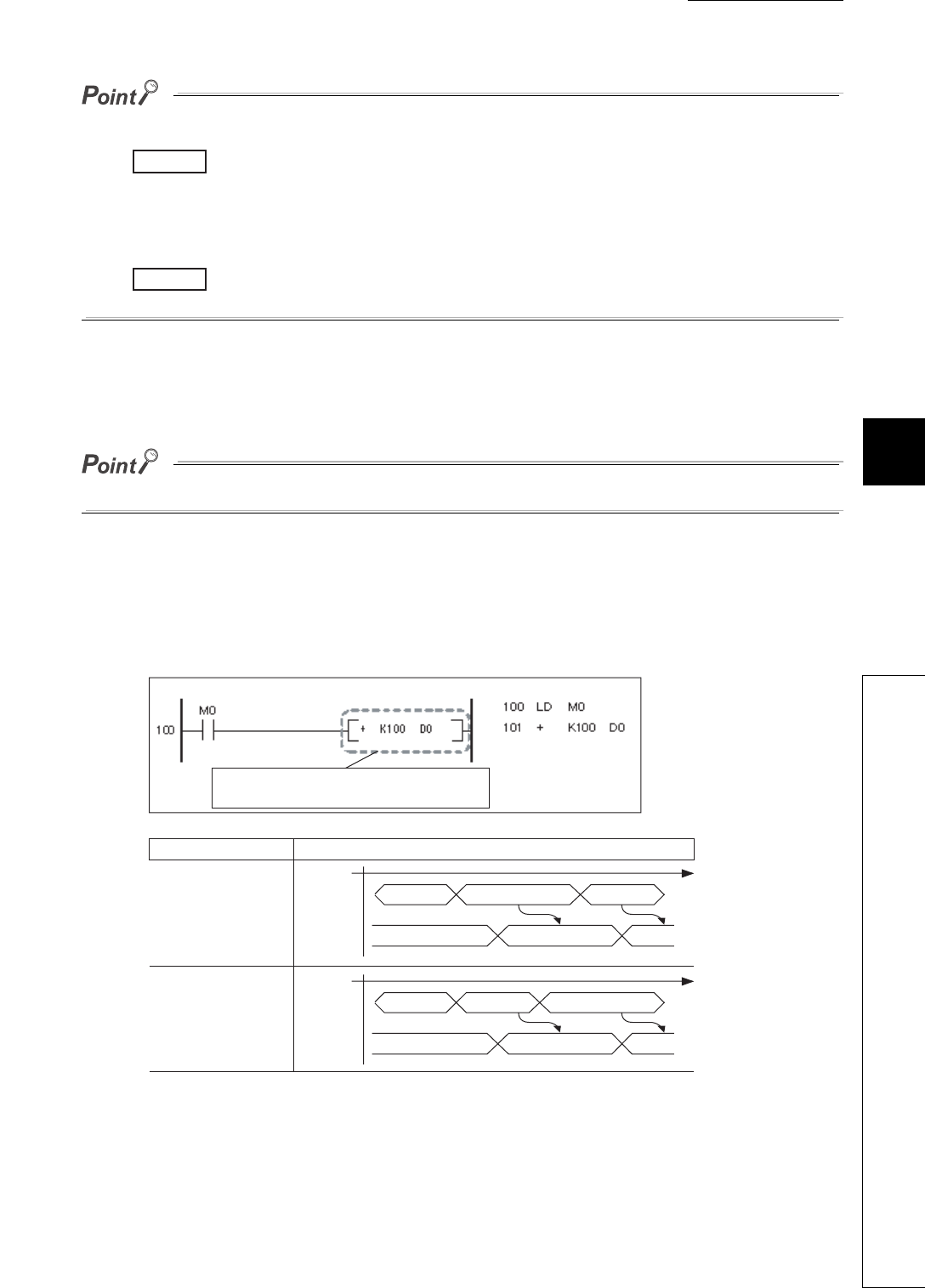

6.11.4 Executional conditioned device test ..................................................................................6 - 48

6.12 Writing Programs While CPU Module is in RUN Status.........................................................6 - 58

6.12.1 Online change (ladder mode)............................................................................................6 - 58

6.12.2 Online change (files) .........................................................................................................6 - 61

6.12.3 Precautions for online change...........................................................................................6 - 63

6.13 Execution Time Measurement ...............................................................................................6 - 69

6.13.1 Program monitor list ..........................................................................................................6 - 69

6.13.2 Interrupt program monitor list............................................................................................6 - 72

6.13.3 Scan time measurement ...................................................................................................6 - 73

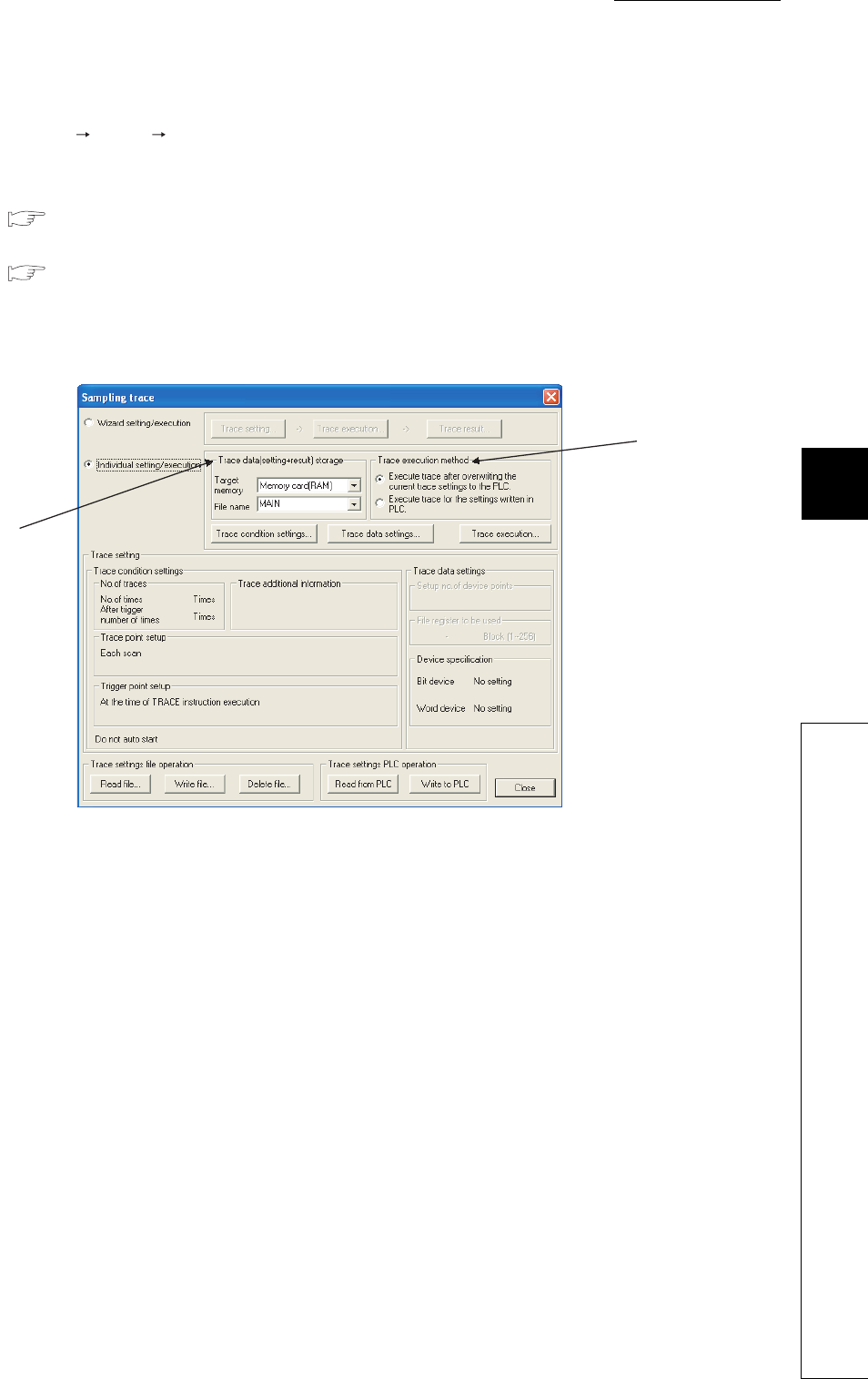

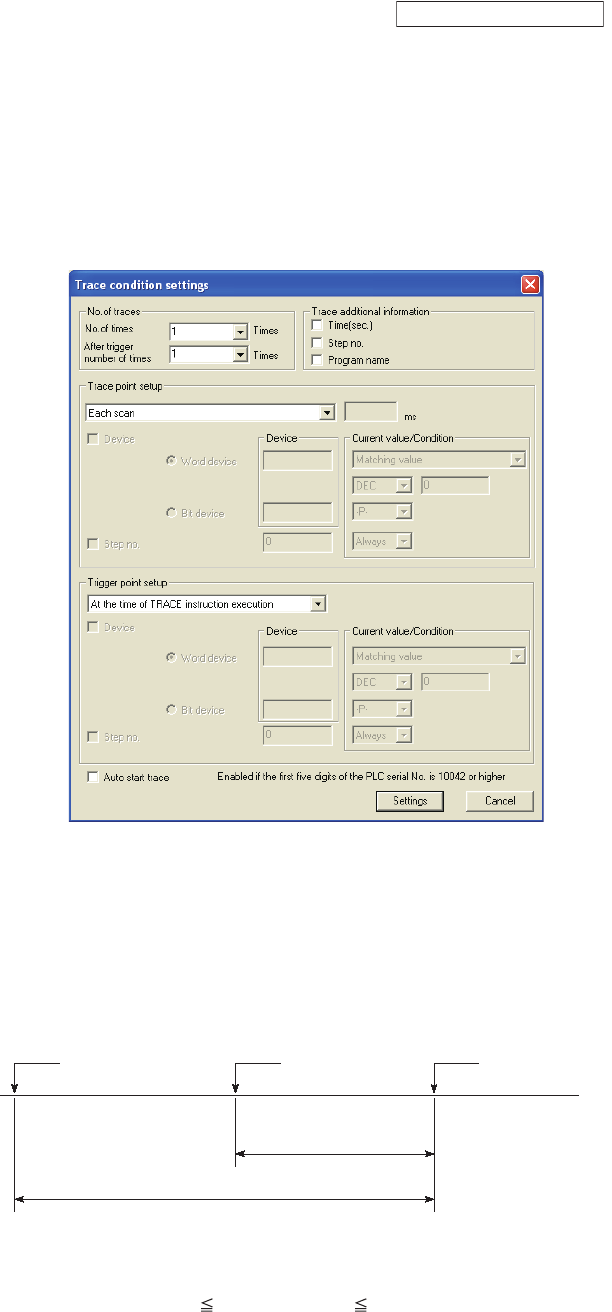

6.14 Sampling Trace Function ....................................................................................................... 6 - 77

6.15 Debug Function from Multiple GX Developers....................................................................... 6 - 91

6.15.1 Simultaneous monitoring from multiple GX Developers function ......................................6 - 91

6.15.2 Online change function from multiple GX Developers ......................................................6 - 93

6.16 Watchdog Timer (WDT) ......................................................................................................... 6 - 95

6.17 Self-diagnostic Function......................................................................................................... 6 - 97

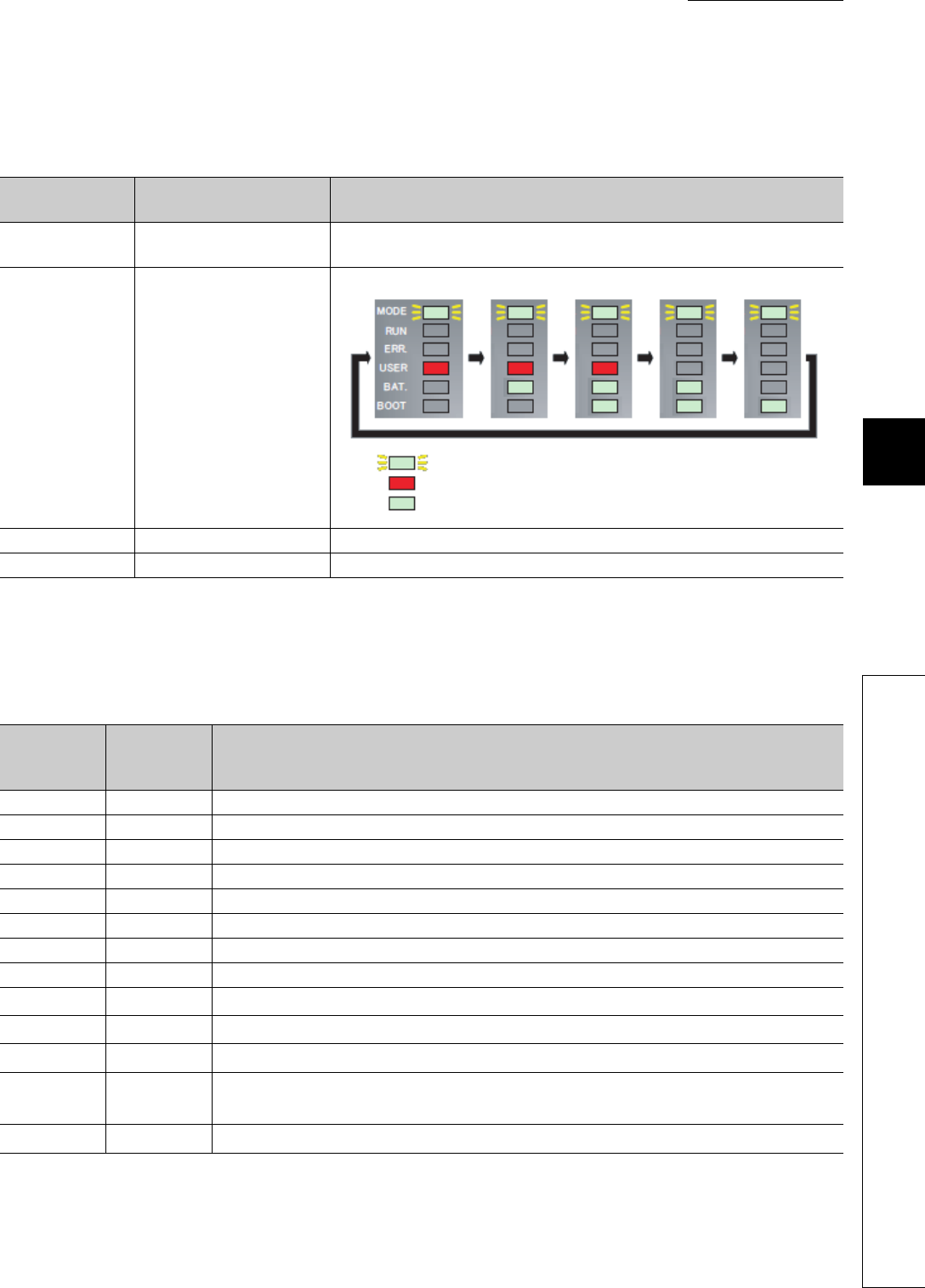

6.17.1 LEDs indicating errors.......................................................................................................6 - 104

6.17.2 Error clear .........................................................................................................................6 - 104

6.18 Error History........................................................................................................................... 6 - 105

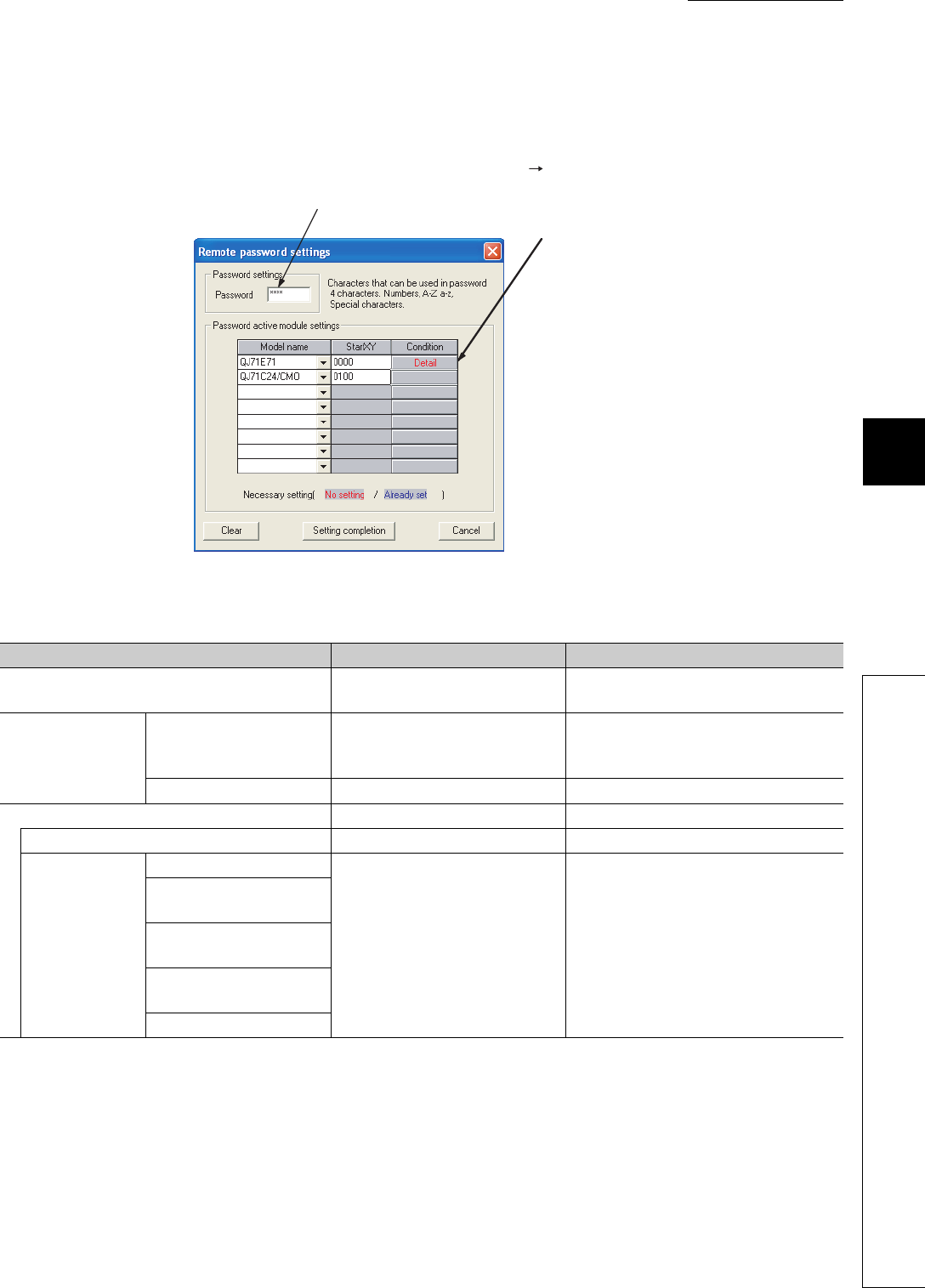

6.19 System Protection.................................................................................................................. 6 - 106

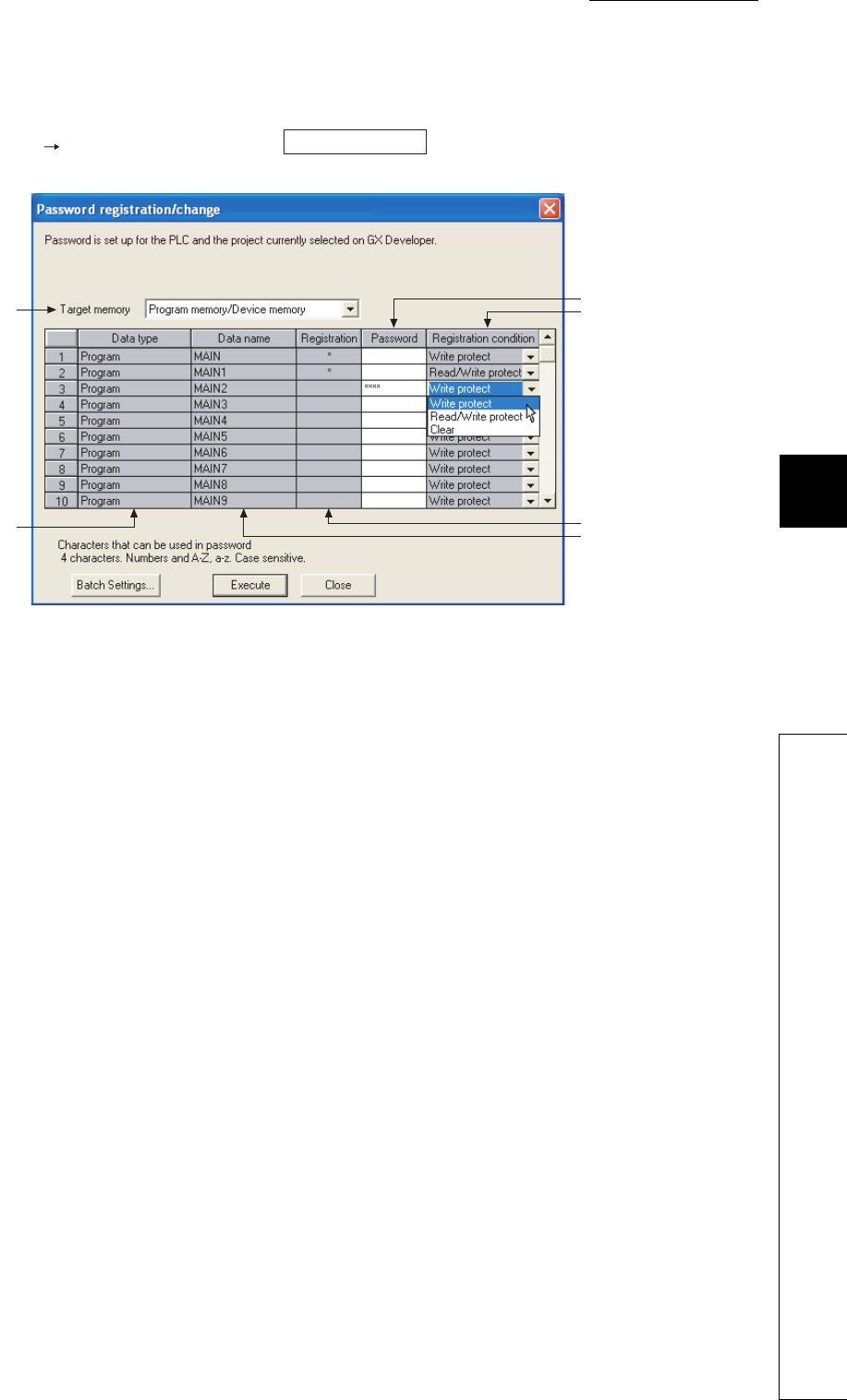

6.19.1 Password registration........................................................................................................6 - 106

6.19.2 Remote password .............................................................................................................6 - 108

6.20 System Display of CPU Module with GX Developer..............................................................6 - 113

6.21 LED Indication........................................................................................................................ 6 - 116

6.21.1 Methods for turning off the LEDs.......................................................................................6 - 116

6.21.2 LED indication priority .......................................................................................................6 - 117

6.22 Interrupt from Intelligent Function Module ............................................................................. 6 - 119

6.23 Serial Communication Function.............................................................................................6 - 120

6.24 Service Processing ................................................................................................................ 6 - 128

6.24.1 Service processing setting ................................................................................................6 - 128

6.25 Initial Device Value................................................................................................................. 6 - 135

6.26 Battery Life-prolonging Function............................................................................................6 - 139

6.27 Memory Check Function........................................................................................................6 - 140

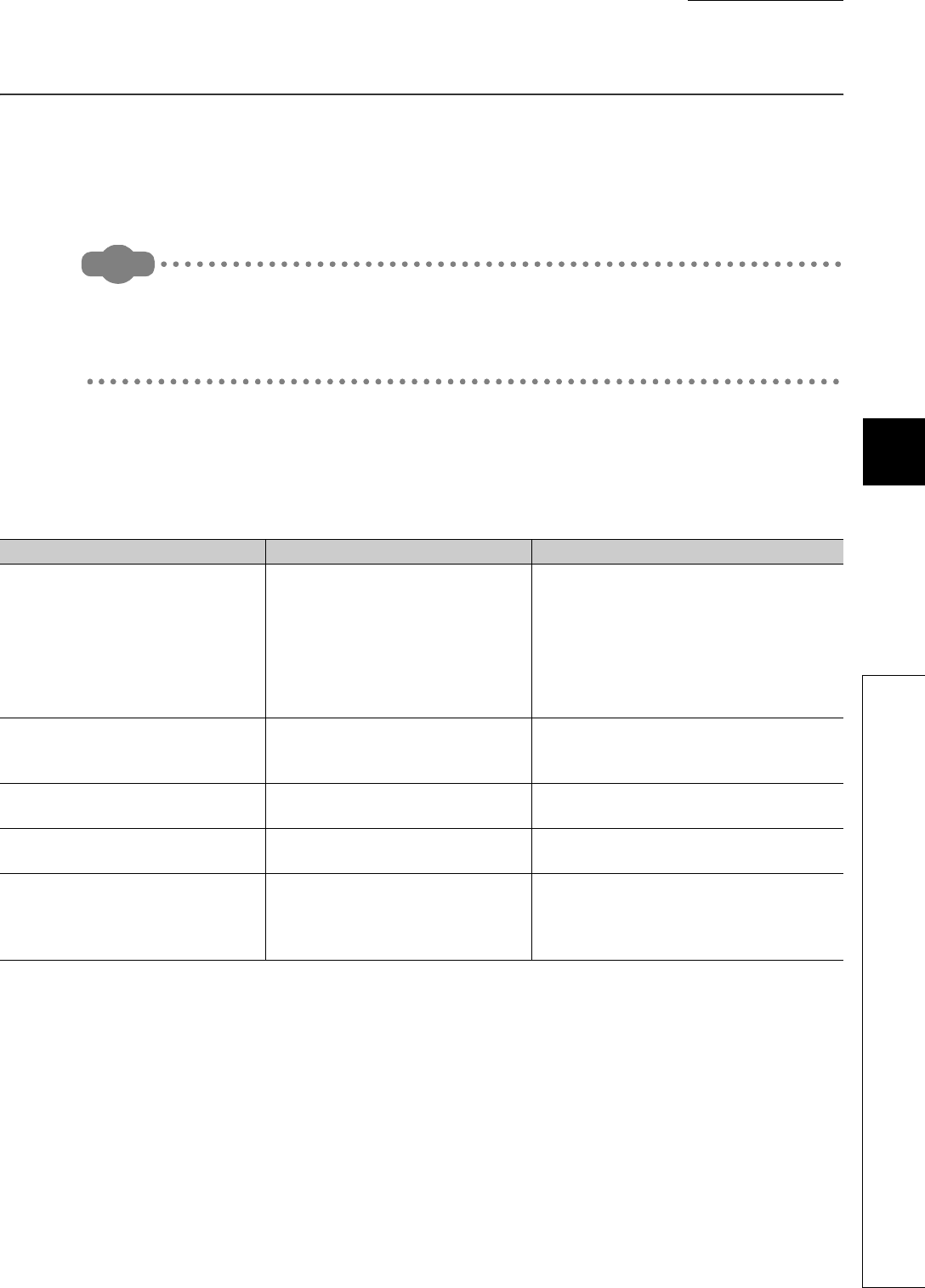

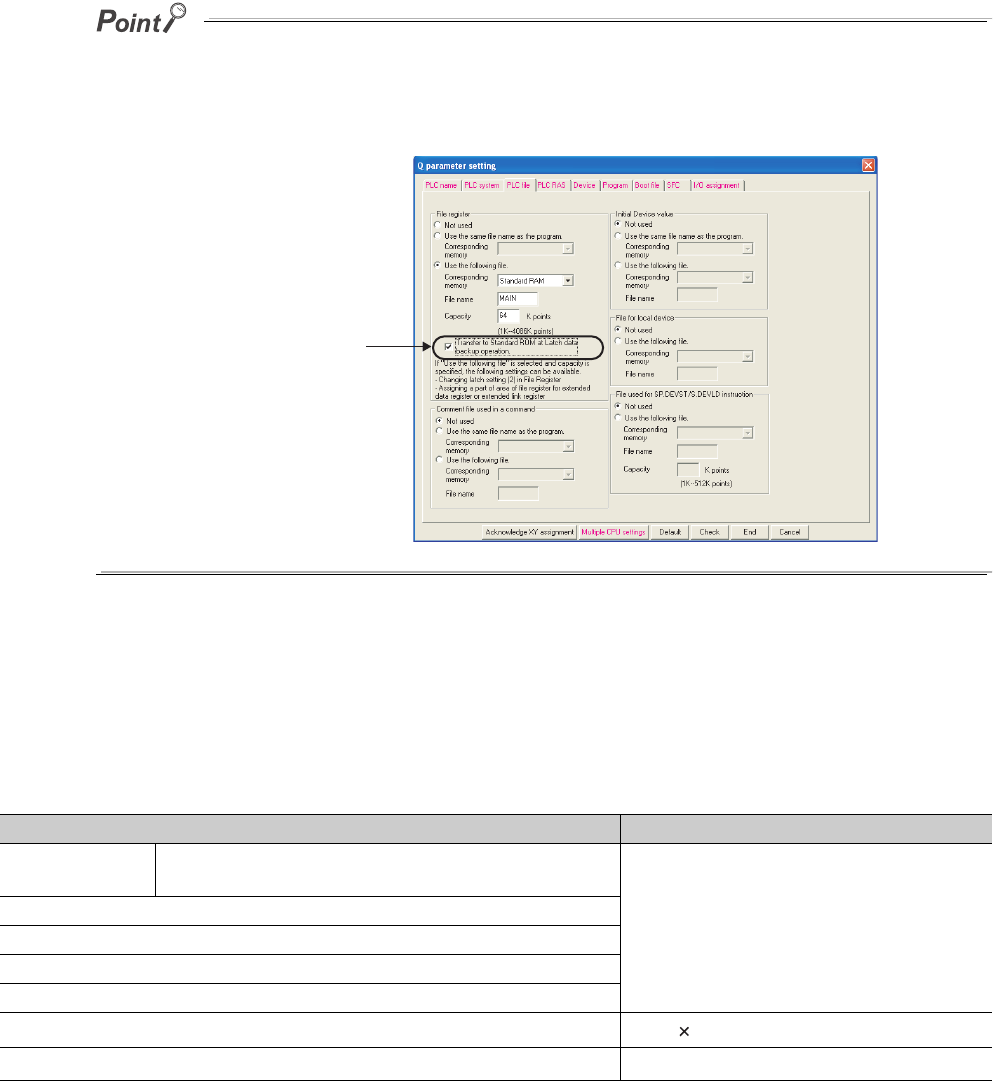

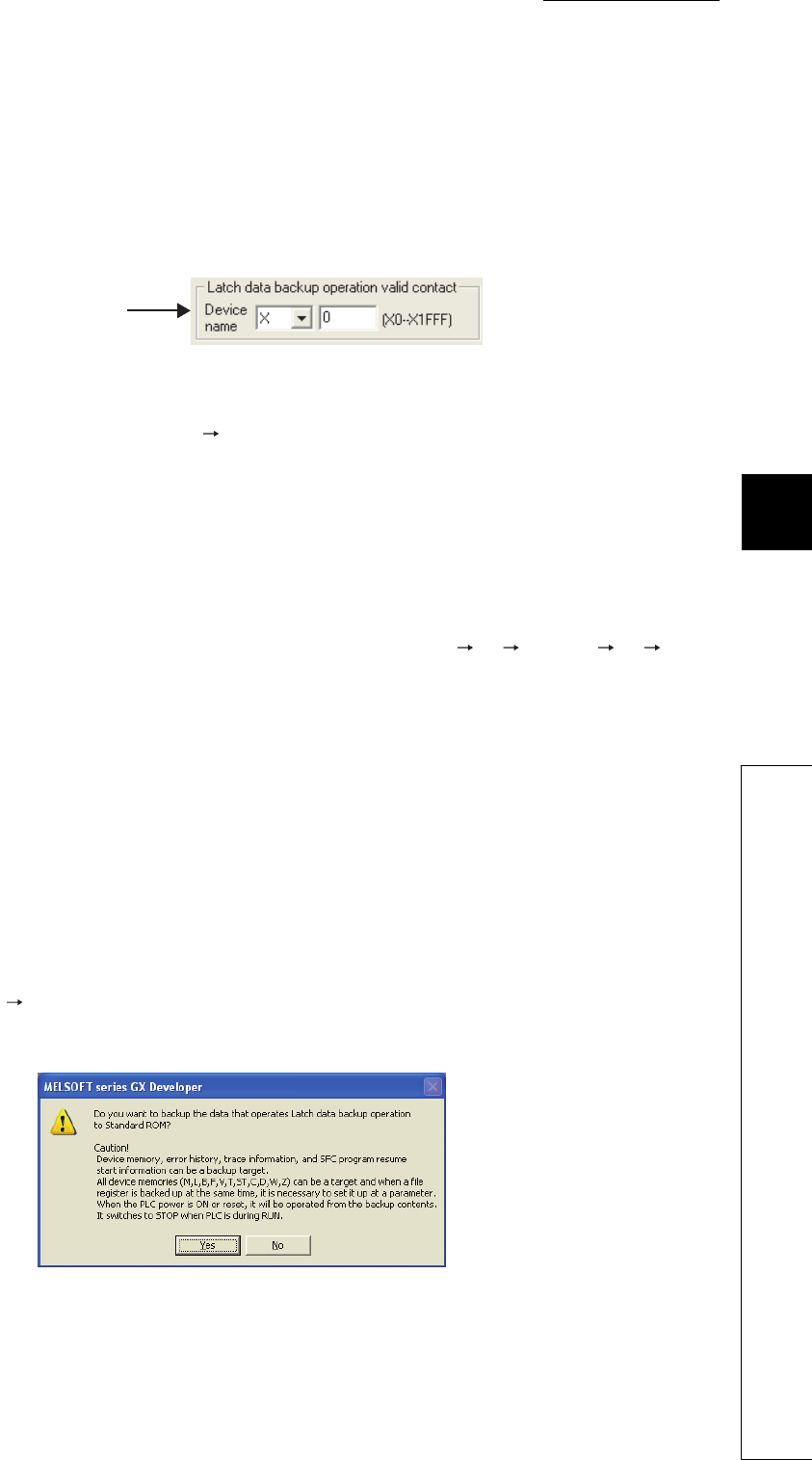

6.28 Latch Data Backup to Standard ROM Function .....................................................................6 - 141

6.29 Writing/Reading Device Data to/from Standard ROM ............................................................ 6 - 146

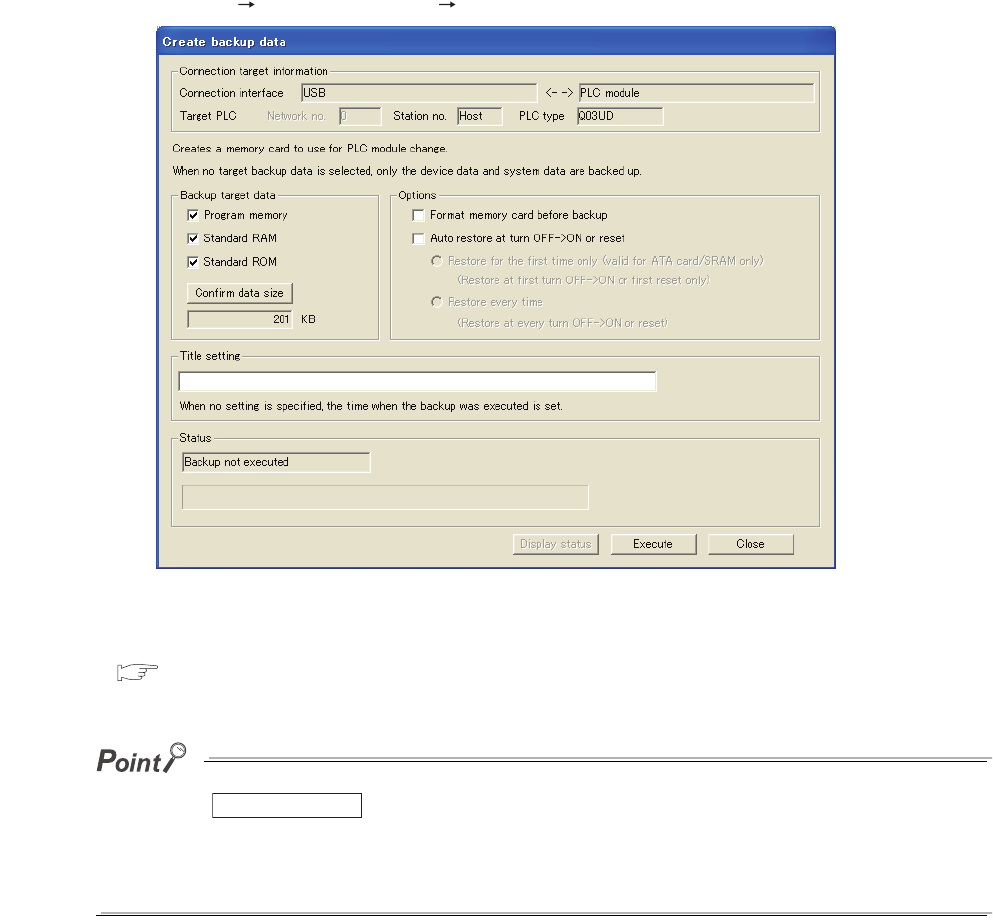

6.30 CPU Module Change Function with Memory Card ................................................................6 - 147

6.30.1 Backup function to memory card.......................................................................................6 - 149

A - 15

6.30.2 Backup data restoration function.......................................................................................6 - 157

6.31 Module model name read ......................................................................................................6 - 161

6.32 Module error collection...........................................................................................................6 - 162

CHAPTER7 COMMUNICATIONS WITH INTELLIGENT FUNCTION

MODULE 7-1 to 7-9

7.1 Communications between CPU Module and Intelligent Function Module ............................. 7 - 1

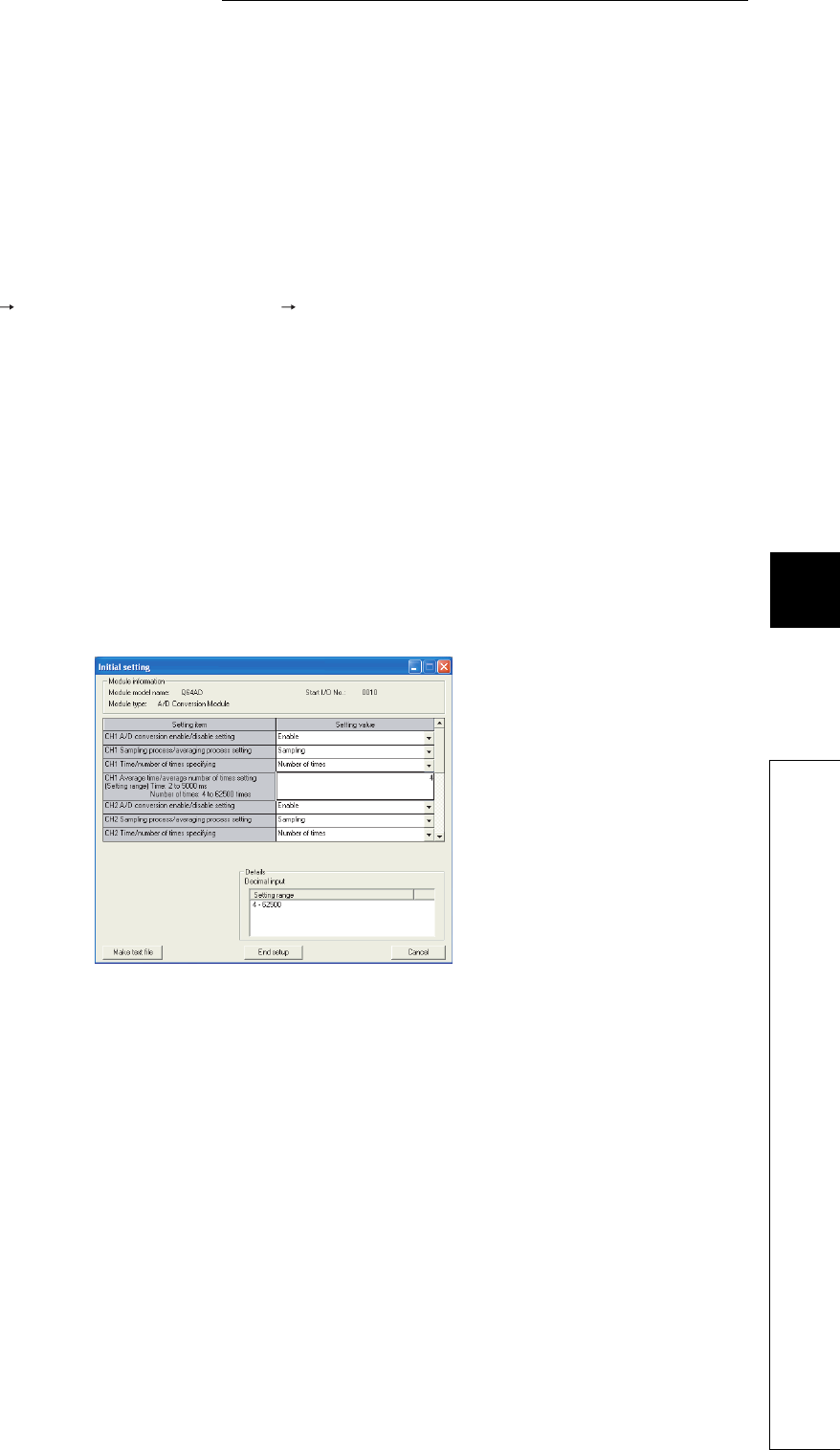

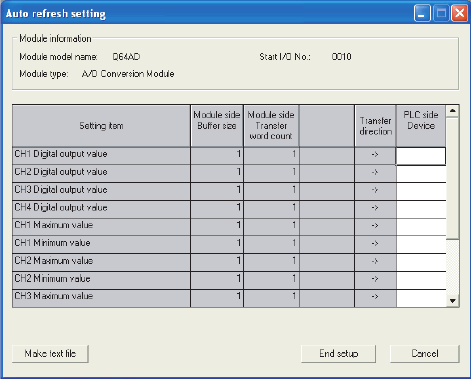

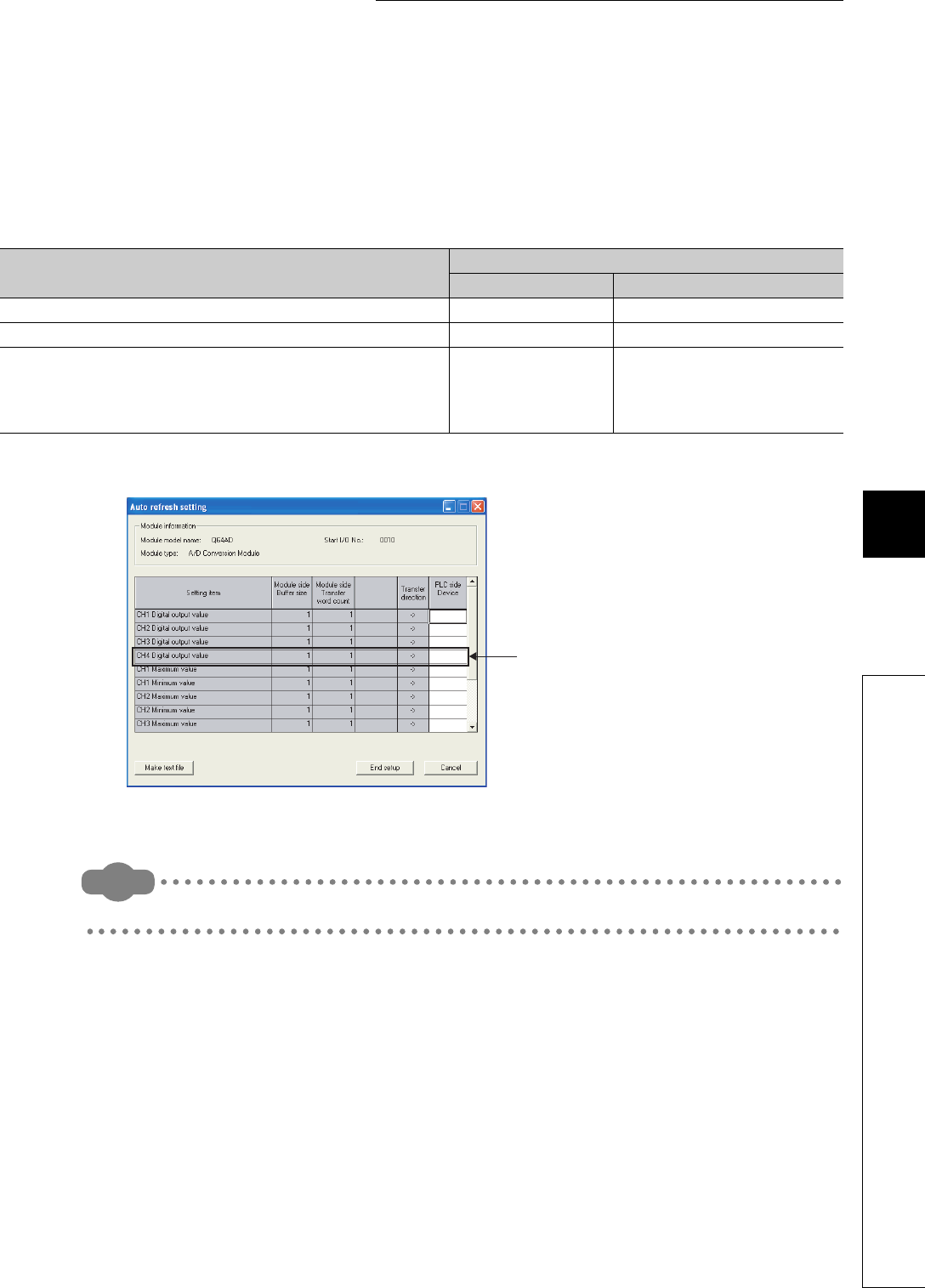

7.1.1 Initial setting and auto refresh setting by GX Configurator................................................7 - 2

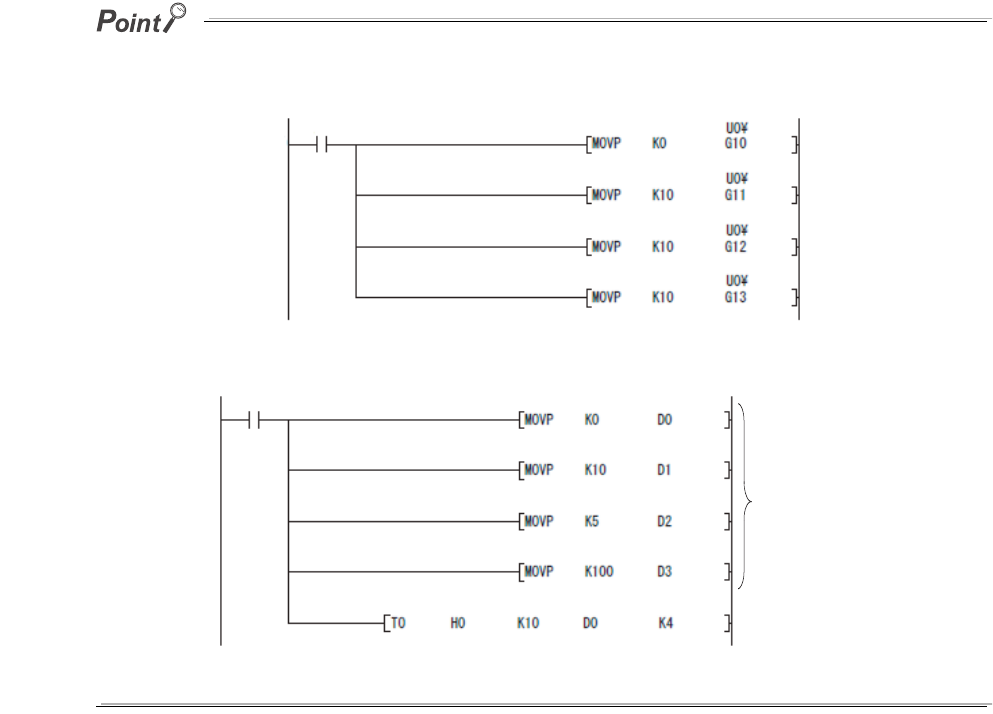

7.1.2 Initial setting by initial device value ...................................................................................7 - 5

7.1.3 Communications with the FROM and TO instructions ......................................................7 - 5

7.1.4 Communications using the intelligent function module device ..........................................7 - 6

7.1.5 Communications using the intelligent function module dedicated instruction ...................7 - 8

CHAPTER8 PARAMETERS 8-1 to 8-26

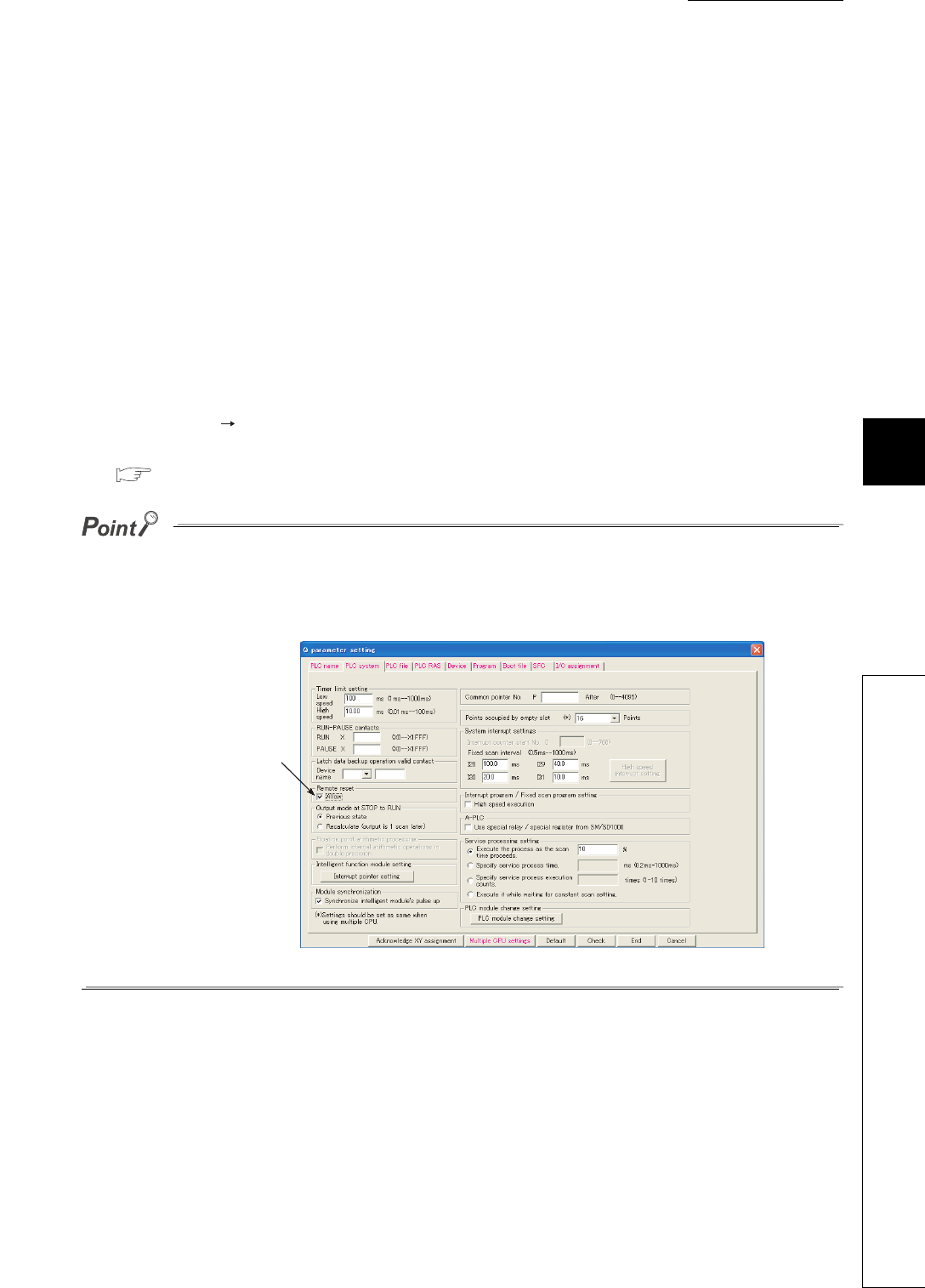

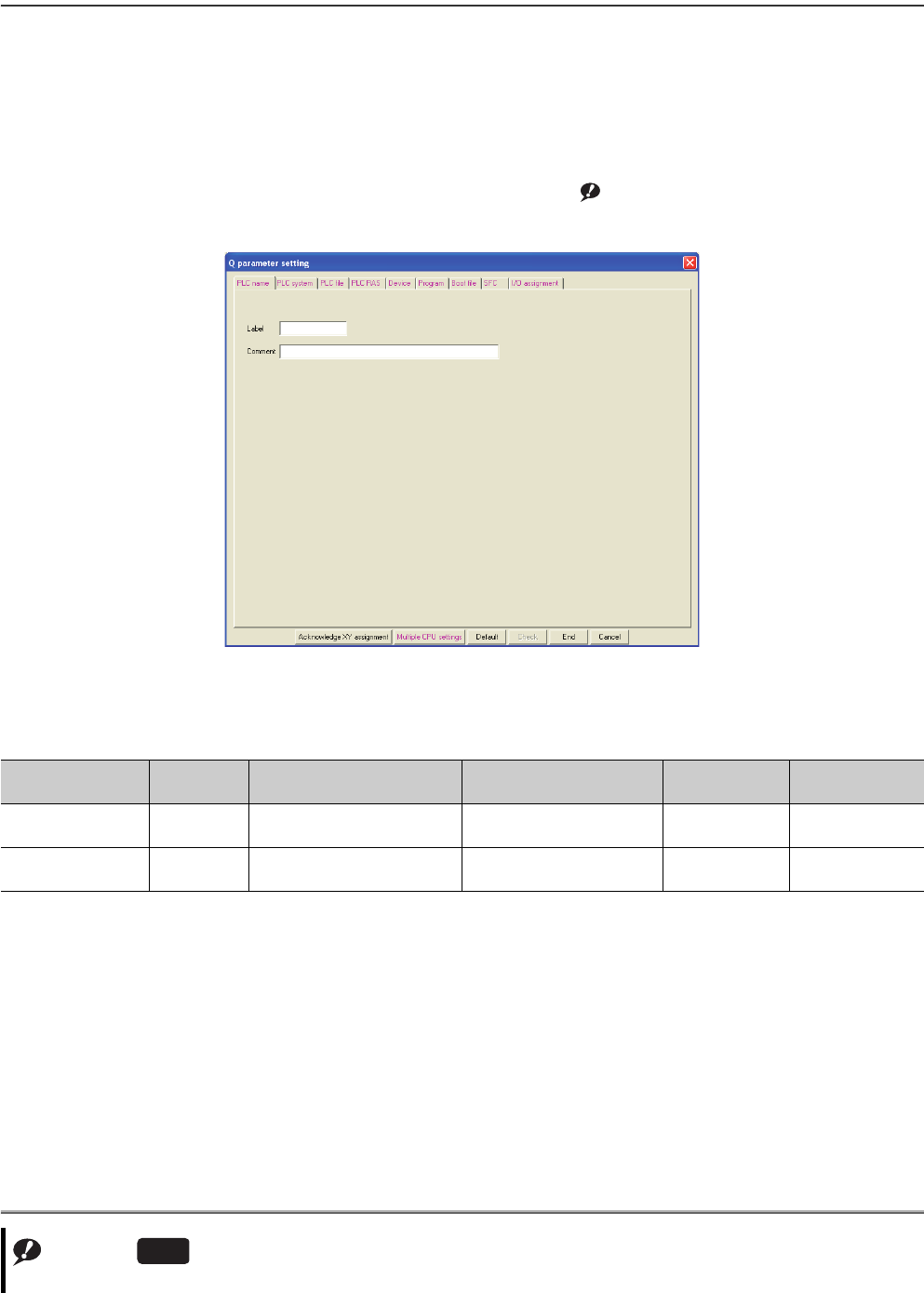

8.1 PLC Parameters ....................................................................................................................8 - 2

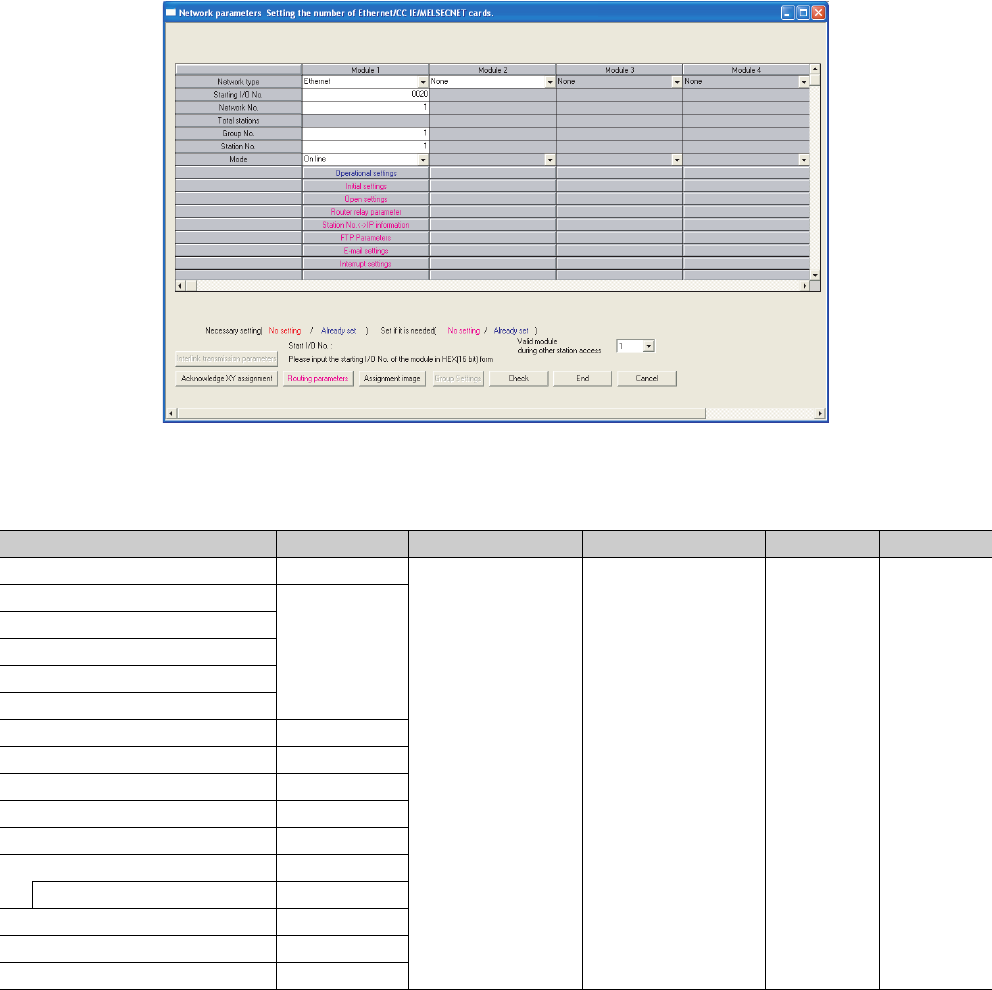

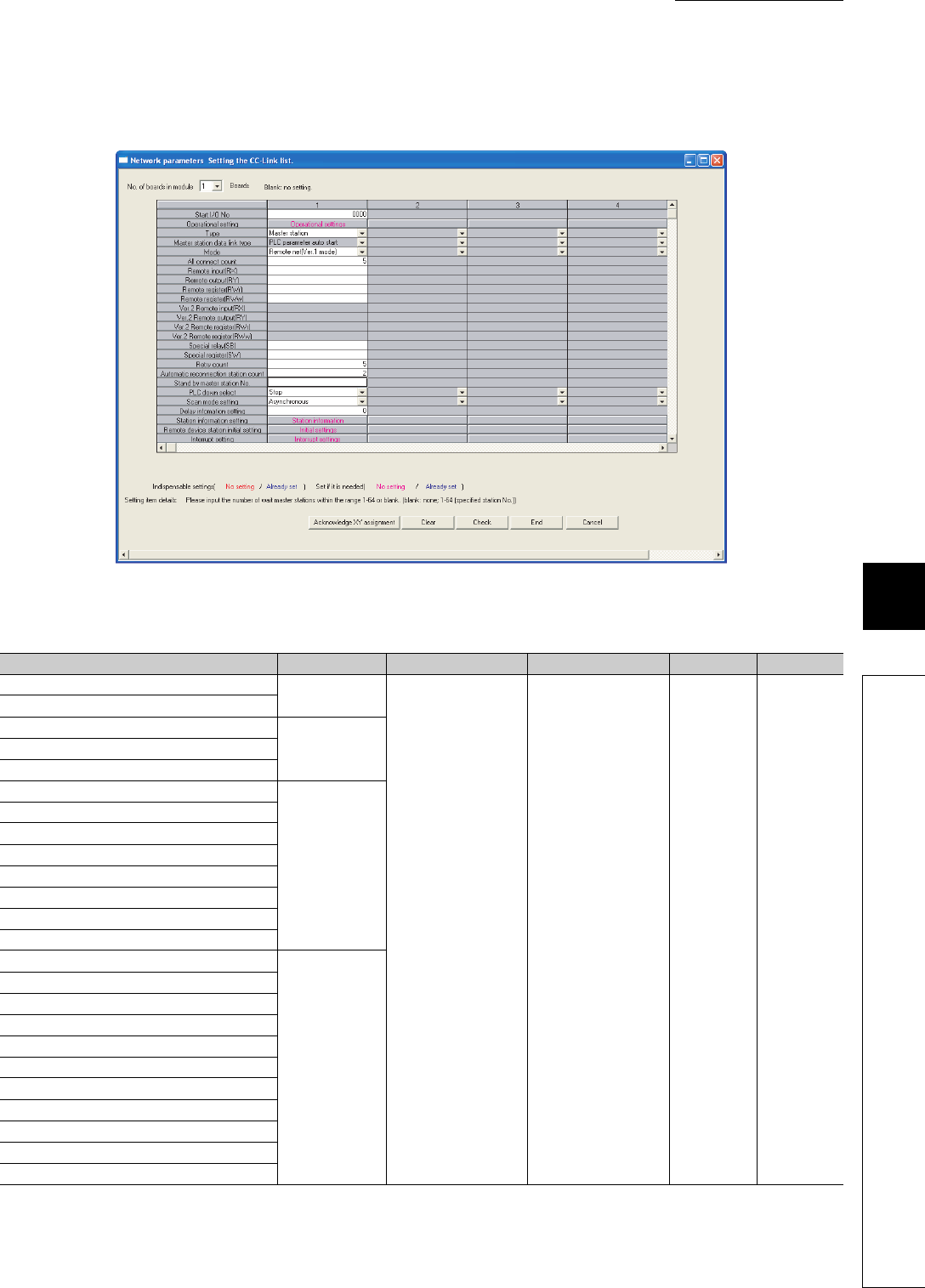

8.2 Network Parameters ..............................................................................................................8 - 21

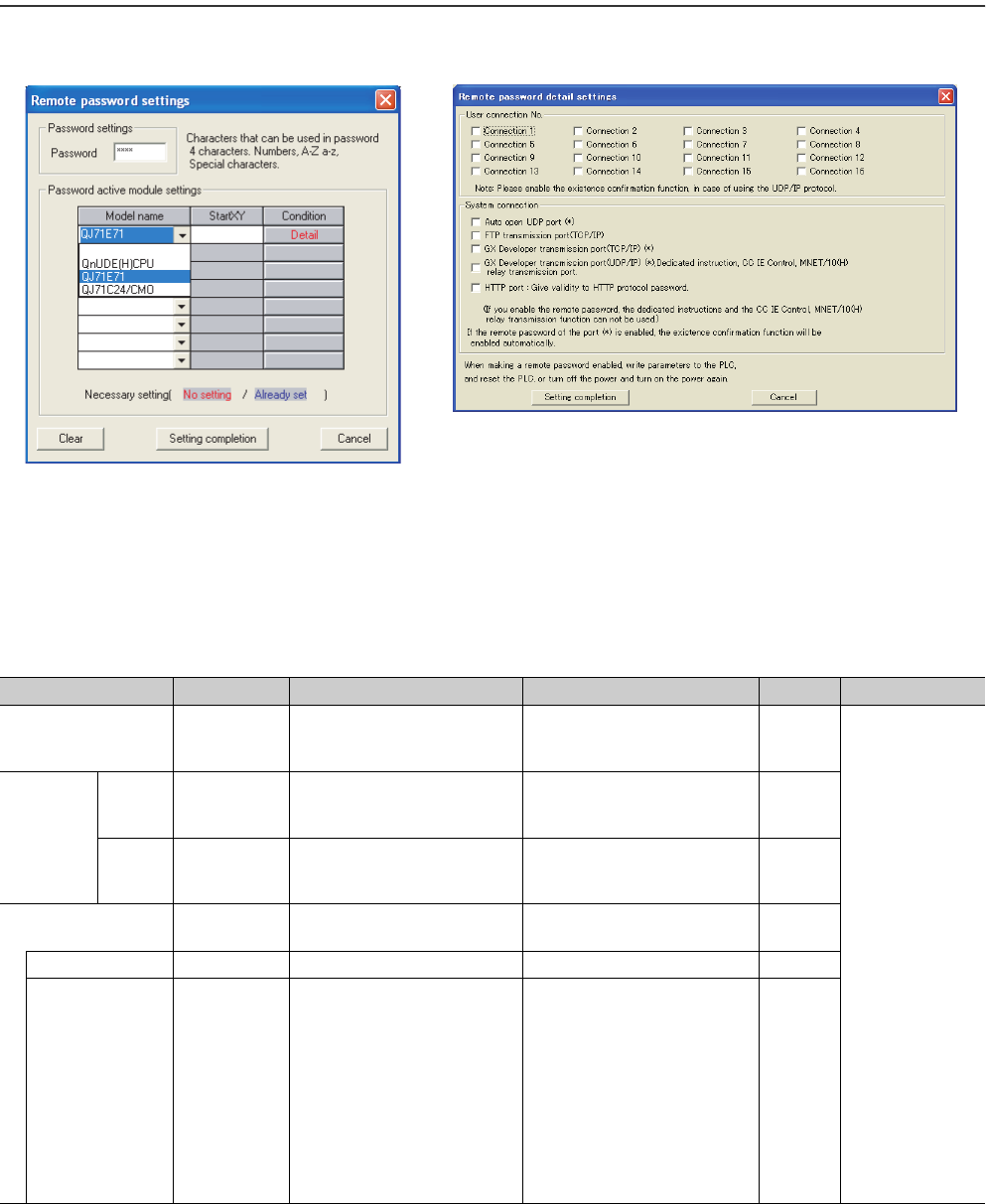

8.3 Remote Password.................................................................................................................. 8 - 26

CHAPTER9 DEVICES 9-1 to 9-94

9.1 Device List .............................................................................................................................9 - 1

9.2 Internal User Device .............................................................................................................. 9 - 3

9.2.1 Input (X) ............................................................................................................................9 - 6

9.2.2 Output (Y)..........................................................................................................................9 - 8

9.2.3 Internal relay (M) ...............................................................................................................9 - 9

9.2.4 Latch relay (L) ...................................................................................................................9 - 10

9.2.5 Annunciator (F) .................................................................................................................9 - 11

9.2.6 Edge relay (V) ...................................................................................................................9 - 15

9.2.7 Link relay (B) .....................................................................................................................9 - 16

9.2.8 Link special relay (SB) ......................................................................................................9 - 18

9.2.9 Step relay (S) ....................................................................................................................9 - 19

9.2.10 Timer (T)............................................................................................................................9 - 20

9.2.11 Counter (C) .......................................................................................................................9 - 27

9.2.12 Data register (D)................................................................................................................9 - 31

9.2.13 Link register (W)................................................................................................................9 - 32

9.2.14 Link special register (SW) .................................................................................................9 - 34

9.3 Internal System Devices ........................................................................................................ 9 - 35

9.3.1 Function devices (FX, FY, FD) ..........................................................................................9 - 35

9.3.2 Special relay (SM) .............................................................................................................9 - 38

9.3.3 Special register (SD) .........................................................................................................9 - 39

9.4 Link Direct Device (J\)............................................................................................................ 9 - 40

9.5 Module Access Devices......................................................................................................... 9 - 43

9.5.1 Intelligent function module device (U\G) ...........................................................................9 - 43

9.5.2 Cyclic transmission area device (U3En\G)........................................................................9 - 45

A - 16

9.6 Index Register (Z)/Standard Device Resister (Z) ...................................................................9 - 46

9.6.1 Index register (Z)...............................................................................................................9 - 46

9.6.2 Standard device register (Z)..............................................................................................9 - 48

9.6.3 Switching from the scan execution type program to the interrupt/fixed scan execution

type program....................................................................................................9 - 49

9.7 File Register (R)..................................................................................................................... 9 - 53

9.7.1 File register data storage location .....................................................................................9 - 54

9.7.2 File register size ................................................................................................................9 - 54

9.7.3 Differences in available accesses by storage memory .....................................................9 - 55

9.7.4 Registration procedure for the file register ........................................................................9 - 56

9.7.5 Specification methods of the file register...........................................................................9 - 61

9.7.6 Precautions for using the file register................................................................................9 - 62

9.8 Extended Data Register (D) and Extended Link Register (W)...............................................9 - 64

9.9 Nesting (N)............................................................................................................................ 9 - 70

9.10 Pointer (P).............................................................................................................................. 9 - 71

9.10.1 Local pointer.....................................................................................................................9 - 72

9.10.2 Common pointer................................................................................................................9 - 74

9.11 Interrupt Pointer(I)..................................................................................................................9 - 76

9.11.1 List of interrupt pointer numbers and interrupt factors ......................................................9 - 77

9.12 Other Devices ........................................................................................................................ 9 - 78

9.12.1 SFC block device (BL) ......................................................................................................9 - 78

9.12.2 Network No. specification device (J).................................................................................9 - 78

9.12.3 I/O No. specification device (U).........................................................................................9 - 79

9.12.4 Macro instruction argument device (VD)...........................................................................9 - 80

9.13 Constants............................................................................................................................... 9 - 81

9.13.1 Decimal constant (K).........................................................................................................9 - 81

9.13.2 Hexadecimal constant (H) .................................................................................................9 - 81

9.13.3 Real number (E)................................................................................................................9 - 82

9.13.4 Character string (" ")..........................................................................................................9 - 83

9.14 Convenient Usage of Devices................................................................................................9 - 84

9.14.1 Global device ....................................................................................................................9 - 84

9.14.2 Local device ......................................................................................................................9 - 85

CHAPTER10 CPU MODULE PROCESSING TIME 10-1 to 10-18

10.1 Scan Time..............................................................................................................................10 - 1

10.1.1 Scan time structure ...........................................................................................................10 - 1

10.1.2 Time required for each processing included in scan time .................................................10 - 2

10.1.3 Factors that increase the scan time ..................................................................................10 - 11

CHAPTER11 PROCEDURES FOR WRITING PROGRAM TO CPU

MODULE 11-1 to 11-10

11.1 Items to be Considered for Creating Programs .....................................................................11 - 1

11.2 Hardware Check .................................................................................................................... 11 - 3

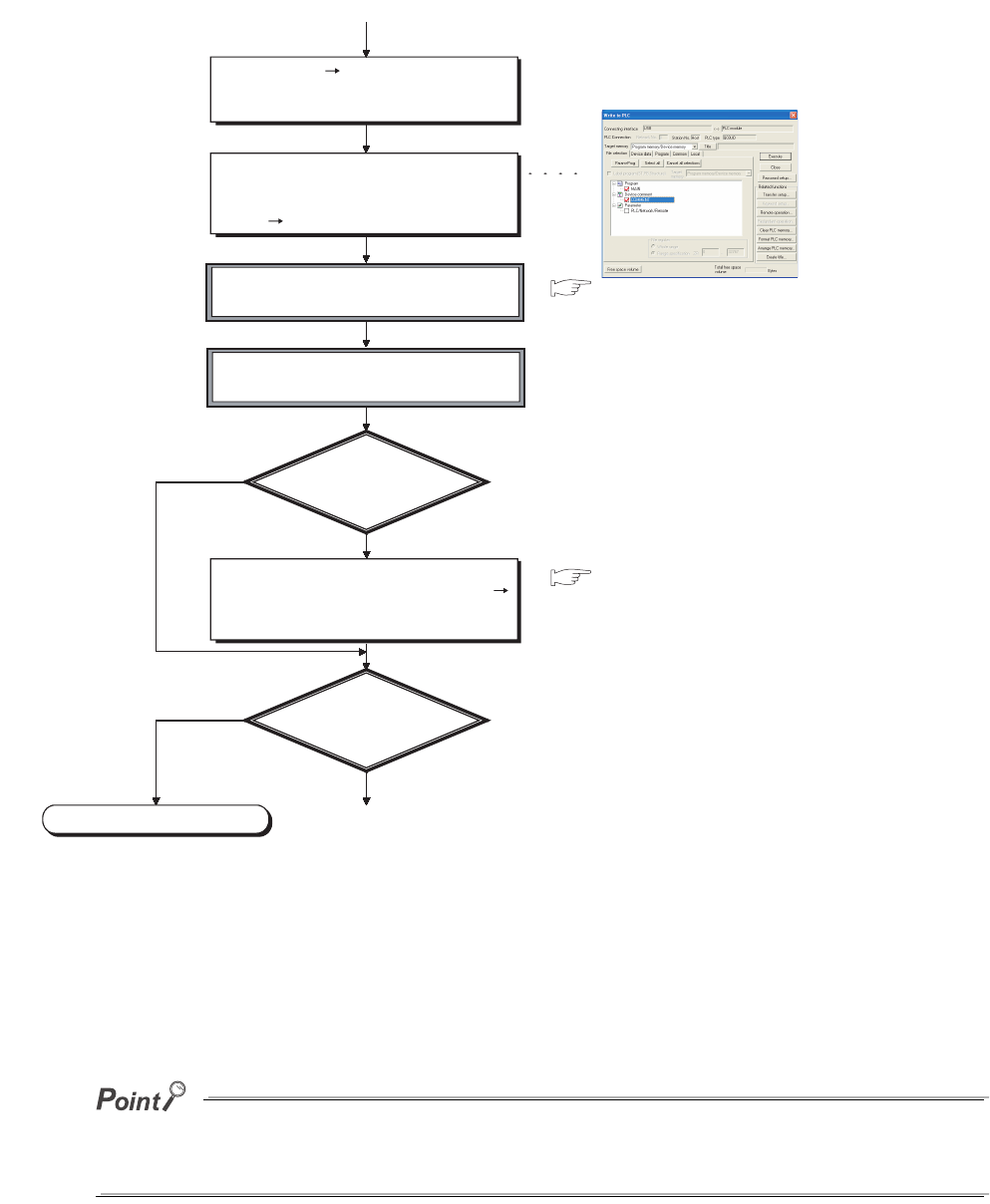

11.3 Procedure for Writing One Program ......................................................................................11 - 5

A - 17

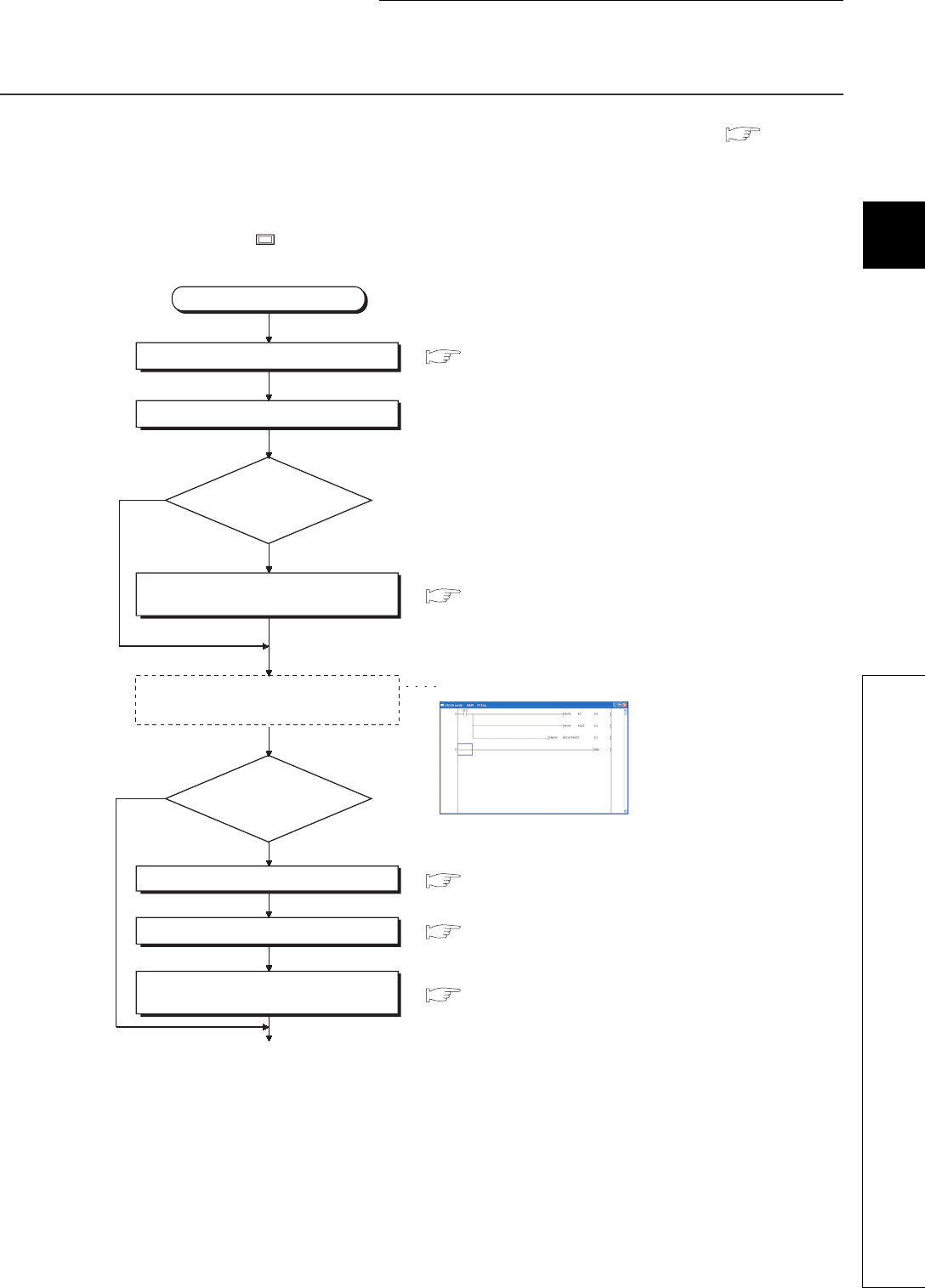

11.4 Procedure for Writing Multiple Programs ...............................................................................11 - 7

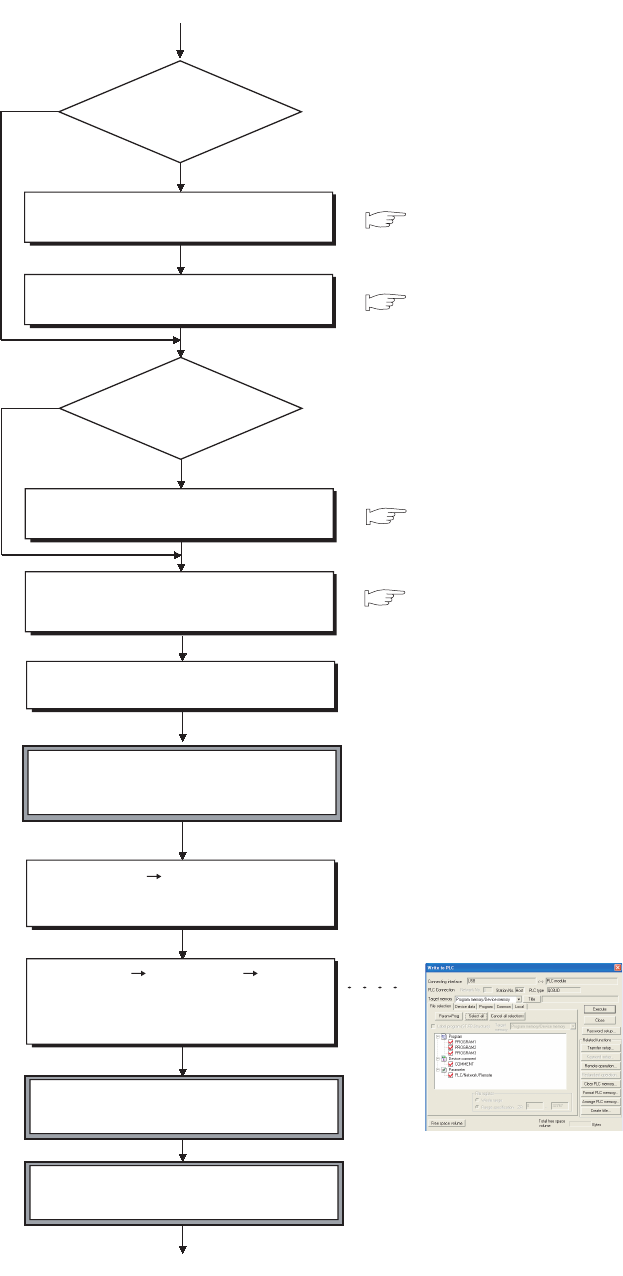

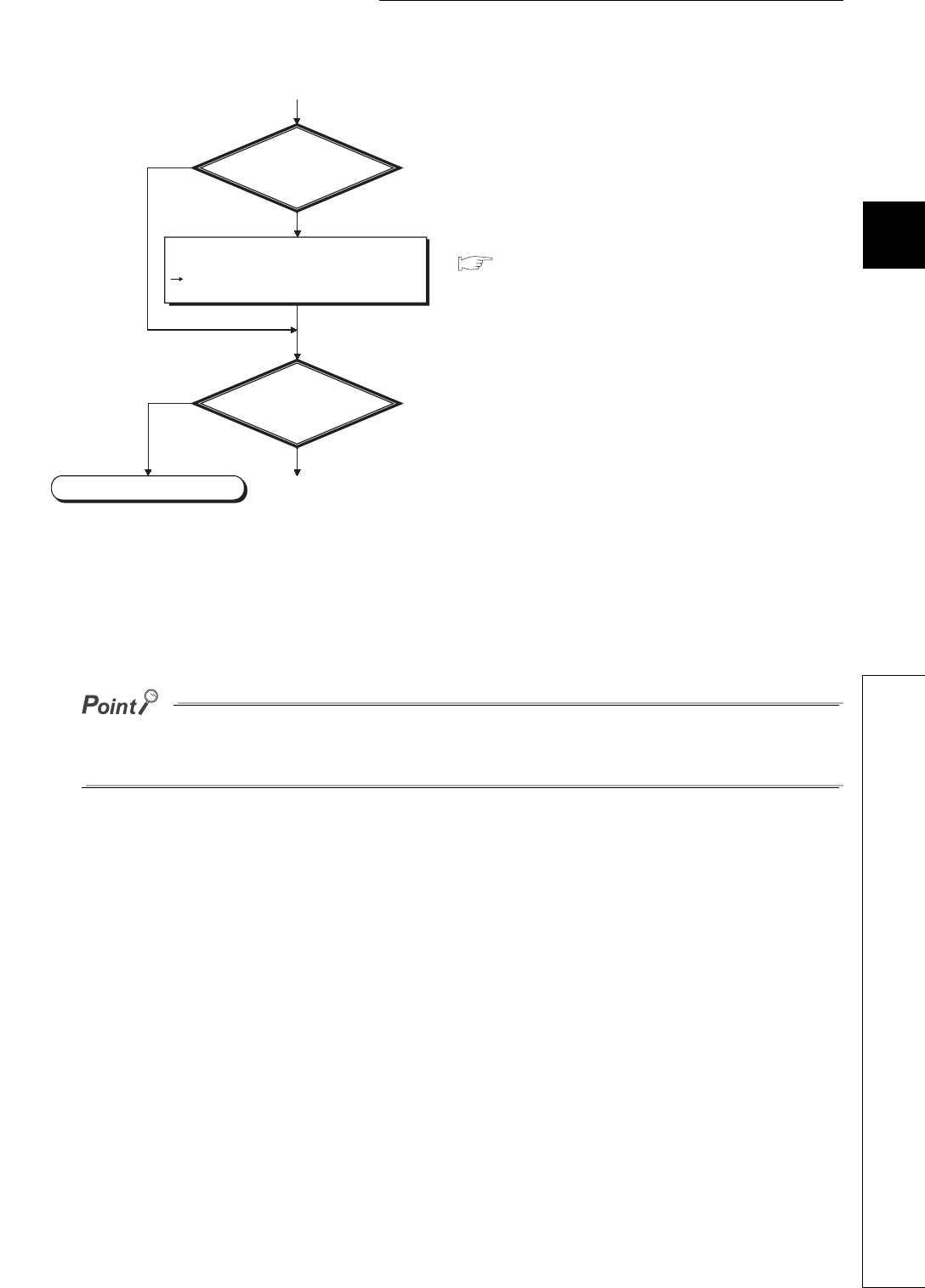

11.5 Procedure for Boot Operation................................................................................................11 - 10

CHAPTER12 SPECIAL RELAY LIST AND SPECIAL REGISTER LIST 12-1 to 12-78

12.1 SPECIAL RELAY LIST........................................................................................................... 12 - 1

12.2 SPECIAL REGISTER LIST....................................................................................................12 - 27

APPENDICES App-1 to App-72

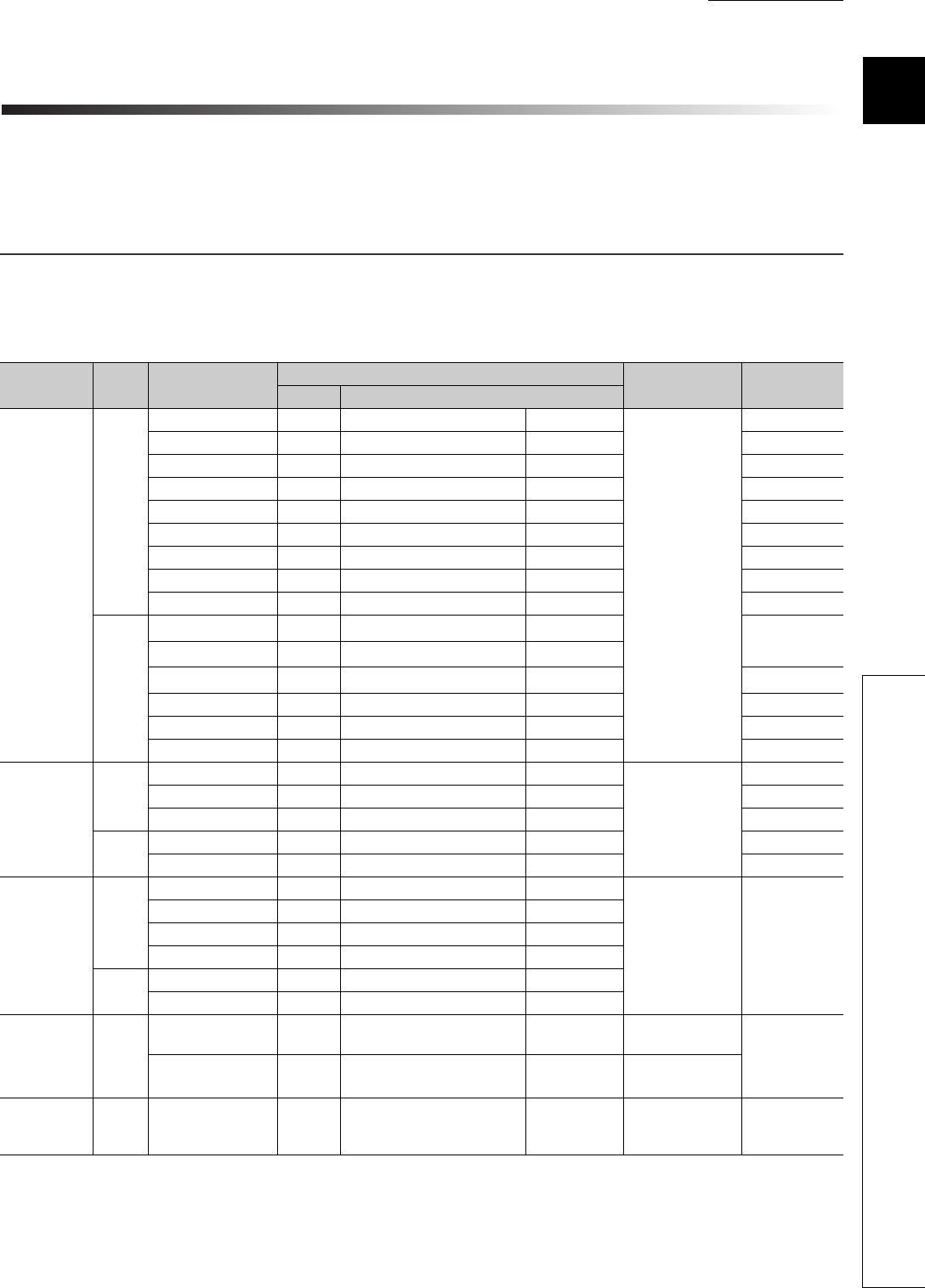

Appendix 1 List of Parameter Numbers .........................................................................................App- 1

Appendix 2 Functions Added or Changed by Version Upgrade.....................................................App- 6

Appendix 3 Method of Replacing Basic Model QCPU or High Performance Model QCPU

with Universal Model QCPU ...............................................................................App- 8

Appendix 3.1 Replacement Precautions ........................................................................... App- 8

Appendix 3.1.1 Replacing Basic model QCPU with Universal model QCPU .......................App- 8

Appendix 3.1.2 Replacing High Performance model QCPU with Universal model QCPU ......App- 12

Appendix 3.2 Applicable devices and software .................................................................. App- 19

Appendix 3.3 Instructions ..............................................................................................App- 23

Appendix 3.3.1 Instructions not supported in the Universal model QCPU and replacing

methods ..........................................................................................App- 23

Appendix 3.3.2 Replacing programs using multiple CPU transmission dedicated

instructions ...................................................................................... App- 25

Appendix 3.3.3 Program replacement examples ...........................................................App- 26

Appendix 3.4 Functions.................................................................................................App- 40

Appendix 3.4.1 Floating-point operation instructions ...................................................... App- 40

Appendix 3.4.2 Error check processing for floating-point data comparison instructions .........App- 48

Appendix 3.4.3 Range check processing for index-modified devices ................................. App- 52

Appendix 3.4.4 Device latch function .......................................................................... App- 55

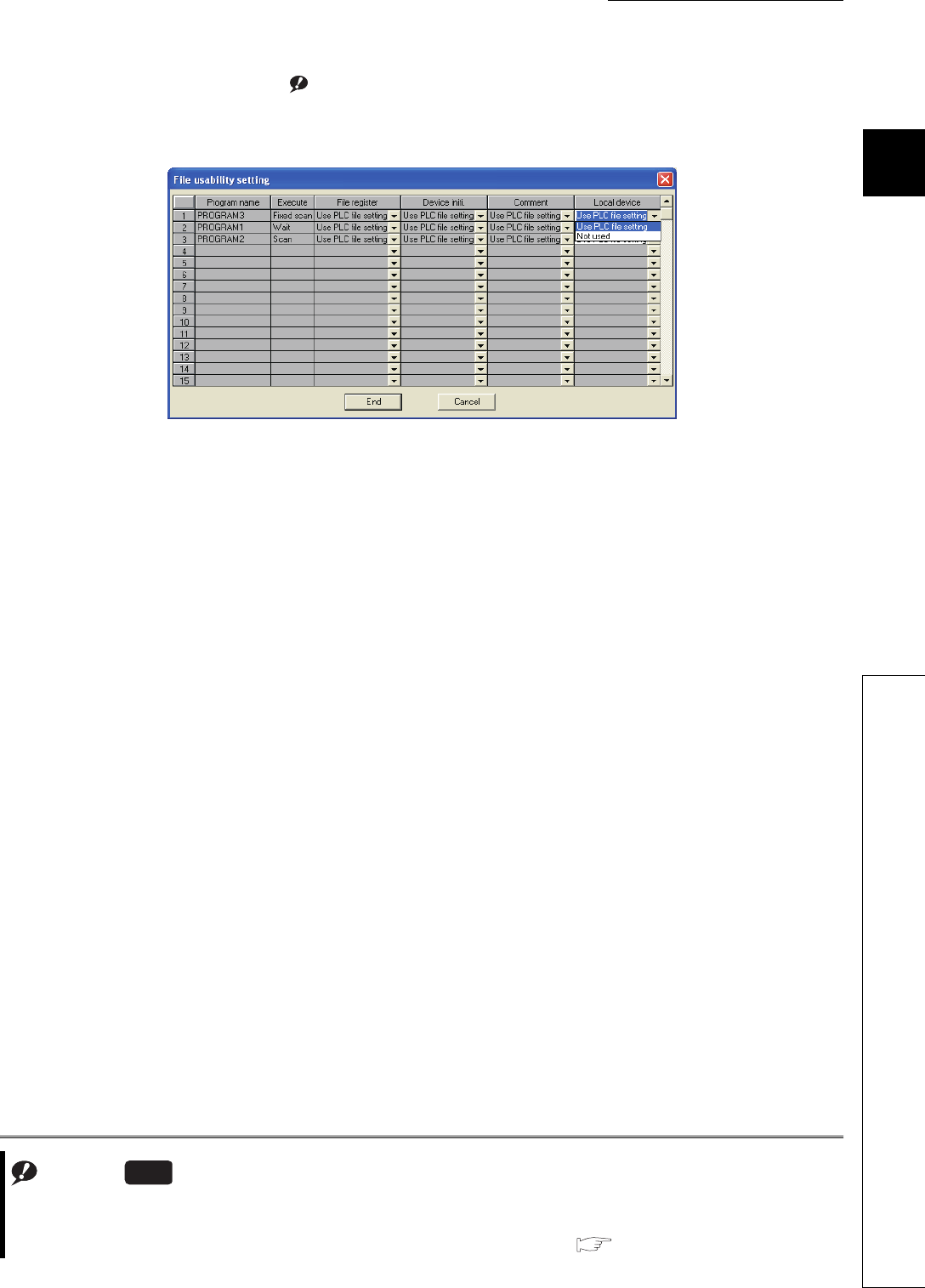

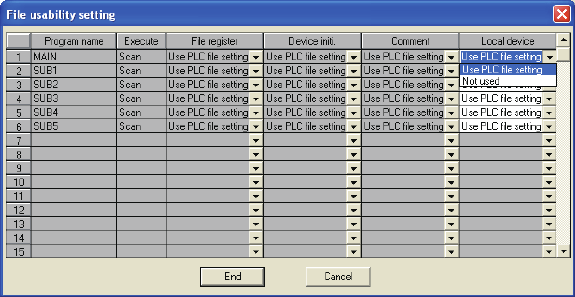

Appendix 3.4.5 File usability setting............................................................................ App- 57

Appendix 3.4.6 Parameter-valid drive and boot file setting ..............................................App- 60

Appendix 3.4.7 External input/output forced on/off function .............................................App- 63

Appendix 3.5 Special Relay and Special Register...............................................................App- 67

Appendix 3.5.1 Special relay list ................................................................................ App- 67

Appendix 3.5.2 Special register list.............................................................................App- 70

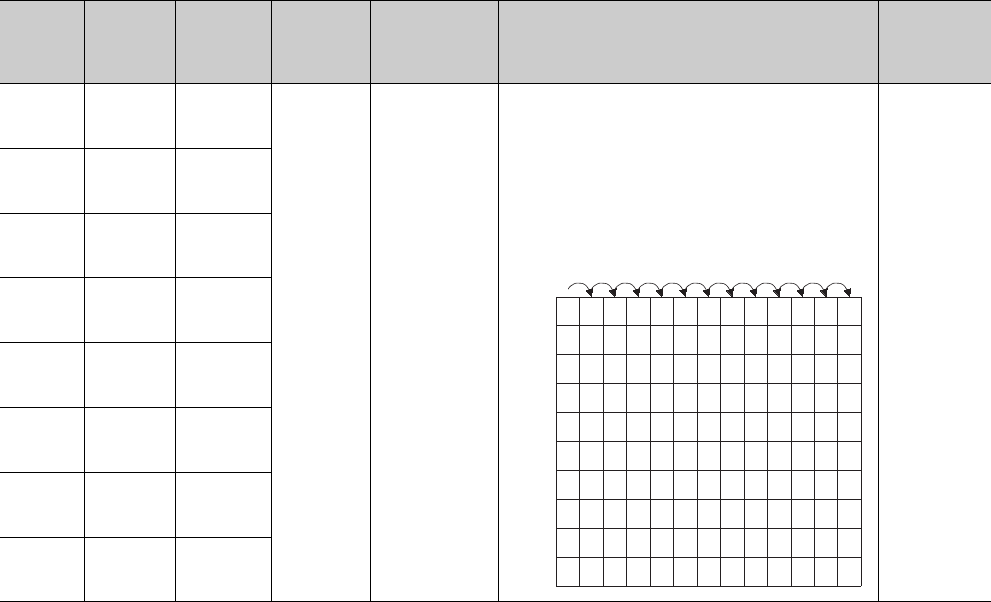

Appendix 4 Device Point Assignment Sheet..................................................................................App- 72

INDEX Index-1 to Index-4

A - 18

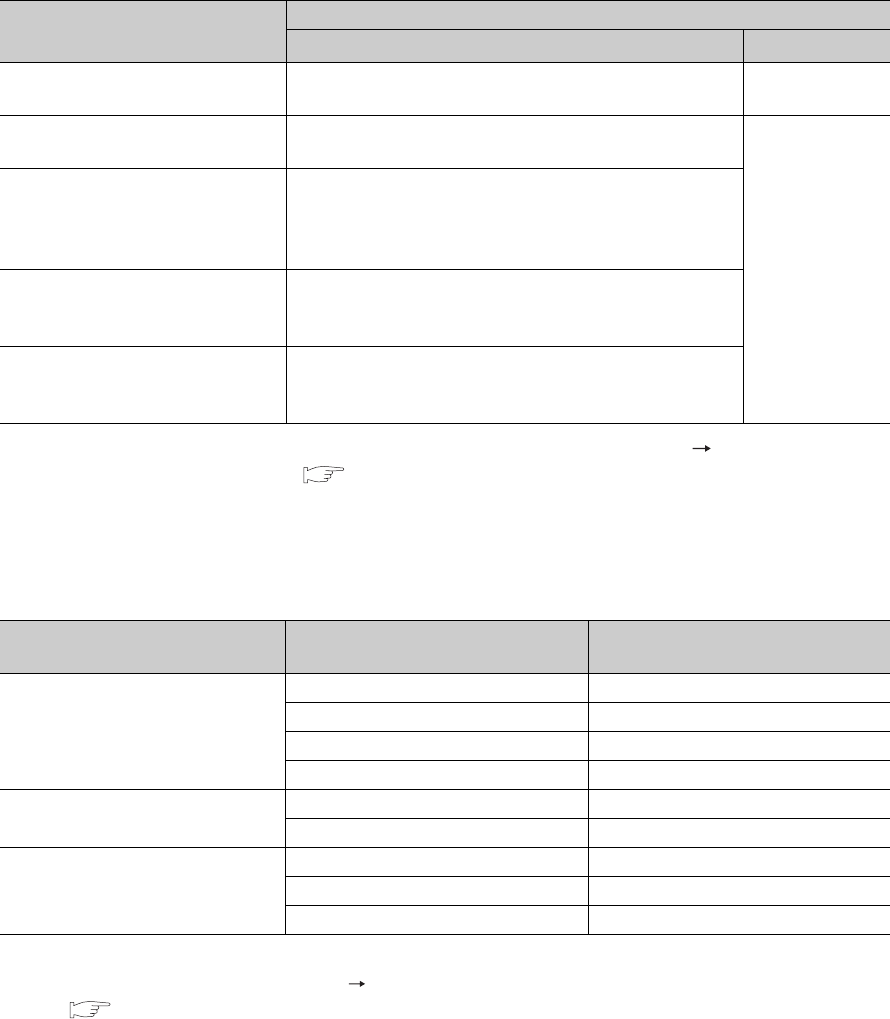

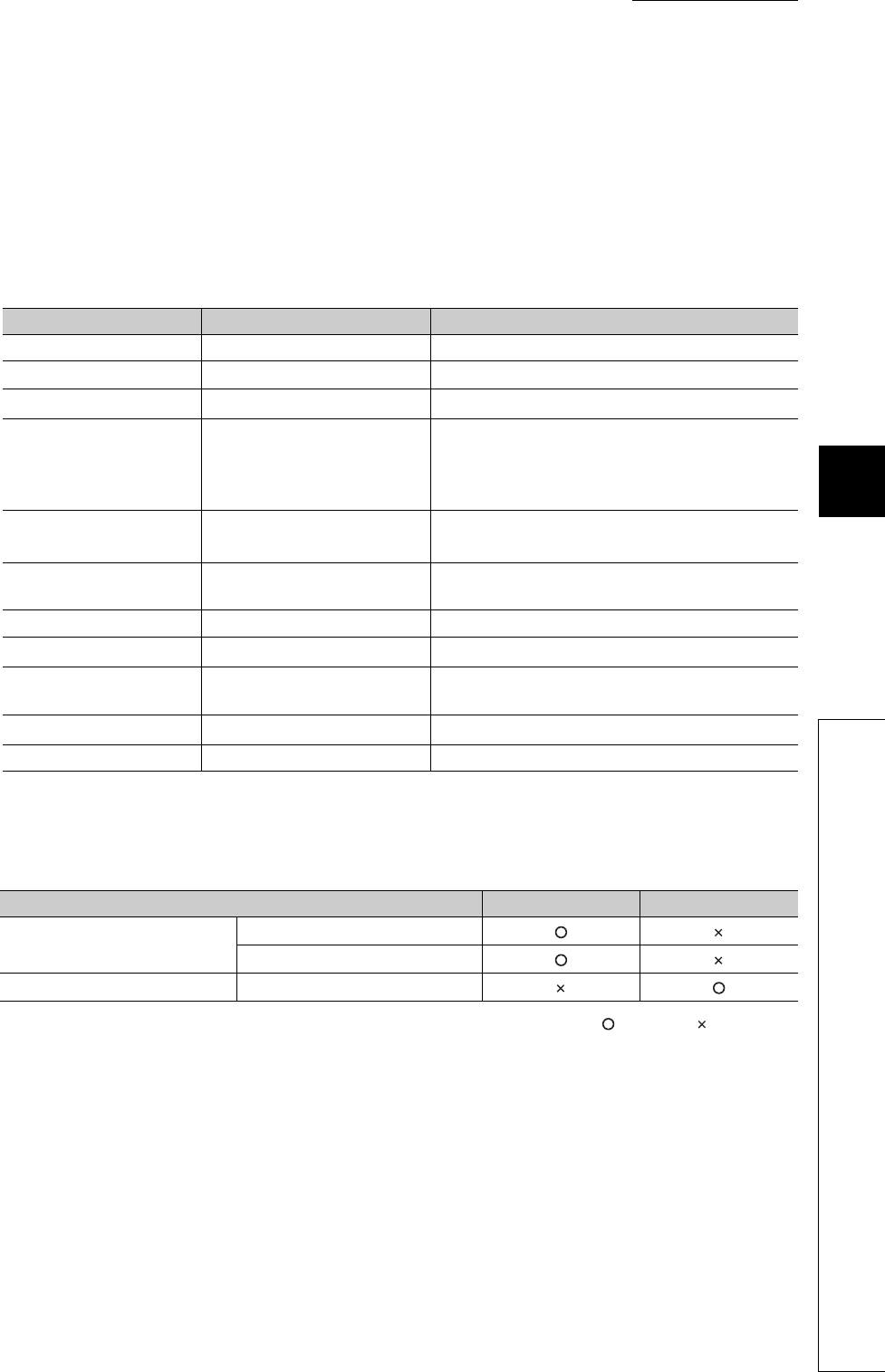

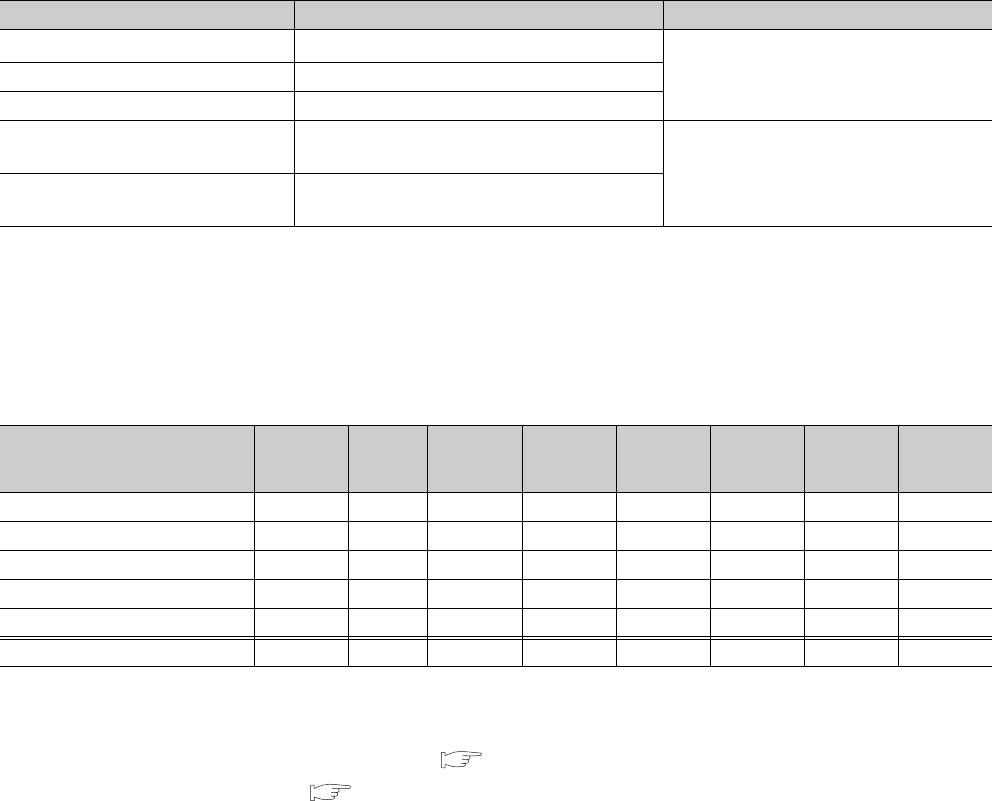

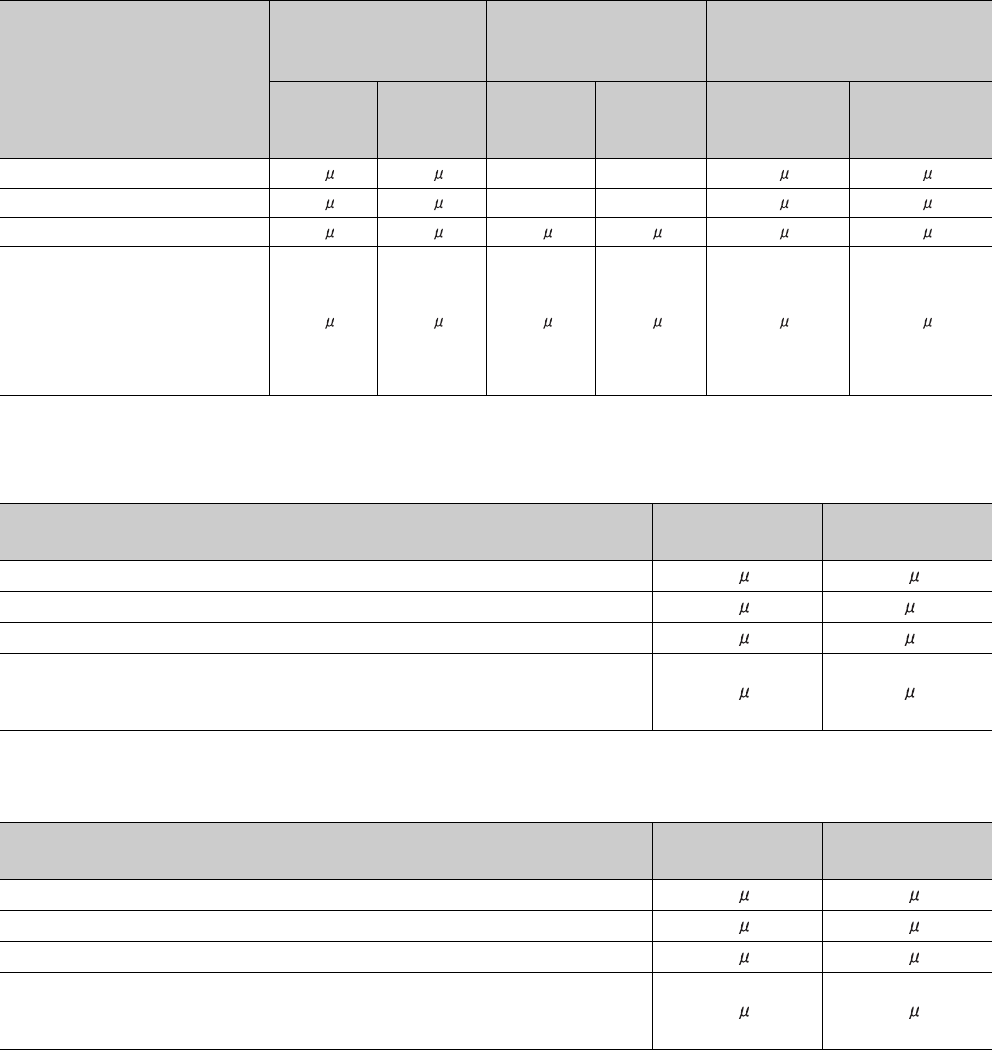

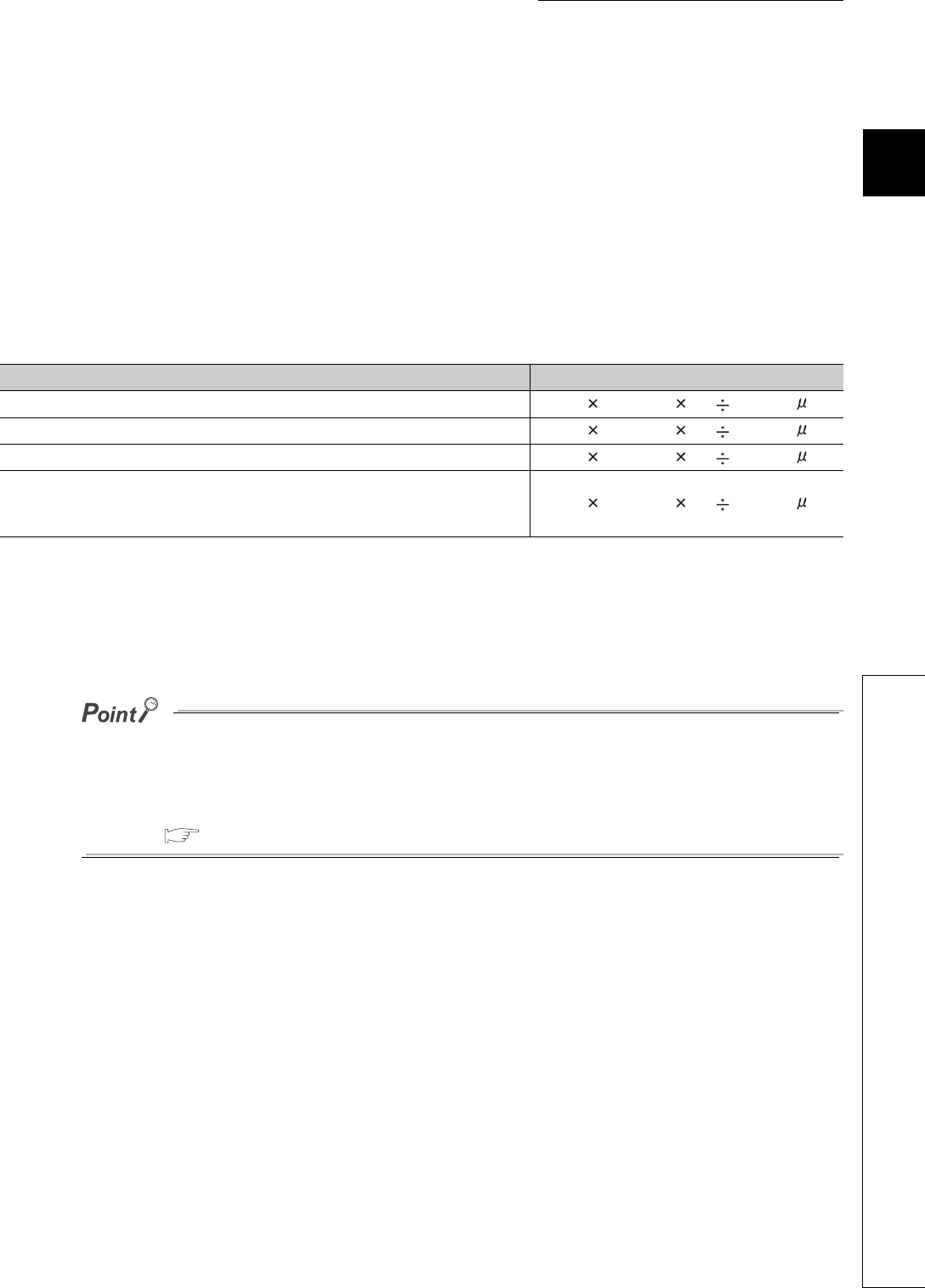

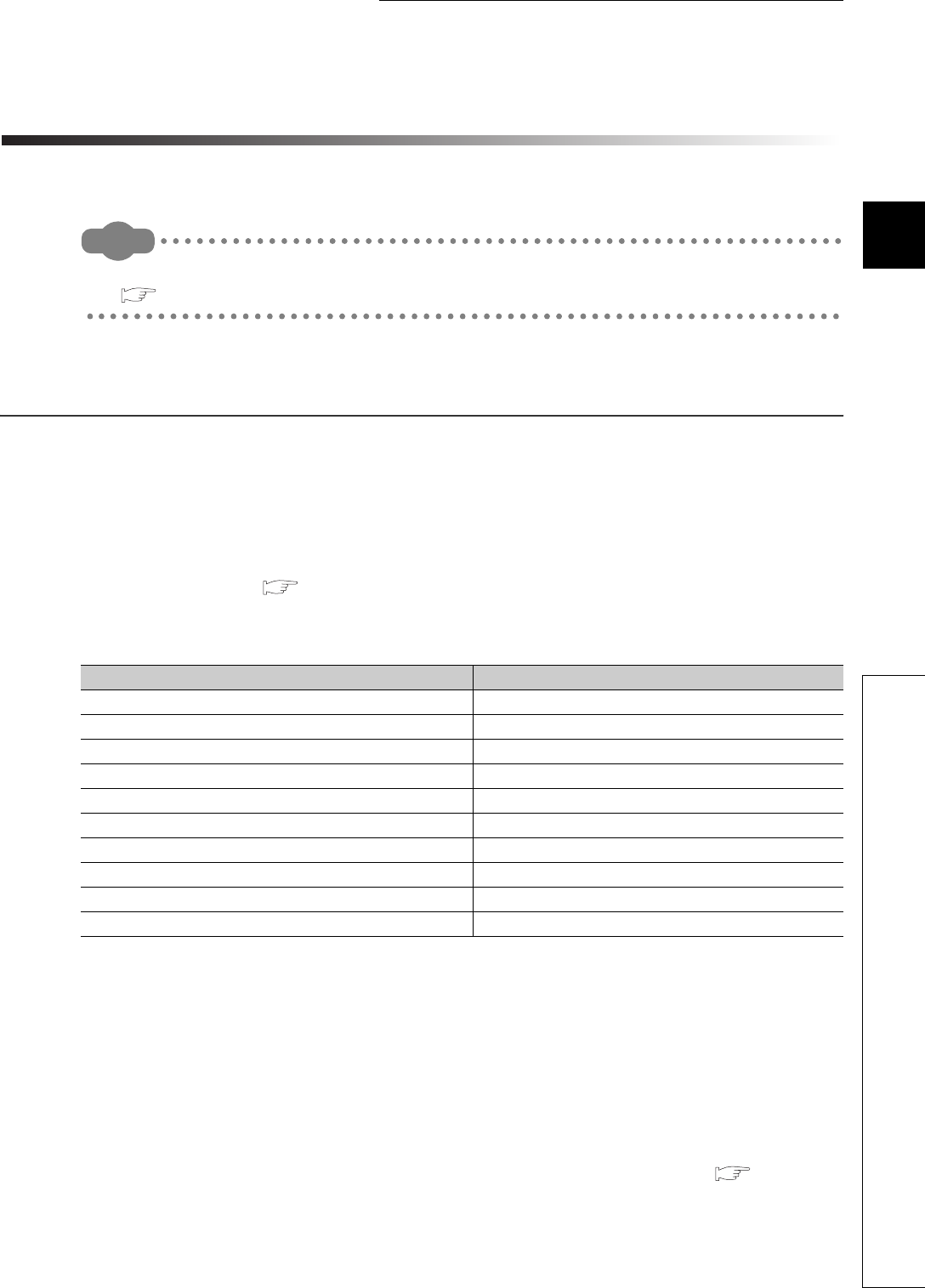

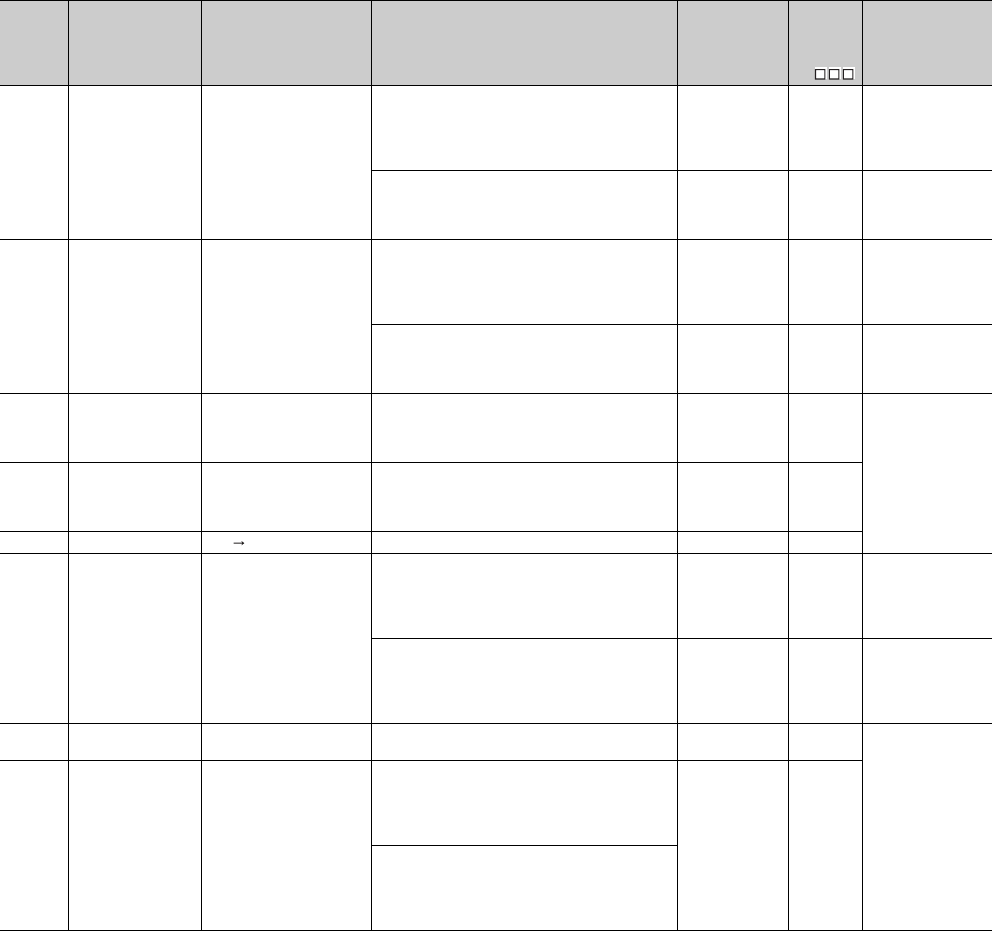

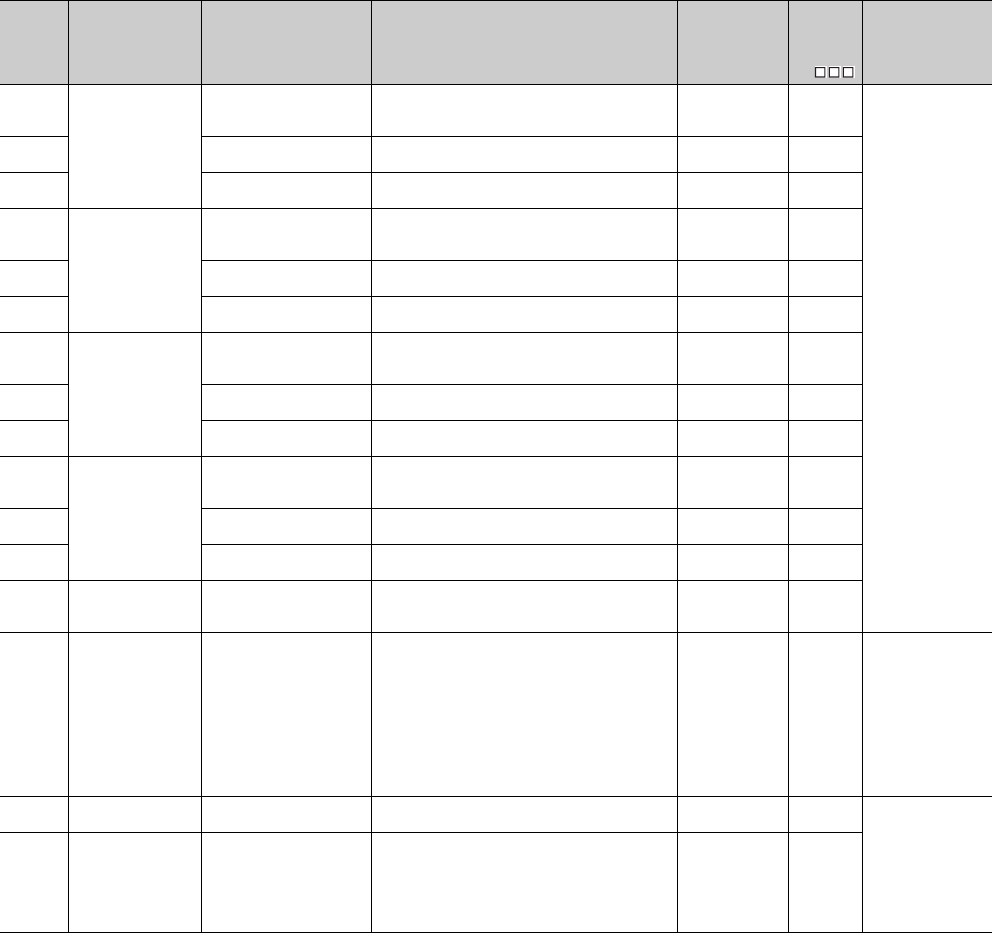

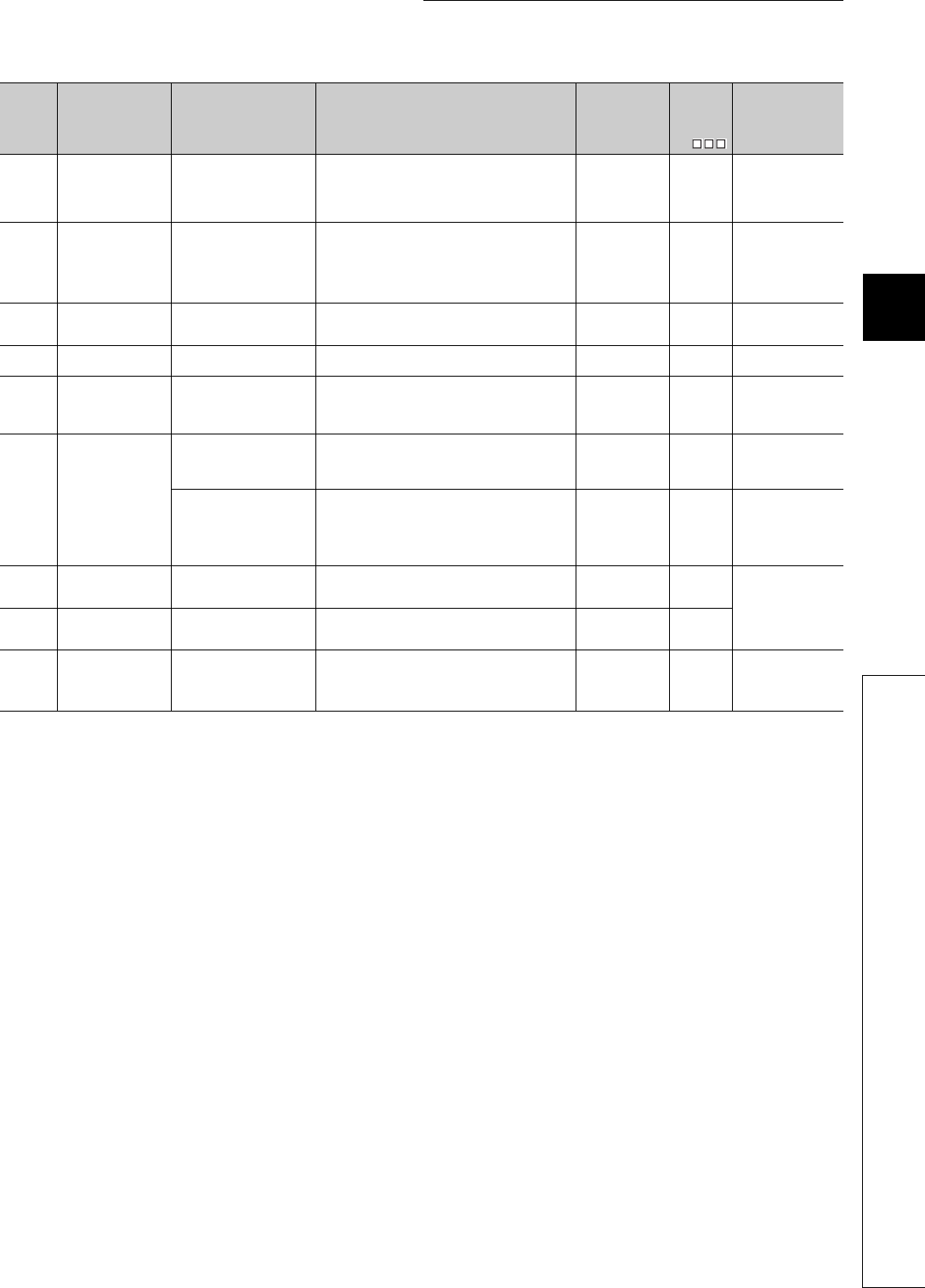

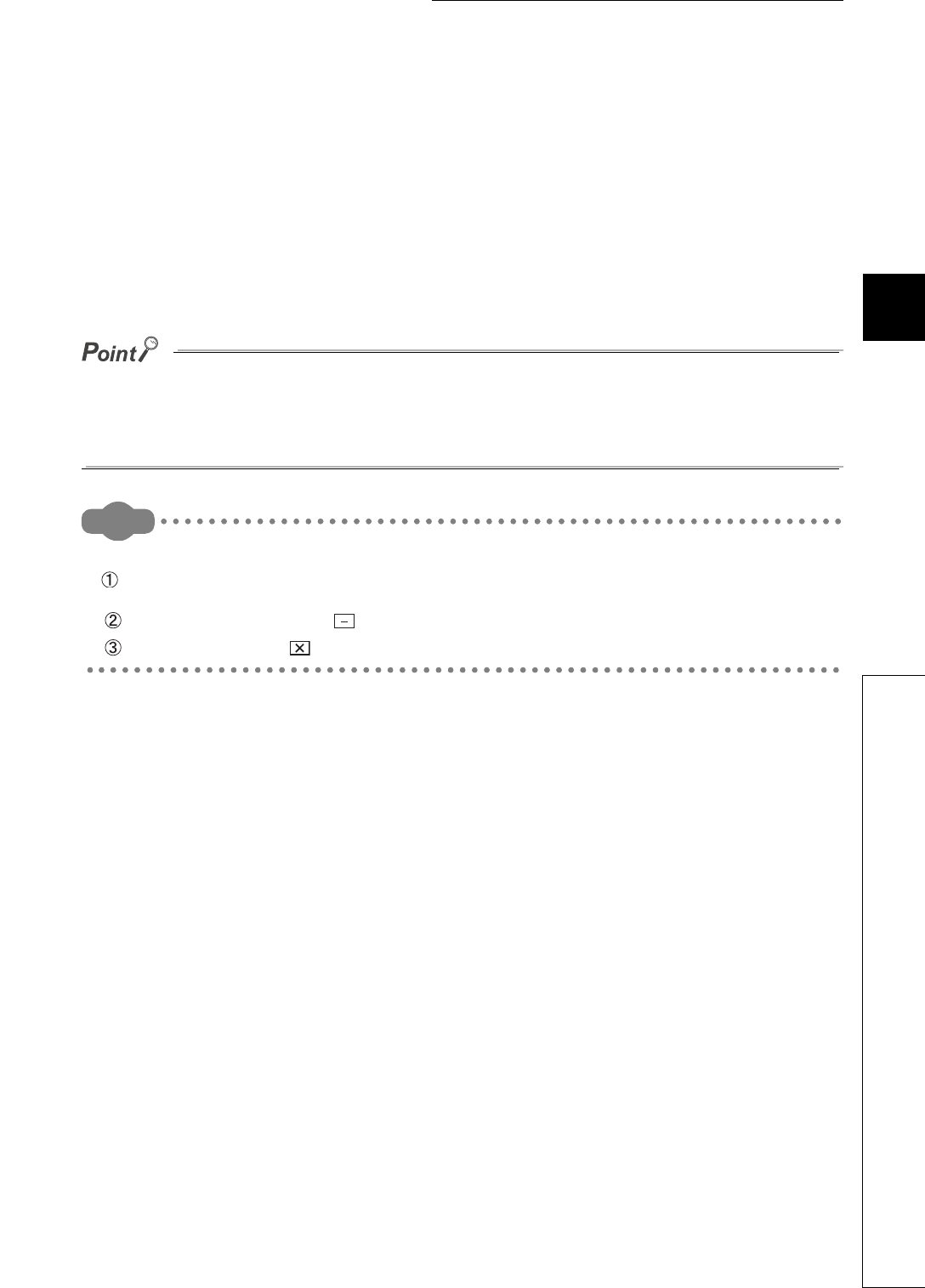

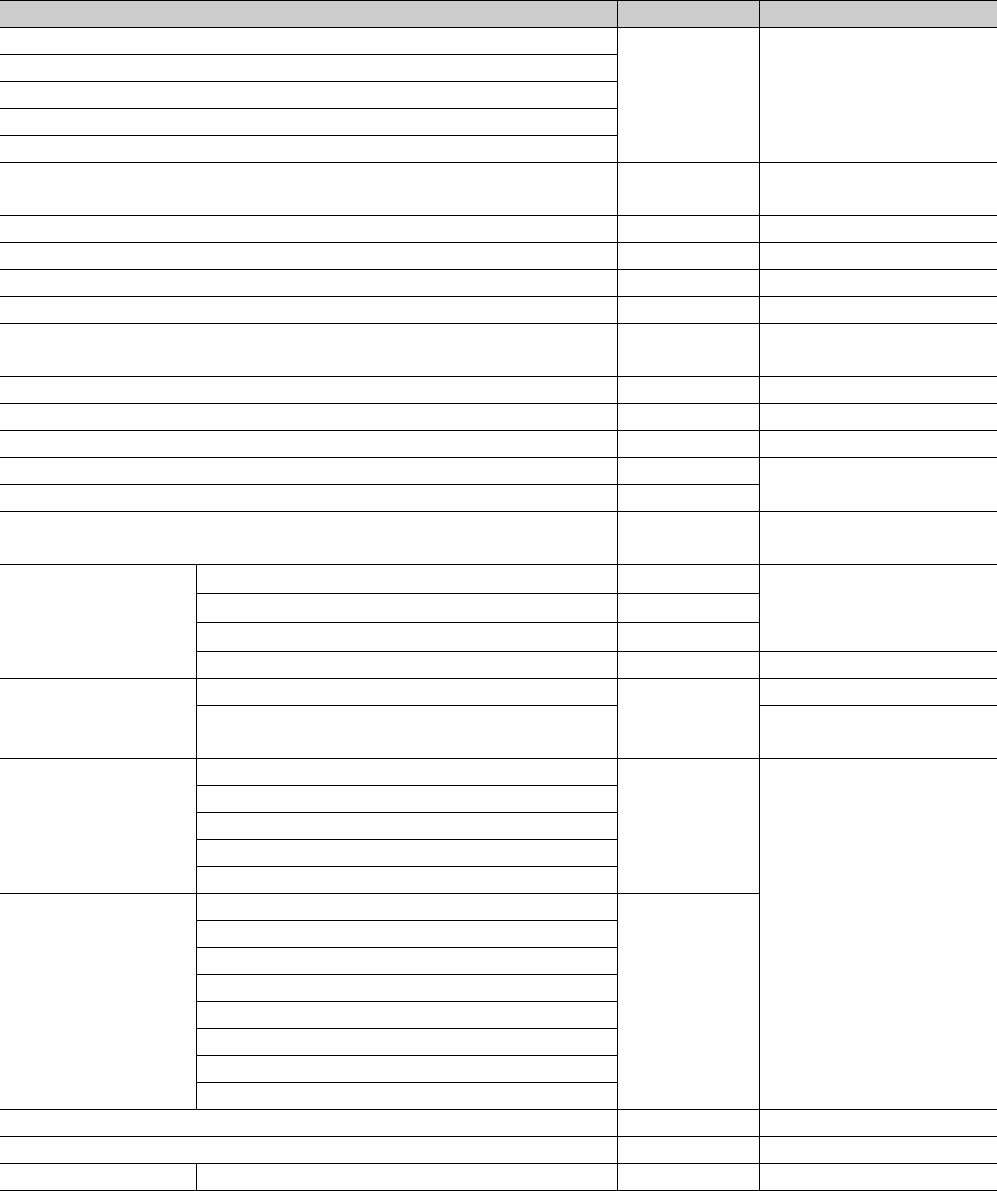

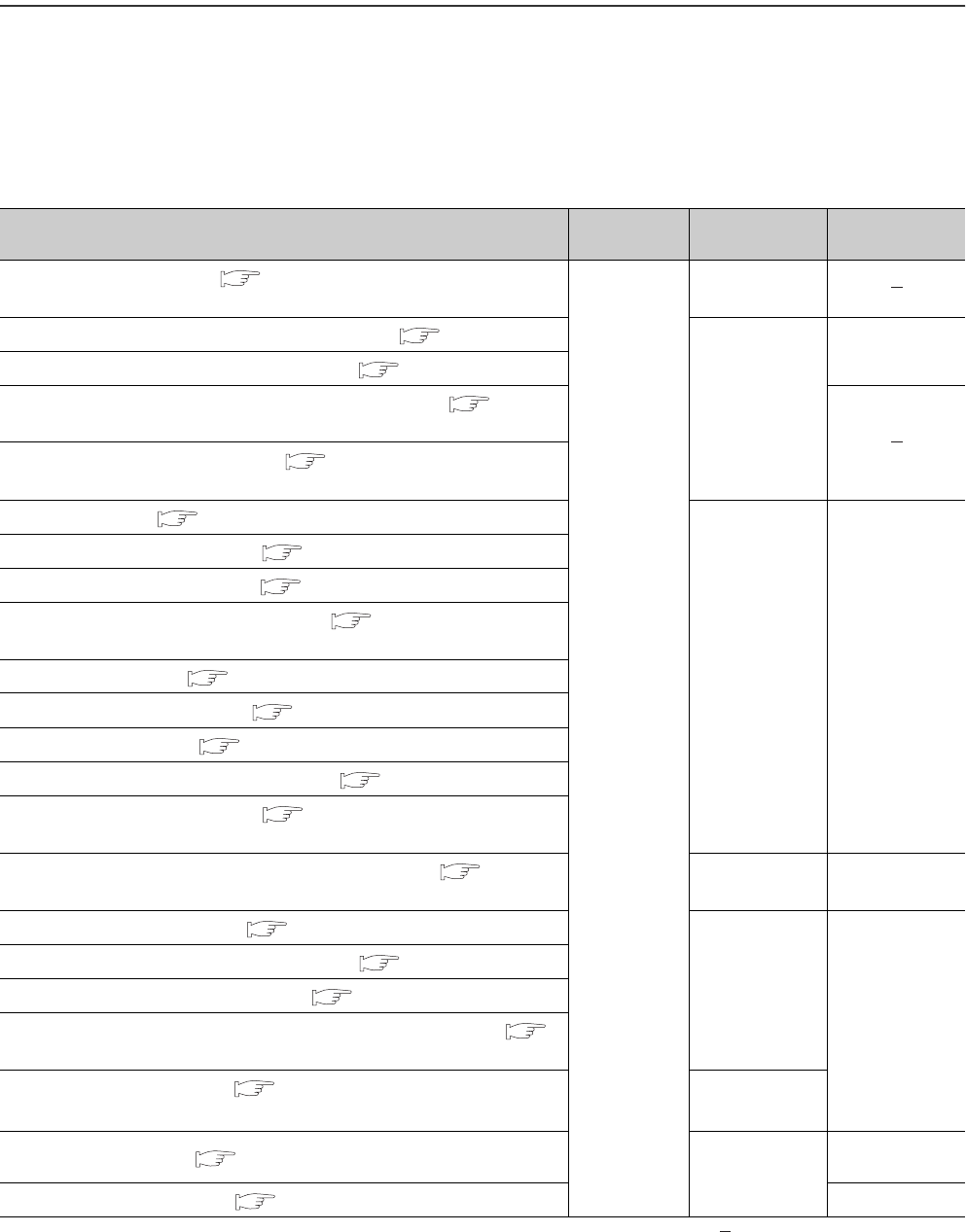

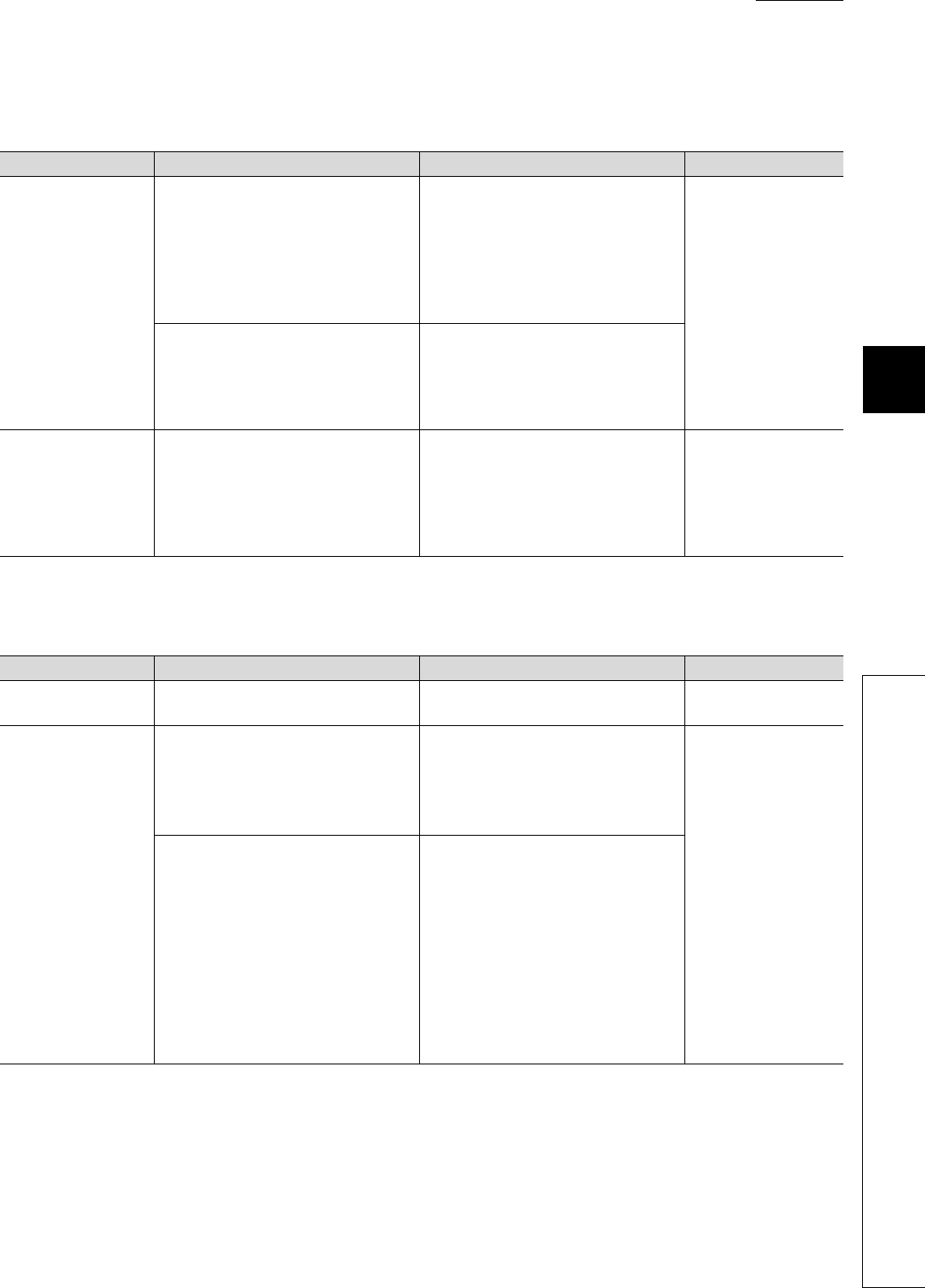

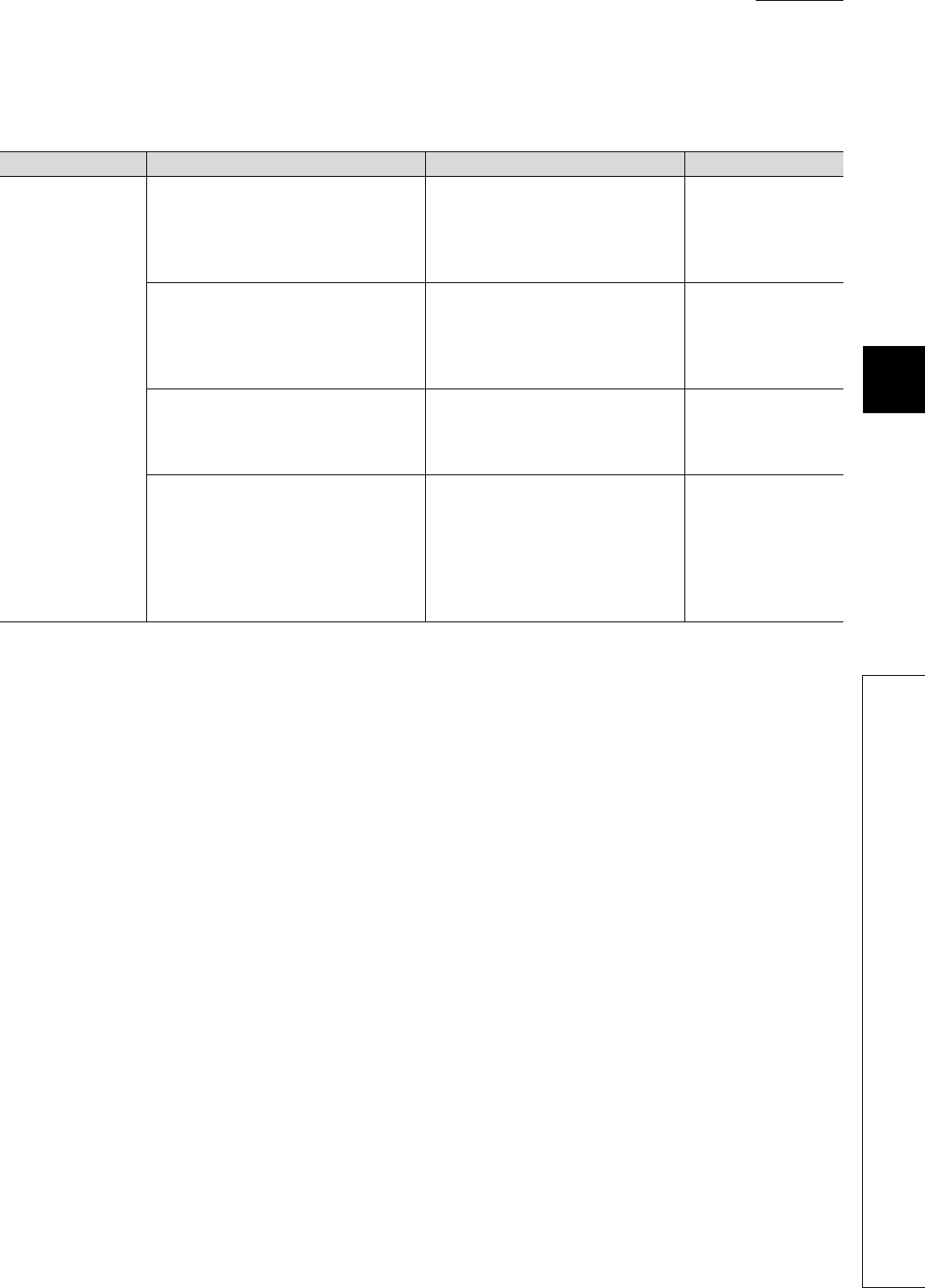

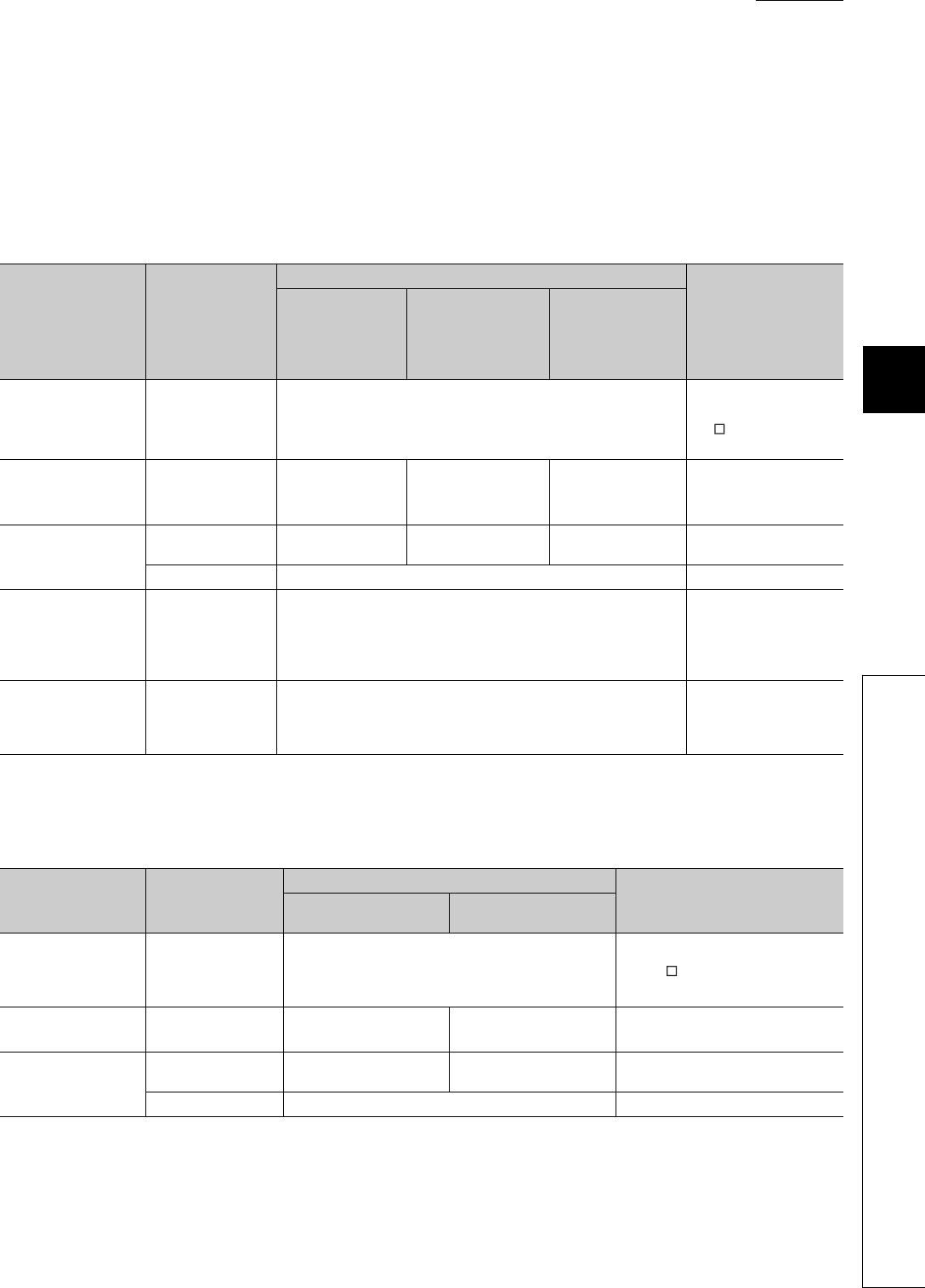

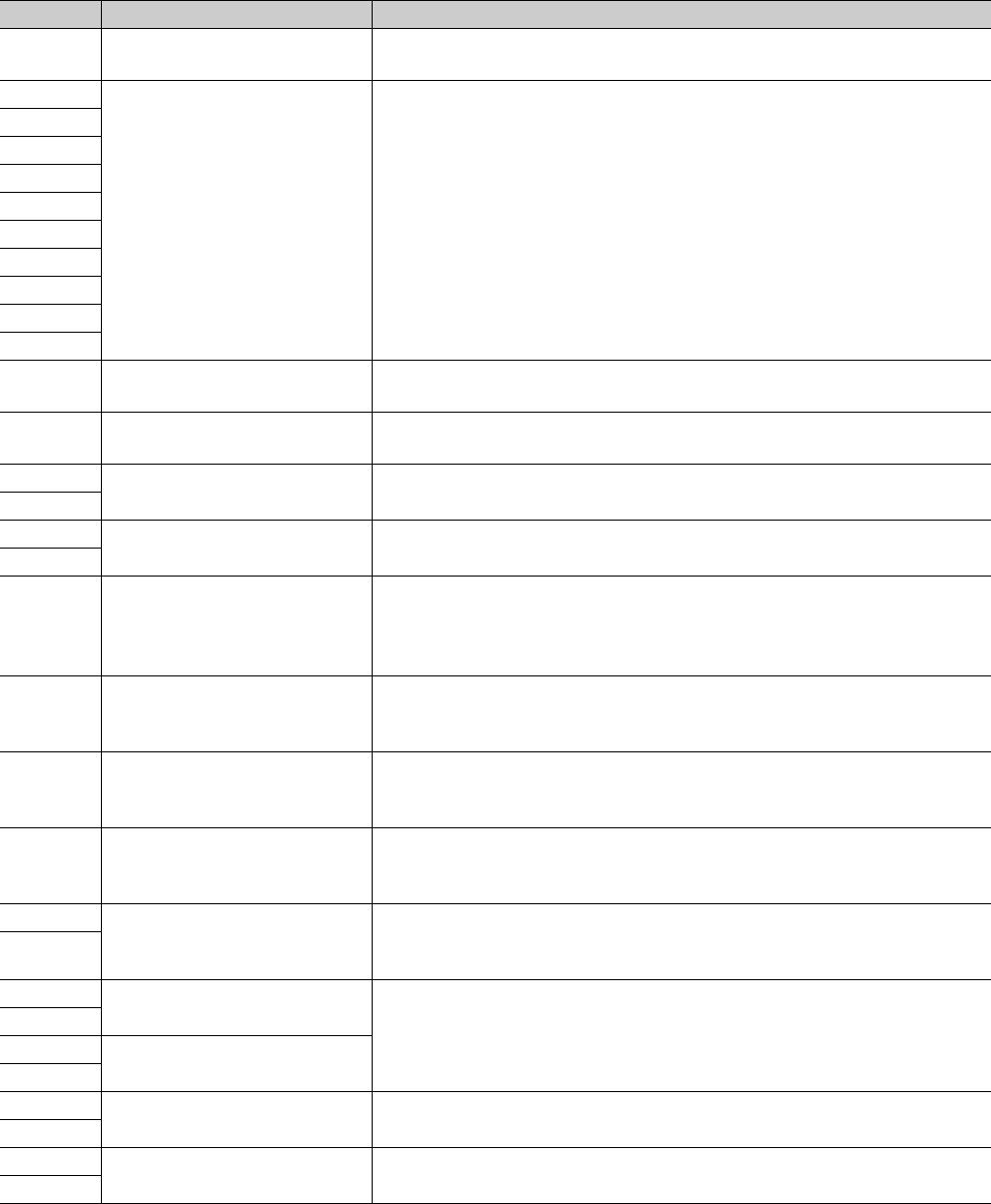

MANUALS

To understand the main specifications, functions, and usage of the CPU module, refer to the basic manuals.

Read other manuals as well when using a different type of CPU module and its functions.

Order each manual as needed, referring to the following list.

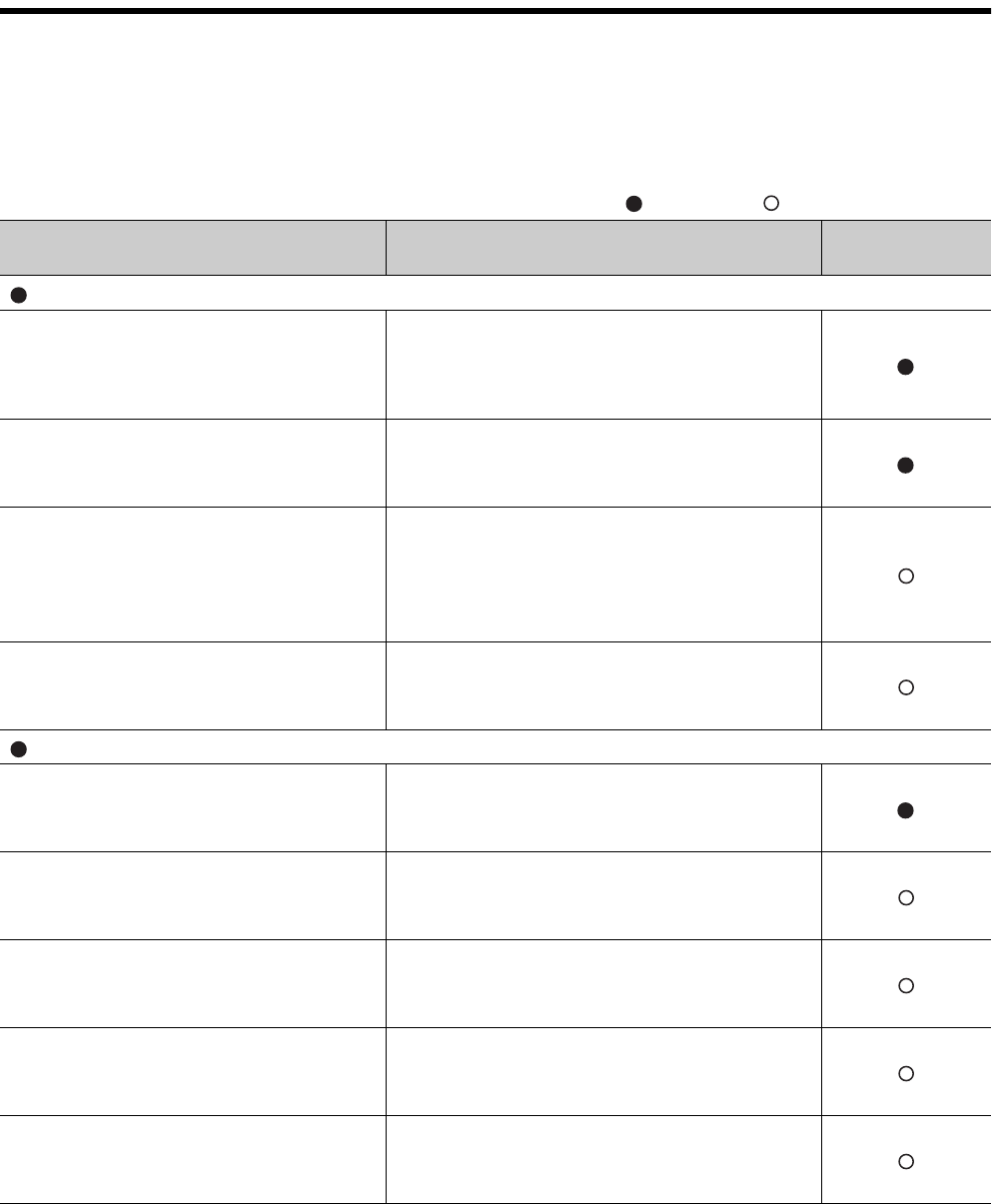

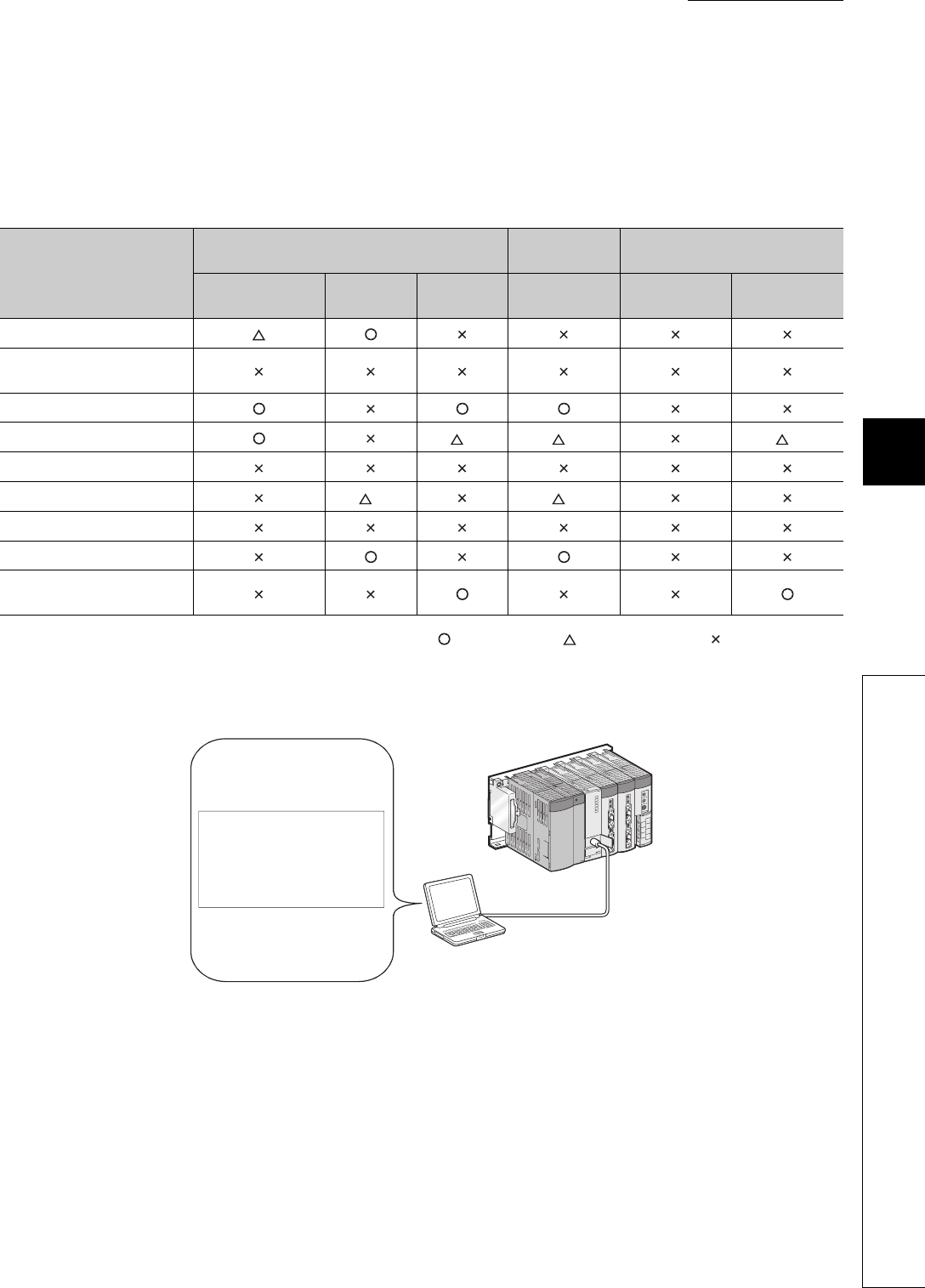

:Basic manual, :Other CPU module manuals

Manual name

< Manual number (model code) > Description Manual type

User's manual

QCPU User's Manual (Hardware Design,

Maintenance and Inspection)

< SH-080483ENG (13JR73) >

Specifications of the hardware (CPU modules, power

supply modules, base units, extension cables, and

memory cards), system maintenance and inspection,

troubleshooting, and error codes

QnUCPU User's Manual (Function

Explanation, Program Fundamentals)

< SH-080807ENG (13JZ27) >

Functions, methods, and devices for programming

QCPU User's Manual (Multiple CPU System)

< SH-080485ENG (13JR75) >

Information on multiple CPU system configuration

(system configuration, I/O numbers, communication

between CPU modules, and communication with the

input/output modules and intelligent function

modules)

QnUCPU User's Manual (Communication via

Built-in Ethernet Port)

< SH-080811ENG (13JZ29) >

Functions for the communication via built-in Ethernet

port of the CPU module

Programming manual

QCPU Programming Manual (Common

Instructions)

< SH-080809ENG (13JW10) >

How to use sequence instructions, basic instructions,

and application instructions

QCPU (Q Mode)/QnACPU Programming

Manual (SFC)

< SH-080041 (13JF60) >

System configuration, performance specifications,

functions, programming, debugging, and error codes

for SFC (MELSAP3) programs

QCPU (Q Mode) Programming Manual

(MELSAP-L)

< SH-080076 (13JF61) >

Programming methods, specifications, and functions

for SFC (MELSAP-L) programs

QCPU (Q Mode) Programming Manual

(Structured Text)

< SH-080366E (13JF68) >

Programming methods using structured languages

QCPU (Q Mode) / QnACPU Programming

Manual (PID Control Instructions)

< SH-080040 (13JF59) >

Dedicated instructions for PID control

A - 19

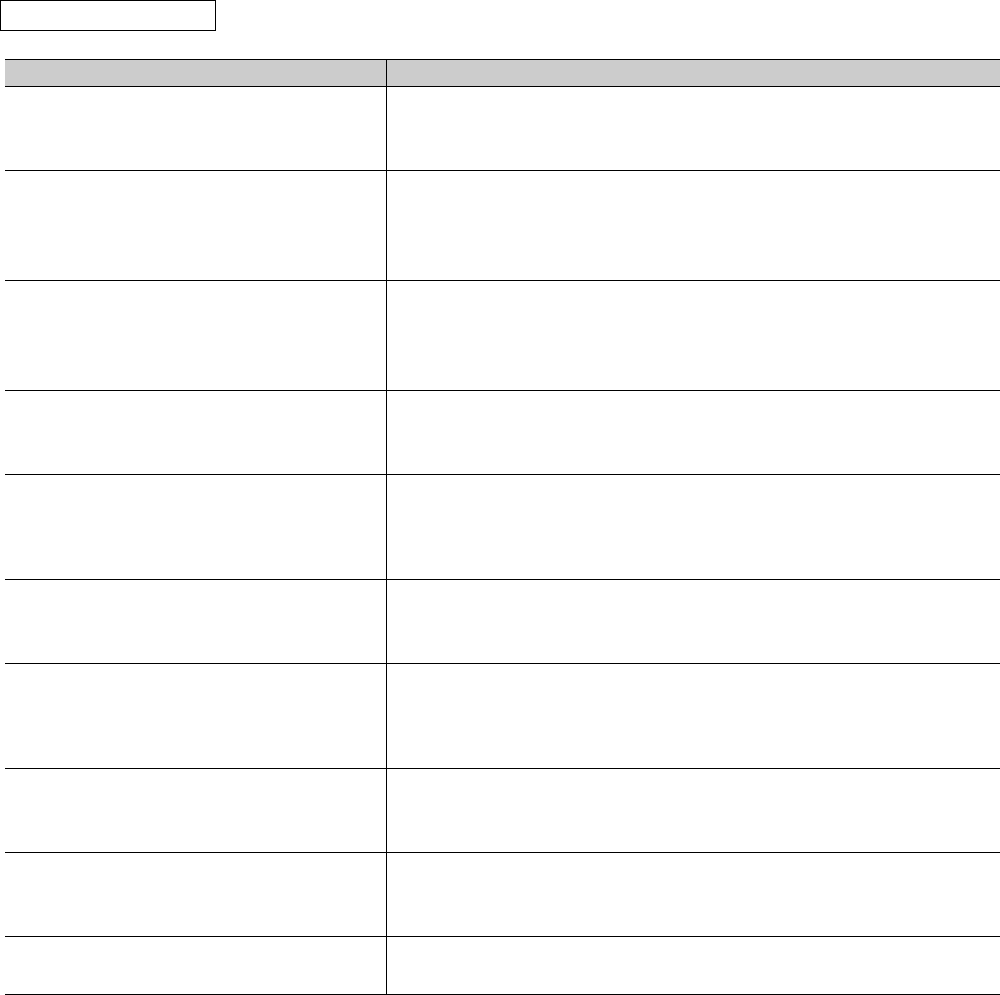

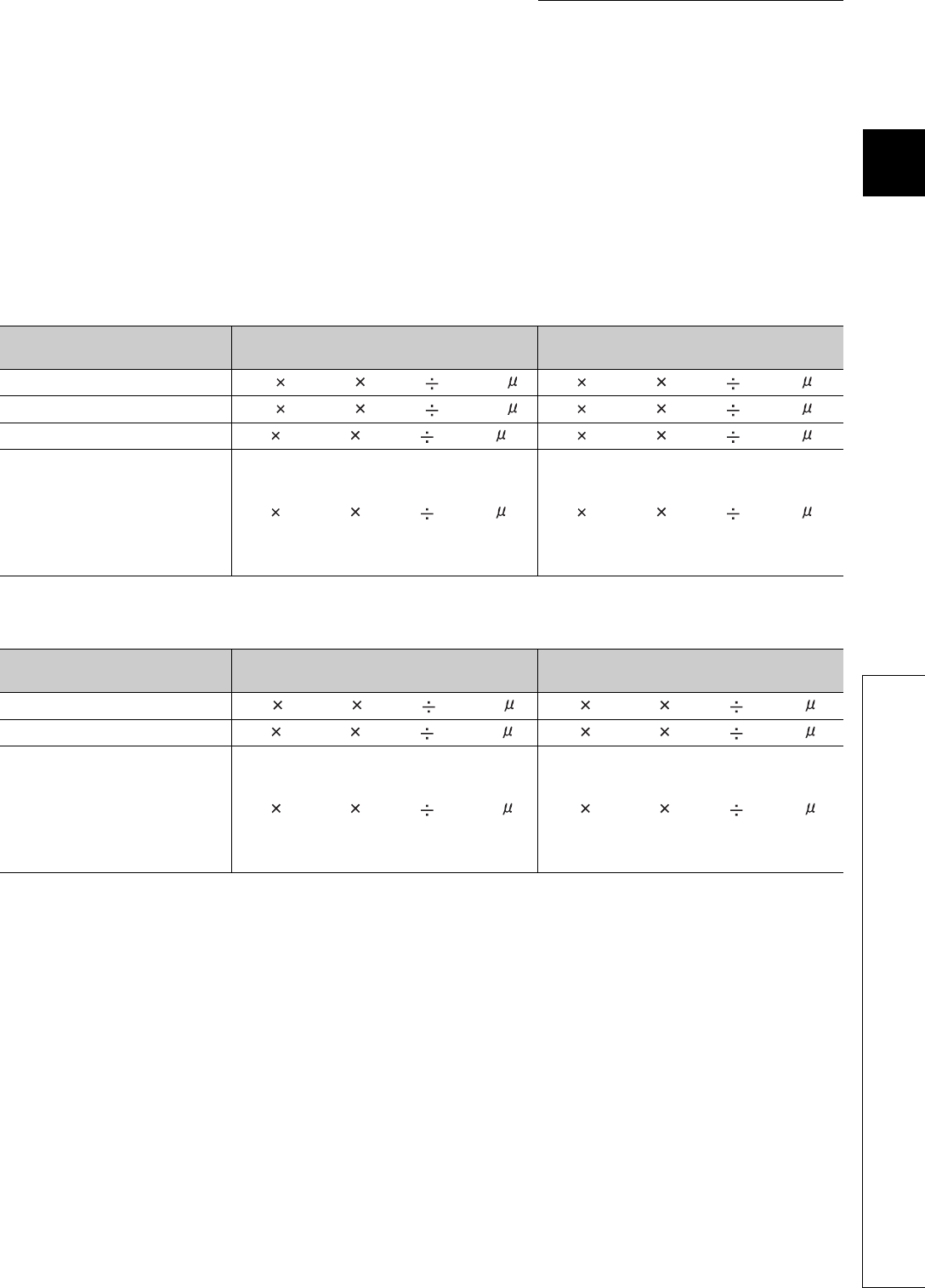

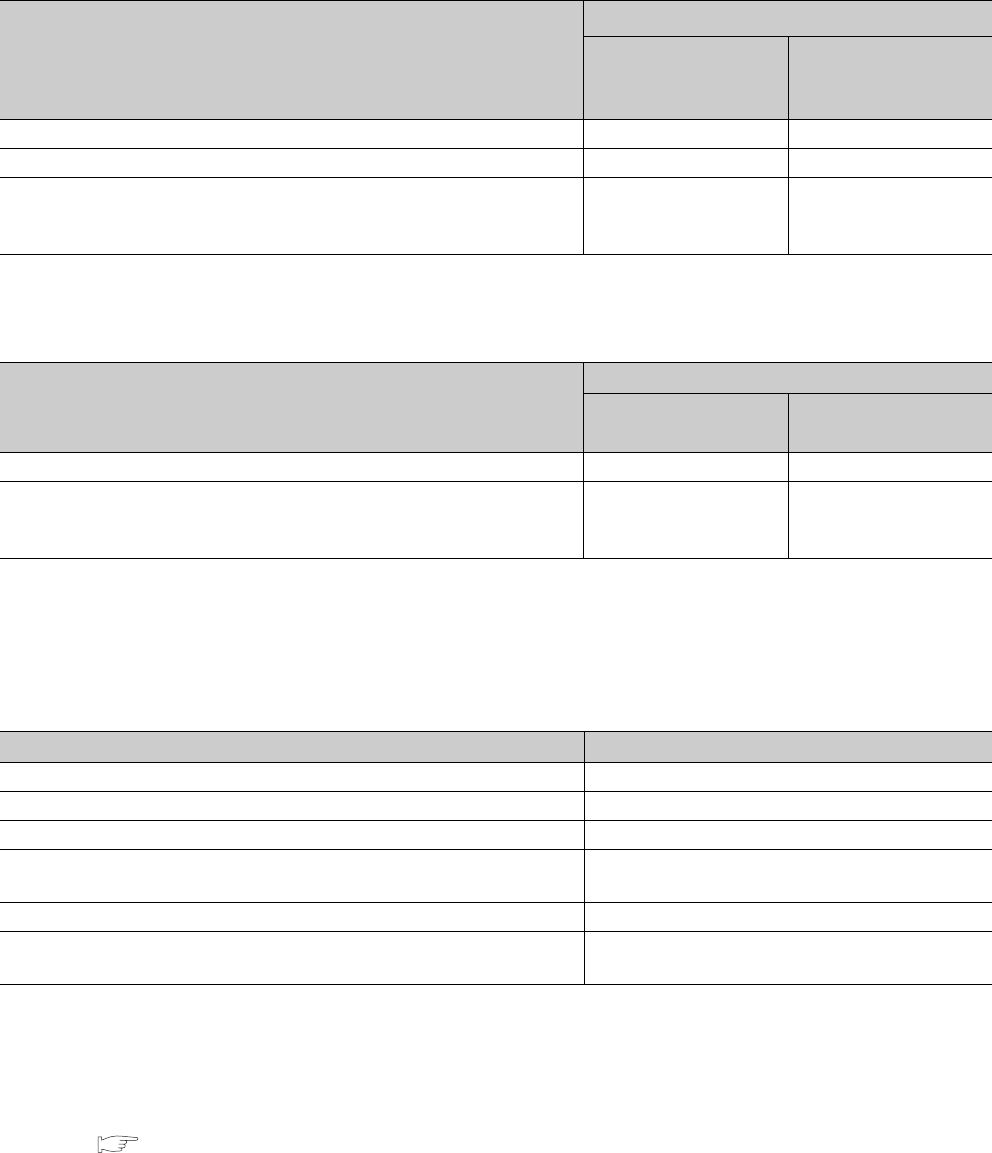

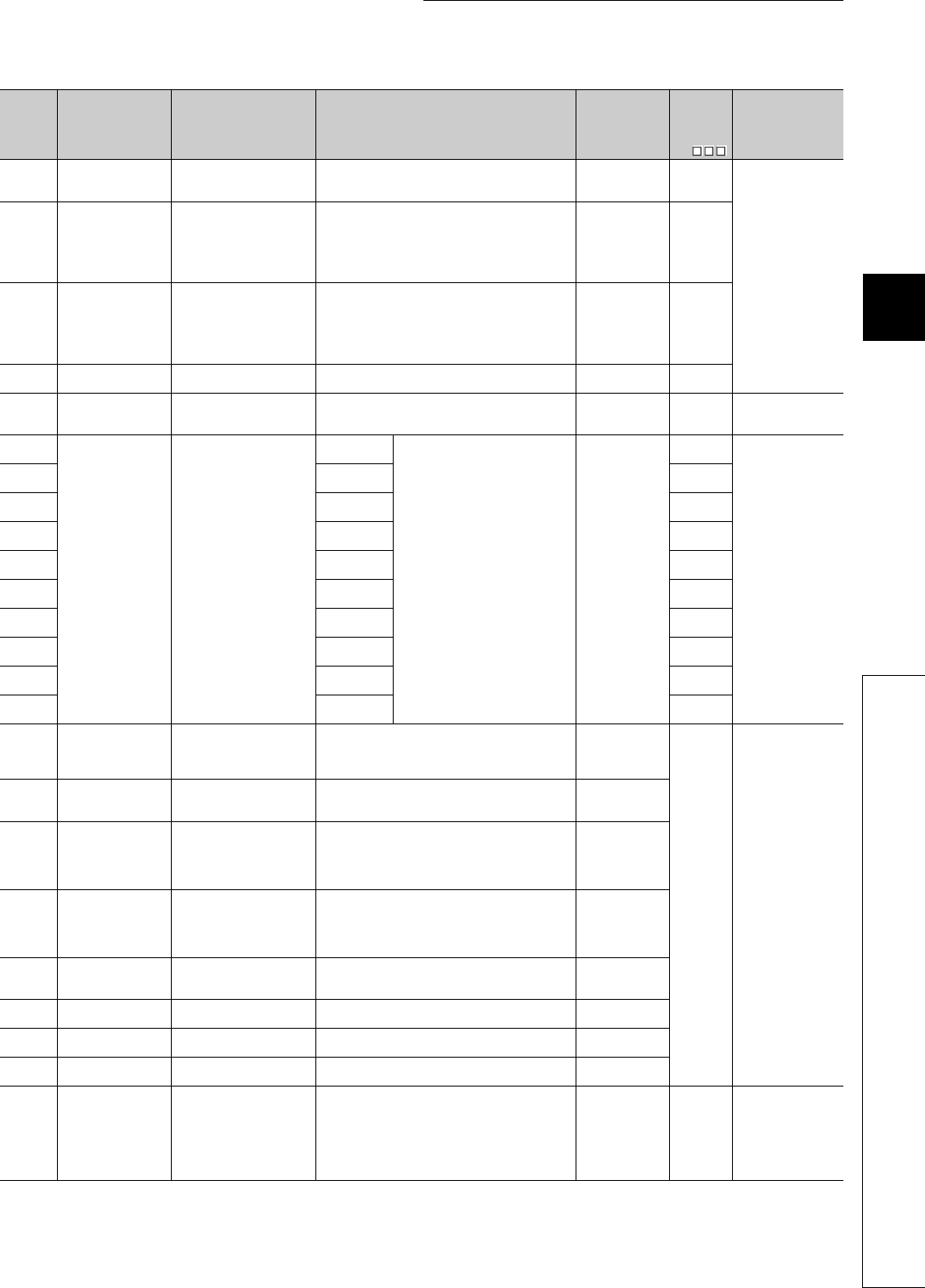

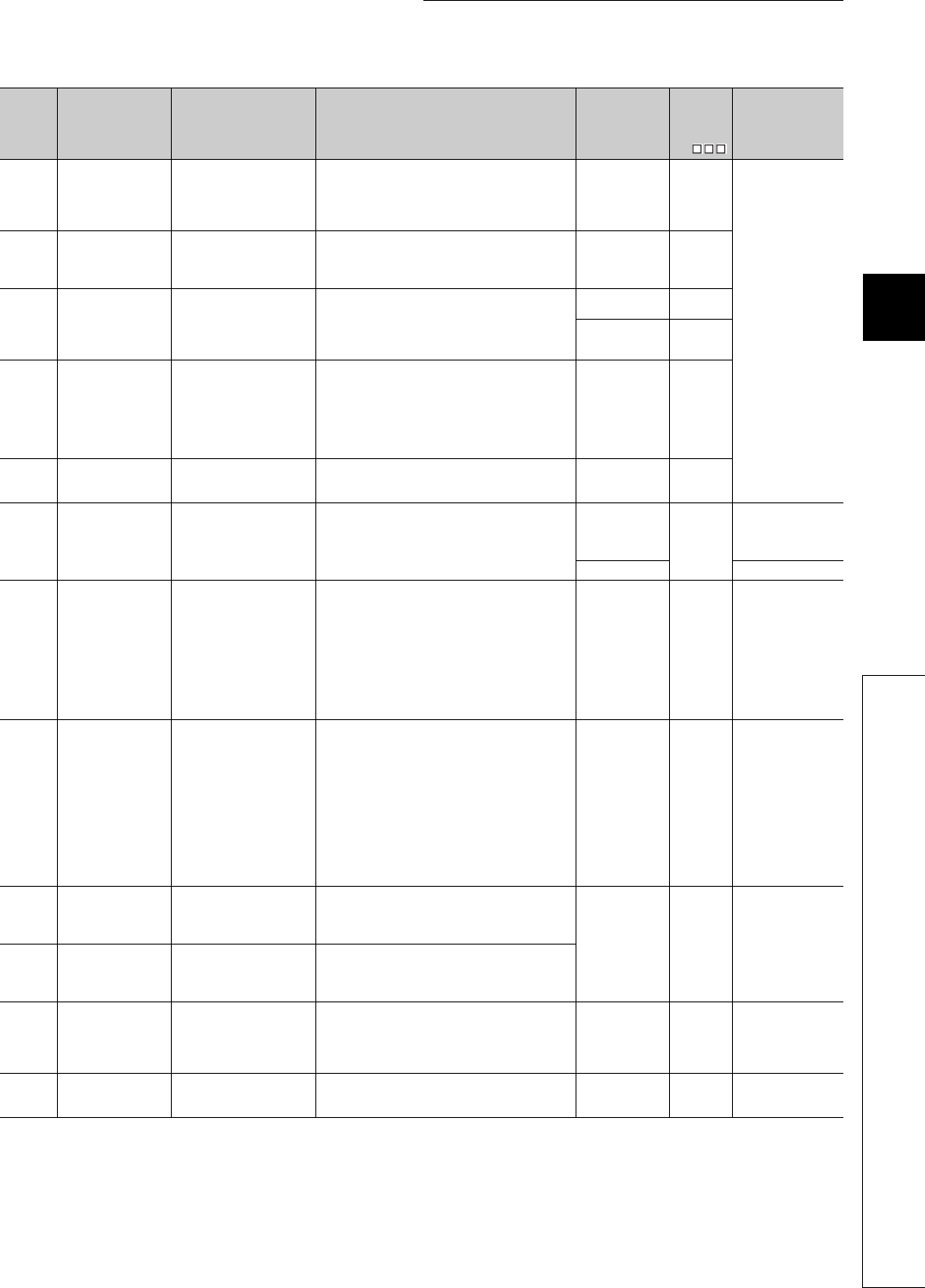

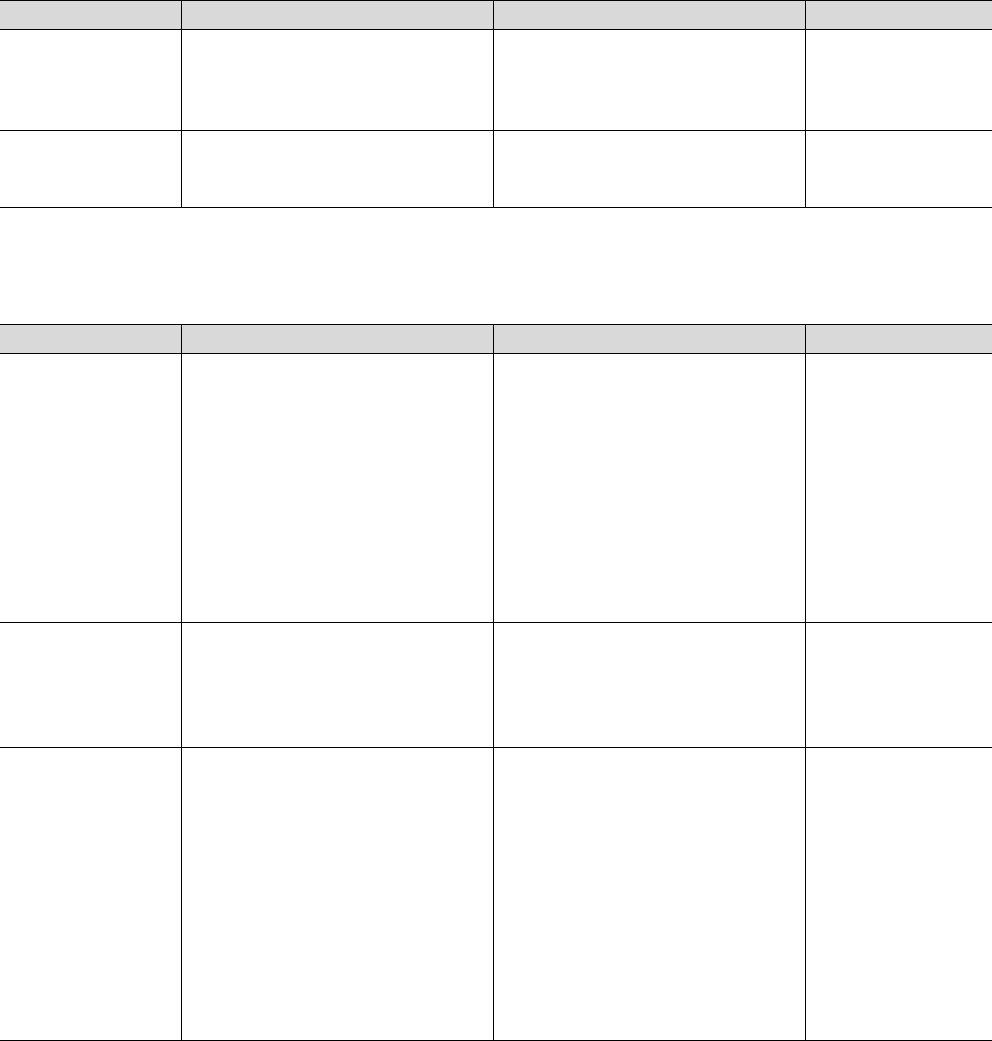

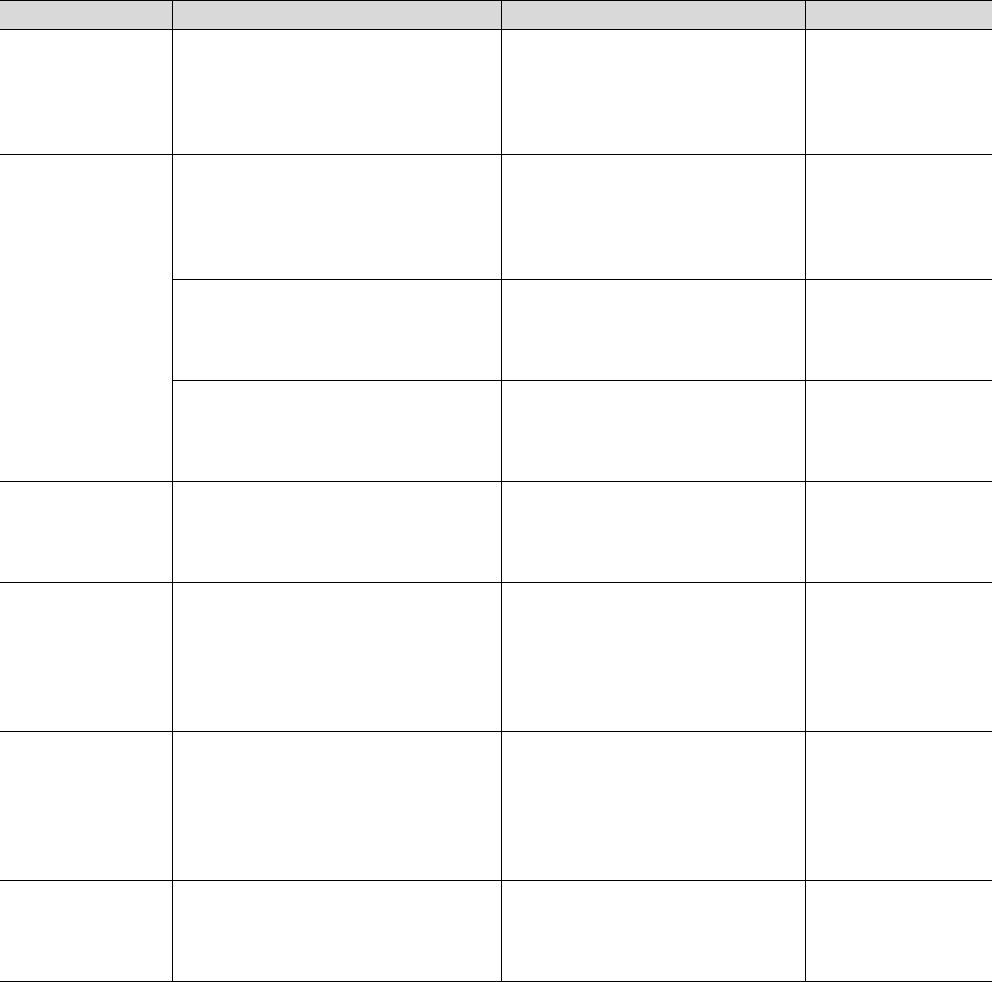

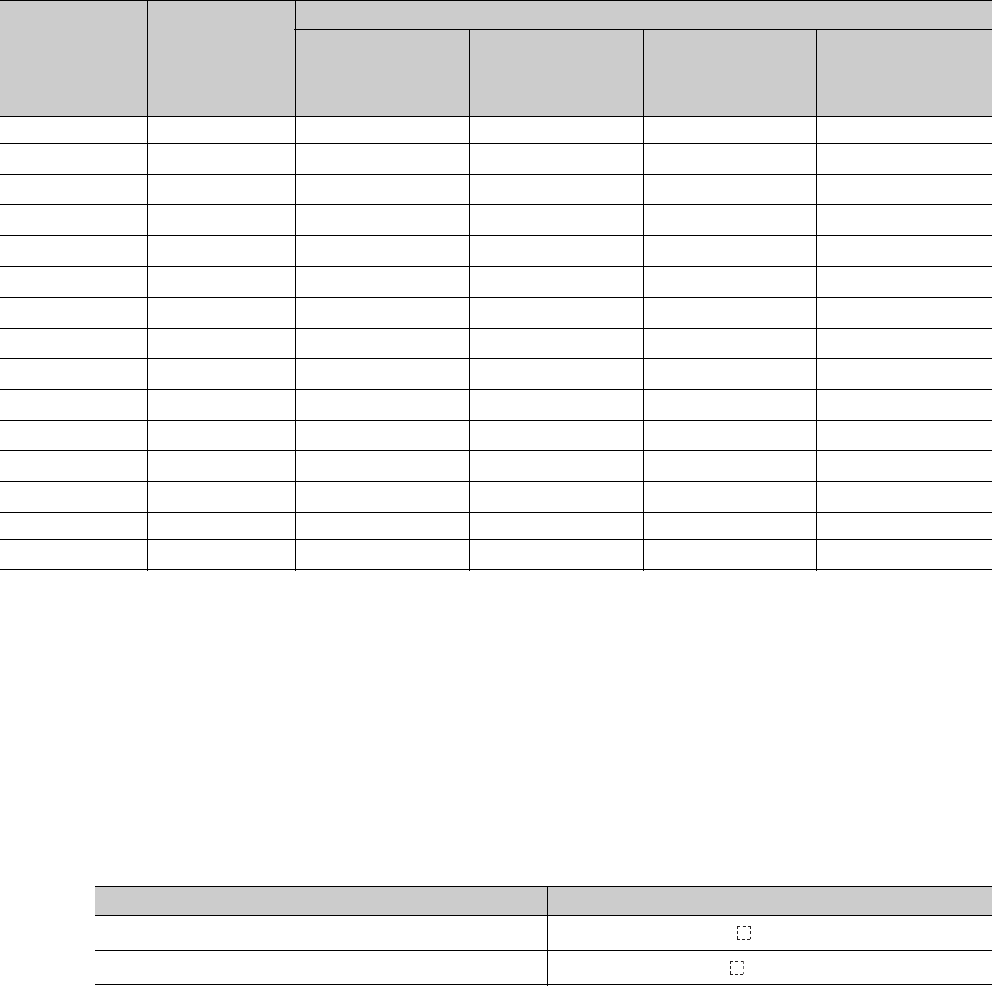

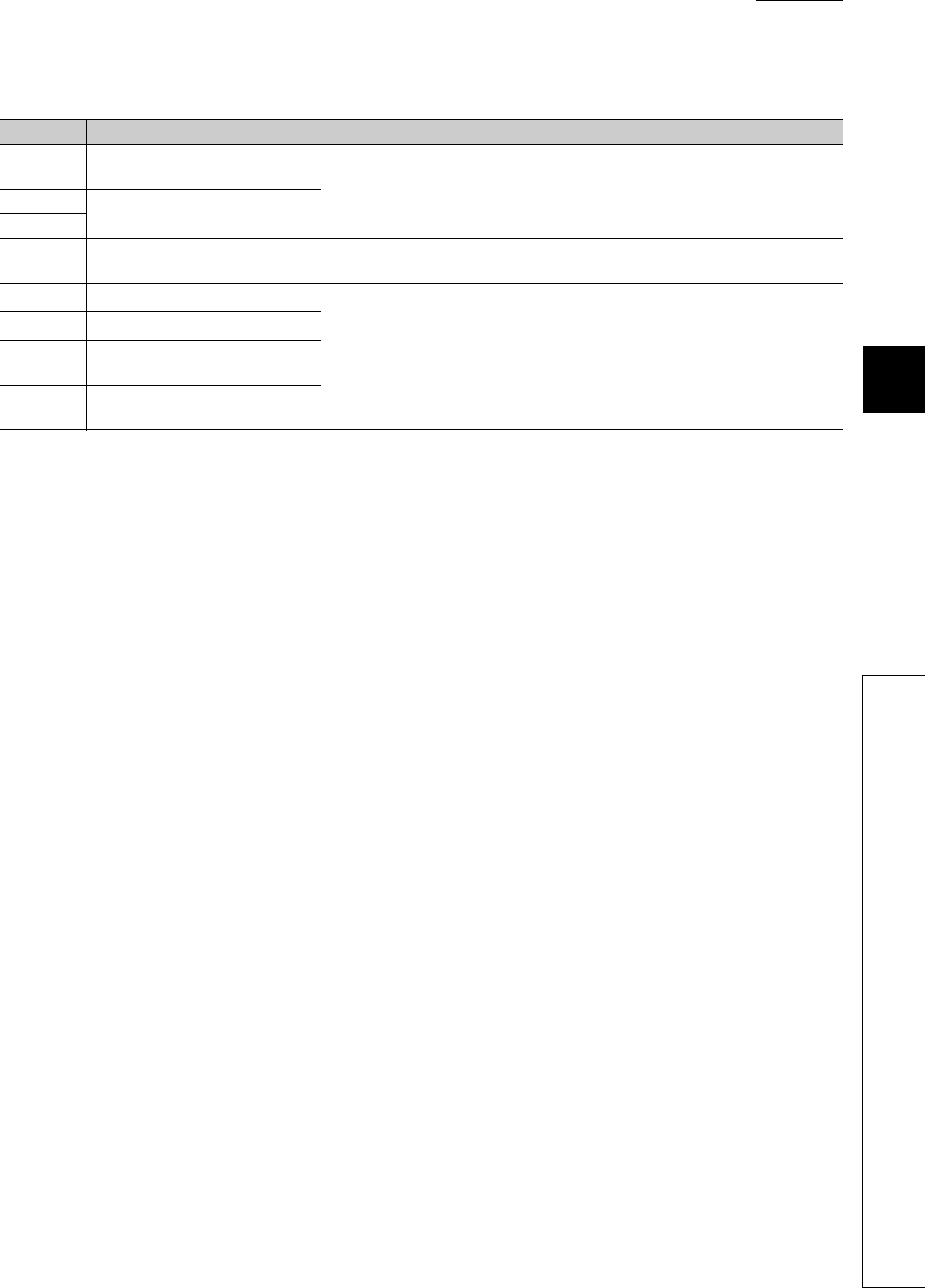

Other relevant manuals

Manual name Description

CC-Link IE Controller Network Reference

Manual

< SH-080668ENG (13JV16) >

Specifications, procedures and settings before system operation, parameter

setting, programming, and troubleshooting of the CC-Link IE controller

network module

Q Corresponding MELSECNET/H Network

System Reference Manual (PLC to PLC

network)

< SH-080049 (13JF92) >

Specifications, procedures and settings before system operation, parameter

setting, programming, and troubleshooting of a MELSECNET/H network

system (PLC to PLC network)

Q Corresponding MELSECNET/H Network

System Reference Manual (Remote I/O

network)

< SH-080124 (13JF96) >

Specifications, procedures and settings before system operation, parameter

setting, programming, and troubleshooting of a MELSECNET/H network

system (remote I/O network)

Q Corresponding Ethernet Interface Module

User's Manual (Basic)

< SH-080009 (13JL88) >

Specifications, procedures for data communication with external devices,

line connection (open/close), fixed buffer communication, random access

buffer communication, and troubleshooting of the Ethernet module

Q Corresponding Ethernet Interface Module

User's Manual (Application)

< SH-080010 (13JL89) >

E-mail function, programmable controller CPU status monitoring function,

communication via MELSECNET/H or MELSECNET/10, communication

using the data link instructions, and file transfer function (FTP server) of the

Ethernet module

CC-Link System Master/Local Module User's

Manual

< SH-080394E (13JR64) >

System configuration, performance specifications, functions, handling,

wiring, and troubleshooting of the QJ61BT11N

Q Corresponding Serial Communication

Module User's Manual (Basic)

< SH-080006 (13JL86) >

Overview, system configuration, specifications, procedures before

operation, basic data communication method with external devices,

maintenance and inspection, and troubleshooting for using the serial

communication module

Q Corresponding Serial Communication

Module User's Manual (Application)

< SH-080007 (13JL87) >

Special functions (specifications, usage, and settings and data

communication method with external devices of the serial communication

module

Q Corresponding MELSEC Communication

Protocol Reference Manual

< SH-080008 (13JF89) >

Communication method using the MC protocol, which reads/writes data to/

from the CPU module via the serial communication module or Ethernet

module

GX Developer Version 8 Operating Manual

< SH-080373E (13JU41) > Operating methods of GX Developer, such as programming and printout

A - 20

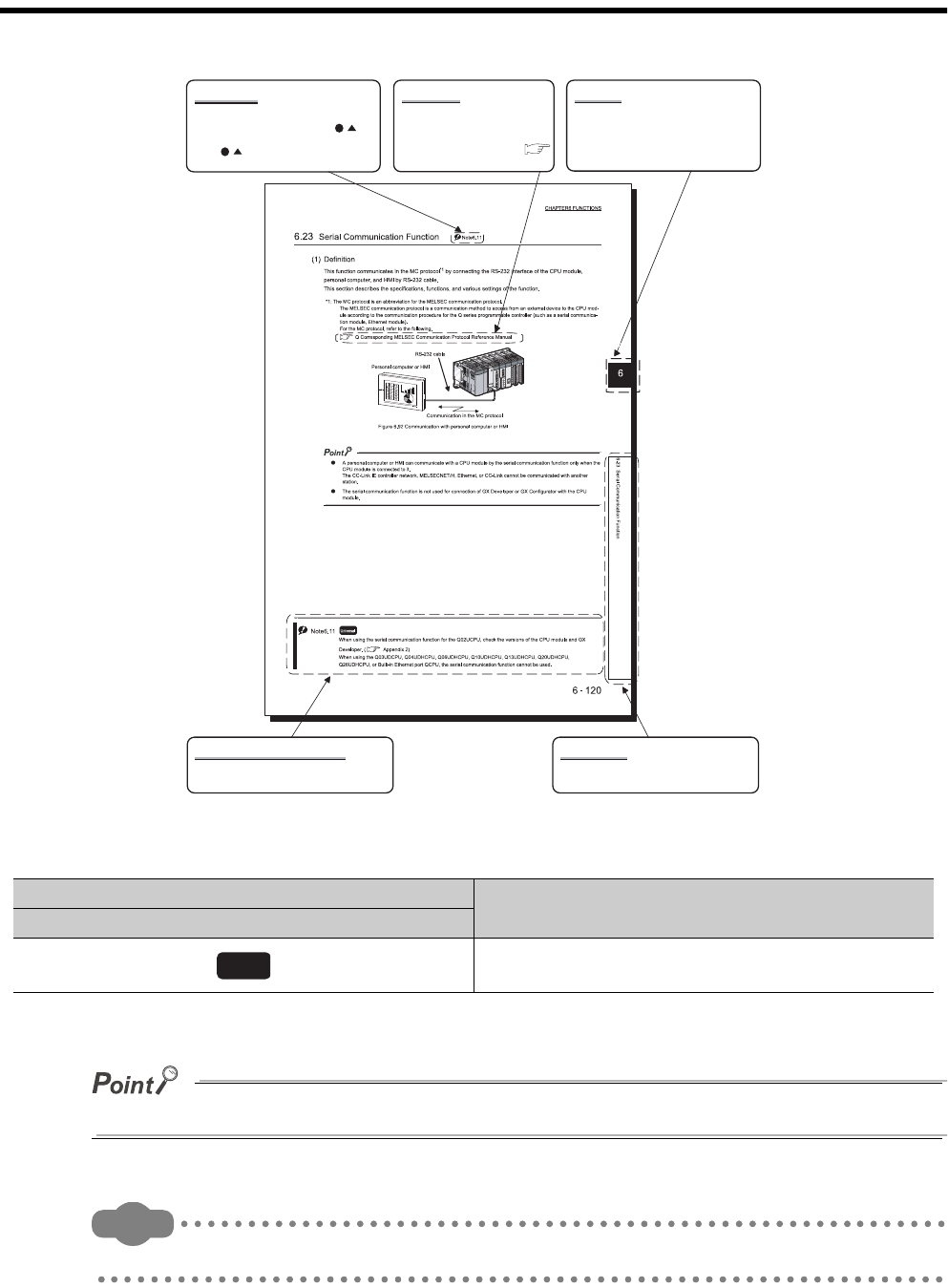

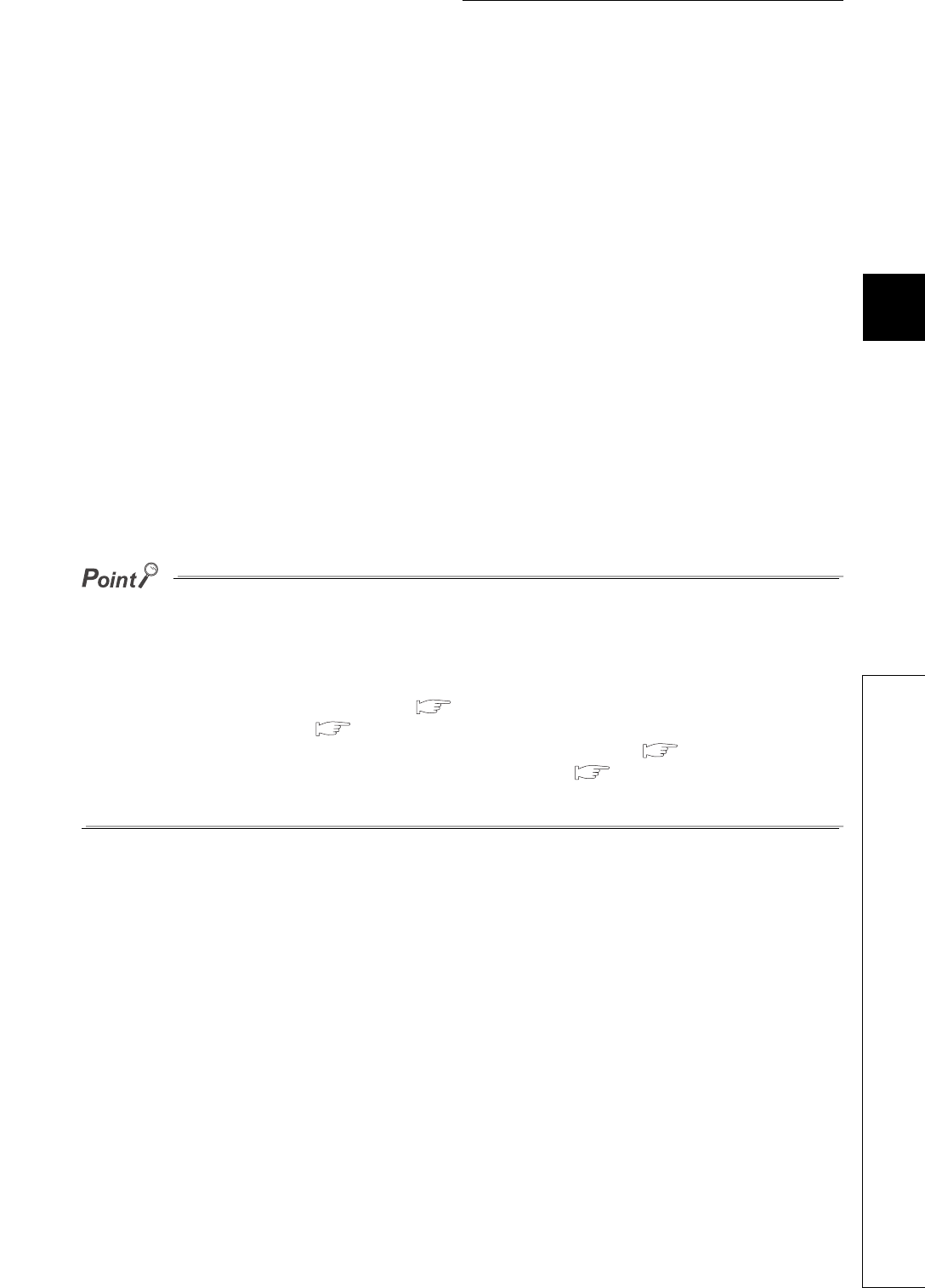

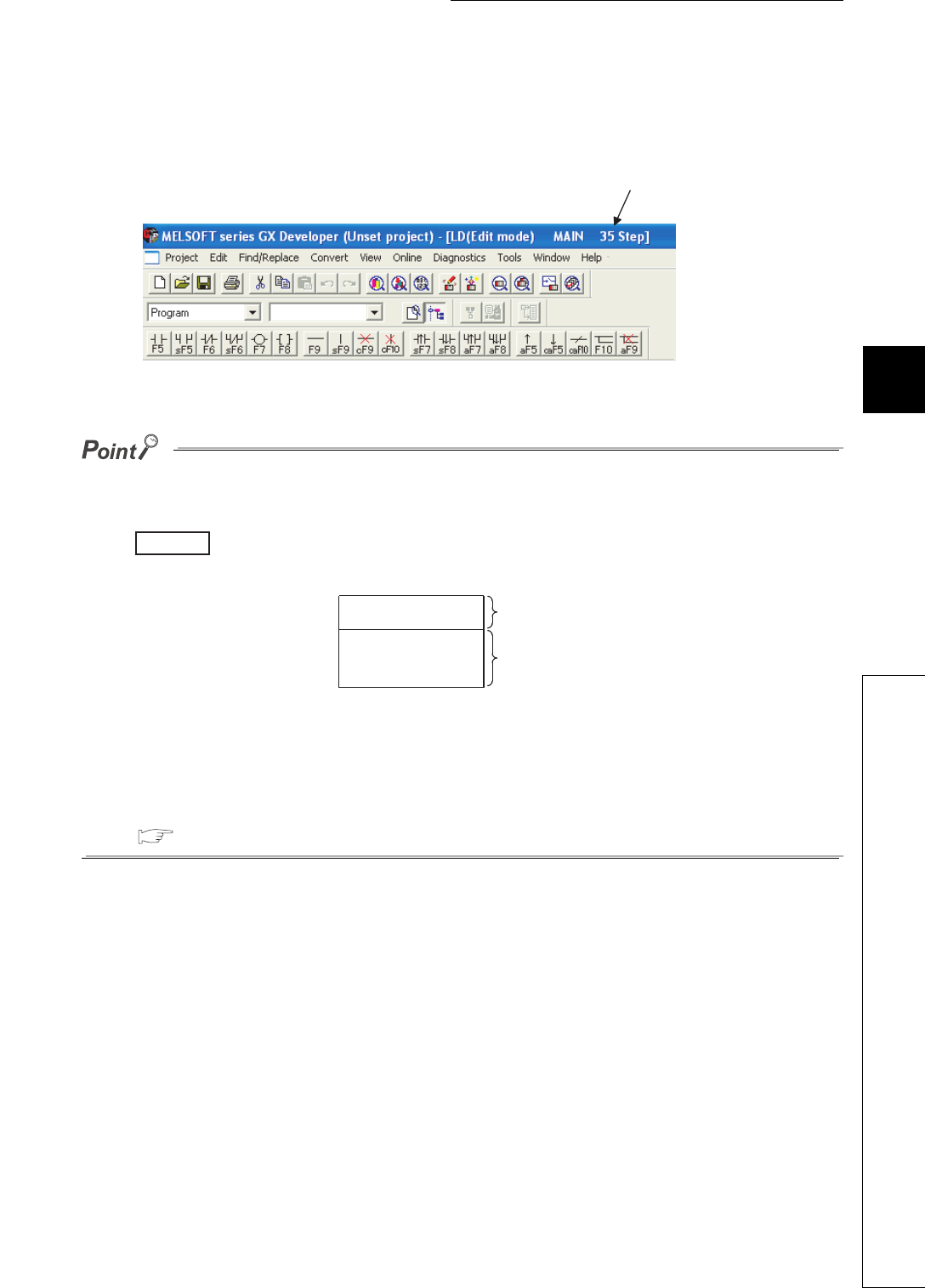

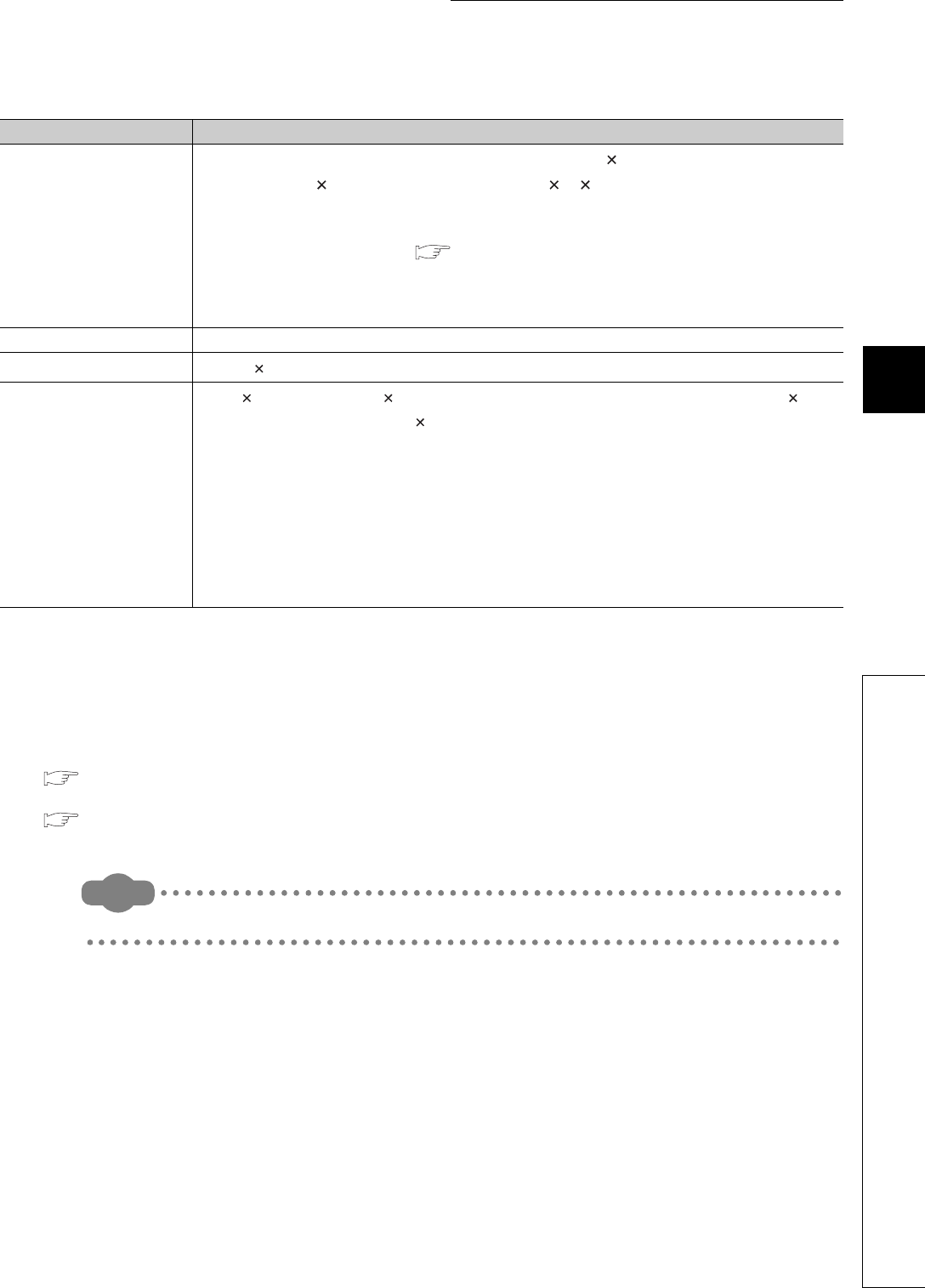

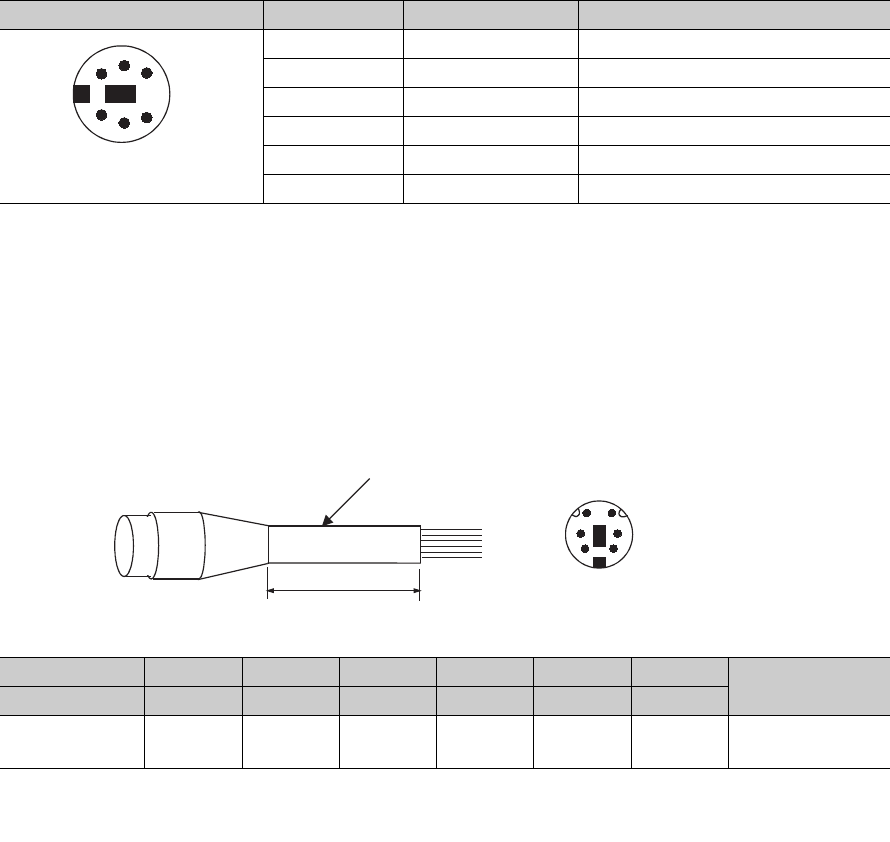

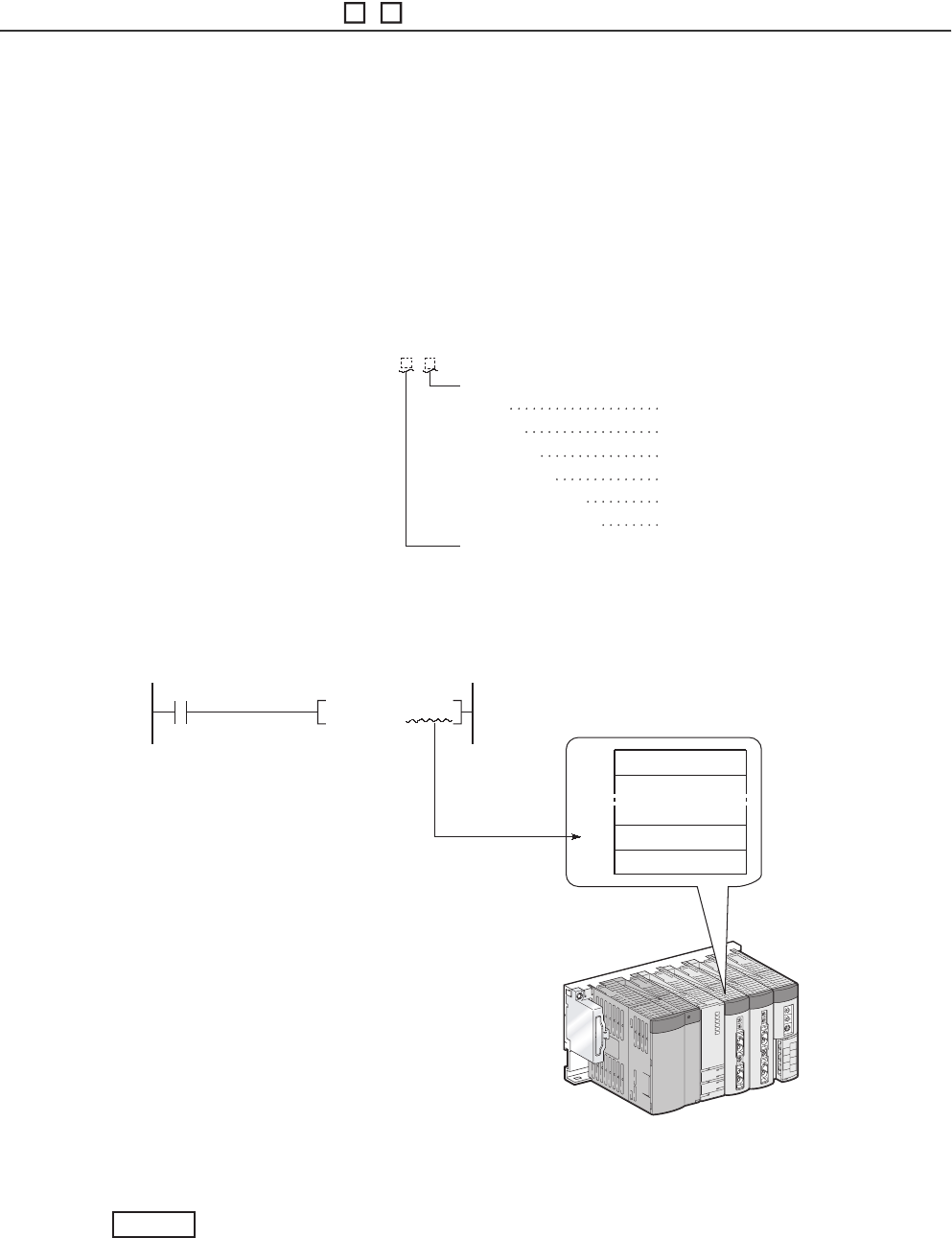

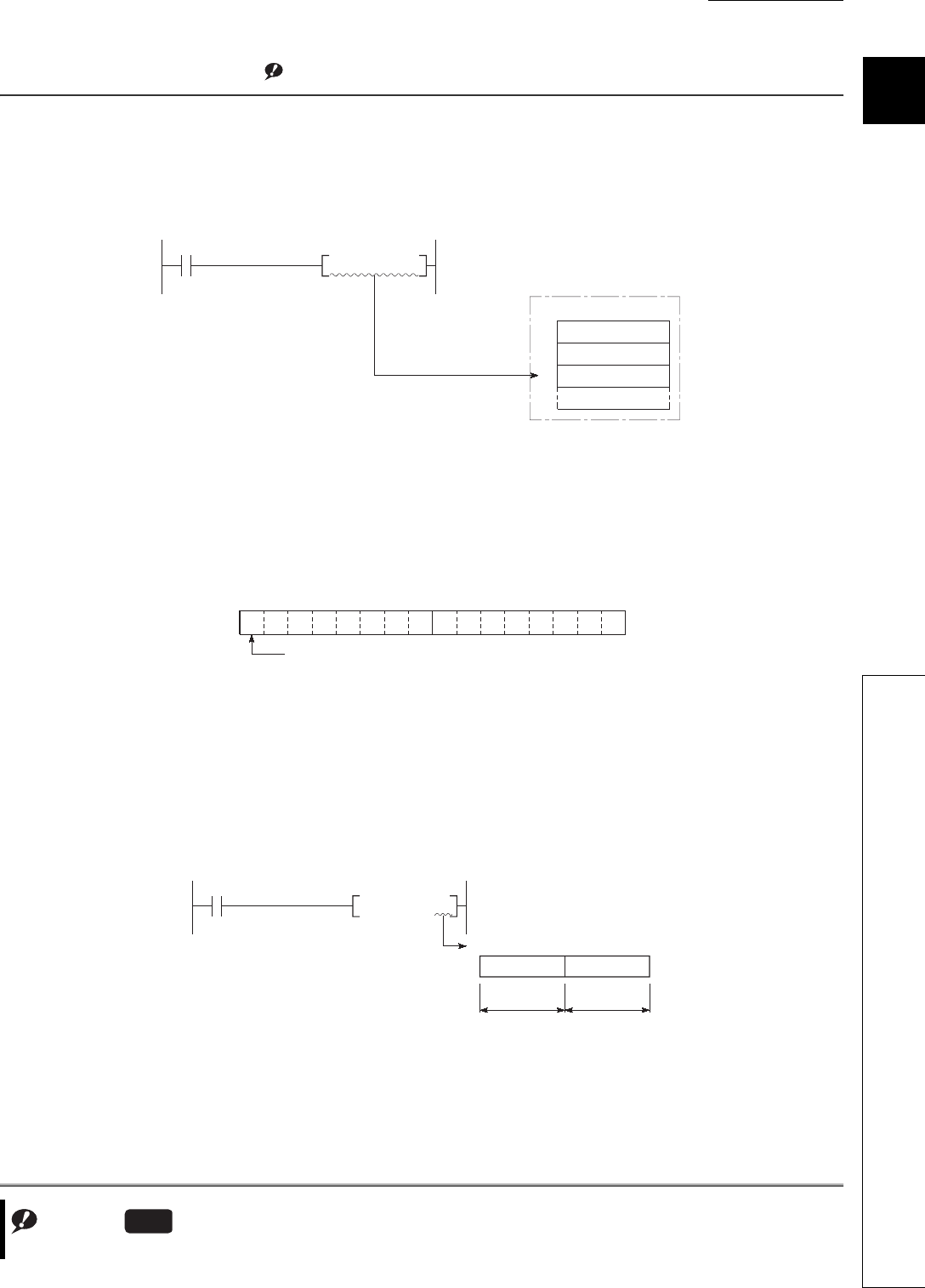

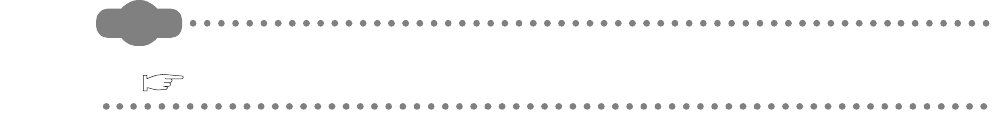

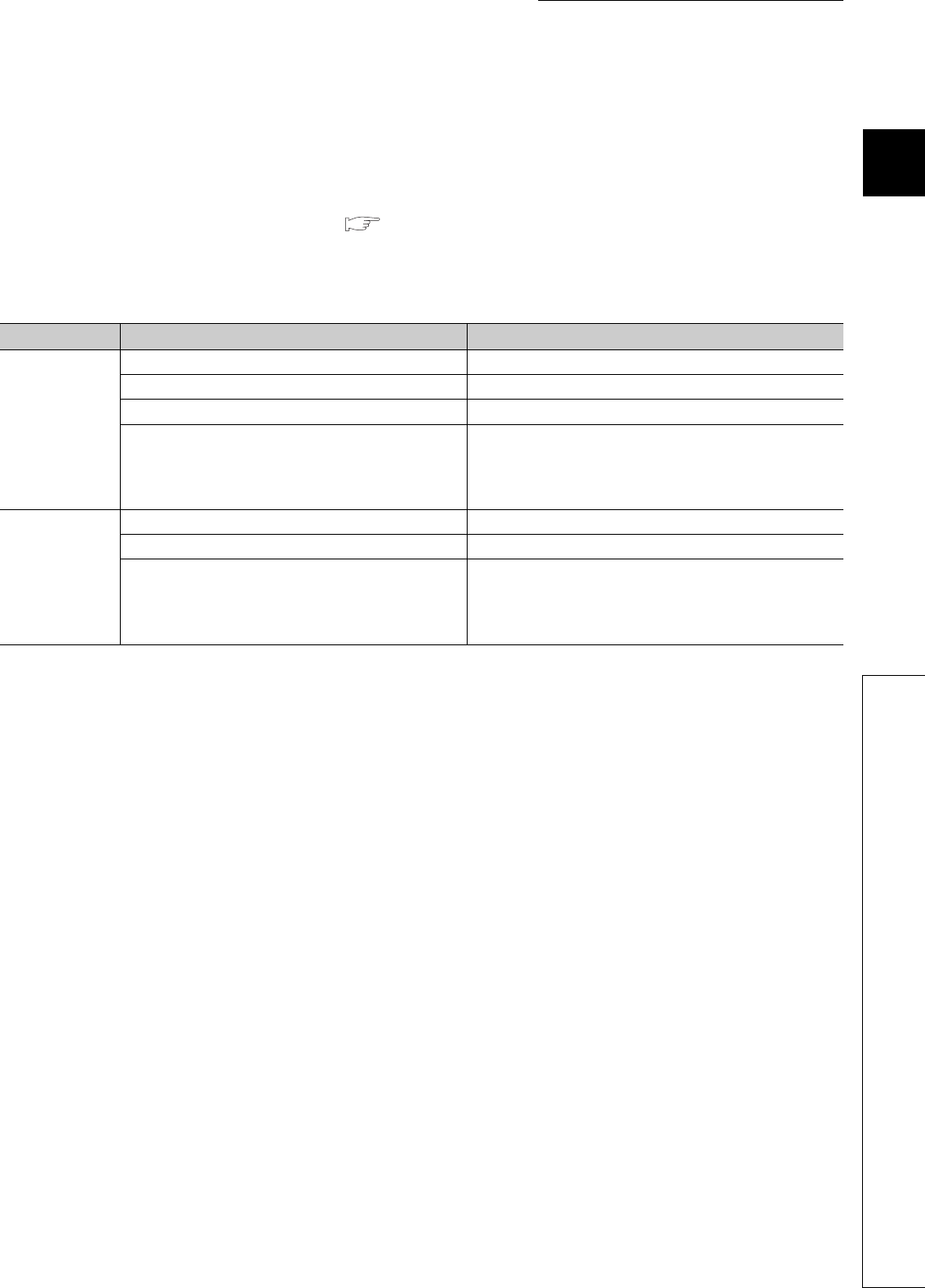

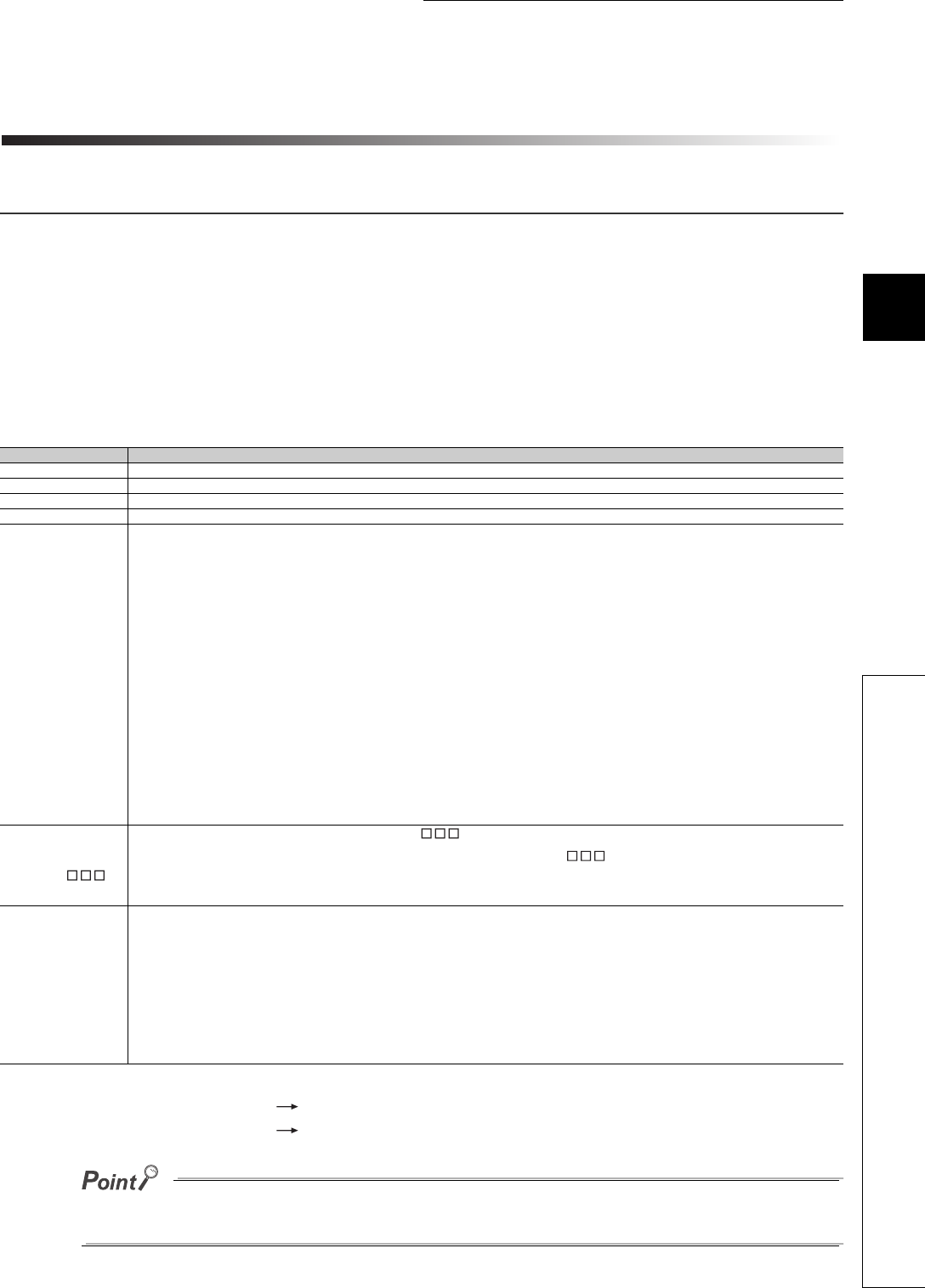

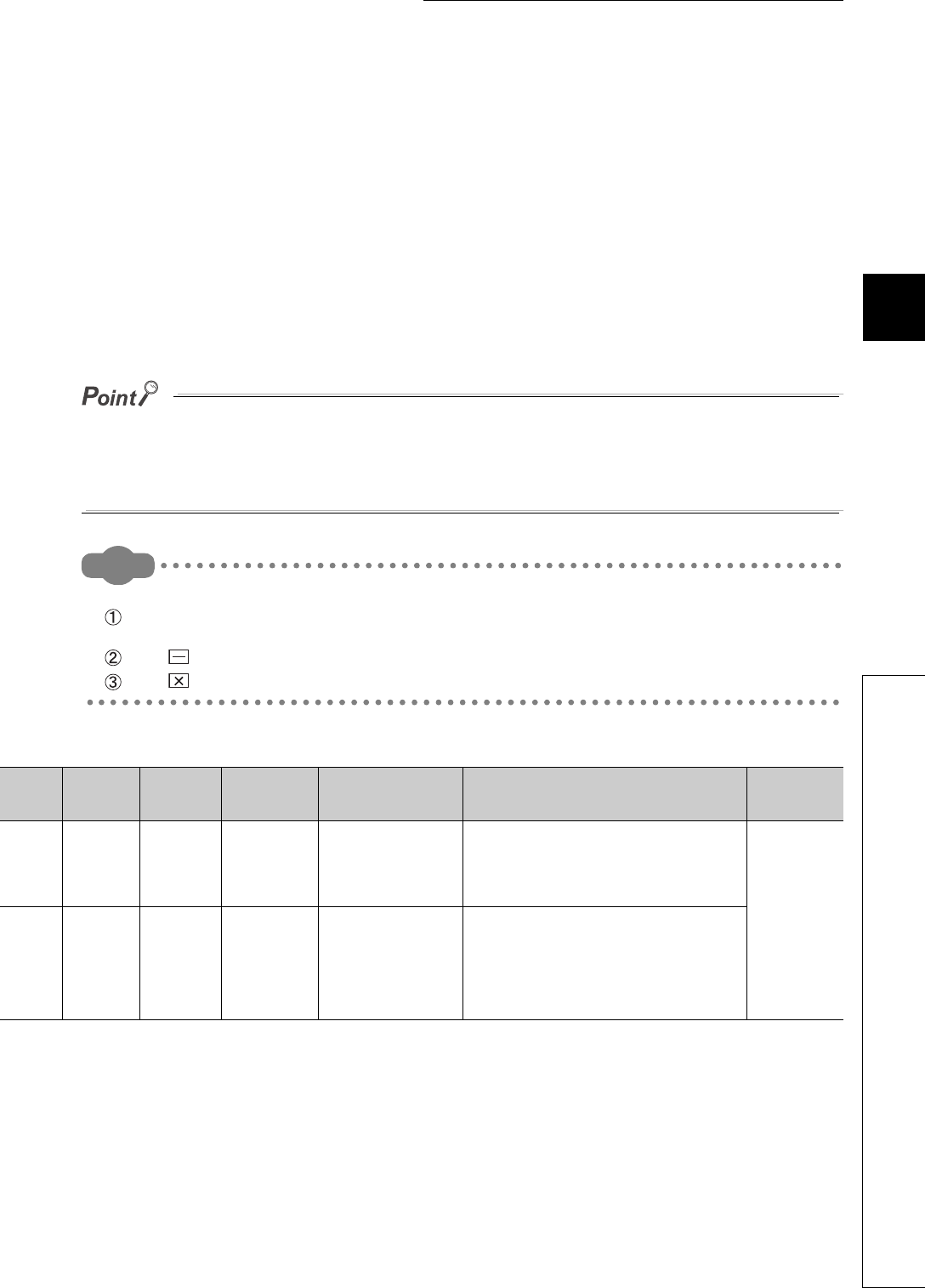

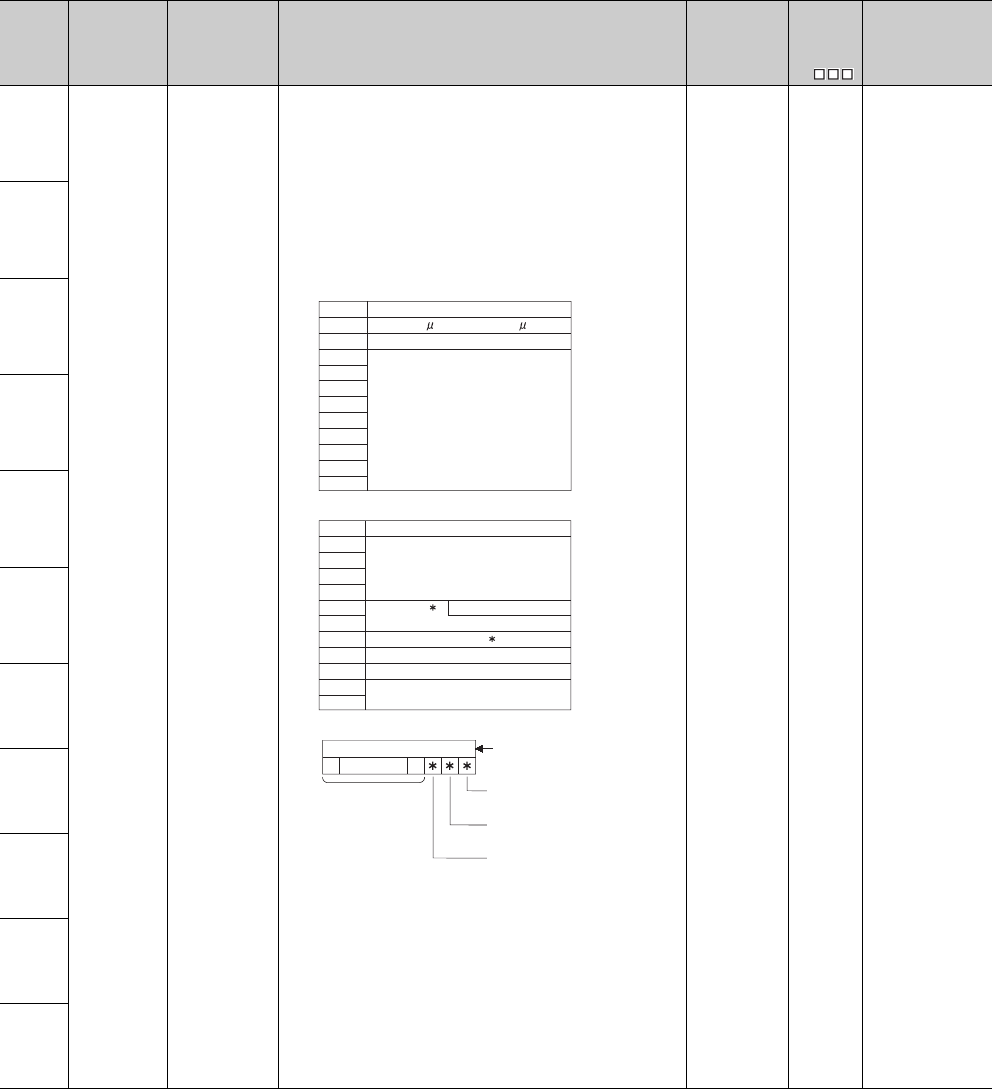

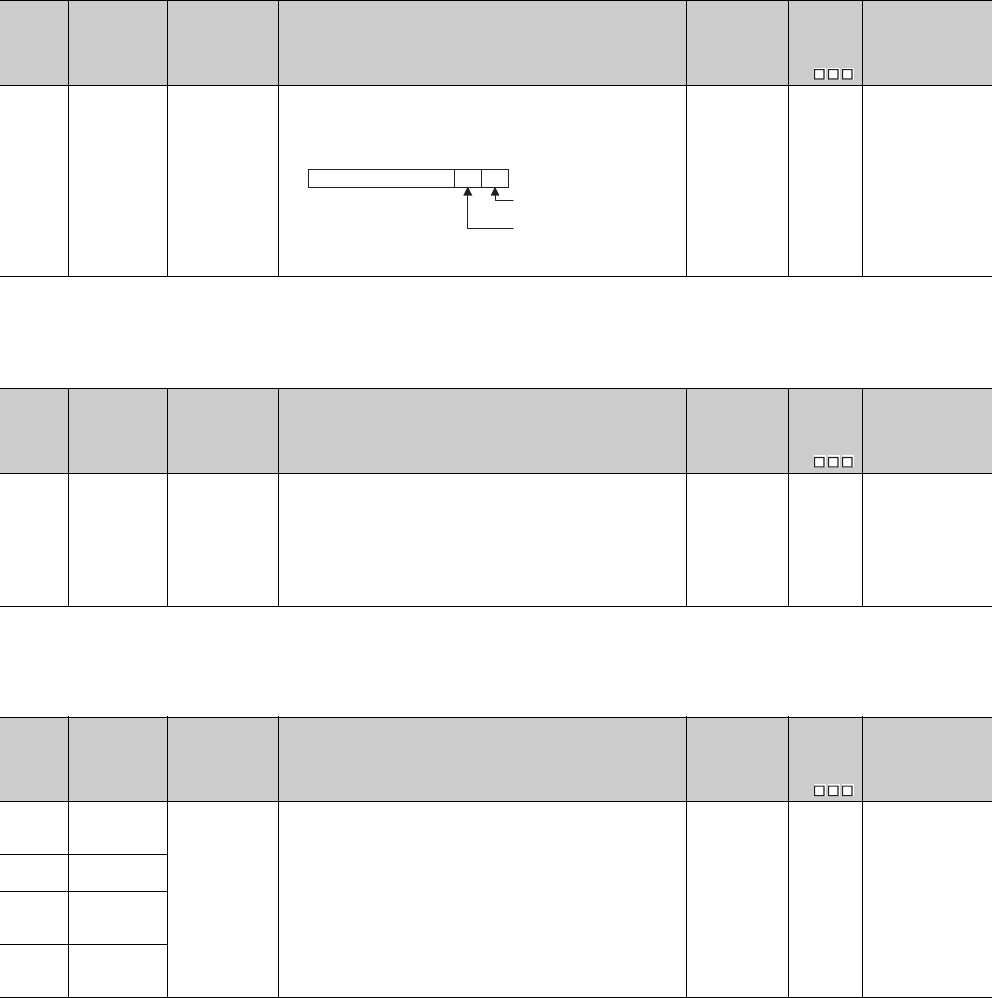

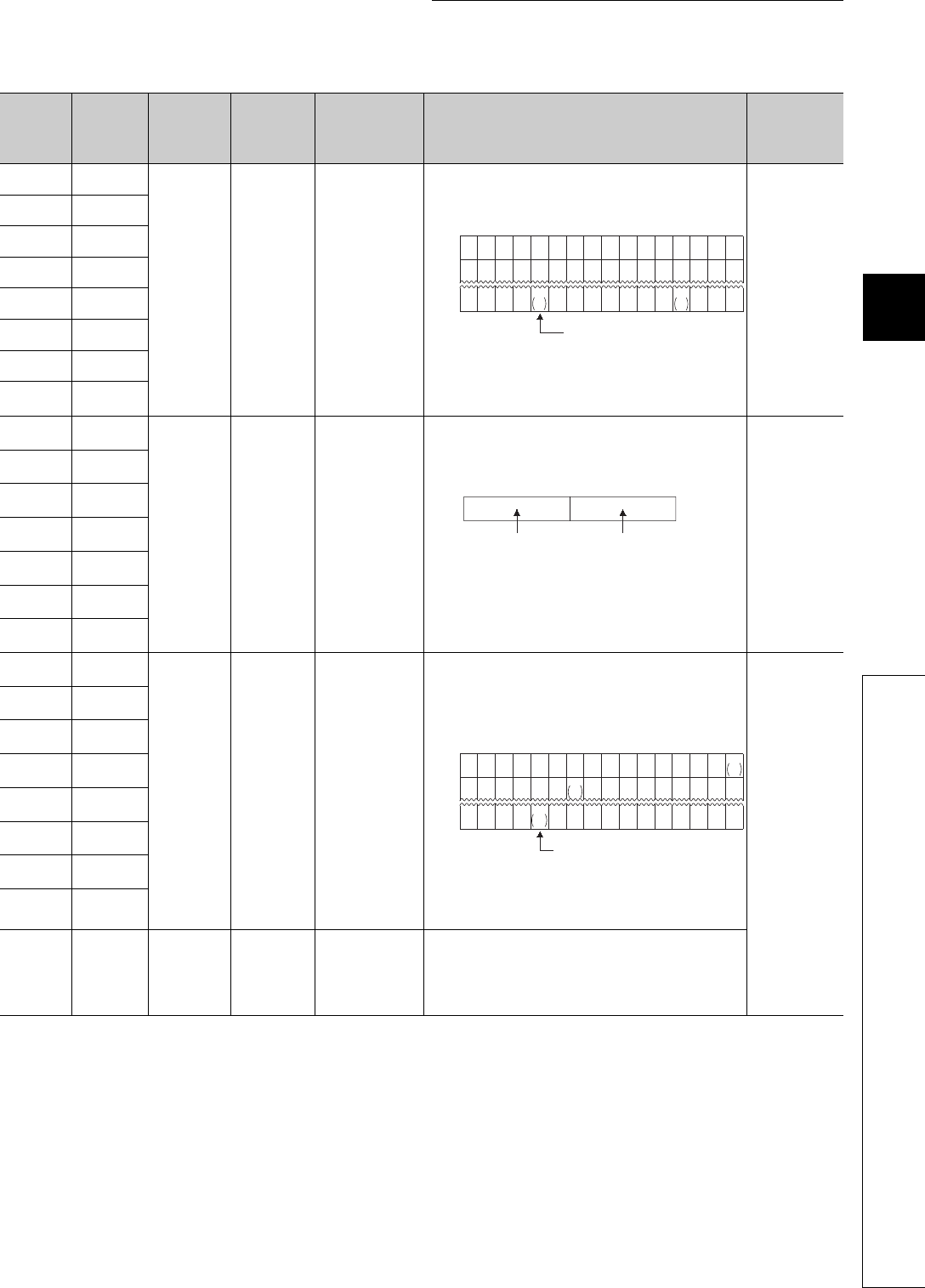

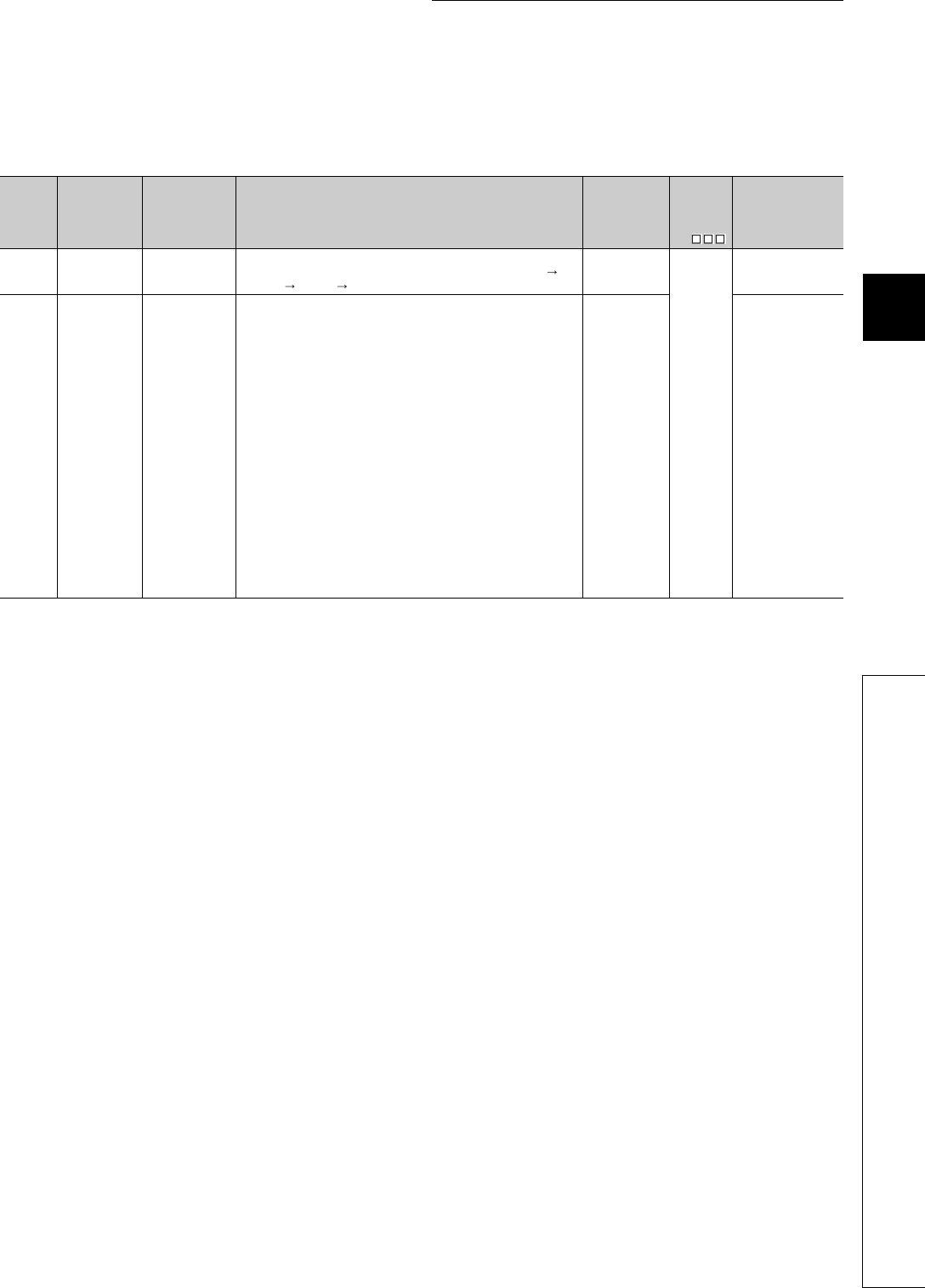

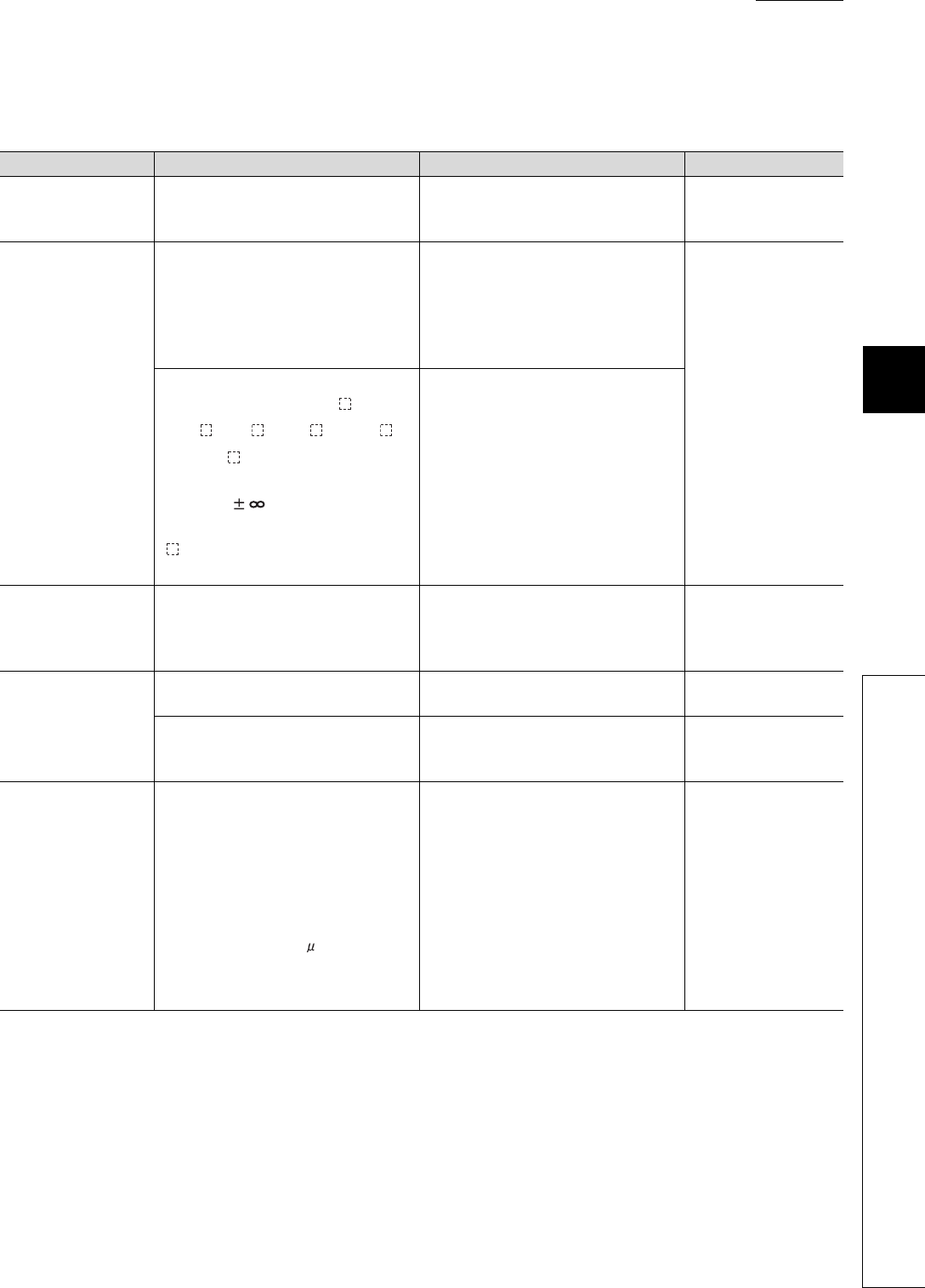

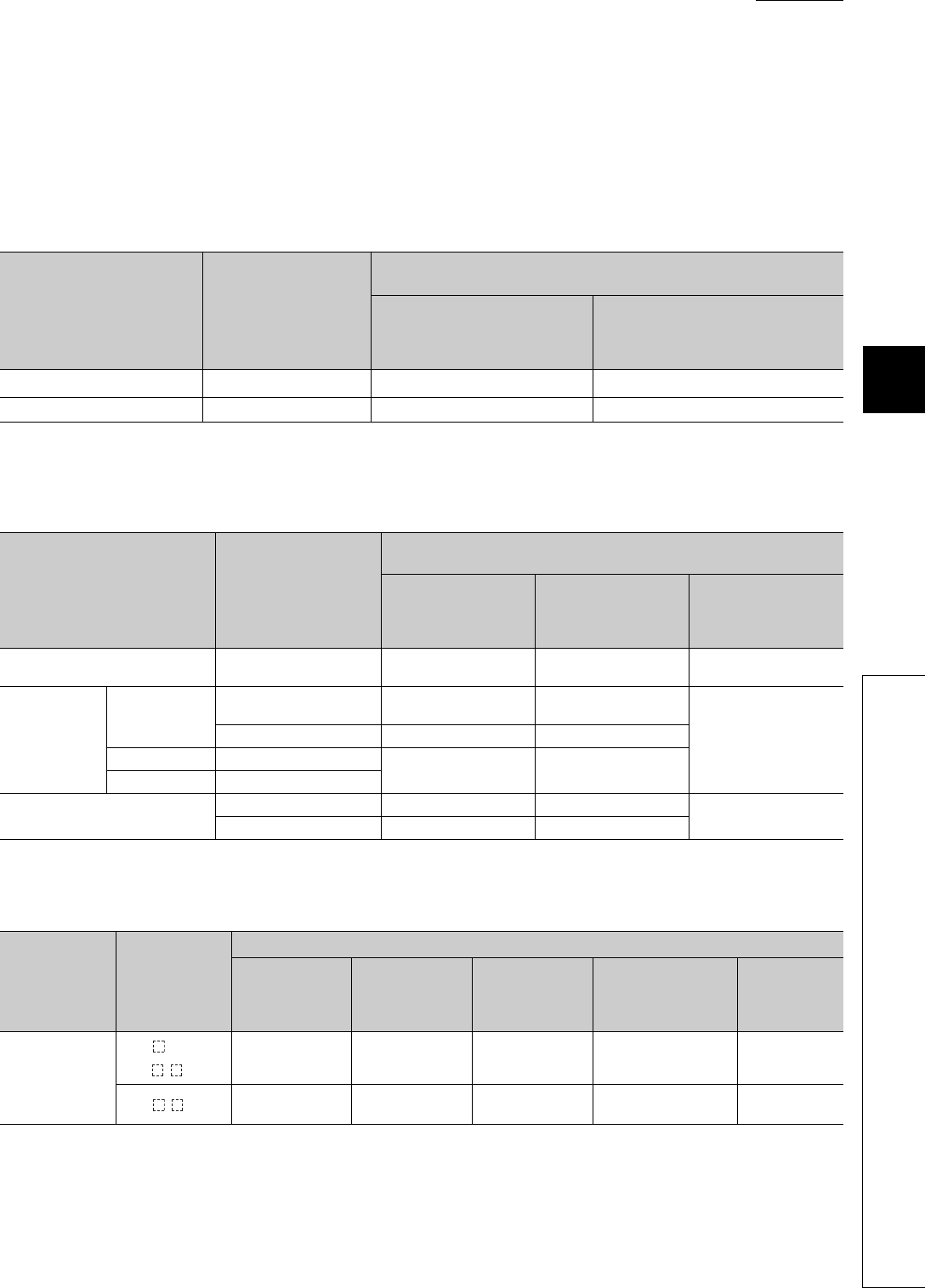

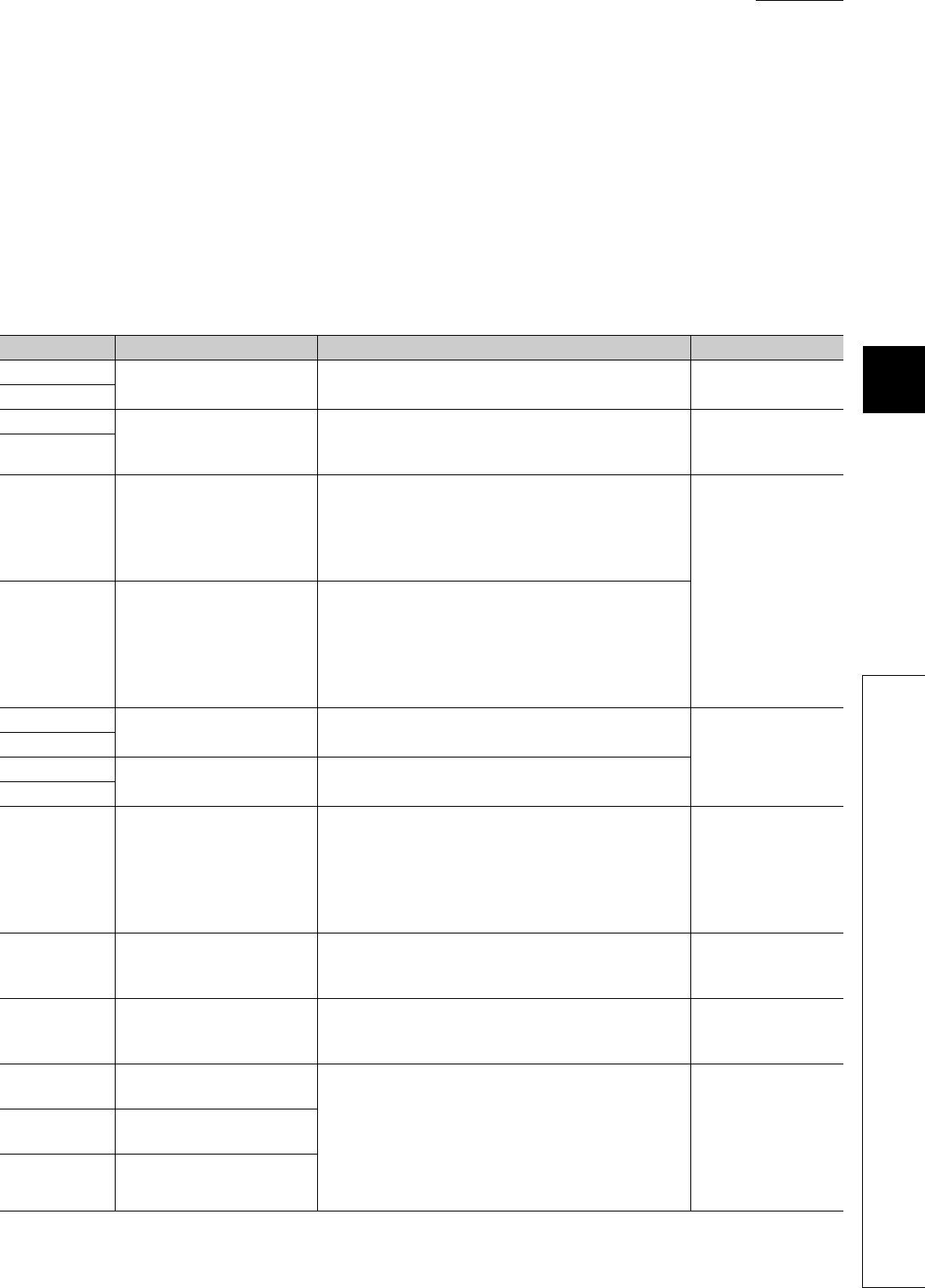

MANUAL PAGE ORGANIZATION

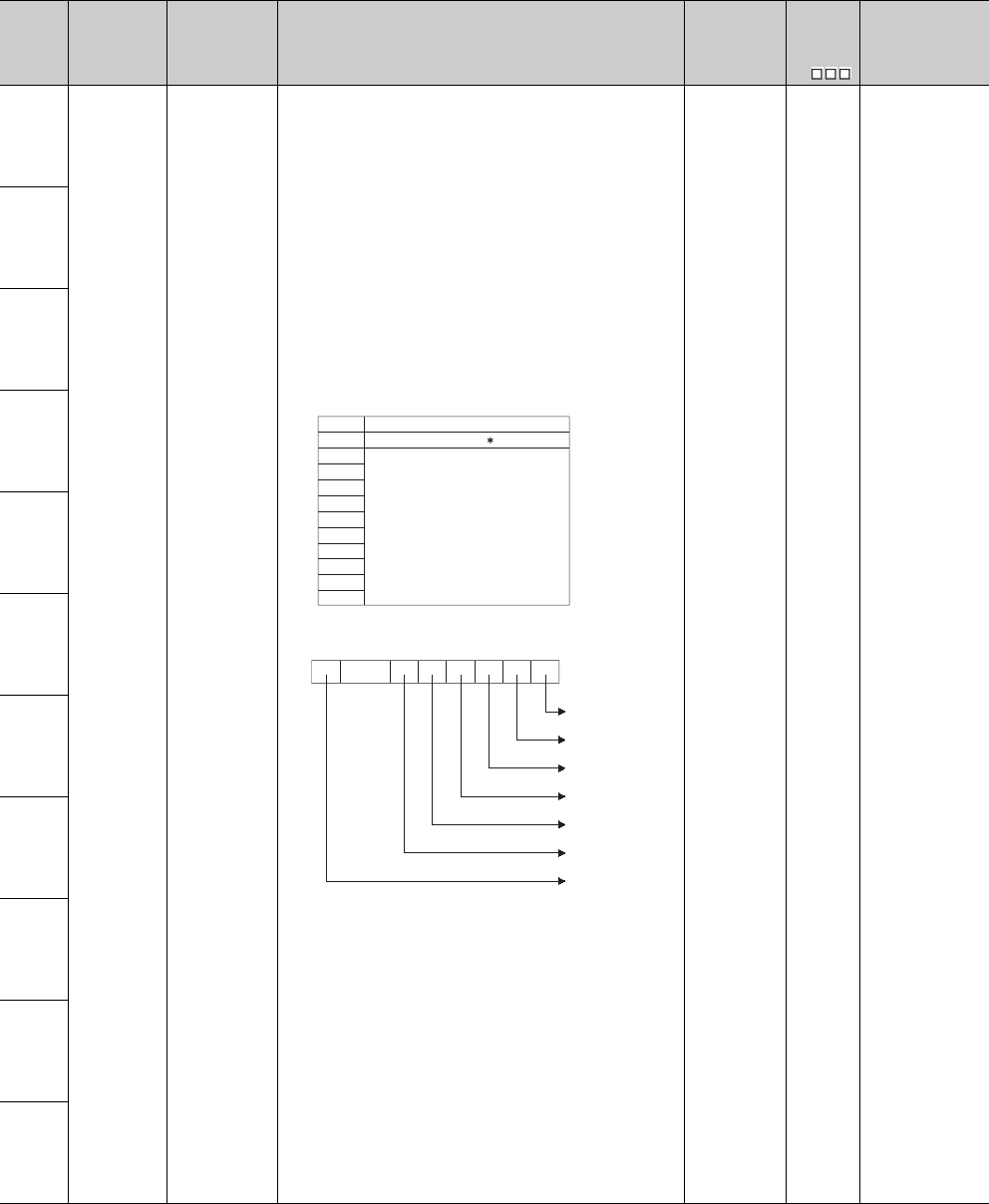

* cining page components, and differs from an actual page.

In addition, this manual uses the following types of explanations.

In addition to description of the page, notes or functions that require special attention are described here.

Remark

The reference related to the page or useful information are described here.

Icons Description

Universal model QCPU

Icons indicate that specifications described on the page

contain some precautions.

Note (detailed explanation)

ReferenceNote (icon)

The section in this manual or

another relevant manual that can

be referred to is shown with .

The chapter of the current page can be

easily identified by this indication on the

right side.

Chapter

The detailed note corresponding to each icon

is described.

Section title

The section number and title of the current

page can be easily identified.

The detailed explanation of "Note . " is

provided under the corresponding

"Note . " at the bottom of the page.

Universal

A - 21

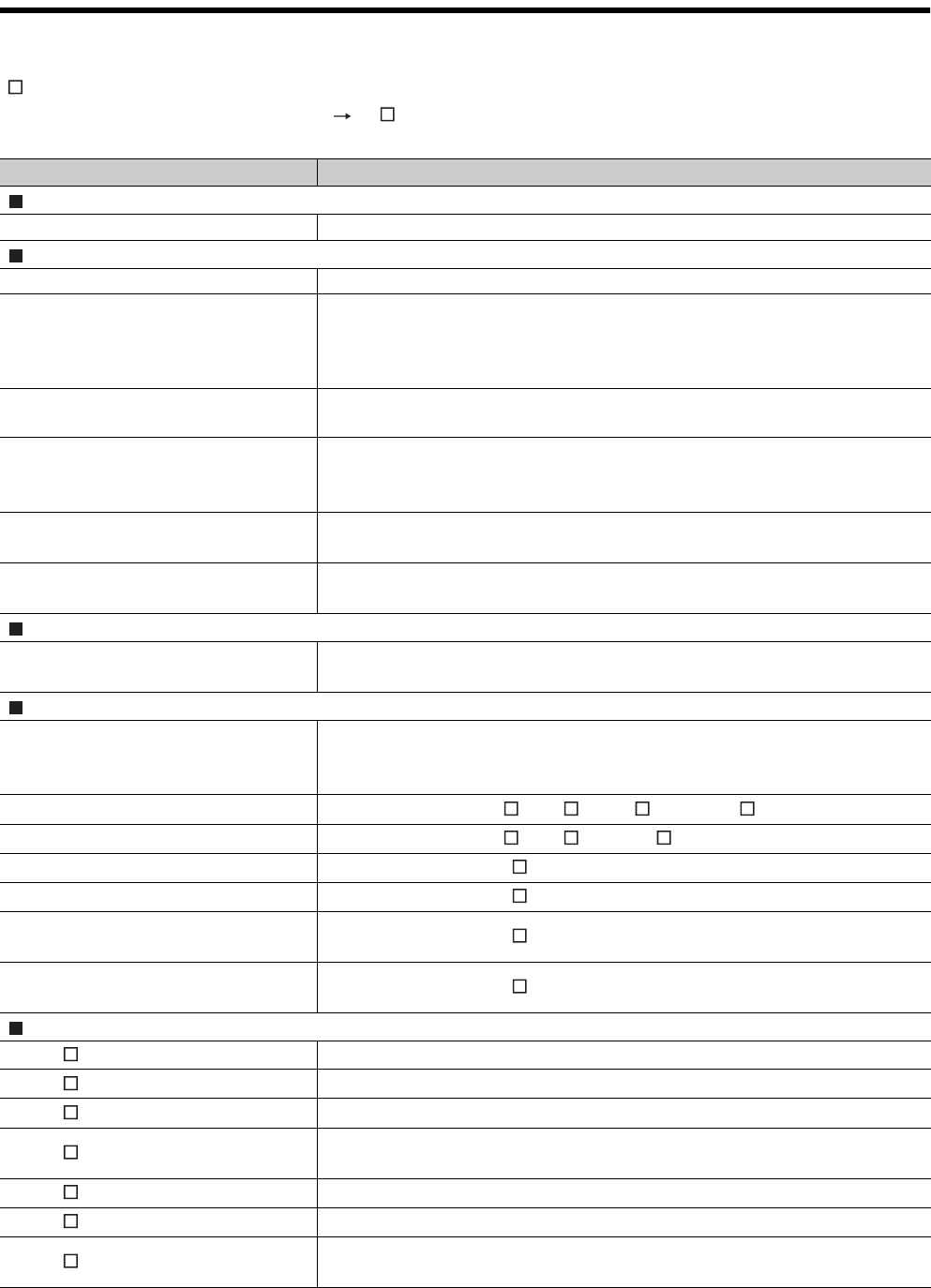

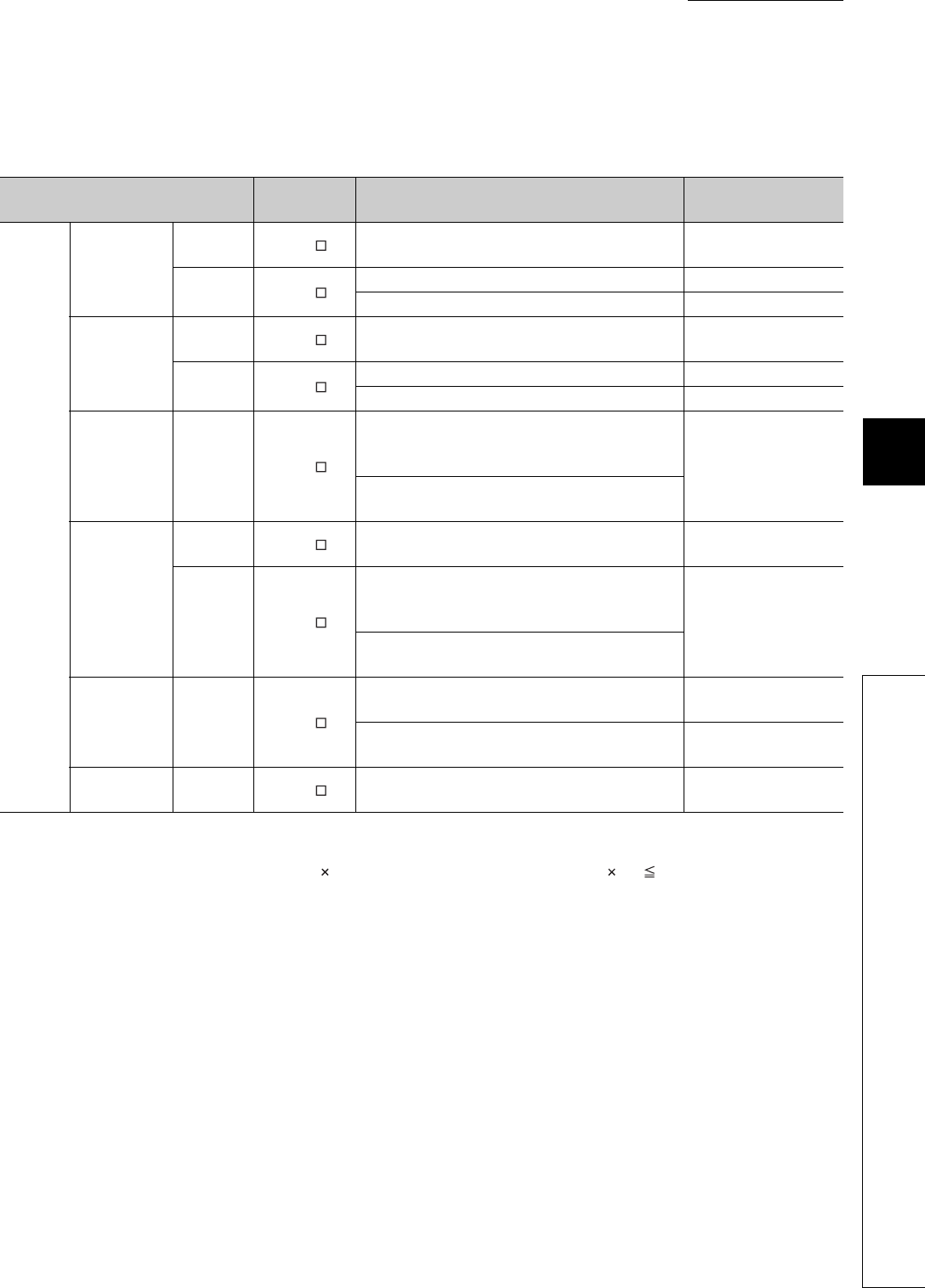

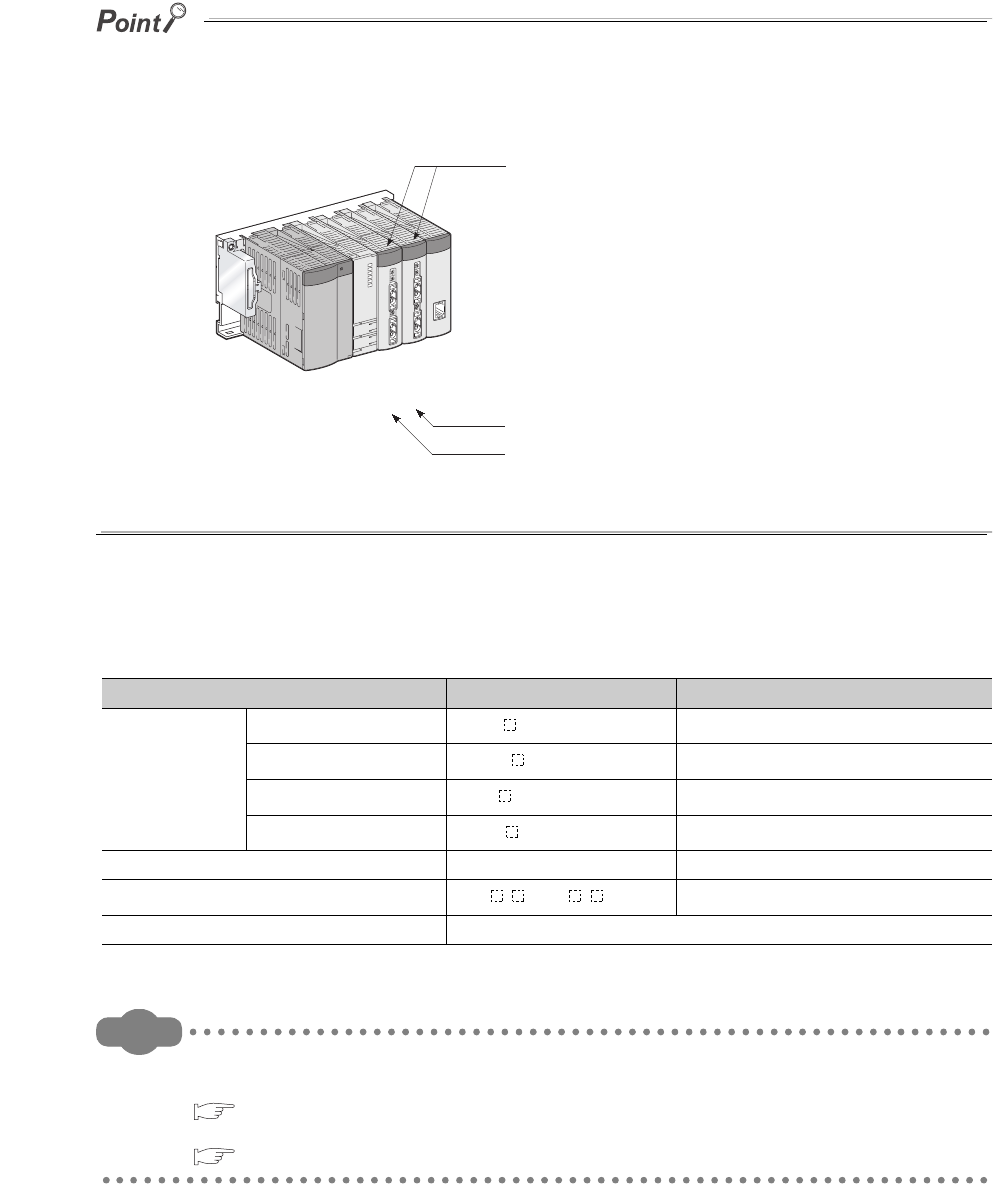

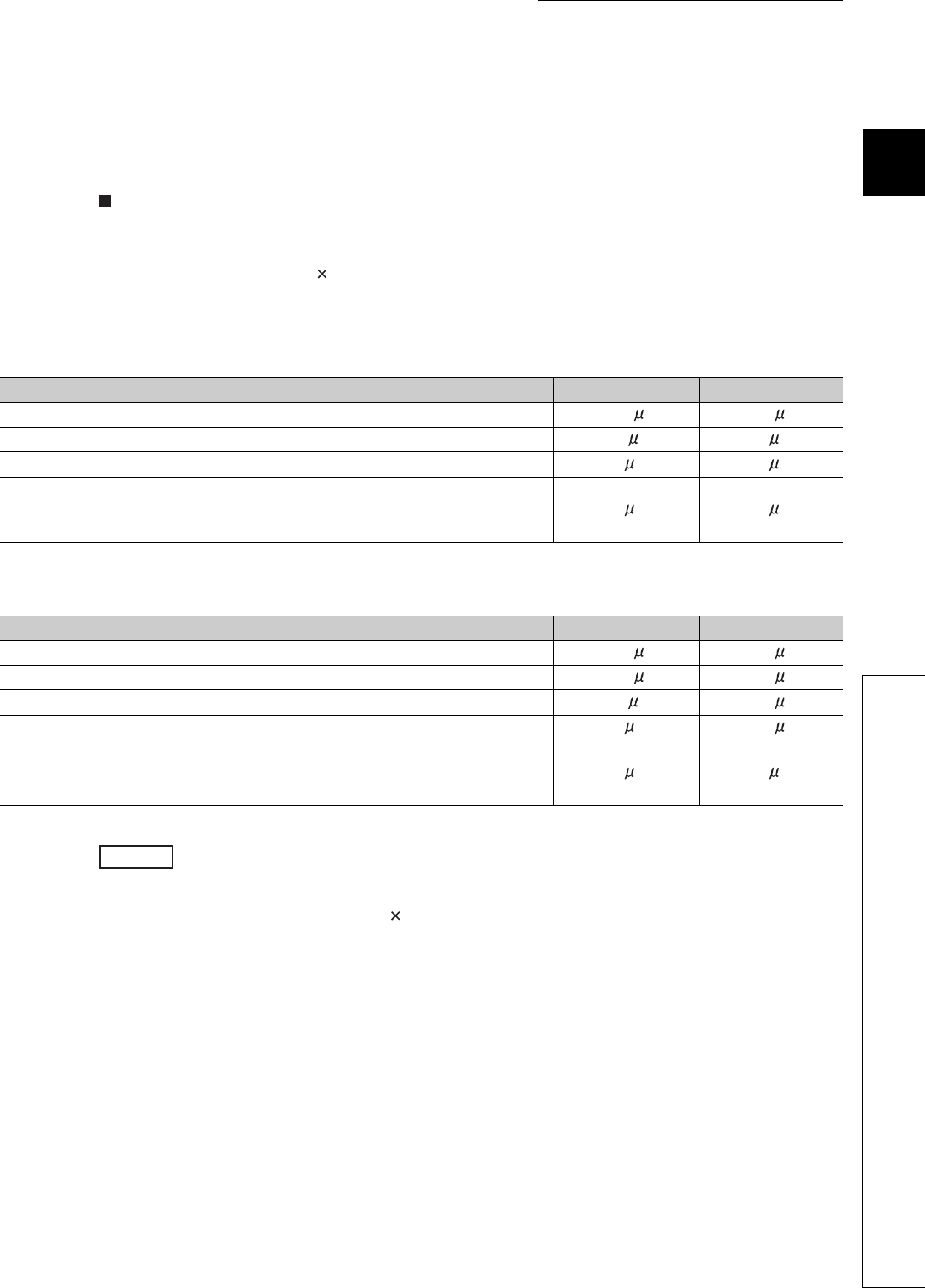

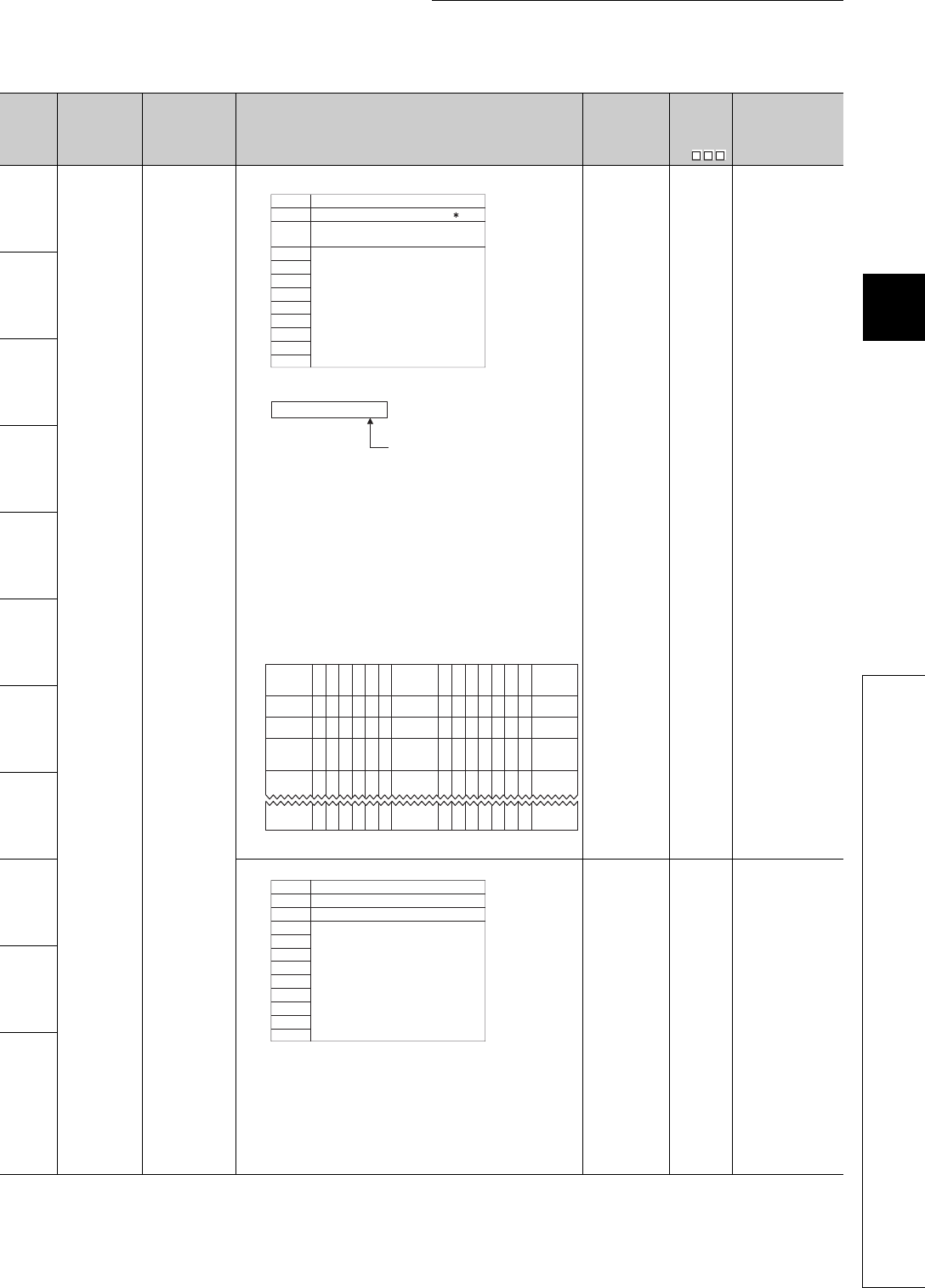

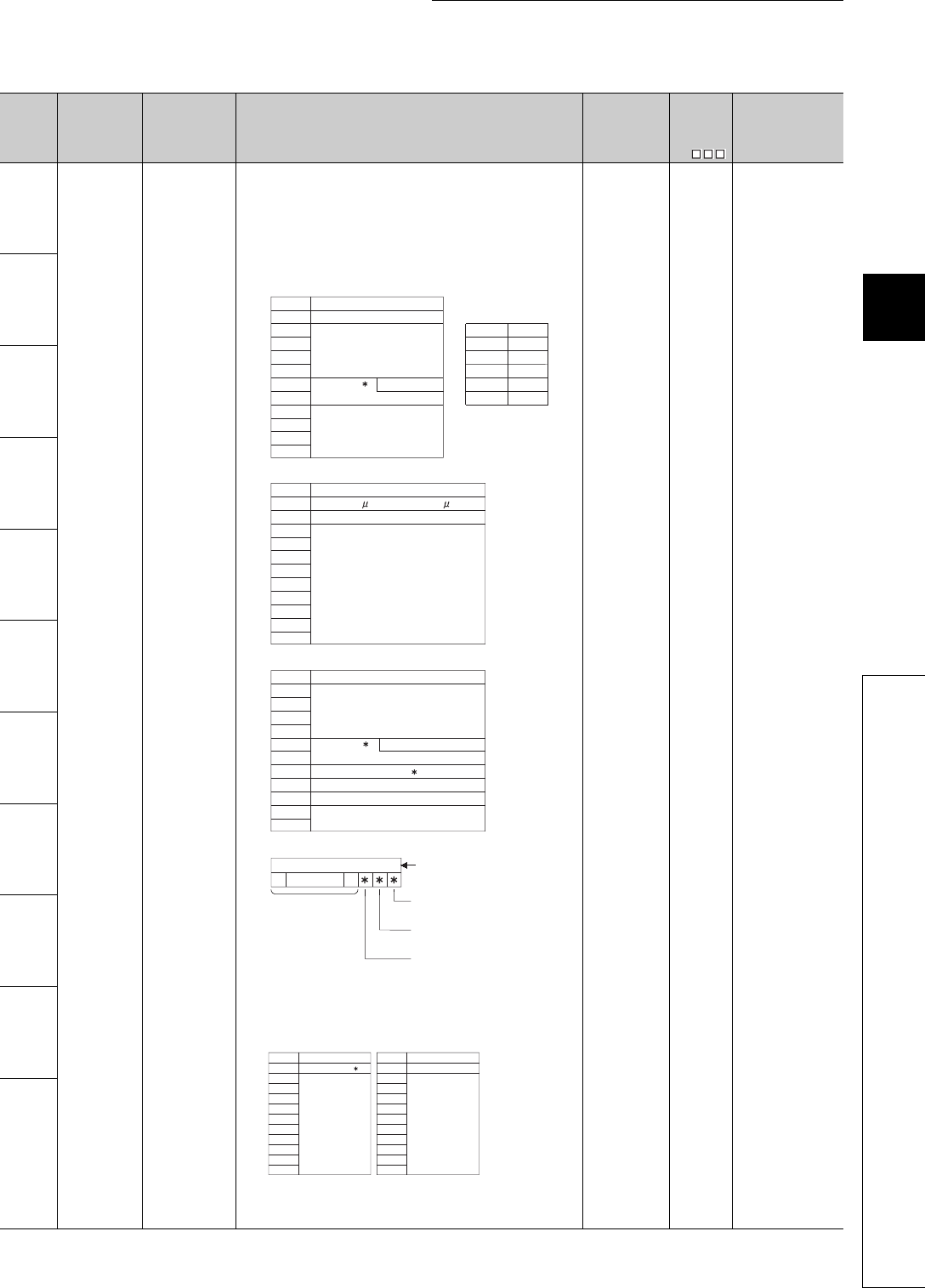

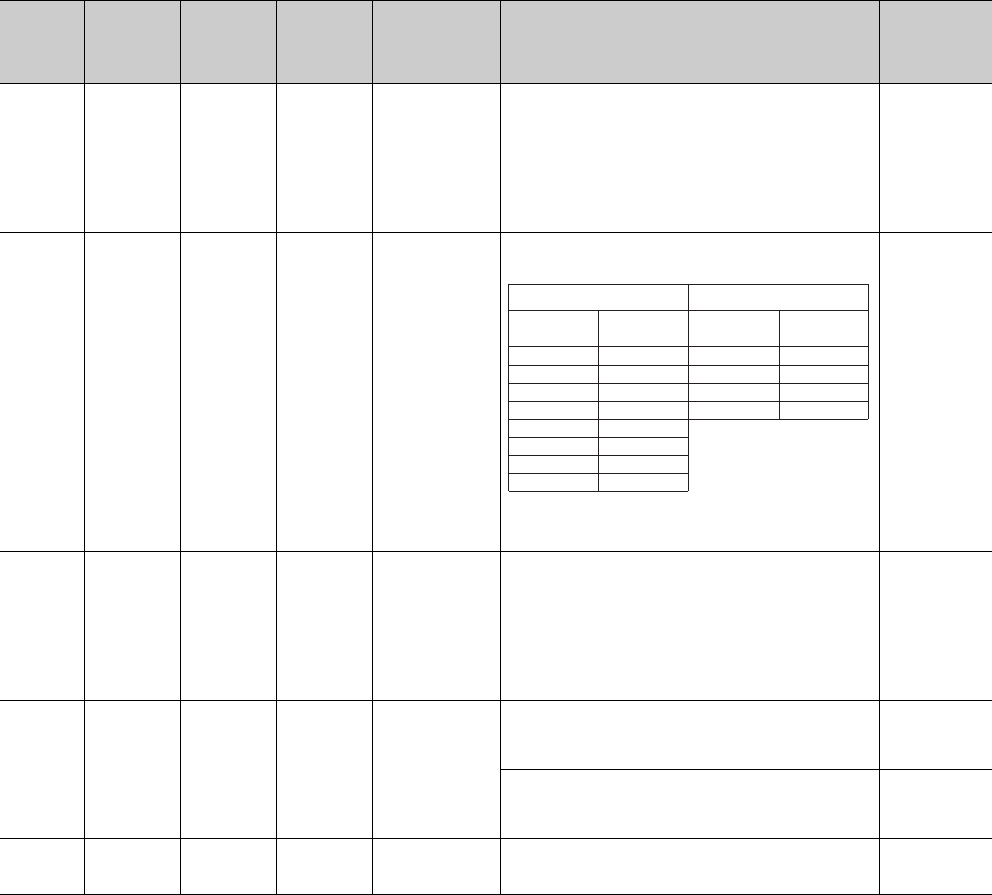

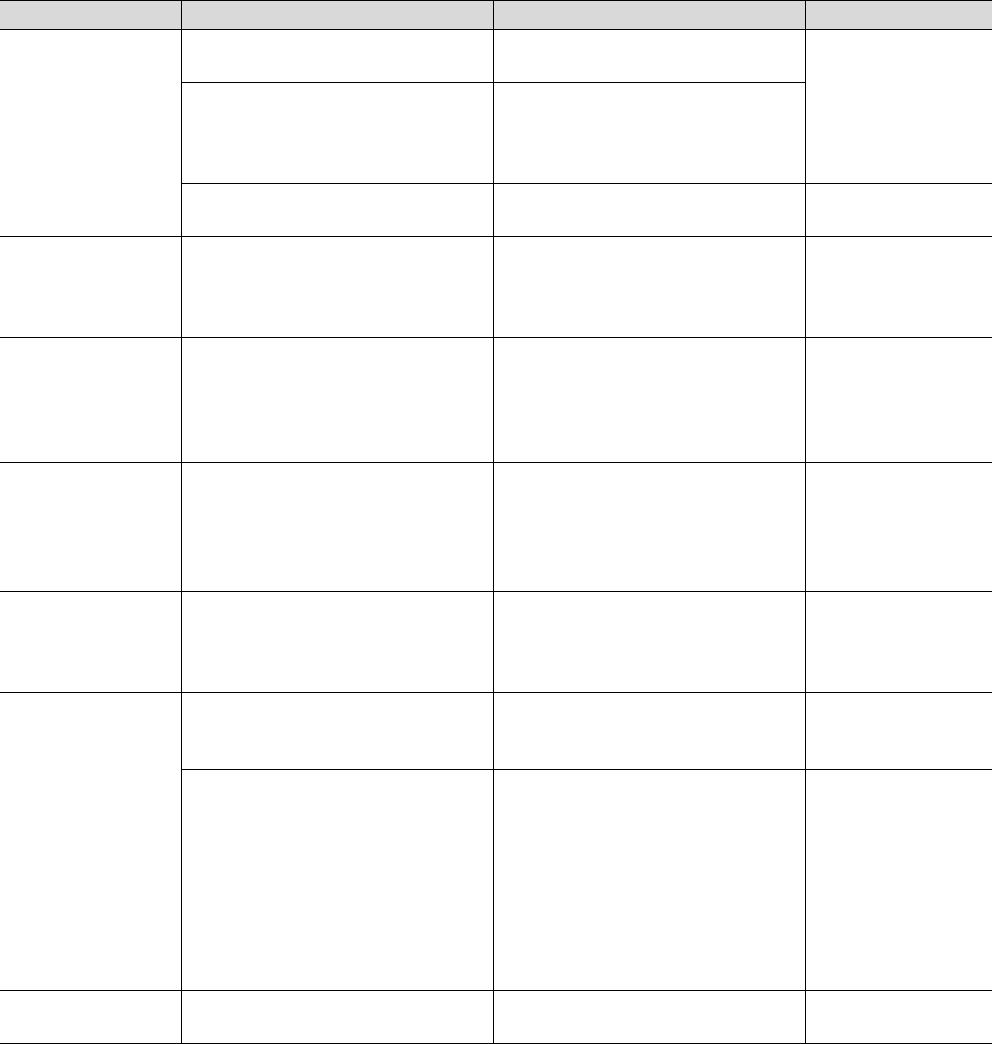

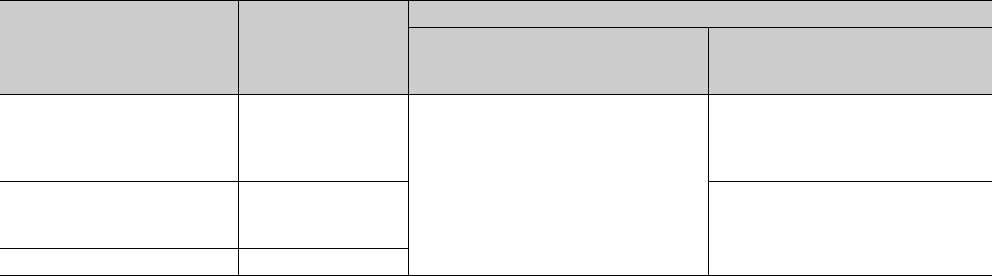

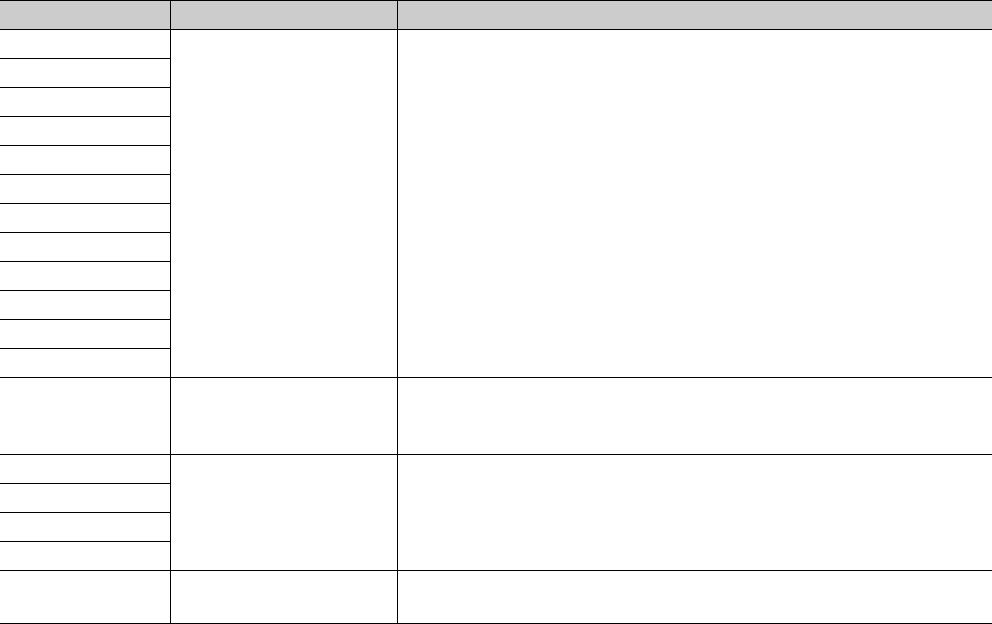

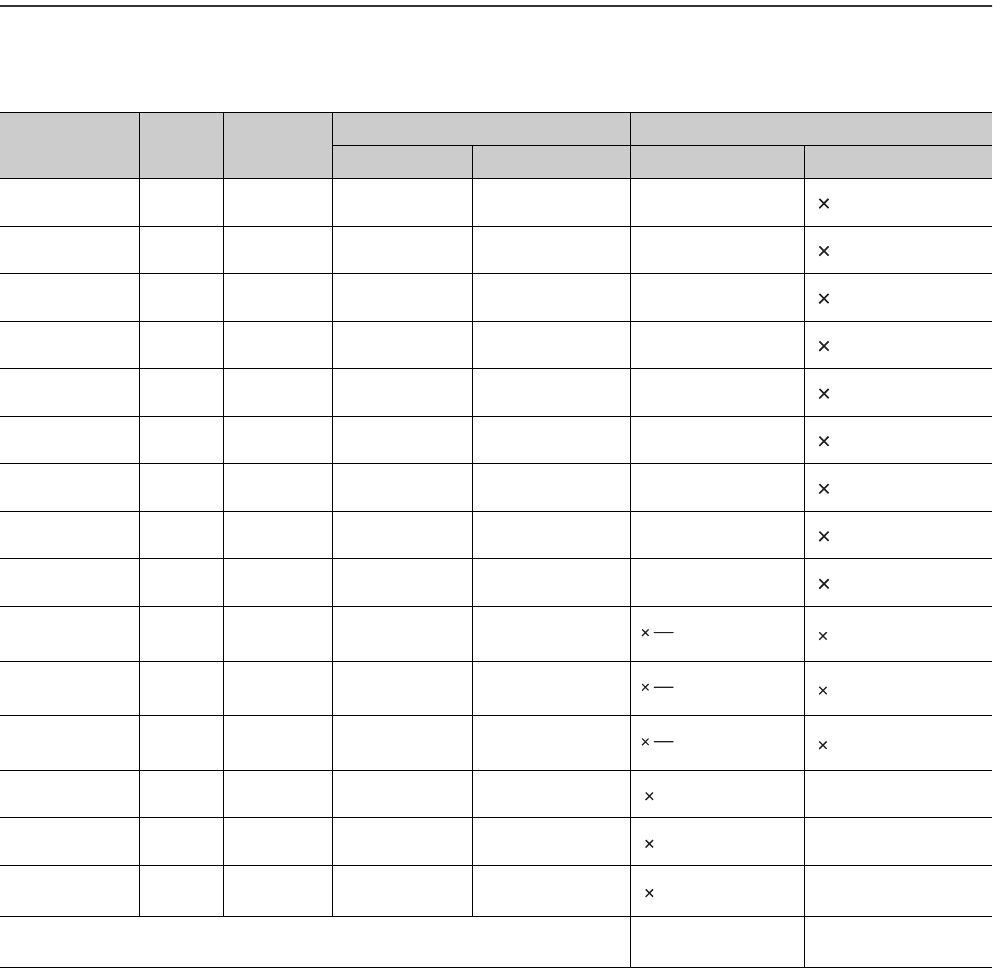

GENERIC TERMS AND ABBREVIATIONS

Unless otherwise specified, this manual uses the following generic terms and abbreviations.

* indicates a part of the model or version.

(Example): Q33B, Q35B, Q38B, Q312B Q3 B

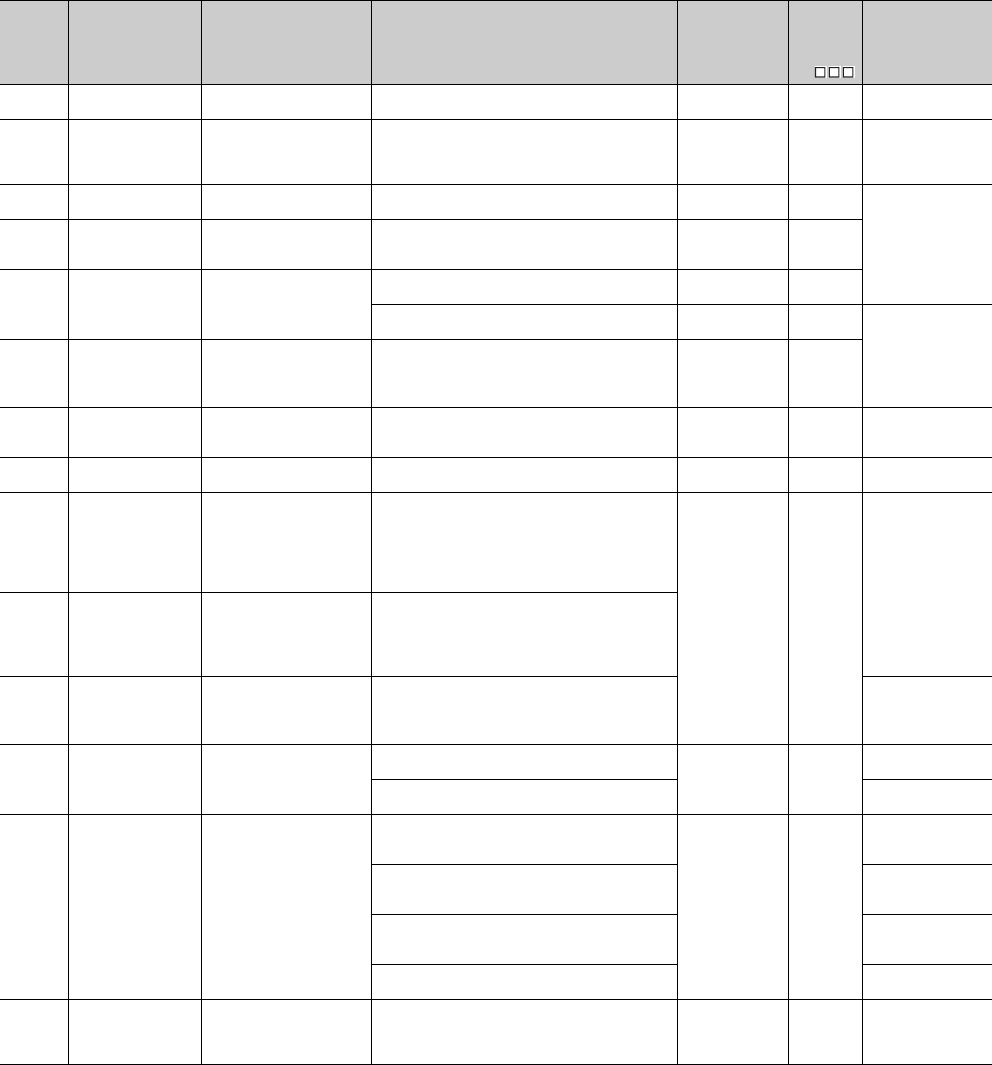

Generic term/abbreviation Description

Series

Q series Abbreviation for Mitsubishi MELSEC-Q series programmable controller

CPU module type

CPU module Generic term for the Universal model QCPU

Universal model QCPU

Generic term for the Q00UJCPU, Q00UCPU, Q01UCPU, Q02UCPU,

Q03UDCPU, Q04UDHCPU, Q06UDHCPU, Q10UDHCPU, Q13UDHCPU,

Q20UDHCPU, Q26UDHCPU, Q03UDECPU, Q04UDEHCPU, Q06UDEHCPU,

Q10UDEHCPU, Q13UDEHCPU, Q20UDEHCPU, and Q26UDEHCPU

Built-in Ethernet port QCPU Generic term for the Q03UDECPU, Q04UDEHCPU, Q06UDEHCPU,

Q10UDEHCPU, Q13UDEHCPU, Q20UDEHCPU, and Q26UDEHCPU

Motion CPU

Generic term for Mitsubishi motion controllers, Q172CPUN, Q173CPUN,

Q172HCPU, Q173HCPU, Q172CPUN-T, Q173CPUN-T, Q172HCPU-T,

Q173HCPU-T, Q172DCPU, and Q173DCPU

PC CPU module Generic term for MELSEC-Q series PC CPU module, PPC-CPU852(MS)-512,

manufactured by CONTEC Co., Ltd.

C Controller module Generic term for the Q06CCPU-V-H01, Q06CCPU-V, Q06CCPU-V-B, and

Q12DCCPU-V C Controller modules

CPU module model

QnUD(H)CPU Generic term for the Q03UDCPU, Q04UDHCPU, Q06UDHCPU, Q10UDHCPU,

Q13UDHCPU, Q20UDHCPU, and Q26UDHCPU

Base unit type

Base unit

Generic term for the main base unit, extension base unit, slim type main base

unit, redundant power main base unit, redundant power extension base unit, and

multiple CPU high speed main base unit

Main base unit Generic term for the Q3 B, Q3 SB, Q3 RB, and Q3 DB

Extension base unit Generic term for the Q5 B, Q6 B, and Q6 RB

Slim type main base unit Another name for the Q3 SB

Redundant power main base unit Another name for the Q3 RB

Redundant power extension base

unit Another name for the Q6 RB

Multiple CPU high speed main base

unit Another name for the Q3 DB

Base unit model

Q3 B Generic term for the Q33B, Q35B, Q38B, and Q312B main base units

Q3 SB Generic term for the Q32SB, Q33SB, and Q35SB slim type main base units

Q3 RB Another name for the Q38RB main base unit for redundant power supply system

Q3 DB Generic term for the Q38DB and Q312DB multiple CPU high speed main base

units

Q5 B Generic term for the Q52B and Q55B extension base units

Q6 B Generic term for the Q63B, Q65B, Q68B, and Q612B extension base units

Q6 RB Another name for the Q68RB extension base unit for redundant power supply

system

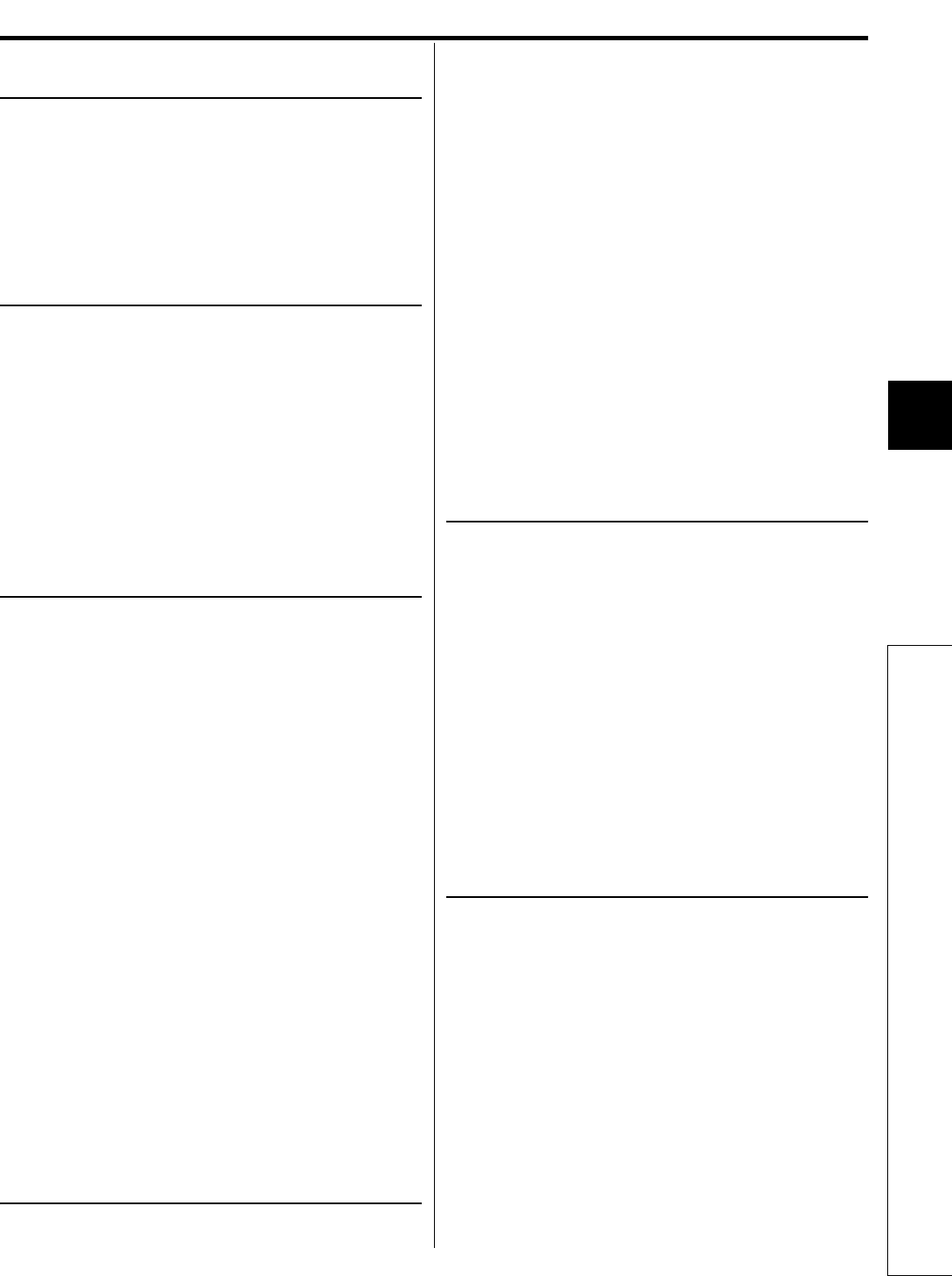

A - 22

Generic term/abbreviation Description

Power supply module

Power supply module Generic term for the Q series power supply module, slim type power supply

module, and redundant power supply module

Q series power supply module Generic term for the Q61P-A1, Q61P-A2, Q61P, Q61P-D, Q62P, Q63P, Q64P, and

Q64PN power supply modules

Slim type power supply module Abbreviation for the Q61SP slim type power supply module

Redundant power supply module Generic term for the Q63RP and Q64RP power supply modules for redundant

power supply

Network

MELSECNET/H Abbreviation for the MELSECNET/H network system

Ethernet Abbreviation for the Ethernet network system

CC-Link Abbreviation for the Control & Communication Link

Memory card

Memory card Generic term for the SRAM card, Flash card, and ATA card

SRAM card Generic term for the Q2MEM-1MBS, Q2MEM-2MBS, Q3MEM-4MBS, and

Q3MEM-8MBS SRAM cards

Flash card Generic term for the Q2MEM-2MBF and Q2MEM-4MBF Flash cards

ATA card Generic term for the Q2MEM-8MBA, Q2MEM-16MBA, and Q2MEM-32MBA ATA

cards

Others

GX Developer Product name for SW D5C-GPPW-E GPP function software package compatible

with the Q series

Extension cable Generic term for the QC05B, QC06B, QC12B, QC30B, QC50B, and QC100B

extension cables

Battery Generic term for the Q6BAT, Q7BAT, and Q8BAT CPU module batteries,

Q2MEM-BAT SRAM card battery, and Q3MEM-BAT SRAM card battery

GOT Generic term for Mitsubishi Graphic Operation Terminal, GOT-A*** series, GOT-F***

series, and GOT1000 series

CHAPTER1 OVERVIEW

1

2

3

4

5

6

7

8

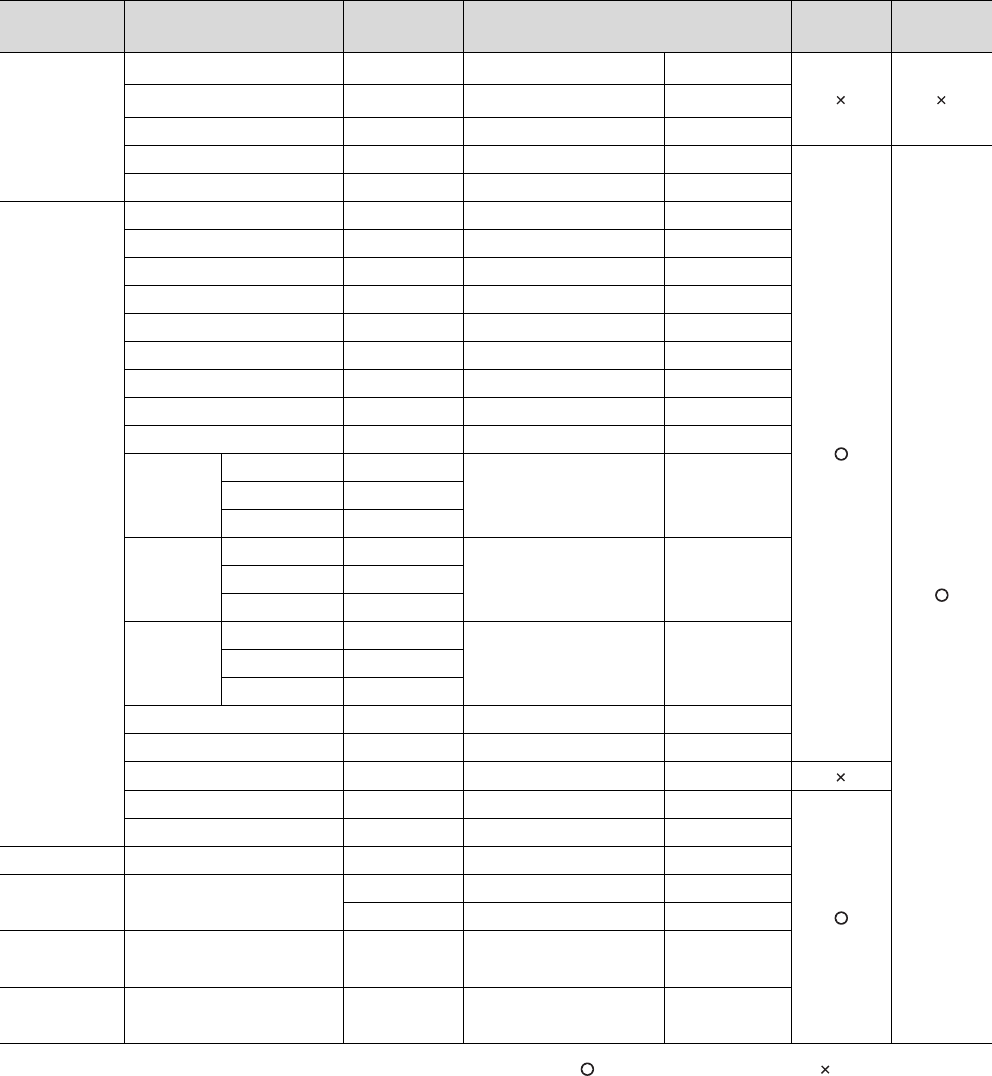

1.1 Processing Order in the CPU Module

1 - 1

CHAPTER1 OVERVIEW

The CPU module performs sequence control by executing programs.

This chapter describes the processing order in the CPU module, locations where the created programs are stored, and

devices and instructions useful for programming.

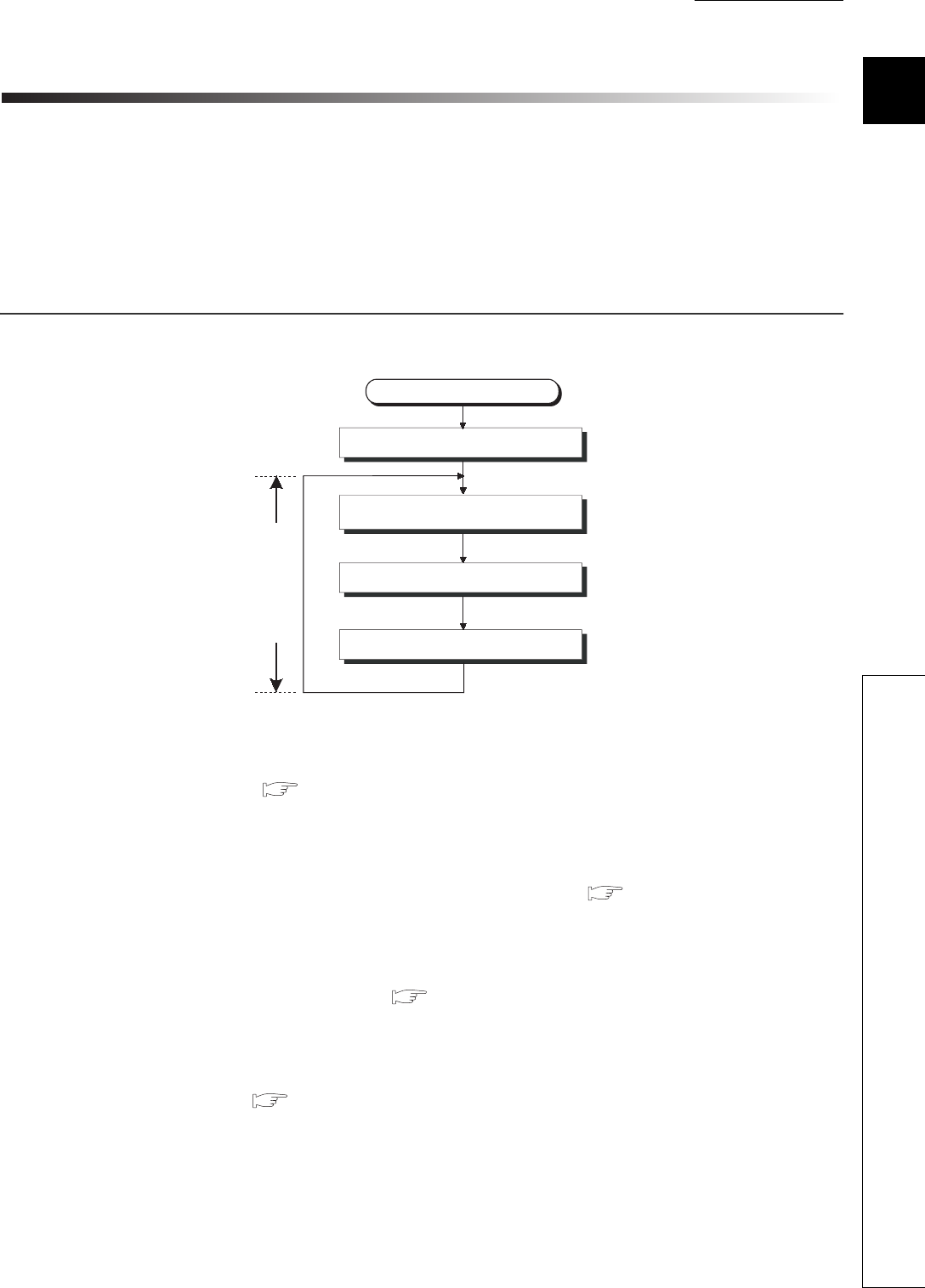

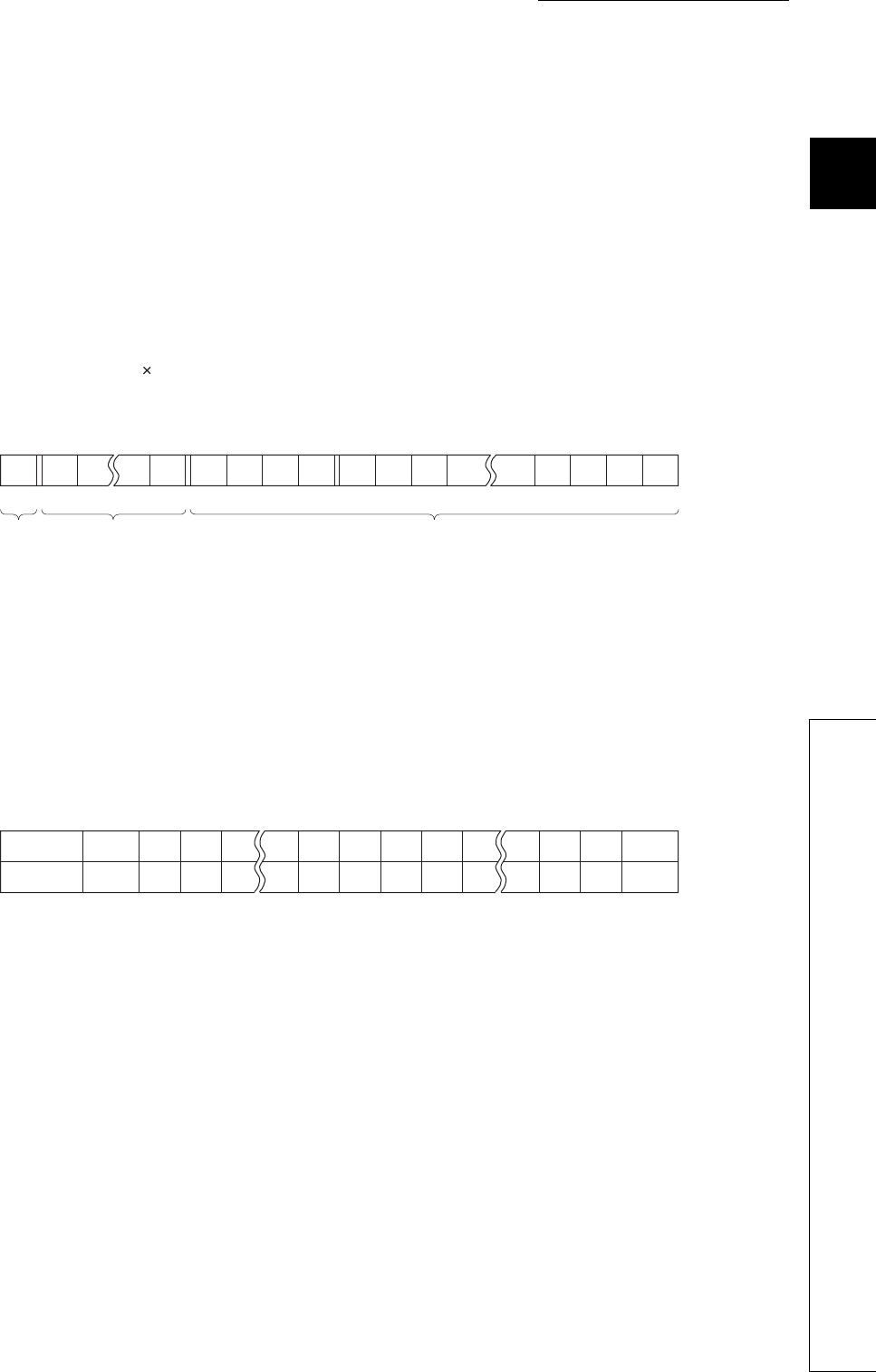

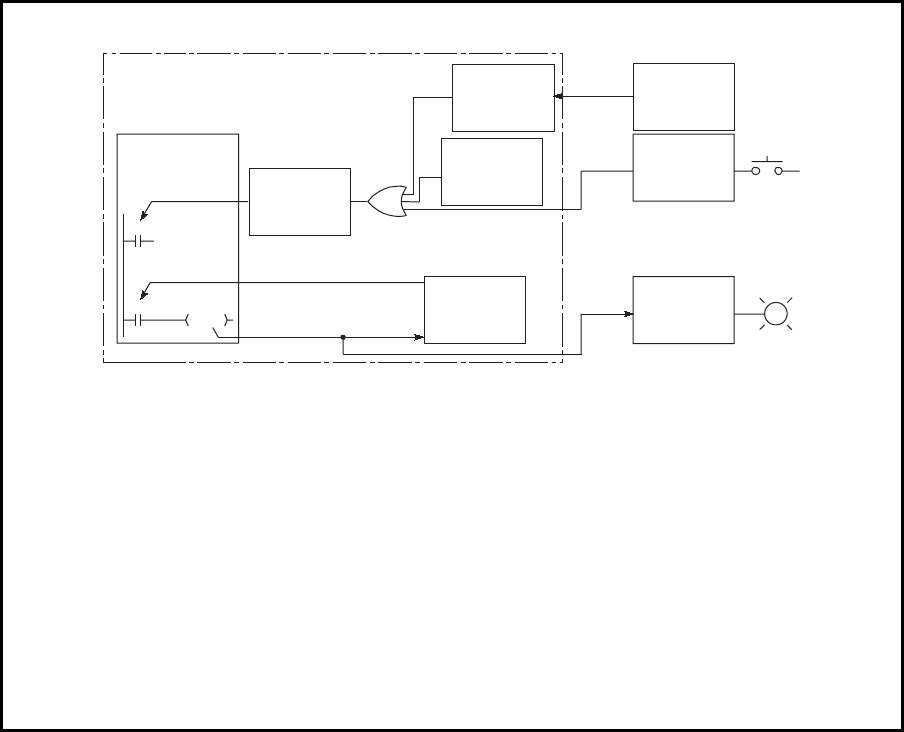

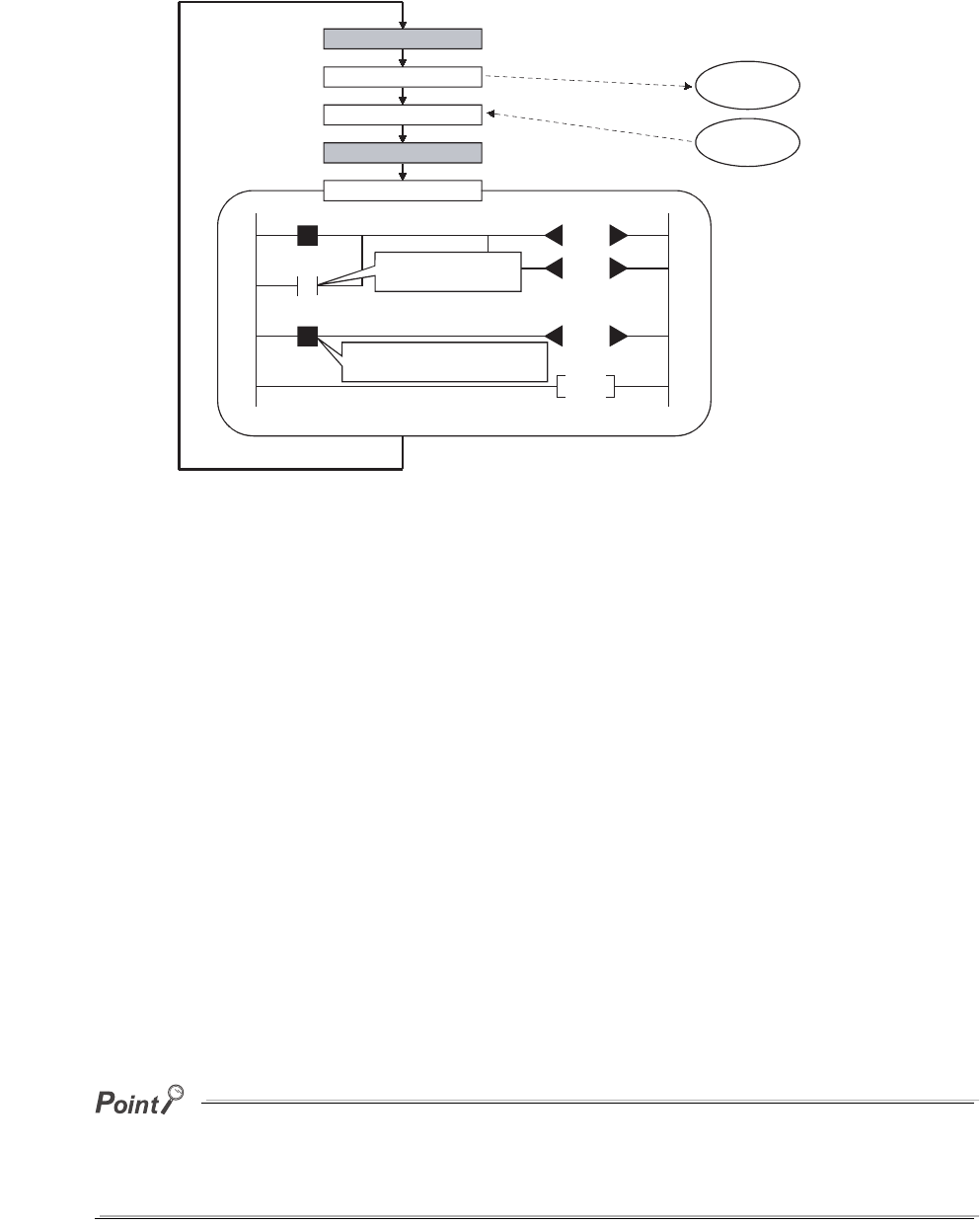

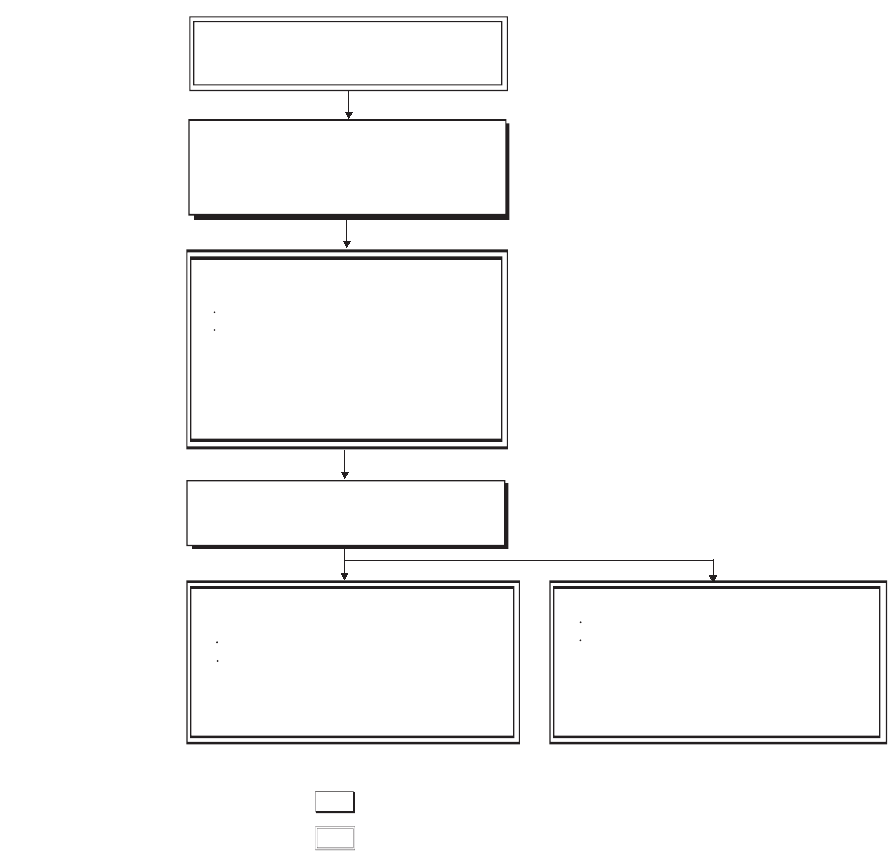

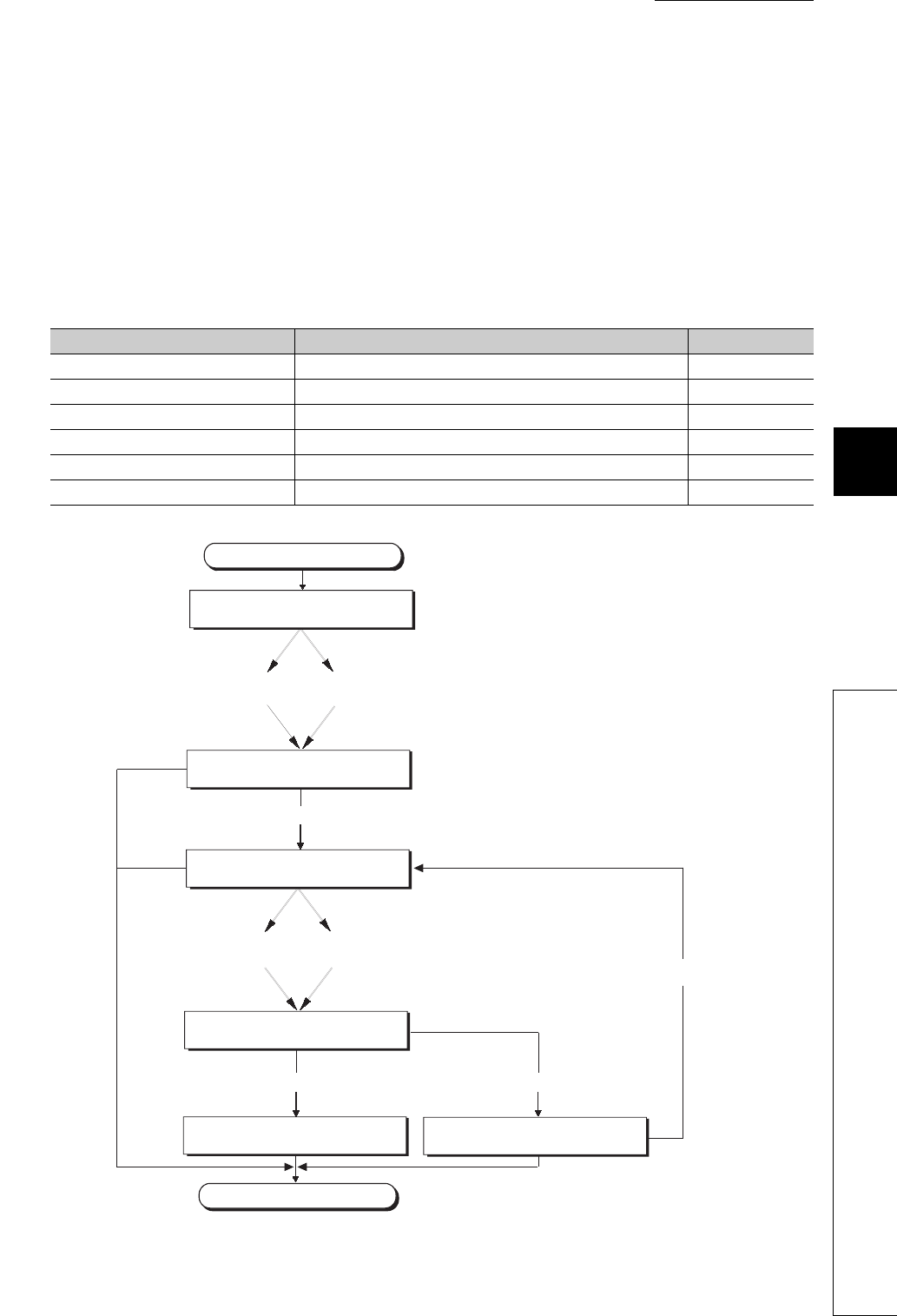

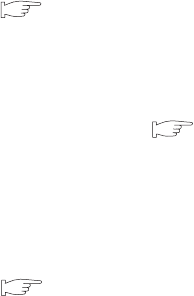

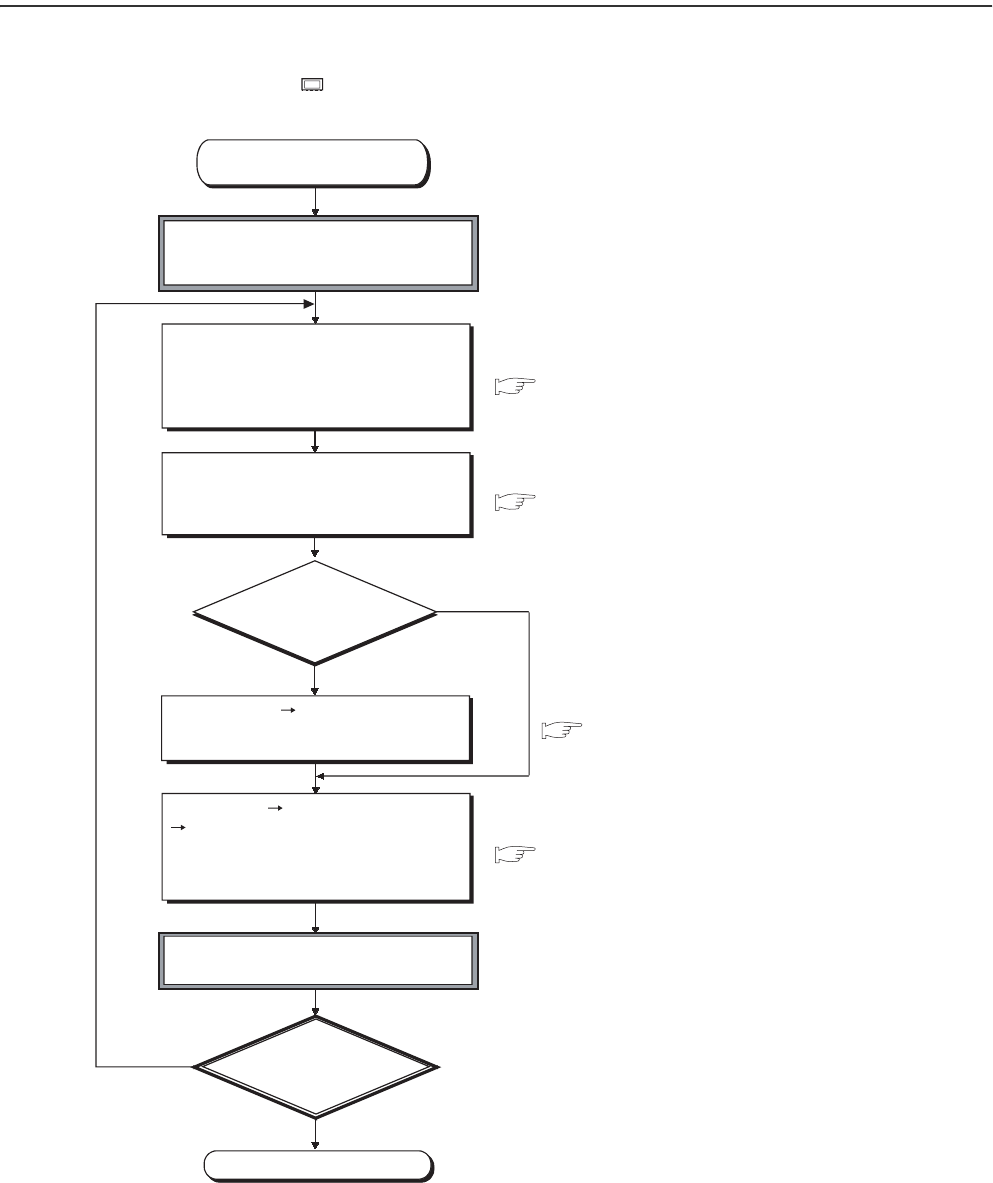

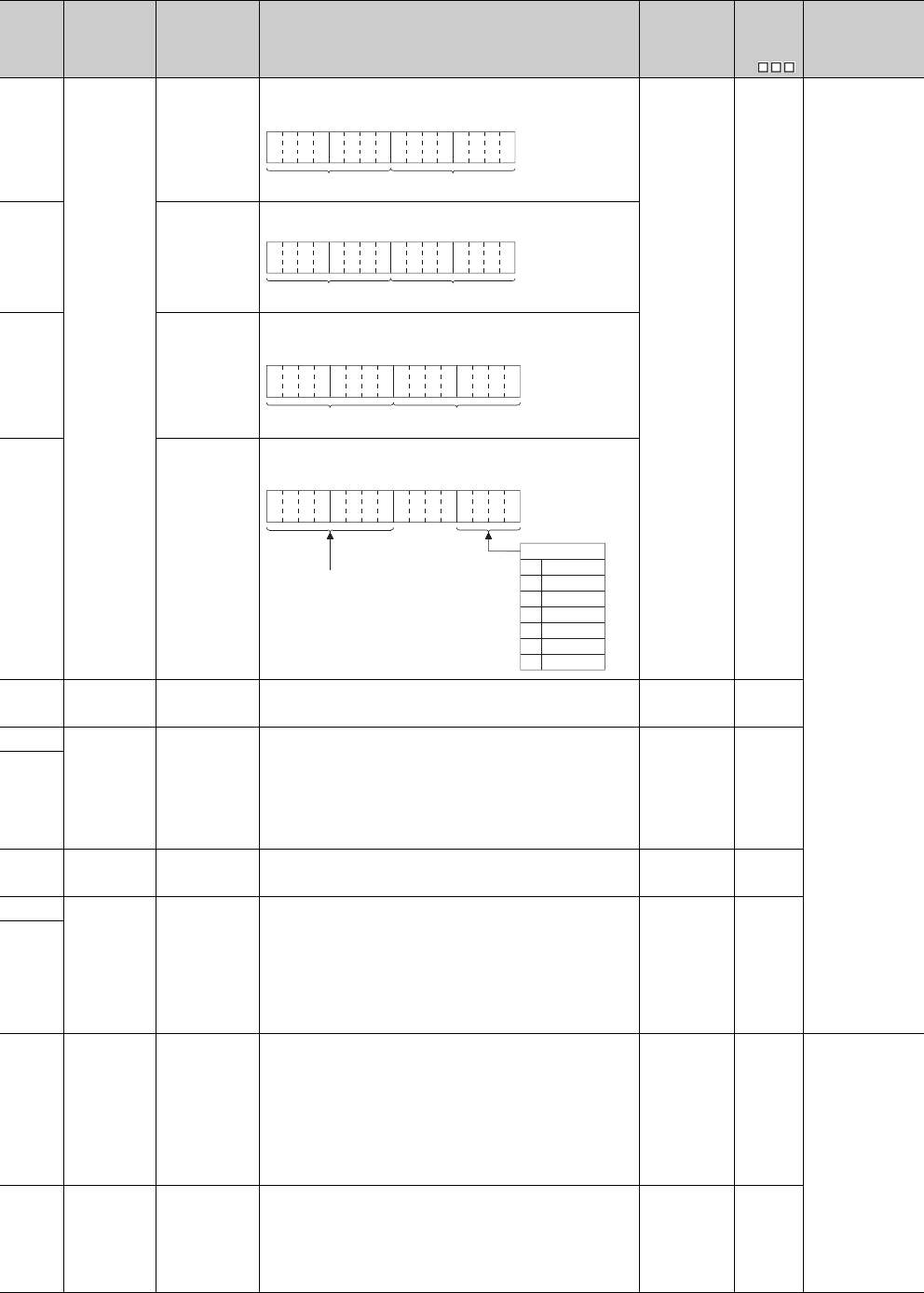

1.1 Processing Order in the CPU Module

The CPU module performs processing in the following order.

(1) Initial processing ( Section 3.1)

The CPU module performs preprocessing required for program operations.

The preprocessing is performed only once when the module is powered on or reset.

(2) Refresh processing with input and output modules ( Section 3.2)

The CPU module takes on/off data from the input module or intelligent function module and outputs on/off data to

the output module or intelligent function module.

(3) Program operation processing ( Section 3.3)

The CPU module sequentially executes the program stored in the module from the step 0 to the END or FEND

instruction.

(4) END processing ( Section 3.4)

The CPU module performs refresh processing with network modules or communicates with external devices.

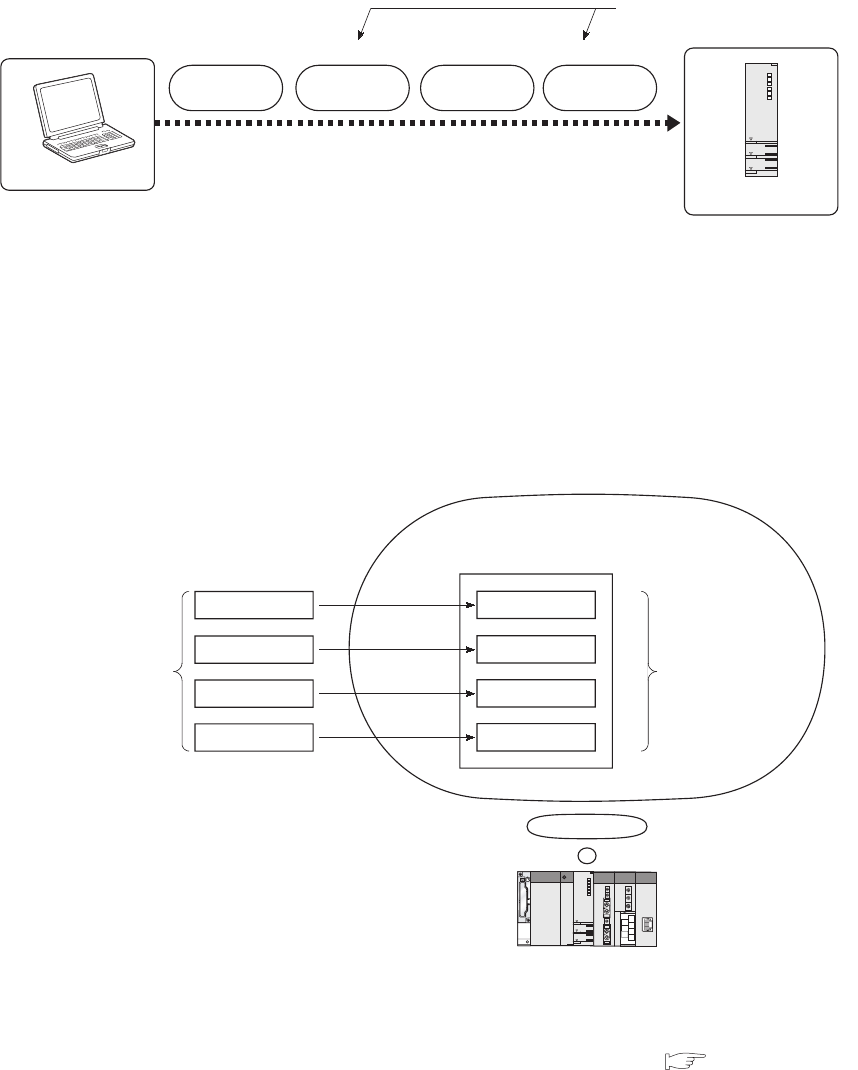

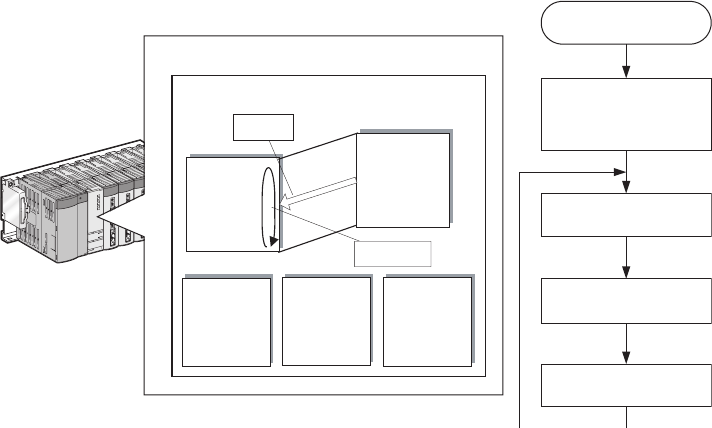

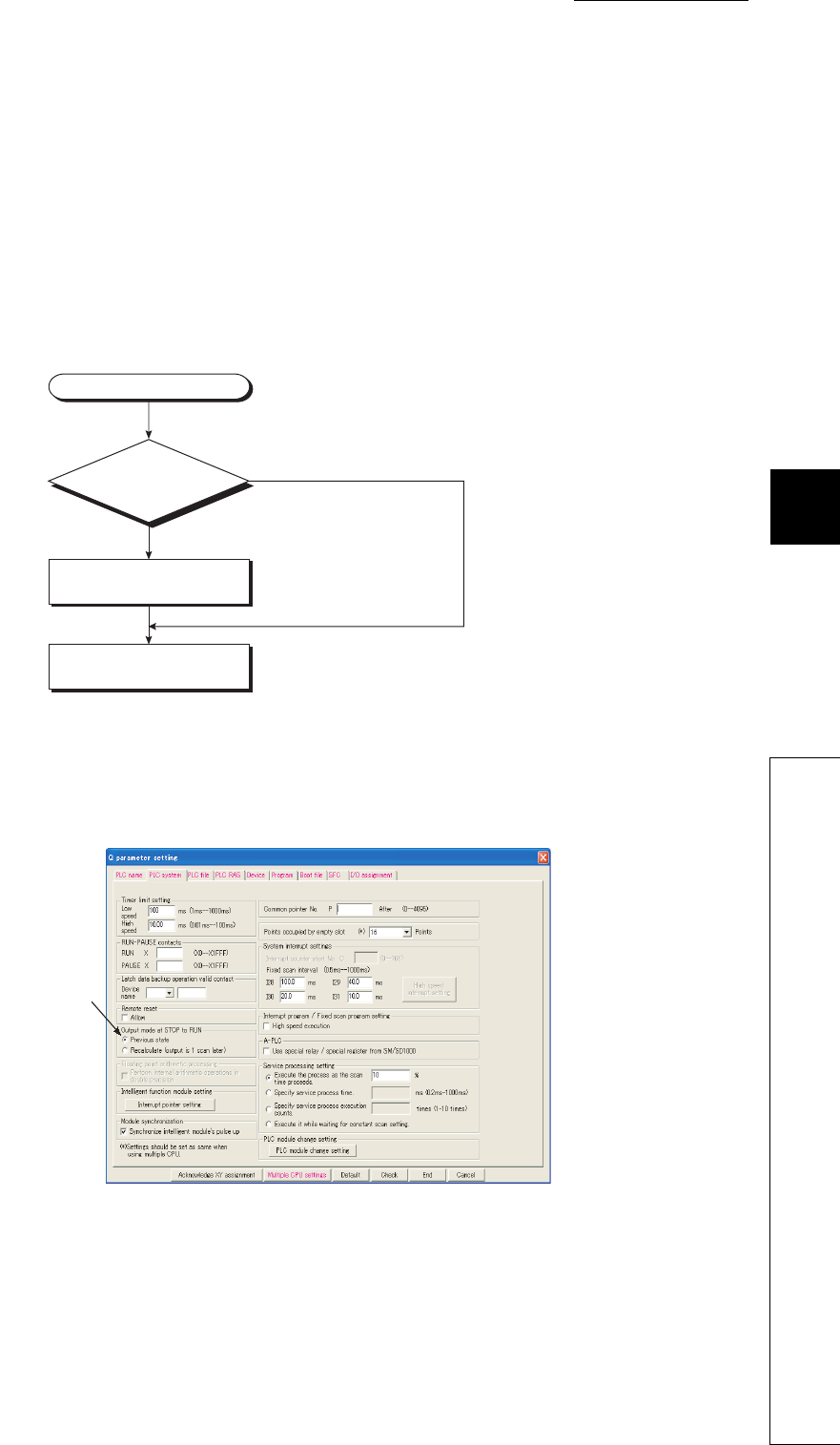

Figure 1.1 Processing order in the CPU module

Power-on or reset

Initial processing

Refresh processing with

input/output modules

Program operation processing

END processing

Scan time

1 - 2

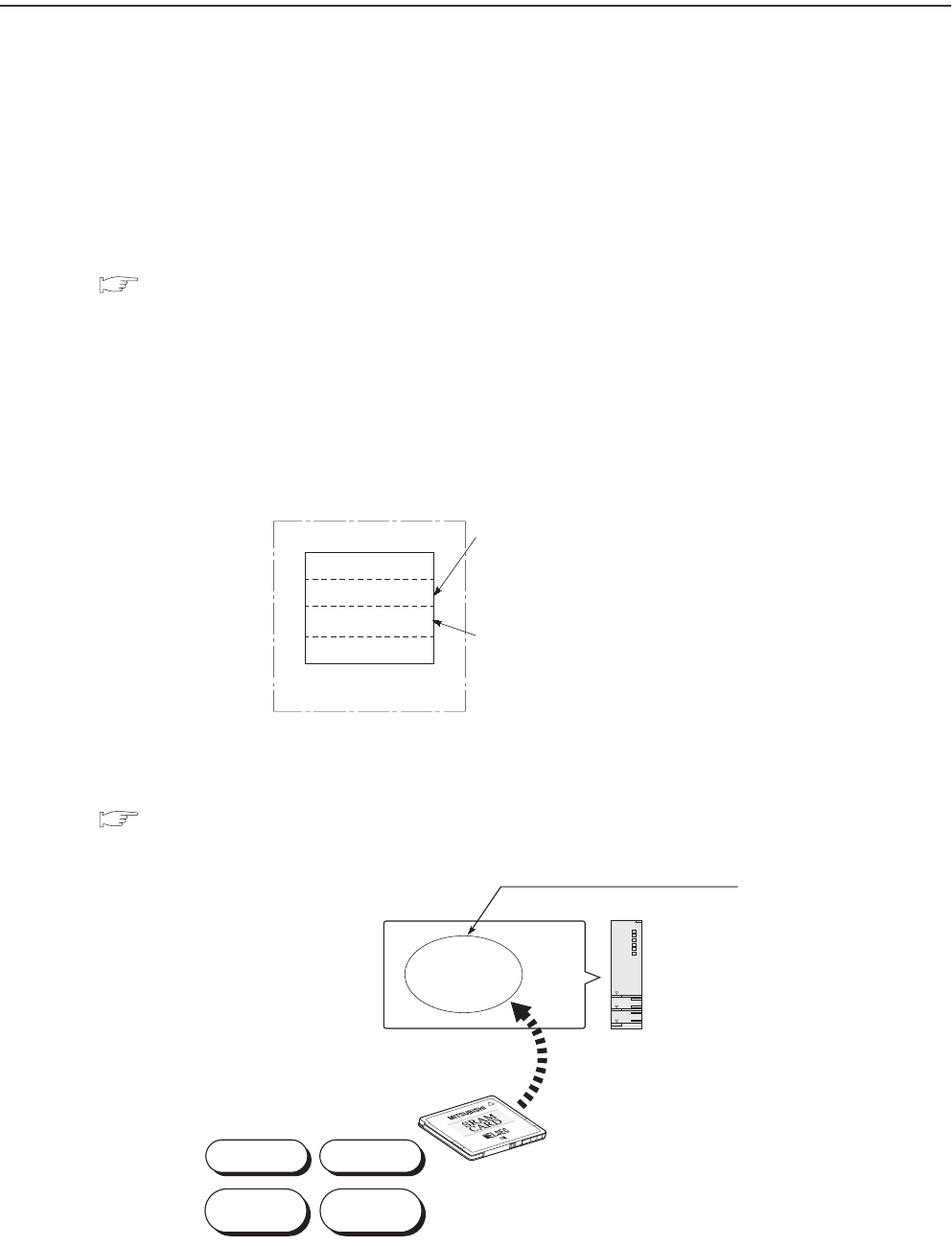

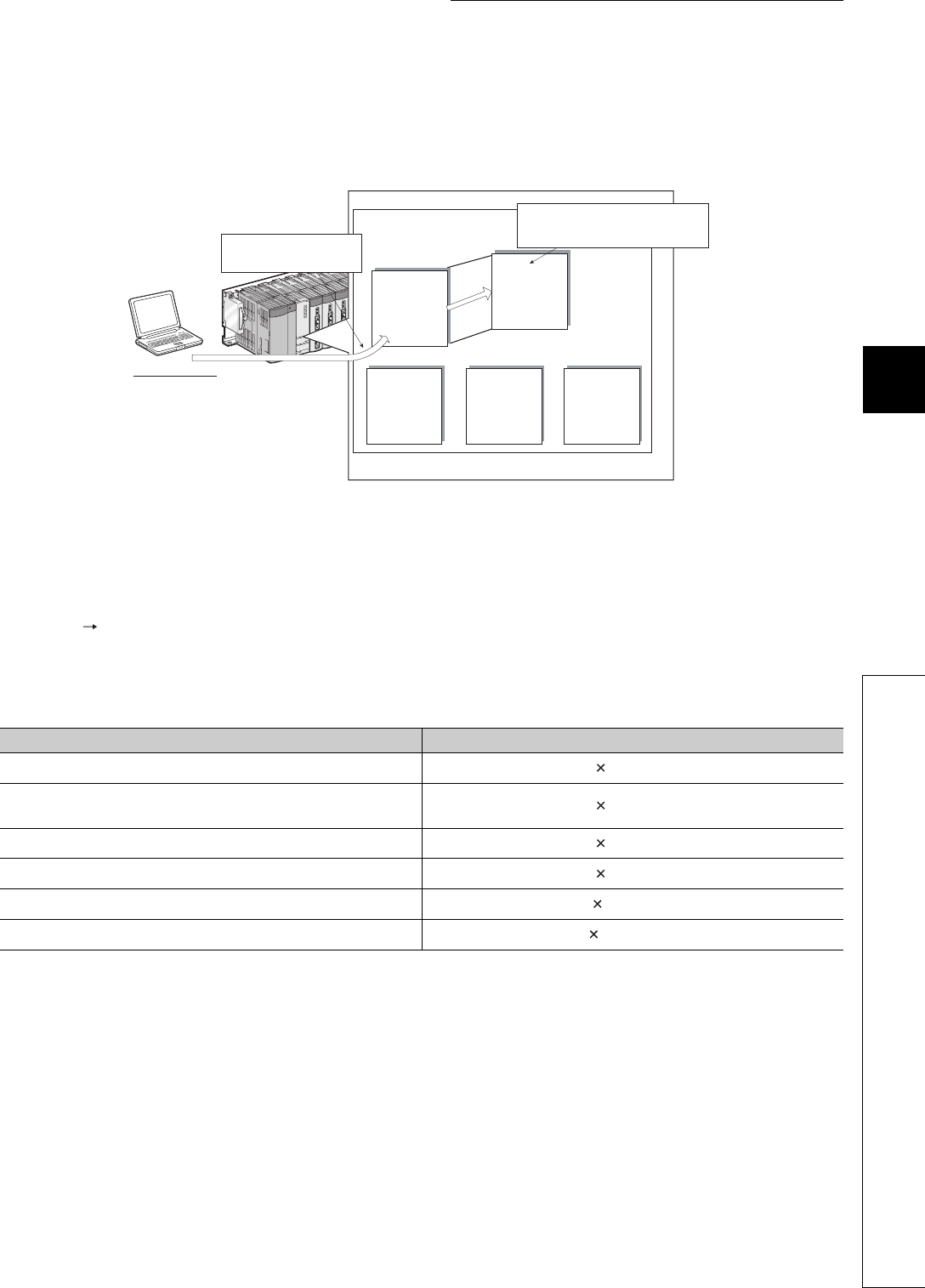

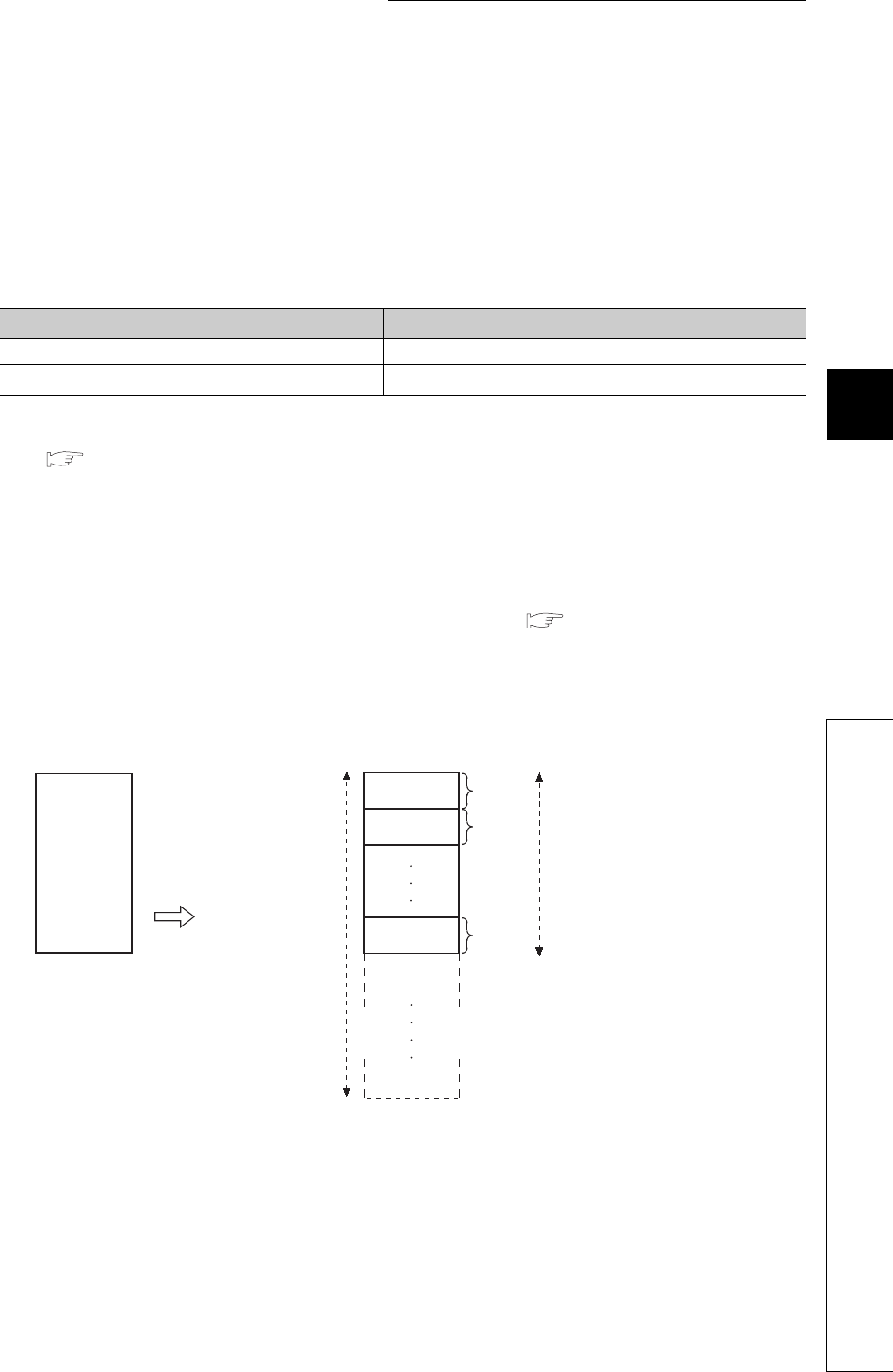

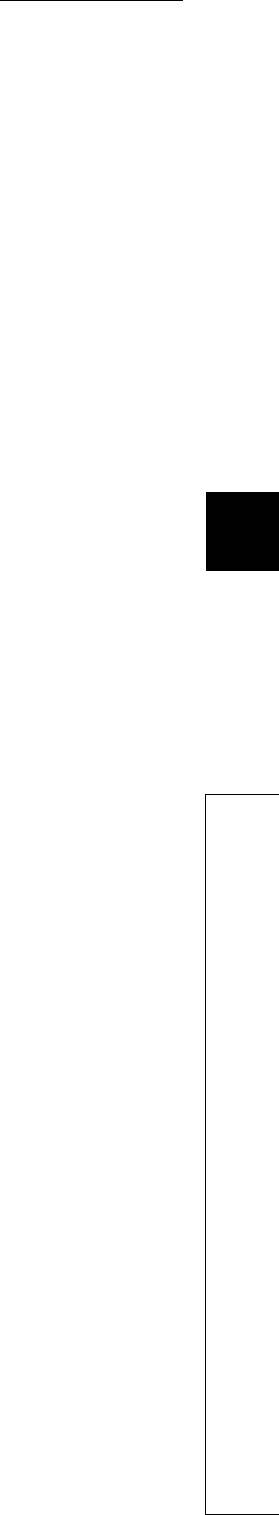

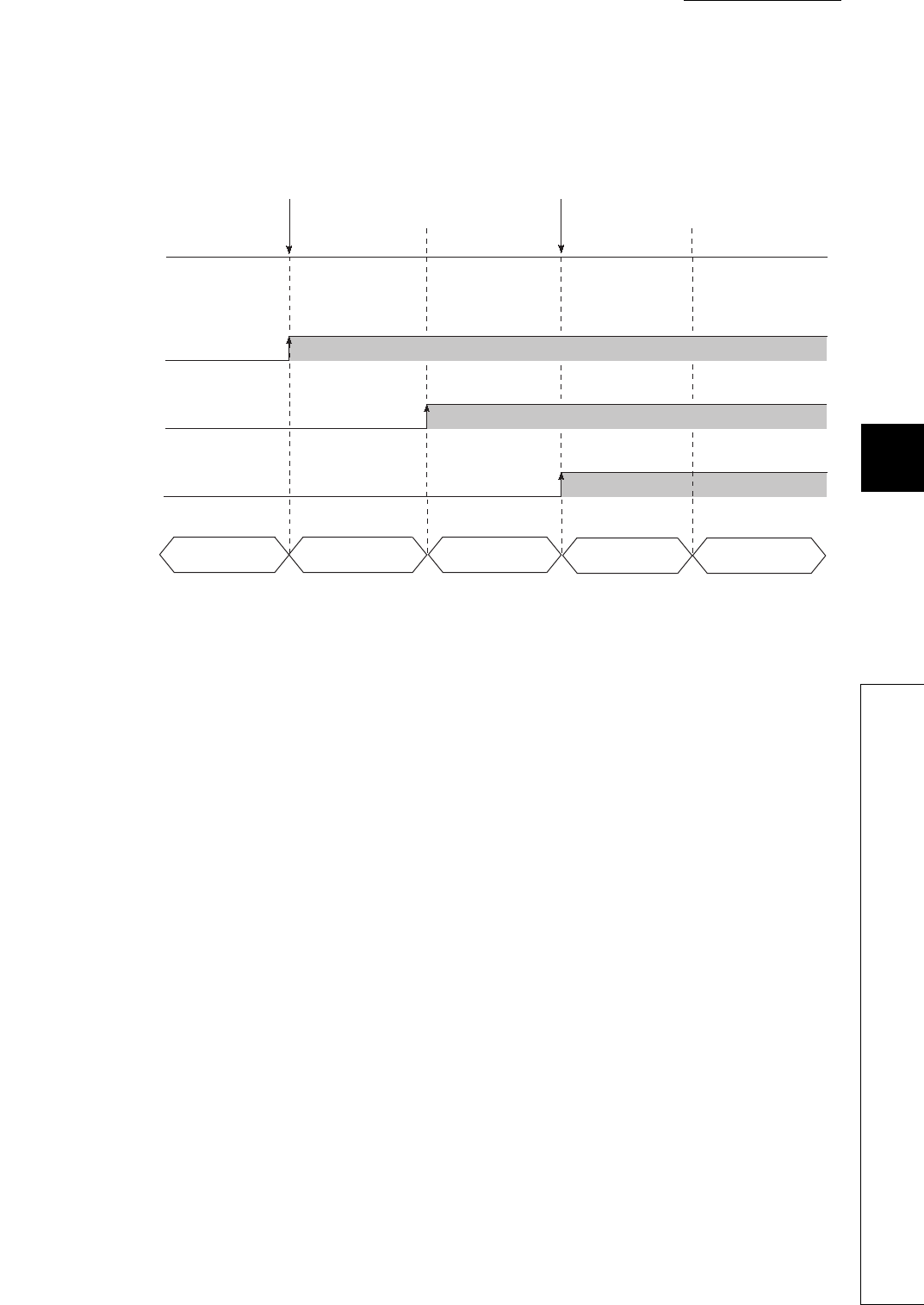

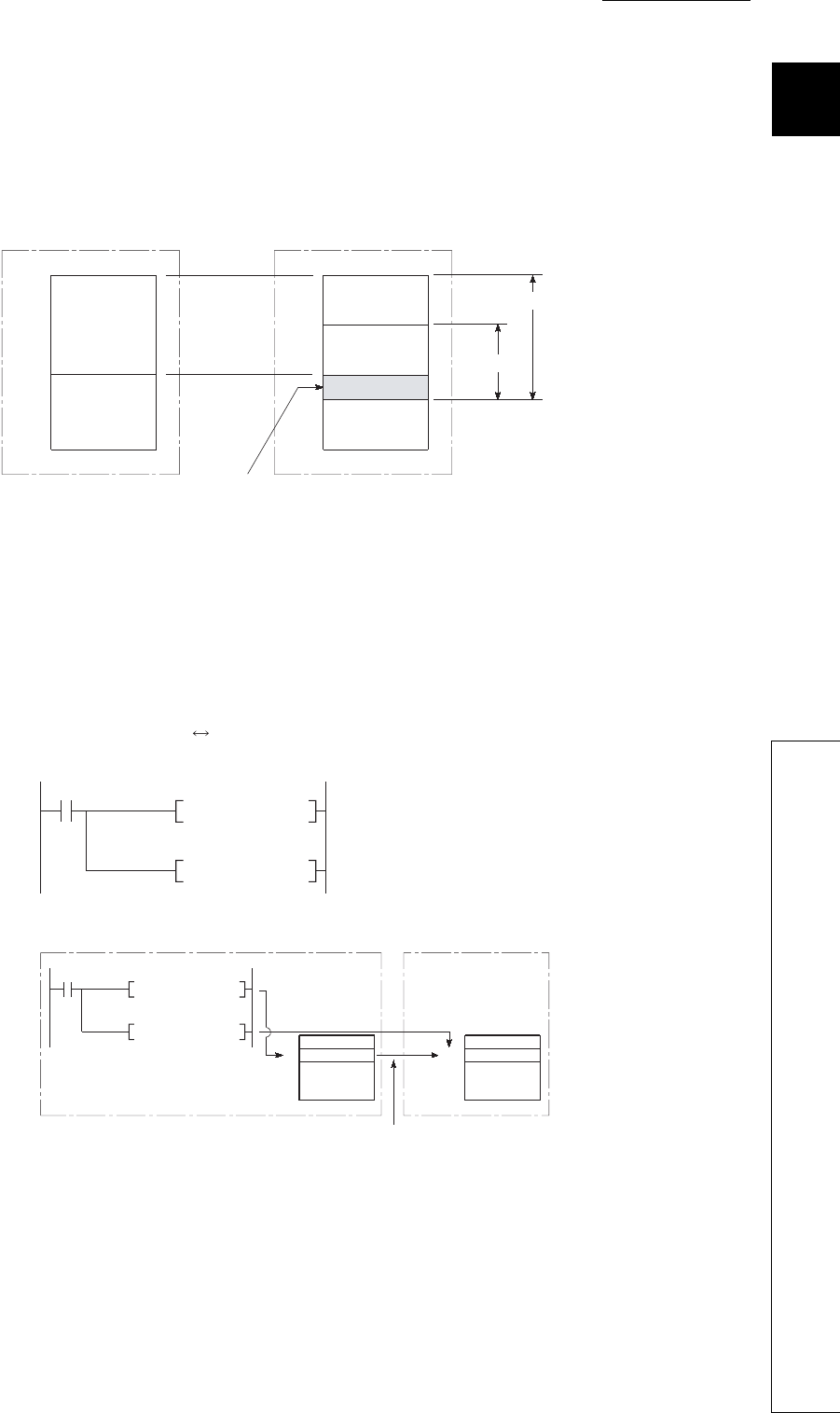

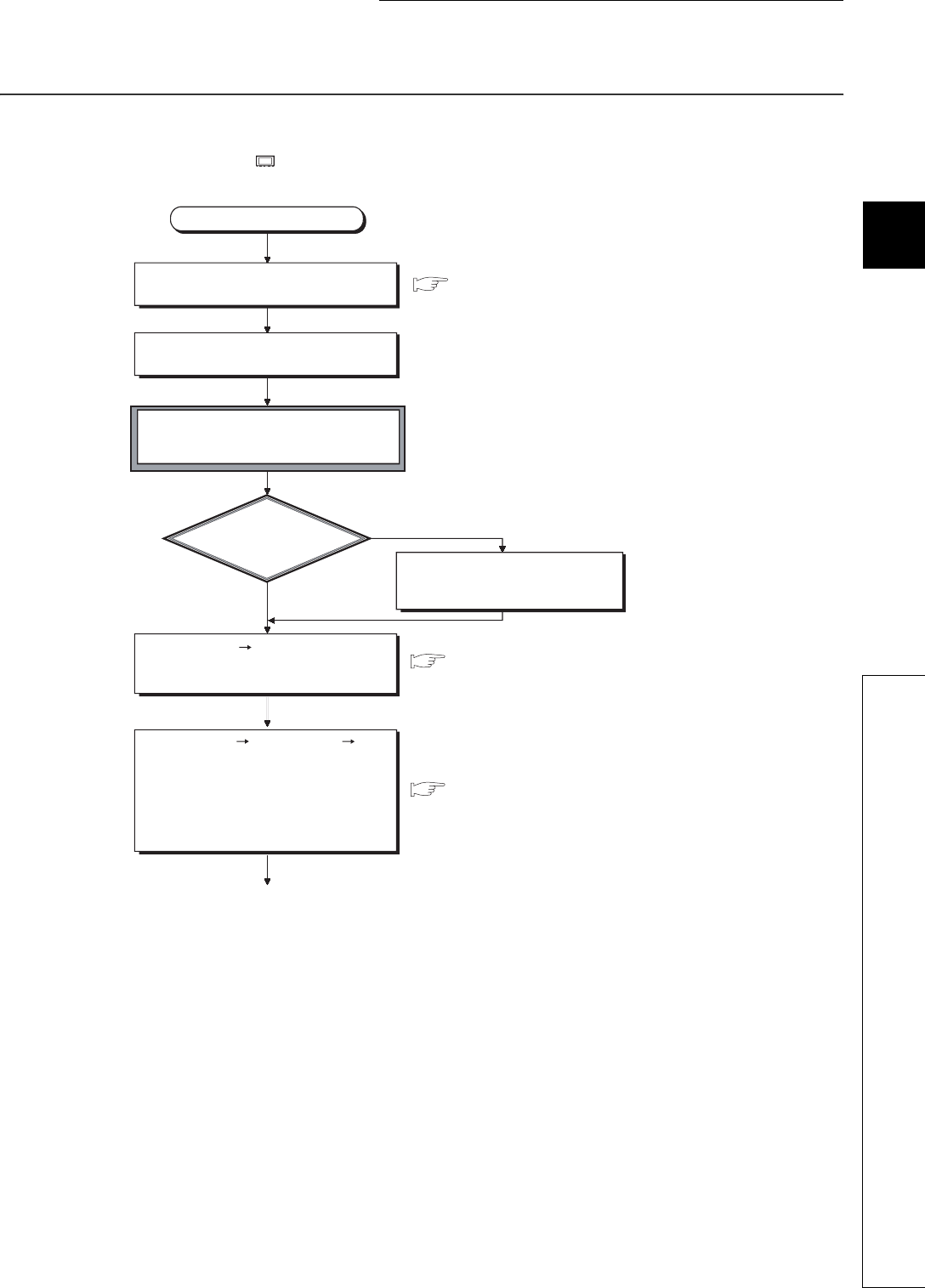

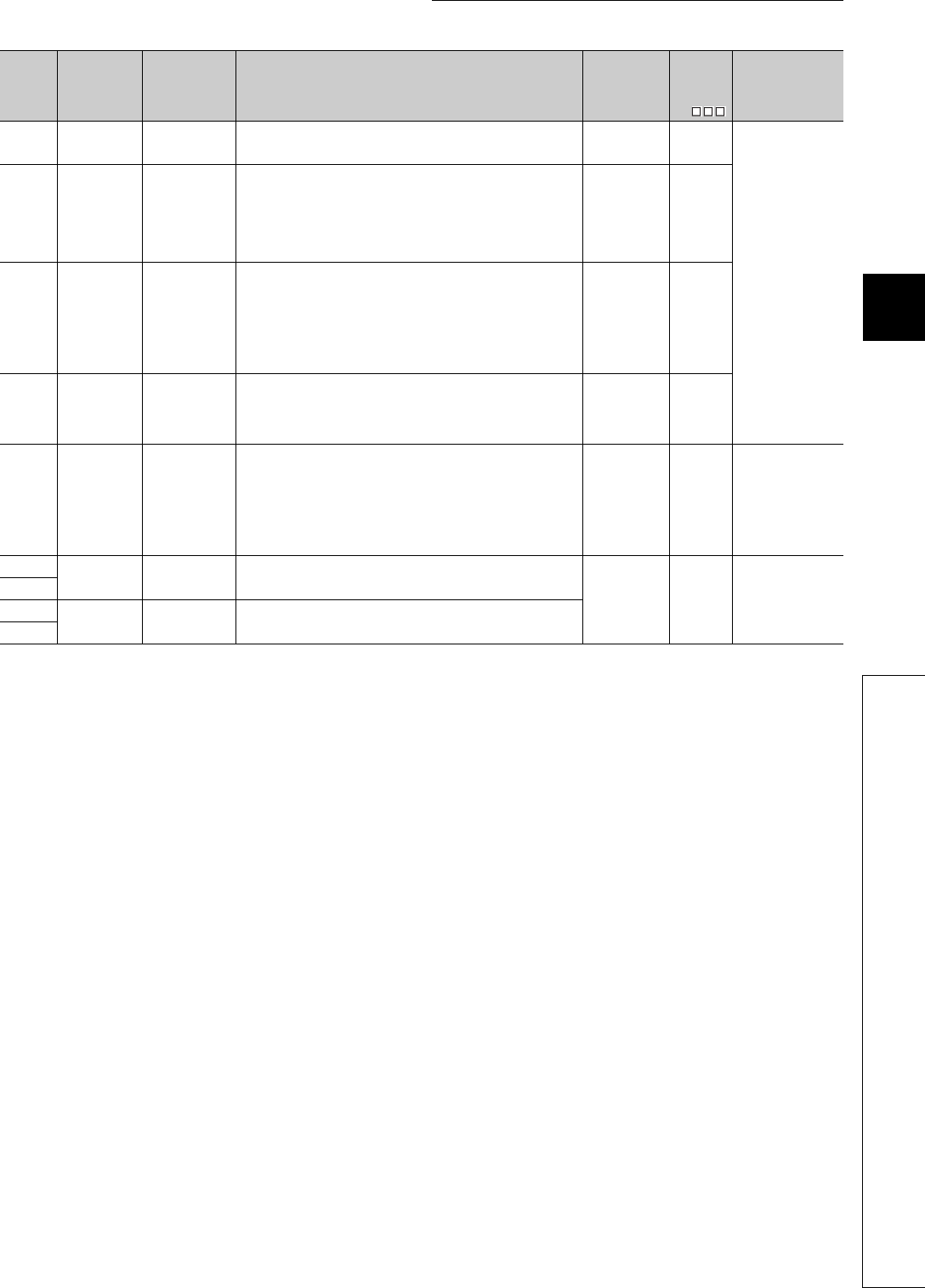

1.2 Storing and Executing Programs

This section describes where to store and how to execute the programs in the CPU module.

(1) Programming

Programs are created with GX Developer.

For details of program configuration and execution conditions, refer to CHAPTER 2.

(2) Storing programs

Created programs and set parameters are stored in the following memories of the CPU module.

( Section 5.1)

• Program memory

• Standard ROM (parameters only)

• Memory card

(3) Executing programs

The CPU module executes the programs stored in the program memory.

To execute the programs stored in a memory card, the programs need to be booted to the program memory

( Section 5.1.8) when the CPU module is powered off and then on or reset.

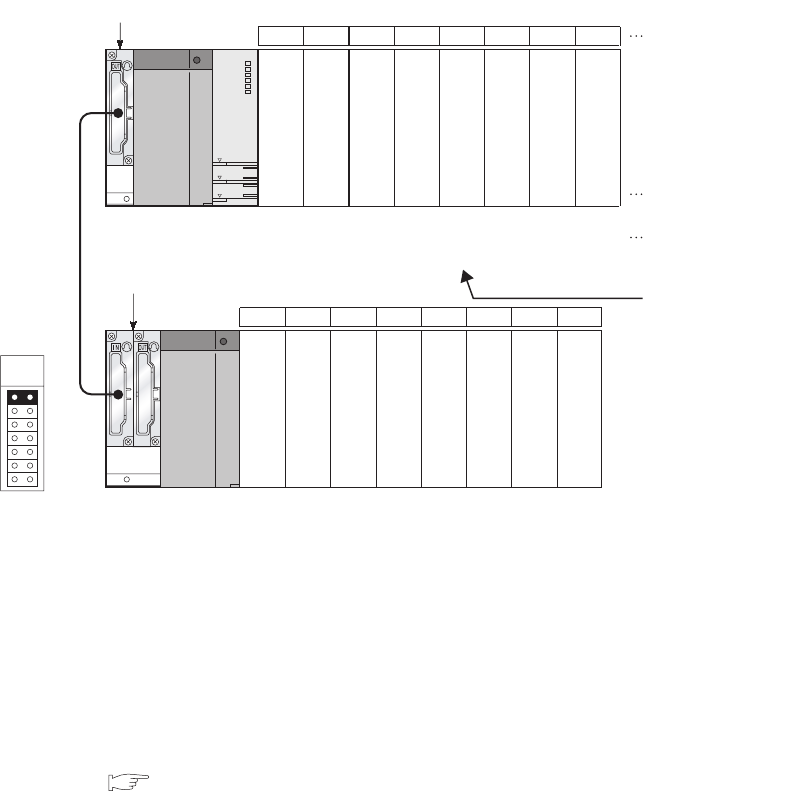

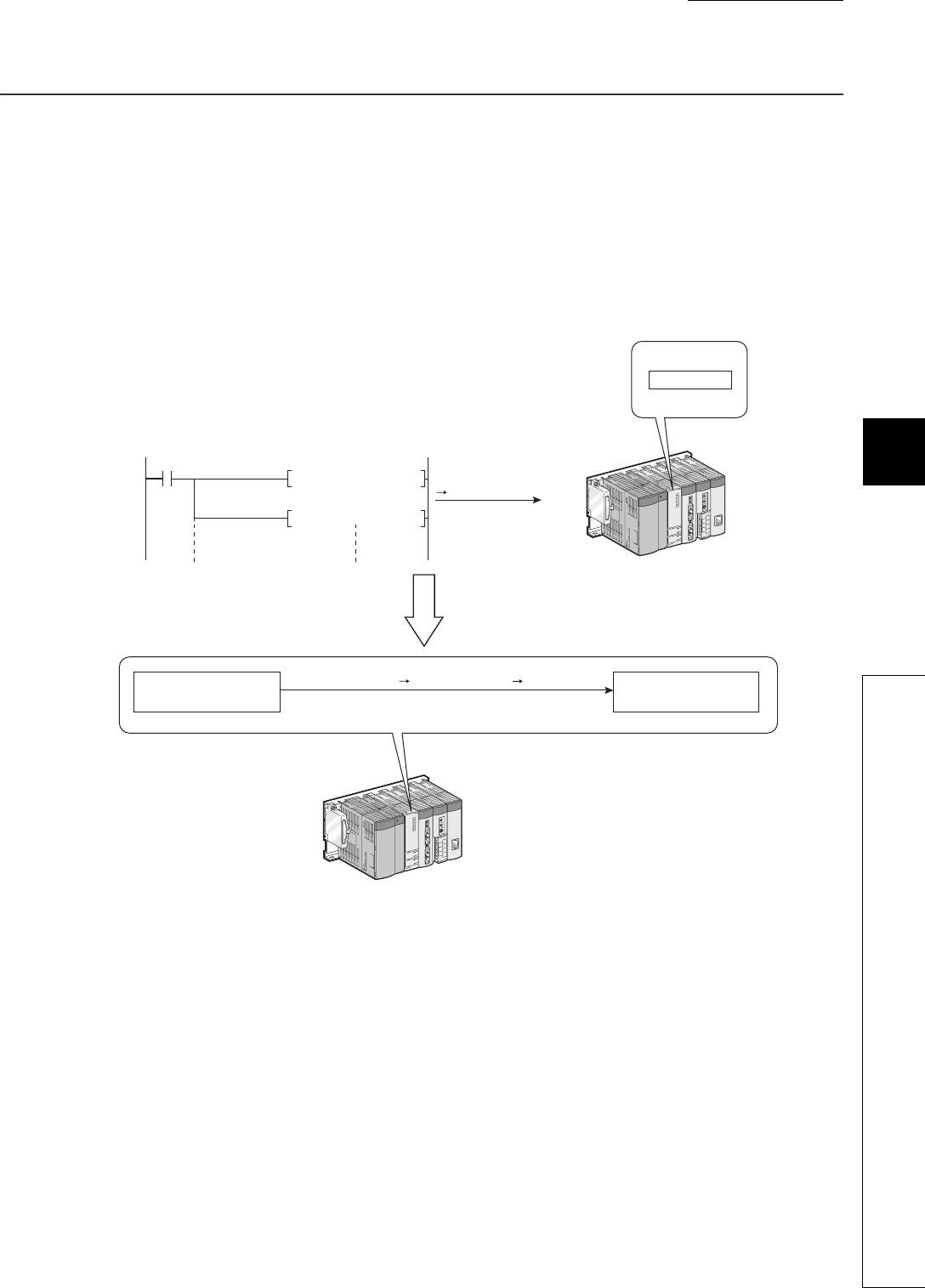

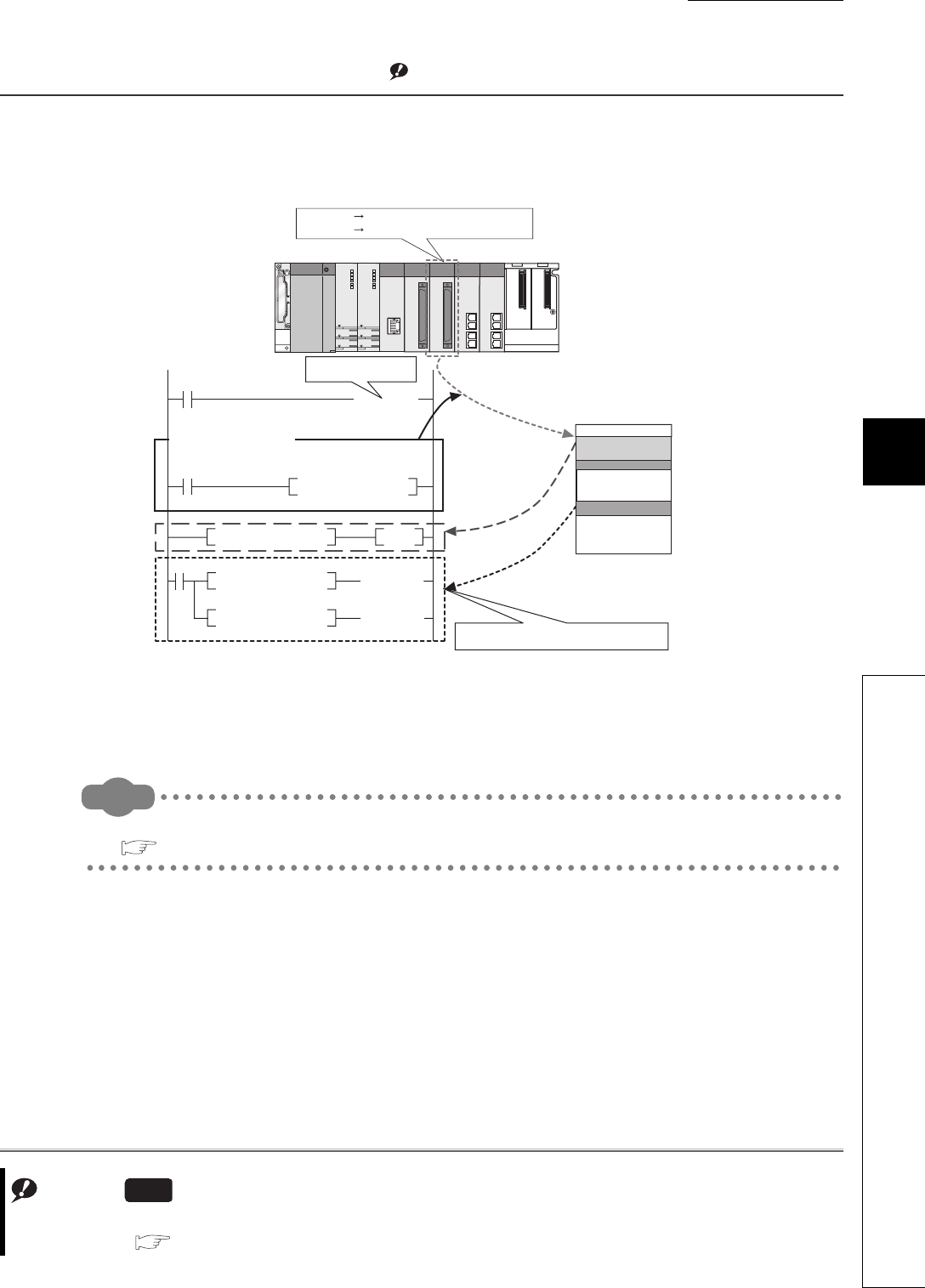

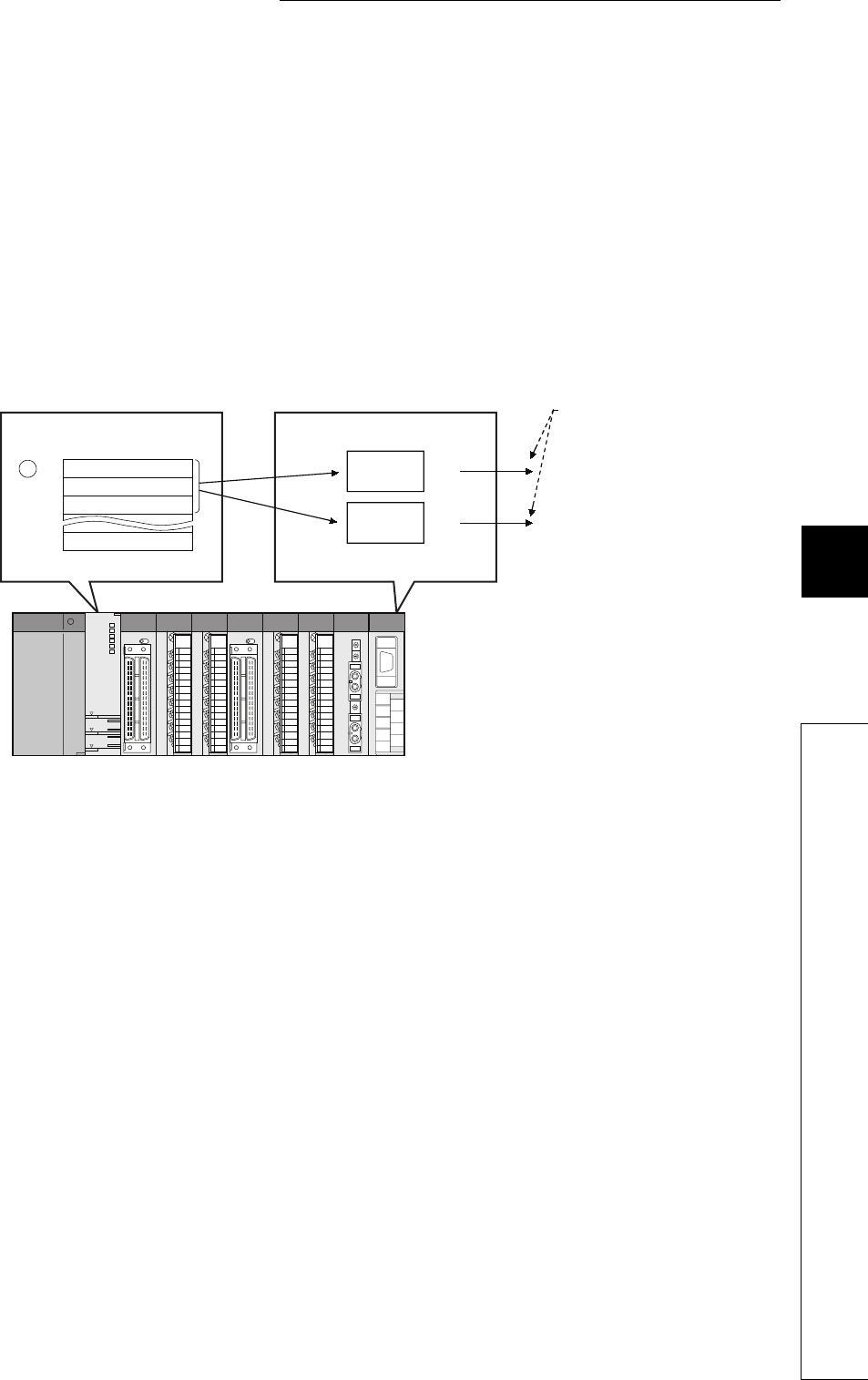

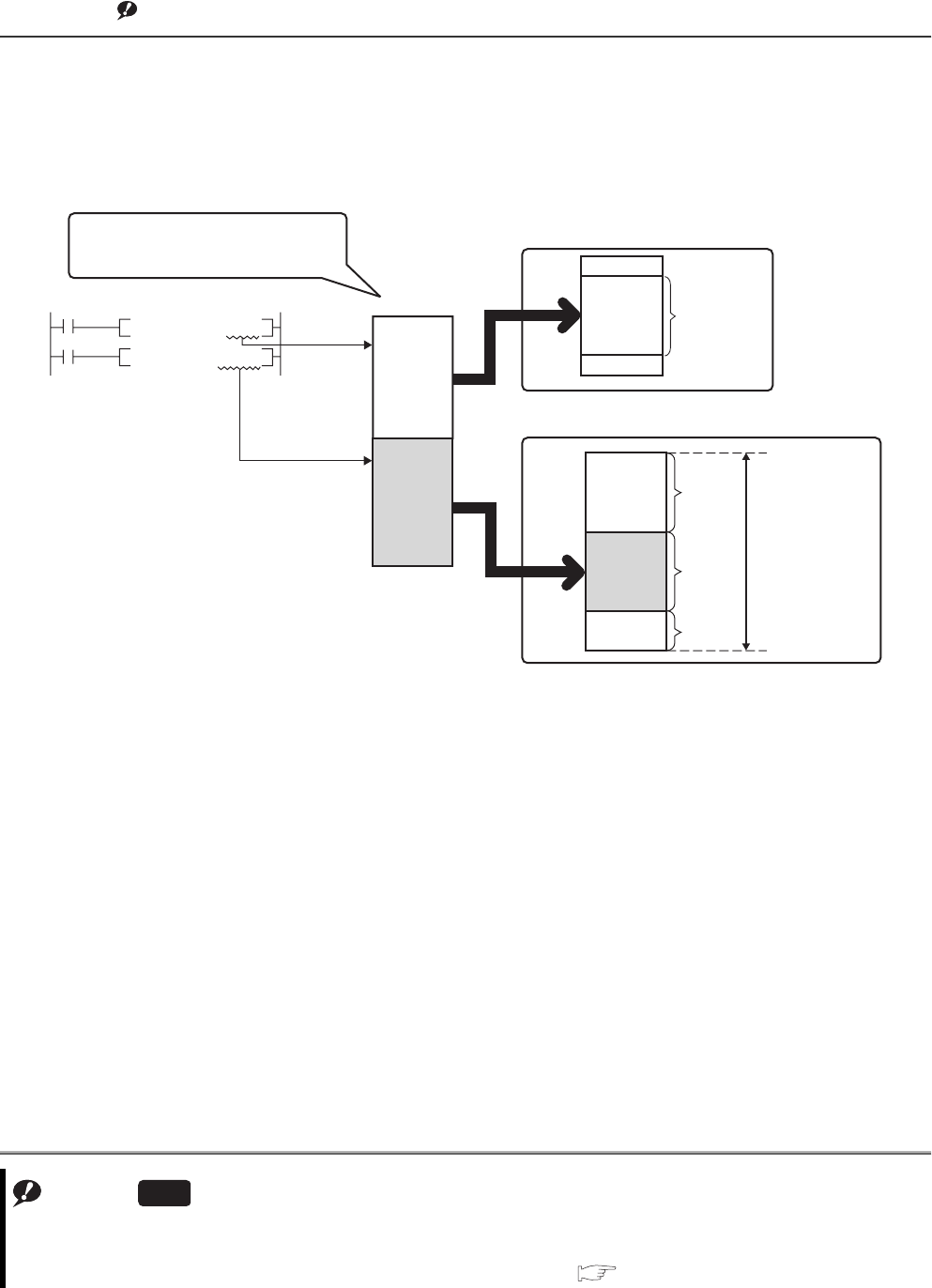

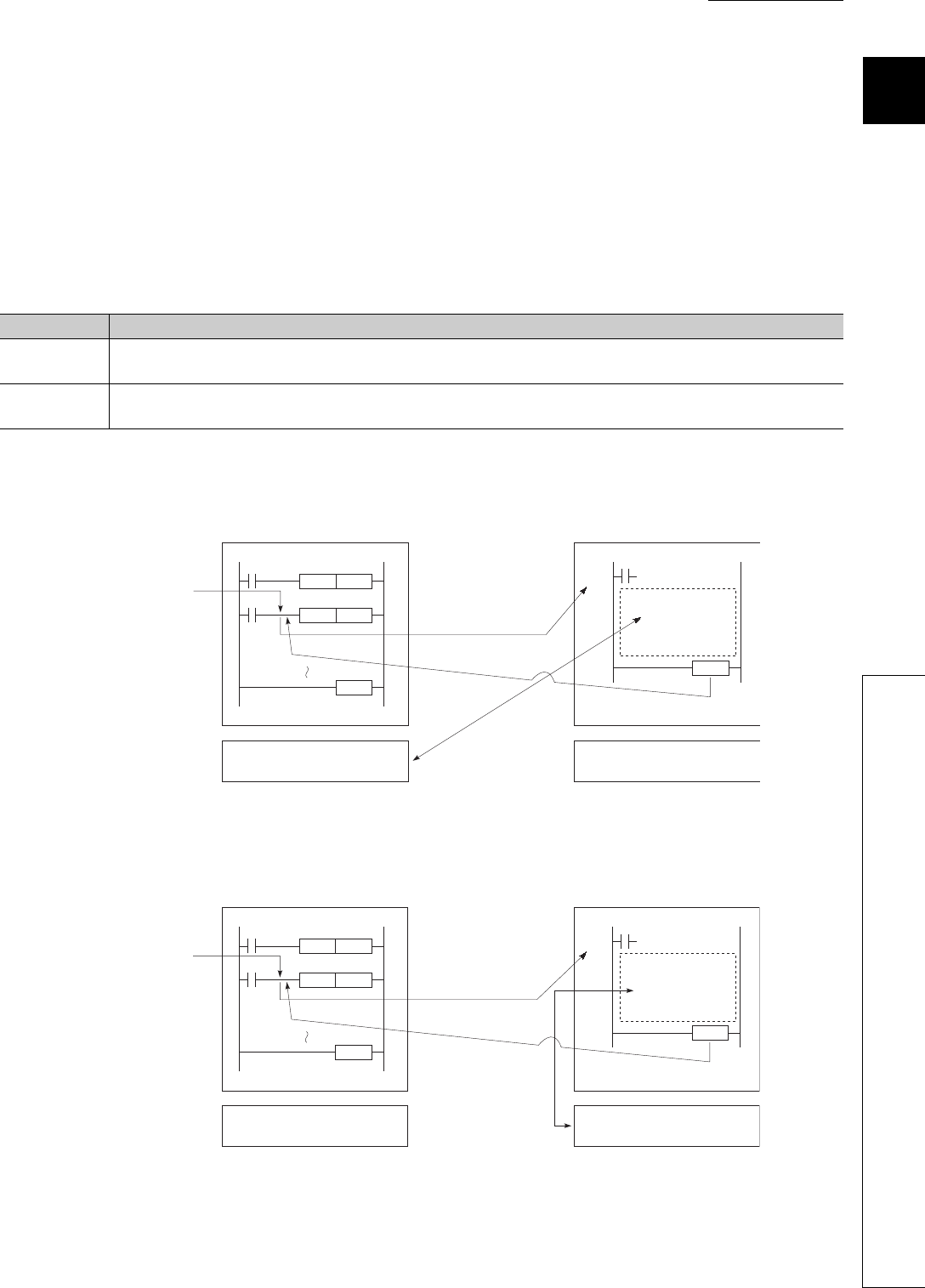

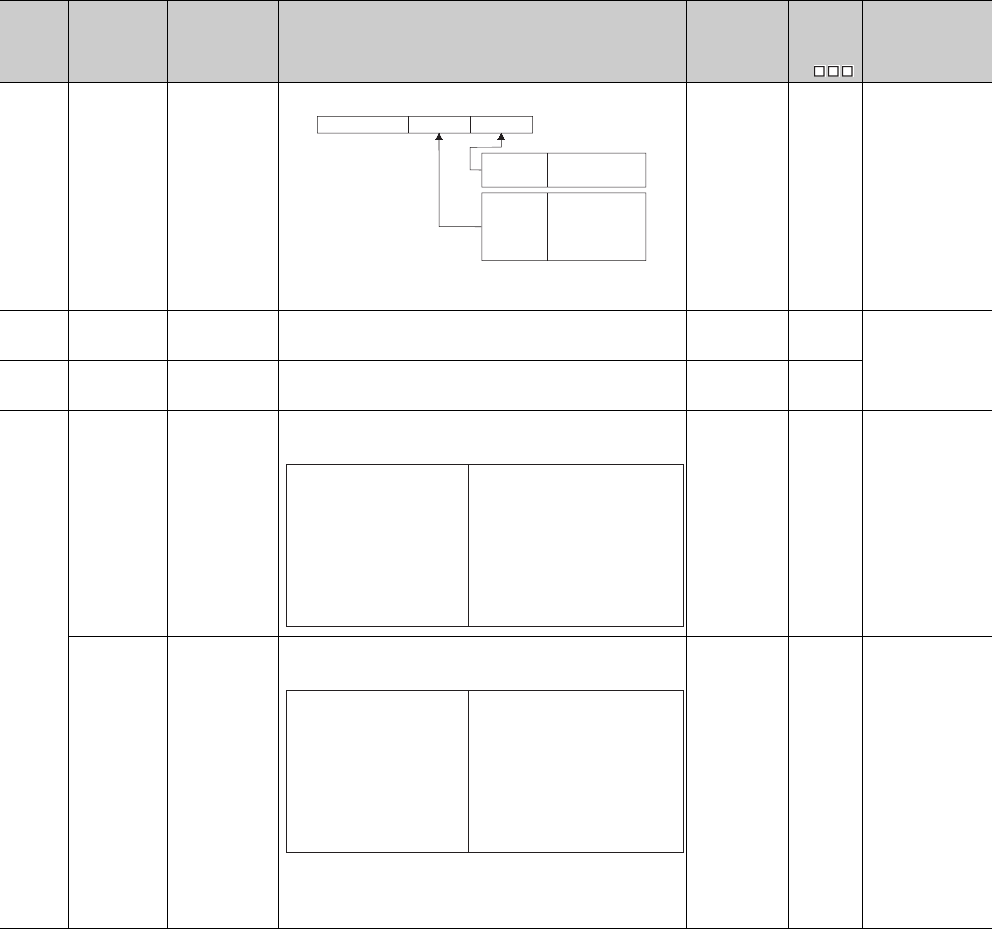

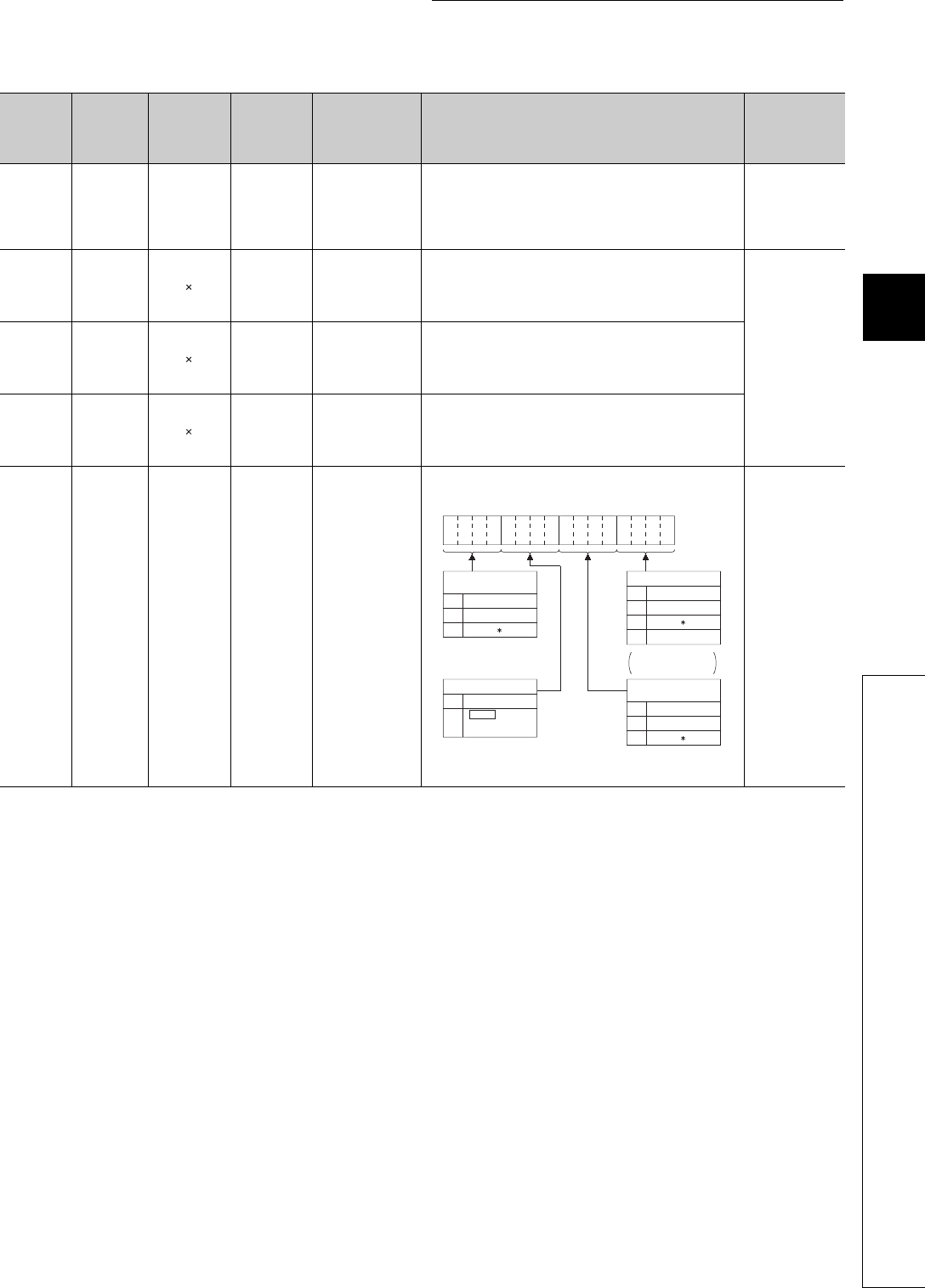

Figure 1.2 Executing programs

Figure 1.3 Executing programs stored in a memory card

CPU module

The CPU module executes

the programs stored here.

Program memory

Parameter

Program

Device comment

Initial device value

Comments are stored

separately from the program.

The CPU module executes the programs

booted from a memory card to here.

Program

memory

Device

comment

Parameter Program

Initial device

value

CPU moduleBoot

Memory card

CHAPTER1 OVERVIEW

1

2

3

4

5

6

7

8

1.3 Structured Programming

1 - 3

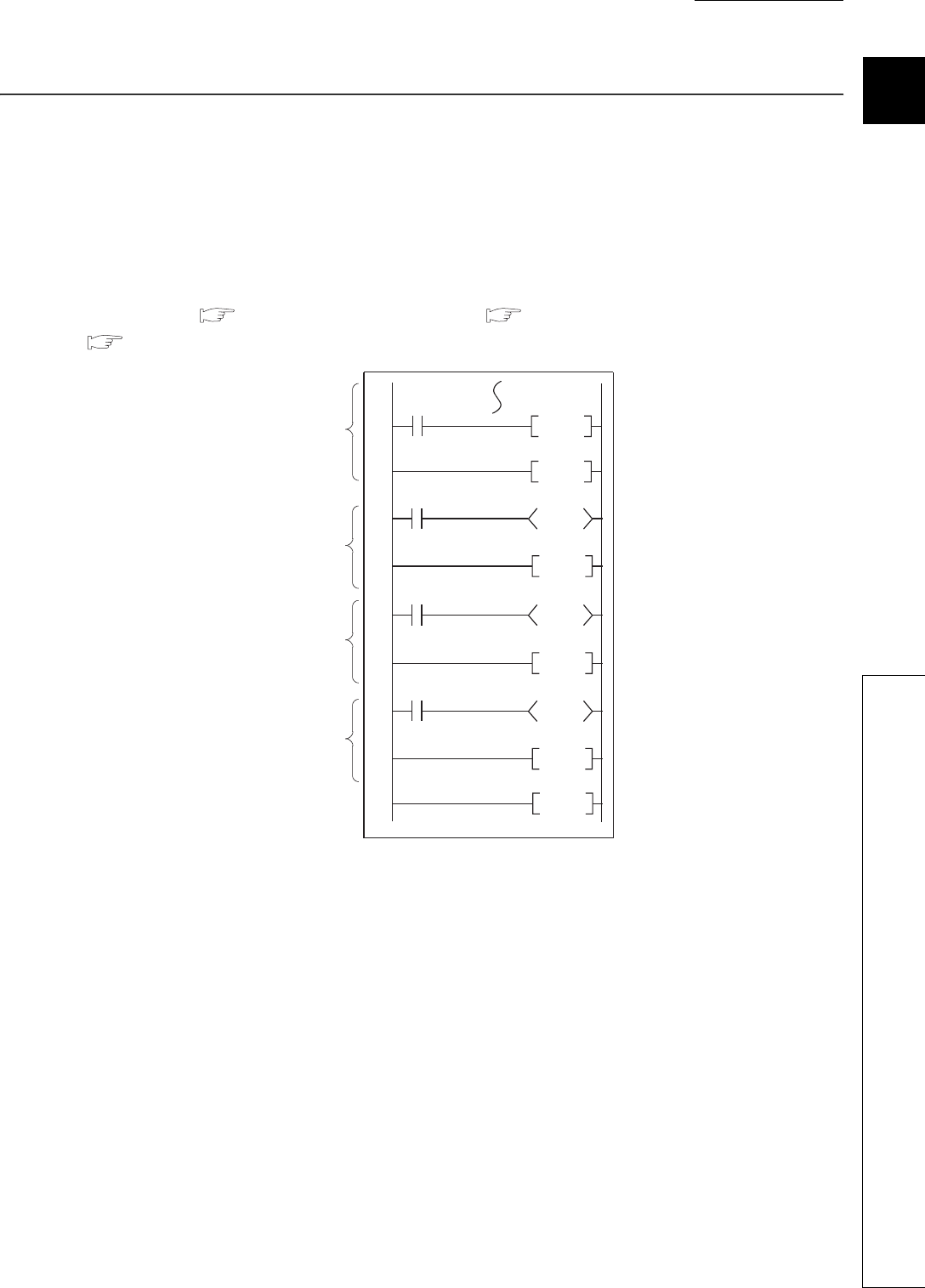

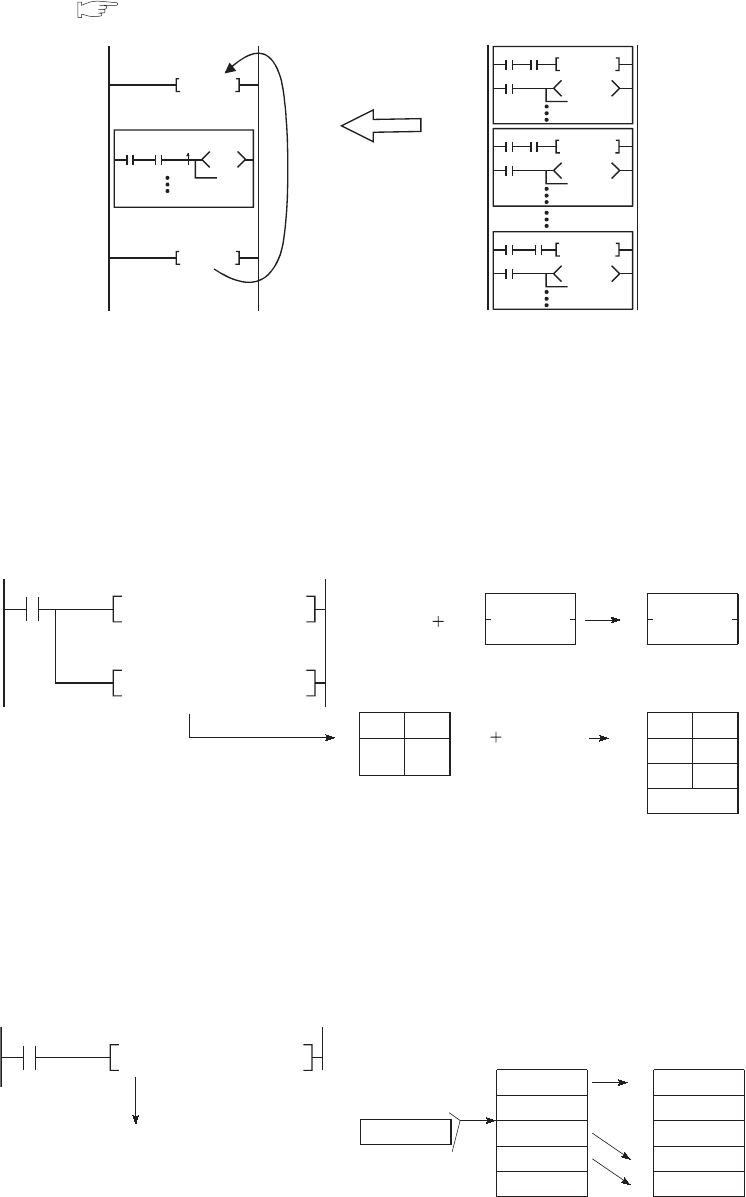

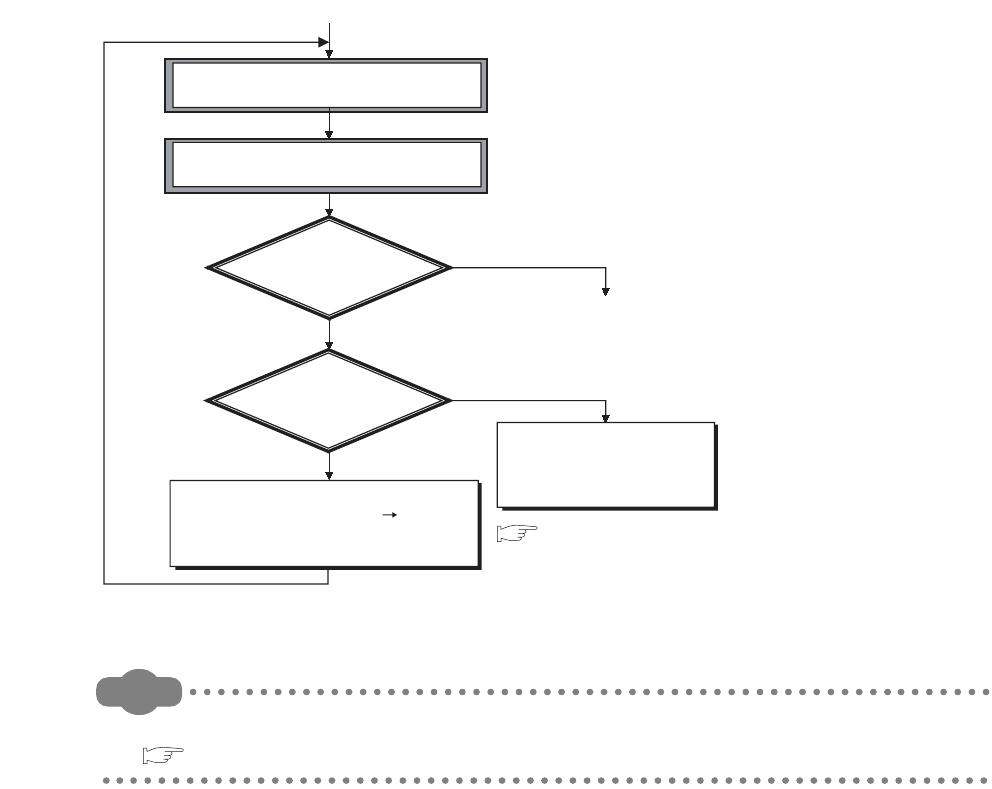

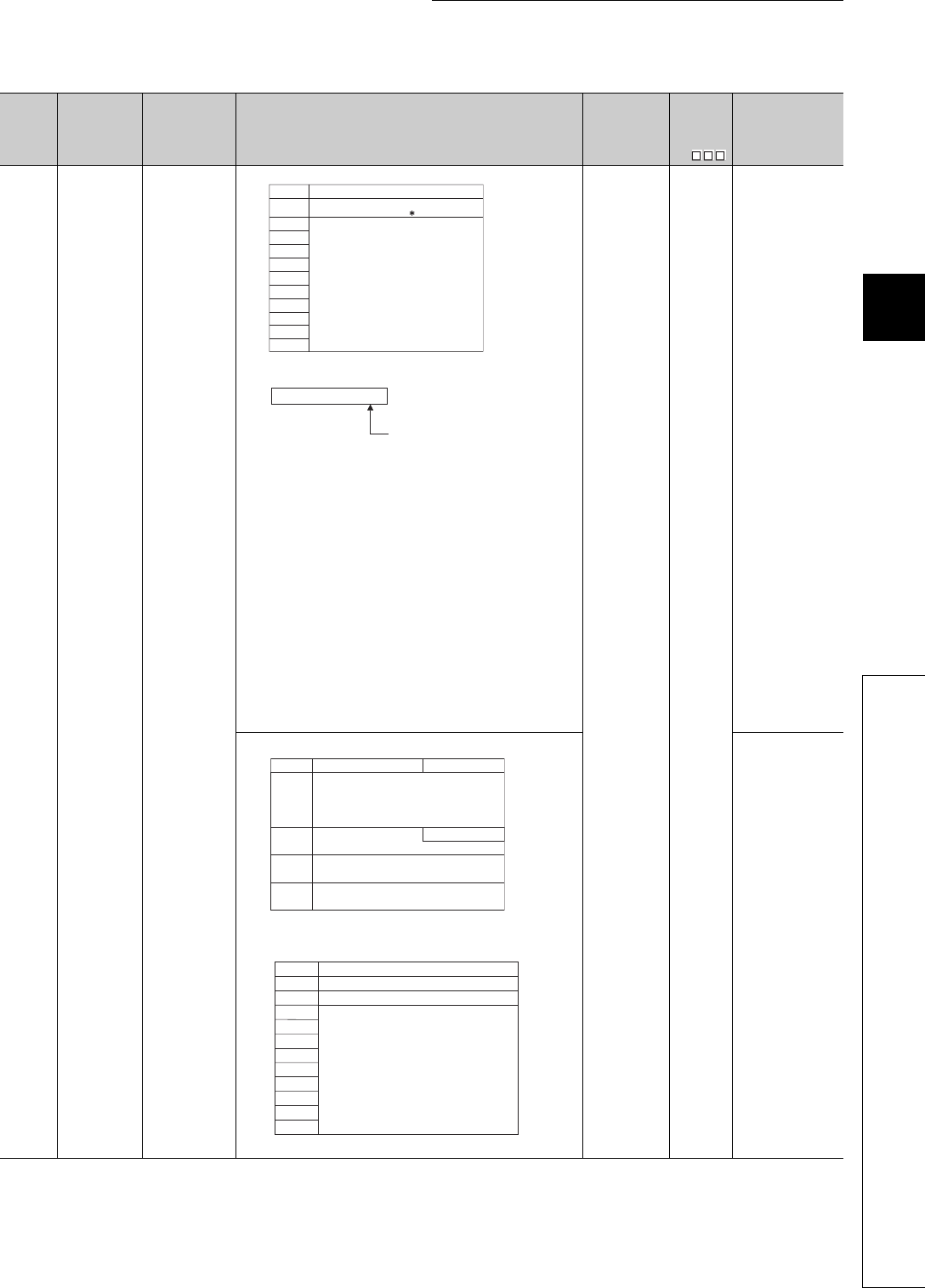

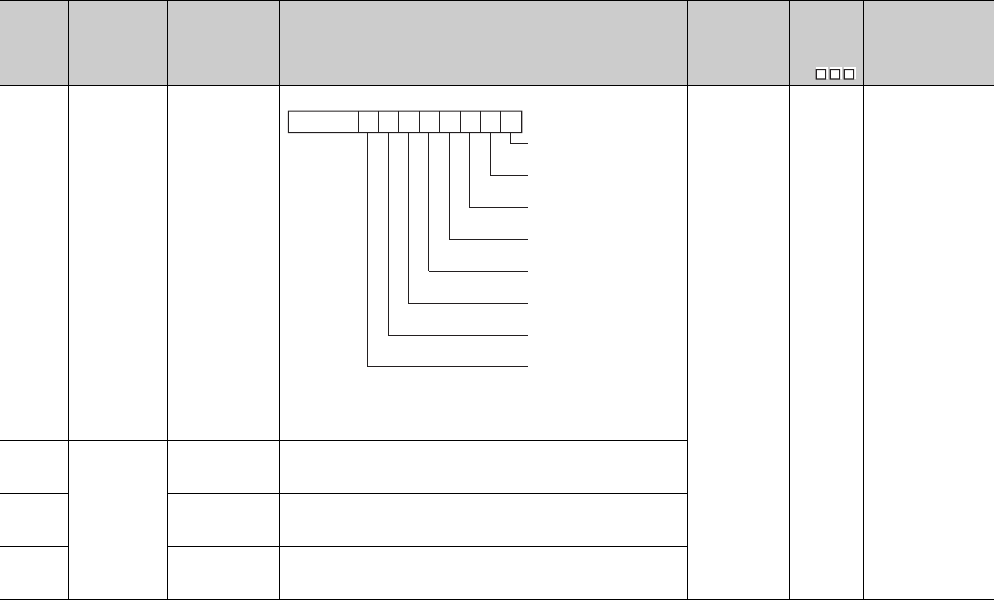

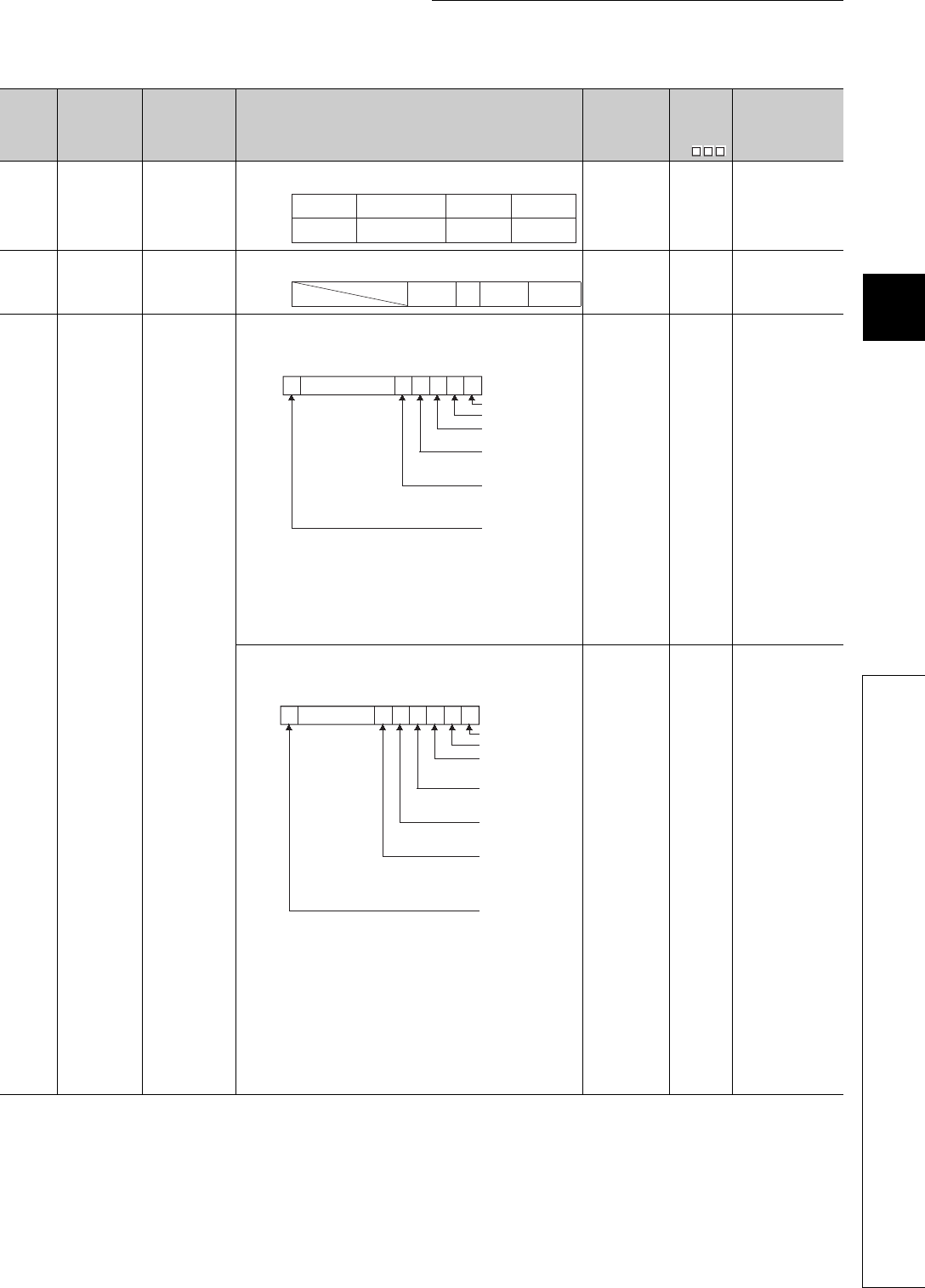

1.3 Structured Programming

The programs to be executed in the CPU module can be structured in the following two ways.

• In one program

• By dividing into multiple files

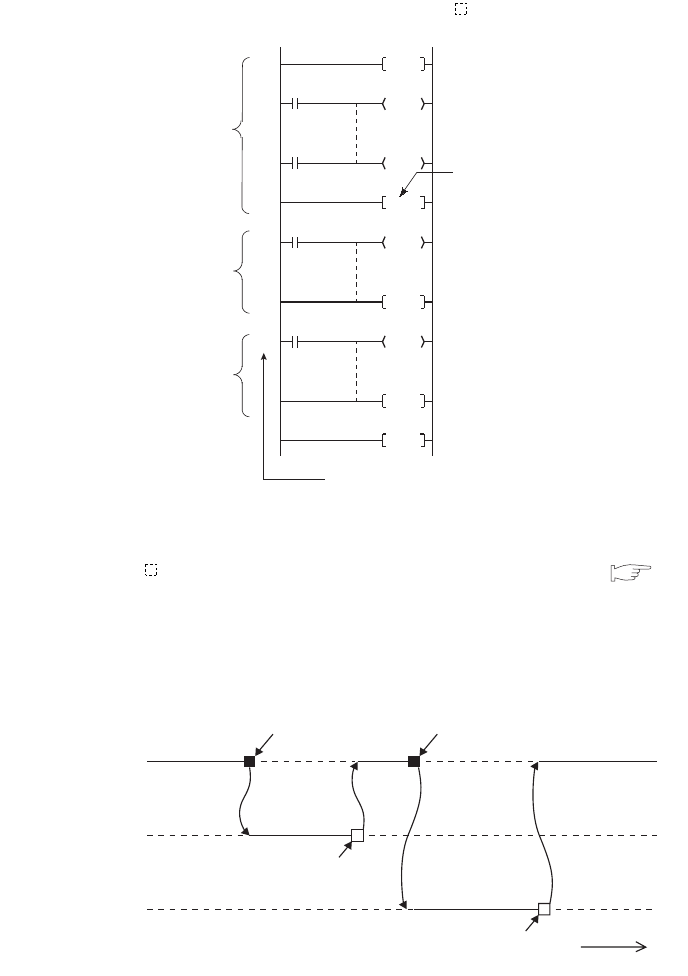

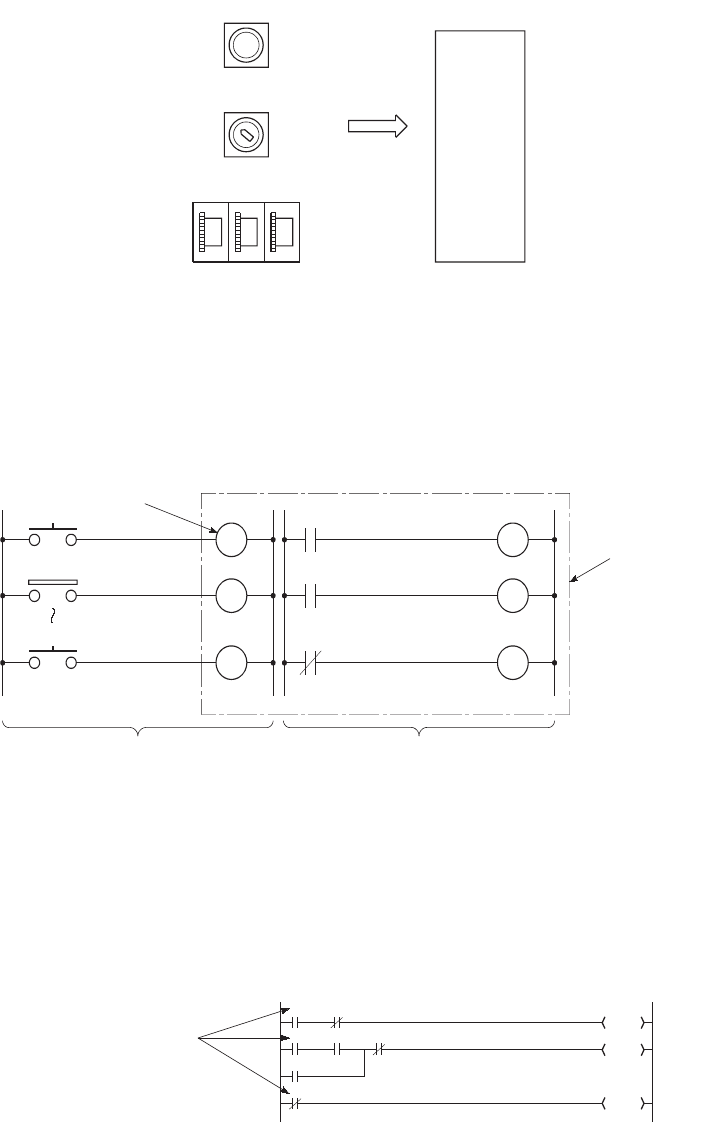

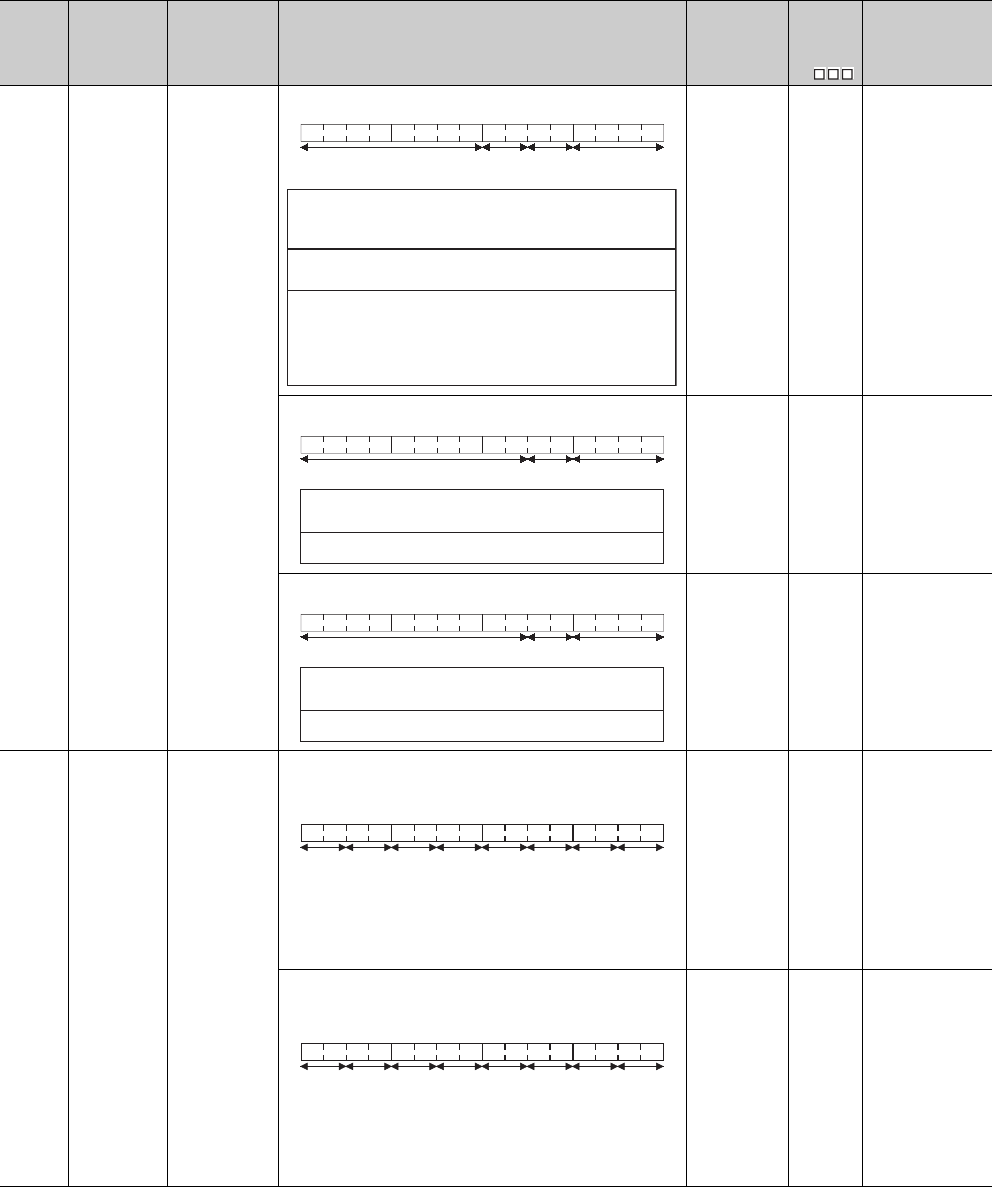

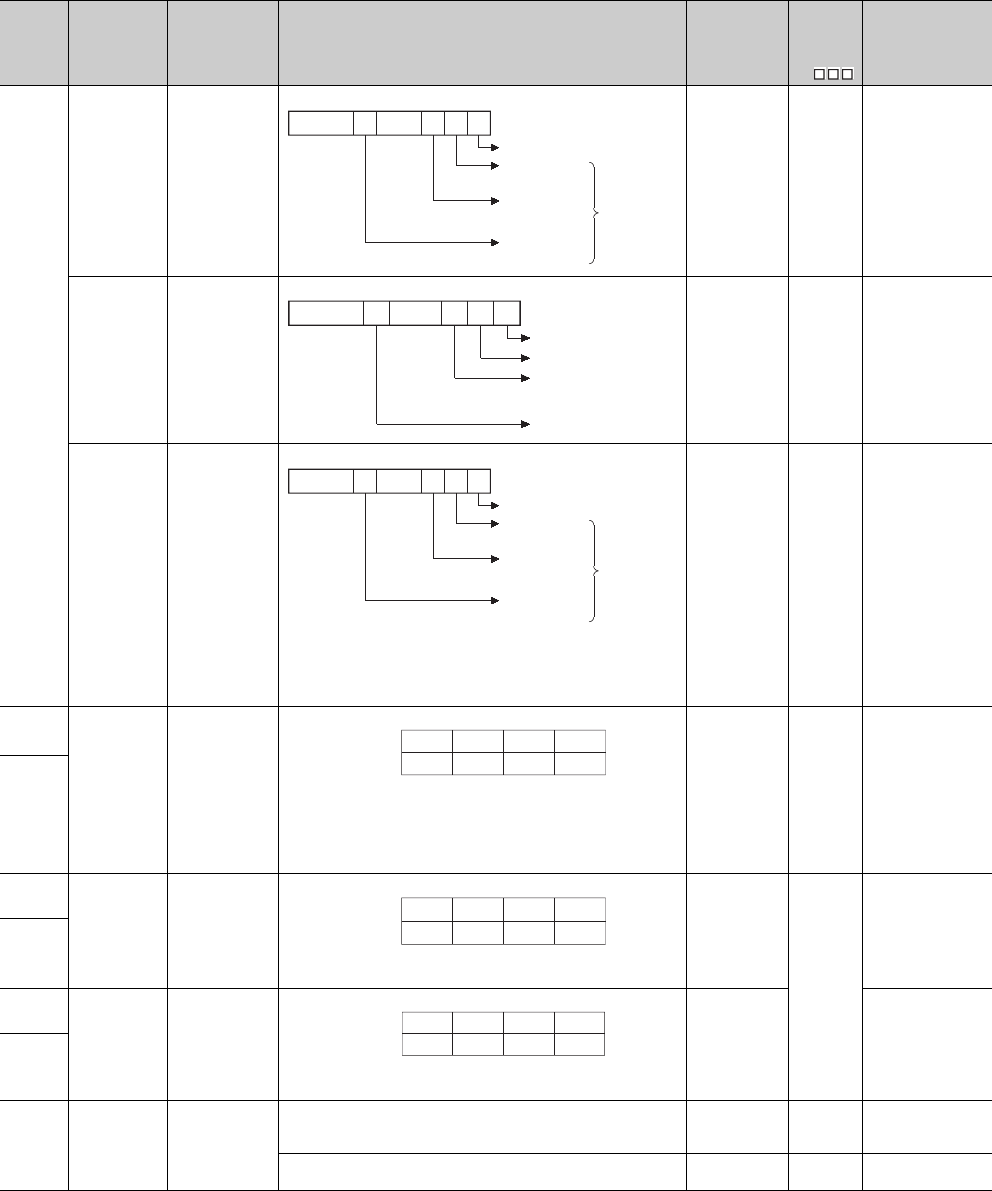

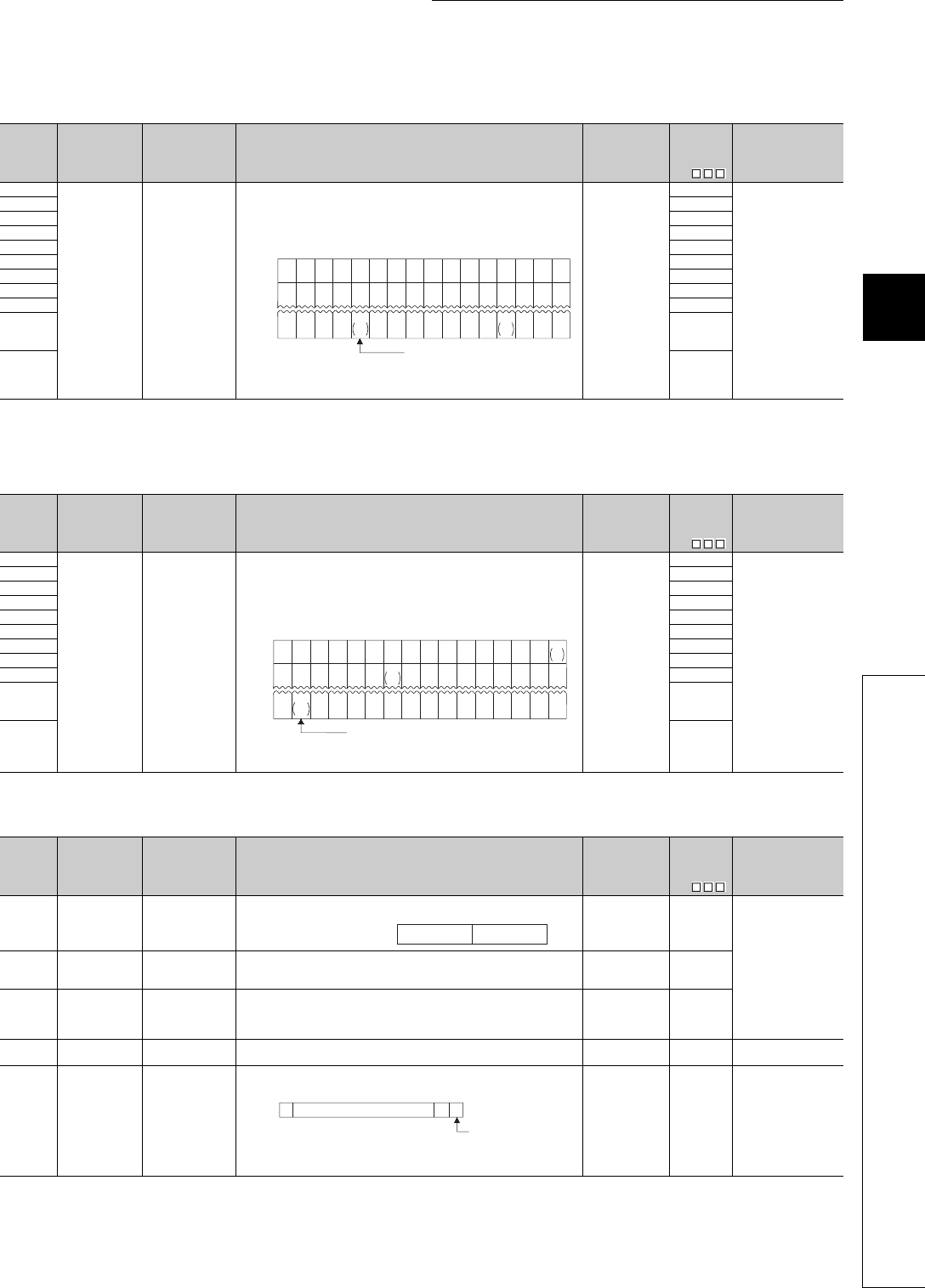

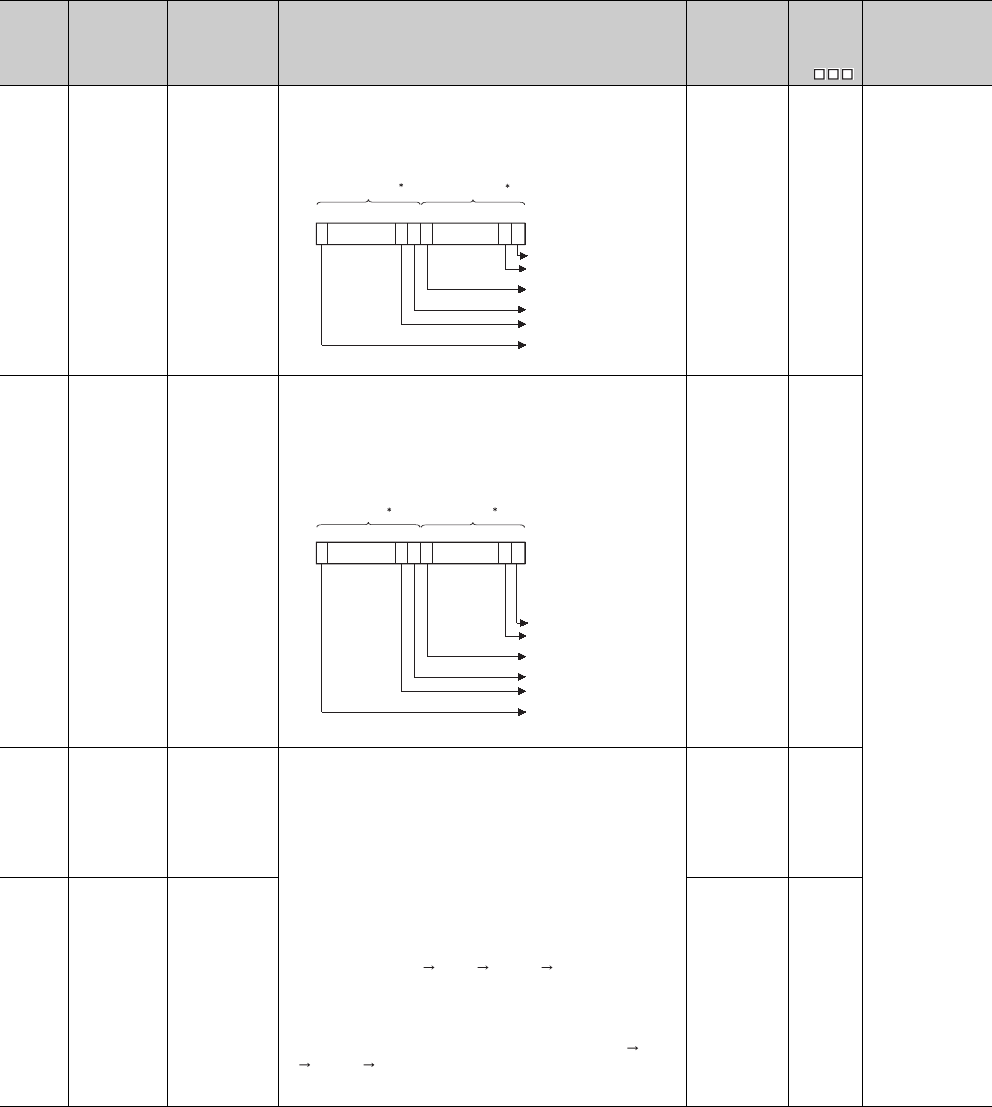

(1) Structuring in one program

Structured programming is available by creating one program as a collection of three program sections: main

routine program ( Section 2.2.1), subroutine program ( Section 2.2.2), and interrupt program

( Section 2.2.3).

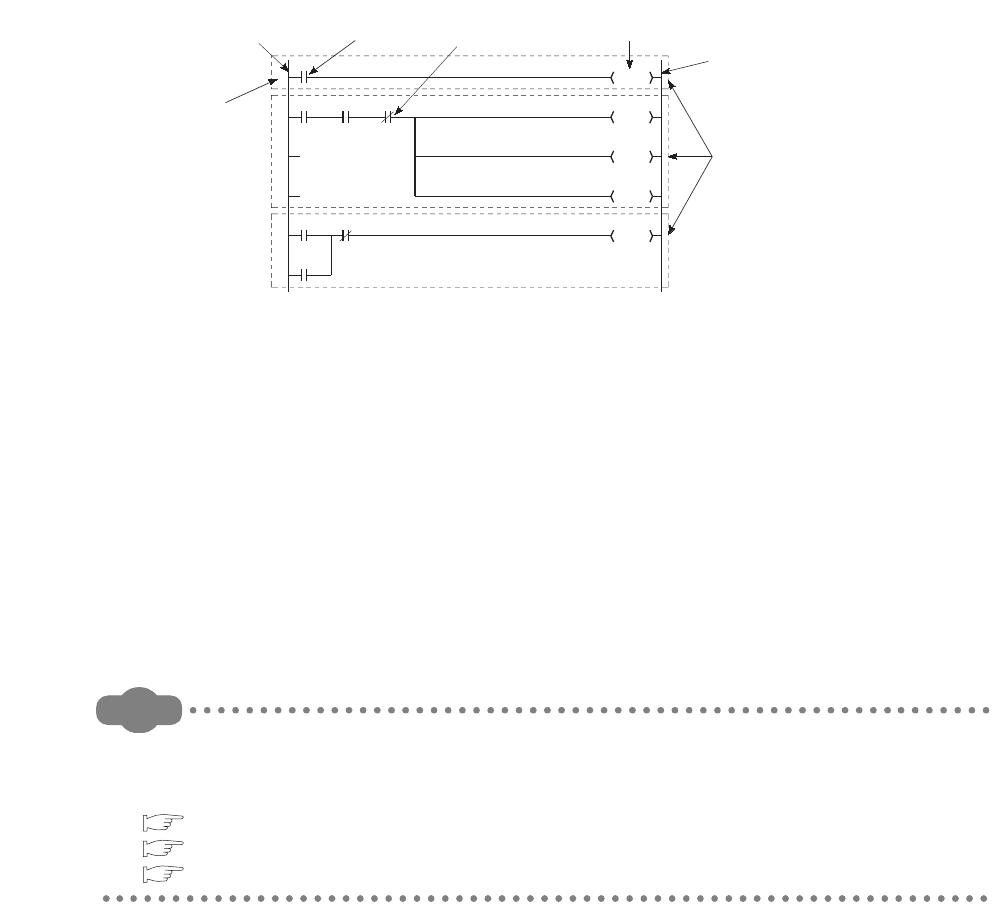

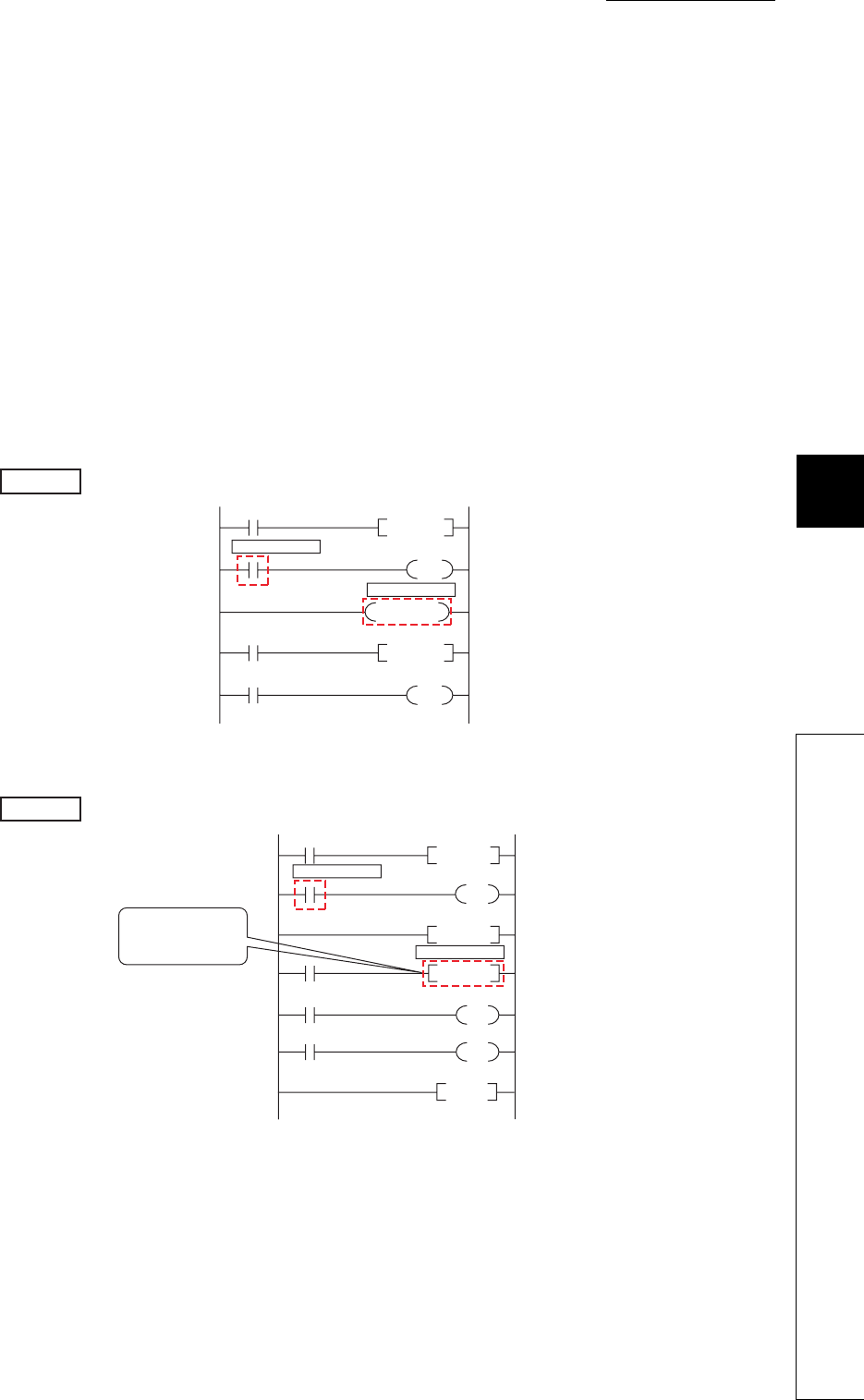

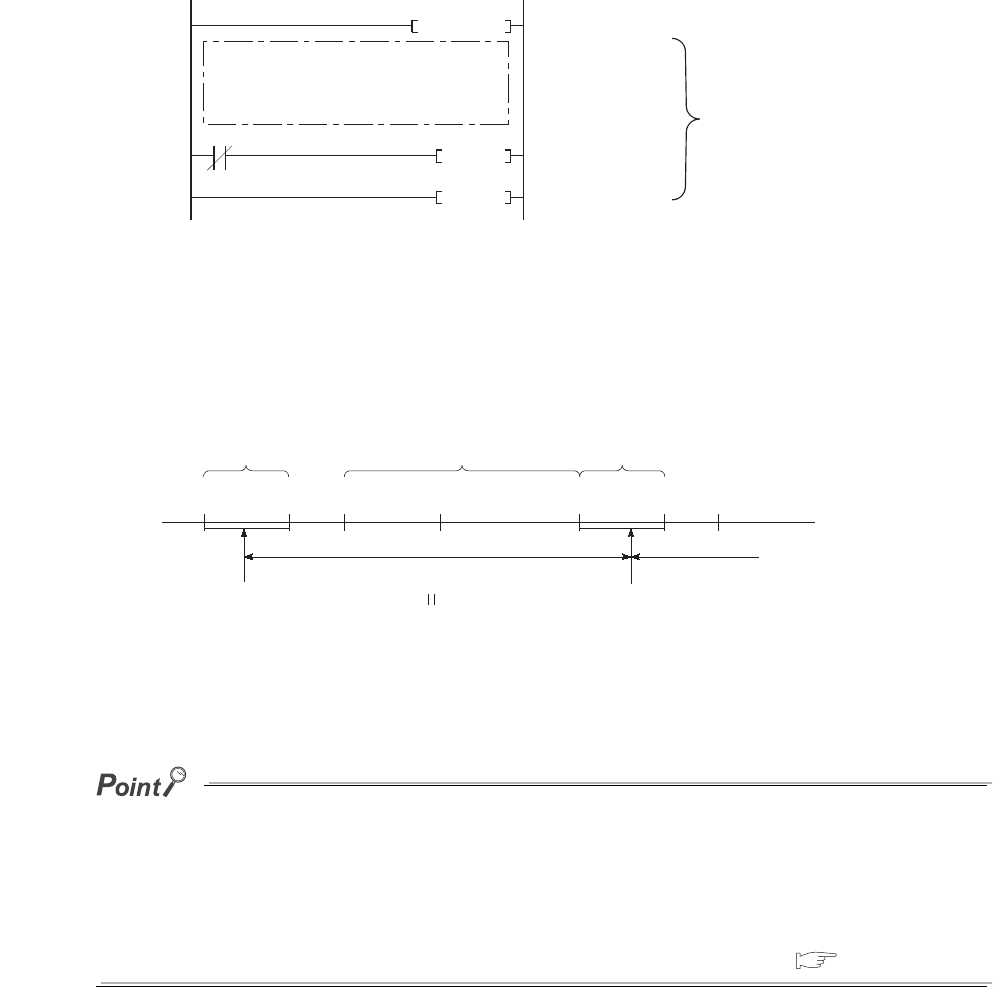

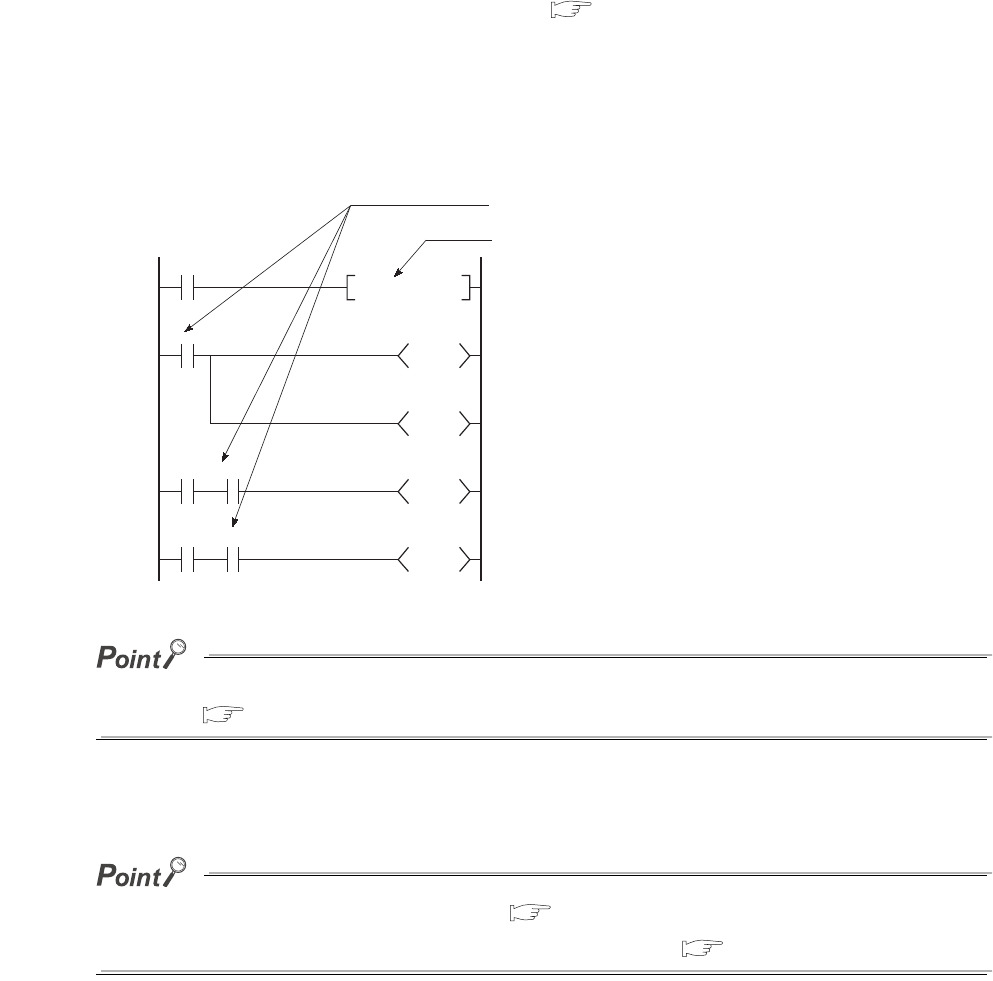

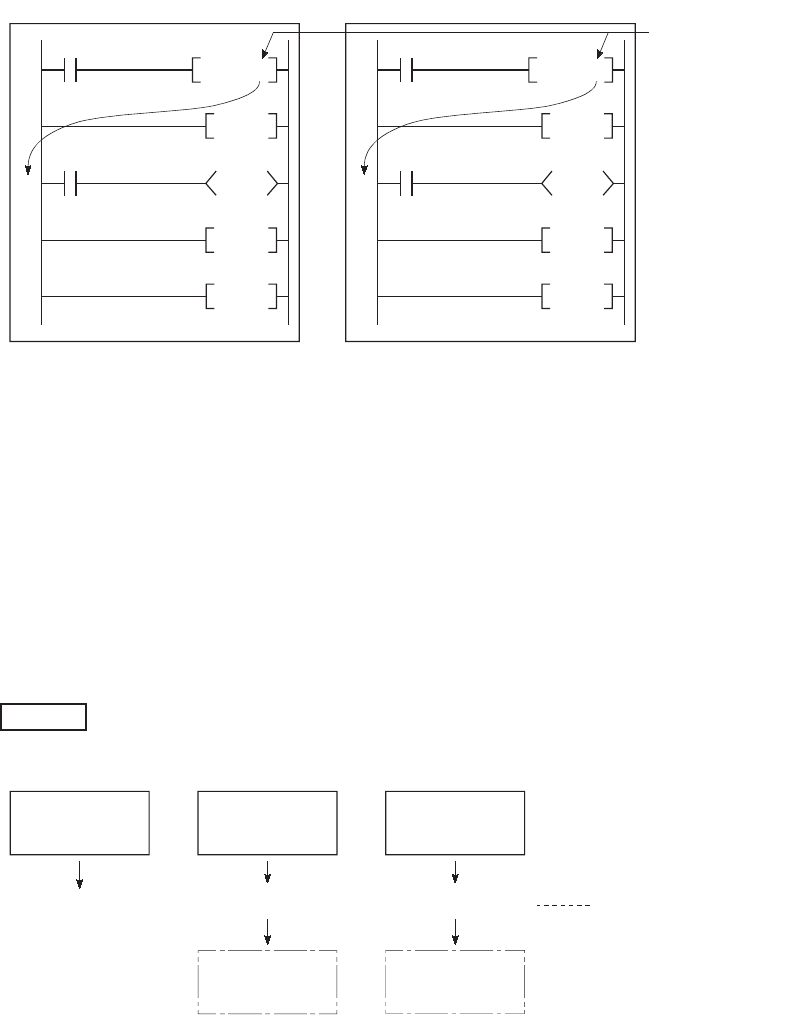

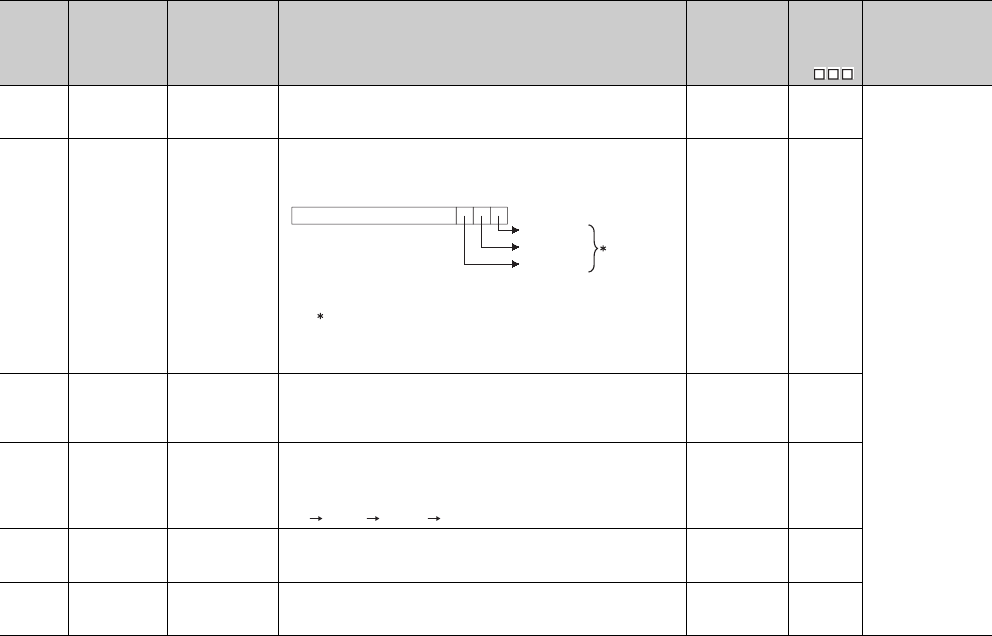

Figure 1.4 Structuring in one program

P8

RET

RET

Y10

Y11

Y12

P1

END

FEND

CALL P1

IRET

I0

Main routine

program

Subroutine

program 1

Subroutine

program 2

Interrupt program

1 - 4

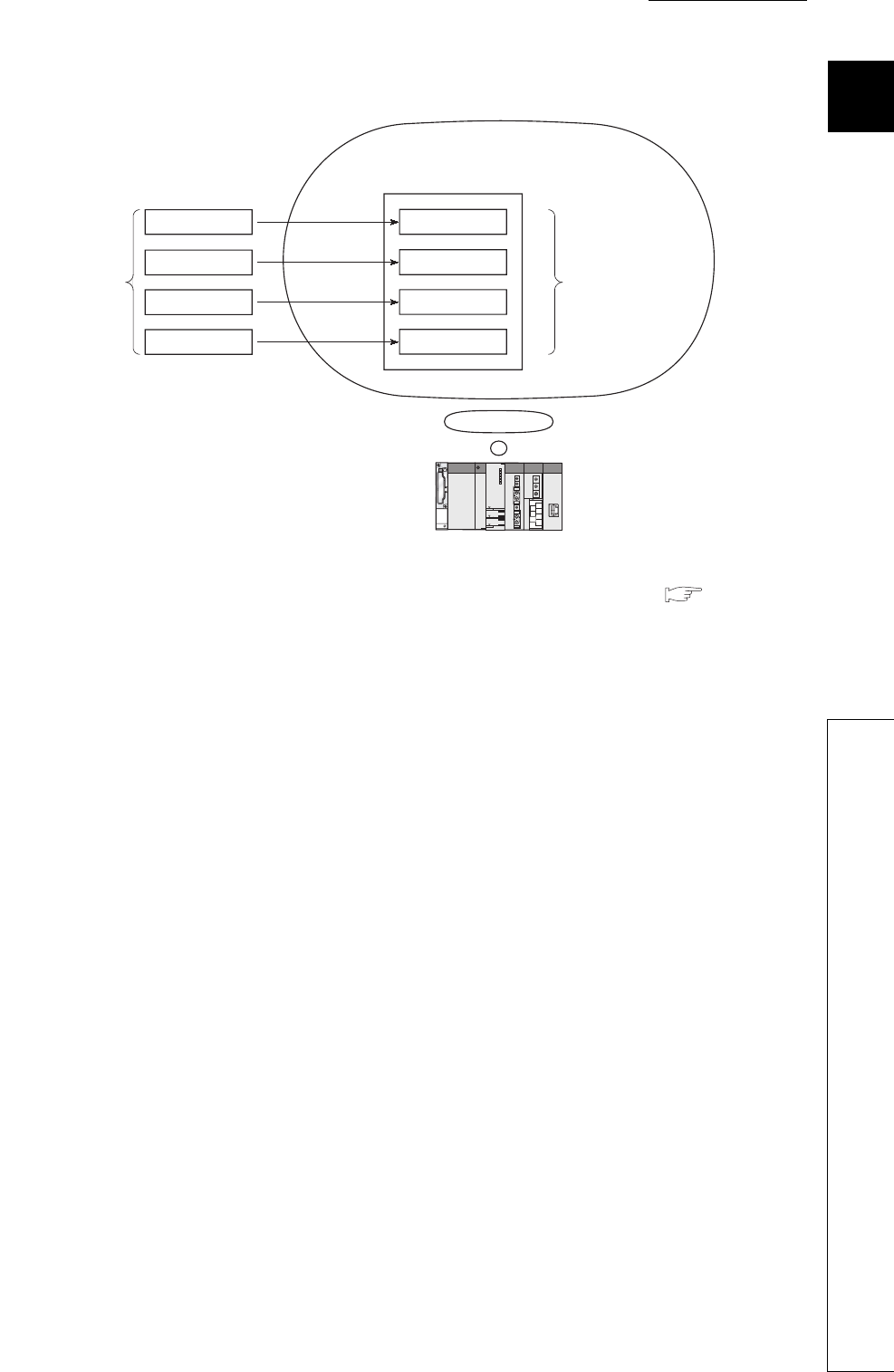

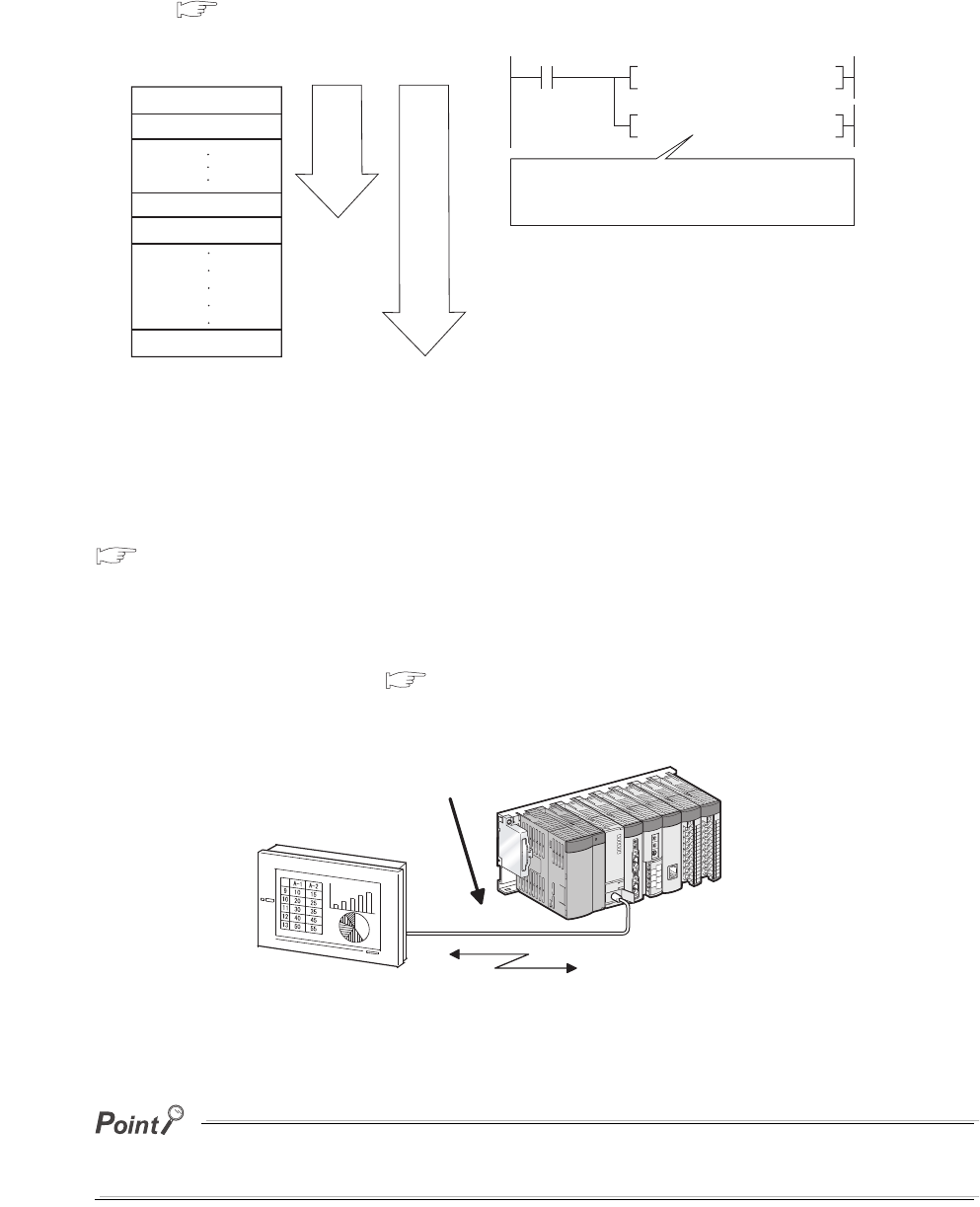

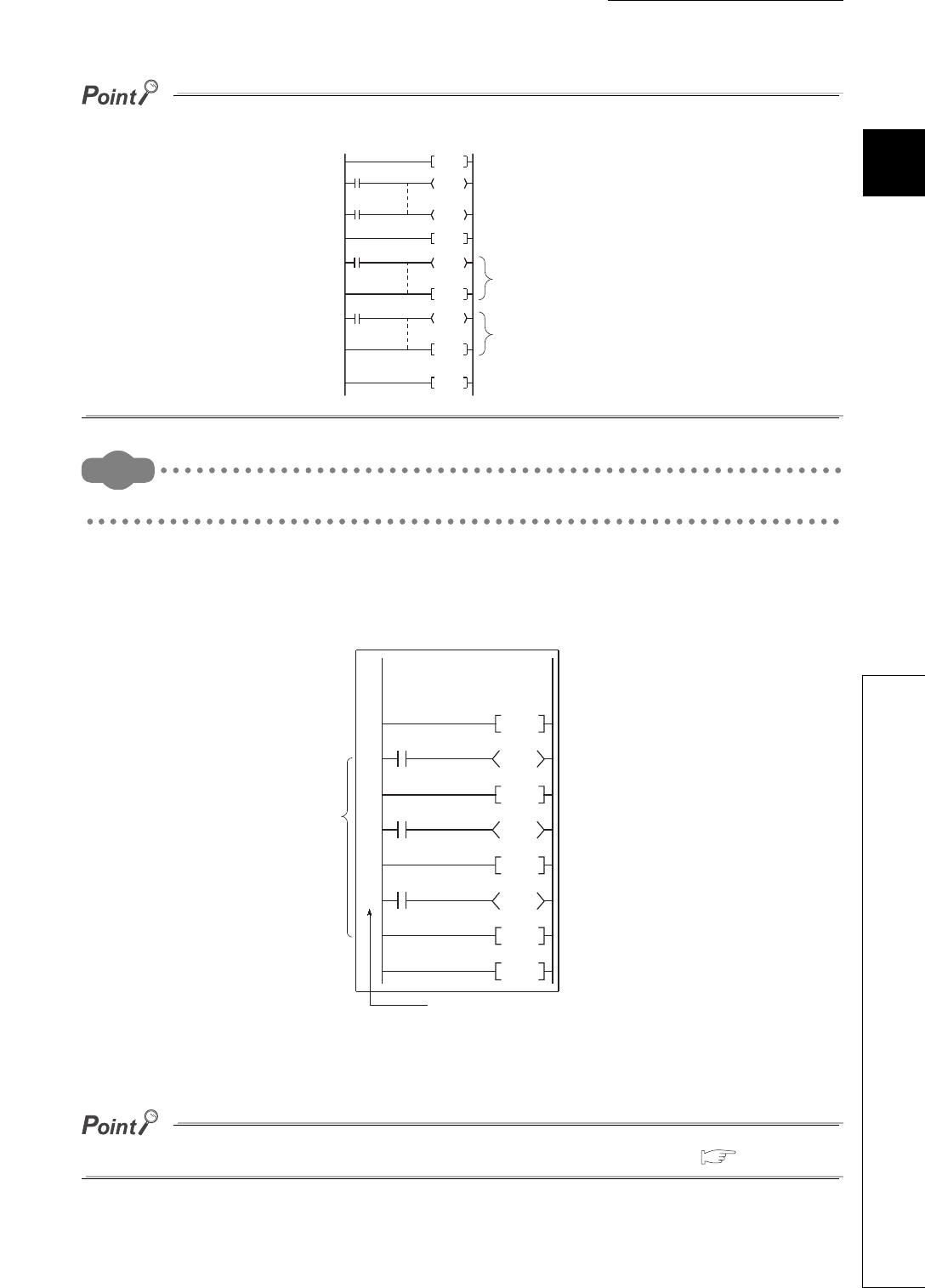

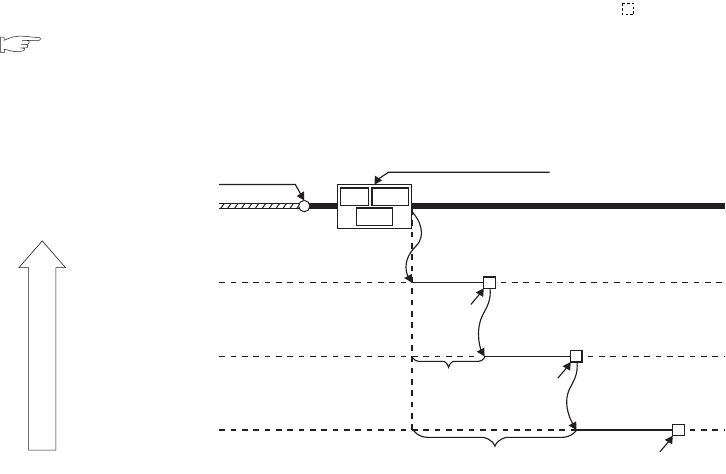

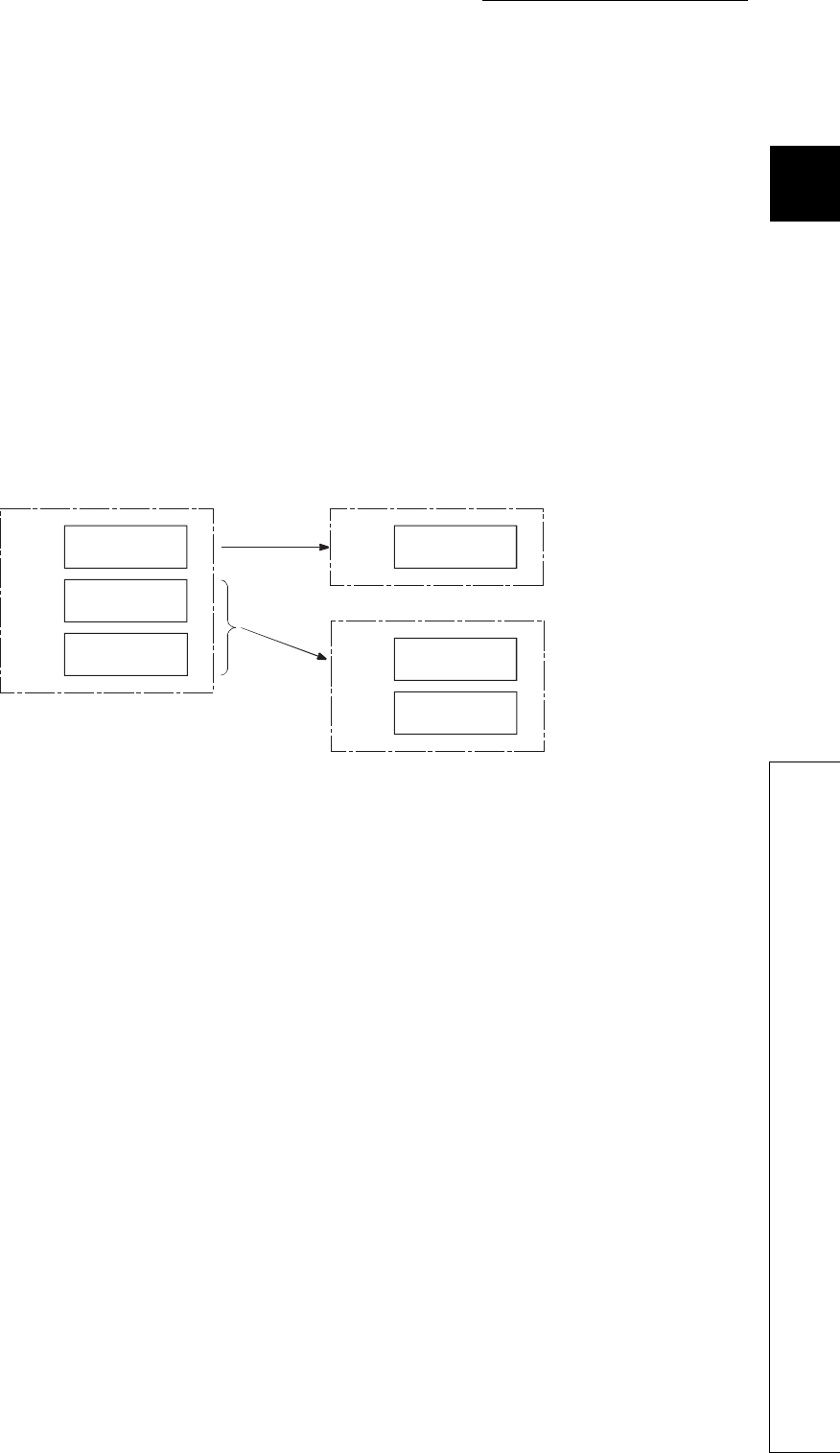

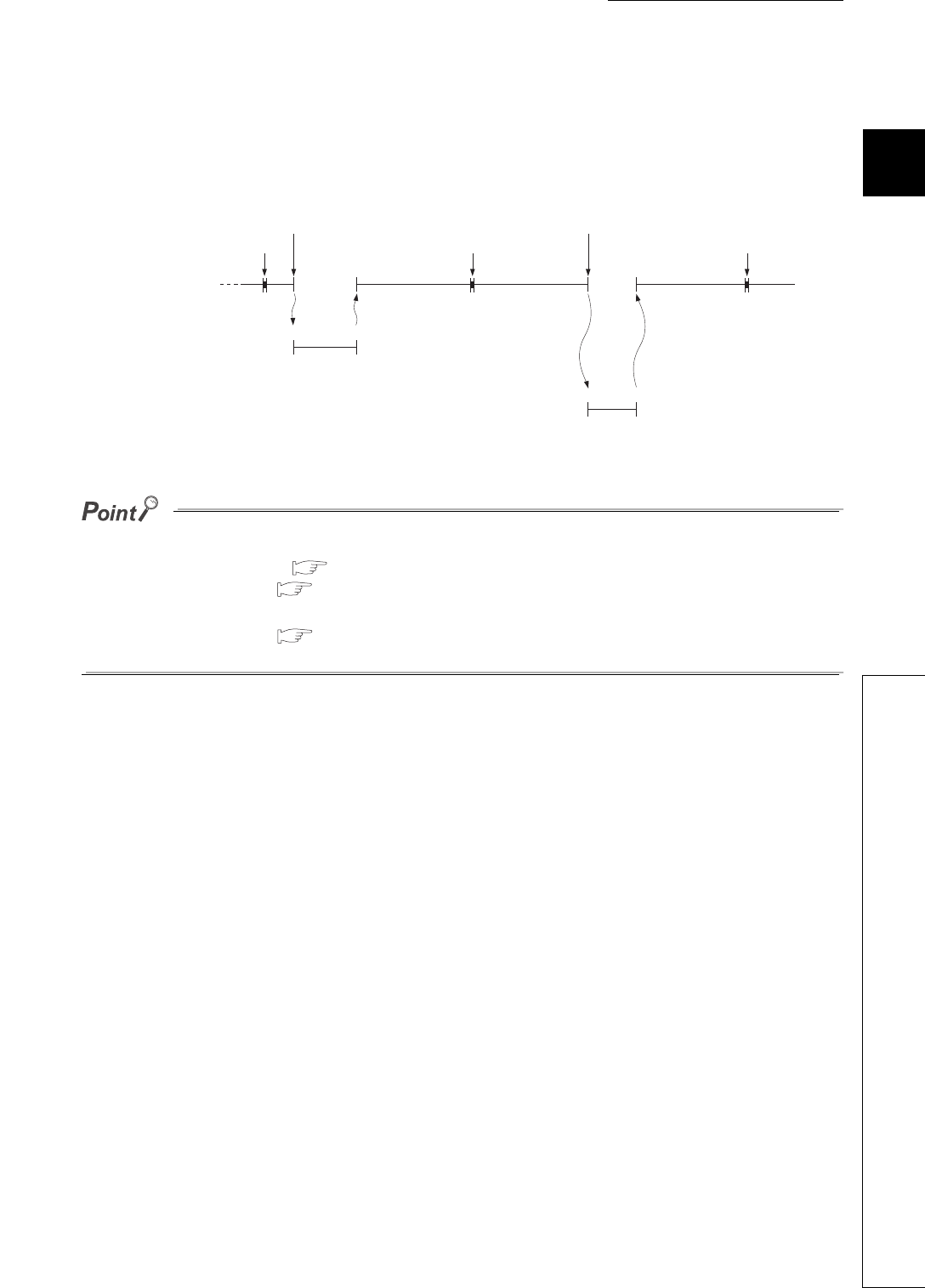

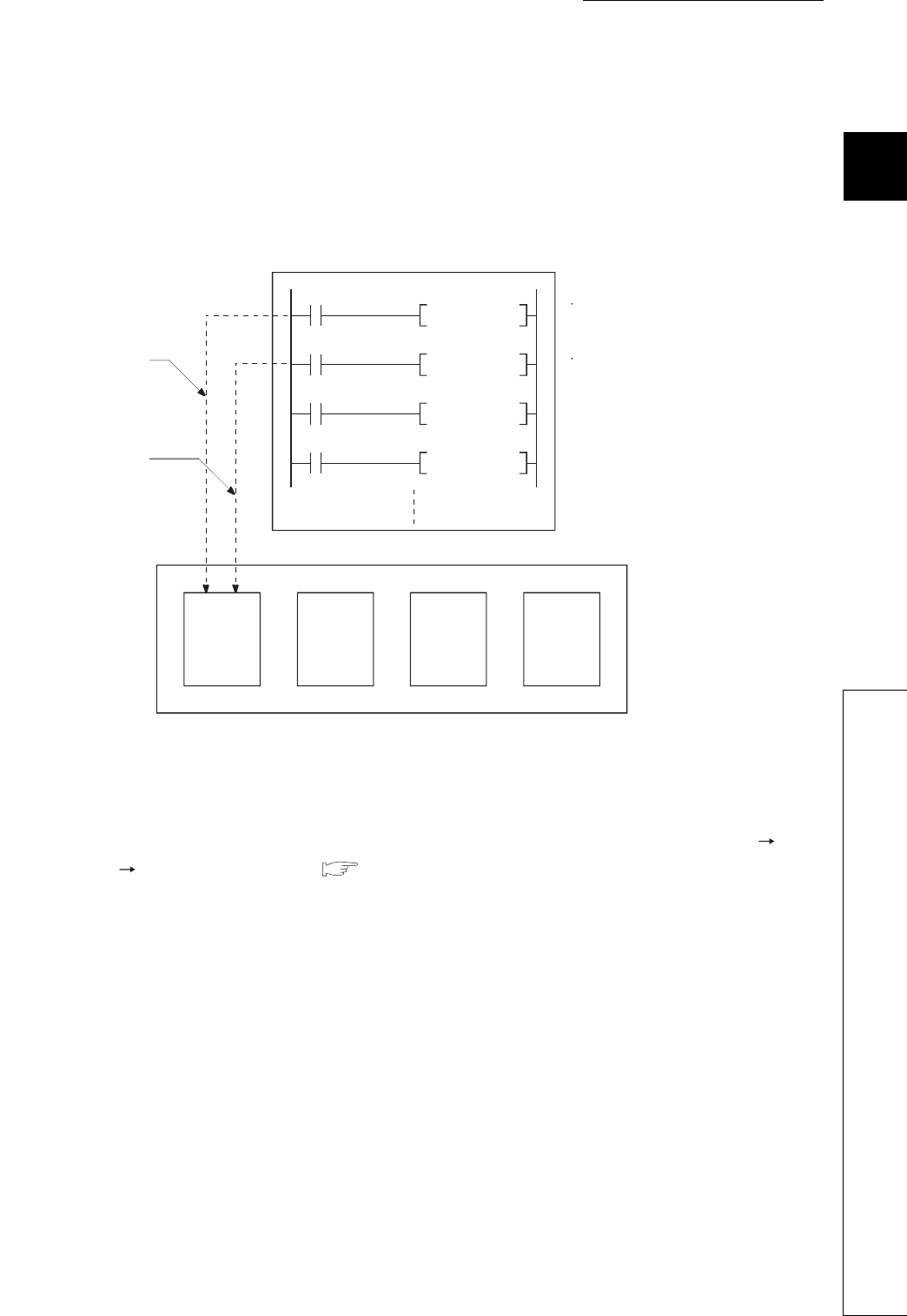

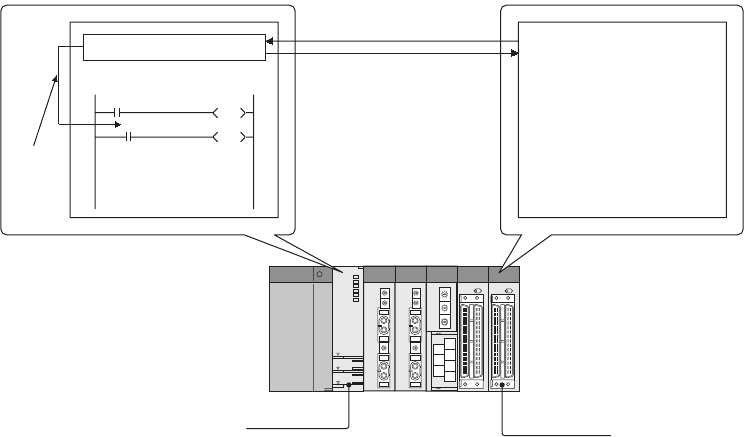

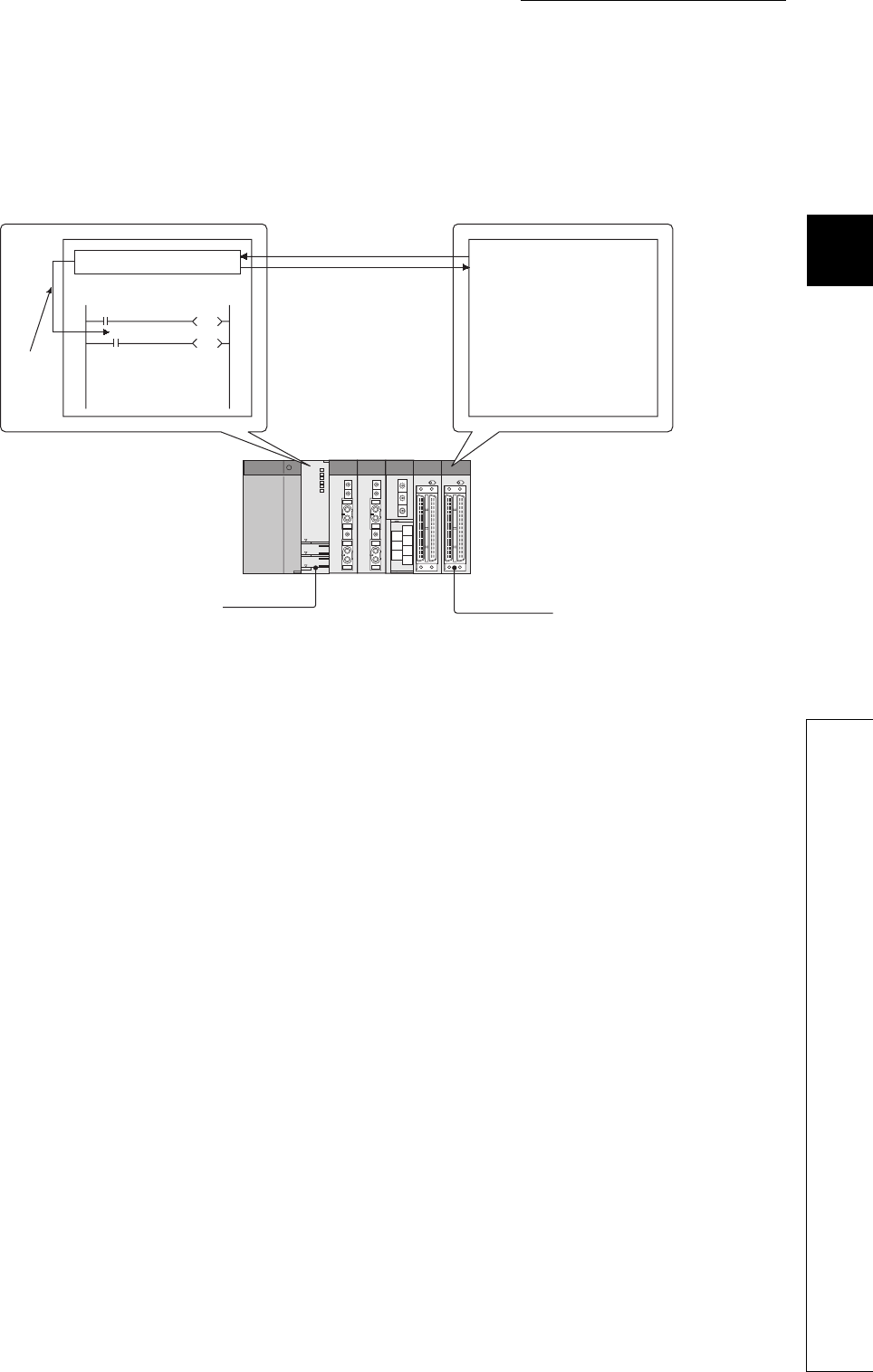

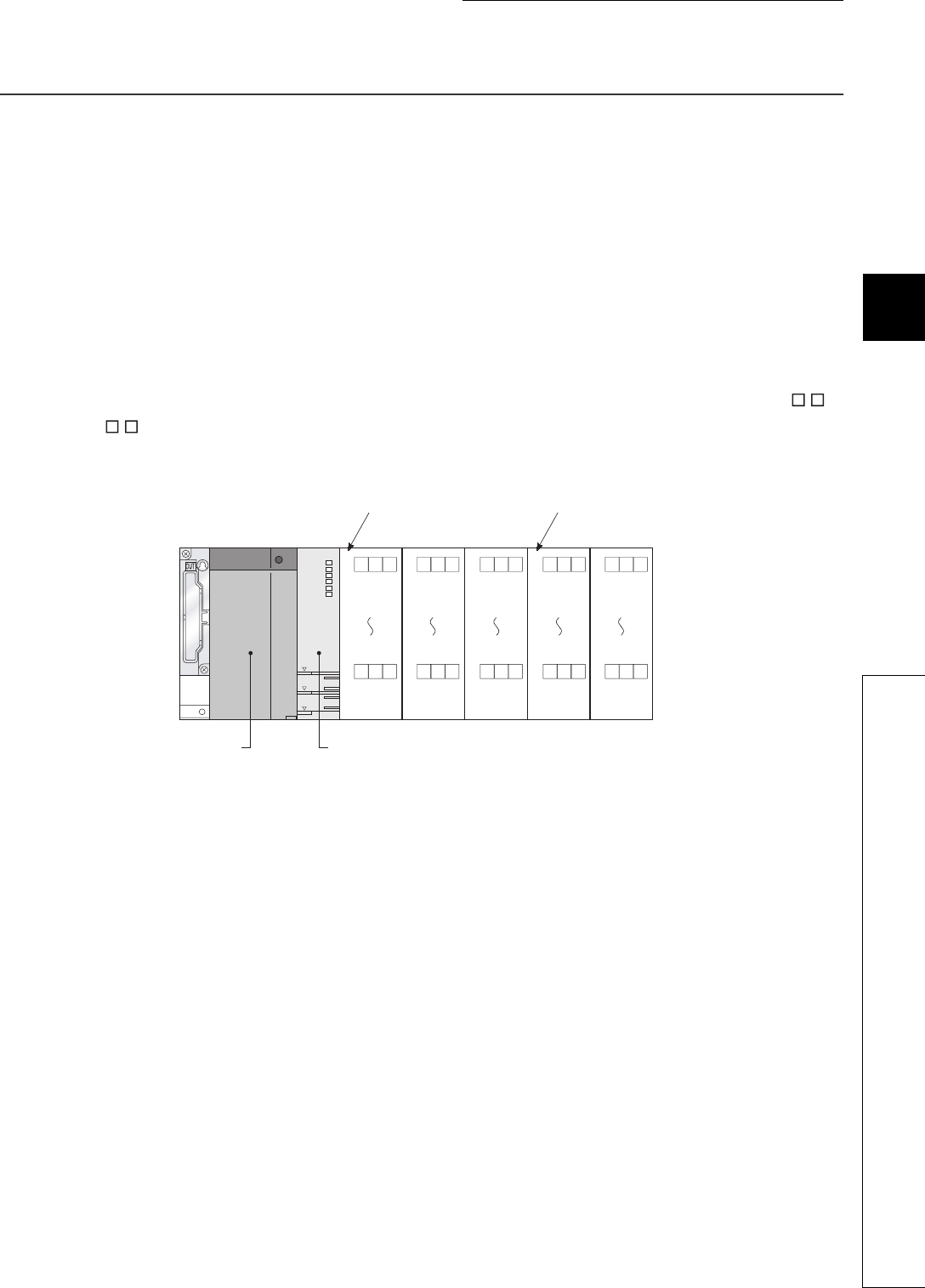

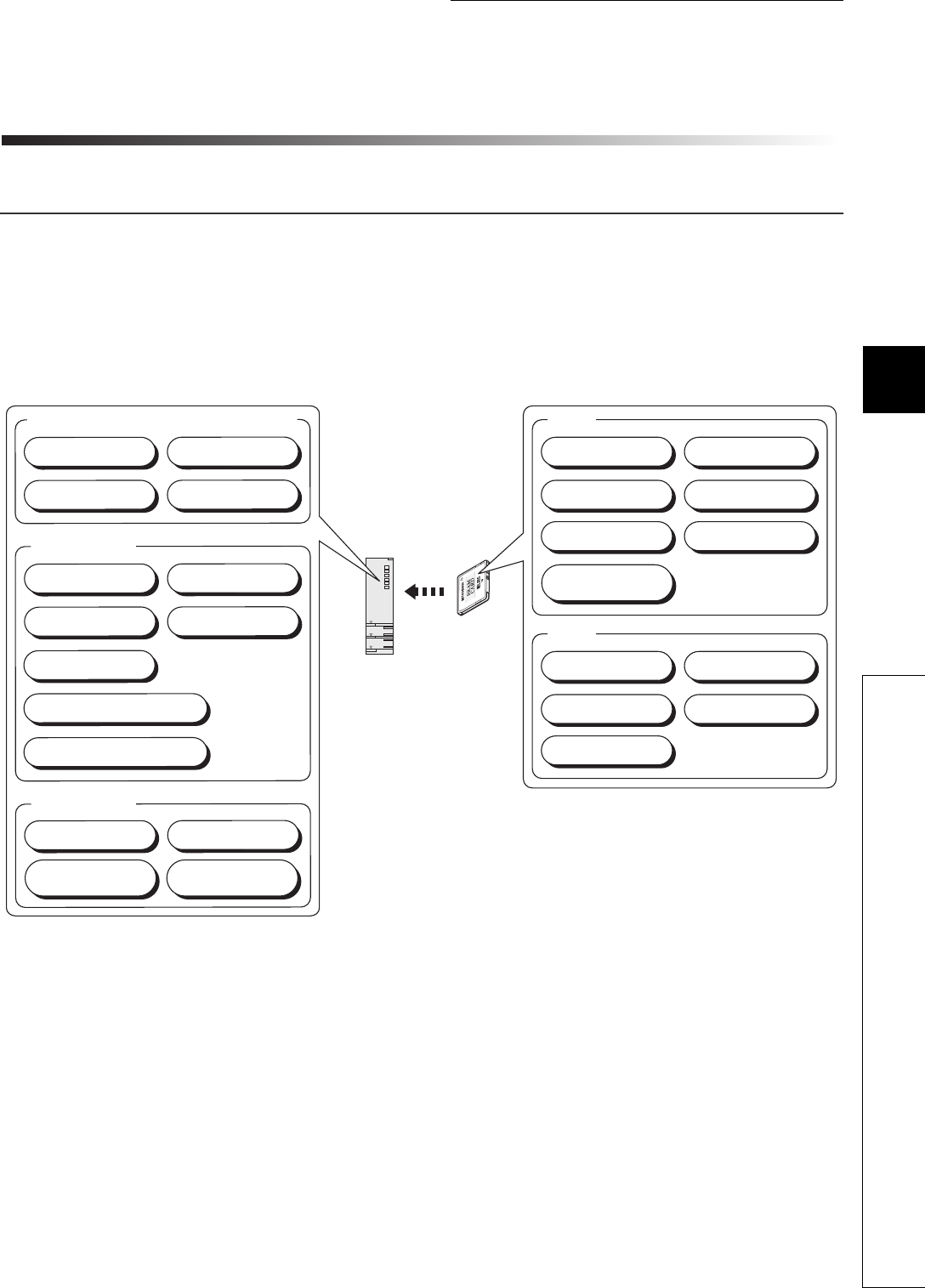

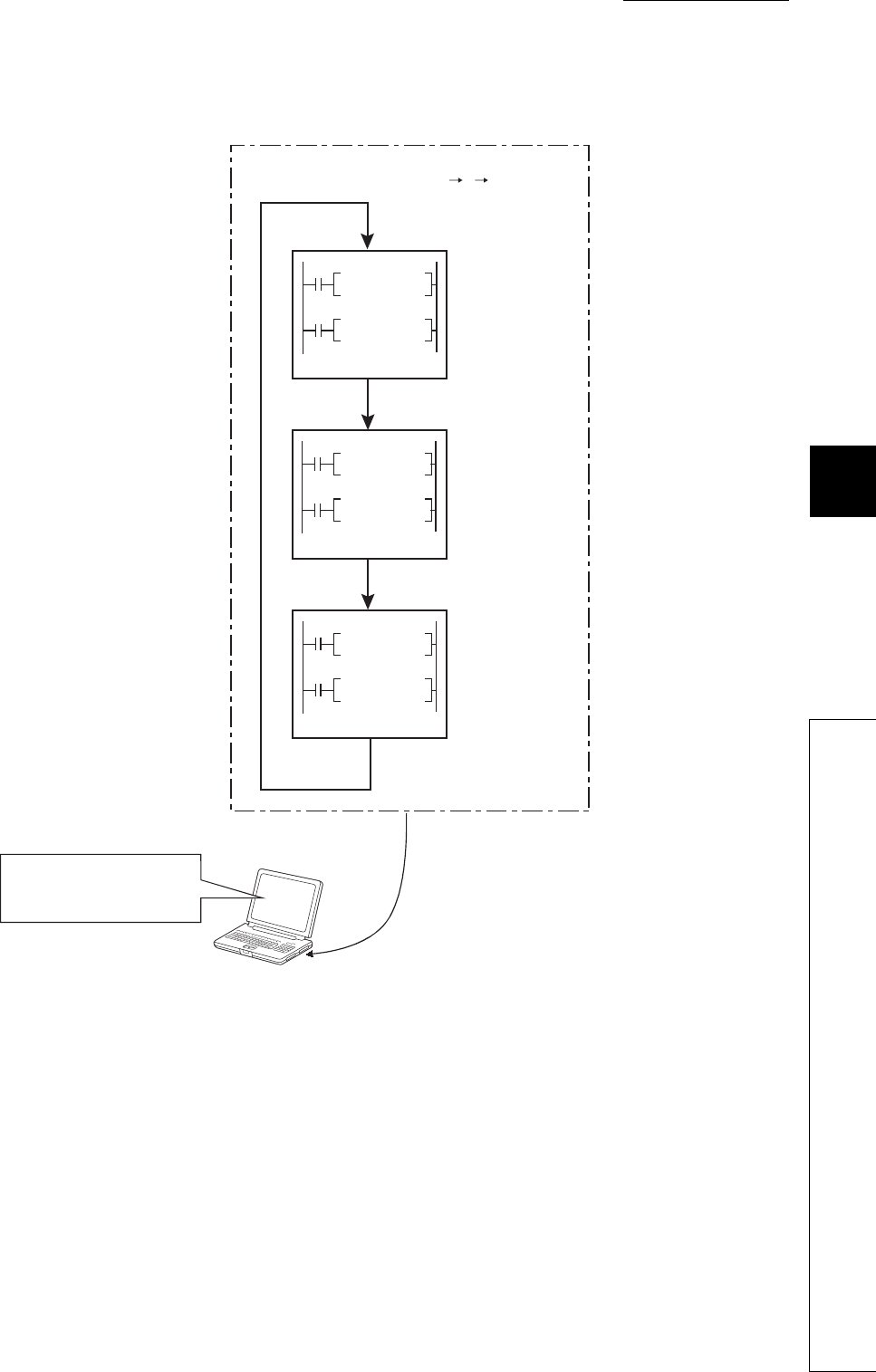

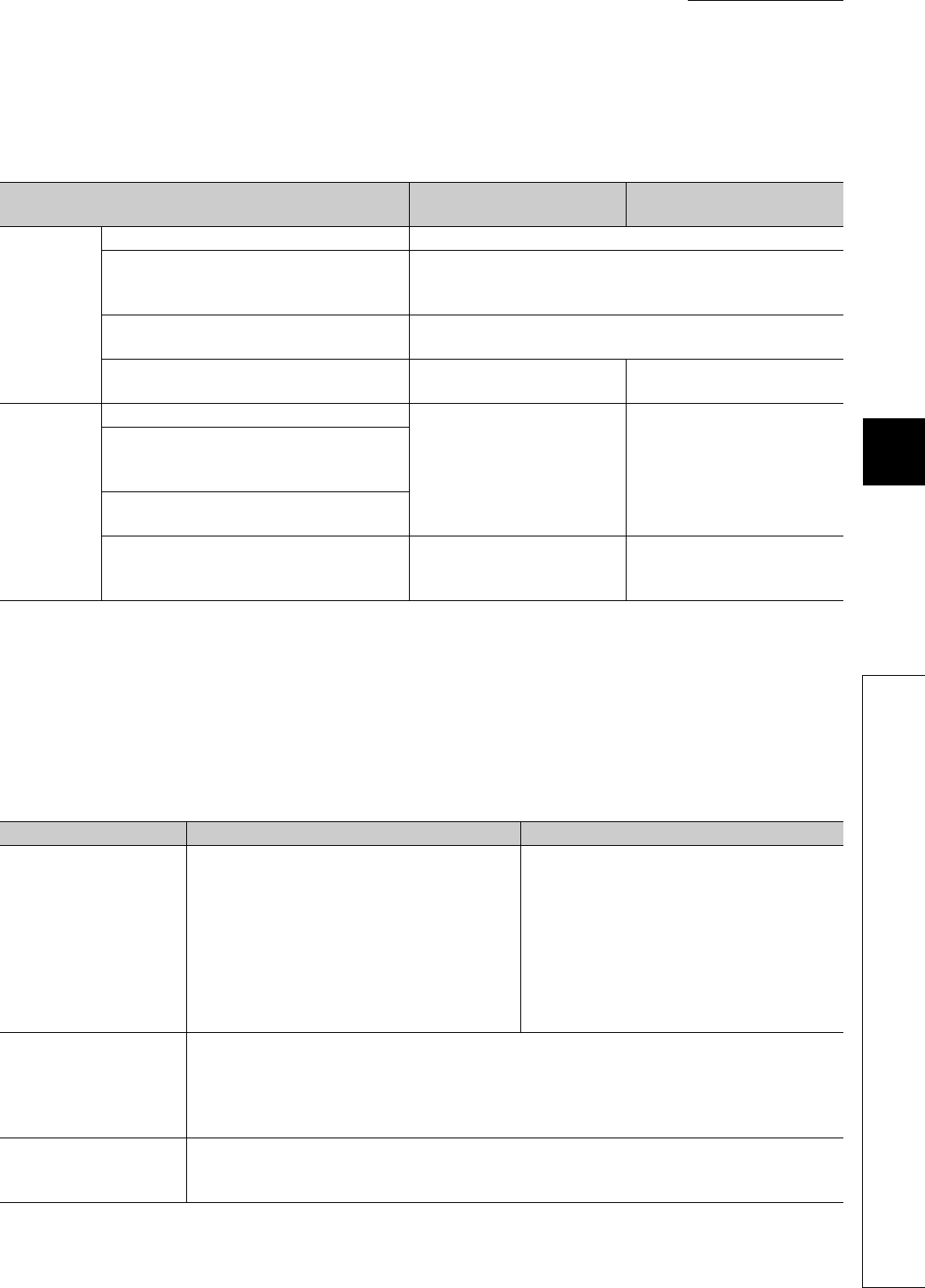

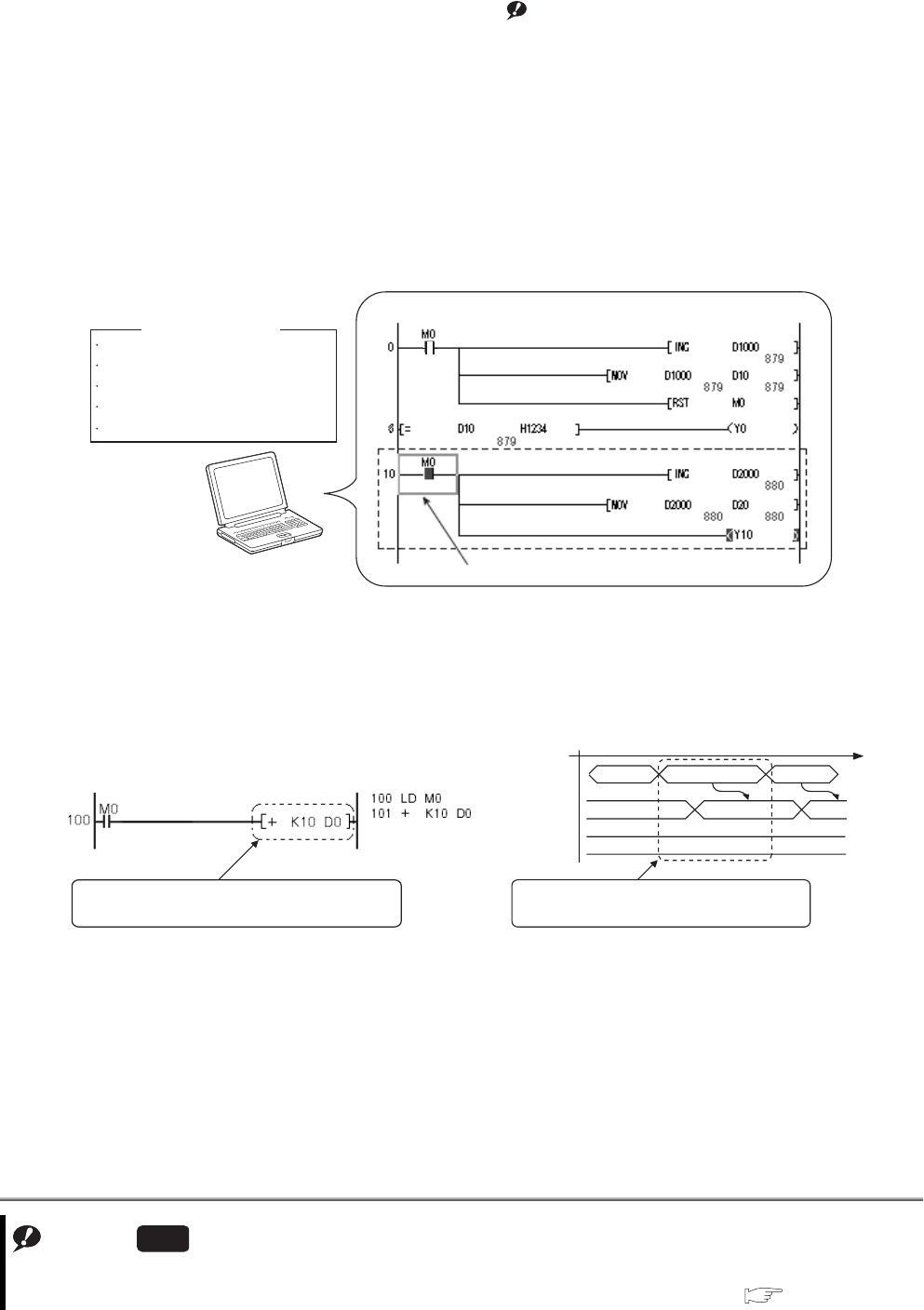

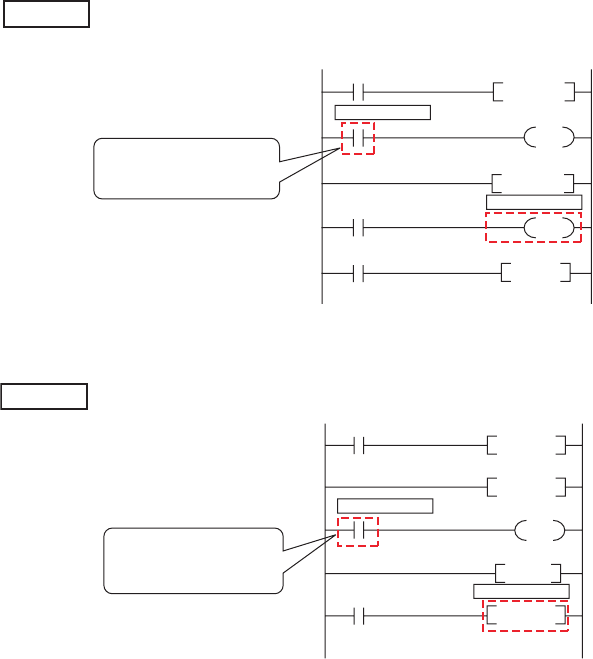

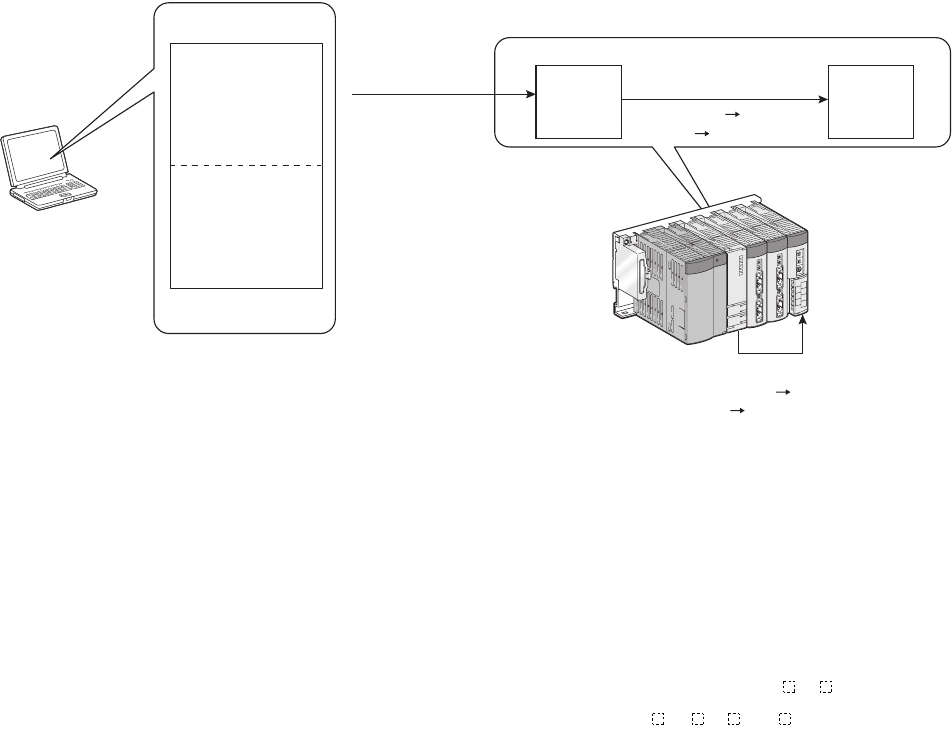

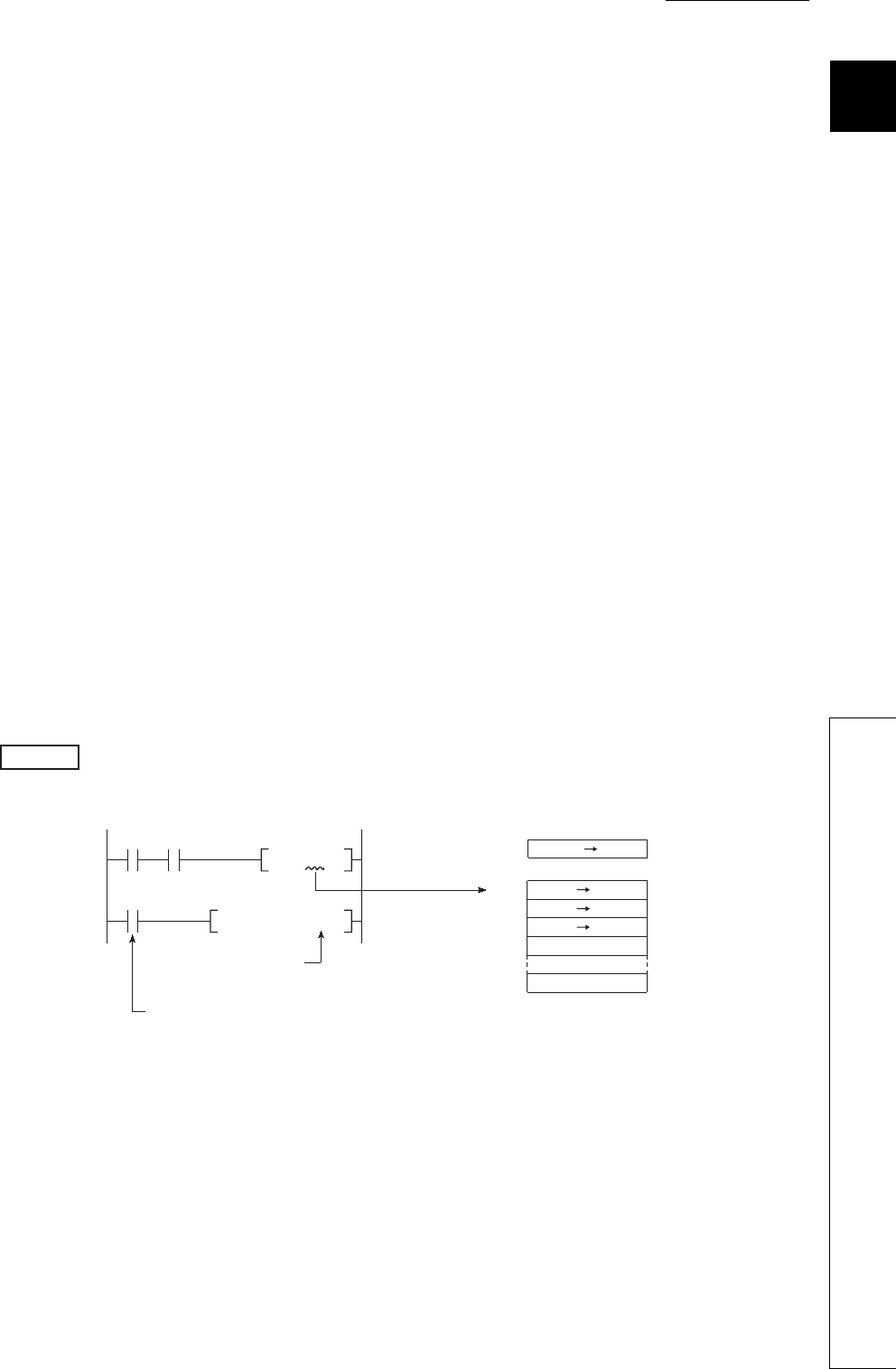

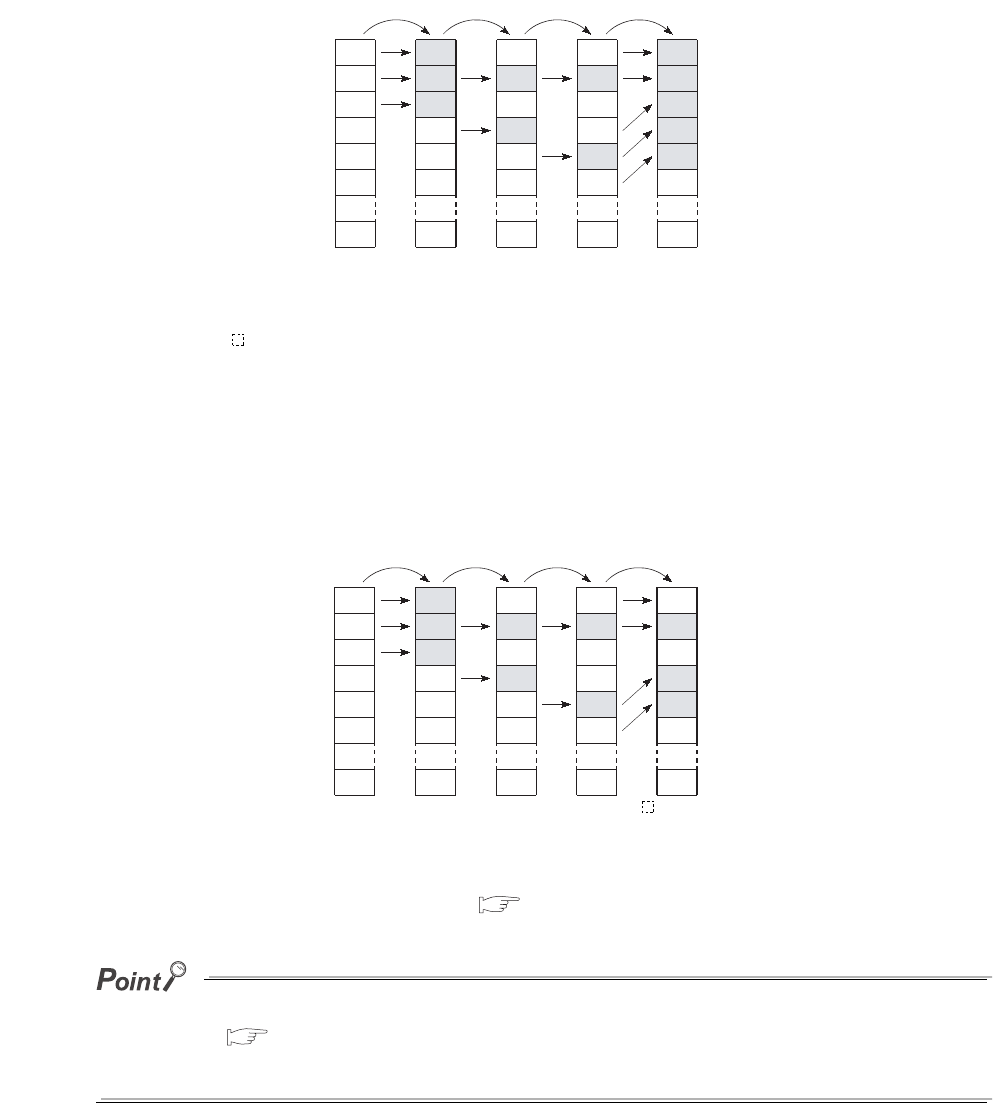

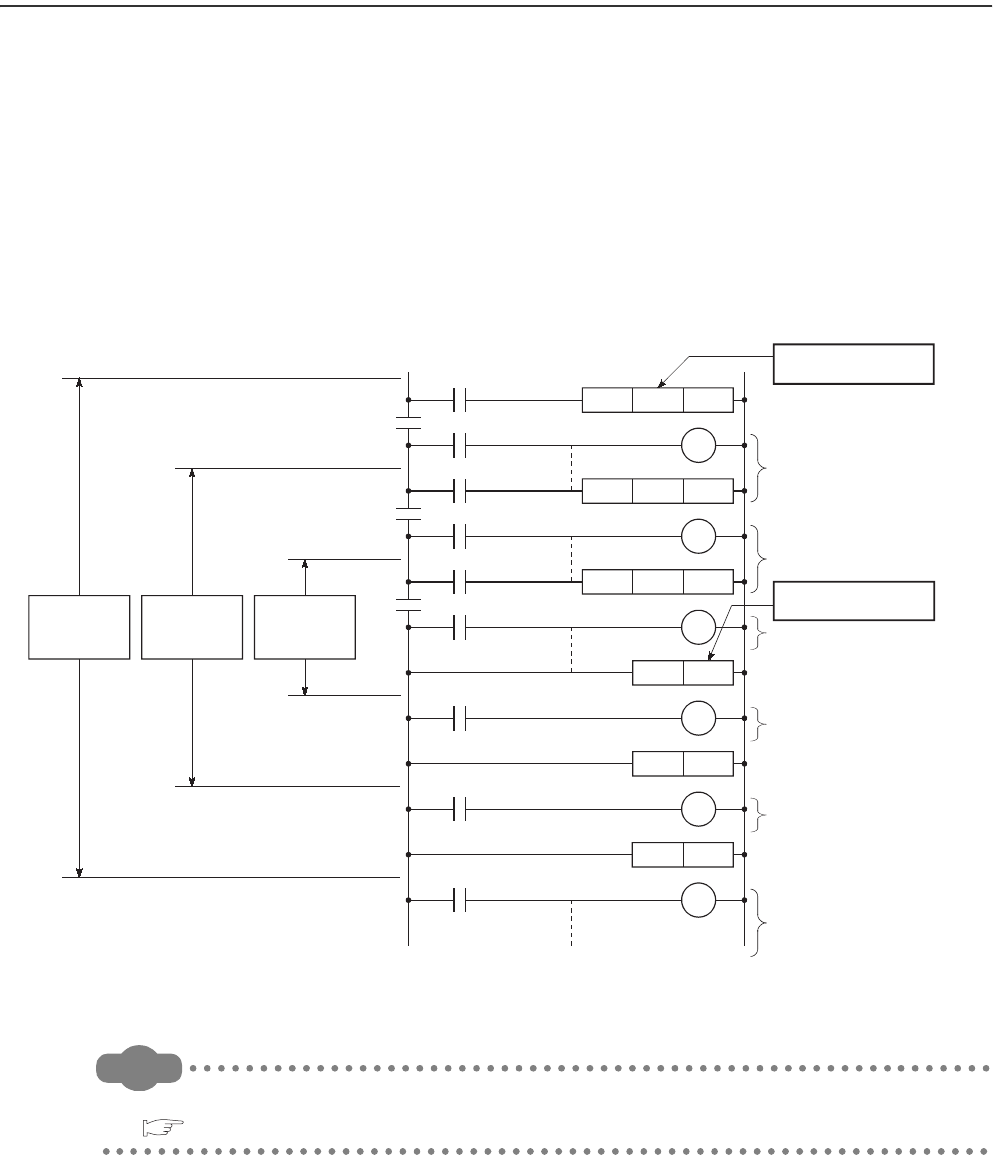

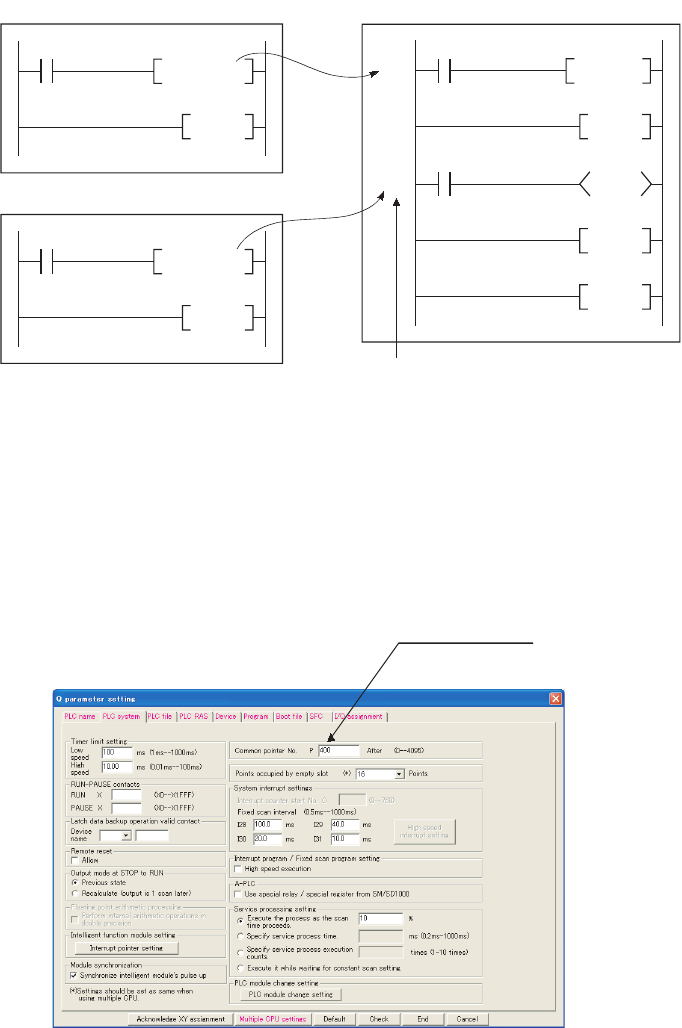

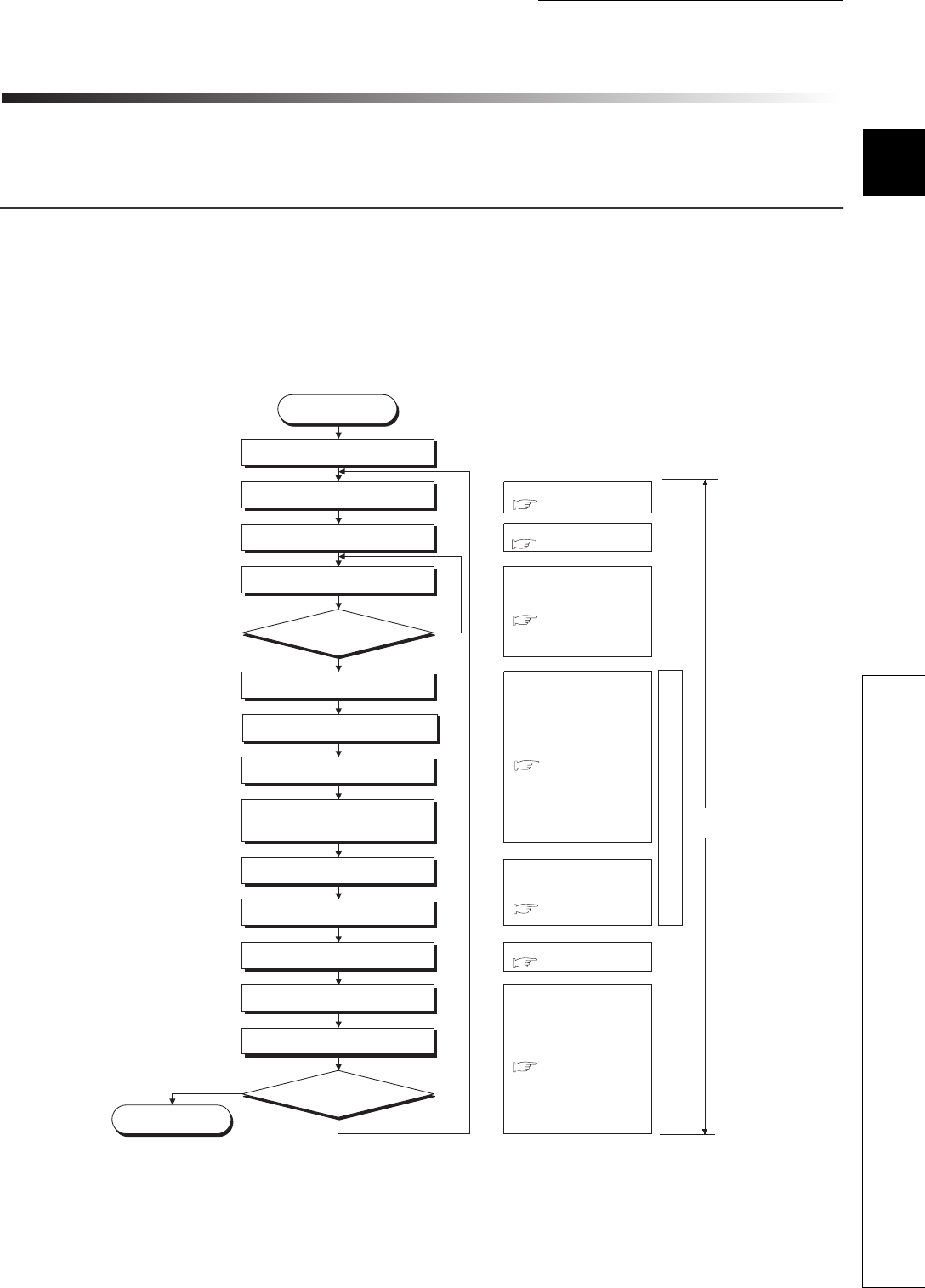

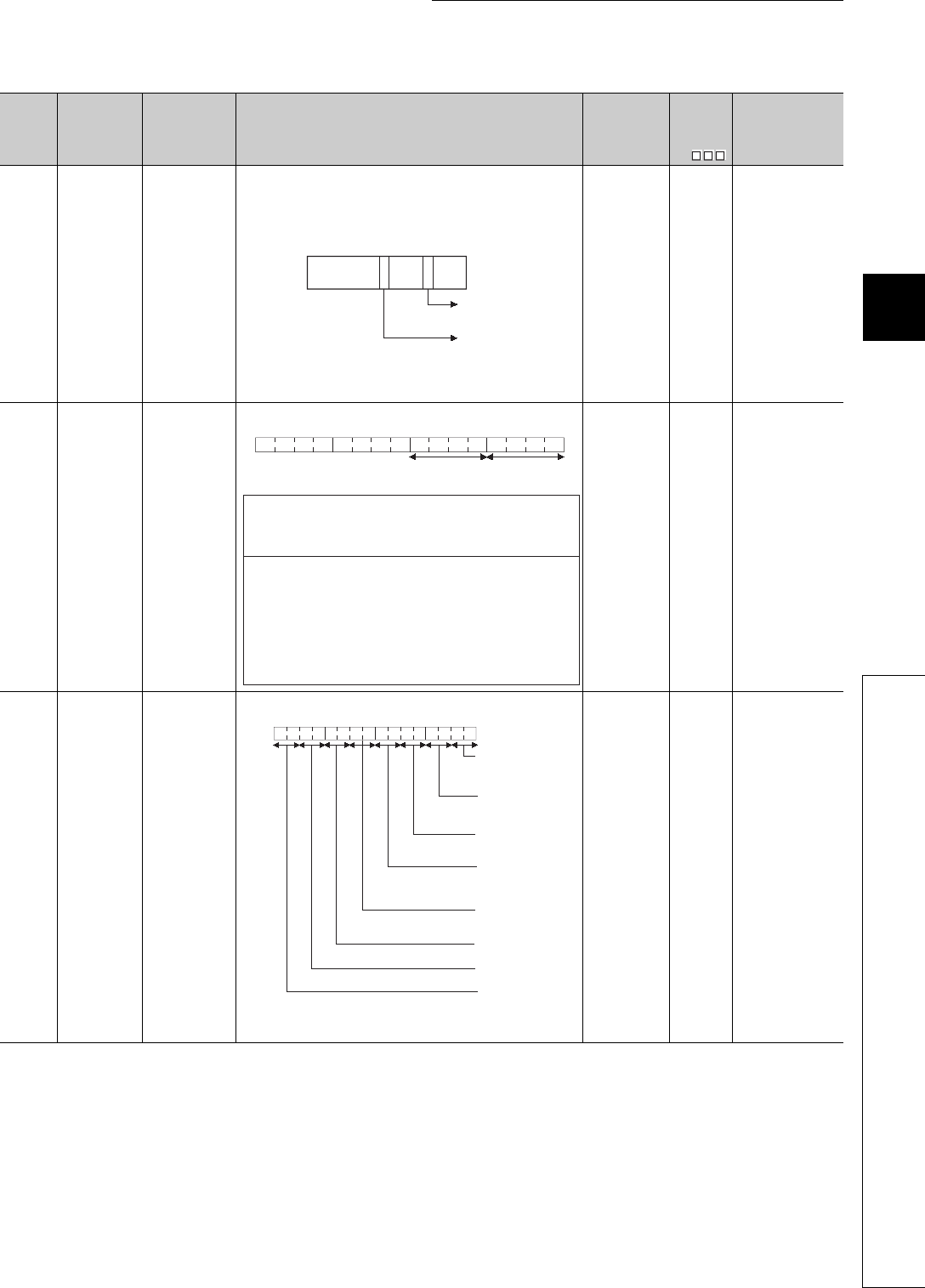

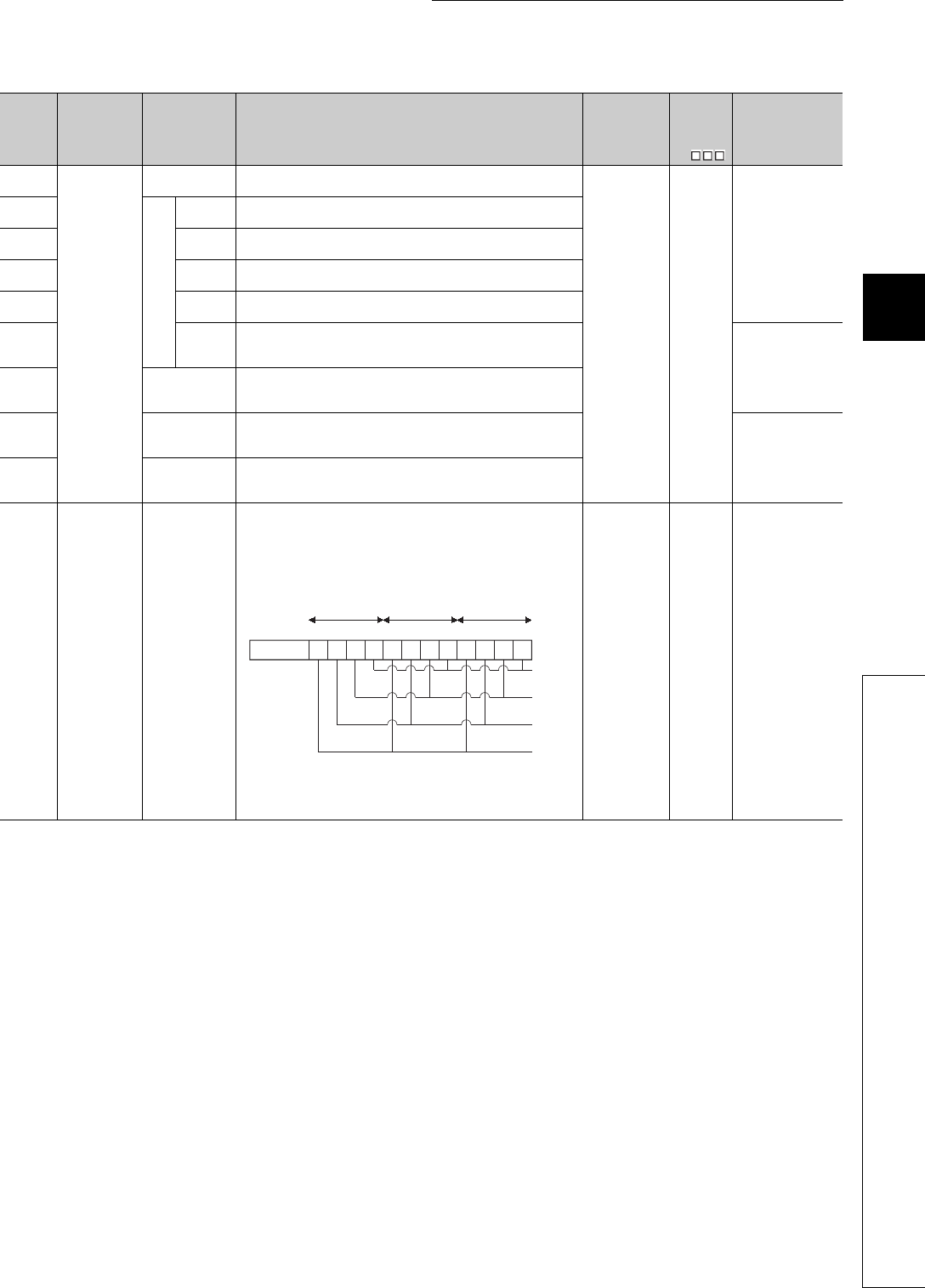

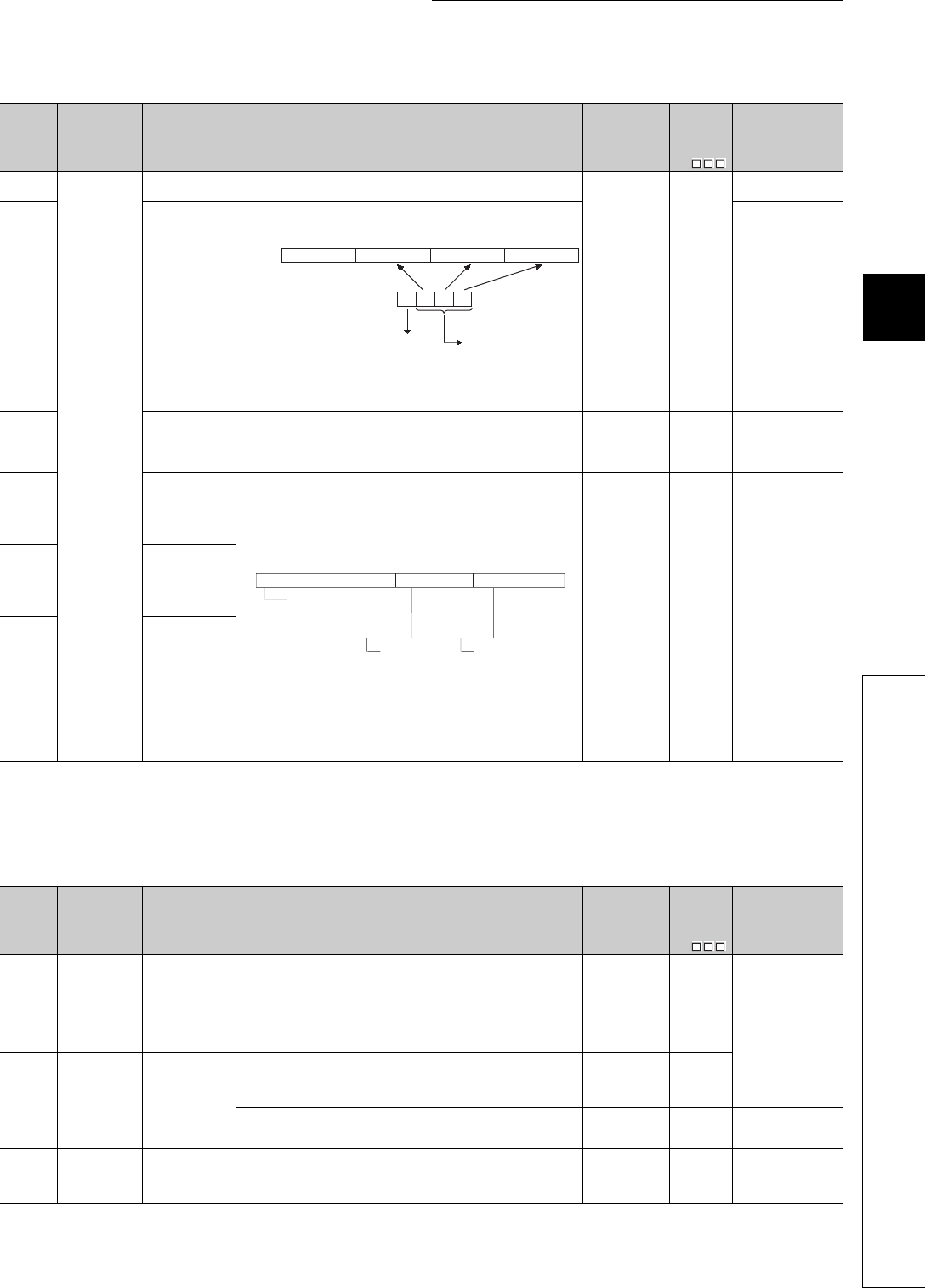

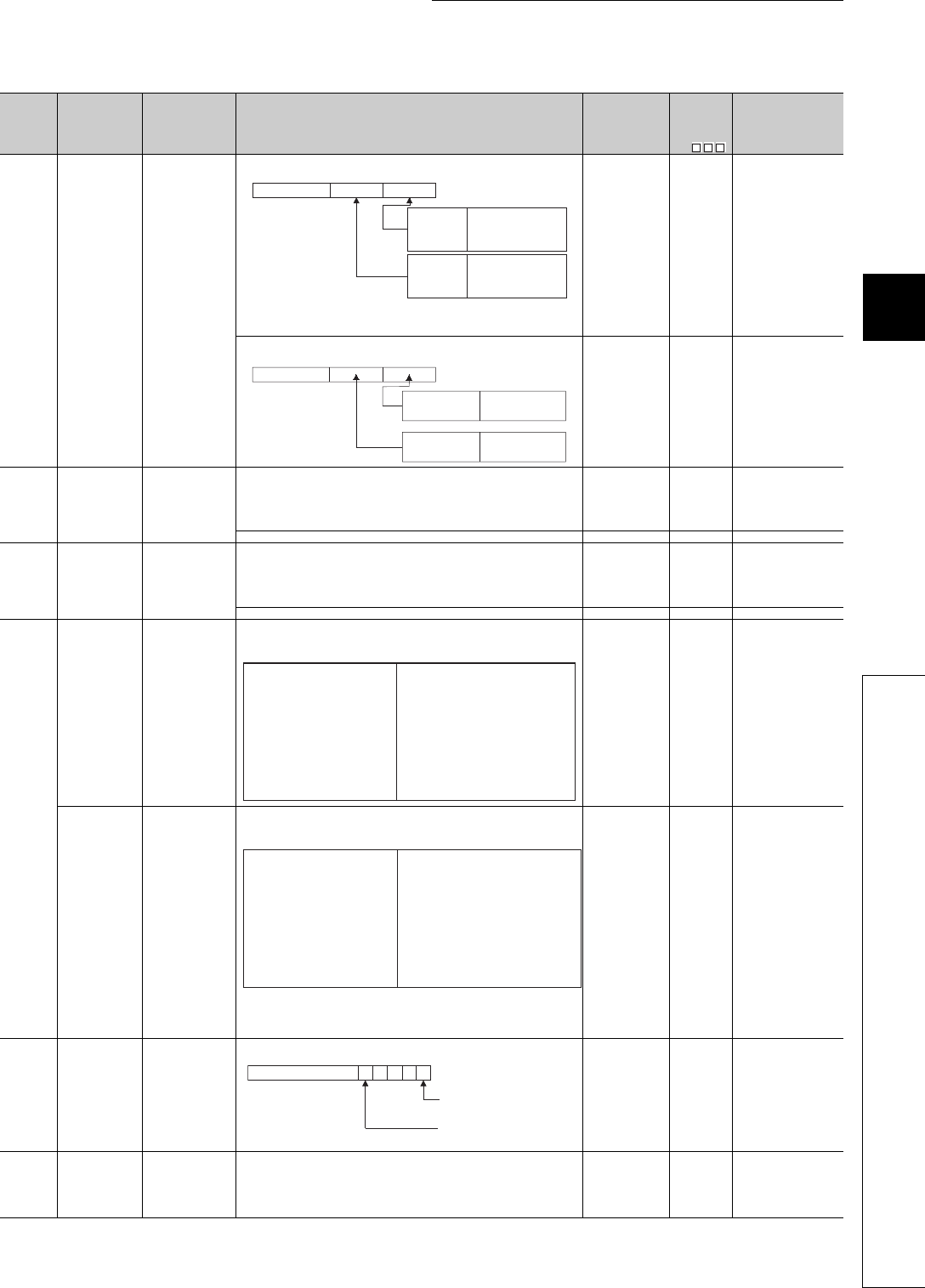

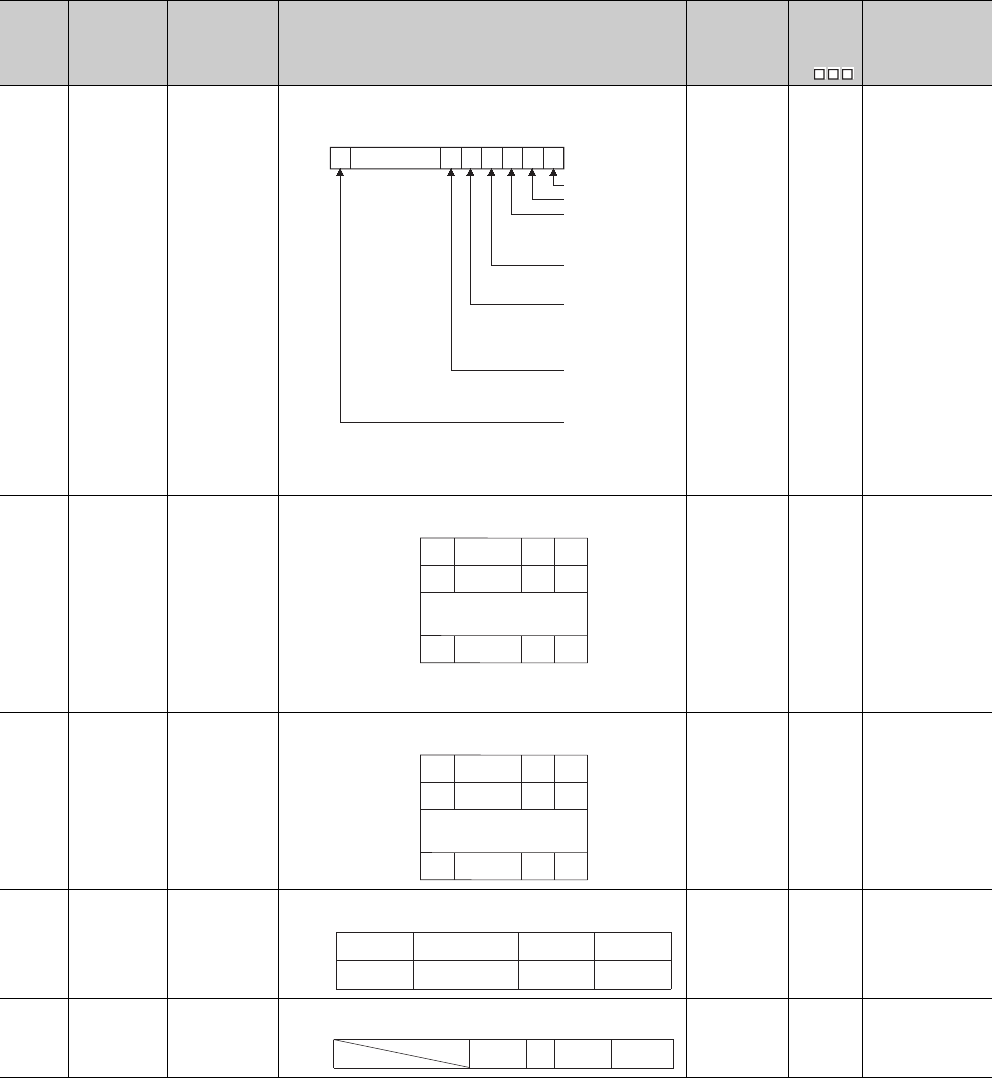

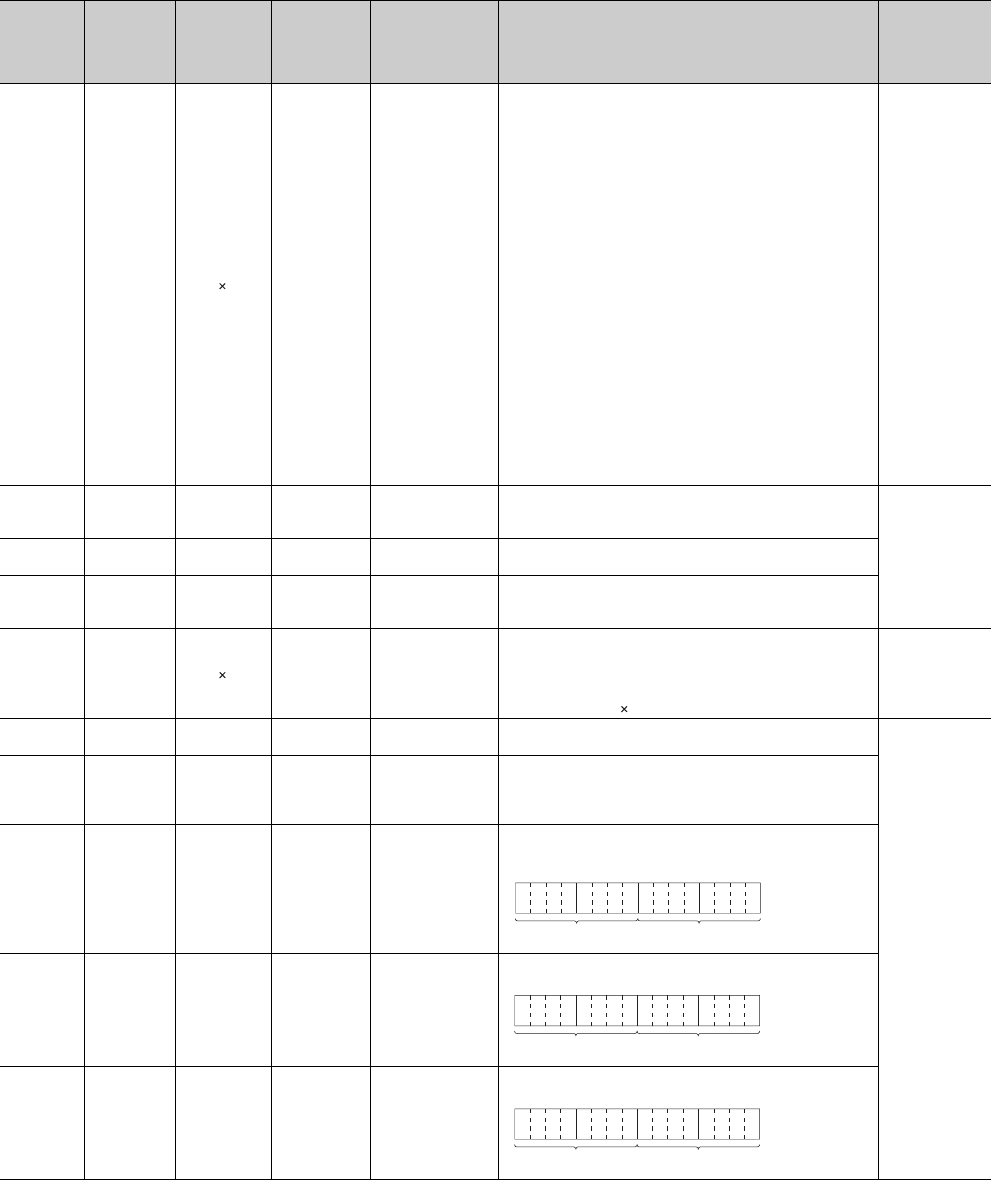

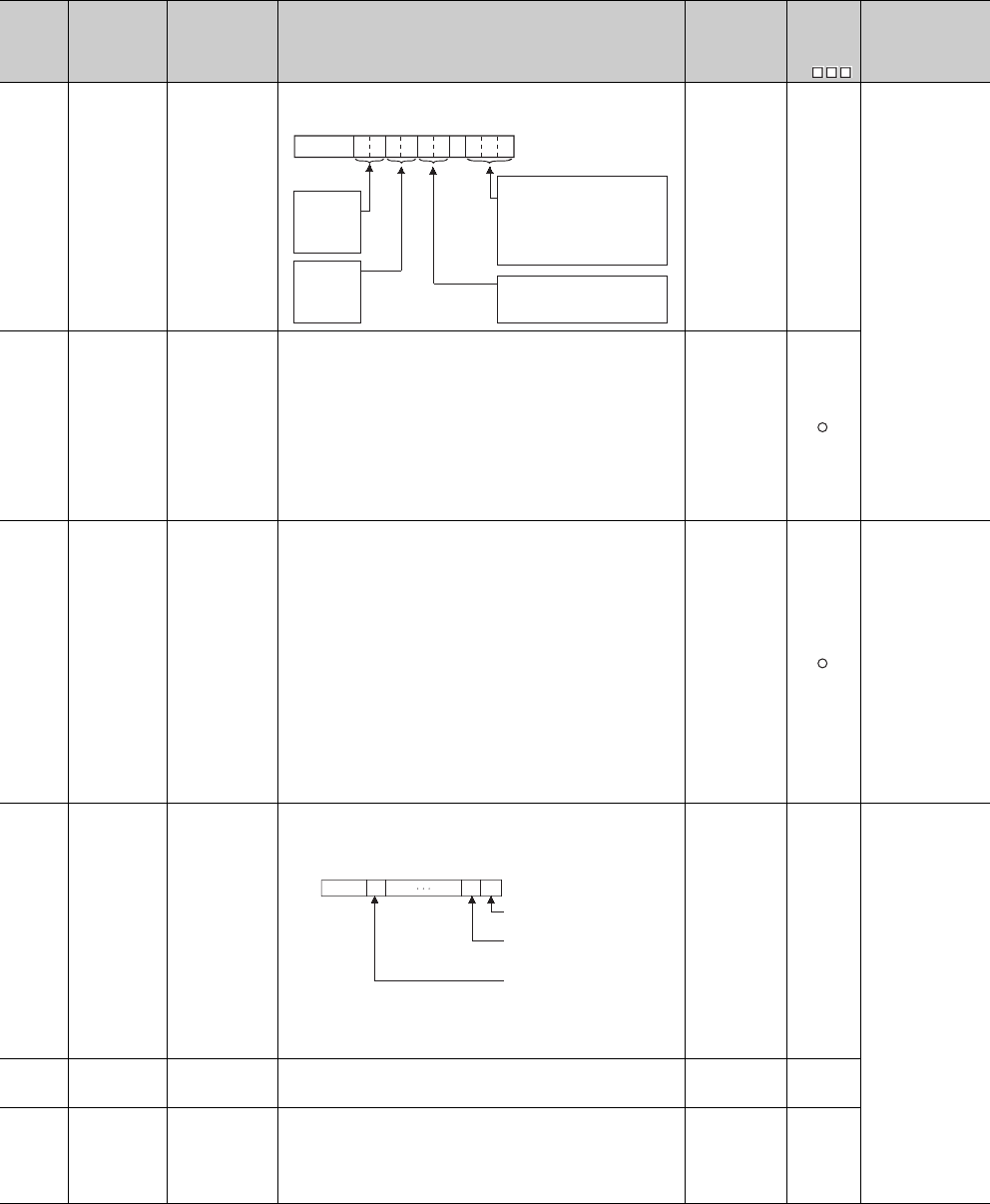

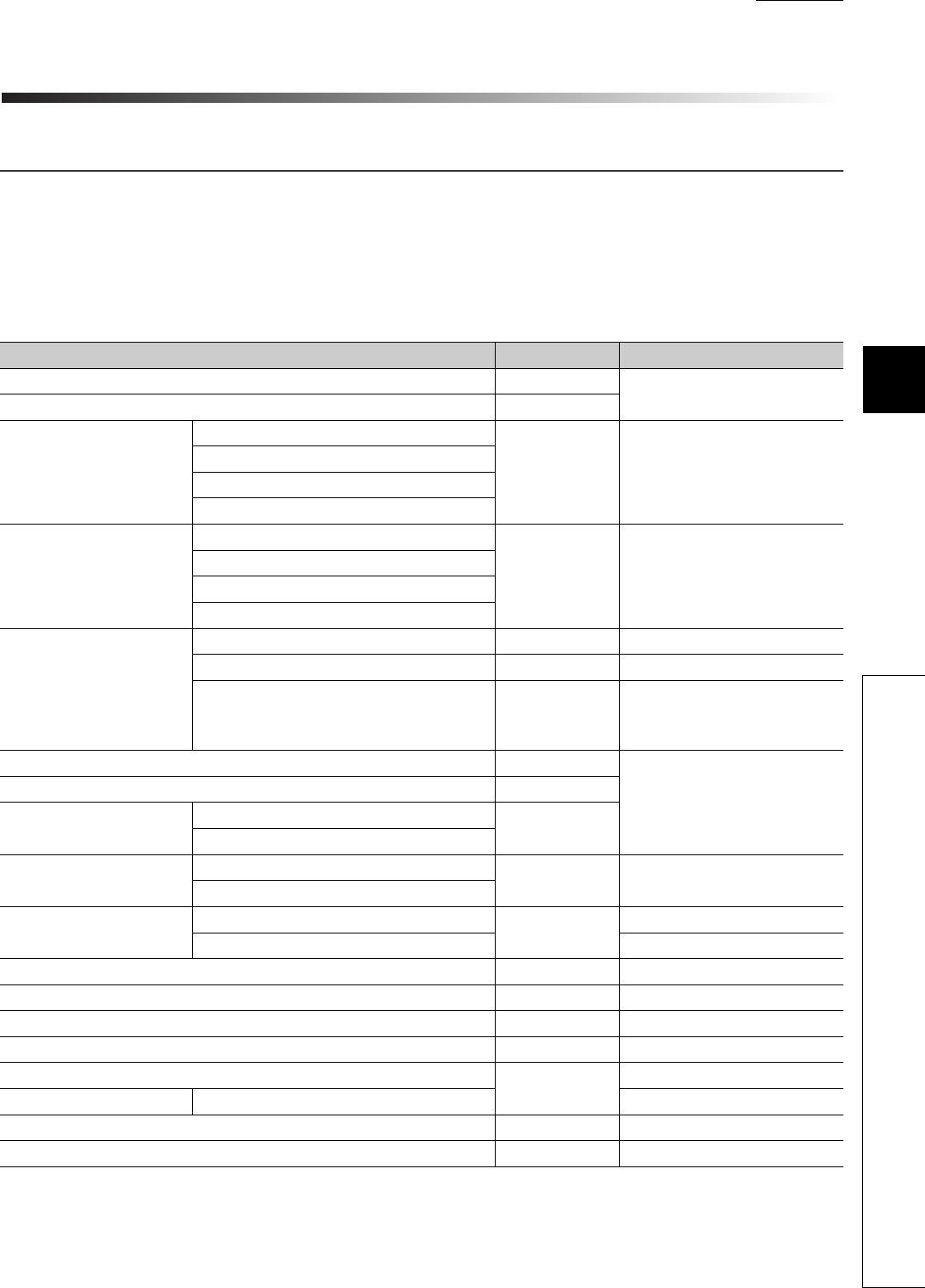

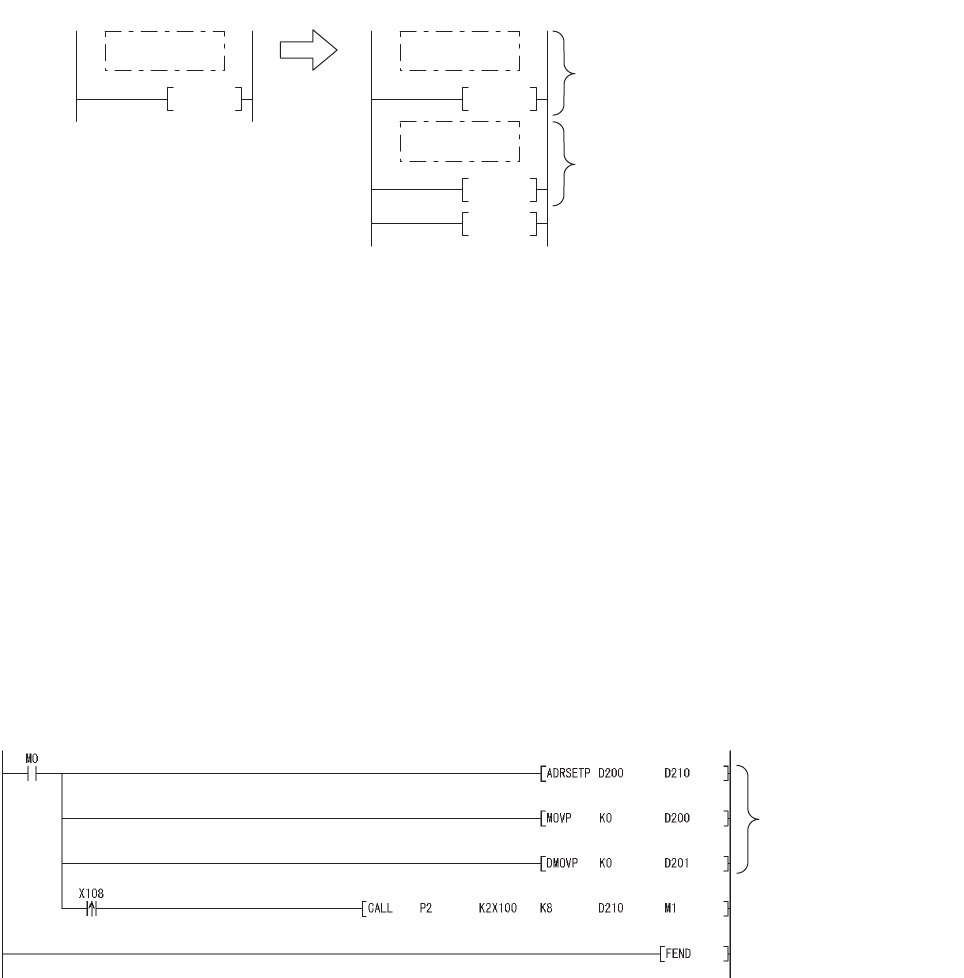

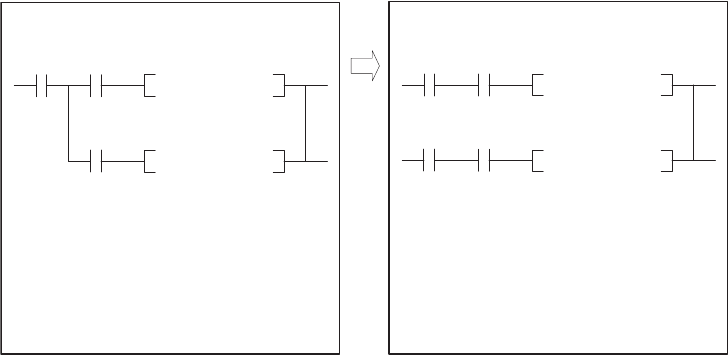

(2) Structuring by dividing into multiple files

A program is stored in a file.

Changing the file name allows the CPU module to store multiple programs.

Dividing into multiple files according to the processes or functions enables simultaneous programming by two or

more designers. Managing the files separately eases reuse and utilization to other programs.

Structured programming is efficient in this way because only the corresponding file needs to be modified or

debugged in case of change in the specifications.

(a) Dividing into multiple files according to the processes*1

*1: The processing contents divided according to the processes can further be divided and managed according to the

functions.

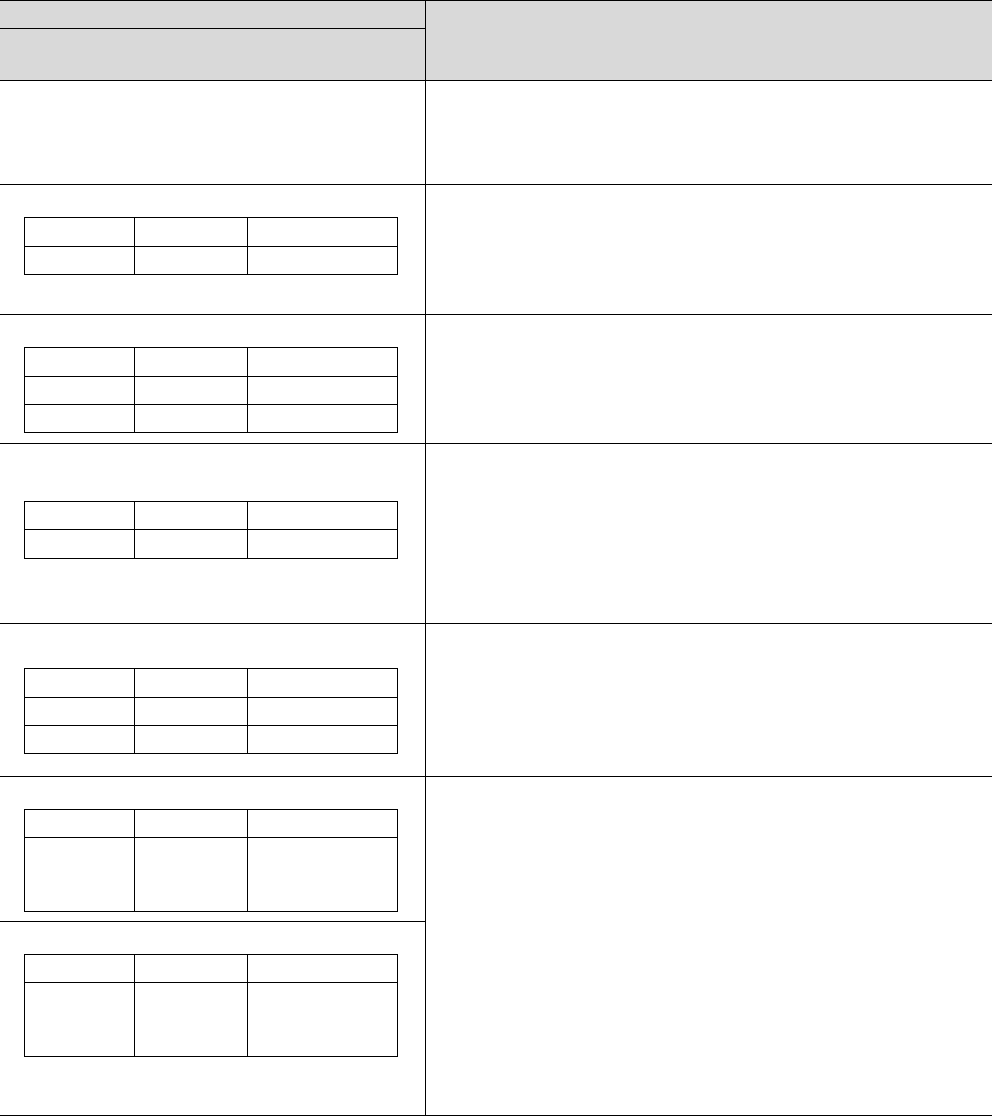

*2: The execution order can be set in the Program tab of the PLC parameter dialog box. ( Section 2.3(2)).

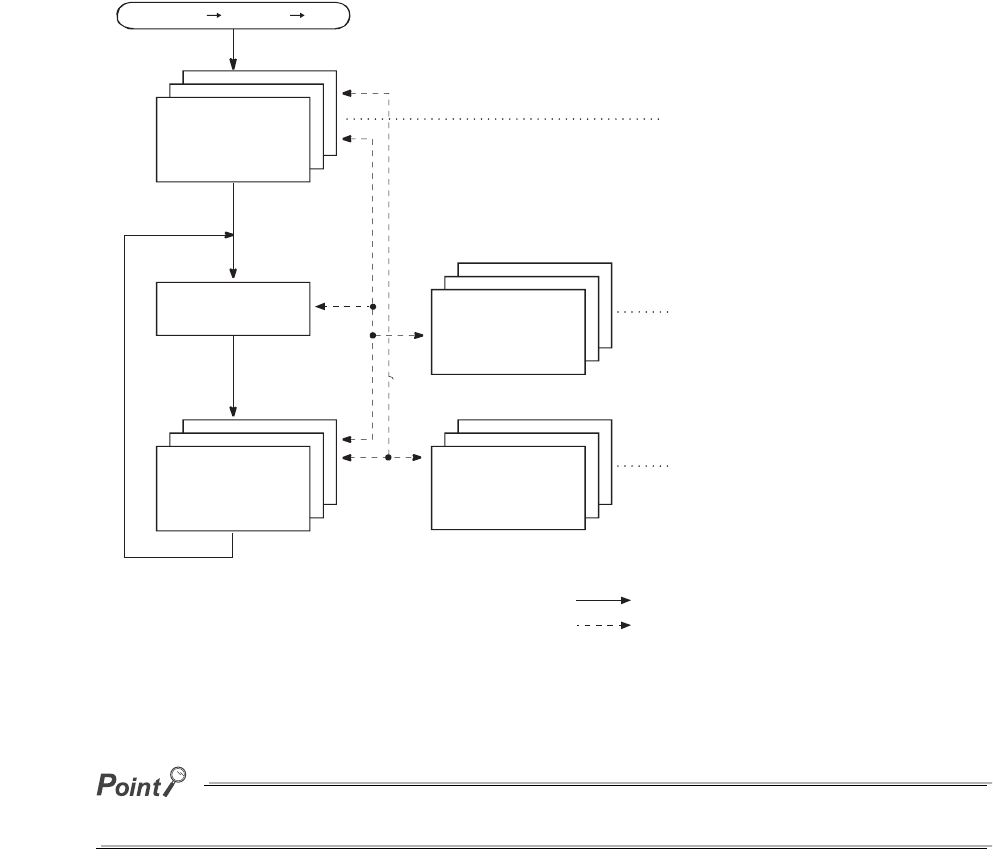

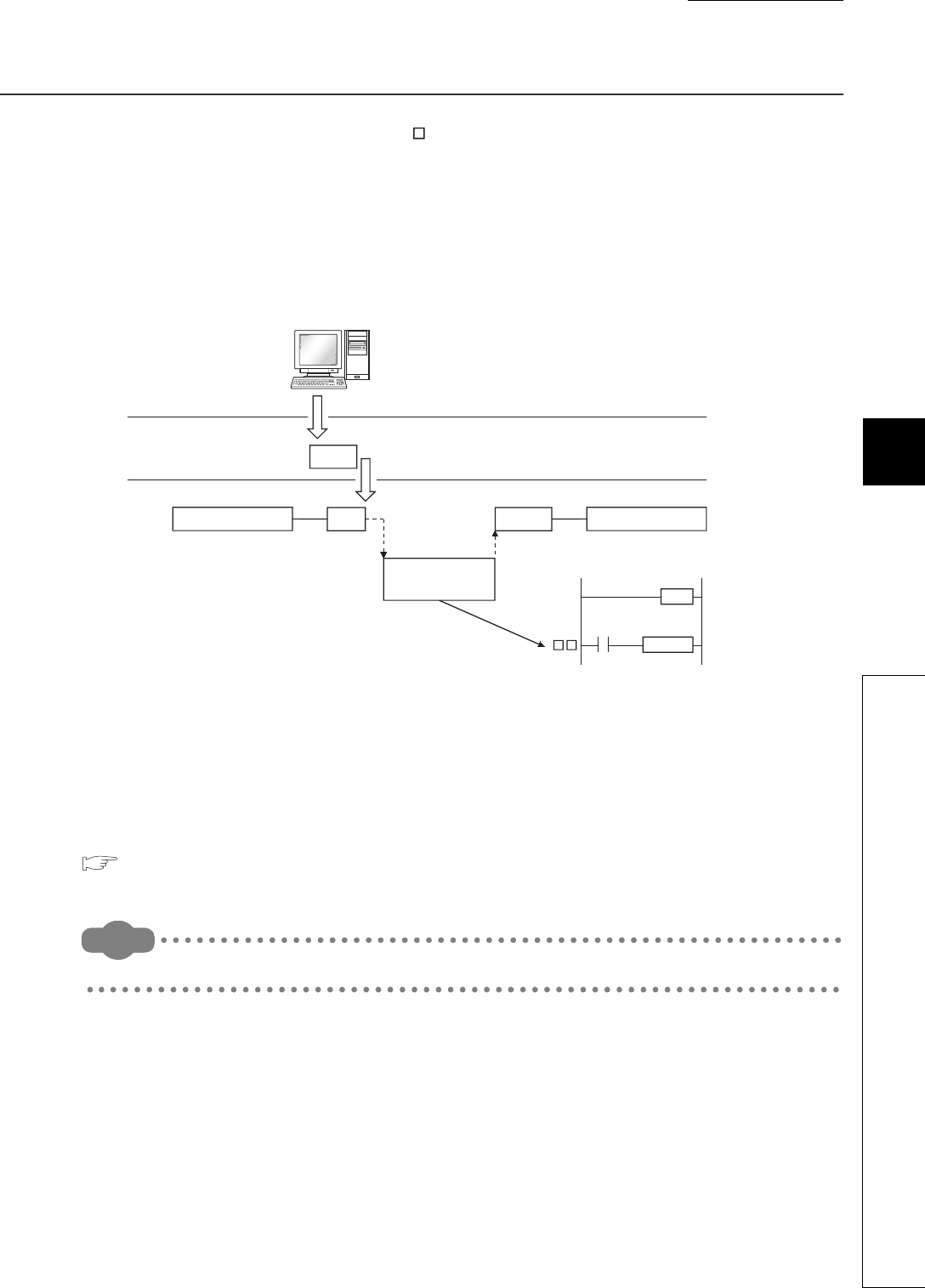

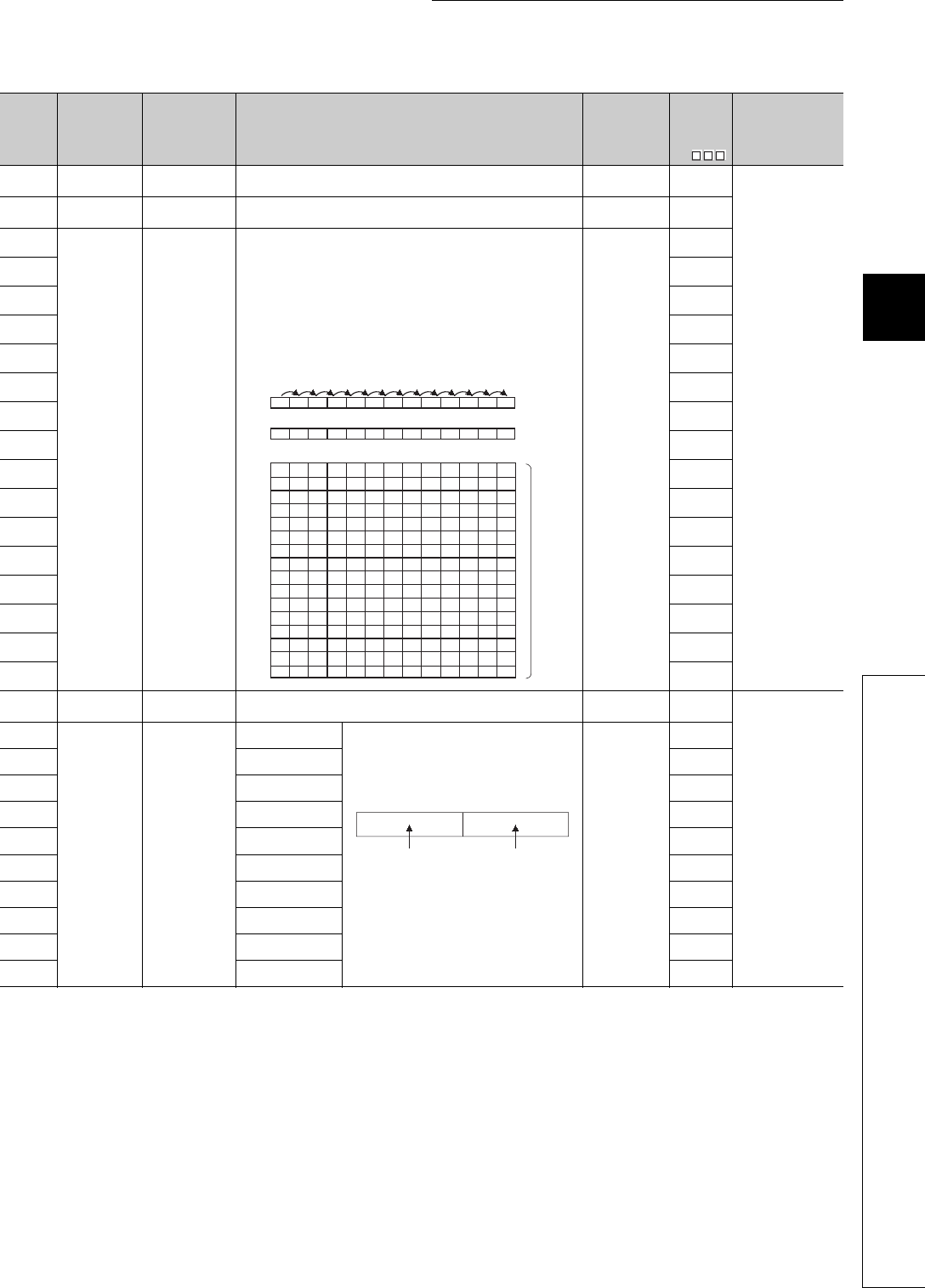

Figure 1.5 Structuring by dividing into multiple files

Figure 1.6 Dividing into multiple files according to the processes

GX Developer

CPU module

Multiple programs can be stored

by changing the file name.

File name: PARAM

Parameter Program Program

Device

comment

File name: ABC File name: ABC File name: DEF

Program memory/memory card

Program ACarrying in

Processing contents

are divided according

to the processes.

Program A to D will

be executed in the

specified order. *2

Manufacturing

Assembly

Carrying out

Program B

Program C

Program D

CHAPTER1 OVERVIEW

1

2

3

4

5

6

7

8

1.3 Structured Programming

1 - 5

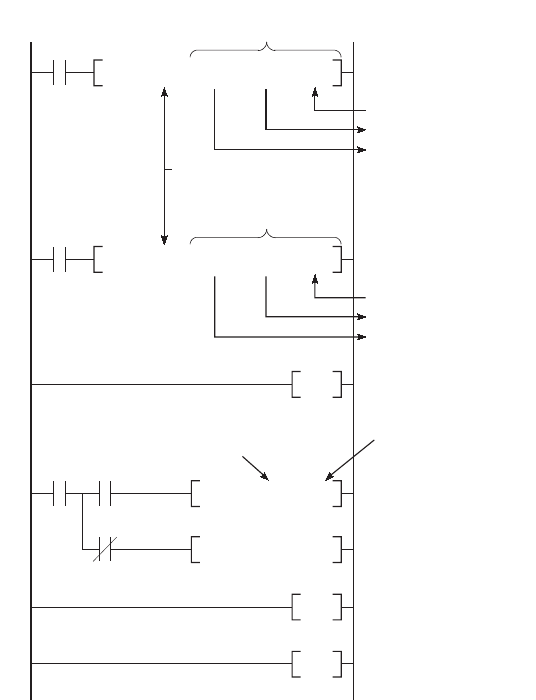

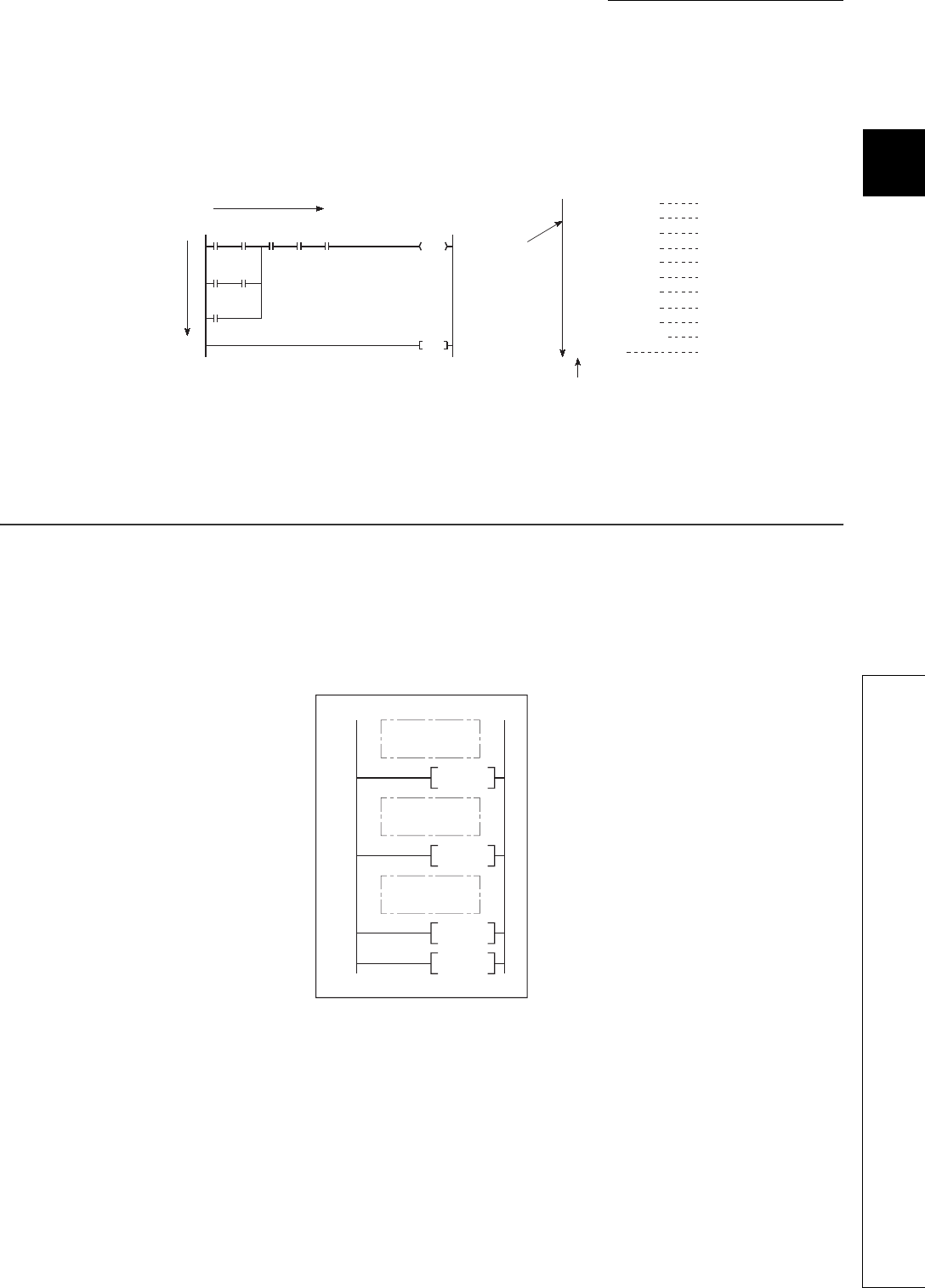

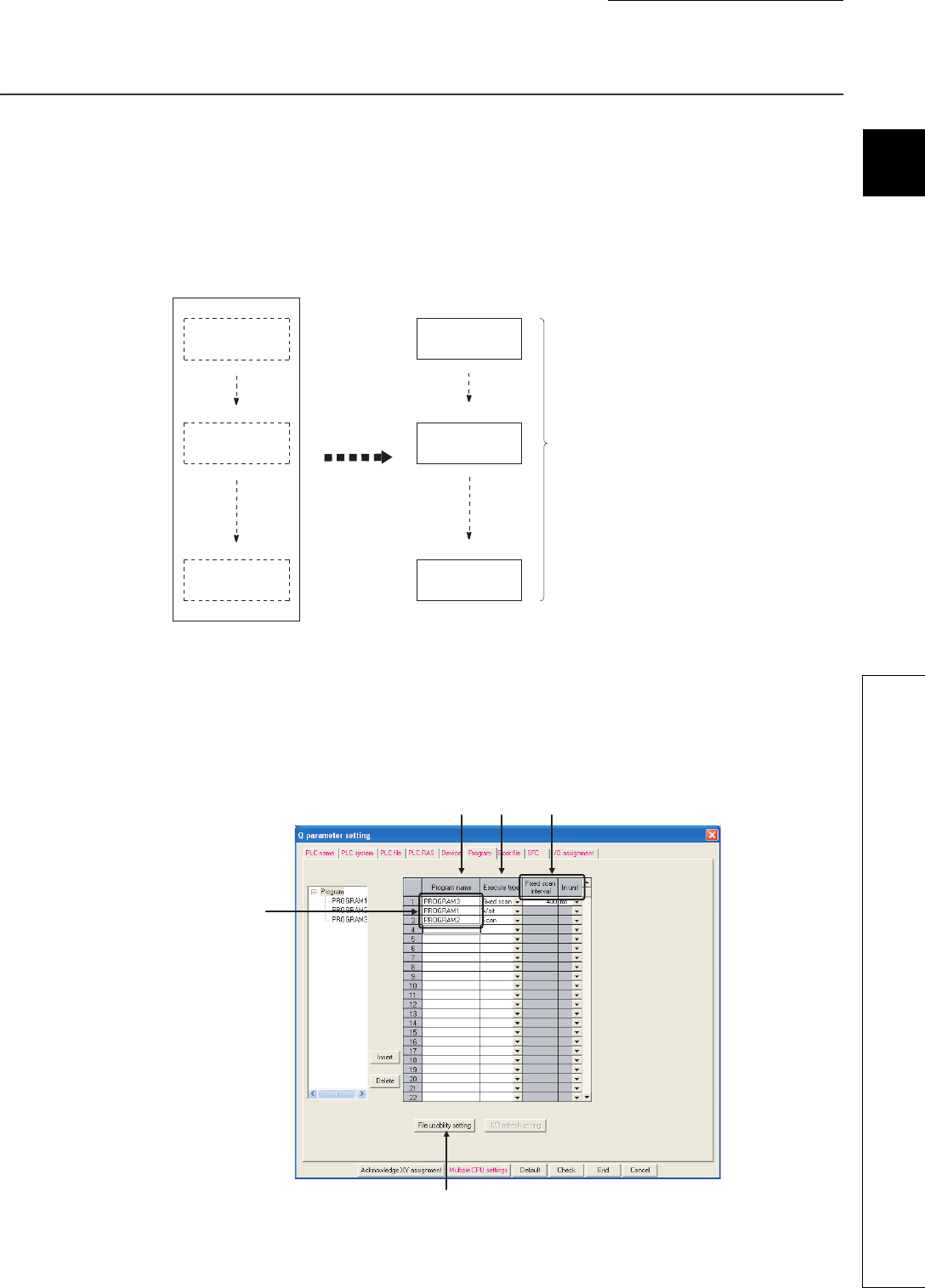

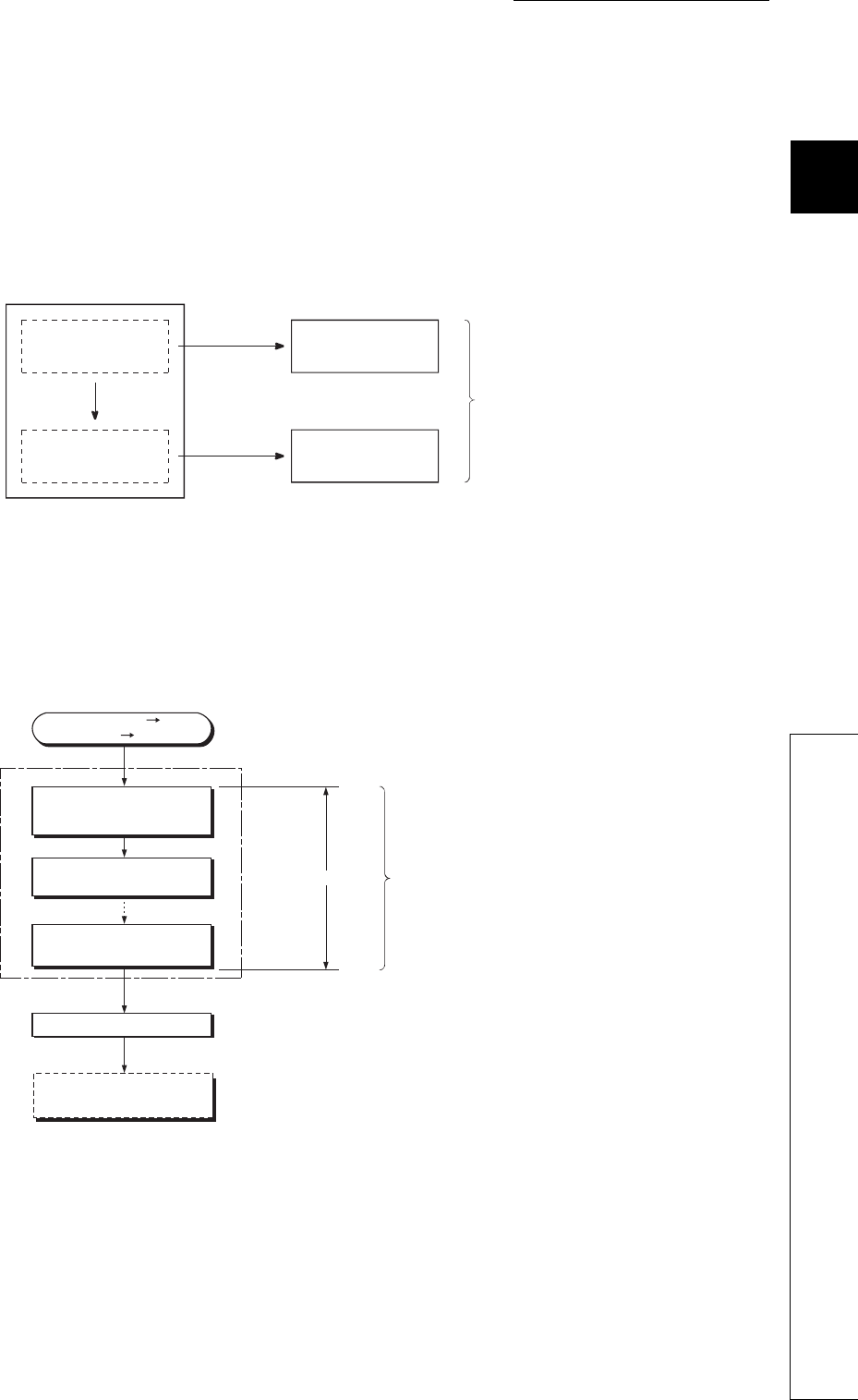

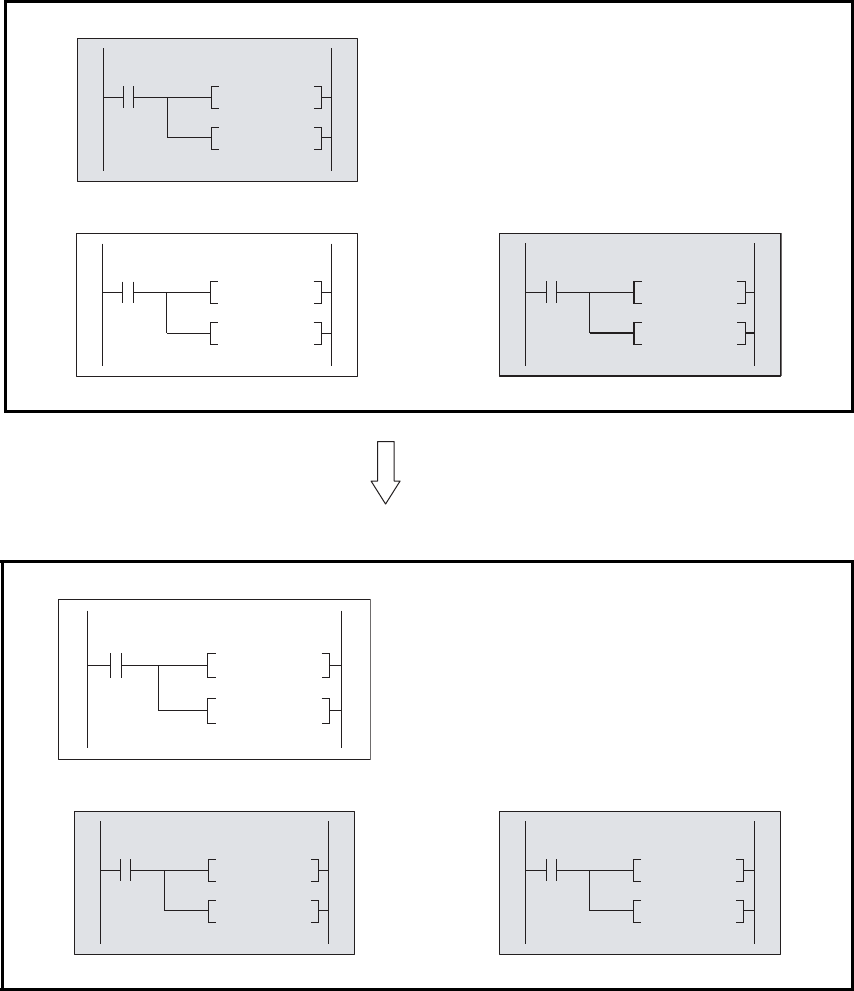

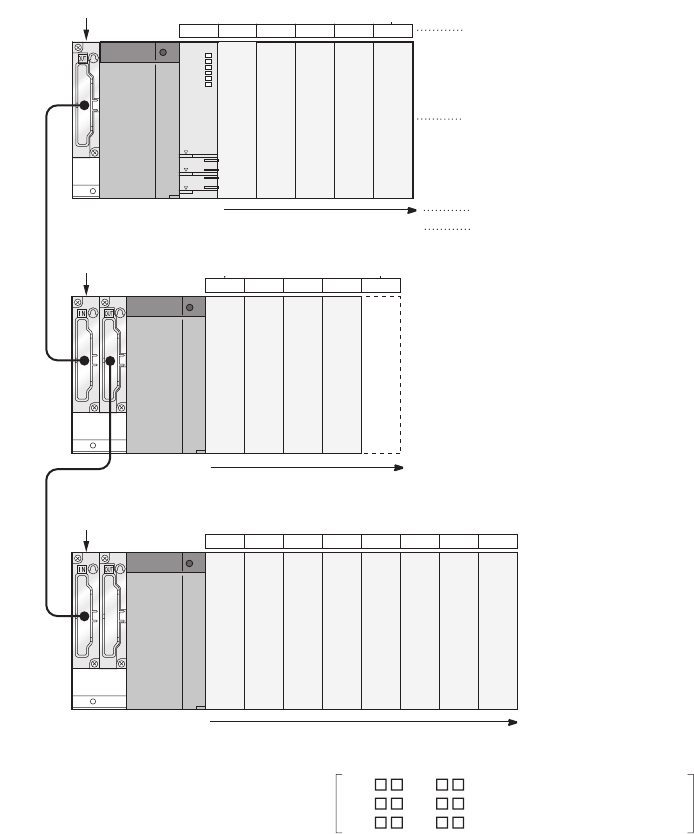

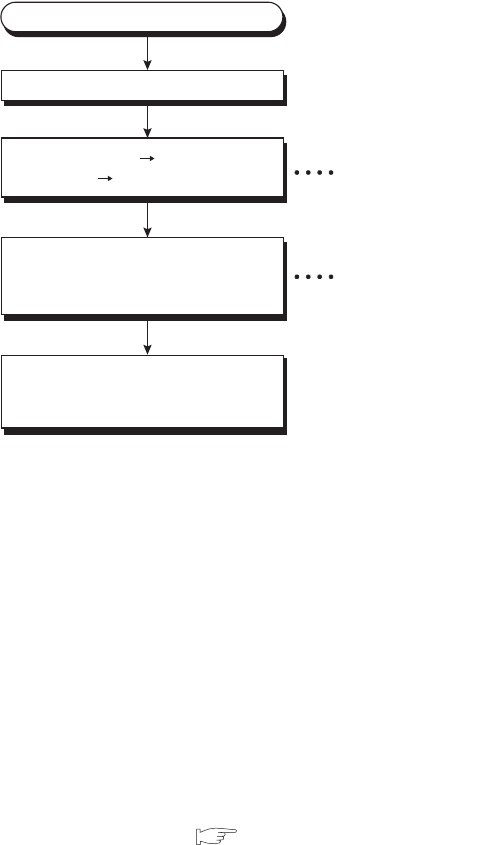

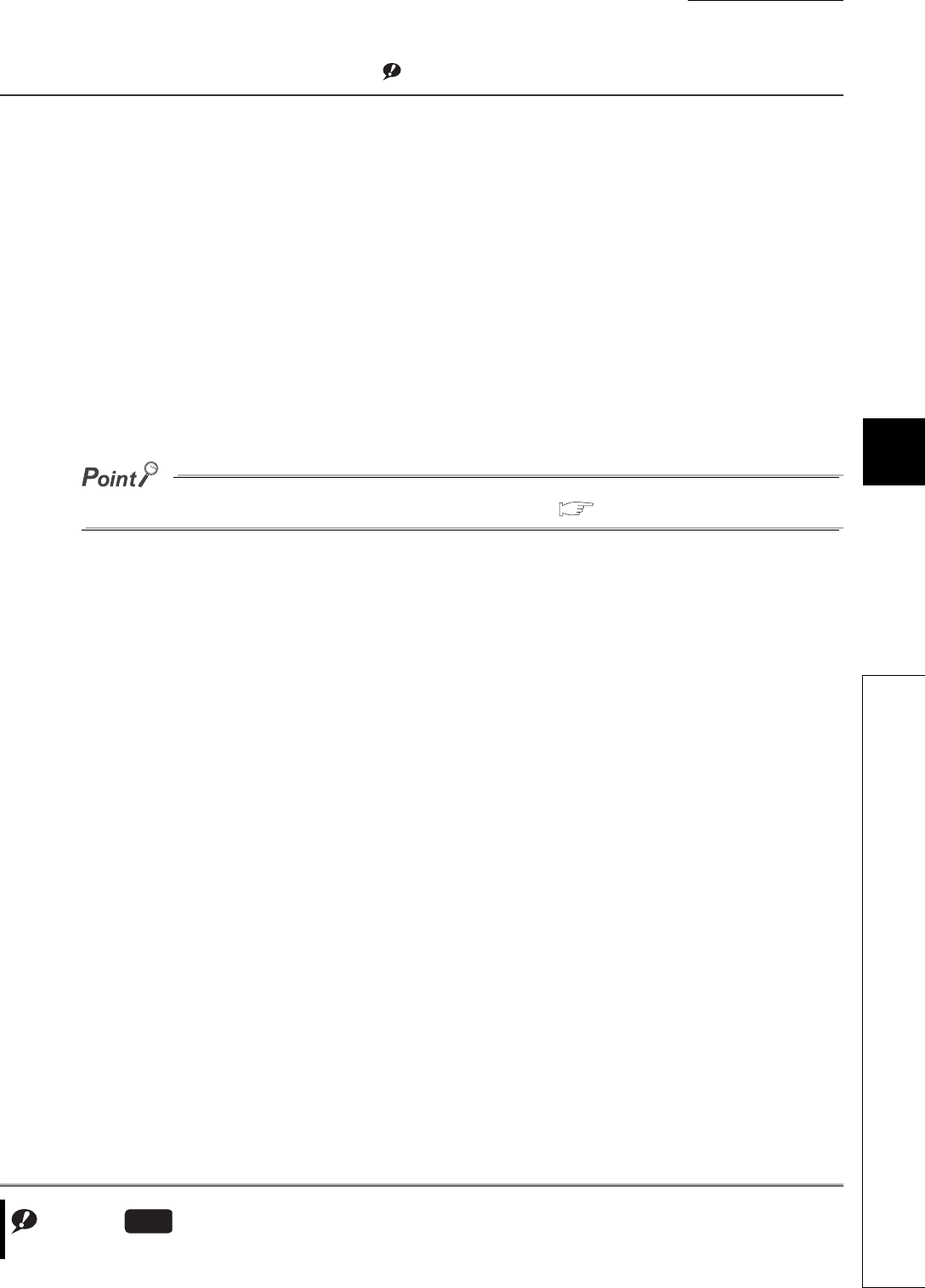

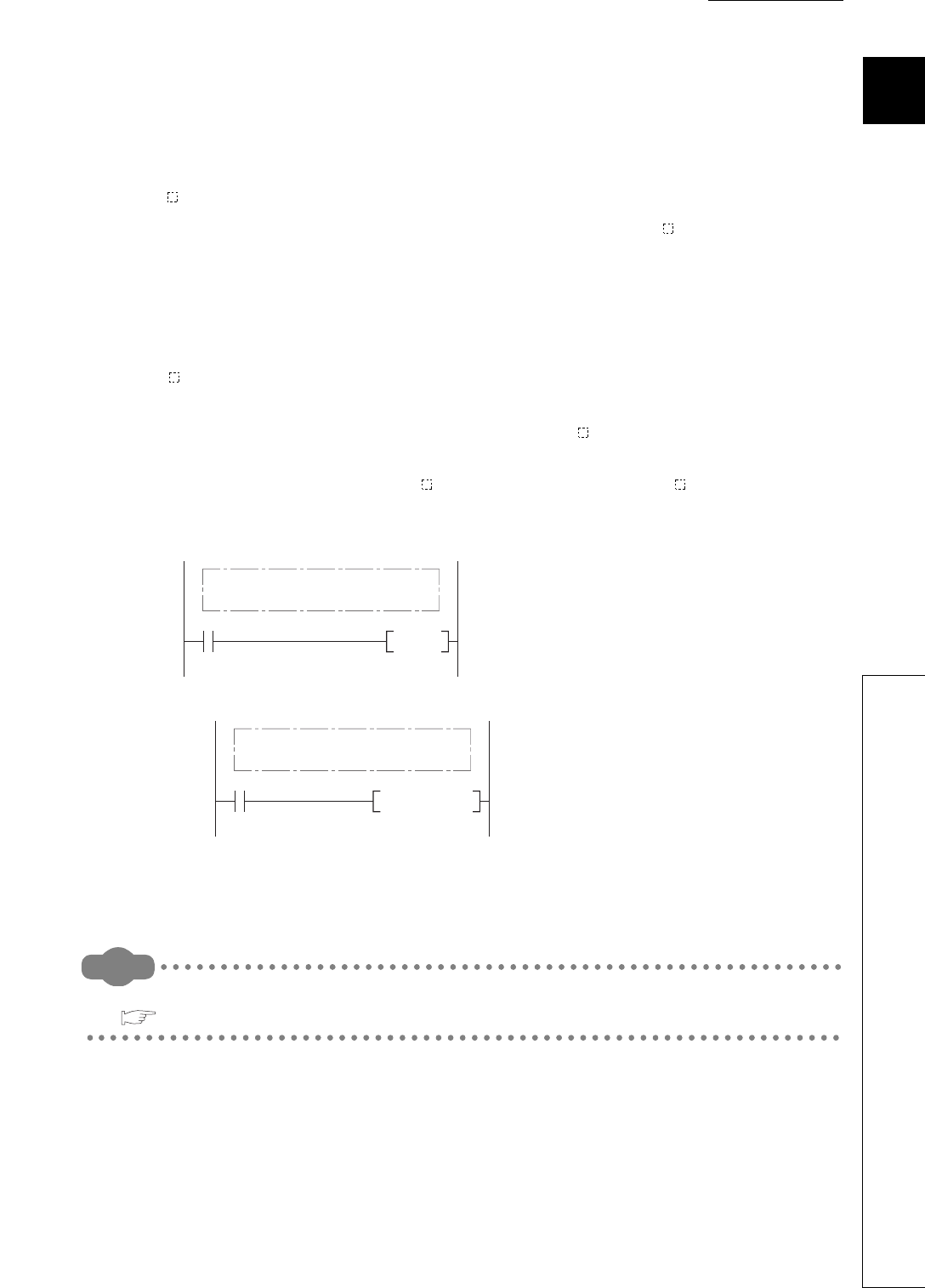

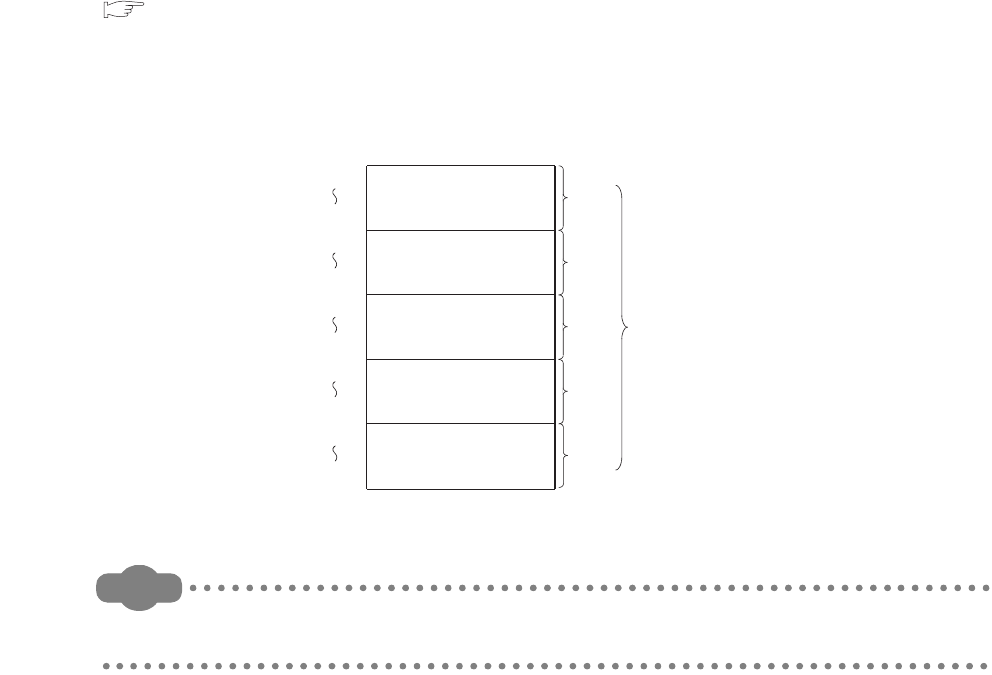

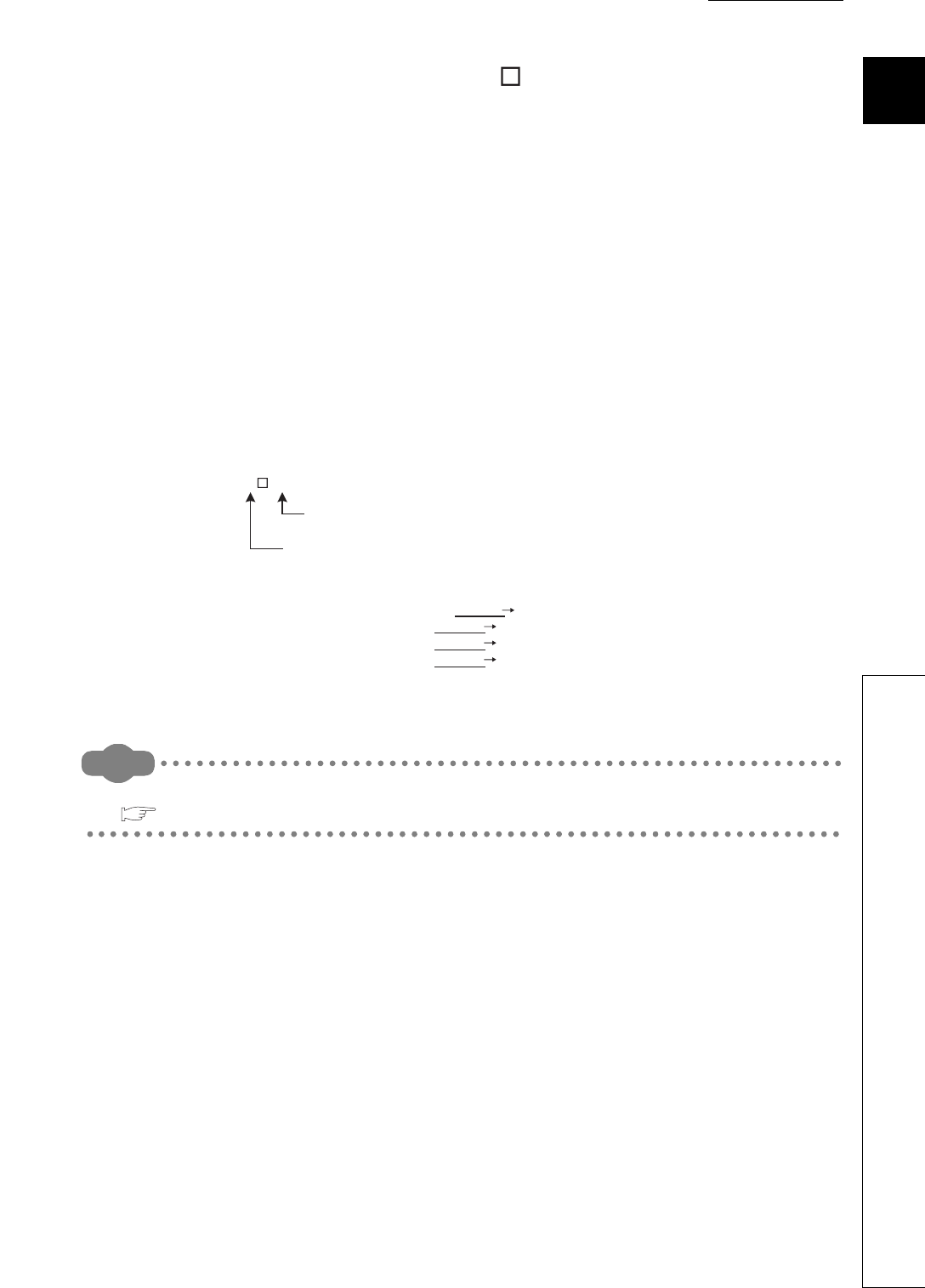

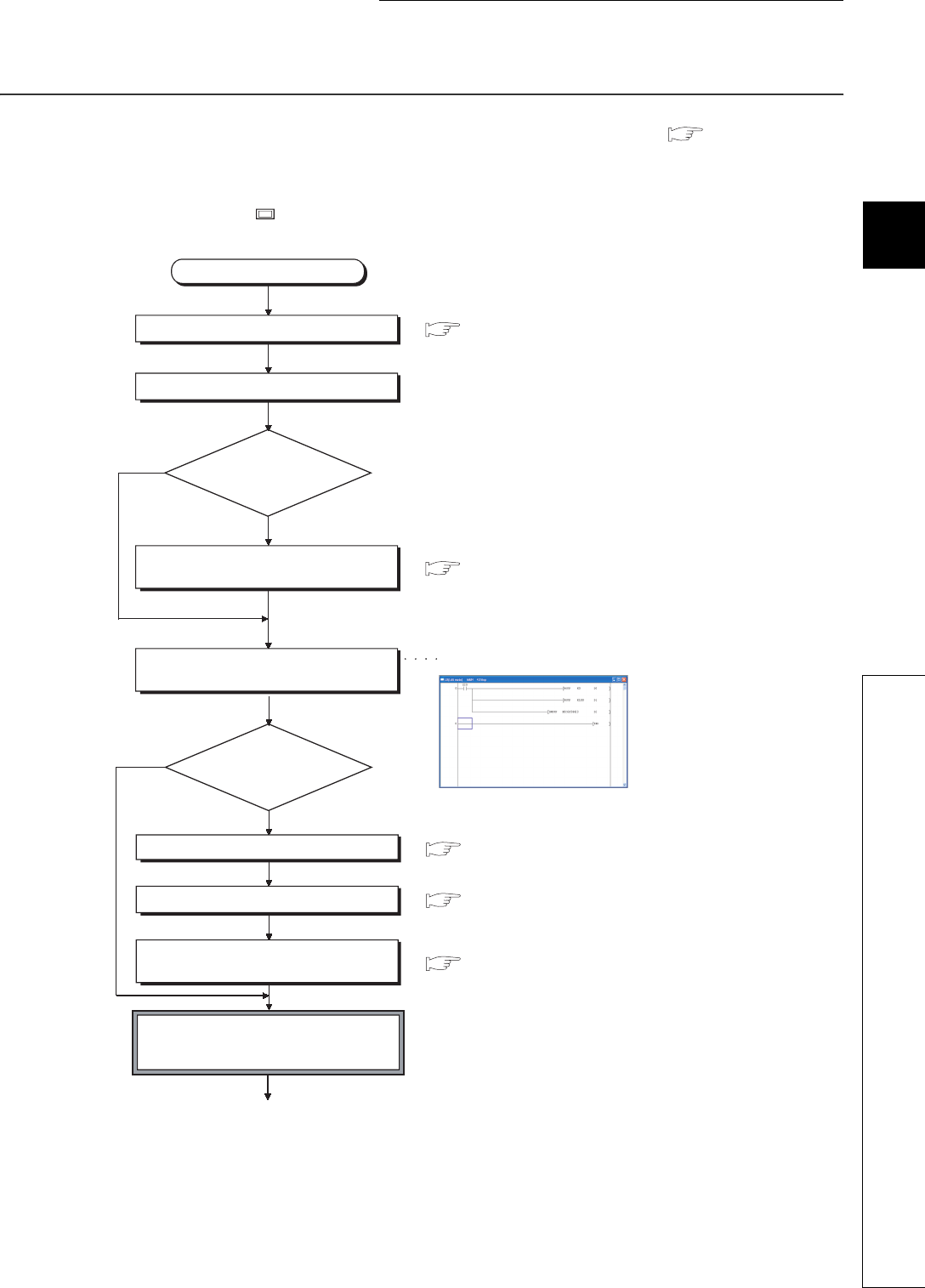

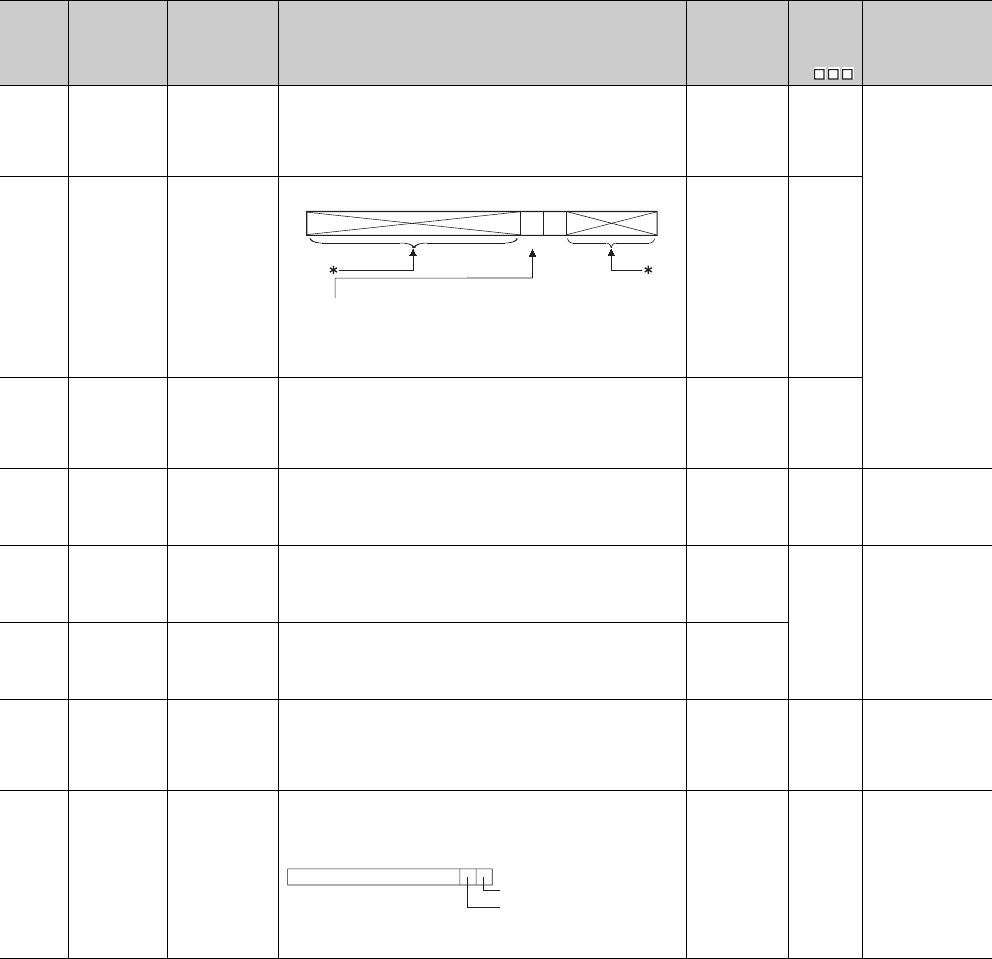

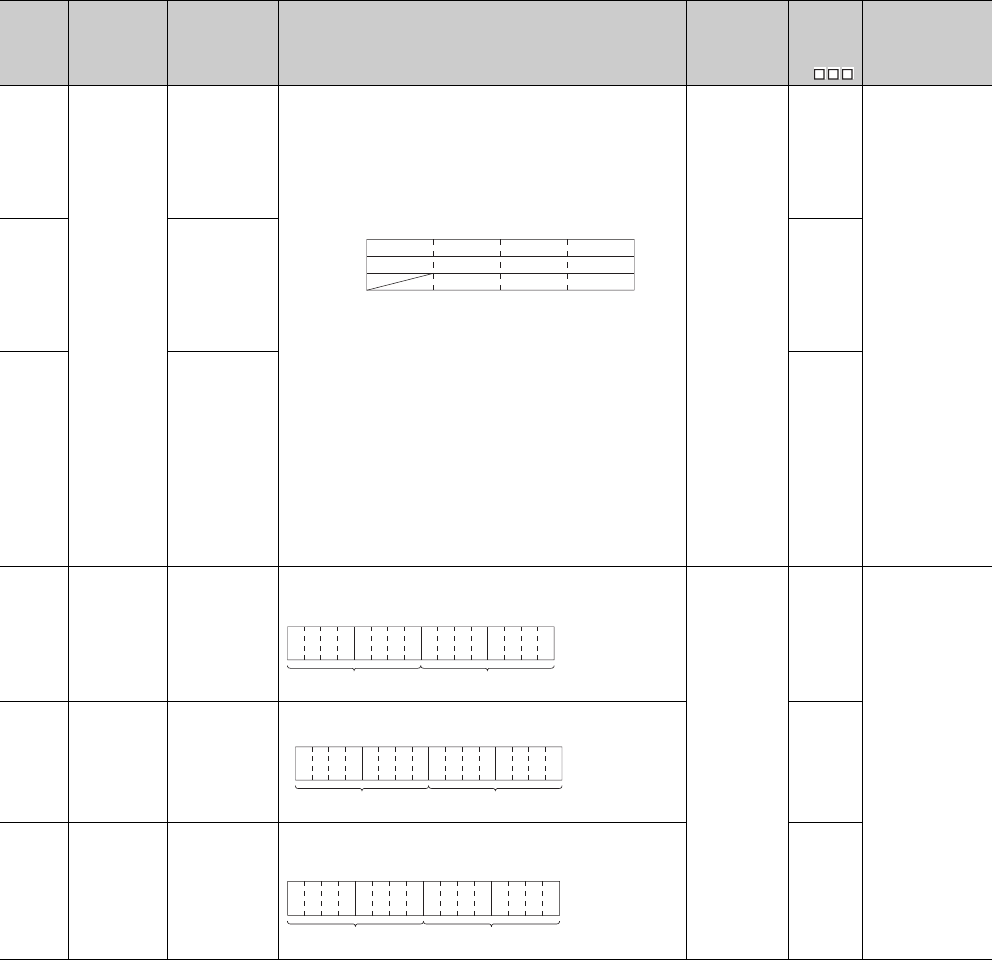

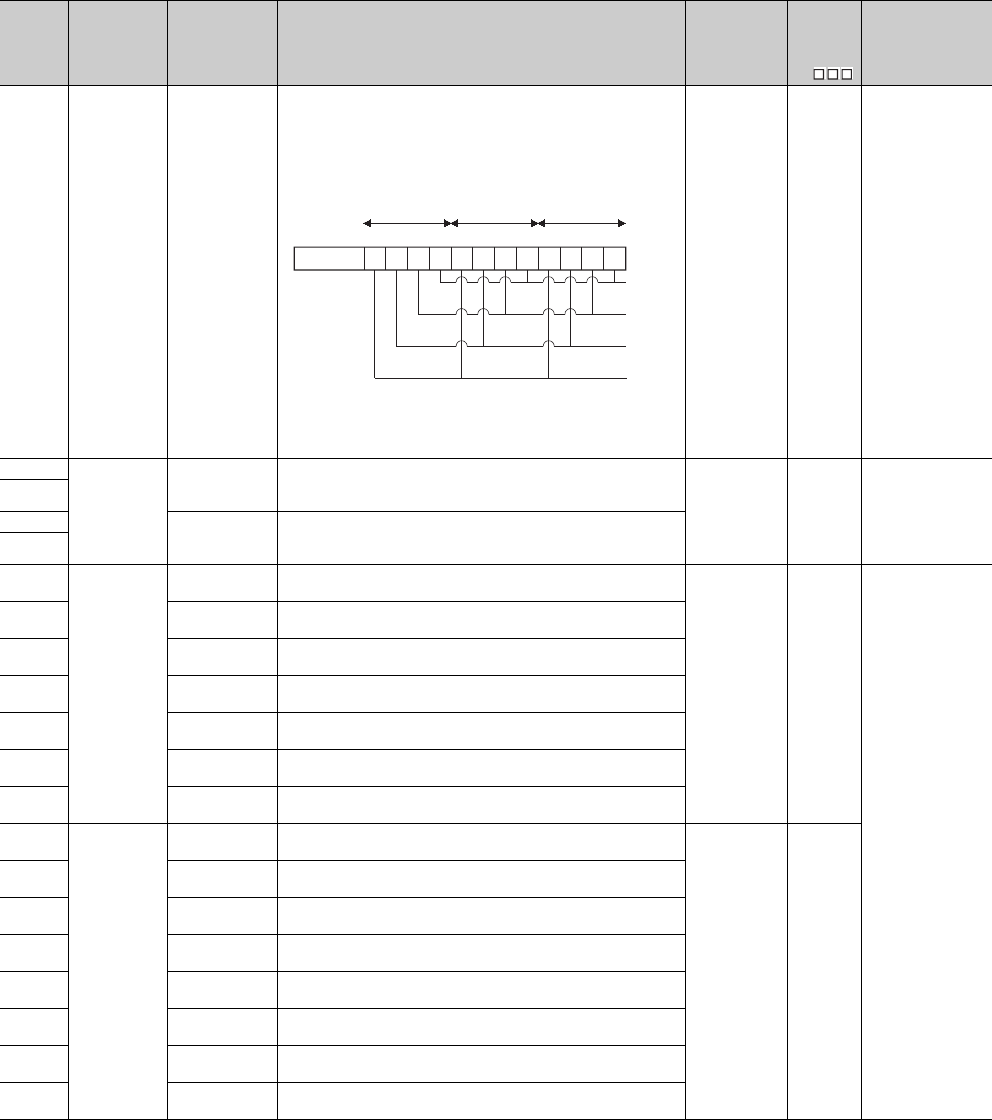

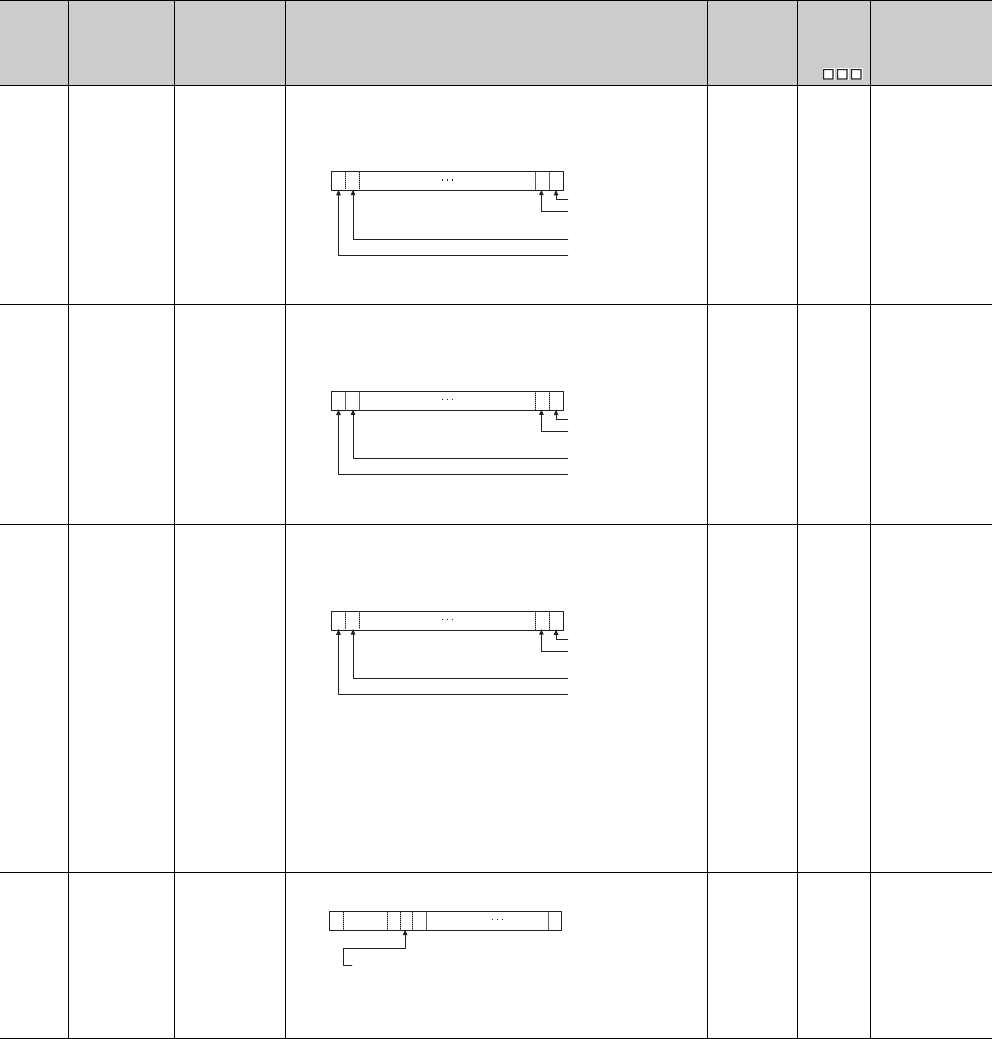

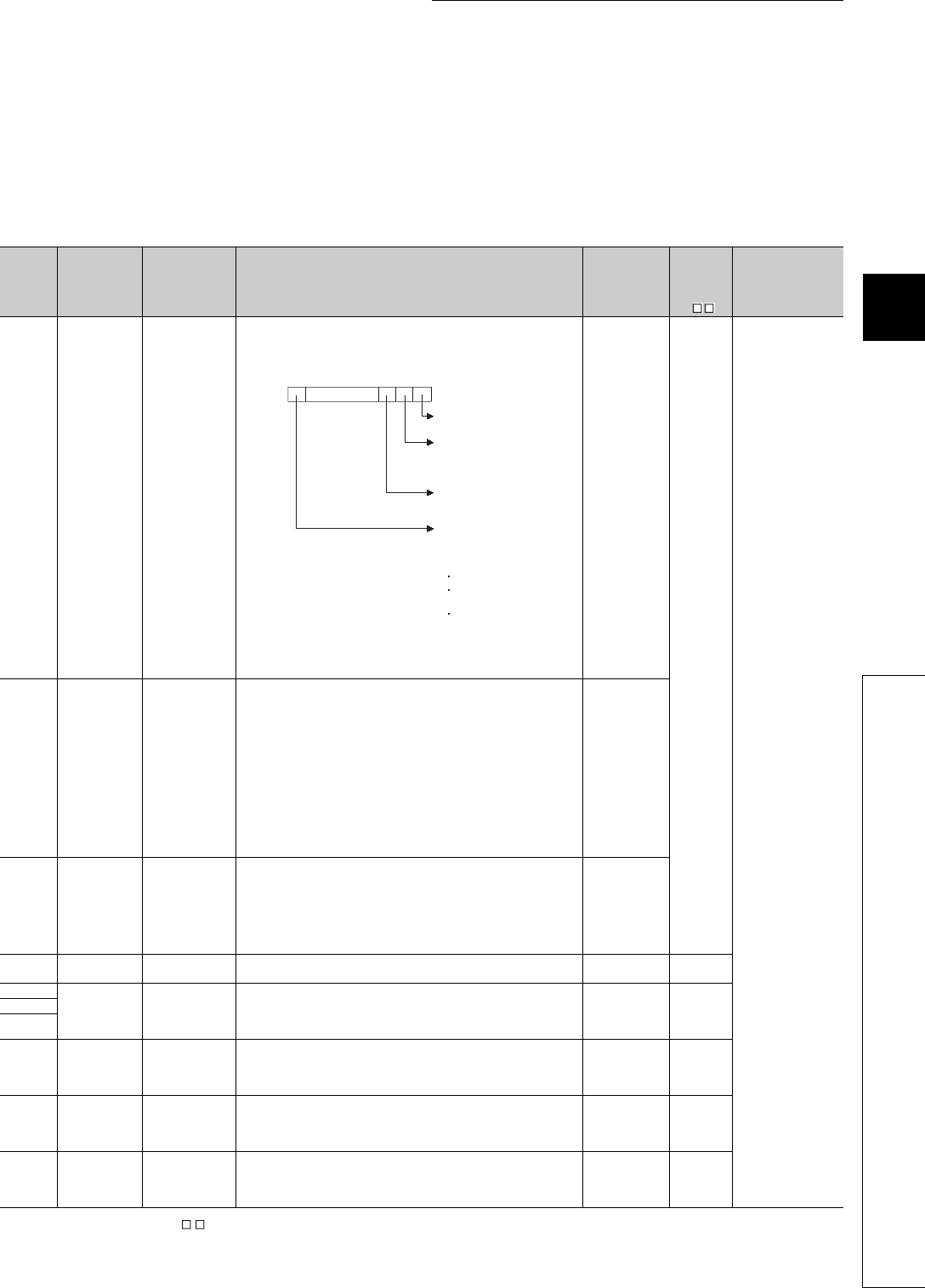

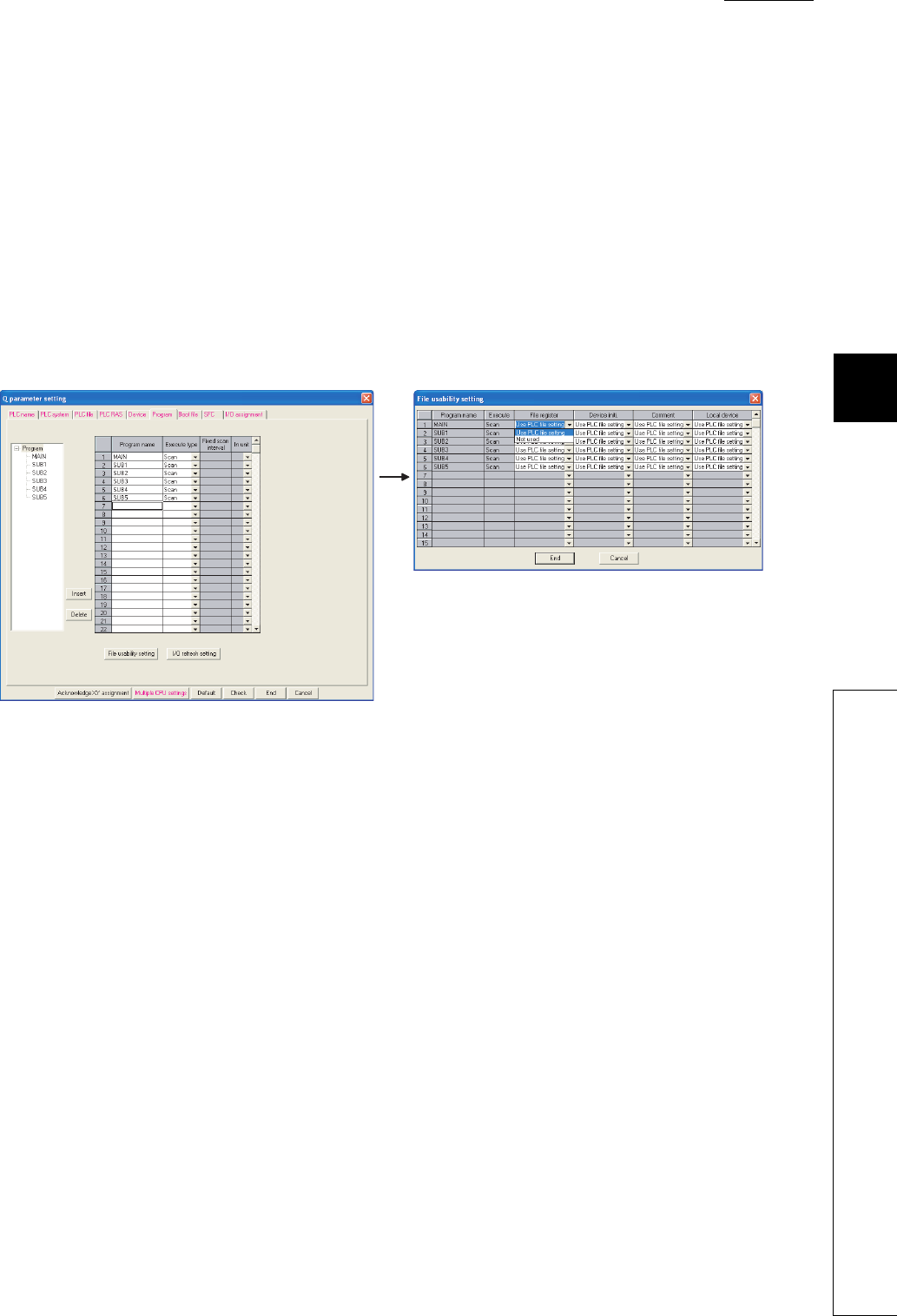

(b) Dividing into multiple files according to the functions

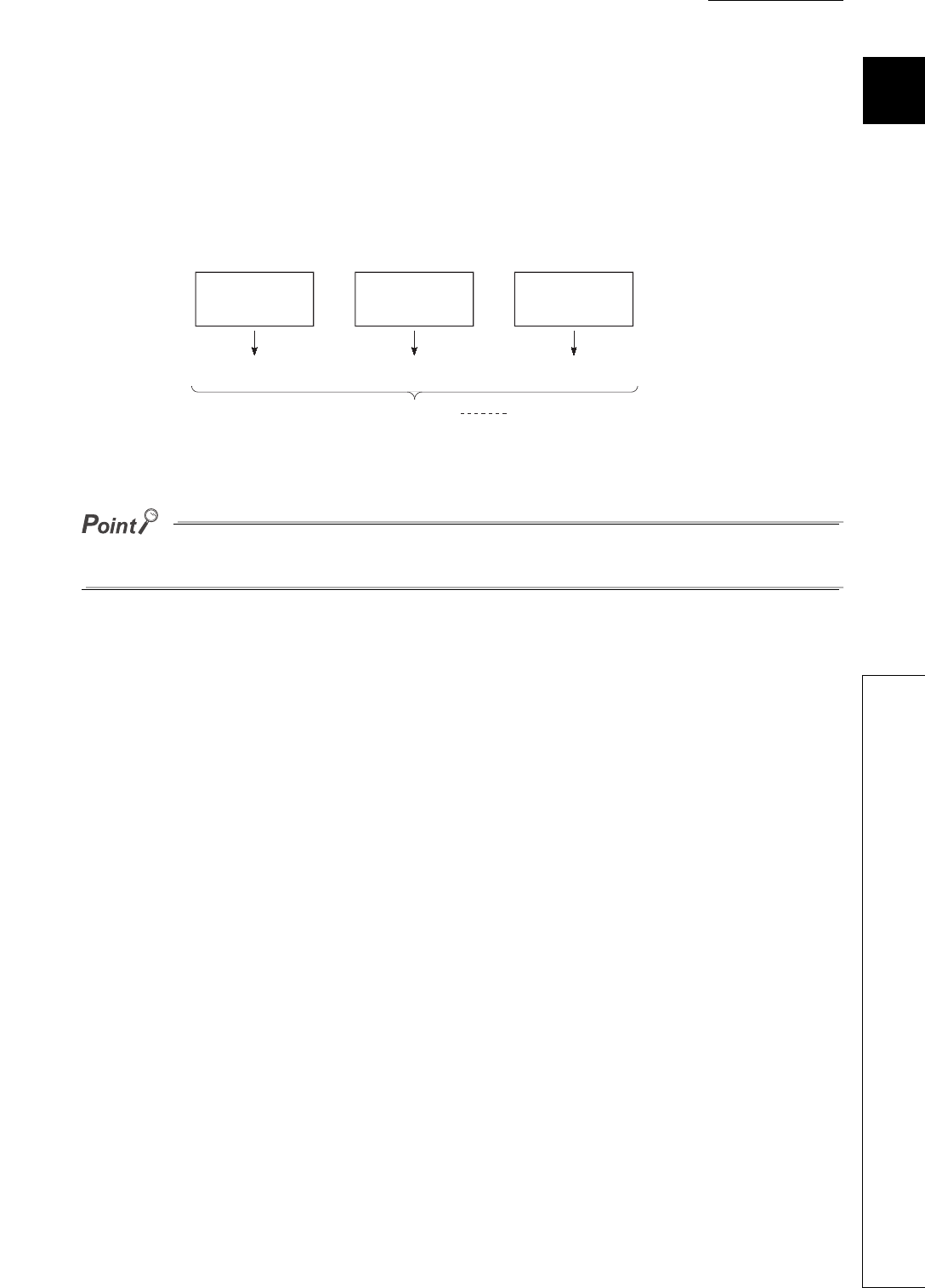

*1: The execution order and conditions can be set in the Program tab of the PLC parameter dialog box. ( Section 2.3(2)).

Figure 1.7 Dividing into multiple files according to the functions

Program memory/memory card

Program A

Initial processing

Processing contents

are divided according

to the functions.

Main processing

Communication

processing

Error processing

Program B

Program C

Program D

The execution order and

conditions for program

A to D can be set. *1

1 - 6

1.4 Devices and Instructions Useful for Programming

The CPU module is provided with devices and instructions useful for programming.

This section describes the outline of these devices and instructions.

(1) Various ways of device specification

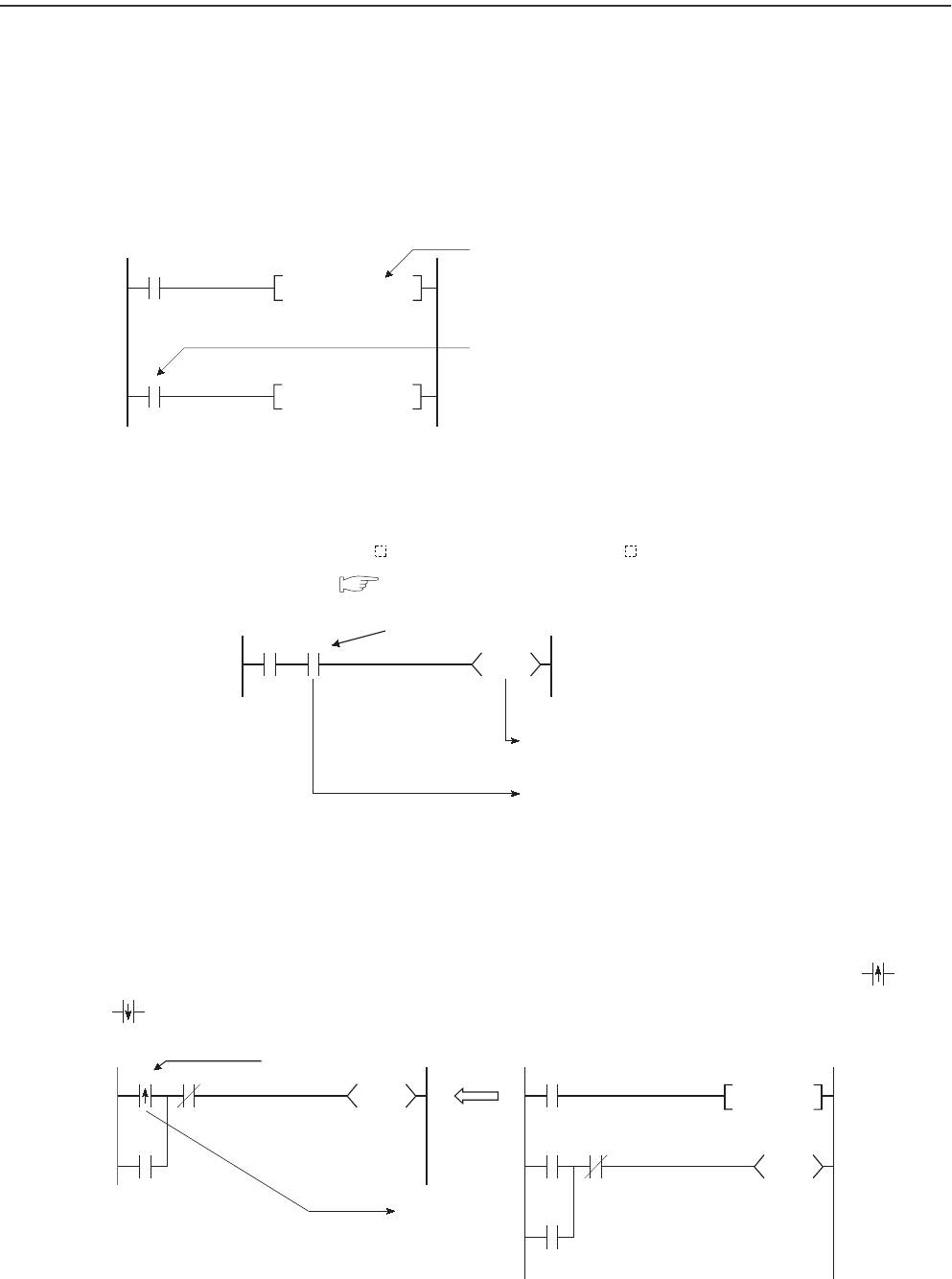

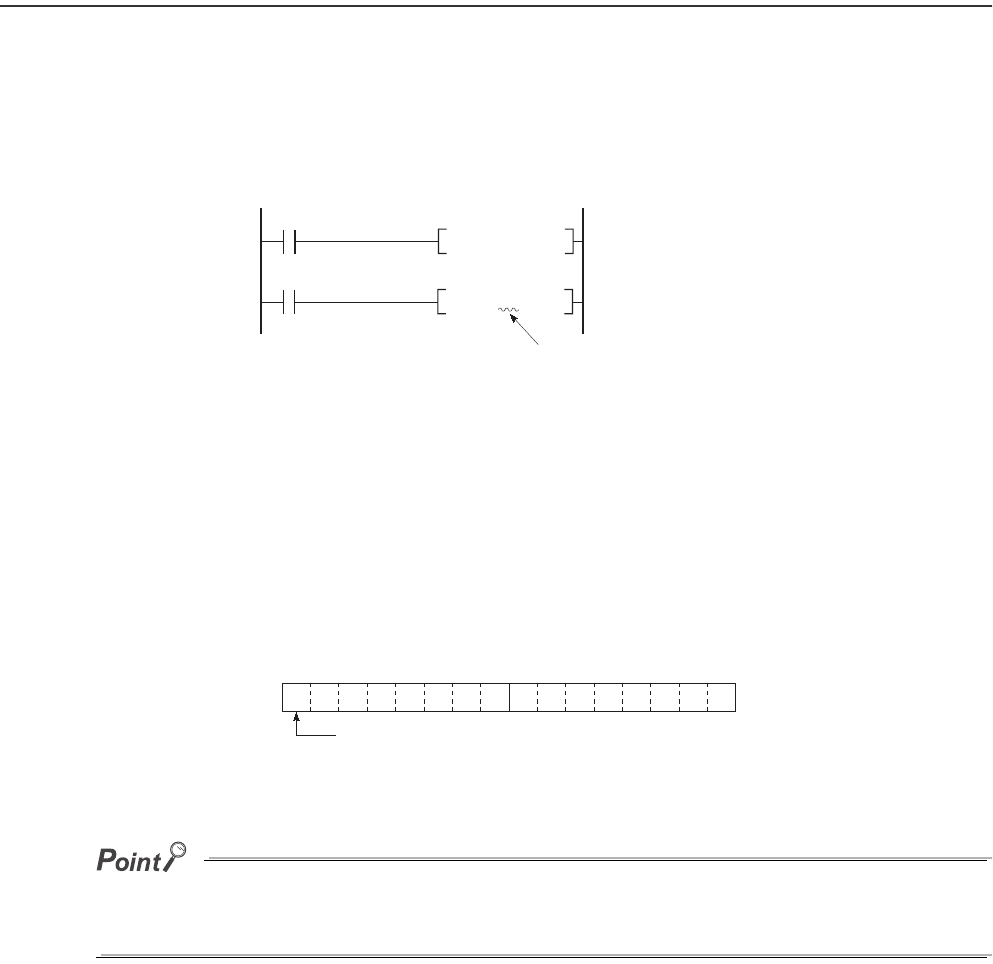

(a) Using each bit of a word device as a contact or coil

By specifying a bit of a word device, the bit can be used as a contact or coil.

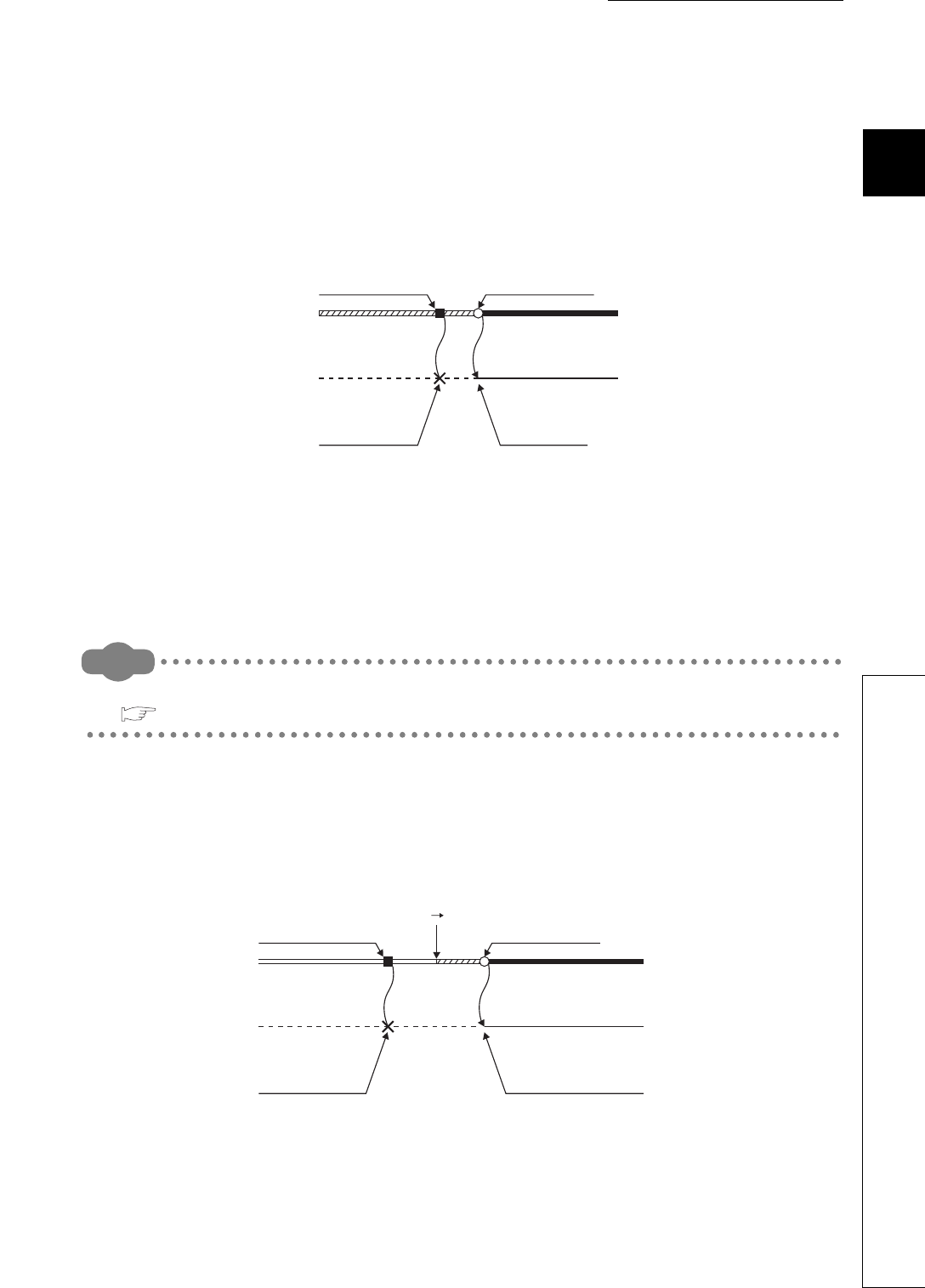

(b) Easy direct processing in units of one point

Use of the direct access input (DX ) and direct access output (DY ) enables easy direct processing (in units

of one point) in the program. ( Section 3.8.2)

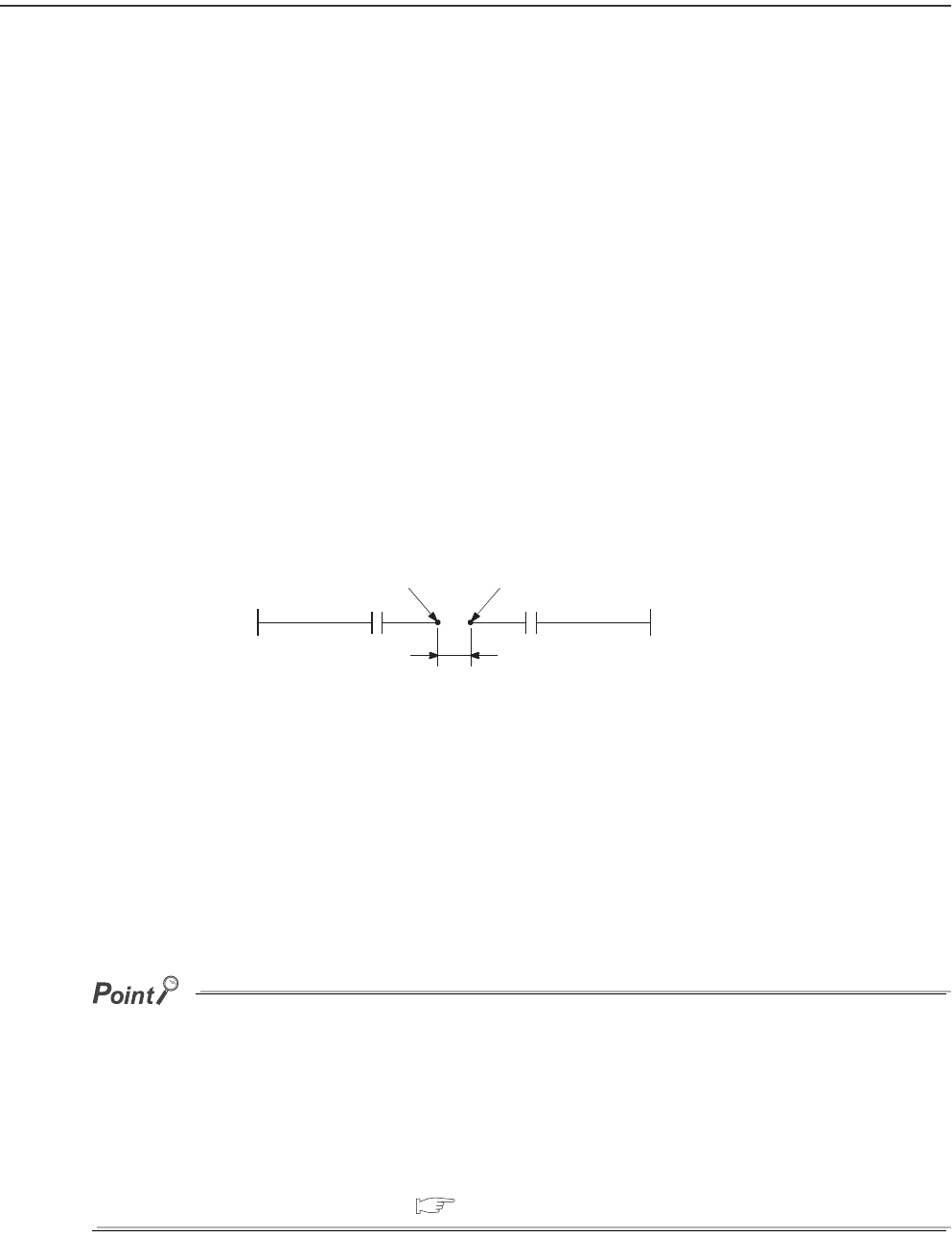

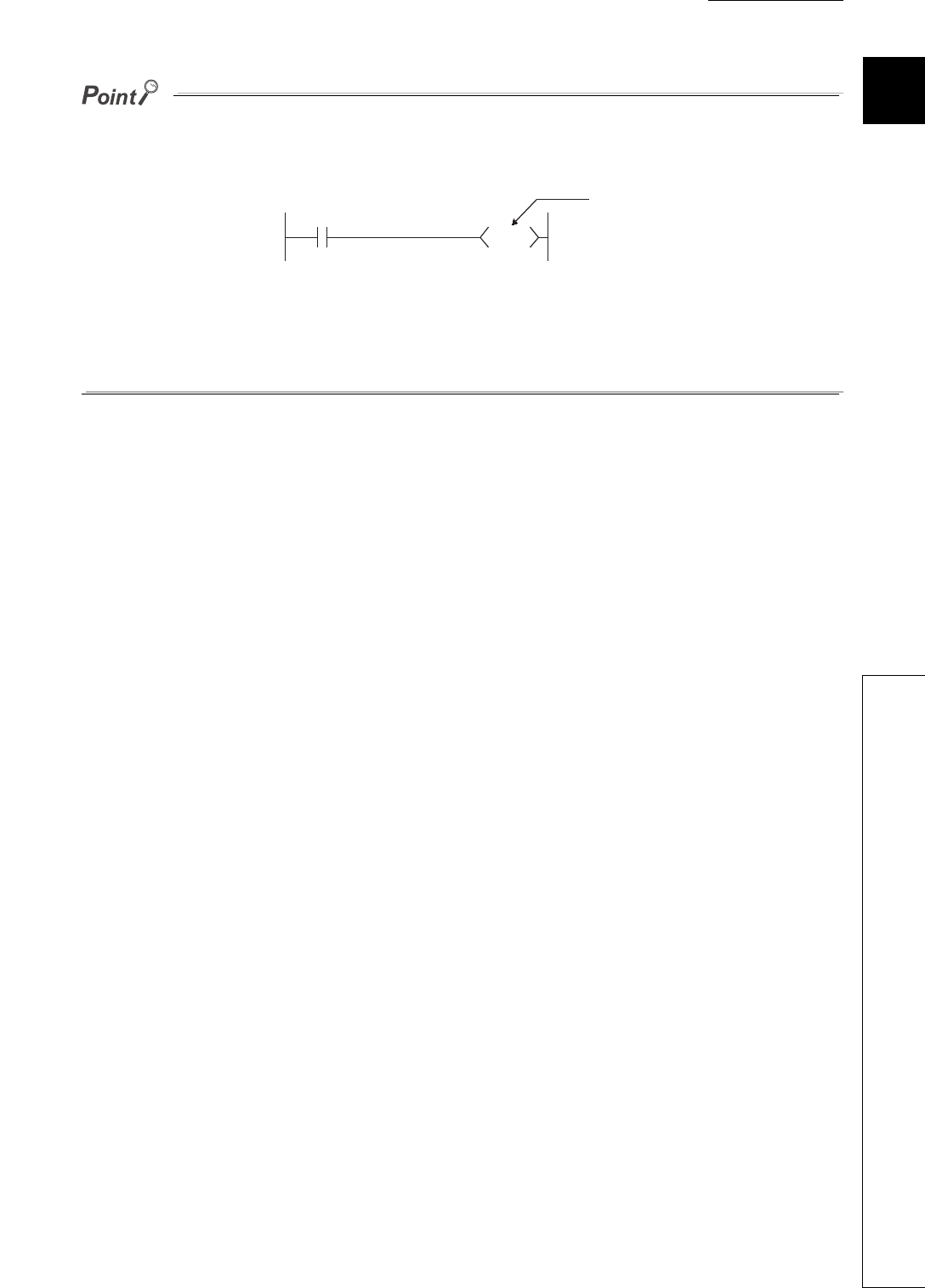

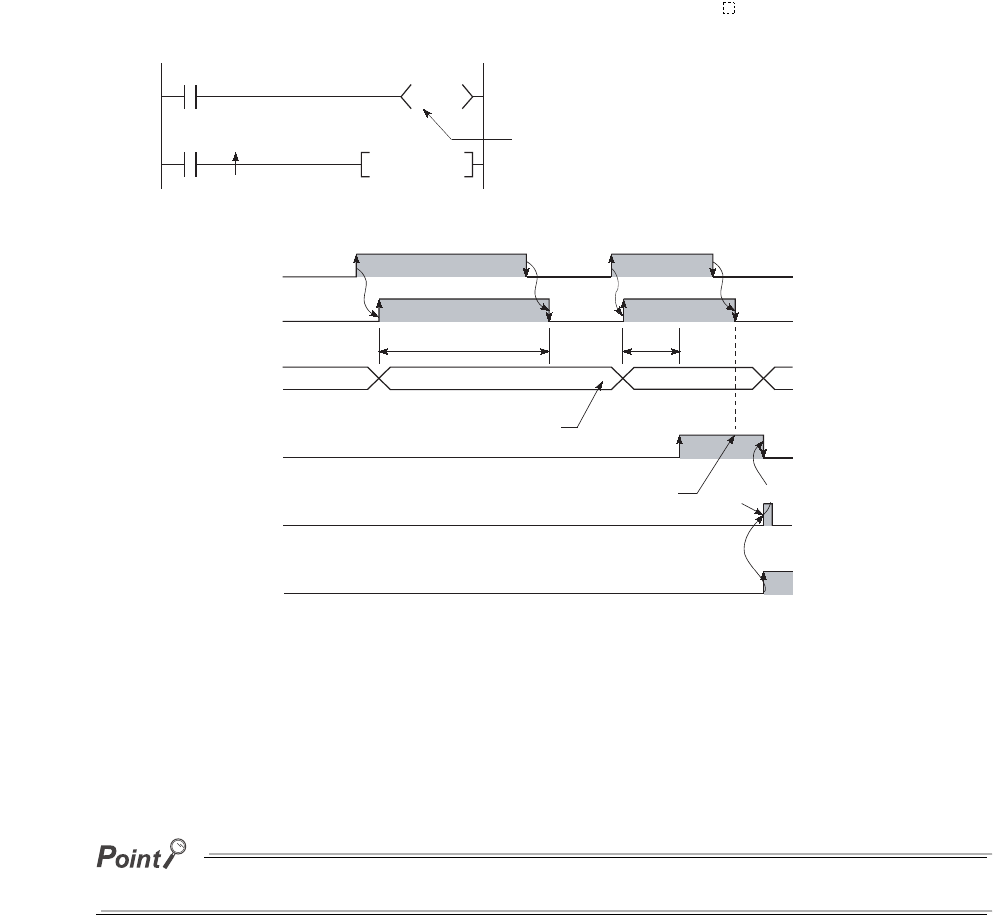

(c) No input pulse conversion required by using a differential contact

Pulse conversion processing for inputs is no longer required with the use of a differential contacts ( and

).

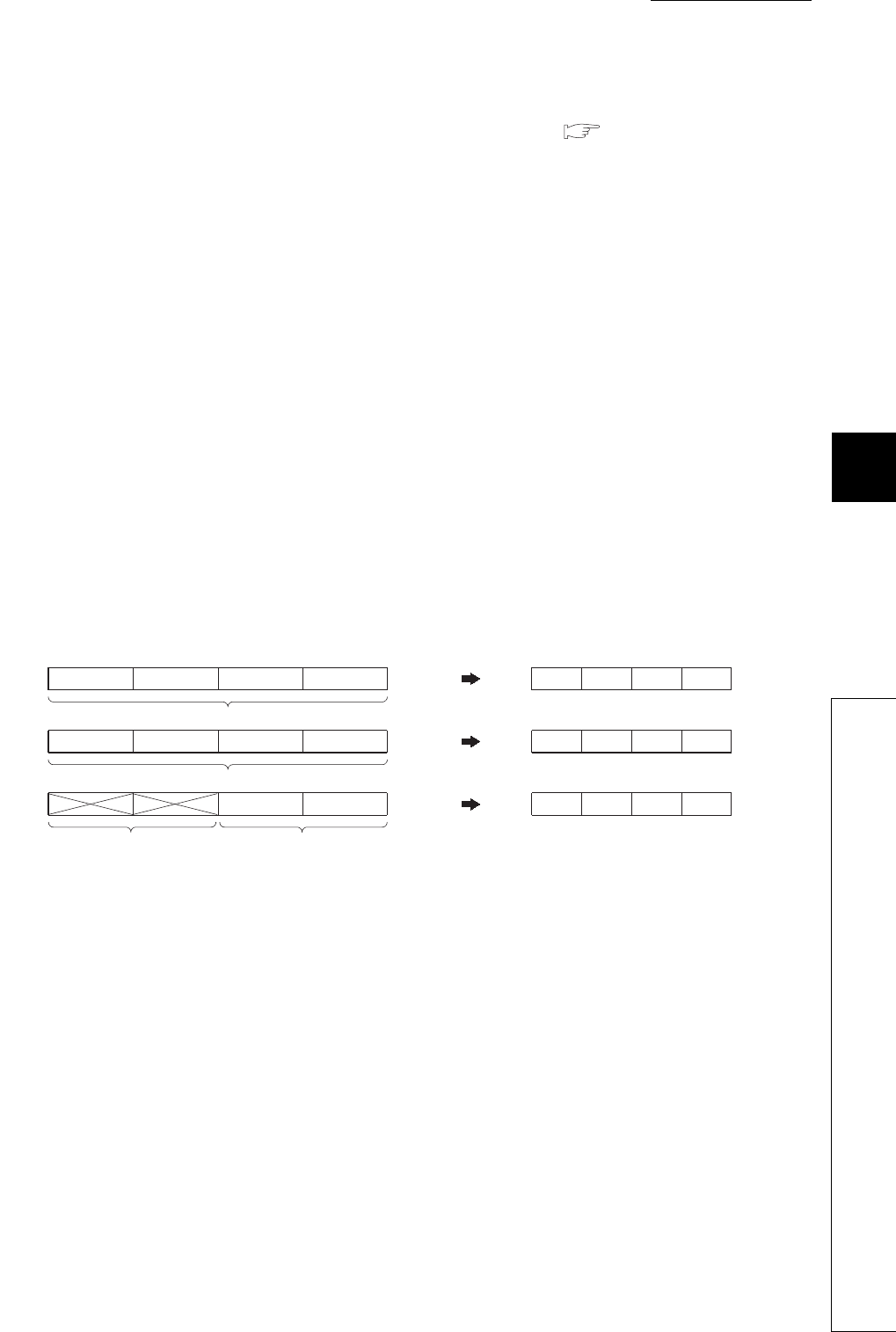

Figure 1.8 Specifying a bit of a word device

Figure 1.9 Direct processing in units of one point

Figure 1.10 Use of a differential contact

D0.5

SET Y10

X0

SET D0.5

A bit-specified word device (turns on

(switches to 1) the 5th bit (b5) of D0.)

A bit-specified word device (turns on/off depending

on the on/off (1/0) status of the 5th bit (b5) of D0.)

M0 DX10

DY100

Direct access input

On/off data is output to the

output module when the

instruction is executed.

On/off data is input from

the input module when the

instruction is executed.

X0 X1

Y100

M0

X0

Y100

Y100

X1

Y100

Differential contact

On at the rising

edge of X0

M0

PLS

CHAPTER1 OVERVIEW

1

2

3

4

5

6

7

8

1.4 Devices and Instructions Useful for Programming

1 - 7

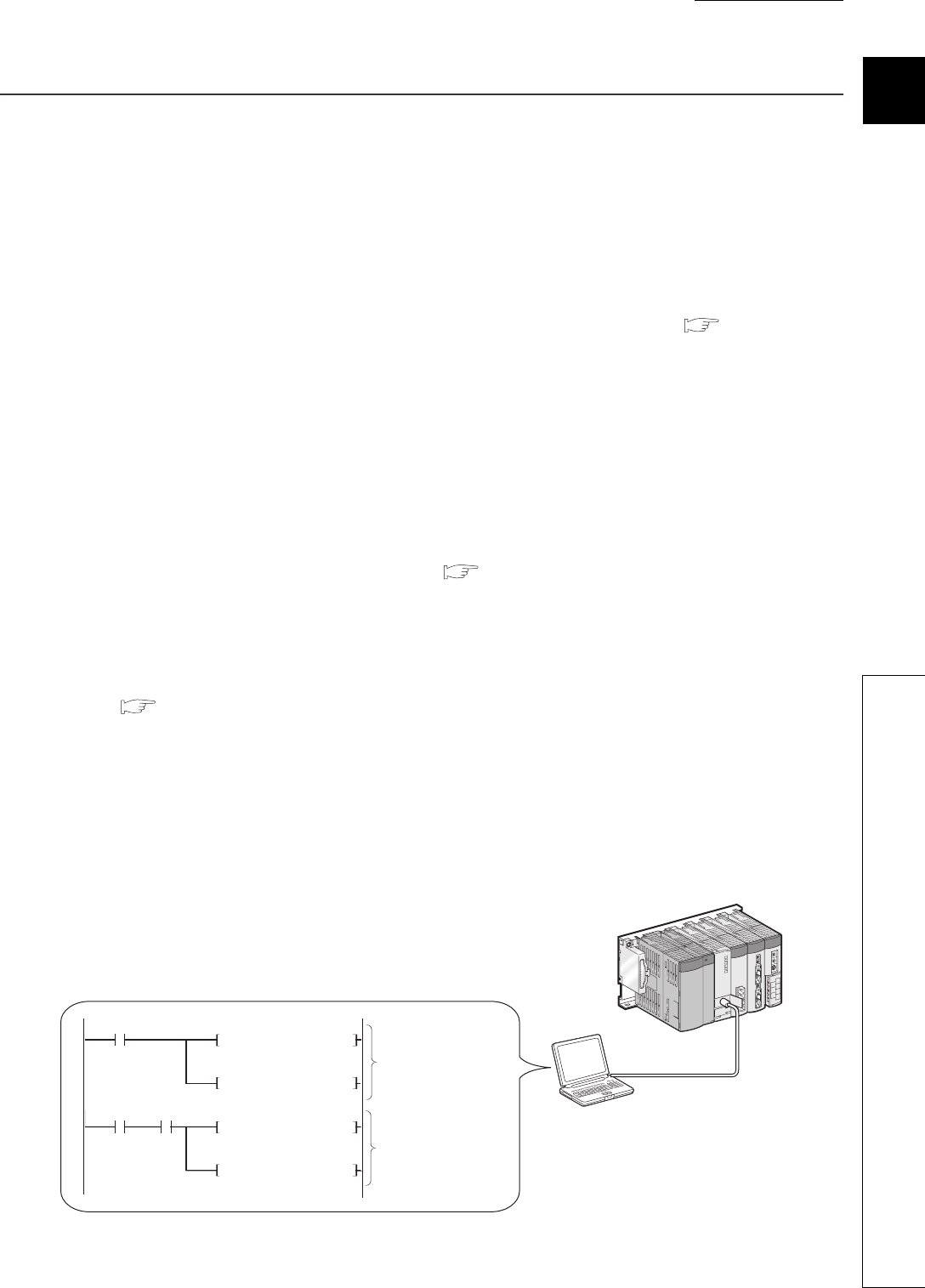

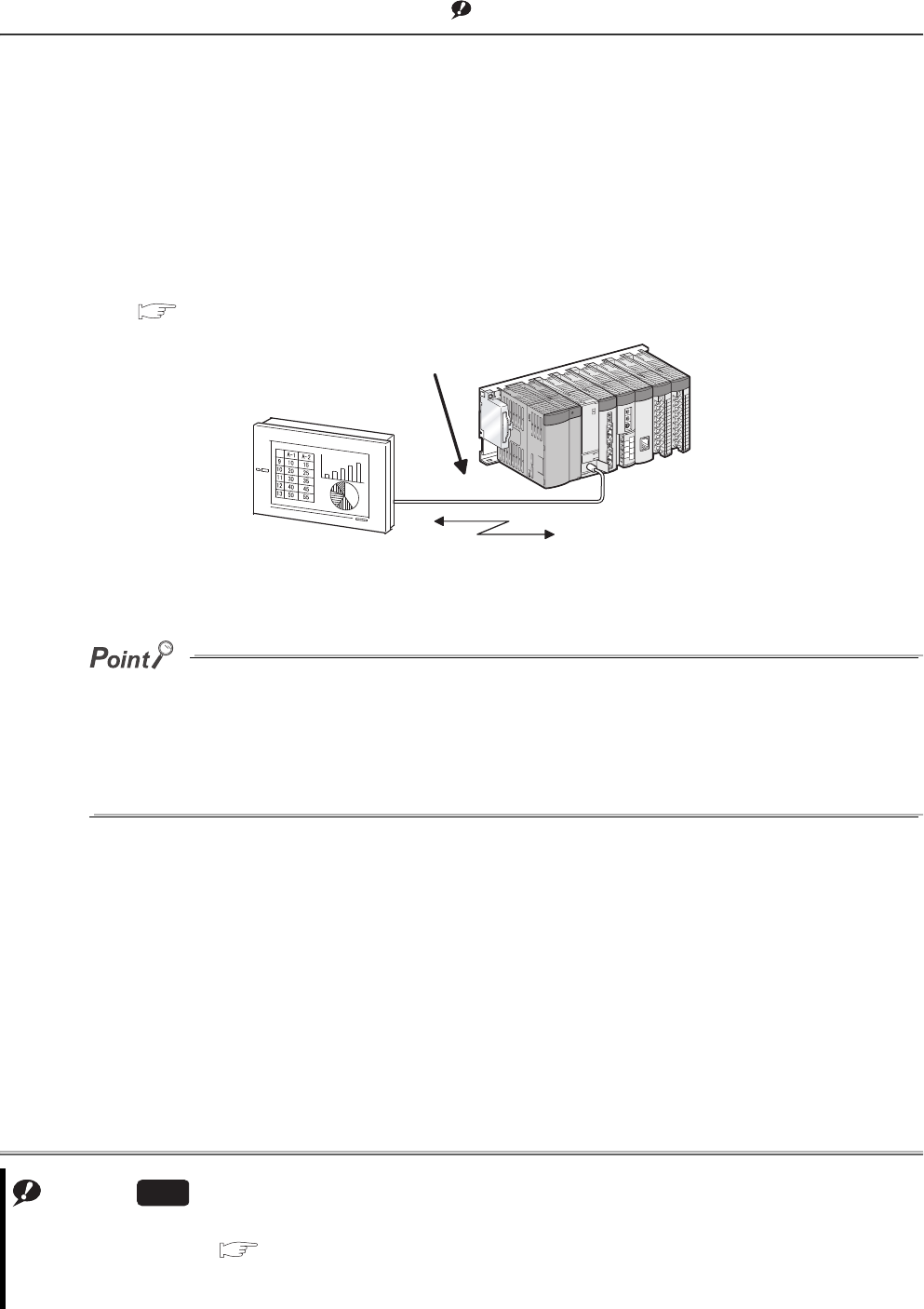

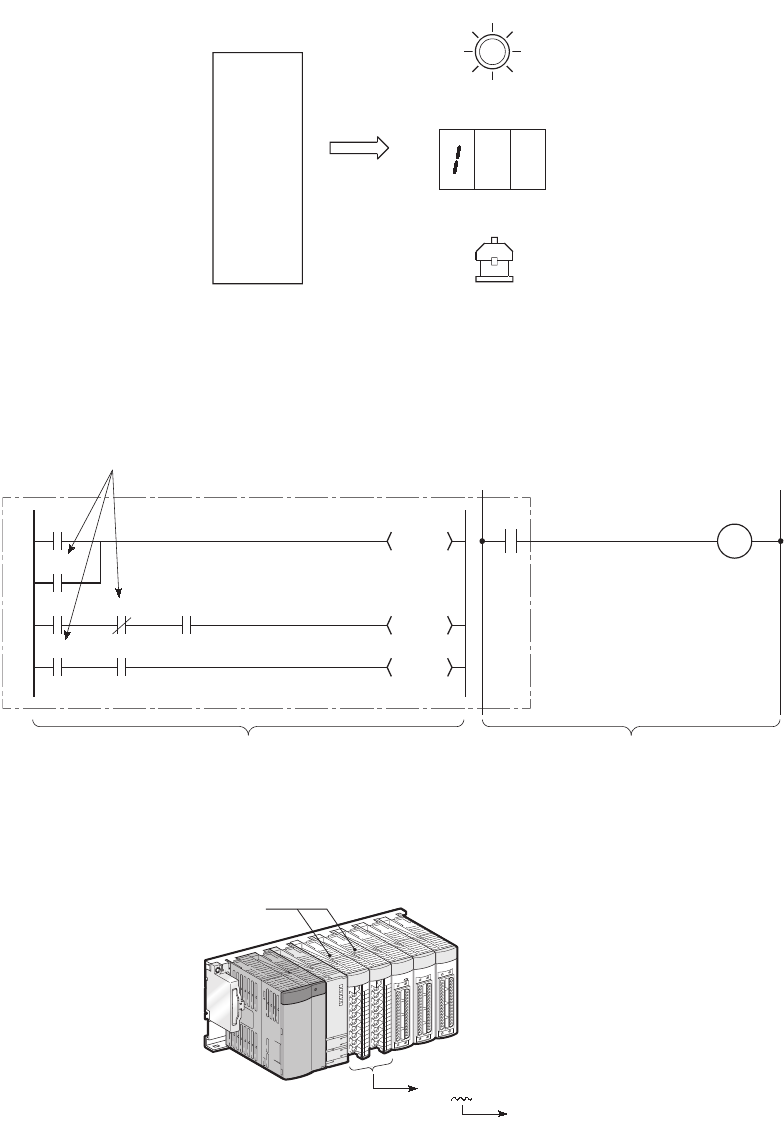

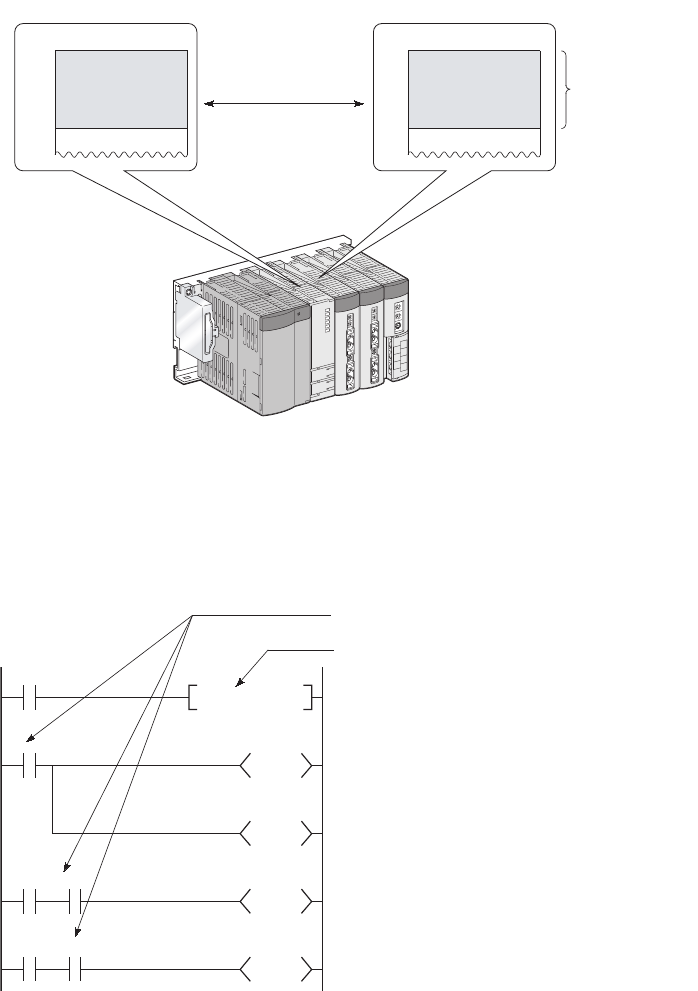

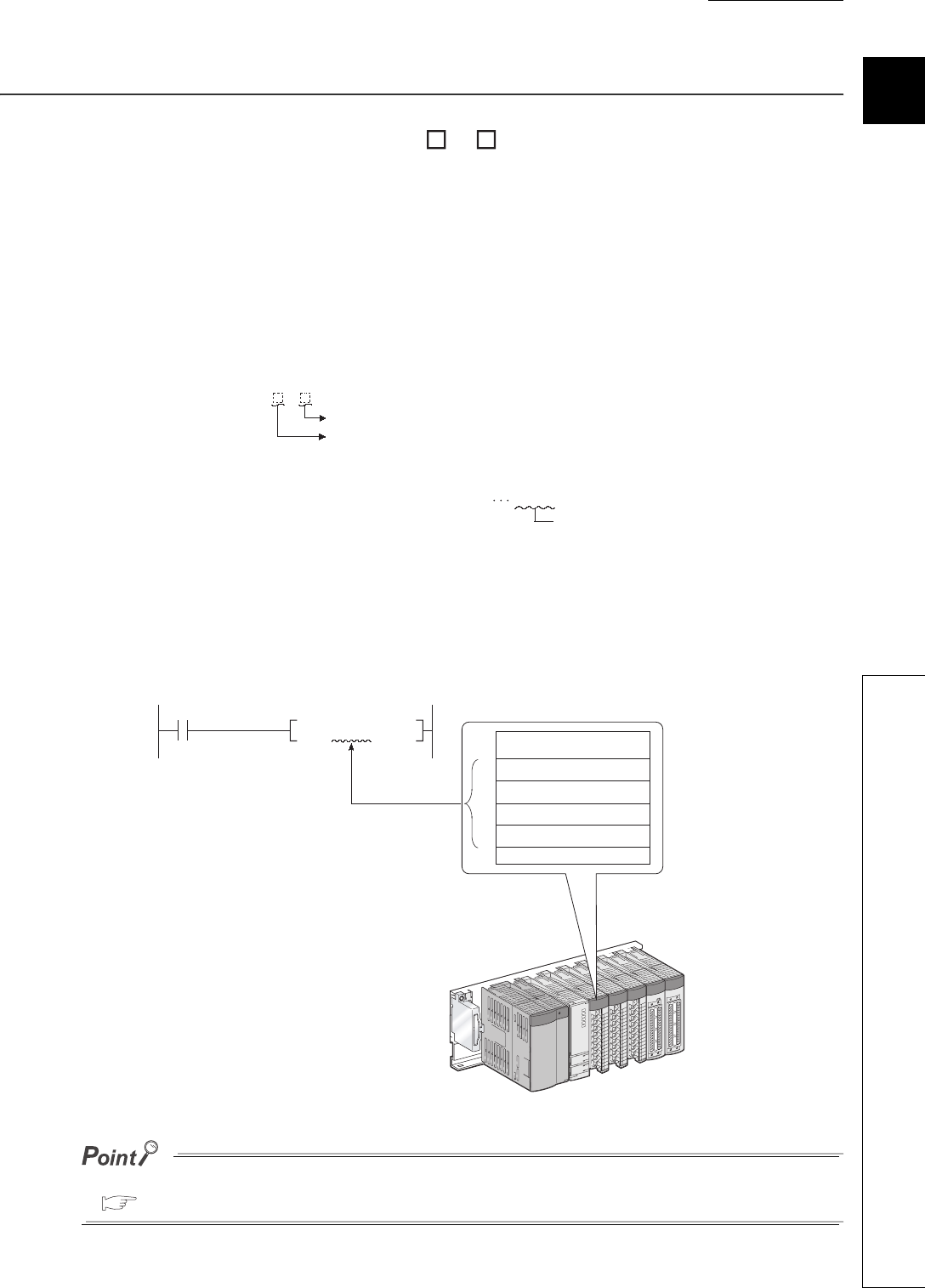

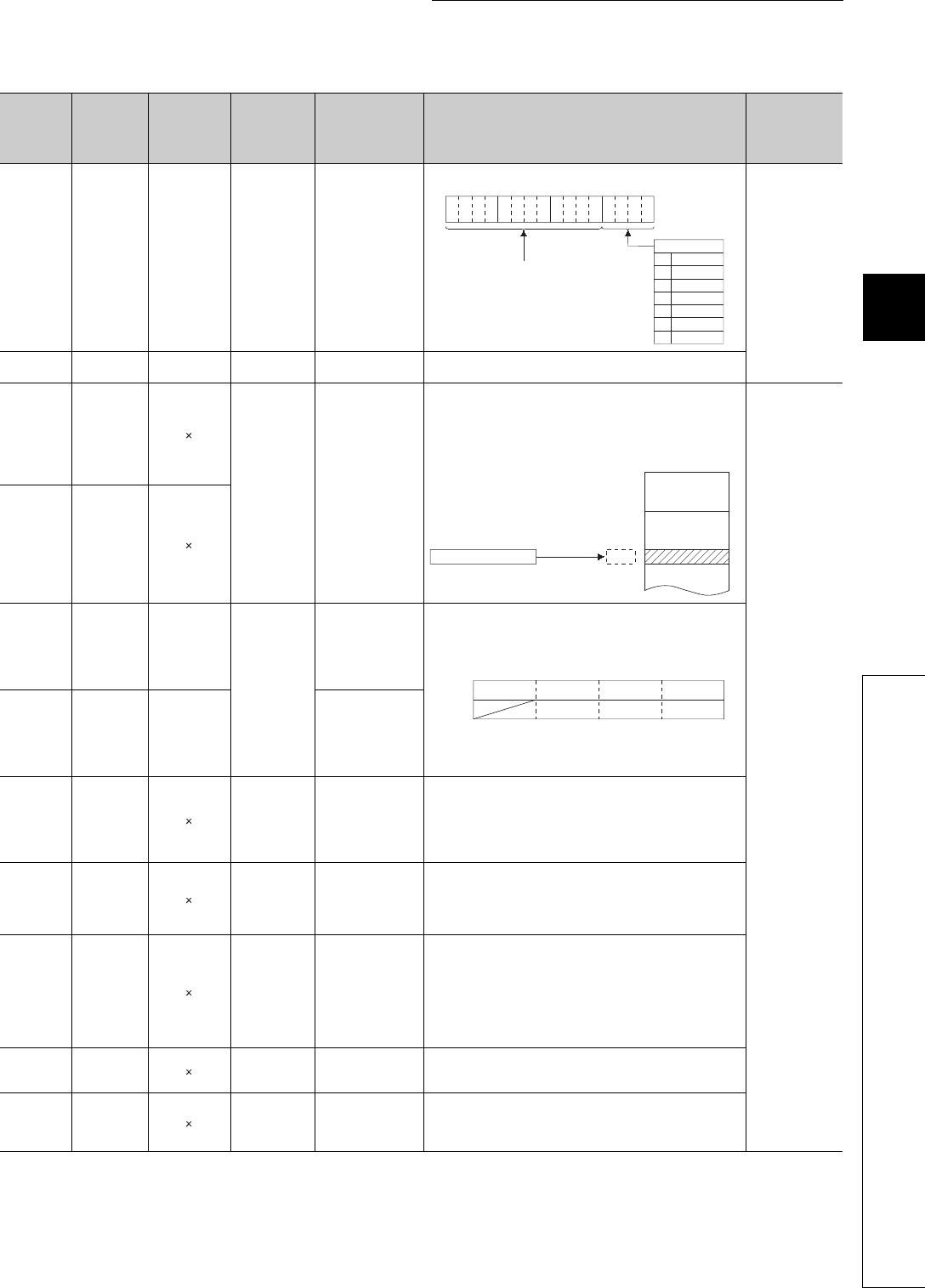

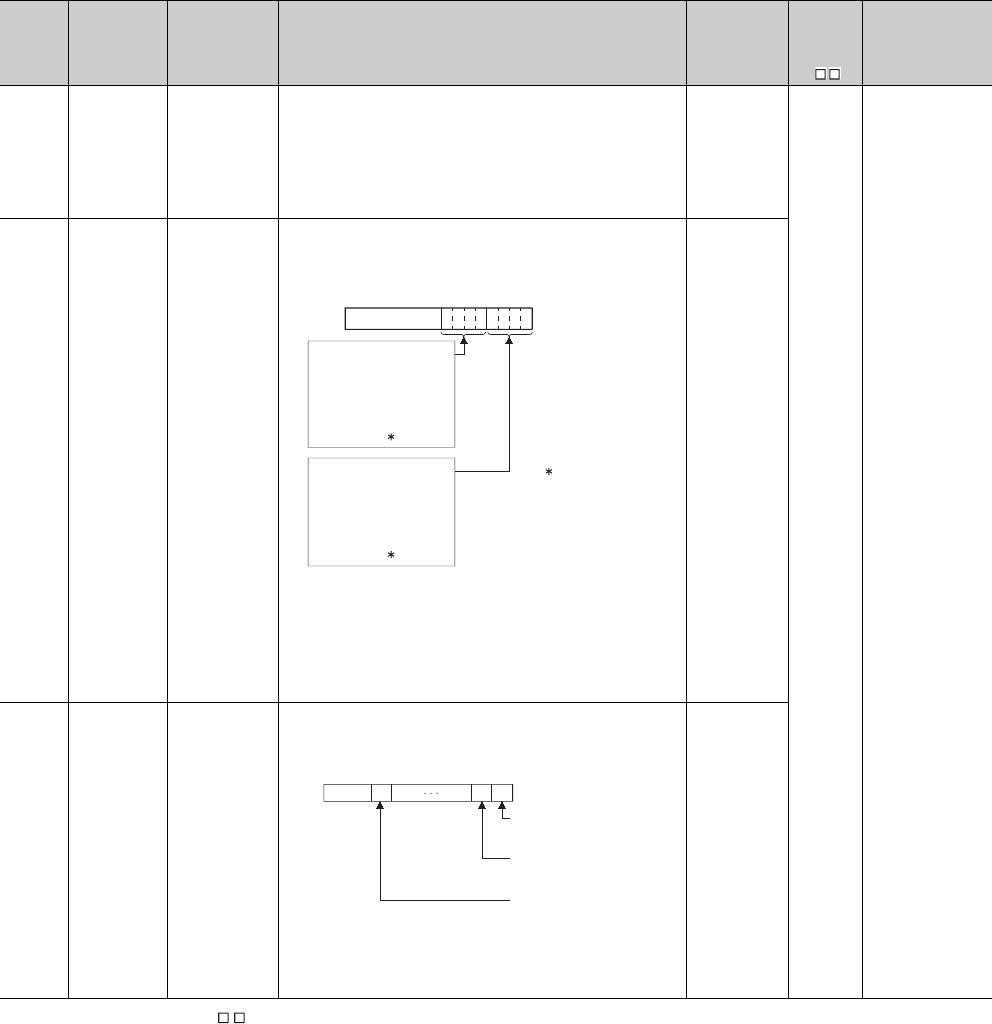

(d) Direct access to the buffer memory of the intelligent function module

The buffer memory of the intelligent function module can be used as a device area in a program.

( Section 9.5.1)

(e) Direct access to the link devices

The link devices (LX, LY, LB, LW, SB, or SW) in network modules can be directly accessed without

the refresh setting. ( Section 9.4)

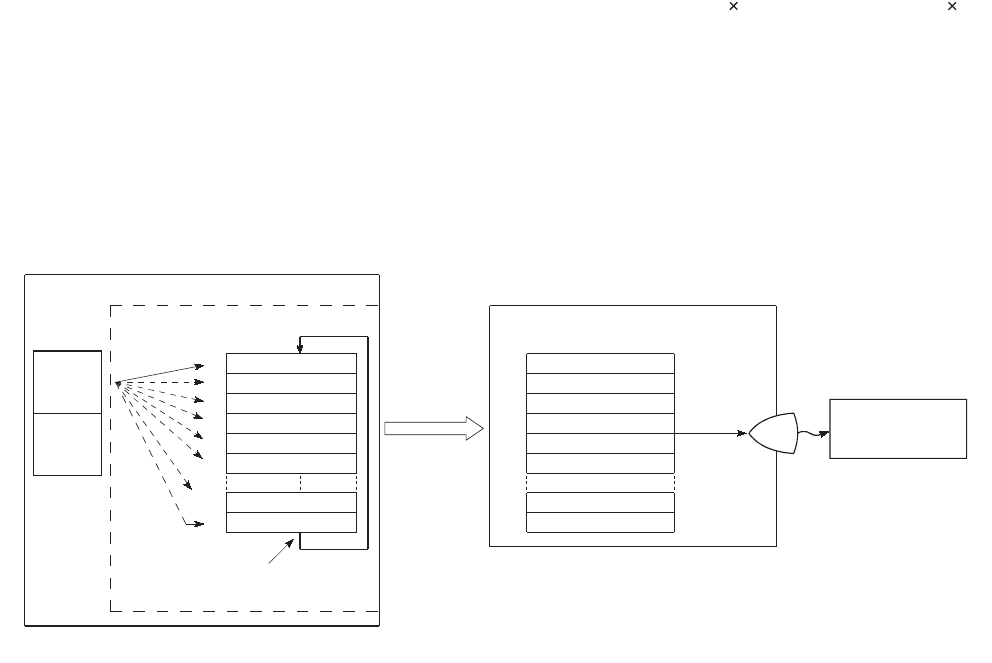

Figure 1.11 Direct access to the buffer memory of the intelligent function module

Figure 1.12 Direct access to the link devices

X0

D0U4\G12

*1

+P

*1:U4\G12

The CPU module can read the

data in the buffer memory

address 12 of the Q64AD.

I/O number: X/Y40 to X/Y4F

Specifying the buffer

memory address

Specifying the I/O number of

the intelligent function module

Power supply module

CPU module

Input module (16 points)

Input module (16 points)

Input module (16 points)

Q64AD (16 points)

Q64AD (16 points)

Q62AD (16 points)

Output module (16 points)

Output module (16 points)

M0 J5\W12

The CPU module can directly read the data in the

link register (LW12) of the number 5 network module.

Network number 5

Specifying the

link register

Specifying the

network number

D0

J5\W12+P

Power supply module

CPU module

Input module (16 points)

Input module (16 points)

Q68AD (16 points)

Q68AD (16 points)

Q62AD (16 points)

Output module (16 points)

Output module (16 points)

QJ71LP21-25

1 - 8

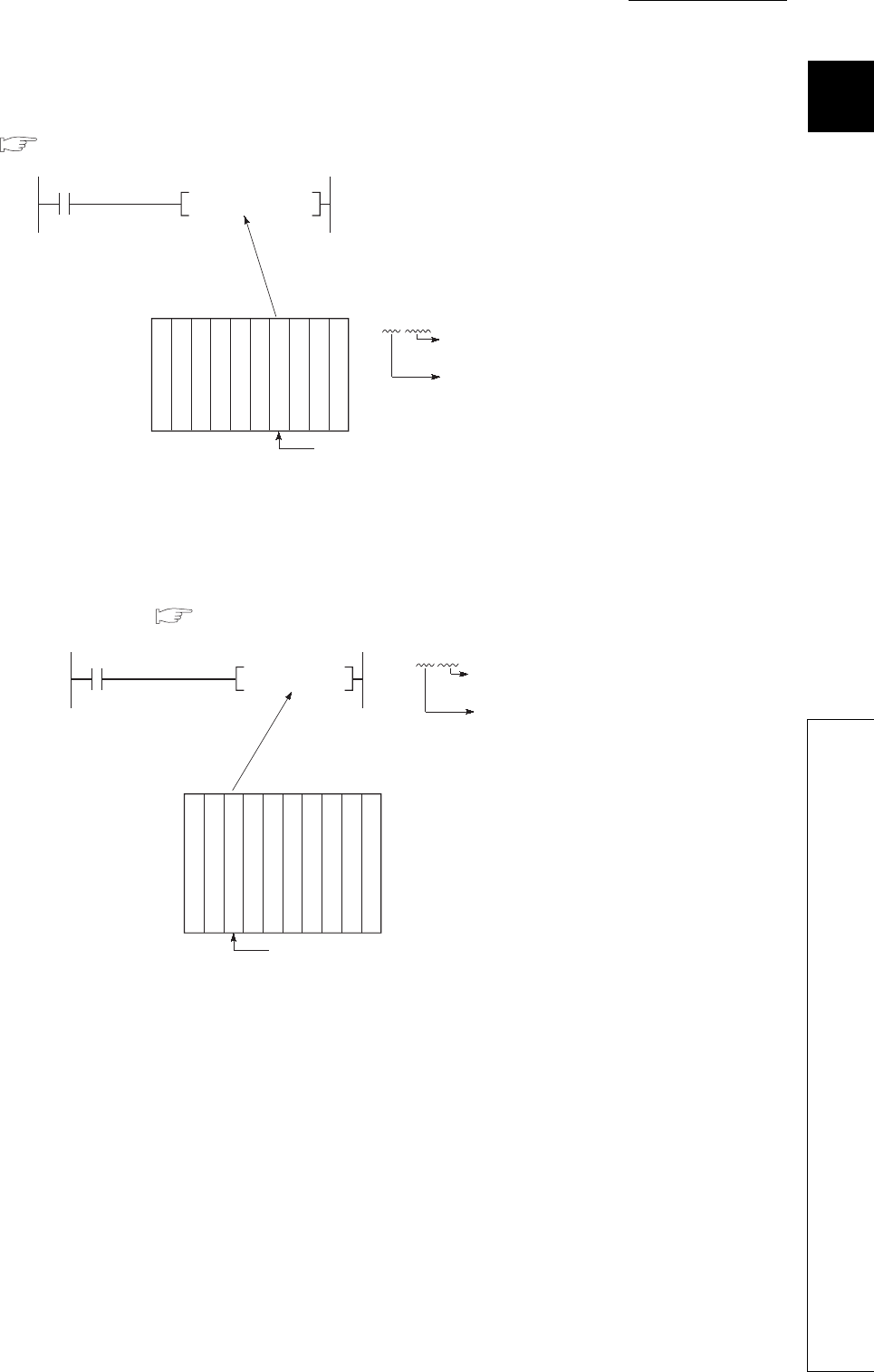

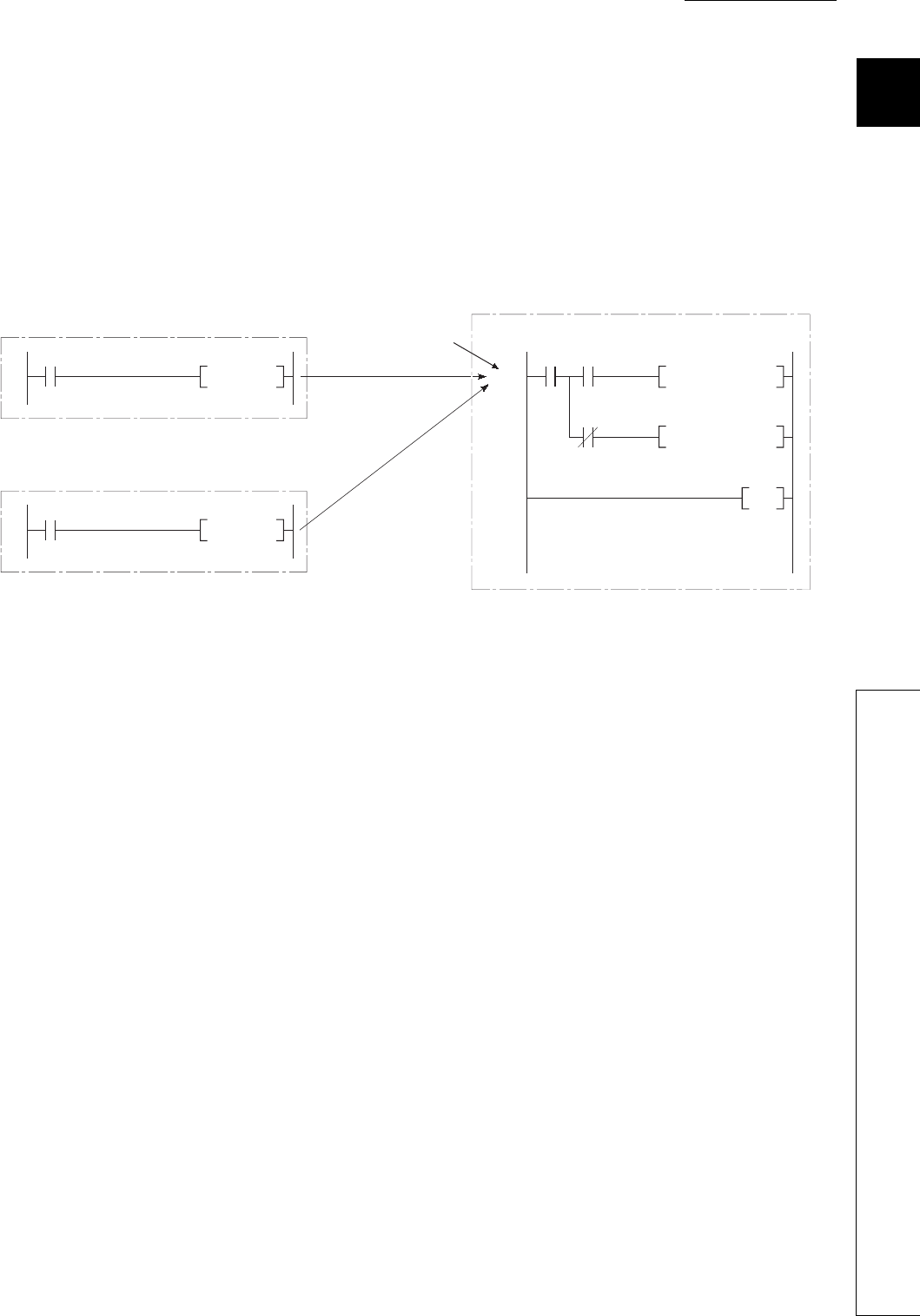

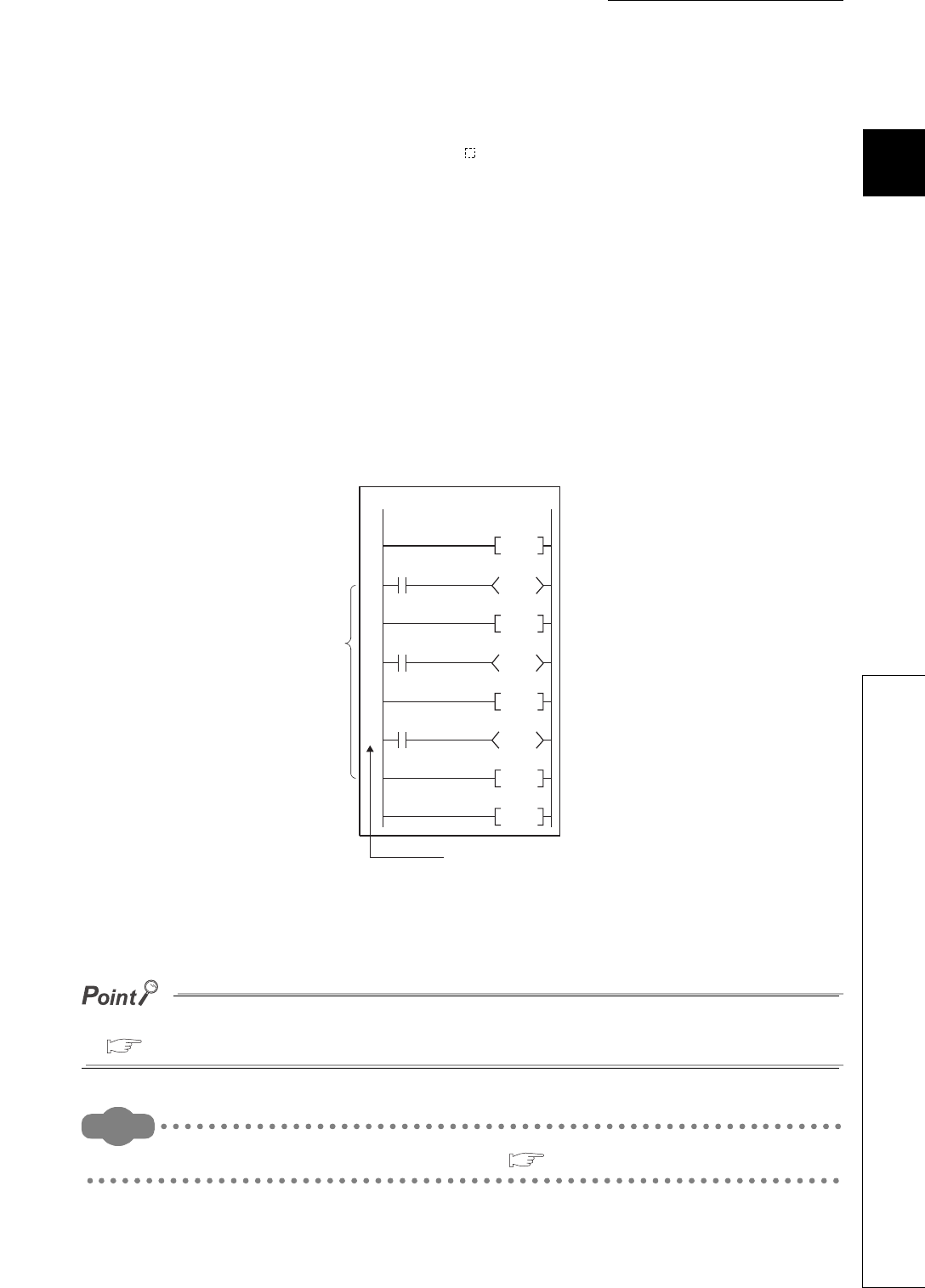

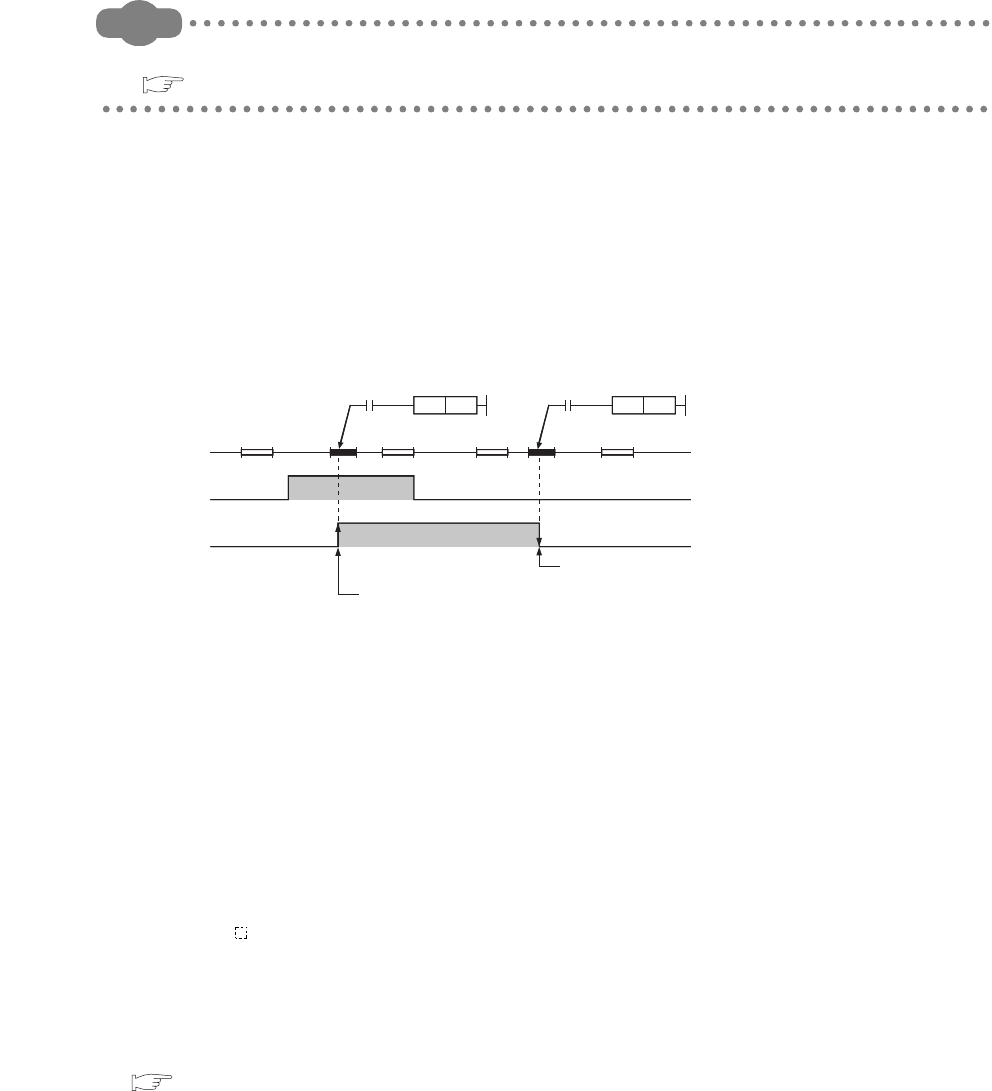

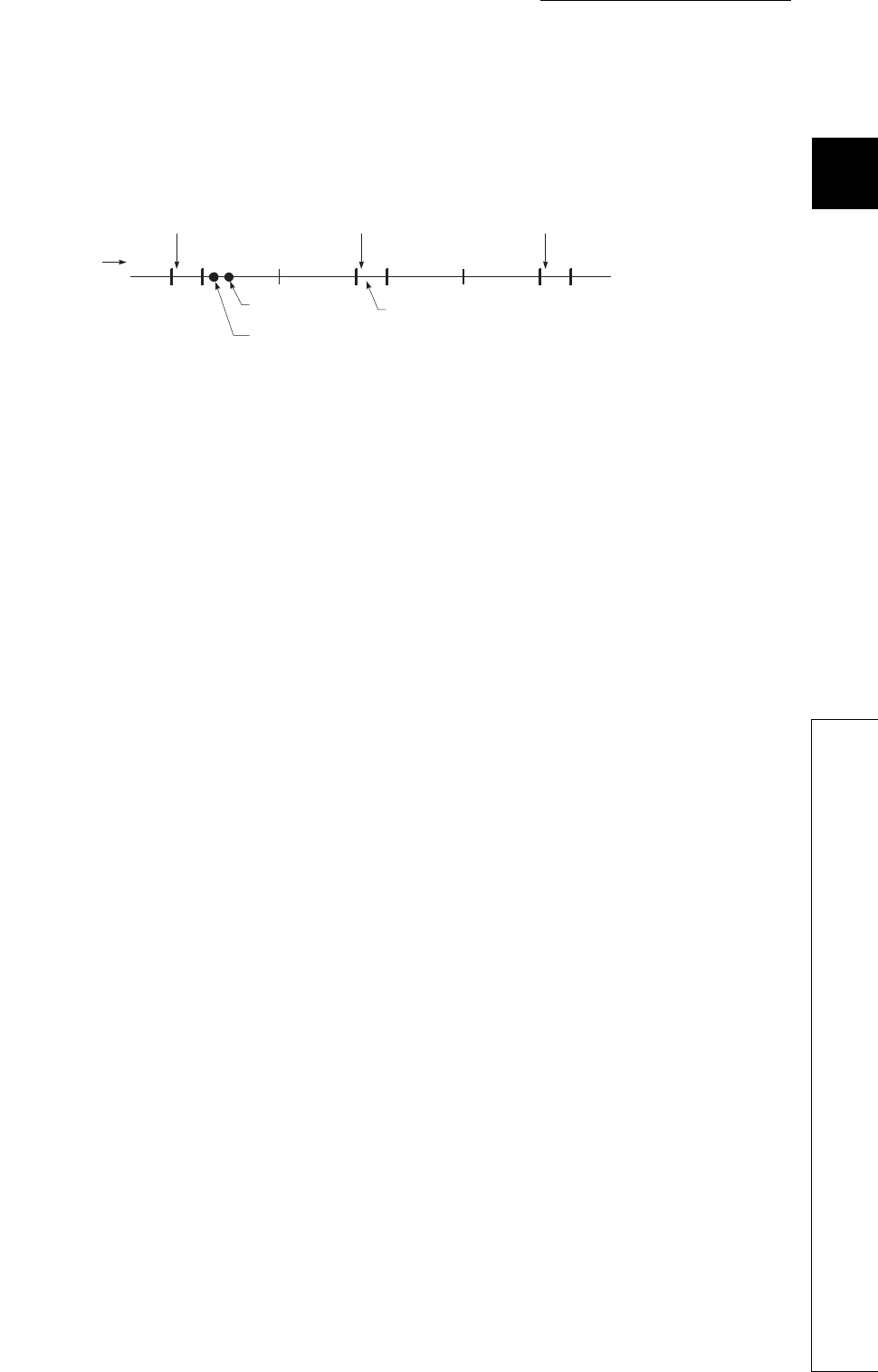

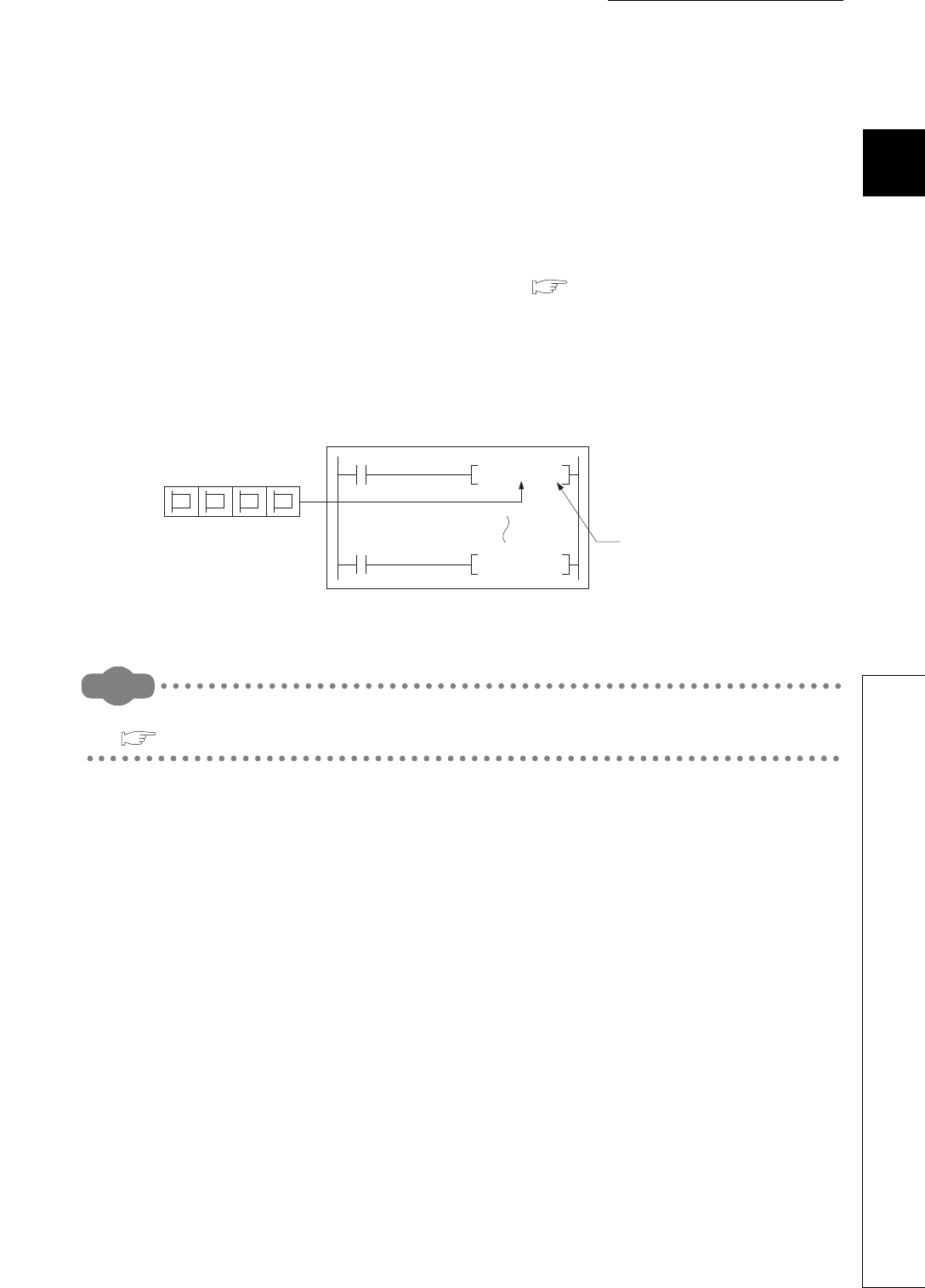

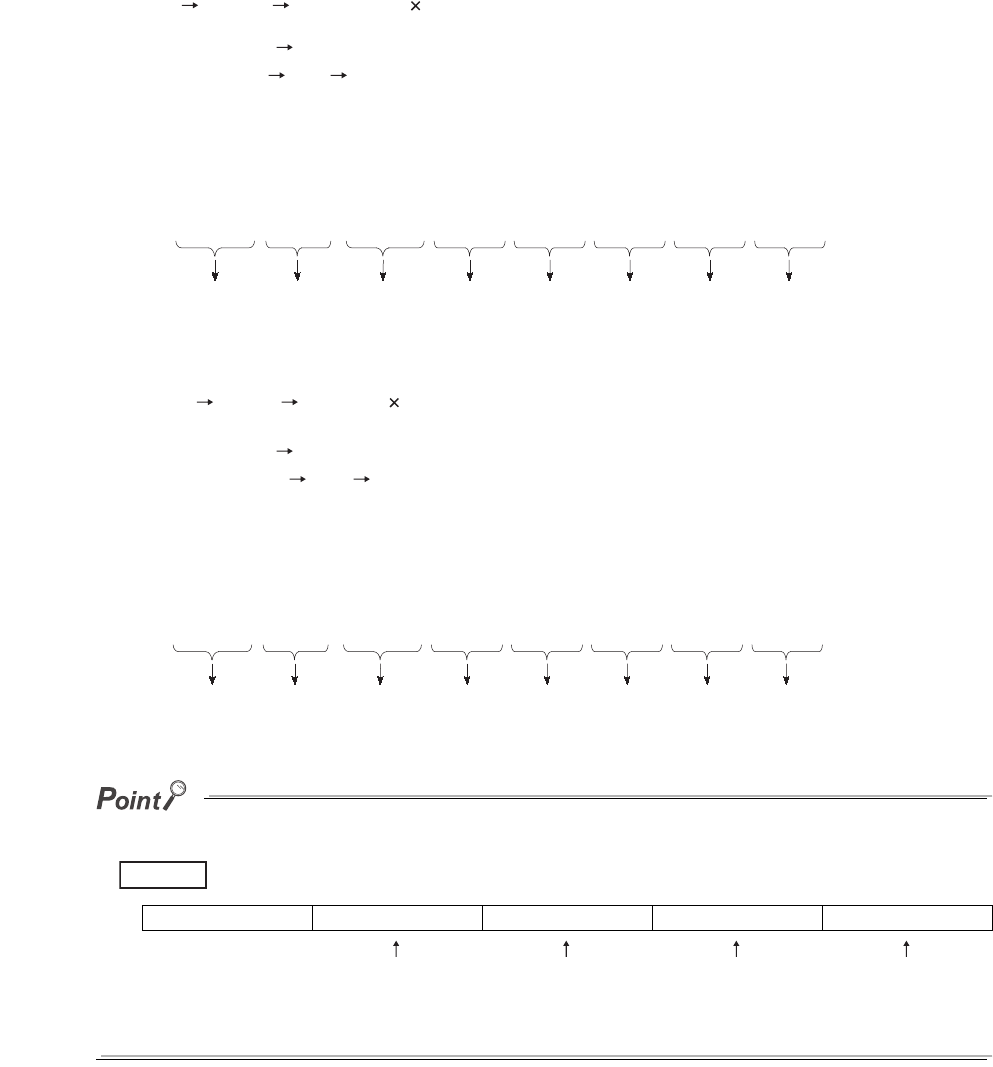

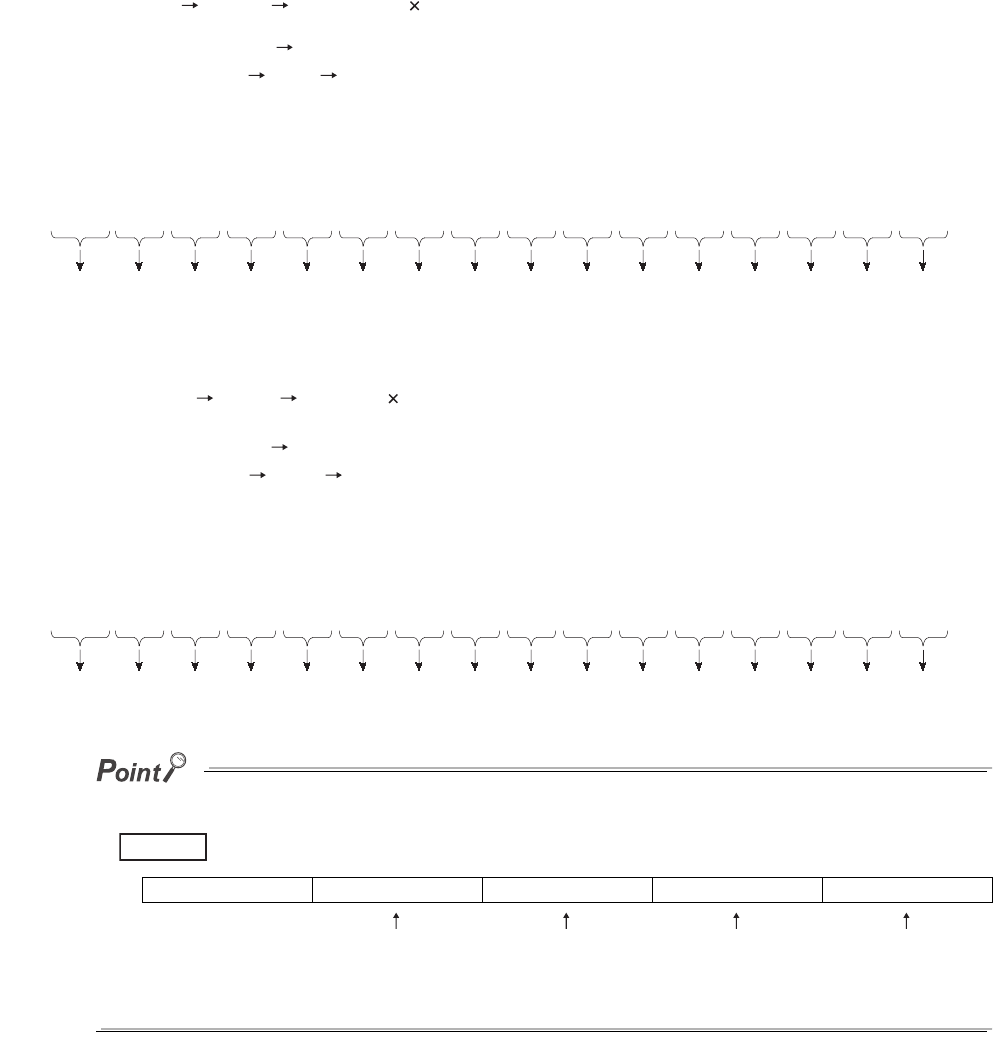

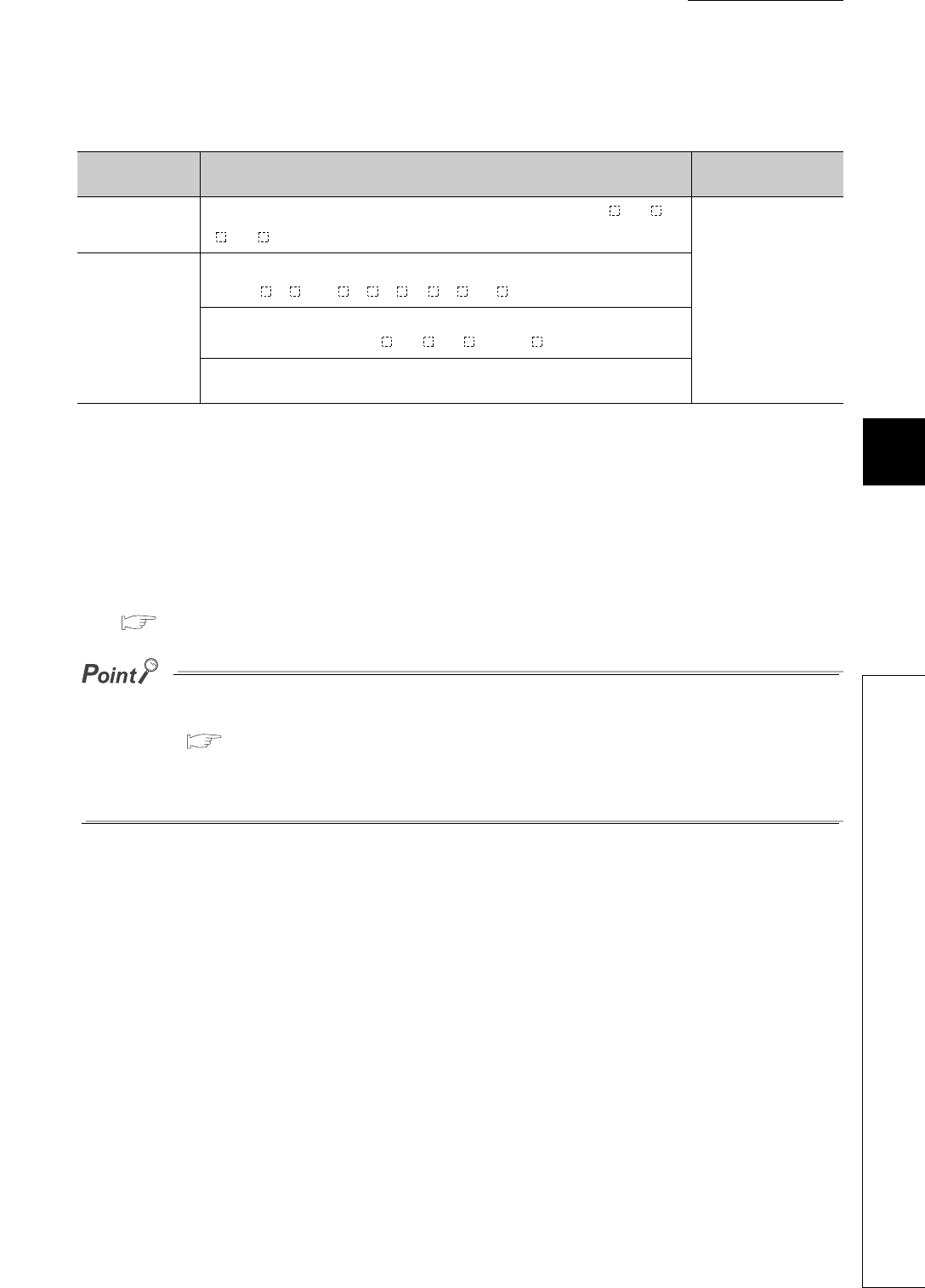

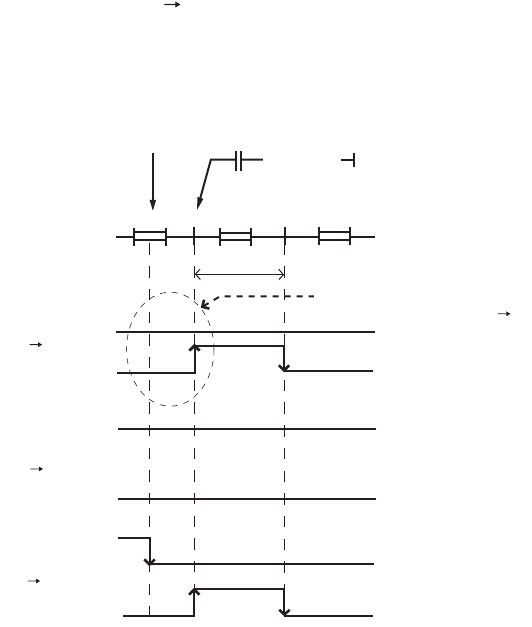

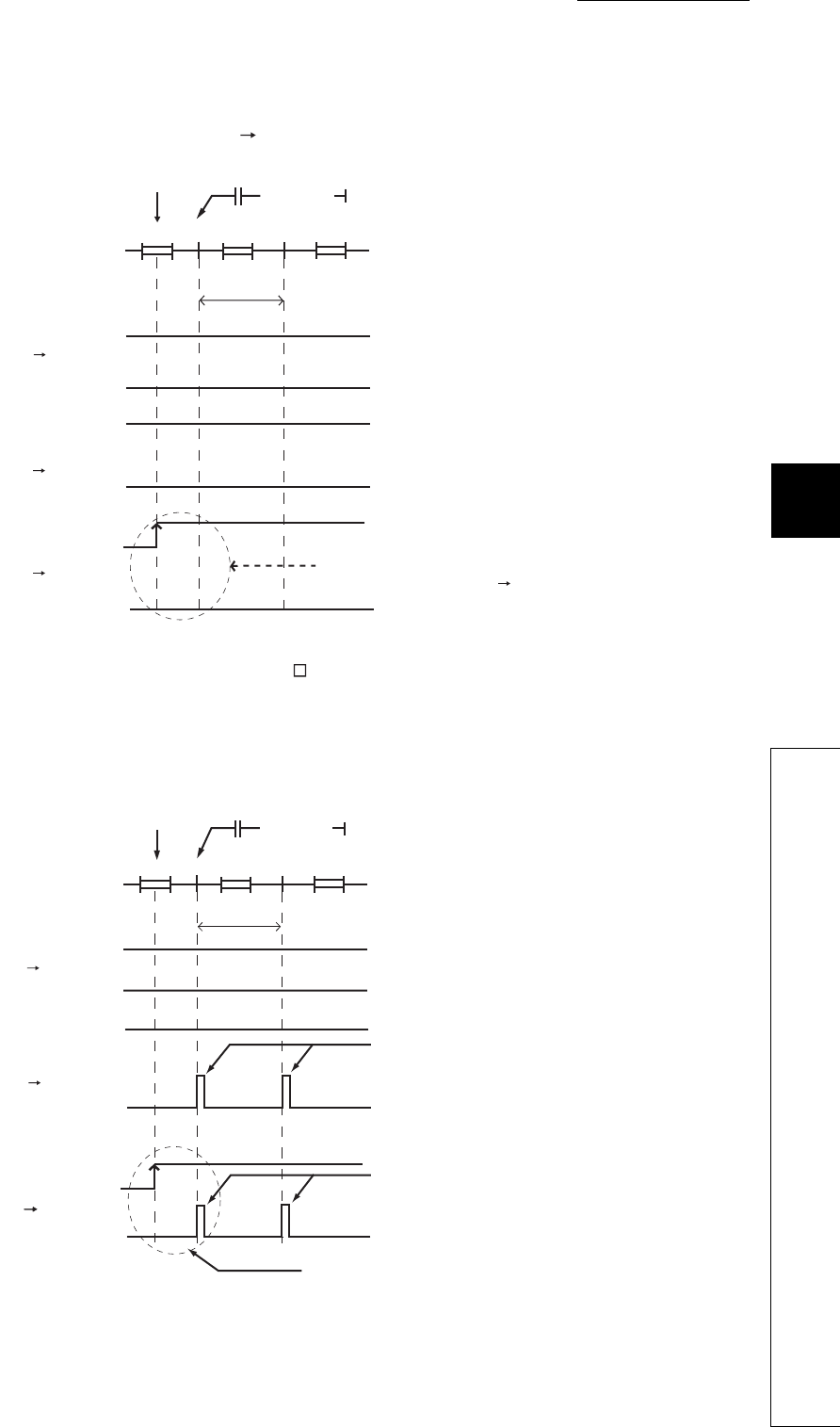

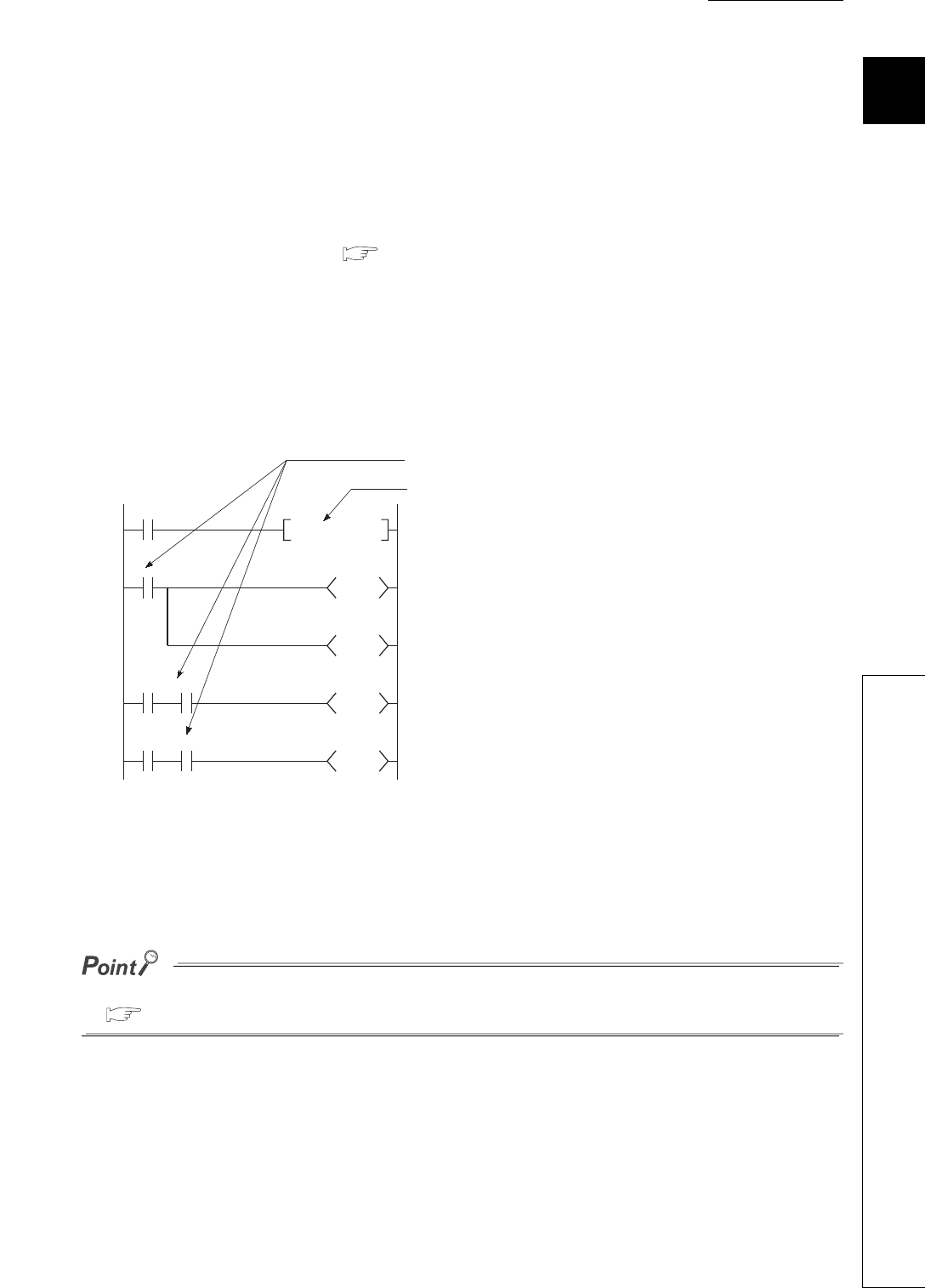

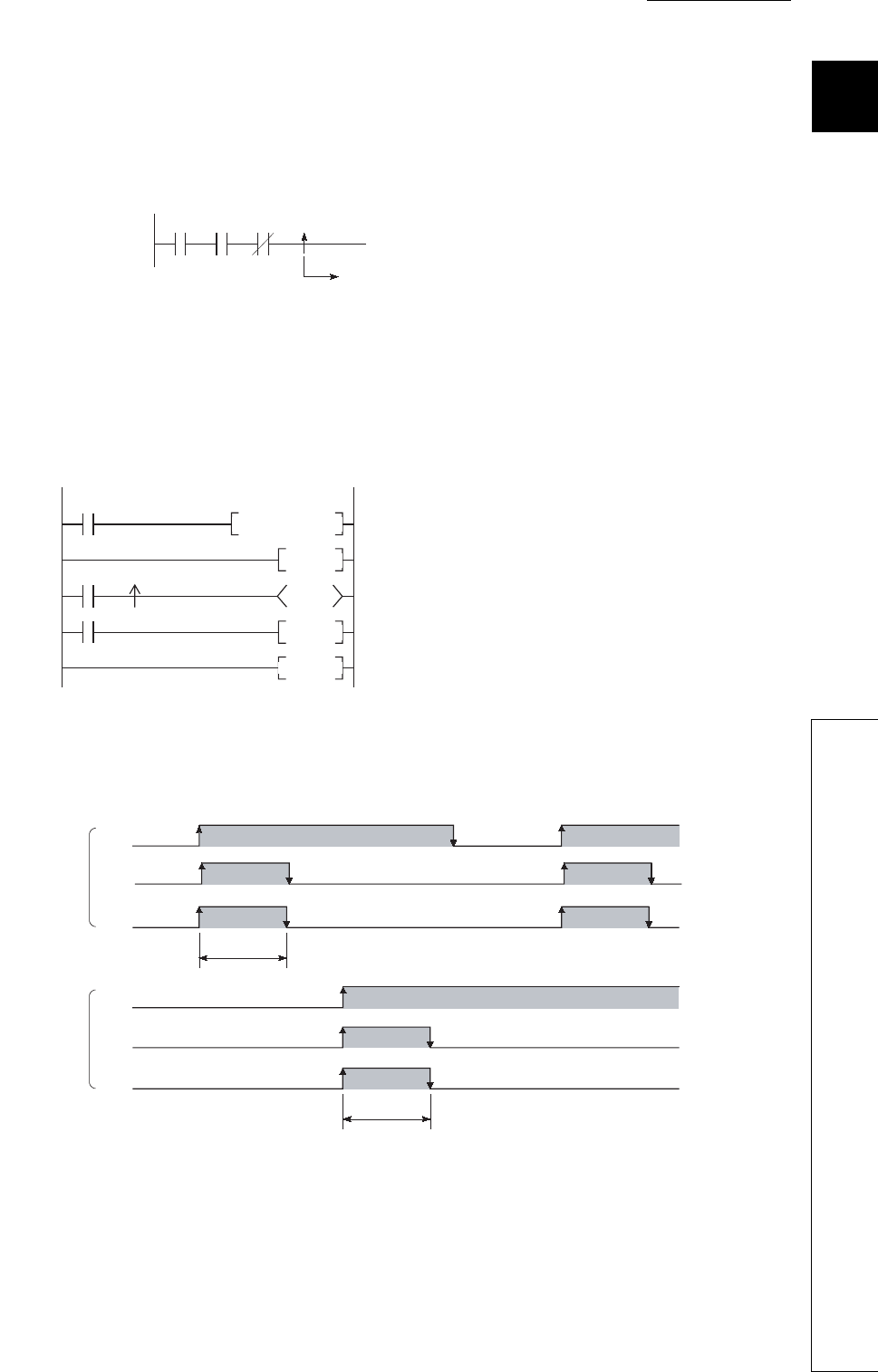

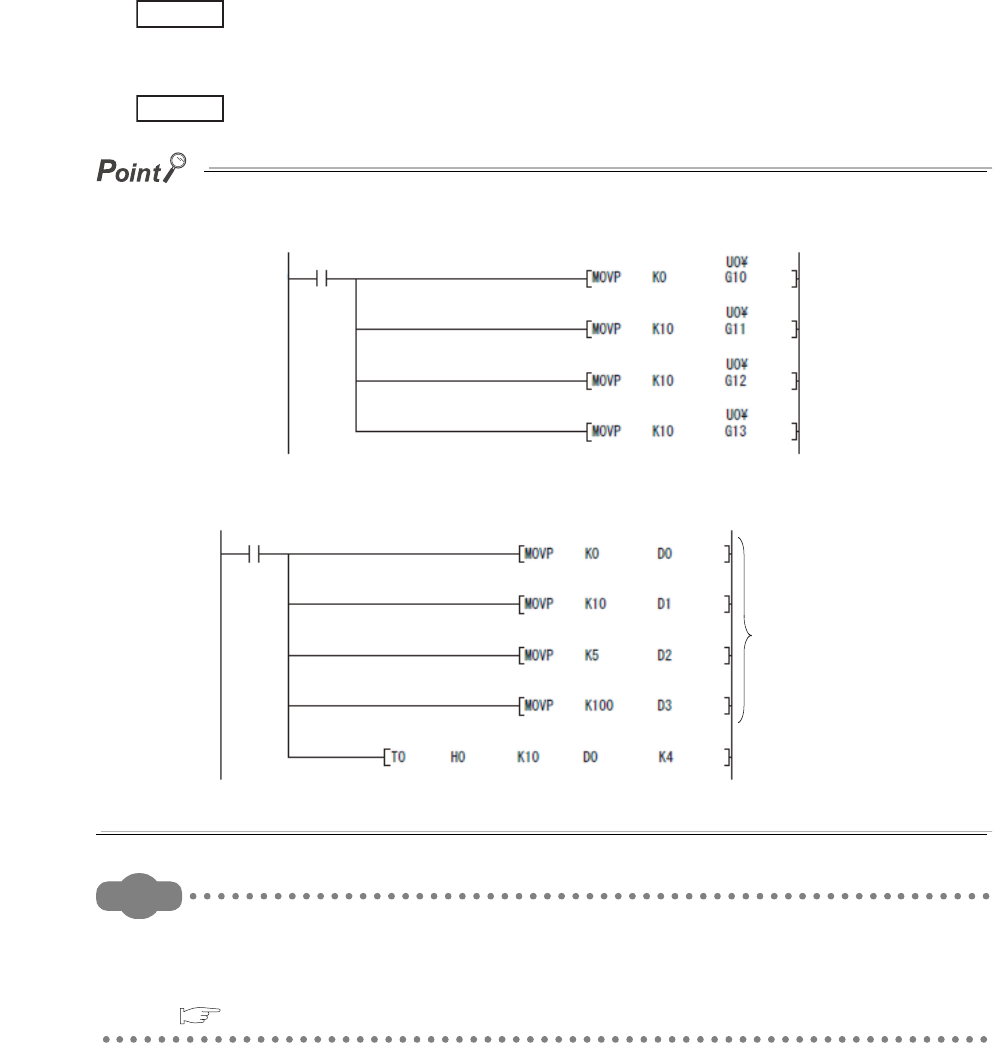

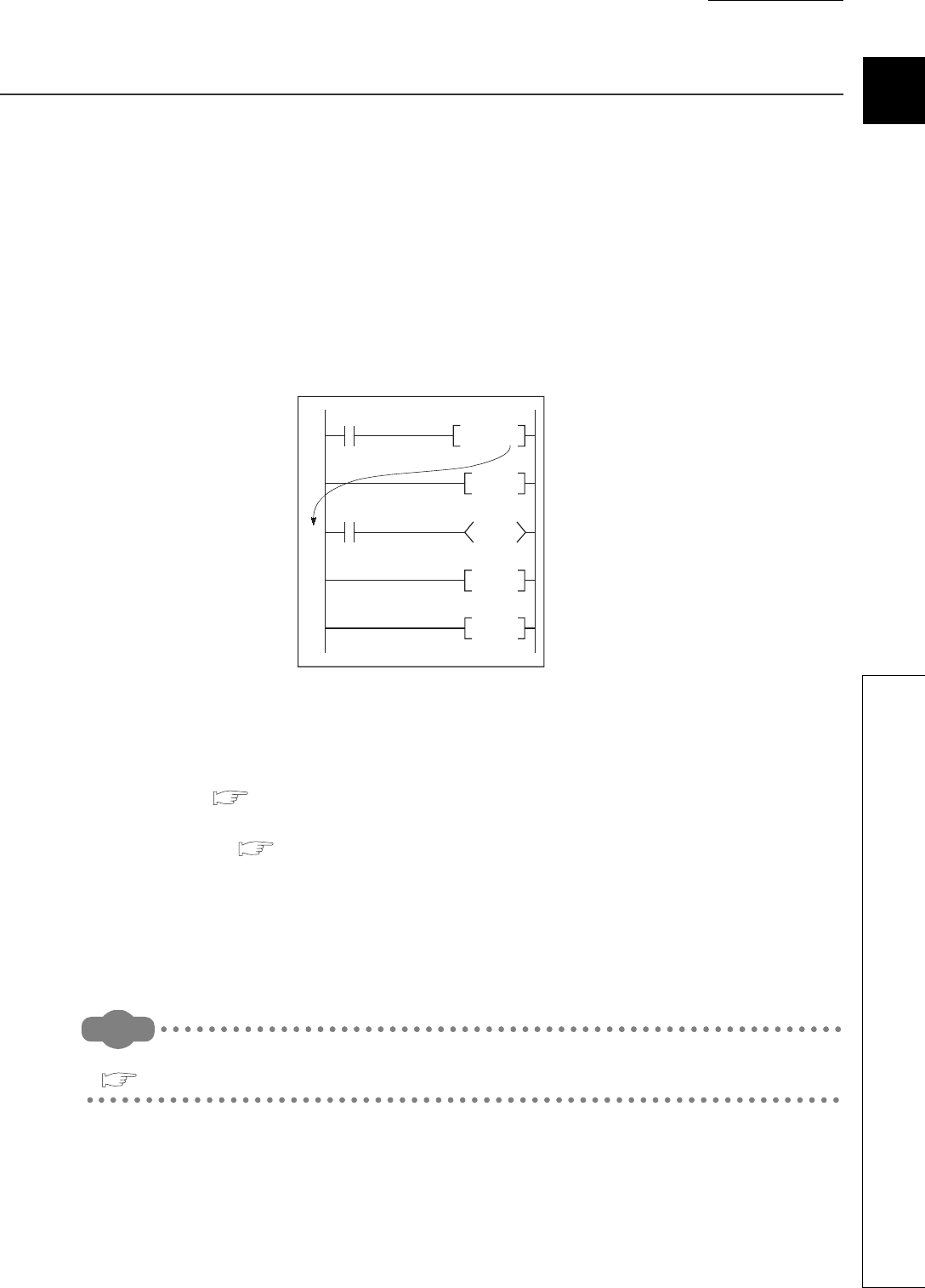

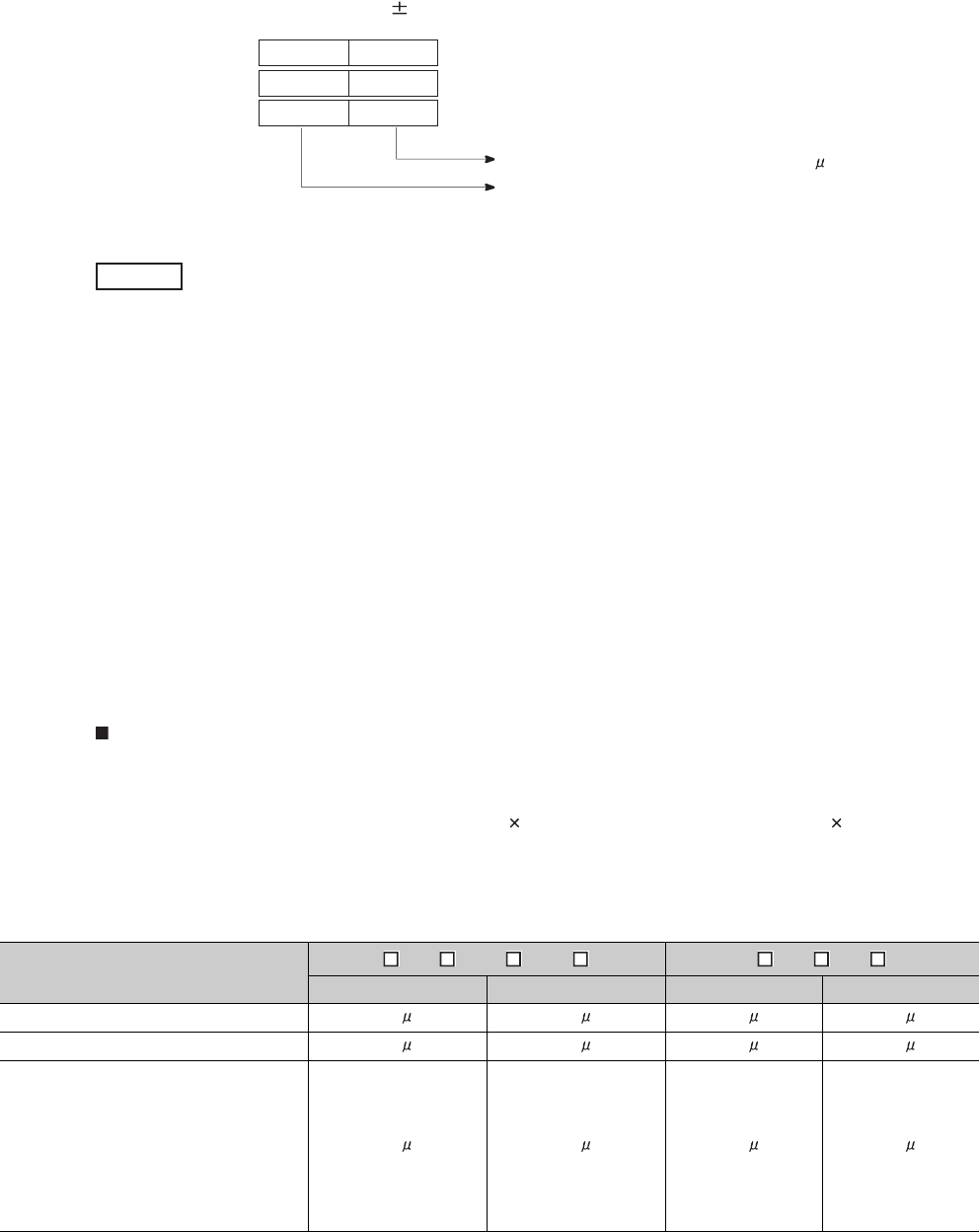

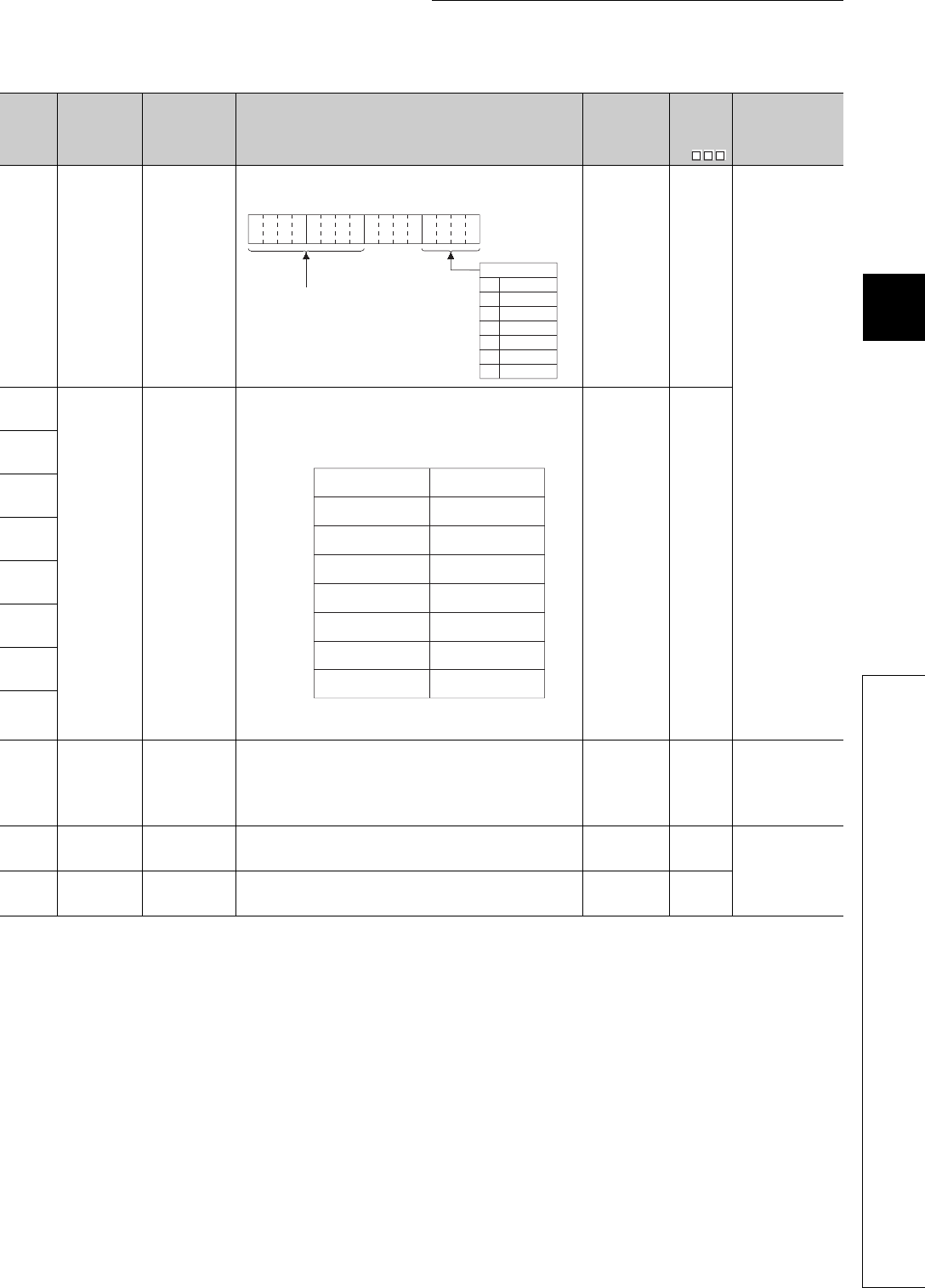

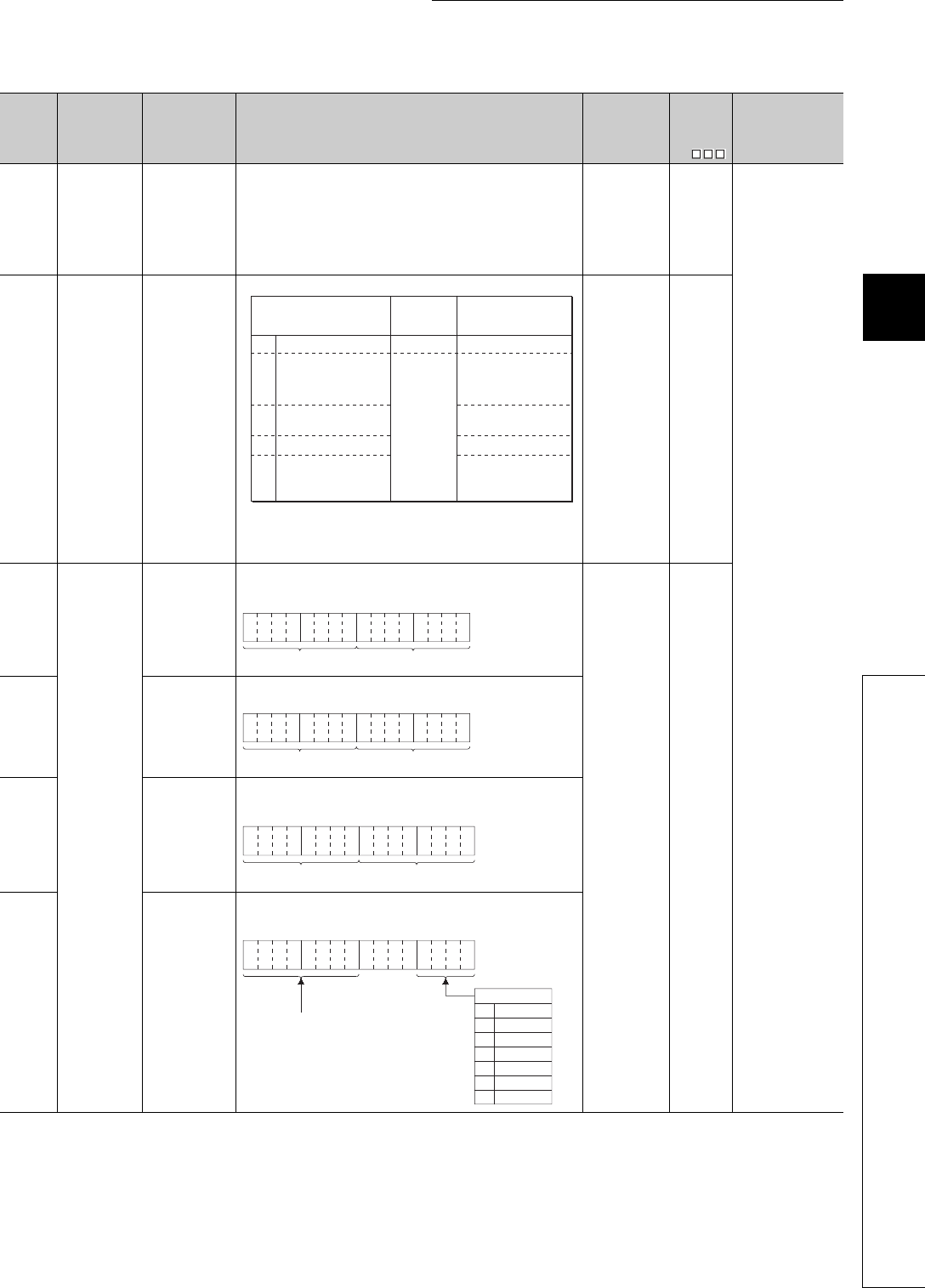

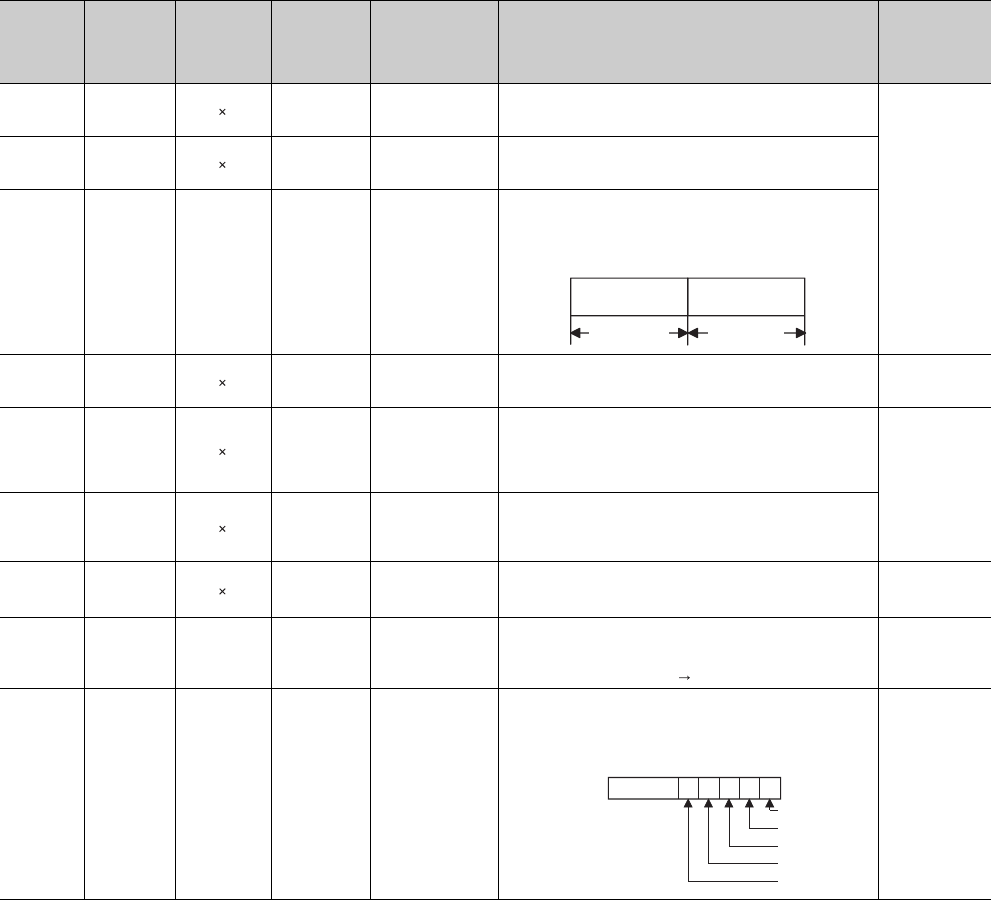

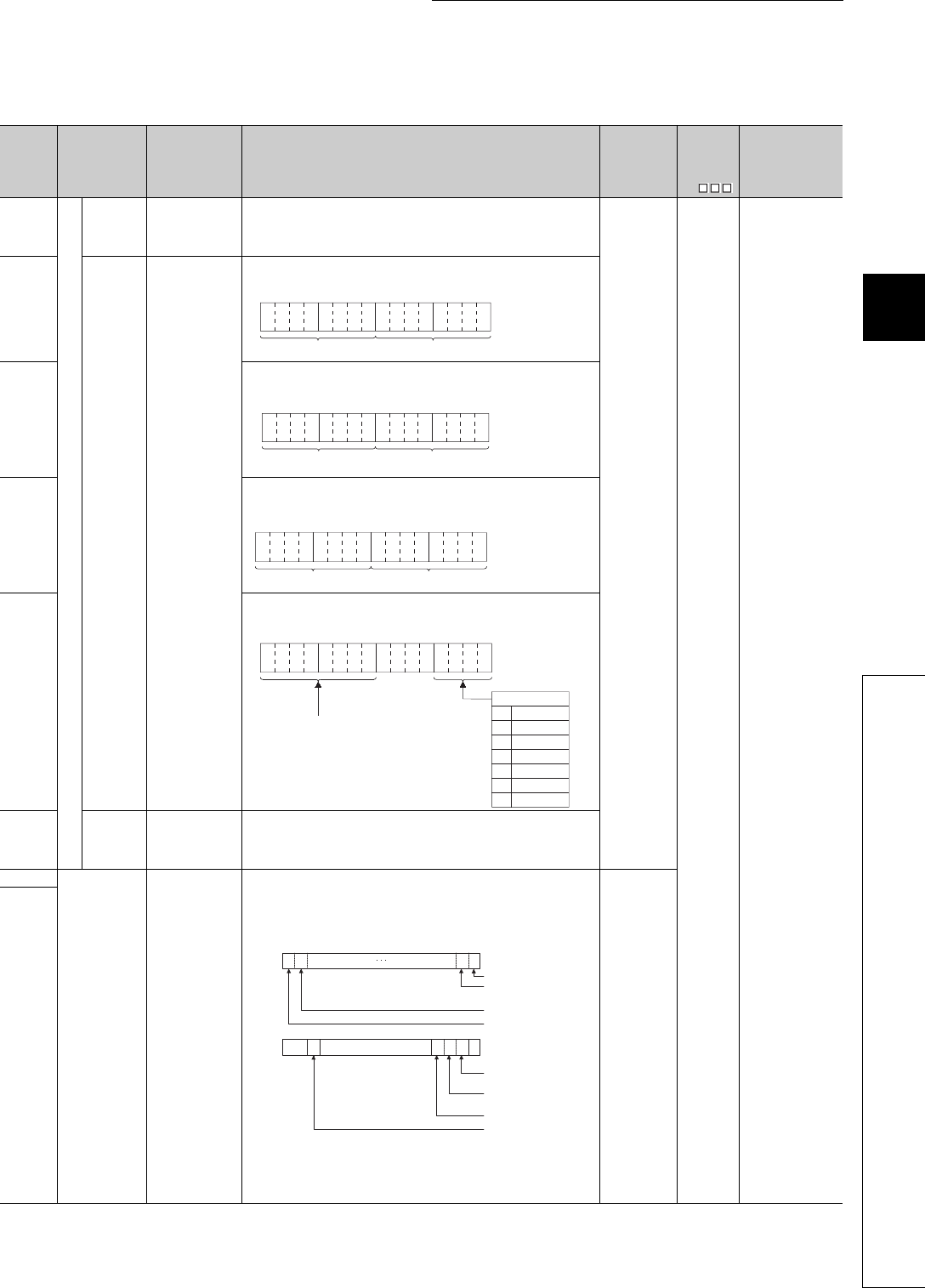

(2) Structural description of programs

Use of the index register and edge relay enables easy structured programming including the pulse conversion

processing. ( Section 9.2.6)

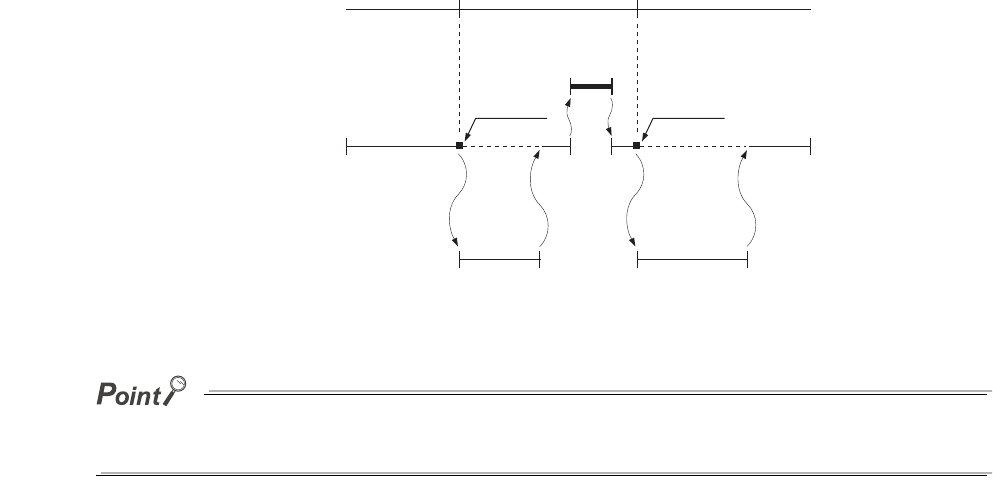

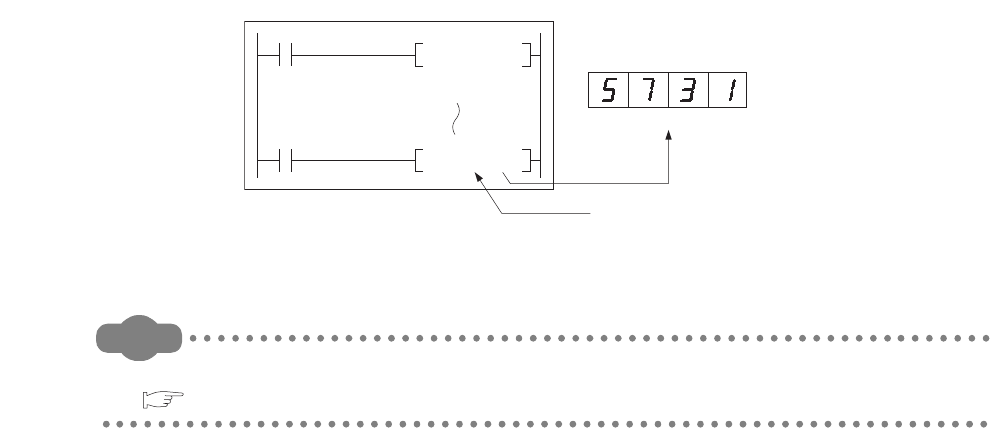

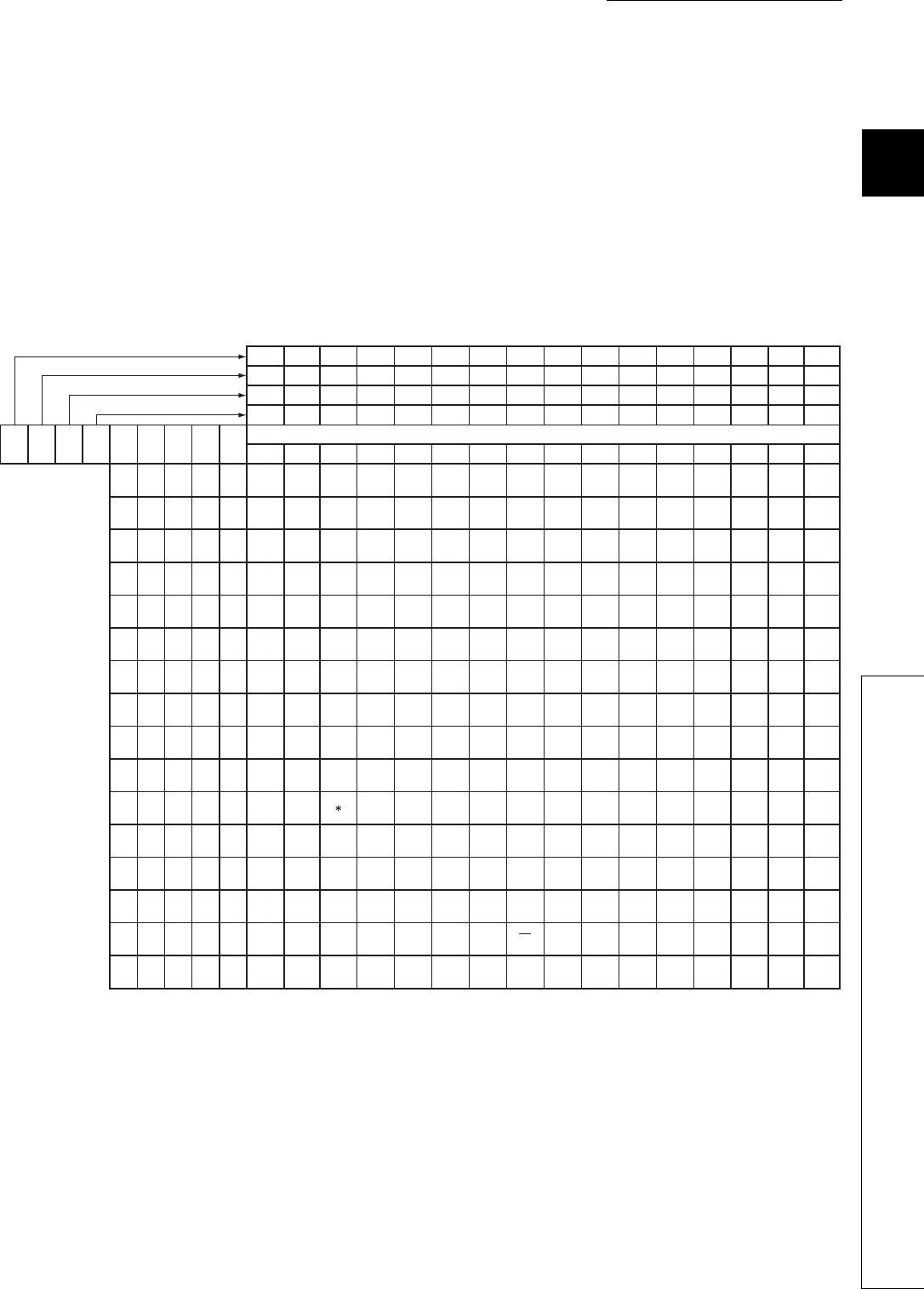

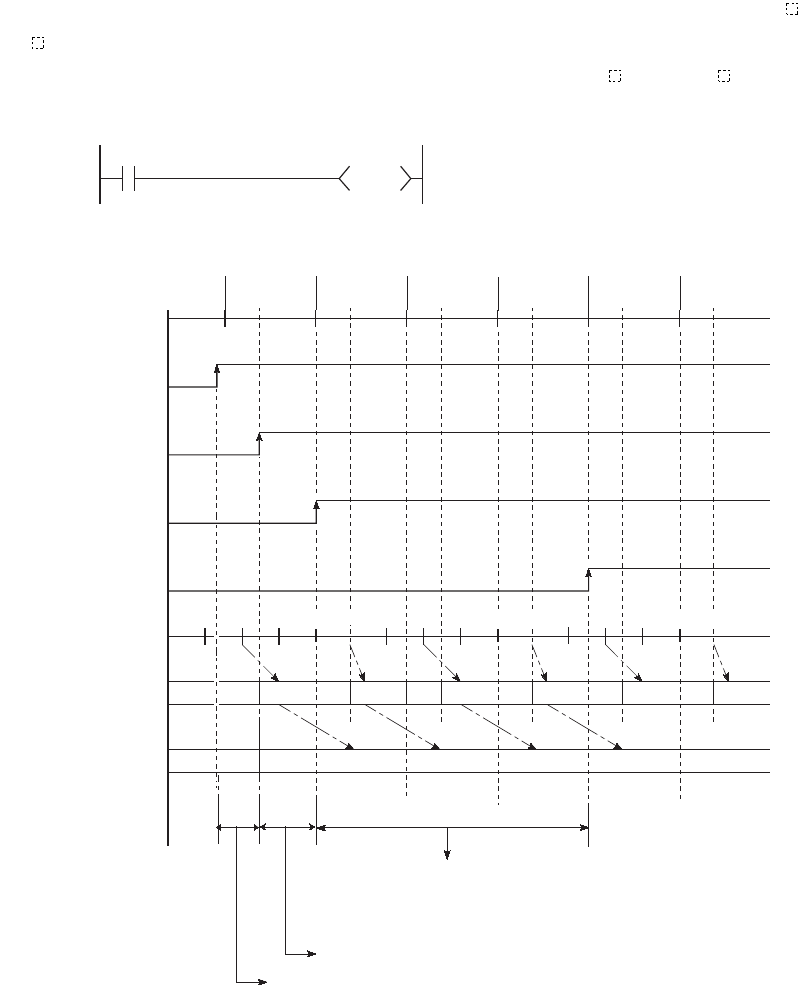

(3) Easy data processing

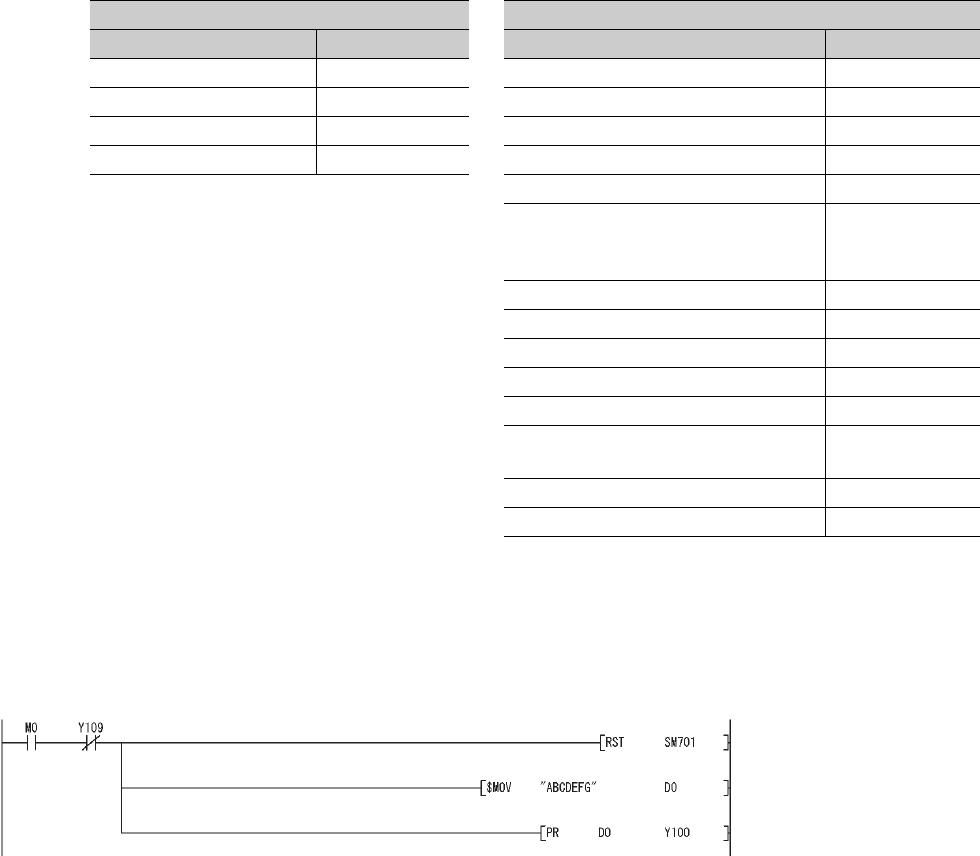

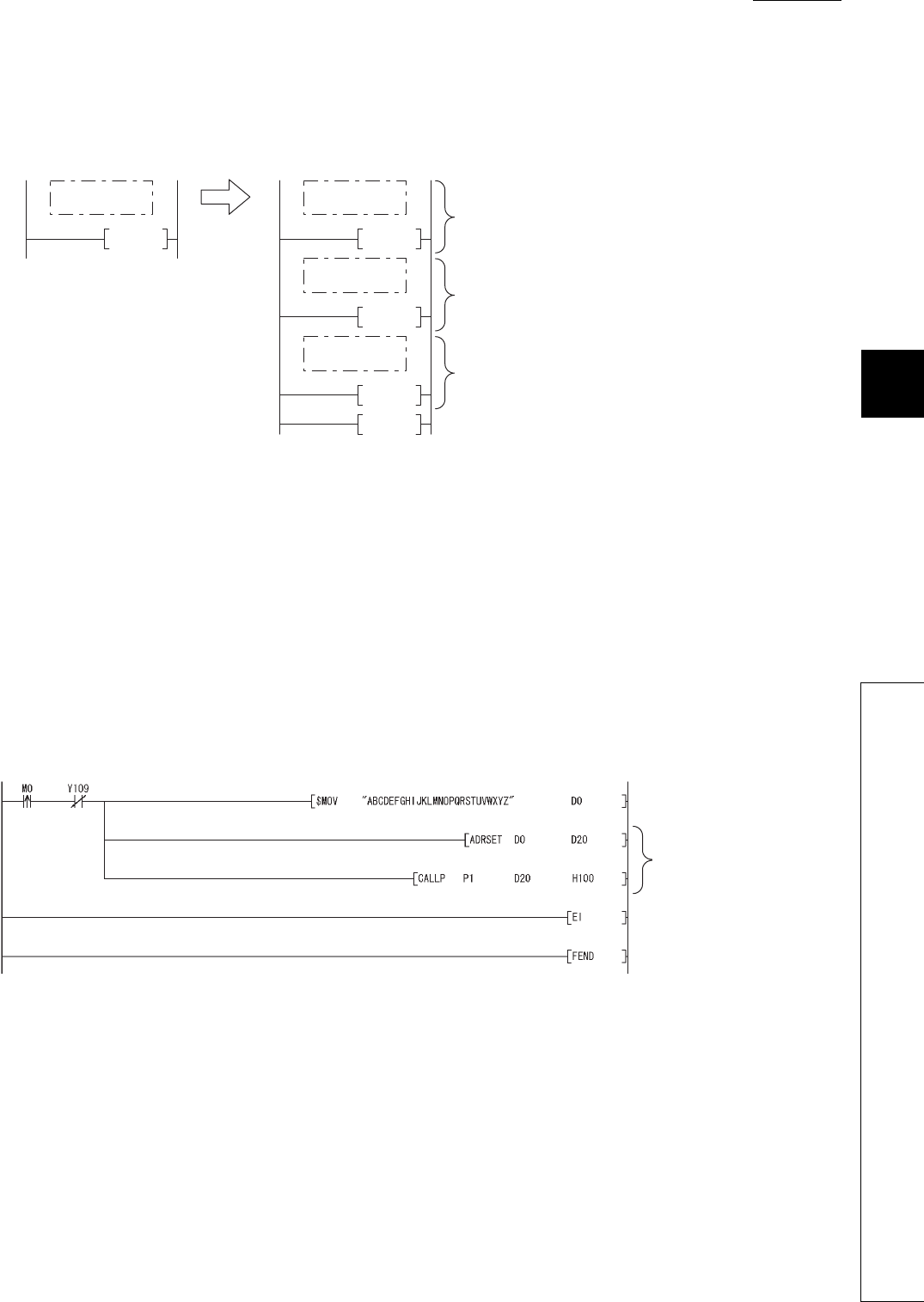

(a) Using real numbers and character string constants without conversion

Real numbers (floating-point data) and character string constants can be used without conversion for

programming.

*1: The NULL character represents "00H" (end of character strings).

(b) High-speed processing of bulk data

Extension of the data table operation instructions, such as the data table processing instruction, allows high-

speed processing of bulk data.

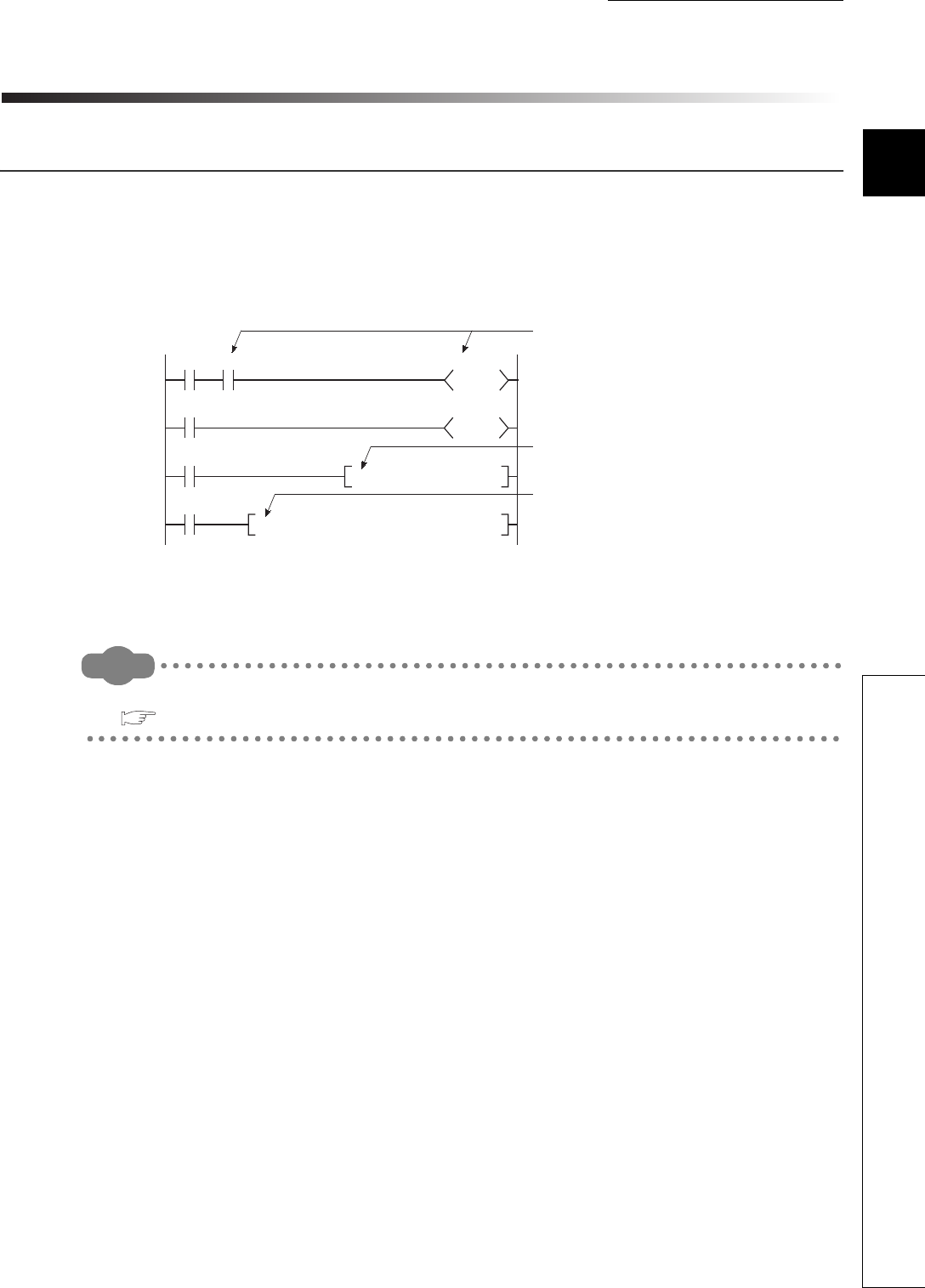

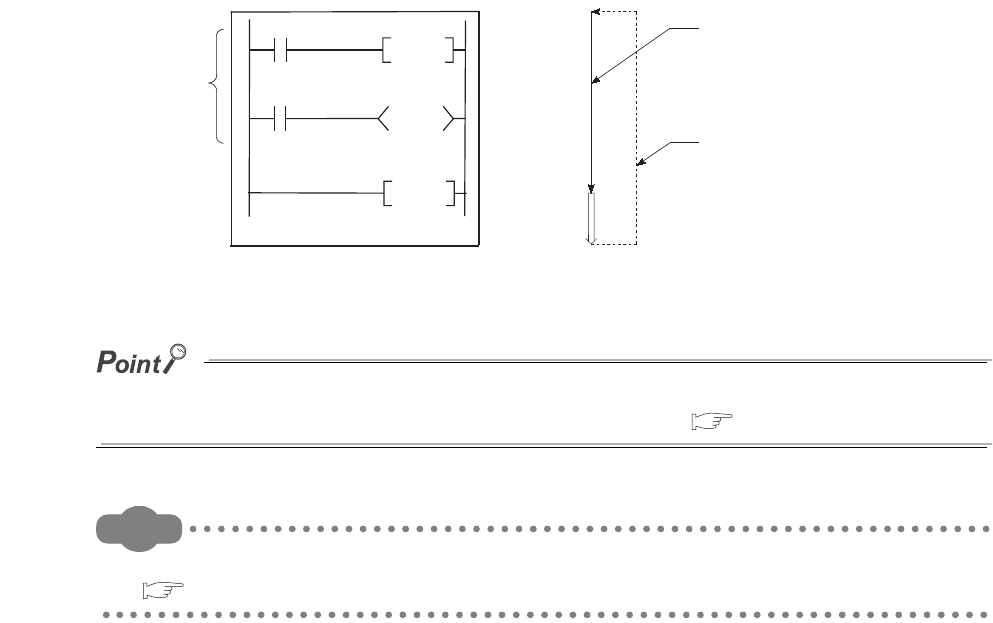

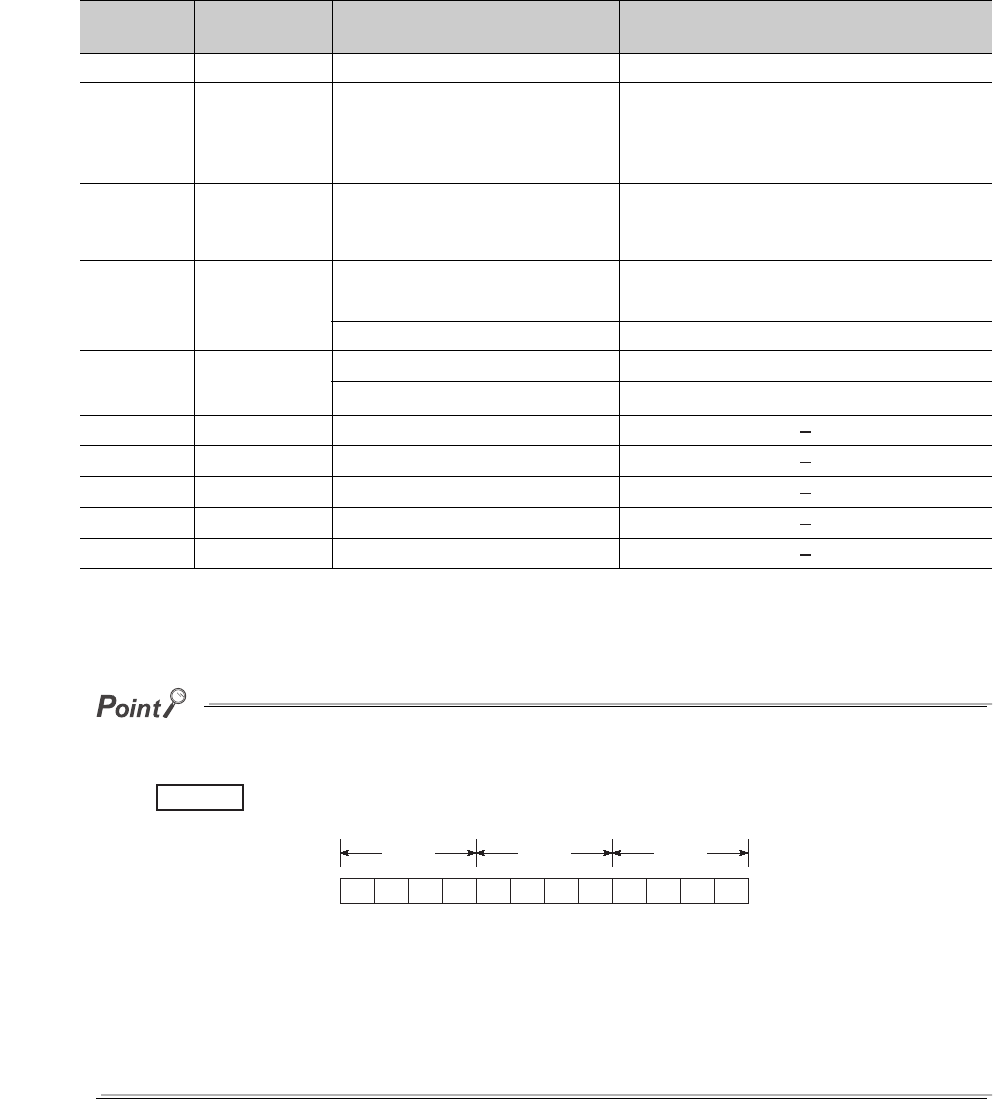

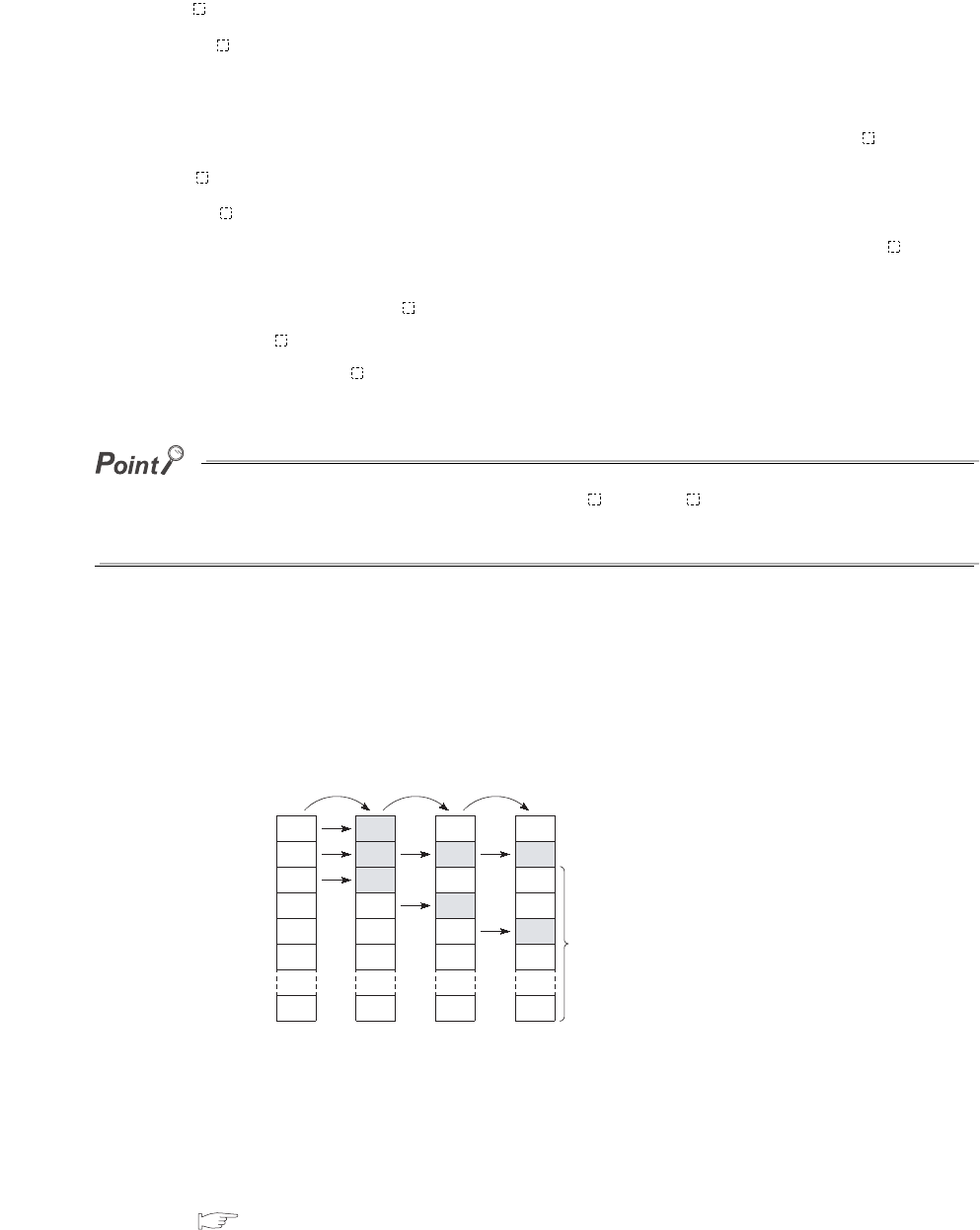

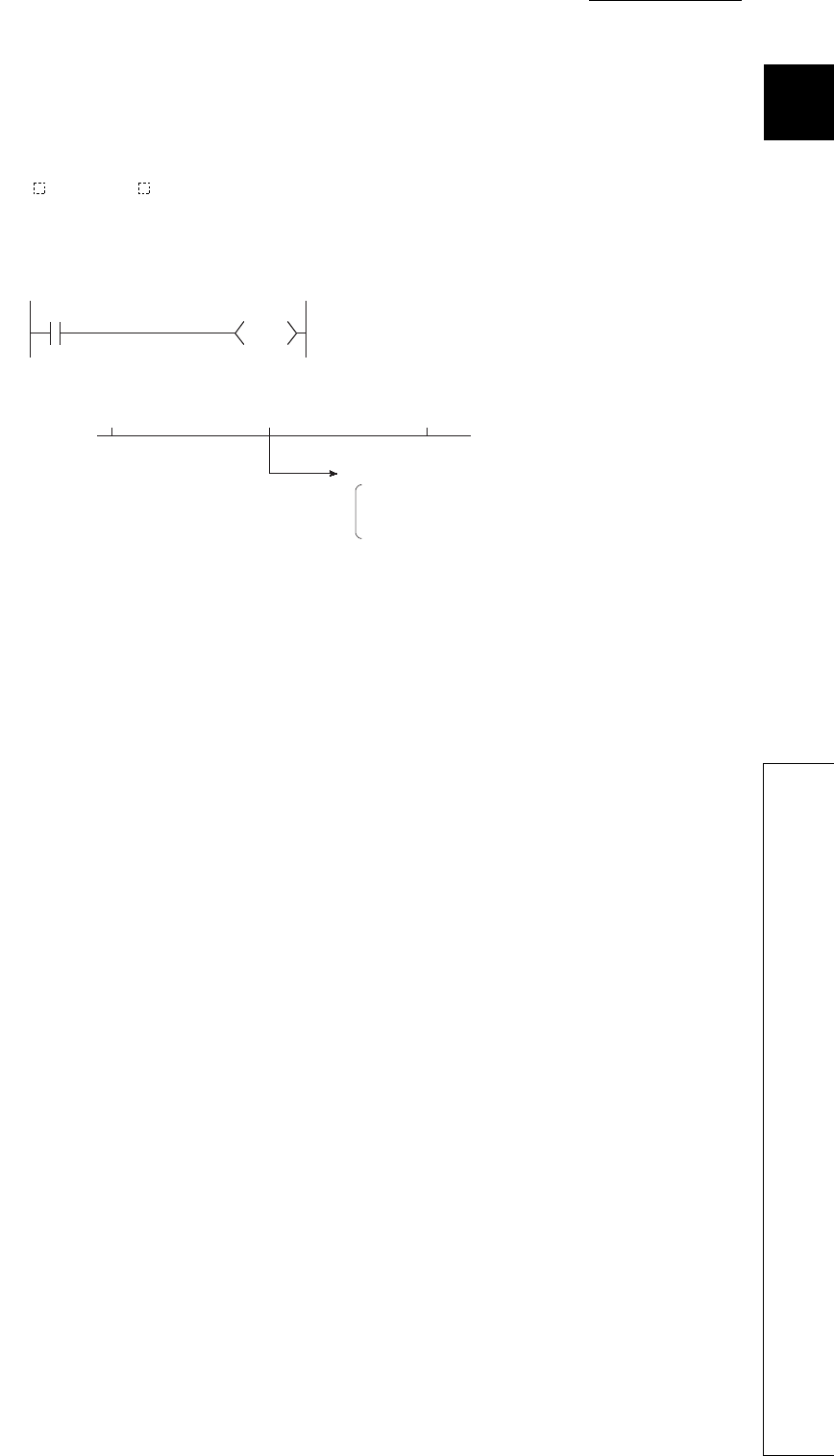

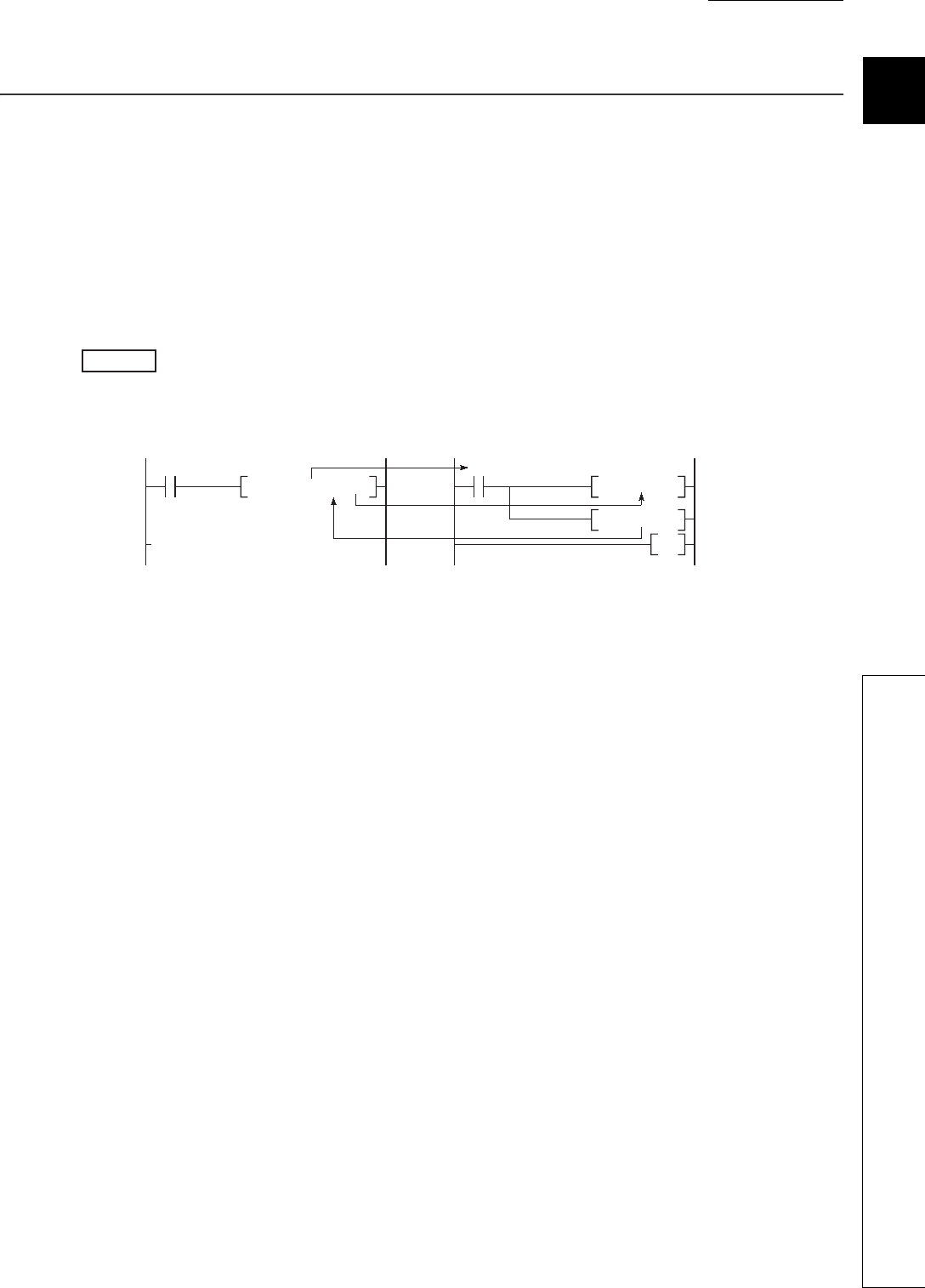

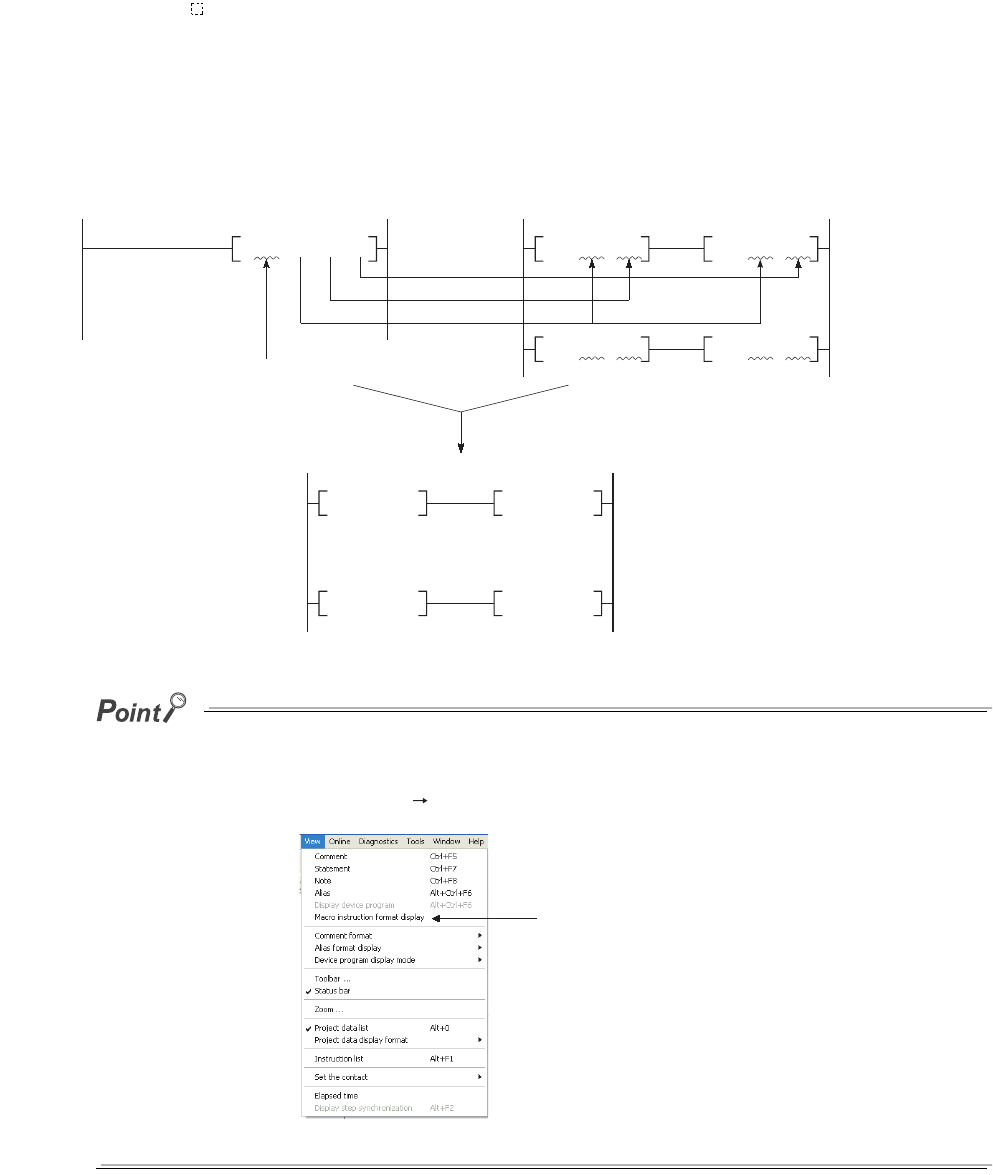

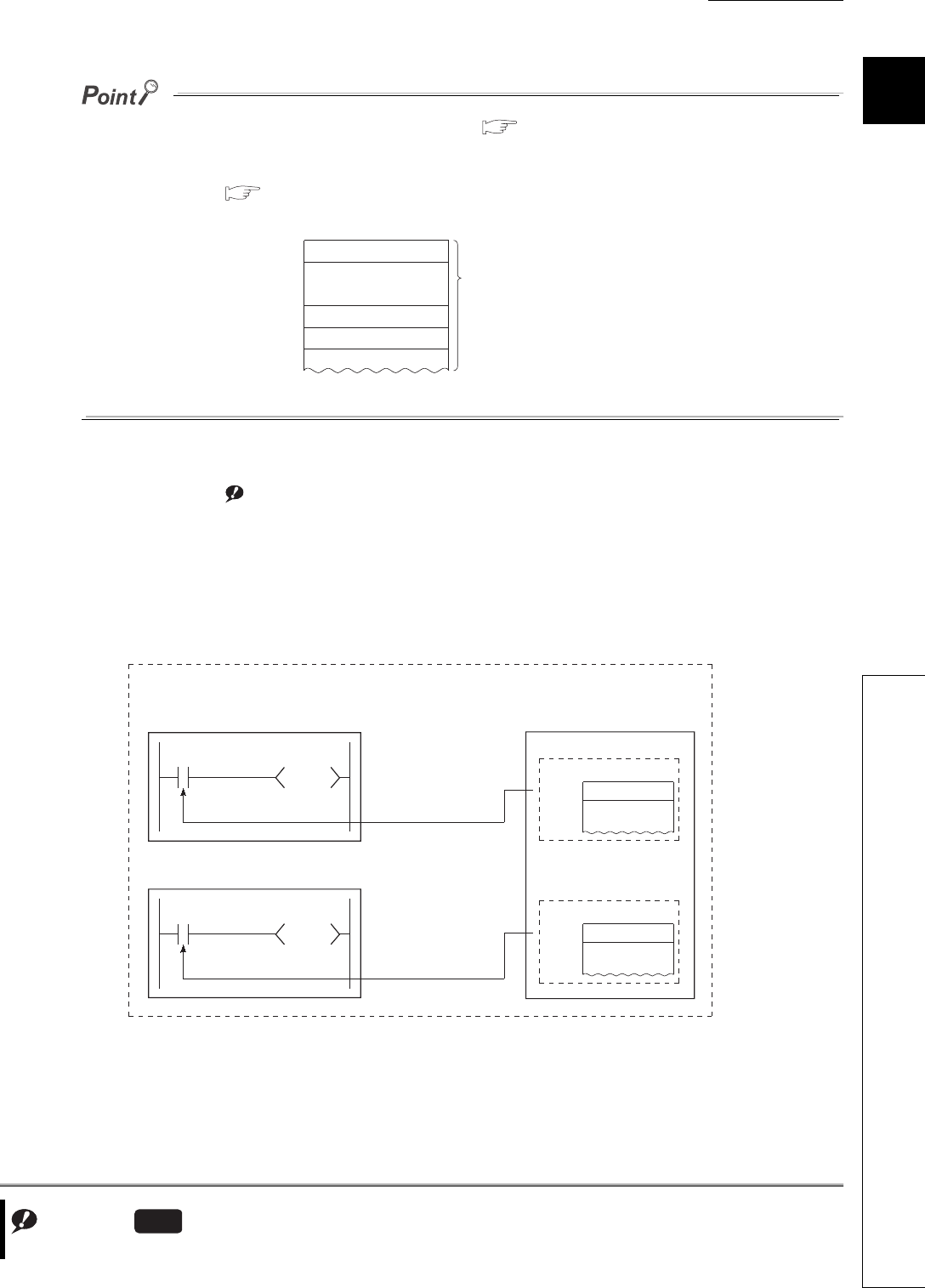

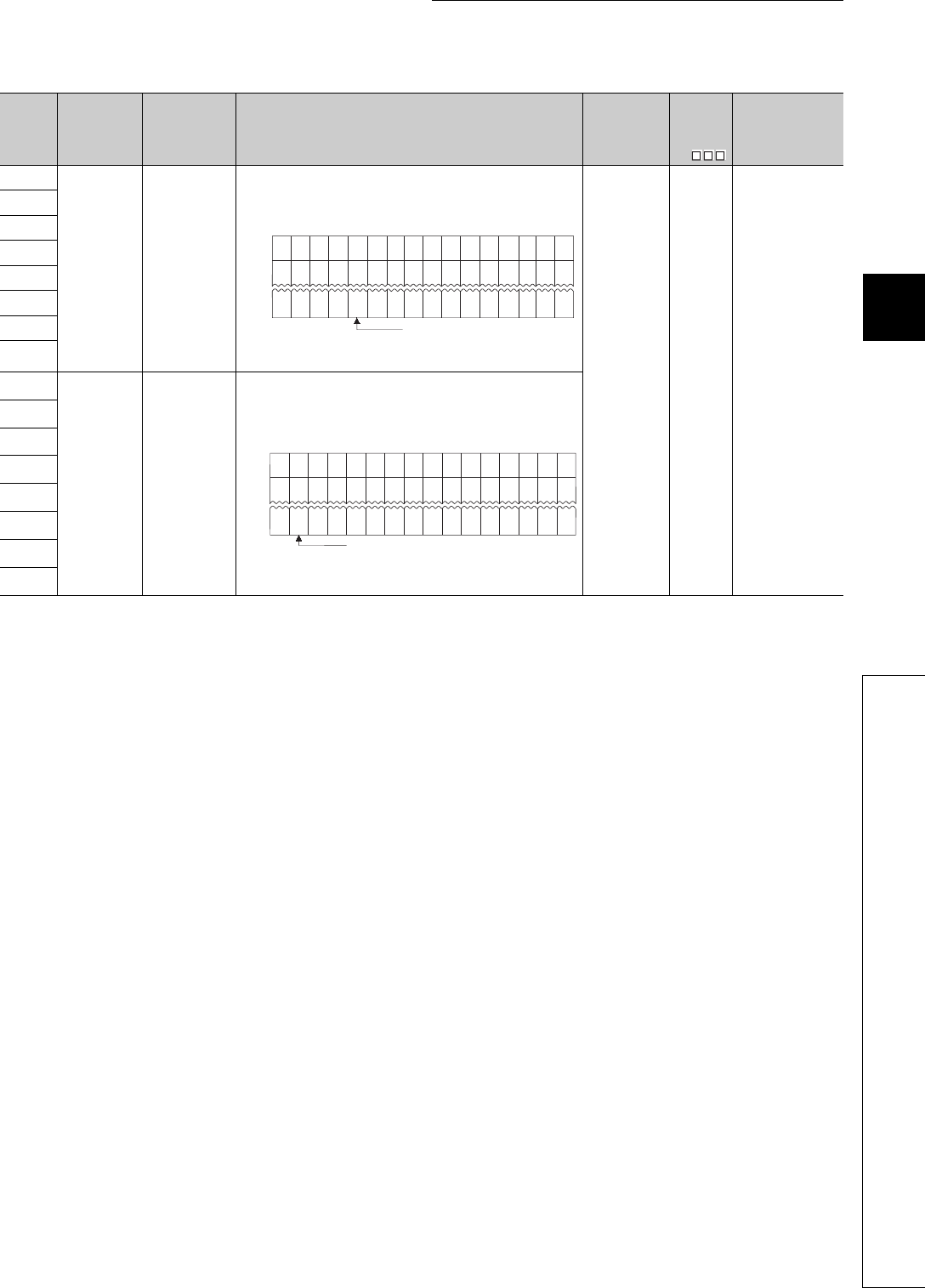

Figure 1.13 Structured programming including the pulse conversion processing

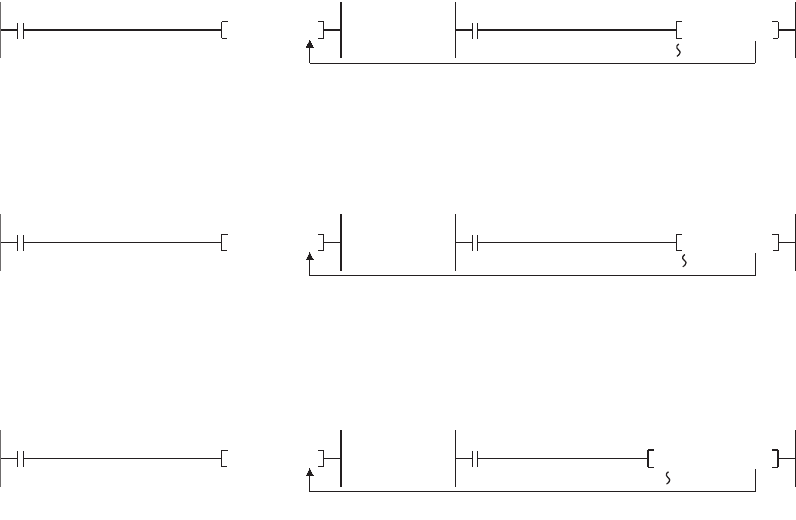

Figure 1.14 Using real numbers and character string constants

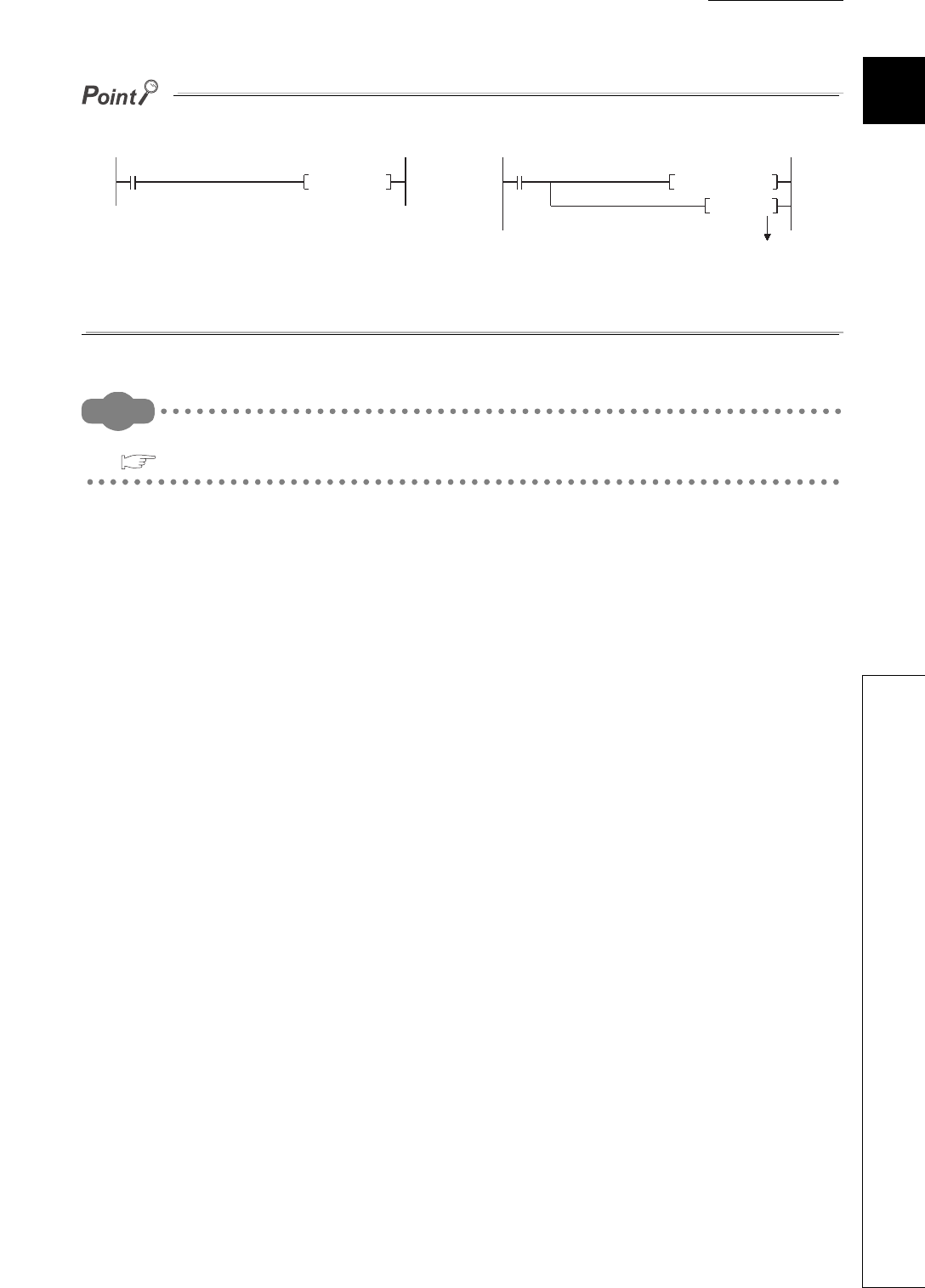

Figure 1.15 Data processing with the table processing instruction

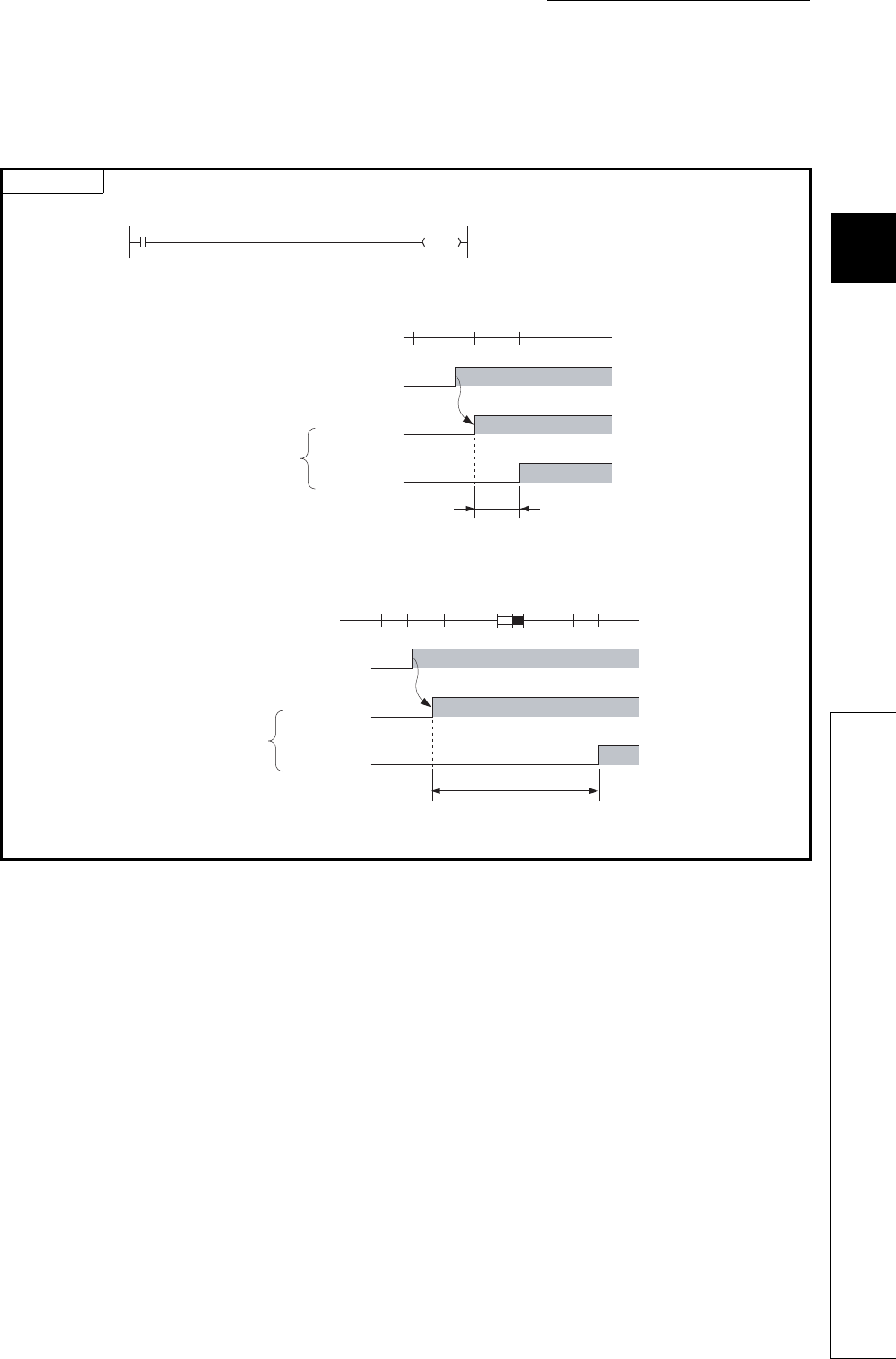

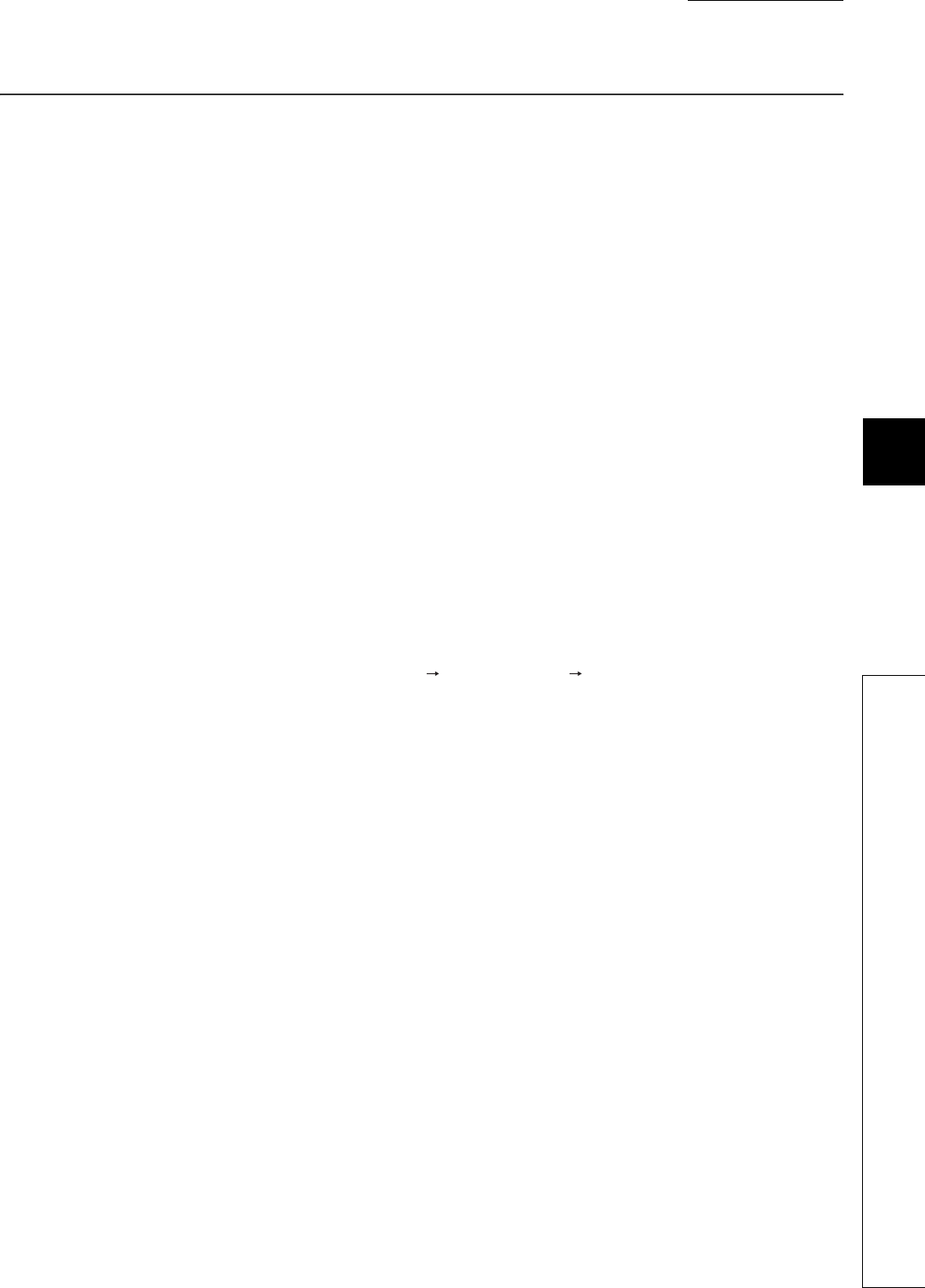

X0 X1 PLS M0

M0 Y8

X10 X11 PLS M10

M10

Y18

X170 X171

PLS M170

M170

Y178

X0Z0 X1Z0

Y8Z2

FOR n

NEXT

V0Z1

Multiple number (n) of

similar programs can

be executed by one

description.

Real number addition instruction

Real number

data

X0

E+P E1.23 E1.23 E3.45 E4.68

D0 D0

D5 D10

D11

D12

D13

D6

"0" "Q" "CPU"

"2"

"0"

"C"

"U"

"Q"

"2"

"P"

D1

R0

R1

R0

$+P D5 "CPU" D10

Real number

data

Real number

data

Character string data link instruction

Character

string data

Character

string data

Character

string data

NULL

*1

NULL *1

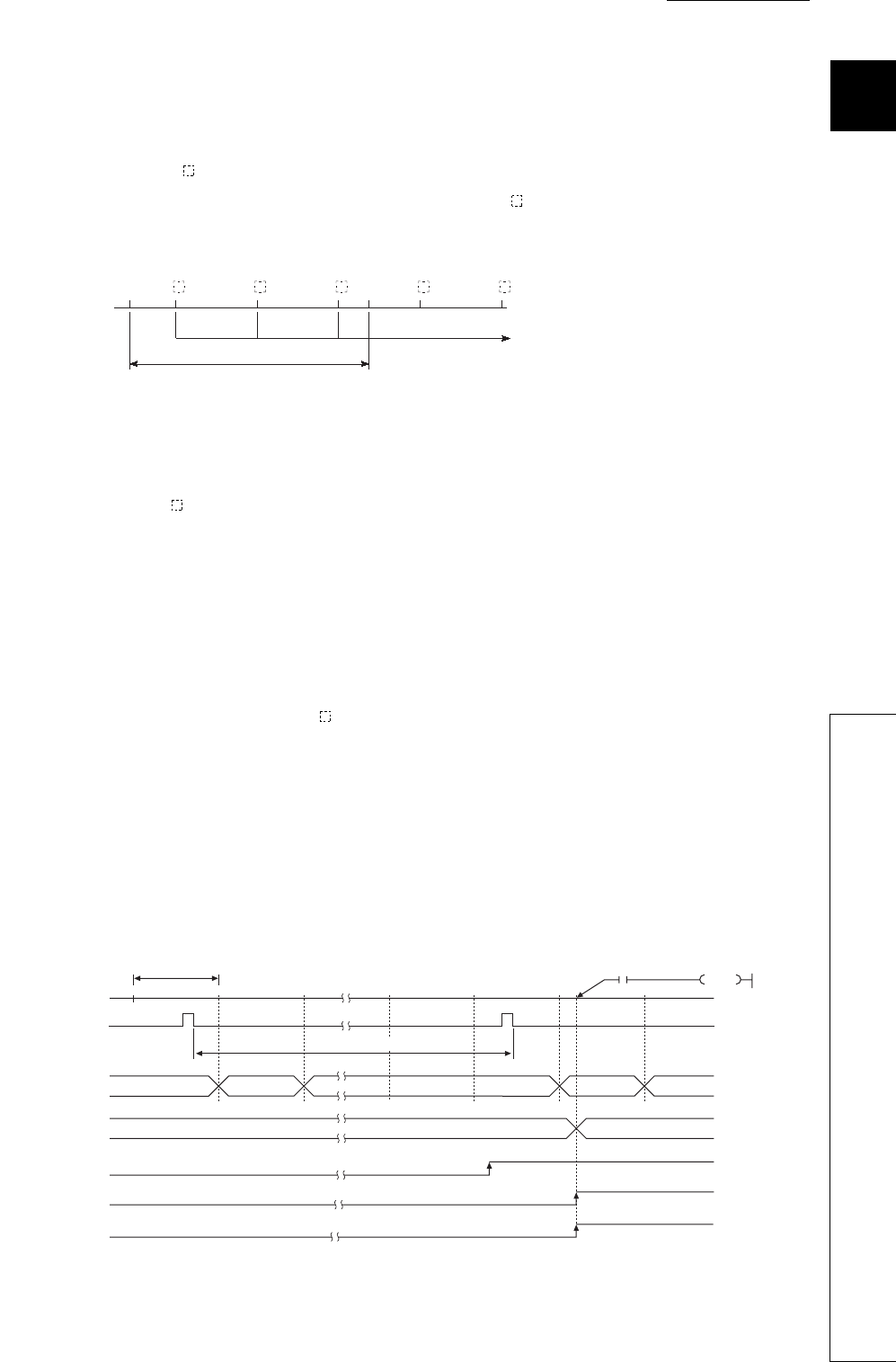

X0

K2R0D0FINSP

R0

R1

R2

R3

3

10

20

30

R4

R0

R1

R2

R3

4

10

15

20

30R4

D0 15

Insertion

position

Instruction for inserting data

to the table

FIF0 table FIF0 table

Device

where the

data is

currently

stored

Device

where

the data

is to be

stored

CHAPTER1 OVERVIEW

1

2

3

4

5

6

7

8

1.4 Devices and Instructions Useful for Programming

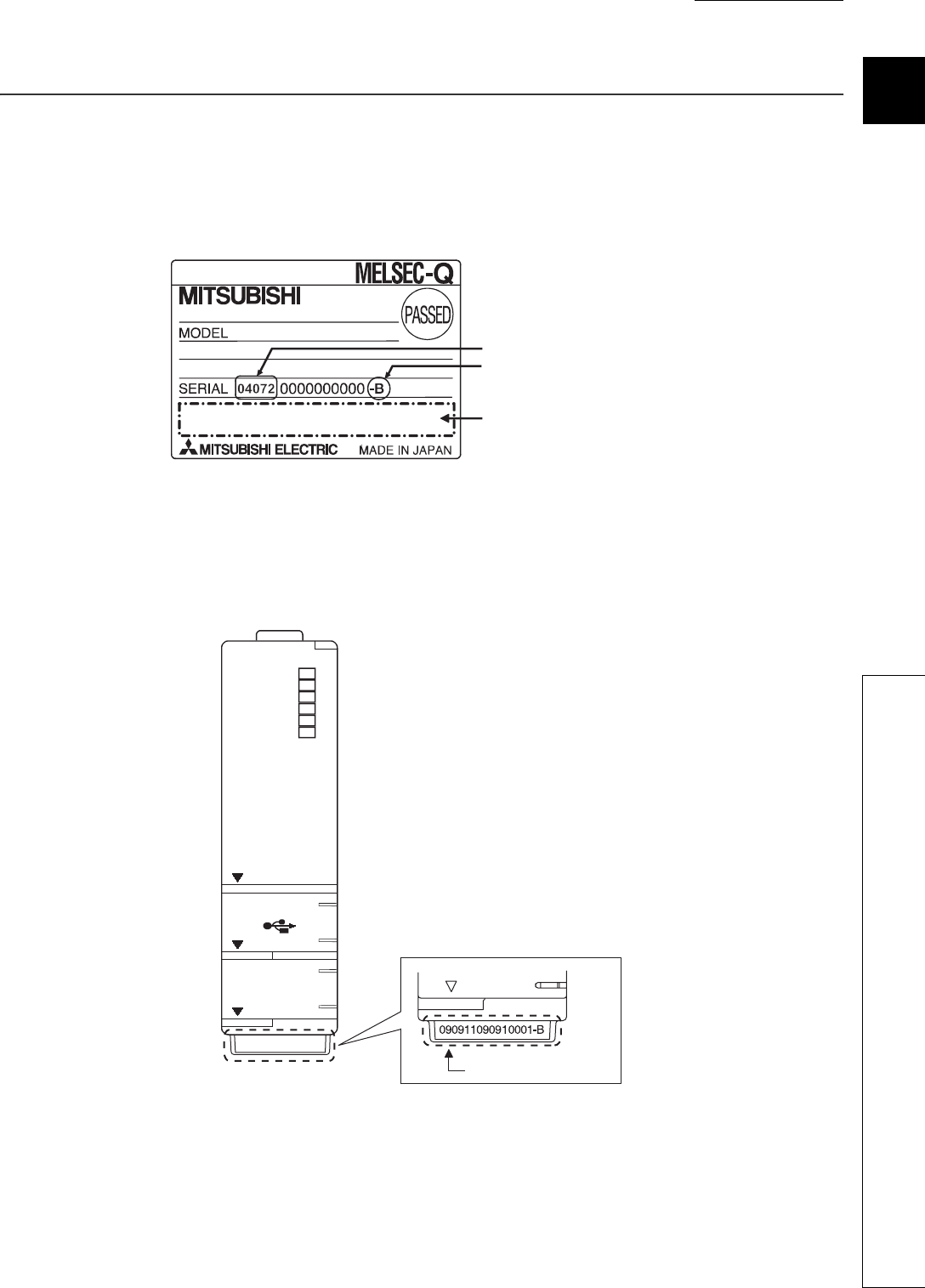

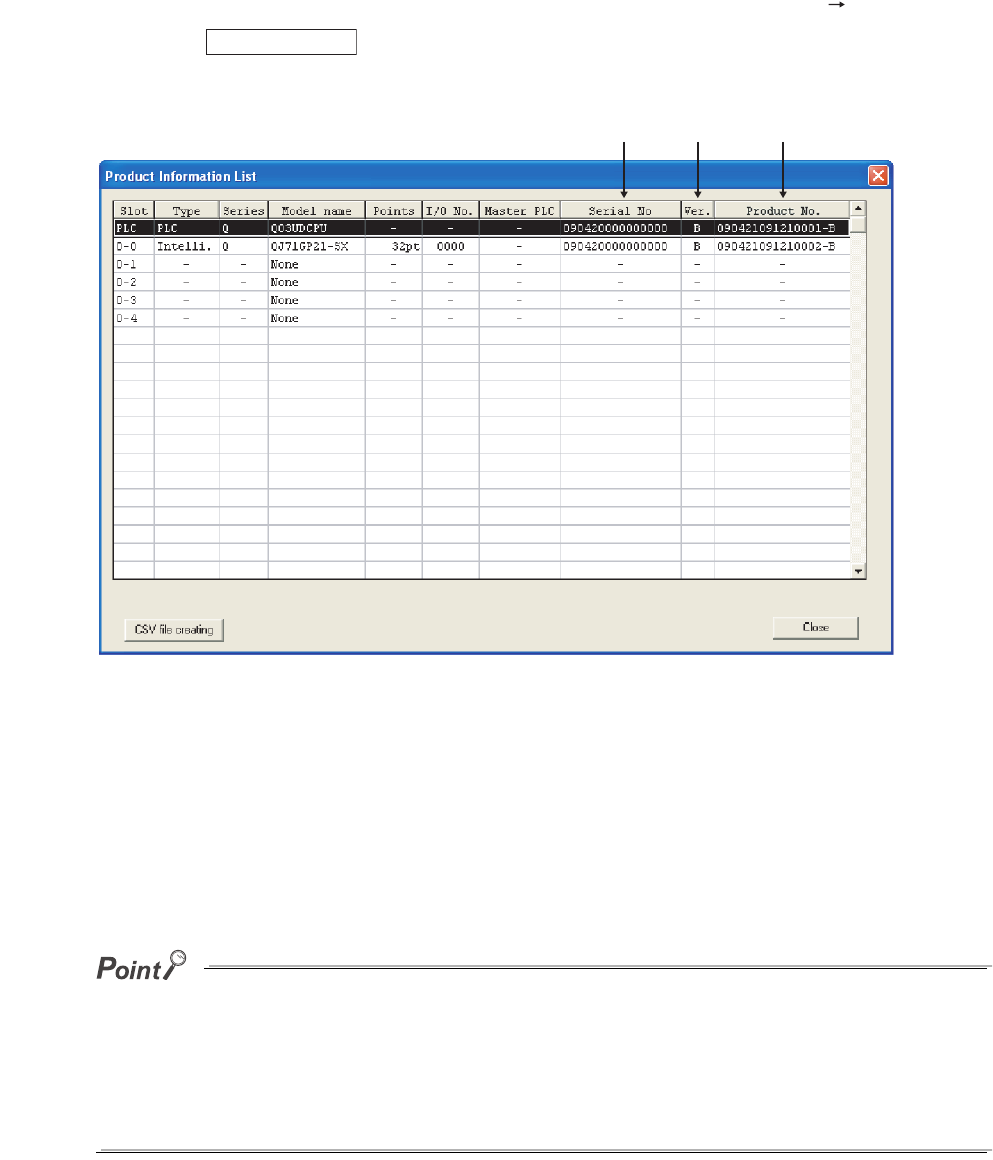

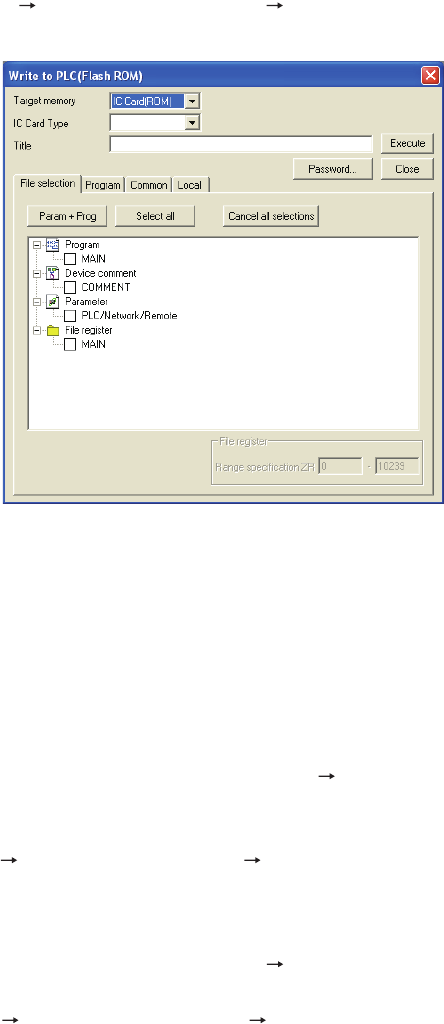

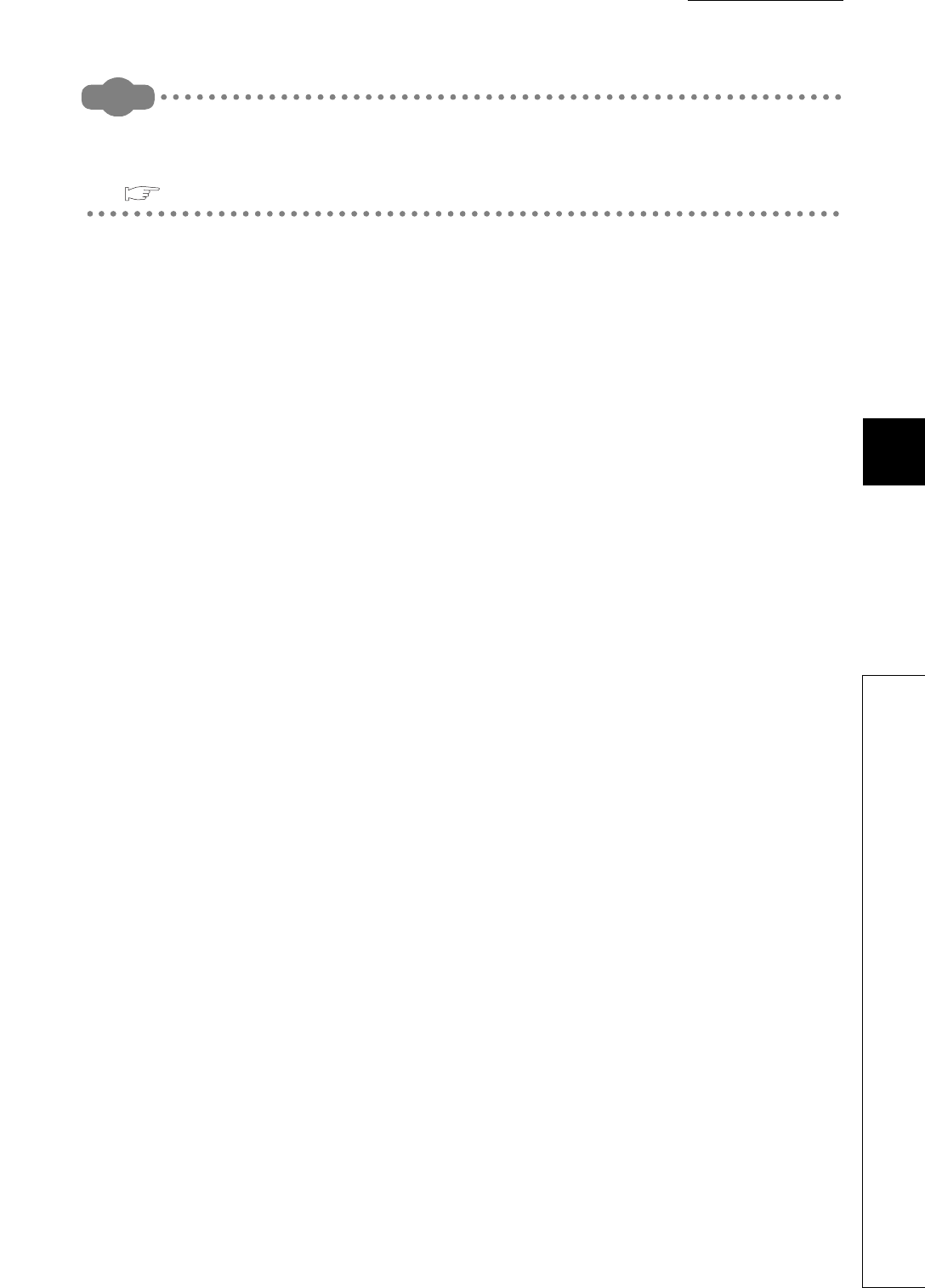

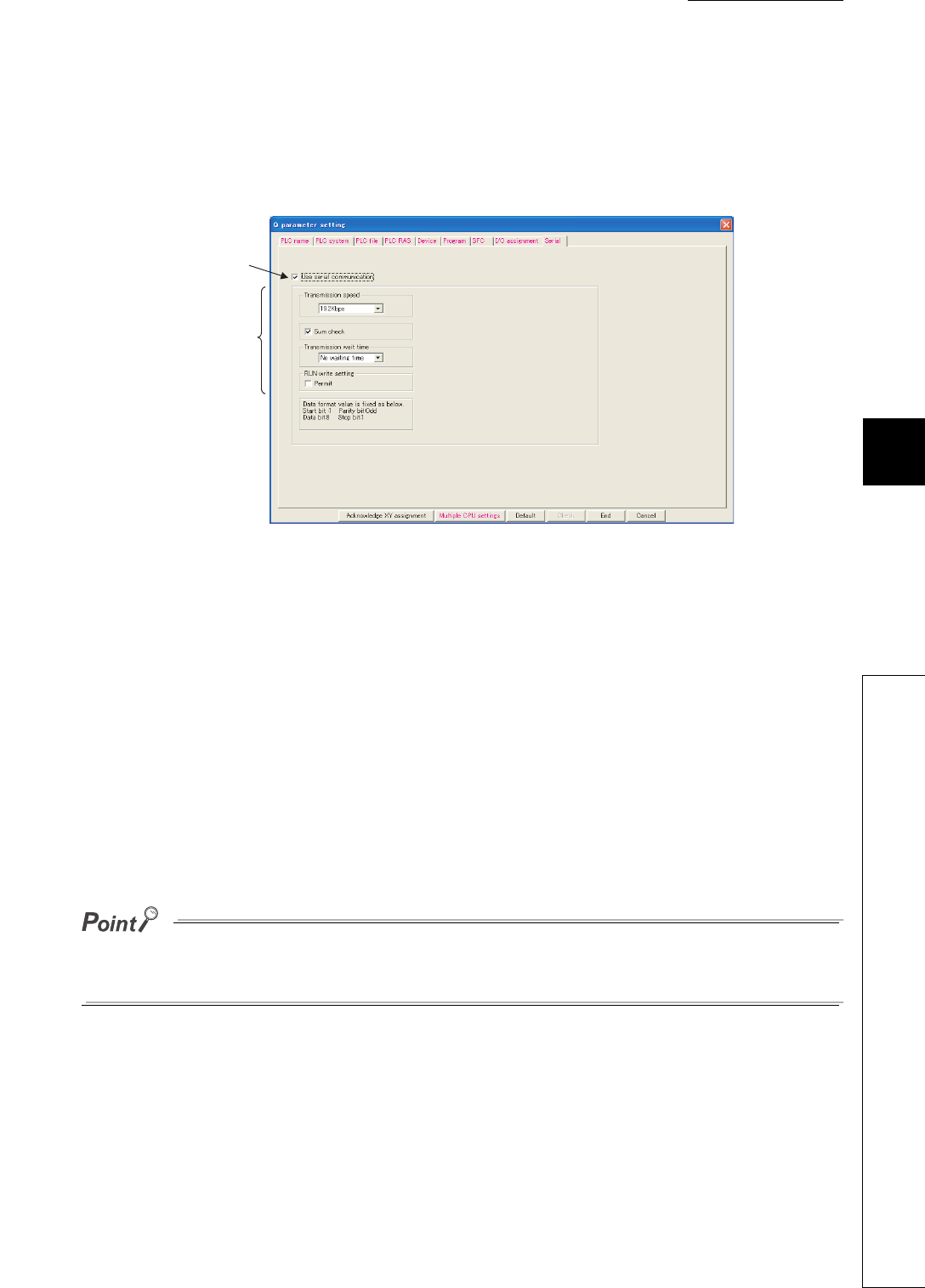

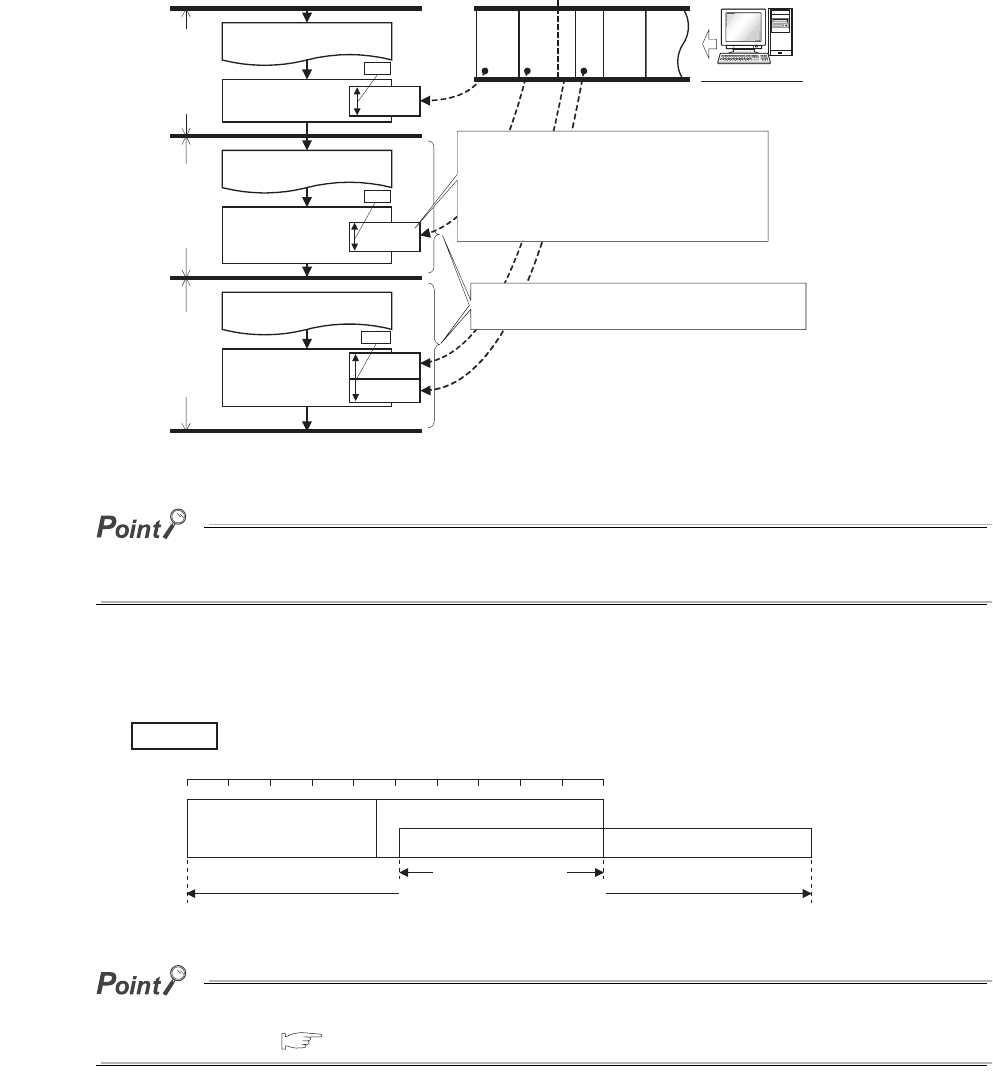

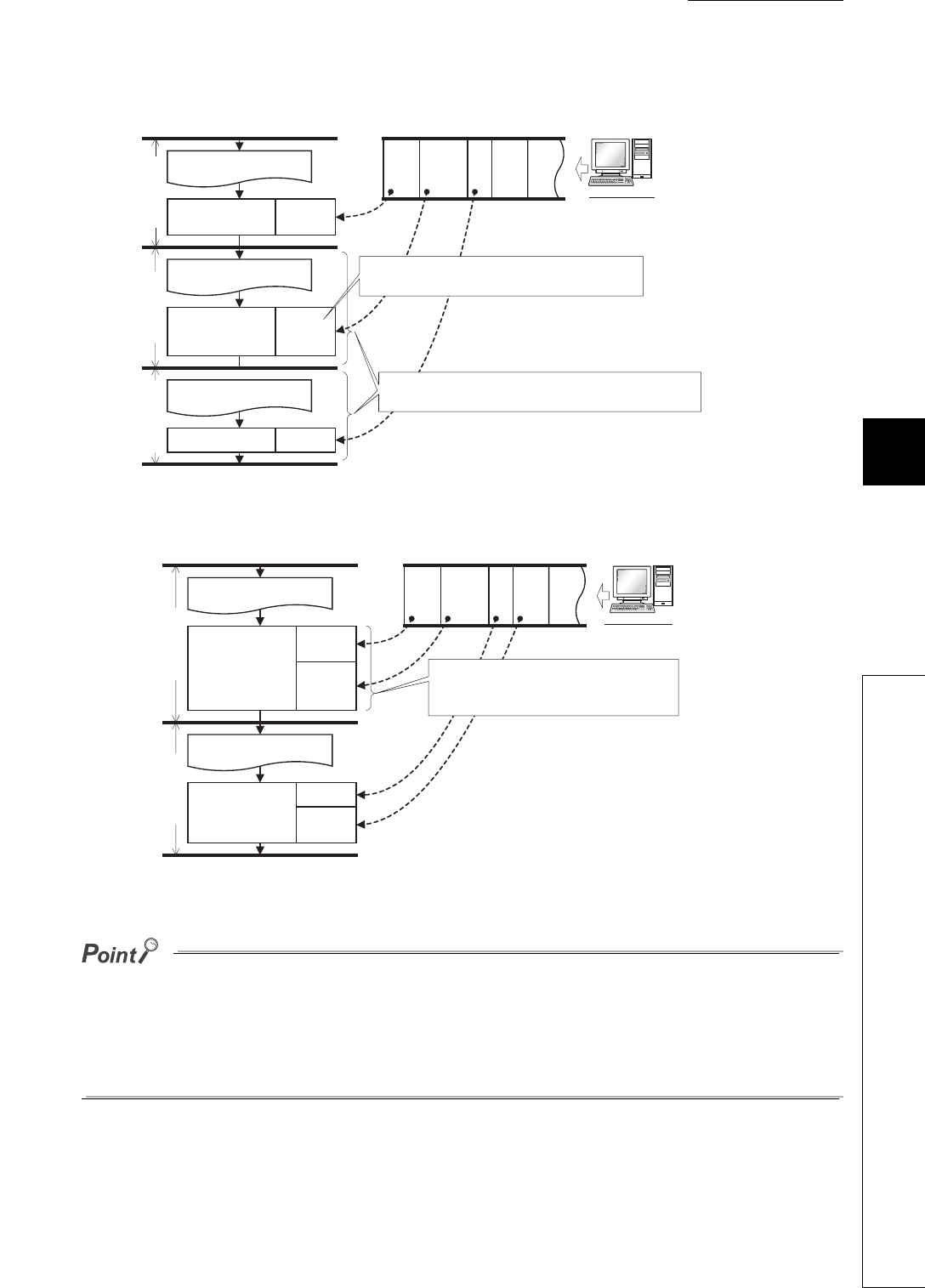

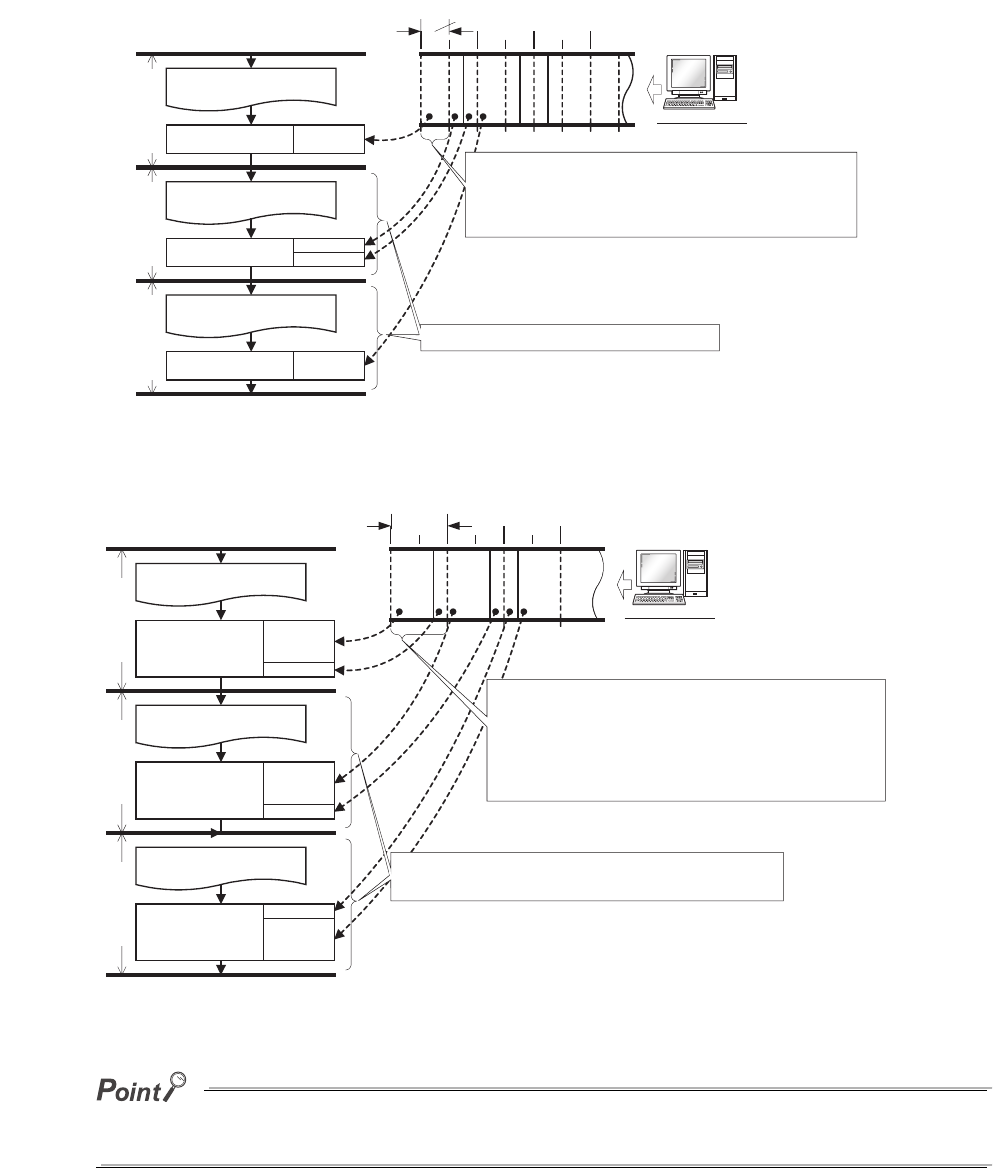

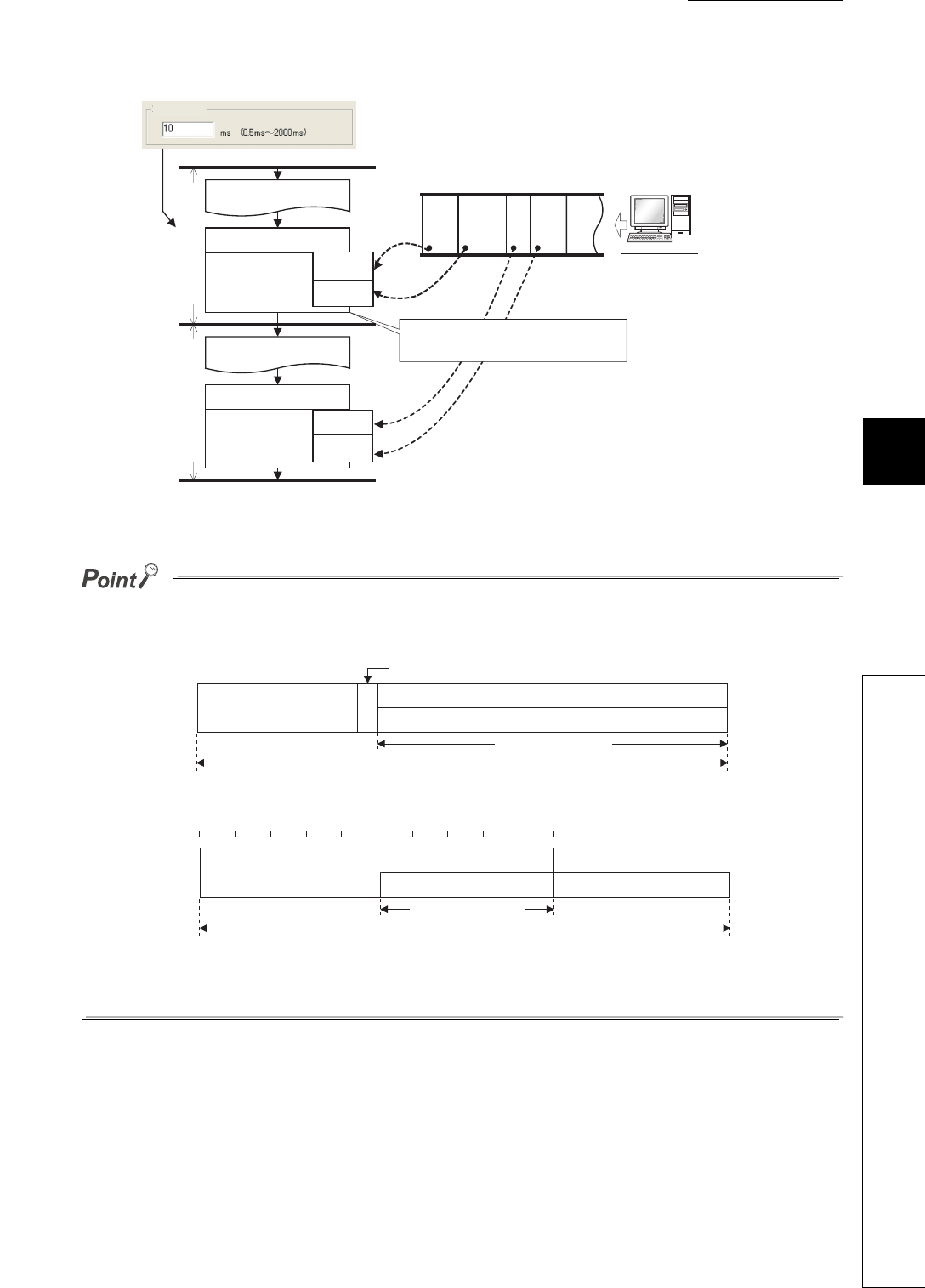

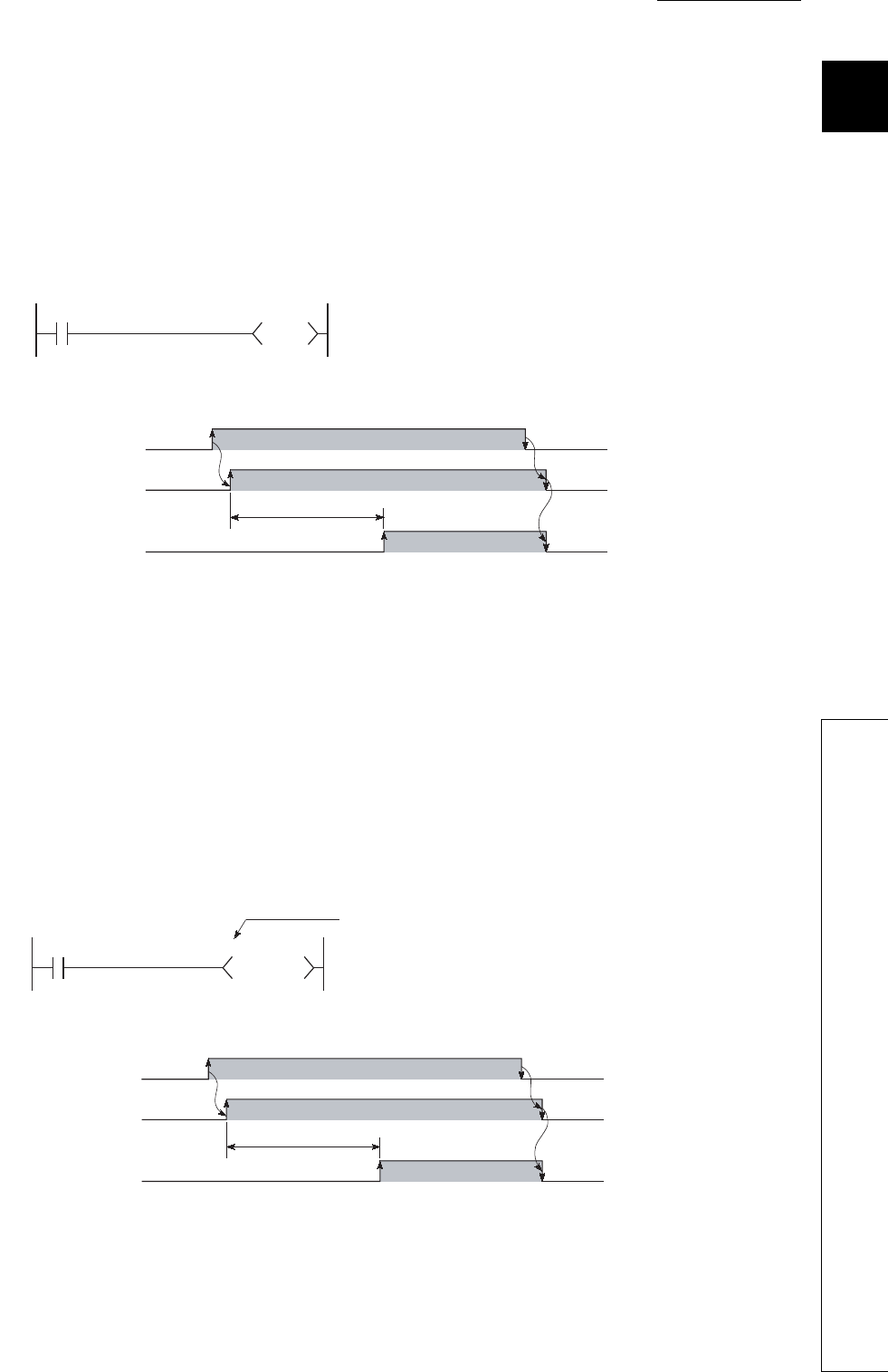

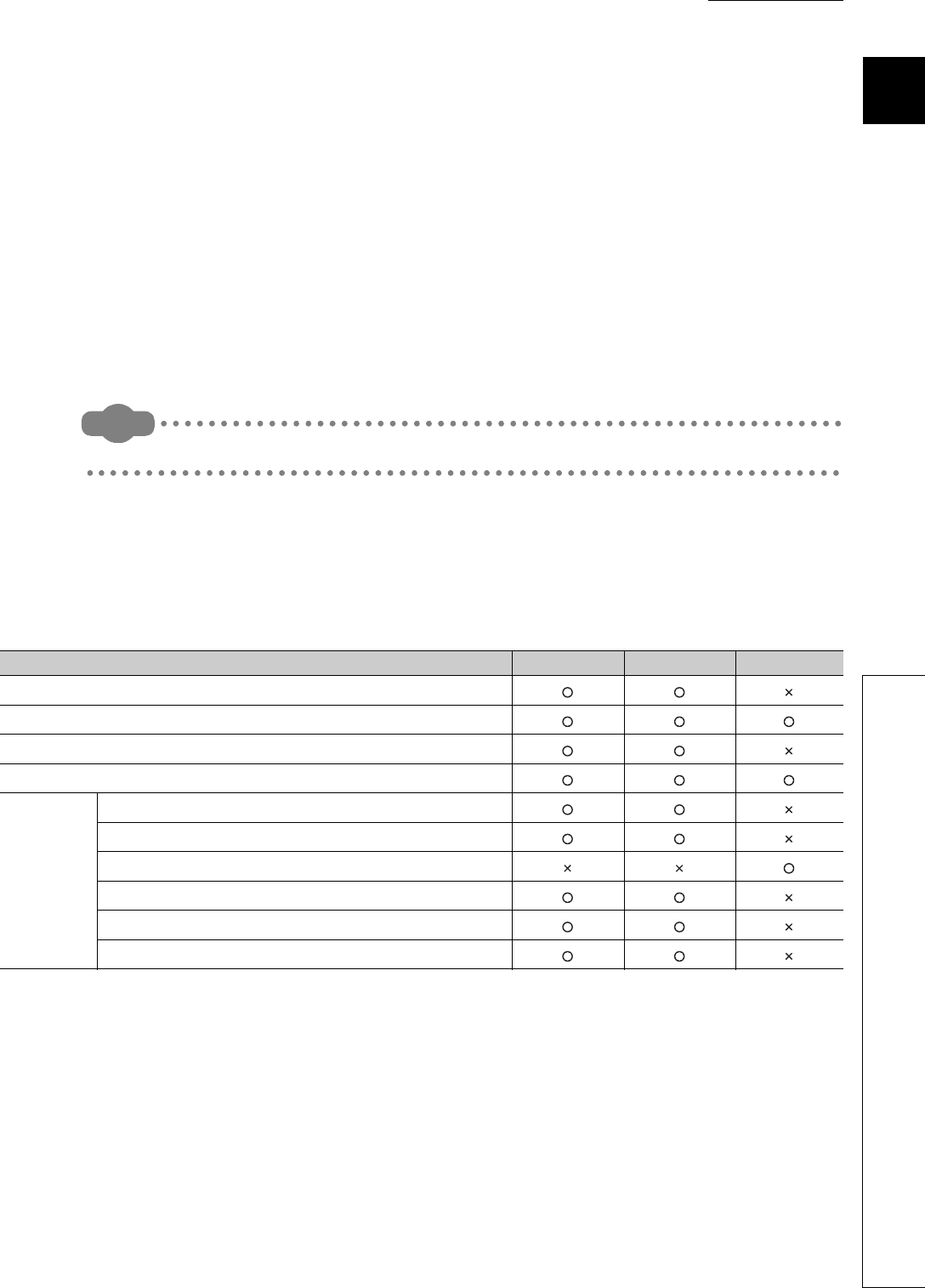

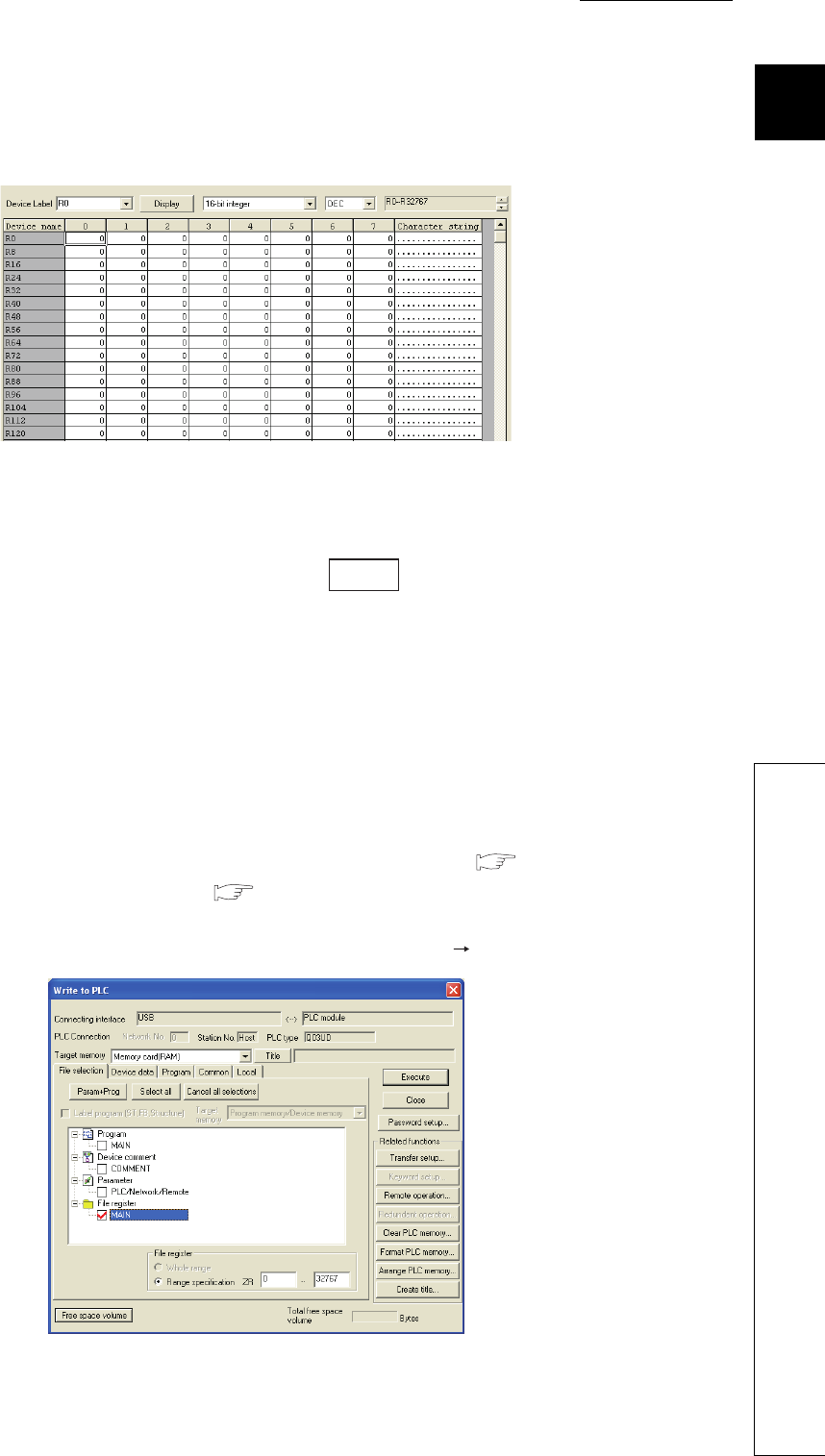

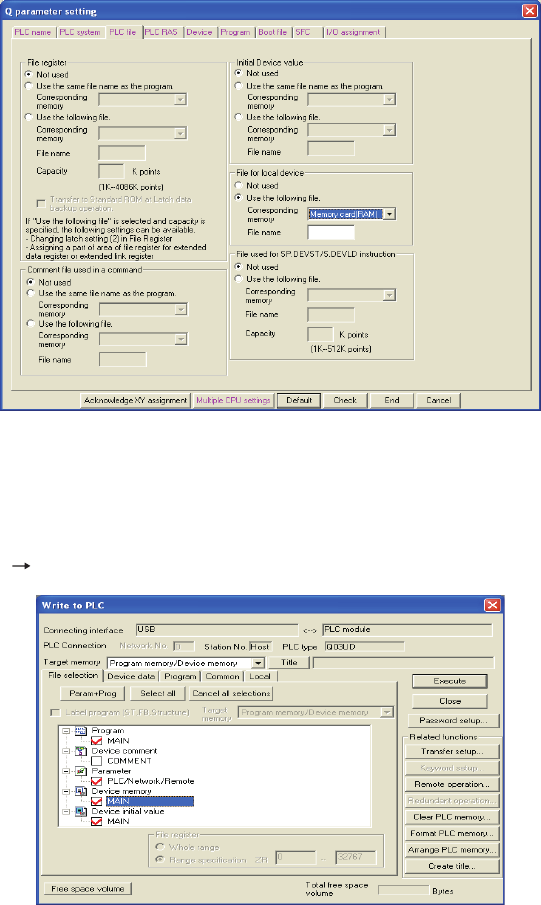

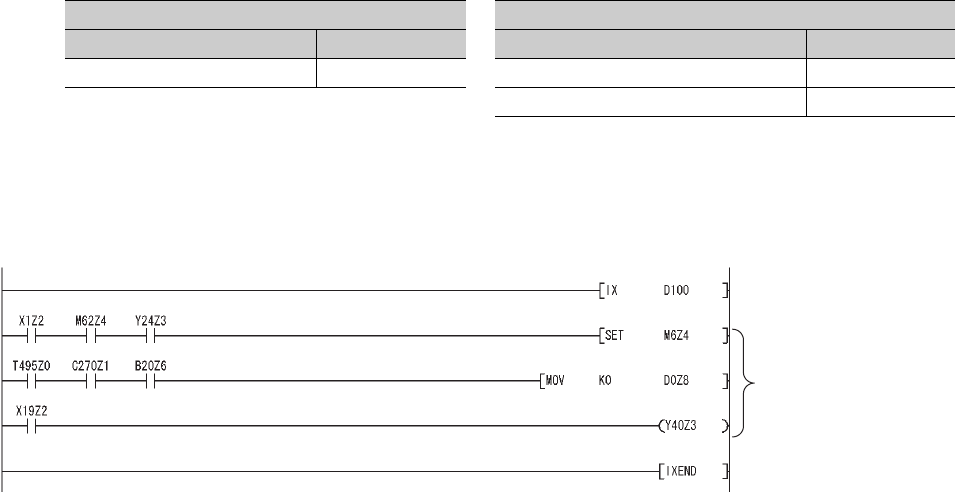

1 - 9