MCUXpresso SDK API Reference Manual MCIMX6G3

User Manual: Pdf

Open the PDF directly: View PDF ![]() .

.

Page Count: 677 [warning: Documents this large are best viewed by clicking the View PDF Link!]

- MCUXpresso SDK API Reference Manual

- Introduction

- Driver errors status

- Architectural Overview

- Trademarks

- ADC: 12-bit Analog to Digital Converter Driver

- ADC_5HC: 12-bit Analog to Digital Converter Driver

- Overview

- Typical use case

- Data Structure Documentation

- Macro Definition Documentation

- Enumeration Type Documentation

- Function Documentation

- ADC_5HC_Init

- ADC_5HC_Deinit

- ADC_5HC_GetDefaultConfig

- ADC_5HC_SetChannelConfig

- ADC_5HC_GetChannelConversionValue

- ADC_5HC_GetChannelStatusFlags

- ADC_5HC_DoAutoCalibration

- ADC_5HC_SetOffsetConfig

- ADC_5HC_EnableDMA

- ADC_5HC_EnableHardwareTrigger

- ADC_5HC_SetHardwareCompareConfig

- ADC_5HC_SetHardwareAverageConfig

- ADC_5HC_GetStatusFlags

- ADC_5HC_ClearStatusFlags

- Variable Documentation

- CACHE: CACHE Memory Controller

- CSI: CMOS Sensor Interface

- Overview

- Frame Buffer Queue

- Typical use case

- Data Structure Documentation

- Macro Definition Documentation

- Typedef Documentation

- Enumeration Type Documentation

- Function Documentation

- CSI_Init

- CSI_Deinit

- CSI_Reset

- CSI_GetDefaultConfig

- CSI_ClearFifo

- CSI_ReflashFifoDma

- CSI_EnableFifoDmaRequest

- CSI_Start

- CSI_Stop

- CSI_SetRxBufferAddr

- CSI_EnableInterrupts

- CSI_DisableInterrupts

- CSI_GetStatusFlags

- CSI_ClearStatusFlags

- CSI_TransferCreateHandle

- CSI_TransferStart

- CSI_TransferStop

- CSI_TransferSubmitEmptyBuffer

- CSI_TransferGetFullBuffer

- CSI_TransferHandleIRQ

- ECSPI: Serial Peripheral Interface Driver

- eLCDIF: Enhanced LCD Interface

- Overview

- Typical use case

- Data Structure Documentation

- Macro Definition Documentation

- Enumeration Type Documentation

- Function Documentation

- ELCDIF_RgbModeInit

- ELCDIF_GetStatus

- ELCDIF_GetLFifoCount

- ELCDIF_EnableInterrupts

- ELCDIF_DisableInterrupts

- ELCDIF_GetInterruptStatus

- ELCDIF_ClearInterruptStatus

- ELCDIF_SetAlphaSurfaceBufferConfig

- ELCDIF_SetAlphaSurfaceBlendConfig

- ELCDIF_SetNextAlphaSurfaceBufferAddr

- ELCDIF_SetOverlayColorKey

- ELCDIF_EnableOverlayColorKey

- ELCDIF_EnableAlphaSurface

- ELCDIF_EnableProcessSurface

- ENET: Ethernet MAC Driver

- Overview

- Typical use case

- Data Structure Documentation

- Macro Definition Documentation

- FSL_ENET_DRIVER_VERSION

- ENET_BUFFDESCRIPTOR_RX_EMPTY_MASK

- ENET_BUFFDESCRIPTOR_RX_SOFTOWNER1_MASK

- ENET_BUFFDESCRIPTOR_RX_WRAP_MASK

- ENET_BUFFDESCRIPTOR_RX_SOFTOWNER2_Mask

- ENET_BUFFDESCRIPTOR_RX_LAST_MASK

- ENET_BUFFDESCRIPTOR_RX_MISS_MASK

- ENET_BUFFDESCRIPTOR_RX_BROADCAST_MASK

- ENET_BUFFDESCRIPTOR_RX_MULTICAST_MASK

- ENET_BUFFDESCRIPTOR_RX_LENVLIOLATE_MASK

- ENET_BUFFDESCRIPTOR_RX_NOOCTET_MASK

- ENET_BUFFDESCRIPTOR_RX_CRC_MASK

- ENET_BUFFDESCRIPTOR_RX_OVERRUN_MASK

- ENET_BUFFDESCRIPTOR_RX_TRUNC_MASK

- ENET_BUFFDESCRIPTOR_TX_READY_MASK

- ENET_BUFFDESCRIPTOR_TX_SOFTOWENER1_MASK

- ENET_BUFFDESCRIPTOR_TX_WRAP_MASK

- ENET_BUFFDESCRIPTOR_TX_SOFTOWENER2_MASK

- ENET_BUFFDESCRIPTOR_TX_LAST_MASK

- ENET_BUFFDESCRIPTOR_TX_TRANMITCRC_MASK

- ENET_BUFFDESCRIPTOR_RX_ERR_MASK

- ENET_FRAME_MAX_FRAMELEN

- ENET_FIFO_MIN_RX_FULL

- ENET_RX_MIN_BUFFERSIZE

- ENET_PHY_MAXADDRESS

- Typedef Documentation

- Enumeration Type Documentation

- Function Documentation

- ENET_GetDefaultConfig

- ENET_Init

- ENET_Deinit

- ENET_Reset

- ENET_SetMII

- ENET_SetSMI

- ENET_GetSMI

- ENET_ReadSMIData

- ENET_StartSMIRead

- ENET_StartSMIWrite

- ENET_StartExtC45SMIRead

- ENET_StartExtC45SMIWrite

- ENET_SetMacAddr

- ENET_GetMacAddr

- ENET_AddMulticastGroup

- ENET_LeaveMulticastGroup

- ENET_ActiveRead

- ENET_EnableSleepMode

- ENET_GetAccelFunction

- ENET_EnableInterrupts

- ENET_DisableInterrupts

- ENET_GetInterruptStatus

- ENET_ClearInterruptStatus

- ENET_SetCallback

- ENET_GetRxErrBeforeReadFrame

- ENET_GetRxFrameSize

- ENET_ReadFrame

- ENET_SendFrame

- ENET_TransmitIRQHandler

- ENET_ReceiveIRQHandler

- ENET_ErrorIRQHandler

- ENET_CommonFrame0IRQHandler

- EPIT: Enhanced Periodic Interrupt Timer

- Overview

- Function groups

- Typical use case

- Data Structure Documentation

- Enumeration Type Documentation

- Function Documentation

- EPIT_SoftwareReset

- EPIT_Init

- EPIT_Deinit

- EPIT_GetDefaultConfig

- EPIT_SetClockSource

- EPIT_SetClockDivider

- EPIT_GetClockDivider

- EPIT_StartTimer

- EPIT_StopTimer

- EPIT_SetTimerPeriod

- EPIT_GetCurrentTimerCount

- EPIT_SetOutputOperationMode

- EPIT_SetOutputCompareValue

- EPIT_EnableInterrupts

- EPIT_DisableInterrupts

- EPIT_GetEnabledInterrupts

- EPIT_GetStatusFlags

- EPIT_ClearStatusFlags

- FlexCAN: Flex Controller Area Network Driver

- GPT: General Purpose Timer

- Overview

- Function groups

- Typical use case

- Data Structure Documentation

- Enumeration Type Documentation

- Function Documentation

- GPT_Init

- GPT_Deinit

- GPT_GetDefaultConfig

- GPT_SoftwareReset

- GPT_SetClockSource

- GPT_GetClockSource

- GPT_SetClockDivider

- GPT_GetClockDivider

- GPT_SetOscClockDivider

- GPT_GetOscClockDivider

- GPT_StartTimer

- GPT_StopTimer

- GPT_GetCurrentTimerCount

- GPT_SetInputOperationMode

- GPT_GetInputOperationMode

- GPT_GetInputCaptureValue

- GPT_SetOutputOperationMode

- GPT_GetOutputOperationMode

- GPT_SetOutputCompareValue

- GPT_GetOutputCompareValue

- GPT_ForceOutput

- GPT_EnableInterrupts

- GPT_DisableInterrupts

- GPT_GetEnabledInterrupts

- GPT_GetStatusFlags

- GPT_ClearStatusFlags

- GPC: General Power Controller Driver

- GPIO: General-Purpose Input/Output Driver

- I2C: Inter-Integrated Circuit Driver

- PWM: Pulse Width Modulation Driver

- UART: Universal Asynchronous Receiver/Transmitter Driver

- MMDC: Multi Mode DDR Controller Driver

- Overview

- Typical use case

- Data Structure Documentation

- struct mmdc_readDQS_calibration_config_t

- struct mmdc_writeLeveling_calibration_config_t

- struct mmdc_read_calibration_config_t

- struct mmdc_fine_tuning_config_t

- struct mmdc_odt_config_t

- struct mmdc_power_config_t

- struct mmdc_zq_config_t

- struct mmdc_cmd_config_t

- struct mmdc_device_timing_t

- struct mmdc_auto_refresh_t

- struct mmdc_exaccess_config_t

- struct mmdc_profiling_config_t

- struct mmdc_performance_config_t

- struct mmdc_device_config_t

- struct mmdc_config_t

- Macro Definition Documentation

- Typedef Documentation

- Enumeration Type Documentation

- _mmdc_status

- mmdc_device_type_t

- mmdc_device_bank_num_t

- mmdc_row_addr_width_t

- mmdc_col_addr_width_t

- mmdc_burst_len_t

- mmdc_cmd_type_t

- mmdc_zq_calmode_t

- mmdc_zq_calfreq_t

- mmdc_refresh_sel_t

- mmdc_profiling_action_t

- mmdc_calibration_type_t

- mmdc_calibaration_waitcycles_t

- mmdc_fine_tuning_dutycycle_t

- mmdc_termination_config_t

- _mmdc_lpddr2_derate

- _mmdc_exaccess_type

- Function Documentation

- MMDC_GetDefaultConfig

- MMDC_Init

- MMDC_Deinit

- MMDC_HandleCommand

- MMDC_GetReadData

- MMDC_EnhancePerformance

- MMDC_EnableAutoRefresh

- MMDC_DisableAutoRefresh

- MMDC_EnablePowerSaving

- MMDC_DisablePowerSaving

- MMDC_Profiling

- MMDC_LPDDR2UpdateDerate

- MMDC_MonitorLPDDR2OperationTemp

- MMDC_ReadDQSGatingCalibration

- MMDC_WriteLevelingCalibration

- MMDC_WriteCalibration

- MMDC_ReadCalibration

- MMDC_DoFineTuning

- MMDC_SetTiming

- MMDC_DeviceInit

- MMDC_EnterConfigurationMode

- MMDC_DoZQCalibration

- MMDC_EnableLowPowerMode

- MMDC_EnableDVFSMode

- MMDC_Reset

- MMDC_SwitchDeviceFrequency

- MMDC_EnableSBS

- MMDC_TriggerSBS

- MMDC_GetAXIAddrBySBS

- MMDC_GetAXIAttributeBySBS

- MMDC_EnableProfiling

- MMDC_ResumeProfiling

- MMDC_ResetProfiling

- MMDC_ExclusiveAccess

- PMU: Power Management Unit

- Overview

- Macro Definition Documentation

- Enumeration Type Documentation

- Function Documentation

- PMU_1P1SetWeakReferenceSource

- PMU_1P1EnableWeakRegulator

- PMU_1P1SetRegulatorOutputVoltage

- PMU_1P1SetBrownoutOffsetVoltage

- PMU_1P1EnablePullDown

- PMU_1P1EnableCurrentLimit

- PMU_1P1EnableBrownout

- PMU_1P1EnableOutput

- PMU_3P0SetRegulatorOutputVoltage

- PMU_3P0SetVBusVoltageSource

- PMU_3P0SetBrownoutOffsetVoltage

- PMU_3P0EnableCurrentLimit

- PMU_3P0EnableBrownout

- PMU_3P0EnableOutput

- PMU_2P5EnableWeakRegulator

- PMU_2P5SetRegulatorOutputVoltage

- PMU_2P5SetBrownoutOffsetVoltage

- PMU_2P1EnablePullDown

- PMU_2P5EnableCurrentLimit

- PMU_2P5nableBrownout

- PMU_2P5EnableOutput

- PMU_CoreEnableIncreaseGateDrive

- PMU_CoreSetRegulatorVoltageRampRate

- PMU_CoreSetSOCDomainVoltage

- PMU_CoreSetARMCoreDomainVoltage

- PMU_GatePower

- PMU_UngatePower

- PMU_EnableLowPowerBandgap

- PXP: Pixel Pipeline

- Overview

- Typical use case

- Data Structure Documentation

- Enumeration Type Documentation

- _pxp_interrupt_enable

- _pxp_flags

- pxp_flip_mode_t

- pxp_rotate_position_t

- pxp_rotate_degree_t

- pxp_interlaced_output_mode_t

- pxp_output_pixel_format_t

- pxp_ps_pixel_format_t

- pxp_as_pixel_format_t

- pxp_alpha_mode_t

- pxp_rop_mode_t

- pxp_block_size_t

- pxp_csc1_mode_t

- pxp_csc2_mode_t

- pxp_lut_lookup_mode_t

- pxp_lut_out_mode_t

- pxp_lut_8k_bank_t

- pxp_ram_t

- _pxp_dither_mode

- _pxp_dither_lut_mode

- _pxp_dither_matrix_size

- Function Documentation

- PXP_Init

- PXP_Deinit

- PXP_Reset

- PXP_Start

- PXP_EnableLcdHandShake

- PXP_EnableContinousRun

- PXP_SetProcessBlockSize

- PXP_GetStatusFlags

- PXP_ClearStatusFlags

- PXP_GetAxiErrorId

- PXP_EnableInterrupts

- PXP_DisableInterrupts

- PXP_SetAlphaSurfaceBufferConfig

- PXP_SetAlphaSurfaceBlendConfig

- PXP_SetAlphaSurfaceOverlayColorKey

- PXP_EnableAlphaSurfaceOverlayColorKey

- PXP_SetAlphaSurfacePosition

- PXP_SetProcessSurfaceBackGroundColor

- PXP_SetProcessSurfaceBufferConfig

- PXP_SetProcessSurfaceScaler

- PXP_SetProcessSurfacePosition

- PXP_SetProcessSurfaceColorKey

- PXP_SetOutputBufferConfig

- PXP_SetOverwrittenAlphaValue

- PXP_EnableOverWrittenAlpha

- PXP_SetRotateConfig

- PXP_SetNextCommand

- PXP_IsNextCommandPending

- PXP_CancelNextCommand

- PXP_SetCsc2Config

- PXP_EnableCsc2

- PXP_SetCsc1Mode

- PXP_EnableCsc1

- PXP_SetLutConfig

- PXP_LoadLutTable

- PXP_EnableLut

- PXP_Select8kLutBank

- QSPI: Quad Serial Peripheral Interface Driver

- Overview

- Data Structure Documentation

- Macro Definition Documentation

- Enumeration Type Documentation

- Function Documentation

- QSPI_Init

- QSPI_GetDefaultQspiConfig

- QSPI_Deinit

- QSPI_SetFlashConfig

- QSPI_SoftwareReset

- QSPI_Enable

- QSPI_GetStatusFlags

- QSPI_GetErrorStatusFlags

- QSPI_ClearErrorFlag

- QSPI_EnableInterrupts

- QSPI_DisableInterrupts

- QSPI_EnableDMA

- QSPI_GetTxDataRegisterAddress

- QSPI_GetRxDataRegisterAddress

- QSPI_SetIPCommandAddress

- QSPI_SetIPCommandSize

- QSPI_ExecuteIPCommand

- QSPI_ExecuteAHBCommand

- QSPI_EnableIPParallelMode

- QSPI_EnableAHBParallelMode

- QSPI_UpdateLUT

- QSPI_ClearFifo

- QSPI_ClearCommandSequence

- QSPI_EnableDDRMode

- QSPI_SetReadDataArea

- QSPI_WriteBlocking

- QSPI_WriteData

- QSPI_ReadBlocking

- QSPI_ReadData

- QSPI_TransferSendBlocking

- QSPI_TransferReceiveBlocking

- QSPI eDMA Driver

- SAI: Serial Audio Interface

- Overview

- Typical use case

- Data Structure Documentation

- Macro Definition Documentation

- Enumeration Type Documentation

- Function Documentation

- SAI_TxInit

- SAI_RxInit

- SAI_TxGetDefaultConfig

- SAI_RxGetDefaultConfig

- SAI_Deinit

- SAI_TxReset

- SAI_RxReset

- SAI_TxEnable

- SAI_RxEnable

- SAI_TxGetStatusFlag

- SAI_TxClearStatusFlags

- SAI_RxGetStatusFlag

- SAI_RxClearStatusFlags

- SAI_TxSoftwareReset

- SAI_RxSoftwareReset

- SAI_TxSetChannelFIFOMask

- SAI_RxSetChannelFIFOMask

- SAI_TxEnableInterrupts

- SAI_RxEnableInterrupts

- SAI_TxDisableInterrupts

- SAI_RxDisableInterrupts

- SAI_TxEnableDMA

- SAI_RxEnableDMA

- SAI_TxGetDataRegisterAddress

- SAI_RxGetDataRegisterAddress

- SAI_TxSetFormat

- SAI_RxSetFormat

- SAI_WriteBlocking

- SAI_WriteData

- SAI_ReadBlocking

- SAI_ReadData

- SAI_TransferTxCreateHandle

- SAI_TransferRxCreateHandle

- SAI_TransferTxSetFormat

- SAI_TransferRxSetFormat

- SAI_TransferSendNonBlocking

- SAI_TransferReceiveNonBlocking

- SAI_TransferGetSendCount

- SAI_TransferGetReceiveCount

- SAI_TransferAbortSend

- SAI_TransferAbortReceive

- SAI_TransferTerminateSend

- SAI_TransferTerminateReceive

- SAI_TransferTxHandleIRQ

- SAI_TransferRxHandleIRQ

- SAI DMA Driver

- SAI eDMA Driver

- SAI SDMA Driver

- SDMA: Smart Direct Memory Access (SDMA) Controller Driver

- Overview

- Typical use case

- Data Structure Documentation

- Macro Definition Documentation

- Typedef Documentation

- Enumeration Type Documentation

- Function Documentation

- SDMA_Init

- SDMA_Deinit

- SDMA_GetDefaultConfig

- SDMA_ResetModule

- SDMA_EnableChannelErrorInterrupts

- SDMA_DisableChannelErrorInterrupts

- SDMA_ConfigBufferDescriptor

- SDMA_SetChannelPriority

- SDMA_SetSourceChannel

- SDMA_StartChannelSoftware

- SDMA_StartChannelEvents

- SDMA_StopChannel

- SDMA_SetContextSwitchMode

- SDMA_GetChannelInterruptStatus

- SDMA_ClearChannelInterruptStatus

- SDMA_GetChannelStopStatus

- SDMA_ClearChannelStopStatus

- SDMA_GetChannelPendStatus

- SDMA_ClearChannelPendStatus

- SDMA_GetErrorStatus

- SDMA_GetRequestSourceStatus

- SDMA_CreateHandle

- SDMA_InstallBDMemory

- SDMA_SetCallback

- SDMA_PrepareTransfer

- SDMA_SubmitTransfer

- SDMA_StartTransfer

- SDMA_StopTransfer

- SDMA_AbortTransfer

- SDMA_HandleIRQ

- SNVS_HP: Secure Non-Volatile Storage

- Overview

- SNVS_HP Driver Initialization and Configuration

- Set & Get Datetime

- Set & Get Alarm

- Start & Stop timer

- Status

- Interrupt

- Typical use case

- Data Structure Documentation

- Enumeration Type Documentation

- Function Documentation

- SNVS_HP_RTC_Init

- SNVS_HP_RTC_Deinit

- SNVS_HP_RTC_GetDefaultConfig

- SNVS_HP_RTC_SetDatetime

- SNVS_HP_RTC_GetDatetime

- SNVS_HP_RTC_SetAlarm

- SNVS_HP_RTC_GetAlarm

- SNVS_HP_RTC_EnableInterrupts

- SNVS_HP_RTC_DisableInterrupts

- SNVS_HP_RTC_GetEnabledInterrupts

- SNVS_HP_RTC_GetStatusFlags

- SNVS_HP_RTC_ClearStatusFlags

- SNVS_HP_RTC_StartTimer

- SNVS_HP_RTC_StopTimer

- Variable Documentation

- SRC: System Reset Controller Driver

- Overview

- Macro Definition Documentation

- Enumeration Type Documentation

- Function Documentation

- SRC_EnableWDOG3Reset

- SRC_SetMixResetStretchCycles

- SRC_EnableCoreDebugResetAfterPowerGate

- SRC_SetWdog3ResetOption

- SRC_DoSoftwareResetARMCoreDebug

- SRC_GetSoftwareResetARMCoreDebugDone

- SRC_DoSoftwareResetARMCore0

- SRC_GetSoftwareResetARMCore0Done

- SRC_AssertEIMReset

- SRC_EnableWDOGReset

- SRC_SetWarmResetBypassCount

- SRC_EnableWarmReset

- SRC_GetStatusFlags

- SRC_GetBootModeWord1

- SRC_GetBootModeWord2

- SRC_SetWarmBootIndication

- SRC_GetResetStatusFlags

- SRC_ClearResetStatusFlags

- SRC_SetGeneralPurposeRegister

- SRC_GetGeneralPurposeRegister

- TSC: Touch Screen Controller Driver

- USDHC: ultra Secured Digital Host Controller Driver

- Overview

- Typical use case

- Data Structure Documentation

- Macro Definition Documentation

- Typedef Documentation

- Enumeration Type Documentation

- _usdhc_status

- _usdhc_capability_flag

- _usdhc_wakeup_event

- _usdhc_reset

- _usdhc_transfer_flag

- _usdhc_present_status_flag

- _usdhc_interrupt_status_flag

- _usdhc_auto_command12_error_status_flag

- _usdhc_standard_tuning

- _usdhc_adma_error_status_flag

- usdhc_adma_error_state_t

- _usdhc_force_event

- usdhc_data_bus_width_t

- usdhc_endian_mode_t

- usdhc_dma_mode_t

- _usdhc_sdio_control_flag

- usdhc_boot_mode_t

- usdhc_card_command_type_t

- usdhc_card_response_type_t

- _usdhc_adma1_descriptor_flag

- _usdhc_adma2_descriptor_flag

- usdhc_burst_len_t

- Function Documentation

- USDHC_Init

- USDHC_Deinit

- USDHC_Reset

- USDHC_SetAdmaTableConfig

- USDHC_EnableInterruptStatus

- USDHC_DisableInterruptStatus

- USDHC_EnableInterruptSignal

- USDHC_DisableInterruptSignal

- USDHC_GetInterruptStatusFlags

- USDHC_ClearInterruptStatusFlags

- USDHC_GetAutoCommand12ErrorStatusFlags

- USDHC_GetAdmaErrorStatusFlags

- USDHC_GetPresentStatusFlags

- USDHC_GetCapability

- USDHC_ForceClockOn

- USDHC_SetSdClock

- USDHC_SetCardActive

- USDHC_AssertHardwareReset

- USDHC_SetDataBusWidth

- USDHC_WriteData

- USDHC_ReadData

- USDHC_SendCommand

- USDHC_EnableWakeupEvent

- USDHC_CardDetectByData3

- USDHC_DetectCardInsert

- USDHC_EnableSdioControl

- USDHC_SetContinueRequest

- USDHC_SetMmcBootConfig

- USDHC_SetForceEvent

- UDSHC_SelectVoltage

- USDHC_RequestTuningForSDR50

- USDHC_RequestReTuning

- USDHC_EnableAutoTuning

- USDHC_SetRetuningTimer

- USDHC_EnableAutoTuningForCmdAndData

- USDHC_EnableManualTuning

- USDHC_AdjustDelayForManualTuning

- USDHC_EnableStandardTuning

- USDHC_GetExecuteStdTuningStatus

- USDHC_CheckStdTuningResult

- USDHC_CheckTuningError

- USDHC_EnableDDRMode

- USDHC_TransferBlocking

- USDHC_TransferCreateHandle

- USDHC_TransferNonBlocking

- USDHC_TransferHandleIRQ

- WDOG: Watchdog Timer Driver

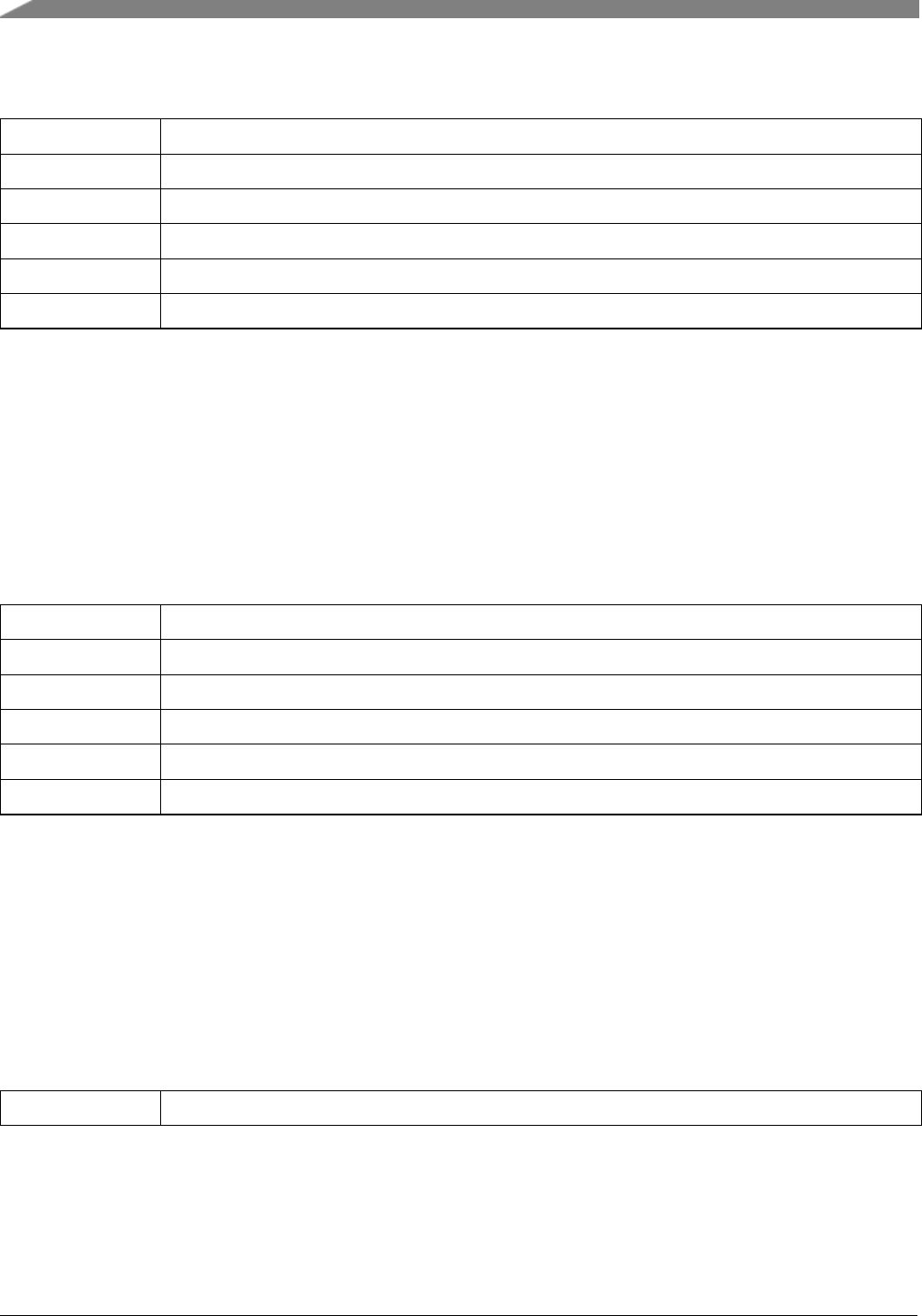

- Clock Driver

- Overview

- Get frequency

- External clock frequency

- Data Structure Documentation

- Macro Definition Documentation

- FSL_SDK_DISABLE_DRIVER_CLOCK_CONTROL

- FSL_CLOCK_DRIVER_VERSION

- ADC_CLOCKS

- ADC_5HC_CLOCKS

- ECSPI_CLOCKS

- ENET_CLOCKS

- EPIT_CLOCKS

- FLEXCAN_CLOCKS

- FLEXCAN_PERIPH_CLOCKS

- GPIO_CLOCKS

- GPT_CLOCKS

- GPT_PERIPH_CLOCKS

- I2C_CLOCKS

- PWM_CLOCKS

- QSPI_CLOCKS

- SAI_CLOCKS

- SDMA_CLOCKS

- SIM_CLOCKS

- TSC_CLOCKS

- UART_CLOCKS

- USDHC_CLOCKS

- WDOG_CLOCKS

- LCDIF_CLOCKS

- LCDIF_PERIPH_CLOCKS

- PXP_CLOCKS

- SNVS_HP_CLOCKS

- SNVS_LP_CLOCKS

- CSI_CLOCKS

- CSI_MCLK_CLOCKS

- FSL_CLOCK_MMDC_IPG_GATE_COUNT

- MMDC_ACLK_CLOCKS

- kCLOCK_CoreSysClk

- CLOCK_GetCoreSysClkFreq

- Enumeration Type Documentation

- Function Documentation

- CLOCK_SetMux

- CLOCK_GetMux

- CLOCK_SetDiv

- CLOCK_GetDiv

- CLOCK_ControlGate

- CLOCK_EnableClock

- CLOCK_DisableClock

- CLOCK_SetMode

- CLOCK_GetFreq

- CLOCK_InitExternalClk

- CLOCK_DeinitExternalClk

- CLOCK_SwitchOsc

- CLOCK_GetOscFreq

- CLOCK_GetRtcFreq

- CLOCK_SetXtalFreq

- CLOCK_SetRtcXtalFreq

- CLOCK_InitArmPll

- CLOCK_InitSysPll

- CLOCK_InitUsb1Pll

- CLOCK_InitUsb2Pll

- CLOCK_InitAudioPll

- CLOCK_InitVideoPll

- CLOCK_InitEnetPll

- CLOCK_DeinitEnetPll

- CLOCK_GetPllFreq

- CLOCK_InitSysPfd

- CLOCK_DeinitSysPfd

- CLOCK_InitUsb1Pfd

- CLOCK_DeinitUsb1Pfd

- CLOCK_GetSysPfdFreq

- CLOCK_GetUsb1PfdFreq

- CLOCK_EnableUsbhs0Clock

- CLOCK_EnableUsbhs0PhyPllClock

- CLOCK_DisableUsbhs0PhyPllClock

- CLOCK_EnableUsbhs1Clock

- CLOCK_EnableUsbhs1PhyPllClock

- CLOCK_DisableUsbhs1PhyPllClock

- Variable Documentation

- Debug Console

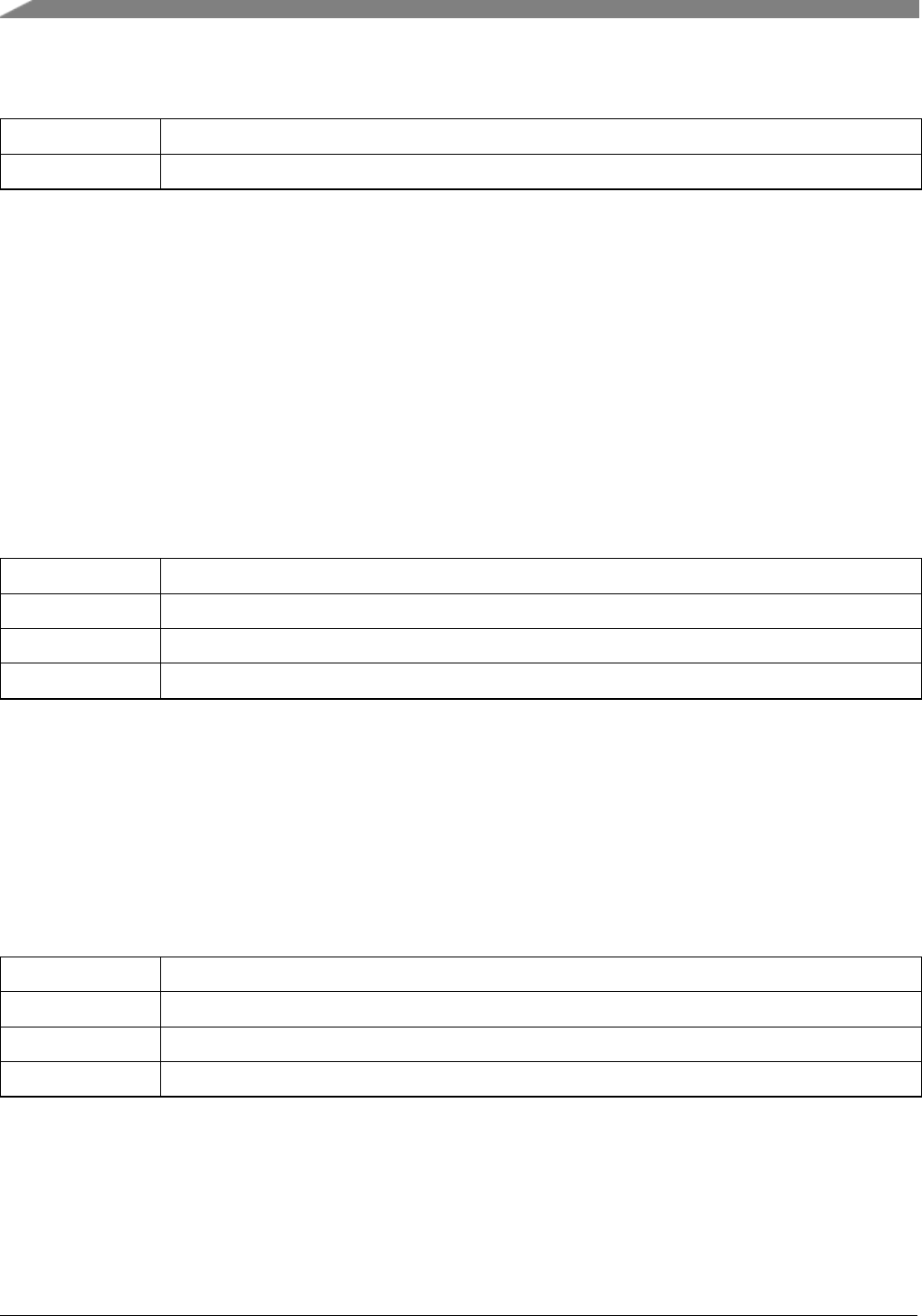

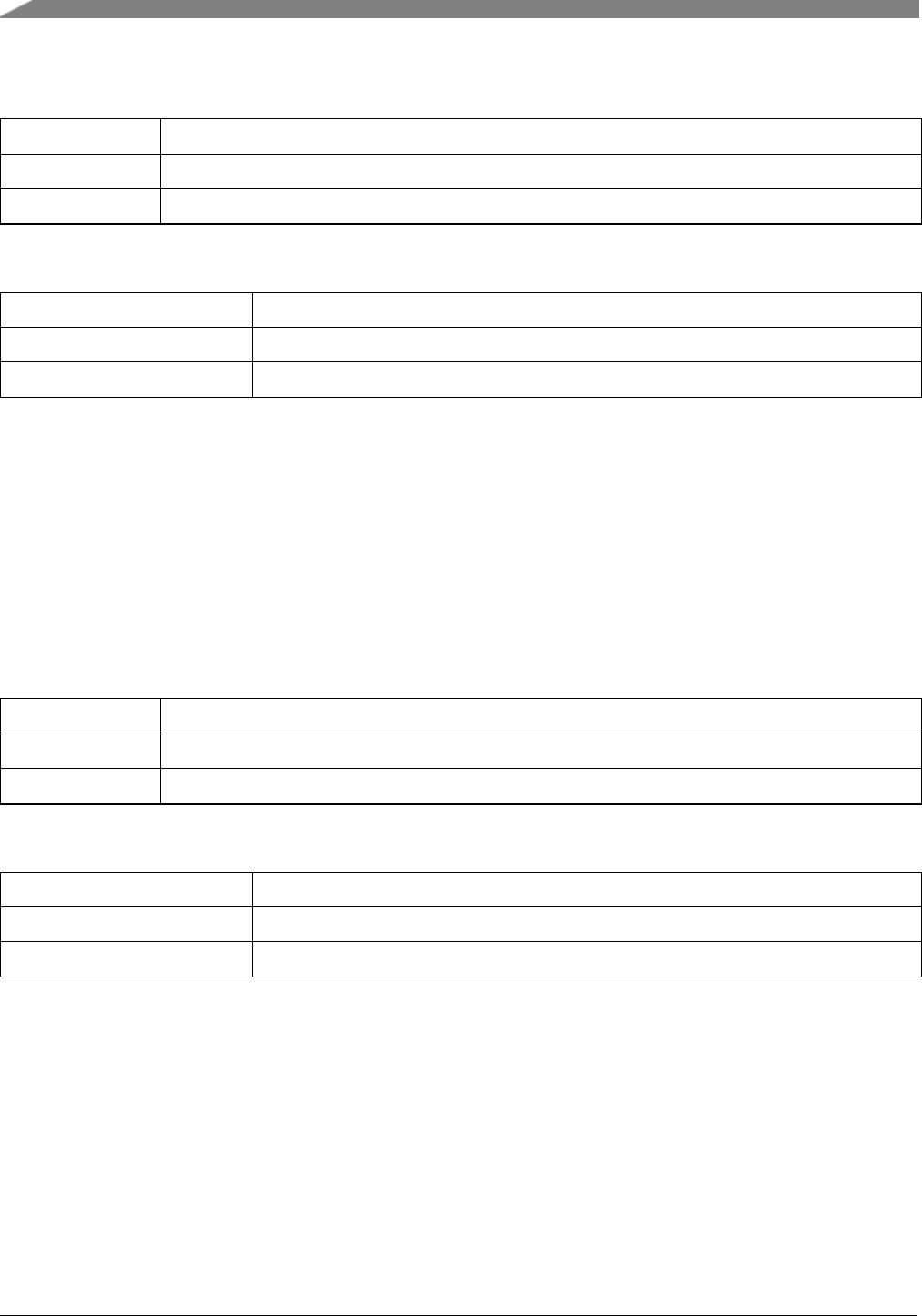

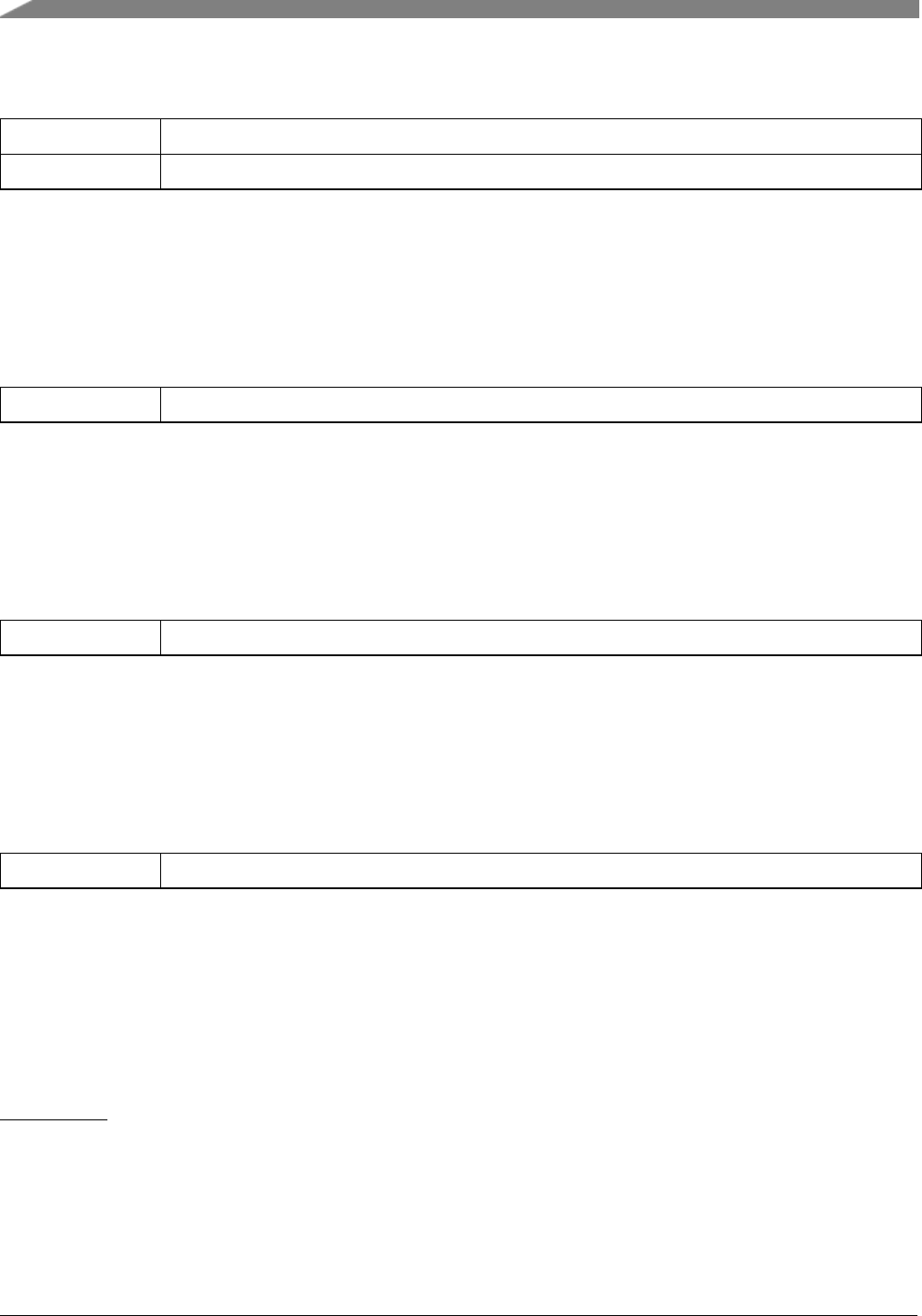

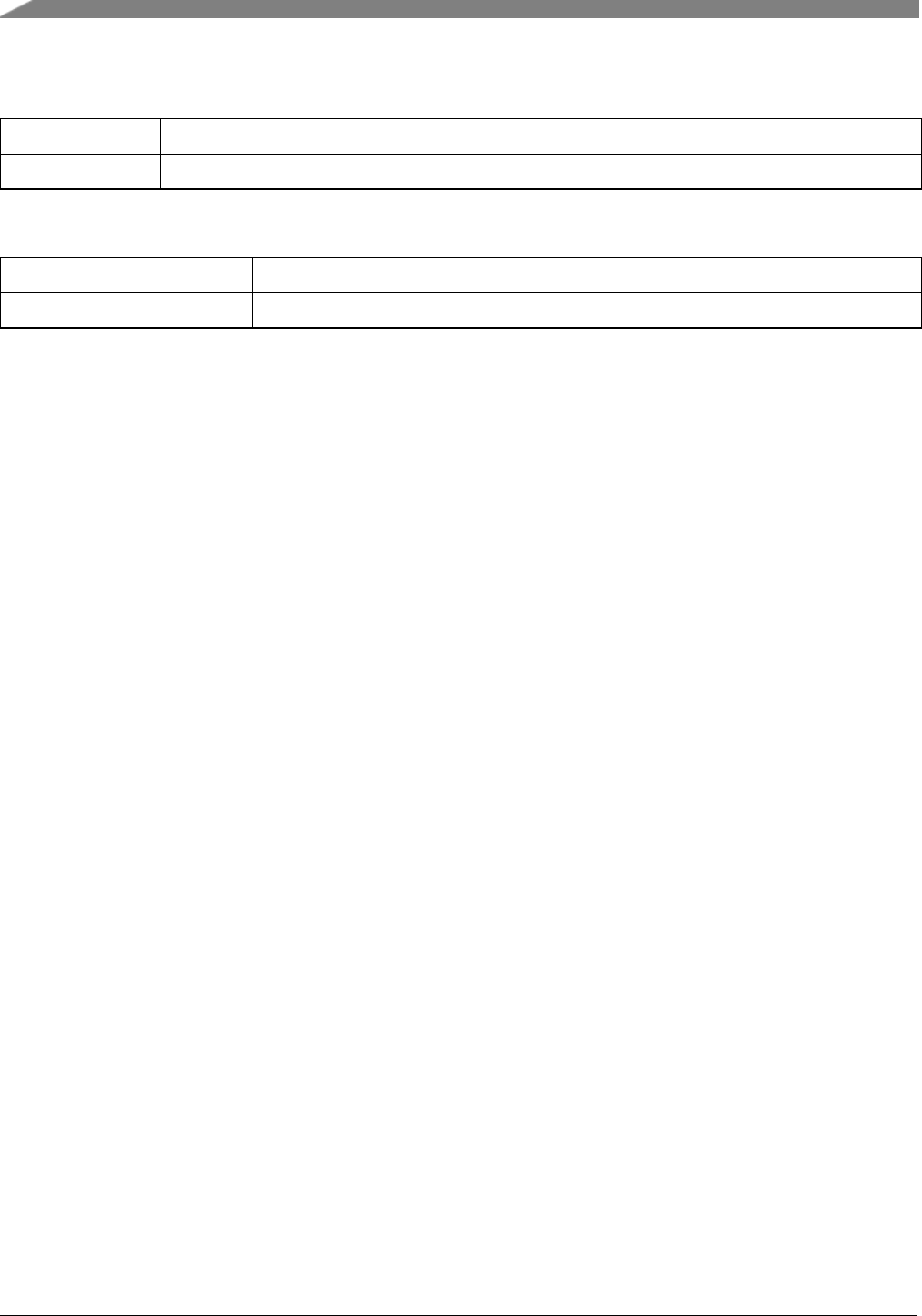

MCUXpresso SDK API Reference Manual

NXP Semiconductors

Document Number: MCUXSDKIMX6ULAPIRM

Rev. 0

Jun 2017

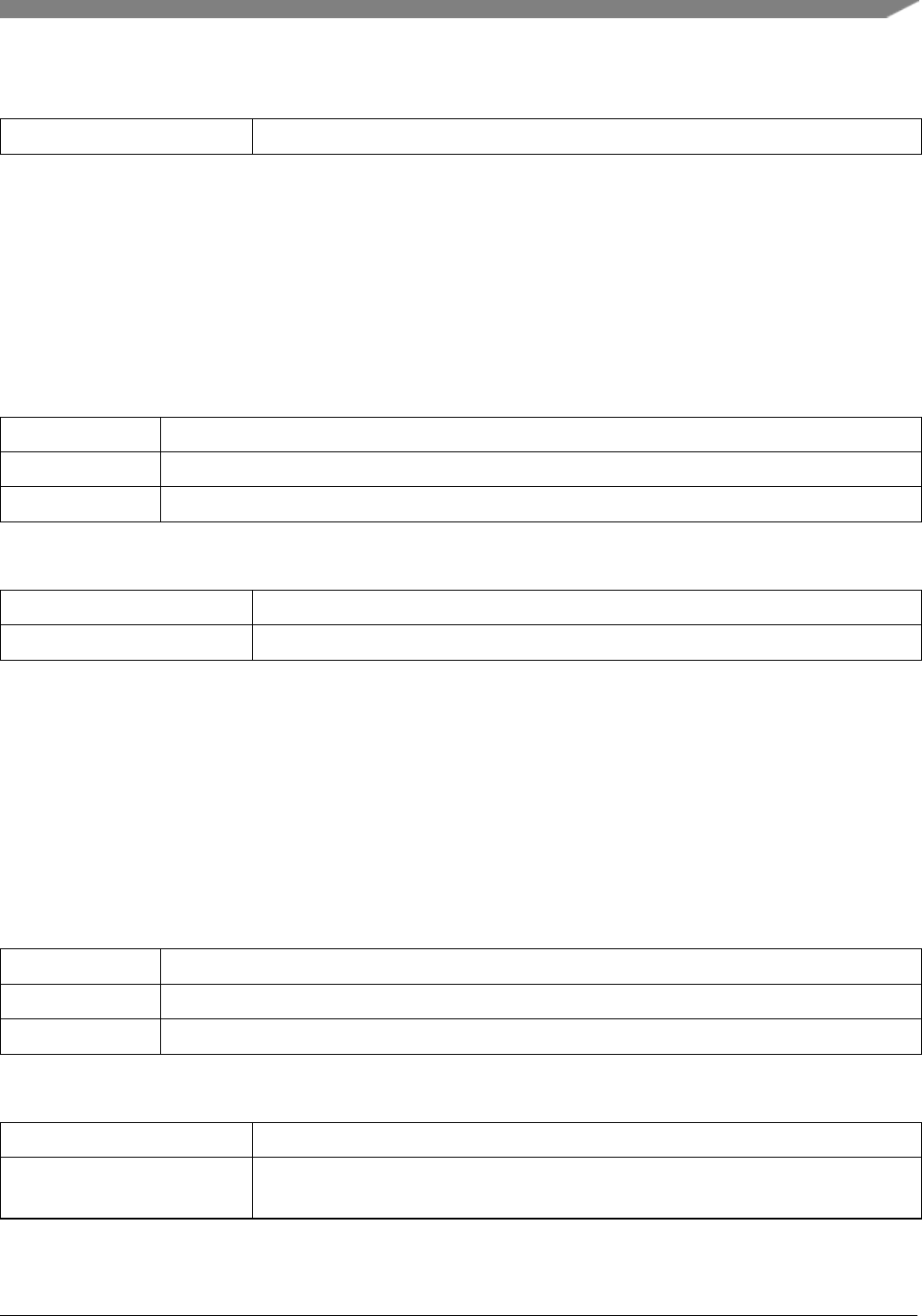

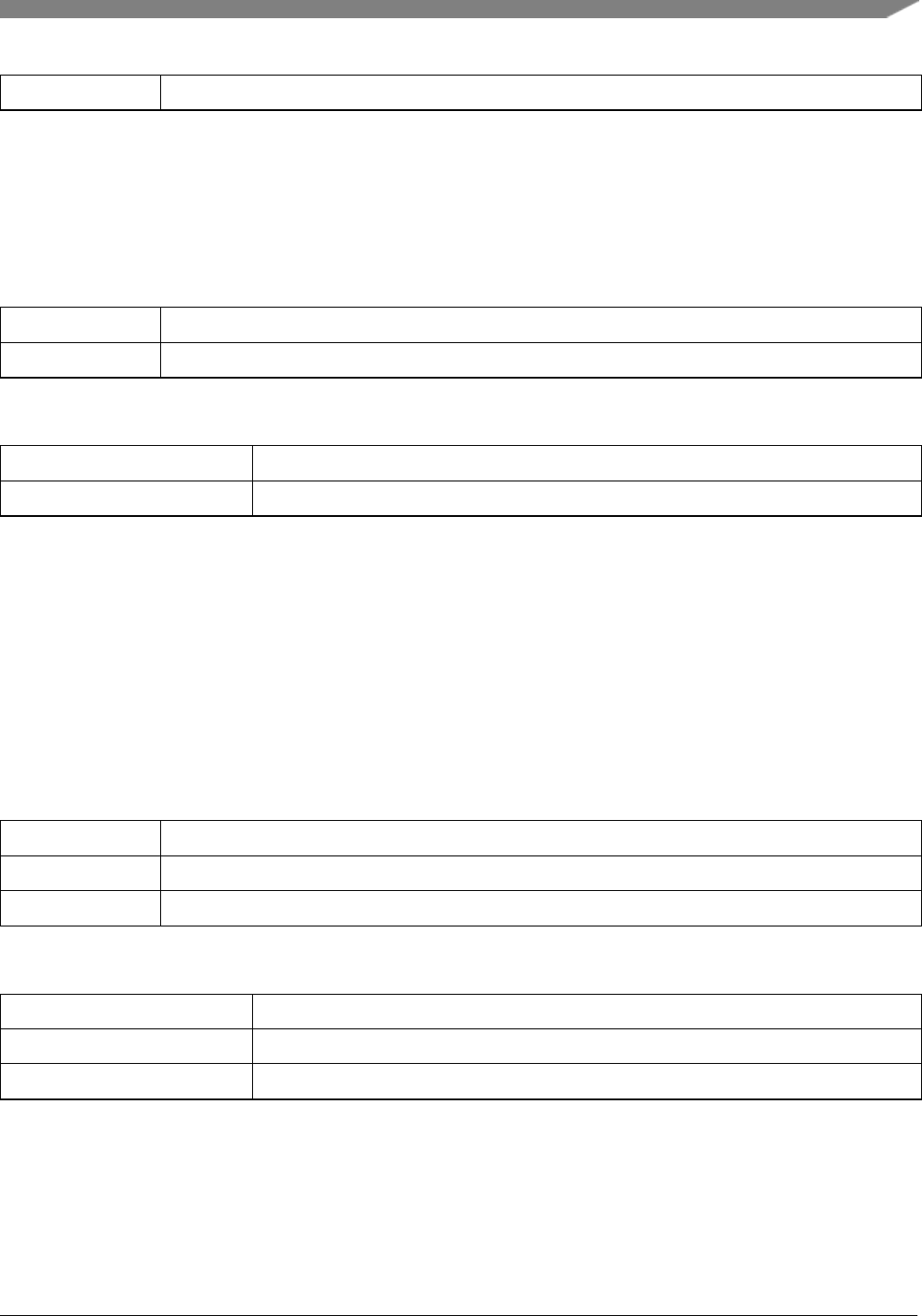

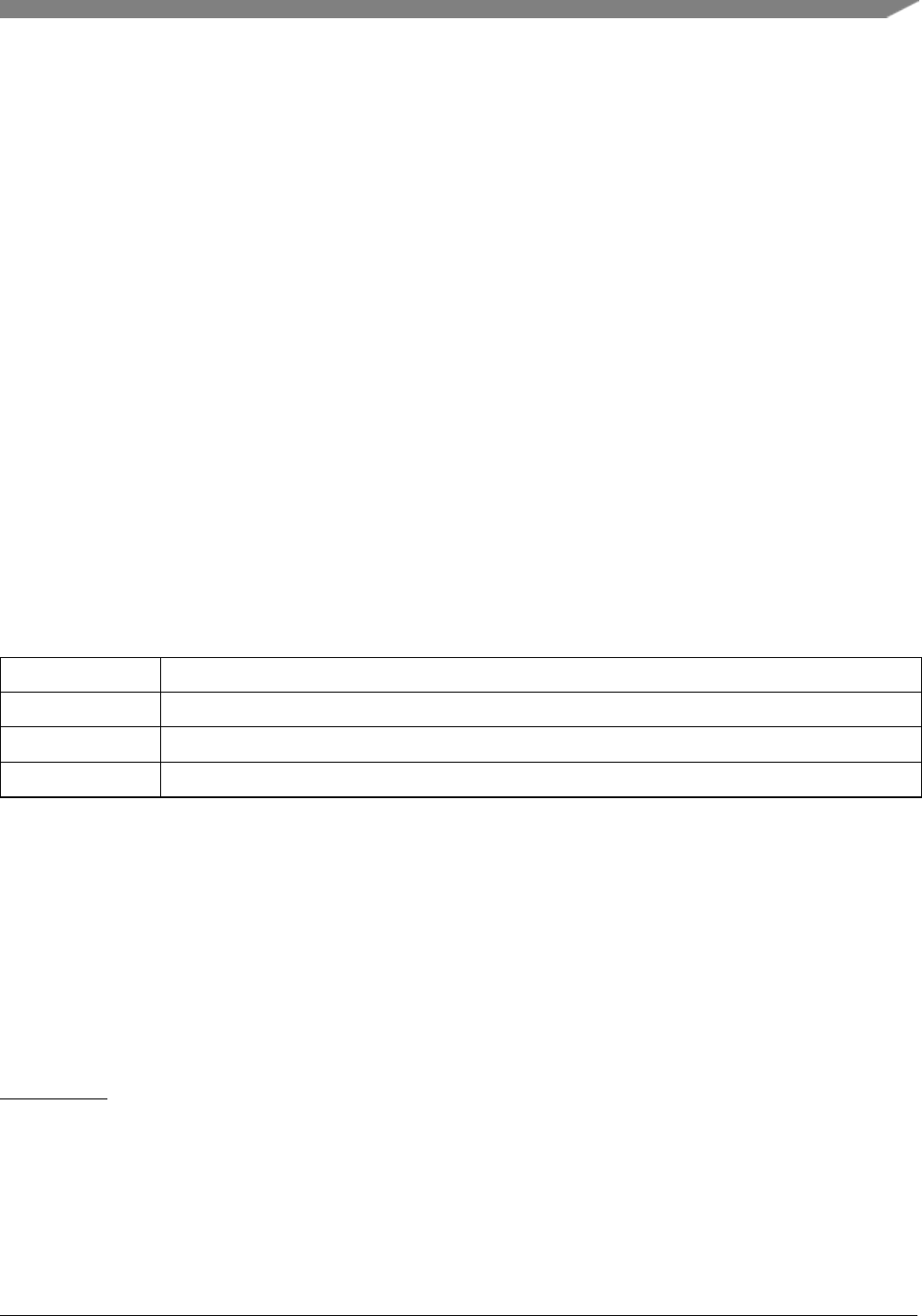

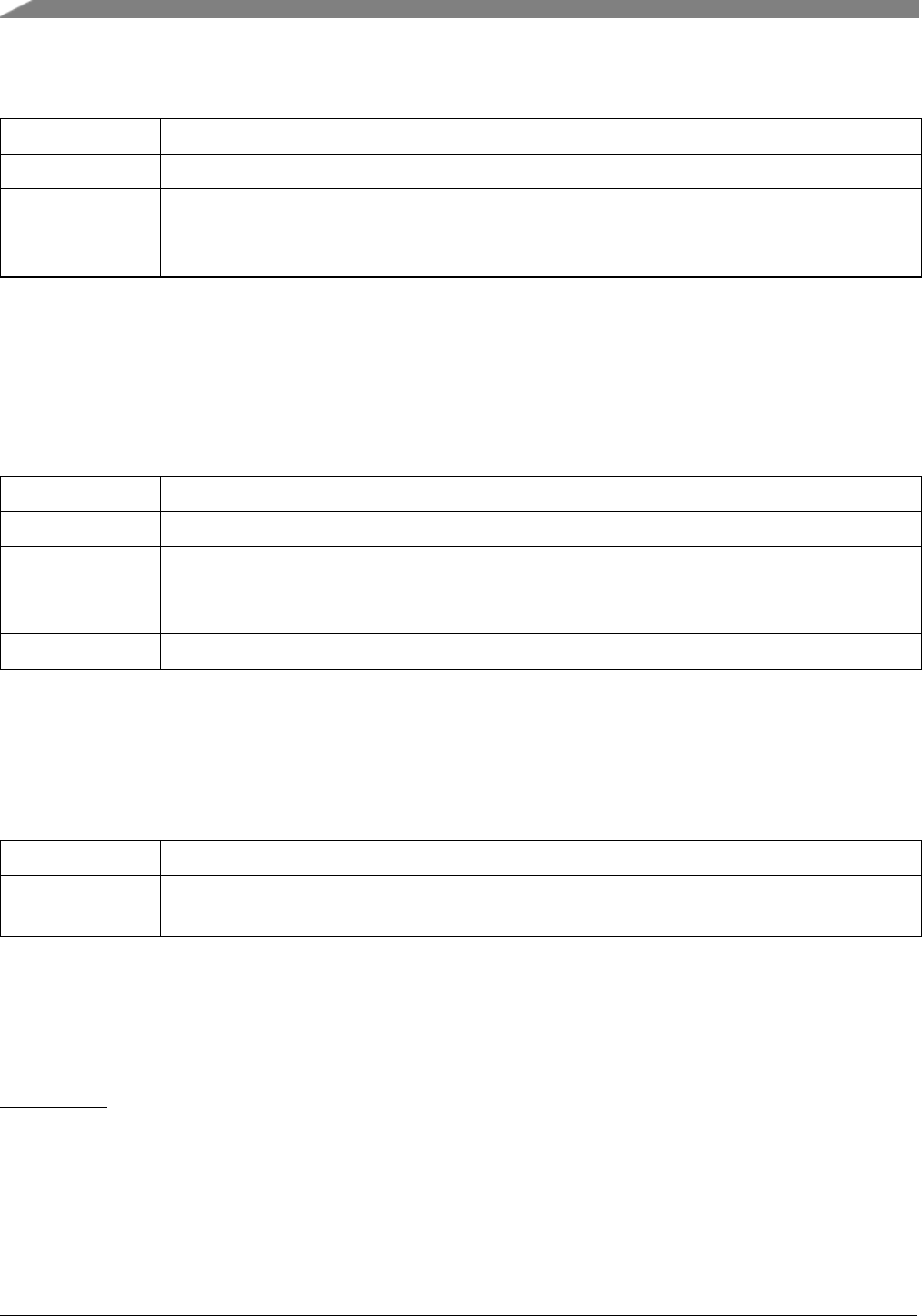

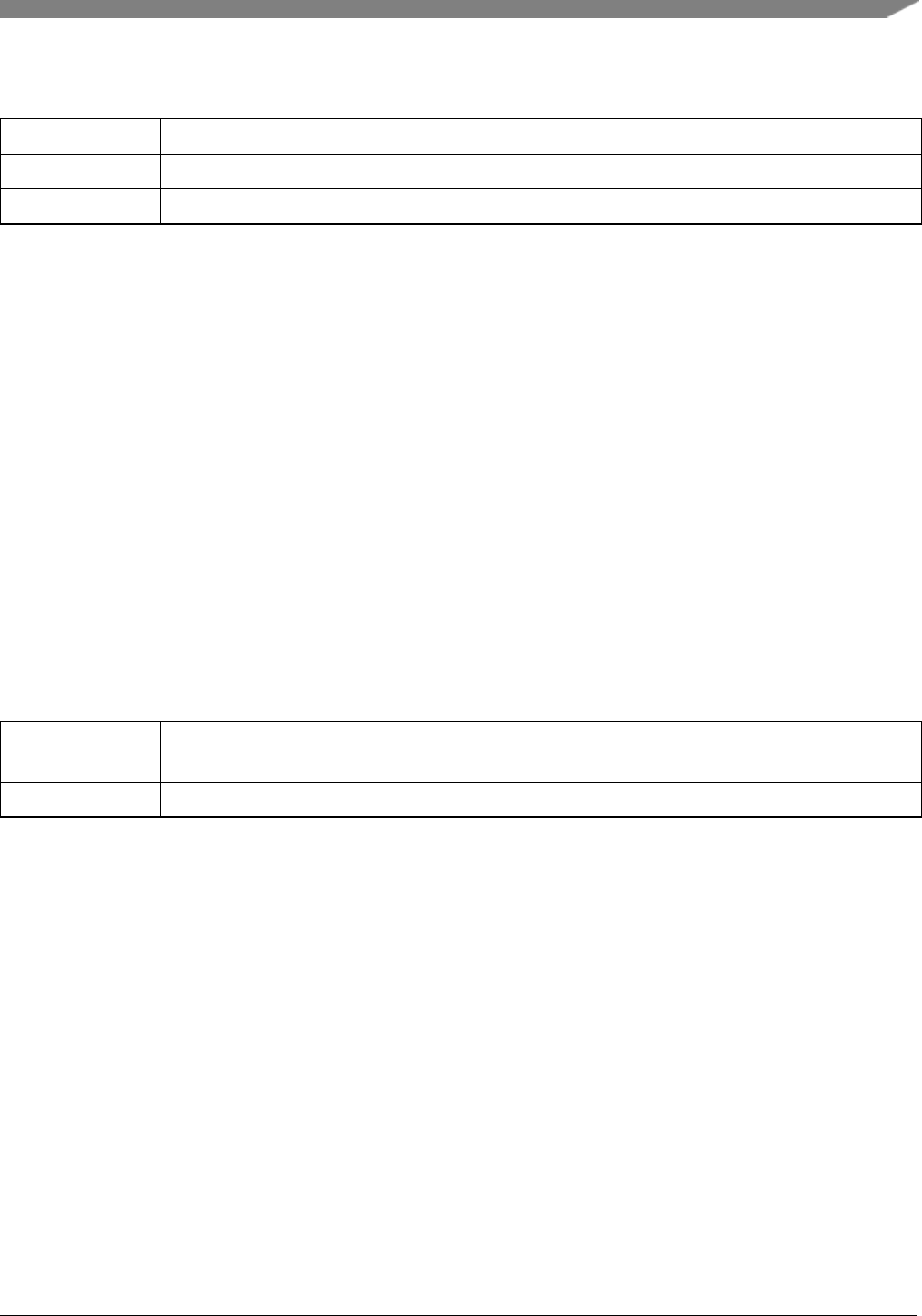

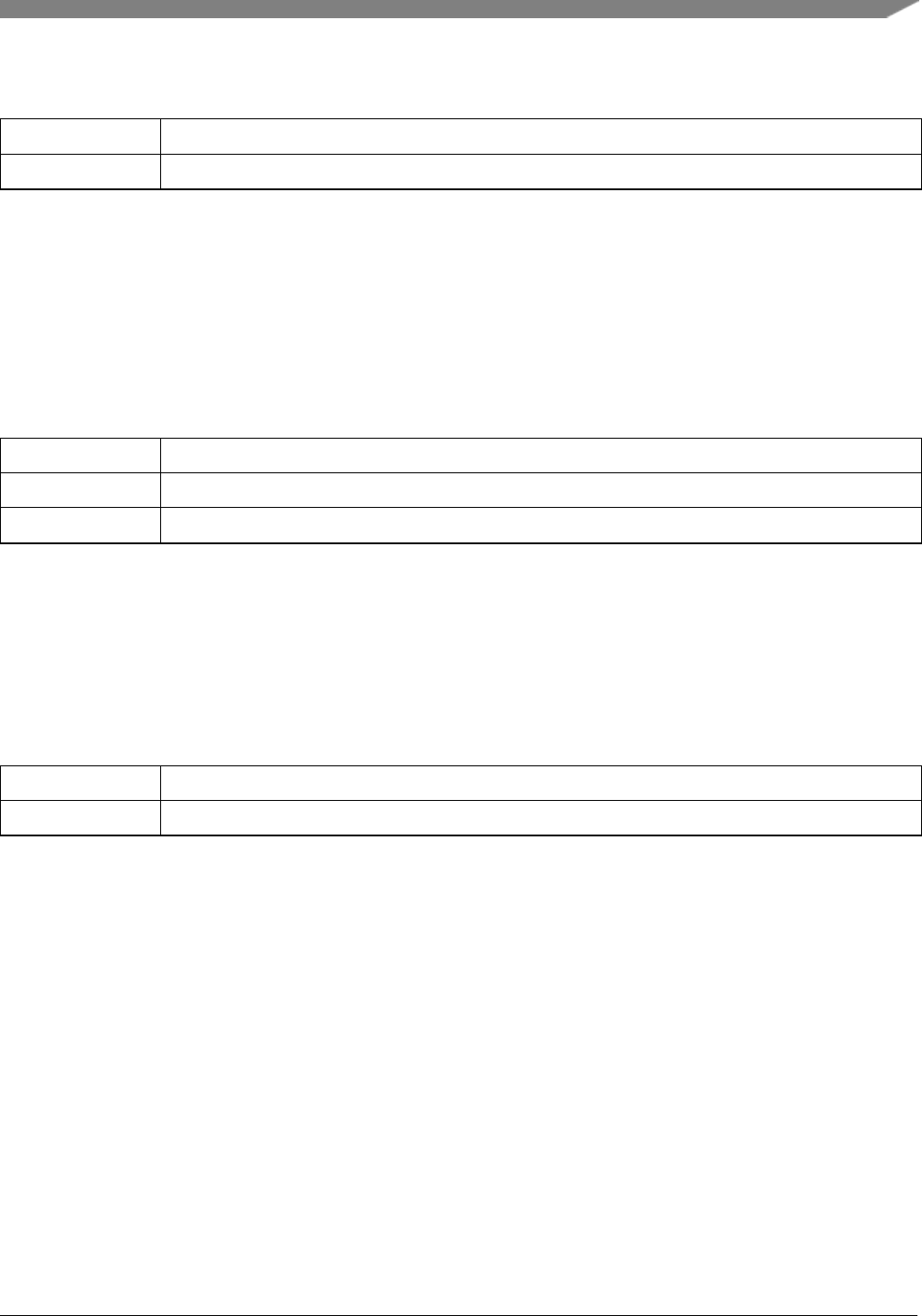

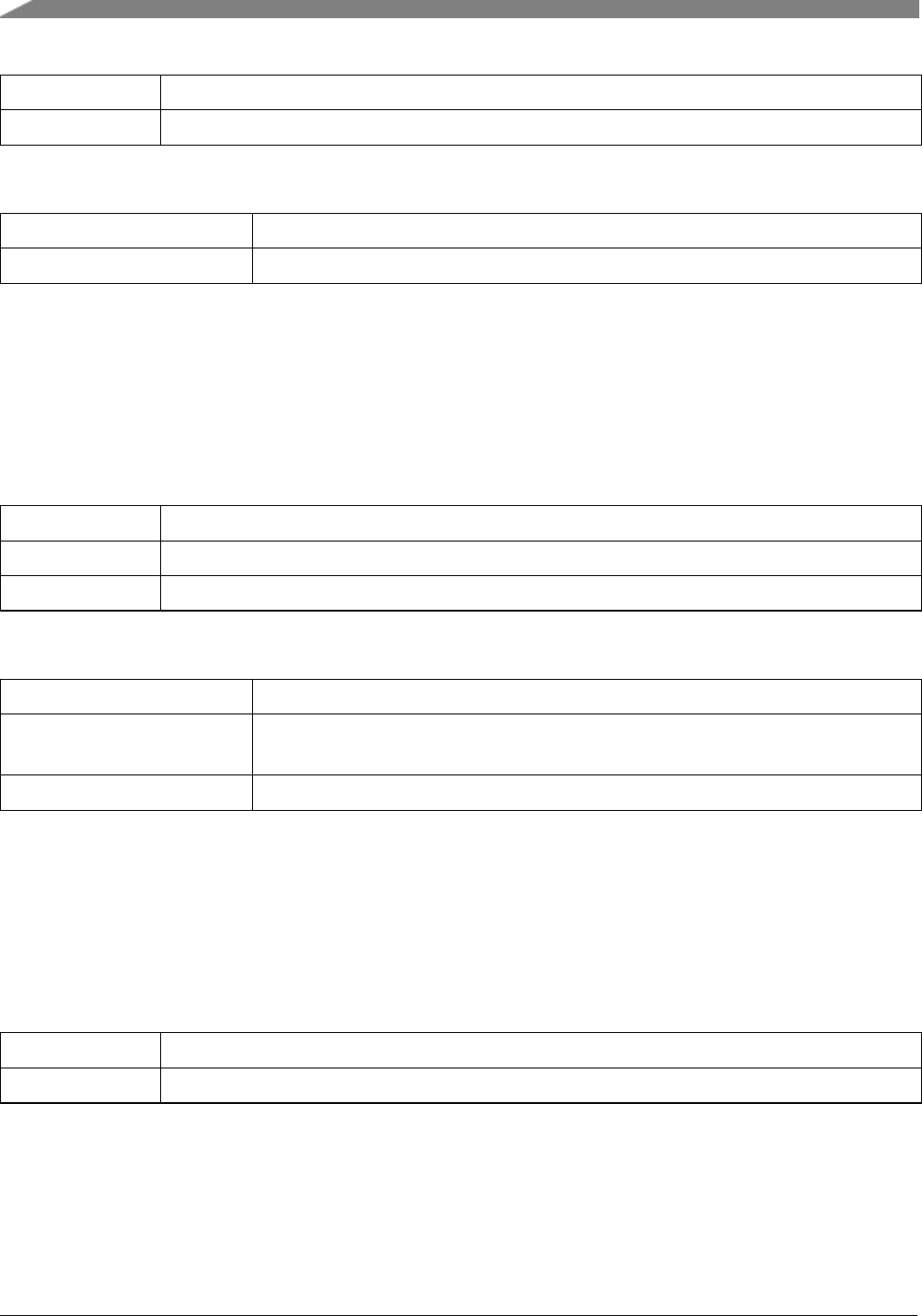

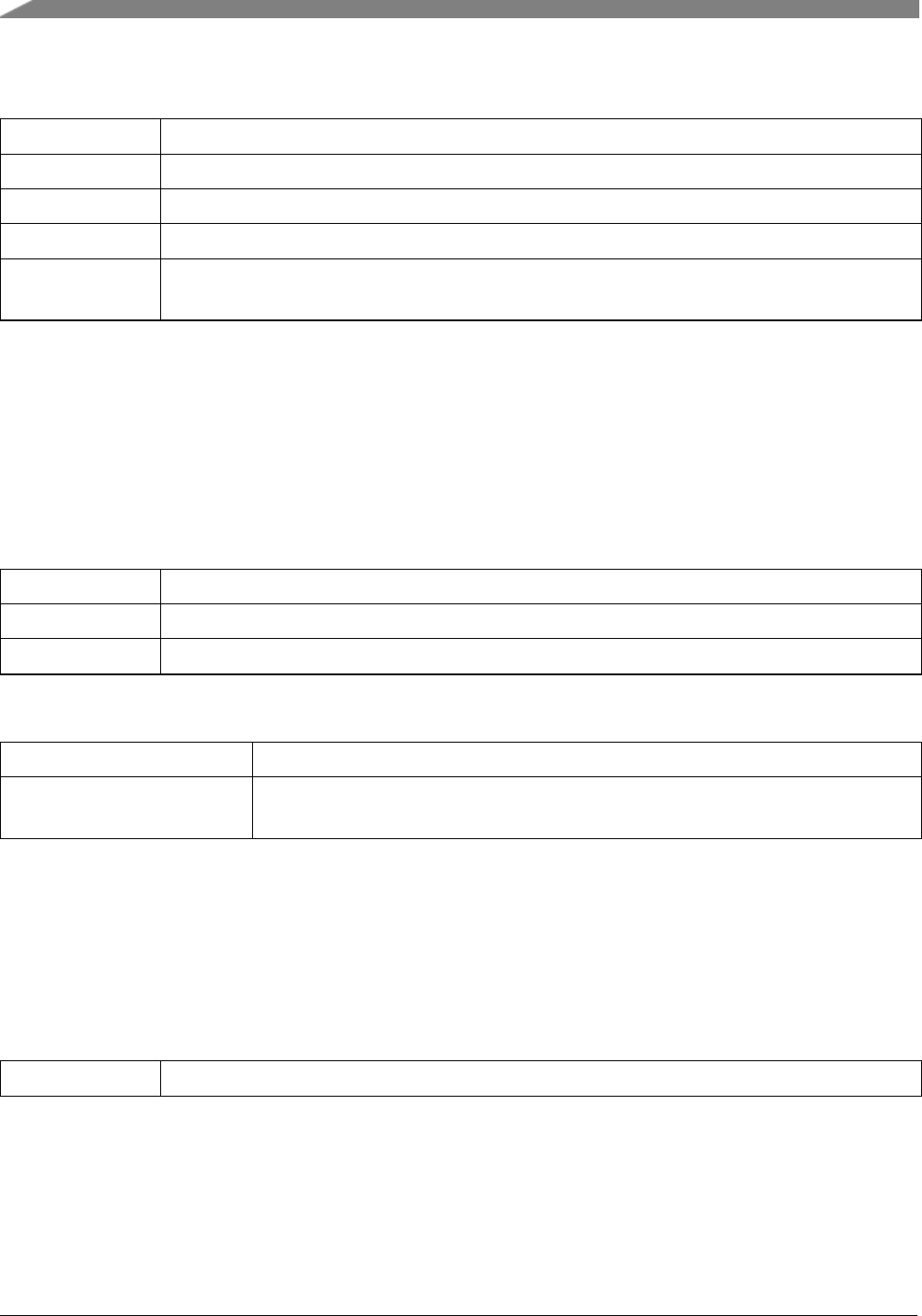

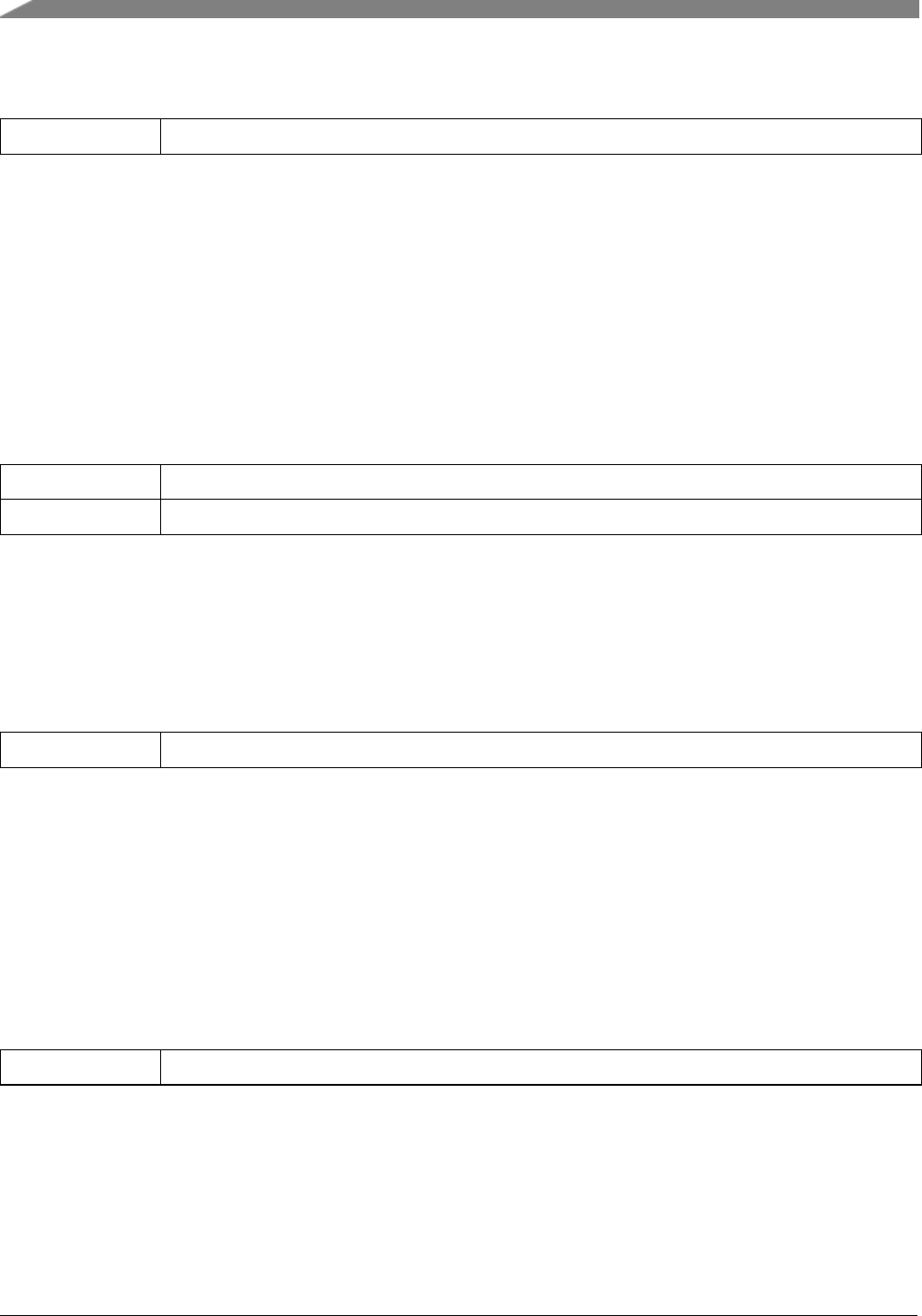

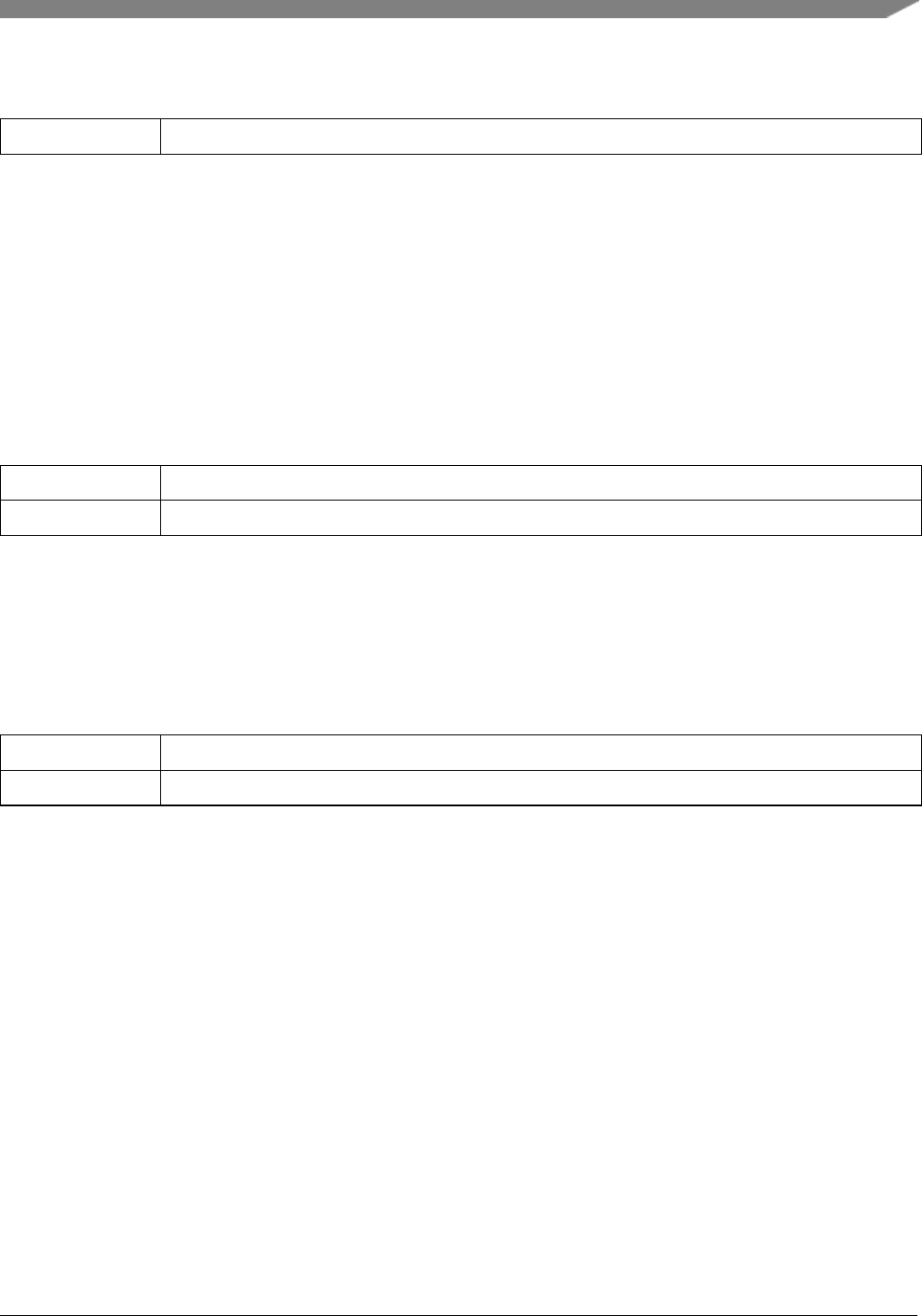

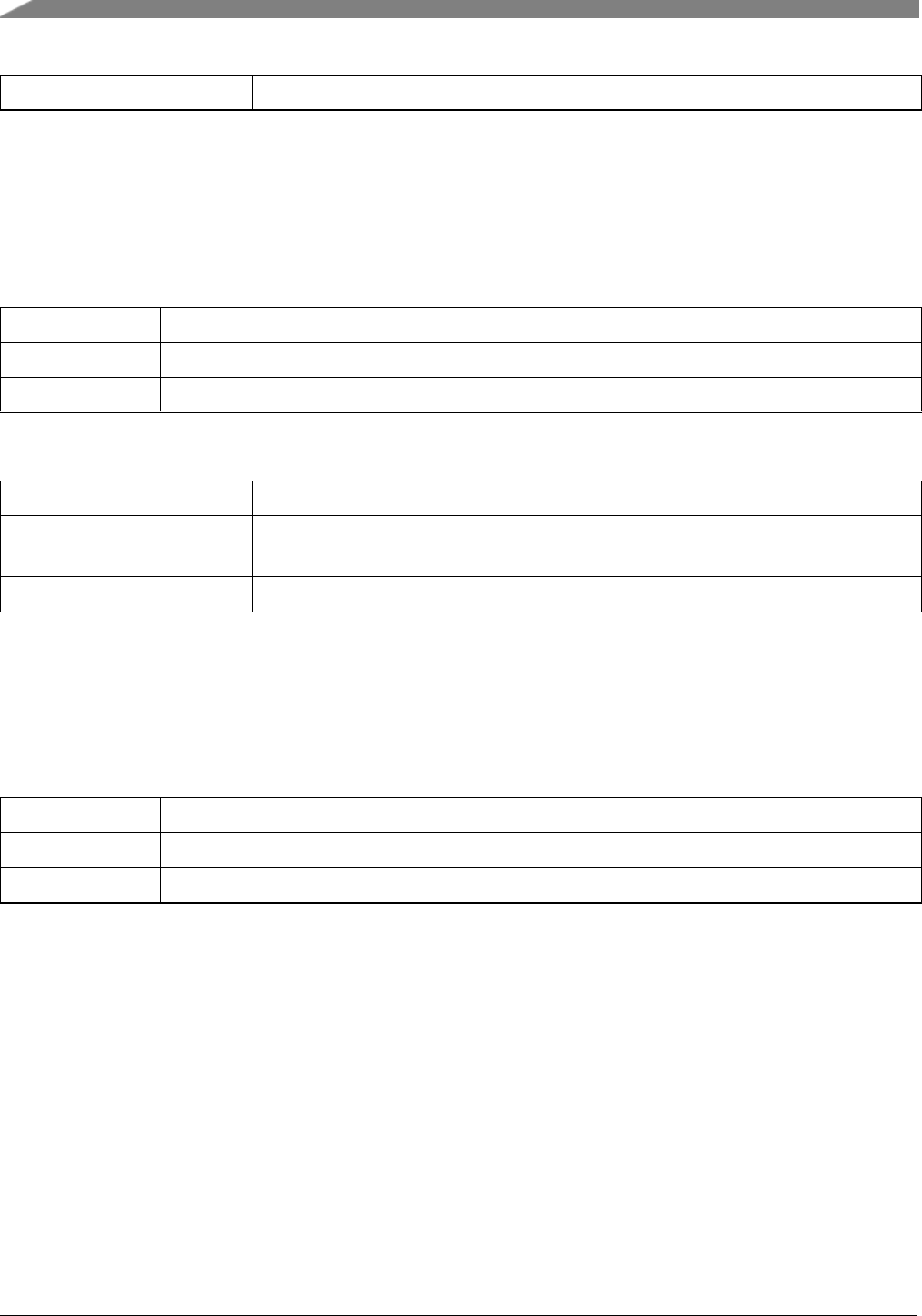

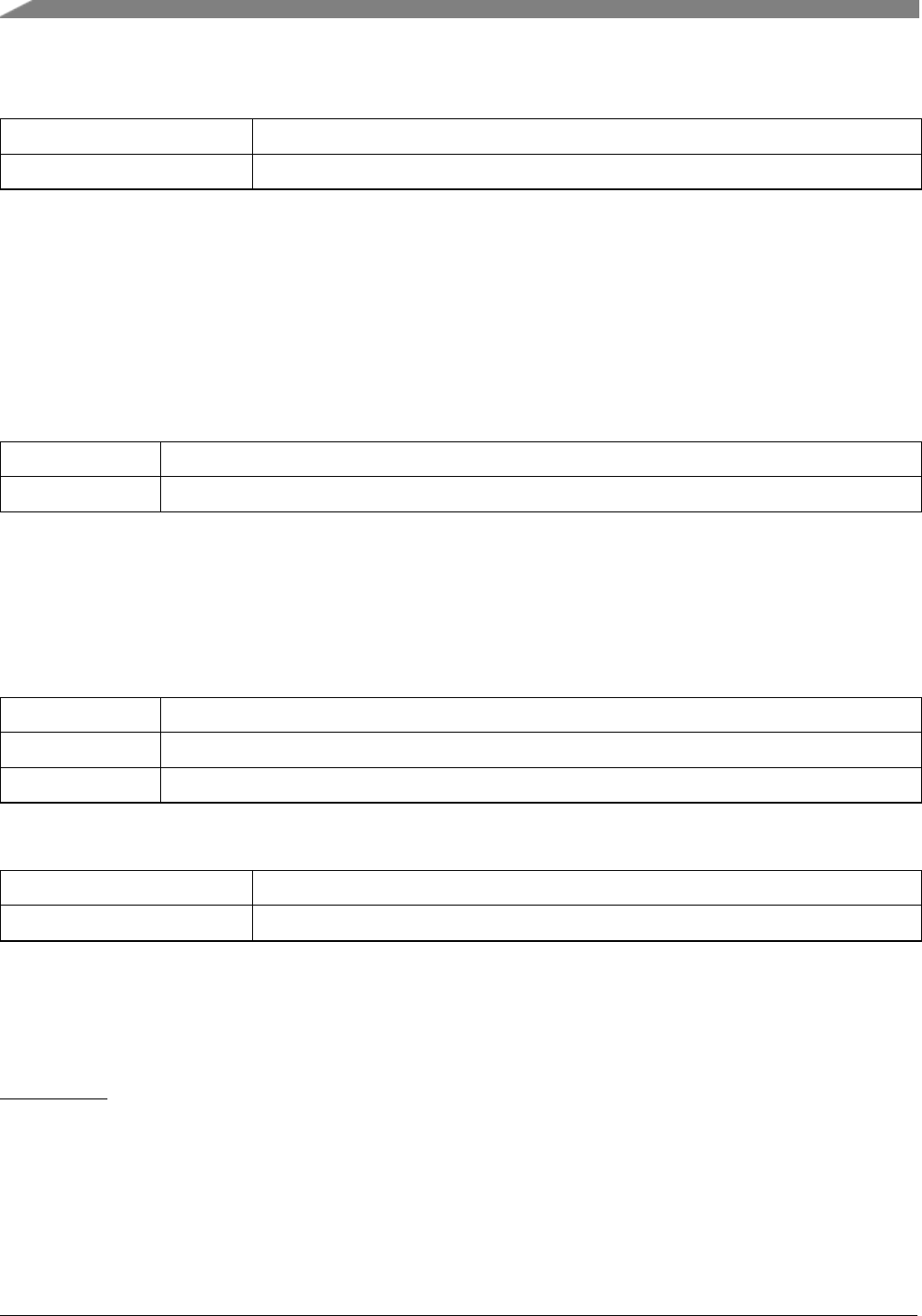

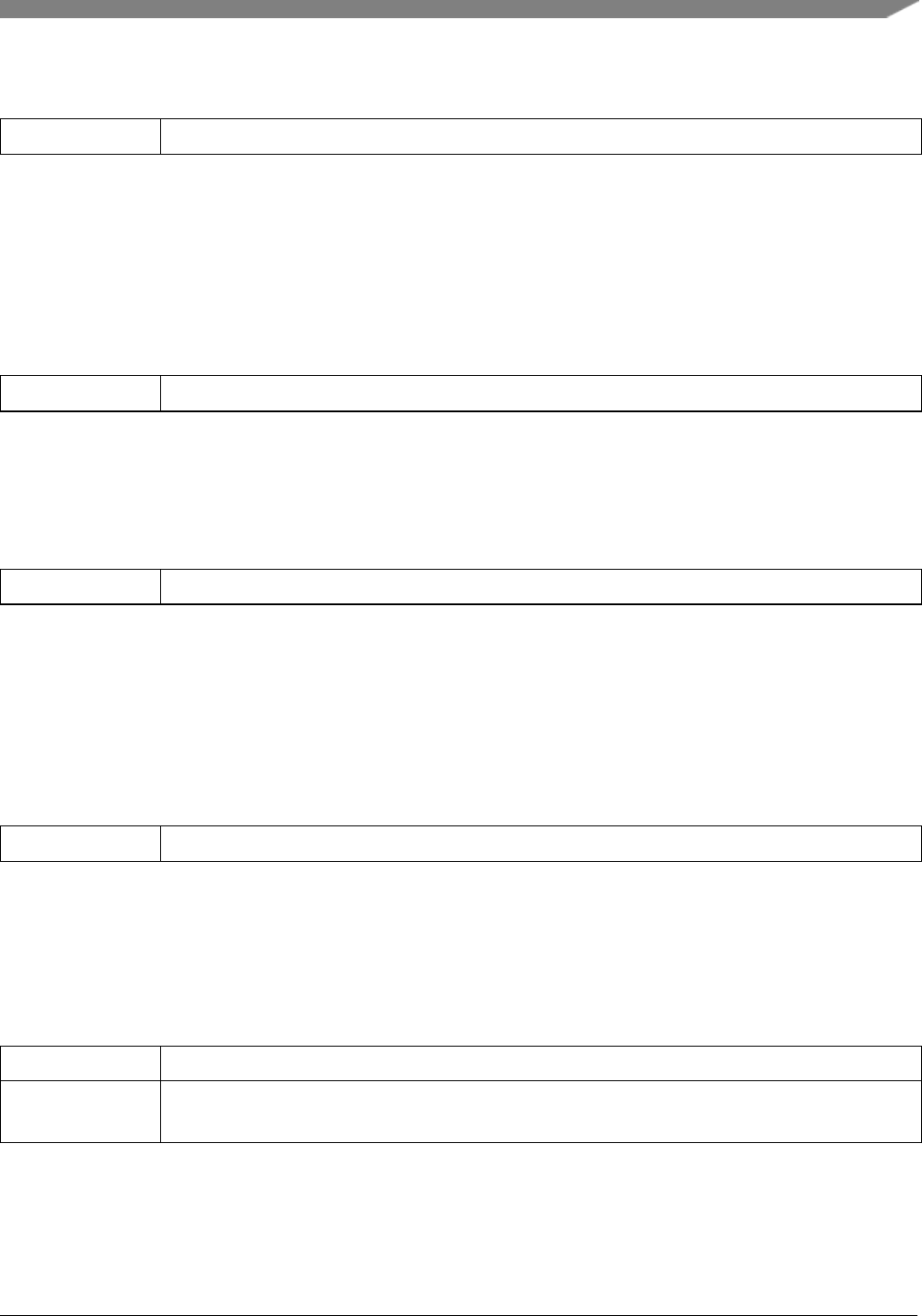

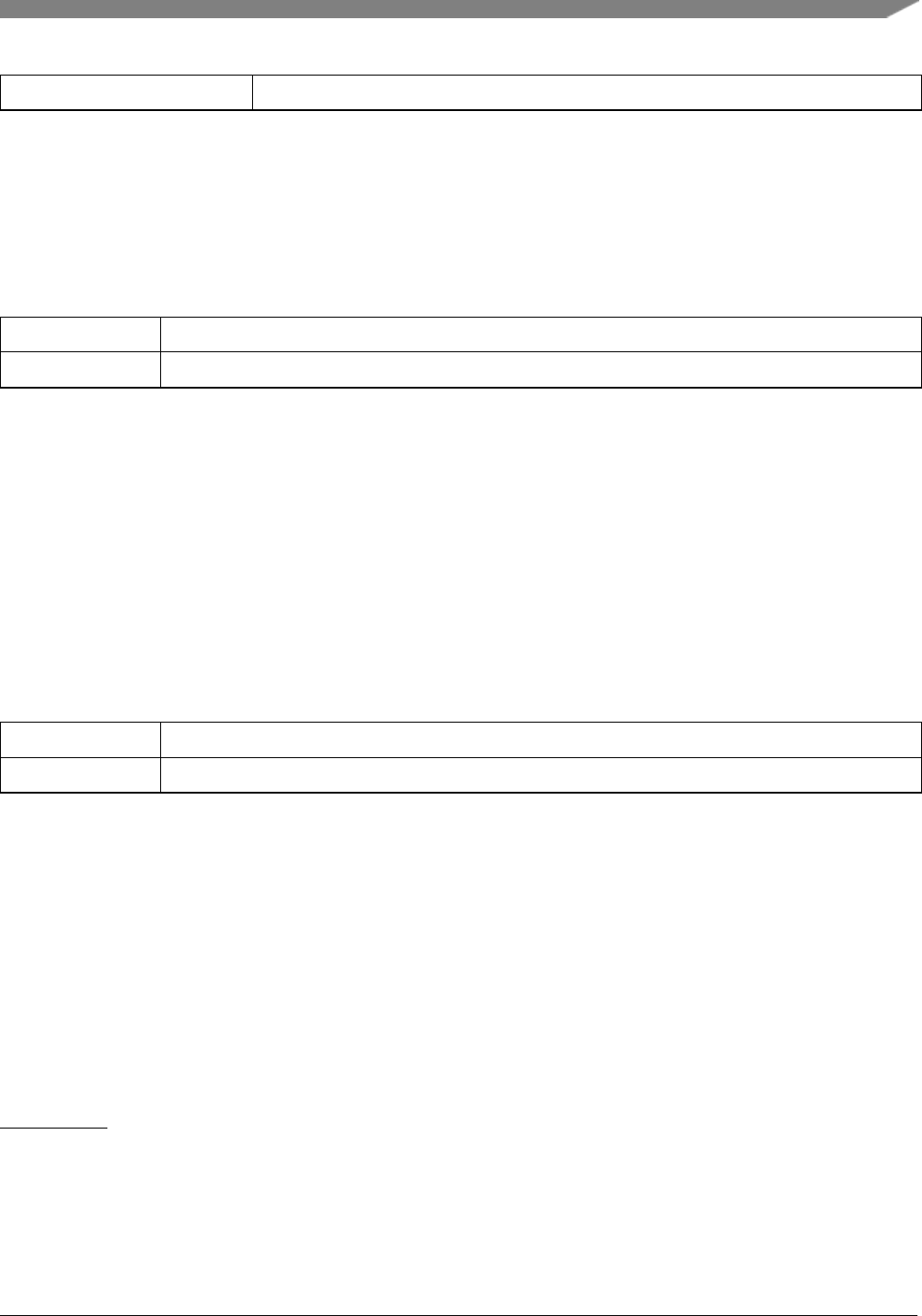

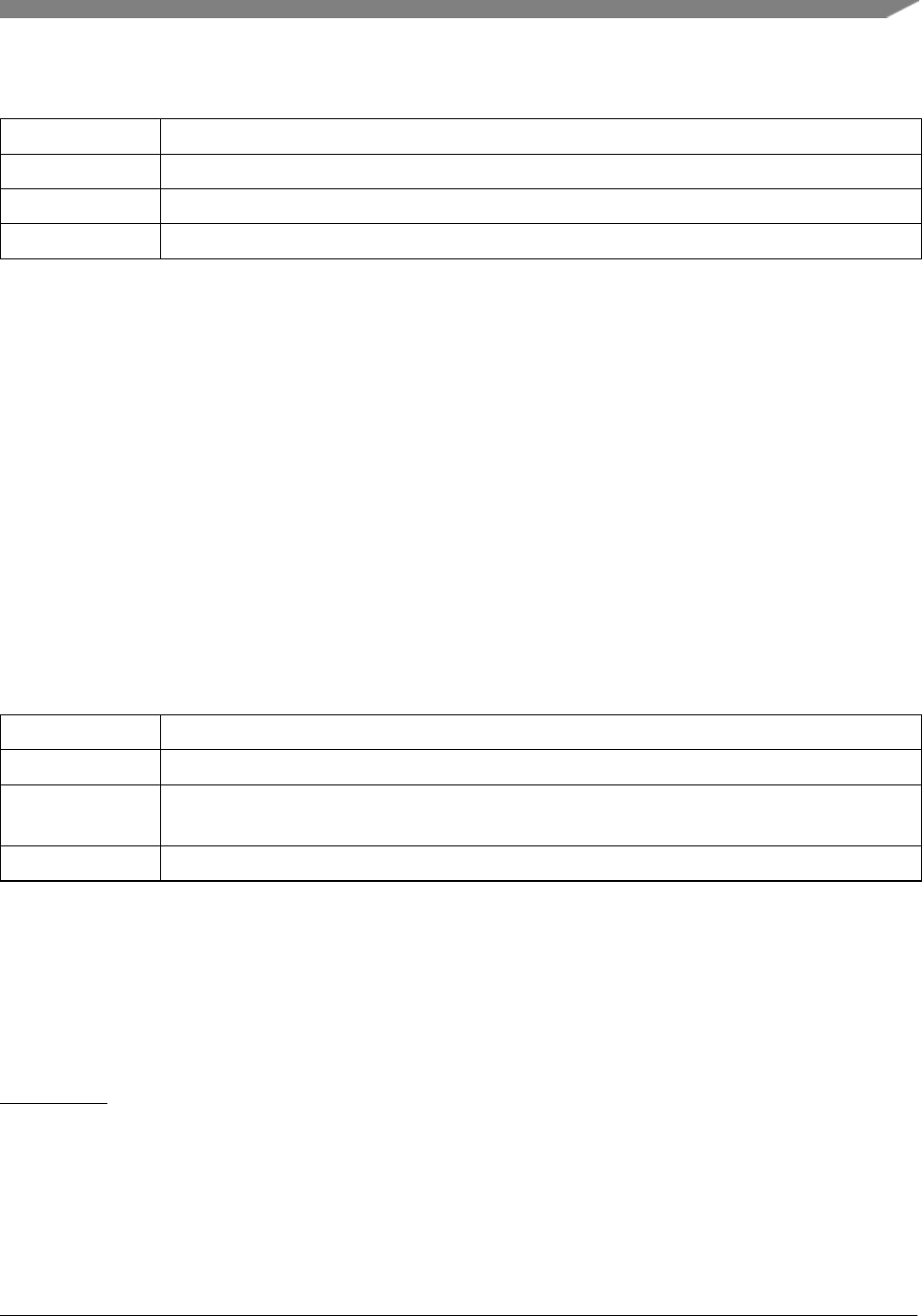

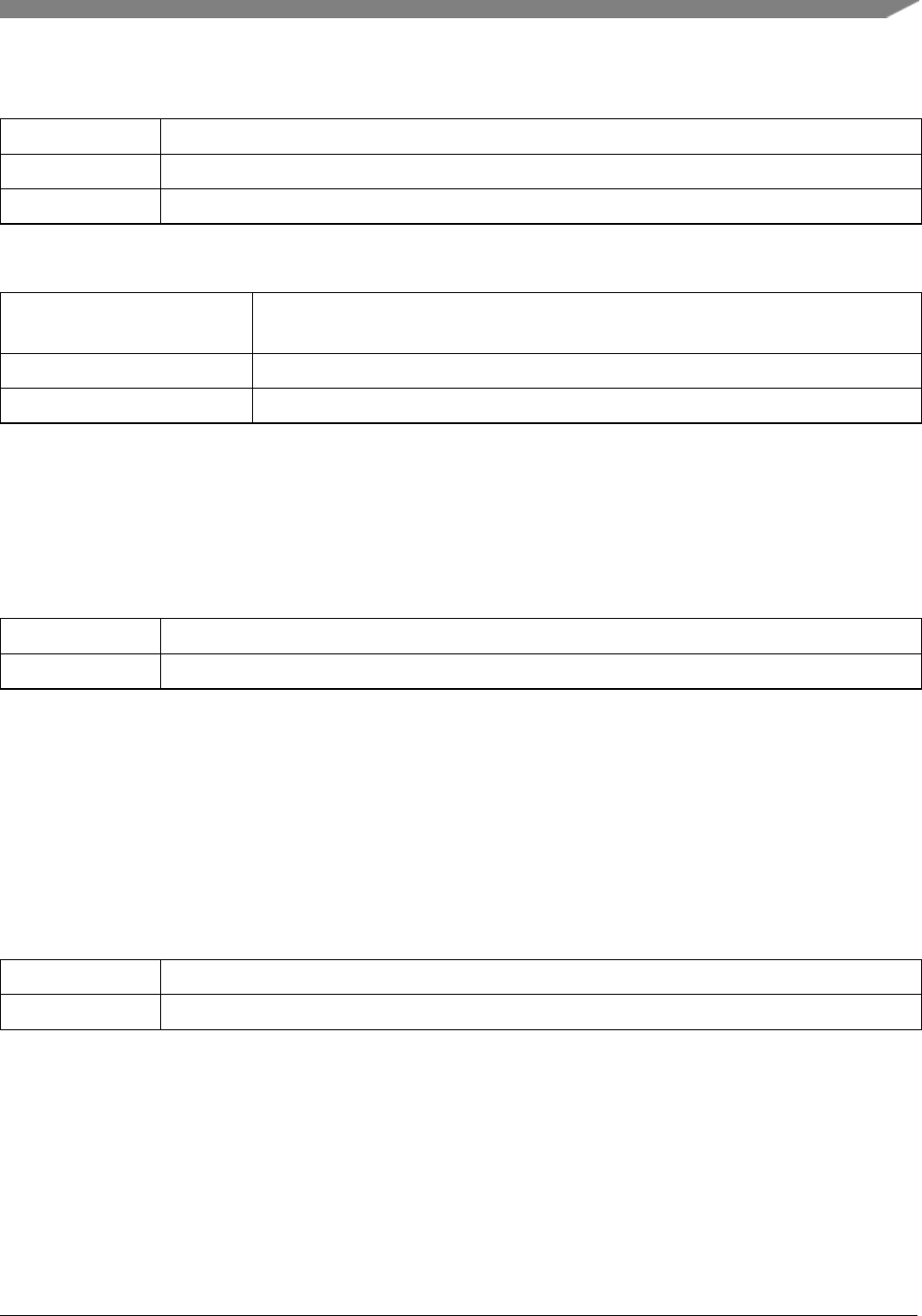

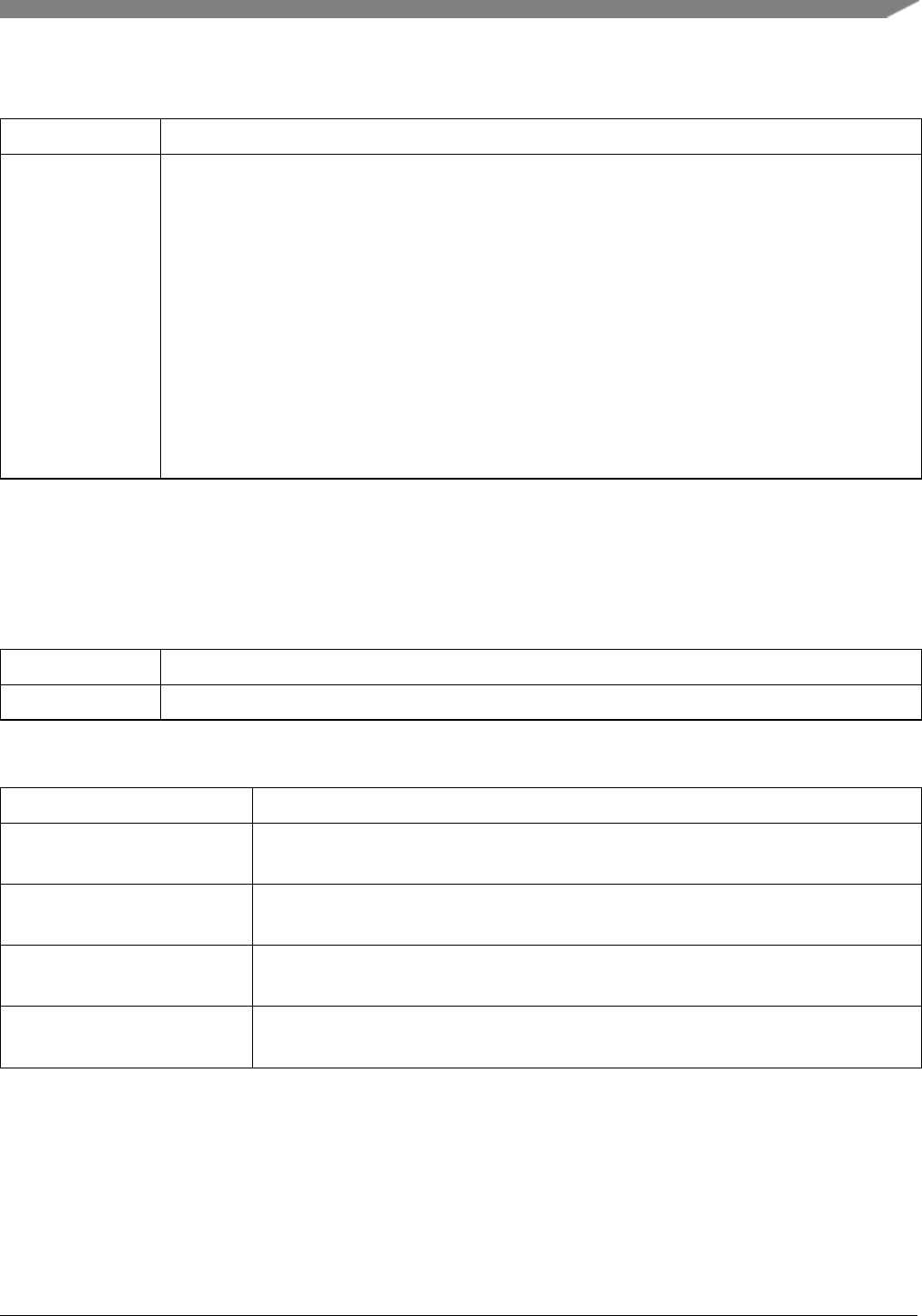

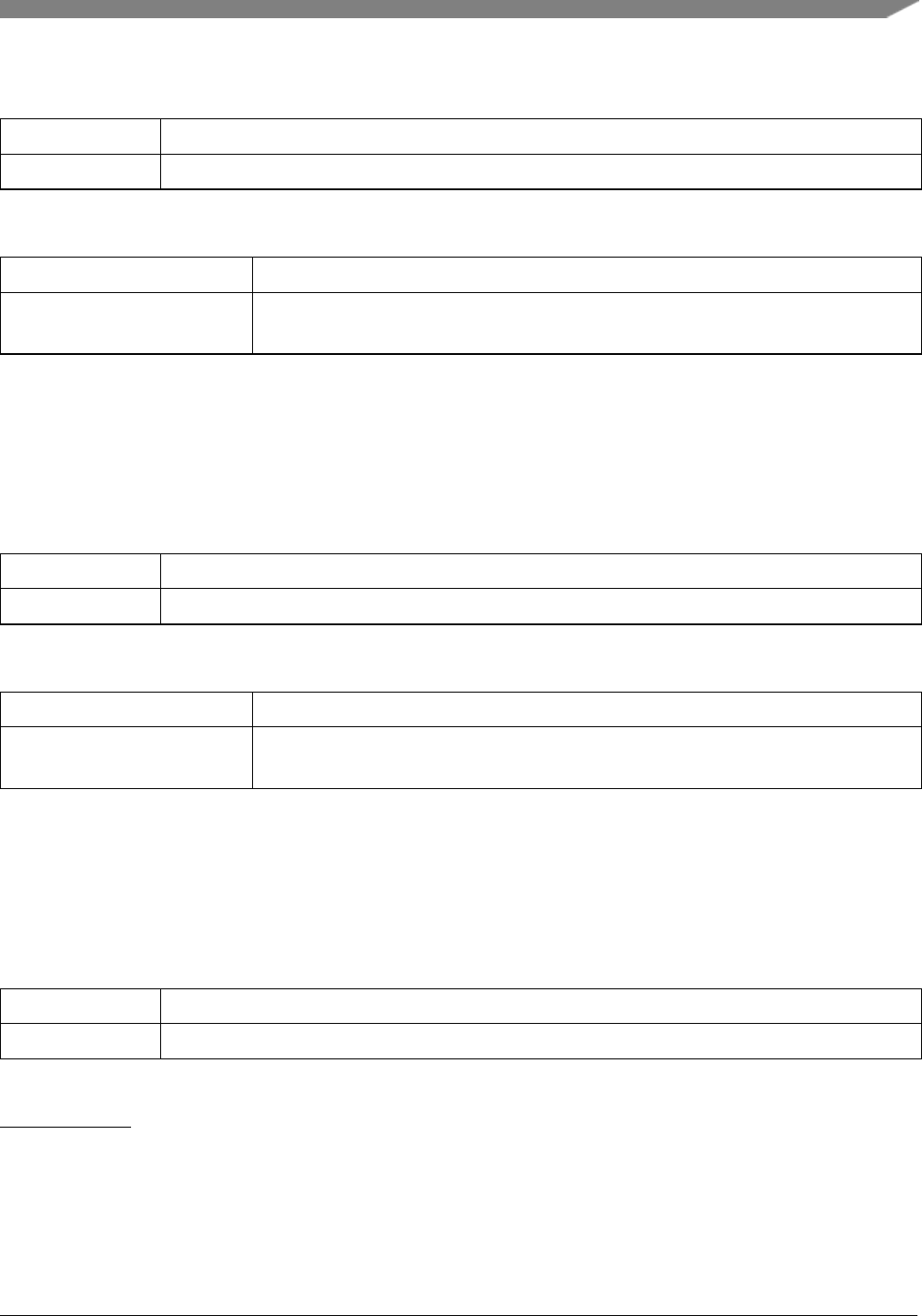

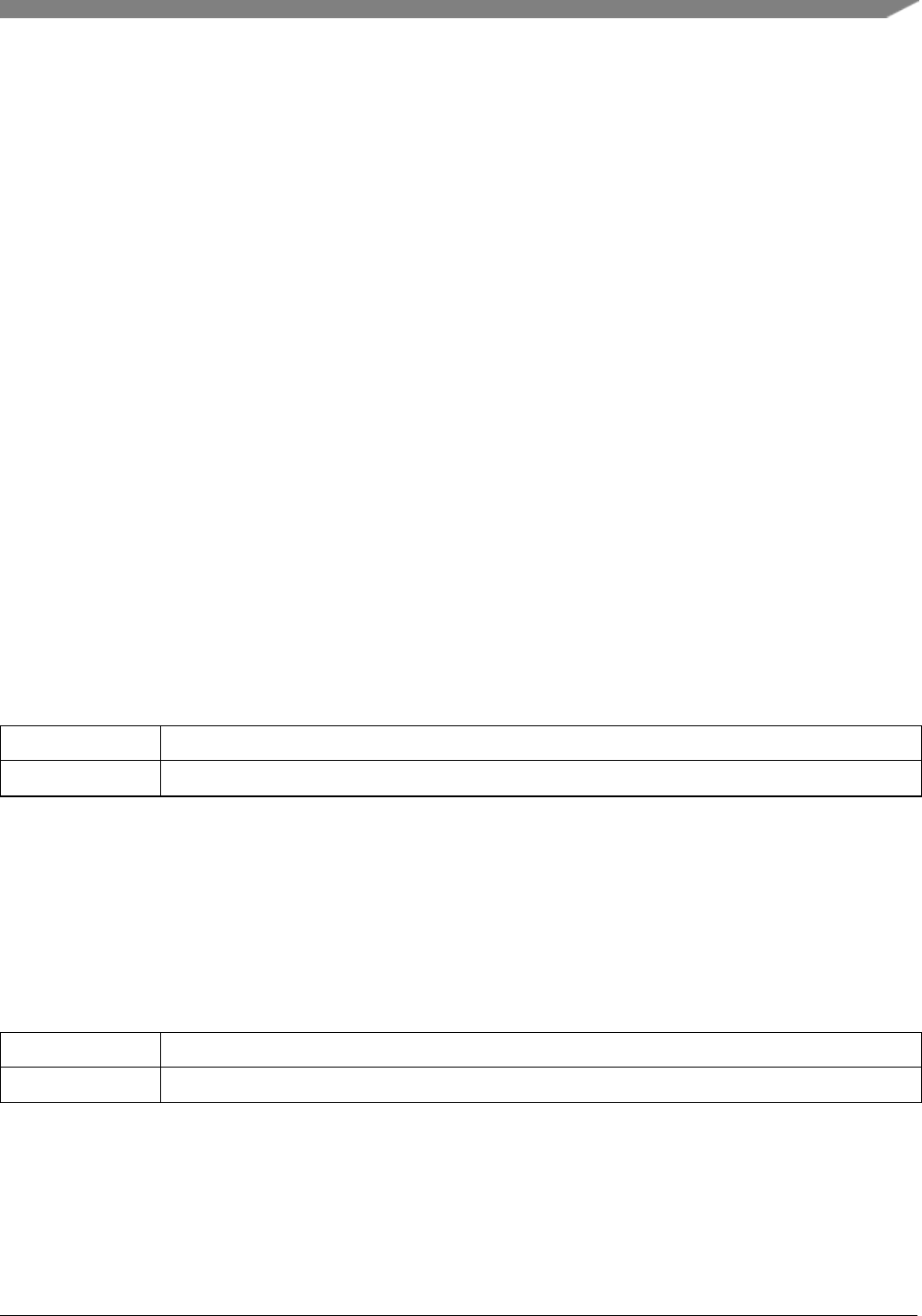

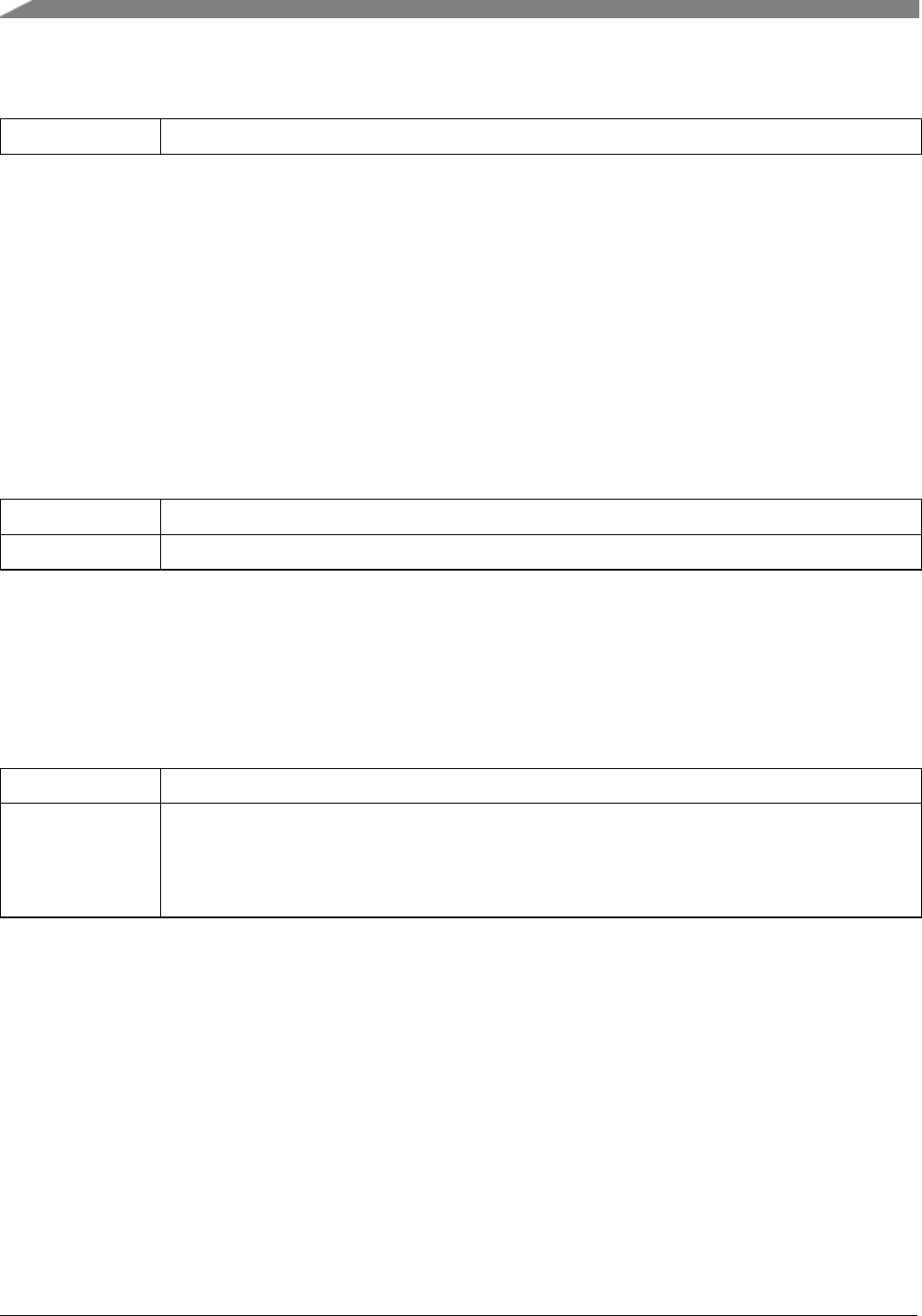

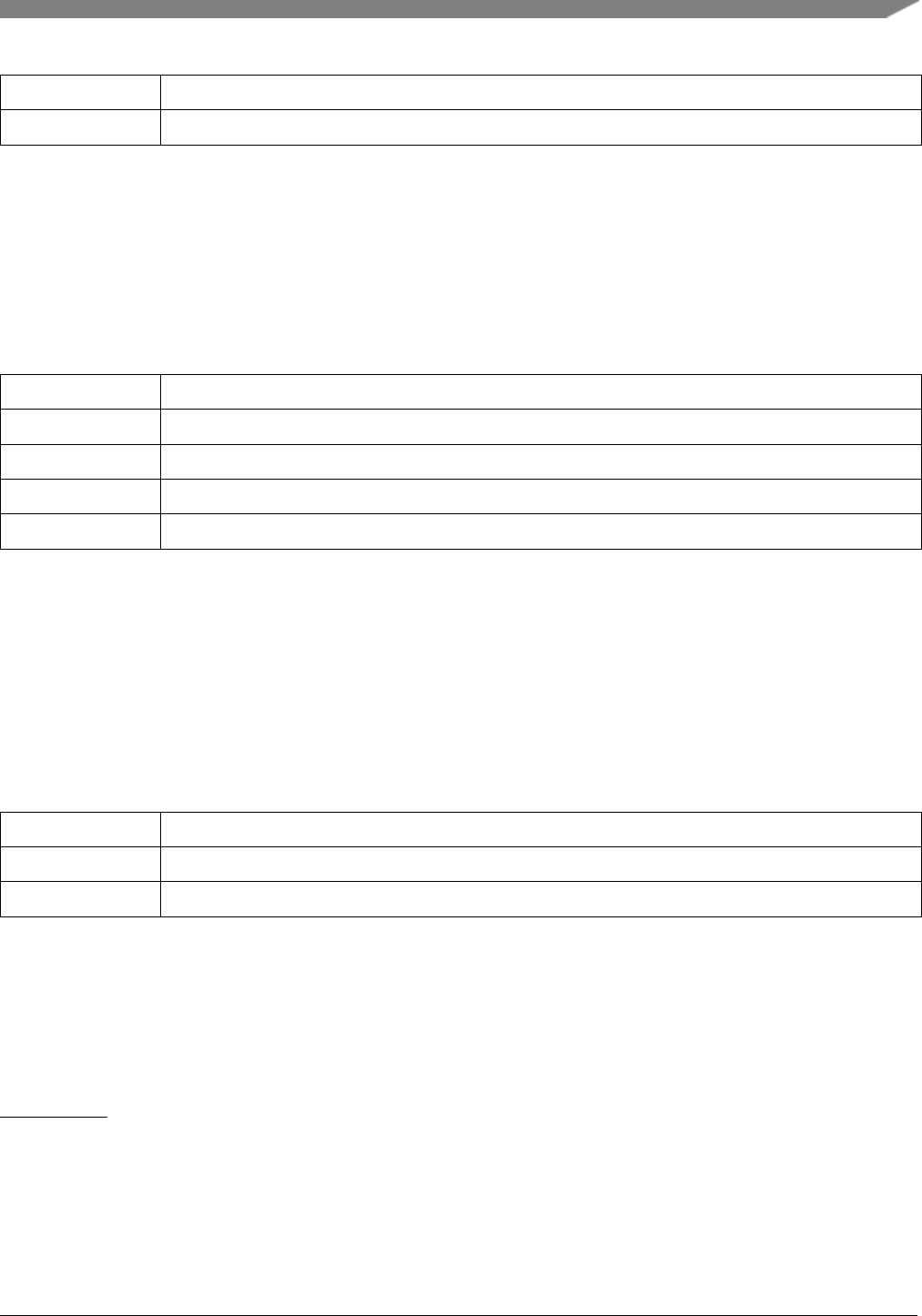

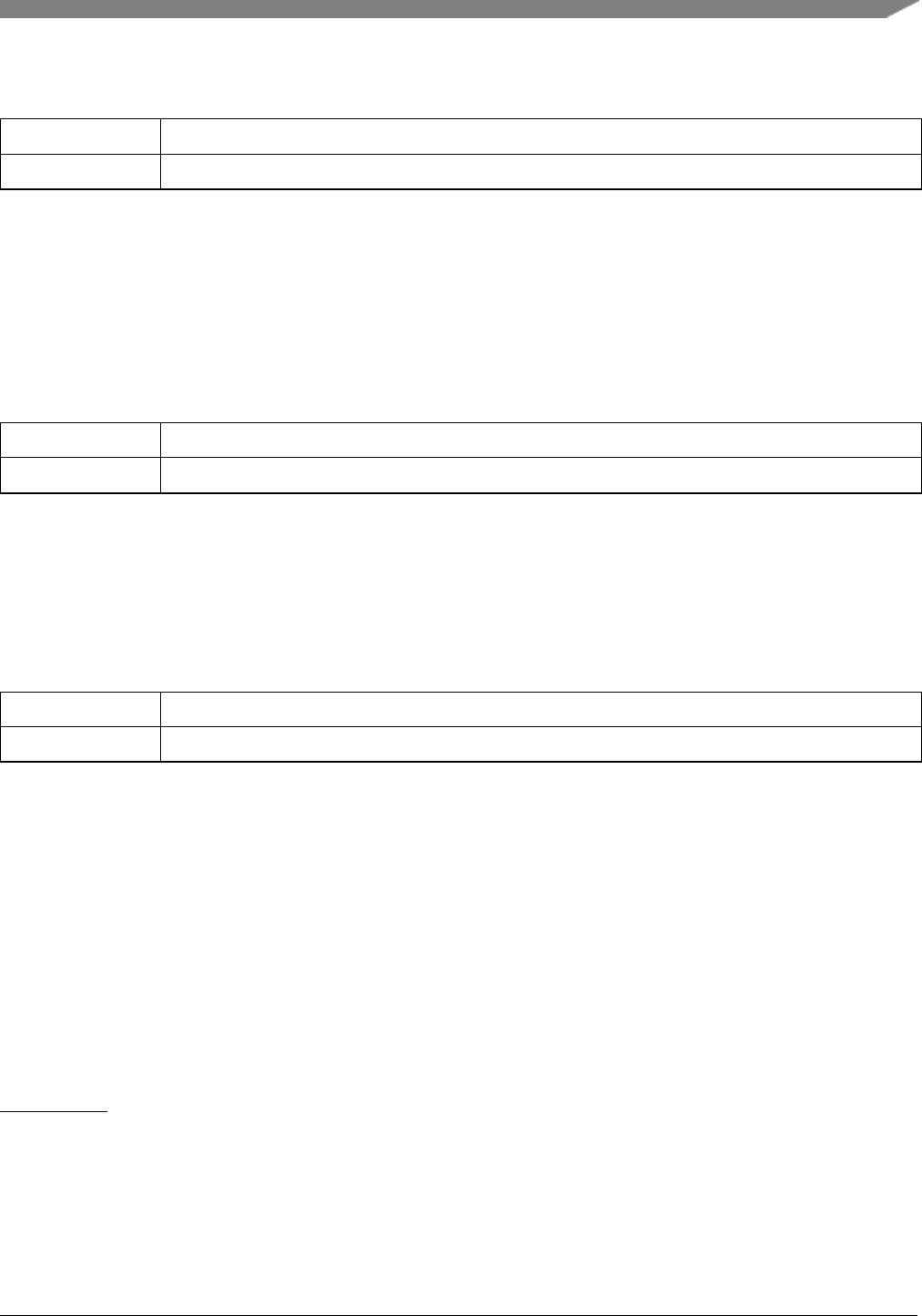

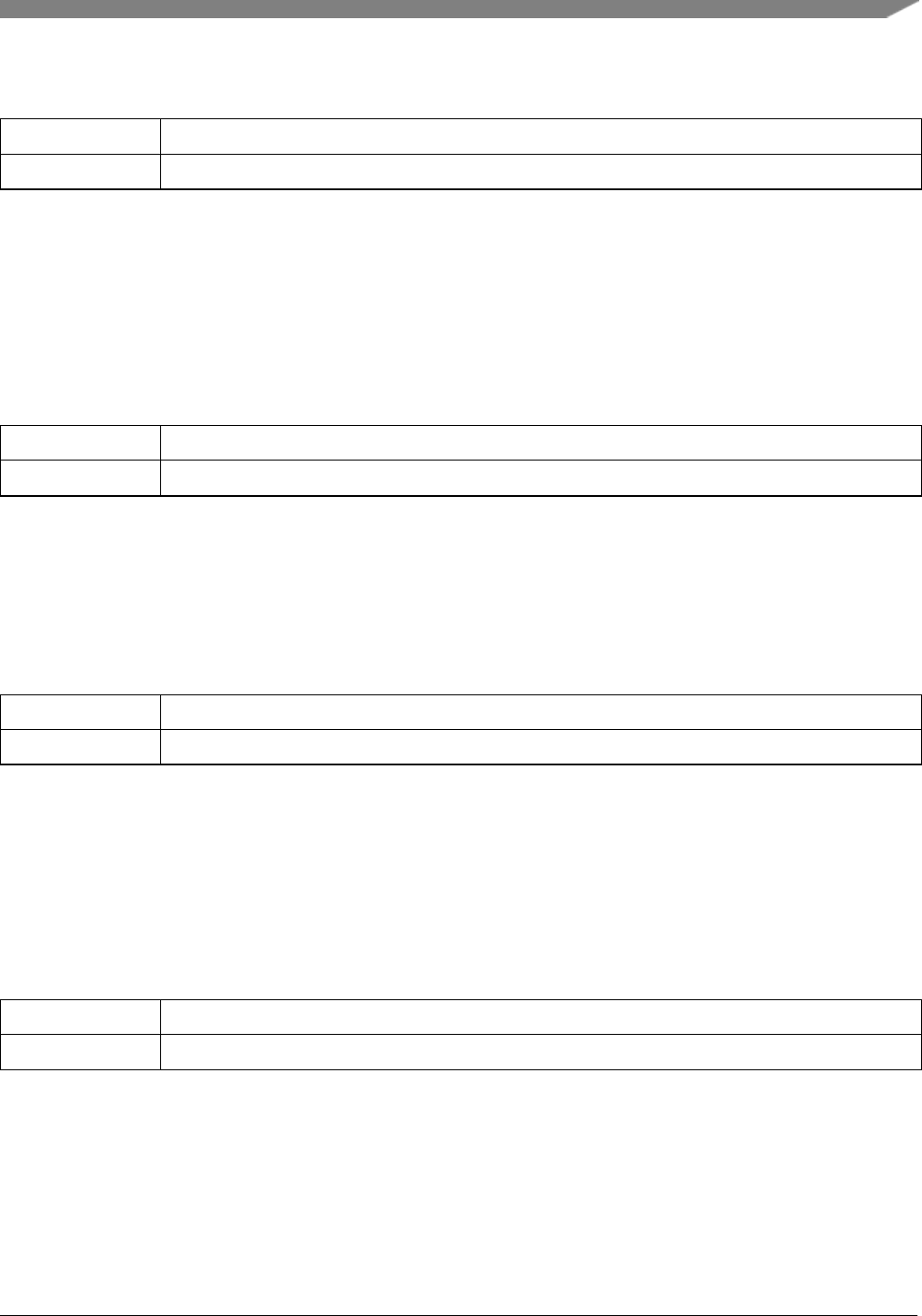

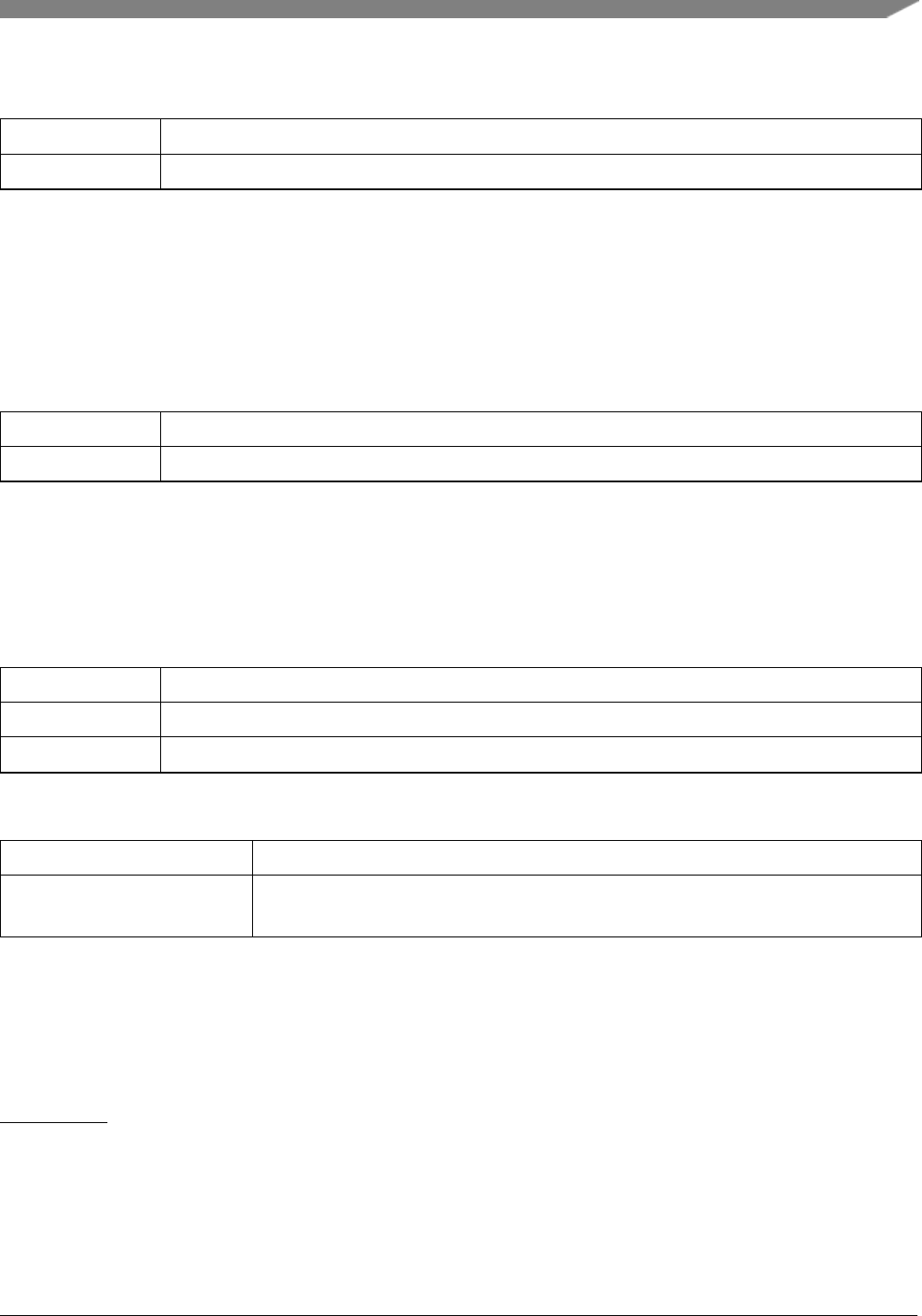

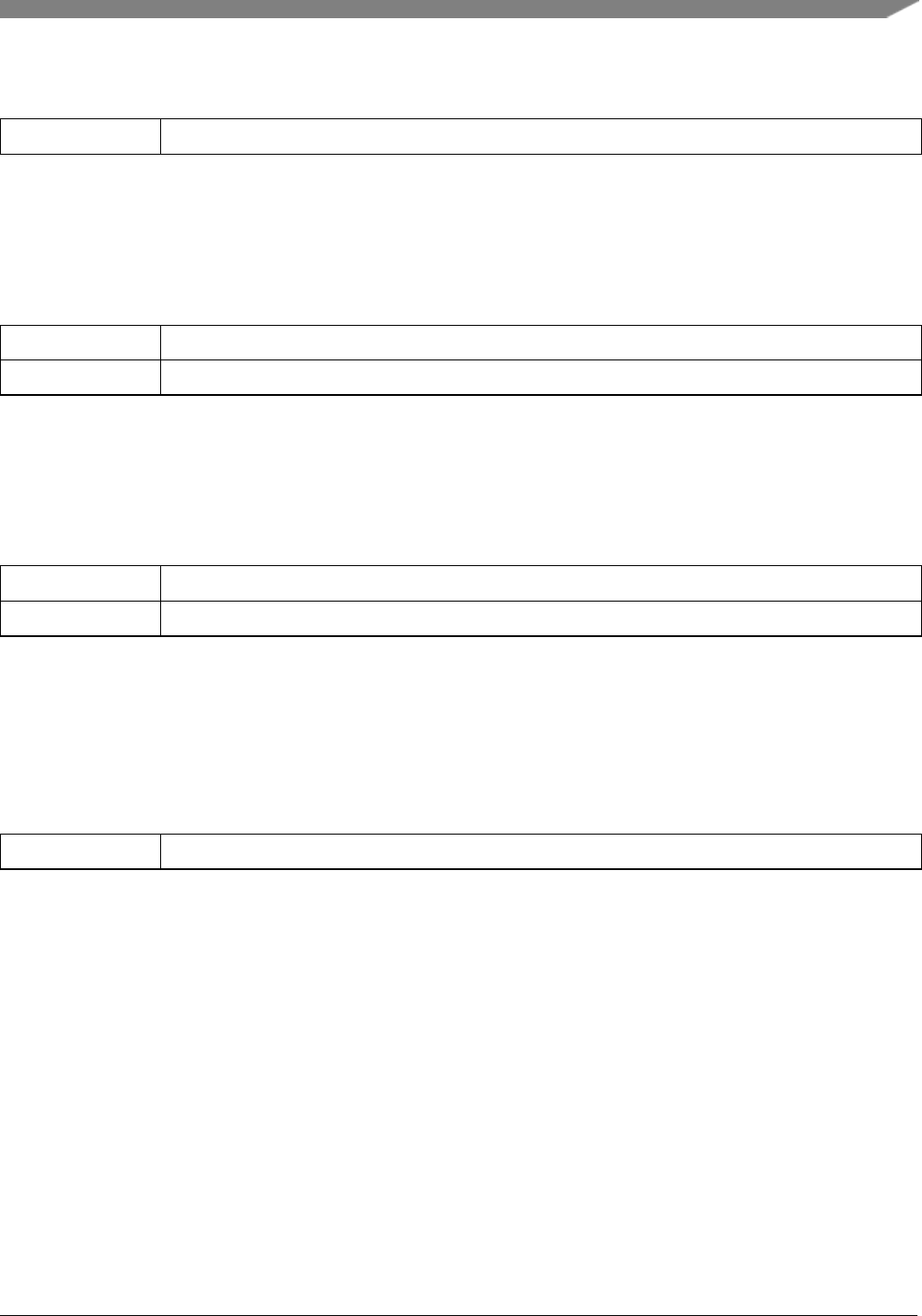

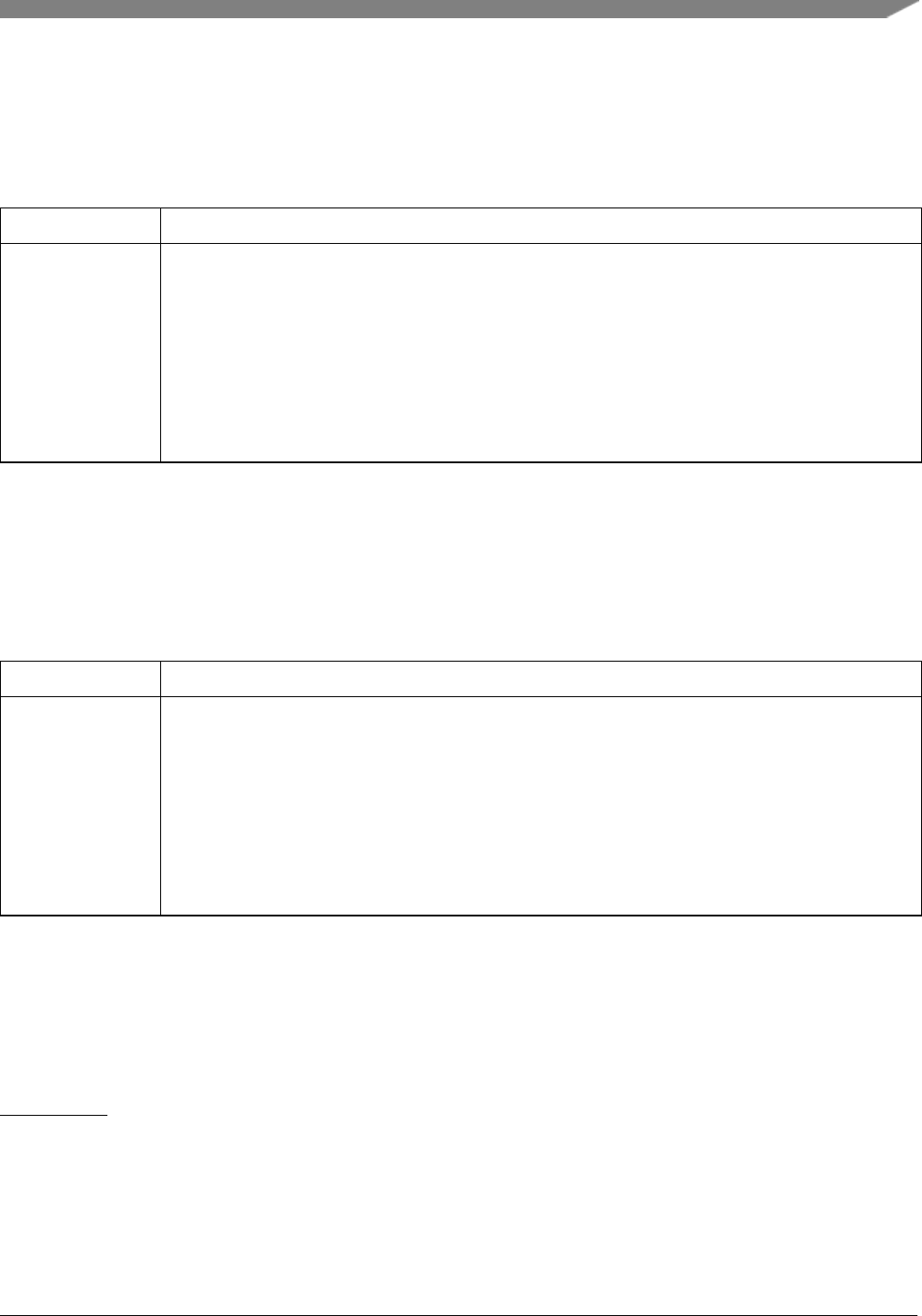

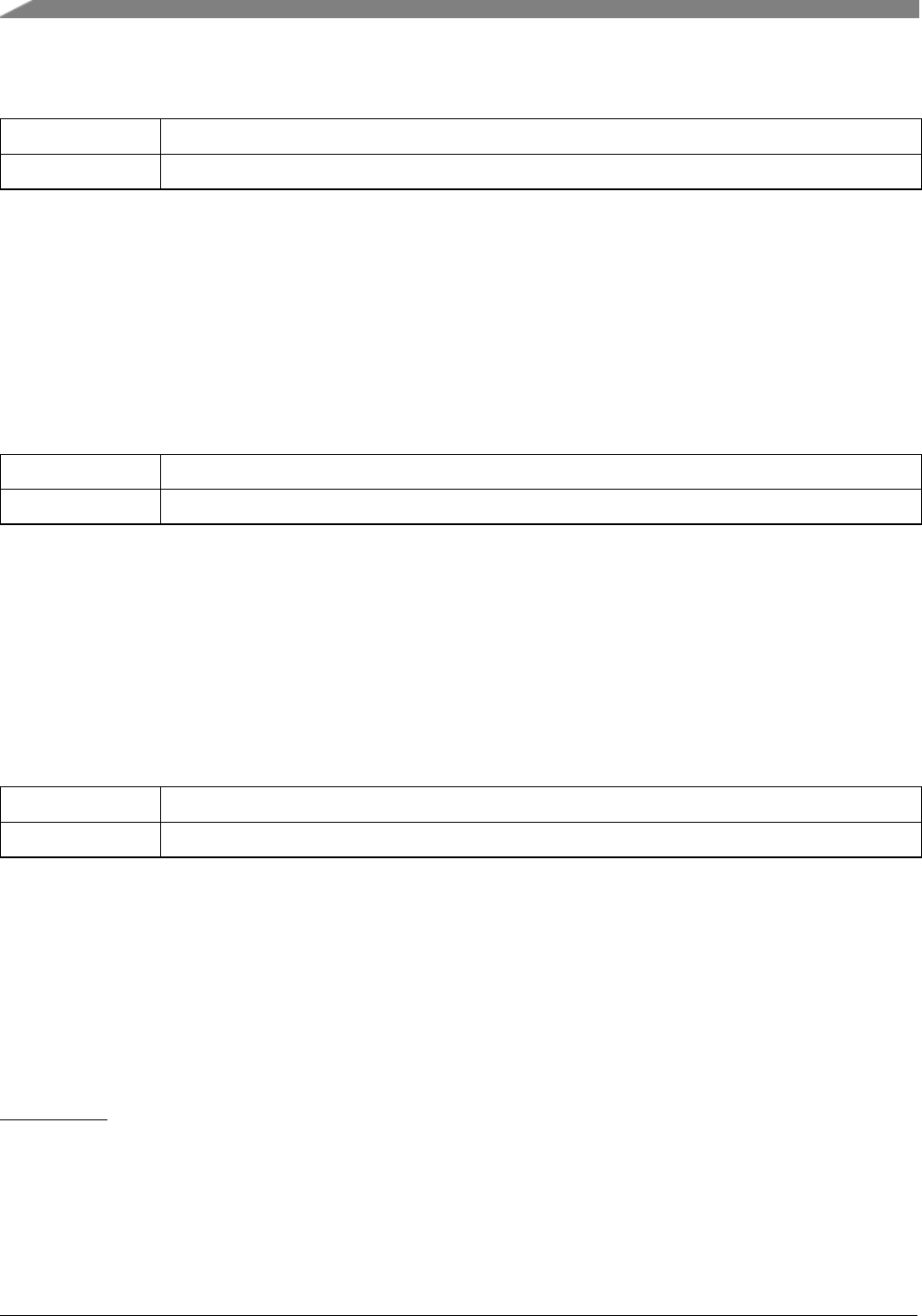

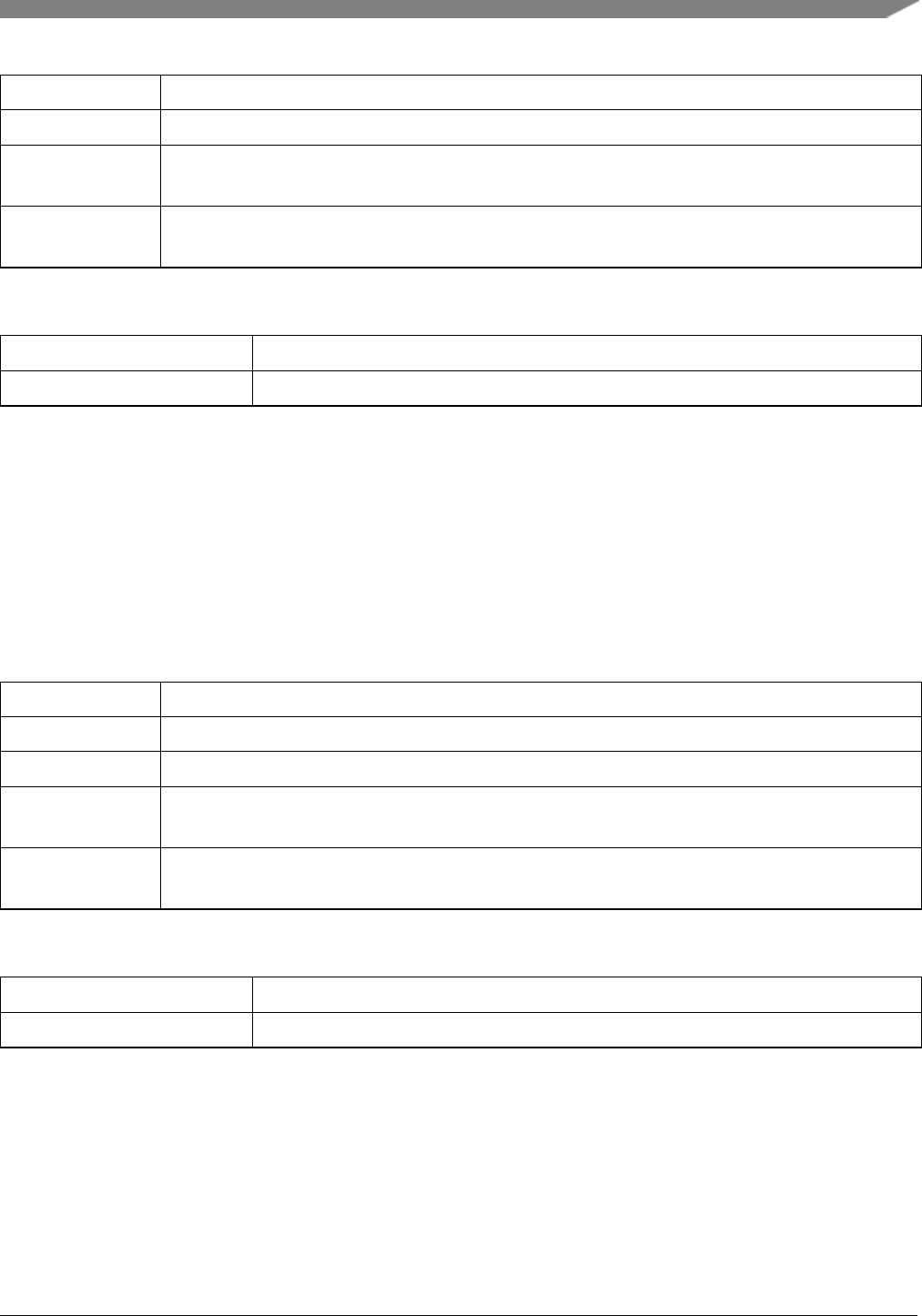

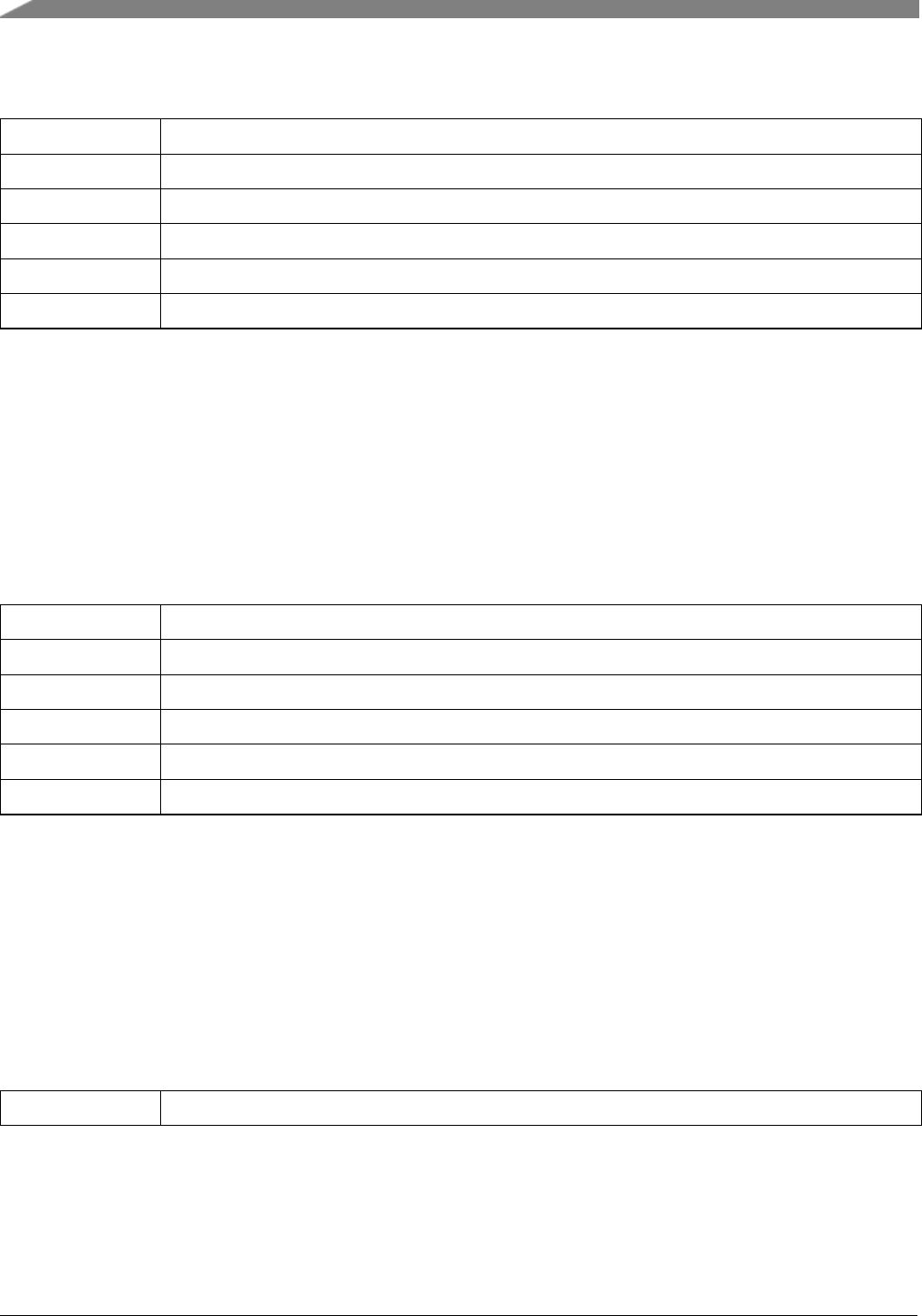

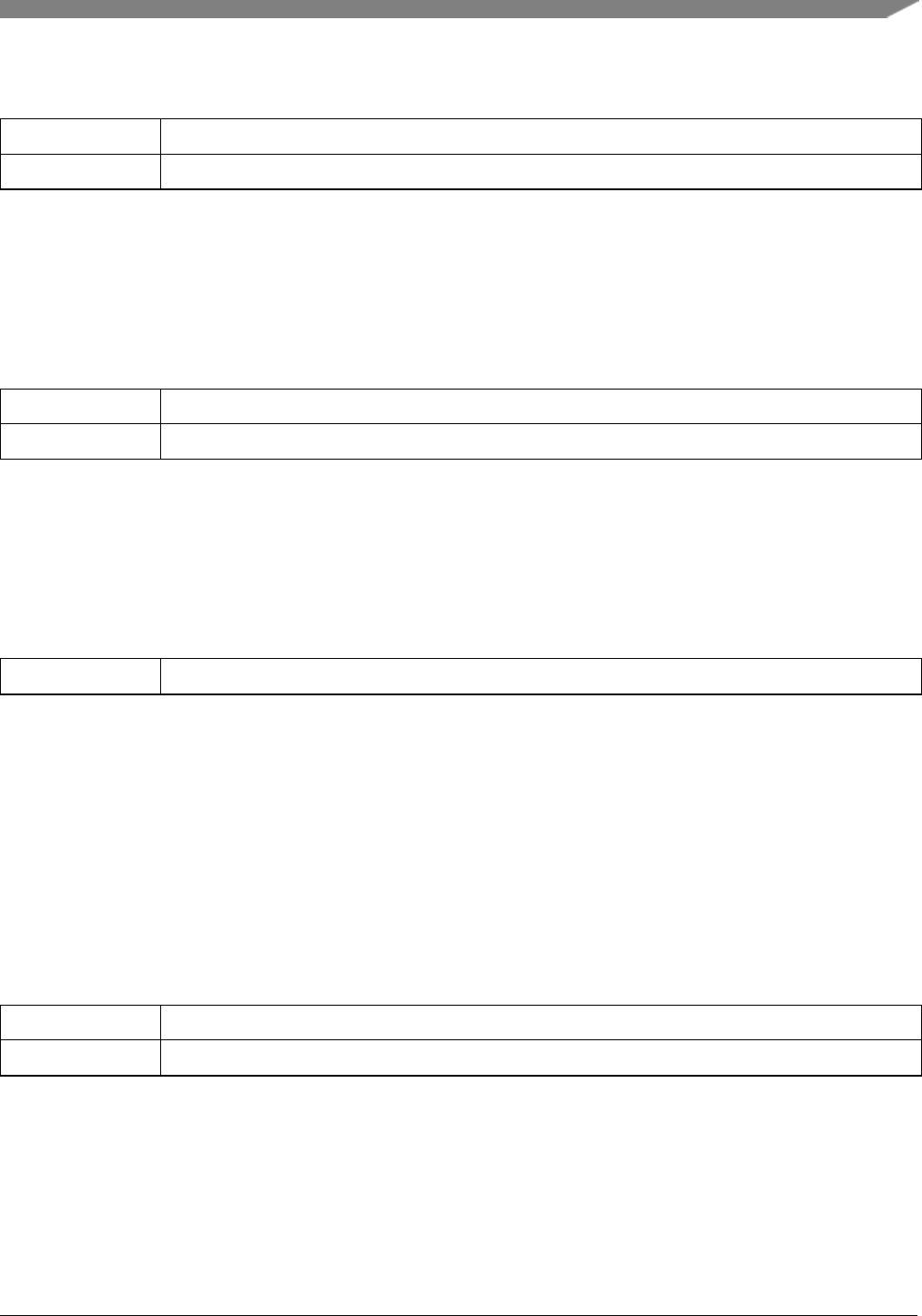

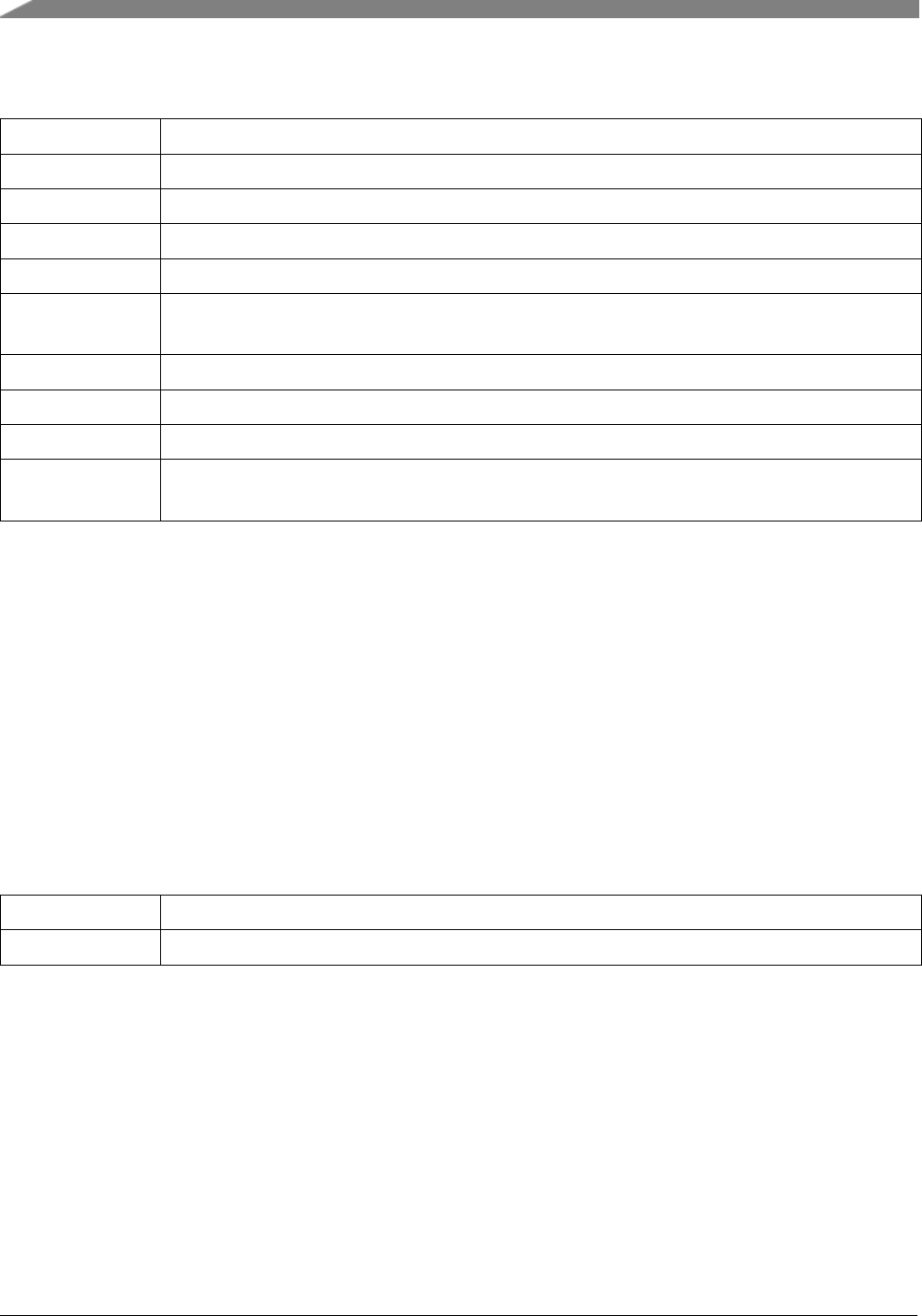

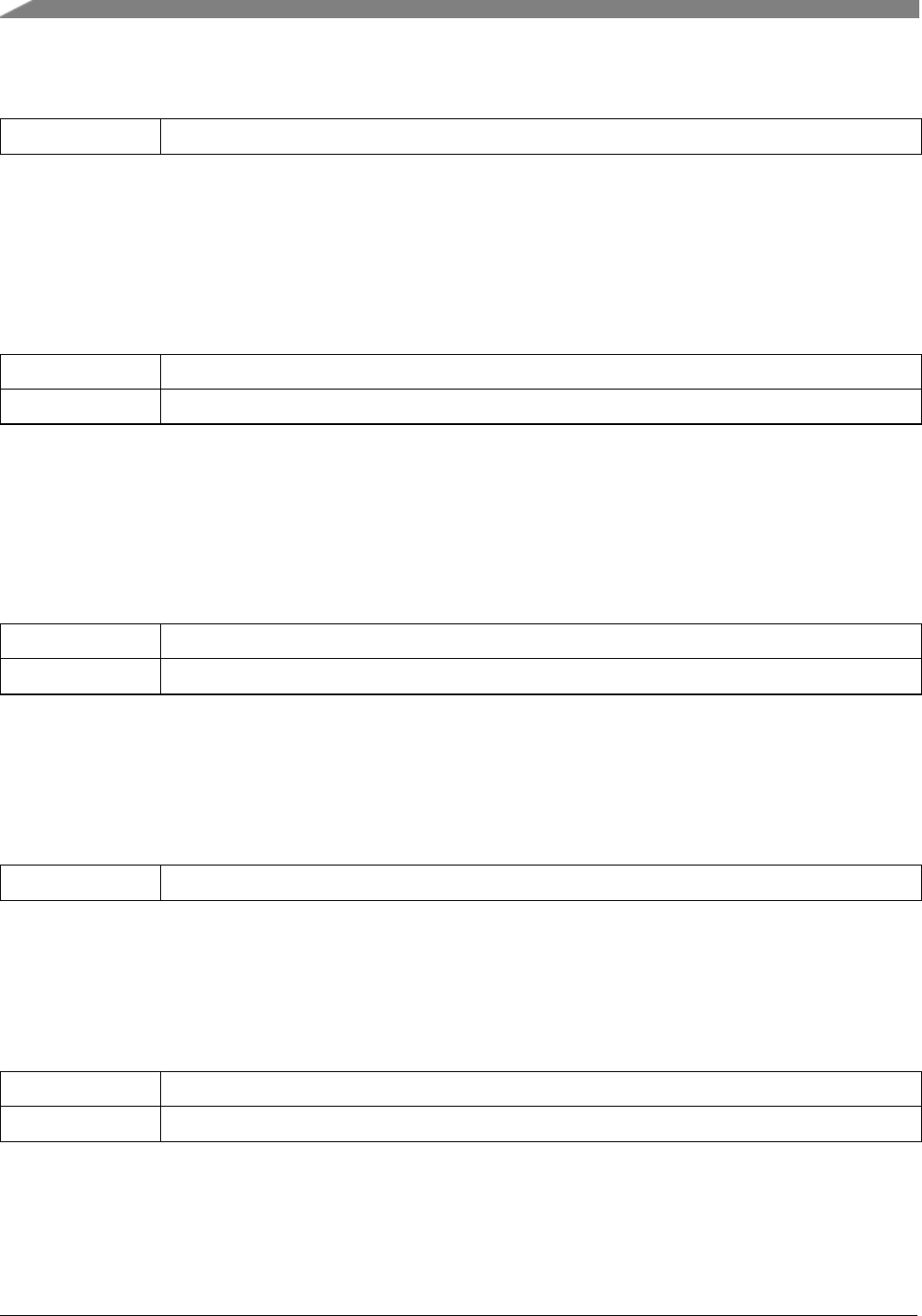

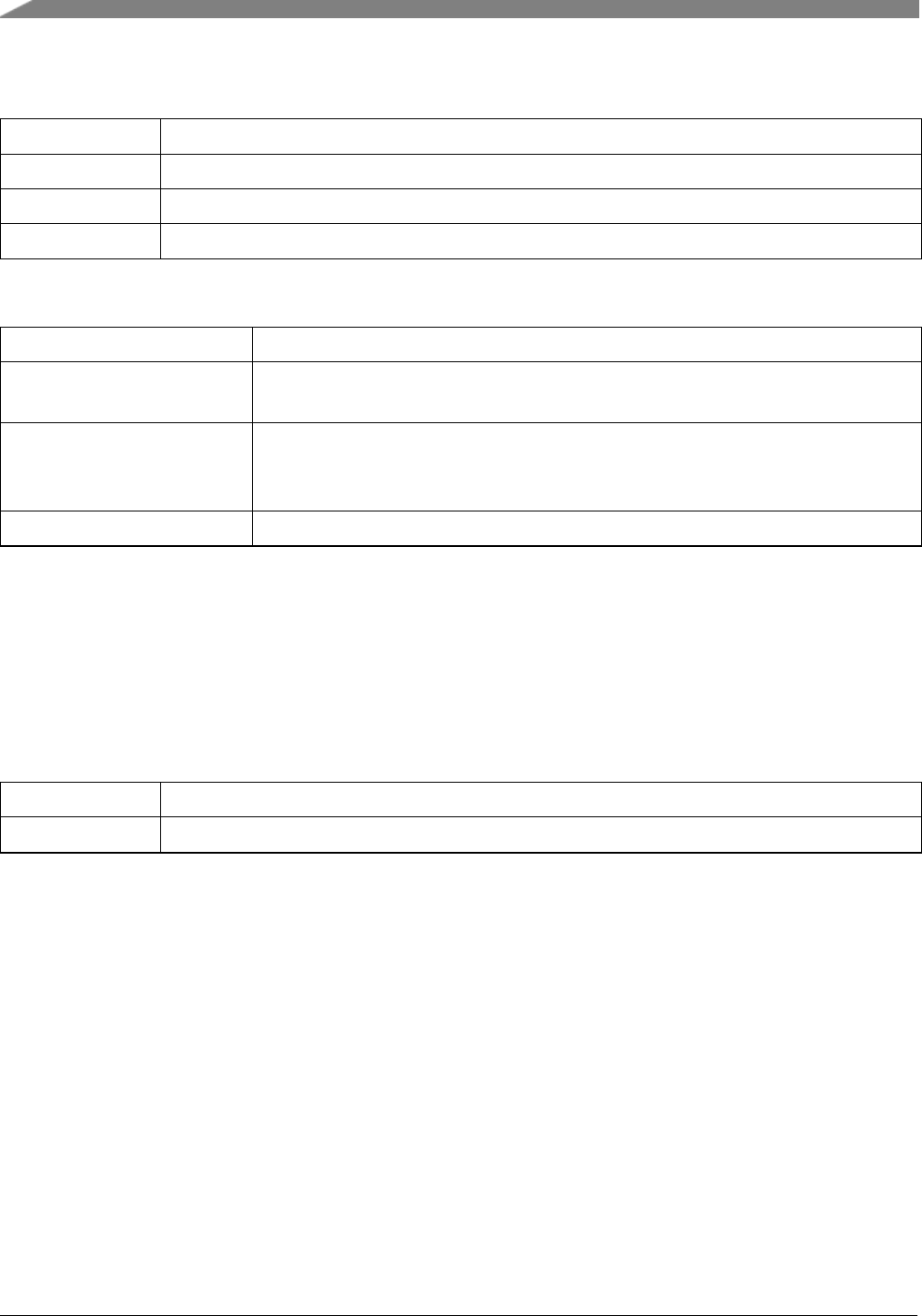

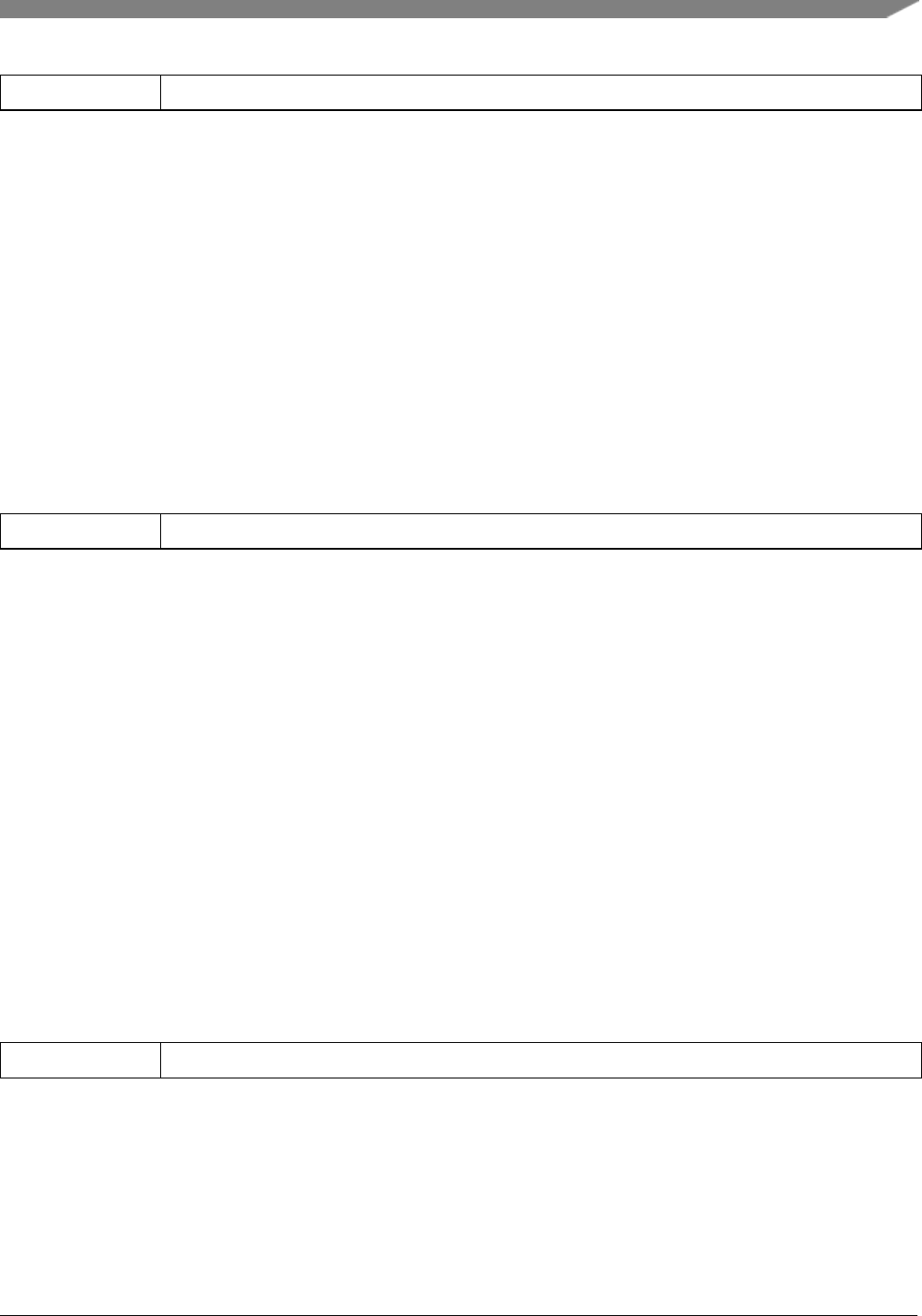

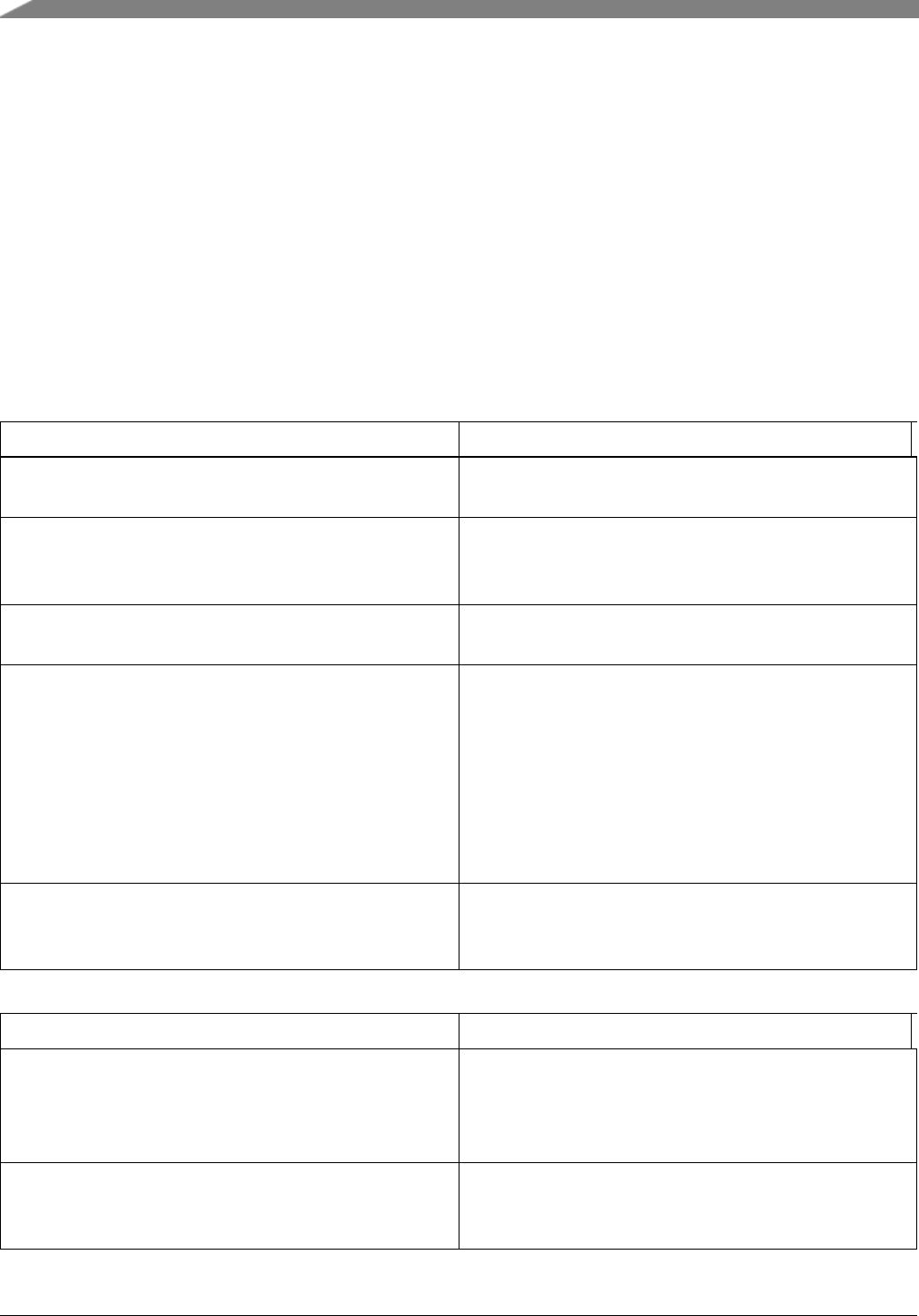

Contents

Chapter Introduction

Chapter Driver errors status

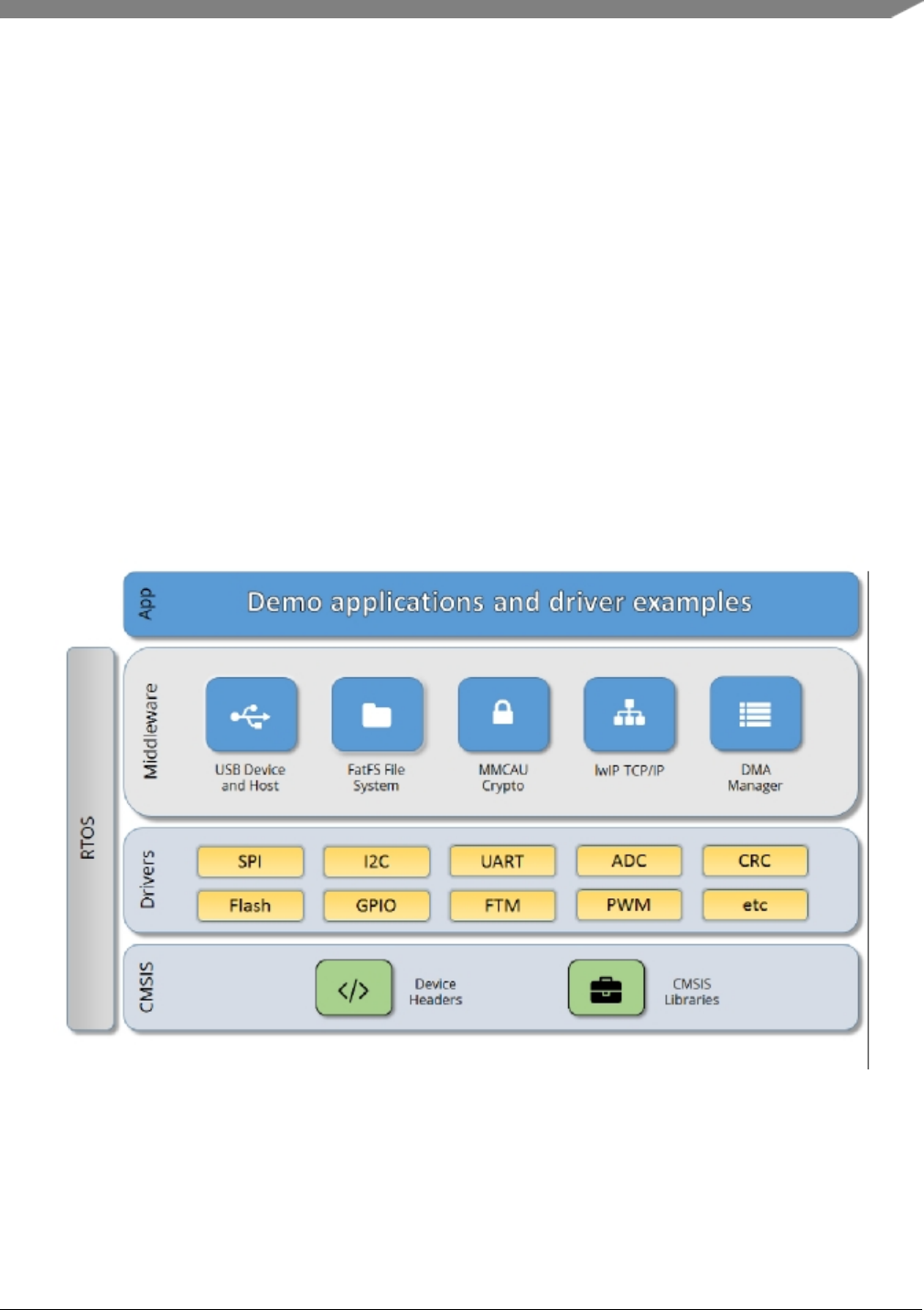

Chapter Architectural Overview

Chapter Trademarks

Chapter ADC: 12-bit Analog to Digital Converter Driver

5.1 Overview ........................................ 11

5.2 Typical use case .................................... 11

5.2.1 Polling Configuration ................................ 11

5.2.2 Polling Configuration ................................ 12

5.3 Data Structure Documentation ............................ 15

5.3.1 struct adc_config_t .................................. 15

5.3.2 struct adc_offest_config_t .............................. 16

5.3.3 struct adc_hardware_compare_config_t ....................... 16

5.3.4 struct adc_channel_config_t ............................. 16

5.4 Macro Definition Documentation ........................... 17

5.4.1 FSL_ADC_DRIVER_VERSION .......................... 17

5.5 Enumeration Type Documentation .......................... 17

5.5.1 adc_status_flags_t .................................. 17

5.5.2 adc_reference_voltage_source_t ........................... 17

5.5.3 adc_sample_period_mode_t ............................. 17

5.5.4 adc_clock_source_t ................................. 17

5.5.5 adc_clock_driver_t .................................. 18

5.5.6 adc_resolution_t ................................... 18

5.5.7 adc_hardware_compare_mode_t .......................... 18

5.5.8 adc_hardware_average_mode_t ........................... 18

5.6 Function Documentation ............................... 19

5.6.1 ADC_Init ....................................... 19

5.6.2 ADC_Deinit ..................................... 19

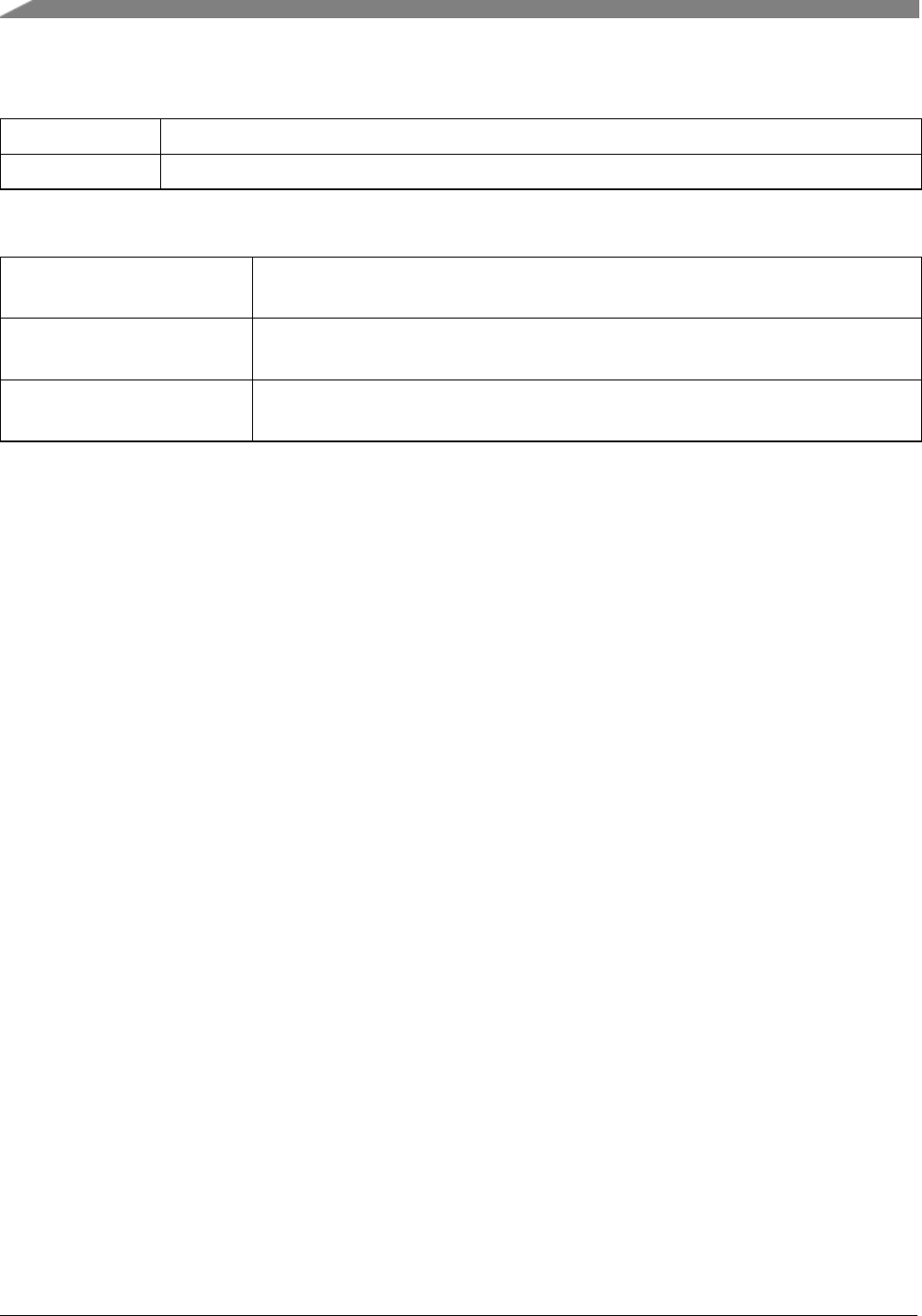

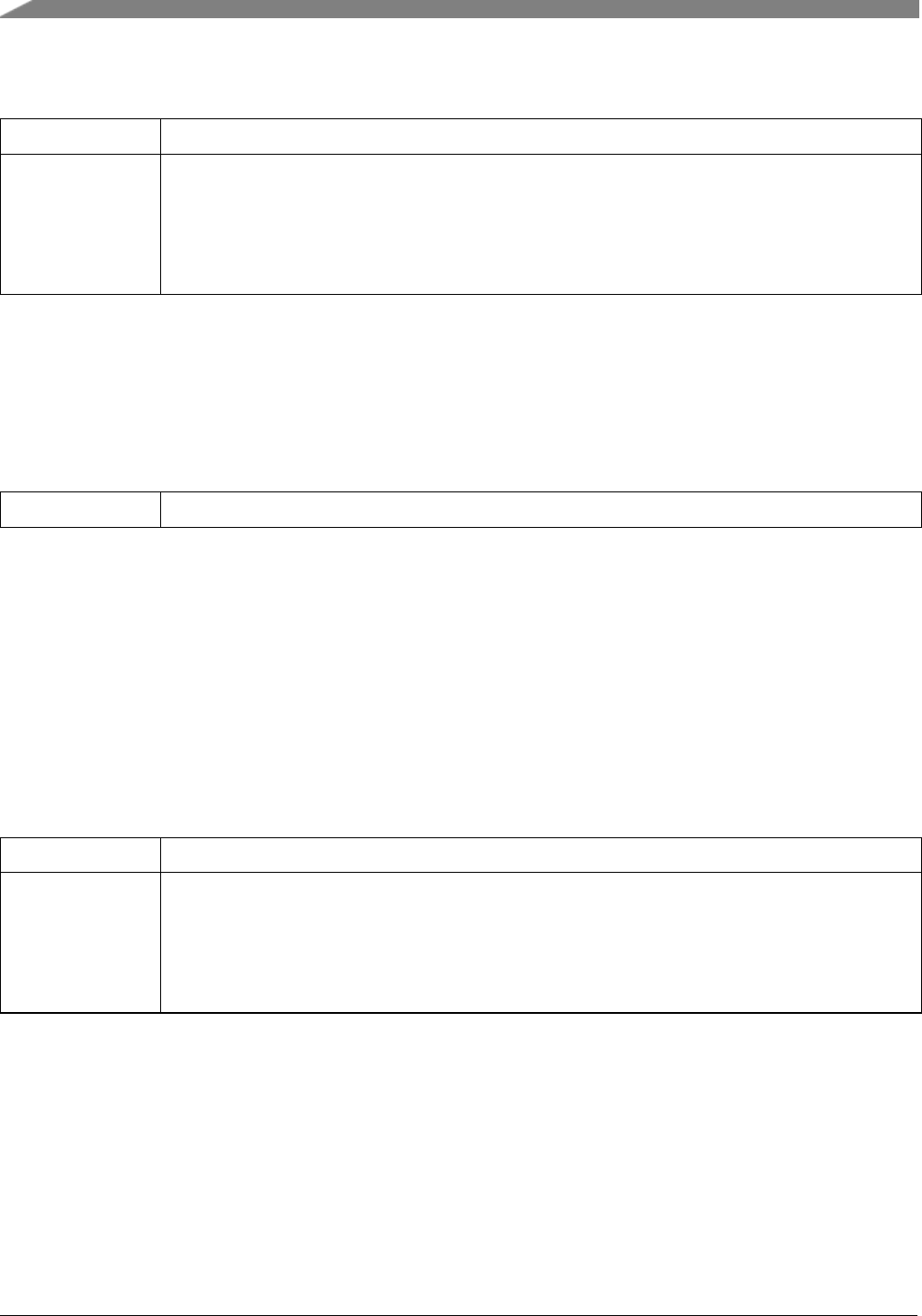

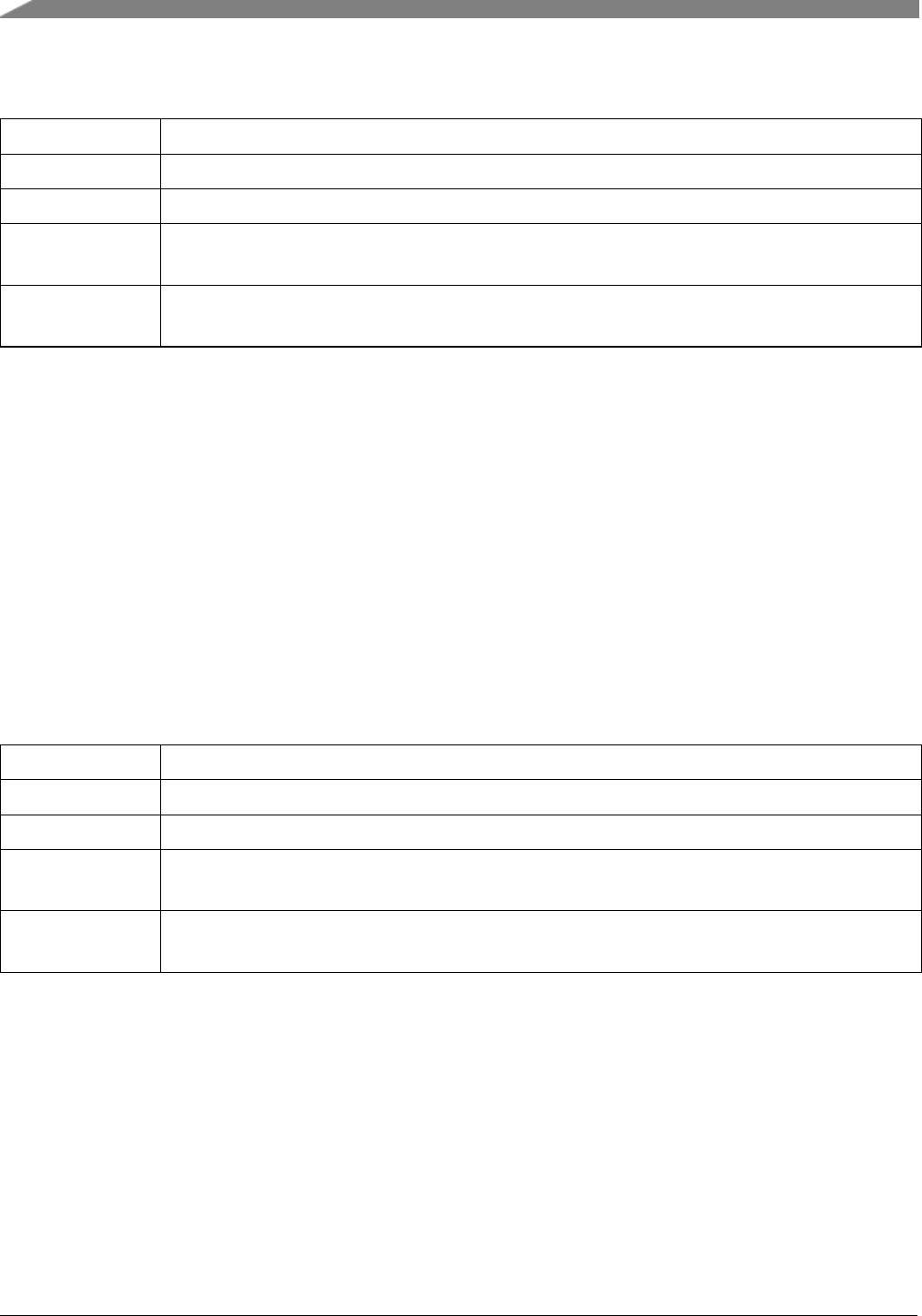

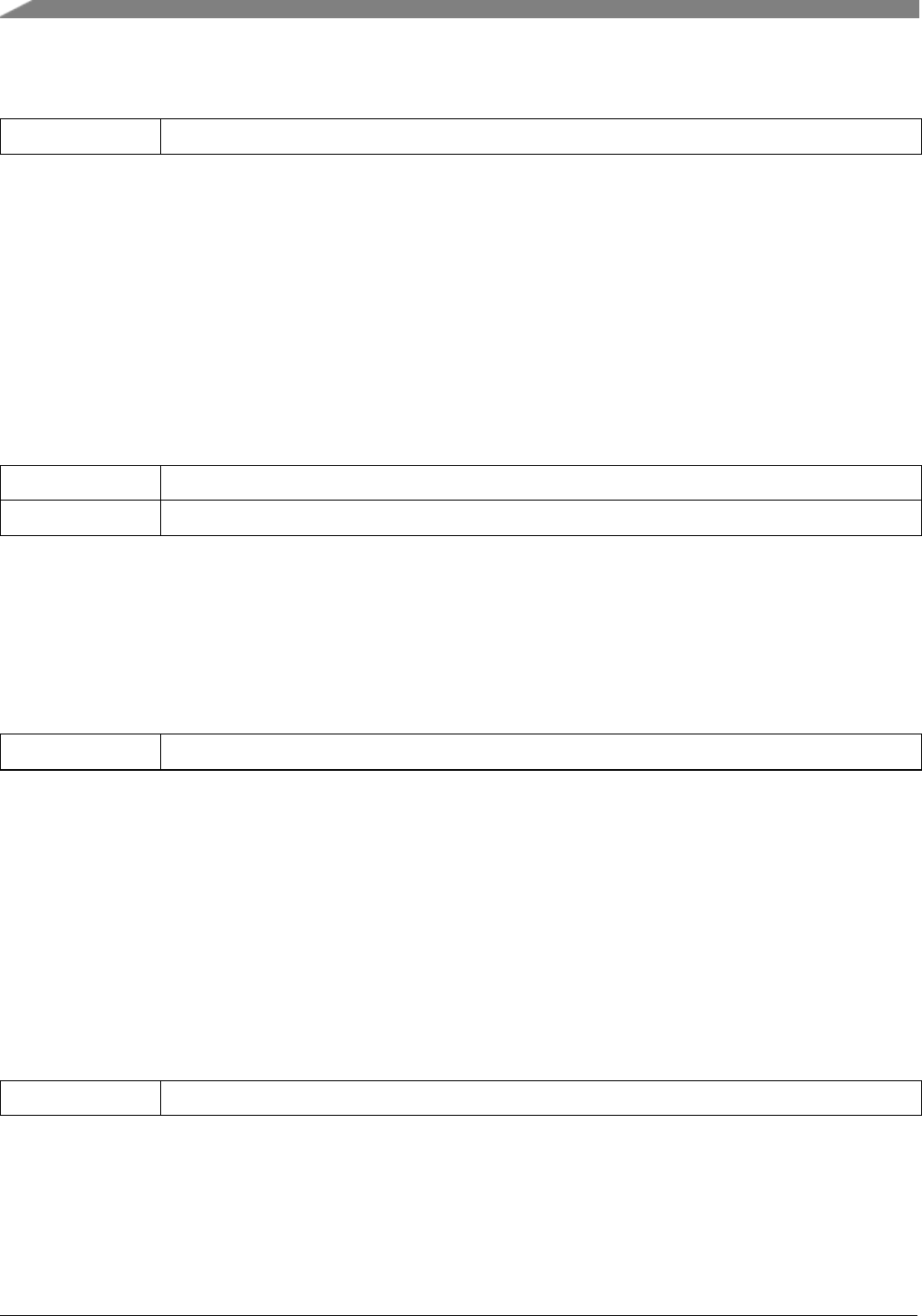

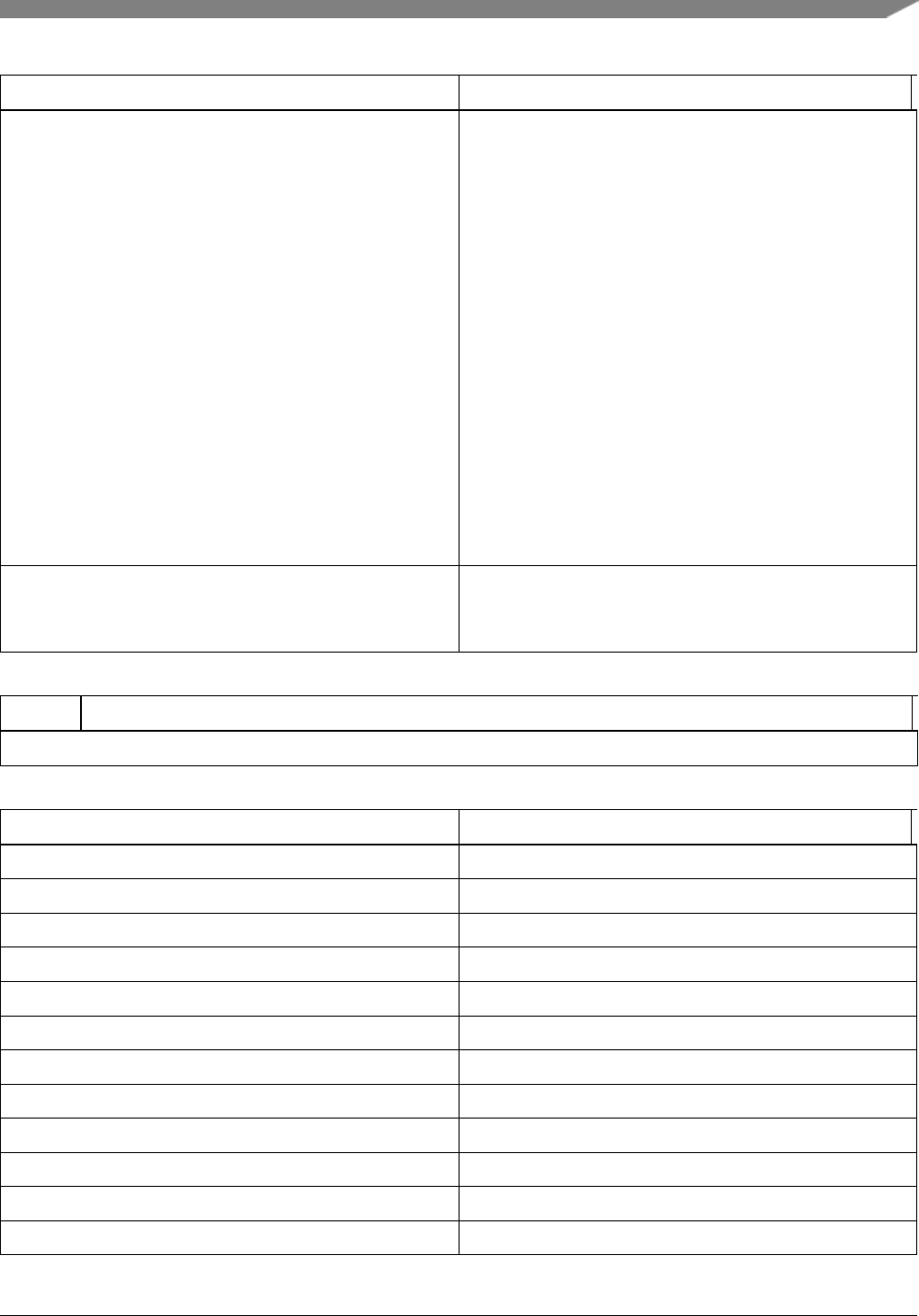

NXP Semiconductors

MCUXpresso SDK API Reference Manual

iii

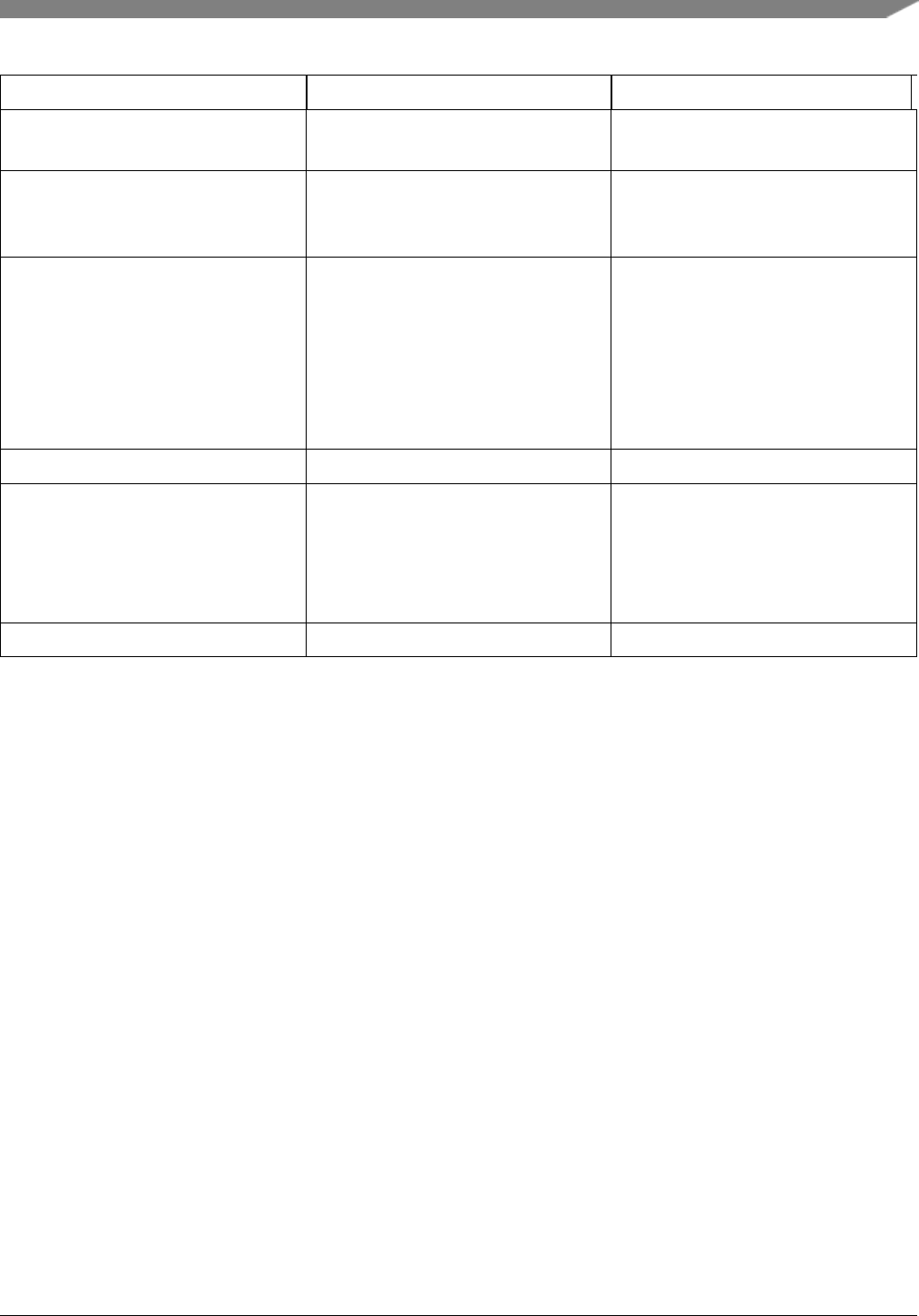

Section

Number

Contents

Title

Page

Number

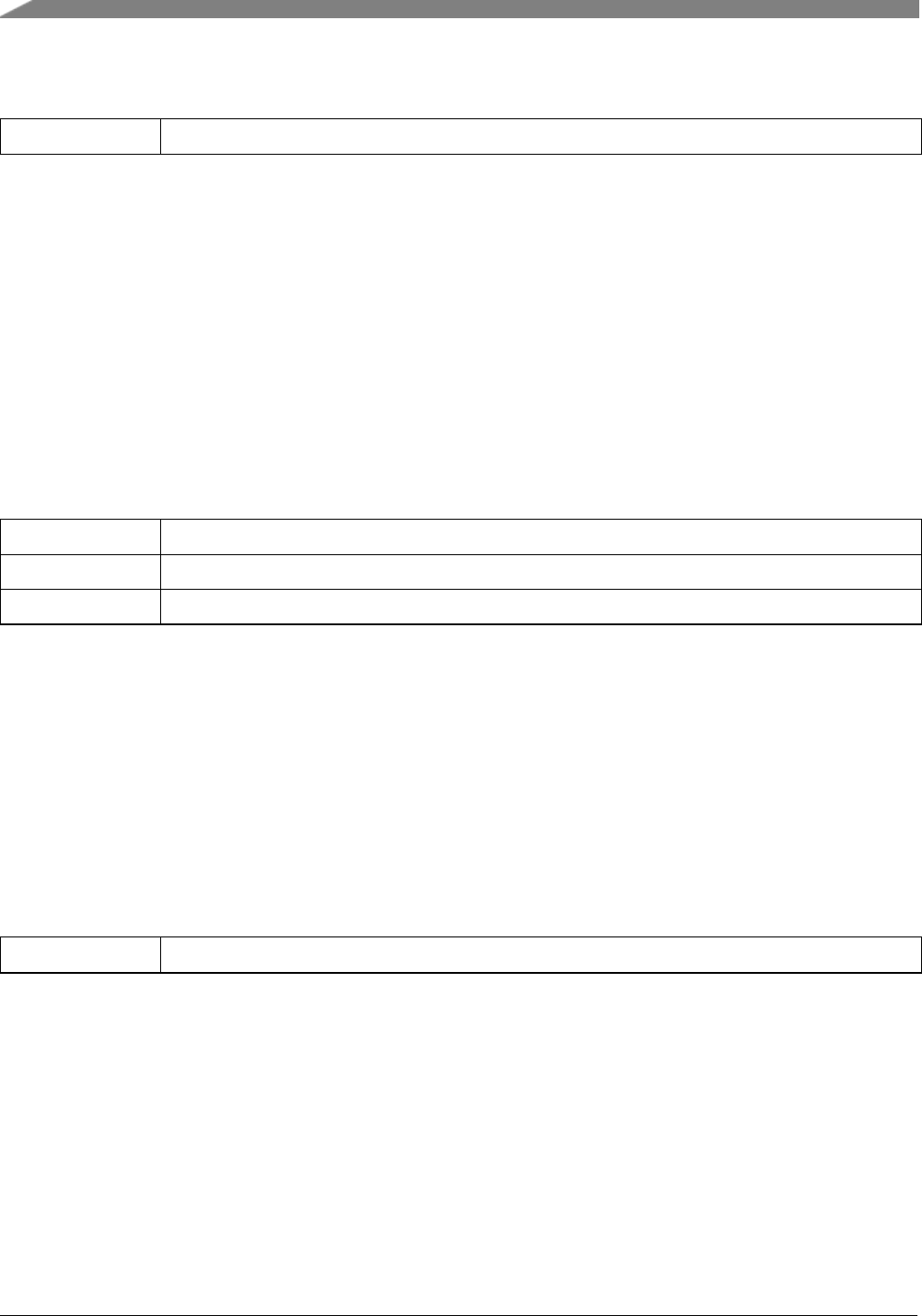

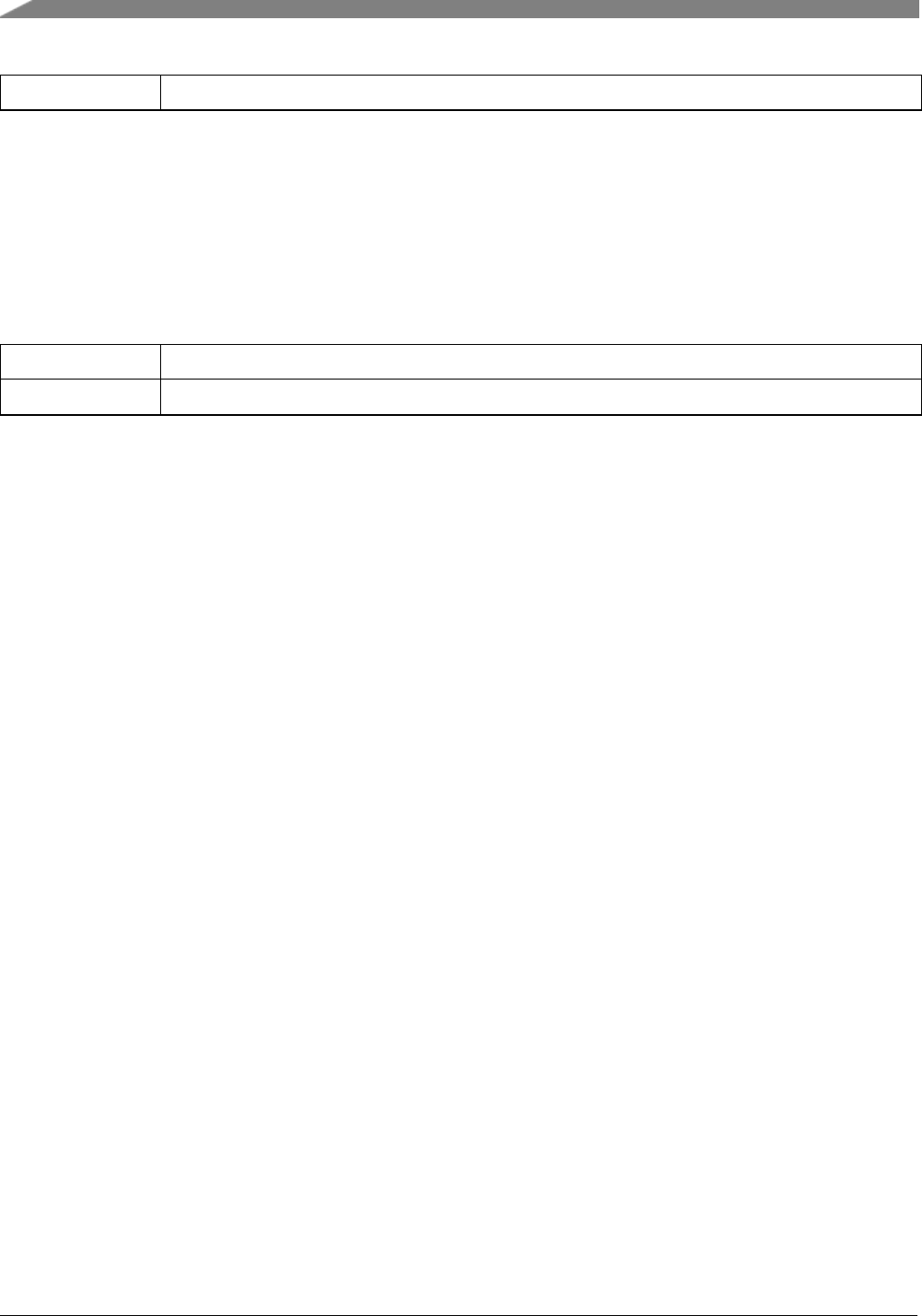

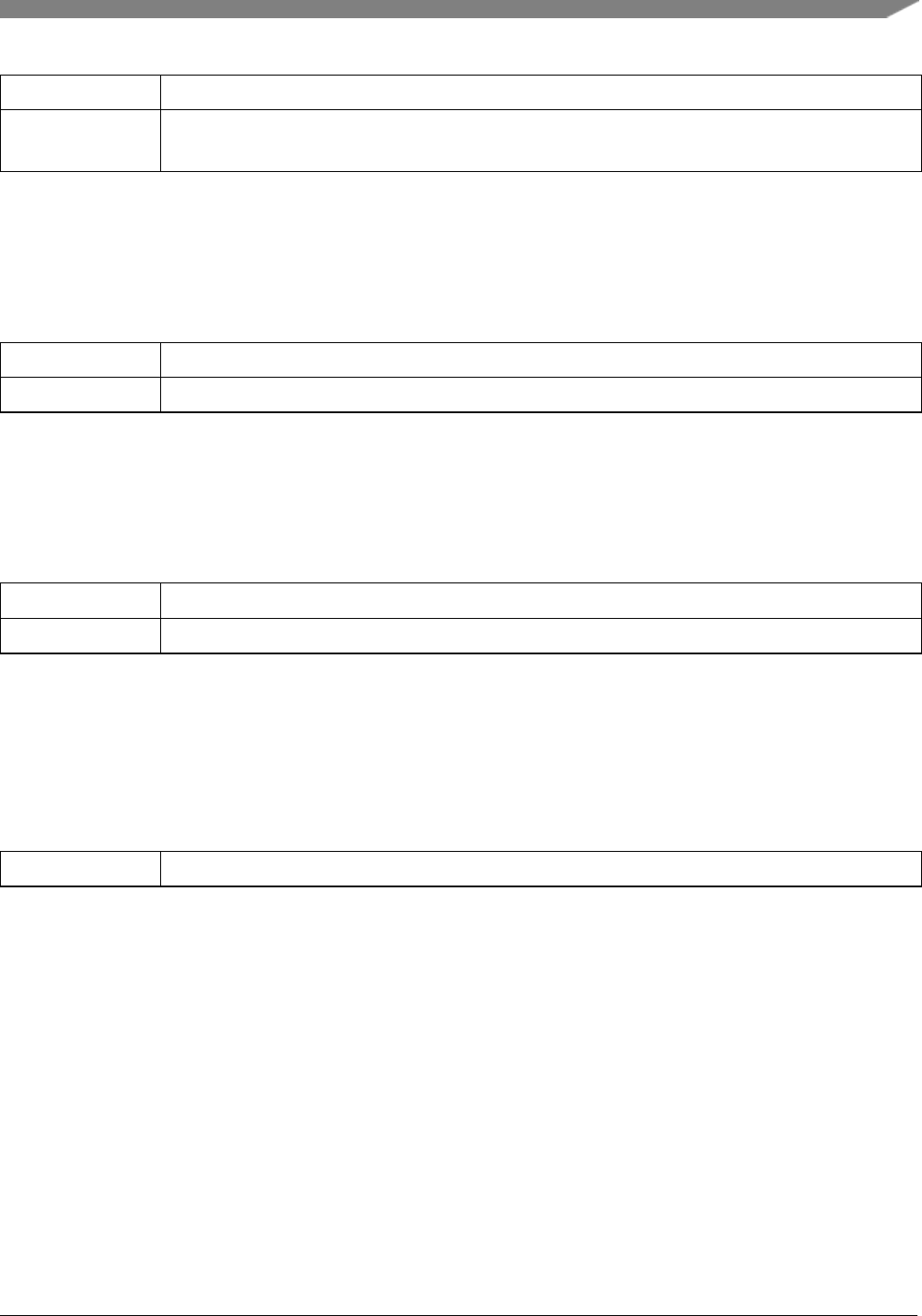

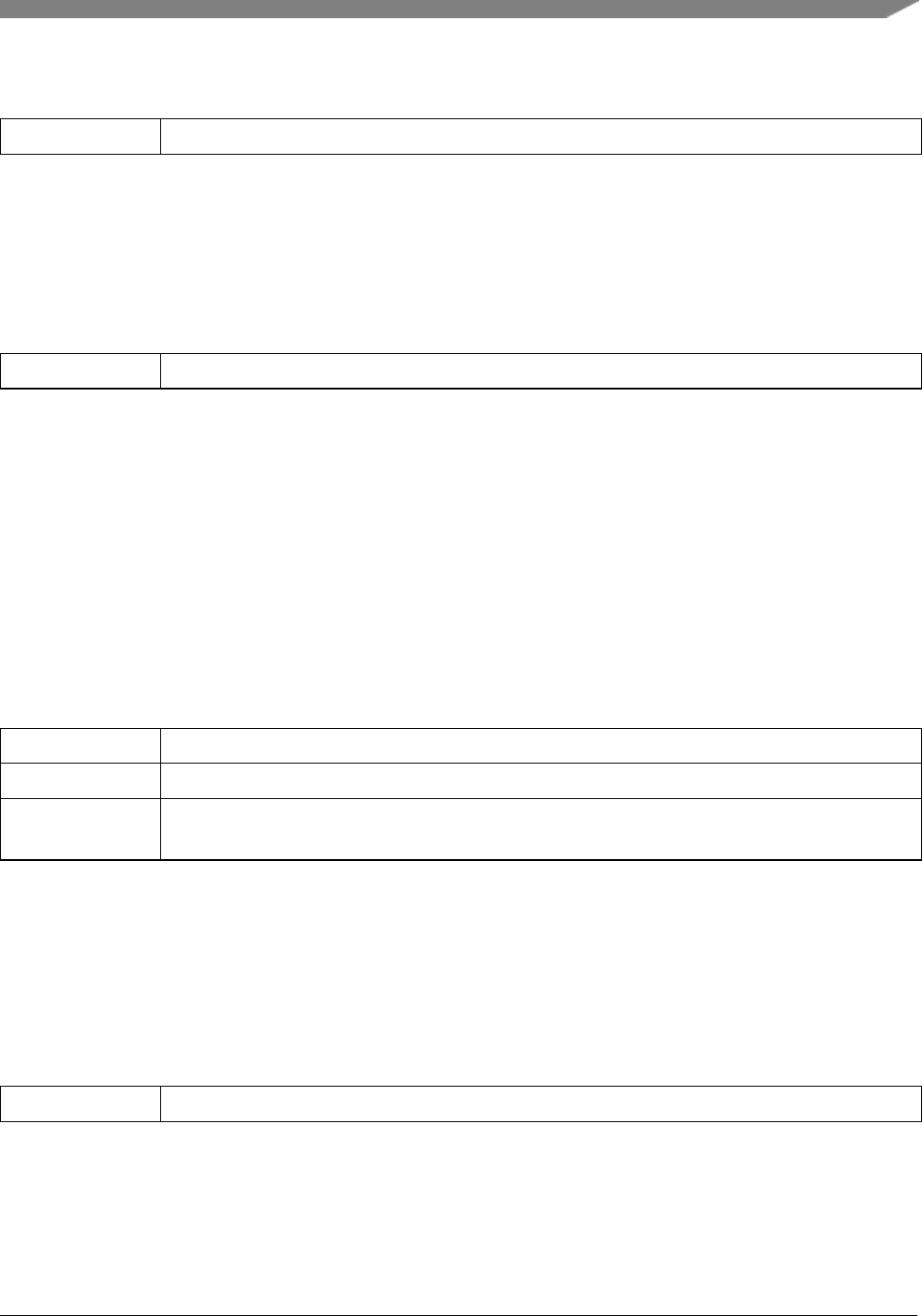

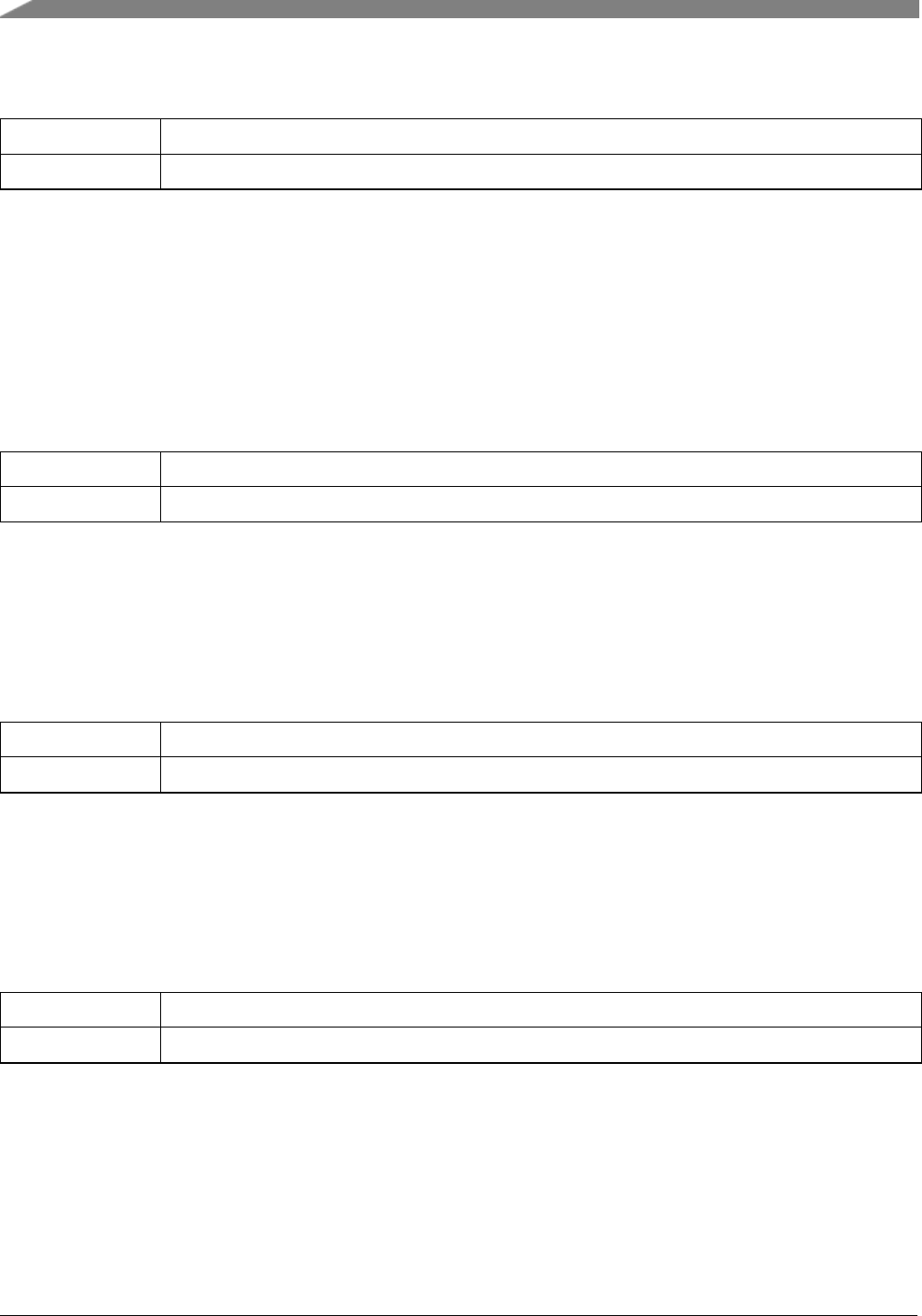

5.6.3 ADC_GetDefaultConfig ............................... 19

5.6.4 ADC_SetChannelConfig ............................... 20

5.6.5 ADC_GetChannelConversionValue ......................... 20

5.6.6 ADC_GetChannelStatusFlags ............................ 21

5.6.7 ADC_DoAutoCalibration .............................. 21

5.6.8 ADC_SetOffsetConfig ................................ 22

5.6.9 ADC_EnableDMA .................................. 22

5.6.10 ADC_EnableHardwareTrigger ........................... 22

5.6.11 ADC_SetHardwareCompareConfig ......................... 22

5.6.12 ADC_SetHardwareAverageConfig ......................... 23

5.6.13 ADC_GetStatusFlags ................................ 23

5.6.14 ADC_ClearStatusFlags ............................... 23

5.7 Variable Documentation ................................ 24

5.7.1 enableOverWrite ................................... 24

5.7.2 enableContinuousConversion ............................ 24

5.7.3 enableHighSpeed .................................. 24

5.7.4 enableLowPower ................................... 24

5.7.5 enableLongSample .................................. 24

5.7.6 enableAsynchronousClockOutput .......................... 24

5.7.7 referenceVoltageSource ............................... 24

5.7.8 samplePeriodMode ................................. 24

5.7.9 clockSource ..................................... 24

5.7.10 clockDriver ...................................... 24

5.7.11 resolution ....................................... 24

5.7.12 enableSigned ..................................... 24

5.7.13 offsetValue ...................................... 24

5.7.14 hardwareCompareMode ............................... 24

5.7.15 value1 ........................................ 25

5.7.16 value2 ........................................ 25

5.7.17 channelNumber ................................... 25

5.7.18 enableInterruptOnConversionCompleted ...................... 25

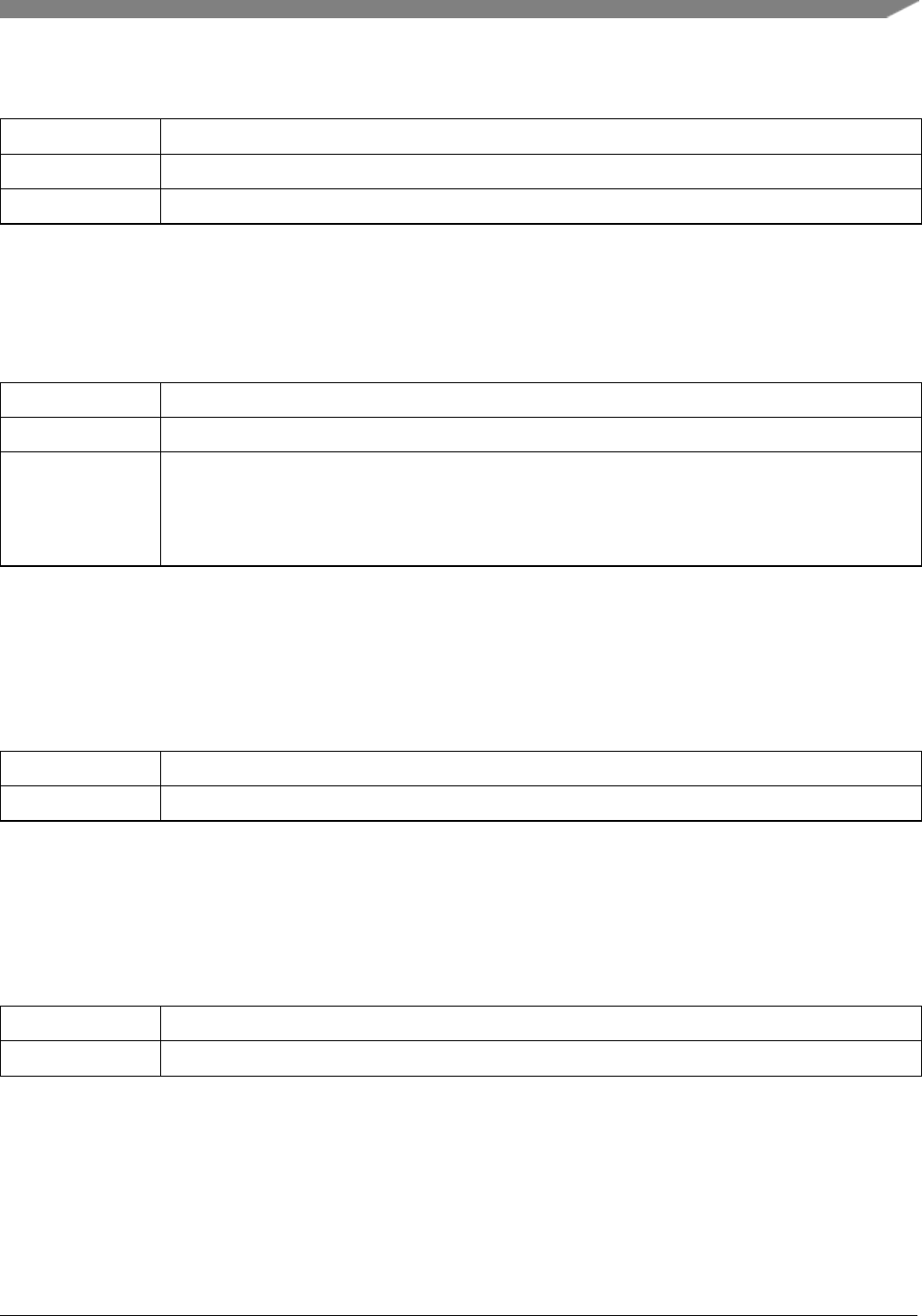

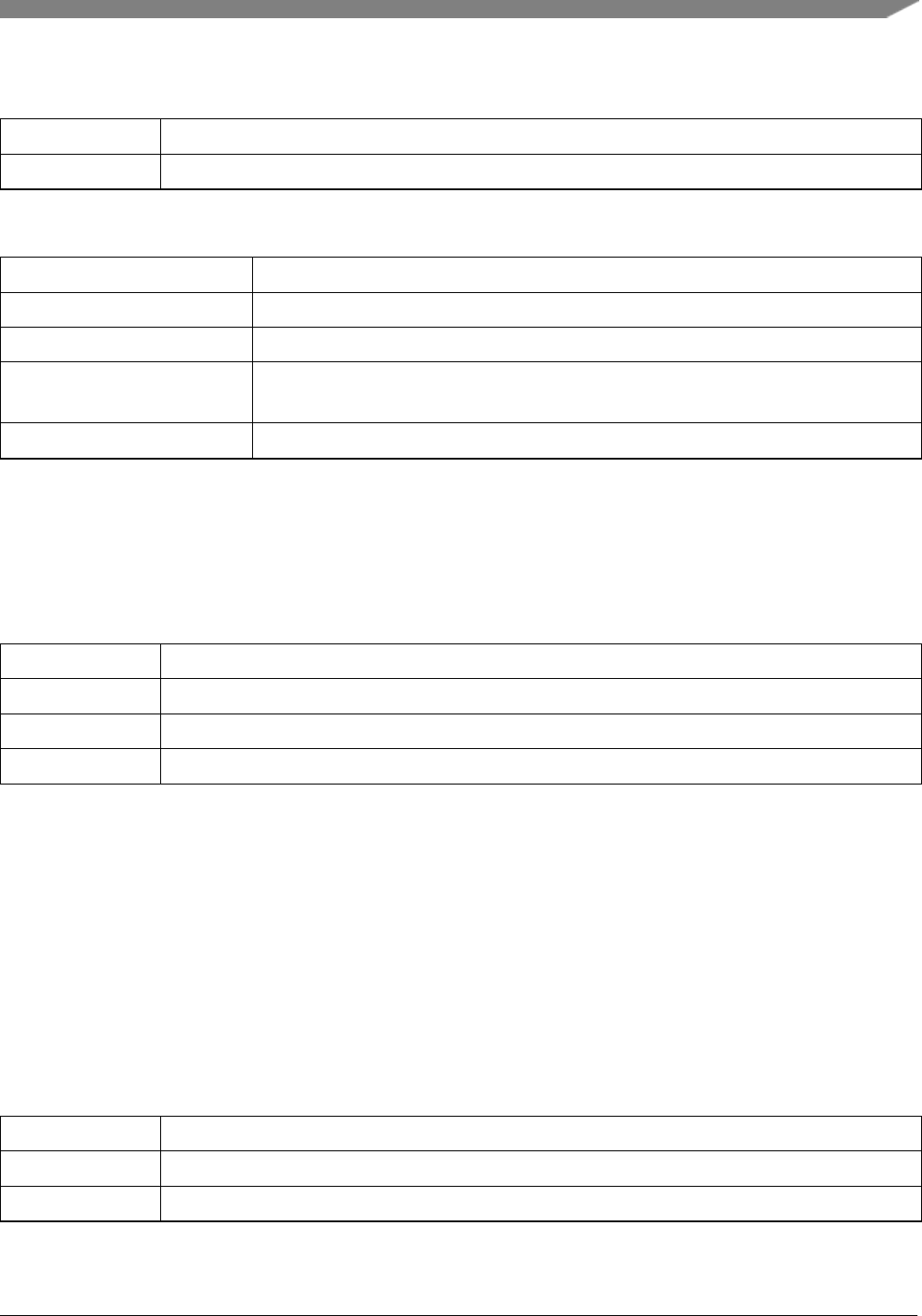

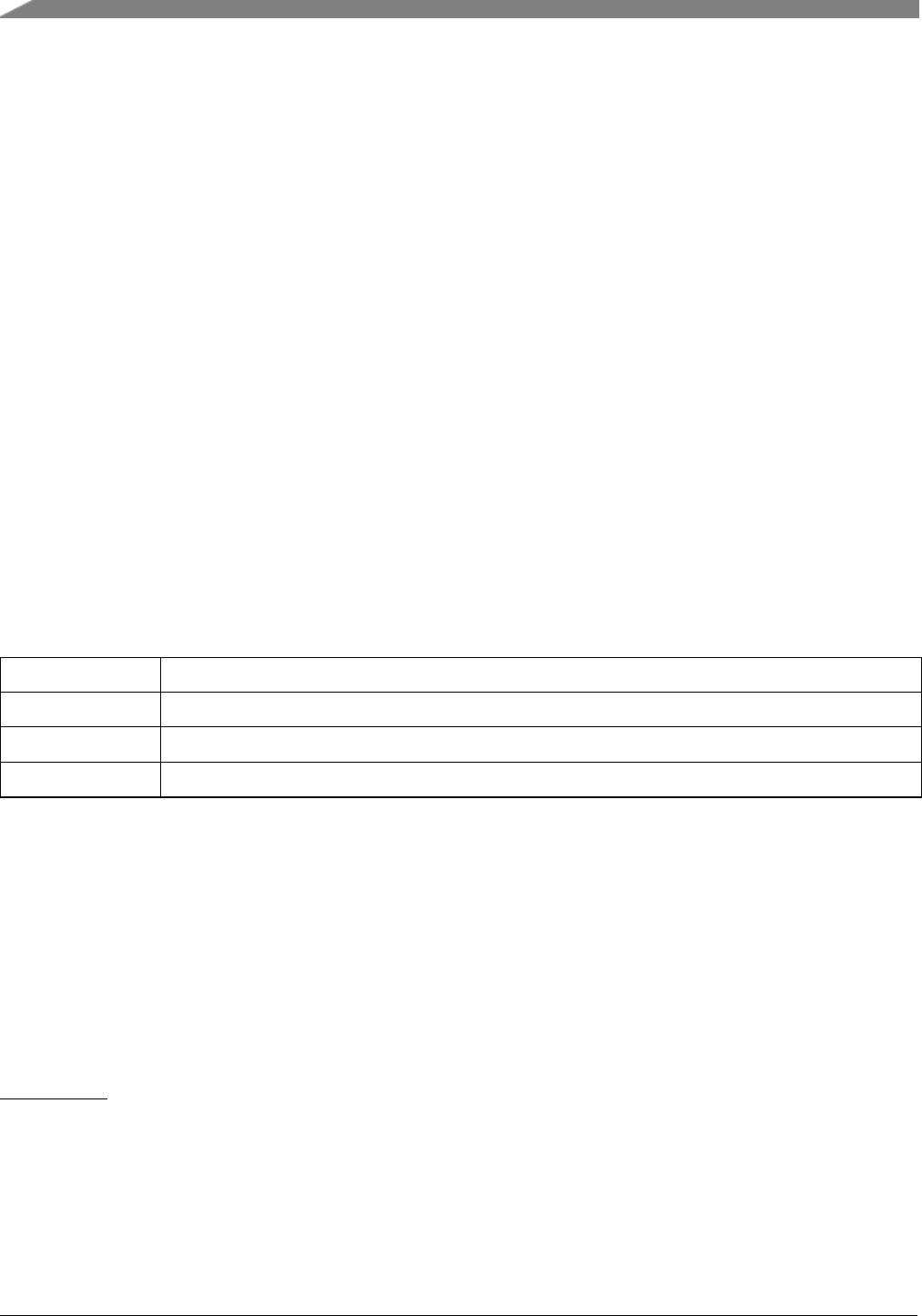

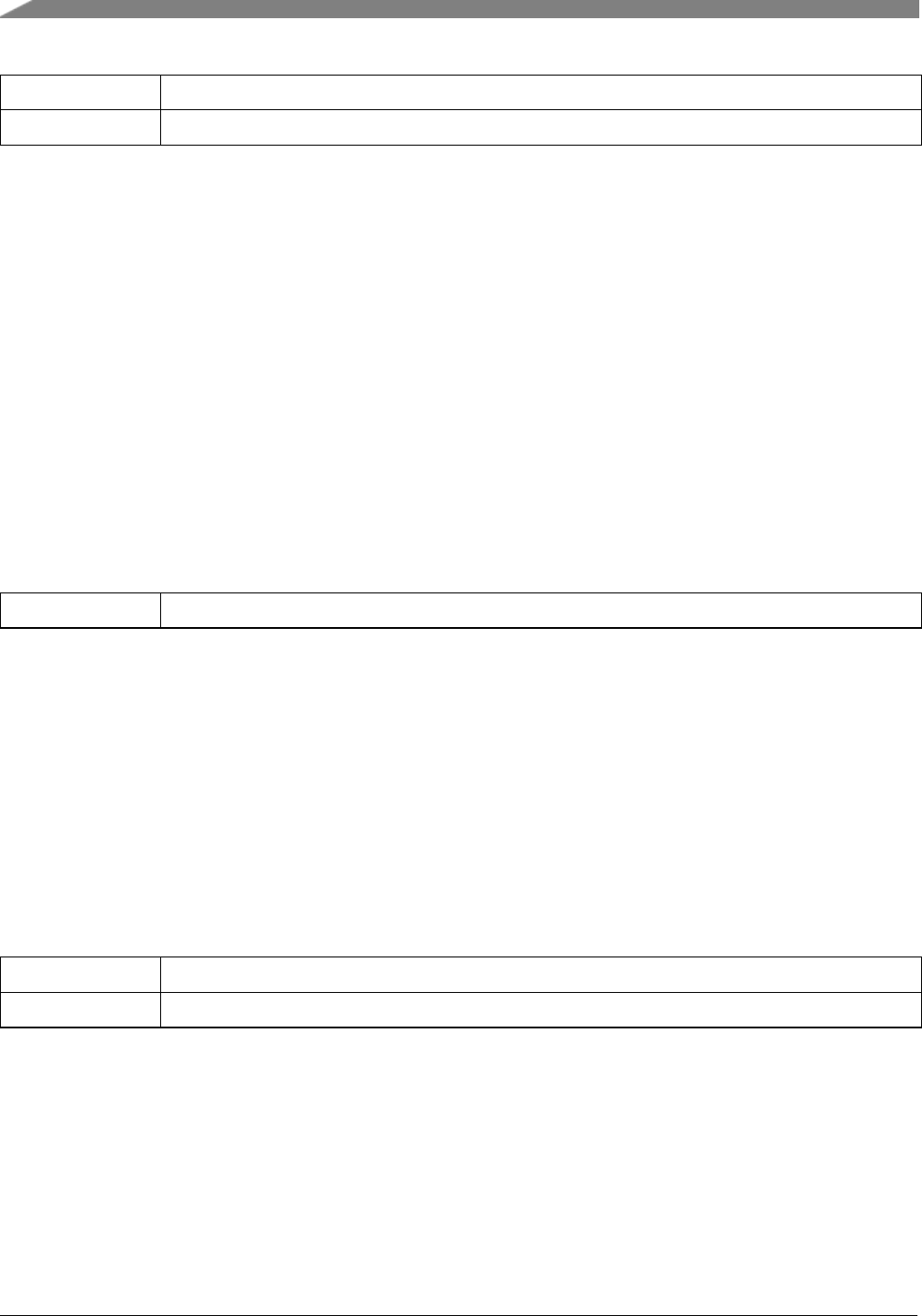

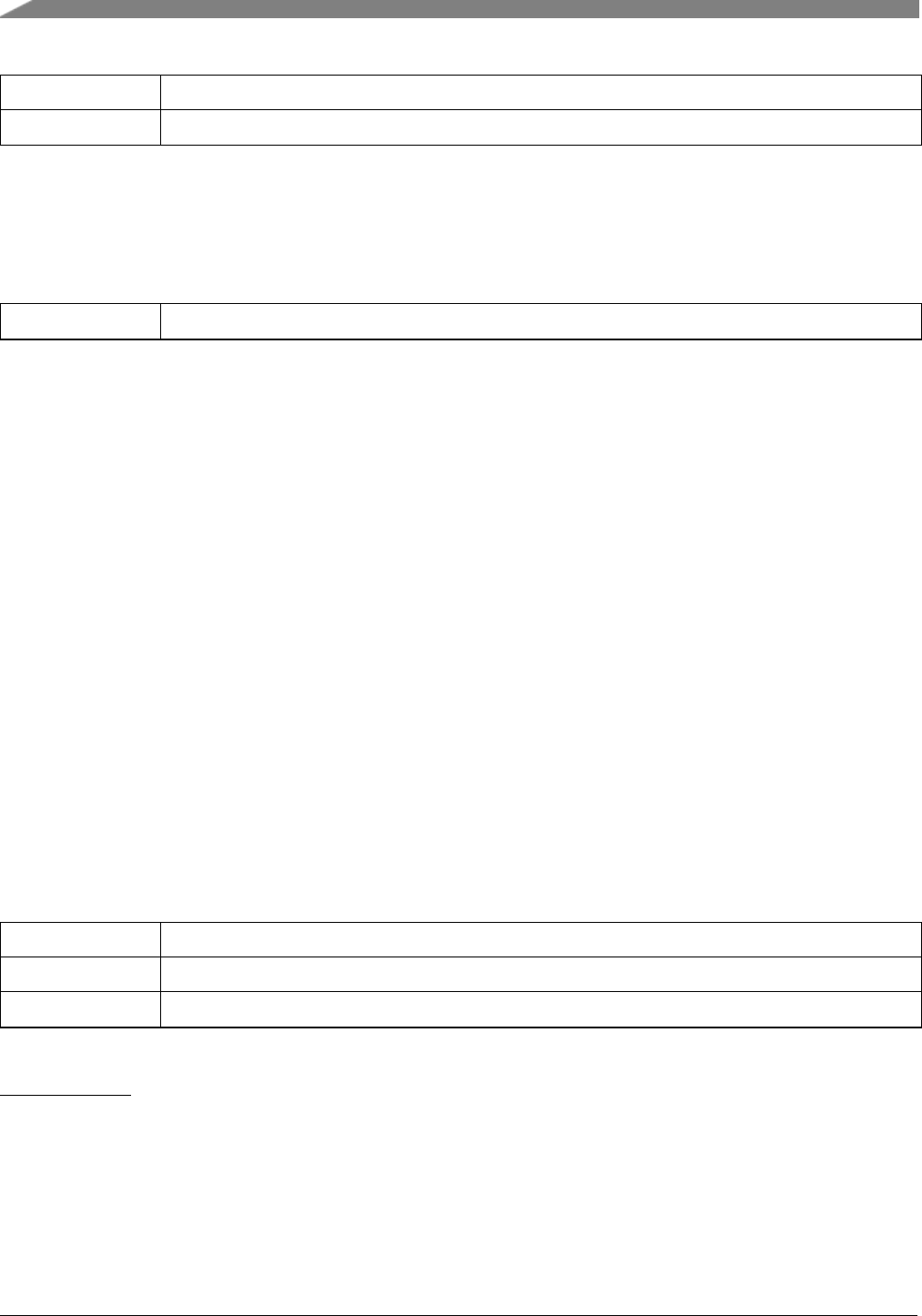

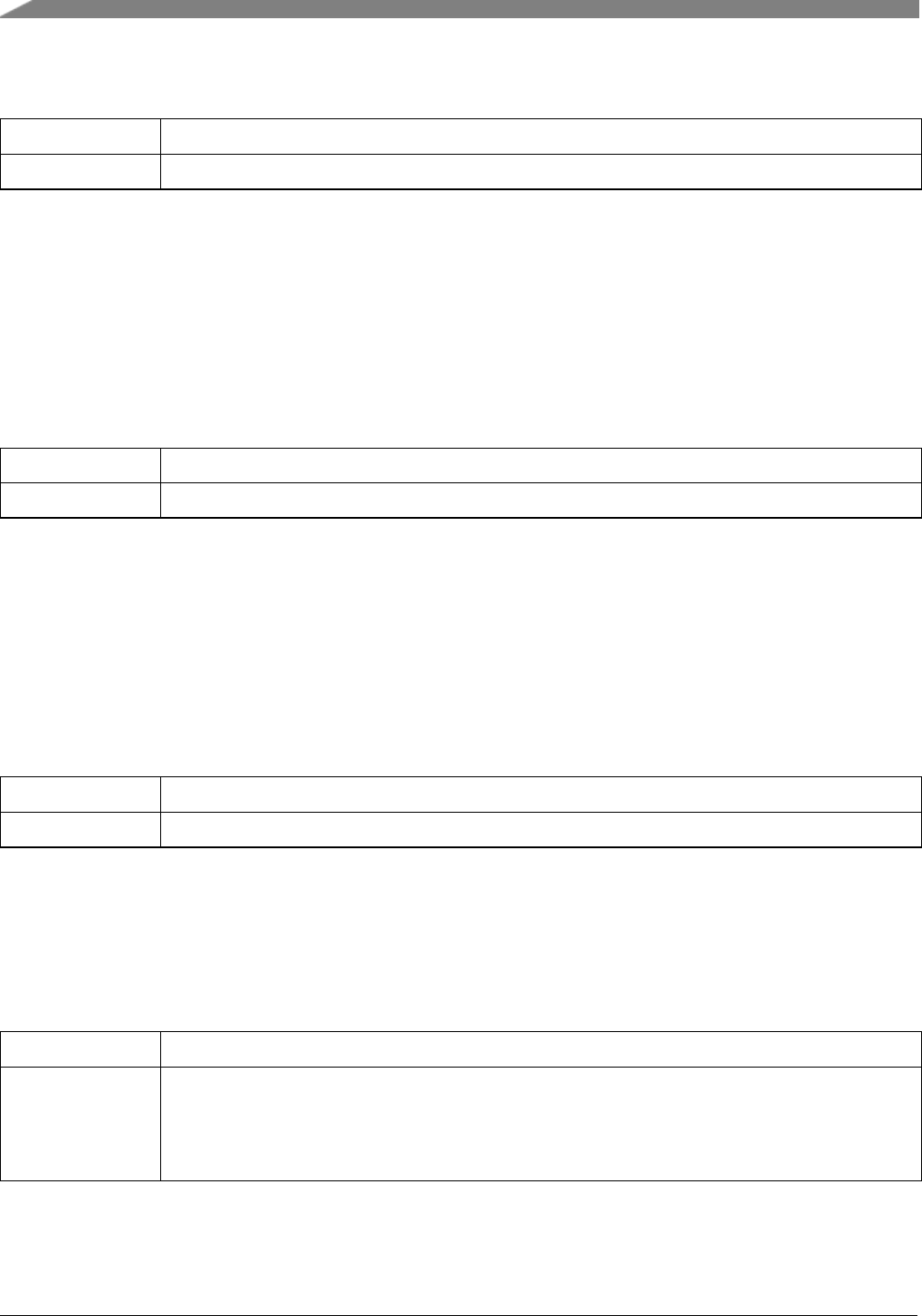

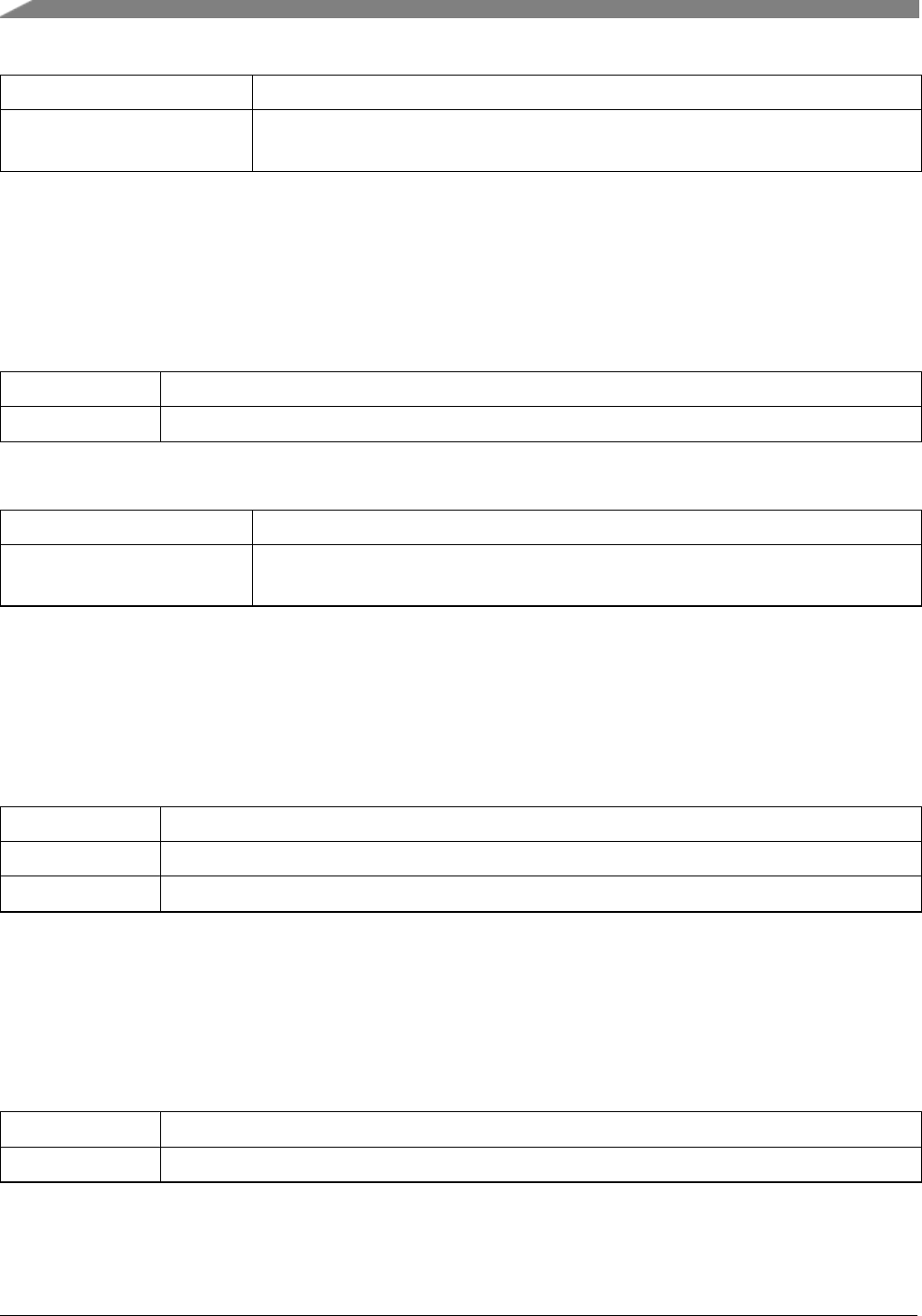

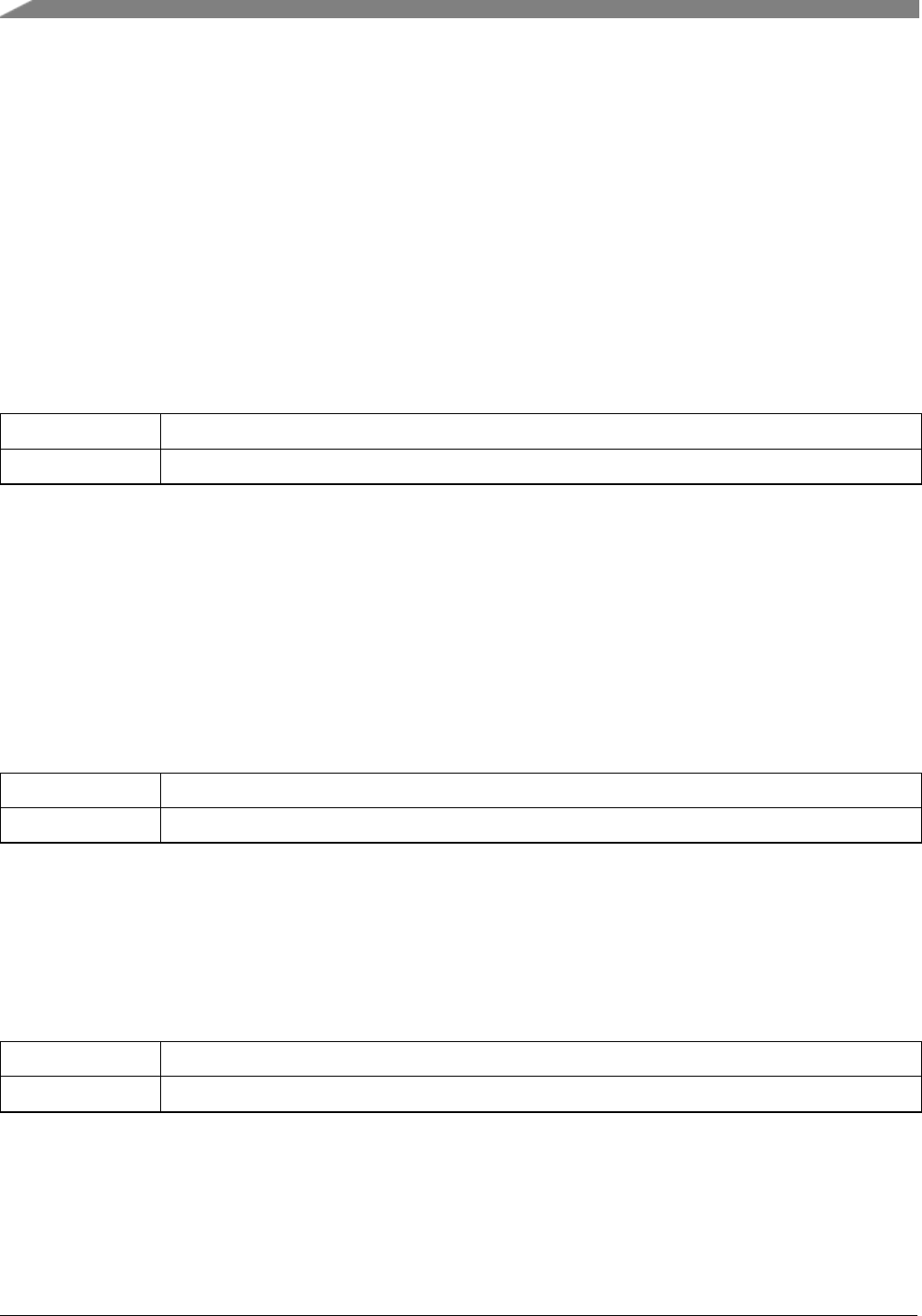

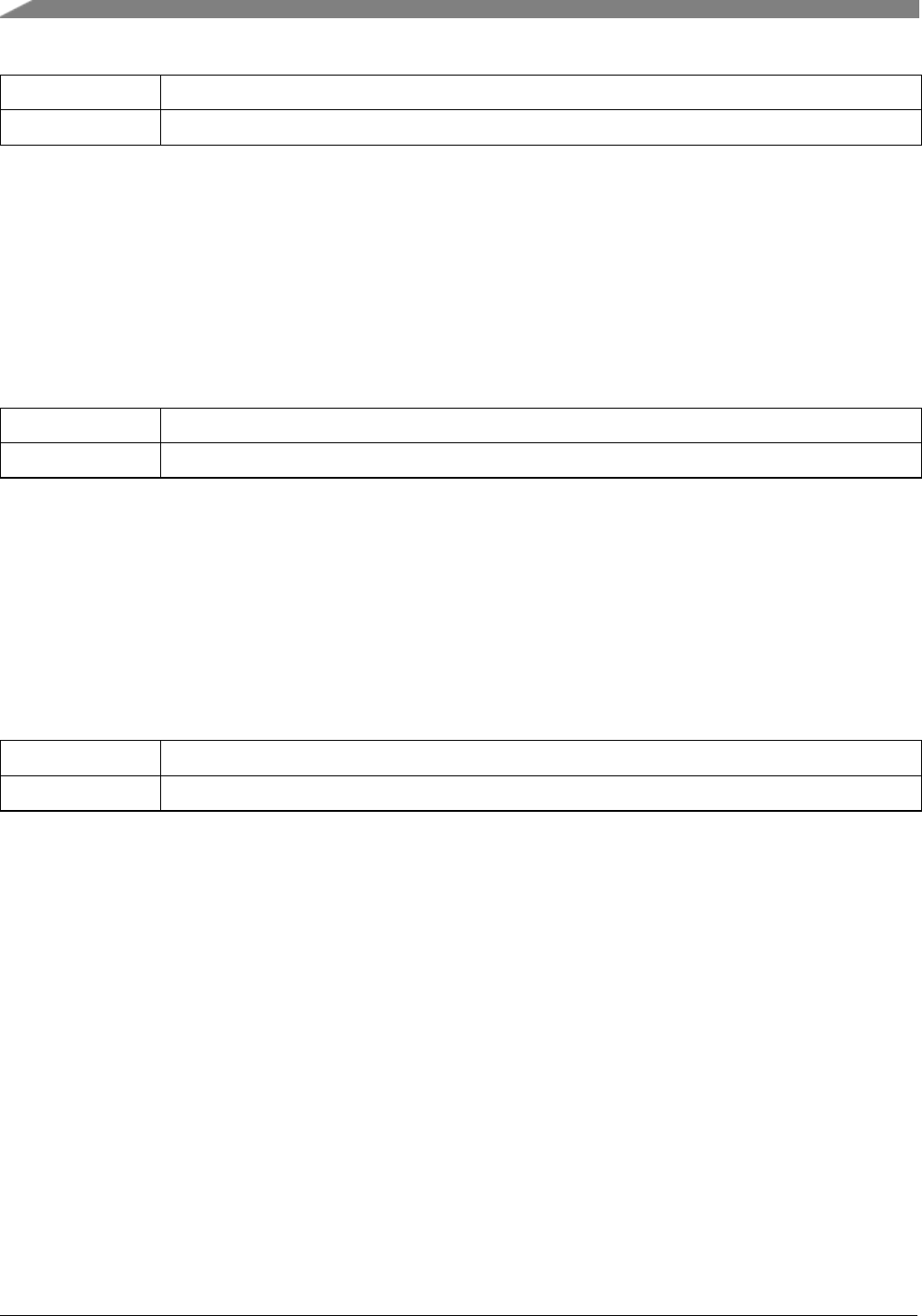

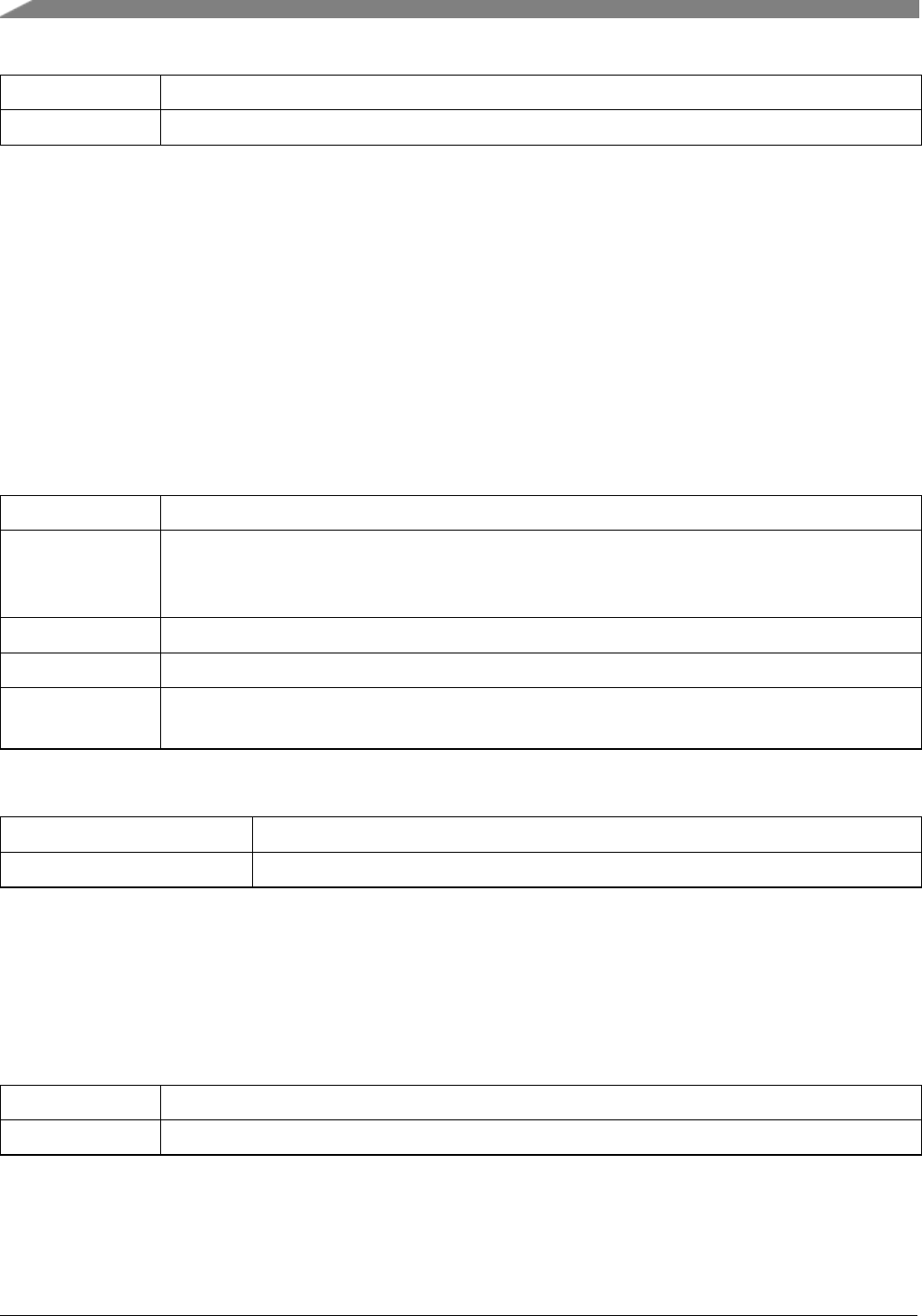

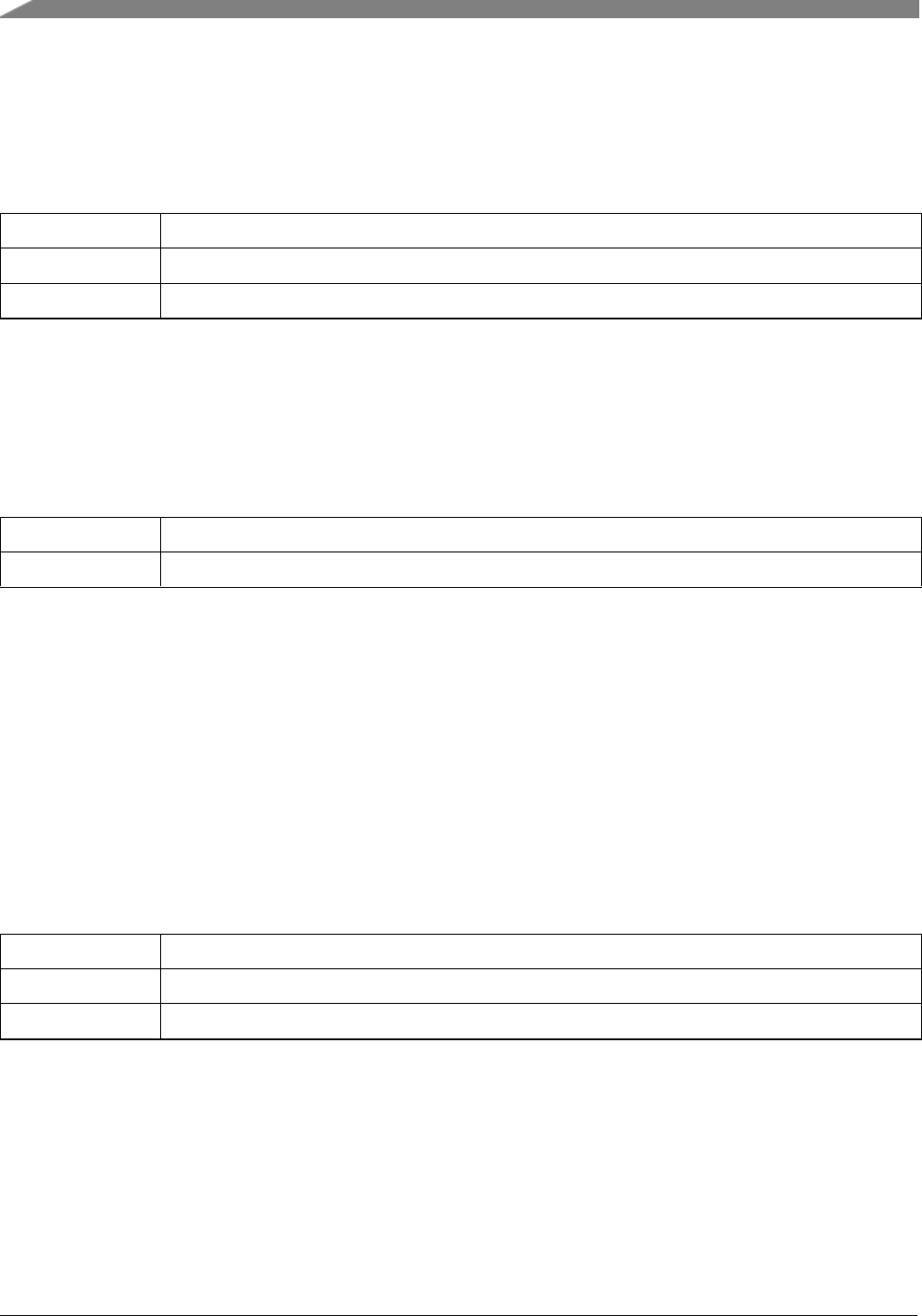

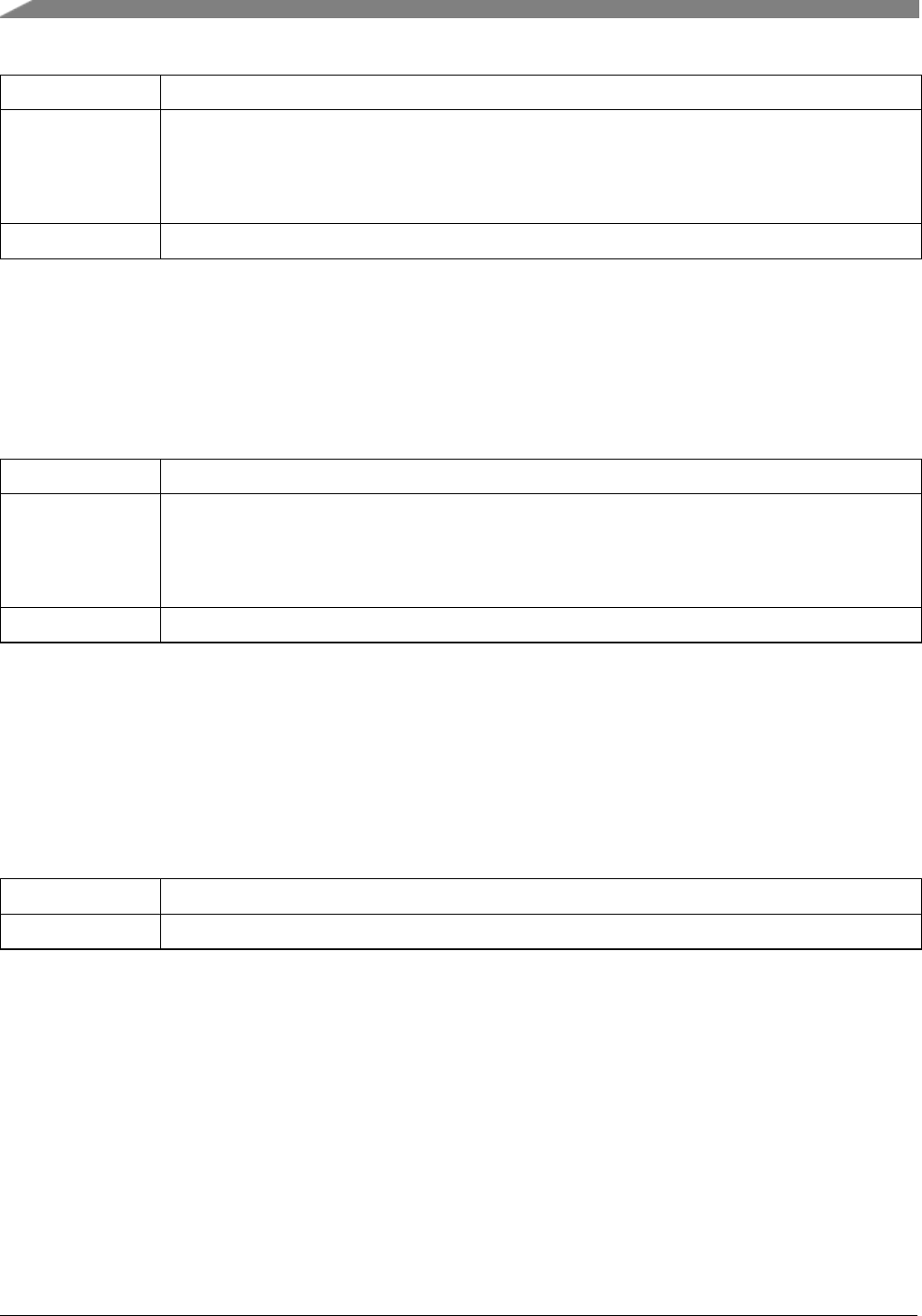

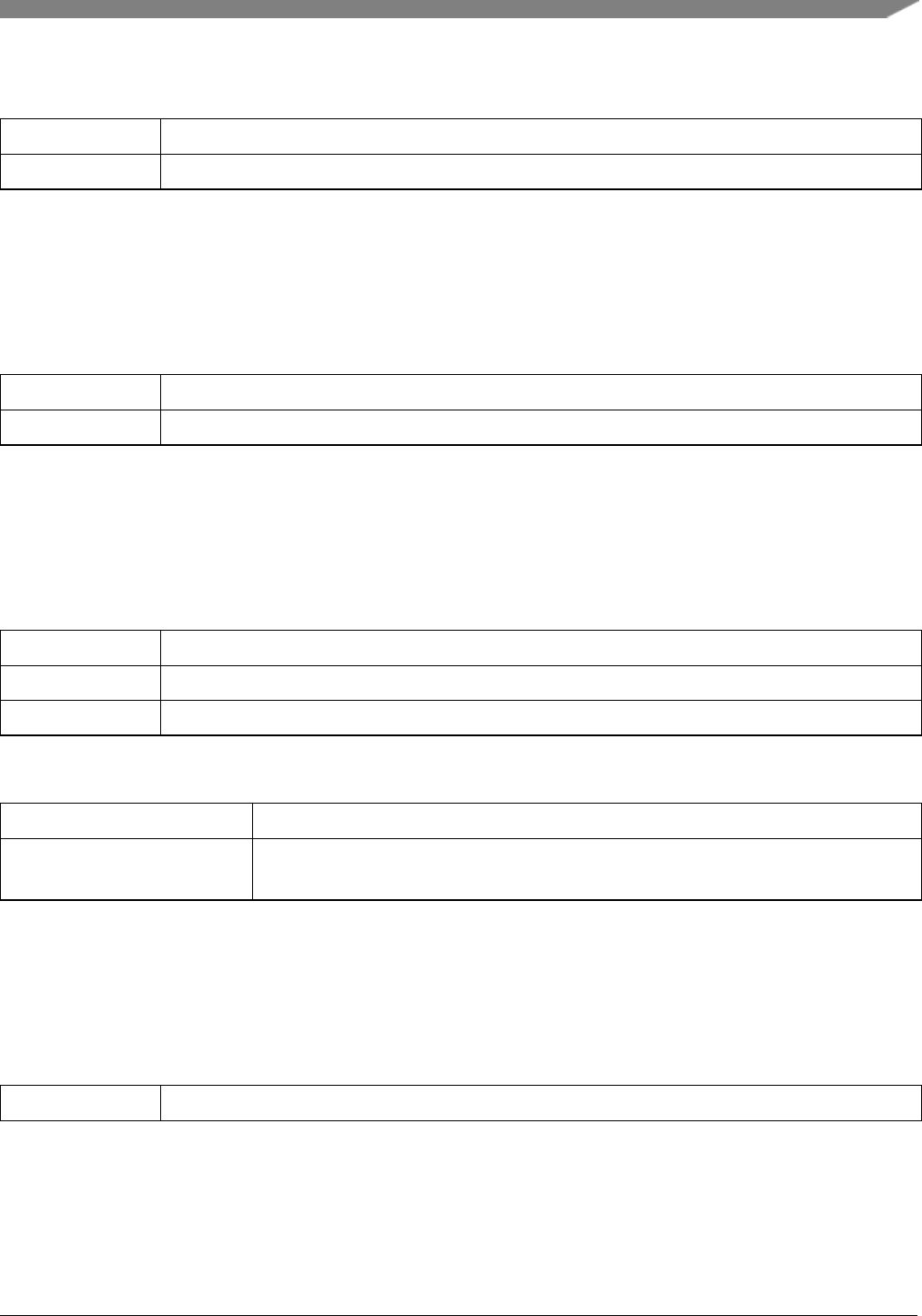

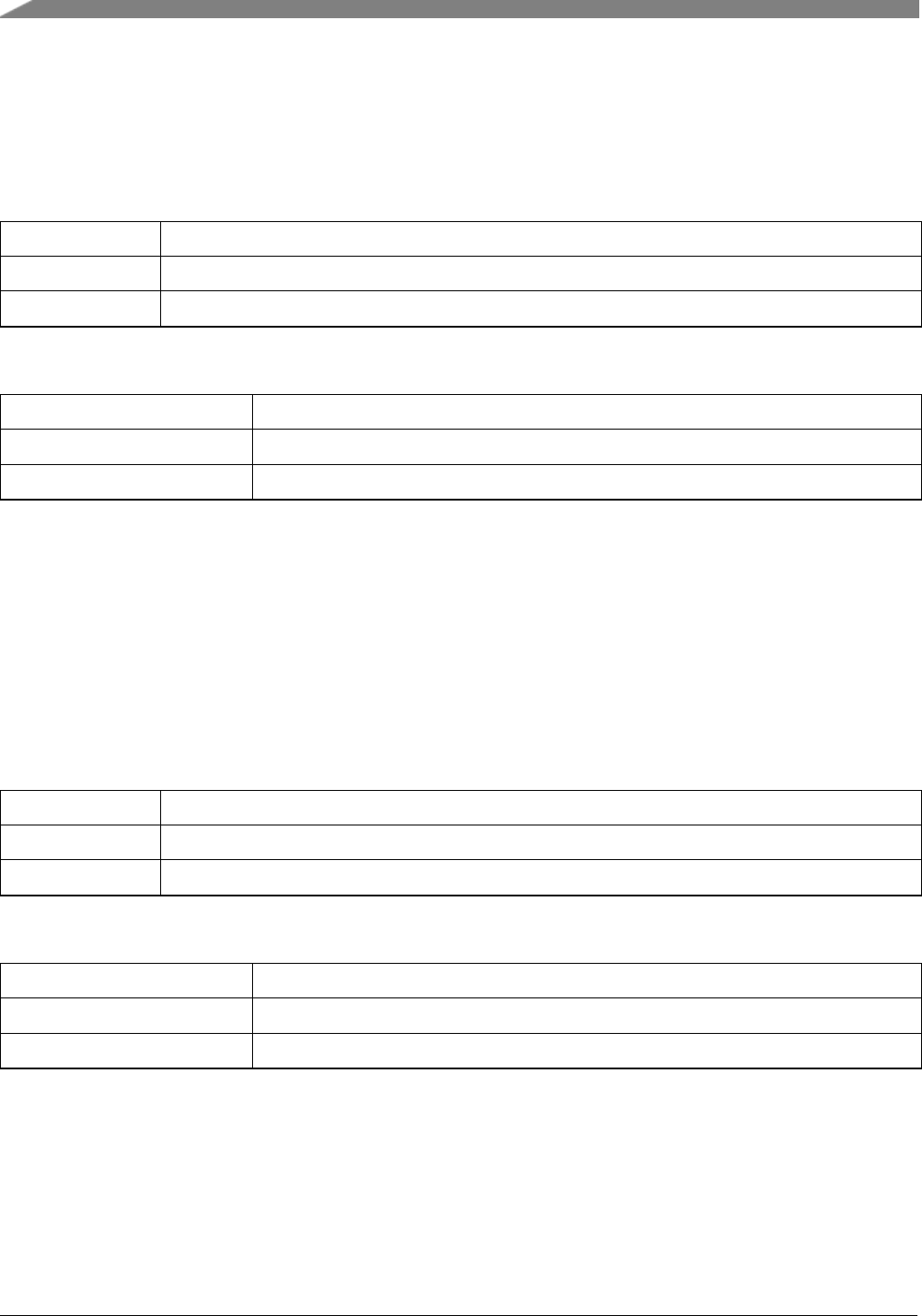

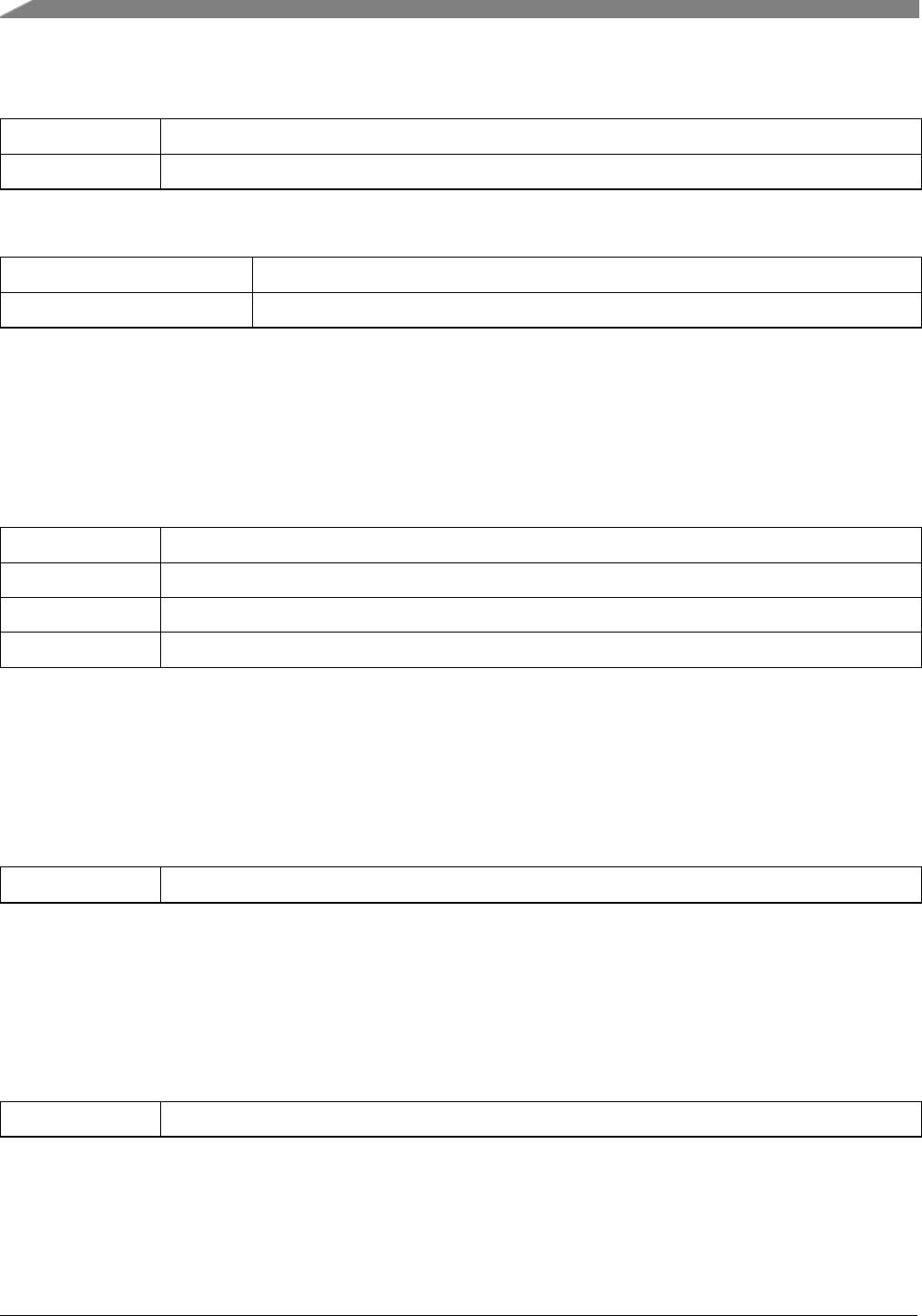

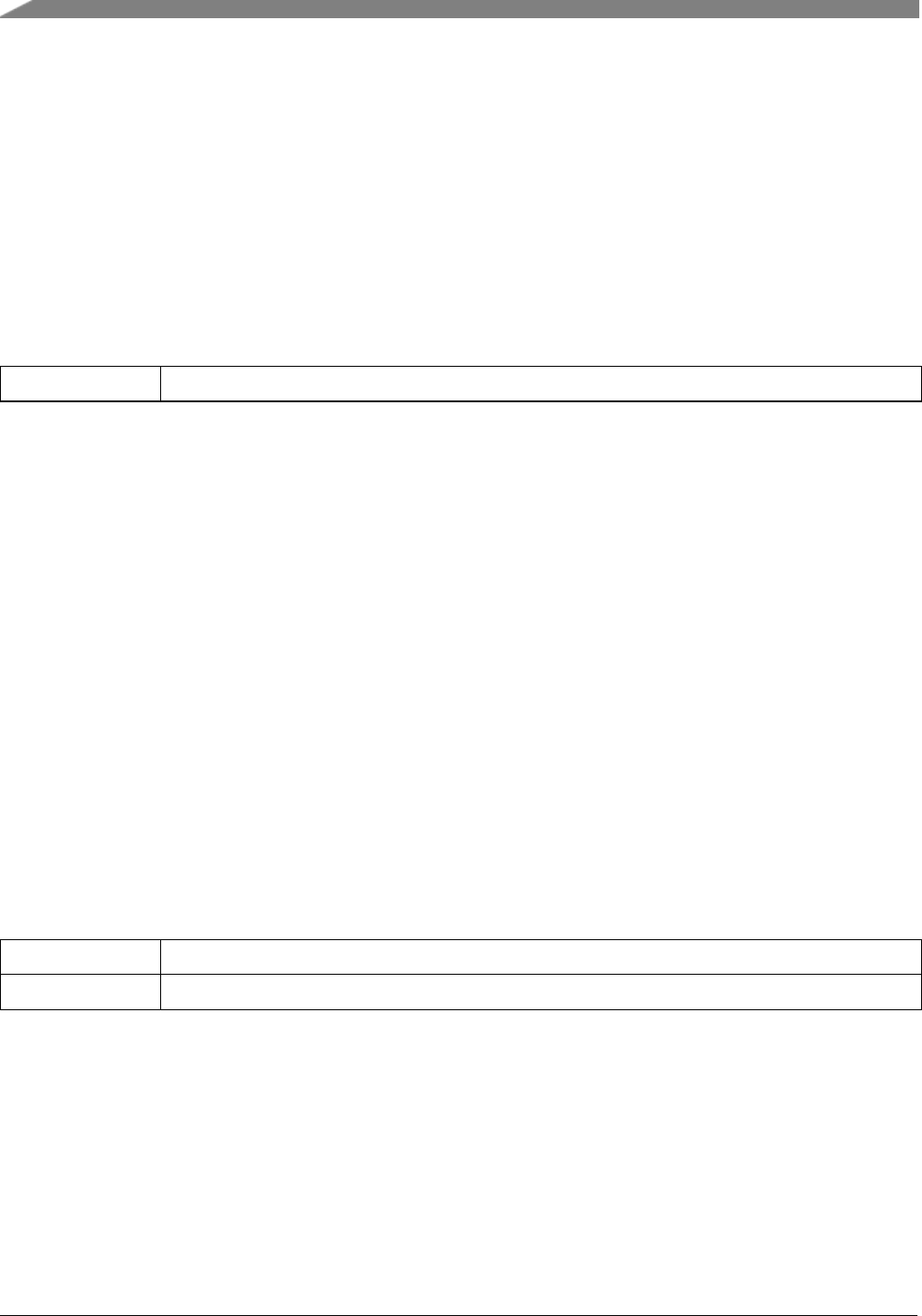

Chapter ADC_5HC: 12-bit Analog to Digital Converter Driver

6.1 Overview ........................................ 27

6.2 Typical use case .................................... 27

6.2.1 Polling Configuration ................................ 27

6.2.2 Polling Configuration ................................ 28

6.3 Data Structure Documentation ............................ 31

6.3.1 struct adc_5hc_config_t ............................... 31

6.3.2 struct adc_5hc_offest_config_t ........................... 32

6.3.3 struct adc_5hc_hardware_compare_config_t .................... 32

iv

MCUXpresso SDK API Reference Manual

NXP Semiconductors

Section

Number

Contents

Title

Page

Number

6.3.4 struct adc_5hc_channel_config_t .......................... 33

6.4 Macro Definition Documentation ........................... 33

6.4.1 FSL_ADC_5HC_DRIVER_VERSION ....................... 33

6.5 Enumeration Type Documentation .......................... 33

6.5.1 adc_5hc_status_flags_t ............................... 33

6.5.2 adc_5hc_reference_voltage_source_t ........................ 33

6.5.3 adc_5hc_sample_period_mode_t .......................... 33

6.5.4 adc_5hc_clock_source_t ............................... 34

6.5.5 adc_5hc_clock_driver_t ............................... 34

6.5.6 adc_5hc_resolution_t ................................ 34

6.5.7 adc_5hc_hardware_compare_mode_t ........................ 34

6.5.8 adc_5hc_hardware_average_mode_t ........................ 35

6.6 Function Documentation ............................... 35

6.6.1 ADC_5HC_Init ................................... 35

6.6.2 ADC_5HC_Deinit .................................. 35

6.6.3 ADC_5HC_GetDefaultConfig ............................ 35

6.6.4 ADC_5HC_SetChannelConfig ........................... 36

6.6.5 ADC_5HC_GetChannelConversionValue ...................... 36

6.6.6 ADC_5HC_GetChannelStatusFlags ......................... 37

6.6.7 ADC_5HC_DoAutoCalibration ........................... 37

6.6.8 ADC_5HC_SetOffsetConfig ............................. 38

6.6.9 ADC_5HC_EnableDMA .............................. 38

6.6.10 ADC_5HC_EnableHardwareTrigger ........................ 38

6.6.11 ADC_5HC_SetHardwareCompareConfig ...................... 38

6.6.12 ADC_5HC_SetHardwareAverageConfig ...................... 39

6.6.13 ADC_5HC_GetStatusFlags ............................. 39

6.6.14 ADC_5HC_ClearStatusFlags ............................ 39

6.7 Variable Documentation ................................ 40

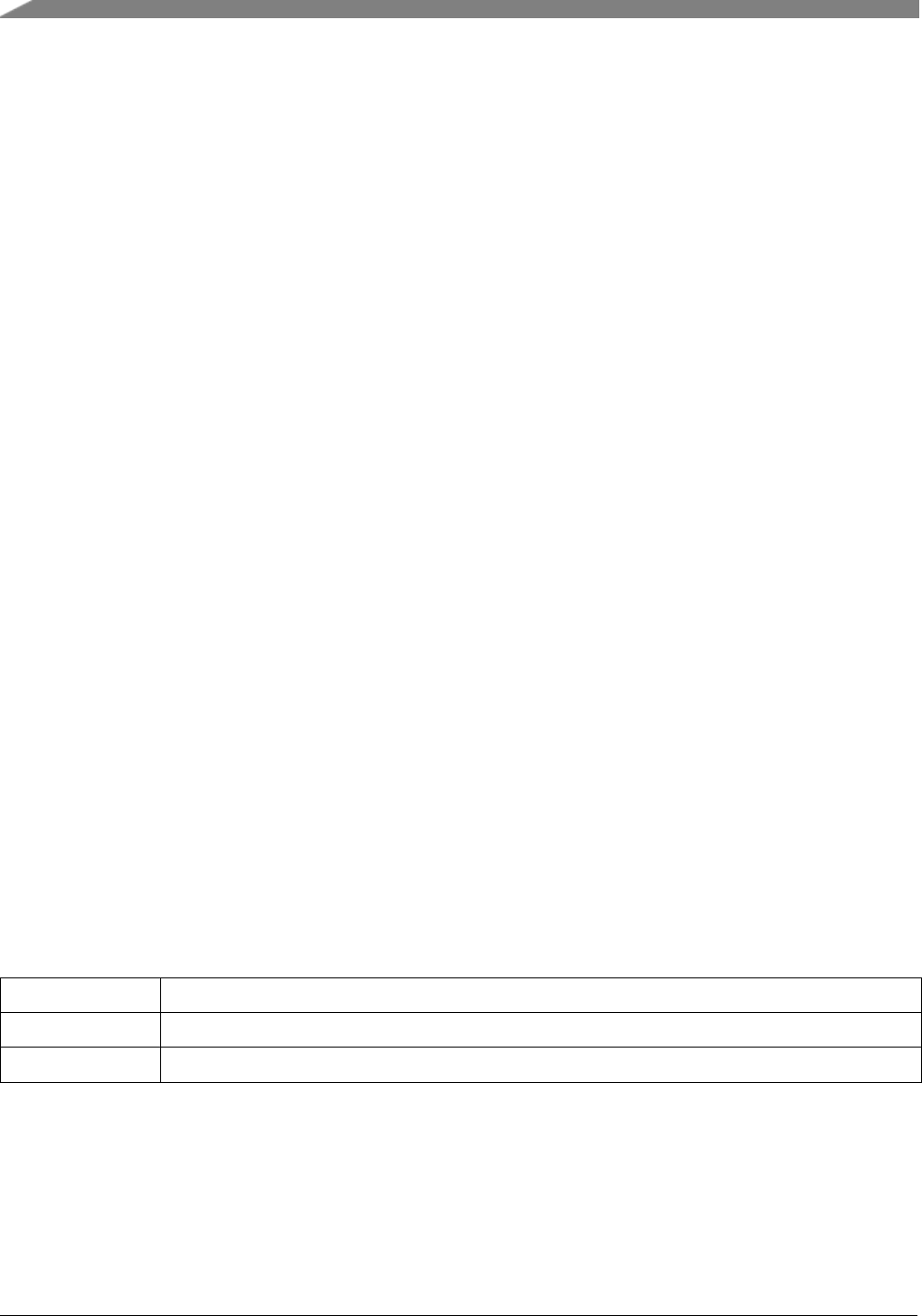

6.7.1 enableOverWrite ................................... 40

6.7.2 enableContinuousConversion ............................ 40

6.7.3 enableHighSpeed .................................. 40

6.7.4 enableLowPower ................................... 40

6.7.5 enableLongSample .................................. 40

6.7.6 enableAsynchronousClockOutput .......................... 40

6.7.7 referenceVoltageSource ............................... 40

6.7.8 samplePeriodMode ................................. 40

6.7.9 clockSource ..................................... 40

6.7.10 clockDriver ...................................... 40

6.7.11 resolution ....................................... 40

6.7.12 enableSigned ..................................... 40

6.7.13 offsetValue ...................................... 40

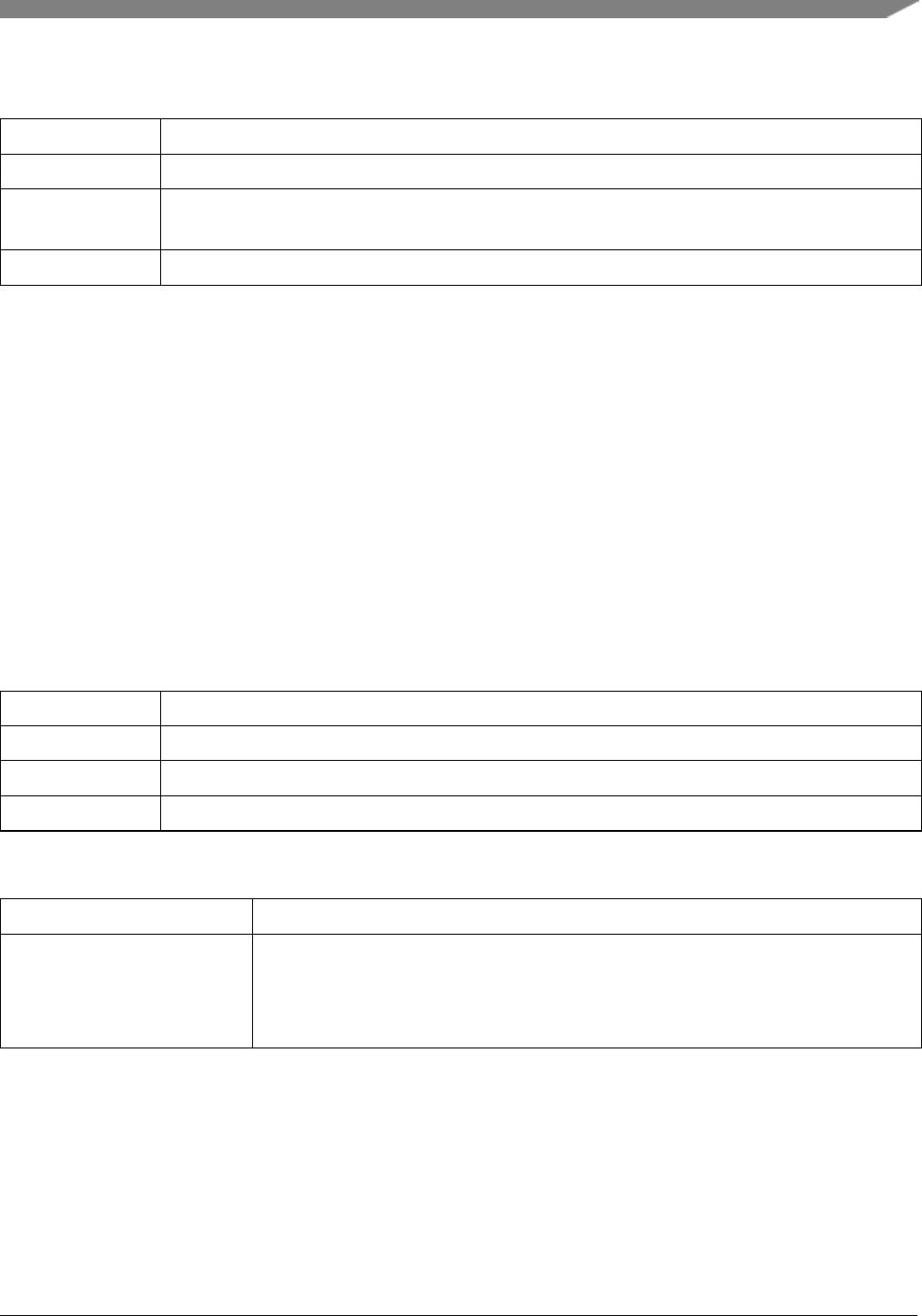

NXP Semiconductors

MCUXpresso SDK API Reference Manual

v

Section

Number

Contents

Title

Page

Number

6.7.14 hardwareCompareMode ............................... 40

6.7.15 value1 ........................................ 41

6.7.16 value2 ........................................ 41

6.7.17 channelNumber ................................... 41

6.7.18 enableInterruptOnConversionCompleted ...................... 41

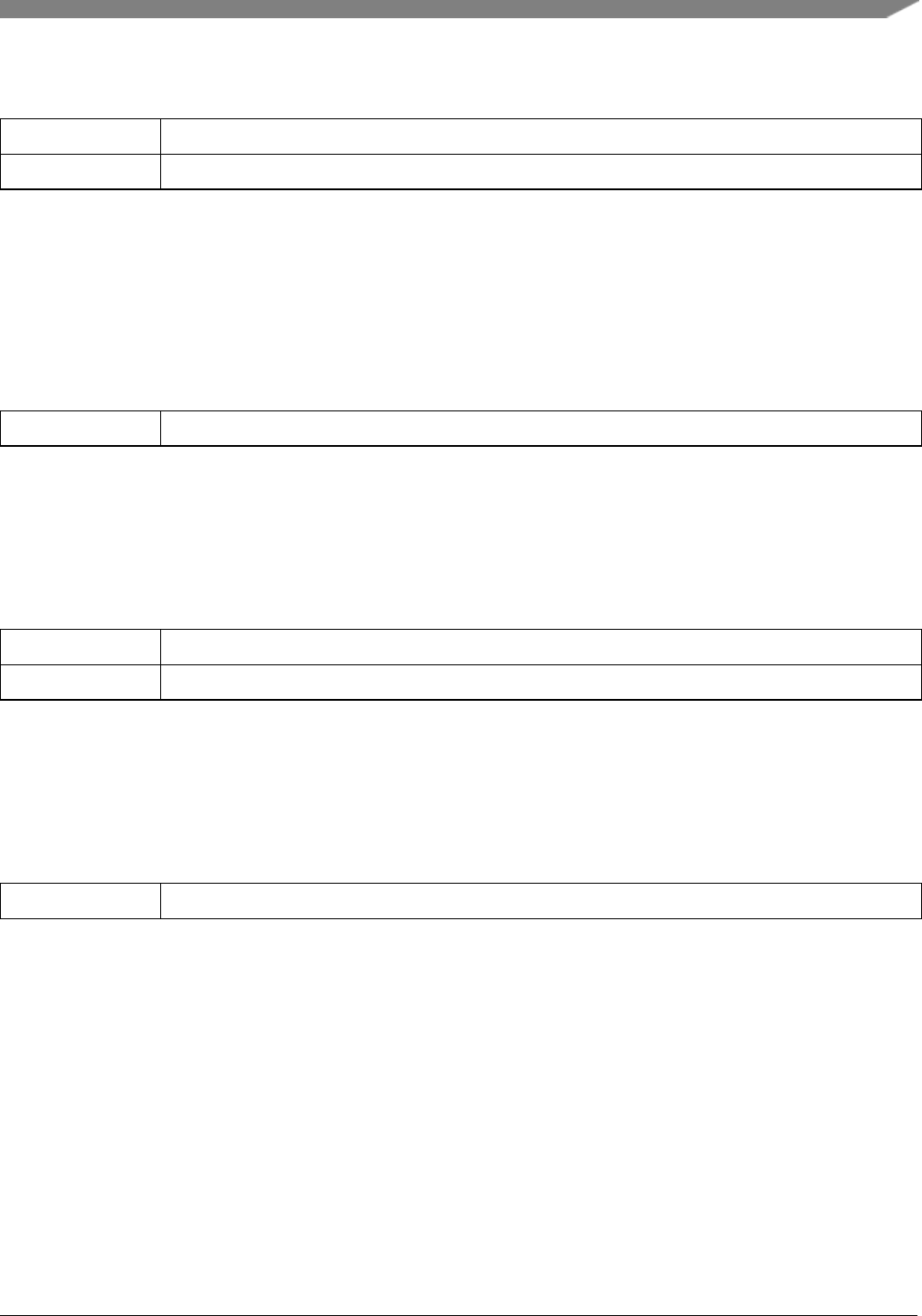

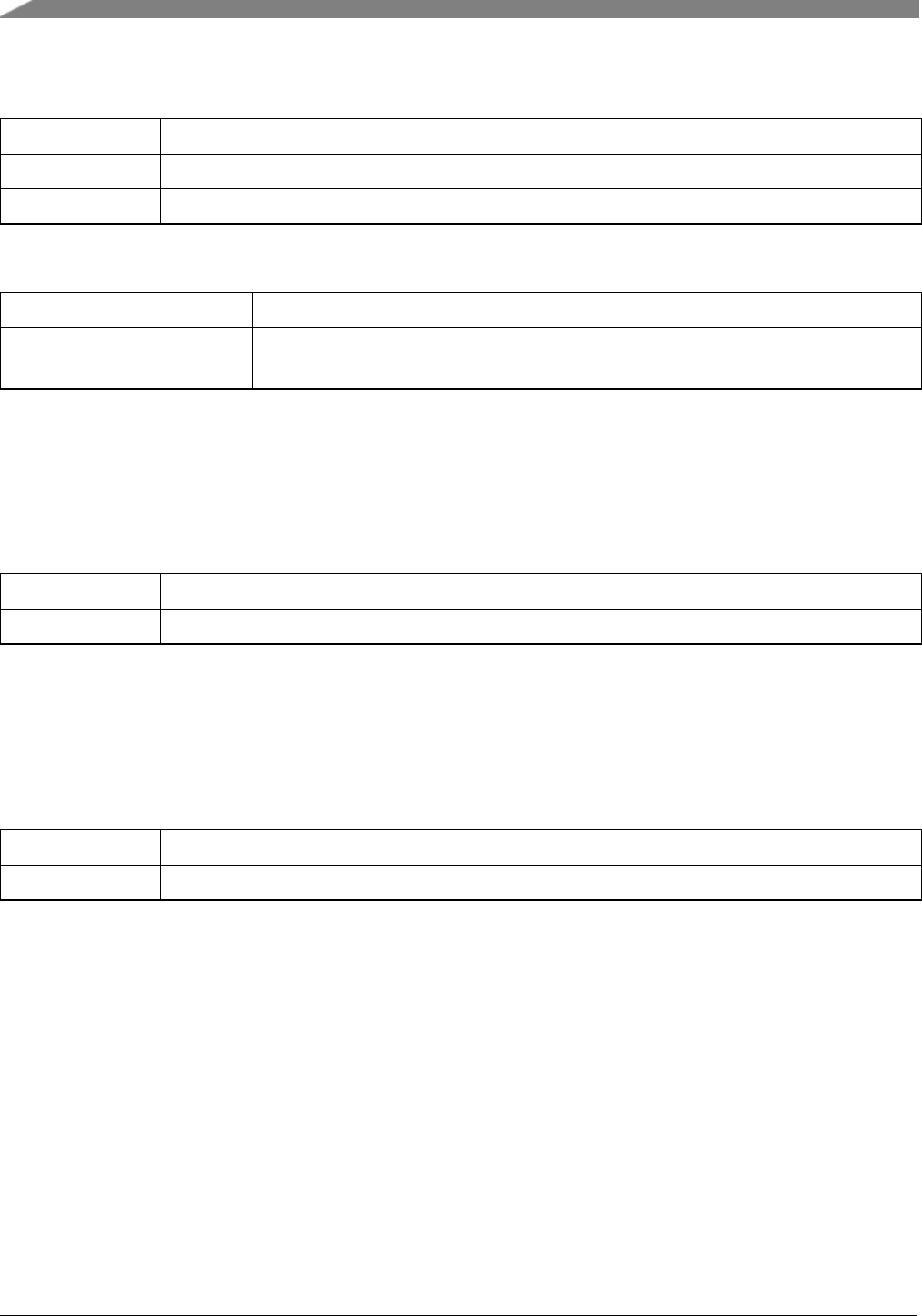

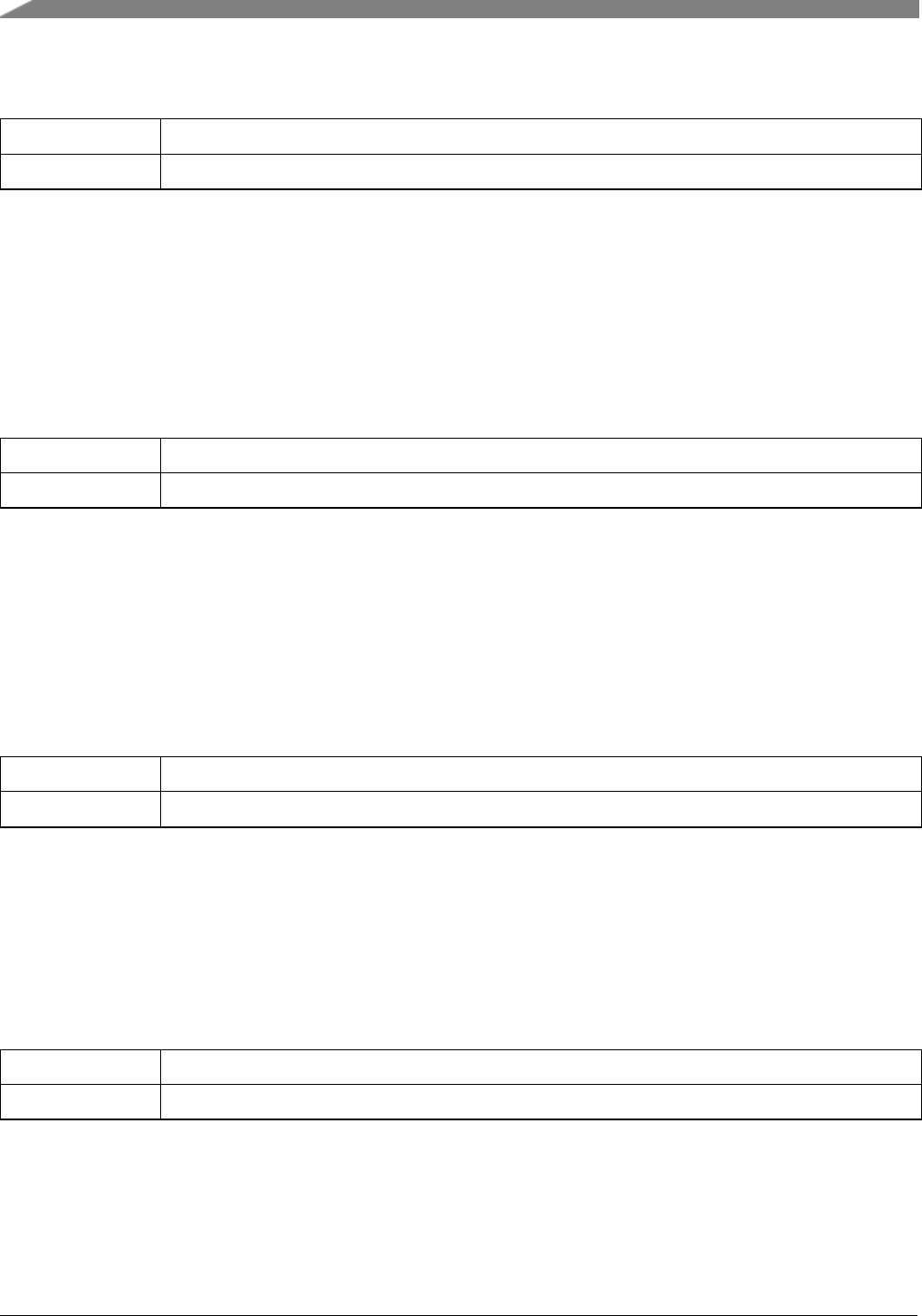

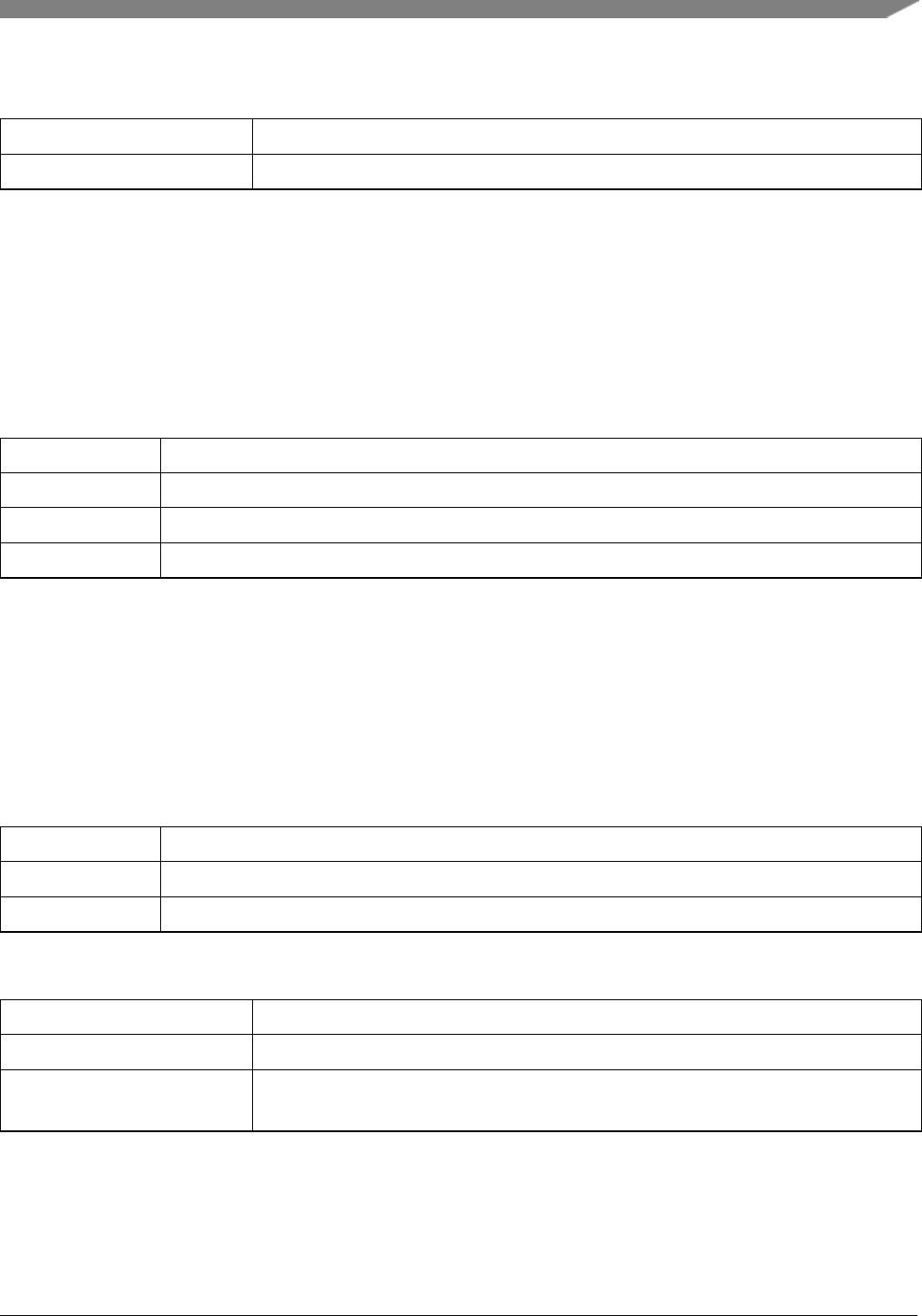

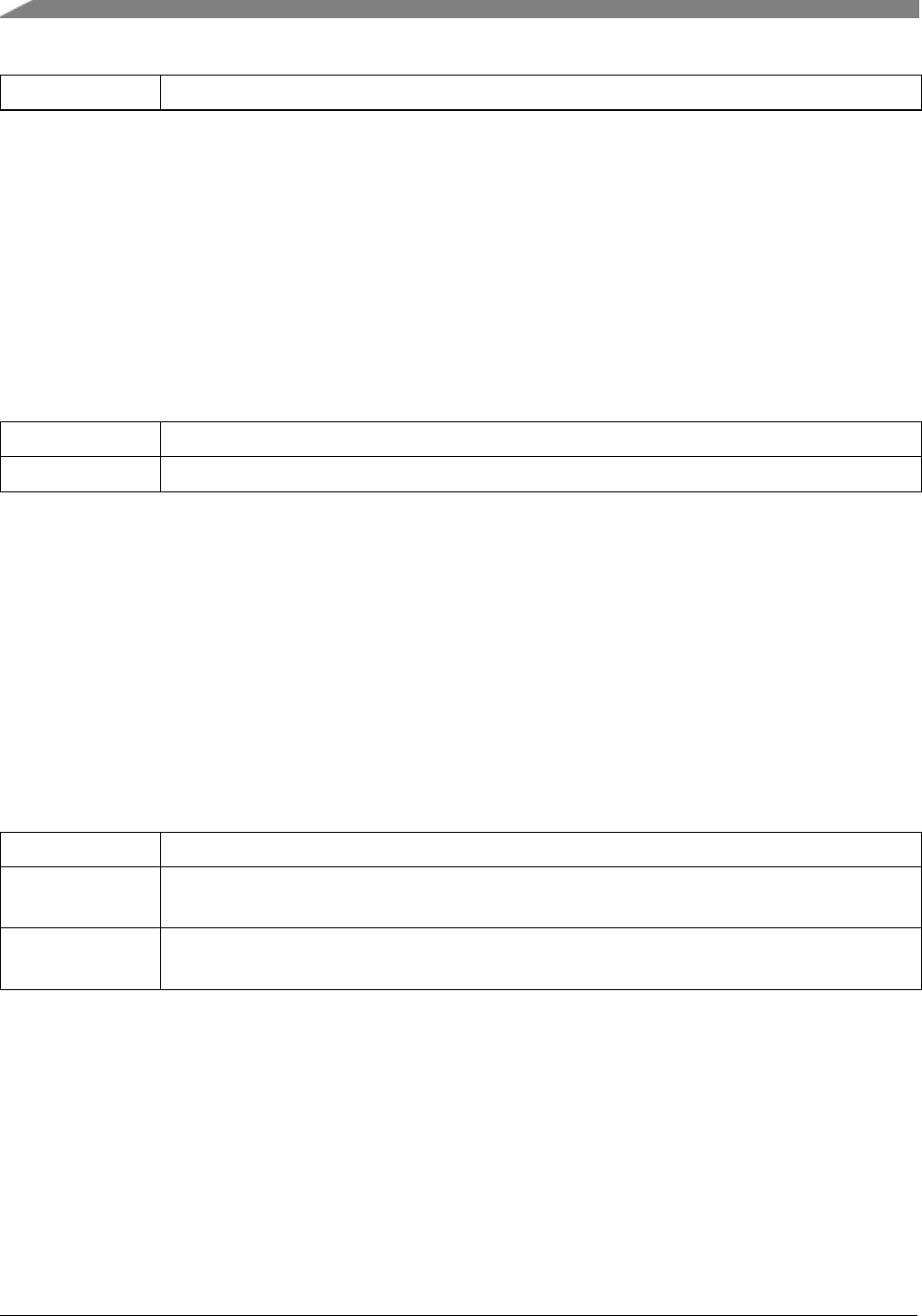

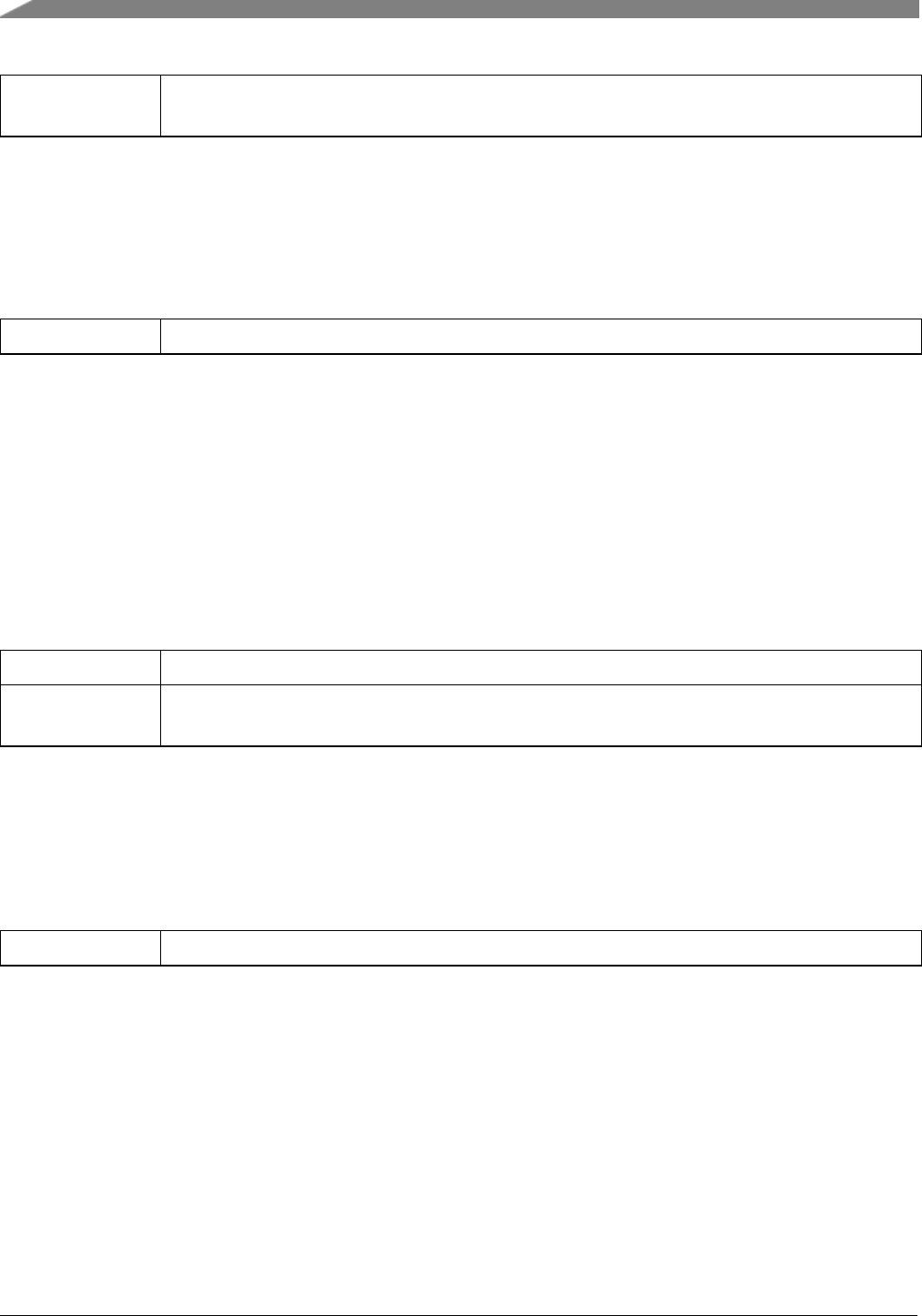

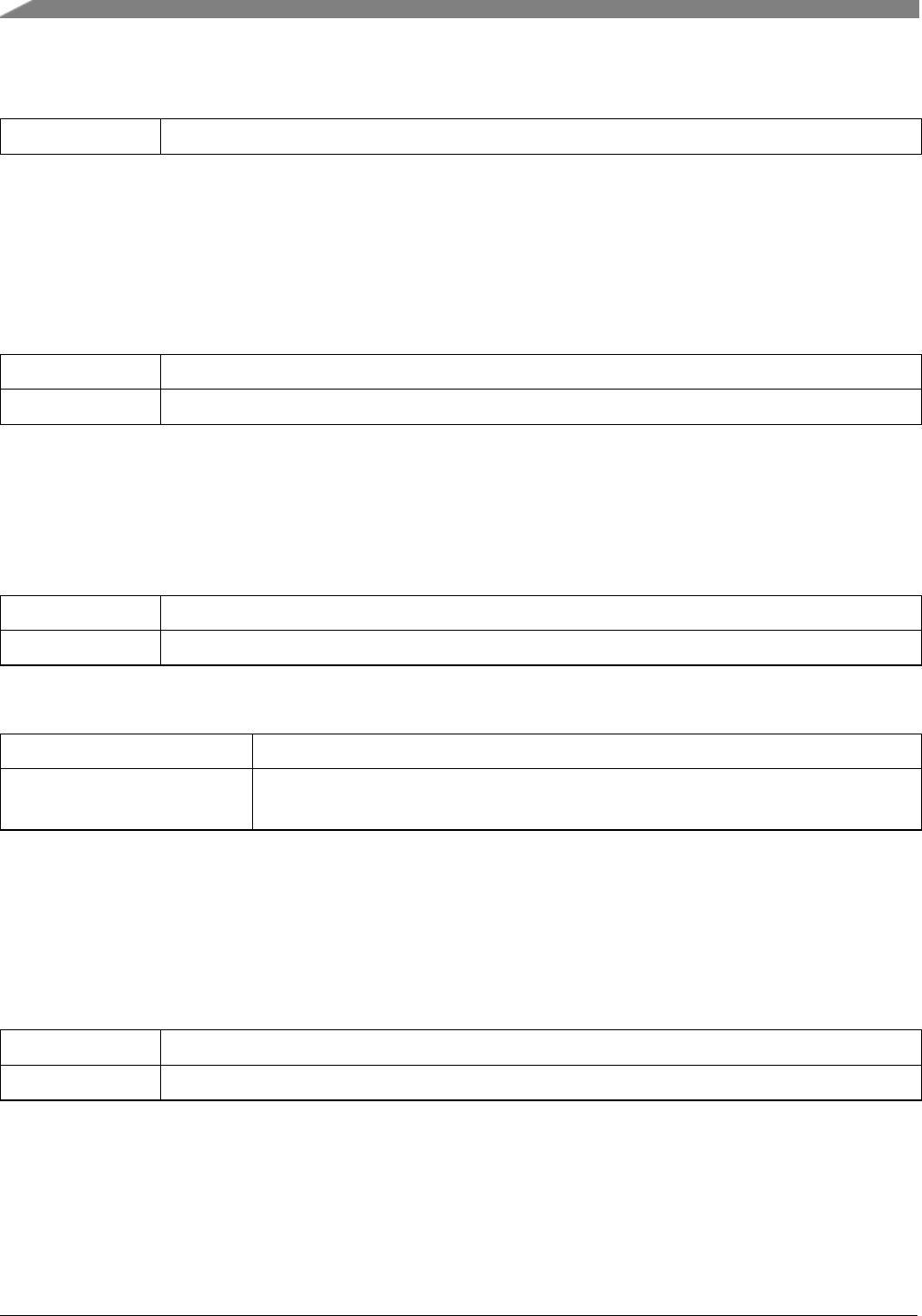

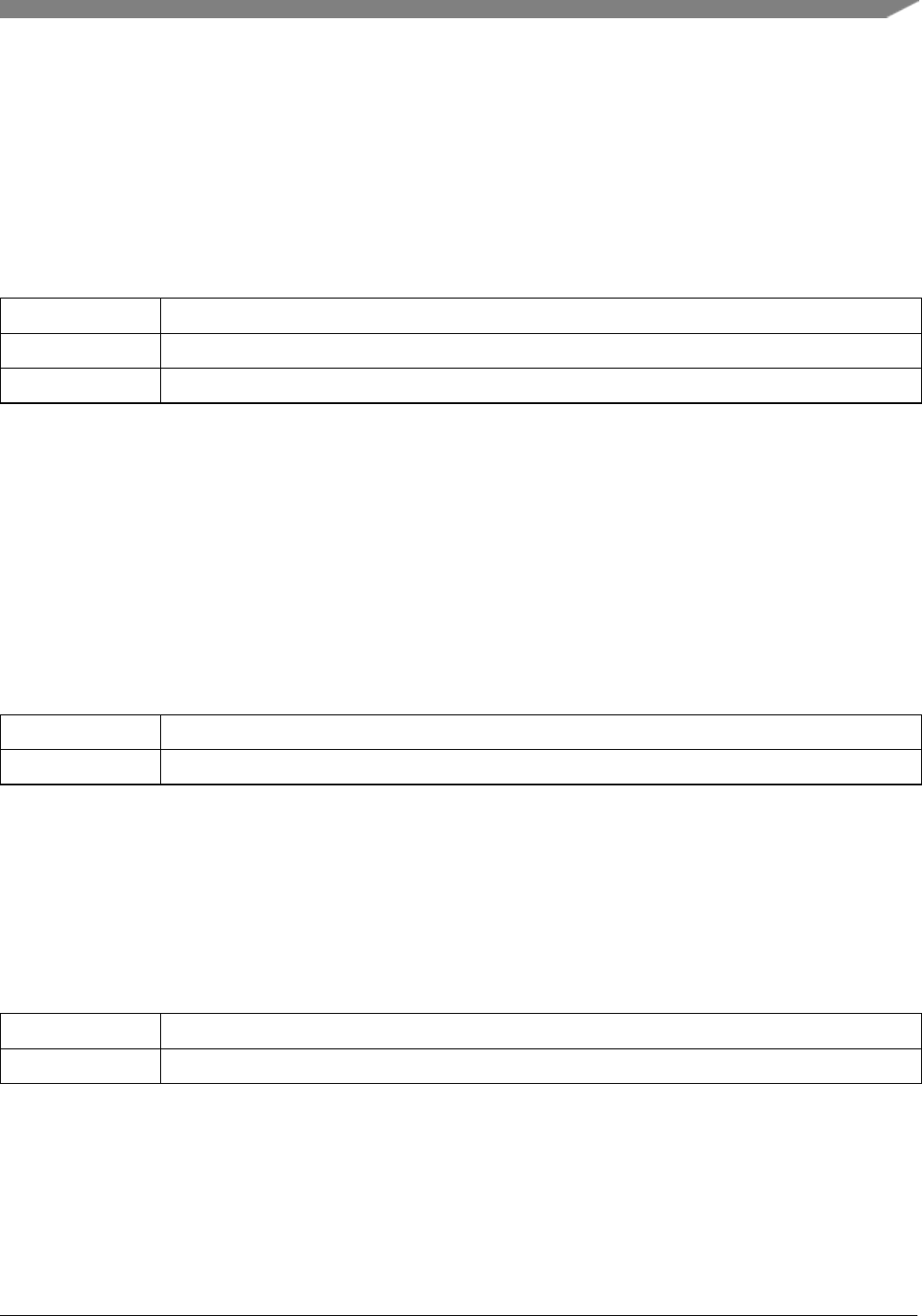

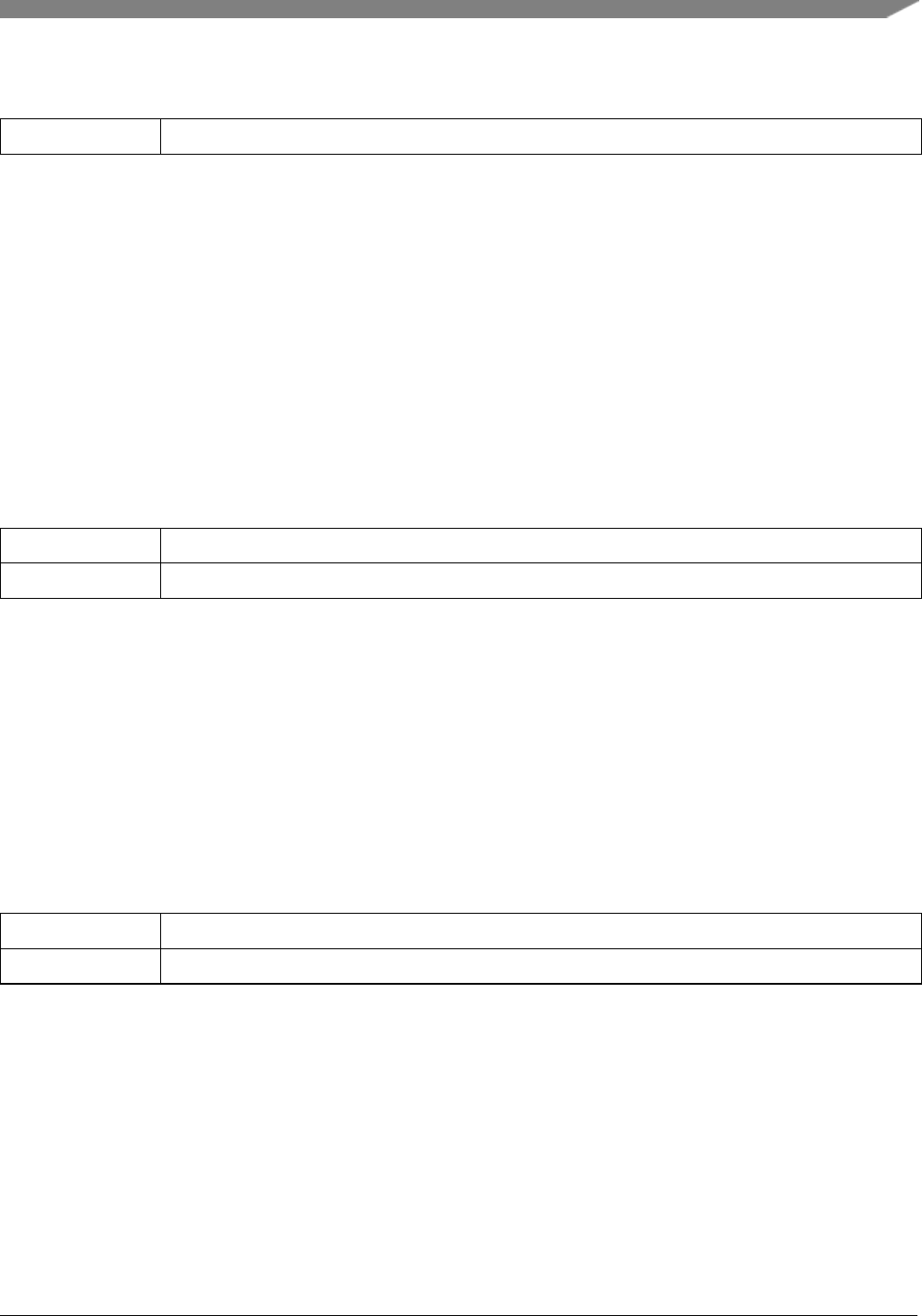

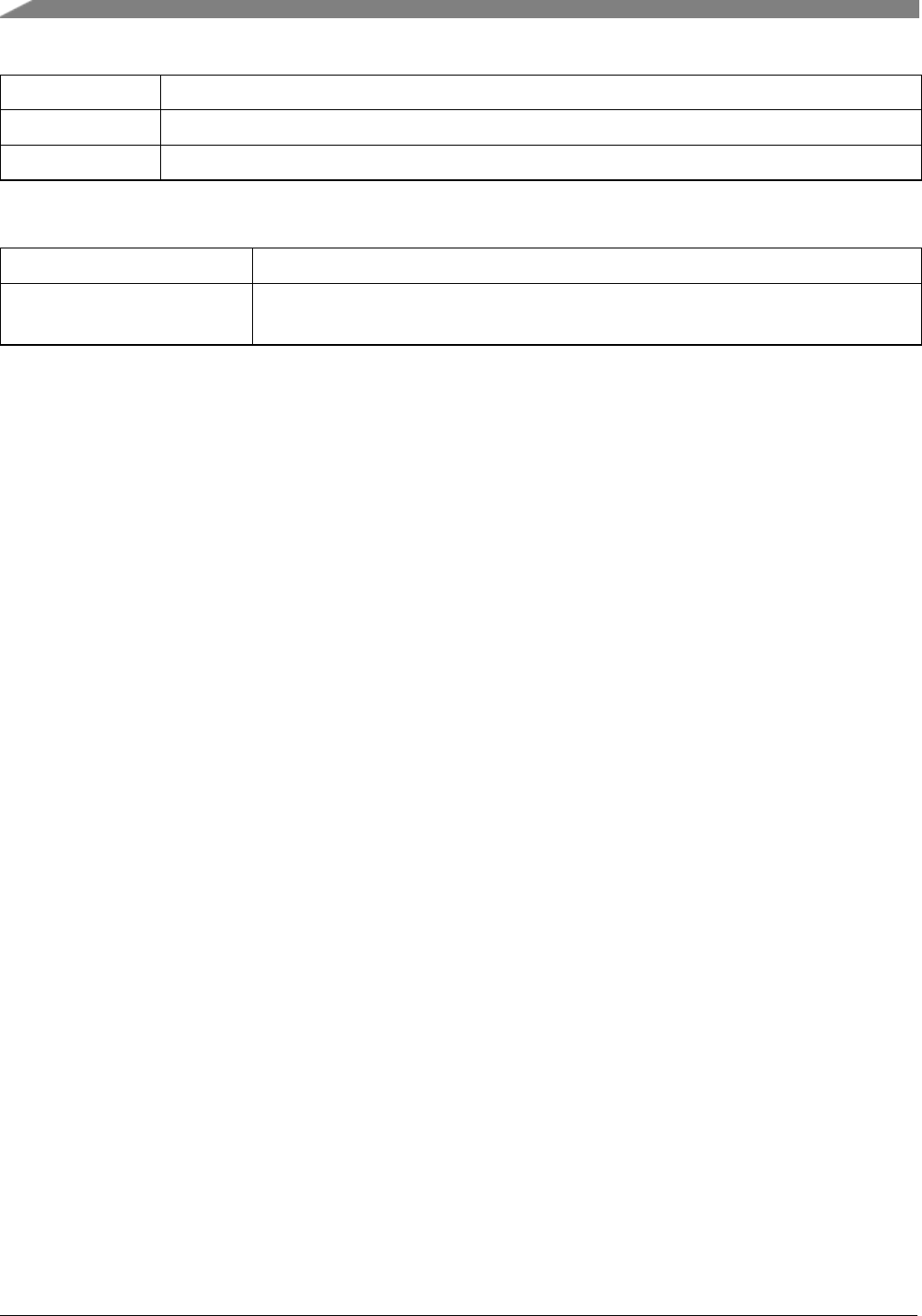

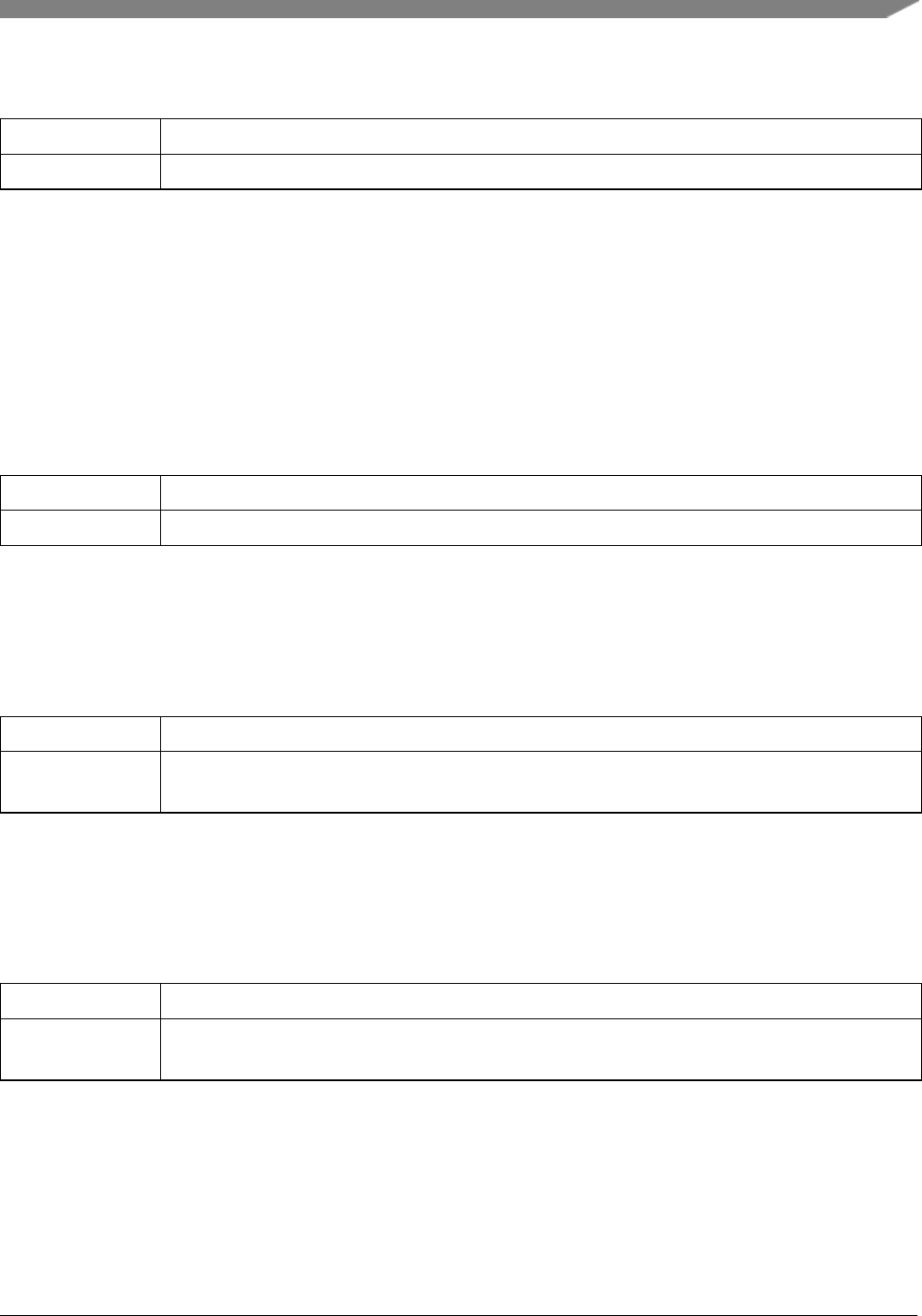

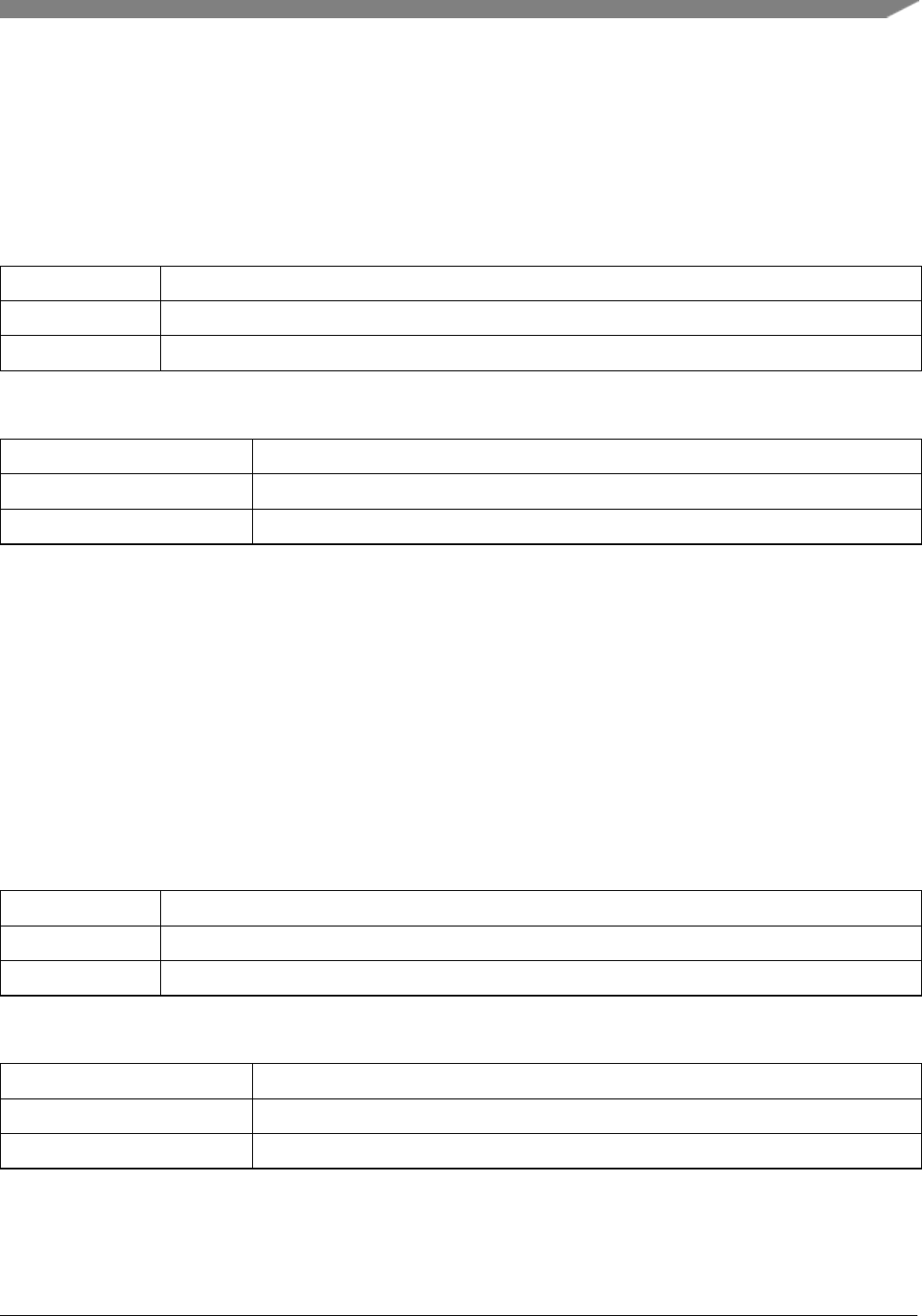

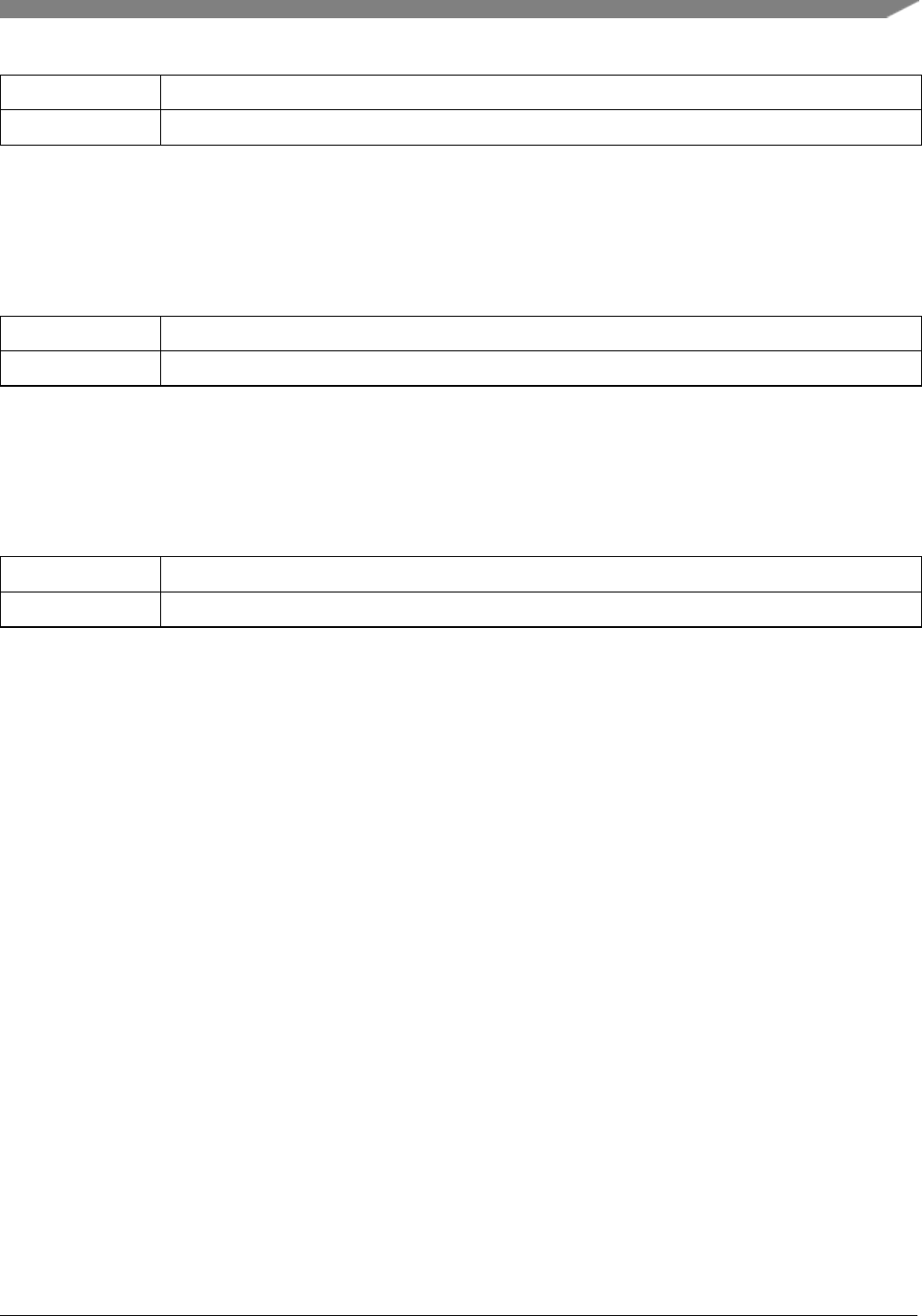

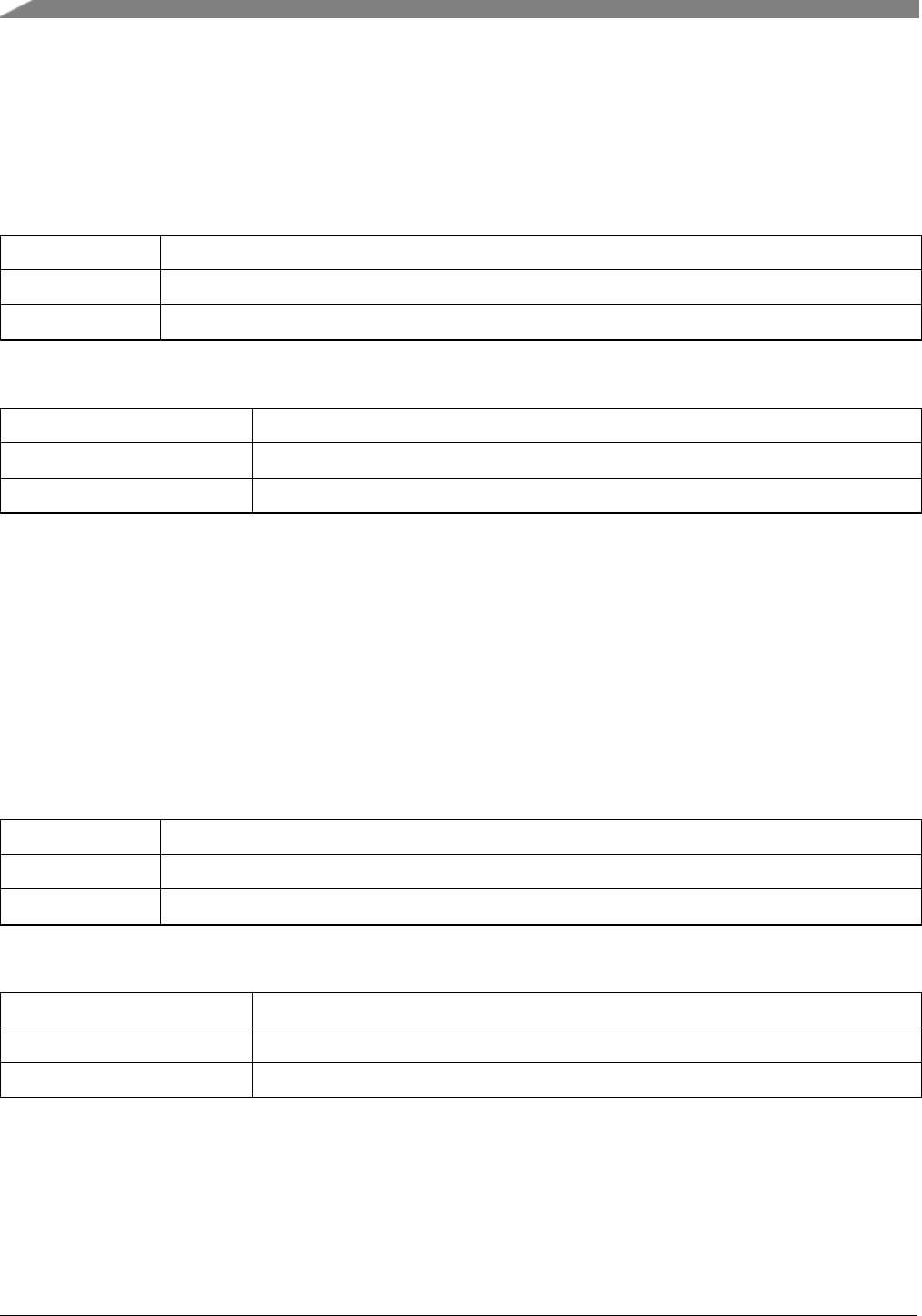

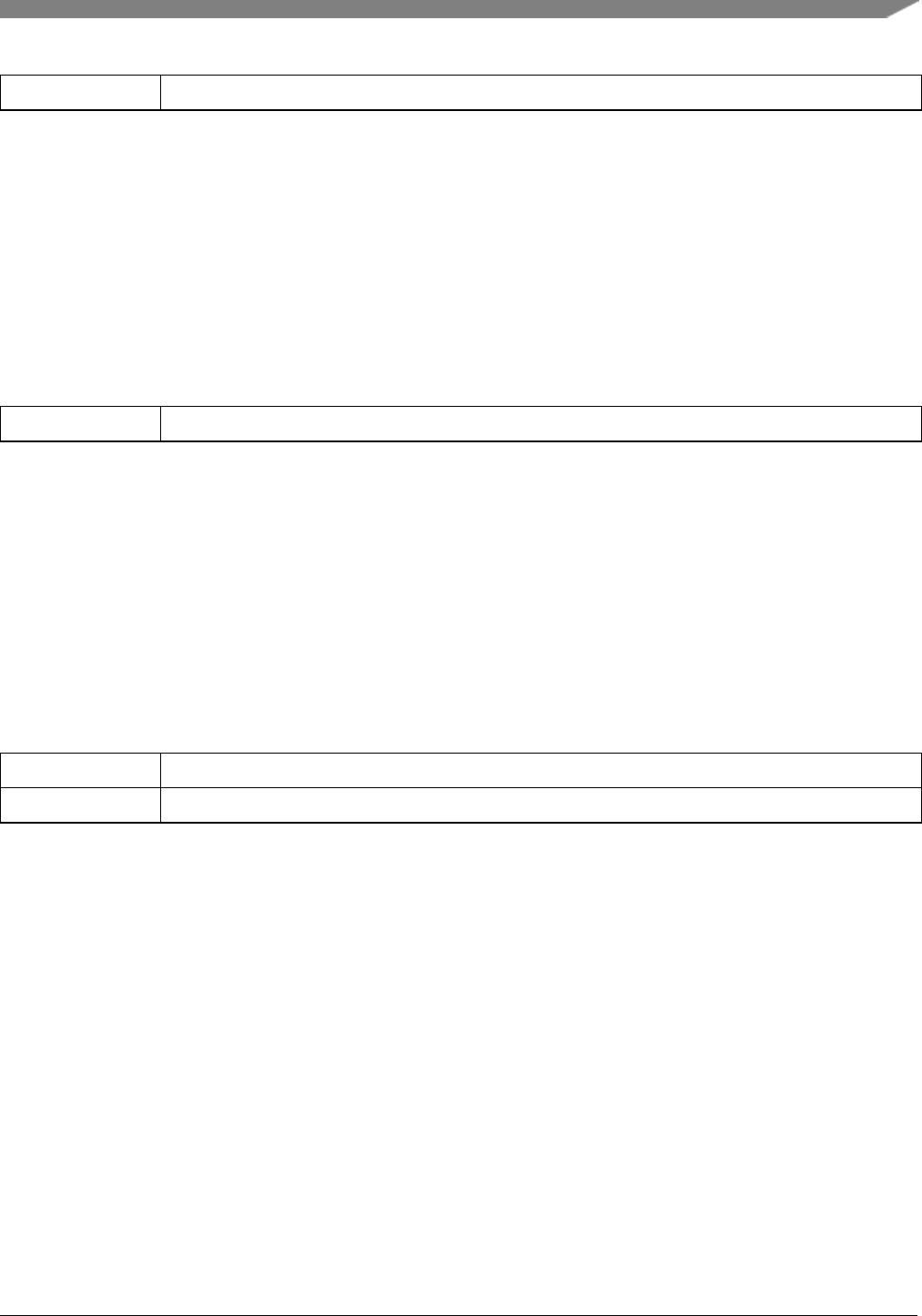

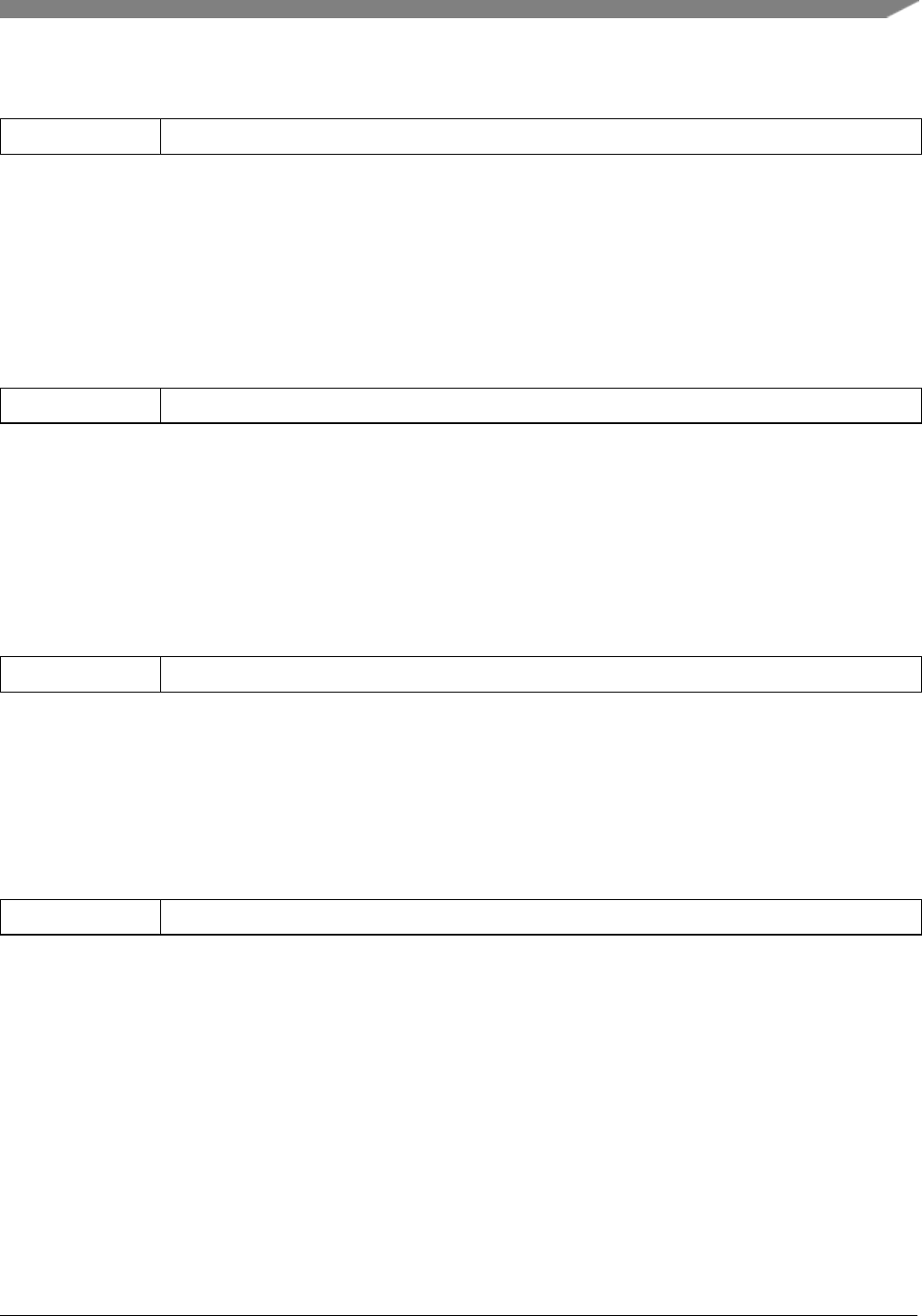

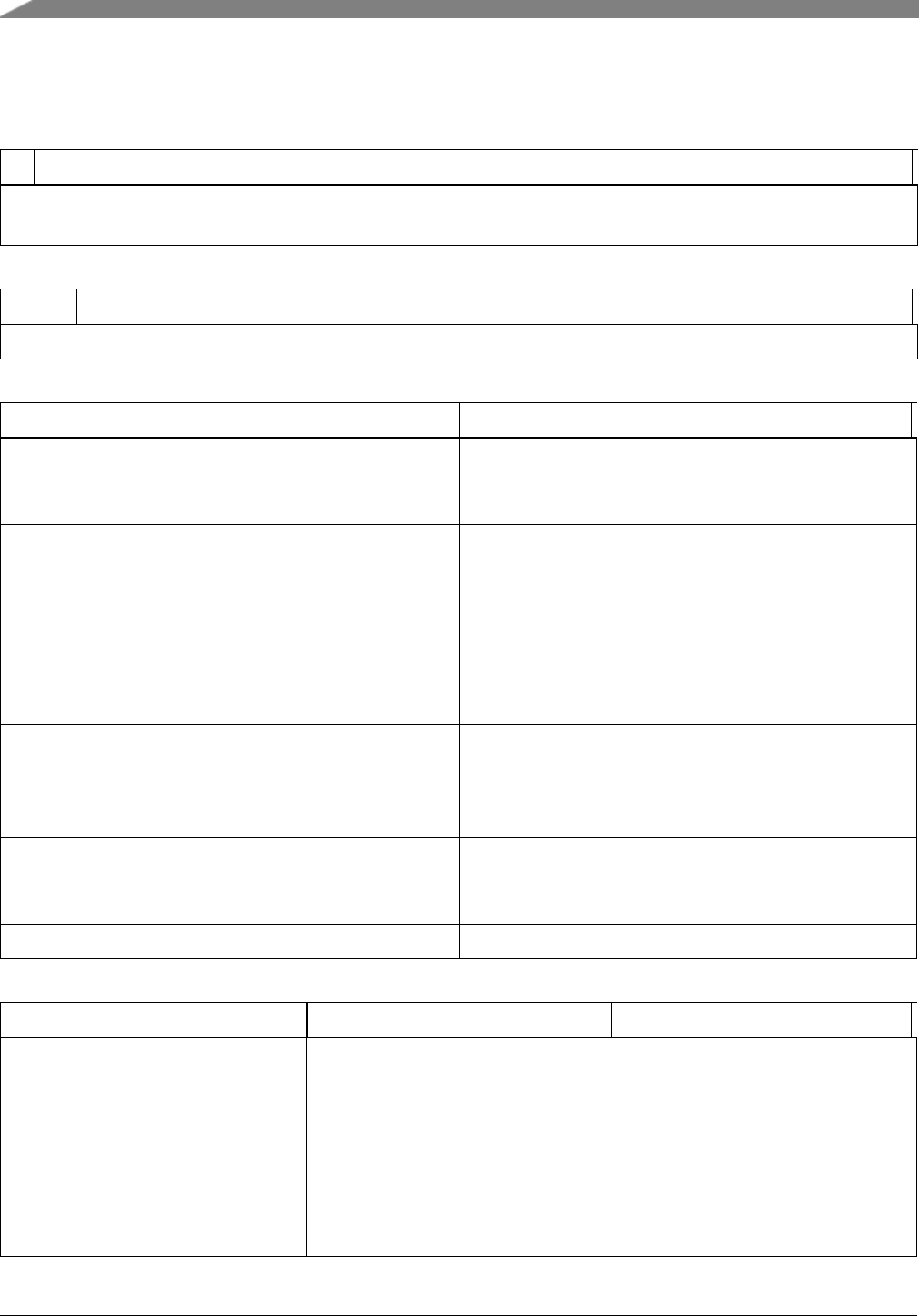

Chapter CACHE: CACHE Memory Controller

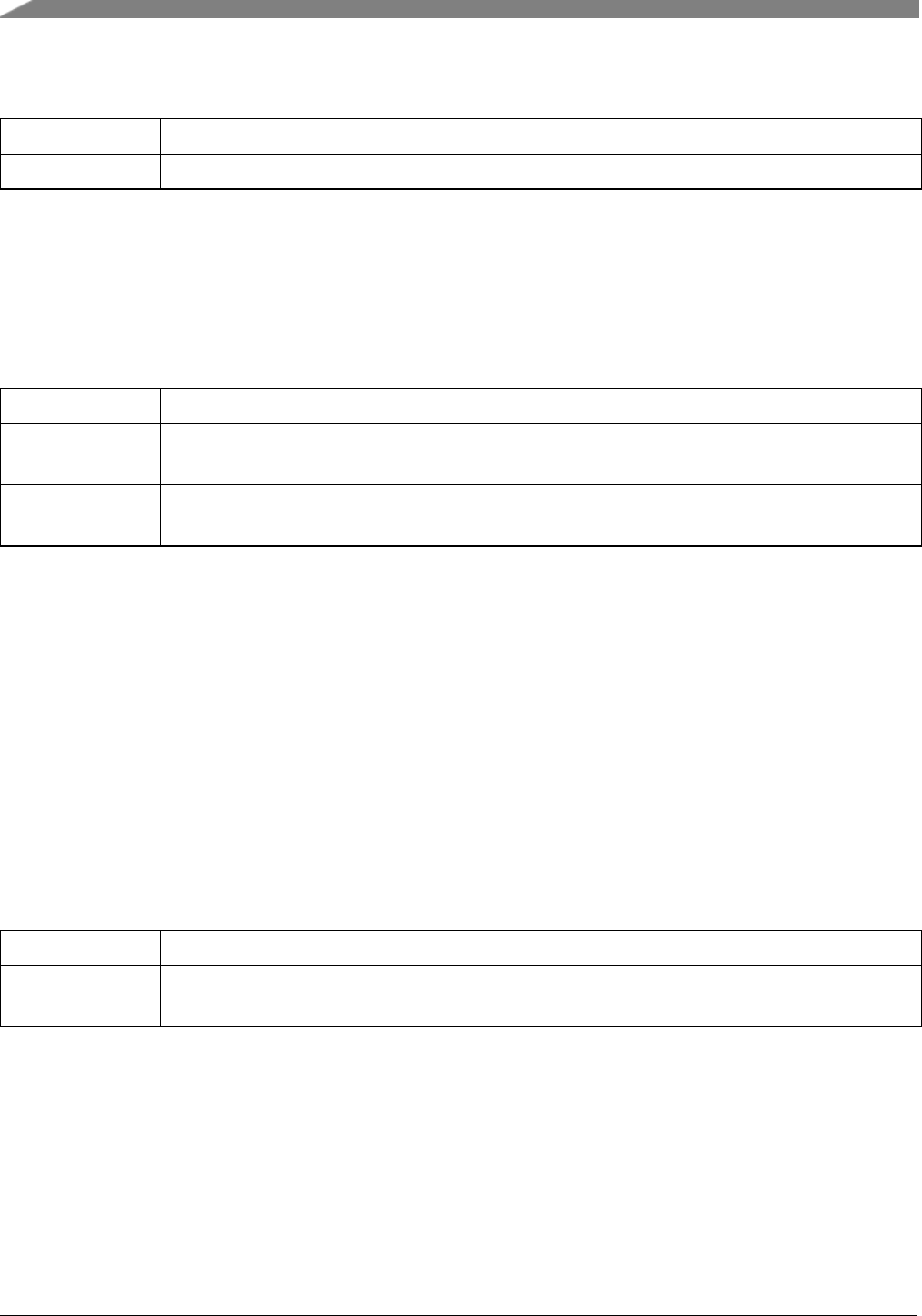

7.1 Overview ........................................ 43

7.2 Function groups .................................... 43

7.3 Macro Definition Documentation ........................... 44

7.3.1 FSL_CACHE_DRIVER_VERSION ........................ 44

7.4 Function Documentation ............................... 44

7.4.1 L1CACHE_InvalidateICacheByRange ....................... 44

7.4.2 L1CACHE_InvalidateDCacheByRange ....................... 45

7.4.3 L1CACHE_CleanDCacheByRange ......................... 46

7.4.4 L1CACHE_CleanInvalidateDCacheByRange .................... 46

7.4.5 ICACHE_InvalidateByRange ............................ 47

7.4.6 DCACHE_InvalidateByRange ............................ 48

7.4.7 DCACHE_CleanByRange .............................. 48

7.4.8 DCACHE_CleanInvalidateByRange ........................ 49

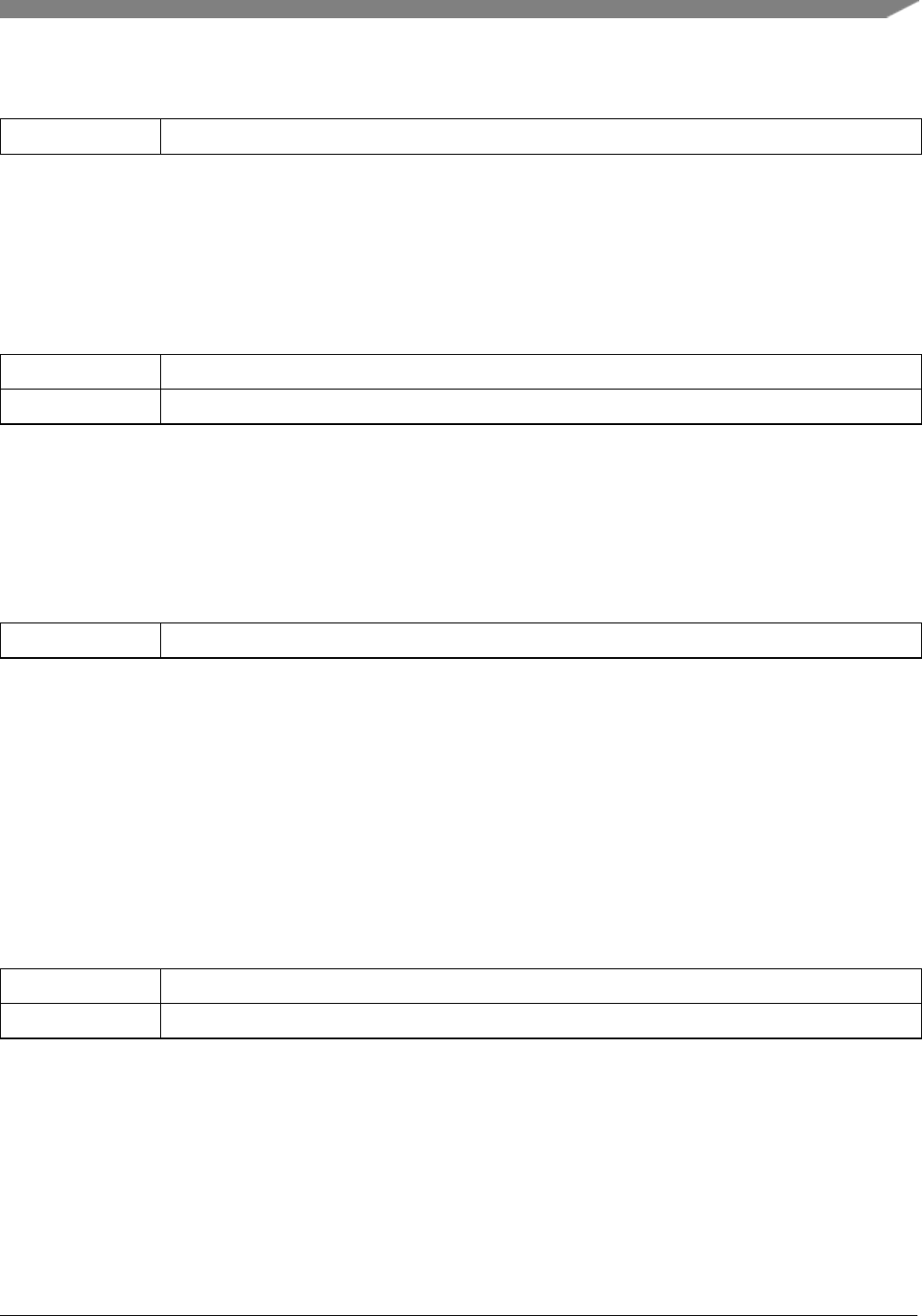

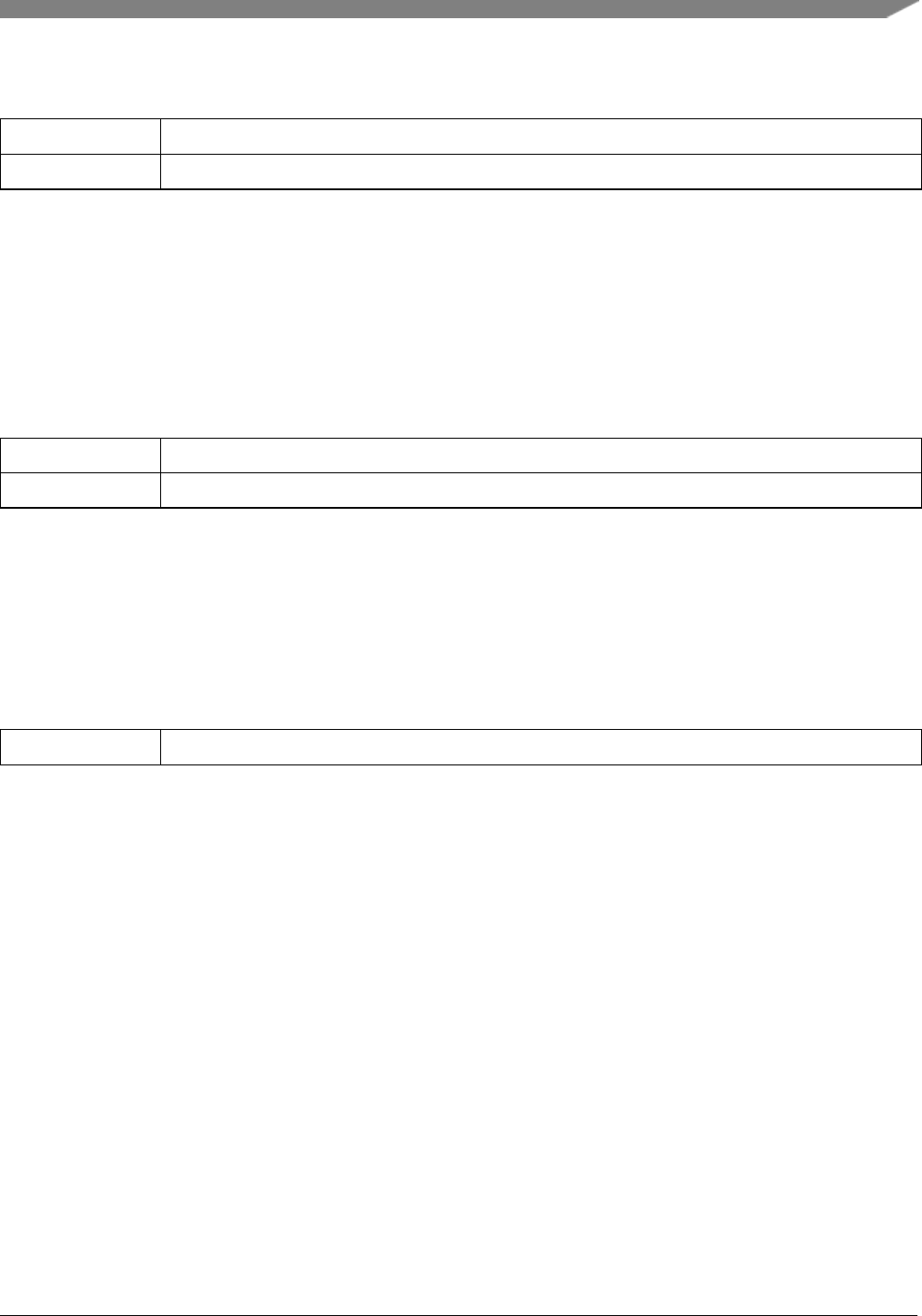

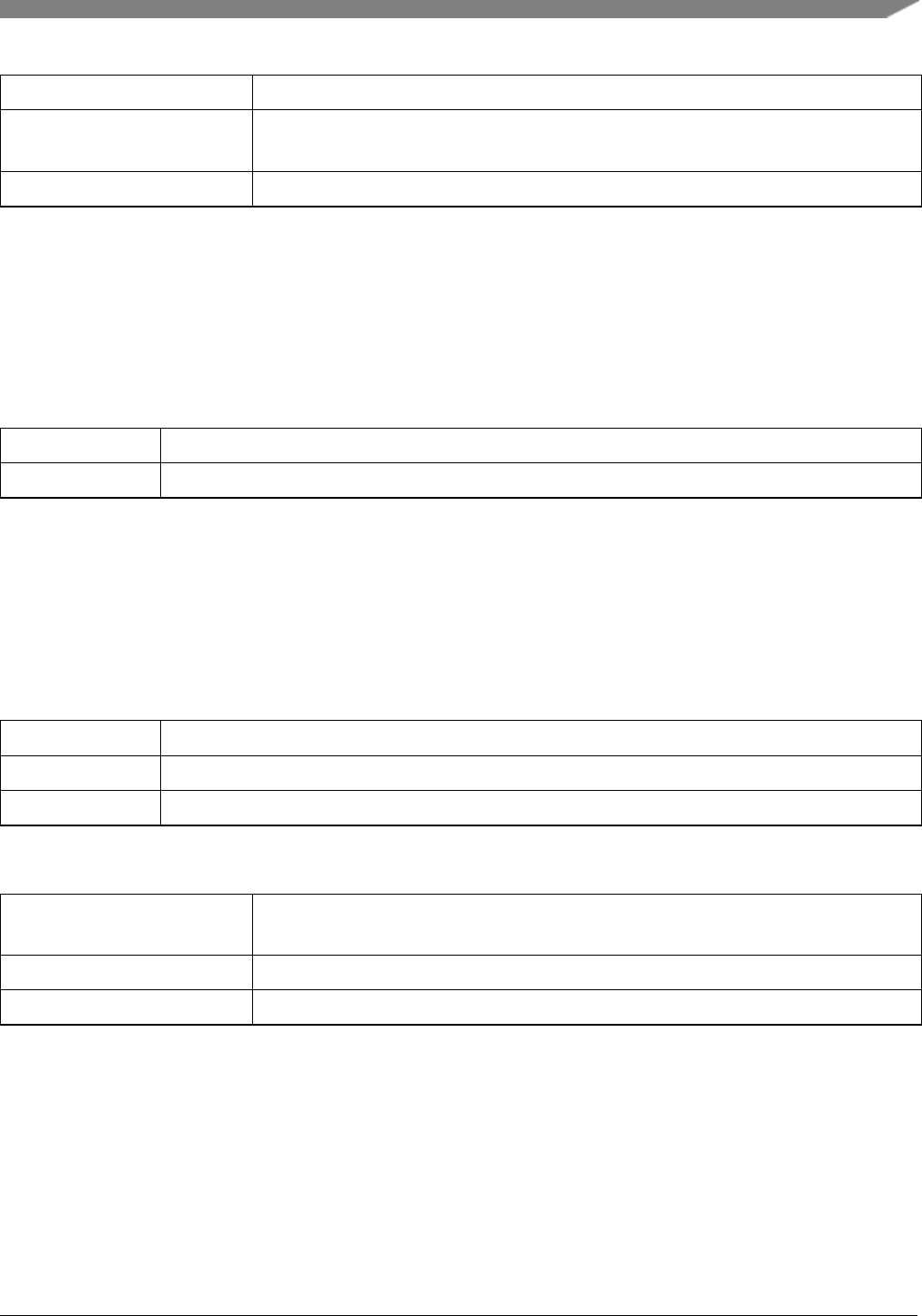

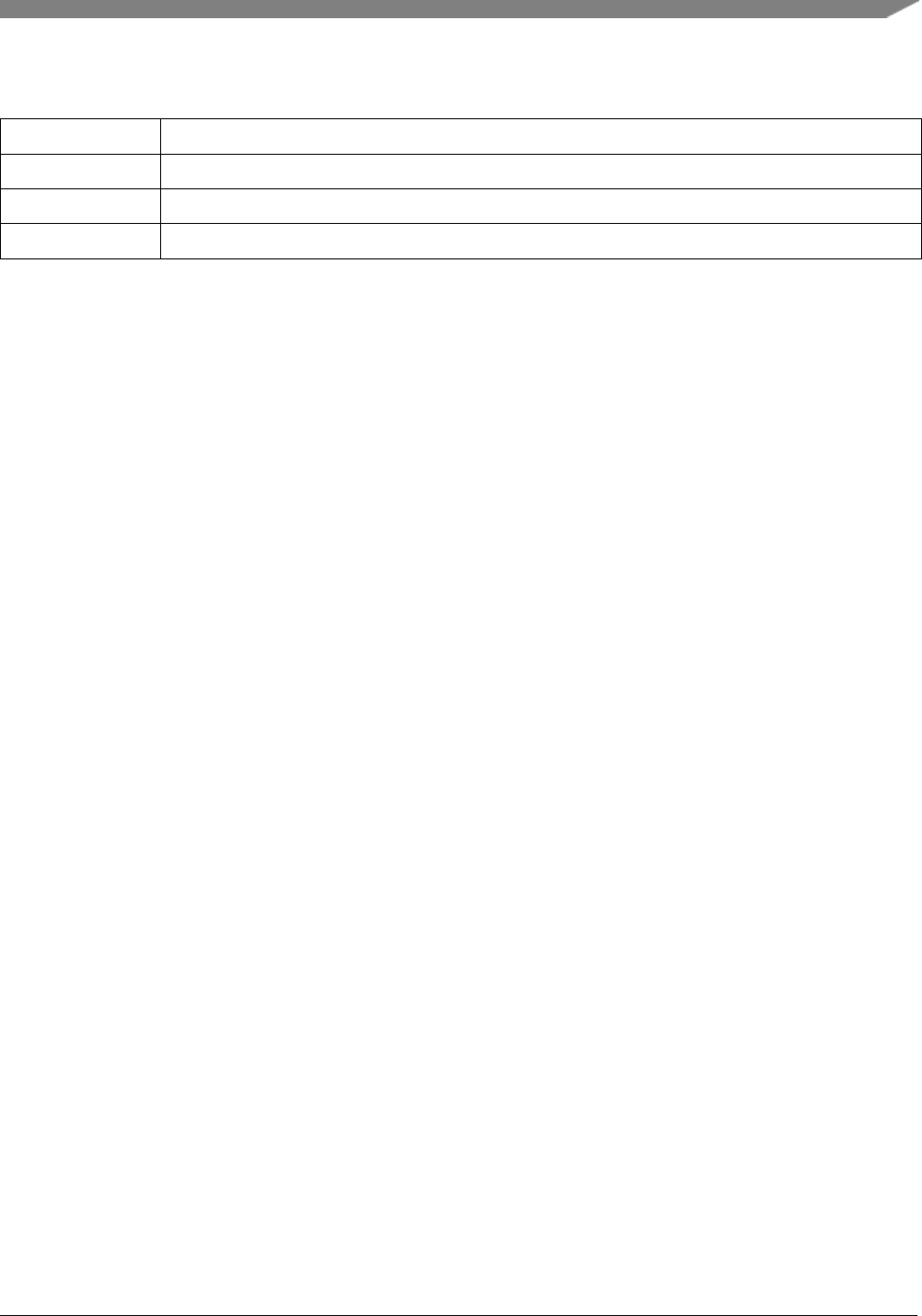

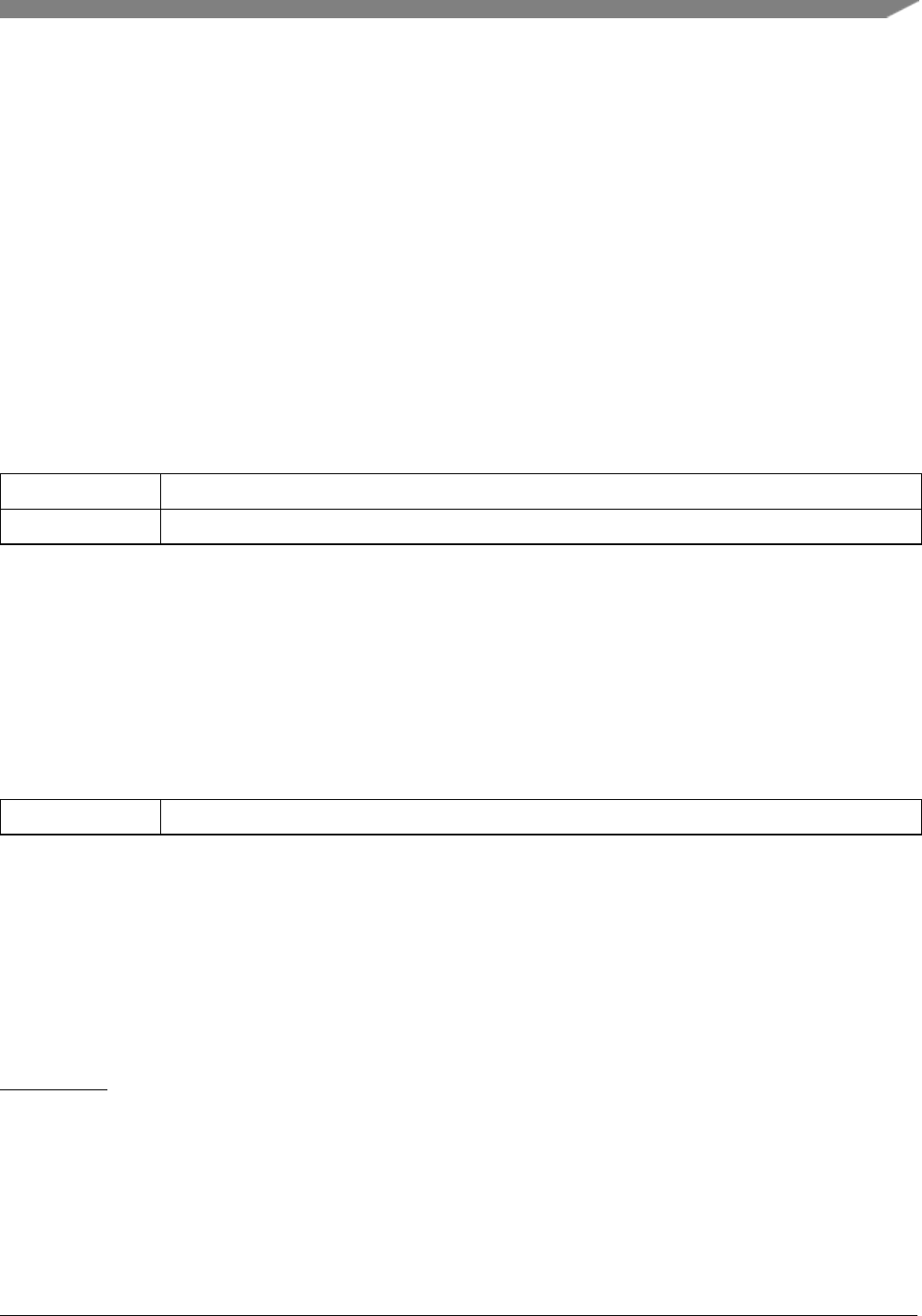

Chapter CSI: CMOS Sensor Interface

8.1 Overview ........................................ 51

8.2 Frame Buffer Queue .................................. 51

8.3 Typical use case .................................... 51

8.3.1 Receive with functional APIs ............................ 51

8.3.2 Receive with transactional APIs ........................... 52

8.4 Data Structure Documentation ............................ 56

8.4.1 struct csi_config_t .................................. 56

8.4.2 struct _csi_handle .................................. 57

8.5 Macro Definition Documentation ........................... 58

8.5.1 CSI_DRIVER_QUEUE_SIZE ........................... 58

8.6 Typedef Documentation ................................ 59

8.6.1 csi_transfer_callback_t ............................... 59

8.7 Enumeration Type Documentation .......................... 59

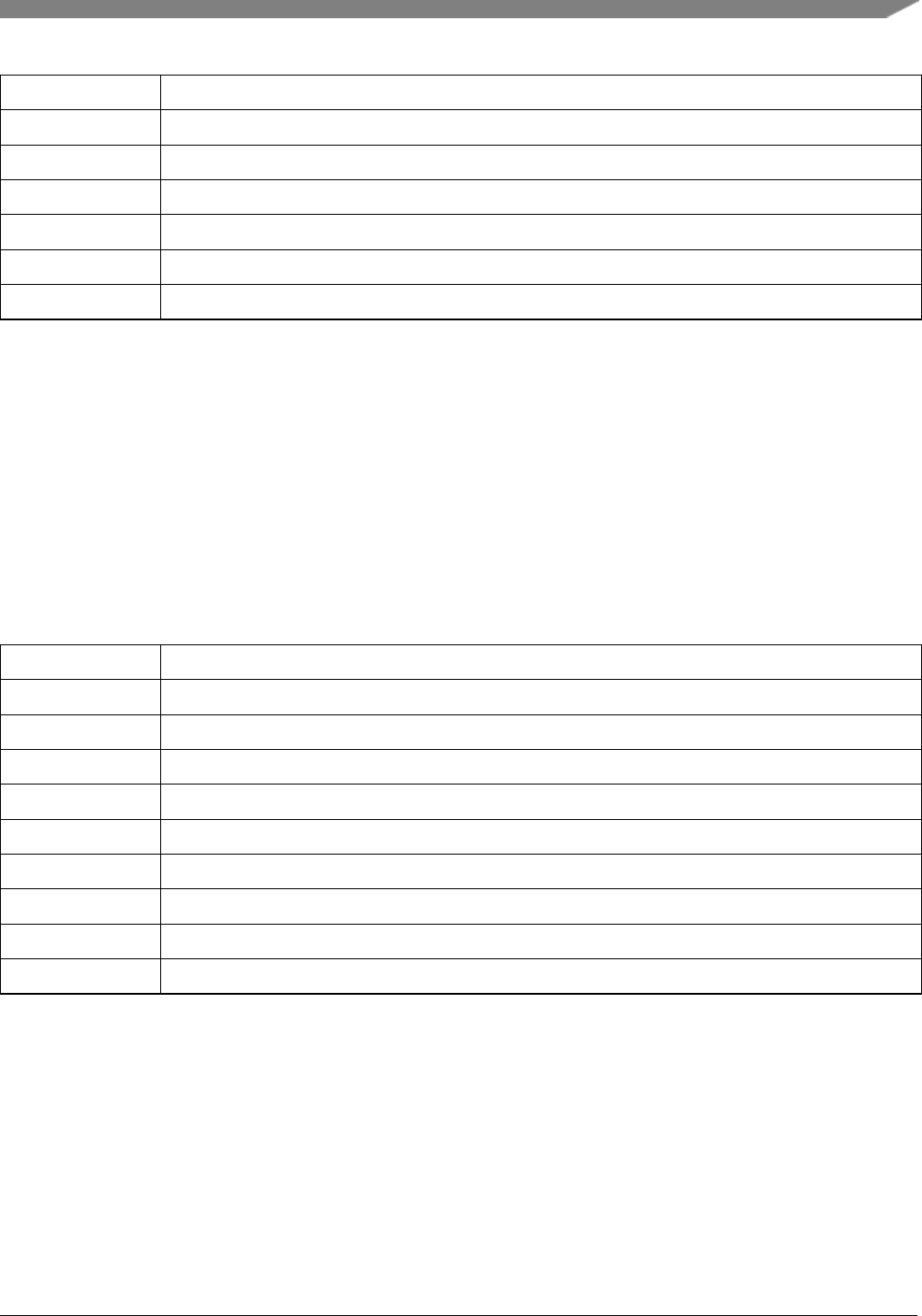

vi

MCUXpresso SDK API Reference Manual

NXP Semiconductors

Section

Number

Contents

Title

Page

Number

8.7.1 _csi_status ...................................... 59

8.7.2 csi_work_mode_t .................................. 59

8.7.3 csi_data_bus_t .................................... 59

8.7.4 _csi_polarity_flags .................................. 59

8.7.5 csi_fifo_t ....................................... 60

8.7.6 _csi_interrupt_enable ................................ 60

8.7.7 _csi_flags ....................................... 60

8.8 Function Documentation ............................... 61

8.8.1 CSI_Init ....................................... 61

8.8.2 CSI_Deinit ...................................... 62

8.8.3 CSI_Reset ...................................... 62

8.8.4 CSI_GetDefaultConfig ................................ 62

8.8.5 CSI_ClearFifo .................................... 63

8.8.6 CSI_ReflashFifoDma ................................ 63

8.8.7 CSI_EnableFifoDmaRequest ............................ 63

8.8.8 CSI_Start ....................................... 63

8.8.9 CSI_Stop ....................................... 64

8.8.10 CSI_SetRxBufferAddr ................................ 64

8.8.11 CSI_EnableInterrupts ................................ 64

8.8.12 CSI_DisableInterrupts ................................ 64

8.8.13 CSI_GetStatusFlags ................................. 64

8.8.14 CSI_ClearStatusFlags ................................ 65

8.8.15 CSI_TransferCreateHandle ............................. 65

8.8.16 CSI_TransferStart .................................. 66

8.8.17 CSI_TransferStop .................................. 66

8.8.18 CSI_TransferSubmitEmptyBuffer .......................... 66

8.8.19 CSI_TransferGetFullBuffer ............................. 67

8.8.20 CSI_TransferHandleIRQ ............................... 67

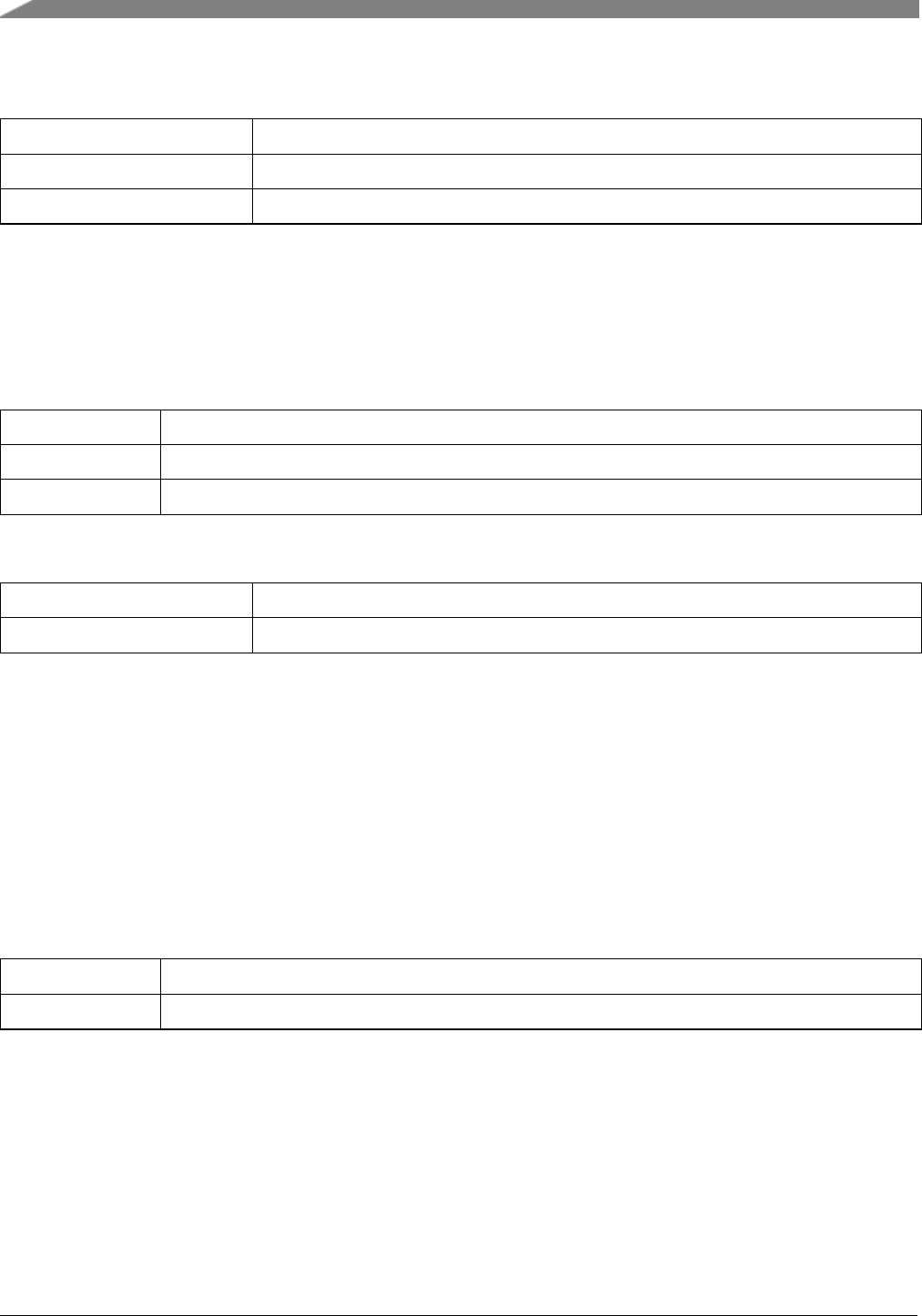

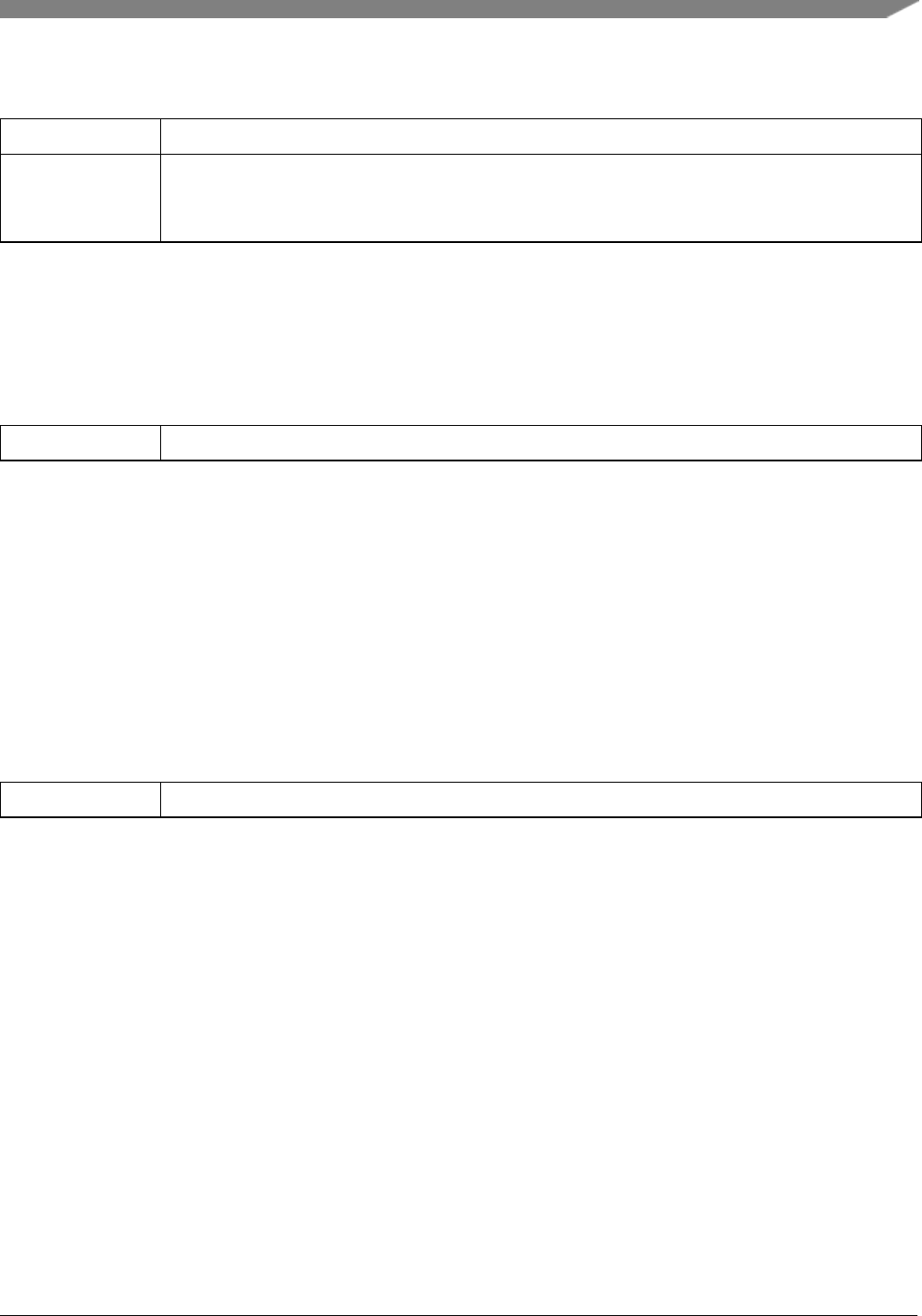

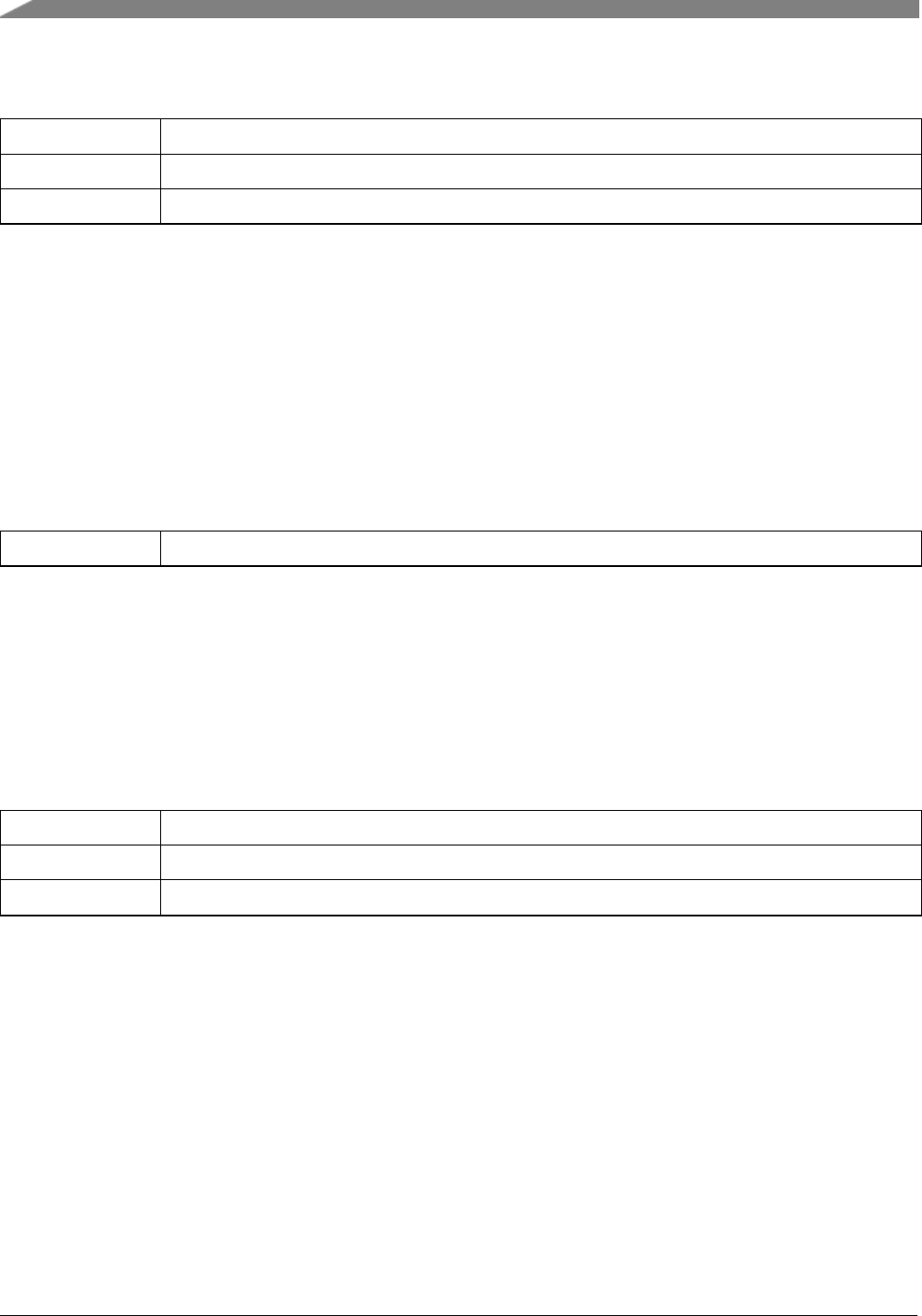

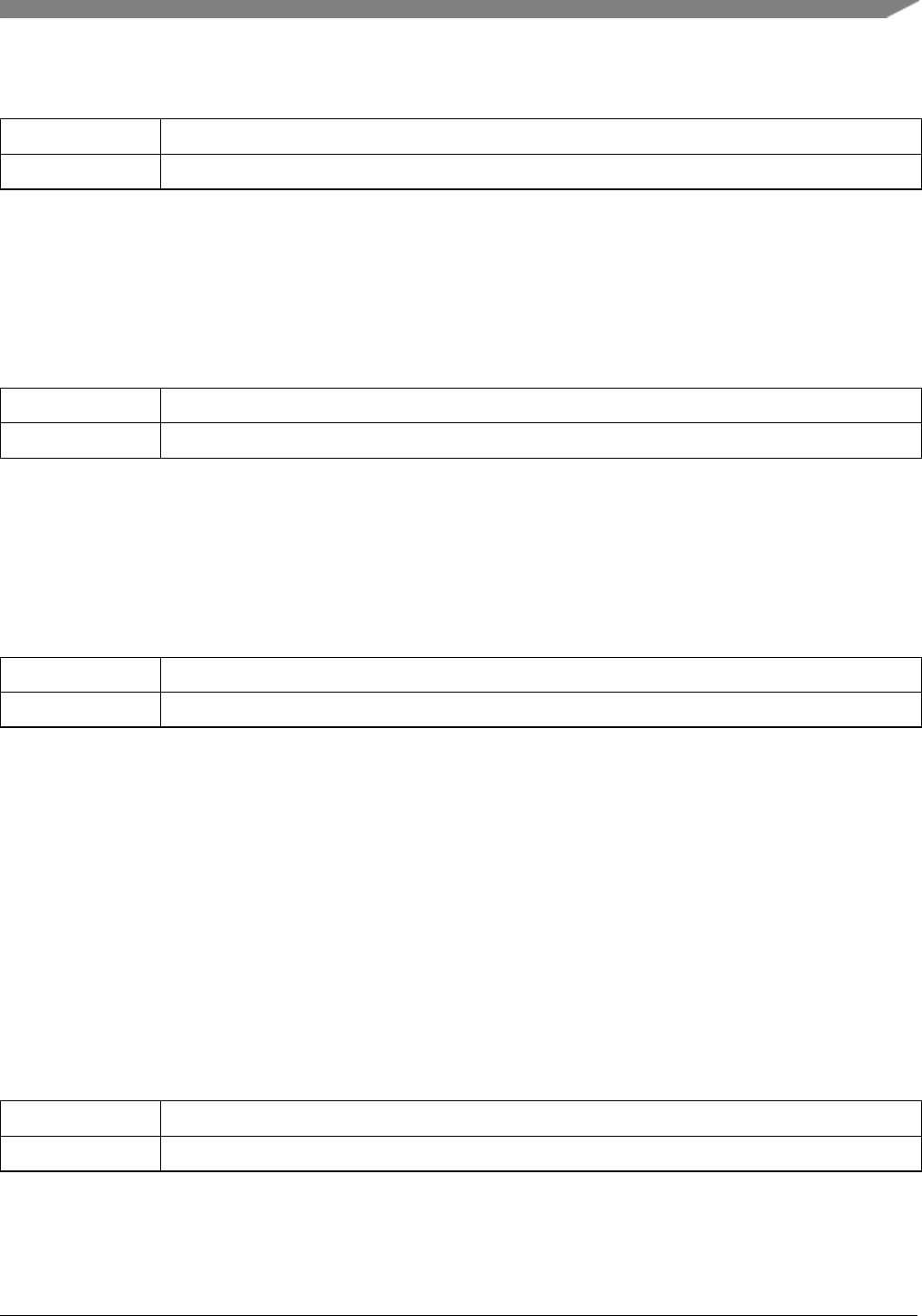

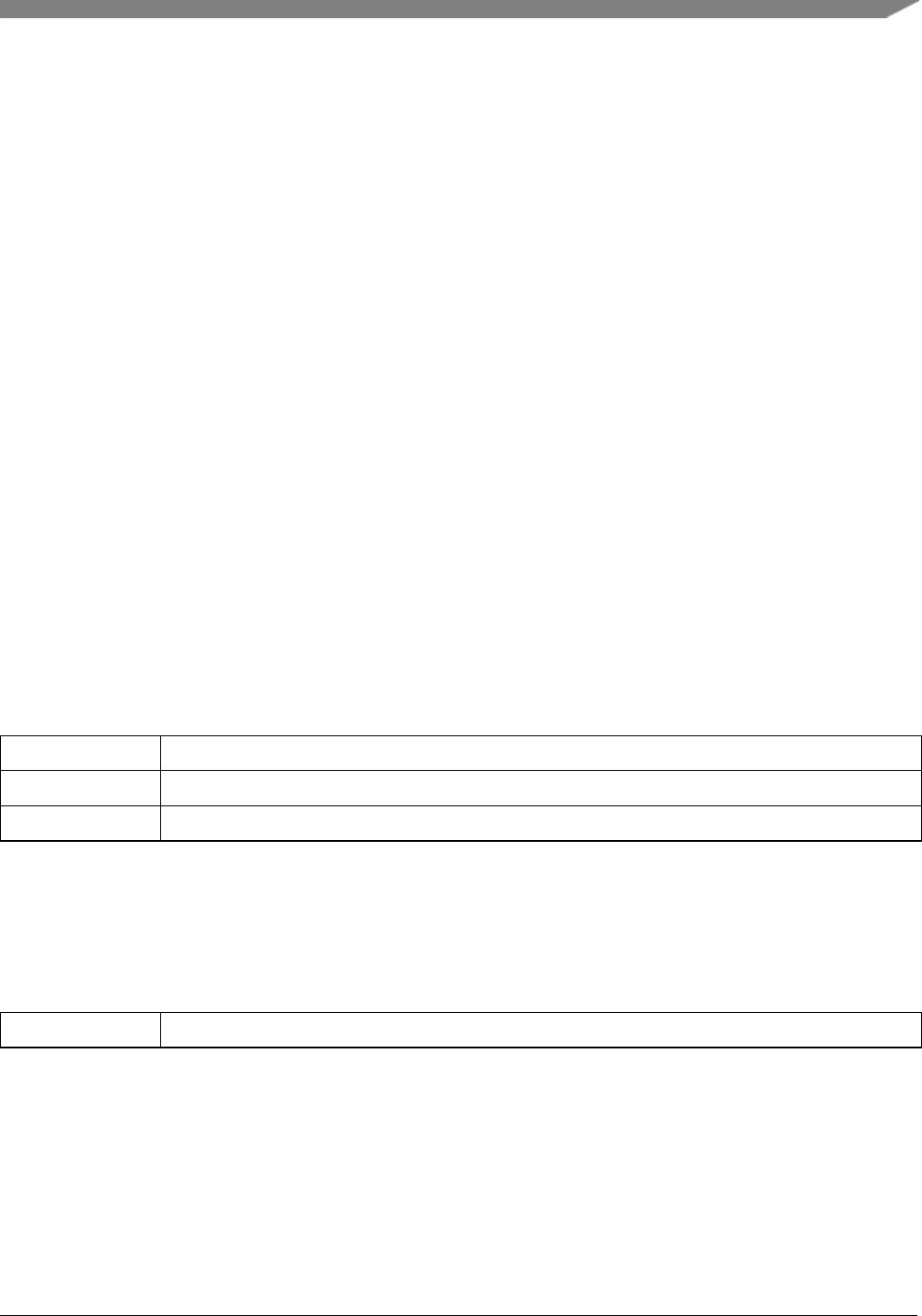

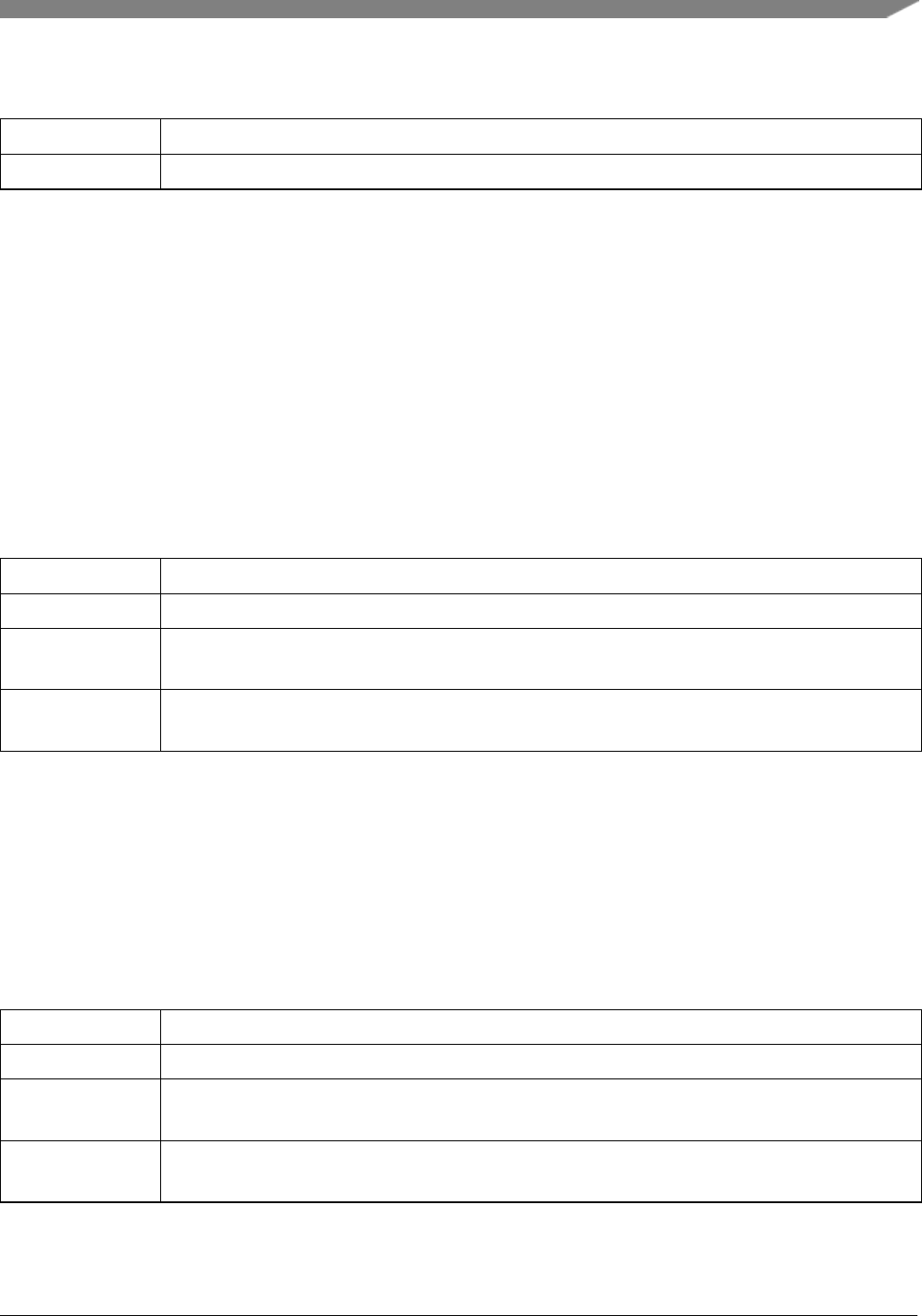

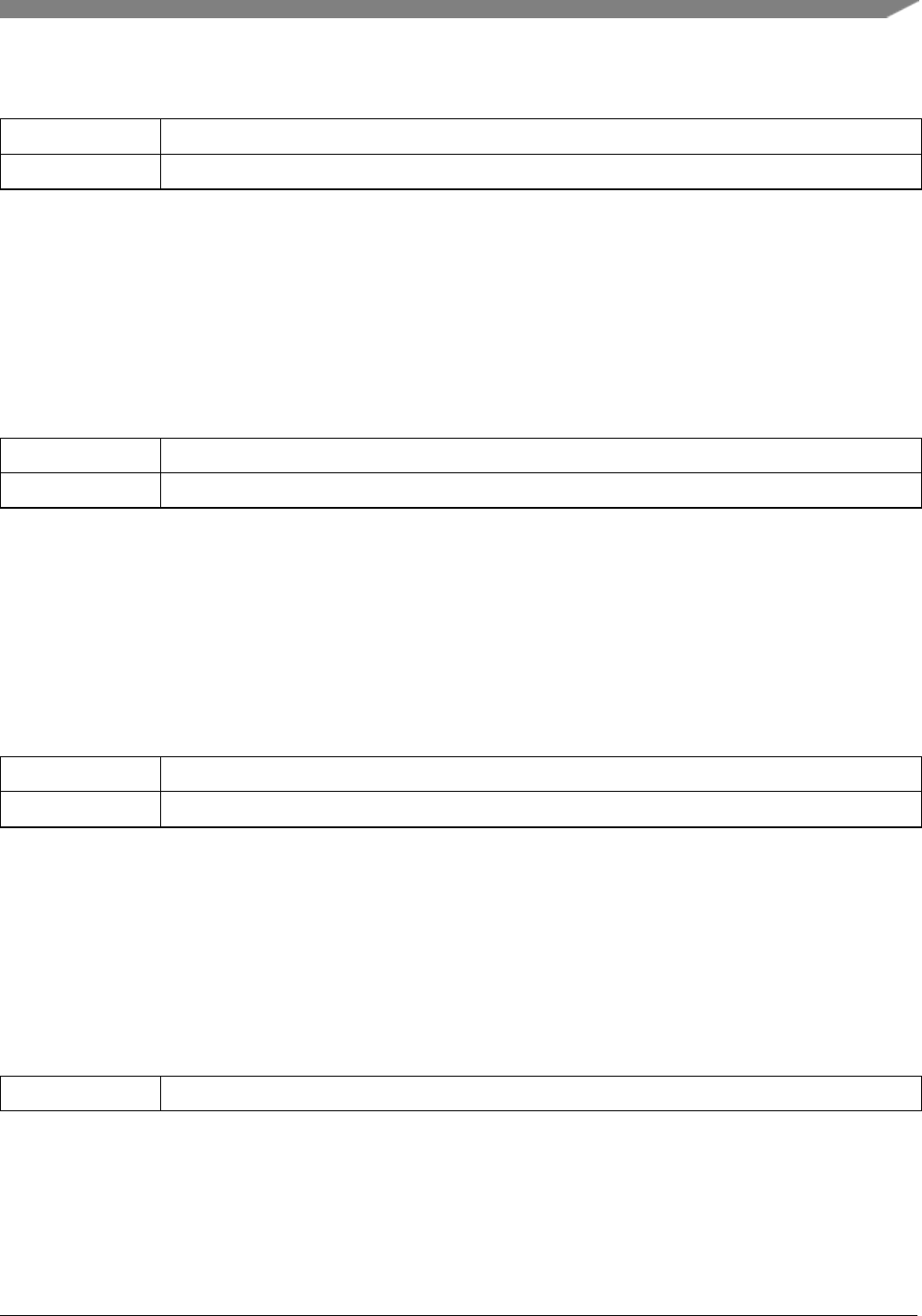

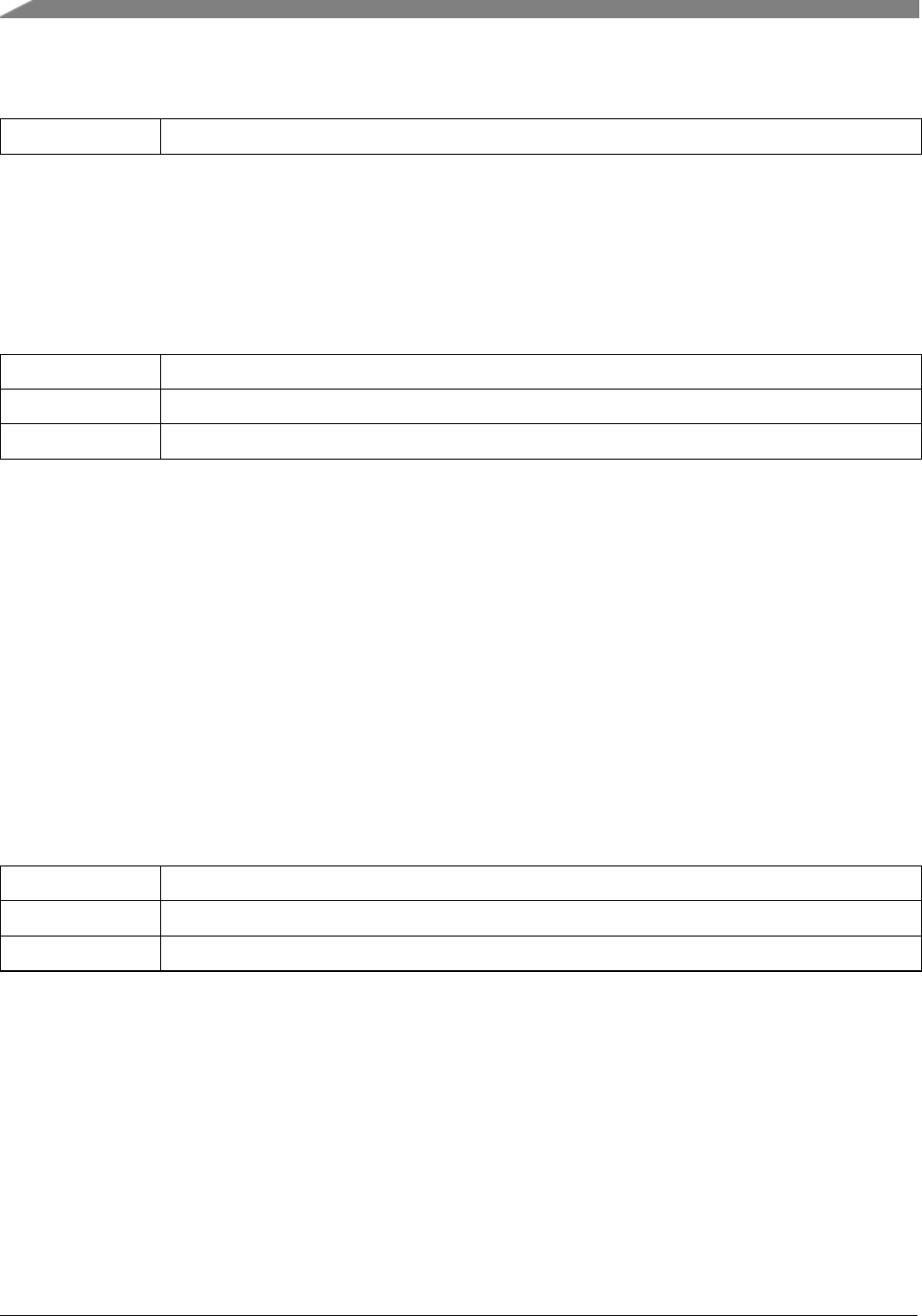

Chapter ECSPI: Serial Peripheral Interface Driver

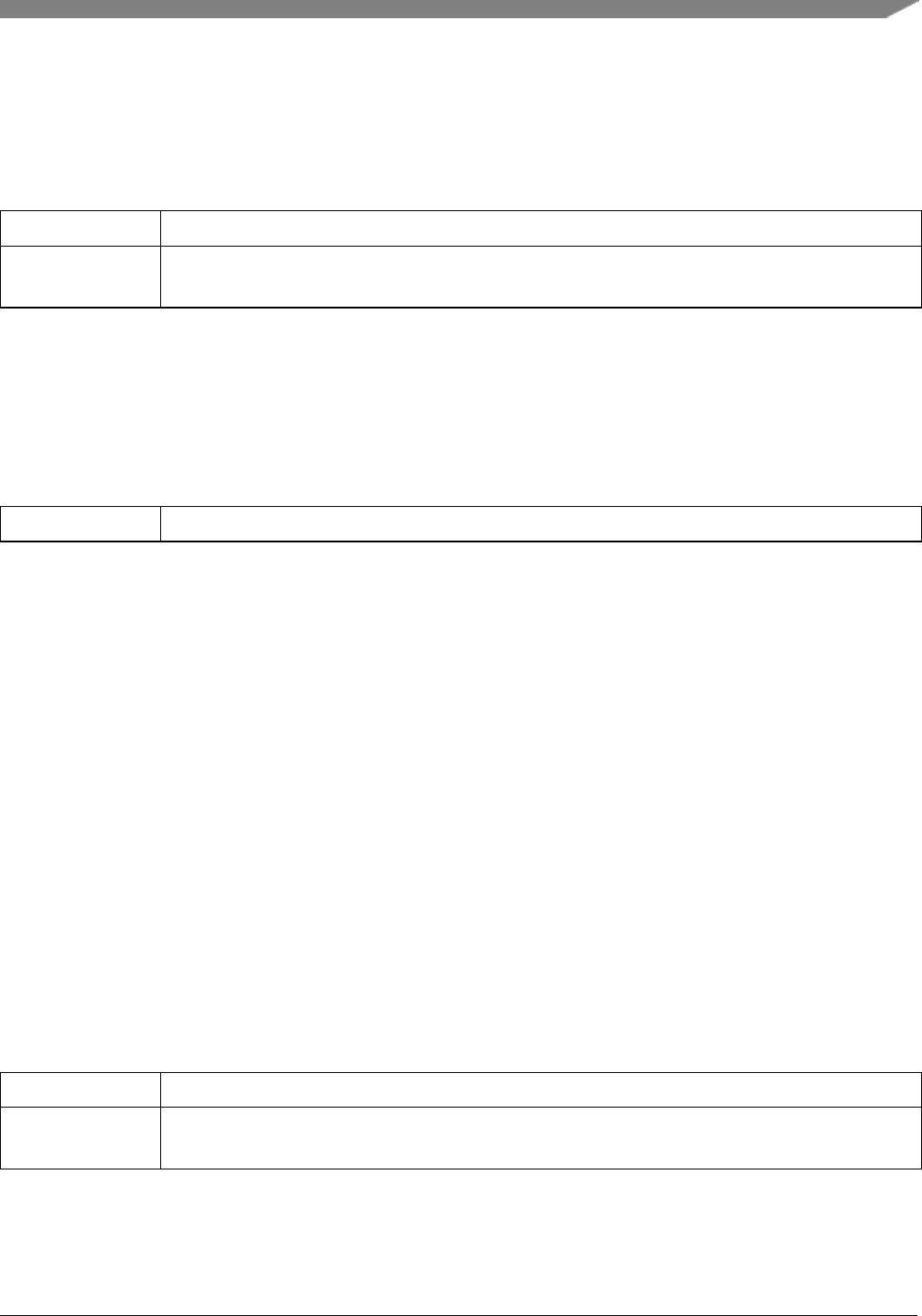

9.1 Overview ........................................ 69

9.2 ECSPI Driver ..................................... 70

9.2.1 Overview ....................................... 70

9.2.2 Typical use case ................................... 70

9.2.3 Data Structure Documentation ............................ 76

9.2.4 Macro Definition Documentation .......................... 78

9.2.5 Enumeration Type Documentation ......................... 78

9.2.6 Function Documentation ............................... 81

9.3 ECSPI FreeRTOS Driver ............................... 93

9.3.1 Overview ....................................... 93

9.3.2 Function Documentation ............................... 93

NXP Semiconductors

MCUXpresso SDK API Reference Manual

vii

Section

Number

Contents

Title

Page

Number

9.4 ECSPI SDMA Driver ................................. 95

9.4.1 Overview ....................................... 95

9.4.2 Data Structure Documentation ............................ 95

9.4.3 Typedef Documentation ............................... 96

9.4.4 Function Documentation ............................... 96

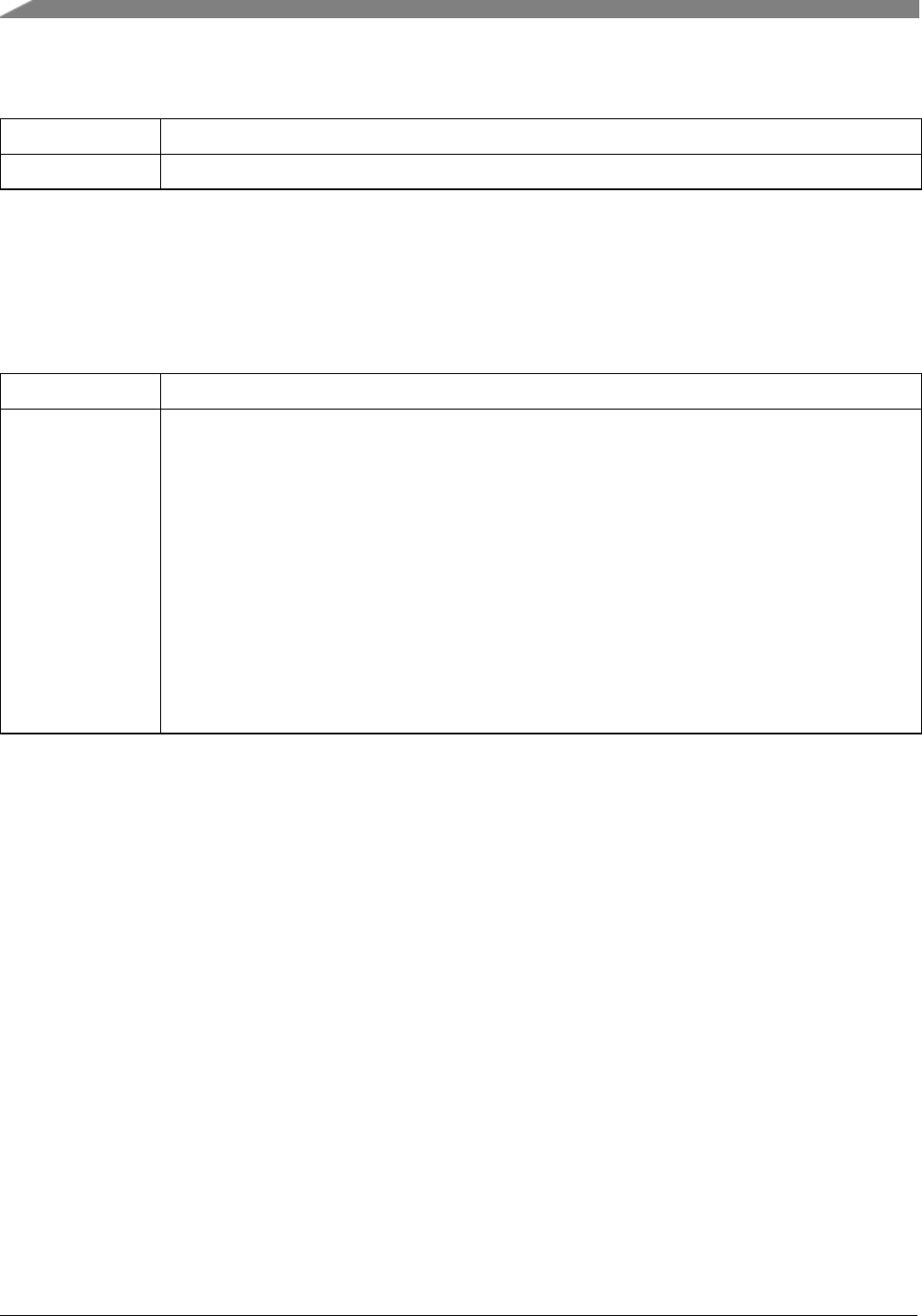

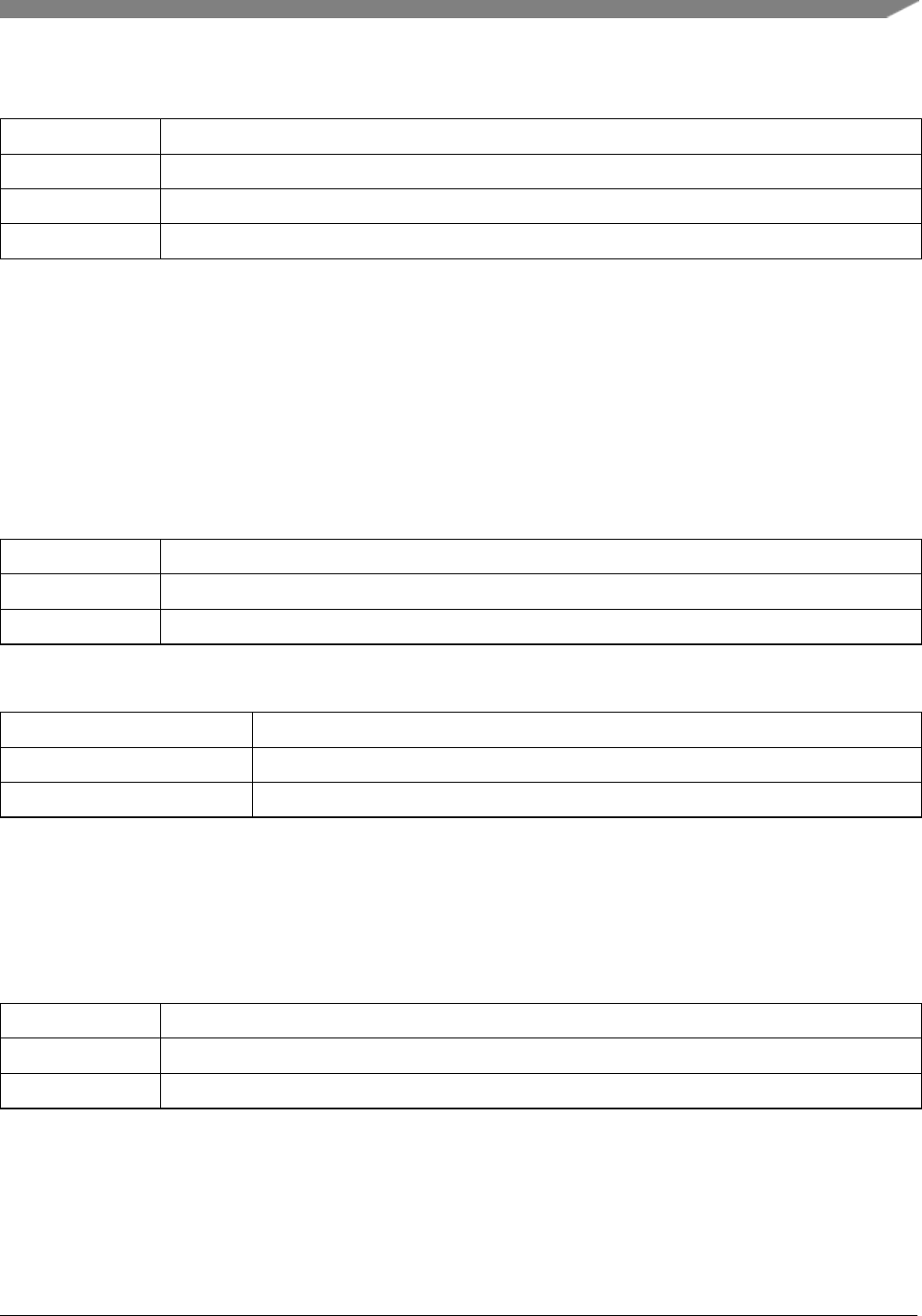

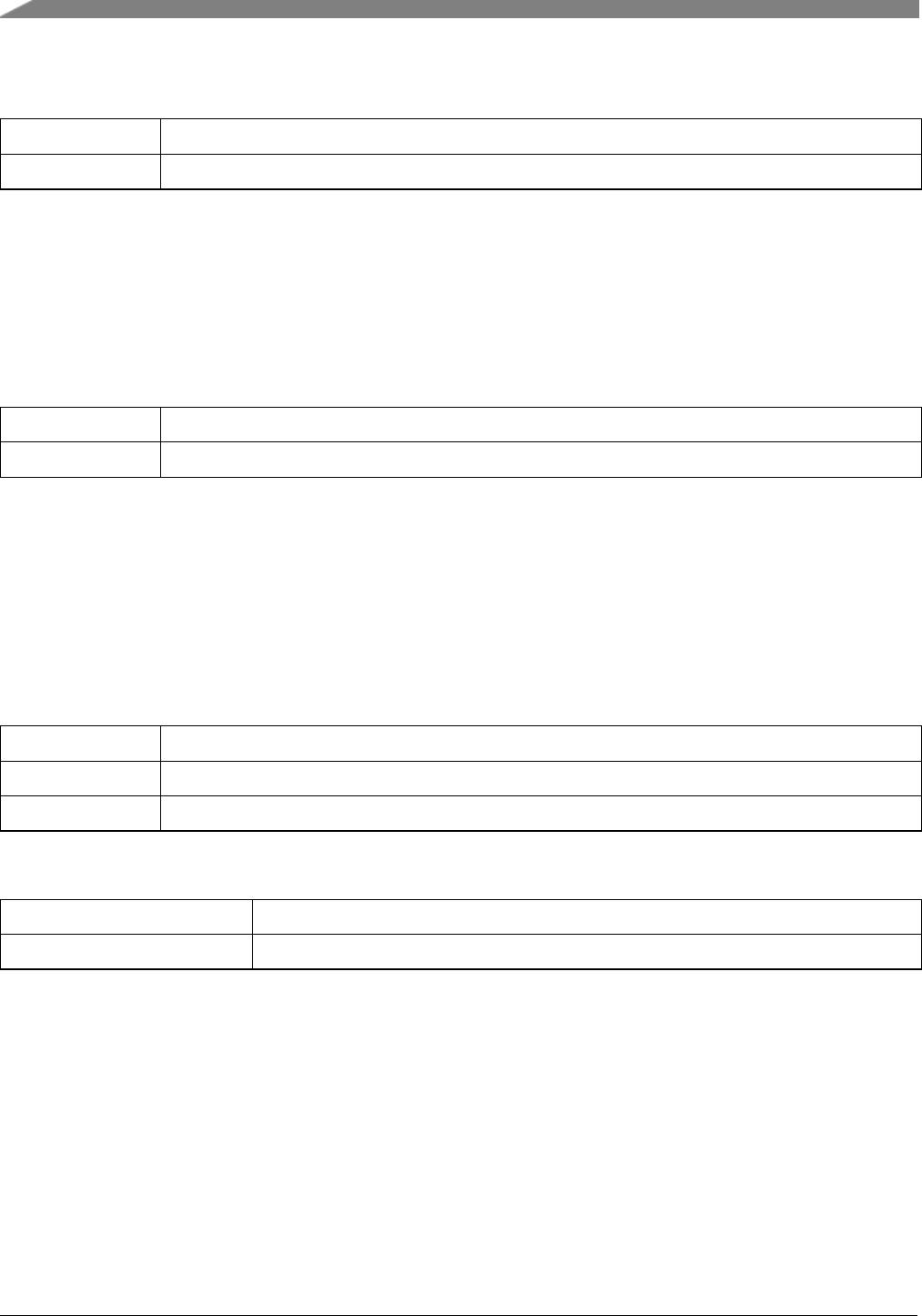

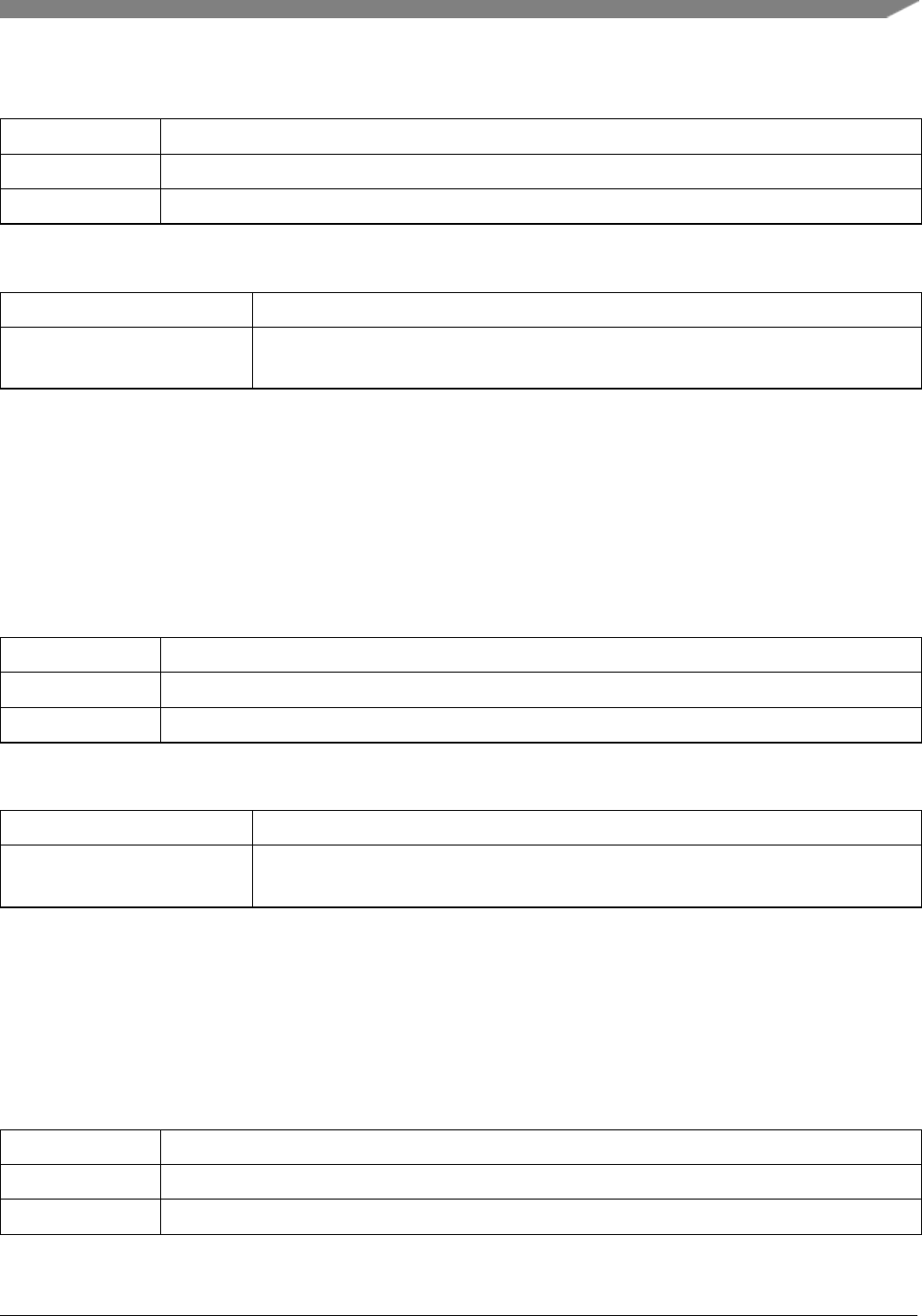

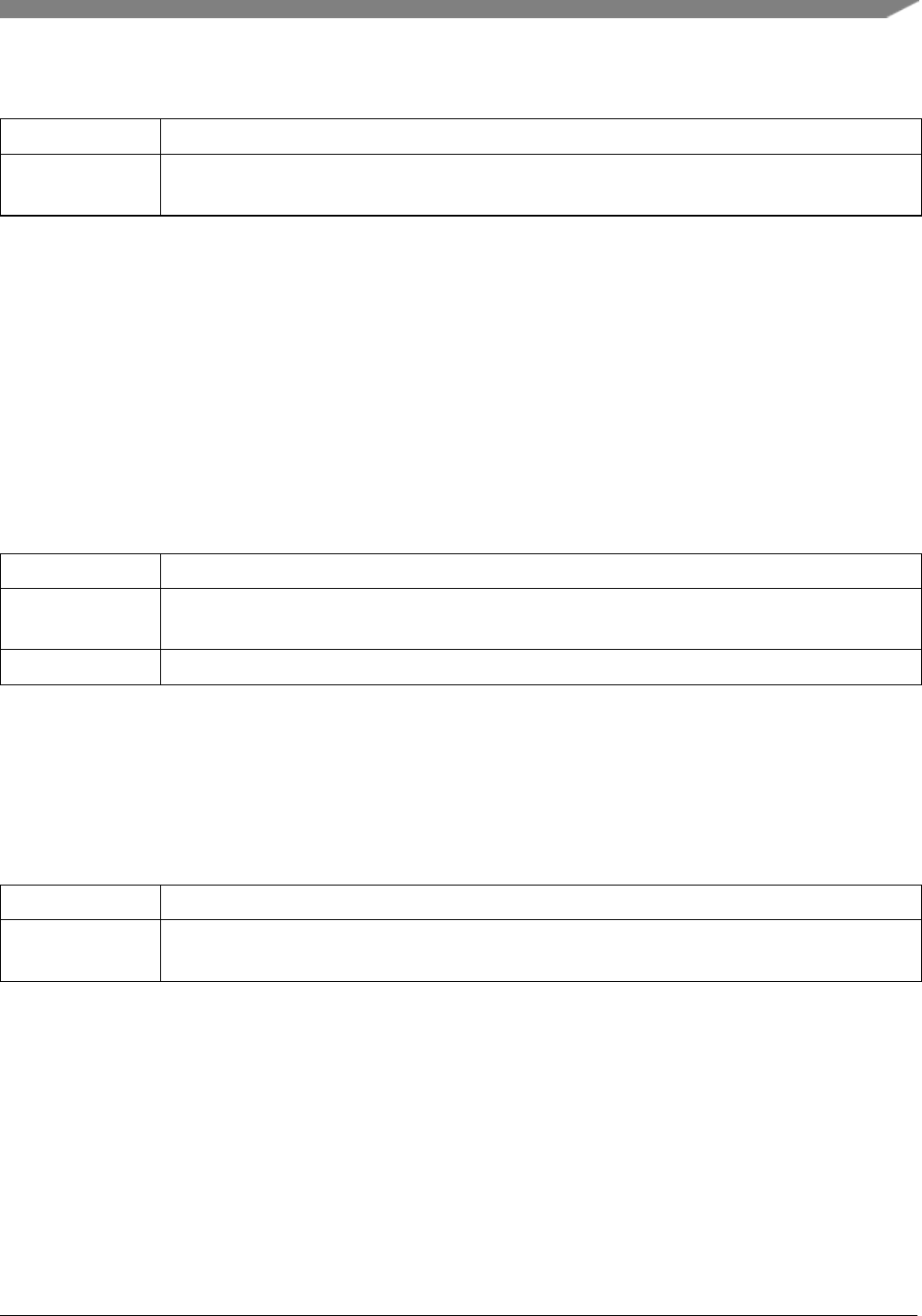

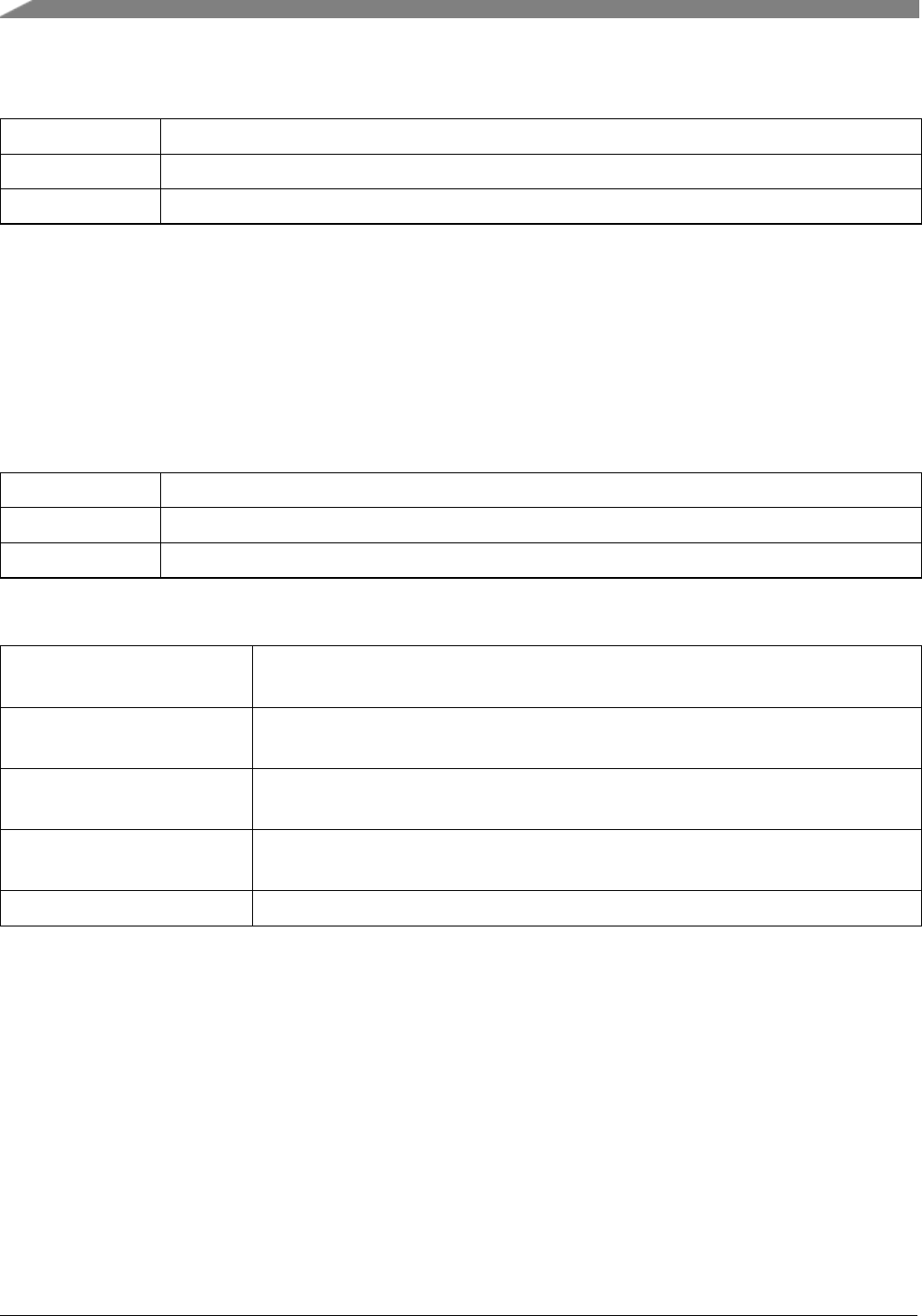

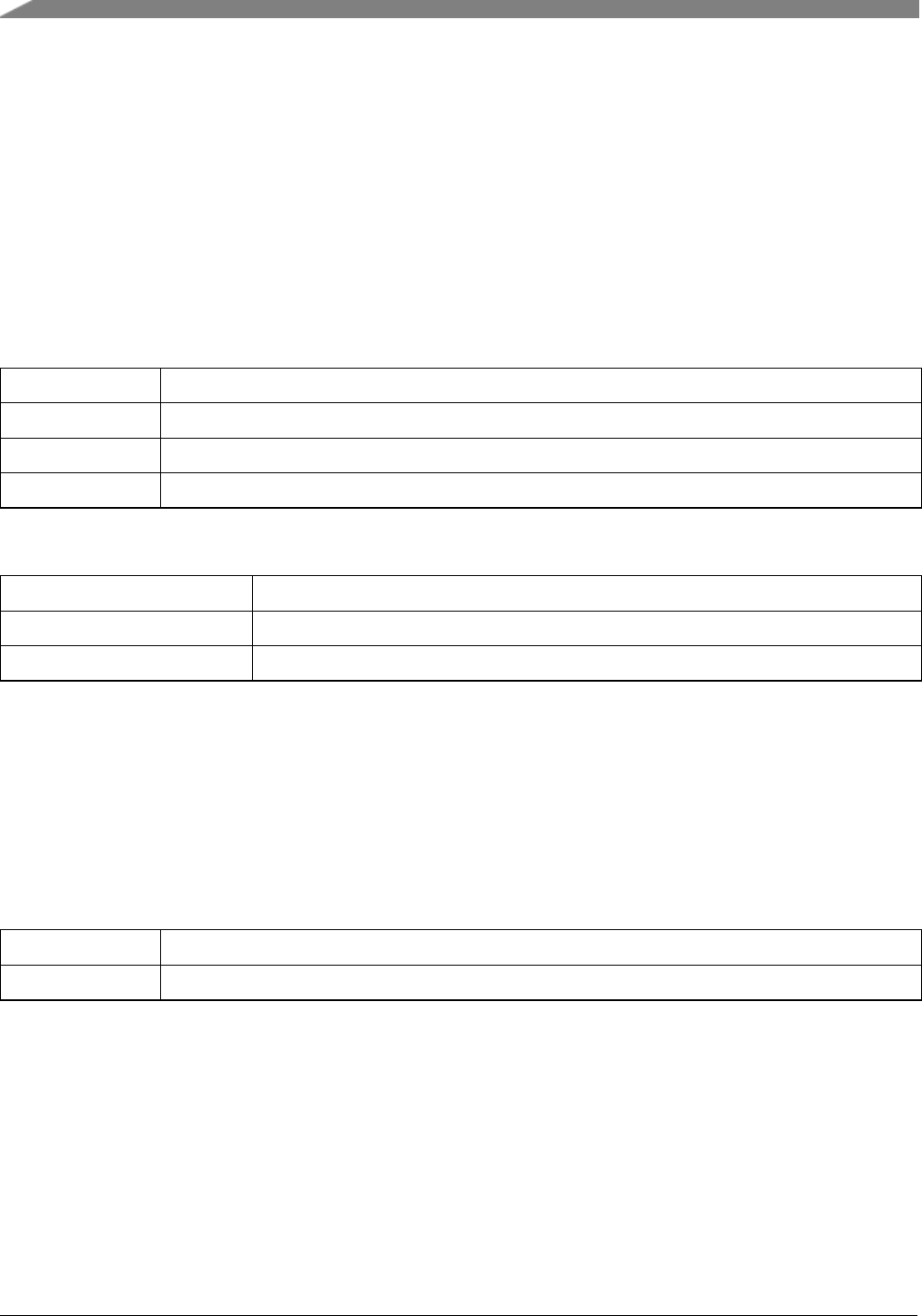

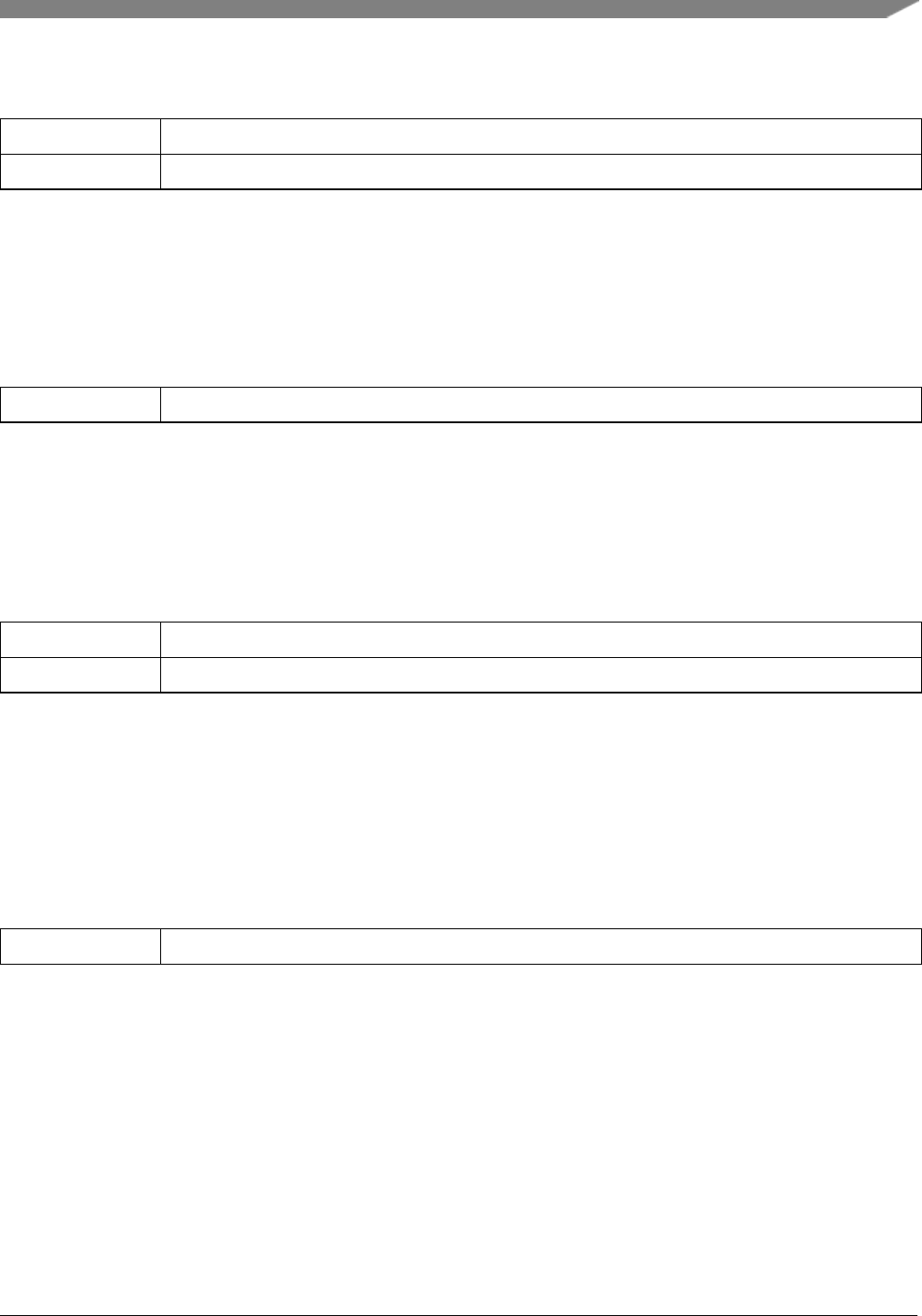

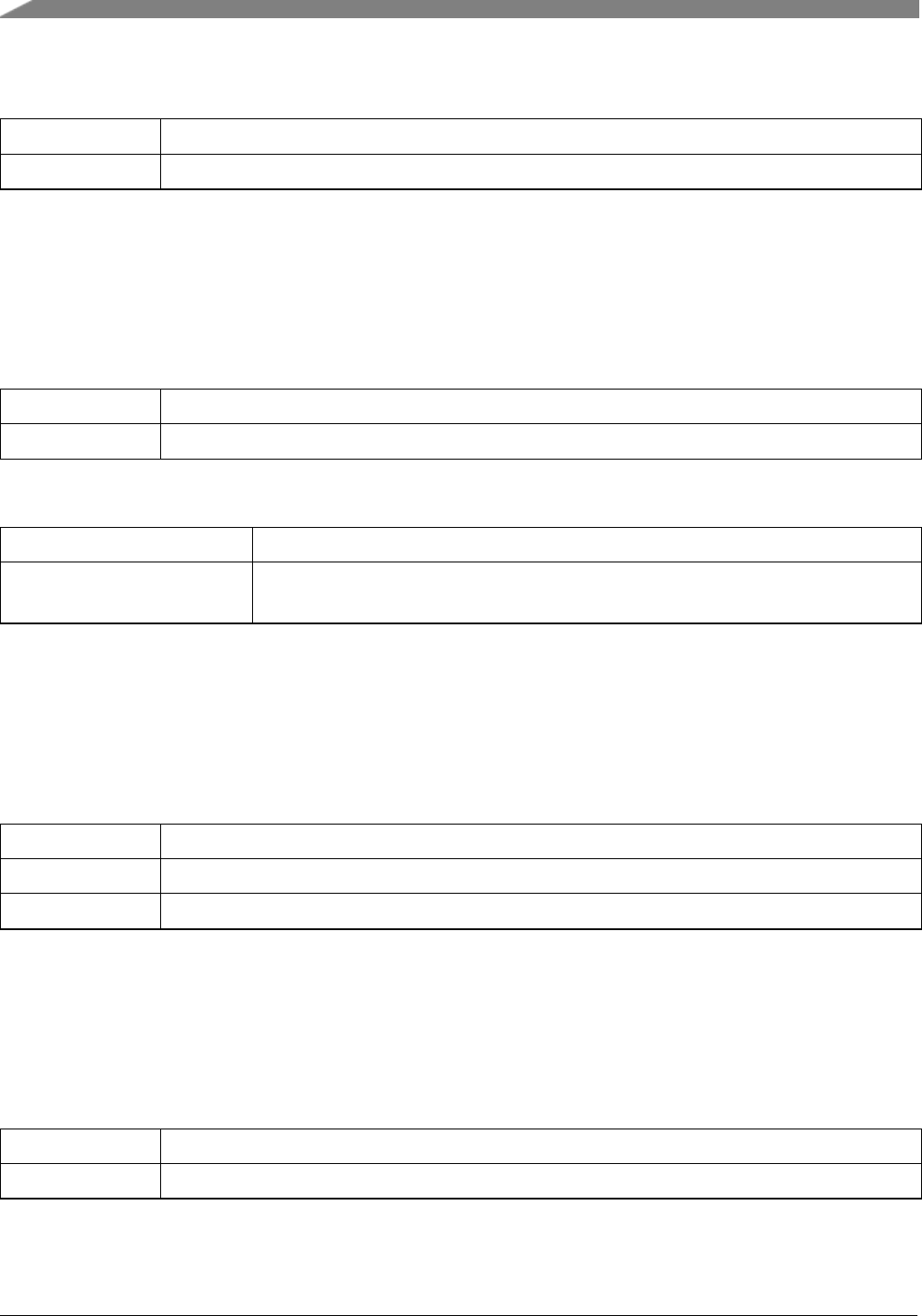

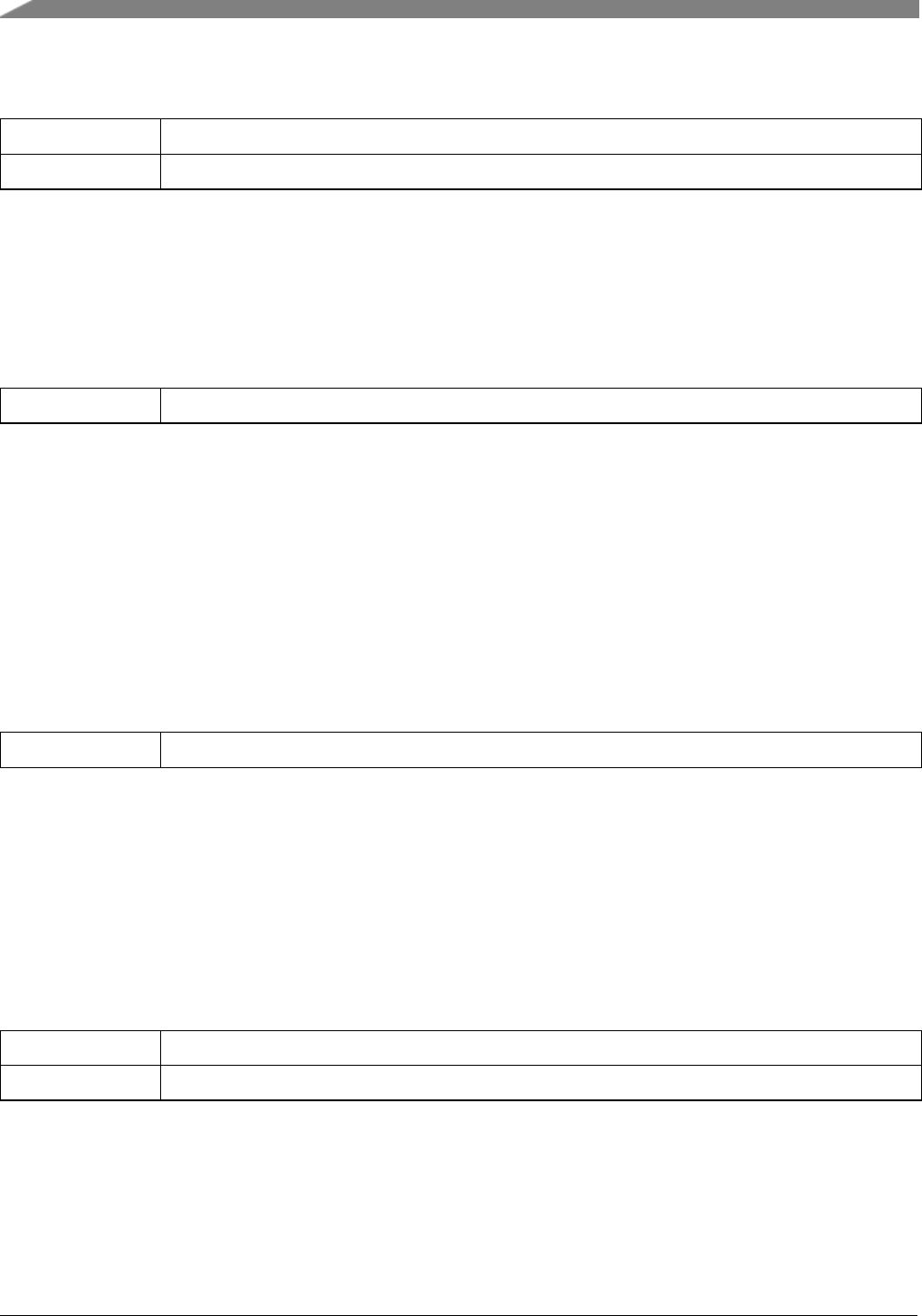

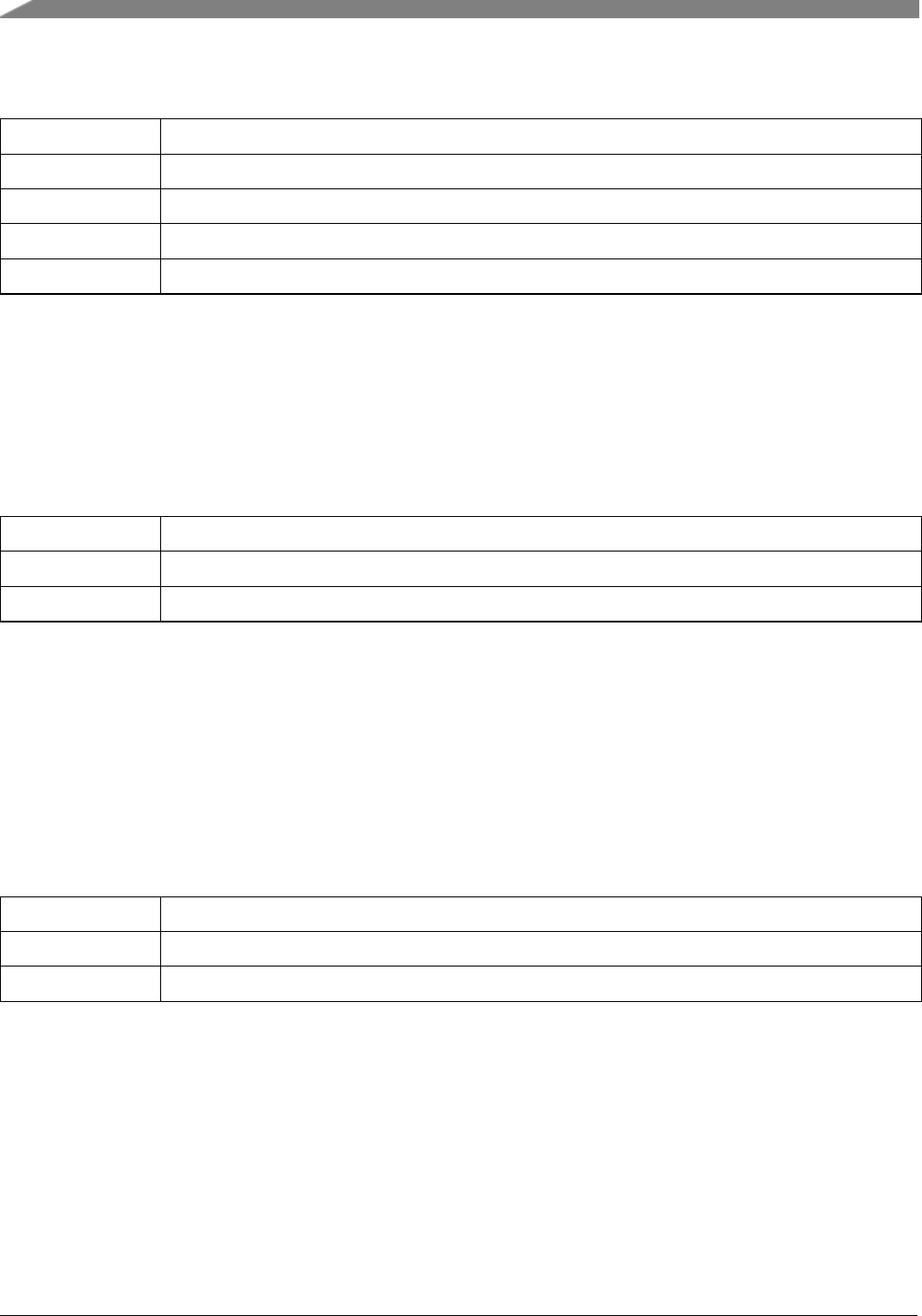

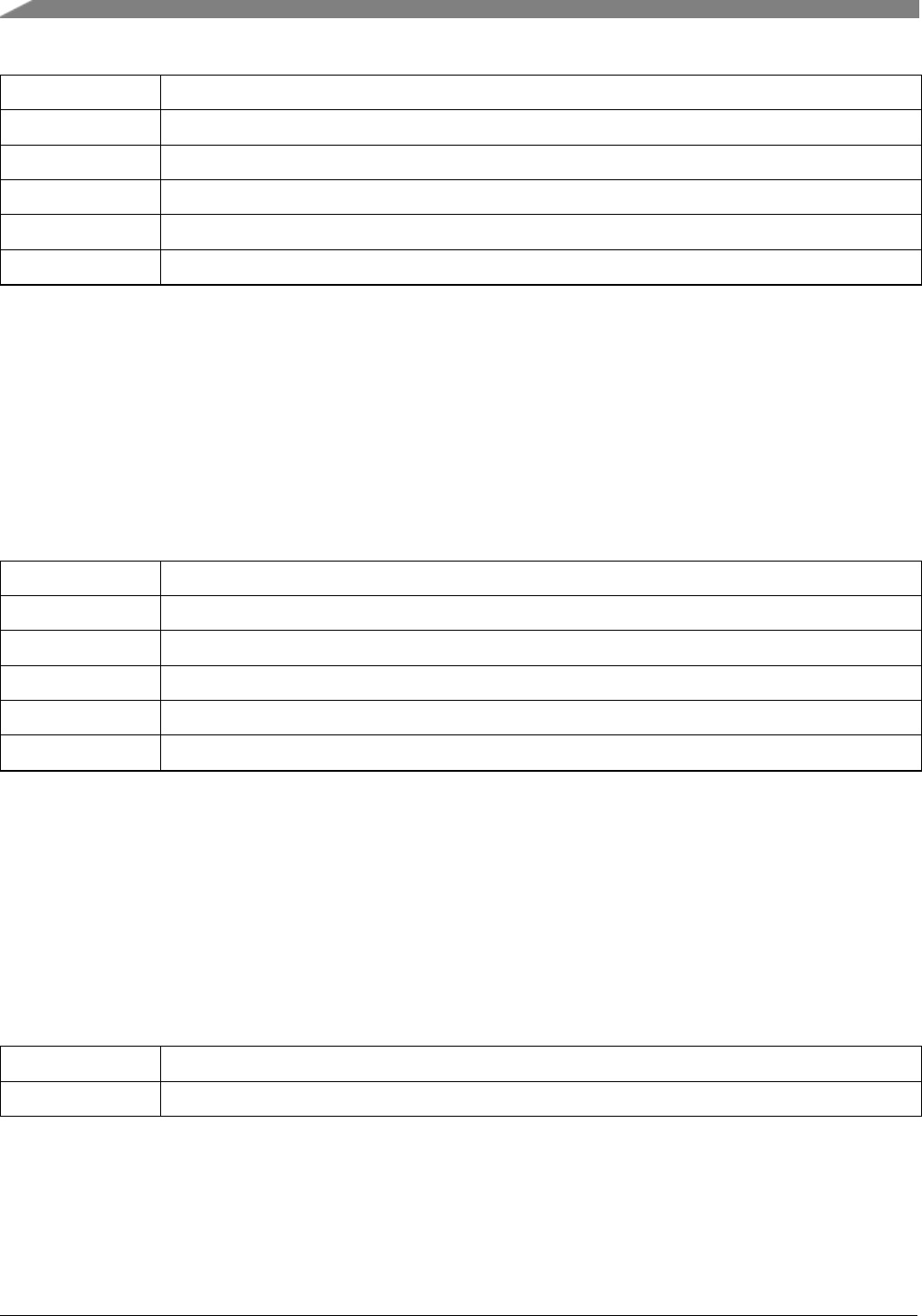

Chapter eLCDIF: Enhanced LCD Interface

10.1 Overview ........................................101

10.2 Typical use case ....................................101

10.2.1 Frame buffer update .................................101

10.2.2 Alpha surface ....................................102

10.3 Data Structure Documentation ............................106

10.3.1 struct elcdif_pixel_format_reg_t ...........................106

10.3.2 struct elcdif_rgb_mode_config_t ..........................106

10.3.3 struct elcdif_as_buffer_config_t ...........................107

10.3.4 struct elcdif_as_blend_config_t ...........................108

10.4 Macro Definition Documentation ...........................108

10.4.1 FSL_ELCDIF_DRIVER_VERSION ........................108

10.5 Enumeration Type Documentation ..........................108

10.5.1 _elcdif_polarity_flags ................................108

10.5.2 _elcdif_interrupt_enable ...............................109

10.5.3 _elcdif_interrupt_flags ................................109

10.5.4 _elcdif_status_flags .................................109

10.5.5 elcdif_pixel_format_t ................................110

10.5.6 elcdif_lcd_data_bus_t ................................110

10.5.7 elcdif_as_pixel_format_t ..............................110

10.5.8 elcdif_alpha_mode_t .................................110

10.5.9 elcdif_rop_mode_t ..................................111

10.6 Function Documentation ...............................111

10.6.1 ELCDIF_RgbModeInit ...............................111

10.6.2 ELCDIF_GetStatus .................................111

10.6.3 ELCDIF_GetLFifoCount ..............................113

10.6.4 ELCDIF_EnableInterrupts ..............................113

10.6.5 ELCDIF_DisableInterrupts .............................113

10.6.6 ELCDIF_GetInterruptStatus .............................114

10.6.7 ELCDIF_ClearInterruptStatus ............................114

10.6.8 ELCDIF_SetAlphaSurfaceBufferConfig ......................114

10.6.9 ELCDIF_SetAlphaSurfaceBlendConfig .......................114

10.6.10 ELCDIF_SetNextAlphaSurfaceBufferAddr .....................115

viii

MCUXpresso SDK API Reference Manual

NXP Semiconductors

Section

Number

Contents

Title

Page

Number

10.6.11 ELCDIF_SetOverlayColorKey ...........................115

10.6.12 ELCDIF_EnableOverlayColorKey .........................115

10.6.13 ELCDIF_EnableAlphaSurface ............................116

10.6.14 ELCDIF_EnableProcessSurface ...........................117

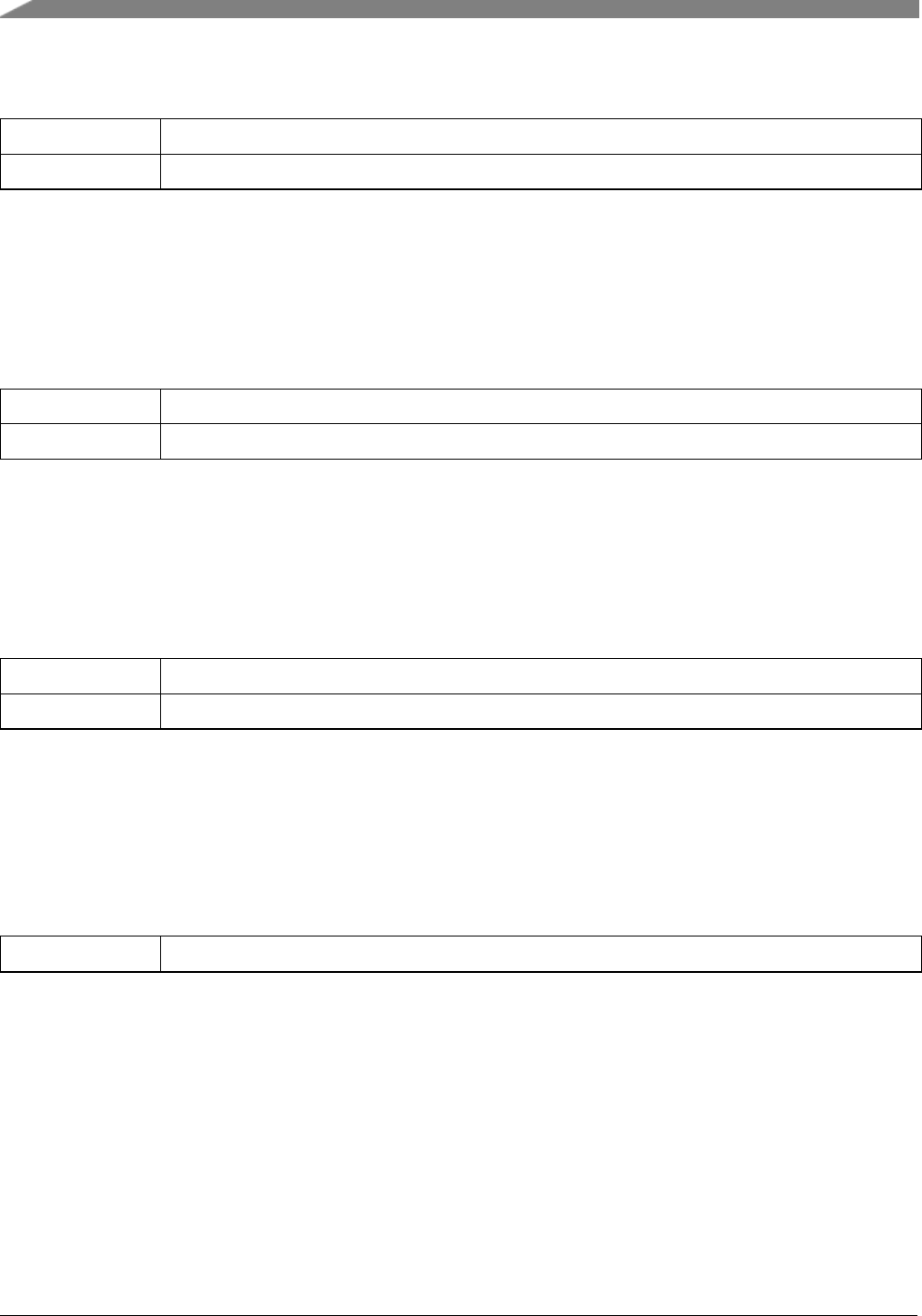

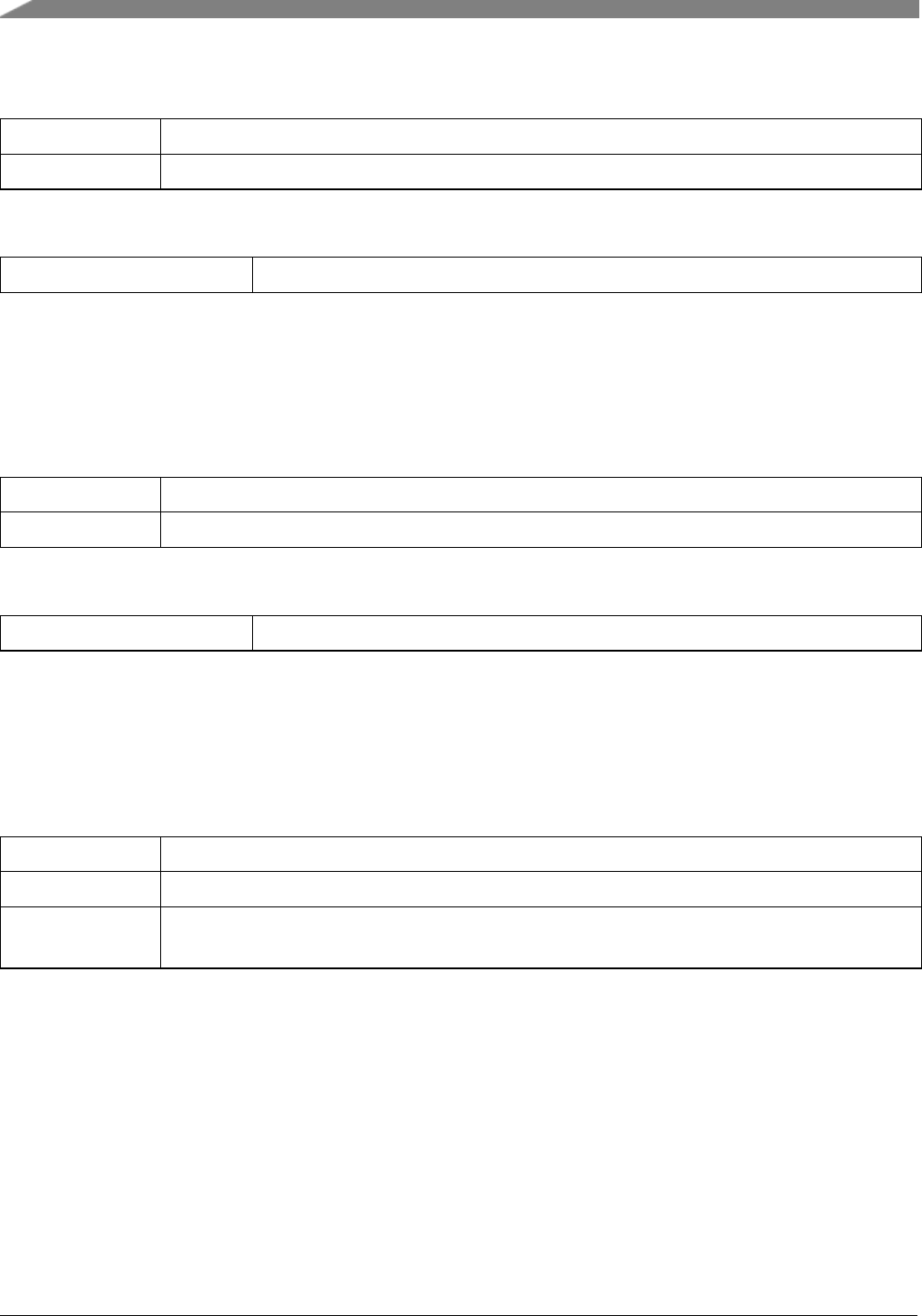

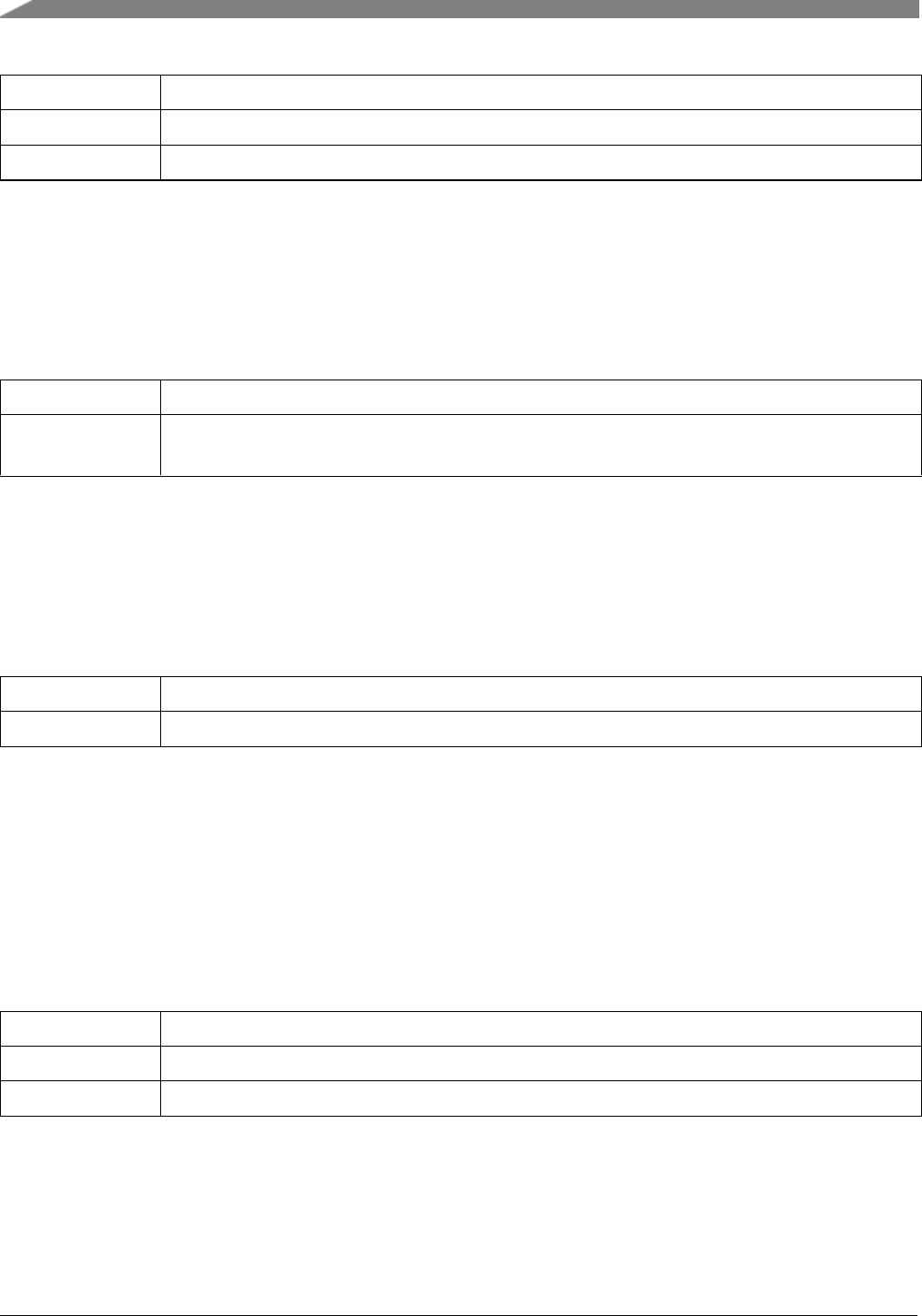

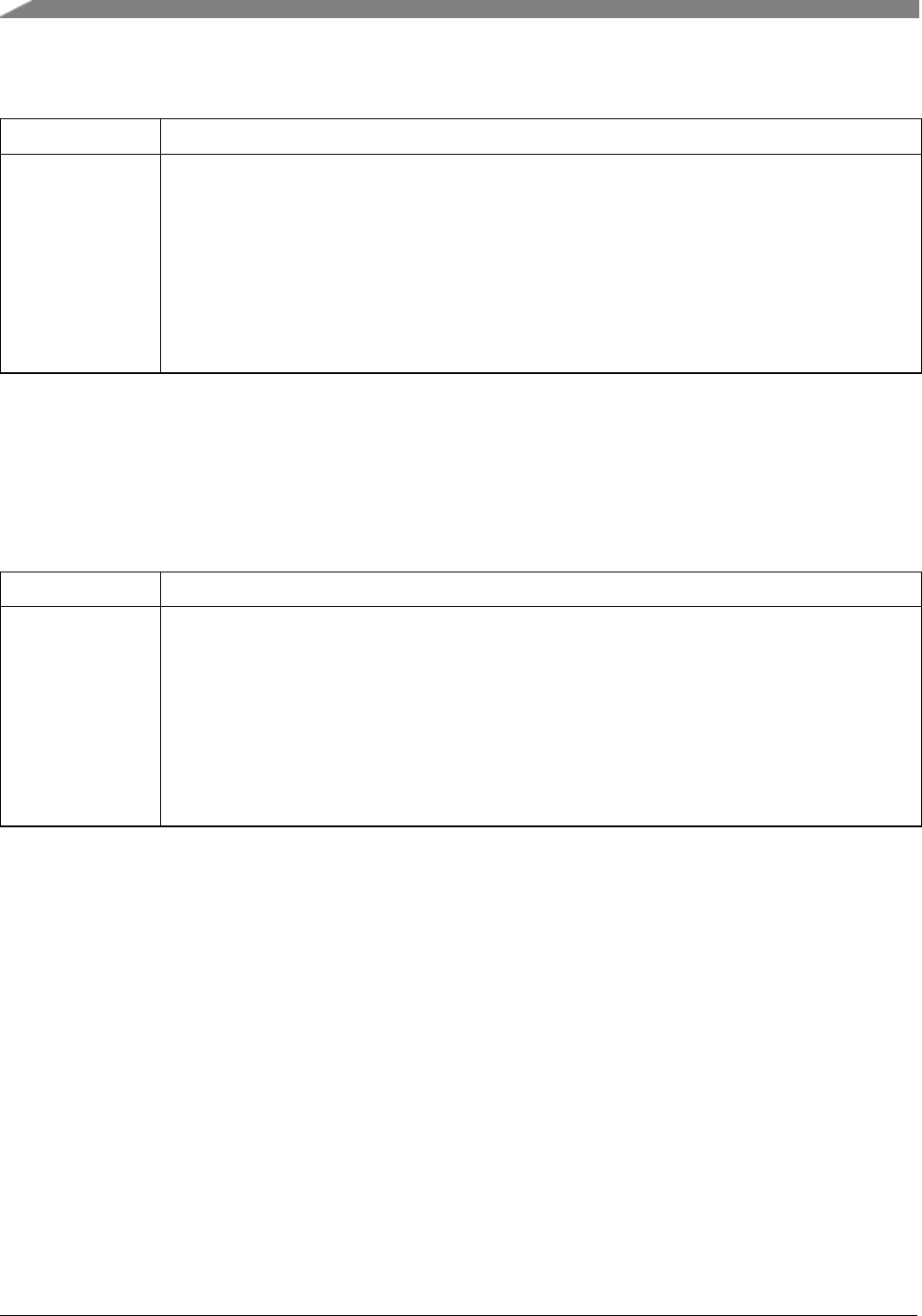

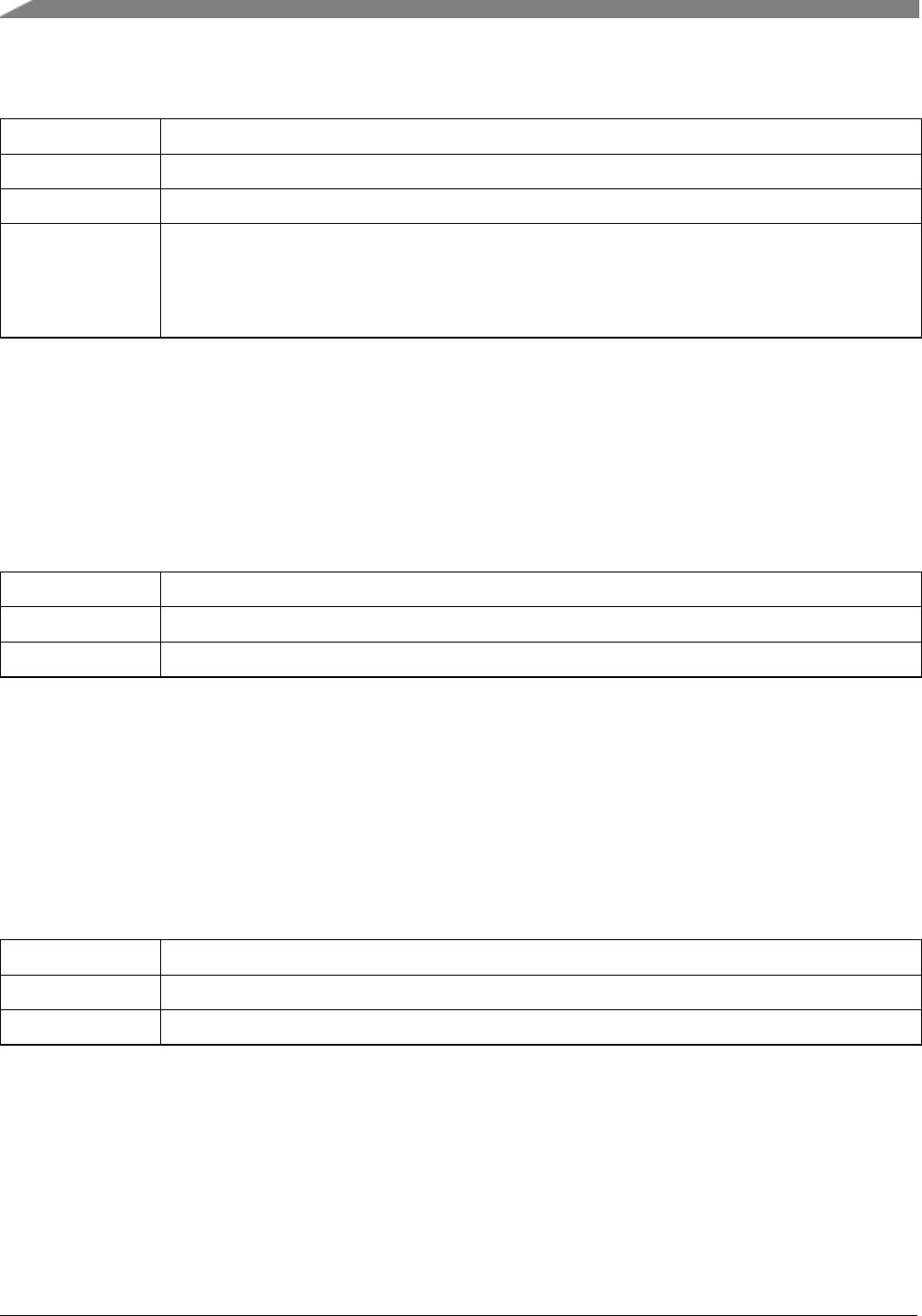

Chapter ENET: Ethernet MAC Driver

11.1 Overview ........................................119

11.2 Typical use case ....................................119

11.2.1 ENET Initialization, receive, and transmit operations ................119

11.3 Data Structure Documentation ............................127

11.3.1 struct enet_rx_bd_struct_t ..............................127

11.3.2 struct enet_tx_bd_struct_t ..............................128

11.3.3 struct enet_data_error_stats_t ............................128

11.3.4 struct enet_buffer_config_t .............................129

11.3.5 struct enet_intcoalesce_config_t ...........................130

11.3.6 struct enet_config_t .................................130

11.3.7 struct _enet_handle .................................132

11.4 Macro Definition Documentation ...........................133

11.4.1 FSL_ENET_DRIVER_VERSION .........................133

11.4.2 ENET_BUFFDESCRIPTOR_RX_EMPTY_MASK ................135

11.4.3 ENET_BUFFDESCRIPTOR_RX_SOFTOWNER1_MASK ............135

11.4.4 ENET_BUFFDESCRIPTOR_RX_WRAP_MASK .................135

11.4.5 ENET_BUFFDESCRIPTOR_RX_SOFTOWNER2_Mask .............135

11.4.6 ENET_BUFFDESCRIPTOR_RX_LAST_MASK .................135

11.4.7 ENET_BUFFDESCRIPTOR_RX_MISS_MASK .................135

11.4.8 ENET_BUFFDESCRIPTOR_RX_BROADCAST_MASK .............135

11.4.9 ENET_BUFFDESCRIPTOR_RX_MULTICAST_MASK .............135

11.4.10 ENET_BUFFDESCRIPTOR_RX_LENVLIOLATE_MASK ...........135

11.4.11 ENET_BUFFDESCRIPTOR_RX_NOOCTET_MASK ..............135

11.4.12 ENET_BUFFDESCRIPTOR_RX_CRC_MASK ..................135

11.4.13 ENET_BUFFDESCRIPTOR_RX_OVERRUN_MASK ..............135

11.4.14 ENET_BUFFDESCRIPTOR_RX_TRUNC_MASK ................135

11.4.15 ENET_BUFFDESCRIPTOR_TX_READY_MASK ................135

11.4.16 ENET_BUFFDESCRIPTOR_TX_SOFTOWENER1_MASK ...........135

11.4.17 ENET_BUFFDESCRIPTOR_TX_WRAP_MASK .................135

11.4.18 ENET_BUFFDESCRIPTOR_TX_SOFTOWENER2_MASK ...........135

11.4.19 ENET_BUFFDESCRIPTOR_TX_LAST_MASK .................135

11.4.20 ENET_BUFFDESCRIPTOR_TX_TRANMITCRC_MASK ............135

11.4.21 ENET_BUFFDESCRIPTOR_RX_ERR_MASK ..................135

11.4.22 ENET_FRAME_MAX_FRAMELEN ........................136

11.4.23 ENET_FIFO_MIN_RX_FULL ...........................136

NXP Semiconductors

MCUXpresso SDK API Reference Manual

ix

Section

Number

Contents

Title

Page

Number

11.4.24 ENET_RX_MIN_BUFFERSIZE ..........................136

11.4.25 ENET_PHY_MAXADDRESS ...........................136

11.5 Typedef Documentation ................................136

11.5.1 enet_callback_t ...................................136

11.6 Enumeration Type Documentation ..........................136

11.6.1 _enet_status .....................................136

11.6.2 enet_mii_mode_t ...................................136

11.6.3 enet_mii_speed_t ..................................136

11.6.4 enet_mii_duplex_t ..................................137

11.6.5 enet_mii_write_t ...................................137

11.6.6 enet_mii_read_t ...................................137

11.6.7 enet_mii_extend_opcode ..............................137

11.6.8 enet_special_control_flag_t .............................137

11.6.9 enet_interrupt_enable_t ...............................138

11.6.10 enet_event_t .....................................138

11.6.11 enet_tx_accelerator_t ................................139

11.6.12 enet_rx_accelerator_t ................................139

11.7 Function Documentation ...............................139

11.7.1 ENET_GetDefaultConfig ..............................139

11.7.2 ENET_Init ......................................139

11.7.3 ENET_Deinit ....................................140

11.7.4 ENET_Reset .....................................140

11.7.5 ENET_SetMII ....................................140

11.7.6 ENET_SetSMI ....................................141

11.7.7 ENET_GetSMI ...................................141

11.7.8 ENET_ReadSMIData ................................141

11.7.9 ENET_StartSMIRead ................................142

11.7.10 ENET_StartSMIWrite ................................142

11.7.11 ENET_StartExtC45SMIRead ............................142

11.7.12 ENET_StartExtC45SMIWrite ............................143

11.7.13 ENET_SetMacAddr .................................143

11.7.14 ENET_GetMacAddr .................................143

11.7.15 ENET_AddMulticastGroup .............................144

11.7.16 ENET_LeaveMulticastGroup ............................145

11.7.17 ENET_ActiveRead ..................................145

11.7.18 ENET_EnableSleepMode ..............................145

11.7.19 ENET_GetAccelFunction ..............................145

11.7.20 ENET_EnableInterrupts ...............................146

11.7.21 ENET_DisableInterrupts ...............................146

11.7.22 ENET_GetInterruptStatus ..............................147

11.7.23 ENET_ClearInterruptStatus .............................147

11.7.24 ENET_SetCallback .................................147

x

MCUXpresso SDK API Reference Manual

NXP Semiconductors

Section

Number

Contents

Title

Page

Number

11.7.25 ENET_GetRxErrBeforeReadFrame .........................148

11.7.26 ENET_GetRxFrameSize ...............................148

11.7.27 ENET_ReadFrame ..................................149

11.7.28 ENET_SendFrame ..................................150

11.7.29 ENET_TransmitIRQHandler ............................150

11.7.30 ENET_ReceiveIRQHandler .............................151

11.7.31 ENET_ErrorIRQHandler ..............................151

11.7.32 ENET_CommonFrame0IRQHandler ........................151

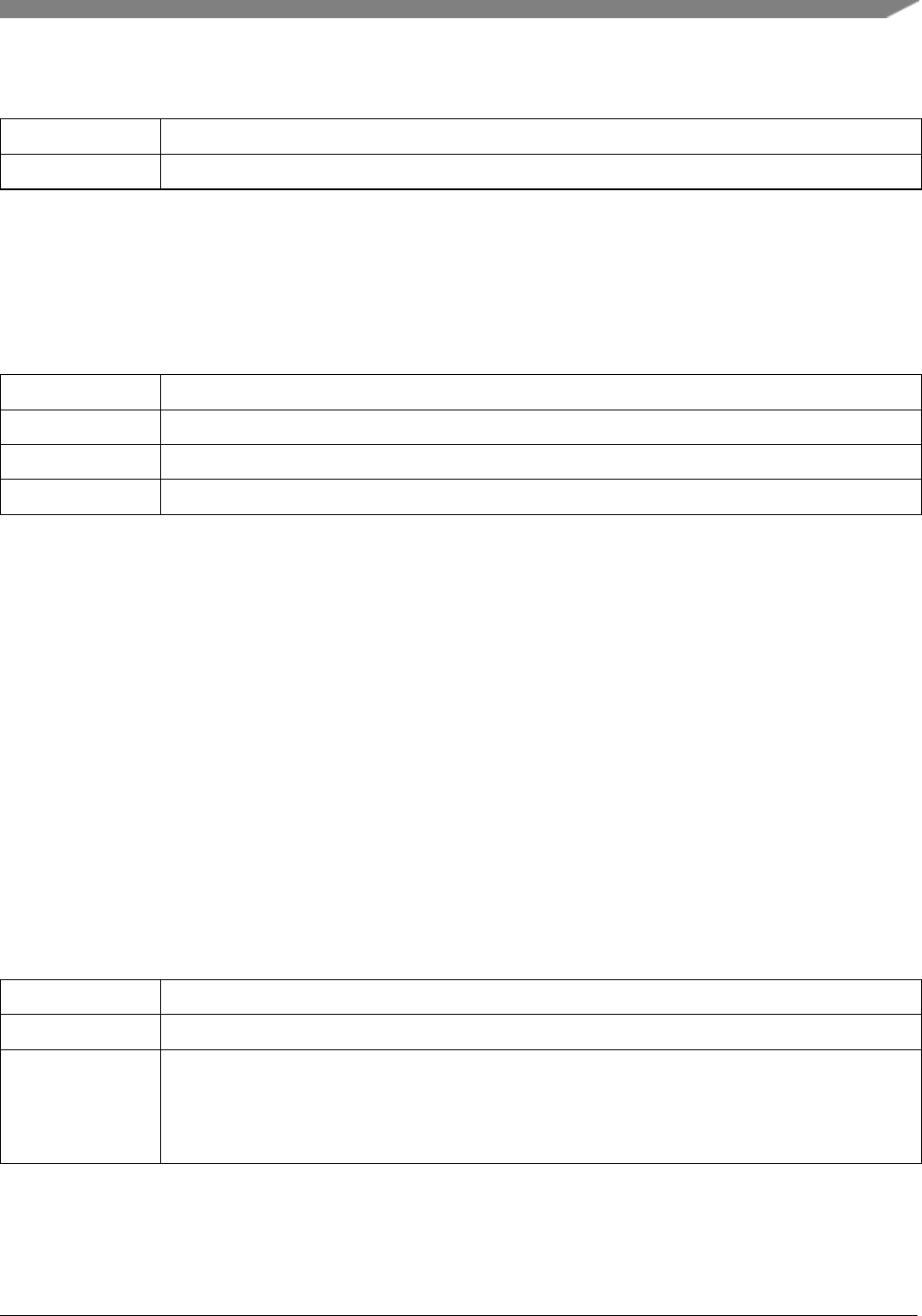

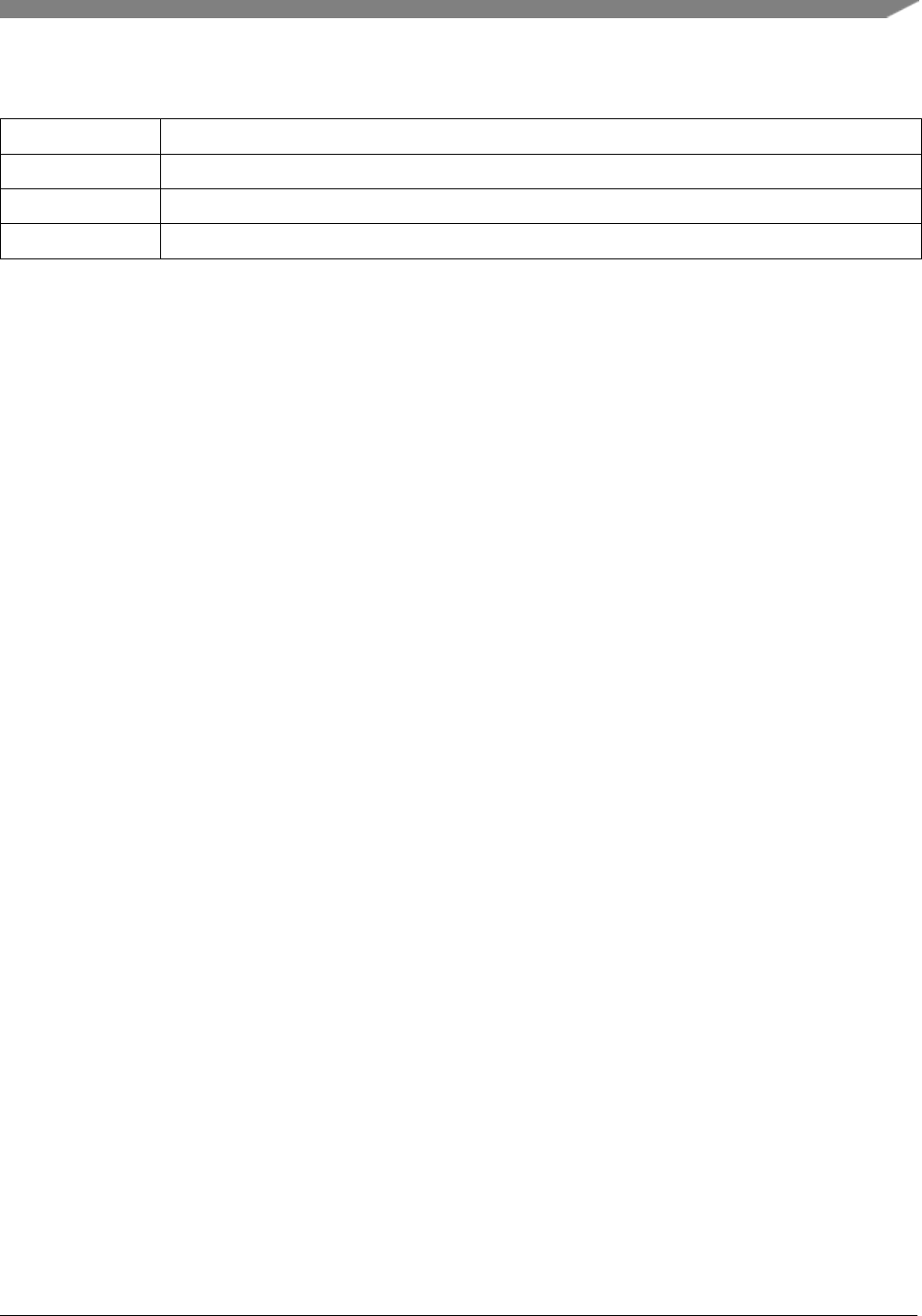

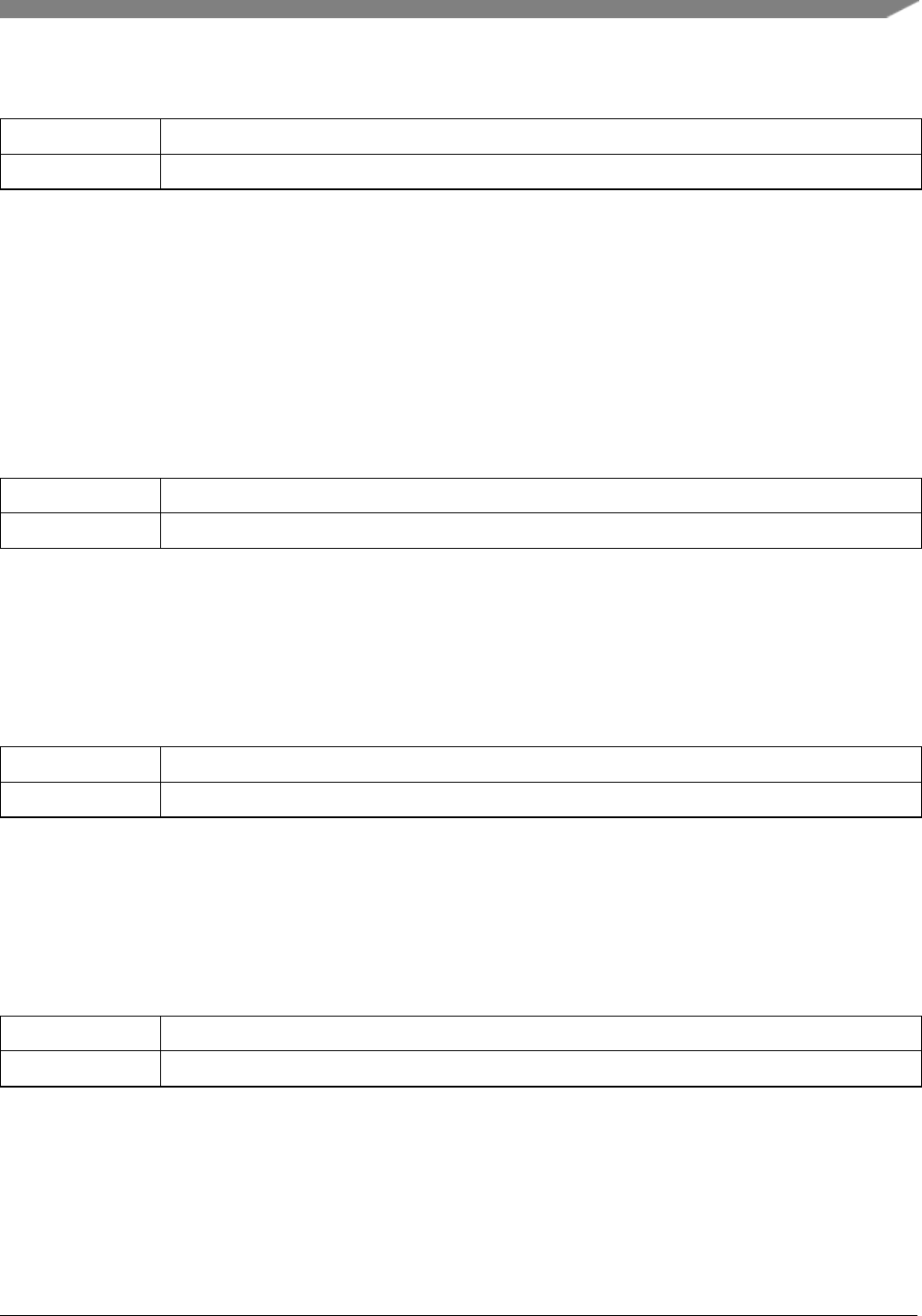

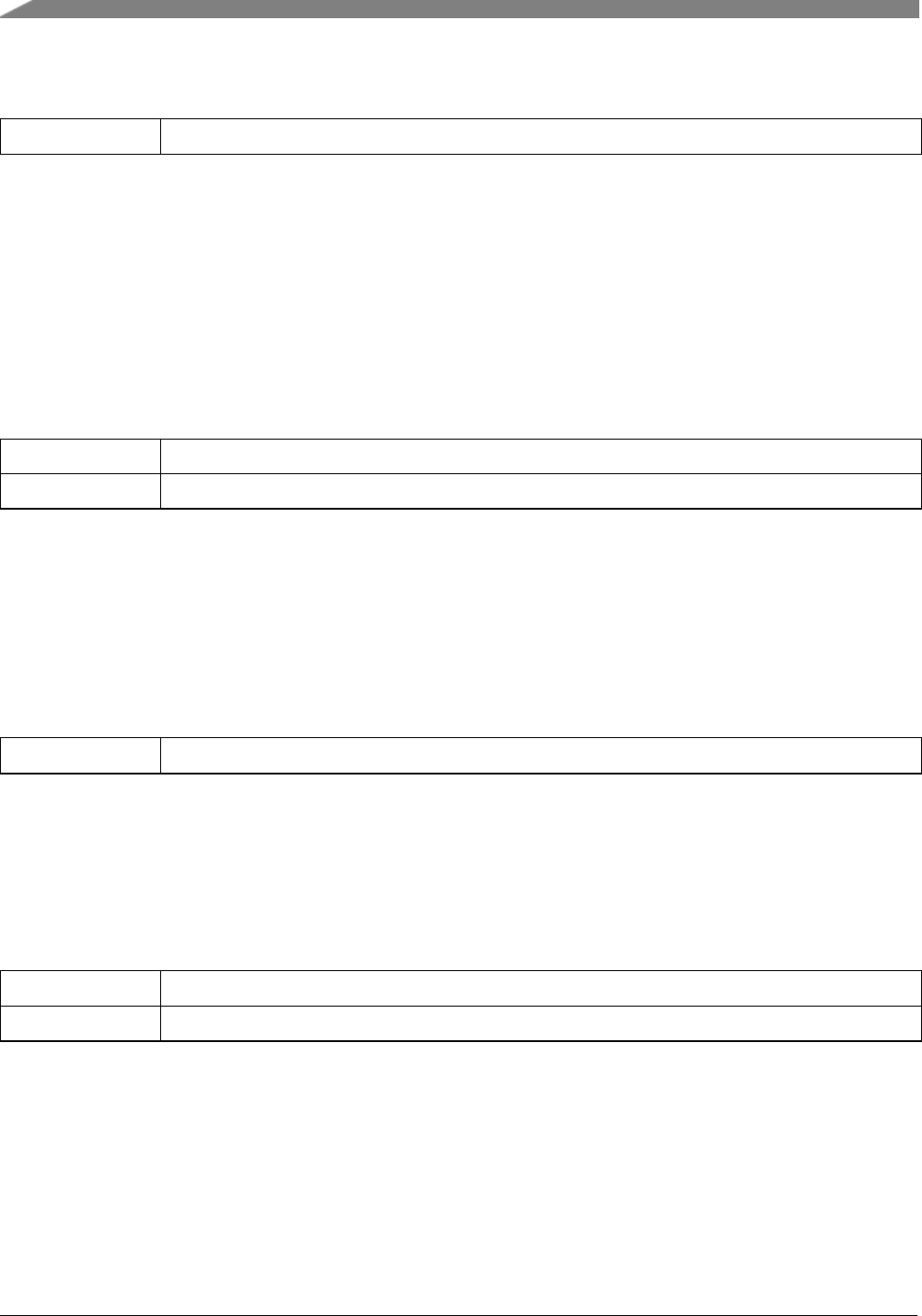

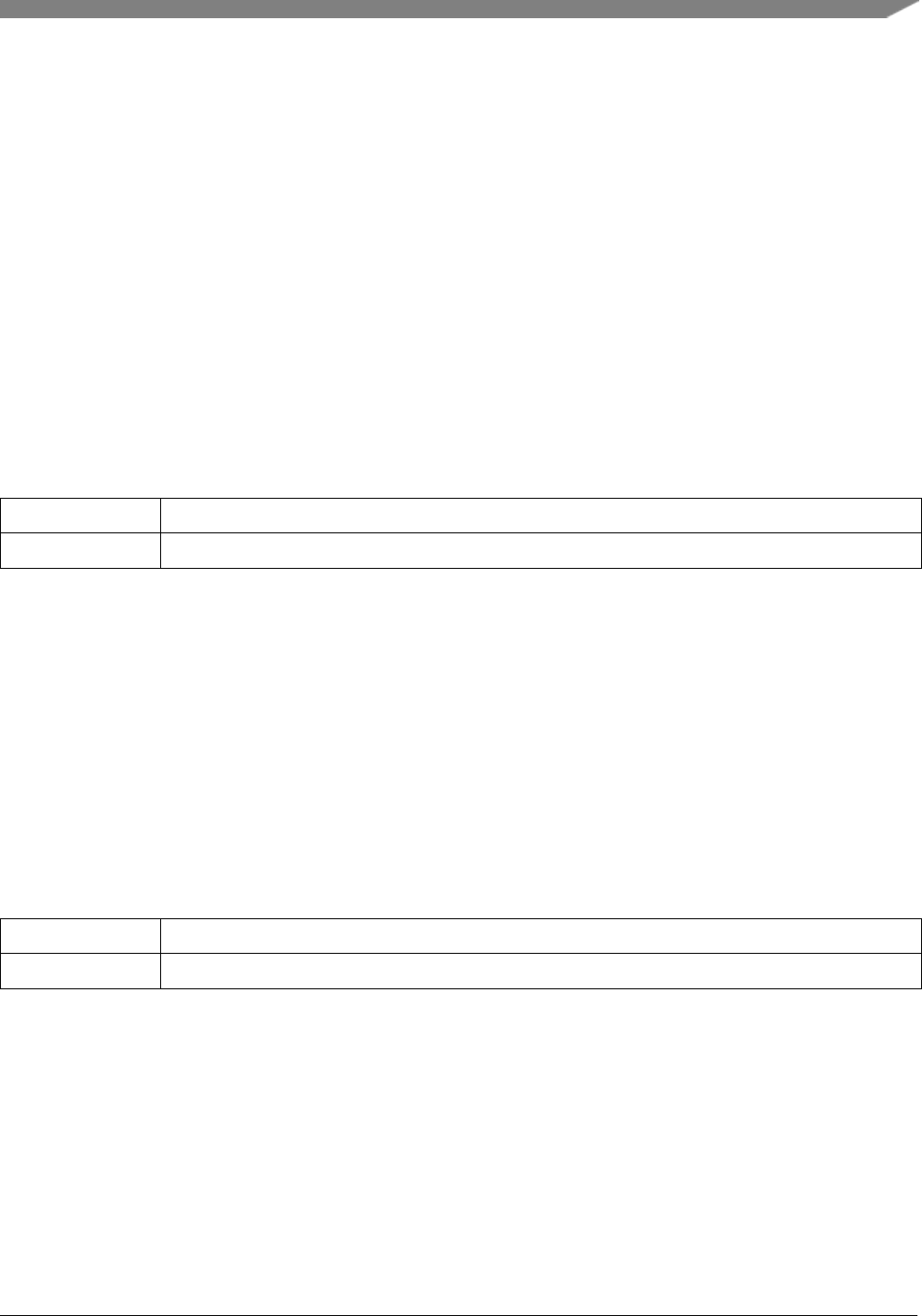

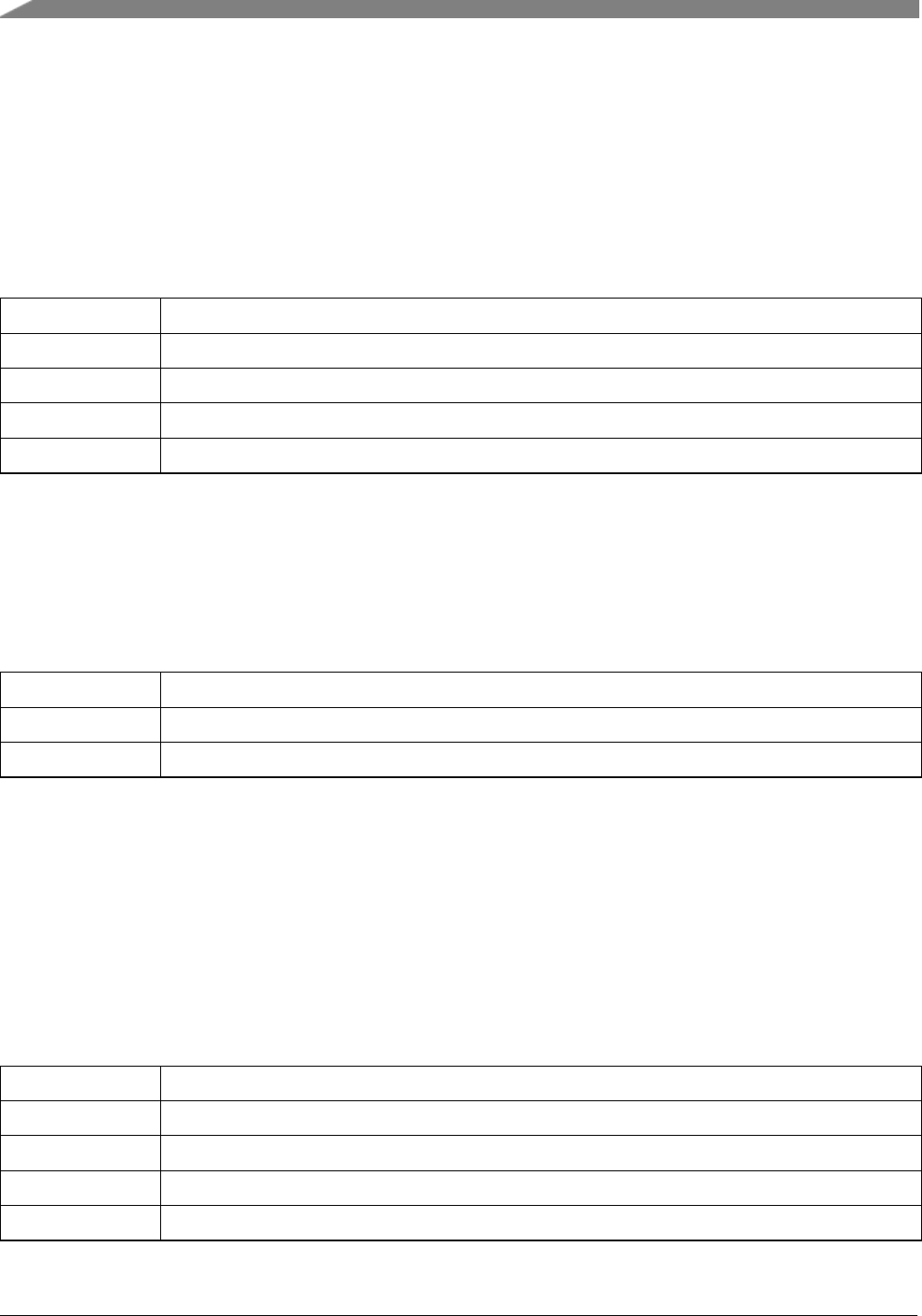

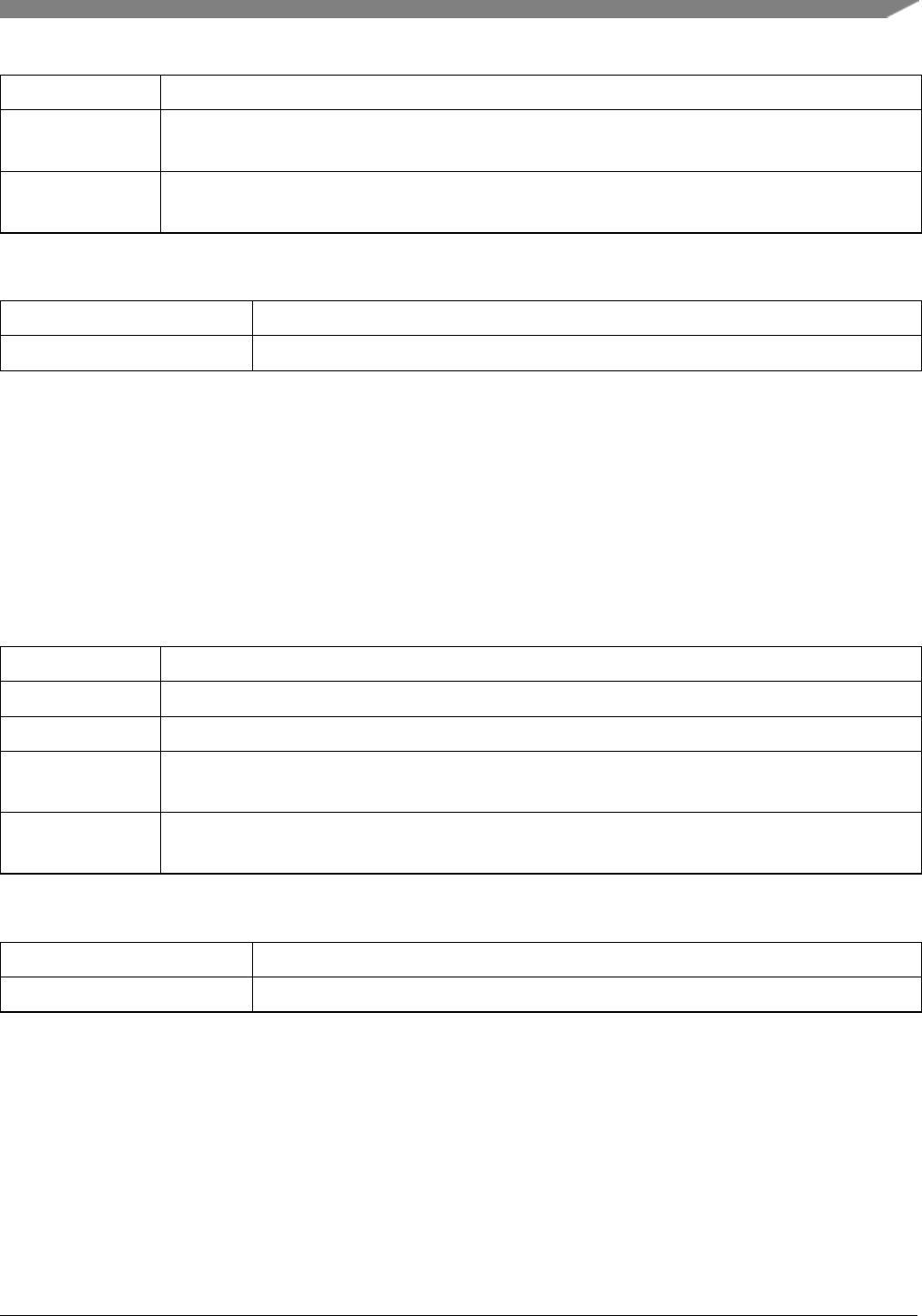

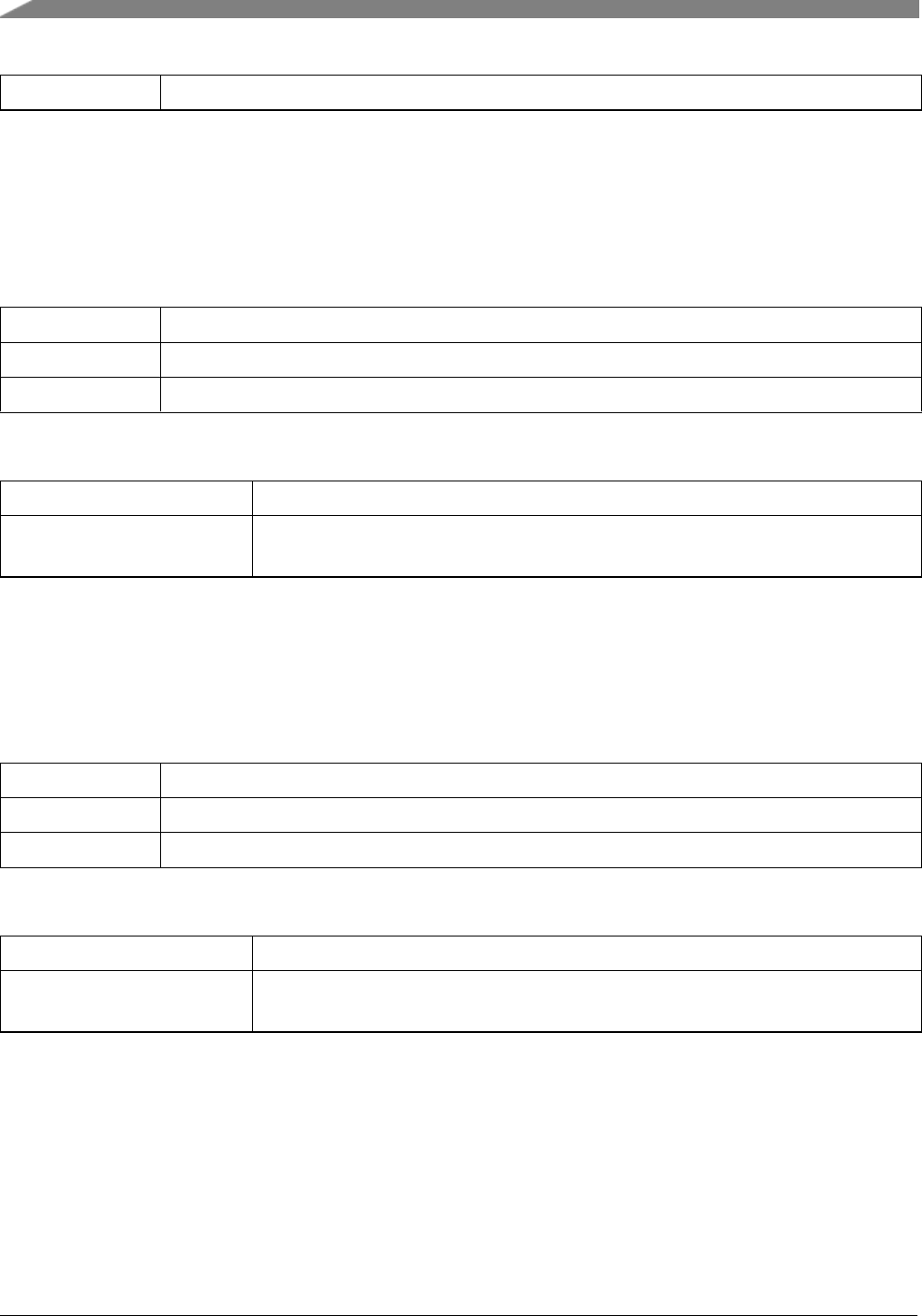

Chapter EPIT: Enhanced Periodic Interrupt Timer

12.1 Overview ........................................153

12.2 Function groups ....................................153

12.2.1 Initialization and deinitialization ..........................153

12.3 Typical use case ....................................153

12.3.1 EPIT interrupt example ...............................153

12.4 Data Structure Documentation ............................156

12.4.1 struct epit_config_t ..................................156

12.5 Enumeration Type Documentation ..........................157

12.5.1 epit_clock_source_t .................................157

12.5.2 epit_output_operation_mode_t ...........................157

12.5.3 epit_interrupt_enable_t ...............................157

12.5.4 epit_status_flags_t ..................................157

12.6 Function Documentation ...............................157

12.6.1 EPIT_SoftwareReset .................................157

12.6.2 EPIT_Init .......................................158

12.6.3 EPIT_Deinit .....................................158

12.6.4 EPIT_GetDefaultConfig ...............................158

12.6.5 EPIT_SetClockSource ................................159

12.6.6 EPIT_SetClockDivider ...............................159

12.6.7 EPIT_GetClockDivider ...............................159

12.6.8 EPIT_StartTimer ...................................159

12.6.9 EPIT_StopTimer ...................................160

12.6.10 EPIT_SetTimerPeriod ................................160

12.6.11 EPIT_GetCurrentTimerCount ............................160

12.6.12 EPIT_SetOutputOperationMode ...........................161

12.6.13 EPIT_SetOutputCompareValue ...........................161

12.6.14 EPIT_EnableInterrupts ...............................161

12.6.15 EPIT_DisableInterrupts ...............................161

12.6.16 EPIT_GetEnabledInterrupts .............................162

NXP Semiconductors

MCUXpresso SDK API Reference Manual

xi

Section

Number

Contents

Title

Page

Number

12.6.17 EPIT_GetStatusFlags ................................162

12.6.18 EPIT_ClearStatusFlags ...............................162

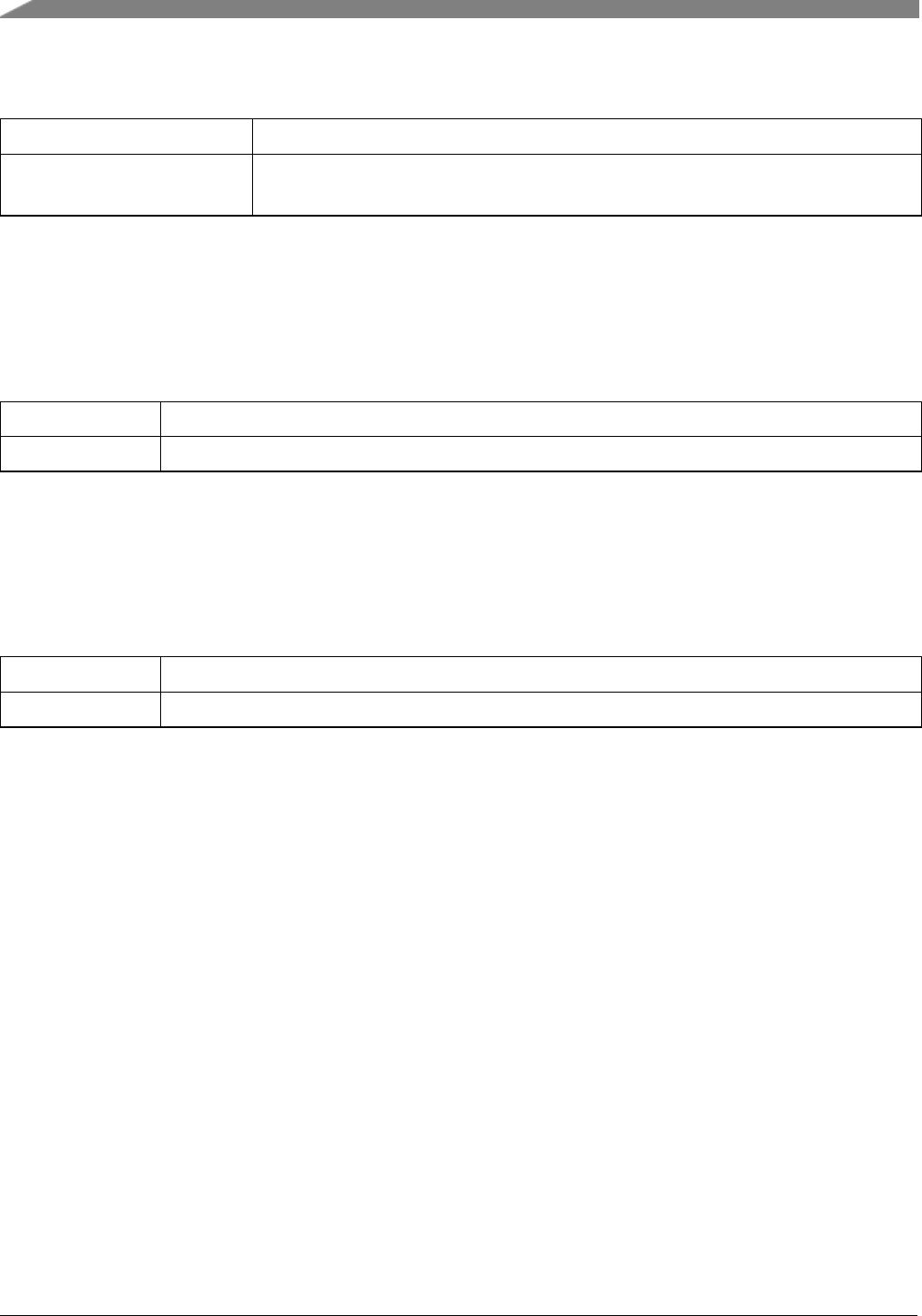

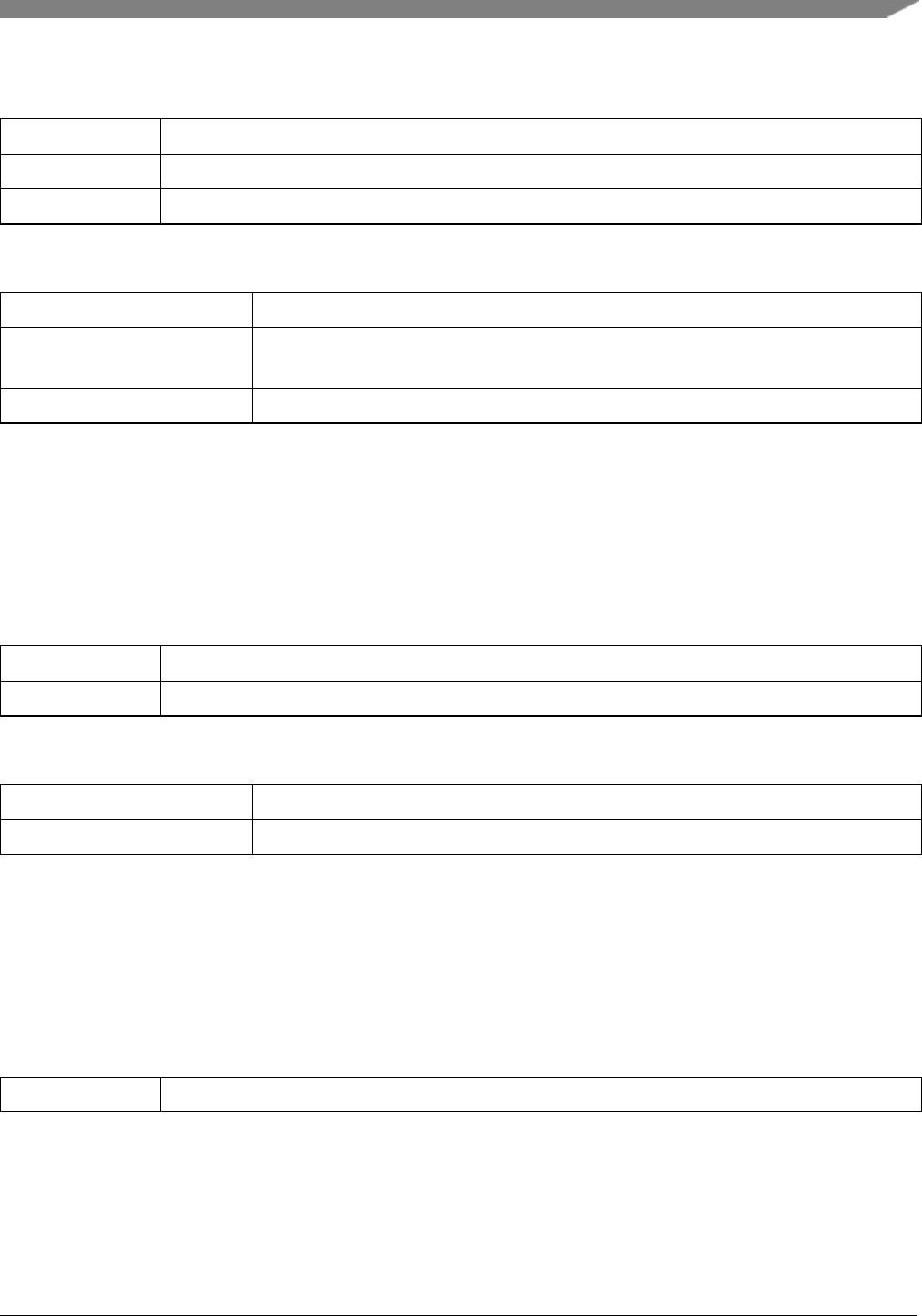

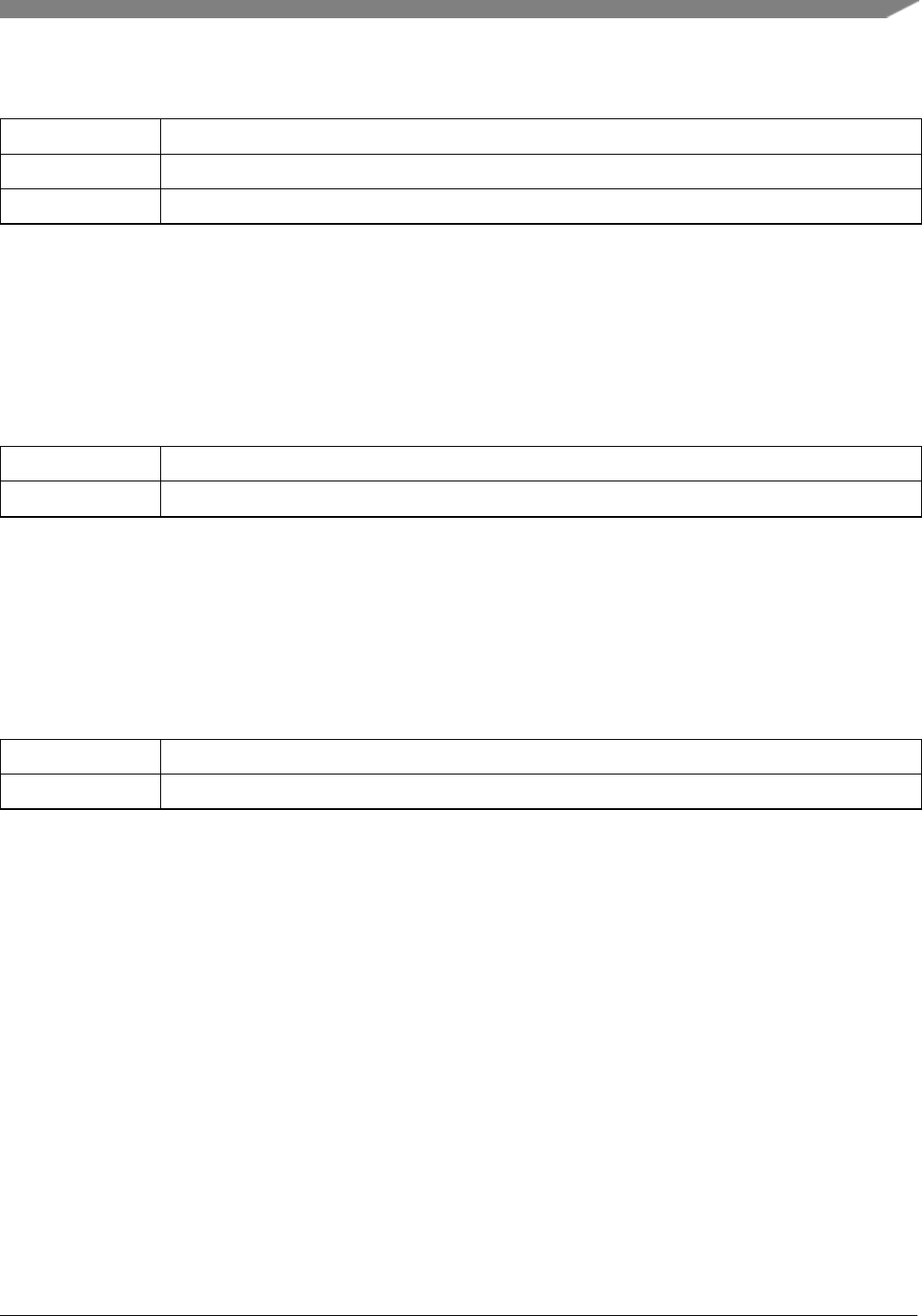

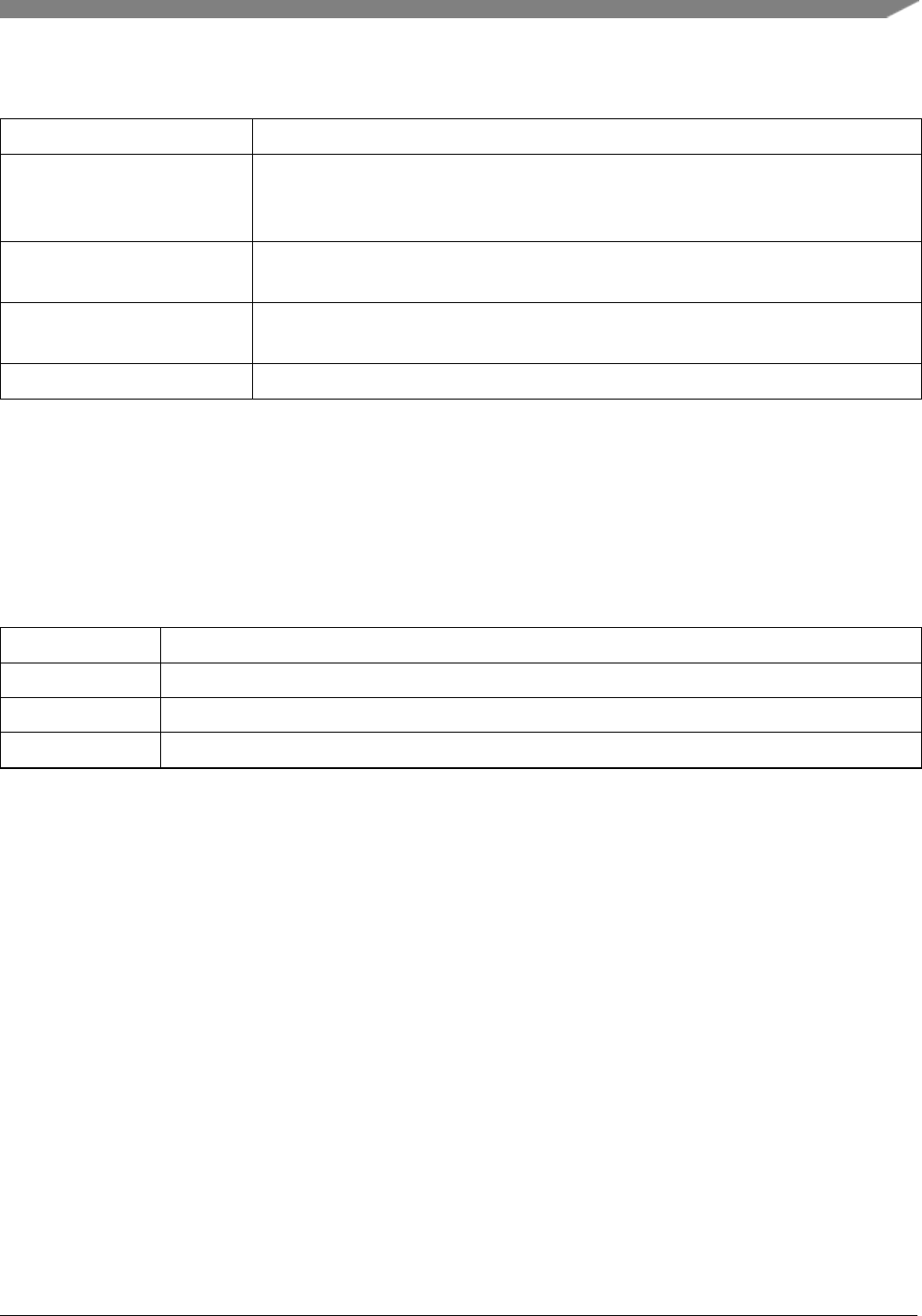

Chapter FlexCAN: Flex Controller Area Network Driver

13.1 Overview ........................................163

13.2 FlexCAN Driver ....................................164

13.2.1 Overview .......................................164

13.2.2 Typical use case ...................................164

13.2.3 Data Structure Documentation ............................172

13.2.4 Macro Definition Documentation ..........................176

13.2.5 Typedef Documentation ...............................181

13.2.6 Enumeration Type Documentation .........................181

13.2.7 Function Documentation ...............................184

13.3 FlexCAN eDMA Driver ................................199

13.3.1 Overview .......................................199

13.3.2 Data Structure Documentation ............................199

13.3.3 Typedef Documentation ...............................200

13.3.4 Function Documentation ...............................200

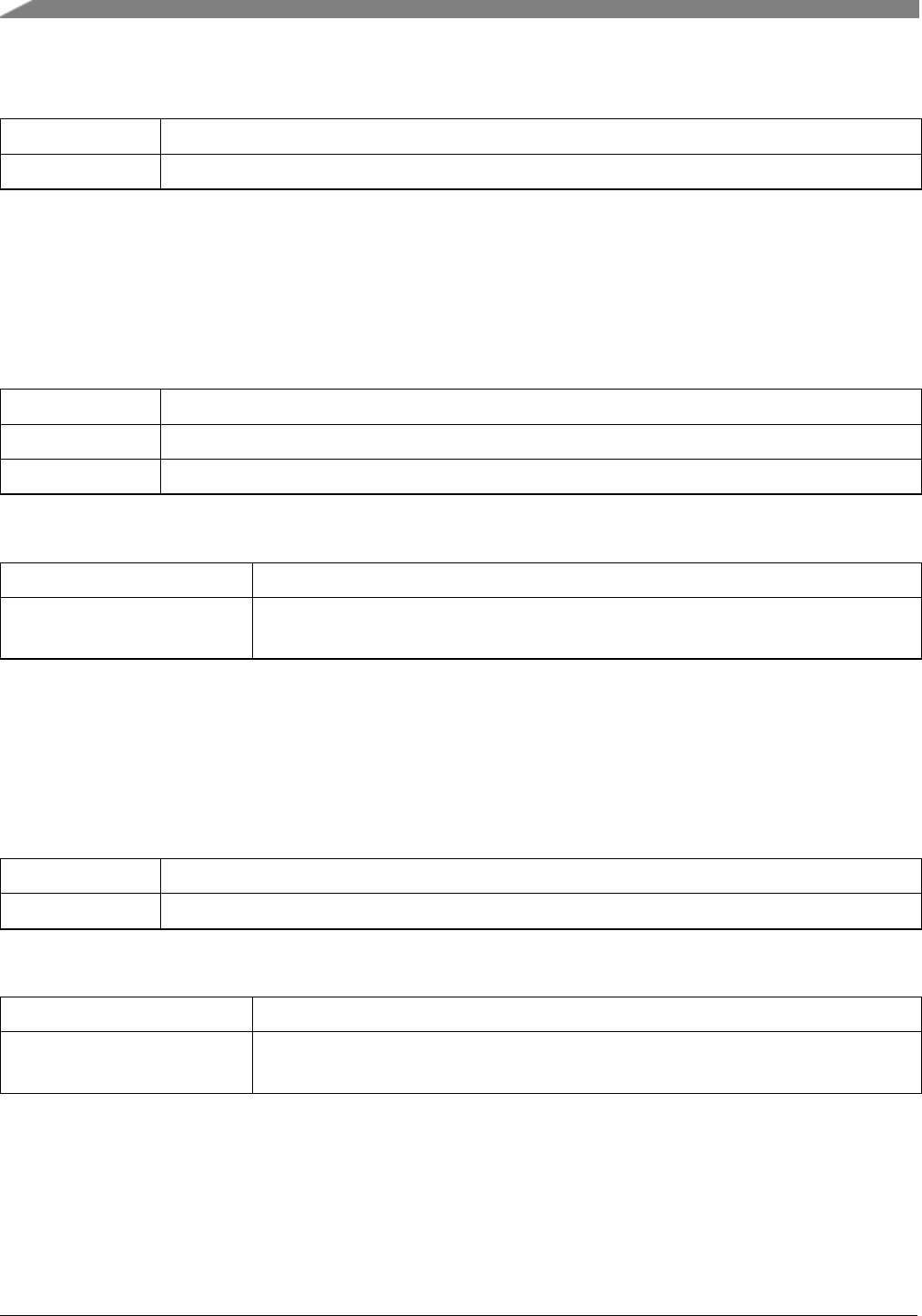

Chapter GPT: General Purpose Timer

14.1 Overview ........................................203

14.2 Function groups ....................................203

14.2.1 Initialization and deinitialization ..........................203

14.3 Typical use case ....................................203

14.3.1 GPT interrupt example ................................203

14.4 Data Structure Documentation ............................207

14.4.1 struct gpt_config_t ..................................207

14.5 Enumeration Type Documentation ..........................208

14.5.1 gpt_clock_source_t .................................208

14.5.2 gpt_input_capture_channel_t ............................208

14.5.3 gpt_input_operation_mode_t ............................208

14.5.4 gpt_output_compare_channel_t ...........................209

14.5.5 gpt_output_operation_mode_t ............................209

14.5.6 gpt_interrupt_enable_t ................................209

14.5.7 gpt_status_flag_t ...................................209

14.6 Function Documentation ...............................210

14.6.1 GPT_Init .......................................210

xii

MCUXpresso SDK API Reference Manual

NXP Semiconductors

Section

Number

Contents

Title

Page

Number

14.6.2 GPT_Deinit .....................................210

14.6.3 GPT_GetDefaultConfig ...............................210

14.6.4 GPT_SoftwareReset .................................210

14.6.5 GPT_SetClockSource ................................211

14.6.6 GPT_GetClockSource ................................211

14.6.7 GPT_SetClockDivider ................................211

14.6.8 GPT_GetClockDivider ................................211

14.6.9 GPT_SetOscClockDivider ..............................212

14.6.10 GPT_GetOscClockDivider .............................212

14.6.11 GPT_StartTimer ...................................212

14.6.12 GPT_StopTimer ...................................212

14.6.13 GPT_GetCurrentTimerCount ............................213

14.6.14 GPT_SetInputOperationMode ............................213

14.6.15 GPT_GetInputOperationMode ...........................213

14.6.16 GPT_GetInputCaptureValue .............................214

14.6.17 GPT_SetOutputOperationMode ...........................215

14.6.18 GPT_GetOutputOperationMode ...........................215

14.6.19 GPT_SetOutputCompareValue ...........................215

14.6.20 GPT_GetOutputCompareValue ...........................216

14.6.21 GPT_ForceOutput ..................................216

14.6.22 GPT_EnableInterrupts ................................216

14.6.23 GPT_DisableInterrupts ...............................217

14.6.24 GPT_GetEnabledInterrupts .............................217

14.6.25 GPT_GetStatusFlags .................................217

14.6.26 GPT_ClearStatusFlags ................................218

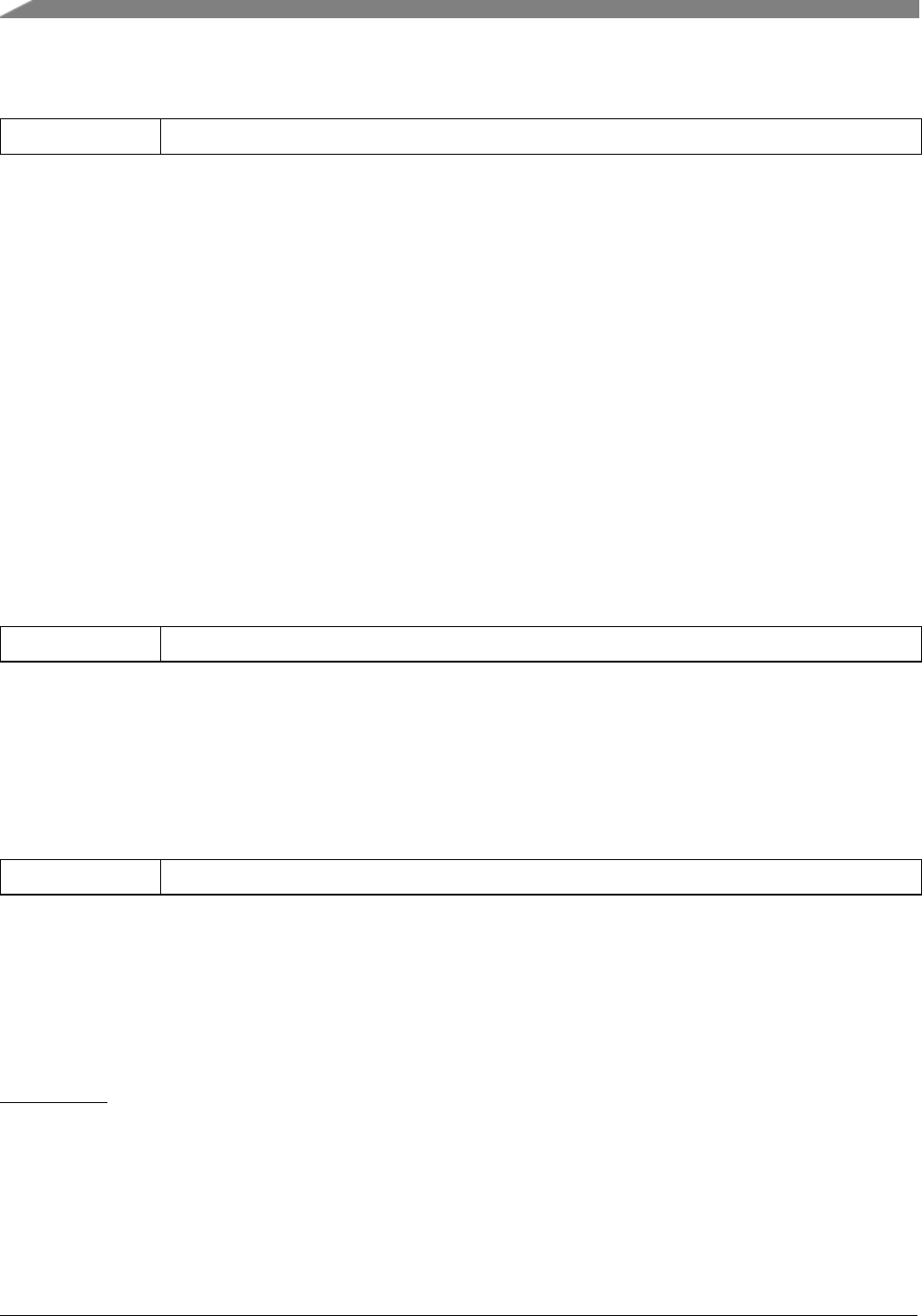

Chapter GPC: General Power Controller Driver

15.1 Overview ........................................221

15.2 Macro Definition Documentation ...........................221

15.2.1 FSL_GPC_DRIVER_VERSION ..........................221

15.3 Function Documentation ...............................222

15.3.1 GPC_AllowIRQs ..................................222

15.3.2 GPC_DisallowIRQs .................................223

15.3.3 GPC_EnableIRQ ...................................223

15.3.4 GPC_DisableIRQ ..................................223

15.3.5 GPC_GetIRQStatusFlag ...............................223

15.3.6 GPC_RequestL2CachePowerDown .........................224

15.3.7 GPC_RequestVADCPowerDown ..........................224

15.3.8 GPC_GetVADCPowerDownFlag ..........................224

15.3.9 GPC_HasDVFS0ChangeRequest ..........................224

15.3.10 GPC_RequestDisplayPowerOn ...........................225

15.3.11 GPC_RequestMEGAPowerOn ...........................225

NXP Semiconductors

MCUXpresso SDK API Reference Manual

xiii

Section

Number

Contents

Title

Page

Number

Chapter GPIO: General-Purpose Input/Output Driver

16.1 Overview ........................................227

16.2 GPIO Driver ......................................228

16.2.1 Overview .......................................228

16.2.2 Typical use case ...................................228

16.2.3 Data Structure Documentation ............................229

16.2.4 Macro Definition Documentation ..........................230

16.2.5 Enumeration Type Documentation .........................230

16.2.6 Function Documentation ...............................230

Chapter I2C: Inter-Integrated Circuit Driver

17.1 Overview ........................................235

17.2 I2C Driver .......................................236

17.2.1 Overview .......................................236

17.2.2 Typical use case ...................................236

17.2.3 Data Structure Documentation ............................242

17.2.4 Macro Definition Documentation ..........................246

17.2.5 Typedef Documentation ...............................246

17.2.6 Enumeration Type Documentation .........................246

17.2.7 Function Documentation ...............................248

17.3 I2C FreeRTOS Driver .................................261

17.3.1 Overview .......................................261

17.3.2 Function Documentation ...............................261

Chapter PWM: Pulse Width Modulation Driver

18.1 Overview ........................................263

18.2 PWM Driver ......................................264

18.2.1 Overview .......................................264

18.2.2 Typical use case ...................................264

18.2.3 Enumeration Type Documentation .........................268

18.2.4 Function Documentation ...............................270

Chapter UART: Universal Asynchronous Receiver/Transmitter Driver

19.1 Overview ........................................277

19.2 UART Driver ......................................278

19.2.1 Overview .......................................278

xiv

MCUXpresso SDK API Reference Manual

NXP Semiconductors

Section

Number

Contents

Title

Page

Number

19.2.2 Typical use case ...................................278

19.2.3 Data Structure Documentation ............................288

19.2.4 Macro Definition Documentation ..........................290

19.2.5 Typedef Documentation ...............................290

19.2.6 Enumeration Type Documentation .........................290

19.2.7 Function Documentation ...............................292

19.2.8 Variable Documentation ...............................307

19.3 UART FreeRTOS Driver ...............................308

19.3.1 Overview .......................................308

19.3.2 Data Structure Documentation ............................308

19.3.3 Function Documentation ...............................309

19.4 UART SDMA Driver .................................312

19.4.1 Overview .......................................312

19.4.2 Data Structure Documentation ............................312

19.4.3 Typedef Documentation ...............................313

19.4.4 Function Documentation ...............................313

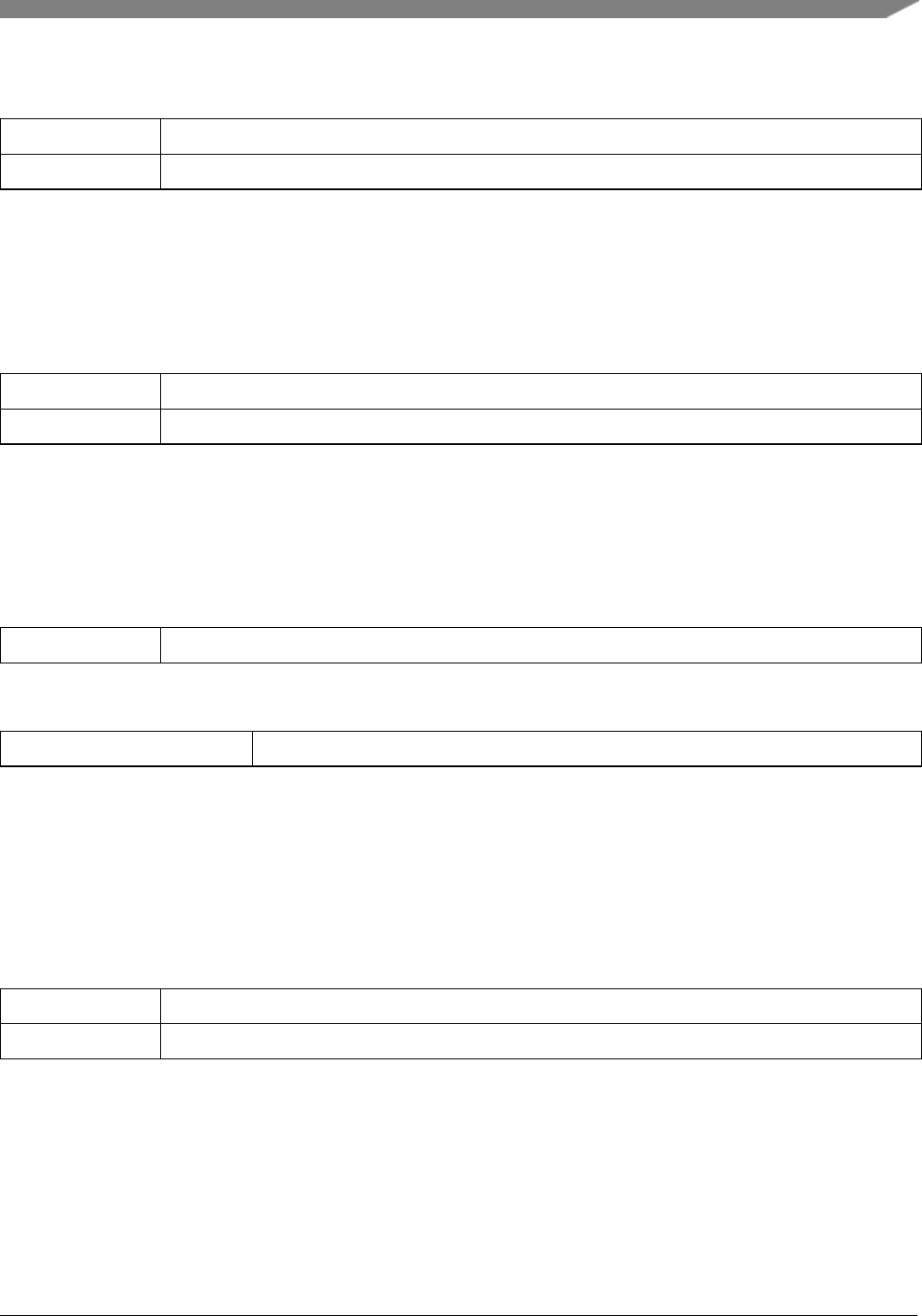

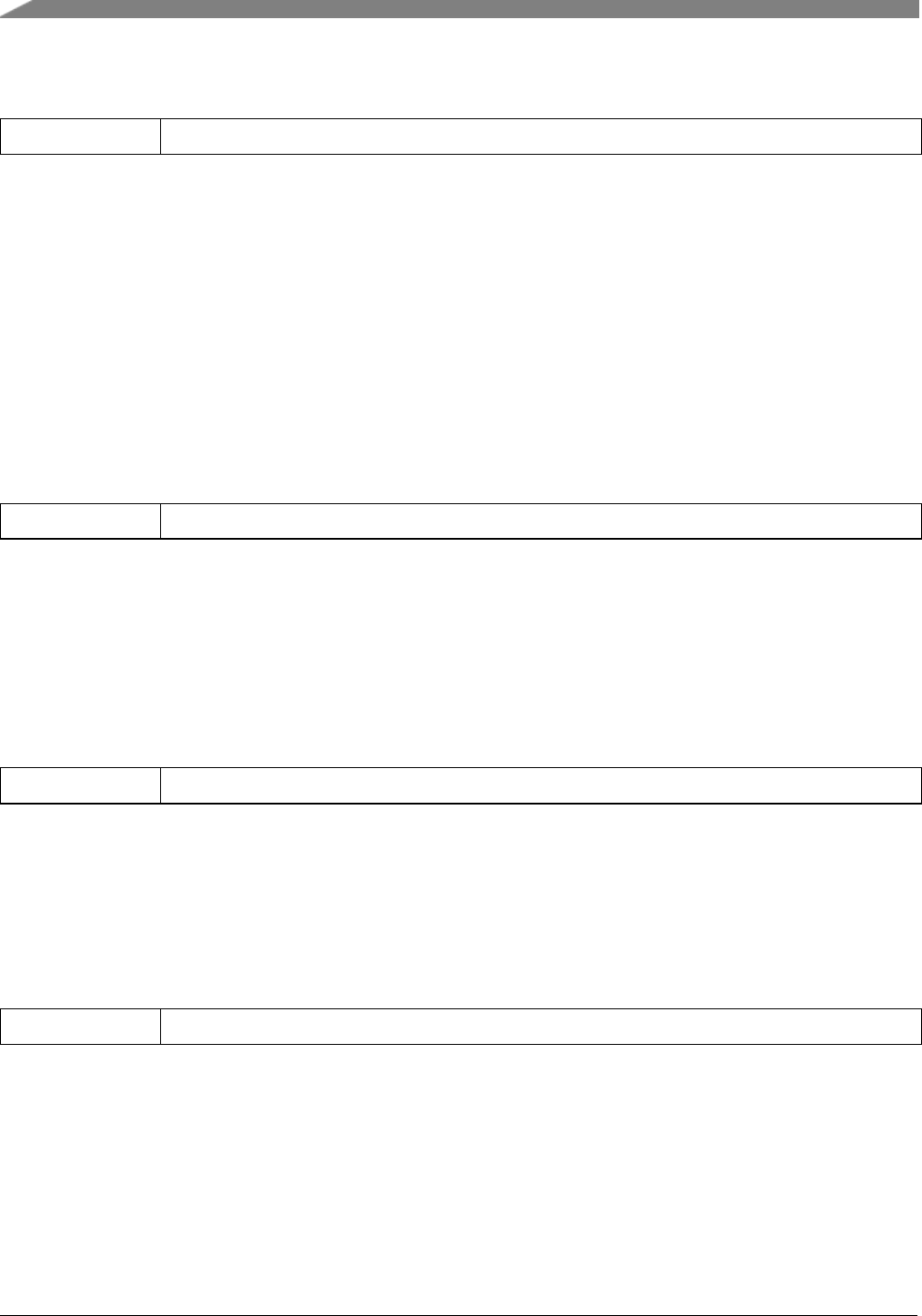

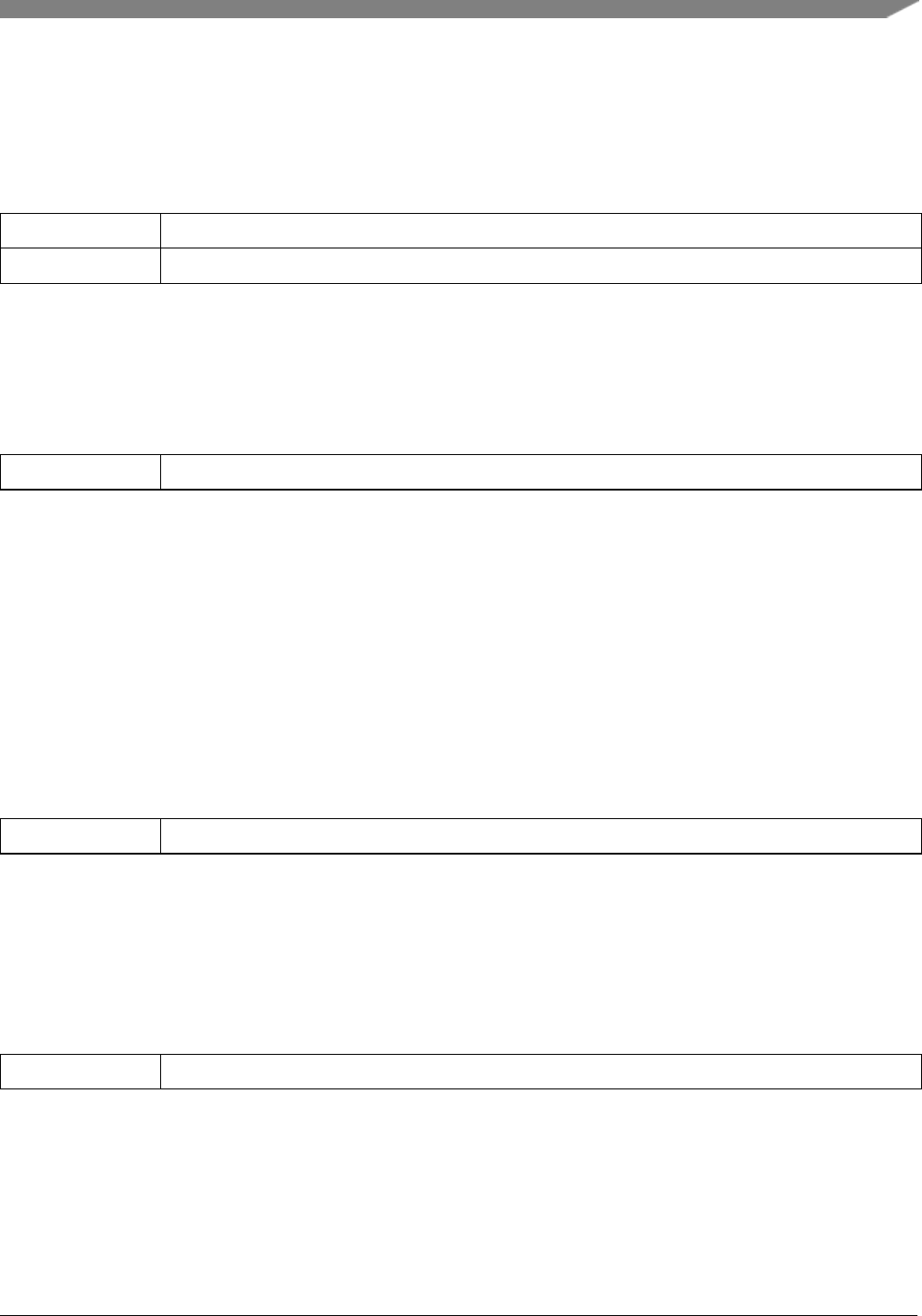

Chapter MMDC: Multi Mode DDR Controller Driver

20.1 Overview ........................................317

20.2 Typical use case ....................................317

20.3 Data Structure Documentation ............................324

20.3.1 struct mmdc_readDQS_calibration_config_t ....................324

20.3.2 struct mmdc_writeLeveling_calibration_config_t ..................325

20.3.3 struct mmdc_read_calibration_config_t .......................326

20.3.4 struct mmdc_fine_tuning_config_t .........................326

20.3.5 struct mmdc_odt_config_t ..............................327

20.3.6 struct mmdc_power_config_t ............................328

20.3.7 struct mmdc_zq_config_t ..............................329

20.3.8 struct mmdc_cmd_config_t .............................329

20.3.9 struct mmdc_device_timing_t ............................330

20.3.10 struct mmdc_auto_refresh_t .............................332

20.3.11 struct mmdc_exaccess_config_t ...........................332

20.3.12 struct mmdc_profiling_config_t ...........................333

20.3.13 struct mmdc_performance_config_t .........................333

20.3.14 struct mmdc_device_config_t ............................334

20.3.15 struct mmdc_config_t ................................334

20.4 Macro Definition Documentation ...........................335

20.4.1 MMDC_READ_DQS_FINE_TUNING_MASK ..................335

20.4.2 MMDC_WRITE_DQS_FINE_TUNING_MASK .................335

NXP Semiconductors

MCUXpresso SDK API Reference Manual

xv

Section

Number

Contents

Title

Page

Number

20.4.3 MMDC_PRE_DEFINE_VALUE_DEFAULT ...................335

20.4.4 MMDC_MEASUREUNIT_ERR_FREQ ......................335

20.5 Typedef Documentation ................................336

20.5.1 MMDC_SwitchFrequency ..............................336

20.6 Enumeration Type Documentation ..........................336

20.6.1 _mmdc_status ....................................336

20.6.2 mmdc_device_type_t ................................336

20.6.3 mmdc_device_bank_num_t .............................336

20.6.4 mmdc_row_addr_width_t ..............................336

20.6.5 mmdc_col_addr_width_t ..............................337

20.6.6 mmdc_burst_len_t ..................................337

20.6.7 mmdc_cmd_type_t ..................................337

20.6.8 mmdc_zq_calmode_t ................................337

20.6.9 mmdc_zq_calfreq_t .................................338

20.6.10 mmdc_refresh_sel_t .................................338

20.6.11 mmdc_profiling_action_t ..............................338

20.6.12 mmdc_calibration_type_t ..............................338

20.6.13 mmdc_calibaration_waitcycles_t ..........................338

20.6.14 mmdc_fine_tuning_dutycycle_t ...........................339

20.6.15 mmdc_termination_config_t .............................339

20.6.16 _mmdc_lpddr2_derate ................................339

20.6.17 _mmdc_exaccess_type ................................339

20.7 Function Documentation ...............................340

20.7.1 MMDC_GetDefaultConfig .............................340

20.7.2 MMDC_Init .....................................341

20.7.3 MMDC_Deinit ....................................341

20.7.4 MMDC_HandleCommand ..............................342

20.7.5 MMDC_GetReadData ................................342

20.7.6 MMDC_EnhancePerformance ............................342

20.7.7 MMDC_EnableAutoRefresh ............................342

20.7.8 MMDC_DisableAutoRefresh ............................343

20.7.9 MMDC_EnablePowerSaving ............................343

20.7.10 MMDC_DisablePowerSaving ............................343

20.7.11 MMDC_Profiling ..................................343

20.7.12 MMDC_LPDDR2UpdateDerate ...........................344

20.7.13 MMDC_MonitorLPDDR2OperationTemp .....................344

20.7.14 MMDC_ReadDQSGatingCalibration ........................344

20.7.15 MMDC_WriteLevelingCalibration .........................345

20.7.16 MMDC_WriteCalibration ..............................345

20.7.17 MMDC_ReadCalibration ..............................346

20.7.18 MMDC_DoFineTuning ...............................347

20.7.19 MMDC_SetTiming .................................347

xvi

MCUXpresso SDK API Reference Manual

NXP Semiconductors

Section

Number

Contents

Title

Page

Number

20.7.20 MMDC_DeviceInit .................................347

20.7.21 MMDC_EnterConfigurationMode ..........................348

20.7.22 MMDC_DoZQCalibration ..............................349

20.7.23 MMDC_EnableLowPowerMode ..........................349

20.7.24 MMDC_EnableDVFSMode .............................349

20.7.25 MMDC_Reset ....................................350

20.7.26 MMDC_SwitchDeviceFrequency ..........................350

20.7.27 MMDC_EnableSBS .................................350

20.7.28 MMDC_TriggerSBS .................................351

20.7.29 MMDC_GetAXIAddrBySBS ............................351

20.7.30 MMDC_GetAXIAttributeBySBS ..........................351

20.7.31 MMDC_EnableProfiling ...............................351

20.7.32 MMDC_ResumeProfiling ..............................352

20.7.33 MMDC_ResetProfiling ...............................353

20.7.34 MMDC_ExclusiveAccess ..............................353

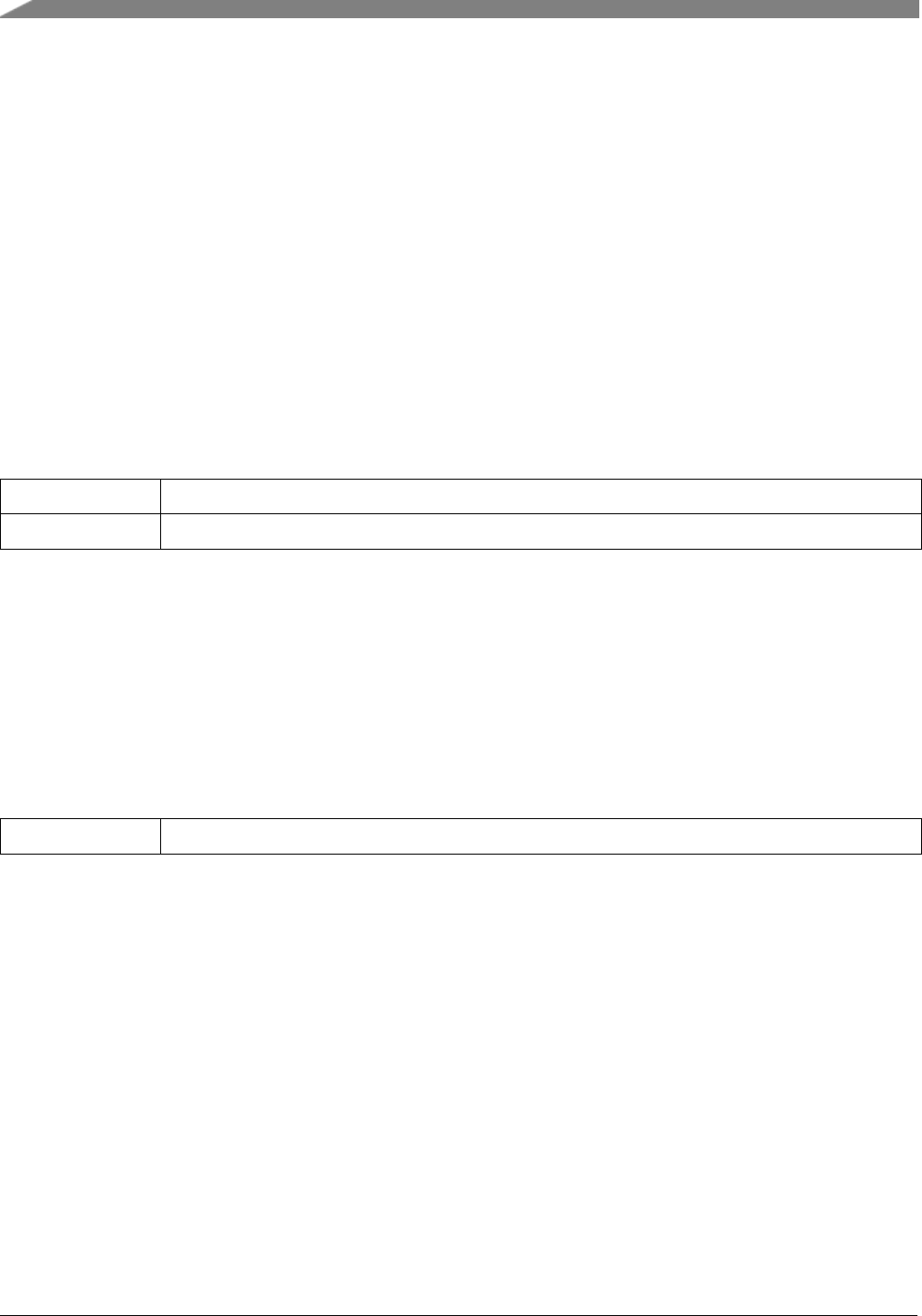

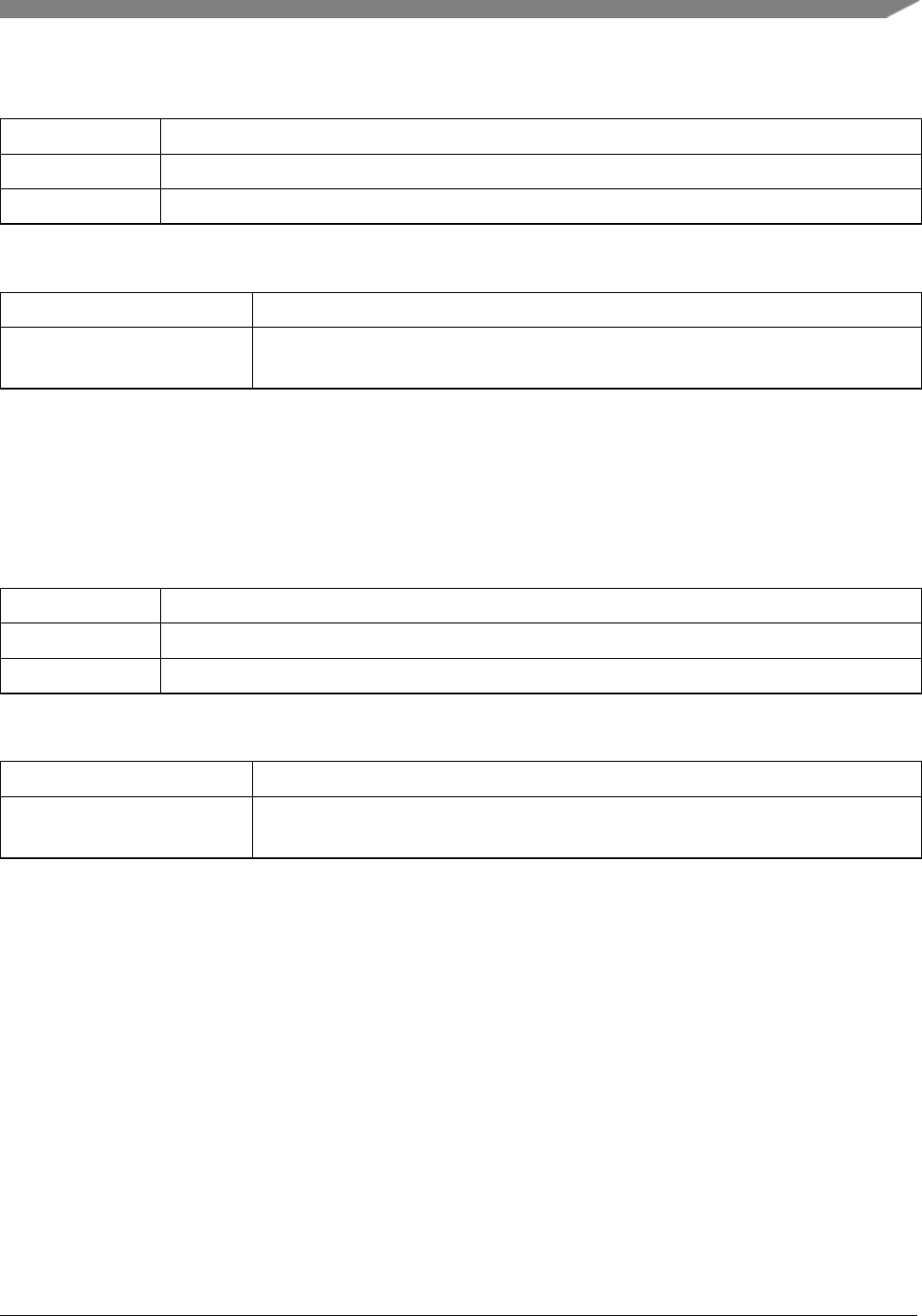

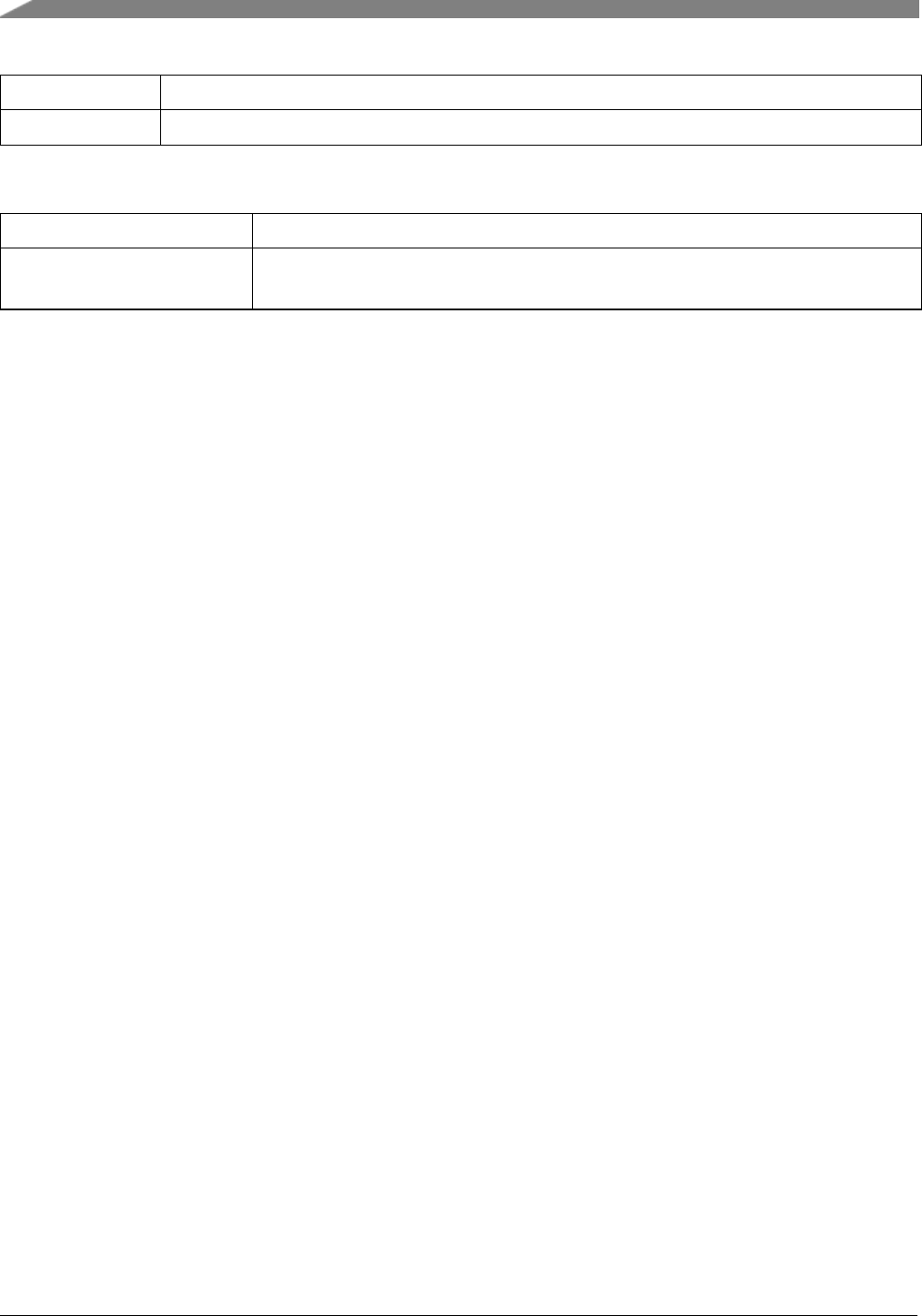

Chapter PMU: Power Management Unit

21.1 Overview ........................................355

21.2 Macro Definition Documentation ...........................357

21.2.1 FSL_PMU_DRIVER_VERSION ..........................357

21.3 Enumeration Type Documentation ..........................358

21.3.1 _pmu_status_flags ..................................358

21.3.2 pmu_1p1_weak_reference_source_t .........................358

21.3.3 pmu_3p0_vbus_voltage_source_t ..........................358

21.3.4 pmu_core_reg_voltage_ramp_rate_t .........................358

21.3.5 _pmu_power_gate ..................................359

21.3.6 pmu_power_bandgap_t ...............................359

21.4 Function Documentation ...............................359

21.4.1 PMU_1P1SetWeakReferenceSource ........................359

21.4.2 PMU_1P1EnableWeakRegulator ..........................359

21.4.3 PMU_1P1SetRegulatorOutputVoltage ........................360

21.4.4 PMU_1P1SetBrownoutOffsetVoltage ........................360

21.4.5 PMU_1P1EnablePullDown .............................360

21.4.6 PMU_1P1EnableCurrentLimit ...........................361

21.4.7 PMU_1P1EnableBrownout .............................361

21.4.8 PMU_1P1EnableOutput ...............................361

21.4.9 PMU_3P0SetRegulatorOutputVoltage ........................361

21.4.10 PMU_3P0SetVBusVoltageSource ..........................362

21.4.11 PMU_3P0SetBrownoutOffsetVoltage ........................362

21.4.12 PMU_3P0EnableCurrentLimit ...........................362

21.4.13 PMU_3P0EnableBrownout .............................363

NXP Semiconductors

MCUXpresso SDK API Reference Manual

xvii

Section

Number

Contents

Title

Page

Number

21.4.14 PMU_3P0EnableOutput ...............................363

21.4.15 PMU_2P5EnableWeakRegulator ..........................363

21.4.16 PMU_2P5SetRegulatorOutputVoltage ........................363

21.4.17 PMU_2P5SetBrownoutOffsetVoltage ........................364

21.4.18 PMU_2P1EnablePullDown .............................364

21.4.19 PMU_2P5EnableCurrentLimit ...........................364

21.4.20 PMU_2P5nableBrownout ..............................365

21.4.21 PMU_2P5EnableOutput ...............................365

21.4.22 PMU_CoreEnableIncreaseGateDrive ........................365

21.4.23 PMU_CoreSetRegulatorVoltageRampRate .....................365

21.4.24 PMU_CoreSetSOCDomainVoltage .........................366

21.4.25 PMU_CoreSetARMCoreDomainVoltage ......................366

21.4.26 PMU_GatePower ..................................367

21.4.27 PMU_UngatePower .................................367

21.4.28 PMU_EnableLowPowerBandgap ..........................367

Chapter PXP: Pixel Pipeline

22.1 Overview ........................................369

22.2 Typical use case ....................................369

22.2.1 PXP normal operation ................................369

22.2.2 PXP operation queue .................................370

22.3 Data Structure Documentation ............................377

22.3.1 struct pxp_output_buffer_config_t ..........................377

22.3.2 struct pxp_ps_buffer_config_t ............................378

22.3.3 struct pxp_as_buffer_config_t ............................379

22.3.4 struct pxp_as_blend_config_t ............................379

22.3.5 struct pxp_csc2_config_t ..............................380

22.3.6 struct pxp_lut_config_t ...............................381

22.3.7 struct pxp_dither_final_lut_data_t ..........................382

22.3.8 struct pxp_dither_config_t ..............................382

22.4 Enumeration Type Documentation ..........................384

22.4.1 _pxp_interrupt_enable ................................384

22.4.2 _pxp_flags ......................................384

22.4.3 pxp_flip_mode_t ...................................384

22.4.4 pxp_rotate_position_t ................................385

22.4.5 pxp_rotate_degree_t .................................385

22.4.6 pxp_interlaced_output_mode_t ...........................385

22.4.7 pxp_output_pixel_format_t .............................385

22.4.8 pxp_ps_pixel_format_t ...............................386

22.4.9 pxp_as_pixel_format_t ................................386

22.4.10 pxp_alpha_mode_t ..................................386

xviii

MCUXpresso SDK API Reference Manual

NXP Semiconductors

Section

Number

Contents

Title

Page

Number

22.4.11 pxp_rop_mode_t ...................................387

22.4.12 pxp_block_size_t ..................................387

22.4.13 pxp_csc1_mode_t ..................................387

22.4.14 pxp_csc2_mode_t ..................................388

22.4.15 pxp_lut_lookup_mode_t ...............................388

22.4.16 pxp_lut_out_mode_t .................................388

22.4.17 pxp_lut_8k_bank_t .................................388

22.4.18 pxp_ram_t ......................................388

22.4.19 _pxp_dither_mode ..................................389

22.4.20 _pxp_dither_lut_mode ................................389

22.4.21 _pxp_dither_matrix_size ...............................389

22.5 Function Documentation ...............................389

22.5.1 PXP_Init .......................................389

22.5.2 PXP_Deinit .....................................390

22.5.3 PXP_Reset ......................................390

22.5.4 PXP_Start ......................................390

22.5.5 PXP_EnableLcdHandShake .............................390

22.5.6 PXP_EnableContinousRun .............................391

22.5.7 PXP_SetProcessBlockSize .............................391

22.5.8 PXP_GetStatusFlags .................................391

22.5.9 PXP_ClearStatusFlags ................................392

22.5.10 PXP_GetAxiErrorId .................................392

22.5.11 PXP_EnableInterrupts ................................392

22.5.12 PXP_DisableInterrupts ...............................394

22.5.13 PXP_SetAlphaSurfaceBufferConfig .........................394

22.5.14 PXP_SetAlphaSurfaceBlendConfig .........................394

22.5.15 PXP_SetAlphaSurfaceOverlayColorKey ......................395

22.5.16 PXP_EnableAlphaSurfaceOverlayColorKey ....................395

22.5.17 PXP_SetAlphaSurfacePosition ...........................395

22.5.18 PXP_SetProcessSurfaceBackGroundColor .....................396

22.5.19 PXP_SetProcessSurfaceBufferConfig ........................396

22.5.20 PXP_SetProcessSurfaceScaler ............................396

22.5.21 PXP_SetProcessSurfacePosition ...........................397

22.5.22 PXP_SetProcessSurfaceColorKey ..........................397

22.5.23 PXP_SetOutputBufferConfig ............................397

22.5.24 PXP_SetOverwrittenAlphaValue ..........................398

22.5.25 PXP_EnableOverWrittenAlpha ...........................398

22.5.26 PXP_SetRotateConfig ................................398

22.5.27 PXP_SetNextCommand ...............................399

22.5.28 PXP_IsNextCommandPending ...........................400

22.5.29 PXP_CancelNextCommand .............................400

22.5.30 PXP_SetCsc2Config .................................400

22.5.31 PXP_EnableCsc2 ..................................400

22.5.32 PXP_SetCsc1Mode .................................401

NXP Semiconductors

MCUXpresso SDK API Reference Manual

xix

Section

Number

Contents

Title

Page

Number

22.5.33 PXP_EnableCsc1 ..................................401

22.5.34 PXP_SetLutConfig ..................................401

22.5.35 PXP_LoadLutTable .................................402

22.5.36 PXP_EnableLut ...................................402

22.5.37 PXP_Select8kLutBank ...............................402

Chapter QSPI: Quad Serial Peripheral Interface Driver

23.1 Overview ........................................405

23.2 Data Structure Documentation ............................409

23.2.1 struct qspi_dqs_config_t ...............................409

23.2.2 struct qspi_flash_timing_t ..............................410

23.2.3 struct qspi_config_t .................................410

23.2.4 struct qspi_flash_config_t ..............................411

23.2.5 struct qspi_transfer_t .................................412

23.3 Macro Definition Documentation ...........................412

23.3.1 FSL_QSPI_DRIVER_VERSION ..........................412

23.4 Enumeration Type Documentation ..........................412

23.4.1 _status_t .......................................412

23.4.2 qspi_read_area_t ...................................412

23.4.3 qspi_command_seq_t ................................412

23.4.4 qspi_fifo_t ......................................413

23.4.5 qspi_endianness_t ..................................413

23.4.6 _qspi_error_flags ...................................413

23.4.7 _qspi_flags ......................................413

23.4.8 _qspi_interrupt_enable ................................414

23.4.9 _qspi_dma_enable ..................................415

23.4.10 qspi_dqs_phrase_shift_t ...............................415

23.5 Function Documentation ...............................415

23.5.1 QSPI_Init ......................................415

23.5.2 QSPI_GetDefaultQspiConfig ............................415

23.5.3 QSPI_Deinit .....................................415

23.5.4 QSPI_SetFlashConfig ................................416

23.5.5 QSPI_SoftwareReset .................................416

23.5.6 QSPI_Enable .....................................416

23.5.7 QSPI_GetStatusFlags ................................416

23.5.8 QSPI_GetErrorStatusFlags .............................417

23.5.9 QSPI_ClearErrorFlag ................................417

23.5.10 QSPI_EnableInterrupts ...............................417

23.5.11 QSPI_DisableInterrupts ...............................418

23.5.12 QSPI_EnableDMA .................................418

xx

MCUXpresso SDK API Reference Manual

NXP Semiconductors

Section

Number

Contents

Title

Page

Number

23.5.13 QSPI_GetTxDataRegisterAddress ..........................418

23.5.14 QSPI_GetRxDataRegisterAddress ..........................418

23.5.15 QSPI_SetIPCommandAddress ...........................419

23.5.16 QSPI_SetIPCommandSize ..............................419

23.5.17 QSPI_ExecuteIPCommand .............................419

23.5.18 QSPI_ExecuteAHBCommand ............................419

23.5.19 QSPI_EnableIPParallelMode ............................420

23.5.20 QSPI_EnableAHBParallelMode ...........................420

23.5.21 QSPI_UpdateLUT ..................................420

23.5.22 QSPI_ClearFifo ...................................420

23.5.23 QSPI_ClearCommandSequence ...........................421

23.5.24 QSPI_EnableDDRMode ...............................421

23.5.25 QSPI_SetReadDataArea ...............................421

23.5.26 QSPI_WriteBlocking ................................421

23.5.27 QSPI_WriteData ...................................422

23.5.28 QSPI_ReadBlocking .................................422

23.5.29 QSPI_ReadData ...................................422

23.5.30 QSPI_TransferSendBlocking ............................423

23.5.31 QSPI_TransferReceiveBlocking ...........................423

23.6 QSPI eDMA Driver ..................................424

23.6.1 Overview .......................................424

23.6.2 Data Structure Documentation ............................425

23.6.3 Function Documentation ...............................425

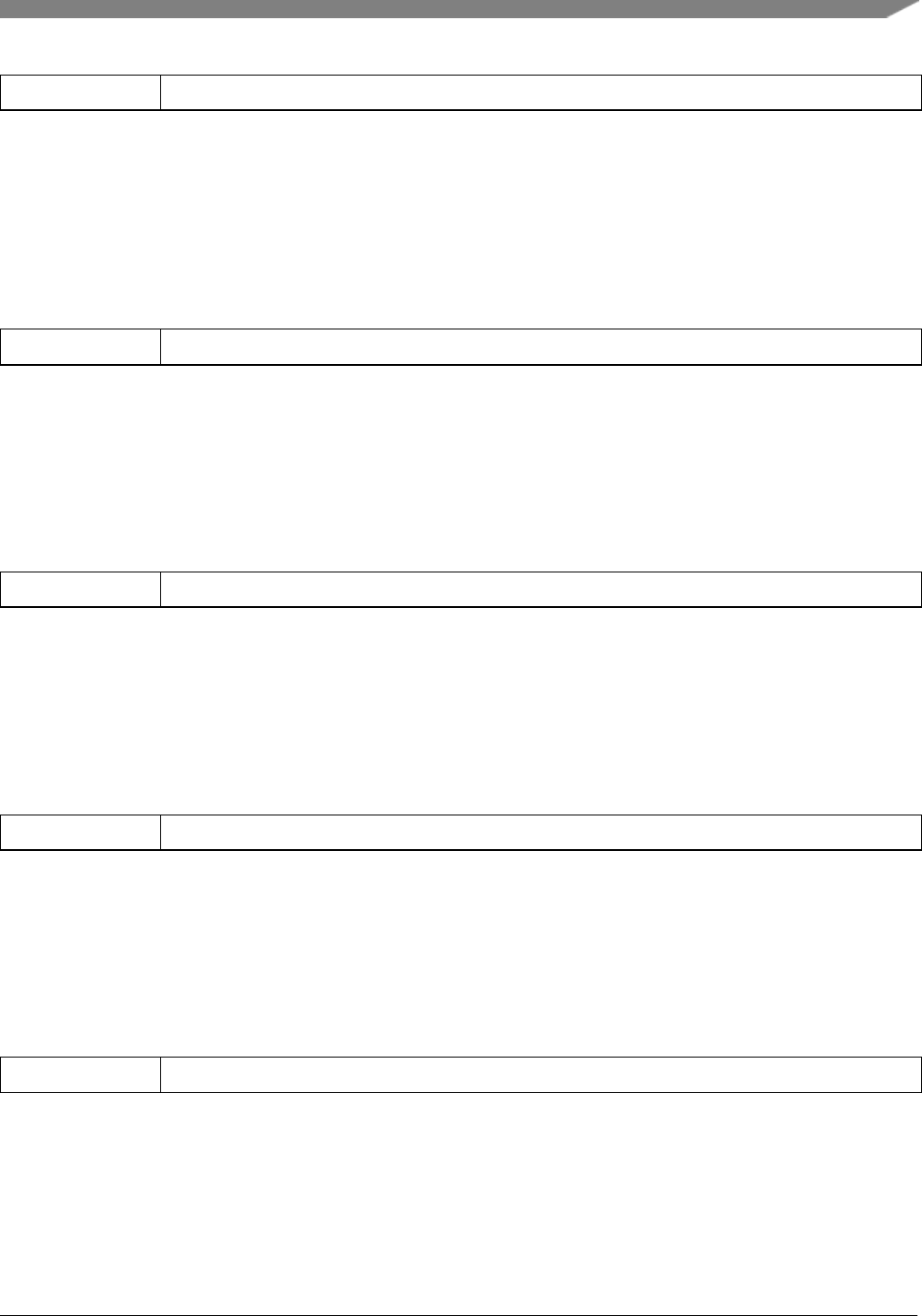

Chapter SAI: Serial Audio Interface

24.1 Overview ........................................429

24.2 Typical use case ....................................429

24.2.1 SAI Send/receive using an interrupt method ....................429

24.2.2 SAI Send/receive using a DMA method .......................430

24.3 Data Structure Documentation ............................436

24.3.1 struct sai_config_t ..................................436

24.3.2 struct sai_transfer_format_t .............................436

24.3.3 struct sai_transfer_t .................................437

24.3.4 struct _sai_handle ..................................437

24.4 Macro Definition Documentation ...........................437

24.4.1 SAI_XFER_QUEUE_SIZE .............................437

24.5 Enumeration Type Documentation ..........................438

24.5.1 _sai_status_t .....................................438

24.5.2 sai_protocol_t ....................................438

NXP Semiconductors

MCUXpresso SDK API Reference Manual

xxi

Section

Number

Contents

Title

Page

Number

24.5.3 sai_master_slave_t ..................................438

24.5.4 sai_mono_stereo_t ..................................438

24.5.5 sai_sync_mode_t ...................................439

24.5.6 sai_mclk_source_t ..................................439

24.5.7 sai_bclk_source_t ..................................439

24.5.8 _sai_interrupt_enable_t ...............................439

24.5.9 _sai_dma_enable_t ..................................439

24.5.10 _sai_flags .......................................440

24.5.11 sai_reset_type_t ...................................440

24.5.12 sai_sample_rate_t ..................................440

24.5.13 sai_word_width_t ..................................440

24.6 Function Documentation ...............................441

24.6.1 SAI_TxInit ......................................441

24.6.2 SAI_RxInit ......................................441

24.6.3 SAI_TxGetDefaultConfig ..............................441

24.6.4 SAI_RxGetDefaultConfig ..............................442

24.6.5 SAI_Deinit ......................................442

24.6.6 SAI_TxReset .....................................442

24.6.7 SAI_RxReset .....................................442

24.6.8 SAI_TxEnable ....................................443

24.6.9 SAI_RxEnable ....................................443

24.6.10 SAI_TxGetStatusFlag ................................443

24.6.11 SAI_TxClearStatusFlags ...............................443

24.6.12 SAI_RxGetStatusFlag ................................444

24.6.13 SAI_RxClearStatusFlags ..............................444

24.6.14 SAI_TxSoftwareReset ................................444

24.6.15 SAI_RxSoftwareReset ................................445

24.6.16 SAI_TxSetChannelFIFOMask ............................445

24.6.17 SAI_RxSetChannelFIFOMask ...........................445

24.6.18 SAI_TxEnableInterrupts ...............................445

24.6.19 SAI_RxEnableInterrupts ...............................446

24.6.20 SAI_TxDisableInterrupts ..............................447

24.6.21 SAI_RxDisableInterrupts ..............................447

24.6.22 SAI_TxEnableDMA .................................448

24.6.23 SAI_RxEnableDMA .................................448

24.6.24 SAI_TxGetDataRegisterAddress ..........................448

24.6.25 SAI_RxGetDataRegisterAddress ..........................449

24.6.26 SAI_TxSetFormat ..................................449

24.6.27 SAI_RxSetFormat ..................................450

24.6.28 SAI_WriteBlocking .................................450

24.6.29 SAI_WriteData ...................................450

24.6.30 SAI_ReadBlocking .................................451

24.6.31 SAI_ReadData ....................................451

24.6.32 SAI_TransferTxCreateHandle ............................451

xxii

MCUXpresso SDK API Reference Manual

NXP Semiconductors

Section

Number

Contents

Title

Page

Number

24.6.33 SAI_TransferRxCreateHandle ............................452

24.6.34 SAI_TransferTxSetFormat ..............................452

24.6.35 SAI_TransferRxSetFormat .............................453

24.6.36 SAI_TransferSendNonBlocking ...........................453