SPE_PEM SPE Programming Environments Manual

User Manual: Pdf

Open the PDF directly: View PDF ![]() .

.

Page Count: 342 [warning: Documents this large are best viewed by clicking the View PDF Link!]

- Contents

- Figures

- Tables

- About This Book

- Chapter 1 Overview

- Chapter 2 SPE Register Model

- 2.1 Overview

- 2.2 Register Model

- Figure 2-1. SPE Register Model

- Figure 2-2. Integer, Fractional, and Floating-Point Data Formats and GPR Usage

- Figure 2-3. 32- and 64-Bit Register Elements and Bit-Numbering Conventions

- 2.2.1 General-Purpose Registers (GPRs)

- 2.2.2 Accumulator Register (ACC)

- 2.2.3 Signal Processing Embedded Floating-Point Status and Control Register (SPEFSCR)

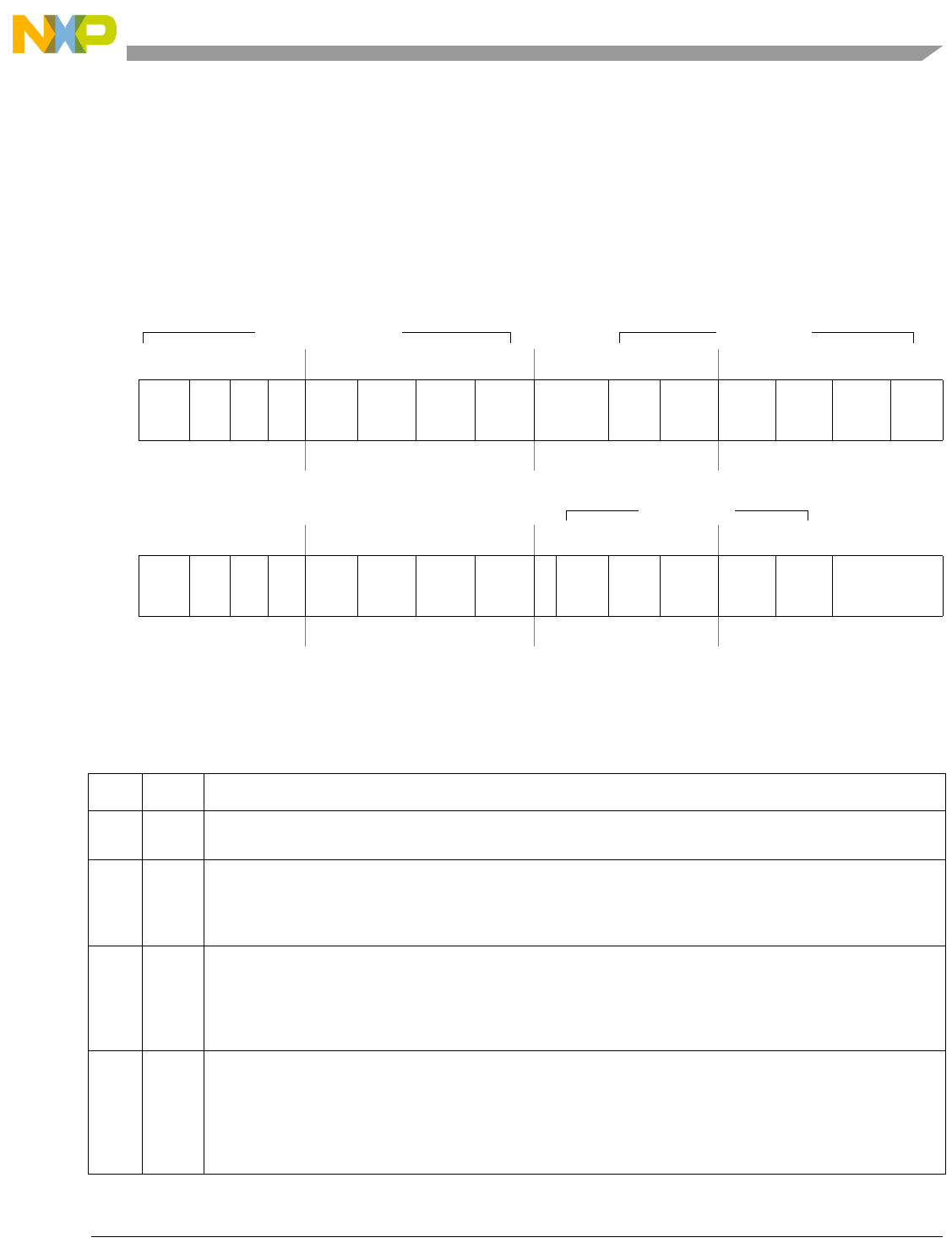

- Figure 2-6. Signal Processing and Embedded Floating-Point Status and Control Register (SPEFSCR)

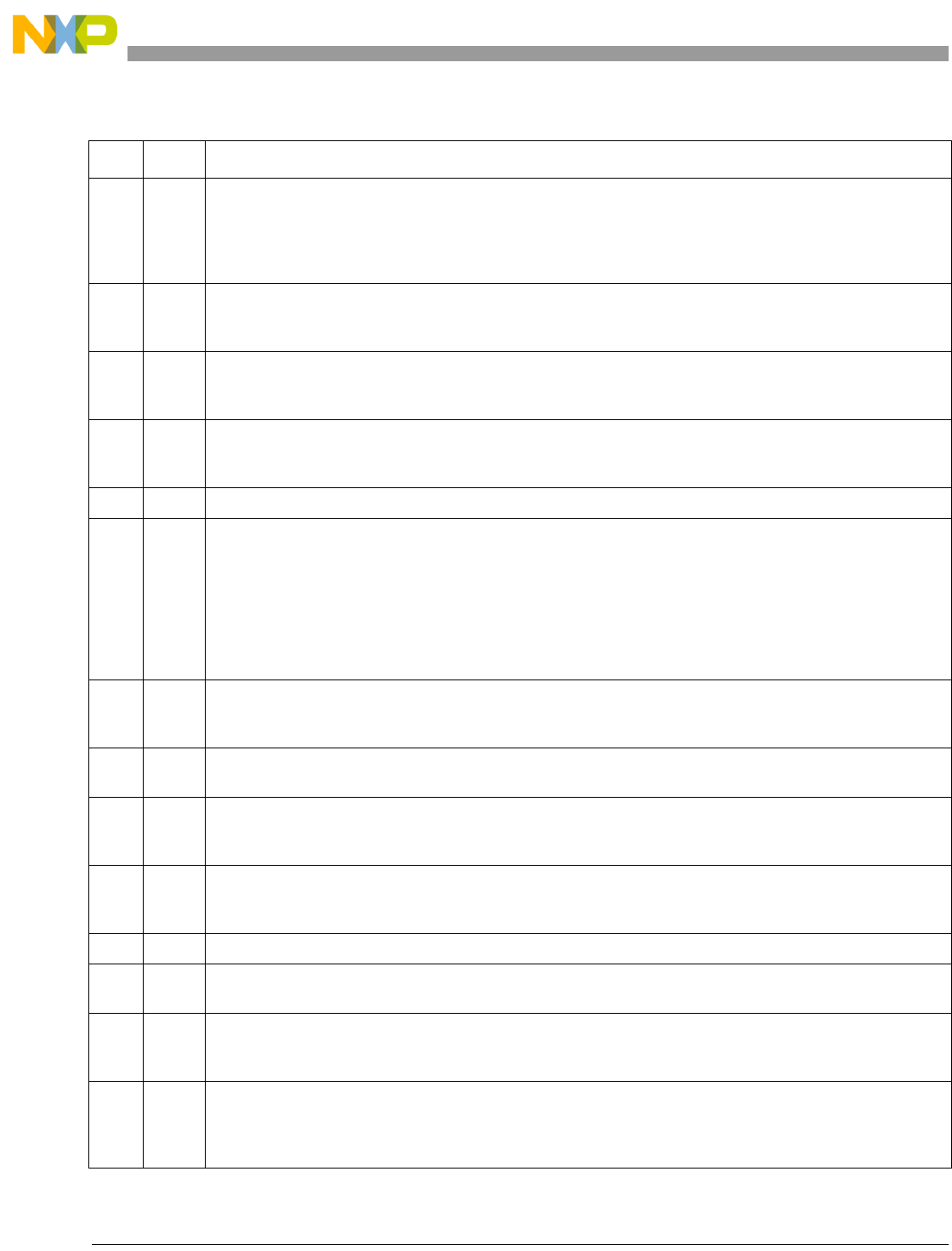

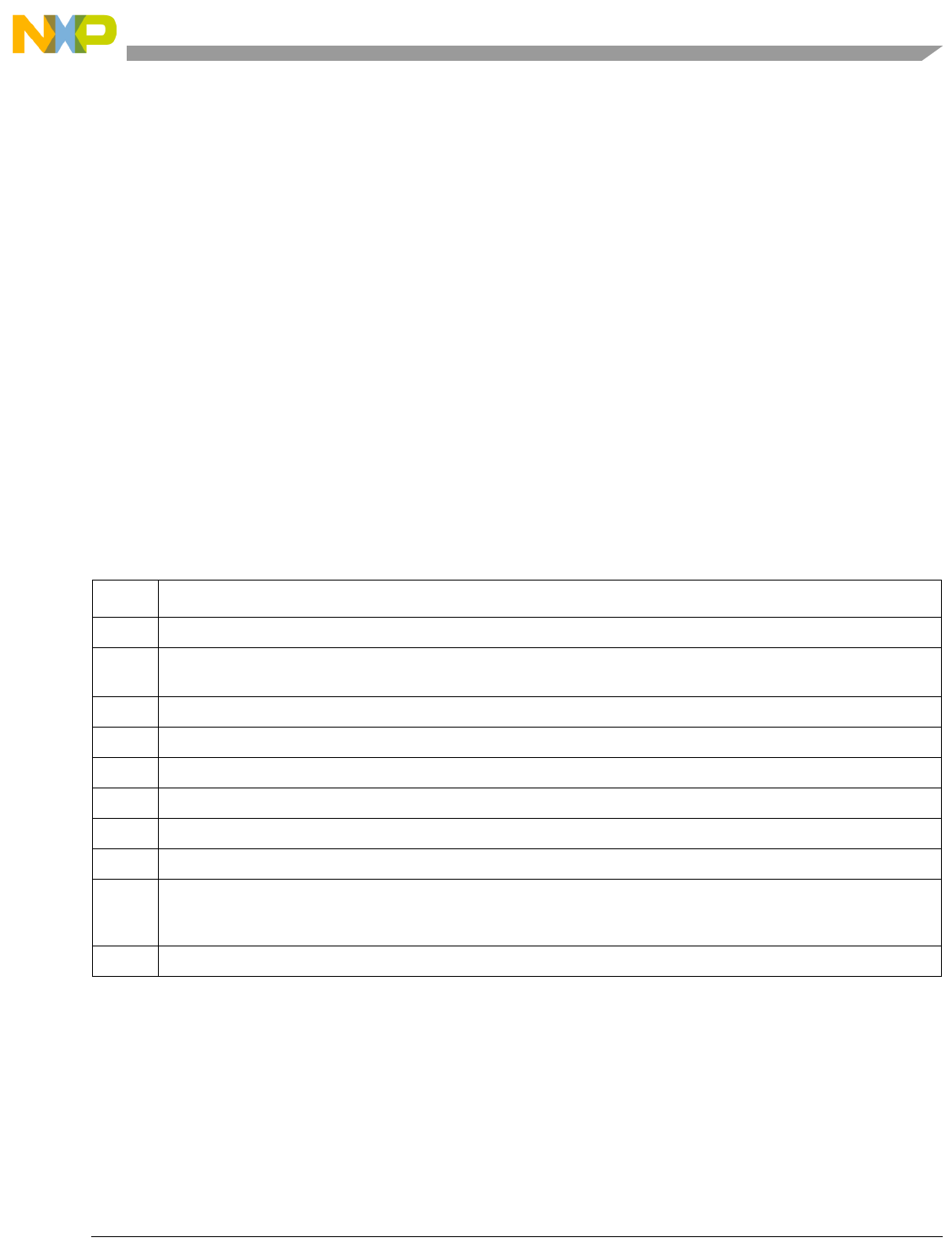

- Table 2-1. SPEFSCR Field Descriptions

- 2.2.3.1 Interrupt Vector Offset Registers (IVORs)

- 2.2.3.2 Exception Bit in the Exception Syndrome Register (ESR)

- 2.2.3.3 Condition Register (CR)

- 2.2.3.4 SPE Available Bit in the Machine State Register (MSR)

- Chapter 3 SPE and Embedded Floating-Point Instruction Model

- 3.1 Overview

- 3.2 SPE Instruction Set

- 3.3 Embedded Floating-Point Instruction Set

- 3.3.1 Embedded Floating-Point Operations

- 3.3.2 Embedded Vector and Scalar Floating-Point Instructions

- 3.3.3 Load/Store Instructions

- Chapter 4 SPE/Embedded Floating-Point Interrupt Model

- Chapter 5 Instruction Set

- 5.1 Notation

- 5.2 Instruction Fields

- 5.3 Description of Instruction Operations

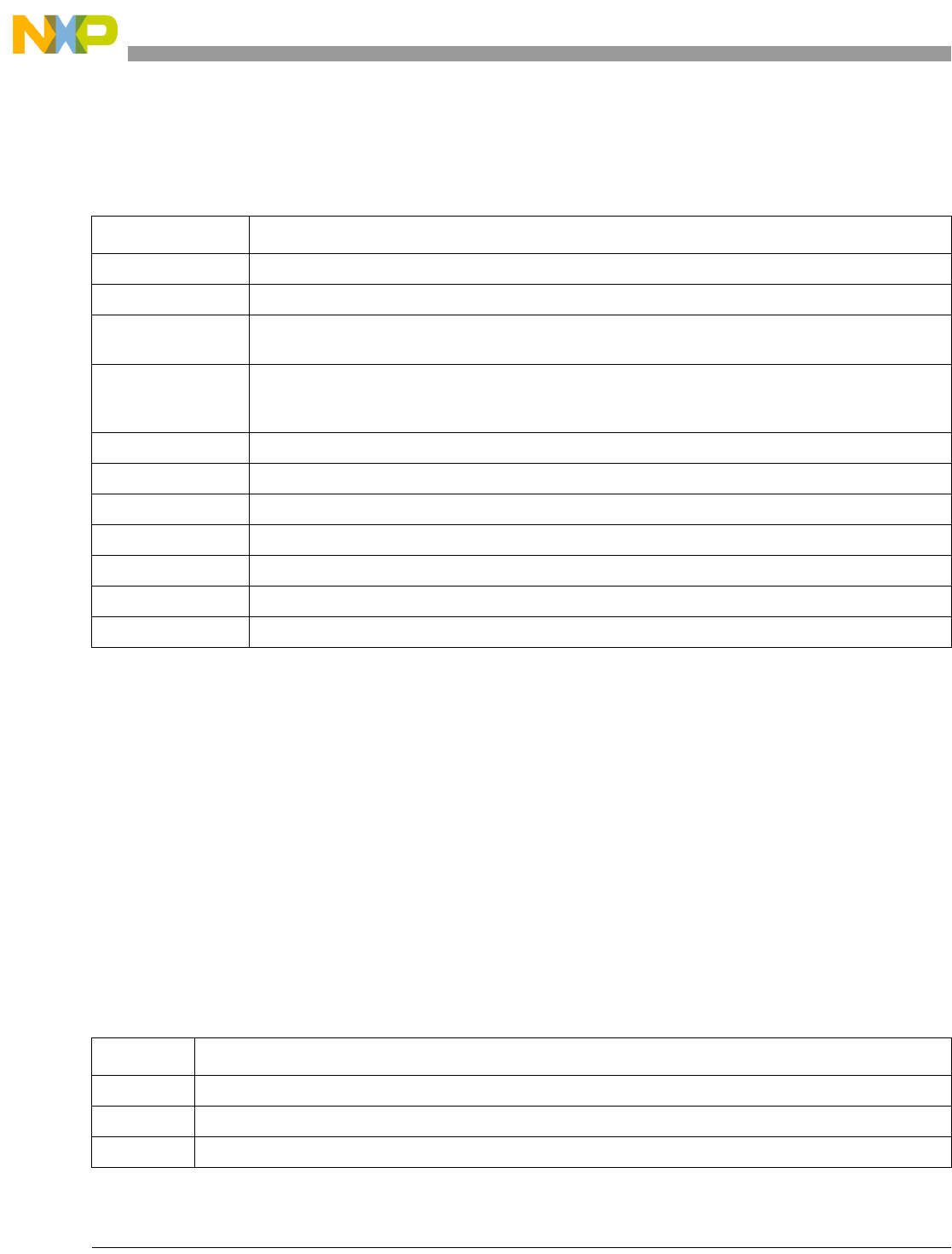

- Table 5-3. RTL Notation

- Table 5-4. Operator Precedence

- 5.3.1 SPE Saturation and Bit-Reverse Models

- 5.3.2 Embedded Floating-Point Conversion Models

- Table 5-5. Conversion Models

- 5.3.2.1 Common Embedded Floating-Point Functions

- 5.3.2.2 Convert from Single-Precision Floating-Point to Integer Word with Saturation

- 5.3.2.3 Convert from Double-Precision Floating-Point to Integer Word with Saturation

- 5.3.2.4 Convert from Double-Precision Floating-Point to Integer Double Word with Saturation

- 5.3.2.5 Convert to Single-Precision Floating-Point from Integer Word with Saturation

- 5.3.2.6 Convert to Double-Precision Floating-Point from Integer Word with Saturation

- 5.3.2.7 Convert to Double-Precision Floating-Point from Integer Double Word with Saturation

- 5.3.3 Integer Saturation Models

- 5.3.4 Embedded Floating-Point Results

- 5.4 Instruction Set

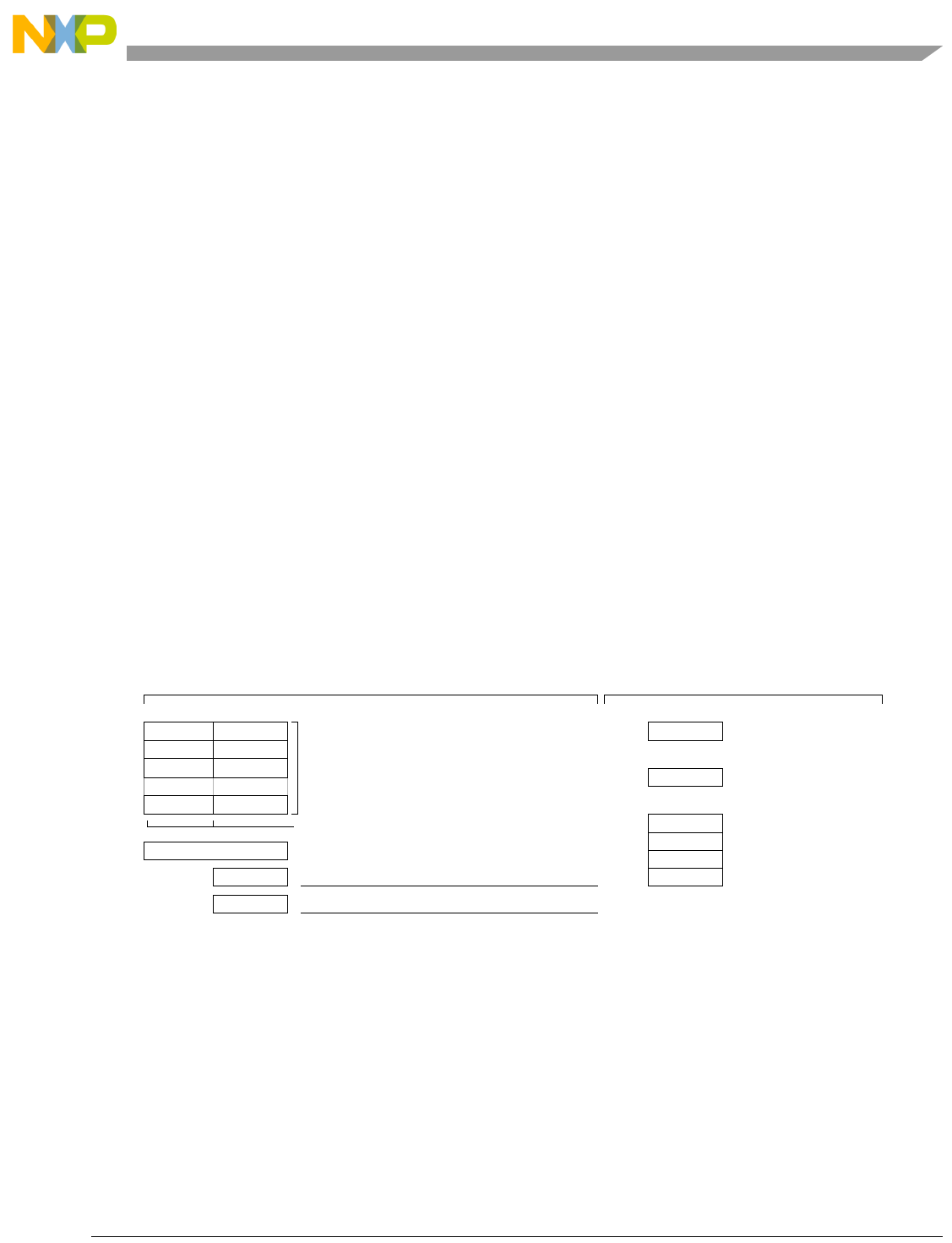

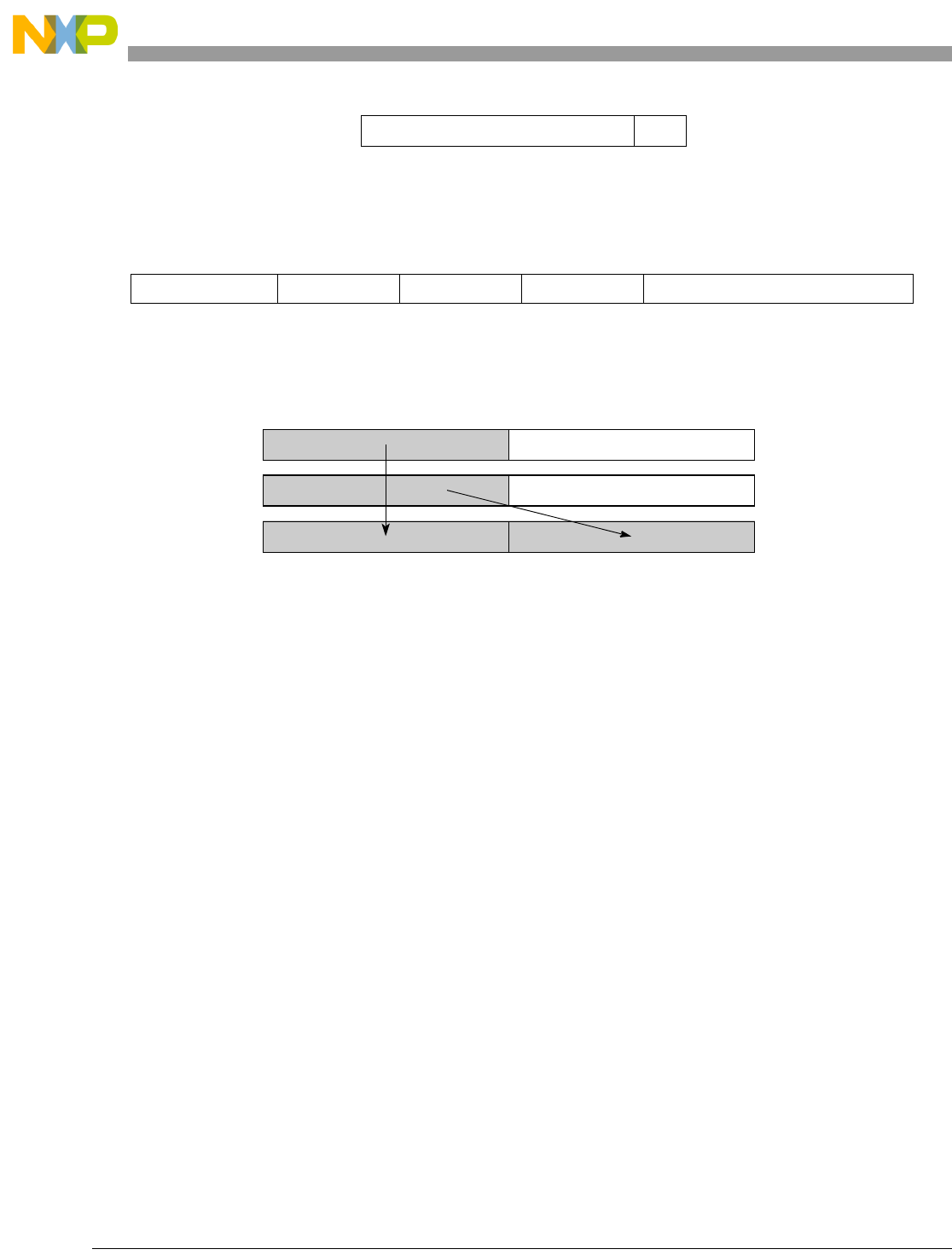

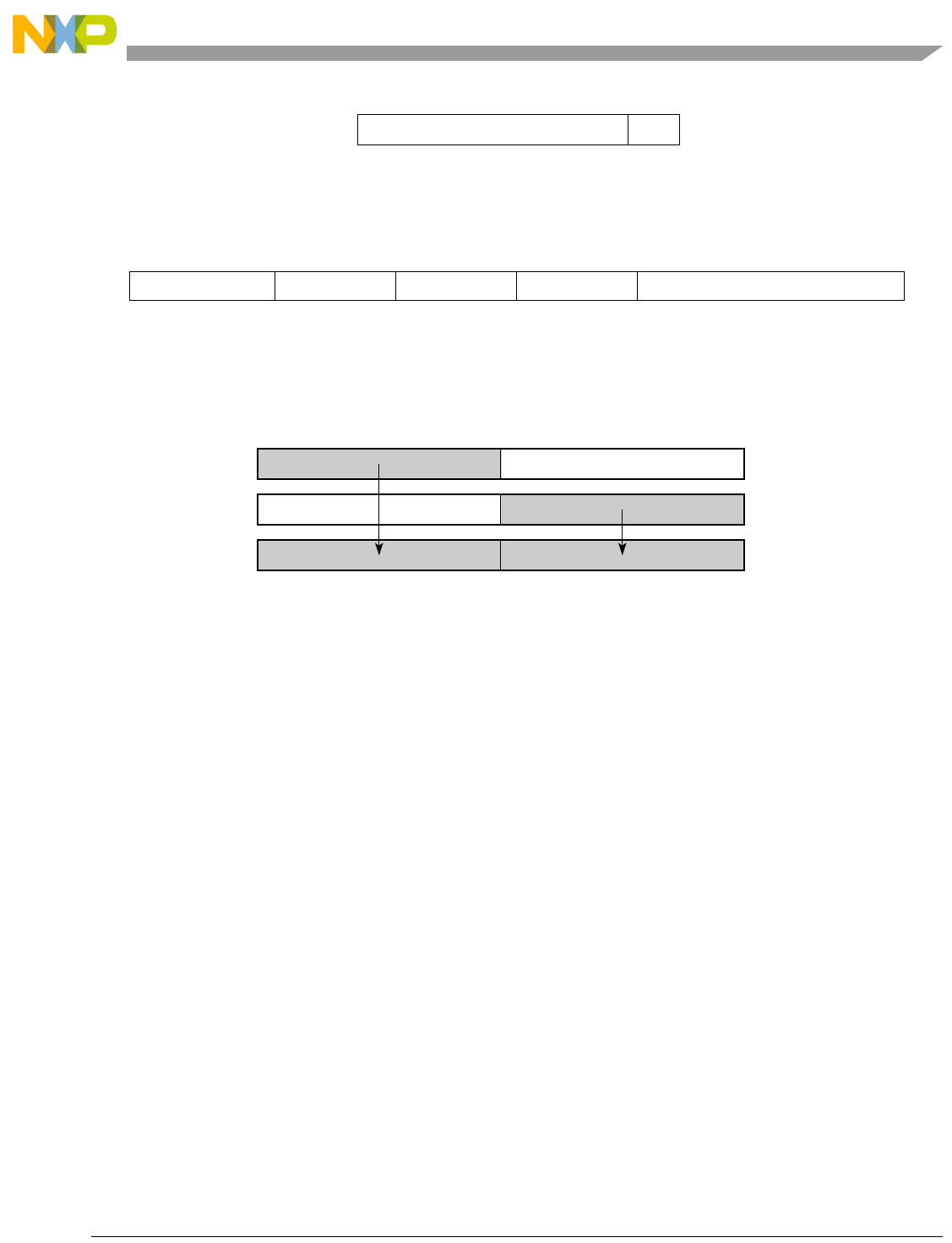

- Figure 5-1. Instruction Description

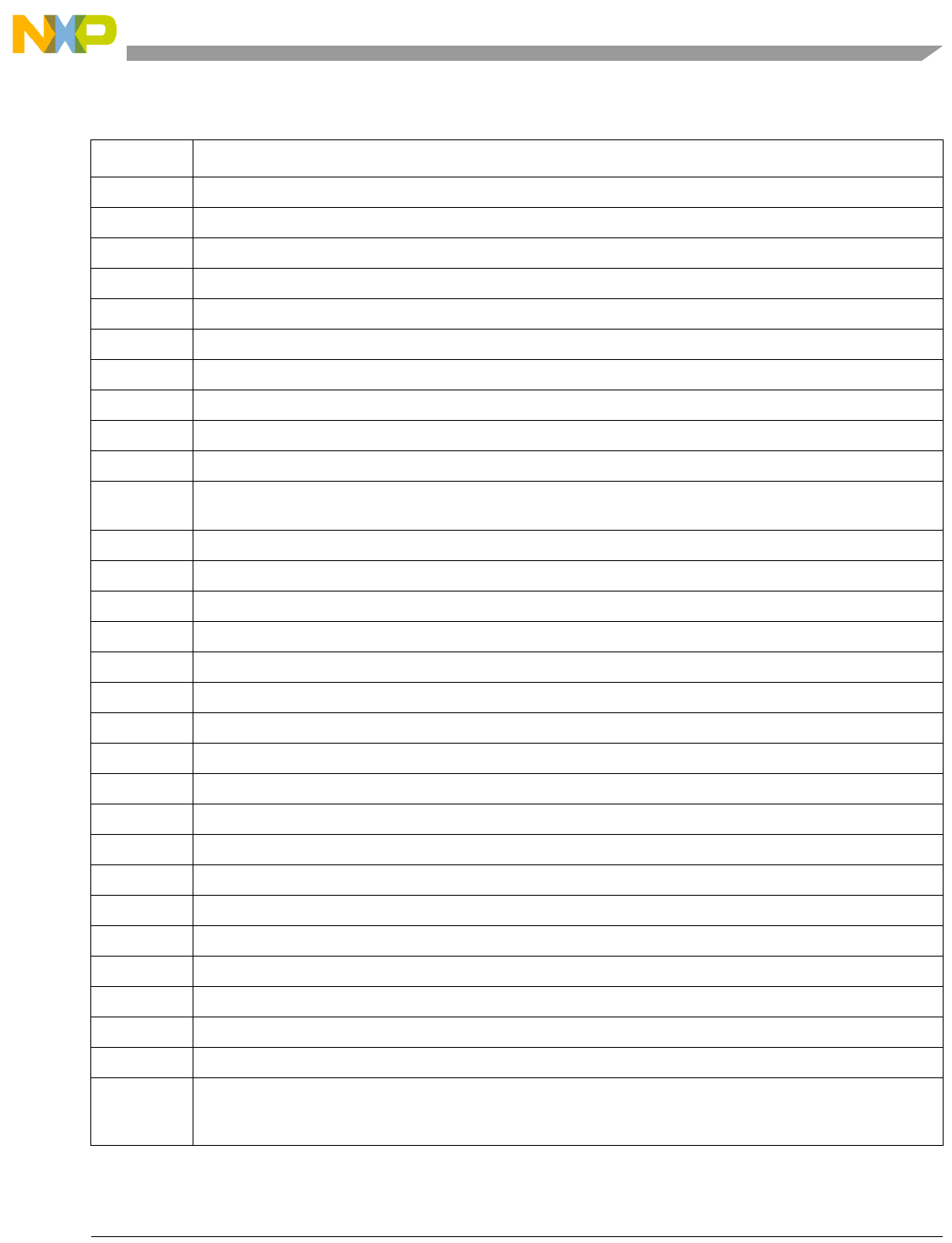

- Table 5-6. Data Samples and Sizes

- Figure 5-2. Vector Absolute Value (evabs)

- Figure 5-3. Vector Add Immediate Word (evaddiw)

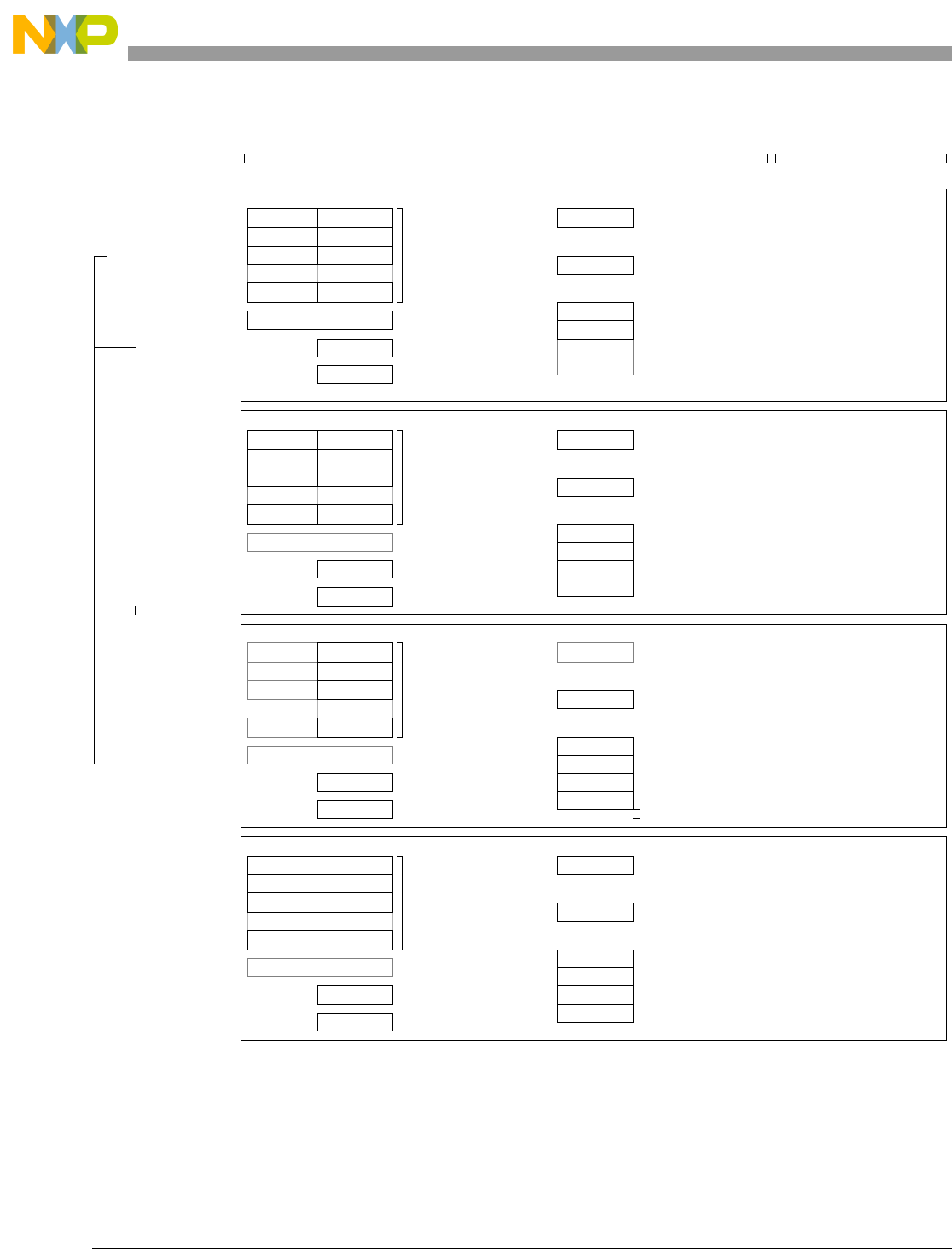

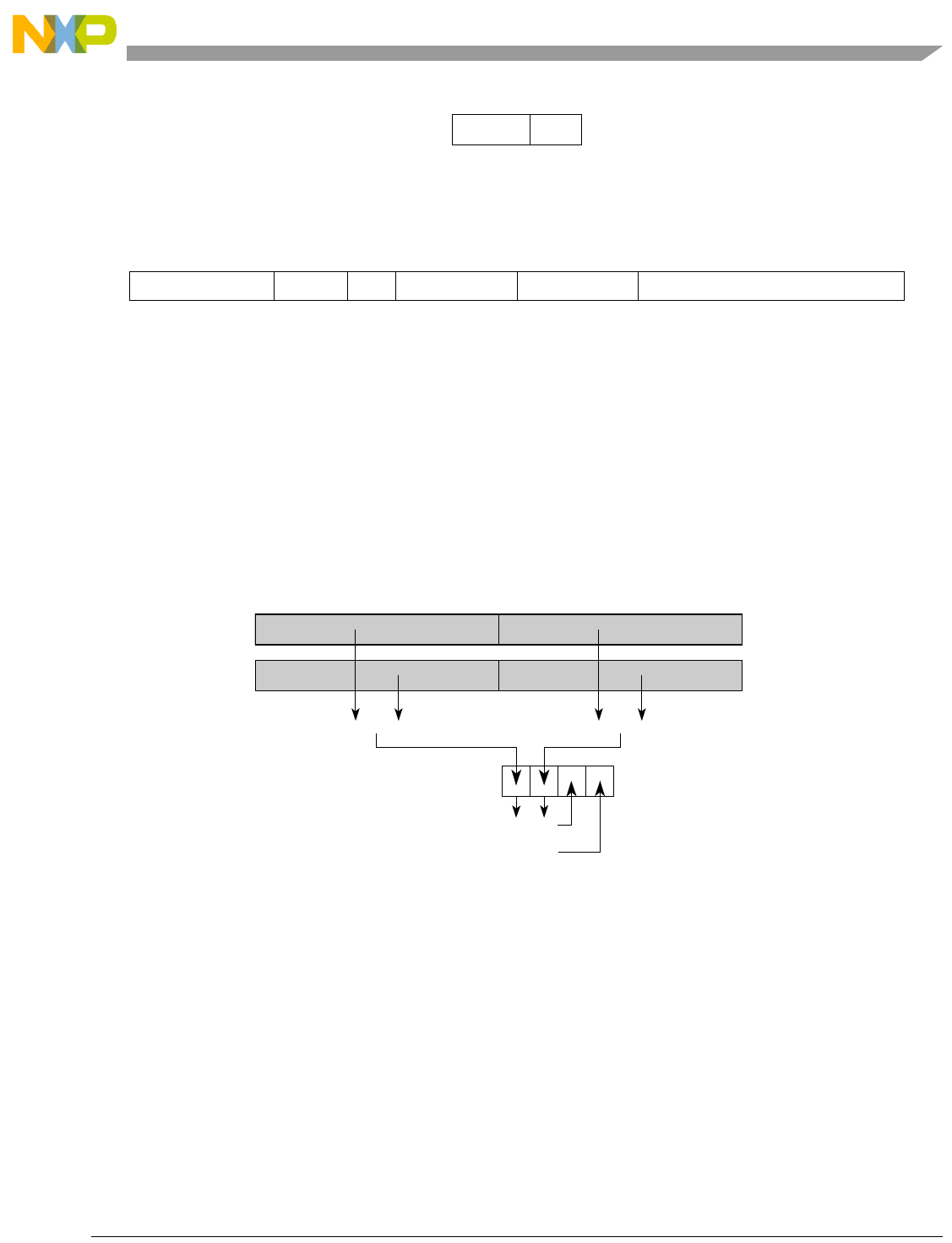

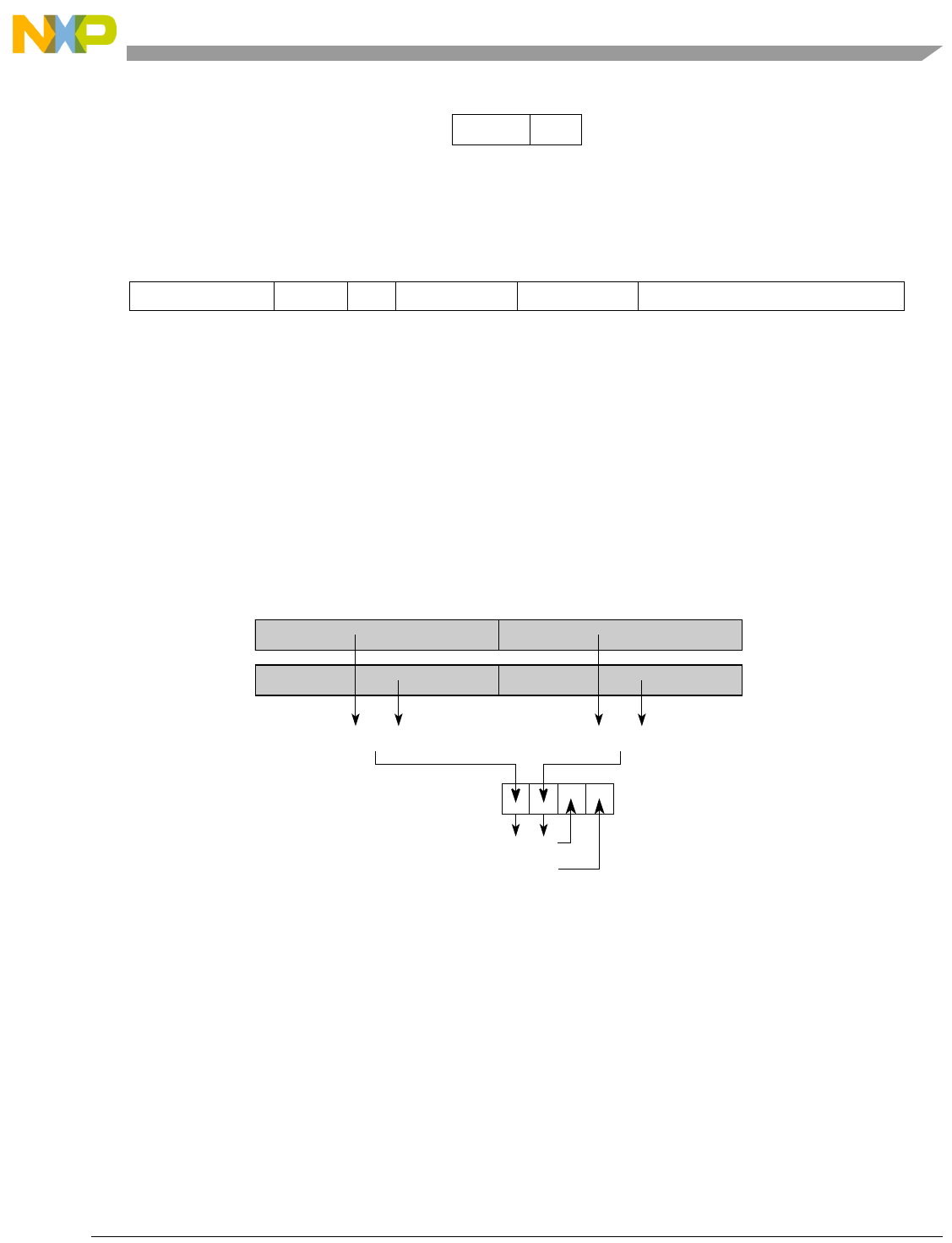

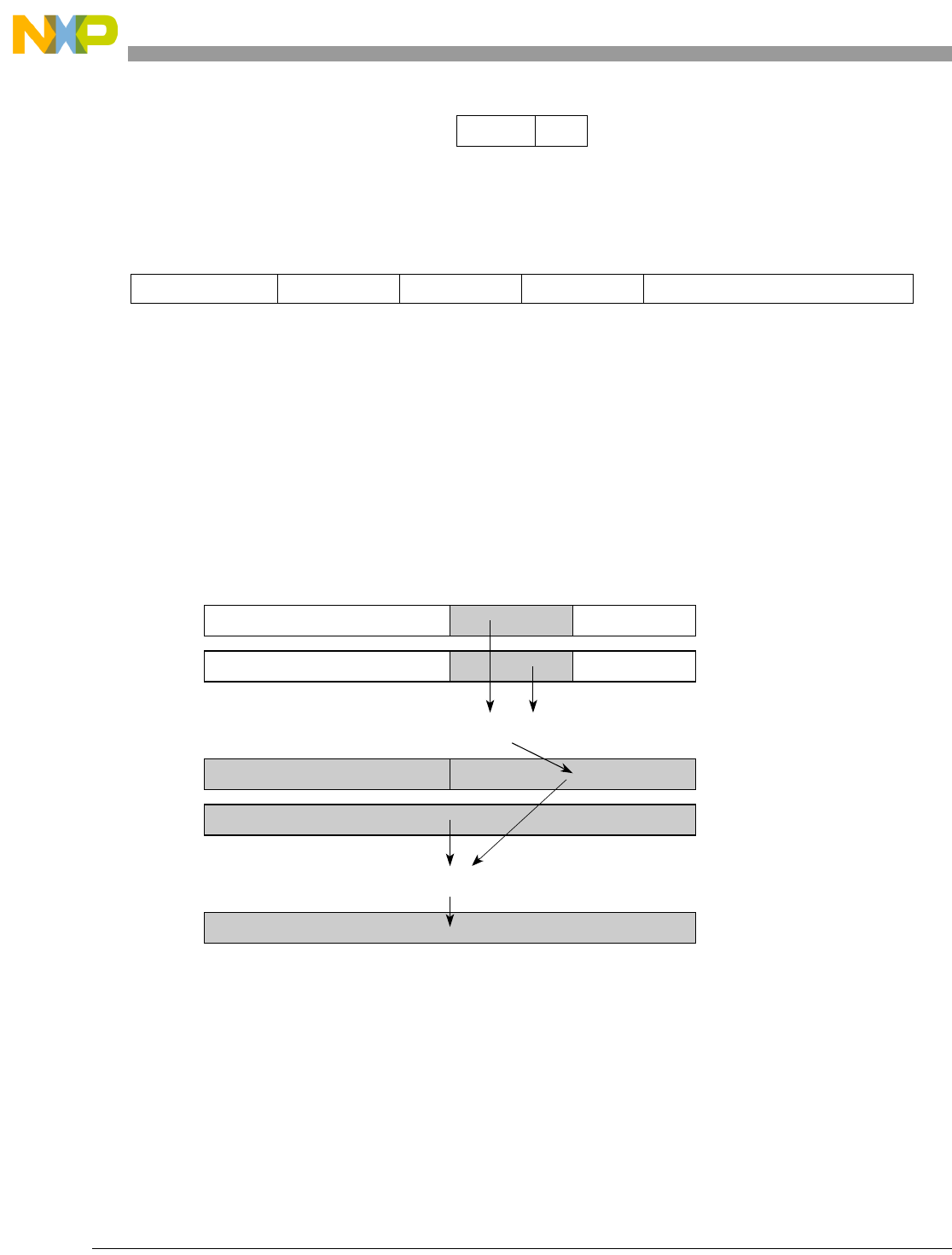

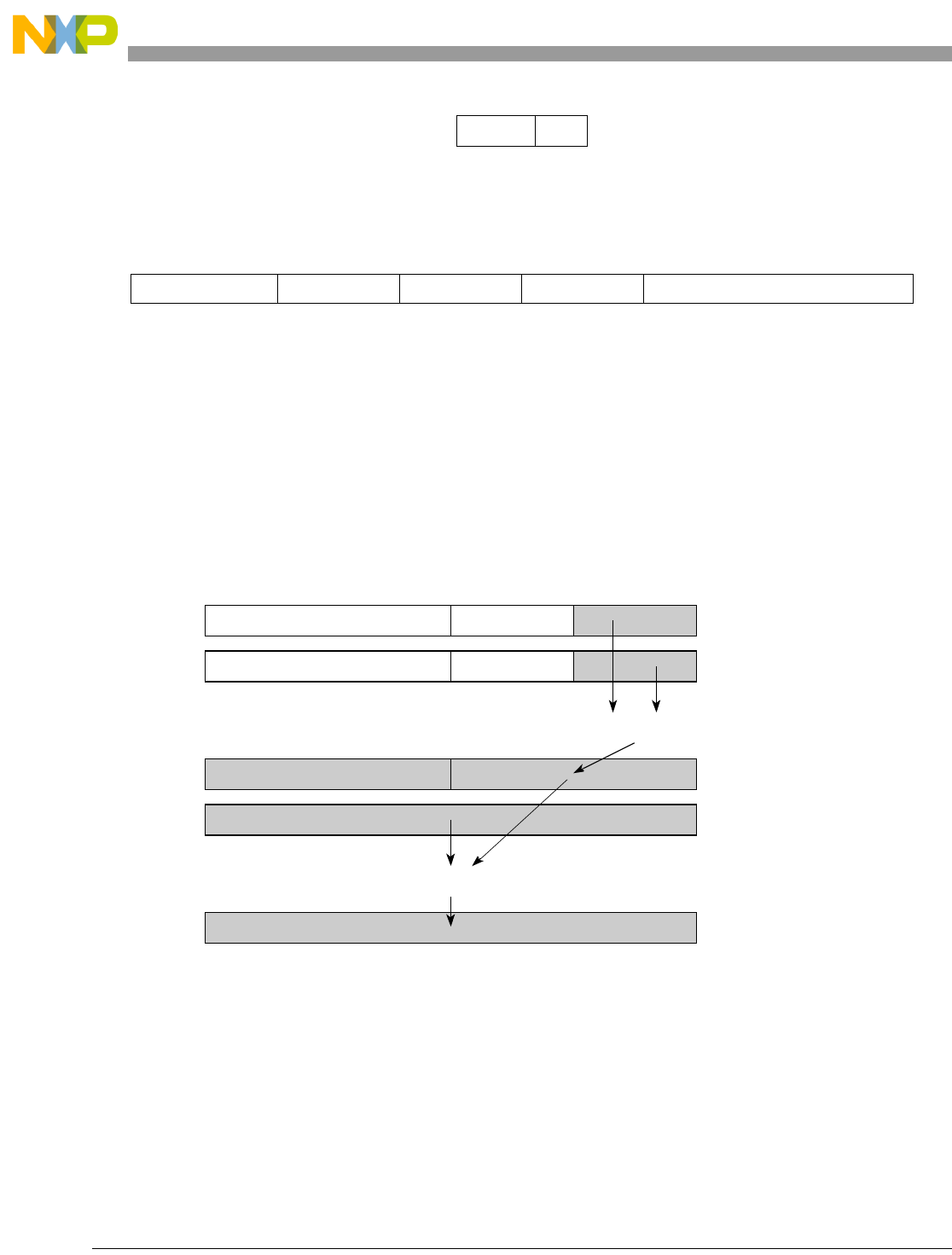

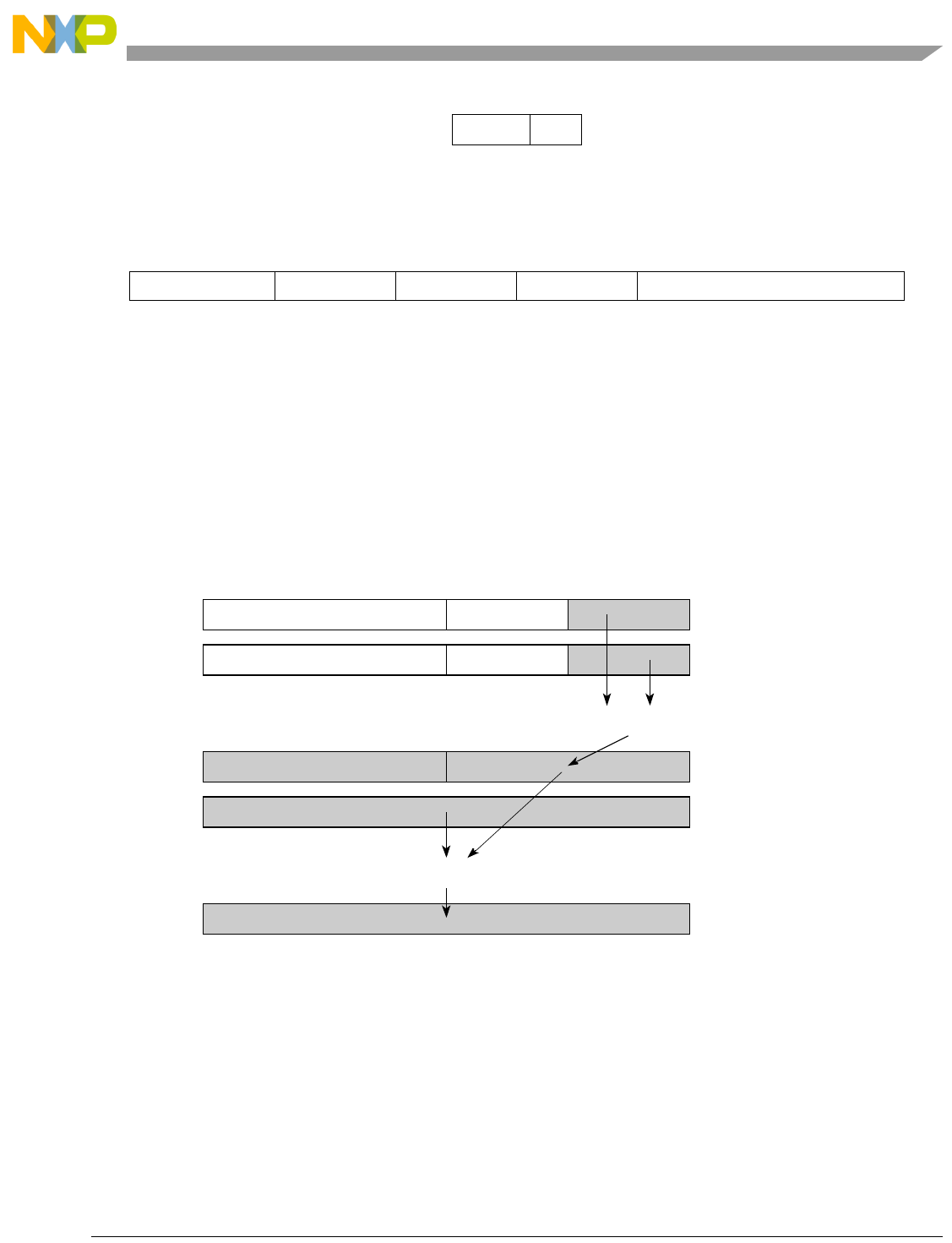

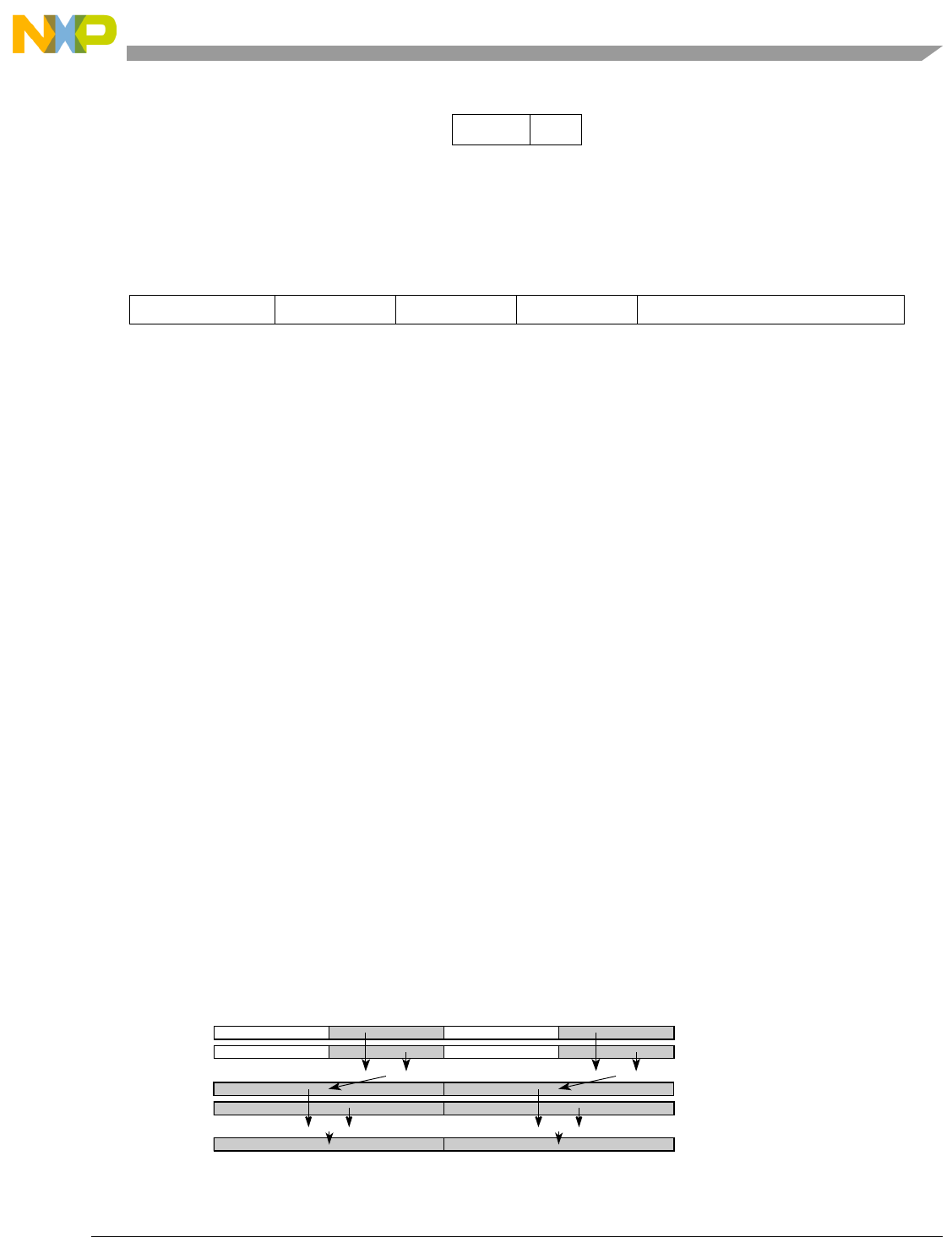

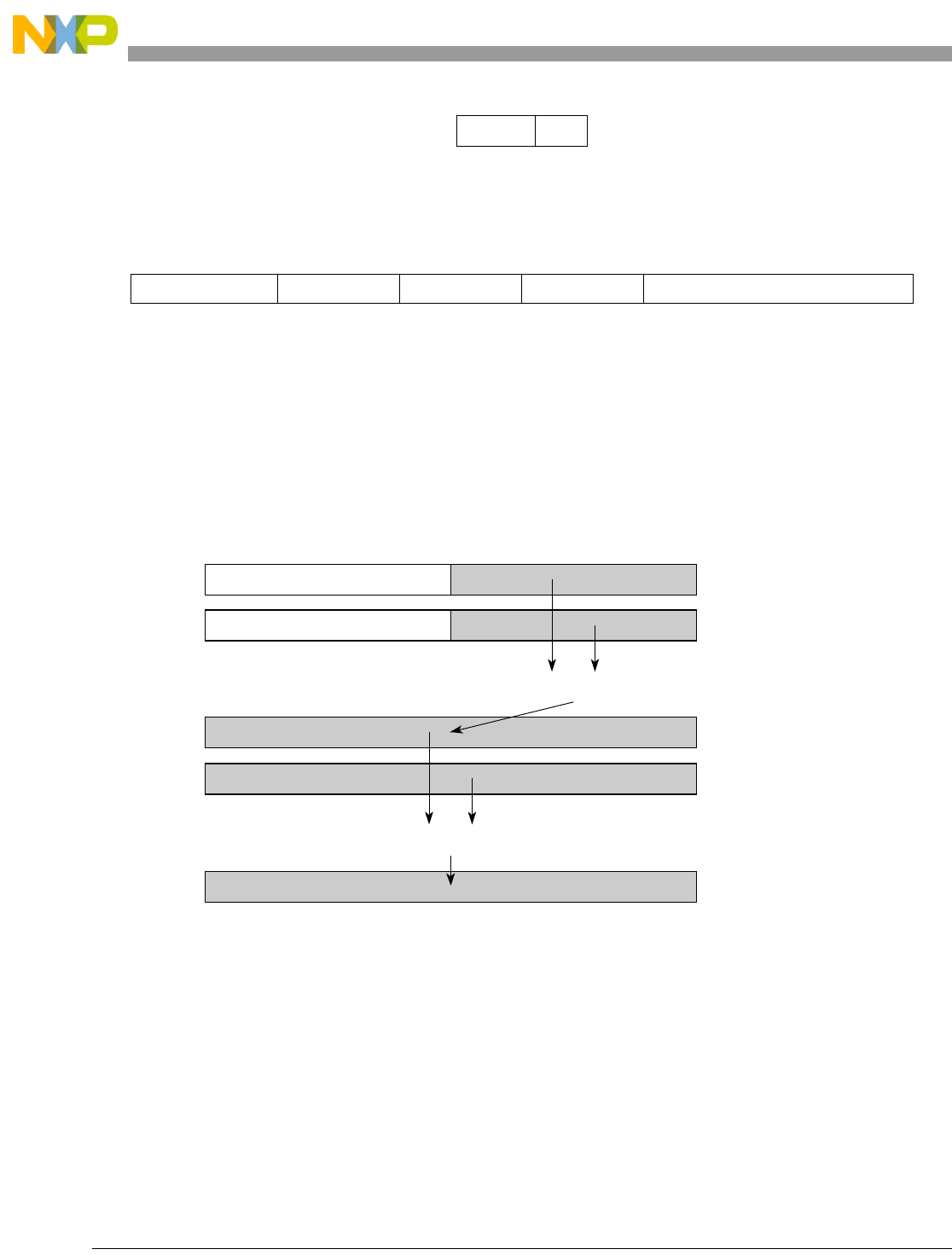

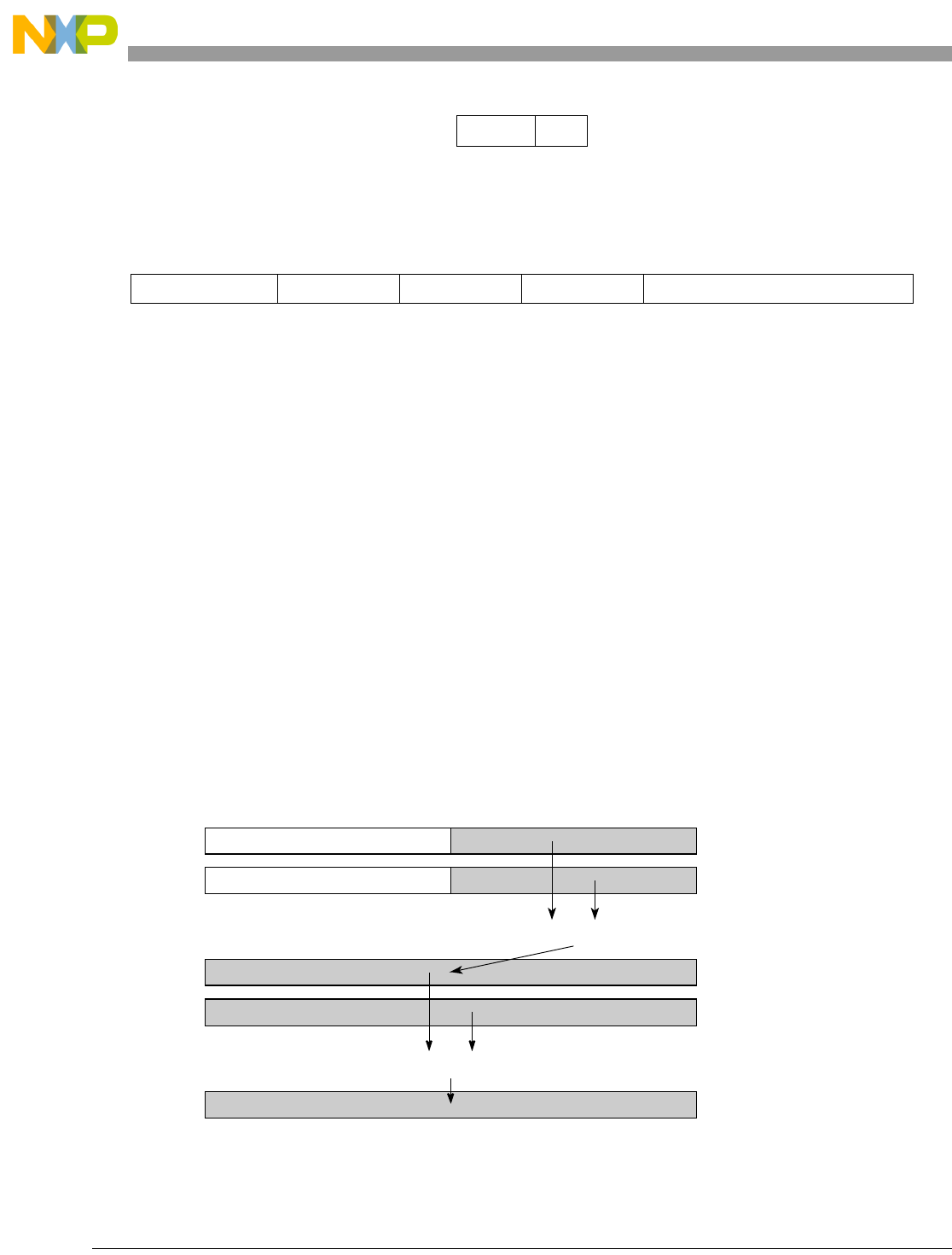

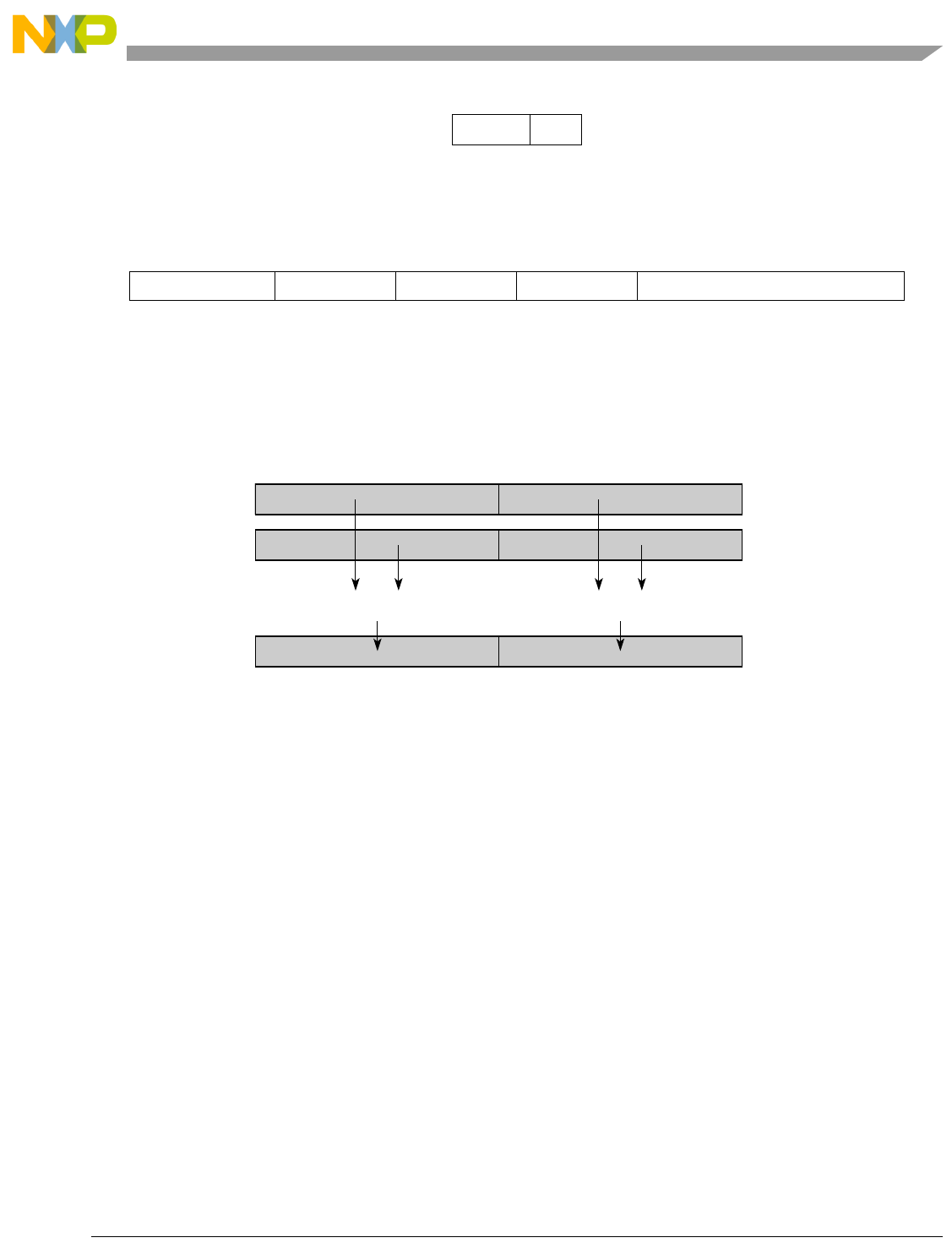

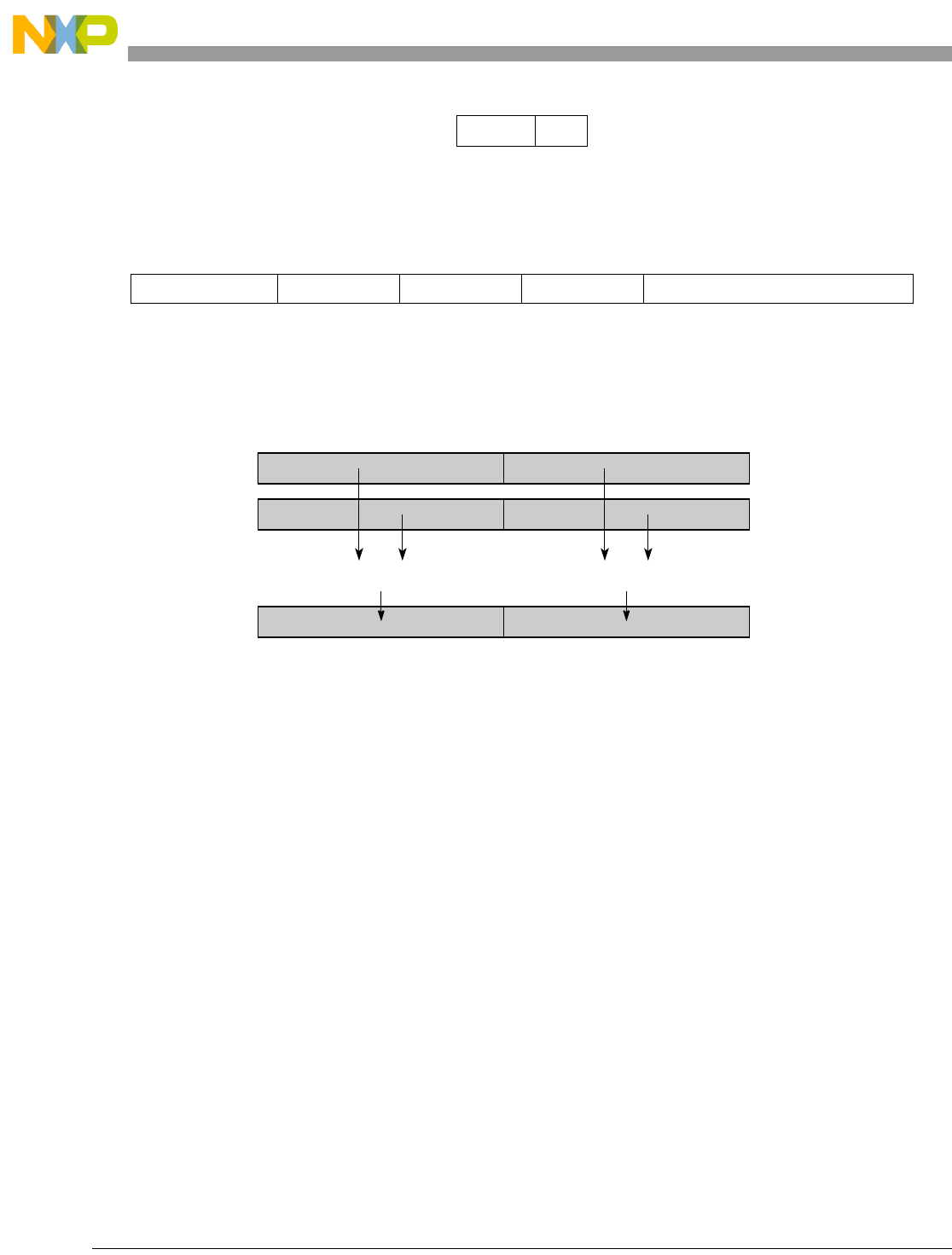

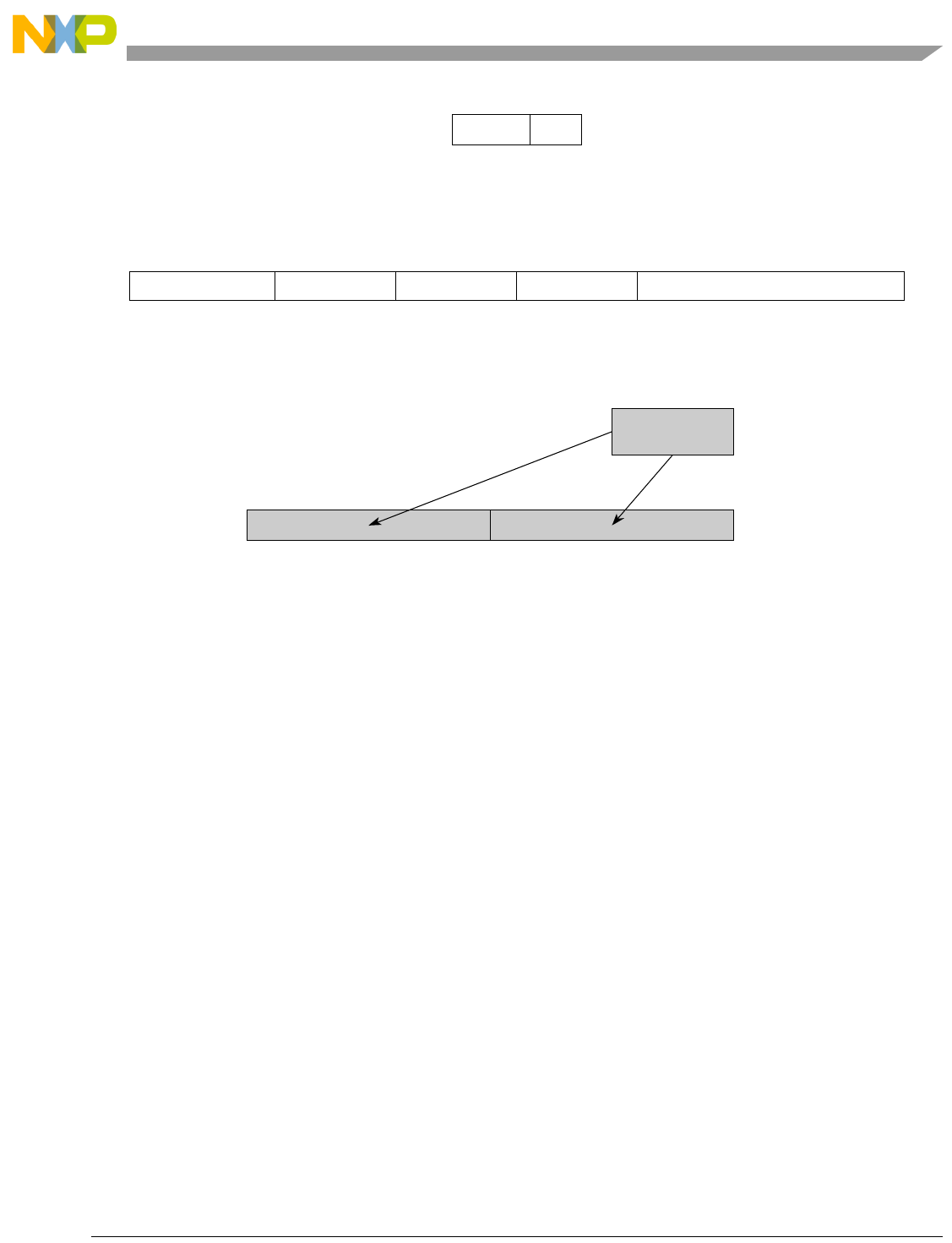

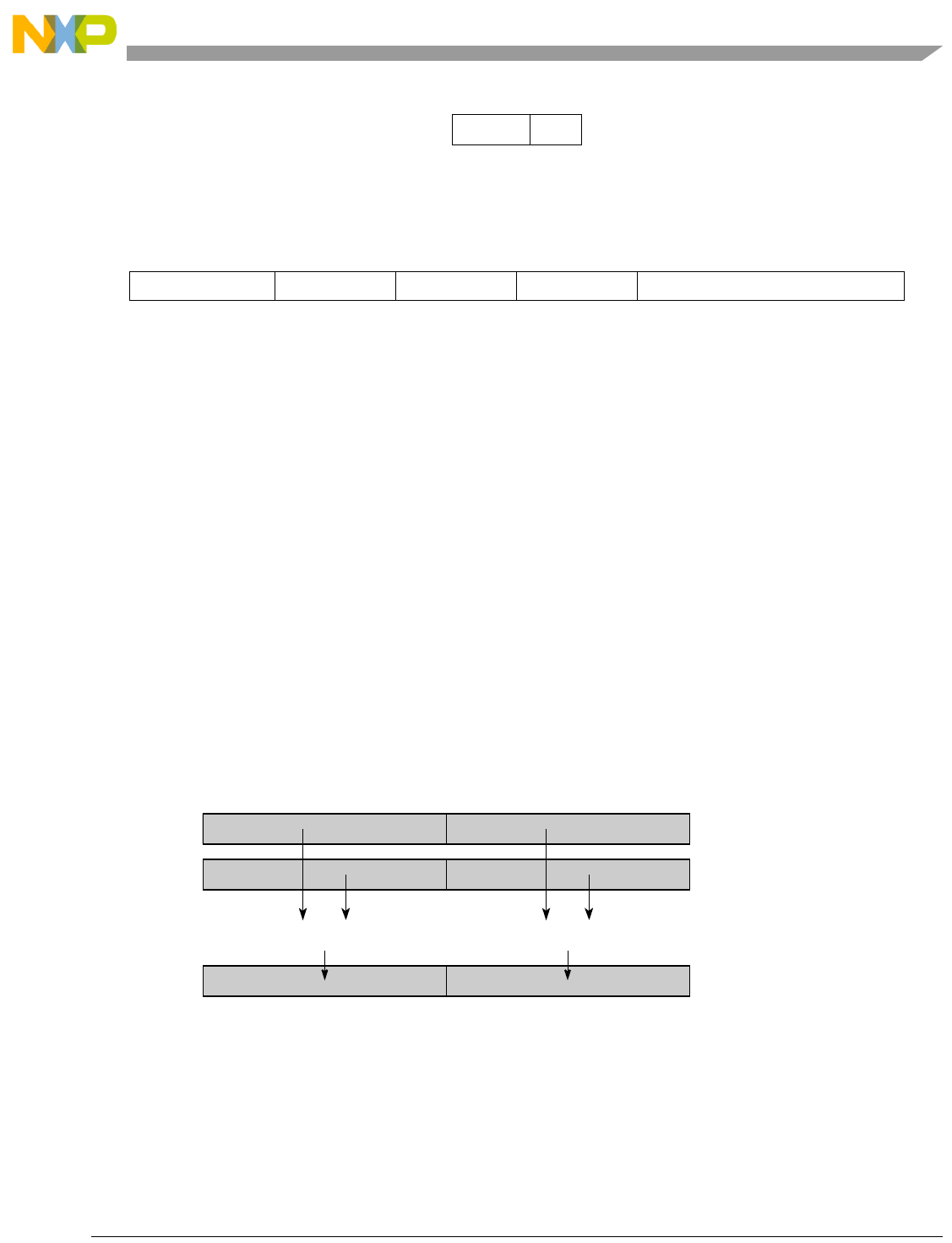

- Figure 0-1. Vector Add Signed, Modulo, Integer to Accumulator Word (evaddsmiaaw)

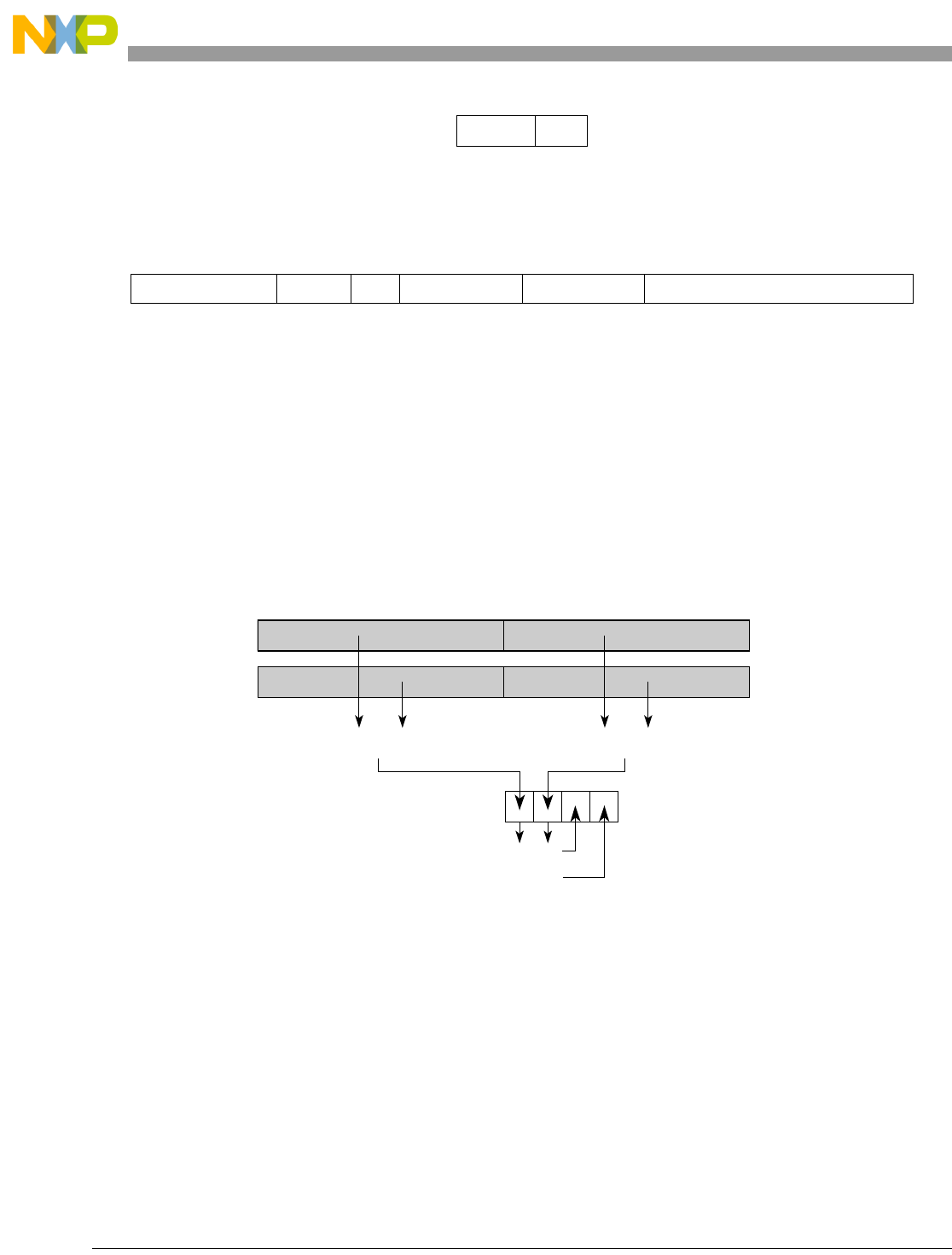

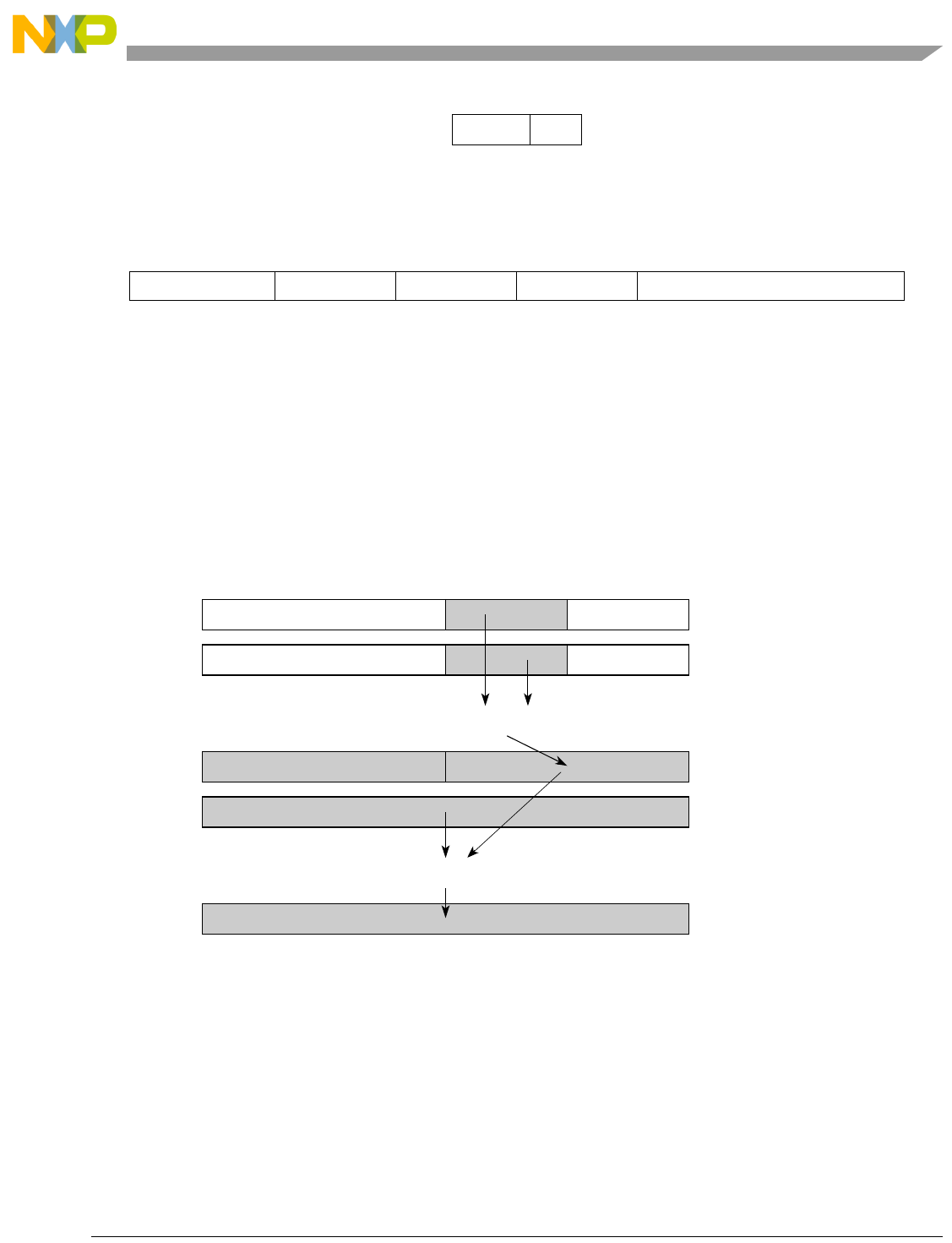

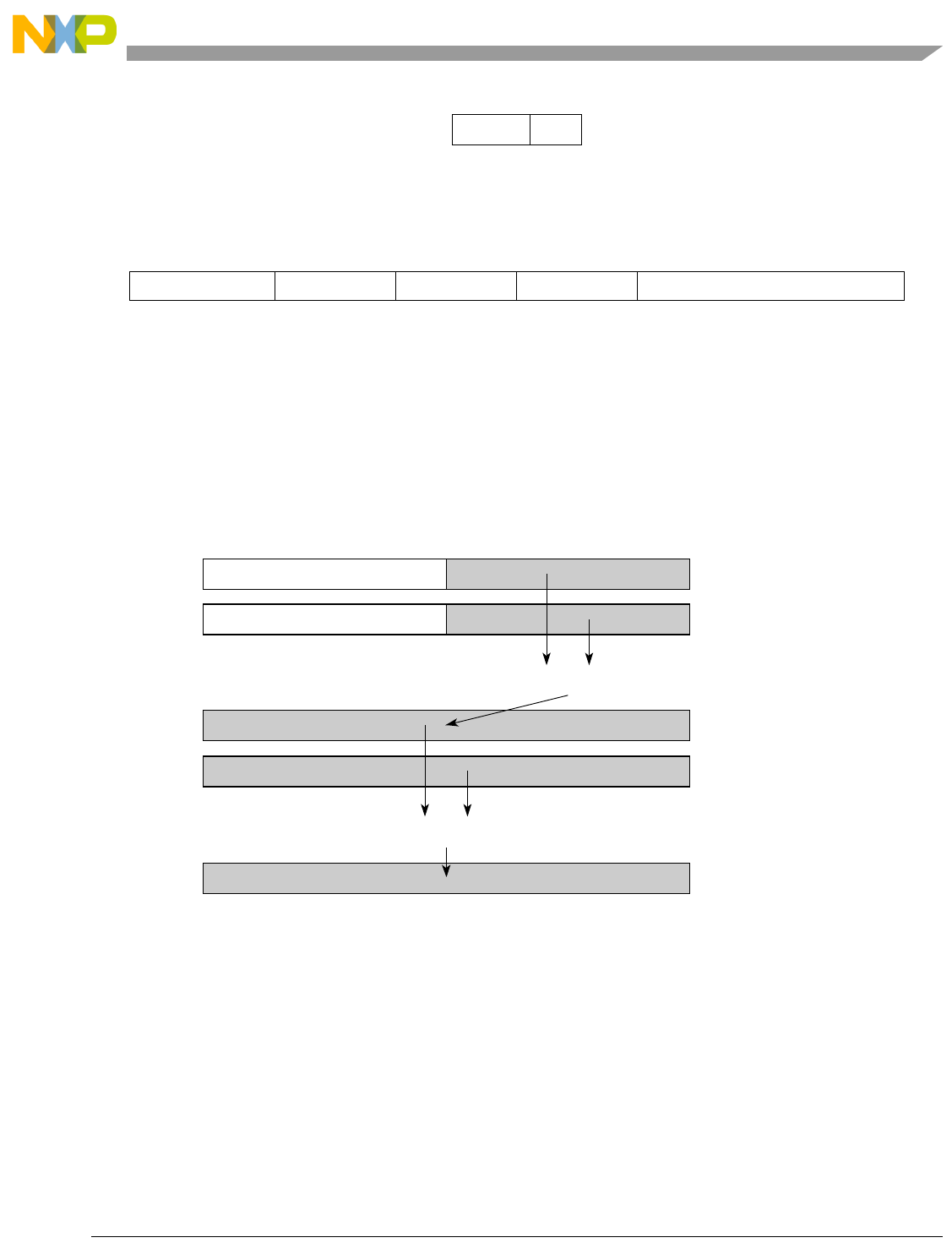

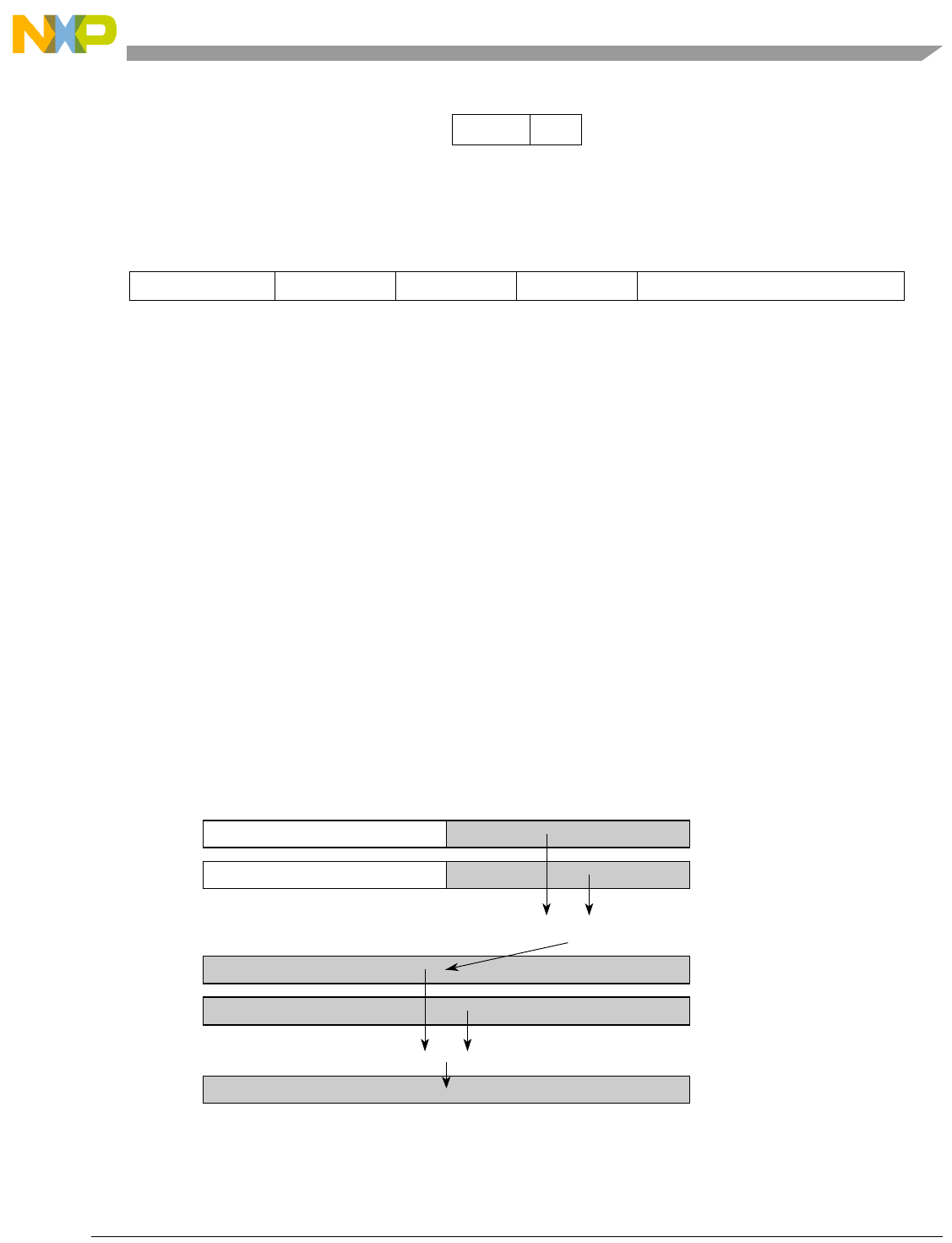

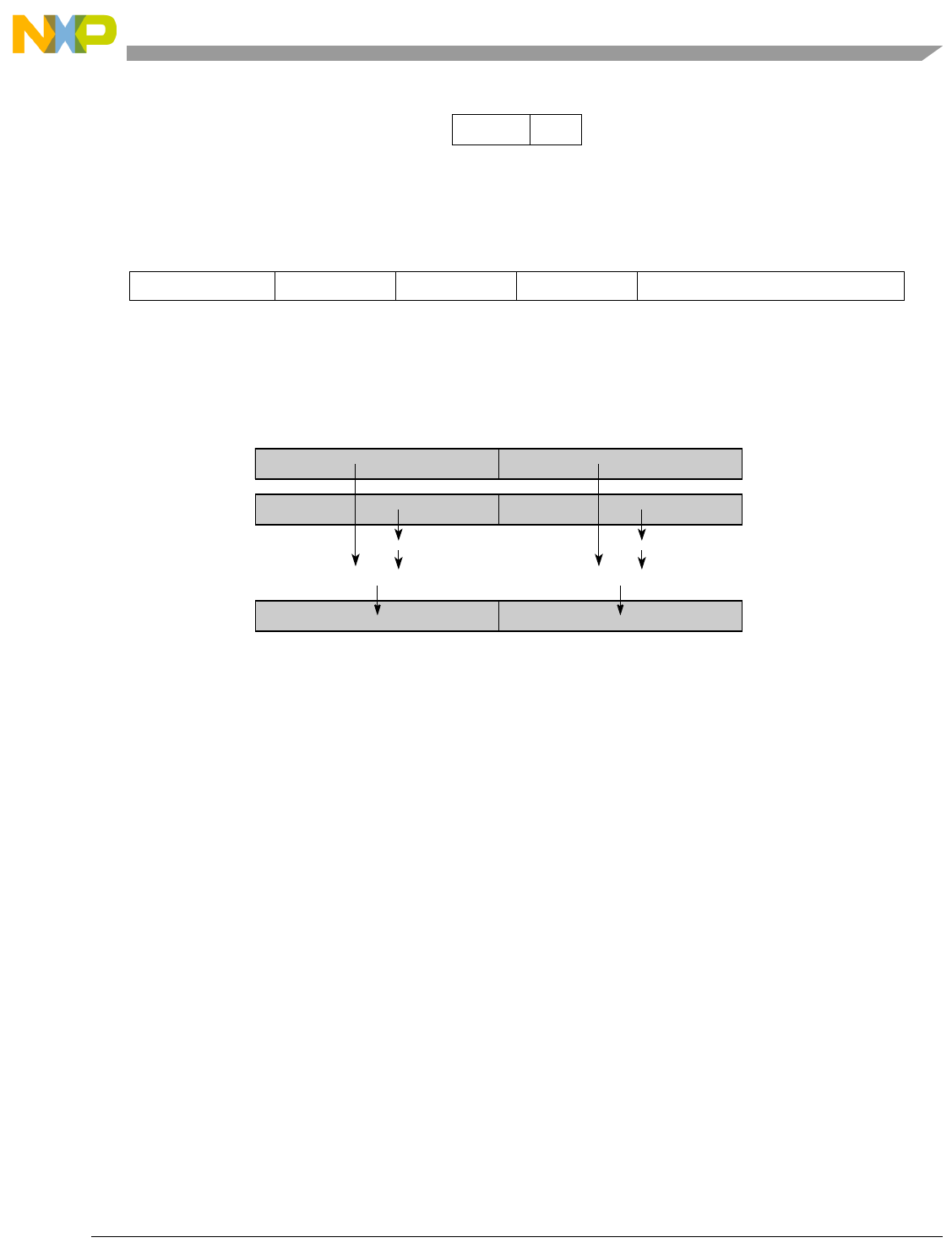

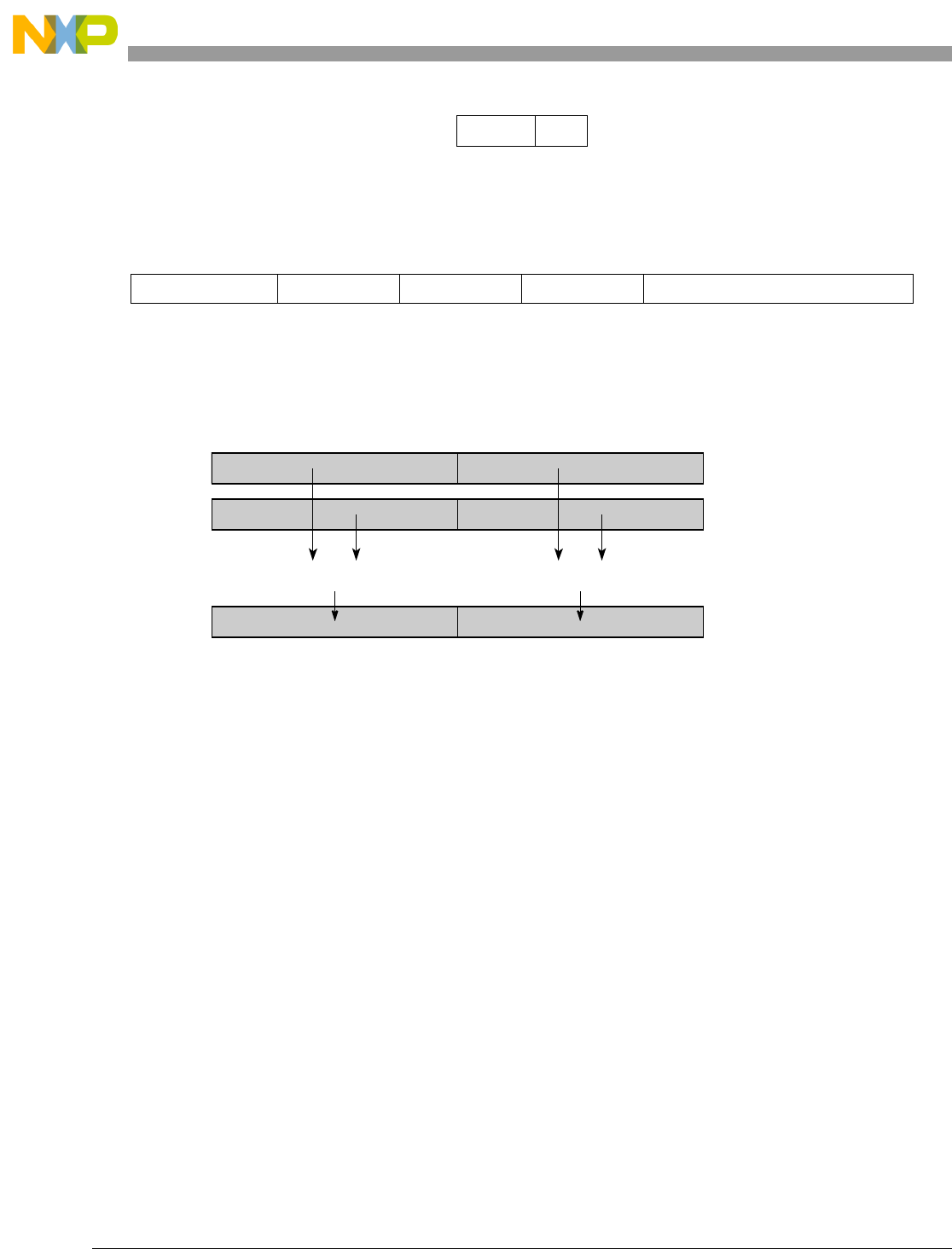

- Figure 5-4. Vector Add Signed, Saturate, Integer to Accumulator Word (evaddssiaaw)

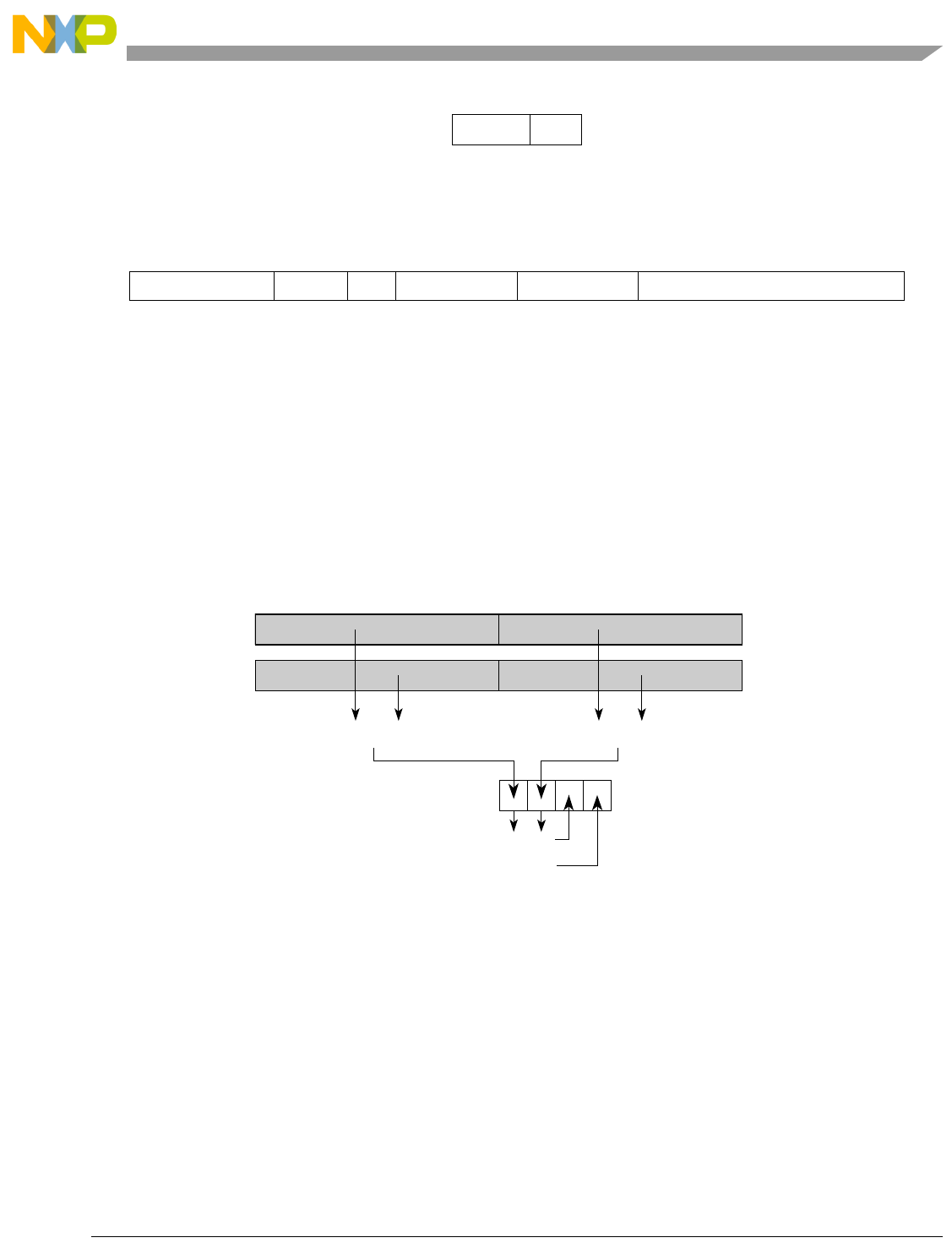

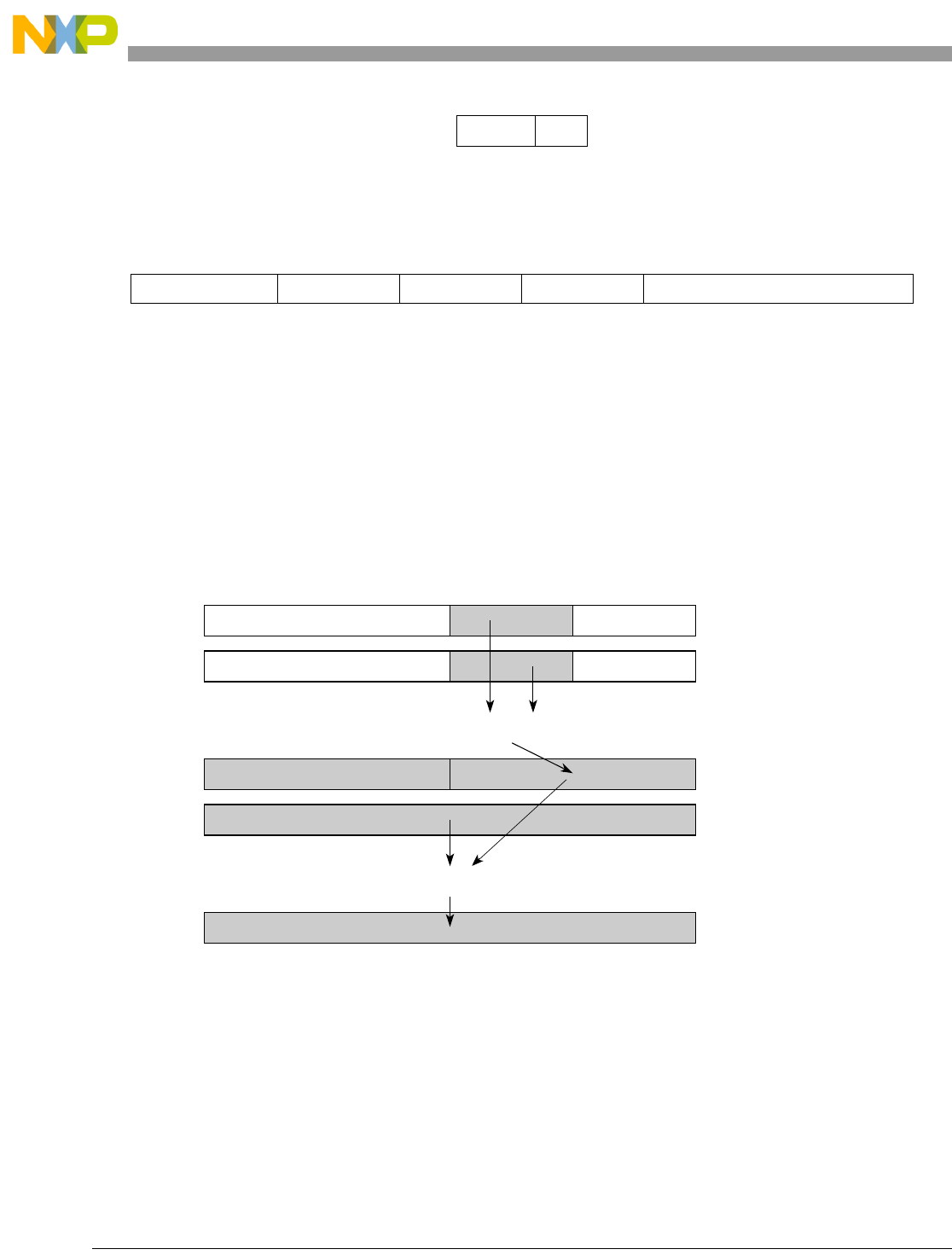

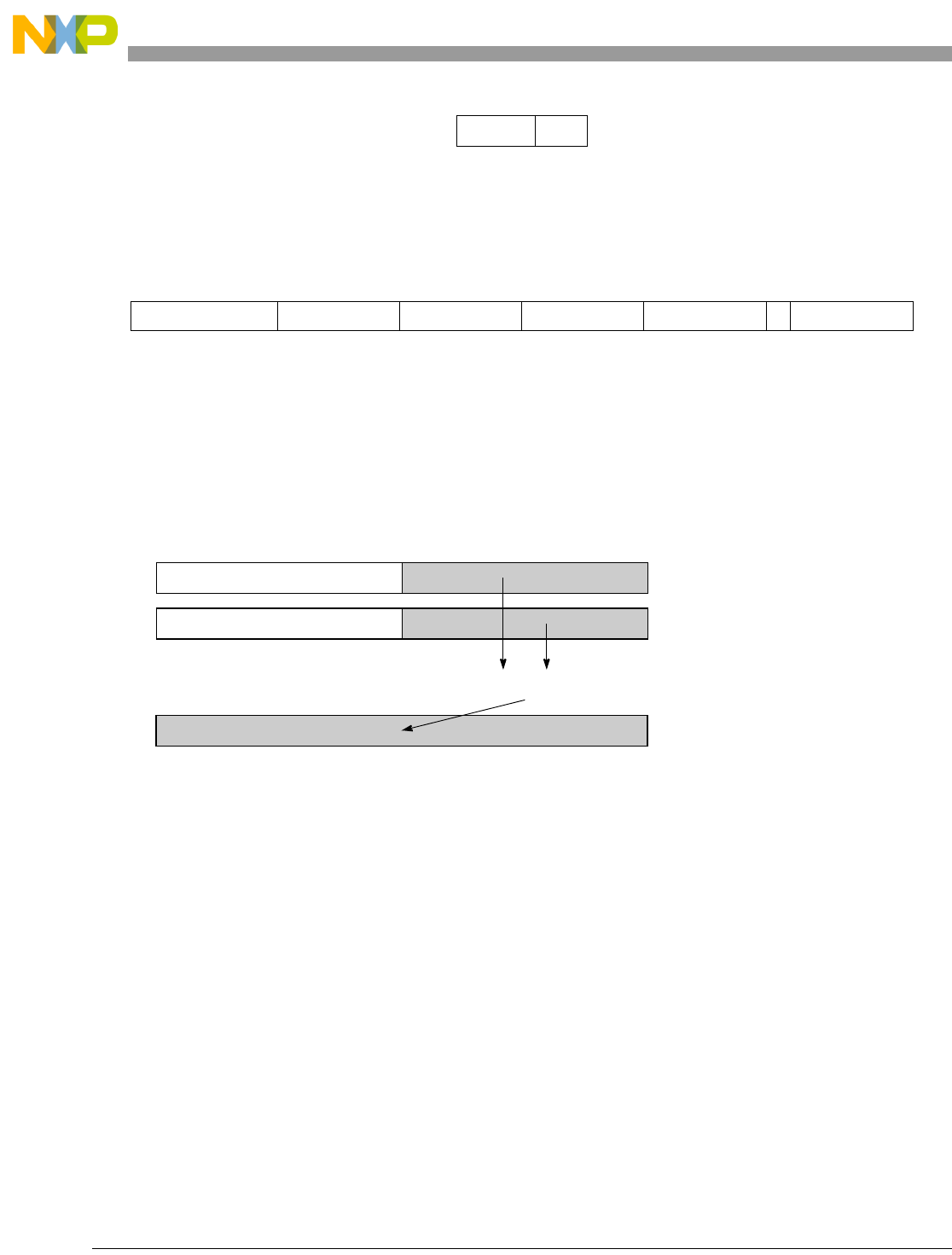

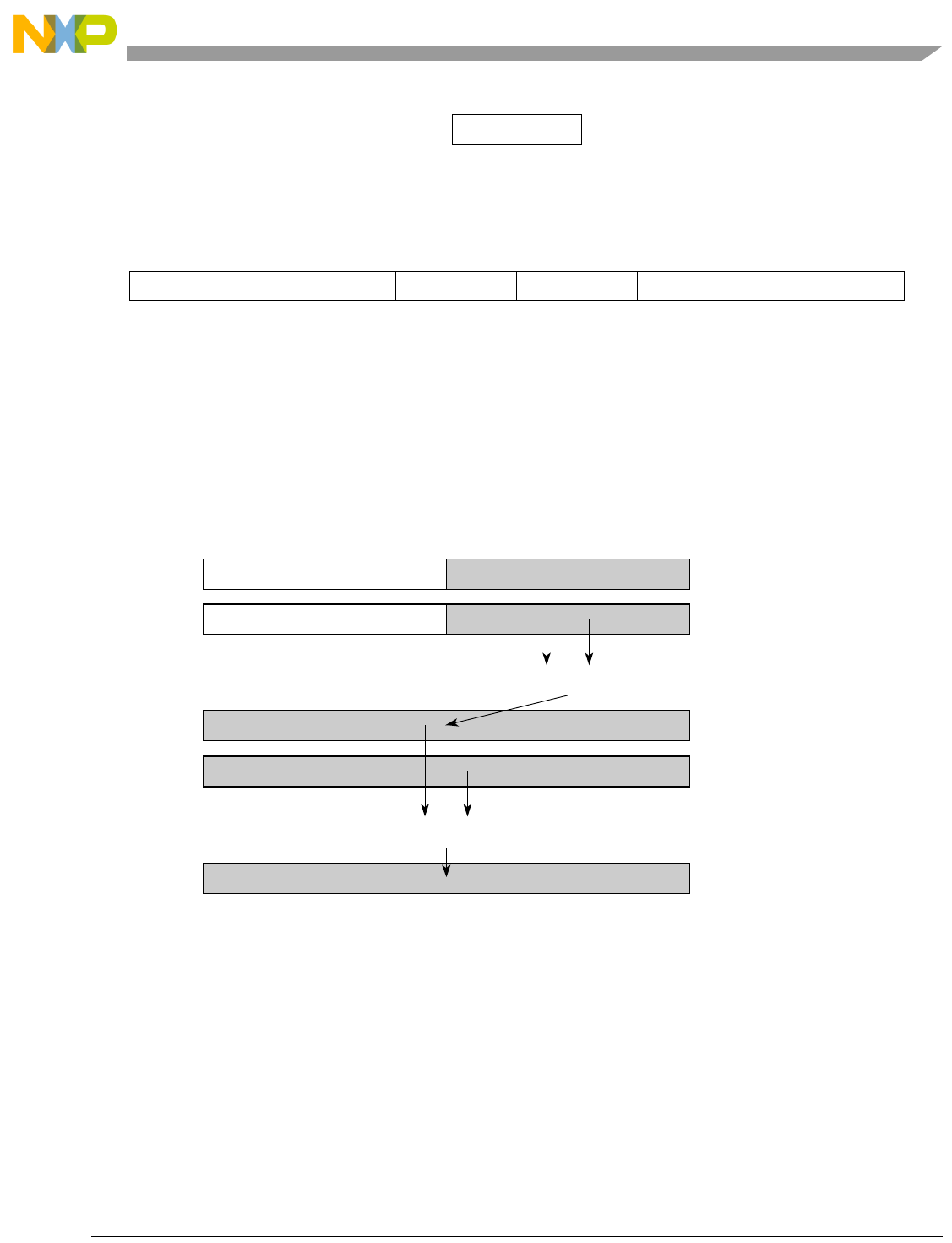

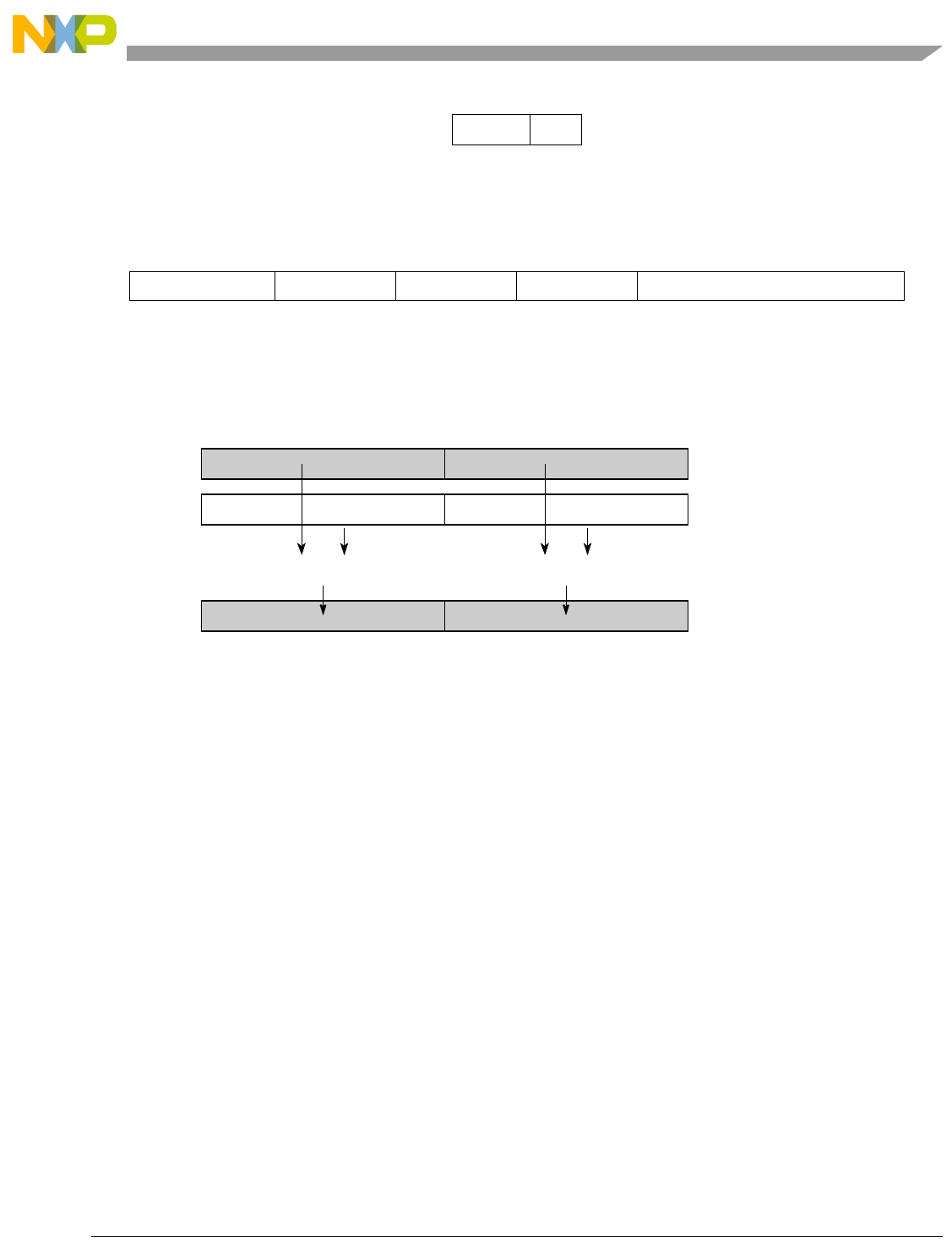

- Figure 5-5. Vector Add Unsigned, Modulo, Integer to Accumulator Word (evaddumiaaw)

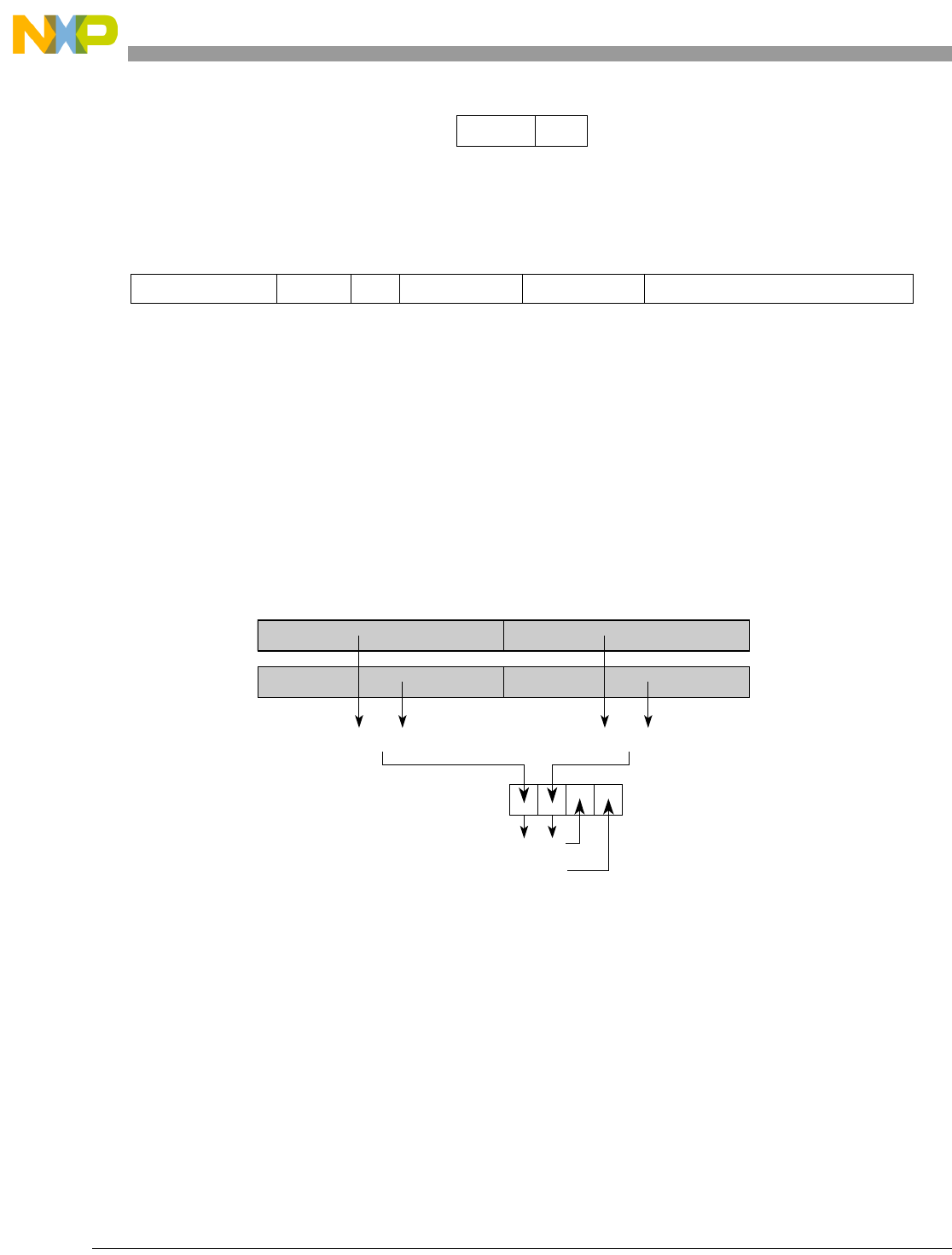

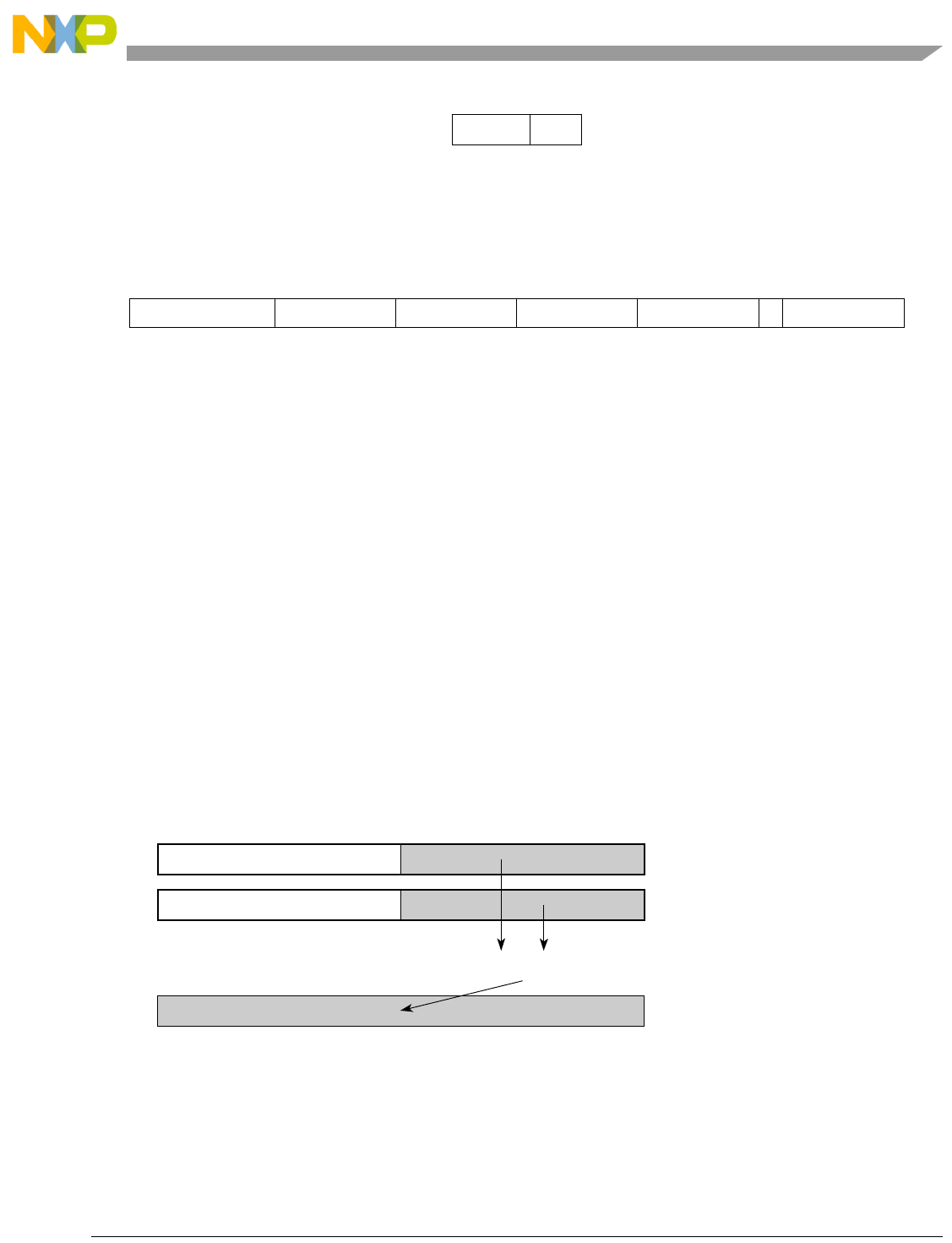

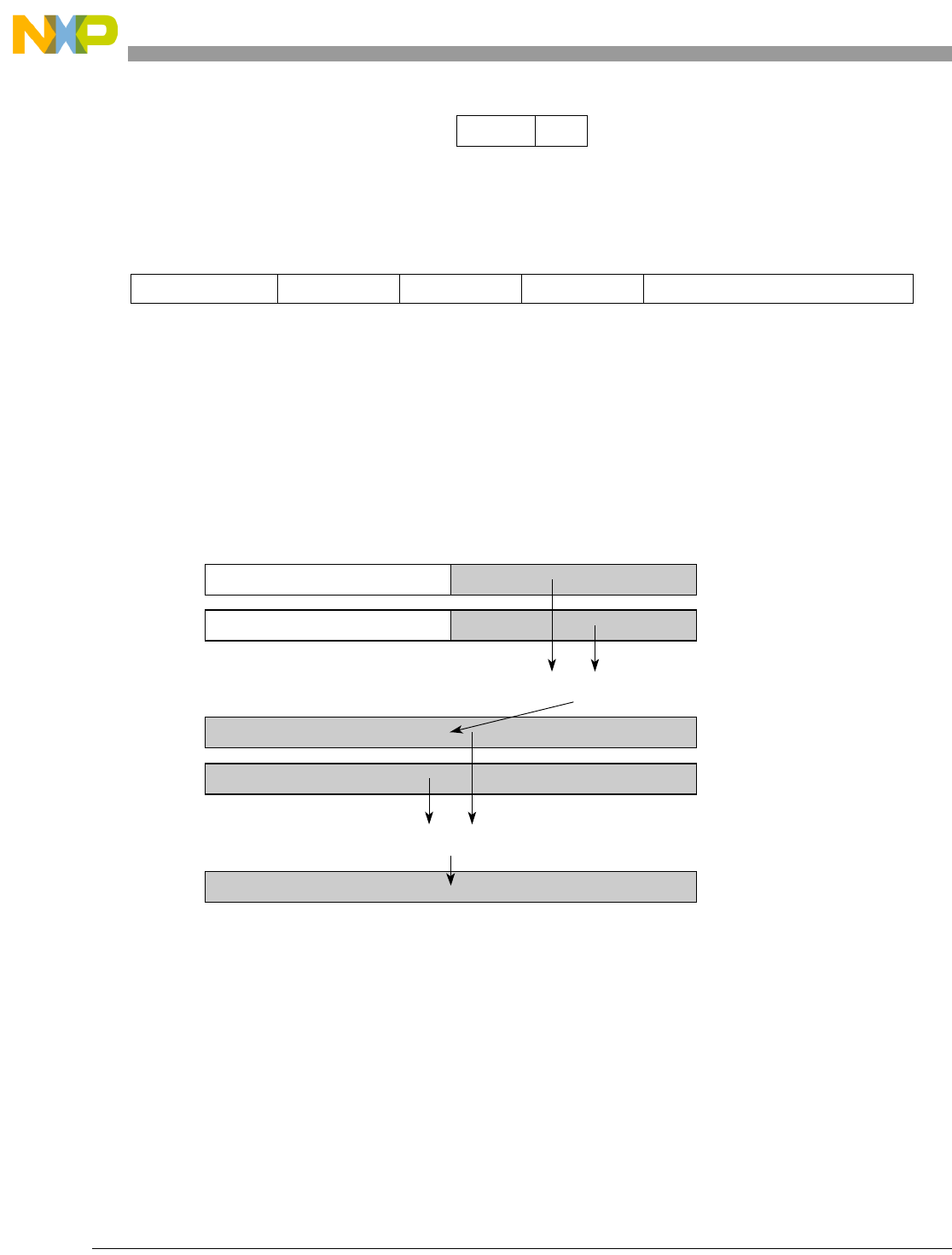

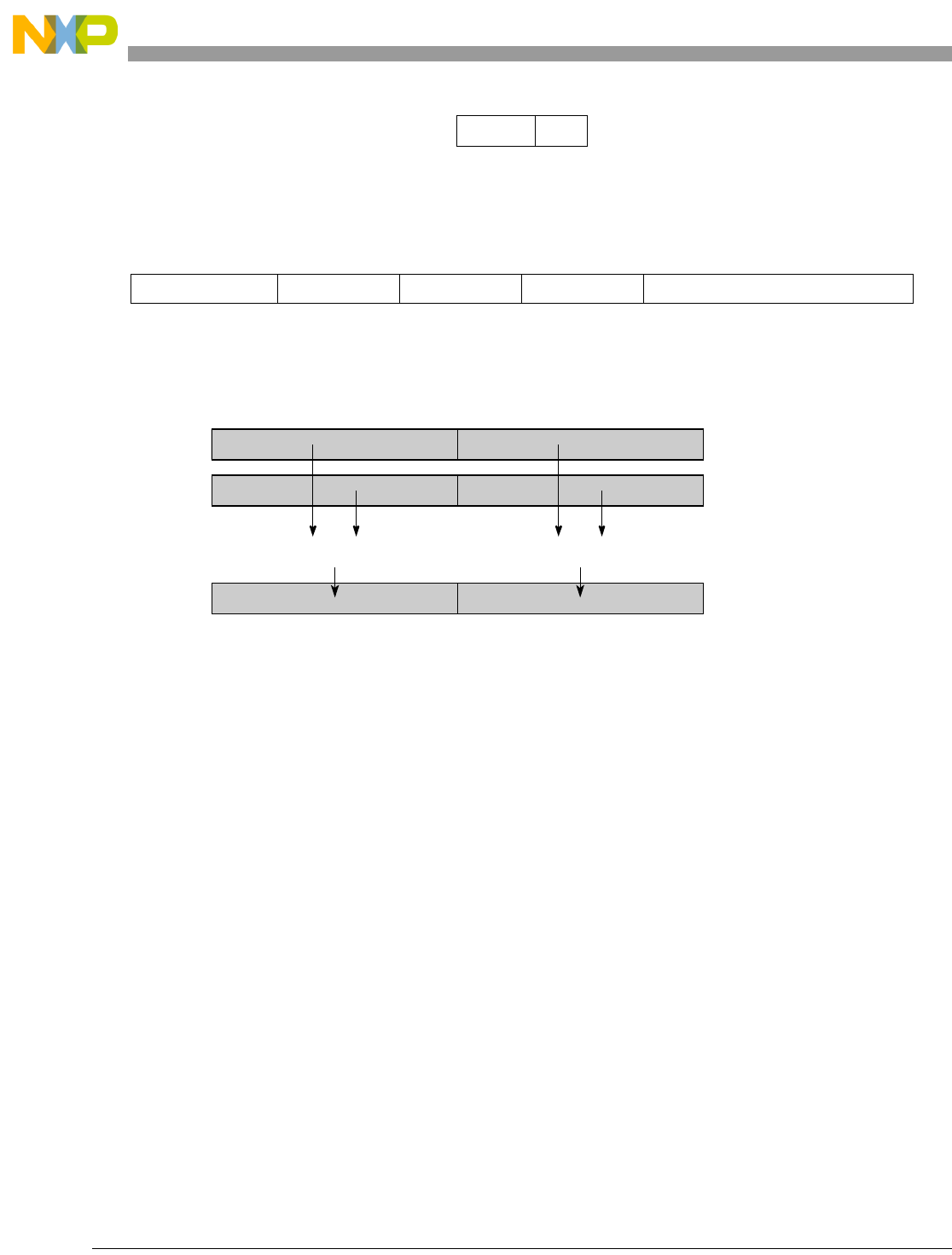

- Figure 5-6. Vector Add Unsigned, Saturate, Integer to Accumulator Word (evaddusiaaw)

- Figure 5-7. Vector Add Word (evaddw)

- Figure 5-8. Vector AND (evand)

- Figure 5-9. Vector AND with Complement (evandc)

- Figure 5-10. Vector Compare Equal (evcmpeq)

- Figure 5-11. Vector Compare Greater Than Signed (evcmpgts)

- Figure 5-12. Vector Compare Greater Than Unsigned (evcmpgtu)

- Figure 5-13. Vector Compare Less Than Signed (evcmplts)

- Figure 5-14. Vector Compare Less Than Unsigned (evcmpltu)

- Figure 5-15. Vector Count Leading Signed Bits Word (evcntlsw)

- Figure 5-16. Vector Count Leading Zeros Word (evcntlzw)

- Figure 5-17. Vector Divide Word Signed (evdivws)

- Figure 5-18. Vector Divide Word Unsigned (evdivwu)

- Figure 5-19. Vector Equivalent (eveqv)

- Figure 5-20. Vector Extend Sign Byte (evextsb)

- Figure 5-21. Vector Extend Sign Half Word (evextsh)

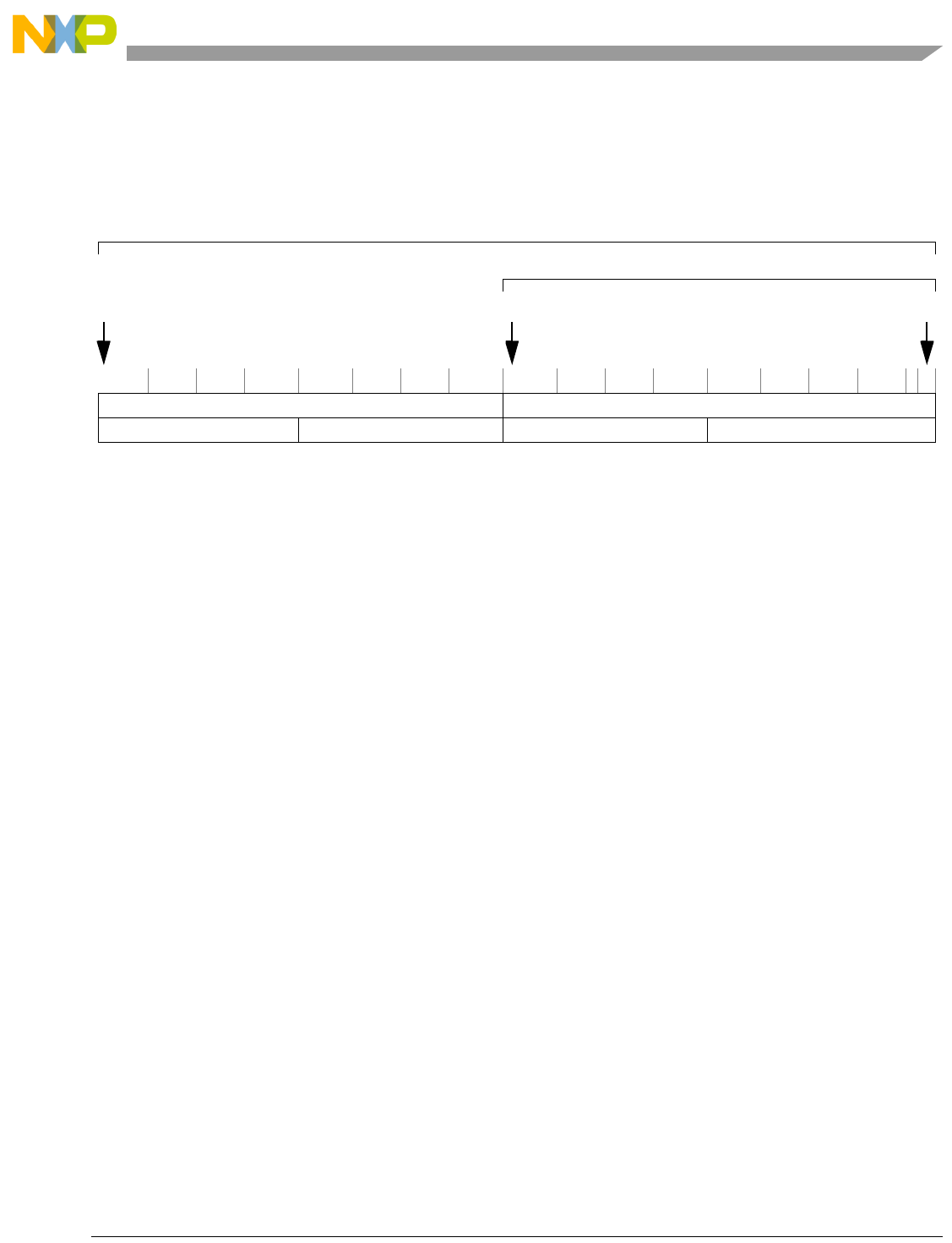

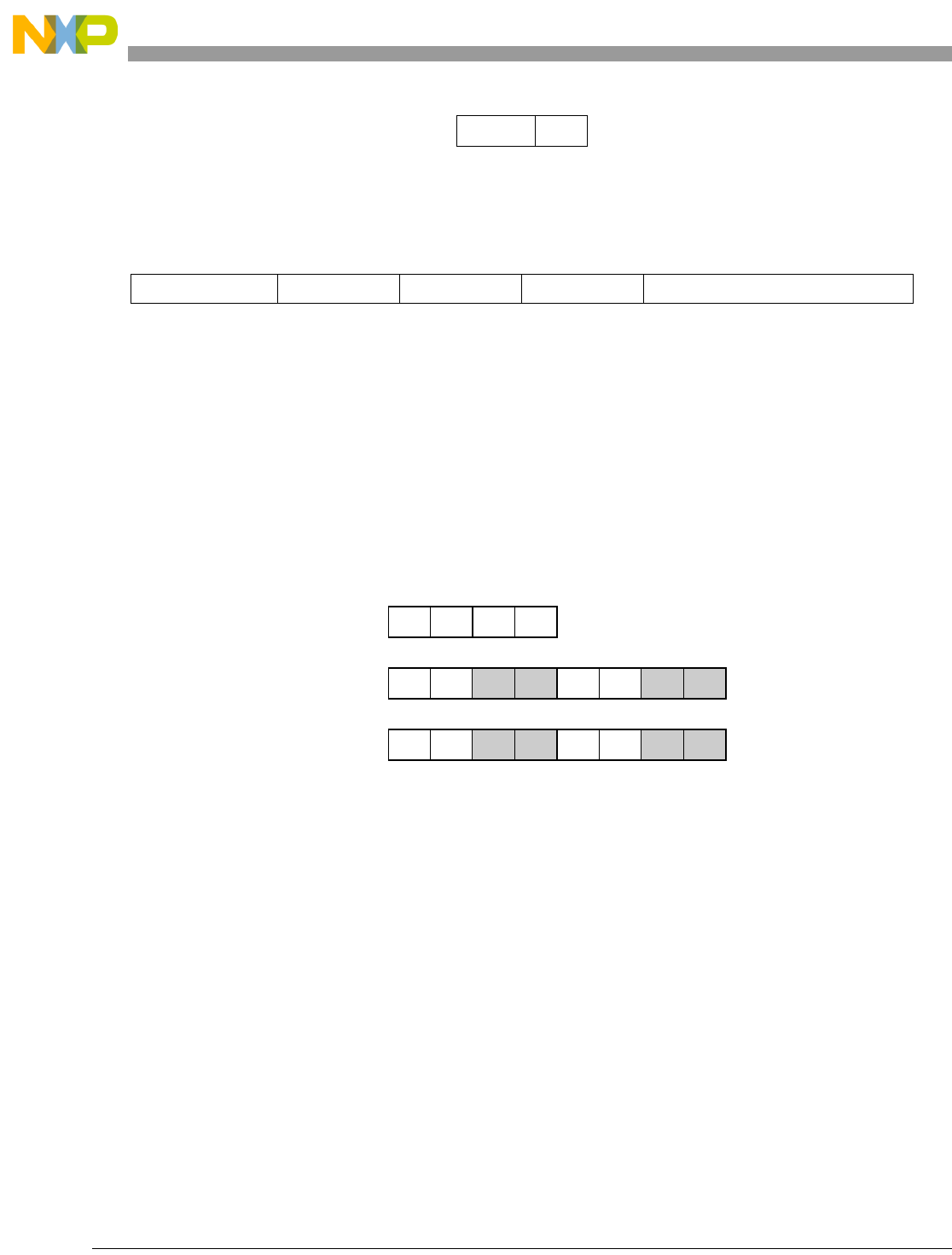

- Figure 5-22. evldd Results in Big- and Little-Endian Modes

- Figure 5-23. evlddx Results in Big- and Little-Endian Modes

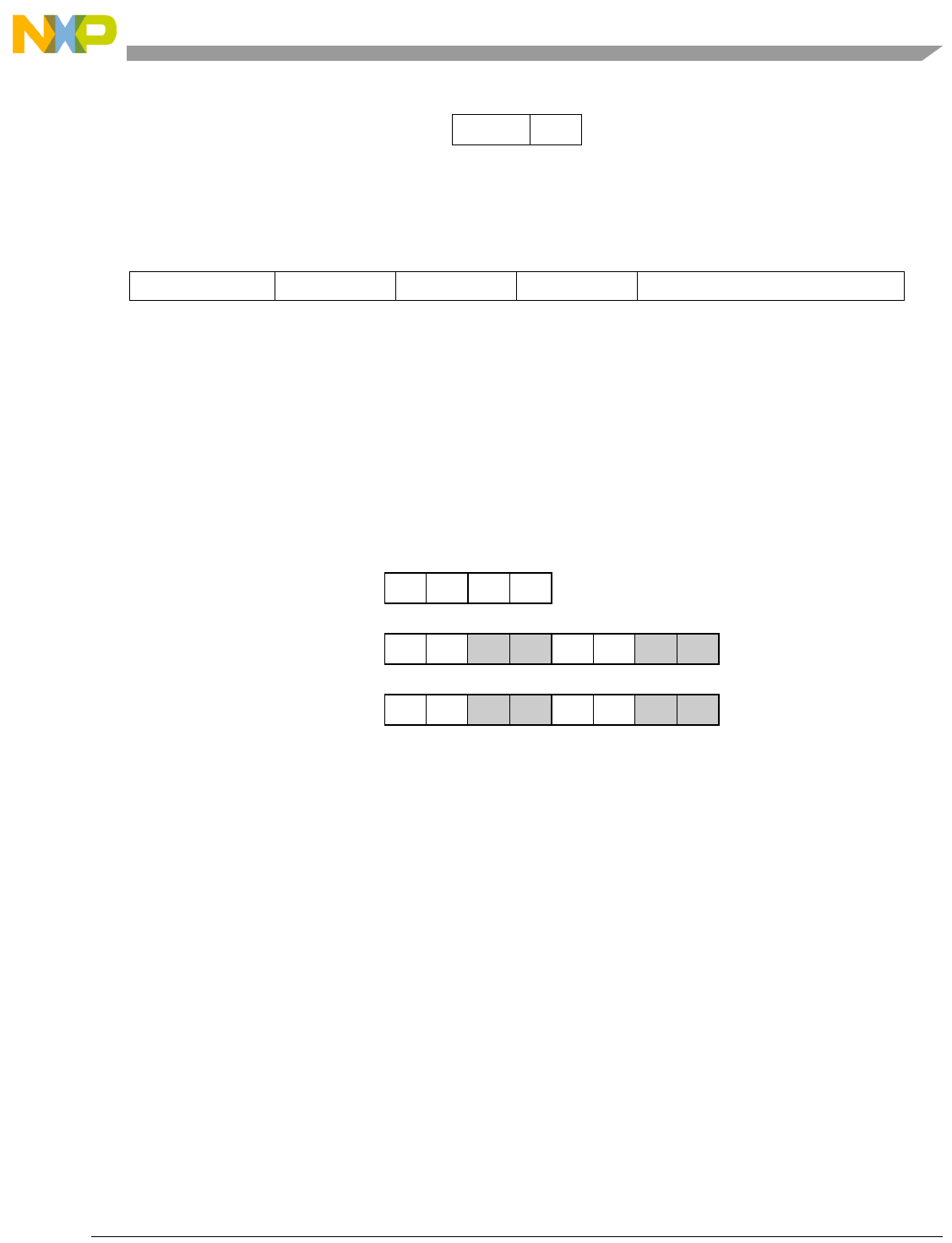

- Figure 5-24. evldh Results in Big- and Little-Endian Modes

- Figure 5-25. evldhx Results in Big- and Little-Endian Modes

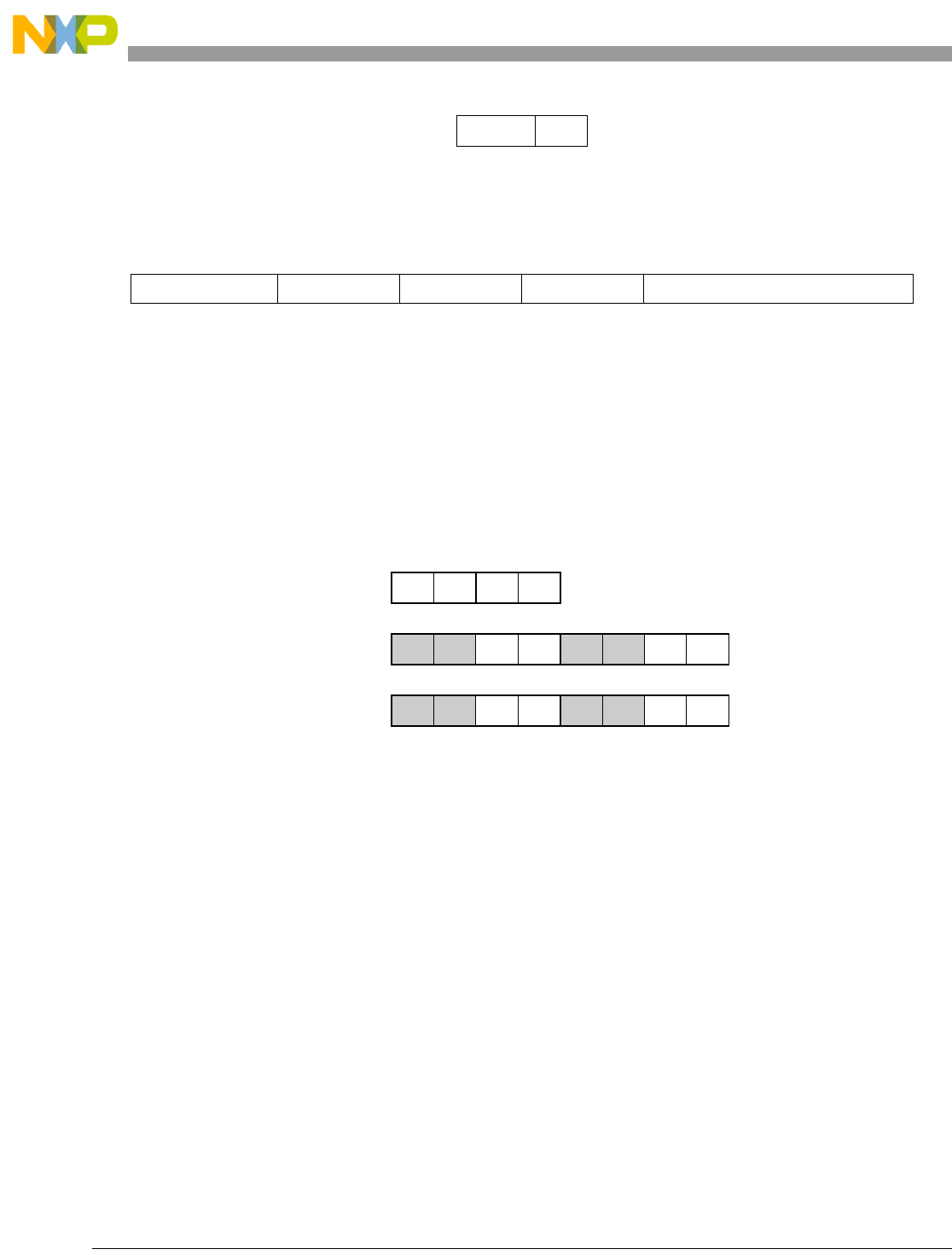

- Figure 5-26. evldw Results in Big- and Little-Endian Modes

- Figure 5-27. evldwx Results in Big- and Little-Endian Modes

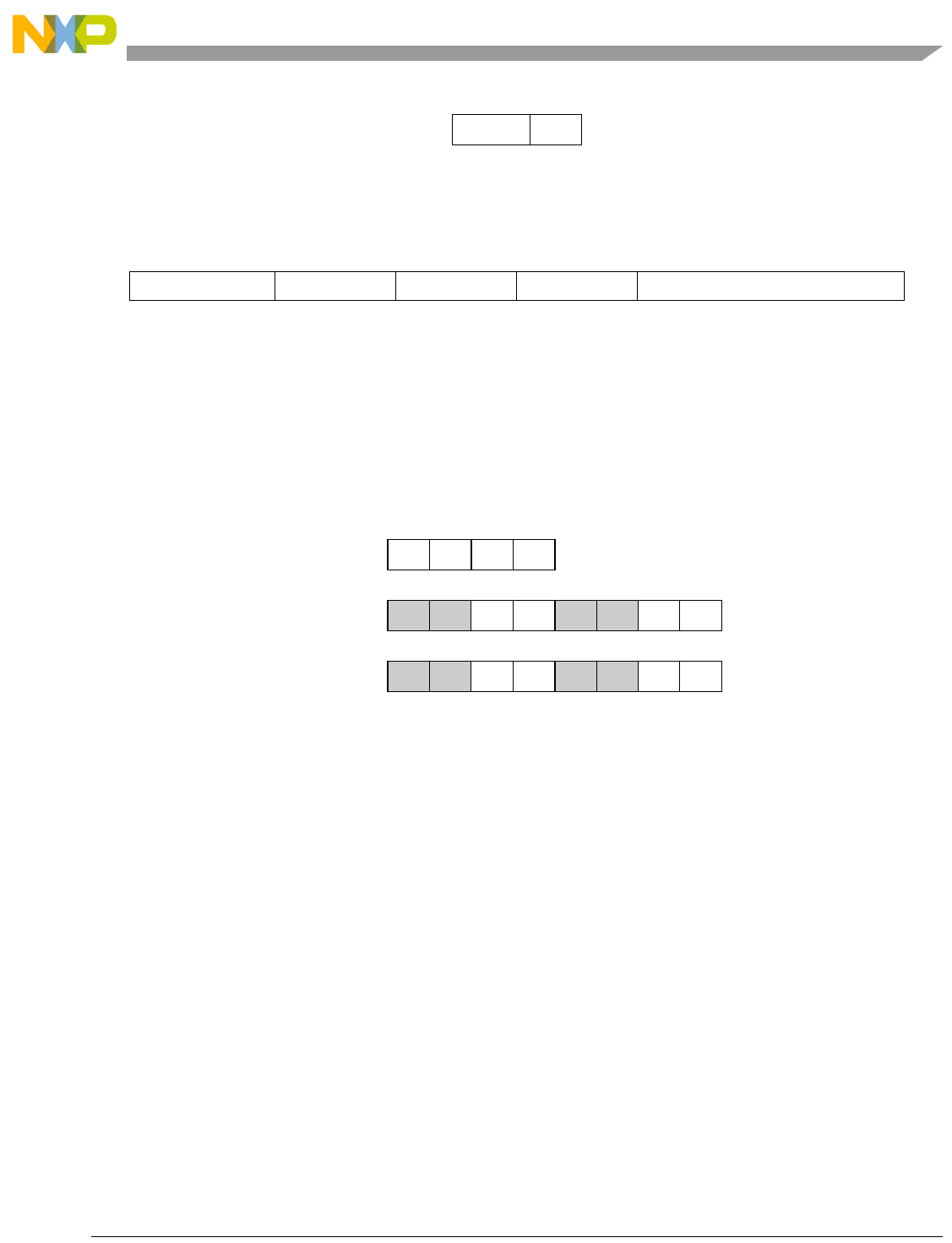

- Figure 5-28. evlhhesplat Results in Big- and Little-Endian Modes

- Figure 5-29. evlhhesplatx Results in Big- and Little-Endian Modes

- Figure 5-30. evlhhossplat Results in Big- and Little-Endian Modes

- Figure 5-31. evlhhossplatx Results in Big- and Little-Endian Modes

- Figure 5-32. evlhhousplat Results in Big- and Little-Endian Modes

- Figure 5-33. evlhhousplatx Results in Big- and Little-Endian Modes

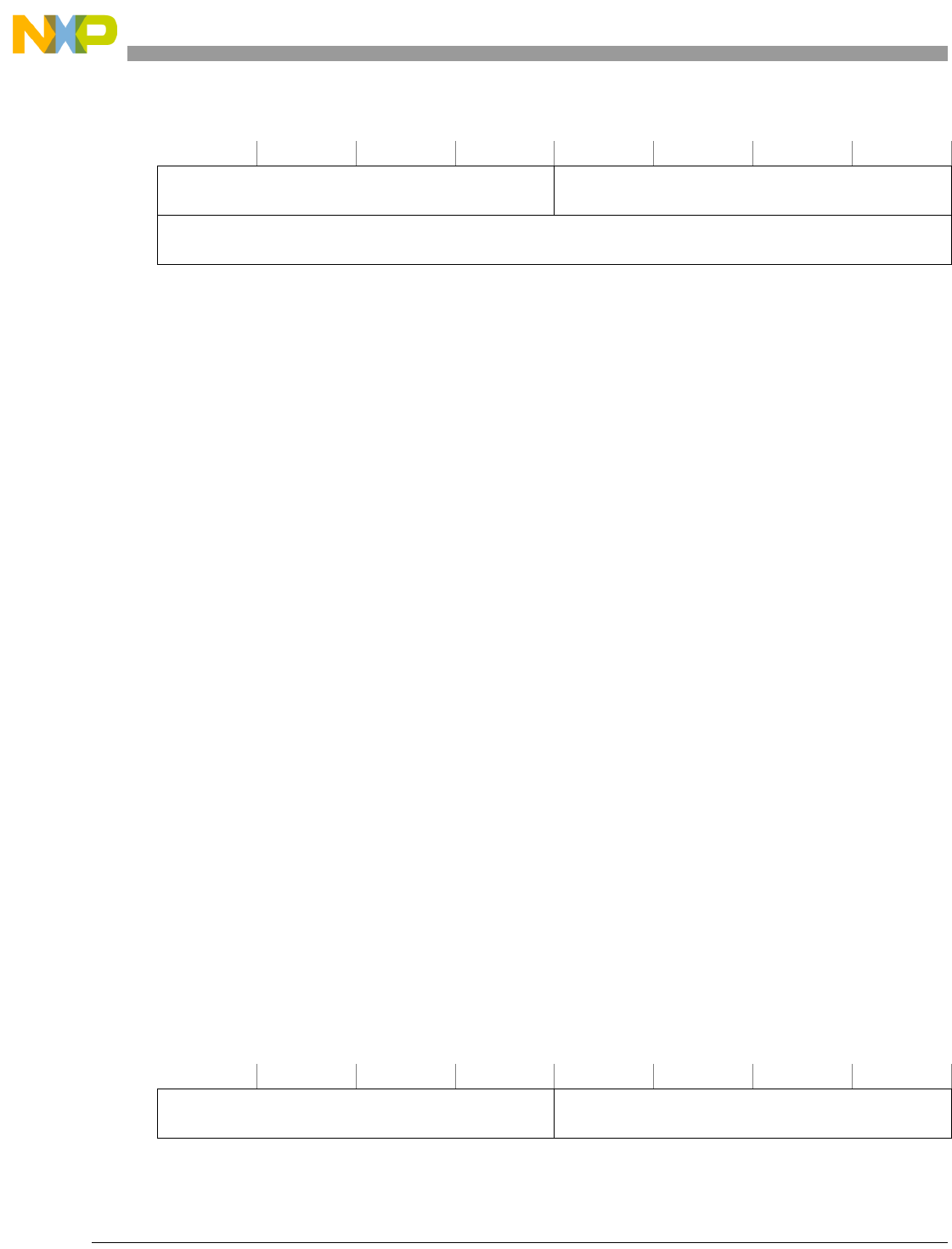

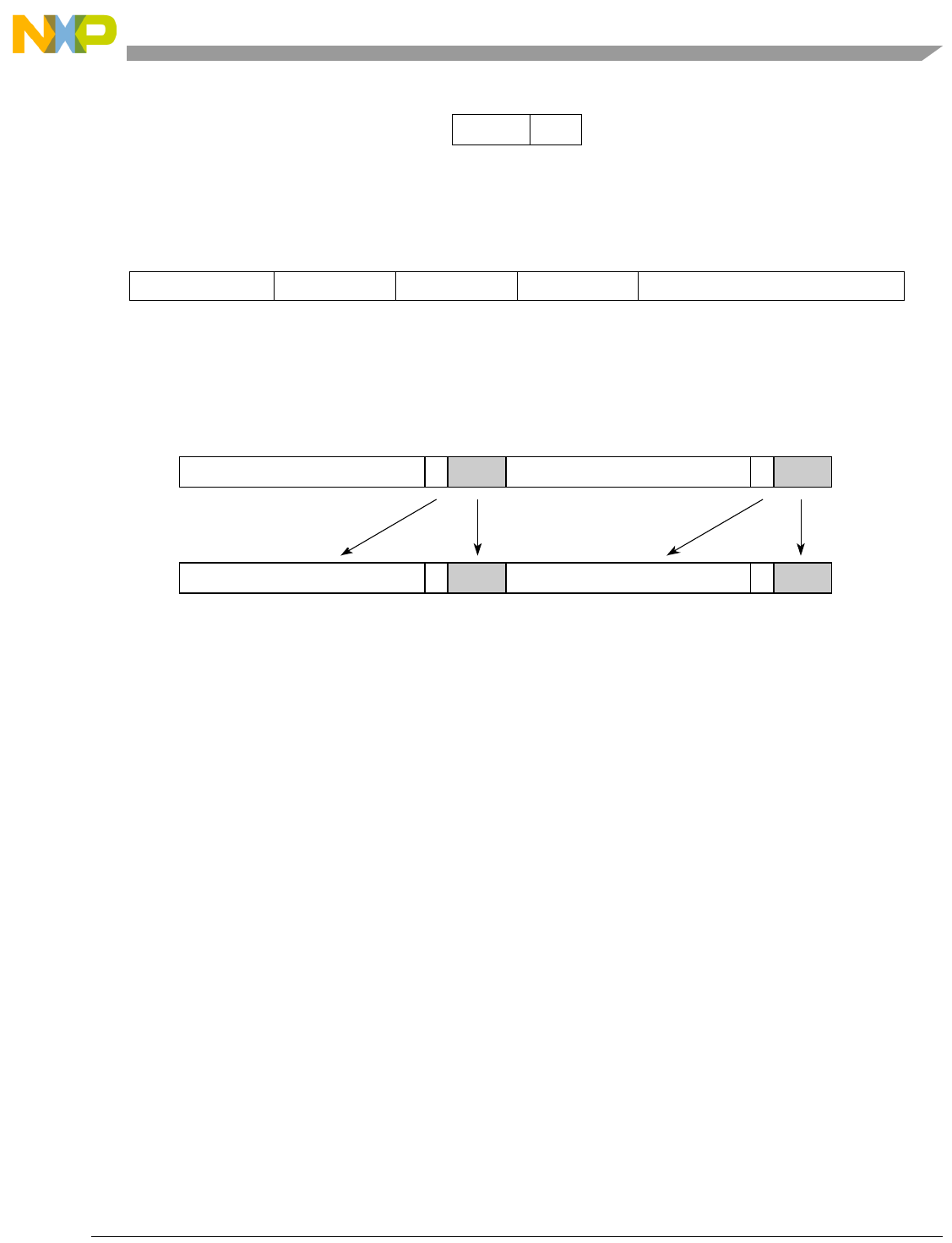

- Figure 5-34. evlwhe Results in Big- and Little-Endian Modes

- Figure 5-35. evlwhex Results in Big- and Little-Endian Modes

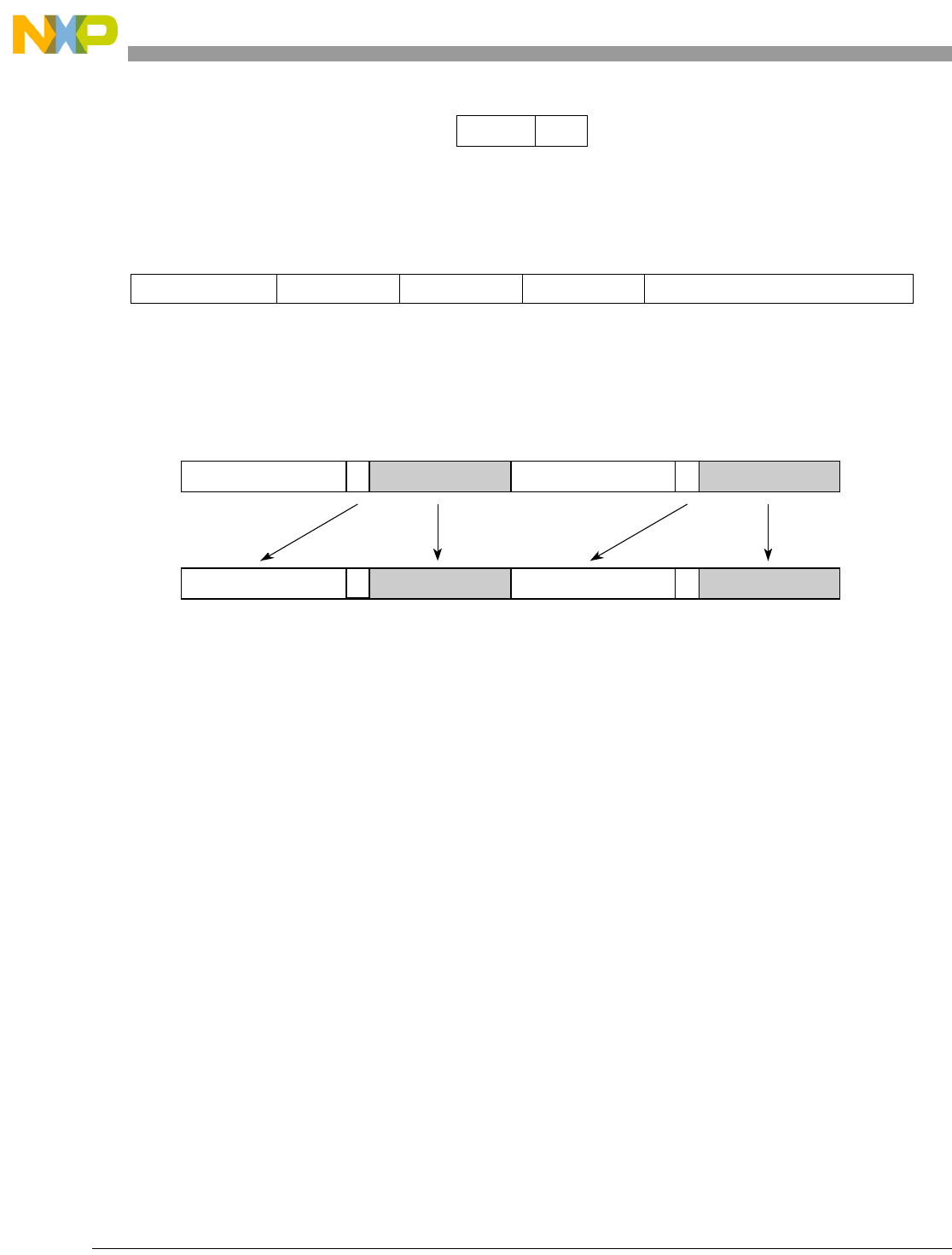

- Figure 5-36. evlwhos Results in Big- and Little-Endian Modes

- Figure 5-37. evlwhosx Results in Big- and Little-Endian Modes

- Figure 5-38. evlwhou Results in Big- and Little-Endian Modes

- Figure 5-39. evlwhoux Results in Big- and Little-Endian Modes

- Figure 5-40. evlwhsplat Results in Big- and Little-Endian Modes

- Figure 5-41. evlwhsplatx Results in Big- and Little-Endian Modes

- Figure 5-42. evlwwsplat Results in Big- and Little-Endian Modes

- Figure 5-43. evlwwsplatx Results in Big- and Little-Endian Modes

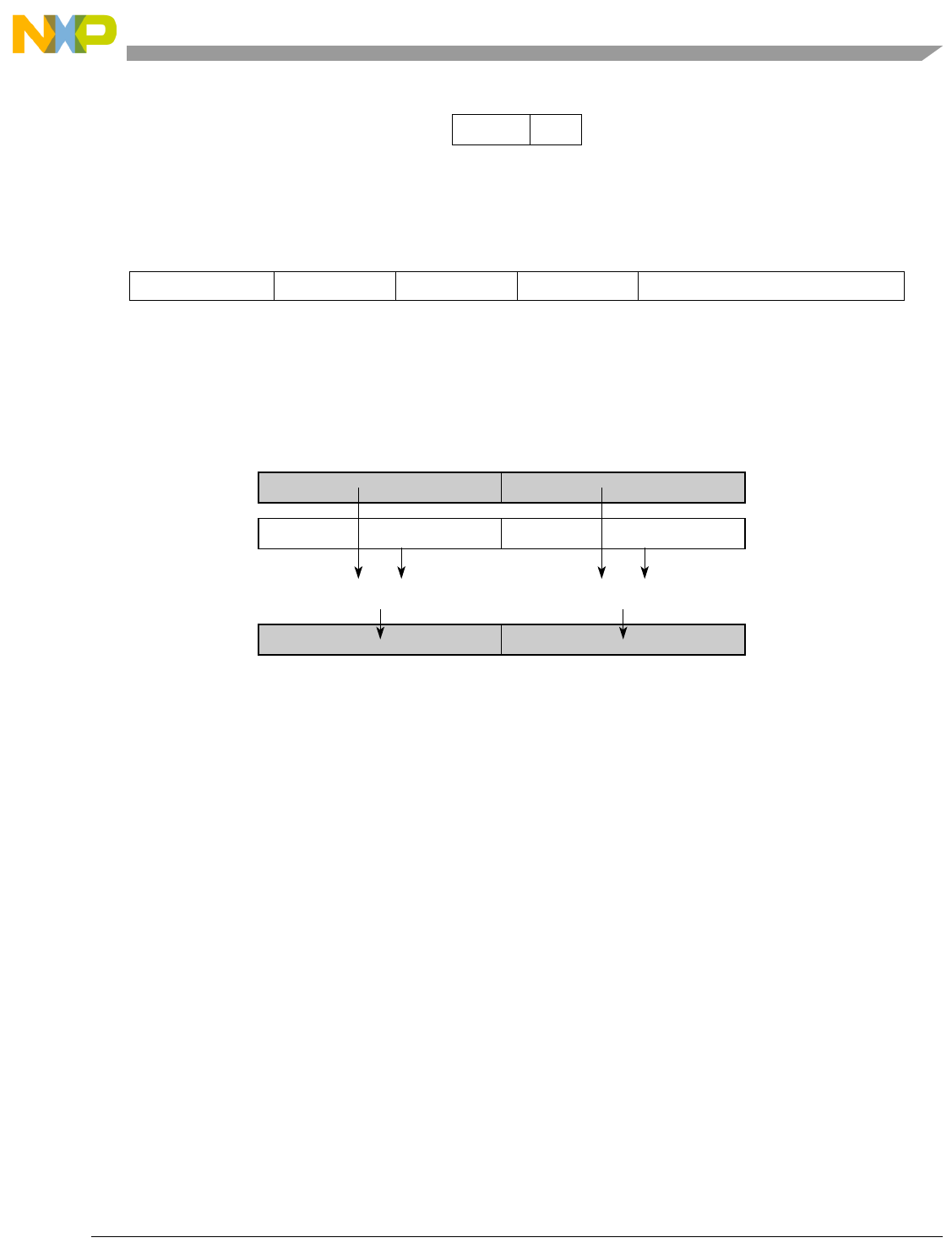

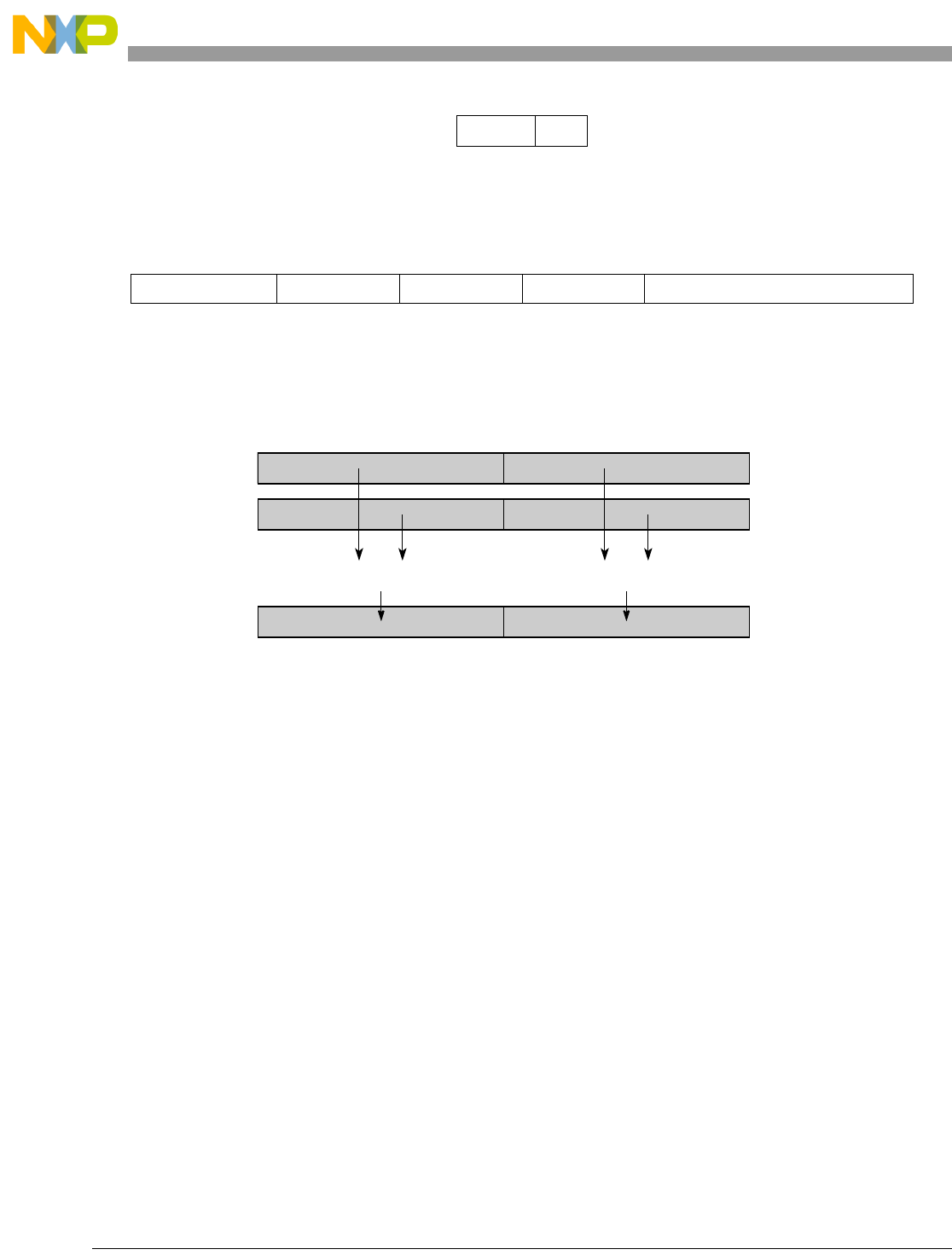

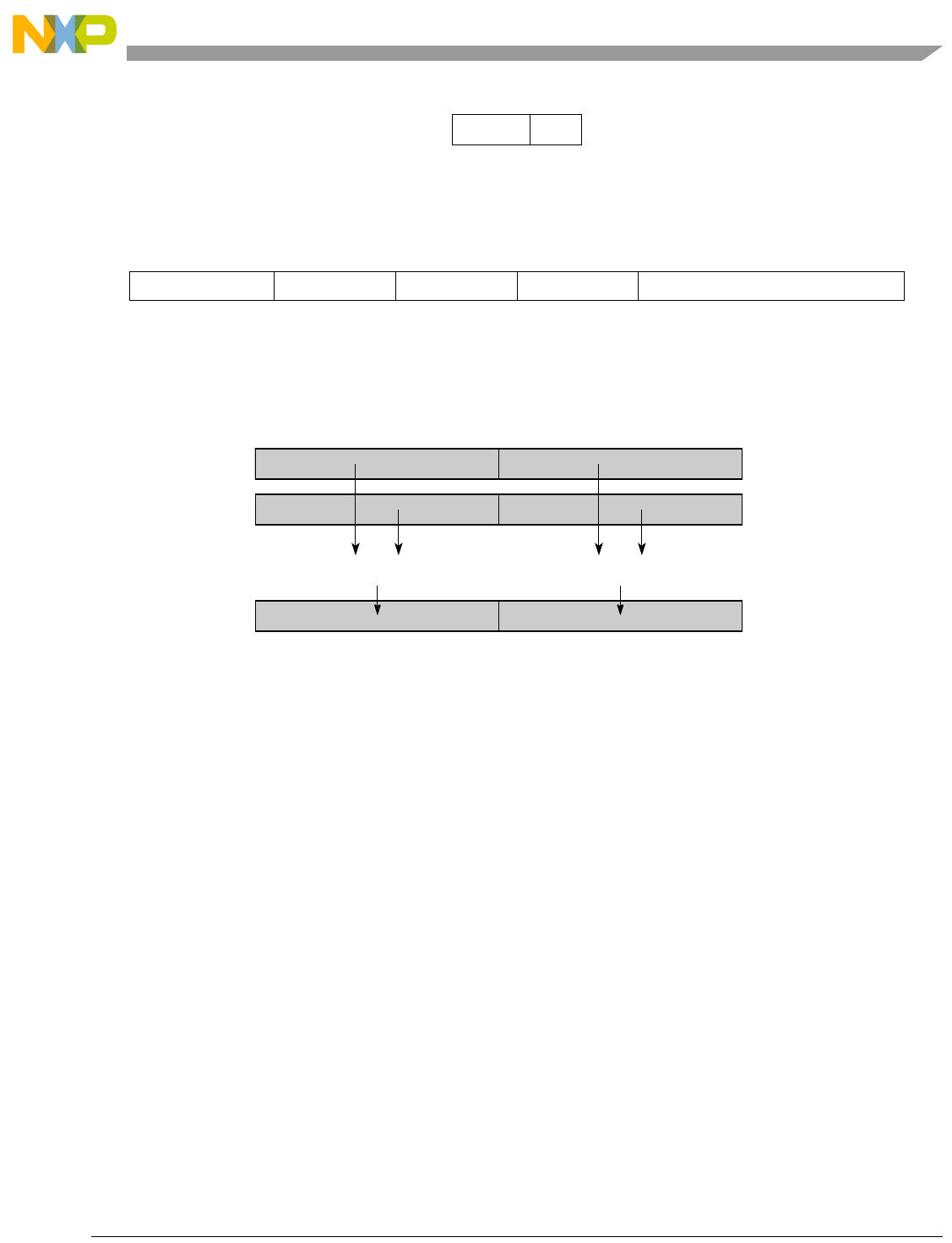

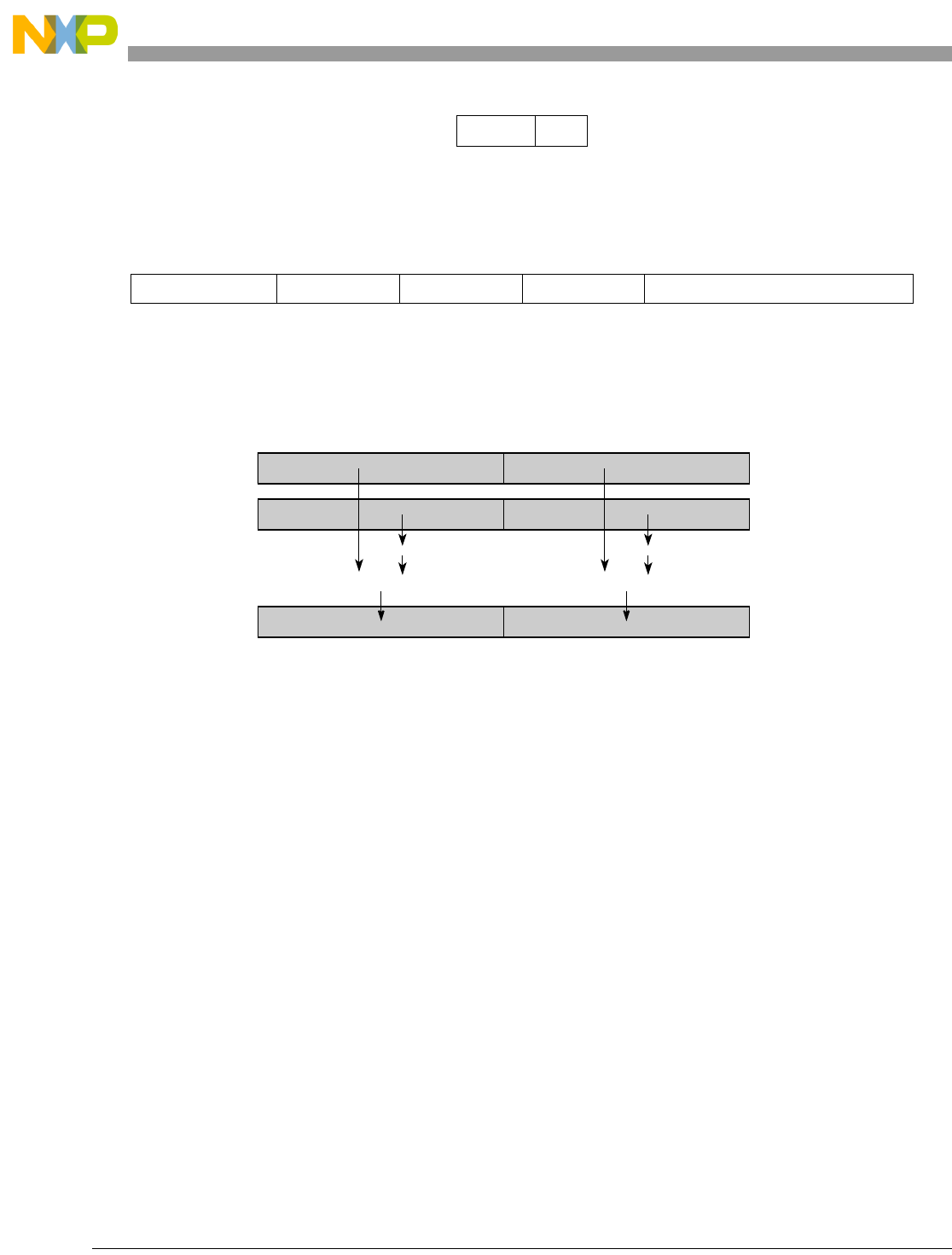

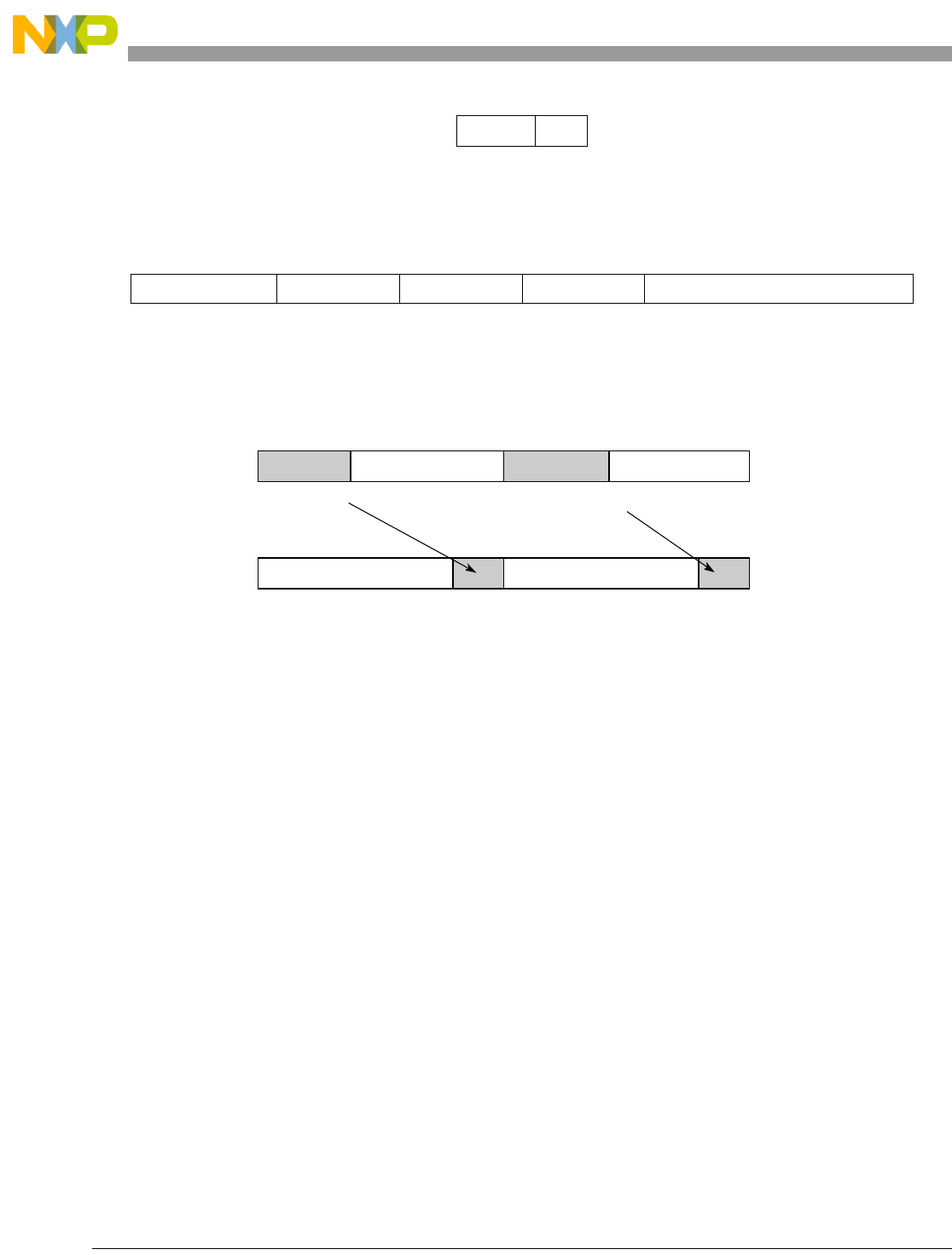

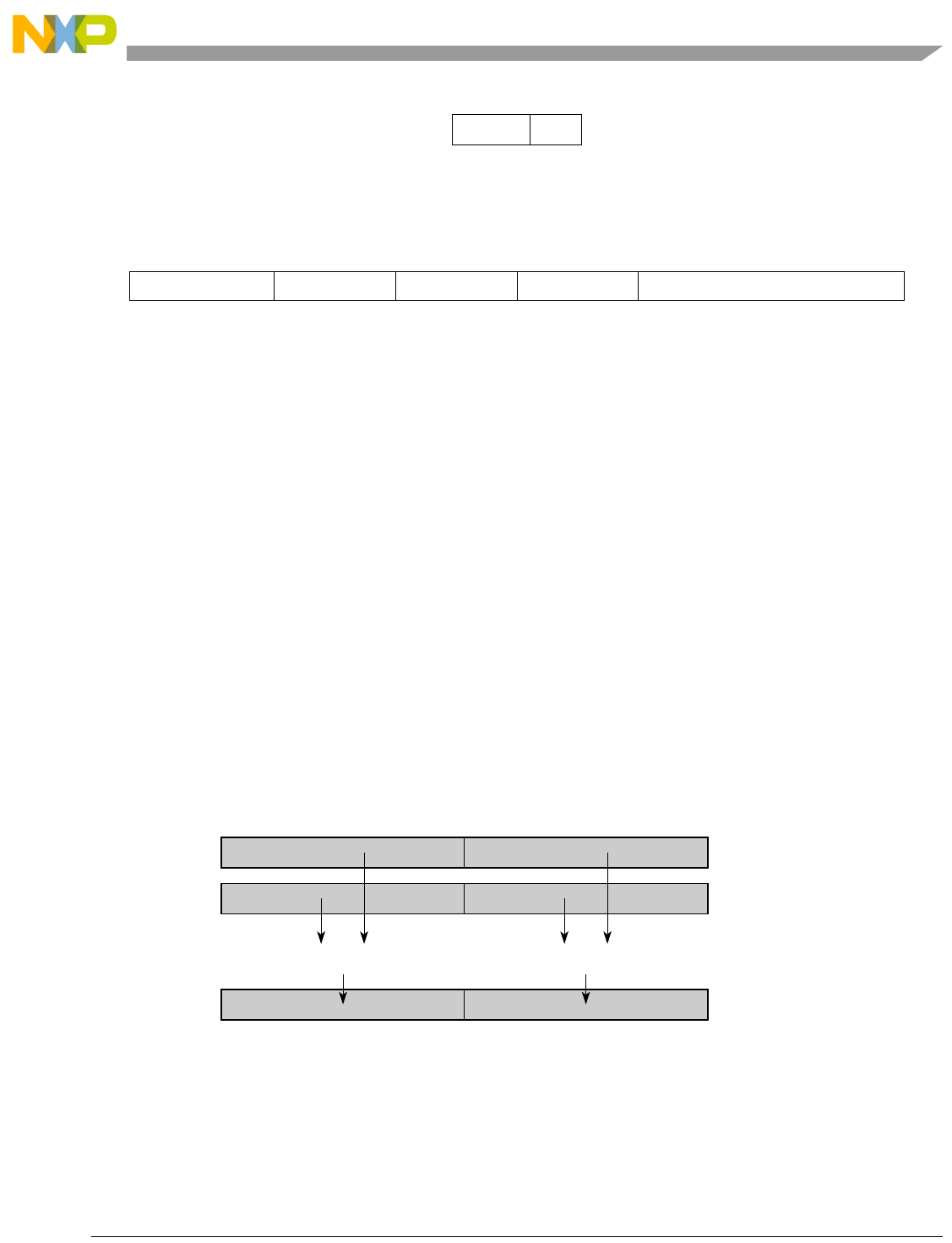

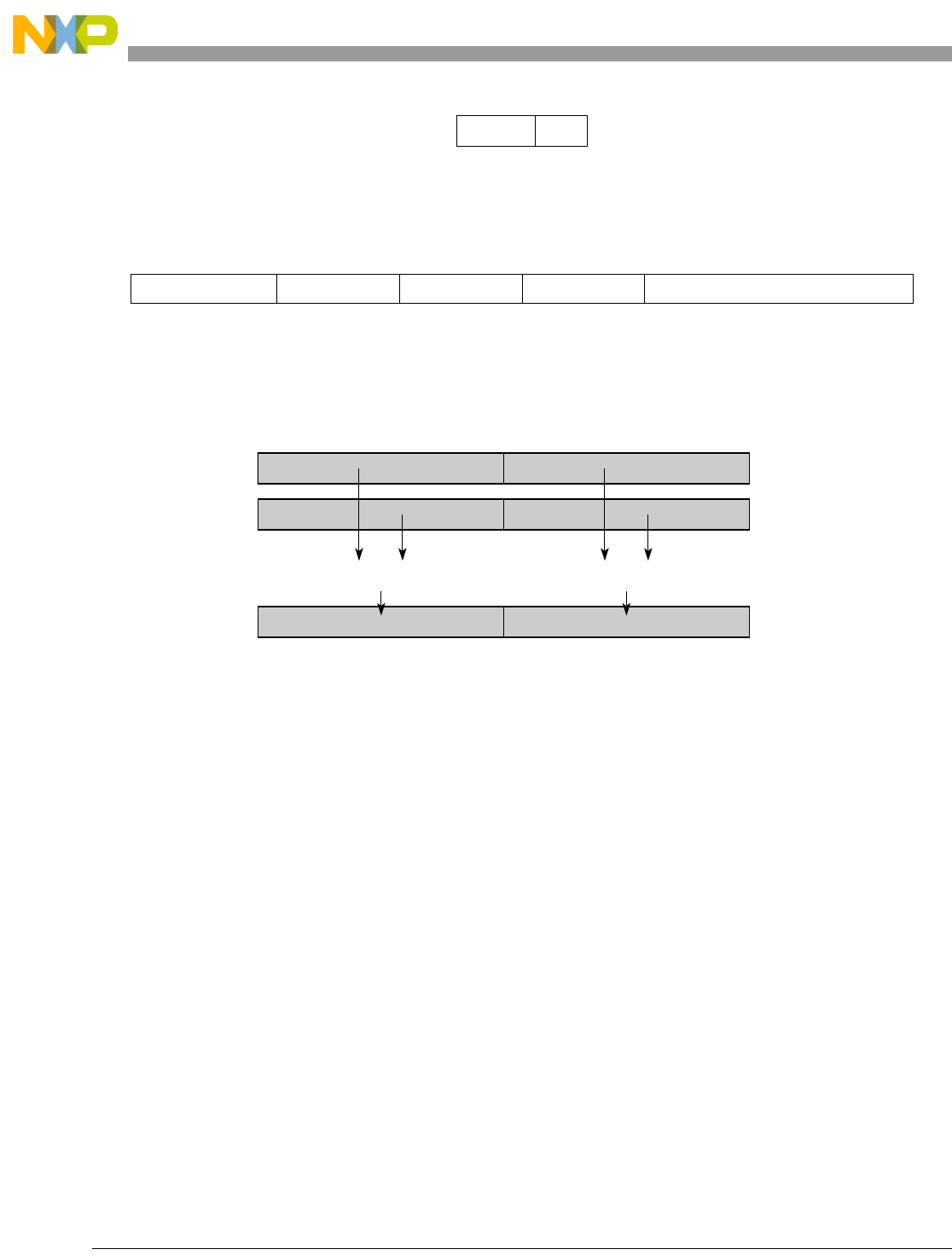

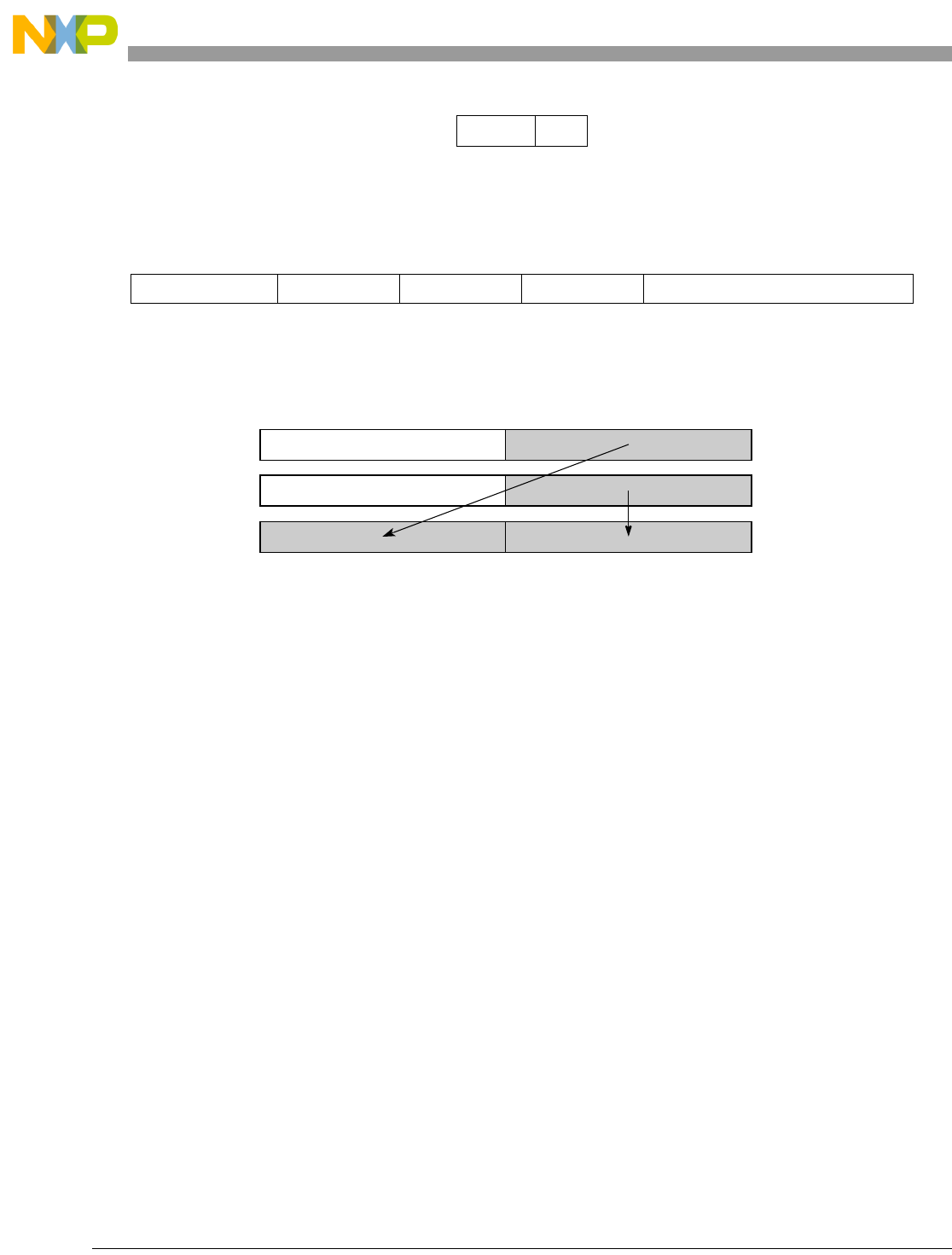

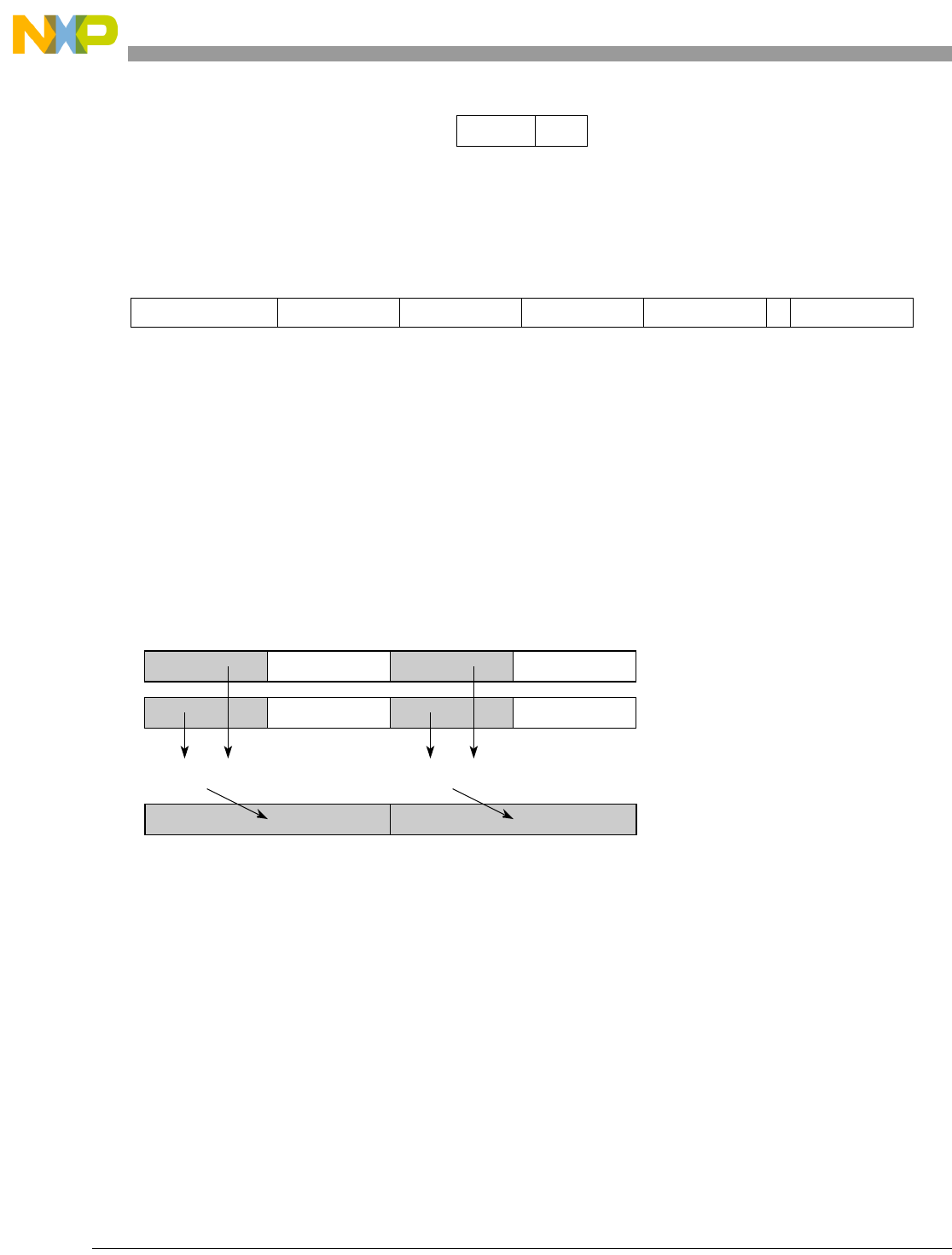

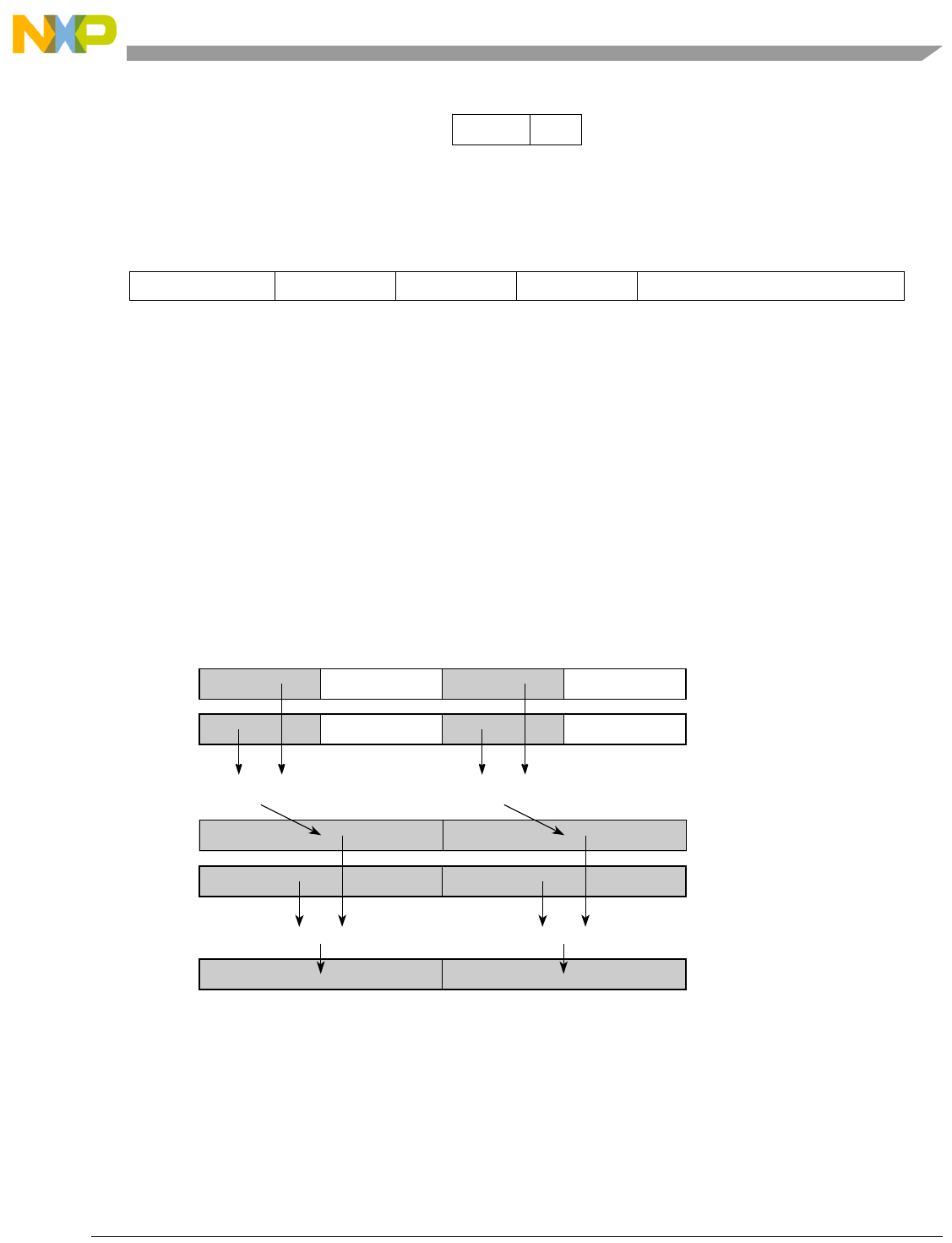

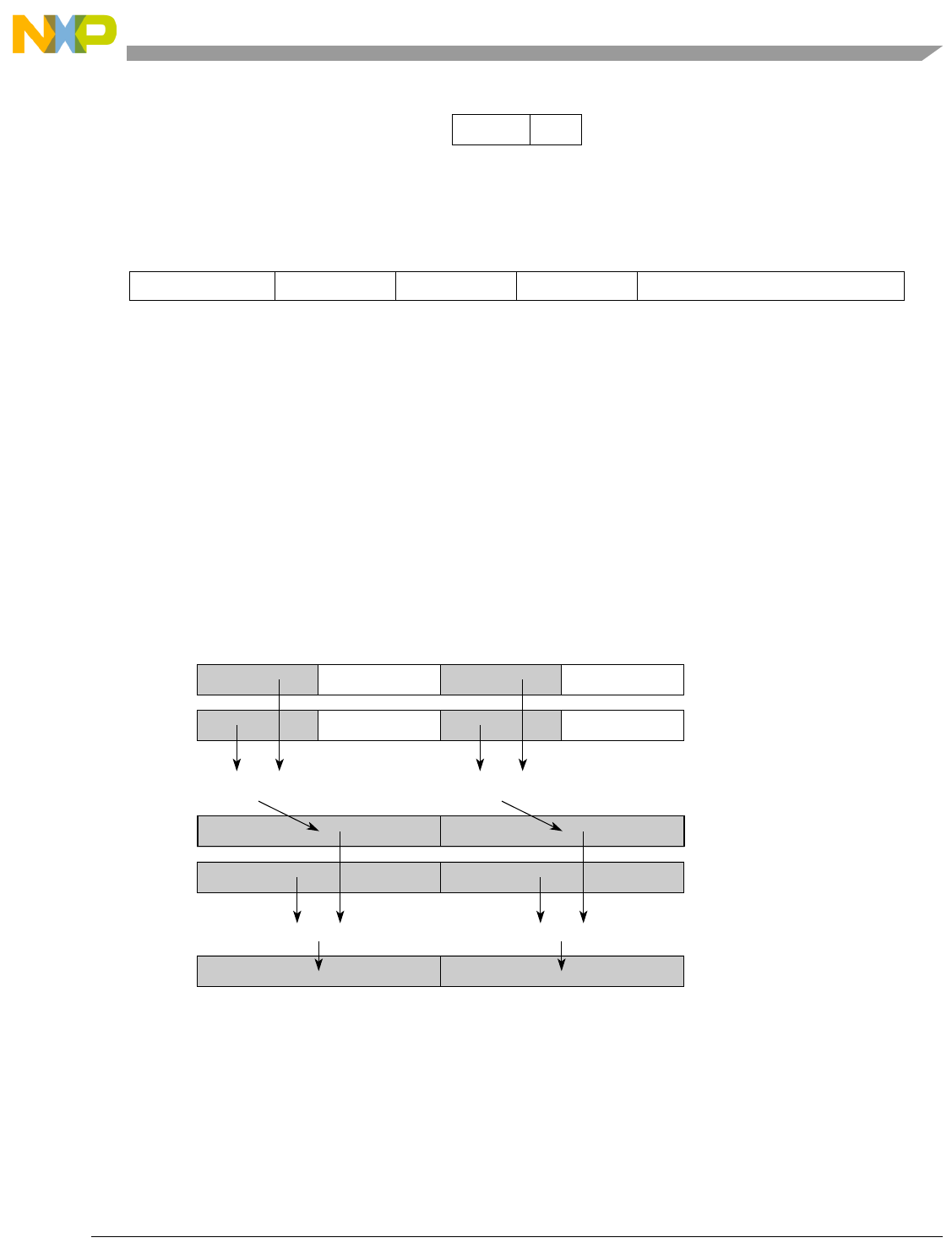

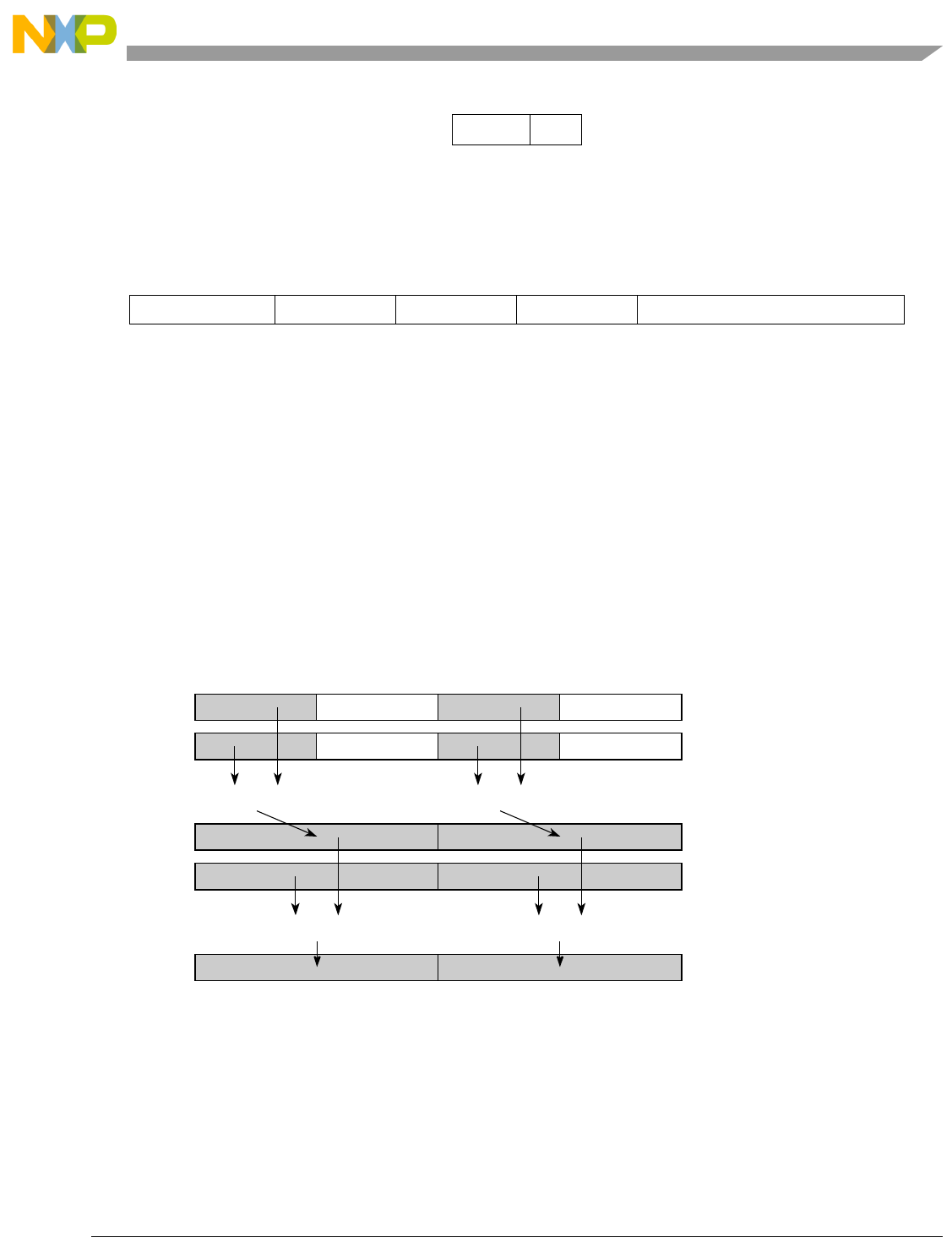

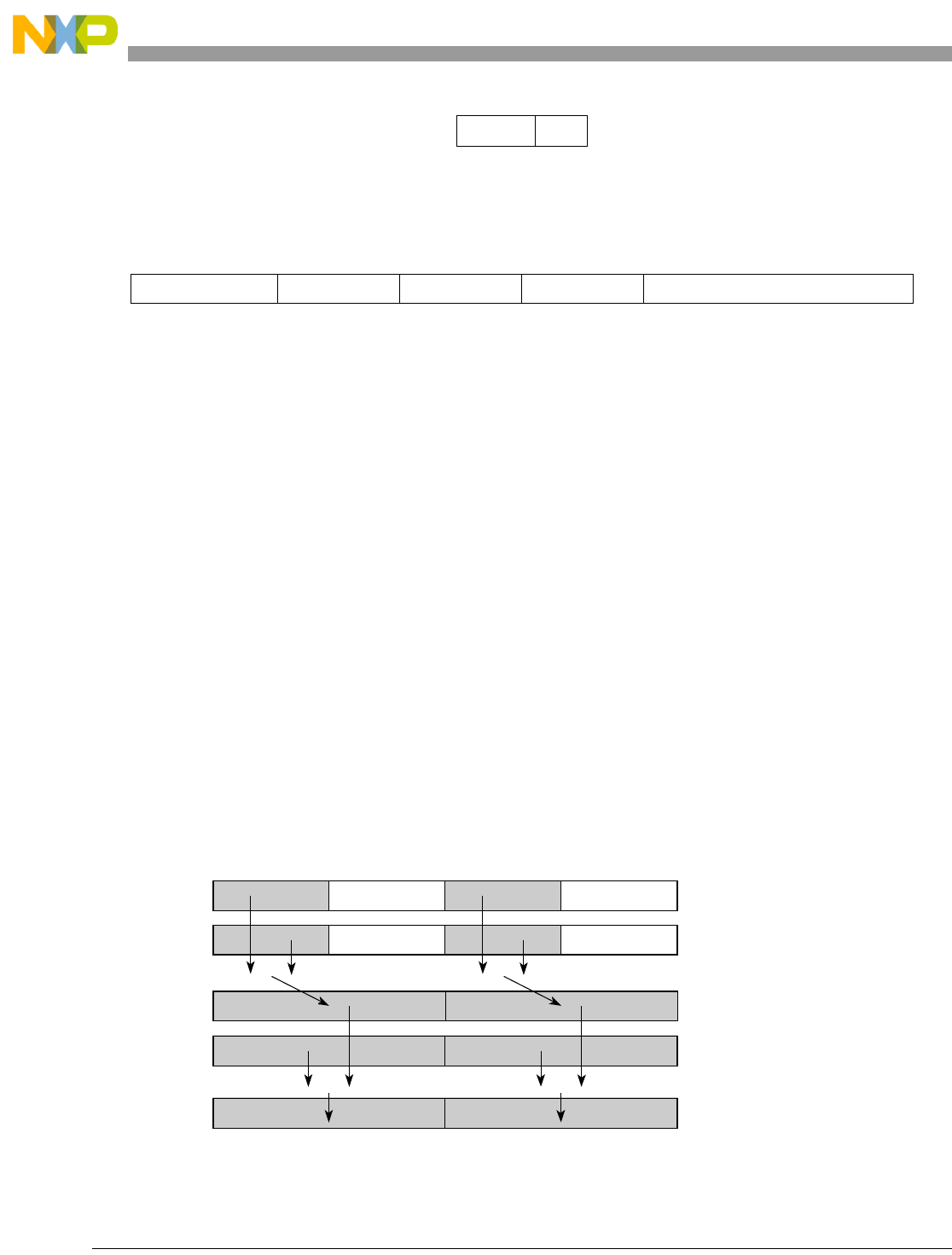

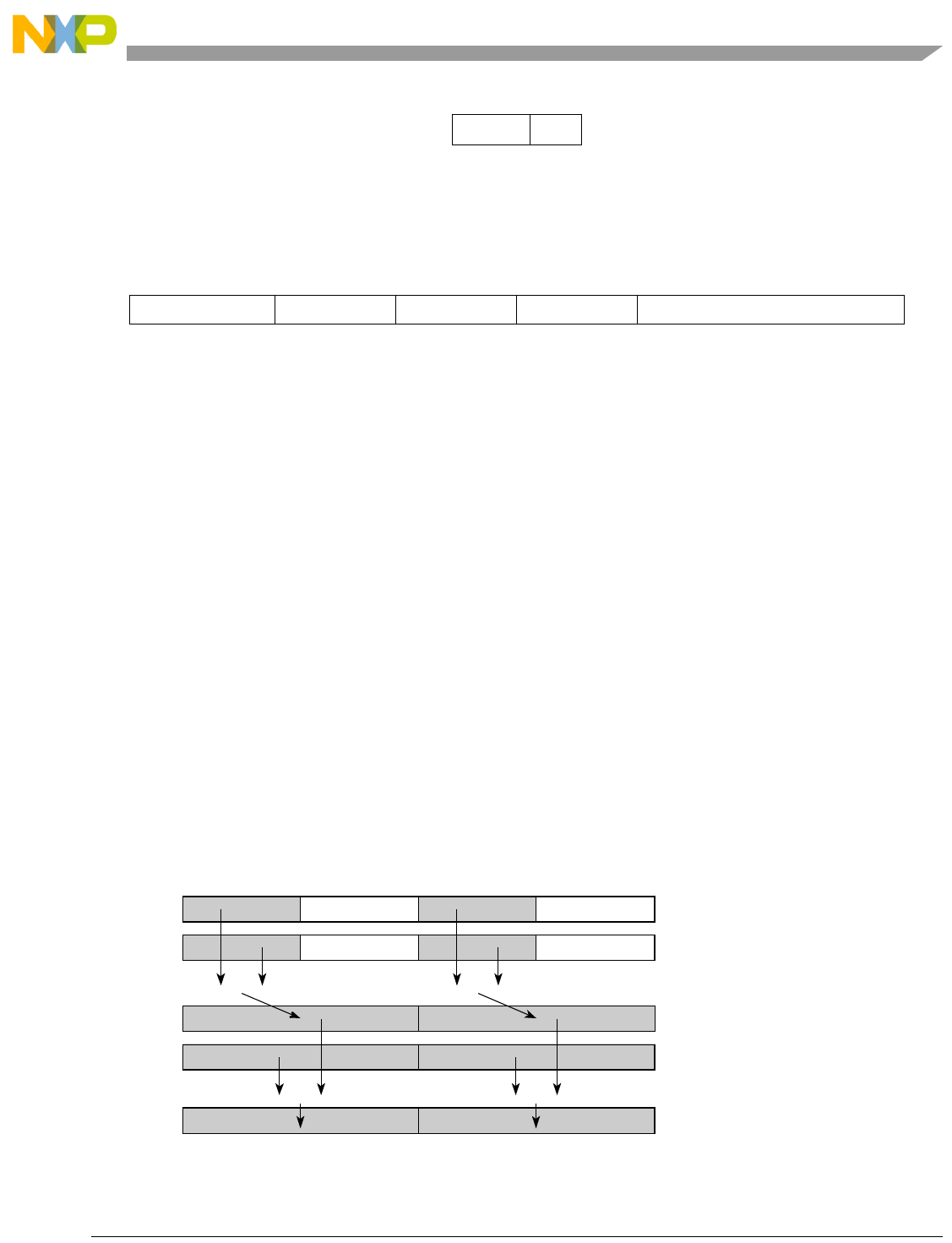

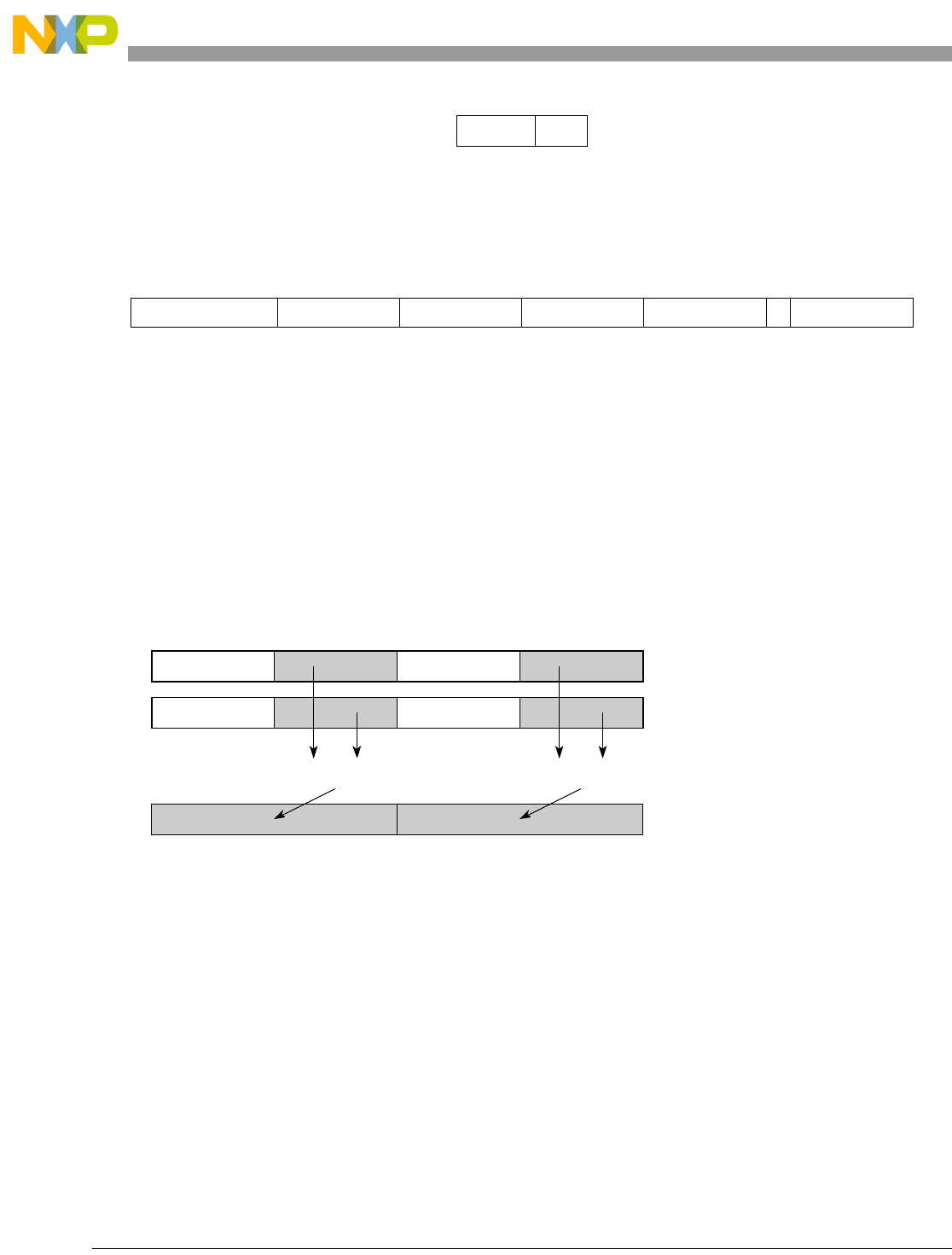

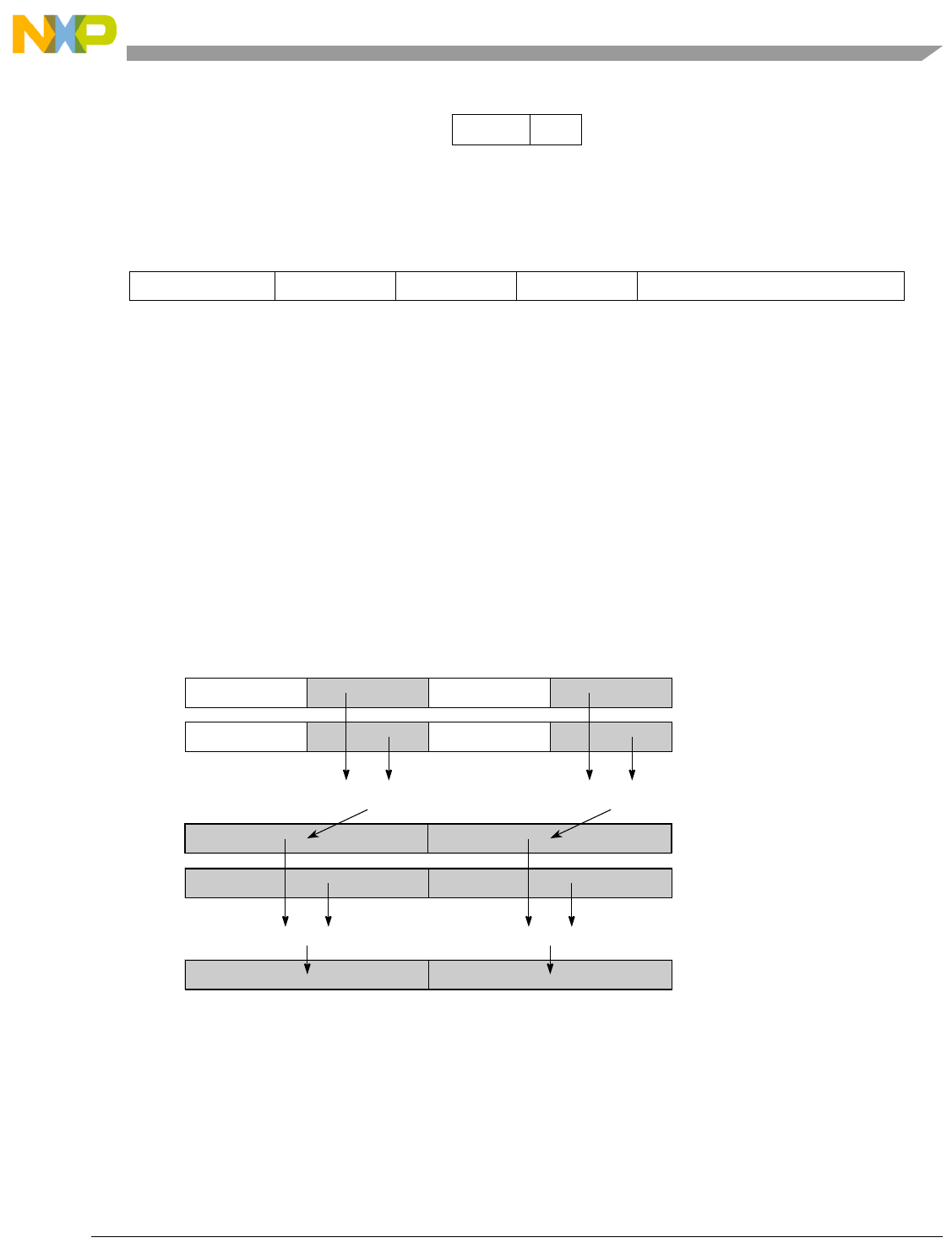

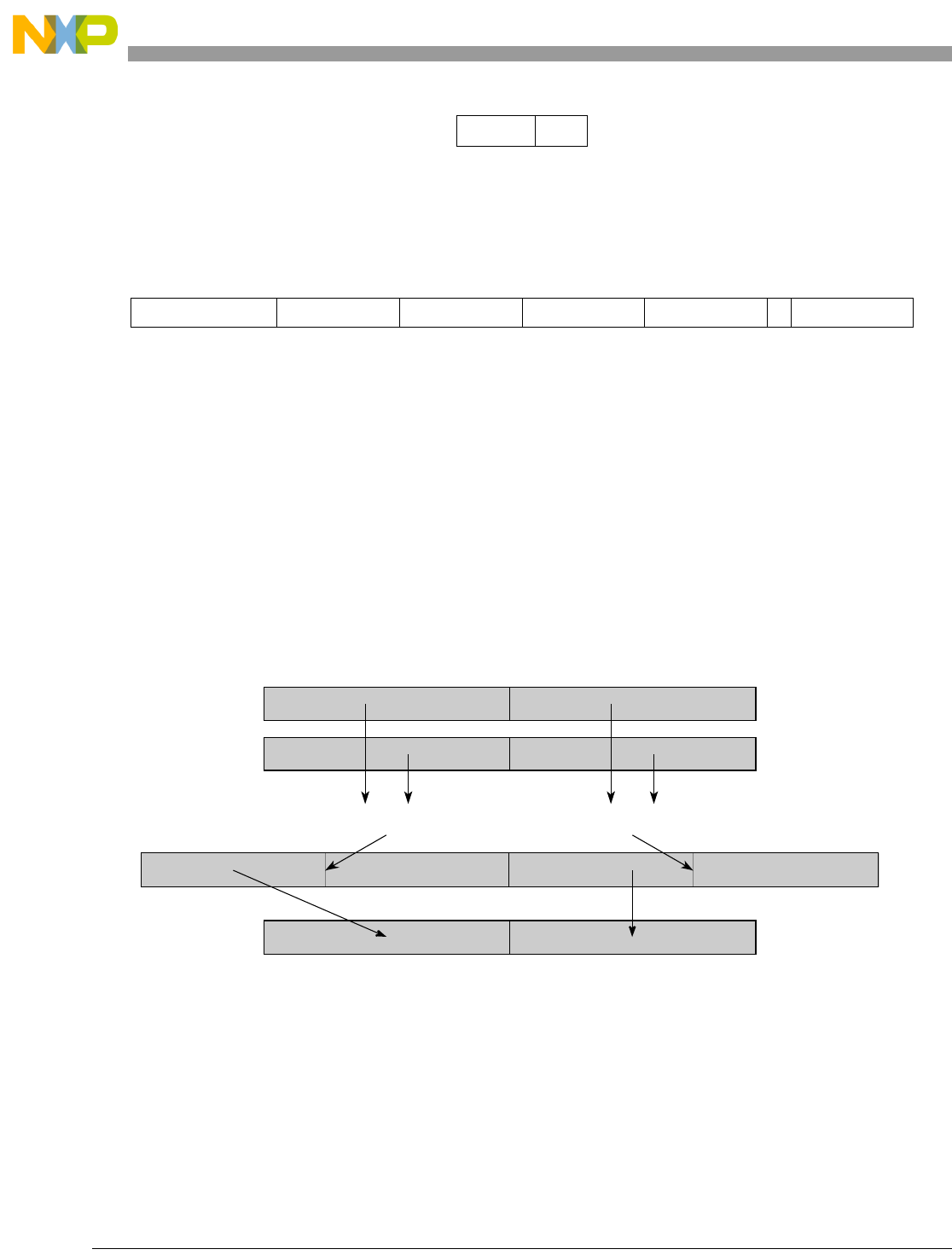

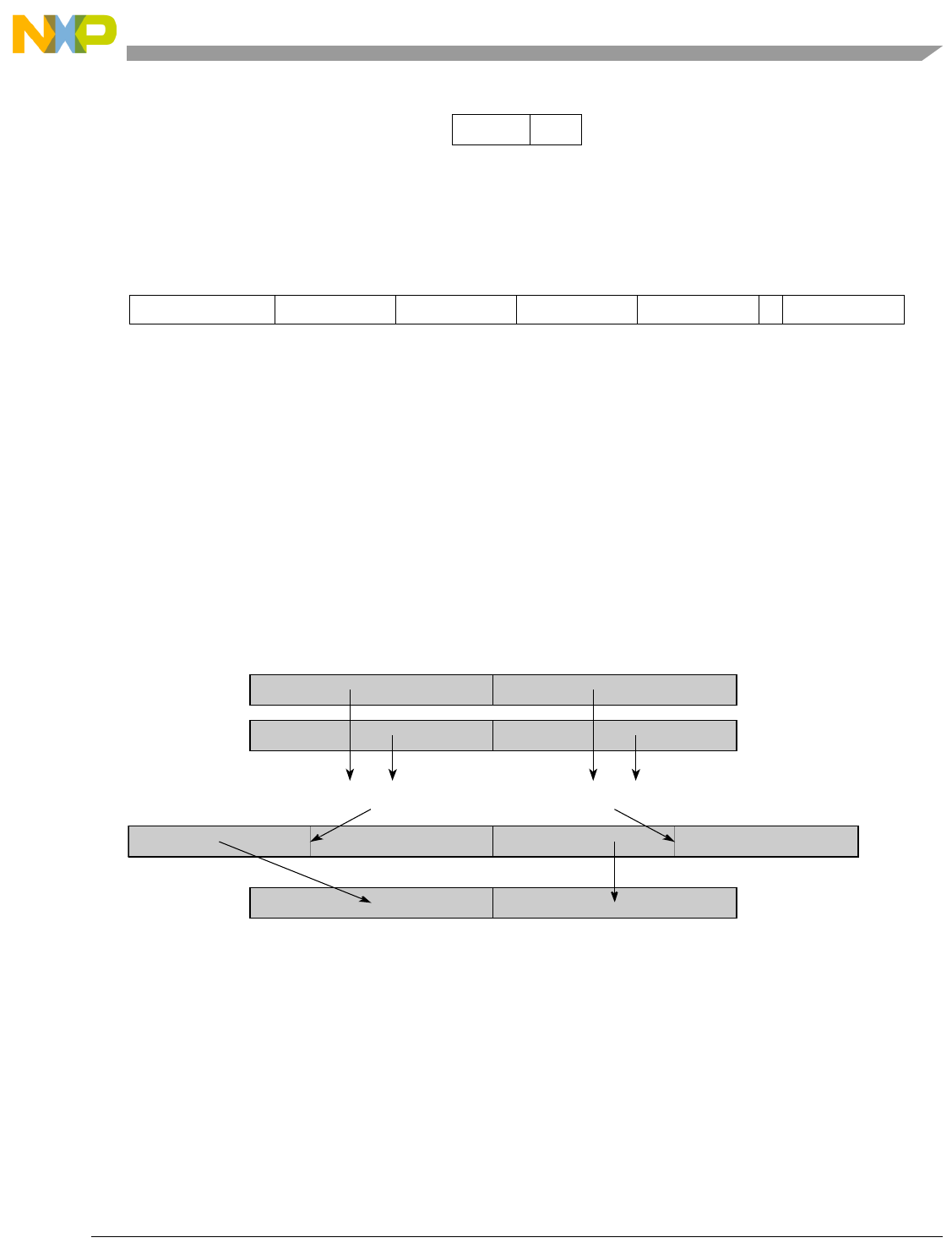

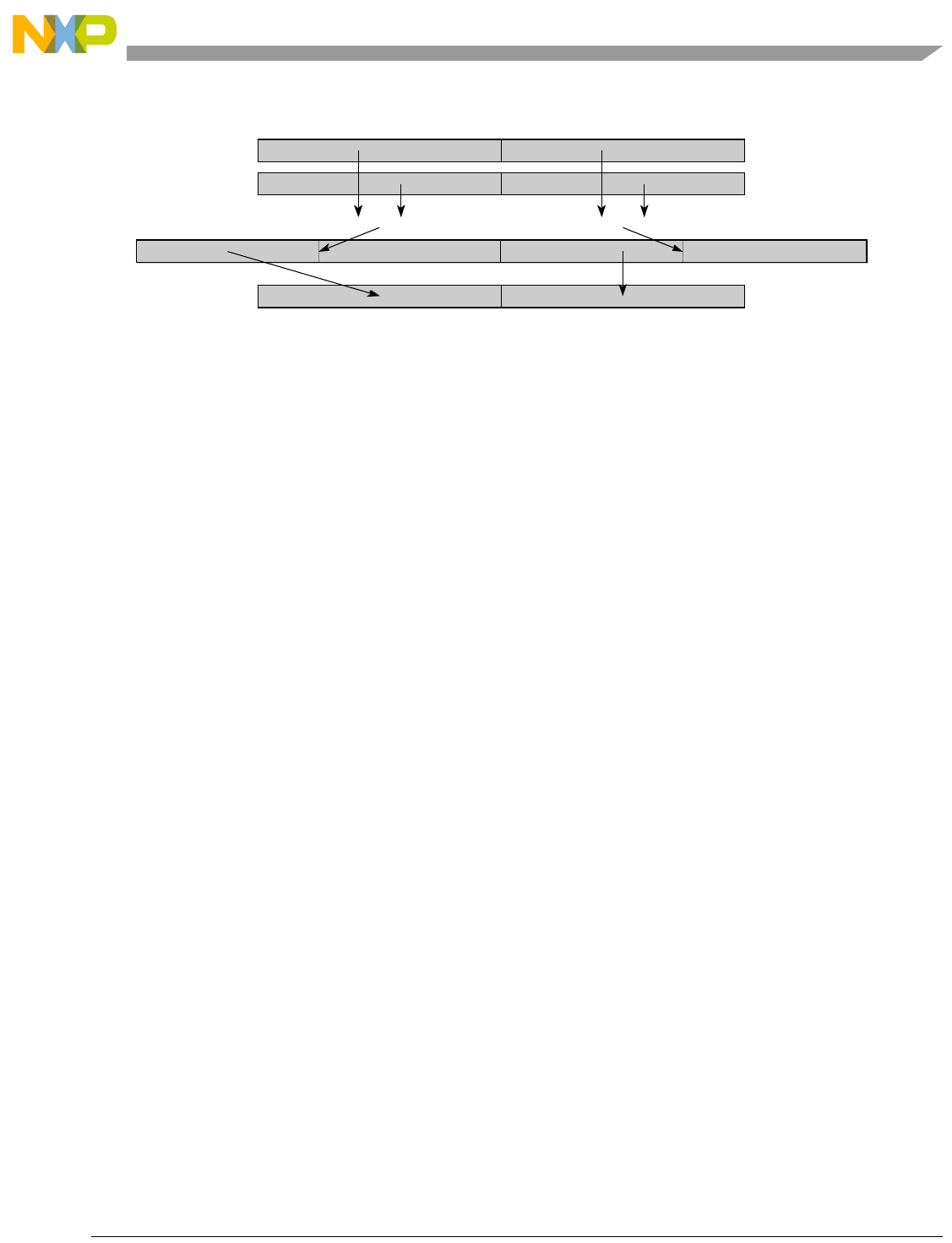

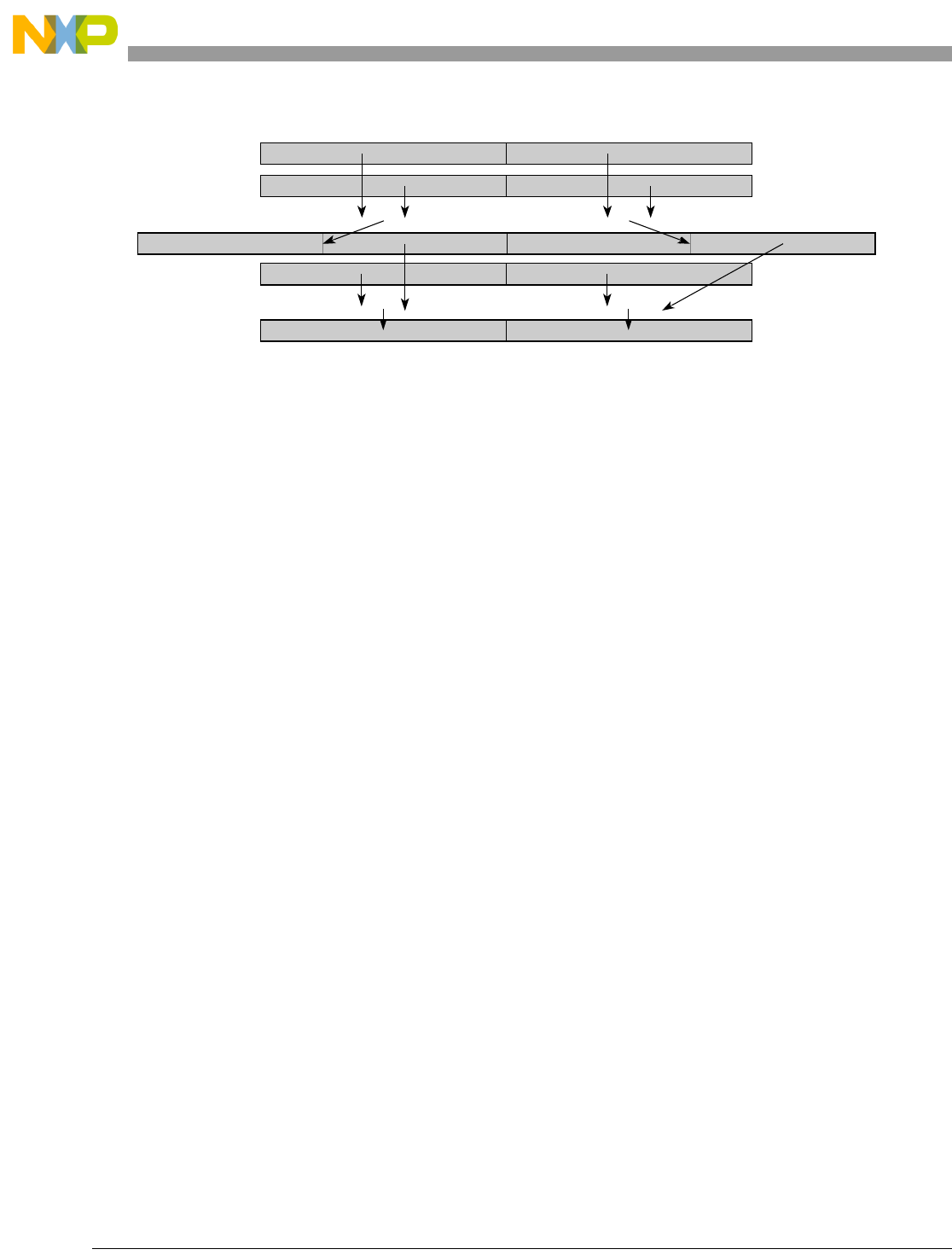

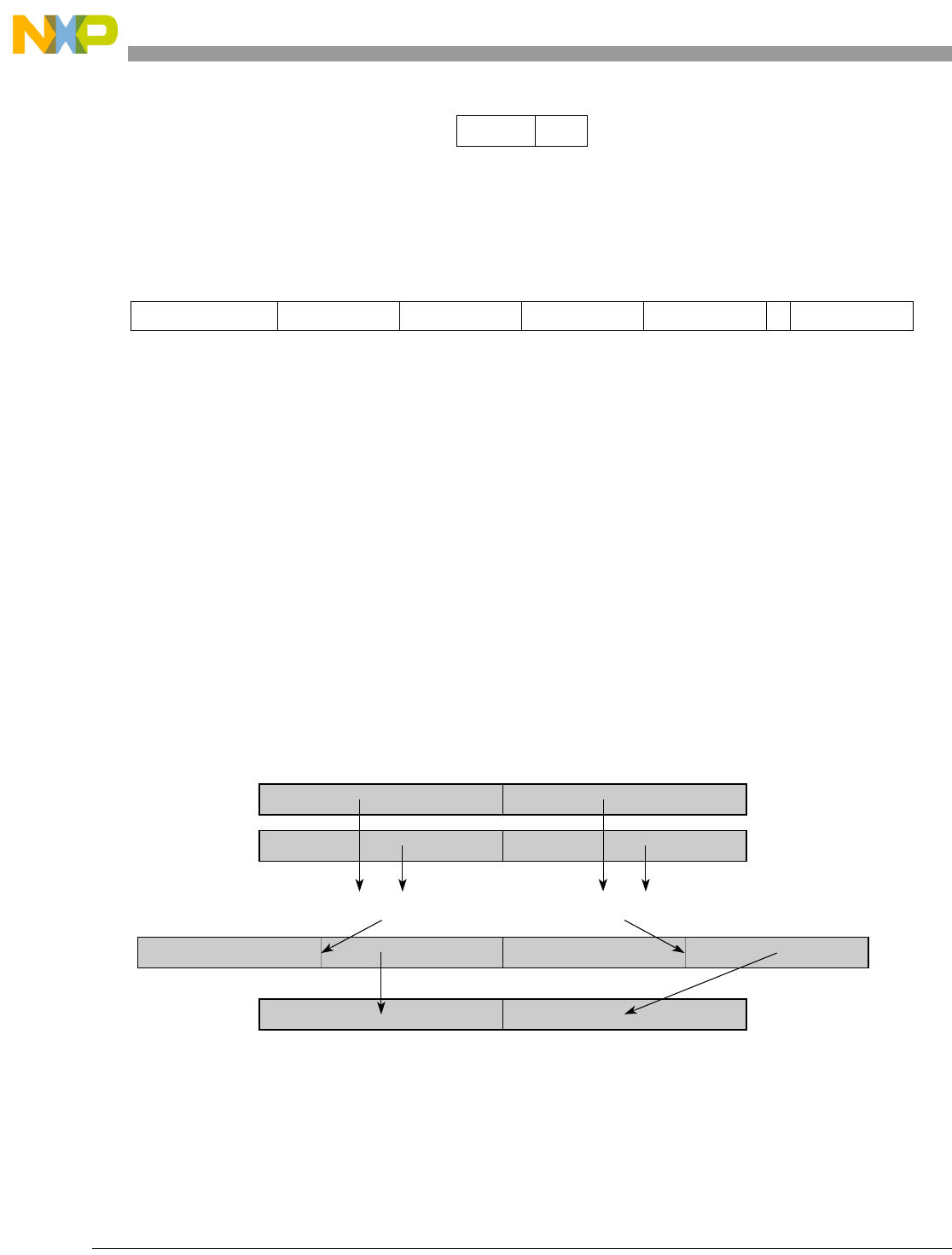

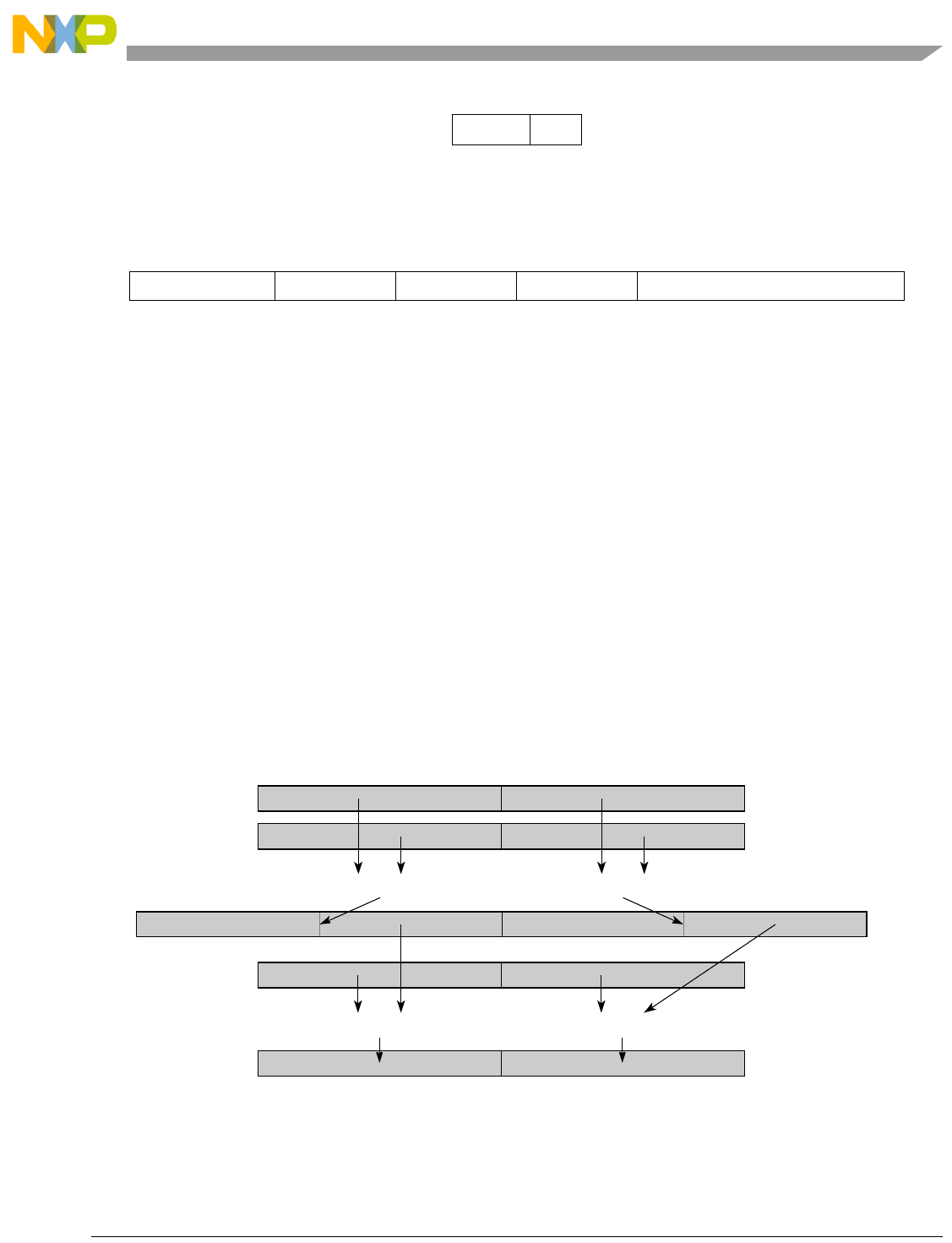

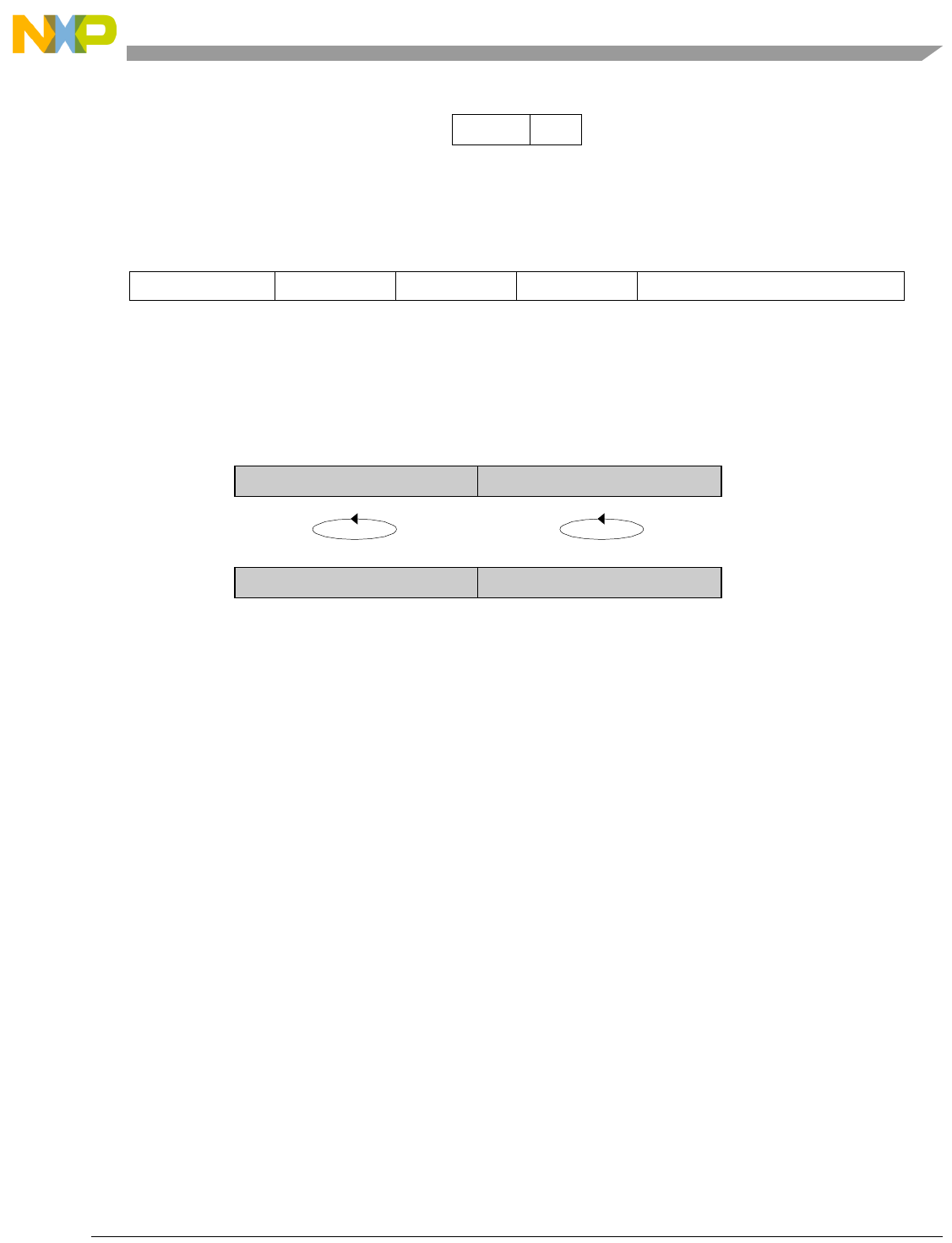

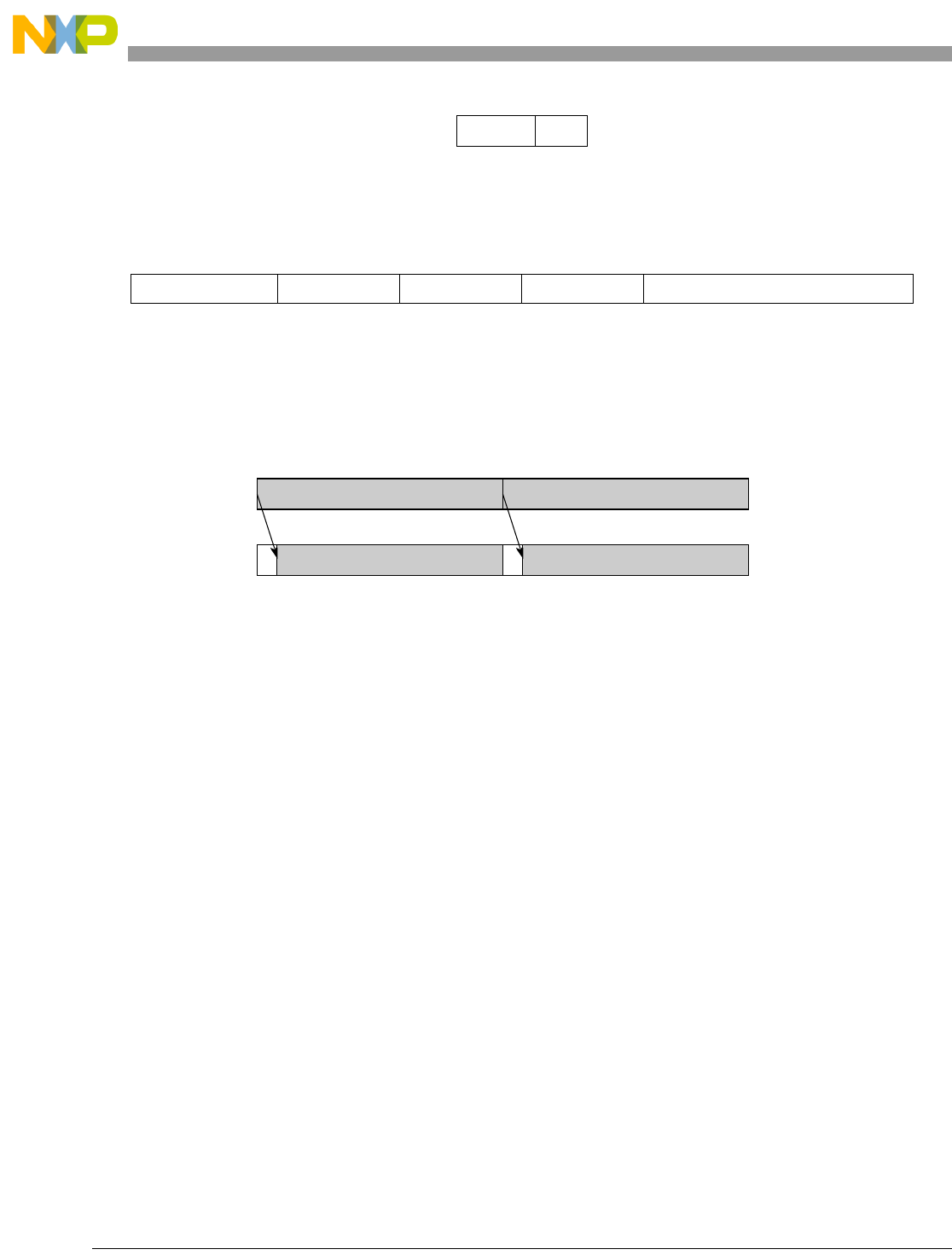

- Figure 5-44. High Order Element Merging (evmergehi)

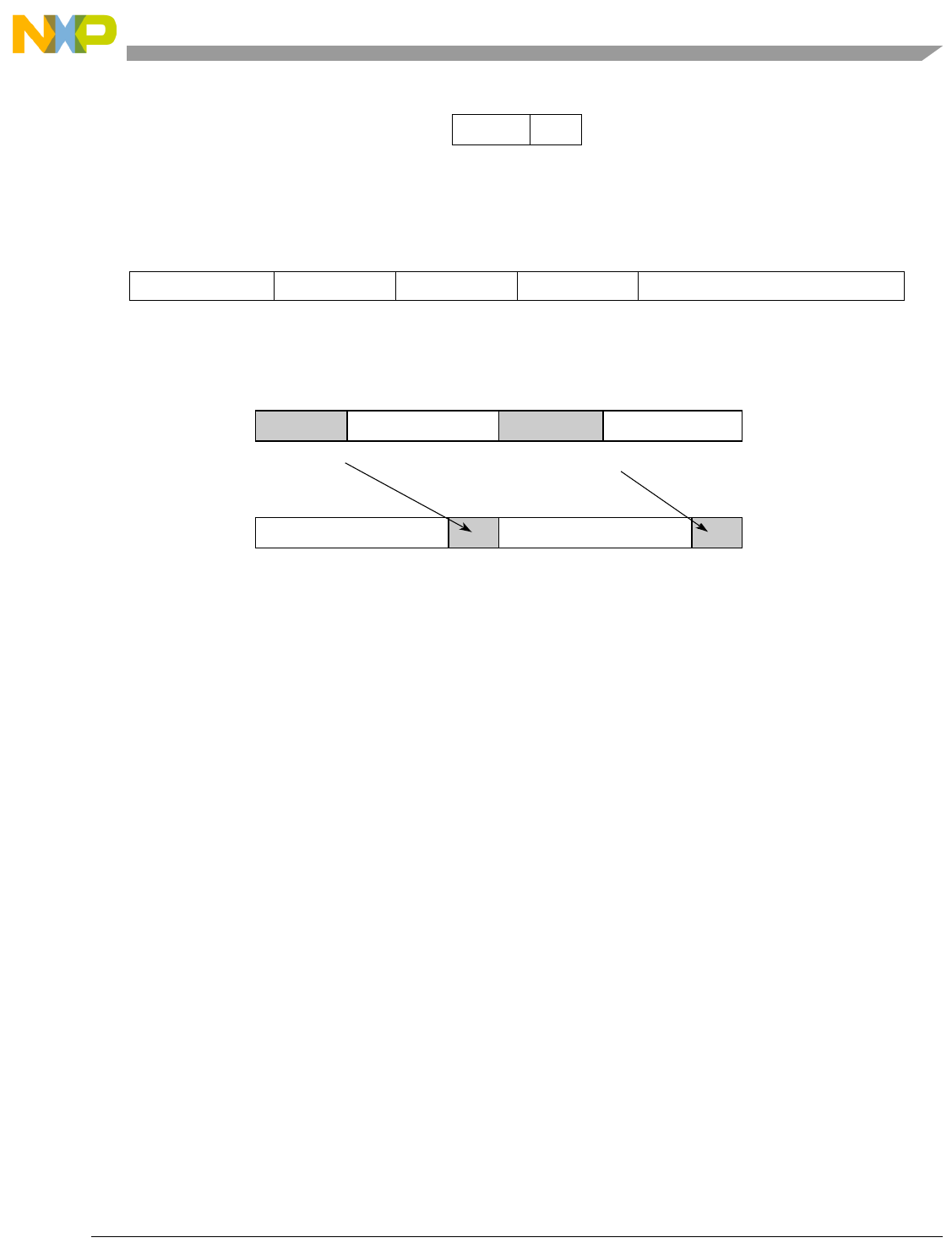

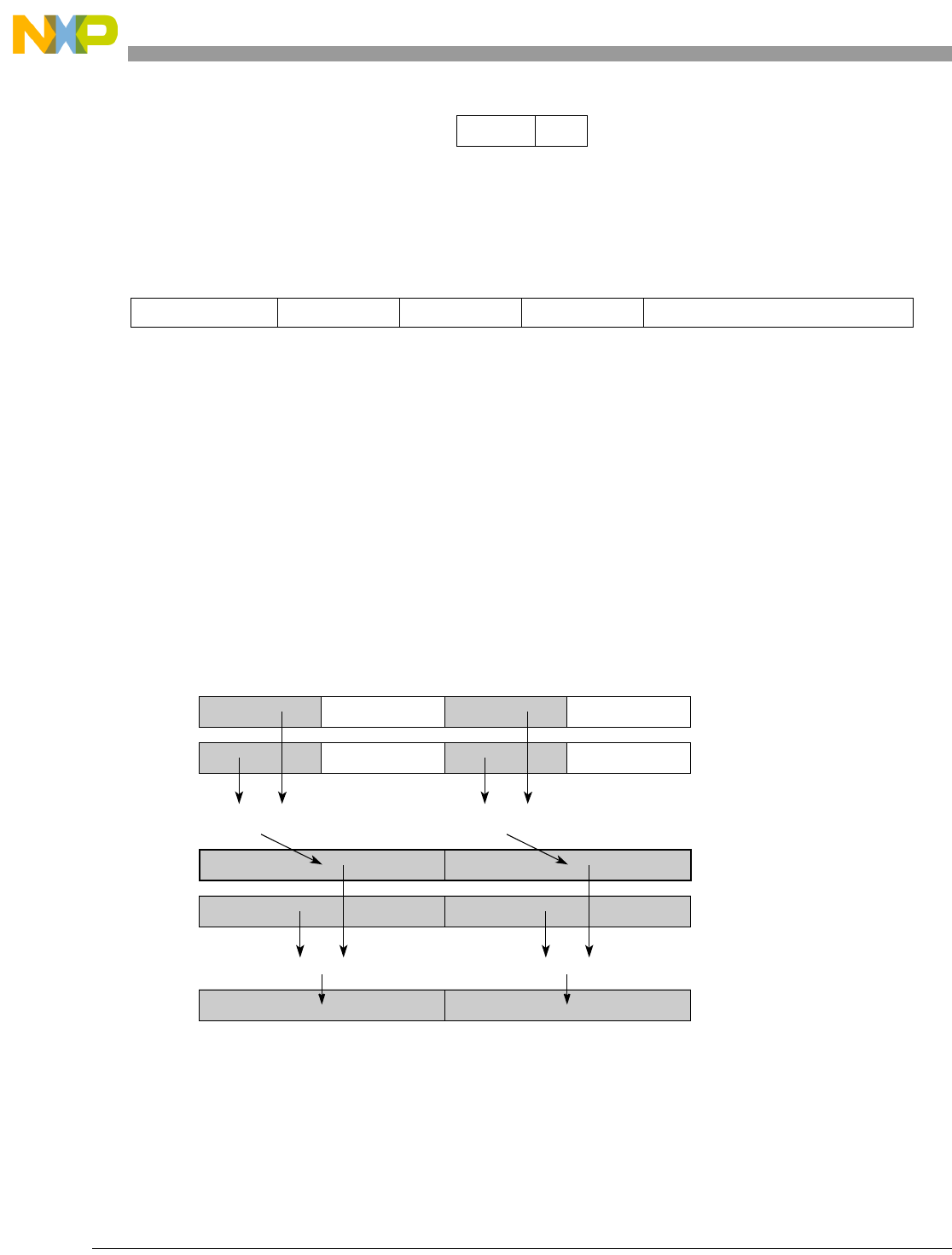

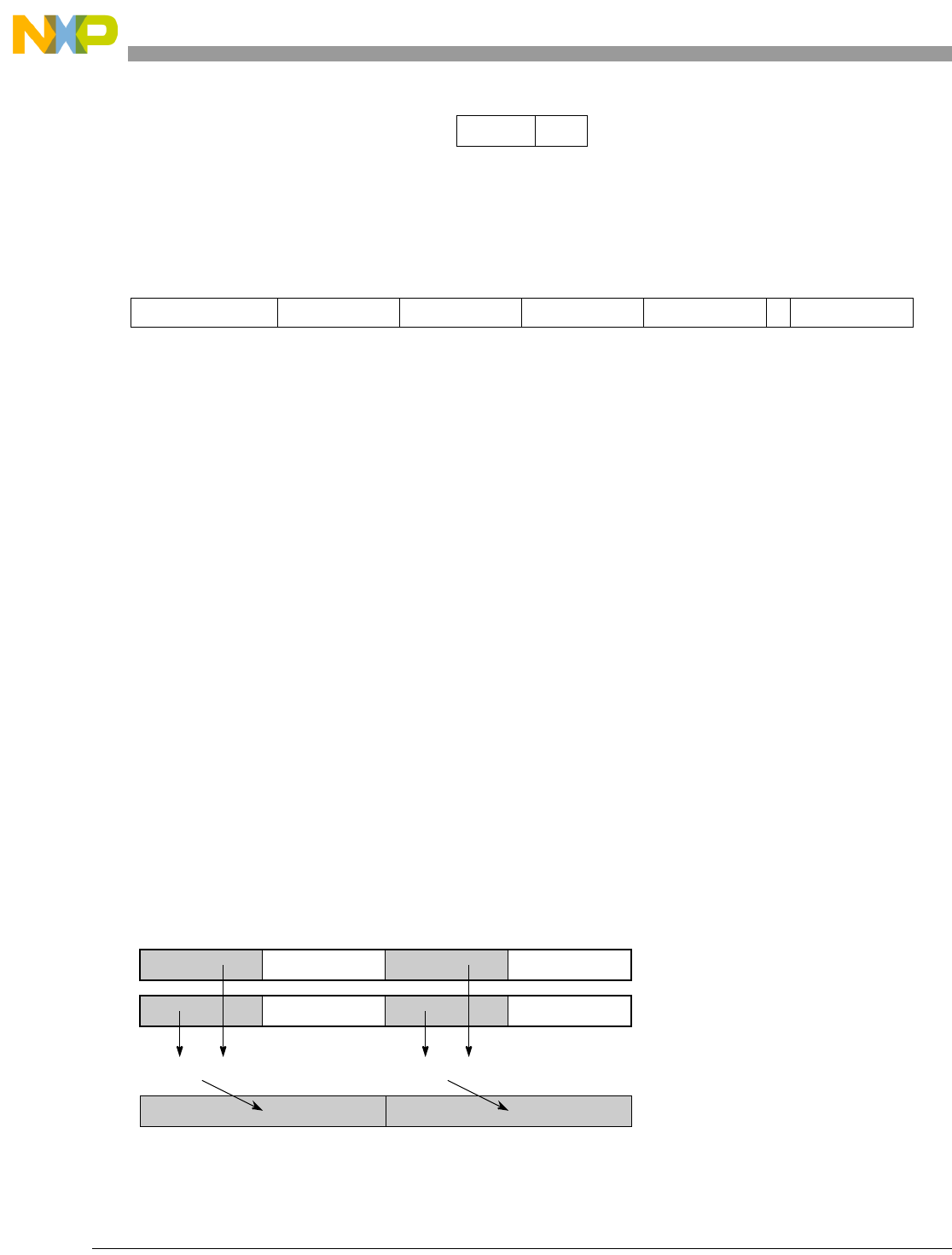

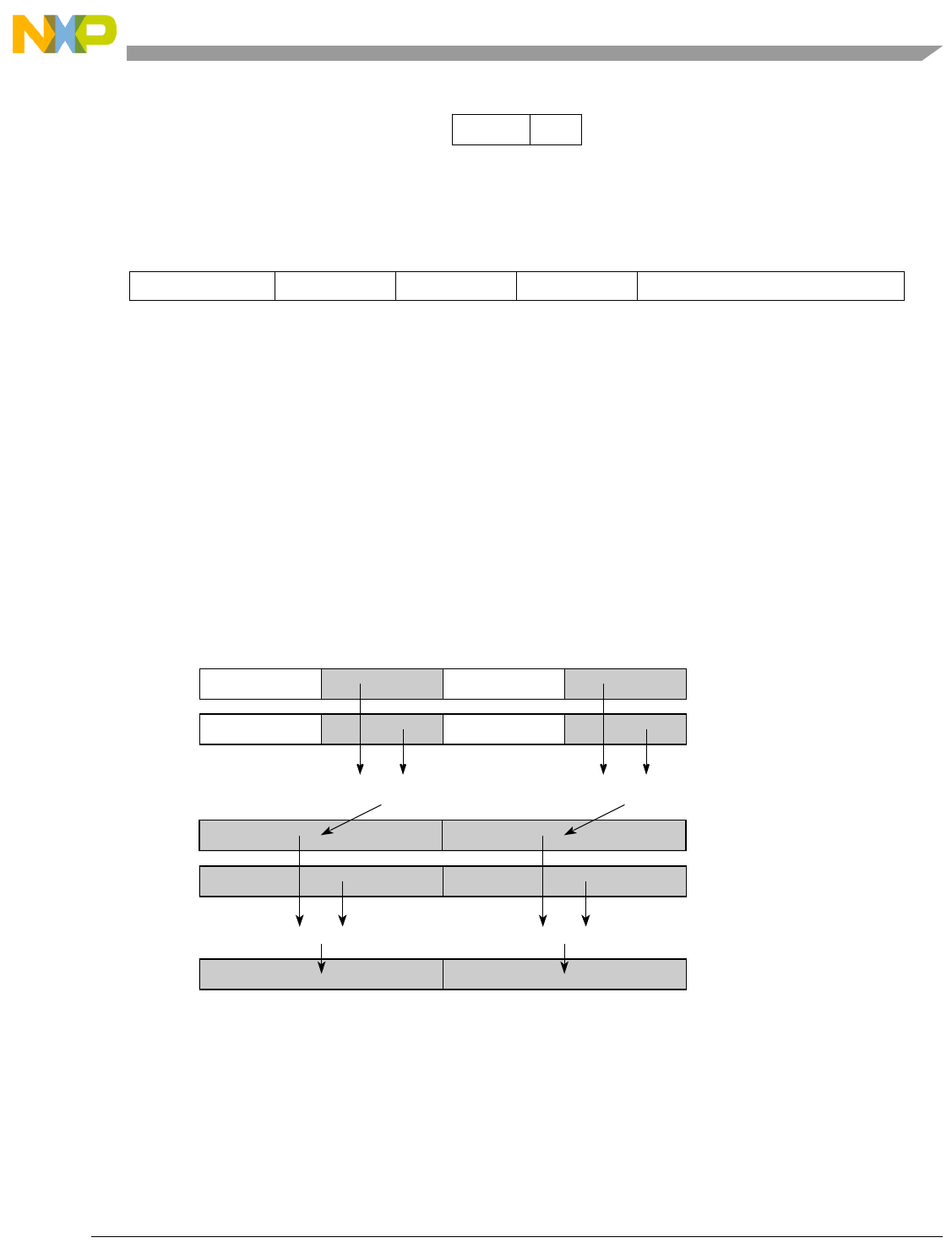

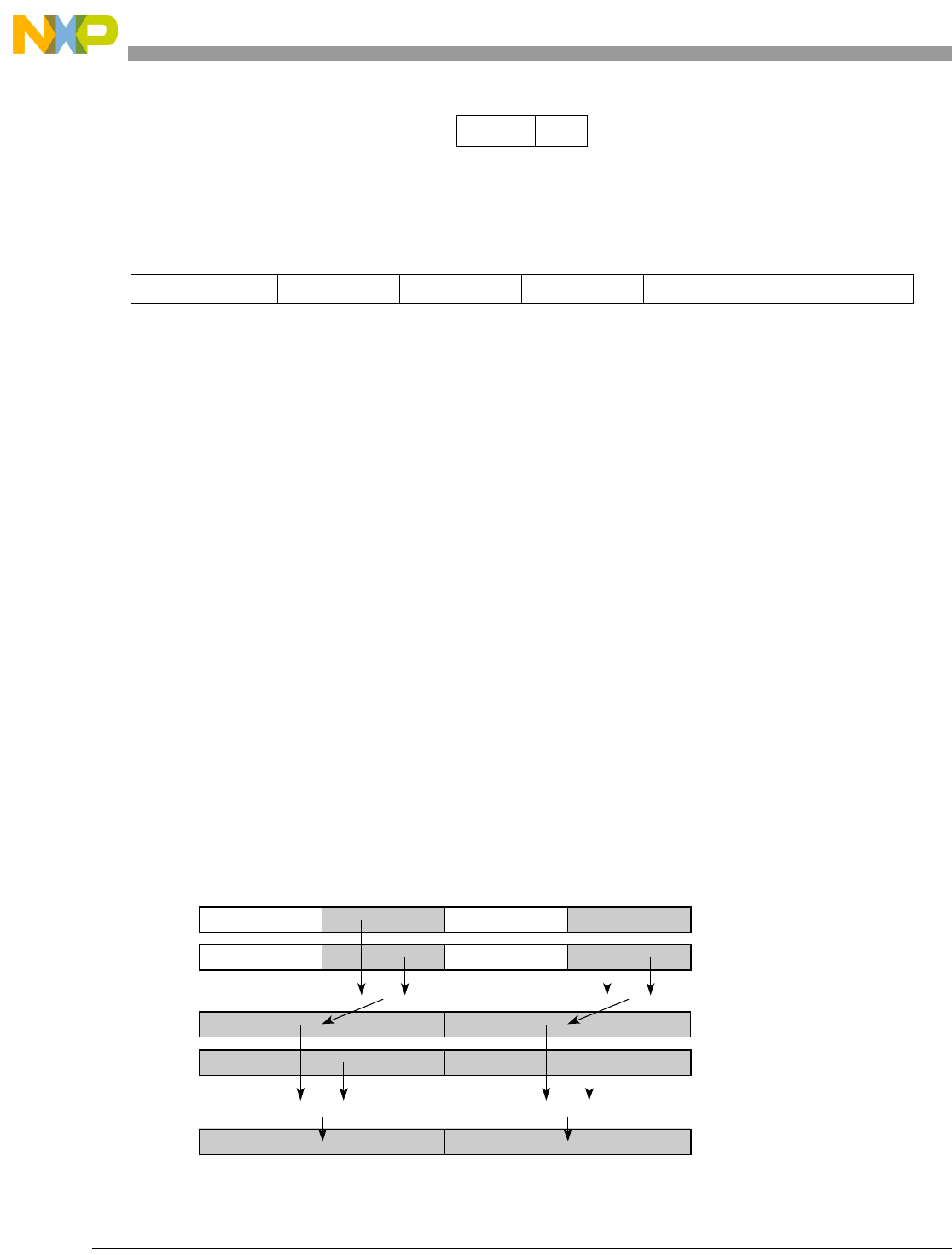

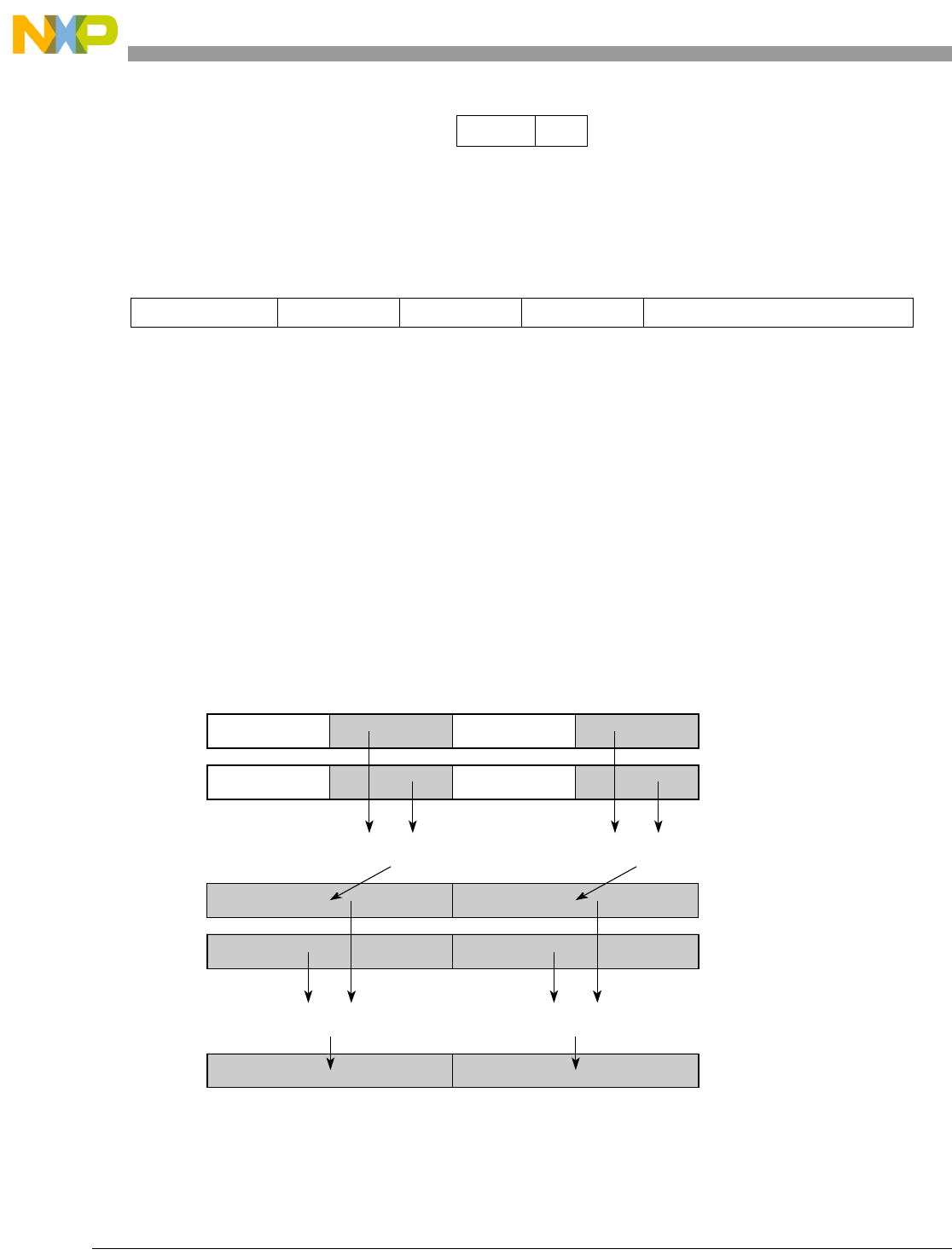

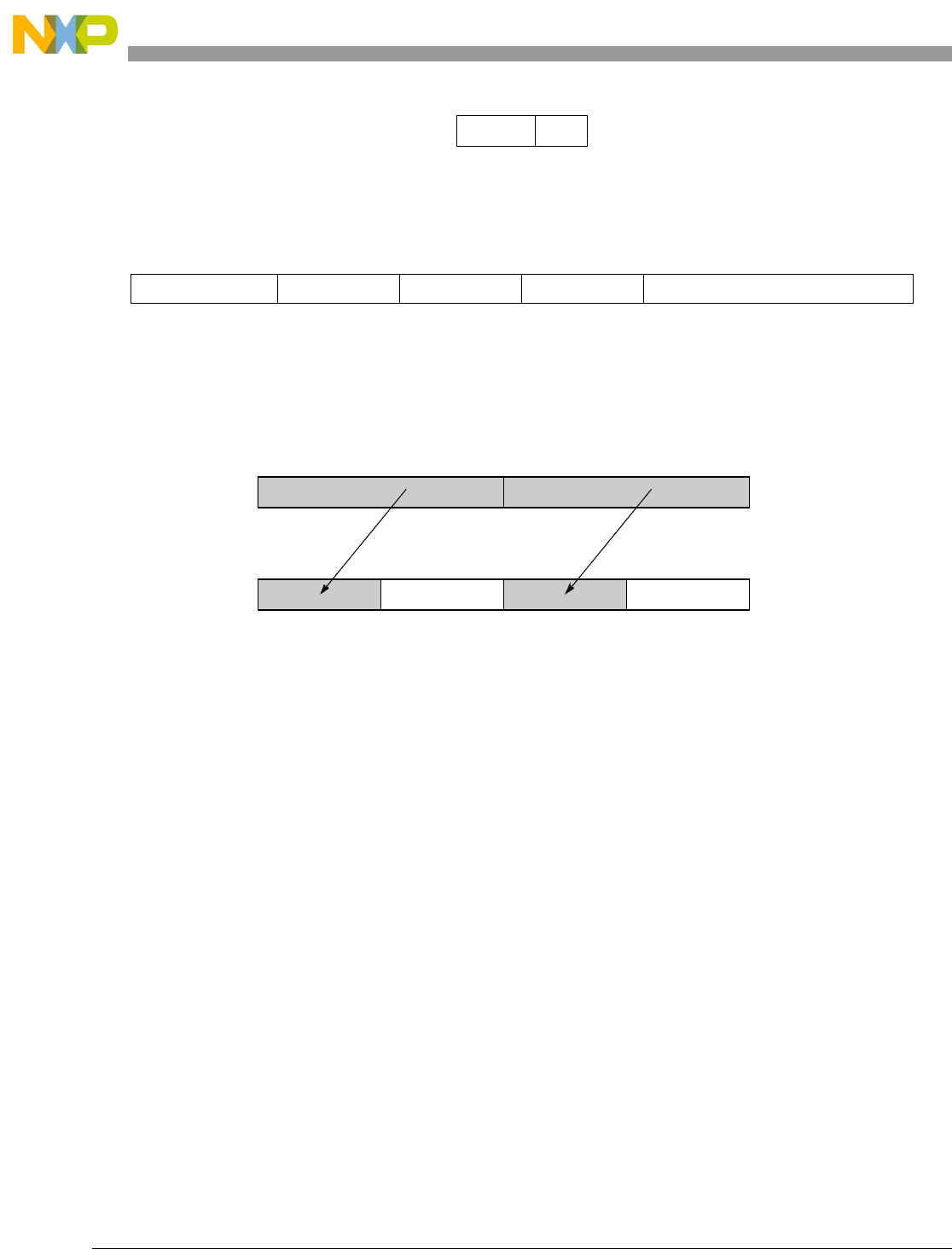

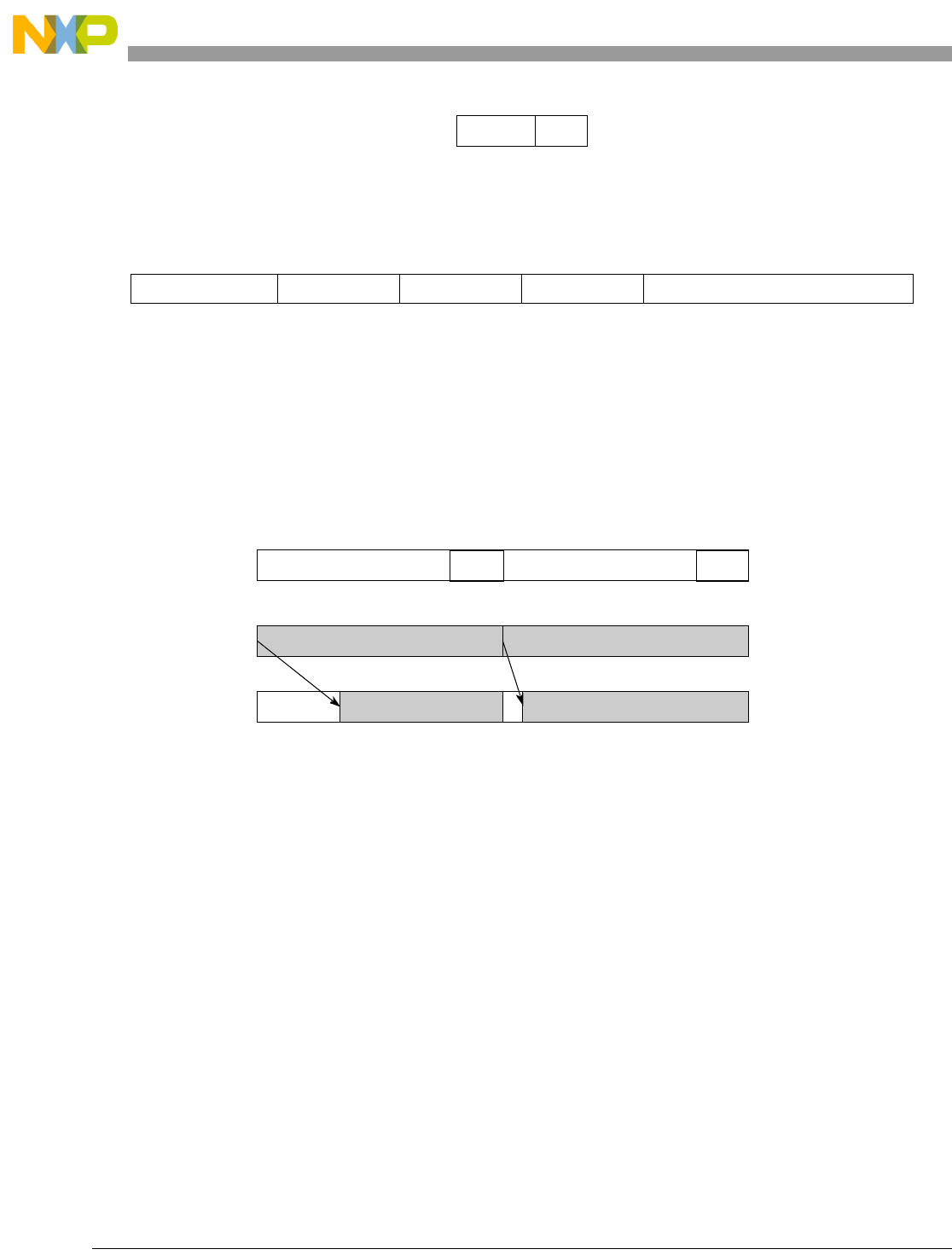

- Figure 5-45. High Order Element Merging (evmergehilo)

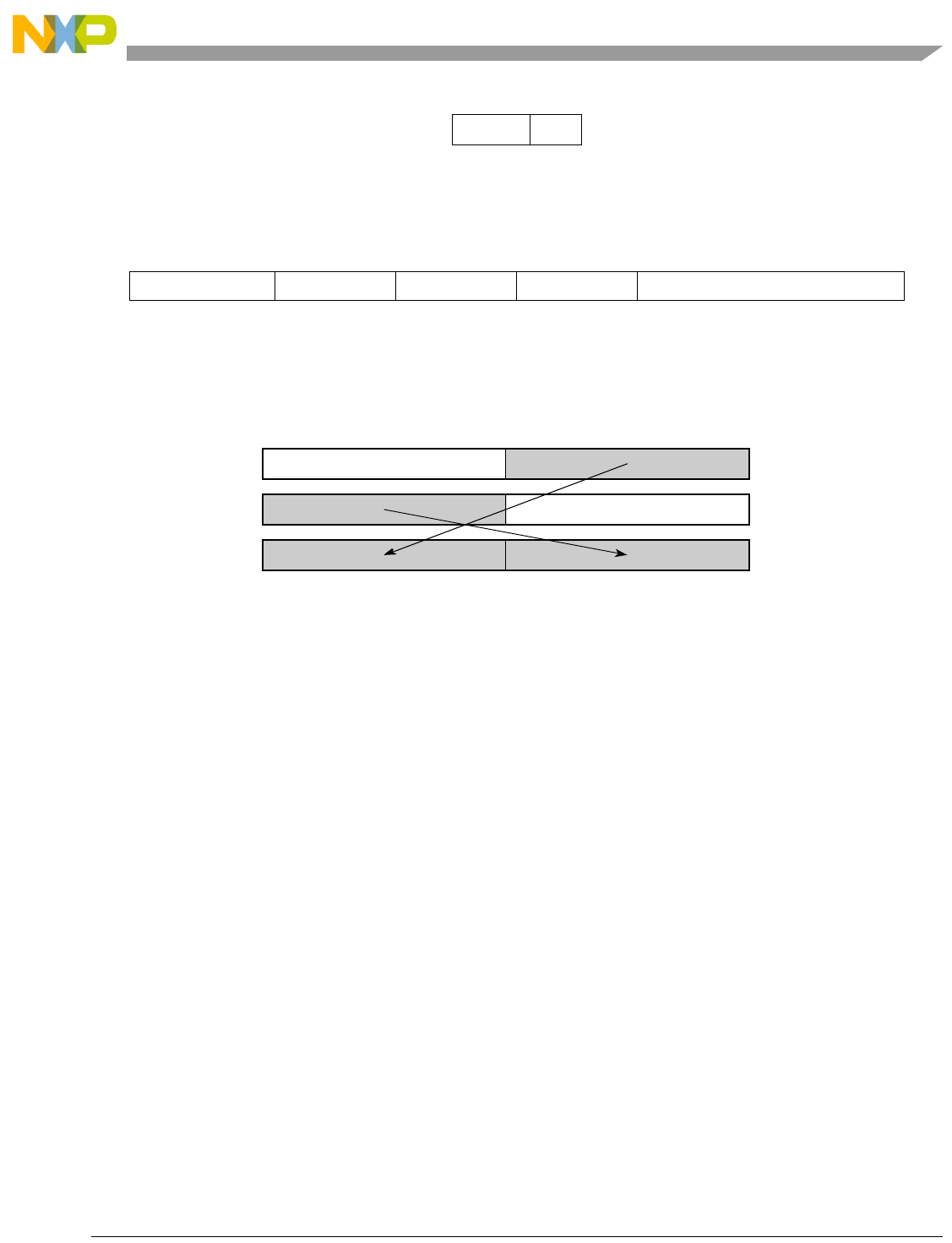

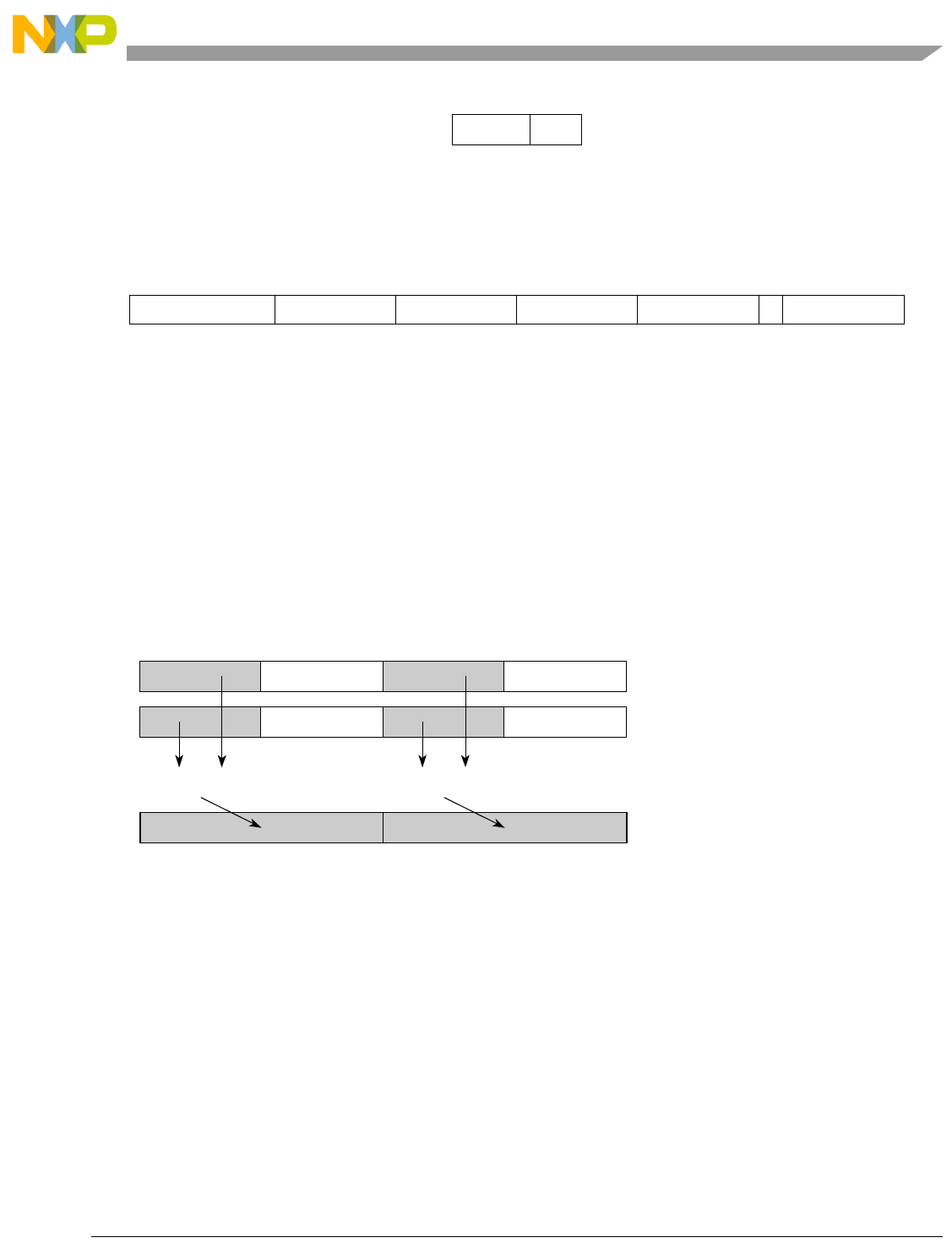

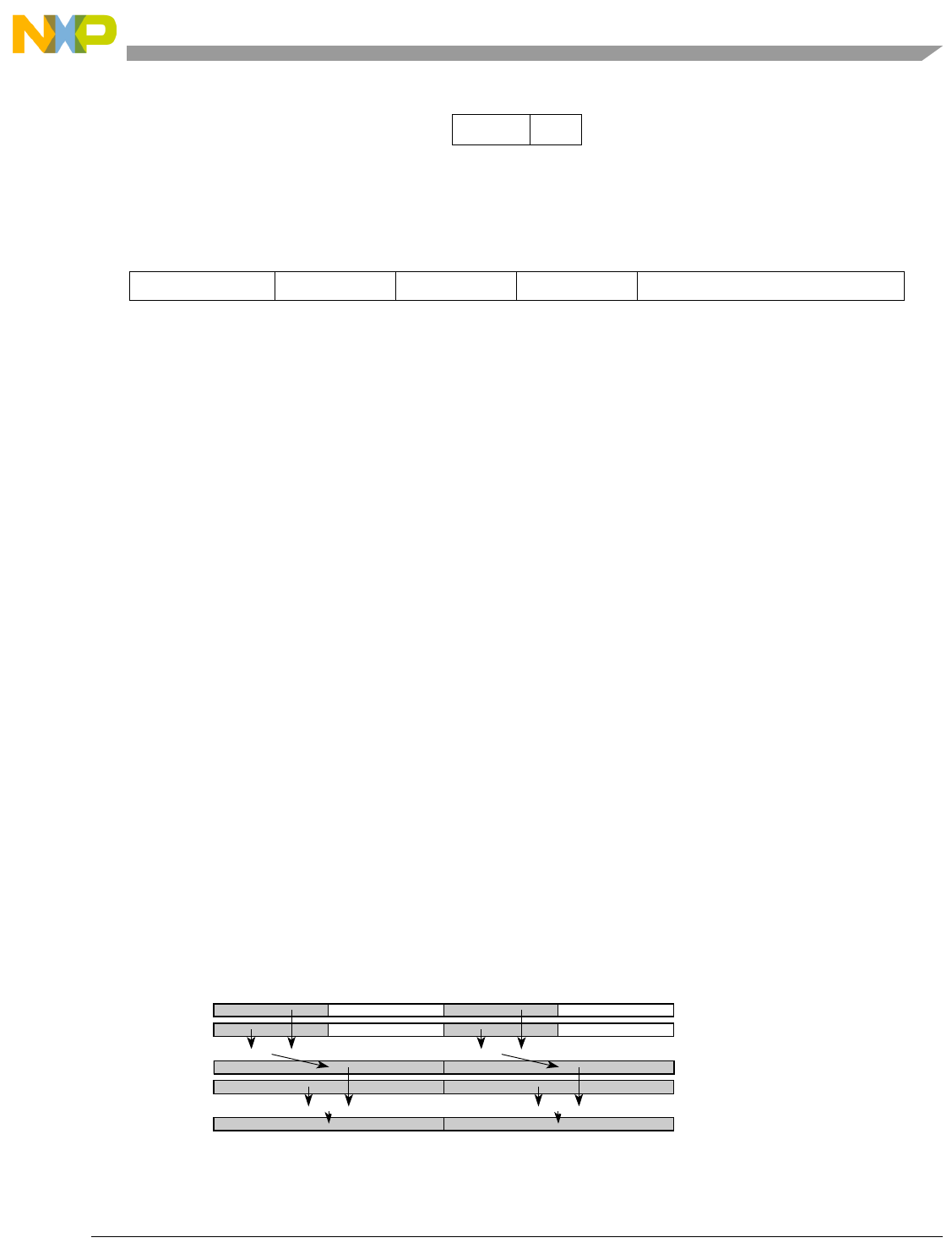

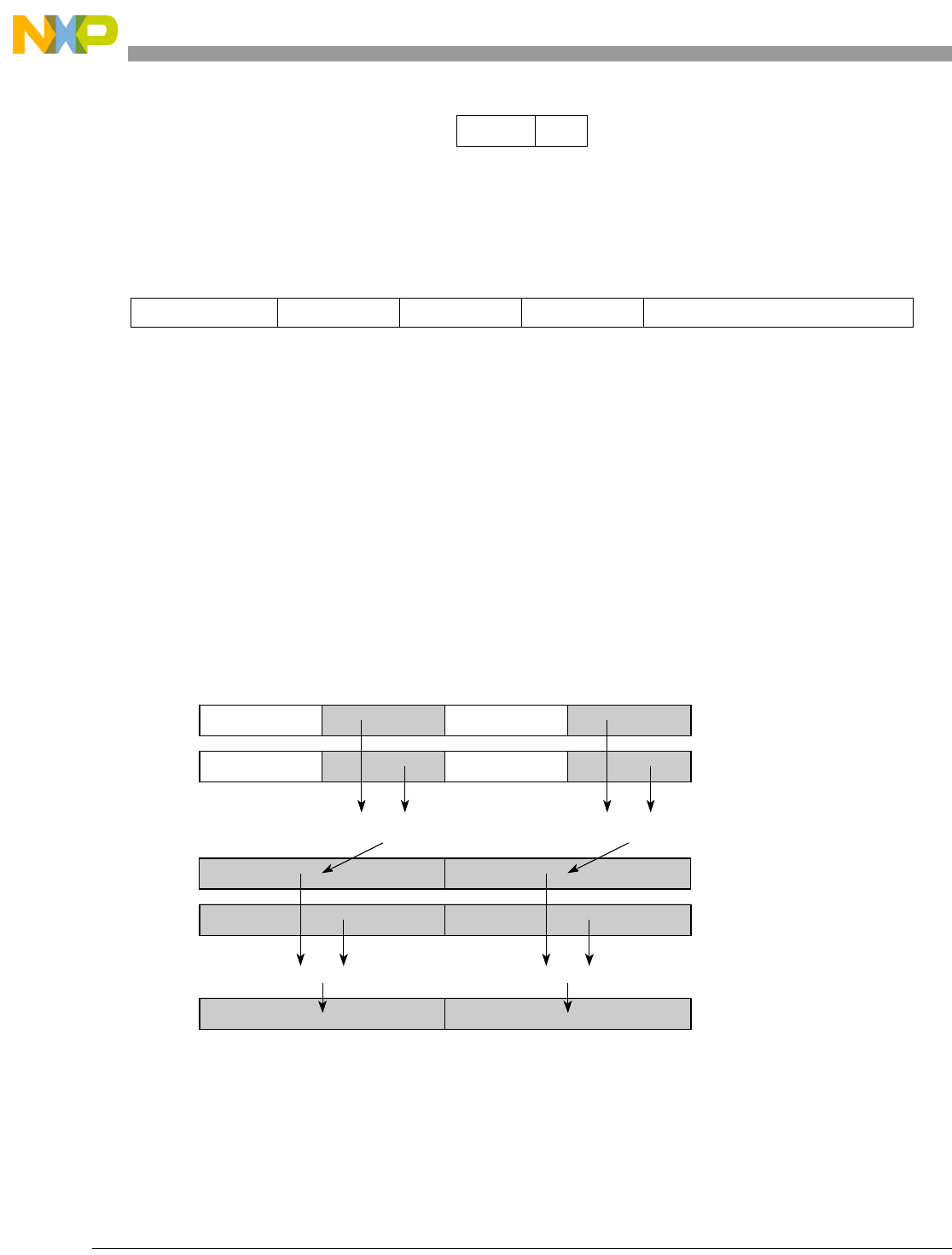

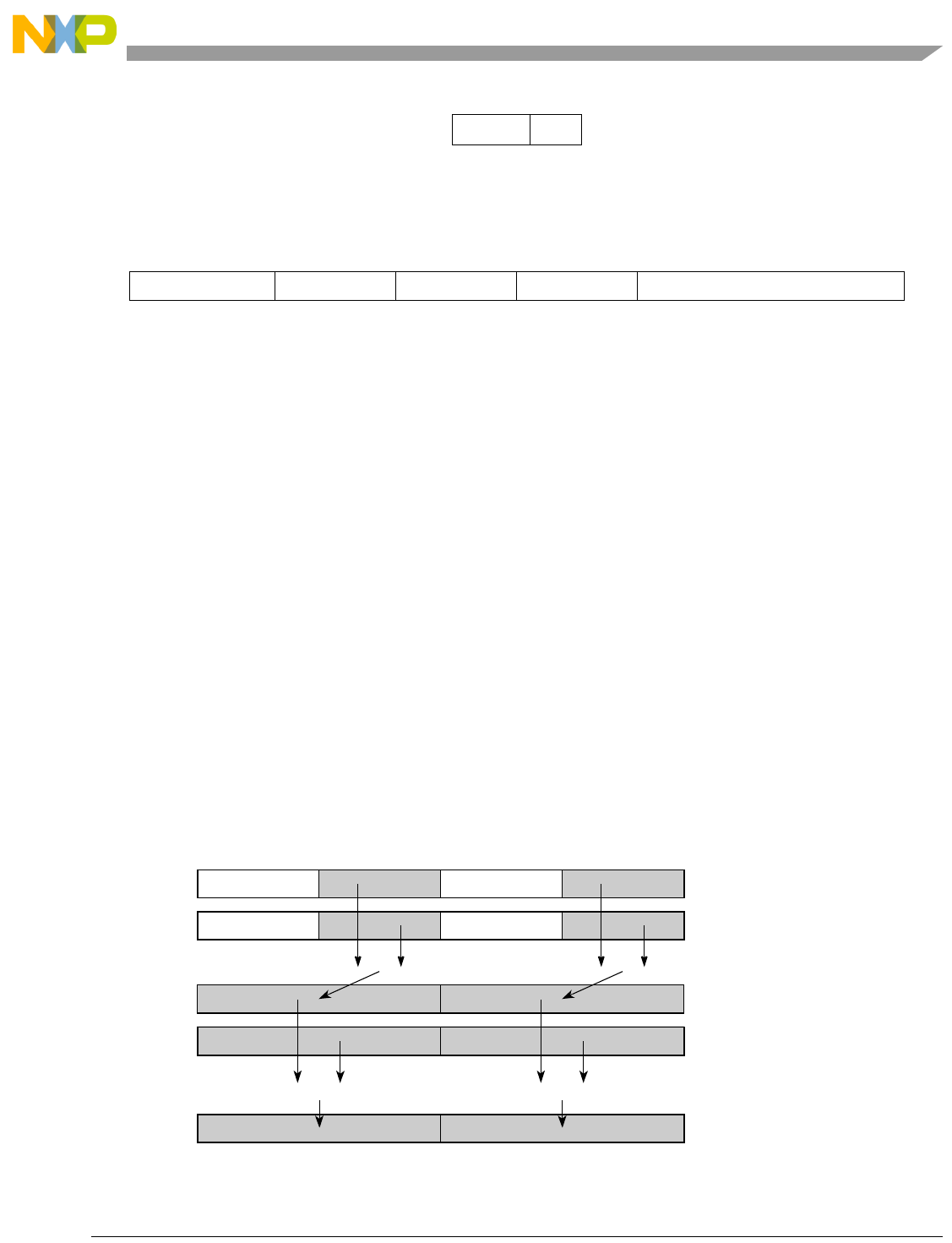

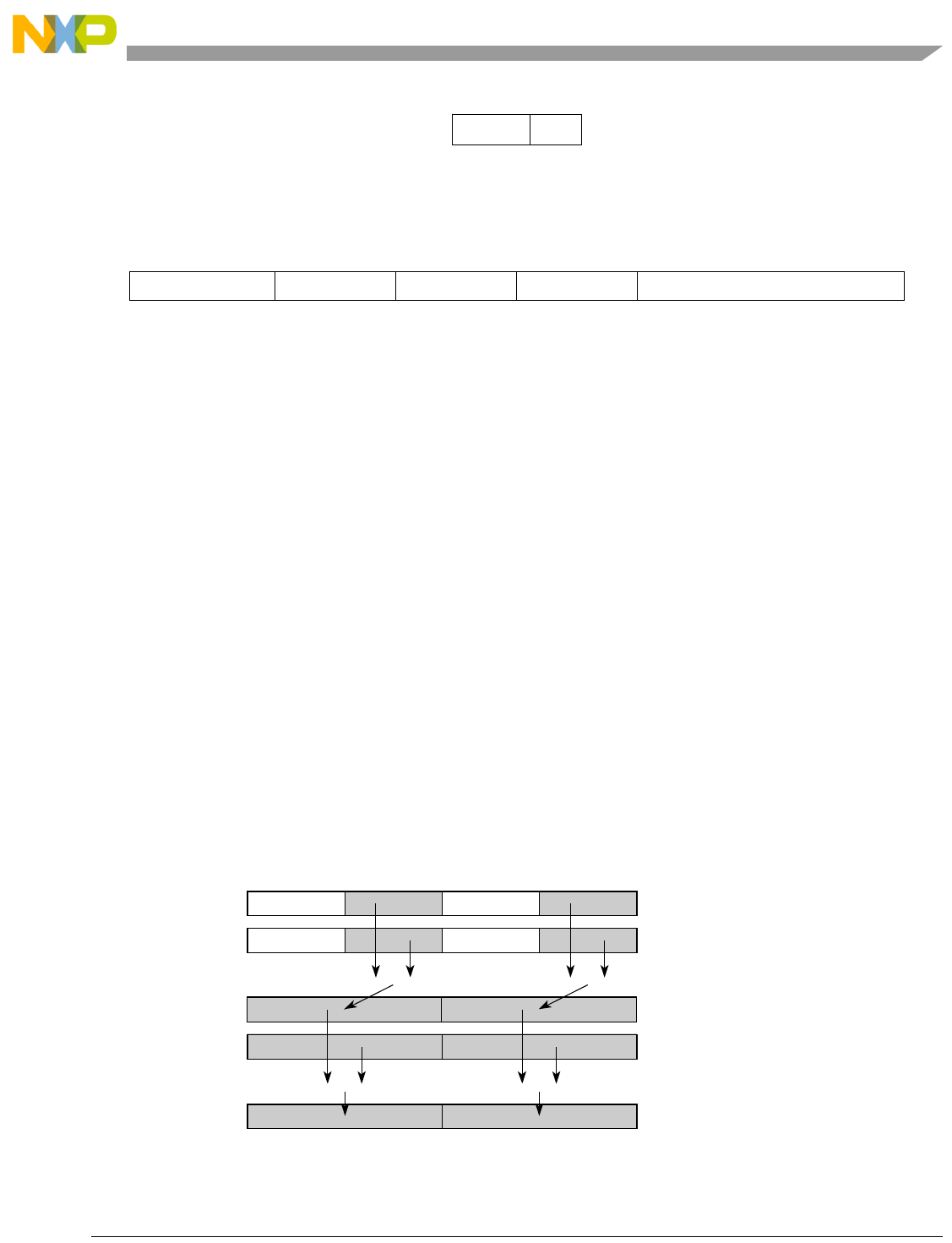

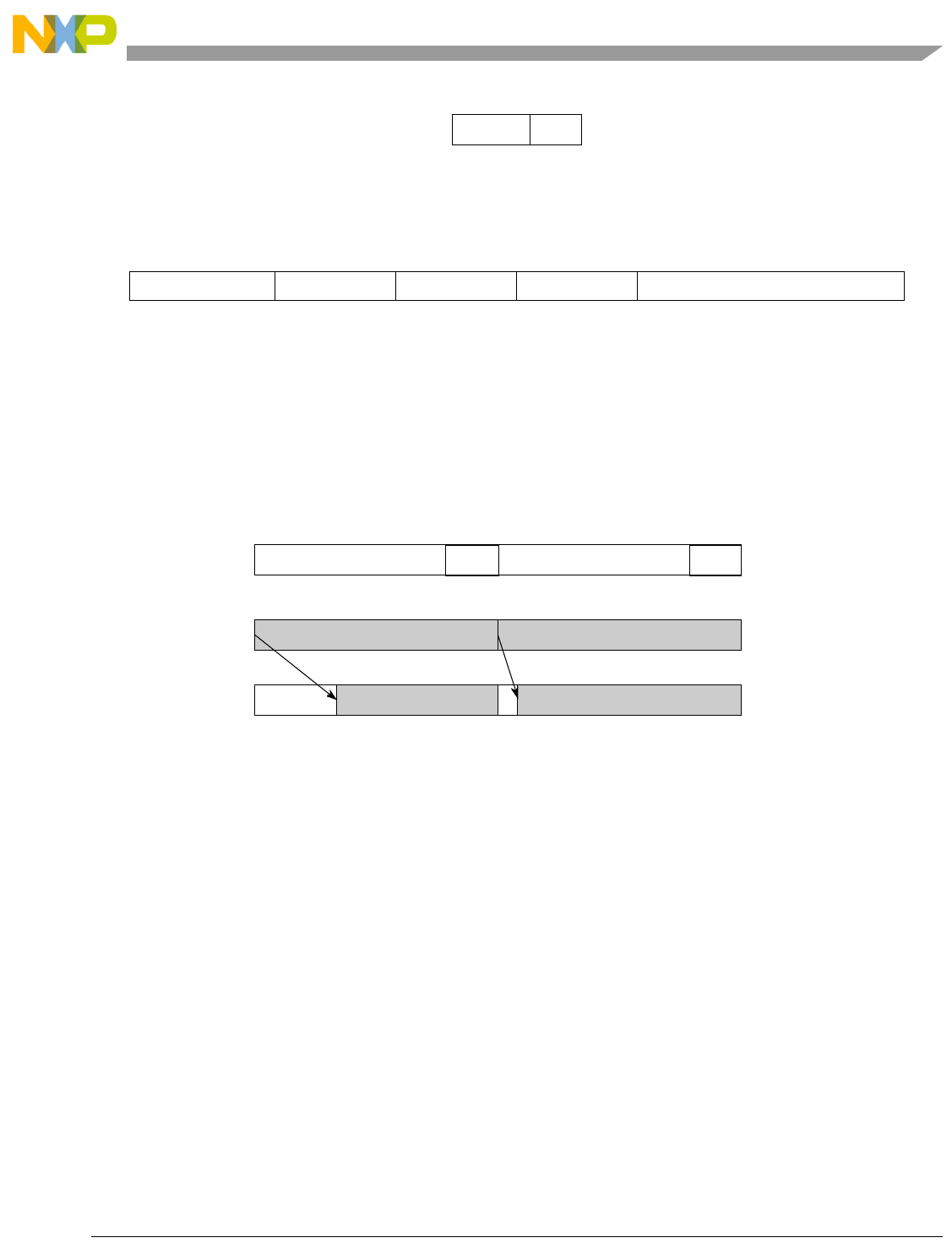

- Figure 5-46. Low Order Element Merging (evmergelo)

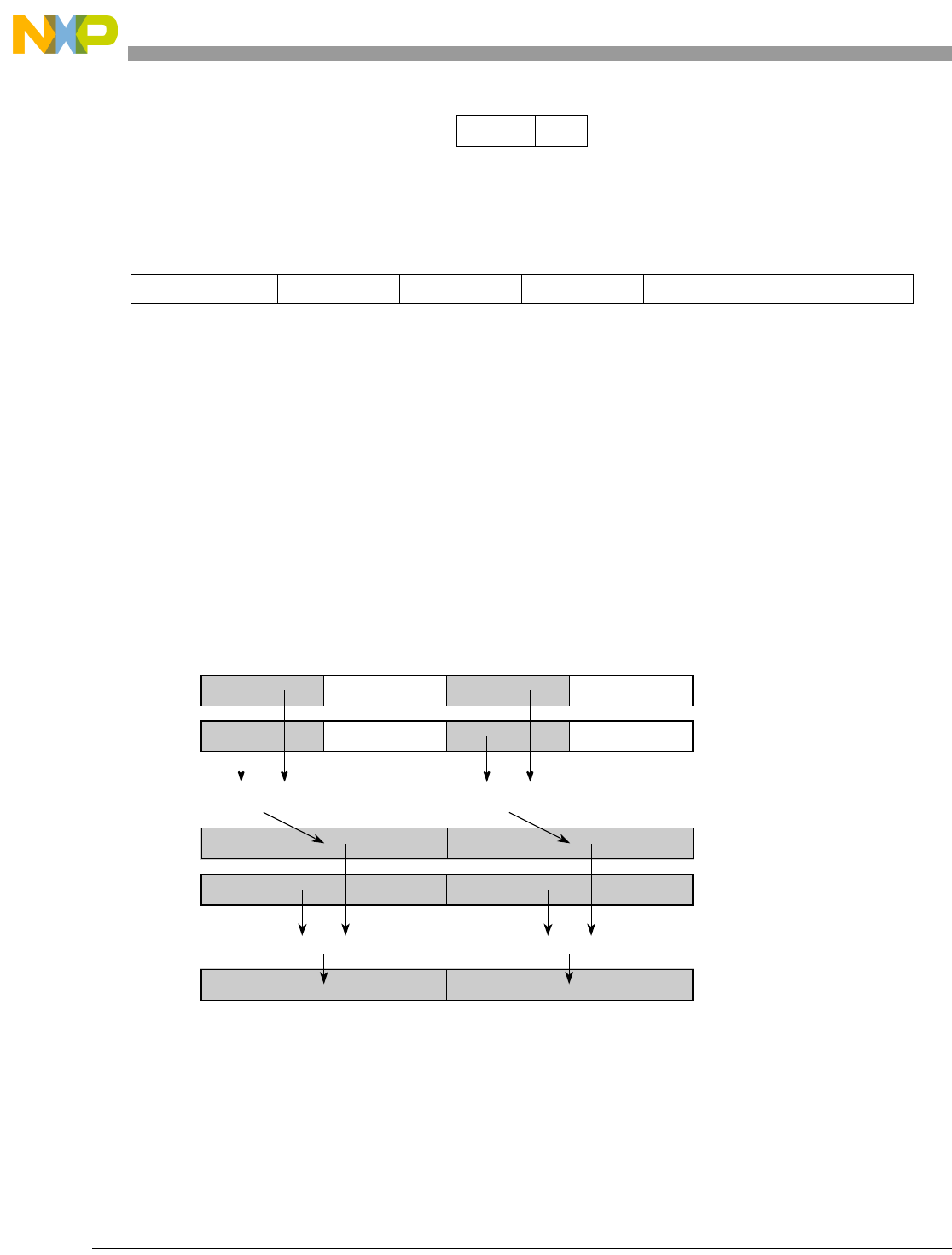

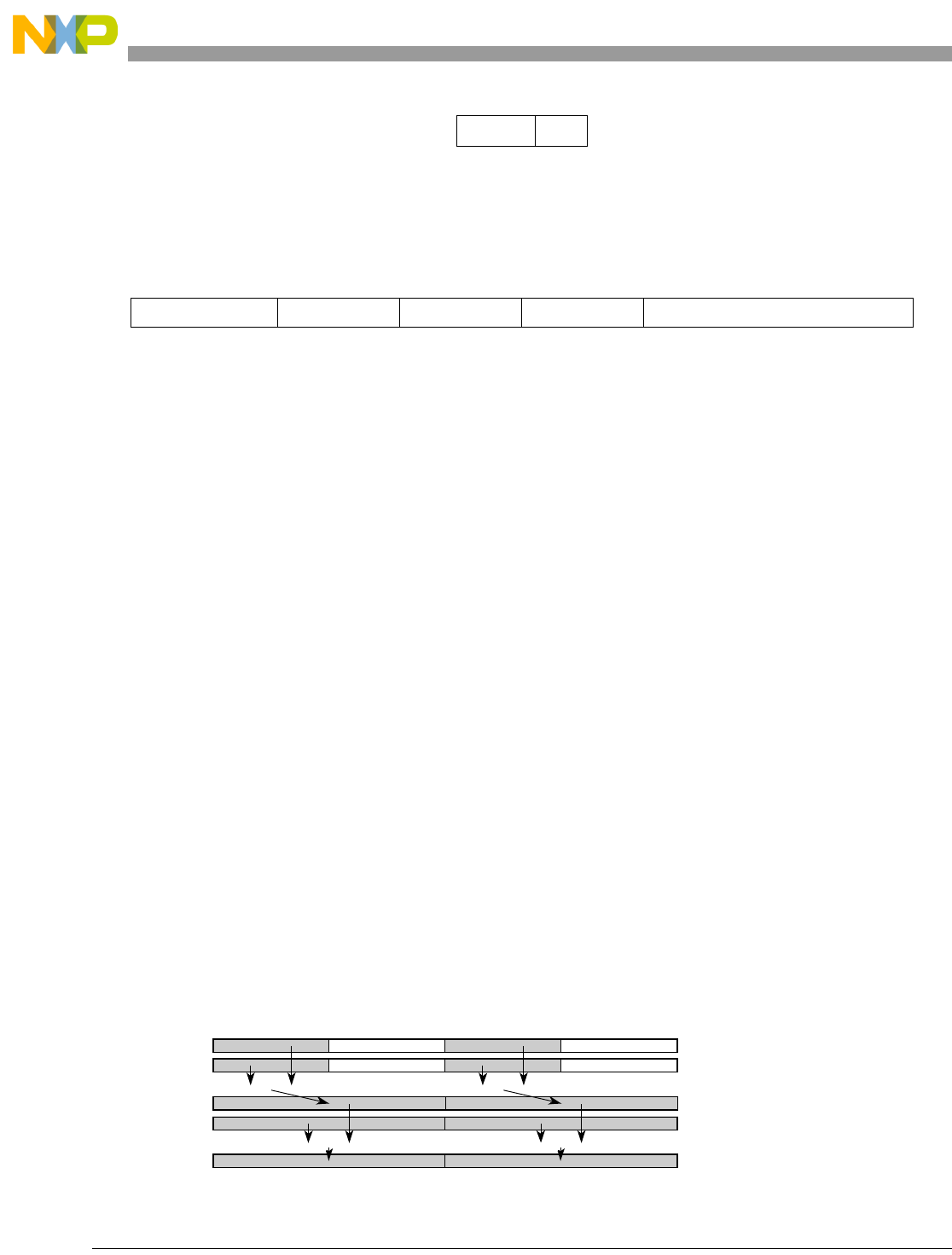

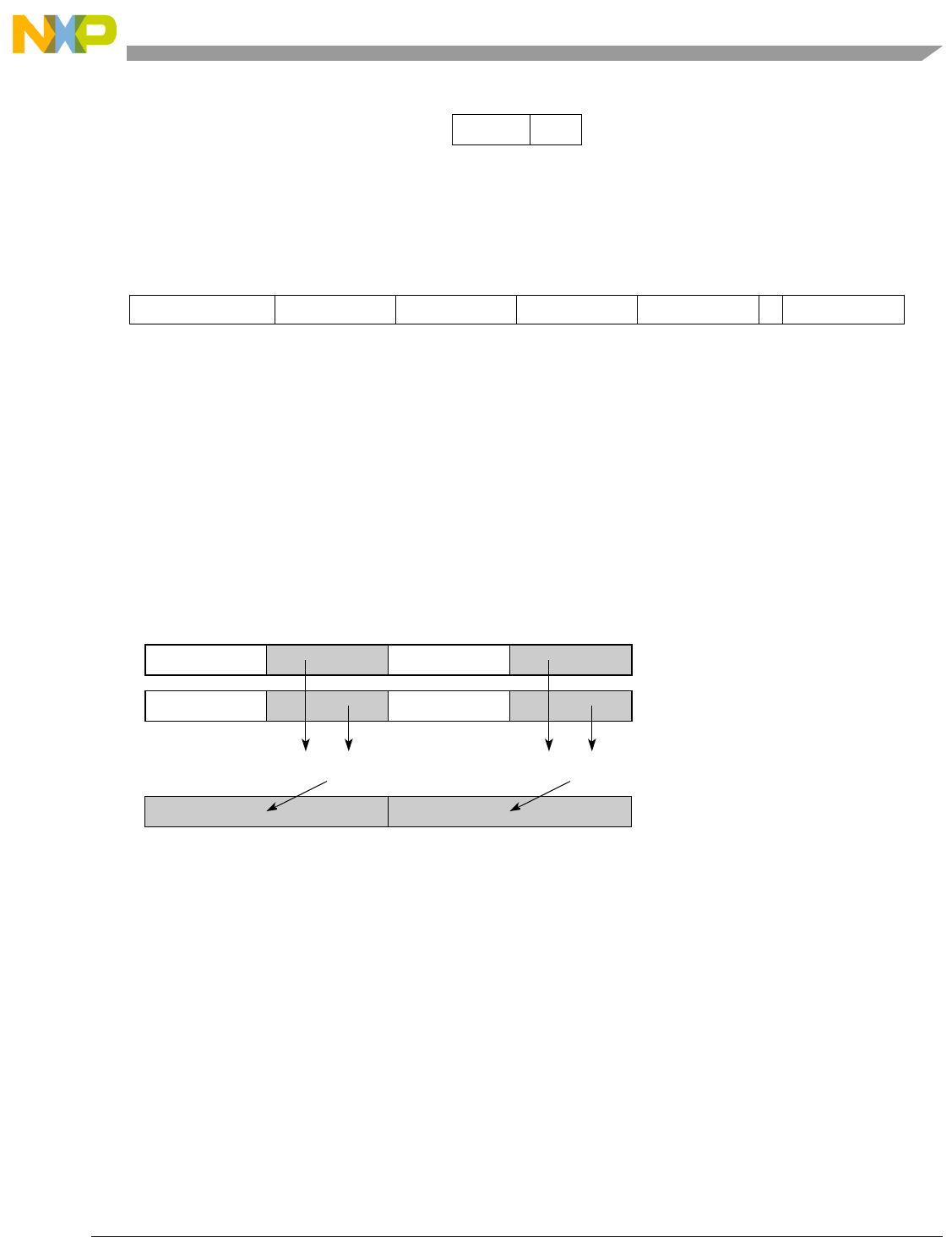

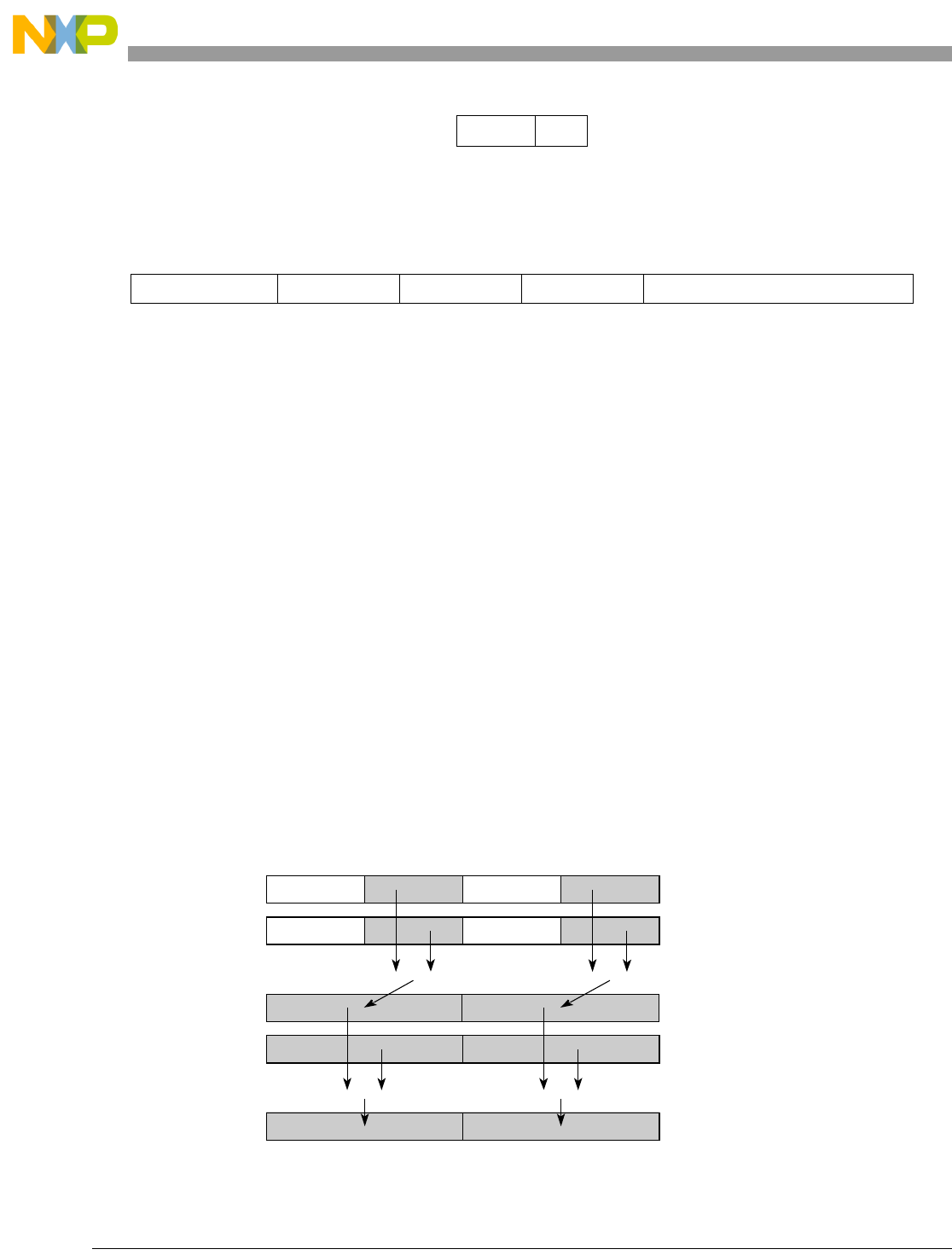

- Figure 5-47. Low Order Element Merging (evmergelohi)

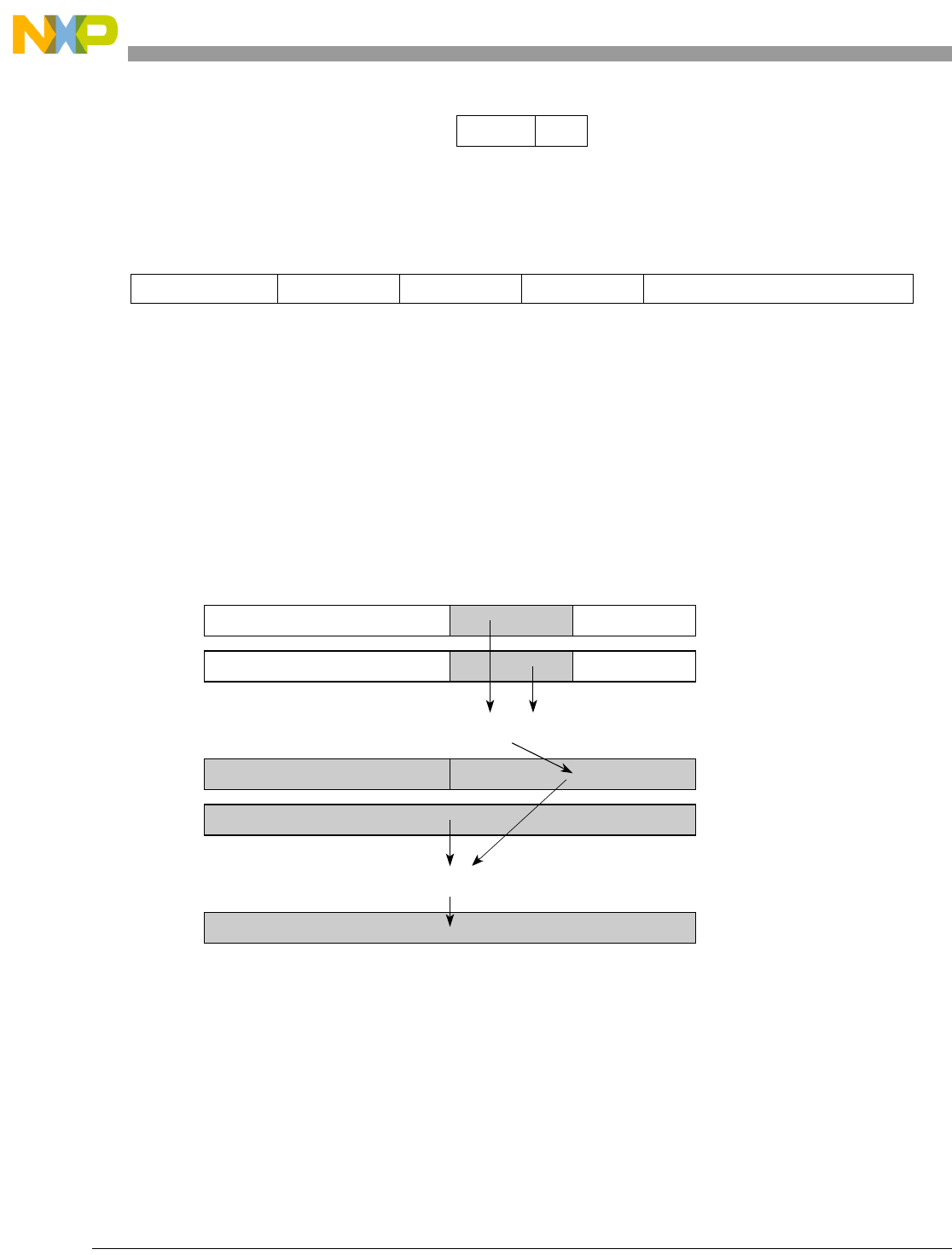

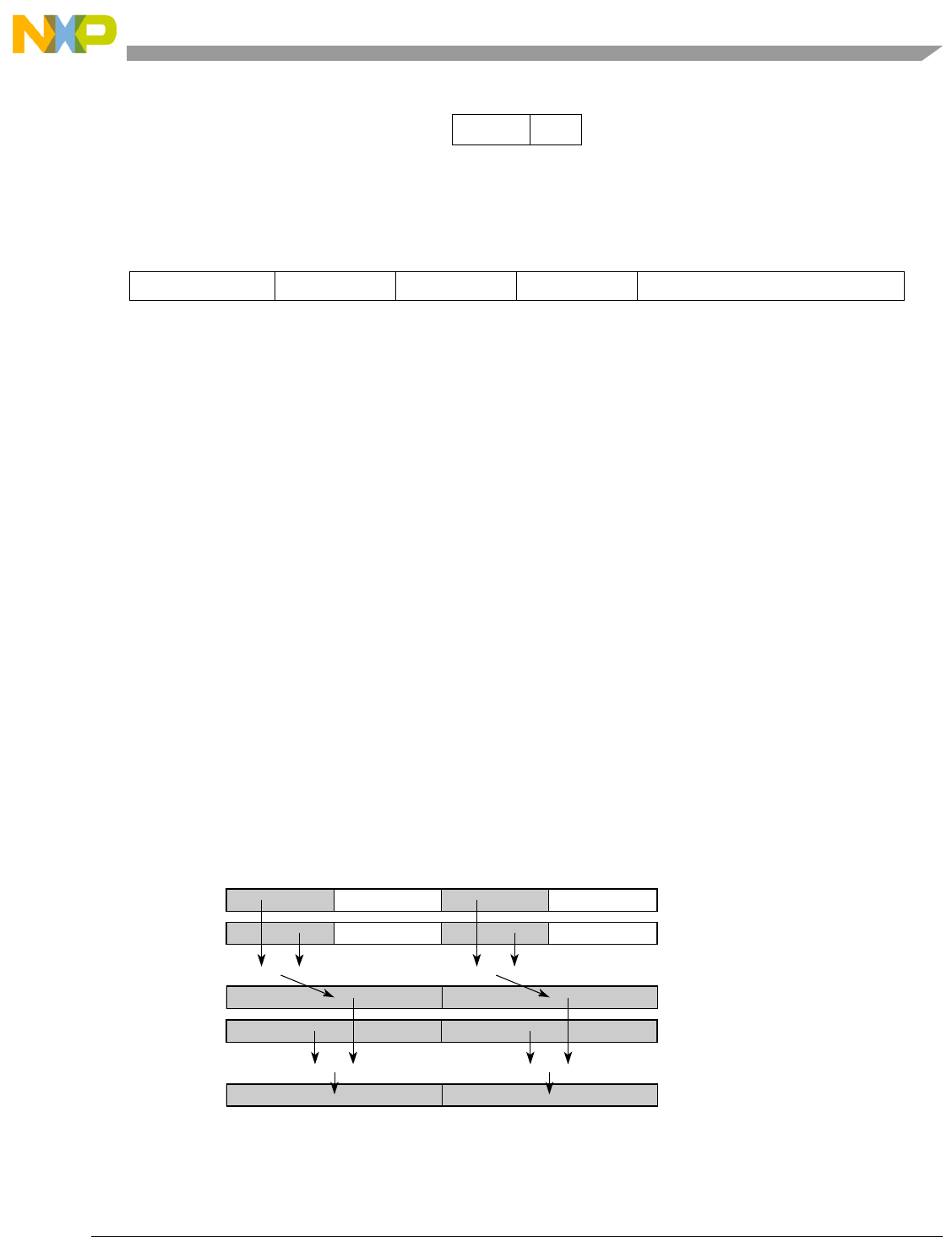

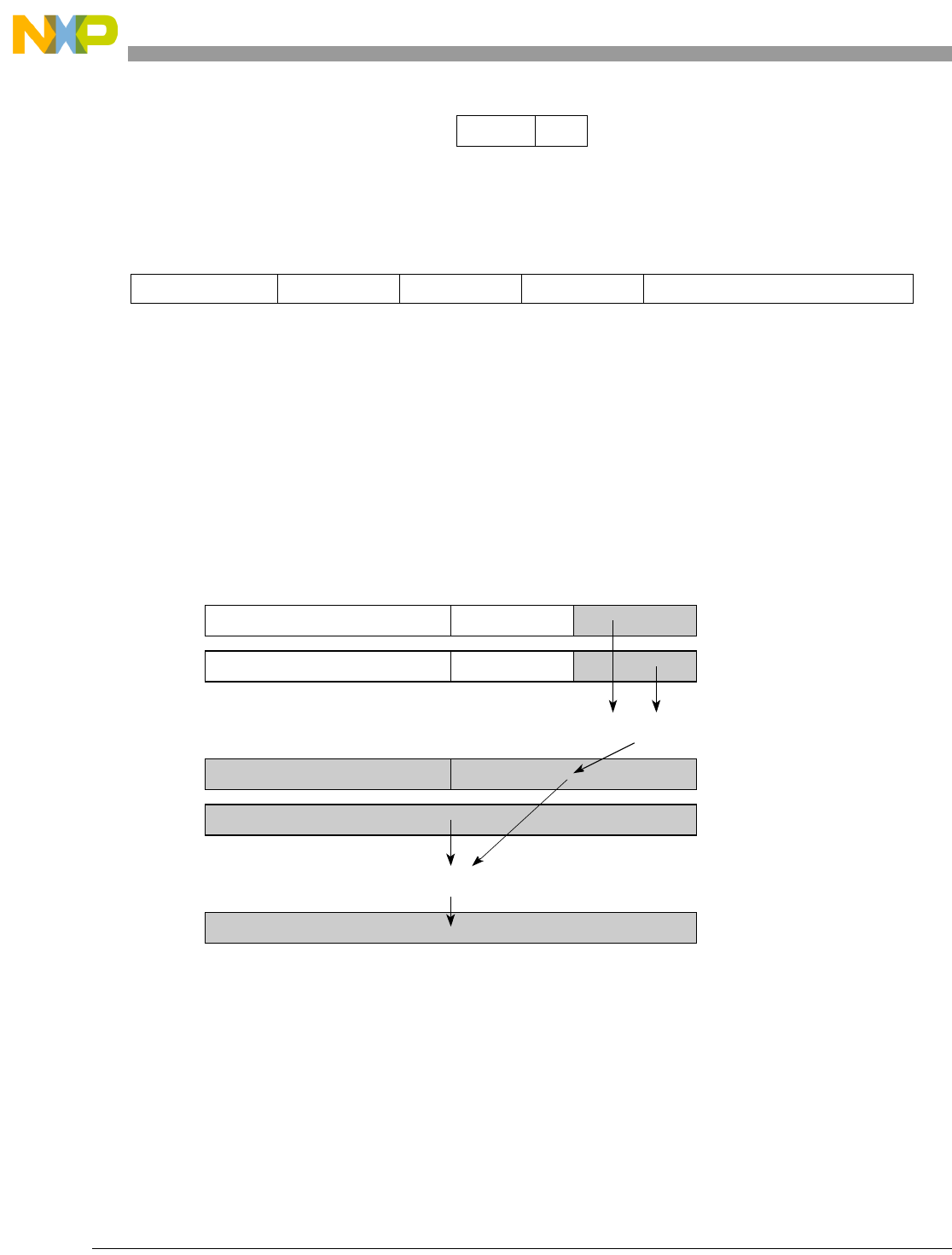

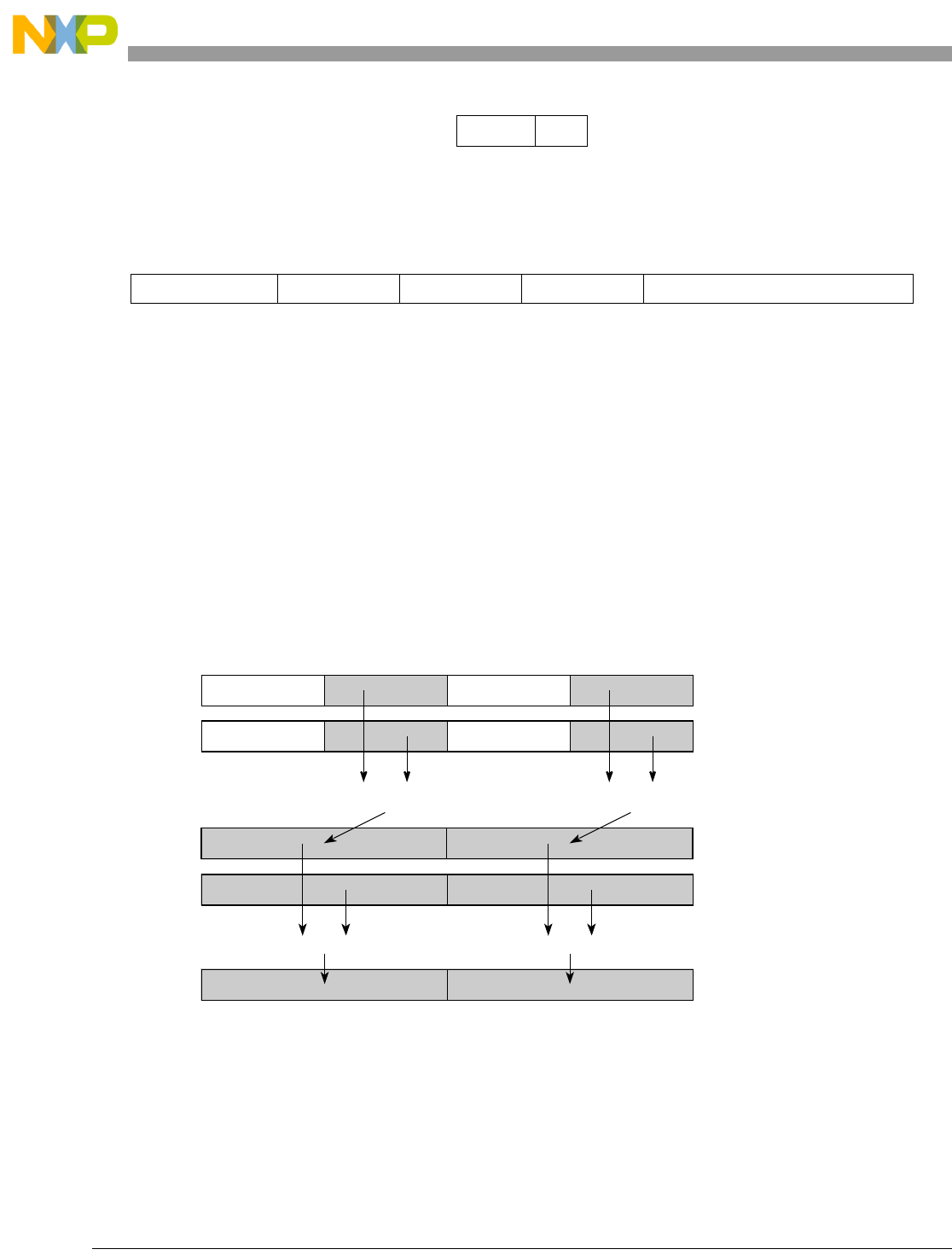

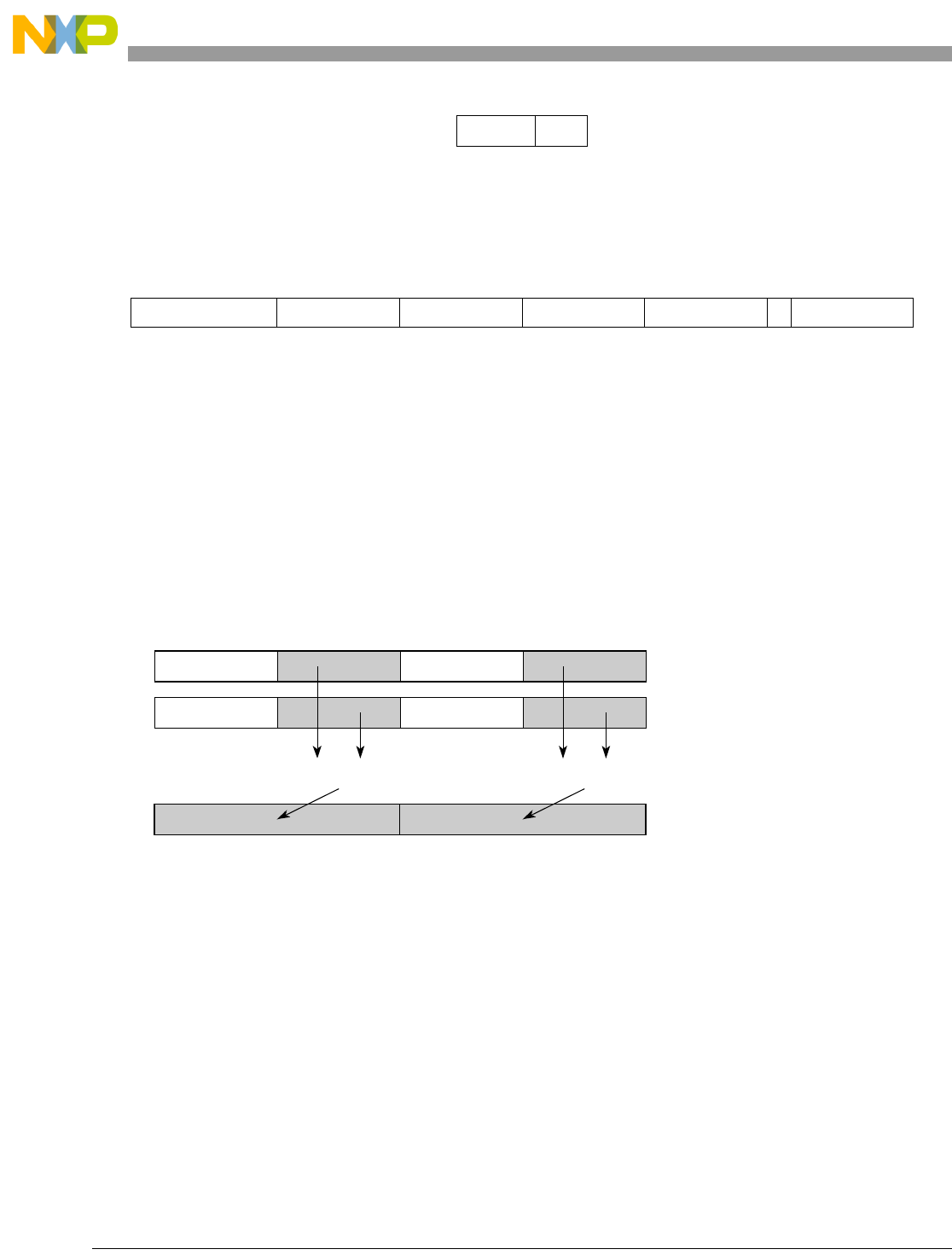

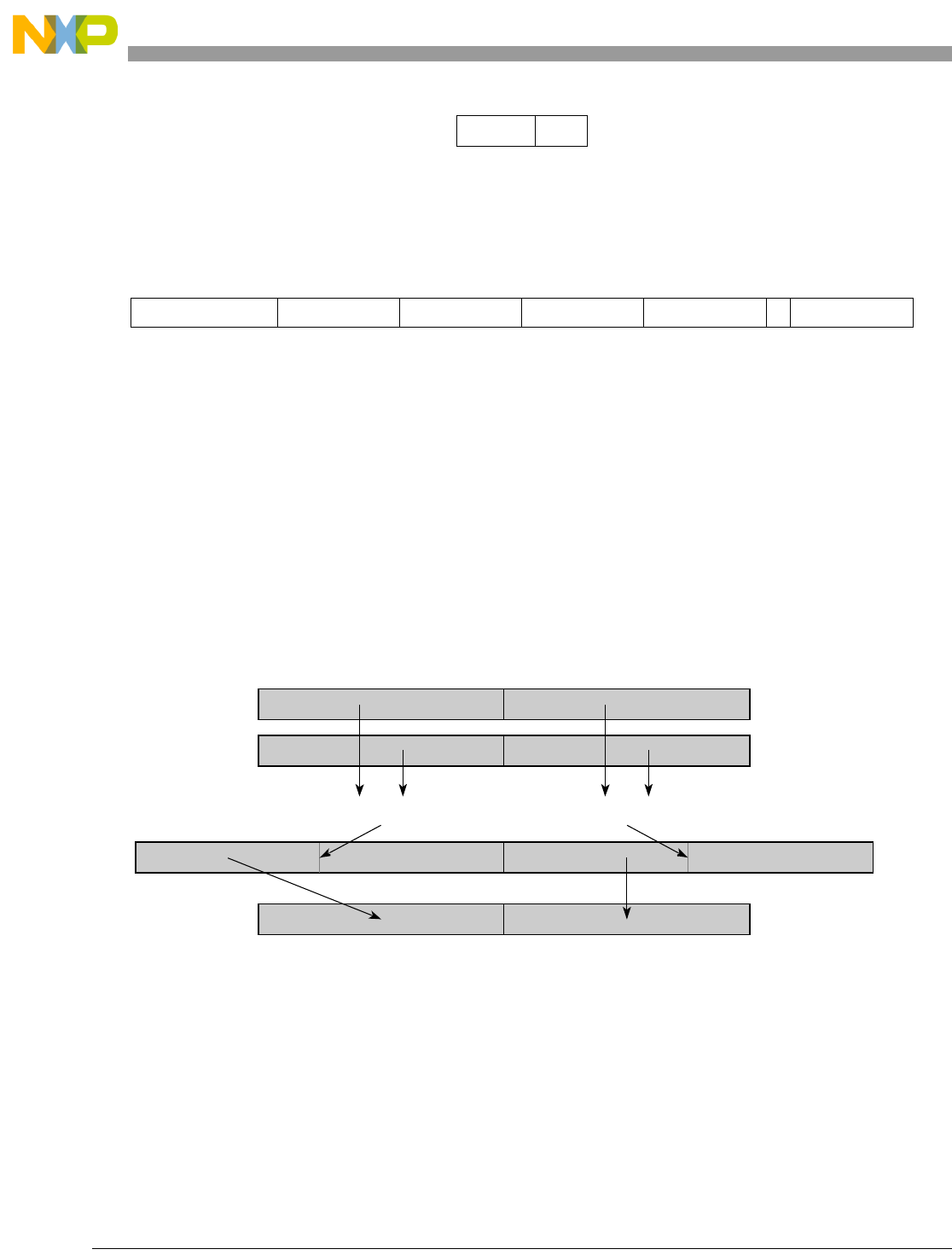

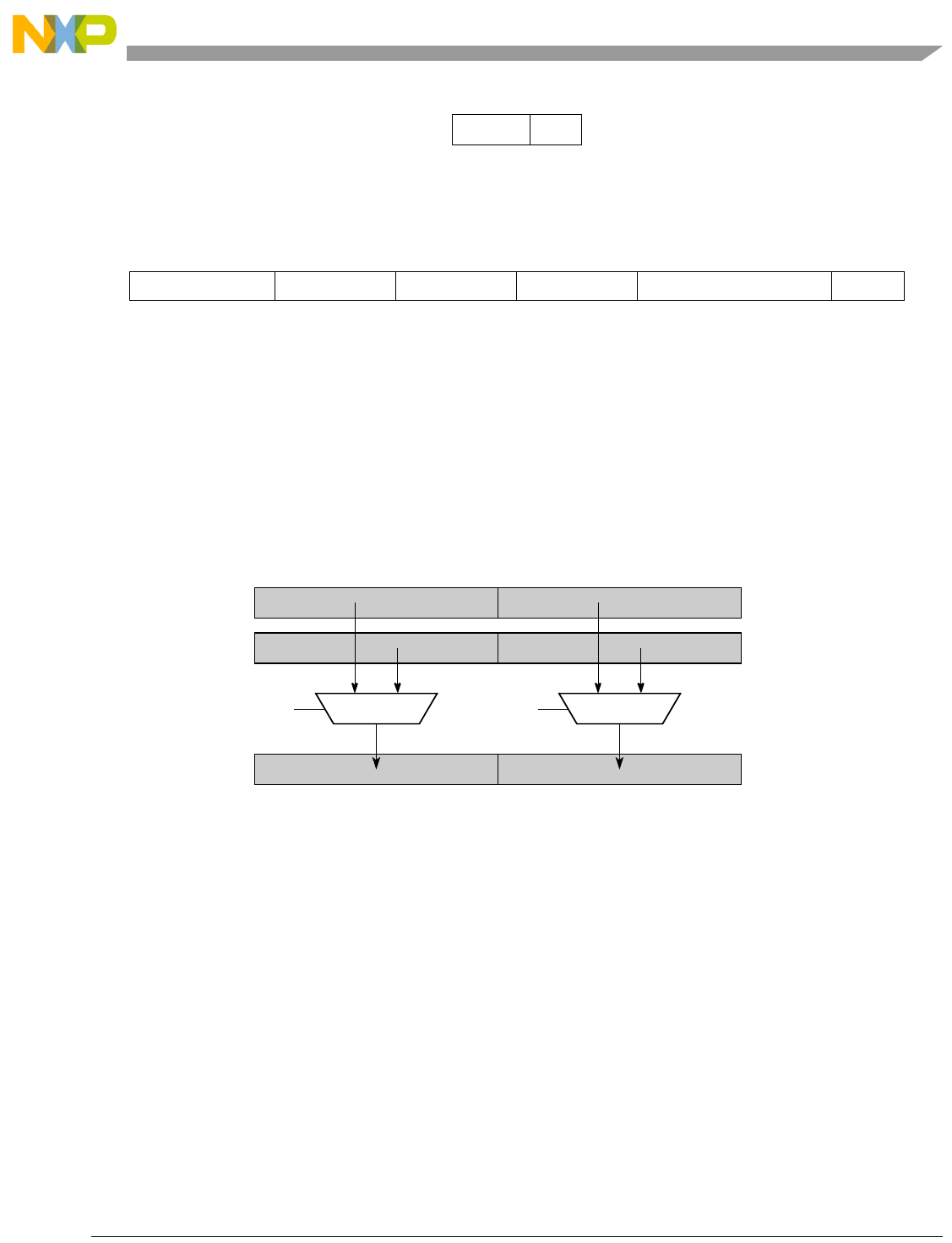

- Figure 5-48. evmhegsmfaa (Even Form)

- Figure 5-49. evmhegsmfan (Even Form)

- Figure 5-50. evmhegsmiaa (Even Form)

- Figure 5-51. evmhegsmian (Even Form)

- Figure 5-52. evmhegumiaa (Even Form)

- Figure 5-53. evmhegumian (Even Form)

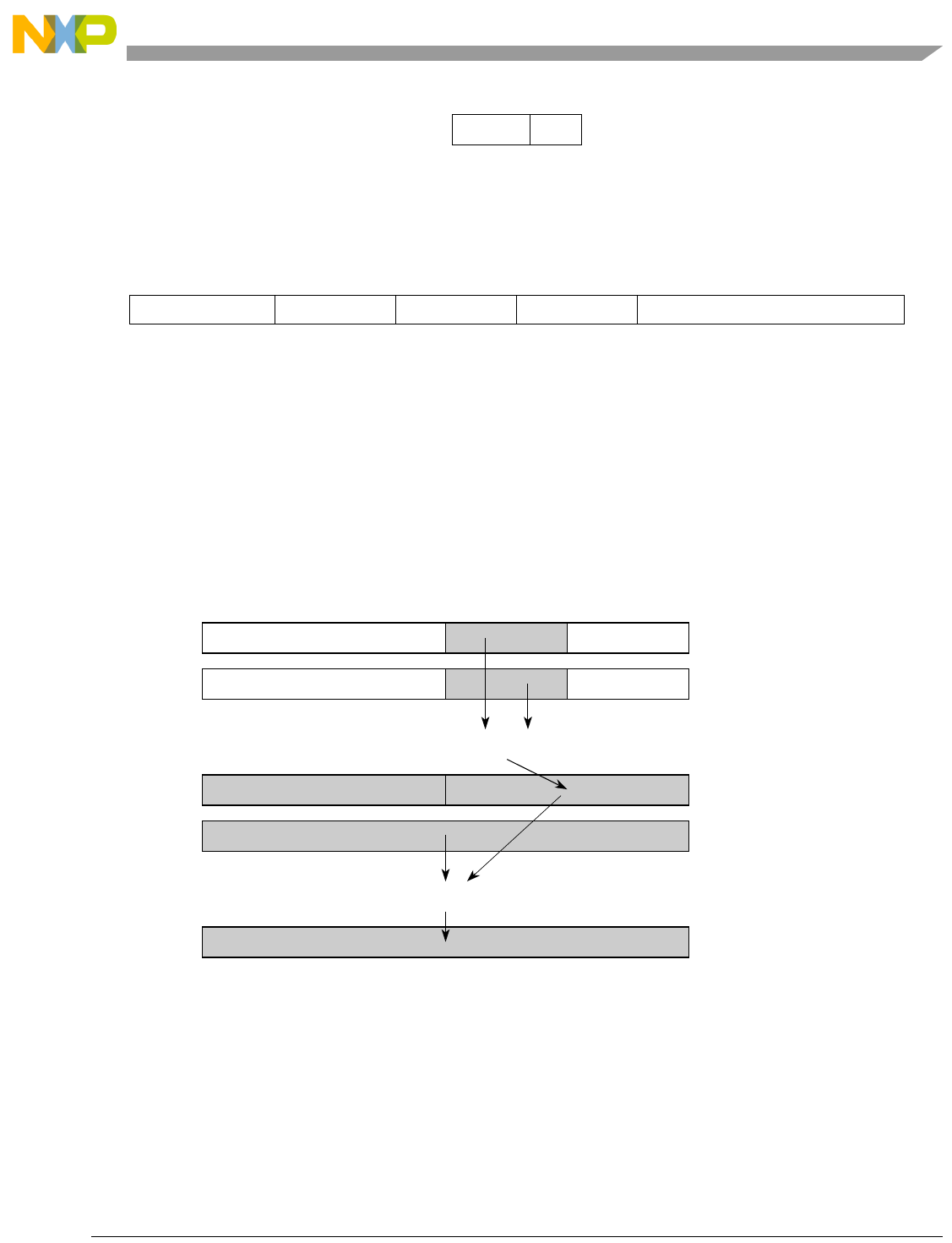

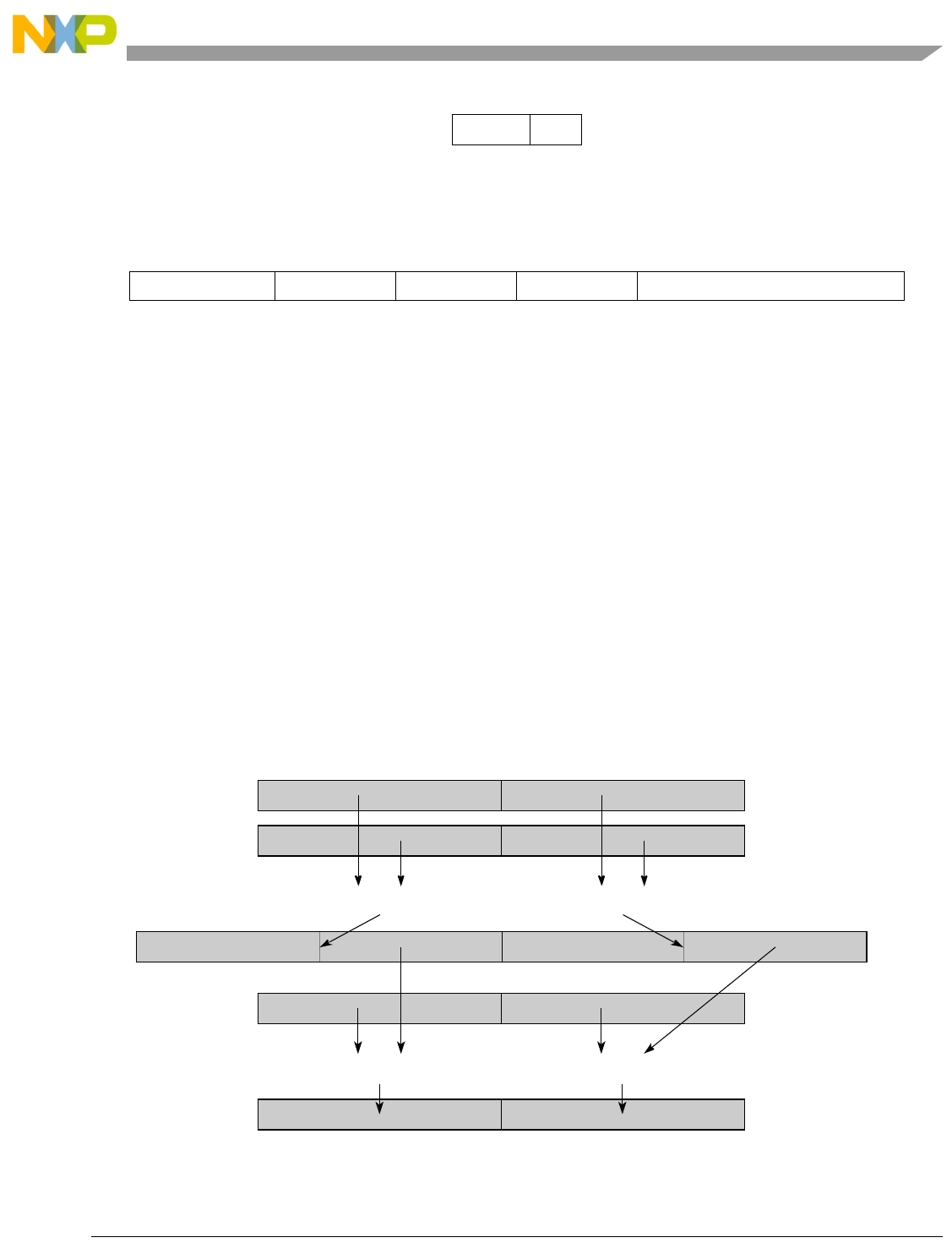

- Figure 5-54. Even Multiply of Two Signed Modulo Fractional Elements (to Accumulator) (evmhesmf)

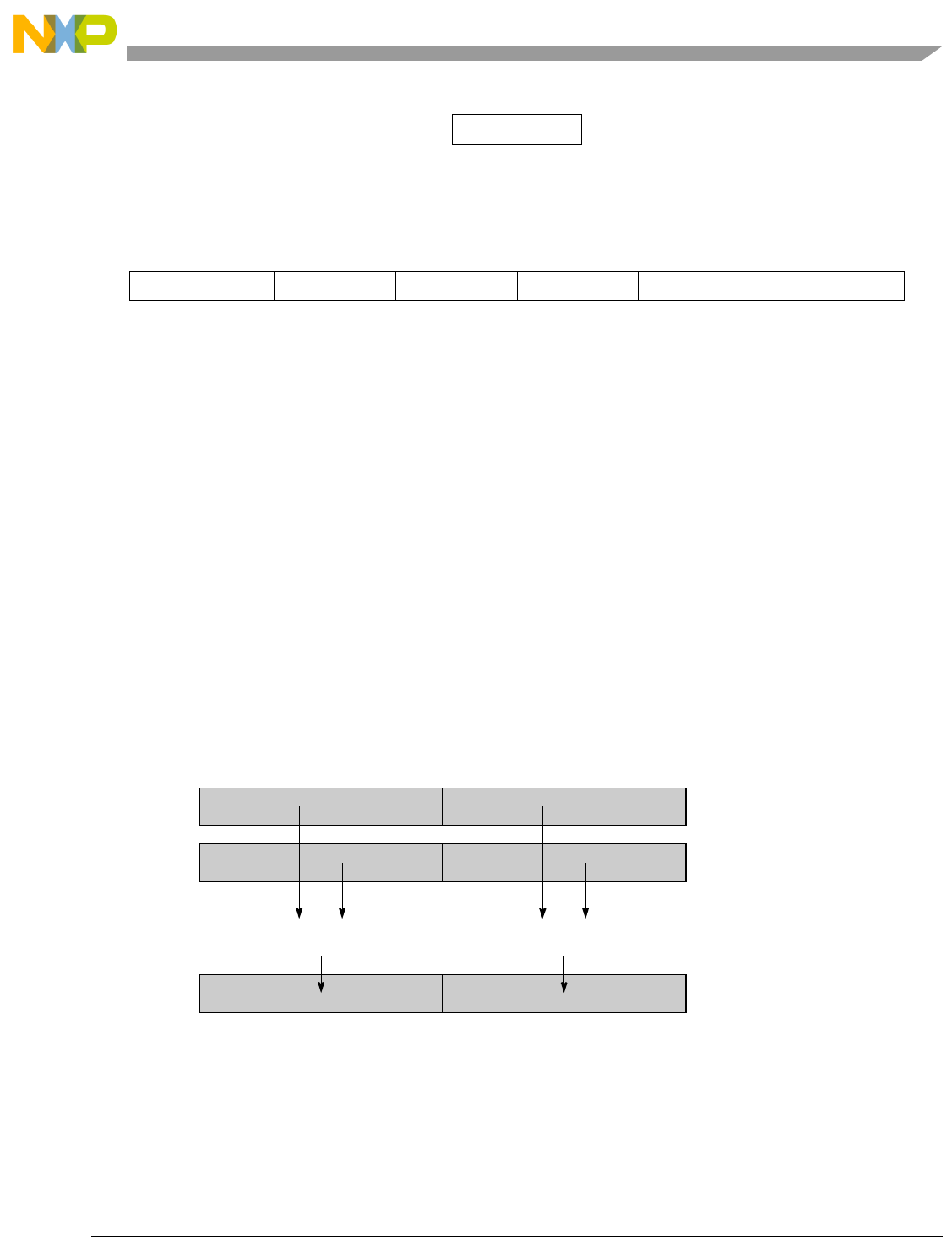

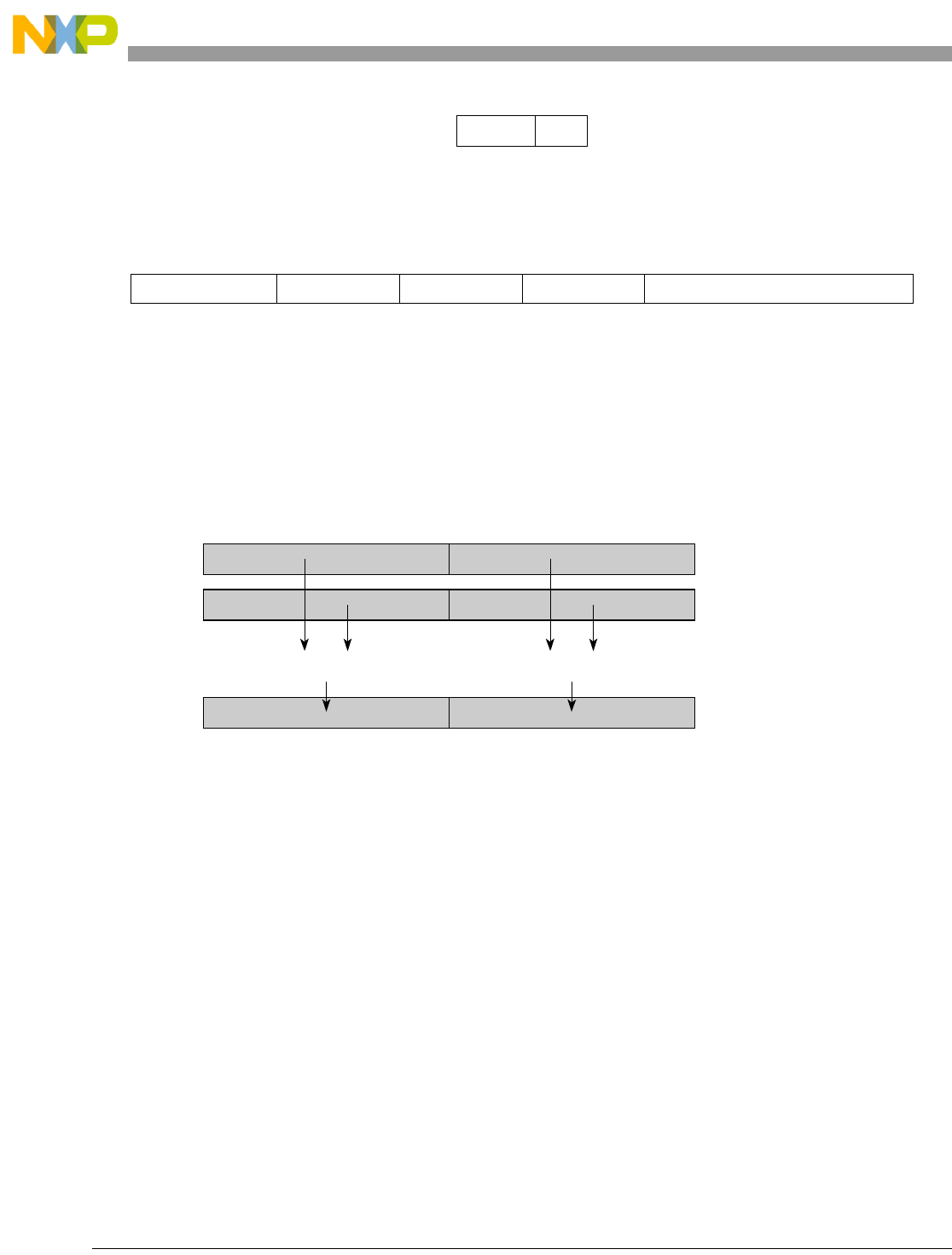

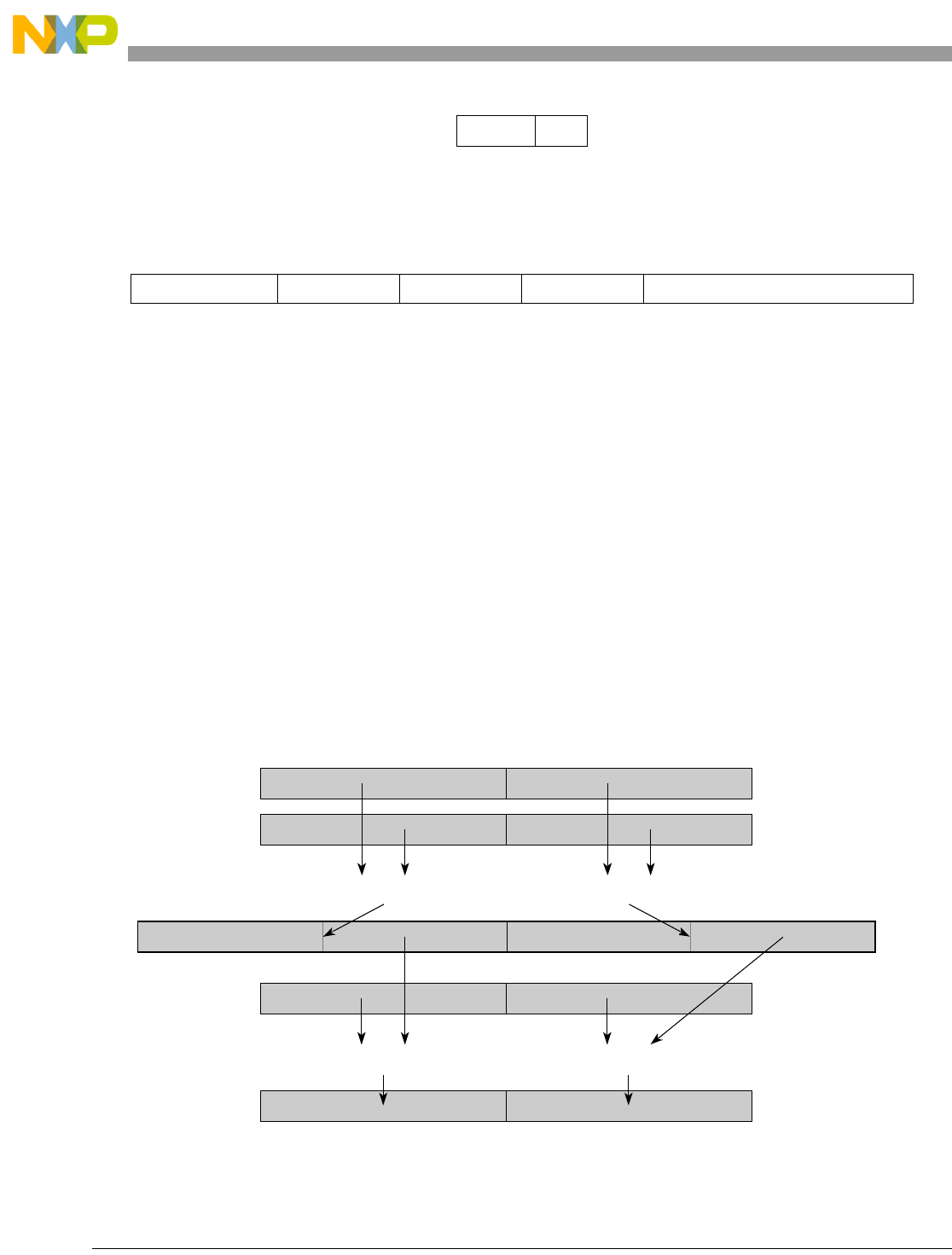

- Figure 5-55. Even Form of Vector Half-Word Multiply (evmhesmfaaw)

- Figure 5-56. Even Form of Vector Half-Word Multiply (evmhesmfanw)

- Figure 5-57. Even Form for Vector Multiply (to Accumulator) (evmhesmi)

- Figure 5-58. Even Form of Vector Half-Word Multiply (evmhesmiaaw)

- Figure 5-59. Even Form of Vector Half-Word Multiply (evmhesmianw)

- Figure 5-60. Even Multiply of Two Signed Saturate Fractional Elements (to Accumulator) (evmhessf)

- Figure 5-61. Even Form of Vector Half-Word Multiply (evmhessfaaw)

- Figure 5-62. Even Form of Vector Half-Word Multiply (evmhessfanw)

- Figure 5-63. Even Form of Vector Half-Word Multiply (evmhessiaaw)

- Figure 5-64. Even Form of Vector Half-Word Multiply (evmhessianw)

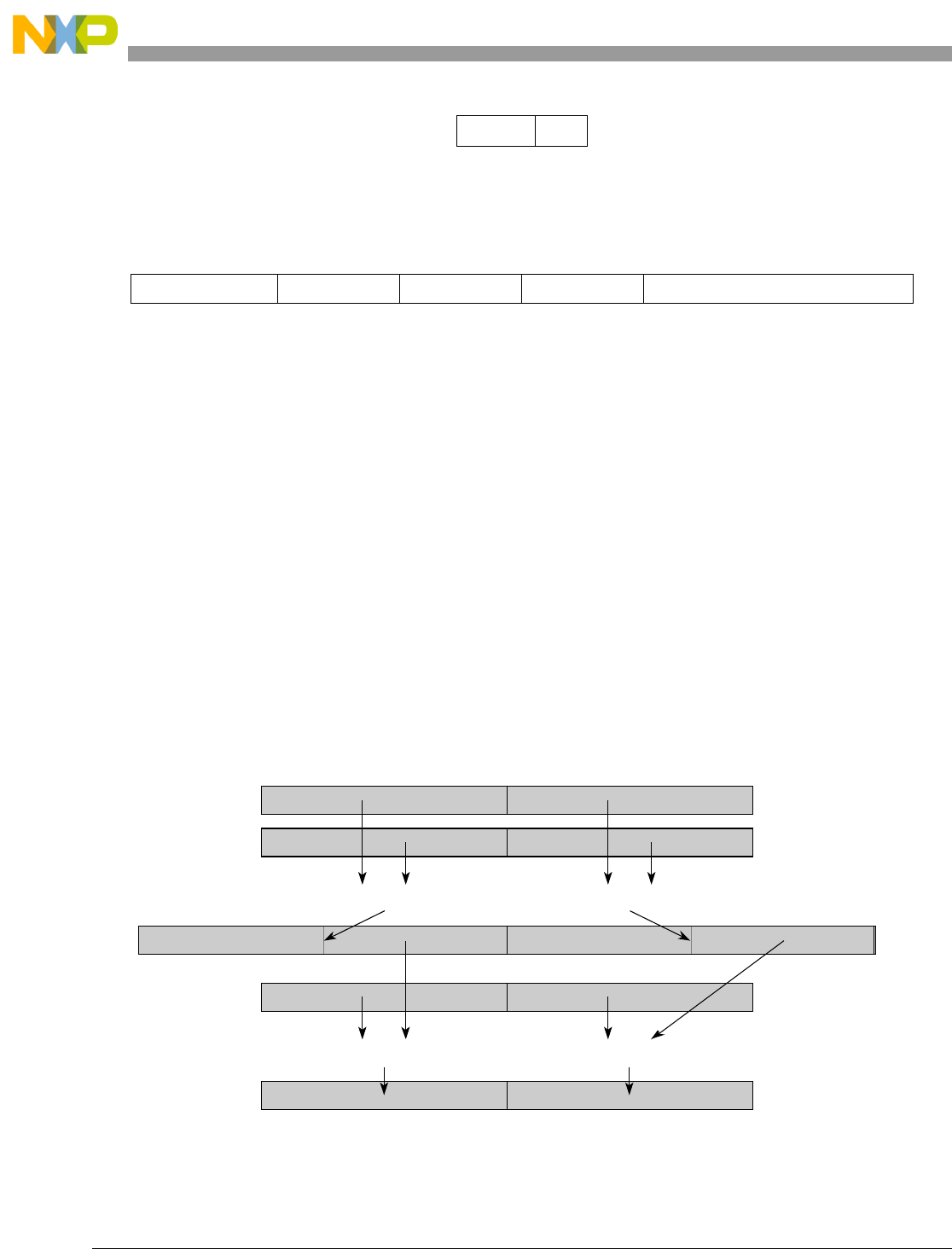

- Figure 5-65. Vector Multiply Half Words, Even, Unsigned, Modulo, Integer (to Accumulator) (evmheumi)

- Figure 5-66. Even Form of Vector Half-Word Multiply (evmheumiaaw)

- Figure 5-67. Even Form of Vector Half-Word Multiply (evmheumianw)

- Figure 5-68. Even Form of Vector Half-Word Multiply (evmheusiaaw)

- Figure 5-69. Even Form of Vector Half-Word Multiply (evmheusianw)

- Figure 5-70. evmhogsmfaa (Odd Form)

- Figure 5-71. evmhogsmfan (Odd Form)

- Figure 5-72. evmhogsmiaa (Odd Form)

- Figure 5-73. evmhogsmian (Odd Form)

- Figure 5-74. evmhogumiaa (Odd Form)

- Figure 5-75. evmhogumian (Odd Form)

- Figure 5-76. Vector Multiply Half Words, Odd, Signed, Modulo, Fractional (to Accumulator) (evmhosmf)

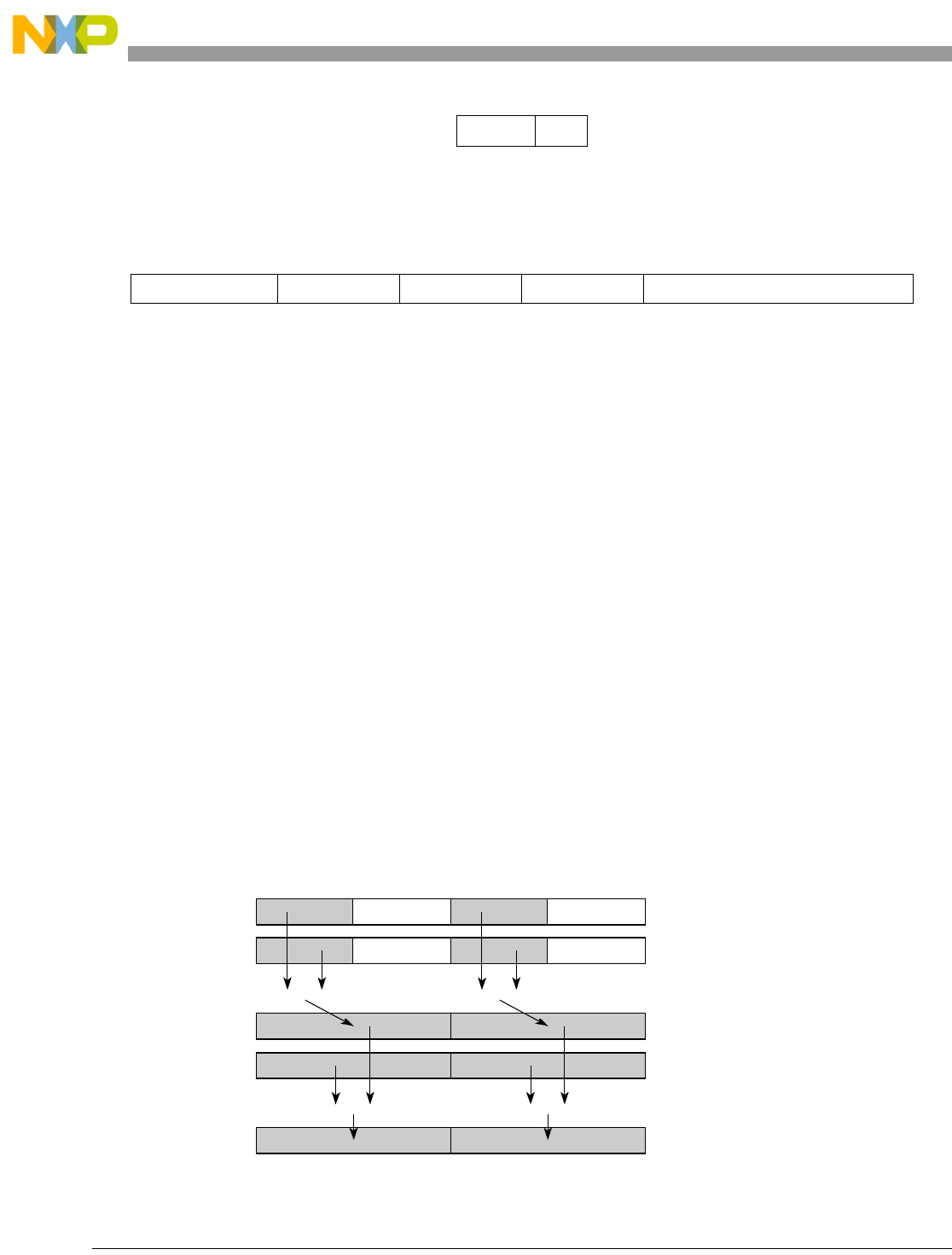

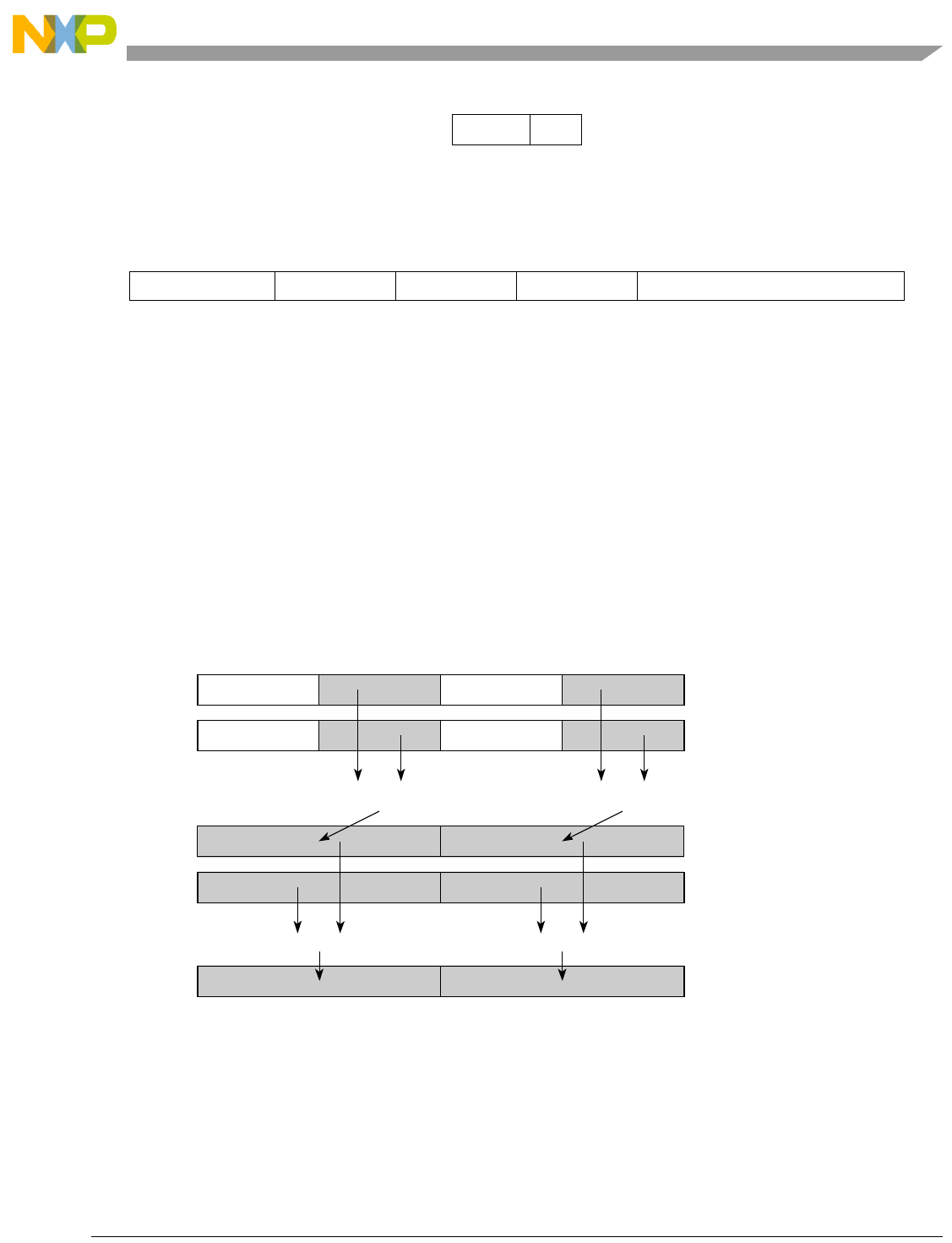

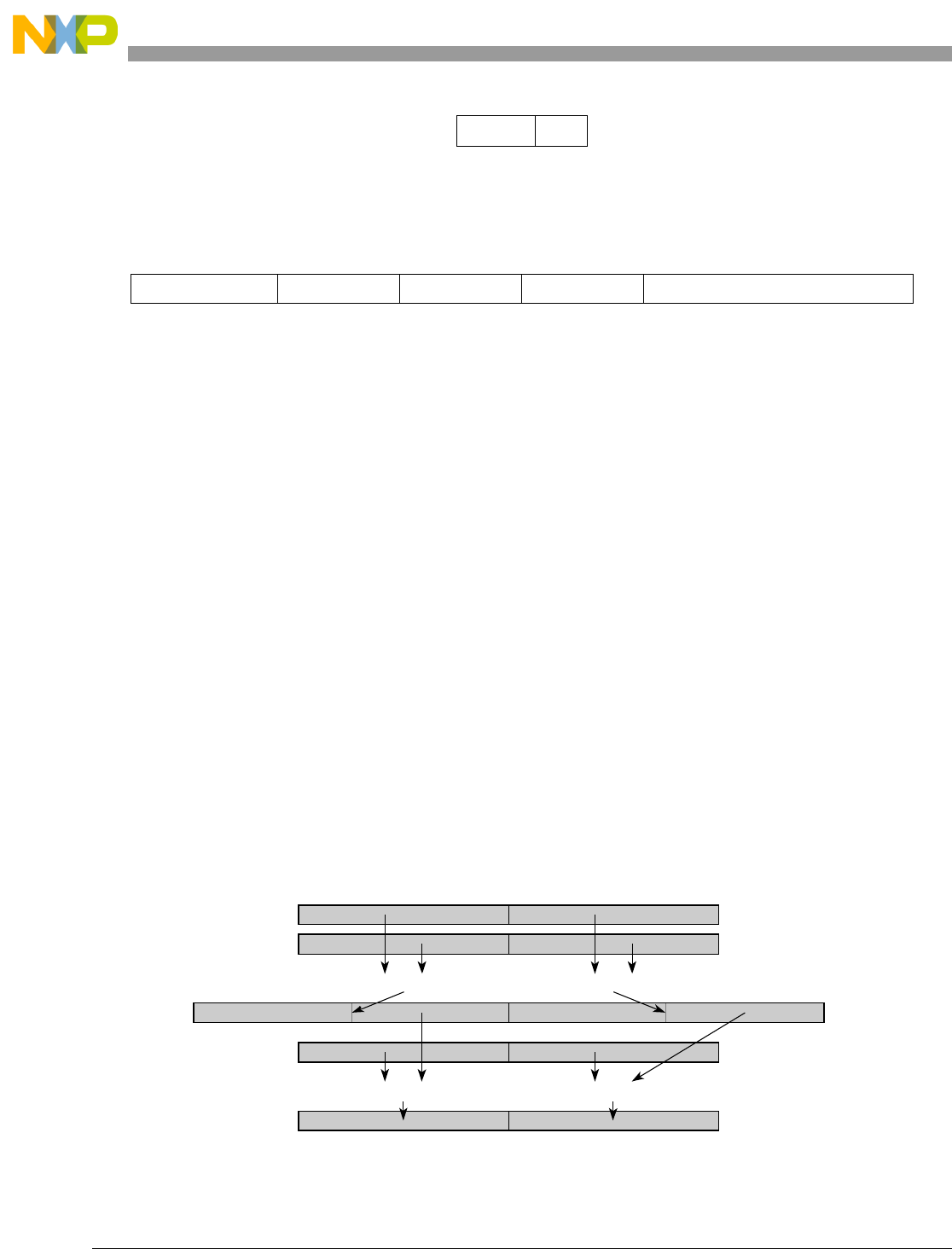

- Figure 5-77. Odd Form of Vector Half-Word Multiply (evmhosmfaaw)

- Figure 5-78. Odd Form of Vector Half-Word Multiply (evmhosmfanw)

- Figure 5-79. Vector Multiply Half Words, Odd, Signed, Modulo, Integer (to Accumulator) (evmhosmi)

- Figure 5-80. Odd Form of Vector Half-Word Multiply (evmhosmiaaw)

- Figure 5-81. Odd Form of Vector Half-Word Multiply (evmhosmianw)

- Figure 5-82. Vector Multiply Half Words, Odd, Signed, Saturate, Fractional (to Accumulator) (evmhossf)

- Figure 5-83. Odd Form of Vector Half-Word Multiply (evmhossfaaw)

- Figure 5-84. Odd Form of Vector Half-Word Multiply (evmhossfanw)

- Figure 5-85. Odd Form of Vector Half-Word Multiply (evmhossiaaw)

- Figure 5-86. Odd Form of Vector Half-Word Multiply (evmhossianw)

- Figure 5-87. Vector Multiply Half Words, Odd, Unsigned, Modulo, Integer (to Accumulator) (evmhoumi)

- Figure 5-88. Odd Form of Vector Half-Word Multiply (evmhoumiaaw)

- Figure 5-89. Odd Form of Vector Half-Word Multiply (evmhoumianw)

- Figure 5-90. Odd Form of Vector Half-Word Multiply (evmhousiaaw)

- Figure 5-91. Odd Form of Vector Half-Word Multiply (evmhousianw)

- Figure 5-92. Initialize Accumulator (evmra)

- Figure 5-93. Vector Multiply Word High Signed, Modulo, Fractional (to Accumulator) (evmwhsmf)

- Figure 5-94. Vector Multiply Word High Signed, Modulo, Integer (to Accumulator) (evmwhsm)

- Figure 5-95. Vector Multiply Word High Signed, Saturate, Fractional (to Accumulator) (evmwhssf)

- Figure 5-96. Vector Multiply Word High Unsigned, Modulo, Integer (to Accumulator) (evmwhumi)

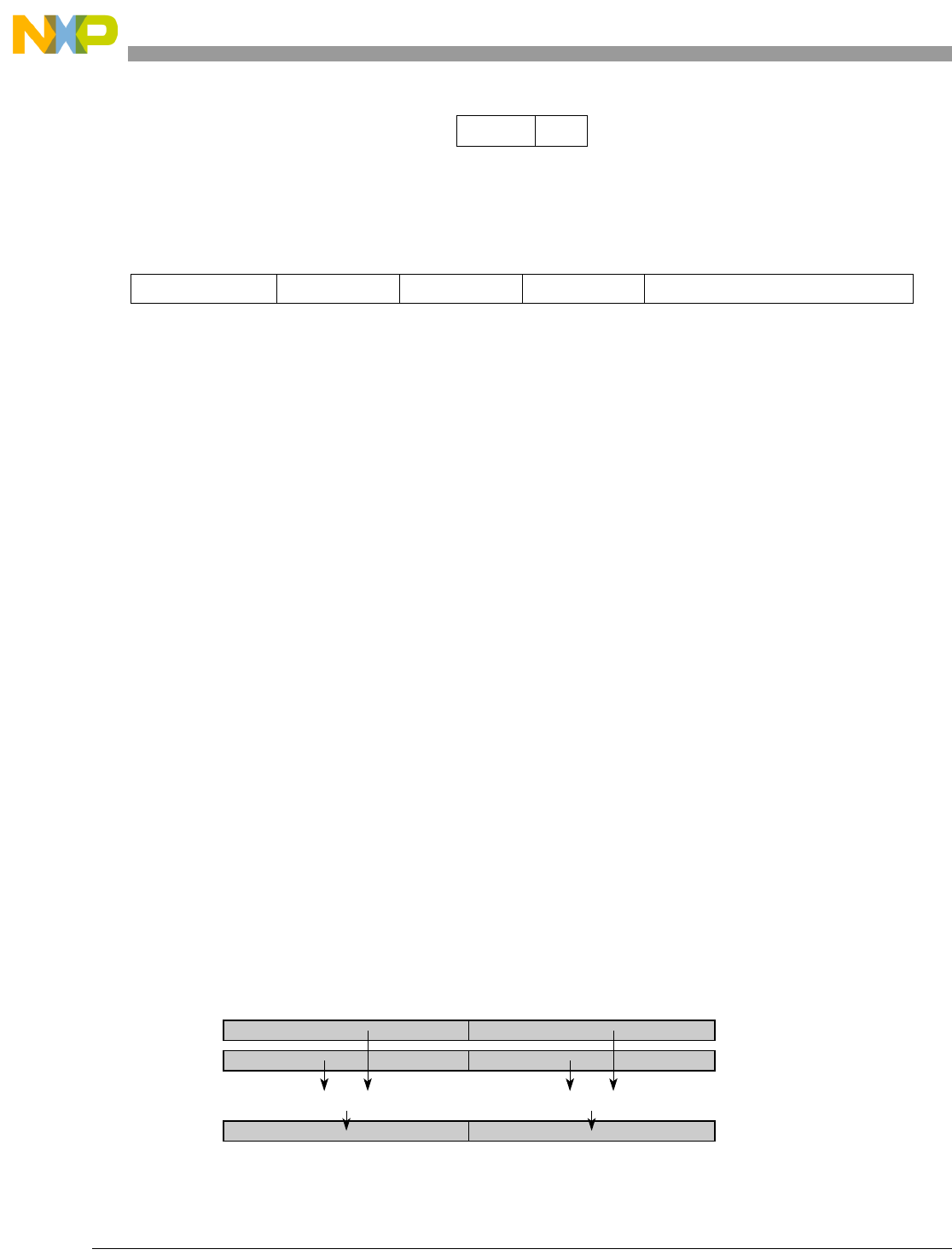

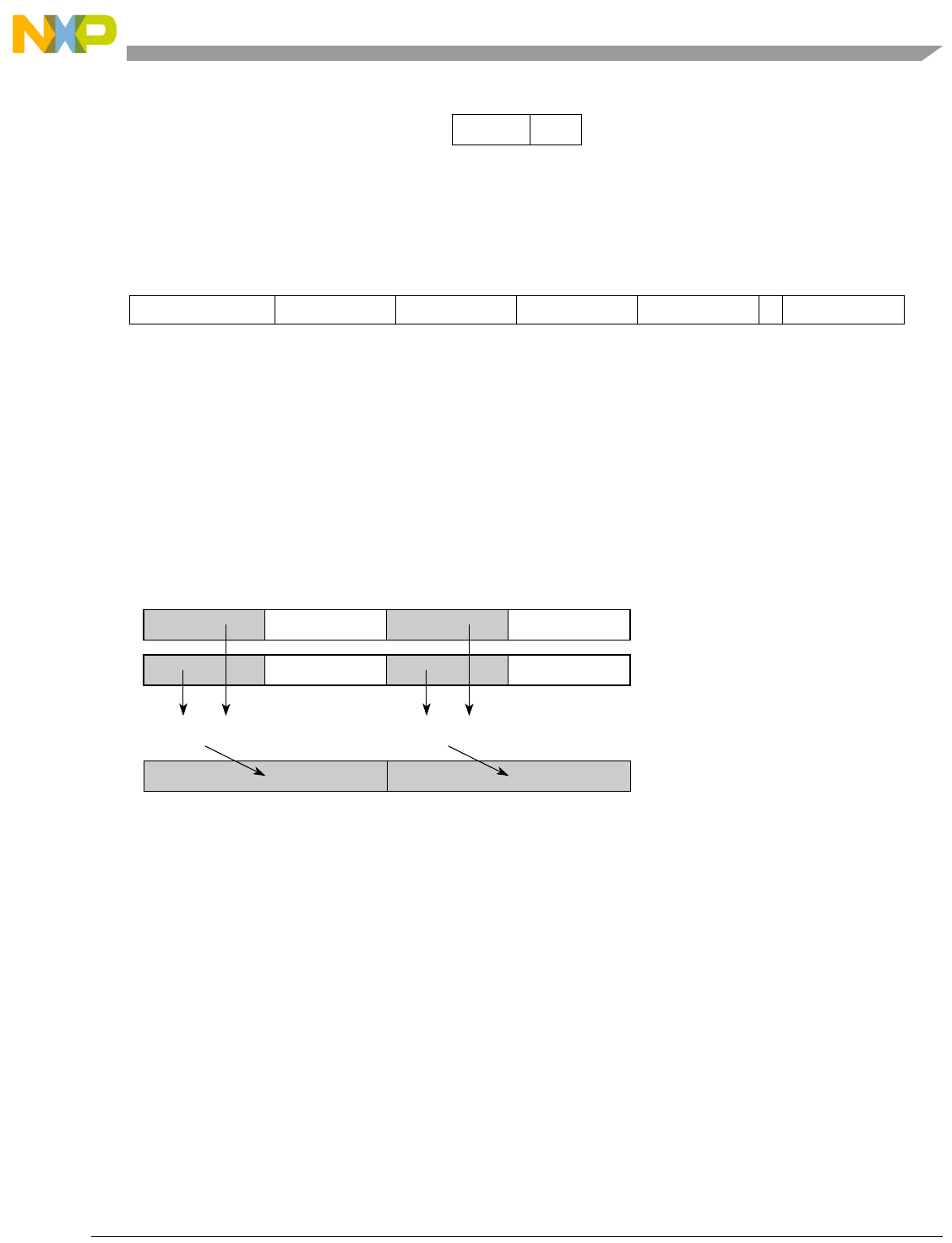

- Figure 5-97. Vector Multiply Word Low Signed, Modulo, Integer and Accumulate in Words (evmwlsmiaaw)

- Figure 5-98. Vector Multiply Word Low Signed, Modulo, Integer and Accumulate Negative in Words (evmwlsmianw)

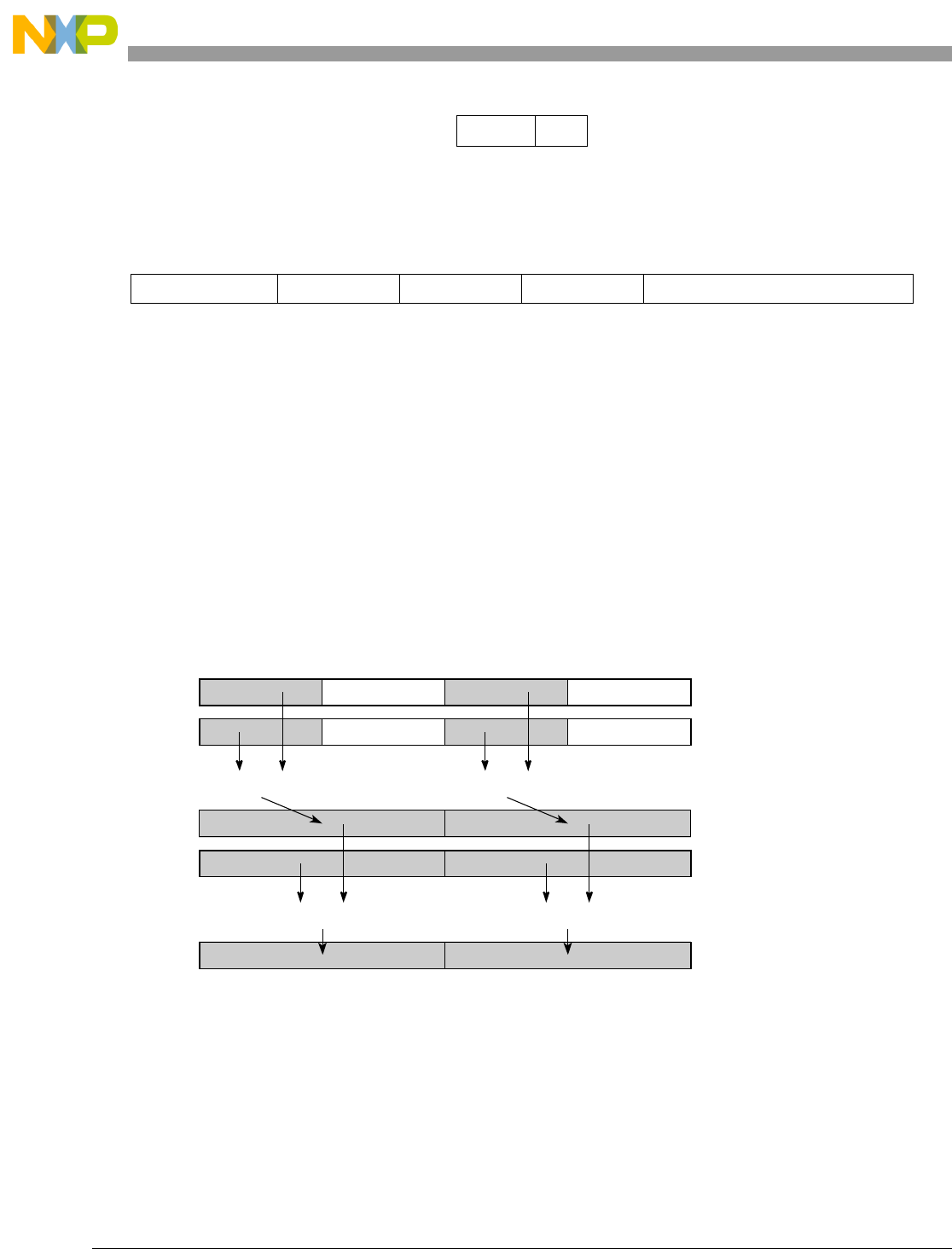

- Figure 5-99. Vector Multiply Word Low Signed, Saturate, Integer and Accumulate in Words (evmwlssiaaw)

- Figure 5-100. Vector Multiply Word Low Signed, Saturate, Integer and Accumulate Negative in Words (evmwlssianw

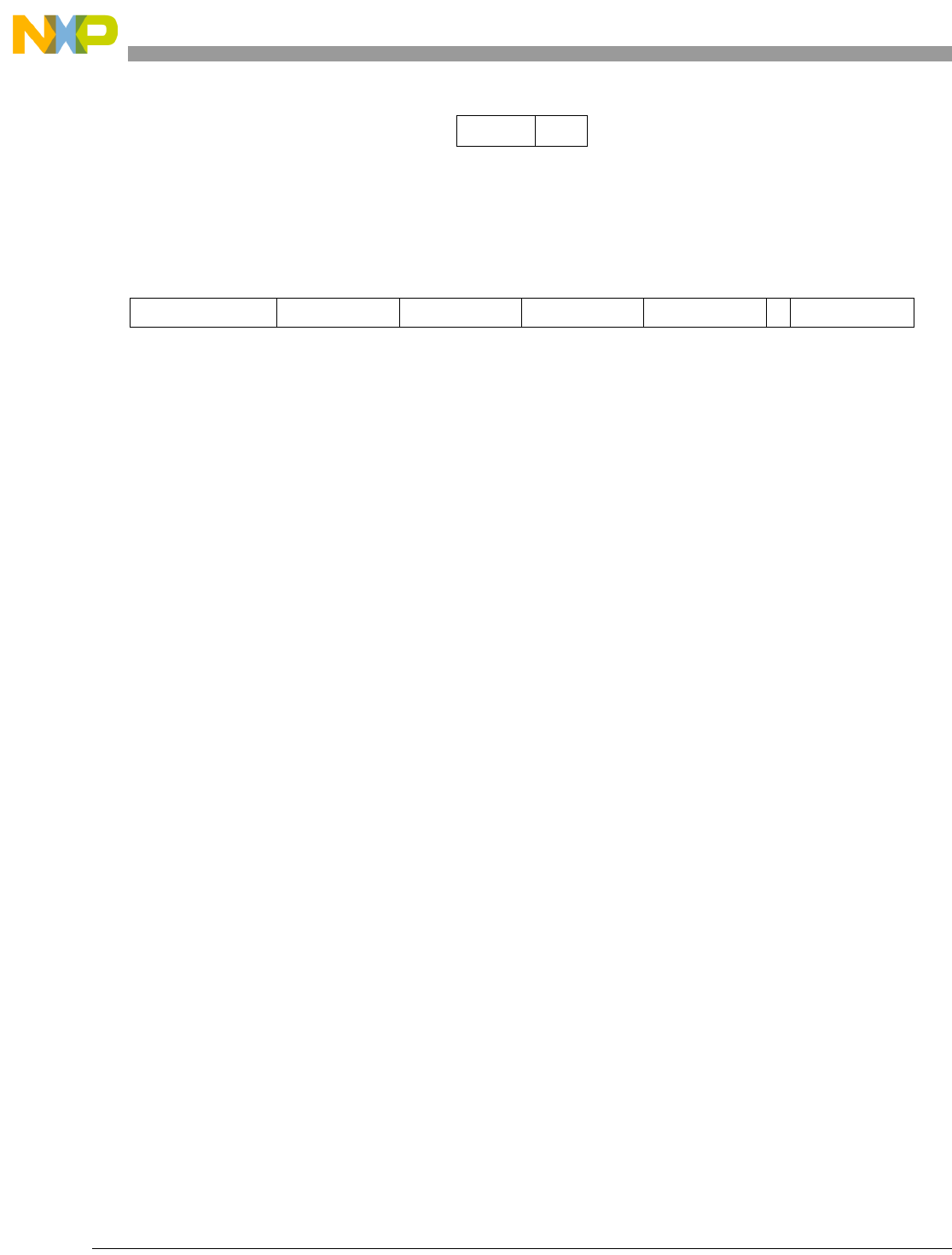

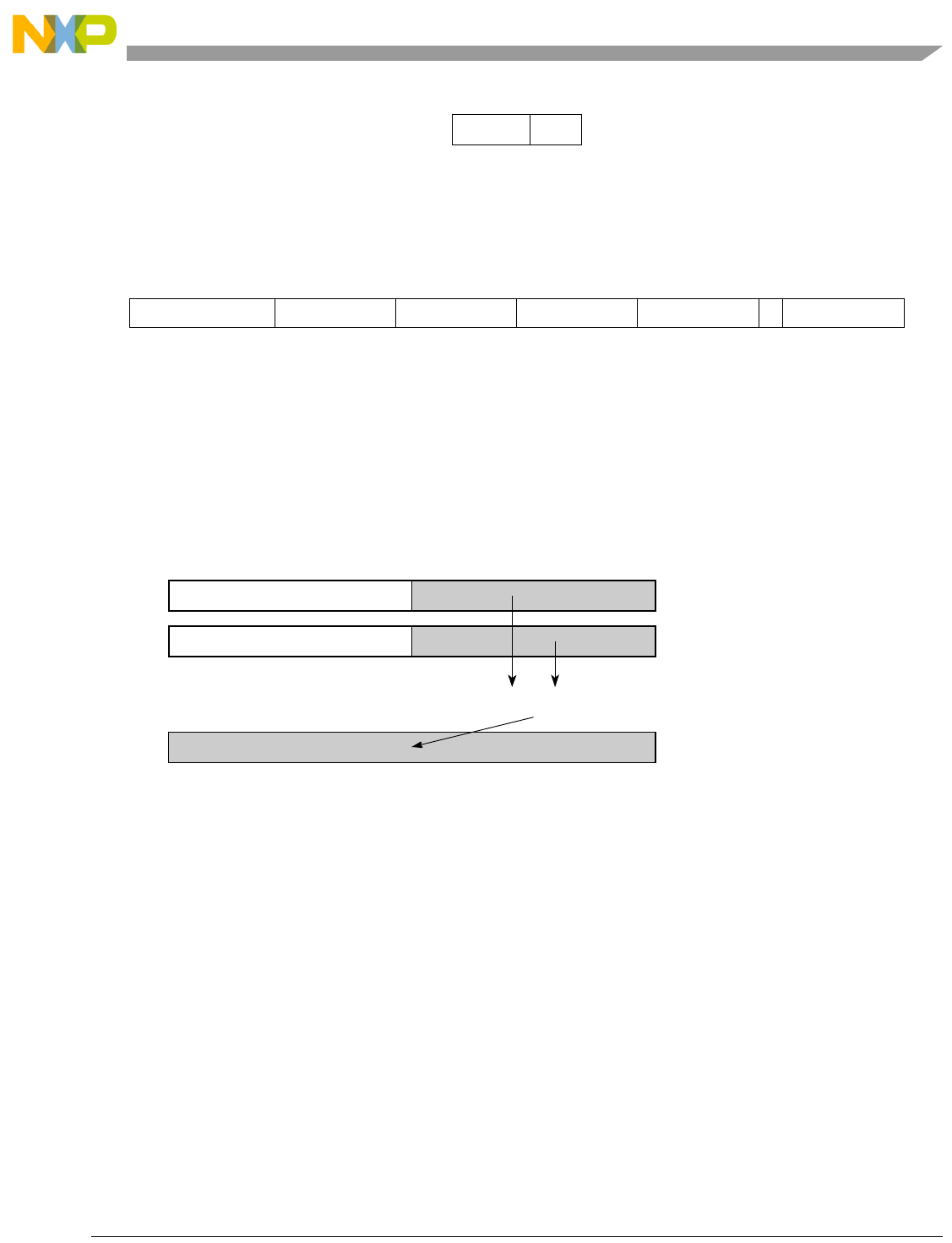

- Figure 5-101. Vector Multiply Word Low Unsigned, Modulo, Integer (evmwlumi)

- Figure 5-102. Vector Multiply Word Low Unsigned, Modulo, Integer and Accumulate in Words (evmwlumiaaw)

- Figure 5-103. Vector Multiply Word Low Unsigned, Modulo, Integer and Accumulate Negative in Words (evmwlumianw)

- Figure 5-104. Vector Multiply Word Low Unsigned, Saturate, Integer and Accumulate in Words (evmwlusiaaw)

- Figure 5-105. Vector Multiply Word Low Unsigned, Saturate, Integer and Accumulate Negative in Words (evmwlusianw)

- Figure 5-106. Vector Multiply Word Signed, Modulo, Fractional (to Accumulator) (evmwsmf)

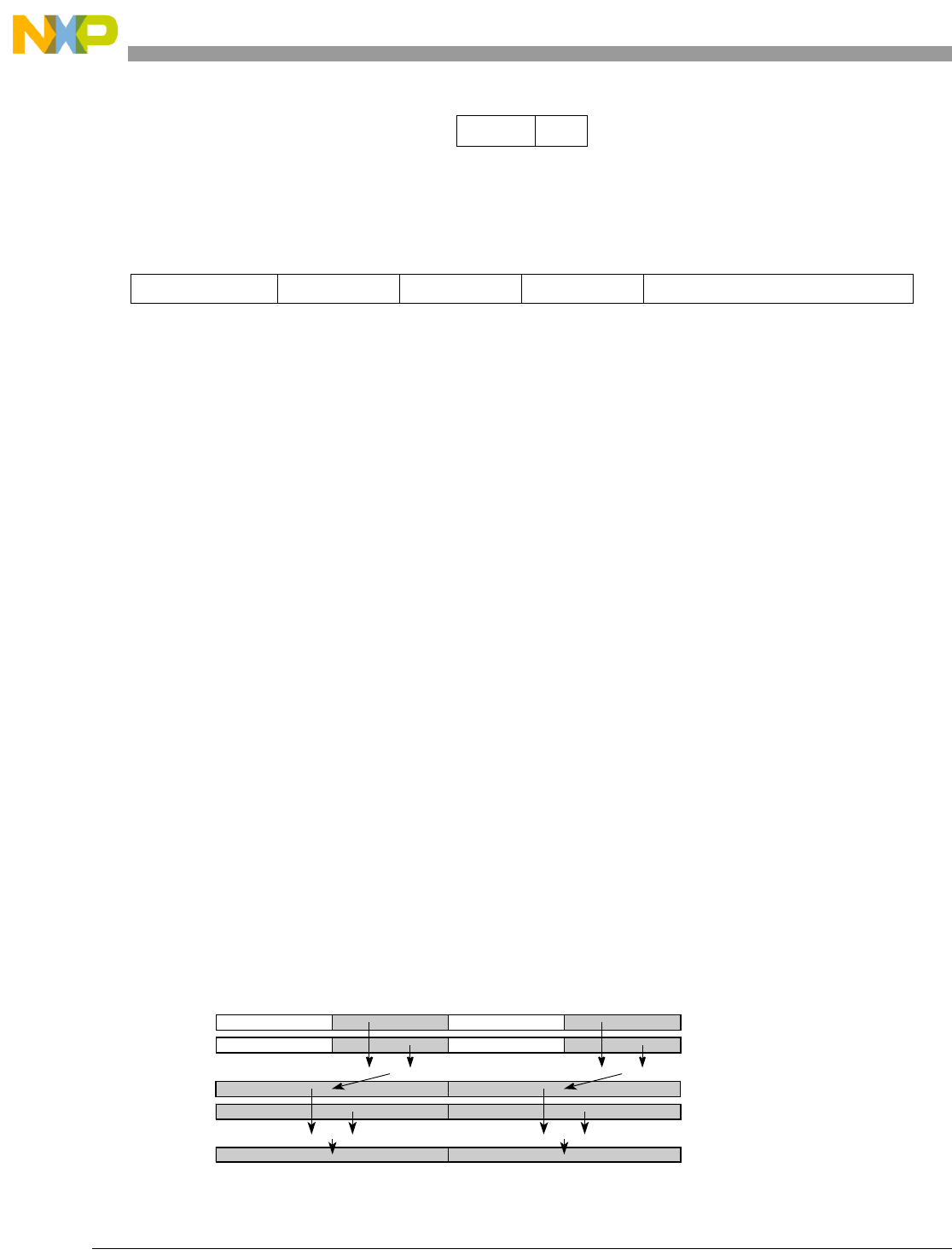

- Figure 5-107. Vector Multiply Word Signed, Modulo, Fractional and Accumulate (evmwsmfaa)

- Figure 5-108. Vector Multiply Word Signed, Modulo, Fractional and Accumulate Negative (evmwsmfan)

- Figure 5-109. Vector Multiply Word Signed, Modulo, Integer (to Accumulator) (evmwsmi)

- Figure 5-110. Vector Multiply Word Signed, Modulo, Integer and Accumulate (evmwsmiaa)

- Figure 5-111. Vector Multiply Word Signed, Modulo, Integer and Accumulate Negative (evmwsmian)

- Figure 5-112. Vector Multiply Word Signed, Saturate, Fractional (to Accumulator) (evmwssf)

- Figure 5-113. Vector Multiply Word Signed, Saturate, Fractional, and Accumulate (evmwssfaa)

- Figure 5-114. Vector Multiply Word Signed, Saturate, Fractional and Accumulate Negative (evmwssfan)

- Figure 5-115. Vector Multiply Word Unsigned, Modulo, Integer (to Accumulator) (evmwumi)

- Figure 5-116. Vector Multiply Word Unsigned, Modulo, Integer and Accumulate (evmwumiaa)

- Figure 5-117. Vector Multiply Word Unsigned, Modulo, Integer and Accumulate Negative (evmwumian)

- Figure 5-118. Vector NAND (evnand)

- Figure 5-119. Vector Negate (evneg)

- Figure 5-120. Vector NOR (evnor)

- Figure 5-121. Vector OR (evor)

- Figure 5-122. Vector OR with Complement (evorc)

- Figure 5-123. Vector Rotate Left Word (evrlw)

- Figure 5-124. Vector Rotate Left Word Immediate (evrlwi)

- Figure 5-125. Vector Round Word (evrndw)

- Figure 5-126. Vector Select (evsel)

- Figure 5-127. Vector Shift Left Word (evslw)

- Figure 5-128. Vector Shift Left Word Immediate (evslwi)

- Figure 5-129. Vector Splat Fractional Immediate (evsplatfi)

- Figure 5-130. evsplati Sign Extend

- Figure 5-131. Vector Shift Right Word Immediate Signed (evsrwis)

- Figure 5-132. Vector Shift Right Word Immediate Unsigned (evsrwiu)

- Figure 5-133. Vector Shift Right Word Signed (evsrws)

- Figure 5-134. Vector Shift Right Word Unsigned (evsrwu)

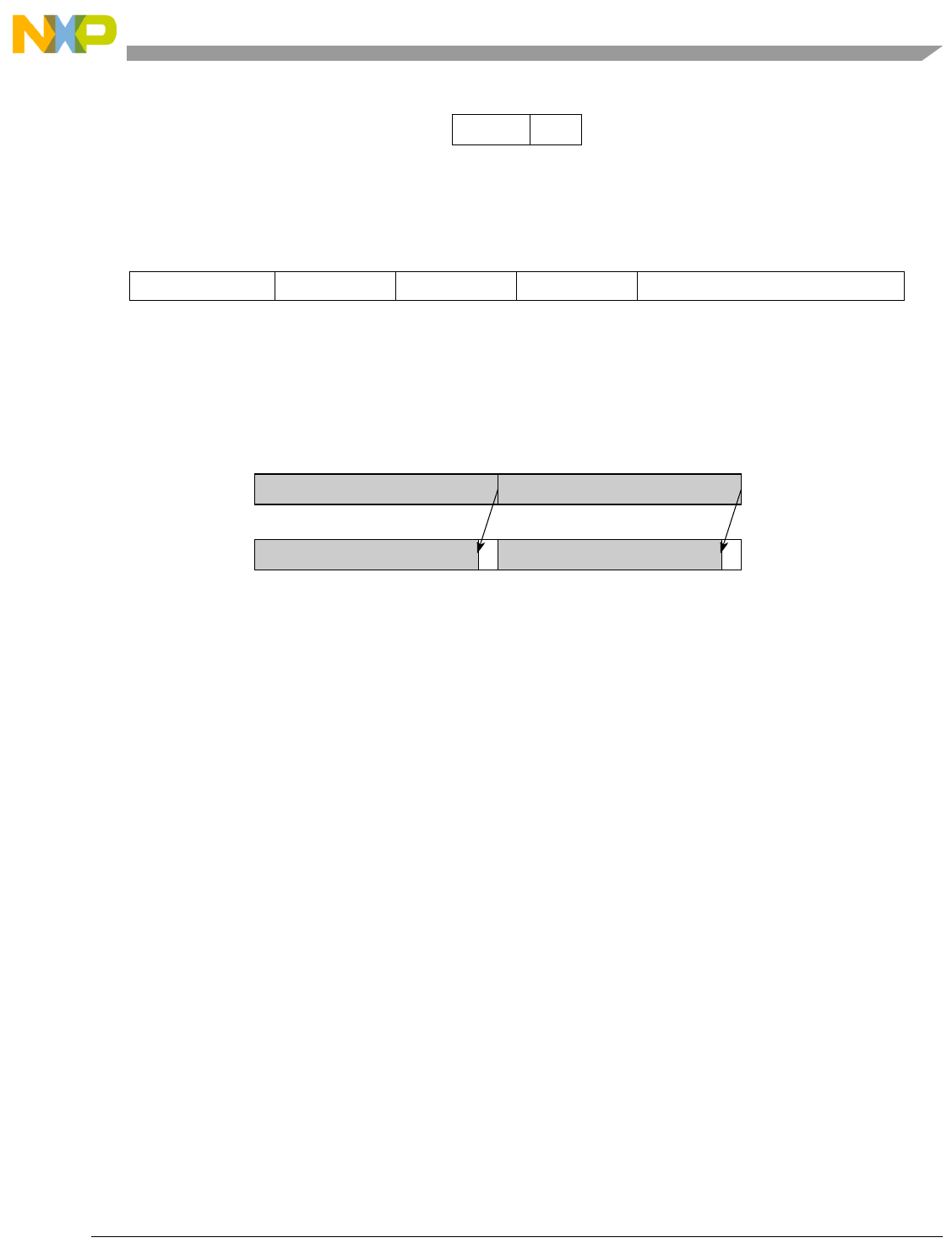

- Figure 5-135. evstdd Results in Big- and Little-Endian Modes

- Figure 5-136. evstddx Results in Big- and Little-Endian Modes

- Figure 5-137. evstdh Results in Big- and Little-Endian Modes

- Figure 5-138. evstdhx Results in Big- and Little-Endian Modes

- Figure 5-139. evstdw Results in Big- and Little-Endian Modes

- Figure 5-140. evstdwx Results in Big- and Little-Endian Modes

- Figure 5-141. evstwhe Results in Big- and Little-Endian Modes

- Figure 5-142. evstwhex Results in Big- and Little-Endian Modes

- Figure 5-143. evstwho Results in Big- and Little-Endian Modes

- Figure 5-144. evstwhox Results in Big- and Little-Endian Modes

- Figure 5-145. evstwwe Results in Big- and Little-Endian Modes

- Figure 5-146. evstwwex Results in Big- and Little-Endian Modes

- Figure 5-147. evstwwo Results in Big- and Little-Endian Modes

- Figure 5-148. evstwwox Results in Big- and Little-Endian Modes

- Figure 5-149. Vector Subtract Signed, Modulo, Integer to Accumulator Word (evsubfsmiaaw)

- Figure 5-150. Vector Subtract Signed, Saturate, Integer to Accumulator Word (evsubfssiaaw)

- Figure 5-151. Vector Subtract Unsigned, Modulo, Integer to Accumulator Word (evsubfumiaaw)

- Figure 5-152. Vector Subtract Unsigned, Saturate, Integer to Accumulator Word (evsubfusiaaw)

- Figure 5-153. Vector Subtract from Word (evsubfw)

- Figure 5-154. Vector Subtract Immediate from Word (evsubifw)

- Figure 5-155. Vector XOR (evxor)

- Appendix A Embedded Floating-Point Results Summary

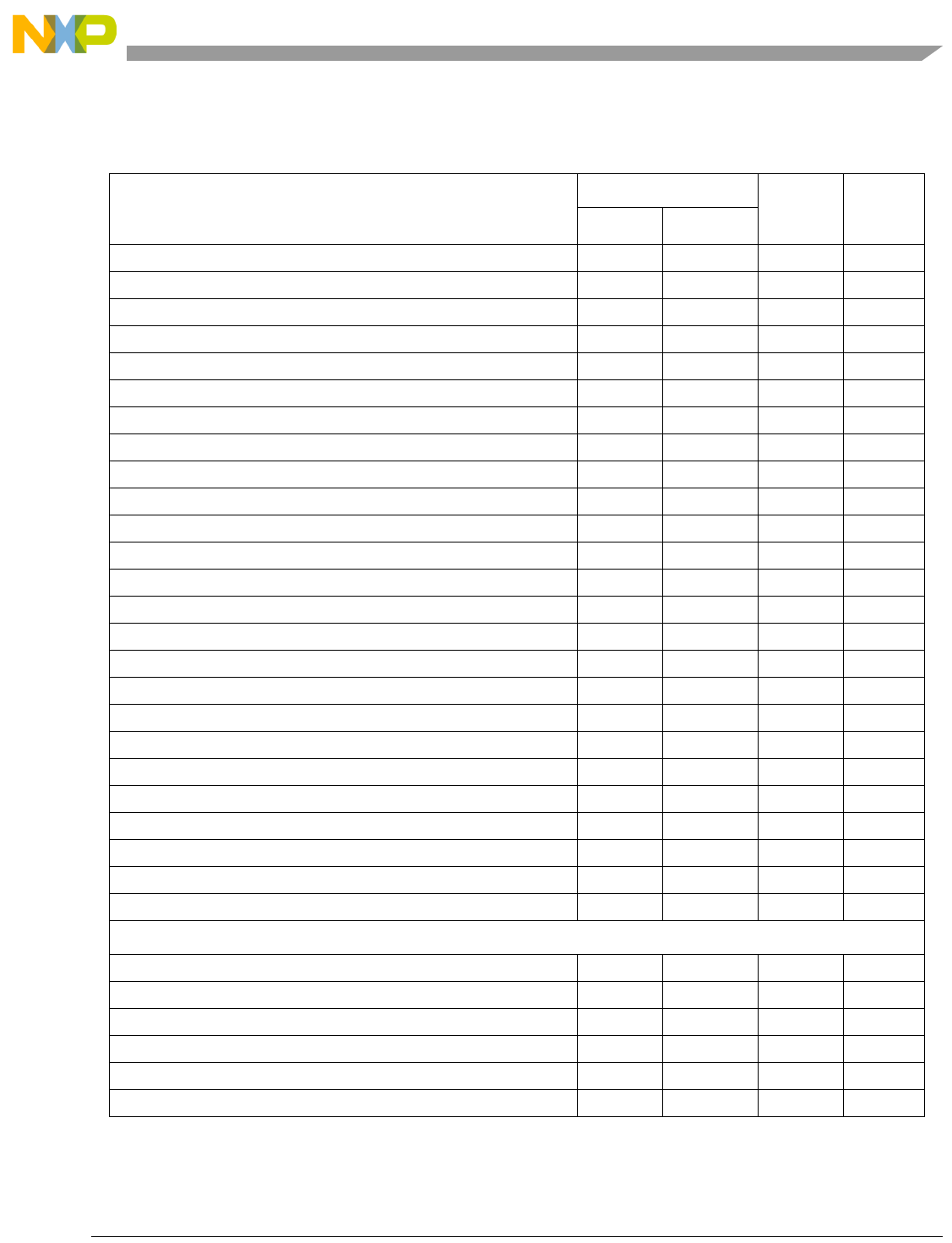

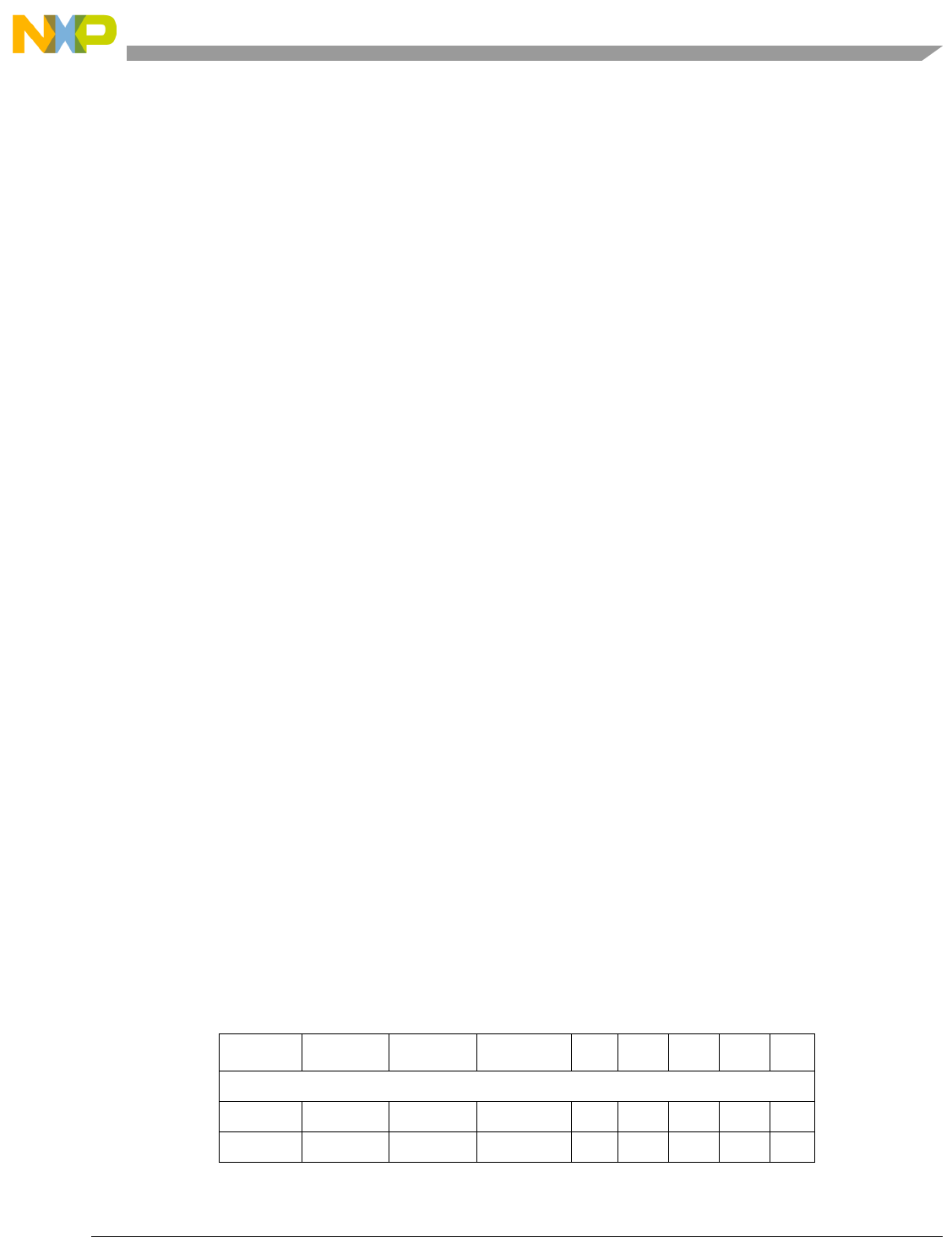

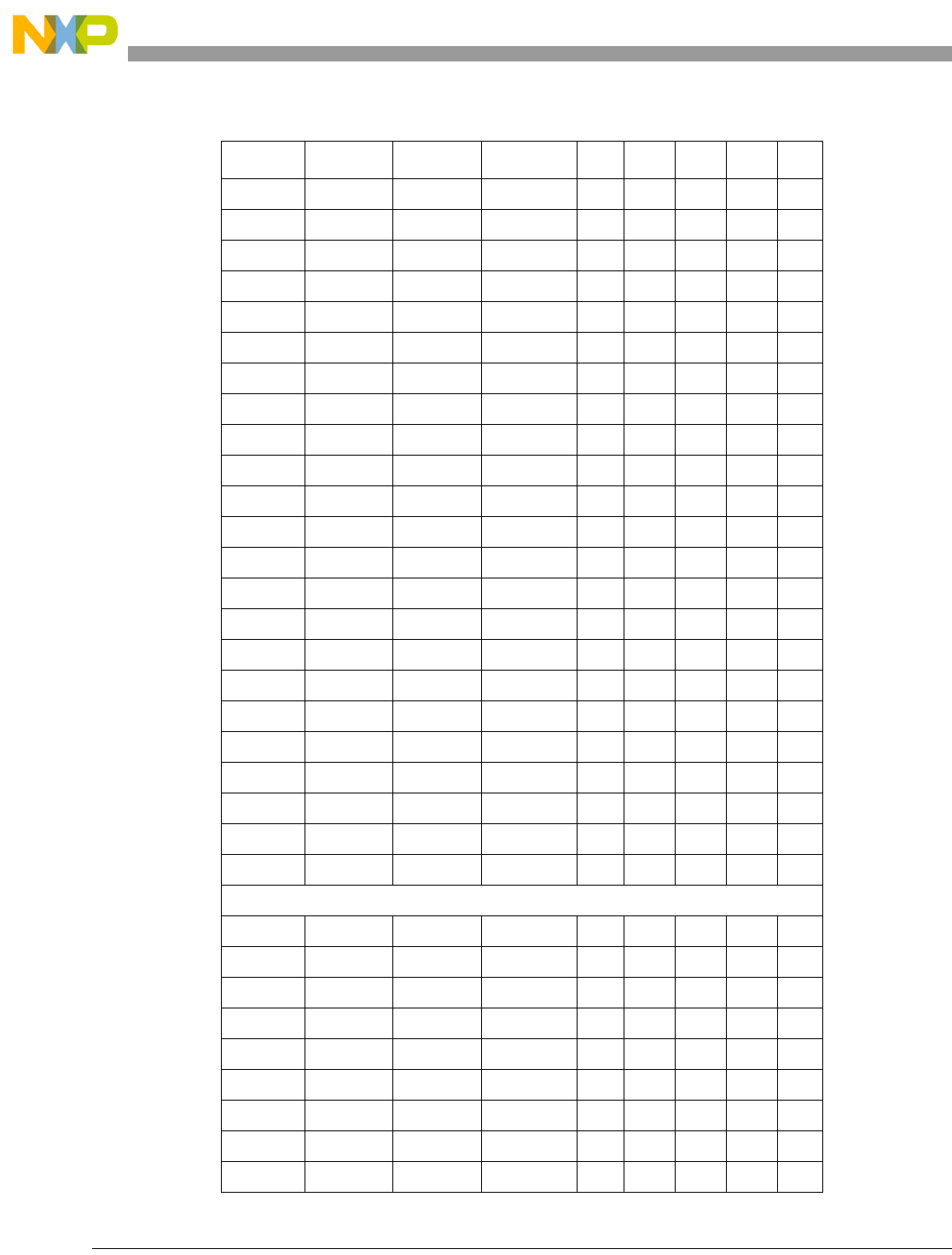

- Table A-1. Embedded Floating-Point Results Summary-Add, Sub, Mul, Div

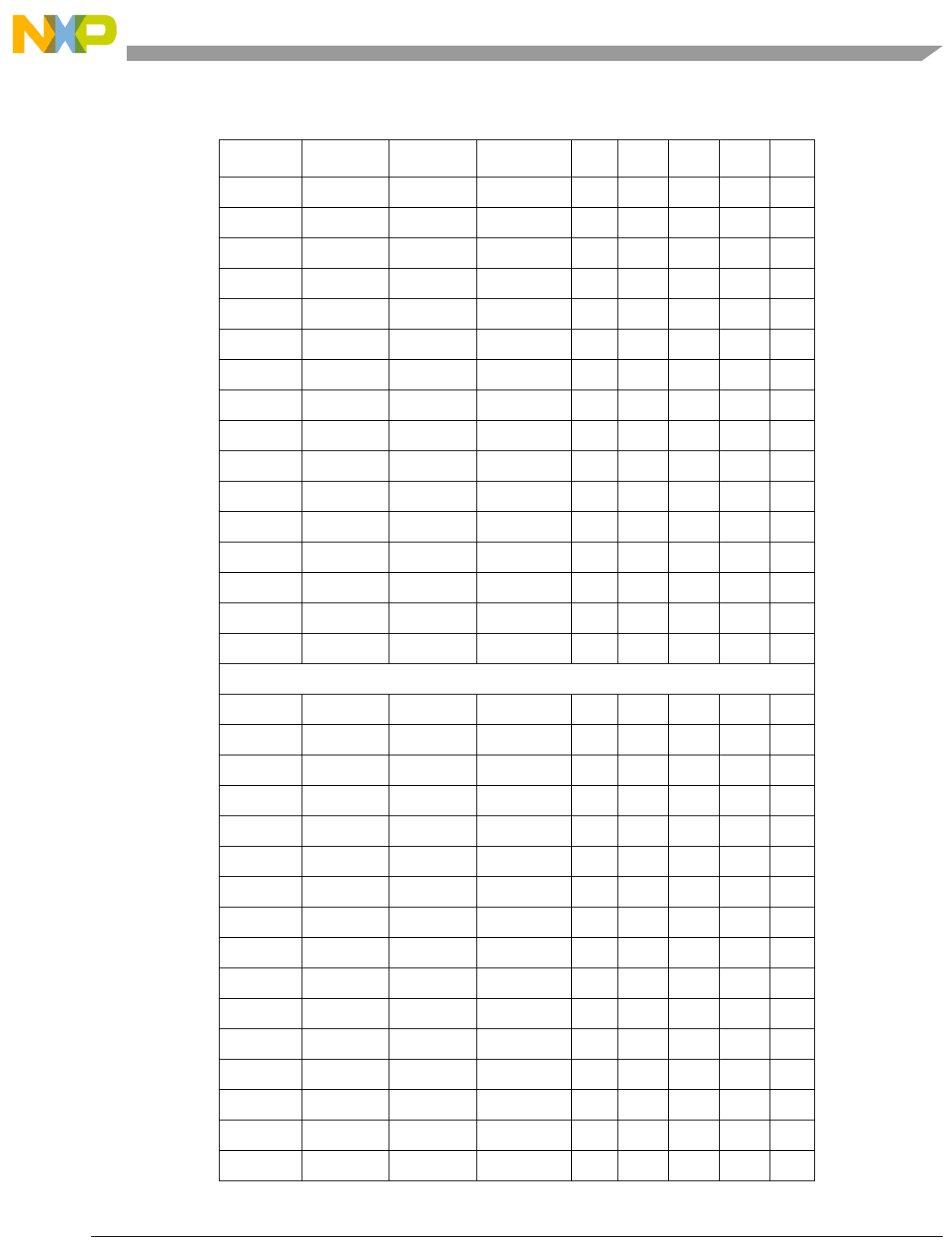

- Table A-2. Embedded Floating-Point Results Summary-Single Convert from Double

- Table A-3. Embedded Floating-Point Results Summary-Double Convert from Single

- Table A-4. Embedded Floating-Point Results Summary-Convert to Unsigned

- Table A-5. Embedded Floating-Point Results Summary-Convert to Signed

- Table A-6. Results Summary-Convert from Unsigned

- Table A-7. Embedded Floating-Point Results Summary-Convert from Signed

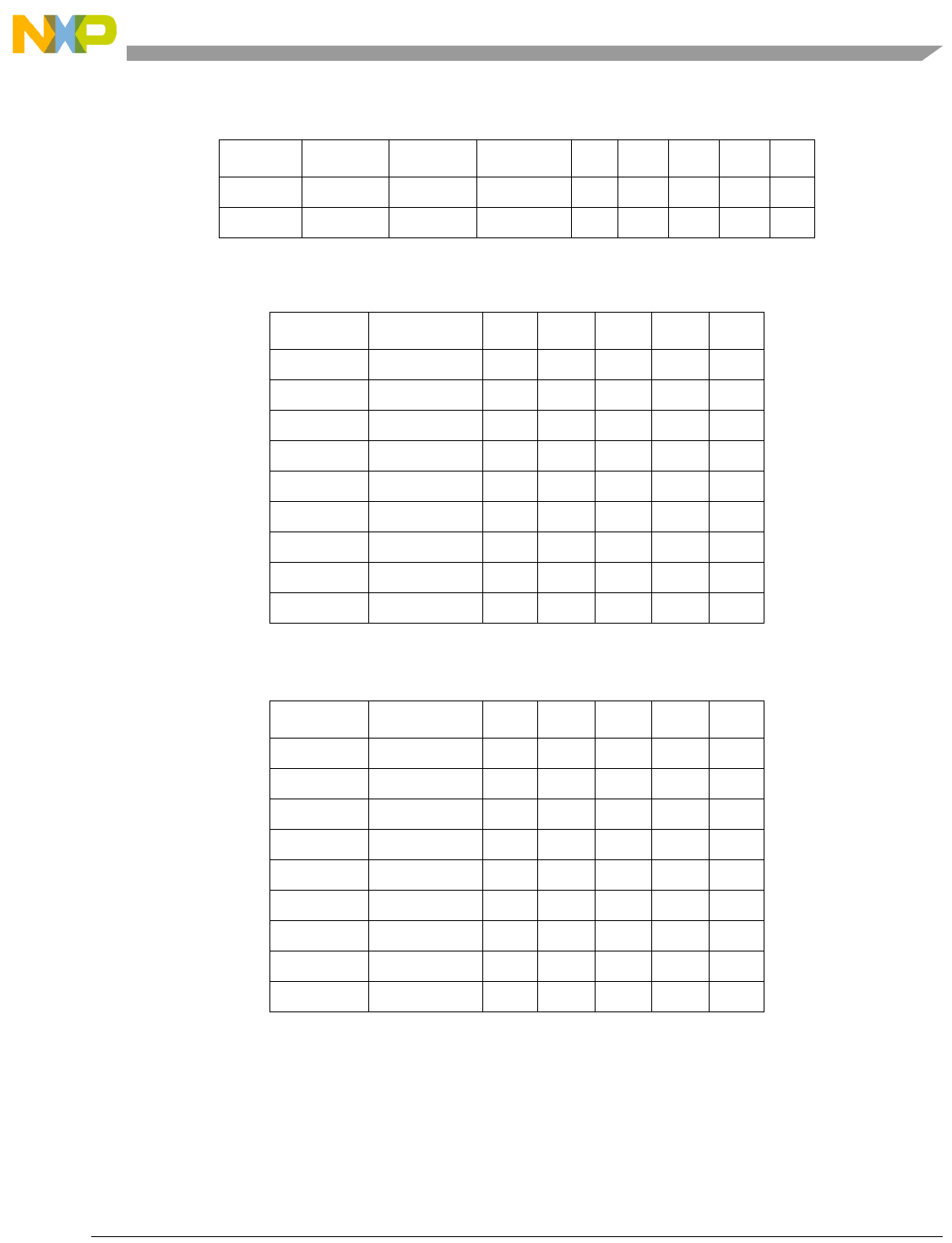

- Table A-8. Embedded Floating-Point Results Summary-*abs, *nabs, *neg

- Appendix B SPE and Embedded Floating-Point Opcode Listings

Signal Processing Engine (SPE)

Programming Environments Manual:

A Supplement to the EREF

SPEPEM

Rev. 0

01/2008

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc.

The Power Architecture and Power.org word marks and the Power and Power.org logos

and related marks are trademarks and service marks licensed by Power.org. The

PowerPC name is a trademark of IBM Corp. and is used under license. IEEE 754 is a

registered trademark of the Institute of Electrical and Electronics Engineers, Inc.

(IEEE). This product is not endorsed or approved by the IEEE. All other product or

service names are the property of their respective owners.

© Freescale Semiconductor, Inc., 2008. Printed in the United States of

America. All rights reserved.

Information in this document is provided solely to enable system and software

implementers to use Freescale Semiconductor products. There are no express or

implied copyright licenses granted hereunder to design or fabricate any integrated

circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to

any products herein. Freescale Semiconductor makes no warranty, representation or

guarantee regarding the suitability of its products for any particular purpose, nor does

Freescale Semiconductor assume any liability arising out of the application or use of

any product or circuit, and specifically disclaims any and all liability, including without

limitation consequential or incidental damages. “Typical” parameters which may be

provided in Freescale Semiconductor data sheets and/or specifications can and do

vary in different applications and actual performance may vary over time. All operating

parameters, including “Typicals” must be validated for each customer application by

customer’s technical experts. Freescale Semiconductor does not convey any license

under its patent rights nor the rights of others. Freescale Semiconductor products are

not designed, intended, or authorized for use as components in systems intended for

surgical implant into the body, or other applications intended to support or sustain life,

or for any other application in which the failure of the Freescale Semiconductor product

could create a situation where personal injury or death may occur. Should Buyer

purchase or use Freescale Semiconductor products for any such unintended or

unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor

and its officers, employees, subsidiaries, affiliates, and distributors harmless against all

claims, costs, damages, and expenses, and reasonable attorney fees arising out of,

directly or indirectly, any claim of personal injury or death associated with such

unintended or unauthorized use, even if such claim alleges that Freescale

Semiconductor was negligent regarding the design or manufacture of the part.

Document Number: SPEPEM

Rev. 0, 01/2008

How to Reach Us:

Home Page:

www.freescale.com

Web Support:

http://www.freescale.com/support

USA/Europe or Locations Not Listed:

Freescale Semiconductor, Inc.

Technical Information Center, EL516

2100 East Elliot Road

Tempe, Arizona 85284

+1-800-521-6274 or

+1-480-768-2130

www.freescale.com/support

Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH

Technical Information Center

Schatzbogen 7

81829 Muenchen, Germany

+44 1296 380 456 (English)

+46 8 52200080 (English)

+49 89 92103 559 (German)

+33 1 69 35 48 48 (French)

www.freescale.com/support

Japan:

Freescale Semiconductor Japan Ltd.

Headquarters

ARCO Tower 15F

1-8-1, Shimo-Meguro, Meguro-ku

Tokyo 153-0064

Japan

0120 191014 or

+81 3 5437 9125

support.japan@freescale.com

Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd.

Technical Information Center

2 Dai King Street

Tai Po Industrial Estate

Tai Po, N.T., Hong Kong

+800 2666 8080

support.asia@freescale.com

For Literature Requests Only:

Freescale Semiconductor

Literature Distribution Center

P.O. Box 5405

Denver, Colorado 80217

+1-800 441-2447 or

+1-303-675-2140

Fax: +1-303-675-2150

LDCForFreescaleSemiconductor

@hibbertgroup.com

Signal Processing Engine (SPE) Programming Environments Manual, Rev. 0

Freescale Semiconductor iii

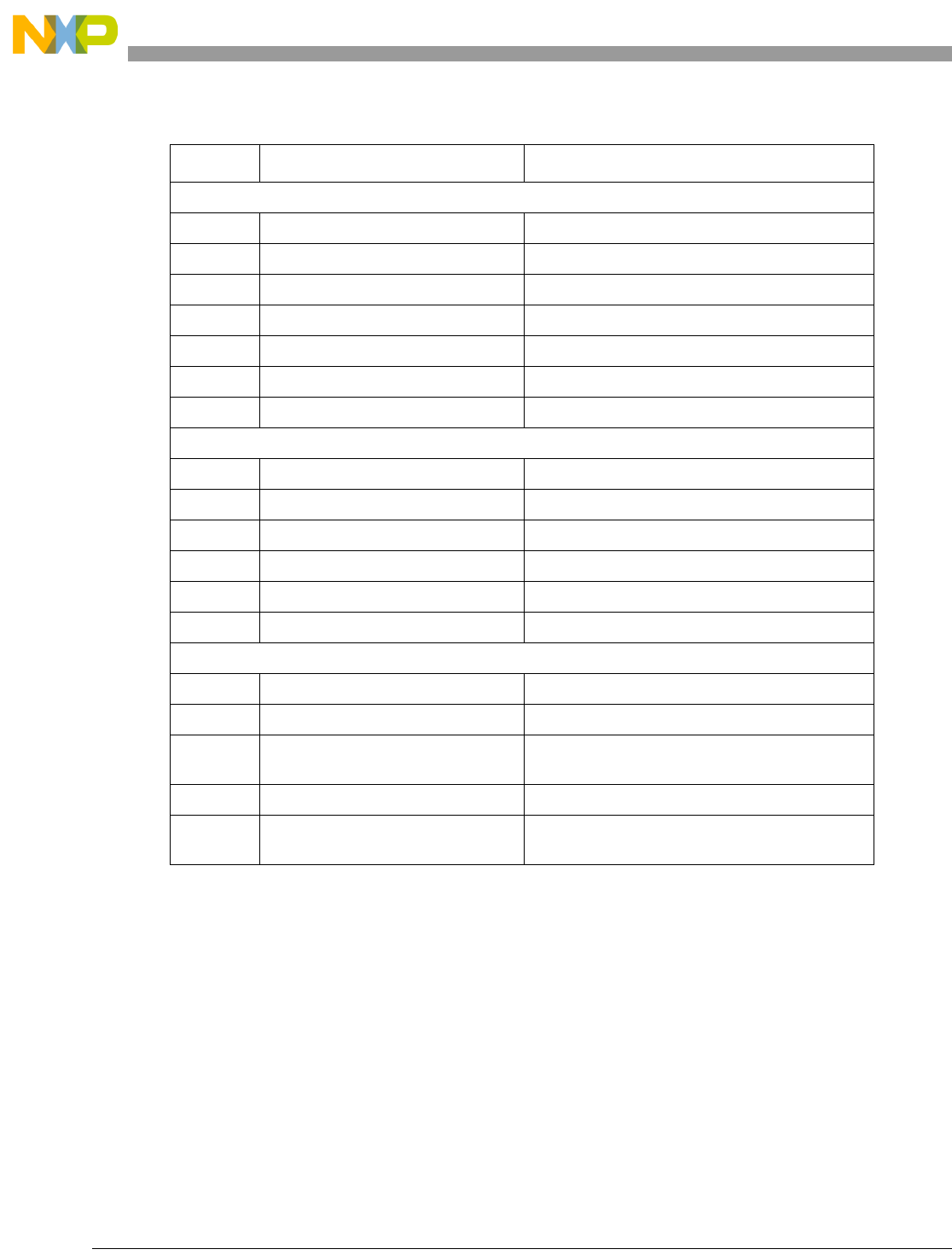

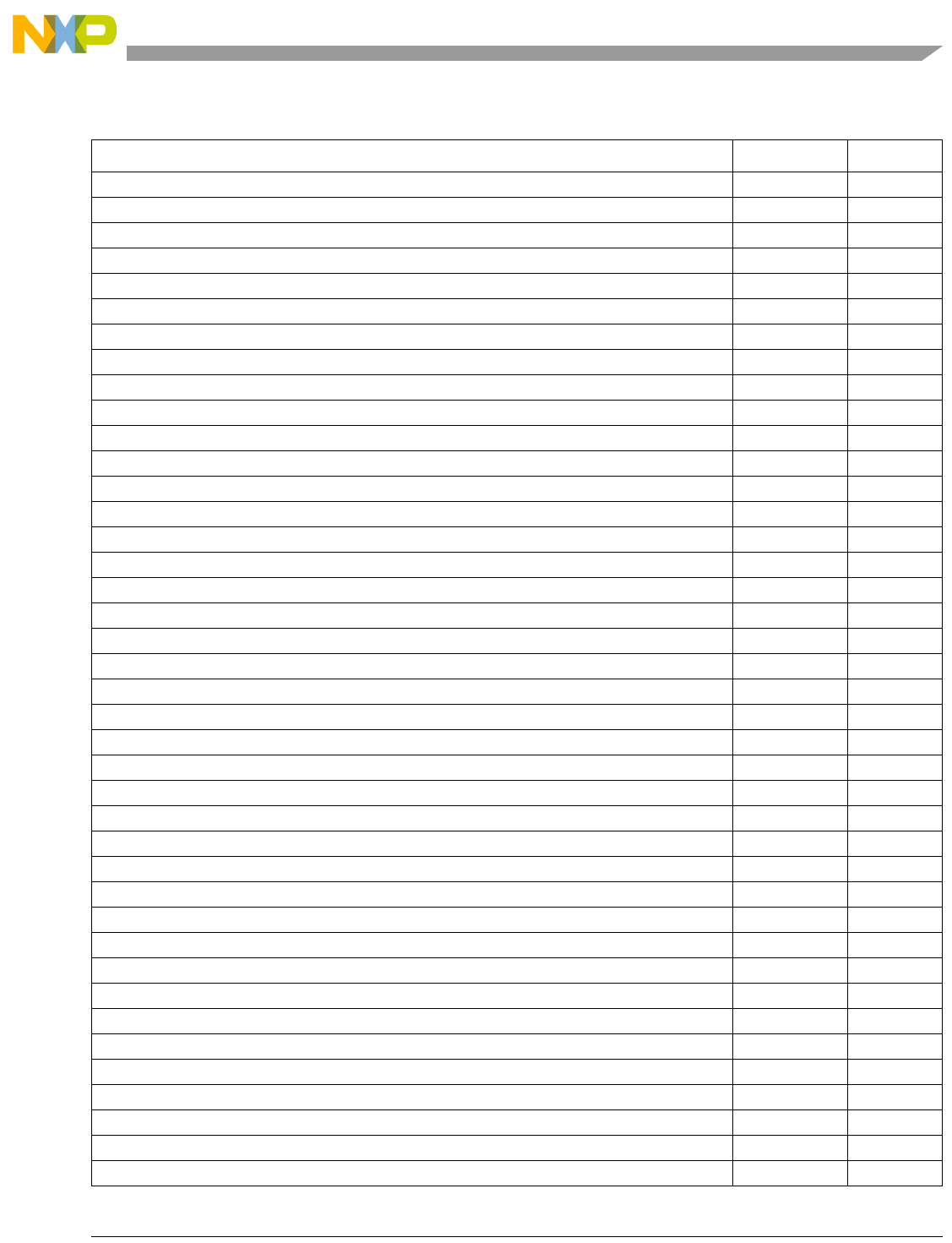

Contents

Paragraph

Number Title

Page

Number

Co nt en t s

About This Book

Chapter 1

Overview

1.1 Overview.......................................................................................................................... 1-1

1.2 Register Model................................................................................................................. 1-2

1.2.1 SPE Instructions...........................................................................................................1-3

1.2.1.1 Embedded Vector and Scalar Floating-Point Instructions....................................... 1-6

1.3 SPE and Embedded Floating-Point Exceptions and Interrupts ....................................... 1-6

Chapter 2

SPE Register Model

2.1 Overview.......................................................................................................................... 2-1

2.2 Register Model................................................................................................................. 2-1

2.2.1 General-Purpose Registers (GPRs).............................................................................. 2-3

2.2.2 Accumulator Register (ACC) ...................................................................................... 2-4

2.2.3 Signal Processing Embedded Floating-Point Status and

Control Register (SPEFSCR) .................................................................................. 2-5

2.2.3.1 Interrupt Vector Offset Registers (IVORs) .............................................................. 2-8

2.2.3.2 Exception Bit in the Exception Syndrome Register (ESR) ..................................... 2-8

2.2.3.3 Condition Register (CR).......................................................................................... 2-8

2.2.3.4 SPE Available Bit in the Machine State Register (MSR)........................................ 2-9

Chapter 3

SPE and Embedded Floating-Point Instruction Model

3.1 Overview.......................................................................................................................... 3-1

3.2 SPE Instruction Set ..........................................................................................................3-1

3.2.1 SPE Data Formats........................................................................................................ 3-2

3.2.1.1 Integer Format ......................................................................................................... 3-2

3.2.1.2 Fractional Format..................................................................................................... 3-2

3.2.2 Computational Operations ........................................................................................... 3-2

3.2.2.1 Data Formats and Register Usage............................................................................ 3-4

3.2.2.1.1 Signed Fractions .................................................................................................. 3-4

3.2.2.1.2 SPE Integer and Fractional Operations ............................................................... 3-4

3.2.2.1.3 SPE Instructions .................................................................................................. 3-5

3.2.3 SPE Simplified Mnemonics....................................................................................... 3-11

3.3 Embedded Floating-Point Instruction Set...................................................................... 3-11

3.3.1 Embedded Floating-Point Operations........................................................................ 3-12

Signal Processing Engine (SPE) Programming Environments Manual, Rev. 0

iv Freescale Semiconductor

Contents

Paragraph

Number Title

Page

Number

3.3.1.1 Operational Modes................................................................................................. 3-12

3.3.1.2 Floating-Point Data Formats.................................................................................. 3-12

3.3.1.3 Overflow and Underflow....................................................................................... 3-13

3.3.1.4 IEEE Std 754™ Compliance ................................................................................. 3-14

3.3.1.5 Sticky Bit Handling for Exception Conditions...................................................... 3-15

3.3.1.6 Implementation Options Summary........................................................................ 3-15

3.3.1.7 Saturation, Shift, and Bit Reverse Models............................................................. 3-15

3.3.1.7.1 Saturation........................................................................................................... 3-16

3.3.1.7.2 Shift Left............................................................................................................ 3-16

3.3.1.7.3 Bit Reverse ........................................................................................................ 3-16

3.3.2 Embedded Vector and Scalar Floating-Point Instructions......................................... 3-16

3.3.3 Load/Store Instructions.............................................................................................. 3-18

3.3.3.1 Floating-Point Conversion Models........................................................................ 3-18

Chapter 4

SPE/Embedded Floating-Point Interrupt Model

4.1 Overview.......................................................................................................................... 4-1

4.2 SPE Interrupts .................................................................................................................. 4-1

4.2.1 Interrupt-Related Registers.......................................................................................... 4-1

4.2.2 Alignment Interrupt ..................................................................................................... 4-2

4.2.3 SPE/Embedded Floating-Point Unavailable Interrupt................................................. 4-2

4.2.4 SPE Embedded Floating-Point Interrupts.................................................................... 4-3

4.2.4.1 Embedded Floating-Point Data Interrupt................................................................. 4-3

4.2.4.2 Embedded Floating-Point Round Interrupt ............................................................. 4-3

4.3 Interrupt Priorities............................................................................................................ 4-4

4.4 Exception Conditions....................................................................................................... 4-4

4.4.1 Floating-Point Exception Conditions .......................................................................... 4-5

4.4.1.1 Denormalized Values on Input................................................................................. 4-5

4.4.1.2 Embedded Floating-Point Overflow and Underflow............................................... 4-5

4.4.1.3 Embedded Floating-Point Invalid Operation/Input Errors ...................................... 4-5

4.4.1.4 Embedded Floating-Point Round (Inexact)............................................................. 4-6

4.4.1.5 Embedded Floating-Point Divide by Zero............................................................... 4-6

4.4.1.6 Default Results......................................................................................................... 4-6

Chapter 5

Instruction Set

5.1 Notation ........................................................................................................................... 5-1

5.2 Instruction Fields ............................................................................................................. 5-2

5.3 Description of Instruction Operations.............................................................................. 5-2

Signal Processing Engine (SPE) Programming Environments Manual, Rev. 0

Freescale Semiconductor v

Contents

Paragraph

Number Title

Page

Number

5.3.1 SPE Saturation and Bit-Reverse Models ..................................................................... 5-4

5.3.1.1 Saturation................................................................................................................. 5-4

5.3.1.2 Bit Reverse............................................................................................................... 5-5

5.3.2 Embedded Floating-Point Conversion Models............................................................ 5-5

5.3.2.1 Common Embedded Floating-Point Functions ....................................................... 5-6

5.3.2.1.1 32-Bit NaN or Infinity Test.................................................................................. 5-6

5.3.2.1.2 Signal Floating-Point Error ................................................................................. 5-6

5.3.2.1.3 Round a 32-Bit Value .......................................................................................... 5-6

5.3.2.1.4 Round a 64-Bit Value .......................................................................................... 5-7

5.3.2.2 Convert from Single-Precision Floating-Point to Integer Word with Saturation .... 5-7

5.3.2.3 Convert from Double-Precision Floating-Point to Integer Word with Saturation... 5-9

5.3.2.4 Convert from Double-Precision Floating-Point to Integer Double

Word with Saturation......................................................................................... 5-10

5.3.2.5 Convert to Single-Precision Floating-Point from Integer Word with Saturation .. 5-11

5.3.2.6 Convert to Double-Precision Floating-Point from Integer Word with Saturation. 5-12

5.3.2.7 Convert to Double-Precision Floating-Point from Integer Double

Word with Saturation......................................................................................... 5-13

5.3.3 Integer Saturation Models.......................................................................................... 5-14

5.3.4 Embedded Floating-Point Results ............................................................................. 5-14

5.4 Instruction Set ................................................................................................................ 5-15

Appendix A

Embedded Floating-Point Results Summary

Appendix B

SPE and Embedded Floating-Point Opcode Listings

B.1 Instructions (Binary) by Mnemonic.................................................................................B-1

B.2 Instructions (Decimal and Hexadecimal) by Opcode ......................................................B-9

B.3 Instructions by Form......................................................................................................B-16

Signal Processing Engine (SPE) Programming Environments Manual, Rev. 0

vi Freescale Semiconductor

Contents

Paragraph

Number Title

Page

Number

Signal Processing Engine (SPE) Programming Environments Manual, Rev. 0

Freescale Semiconductor vii

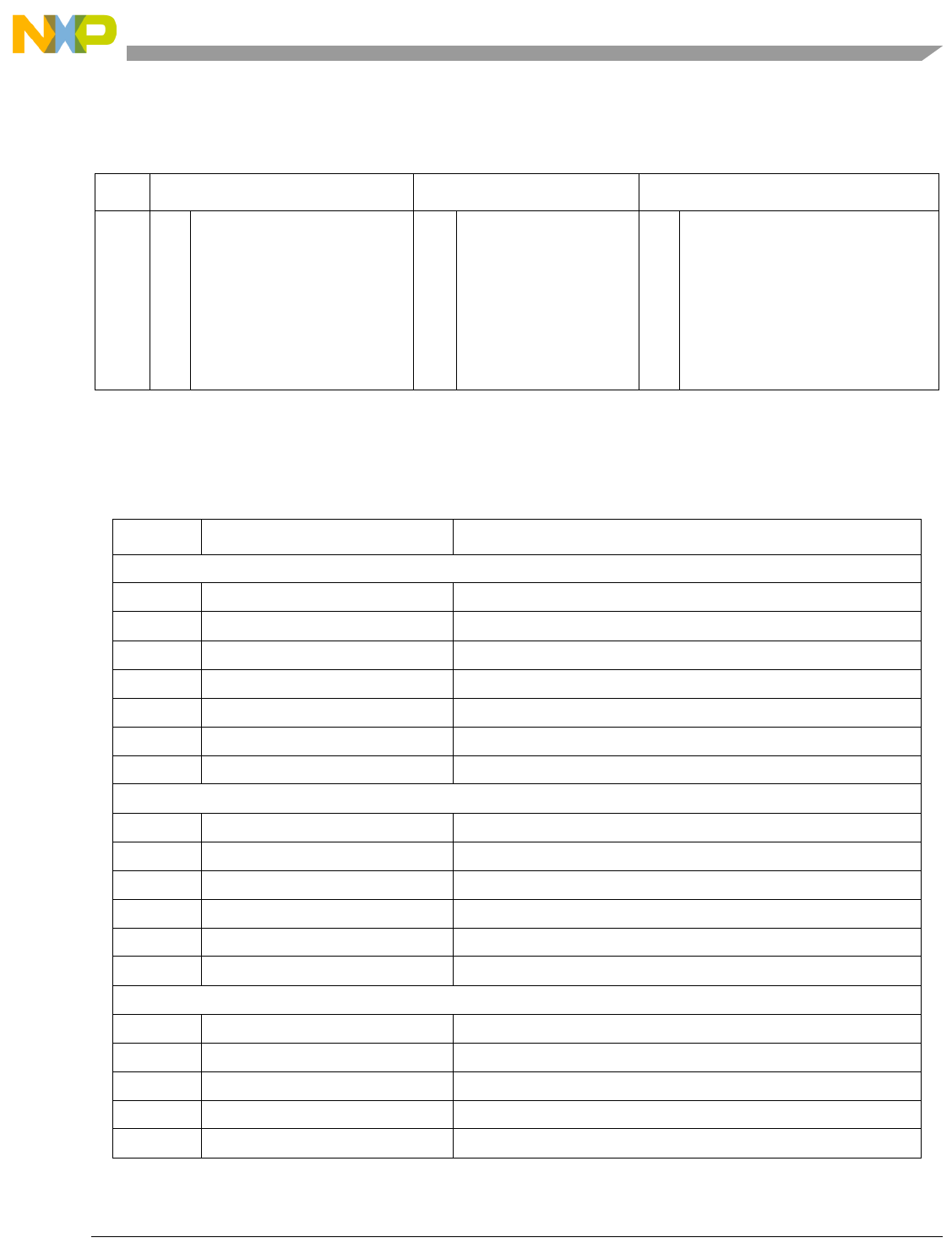

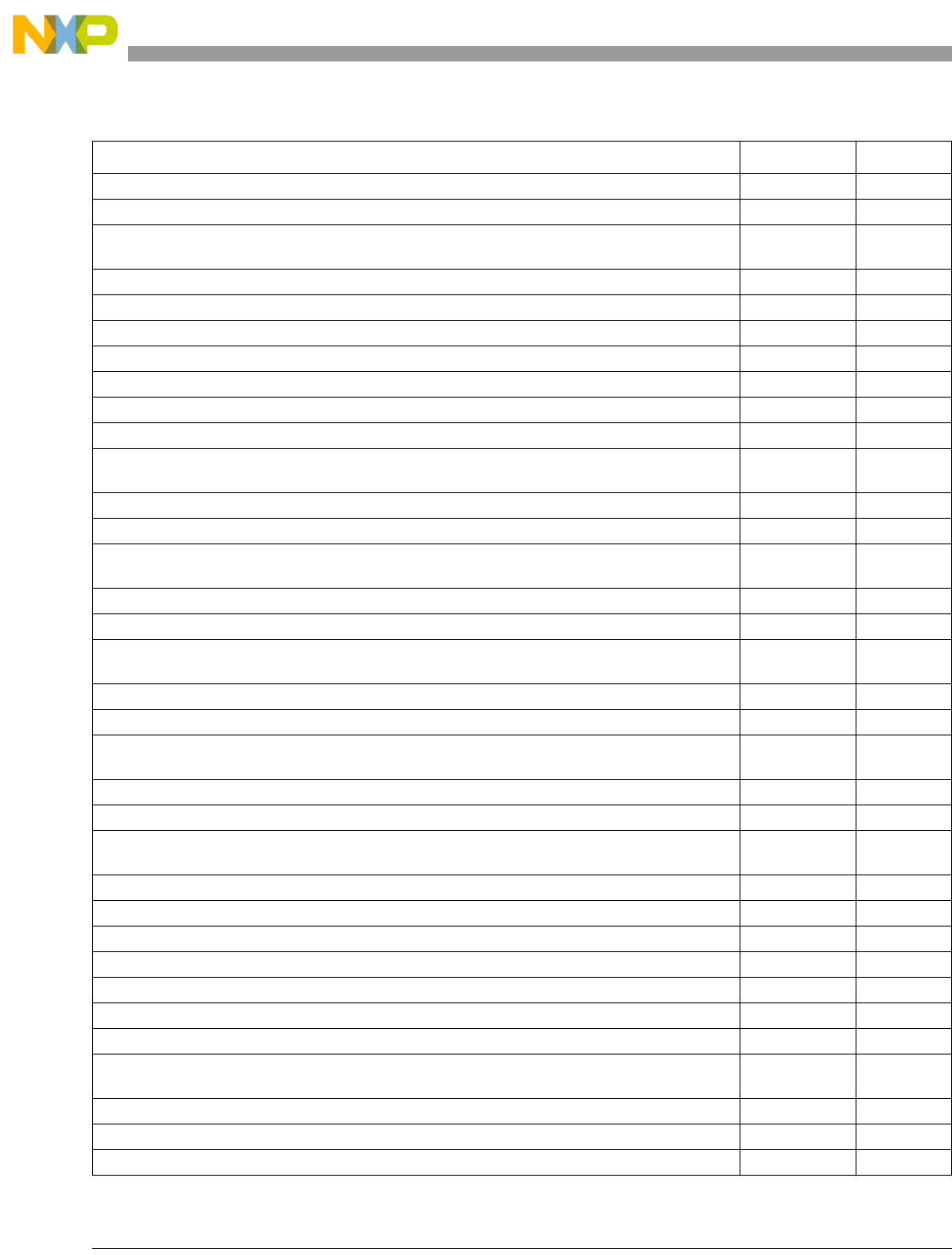

Figures

Figure

Number Title

Page

Number

Figures

1-1 SPE Register Model ................................................................................................................ 1-2

1-2 Two-Element Vector Operations ............................................................................................. 1-3

2-1 SPE Register Model ................................................................................................................ 2-1

2-2 Integer, Fractional, and Floating-Point Data Formats and GPR Usage.................................. 2-2

2-3 32- and 64-Bit Register Elements and Bit-Numbering Conventions...................................... 2-3

2-4 General Purpose Registers (GPR0–GRP31) ........................................................................... 2-4

2-5 Accumulator (ACC)................................................................................................................ 2-4

2-6 Signal Processing and Embedded Floating-Point Status and Control

Register (SPEFSCR) .......................................................................................................... 2-5

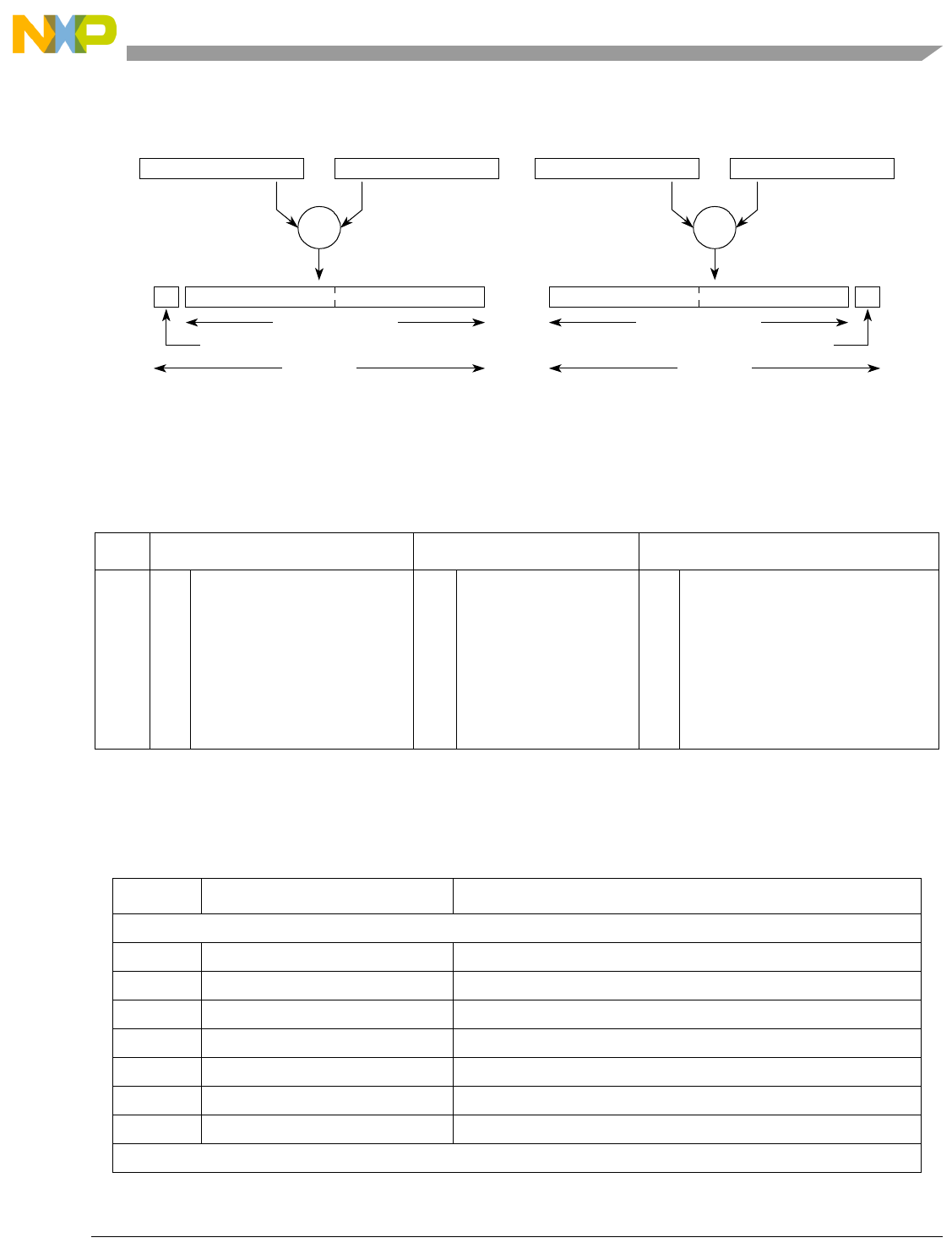

3-1 Two-Element Vector Operations ............................................................................................. 3-3

3-2 Integer and Fractional Operations........................................................................................... 3-5

3-3 Floating-Point Data Format .................................................................................................. 3-12

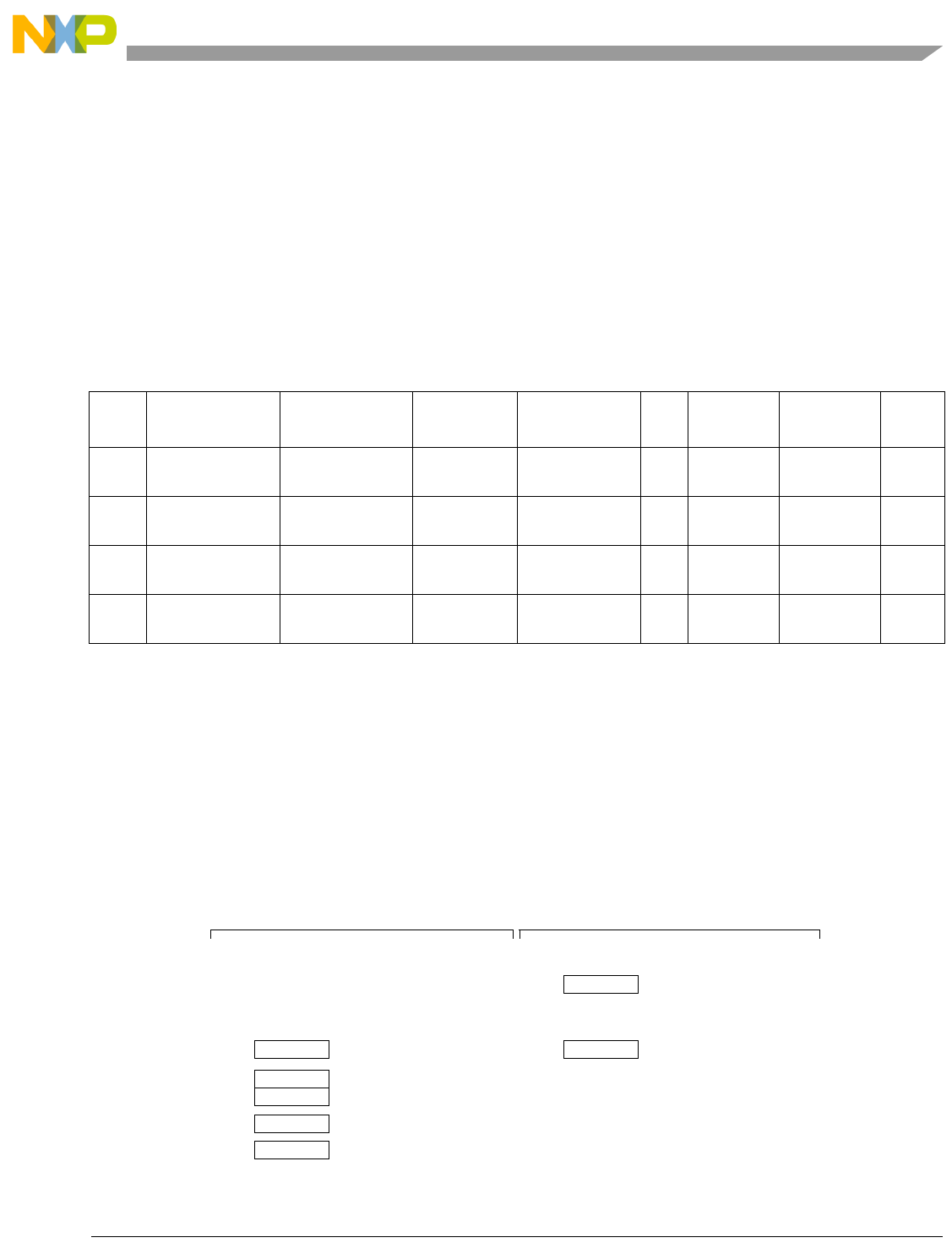

4-1 SPE Interrupt-Related Registers ............................................................................................. 4-1

5-1 Instruction Description.......................................................................................................... 5-15

5-2 Vector Absolute Value (evabs) ............................................................................................. 5-68

5-3 Vector Add Immediate Word (evaddiw)............................................................................... 5-69

0-1 Vector Add Signed, Modulo, Integer to Accumulator Word (evaddsmiaaw)...................... 5-70

5-4 Vector Add Signed, Saturate, Integer to Accumulator Word (evaddssiaaw)....................... 5-71

5-5 Vector Add Unsigned, Modulo, Integer to Accumulator Word (evaddumiaaw)................. 5-72

5-6 Vector Add Unsigned, Saturate, Integer to Accumulator Word (evaddusiaaw) .................. 5-73

5-7 Vector Add Word (evaddw).................................................................................................. 5-74

5-8 Vector AND (evand)............................................................................................................. 5-75

5-9 Vector AND with Complement (evandc) ............................................................................. 5-76

5-10 Vector Compare Equal (evcmpeq) ....................................................................................... 5-77

5-11 Vector Compare Greater Than Signed (evcmpgts)............................................................... 5-78

5-12 Vector Compare Greater Than Unsigned (evcmpgtu).......................................................... 5-79

5-13 Vector Compare Less Than Signed (evcmplts) .................................................................... 5-80

5-14 Vector Compare Less Than Unsigned (evcmpltu) ............................................................... 5-81

5-15 Vector Count Leading Signed Bits Word (evcntlsw)............................................................ 5-82

5-16 Vector Count Leading Zeros Word (evcntlzw)..................................................................... 5-83

5-17 Vector Divide Word Signed (evdivws) ................................................................................. 5-84

5-18 Vector Divide Word Unsigned (evdivwu) ............................................................................ 5-85

5-19 Vector Equivalent (eveqv) .................................................................................................... 5-86

5-20 Vector Extend Sign Byte (evextsb)....................................................................................... 5-87

5-21 Vector Extend Sign Half Word (evextsh) ............................................................................. 5-88

5-22 evldd Results in Big- and Little-Endian Modes ................................................................. 5-112

5-23 evlddx Results in Big- and Little-Endian Modes ............................................................... 5-113

5-24 evldh Results in Big- and Little-Endian Modes ................................................................. 5-114

5-25 evldhx Results in Big- and Little-Endian Modes ............................................................... 5-115

5-26 evldw Results in Big- and Little-Endian Modes................................................................. 5-116

5-27 evldwx Results in Big- and Little-Endian Modes............................................................... 5-117

Signal Processing Engine (SPE) Programming Environments Manual, Rev. 0

viii Freescale Semiconductor

Figures

Figure

Number Title

Page

Number

5-28 evlhhesplat Results in Big- and Little-Endian Modes ....................................................... 5-118

5-29 evlhhesplatx Results in Big- and Little-Endian Modes ..................................................... 5-119

5-30 evlhhossplat Results in Big- and Little-Endian Modes...................................................... 5-120

5-31 evlhhossplatx Results in Big- and Little-Endian Modes.................................................... 5-121

5-32 evlhhousplat Results in Big- and Little-Endian Modes..................................................... 5-122

5-33 evlhhousplatx Results in Big- and Little-Endian Modes................................................... 5-123

5-34 evlwhe Results in Big- and Little-Endian Modes............................................................... 5-124

5-35 evlwhex Results in Big- and Little-Endian Modes............................................................. 5-125

5-36 evlwhos Results in Big- and Little-Endian Modes............................................................. 5-126

5-37 evlwhosx Results in Big- and Little-Endian Modes ........................................................... 5-127

5-38 evlwhou Results in Big- and Little-Endian Modes ............................................................ 5-128

5-39 evlwhoux Results in Big- and Little-Endian Modes .......................................................... 5-129

5-40 evlwhsplat Results in Big- and Little-Endian Modes ........................................................ 5-130

5-41 evlwhsplatx Results in Big- and Little-Endian Modes ...................................................... 5-131

5-42 evlwwsplat Results in Big- and Little-Endian Modes........................................................ 5-132

5-43 evlwwsplatx Results in Big- and Little-Endian Modes...................................................... 5-133

5-44 High Order Element Merging (evmergehi)........................................................................ 5-134

5-45 High Order Element Merging (evmergehilo)..................................................................... 5-135

5-46 Low Order Element Merging (evmergelo)......................................................................... 5-136

5-47 Low Order Element Merging (evmergelohi) ..................................................................... 5-137

5-48 evmhegsmfaa (Even Form)................................................................................................ 5-138

5-49 evmhegsmfan (Even Form)................................................................................................ 5-139

5-50 evmhegsmiaa (Even Form)................................................................................................ 5-140

5-51 evmhegsmian (Even Form)................................................................................................ 5-141

5-52 evmhegumiaa (Even Form) ............................................................................................... 5-142

5-53 evmhegumian (Even Form) ............................................................................................... 5-143

5-54 Even Multiply of Two Signed Modulo Fractional

Elements (to Accumulator) (evmhesmf) ....................................................................... 5-144

5-55 Even Form of Vector Half-Word Multiply (evmhesmfaaw).............................................. 5-145

5-56 Even Form of Vector Half-Word Multiply (evmhesmfanw).............................................. 5-146

5-57 Even Form for Vector Multiply (to Accumulator) (evmhesmi) ......................................... 5-147

5-58 Even Form of Vector Half-Word Multiply (evmhesmiaaw).............................................. 5-148

5-59 Even Form of Vector Half-Word Multiply (evmhesmianw).............................................. 5-149

5-60 Even Multiply of Two Signed Saturate Fractional

Elements (to Accumulator) (evmhessf) ........................................................................ 5-150

5-61 Even Form of Vector Half-Word Multiply (evmhessfaaw)................................................ 5-151

5-62 Even Form of Vector Half-Word Multiply (evmhessfanw) ............................................... 5-152

5-63 Even Form of Vector Half-Word Multiply (evmhessiaaw)................................................ 5-153

5-64 Even Form of Vector Half-Word Multiply (evmhessianw)................................................ 5-154

5-65 Vector Multiply Half Words, Even, Unsigned, Modulo,

Integer (to Accumulator) (evmheumi) .......................................................................... 5-155

Signal Processing Engine (SPE) Programming Environments Manual, Rev. 0

Freescale Semiconductor ix

Figures

Figure

Number Title

Page

Number

5-66 Even Form of Vector Half-Word Multiply (evmheumiaaw) ............................................. 5-156

5-67 Even Form of Vector Half-Word Multiply (evmheumianw) ............................................. 5-157

5-68 Even Form of Vector Half-Word Multiply (evmheusiaaw) ............................................... 5-158

5-69 Even Form of Vector Half-Word Multiply (evmheusianw) ............................................... 5-159

5-70 evmhogsmfaa (Odd Form)................................................................................................. 5-160

5-71 evmhogsmfan (Odd Form)................................................................................................. 5-161

5-72 evmhogsmiaa (Odd Form) ................................................................................................. 5-162

5-73 evmhogsmian (Odd Form)................................................................................................. 5-163

5-74 evmhogumiaa (Odd Form) ................................................................................................ 5-164

5-75 evmhogumian (Odd Form) ................................................................................................ 5-165

5-76 Vector Multiply Half Words, Odd, Signed, Modulo,

Fractional (to Accumulator) (evmhosmf)...................................................................... 5-166

5-77 Odd Form of Vector Half-Word Multiply (evmhosmfaaw) ............................................... 5-167

5-78 Odd Form of Vector Half-Word Multiply (evmhosmfanw)............................................... 5-168

5-79 Vector Multiply Half Words, Odd, Signed, Modulo,

Integer (to Accumulator) (evmhosmi)........................................................................... 5-169

5-80 Odd Form of Vector Half-Word Multiply (evmhosmiaaw) ............................................... 5-170

5-81 Odd Form of Vector Half-Word Multiply (evmhosmianw) ............................................... 5-171

5-82 Vector Multiply Half Words, Odd, Signed, Saturate,

Fractional (to Accumulator) (evmhossf)........................................................................ 5-173

5-83 Odd Form of Vector Half-Word Multiply (evmhossfaaw)................................................. 5-174

5-84 Odd Form of Vector Half-Word Multiply (evmhossfanw)................................................. 5-175

5-85 Odd Form of Vector Half-Word Multiply (evmhossiaaw) ................................................. 5-176

5-86 Odd Form of Vector Half-Word Multiply (evmhossianw)................................................. 5-177

5-87 Vector Multiply Half Words, Odd, Unsigned, Modulo,

Integer (to Accumulator) (evmhoumi) .......................................................................... 5-178

5-88 Odd Form of Vector Half-Word Multiply (evmhoumiaaw)............................................... 5-179

5-89 Odd Form of Vector Half-Word Multiply (evmhoumianw) .............................................. 5-180

5-90 Odd Form of Vector Half-Word Multiply (evmhousiaaw) ................................................ 5-181

5-91 Odd Form of Vector Half-Word Multiply (evmhousianw)................................................ 5-182

5-92 Initialize Accumulator (evmra).......................................................................................... 5-183

5-93 Vector Multiply Word High Signed, Modulo,

Fractional (to Accumulator) (evmwhsmf)..................................................................... 5-184

5-94 Vector Multiply Word High Signed, Modulo,

Integer (to Accumulator) (evmwhsm) ........................................................................... 5-185

5-95 Vector Multiply Word High Signed, Saturate,

Fractional (to Accumulator) (evmwhssf)....................................................................... 5-187

5-96 Vector Multiply Word High Unsigned, Modulo,

Integer (to Accumulator) (evmwhumi) ......................................................................... 5-188

5-97 Vector Multiply Word Low Signed, Modulo, Integer and

Accumulate in Words (evmwlsmiaaw) ......................................................................... 5-189

Signal Processing Engine (SPE) Programming Environments Manual, Rev. 0

xFreescale Semiconductor

Figures

Figure

Number Title

Page

Number

5-98 Vector Multiply Word Low Signed, Modulo, Integer and

Accumulate Negative in Words (evmwlsmianw).......................................................... 5-190

5-99 Vector Multiply Word Low Signed, Saturate, Integer and

Accumulate in Words (evmwlssiaaw) ........................................................................... 5-192

5-100 Vector Multiply Word Low Signed, Saturate, Integer and

Accumulate Negative in Words (evmwlssianw............................................................. 5-193

5-101 Vector Multiply Word Low Unsigned, Modulo, Integer (evmwlumi) ............................... 5-194

5-102 Vector Multiply Word Low Unsigned, Modulo, Integer and

Accumulate in Words (evmwlumiaaw)......................................................................... 5-195

5-103 Vector Multiply Word Low Unsigned, Modulo, Integer and

Accumulate Negative in Words (evmwlumianw) ......................................................... 5-196

5-104 Vector Multiply Word Low Unsigned, Saturate, Integer and

Accumulate in Words (evmwlusiaaw)........................................................................... 5-197

5-105 Vector Multiply Word Low Unsigned, Saturate, Integer and

Accumulate Negative in Words (evmwlusianw)........................................................... 5-198

5-106 Vector Multiply Word Signed, Modulo,

Fractional (to Accumulator) (evmwsmf) ....................................................................... 5-199

5-107 Vector Multiply Word Signed, Modulo, Fractional and

Accumulate (evmwsmfaa)............................................................................................. 5-200

5-108 Vector Multiply Word Signed, Modulo, Fractional and

Accumulate Negative (evmwsmfan)............................................................................. 5-201

5-109 Vector Multiply Word Signed, Modulo,

Integer (to Accumulator) (evmwsmi) ............................................................................ 5-202

5-110 Vector Multiply Word Signed, Modulo, Integer and

Accumulate (evmwsmiaa)............................................................................................. 5-203

5-111 Vector Multiply Word Signed, Modulo, Integer and

Accumulate Negative (evmwsmian) ............................................................................. 5-204

5-112 Vector Multiply Word Signed, Saturate,

Fractional (to Accumulator) (evmwssf)......................................................................... 5-205

5-113 Vector Multiply Word Signed, Saturate, Fractional, and

Accumulate (evmwssfaa) .............................................................................................. 5-206

5-114 Vector Multiply Word Signed, Saturate, Fractional and

Accumulate Negative (evmwssfan)............................................................................... 5-207

5-115 Vector Multiply Word Unsigned, Modulo,

Integer (to Accumulator) (evmwumi)............................................................................ 5-208

5-116 Vector Multiply Word Unsigned, Modulo, Integer and

Accumulate (evmwumiaa) ............................................................................................ 5-209

5-117 Vector Multiply Word Unsigned, Modulo, Integer and

Accumulate Negative (evmwumian)............................................................................. 5-210

5-118 Vector NAND (evnand)...................................................................................................... 5-211

5-119 Vector Negate (evneg) ........................................................................................................ 5-212

Signal Processing Engine (SPE) Programming Environments Manual, Rev. 0

Freescale Semiconductor xi

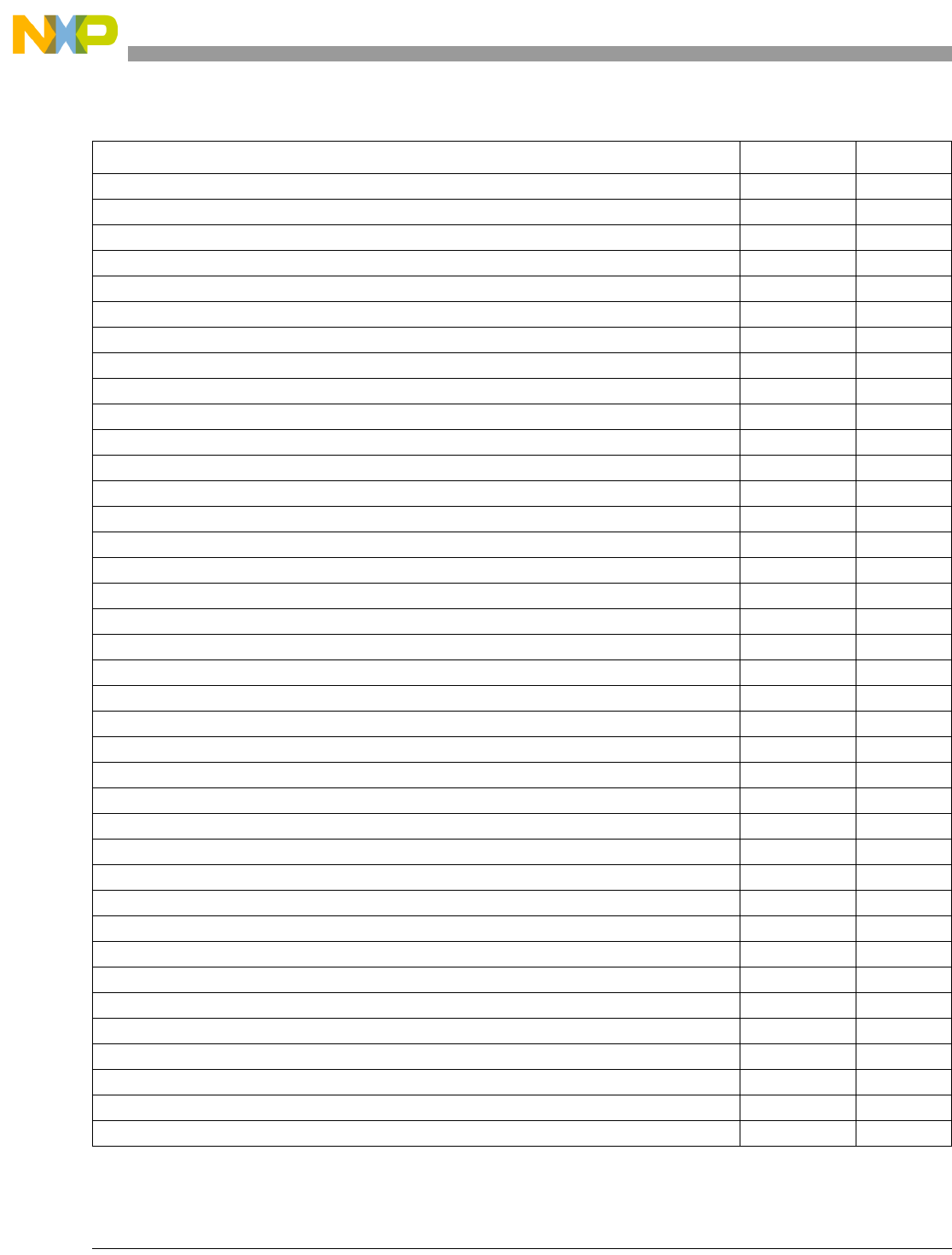

Figures

Figure

Number Title

Page

Number

5-120 Vector NOR (evnor) ........................................................................................................... 5-213

5-121 Vector OR (evor) ................................................................................................................ 5-214

5-122 Vector OR with Complement (evorc)................................................................................. 5-215

5-123 Vector Rotate Left Word (evrlw) ........................................................................................ 5-216

5-124 Vector Rotate Left Word Immediate (evrlwi)..................................................................... 5-217

5-125 Vector Round Word (evrndw) ............................................................................................ 5-218

5-126 Vector Select (evsel)............................................................................................................ 5-219

5-127 Vector Shift Left Word (evslw)........................................................................................... 5-220

5-128 Vector Shift Left Word Immediate (evslwi)........................................................................ 5-221

5-129 Vector Splat Fractional Immediate (evsplatfi).................................................................... 5-222

5-130 evsplati Sign Extend........................................................................................................... 5-223

5-131 Vector Shift Right Word Immediate Signed (evsrwis) ....................................................... 5-224

5-132 Vector Shift Right Word Immediate Unsigned (evsrwiu) .................................................. 5-225

5-133 Vector Shift Right Word Signed (evsrws) .......................................................................... 5-226

5-134 Vector Shift Right Word Unsigned (evsrwu)...................................................................... 5-227

5-135 evstdd Results in Big- and Little-Endian Modes................................................................ 5-228

5-136 evstddx Results in Big- and Little-Endian Modes.............................................................. 5-229

5-137 evstdh Results in Big- and Little-Endian Modes................................................................ 5-230

5-138 evstdhx Results in Big- and Little-Endian Modes.............................................................. 5-231

5-139 evstdw Results in Big- and Little-Endian Modes............................................................... 5-232

5-140 evstdwx Results in Big- and Little-Endian Modes............................................................. 5-233

5-141 evstwhe Results in Big- and Little-Endian Modes ............................................................. 5-234

5-142 evstwhex Results in Big- and Little-Endian Modes ........................................................... 5-235

5-143 evstwho Results in Big- and Little-Endian Modes............................................................. 5-236

5-144 evstwhox Results in Big- and Little-Endian Modes........................................................... 5-237

5-145 evstwwe Results in Big- and Little-Endian Modes ............................................................ 5-238

5-146 evstwwex Results in Big- and Little-Endian Modes .......................................................... 5-239

5-147 evstwwo Results in Big- and Little-Endian Modes ............................................................ 5-240

5-148 evstwwox Results in Big- and Little-Endian Modes .......................................................... 5-241

5-149 Vector Subtract Signed, Modulo, Integer to

Accumulator Word (evsubfsmiaaw).............................................................................. 5-242

5-150 Vector Subtract Signed, Saturate, Integer to

Accumulator Word (evsubfssiaaw) ............................................................................... 5-243

5-151 Vector Subtract Unsigned, Modulo, Integer to

Accumulator Word (evsubfumiaaw)............................................................................. 5-244

5-152 Vector Subtract Unsigned, Saturate, Integer to

Accumulator Word (evsubfusiaaw)............................................................................... 5-245

5-153 Vector Subtract from Word (evsubfw)................................................................................ 5-246

5-154 Vector Subtract Immediate from Word (evsubifw) ............................................................ 5-247

5-155 Vector XOR (evxor)............................................................................................................ 5-248

Signal Processing Engine (SPE) Programming Environments Manual, Rev. 0

xii Freescale Semiconductor

Figures

Figure

Number Title

Page

Number

Signal Processing Engine (SPE) Programming Environments Manual, Rev. 0

Freescale Semiconductor xiii

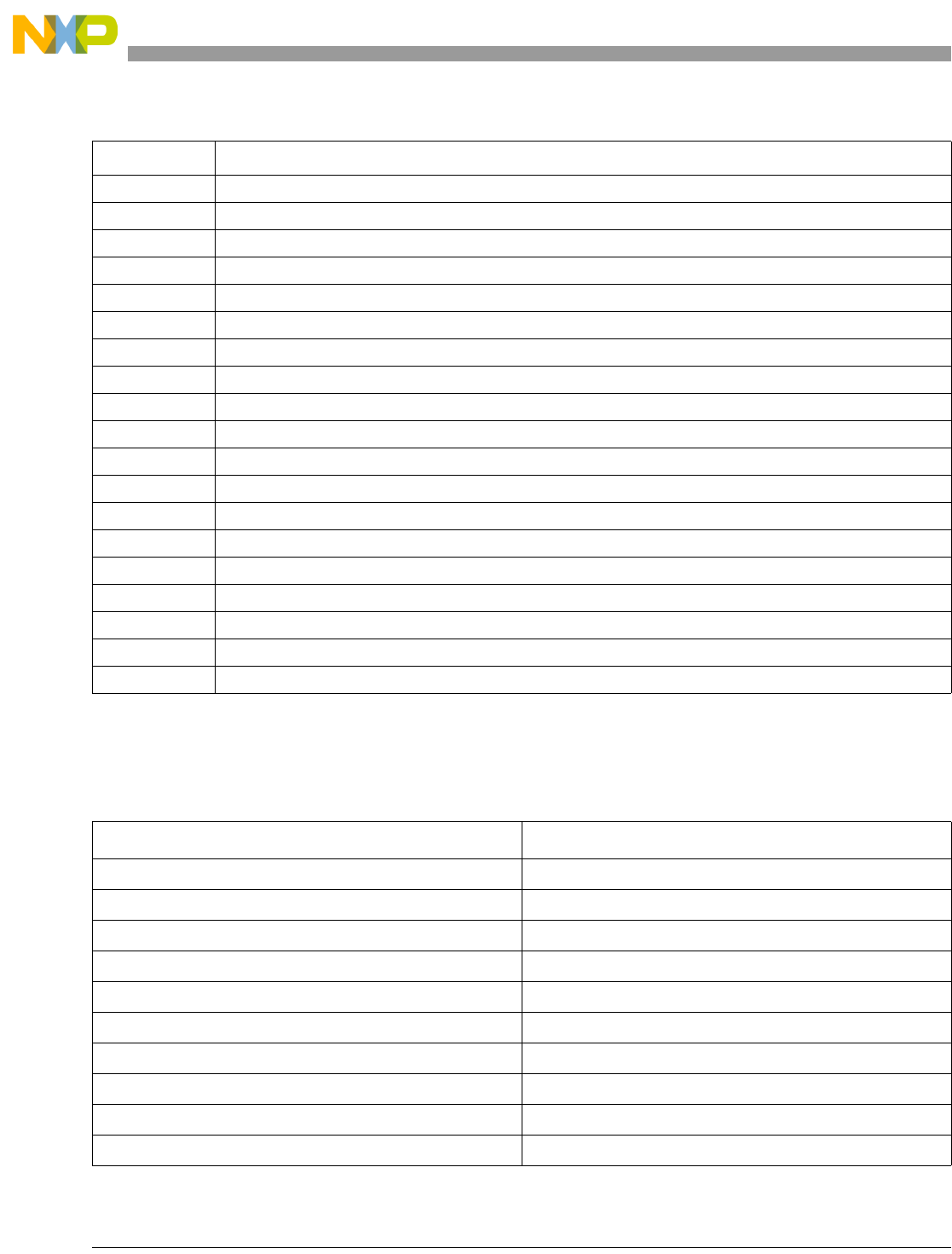

Tables

Table

Number Title

Page

Number

Ta bl e s

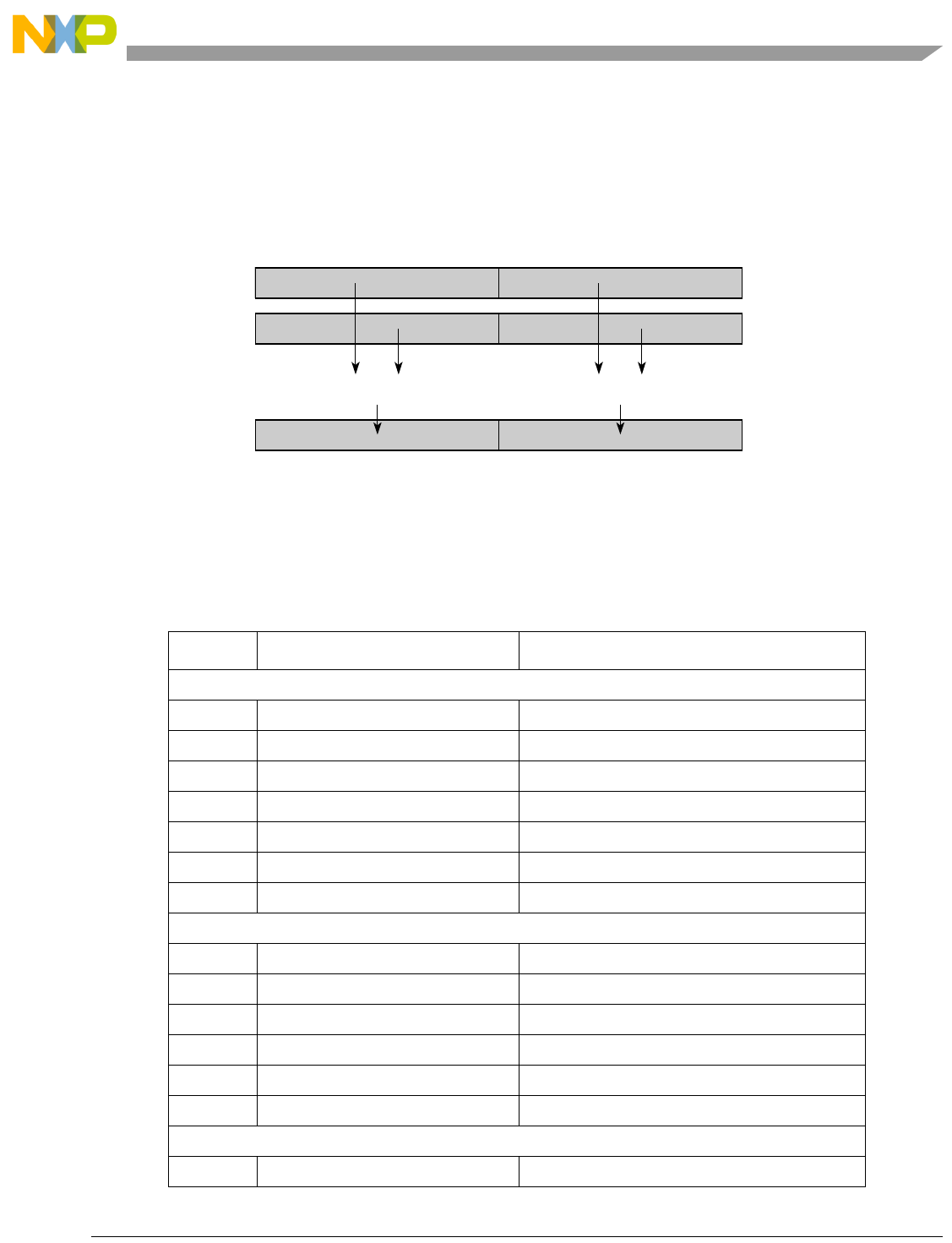

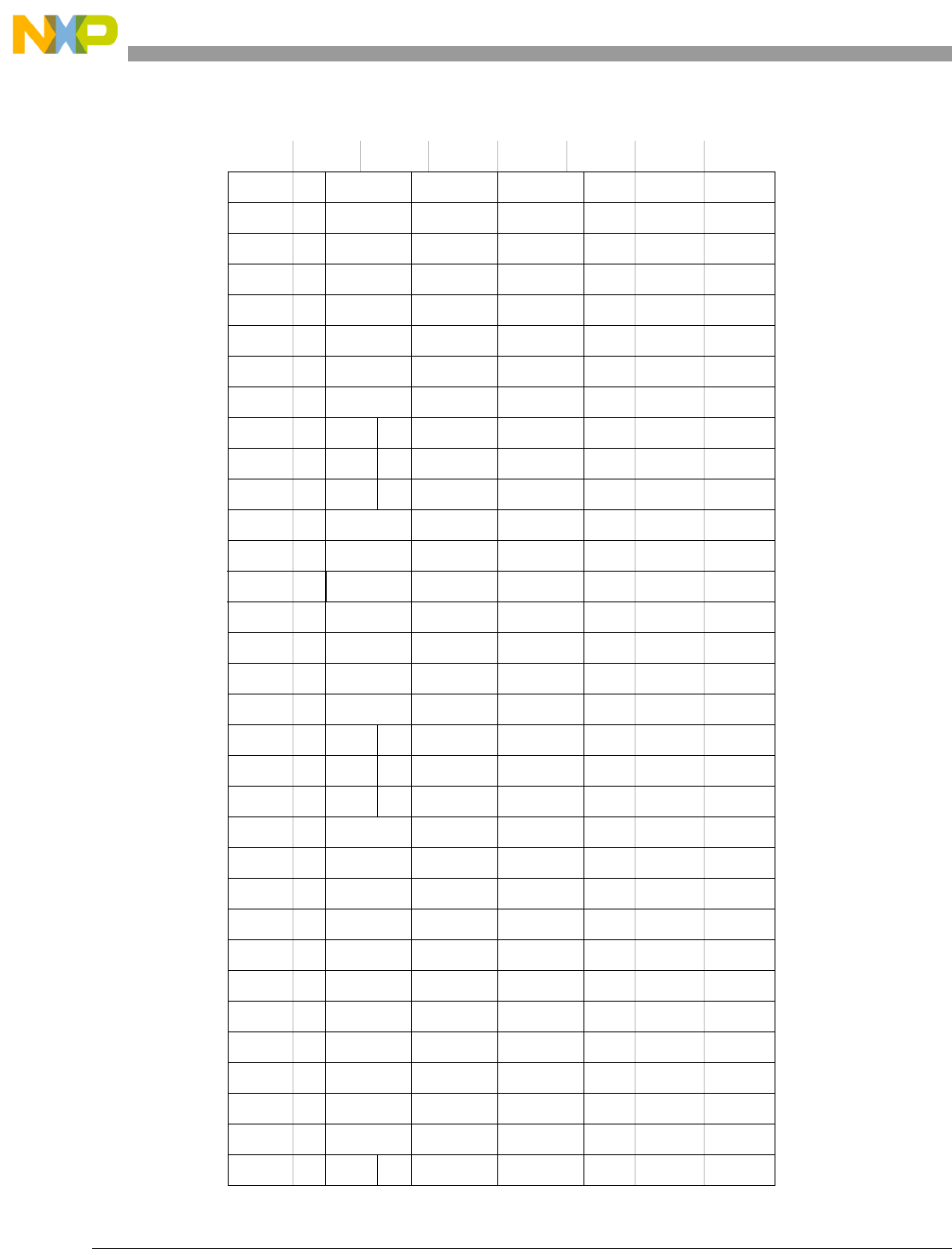

1-1 SPE Vector Multiply Instruction Mnemonic Structure ........................................................... 1-1

1-2 Mnemonic Extensions for Multiply Accumulate Instructions................................................ 1-4

1-3 SPE Vector Multiply Instruction Mnemonic Structure ........................................................... 1-5

1-4 Mnemonic Extensions for Multiply-Accumulate Instructions................................................ 1-5

2-1 SPEFSCR Field Descriptions ................................................................................................. 2-5

2-2 SPE Instructions that Use the CR ........................................................................................... 2-8

2-3 Embedded Floating-Point Instructions that Use the CR ......................................................... 2-8

3-1 Mnemonic Extensions for Multiply Accumulate Instructions................................................ 3-3

3-2 SPE Vector Multiply Instruction Mnemonic Structure ........................................................... 3-5

3-3 Mnemonic Extensions for Multiply-Accumulate Instructions................................................ 3-5

3-4 SPE Instructions...................................................................................................................... 3-6

3-5 SPE Simplified Mnemonics .................................................................................................. 3-11

3-6 Vector and Scalar Floating-Point Instructions ...................................................................... 3-17

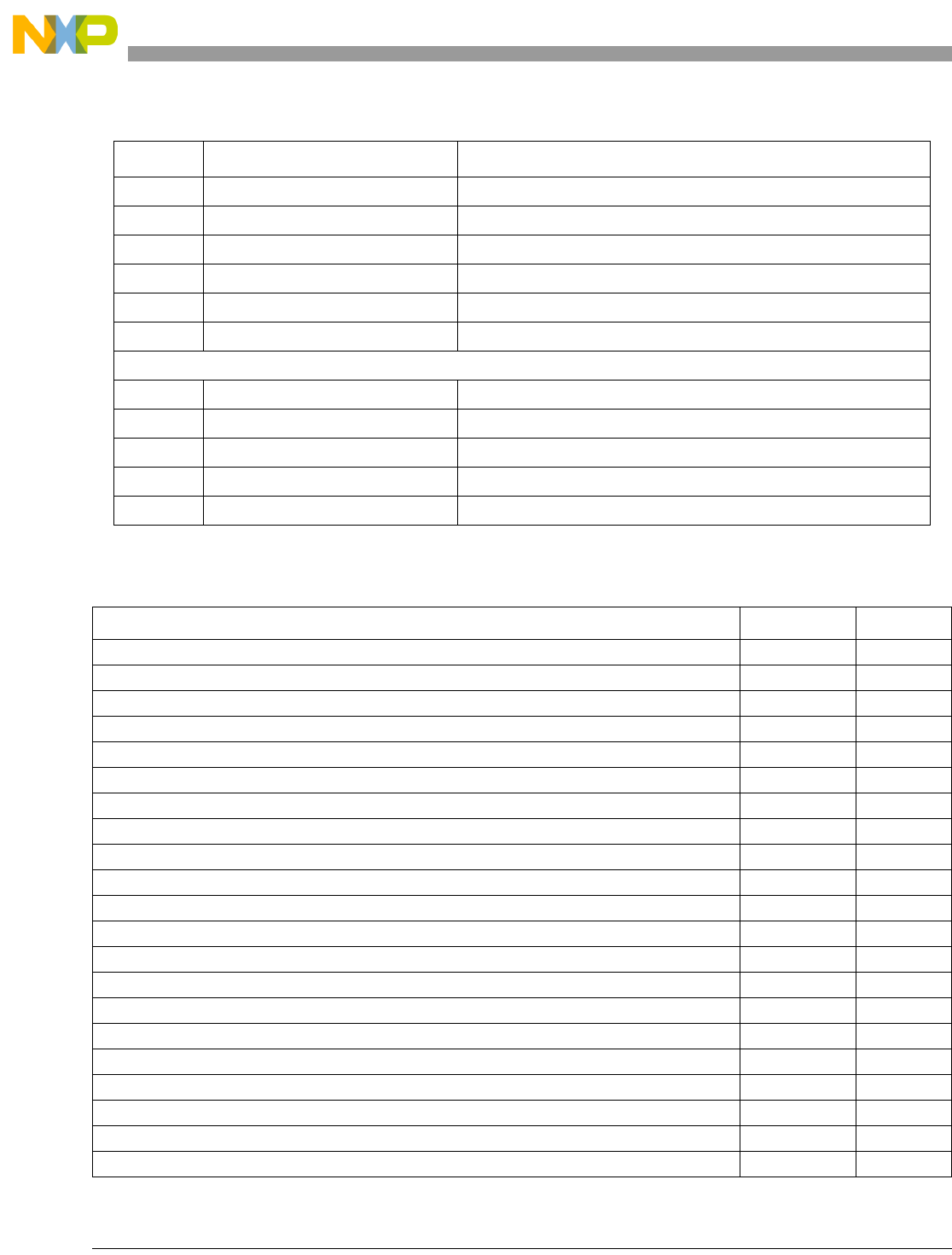

4-1 SPE/SPE Embedded Floating-Point Interrupt and Exception Types...................................... 4-1

5-1 Notation Conventions ............................................................................................................. 5-1

5-2 Instruction Field Descriptions................................................................................................. 5-2

5-3 RTL Notation .......................................................................................................................... 5-2

5-4 Operator Precedence ............................................................................................................... 5-4

5-5 Conversion Models ................................................................................................................. 5-5

5-6 Data Samples and Sizes ........................................................................................................ 5-16

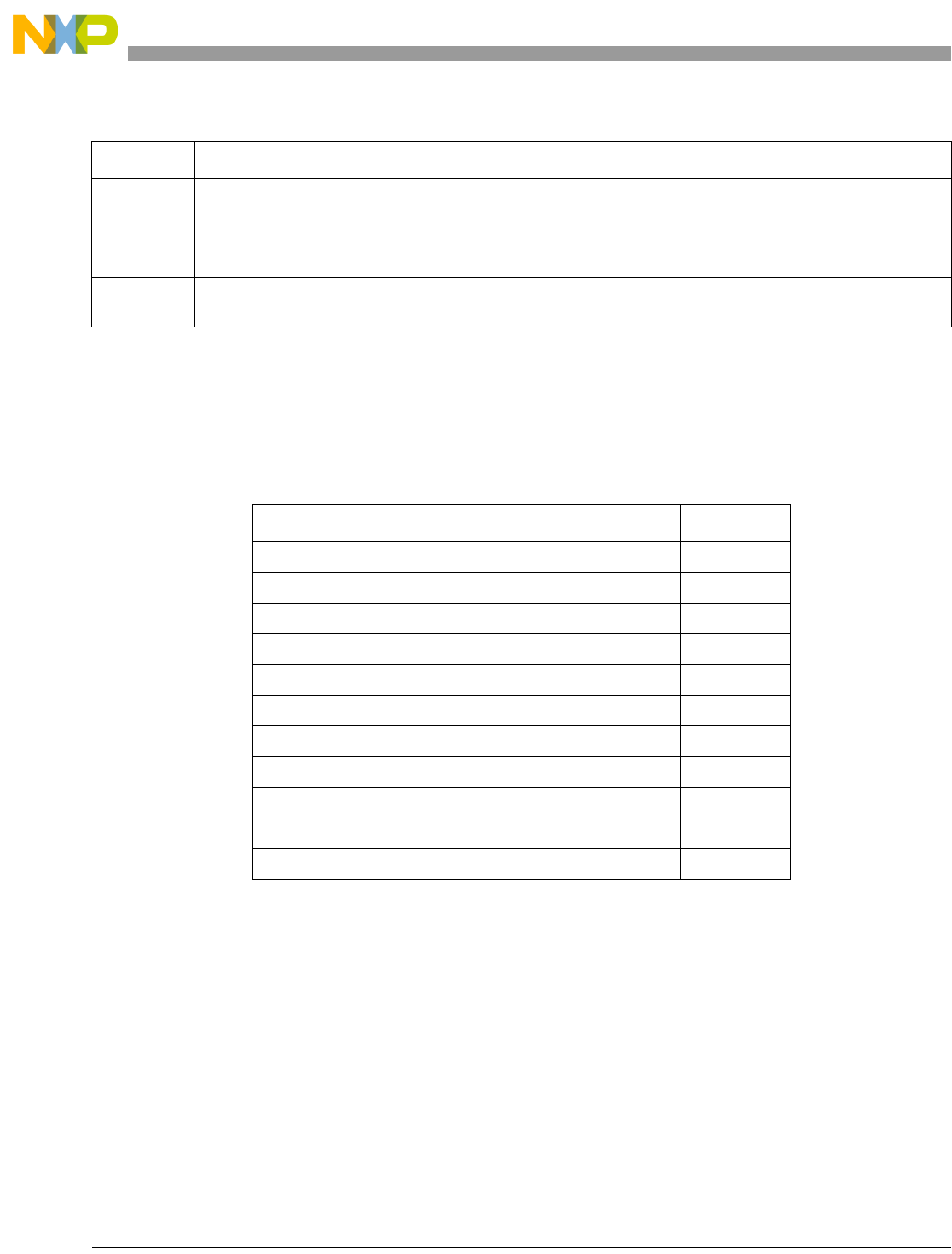

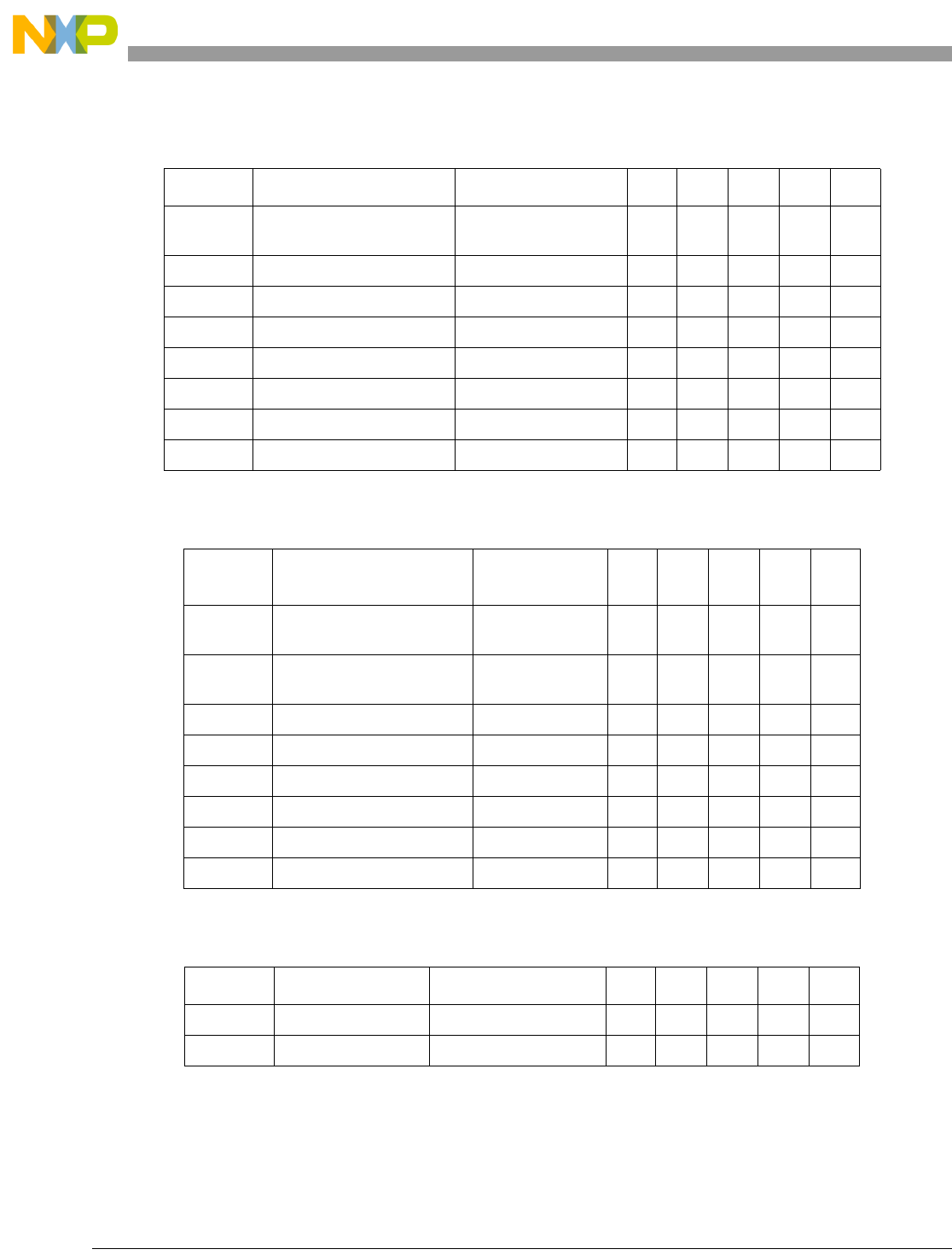

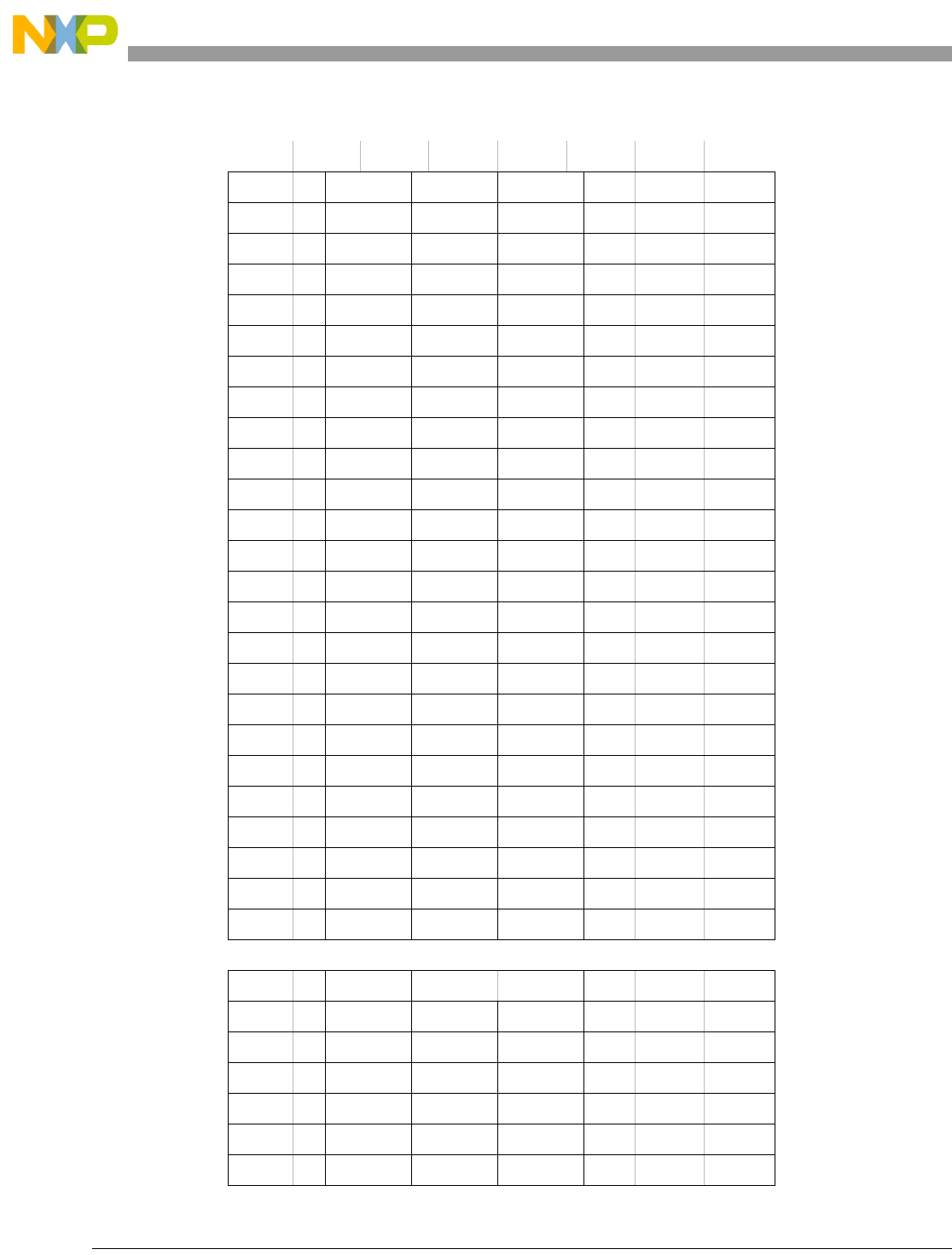

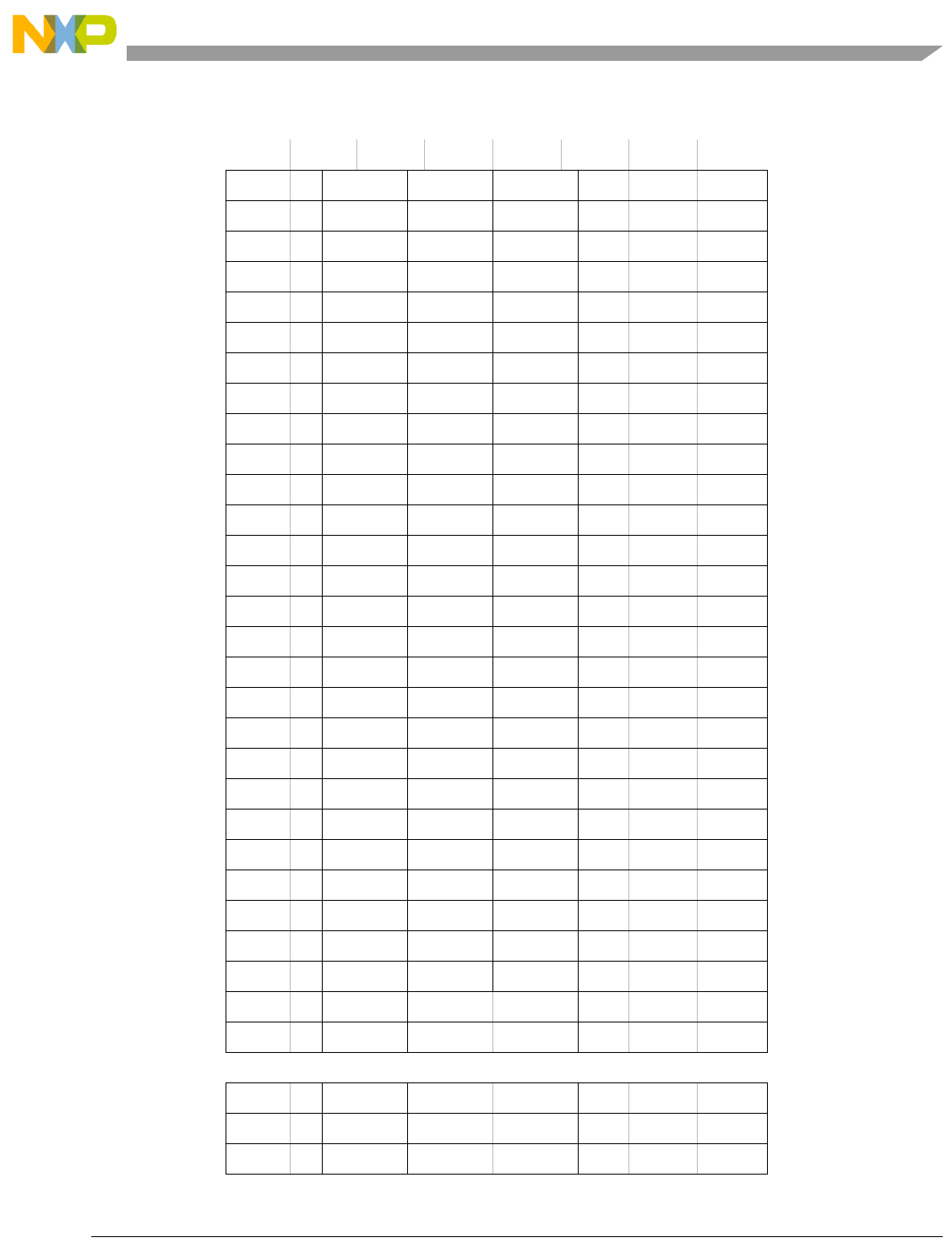

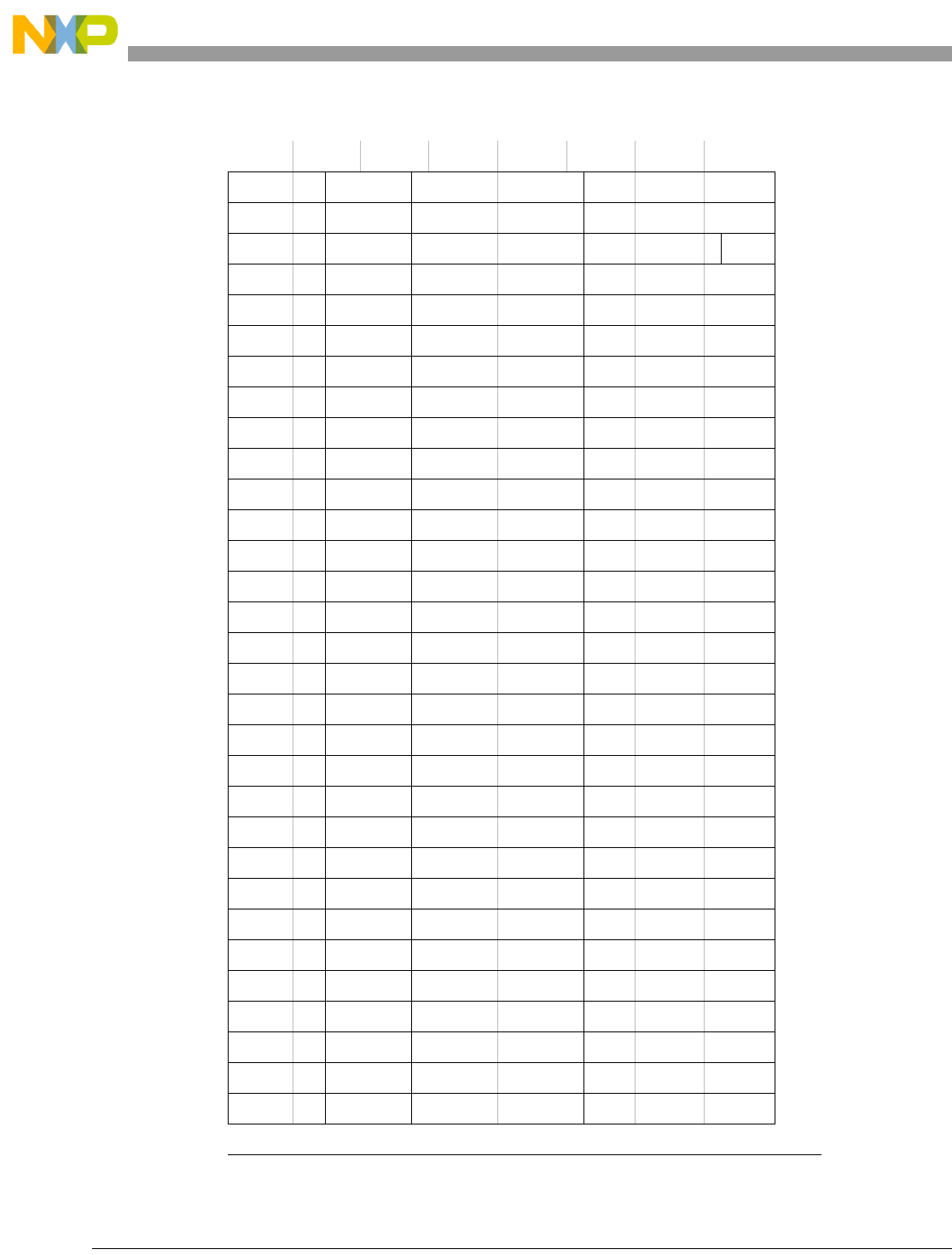

A-1 Embedded Floating-Point Results Summary—Add, Sub, Mul, Div ..................................... A-1

A-2 Embedded Floating-Point Results Summary—Single Convert from Double ....................... A-5

A-3 Embedded Floating-Point Results Summary—Double Convert from Single ....................... A-5

A-4 Embedded Floating-Point Results Summary—Convert to Unsigned.................................... A-6

A-5 Embedded Floating-Point Results Summary—Convert to Signed ........................................ A-6

A-6 Results Summary—Convert from Unsigned ......................................................................... A-6

A-7 Embedded Floating-Point Results Summary—Convert from Signed ................................... A-7

A-8 Embedded Floating-Point Results Summary—*abs, *nabs, *neg......................................... A-7

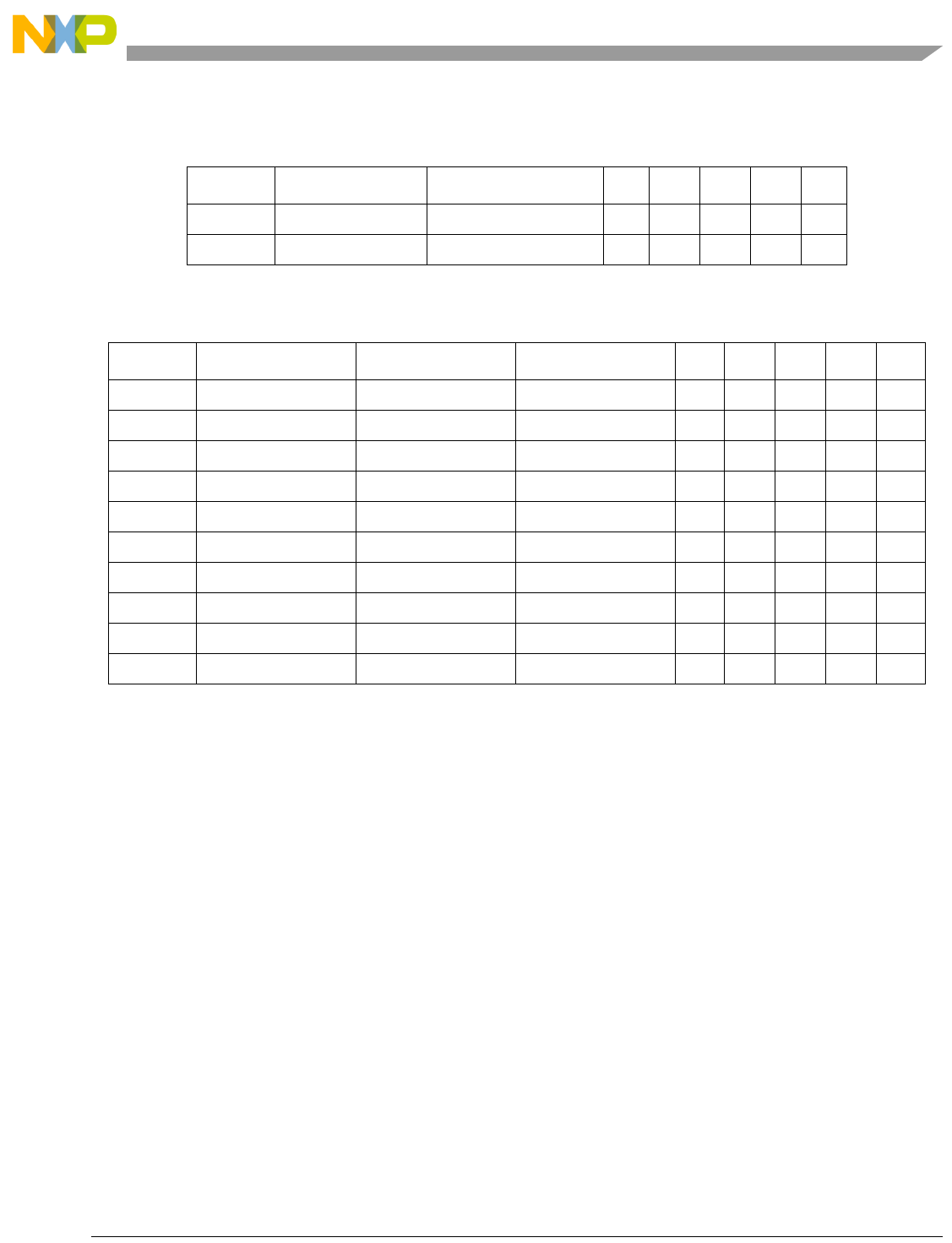

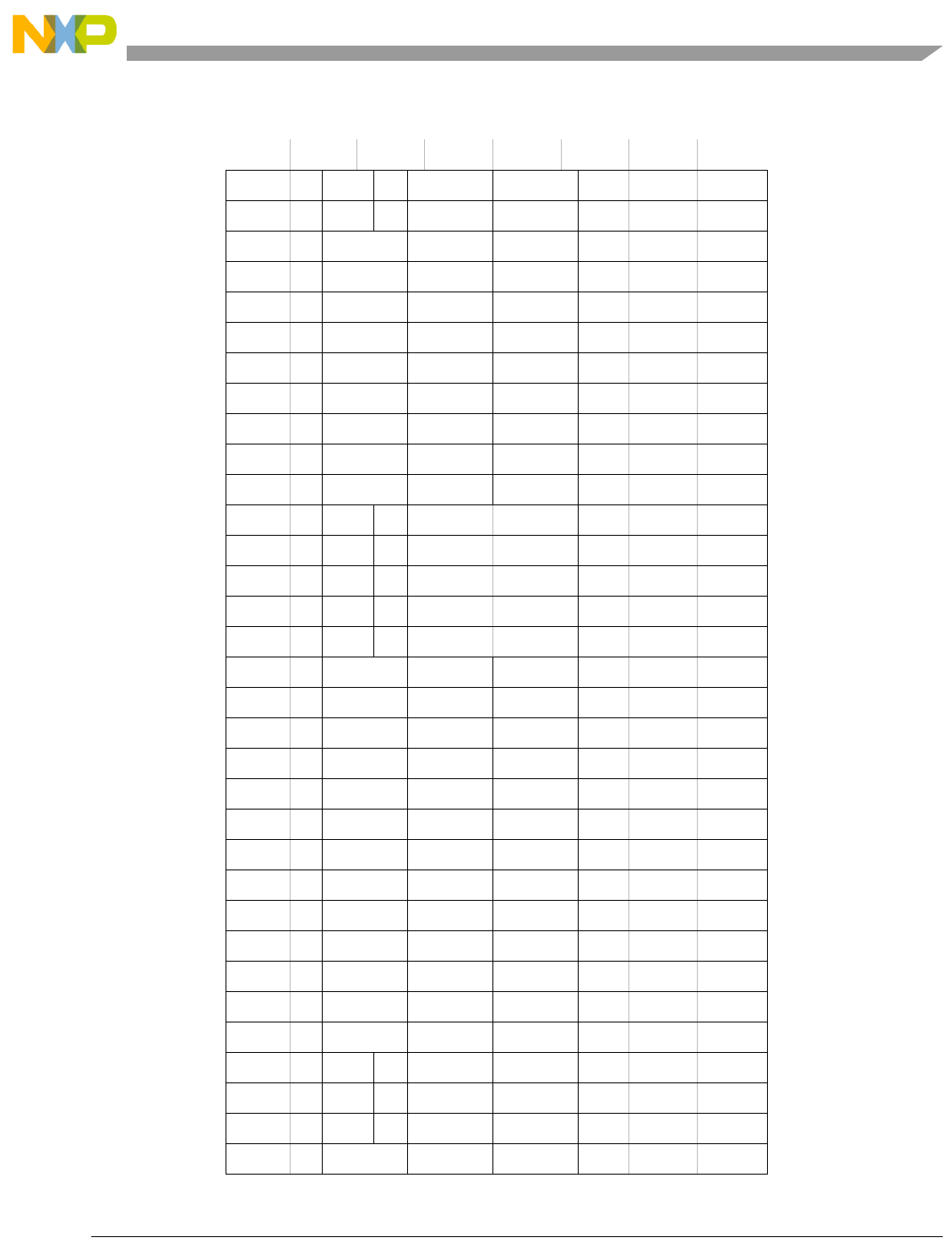

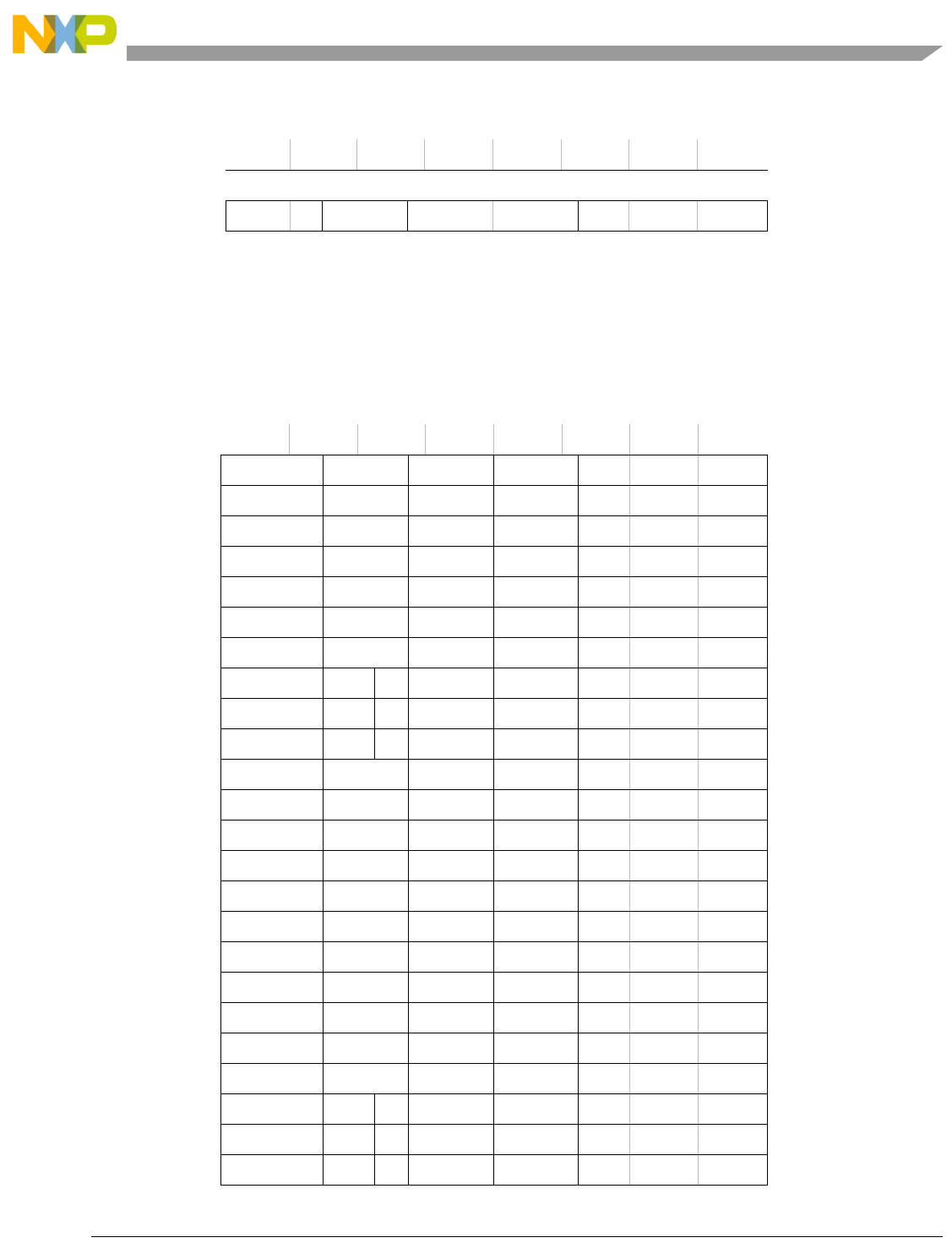

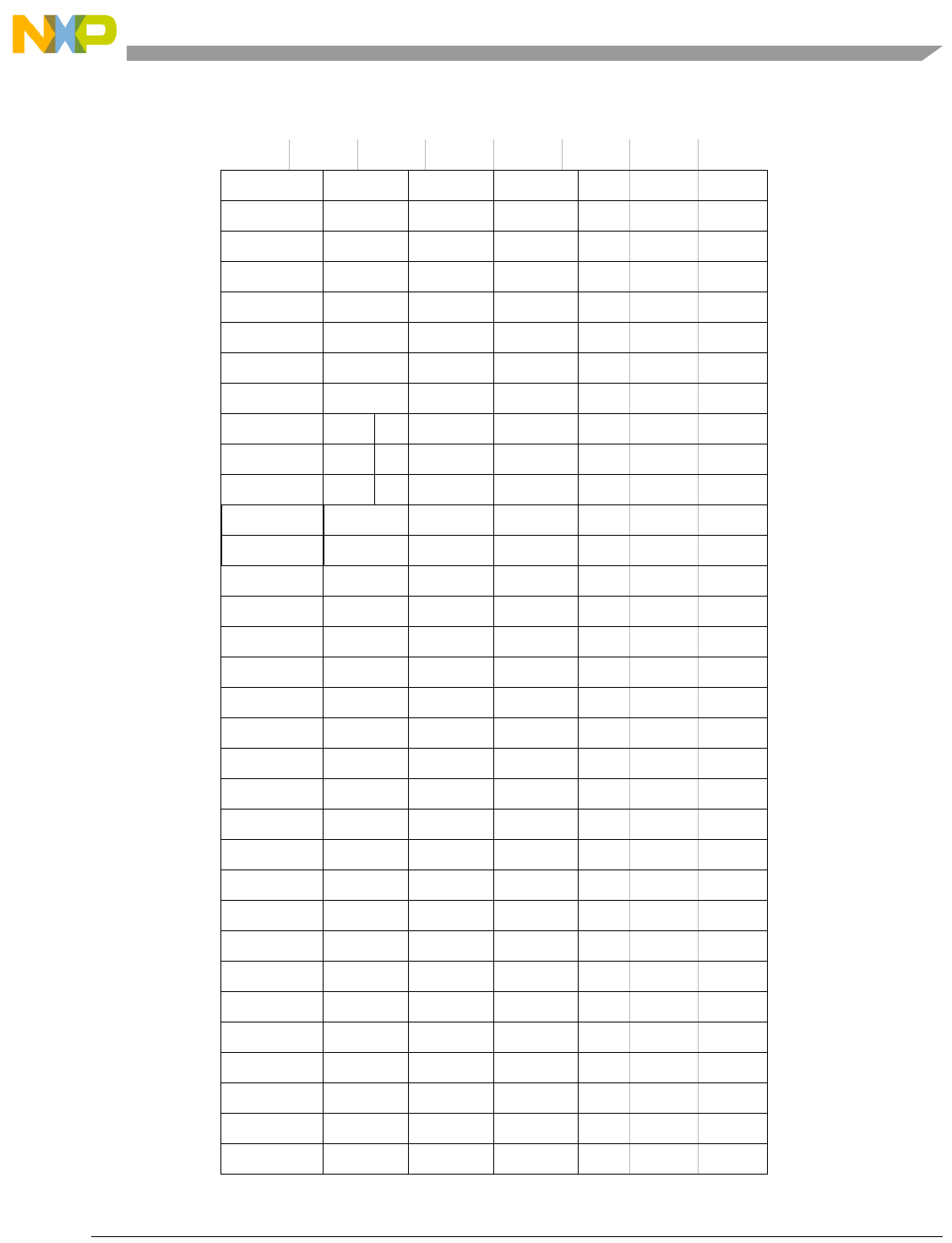

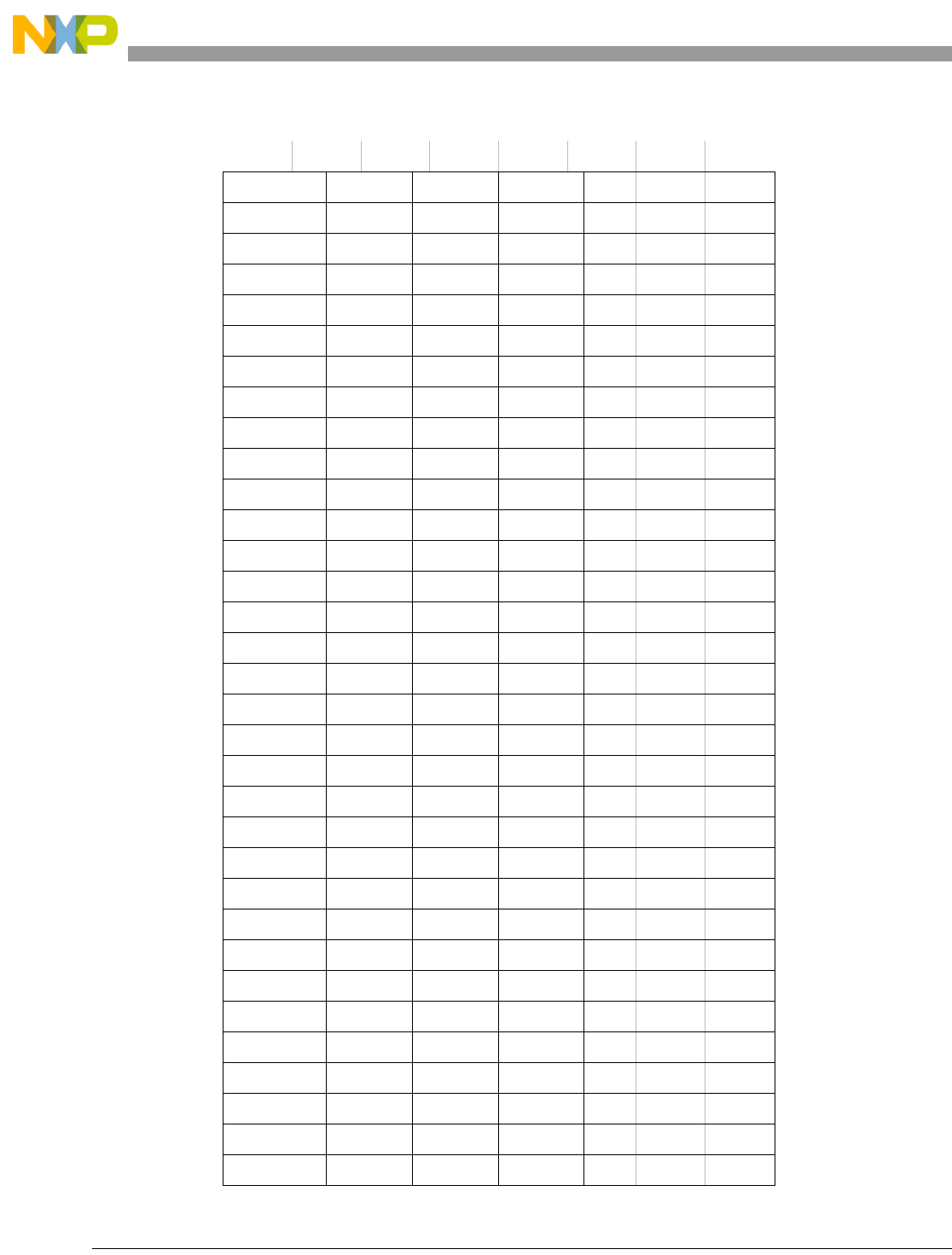

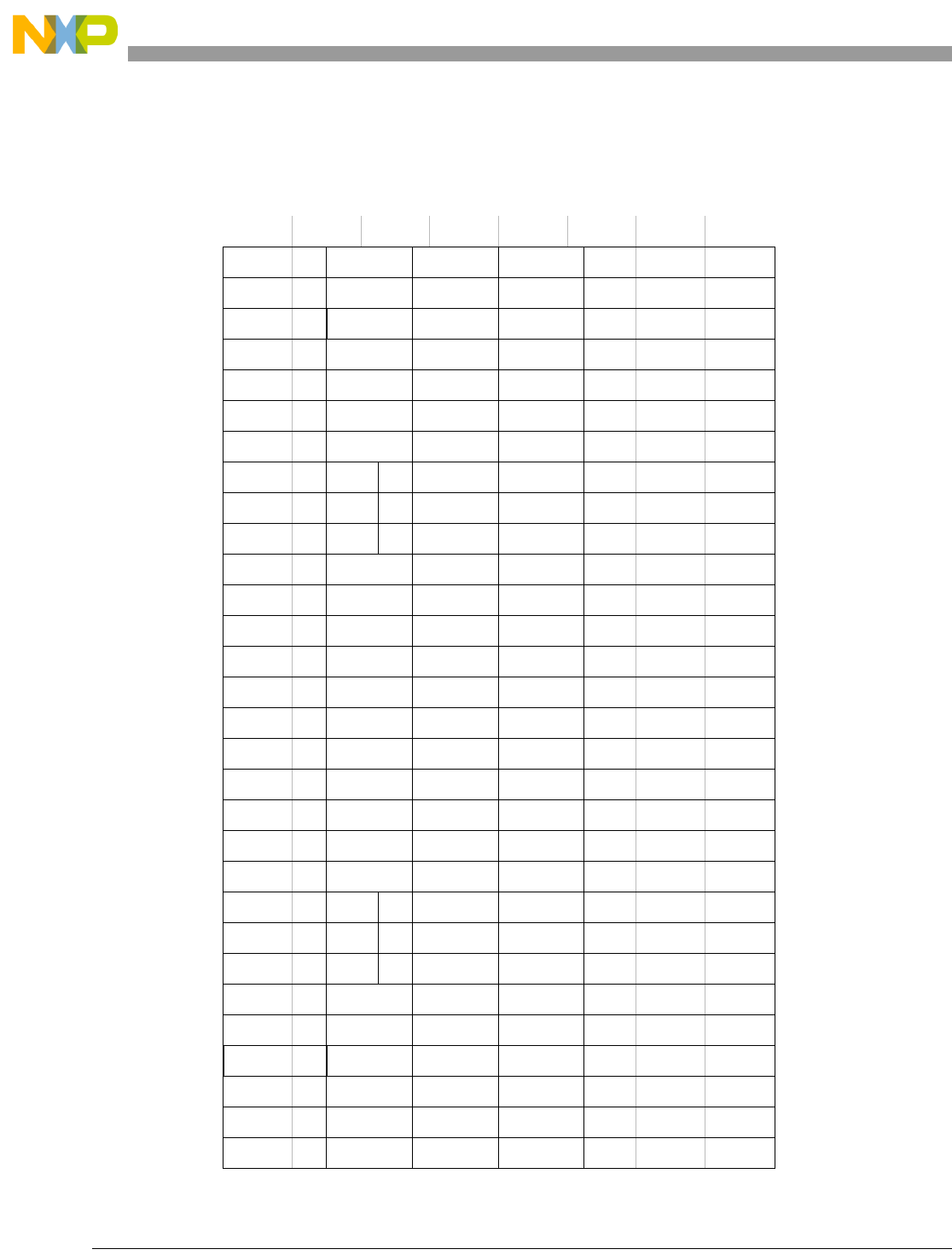

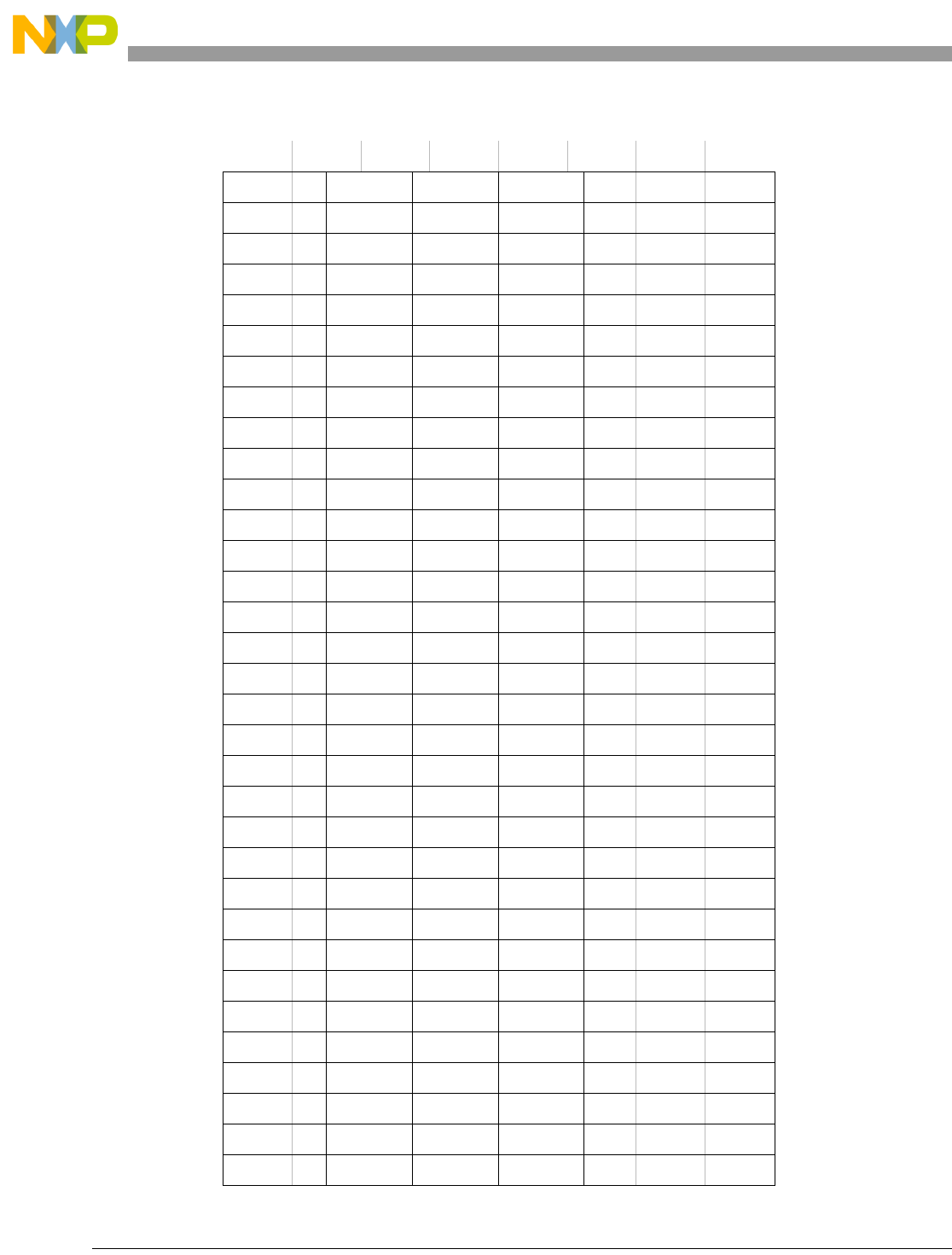

B-1 Instructions (Binary) by Mnemonic........................................................................................B-1

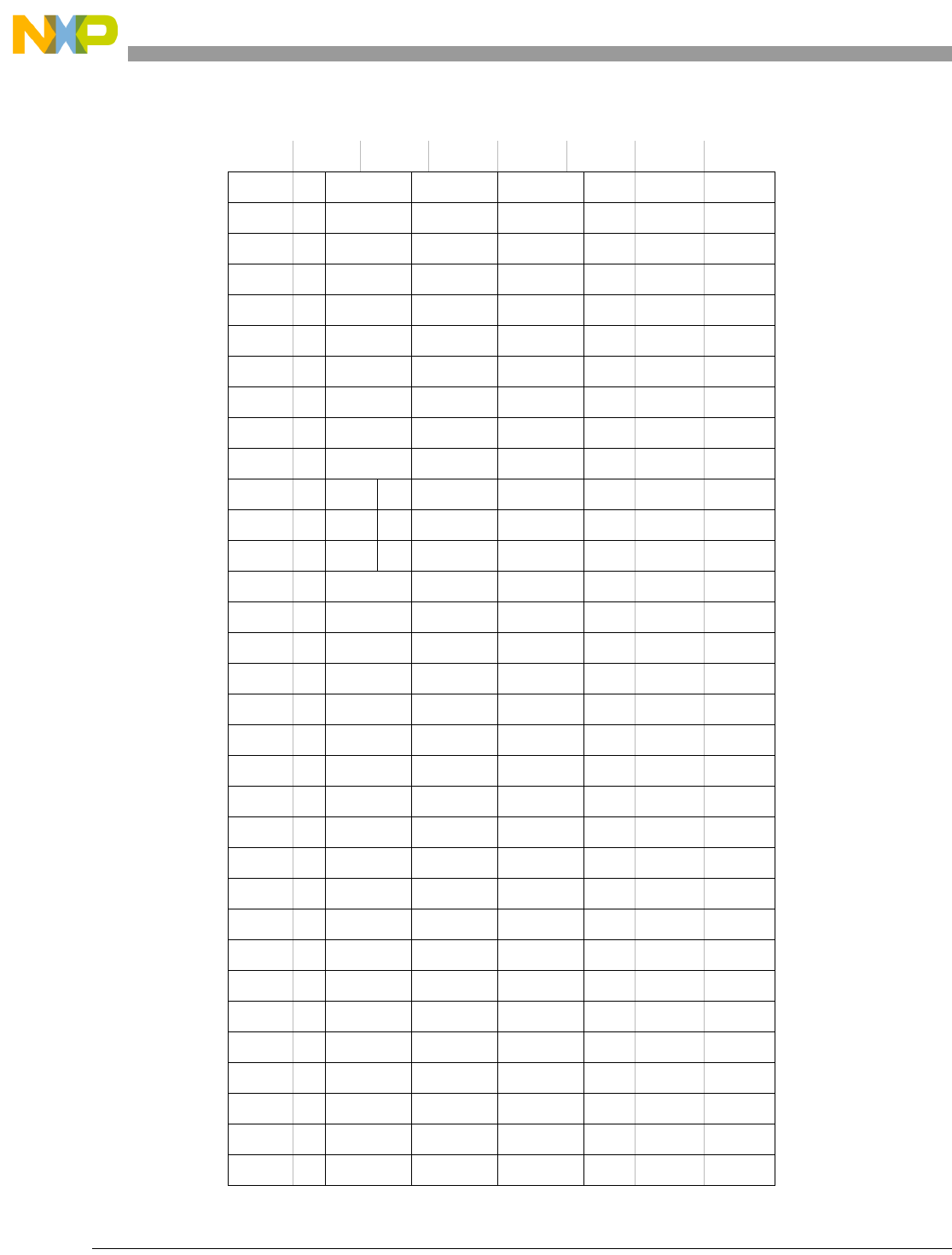

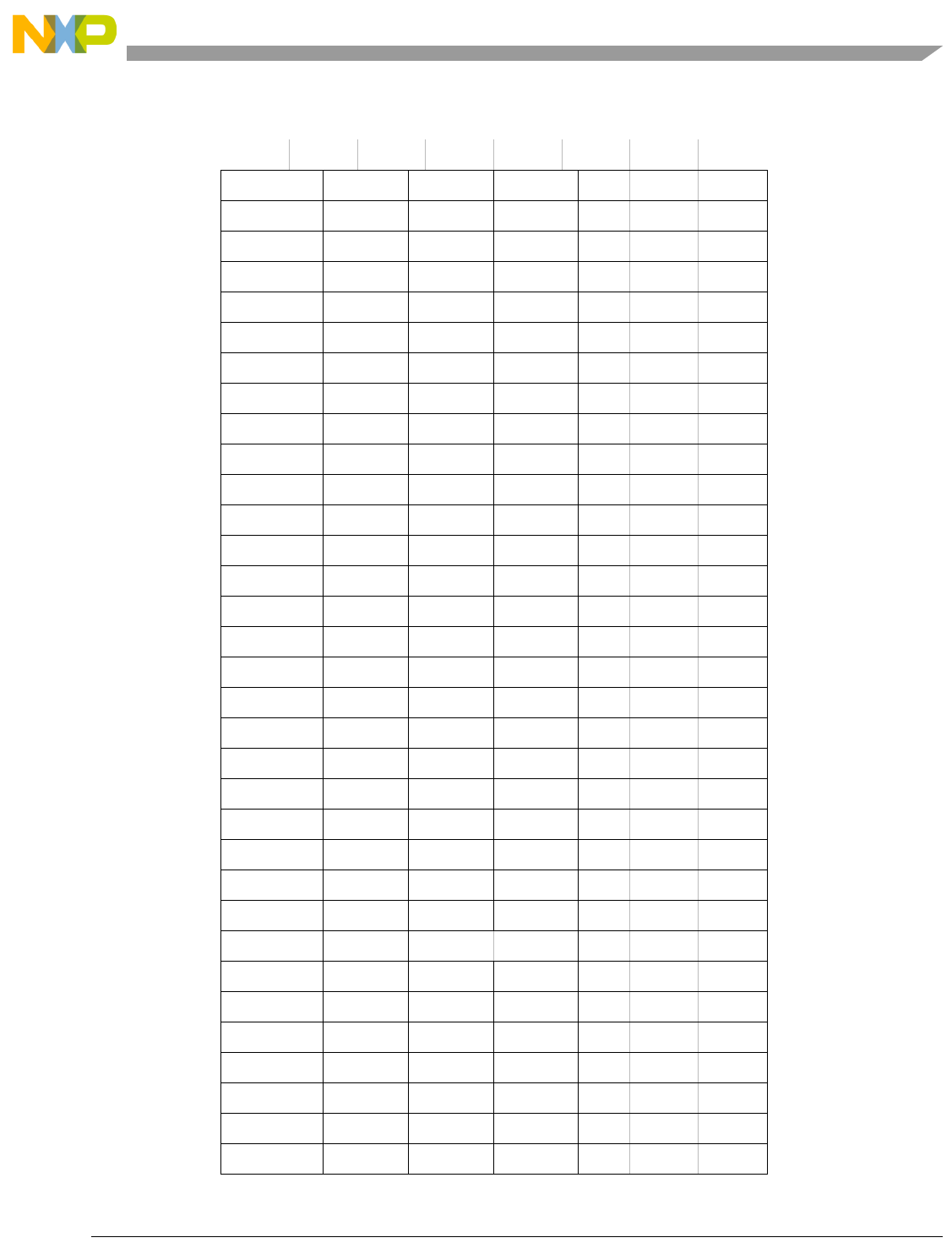

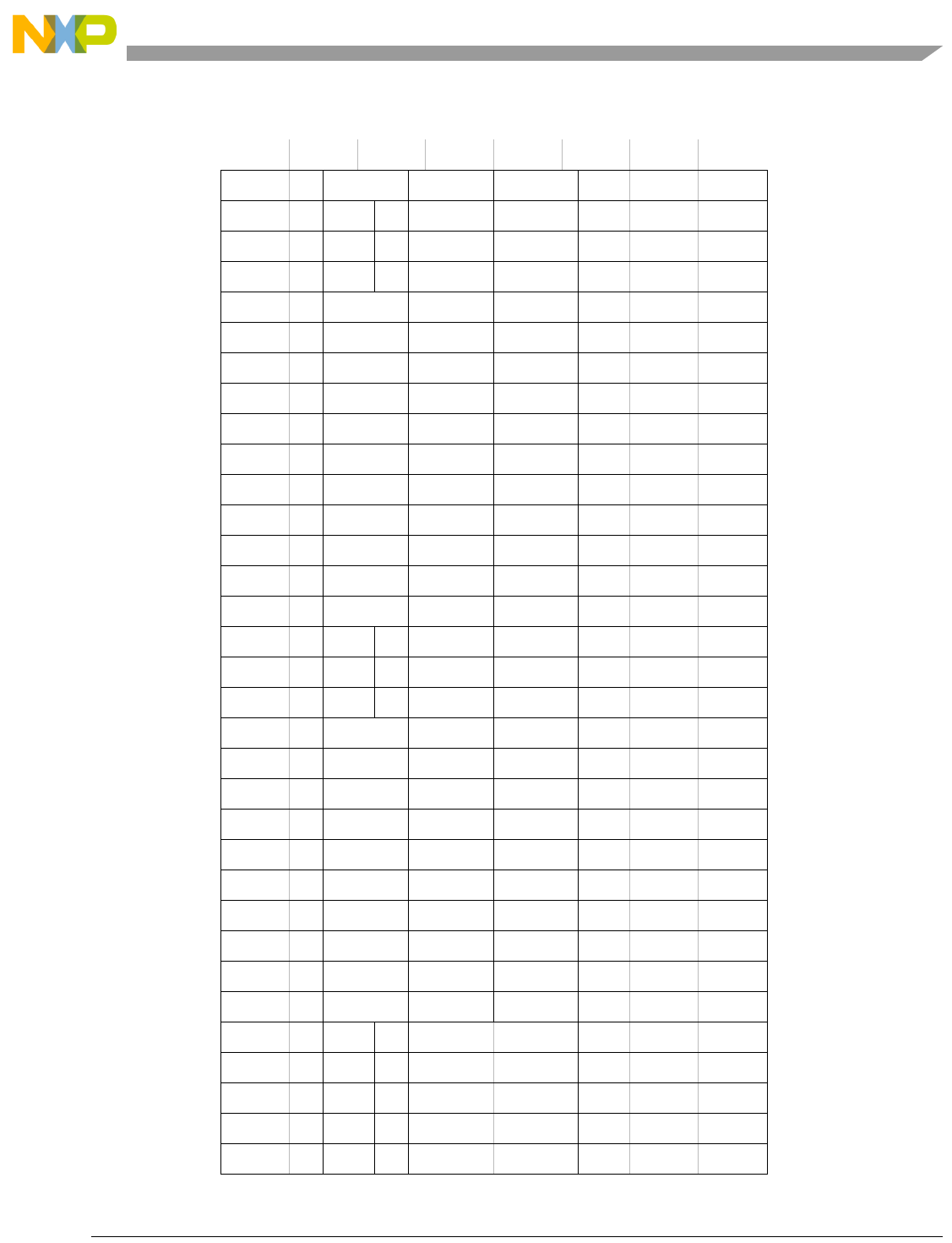

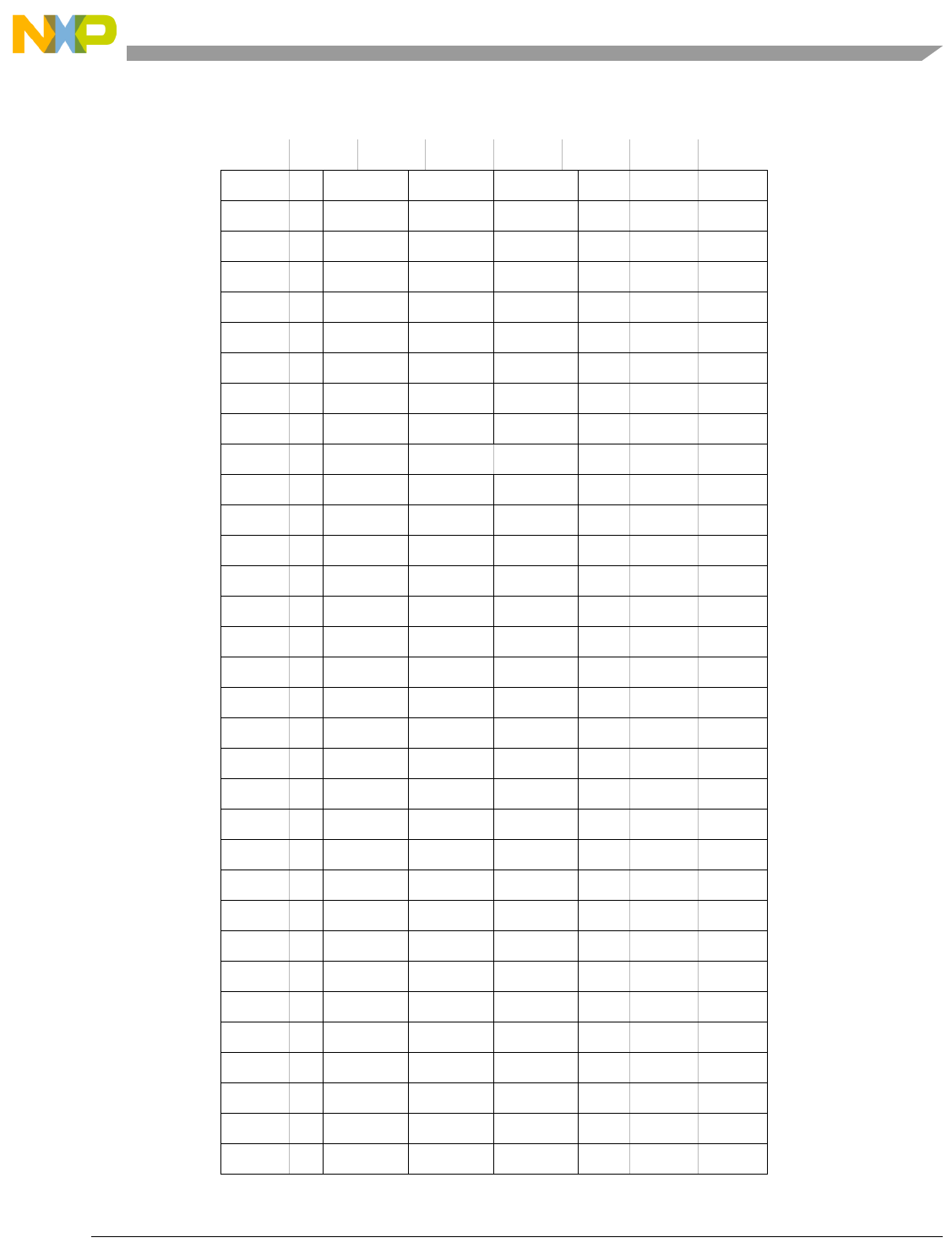

B-2 Instructions (Decimal and Hexadecimal) by Opcode .............................................................B-9

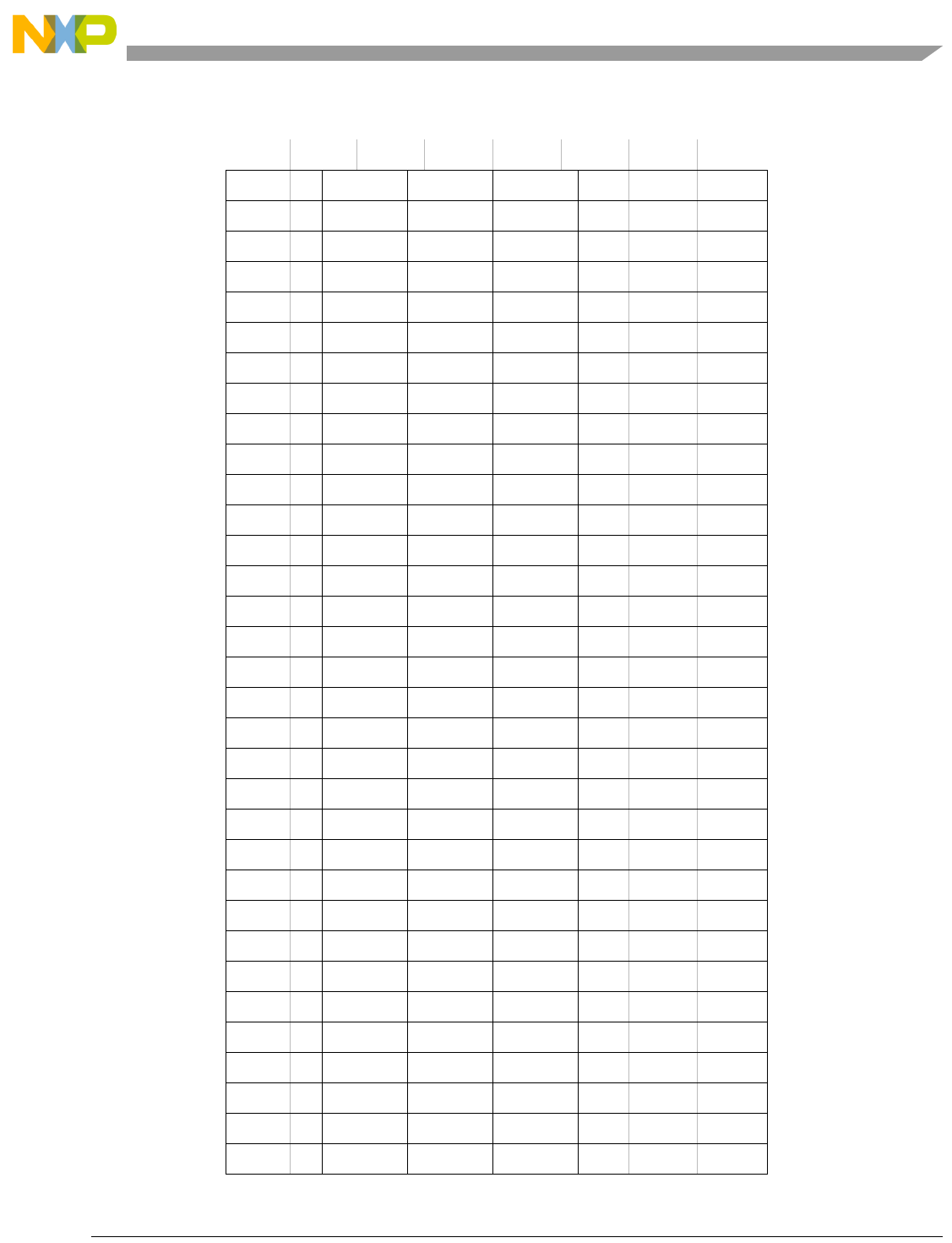

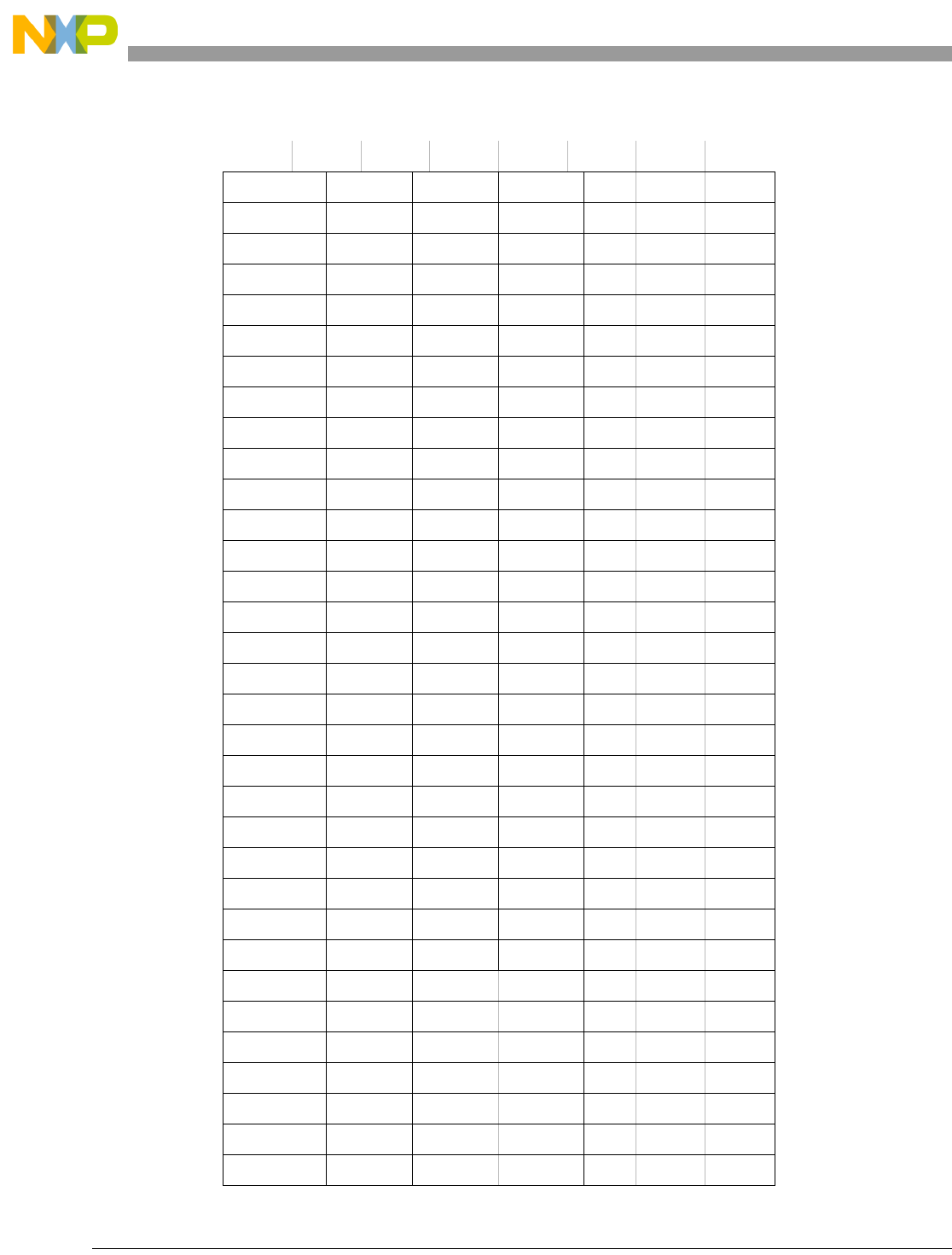

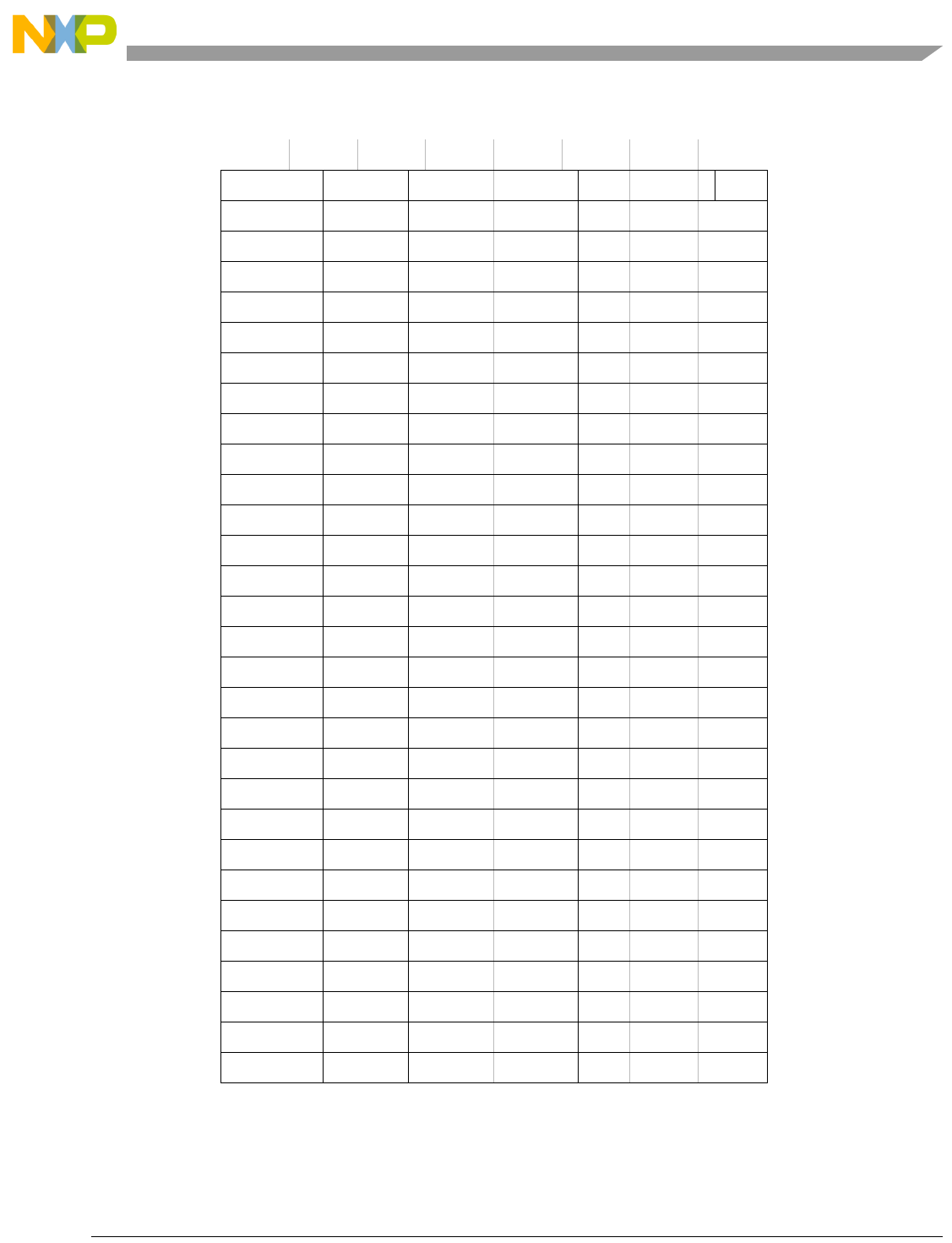

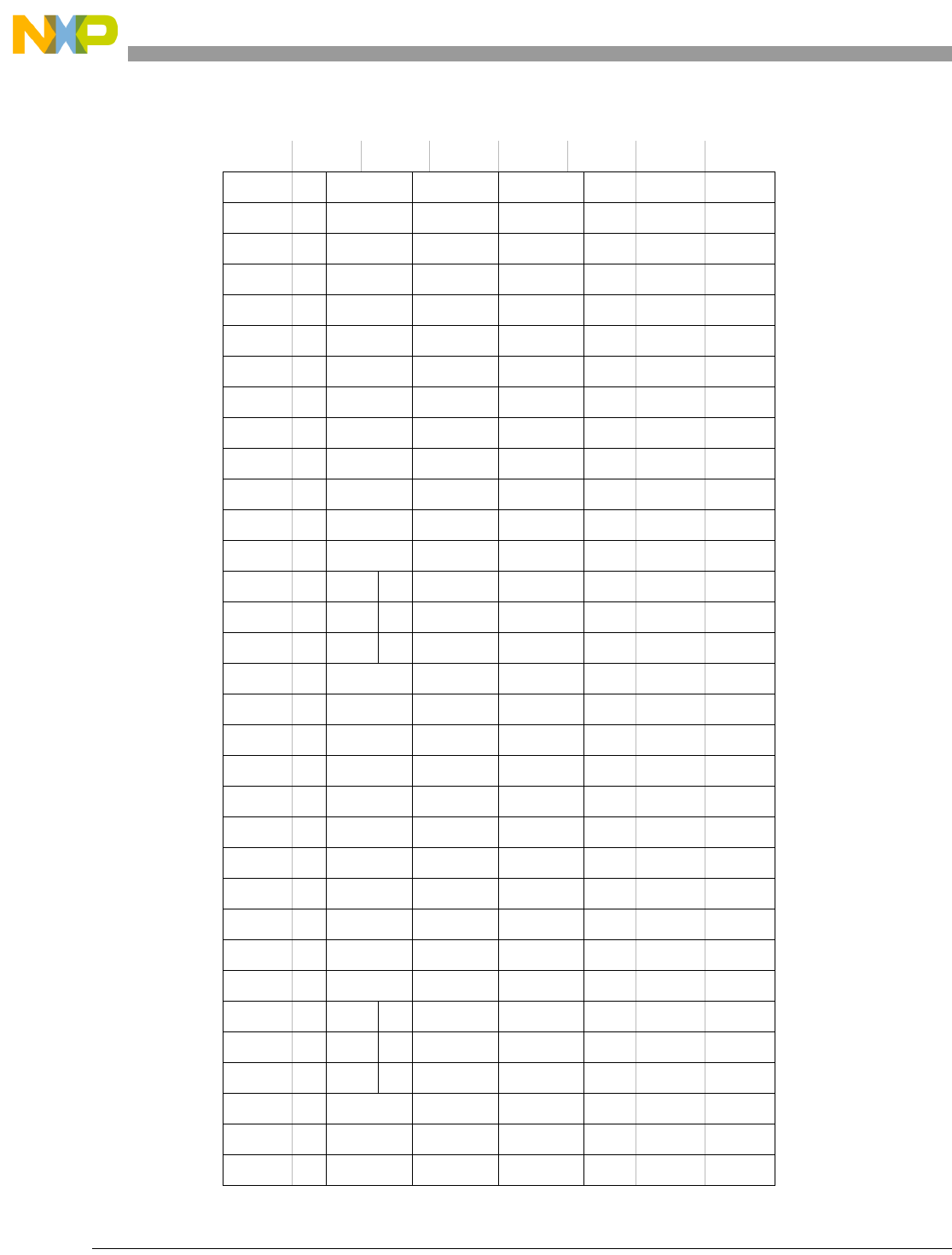

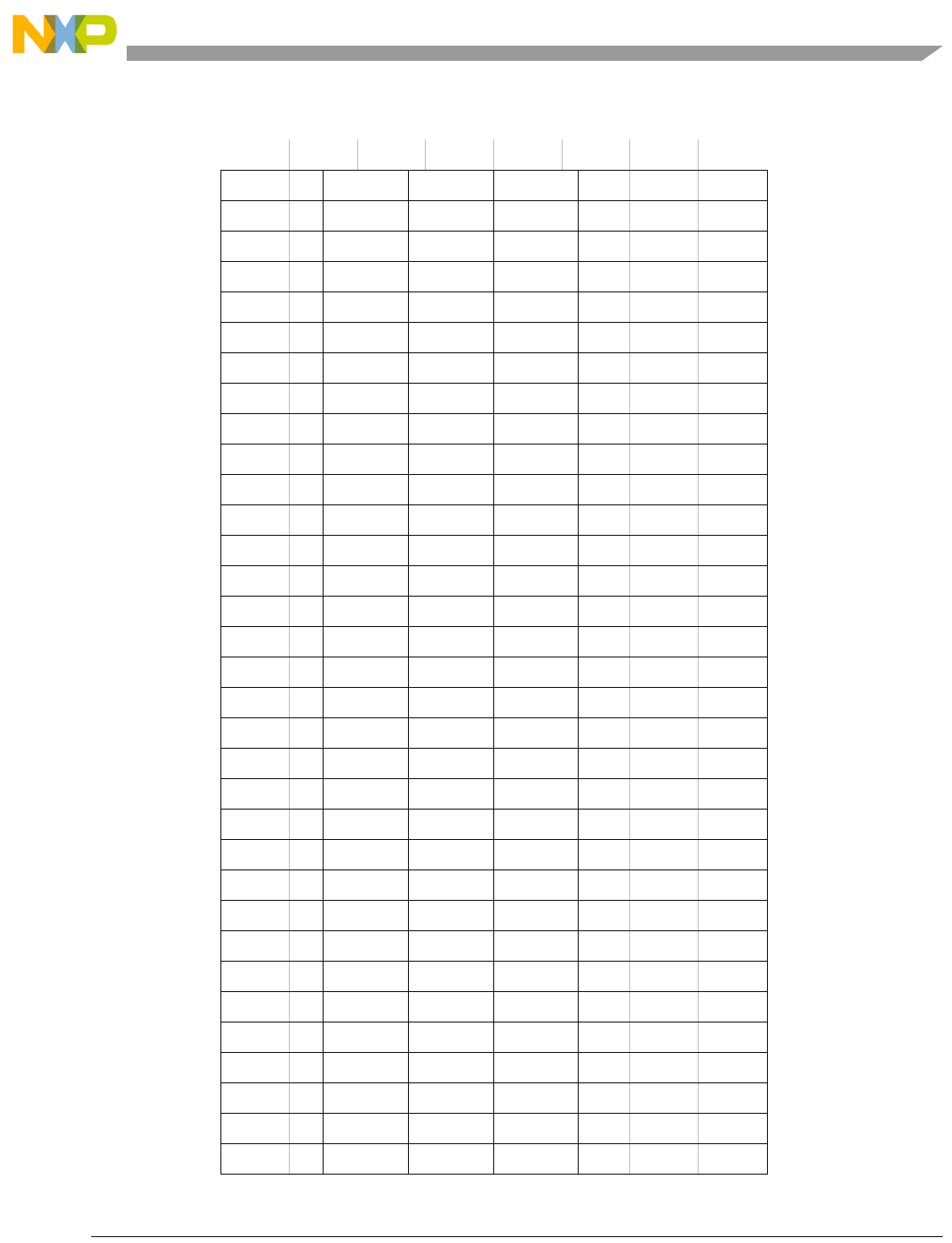

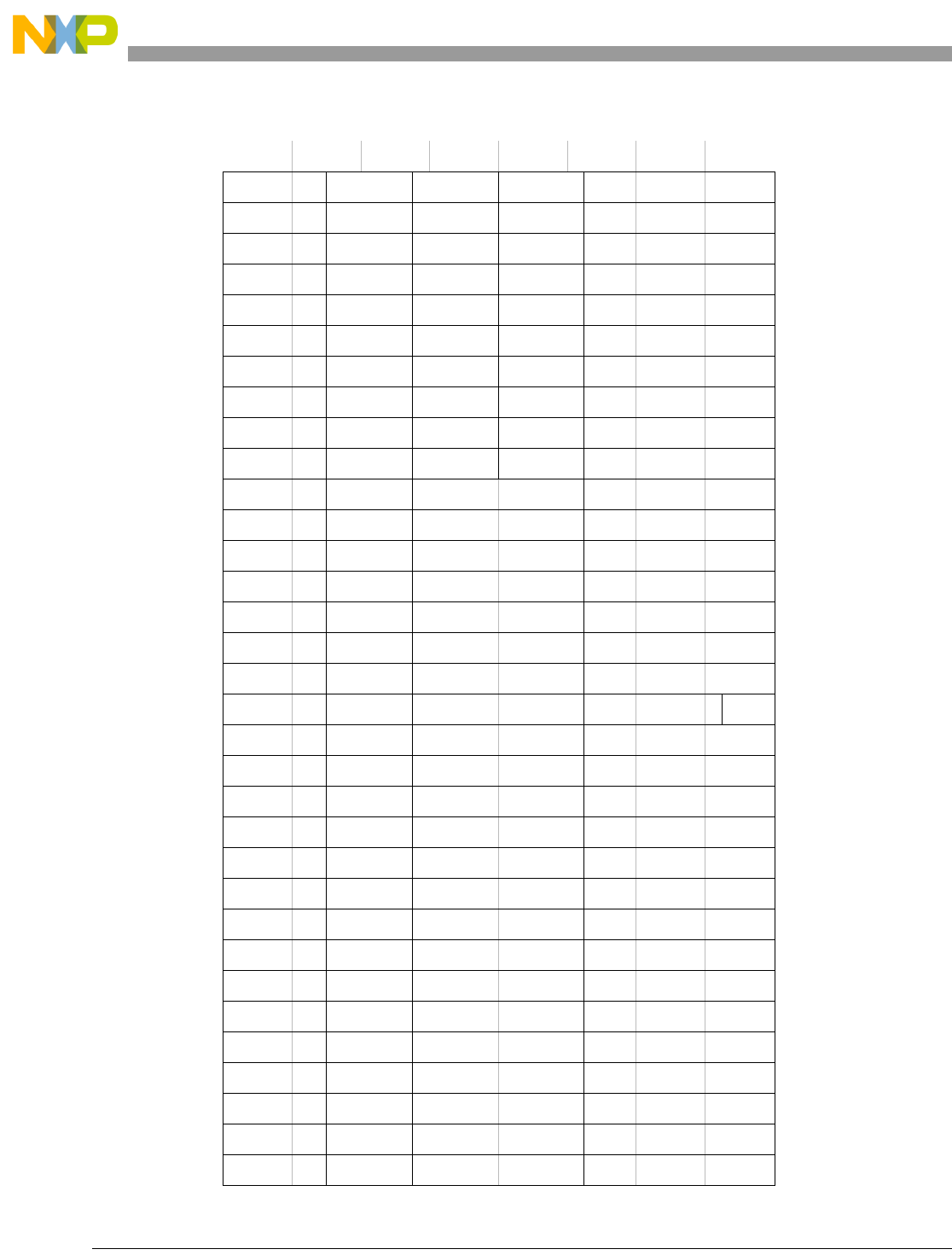

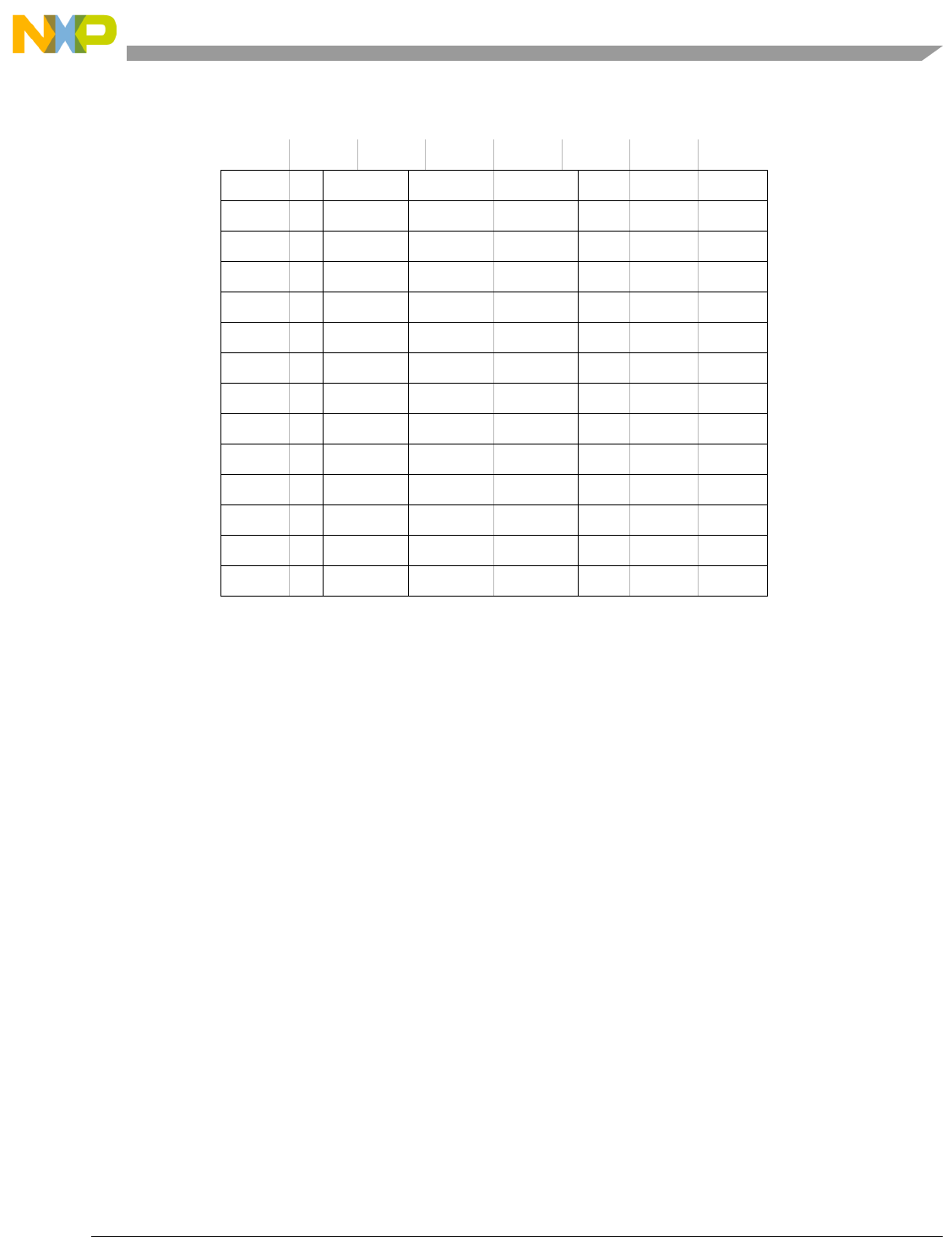

B-3 Instructions (Binary) by Form...............................................................................................B-16

Signal Processing Engine (SPE) Programming Environments Manual, Rev. 0

xiv Freescale Semiconductor

Tables

Table

Number Title

Page

Number

Signal Processing Engine (SPE) Programming Environments Manual, Rev. 0

Freescale Semiconductor xv

About This Book

The primary objective of this manual is to help programmers provide software compatible with processors

that implement the signal processing engine (SPE) and embedded floating-point instruction sets.

To locate any published errata or updates for this document, refer to the web at http://www.freescale.com.

This book is used as a reference guide for assembler programmers. It uses a standardized format instruction

to describe each instruction, showing syntax, instruction format, register translation language (RTL) code

that describes how the instruction works, and a listing of which, if any, registers are affected. At the bottom

of each instruction entry is a figure that shows the operations on elements within source operands and

where the results of those operations are placed in the destination operand.

The SPE Programming Interface Manual (SPEPIM) is a reference guide for high-level programmers. The

VLEPIM describes how programmers can access SPE functionality from programming languages such as

C and C++. It defines a programming model for use with the SPE instruction set. Processors that

implement the Power ISA™ (instruction set architecture) use the SPE instruction set as an extension to the

base and embedded categories of the Power ISA.

Because it is important to distinguish among the categories of the Power ISA to ensure compatibility

across multiple platforms, those distinctions are shown clearly throughout this book. This document stays

consistent with the Power ISA in referring to three levels, or programming environments, which are as

follows:

• User instruction set architecture (UISA)—The UISA defines the level of the architecture to which

user-level software should conform. The UISA defines the base user-level instruction set,

user-level registers, data types, memory conventions, and the memory and programming models

seen by application programmers.

• Virtual environment architecture (VEA)—The VEA, which is the smallest component of the

architecture, defines additional user-level functionality that falls outside typical user-level software

requirements. The VEA describes the memory model for an environment in which multiple

processors or other devices can access external memory and defines aspects of the cache model and

cache control instructions from a user-level perspective. VEA resources are particularly useful for

optimizing memory accesses and for managing resources in an environment in which other

processors and other devices can access external memory.

Implementations that conform to the VEA also conform to the UISA but may not necessarily

adhere to the OEA.

• Operating environment architecture (OEA)—The OEA defines supervisor-level resources

typically required by an operating system. It defines the memory management model,

supervisor-level registers, and the exception model.

Implementations that conform to the OEA also conform to the UISA and VEA.

Signal Processing Engine (SPE) Programming Environments Manual, Rev. 0

xvi Freescale Semiconductor

Most of the discussions on the SPE are at the UISA level. For ease in reference, this book and the processor

reference manuals have arranged the architecture information into topics that build on one another,

beginning with a description and complete summary of registers and instructions (for all three

environments) and progressing to more specialized topics such as the cache, exception, and memory

management models. As such, chapters may include information from multiple levels of the architecture,

but when discussing OEA and VEA, the level is noted in the text.

It is beyond the scope of this manual to describe individual devices that implement SPE. It must be kept

in mind that each processor that implements the Power ISA is unique in its implementation.

The information in this book is subject to change without notice, as described in the disclaimers on the title

page of this book. As with any technical documentation, it is the readers’ responsibility to be sure they are

using the most recent version of the documentation. For more information, contact your sales

representative or visit our web site at http://www.freescale.com.

Audience

This manual is intended for system software and hardware developers, and for application programmers

who want to develop products using the SPE. It is assumed that the reader understands operating systems,

microprocessor system design, the basic principles of RISC processing, and details of the Power ISA.

This book describes how SPE interacts with the other components of the architecture.

Organization

Following is a summary and a brief description of the major sections of this manual:

•Chapter 1, “Overview,” is useful for those who want a general understanding of the features and

functions of the SPE. This chapter provides an overview of how the VLE defines the register set,

operand conventions, addressing modes, instruction set, and interrupt model.

•Chapter 2, “SPE Register Model,” lists the register resources defined by the SPE and embedded

floating-point ISAs. It also lists base category resources that are accessed by SPE and embedded

floating-point instructions.

•Chapter 3, “SPE and Embedded Floating-Point Instruction Model,” describes the SPE and

embedded floating-point instruction set, including operand conventions, addressing modes, and

instruction syntax. It also provides a brief description of instructions grouped by category.

•Chapter 5, “Instruction Set,” functions as a handbook for the SPE and embedded floating-point

instruction set. Instructions are sorted by mnemonic. Each instruction description includes the

instruction formats and figures where it helps in understanding what the instruction does.

•Appendix A, “Embedded Floating-Point Results Summary,” summarizes the results of various

types of embedded floating-point operations on various combinations of input operands.

•Appendix B, “SPE and Embedded Floating-Point Opcode Listings,” lists all SPE and

embedded-floating point instructions, grouped according to mnemonic and opcode.

This manual also includes an index.

Signal Processing Engine (SPE) Programming Environments Manual, Rev. 0

Freescale Semiconductor xvii

Suggested Reading

This section lists additional reading that provides background for the information in this manual as well as

general information about the VLE and the Power ISA.

General Information

The following documentation provides useful information about the Power Architecture™ technology and

computer architecture in general:

•Computer Architecture: A Quantitative Approach, Third Edition, by John L. Hennessy and

David A. Patterson.

•Computer Organization and Design: The Hardware/Software Interface, Third Edition,

David A. Patterson and John L. Hennessy.

Related Documentation

Freescale documentation is available from the sources listed on the back of the title page; the document

order numbers, when applicable, are included in parentheses for ease in ordering:

•EREF: A Programmer's Reference Manual for Freescale Embedded Processors (EREFRM).

Describes the programming, memory management, cache, and interrupt models defined by the

Power ISA for embedded environment processors.

•Power ISA™. The latest version of the Power ISA can be downloaded from the website

www.power.org.

•Variable-Length Encoding (VLE) Extension Programming Interface Manual (VLEPIM). Provides

the VLE-specific extensions to the e500 application binary interface.

•e500 Application Binary Interface User's Guide (E500ABIUG). Establishes a standard binary

interface for application programs on systems that implement the interfaces defined in the System

V Interface Definition, Issue 3. This includes systems that have implemented UNIX System V

Release 4.

• Reference manuals. The following reference manuals provide details information about processor

cores and integrated devices:

— Core reference manuals—These books describe the features and behavior of individual

microprocessor cores and provide specific information about how functionality described in

the EREF is implemented by a particular core. They also describe implementation-specific

features and microarchitectural details, such as instruction timing and cache hardware details,

that lie outside the architecture specification.

— Integrated device reference manuals—These manuals describe the features and behavior of

integrated devices that implement a Power ISA processor core. It is important to understand

that some features defined for a core may not be supported on all devices that implement that

core.

Also, some features are defined in a general way at the core level and have meaning only in the

context of how the core is implemented. For example, any implementation-specific behavior

of register fields can be described only in the reference manual for the integrated device.

Signal Processing Engine (SPE) Programming Environments Manual, Rev. 0

xviii Freescale Semiconductor

Each of these documents include the following two chapters that are pertinent to the core:

– A core overview. This chapter provides a general overview of how the core works and

indicates which of a core’s features are implemented on the integrated device.

– A register summary chapter. This chapter gives the most specific information about how

register fields can be interpreted in the context of the implementation.

These reference manuals also describe how the core interacts with other blocks on the integrated

device, especially regarding topics such as reset, interrupt controllers, memory and cache

management, debug, and global utilities.

• Addenda/errata to reference manuals—Errata documents are provided to address errors in

published documents.

Because some processors have follow-on parts, often an addendum is provided that describes the

additional features and functionality changes. These addenda, which may also contain errata, are

intended for use with the corresponding reference manuals.

Always check the Freescale website for updates to reference manuals.

• Hardware specifications—Hardware specifications provide specific data regarding bus timing;

signal behavior; AC, DC, and thermal characteristics; and other design considerations.

• Product brief—Each integrated device has a product brief that provides an overview of its features.

This document is roughly the equivalent to the overview (Chapter 1) of the device’s reference

manual.

• Application notes—These short documents address specific design issues useful to programmers

and engineers working with Freescale processors.

Additional literature is published as new processors become available. For current documentation, refer to

http://www.freescale.com.

Conventions

This document uses the following notational conventions:

cleared/set When a bit takes the value zero, it is said to be cleared; when it takes a value of

one, it is said to be set.

mnemonics Instruction mnemonics are shown in lowercase bold

italics Italics indicate variable command parameters, for example, bcctrx

Book titles in text are set in italics

0x0 Prefix to denote hexadecimal number

0b0 Prefix to denote binary number

rA, rB Instruction syntax used to identify a source general-purpose register (GPR)

rD Instruction syntax used to identify a destination GPR

frA, frB, frC Instruction syntax used to identify a source floating-point register (FPR)

frD Instruction syntax used to identify a destination FPR

REG[FIELD] Abbreviations for registers are shown in uppercase text. Specific bits, fields, or

ranges appear in brackets.

Signal Processing Engine (SPE) Programming Environments Manual, Rev. 0

Freescale Semiconductor xix

x In some contexts, such as signal encodings, an unitalicized x indicates a don’t

care.

xAn italicized x indicates an alphanumeric variable

nAn italicized n indicates a numeric variable

¬ NOT logical operator

& AND logical operator

| OR logical operator

Indicates reserved bits or bit fields in a register. Although these bits may be written

to as ones or zeros, they are always read as zeros.

Additional conventions used with instruction encodings are described in Section 5.1, “Notation.”

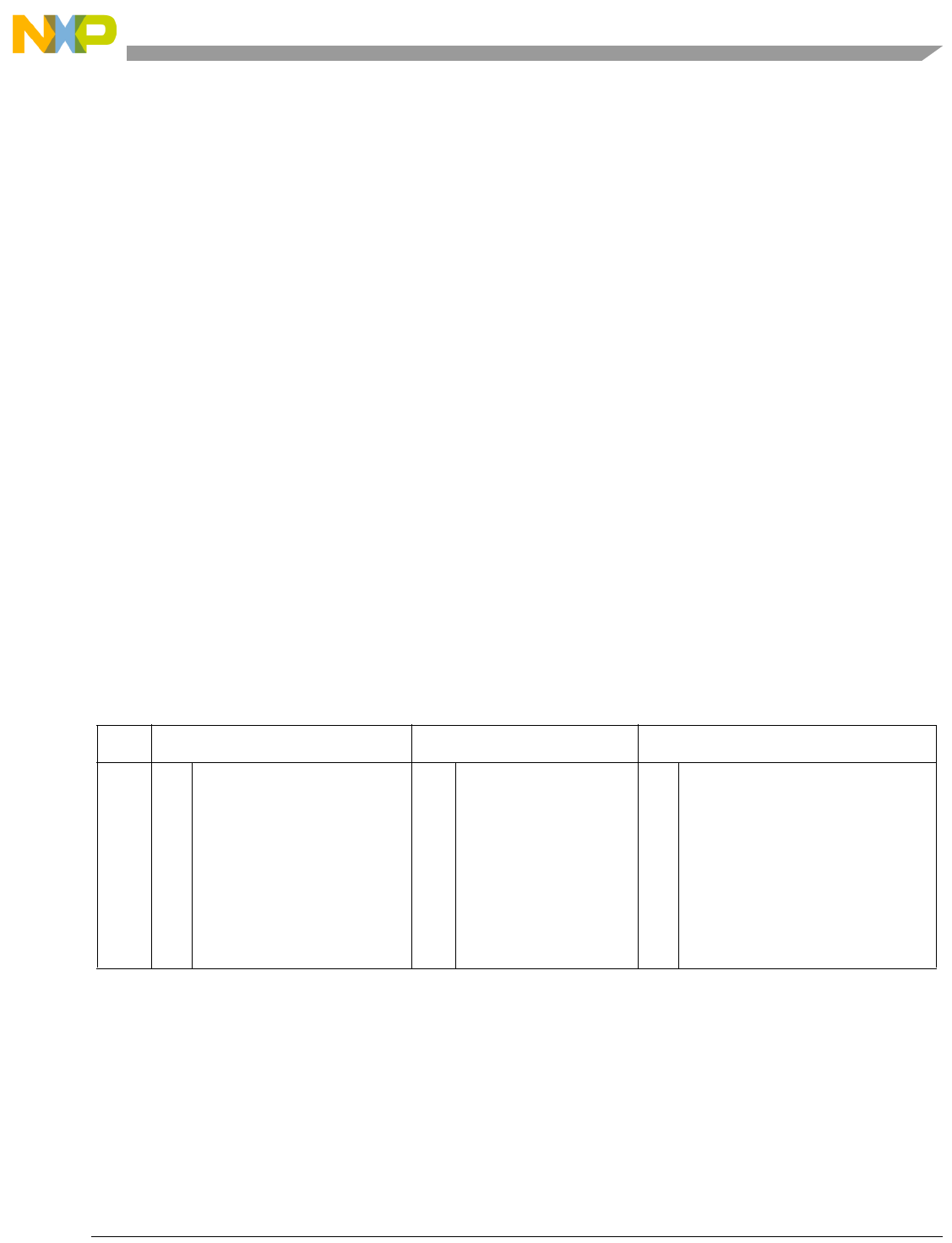

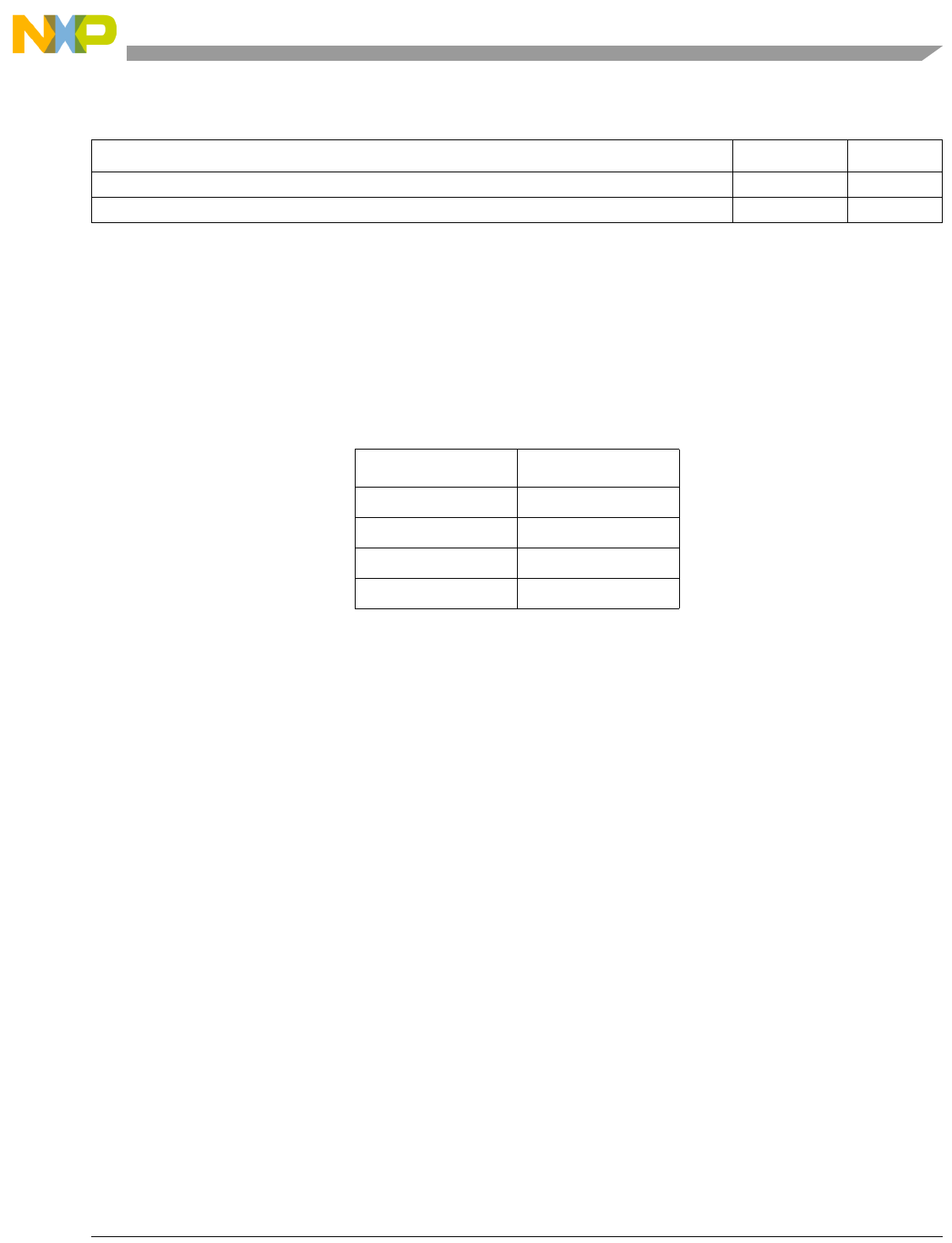

Acronyms and Abbreviations

Table i contains acronyms and abbreviations that are used in this document. Note that the meanings for

some acronyms (such as XER) are historical, and the words for which an acronym stands may not be

intuitively obvious.

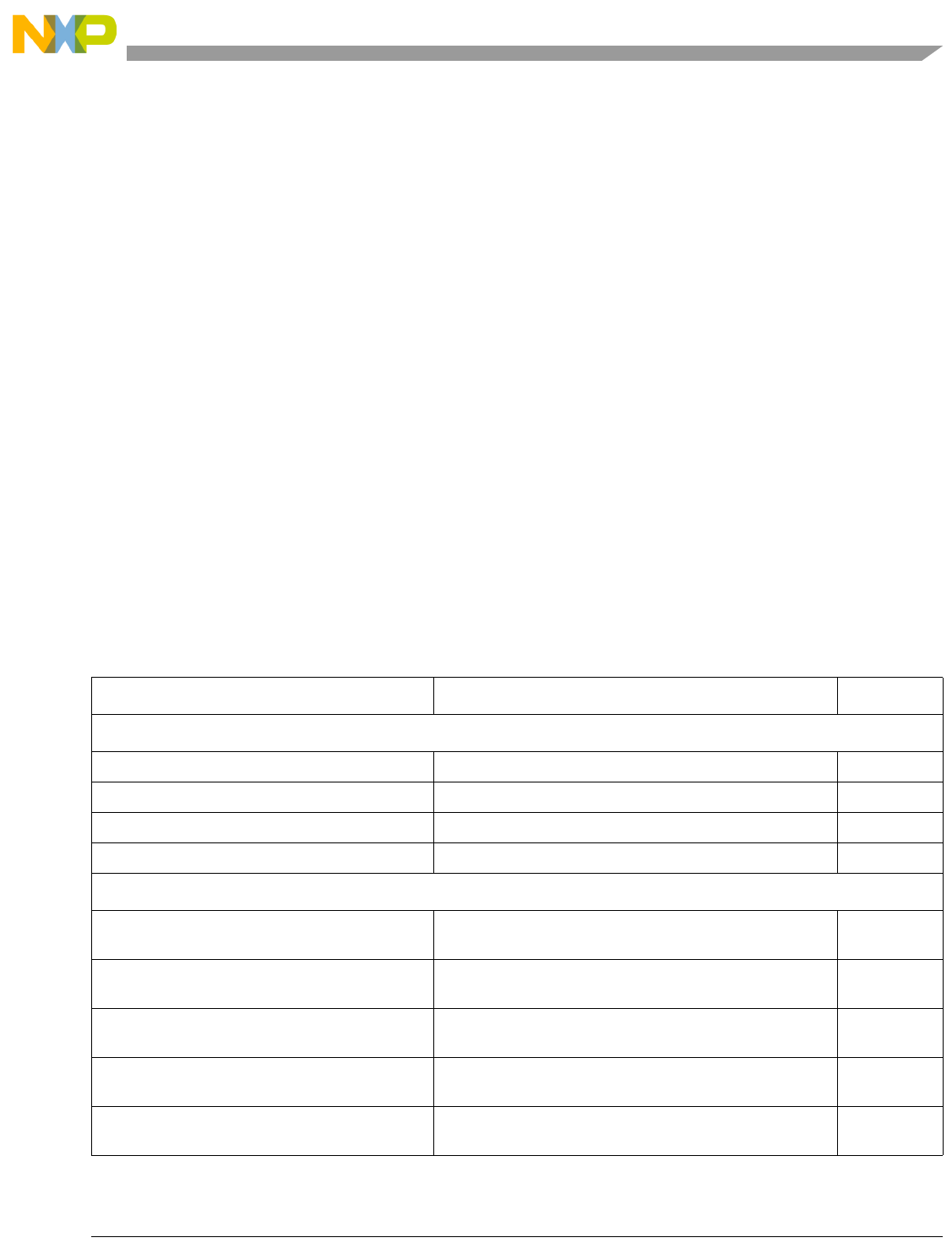

Table i. Acronyms and Abbreviated Terms

Term Meaning

CR Condition register

CTR Count register

DEC Decrementer register

EA Effective address

EREF

A Programmer's Reference Manual for Freescale Embedded Processors (Including the e200 and e500

Families)

GPR General-purpose register

IEEE Institute of Electrical and Electronics Engineers

IU Integer unit

LR Link register

LRU Least recently used

LSB Least significant byte

lsb Least significant bit

LSU Load/store unit

MMU Memory management unit

MSB Most significant byte

msb Most significant bit

MSR Machine state register

NaN Not a number

No-op No operation

OEA Operating environment architecture

0 0 0 0

Signal Processing Engine (SPE) Programming Environments Manual, Rev. 0

xx Freescale Semiconductor

Terminology Conventions

Table ii lists certain terms used in this manual that differ from the architecture terminology conventions.

PMC

n

Performance monitor counter register

PVR Processor version register

RISC Reduced instruction set computing

RTL Register transfer language

SIMM Signed immediate value

SPR Special-purpose register

SRR0 Machine status save/restore register 0

SRR1 Machine status save/restore register 1

TB Time base facility

TBL Time base lower register

TBU Time base upper register

TLB Translation lookaside buffer

UIMM Unsigned immediate value

UISA User instruction set architecture

VA Virtual address

VEA Virtual environment architecture

VLEPEM

Variable-Length Encoding (VLE) Programming Environments Manual

VLEPIM

Variable-Length Encoding (VLE) Extension Programming Interface Manual (VLEPIM)

XER Register used for indicating conditions such as carries and overflows for integer operations

Table ii. Terminology Conventions

The Architecture Specification This Manual

Extended mnemonics Simplified mnemonics

Fixed-point unit (FXU) Integer unit (IU)

Privileged mode (or privileged state) Supervisor-level privilege

Problem mode (or problem state) User-level privilege

Real address Physical address

Relocation Translation

Storage (locations) Memory

Storage (the act of) Access

Store in Write back

Store through Write through

Table i. Acronyms and Abbreviated Terms (continued)

Term Meaning

Signal Processing Engine (SPE) Programming Environments Manual, Rev. 0

Freescale Semiconductor xxi

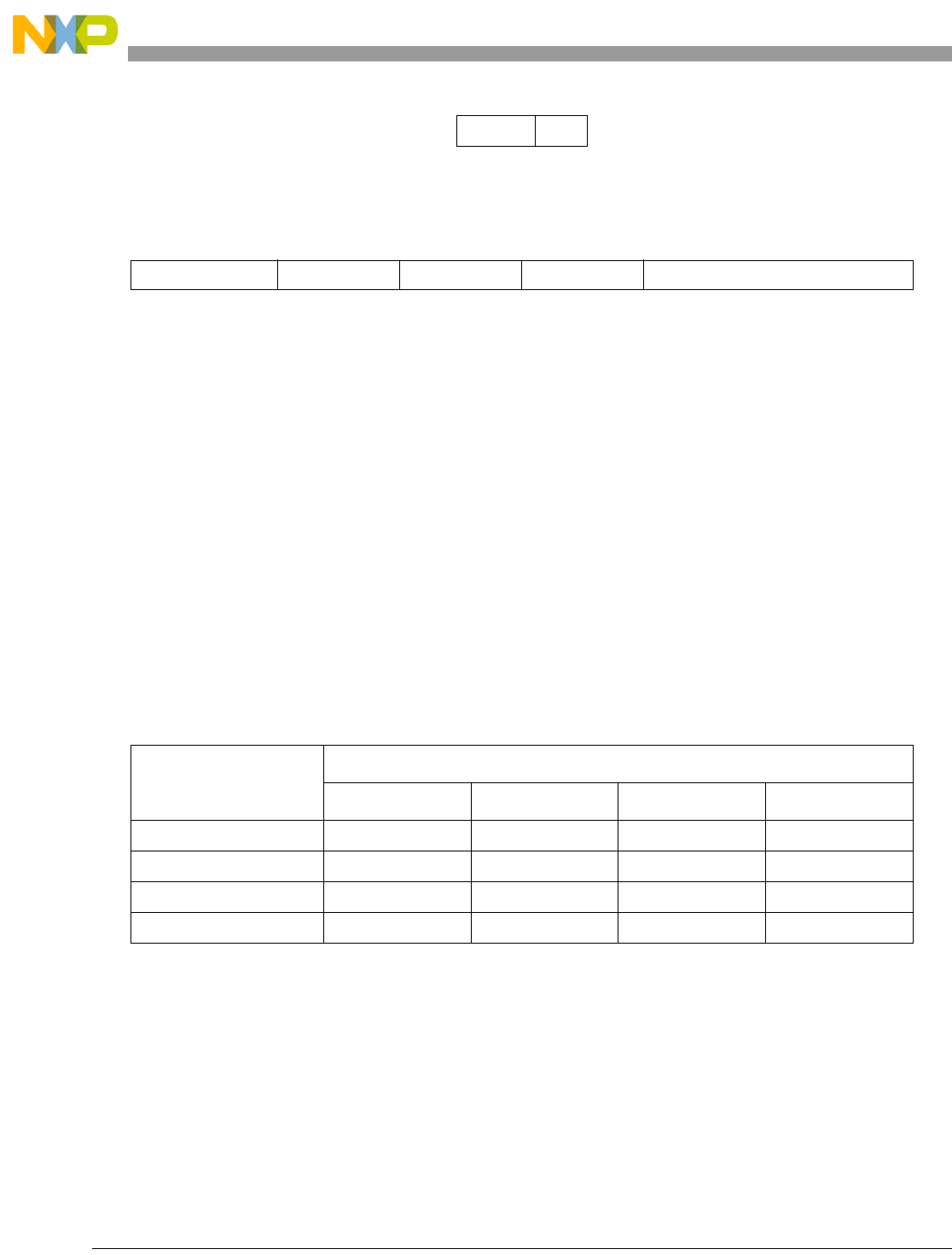

Table iii describes instruction field notation conventions used in this manual.

Table iii. Instruction Field Conventions

The Architecture Specification Equivalent to:

BA, BB, BT crbA, crbB, crbD (respectively)

BF, BFA crfD, crfS (respectively)

Dd

DS ds

/, //, /// 0...0 (shaded)

RA, RB, RT, RS rA, rB, rD, rS (respectively)

SI SIMM

UIMM

UI UIMM

Signal Processing Engine (SPE) Programming Environments Manual, Rev. 0

xxii Freescale Semiconductor

Signal Processing Engine (SPE) Programming Environments Manual, Rev. 0

Freescale Semiconductor 1-1

Chapter 1

Overview

This chapter provides a general description of the signal processing engine (SPE) and the SPE embedded

floating-point resources defined as part of the Power ISA™ (instruction set architecture).

1.1 Overview

The SPE is a 64-bit, two-element, single-instruction multiple-data (SIMD) ISA, originally designed to

accelerate signal processing applications normally suited to DSP operation. The two-element vectors fit

within GPRs extended to 64 bits. SPE also defines an accumulator register (ACC) to allow for

back-to-back operations without loop unrolling. Like the VEC category, SPE is primarily an extension of

Book I but identifies some resources for interrupt handling in Book III-E.

In addition to add and subtract to accumulator operations, the SPE supports a number of forms of multiply

and multiply-accumulate operations, as well as negative accumulate forms. These instructions are

summarized in Table 1-3. The SPE supports signed, unsigned, and fractional forms. For these instructions,

the fractional form does not apply to unsigned forms, because integer and fractional forms are identical for

unsigned operands.

Mnemonics for SPE instructions generally begin with the letters ‘ev’ (embedded vector).

The SPE is part of the Power ISA specification (where it is referred to as the category SPE). Closely

associated with the SPE are the embedded floating-point categories, which may be implemented if the SPE

is implemented and which consist of the following:

• Single-precision scalar (SP.FS)

• Single-precision vector (SP.FV)

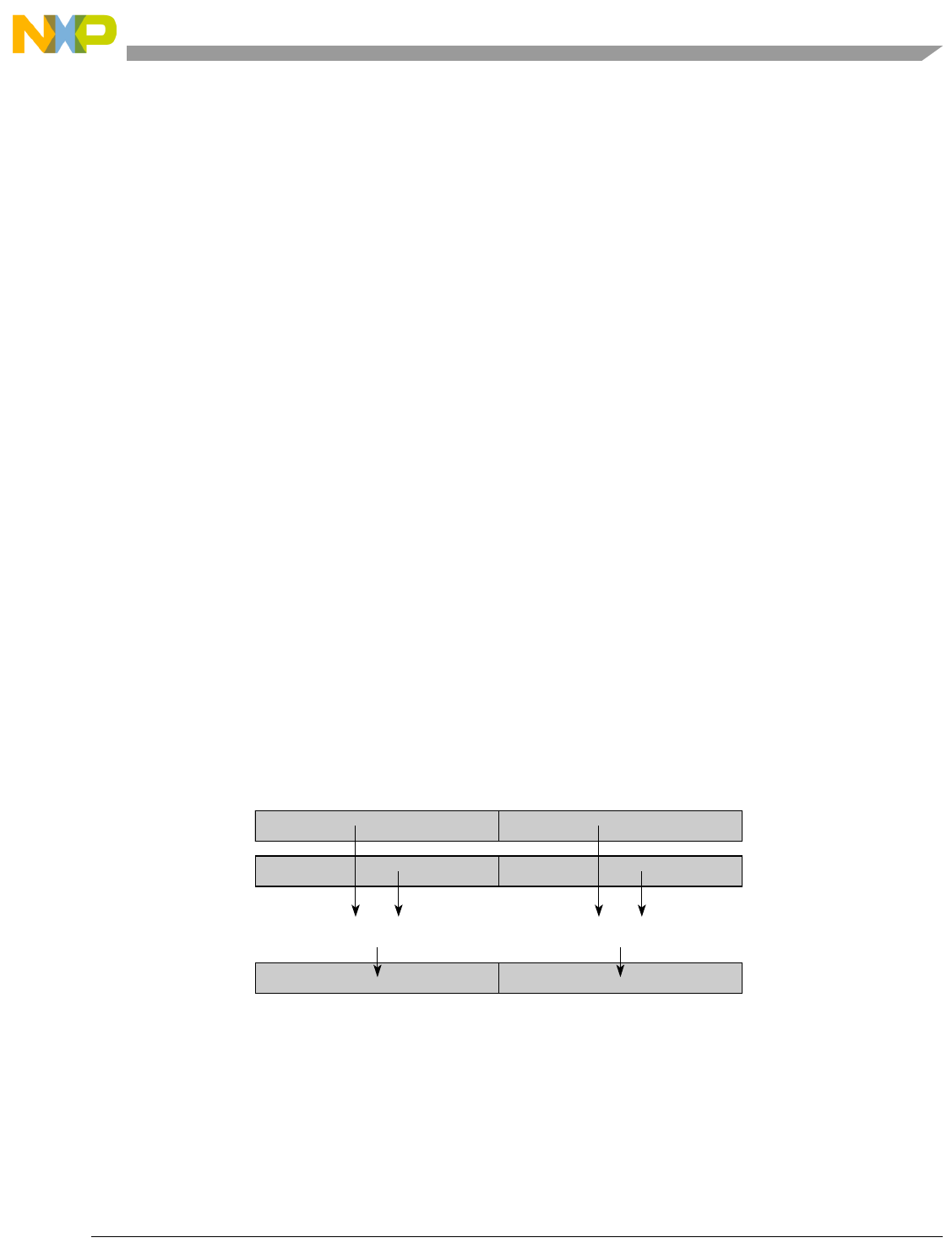

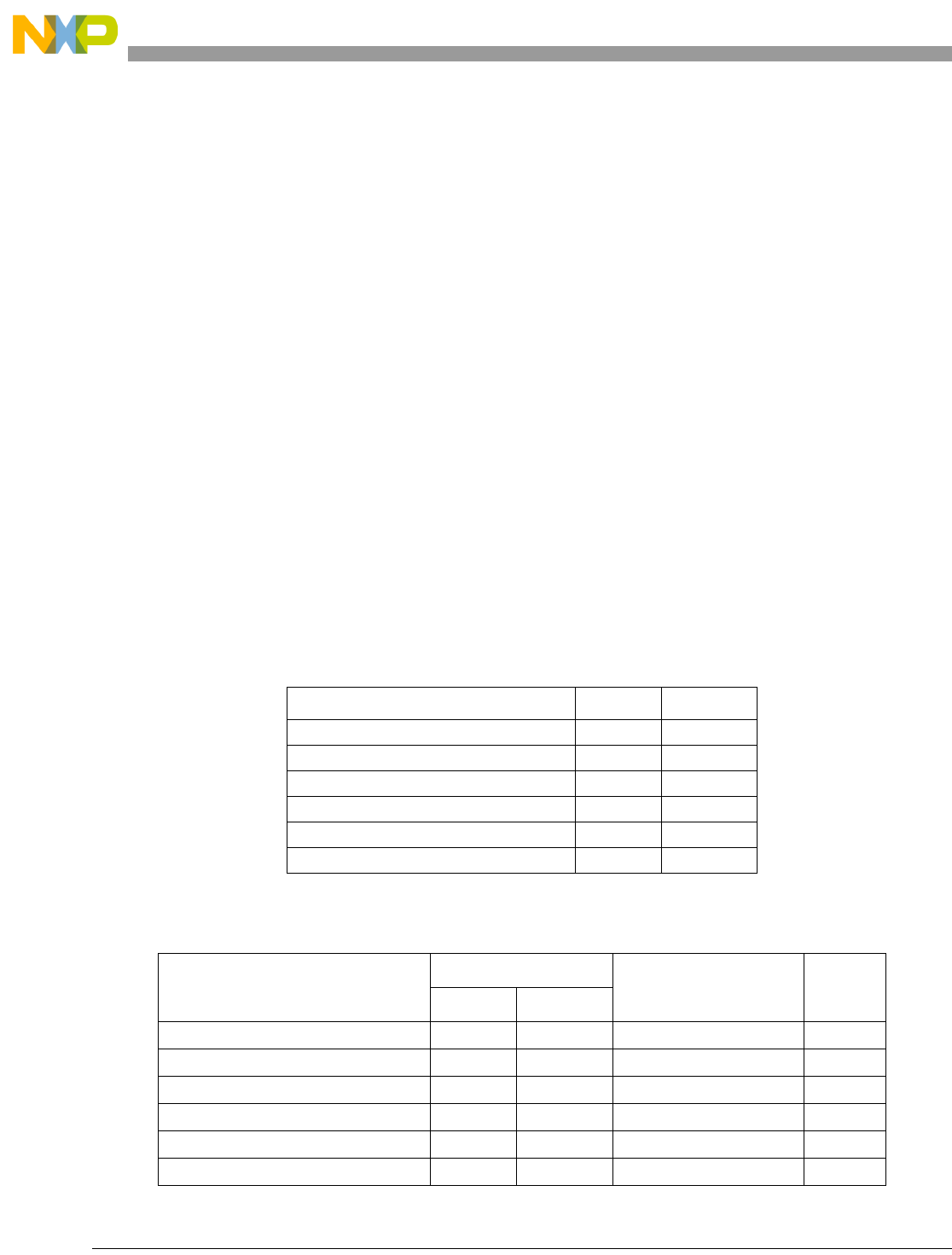

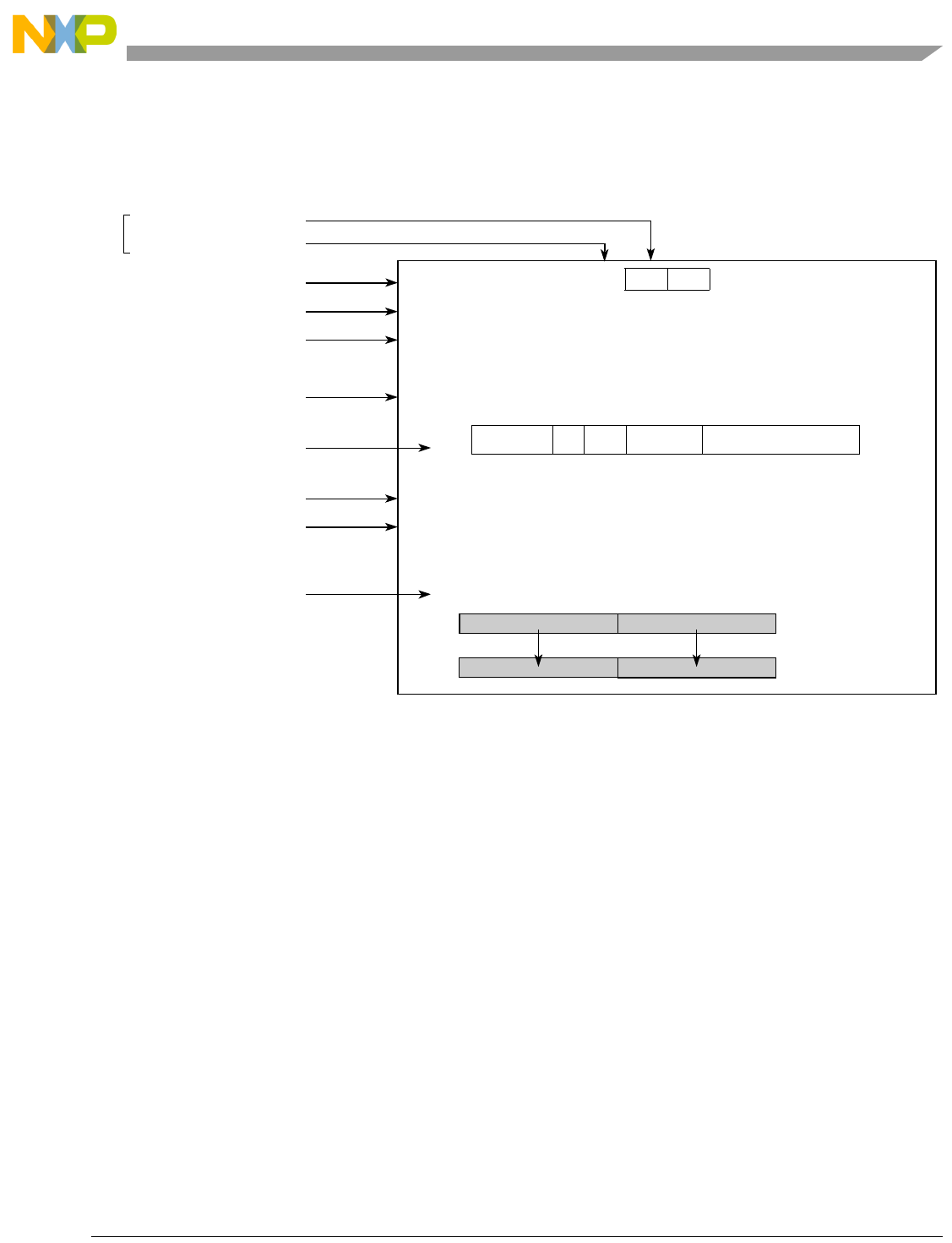

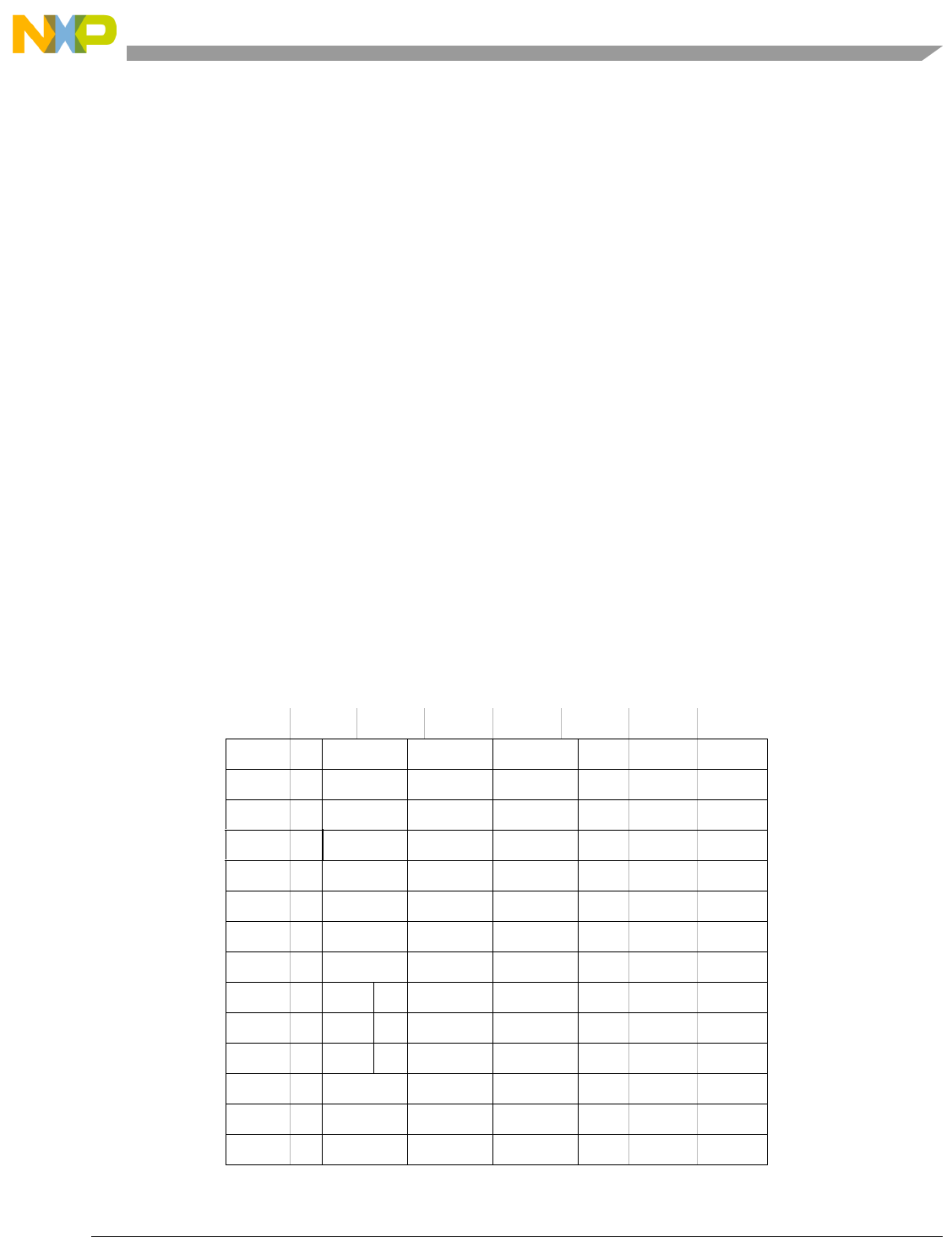

Table 1-1. SPE Vector Multiply Instruction Mnemonic Structure

Prefix Multiply Element Data Type Element Accumulate Element

evm

ho

he

hog

heg

wh

wl

whg

wlg

w

half odd (16x16->32)

half even (16x16->32)

half odd guarded (16x16->32)

half even guarded (16x16->32)

word high (32x32->32)

word low (32x32->32)

word high guarded (32x32->32)

word low guarded (32x32->32)

word (32x32->64)

usi

umi

ssi

ssf1

smi

smf1

1Low word versions of signed saturate and signed modulo fractional instructions are not supported. Attempting to execute an

opcode corresponding to these instructions causes boundedly undefined results.

unsigned saturate integer

unsigned modulo integer

signed saturate integer

signed saturate fractional

signed modulo integer

signed modulo fractional

a

aa

an

aaw

anw

write to ACC

write to ACC & added ACC

write to ACC & negate ACC

write to ACC & ACC in words

write to ACC & negate ACC in words

Overview

Signal Processing Engine (SPE) Programming Environments Manual, Rev. 0