Shane Cook CUDA Programming A Developer's Guide To Parallel Computing With GPUs Morgan Kaufmann (2012)

User Manual: Pdf

Open the PDF directly: View PDF ![]() .

.

Page Count: 591 [warning: Documents this large are best viewed by clicking the View PDF Link!]

- Front Cover

- CUDA Programming: A Developer’s Guide to Parallel Computing with GPUs

- Copyright

- Contents

- Preface

- Chapter 1 - A Short History of Supercomputing

- Chapter 2 - Understanding Parallelism with GPUs

- Chapter 3 - CUDA Hardware Overview

- Chapter 4 - Setting Up CUDA

- Chapter 5 - Grids, Blocks, and Threads

- Chapter 6 - Memory Handling with CUDA

- Chapter 7 - Using CUDA in Practice

- Chapter 8 - Multi-CPU and Multi-GPU Solutions

- Chapter 9 - Optimizing Your Application

- Chapter 10 - Libraries and SDK

- Chapter 11 - Designing GPU-Based Systems

- Chapter 12 - Common Problems, Causes, and Solutions

- Index

CUDA Programming

A Developer’s Guide to Parallel

Computing with GPUs

This page intentionally left blank

CUDA Programming

A Developer’s Guide to Parallel

Computing with GPUs

Shane Cook

AMSTERDAM • BOSTON • HEIDELBERG • LONDON

NEW YORK • OXFORD • PARIS • SAN DIEGO

SAN FRANCISCO • SINGAPORE • SYDNEY • TOKYO

Morgan Kaufmann is an Imprint of Elsevier

Acquiring Editor: Todd Green

Development Editor: Robyn Day

Project Manager: Andre Cuello

Designer: Kristen Davis

Morgan Kaufmann is an imprint of Elsevier

225 Wyman Street, Waltham, MA 02451, USA

Ó2013 Elsevier Inc. All rights reserved.

No part of this publication may be reproduced or transmitted in any form or by any means, electronic or

mechanical, including photocopying, recording, or any information storage and retrieval system, without

permission in writing from the publisher. Details on how to seek permission, further information about the

Publisher’s permissions policies and our arrangements with organizations such as the Copyright Clearance

Center and the Copyright Licensing Agency, can be found at our website: www.elsevier.com/permissions.

This book and the individual contributions contained in it are protected under copyright by the Publisher

(other than as may be noted herein).

Notices

Knowledge and best practice in this field are constantly changing. As new research and experience broaden our

understanding, changes in research methods or professional practices, may become necessary. Practitioners

and researchers must always rely on their own experience and knowledge in evaluating and using any information

or methods described herein. In using such information or methods they should be mindful of their own safety and

the safety of others, including parties for whom they have a professional responsibility.

To the fullest extent of the law, neither the Publisher nor the authors, contributors, or editors, assume any

liability for any injury and/or damage to persons or property as a matter of products liability, negligence or

otherwise, or from any use or operation of any methods, products, instructions, or ideas contained in the

material herein.

Library of Congress Cataloging-in-Publication Data

Application submitted

British Library Cataloguing-in-Publication Data

A catalogue record for this book is available from the British Library.

ISBN: 978-0-12-415933-4

For information on all MK publications

visit our website at http://store.elsevier.com

Printed in the United States of America

13 14 10 9 8 7 6 5 4 3 2 1

Contents

Preface ................................................................................................................................................ xiii

CHAPTER 1 A Short History of Supercomputing................................................1

Introduction ................................................................................................................ 1

Von Neumann Architecture........................................................................................ 2

Cray............................................................................................................................. 5

Connection Machine................................................................................................... 6

Cell Processor............................................................................................................. 7

Multinode Computing ................................................................................................ 9

The Early Days of GPGPU Coding ......................................................................... 11

The Death of the Single-Core Solution ................................................................... 12

NVIDIA and CUDA................................................................................................. 13

GPU Hardware ......................................................................................................... 15

Alternatives to CUDA .............................................................................................. 16

OpenCL ............................................................................................................... 16

DirectCompute .................................................................................................... 17

CPU alternatives.................................................................................................. 17

Directives and libraries ....................................................................................... 18

Conclusion ................................................................................................................ 19

CHAPTER 2 Understanding Parallelism with GPUs ......................................... 21

Introduction .............................................................................................................. 21

Traditional Serial Code ............................................................................................ 21

Serial/Parallel Problems ........................................................................................... 23

Concurrency.............................................................................................................. 24

Locality................................................................................................................ 25

Types of Parallelism ................................................................................................. 27

Task-based parallelism ........................................................................................ 27

Data-based parallelism ........................................................................................ 28

Flynn’s Taxonomy .................................................................................................... 30

Some Common Parallel Patterns.............................................................................. 31

Loop-based patterns ............................................................................................ 31

Fork/join pattern.................................................................................................. 33

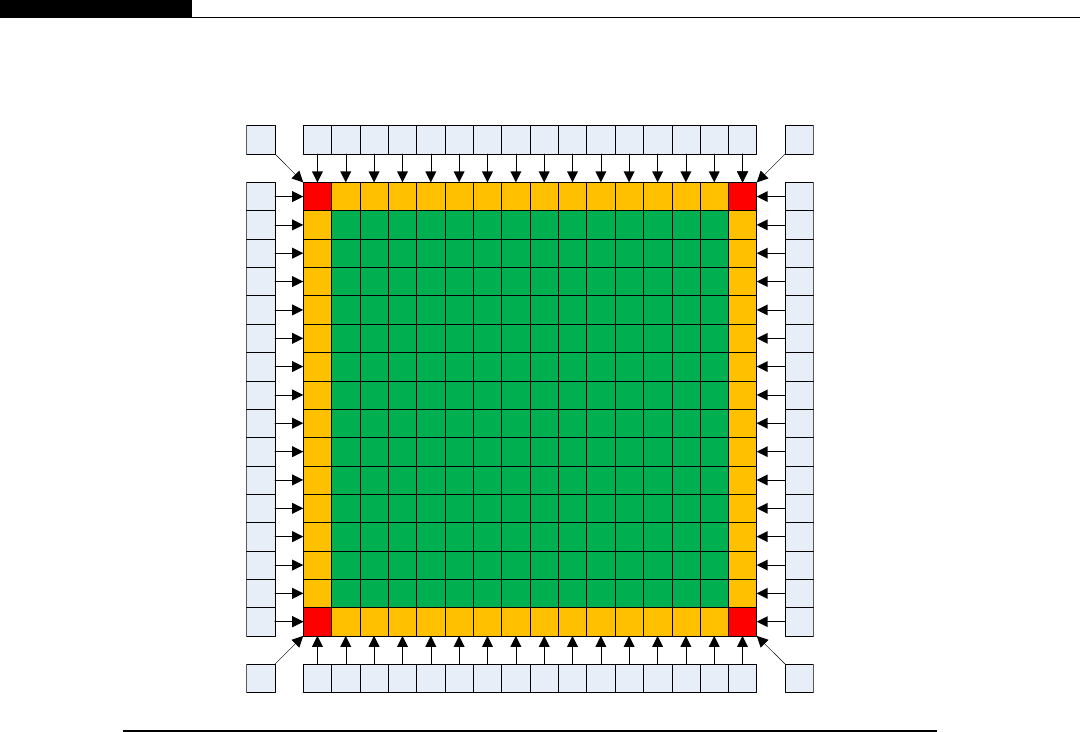

Tiling/grids .......................................................................................................... 35

Divide and conquer ............................................................................................. 35

Conclusion ................................................................................................................ 36

CHAPTER 3 CUDA Hardware Overview........................................................... 37

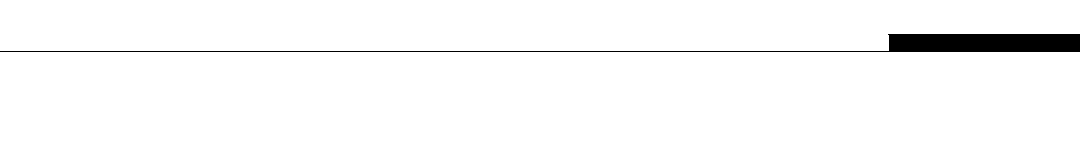

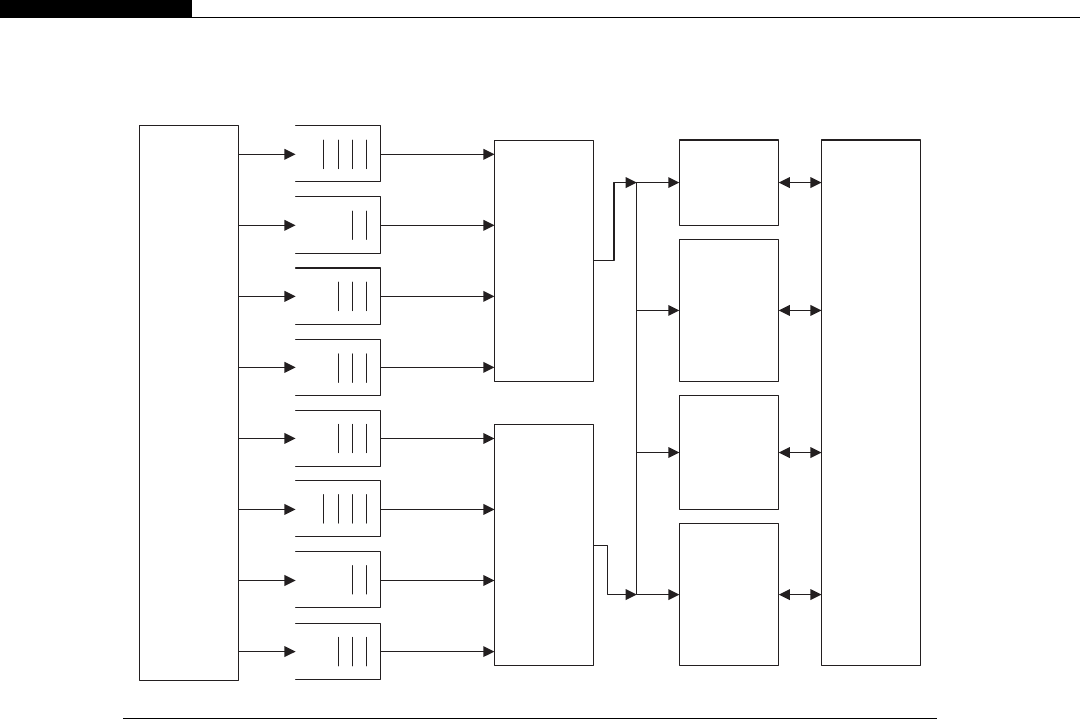

PC Architecture ........................................................................................................ 37

GPU Hardware ......................................................................................................... 42

v

CPUs and GPUs ....................................................................................................... 46

Compute Levels........................................................................................................ 46

Compute 1.0 ........................................................................................................ 47

Compute 1.1 ........................................................................................................ 47

Compute 1.2 ........................................................................................................ 49

Compute 1.3 ........................................................................................................ 49

Compute 2.0 ........................................................................................................ 49

Compute 2.1 ........................................................................................................ 51

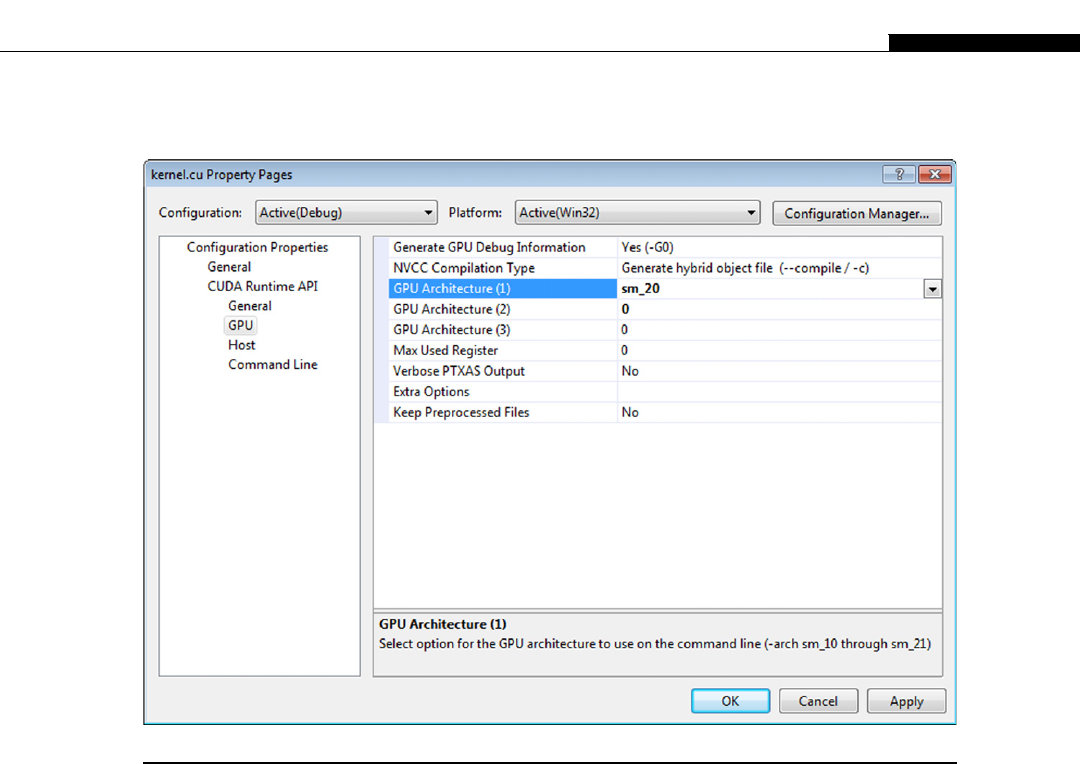

CHAPTER 4 Setting Up CUDA........................................................................ 53

Introduction .............................................................................................................. 53

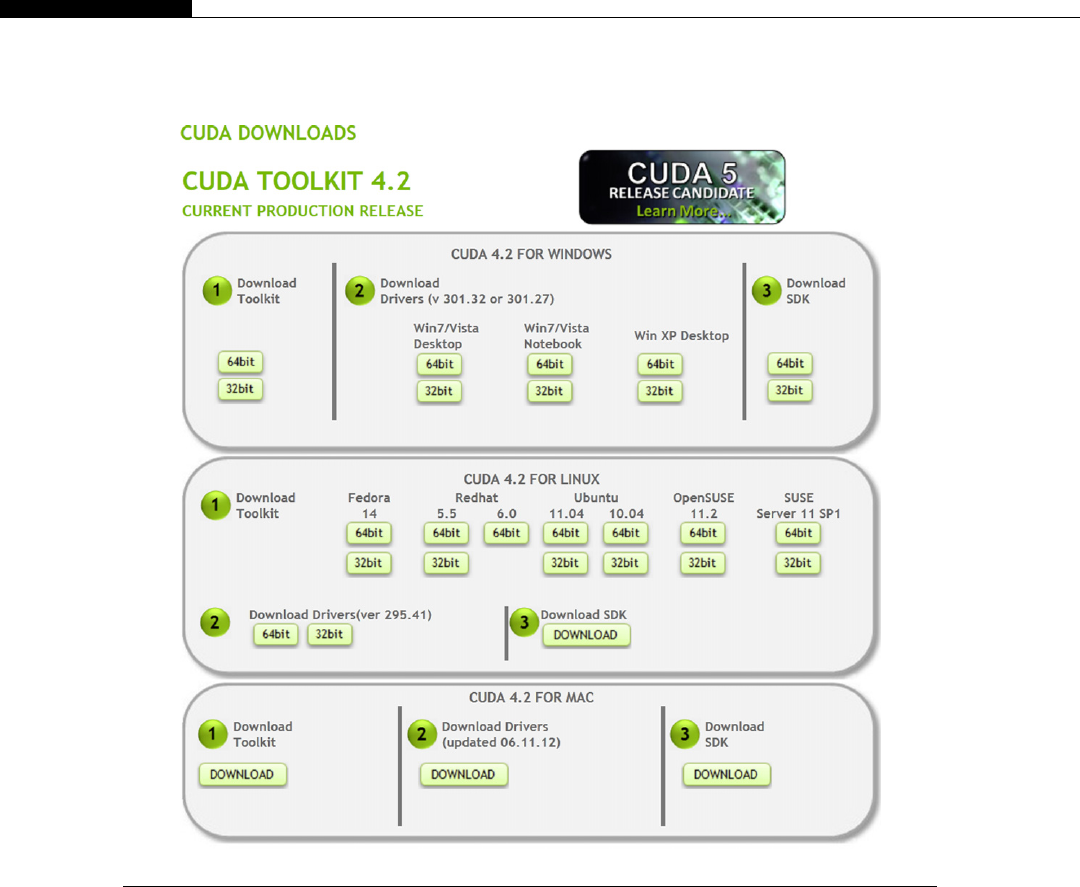

Installing the SDK under Windows ......................................................................... 53

Visual Studio ............................................................................................................ 54

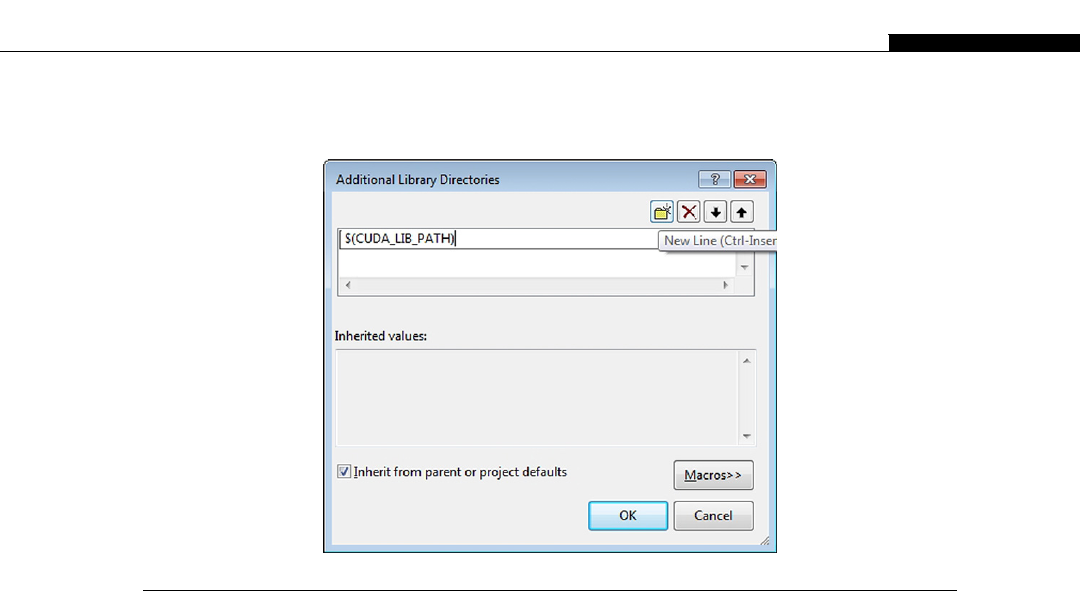

Projects ................................................................................................................ 55

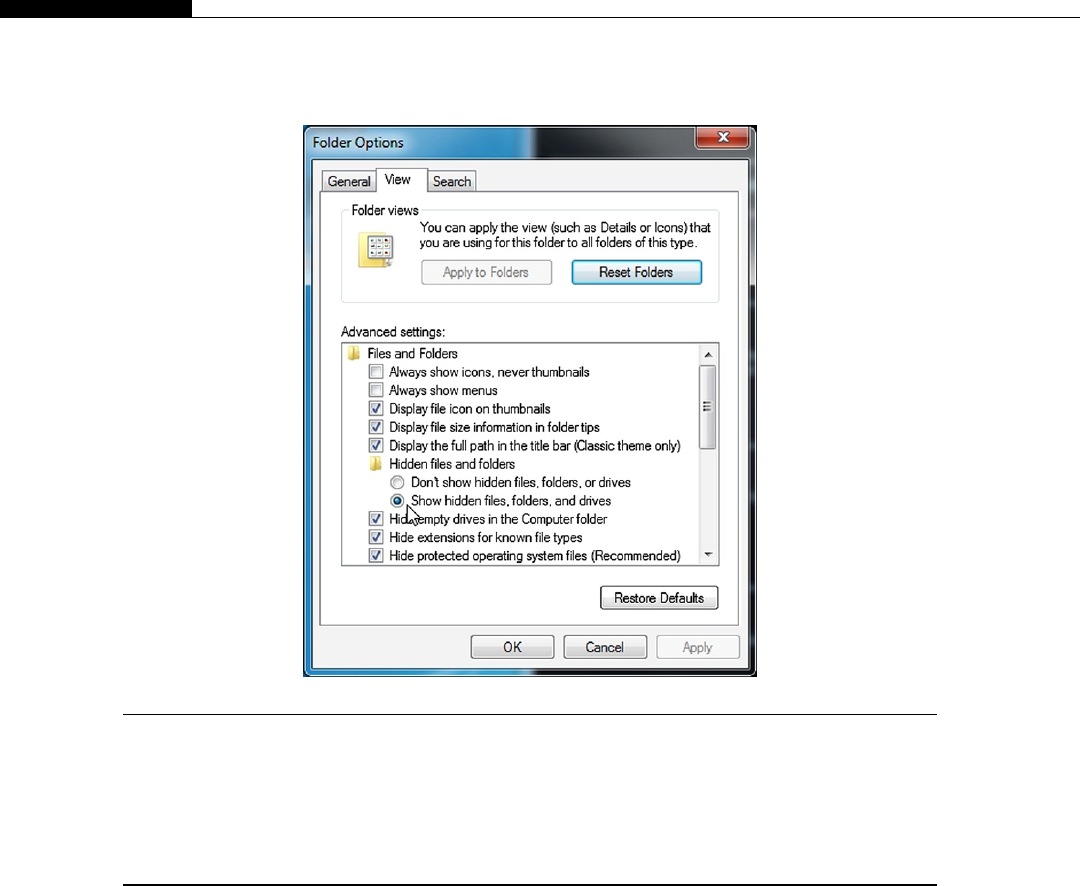

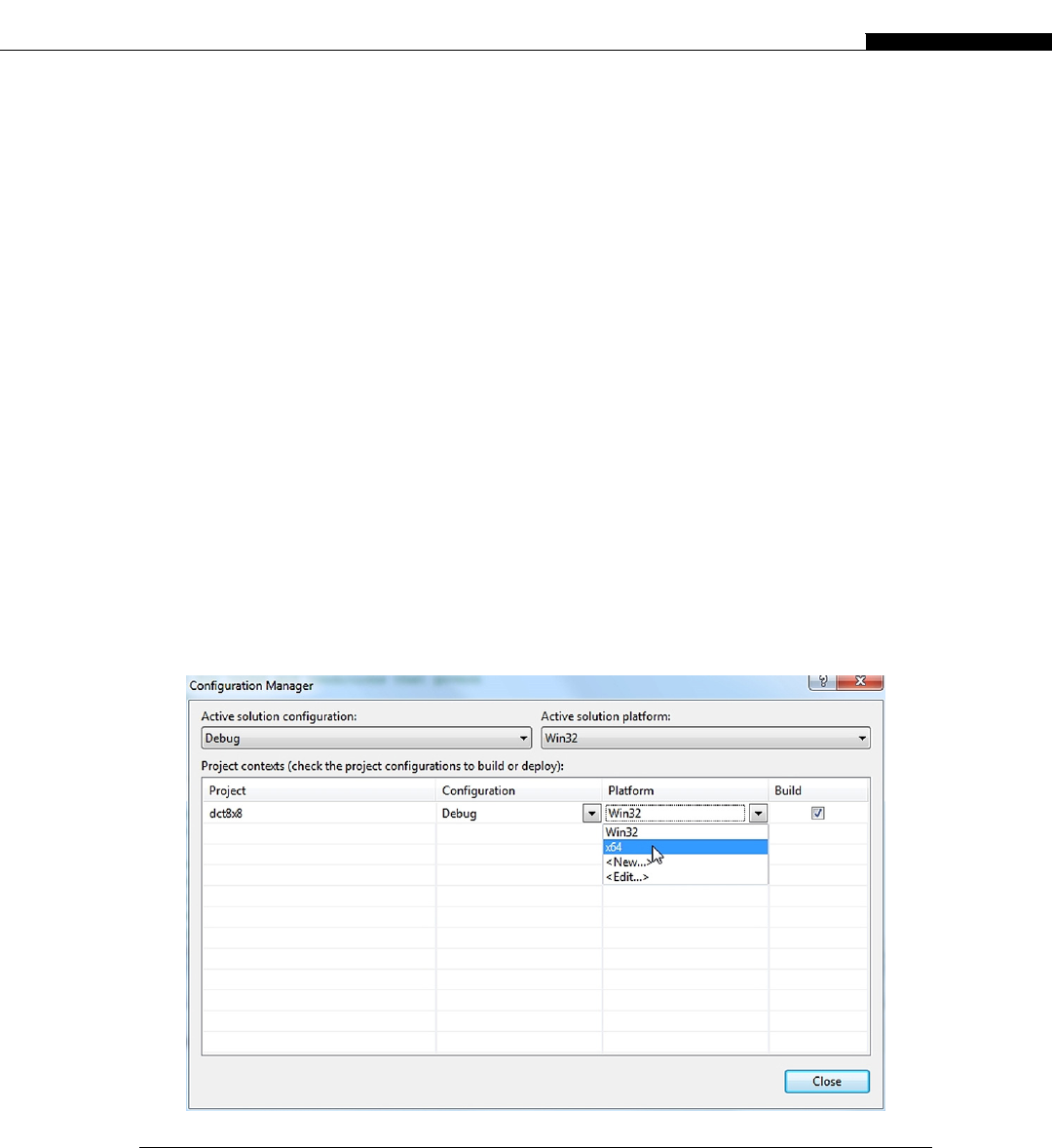

64-bit users .......................................................................................................... 55

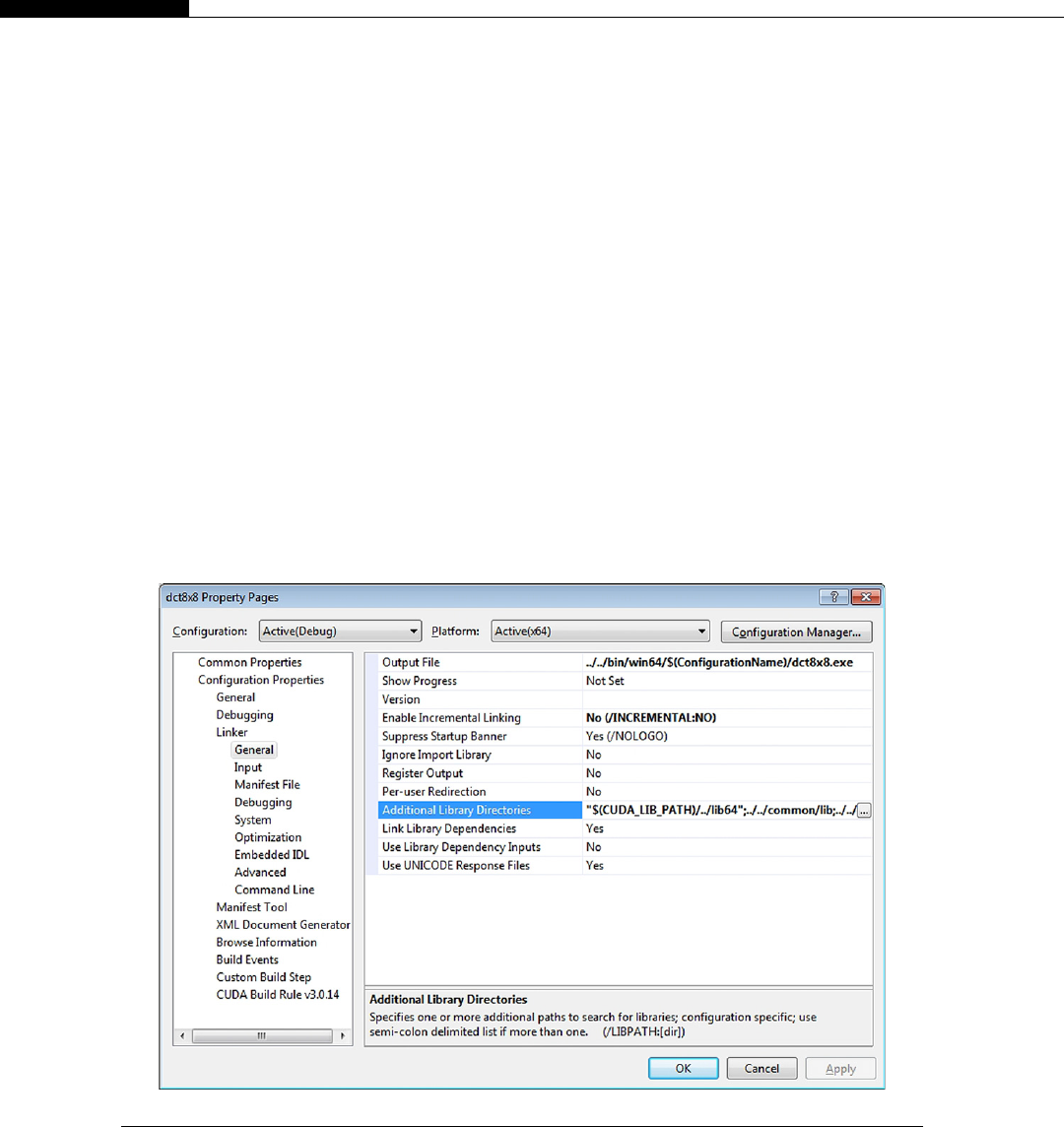

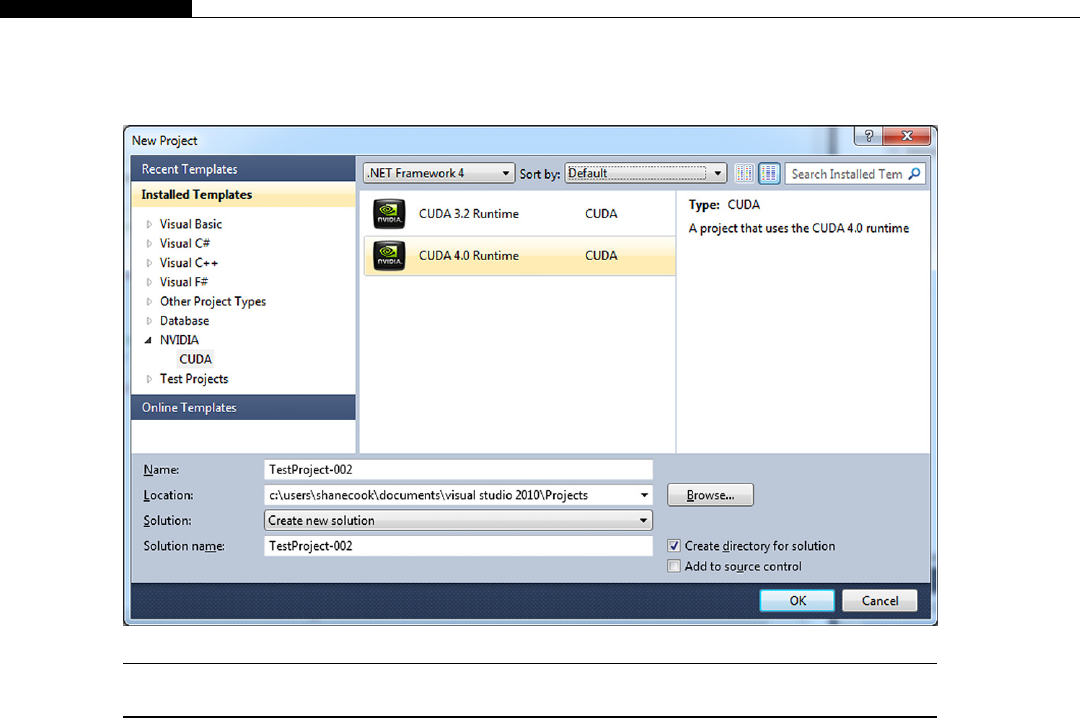

Creating projects ................................................................................................. 57

Linux......................................................................................................................... 58

Kernel base driver installation (CentOS, Ubuntu 10.4) ..................................... 59

Mac ........................................................................................................................... 62

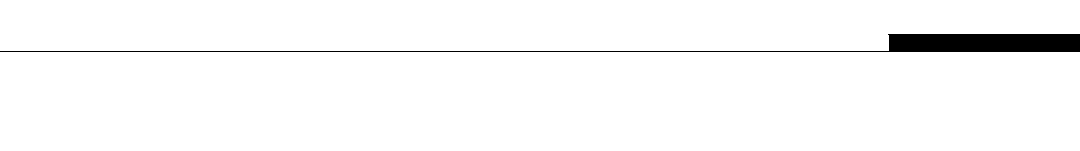

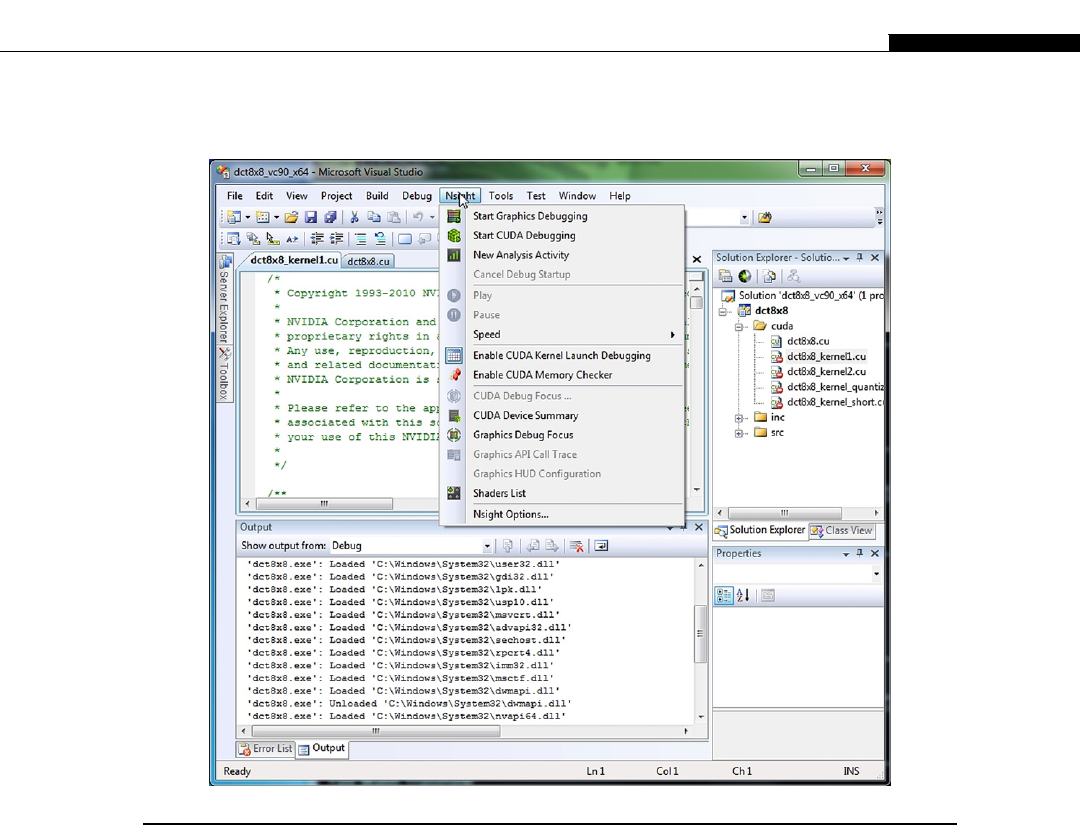

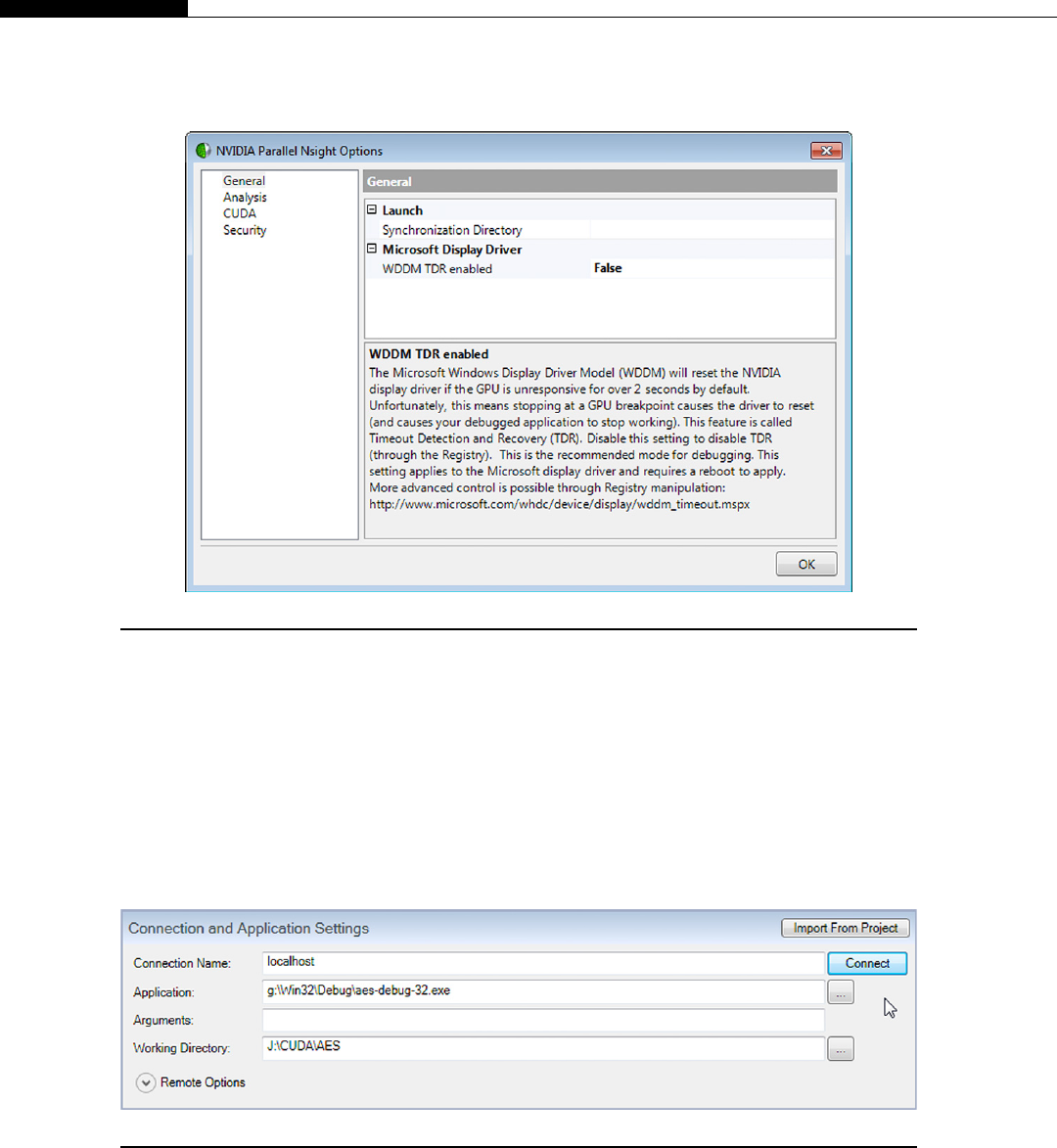

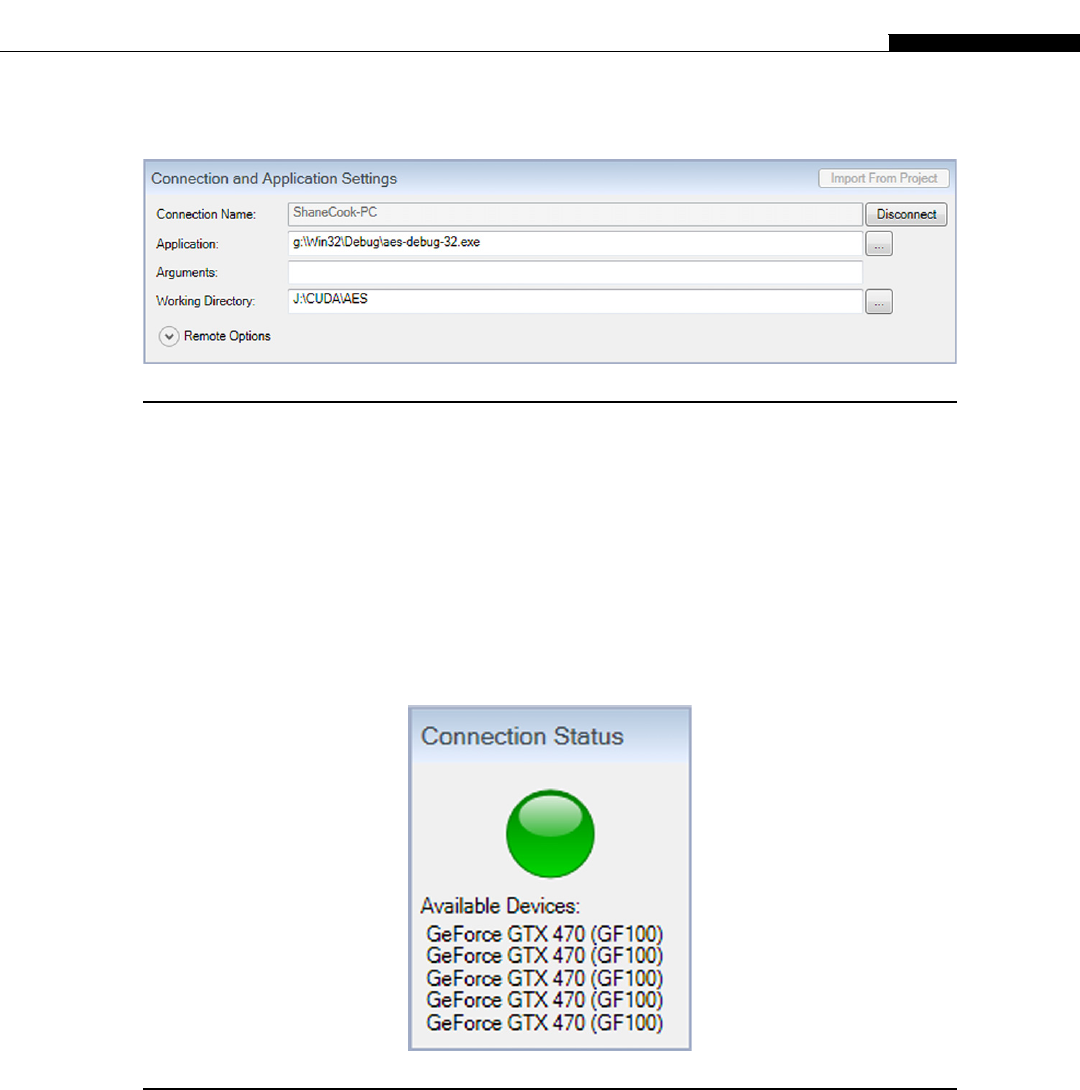

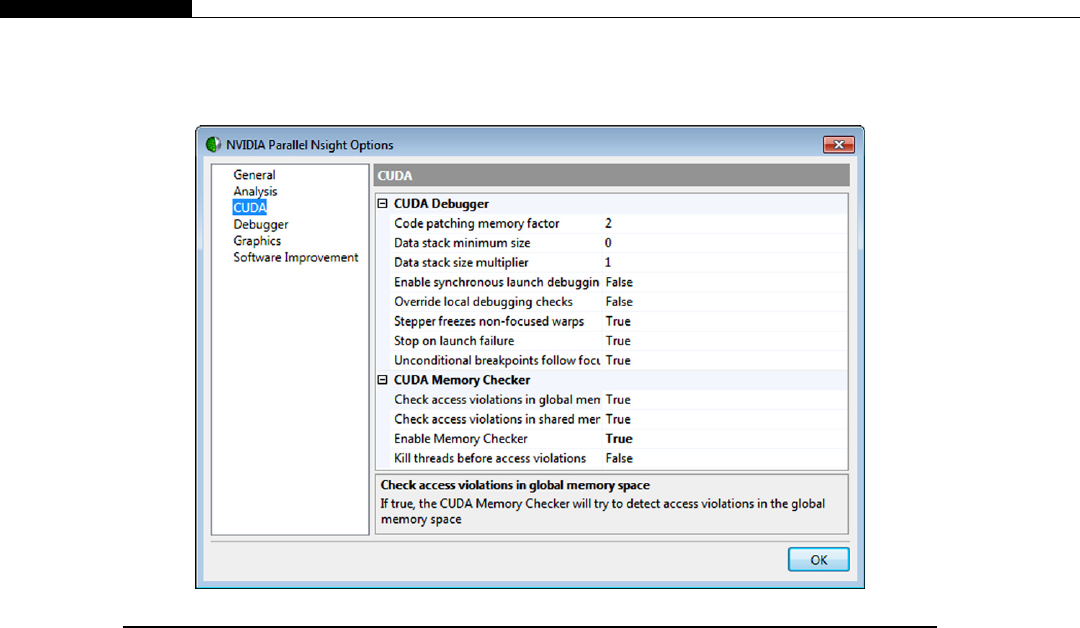

Installing a Debugger ............................................................................................... 62

Compilation Model................................................................................................... 66

Error Handling.......................................................................................................... 67

Conclusion ................................................................................................................ 68

CHAPTER 5 Grids, Blocks, and Threads......................................................... 69

What it all Means ..................................................................................................... 69

Threads ..................................................................................................................... 69

Problem decomposition....................................................................................... 69

How CPUs and GPUs are different .................................................................... 71

Task execution model.......................................................................................... 72

Threading on GPUs............................................................................................. 73

A peek at hardware ............................................................................................. 74

CUDA kernels ..................................................................................................... 77

Blocks ....................................................................................................................... 78

Block arrangement .............................................................................................. 80

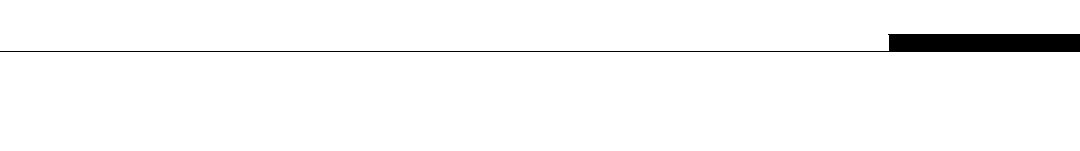

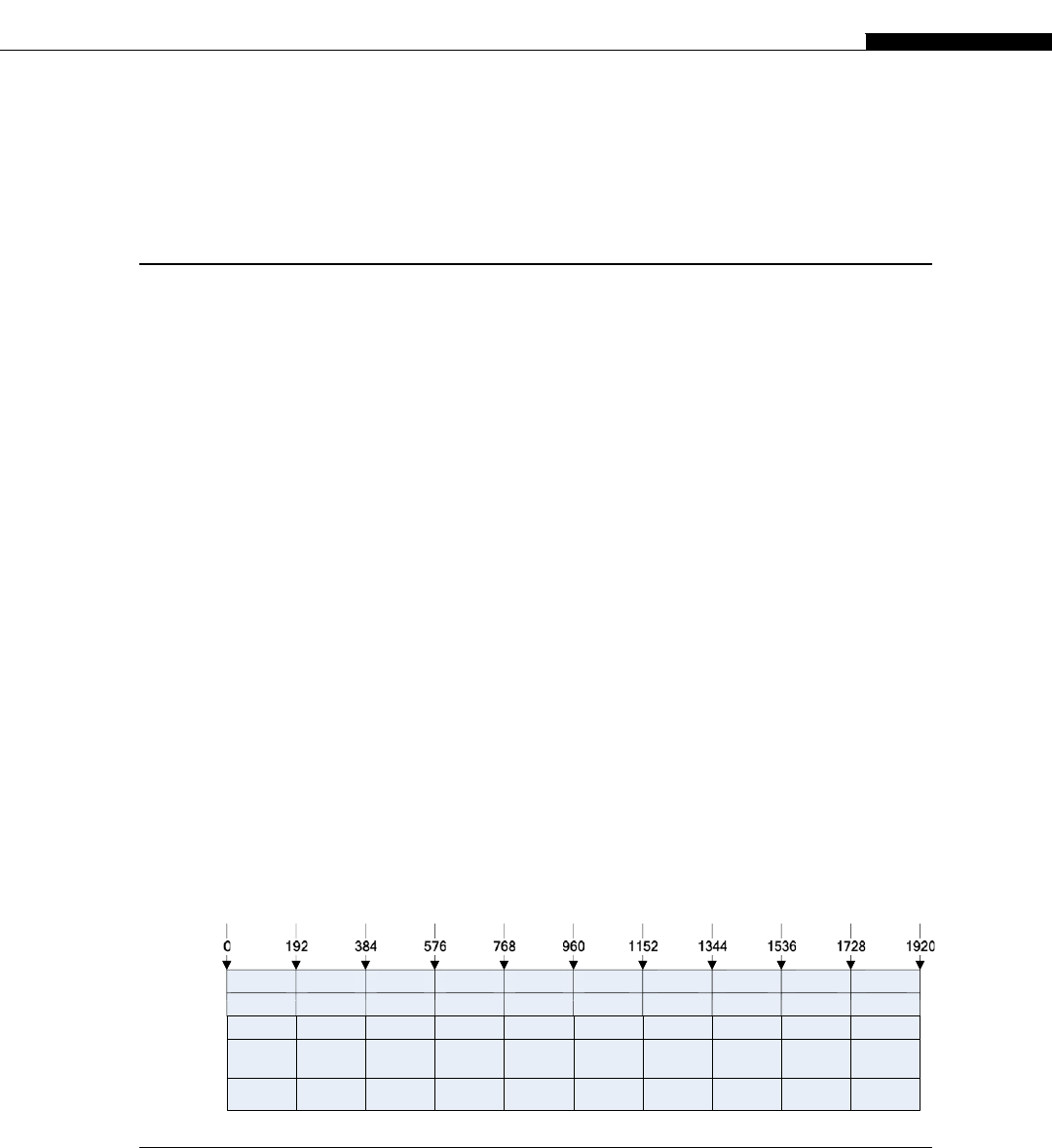

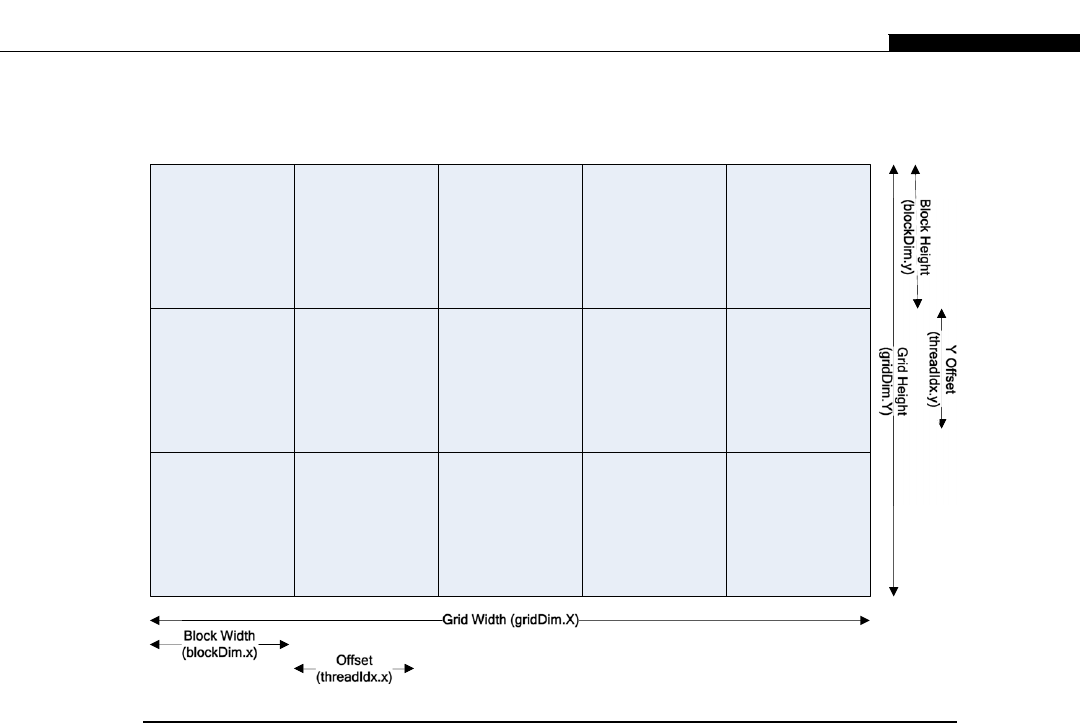

Grids ......................................................................................................................... 83

Stride and offset .................................................................................................. 84

Xand Ythread indexes........................................................................................ 85

Warps ........................................................................................................................ 91

Branching ............................................................................................................ 92

GPU utilization.................................................................................................... 93

Block Scheduling ..................................................................................................... 95

vi Contents

A Practical ExampledHistograms .......................................................................... 97

Conclusion .............................................................................................................. 103

Questions ........................................................................................................... 104

Answers ............................................................................................................. 104

CHAPTER 6 Memory Handling with CUDA .................................................... 107

Introduction ............................................................................................................ 107

Caches..................................................................................................................... 108

Types of data storage ........................................................................................ 110

Register Usage........................................................................................................ 111

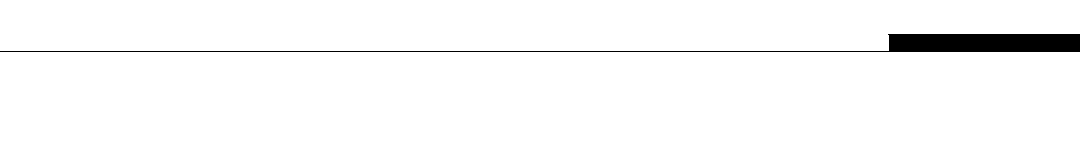

Shared Memory ...................................................................................................... 120

Sorting using shared memory ........................................................................... 121

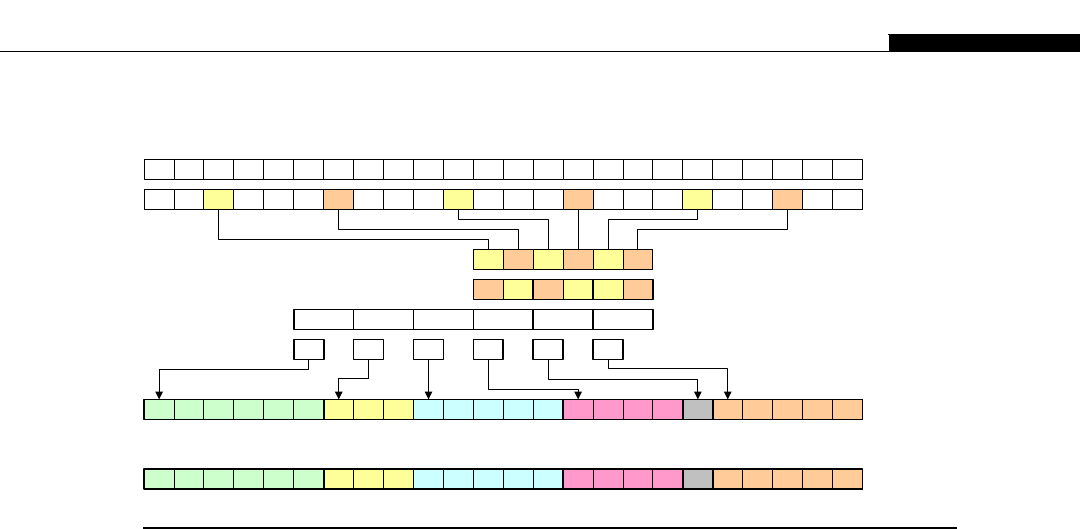

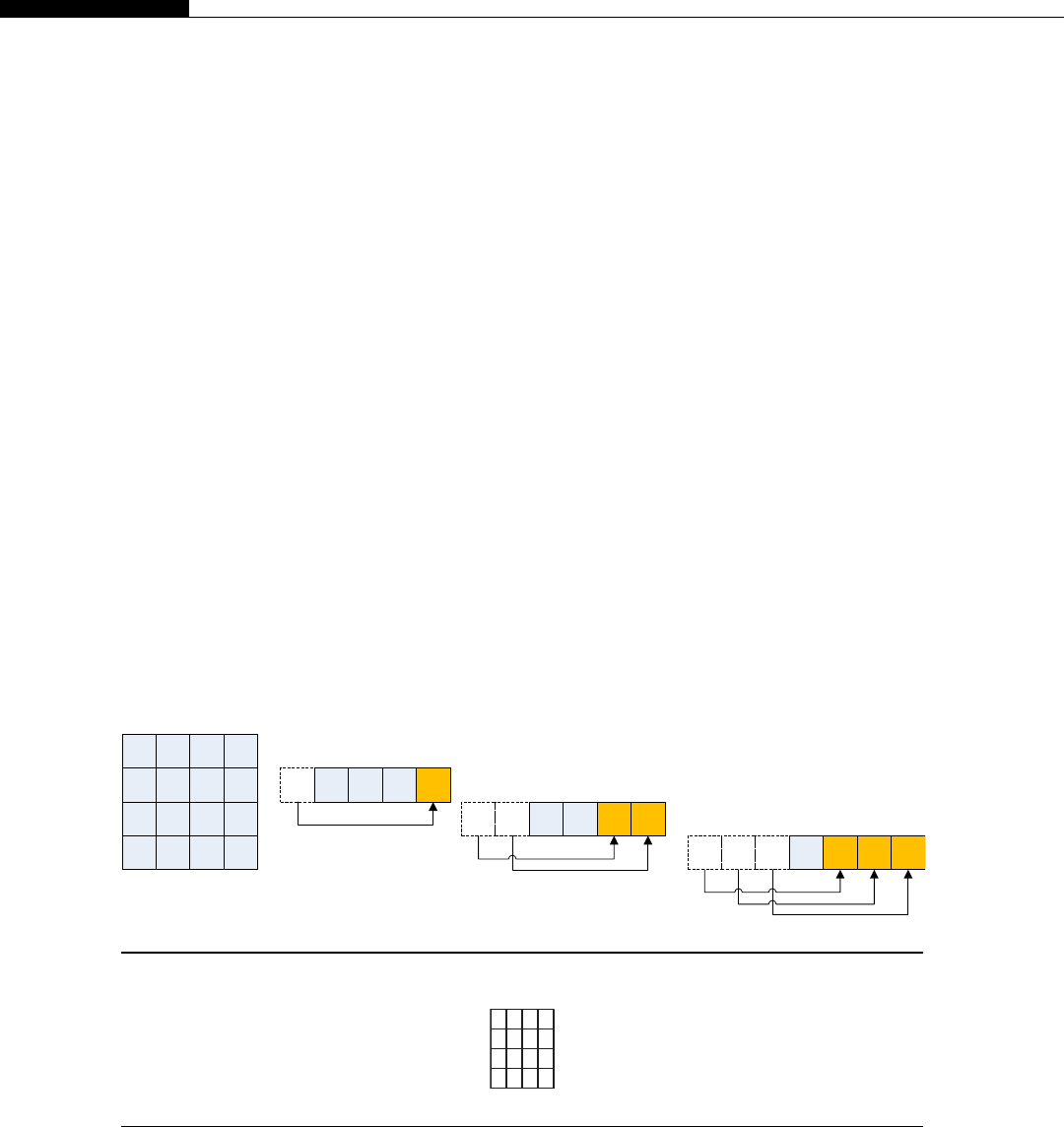

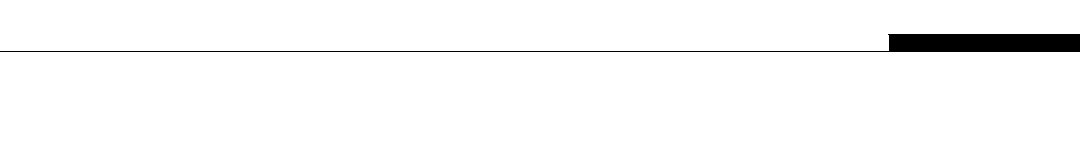

Radix sort .......................................................................................................... 125

Merging lists...................................................................................................... 131

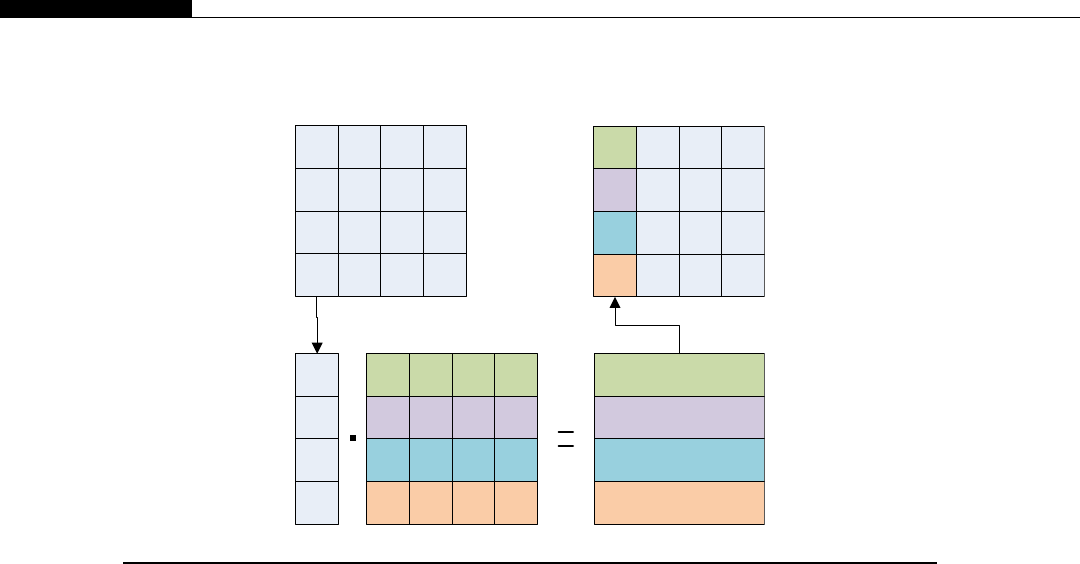

Parallel merging ................................................................................................ 137

Parallel reduction............................................................................................... 140

A hybrid approach............................................................................................. 144

Shared memory on different GPUs................................................................... 148

Shared memory summary ................................................................................. 148

Questions on shared memory............................................................................ 149

Answers for shared memory ............................................................................. 149

Constant Memory ................................................................................................... 150

Constant memory caching................................................................................. 150

Constant memory broadcast.............................................................................. 152

Constant memory updates at runtime ............................................................... 162

Constant question .............................................................................................. 166

Constant answer ................................................................................................ 167

Global Memory ...................................................................................................... 167

Score boarding................................................................................................... 176

Global memory sorting ..................................................................................... 176

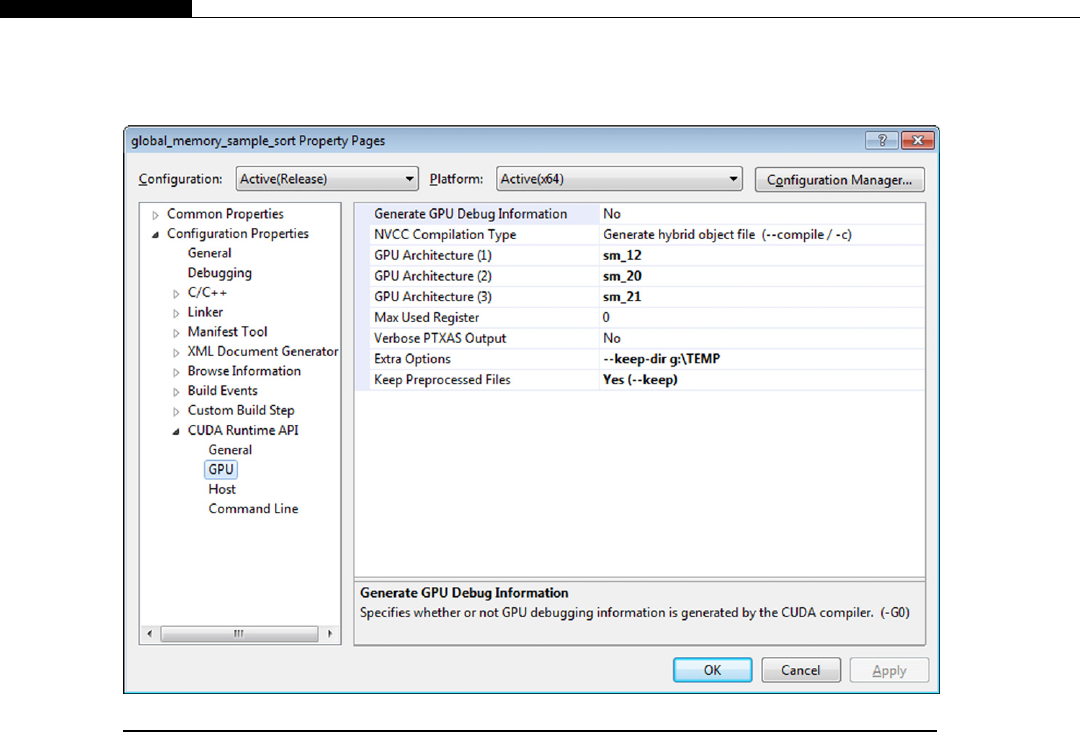

Sample sort........................................................................................................ 179

Questions on global memory ............................................................................ 198

Answers on global memory .............................................................................. 199

Texture Memory ..................................................................................................... 200

Texture caching ................................................................................................. 200

Hardware manipulation of memory fetches ..................................................... 200

Restrictions using textures ................................................................................ 201

Conclusion .............................................................................................................. 202

CHAPTER 7 Using CUDA in Practice............................................................ 203

Introduction ............................................................................................................ 203

Serial and Parallel Code......................................................................................... 203

Design goals of CPUs and GPUs ..................................................................... 203

Contents vii

Algorithms that work best on the CPU versus the GPU.................................. 206

Processing Datasets ................................................................................................ 209

Using ballot and other intrinsic operations....................................................... 211

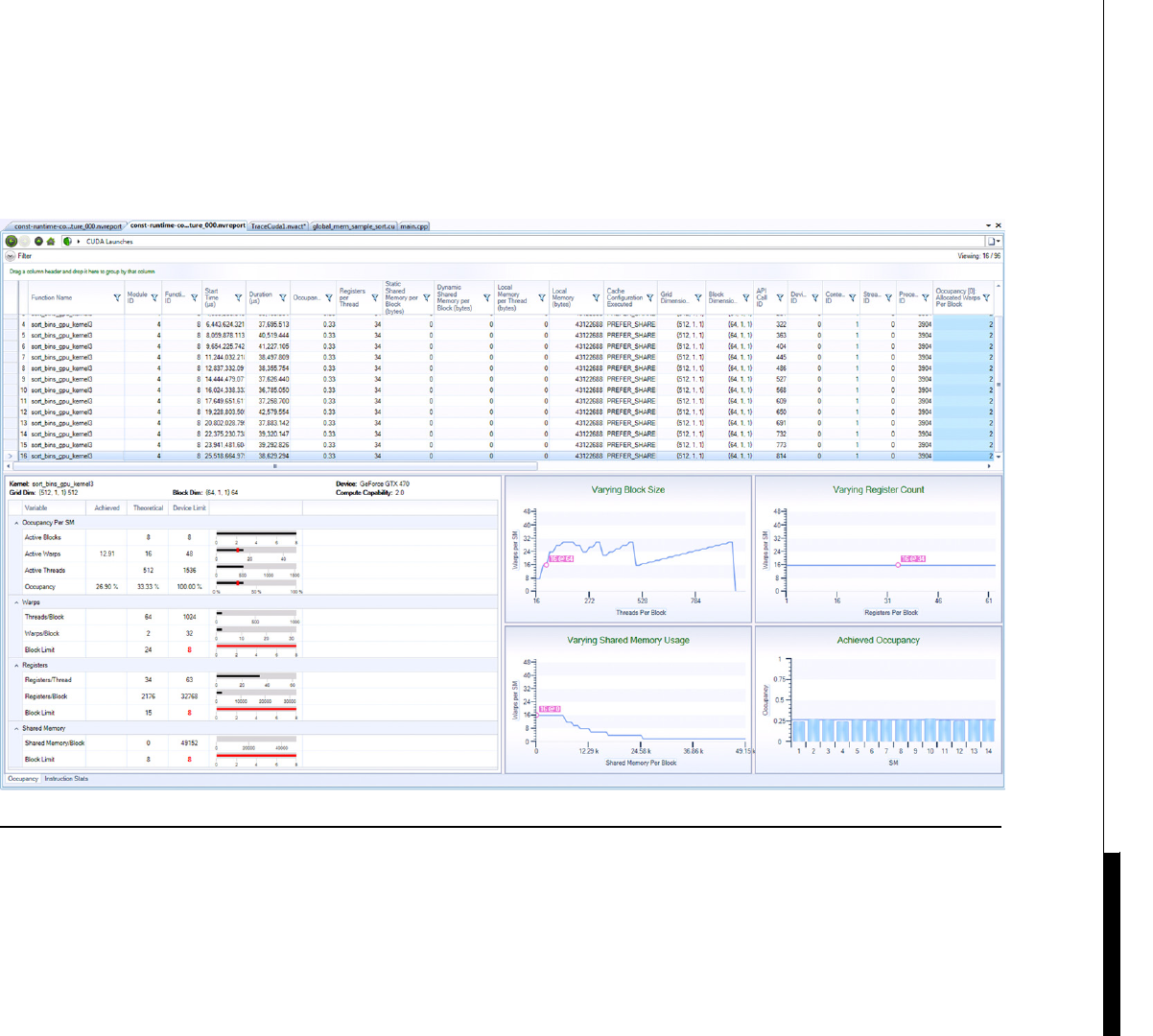

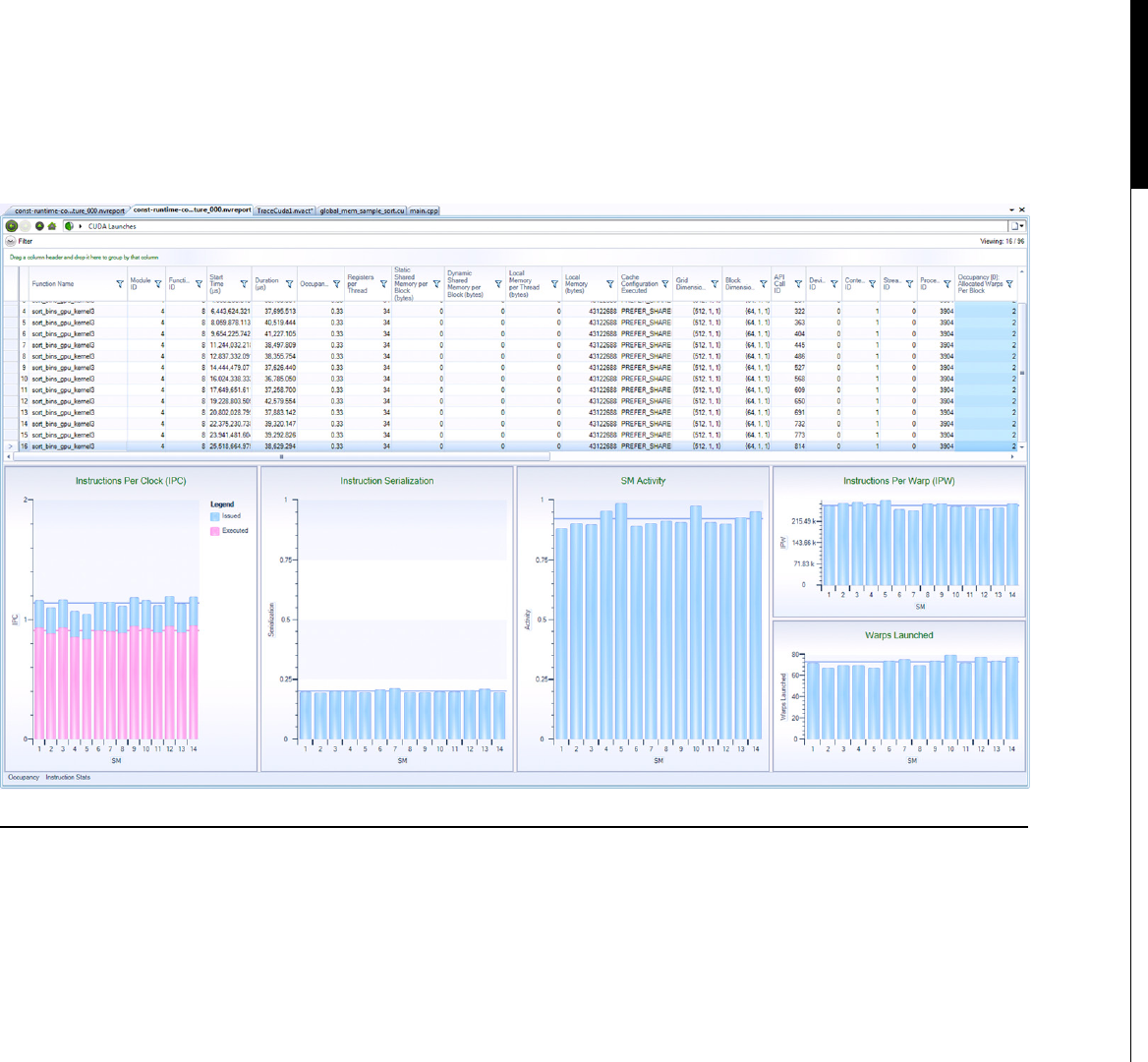

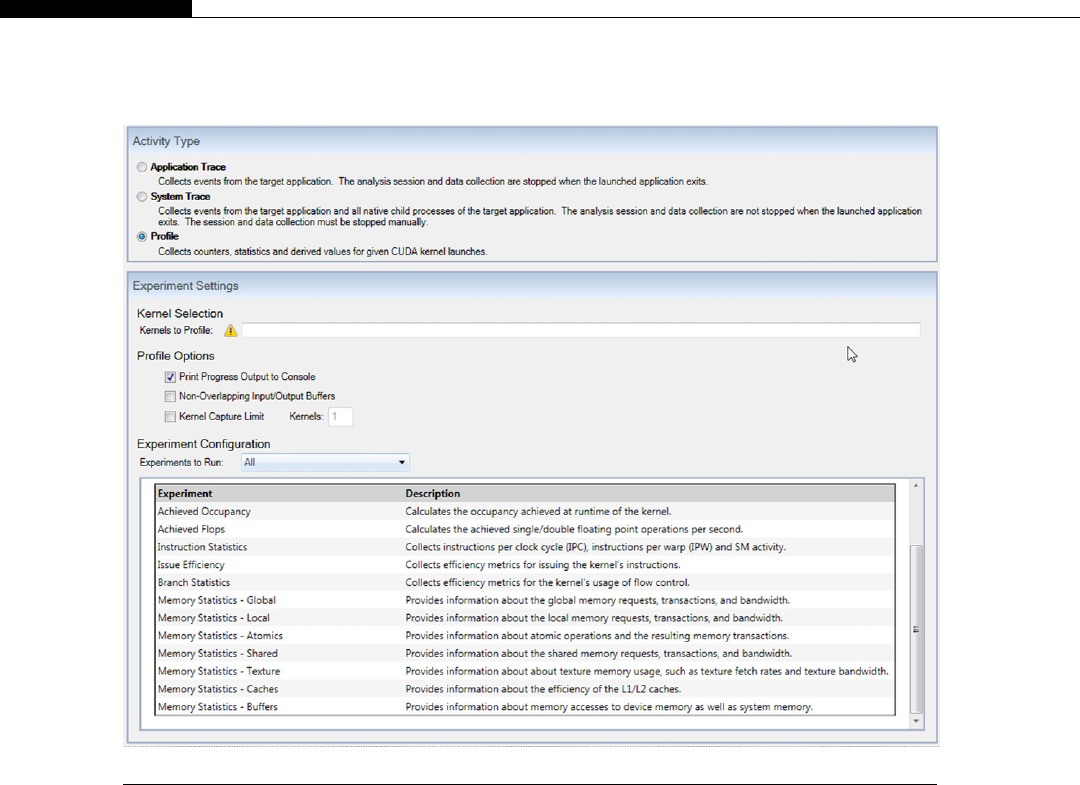

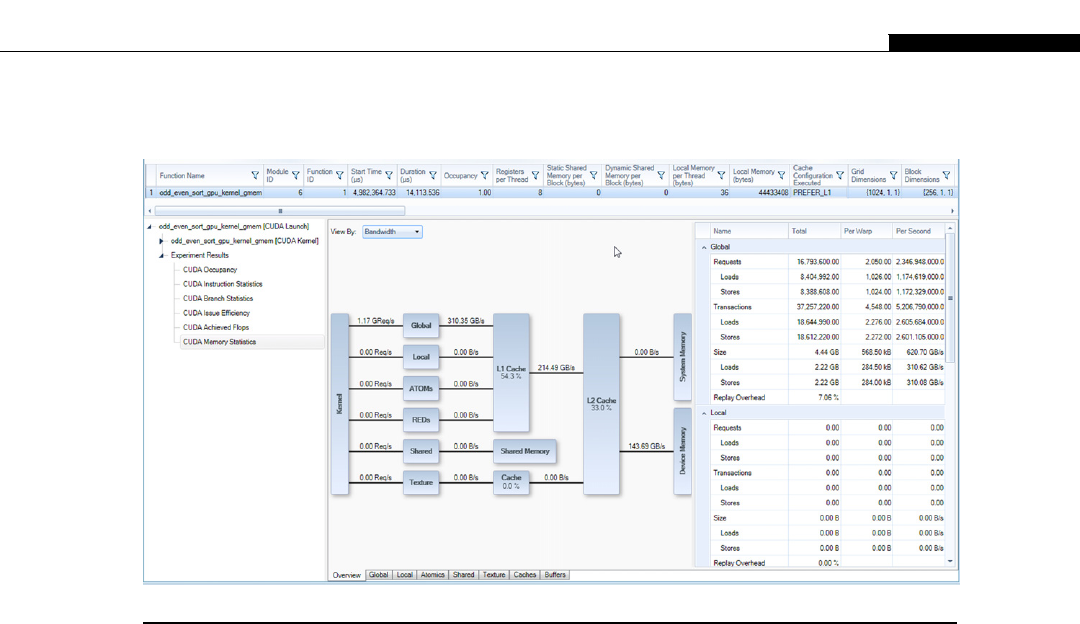

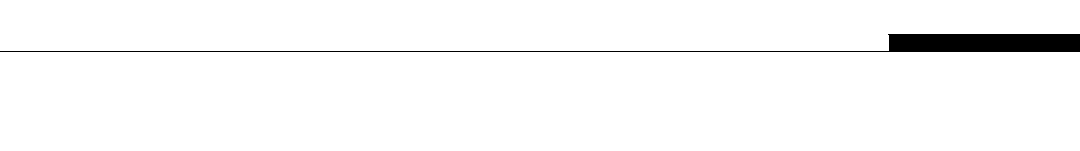

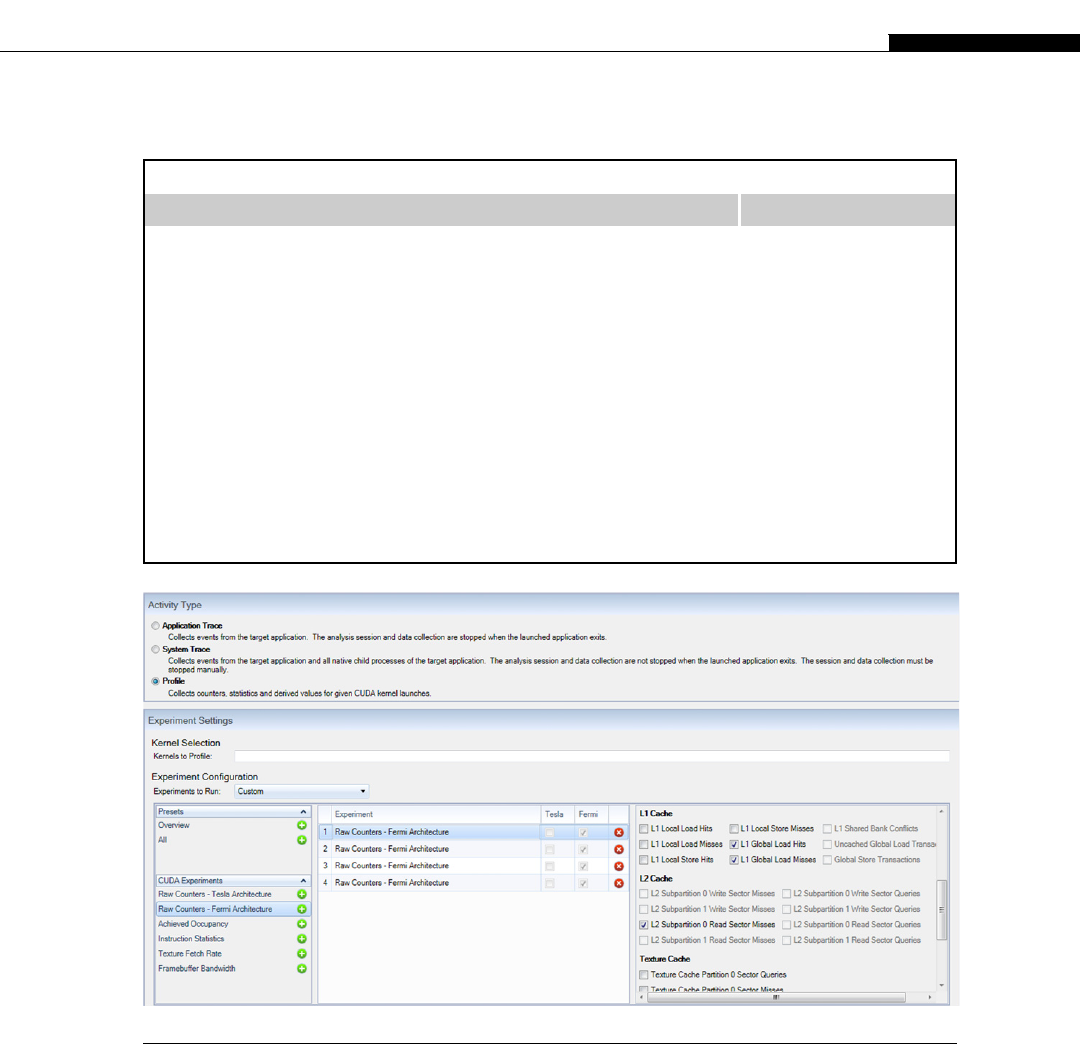

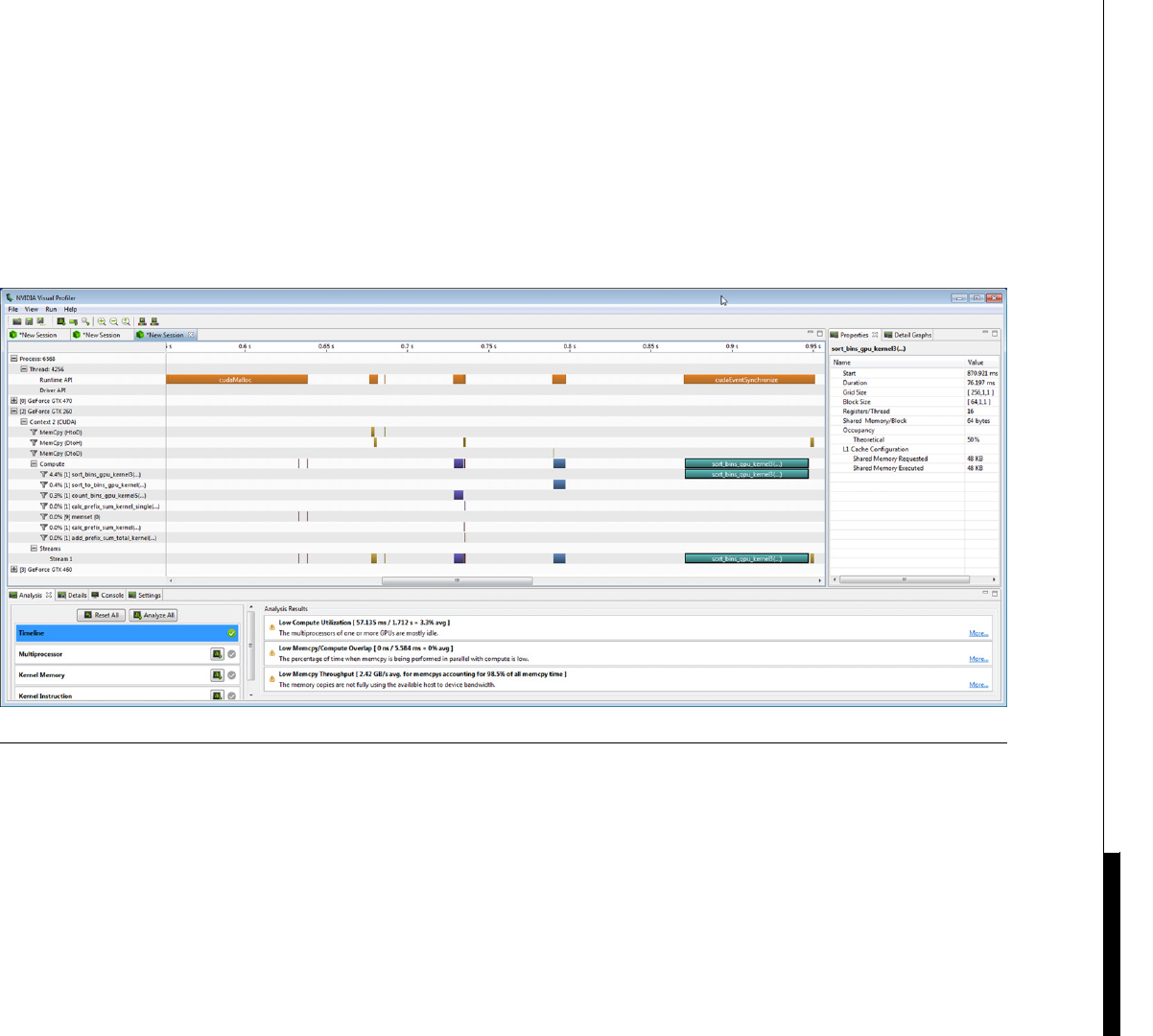

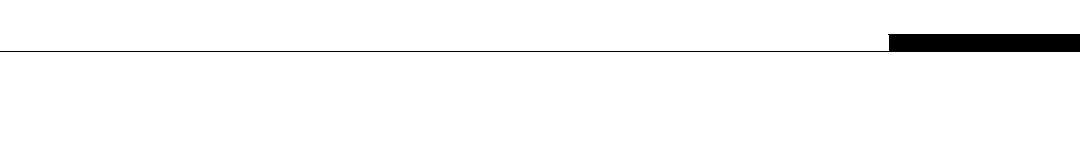

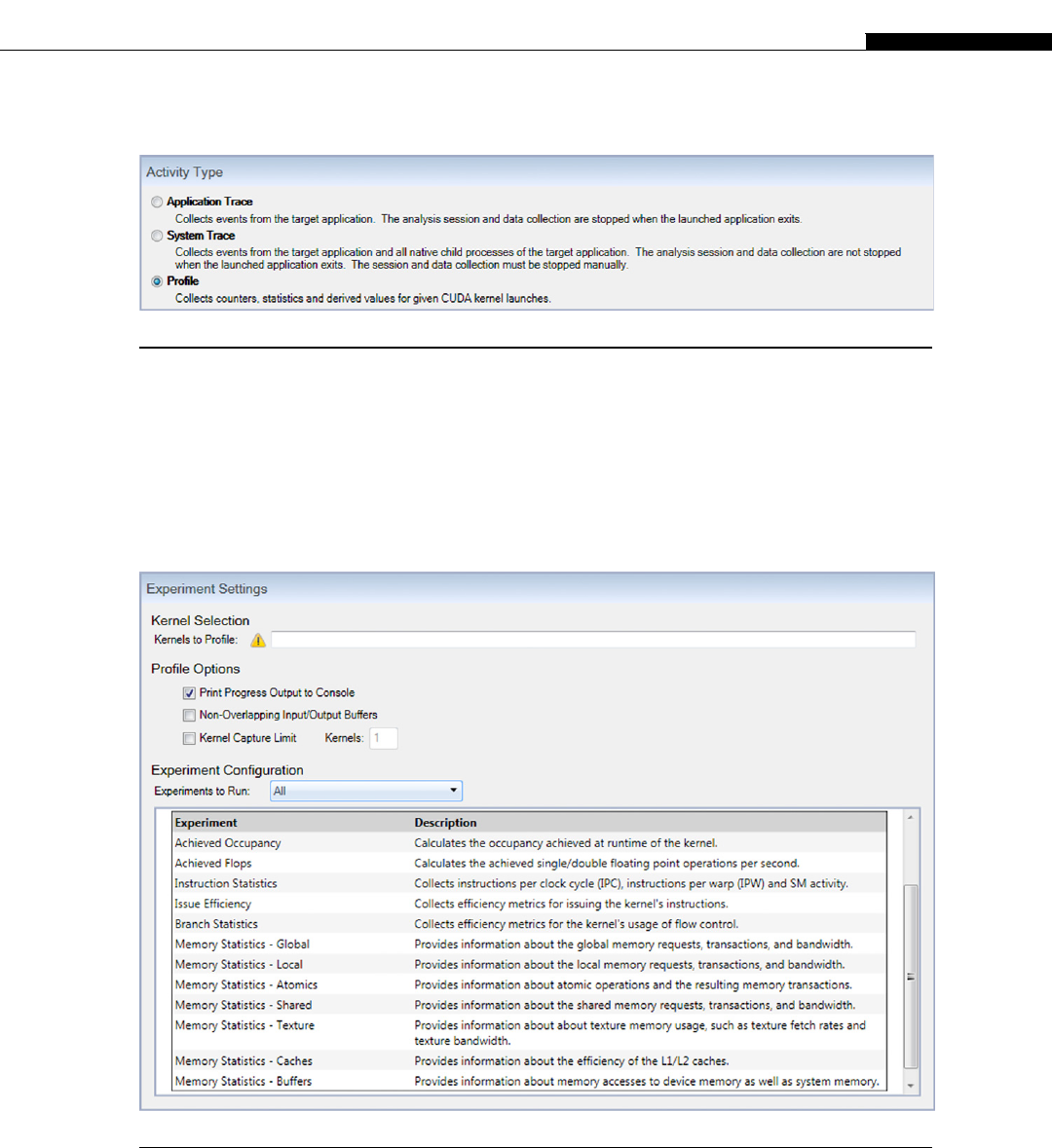

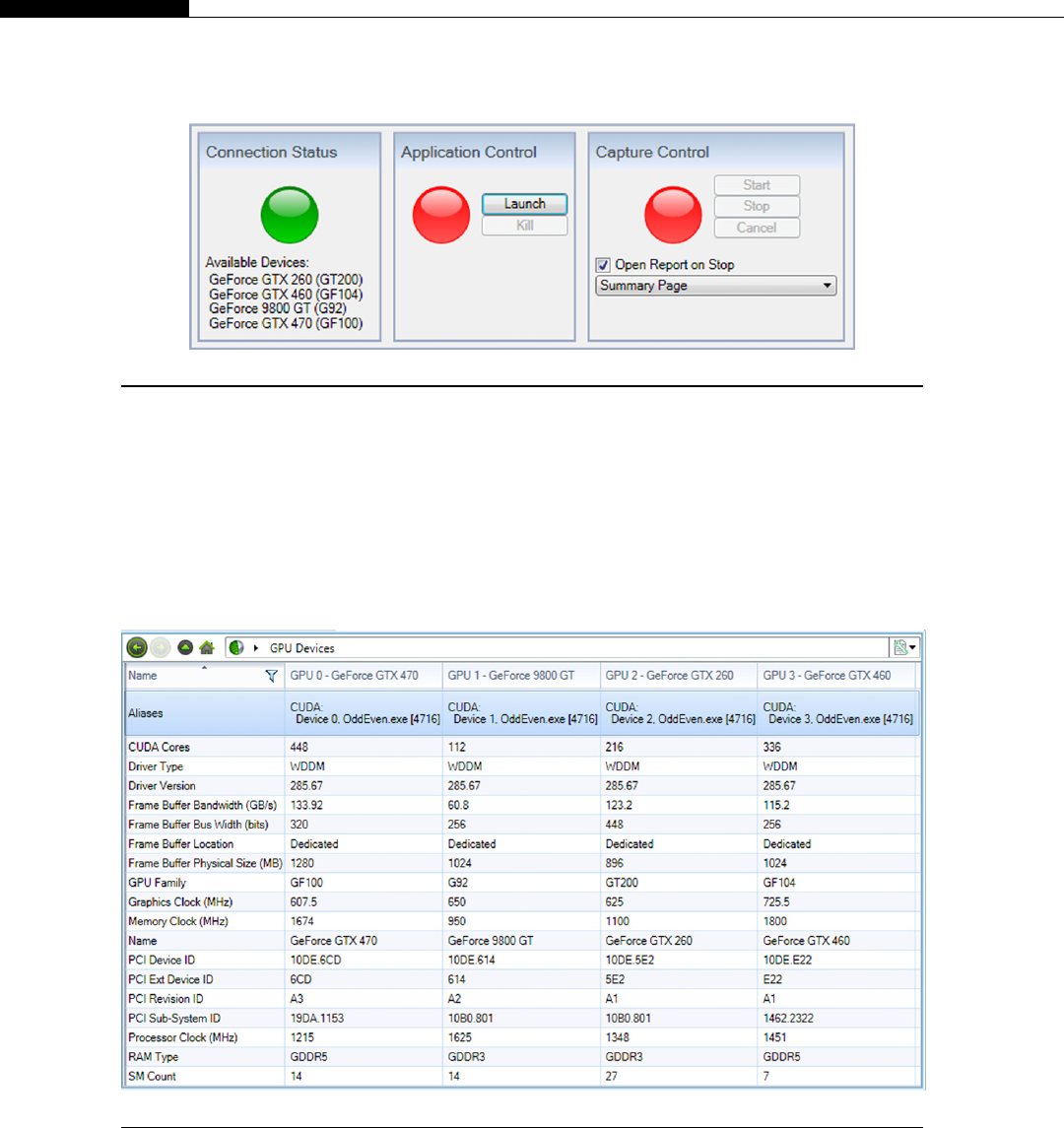

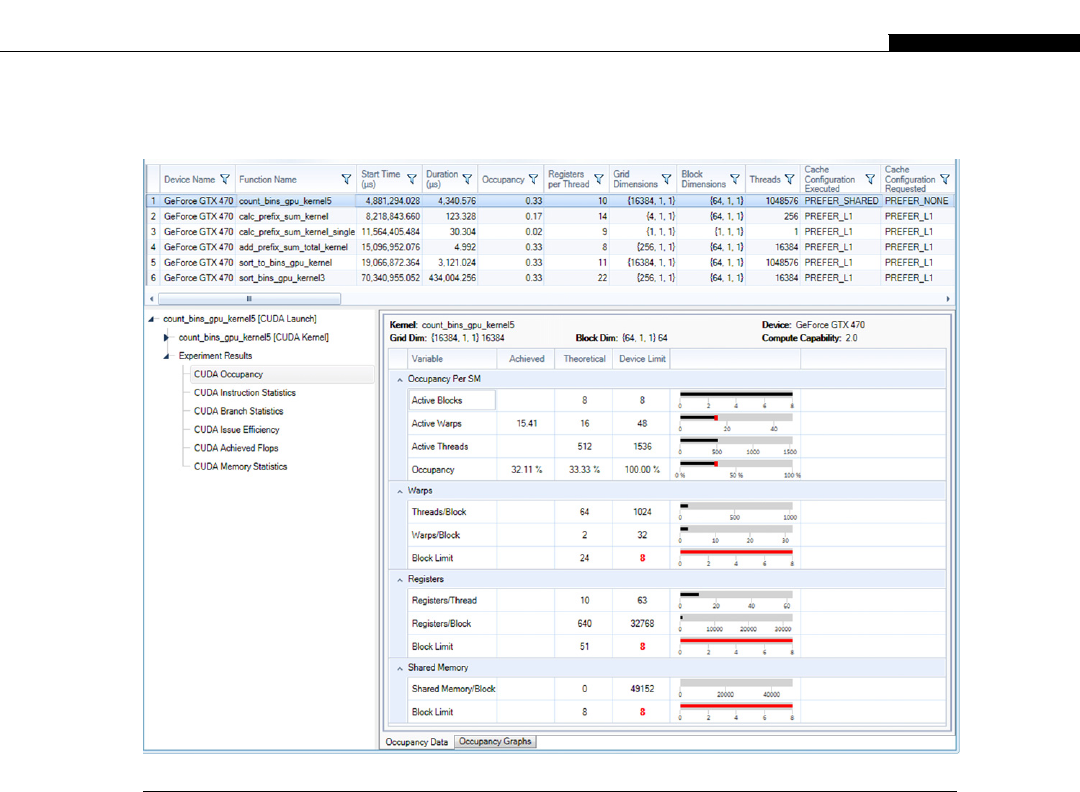

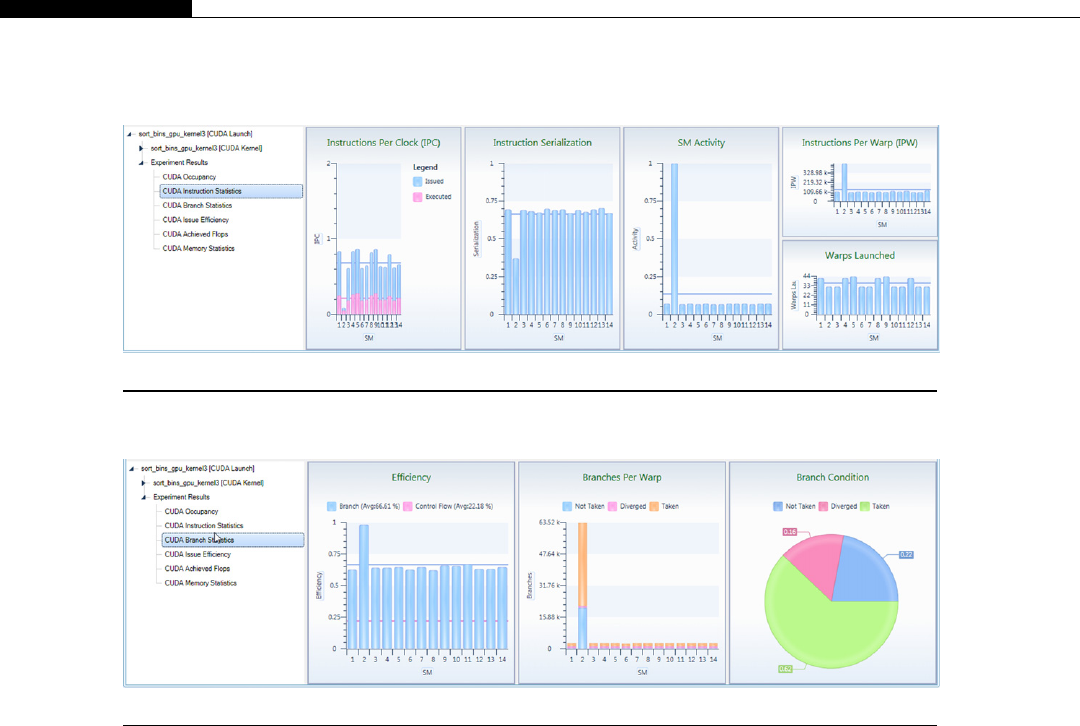

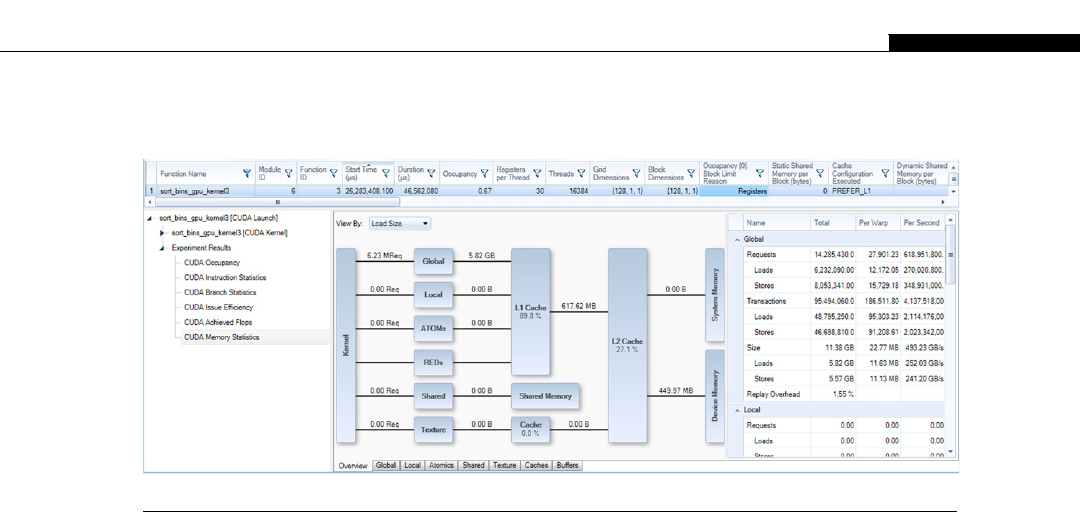

Profiling .................................................................................................................. 219

An Example Using AES ........................................................................................ 231

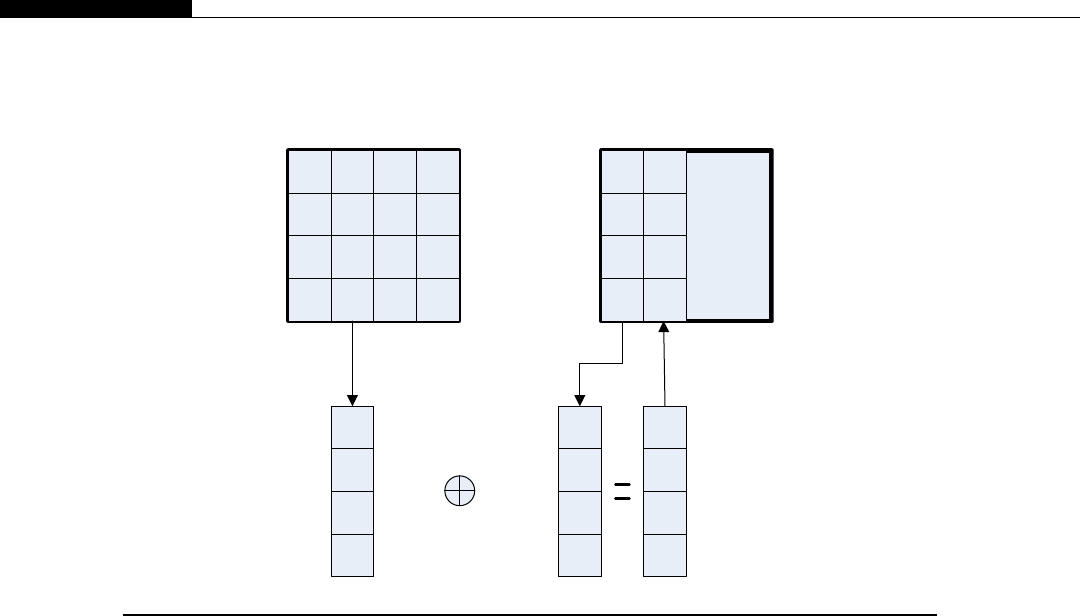

The algorithm .................................................................................................... 232

Serial implementations of AES ........................................................................ 236

An initial kernel ................................................................................................ 239

Kernel performance........................................................................................... 244

Transfer performance ........................................................................................ 248

A single streaming version ............................................................................... 249

How do we compare with the CPU .................................................................. 250

Considerations for running on other GPUs ...................................................... 260

Using multiple streams...................................................................................... 263

AES summary ................................................................................................... 264

Conclusion .............................................................................................................. 265

Questions ........................................................................................................... 265

Answers ............................................................................................................. 265

References .............................................................................................................. 266

CHAPTER 8 Multi-CPU and Multi-GPU Solutions .......................................... 267

Introduction ............................................................................................................ 267

Locality................................................................................................................... 267

Multi-CPU Systems................................................................................................ 267

Multi-GPU Systems................................................................................................ 268

Algorithms on Multiple GPUs ............................................................................... 269

Which GPU?........................................................................................................... 270

Single-Node Systems.............................................................................................. 274

Streams ................................................................................................................... 275

Multiple-Node Systems .......................................................................................... 290

Conclusion .............................................................................................................. 301

Questions ........................................................................................................... 302

Answers ............................................................................................................. 302

CHAPTER 9 Optimizing Your Application...................................................... 305

Strategy 1: Parallel/Serial GPU/CPU Problem Breakdown .................................. 305

Analyzing the problem...................................................................................... 305

Time................................................................................................................... 305

Problem decomposition..................................................................................... 307

Dependencies..................................................................................................... 308

Dataset size........................................................................................................ 311

viii Contents

Resolution.......................................................................................................... 312

Identifying the bottlenecks................................................................................ 313

Grouping the tasks for CPU and GPU.............................................................. 317

Section summary............................................................................................... 320

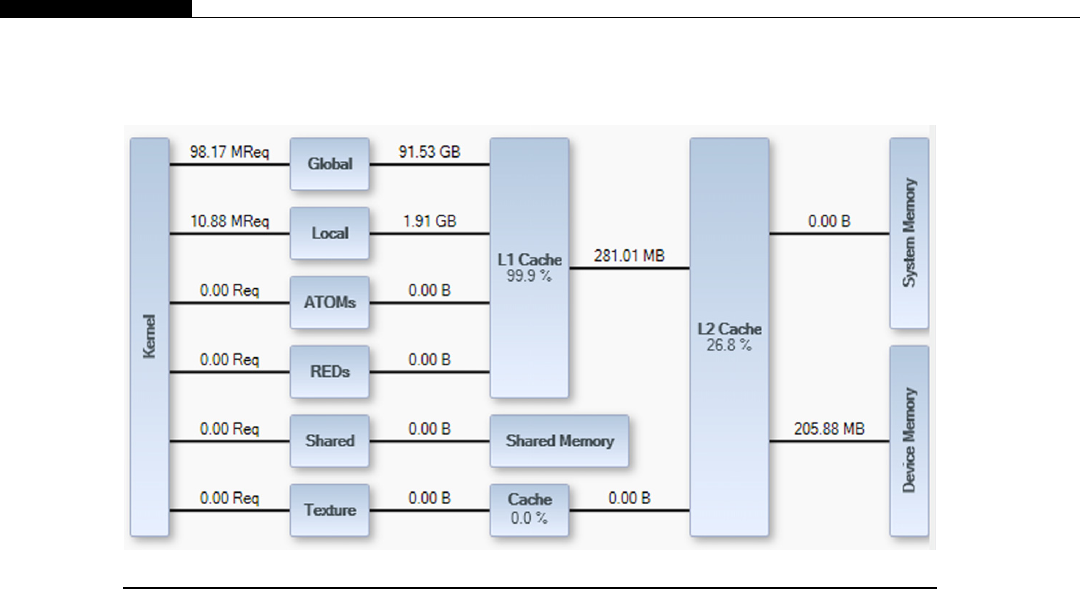

Strategy 2: Memory Considerations ...................................................................... 320

Memory bandwidth ........................................................................................... 320

Source of limit................................................................................................... 321

Memory organization ........................................................................................ 323

Memory accesses to computation ratio ............................................................ 325

Loop and kernel fusion ..................................................................................... 331

Use of shared memory and cache..................................................................... 332

Section summary............................................................................................... 333

Strategy 3: Transfers .............................................................................................. 334

Pinned memory ................................................................................................. 334

Zero-copy memory............................................................................................ 338

Bandwidth limitations ....................................................................................... 347

GPU timing ....................................................................................................... 351

Overlapping GPU transfers ............................................................................... 356

Section summary............................................................................................... 360

Strategy 4: Thread Usage, Calculations, and Divergence ..................................... 361

Thread memory patterns ................................................................................... 361

Inactive threads.................................................................................................. 364

Arithmetic density............................................................................................. 365

Some common compiler optimizations ............................................................ 369

Divergence......................................................................................................... 374

Understanding the low-level assembly code .................................................... 379

Register usage ................................................................................................... 383

Section summary............................................................................................... 385

Strategy 5: Algorithms ........................................................................................... 386

Sorting ............................................................................................................... 386

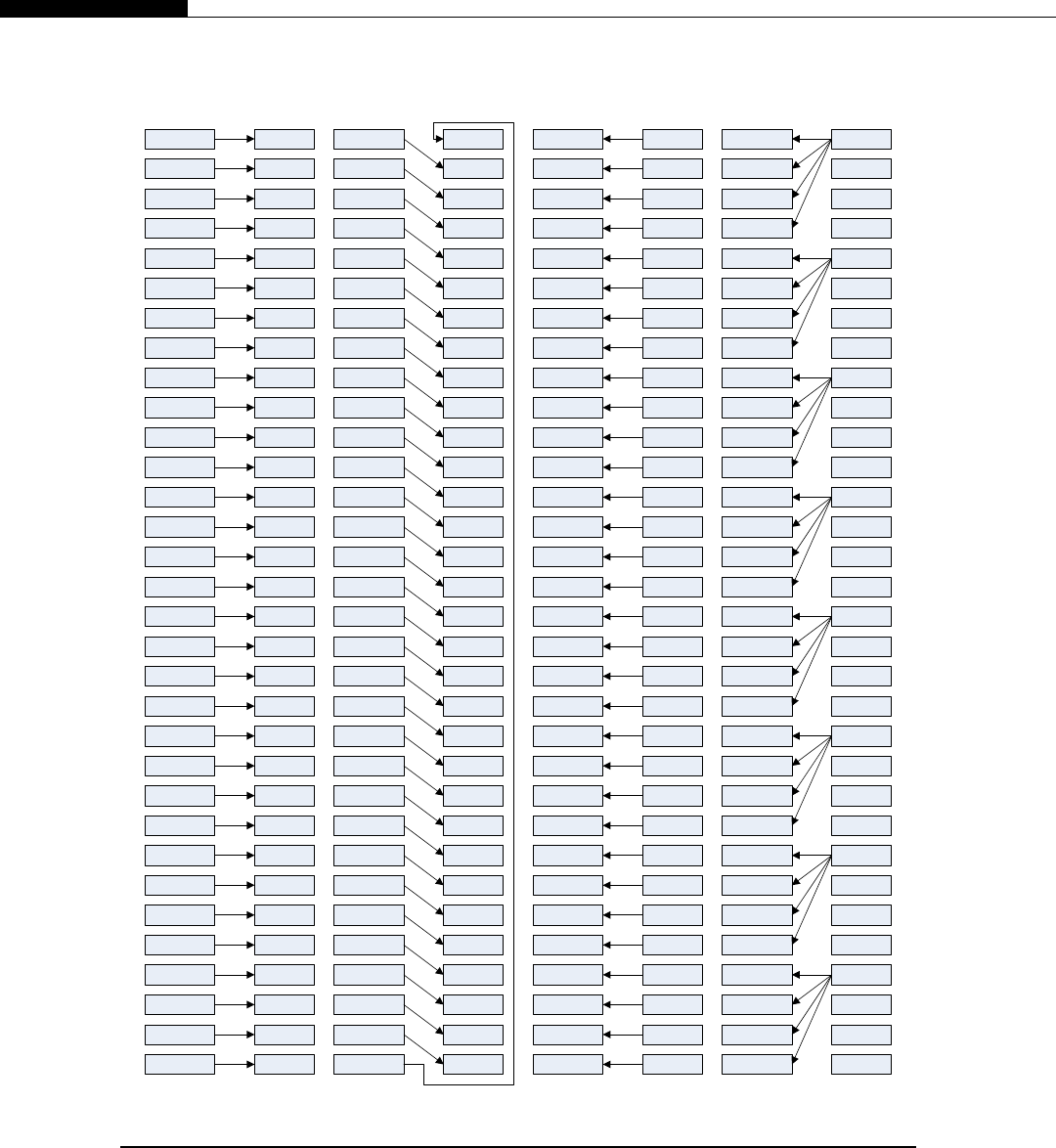

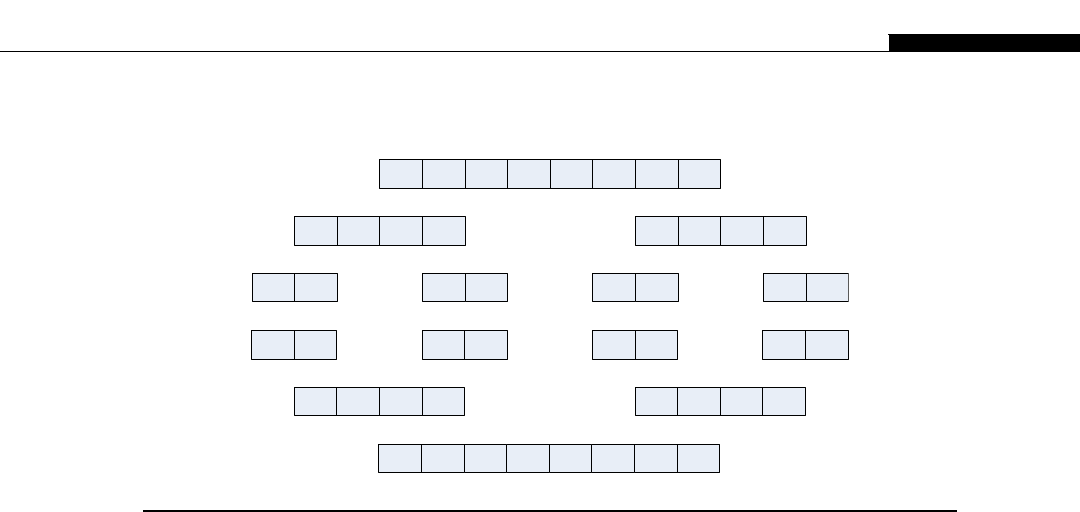

Reduction........................................................................................................... 392

Section summary............................................................................................... 414

Strategy 6: Resource Contentions .......................................................................... 414

Identifying bottlenecks...................................................................................... 414

Resolving bottlenecks ....................................................................................... 427

Section summary............................................................................................... 434

Strategy 7: Self-Tuning Applications..................................................................... 435

Identifying the hardware ................................................................................... 436

Device utilization .............................................................................................. 437

Sampling performance ...................................................................................... 438

Section summary............................................................................................... 439

Conclusion .............................................................................................................. 439

Questions on Optimization................................................................................ 439

Answers ............................................................................................................. 440

Contents ix

CHAPTER 10 Libraries and SDK .................................................................. 441

Introduction.......................................................................................................... 441

Libraries ............................................................................................................... 441

General library conventions ........................................................................... 442

NPP (Nvidia Performance Primitives) ........................................................... 442

Thrust .............................................................................................................. 451

CuRAND......................................................................................................... 467

CuBLAS (CUDA basic linear algebra) library.............................................. 471

CUDA Computing SDK ...................................................................................... 475

Device Query .................................................................................................. 476

Bandwidth test ................................................................................................ 478

SimpleP2P....................................................................................................... 479

asyncAPI and cudaOpenMP........................................................................... 482

Aligned types .................................................................................................. 489

Directive-Based Programming ............................................................................ 491

OpenACC........................................................................................................ 492

Writing Your Own Kernels.................................................................................. 499

Conclusion ........................................................................................................... 502

CHAPTER 11 Designing GPU-Based Systems................................................ 503

Introduction.......................................................................................................... 503

CPU Processor ..................................................................................................... 505

GPU Device ......................................................................................................... 507

Large memory support ................................................................................... 507

ECC memory support..................................................................................... 508

Tesla compute cluster driver (TCC)............................................................... 508

Higher double-precision math ........................................................................ 508

Larger memory bus width .............................................................................. 508

SMI ................................................................................................................. 509

Status LEDs .................................................................................................... 509

PCI-E Bus ............................................................................................................ 509

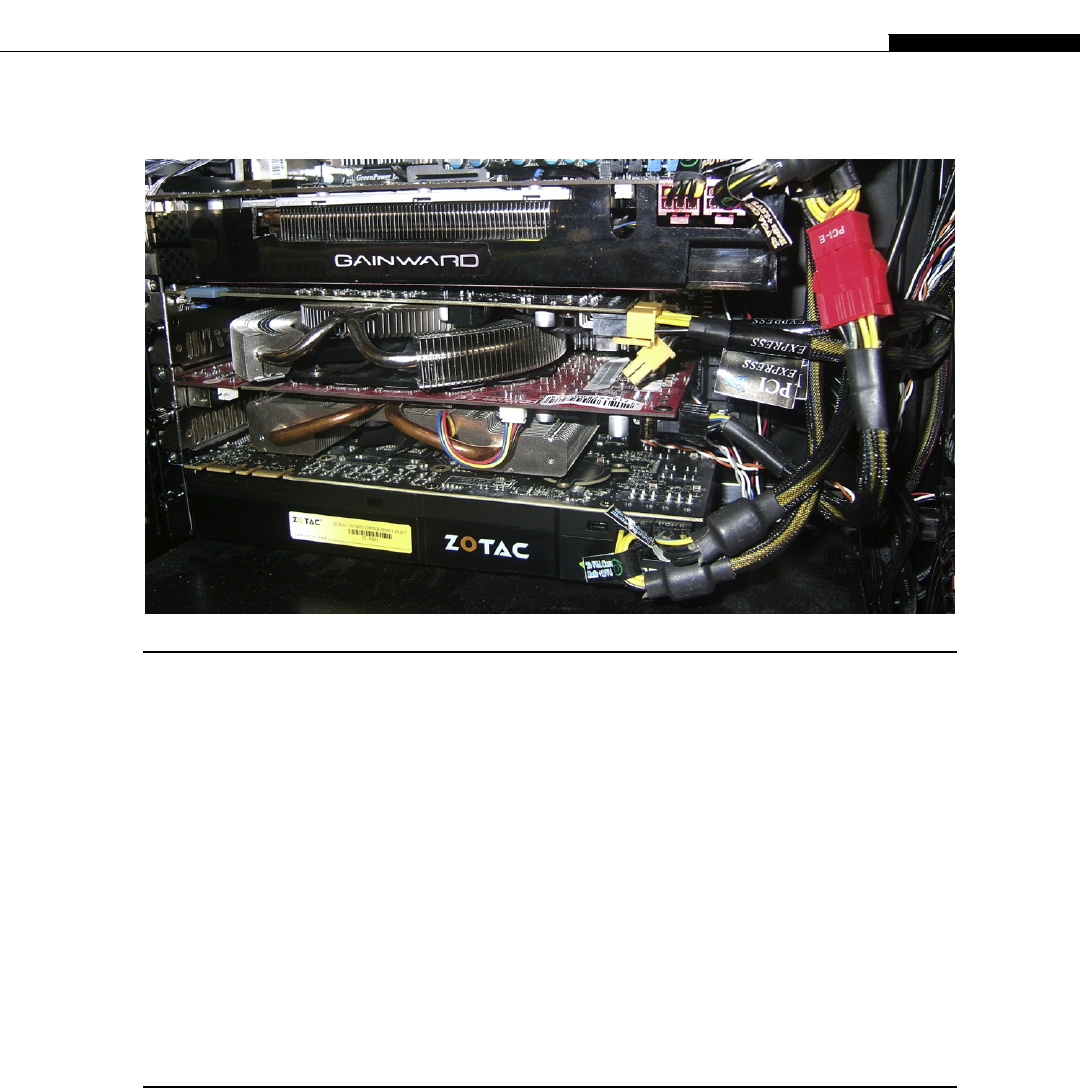

GeForce cards ...................................................................................................... 510

CPU Memory ....................................................................................................... 510

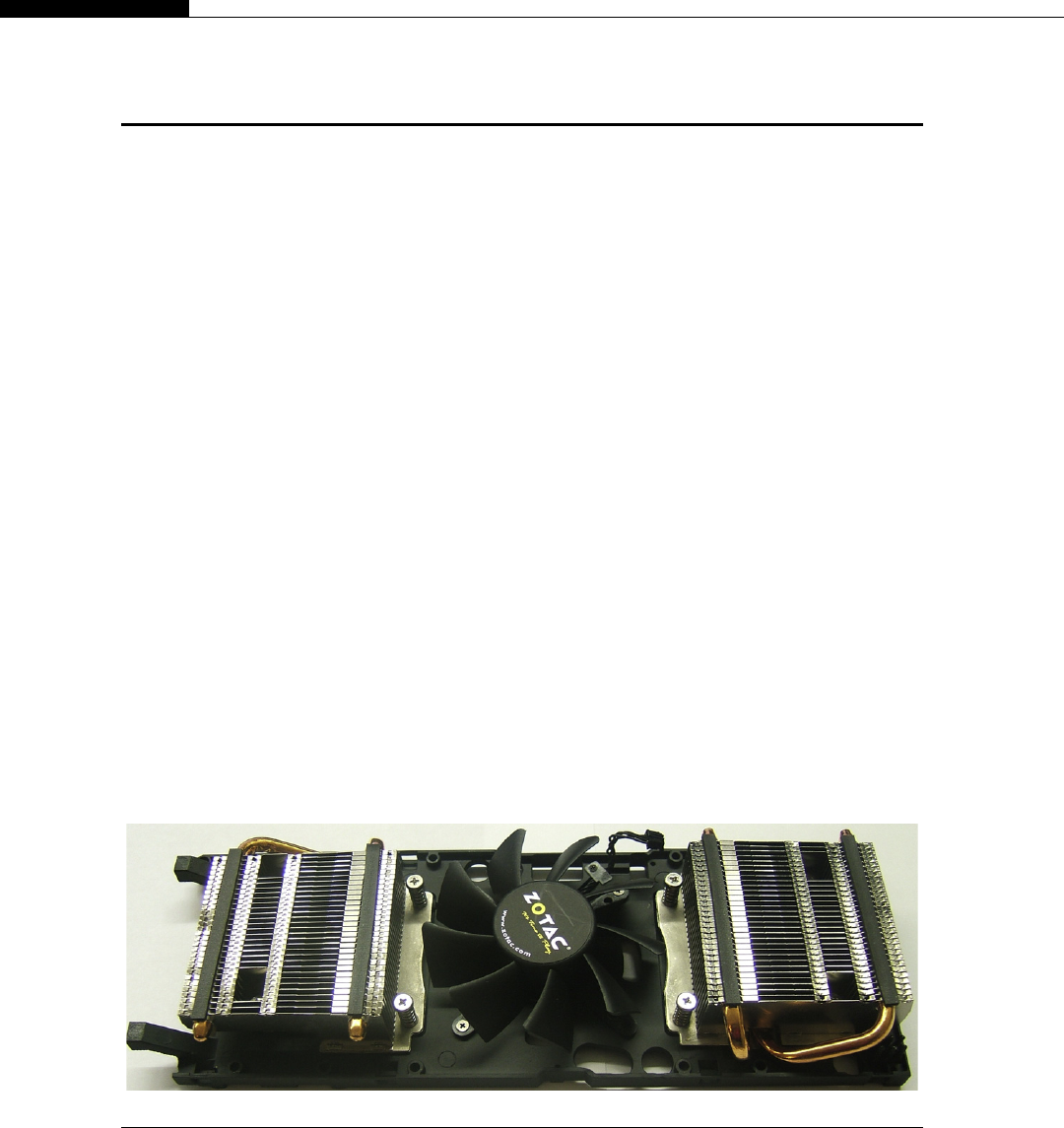

Air Cooling .......................................................................................................... 512

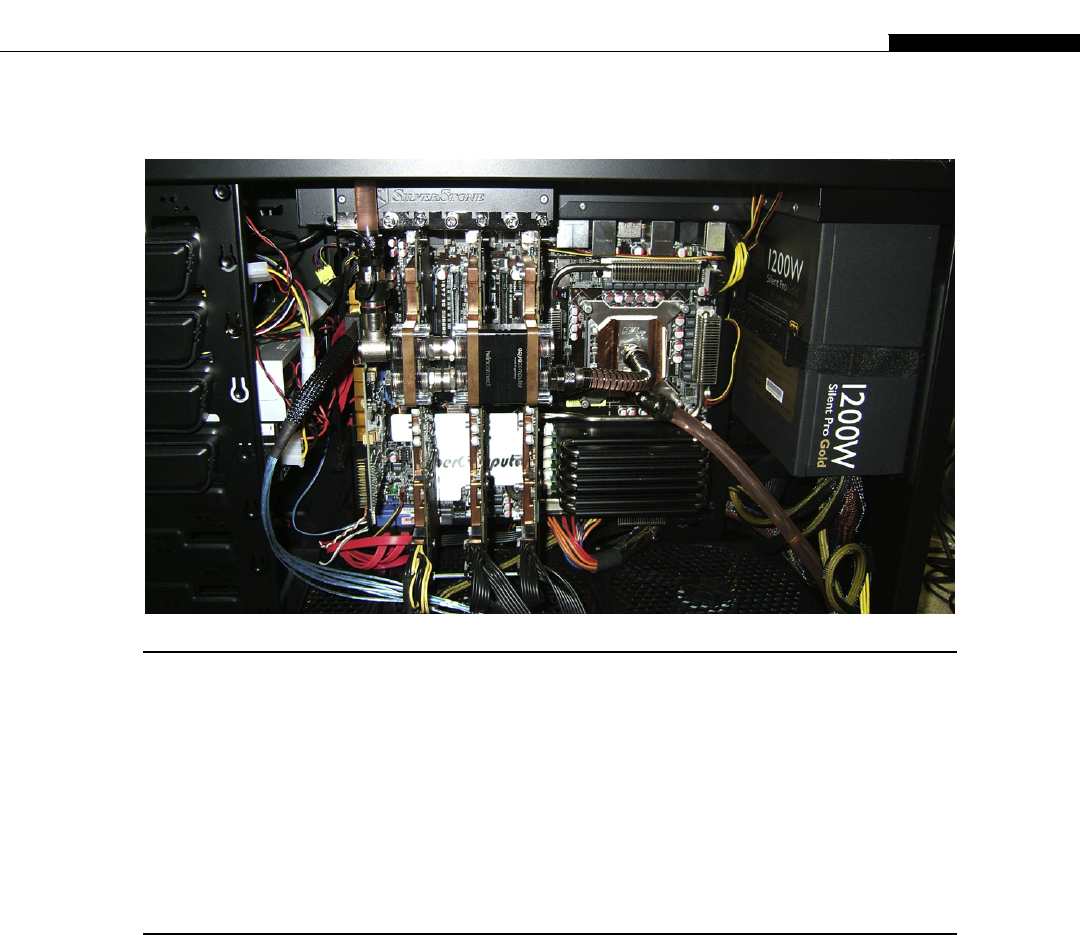

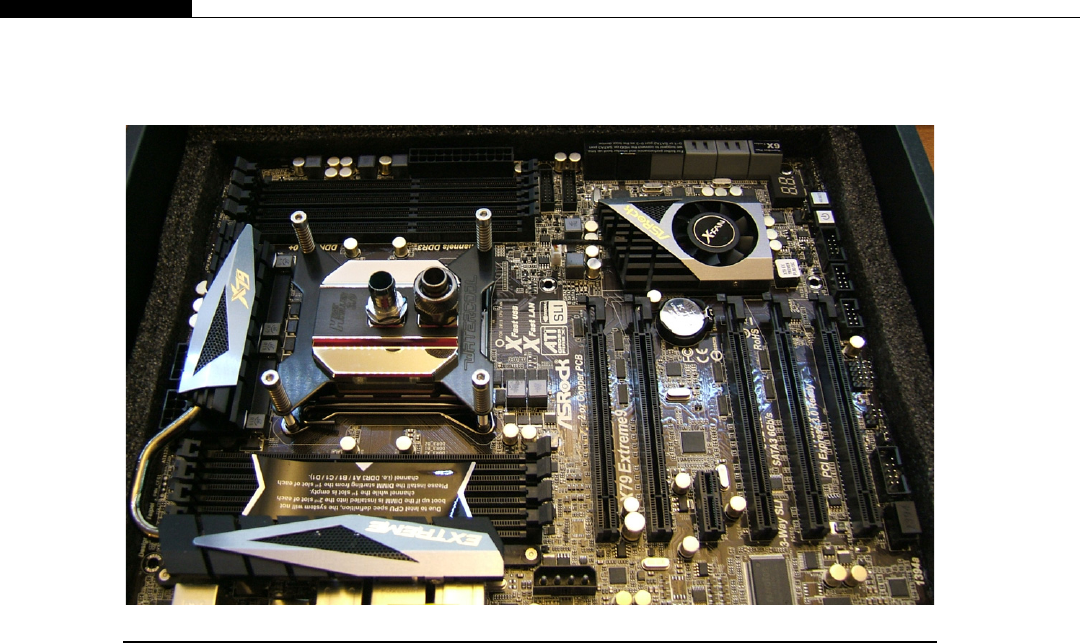

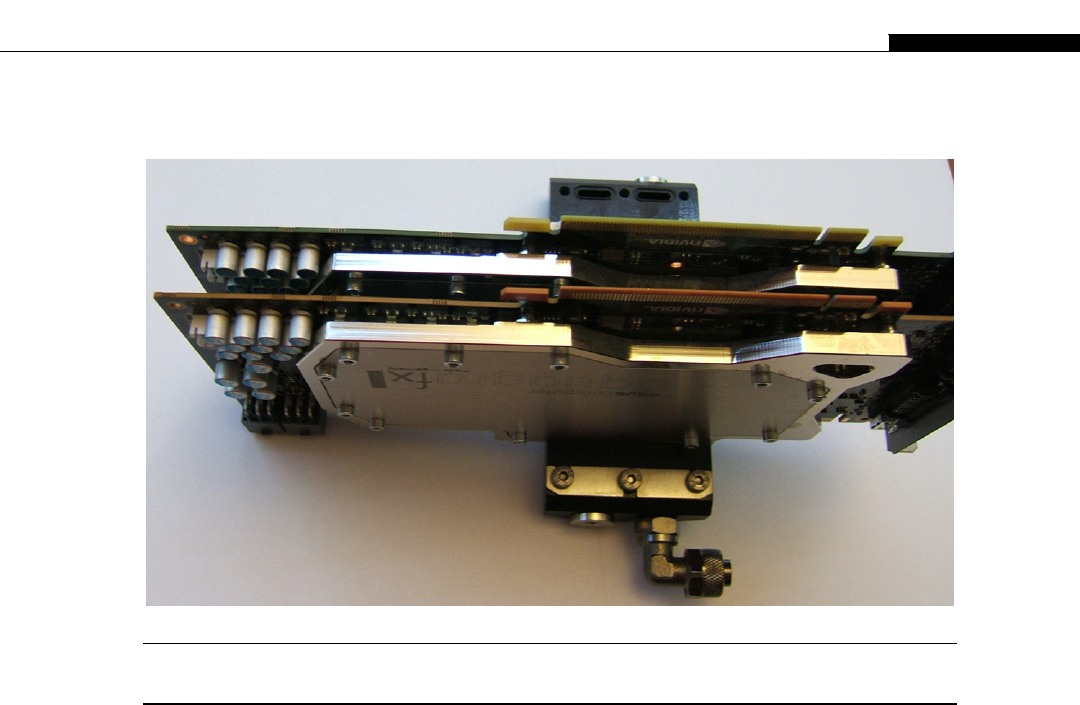

Liquid Cooling..................................................................................................... 513

Desktop Cases and Motherboards ....................................................................... 517

Mass Storage........................................................................................................ 518

Motherboard-based I/O................................................................................... 518

Dedicated RAID controllers........................................................................... 519

HDSL .............................................................................................................. 520

Mass storage requirements ............................................................................. 521

Networking ..................................................................................................... 521

Power Considerations .......................................................................................... 522

xContents

Operating Systems ............................................................................................... 525

Windows ......................................................................................................... 525

Linux............................................................................................................... 525

Conclusion ........................................................................................................... 526

CHAPTER 12 Common Problems, Causes, and Solutions............................... 527

Introduction.......................................................................................................... 527

Errors With CUDA Directives............................................................................. 527

CUDA error handling ..................................................................................... 527

Kernel launching and bounds checking ......................................................... 528

Invalid device handles .................................................................................... 529

Volatile qualifiers ............................................................................................ 530

Compute level–dependent functions .............................................................. 532

Device, global, and host functions................................................................. 534

Kernels within streams ................................................................................... 535

Parallel Programming Issues ............................................................................... 536

Race hazards ................................................................................................... 536

Synchronization .............................................................................................. 537

Atomic operations........................................................................................... 541

Algorithmic Issues ............................................................................................... 544

Back-to-back testing ....................................................................................... 544

Memory leaks ................................................................................................. 546

Long kernels ................................................................................................... 546

Finding and Avoiding Errors ............................................................................... 547

How many errors does your GPU program have?......................................... 547

Divide and conquer......................................................................................... 548

Assertions and defensive programming ......................................................... 549

Debug level and printing ................................................................................ 551

Version control................................................................................................ 555

Developing for Future GPUs............................................................................... 555

Kepler.............................................................................................................. 555

What to think about........................................................................................ 558

Further Resources ................................................................................................ 560

Introduction..................................................................................................... 560

Online courses ................................................................................................ 560

Taught courses ................................................................................................ 561

Books .............................................................................................................. 562

NVIDIA CUDA certification.......................................................................... 562

Conclusion ........................................................................................................... 562

References............................................................................................................ 563

Index ................................................................................................................................................. 565

Contents xi

This page intentionally left blank

Preface

Over the past five years there has been a revolution in computing brought about by a company that for

successive years has emerged as one of the premier gaming hardware manufacturersdNVIDIA. With

the introduction of the CUDA (Compute Unified Device Architecture) programming language, for the

first time these hugely powerful graphics coprocessors could be used by everyday C programmers to

offload computationally expensive work. From the embedded device industry, to home users, to

supercomputers, everything has changed as a result of this.

One of the major changes in the computer software industry has been the move from serial

programming to parallel programming. Here, CUDA has produced great advances. The graphics

processor unit (GPU) by its very nature is designed for high-speed graphics, which are inherently

parallel. CUDA takes a simple model of data parallelism and incorporates it into a programming

model without the need for graphics primitives.

In fact, CUDA, unlike its predecessors, does not require any understanding or knowledge of

graphics or graphics primitives. You do not have to be a games programmer either. The CUDA

language makes the GPU look just like another programmable device.

Throughout this book I will assume readers have no prior knowledge of CUDA, or of parallel

programming. I assume they have only an existing knowledge of the C/C++ programming language.

As we progress and you become more competent with CUDA, we’ll cover more advanced topics,

taking you from a parallel unaware programmer to one who can exploit the full potential of CUDA.

For programmers already familiar with parallel programming concepts and CUDA, we’ll be

discussing in detail the architecture of the GPUs and how to get the most from each, including the latest

Fermi and Kepler hardware. Literally anyone who can program in C or C++ can program with CUDA

in a few hours given a little training. Getting from novice CUDA programmer, with a several times

speedup to 10 times–plus speedup is what you should be capable of by the end of this book.

The book is very much aimed at learning CUDA, but with a focus on performance, having first

achieved correctness. Your level of skill and understanding of writing high-performance code, espe-

cially for GPUs, will hugely benefit from this text.

This book is a practical guide to using CUDA in real applications, by real practitioners. At the same

time, however, we cover the necessary theory and background so everyone, no matter what their

background, can follow along and learn how to program in CUDA, making this book ideal for both

professionals and those studying GPUs or parallel programming.

The book is set out as follows:

Chapter 1: A Short History of Supercomputing. This chapter is a broad introduction to the

evolution of streaming processors covering some key developments that brought us to GPU

processing today.

Chapter 2: Understanding Parallelism with GPUs. This chapter is an introduction to the

concepts of parallel programming, such as how serial and parallel programs are different and

how to approach solving problems in different ways. This chapter is primarily aimed at existing

serial programmers to give a basis of understanding for concepts covered later in the book.

xiii

Chapter 3: CUDA Hardware Overview. This chapter provides a fairly detailed explanation of the

hardware and architecture found around and within CUDA devices. To achieve the best

performance from CUDA programming, a reasonable understanding of the hardware both

within and outside the device is required.

Chapter 4: Setting Up CUDA. Installation and setup of the CUDA SDK under Windows, Mac,

and the Linux variants. We also look at the main debugging environments available for CUDA.

Chapter 5: Grids, Blocks, and Threads. A detailed explanation of the CUDA threading model,

including some examples of how the choices here impact performance.

Chapter 6: Memory Handling with CUDA. Understanding the different memory types and how

they are used within CUDA is the single largest factor influencing performance. Here we take

a detailed explanation, with examples, of how the various memory types work and the pitfalls

of getting it wrong.

Chapter 7: Using CUDA in Practice. Detailed examination as to how central processing units

(CPUs) and GPUs best cooperate with a number of problems and the issues involved in CPU/

GPU programming.

Chapter 8: Multi-CPU and Multi-GPU Solutions. We look at how to program and use multiple

GPUs within an application.

Chapter 9: Optimizing Your Application. A detailed breakdown of the main areas that limit

performance in CUDA. We look at the tools and techniques that are available for analysis of

CUDA code.

Chapter 10: Libraries and SDK. A look at some of the CUDA SDK samples and the libraries

supplied with CUDA, and how you can use these within your applications.

Chapter 11: Designing GPU-Based Systems. This chapter takes a look at some of the issues

involved with building your own GPU server or cluster.

Chapter 12: Common Problems, Causes, and Solutions. A look at the type of mistakes most

programmers make when developing applications in CUDA and how these can be detected and

avoided.

xiv Preface

A Short History of Supercomputing 1

INTRODUCTION

So why in a book about CUDA are we looking at supercomputers? Supercomputers are typically at the

leading edge of the technology curve. What we see here is what will be commonplace on the desktop in

5 to 10 years. In 2010, the annual International Supercomputer Conference in Hamburg, Germany,

announced that a NVIDIA GPU-based machine had been listed as the second most powerful computer

in the world, according to the top 500 list (http://www.top500.org). Theoretically, it had more peak

performance than the mighty IBM Roadrunner, or the then-leader, the Cray Jaguar, peaking at near to 3

petaflops of performance. In 2011, NVIDIA CUDA-powered GPUs went on to claim the title of the

fastest supercomputer in the world. It was suddenly clear to everyone that GPUs had arrived in a very

big way on the high-performance computing landscape, as well as the humble desktop PC.

Supercomputing is the driver of many of the technologies we see in modern-day processors.

Thanks to the need for ever-faster processors to process ever-larger datasets, the industry produces

ever-faster computers. It is through some of these evolutions that GPU CUDA technology has come

about today.

Both supercomputers and desktop computing are moving toward a heterogeneous computing

routedthat is, they are trying to achieve performance with a mix of CPU (Central Processor Unit) and

GPU (Graphics Processor Unit) technology. Two of the largest worldwide projects using GPUs are

BOINC and Folding@Home, both of which are distributed computing projects. They allow ordinary

people to make a real contribution to specific scientific projects. Contributions from CPU/GPU hosts

on projects supporting GPU accelerators hugely outweigh contributions from CPU-only hosts. As of

November 2011, there were some 5.5 million hosts contributing a total of around 5.3 petaflops, around

half that of the world’s fastest supercomputer, in 2011, the Fujitsu “K computer” in Japan.

The replacement for Jaguar, currently the fastest U.S. supercomputer, code-named Titan, is

planned for 2013. It will use almost 300,000 CPU cores and up to 18,000 GPU boards to achieve

between 10 and 20 petaflops per second of performance. With support like this from around the world,

GPU programming is set to jump into the mainstream, both in the HPC industry and also on the

desktop.

You can now put together or purchase a desktop supercomputer with several teraflops of perfor-

mance. At the beginning of 2000, some 12 years ago, this would have given you first place in the top

500 list, beating IBM ASCI Red with its 9632 Pentium processors. This just shows how much a little

over a decade of computing progress has achieved and opens up the question about where we will be

a decade from now. You can be fairly certain GPUs will be at the forefront of this trend for some time

CHAPTER

CUDA Programming. http://dx.doi.org/10.1016/B978-0-12-415933-4.00001-6

Copyright Ó2013 Elsevier Inc. All rights reserved.

1

to come. Thus, learning how to program GPUs effectively is a key skill any good developer needs

to acquire.

VON NEUMANN ARCHITECTURE

Almost all processors work on the basis of the process developed by Von Neumann, considered one of

the fathers of computing. In this approach, the processor fetches instructions from memory, decodes,

and then executes that instruction.

A modern processor typically runs at anything up to 4 GHz in speed. Modern DDR-3 memory, when

paired with say a standard Intel I7 device, can run at anything up to 2 GHz. However, the I7 has at least four

processors or cores in one device, or double that if you count its hyperthreading ability as a real processor.

A DDR-3 triple-channel memory setup on a I7 Nehalem system would produce the theoretical

bandwidth figures shown in Table 1.1. Depending on the motherboard, and exact memory pattern, the

actual bandwidth could be considerably less.

You run into the first problem with memory bandwidth when you consider the processor clock

speed. If you take a processor running at 4 GHz, you need to potentially fetch, every cycle, an

instruction (an operator) plus some data (an operand).

Each instruction is typically 32 bits, so if you execute nothing but a set of linear instructions, with no

data, on every core, you get 4.8 GB/s O4¼1.2 GB instructions per second. This assumes the processor

can dispatch one instruction per clock on average*. However, you typically also need to fetch and write

back data, which if we say is on a 1:1 ratio with instructions, means we effectively halve our throughput.

The ratio of clock speed to memory is an important limiter for both CPU and GPU throughput and

something we’ll look at later. We find when you look into it, most applications, with a few exceptions on

both CPU and GPU, are often memory bound and not processor cycle or processor clock/load bound.

CPU vendors try to solve this problem by using cache memory and burst memory access. This

exploits the principle of locality. It you look at a typical C program, you might see the following type of

operation in a function:

void some_function

{

int array[100];

int i ¼0;

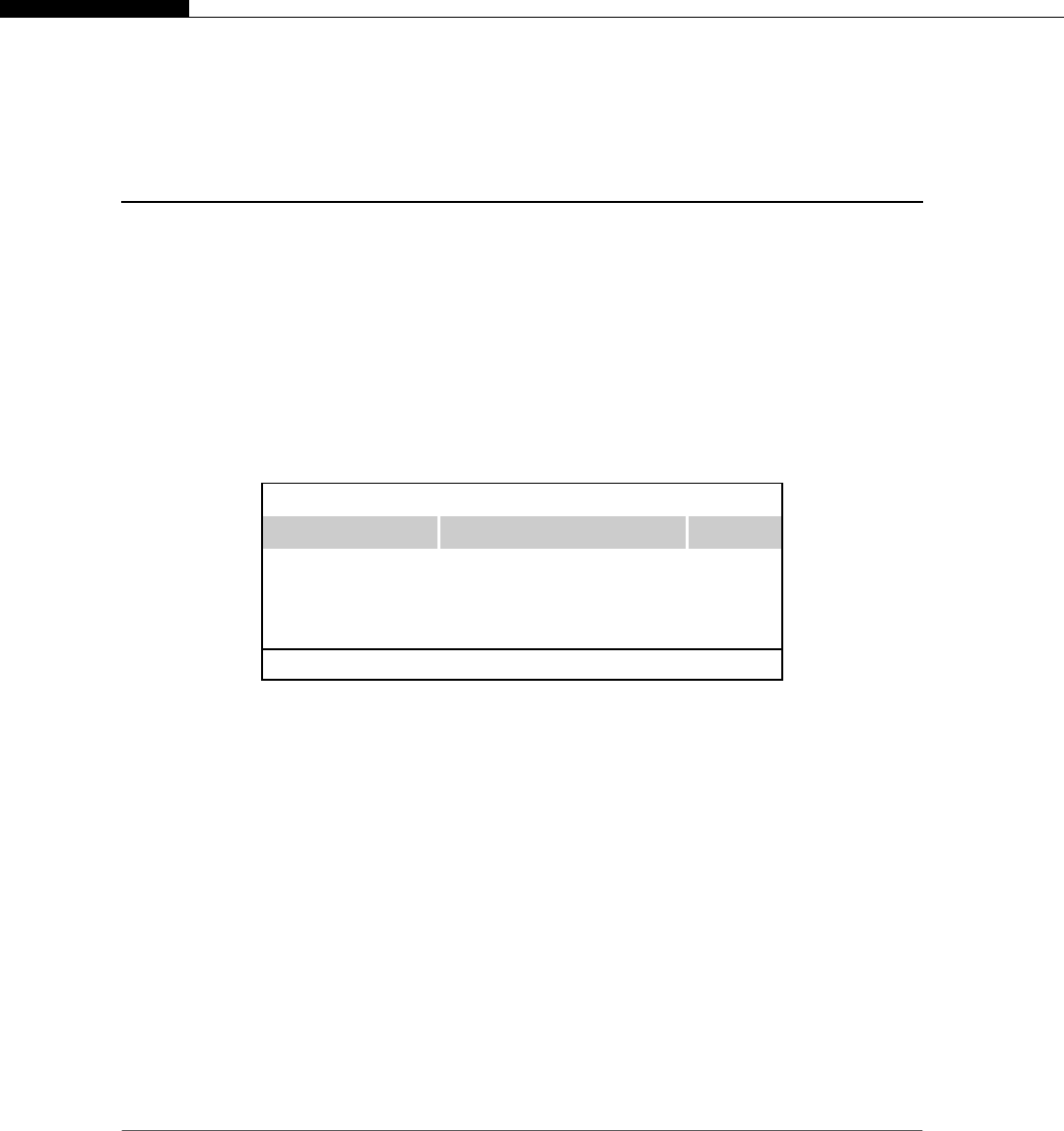

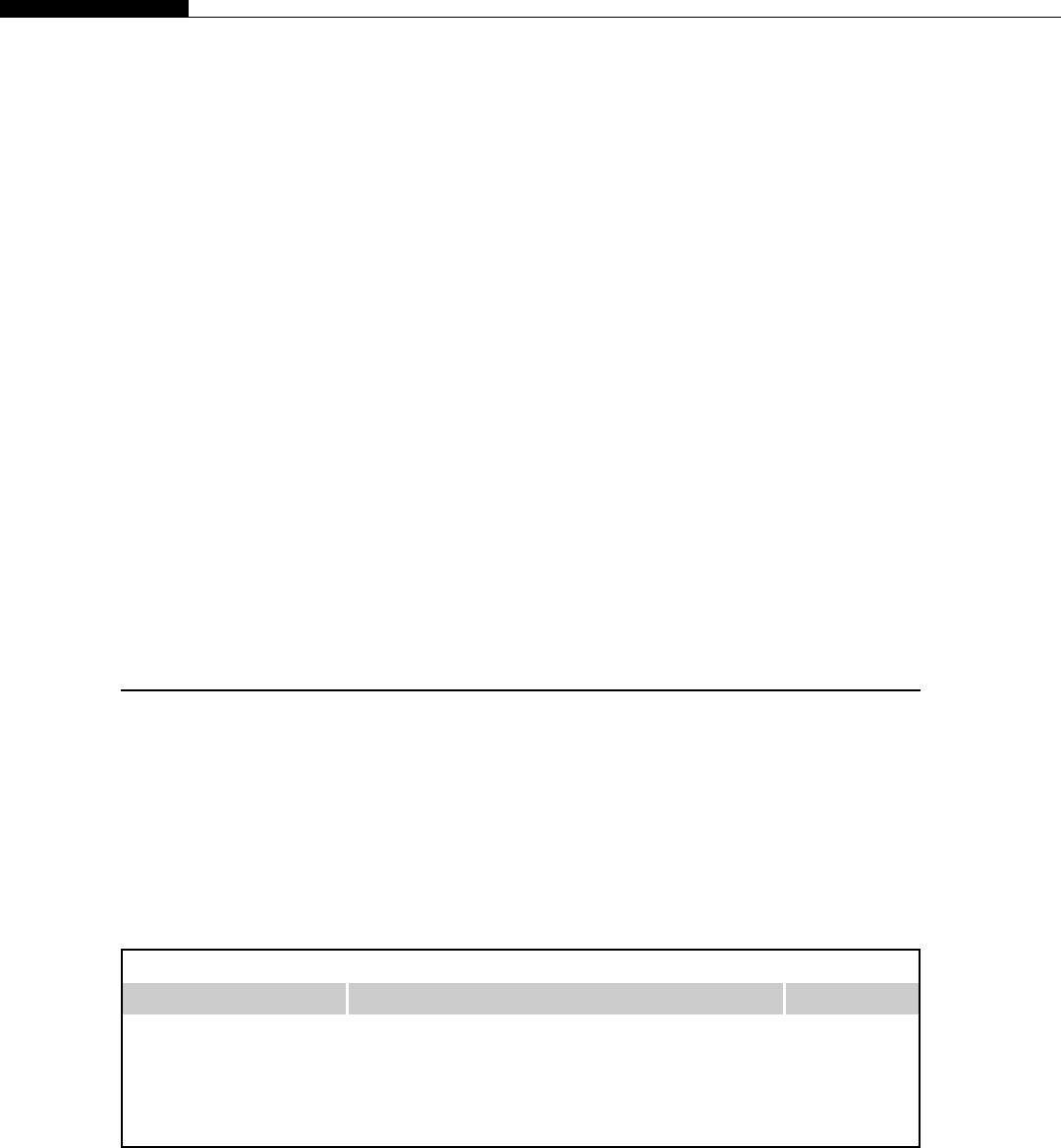

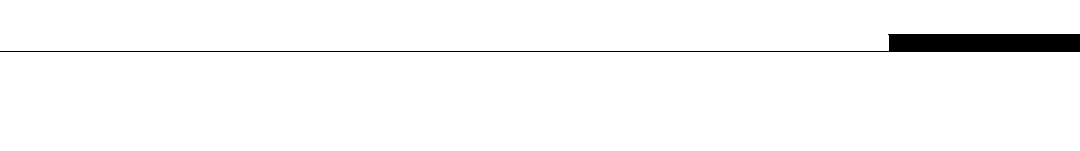

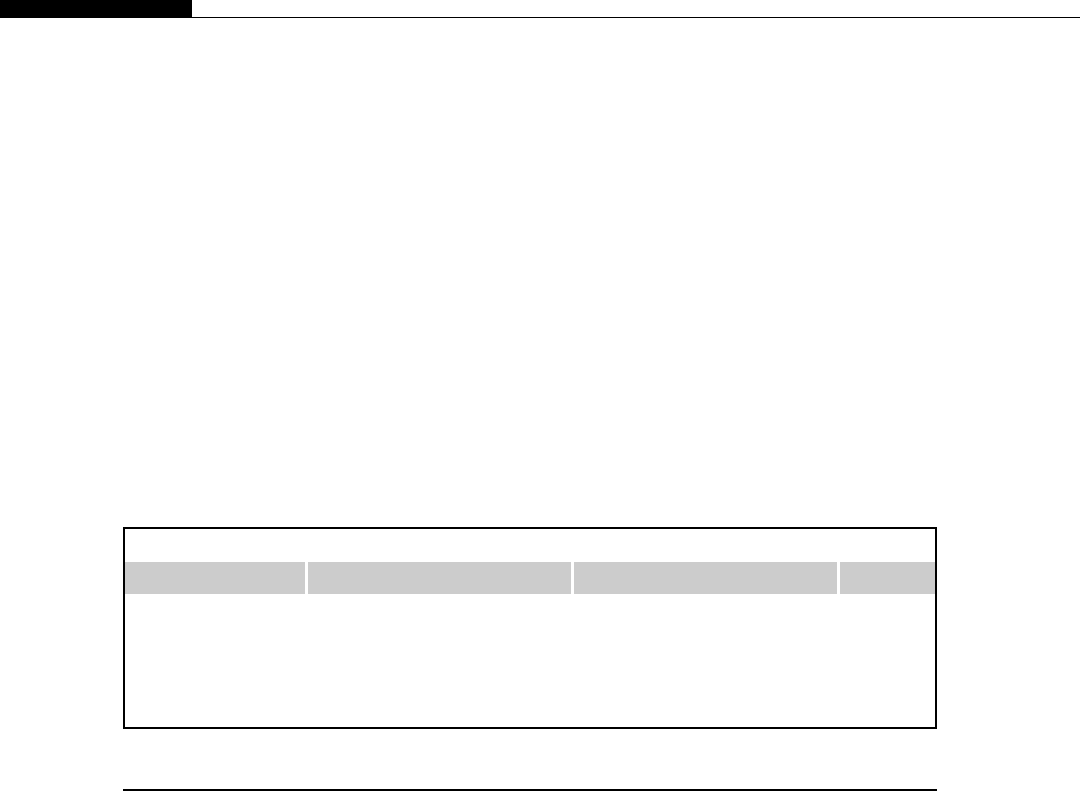

Table 1.1 Bandwidth on I7 Nehalem Processor

QPI Clock Theoretical Bandwidth Per Core

4.8 GT/s

(standard part)

19.2 GB/s 4.8 GB/s

6.4 GT/s

(extreme edition)

25.6 GB/s 6.4 GB/s

Note: QPI ¼Quick Path Interconnect.

*

The actual achieved dispatch rate can be higher or lower than one, which we use here for simplicity.

2 CHAPTER 1 A Short History of Supercomputing

for (i¼0; i<100; iþþ)

{

array[i] ¼i * 10;

}

}

If you look at how the processor would typically implement this, you would see the address of

array loaded into some memory access register. The parameter iwould be loaded into another

register. The loop exit condition, 100, is loaded into another register or possibly encoded into the

instruction stream as a literal value. The computer would then iterate around the same instructions,

over and over again 100 times. For each value calculated, we have control, memory, and calculation

instructions, fetched and executed.

This is clearly inefficient, as the computer is executing the same instructions, but with

different data values. Thus, the hardware designers implement into just about all processors

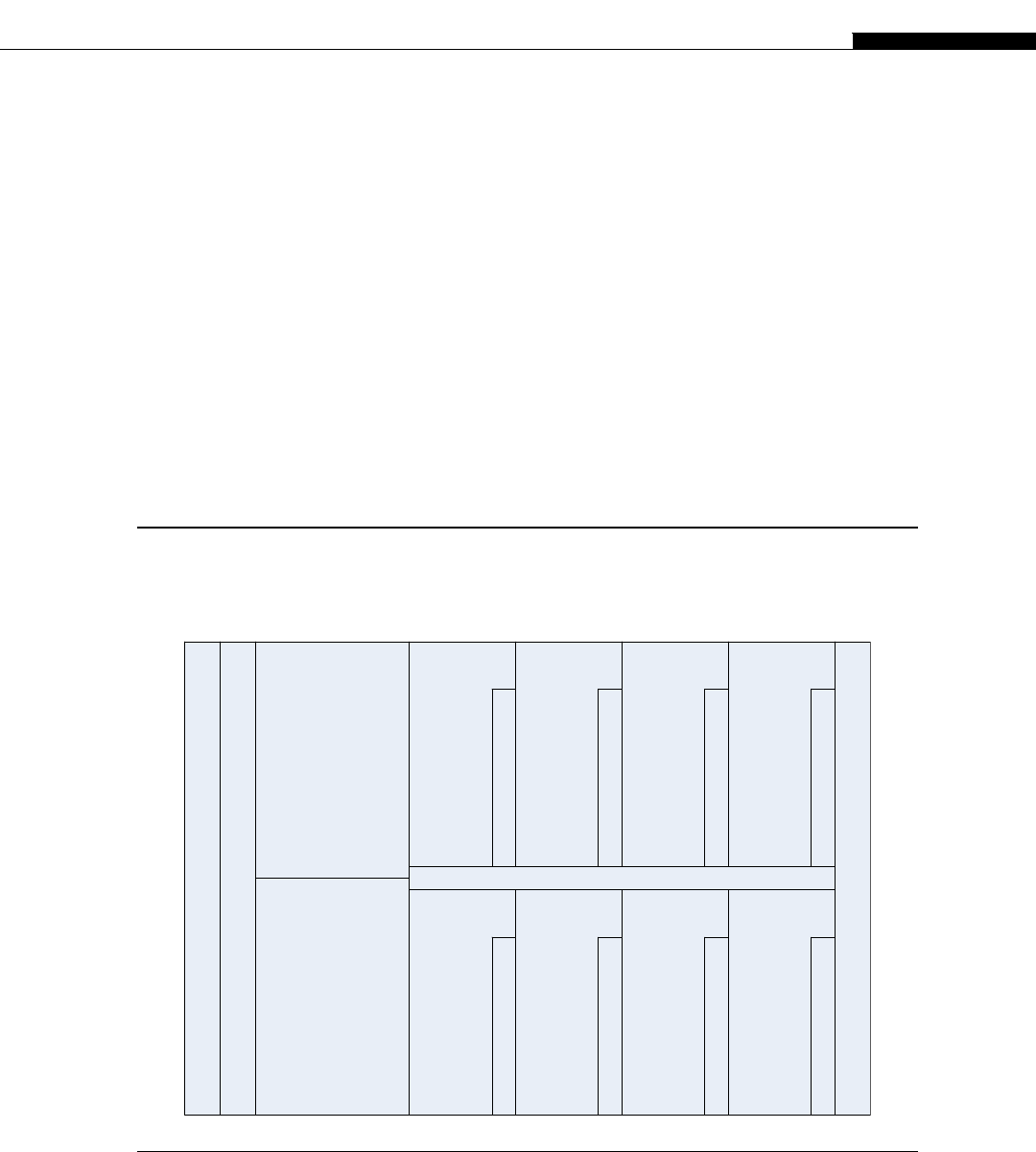

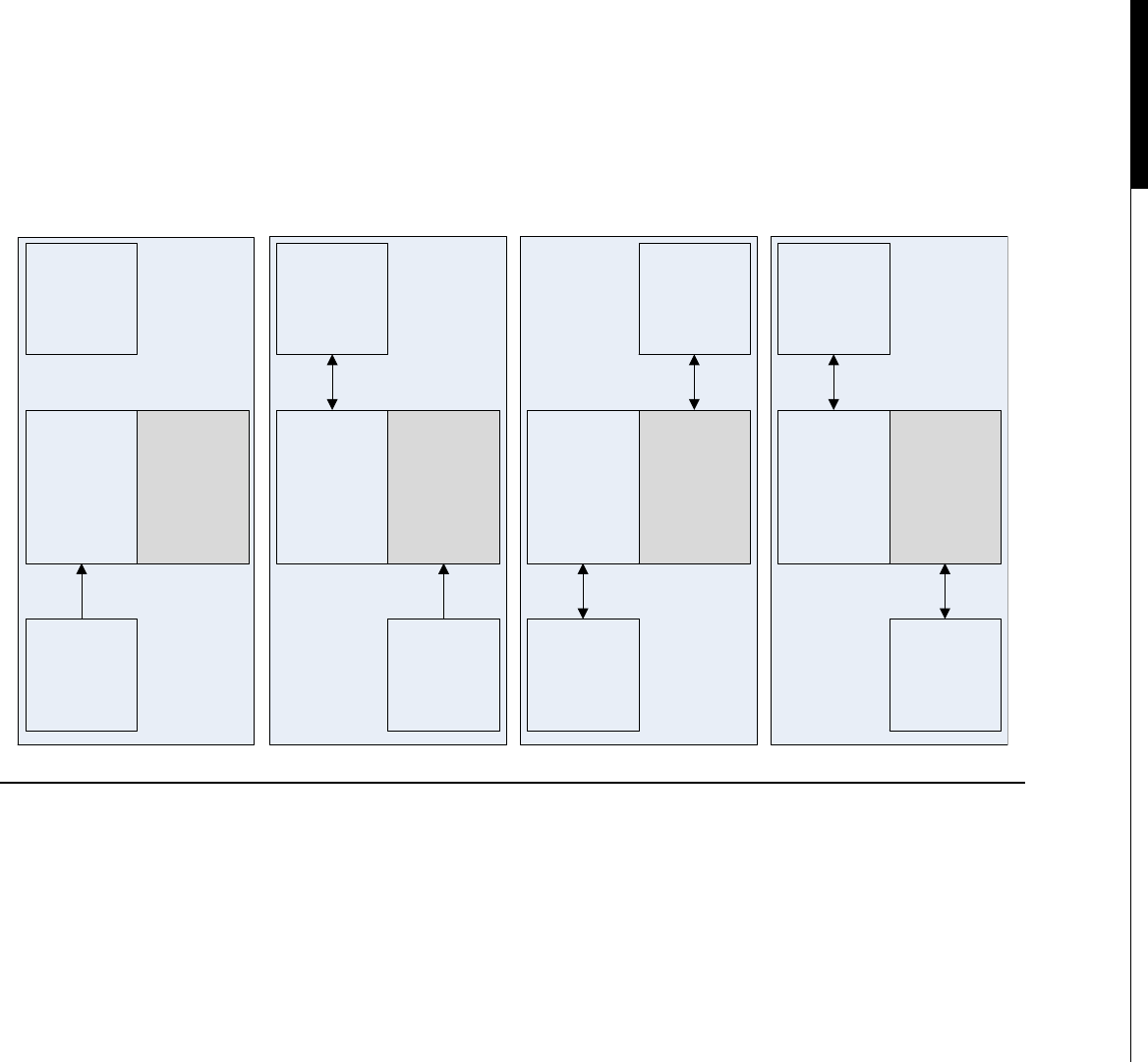

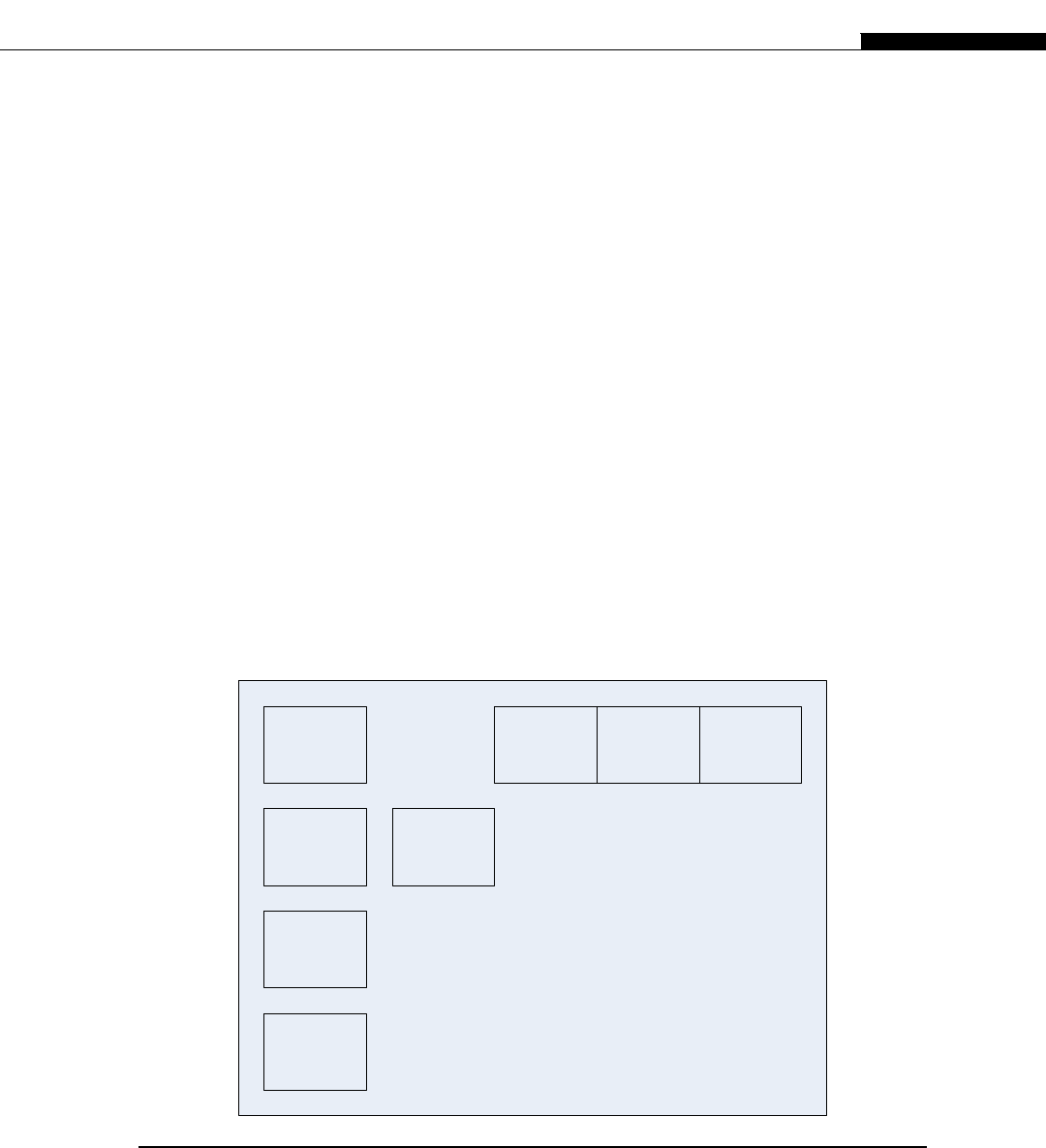

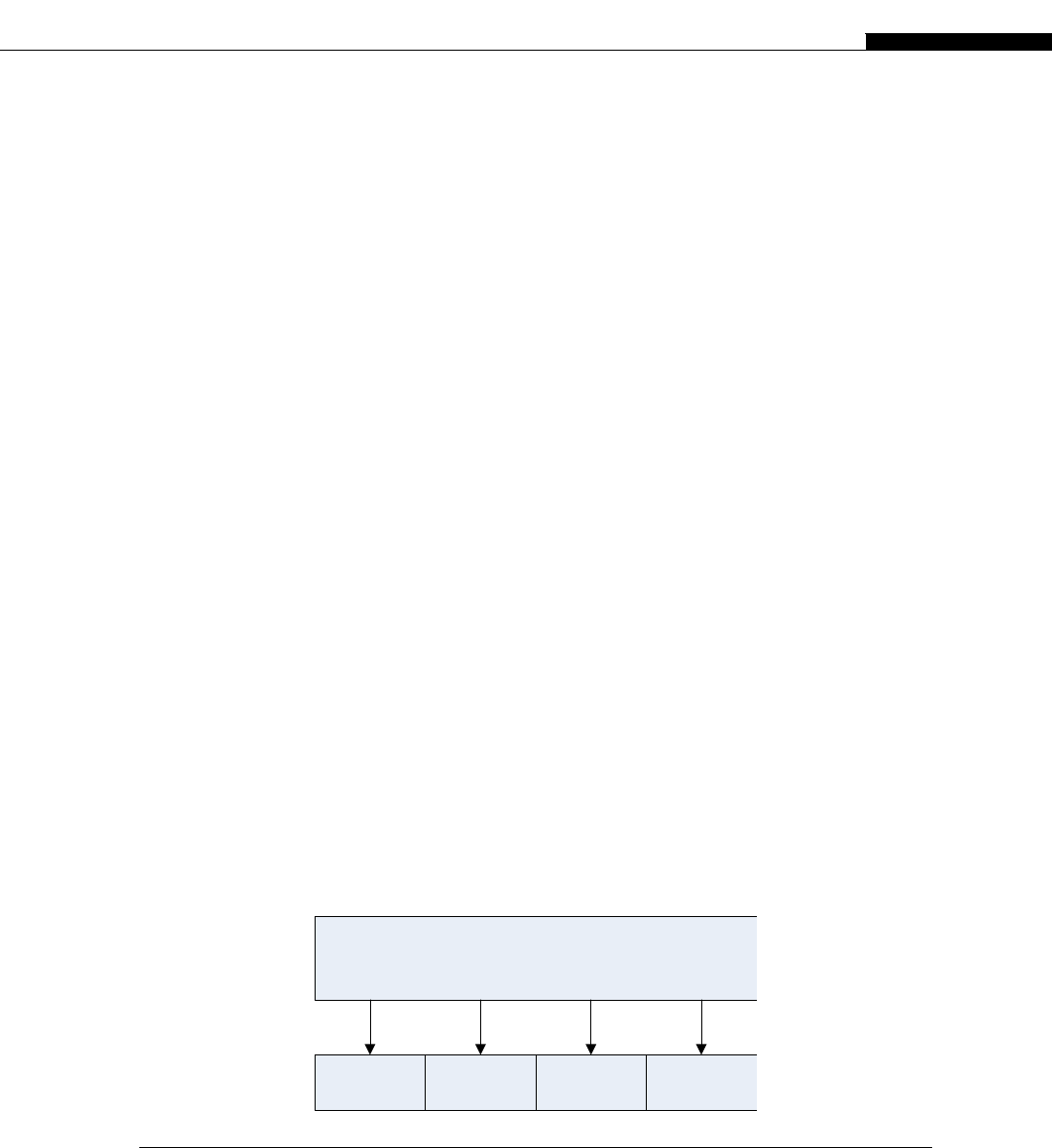

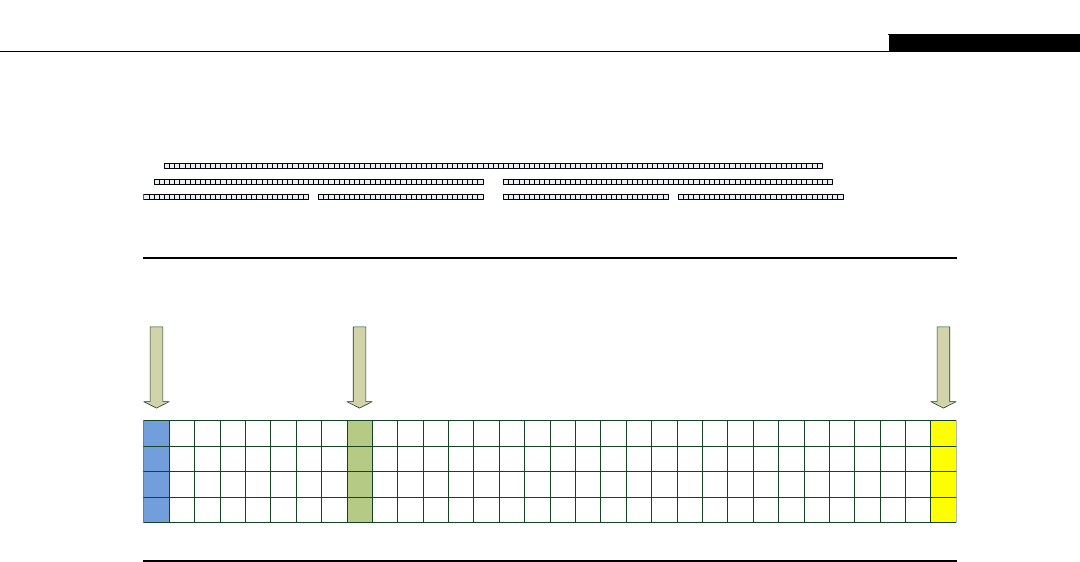

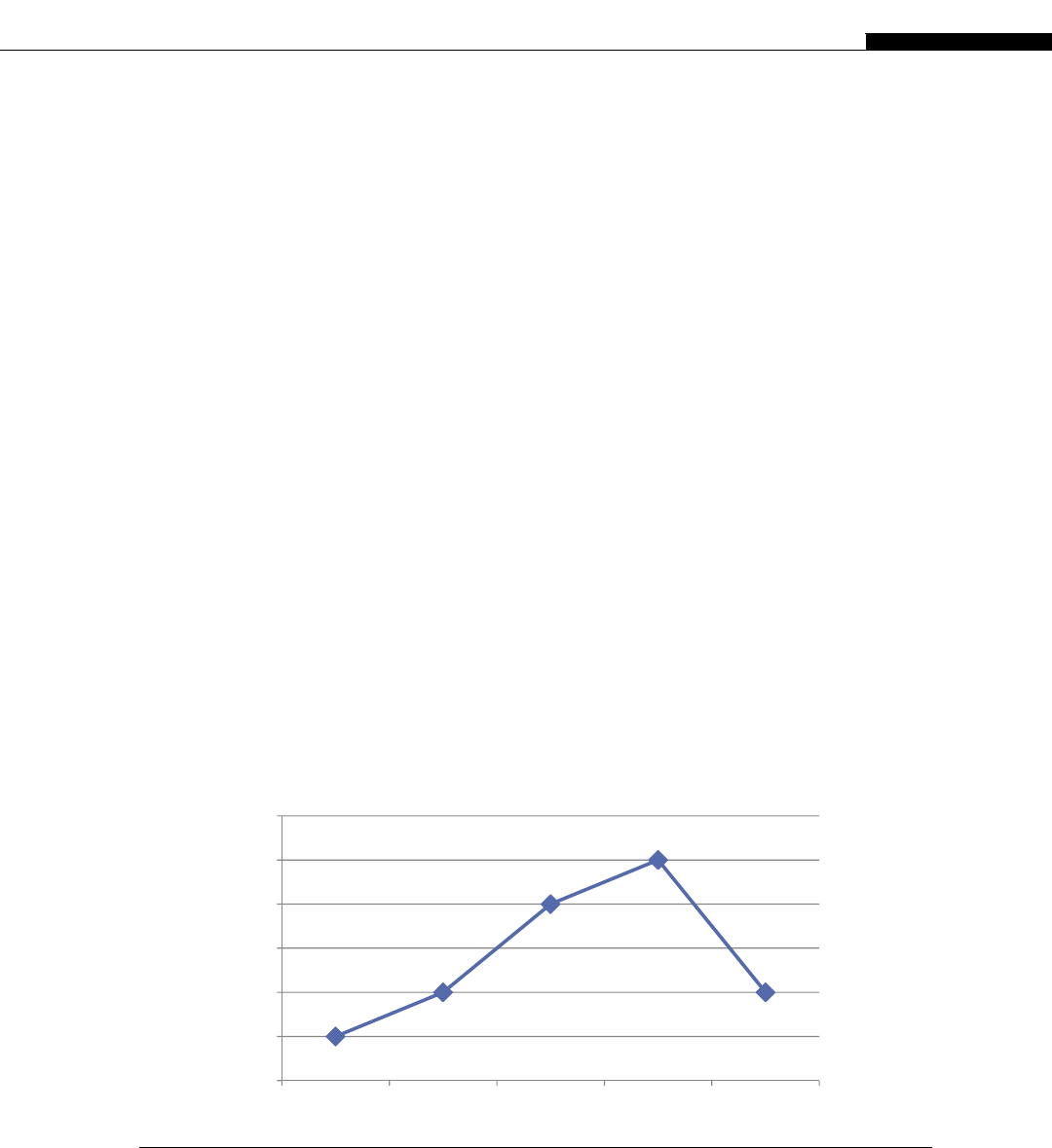

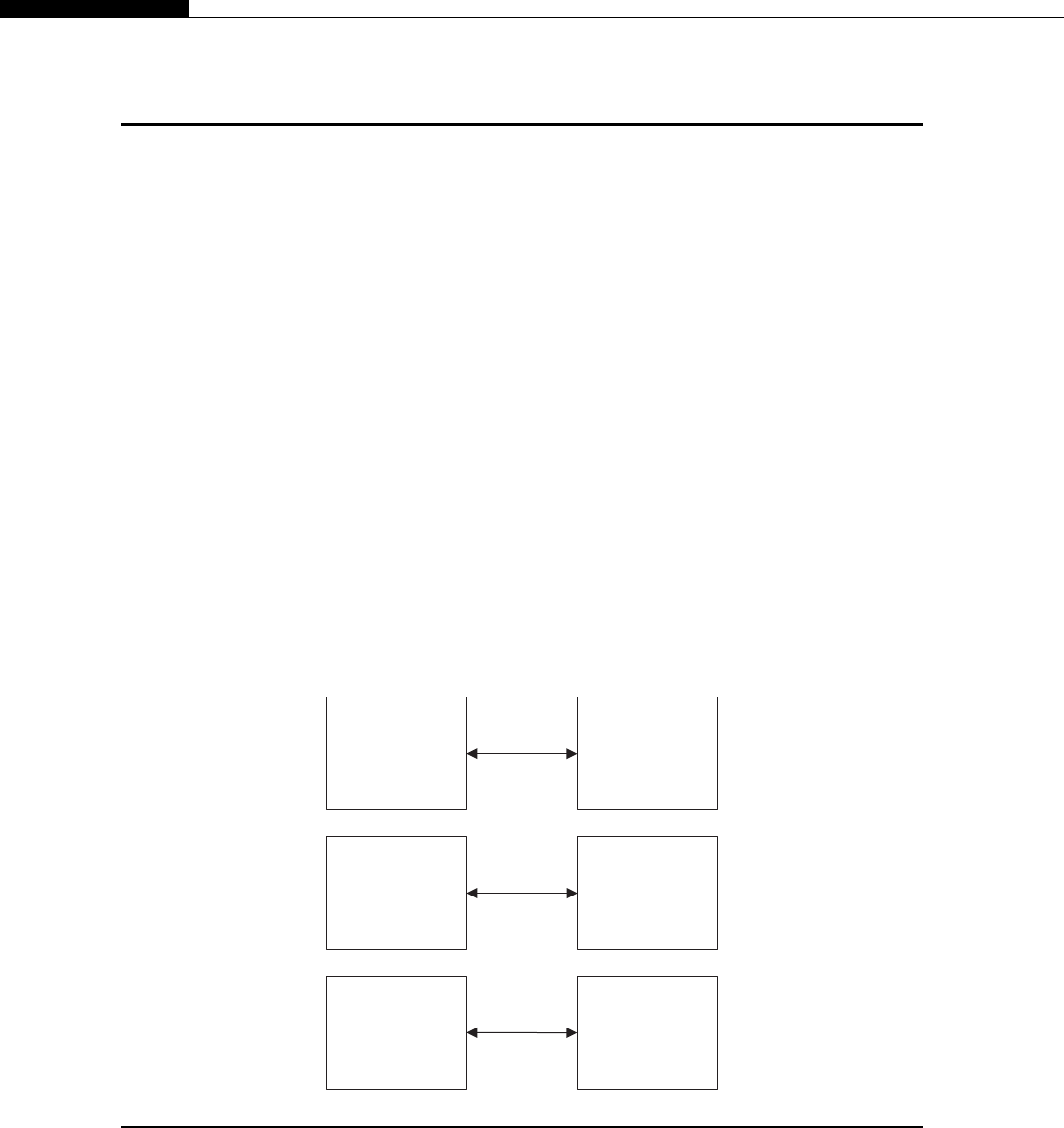

a small amount of cache, and in more complex processors, many levels of cache (Figure 1.1).

When the processor would fetch something from memory, the processor first queries the cache,

and if the data or instructions are present there, the high-speed cache provides them to the

processor.

DRAM

L3 Cache

L2 Cache

L1 Instruction L1 Data

Processor Core

L2 Cache

L1 Instruction L1 Data

Processor Core

L2 Cache

L1 Instruction L1 Data

Processor Core

L2 Cache

L1 Instruction L1 Data

Processor Core

FIGURE 1.1

Typical modern CPU cache organization.

Von Neumann Architecture 3

If the data is not in the first level (L1) cache, then a fetch from the second or third level (L2 or L3)

cache is required, or from the main memory if no cache line has this data already. The first level cache

typically runs at or near the processor clock speed, so for the execution of our loop, potentially we do

get near the full processor speed, assuming we write cache as well as read cache. However, there is

a cost for this: The size of the L1 cache is typically only 16 K or 32 K in size. The L2 cache is

somewhat slower, but much larger, typically around 256 K. The L3 cache is much larger, usually

several megabytes in size, but again much slower than the L2 cache.

With real-life examples, the loop iterations are much, much larger, maybe many megabytes in size.

Even if the program can remain in cache memory, the dataset usually cannot, so the processor, despite

all this cache trickery, is quite often limited by the memory throughput or bandwidth.

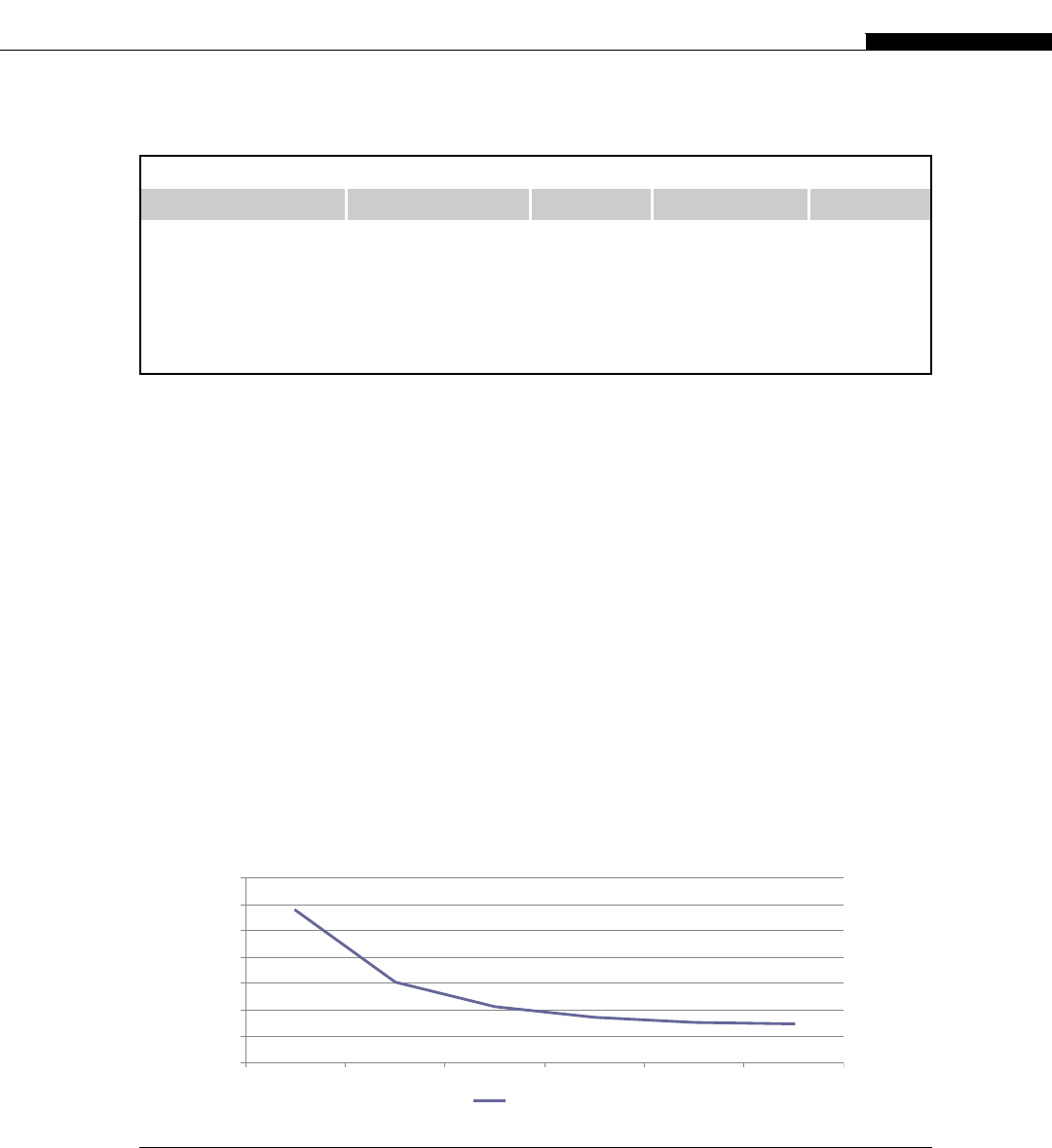

When the processor fetches an instruction or data item from the cache instead of the main memory,

it’s called a cache hit. The incremental benefit of using progressively larger caches drops off quite

rapidly. This in turn means the ever-larger caches we see on modern processors are a less and less

useful means to improve performance, unless they manage to encompass the entire dataset of the

problem.

The Intel I7-920 processor has some 8 MB of internal L3 cache. This cache memory is not free, and

if we look at the die for the Intel I7 processor, we see around 30% of the size of the chip is dedicated to

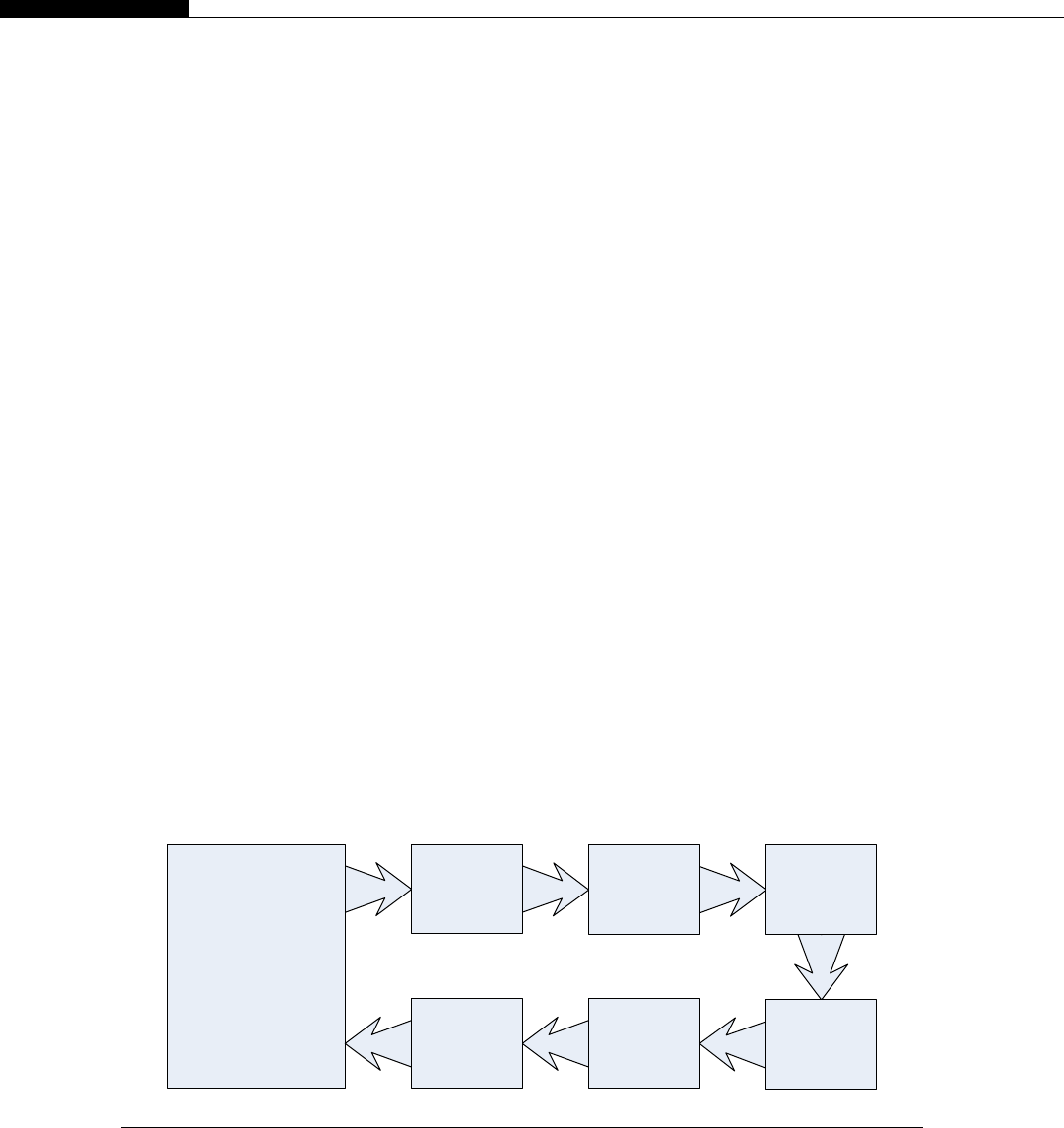

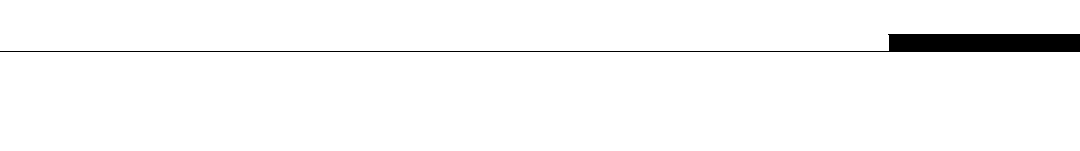

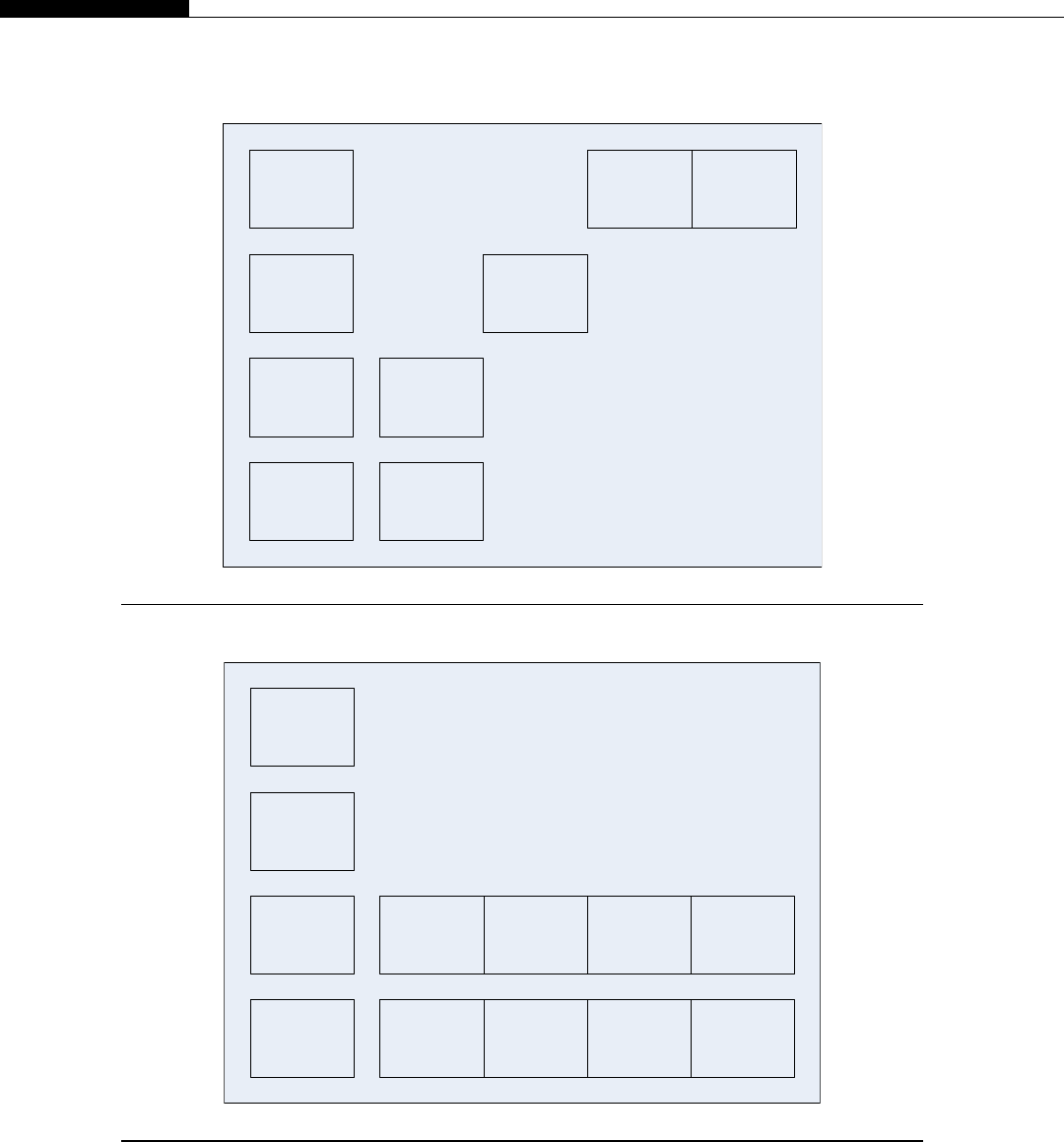

the L3 cache memory (Figure 1.2).

As cache sizes grow, so does the physical size of the silicon used to make the processors. The

larger the chip, the more expensive it is to manufacture and the higher the likelihood that it will

contain an error and be discarded during the manufacturing process. Sometimes these faulty devices

are sold cheaply as either triple- or dual-core devices, with the faulty cores disabled. However,

the effect of larger, progressively more inefficient caches ultimately results in higher costs to the

end user.

M

i

s

c

I

O

Core 1

Q

P

I

1Shared L3 Cache

Core 2 Core 4Core 3

Q

u

e

u

e

M

i

s

c

I

O

Q

P

I

2

FIGURE 1.2

Layout of I7 Nehalem processor on processor die.

4 CHAPTER 1 A Short History of Supercomputing

CRAY

The computing revolution that we all know today started back in the 1950s with the advent of the first

microprocessors. These devices, by today’s standards, are slow and you most likely have a far more

powerful processor in your smartphone. However, these led to the evolution of supercomputers, which are

machines usually owned by governments, large academic institutions, or corporations. They are thou-

sands of times more powerful than the computers in general use today. They cost millions of dollars to

produce, occupy huge amounts of space, usually have special cooling requirements, and require a team of

engineers to look after them. They consume huge amounts of power, to the extent they are often as

expensive to run each year as they cost to build. In fact, power is one of the key considerations when

planning such an installation and one of the main limiting factors in the growth of today’s supercomputers.

One of the founders of modern supercomputers was Seymour Cray with his Cray-1, produced by

Cray Research back in 1976. It had many thousands of individual cables required to connect every-

thing togetherdso much so they used to employ women because their hands were smaller than those

of most men and they could therefore more easily wire up all the thousands of individual cables.

These machines would typically have an uptime (the actual running time between breakdowns)

measured in hours. Keeping them running for a whole day at a time would be considered a huge

FIGURE 1.3

Wiring inside the Cray-2 supercomputer.

Cray 5

achievement. This seems quite backward by today’s standards. However, we owe a lot of what we have

today to research carried out by Seymour Cray and other individuals of this era.

Cray went on to produce some of the most groundbreaking supercomputers of his time under various

Cray names. The original Cray-1 cost some $8.8 million USD and achieved a massive 160 MFLOPS

(million floating-point operations per second). Computing speed today is measured in TFLOPS

(tera floating-point operations per second), a million times larger than the old MFLOPS measurement

(10

12

vs. 10

6

). A single Fermi GPU card today has a theoretical peak in excess of 1 teraflop of

performance.

The Cray-2 was a significant improvement on the Cray-1. It used a shared memory architecture,

split into banks. These were connected to one, two, or four processors. It led the way for the creation of

today’s server-based symmetrical multiprocessor (SMP) systems in which multiple CPUs shared the

same memory space. Like many machines of its era, it was a vector-based machine. In a vector

machine the same operation acts on many operands. These still exist today, in part as processor

extensions such as MMX, SSE, and AVX. GPU devices are, at their heart, vector processors that share

many similarities with the older supercomputer designs.

The Cray also had hardware support for scatter- and gather-type primitives, something we’ll see is

quite important in parallel computing and something we look at in subsequent chapters.

Cray still exists today in the supercomputer market, and as of 2010 held the top 500 position with

their Jaguar supercomputer at the Oak Ridge National Laboratory (http://www.nccs.gov/computing-

resources/jaguar/). I encourage you to read about the history of this great company, which you can

find on Cray’s website (http://www.cray.com), as it gives some insight into the evolution of computers

and as to where we are today.

CONNECTION MACHINE

Back in 1982 a corporation called Thinking Machines came up with a very interesting design, that of

the Connection Machine.

It was a relatively simple concept that led to a revolution in today’s parallel computers. They used

a few simple parts over and over again. They created a 16-core CPU, and then installed some 4096 of

these devices in one machine. The concept was different. Instead of one fast processor churning

through a dataset, there were 64 K processors doing this task.

Let’s take the simple example of manipulating the color of an RGB (red, green, blue) image. Each

color is made up of a single byte, with 3 bytes representing the color of a single pixel. Let’s suppose we

want to reduce the blue level to zero.

Let’s assume the memory is configured in three banks of red, blue, and green, rather than being

interleaved. With a conventional processor, we would have a loop running through the blue memory

and decrement every pixel color level by one. The operation is the same on each item of data, yet each

time we fetch, decode, and execute the instruction stream on each loop iteration.

The Connection Machine used something called SIMD (single instruction, multiple data), which is

used today in modern processors and known by names such as SSE (Streaming SIMD Extensions),

MMX (Multi-Media eXtension), and AVX (Advanced Vector eXtensions). The concept is to define

a data range and then have the processor apply that operation to the data range. However, SSE and

MMX are based on having one processor core. The Connection Machine had 64 K processor cores,

each executing SIMD instructions on its dataset.

6 CHAPTER 1 A Short History of Supercomputing

Processors such as the Intel I7 are 64-bit processors, meaning they can process up to 64 bits at

a time (8 bytes). The SSE SIMD instruction set extends this to 128 bits. With SIMD instructions on

such a processor, we eliminate all redundant instruction memory fetches, and generate one sixteenth of

the memory read and write cycles compared with fetching and writing 1 byte at a time. AVX extends

this to 256 bits, making it even more effective.

For a high-definition (HD) video image of 1920 1080 resolution, the data size is 2,073,600 bytes,

or around 2 MB per color plane. Thus, we generate around 260,000 SIMD cycles for a single

conventional processor using SSE/MMX. By SIMD cycle, we mean one read, compute, and write

cycle. The actual number of processor clocks may be considerably different than this, depending on the

particular processor architecture.

The Connection Machine used 64 K processors. Thus, the 2 MB frame would have resulted in about

32 SIMD cycles for each processor. Clearly, this type of approach is vastly superior to the modern

processor SIMD approach. However, there is of course a caveat. Synchronizing and communication

between processors becomes the major issue when moving from a rather coarse-threaded approach of

today’s CPUs to a hugely parallel approach used by such machines.

CELL PROCESSOR

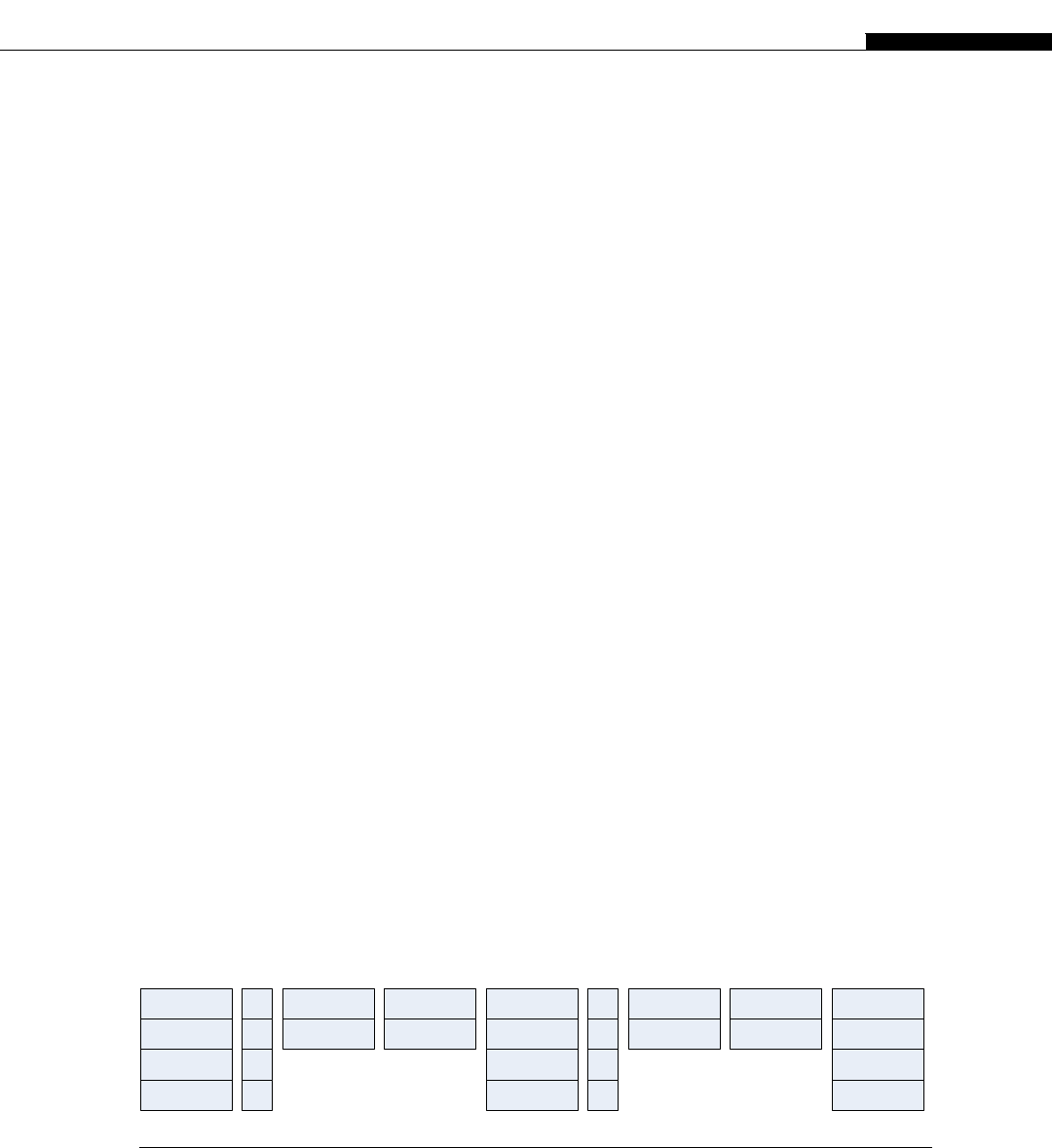

Another interesting development in supercomputers stemmed from IBM’s invention of the Cell

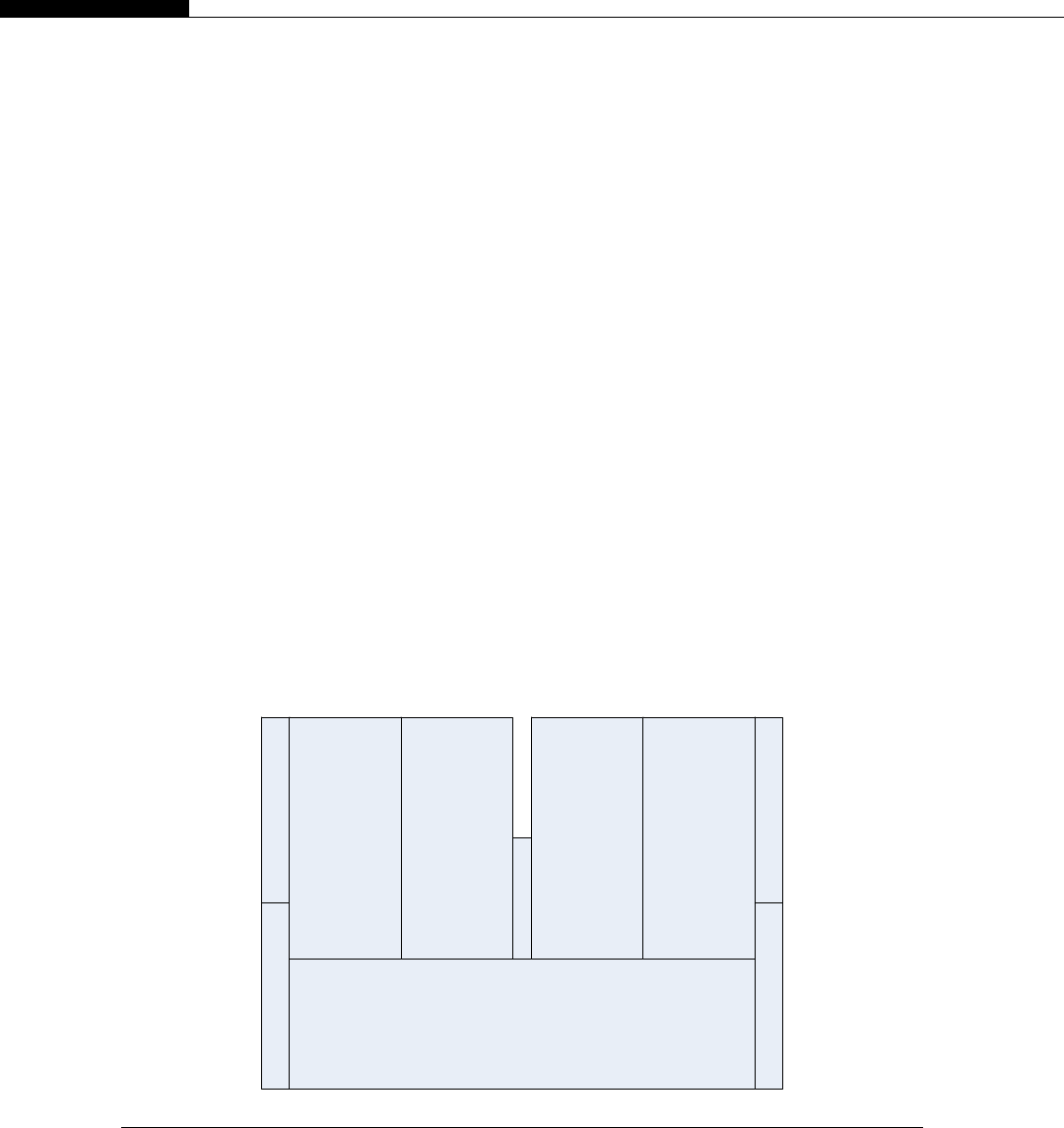

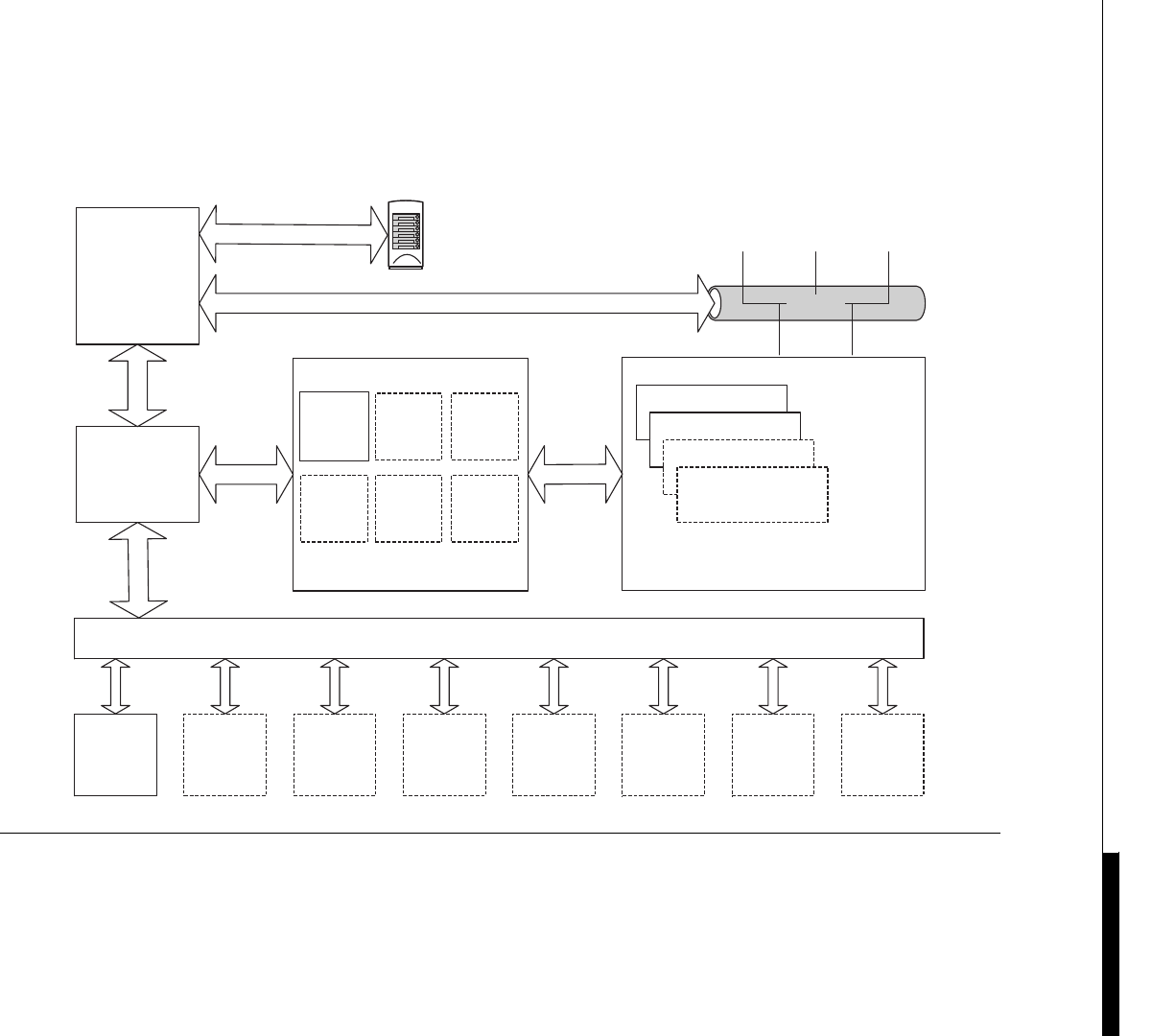

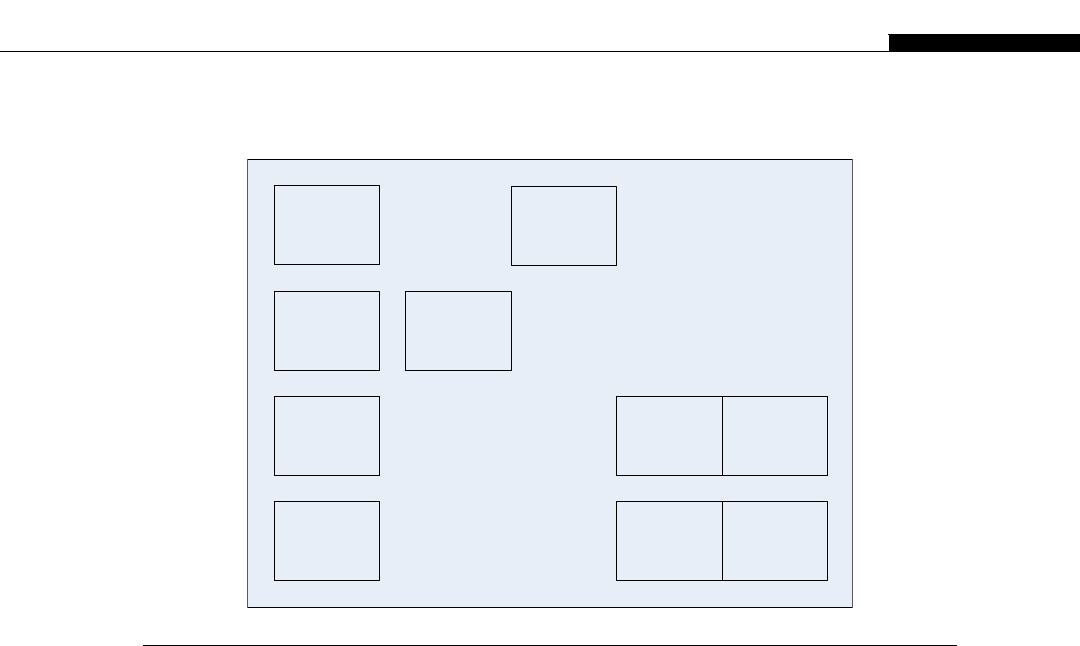

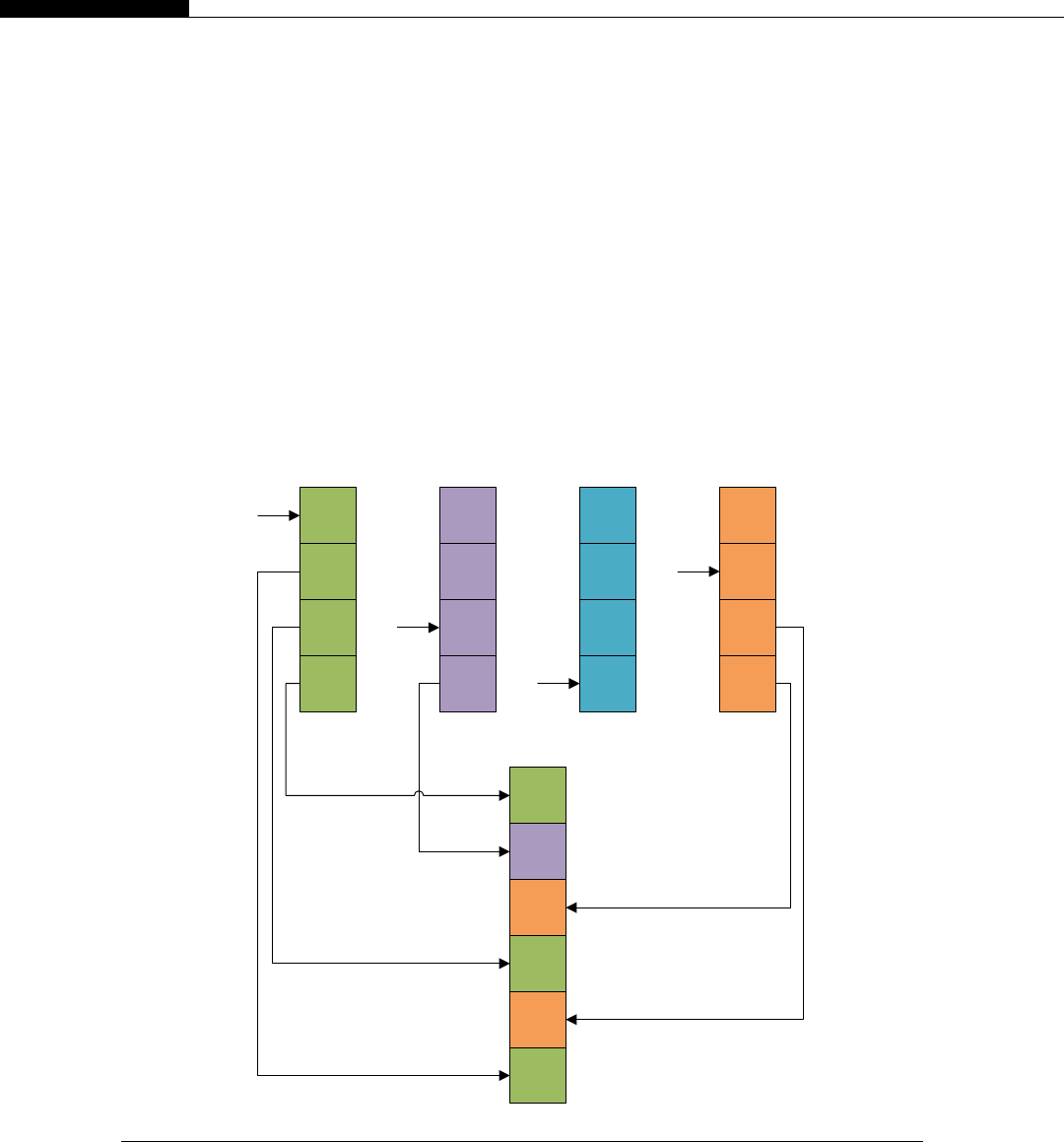

processor (Figure 1.4). This worked on the idea of having a regular processor act as a supervisory

R

A

M

B

U

S

I

N

T

E

R

F

A

C

E

M

E

M

O

R

Y

C

O

N

T

R

O

L

L

E

R

L2 Cache

(512K)

Power PC Core

SPE

SPE

Interconnect Bus

SPE SPE SPE

SPE SPE SPE

I/O

C

O

N

T

R

O

L

L

E

R

L

O

C

A

L

M

E

M

O

R

Y

L

O

C

A

L

M

E

M

O

R

Y

L

O

C

A

L

M

E

M

O

R

Y

L

O

C

A

L

M

E

M

O

R

Y

L

O

C

A

L

M

E

M

O

R

Y

L

O

C

A

L

M

E

M

O

R

Y

L

O

C

A

L

M

E

M

O

R

Y

L

O

C

A

L

M

E

M

O

R

Y

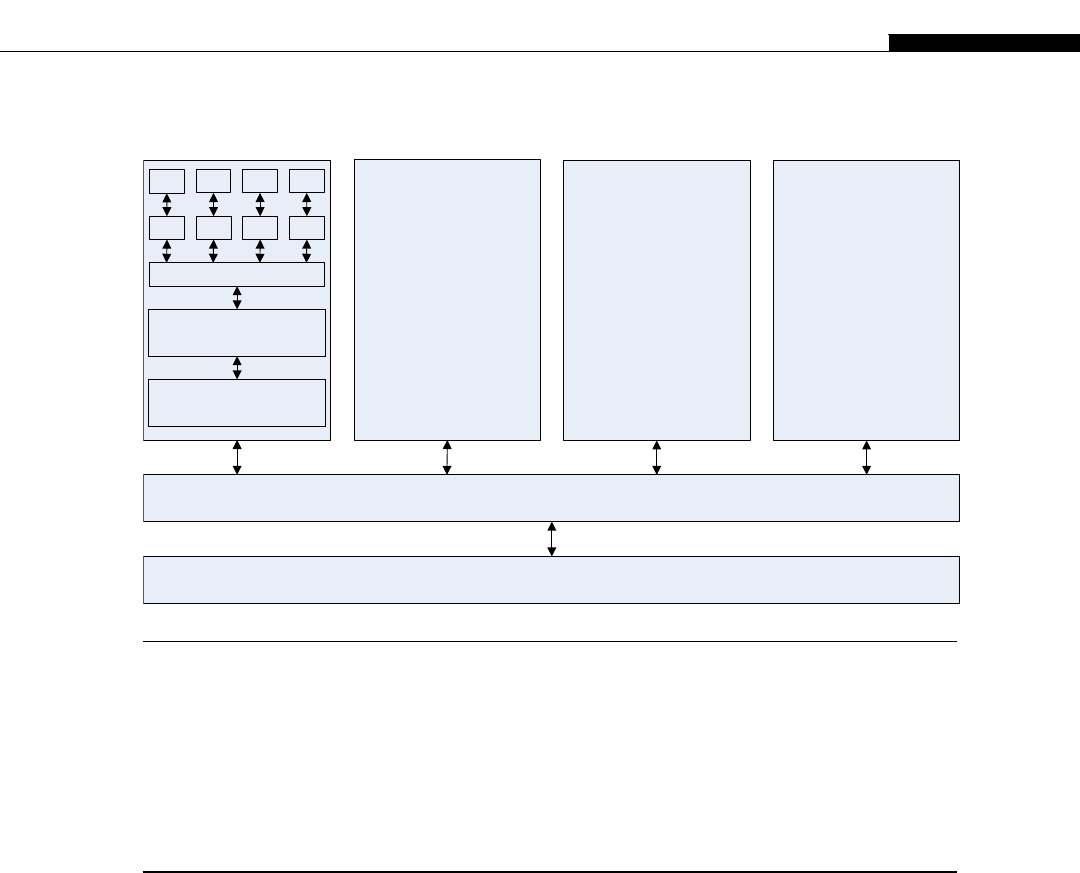

FIGURE 1.4

IBM cell processor die layout (8 SPE version).

Cell Processor 7

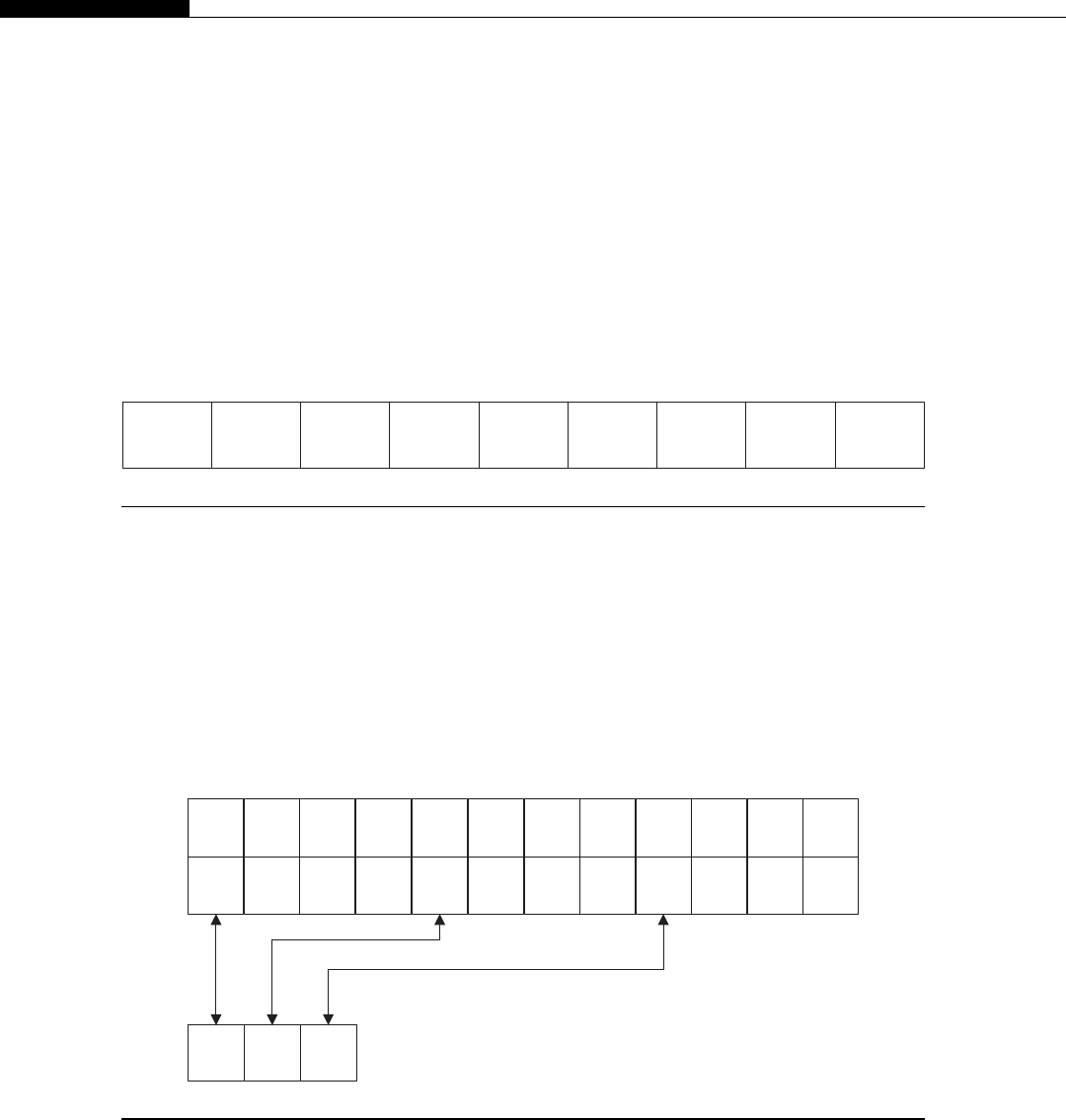

processor, connected to a number of high-speed stream processors. The regular PowerPC (PPC)

processor in the Cell acts as an interface to the stream processors and the outside world. The

stream SIMD processors, or SPEs as IBM called them, would process datasets managed by the

regular processor.

The Cell is a particularly interesting processor for us, as it’s a similar design to what NVIDIA later

used in the G80 and subsequent GPUs. Sony also used it in their PS3 console machines in the games

industry, a very similar field to the main use of GPUs.

To program the Cell, you write a program to execute on the PowerPC core processor. It then

invokes a program, using an entirely different binary, on each of the stream processing elements

(SPEs). Each SPE is actually a core in itself. It can execute an independent program from its own local

memory, which is different from the SPE next to it. In addition, the SPEs can communicate with one

another and the PowerPC core over a shared interconnect. However, this type of hybrid architecture is

not easy to program. The programmer must explicitly manage the eight SPEs, both in terms of

programs and data, as well as the serial program running on the PowerPC core.

With the ability to talk directly to the coordinating processor, a series of simple steps can be

achieved. With our RGB example earlier, the PPC core fetches a chunk of data to work on. It allocates

these to the eight SPEs. As we do the same thing in each SPE, each SPE fetches the byte, decrements it,

and writes its bit back to its local memory. When all SPEs are done, the PC core fetches the data from

each SPE. It then writes its chunk of data (or tile) to the memory area where the whole image is being

assembled. The Cell processor is designed to be used in groups, thus repeating the design of the

Connection Machine we covered earlier.

The SPEs could also be ordered to perform a stream operation, involving multiple steps, as each

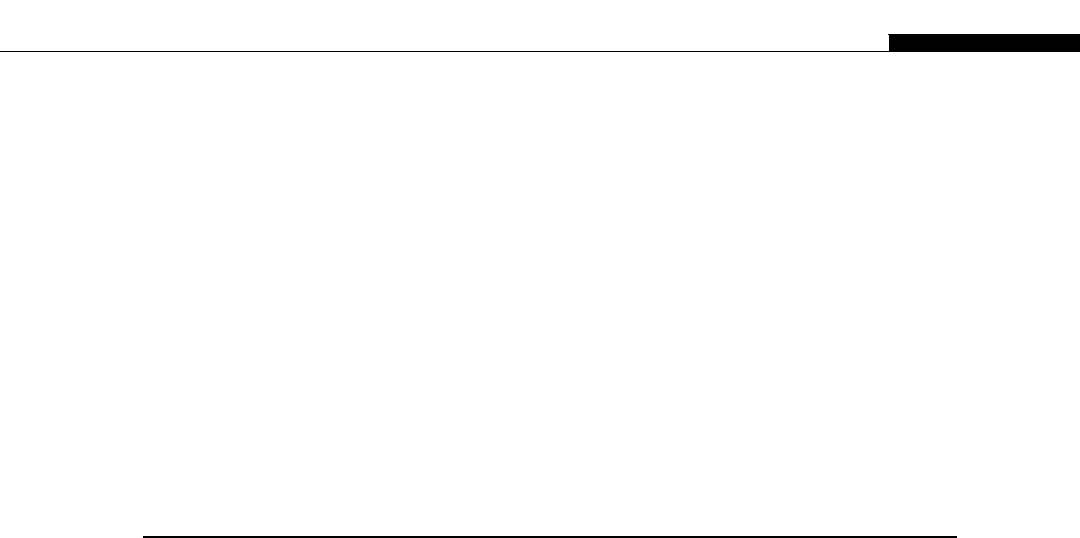

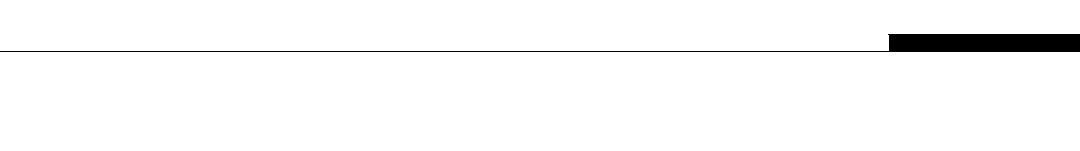

SPE is connected to a high-speed ring (Figure 1.5).

The problem with this sort of streaming or pipelining approach is it runs only as fast as the slowest

node. It mirrors a production line in a factory. The whole line can only run as fast as the slowest point.

Each SPE (worker) only has a small set of tasks to perform, so just like the assembly line worker, it can

do this very quickly and efficiently. However, just like any processor, there is a bandwidth limit and

overhead of passing data to the next stage. Thus, while you gain efficiencies from executing

a consistent program on each SPE, you lose on interprocessor communication and are ultimately

Power PC Core

SPE 0

(Clamp)

SPE 1

(DCT)

SPE 2

(Filter 1)

SPE 3

(Filter 2)

SPE 5

(Restore)

SPE 4

(IDCT)

FIGURE 1.5

Example routing stream processor routing on Cell.

8 CHAPTER 1 A Short History of Supercomputing

limited by the slowest process step. This is a common problem with any pipeline-based model of

execution.

The alternative approach of putting everything on one SPE and then having each SPE process a small

chunk of data is often a more efficient approach. This is the equivalent to training all assembly line

workers to assemble a complete widget. For simple tasks, this is easy, but each SPE has limits on available

program and data memory. The PowerPC core must now also deliver and collect data from eight SPEs,

instead of just two, so the management overhead and communication between host and SPEs increases.

IBM used a high-powered version of the Cell processor in their Roadrunner supercomputer,

which as of 2010 was the third fastest computer on the top 500 list. It consists of 12,960 PowerPC

cores, plus a total of 103,680 stream processors. Each PowerPC board is supervised by a dual-core

AMD (Advanced Micro Devices) Opteron processor, of which there are 6912 in total. The Opteron

processors act as coordinators among the nodes. Roadrunner has a theoretical throughput of 1.71

petaflops, cost $125 million USD to build, occupies 560 square meters, and consumes 2.35 MW of

electricity when operating!

MULTINODE COMPUTING

As you increase the requirements (CPU, memory, storage space) needed on a single machine, costs

rapidly increase. While a 2.6 GHz processor may cost you $250 USD, the same processor at 3.4 GHz

may be $1400 for less than a 1 GHz increase in clock speed. A similar relationship is seen for both

speed and size memory, and storage capacity.

Not only do costs scale as computing requirements scale, but so do the power requirements and the

consequential heat dissipation issues. Processors can hit 4–5 GHz, given sufficient supply of power and

cooling.

In computing you often find the law of diminishing returns. There is only so much you can put into

a single case. You are limited by cost, space, power, and heat. The solution is to select a reasonable

balance of each and to replicate this many times.

Cluster computing became popular in 1990s along with ever-increasing clock rates. The concept

was a very simple one. Take a number of commodity PCs bought or made from off-the-shelf parts and

connect them to an off-the-shelf 8-, 16-, 24-, or 32-port Ethernet switch and you had up to 32 times the

performance of a single box. Instead of paying $1600 for a high performance processor, you paid $250

and bought six medium performance processors. If your application needed huge memory capacity, the

chances were that maxing out the DIMMs on many machines and adding them together was more than

sufficient. Used together, the combined power of many machines hugely outperformed any single

machine you could possible buy with a similar budget.

All of a sudden universities, schools, offices, and computer departments could build machines

much more powerful than before and were not locked out of the high-speed computing market due to

lack of funds. Cluster computing back then was like GPU computing todayda disruptive technology

that changed the face of computing. Combined with the ever-increasing single-core clock speeds it

provided a cheap way to achieve parallel processing within single-core CPUs.

Clusters of PCs typically ran a variation of LINUX with each node usually fetching its boot

instructions and operating system (OS) from a central master node. For example, at CudaDeveloper we

have a tiny cluster of low-powered, atom-based PCs with embedded CUDA GPUs. It’s very cheap to

Multinode Computing 9

buy and set up a cluster. Sometimes they can simply be made from a number of old PCs that are being

replaced, so the hardware is effectively free.

However, the problem with cluster computing is it’s only as fast as the amount of internode

communication that is necessary for the problem. If you have 32 nodes and the problem breaks down into

32 nice chunks and requires no internode communication, you have an application that is ideal for

a cluster. If every data point takes data from every node, you have a terrible problem to put into a cluster.

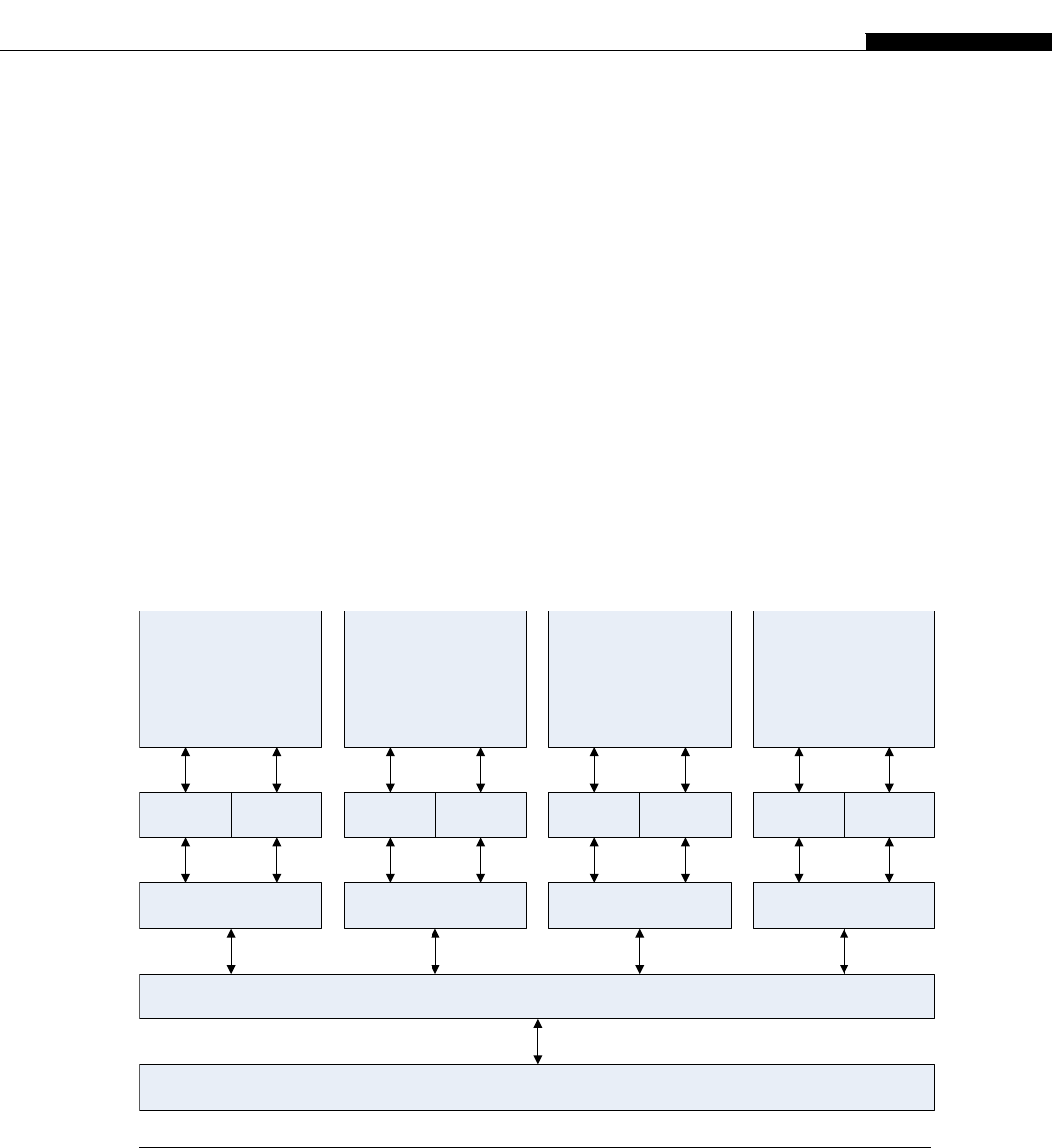

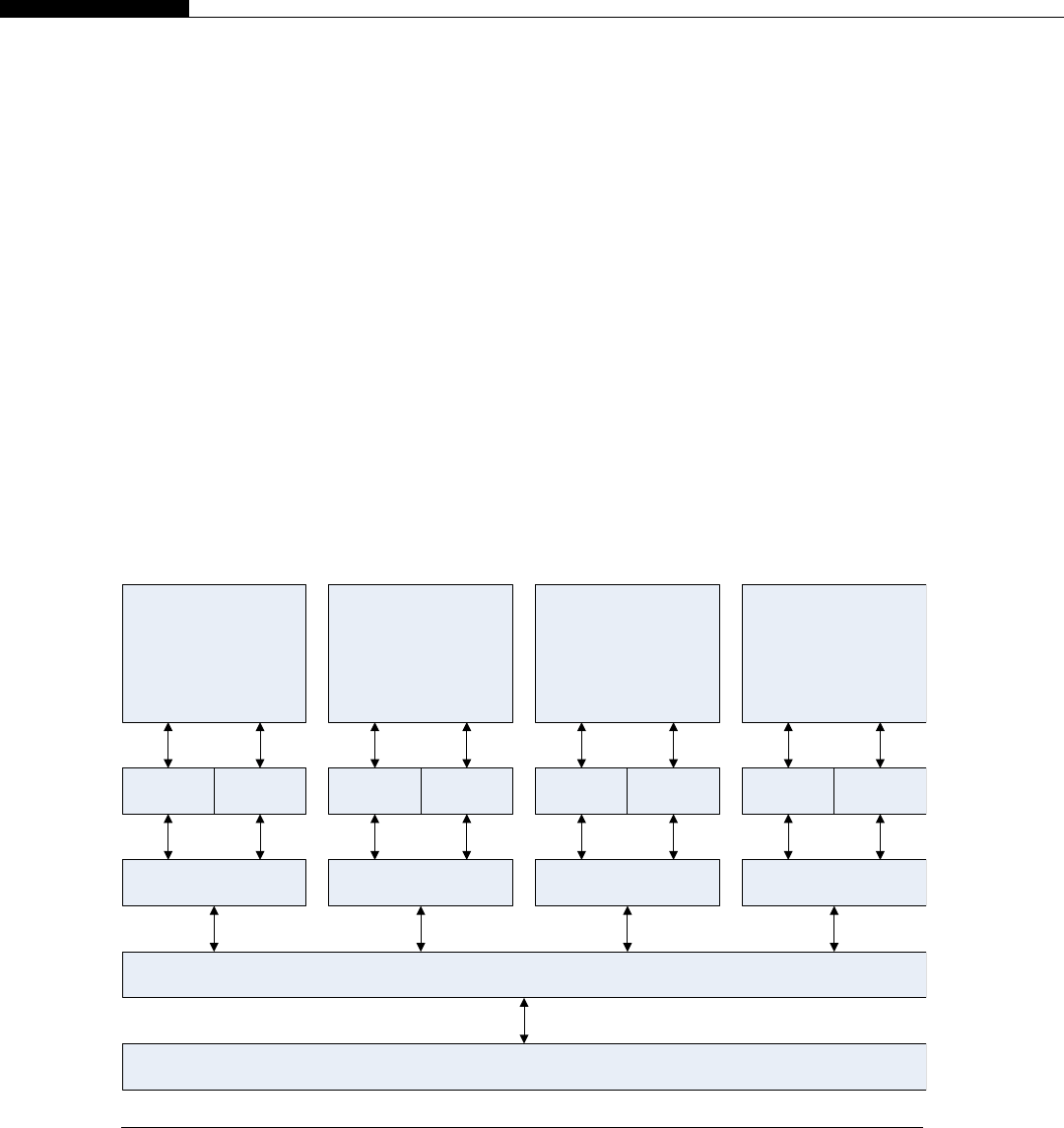

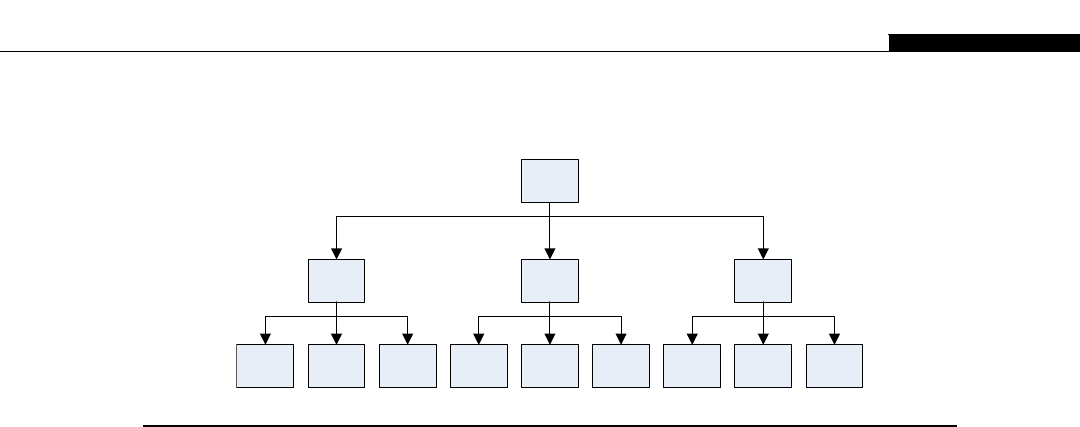

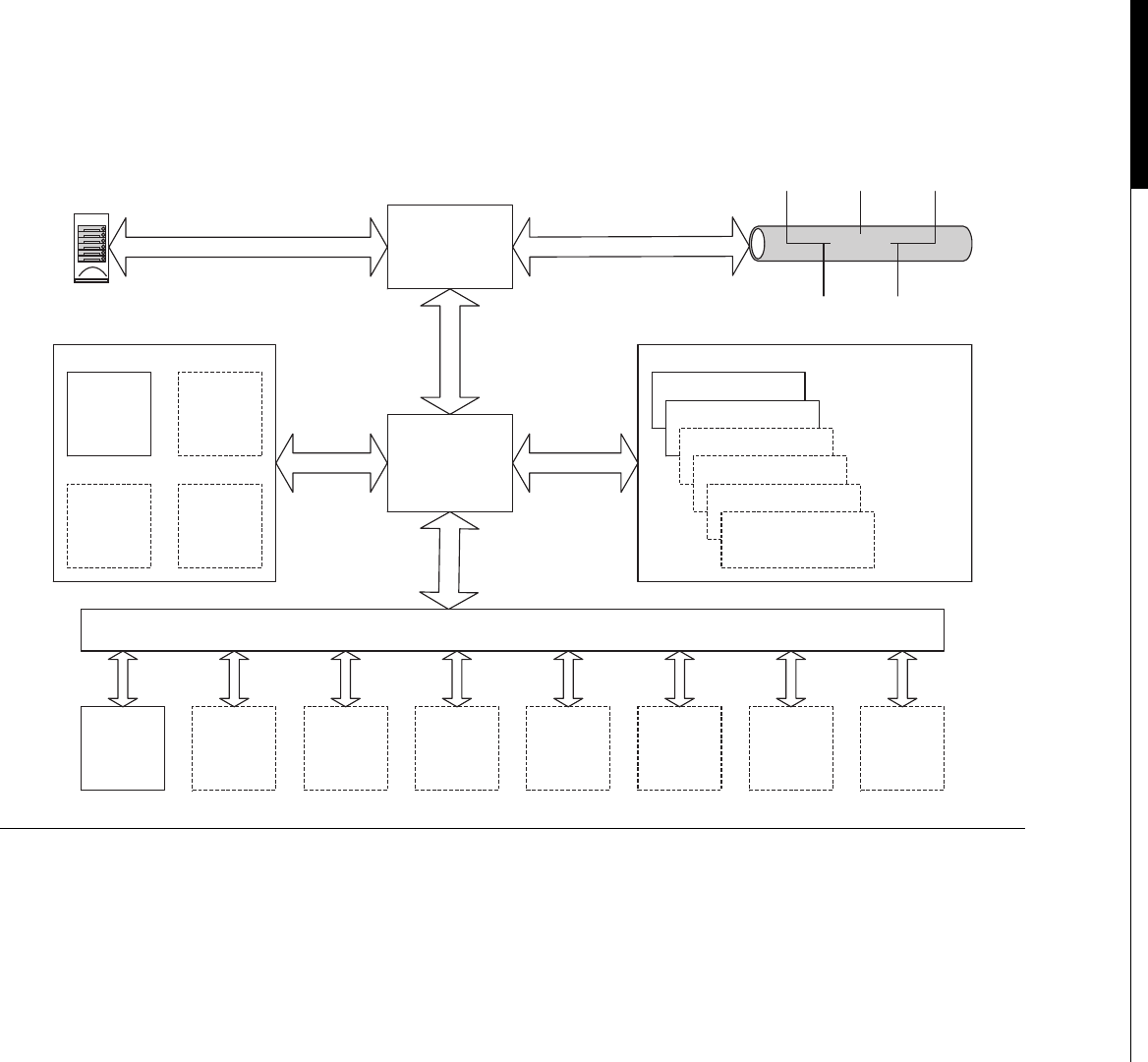

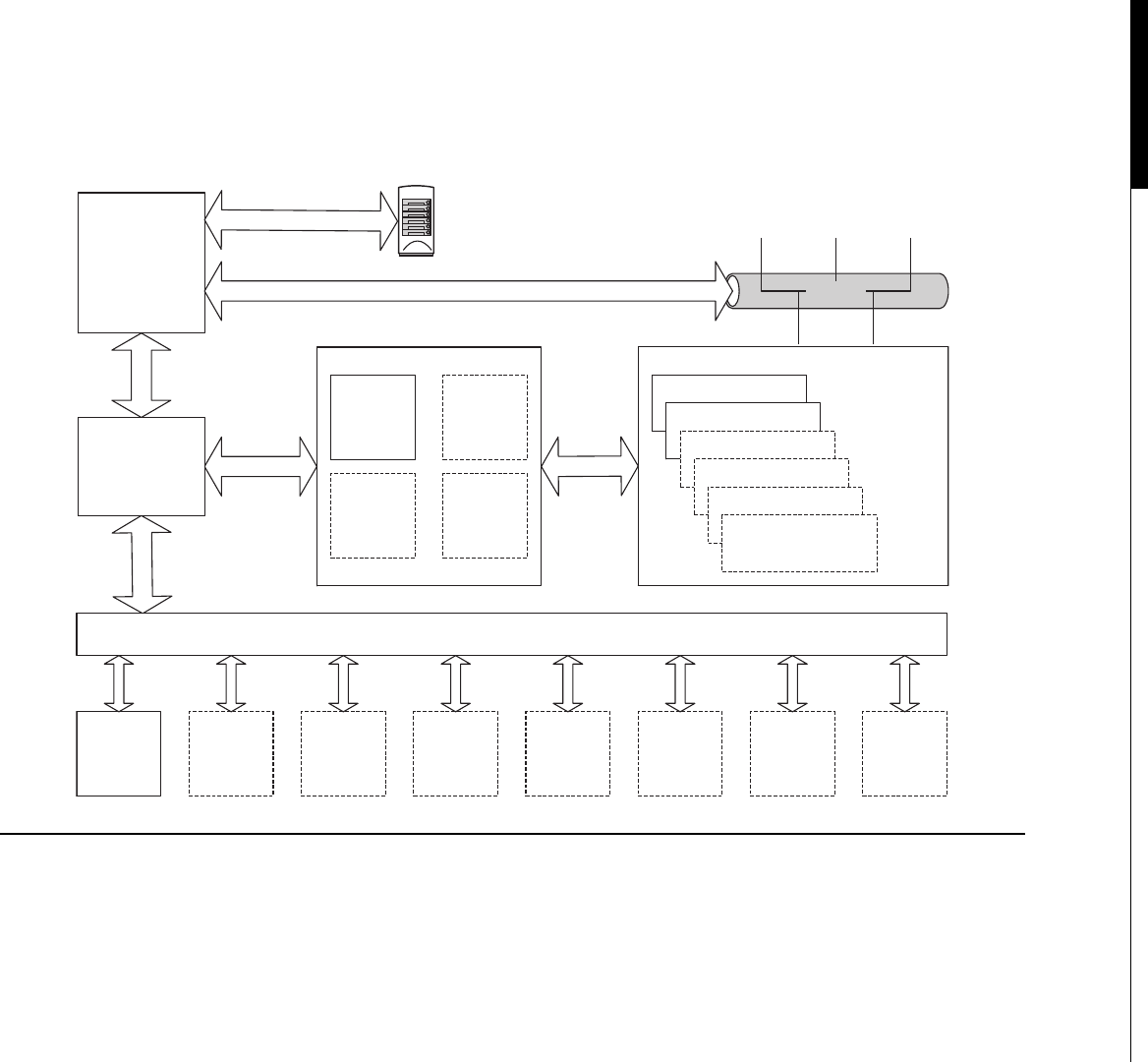

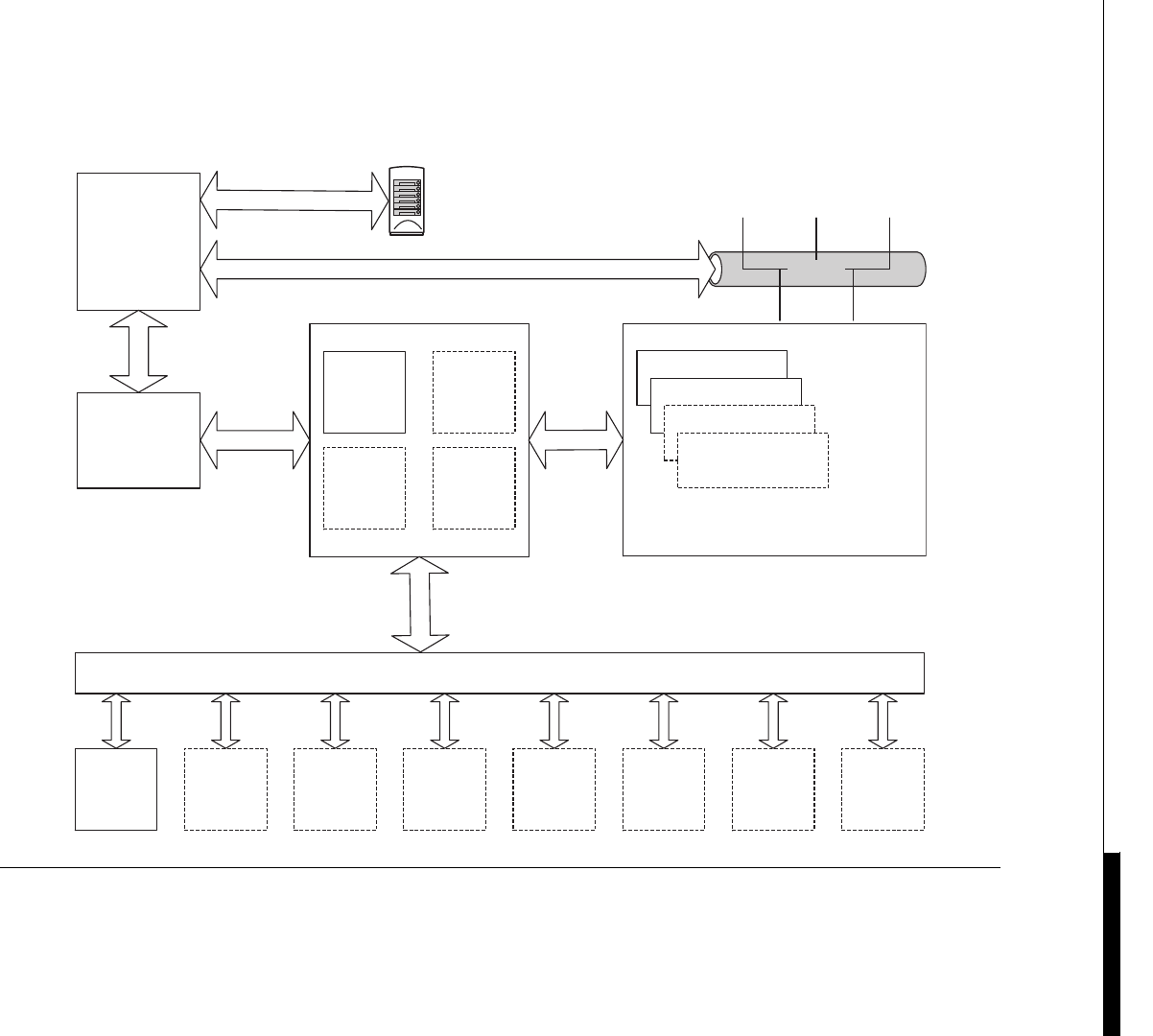

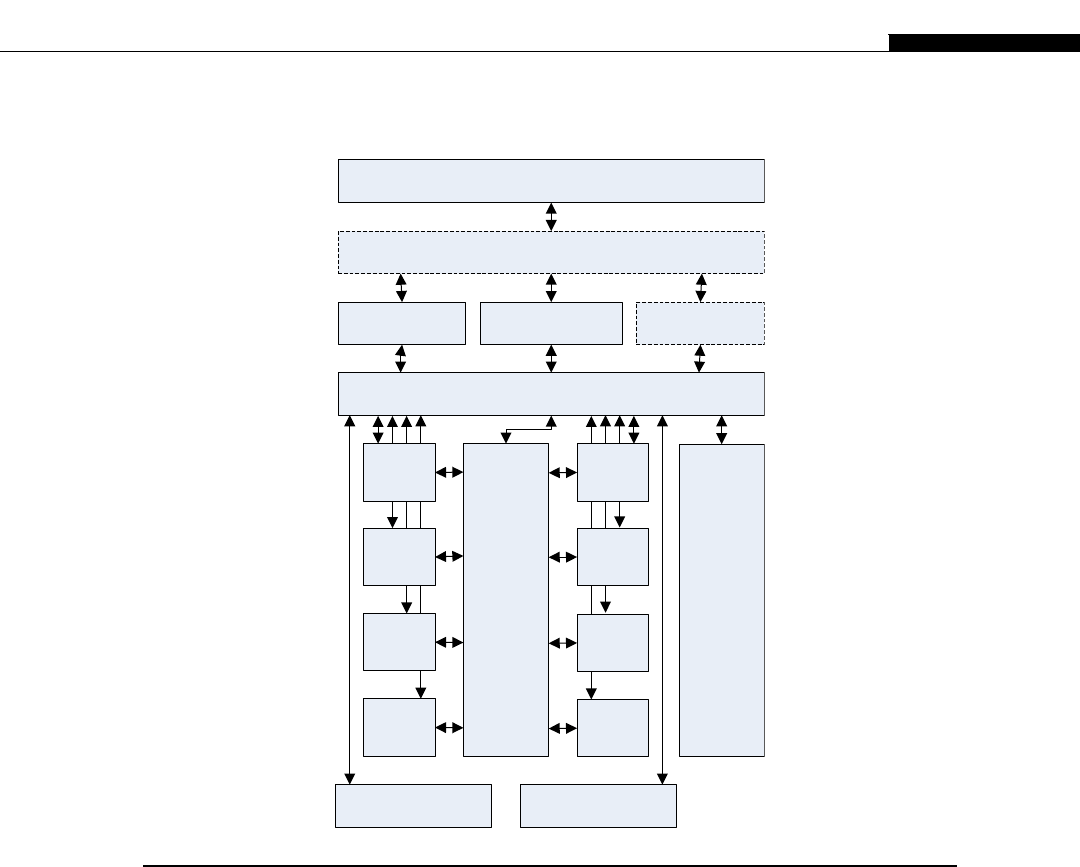

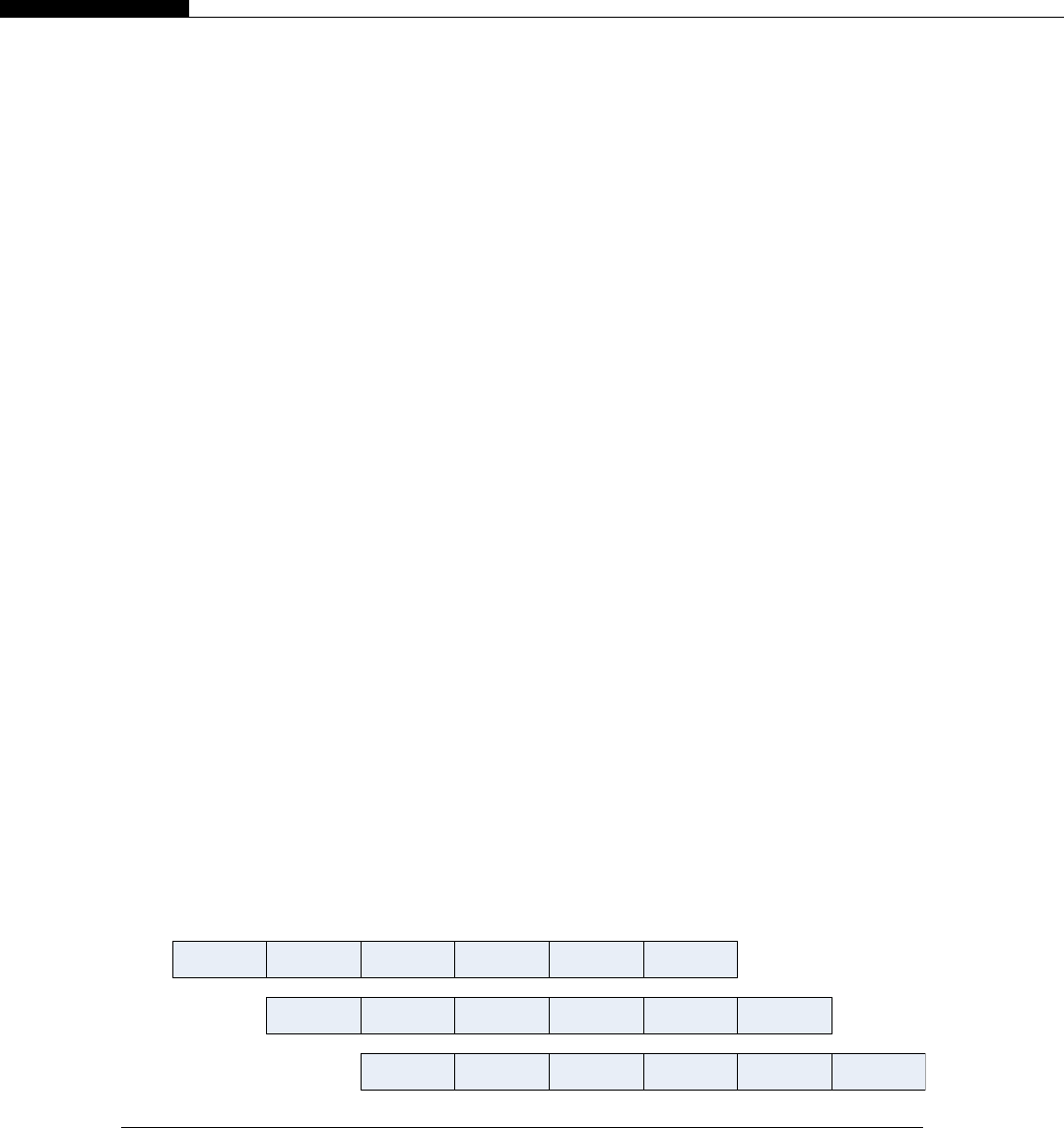

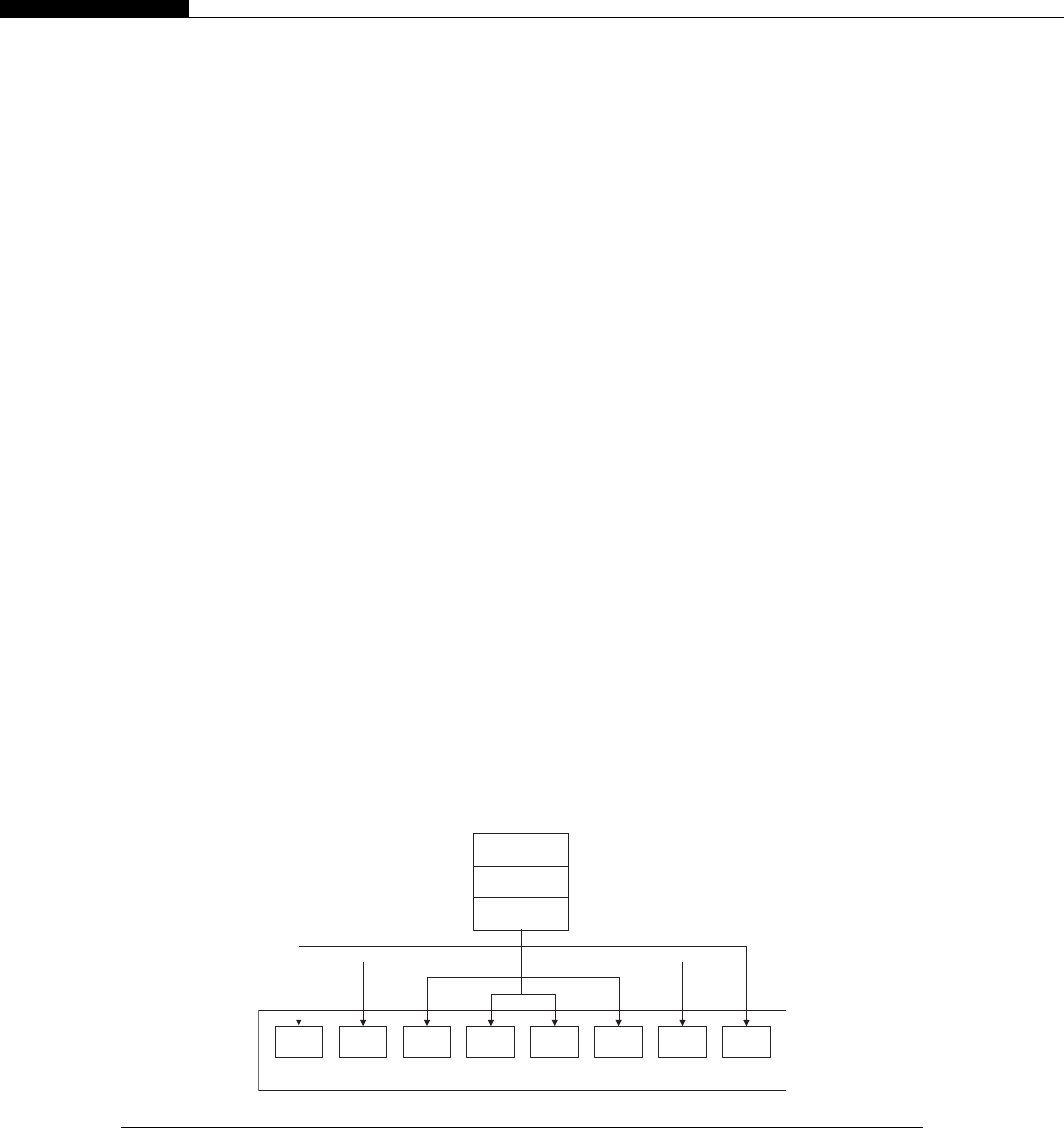

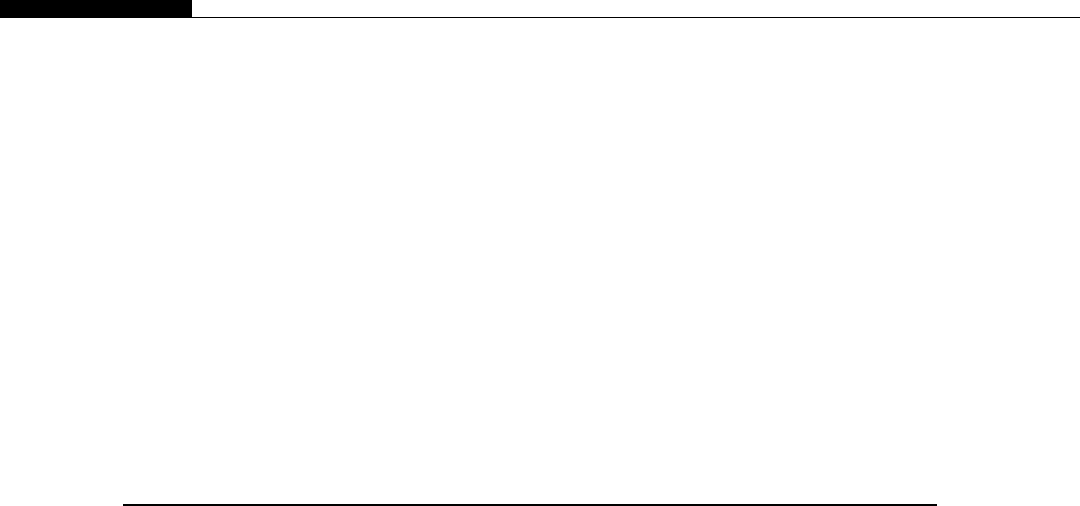

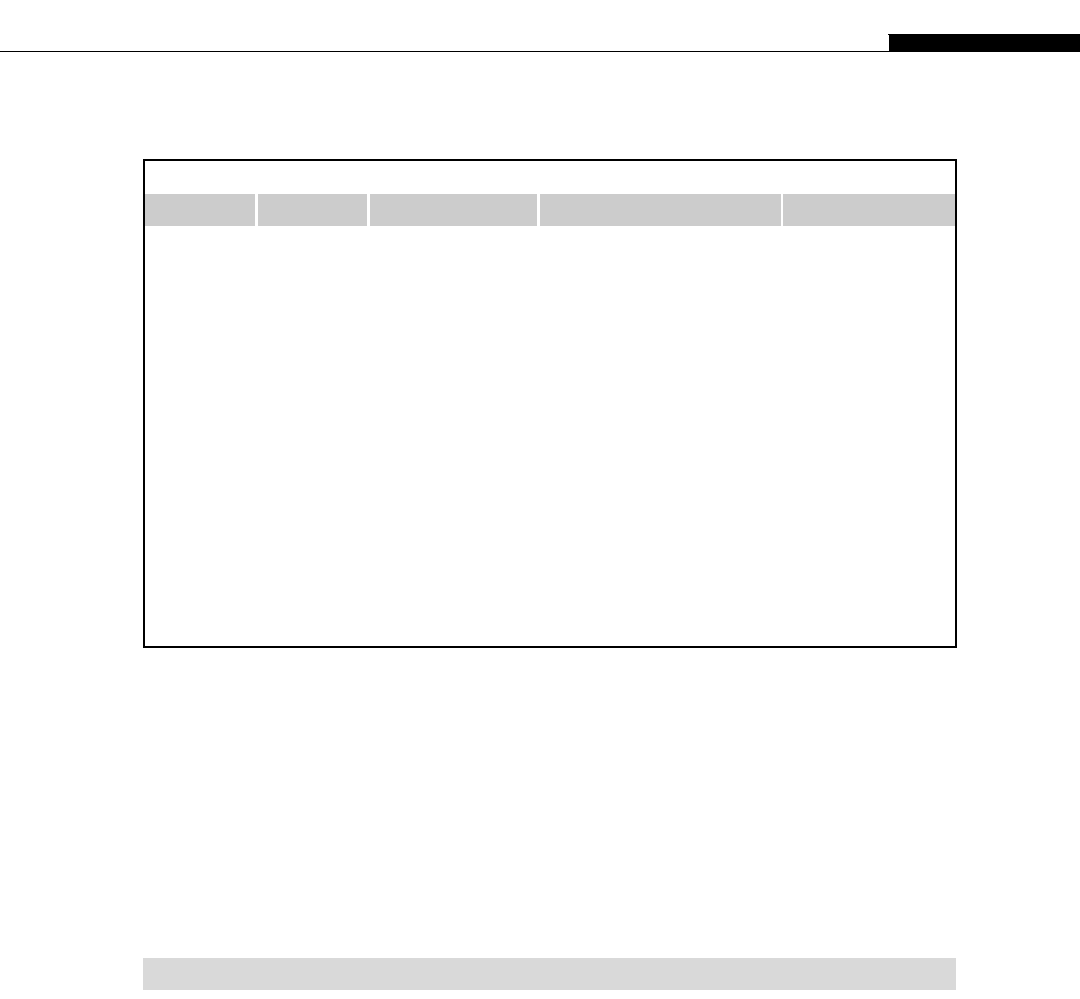

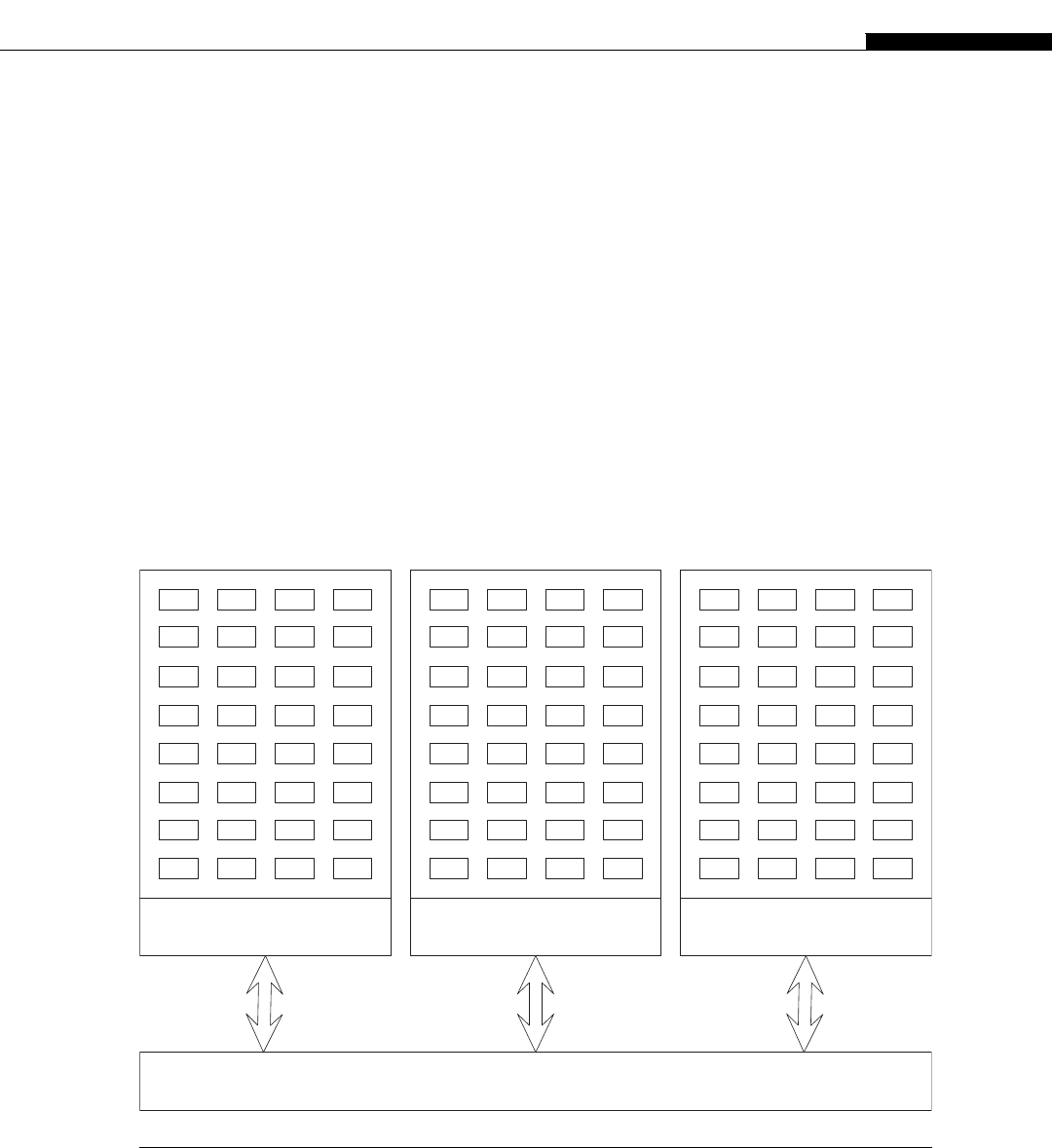

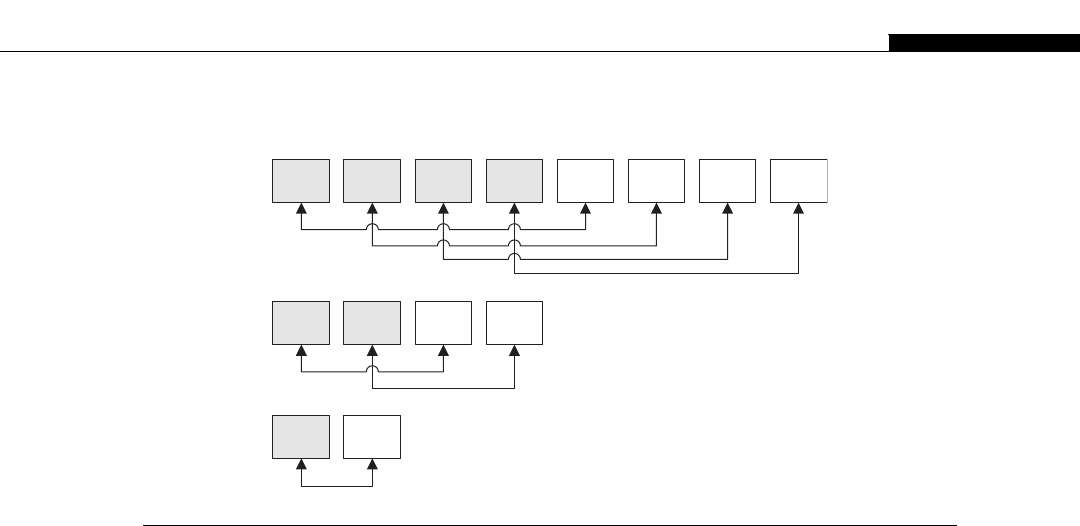

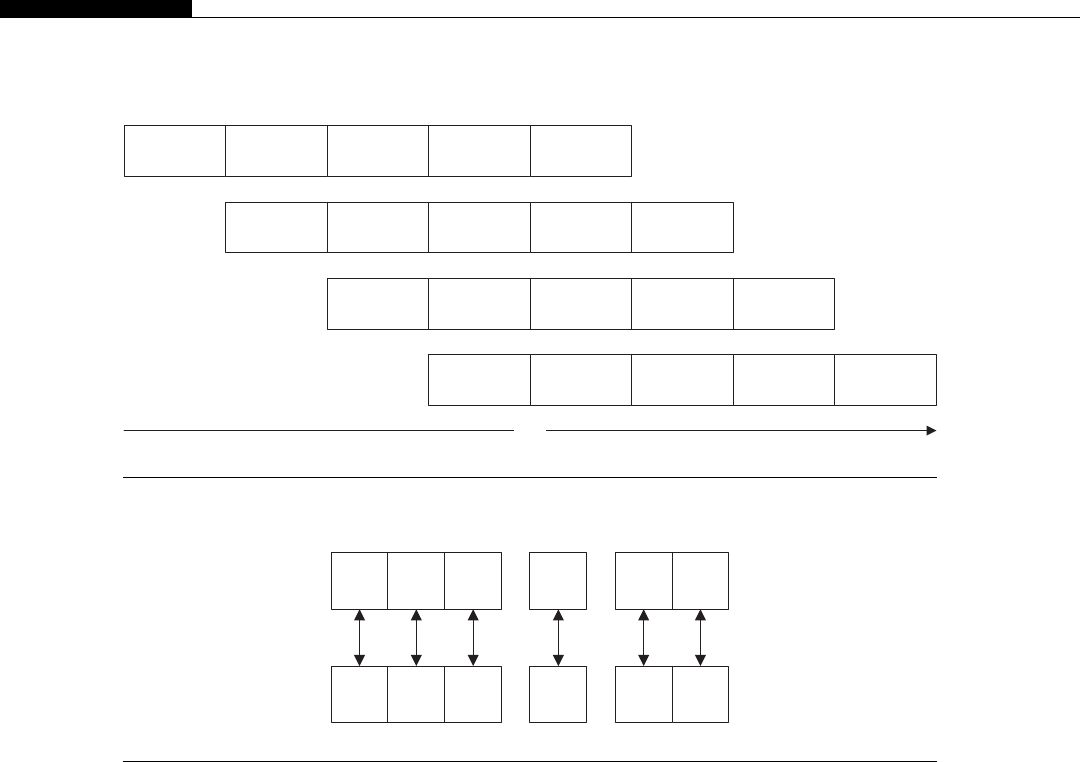

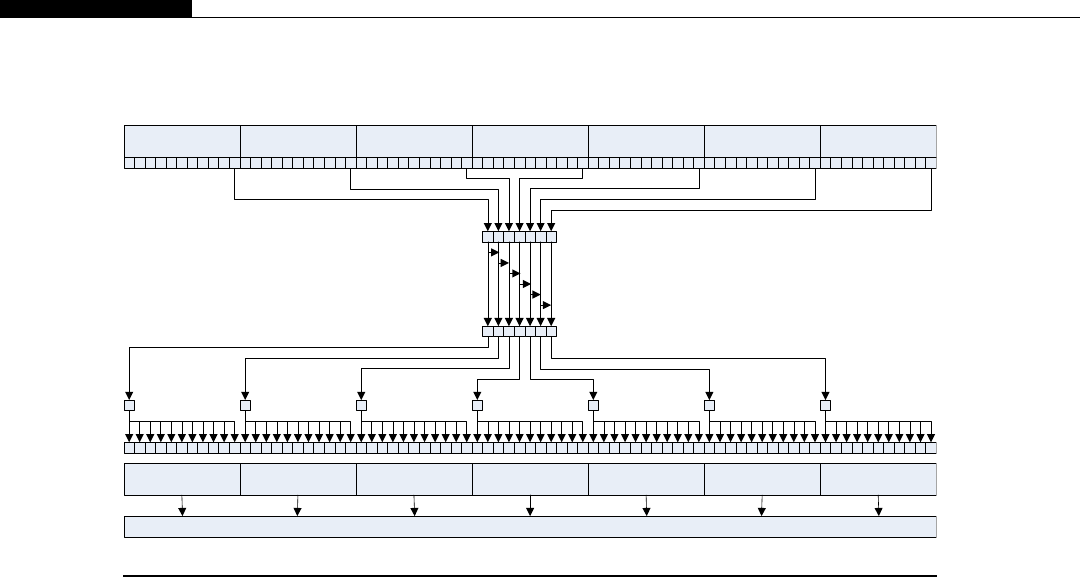

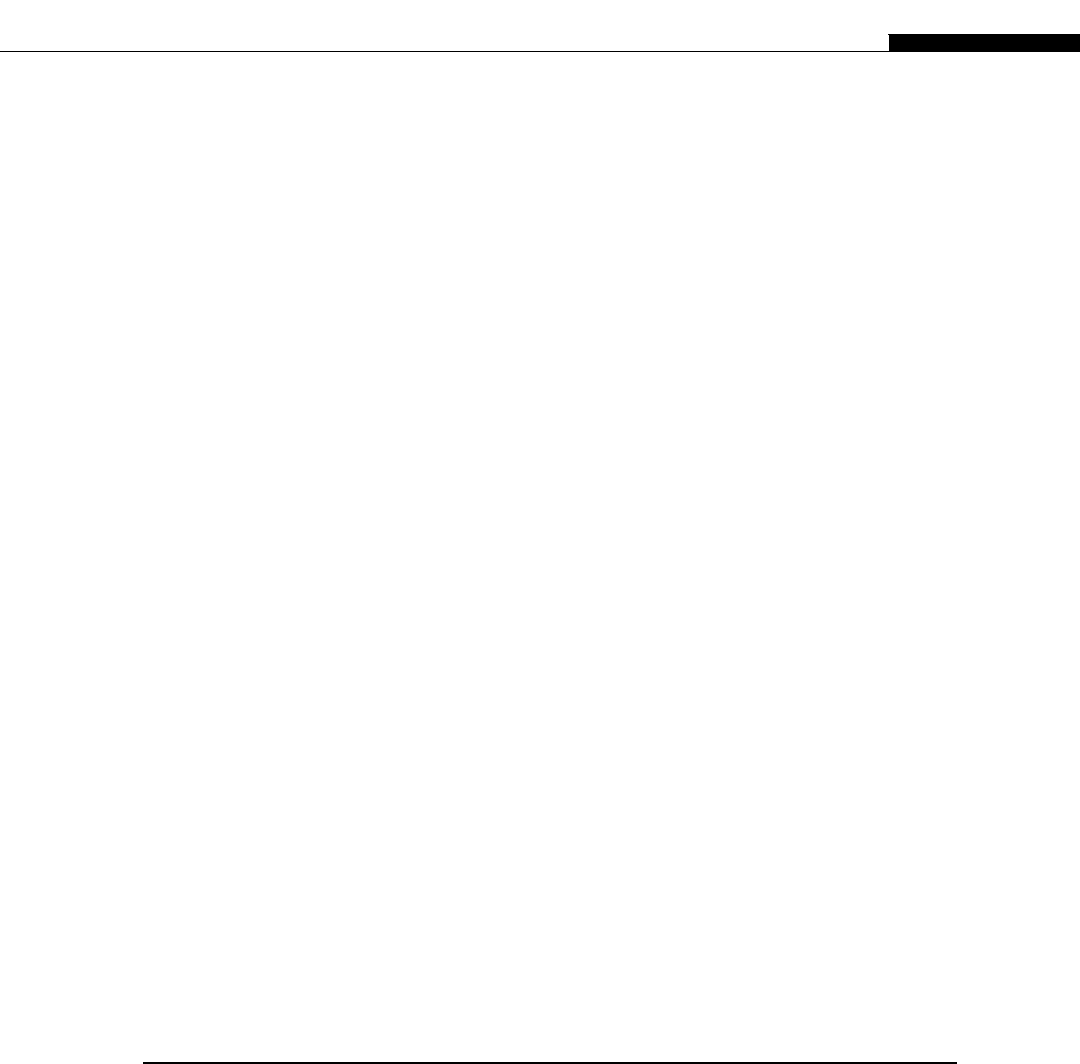

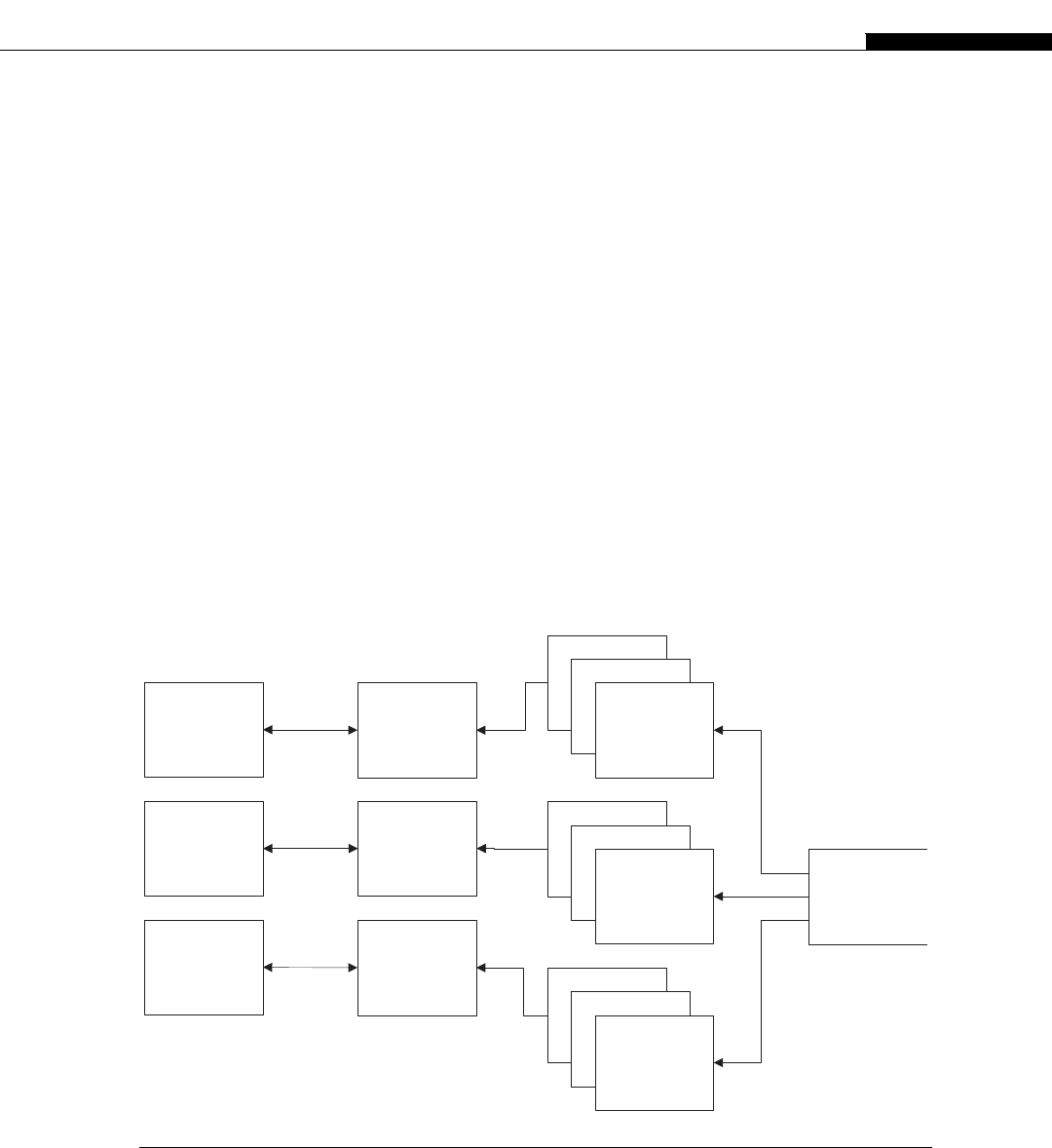

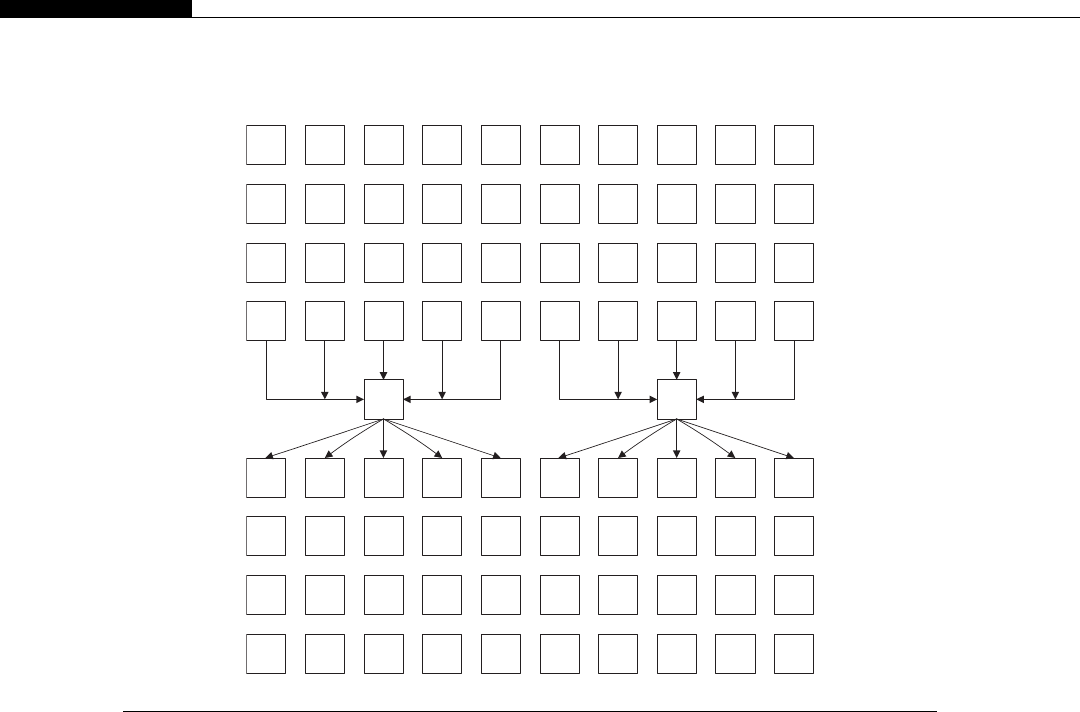

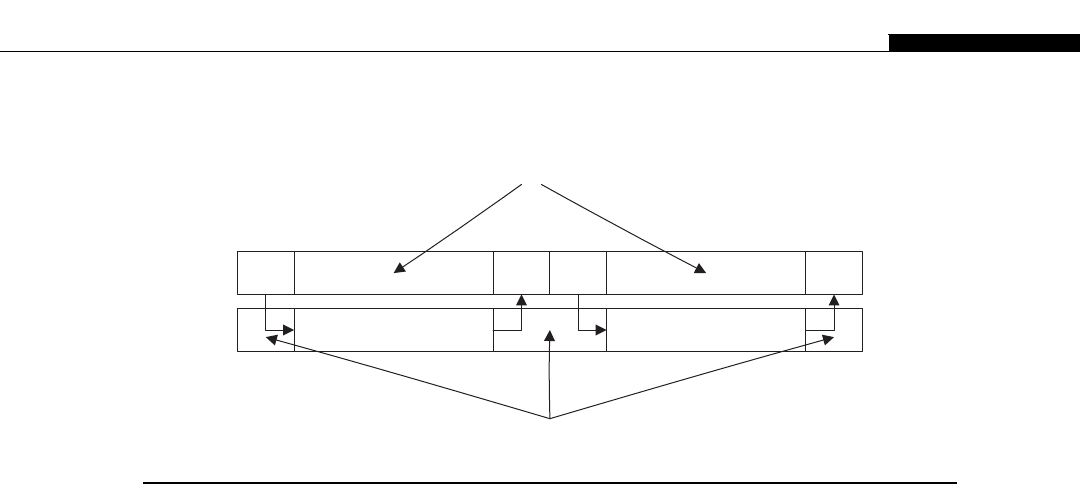

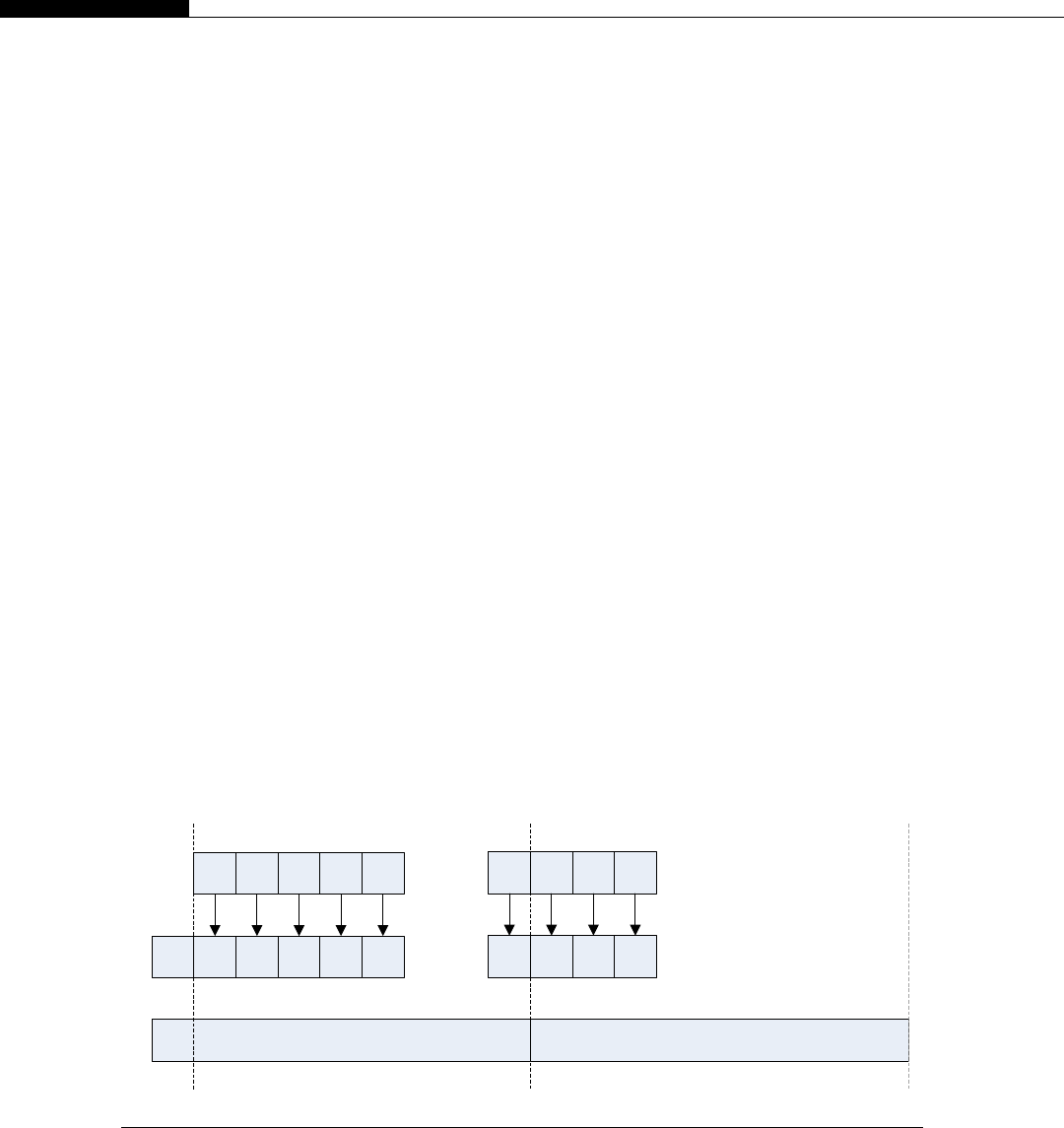

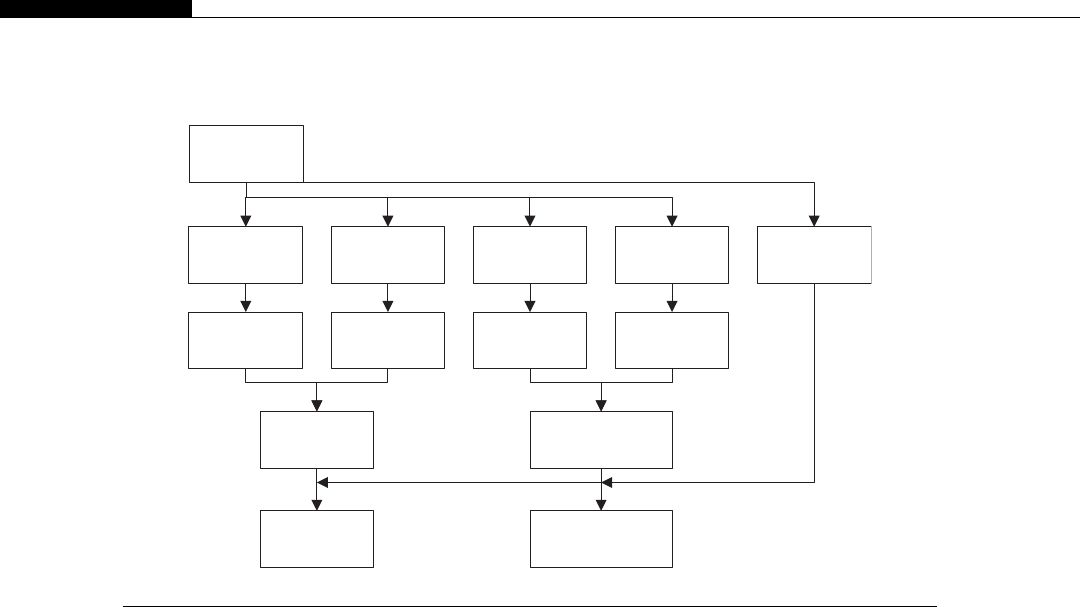

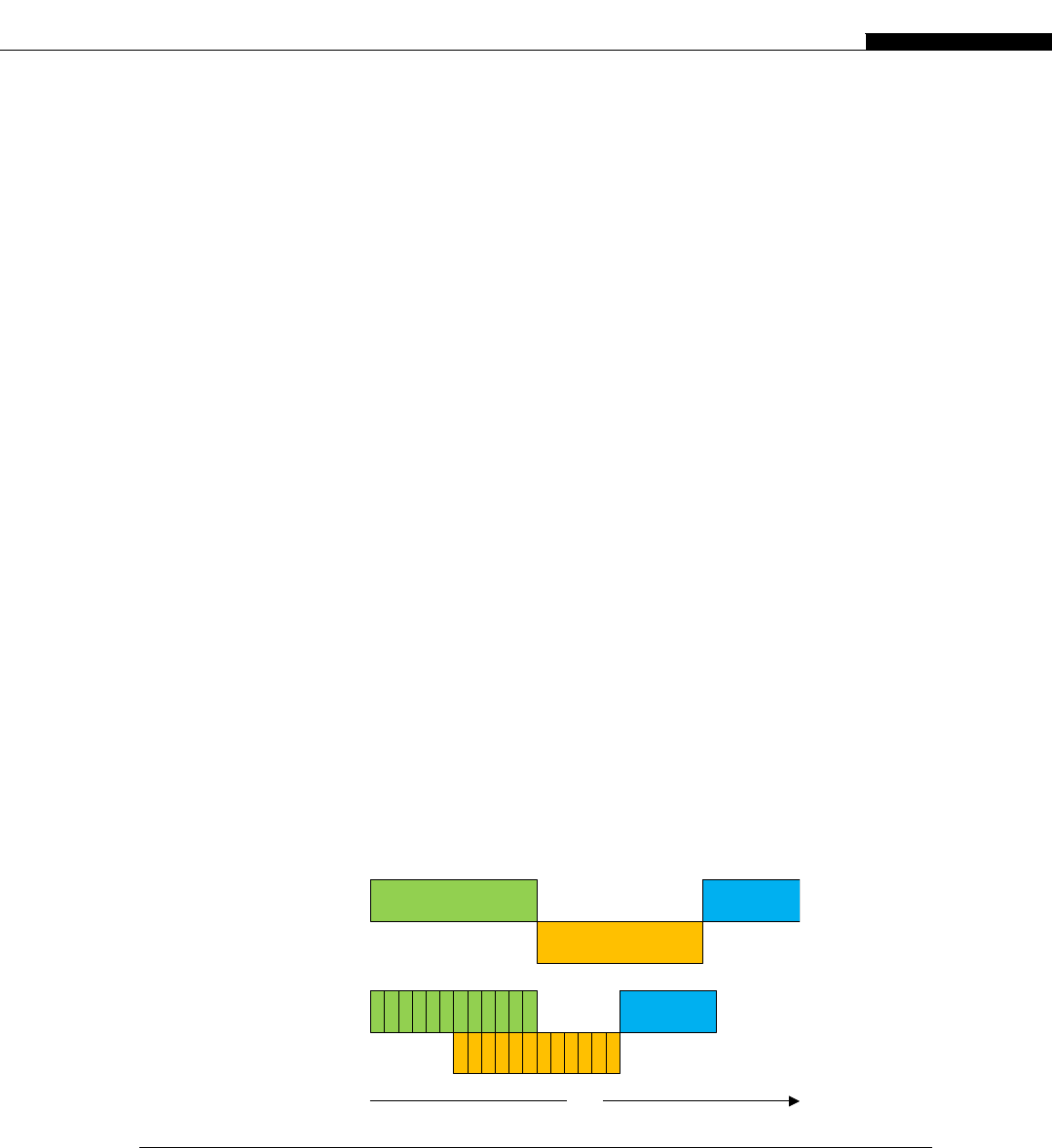

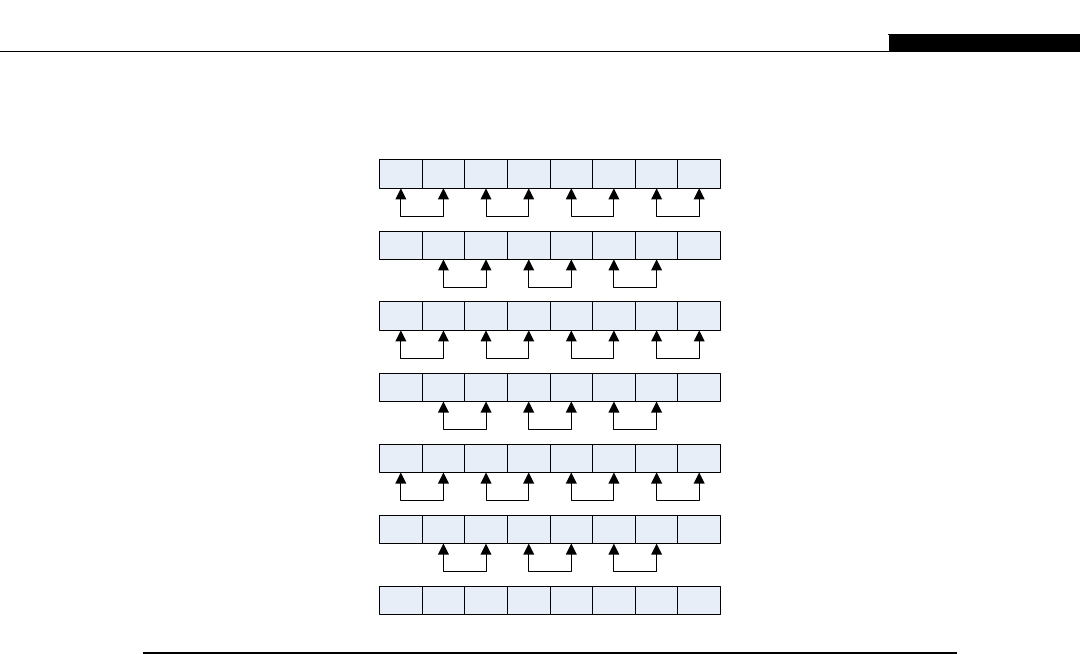

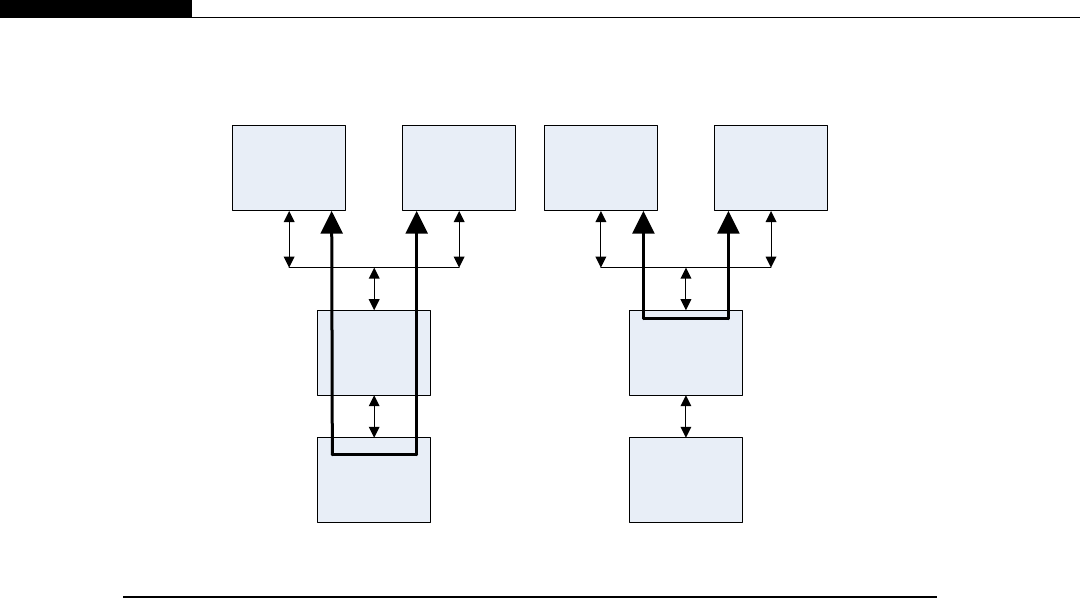

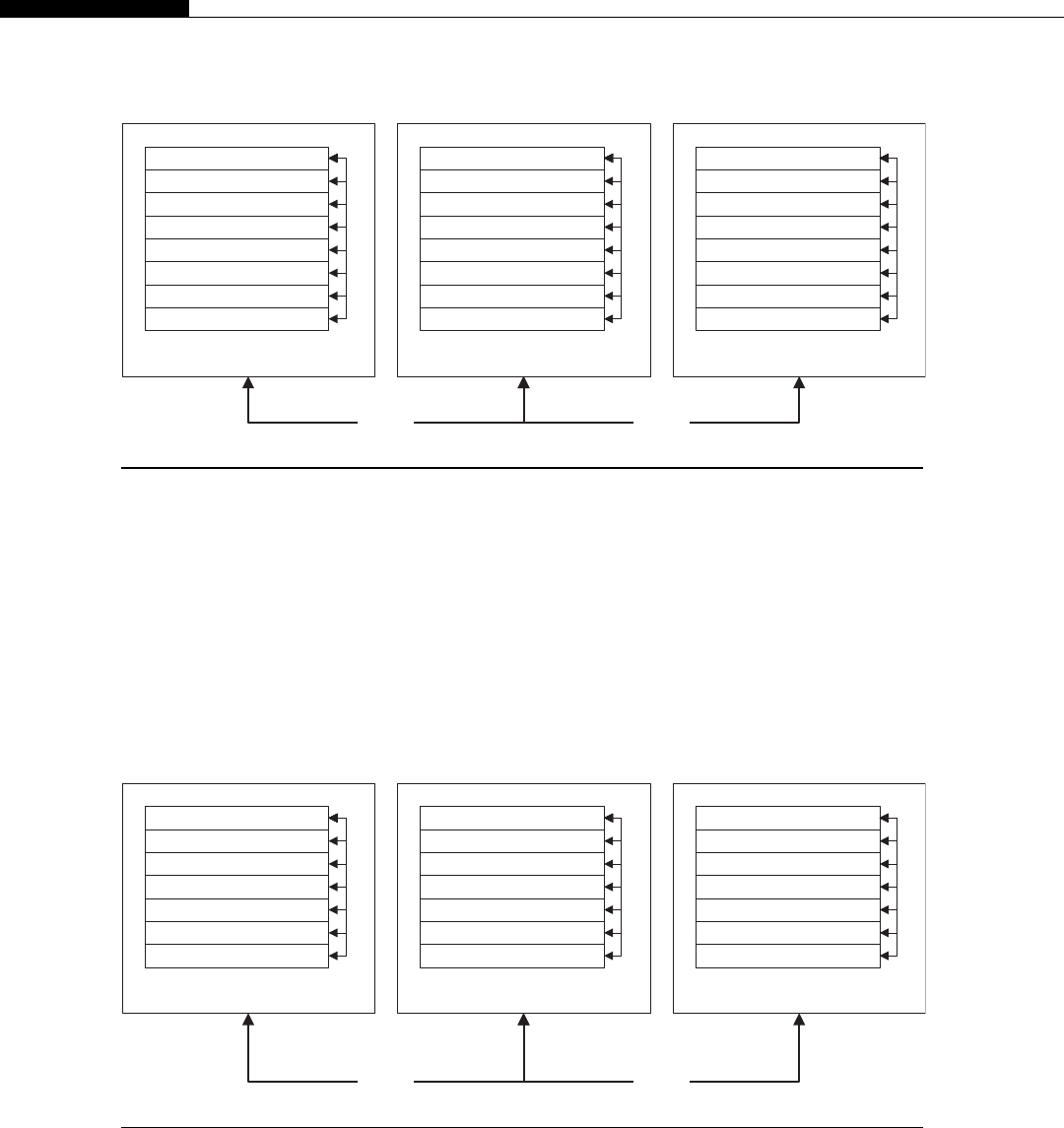

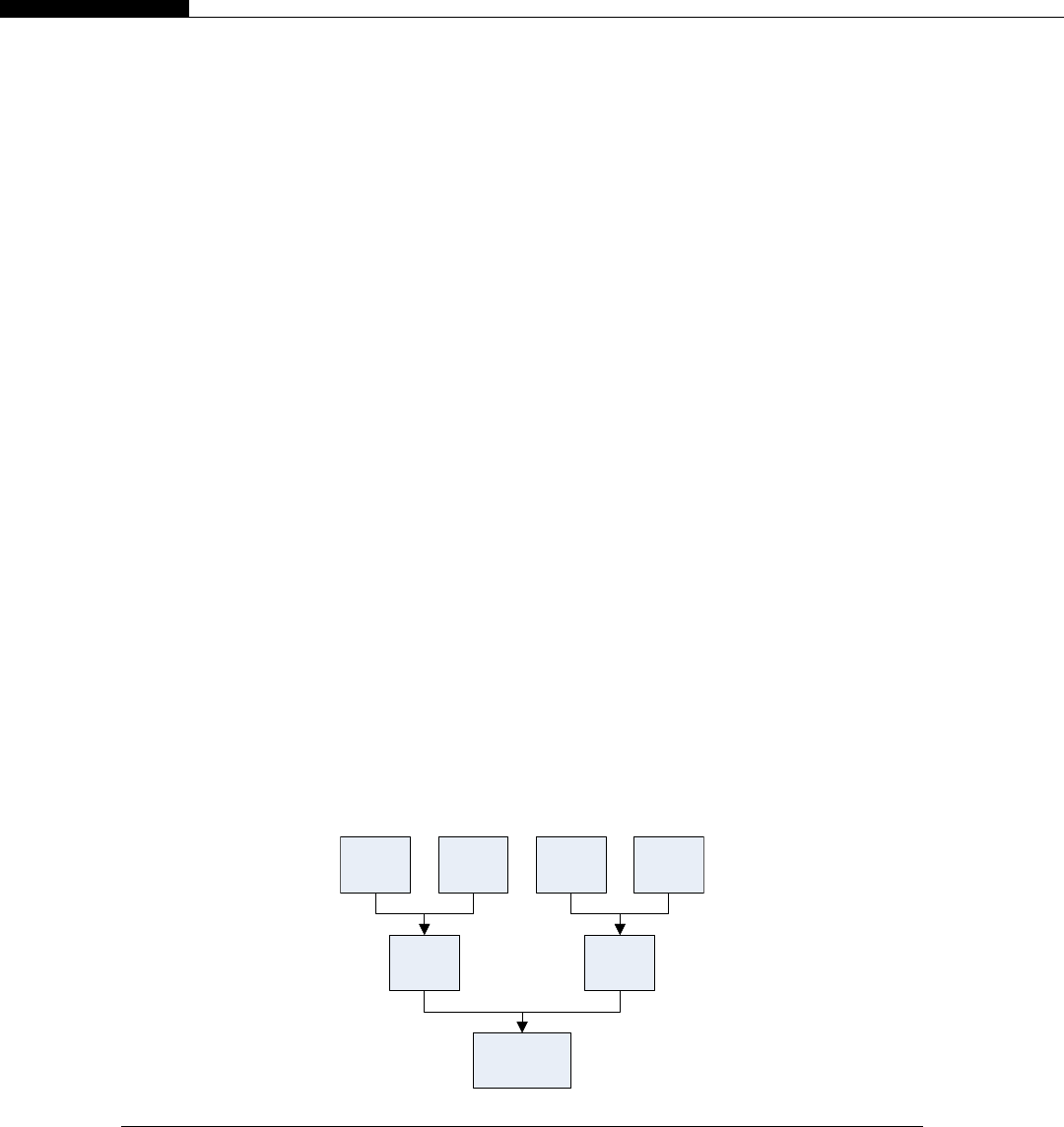

Clusters are seen inside modern CPUs and GPUs. Look back at Figure 1.1, the CPU cache hier-

archy. If we consider each CPU core as a node, the L2 cache as DRAM (Dynamic Random Access

Memory), the L3 cache as the network switch, and the DRAM as mass storage, we have a cluster in

miniature (Figure 1.6).

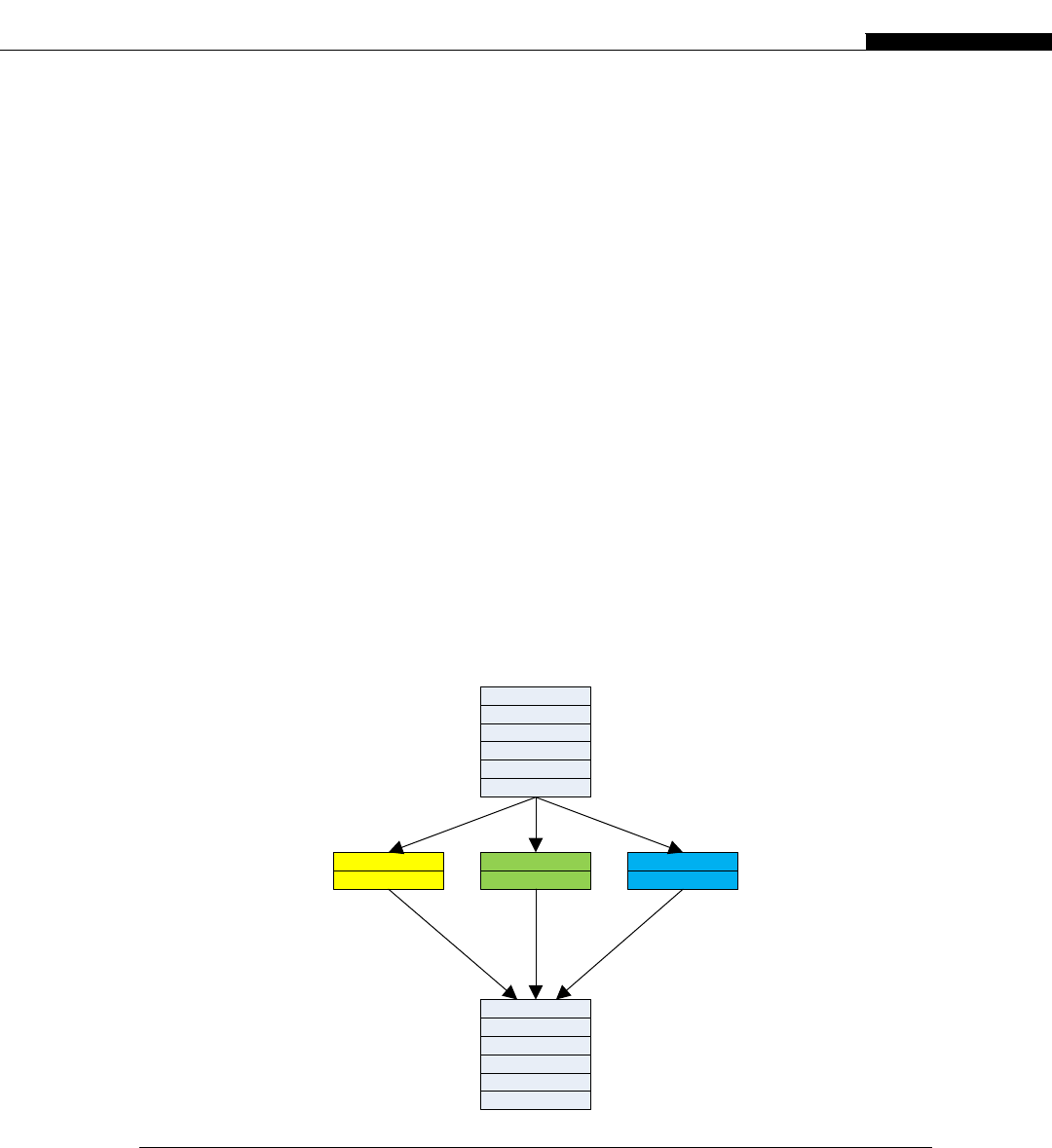

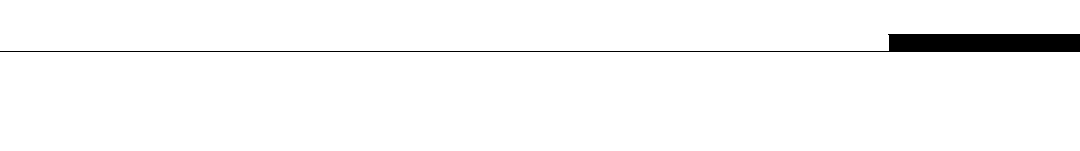

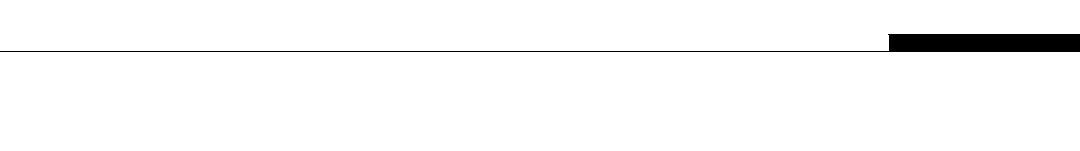

The architecture inside a modern GPU is really no different. You have a number of streaming

multiprocessors (SMs) that are akin to CPU cores. These are connected to a shared memory/L1

cache. This is connected to an L2 cache that acts as an inter-SM switch. Data can be held in global

memory storage where it’s then extracted and used by the host, or sent via the PCI-E switch directly

to the memory on another GPU. The PCI-E switch is many times faster than any network’s

interconnect.

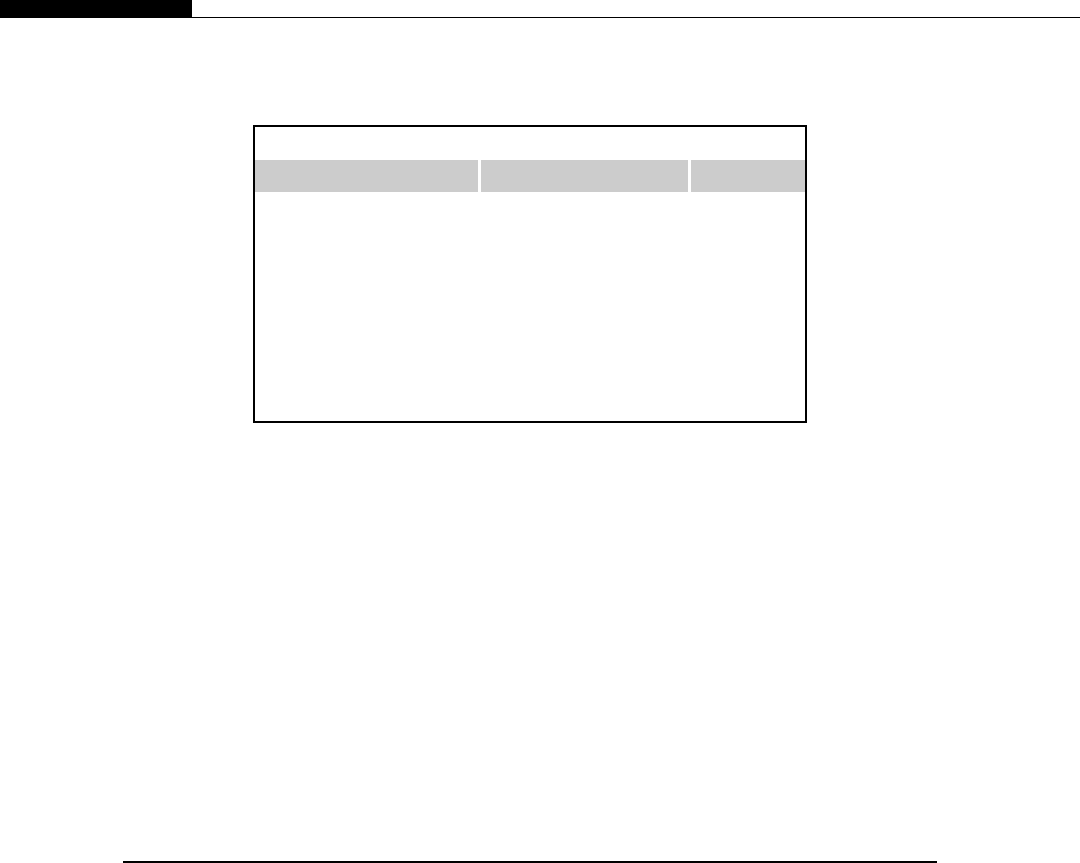

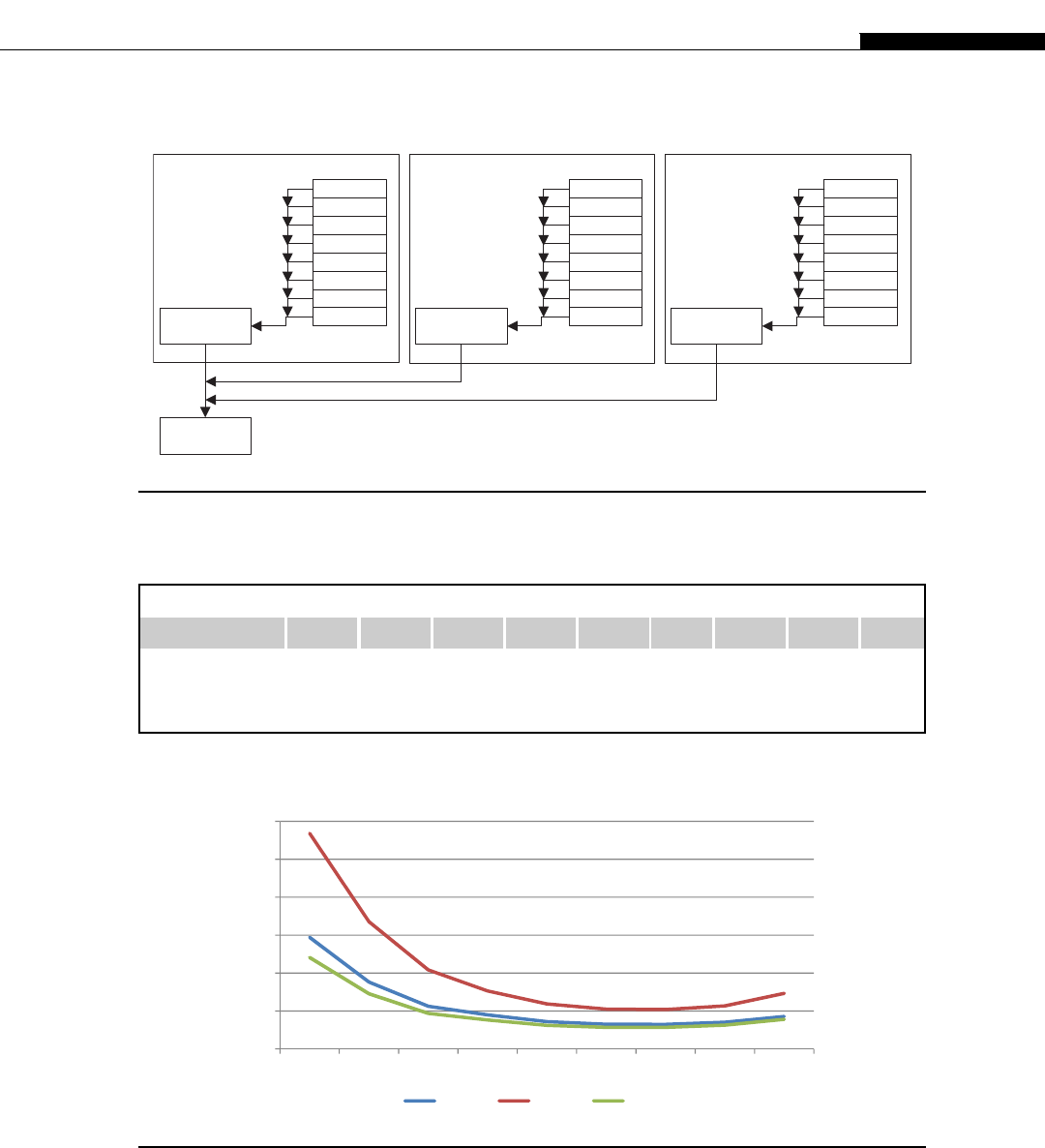

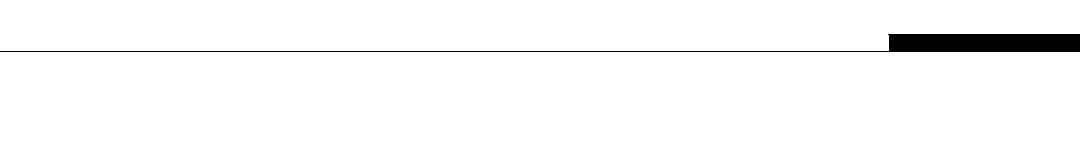

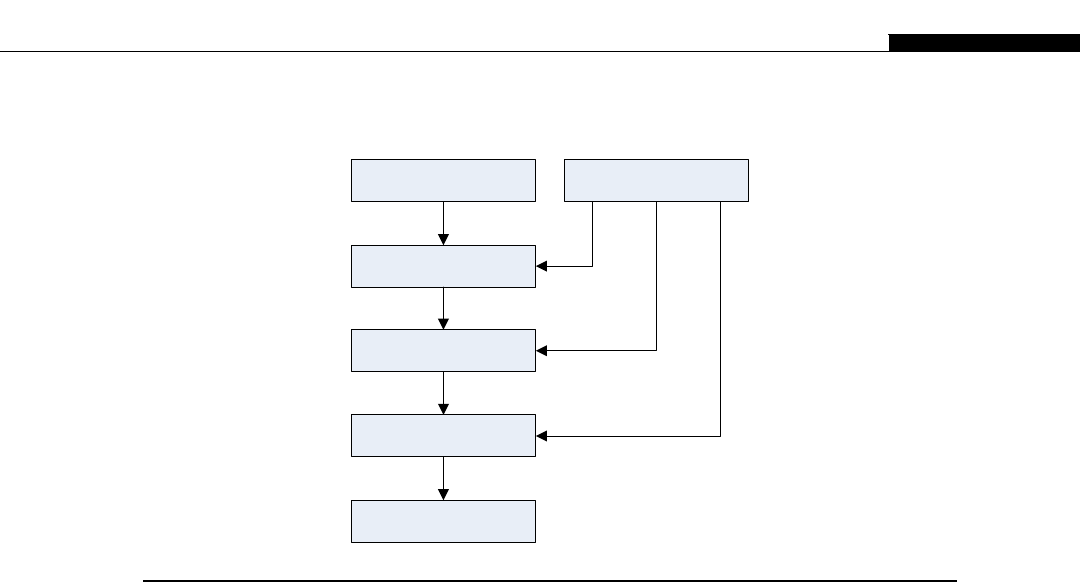

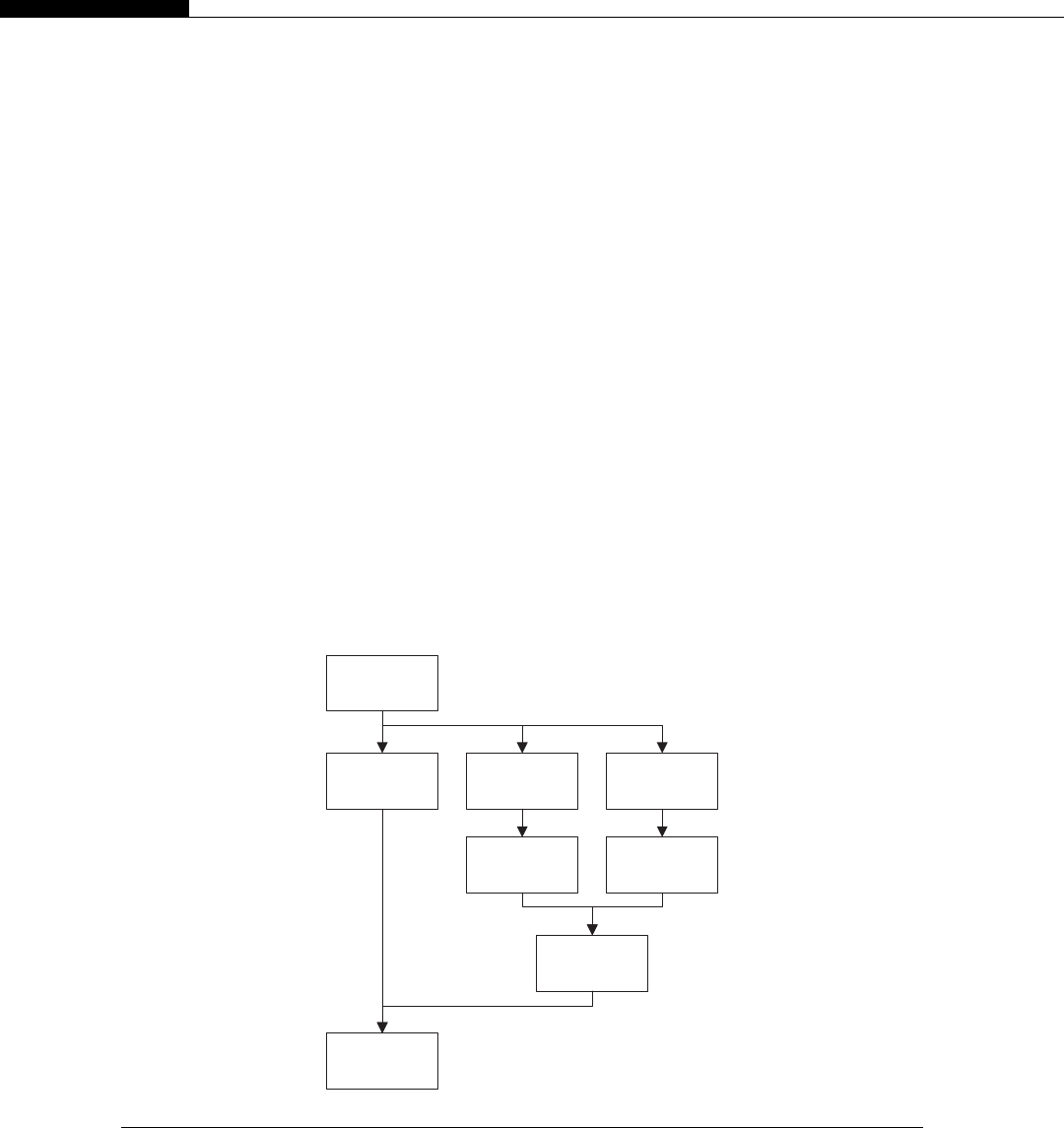

The node may itself be replicated many times, as shown in Figure 1.7. This replication within

a controlled environment forms a cluster. One evolution of the cluster designs are distributed

Network Storage

Network Switch

Network Interface

DRAM Local

Storage

Processor Node

Network Interface

DRAM Local

Storage

Processor Node

Network Interface

DRAM Local

Storage

Processor Node

Network Interface

DRAM Local

Storage

Processor Node

FIGURE 1.6

Typical cluster layout.

10 CHAPTER 1 A Short History of Supercomputing

applications. Distributed applications run on many nodes, each of which may contain many processing

elements including GPUs. Distributed applications may, but do not need to, run in a controlled

environment of a managed cluster. They can connect arbitrary machines together to work on some

common problem, BOINC and Folding@Home being two of the largest examples of such applications

that connect machines together over the Internet.

THE EARLY DAYS OF GPGPU CODING

Graphics processing units (GPUs) are devices present in most modern PCs. They provide a number of

basic operations to the CPU, such as rendering an image in memory and then displaying that image

onto the screen. A GPU will typically process a complex set of polygons, a map of the scene to be

rendered. It then applies textures to the polygons and then performs shading and lighting calculations.

The NVIDIA 5000 series cards brought for the first time photorealistic effects, such as shown in the

Dawn Fairy demo from 2003.

Have a look at http://www.nvidia.com/object/cool_stuff.html#/demos anddownloadsomeof

the older demos and you’ll see just how much GPUs have evolved over the past decade. See

Table 1.2.

One of the important steps was the development of programmable shaders. These were effectively

little programs that the GPU ran to calculate different effects. No longer was the rendering fixed in the

GPU; through downloadable shaders, it could be manipulated. This was the first evolution of general-

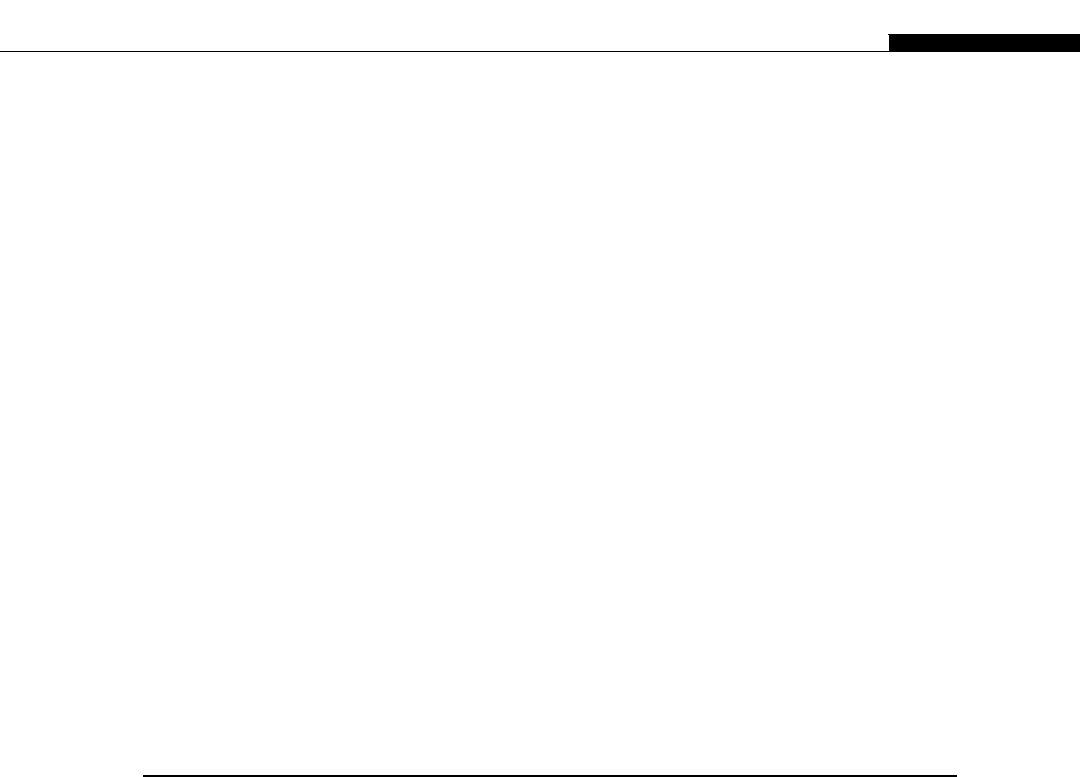

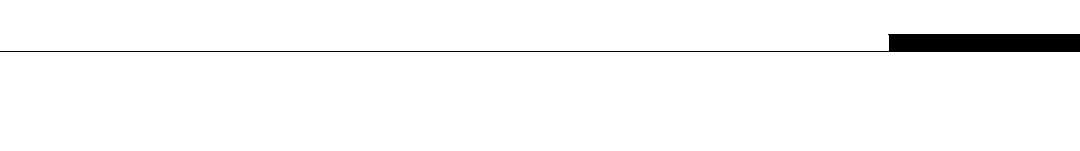

Host Memory / CPU

PCI-E Switch

PCI-E Interface

GMEM

SM

GPU

L1

L2 Cache

SM SM SM

L1 L1 L1

GPU GPU

FIGURE 1.7

GPUs compared to a cluster.

The Early Days of GPGPU Coding 11

purpose graphical processor unit (GPGPU) programming, in that the design had taken its first steps in

moving away from fixed function units.

However, these shaders were operations that by their very nature took a set of 3D points that

represented a polygon map. The shaders applied the same operation to many such datasets, in a hugely

parallel manner, giving huge throughput of computing power.

Now although polygons are sets of three points, and some other datasets such as RGB photos can be

represented by sets of three points, a lot of datasets are not. A few brave researchers made use of GPU

technology to try and speed up general-purpose computing. This led to the development of a number of

initiatives (e.g., BrookGPU, Cg, CTM, etc.), all of which were aimed at making the GPU a real

programmable device in the same way as the CPU. Unfortunately, each had its own advantages and

problems. None were particularly easy to learn or program in and were never taught to people in large

numbers. In short, there was never a critical mass of programmers or a critical mass of interest from

programmers in this hard-to-learn technology. They never succeeded in hitting the mass market,

something CUDA has for the first time managed to do, and at the same time provided programmers

with a truly general-purpose language for GPUs.

THE DEATH OF THE SINGLE-CORE SOLUTION

One of the problems with today’s modern processors is they have hit a clock rate limit at around 4 GHz.

At this point they just generate too much heat for the current technology and require special and

expensive cooling solutions. This is because as we increase the clock rate, the power consumption

rises. In fact, the power consumption of a CPU, if you fix the voltage, is approximately the cube of its

clock rate. To make this worse, as you increase the heat generated by the CPU, for the same clock rate,

the power consumption also increases due to the properties of the silicon. This conversion of power

into heat is a complete waste of energy. This increasingly inefficient use of power eventually means

you are unable to either power or cool the processor sufficiently and you reach the thermal limits of the

device or its housing, the so-called power wall.

Faced with not being able to increase the clock rate, making forever-faster processors, the processor

manufacturers had to come up with another game plan. The two main PC processor manufacturers, Intel

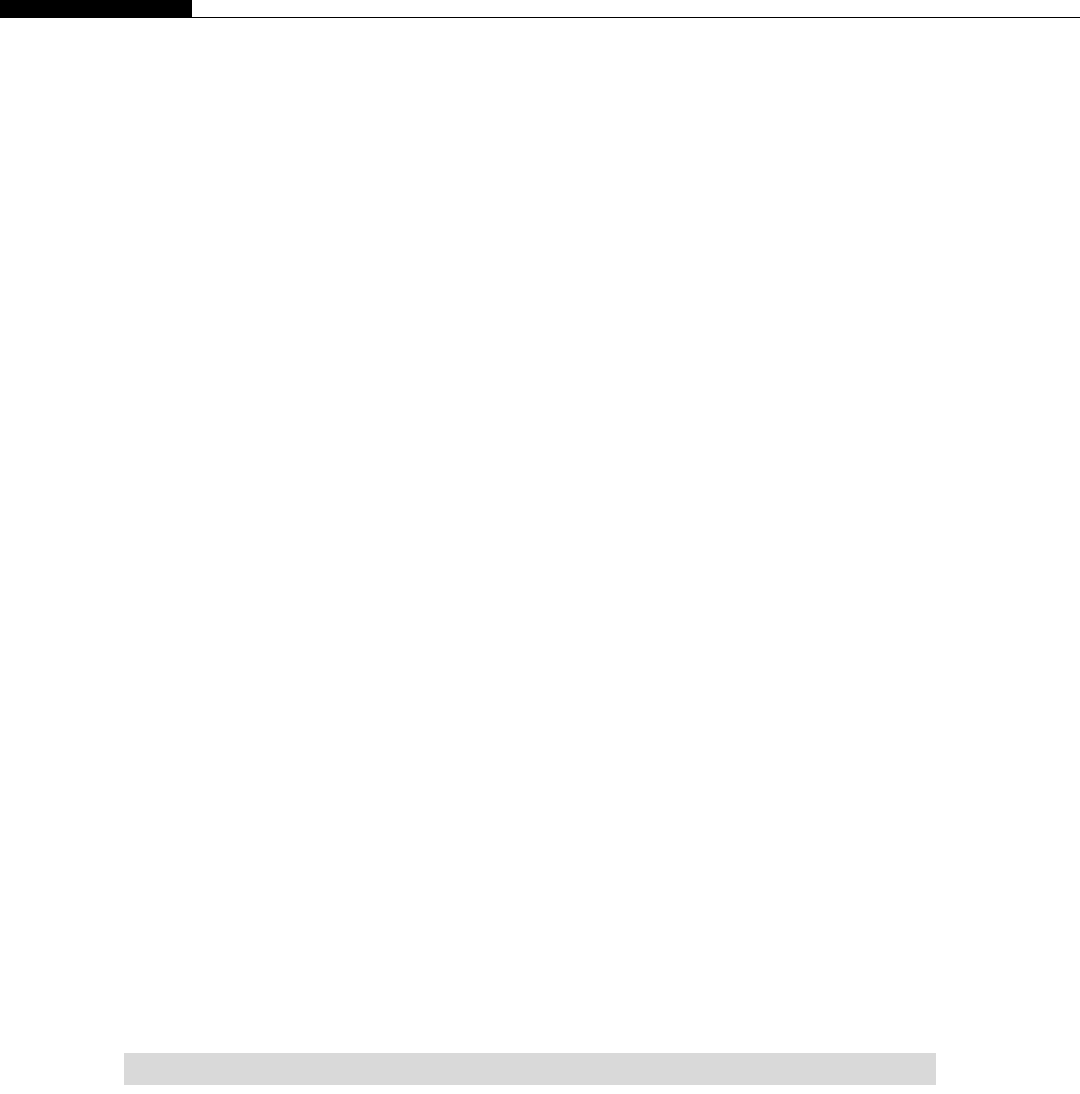

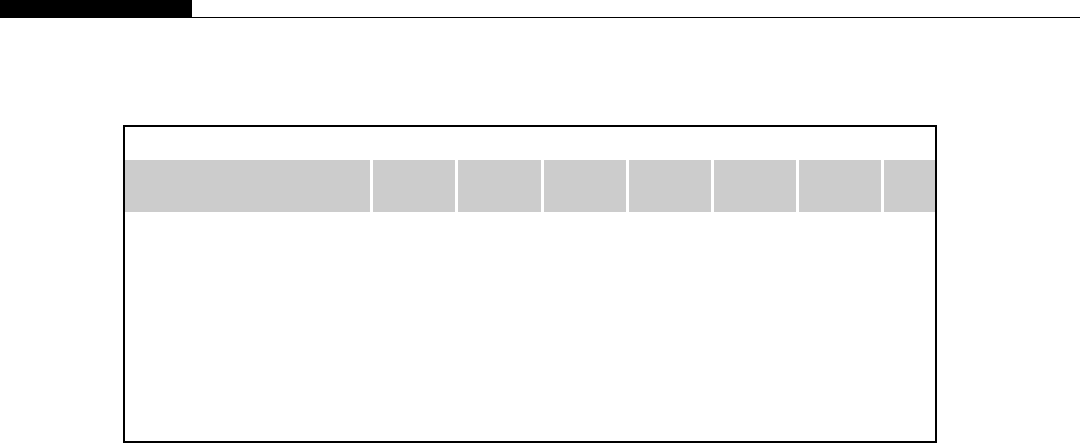

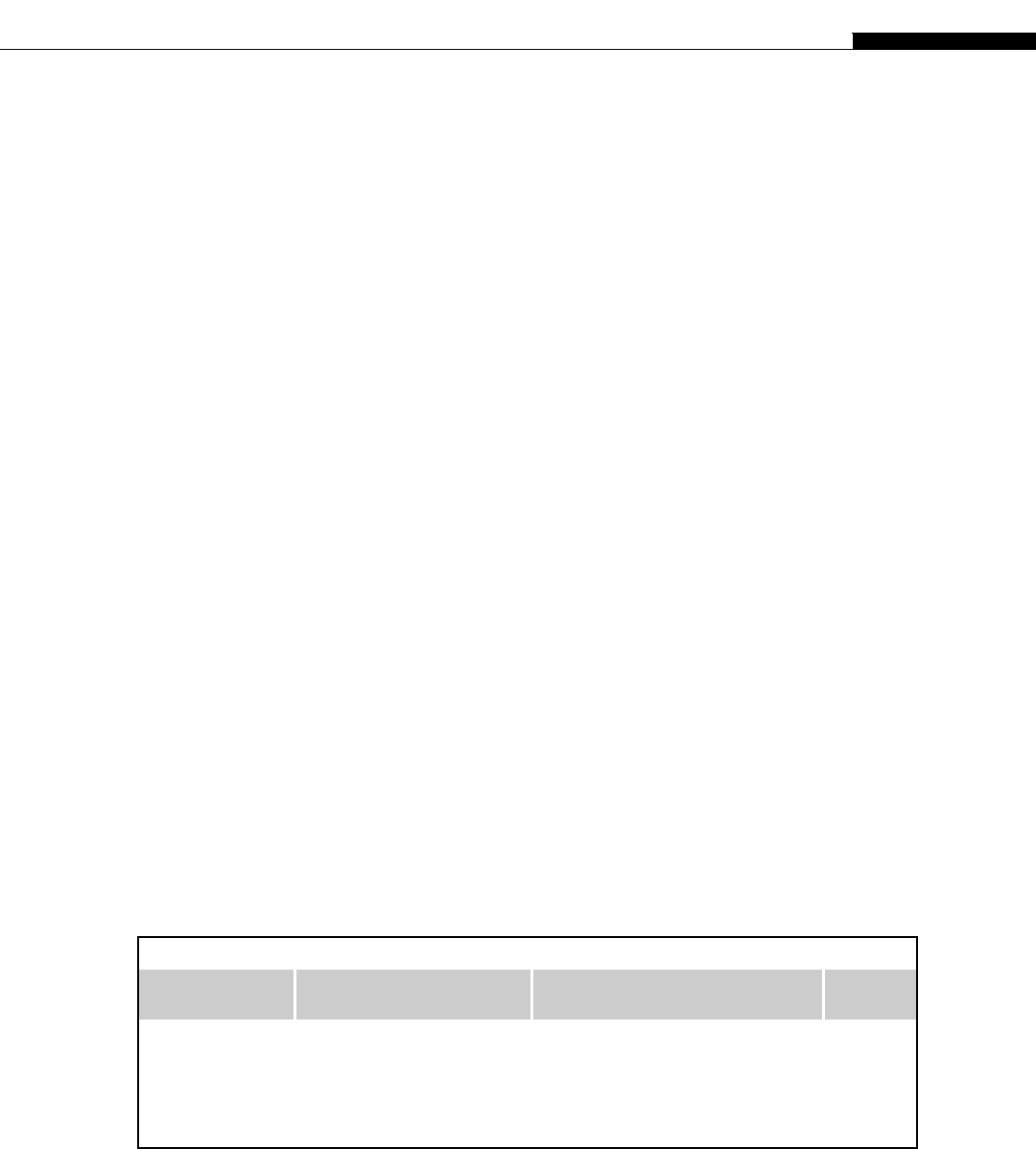

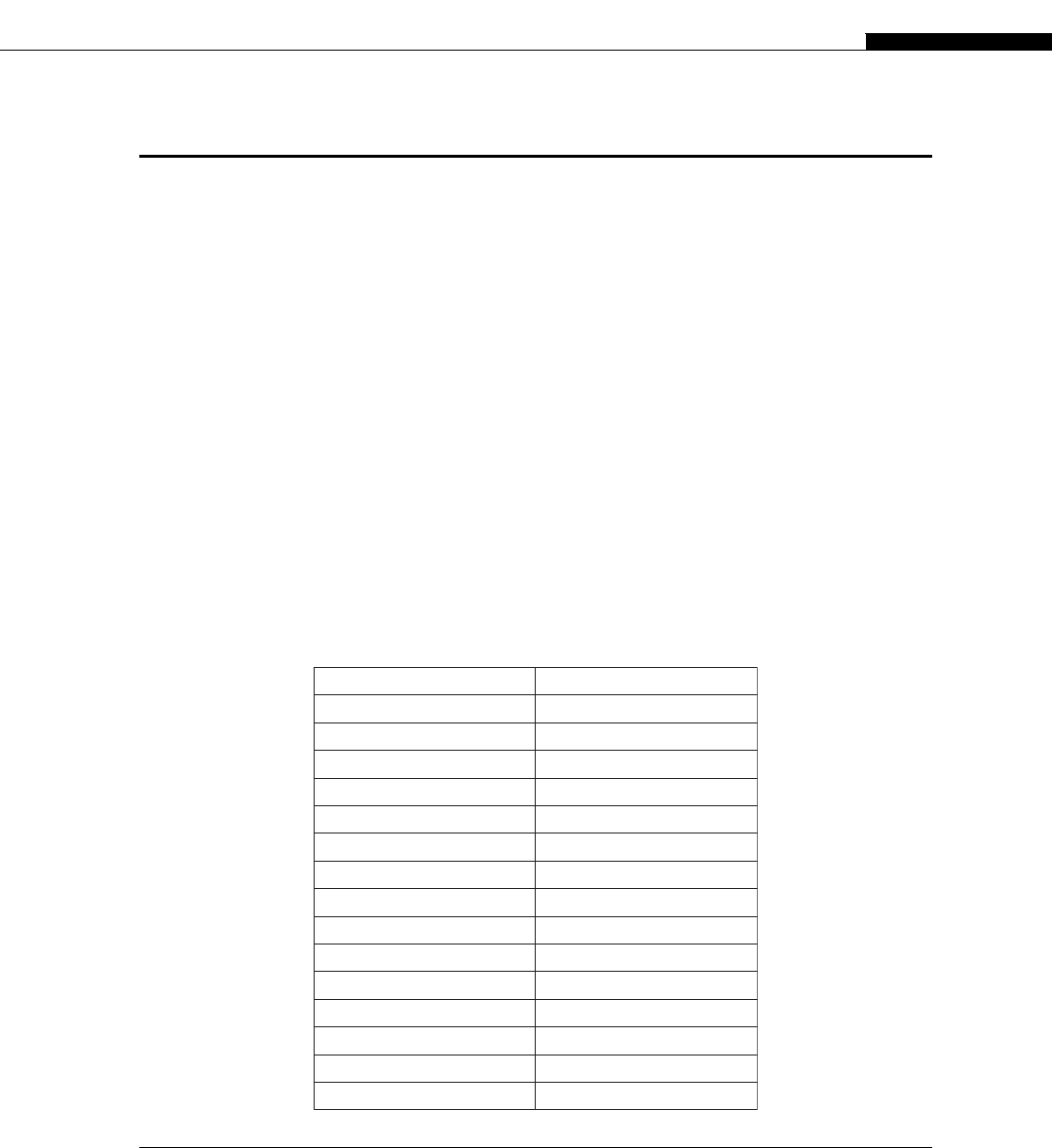

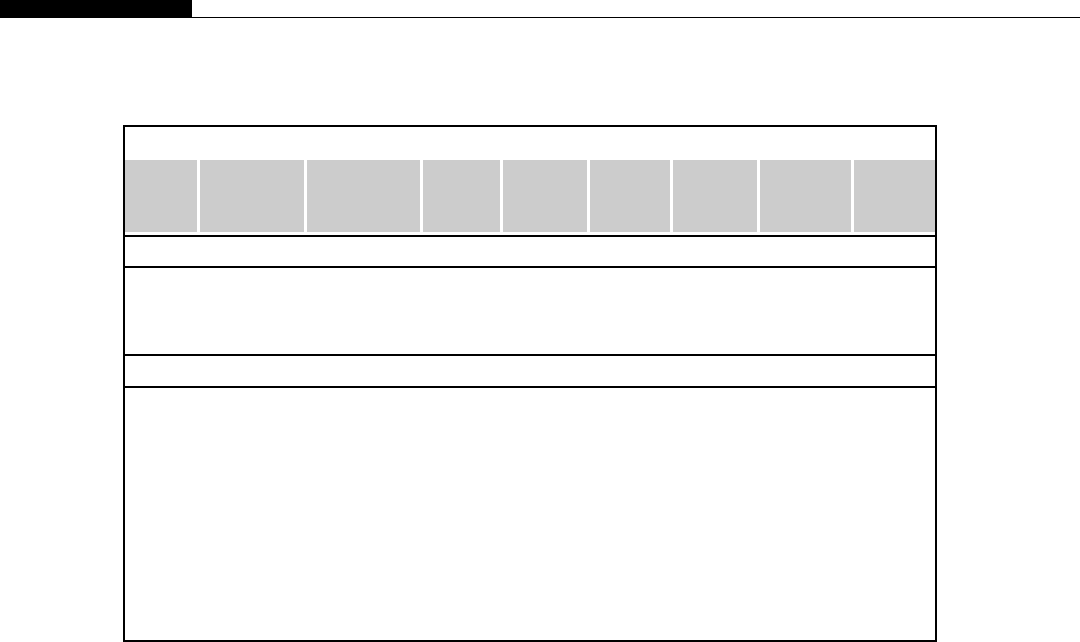

Table 1.2 GPU Technology Demonstrated over the Years

Demo Card Year

Dawn GeForce FX 2003

Dusk Ultra GeForce FX 2003

Nalu GeForce 6 2004

Luna GeForce 7 2005

Froggy GeForce 8 2006

Human Head GeForce 8 2007

Medusa GeForce 200 2008

Supersonic Sled GeForce 400 2010

A New Dawn GeForce 600 2012

12 CHAPTER 1 A Short History of Supercomputing

and AMD, have had to adopt a different approach. They have been forced down the route of adding more

cores to processors, rather than continuously trying to increase CPU clock rates and/or extract more

instructions per clock through instruction-level parallelism. We have dual, tri, quad, hex, 8, 12, and soon

even 16 and 32 cores and so on. This is the future of where computing is now going for everyone, the

GPU and CPU communities. The Fermi GPU is effectively already a 16-core device in CPU terms.

There is a big problem with this approachdit requires programmers to switch from their traditional

serial, single-thread approach, to dealing with multiple threads all executing at once. Now the

programmer has to think about two, four, six, or eight program threads and how they interact and

communicate with one another. When dual-core CPUs arrived, it was fairly easy, in that there were

usually some background tasks being done that could be offloaded onto a second core. When quad-

core CPUs arrived, not many programs were changed to support it. They just carried on being sold as

single-thread applications. Even the games industry didn’t really move to quad-core programming

very quickly, which is the one industry you’d expect to want to get the absolute most out of today’s

technology.

In some ways the processor manufacturers are to blame for this, because the single-core application

runs just fine on one-quarter of the quad-core device. Some devices even increase the clock rate

dynamically when only one core is active, encouraging programmers to be lazy and not make use of

the available hardware.

There are economic reasons too. The software development companies need to get the product to

market as soon as possible. Developing a better quad-core solution is all well and good, but not if the

market is being grabbed by a competitor who got there first. As manufacturers still continue to make

single- and dual-core devices, the market naturally settles on the lowest configuration, with the widest

scope for sales. Until the time that quad-core CPUs are the minimum produced, market forces work

against the move to multicore programming in the CPU market.

NVIDIA AND CUDA

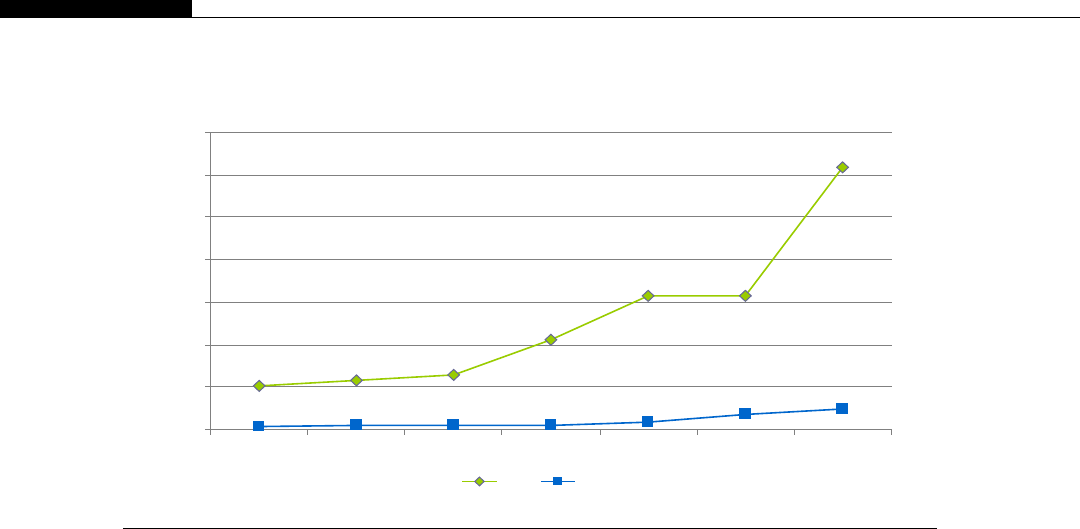

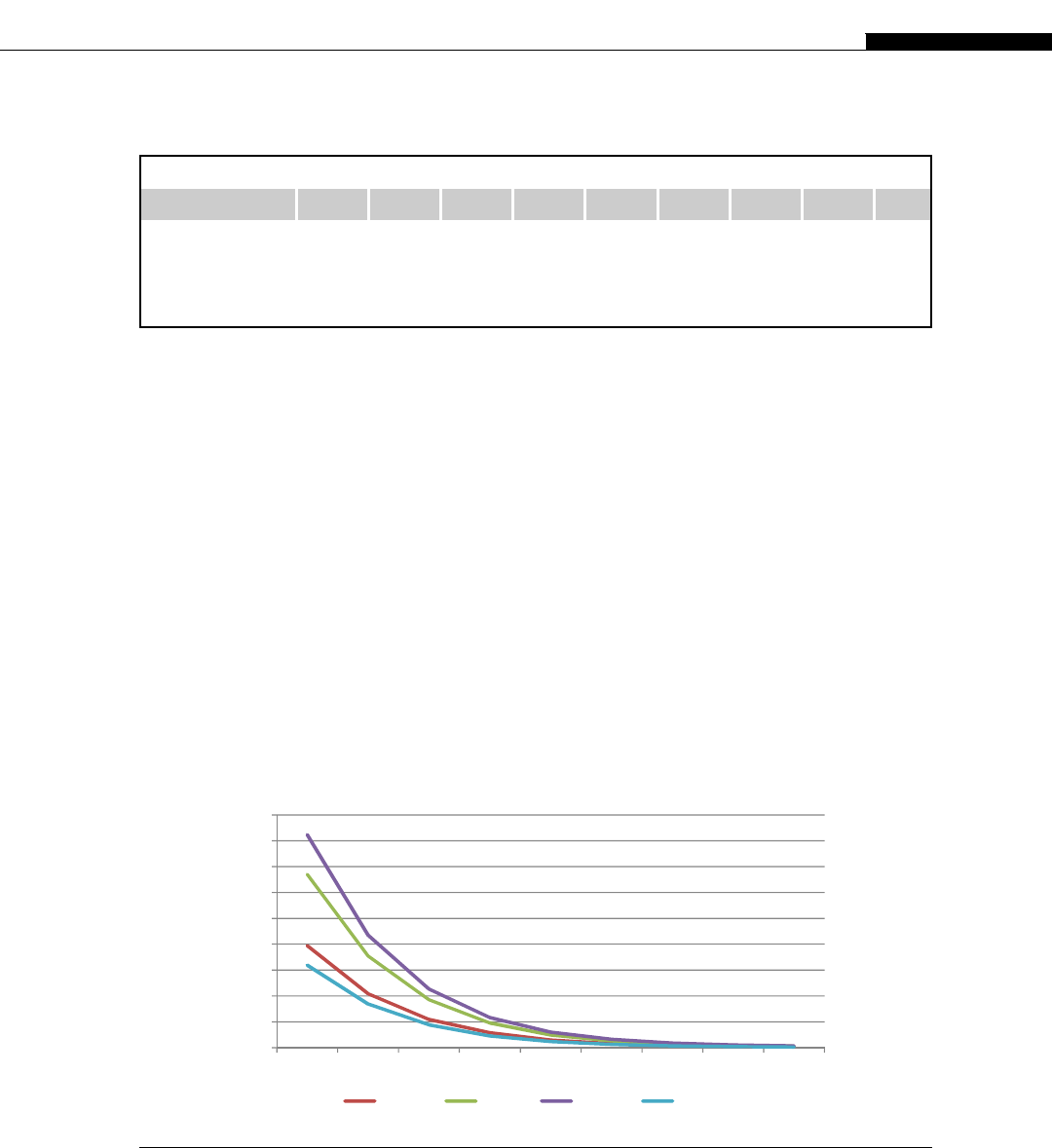

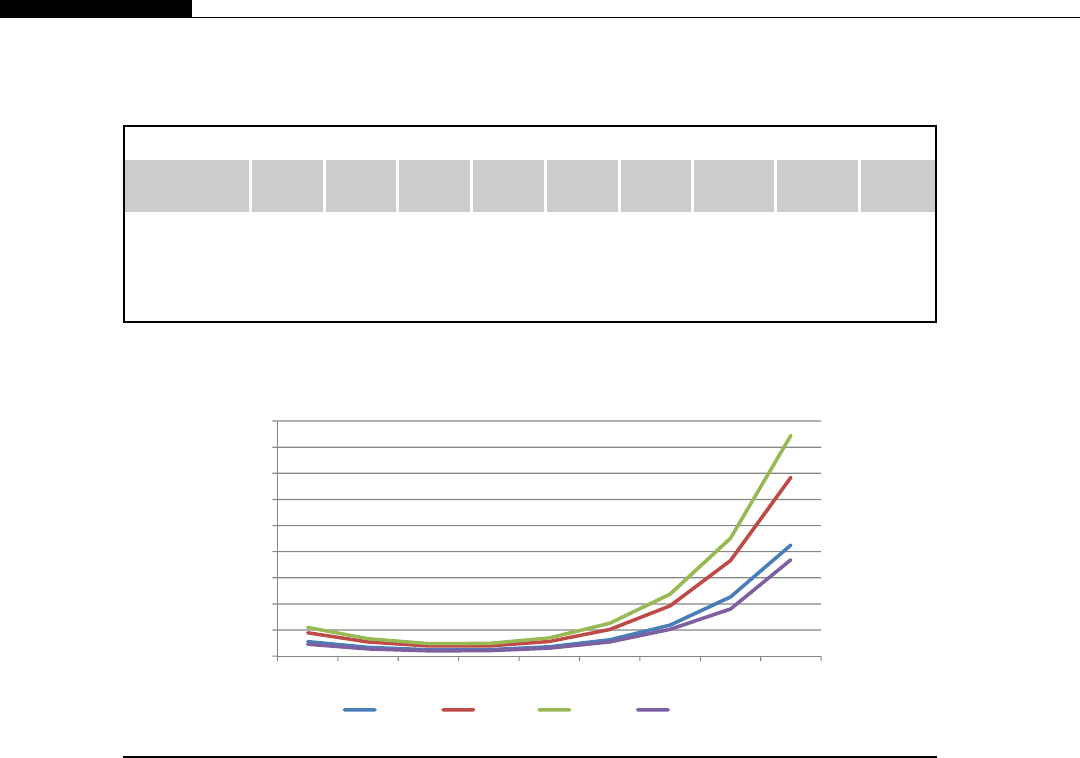

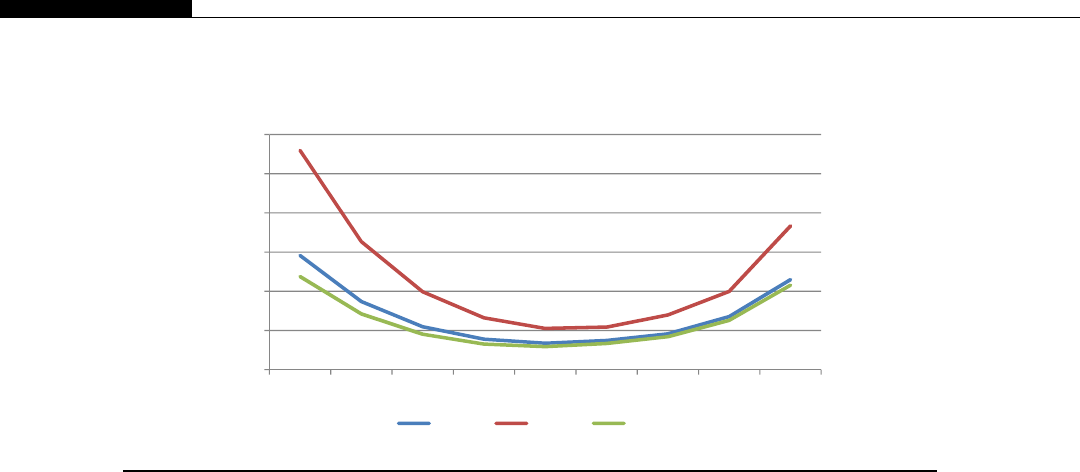

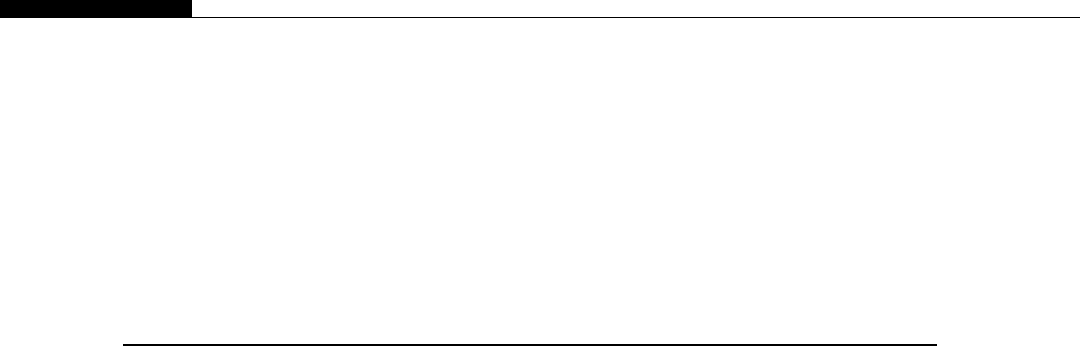

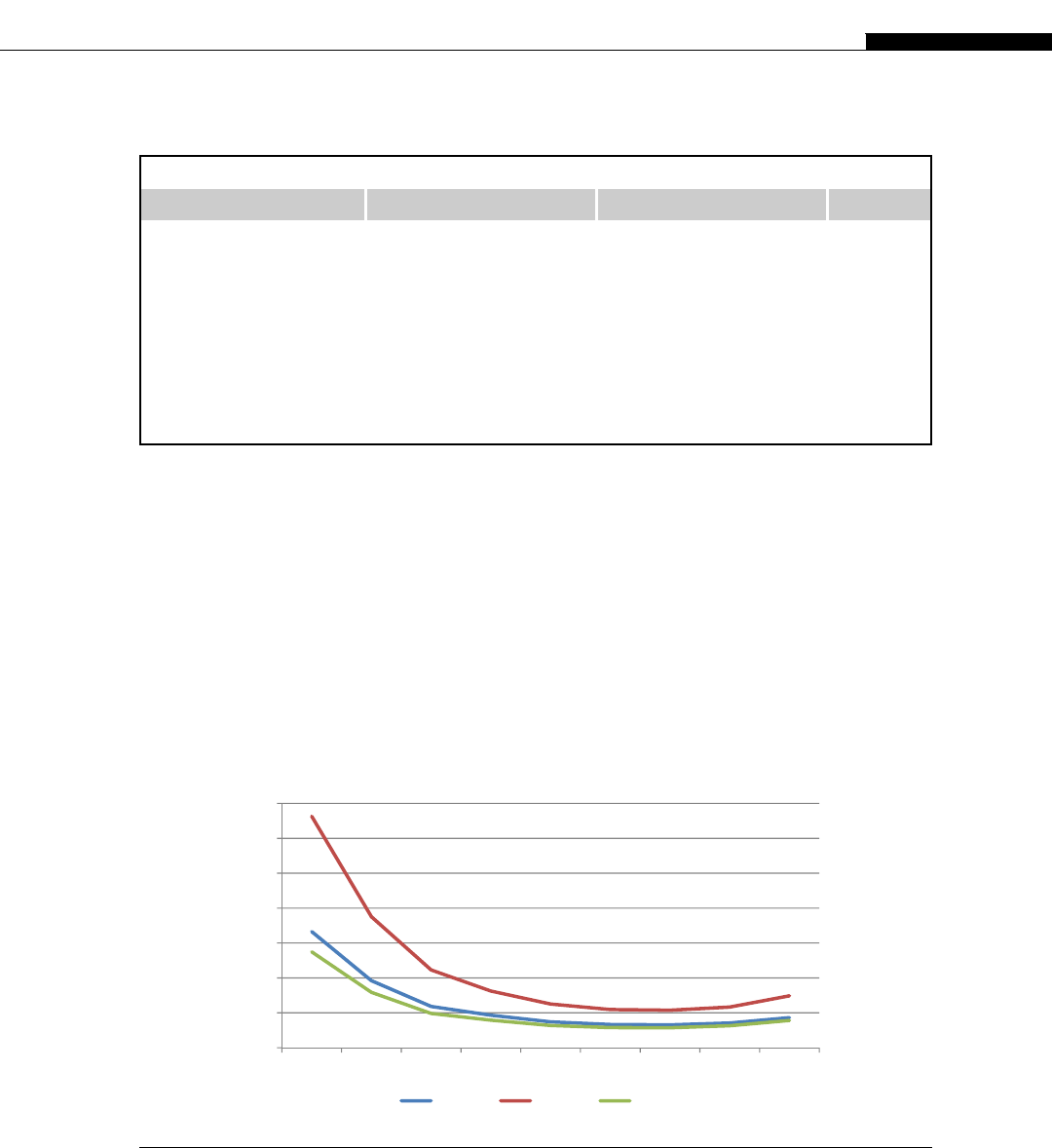

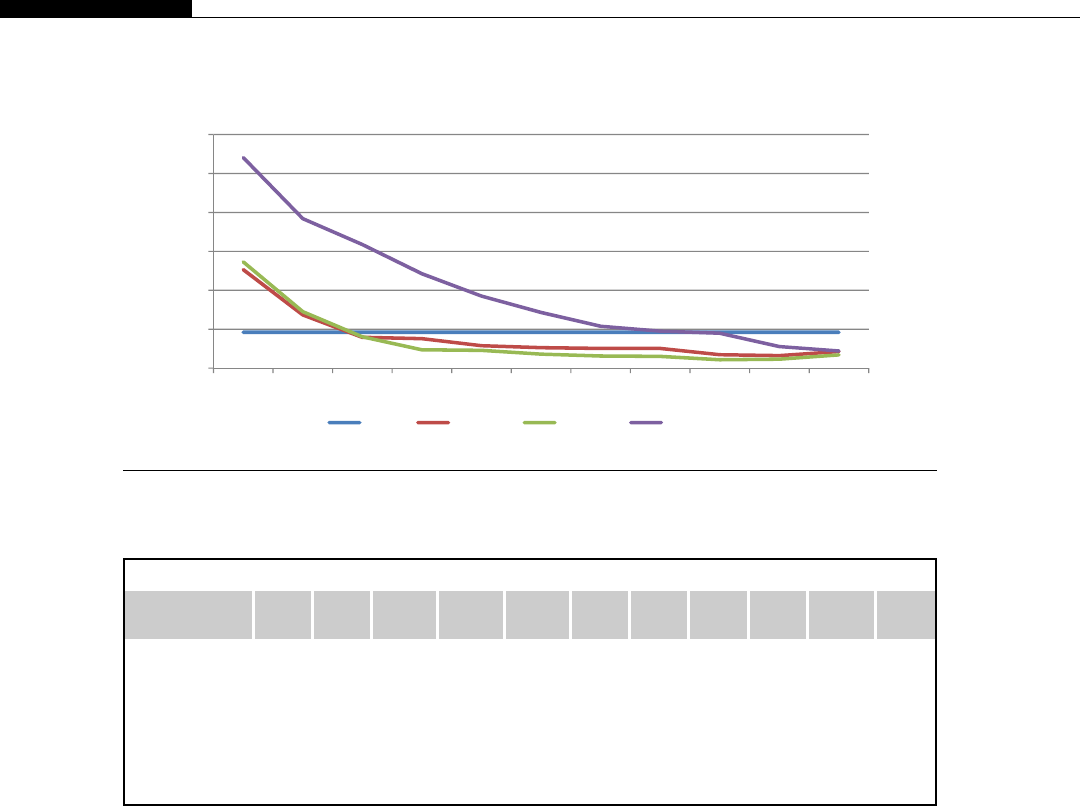

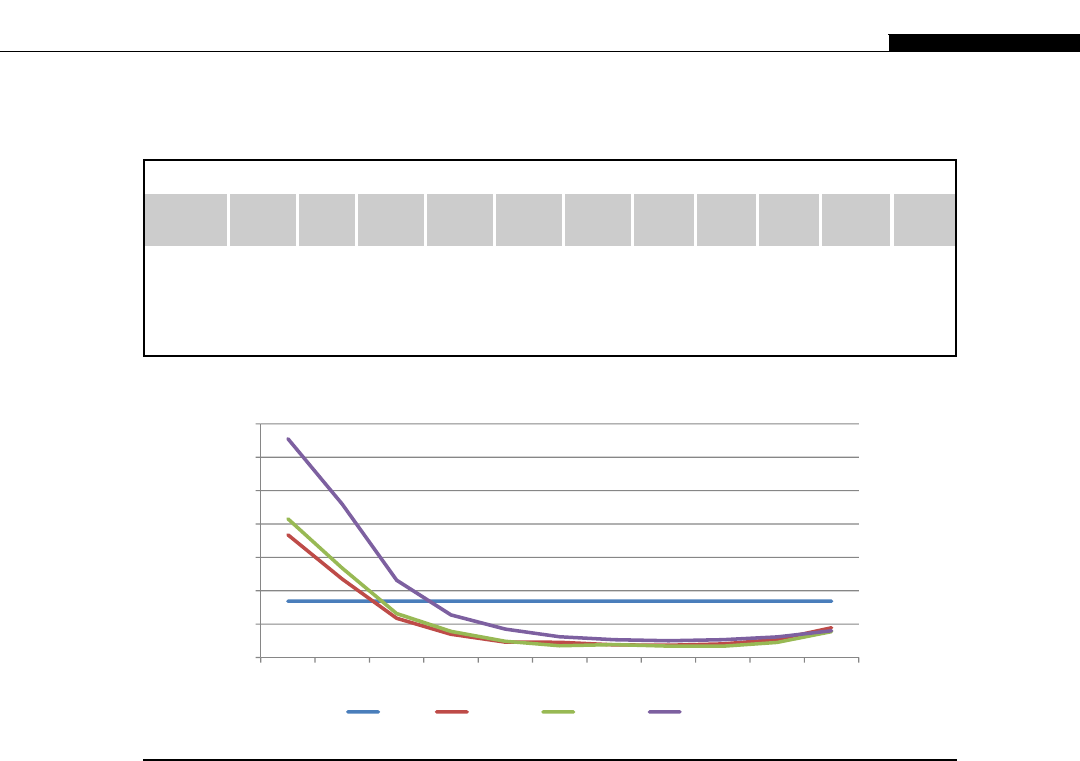

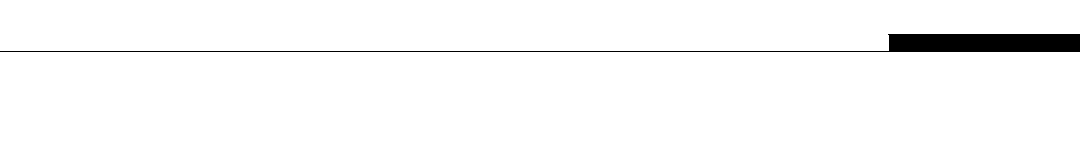

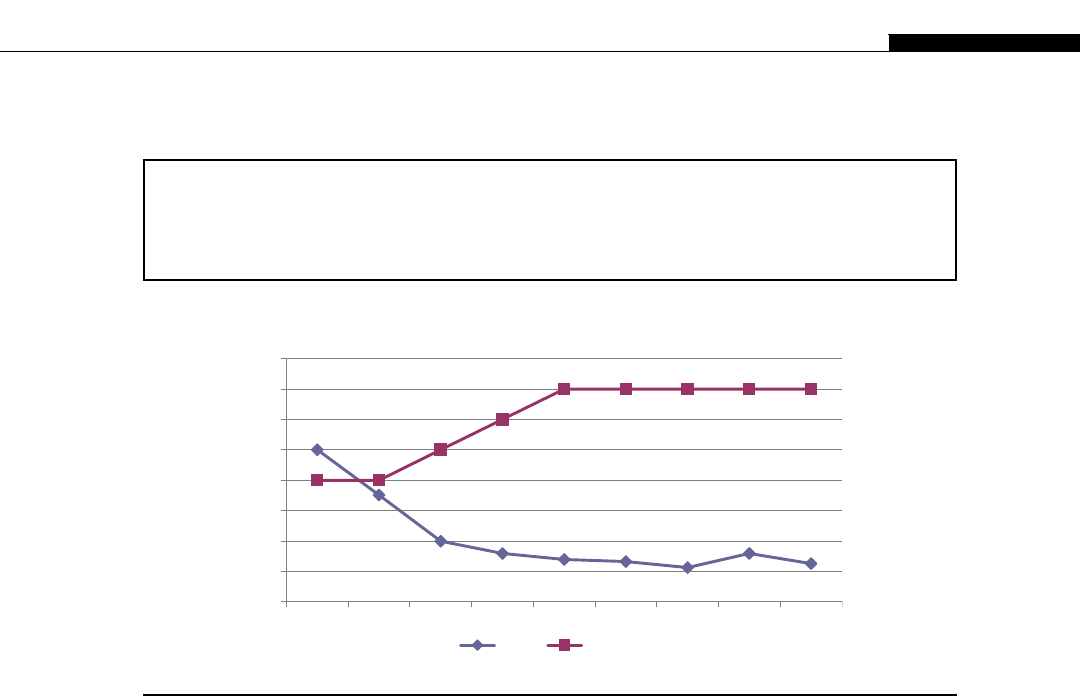

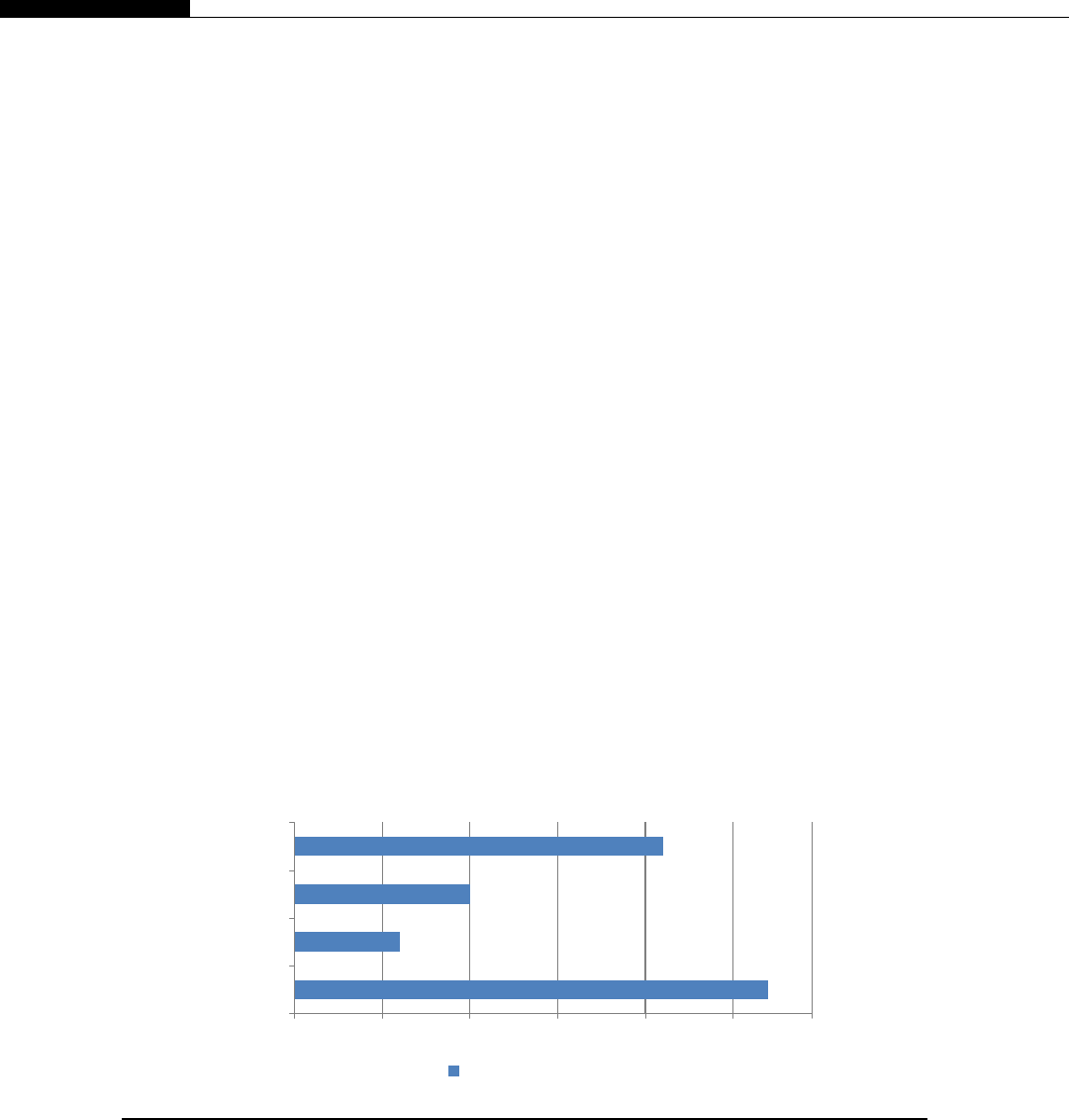

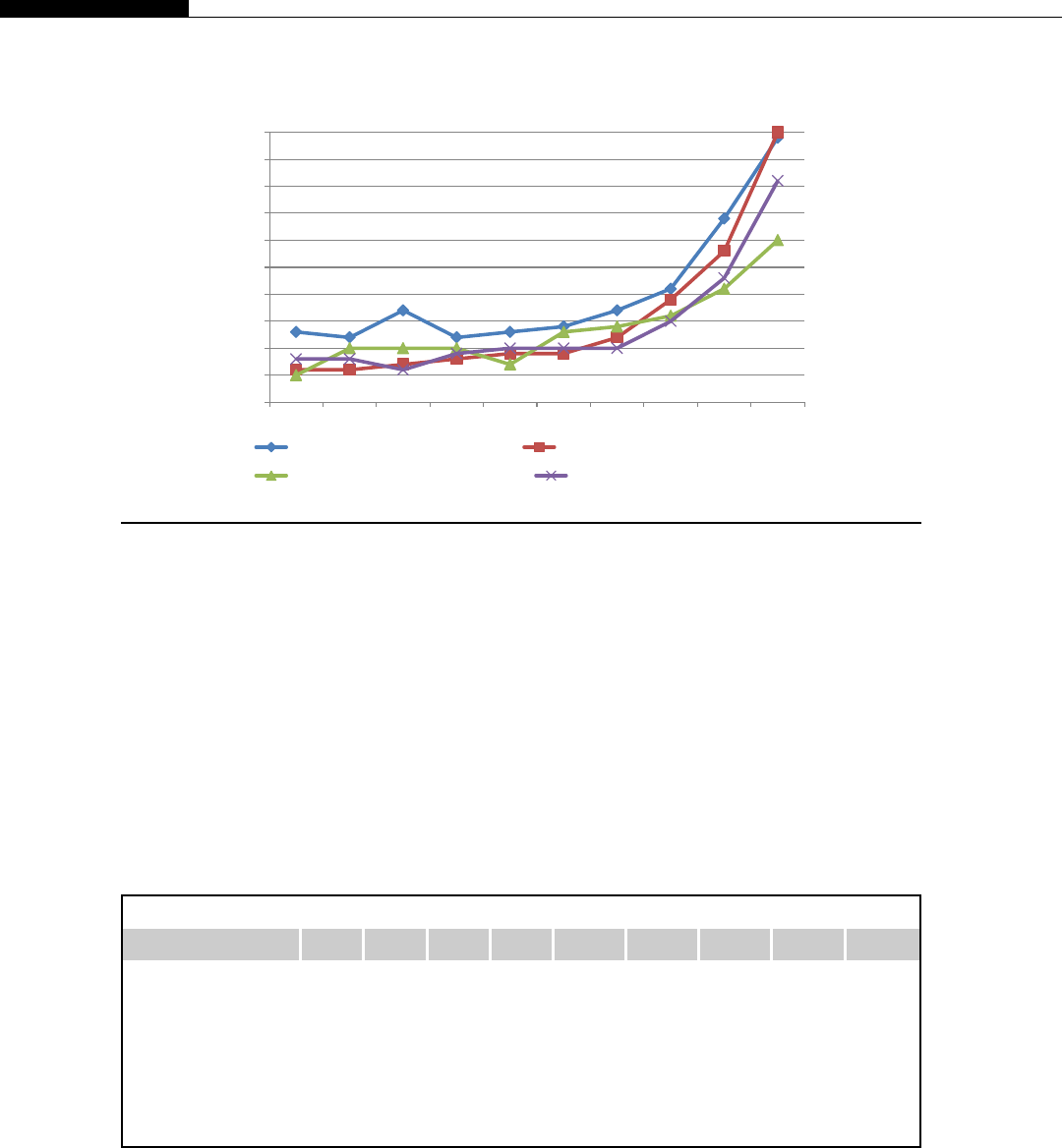

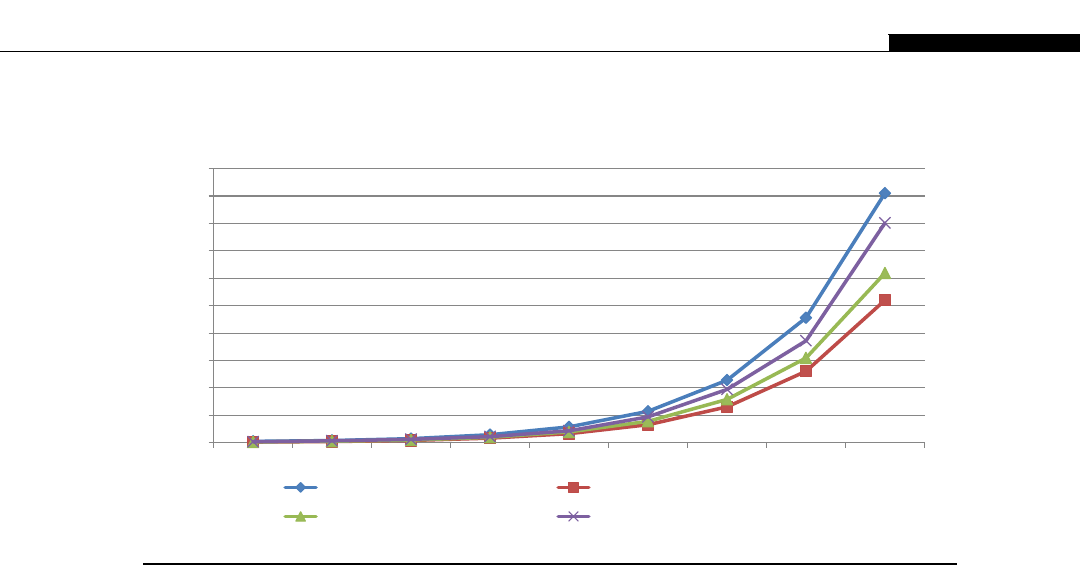

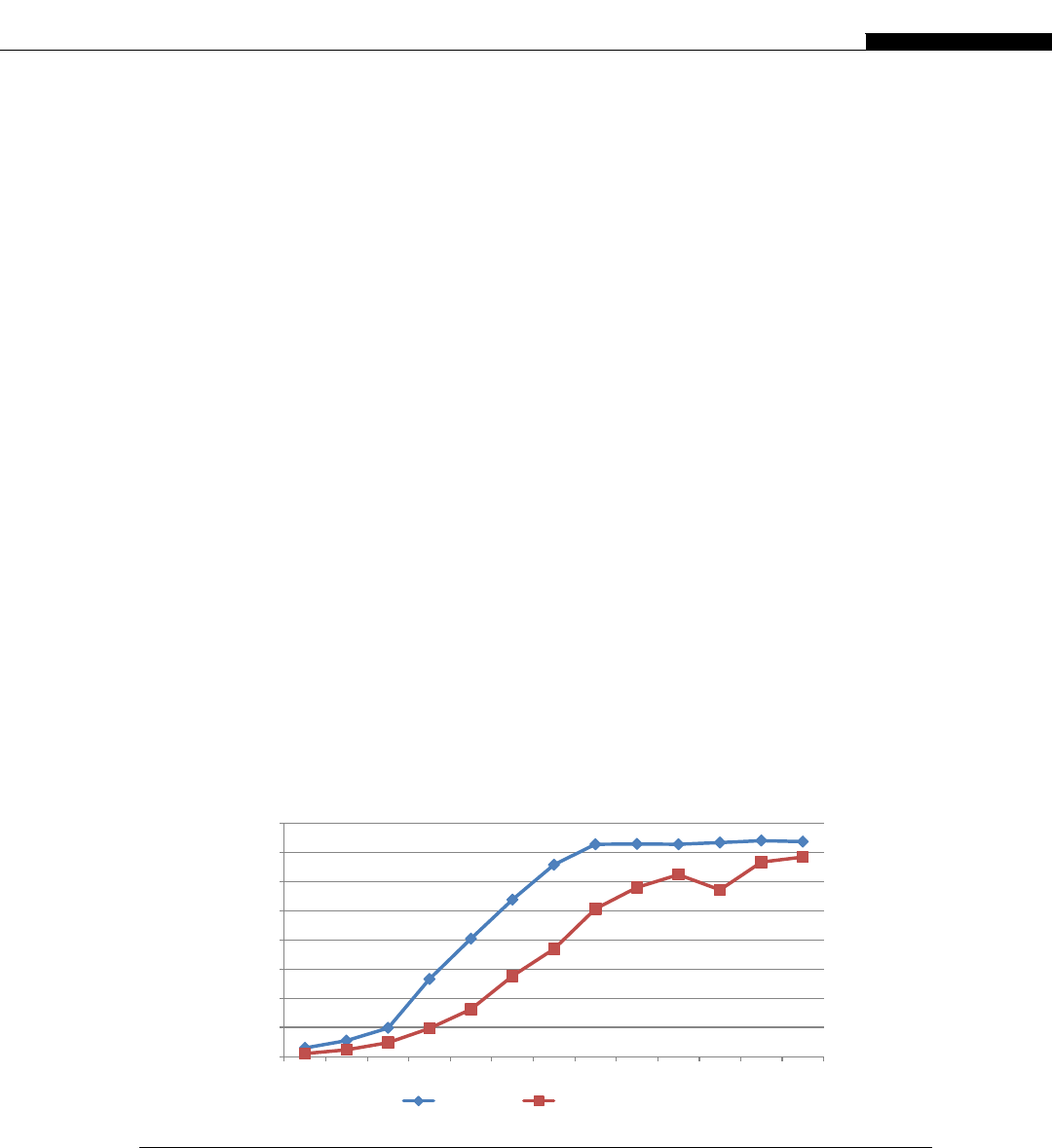

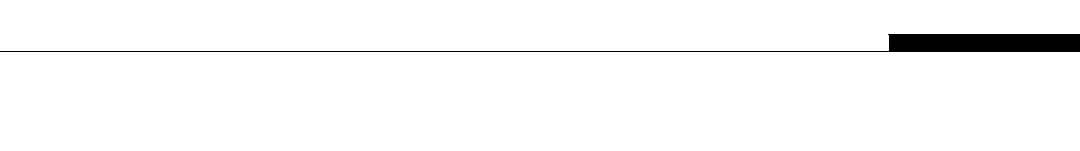

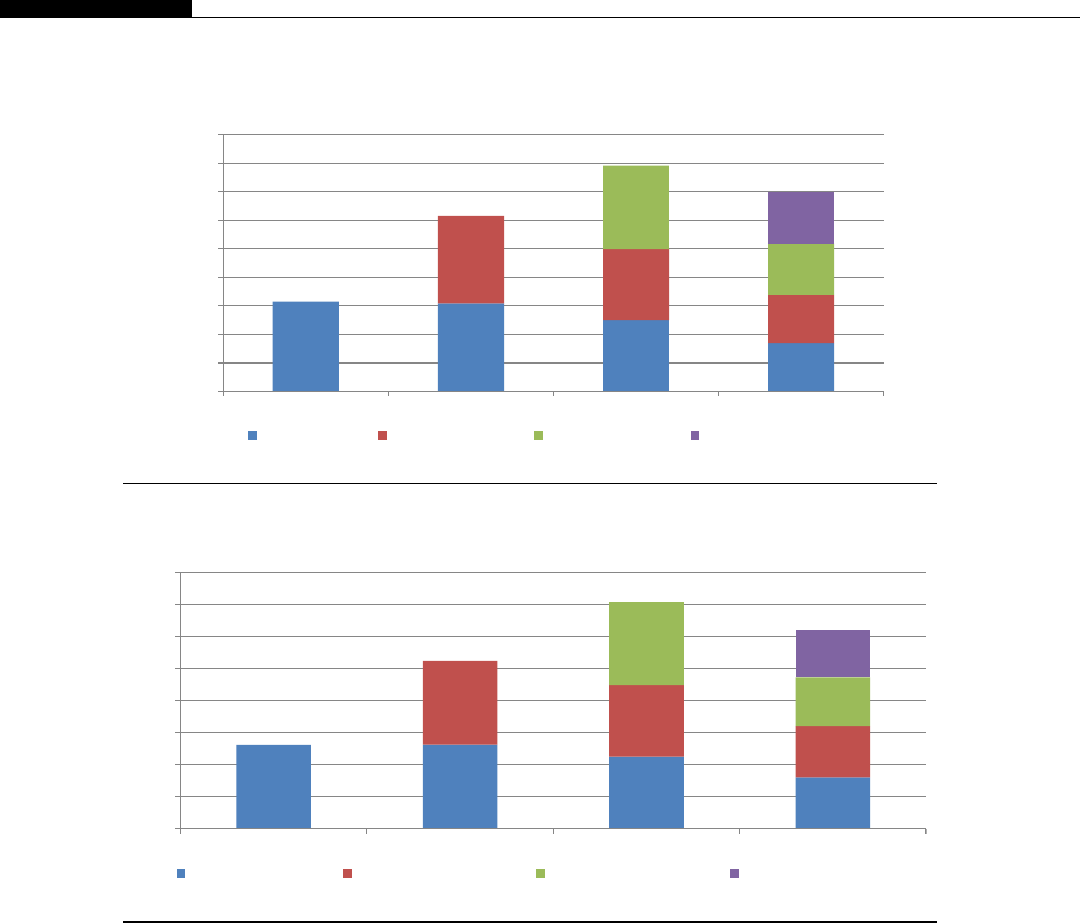

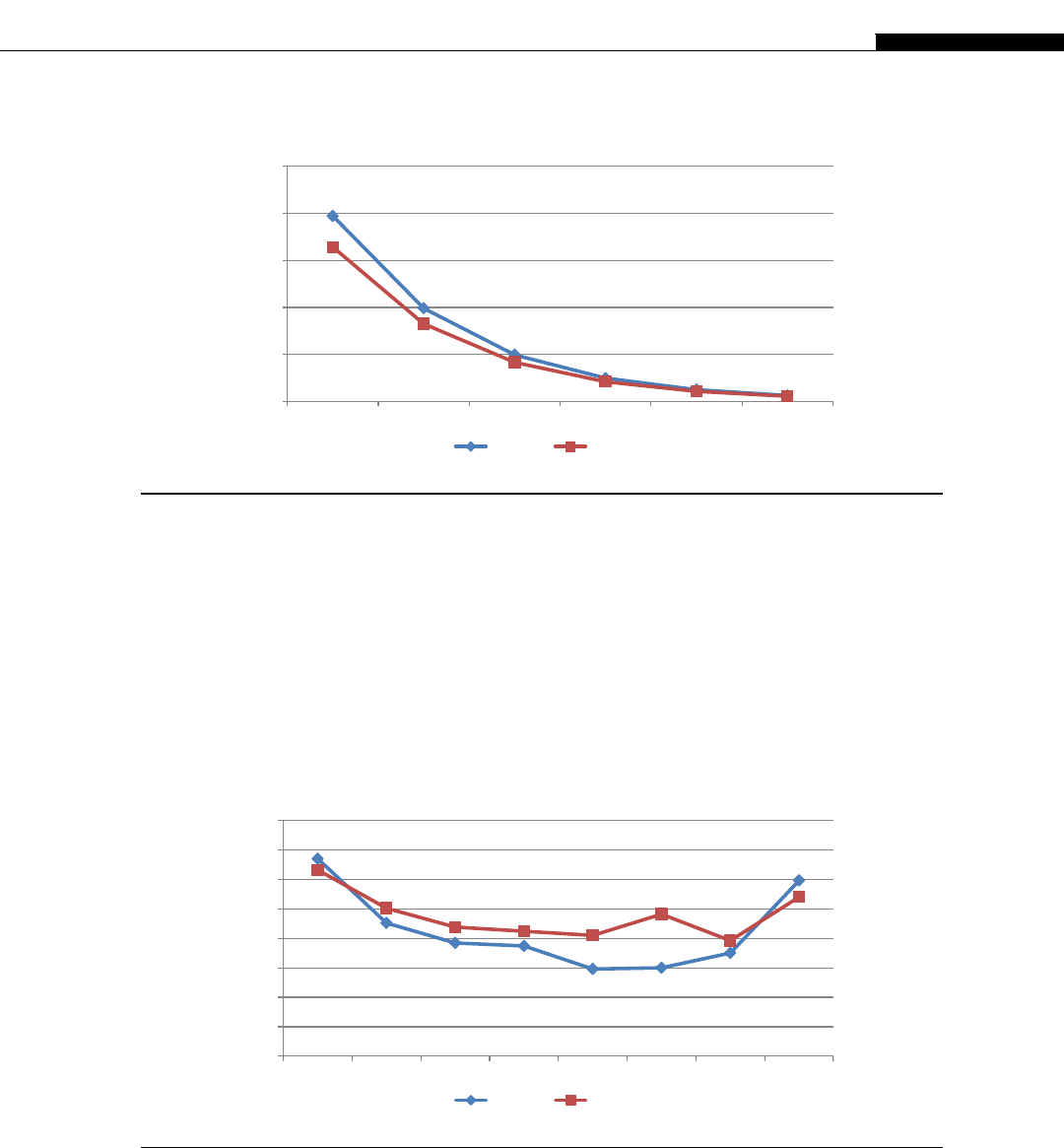

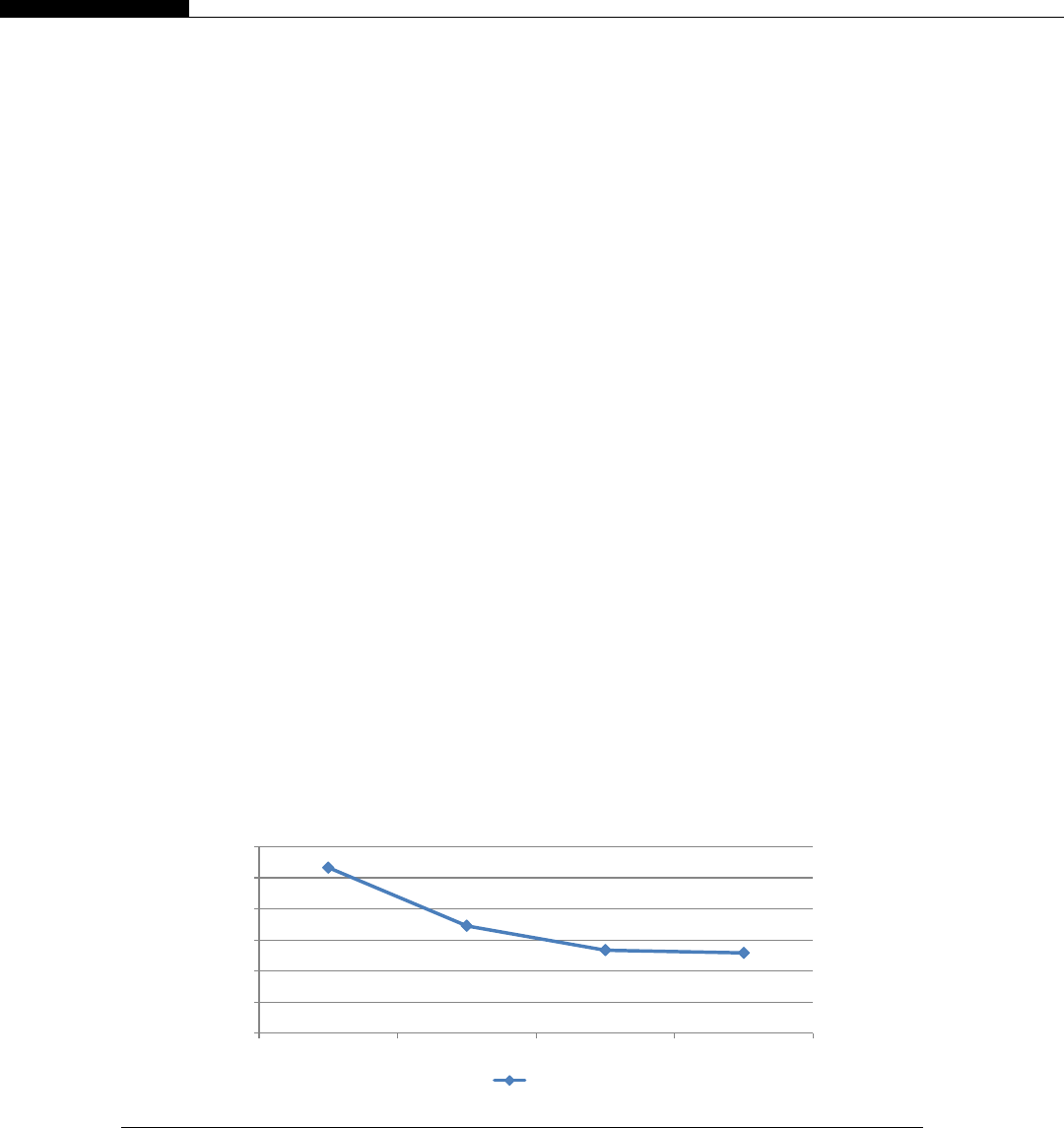

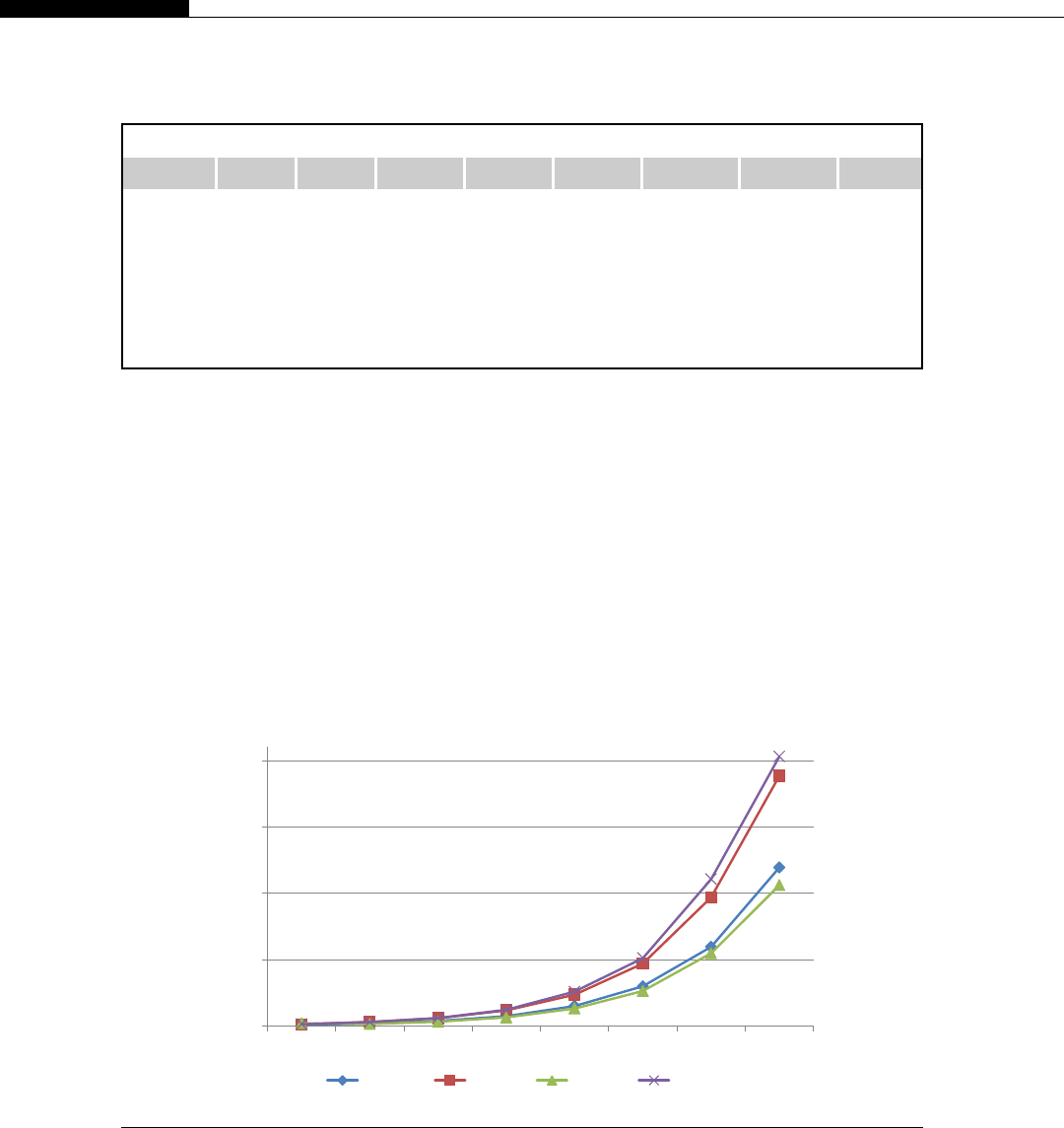

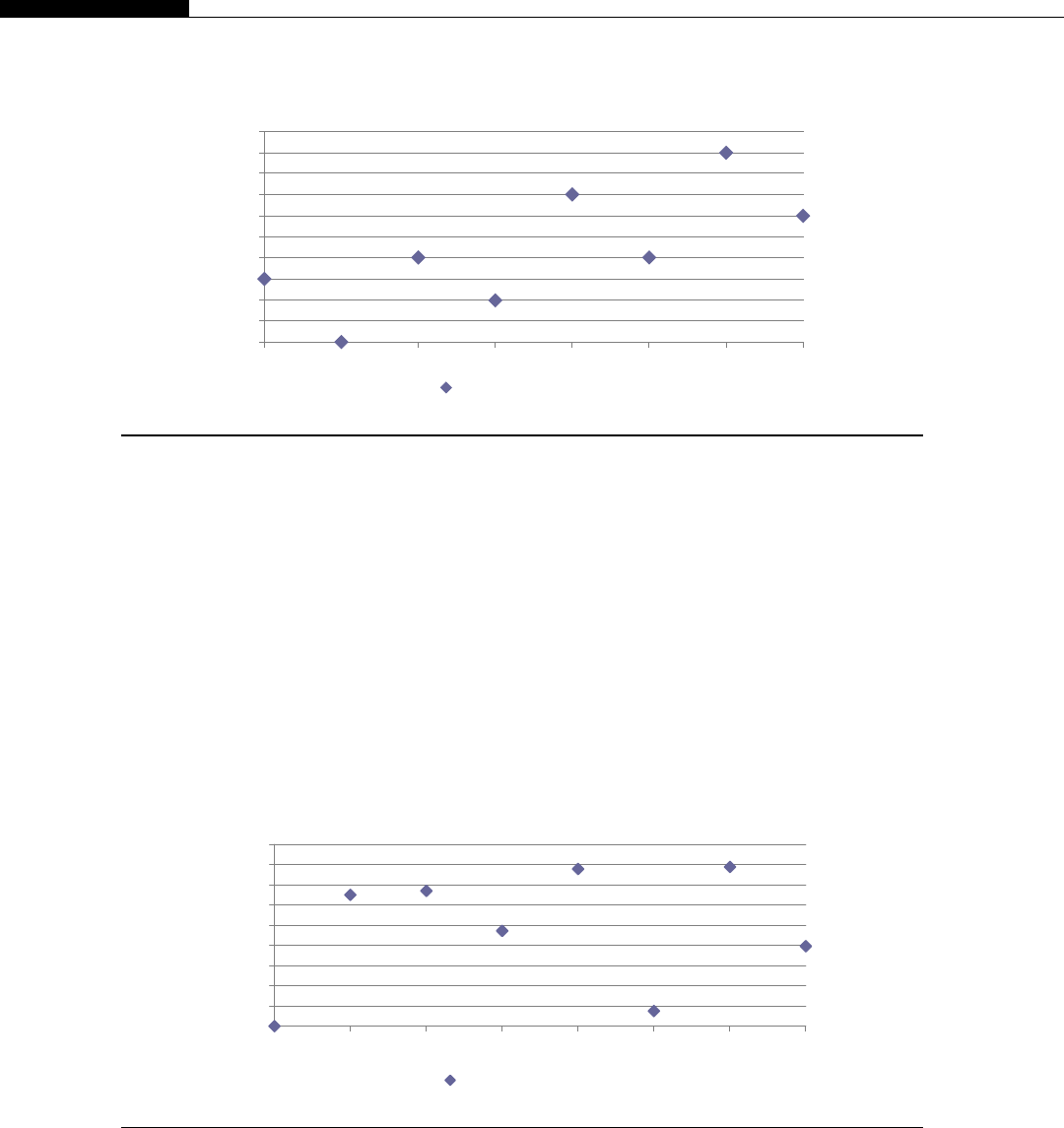

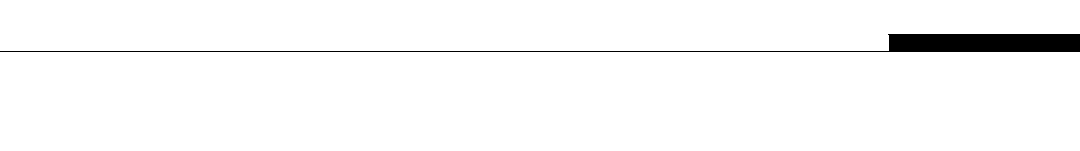

If you look at the relative computational power in GPUs and CPUs, we get an interesting graph

(Figure 1.8). We start to see a divergence of CPU and GPU computational power until 2009 when we

see the GPU finally break the 1000 gigaflops or 1 teraflop barrier. At this point we were moving from

the G80 hardware to the G200 and then in 2010 to the Fermi evolution. This is driven by the intro-

duction of massively parallel hardware. The G80 is a 128 CUDA core device, the G200 is a 256 CUDA

core device, and the Fermi is a 512 CUDA core device.

We see NVIDIA GPUs make a leap of 300 gigaflops from the G200 architecture to the Fermi

architecture, nearly a 30% improvement in throughput. By comparison, Intel’s leap from their core 2

architecture to the Nehalem architecture sees only a minor improvement. Only with the change to

Sandy Bridge architecture do we see significant leaps in CPU performance. This is not to say one is

better than the other, for the traditional CPUs are aimed at serial code execution and are extremely

good at it. They contain special hardware such as branch prediction units, multiple caches, etc., all of

which target serial code execution. The GPUs are not designed for this serial execution flow and only