VU User’s Manual Users

User Manual: Pdf

Open the PDF directly: View PDF ![]() .

.

Page Count: 368 [warning: Documents this large are best viewed by clicking the View PDF Link!]

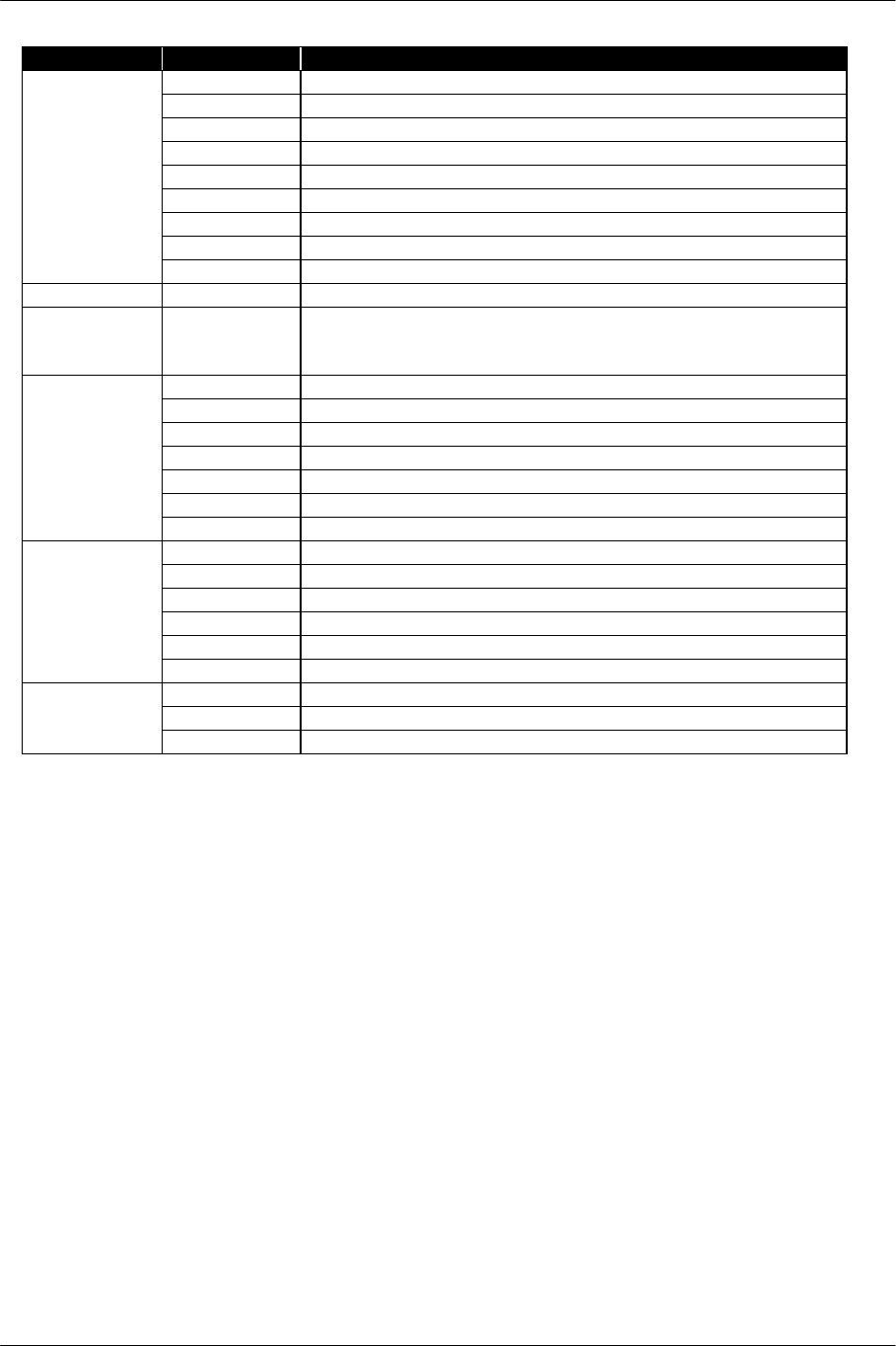

- VU USER'S MANUAL

- About This Manual

- Changes Since Release of 5th Edition

- VU Overview

- Data/Calculation Basic Specifications

- Micro Mode

- Micro Mode Instruction Reference

- Micro Mode Instruction Set

- Upper Instruction Reference

- ABS : Absolute Value

- ADD : Add

- ADDi : Add to I Register

- ADDq : Add to Q Register

- ADDbc : Broadcast Add

- ADDA : Add; to Accumulator

- ADDAi : Add I Register; to Accumulator

- ADDAq : Add Q Register; to Accumulator

- ADDAbc : Broadcast Add; to Accumulator

- CLIP : Clipping Judgment

- FTOI0 : Convert to Fixed Point

- FTOI4 : Convert to Fixed Point

- FTOI12 : Convert to Fixed Point

- FTOI15 : Convert to Fixed Point

- ITOF0 : Convert to Floating-Point Number

- ITOF4 : Convert to Floating-Point Number

- ITOF12 : Convert to Floating-Point Number

- ITOF15 : Convert to Floating-Point Number

- MADD : Product Sum

- MADDi : Product Sum; with I Register

- MADDq : Product Sum; by Q Register

- MADDbc : Broadcast Product Sum

- MADDA : Product Sum; to Accumulator

- MADDAi : Product Sum; by I register, to Accumulator

- MADDAq : Product Sum; by Q Register, to Accumulator

- MADDAbc : Broadcast Product Sum; to Accumulator

- MAX : Maximum Value

- MAXi : Maximum Value

- MAXbc : Maximum Value

- MINI : Minimum Value

- MINIi : Minimum Value

- MINIbc : Minimum Value

- MSUB : Multiply and Subtract

- MSUBi : Multiply and Subtract; with I Register

- MSUBq : Multiply and Subtract; by Q Register

- MSUBbc : Broadcast Multiply and Subtract

- MSUBA : Multiply and Subtract; to Accumulator

- MSUBAi : Multiply and Subtract; with I Register, to Accumulator

- MSUBAq : Multiply and Subtract; by Q Register, to Accumulator

- MSUBAbc : Broadcast Multiply and Subtract; to Accumulator

- MUL : Multiply

- MULi : Multiply by I Register

- MULq : Multiply by Q Register

- MULbc : Multiply by Broadcast

- MULA : Multiply; to Accumulator

- MULAi : Multiply by I Register, to Accumulator

- MULAq : Multiply by Q Register, to Accumulator

- MULAbc : Broadcast Multiply by broadcast, to Accumulator

- NOP : No Operation

- OPMULA : Vector Outer Product

- OPMSUB : Vector Outer Product

- SUB : Subtract

- SUBi : Subtract I Register

- SUBq : Subtract Q Register

- SUBbc : Broadcast Subtract

- SUBA : Substract; to Accumulator

- SUBAi : Subtract I Register; to Accumulator

- SUBAq : Subtract Q Register; to Accumulator

- SUBAbc : Broadcast Subtract; to Accumulator

- Lower Instruction Reference

- B : Unconditional Branch

- BAL : Unconditional Branch with Saving Address

- DIV : Divide

- EATAN : Arctangent

- EATANxy : Arctangent

- EATANxz : Arctangent

- EEXP : Exponent

- ELENG : Length

- ERCPR : Reciprocal Number

- ERLENG : Reciprocal Number of Length

- ERSADD : Reciprocal Number

- ERSQRT : Reciprocal Number of Square Root

- ESADD : Sum of Square Numbers

- ESIN : Sine

- ESQRT : Square Root

- ESUM : Sum of Each Field

- FCAND : Test Clipping Flag

- FCEQ : Test Clipping Flag

- FCGET : Get Clipping Flag

- FCOR : Test Clipping Flag

- FCSET : Setting Clipping Flag

- FMAND : Test MAC Flag Check

- FMEQ : Test MAC Flag Check

- FMOR : Test MAC Flag Check

- FSAND : Test Status Flag Check

- FSEQ : Test Status Flag Check

- FSOR : Test Status Flag

- FSSET : Set Sticky Flags

- IADD : ADD Integer

- IADDI : Add Immediate Value Integer

- IADDIU : Add Immediate Integer

- IAND : Logical Product

- IBEQ : Conditional Branch

- IBGEZ : Conditional Branch

- IBGTZ : Conditional Branch

- IBLEZ : Conditional Branch

- IBLTZ : Conditional Branch

- IBNE : Conditional Branch

- ILW : Integer Load with Offset Specification

- ILWR : Integer Load

- IOR : Logical Sum

- ISUB : Integer Subtract

- ISUBIU : Immediate Value Integer Subtract

- ISW : Integer Store with Offset

- ISWR : Integer Store

- JALR : Unconditional Jump with Address Saving

- JR : Unconditional Jump

- LQ : Load Qword

- LQD : Load Qword with Pre-Decrement

- LQI : Load with Post-Increment

- MFIR : Move from Integer Register to Floating-Point Register

- MFP : Move from P Register to Floating-Point Register

- MOVE : Transfer between Floating-Point Registers

- MR32 : Move with Rotate

- MTIR : Move from Floating-Point Register to Integer Register

- RGET : Get Random Number

- RINIT : Random Number Intialize

- RNEXT : Next Random Number

- RSQRT : Square Root Division

- RXOR : Random Number Set

- SQ : Store Qword with Offset

- SQD : Store Qword with Pre-Decrement

- SQI : Store with Post-Increment

- SQRT : Square Root

- WAITP : P Register Syncronize

- WAITQ : Q Register Syncronize

- XGKICK : GIF Control

- XITOP : VIF Control

- XTOP : VIF Control

- Macro Mode

- Macro Mode Instruction Reference

- Macro Instruction Operation Code

- Macro Instruction Set

- BC2F : Branch on COP2 Conditional Signal

- BC2FL : Branch on COP2 Conditional Signal

- BC2T : Branch on COP2 Conditional Signal

- BC2TL : Branch on COP2 Conditional signal

- CFC2 : Transfer Integer Data from VU to EE Core

- CTC2 : Transfer Integer Data from EE Core to VU

- LQC2 : Floating-Point Data Transfer from EE Core to VU

- QMFC2 : Floating-Point Data Transfer from VU to EE Core

- QMTC2 : Floating-Point Data Transfer from EE Core to VU

- SQC2 : Floating-Point Data Transfer from VU to EE Core

- VABS : Absolute Value

- VADD : Add

- VADDi : Add to I Register

- VADDq : Add to Q Register

- VADDbc : Broadcast Add

- VADDA : Add to Accumulator

- VADDAi : Add I Register to Accumulator

- VADDAq : Add Q Register to Accumulator

- VADDAbc : Broadcast Add to Accumulator

- VCALLMS : Start Micro Sub-Routine

- VCALLMSR : Start Micro Sub-Routine by Register

- VCLIP : Clipping Judgment

- VDIV : Divide

- VFTOI0 : Conversion to Fixed Point

- VFTOI4 : Conversion to Fixed Point

- VFTOI12 : Conversion to Fixed Point

- VFTOI15 : Conversion to Fixed Point

- VIADD : Add Integer

- VIADDI : Add Immediate Value Integer

- VIAND : Logical Product

- VILWR : Integer Load

- VIOR : Logical Sum

- VISUB : Integer Subtract

- VISWR : Integer Store

- VITOF0 : Conversion to Floating-Point Number

- VITOF4 : Conversion to Floating-Point Number

- VITOF12 : Conversion to Floating-Point Number

- VITOF15 : Conversion to Floating-Point Number

- VLQD : Load with Pre-Decrement

- VLQI : Load with Post-Increment

- VMADD : Product Sum

- VMADDi : Product Sum; with I Register

- VMADDq : Product Sum; with Q Register

- VMADDbc : Broadcast Product Sum

- VMADDA : Product Sum; to Accumulator

- VMADDAi : Product Sum; with I Register, to Accumulator

- VMADDAq : Product Sum; with Q Register, to Accumulator

- VMADDAbc : Broadcast Product Sum; to Accumulator

- VMAX : Maximum Value

- VMAXi : Maximum Value

- VMAXbc : Maximum Value

- VMFIR : Transfer from Integer Register to Floating-Point Register

- VMINI : Minimum Value

- VMINIi : Minimum Value

- VMINIbc : Minimum Value

- VMOVE : Transfer between Floating-Point Registers

- VMR32 : Vector Rotate

- VMSUB : Multiply and Subtract

- VMSUBi : Multiply and Subtract with I Register

- VMSUBq : Multiply and Subtract; Q Register

- VMSUBbc : Broadcast Multiply and Subtract

- VMSUBA : Multiply and Subtract; to Accumulator

- VMSUBAi : Multiply and Subtract; with I Register, to Accumulator

- VMSUBAq : Multiply and Subtract; with Q Register, to Accumulator

- VMSUBAbc : Broadcast Multiply and Subtract; to Accumulator

- VMTIR : Transfer from Floating-Point Register to Integer Register

- VMUL : Multiply

- VMULi : Multiply; by I Register

- VMULq : Multiply; by Q Register

- VMULbc : Broadcast Multiply

- VMULA : Multiply; to Accumulator

- VMULAi : Multiply by I Register; to Accumulator

- VMULAq : Multiply by Q Register; to Accumulator

- VMULAbc : Broadcast Multiply; to Accumulator

- VNOP : No Operation

- VOPMULA : Vector Outer Product

- VOPMSUB : Vector Outer Product

- VRGET : Get Random Numbers

- VRINIT : Random Number Initial Set

- VRNEXT : New Random Numbers

- VRSQRT : Square Root Division

- VRXOR : Random Number Set

- VSQD : Store with Pre-Decrement

- VSQI : Store with Post-Increment

- VSQRT : Square Root

- VSUB : Subtract

- VSUBi : Subtract I Register

- VSUBq : Subtract Q Register

- VSUBbc : Broadcast Subtract

- VSUBA : Subtract; to Accumulator

- VSUBAi : Subtract I Register; to Accumulator

- VSUBAq : Subtract Q Register; to Accumulator

- VSUBAbc : Broadcast Subtract; to Accumulator

- VWAITQ : Q Register Synchronize

- Appendix

VU User's Manual

Copyright © 2002 Sony Computer Entertainment Inc.

All Rights Reserved.

SCE Confidential

SCE CONFIDENTIAL VU User's Manual Version 6.0

© SCEI

-2-

© 2002 Sony Computer Entertainment Inc.

Publication date: April 2002

Sony Computer Entertainment Inc.

1-1, Akasaka 7-chome, Minato-ku

Tokyo 107-0052 Japan

Sony Computer Entertainment America

919 East Hillsdale Blvd.

Foster City, CA 94404, U.S.A.

Sony Computer Entertainment Europe

30 Golden Square

London W1F 9LD, U.K.

The VU User’s Manual is supplied pursuant to and subject to the terms of the Sony Computer Entertainment

PlayStation® license agreements.

The VU User’s Manual is intended for distribution to and use by only Sony Computer Entertainment licensed

Developers and Publishers in accordance with the PlayStation® license agreements.

Unauthorized reproduction, distribution, lending, rental or disclosure to any third party, in whole or in part, of

this book is expressly prohibited by law and by the terms of the Sony Computer Entertainment PlayStation®

license agreements.

Ownership of the physical property of the book is retained by and reserved by Sony Computer Entertainment.

Alteration to or deletion, in whole or in part, of the book, its presentation, or its contents is prohibited.

The information in the VU User’s Manual is subject to change without notice. The content of this book is

Confidential Information of Sony Computer Entertainment.

® and PlayStation® are registered trademarks, and GRAPHICS SYNTHESIZERTM and

EMOTION ENGINETM are trademarks of Sony Computer Entertainment Inc. All other trademarks are property

of their respective owners and/or their licensors.

SCE CONFIDENTIAL VU User's Manual Version 6.0

© SCEI

-3-

About This Manual

The "VU User's Manual" describes the operational functions of the VPU (Vector Operation Unit) built into the

Emotion Engine. For information on data and microprogram transfers to the VPU, refer to the "EE User's

Manual".

- Chapter 1 "VU Overview" describes the configurations of the VPU and the VU (the core of the VPU), the

differences between the two VPUs (VPU0/VPU1) that are embedded, and the operation modes.

- Chapter 2 "Data/Calculation Basic Specifications" describes the numerical data formats used by the VU,

rounding-off operations in calculations, and exception specifications. Note that the description does not

fully conform to the requirements of the IEEE 754 standard.

- Chapter 3 "Micro Mode" describes the architecture and operation of micro mode, in which the VU operates

as a stand-alone processor.

- Chapter 4 "Micro Mode Instruction Reference" describes the individual micro mode instructions.

- Chapter 5 "Macro Mode" describes the architecture and operation of macro mode, in which VPU0 operates

as a coprocessor of the EE Core. This chapter also explains how to control VPU1 from the EE Core.

- Chapter 6 "Macro Mode Instruction Reference" describes the individual macro mode instructions.

- Chapter 7 "Appendix" gives other information, including sample micro programs.

Changes Since Release of 5th Edition

Since release of the 5th Edition of the VU User’s Manual, the following changes have been made.

Note that each of these changes is indicated by a revision bar in the margin of the affected page.

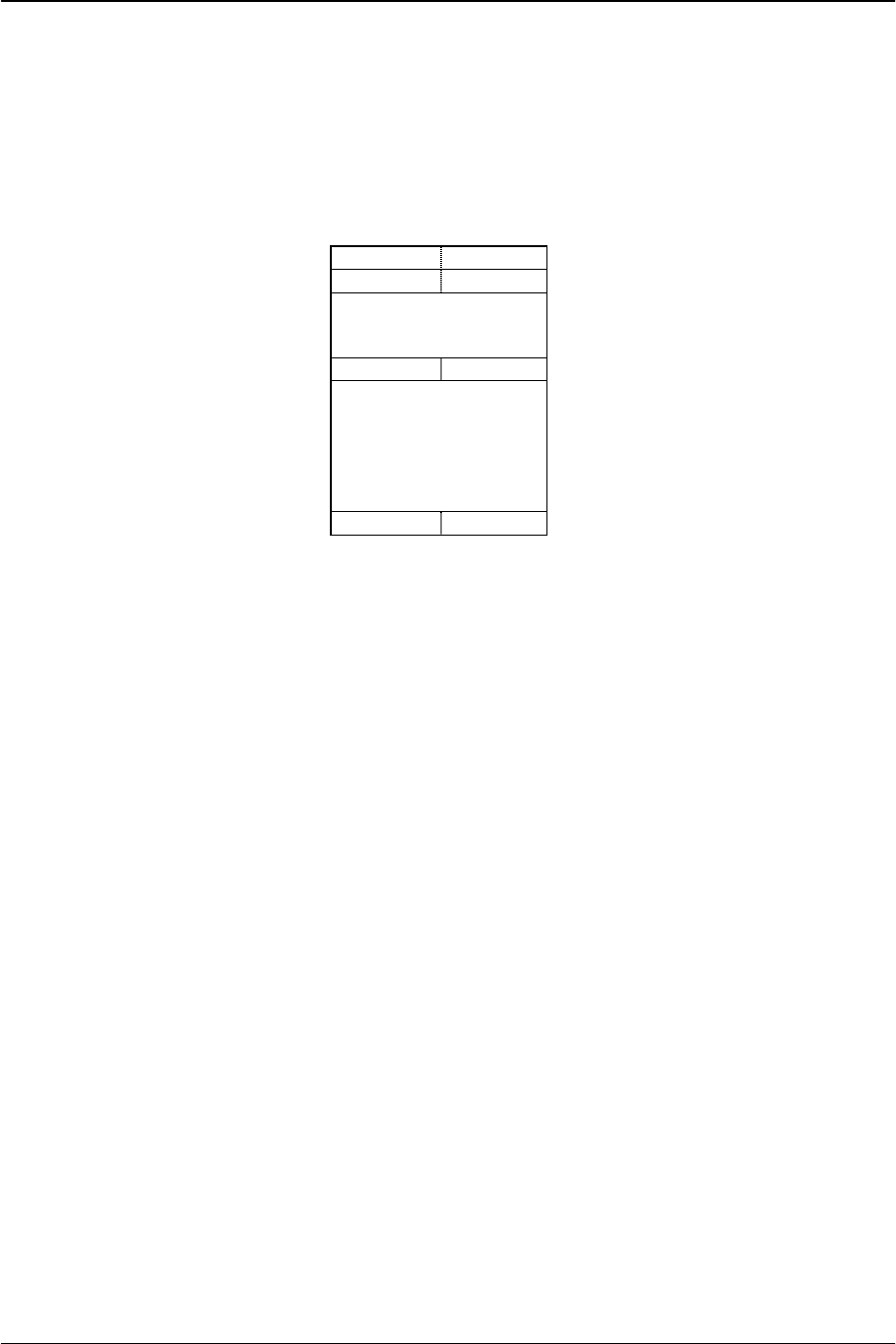

Ch. 1: VU Overview

• Information about the derivation of the M series polynomial was added to “RANDU” in section 1.1.2.

Lower Execution Unit, on page 17.

Ch. 3: Micro Mode

• A correction was made to the description following the figure in Section 3.4.9. XGKICK Pipeline, on

page 52.

Ch. 4: Micro Mode Instruction Reference

• A correction was made to the “Operation Code” figure in the EATANxz reference on page 134.

• A correction was made to “Example” in the IBGTZ reference on page 164.

• A correction was made to “Example” in the IBLEZ reference on page 165.

• A correction was made to “Example” in the IBLTZ reference on page 166.

• A correction was made to “Mnemonic” in the ISW reference on page 173.

• Information about the XGKIXK pipeline and XGKICK synchronization was added to “Remarks” in

the XGKICK reference on page 196.

• Information was added to “Operation” in the XITOP reference on page 197.

Ch. 6: Macro Mode Instruction Reference

• A correction was made to “Operation” in the QMTC2 reference on page 238.

SCE CONFIDENTIAL VU User's Manual Version 6.0

© SCEI

-4-

(This page is left blank intentionally)

SCE CONFIDENTIAL VU User's Manual Version 6.0

© SCEI

-5-

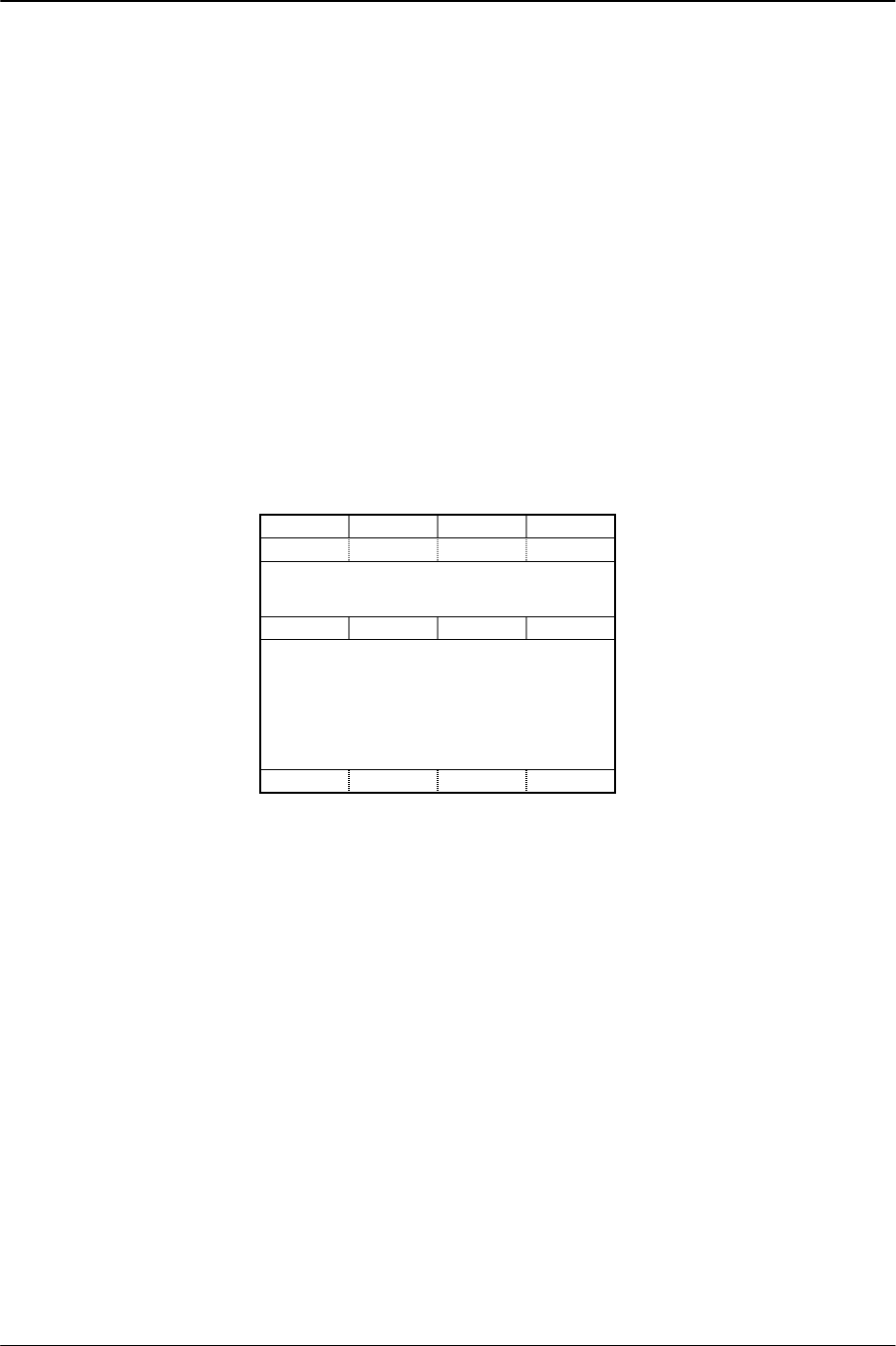

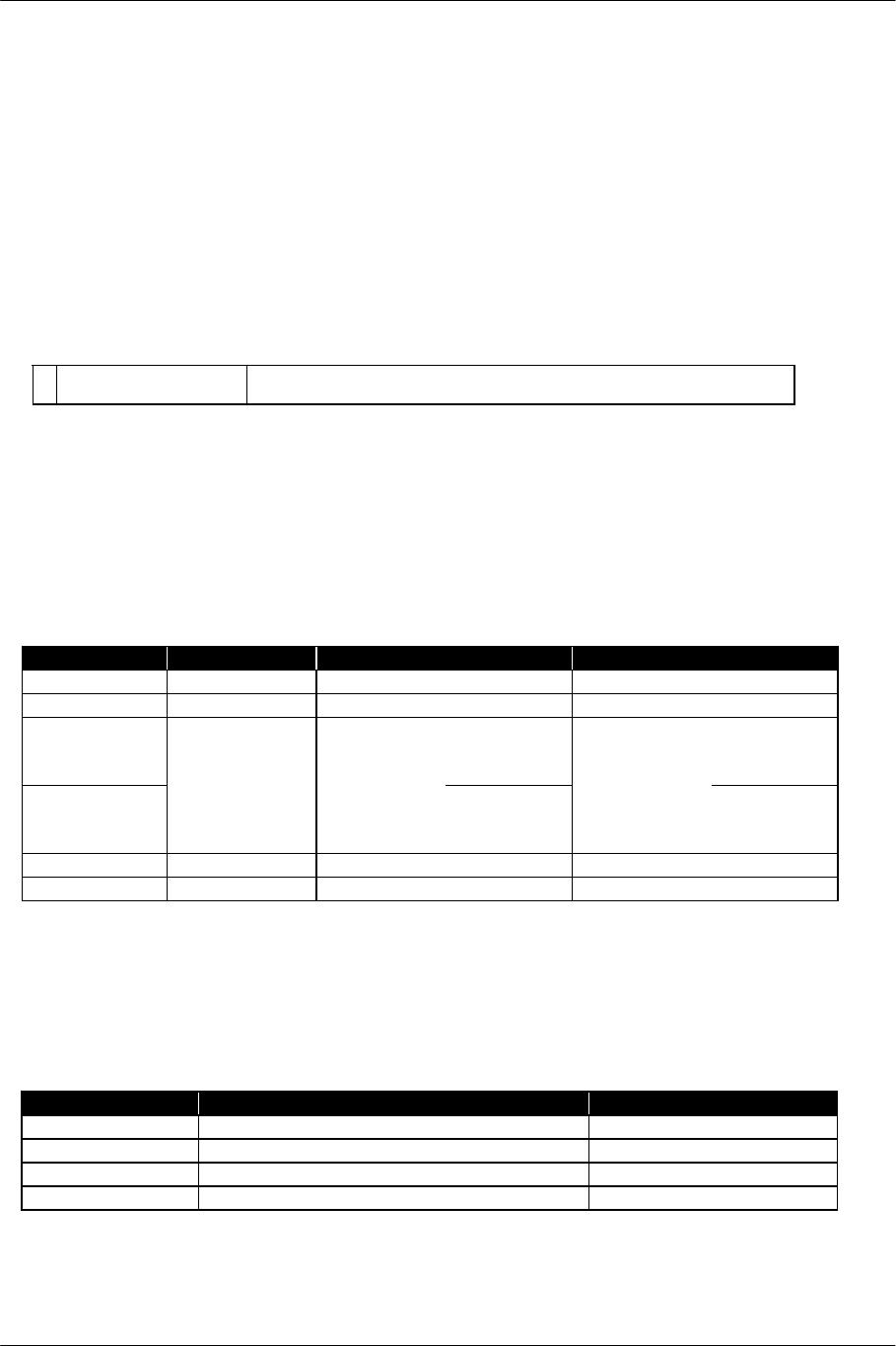

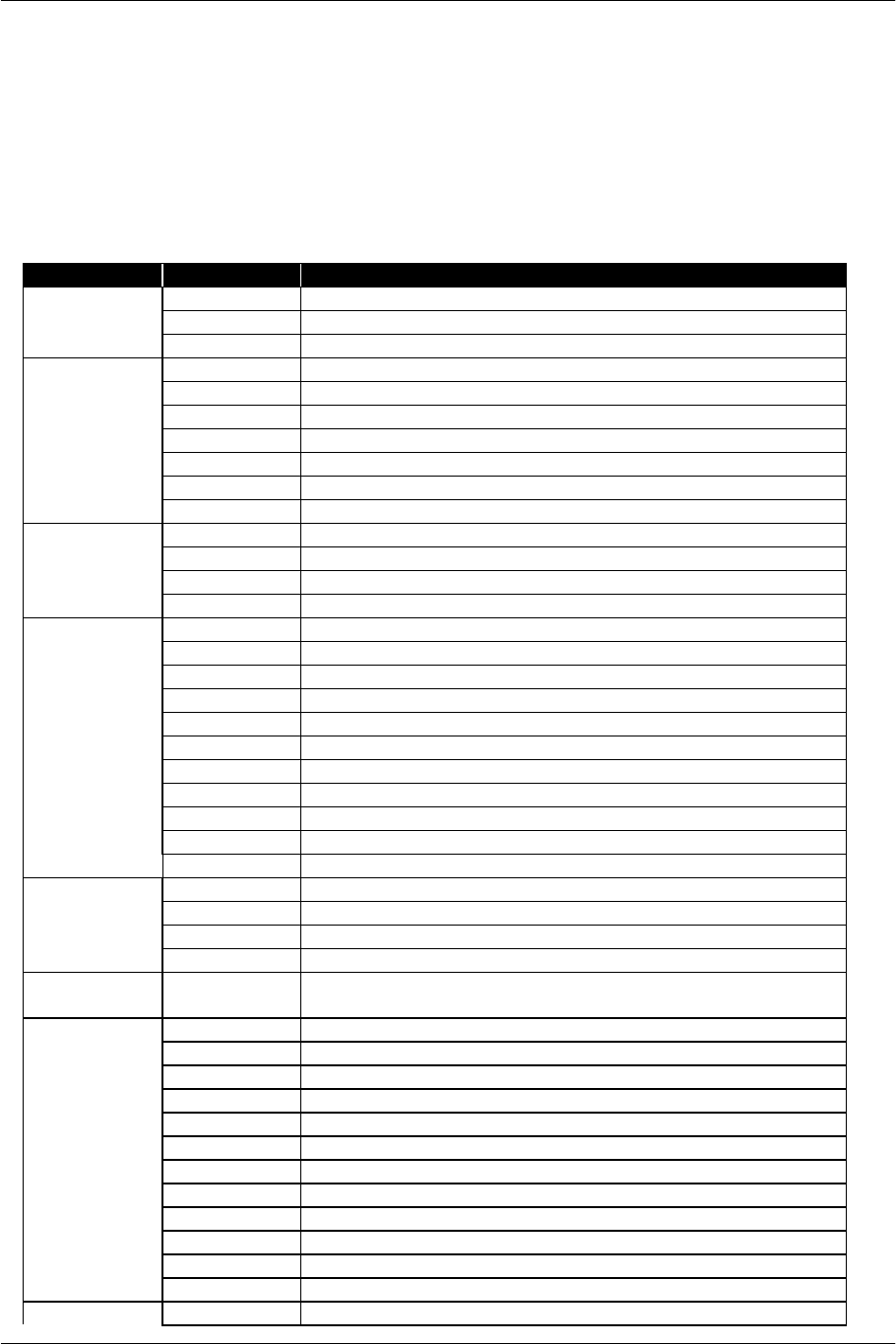

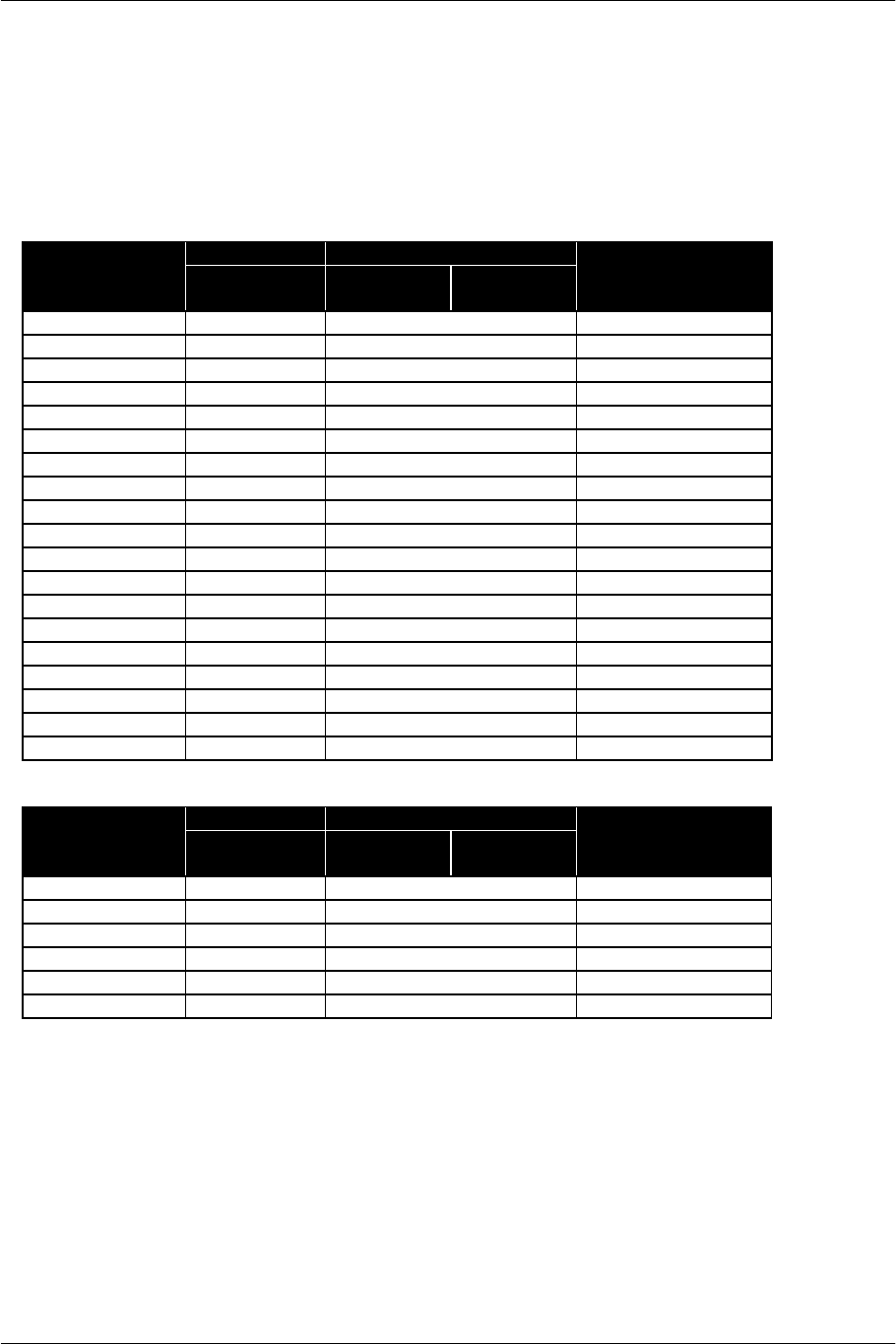

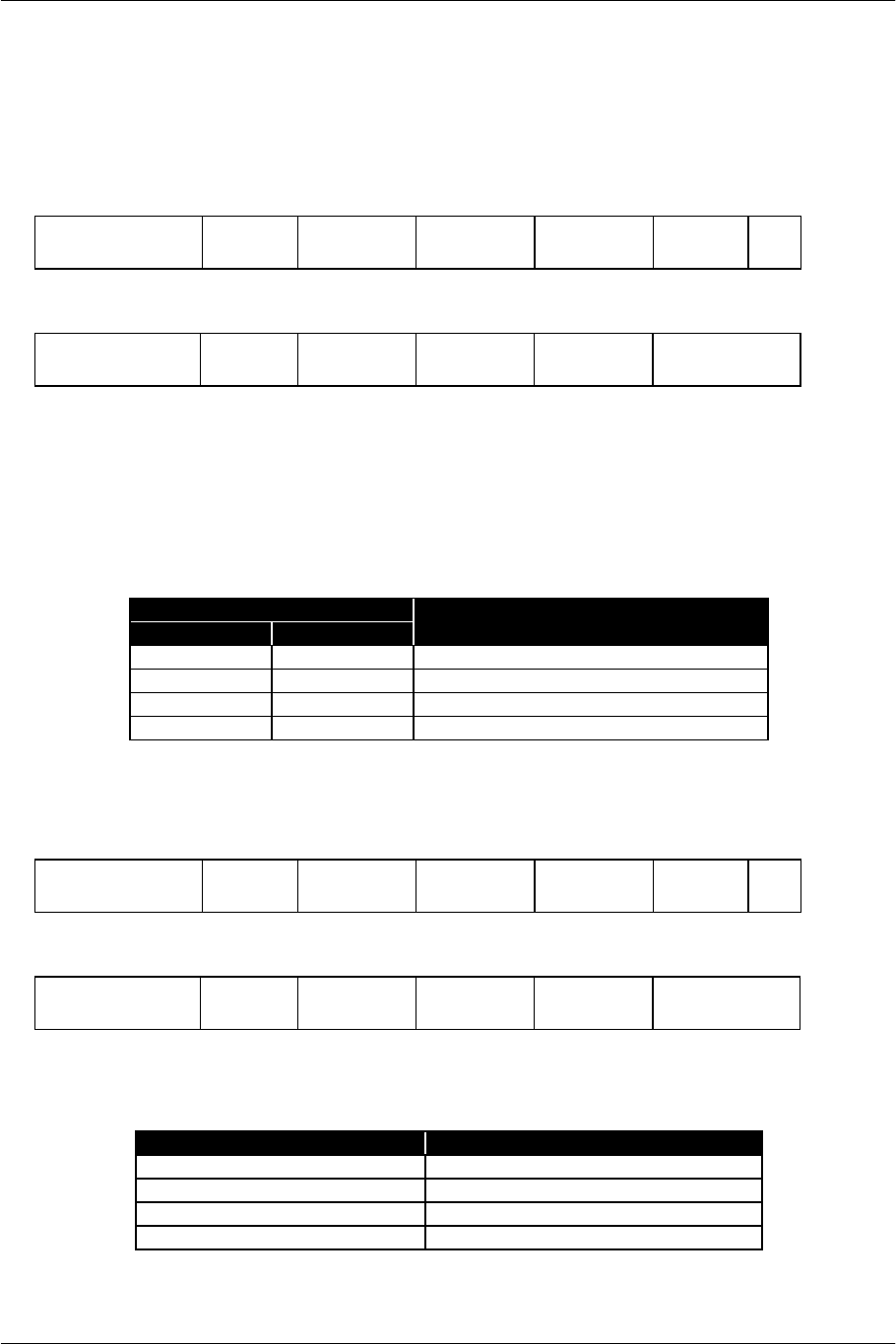

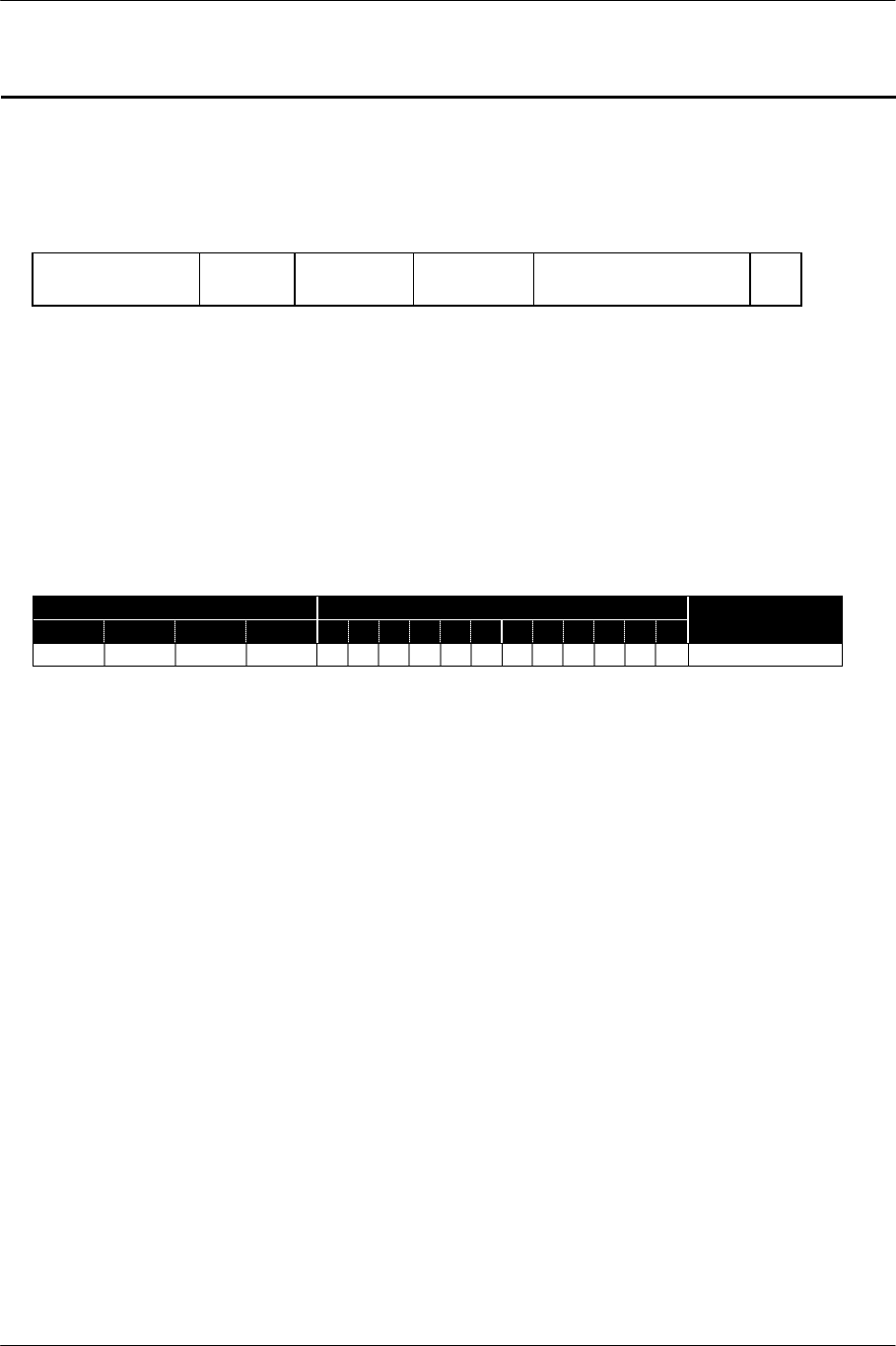

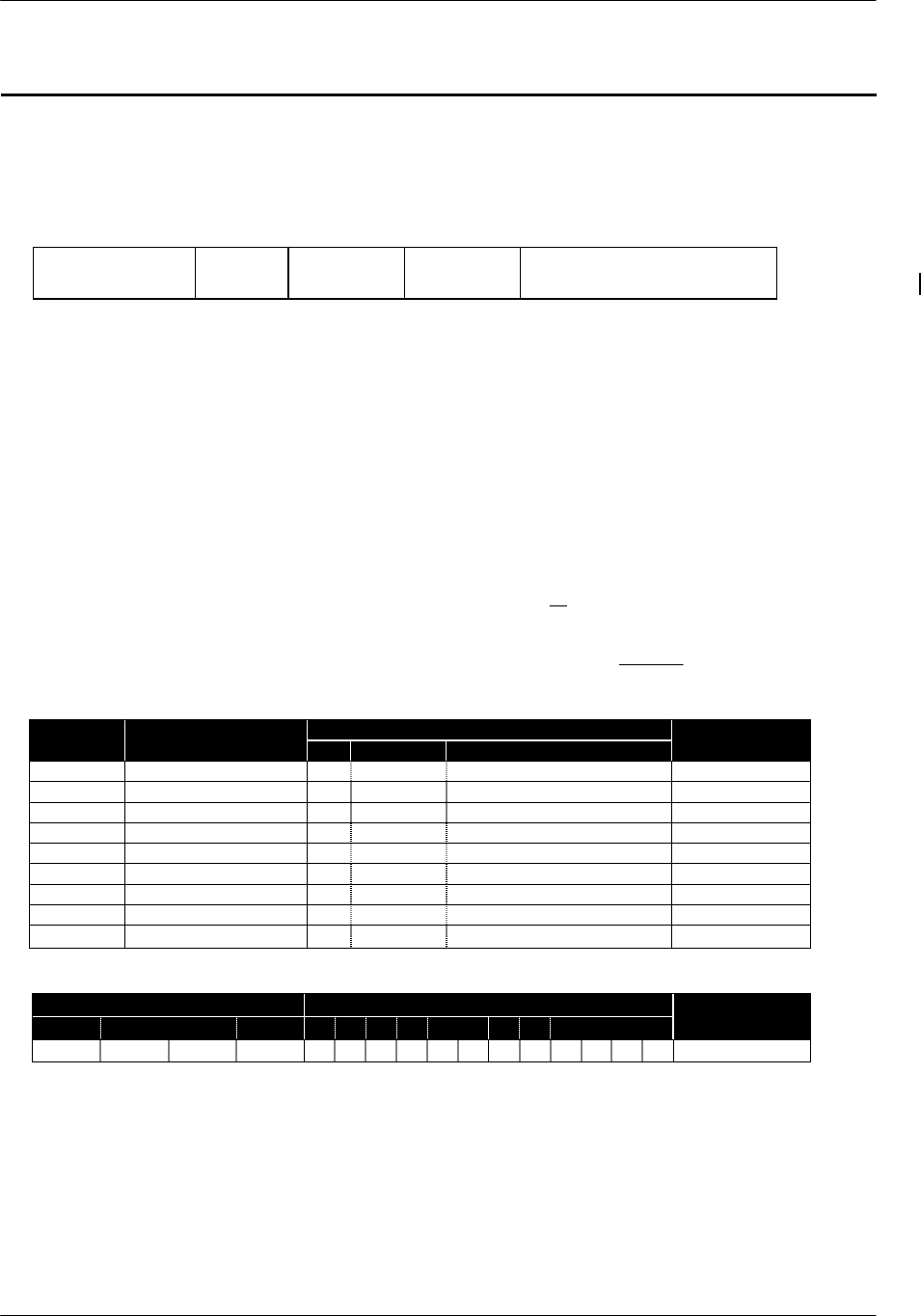

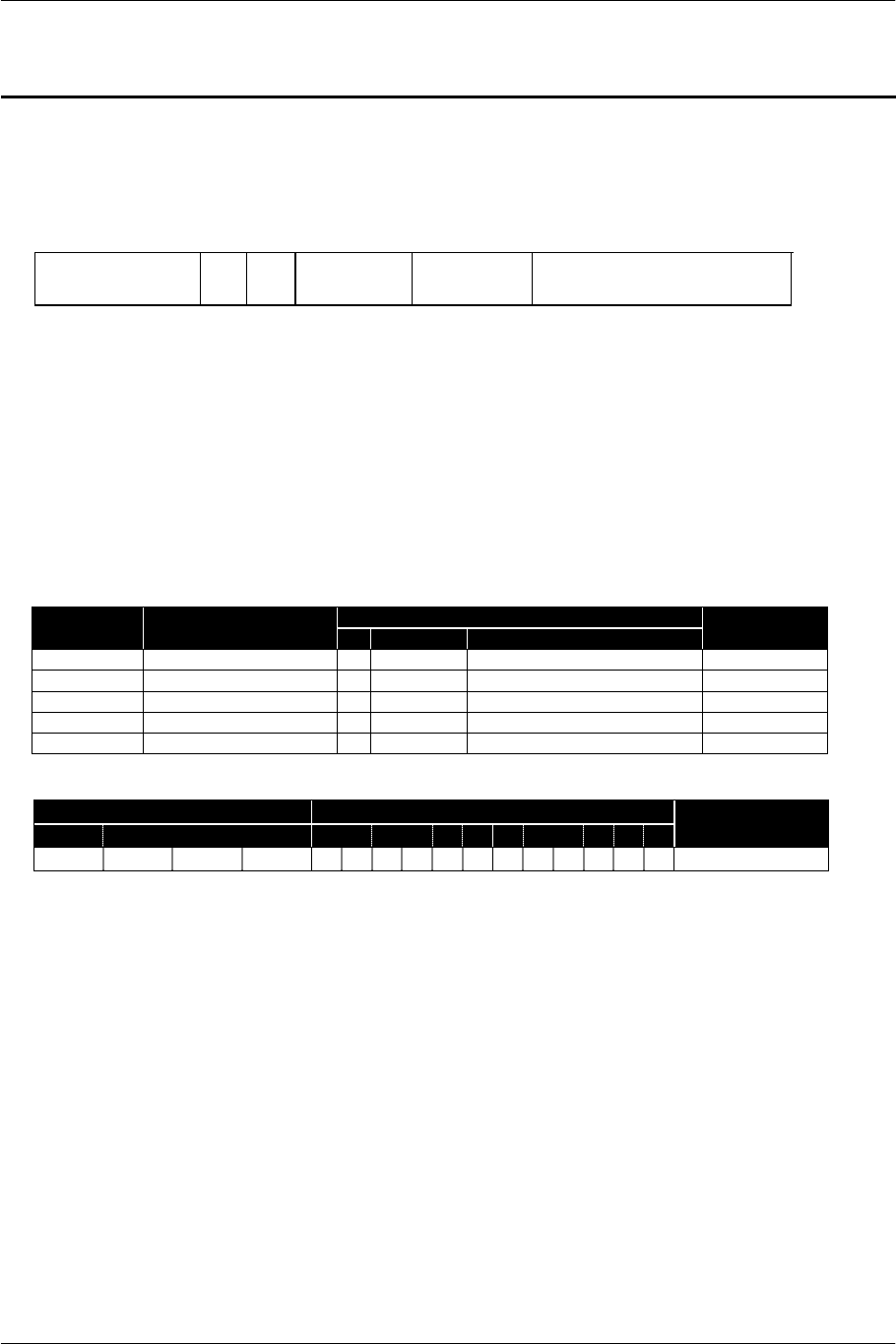

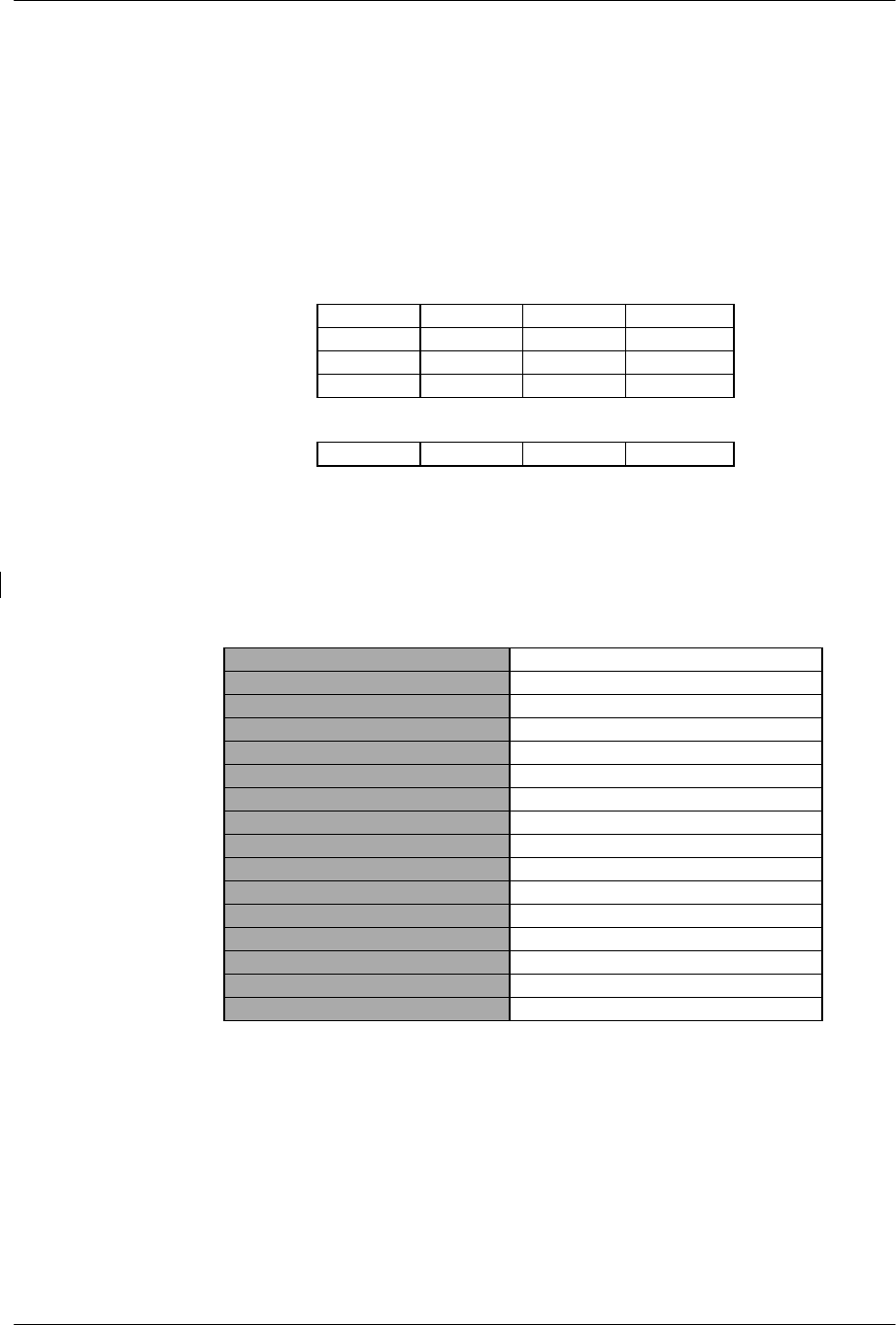

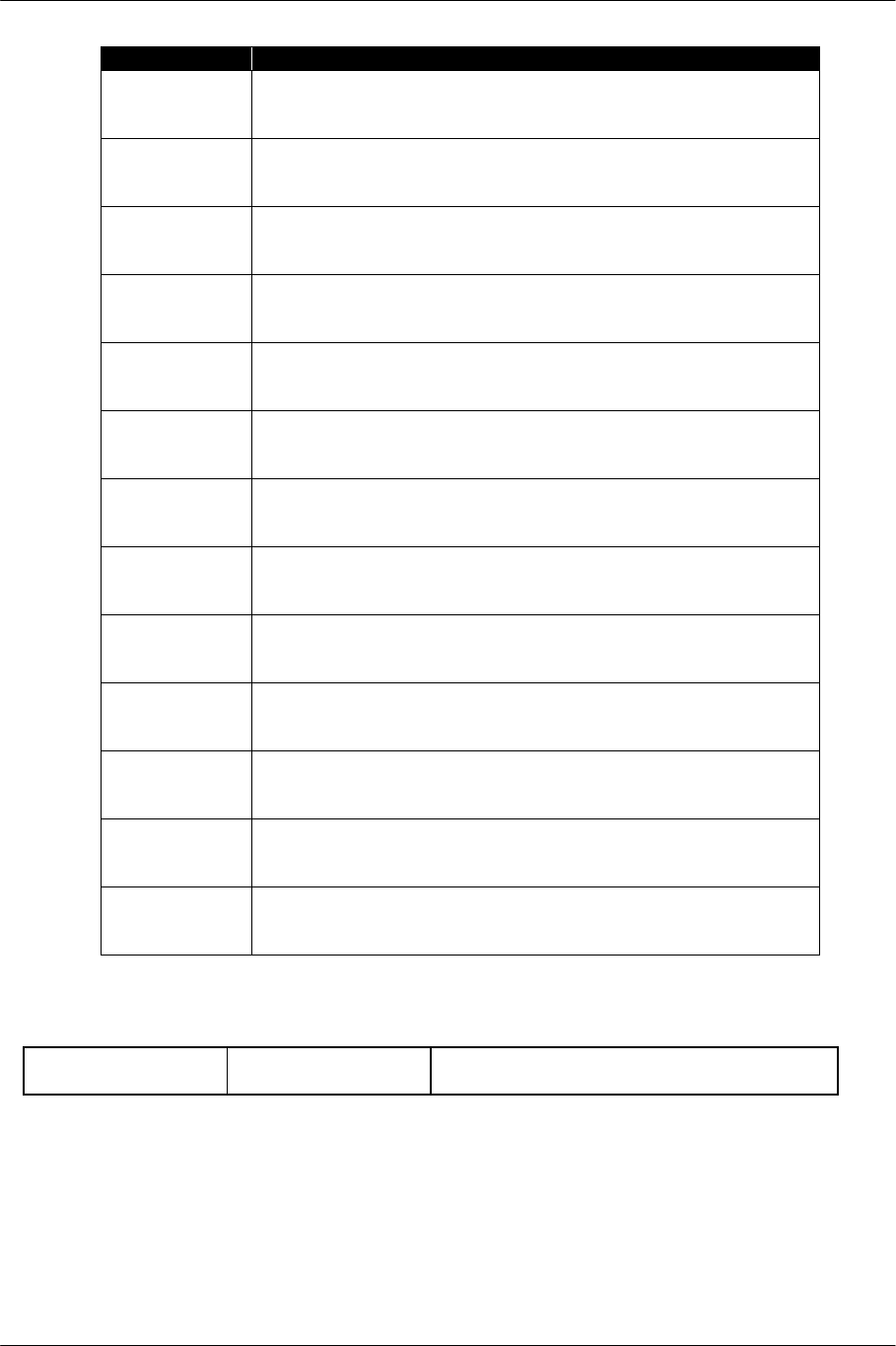

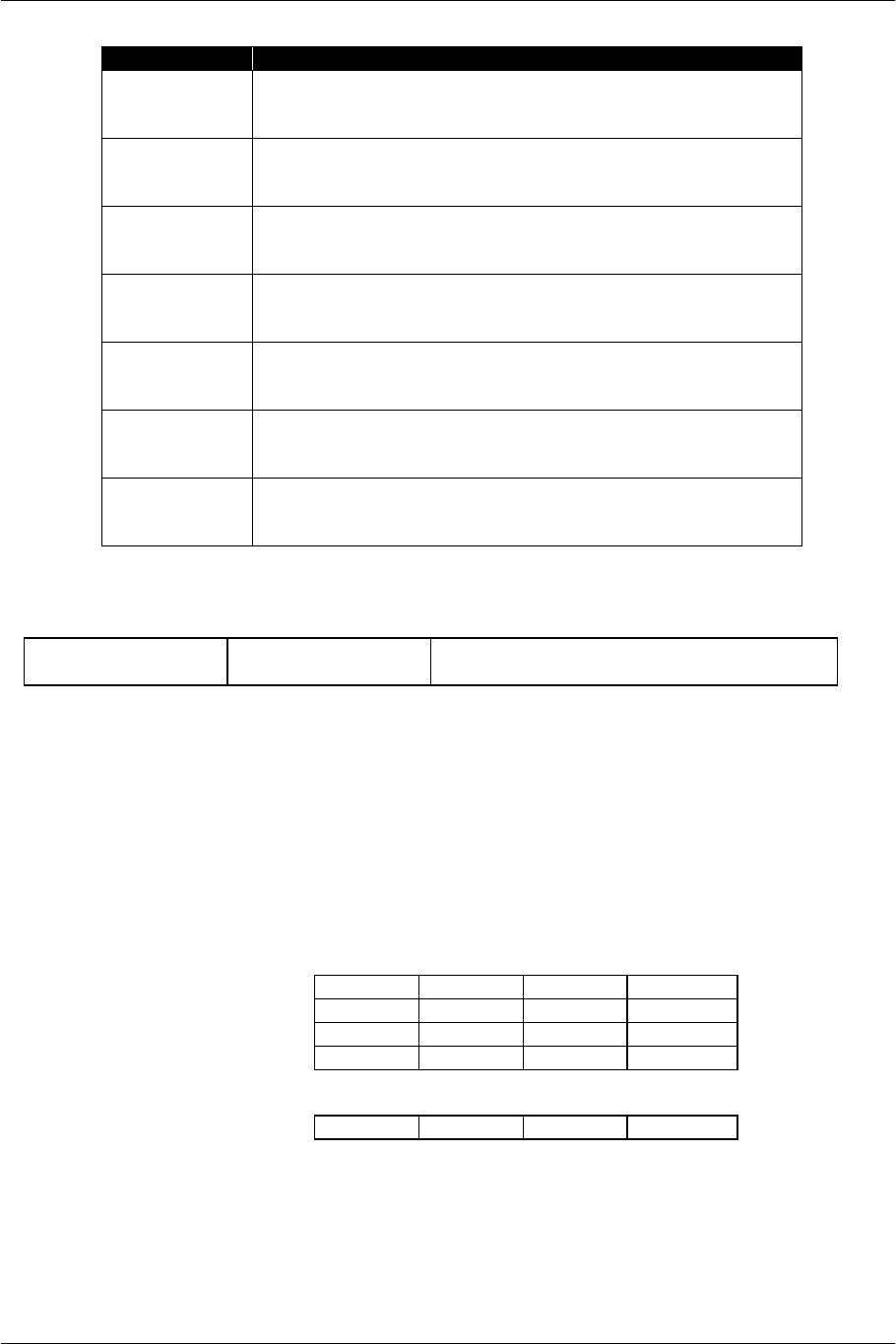

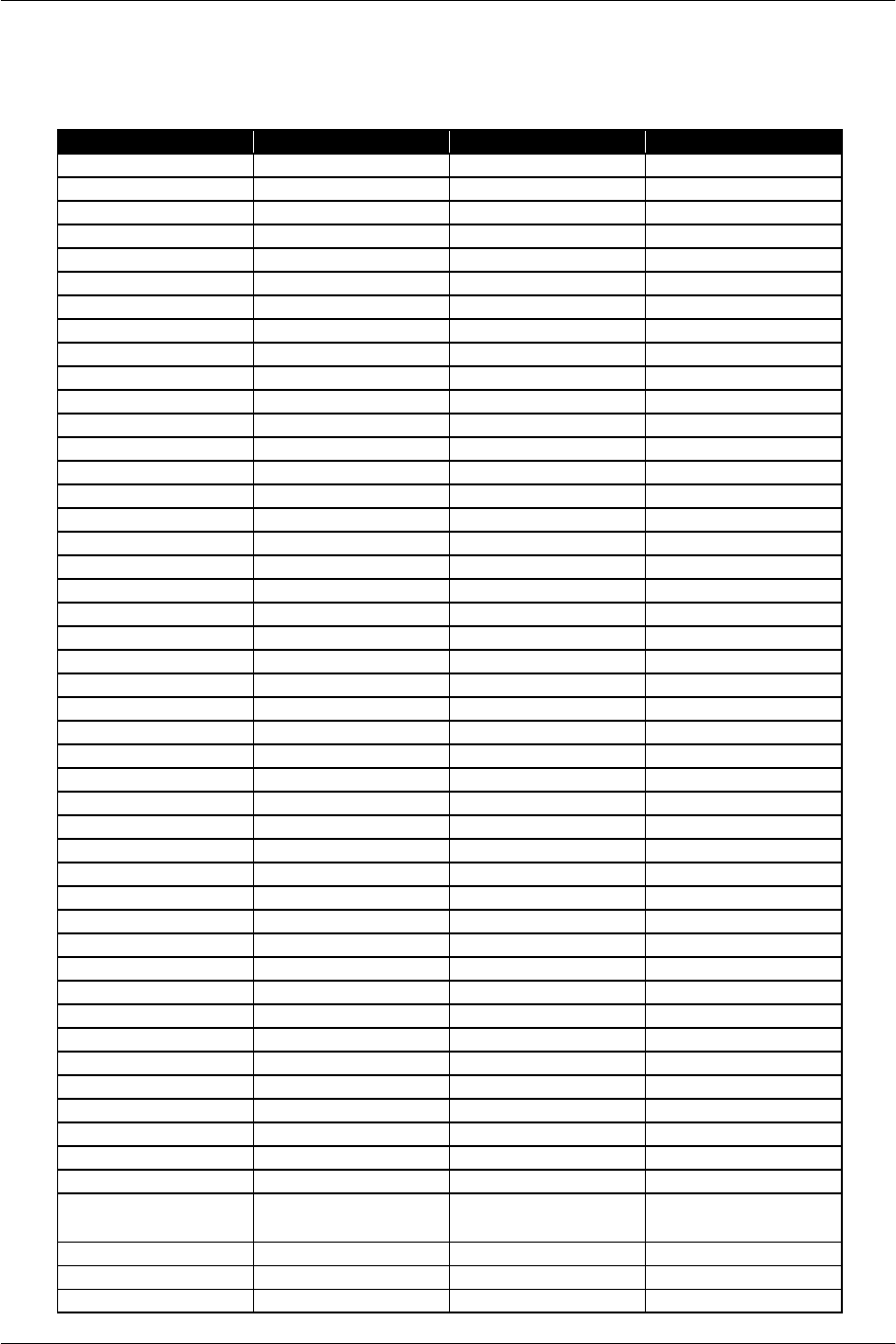

Glossary

Term Definition

EE Emotion Engine. CPU of the PlayStation 2.

EE Core Generalized computation and control unit of EE. Core of the CPU.

COP0 EE Core system control coprocessor.

COP1 EE Core floating-point operation coprocessor. Also referred to as FPU.

COP2 Vector operation unit coupled as a coprocessor of EE Core. VPU0.

GS Graphics Synthesizer.

Graphics processor connected to EE.

GIF EE Interface unit to GS.

IOP Processor connected to EE for controlling input/output devices.

SBUS Bus connecting EE to IOP.

VPU (VPU0/VPU1) Vector operation unit.

EE contains 2 VPUs: VPU0 and VPU1.

VU (VU0/VU1) VPU core operation unit.

VIF (VIF0/VIF1) VPU data decompression unit.

VIFcode Instruction code for VIF.

SPR Quick-access data memory built into EE Core (Scratchpad memory).

IPU EE Image processor unit.

word Unit of data length: 32 bits

qword Unit of data length: 128 bits

Slice Physical unit of DMA transfer: 8 qwords or less

Packet Data to be handled as a logical unit for transfer processing.

Transfer list A group of packets transferred in serial DMA transfer processing.

Tag Additional data indicating data size and other attributes of packets.

DMAtag Tag positioned first in DMA packet to indicate address/size of data and address

of the following packet.

GS primitive Data to indicate image elements such as point and triangle.

Context A set of drawing information (e.g. texture, distant fog color, and dither matrix)

applied to two or more primitives uniformly. Also referred to as the drawing

environment.

GIFtag Additional data to indicate attributes of GS primitives.

Display list A group of GS primitives to indicate batches of images.

SCE CONFIDENTIAL VU User's Manual Version 6.0

© SCEI

-6-

(This page is left blank intentionally)

SCE CONFIDENTIAL VU User's Manual Version 6.0

© SCEI

-7-

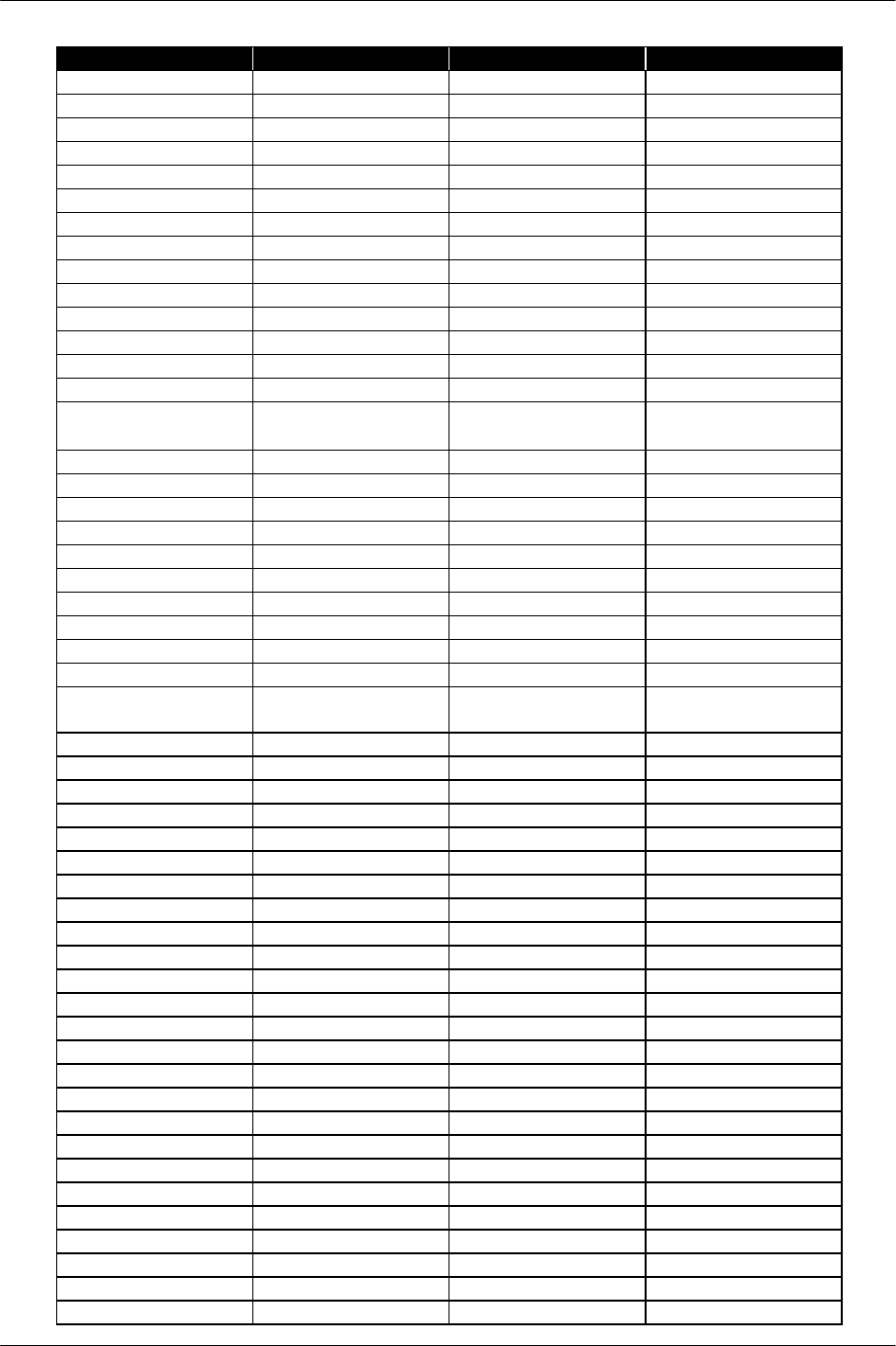

Contents

1. VU Overview .........................................................................................................................................................................15

1.1. VPU Structure ................................................................................................................................................................16

1.1.1. Upper Execution Unit ...........................................................................................................................................16

1.1.2. Lower Execution Unit ...........................................................................................................................................17

1.1.3. Floating-Point Registers ........................................................................................................................................18

1.1.4. Integer Register.......................................................................................................................................................18

1.1.5. VU Mem..................................................................................................................................................................18

1.1.6. Micro Mem..............................................................................................................................................................19

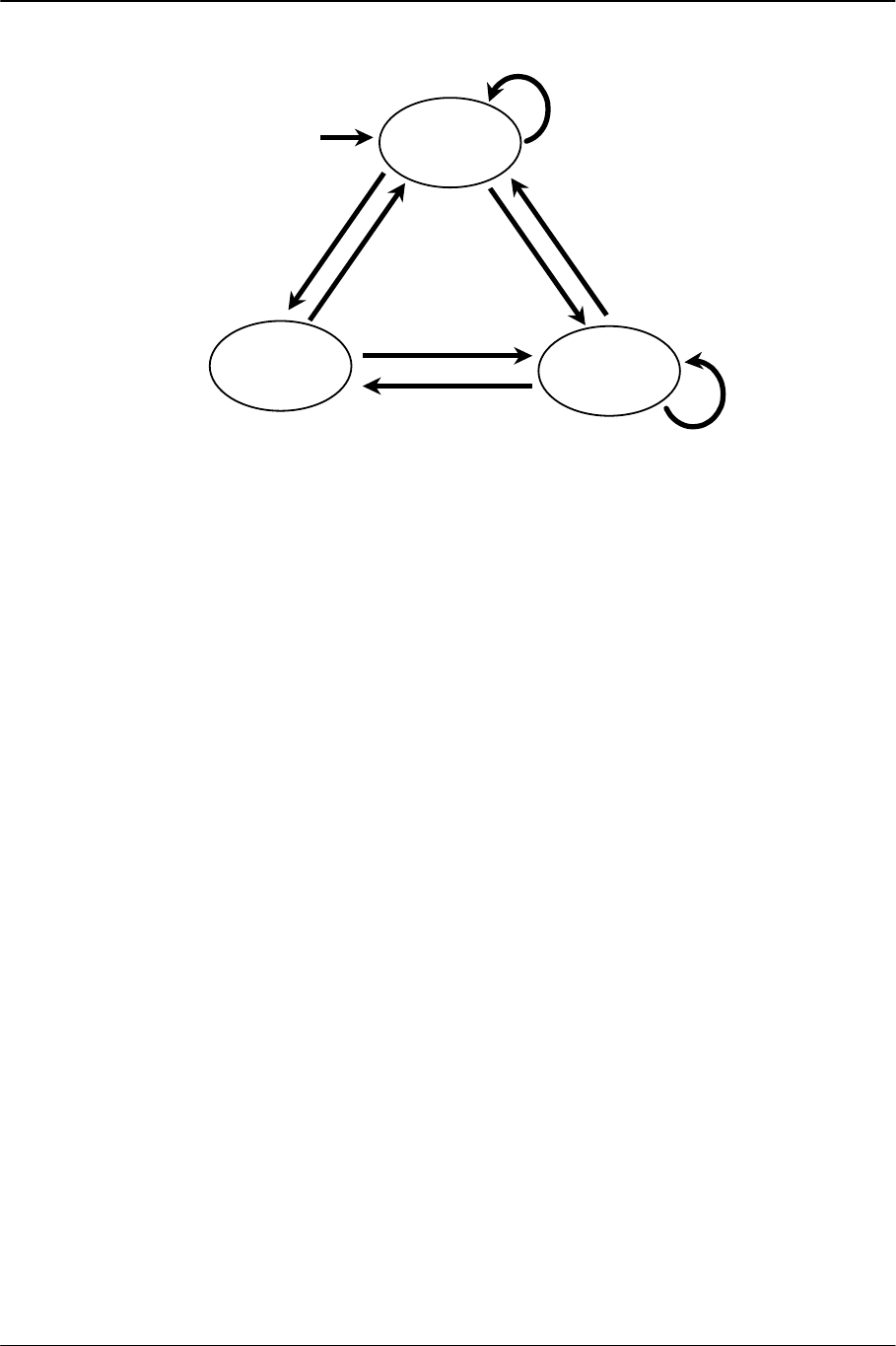

1.2. VU Execution Mode .....................................................................................................................................................20

1.3. VU Operation Status.....................................................................................................................................................21

1.3.1. Ready State ..............................................................................................................................................................21

1.3.2. Run State .................................................................................................................................................................21

1.3.3. Stop State.................................................................................................................................................................21

1.4. VU Usage........................................................................................................................................................................23

1.4.1. VU1 Usage Outline................................................................................................................................................23

1.4.2. VU0 Usage Outline................................................................................................................................................23

2. Data/Calculation Basic Specifications................................................................................................................................25

2.1. Data Format ................................................................................................................................................................... 26

2.1.1. Floating-Point Values ............................................................................................................................................26

2.1.2. Fixed-Point Values.................................................................................................................................................26

2.2. Rounding Off Floating-Point Values..........................................................................................................................27

2.3. Exception Processing ....................................................................................................................................................28

2.4. Differences from IEEE 754......................................................................................................................................... 29

3. Micro Mode............................................................................................................................................................................31

3.1. Micro Mode Register Set...............................................................................................................................................32

3.1.1. Floating-Point Registers ........................................................................................................................................32

3.1.2. Integer Registers.....................................................................................................................................................32

3.1.3. ACC Registers......................................................................................................................................................... 33

3.1.4. I Register..................................................................................................................................................................33

3.1.5. Q Register................................................................................................................................................................34

3.1.6. R Register ................................................................................................................................................................ 34

3.1.7. P Register................................................................................................................................................................. 34

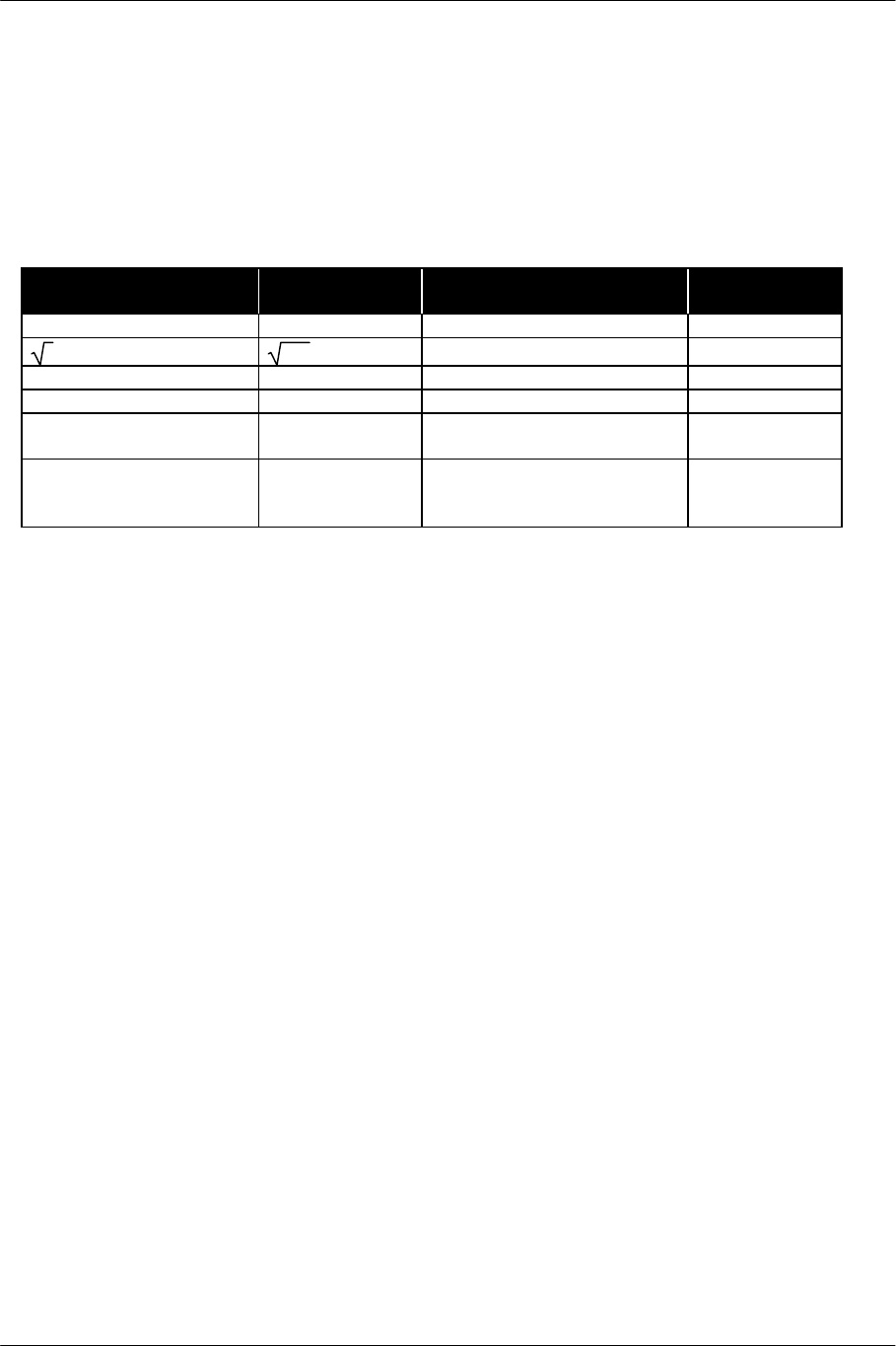

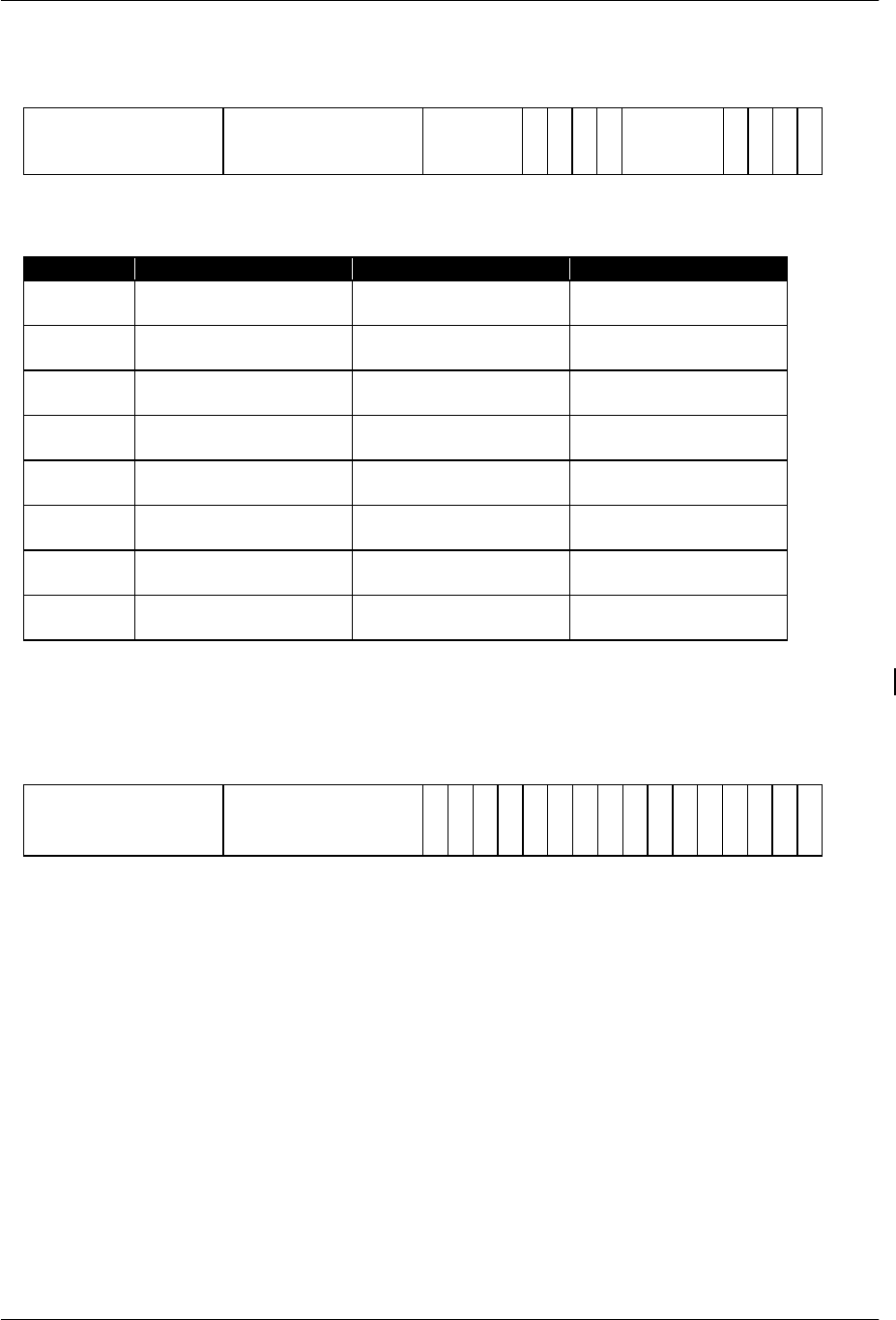

3.2. Micro Instruction Set Overview .................................................................................................................................. 35

3.2.1. Upper Instructions ................................................................................................................................................. 35

3.2.2. Lower Instructions.................................................................................................................................................37

3.3. Flags................................................................................................................................................................................. 39

3.3.1. MAC Flags............................................................................................................................................................... 39

3.3.2. Status Flags (SF) .....................................................................................................................................................39

3.3.3. Clipping Flags (CF) ................................................................................................................................................ 40

3.3.4. Flag Set Instructions ..............................................................................................................................................40

SCE CONFIDENTIAL VU User's Manual Version 6.0

© SCEI

-8-

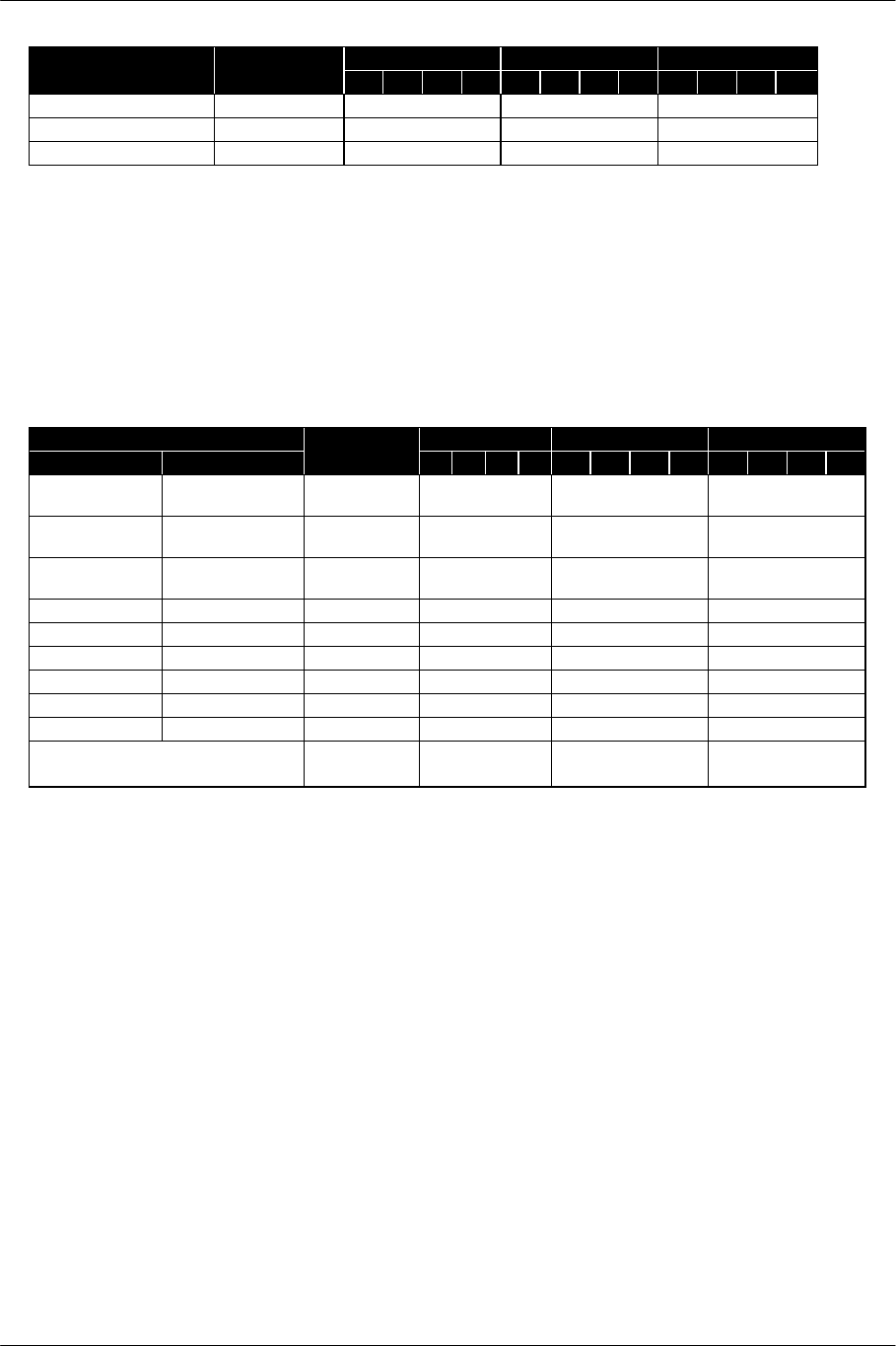

3.3.5. Flag Changes for Each Instruction.......................................................................................................................41

3.3.6. Flag Changes for Exception Occurrences...........................................................................................................41

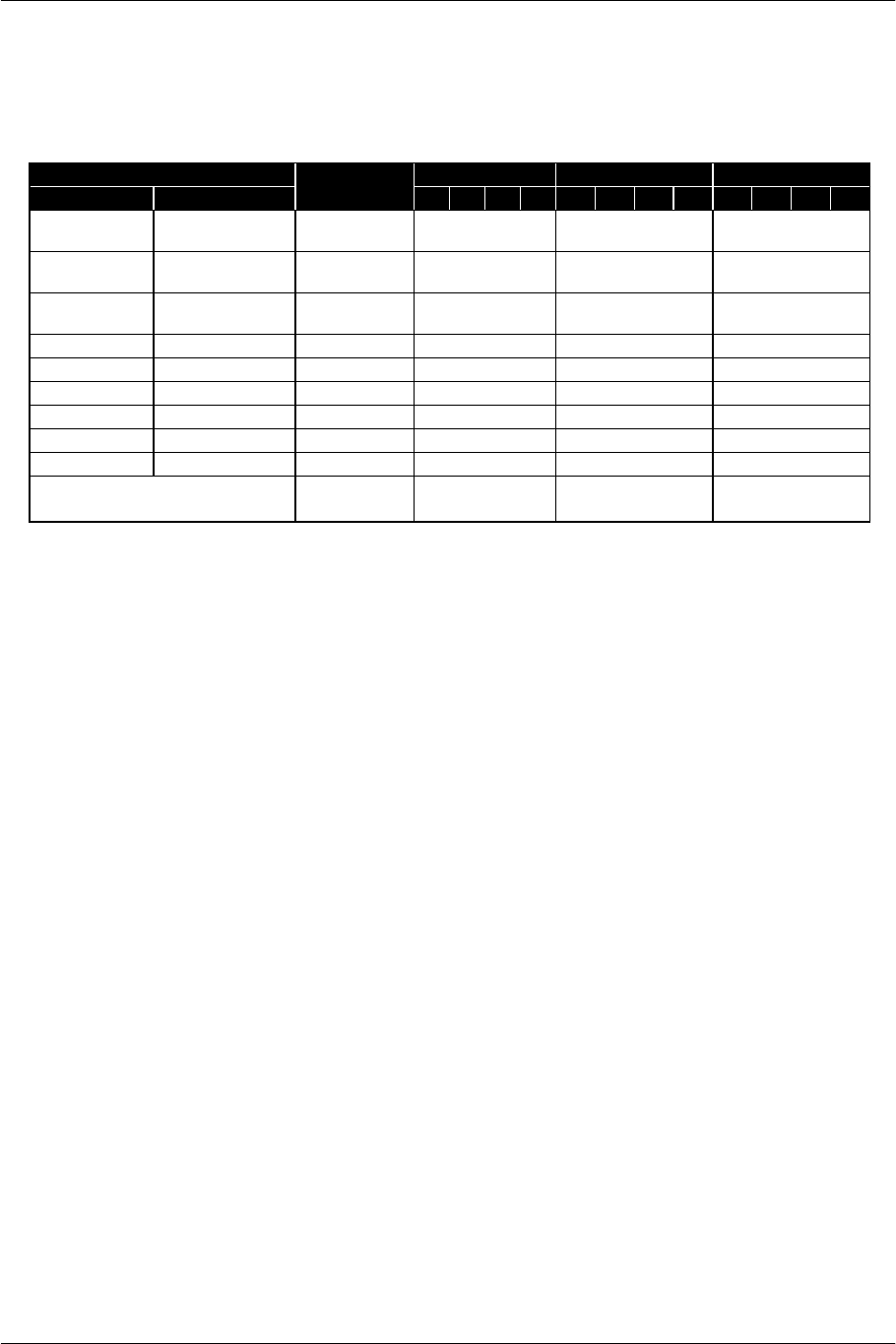

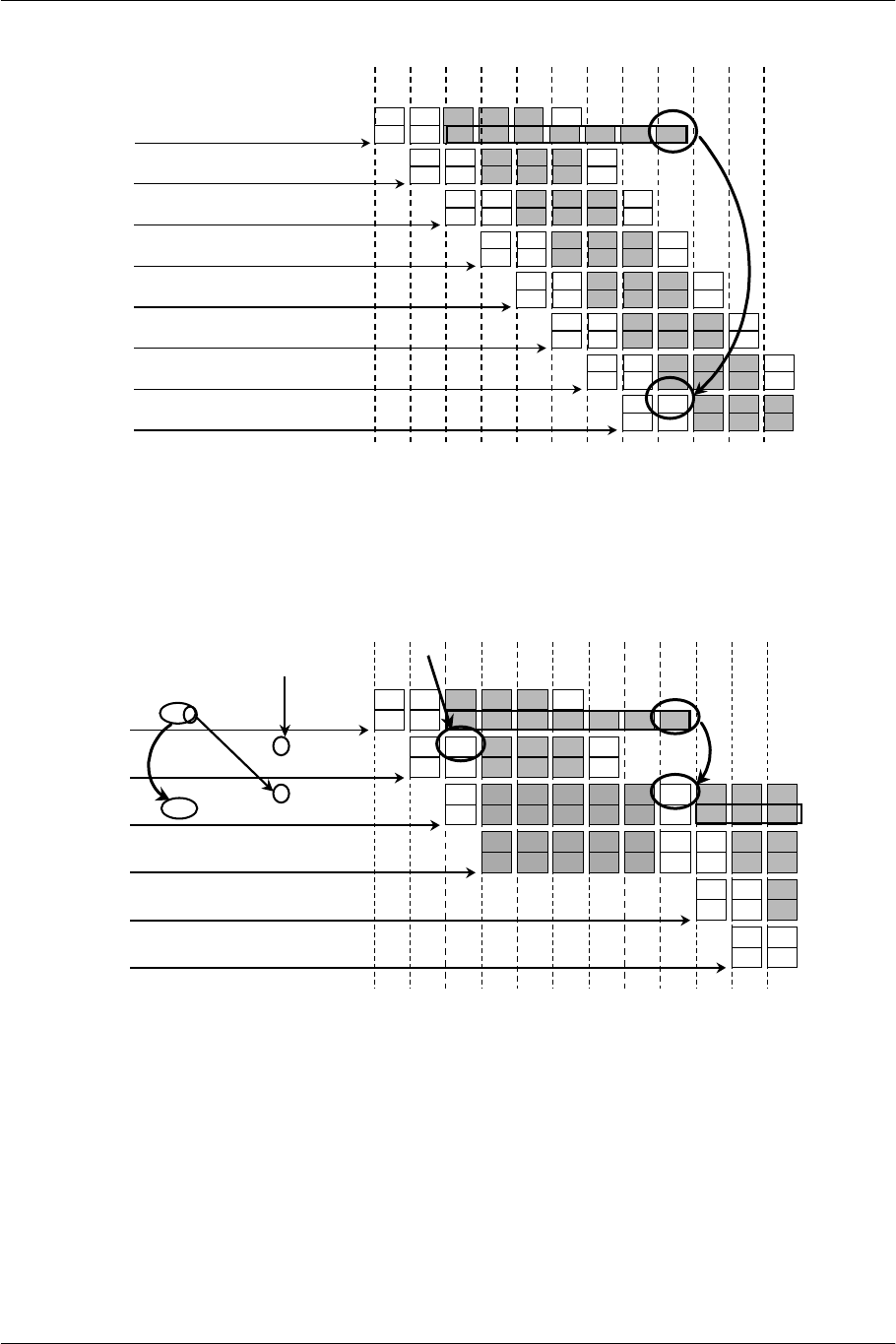

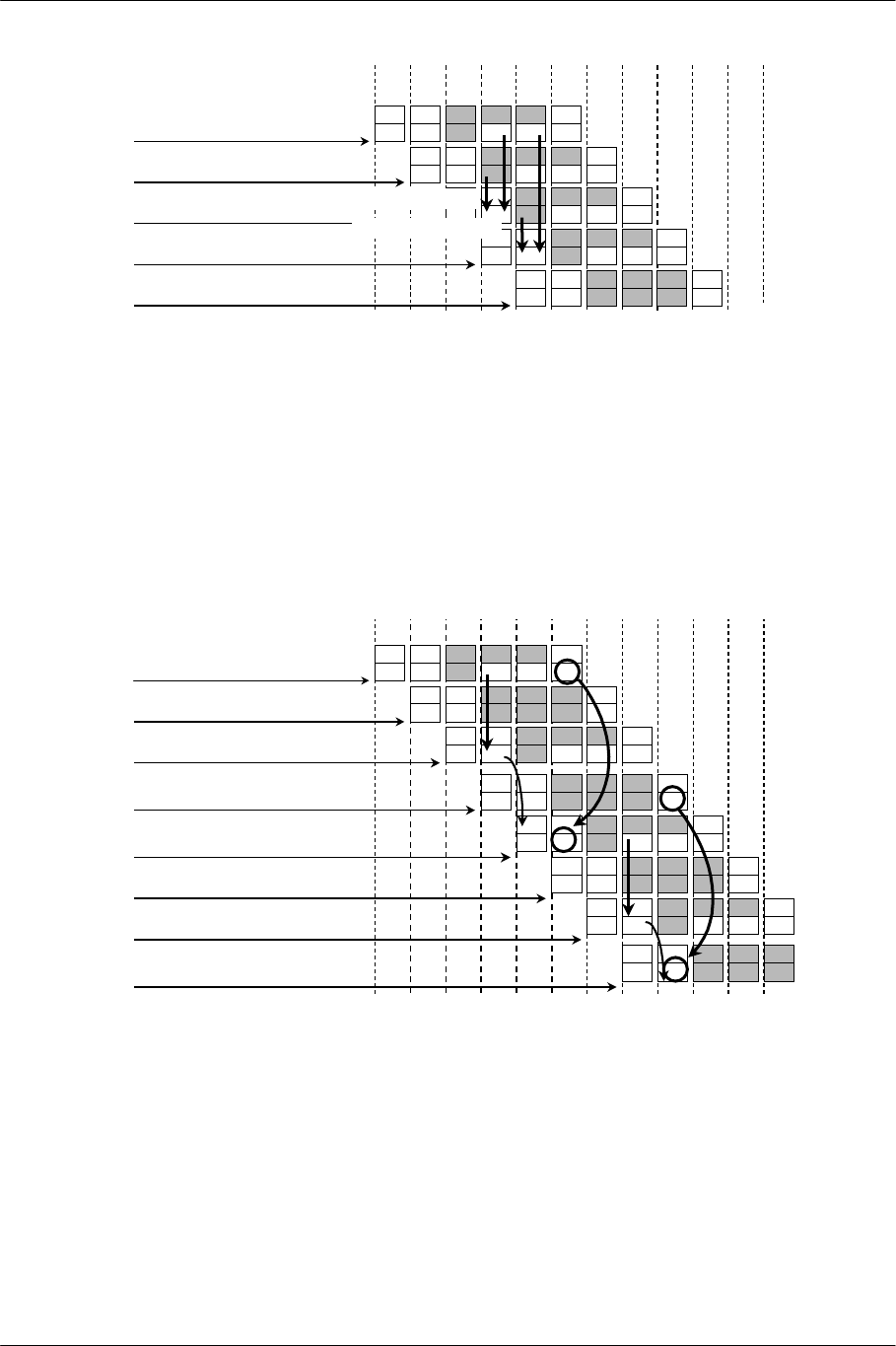

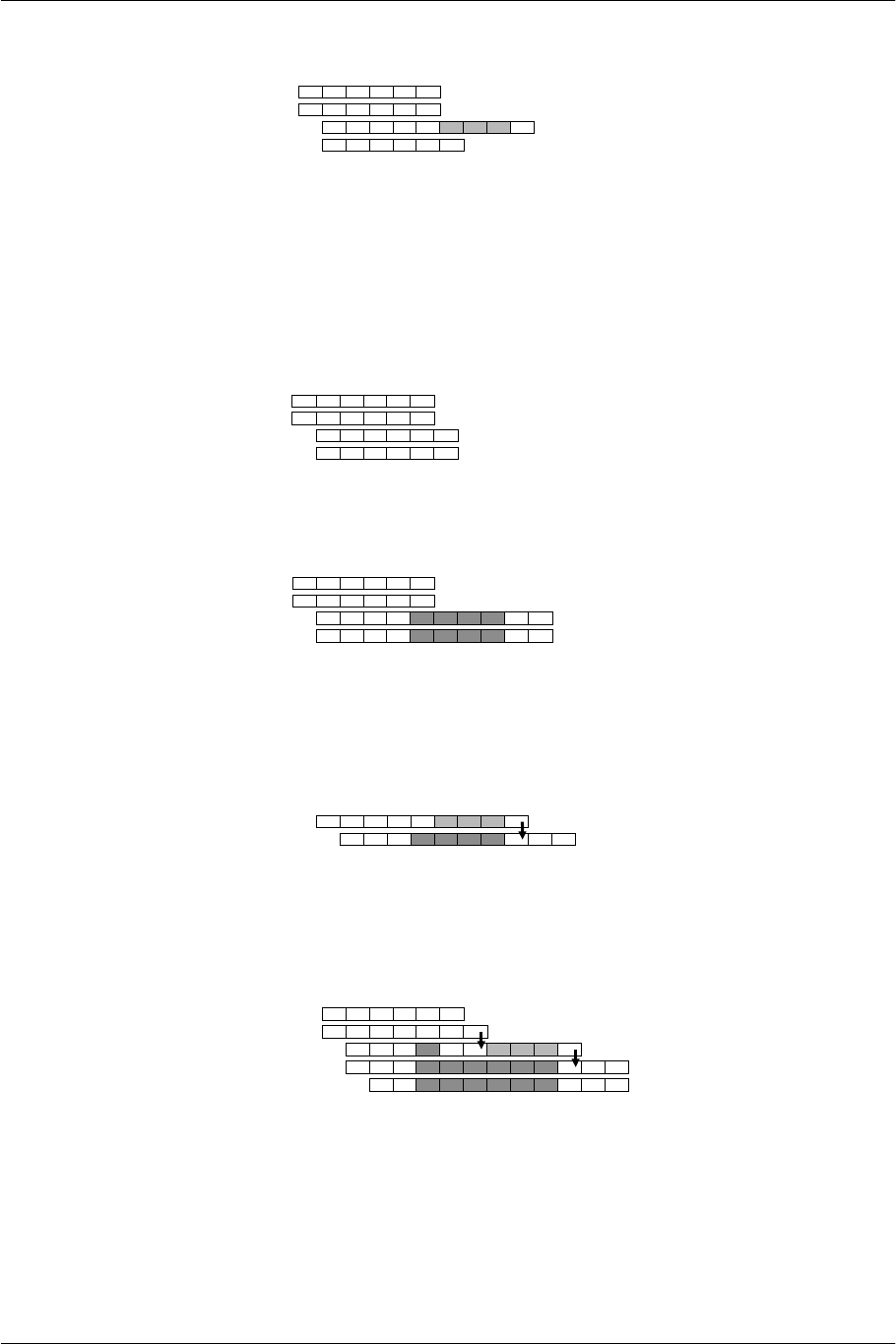

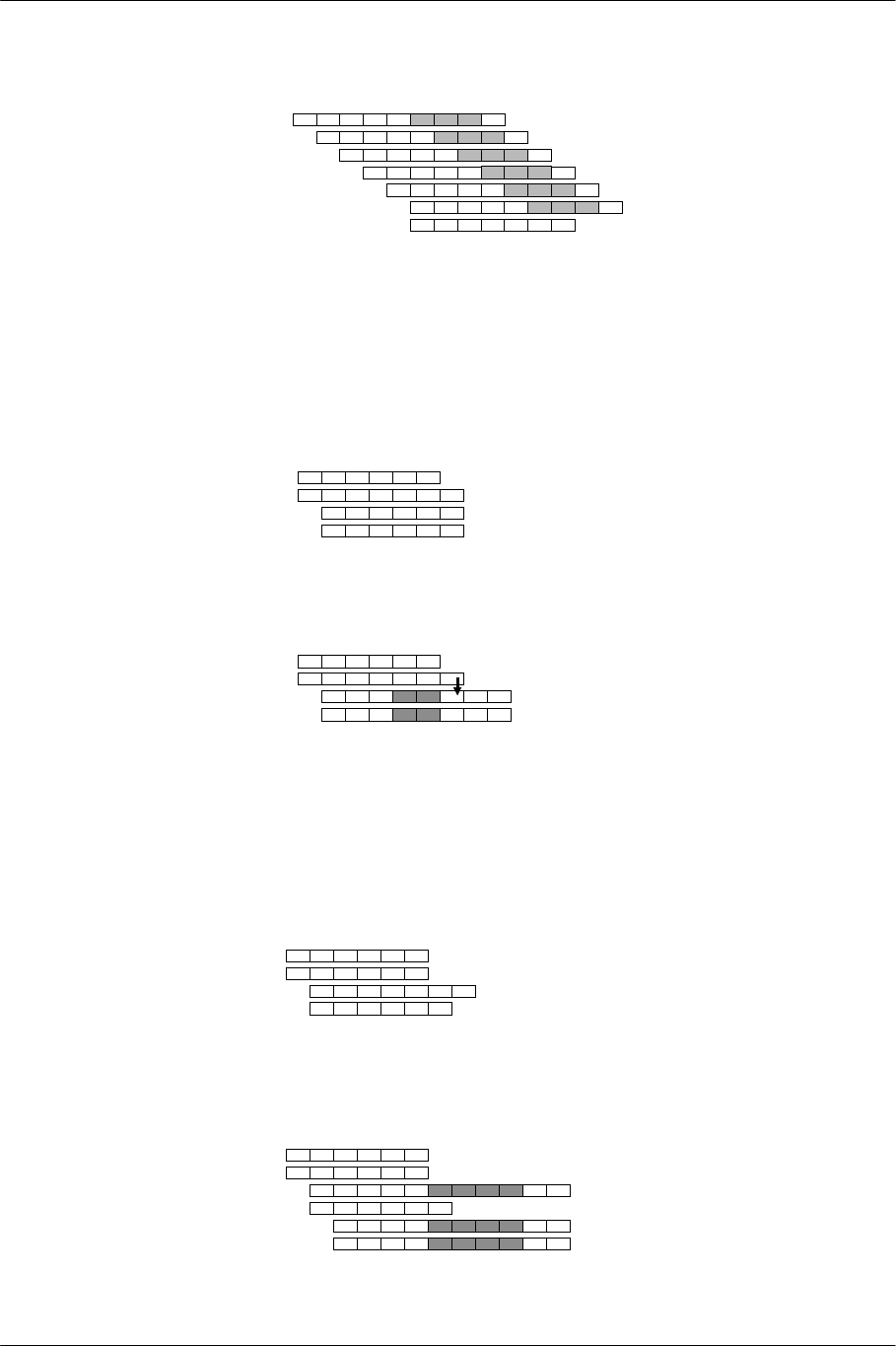

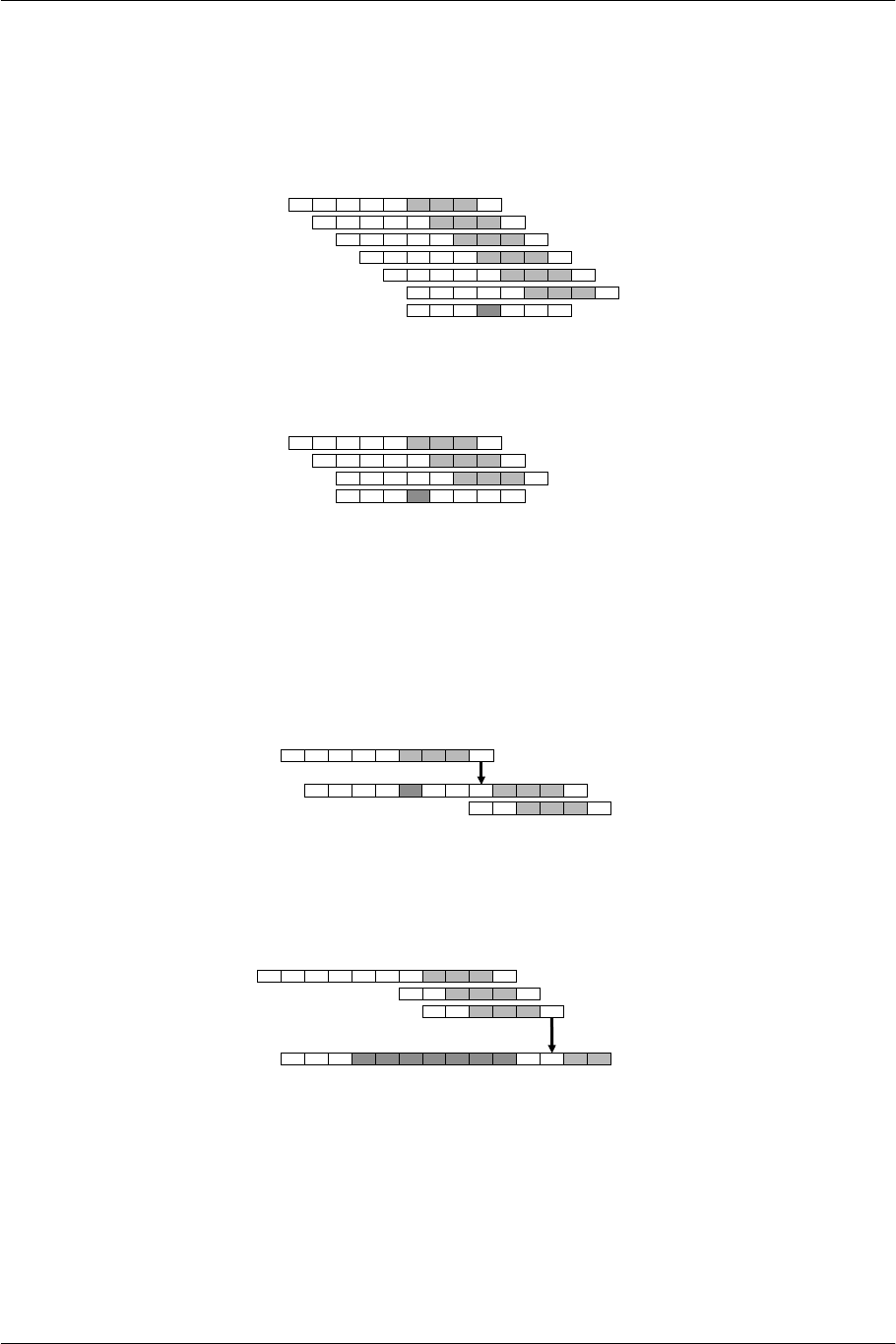

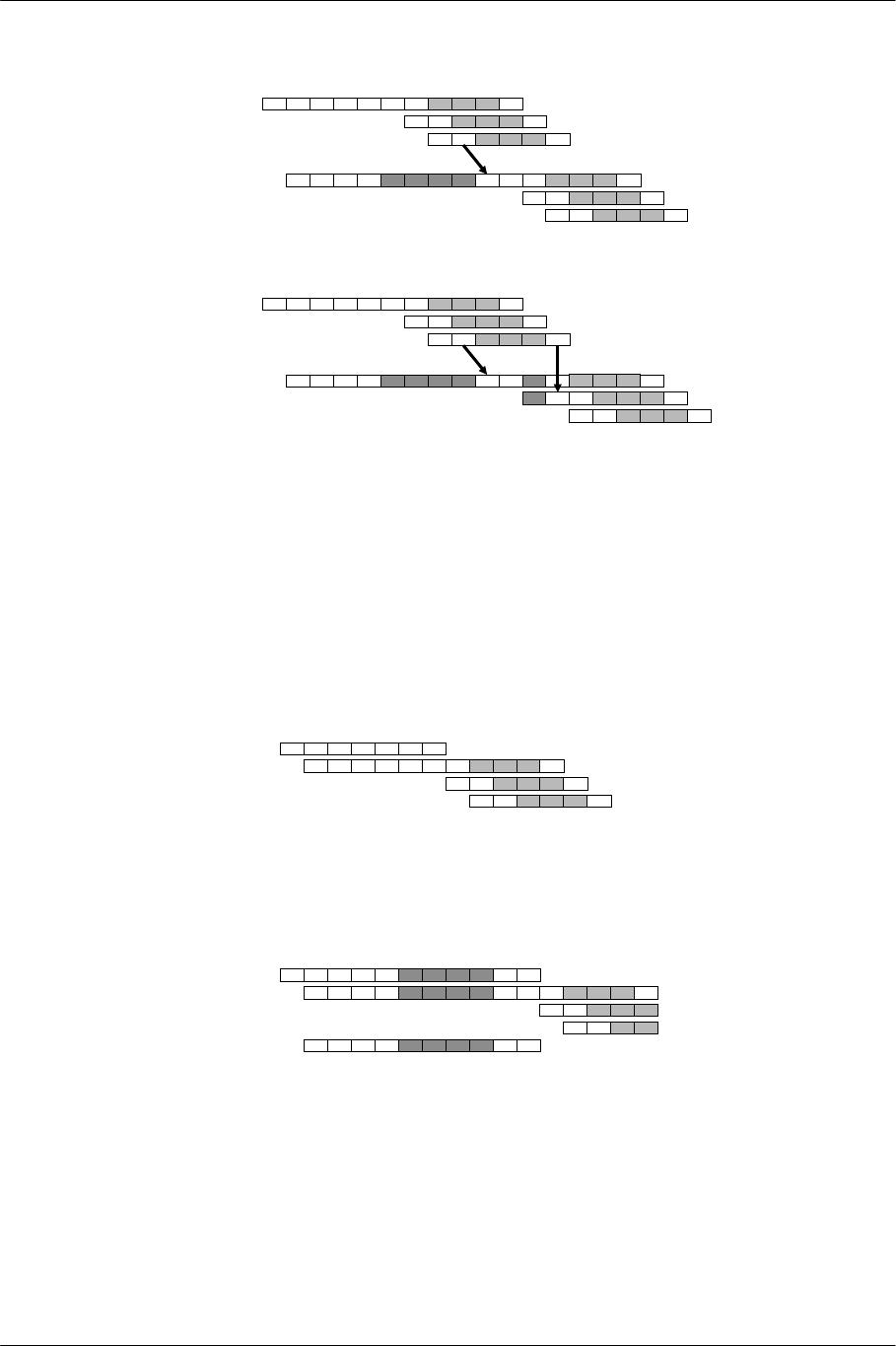

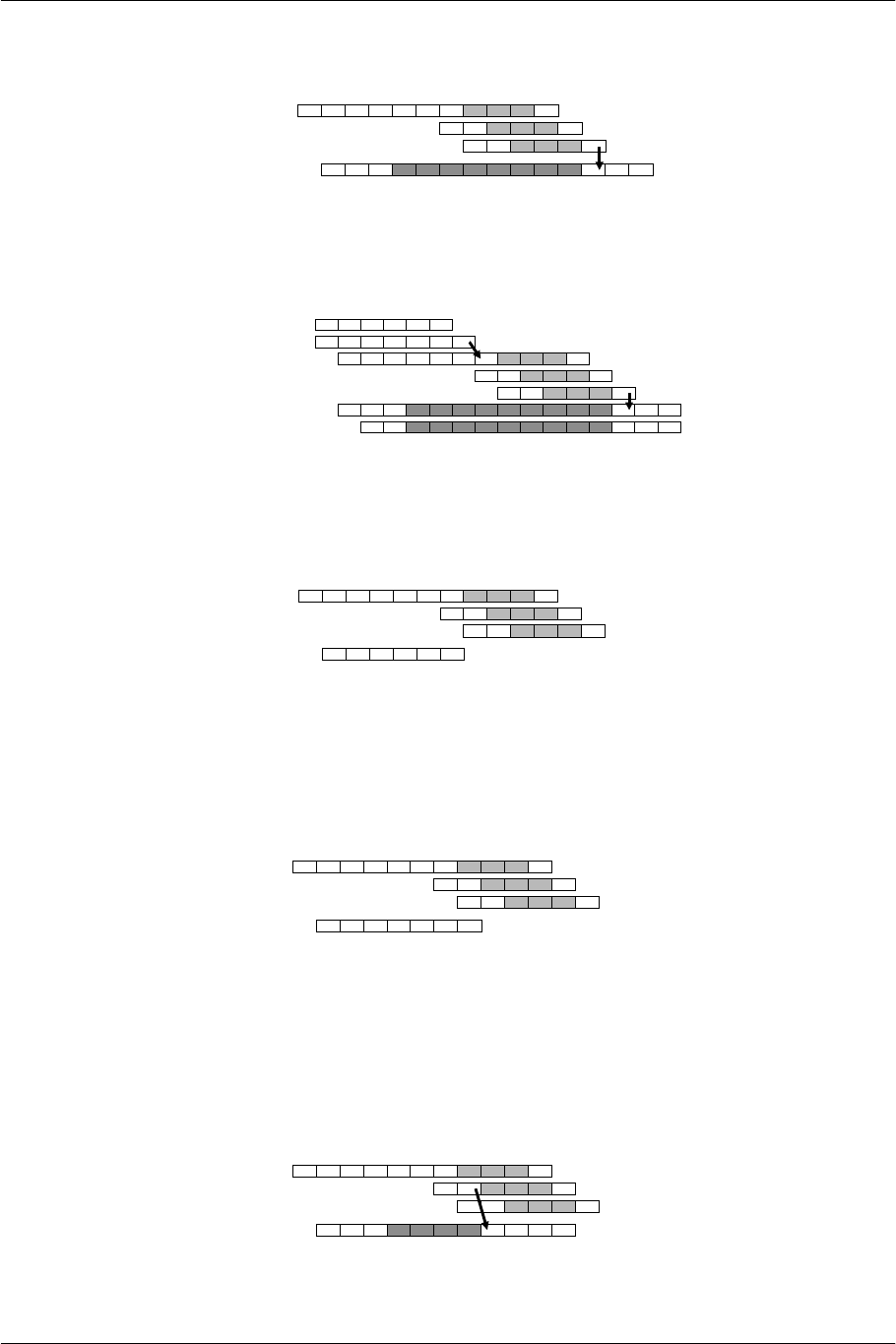

3.4. Pipeline Operation .........................................................................................................................................................44

3.4.1. Hazards.....................................................................................................................................................................44

3.4.2. Upper Instruction and Lower Instruction...........................................................................................................44

3.4.3. Priority for Writing to a Register ..........................................................................................................................44

3.4.4. FMAC Pipeline........................................................................................................................................................45

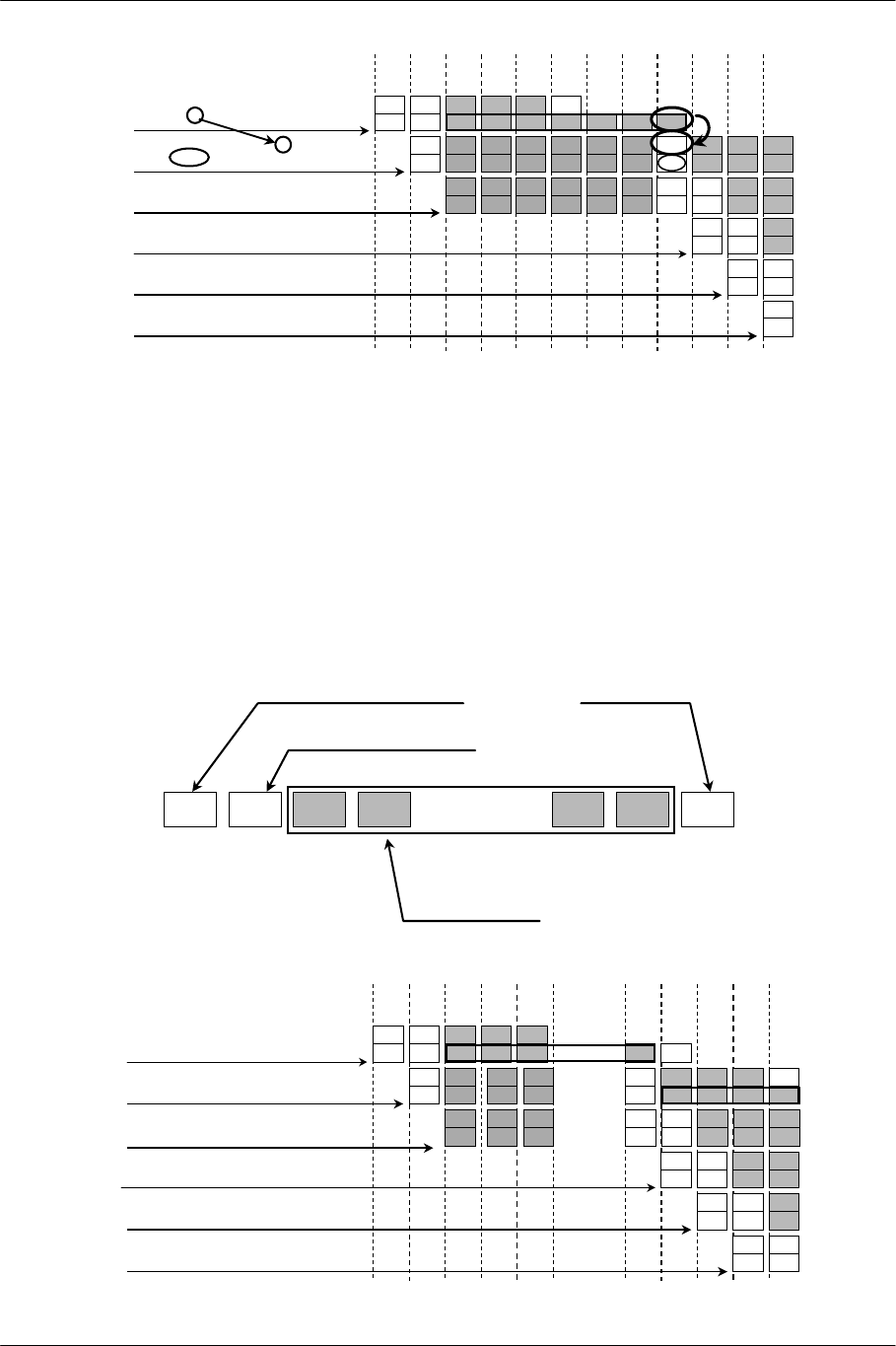

3.4.5. FDIV Pipeline .........................................................................................................................................................46

3.4.6. EFU Pipeline ...........................................................................................................................................................48

3.4.7. IALU Pipeline .........................................................................................................................................................49

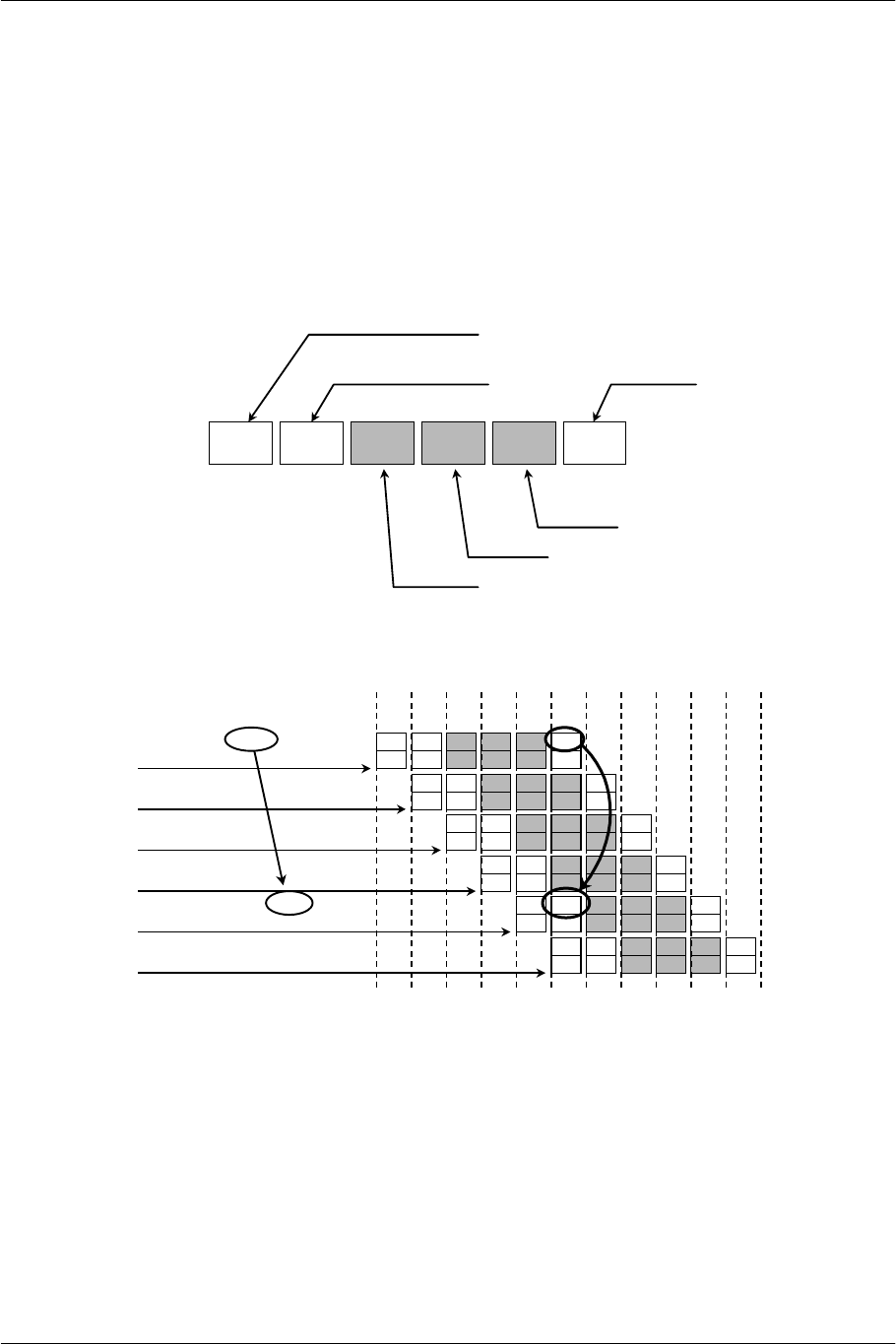

3.4.8. Conditional Branching and Pipeline.....................................................................................................................50

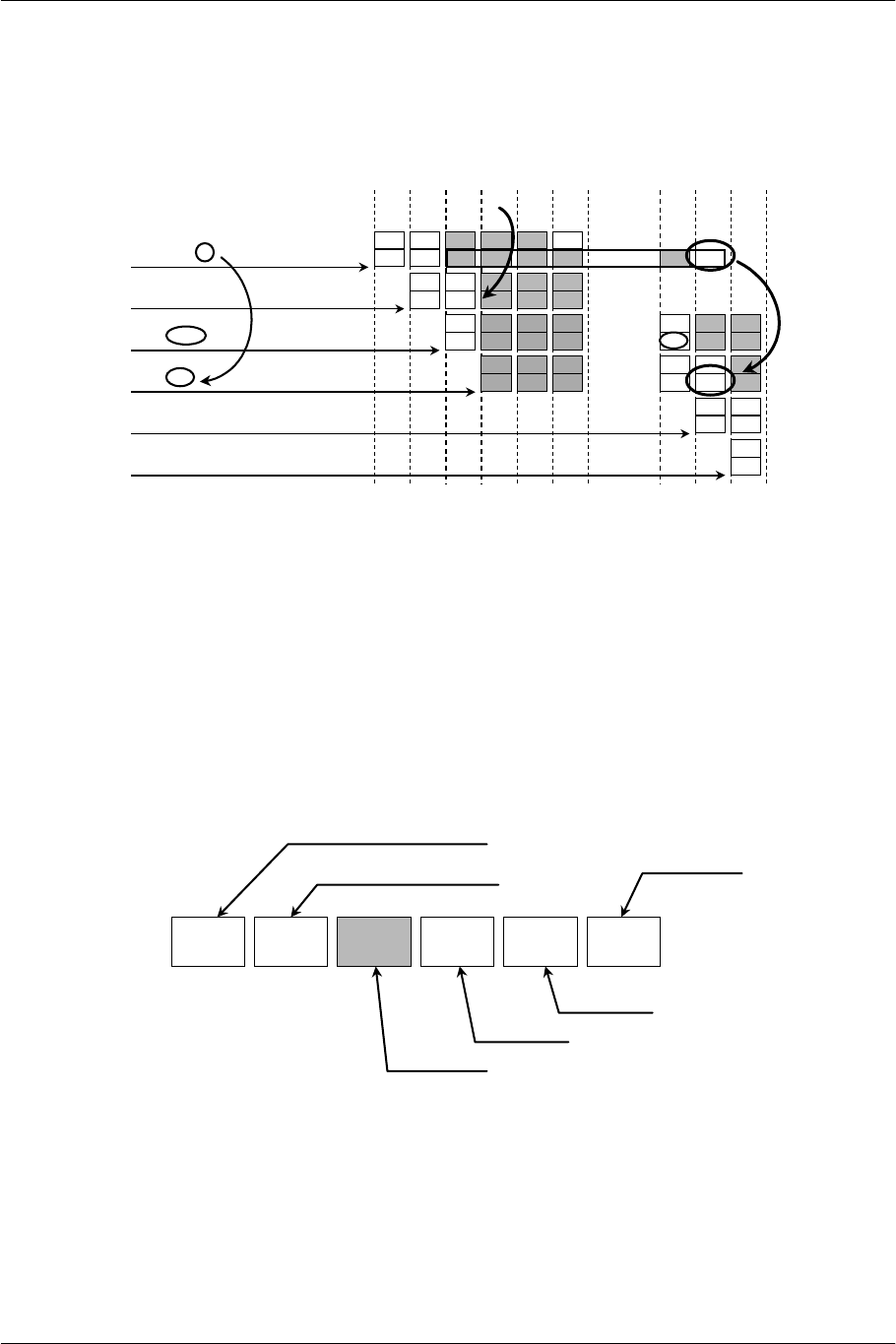

3.4.9. XGKICK Pipeline ..................................................................................................................................................52

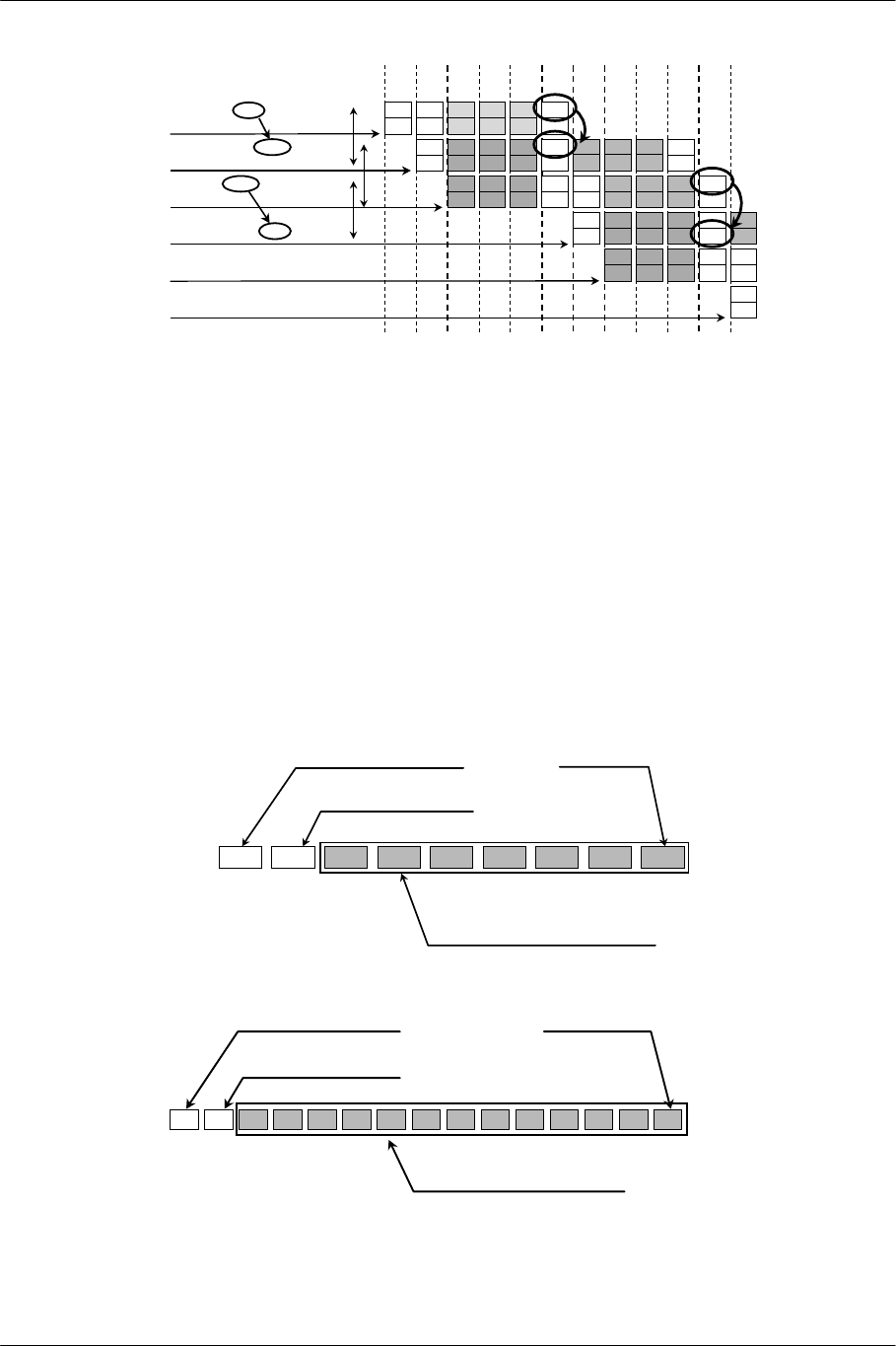

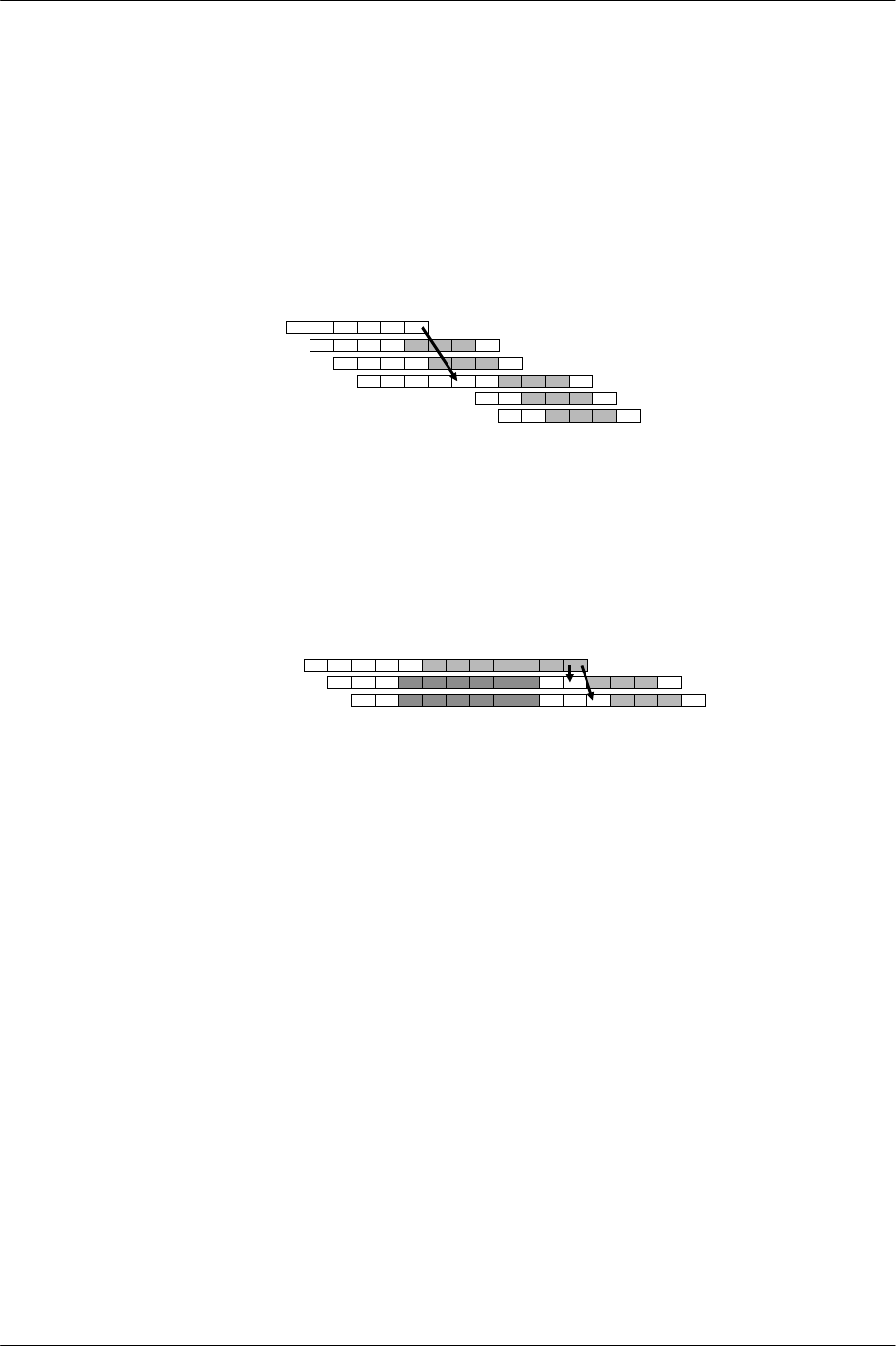

3.5. Micro Subroutine Execution.........................................................................................................................................53

3.5.1. How to Execute a Micro Subroutine ...................................................................................................................53

3.5.2. How to Terminate a Micro Subroutine ...............................................................................................................53

3.5.3. Operation of Execution and Termination...........................................................................................................53

3.6. Other Functions .............................................................................................................................................................55

3.6.1. Data Transfer with VU Mem/Micro Mem .........................................................................................................55

3.6.2. Debug Support Function.......................................................................................................................................55

4. Micro Mode Instruction Reference .....................................................................................................................................57

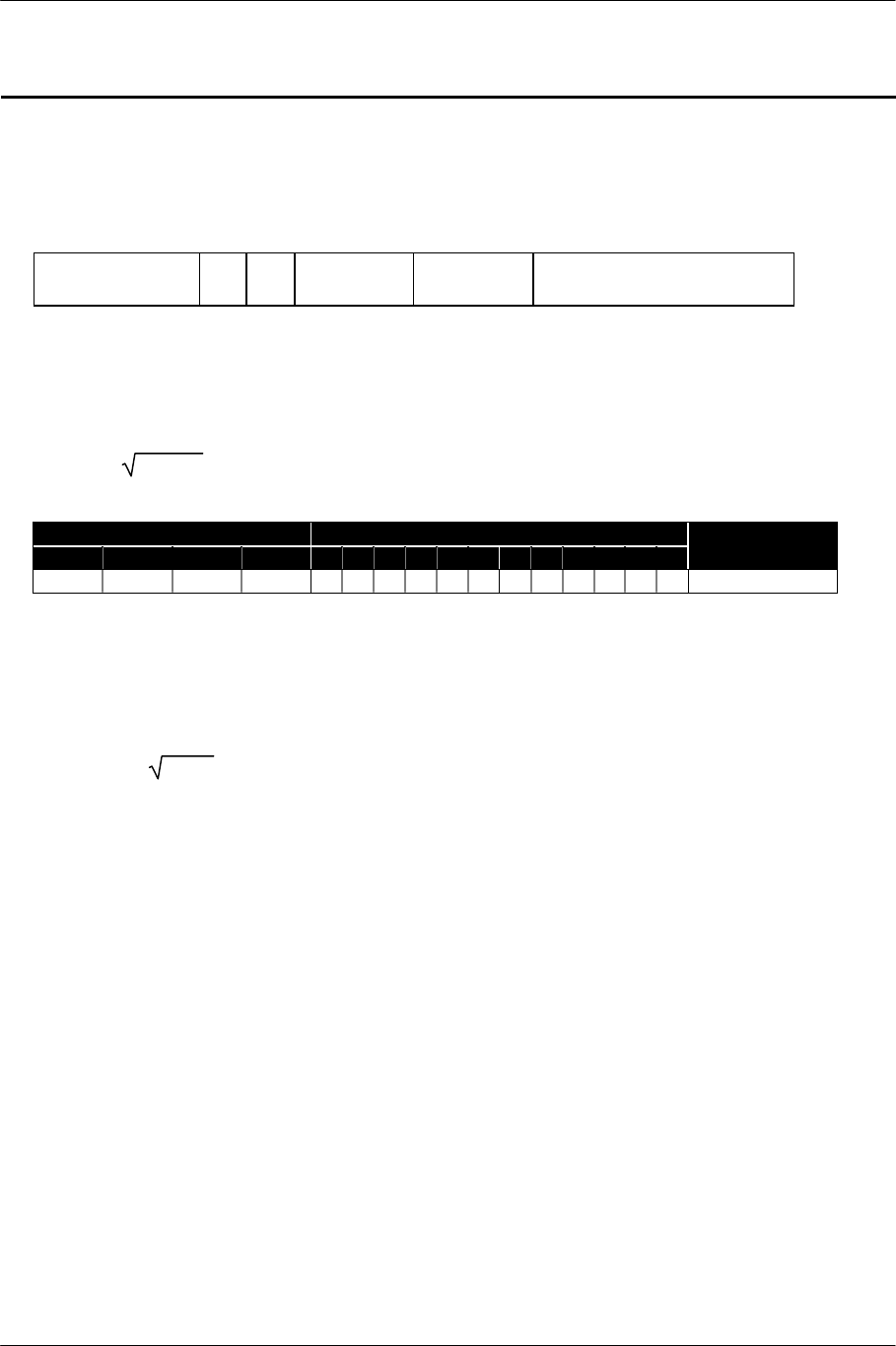

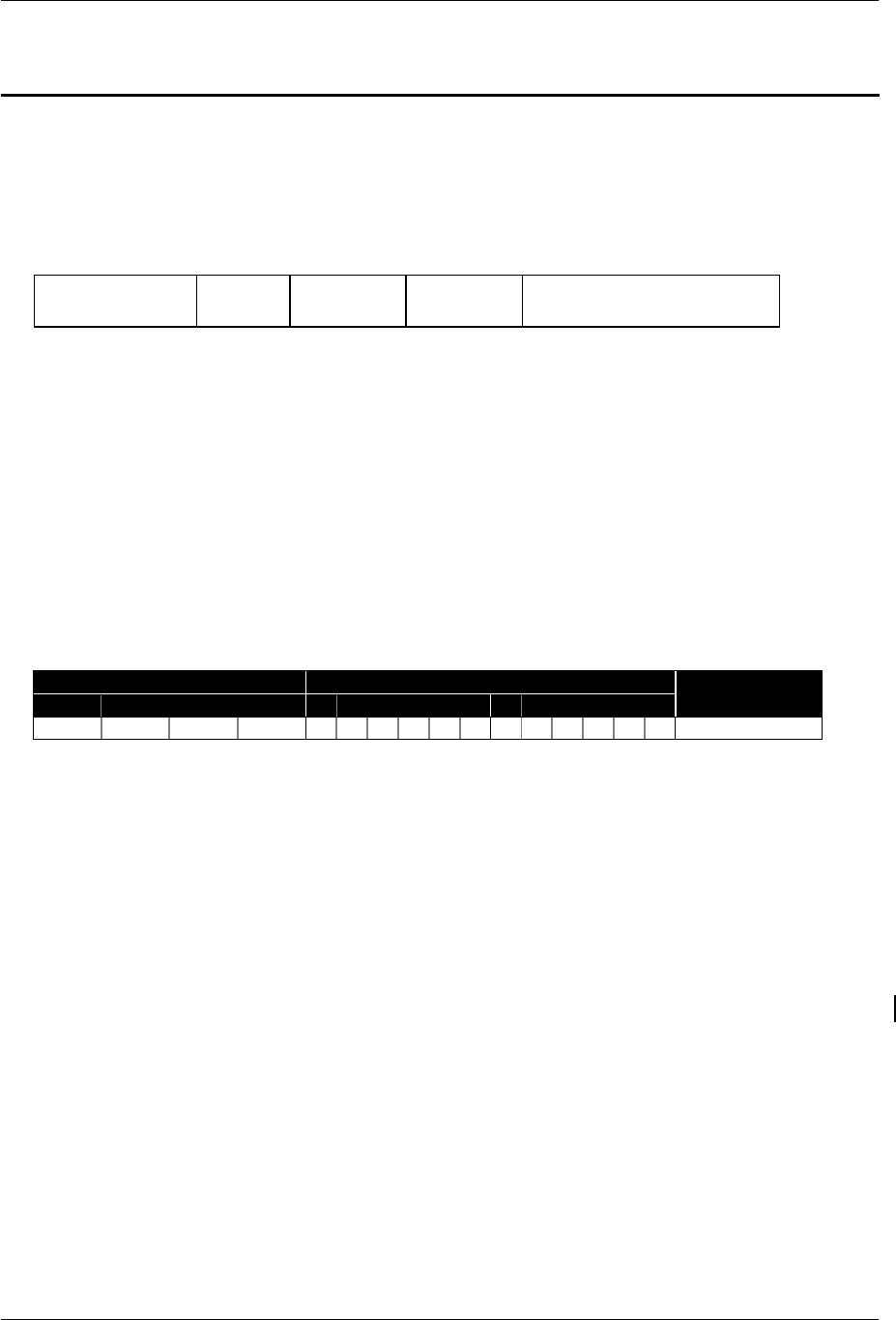

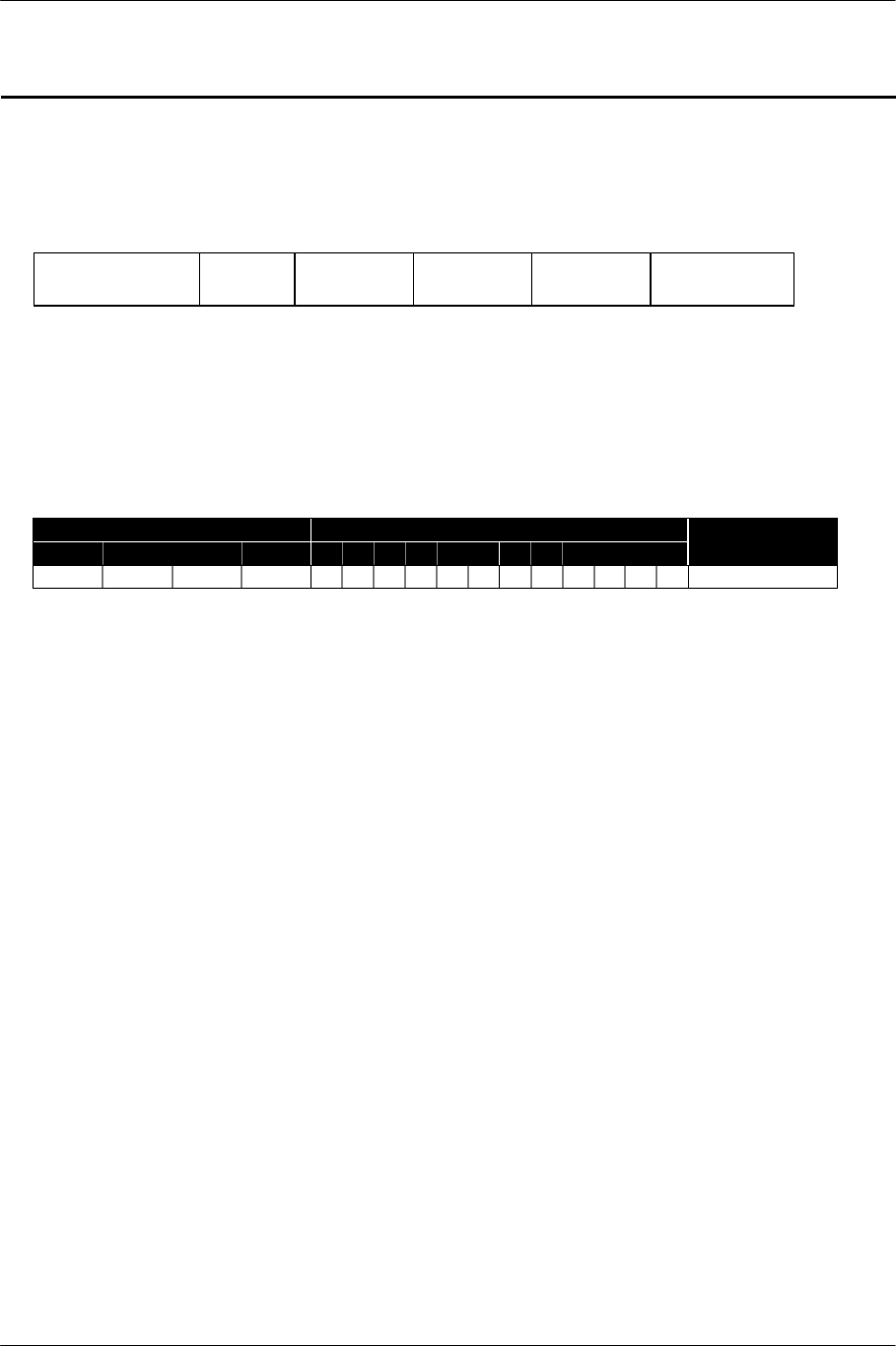

4.1. Micro Mode Instruction Set..........................................................................................................................................58

4.1.1. Types of Upper Instruction...................................................................................................................................58

4.1.2. Types of Lower Instructions.................................................................................................................................59

4.1.3. Operation Fields for Micro Instructions .............................................................................................................61

4.2. Upper Instruction Reference ........................................................................................................................................65

ABS : Absolute Value...................................................................................................................................................66

ADD : Add....................................................................................................................................................................67

ADDi : Add to I Register ............................................................................................................................................68

ADDq : Add to Q Register .........................................................................................................................................69

ADDbc : Broadcast Add .............................................................................................................................................70

ADDA : Add; to Accumulator ...................................................................................................................................71

ADDAi : Add I Register; to Accumulator.................................................................................................................72

ADDAq : Add Q Register; to Accumulator .............................................................................................................73

ADDAbc : Broadcast Add; to Accumulator.............................................................................................................74

CLIP : Clipping Judgment ...........................................................................................................................................75

FTOI0 : Convert to Fixed Point.................................................................................................................................77

FTOI4 : Convert to Fixed Point.................................................................................................................................78

FTOI12 : Convert to Fixed Point ..............................................................................................................................79

FTOI15 : Convert to Fixed Point ..............................................................................................................................80

ITOF0 : Convert to Floating-Point Number............................................................................................................81

ITOF4 : Convert to Floating-Point Number............................................................................................................82

ITOF12 : Convert to Floating-Point Number..........................................................................................................83

ITOF15 : Convert to Floating-Point Number..........................................................................................................84

MADD : Product Sum.................................................................................................................................................85

MADDi : Product Sum; with I Register ....................................................................................................................86

MADDq : Product Sum; by Q Register.....................................................................................................................87

SCE CONFIDENTIAL VU User's Manual Version 6.0

© SCEI

-9-

MADDbc : Broadcast Product Sum..........................................................................................................................88

MADDA : Product Sum; to Accumulator................................................................................................................ 89

MADDAi : Product Sum

;

by I register, to Accumulator ........................................................................................90

MADDAq : Product Sum; by Q Register, to Accumulator.................................................................................... 91

MADDAbc : Broadcast Product Sum; to Accumulator ......................................................................................... 92

MAX : Maximum Value ..............................................................................................................................................93

MAXi : Maximum Value.............................................................................................................................................94

MAXbc : Maximum Value .......................................................................................................................................... 95

MINI : Minimum Value .............................................................................................................................................. 96

MINIi : Minimum Value .............................................................................................................................................97

MINIbc : Minimum Value .......................................................................................................................................... 98

MSUB : Multiply and Subtract.................................................................................................................................... 99

MSUBi : Multiply and Subtract; with I Register.....................................................................................................100

MSUBq : Multiply and Subtract; by Q Register .....................................................................................................101

MSUBbc : Broadcast Multiply and Subtract........................................................................................................... 102

MSUBA : Multiply and Subtract; to Accumulator.................................................................................................103

MSUBAi : Multiply and Subtract; with I Register, to Accumulator ....................................................................104

MSUBAq : Multiply and Subtract; by Q Register, to Accumulator.....................................................................105

MSUBAbc : Broadcast Multiply and Subtract; to Accumulator ..........................................................................106

MUL : Multiply...........................................................................................................................................................107

MULi : Multiply by I Register...................................................................................................................................108

MULq : Multiply by Q Register................................................................................................................................109

MULbc : Multiply by Broadcast ...............................................................................................................................110

MULA : Multiply; to Accumulator ..........................................................................................................................111

MULAi : Multiply by I Register, to Accumulator ..................................................................................................112

MULAq : Multiply by Q Register, to Accumulator ...............................................................................................113

MULAbc : Broadcast Multiply by broadcast, to Accumulator.............................................................................114

NOP : No Operation.................................................................................................................................................115

OPMULA : Vector Outer Product..........................................................................................................................116

OPMSUB : Vector Outer Product...........................................................................................................................117

SUB : Subtract ............................................................................................................................................................118

SUBi : Subtract I Register..........................................................................................................................................119

SUBq : Subtract Q Register ......................................................................................................................................120

SUBbc : Broadcast Subtract......................................................................................................................................121

SUBA : Substract; to Accumulator ..........................................................................................................................122

SUBAi : Subtract I Register; to Accumulator.........................................................................................................123

SUBAq : Subtract Q Register; to Accumulator......................................................................................................124

SUBAbc : Broadcast Subtract; to Accumulator .....................................................................................................125

4.3. Lower Instruction Reference......................................................................................................................................126

B : Unconditional Branch..........................................................................................................................................127

BAL : Unconditional Branch with Saving Address ...............................................................................................128

DIV : Divide ............................................................................................................................................................... 129

EATAN : Arctangent ................................................................................................................................................130

EATANxy : Arctangent ............................................................................................................................................132

EATANxz : Arctangent ............................................................................................................................................134

EEXP : Exponent......................................................................................................................................................136

SCE CONFIDENTIAL VU User's Manual Version 6.0

© SCEI

-10-

ELENG : Length....................................................................................................................................................... 137

ERCPR : Reciprocal Number .................................................................................................................................. 138

ERLENG : Reciprocal Number of Length............................................................................................................ 139

ERSADD : Reciprocal Number .............................................................................................................................. 140

ERSQRT : Reciprocal Number of Square Root.................................................................................................... 141

ESADD : Sum of Square Numbers ........................................................................................................................ 142

ESIN : Sine................................................................................................................................................................. 143

ESQRT : Square Root............................................................................................................................................... 144

ESUM : Sum of Each Field...................................................................................................................................... 145

FCAND : Test Clipping Flag................................................................................................................................... 146

FCEQ : Test Clipping Flag....................................................................................................................................... 147

FCGET : Get Clipping Flag..................................................................................................................................... 148

FCOR : Test Clipping Flag....................................................................................................................................... 149

FCSET : Setting Clipping Flag................................................................................................................................. 150

FMAND : Test MAC Flag Check ........................................................................................................................... 151

FMEQ : Test MAC Flag Check............................................................................................................................... 152

FMOR : Test MAC Flag Check............................................................................................................................... 153

FSAND : Test Status Flag Check............................................................................................................................ 154

FSEQ : Test Status Flag Check................................................................................................................................ 155

FSOR : Test Status Flag............................................................................................................................................ 156

FSSET : Set Sticky Flags........................................................................................................................................... 157

IADD : ADD Integer ............................................................................................................................................... 158

IADDI : Add Immediate Value Integer ................................................................................................................. 159

IADDIU : Add Immediate Integer ......................................................................................................................... 160

IAND : Logical Product ........................................................................................................................................... 161

IBEQ : Conditional Branch...................................................................................................................................... 162

IBGEZ : Conditional Branch................................................................................................................................... 163

IBGTZ : Conditional Branch................................................................................................................................... 164

IBLEZ : Conditional Branch ................................................................................................................................... 165

IBLTZ : Conditional Branch.................................................................................................................................... 166

IBNE : Conditional Branch...................................................................................................................................... 167

ILW : Integer Load with Offset Specification ....................................................................................................... 168

ILWR : Integer Load................................................................................................................................................. 169

IOR : Logical Sum ..................................................................................................................................................... 170

ISUB : Integer Subtract............................................................................................................................................. 171

ISUBIU : Immediate Value Integer Subtract......................................................................................................... 172

ISW : Integer Store with Offset............................................................................................................................... 173

ISWR : Integer Store ................................................................................................................................................. 174

JALR : Unconditional Jump with Address Saving ................................................................................................ 175

JR : Unconditional Jump........................................................................................................................................... 176

LQ : Load Qword...................................................................................................................................................... 177

LQD : Load Qword with Pre-Decrement.............................................................................................................. 178

LQI : Load with Post-Increment............................................................................................................................. 179

MFIR : Move from Integer Register to Floating-Point Register......................................................................... 180

MFP : Move from P Register to Floating-Point Register..................................................................................... 181

MOVE : Transfer between Floating-Point Registers............................................................................................ 182

SCE CONFIDENTIAL VU User's Manual Version 6.0

© SCEI

-11-

MR32 : Move with Rotate.........................................................................................................................................183

MTIR : Move from Floating-Point Register to Integer Register .........................................................................184

RGET : Get Random Number ................................................................................................................................185

RINIT : Random Number Intialize.........................................................................................................................186

RNEXT : Next Random Number ...........................................................................................................................187

RSQRT : Square Root Division ...............................................................................................................................188

RXOR : Random Number Set .................................................................................................................................189

SQ : Store Qword with Offset .................................................................................................................................190

SQD : Store Qword with Pre-Decrement ..............................................................................................................191

SQI : Store with Post-Increment..............................................................................................................................192

SQRT : Square Root ..................................................................................................................................................193

WAITP : P Register Syncronize ...............................................................................................................................194

WAITQ : Q Register Syncronize .............................................................................................................................195

XGKICK : GIF Control...........................................................................................................................................196

XITOP : VIF Control................................................................................................................................................196

XTOP : VIF Control .................................................................................................................................................198

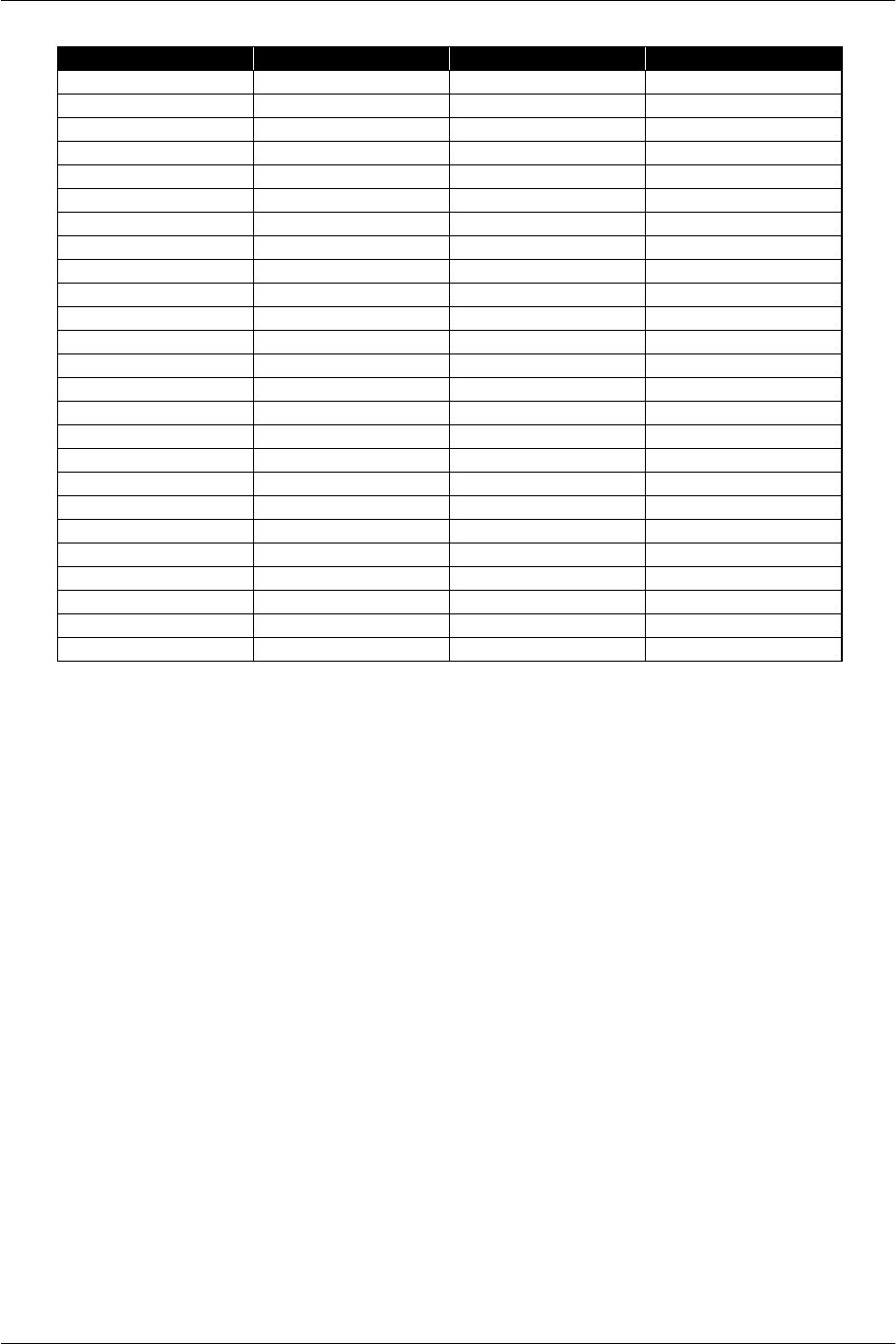

5. Macro Mode.........................................................................................................................................................................199

5.1. Macro Mode Register Set............................................................................................................................................200

5.1.1. Floating-Point Registers ......................................................................................................................................200

5.1.2. Integer Registers...................................................................................................................................................200

5.1.3. Control Registers..................................................................................................................................................200

5.1.4. Special Registers ...................................................................................................................................................205

5.2. Macro Instruction Set Overview................................................................................................................................206

5.2.1. MIPS COP2 Instructions ....................................................................................................................................206

5.2.2. Coprocessor Transfer Instructions ....................................................................................................................206

5.2.3. Coprocessor Branch Instructions ......................................................................................................................206

5.2.4. Coprocessor Calculation Instructions ...............................................................................................................206

5.2.5. Micro Subroutine Execution Instructions ........................................................................................................208

5.3. Flags............................................................................................................................................................................... 209

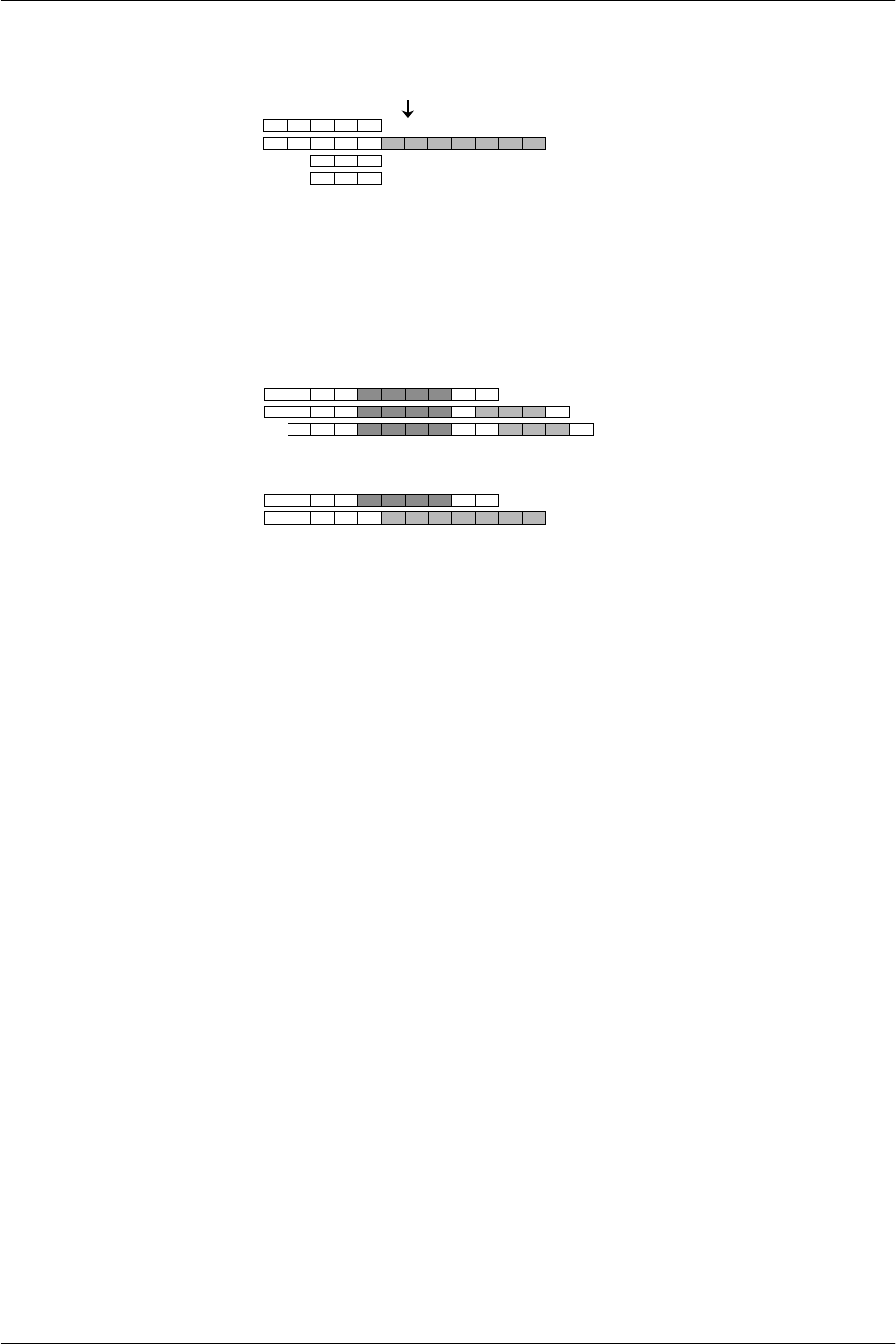

5.4. Macro Mode Pipeline ..................................................................................................................................................210

5.4.1. Pipeline Structure of Macroinstructions............................................................................................................210

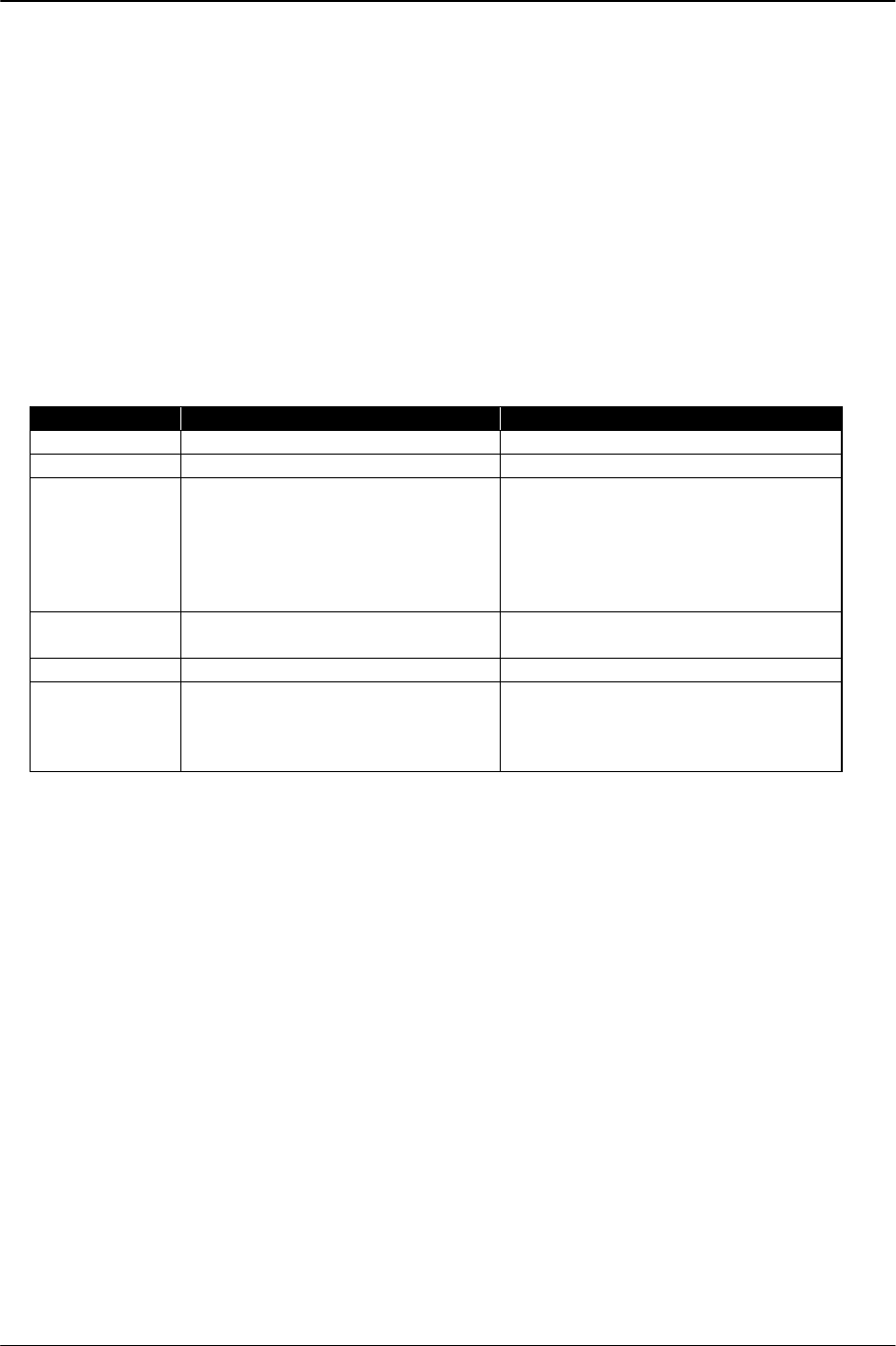

5.4.2. Hazards in Macro Mode......................................................................................................................................210

5.4.3. Macroinstruction Operation ...............................................................................................................................211

5.4.4. Operation when Transferring Data with EE Core..........................................................................................211

5.4.5. Operation when Executing a Micro Subroutine ..............................................................................................215

5.4.6. Micro Subroutine and Data Transfer Operations............................................................................................216

5.4.7. Q Register Synchronization ................................................................................................................................218

5.4.8. Notes on Other Pipeline Operations.................................................................................................................218

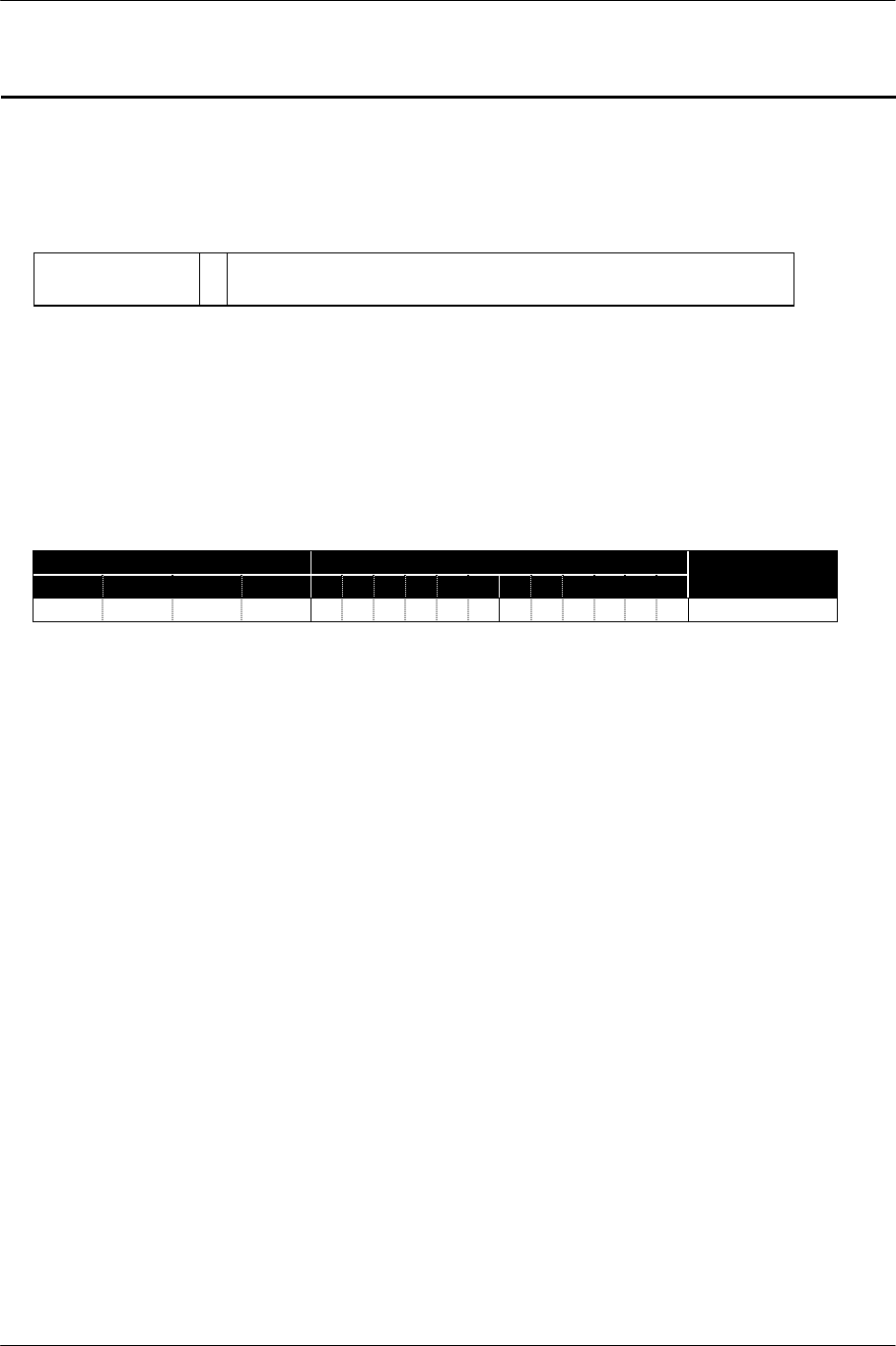

5.5. VU1 Control.................................................................................................................................................................220

5.5.1. MIPS COP2 Condition Signal............................................................................................................................220

5.5.2. MIPS COP2 Control Register ............................................................................................................................220

5.5.3. Floating-Point Registers ......................................................................................................................................221

5.5.4. Integer Registers...................................................................................................................................................222

5.5.5. Control Registers..................................................................................................................................................222

6. Macro Mode Instruction Reference..................................................................................................................................225

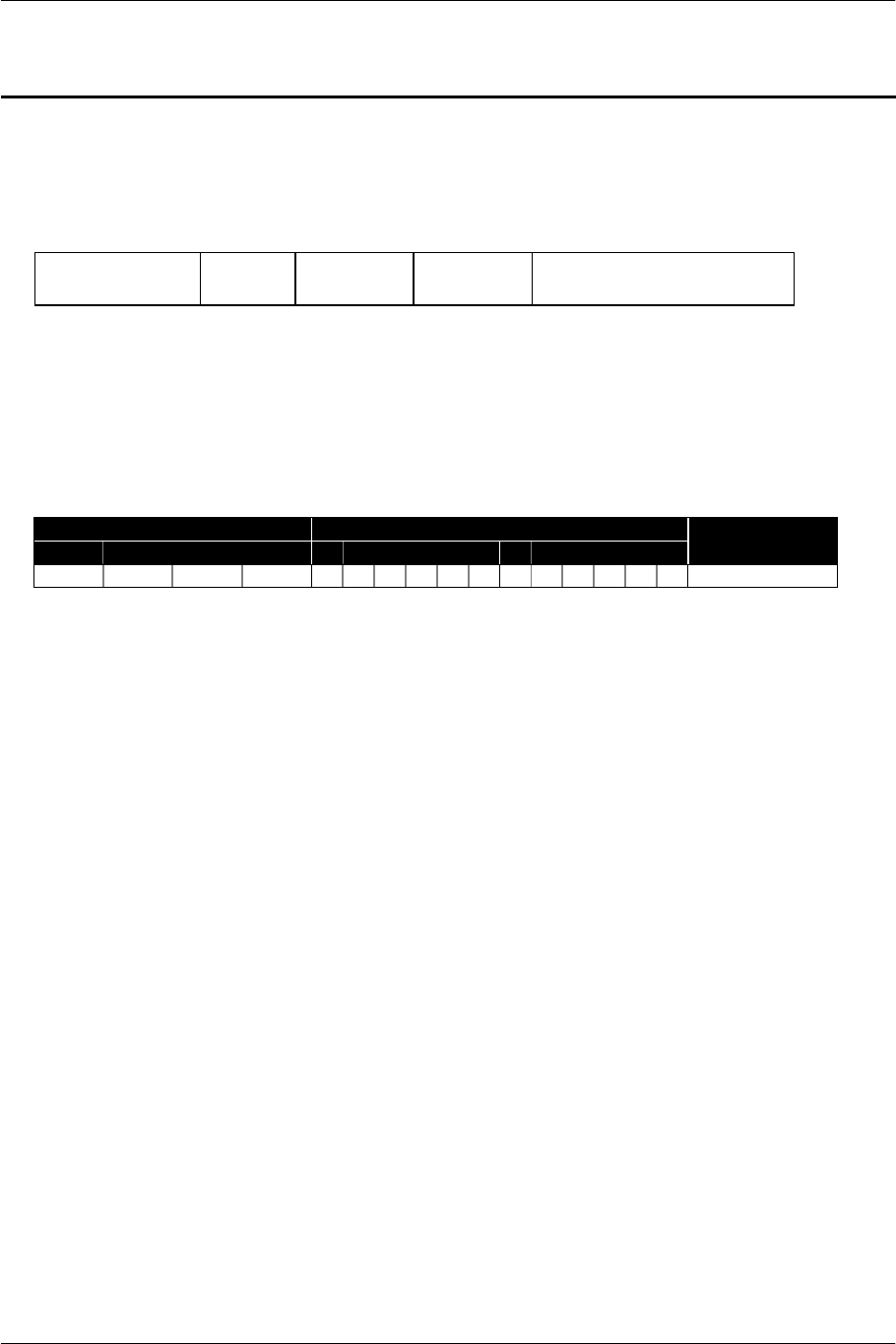

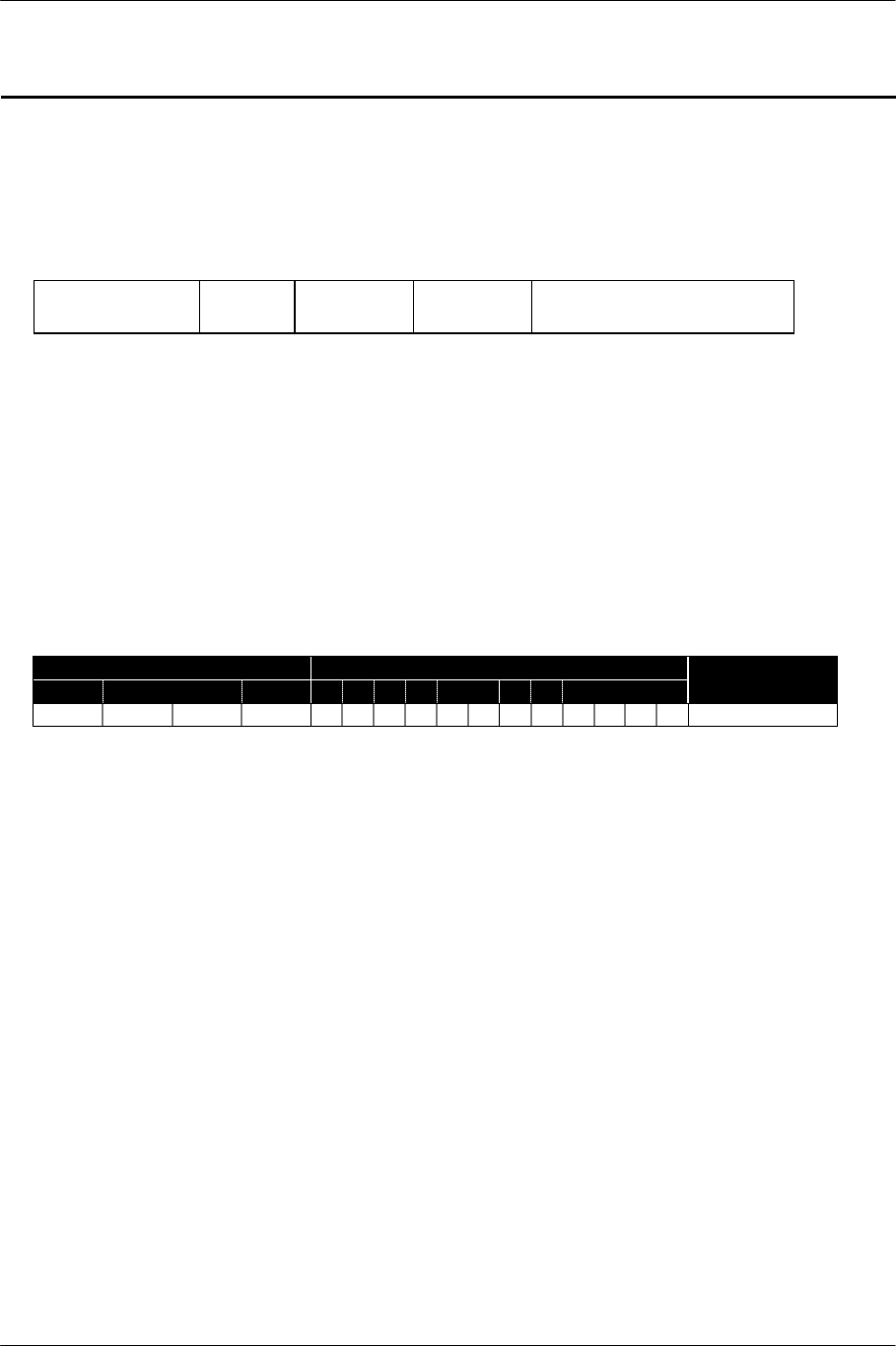

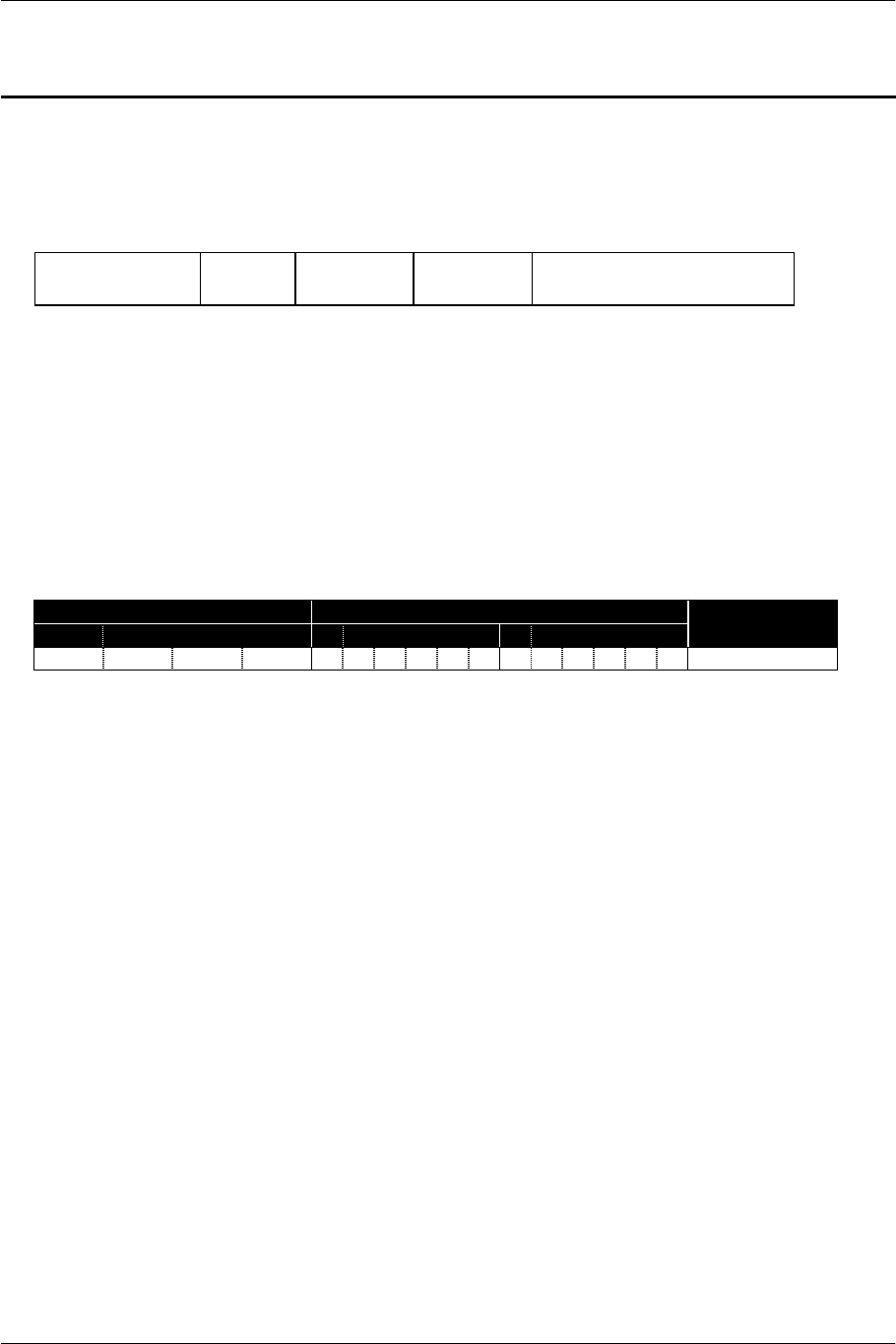

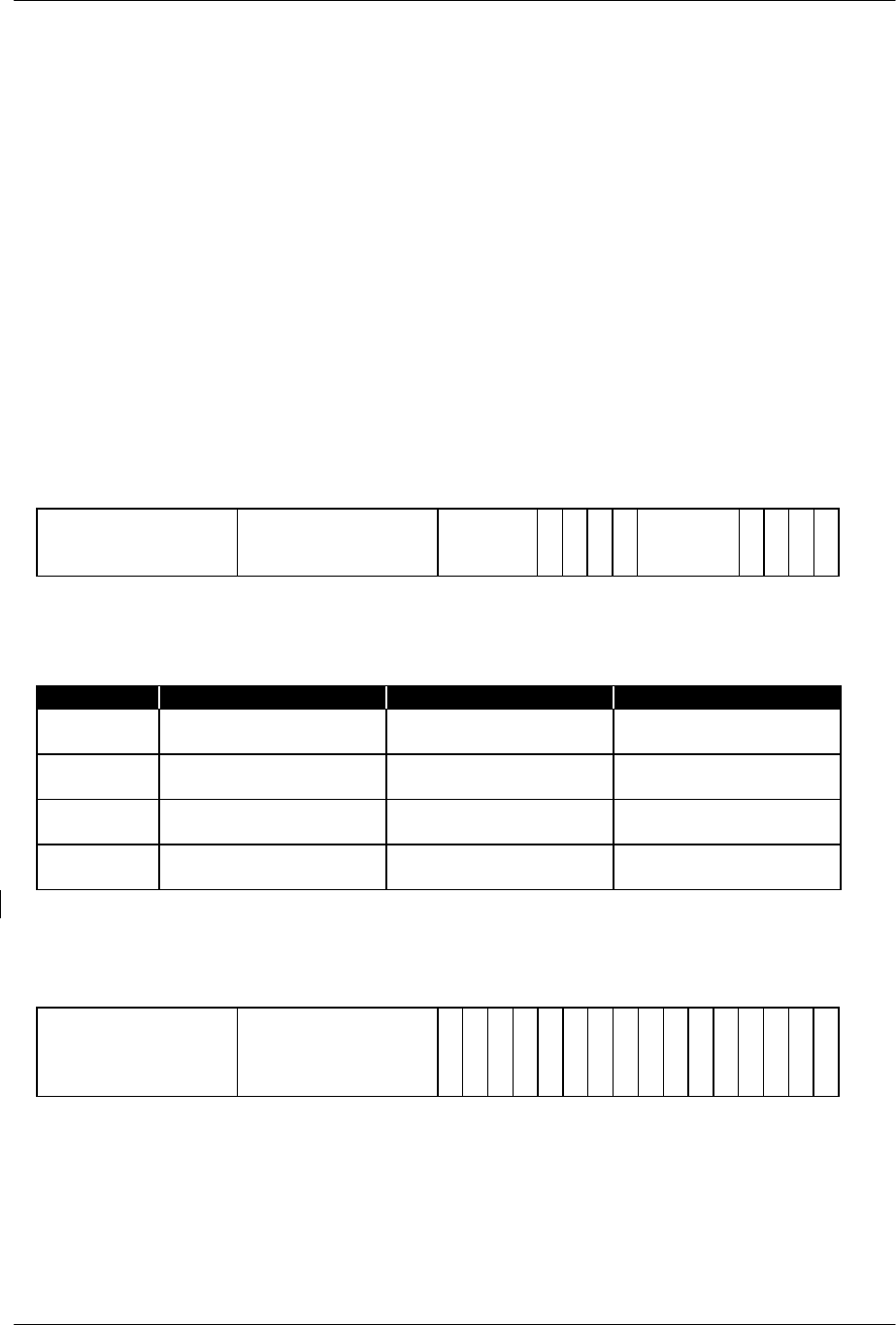

6.1. Macro Instruction Operation Code...........................................................................................................................226

SCE CONFIDENTIAL VU User's Manual Version 6.0

© SCEI

-12-

6.1.1. Macro Instruction Operation Type ................................................................................................................... 226

6.1.2. Macro Instruction Operation Field ................................................................................................................... 227

6.2. Macro Instruction Set ................................................................................................................................................. 229

BC2F : Branch on COP2 Conditional Signal......................................................................................................... 230

BC2FL : Branch on COP2 Conditional Signal...................................................................................................... 231

BC2T : Branch on COP2 Conditional Signal ........................................................................................................ 232

BC2TL : Branch on COP2 Conditional signal ...................................................................................................... 233

CFC2 : Transfer Integer Data from VU to EE Core ........................................................................................... 234

CTC2 : Transfer Integer Data from EE Core to VU ........................................................................................... 235

LQC2 : Floating-Point Data Transfer from EE Core to VU.............................................................................. 236

QMFC2 :

Floating-Point Data Transfer from VU to EE Core........................................................................... 237

QMTC2 :

Floating-Point Data Transfer from EE Core to VU .......................................................................... 238

SQC2 :

Floating-Point Data Transfer from VU to EE Core............................................................................... 239

VABS : Absolute Value............................................................................................................................................. 240

VADD : Add.............................................................................................................................................................. 241

VADDi : Add to I Register ...................................................................................................................................... 242

VADDq : Add to Q Register ................................................................................................................................... 243

VADDbc : Broadcast Add ....................................................................................................................................... 244

VADDA : Add to Accumulator .............................................................................................................................. 245

VADDAi : Add I Register to Accumulator ........................................................................................................... 246

VADDAq : Add Q Register to Accumulator ........................................................................................................ 247

VADDAbc : Broadcast Add to Accumulator........................................................................................................ 248

VCALLMS : Start Micro Sub-Routine.................................................................................................................... 249

VCALLMSR : Start Micro Sub-Routine by Register............................................................................................. 250

VCLIP : Clipping Judgment..................................................................................................................................... 251

VDIV : Divide............................................................................................................................................................ 252

VFTOI0 : Conversion to Fixed Point..................................................................................................................... 253

VFTOI4 : Conversion to Fixed Point..................................................................................................................... 254

VFTOI12 : Conversion to Fixed Point .................................................................................................................. 255

VFTOI15 : Conversion to Fixed Point .................................................................................................................. 256

VIADD : Add Integer............................................................................................................................................... 257

VIADDI : Add Immediate Value Integer .............................................................................................................. 258

VIAND : Logical Product ........................................................................................................................................ 259

VILWR : Integer Load.............................................................................................................................................. 260

VIOR : Logical Sum.................................................................................................................................................. 261

VISUB : Integer Subtract.......................................................................................................................................... 262

VISWR : Integer Store .............................................................................................................................................. 263

VITOF0 : Conversion to Floating-Point Number................................................................................................ 264

VITOF4 : Conversion to Floating-Point Number................................................................................................ 265

VITOF12 : Conversion to Floating-Point Number.............................................................................................. 266

VITOF15 : Conversion to Floating-Point Number.............................................................................................. 267

VLQD : Load with Pre-Decrement ........................................................................................................................ 268

VLQI : Load with Post-Increment.......................................................................................................................... 269

VMADD : Product Sum........................................................................................................................................... 270

VMADDi : Product Sum; with I Register .............................................................................................................. 271

VMADDq : Product Sum; with Q Register........................................................................................................... 272

SCE CONFIDENTIAL VU User's Manual Version 6.0

© SCEI

-13-

VMADDbc : Broadcast Product Sum.....................................................................................................................273

VMADDA : Product Sum; to Accumulator...........................................................................................................274

VMADDAi : Product Sum; with I Register, to Accumulator..............................................................................275

VMADDAq : Product Sum; with Q Register, to Accumulator ...........................................................................276

VMADDAbc : Broadcast Product Sum; to Accumulator ....................................................................................277

VMAX : Maximum Value .........................................................................................................................................278

VMAXi : Maximum Value........................................................................................................................................279

VMAXbc : Maximum Value.....................................................................................................................................280

VMFIR : Transfer from Integer Register to Floating-Point Register..................................................................281

VMINI : Minimum Value .........................................................................................................................................282

VMINIi : Minimum Value ........................................................................................................................................283

VMINIbc : Minimum Value.....................................................................................................................................284

VMOVE : Transfer between Floating-Point Registers.........................................................................................285

VMR32 : Vector Rotate.............................................................................................................................................286

VMSUB : Multiply and Subtract ..............................................................................................................................287

VMSUBi : Multiply and Subtract with I Register...................................................................................................288

VMSUBq : Multiply and Subtract; Q Register........................................................................................................289

VMSUBbc : Broadcast Multiply and Subtract........................................................................................................290

VMSUBA : Multiply and Subtract; to Accumulator..............................................................................................291

VMSUBAi : Multiply and Subtract; with I Register, to Accumulator .................................................................292

VMSUBAq : Multiply and Subtract; with Q Register, to Accumulator ..............................................................293

VMSUBAbc : Broadcast Multiply and Subtract; to Accumulator .......................................................................294

VMTIR : Transfer from Floating-Point Register to Integer Register .................................................................295

VMUL : Multiply........................................................................................................................................................296

VMULi : Multiply; by I Register...............................................................................................................................297

VMULq : Multiply; by Q Register............................................................................................................................298

VMULbc : Broadcast Multiply .................................................................................................................................299

VMULA : Multiply; to Accumulator .......................................................................................................................300

VMULAi : Multiply by I Register; to Accumulator ...............................................................................................301

VMULAq : Multiply by Q Register; to Accumulator ............................................................................................302

VMULAbc : Broadcast Multiply; to Accumulator.................................................................................................303

VNOP : No Operation..............................................................................................................................................304

VOPMULA : Vector Outer Product.......................................................................................................................305

VOPMSUB : Vector Outer Product........................................................................................................................306

VRGET : Get Random Numbers............................................................................................................................307

VRINIT : Random Number Initial Set...................................................................................................................308

VRNEXT : New Random Numbers.......................................................................................................................309

VRSQRT : Square Root Division ............................................................................................................................310

VRXOR : Random Number Set ..............................................................................................................................311

VSQD : Store with Pre-Decrement.........................................................................................................................312

VSQI : Store with Post-Increment ..........................................................................................................................313

VSQRT : Square Root ...............................................................................................................................................314

VSUB : Subtract .........................................................................................................................................................315

VSUBi : Subtract I Register ......................................................................................................................................316

VSUBq : Subtract Q Register ...................................................................................................................................317

VSUBbc : Broadcast Subtract...................................................................................................................................318

SCE CONFIDENTIAL VU User's Manual Version 6.0

© SCEI

-14-

VSUBA : Subtract; to Accumulator ........................................................................................................................ 319

VSUBAi : Subtract I Register; to Accumulator ..................................................................................................... 320

VSUBAq : Subtract Q Register; to Accumulator .................................................................................................. 321

VSUBAbc : Broadcast Subtract; to Accumulator.................................................................................................. 322

VWAITQ : Q Register Synchronize ....................................................................................................................... 323

7. Appendix.............................................................................................................................................................................. 325

7.1. Sample Micro Programs ............................................................................................................................................. 326

7.2. EFU Processing........................................................................................................................................................... 353

7.3. Micro Subroutine Debugging .................................................................................................................................... 362

7.3.1. Debug Flow.......................................................................................................................................................... 362

7.3.2. Notes on Re-execution........................................................................................................................................ 363

7.4. Throughput / Latency List ........................................................................................................................................ 365

SCE CONFIDENTIAL VU User's Manual Version 6.0

© SCEI

-15-

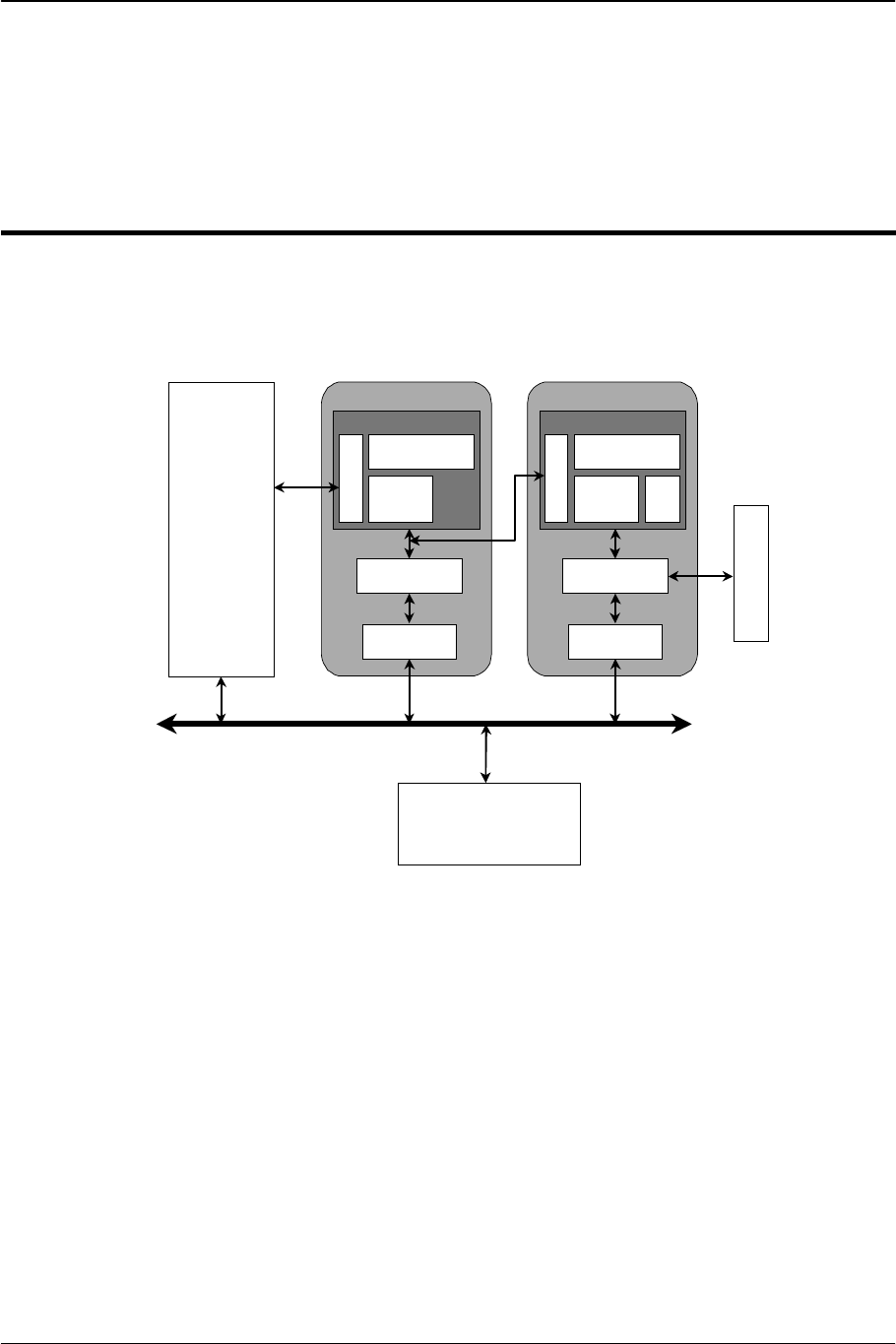

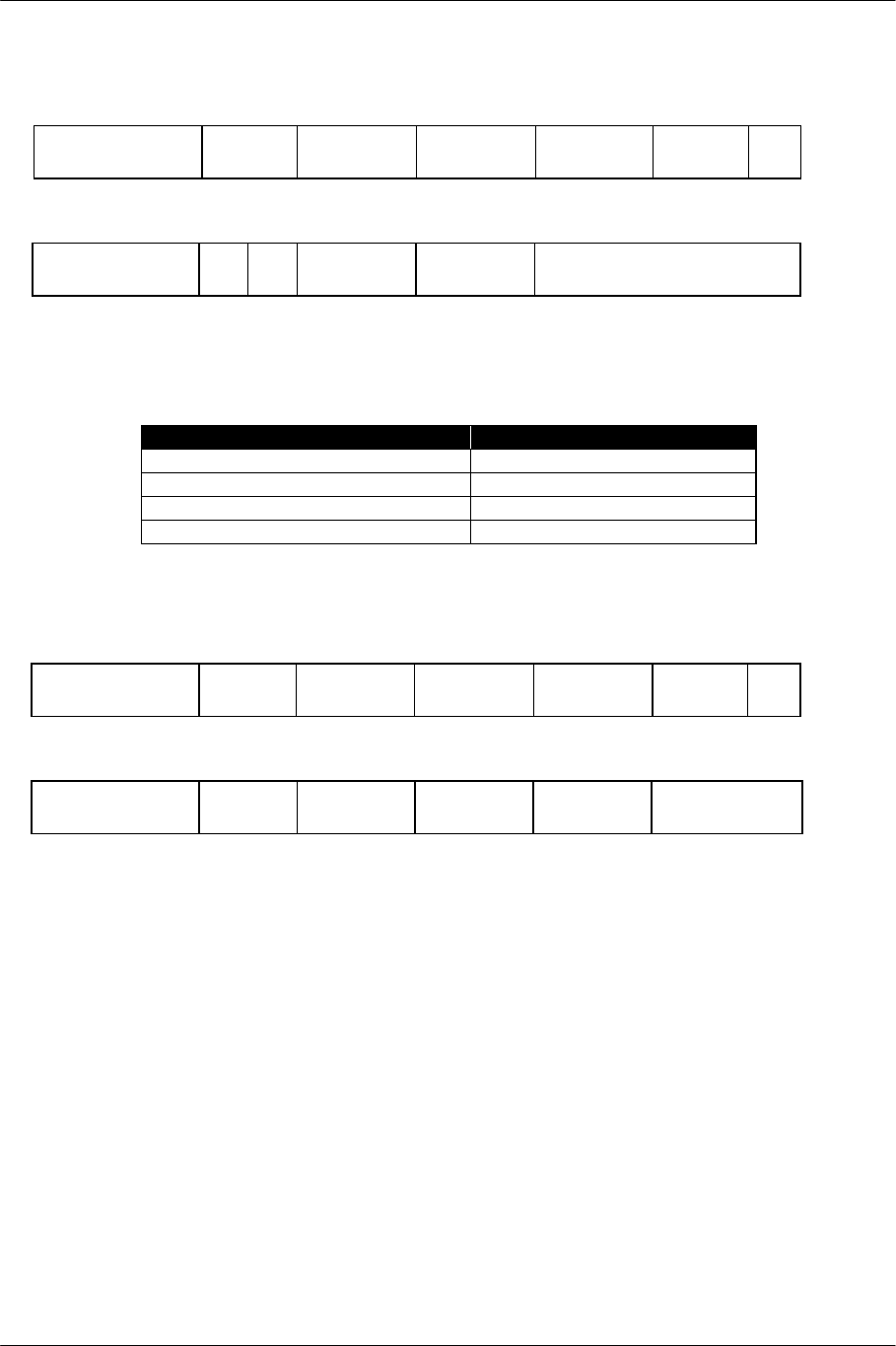

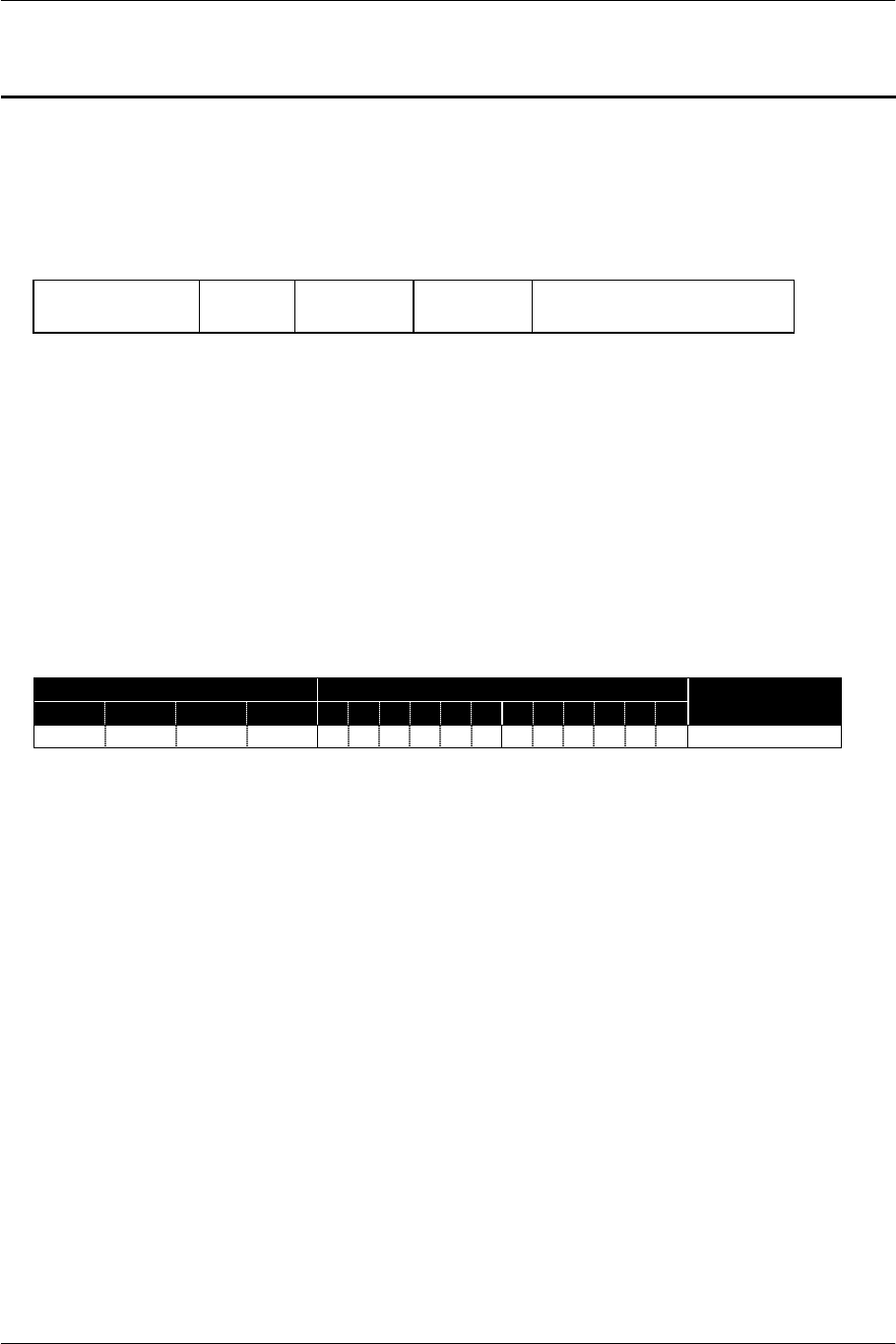

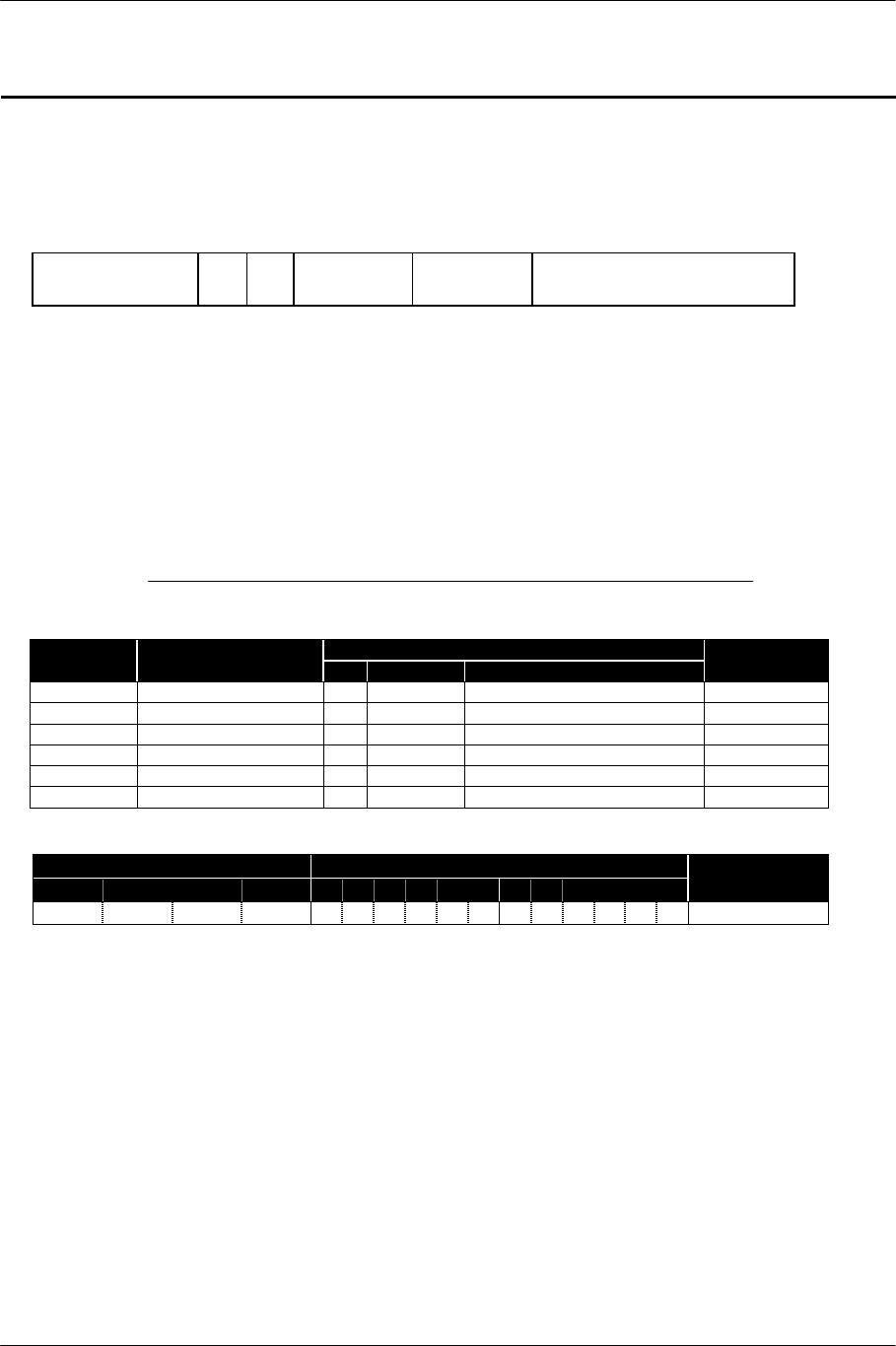

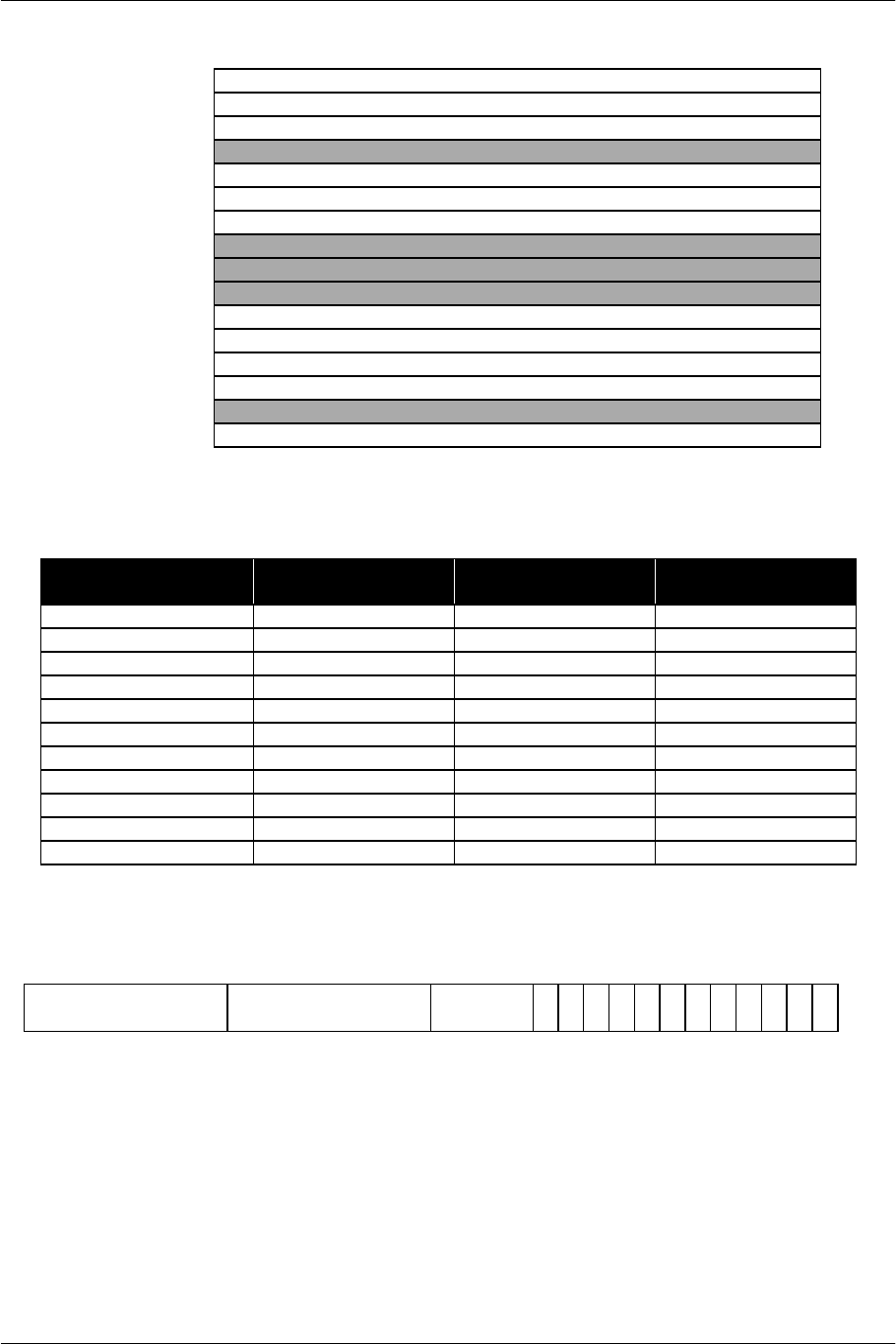

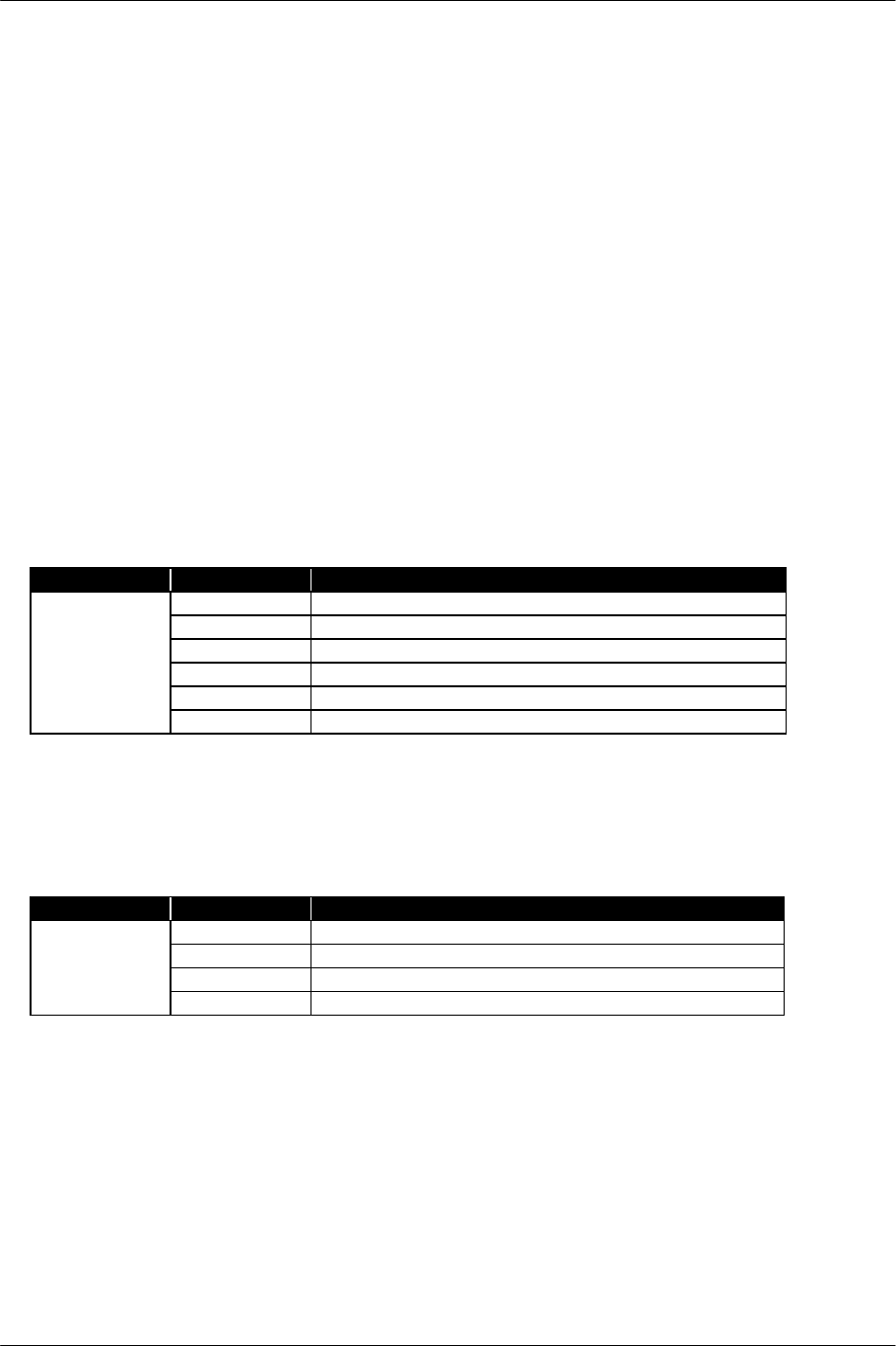

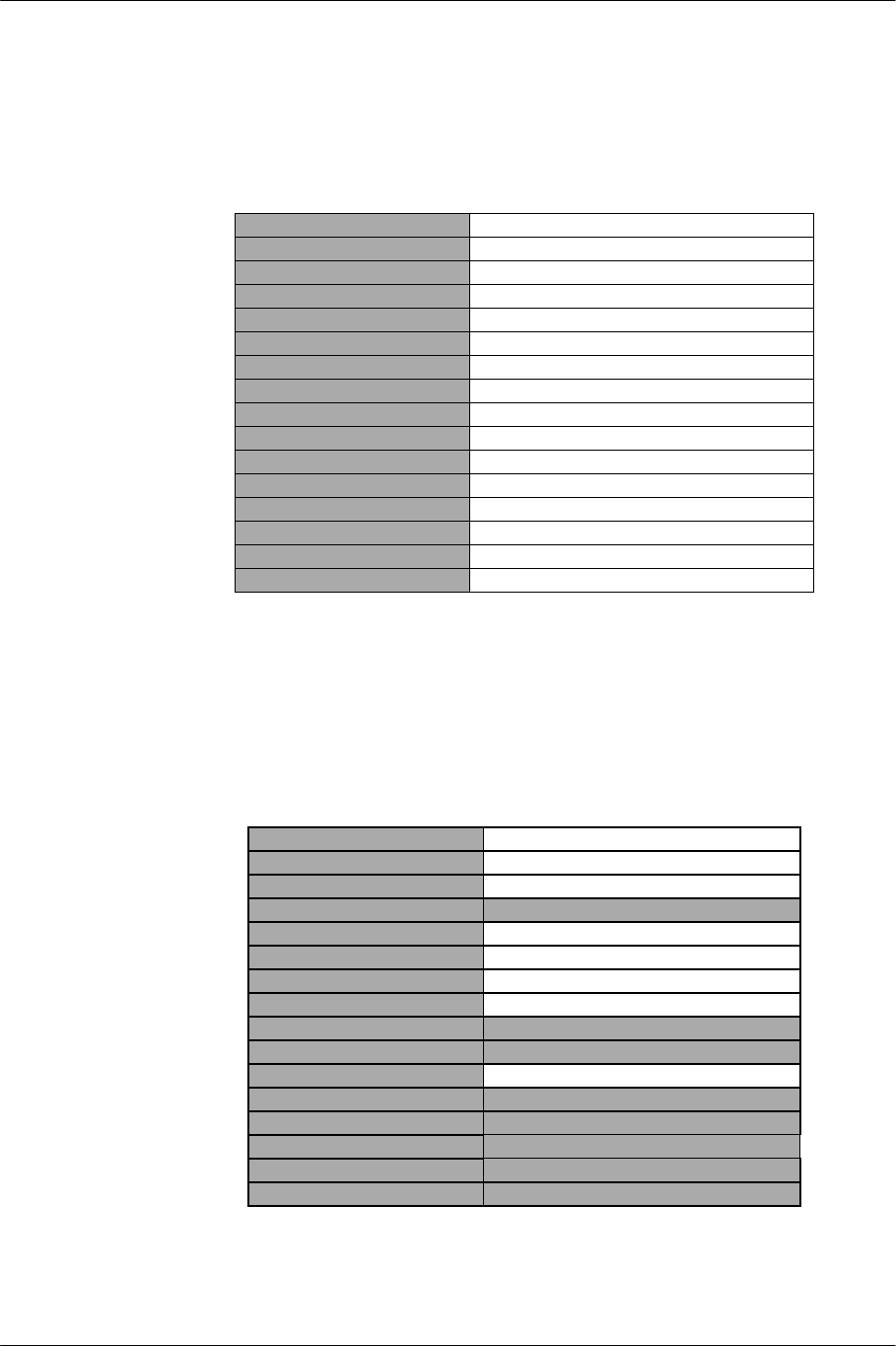

1. VU Overview

The VU is a vector ALU that efficiently performs four-element floating-point vector calculations. It is part of

the VPU, along with the VU Mem (VU Data Memory) and the VIF (compressed data expansion engine).

Two VPUs are mounted on the EE as shown in Figure 1-1.

Main Memory

GIF

EE

core

VIF0

VU0

Micro Mem0

4KByte

VU Mem0

4KByte

VUcore

VU regs.

VPU0

VIF1

VU1

Micro Mem1

16KByte

VU Mem1

16KByte

VUcore

VU regs

.

VPU1

EFU

Figure 1-1 VPU System Outline

VU0 is joined to the EE Core as COP2 via a coprocessor connection. It assists the EE Core in non-stationary

geometry processing. It has a 4-Kbyte instruction memory (MicroMem0) and a 4-Kbyte data memory (VU

Mem0).

VU1 operates independently, and is chiefly in charge of background stationary geometry processing. VU1 has

an Elementary Function Unit (EFU), as well as a 16-Kbyte instruction memory (MicroMem1) and a 16-Kbyte

data memory (VU Mem1). VU1 is also connected to the GIF (the interface unit to the Graphics Synthesizer),

and the GIF control instruction (XGKICK instruction) is mounted. VU1's floating-point and integer registers

are mapped to VPU0's VU Mem0.

SCE CONFIDENTIAL VU User's Manual Version 6.0

© SCEI

-16-

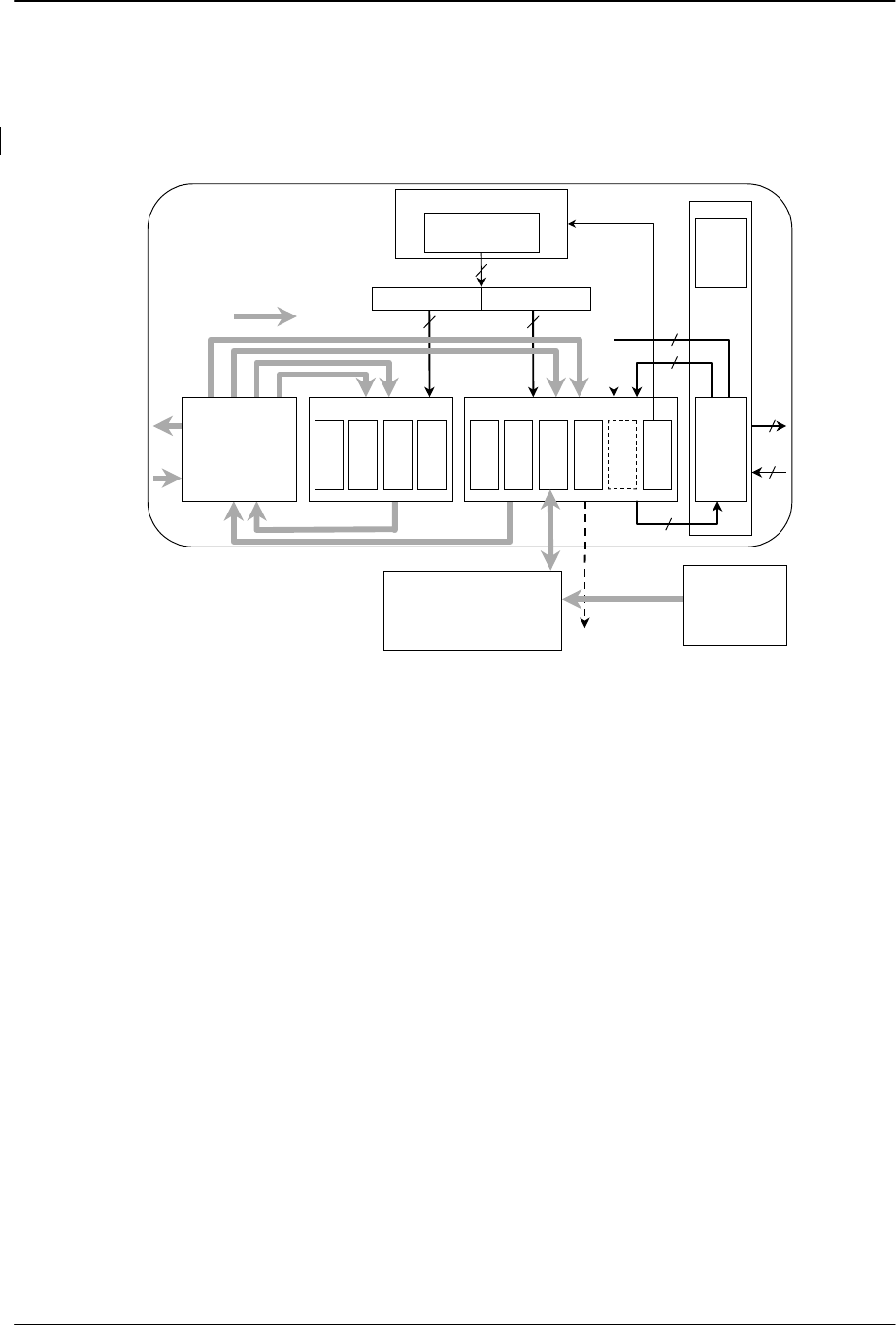

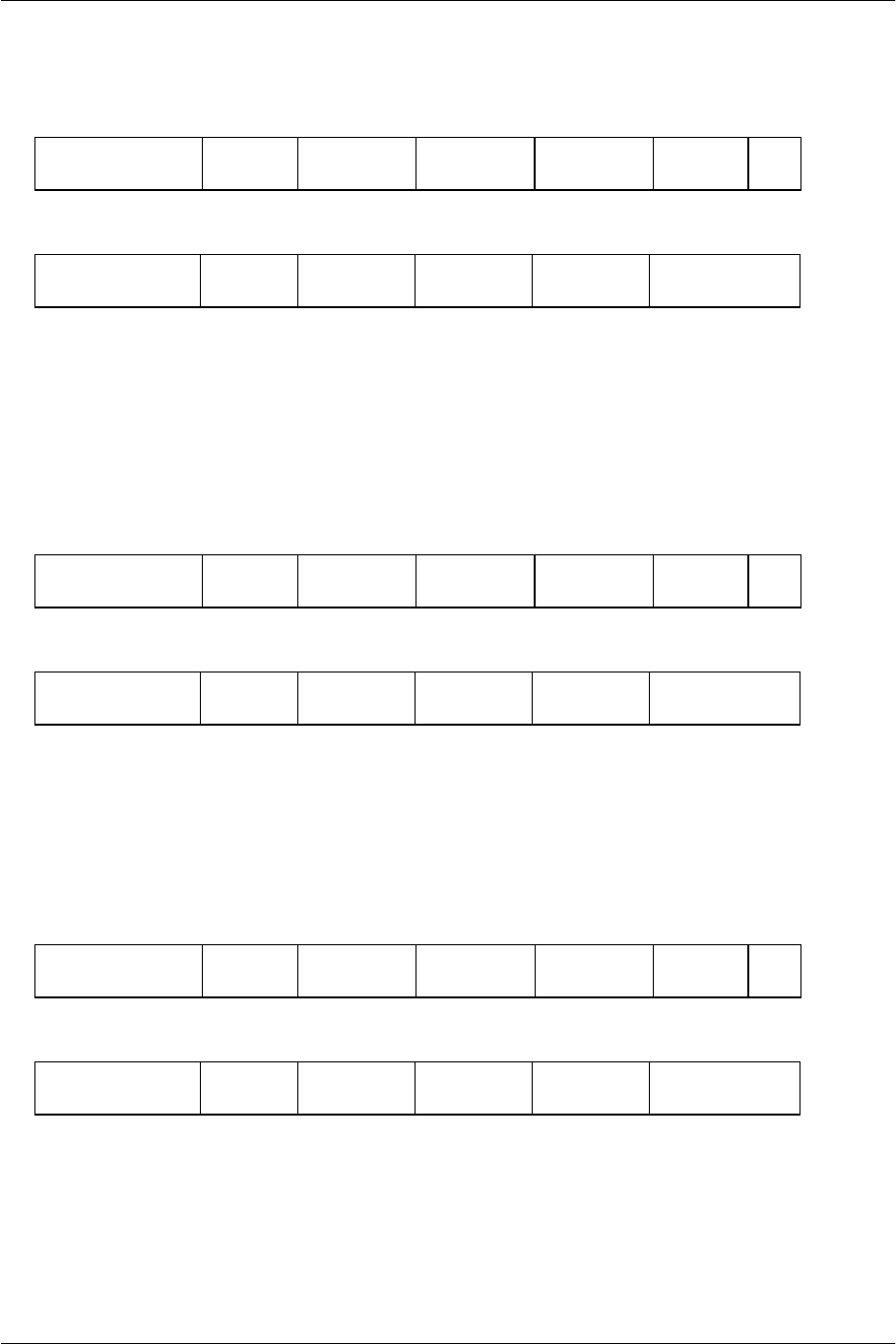

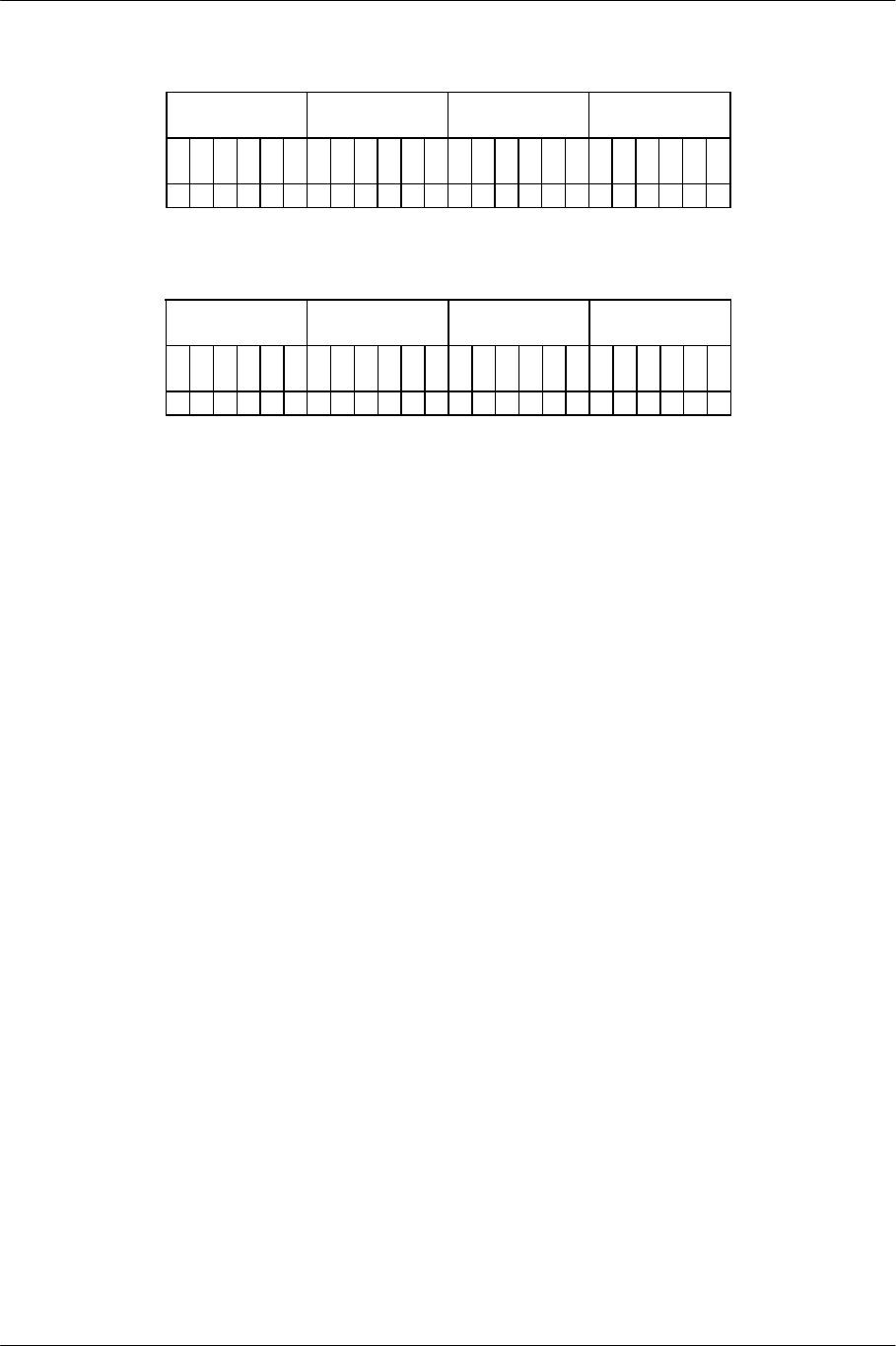

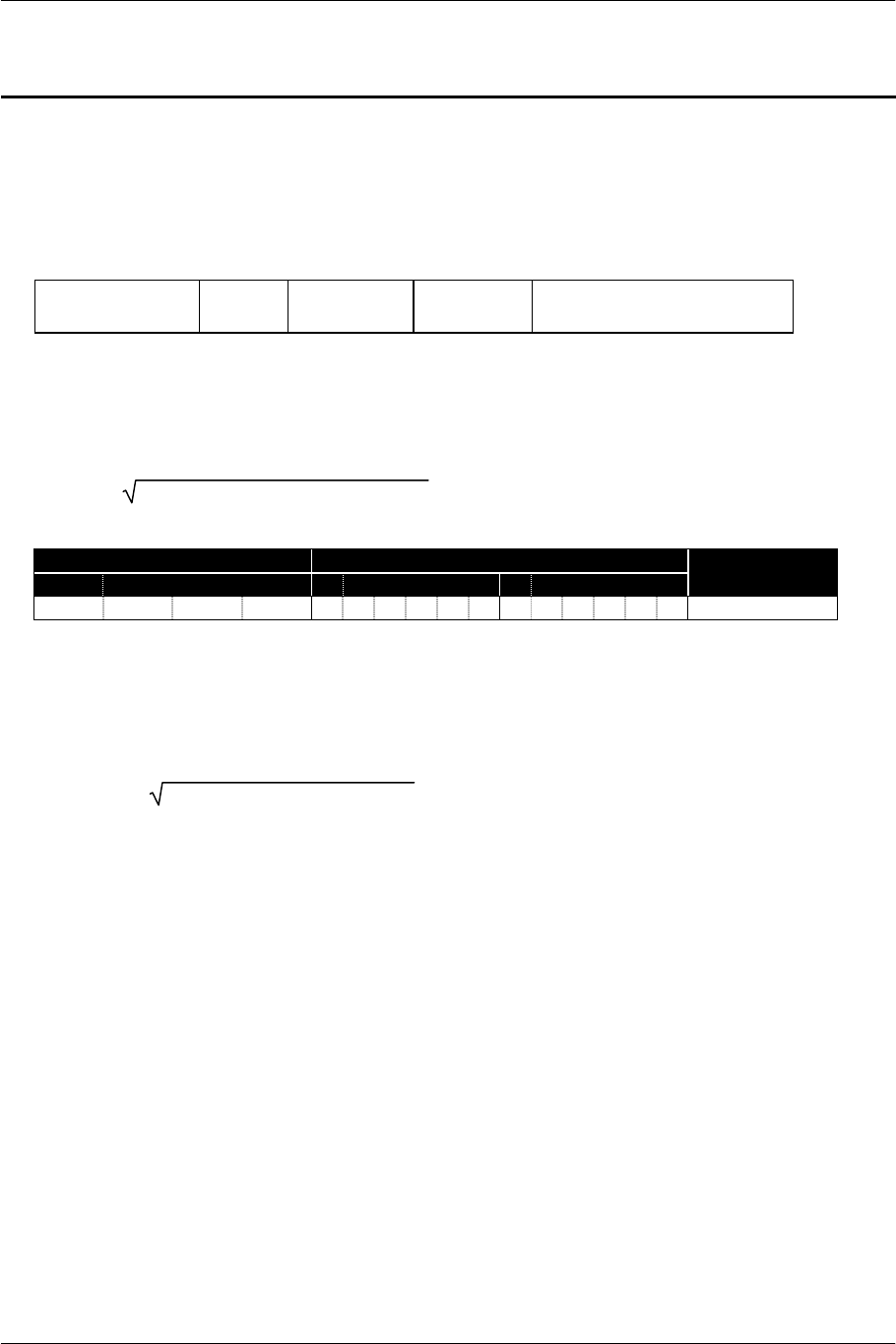

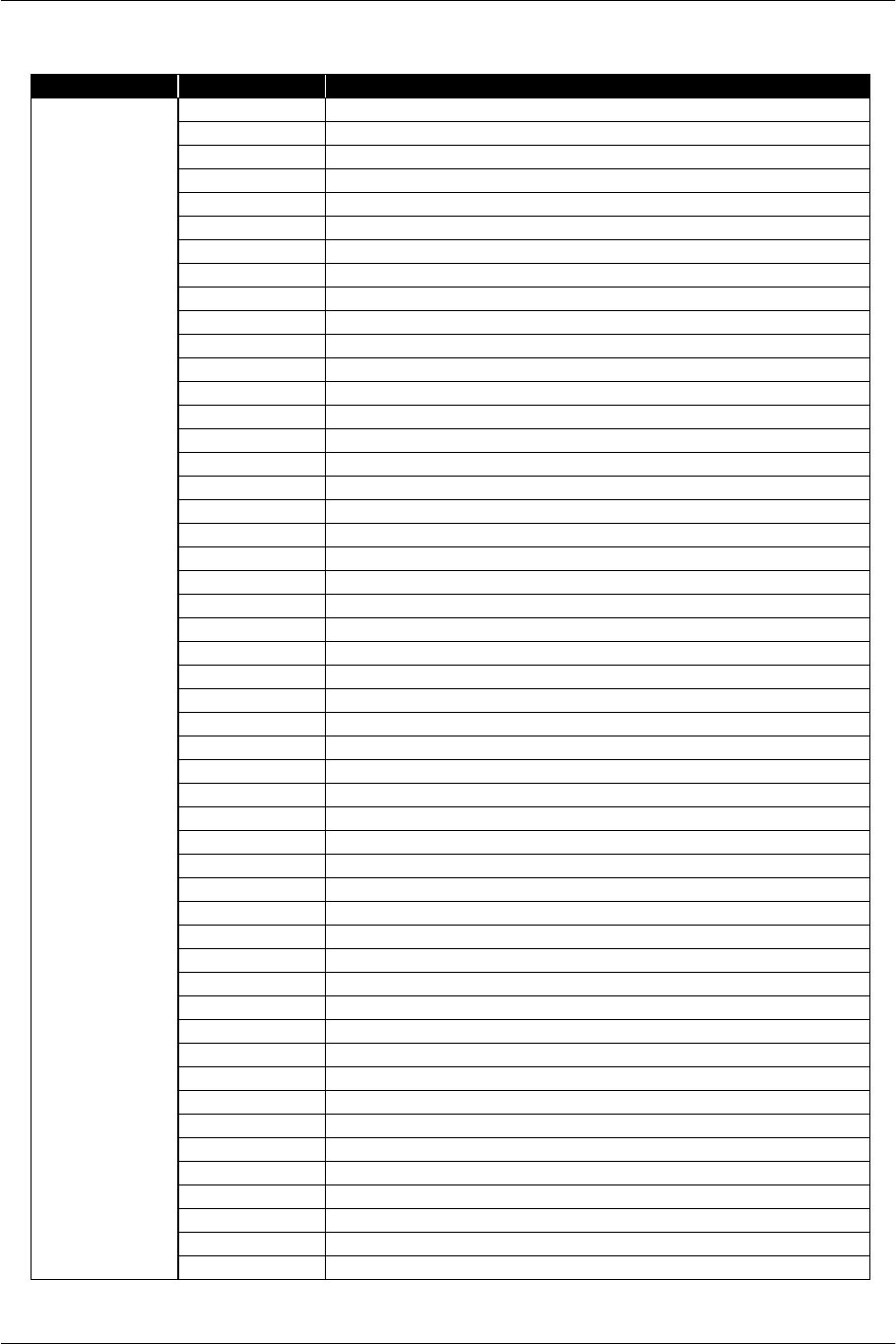

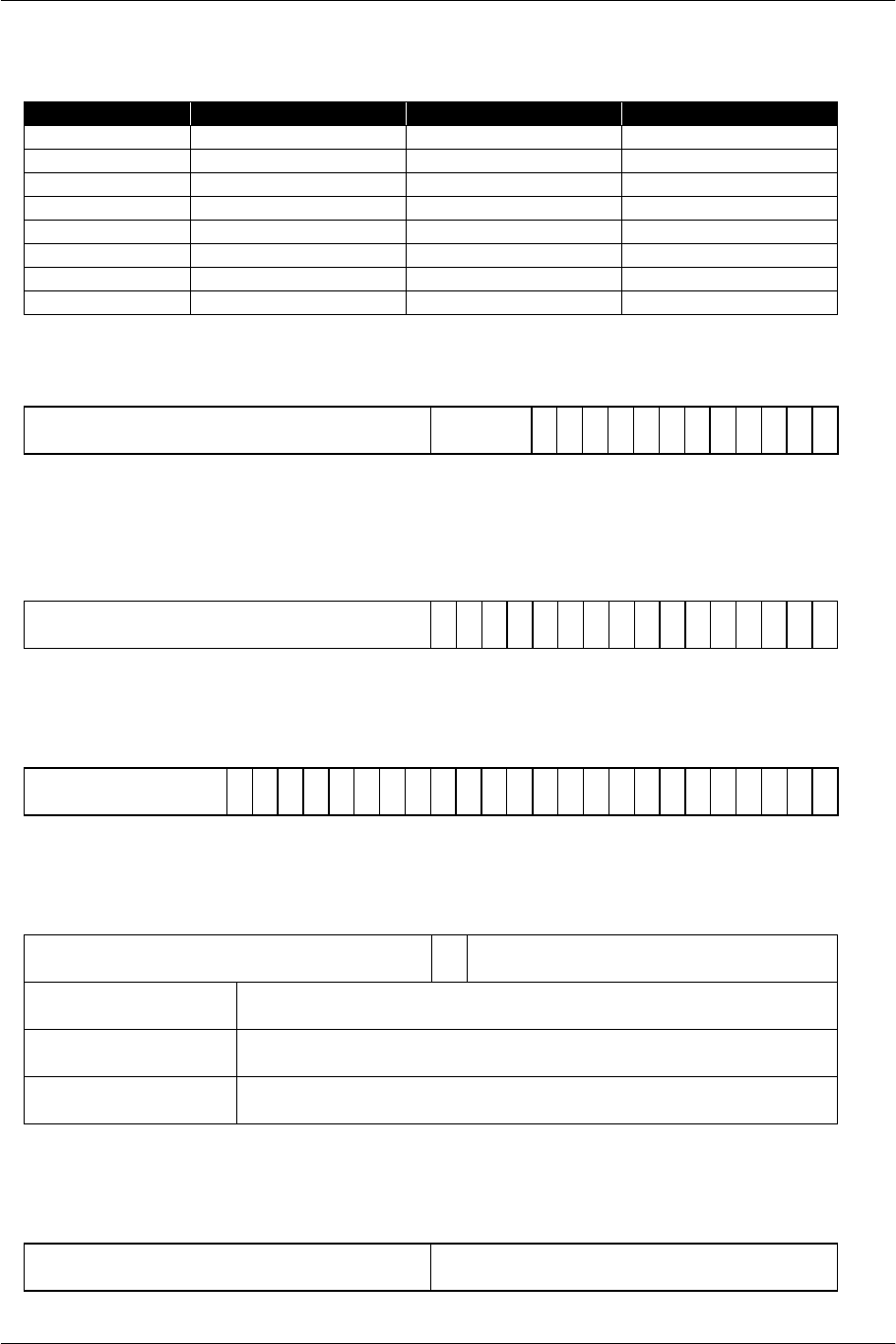

1.1. VPU Structure

Figure 1-2 is a block diagram of the VPU including the VU.

Micro Mem

4KByte or 16KByte

Upper Instruction Lower Instruction

63 0

64

32 32

bold line : 128 bit

Micro instruction fetch unit

FMACw

FMACz

FMACy

FMACx

Upper Execution Unit

RANDU/etc

LSU

IALU

EFU

Lower Execution Unit

floating

registers

VF00-VF31

(COP2 data registers)

127 0

BRU

VU Mem

4KByte or 16KByte

integer

registers

VI00`VI15

16

16

16

QMTC2

/ LQC2

QMFC2

/ SQC2

CTC2

32

CFC2

32

special

registers

VI16`VI31

COP2

control

registers

External Units

Vector Unit :VU

Vector Processing Unit:VPU

FDIV

VIF

Figure 1-2 VU Outline Block Diagram

The VPU consists of the VU, VU Mem (VU Data Memory), and the VIF (compressed data expansion engine).

The VU loads data in 128-bit units (single-precision floating-point number x 4) from the VU Mem, performs

calculations according to micro programs in the VU's internal MicroMem, and stores the results in the VU Mem.

The VU Mem may be used as a temporary area depending on the micro program.

Micro programs employ 64-bit length LIW (Long Instruction Word) instruction sets. They can concurrently

execute a floating-point product-sum calculation in the upper 32 bits (the Upper instruction field) and a floating-

point division or integer calculation in the lower 32 bits (the Lower instruction field).

There are 32 128-bit floating-point registers (single-precision floating-point x 4). There are 16 16-bit integer

registers.

1.1.1. Upper Execution Unit

FMAC

This unit adds, subtracts, multiplies, and does product-sum operations on floating-point numbers. Four

units are mounted in order to efficiently execute four-element vector calculations: FMACx, FMACy,

FMACz, and FMACw. To increase the efficiency of pipeline processing, the latency of the instructions that

use the FMAC has been unified at four cycles.

SCE CONFIDENTIAL VU User's Manual Version 6.0

© SCEI

-17-

1.1.2. Lower Execution Unit

FDIV

This unit performs self-synchronous high-speed floating-point division/square root calculations. It uses a

single-precision floating-point value as input, then stores the calculation result in the dedicated Q register.

The next FDIV instruction cannot be executed while the FDIV is executing. The FDIV stalls if this is

attempted.

LSU

This unit controls Load/Store to and from VU Mem.

Load/Store must be performed in units of 128 bits, but the x, y, z, and w field units can be masked.

There are two ways of specifying addresses. The first specifies a base (Integer) register and offsets in the

operation code field. The second specifies the base register only, not the offsets, and performs post-

incrementing or pre-decrementing. Incrementing/Decrementing is +1/-1 in 128-bit word address units.

IALU

This unit performs 16-bit integer calculations.

Loop counter calculation and Load/Store address calculation are performed using the Integer registers.

BRU

This unit controls jumping and conditional branching.

Most instructions specify PC-relative addresses for the jump target address. The offset is specified by an 11-

bit immediate value, so it is possible to jump within a range of 8 Kbytes before and after the PC. The JR and

JALR instructions are register indirect jump instructions, which use the data in a register as an absolute

address.

Conditional branching is performed by a comparison with one or two Integer registers. When doing

conditional branching based on the results of floating-point calculations, the results of the AND operation

with the MAC flag, status flag, or clipping flag and the appropriate mask value are temporarily stored in an

Integer register. Branching is performed by comparing with this register.

RANDU

This unit generates floating-point random numbers in the range +1.0<r<+2.0. Using the M series, the

mantissa is created from the type that the user specified. Due to a feature of the M series, +1.0 does not

appear in the random numbers. When 0 is specified as the type, only +1.0 is created, not a random number.

This M series is represented by the following polynomial:

p(x) = x23 + x5 + 1

EFU

This is the Elementary Function Unit, which performs calculations such as exponential, logarithmic, and

trigonometric functions. This unit is mounted only on VU1.

The EFU uses a scalar value (a single floating-point value) or vector value (four floating-point values) as

input, then stores the scalar value from the calculation result in the dedicated P register. Calculation latency

varies for each function. The next EFU instruction cannot be executed while the EFU is executing. The

EFU stalls if this is attempted.

SCE CONFIDENTIAL VU User's Manual Version 6.0

© SCEI

-18-

1.1.3. Floating-Point Registers

The VU has 32 128-bit floating-point registers (VF00 – VF31), which are equivalent to four single-precision

floating-point values each. For a product-sum calculation, two 128-bit registers can be specified as source

registers and one 128-bit register can be specified as the destination register.

1.1.4. Integer Register

The VU has sixteen 16-bit Integer registers (VI00 – VI15). These registers are used for loop counters and

load/store address calculations.

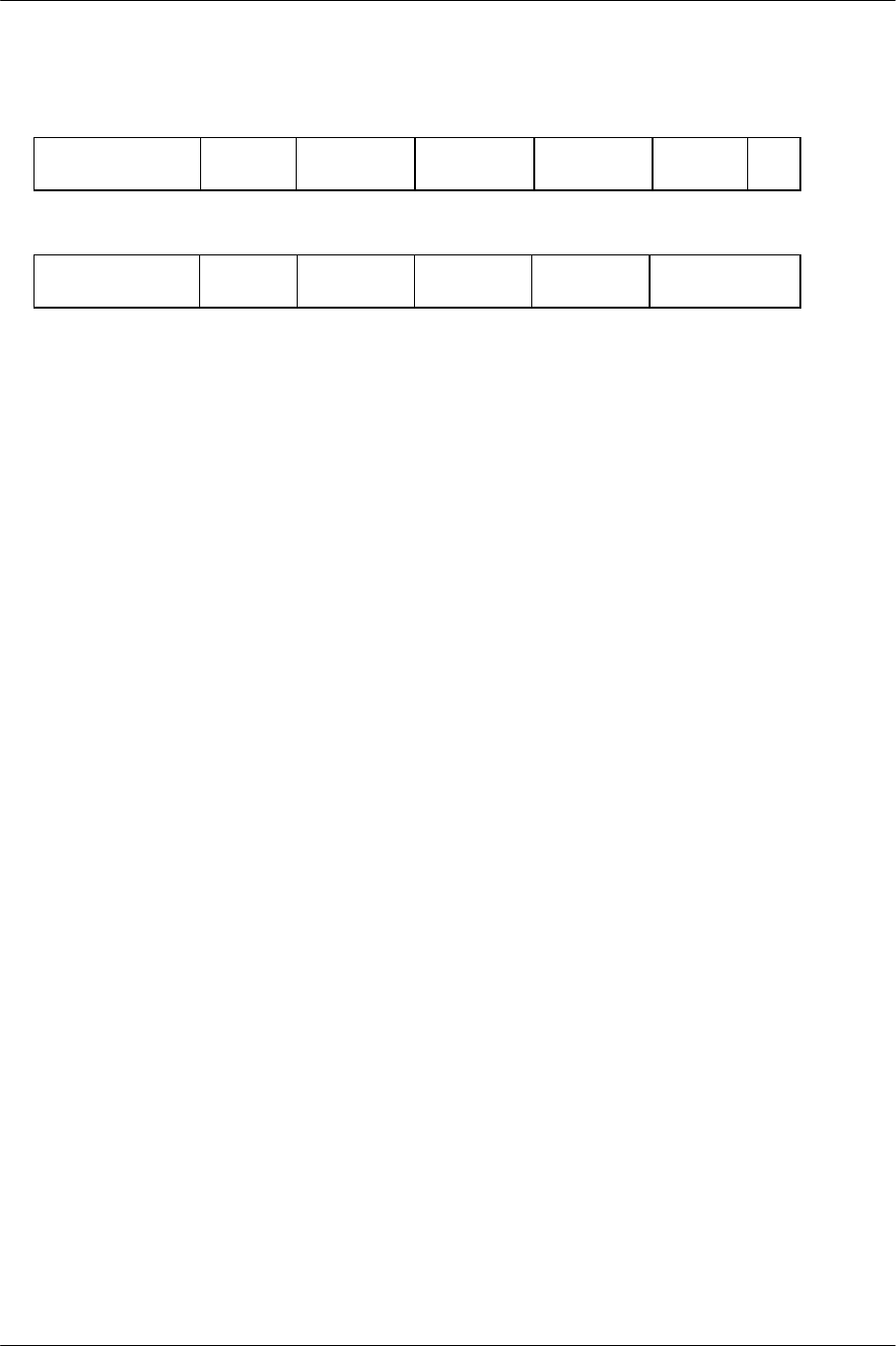

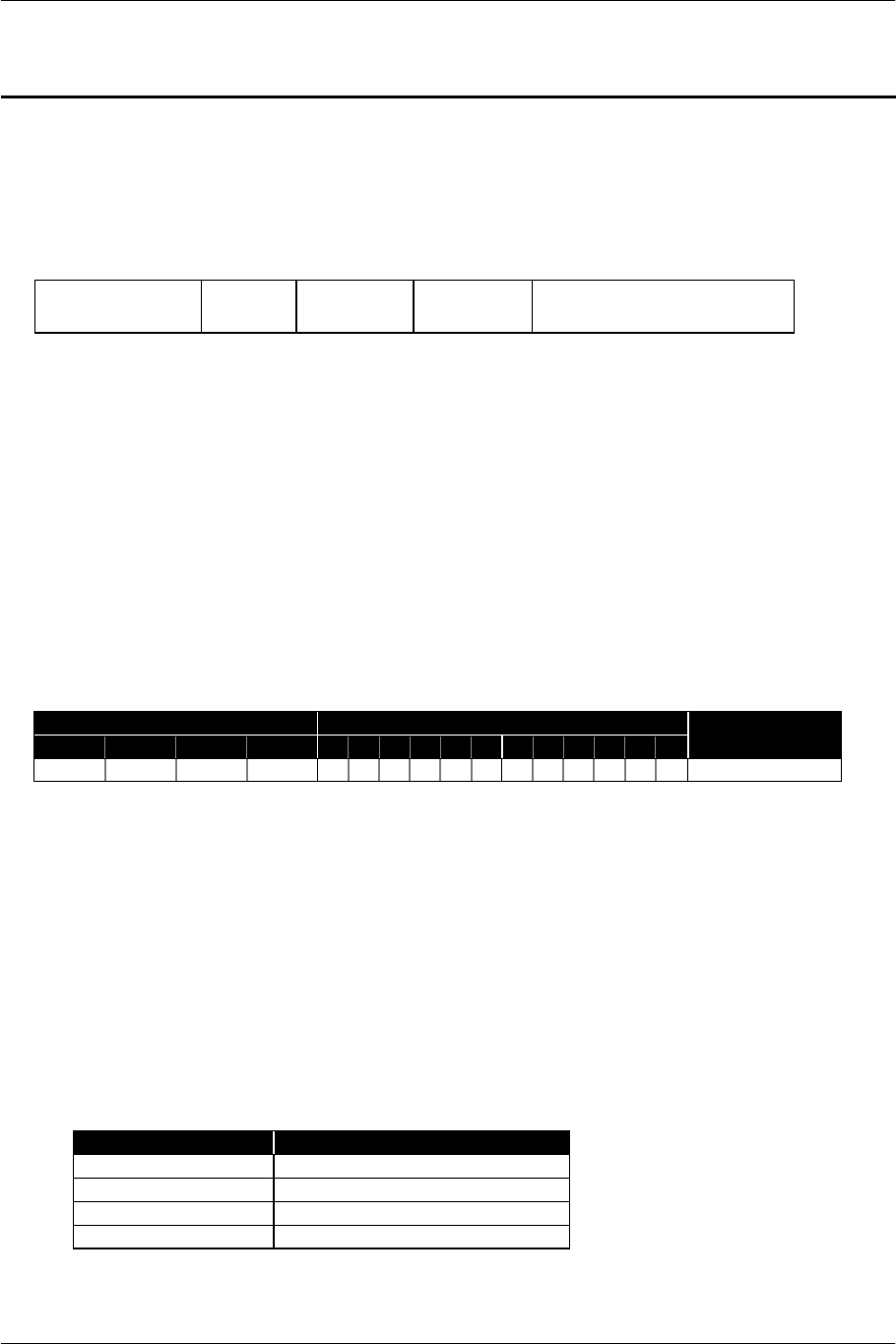

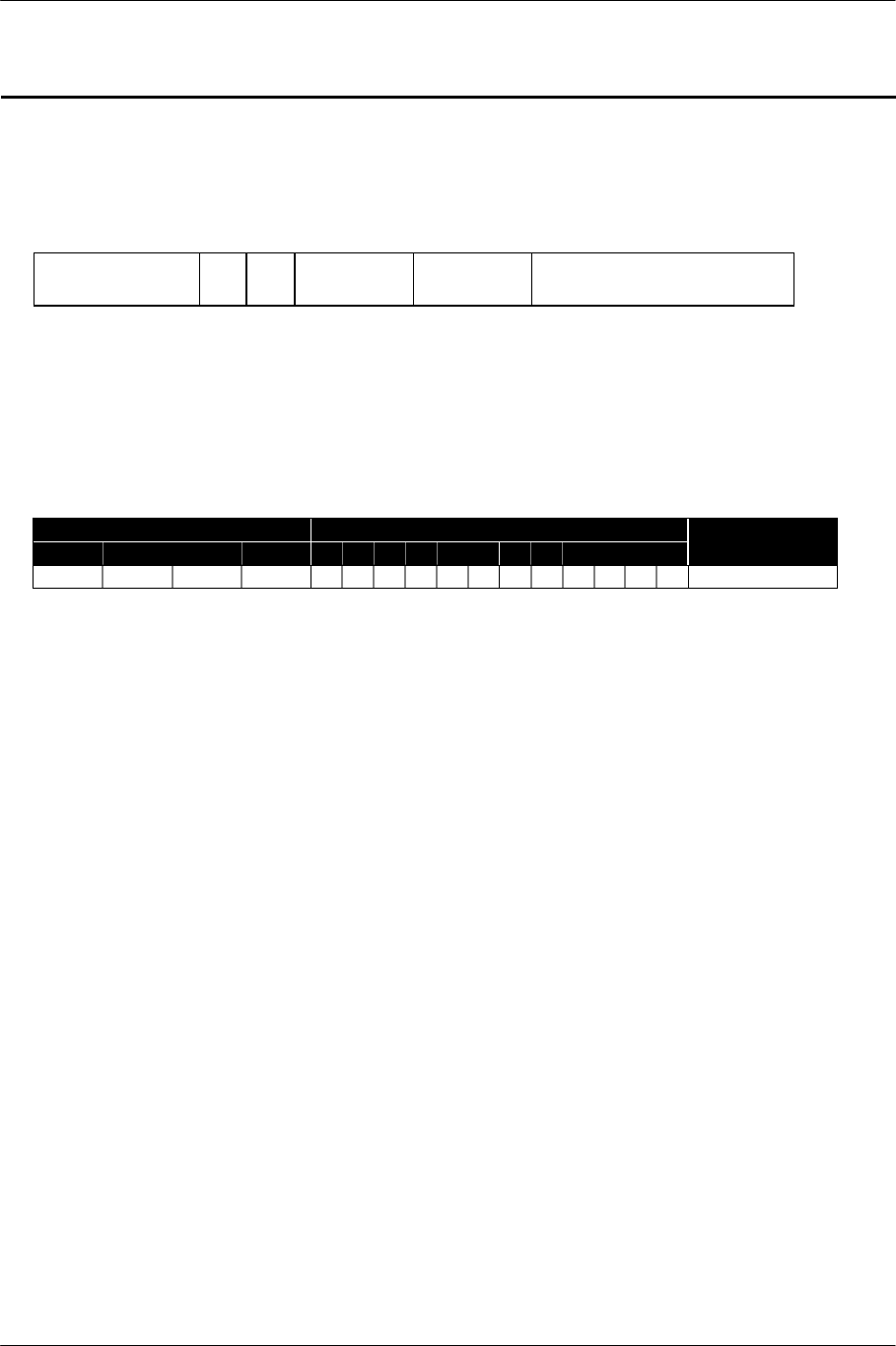

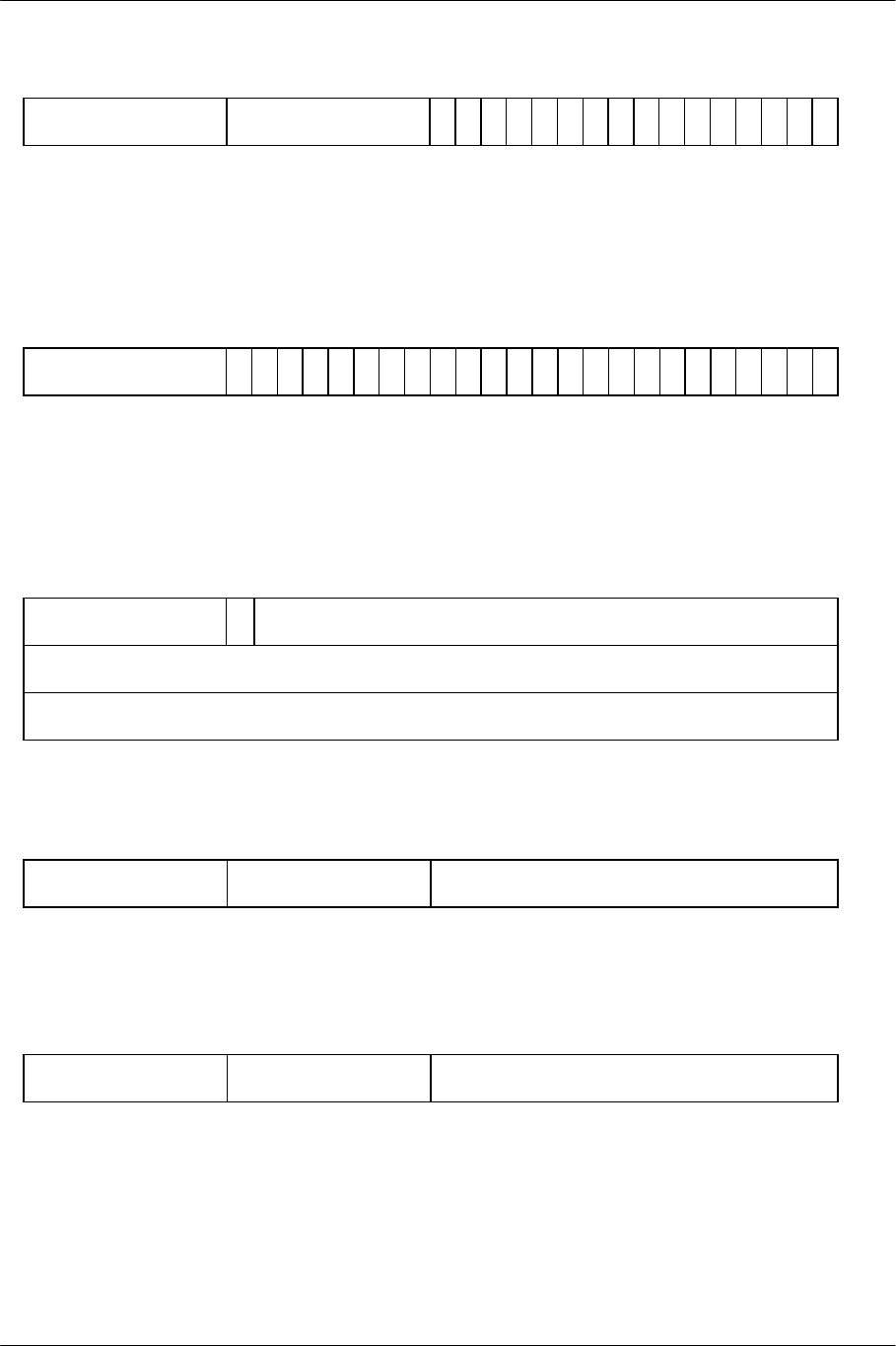

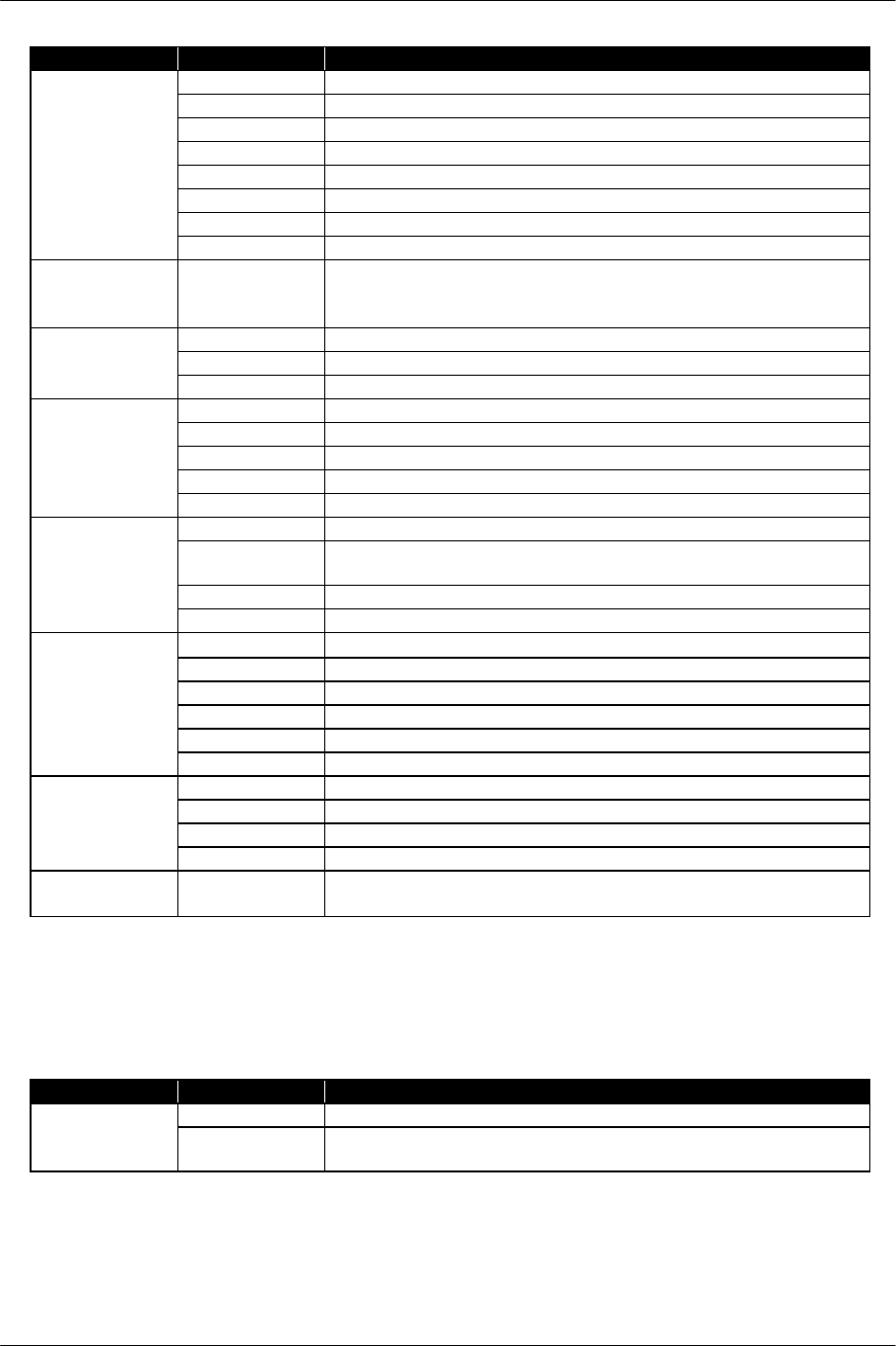

1.1.5. VU Mem

The VU data memory capacity is 4 Kbytes for VU0, and 16 Kbytes for VU1. This memory is connected to the

LSU (Load/Store Unit) at a width of 128 bits, and the address is qword (16 bytes) aligned. The effective data

address must be divisible by 16: the address divided by 16 is specified in some instructions.

Address

0x0000 w z y x

0x0010 w z y x

:

:

0x0ff0 w z y x

:

Mounted on VU1 only

:

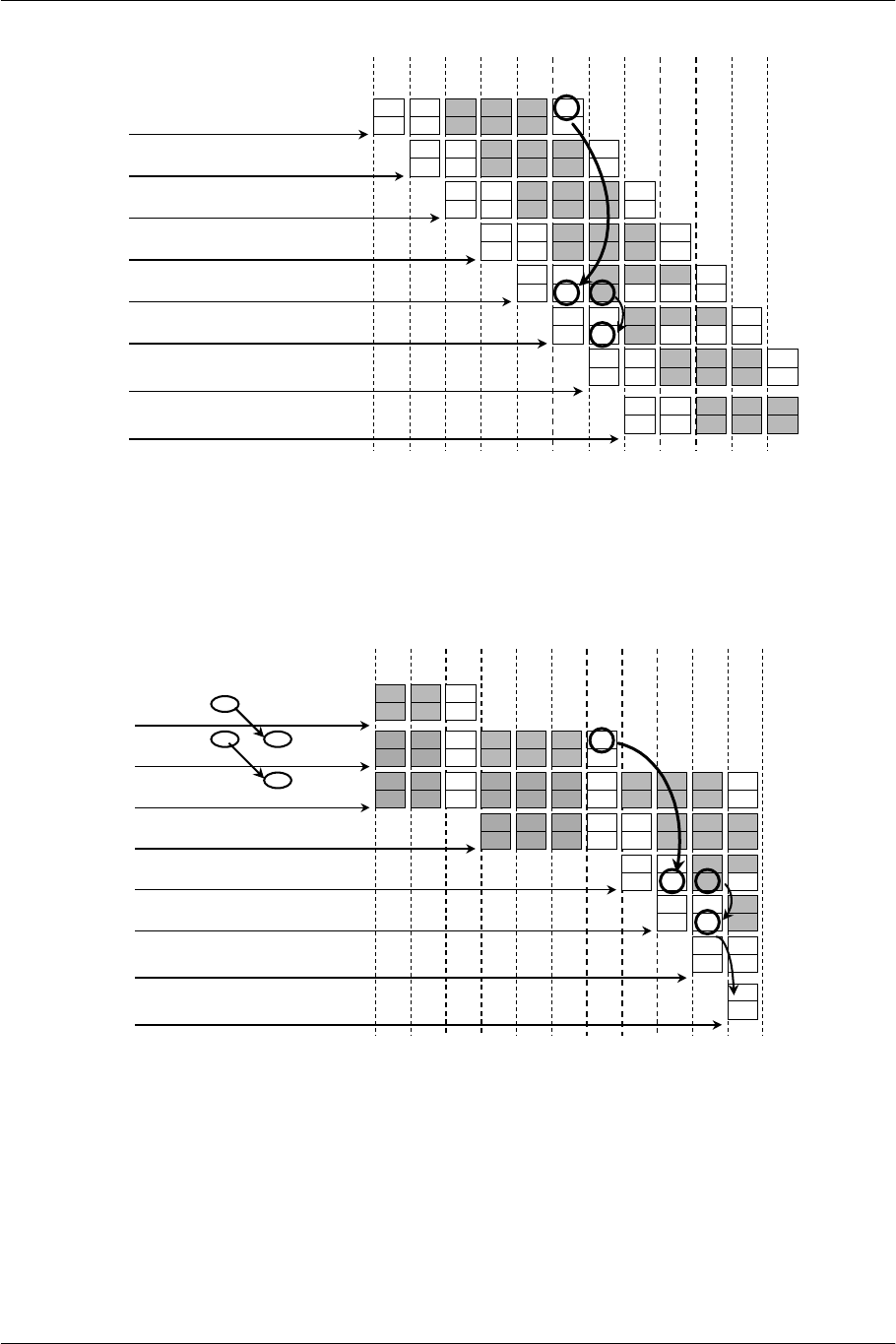

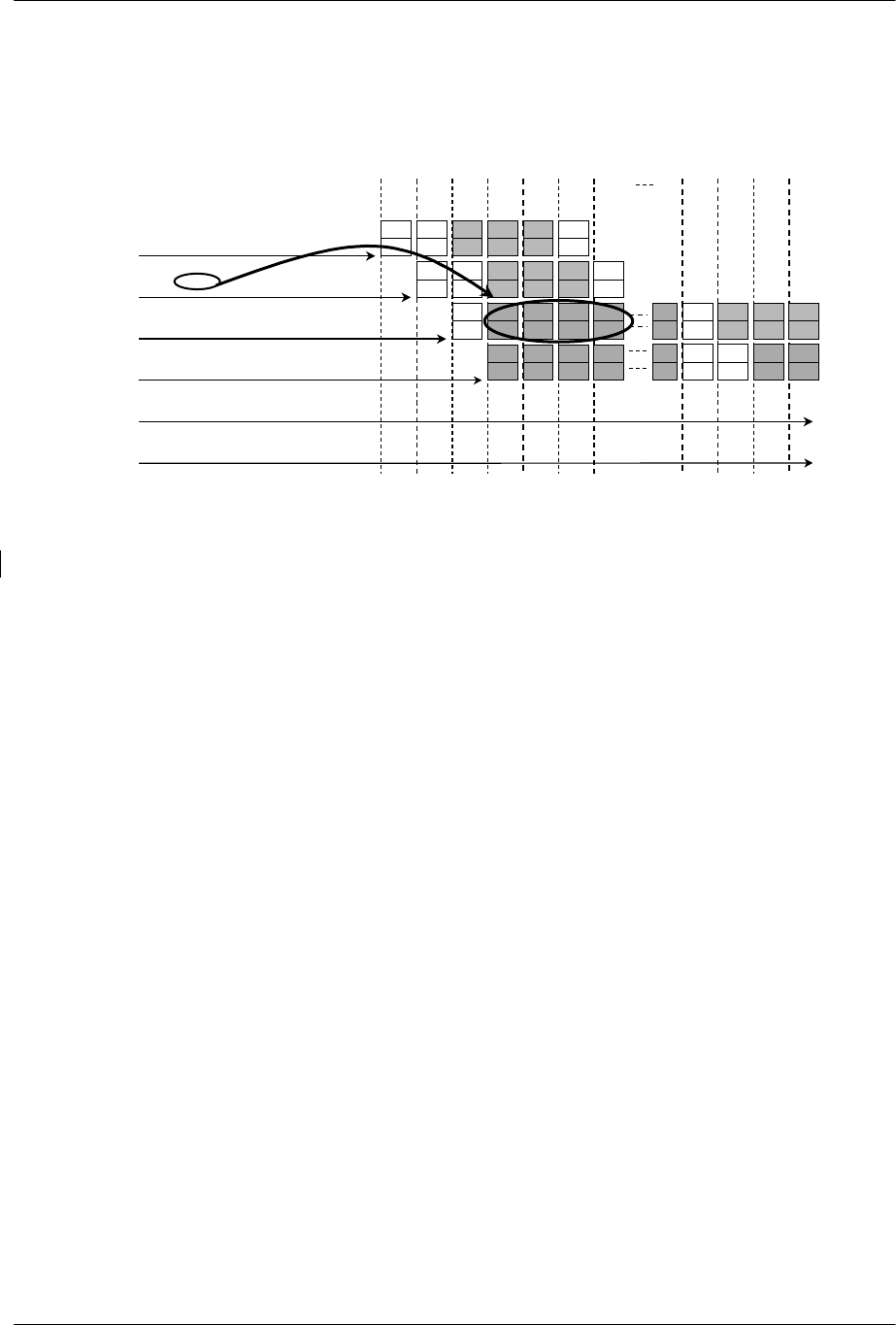

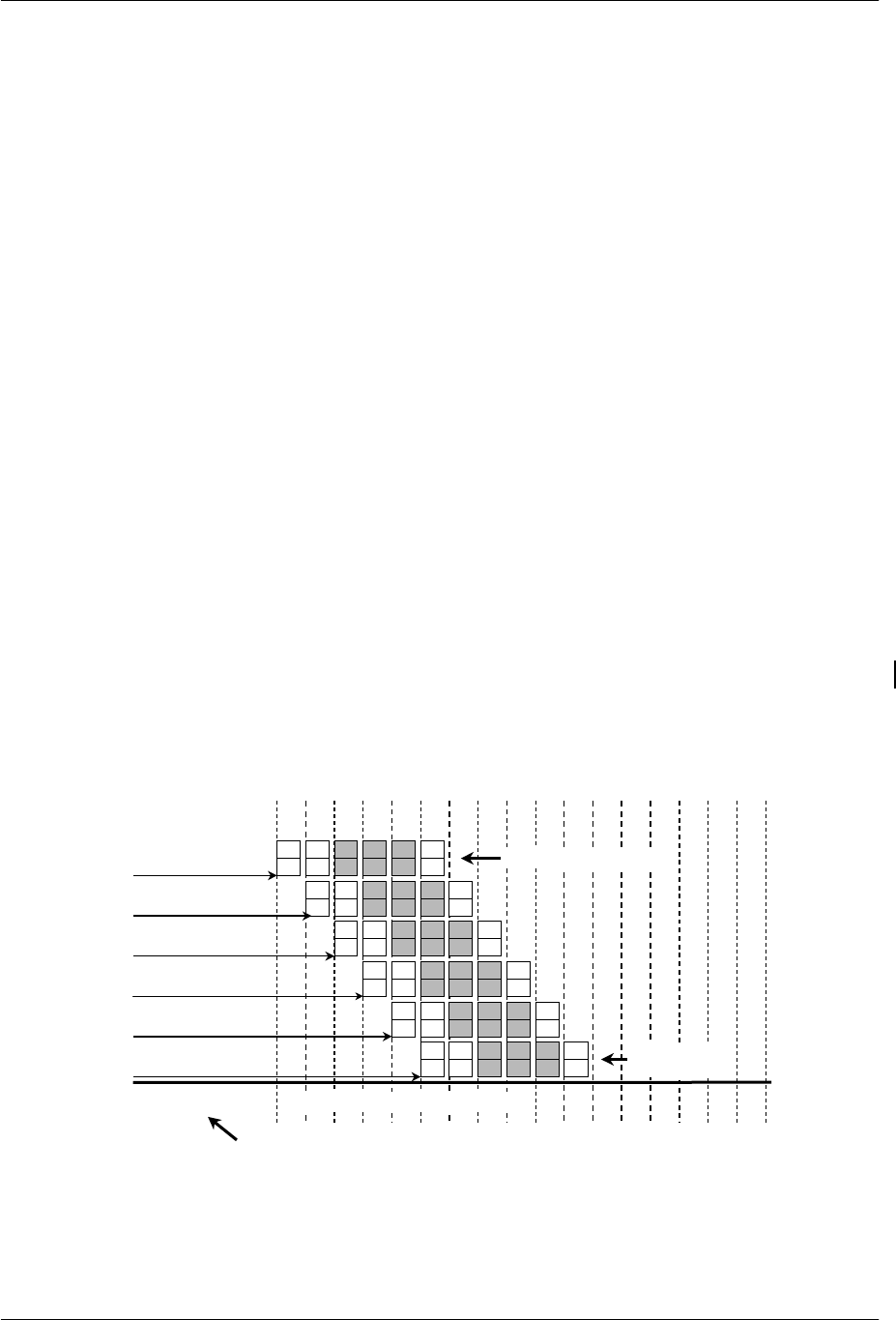

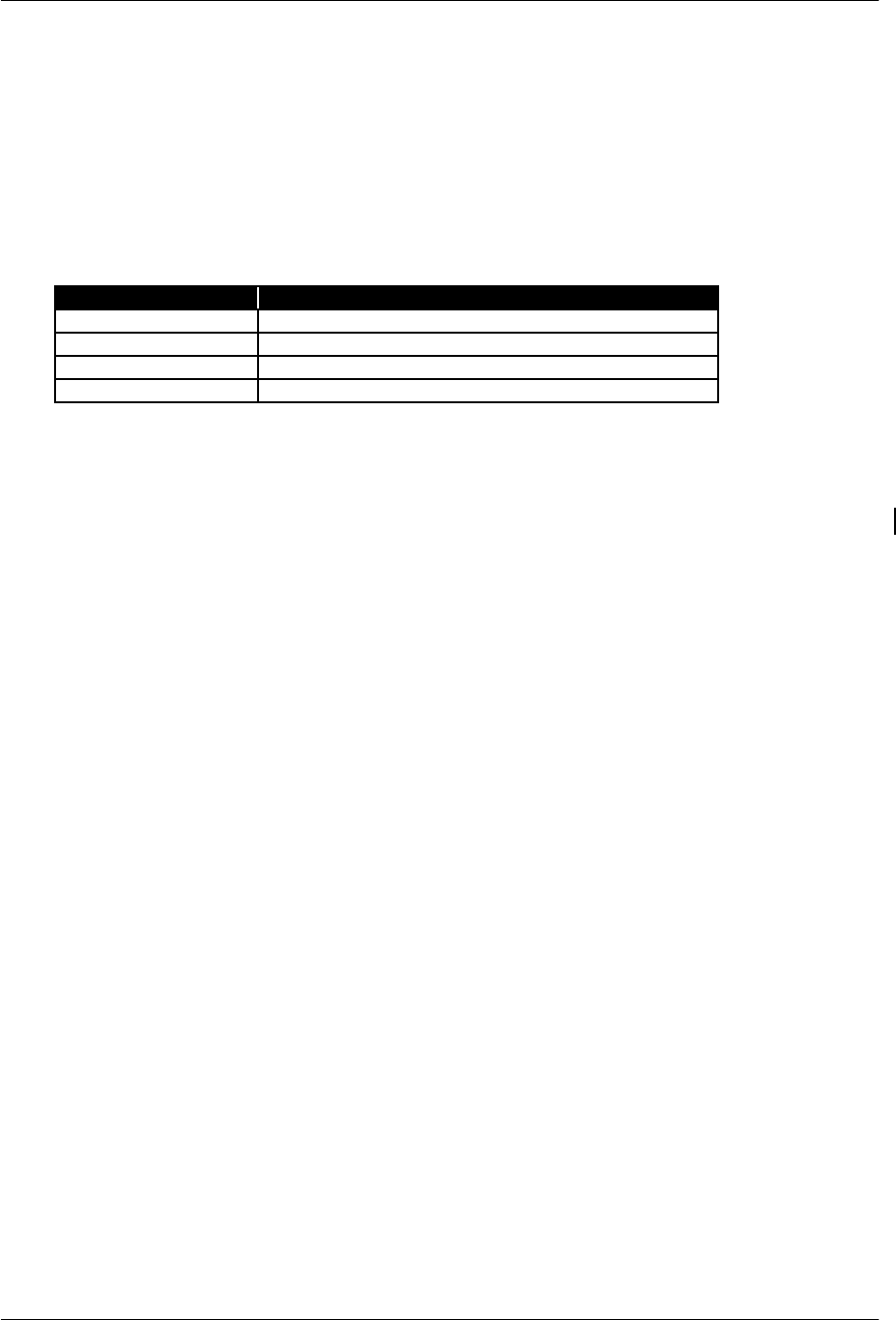

0x3ff0 w z y x