Z80_Asm Z80 Asm

User Manual: Pdf Z80_Asm

Open the PDF directly: View PDF ![]() .

.

Page Count: 16

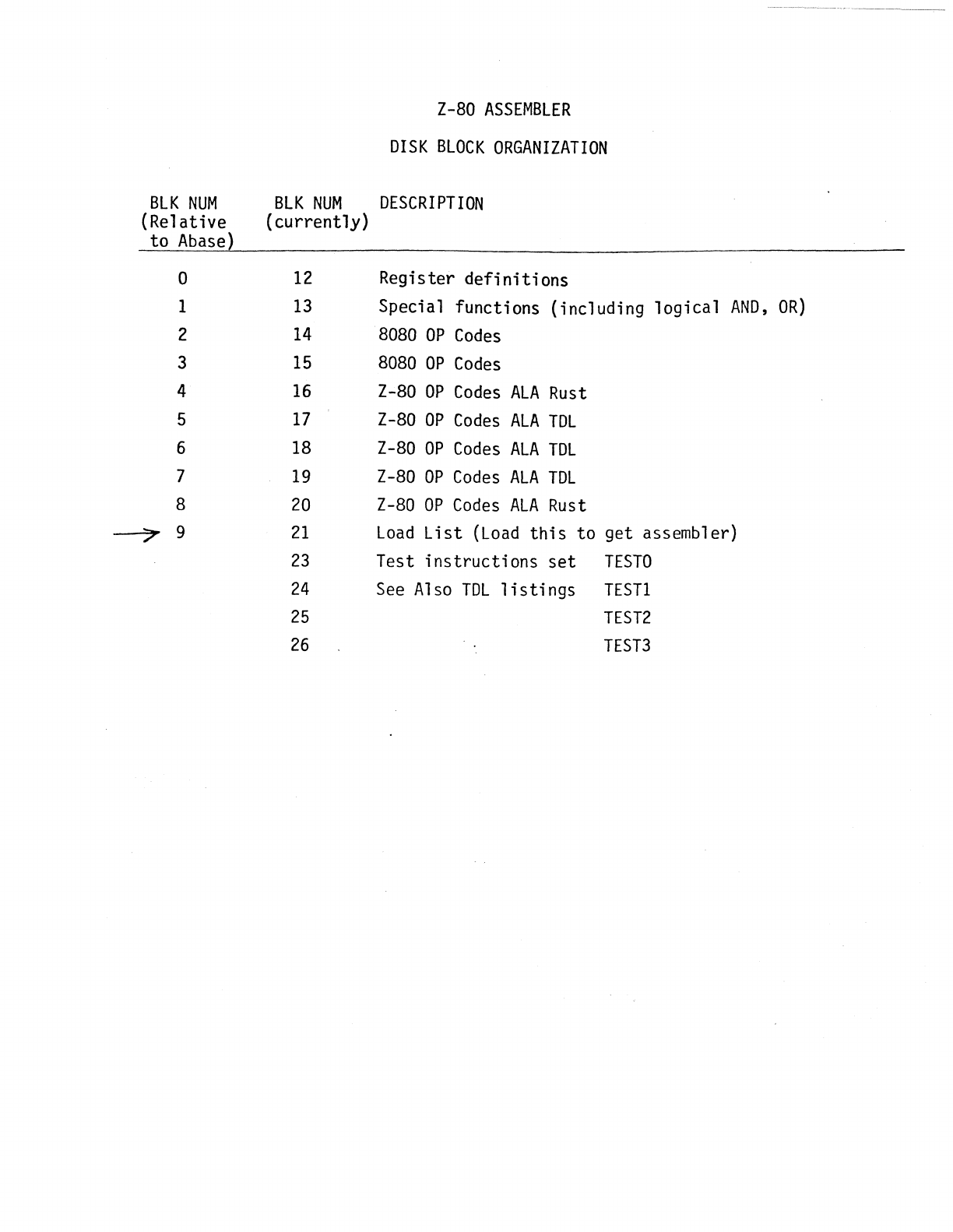

Z-80

ASSEMBLER

DISK

BLOCK

ORGANIZATION

BLK

NUM

BLK

NUM

DESCRIPTION

(Relative

(currently)

to

Abase)

o

12

Register

definitions

1

13

Special functions (including

logical

AND,

OR)

2

14

8080

OP

Codes

3

15

8080

OP

Codes

4

16

Z-80

OP

Codes

ALA

Rust

5

17

Z-80

OP

Codes

ALA

TDL

6

18

Z-80

OP

Codes

ALA

TDL

7

19

Z-80

OP

Codes

ALA

TDL

8

20

Z-80

OP

Codes

ALA

Rust

~

9

21

Load

List

(Load

this

to

get assembler)

23

Test

instructions

set

TESTO

24

See

Also

TDL

listings

TEST

1

25

26

TEST2

TEST3

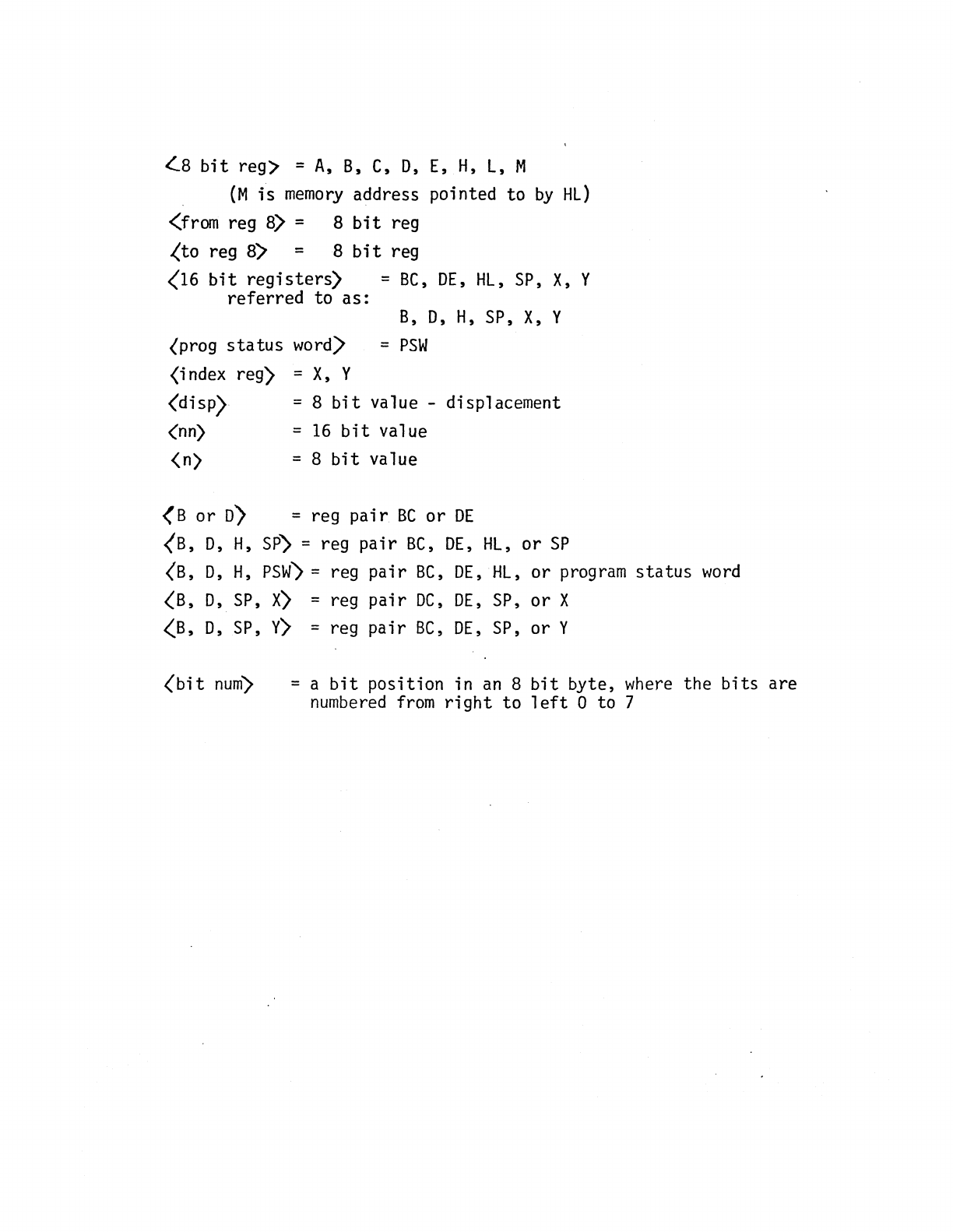

~8

bit

reg)

=

A,

B, C,

D,

E,

H,

L,

M

(M

is

memory

address pointed

to

by

HL)

<from reg

8)

= 8

bit

reg

~to

reg

8)

= 8

bit

reg

<16

bit

registers)

=

BC,

DE,

HL,

SP,

X,

V

referred

to

as:

B,

D,

H,

SP,

X,

V

(prog

status

word) =

PSW

{index

reg)

=

X,

V

<disp) = 8

bit

value -displacement

<nn)

=

16

bit

value

<n) = 8

bit

value

(B

or

D)

= reg

pair

BC

or

DE

<B,

D,

H,

SP) = reg

pair

BC,

DE,

HL,

or

SP

<B,

D,

H,

PSW)

= reg

pair

BC,

DE,

HL,

or

program

status

<B,

D,

SP,

X)

= reg pai r

DC,

DE,

SP,

or

X

<B,

D,

SP,

V)

= reg

pair

BC,

DE,

SP,

or

Y

word

(bit

num)

= a

bit

position

in

an

8

bit

byte,

where

the

bits

are

numbered

from

right

to

left

0 to 7

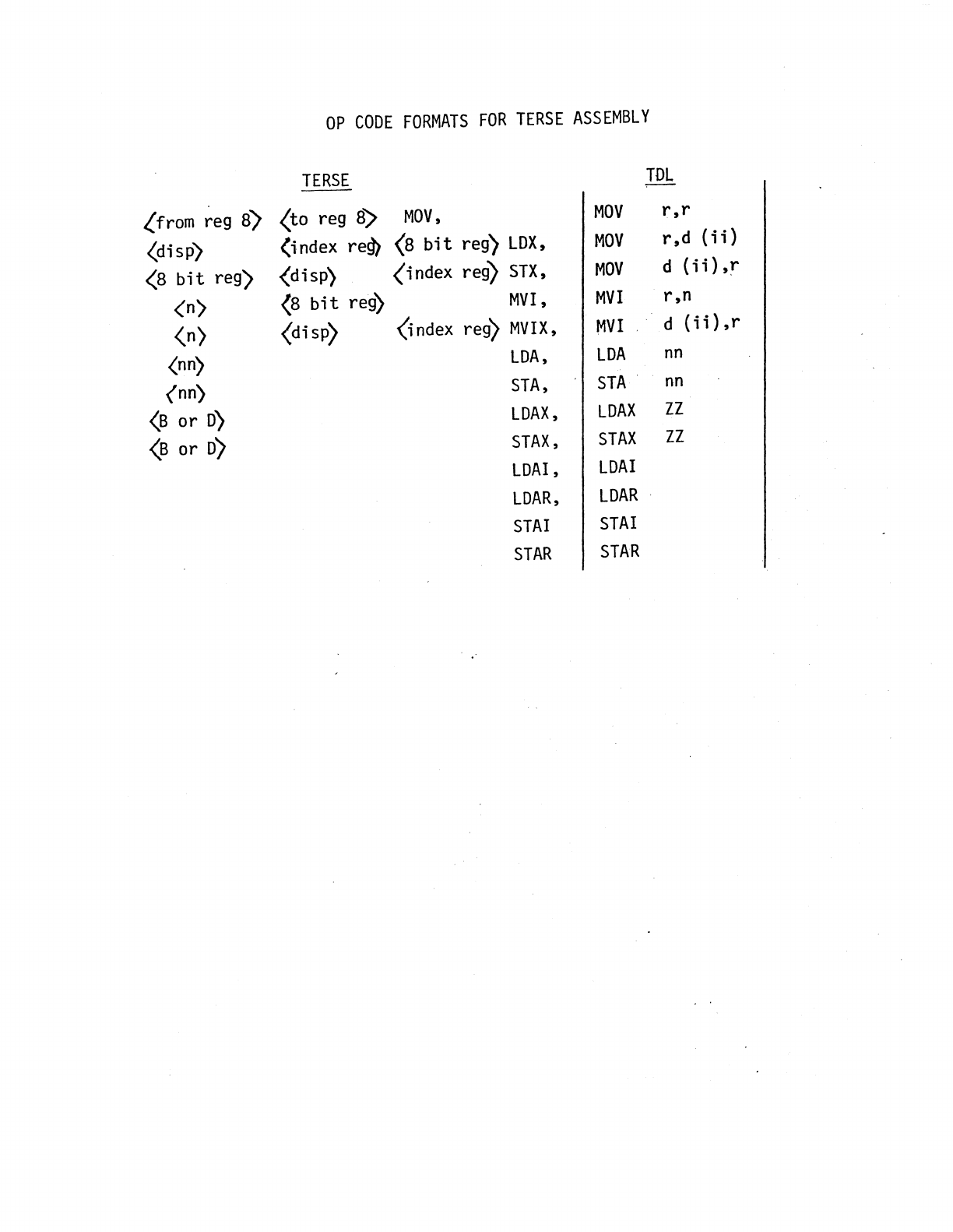

OP

CODE

FORMATS

FOR

TERSE

ASSEMBLY

TERSE

TOL

-,

-

~from

reg

8)

<to reg

8)

MOV,

MOV

r,r

<disp)

(i

ndex

re~

(8 bi t

reg)

LDX,

MOV

r,d

(ii)

<8

bit

reg)

<disp) <index

reg)

STX,

MOV

d

(ii),!'

<n)

{8

bit

reg)

MVI,

MVI

r,n

(n)

<disP) <index reg)

MVIX,

MV!

' ' d

(ii),r

<nn)

LDA,

LDA

nn

(nn)

STA,

STA'

nn

(B

or

D)

LDAX,

LDAX

II

<B

or

D)

STAX,

STAX

II

LDAI,

LDA!

LDAR,

LDAR

'

STAI

STAI

STAR

STAR

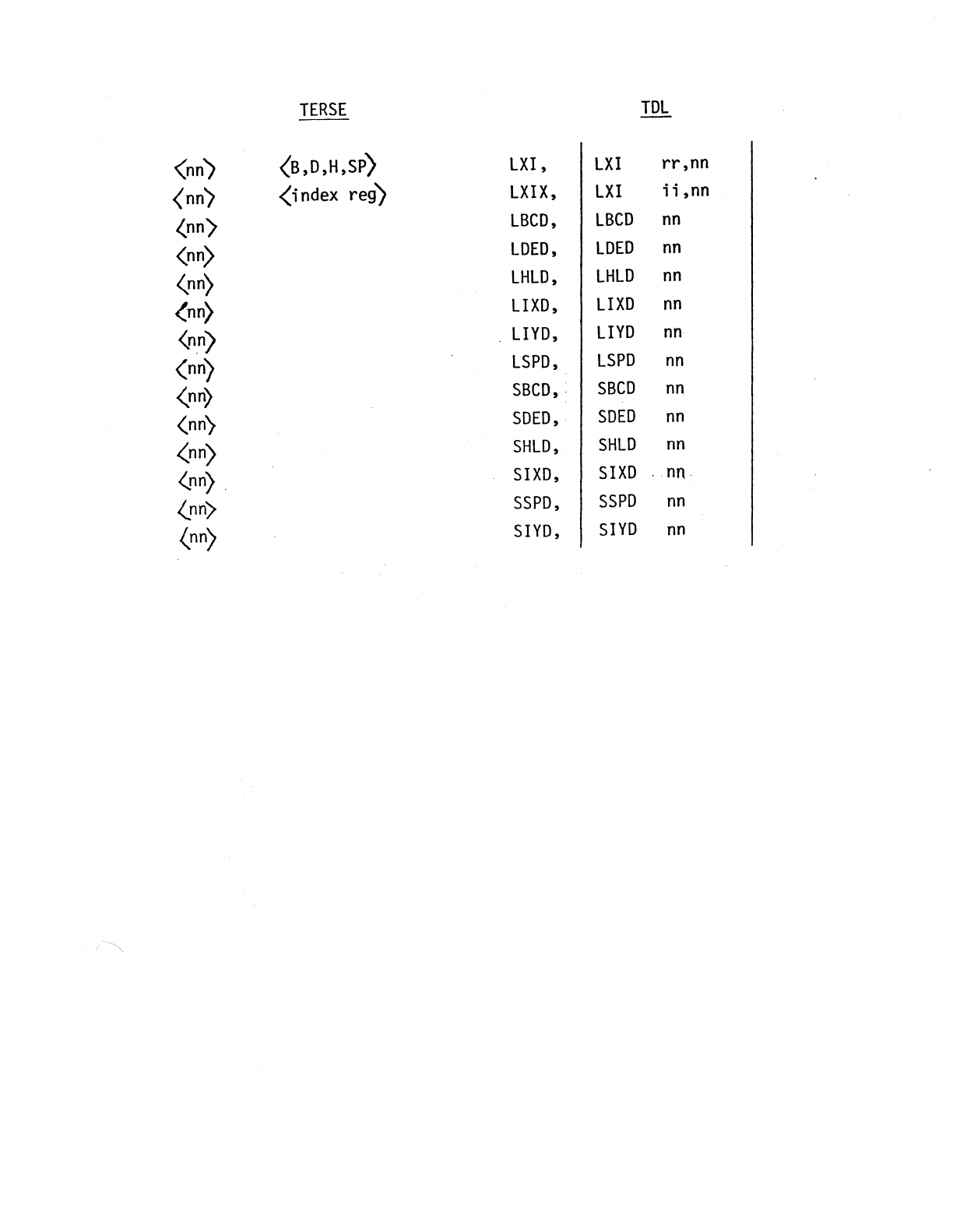

TERSE

TDL

(nn)

<B,D,H,SP)

LXI,

LXI

rr,nn

<nn)

<index

reg)

LXIX,

LXI

ii,nn

<.nn)

LBCD,

LBCD

nn

(nn)

LDED,

LDED

nn

(nn)

LHLD,

LHLD

nn

<nn)

LIXD,

LIXD

nn

(n,n) .

LIYD,

LIYD

nn

(nn)

LSPD,

LSPD

nn

(nn)

SBCD,

:

SBCD

nn

(nn'}

SDED,

'

SDED

nn

<nn)

SHLD,

SHLD

nn

(nn)

,

SIXD,

SIXD

nn

(nn)

SSPD,

SSPD

nn

(nn)

SIYD,

SIYD

nn

i~

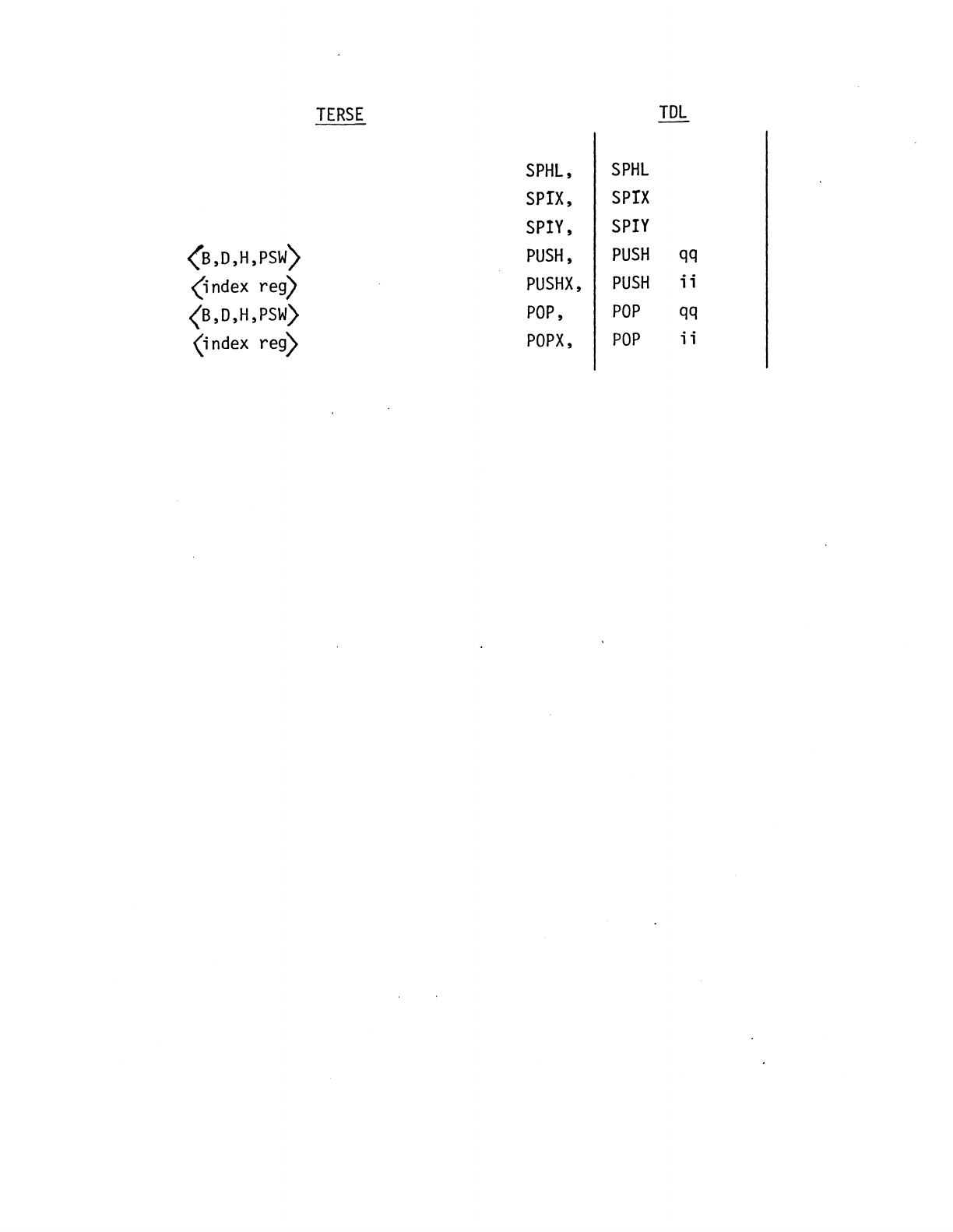

TERSE

TDL

SPHL,

SPHL

sprx,

SPIX

SPIY,

SPIY

(S,D,H,PSW)

PUSH,

PUSH

qq

(index

reg)

PUSHX,

PUSH

ii

<S

,D,H,

PSW)

POP,

POP

qq

(index

reg)

POPX,

POP

i i

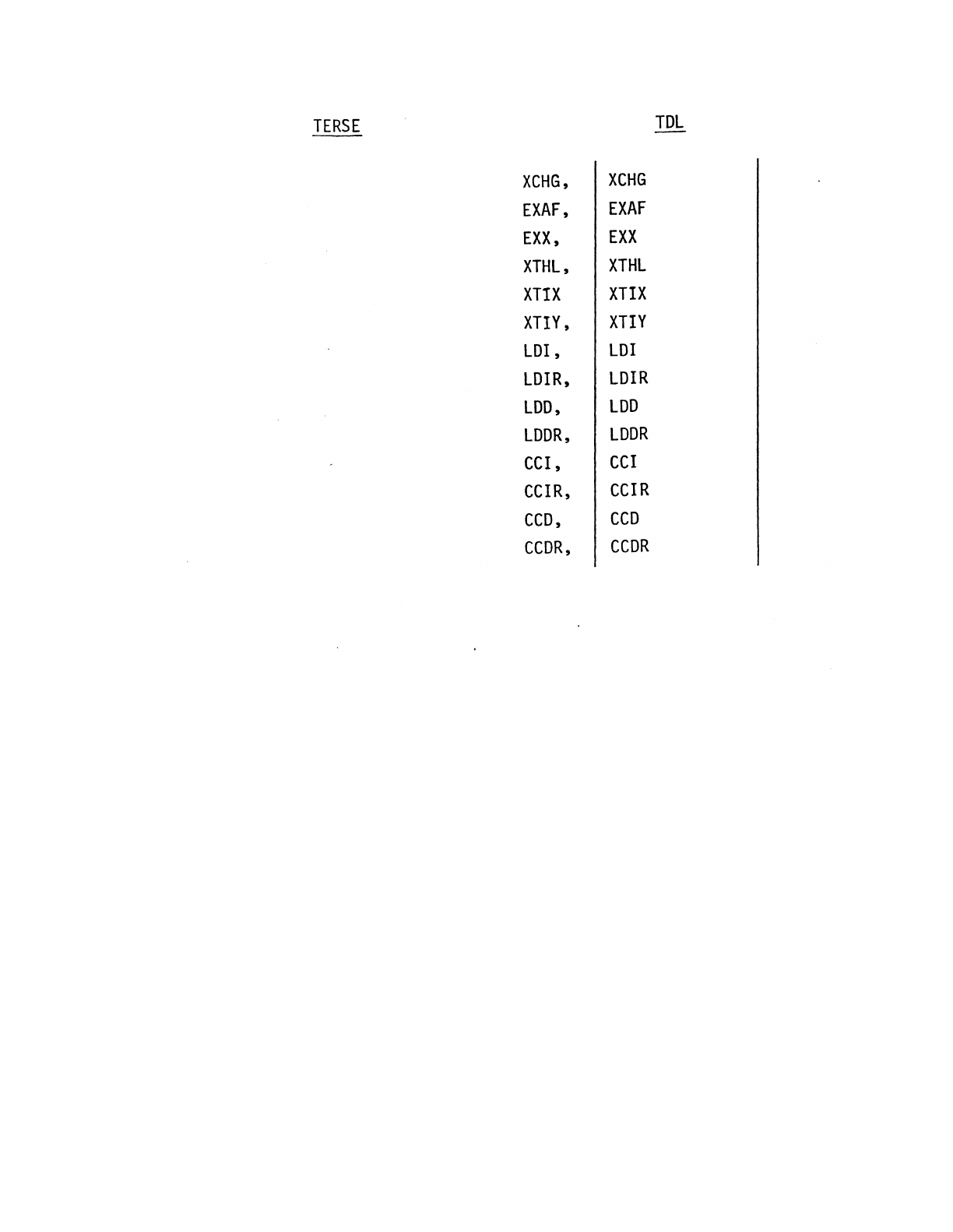

TERSE

TDL

XCHG,

XCHG

EXAF,

EXAF

EXX,

EXX

XTHL,

XTHL

XTIX XTIX

XTIY,

XTIY

LOI,

LOI

LOIR,

LDIR

LOO,

LDD

LDDR,

LODR

CCI,

CCI

CCIR,

CCIR

CCD,

CCO

CCDR,

CCDR

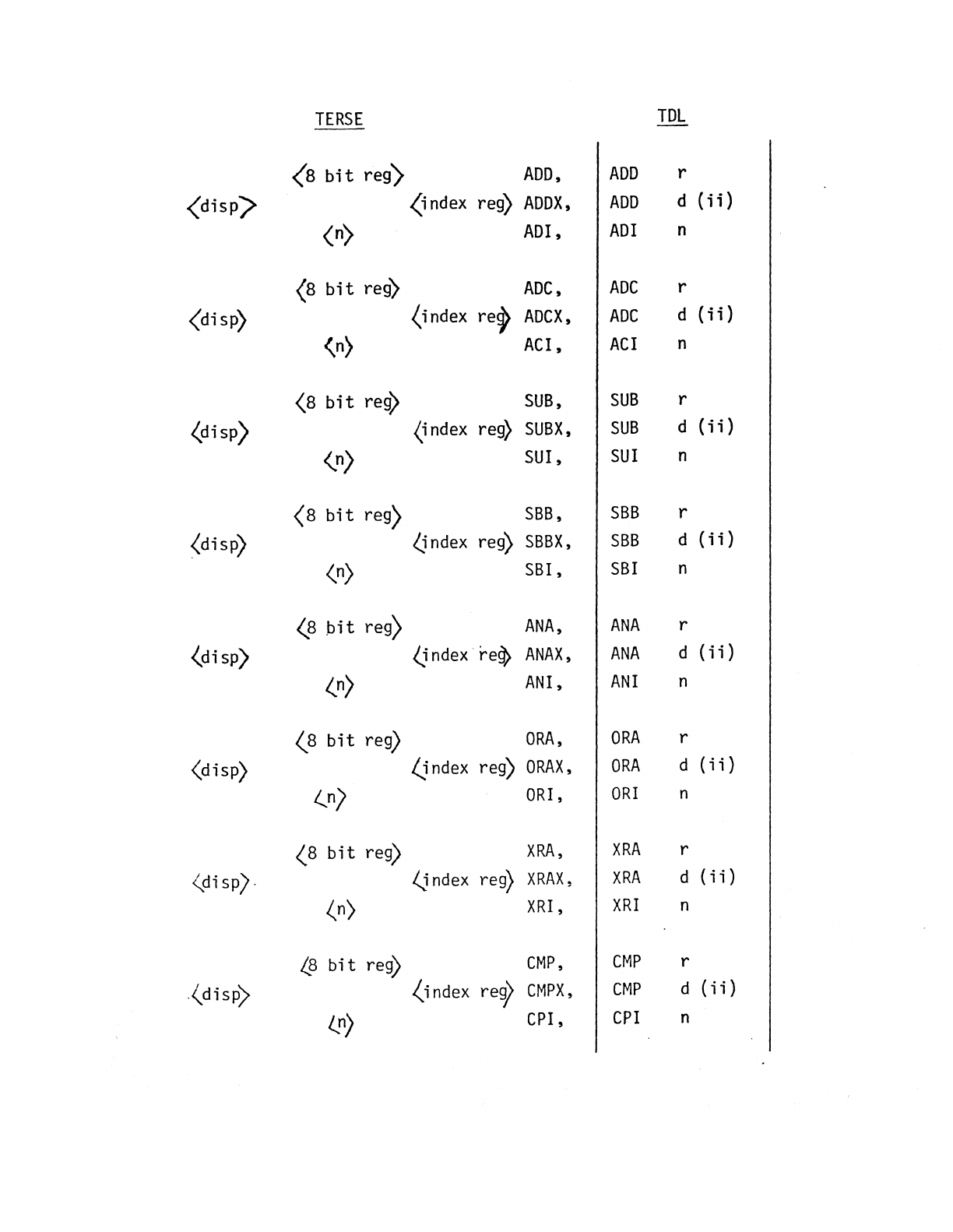

TERSE

TDL

<8

bit

reg)

ADD,

ADD

r

<disp/

<i

nd

ex

reg)

ADDX,

ADD

d

(ii)

<n)

ADI,

ADI

n

<8

bit

reg)

ADC,

ADC

r

<disp)

<index

re~

ADCX,

ADC

d

(i

i)

<n)

ACI,

ACI

n

(8

bit

reg)

SUB,

SUB

r

<'disp)

(i

ndex reg)

SUB

X ,

SUB

d

(ii)

(n)

SUI,

SUI

n

<8

bit

reg)

SBB,

SBB

r

<disp)

(J

ndex

reg)

SBBX,

SBB

d

(i

1)

(n)

SBI,

SBI

n

(8

.bit

reg)

ANA,

ANA

r

<'disp)

(j

ndex . re!l)

ANAX,

ANA

d

(ii)

(n)

ANI,

ANI

n

(8

bit

reg)

ORA,

ORA

r

(disp)

/.j

ndex

reg)

ORAX,

ORA

d

(i

i)

(n;

ORI,

OR!

n

/...8

bit

reg)

XRA,

XRA

r

(di

spj.

/..j

ndex

reg)

XRAX,

XRA

d

(i

i)

(n)

XRI,

XRI

n

/....8

bi t

reg)

CMP,

CMP

r

.(disp>

~.i

ndex

regj

CMPX,

CMP

d

(ii)

/.!I)

CPI,

CPI

n

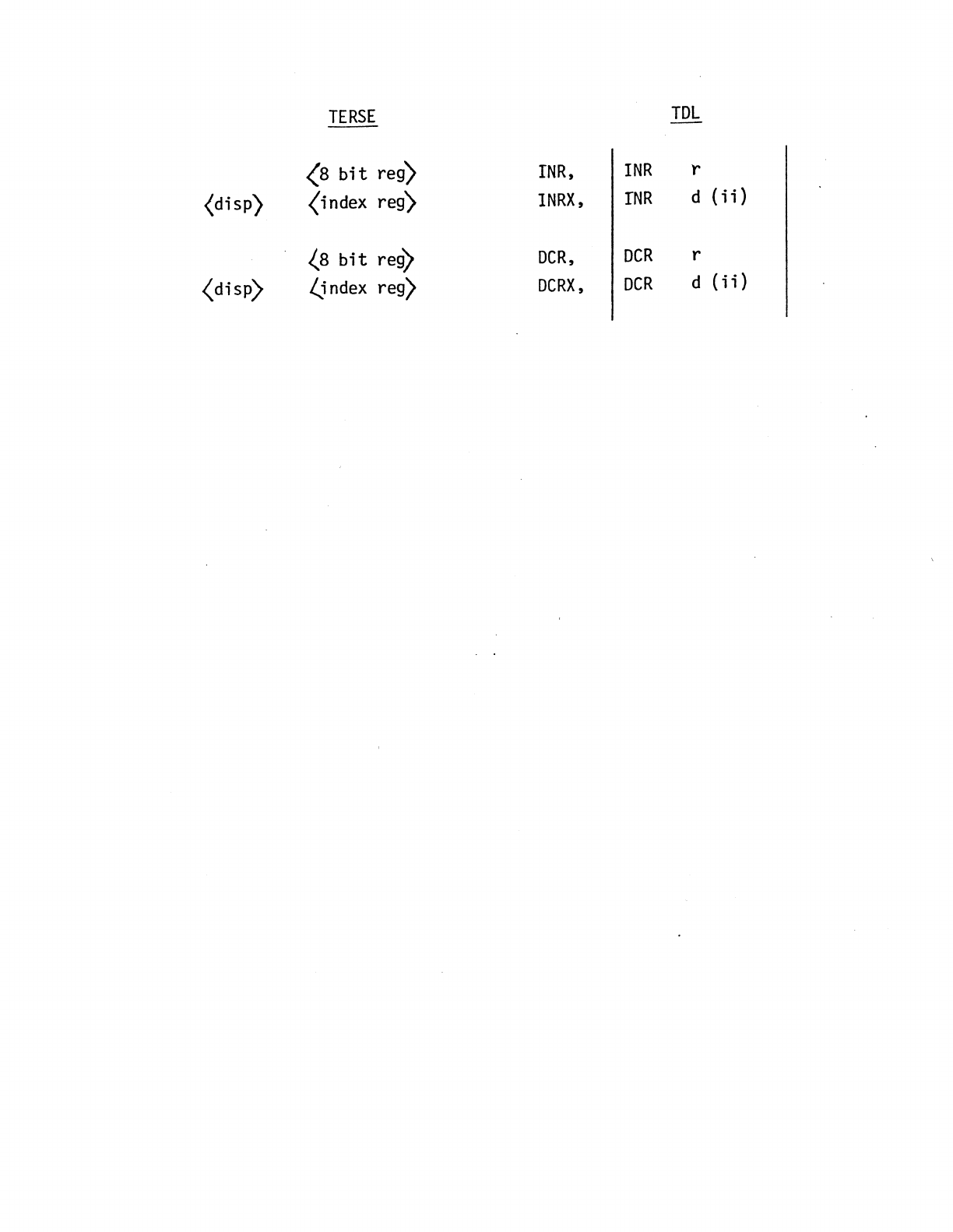

TERSE

TOL

(8

bit

reg)

INR,

INR

r

<disp)

<index

reg)

INRX,

INR

d

(ii)

"8

bit

reg)

OCR,

OCR

r

<disp)

(jndex

reg)

OCRX,

OCR

d

(ii)

\

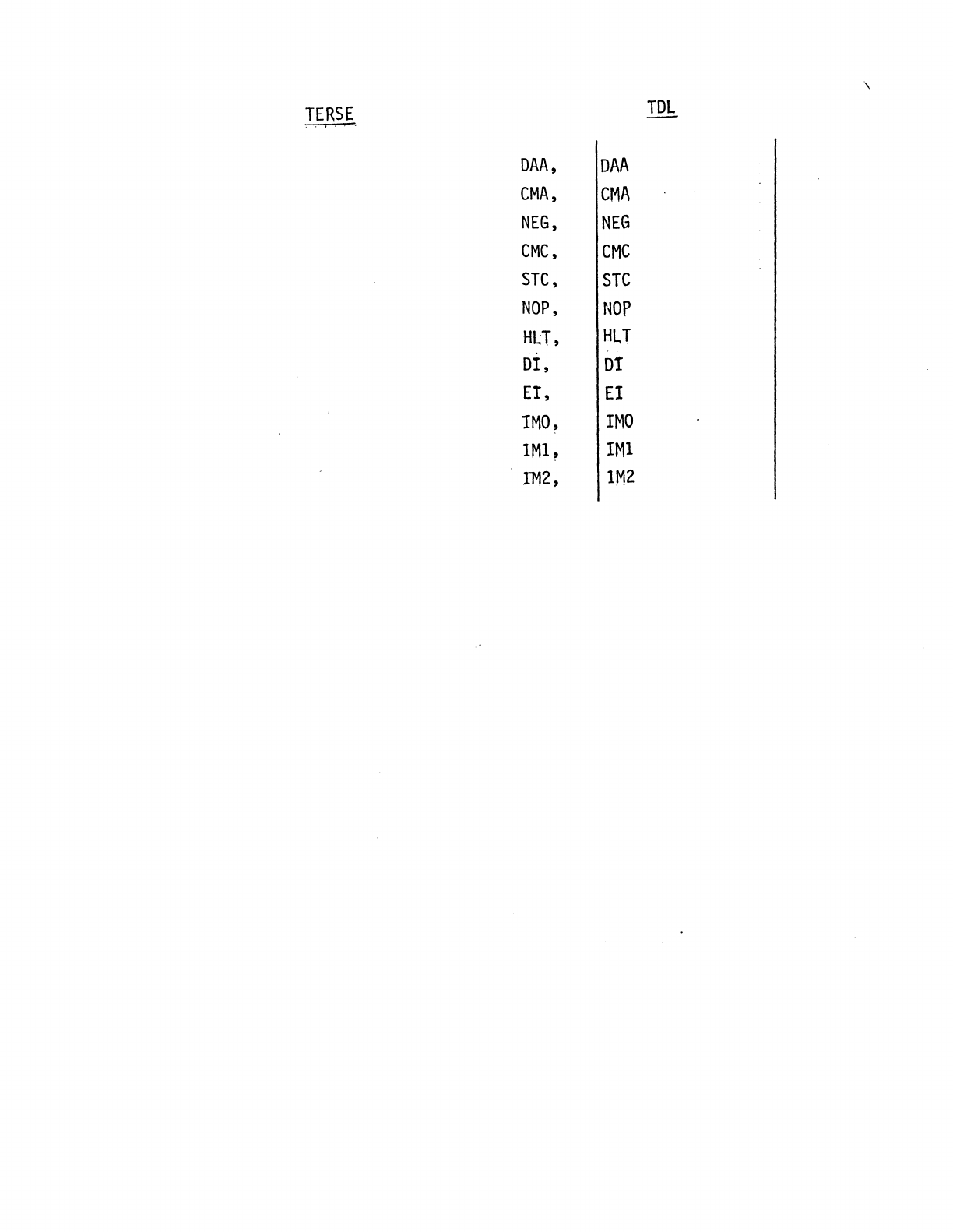

TERSE

TOL

....

OAA,

OAA

CMA,

CMA

NEG,

NEG

CMC,

CMC

STC,

STC

NOP,

NOP

HLT,

HLT

01,

Dr

Et,

E1

TMO,

TMO

1Ml,

1Ml

1M2,

1M2

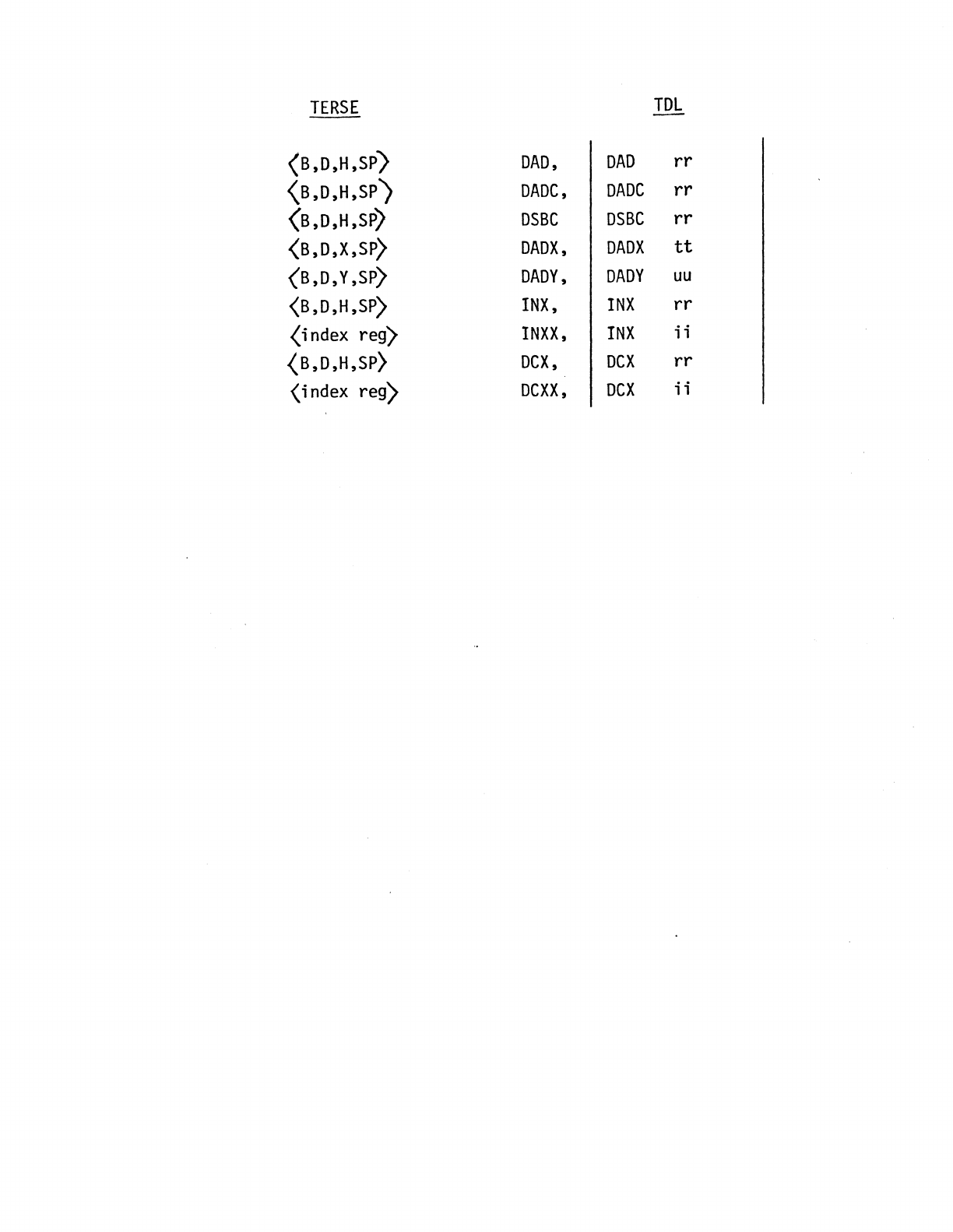

TERSE

TDL

(B,D,H,SP)

DAD,

DAD

rr

<B,D,H,SP)

DADC,

DADC

rr

(B

,D,H

,SP)

DSBC

DSBC

rr

<B,D,X,SP>

DADX,

DAD

X

tt

(B,D, Y ,SP)

DADY,

DADY

uu

<B,D,H,SP)

INX,

INX

rr

<index

reg)

INXX,

INX

ii

{B,D,H,SP)

DCX,

DCX

rr

(index reg>

DCXX,

DCX

ii

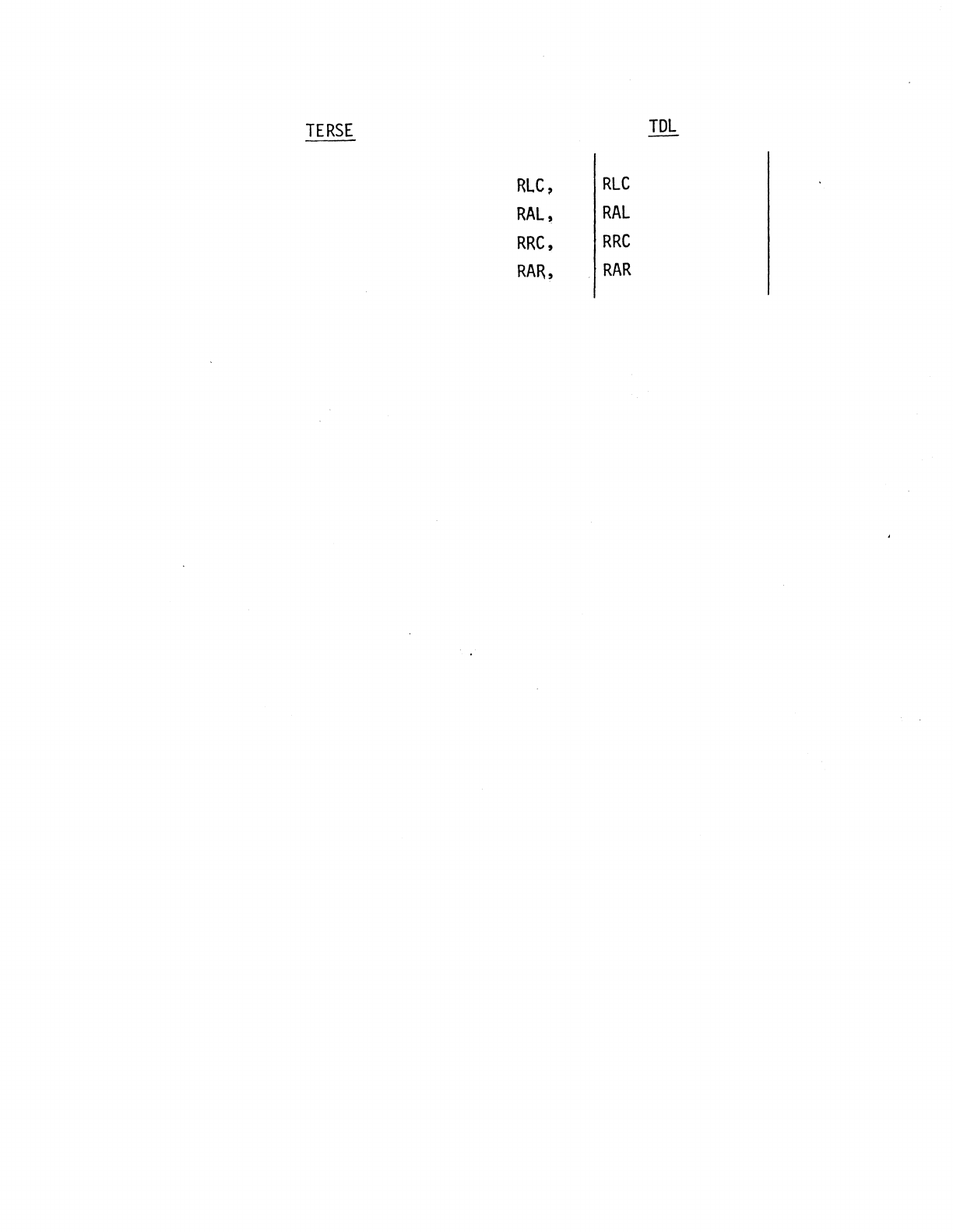

TERSE

RLC~

RAL,

RRC,

RAR,

RLC

RAL

RRC

RAR

TDL

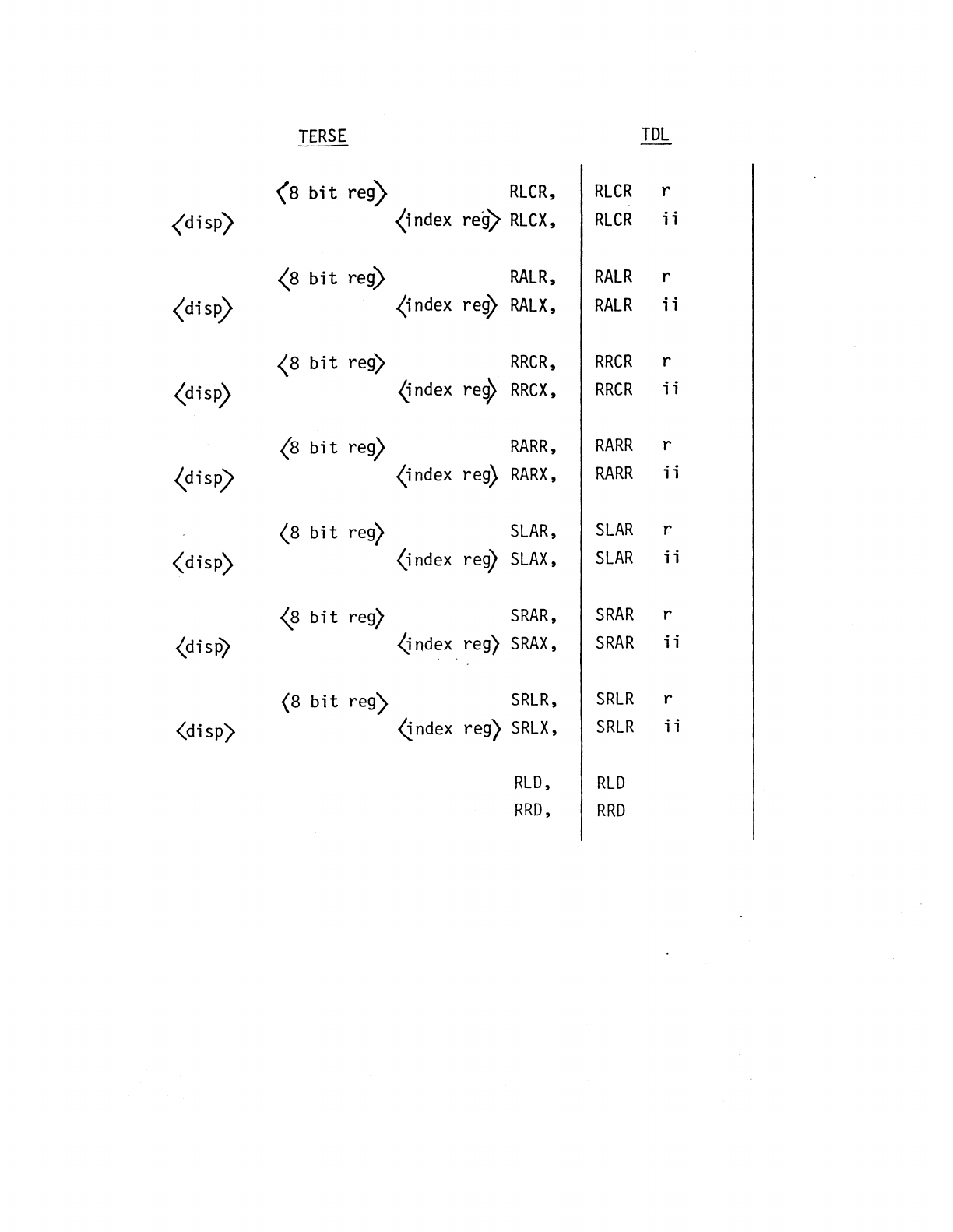

TERSE

TDL

(8

bit

reg)

RLCR,

RLCR

r

<disp)

<i

ndex

reg)

RLCX,

RLCR

ii

<8

bit

reg)

RALR,

RALR

r

<disp)

<index reg)

RALX,

RALR

ii

<8

bit

reg)

RRCR,

RRCR

r

<disp)

(index reg)

RRCX,

RRCR

ii

(8

bit

reg)

RARR,

RARR

r

(disp'/

(index reg)

RARX,

RARR

ii

(8

bit

reg>

SLAR,

SLAR

r

<disp)

(index reg)

SLAX,

SLAR

ii

\8

bit

reg,

SRAR,

SRAR

r

(di

sp) <Jndex

reg)

SRAX,

SRAR

ii

(8

bit

reg)

SRLR,

SRLR

r

<di

sp)

<!ndex

reg)

SRLX,

SRLR

ii

RLD,

RLD

RRD,

RRD

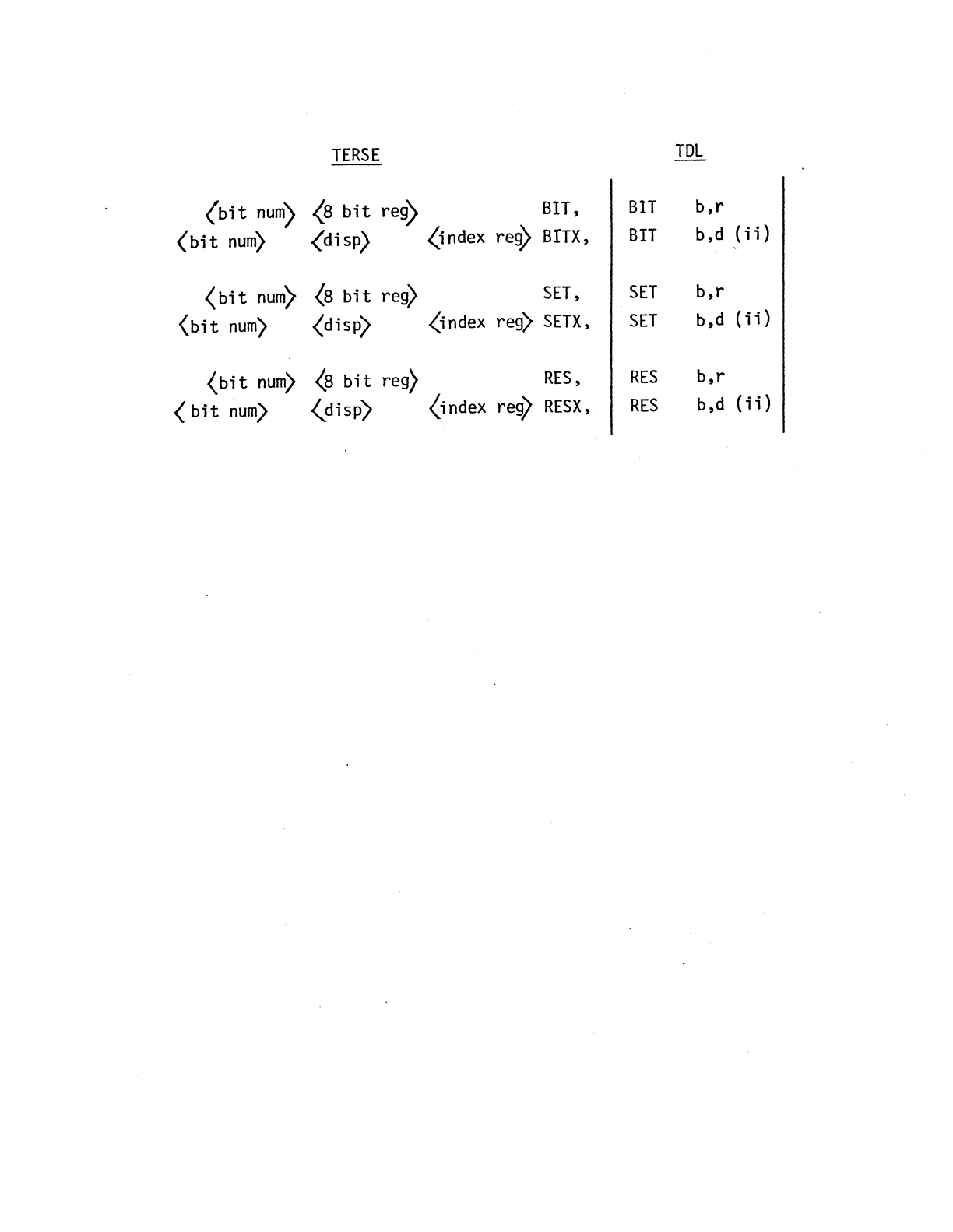

TERSE

TDL

(bit

nurn)

<8

bit

reg)

BIT,

BIT

b,r

(bit

nurn)

(disp)

(i

ndex

reg)

BITX,

BIT

b,d

(ii)

,

<bit

nurn>

(8

bit

reg)

SET,

SET

b,r

(bit

nurn)

<disp)

<index

reg)

SETX,

SET

b,d

(ii)

(bit

nurn)

<8

bit

reg)

RES,

RES

b,r

<

bit

nurn)

(disp)

<index

reg!

RESX,

RES

b,d

(ii)

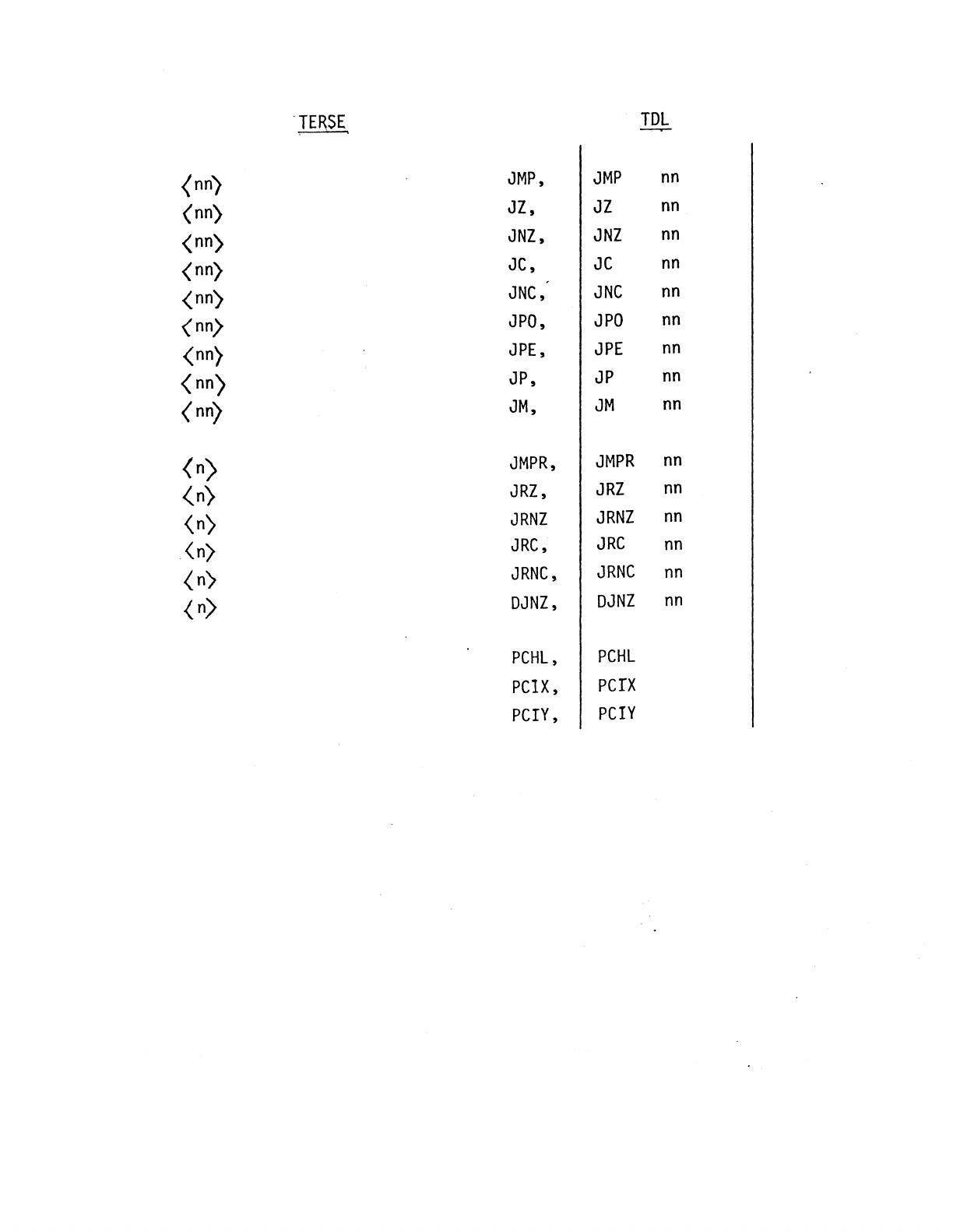

·TERSE

TDL

<nn)

JMP,

JMP

nn

(nn) JZ,

JZ

nn

<nn)

JNZ,

JNZ

nn

<nn)

JC,

JC

nn

<nn)

JNC,

JNC

nn

<nn>

JPO,

JPO

nn

(nn)

JPE,

JPE

nn

<nn) JP,

JP

nn

(nn)

JM,

JM

nn

{n)

JMPR,

JMPR

nn

<n}

JRZ,

JRZ

nn

(n)

JRNZ

JRNZ

nn

(n)

JRC,

JRC

nn

{n}

JRNC,

JRNC

nn

{n)

DJNZ,

DJNZ

nn

PCHL,

PCHL

PClX,

pcrx

PCIY

,

PCIY

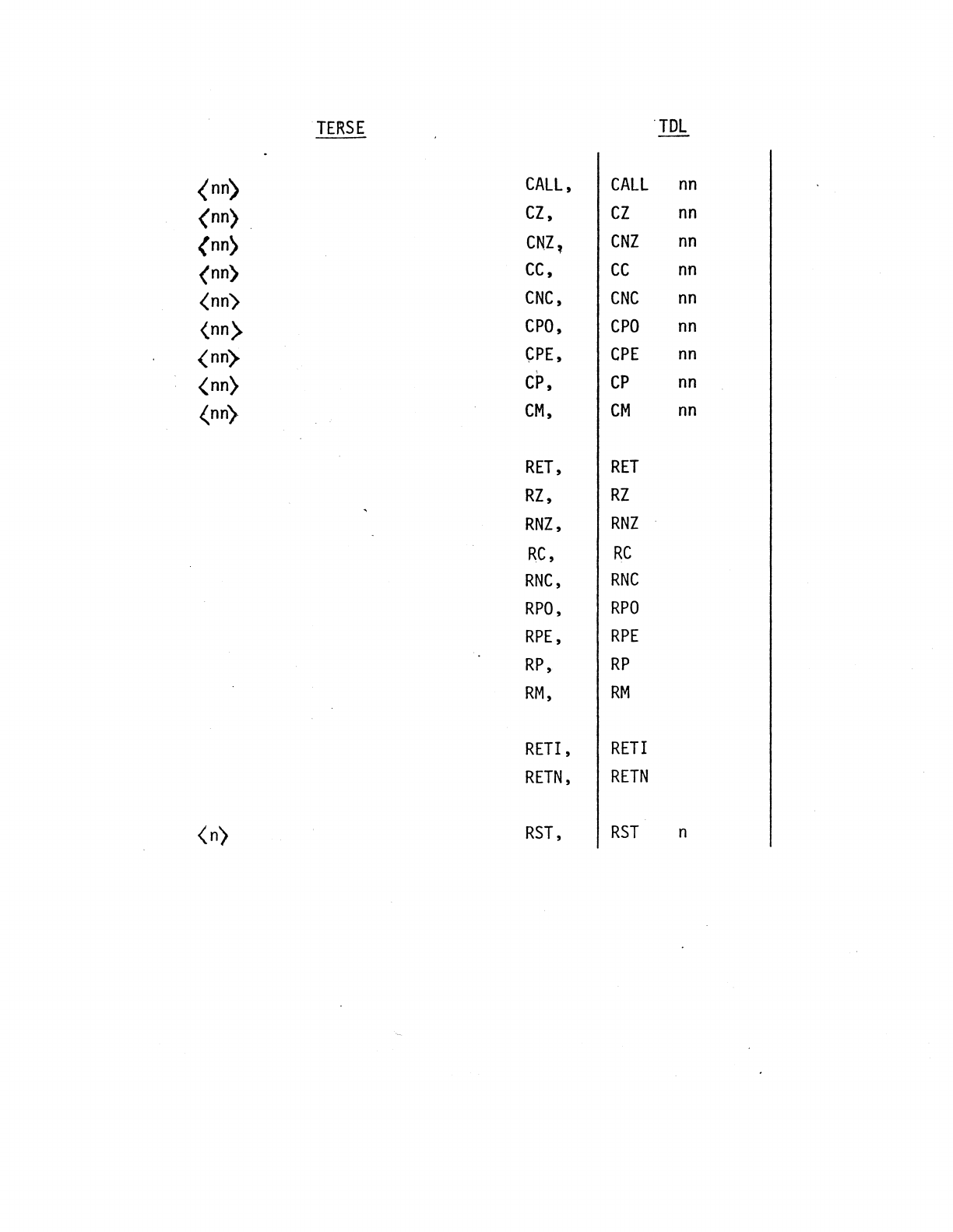

TERSE

"TDL

<nn)

CALL,

CALL

nn

<nn) "

CZ,

CZ

nn

(nn>

CNZ,

CNZ

nn

<nn)

CC,

CC

nn

<nn)

CNC,

CNC

nn

{nn>

CPO,

CPO

nn

<nn>

CPE,

CPE

nn

,

<nn}

CP,

CP

nn

(nn)

CM,

CM

nn

RET,

RET

RZ,

RZ

RNZ,

RNZ

RC,

RC

RNC,

RNC

RPO,

RPO

RPE,

RPE

RP,

RP

RM,

RM

RET!

,

RET!

RETN,

RETN

<n)

RST,

RST

n

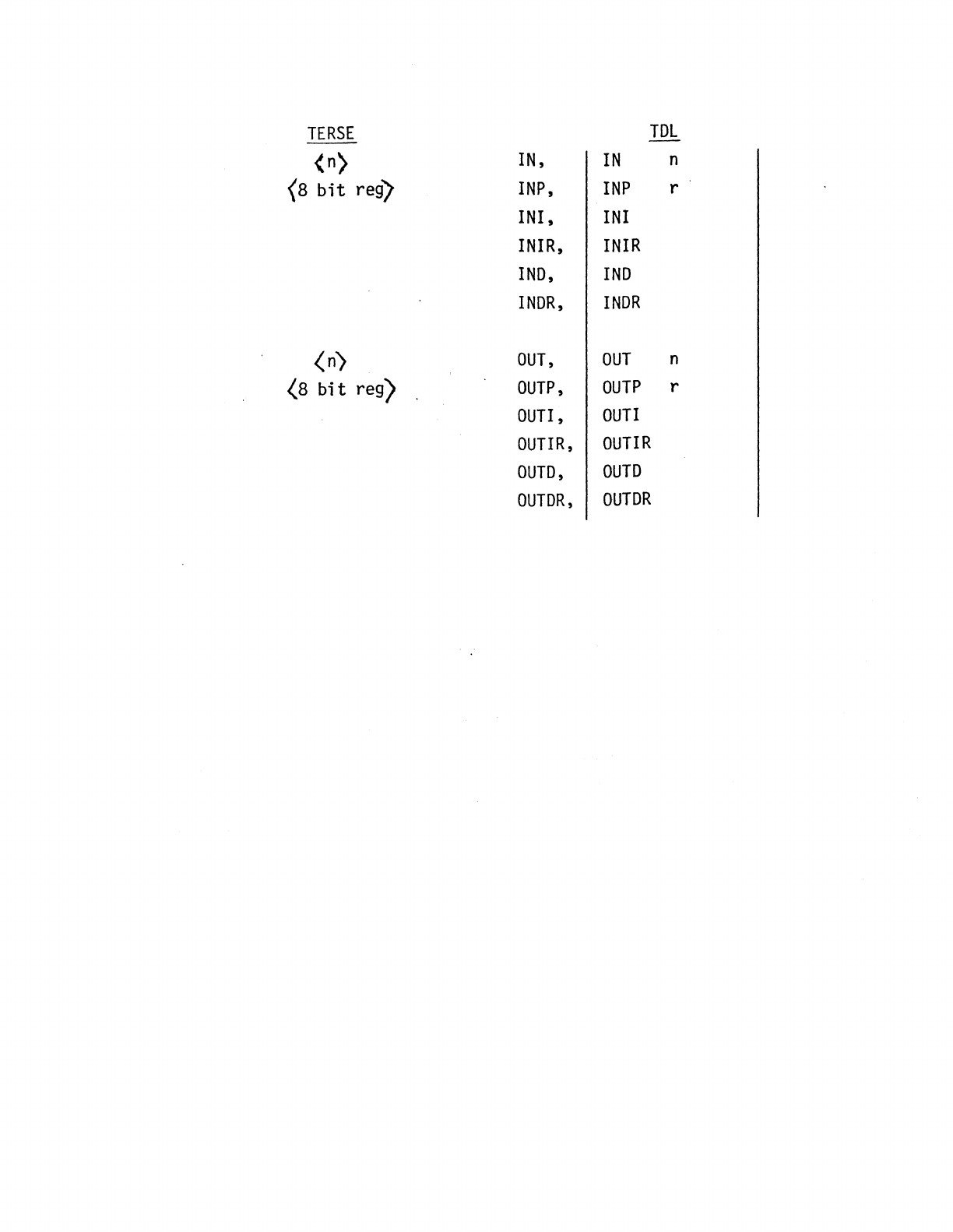

TERSE

TDL

{n}

IN,

IN

n

(8

bit

reg)

INP,

INP

r

INI,

INI

INIR,

INIR

IND,

IND

INDR,

INDR

<n)

OUT,

OUT

n

{8

bit

reg)

OUTP,

OUTP

r

OUTI

,

OUTI

OUTIR,

OUTIR

OUTD,

OUTO

OUTOR,

OUTOR