ARMv4T Partial Instruction Set Summary Instructions

User Manual: Pdf

Open the PDF directly: View PDF ![]() .

.

Page Count: 2

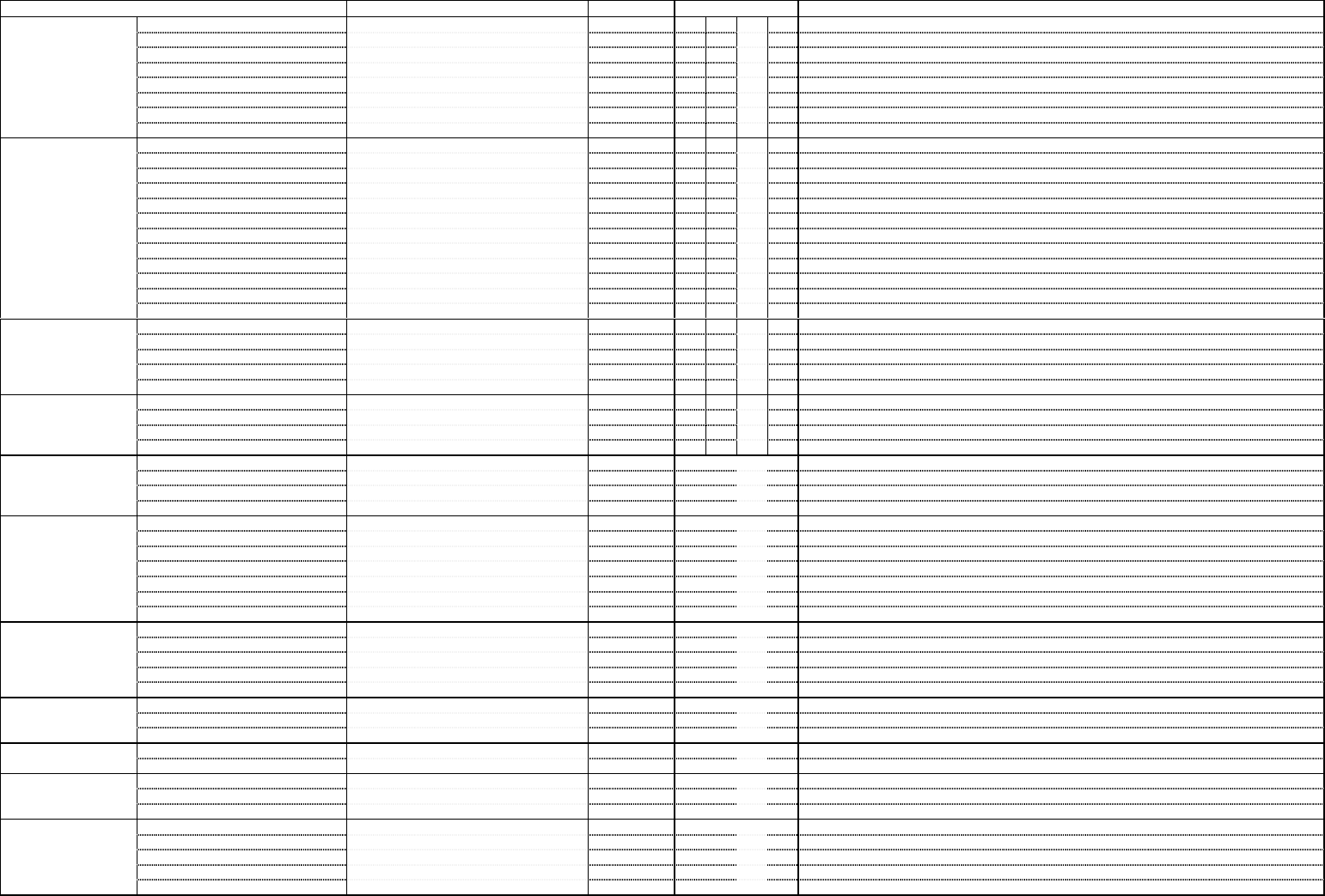

- ARMv4T Partial Instruction Set Summary

- ARMv4T Partial Instruction Set Tables

- Register Names and Aliases

- Program Status Register Format

- Program Status Register Modes

- Program Status Register Fields: fields

- Optional Condition Field: cond

- Data Processing Mode: shifter_op

- Load or Store Word/Unsigned Byte Mode: am2

- Load or Store with Translation Mode: am2P

- Load or Store Half-Word/Signed Byte Mode: am3

- Load Multiple Data Mode: am4L

- Store Multiple Data Mode: am4S

- Exception Vector Table

- Miscellaneous

ARMv4T Partial Instruction Set Summary

Operation Syntax Page Num. S updates Action and Comments

Move Move mov{cond}{s} Rd, shift_op A4–56 (156) N Z C Rd := shift_op

with NOT mvn{cond}{s} Rd, shift_op A4–68 (168) N Z C Rd := NOT(shift_op)

CPSR to register mrs{cond} Rd, cpsr A4–60 (160) Rd := CPSR

SPSR to register mrs{cond} Rd, spsr A4–60 (160) Rd := SPSR; Not valid in System or User modes

register to CPSR msr{cond} cpsr_fields, RmA4–62 (162) CPSR := Rd (selected bytes only)

register to SPSR msr{cond} spsr_fields, RmA4–62 (162) SPSR := Rd (selected bytes only); Not valid in System or User modes

immediate to CPSR msr{cond} cpsr_fields, #imm8r A4–62 (162) CPSR := imm8r (selected bytes only)

immediate to SPSR msr{cond} spsr_fields, #imm8r A4–62 (162) SPSR := imm8r (selected bytes only); Not valid in System or User modes

Arithmetic Add add{cond}{s} Rd, Rn, shift_op A4–6 (106) N Z C V Rd := Rn + shift_op

with carry adc{cond}{s} Rd, Rn, shift_op A4–4 (104) N Z C V Rd := Rn + shift_op + Carry

Subtract sub{cond}{s} Rd, Rn, shift_op A4–98 (198) N Z C V Rd := Rn – shift_op

with carry sbc{cond}{s} Rd, Rn, shift_op A4–76 (176) N Z C V Rd := Rn – shift_op – NOT(Carry)

reverse subtract rsb{cond}{s} Rd, Rn, shift_op A4–72 (172) N Z C V Rd := shift_op – Rn

reverse subtract with carry rsc{cond}{s} Rd, Rn, shift_op A4–74 (174) N Z C V Rd := shift_op – Rn – NOT(Carry)

Multiply mul{cond}{s} Rd, Rm, RsA4–66 (166) N Z C? Rd := Rm × Rs (lower 32 bits only)

with accumulate mla{cond}{s} Rd, Rm, Rs, RnA4–54 (154) N Z C? Rd := (Rm × Rs) + Rn (lower 32 bits only)

unsigned long umull{cond}{s} RdLo, RdHi, Rm, RsA4–111 (211) N Z C? V? RdHi,RdLo := unsigned(Rm × Rs)

unsigned long with accumulate umlal{cond}{s} RdLo, RdHi, Rm, RsA4–109 (209) N Z C? V? RdHi,RdLo := unsigned(RdHi,RdLo + Rm × Rs)

signed long smull{cond}{s} RdLo, RdHi, Rm, RsA4–80 (180) N Z C? V? RdHi,RdLo := signed(Rm × Rs)

signed long with accumulate smlal{cond}{s} RdLo, RdHi, Rm, RsA4–78 (178) N Z C? V? RdHi,RdLo := signed(RdHi,RdLo + Rm × Rs)

Logical AND and{cond}{s} Rd, Rn, shift_op A4–8 (108) N Z C Rd := Rn AND shift_op

OR orr{cond}{s} Rd, Rn, shift_op A4–70 (170) N Z C Rd := Rn OR shift_op

XOR eor{cond}{s} Rd, Rn, shift_op A4–26 (126) N Z C Rd := Rn XOR shift_op

Bit clear bic{cond}{s} Rd, Rn, shift_op A4–12 (112) N Z C Rd := Rn AND NOT(shift_op)

Rotates and shifts Usually mov{cond}{s} Rd, shift_op A4–56 (156) N Z C Usually Rd := shift_op; May use other instructions (eg, add, sub)

Compare Compare cmp{cond} Rn, shift_op A4–25 (125) N Z C V Update CPSR flags for Rn – shift_op

negated cmn{cond} Rn, shift_op A4–23 (123) N Z C V Update CPSR flags for Rn + shift_op

Bitwise test tst{cond} Rn, shift_op A4–107 (207) N Z C Update CPSR flags for Rn AND shift_op

Equivalence test teq{cond} Rn, shift_op A4–106 (206) N Z C Update CPSR flags for Rn XOR shift_op

Branch Branch b{cond} label A4–10 (110) R15 := address of label; Jump to label

with link bl{cond} label A4–10 (110) R14 := R15 – 4; R15 := address of label; Call subroutine/function at label

and exchange bx{cond} RmA4–19 (119) R15 := Rm; Changes to Thumb mode if bit 0 of Rm is 1

Return from subroutine Usually mov pc, lr or bx lr A4–11 (111) R15 := R14

Load Load word ldr{cond} Rd, am2 A4–37 (137) Rd := word stored at address am2

using User mode privileges ldr{cond}t Rd, am2P A4–50 (150) Rd := word stored at address am2P; Usually used in non-User modes

Load byte ldr{cond}b Rd, am2 A4–40 (140) Rd := ZeroExtend(byte at address am2)

signed ldr{cond}sb Rd, am3 A4–46 (146) Rd := SignExtend(byte at address am3)

using User mode privileges ldr{cond}bt Rd, am2P A4–42 (142) Rd := ZeroExtend(byte at address am2P); Usually used in non-User modes

Load half-word ldr{cond}h Rd, am3 A4–44 (144) Rd := ZeroExtend(half-word at address am3)

signed ldr{cond}sh Rd, am3 A4–48 (148) Rd := SignExtend(half-word at address am3)

Store Store word str{cond} Rd, am2 A4–88 (188) Store word in Rd at address am2

using User mode privileges str{cond}t Rd, am2P A4–96 (196) Store word in Rd at address am2P; Usually used in non-User modes

Store byte str{cond}b Rd, am2 A4–90 (190) Store byte in Rd[7..0] at address am2

using User mode privileges str{cond}bt Rd, am2P A4–92 (192) Store byte in Rd[7..0] at address am2P; Usually used in non-User modes

Store half-word str{cond}h Rd, am3 A4–94 (194) Store half-word in Rd[15..0] at address am3

Load Multiple Pop, or Block data load ldm{cond}{am4L} Rd{!}, {reglist}A4–30 (130) Load all listed registers from address in Rd

using User mode privileges ldm{cond}{am4L} Rd{!}, {reglist–pc}^ A4–32 (132) Load all listed registers (PC register not listed) from address in Rd; Not valid in User mode

return and restore CPSR ldm{cond}{am4L} Rd{!}, {reglist+pc}^ A4–34 (134) Load registers, CPSR := SPSR, branch to PC; Not valid in User or System modes

Store Multiple Push, or Block data store stm{cond}{am4S} Rd{!}, {reglist}A4–84 (184) Store all listed registers to address in Rd

using User mode privileges stm{cond}{am4S} Rd{!}, {reglist}^ A4–86 (186) Store all listed registers to address in Rd; Usually used in non-User modes

Miscellaneous Swap word swp{cond} Rd, Rm, [Rn]A4–102 (202) temp := word at address in Rn, store Rm to address in Rn, Rd := temp

Swap byte swp{cond}b Rd, Rm, [Rn]A4–104 (204) temp := ZeroExtend(byte at address in Rn), store Rm[7..0] to address in Rn, Rd := temp

Software interrupt swi{cond} imm24 A4–100 (200) Branch-and-link to address 0x00000008 in Supervisor mode

Pseudo-instructions No operation nop{cond}Does nothing; translates to mov{cond} r0, r0

Load variable ldr{cond} Rd, label Rd := word stored at address label; translates to ldr{cond} Rd, [r15, #offset]

Move constant ldr{cond} Rd, =imm32 mov Rd, #imm32 or ldr Rd, [r15, #offset]

Load address adr{cond} Rd, label add Rd, r15, #offset

long version adr{cond}l Rd, label Two-instruction form of adr

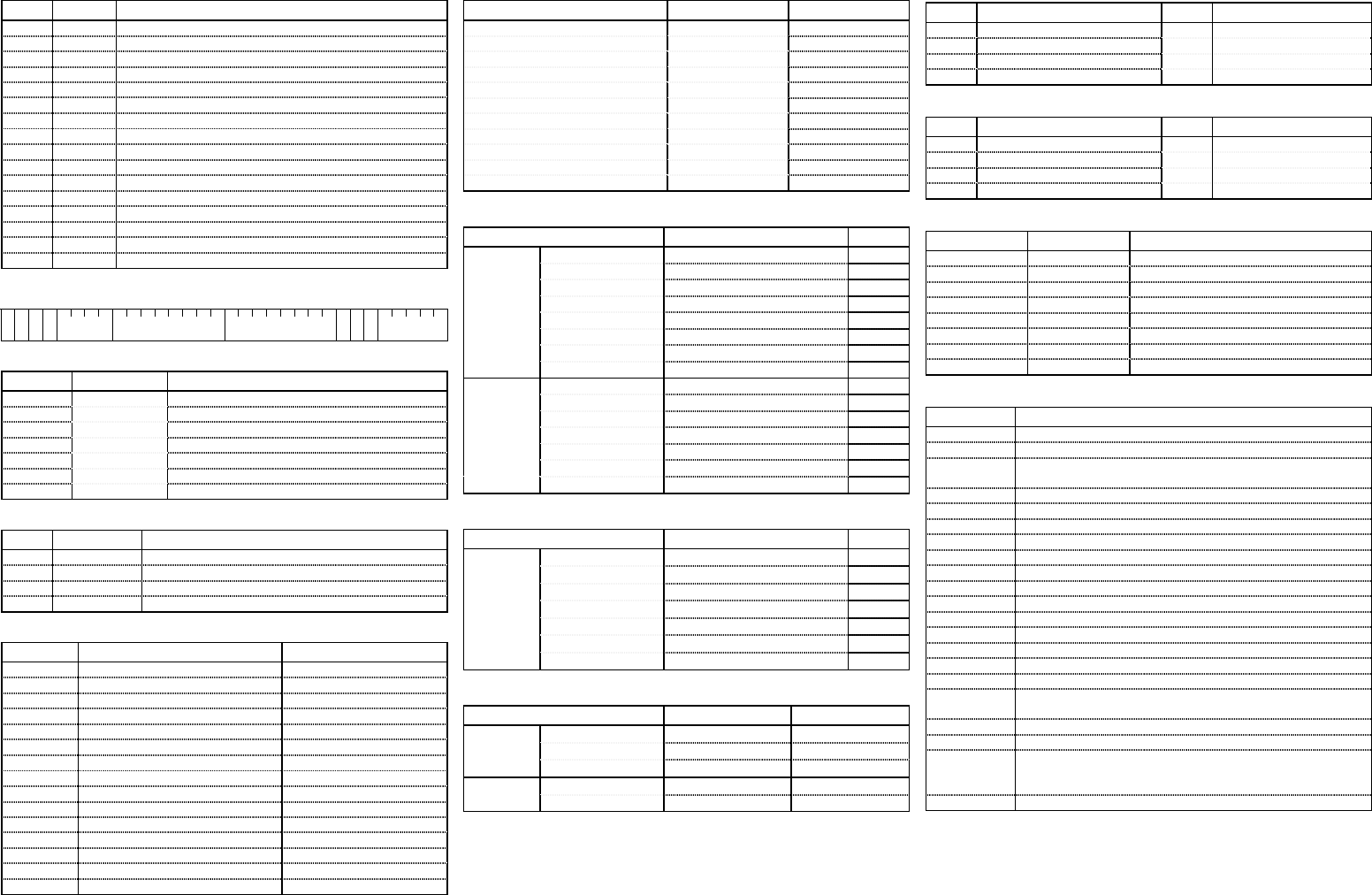

ARMv4T Partial Instruction Set Tables

Register Names and Aliases

Reg Aliases Purpose in ARM Thumb Procedure Call Standard

r0 a1 Argument/result/scratch register 1

r1 a2 Argument/result/scratch register 2

r2 a3 Argument/result/scratch register 3

r3 a4 Argument/result/scratch register 4

r4 v1 Variable register 1

r5 v2 Variable register 2

r6 v3 Variable register 3

r7 v4 Variable register 4

r8 v5 Variable register 5

r9 v6 or sb Variable register 6; sometimes Stack Base register

r10 v7 or sl Variable register 7; sometimes Stack Limit register

r11 v8 or fp Variable register 8; usually Frame Pointer register

r12 ip Intra-procedure-call scratch register

r13 sp Stack Pointer

r14 lr Link Register

r15 pc Program Counter

Program Status Register Format

31 28 24 16 87654 0

NZCV Undef. Undef. Undef. IFT Mode

Program Status Register Modes

Value Mode Accessible registers

0b10000 User PC, R14–R0, CPSR

0b10001 Fast Interrupt PC, R14_fiq–R8_fiq, R7–R0, CPSR, SPSR_fiq

0b10010 Interrupt PC, R14_irq–R13_irq, R12–R0, CPSR, SPSR_irq

0b10011 Supervisor PC, R14_svc–R13_svc, R12–R0, CPSR, SPSR_svc

0b10111 Abort PC, R14_abt–R13_abt, R12–R0, CPSR, SPSR_abt

0b11011 Undefined PC, R14_und–R13_und, R12–R0, CPSR, SPSR_und

0b11111 System PC, R14–R0, CPSR

Program Status Register Fields: fields

Suffix Bits in PSRs Description

c0–7 Control field mask

x8–15 Extension field mask (no bits currently defined)

s16–23 Status field mask (no bits currently defined)

f24–31 Flags field mask (bits 24–27 undefined)

Optional Condition Field: cond

Mnemonic Description Condition flags state

EQ Equal Z set

NE Not equal Z clear

CS or HS Carry set/unsigned higher or same C set

CC or LO Carry clear/unsigned lower C clear

MI Minus/negative N set

PL Plus/positive or zero N clear

VS Overflow V set

VC No overflow V clear

HI Unsigned higher C set and Z clear

LS Unsigned lower or same C clear or Z set

GE Signed greater than or equal N equal to V

LT Signed less than N not equal to V

GT Signed greater than Z clear and N equal to V

LE Signed less than or equal Z set and N not equal to V

AL Always (unconditional, default) Irrelevant

Data Processing Mode: shifter_op

Operation Syntax Comments

Immediate value #imm8r

Register Rm

Logical shift left immediate Rm, lsl #imm5 Allowed 0–31 only

Logical shift left by register Rm, lsl Rs

Logical shift right immediate Rm, lsr #imm5 Allowed 1–32 only

Logical shift right by register Rm, lsr Rs

Arithmetic shift right immediate Rm, asr #imm5 Allowed 1–32 only

Arithmetic shift right by register Rm, asr Rs

Rotate right immediate Rm, ror #imm5 Allowed 1–31 only

Rotate right by register Rm, ror Rs

Rotate right with extend Rm, rrx

Load or Store Word/Unsigned Byte Mode: am2

Operation Syntax Cmts.

Pre-indexed Immediate offset [Rn, #±imm12]{!}

Zero offset [Rn][Rn, #0]

Register offset [Rn, ±Rm]{!}

Scaled register offset [Rn, ±Rm, lsl #imm5]{!}0–31 only

[Rn, ±Rm, lsr #imm5]{!} 1–32 only

[Rn, ±Rm, asr #imm5]{!}1–32 only

[Rn, ±Rm, ror #imm5]{!}1–31 only

[Rn, ±Rm, rrx]{!}

Post-indexed Immediate offset [Rn], #±imm12

Register offset [Rn], ±Rm

Scaled register offset [Rn], ±Rm, lsl #imm5 0–31 only

[Rn], ±Rm, lsr #imm5 1–32 only

[Rn], ±Rm, asr #imm5 1–32 only

[Rn], ±Rm, ror #imm5 1–31 only

[Rn], ±Rm, rrx

Load or Store with Translation Mode: am2P

Operation Syntax Cmts.

Post-indexed Immediate offset [Rn], #±imm12

Register offset [Rn], ±Rm

Scaled register offset [Rn], ±Rm, lsl #imm5 0–31 only

[Rn], ±Rm, lsr #imm5 1–32 only

[Rn], ±Rm, asr #imm5 1–32 only

[Rn], ±Rm, ror #imm5 1–31 only

[Rn], ±Rm, rrx

Load or Store Half-Word/Signed Byte Mode: am3

Operation Syntax Comments

Pre-indexed Immediate offset [Rn, #±imm8]{!}Note: not imm8r

Zero offset [Rn]Same as [Rn, #0]

Register offset [Rn, ±Rm]{!}

Post-indexed Immediate offset [Rn], #±imm8 Note: not imm8r

Register offset [Rn], ±Rm

Load Multiple Data Mode: am4L

Suffix Non-stack Addressing Mode Suffix Stack Addressing Mode

ia Increment after fd Full descending

ib Increment before ed Empty descending

da Decrement after fa Full ascending

db Decrement before ea Empty ascending

Store Multiple Data Mode: am4S

Suffix Non-stack Addressing Mode Suffix Stack Addressing Mode

ia Increment after ea Empty ascending

ib Increment before fa Full ascending

da Decrement after ed Empty descending

db Decrement before fd Full descending

Exception Vector Table

Address Mode Exception Type

0x00000000 Supervisor Reset

0x00000004 Undefined Undefined instruction

0x00000008 Supervisor Software interrupt

0x0000000C Abort Prefetch abort (instruction fetch abort)

0x00000010 Abort Data abort (data access memory abort)

0x00000014 (None) (Not used)

0x00000018 Interrupt Normal-priority interrupt

0x0000001C Fast Interrupt High-priority (fast) interrupt

Miscellaneous

Symbol Meaning

imm5 Immediate 5-bit number, either 0–31, 1–32 or 1–31

imm8 Immediate 8-bit number, between 0–255

imm8r A 32-bit number that can be formed by rotating an 8-bit

number (0–255) by an even number between 0 and 30

imm12 Immediate 12-bit number, between 0–4095

imm24 Immediate 24-bit number, between 0–16,777,215

imm32 Immediate 32-bit number, between 0–4,294,967,295

{s}If present, the instruction will update the condition flags

N Negative flag: 1 if result is negative

Z Zero flag: 1 if result is zero

C Carry flag

VSigned Overflow flag

C? Carry flag ends in an unpredictable state, if flags are set

V? Overflow flag ends in an unpredictable state, if flags are set

I Interrupt Disable bit in the PSRs: 1 to disable interrupts

F Fast Interrupt Disable bit: 1 to disable fast interrupts

T ARM or Thumb state: 0 for ARM execution, 1 for Thumb

{reglist}List of registers separated by commas or dashes, sur-

rounded by braces, eg, {r0,r1,r2} or {r0–r3,r5}

{reglist–pc}List of registers that does not include PC (R15)

{reglist+pc}List of registers that does include PC (R15)

{!}If present, the instruction updates the base register after

the memory transfer.

Post-indexed accesses always update the base register

±Either + or - may be supplied; + is assumed if not present

This document contains a summary of the ARMv4T instruction set architecture in tabular format. It does not list every instruction available in the

ARM architecture: the coprocessor instructions, in particular, have not been listed. Page numbers refer to both the printed and on-line versions of

the ARM Architecture Reference Manual, Second Edition, published by Addison-Wesley in December 2000 (ISBN 0-201-73719-1).

This document was created by John Zaitseff for the Digital Systems Laboratory at the University of New South Wales.

Copyright © 2003, School of Electrical Engineering and Telecommunications, University of New South Wales, Sydney, Australia. All rights reserved.