Samsung Spinpoint 2 5 Hard Disk Drive M8 Users Manual PM M8, Rev. 2.3 Docx

M8 to the manual f6ce8481-0882-4d9a-86af-bb3785a28f35

2015-01-23

: Samsung Samsung-Spinpoint-2-5-Hard-Disk-Drive-M8-Users-Manual-276507 samsung-spinpoint-2-5-hard-disk-drive-m8-users-manual-276507 samsung pdf

Open the PDF directly: View PDF ![]() .

.

Page Count: 84

M8 Product Manual

2.5” Hard Disk Drive

June 05, 2012. Rev 2.3

© 2012 Seagate Technology LLC. All rights reserved. Seagate and Seagate Technology are registered

trademarks of Seagate Technology LLC in the United States and/or other countries. Momentus is either a

trademark or registered trademark of Seagate Technology LLC or one of its affiliated companies in the

United States and/or other countries. All other trademarks or registered trademarks are the property of

their respective owners. When referring to drive capacity, one gigabyte, or GB, equals one billion bytes and

one terabyte, or TB, equals one trillion bytes. Your computer’s operating system may use a different

standard of measurement and report a lower capacity. In addition, some of the listed capacity is used for

formatting and other functions, and thus will not be available for data storage. Actual data rates may vary

depending on operating environment and other factors. The export or re-export of hardware or software

containing encryption may be regulated by the U.S. Department of Commerce, Bureau of Industry and

Security (for more information, visit www.bis.doc.gov), and controlled for import and use outside of the U.S.

Seagate reserves the right to change, without notice, product offerings or specifications.

Spinpoint M8 Product Manual REV 2.3

TABLE OF

CONTENTS

CHAPTER 1

SCOPE .............................................................................................................................1

1.1 USER DEFINITION

..............................................................................................................................1

1.2 MANUAL ORGANIZATION

..................................................................................................................1

1.3 SATA

.................................................................................................................................................2

1.4 REFERENCE

........................................................................................................................................2

CHAPTER 2 DESCRIPTION

..............................................................................................................3

2.1 INTRODUCTION

..................................................................................................................................3

2.2 KEY FEATURES

..................................................................................................................................4

2.3 STANDARDS AND

R

EGULATIONS

........................................................................................................5

2.4 HARDWARE

R

EQUIREMENTS

.............................................................................................................5

CHAPTER 3 SPECIFICATIONS

........................................................................................................6

3.1 SPECIFICATION SUMMARY

................................................................................................................6

3.2 PHYSICAL SPECIFICATIONS

...............................................................................................................7

3.3 LOGICAL

C

ONFIGURATIONS

..............................................................................................................7

3.4 PERFORMANCE SPECIFICATIONS

......................................................................................................8

3.5 POWER CONSUMPTION

......................................................................................................................9

3.6 ENVIRONMENTAL SPECIFICATIONS

................................................................................................10

3.7 RELIABILITY SPECIFICATIONS

........................................................................................................12

CHAPTER 4

INSTALLATION..........................................................................................................13

4.1 SPACE

R

EQUIREMENTS

....................................................................................................................13

4.2 UNPACKING

I

NSTRUCTIONS

.............................................................................................................14

4.3 MOUNTING

.......................................................................................................................................14

4.3.1

Orientation......................................................................................................................15

4.3.2

Clearance........................................................................................................................16

4.3.3 Ventilation

......................................................................................................................17

4.4 CABLE

C

ONNECTORS

.......................................................................................................................17

4.4.1 SATA Connectivity

..........................................................................................................17

4.5 DRIVE

I

NSTALLATION

......................................................................................................................22

CHAPTER 5 DISK DRIVE

OPERATION........................................................................................23

5.1 HEAD / DISK ASSEMBLY (HDA)

......................................................................................................23

5.1.1 Base Casting Assembly

...................................................................................................23

5.1.2 DC Spindle Motor

Assembly...........................................................................................23

5.1.3 Disk Stack Assembly

.......................................................................................................25

5.1.4 Head Stack

Assembly ......................................................................................................25

5.1.5 Voice Coil Motor and Actuator Latch

Assemblies ..........................................................25

5.1.6 Air Filtration

System.......................................................................................................25

5.1.7 Load/Unload

Mechanism................................................................................................25

5.2 DRIVE ELECTRONICS

.......................................................................................................................26

5.2.1 Digital Signal Process and Interface Controller

............................................................26

5.2.2 Disk Controller

...............................................................................................................26

5.2.2.1 The Host Interface Control Block ................................................................................................. 28

5.2.2.2 The Buffer Control Block ............................................................................................................. 28

5.2.2.3 The Disk Control Block ................................................................................................................ 29

5.2.2.4 The Disk LDPC Control Block ..................................................................................................... 29

5.2.2.5 Frequency Synthesizer .................................................................................................................. 29

5.2.2.6 Power Management....................................................................................................................... 30

5.2.3 Read/Write

IC .................................................................................................................30

5.2.3.1 Time Base Generator..................................................................................................................... 30

5.2.3.2 Automatic Gain Control ................................................................................................................ 30

5.2.3.3 Asymmetry Correction Circuitry (ASC) ....................................................................................... 30

5.2.3.4 Analog Anti-Aliasing Low Pass Filter .......................................................................................... 31

Spinpoint M8 Product Manual REV 2.3

5.2.3.5 Analog to Digital Converter (ADC) and FIR ................................................................................ 31

5.3 SERVO SYSTEM

................................................................................................................................32

5.4 READ AND WRITE OPERATIONS

......................................................................................................32

5.4.1 The Read

Channel...........................................................................................................32

5.4.2 The Write

Channel ..........................................................................................................33

5.5 FIRMWARE FEATURES

.....................................................................................................................33

5.5.1 Read Caching

.................................................................................................................33

5.5.2 Write

Caching

.................................................................................................................34

5.5.3 Defect Management

........................................................................................................35

5.5.4 Automatic Defect Allocation

...........................................................................................35

5.5.5 Multi-burst ECC Correction

...........................................................................................35

5.5.6

SMART............................................................................................................................35

CHAPTER 6 SATA II INTERFACE

.................................................................................................37

6.1 INTRODUCTION

................................................................................................................................37

SATA

Terminology....................................................................................................................................37

6.2 PHYSICAL INTERFACE

.....................................................................................................................39

6.3 SIGNAL SUMMARY

...........................................................................................................................39

6.3.1 Signal

Descriptions.........................................................................................................39

6.3.2 I/O Register - Address

....................................................................................................40

6.3.3 Control Block Register Descriptions

..............................................................................40

6.3.3.1 Alternate Status Register (ex. 3F6h) ............................................................................................. 40

6.3.3.2 Device Control Register (ex. 3F6h)............................................................................................... 41

6.3.4 Command Block Register Descriptions

..........................................................................41

6.3.4.1 Data Register (Ex. 1F0h)............................................................................................................... 41

6.3.4.2 Features Register and Feature Extended Register (Ex. 1F1h) ....................................................... 41

6.3.4.3 Sector Number Register and Sector Number Extended Register (Ex. 1F3h) ................................ 41

6.3.4.4 Error Register (Ex. 1F1h) .............................................................................................................. 41

6.3.4.5 Sector Count Register and Sector Count Extended Register (Ex. 1F2h) ....................................... 42

6.3.4.6 Cylinder High Register and Cylinder High Extended Register (Ex. 1F5h) ................................... 42

6.3.4.7 Cylinder Low Register and Cylinder Low Extended Register (Ex. 1F4h) .................................... 42

6.3.4.8 Command Register (Ex. 1F7h)...................................................................................................... 42

6.3.4.9 Device Register (Ex. 1F6h) ........................................................................................................... 42

6.3.4.10 Status Register (Ex. 1F7h) ............................................................................................................ 43

CHAPTER 7 SATA II FEATURE

SET .............................................................................................44

7.1 DEVICE ACTIVITY SIGNAL

..............................................................................................................44

7.2 STAGGERED SPIN-UP DISABLE CONTROL

.......................................................................................44

7.3 AUTO-ACTIVATE IN DMA SETUP FIS

............................................................................................44

7.4 NATIVE COMMAND QUEUING (NCQ)

.............................................................................................44

7.5 PHY. EVENT COUNTERS

..................................................................................................................45

7.6 SOFTWARE SETTINGS

P

RESERVATION

............................................................................................46

7.7 SATA POWER

M

ANAGEMENT

.........................................................................................................46

CHAPTER 8 ATA COMMAND DESCRIPTIONS

..........................................................................47

8.1 COMMAND

T

ABLE

............................................................................................................................47

8.2 COMMAND

D

ESCRIPTIONS

...............................................................................................................48

8.2.1 Check Power Mode

(E5h)...............................................................................................48

8.2.2 Download Micro Code

(92h)

..........................................................................................49

8.2.3 Device Configuration Overlay

(B1h)

..............................................................................49

8.2.4 Execute Device Diagnostics

(90h) ..................................................................................51

8.2.5 Flush Cache (E7h, EAh:

extended).................................................................................51

8.2.6 Format Track (50h)

........................................................................................................51

8.2.7 Identify Device (ECh)

.....................................................................................................51

8.2.8 Idle

(E3h)

........................................................................................................................57

8.2.9 Idle Immediate (E1h)

......................................................................................................57

8.2.10 Initialize Device Parameters

(91h)

.................................................................................58

8.2.11 NOP

(00h).......................................................................................................................58

8.2.12 Read Buffer

(E4h) ...........................................................................................................58

8.2.13 Read DMA (C8h,

25h:extended).....................................................................................58

Spinpoint M8 Product Manual REV 2.3

8.2.14 Read FPDMA Queued

(60h)...........................................................................................58

8.2.15 Read Log Extended

(2Fh) ...............................................................................................59

8.2.16 Read Long (22h)

.............................................................................................................59

8.2.17 Read Multiple Command (C4h,

29h:extended)...............................................................59

8.2.18 Read Native Max Address (F8h, 27h :extended)

.........................................................60

8.2.19 Read Sector(s) (20h, 24h:

extended)...............................................................................60

8.2.20 Read Verify Sector(s) (40h, 41h :extended)

....................................................................60

8.2.21 Recalibrate

(10h) ............................................................................................................61

8.2.22 Security Disable Password (F6h)

...................................................................................61

8.2.23 Security Erase Prepare

(F3h)

.........................................................................................61

8.2.24 Security Erase Unit

(F4h)...............................................................................................61

8.2.25 Security Freeze Lock

(F5h).............................................................................................62

8.2.26 Security Set Password

(F1h)...........................................................................................62

8.2.27 Security Unlock

(F2h).....................................................................................................63

8.2.28 Seek (7xh)

.......................................................................................................................63

8.2.29 Set Features

(EFh)..........................................................................................................63

8.2.30 Set Max Address (F9h, 37h: extended)

...........................................................................65

8.2.31 Set Multiple Mode

(C6h).................................................................................................65

8.2.32 Sleep (E6h)

.....................................................................................................................65

8.2.33 Standby (E2h)

.................................................................................................................65

8.2.34 SMART

(B0h)..................................................................................................................66

8.2.34.1 Smart disable operations (D9h) ..................................................................................................... 66

8.2.34.2 Smart enable/disable attribute auto-save (D2h)............................................................................. 66

8.2.34.3 Smart enable operations (D8h) ...................................................................................................... 67

8.2.34.4 Smart execute off-line immediate (D4h) ....................................................................................... 67

8.2.34.5 Smart read data (D0h) ................................................................................................................... 68

8.2.34.6 SMART read log sector (D5h) ...................................................................................................... 74

8.2.34.7 SMART return status (DAh) ......................................................................................................... 74

8.2.34.8 SMART write log sector (D6h) ..................................................................................................... 74

8.2.35 Standby (E2h)

.................................................................................................................74

8.2.36 Standby Immediate

(E0h)................................................................................................74

8.2.37 Write Buffer (E8h)

..........................................................................................................74

8.2.38 Write DMA (CAh,

35h:extended)....................................................................................74

8.2.39 Write FPDMA Queued

(61h)

..........................................................................................75

8.2.40 Write Long

(32h).............................................................................................................75

8.2.41 Write Multiple Command (C5h, 39h:extended)

..............................................................75

8.2.42 Write Sector(s) (30h, 34h:extended)

............................................................................76

CHAPTER 9

MAINTENANCE..........................................................................................................77

9.1 GENERAL INFORMATION

.................................................................................................................77

9.2 MAINTENANCE PRECAUTIONS

........................................................................................................77

9.3 SERVICE AND REPAIR

......................................................................................................................79

Spinpoint M8 Product Manual REV 2.3

TABLE OF

TABLES

Table 3-1 : Specifications ..........................................................................................................................6

Table 3-2 : Physical Specifications ............................................................................................................7

Table 3-3 : Logical Configurations ............................................................................................................7

Table 3-4 : Performance Specifications .....................................................................................................8

Table 3-5 : Power consumption .................................................................................................................9

Table 3-6 : Environmental

Specifications

................................................................................................10

Table 3-7 : Reliability Specifications.......................................................................................................12

Table 4-1 SATA Connector Pin Definitions ............................................................................................19

Table 7-1 Phy Event Counter Supports....................................................................................................45

Table 8-1 Command Code Parameters ....................................................................................................47

Table 8-2 Device Configuration Overlay Feature Register Values..........................................................49

Table 8-3 Device Configuration Identify data structure ..........................................................................50

Table 8-4 Diagnostic

Codes

.....................................................................................................................51

Table 8-5 IDENTIFY DEVICE information ...........................................................................................52

Table 8-6 Automatic Standby Timer Periods...........................................................................................57

Table 8-7 Security password content .......................................................................................................61

Table 8-8 Security Erase Unit Password..................................................................................................62

Table 8-9 Security Set Password data content .........................................................................................62

Table 8-10 Identifier and security level bit interaction ............................................................................63

Table 8-11 Set Features Register Definitions ..........................................................................................64

Table 8-12 Transfer Mode Values ...........................................................................................................64

Table 8-13 Set Max Feature Register Values ..........................................................................................65

Table 8-14 SMART Feature Registers Values.........................................................................................66

Table 8-15 Device SMART Data Structure .............................................................................................68

Table 8-16 SMART Attribute Status Flags..............................................................................................69

Table 8-17 SMART Attribute Data List ..................................................................................................71

Table 8-18 Off-line Data Collection Status Values .................................................................................71

Table 8-19 Self-test Execution Status Values ..........................................................................................72

SCOPE

Spinpoint M8 Product Manual REV 2.3

1

CHAPTER 1 SCOPE

Welcome to the SpinpointTM M8 series of SamsungTM hard disk drive. This series of drives consists of the

following models: ST250LM004, ST320LM001, ST500LM012, ST640LM001, ST750LM022, and

ST1000LM024. This chapter provides an overview of the contents of this manual, including the

intended user,

manual organization, terminology and conventions. In addition, it provides a list of references that might be

helpful to the reader.

1.1 User Definition

The Spinpoint M8 product manual is intended for the following readers:

Original Equipment Manufacturers (OEMs)

Distributors

1.2 Manual Organization

This manual provides information about installation, principles of operation, and interface command

implementation. It is organized into the following chapters:

Chapter 1 - SCOPE

Chapter 2 - DESCRIPTION

Chapter 3

- SPECIFICATIONS

Chapter 4 - INSTALLATION

Chapter 5 - DISK DRIVE OPERATION

Chapter 6 - SATA INTERFACE

Chapter 7 - MAINTENANCE

In addition, this manual contains a glossary of terms to help you understand important information

SCOPE

Spinpoint M8 Product Manual REV 2.3

2

1.3 SATA

The ATA (Advanced Technology Attachment) interface which was developed based on the IDE

(Integrated Drive Electronics) has been around from 1980’s. As the PC processor speed has improved,

so have the data rates of the HDD. The parallel ATA is reaching its limit of 133 MB/s data transfer rate.

Serial implementation of ATA (SATA) will allow the data rate to run even faster so the processor will

be utilized more efficiently. Serial ATA has been developed to provide the next generation storage

interface.

SATA interface replaces 2 inch wide, 40 pin parallel interface connector with 0.25 inch wide 7 pin

serial interface connector. The maximum length of the SATA interface cable can be extended to 1

meter (approximately 39 inches) compared to 18 inch of parallel ATA. SATA also allows a data

transfer speed of 150 MB/s and has a roadmap up to 600 MB/s to support storage evolution of the

next decade. Even though SATA will not directly interface with Parallel or traditional

ATA (PATA) hardware, it is compliant with ATA protocol and therefore software compatible. The cable

geometry with smaller footprint connector reduces board space requirements and improves air flow

and heat exchange inside computer systems.

SATA uses point to point connection topology and each channel works independently. There is no

sharing of interface, master/slave drive configuration, and no master/slave jumper settings. This is

different from Parallel ATA (PATA) architecture where 2 drives per port are supported by a shared bus

and drives are designated as master or slave drive based on jumper pin or cable selection. Unlike

parallel ATA, SATA drives are hot-plug and hot-swappable.

1.4 Reference

For additional information about the AT interface, refer to:

ATA-2 (AT Attachment 2), Revision 3, January, 1995

ATA-3 (Attachment-3 Interface) Revision 7b, 27 January, 1997

ATA-4 (AT Attachment with Packet Interface Extension) Revision 18, 19 August, 1998

ATA-5 (AT Attachment with Packet Interface Extension) Revision 3, 29 February, 2000

ATA-6 (AT Attachment with Packet Interface Extension) Revision 2a, 26 September, 2001

ATA-7 (AT Attachment with Packet Interface Extension) Revision 1, 28 August, 2002

ATA-8 (AT Attachment with Packet Interface Extension) Revision 0, 16 September, 2008

For introduction about SATA interface please refer to:

SATA 1.0 Design Guides, April 5, 2002. (URL: http:// www.serialdata.org retrieved on May 22, 2003)

Serial ATA: A comparison with Ultra ATA Technology

(URL: http://www.intel.com retrieved April 18,2003)

Serial ATA: High Speed Serialized AT Attachment, Rev. 1.0a, January 7, 2003, Serial Workgroup.

(URL: http://www.serialdata.org retrieved on May 22, 2003)

Serial ATA II: Port Multiplier 1.0 Specification, April 29th, 2003. (URL: http://www.serialdata.org

retrieved on May 22, 2003)

Spinpoint M8 Product Manual REV 2.3

3

DESCRIPTION

CHAPTER 2 DESCRIPTION

This chapter summarizes general functions and key features of the Spinpoint M8 hard disk drive, as well as the

standards and regulations they meet.

2.1 Introduction

The Samsung Spinpoint M8 2.5 inch hard disk drive is high capacity, high performance random access storage device,

which uses non-removable 2.5-inch disks as storage media. Each disk incorporates thin film metallic media technology

for enhanced performance and reliability. And for each disk surface there is a corresponding movable head actuator

assembly to randomly access the data tracks and write or read the user data.

The Spinpoint M8 hard disk drive includes the AT controller embedded in the disk drive PCB electronics. The drive's

electrical interface is compatible with all mandatory, optional and vendor-specific commands within the ATA

specification.

Drive size conforms to the industry standard 2.5-inch form factor with a SATA 15-pin DC power connector, and the

standard SATA 7-pin Interface connector.

The Spinpoint M8 hard disk drive incorporates TuMR head and Noise Predictive PRML (Partial Response

Maximum Likelihood) signal processing technologies. These advanced technologies allow for areal density of about

700.0 Gigabits per square inch and storage capacity of over 500.0 Gigabytes per disk.

The heads, disk(s), and actuator housing are environmentally sealed within an aluminum-alloy base and cover. As the

disks spin, air circulates within this base and cover, commonly referred to as the head and disk assembly (HDA), through

a non-replaceable absolute filter ensuring a contamination free environment for the heads and disks throughout the life of

the drive.

Spinpoint M8 Product Manual REV 2.3

4

DESCRIPTION

2.2 Key Features

Key features of the Spinpoint M8 SATA hard disk drive includes:

Formatted capacities are 250, 320, 500, 640, 750 GB, 1TB

9.5 ± 0.2 mm height form factor

5400 RPM Class

12 ms average seek time

High accuracy rotary voice coil actuator with embedded sector servo

Support ATA standard PIO Mode 4/DMA Mode 2/Ultra DMA Mode 5 (UDMA 100)

Serial ATA (SATA) Interface

Supports SATA interface 3.0 Gbps (1.5 Gbps) speed

Native SATA device without using SATA bridge

chip

Support SATA 3.0 and SATA II

features

Asynchronous Signal Recovery (ASR)

Pin-11 Device Activity Signal (Activity LED)

Pin-11 Staggered Spin-up Control

Auto-Activate DMA Setup FIS

Native Command Queuing with queue depth of 32 (First Party DMA)

Physical Event Counters

Software Settings Preservation

SATA Device Hot Plug Capability

Device Initiated Power Management

Supports LBA Addressing modes

Supports all logical geometries as programmed by the host

Transparent media defect mapping

High performance in-line defective sector skipping

Auto-reassignment

Automatic error correction and retries

On-the-fly (OTF) error correction

Noise predictive PRML read channel

TA detection and correction

TuMR/PMR head

SMART III support

1MB = 1,000,000 Bytes, 1GB = 1,000,000,000 Bytes

Accessible capacity may vary as some OS uses binary numbering system for reported capacity.

Spinpoint M8 Product Manual REV 2.3

5

DESCRIPTION

2.3 Standards and Regulations

The Spinpoint M8 / Momentus® series hard disk drive depends upon its host equipment to provide power and

appropriate environmental conditions to achieve optimum performance and compliance with applicable industry and

governmental regulations. Special attention has been given in the areas of safety, power distribution, shielding,

audible noise control, and temperature regulation.

The Spinpoint M8 hard disk drive satisfies the following standards and regulations:

Underwriters Laboratory (UL): Standard 1950. Information technology equipment including business

equipment.

Technisher Überwachungs Verein (TUV): Standard EN 60 950. Information technology equipment

including business equipment.

2.4 Hardware Requirements

The Spinpoint M8 hard disk drive is designed for use with host computers and controllers that are ATA

compatible. It is connected to a PC either by:

Using an adapter board with SATA interface, or

Plugging a cable from the drive directly into a PC motherboard with a SATA interface

SPECIFICATIONS

Spinpoint M8 Product Manual REV 2.3

6

CHAPTER 3 SPECIFICATIONS

This chapter gives a detail description of the physical, electrical and environmental characteristics of the Spinpoint M8

hard disk drive.

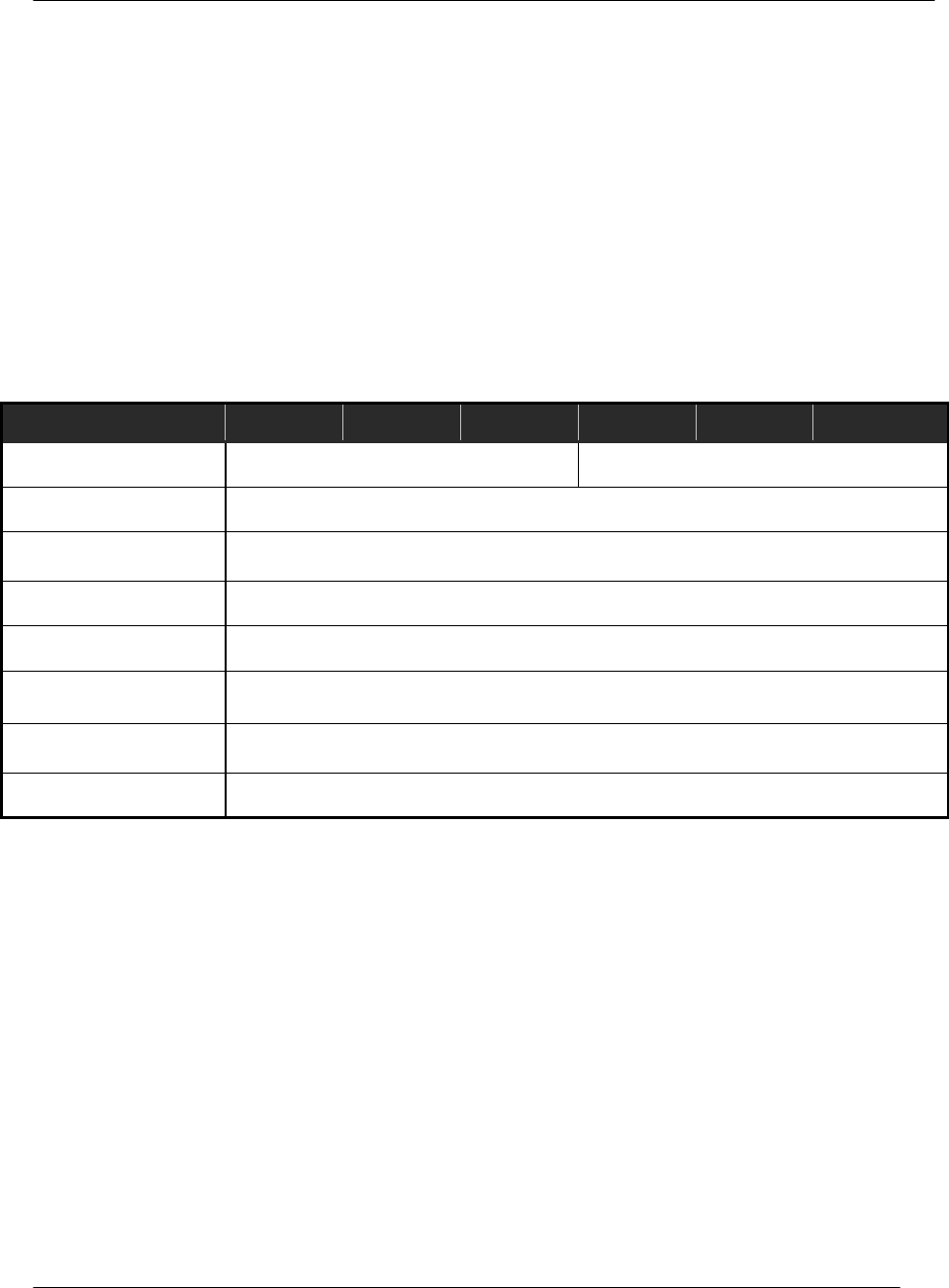

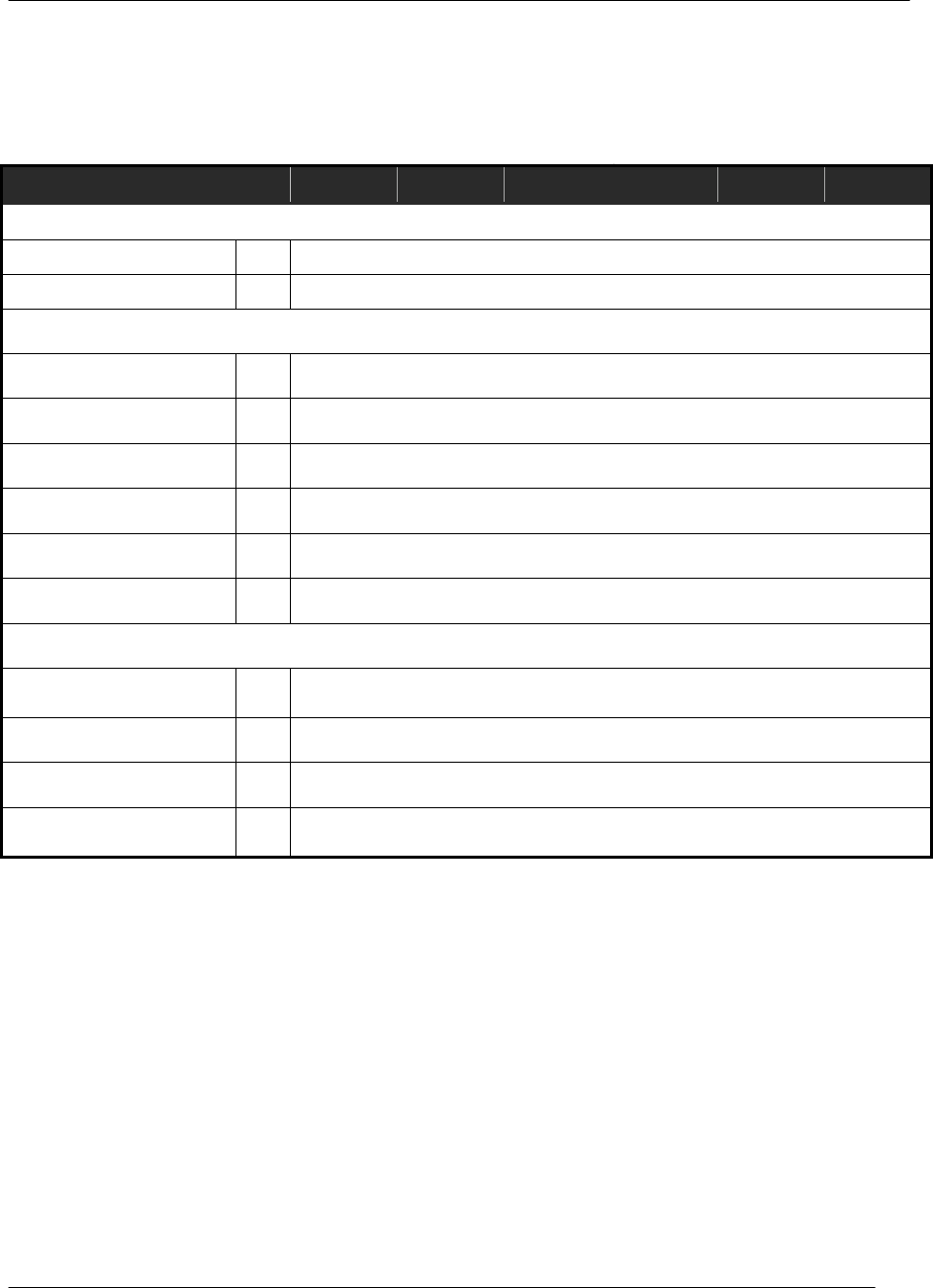

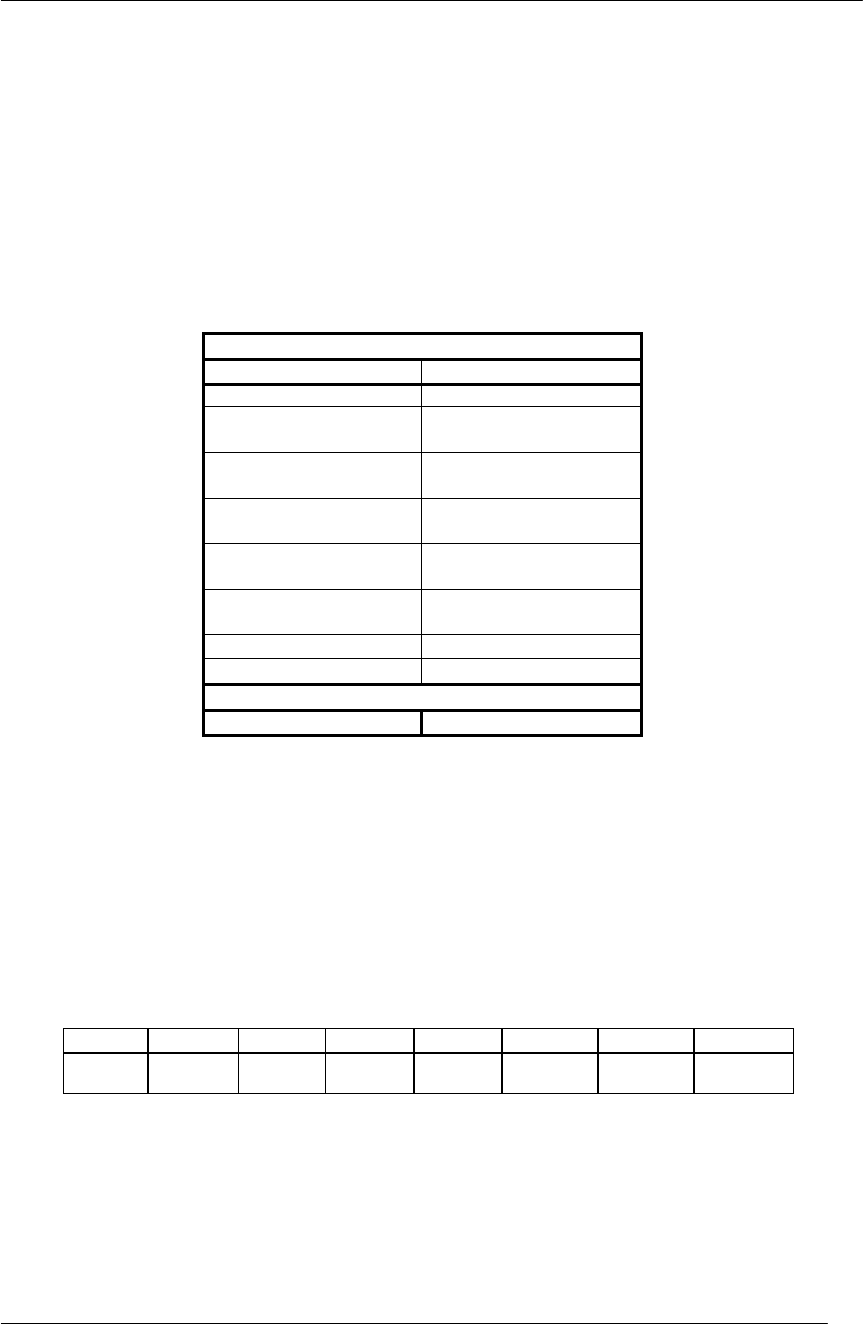

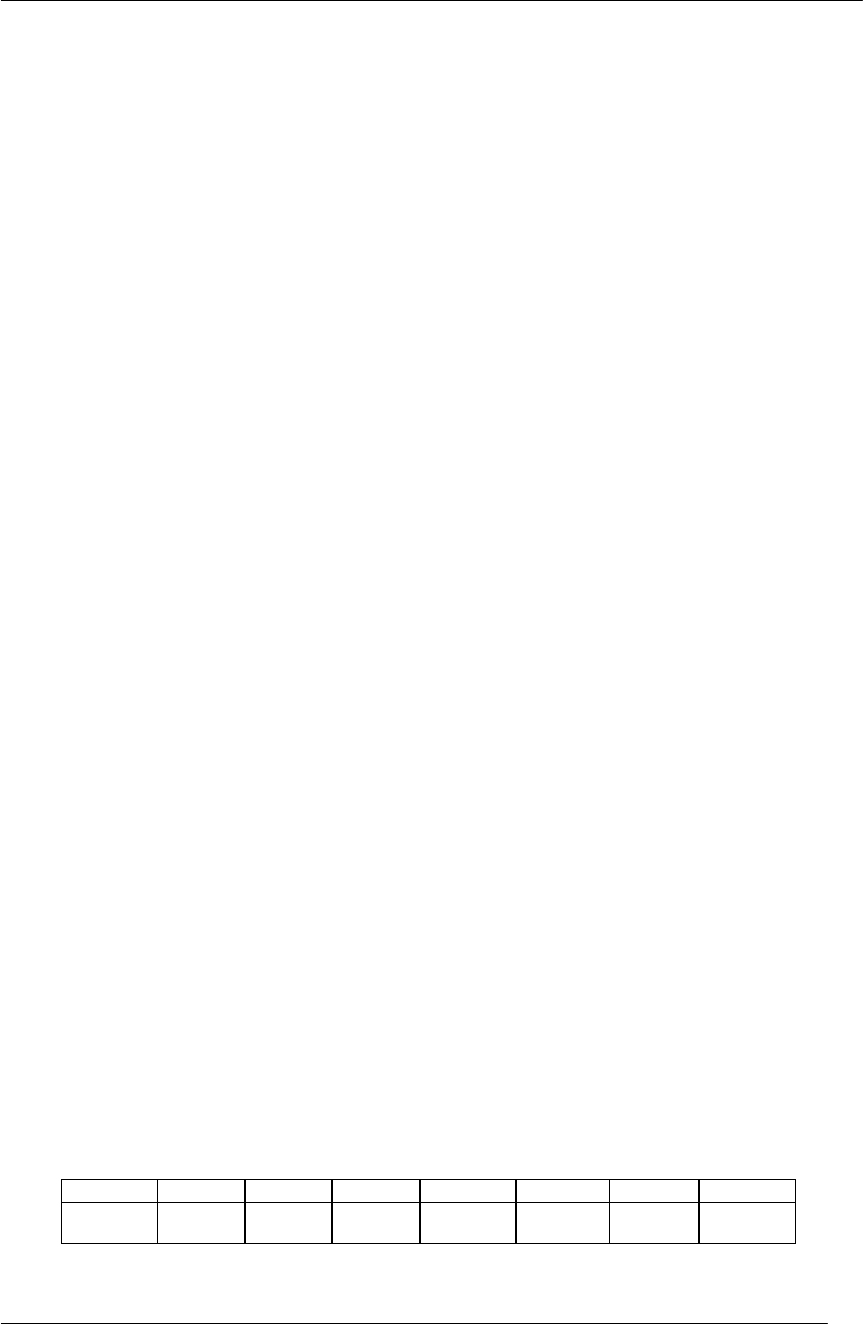

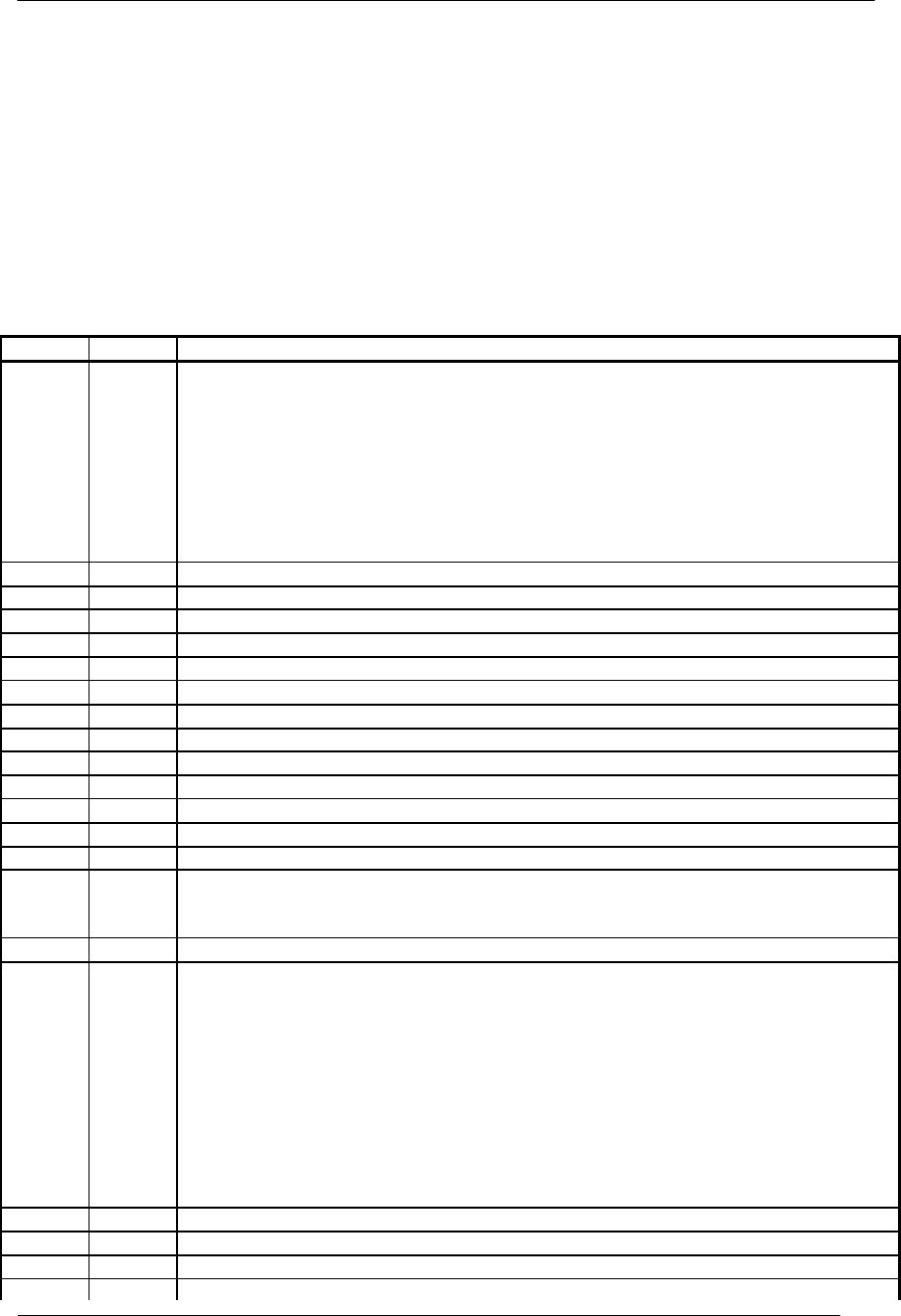

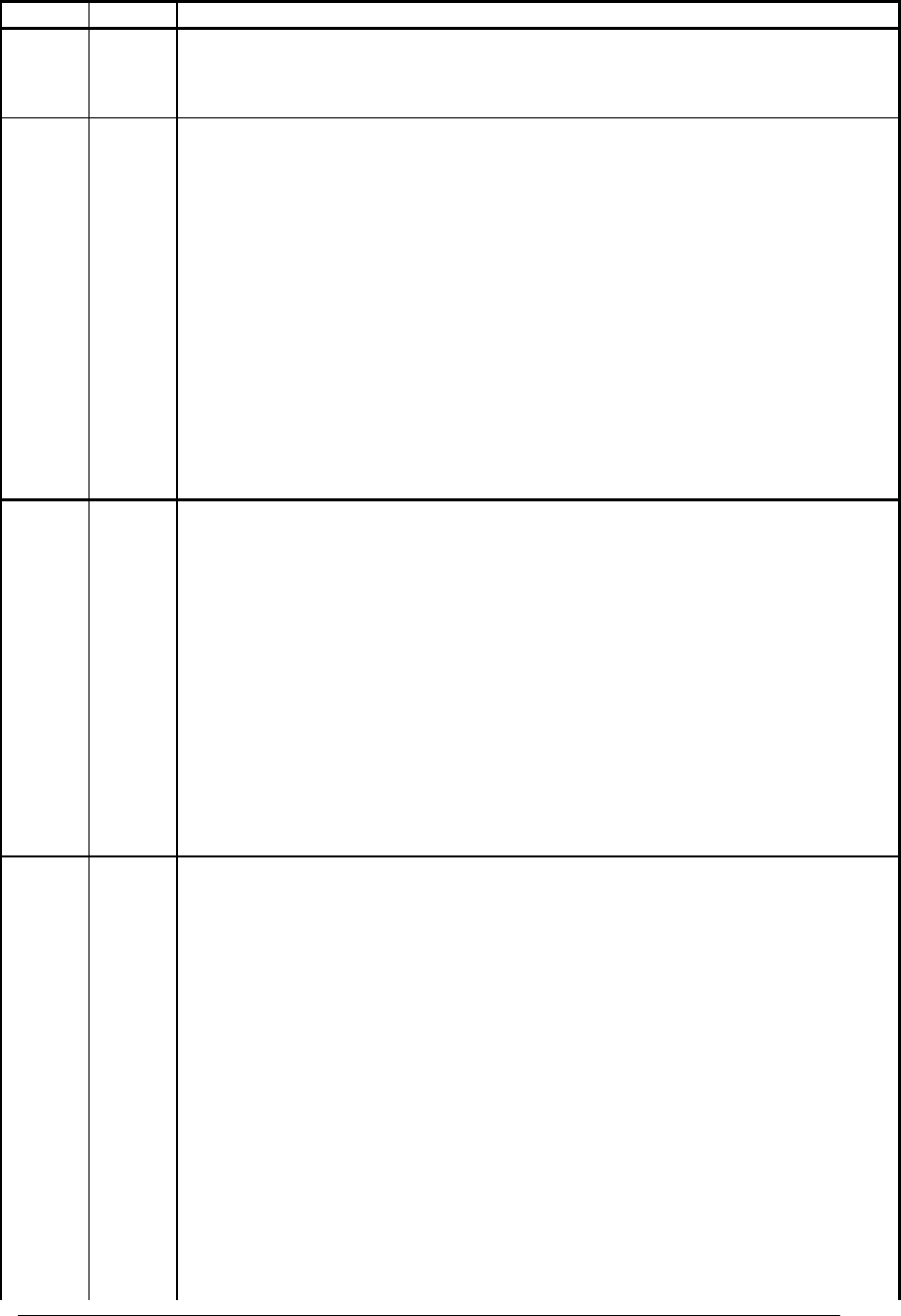

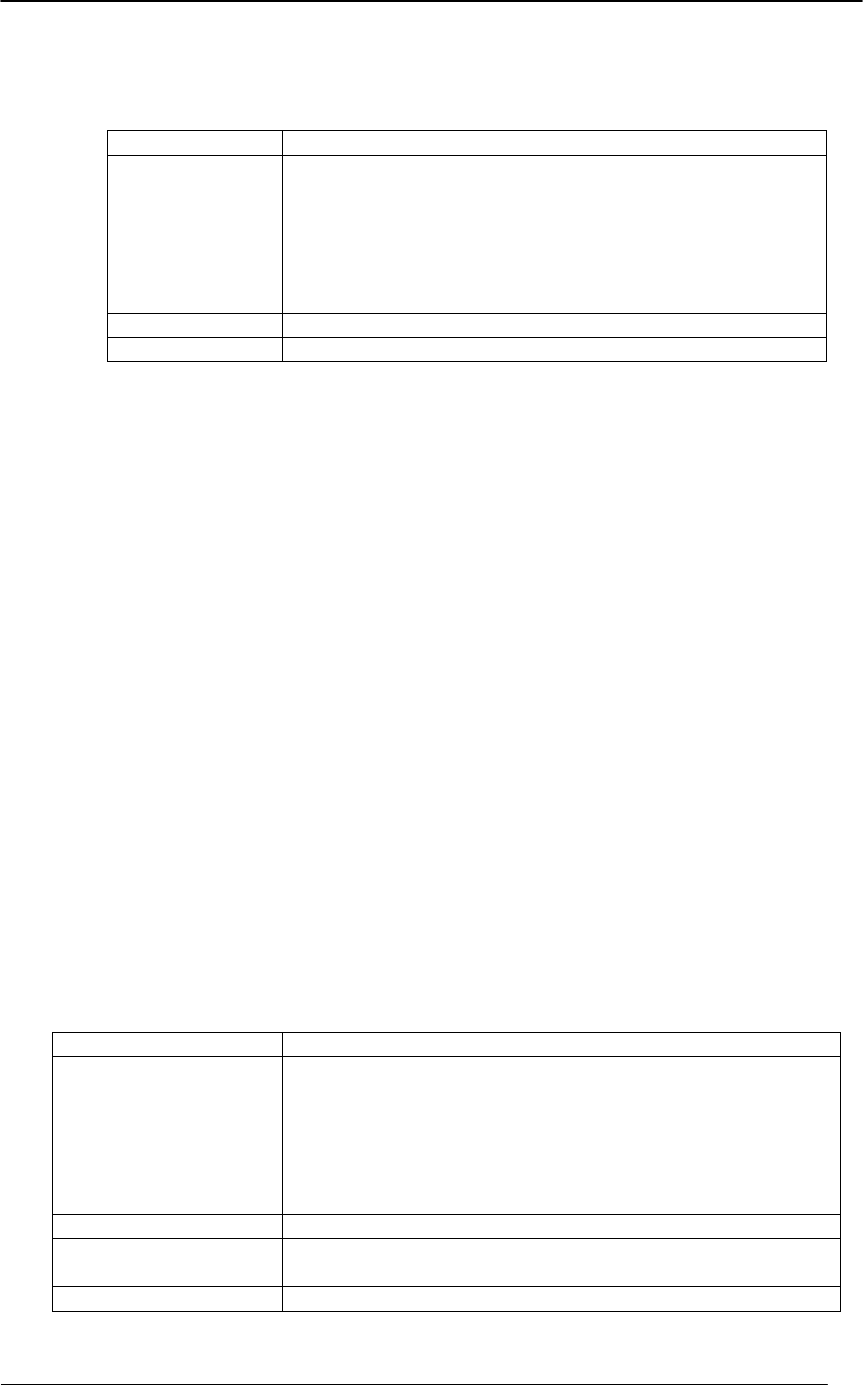

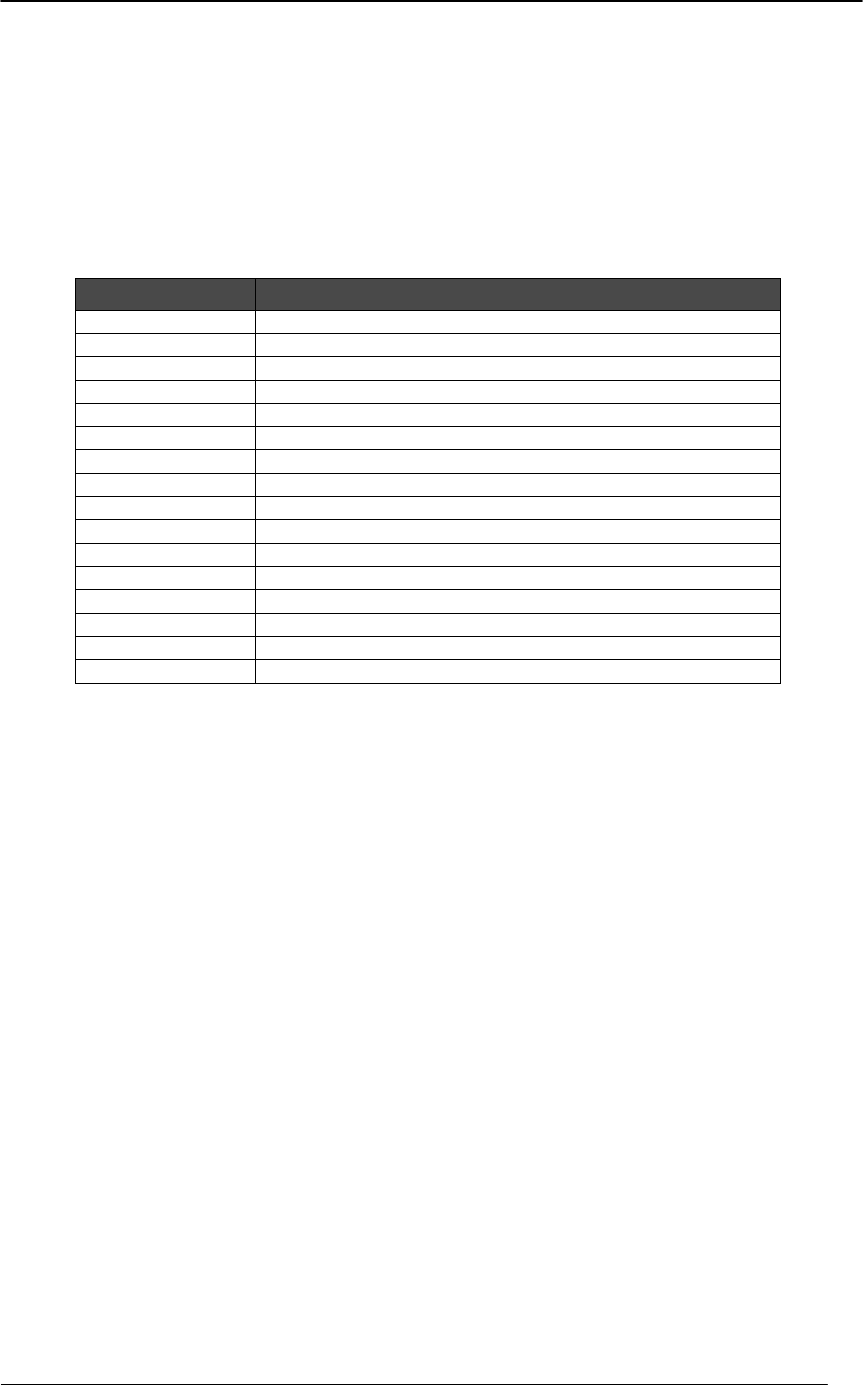

3.1 Specification Summary

Table 3-1:

Specifications

DESCRIPTION

ST250LM004

ST320LM001

ST500LM012

ST640LM001

ST750LM022

ST1000LM024

Number of R/W heads

2

4

Maximum KBPI

179K

Flexible data TPI

400

Encoding method

Noise Predictive

PRML

Interface

SATA 3.0 Gbps (1.5

Gbps)

Actuator type

Rotary Voice

Coil

Servo type

Embedded Sector

Servo

Spindle speed (RPM)

5400 RPM

Class

SPECIFICATIONS

Spinpoint M8 Product Manual REV 2.3

7

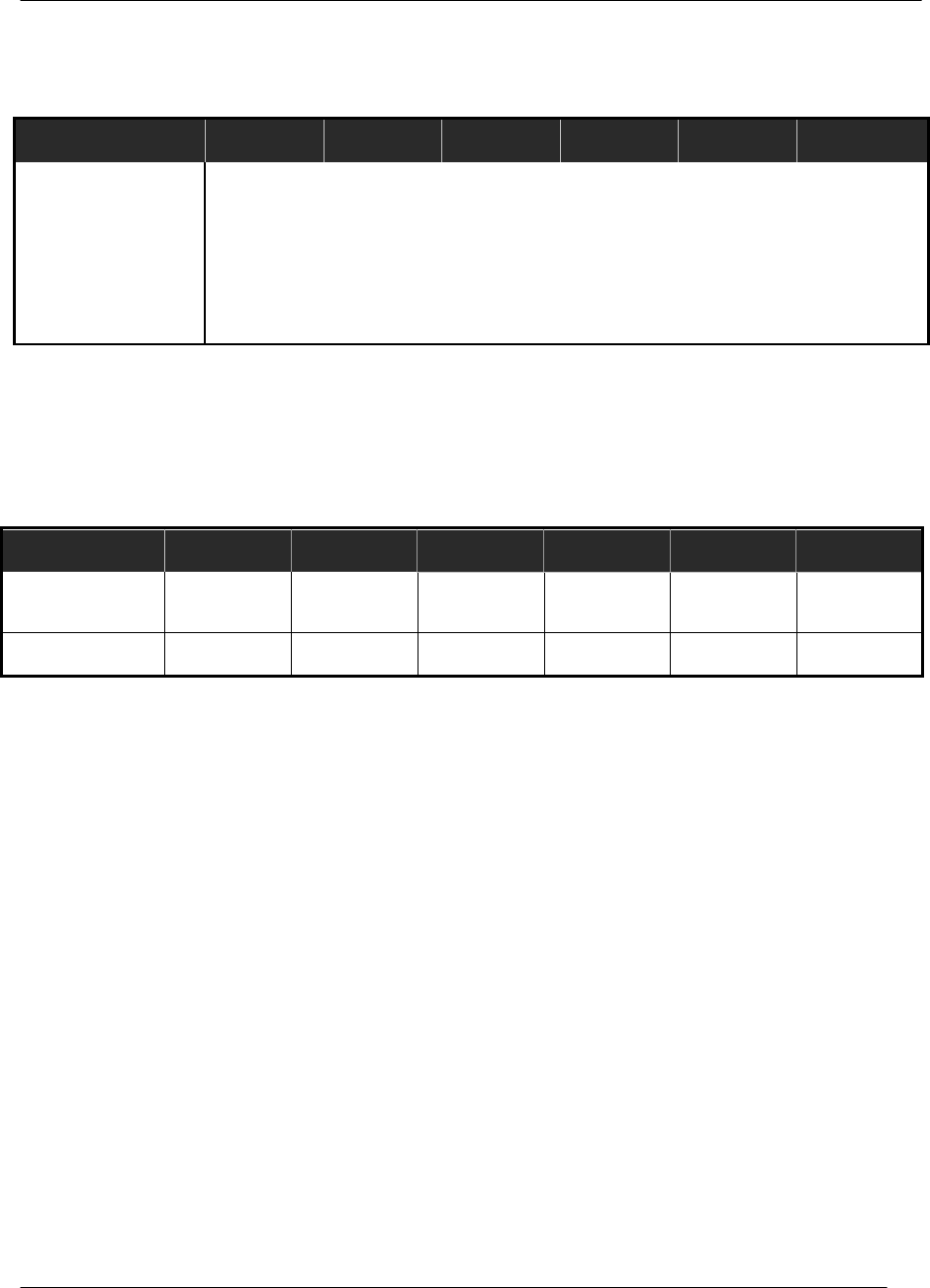

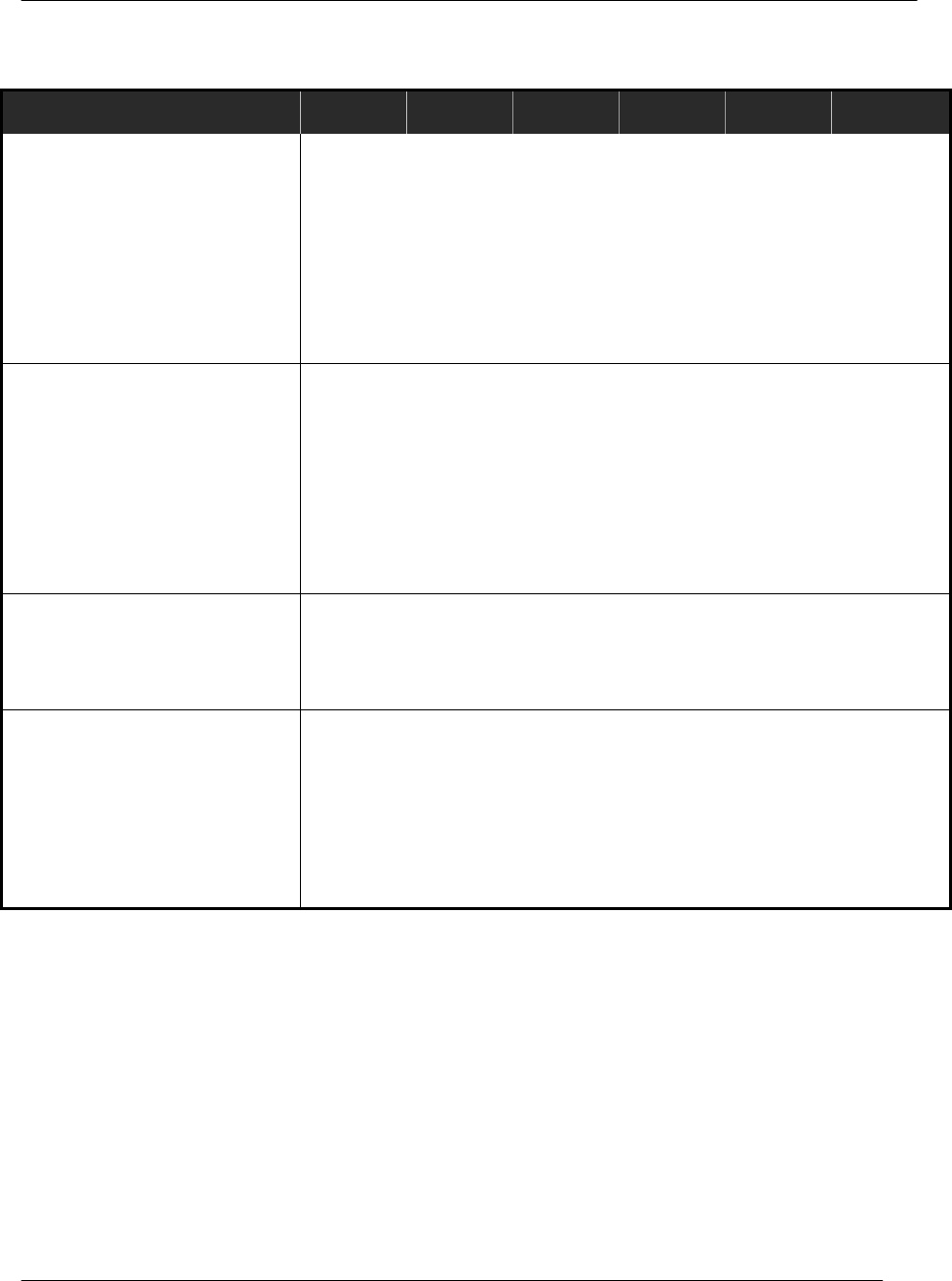

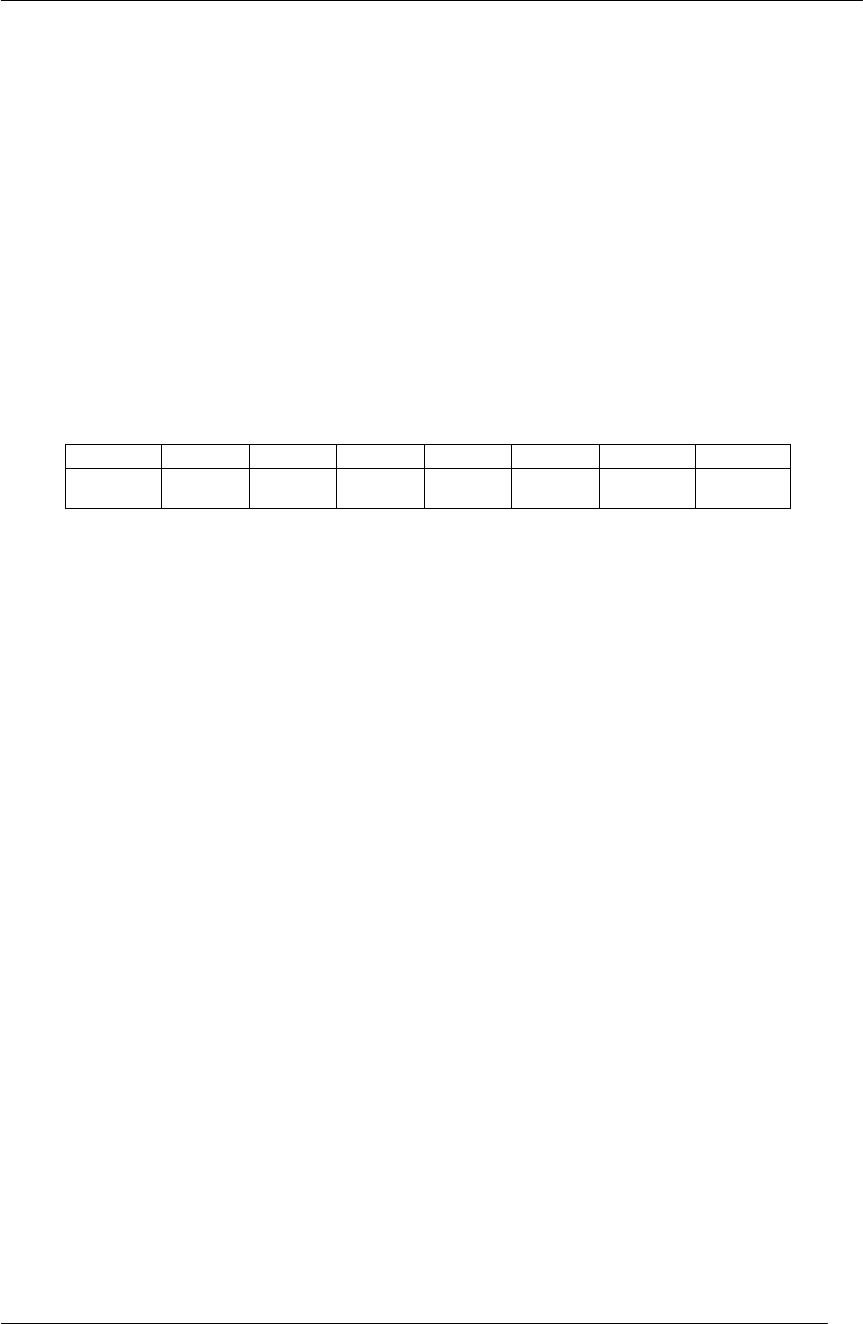

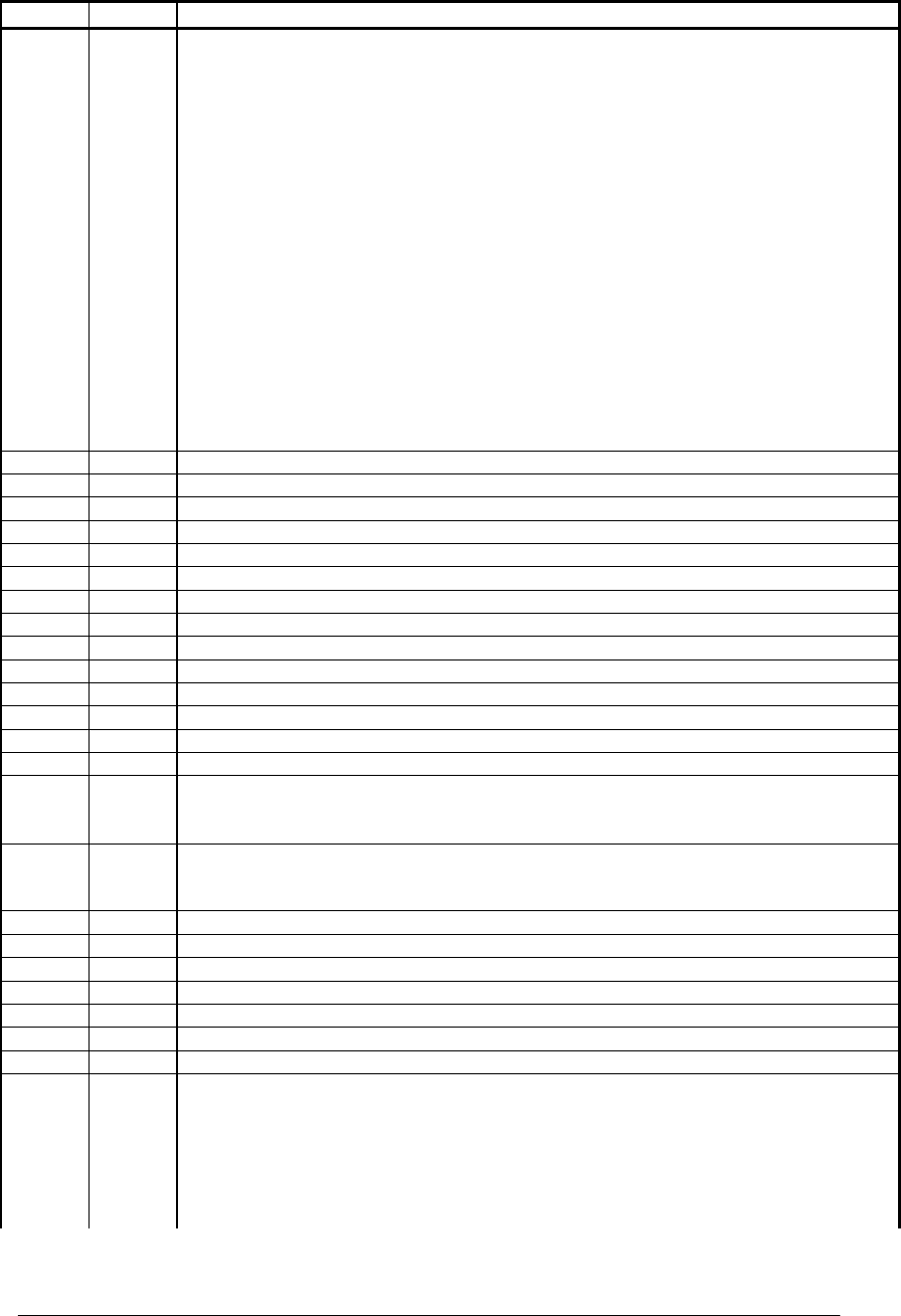

3.2 Physical Specifications

Table 3-2: Physical Specifications

DESCRIPTION

ST250LM004

ST320LM001

ST500LM012

ST640LM001

ST750LM022

ST1000LM024

Physical dimensions

Length (mm)

Width (mm)

Height (mm)

Weight (g, max)

100.3 ±

0.4

69.85 ±

0.25

9.5 ±

0.2

1 Disk 99 / 2 Disk

107

3.3 Logical Configurations

Table 3-3: Logical Configurations

DESCRIPTION

ST250LM004

ST320LM001

ST500LM012

ST640LM001

ST750LM022

ST1000LM024

Total Number of

logical sectors

488,397,168

625,142,448

976,773,168

1,250,263,728

1,465,149,168

1,953,525,168

Capacity 250GB 320GB 500GB 640GB 750GB

1TB

* 1MB = 1,000,000 Bytes, 1GB = 1,000,000,000 Bytes

* Accessible capacity may vary as some OS uses binary numbering system for reported capacity.

SPECIFICATIONS

Spinpoint M8 Product Manual REV 2.3

8

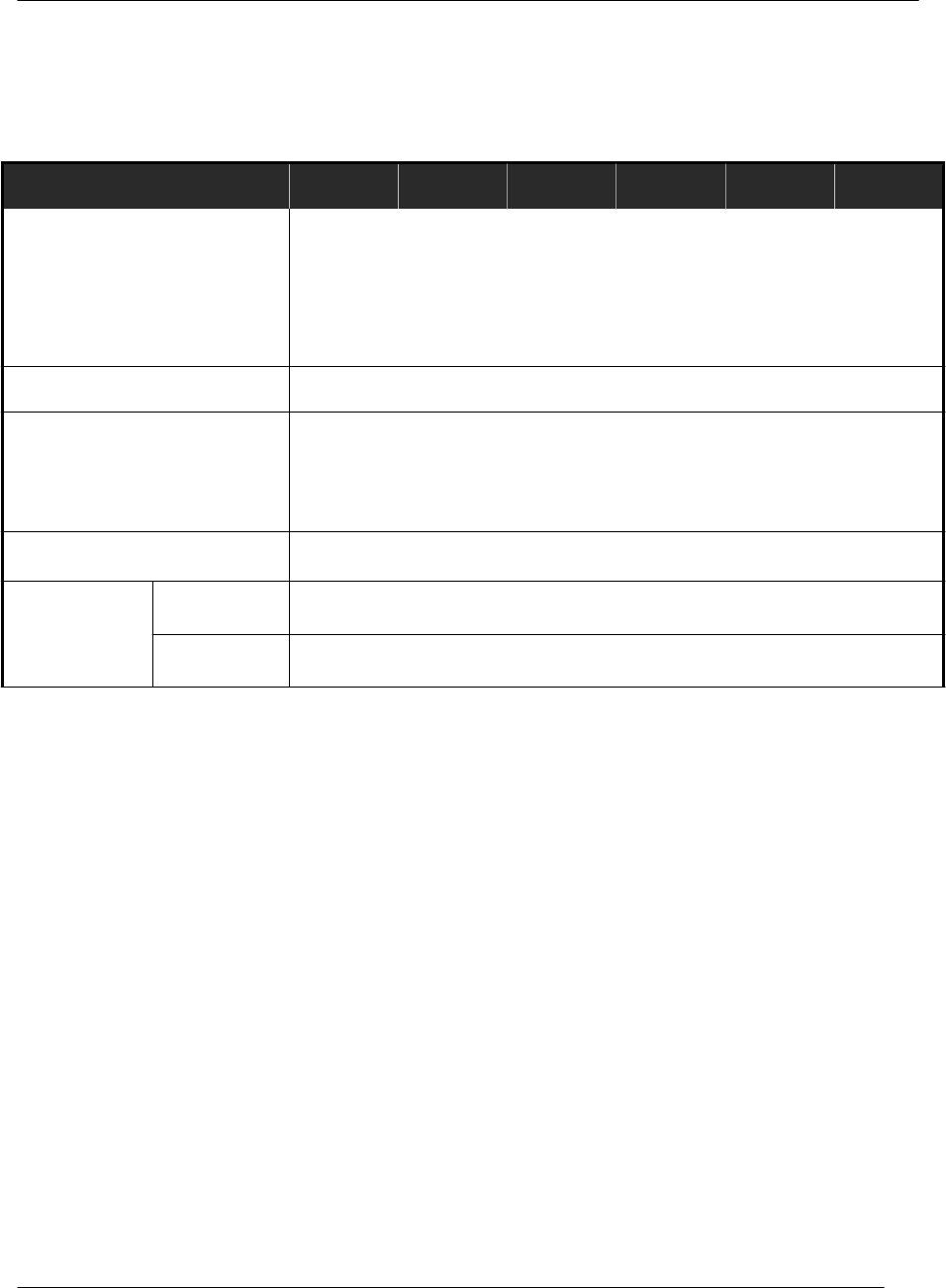

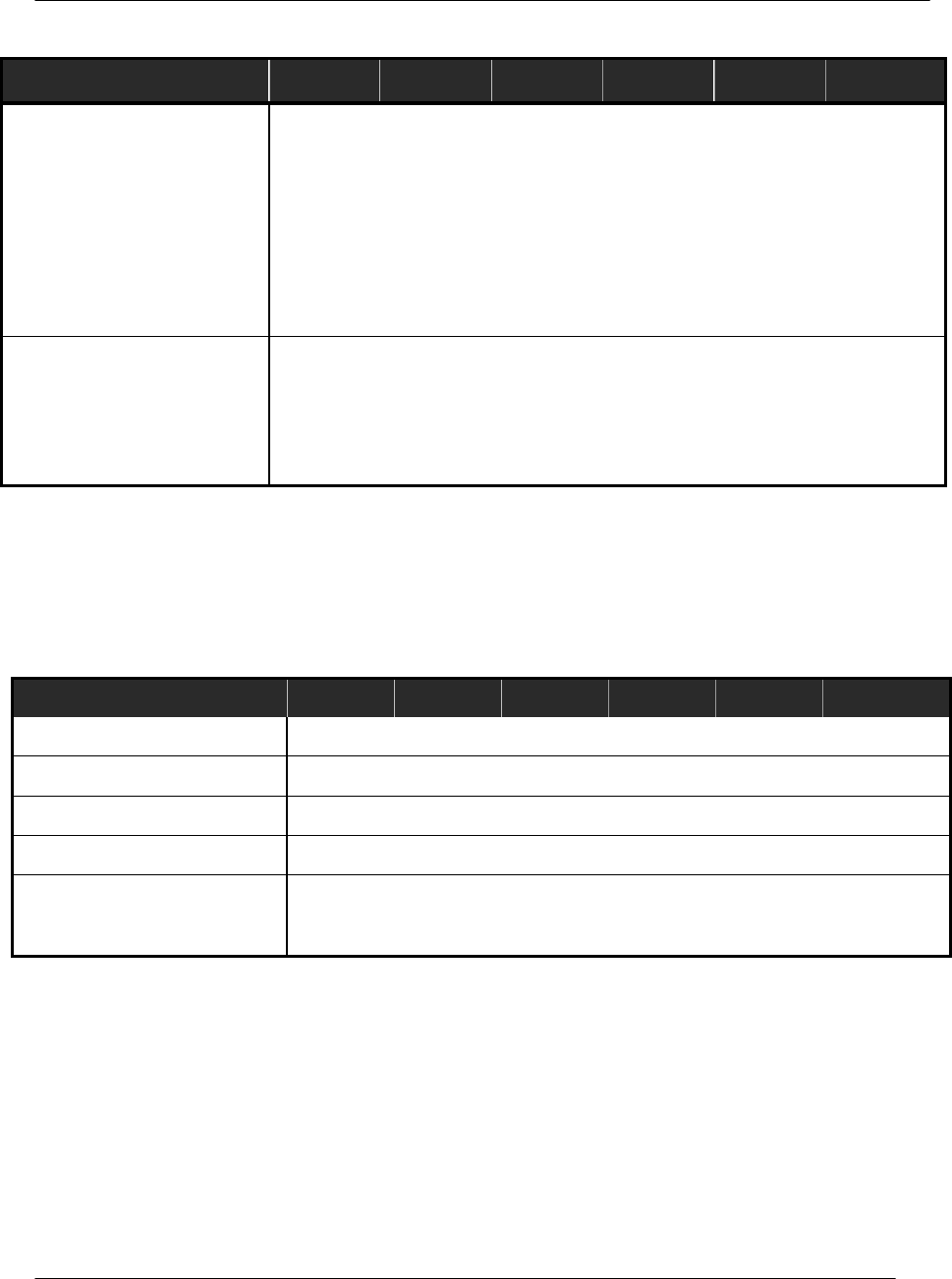

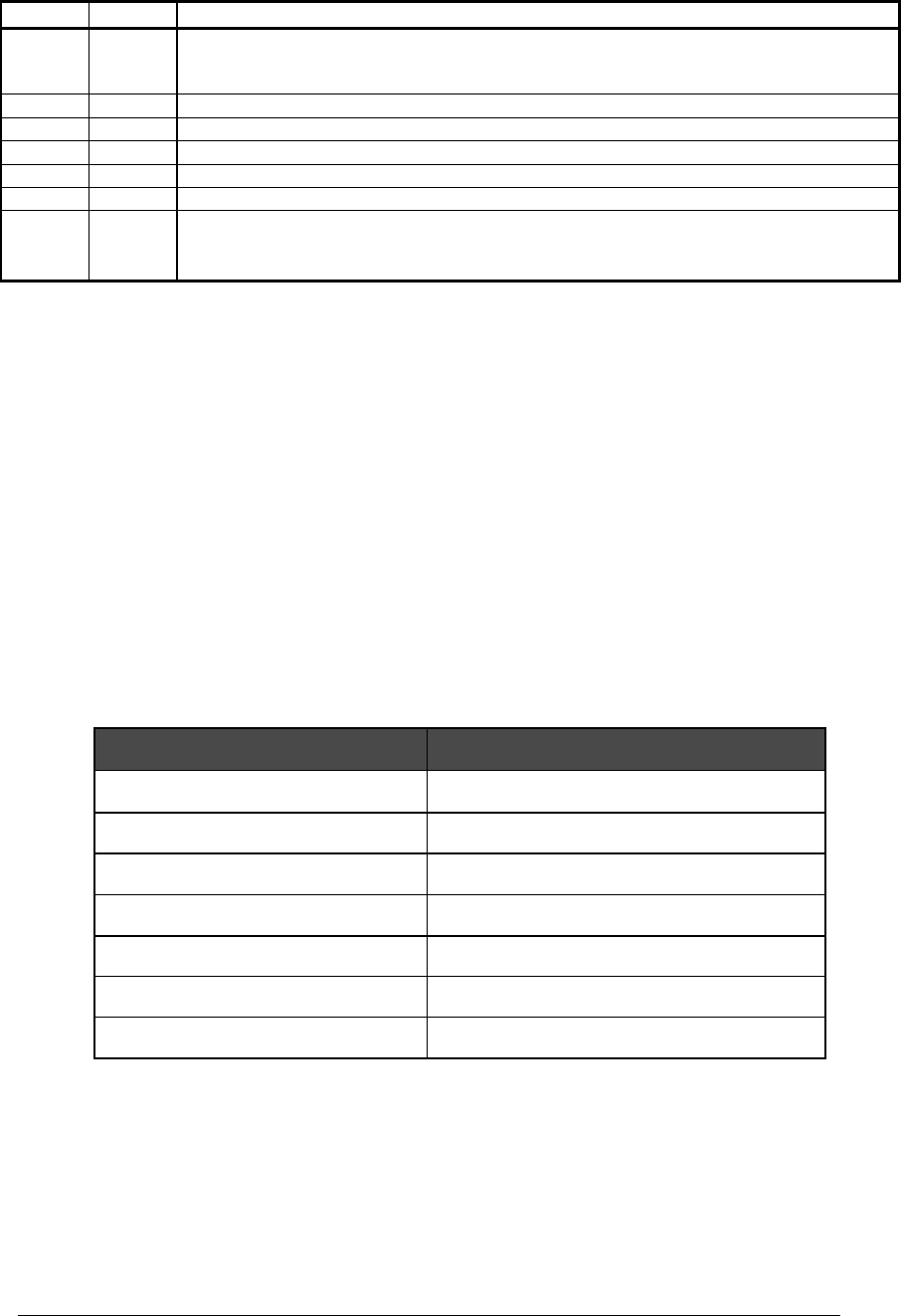

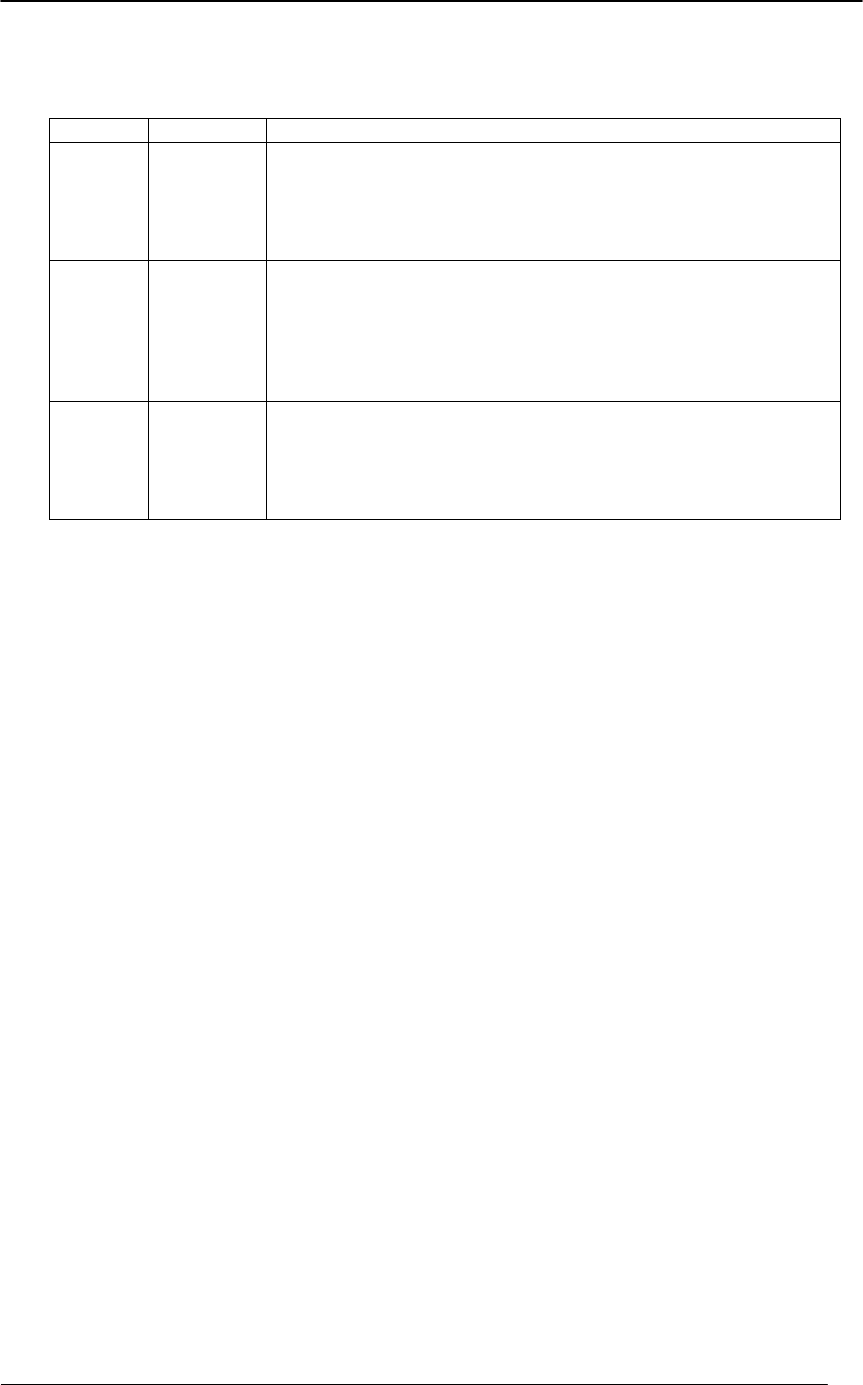

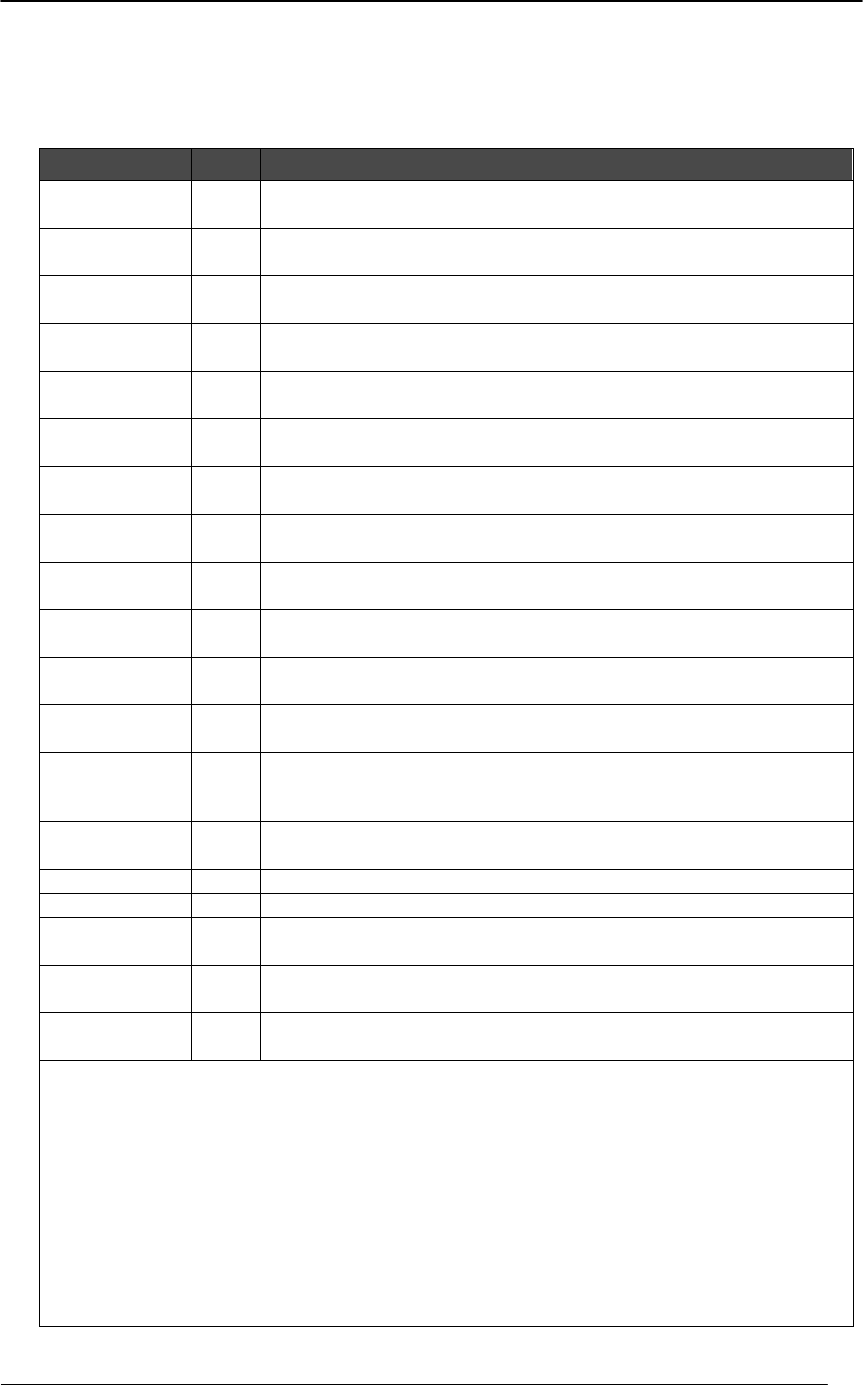

3.4 Performance Specifications

Table 3-4: Performance Specifications

DESCRIPTION ST250LM004 ST320LM001 ST500LM012 ST640LM001 ST750LM022 ST1000LM024

Seek Time (RD/WRT,

Typ)

Average seek time

Track to track seek time

Full stroke seek time

12/14 ms

2/4 ms

22/24 ms

` Average Latency 5.6 ms

Data Transfer Rate

(Max)

buffer to/from

media

host to/from buffer

145Mbits/s

300 MB/s

Rotational Speed 5400 RPM Class

Startup Time

(Typ / Max)

Power on to

Drive Ready 4 sec / 8 sec

Standby to

Drive Ready 3.5 sec / 8 sec

NOTES:

Seek time is defined as the time from the receipt of a read, write or seek command until the actuator has

repositioned and settled on the desired track with the drive operating at nominal DC input voltages and

nominal operating temperature.

Average seek time is determined by averaging the time to complete 1,000 seeks of random length.

Average latency is the time required for the drive to rotate 1/2 of a revolution and on average is

incurred after a seek completion prior to reading or writing user data.

Spin up time is the time elapsed between the supply voltages reaching operating range and the drive

being ready to accept all commands.

Actual rotational speed can be different a little.

Spinpoint M8 Product Manual REV 2.3

9

SPECIFICATIONS

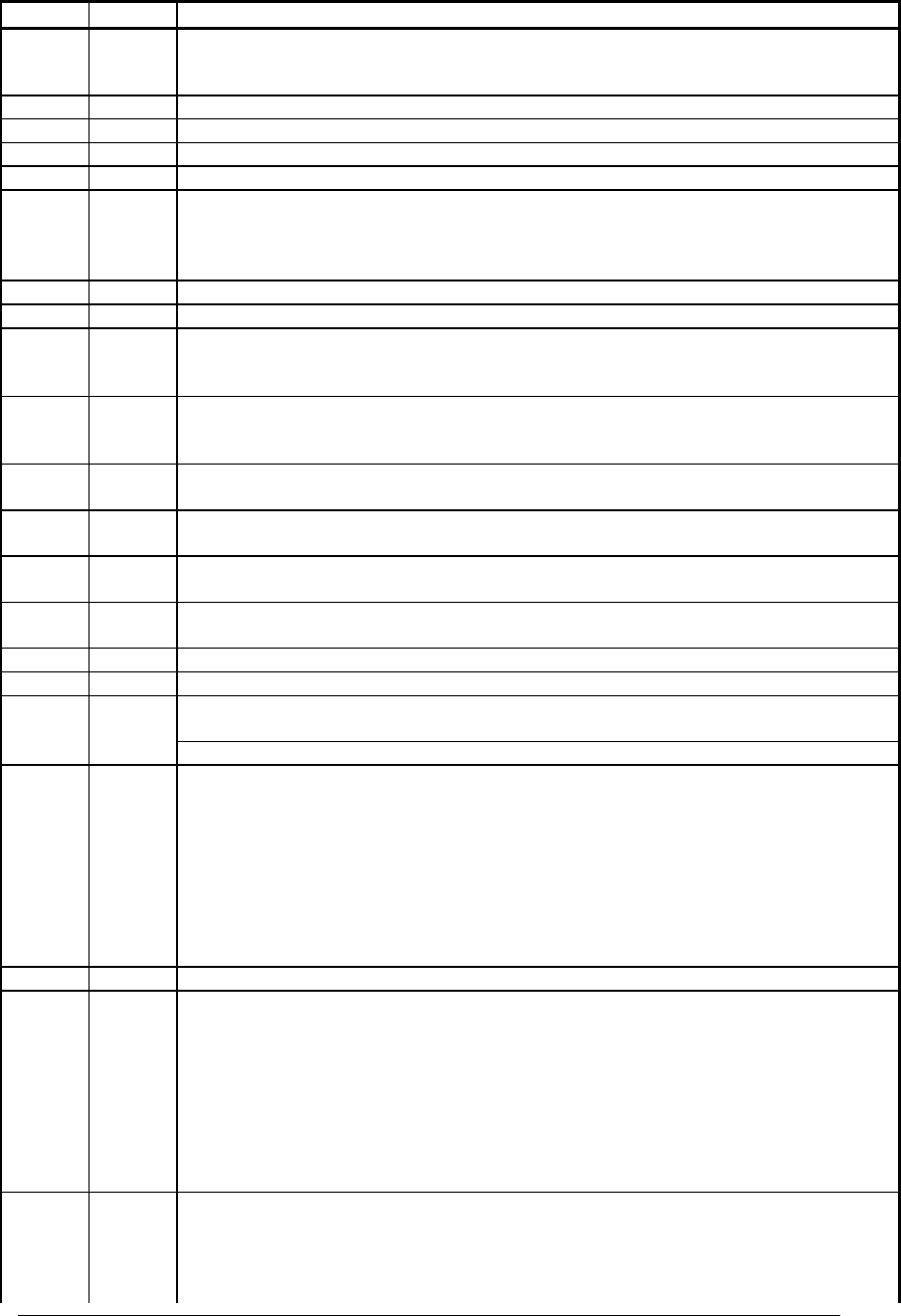

3.5 Power consumption

Table 3-5: Power consumption

DESCRIPTION

ST250LM004

ST320LM001

ST500LM012

ST640LM001

ST750LM022

ST1000LM024

Rated

Voltage V +5

Current A 0.85

Power Consumption

Start Up (25 C)

mA

1000

Low Power Idle (25 C)

Watt

0.7

Read/Write (25 C)

Watt

2.2

Seek (25 C)

Watt

2.0

Stand by (25 C)

Watt

0.2

Sleep (25 C)

Watt

0.2

Power Requirements

Tolerance For + 5V

%

+/-

5

Ripple, 0-30MHz

mV

p-p

100

Supply Rise Time

us/

msec

10us-100ms

Supply Fall Time

Sec

<

5

1) Random seek: 30% Duty cycle seek commands with logical random location.

2) Read/Write @ OD: On track Read/Write operation at OD, 256 sector commands.

Spinpoint M8 Product Manual REV 2.3

10

SPECIFICATIONS

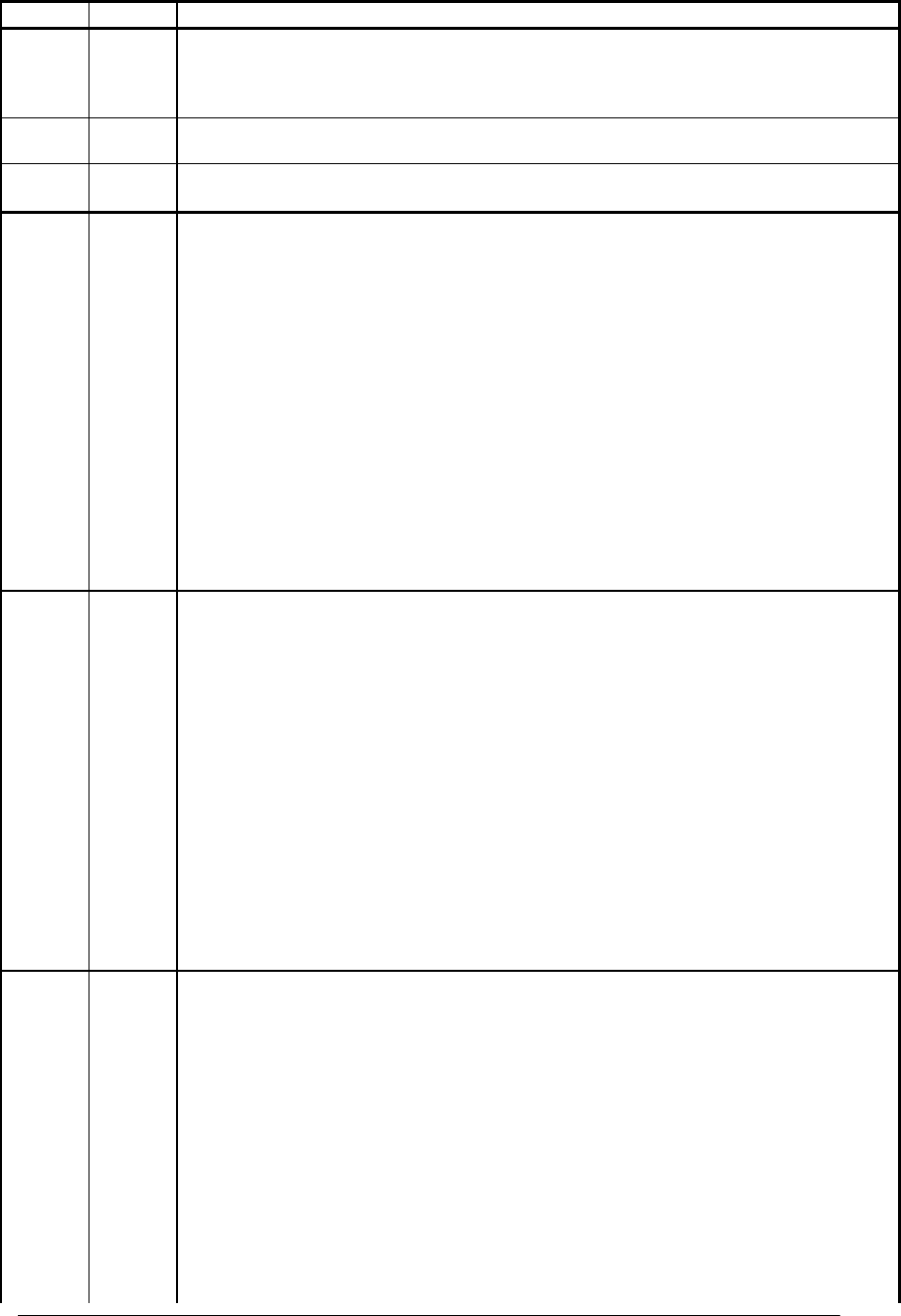

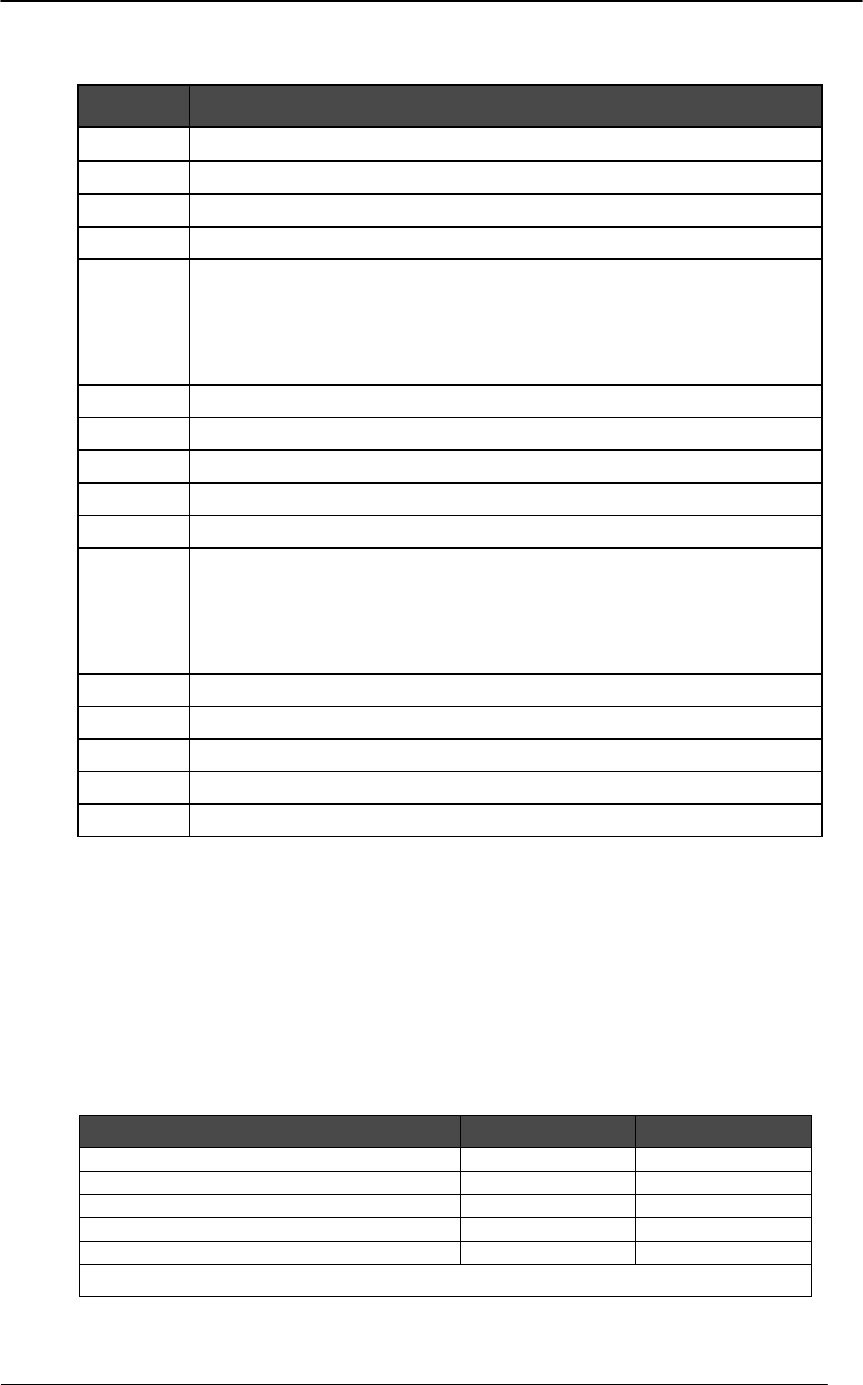

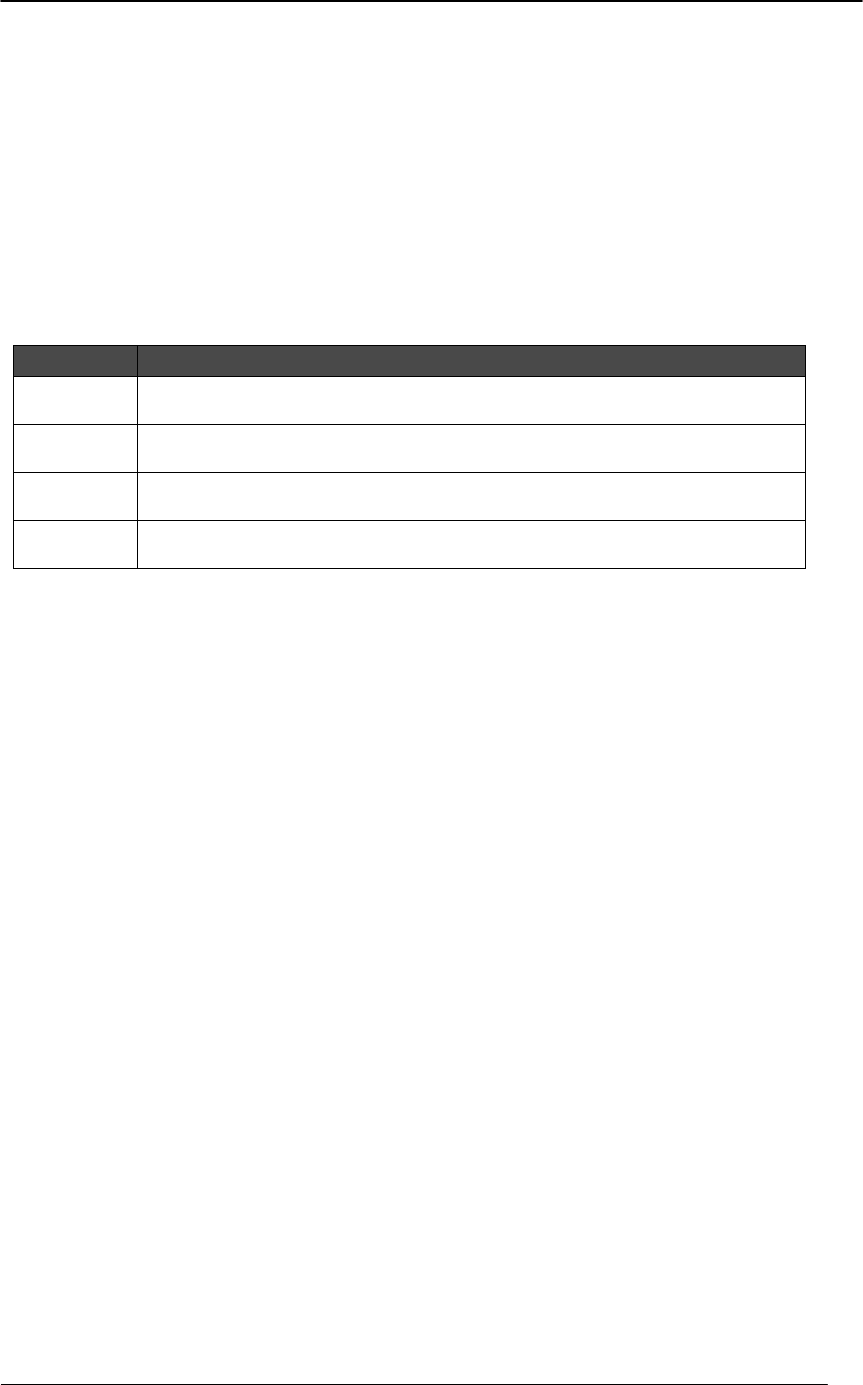

3.6 Environmental Specifications

Table 3-6: Environmental Specifications

DESCRIPTION

ST250LM004

ST320LM001

ST500LM012

ST640LM001

ST750LM022

ST1000LM024

Ambient Temperature

Operating

Non-operating

Max. gradient

(Temperature/Humidity)

(Drive temperature measured on position of figure 3-1 should be max 65C in range of

5C-55C, specified operation temperature.)

5

C

55 C

-40

C

70 C

20 C/20%/hr

Relative Humidity (non condensing)

Operation

Non-operation

Maximum wet bulb temperature

Operating

Non-operating

5~90 %

5~95 %

30 C

40 C

Altitude (relative to sea level)

Operating

Non-operating

-300 ft /3000 m

-400 ft / 15,000 m

Vibration

Operating :

10-500 Hz, Random :

Non-operating :

10-500 Hz, Random

1.5 Grms

5.85 Grms

Spinpoint M8 Product Manual REV 2.3

11

SPECIFICATIONS

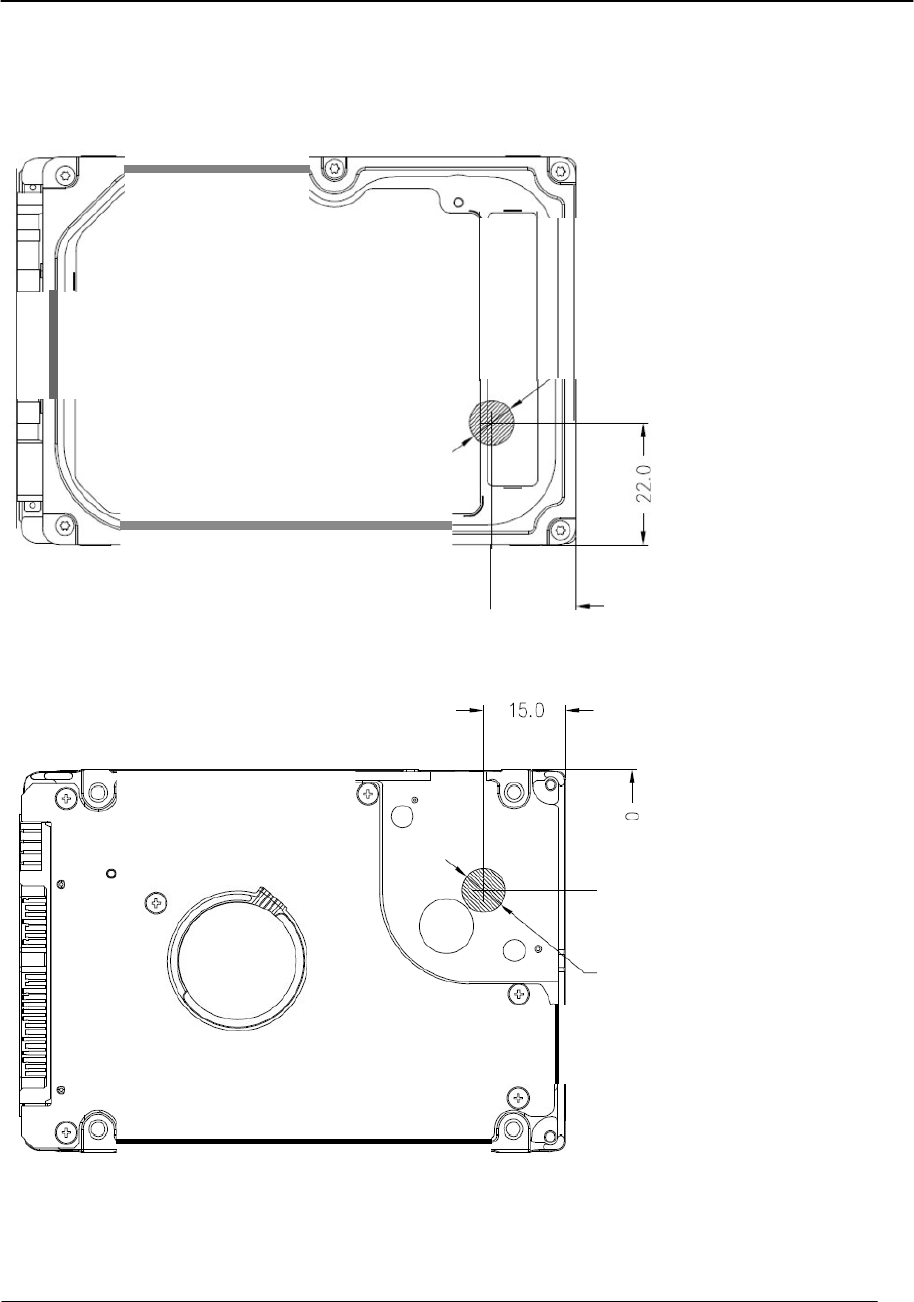

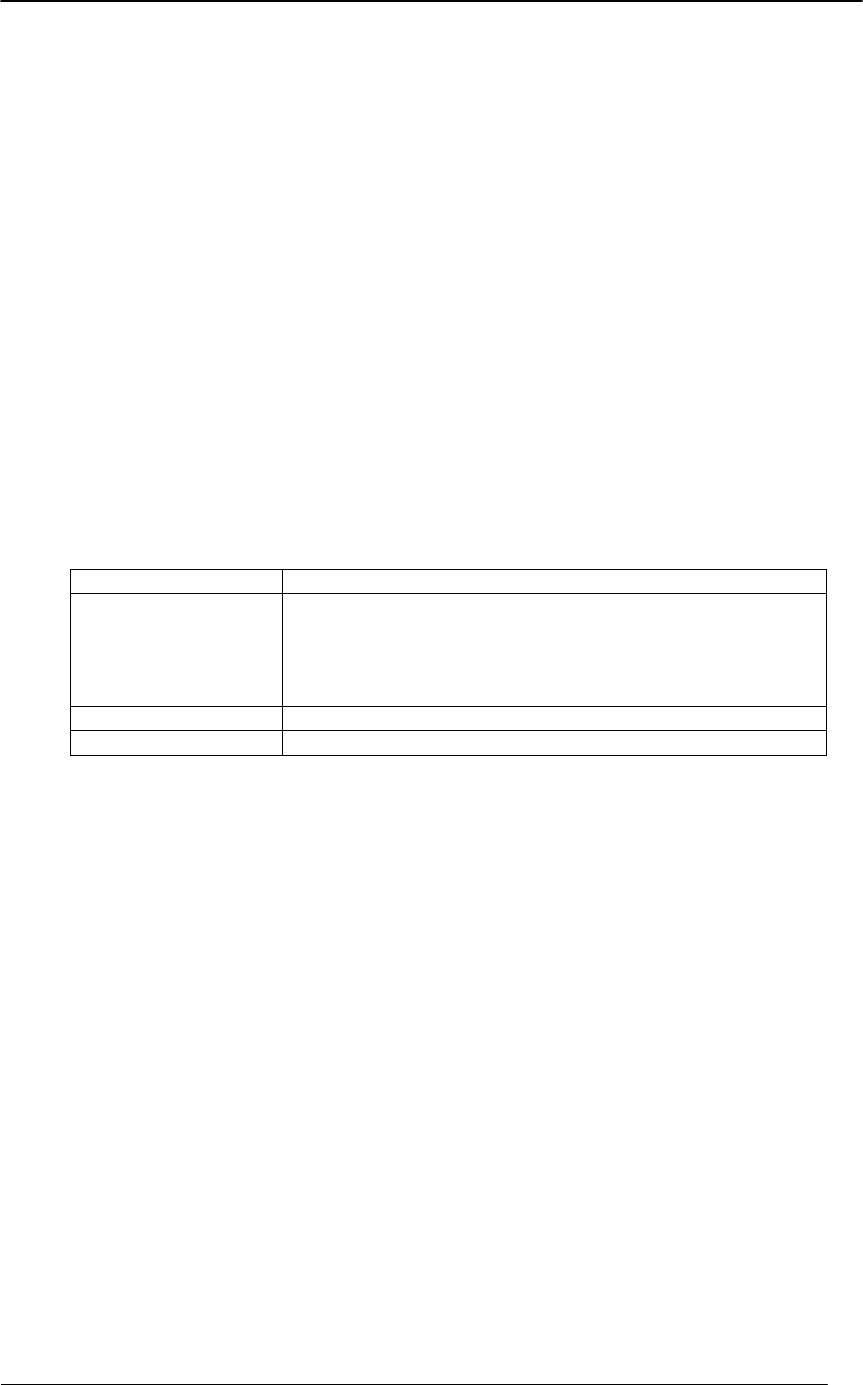

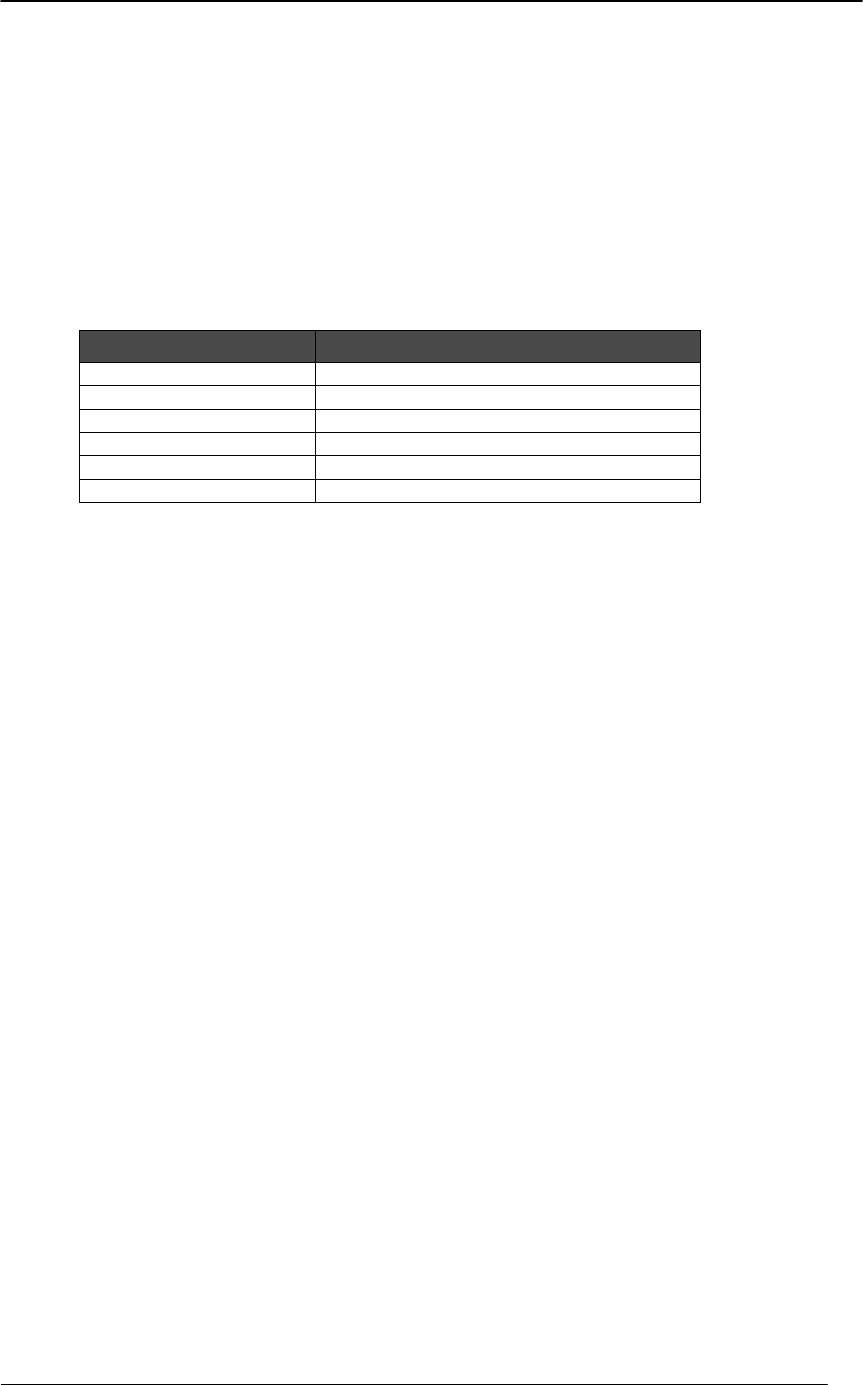

o

08.0

Recommended case temperature

measurement position

1

5.0

N

N

08

.

0

Recommended case temperature

measurement position

o

Figure 3-1

:

Measurement Position.

Spinpoint M8 Product Manual REV 2.3

12

SPECIFICATIONS

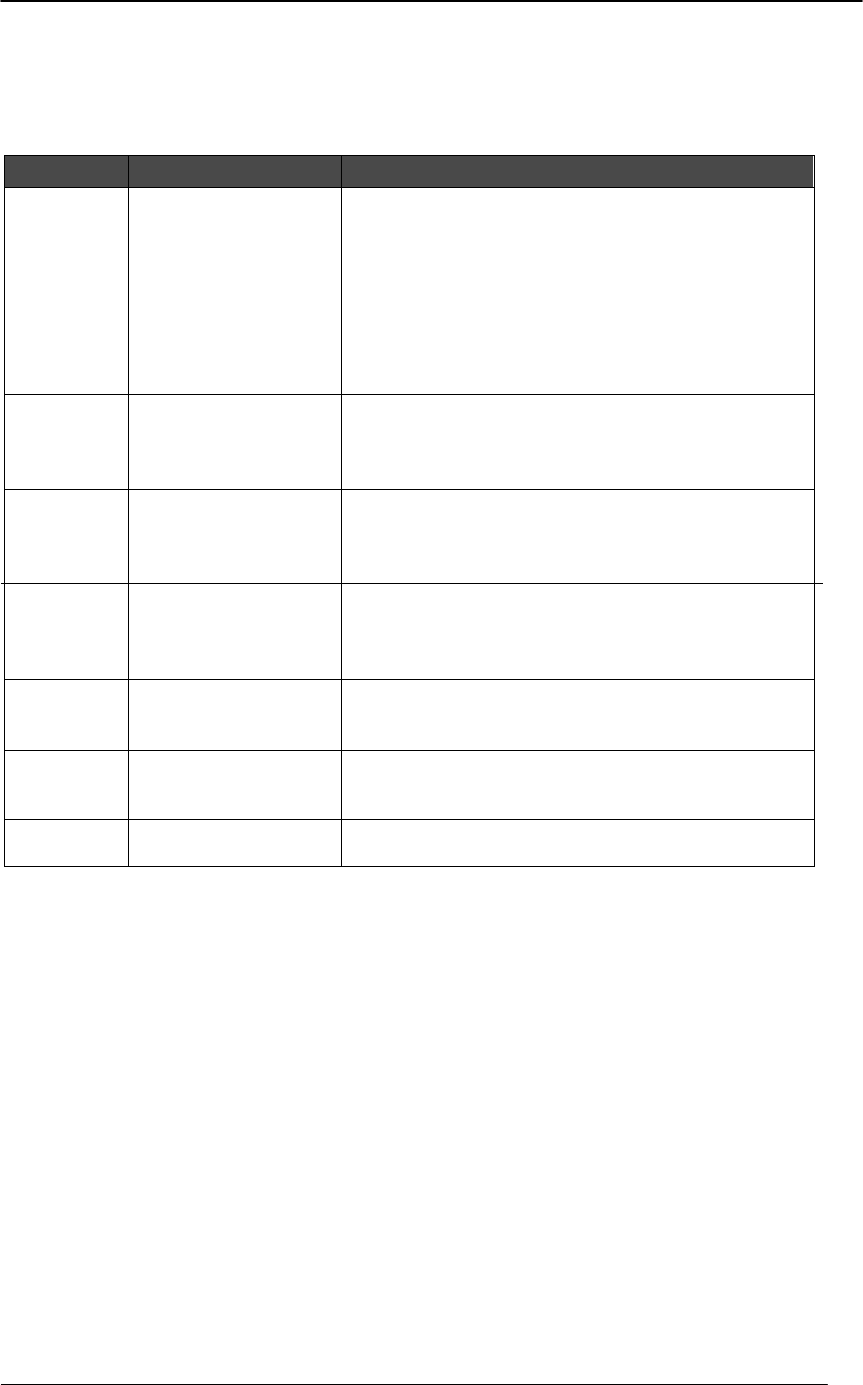

Table 3-6: Environmental Specifications (continued)

DESCRIPTION

ST250LM004

ST320LM001

ST500LM012

ST640LM001

ST750LM022

ST1000LM024

Linear Shock (1/2 sine pulse)

Operating 2.0 ms

Non-operating 2.0 ms

Rotational Shock

Operating 2.0 ms

Non-operating 2.0 ms

325G

750G

3K rad/sec

2

30K rad/sec

2

Acoustic

Noise

(Typical Sound Power)

Idle

Seek

2.4

Bels

2.6

Bels

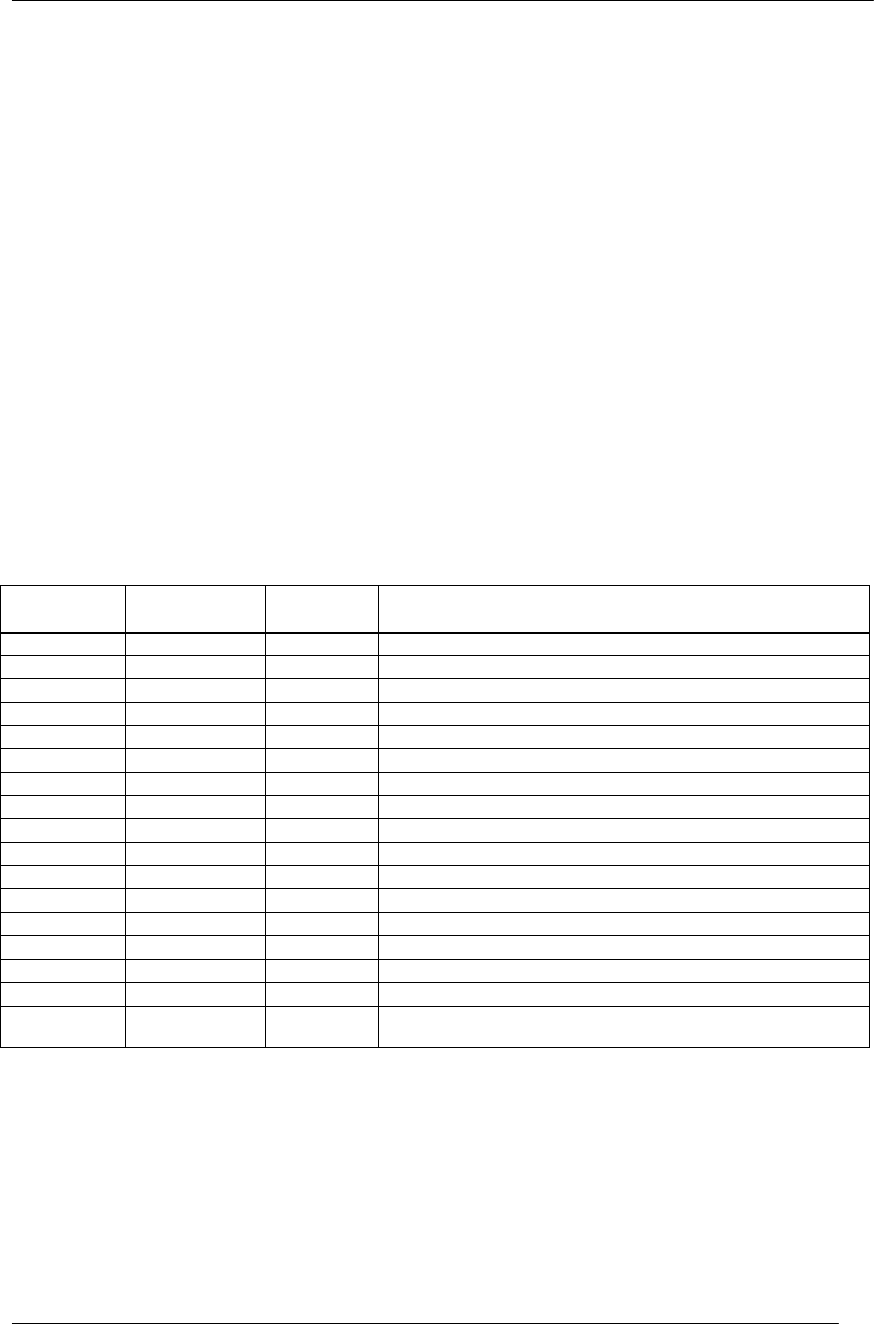

3.7 Reliability Specifications

Table 3-7: Reliability

Specifications

DESCRIPTION

ST250LM004

ST320LM001

ST500LM012

ST640LM001

ST750LM022

ST1000LM024

Recoverable Read Error

<10 in 1011

bits

Non-Recoverable Read Error

<1 sector in 1014

bits

MTBF (POH)

550,000

hours

MTTR (Typical)

5

minutes

Load/Unload Cycles

Ambient

600,000

INSTALLATION

Spinpoint

M8 Product Manual REV

2.3

13

CHAPTER 4 INSTALLATION

This chapter describes how to unpack, mount, configure and connect a Spinpoint M8 hard disk drive.

It also describes how to install the drive in systems.

4.1 Space Requirements

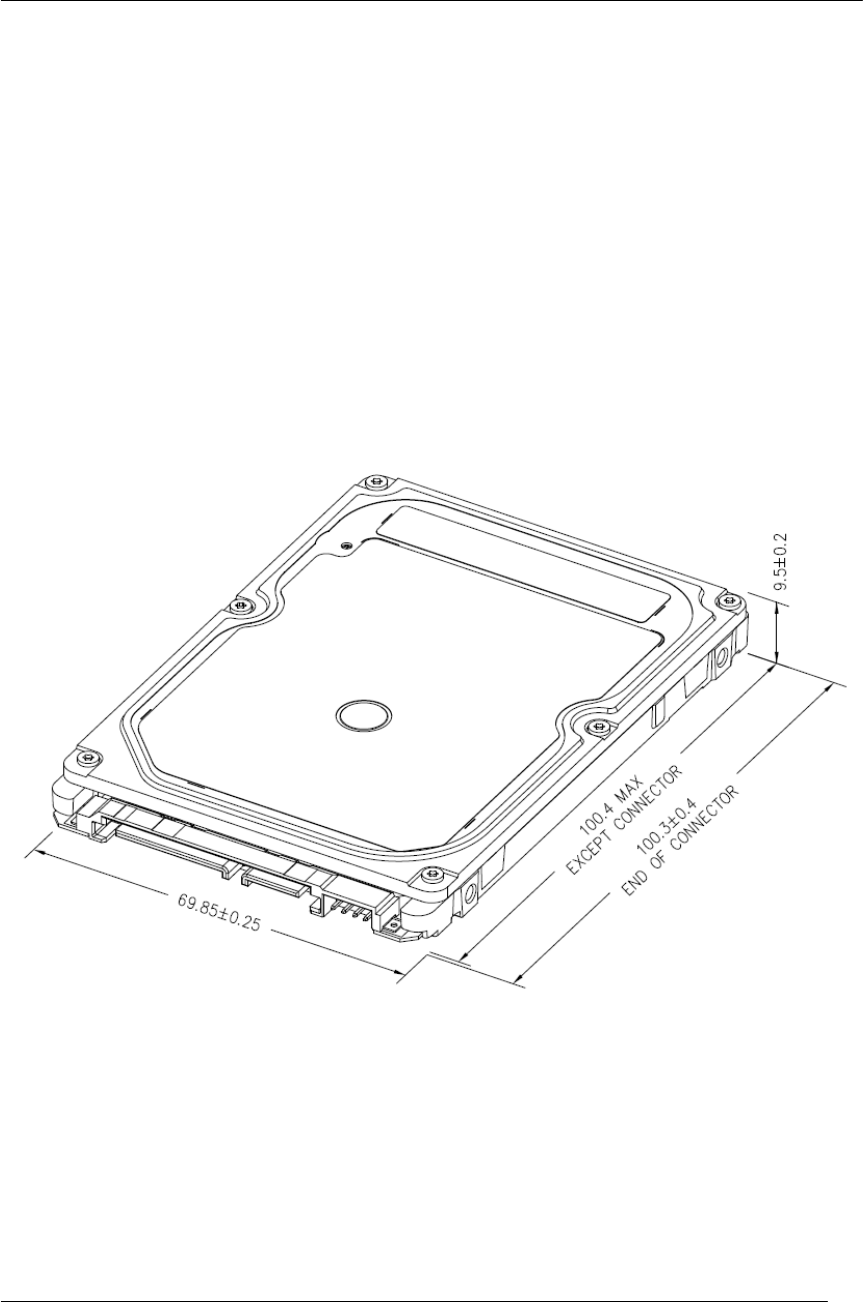

Figure 4-1 shows the external dimensions of the drive.

Figure 4-1: Mechanical Dimension

INSTALLATION

Spinpoint

M8 Product Manual REV

2.3

14

4.2 Unpacking Instructions

(1) Open the shipping container of the Spinpoint M8 hard disk drive.

(2) Lift the packing assembly that contains the drive out of the shipping container.

(3) Remove the drive from the packing assembly. When you are ready to install the drive, remove it from

the ESD (Electro Static Discharge) protection bag. Take precautions to protect the drive from ESD

damage after removing it from the bag.

CAUTION: During shipment and handling, the anti-static ESD protection bag

prevents electronic component damage due to electrostatic discharge.

To avoid accidental damage to the drive, do not use a sharp instrument to

open the ESD protection bag.

(4) Save the packing material for possible future use.

4.3 Mounting

Refer to your system manual for complete mounting details.

(1) Be sure that the system power is off.

(2) For mounting, use four M3 screws.

CAUTION: Torque applied to the screws is recommended to be 3.5 [kg* cm]

±0.5

(

3.0 [inch *pounds] ±0.5)

INSTALLATION

Spinpoint

M8 Product Manual REV

2.3

15

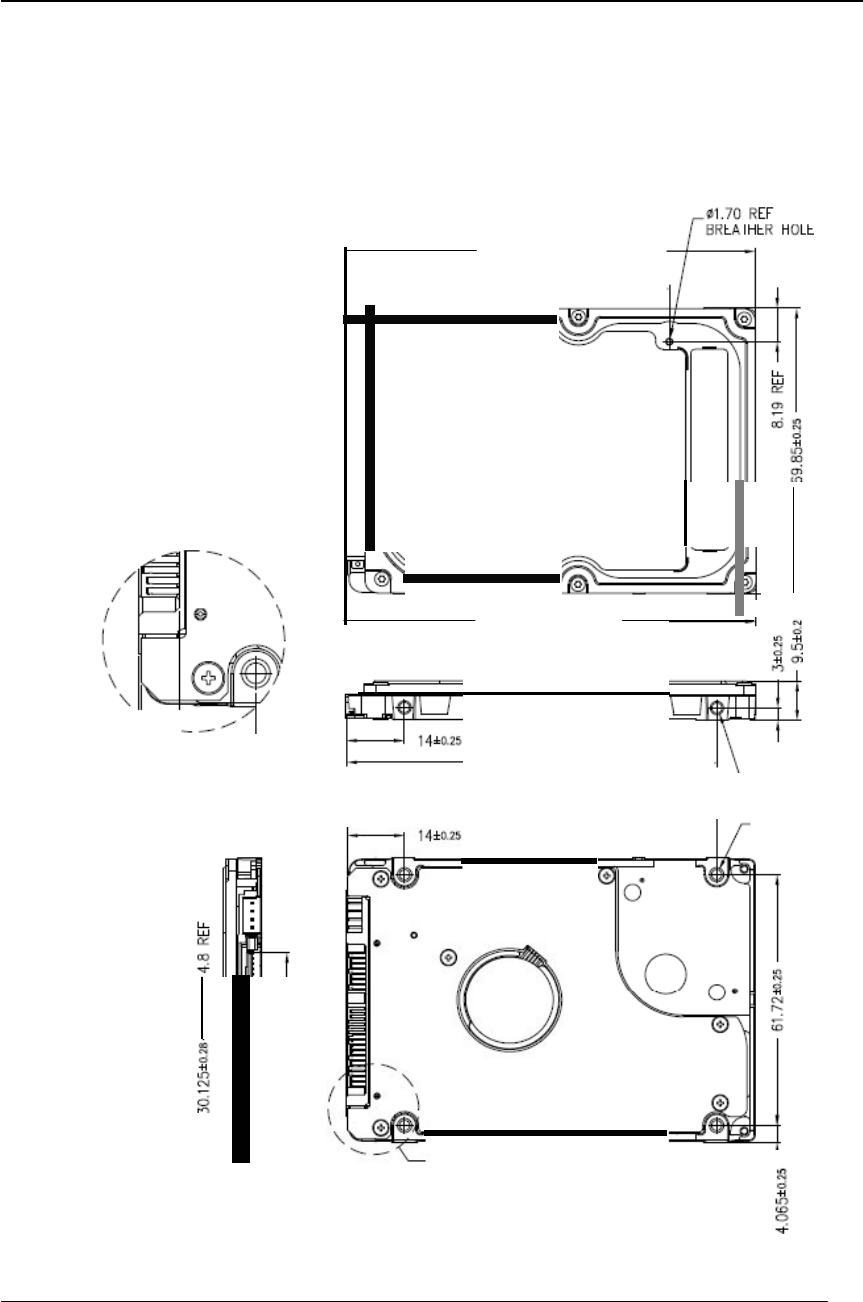

4.3.1 Orientation

Figure 4-2 shows the physical dimensions and mounting holes located on each side of the drive. The

mounting holes on Spinpoint M8 hard disk drive allow the drive to be mounted in any direction.

1

00

.

4

M

AX

E

XC

E

P

T

CO

NN

E

C

T

OR

1

-

----

78

.

98

REF

--- -

-

1

o

O

.:;

REF

--

4.9 REF

9

.

4±

0

.

JS

OETAIL A

100

.3

±0

.

<

END OF CONNECTOR

o

1

-

-----

-

-

9

0

.

6

±

02>

-----

- -

1

C/

L

OF

C/

L

OF

H

DO

CONNECTOR

'+

-lHI

-

'-t

-lli

llft-

!l1

::i

o

3

.

5

±038

-

OETAIL

A

Figure4-2:

Mounting

Dimensions

INSTALLATION

Spinpoint

M8 Product Manual REV

2.3

16

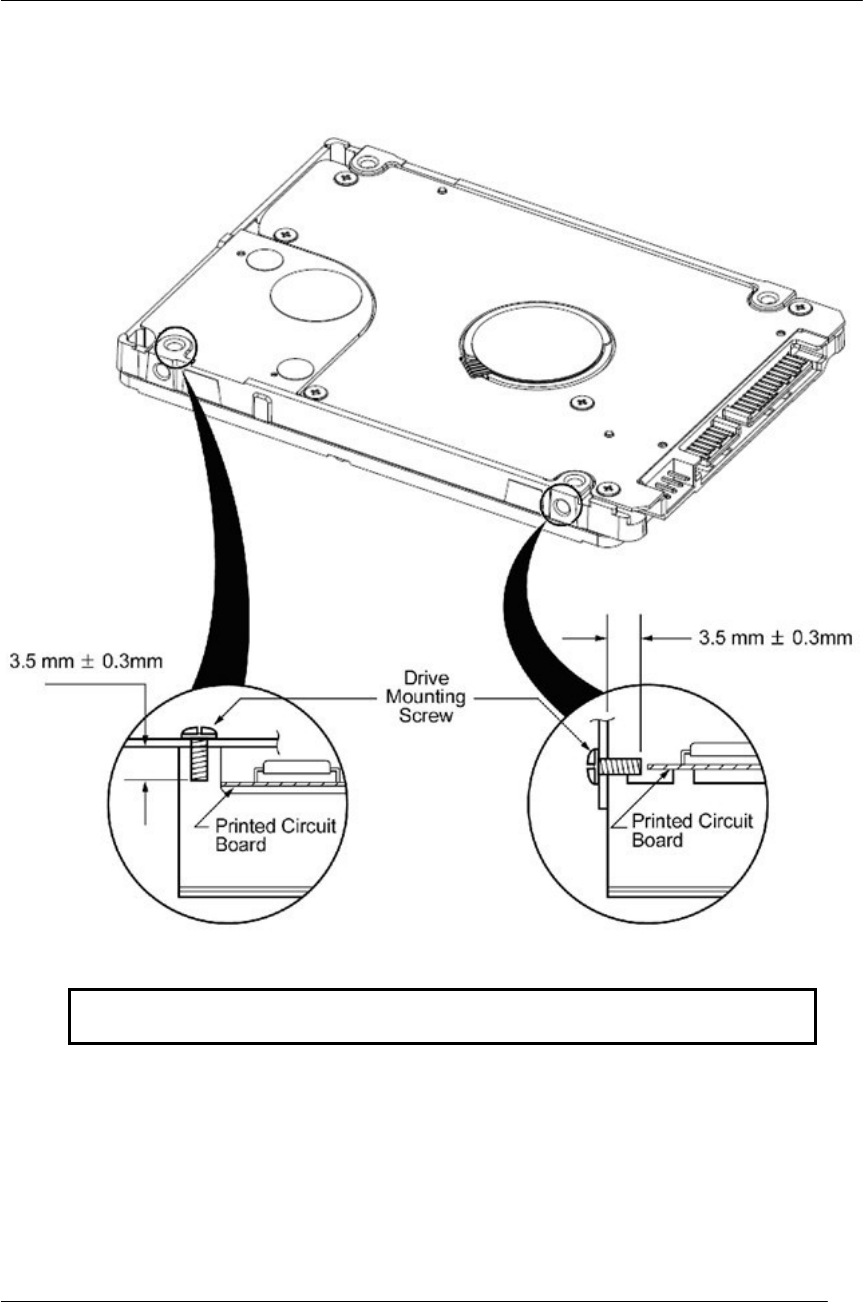

4.3.2 Clearance

The printed circuit board (PCB) is designed to be very close to the mounting holes. Do not exceed the

specified length for the mounting screw described in Figure 4-3. The specified screw length allows full use of

the mounting-hole threads, while avoiding damage or placing unwanted stress on the PCB.

Figure 4-3: Mounting-Screw Clearance

CAUTION: Using mounting screws that are longer than the maximum

lengths specified in Figure 4-3 voids the warranty of the drive.

INSTALLATION

Spinpoint

M8 Product Manual REV

2.3

17

4.3.3 Ventilation

The Spinpoint M8 hard disk drive is designed to operate without the need of a cooling fan provided the

ambient air temperature does not exceed 55ºC. Any user-designed cabinet must provide adequate air

circulation to prevent exceeding the maximum temperature.

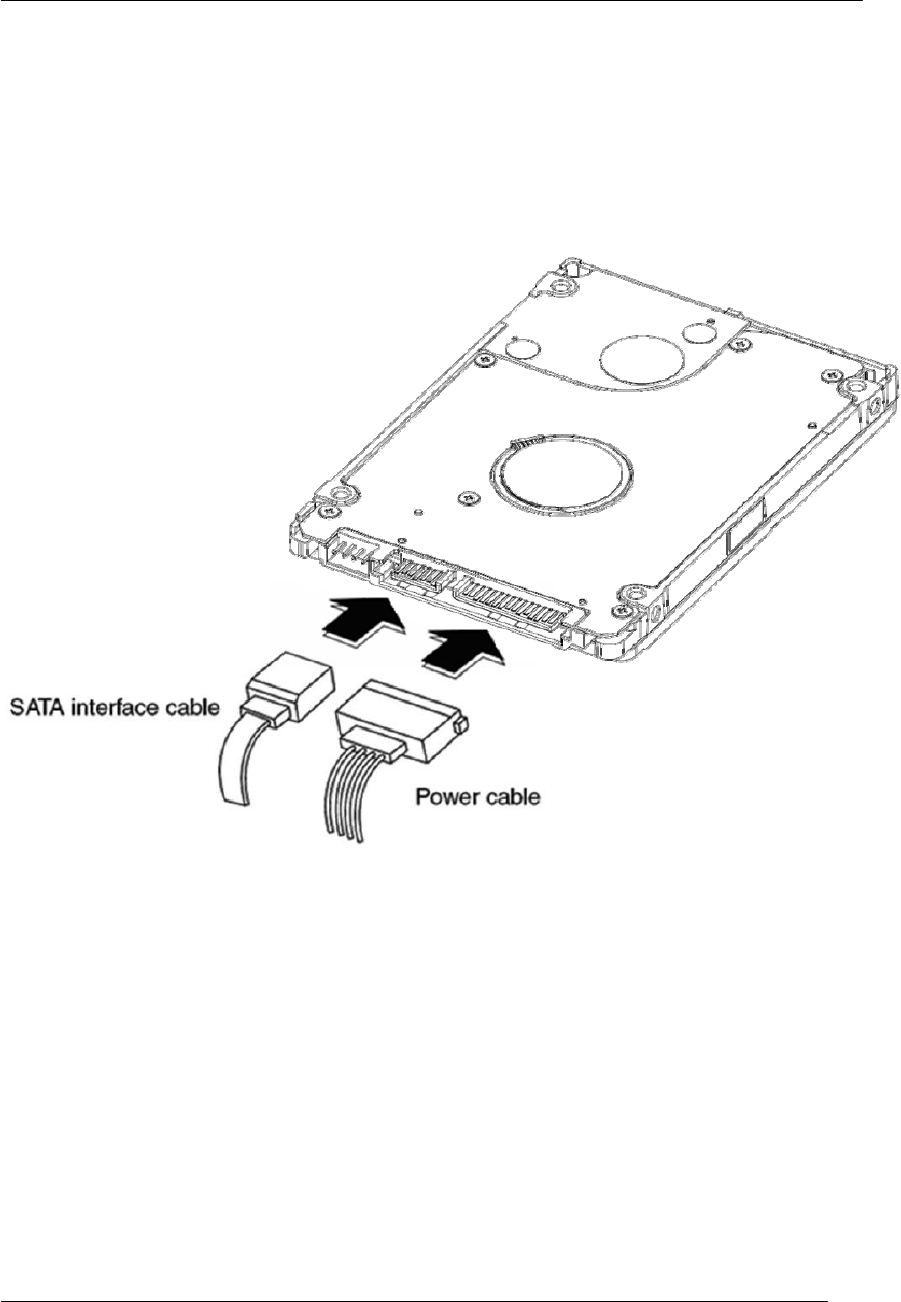

4.4 Cable Connectors

The Interface/Power connector consists of two cables; a SATA 15-pin DC power connector, and the

standard SATA 7-pin Interface connector.

4.4.1 SATA Connectivity

The SATA interface is connected within a point to point configuration with the SATA host port. There is

no master or slave relationship within the devices. Thus SATA does not require master/slave jumper. The

drive interface section of the host adapter employs a new design which processed data into a serial data-

control system.

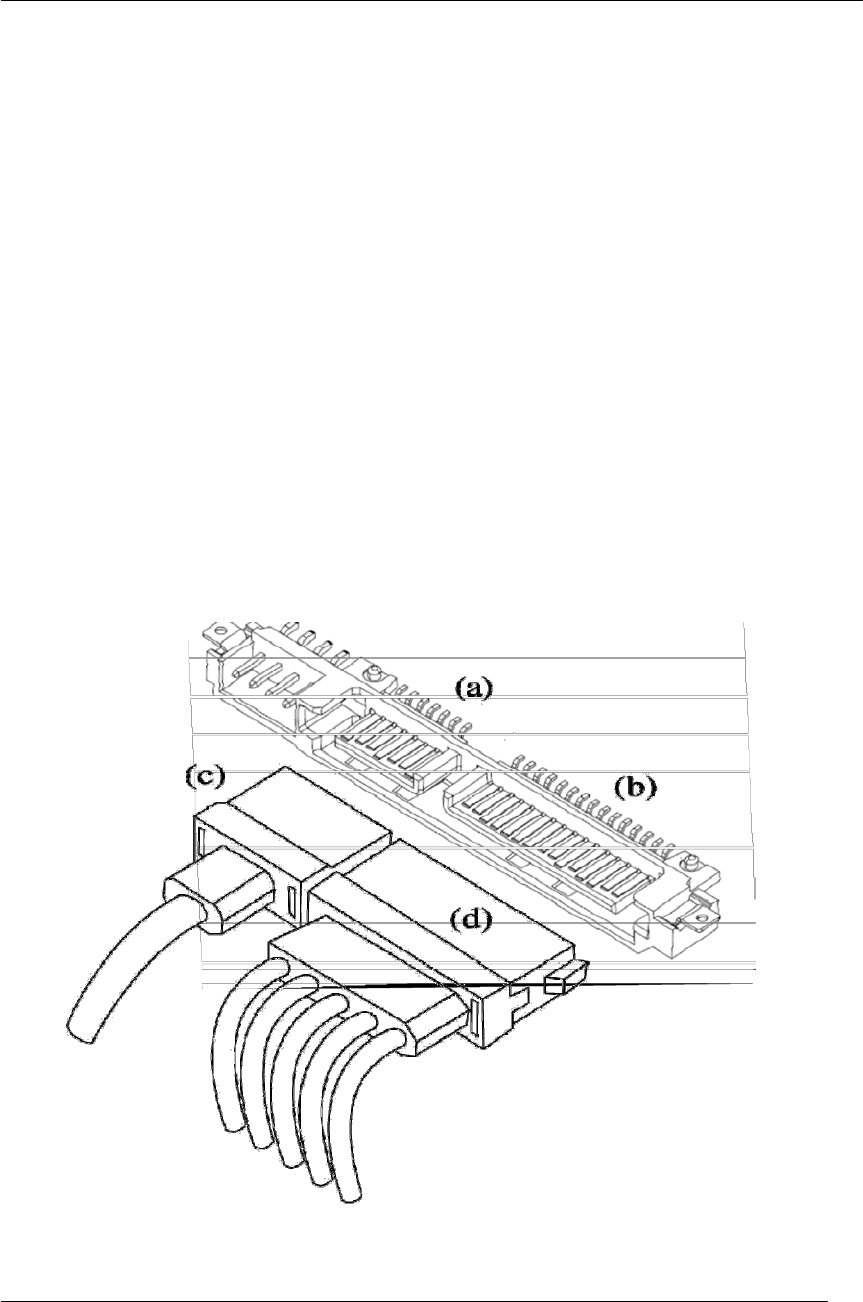

Figure 4.4 illustrates the connection for the SATA.

There are two cables for SATA drives. One is for data transmission. The other is for power. Figure 4-4

illustrates (a) device signal plug connector, (b) device power plug connector, (c) signal cable receptacle

connector mating with (a), and (d) power cable receptacle connector to be mated with (b). For more

information, please refer to SATA Specifications cited in the reference.

.

Figure 4-4 Serial ATA

Connector

INSTALLATION

Spinpoint

M8 Product Manual REV

2.3

18

v

Computer

mainboard

or

...

Serial

ATA

host

adapter

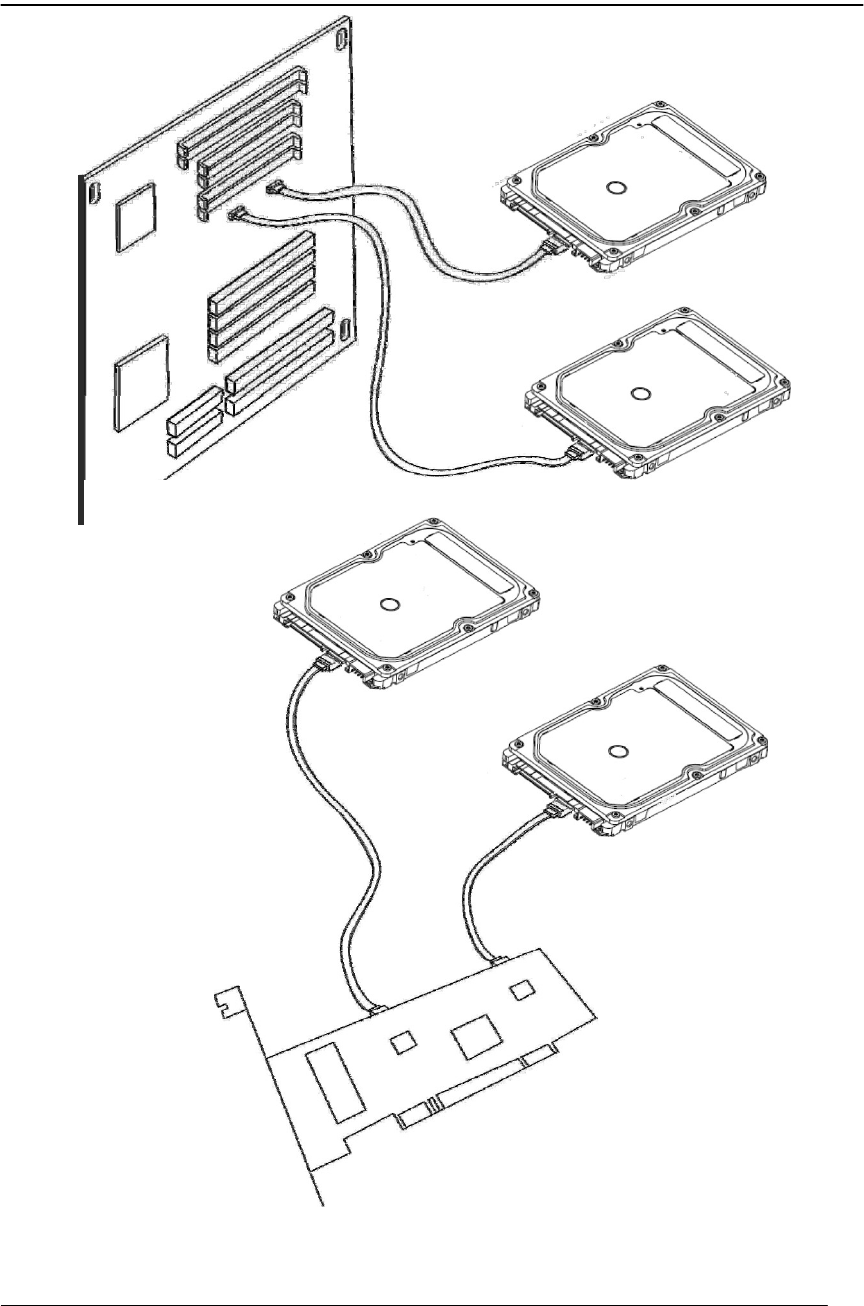

Figure 4-5 Connectivity to

Drives

INSTALLATION

Spinpoint

M8 Product Manual REV

2.3

19

Figure 4-5 illustrates Connectivity of SATA to drives. It can be used with a SATA host bus adapter (lower

picture) or directly into motherboard that has the SATA built-in host bus adapter (upper picture).

SATA Device Connector Definition

Please note that all pins are in a single row, with a 1.27 mm (50 mil) pitch diameter. There are three

power pins for each voltage source. One pin from each voltage is utilized for pre-charge when installed in

a blind- mate backplane configuration.

The notes on the mating sequence apply to the case of backplane blind mate connector.

When the drive is inserted, the ground pins and the pre-charge pins are in contact first followed by the

remaining pins.

Table 4-1 lists the signals connection on the SATA interface and power connector. It is based on SATA 1.0a

Specifications. Note that pin numbers is designated from the pin farthest from power segment.

Table 4-1 SATA Connector Pin

Definitions

Data Signal

Connector

Pin Function Definition

*S1 Ground Ground

S2 Rx+ Differential Signal pair

S3 Rx- Differential Signal pair

*S4 Ground Ground

S5 Tx- Differential Signal Pair

S6 Tx+ Differential Signal pair

*S7 Ground Ground

Key and spacing separate

signal and power segment

Power

Management

P1 V

33

3.3

v

P2 V33 3.3

v

*P3 V33 3.3 v

*P4 Ground Ground

*P5 Ground Ground

*P6 Ground Ground

*P7 V5 5 v

P8 V5 5 v

P9 V5 5 v

*P10 Ground Ground

P11 Device Activity This pin was reserved in SATA 1.0a

/ Stagger Spin-

up Control

*P12 Ground Ground

*P13 V12 12 v

P14 V12 12 v

P15 V12 12 v

* First Mate

INSTALLATION

Spinpoint

M8 Product Manual REV

2.3

20

SATA-Bus Interface

Connector

The SATA-Bus interface connector on the drive connects the drive to an SATA host bus adapter or an

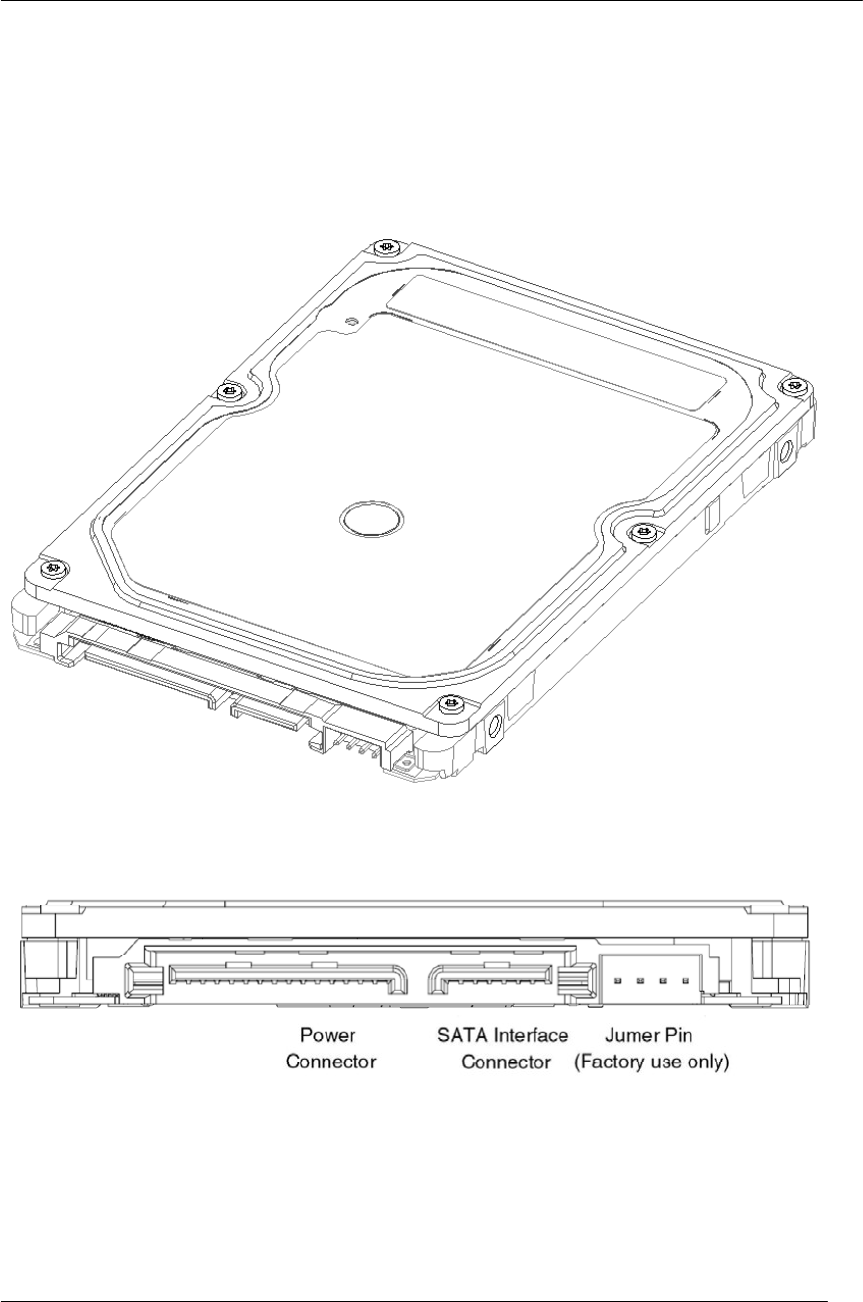

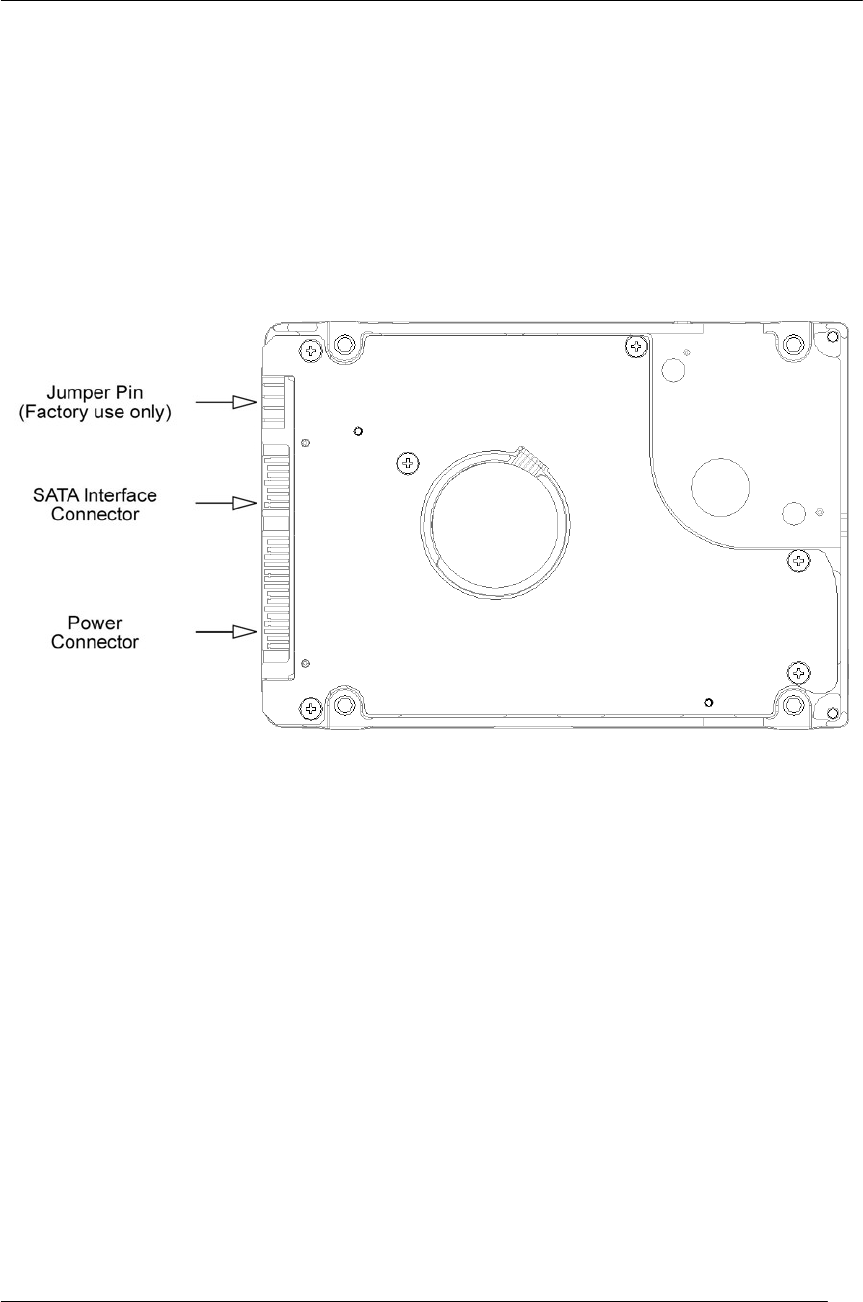

on- board SATA adapter in the computer. Figures 4.6 illustrates the power, SATA, and factory use only

jumper. Figure 4.7 shows pin locations on the SATA drive.

Figure 4-6 HDD Power, SATA Interface, and Factory Jumper Connector

INSTALLATION

Spinpoint

M8 Product Manual REV

2.3

21

Figure 4-7 Pin Locations on the Drive PCBA

Spinpoint

M8 Product Manual REV

2.3

22

INSTALLATION

4.5 Drive Installation

The Spinpoint M8 hard disk drive can be installed in a SATA compatible system

Figure 4-8 indicates the interface and power cable connections required for proper drive installation.

Figure 4-8 DC Power Connector and SATA-Bus Interface Cable Connections

Spinpoint

M8 Product Manual REV

2.3

23

CHAPTER 5 DISK DRIVE OPERATION

This chapter describes the operation of the Spinpoint M8 hard disk drive functional subsystems. It is intended

as a guide to the operation of the drive, rather than a detailed theory of operation.

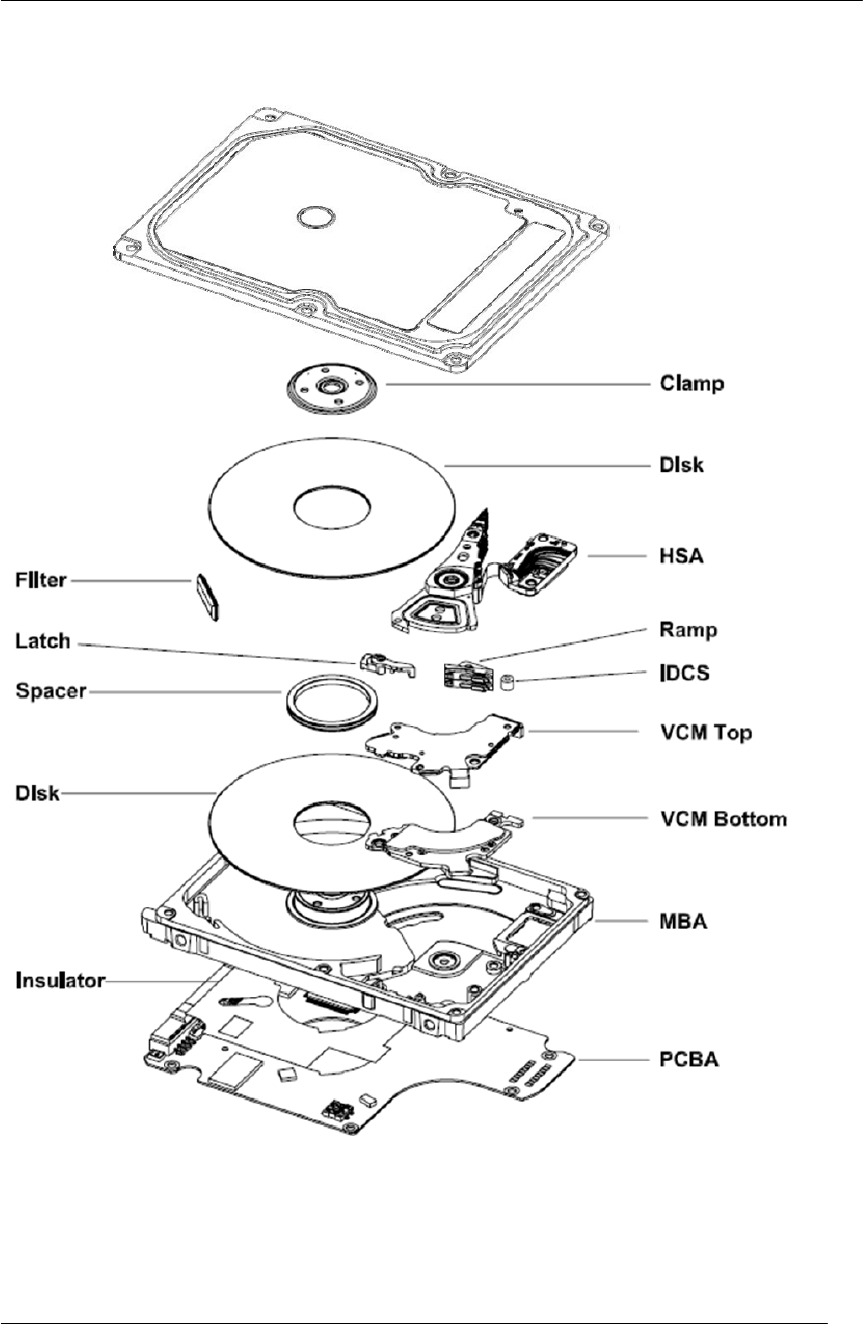

5.1 Head / Disk Assembly (HDA)

The Spinpoint M8 hard disk drive consists of a mechanical sub-assembly and a printed circuit board

assembly (PCBA), as shown in Figure 5-1. This section describes the mechanism of the drive.

The head / disk assembly (HDA) contains the mechanical sub-assemblies of the drive, which are sealed

between the aluminum-alloy base and cover. The HDA consists of the base casting assembly (which

includes the DC spindle motor assembly), the disk stack assembly, the head stack assembly, and the rotary

voice coil motor assembly (which includes the actuator latch assembly). The HDA is assembled in a clean

room. These subassemblies cannot be adjusted or field repaired.

CAUTION: To avoid contamination in the HDA, never remove or adjust its cover

and seals. Disassembling the HDA voids your warranty.

The Spinpoint M8 hard disk drive models and capacities are distinguished by the number of heads and

disks. The ST250LM004 have one (1) disk and two (2) read/write heads. The ST320LM001 have one (1)

disk

and two

(2) read/write heads. The ST500LM012 has one (1) disk and two (2) heads. The ST640LM001

have two (2) disks and four (4) read/write heads. The ST750LM022 have two (2) disks and four (4)

read/write heads. The ST1000LM024 has two (2) disks and four (4) read/write heads.

5.1.1 Base Casting Assembly

A one piece, aluminum-alloy base casting provides a mounting surface for the drive mechanism and PCBA.

The base casting also serves as the flange for the DC spindle motor assembly. A gasket provides a seal

between the base and cover castings that enclose the drive mechanism.

5.1.2 DC Spindle Motor Assembly

The DC spindle motor assembly consists of the brush-less three-phase motor, spindle bearing (FDB)

assembly, disk mounting hub, and a labyrinth seal. The entire spindle motor assembly is

completely enclosed in the HDA and integrated to the base casting. The labyrinth seal prevents bearing

lubricant from coming out into the HDA. The motor rotates the spindle shaft at 5400 rpm.

Spinpoint

M8 Product Manual REV

2.3

24

--

C

over

Assembly

Figure 5-1:

Exploded Mechanical

Vi

e

w

Spinpoint

M8 Product Manual REV

2.3

25

5.1.3 Disk Stack Assembly

The disk stack assembly in the Spinpoint M8 hard disk drive consists of 1 or 2 disks and disk spacers secured

on the hub of the spindle motor assembly by a disk clamp. The glass disks have a sputtered thin-film magnetic

coating.

5.1.4 Head Stack Assembly

The head stack assembly consists of an E-block/coil sub-assembly, read/write heads, a flexible circuit, and

bearings. The E-block/coil sub-assembly is assembled with an E-block and over-molded coil. Read/write

heads are mounted to spring-stainless steel flexures that are then swage mounted onto the E-block arms.

The flexible circuit connects the read/write heads with the PCBA via a connector through the base casting.

The flexible circuit contains a read/write Preamplifier IC.

5.1.5 Voice Coil Motor and Actuator Latch Assemblies

The rotary voice coil motor consists of upper and lower permanent magnets and magnetic yokes fixed to the

base casting and a rotary over-molded coil on the head stack assembly. Each magnet consists of two

alternating poles and is attached to the magnet yoke. Pawl latch and rubber crash stops mounted on a

magnetic yoke physically prevent the head(s) from moving beyond the designed inner boundary into the

spindle or off the disk surface. Current from the power amplifier induces a magnetic field in the voice coil.

Fluctuations in the field around the permanent magnets move the voice coil so that heads can be positioned in

the requested cylinder.

5.1.6 Air Filtration System

Heads fly very close to the disk surfaces. Therefore, it is very important that air circulating within the drive

be maintained free of particles. Samsung HDAs are assembled in a purified air environment to ensure

cleanliness and then sealed with a gasket. To retain this clean air environment, the Spinpoint M8 hard disk

drive is equipped with a re-circulating filter, which is located in the path of the airflow close to the rotating

disk and is designed to trap any particles that may develop inside HDA.

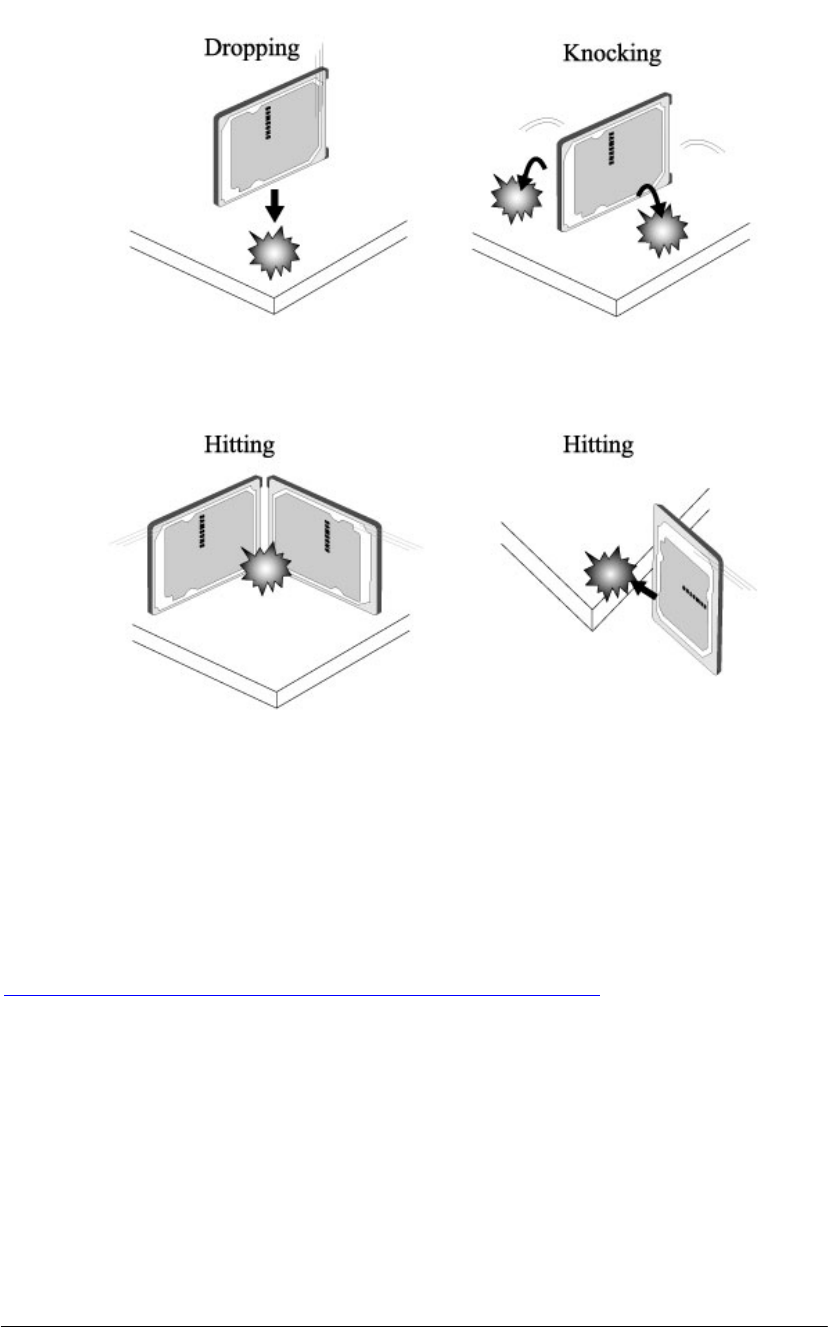

5.1.7 Load/Unload Mechanism

Portable computer is exposed to heavy handling environment comparing with desk top computer.

Load/Unload mechanism provides to protect data loss caused by head hitting to disk due to the abnormal shock

and vibration in the transportation and handling. When power is shut down, head will move to parking position

on the ramp.

Spinpoint

M8 Product Manual REV

2.3

26

5.2 Drive Electronics

The Spinpoint M8 hard disk drive attains its intelligence and performance through the specialized

electronic components mounted on the PCBA. The components are mounted on one side of the PCBA.

The Preamplifier IC is the only electrical component that is not on the PCBA. It is mounted on the flexible

circuit inside the HDA. Locating the Preamplifier IC as close as possible to the read/write heads via surface

mount technology improves the signal to noise ratio.

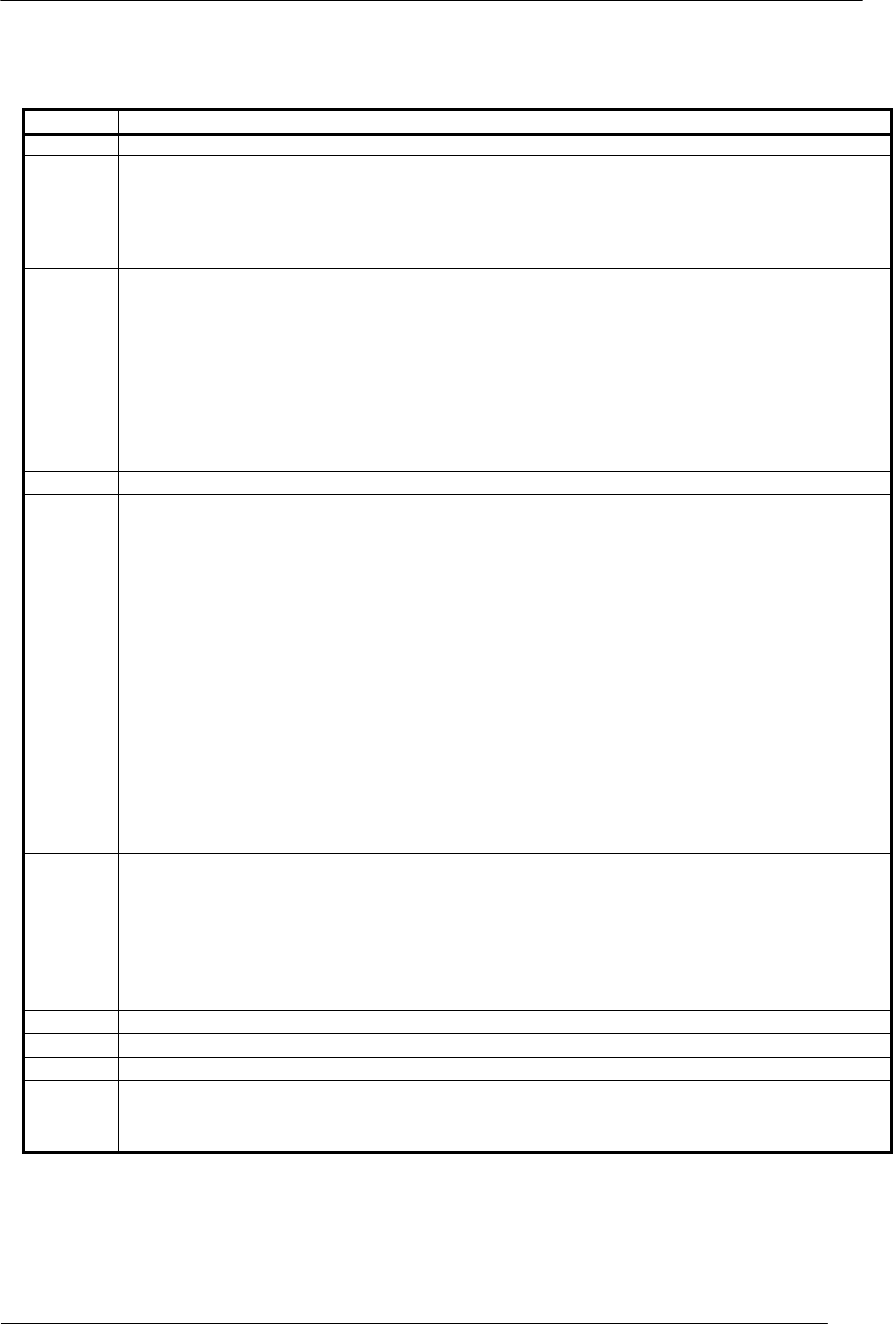

5.2.1 Digital Signal Process and Interface Controller

The DSP core controller has a dual ARM CPU that incorporates a true 32-bit digital signal processor

(DSP),

a

bus controller unit (BCU), an interrupt controller unit (ICU), a general purpose timer (GPT), and SRAM.

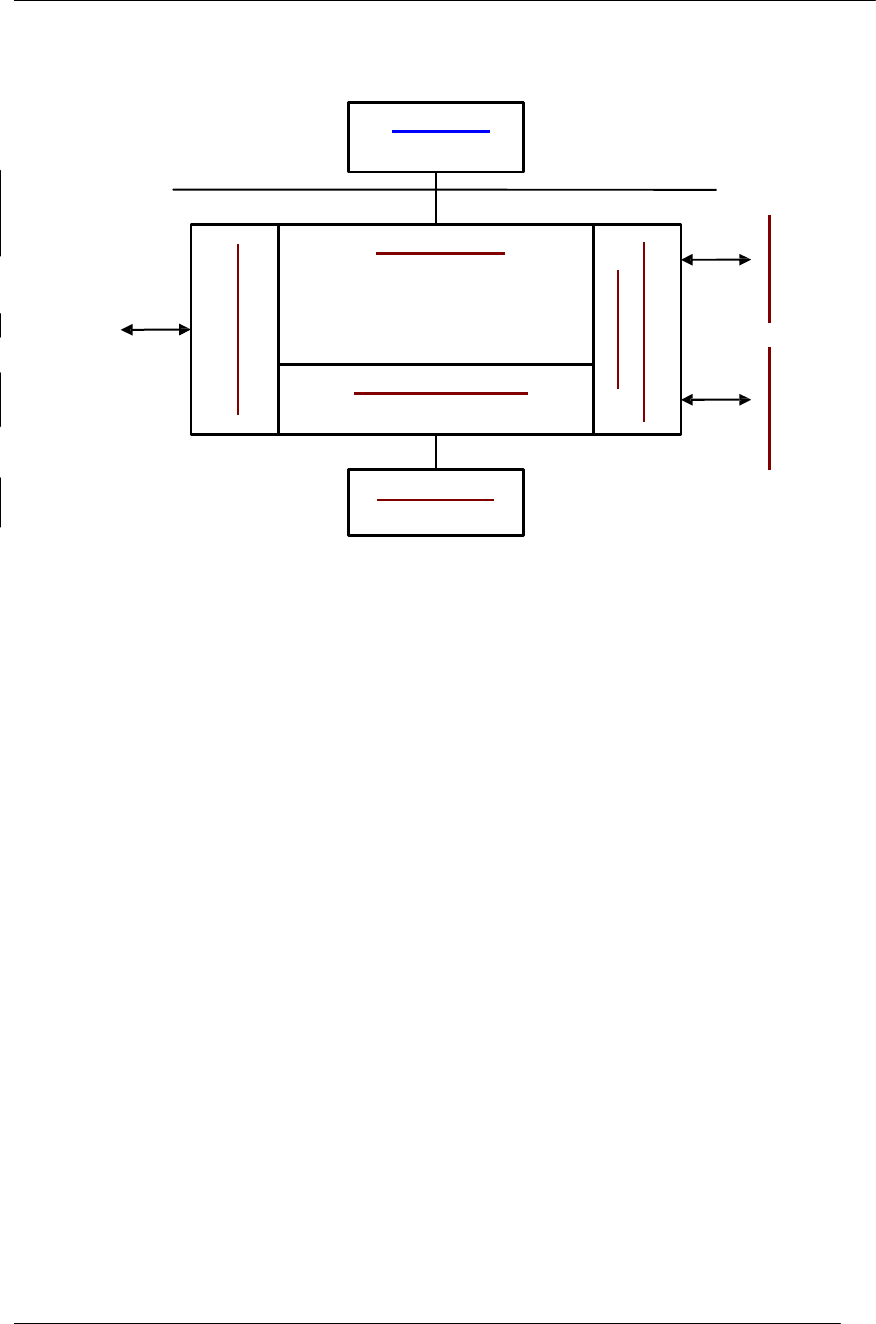

5.2.2 Disk Controller

The AT disk controller works in conjunction with the DSP core to perform the ATA interface control, buffer

data flow management, disk format/read/write control, and error correction functions of an embedded disk

drive controller. The DSP communicates with the disk controller module by reading from and writing to its

various internal registers.

To the DSP core, the registers of the disk controller appear as unique memory or I/O locations that are

randomly accessed and operated upon. By reading from and writing to the registers, the DSP core initiates

operations and examines the status of the different functional blocks. Once an operation is

started, successful completion or an error condition may cause the disk controller to interrupt the DSP

core, which then examines the status registers of the disk controller and determines an appropriate course of

action. The local DSP core may also poll the device to ascertain successful completion or error conditions.

Figure 5-2 illustrates the relationships between the various blocks within the AT disk controller. These

blocks will be referred to throughout this document.

Spinpoint

M8 Product Manual REV

2.3

27

Disk Preamp

Motor Control

Format Sequencer

&

Read

Channel

Host Interface Block

SATA Host Bus (

3 Gbps)

32-bit

ARM

Disk

Controller

Buffer Control

Block

DDR

Figure 5-2: Spinpoint M8 Functional Block Diagram

Spinpoint

M8 Product Manual REV

2.3

28

5.2.2.1 The Host Interface Control Block

The SATA Disk Controller provides direct interface to an SATA bus. It is compatible with ATA 7 Specs. It

provides a means for the host to access the Task File registers used to control the transfer of data between

host memory and the disk drive.

The SATA Host Interface Control block can be programmed to execute various host read/write commands either

completely automatically without any DSP intervention, semi-automatically with minimal DSP intervention, or

manually with the aid of the DSP.

The Disk Controller has significant advances in ATA automation. The highlights of ATA automation includes:

Automatic data transfer management for multi-sector Read/Write commands without DSP intervention.

Automatic execution of read commands (Auto-Read command execution) for cached data in the buffer by

matching the first sector.

Automatic Task File registers updates during automatic multi-sector transfers.

Automatic NCQ queue tag validation

Spinpoint M8 supports PIO, DMA, and FPDMA data transfers. The supported DMA type transfers include multi-

word (MWDMA) and synchronous Ultra DMA (UDMA) transfers. The bus emulates automatically switched

between 16- and 8-bit mode while performing Read Long and Write Long commands at the time of ECC byte

transfers.

Additional functionality is provided in the Host Interface Block by the following features:

Programmable transfer length for automatic ECC byte transfer on the AT bus.

Support of both LBA and CHS Task File registers formats.

Automatic detection of both the Software Reset and COMRESET.

Support for PIO modes 0 through 4.

Support for multiword DMA modes 0 through 2.

Support for multiword DMA modes 0 through 2. Support for synchronous DMA (UDMA) transfer mode

0 through 7. (Mode 7 is referring to 150

MB/S)

Support for First Party DMA (FDMA) for NCQ commands.

5.2.2.2 The Buffer Control Block

The Buffer Control block manages the flow of data into and out of the buffer. Significant automation allows buffer

activity to take place automatically during read/write operations between the host and the disk. This automation

works together with automation within the Host Interface Control and Disk Control blocks to provide more

bandwidth for the local microprocessor to perform non-data flow functions.

The buffer control circuitry keeps track of buffer full and empty conditions and automatically works with the Disk

Control block to stop transfers to or from the disk when necessary. In addition, transfers to or from the host are

automatically stopped or started based on buffer full or empty status.

A prioritized five ports architecture is implemented. All ports, except the refresh port, utilize 22-bit buffer address

pointers.

The data path to the buffer RAM can be configured as 16-bit path in ATA mode.

Spinpoint

M8 Product Manual REV

2.3

29

Additional functionality is provided in the Buffer Control block through the following features:

Increased automation to support minimal latency read operations with minimal latency.

Capability to support the execution of multiple consecutive Auto-Write commands without loss of data

due to overwriting of data.

Auto write pointer.

A disk sector counter that can monitor the transfers between the disk and buffer.

Read/Write cache support.

5.2.2.3 The Disk Control Block

The Spinpoint M8 Disk Control block manages the flow of data between the disk and the buffer. It is capable

of performing completely automated track read and write operations at a maximum data rate of 800 Mb/s in byte

wide NRZ mode. Many flexible features and elements of automation have been incorporated to complement the

automation contributed by the Host and Buffer blocks.

The Disk Control block consists of the programmable sequencer (Disk Sequencer), CDR/data split logic, disk FIFO,

fault tolerant sync detect logic, and other support logic.

The programmable sequencer contains a 31-by-4 byte programmable SRAM and associated control logic, which is

programmed by the user to automatically control all single track format, read, and write operations. From within the

sequencer micro program, the Disk Control block can automatically deal with such real time functions as defect

skipping, servo burst data splitting, branching on critical buffer status and data compare operations. Once the Disk

Sequencer is started, it executes each word in logical order. At the completion of the current instruction word, it

either continues to the next instruction, continues to execute some other instruction based upon an internal or

external condition having been met, or it stops.

During instruction execution or while stopped, registers can be accessed by the DSP to obtain status

information reflecting the Disk Sequencer operations taking place.

5.2.2.4 The Disk LDPC Control Block

The Disk Control Block supports a programmable LDPC code. Error detection and correction is handled in

the Disk Control block. Automatic on-the-fly hardware correction will take place. Correction is guaranteed to

complete before the parity bits of the sector following the sector where the error occurred utilizing standard

ATA size sectors.

5.2.2.5 Frequency Synthesizer

The frequency synthesizer is a clock frequency generation circuit used to generate a DSP clock, AT disk

controller and servo clock from the External Reference clock input.

Spinpoint

M8 Product Manual REV

2.3

30

5.2.2.6 Power Management

Power management features are incorporated into each block of the Spinpoint M8. This allows the designer

to tailor the amount of power management to the specified design. Other power management features include:

Independent power management control for each block.

DSP block powered down and up when needed.

Disk Sequencer and associated disk logic powered up when the Disk Sequencer is started.

Weak pull-up structure on input pins to prevent undesirable power consumption due to floating CMOS

inputs.

5.2.3 Read/Write IC

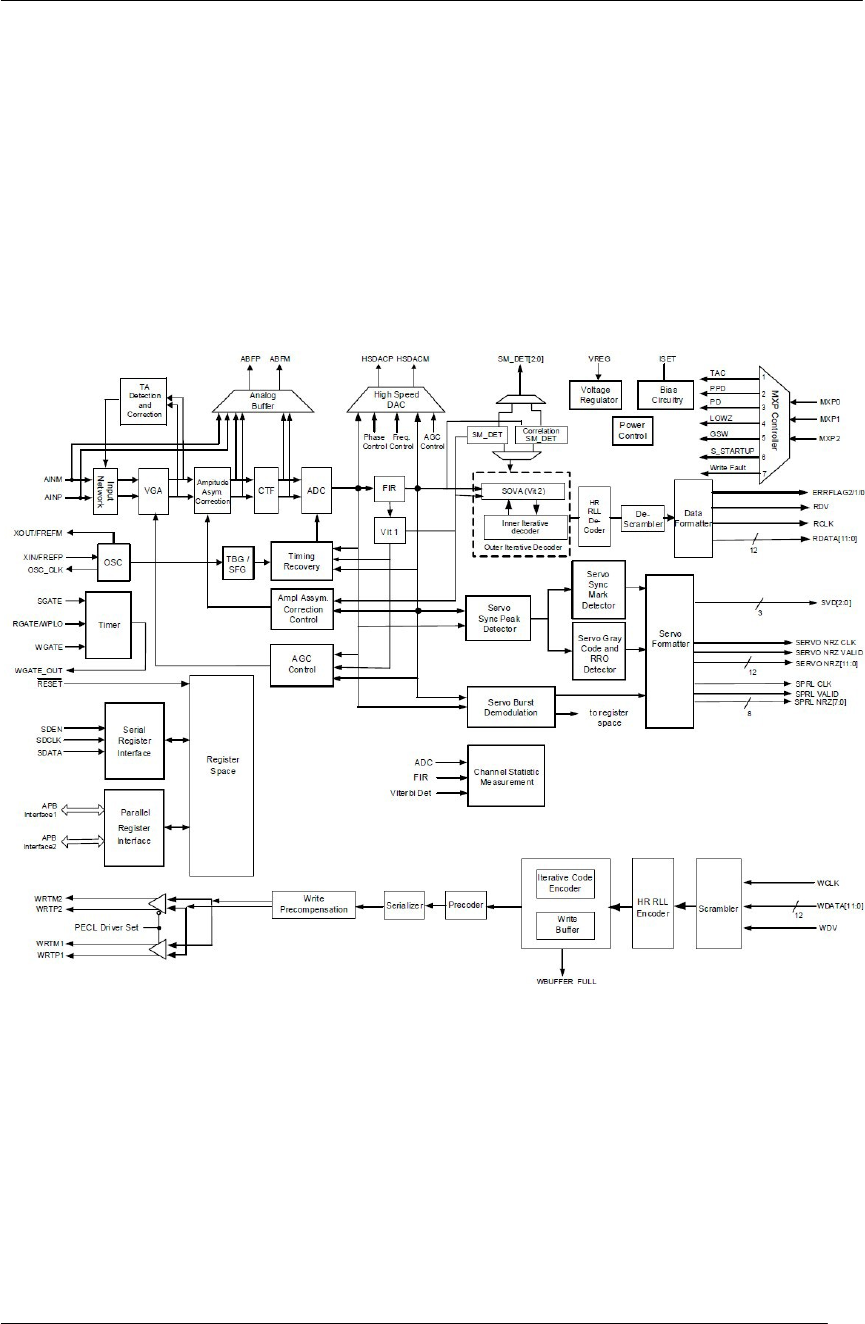

The Read/Write IC, shown in Figure 5-3 provides read/write-processing functions for the drive. The

Read/Write IC receives the Read GATE and Write GATE signals, write data, and servo AGC and gates from the

Interface Controller. The Read/Write IC sends decoded read data and the read reference clock. It receives

write data from the Interface Controller.

The 88C9310 which is embedded in 88i9322 is a sampled-data digital PRML channel designed to work with a disk

controller and a read/write preamplifier to provide the signal processing elements required to build a state of the art

high density, high speed disk drive. The 88C9310 implements a noise predictive, PRML Viterbi read channel

(supporting) zone-bit recording,

The read/write channel functions include a time base generator, AGC circuitry, asymmetry correction circuitry

(ASC), analog anti-aliasing low-pass filter, analog to digital converter (ADC), digital FIR filter, timing recovery

circuits, Viterbi detector, sync mark detection, Iterative code ENDEC, serializer and de-serializer, and write pre-

compensation circuits. Servo functions include servo data detection and PES demodulation. Additionally the

88C9310 contains specialized circuitry to perform various parametric measurements on the processed read signal.

This allows for implementation of self-tuning and optimization capability in every drive built using the 88C9310.

A 12-bit NRZ interface is provided to support high speed data transfers and from the controller.

Programming of the 88C9310 is performed through a serial interface. The serial interface is also used to read

various channel parameters that are computed on the fly.

5.2.3.1 Time Base Generator

The time base generator provides the write frequency and serves as a reference clock to the synchronizer

during non-read mode.

5.2.3.2 Automatic Gain Control

The AGC accepts a differential signal from the pre-amp, and provide constant output amplitude to the analog

filter. It’s capable of accepting signal ranges from 50 mV to 400mVppd.

5.2.3.3 Asymmetry Correction Circuitry (ASC)

The ASC circuit is designed to correct for amplitude asymmetry introduced by MR heads. The compensation

range of this circuit is +/-25%. This circuit allows optimal bias current to be used independent of the

asymmetry effect.

Spinpoint

M8 Product Manual REV

2.3

31

5.2.3.4 Analog Anti-Aliasing Low Pass Filter

The 7th order equal-ripple analog filter provides filtering of the analog signal from AGC before it’s being

converted to digital signal with the ADC. Its main function is to avoid aliasing for the ADC circuit.

5.2.3.5 Analog to Digital Converter (ADC) and FIR

The output of the analog filter is quantified using a 6 bit FLASH ADC. The digitized data is then equalized

by the FIR to the NPV target response for Viterbi detection. The FIR filter consists of 10 independent

programmable taps.

Figure 5-3: Read/Write

88C9310

Spinpoint

M8 Product Manual REV

2.3

32

5.3 Servo System

The Servo System controls the position of the read/write heads and holds them on track during read/write

operations. The Servo System also compensates for MR write/read offsets and thermal offsets between heads on

different surfaces and for vibration and shock applied to the drive.

The Spinpoint M8 hard disk drive is an Embedded Sector Servo System. Positioning information is radially located

in evenly spaced servo sectors on each track.

Radial position information can be provided from these sectors for each data head. Because the drive incorporates

multiple data zones and each zone has a different bit density, split data fields are necessary for optimal use of the

non-servo area of the disk. The servo area remains phase-coherent across the surface of the disk, even though the

disk has various data zones. The main advantage of the Embedded Sector Servo System is that it eliminates the

problems of static and dynamic offsets between heads on different surfaces. The Spinpoint M8 hard disk drive

Servo System is classified as a digital servo system because track-following and seek control, bias cancellation, and

other typical tasks are done in a Digital Signal Processor (DSP).

The Servo system has three modes of operation: track-following mode, settle mode, and velocity control mode.

1. Track-following mode is used when heads are “on-track.” This is a position loop with an

integrator in the compensation.

2. Settle mode is used for all accesses; head switches, short-track seeks and long-track seeks.

Settle mode is a position loop with velocity damping. Settle mode does not use feed forward.

3. Velocity control mode is used for acceleration and deceleration of the actuator for seeking of

two or more tracks. A seek operation of this length is accomplished with a velocity control

loop. The drive’s ROM stores the velocity profile in a look-up table.

5.4 Read and Write Operations

The following two sections describe the read and write channels.

5.4.1 The Read Channel

The drive has one read/write head for each of the data surfaces. The signal path for the Read Channel starts at the

read/write heads. When the magnetic flux transitions recorded on a disk pass under the head, they generate low-

amplitude, differential output voltages. The read/write head transfers these signals to the flexible circuit’s

amplifier, which amplifies the signal.

The flexible circuit transmits the pre-amplified signal from the HDA to the PCBA. The EPRML channel on the

PCBA shapes, filters, detects, synchronizes, and decodes the data from the disk. The Read/Write IC then sends the

resynchronized data output to the 88i9322 (Rev2.0) DSP & Interface/Disk Controller.

The 88i9322 (Rev2.0) Disk Controller manages the flow of data between the Data Synchronizer on the Read/Write

IC and its AT Interface Controller. It also controls data access for the external RAM buffer. The ENDEC of

88C9310 decodes the LDPC with post-processor format to produce a serial bit stream. This NRZ (Non Return to

Zero) serial data is converted to 12-bits.

Spinpoint

M8 Product Manual REV

2.3

33

The Sequencer module identifies the data as belonging to the target sector. After a full sector is read, the

88i9322 (Rev2.0) checks to see if the firmware needs to apply an ECC algorithm to the data. The Buffer Control

section of the 88i9322 (Rev2.0) stores the data in the cache and transmits the data to the AT bus.

5.4.2 The Write Channel

The signal path for the Write Channel follows the reverse order of that for the Read Channel. The host transmits data

via the AT bus to the 88i9322 (Rev2.0) Interface Controller. The Buffer Controller section of the 88i9322 (Rev2.0)

stores the data in the cache. Because the data is transmitted to the drive at a rate that exceeds the rate at which the

drive can write data to the disk, data is stored temporarily in the cache. Thus, the host can present data to the drive at

a rate independent of the rate at which the drive can write data to the disk.

Upon correct identification of the target address, the data is shifted to the Sequencer, which generates and appends

an error correcting code. The Sequencer then converts the bytes of data to a serial bit stream. The AT controller also

generates a preamble field, inserts an address mark, and transmits the data to the ENDEC in the R/W IC where the

data is encoded into the LDPC format and pre-compensates for non-linear transition shift. The amount of write

current is set by the 88i9322 (Rev2.0) DSP and Interface/Disk Controller through the serial interface to the

preamplifier.

The 88i9322 (Rev2.0) switches the Preamplifier and Write Driver IC to write mode and selects a head. Once the

Preamplifier and Write Driver IC receives a write gate signal, it transmits current reversals to the head, which writes

magnetic transitions on the disk.

5.5 Firmware Features

This section describes the following firmware features:

Read Caching

Write Caching

Track Skewing

Defect Management

Automatic Defect Allocation

ECC Correction

SMART (Self-monitoring and reporting technology)

ATA security mode features

ATA host protected area

ATA streaming features

ATA power up in stand by feature set

ATA advanced power management (APM) feature set

ATA device configuration overlay (DCO) feature set

5.5.1 Read Caching

The Spinpoint M8 hard disk drive uses Read Cache to enhance drive performance and significantly improve system

throughput. Use the SET FEATURES command to enable or disable Read Caching. Read caching anticipates

host-system requests for data and stores that data for faster future access. When the host requests a certain segment

of data, the cache feature utilizes a prefetch strategy to get the data in advance and automatically read and store the

following data from the disk into fast RAM. If the host requests this data, the RAM is accessed rather than the disk.

Spinpoint

M8 Product Manual REV

2.3

34

There is a high probability that subsequent data requested will be in the cache, because more than 50 percent of all

disk requests are sequential. It takes microseconds rather than milliseconds to retrieve this cached data. Thus Read

Caching can provide substantial time savings during at least half of all disk requests. For example, Read Caching

could save most of the disk transaction time by eliminating the seek and rotational latency delays that prominently

dominate the typical disk transaction.

Read Caching operates by continuing to fill its cache memory with adjacent data after transferring data requested by

the host. Unlike a non-caching controller, the 88i6526 (Rev2.0) Interface Controller continues a read operation

after the requested data has been transferred to the host system. This read operation terminates after a

programmed amount of subsequent data has been read into the cache memory.

The cache memory consists of a sync DRAM buffer allocated to hold the data. It can be directly accessed by

the host by means of read and write commands. The unit of data stored is the logical block, or a multiple of the 512-

byte sector. Therefore, all accesses to cache memory must be in multiples of the sector size. The following

commands empty the cache:

IDENTIFY DRIVE (ECh)

FORMAT TRACK (50h)

EXECUTE DRIVE DIAGNOSTIC (90h)

READ LONG (23h)

WRITE VERIFY (3Ch)

INITIALIZE DEVICE PARAMETER (91h)

SLEEP (99h, E6h)

STANDBY IMMEDIATELY (94h, E0h)

READ BUFFER (E4h)

WRITE BUFFER (E8h)

WRITE SAME (E9h)

5.5.2 Write Caching

Write caching improves both single and multi-sector write performance by reducing delays introduced by

rotational latency. When the drive writes a pattern of multiple sequential data, it stores the data to a cache

buffer and immediately sends a COMMAND COMPLETE message to the host before it writes the data to the

disk.

The data is then written collectively to the drive thereby minimizing the disk seeking operation. Data is

held in cache no longer than the maximum seek time plus rotational latency. Host retries must be enabled

for Write Caching to be active.

If the data request is random, the data of the previous command is written to the disk before COMMAND

COMPLETE is posted for the current command. Read commands work similarly. The previous write is

allowed to finish before the read operation starts.

If a defective sector is found during a write, the sector is automatically relocated before the write occurs.

This ensures that cached data that already has been reported as written successfully gets written, even if an

error should occur.

Spinpoint

M8 Product Manual REV

2.3

35

If the sector is not automatically relocated, the drive drops out of write caching and reports the error as an ID Not

Found. If the write command is still active on the AT interface, the error is reported during that command.

Otherwise, it is reported on the next command.

5.5.3 Defect Management

The Spinpoint M8 hard disk drive media is scanned for defects. After defect scanning, the defective sectors are

saved in the defect list. A defect encountered in the manufacturing process is slipped to the next physical sector

location. All logical sector numbers are pushed down to maintain a sequential order of data. The read/write

operation can “slip” over the defective sectors so that the only performance impact is idle time.

5.5.4 Automatic Defect Allocation

The automatic defect allocation feature automatically maps out defective sectors encountered during read sector

or write sector operations. These types of defective sectors are typically caused by grown defects. During write

operations, if write errors are encountered, all sectors within the target servo frame are mapped out. Original data