THALES DIS AlS Deutschland ELS61-AUS LTE/WCDMA Module User Manual els61 aus hid

Gemalto M2M GmbH LTE/WCDMA Module els61 aus hid

TempConfidential_QIPELS61-AUS_User Manual

M2M.GEMALTO.COM

Cinterion® ELS61-AUS

Hardware Interface Description

Version: 00.031

DocId: ELS61-AUS_HID_v00.031

GENERAL NOTE

THE USE OF THE PRODUCT INCLUDING THE SOFTWARE AND DOCUMENTATION (THE "PROD-

UCT") IS SUBJECT TO THE RELEASE NOTE PROVIDED TOGETHER WITH PRODUCT. IN ANY

EVENT THE PROVISIONS OF THE RELEASE NOTE SHALL PREVAIL. THIS DOCUMENT CONTAINS

INFORMATION ON GEMALTO M2M PRODUCTS. THE SPECIFICATIONS IN THIS DOCUMENT ARE

SUBJECT TO CHANGE AT GEMALTO M2M'S DISCRETION. GEMALTO M2M GMBH GRANTS A NON-

EXCLUSIVE RIGHT TO USE THE PRODUCT. THE RECIPIENT SHALL NOT TRANSFER, COPY,

MODIFY, TRANSLATE, REVERSE ENGINEER, CREATE DERIVATIVE WORKS; DISASSEMBLE OR

DECOMPILE THE PRODUCT OR OTHERWISE USE THE PRODUCT EXCEPT AS SPECIFICALLY

AUTHORIZED. THE PRODUCT AND THIS DOCUMENT ARE PROVIDED ON AN "AS IS" BASIS ONLY

AND MAY CONTAIN DEFICIENCIES OR INADEQUACIES. TO THE MAXIMUM EXTENT PERMITTED

BY APPLICABLE LAW, GEMALTO M2M GMBH DISCLAIMS ALL WARRANTIES AND LIABILITIES.

THE RECIPIENT UNDERTAKES FOR AN UNLIMITED PERIOD OF TIME TO OBSERVE SECRECY

REGARDING ANY INFORMATION AND DATA PROVIDED TO HIM IN THE CONTEXT OF THE DELIV-

ERY OF THE PRODUCT. THIS GENERAL NOTE SHALL BE GOVERNED AND CONSTRUED

ACCORDING TO GERMAN LAW.

Copyright

Transmittal, reproduction, dissemination and/or editing of this document as well as utilization of its con-

tents and communication thereof to others without express authorization are prohibited. Offenders will be

held liable for payment of damages. All rights created by patent grant or registration of a utility model or

design patent are reserved.

Copyright © 2016, Gemalto M2M GmbH, a Gemalto Company

Trademark Notice

Gemalto, the Gemalto logo, are trademarks and service marks of Gemalto and are registered in certain

countries. Microsoft and Windows are either registered trademarks or trademarks of Microsoft Corpora-

tion in the United States and/or other countries. All other registered trademarks or trademarks mentioned

in this document are property of their respective owners.

ELS61-AUS_HID_v00.031 2016-06-03

Confidential / Preliminary

Cinterion® ELS61-AUS Hardware Interface Description

2

Page 2 of 102

Document Name: Cinterion® ELS61-AUS Hardware Interface Description

Version: 00.031

Date: 2016-06-03

DocId: ELS61-AUS_HID_v00.031

Status Confidential / Preliminary

Cinterion® ELS61-AUS Hardware Interface Description

Contents

102

ELS61-AUS_HID_v00.031 2016-06-03

Confidential / Preliminary

Page 3 of 102

Contents

1 Introduction ................................................................................................................. 9

1.1 Key Features at a Glance .................................................................................. 9

1.2 ELS61-AUS System Overview......................................................................... 12

1.3 Circuit Concept ................................................................................................ 13

2 Interface Characteristics .......................................................................................... 15

2.1 Application Interface ........................................................................................ 15

2.1.1 Pad Assignment.................................................................................. 15

2.1.2 Signal Properties................................................................................. 17

2.1.2.1 Absolute Maximum Ratings ................................................ 22

2.1.3 USB Interface...................................................................................... 23

2.1.3.1 Reducing Power Consumption............................................ 24

2.1.4 Serial Interface ASC0 ......................................................................... 25

2.1.5 Serial Interface ASC1 ......................................................................... 27

2.1.6 UICC/SIM/USIM Interface................................................................... 29

2.1.6.1 Enhanced ESD Protection for SIM Interface....................... 31

2.1.7 RTC Backup........................................................................................ 32

2.1.8 GPIO Interface .................................................................................... 33

2.1.9 I2C Interface ........................................................................................ 35

2.1.10 SPI Interface ....................................................................................... 37

2.1.11 PWM Interfaces .................................................................................. 38

2.1.12 Pulse Counter ..................................................................................... 38

2.1.13 Control Signals.................................................................................... 38

2.1.13.1 Status LED .......................................................................... 38

2.1.13.2 Power Indication Circuit ...................................................... 39

2.1.13.3 Host Wakeup....................................................................... 39

2.1.13.4 Fast Shutdown .................................................................... 40

2.2 RF Antenna Interface....................................................................................... 41

2.2.1 Antenna Interface Specifications ........................................................ 41

2.2.2 Antenna Installation ............................................................................ 43

2.2.3 RF Line Routing Design...................................................................... 44

2.2.3.1 Line Arrangement Examples ............................................... 44

2.2.3.2 Routing Example................................................................. 49

2.3 Sample Application .......................................................................................... 50

2.3.1 Sample Level Conversion Circuit........................................................ 52

3 Operating Characteristics ........................................................................................ 53

3.1 Operating Modes ............................................................................................. 53

3.2 Power Up/Power Down Scenarios................................................................... 54

3.2.1 Turn on ELS61-AUS ........................................................................... 54

3.2.1.1 Connecting ELS61-AUS BATT+ Lines ................................ 54

3.2.1.2 Switch on ELS61-AUS Using ON Signal............................. 56

Cinterion® ELS61-AUS Hardware Interface Description

Contents

102

ELS61-AUS_HID_v00.031 2016-06-03

Confidential / Preliminary

Page 4 of 102

3.2.2 Restart ELS61-AUS ............................................................................ 57

3.2.2.1 Restart ELS61-AUS via AT+CFUN Command.................... 57

3.2.2.2 Restart ELS61-AUS Using EMERG_RST........................... 58

3.2.3 Signal States after Startup .................................................................. 59

3.2.4 Turn off ELS61-AUS ........................................................................... 60

3.2.4.1 Switch off ELS61-AUS Using AT Command ....................... 60

3.2.5 Automatic Shutdown ........................................................................... 61

3.2.5.1 Thermal Shutdown .............................................................. 61

3.2.5.2 Undervoltage Shutdown...................................................... 62

3.2.5.3 Overvoltage Shutdown........................................................ 62

3.3 Power Saving................................................................................................... 63

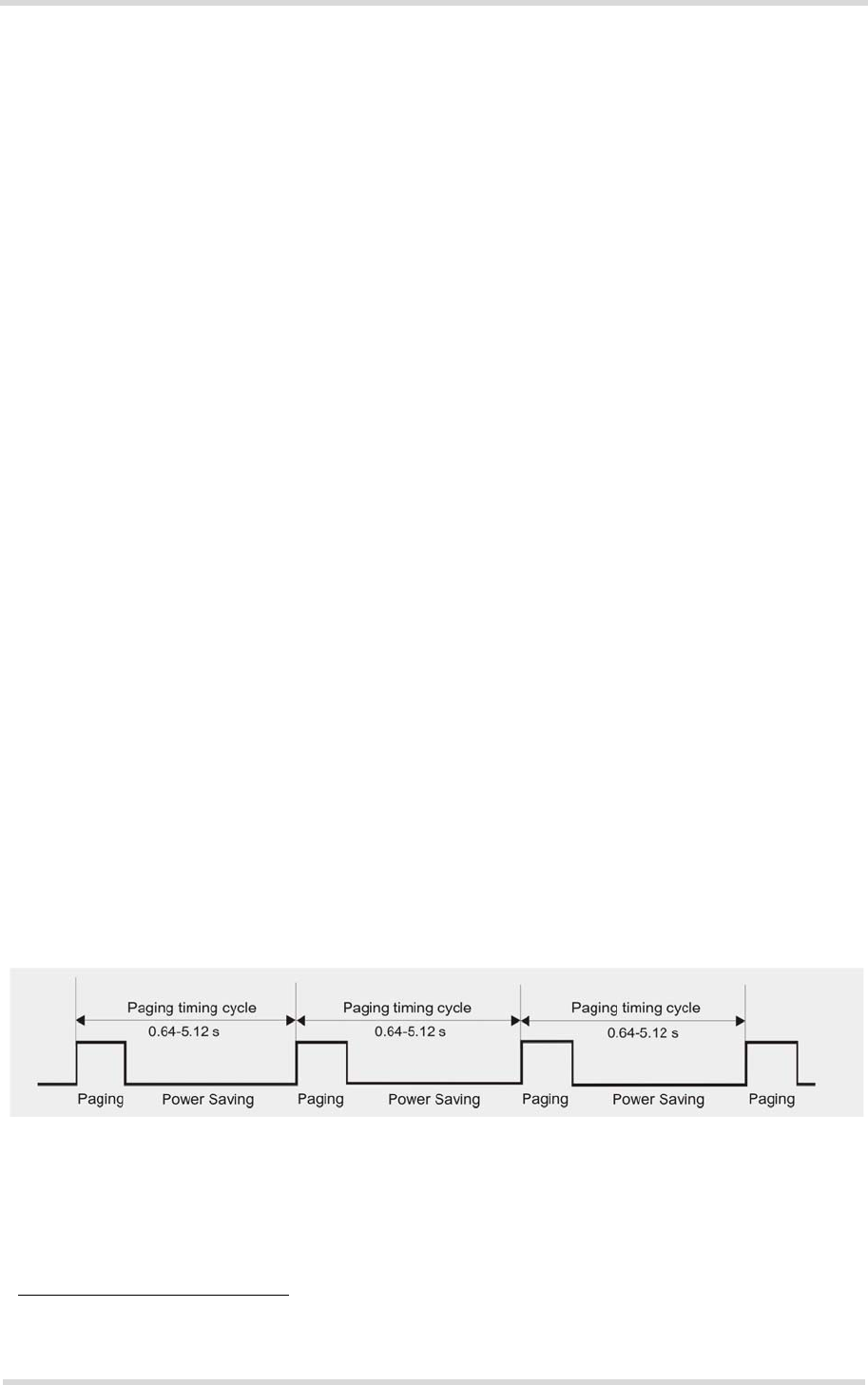

3.3.1 Power Saving while Attached to WCDMA Networks .......................... 63

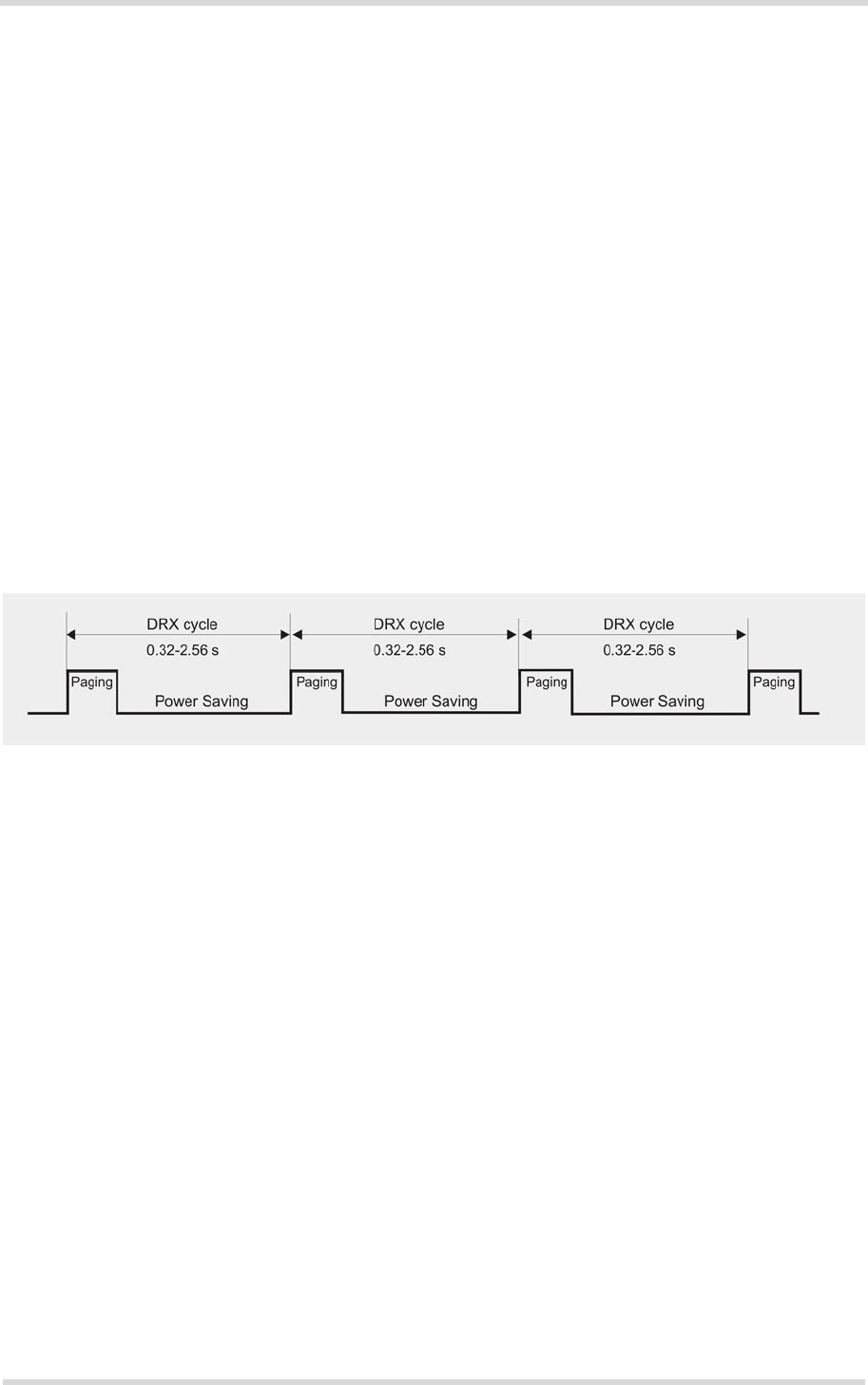

3.3.2 Power Saving while Attached to LTE Networks.................................. 64

3.3.3 Wake-up via RTS0.............................................................................. 65

3.4 Power Supply................................................................................................... 66

3.4.1 Power Supply Ratings......................................................................... 66

3.4.2 Measuring the Supply Voltage (VBATT+)........................................... 68

3.4.3 Monitoring Power Supply by AT Command ........................................ 68

3.5 Operating Temperatures.................................................................................. 69

3.6 Electrostatic Discharge .................................................................................... 70

3.6.1 ESD Protection for Antenna Interfaces ............................................... 70

3.7 Blocking against RF on Interface Lines ........................................................... 71

3.8 Reliability Characteristics................................................................................. 73

4 Mechanical Dimensions, Mounting and Packaging............................................... 74

4.1 Mechanical Dimensions of ELS61-AUS........................................................... 74

4.2 Mounting ELS61-AUS onto the Application Platform....................................... 76

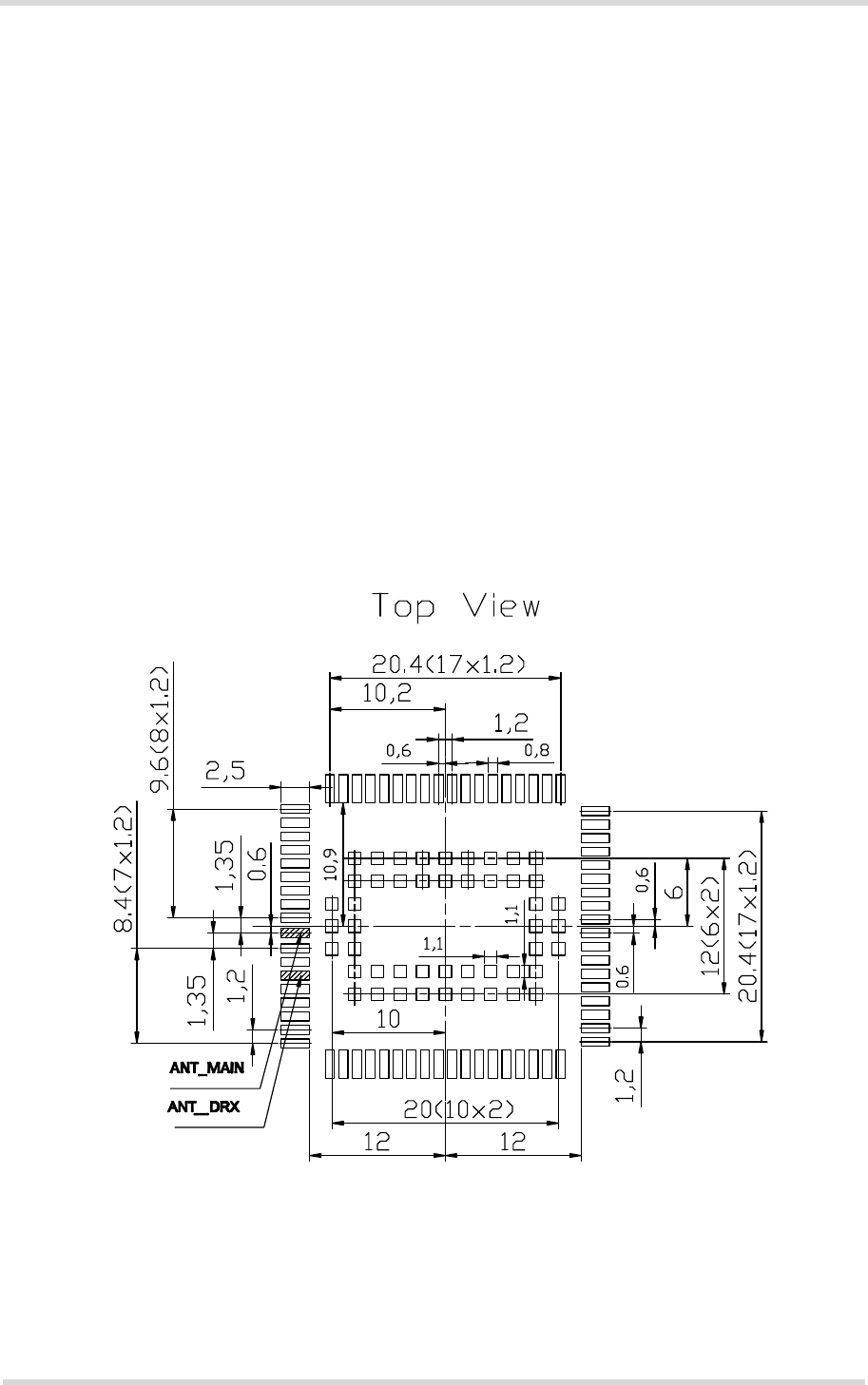

4.2.1 SMT PCB Assembly ........................................................................... 76

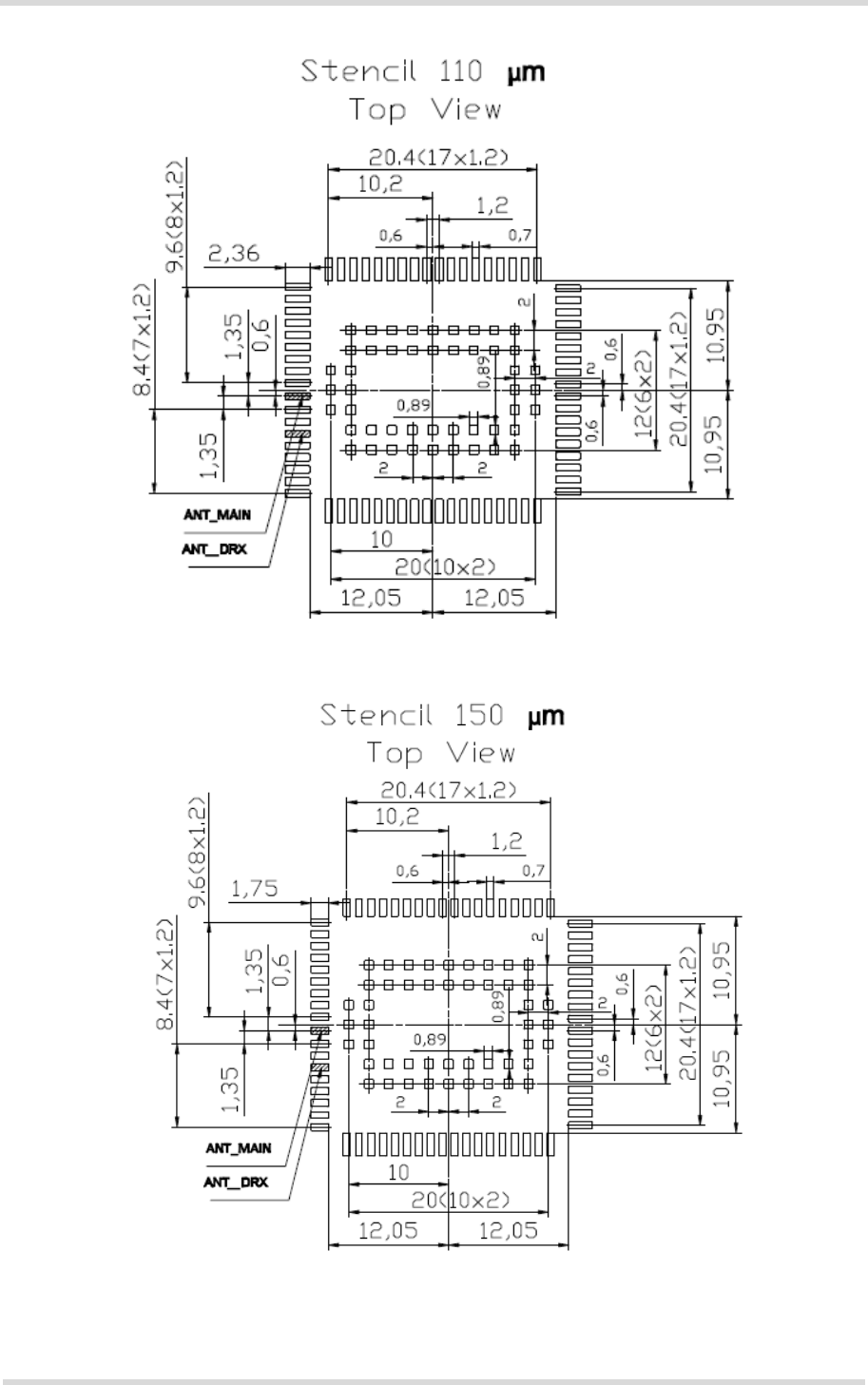

4.2.1.1 Land Pattern and Stencil..................................................... 76

4.2.1.2 Board Level Characterization.............................................. 78

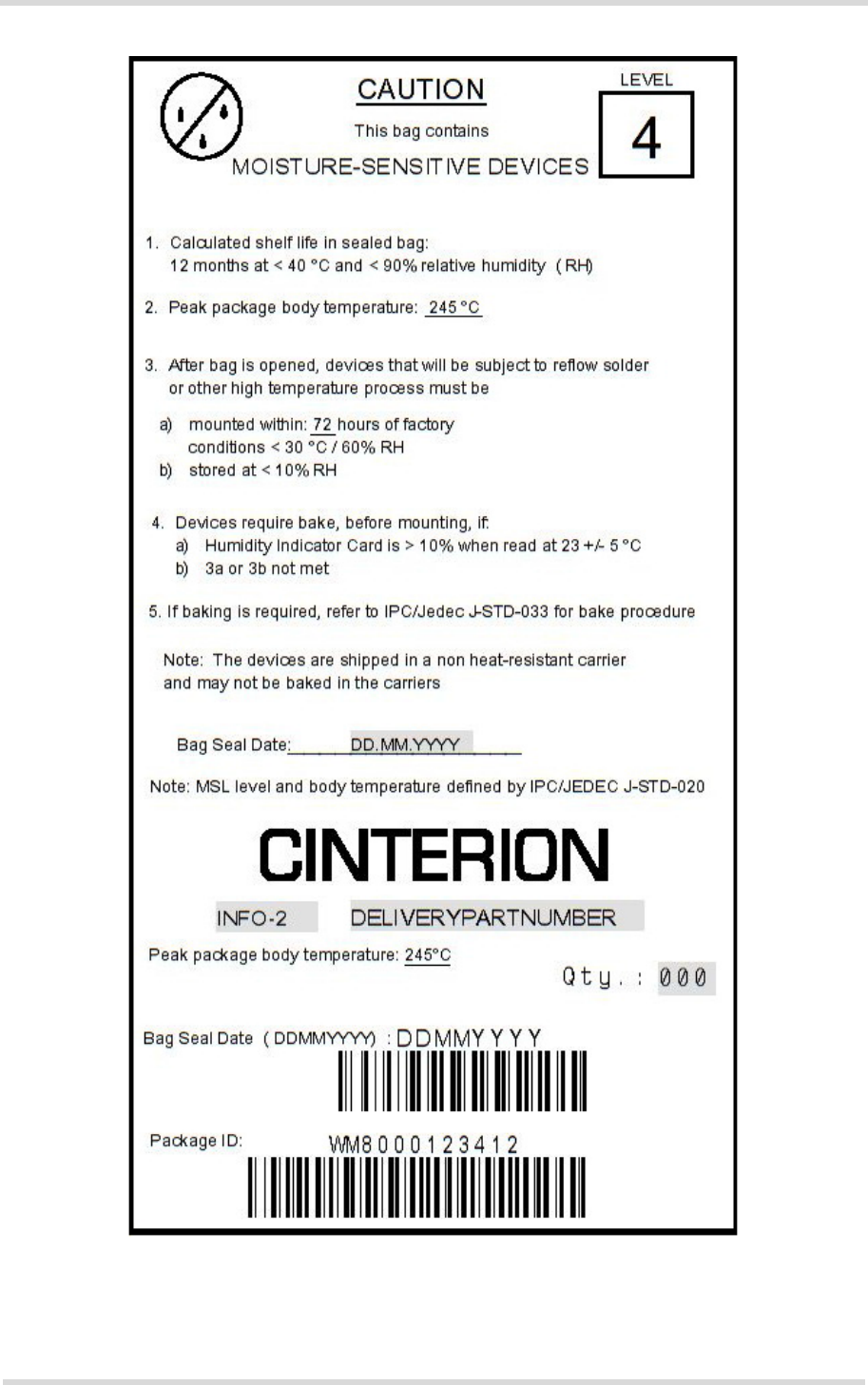

4.2.2 Moisture Sensitivity Level ................................................................... 78

4.2.3 Soldering Conditions and Temperature .............................................. 79

4.2.3.1 Reflow Profile ...................................................................... 79

4.2.3.2 Maximum Temperature and Duration.................................. 80

4.2.4 Durability and Mechanical Handling.................................................... 81

4.2.4.1 Storage Conditions.............................................................. 81

4.2.4.2 Processing Life.................................................................... 82

4.2.4.3 Baking ................................................................................. 82

4.2.4.4 Electrostatic Discharge ....................................................... 82

4.3 Packaging ........................................................................................................ 83

4.3.1 Tape and Reel .................................................................................... 83

4.3.1.1 Orientation........................................................................... 83

4.3.1.2 Barcode Label ..................................................................... 84

Cinterion® ELS61-AUS Hardware Interface Description

Contents

102

ELS61-AUS_HID_v00.031 2016-06-03

Confidential / Preliminary

Page 5 of 102

4.3.2 Shipping Materials .............................................................................. 85

4.3.2.1 Moisture Barrier Bag ........................................................... 85

4.3.2.2 Transportation Box .............................................................. 87

4.3.3 Trays ................................................................................................... 88

5 Regulatory and Type Approval Information ........................................................... 89

5.1 Directives and Standards................................................................................. 89

5.2 SAR requirements specific to portable mobiles ............................................... 92

5.3 Reference Equipment for Type Approval......................................................... 93

5.4 Compliance with FCC Rules and Regulations ................................................. 94

6 Document Information.............................................................................................. 95

6.1 Revision History ............................................................................................... 95

6.2 Related Documents ......................................................................................... 95

6.3 Terms and Abbreviations ................................................................................. 96

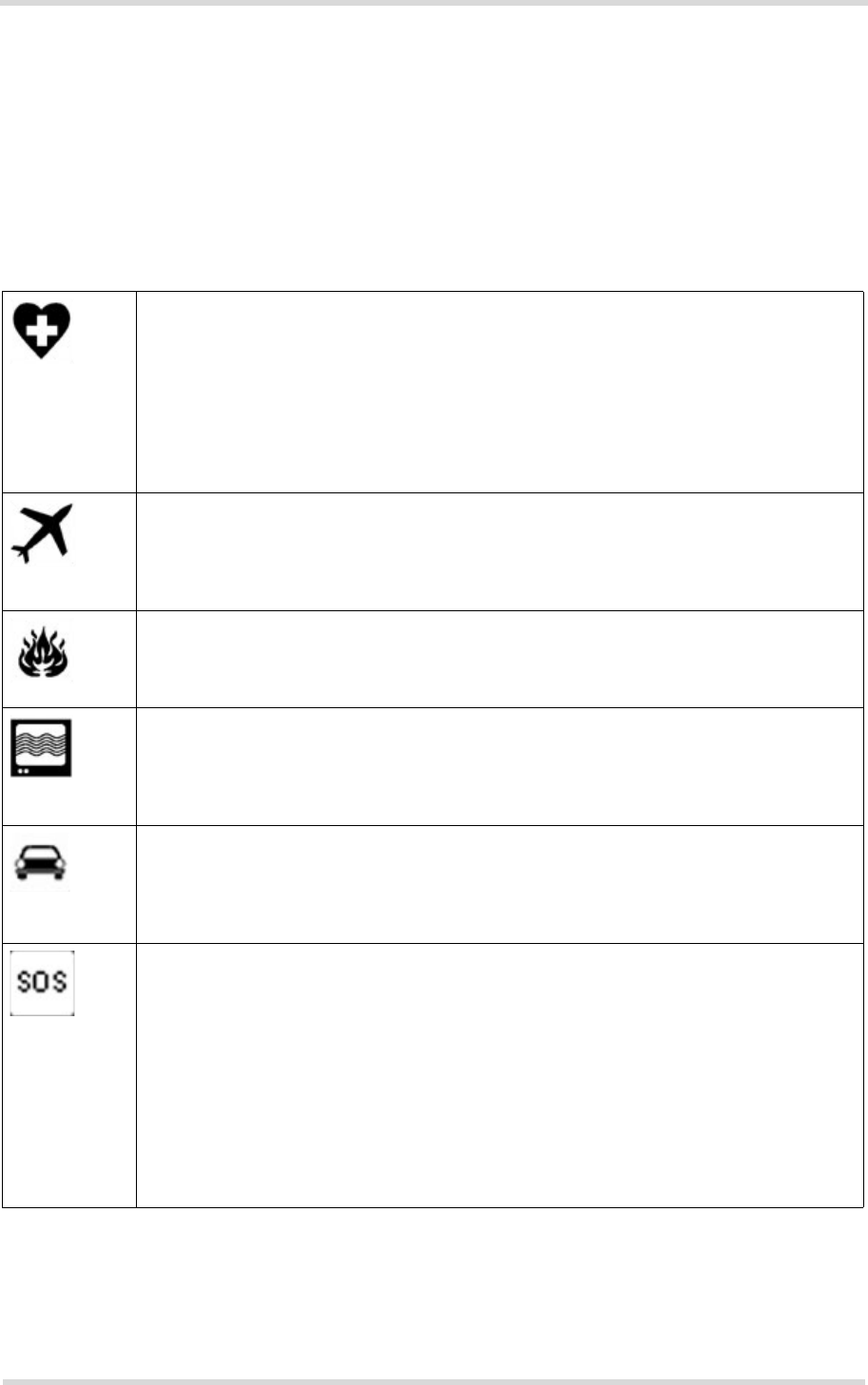

6.4 Safety Precaution Notes .................................................................................. 99

7 Appendix.................................................................................................................. 100

7.1 List of Parts and Accessories......................................................................... 100

Cinterion® ELS61-AUS Hardware Interface Description

Tables

114

ELS61-AUS_HID_v00.031 2016-06-03

Confidential / Preliminary

Page 6 of 102

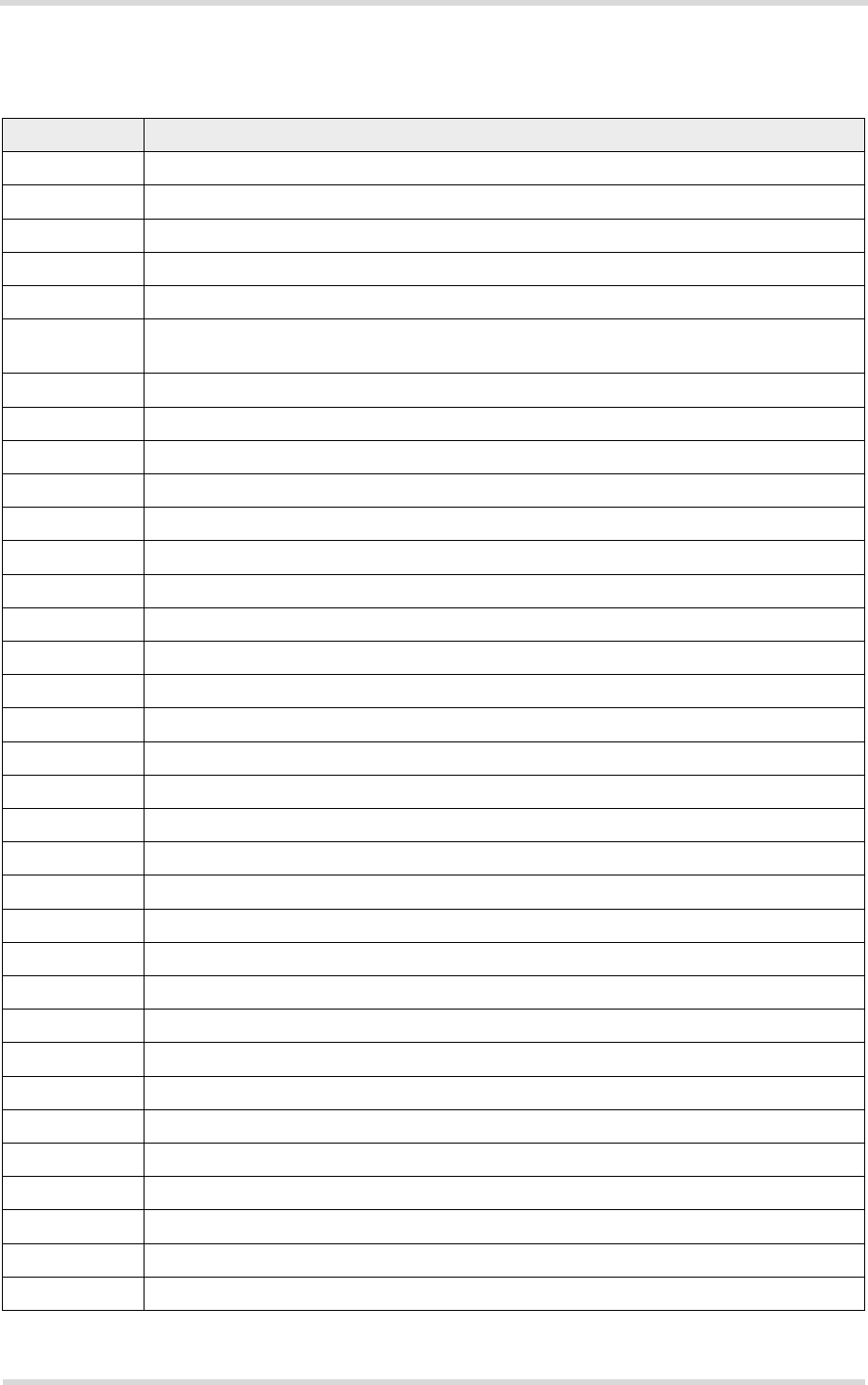

Tables

Table 1: Pad assignments............................................................................................ 16

Table 2: Signal properties ............................................................................................ 17

Table 3: Absolute maximum ratings............................................................................. 22

Table 4: Signals of the SIM interface (SMT application interface) ............................... 29

Table 5: GPIO lines and possible alternative assignment............................................ 33

Table 6: Host wakeup lines.......................................................................................... 39

Table 7: Return loss in the active band........................................................................ 41

Table 8: RF Antenna interface UMTS/LTE (at operating temperature range) ............. 41

Table 9: Overview of operating modes ........................................................................ 53

Table 10: Signal states................................................................................................... 59

Table 11: Temperature dependent behavior.................................................................. 61

Table 12: Voltage supply ratings.................................................................................... 66

Table 13: Current consumption ratings (TBD) ............................................................... 67

Table 14: Board temperature ......................................................................................... 69

Table 15: Electrostatic values ........................................................................................ 70

Table 16: EMI measures on the application interface.................................................... 72

Table 17: Summary of reliability test conditions............................................................. 73

Table 18: Reflow temperature ratings............................................................................ 79

Table 19: Storage conditions ......................................................................................... 81

Table 20: Directives ....................................................................................................... 89

Table 21: Standards of Australian Type Approval.......................................................... 89

Table 22: Requirements of quality ................................................................................. 90

Table 23: Standards of the Ministry of Information Industry of the

People’s Republic of China............................................................................ 90

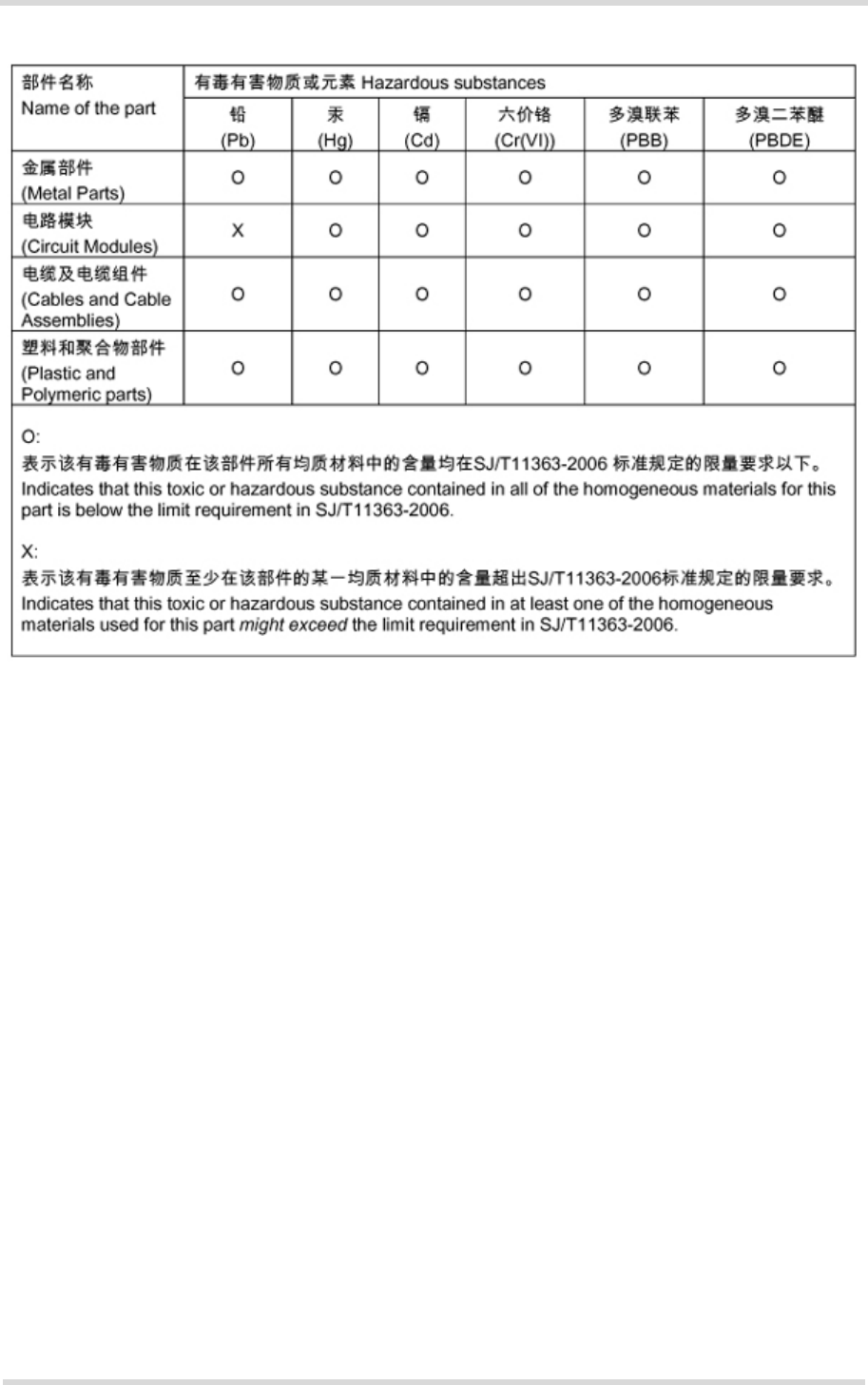

Table 24: Toxic or hazardous substances or elements with defined concentration

limits............................................................................................................... 91

Table 25: List of parts and accessories........................................................................ 100

Table 26: Molex sales contacts (subject to change) .................................................... 101

Cinterion® ELS61-AUS Hardware Interface Description

Figures

114

ELS61-AUS_HID_v00.031 2016-06-03

Confidential / Preliminary

Page 7 of 102

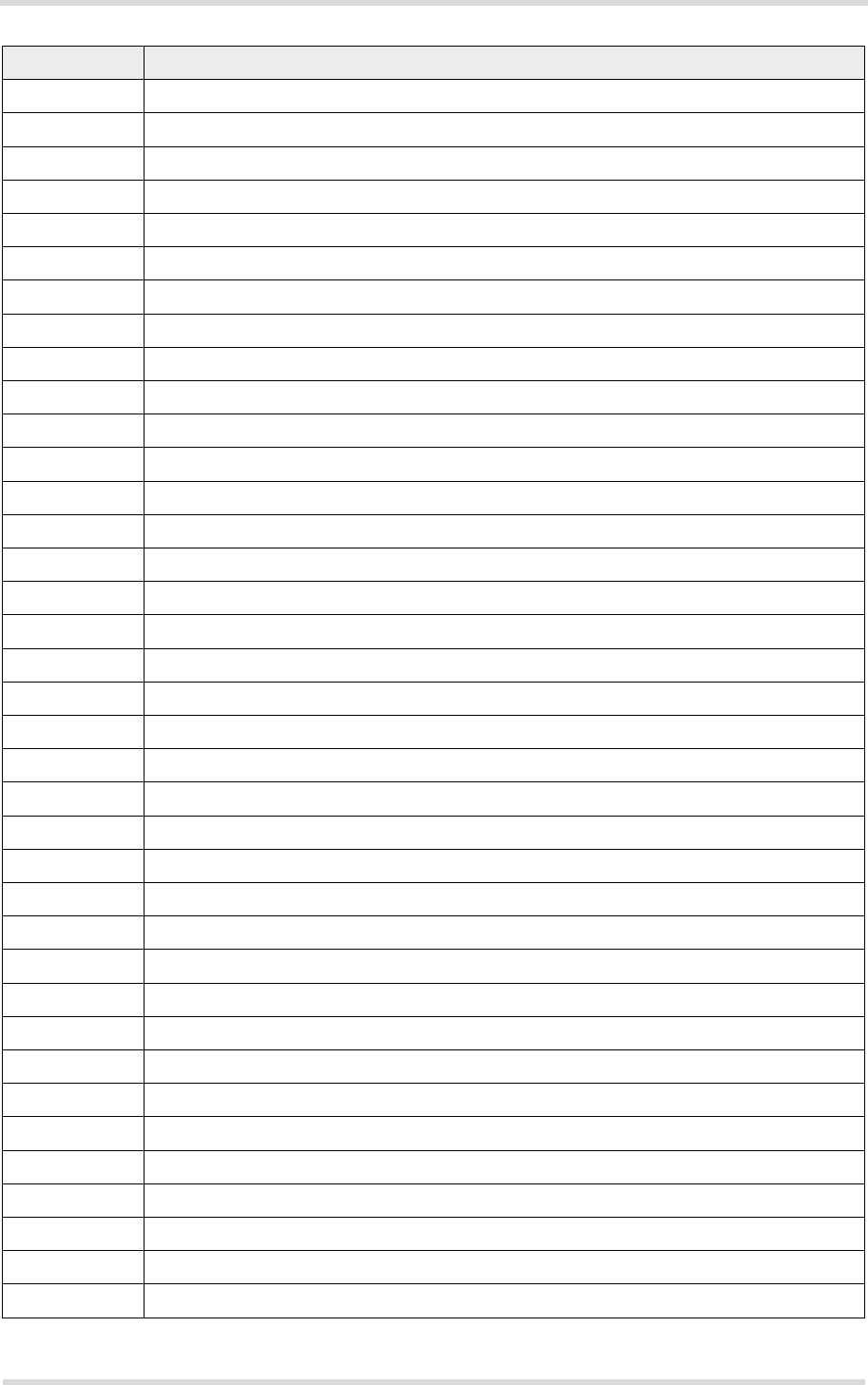

Figures

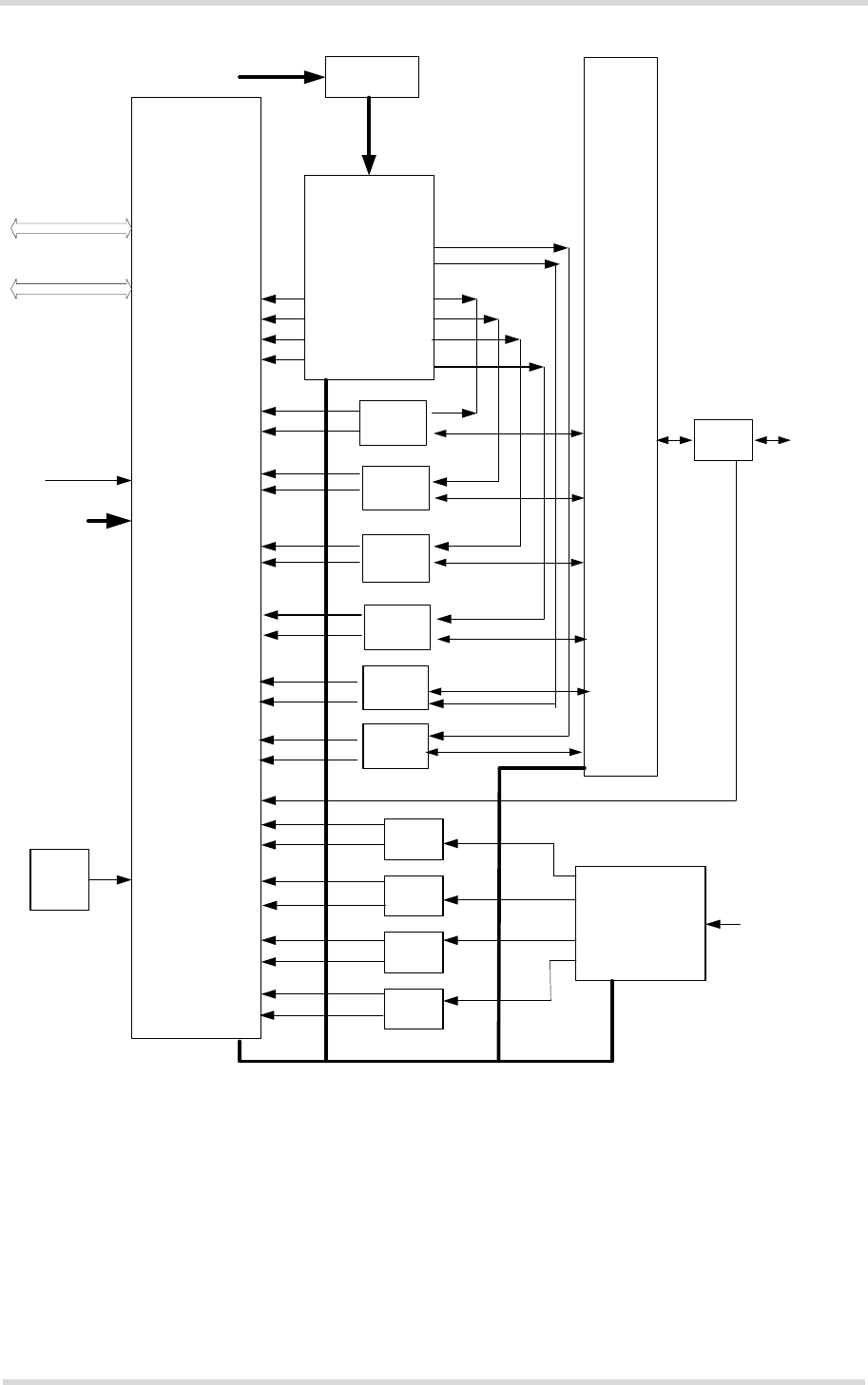

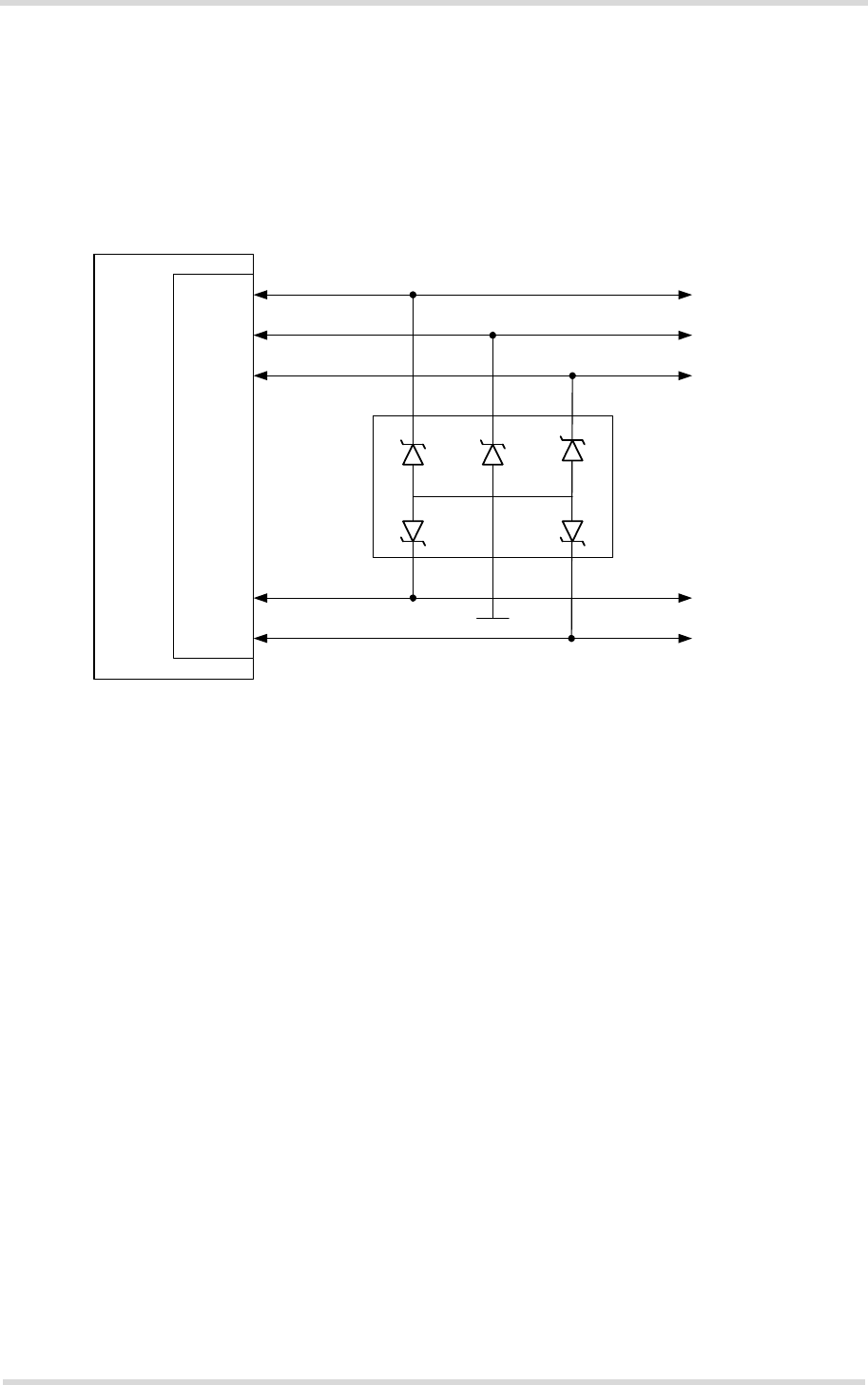

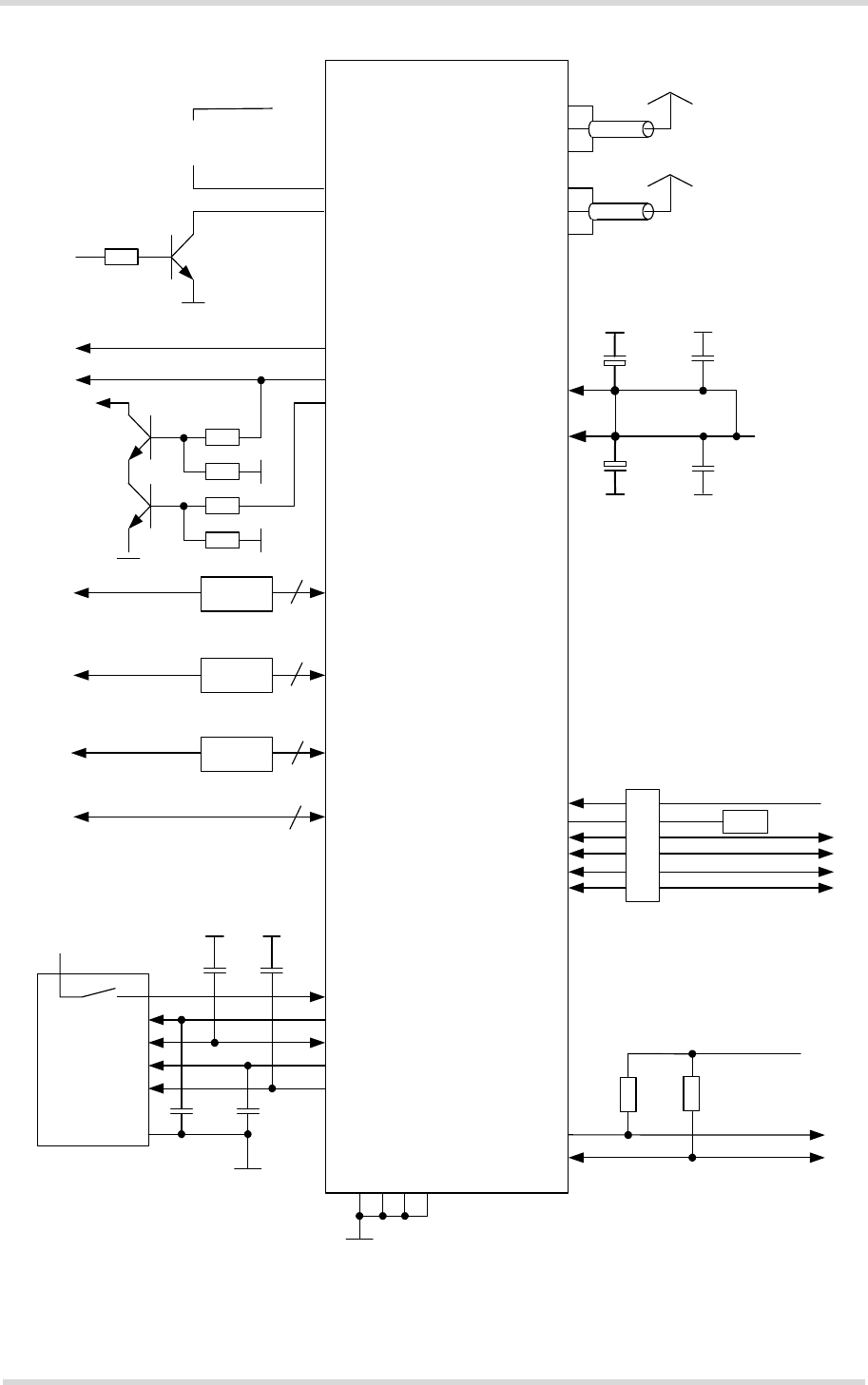

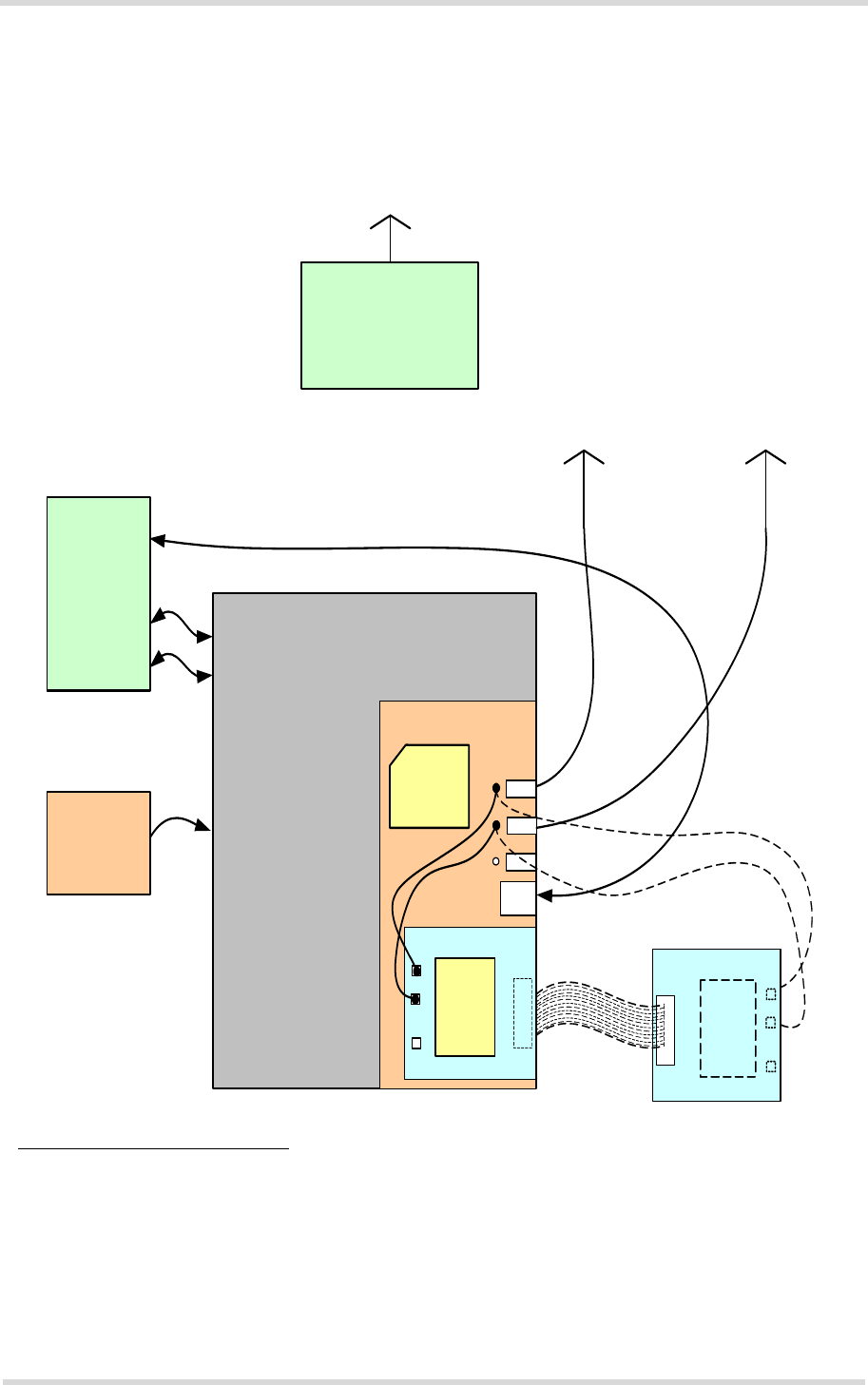

Figure 1: ELS61-AUS system overview ........................................................................ 12

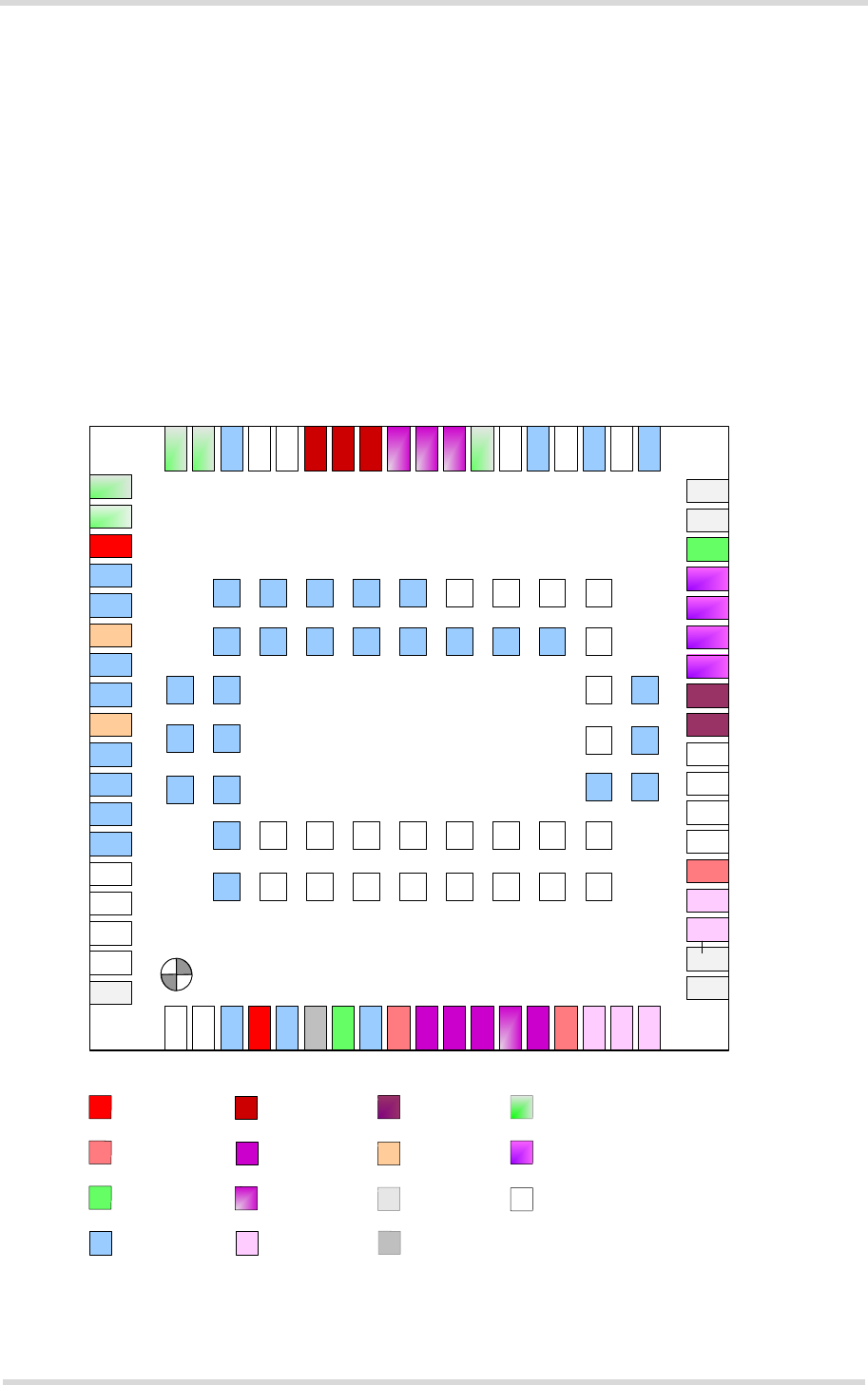

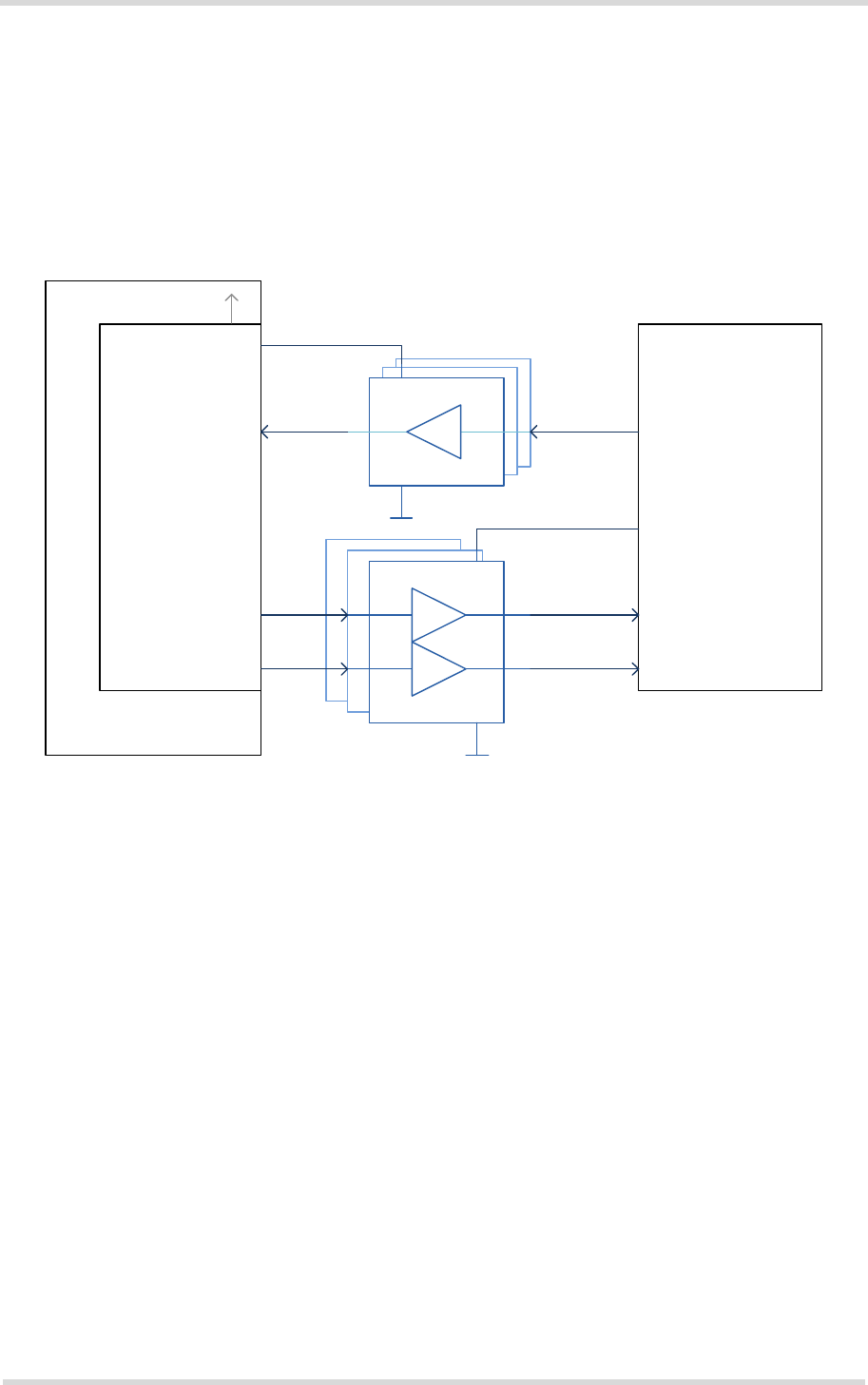

Figure 2: ELS61-AUS block diagram ............................................................................ 13

Figure 3: ELS61-AUS RF section block diagram .......................................................... 14

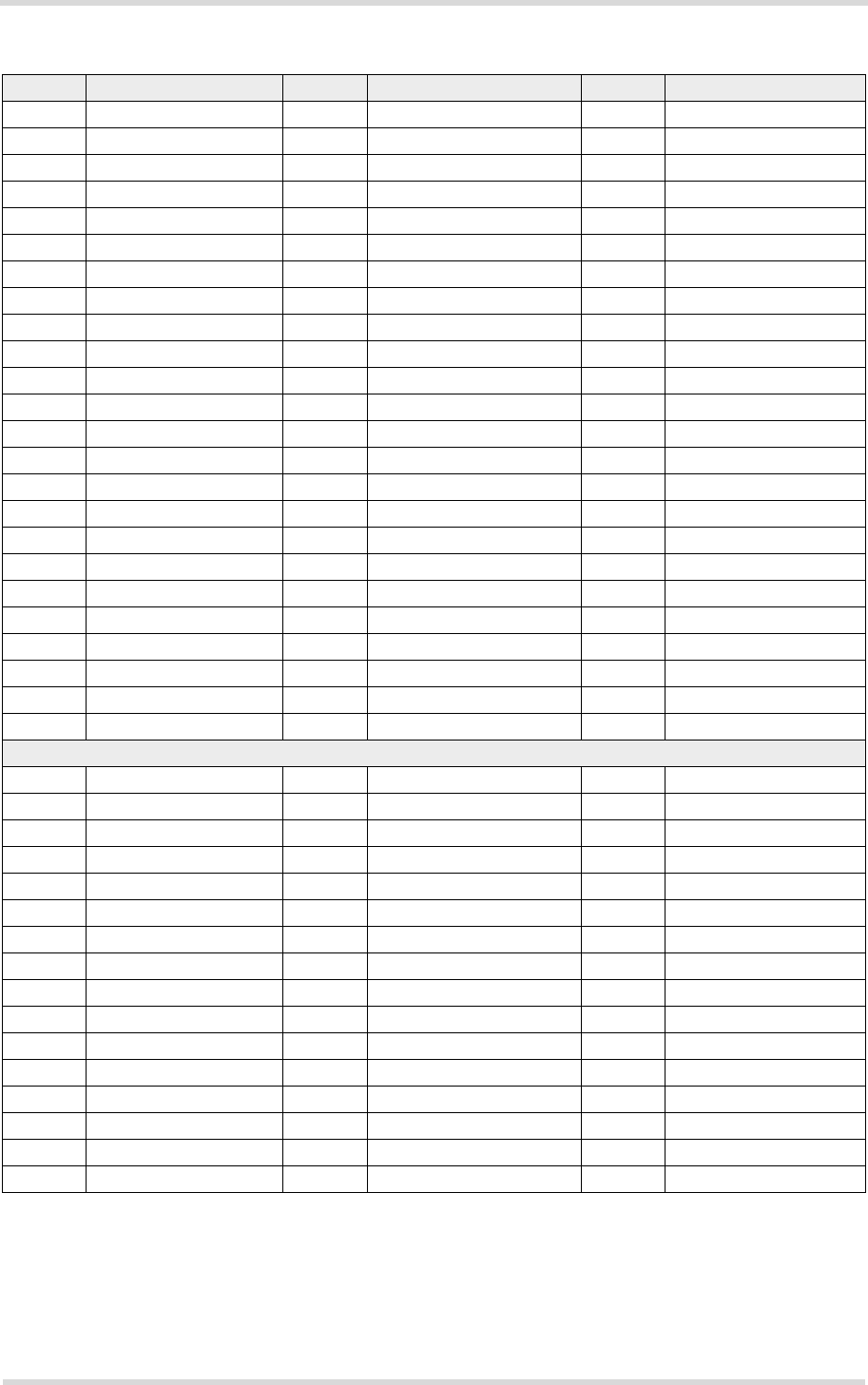

Figure 4: Numbering plan for connecting pads (bottom view)....................................... 15

Figure 5: USB circuit ..................................................................................................... 23

Figure 6: Serial interface ASC0..................................................................................... 25

Figure 7: ASC0 startup behavior................................................................................... 26

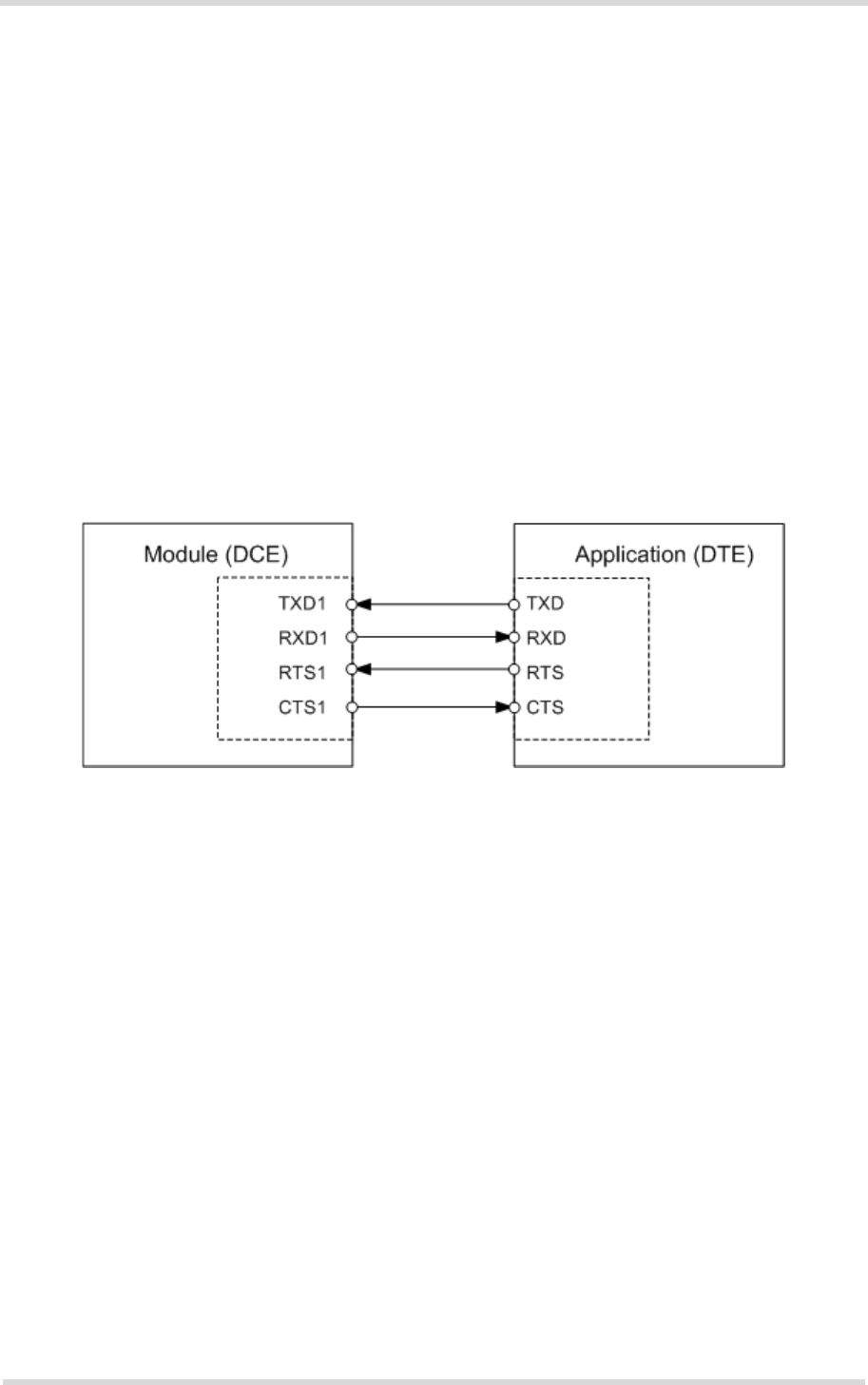

Figure 8: Serial interface ASC1..................................................................................... 27

Figure 9: ASC1 startup behavior................................................................................... 28

Figure 10: External UICC/SIM/USIM card holder circuit ................................................. 30

Figure 11: SIM interface - enhanced ESD protection...................................................... 31

Figure 12: RTC supply variants....................................................................................... 32

Figure 13: GPIO startup behavior ................................................................................... 34

Figure 14: I2C interface connected to V180 .................................................................... 35

Figure 15: I2C startup behavior ....................................................................................... 36

Figure 16: Characteristics of SPI modes......................................................................... 37

Figure 17: Status signaling with LED driver .................................................................... 38

Figure 18: Power indication circuit .................................................................................. 39

Figure 19: Fast shutdown timing ..................................................................................... 40

Figure 20: Antenna pads (bottom view) .......................................................................... 43

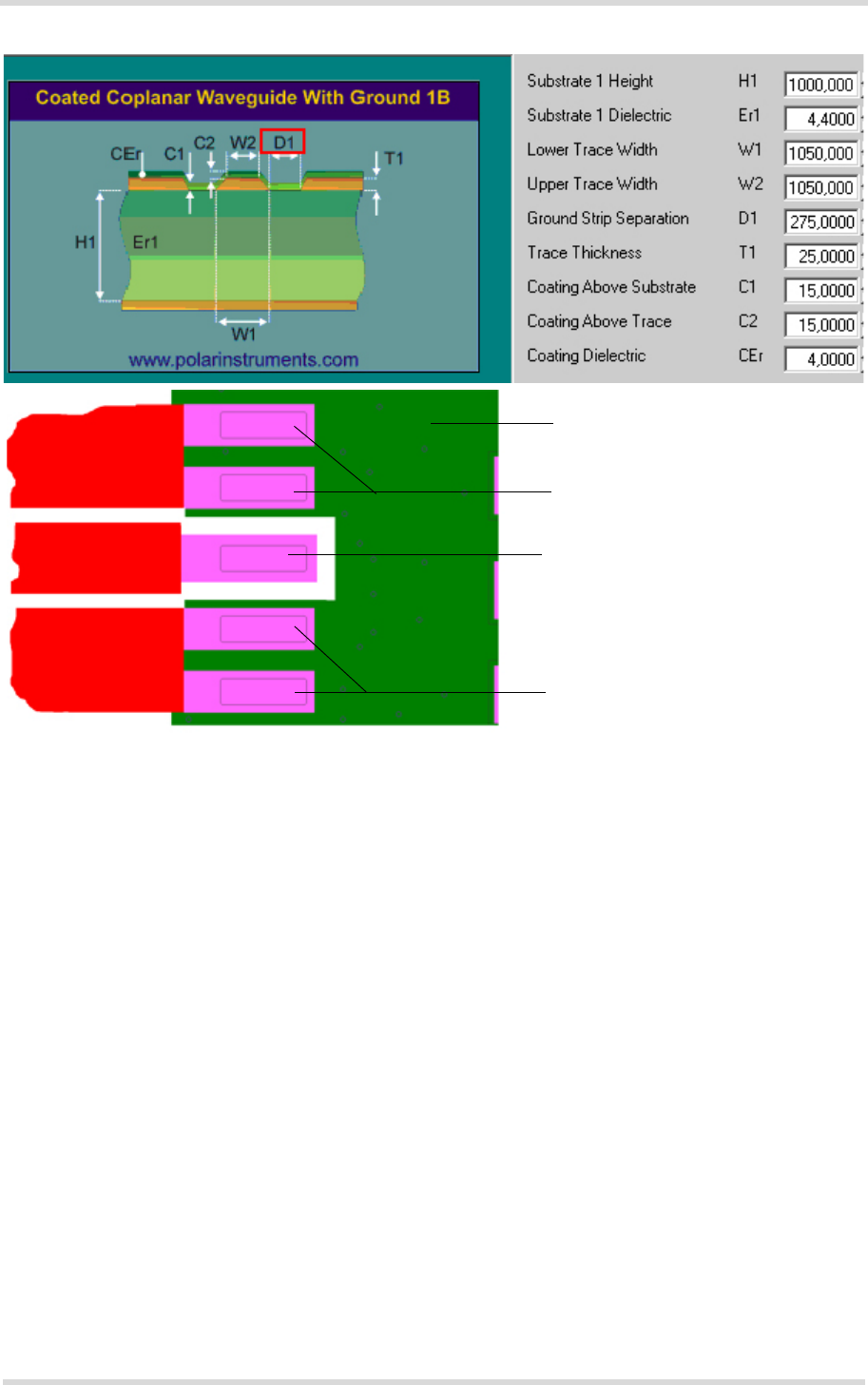

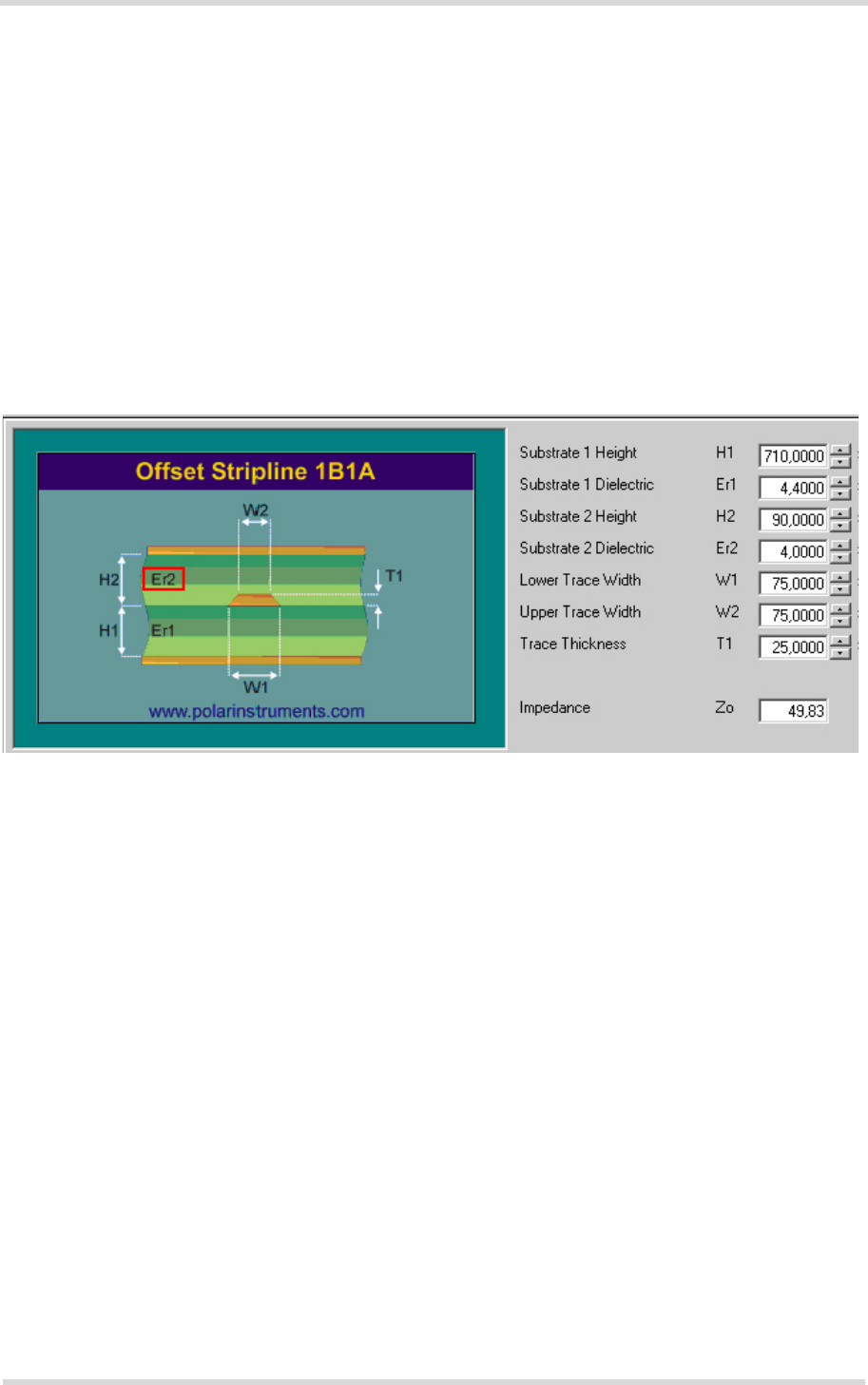

Figure 21: Embedded Stripline with 65µm prepreg (1080) and 710µm core .................. 44

Figure 22: Micro-Stripline on 1.0mm standard FR4 2-layer PCB - example 1 ................ 45

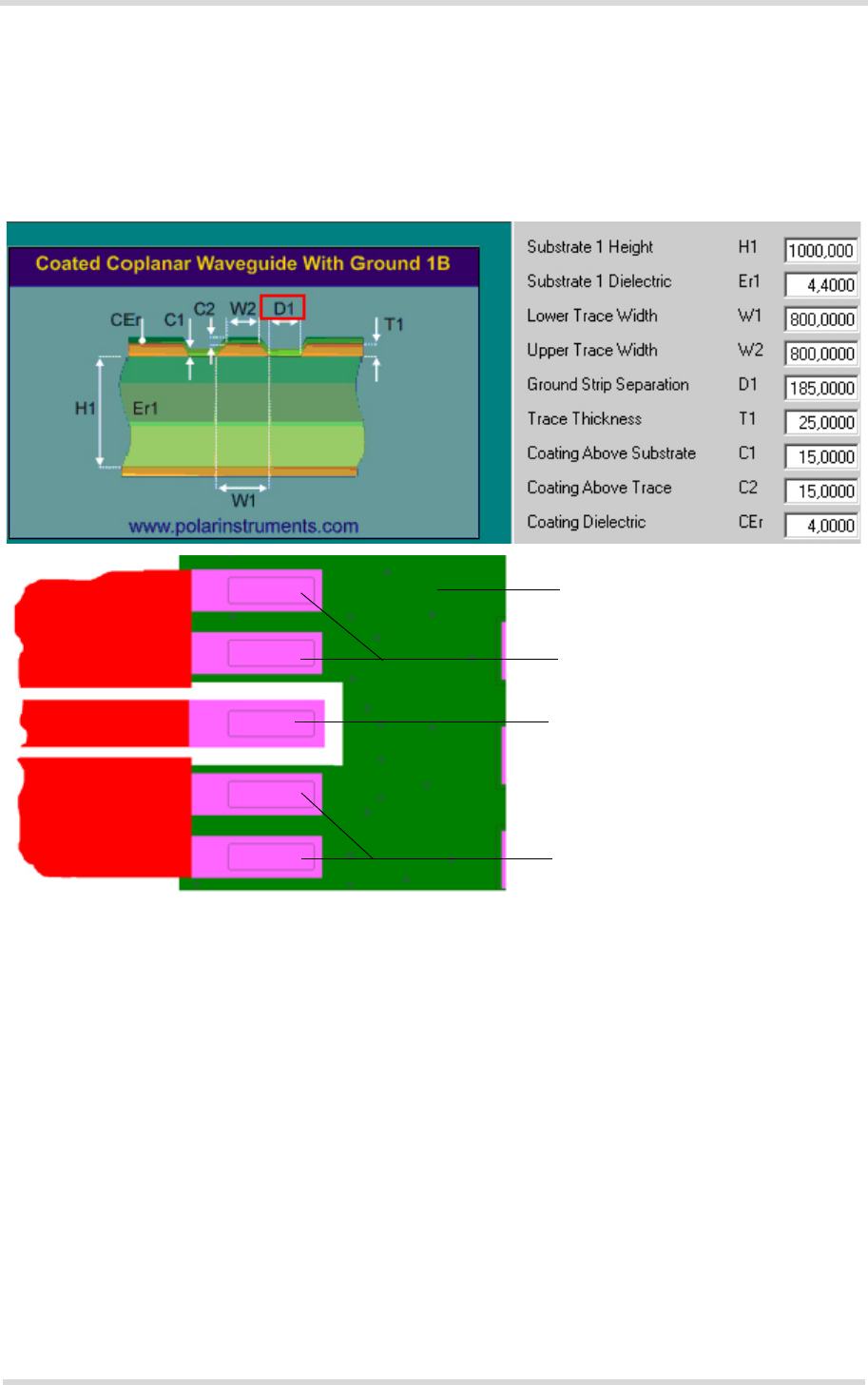

Figure 23: Micro-Stripline on 1.0mm Standard FR4 PCB - example 2............................ 46

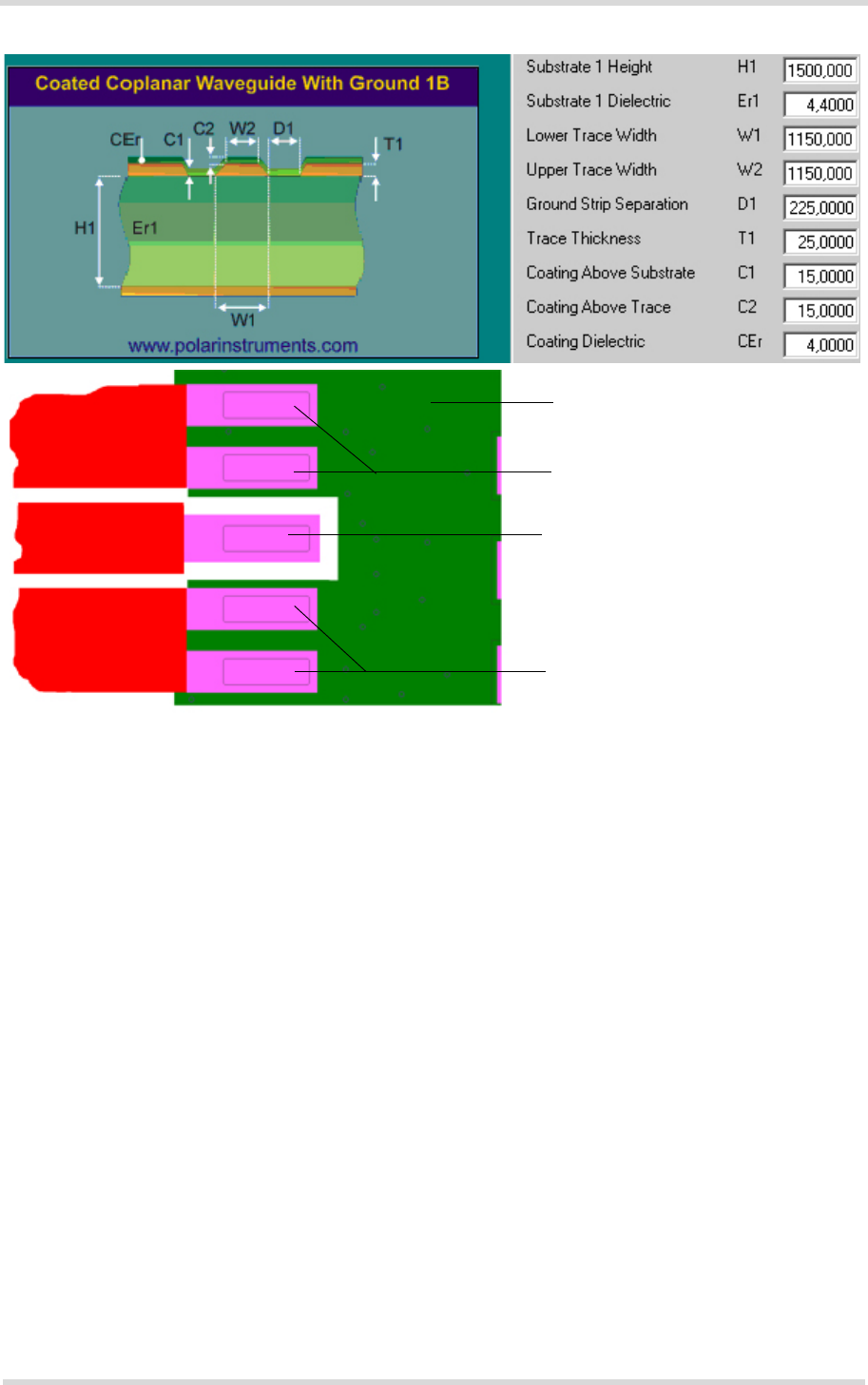

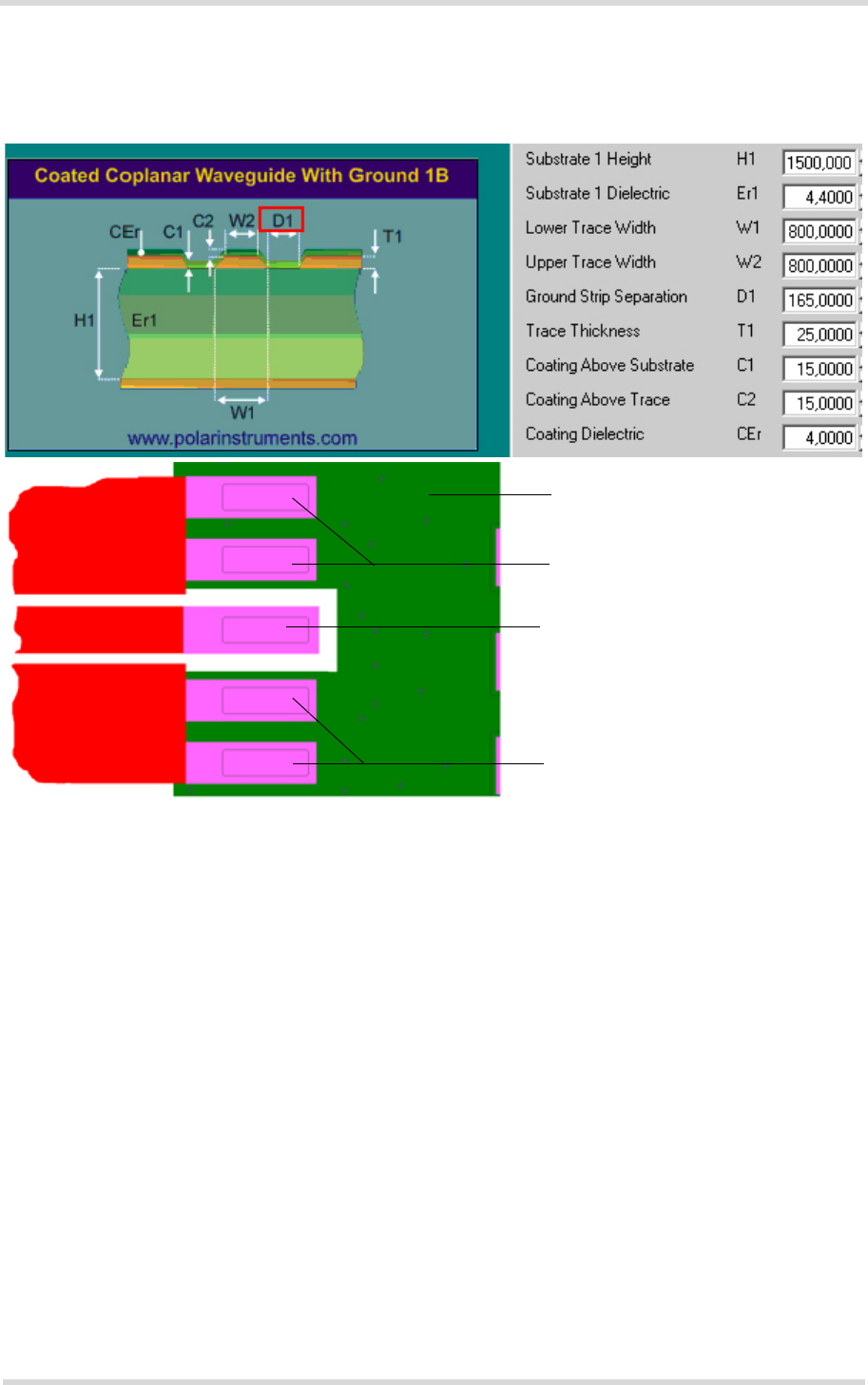

Figure 24: Micro-Stripline on 1.5mm Standard FR4 PCB - example 1............................ 47

Figure 25: Micro-Stripline on 1.5mm Standard FR4 PCB - example 2............................ 48

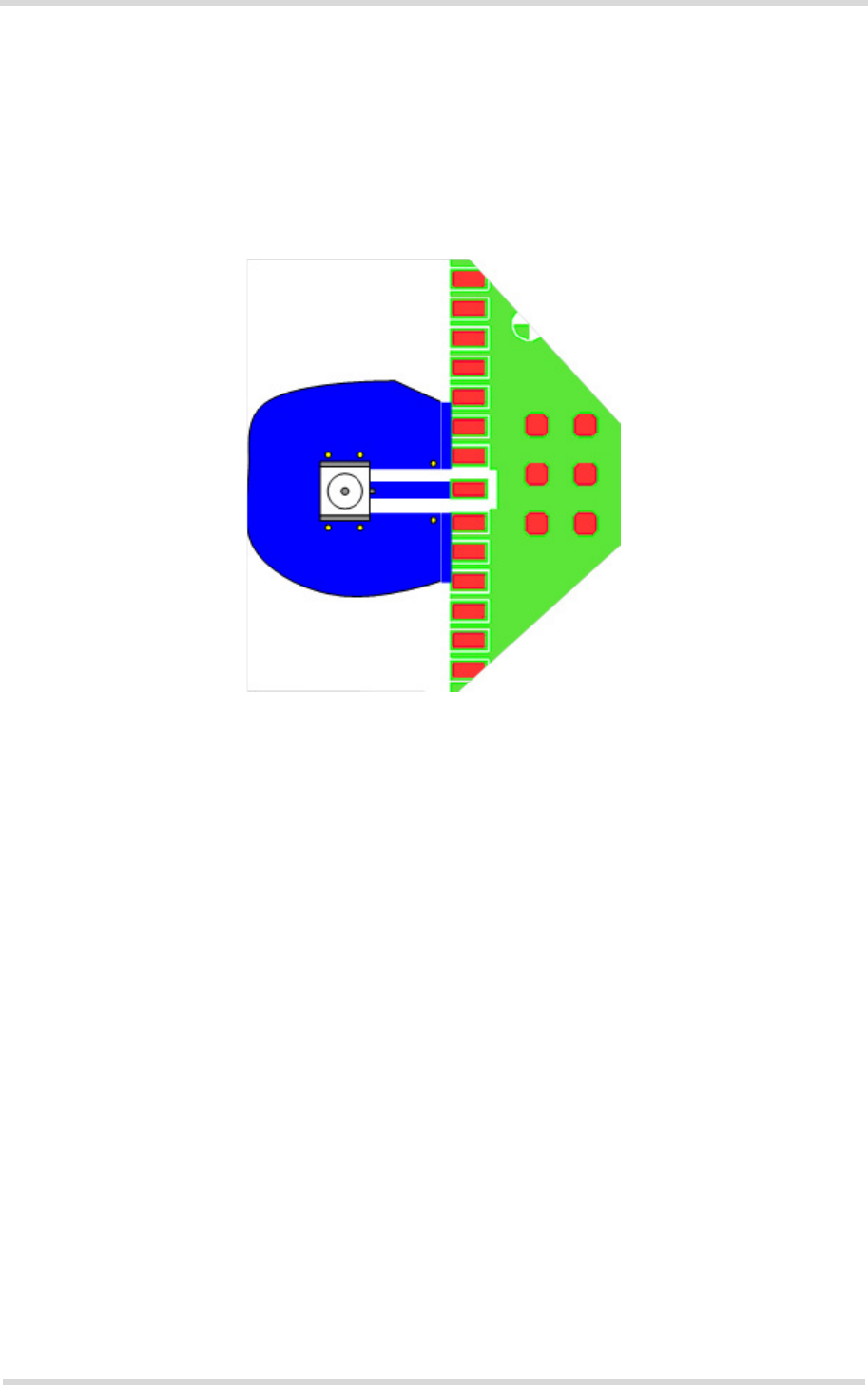

Figure 26: Routing to application‘s RF connector - top view........................................... 49

Figure 27: Schematic diagram of ELS61-AUS sample application ................................. 51

Figure 28: Sample level conversion circuit...................................................................... 52

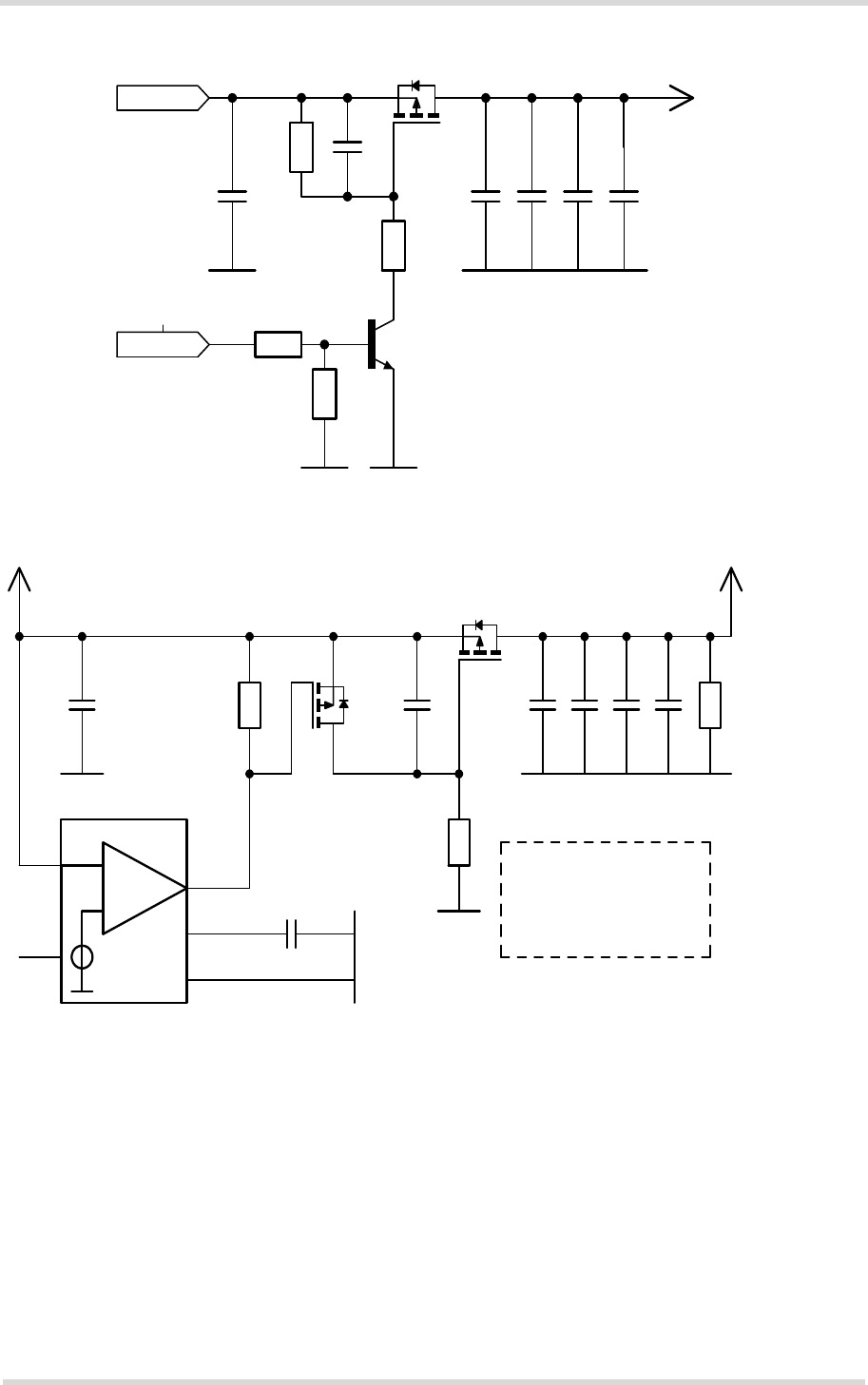

Figure 29: Sample circuit for applying power using an external µC ................................ 55

Figure 30: Sample circuit for applying power using an external voltage supervisory

circuit.............................................................................................................. 55

Figure 31: ON circuit options........................................................................................... 56

Figure 32: ON timing ....................................................................................................... 57

Figure 33: Emergency restart timing ............................................................................... 58

Figure 34: Switch off behavior......................................................................................... 60

Figure 35: Power saving and paging in WCDMA networks............................................. 63

Figure 36: Power saving and paging in LTE networks.................................................... 64

Figure 37: Wake-up via RTS0......................................................................................... 65

Figure 38: Position of reference points BATT+ and GND ............................................... 68

Figure 39: ESD protection for RF antenna interface ....................................................... 70

Figure 40: EMI circuits..................................................................................................... 71

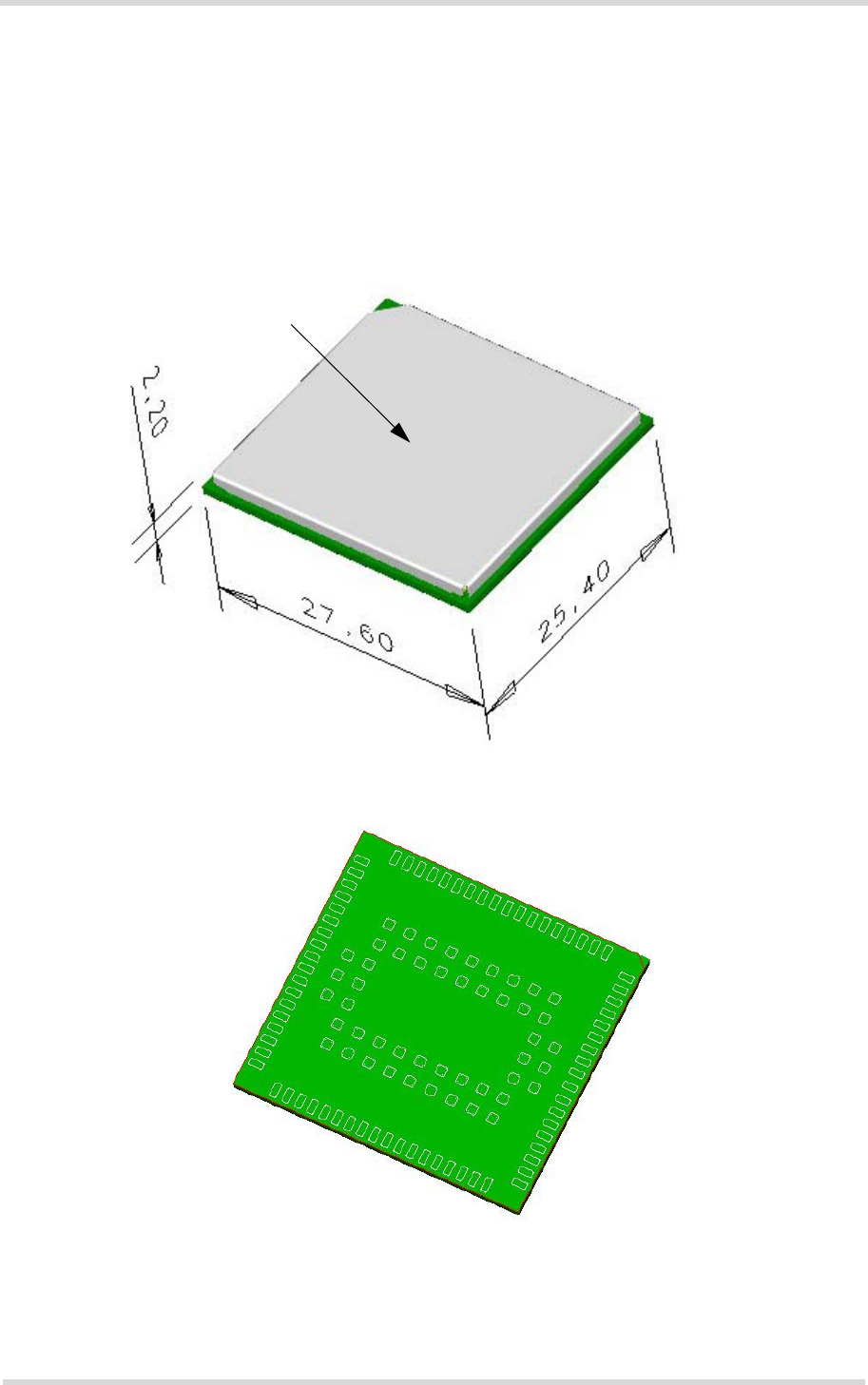

Figure 41: ELS61-AUS– top and bottom view................................................................. 74

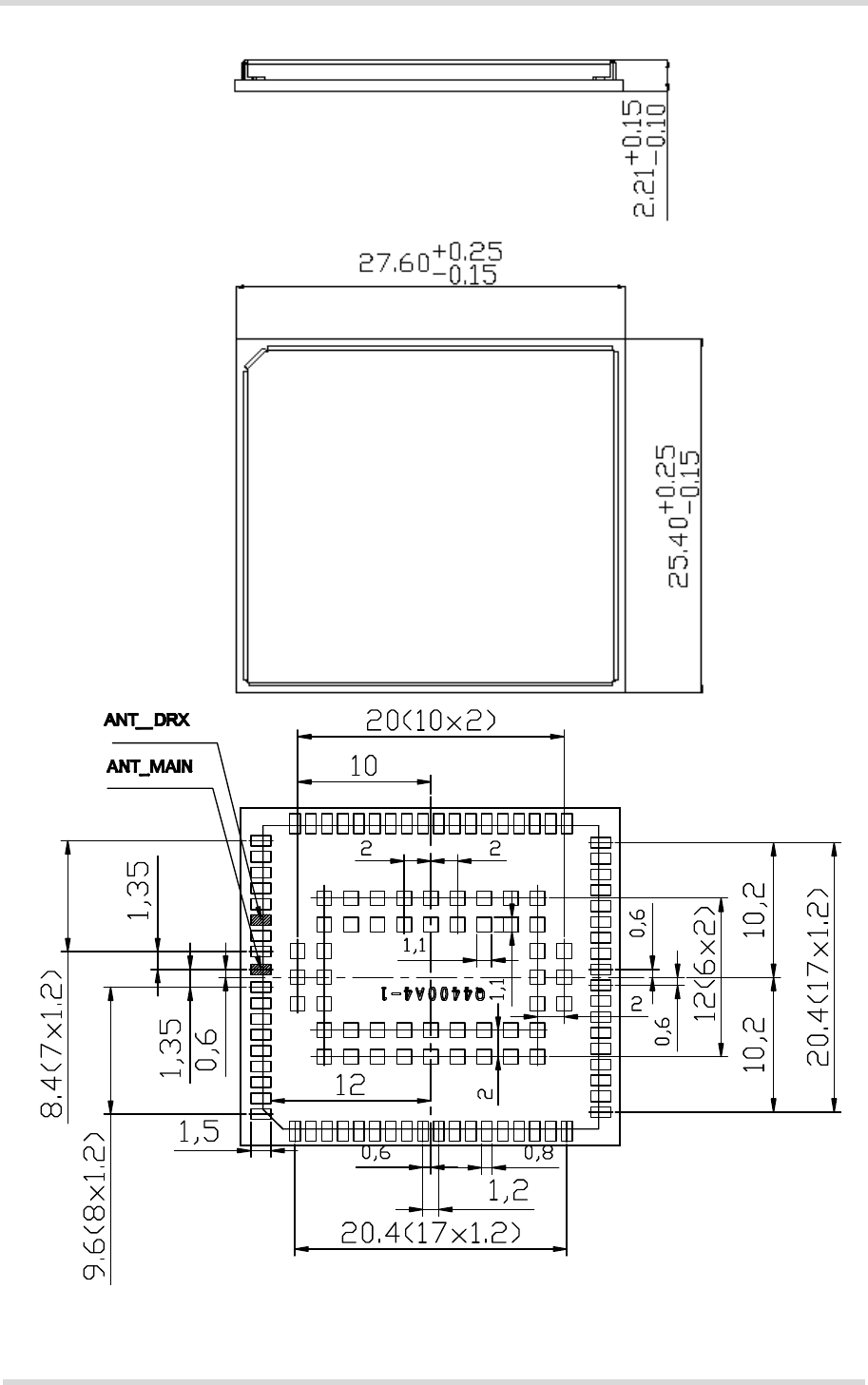

Figure 42: Dimensions of ELS61-AUS (all dimensions in mm) ....................................... 75

Figure 43: Land pattern (top view) .................................................................................. 76

Figure 44: Recommended design for 110µm micron thick stencil (top view).................. 77

Figure 45: Recommended design for 150µm micron thick stencil (top view).................. 77

Figure 46: Reflow Profile................................................................................................. 79

Figure 47: Carrier tape .................................................................................................... 83

Figure 48: Reel direction ................................................................................................. 83

Figure 49: Barcode label on tape reel ............................................................................. 84

Cinterion® ELS61-AUS Hardware Interface Description

Figures

114

ELS61-AUS_HID_v00.031 2016-06-03

Confidential / Preliminary

Page 8 of 102

Figure 50: Moisture barrier bag (MBB) with imprint......................................................... 85

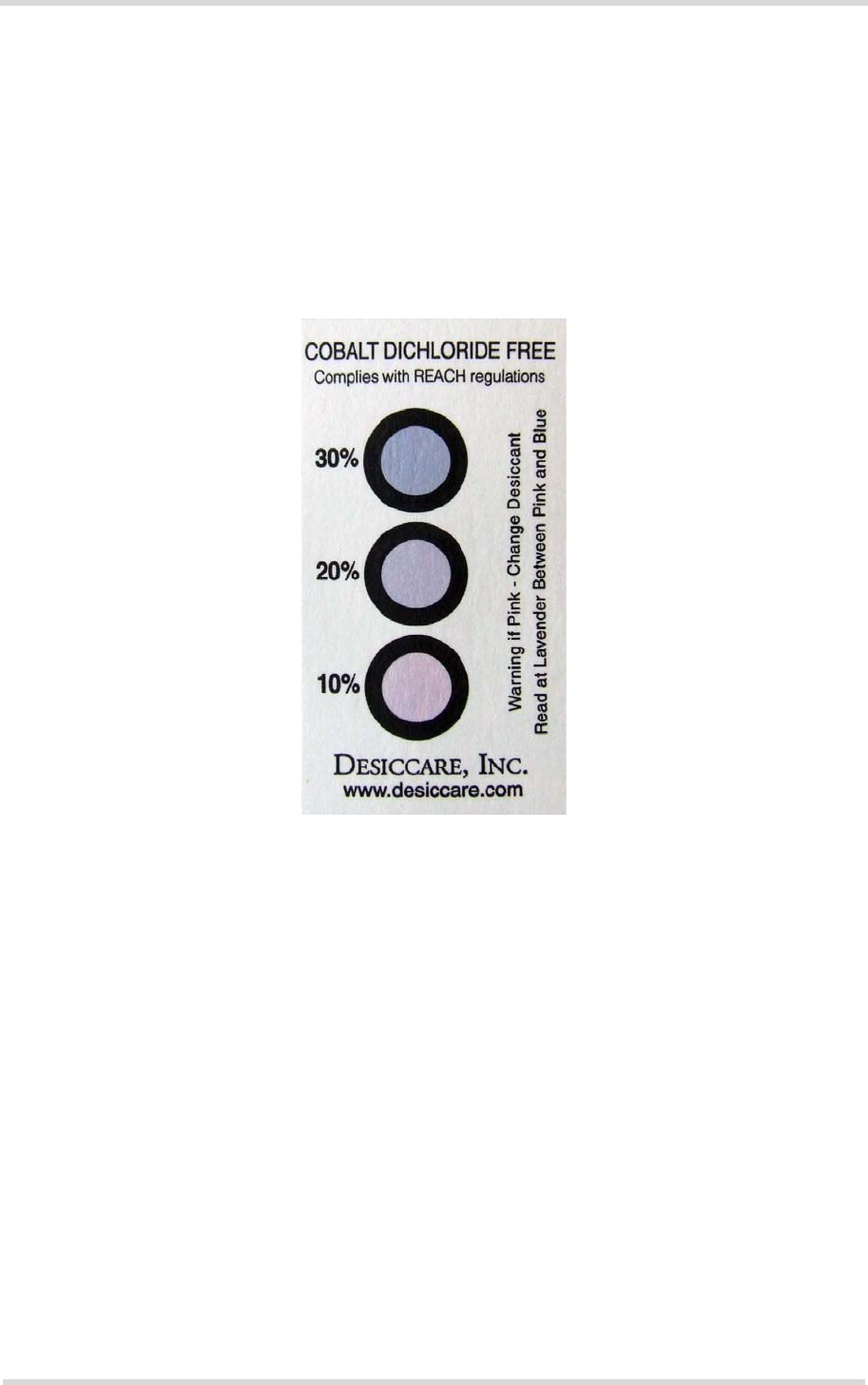

Figure 51: Moisture Sensitivity Label .............................................................................. 86

Figure 52: Humidity Indicator Card - HIC ........................................................................ 87

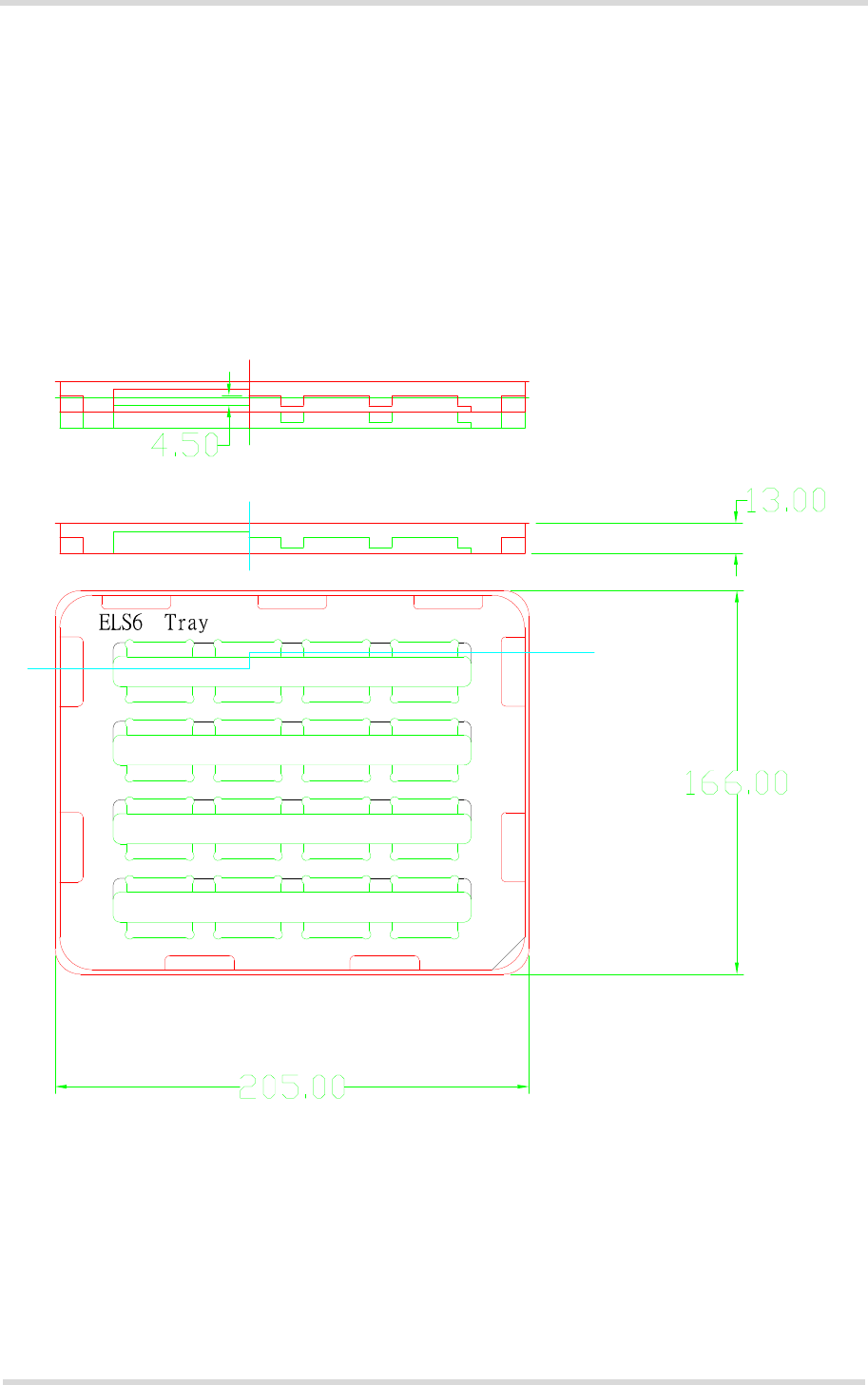

Figure 53: Tray dimensions............................................................................................. 88

Figure 54: Reference equipment for Type Approval ....................................................... 93

Cinterion® ELS61-AUS Hardware Interface Description

1 Introduction

14

ELS61-AUS_HID_v00.031 2016-06-03

Confidential / Preliminary

Page 9 of 102

1 Introduction

This document1 describes the hardware of the Cinterion® ELS61-AUS module. It helps you

quickly retrieve interface specifications, electrical and mechanical details and information on

the requirements to be considered for integrating further components.

1.1 Key Features at a Glance

1. The document is effective only if listed in the appropriate Release Notes as part of the technical docu-

mentation delivered with your Gemalto M2M product.

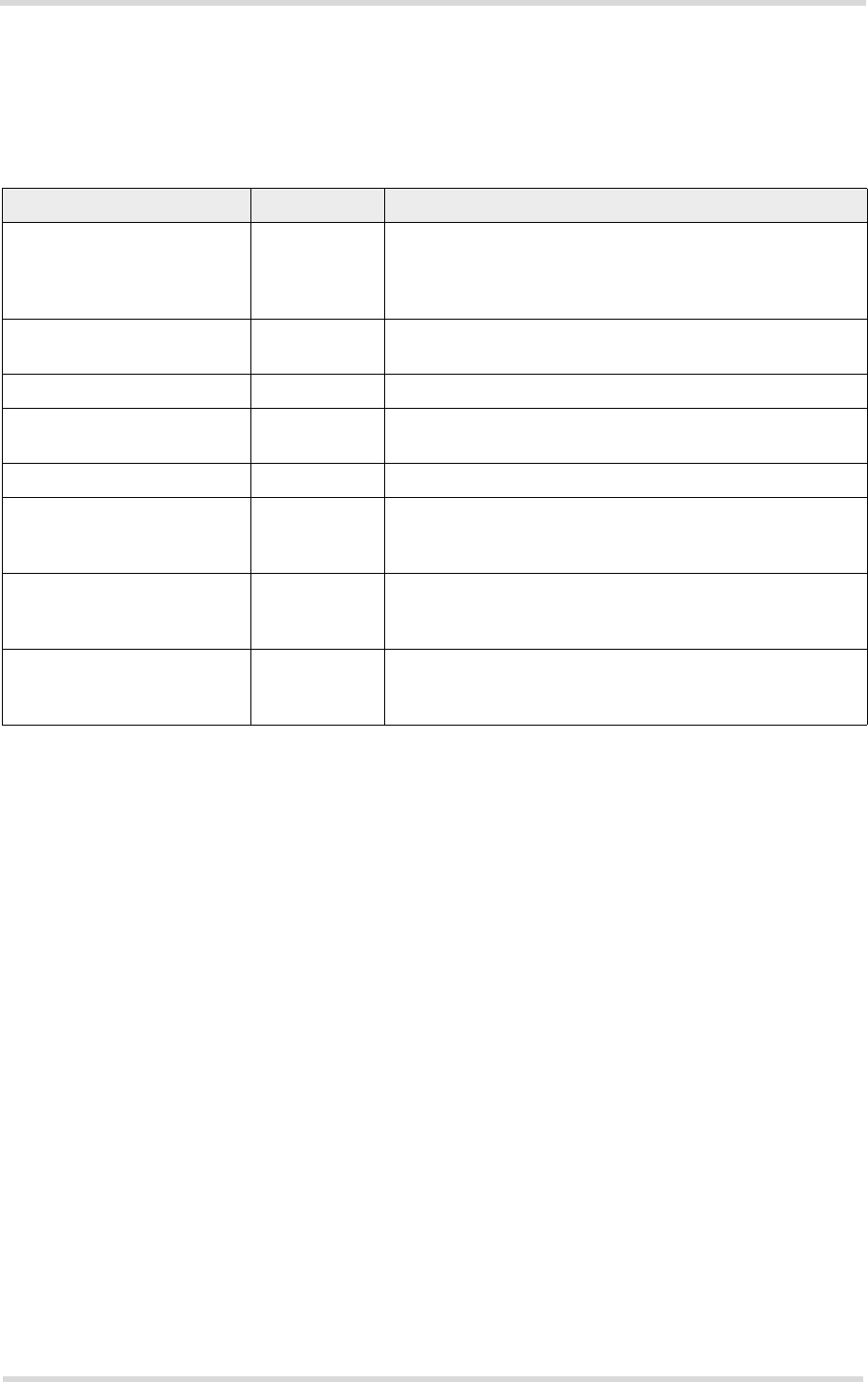

Feature Implementation

General

Frequency bands UMTS/HSPA+: Triple band, 850 (BdV) / 900 (BdVIII) / 2100 MHz (BdI)

LTE: Quad band, 700 (Bd28) / 900 (Bd8) / 850 (Bd5) / 1800MHz (Bd3)

Output power (according

to Release 99)

Class 3 (+24dBm +1/-3dB) for UMTS 2100,WCDMA FDD BdI

Class 3 (+24dBm +1/-3dB) for UMTS 900, WCDMA FDD BdV

Class 3 (+24dBm +1/-3dB) for UMTS 850, WCDMA FDD BdVIII

Output power (according

to Release 8)

Class 3 (+23dBm ±2dB) for LTE 700, LTE FDD Bd28

Class 3 (+23dBm ±2dB) for LTE 900, LTE FDD Bd8

Class 3 (+23dBm ±2dB) for LTE 850, LTE FDD Bd5

Class 3 (+23dBm ±2dB) for LTE 1800, LTE FDD Bd3

Power supply 3.0V to 4.5V

Operating temperature

(board temperature)

Normal operation: -30°C to +85°C

Extended operation: -40°C to +90°C

Physical Dimensions: 27.6mm x 25.4mm x 2.2mm

Weight: approx. 3.5g

RoHS All hardware components fully compliant with EU RoHS Directive

LTE features

3GPP Release 9 UE CAT 1 supported

DL 10.2Mbps, UL 5.2Mbps

HSPA features

3GPP Release 8 DL 7.2Mbps, UL 5.7Mbps

HSDPA Cat.8 / HSUPA Cat.6 data rates

Compressed mode (CM) supported according to 3GPP TS25.212

UMTS features

3GPP Release 4 PS data rate – 384 kbps DL / 384 kbps UL

CS data rate – 64 kbps DL / 64 kbps UL

Cinterion® ELS61-AUS Hardware Interface Description

1.1 Key Features at a Glance

14

ELS61-AUS_HID_v00.031 2016-06-03

Confidential / Preliminary

Page 10 of 102

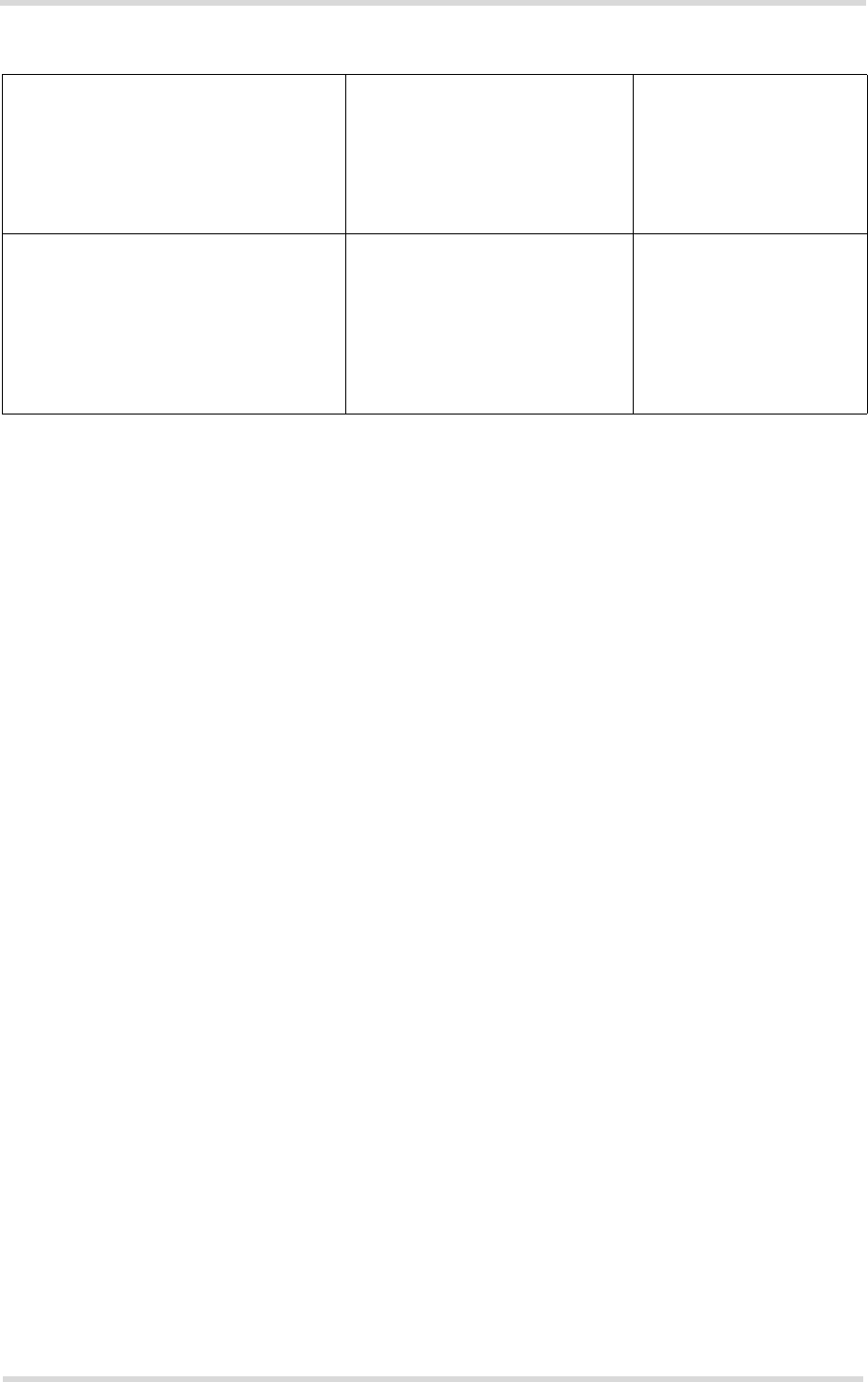

SMS Point-to-point MT and MO

Cell broadcast

Text and PDU mode

Storage: SIM card plus SMS locations in mobile equipment

Software

AT commands Hayes 3GPP TS 27.007, TS 27.005, Gemalto M2M

AT commands for RIL compatibility

Java™ Open Platform Java™ Open Platform with

• Java™ profile IMP-NG & CLDC 1.1 HI

• Secure data transmission via HTTPS/SSL

• Multi-threading programming and multi-application execution

Major benefits: seamless integration into Java applications, ease of pro-

gramming, no need for application microcontroller, extremely cost-efficient

hardware and software design – ideal platform for industrial applications.

The memory space available for Java programs is around 30MB in the flash

file system and around 18MB RAM. Application code and data share the

space in the flash file system and in RAM.

Microsoft™ compatibility RIL for Pocket PC and Smartphone

SIM Application Toolkit SAT letter classes b, c, e; with BIP

Firmware update Generic update from host application over ASC0 or USB modem.

Interfaces

Module interface Surface mount device with solderable connection pads (SMT application

interface). Land grid array (LGA) technology ensures high solder joint reli-

ability and allows the use of an optional module mounting socket.

For more information on how to integrate SMT modules see also [3]. This

application note comprises chapters on module mounting and application

layout issues as well as on additional SMT application development equip-

ment.

USB USB 2.0 High Speed (480Mbit/s) device interface, Full Speed (12Mbit/s)

compliant

2 serial interfaces ASC0 (shared with GPIO lines):

• 8-wire modem interface with status and control lines, unbalanced, asyn-

chronous

• Adjustable baud rates: 1,200bps to 921,600bps

• Autobauding: 1,200bps to 230,400bps

• Supports RTS0/CTS0 hardware flow control.

ASC1 (shared with GPIO lines):

• 4-wire, unbalanced asynchronous interface

• Adjustable baud rates: 1,200bps to 921,60bps

• Autobauding: 1,200bps to 230,400bps

• Supports RTS1/CTS1 hardware flow control

UICC interface Supported SIM/USIM cards: 3V, 1.8V

Feature Implementation

Cinterion® ELS61-AUS Hardware Interface Description

1.1 Key Features at a Glance

14

ELS61-AUS_HID_v00.031 2016-06-03

Confidential / Preliminary

Page 11 of 102

GPIO interface 22 GPIO lines comprising:

13 lines shared with ASC0, ASC1 and SPI lines, with network status indica-

tion, PWM functionality, fast shutdown and pulse counter

9 GPIO lines not shared

I2C interface Supports I2C serial interface

SPI interface Serial peripheral interface, shared with GPIO lines

Antenna interface pads 50Ω. UMTS/LTE main antenna, LTE Rx Diversity antenna

Power on/off, Reset

Power on/off Switch-on by hardware signal ON

Switch-off by AT command

Switch off by hardware signal FST_SHDN instead of AT command

Automatic switch-off in case of critical temperature or voltage conditions

Reset Orderly shutdown and reset by AT command

Emergency reset by hardware signal EMERG_RST

Special features

Real time clock Timer functions via AT commands

Evaluation kit

Evaluation module ELS61-AUS module soldered onto a dedicated PCB that can be connected

to an adapter in order to be mounted onto the DSB75.

DSB75 DSB75 Development Support Board designed to test and type approve

Gemalto M2M modules and provide a sample configuration for application

engineering. A special adapter is required to connect the ELS61-AUS eval-

uation module to the DSB75.

Feature Implementation

Cinterion® ELS61-AUS Hardware Interface Description

1.2 ELS61-AUS System Overview

14

ELS61-AUS_HID_v00.031 2016-06-03

Confidential / Preliminary

Page 12 of 102

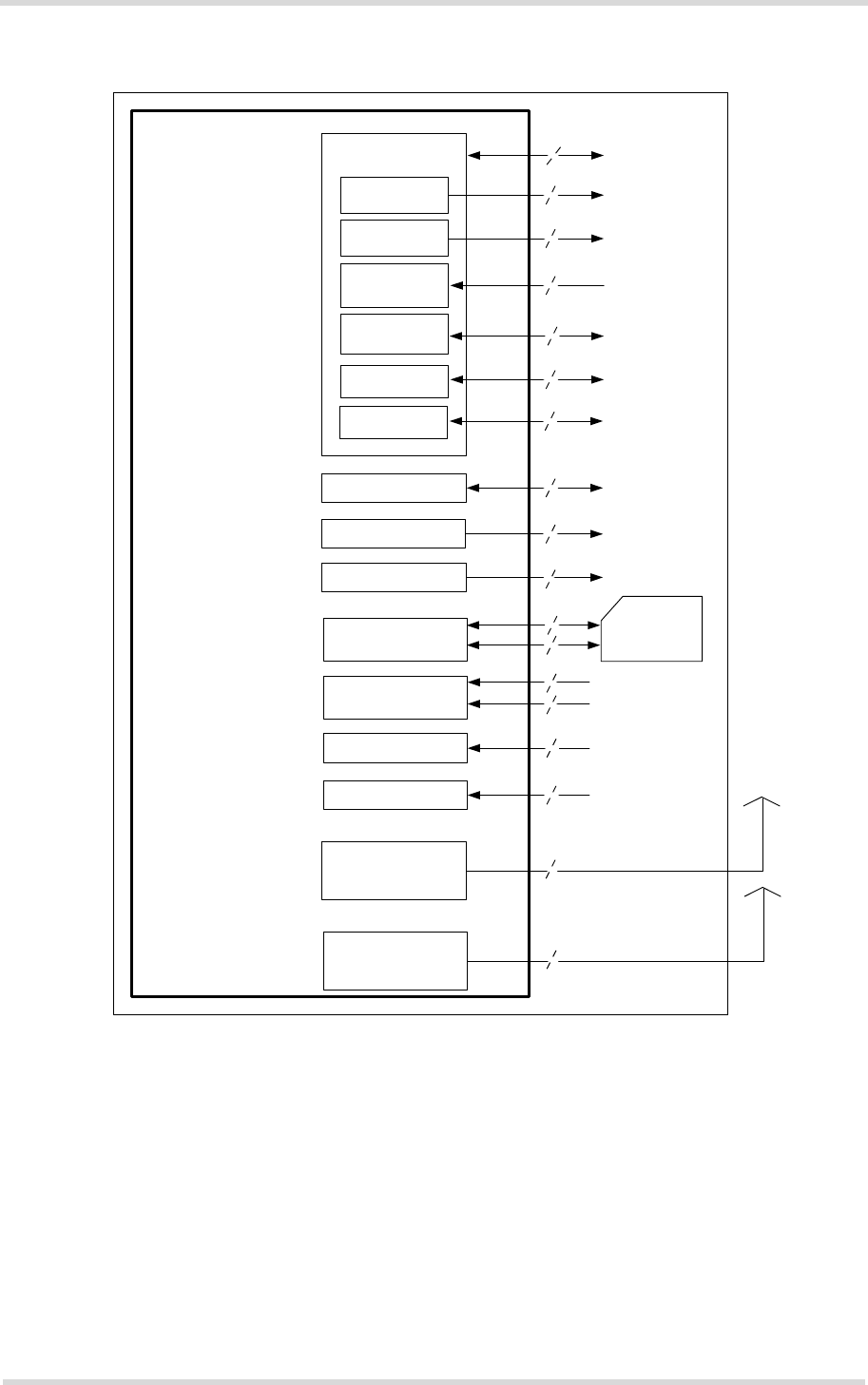

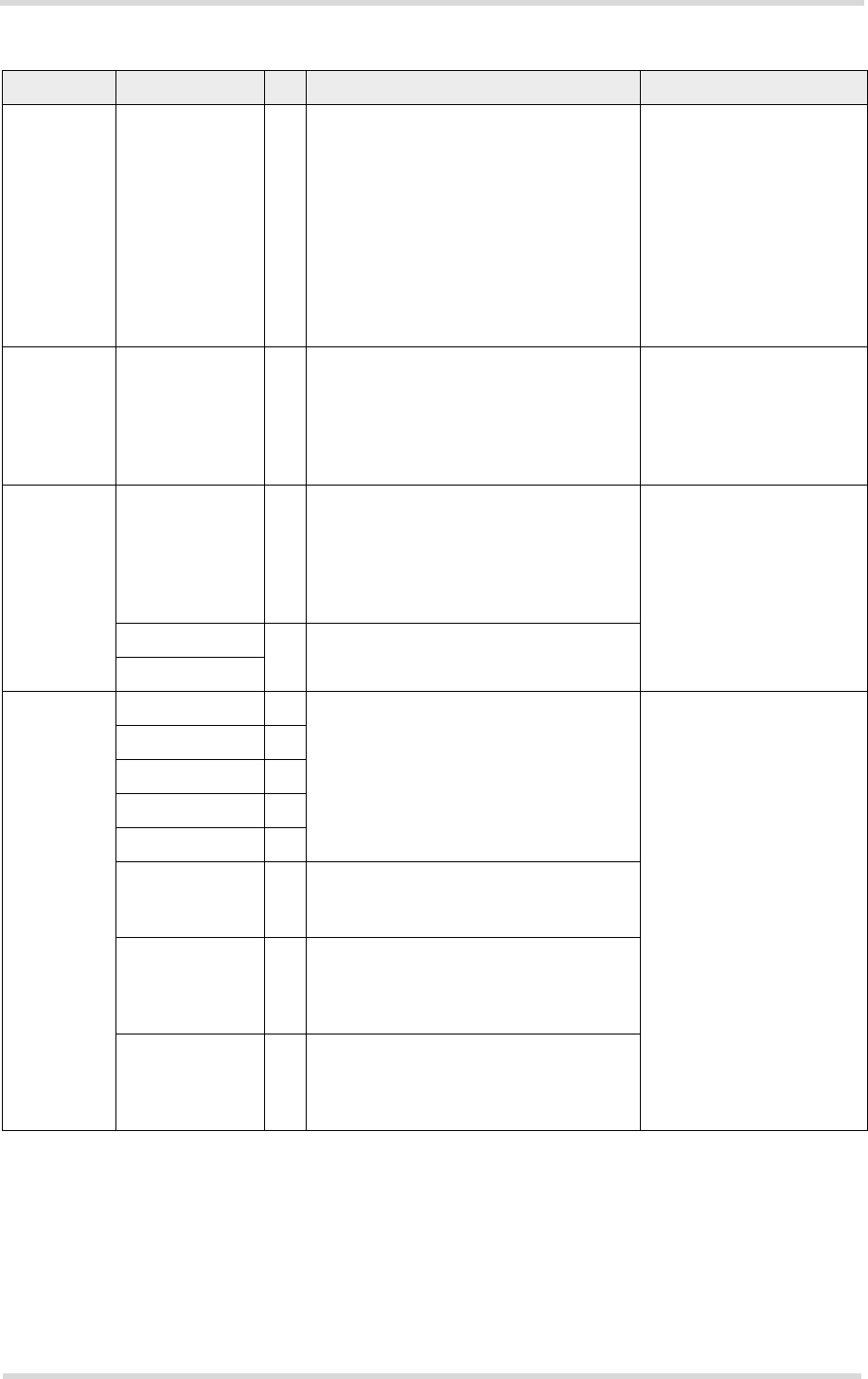

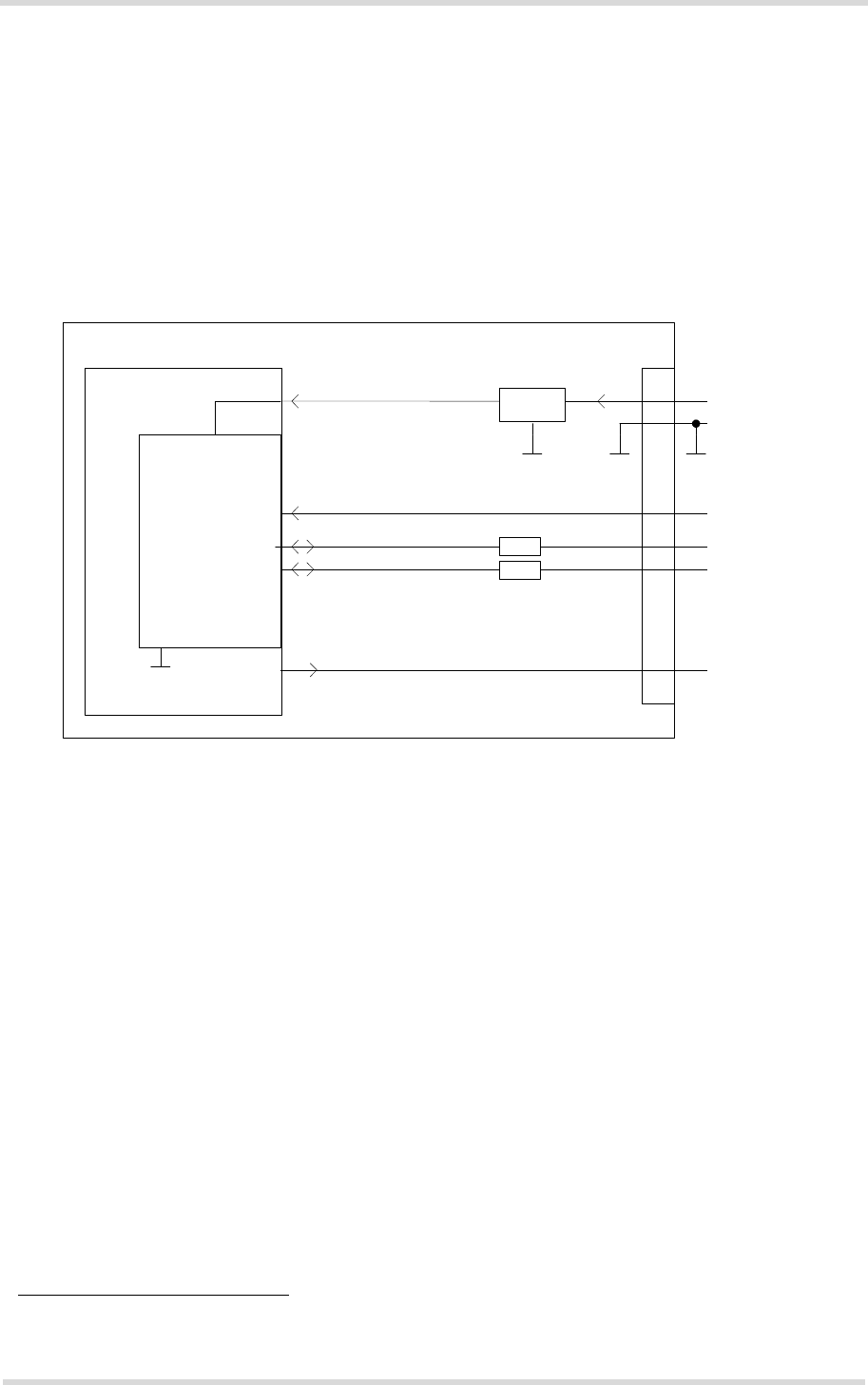

1.2 ELS61-AUS System Overview

Figure 1: ELS61-AUS system overview

GPIO

interface

I2C

USB

ASC0 lines

ASC1/SPI

CONTROL

RTC

POWER

Rx diversity

antenna

(LTE)

Module

SIM interface

(with SIM detection)

SIM card

Application

Power supply

Backup supply

Emergency reset

ON

Serial interface/

SPI interface

Serial modem

interface lines

I2C

GPIO

3

4

4

5

2

9

1

1

1

2

USB

Rx diversity

1

Status LED

1

DAC (PWM) PWM

2

Fast

shutdown Fast shutdown

1

1

COUNTER Pulse counter

1

ASC0 lines

Serial modem

interface lines/

SPI interface

4

Main antenna

(UMTS/LTE)

Main antenna

1

Cinterion® ELS61-AUS Hardware Interface Description

1.3 Circuit Concept

14

ELS61-AUS_HID_v00.031 2016-06-03

Confidential / Preliminary

Page 13 of 102

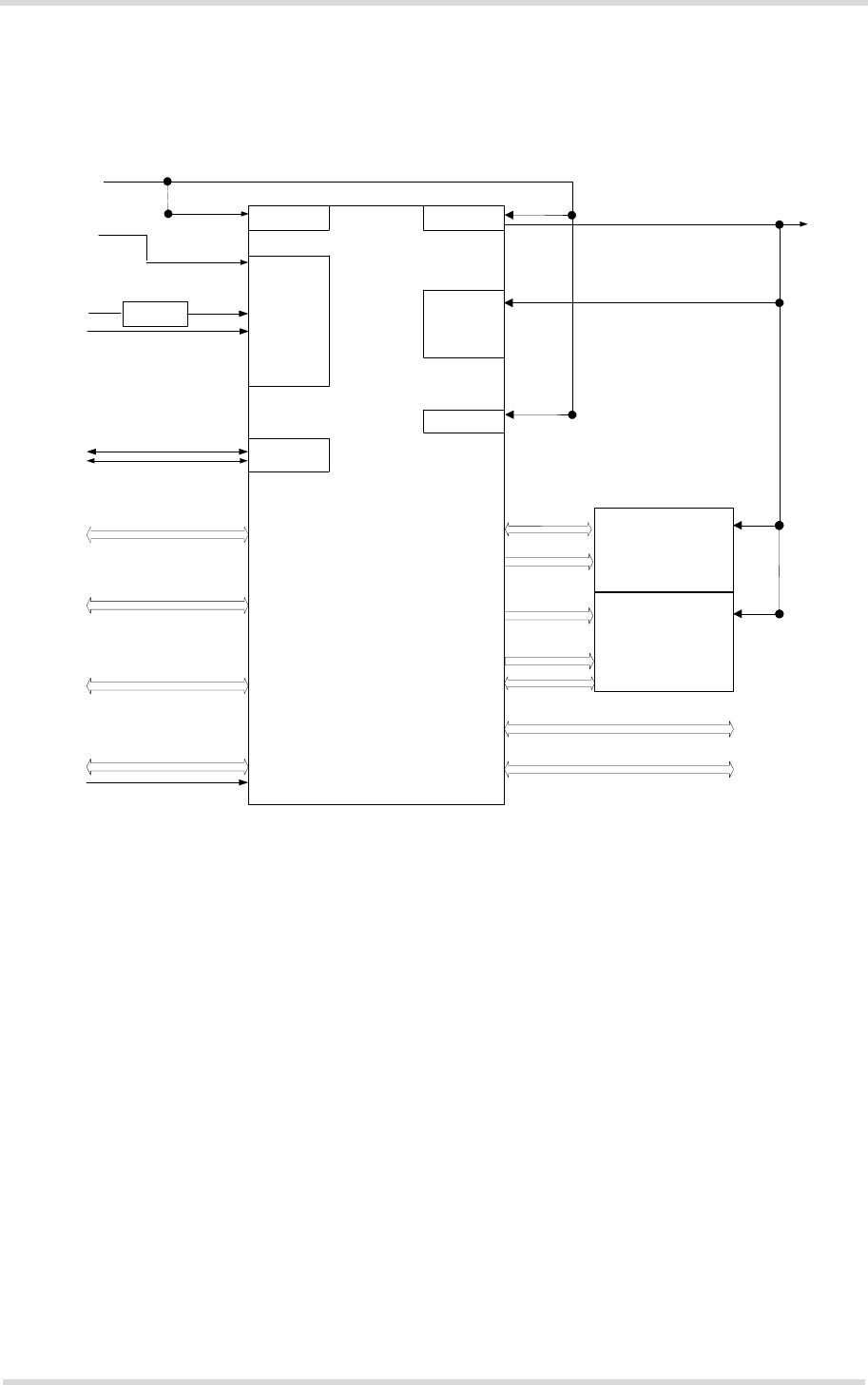

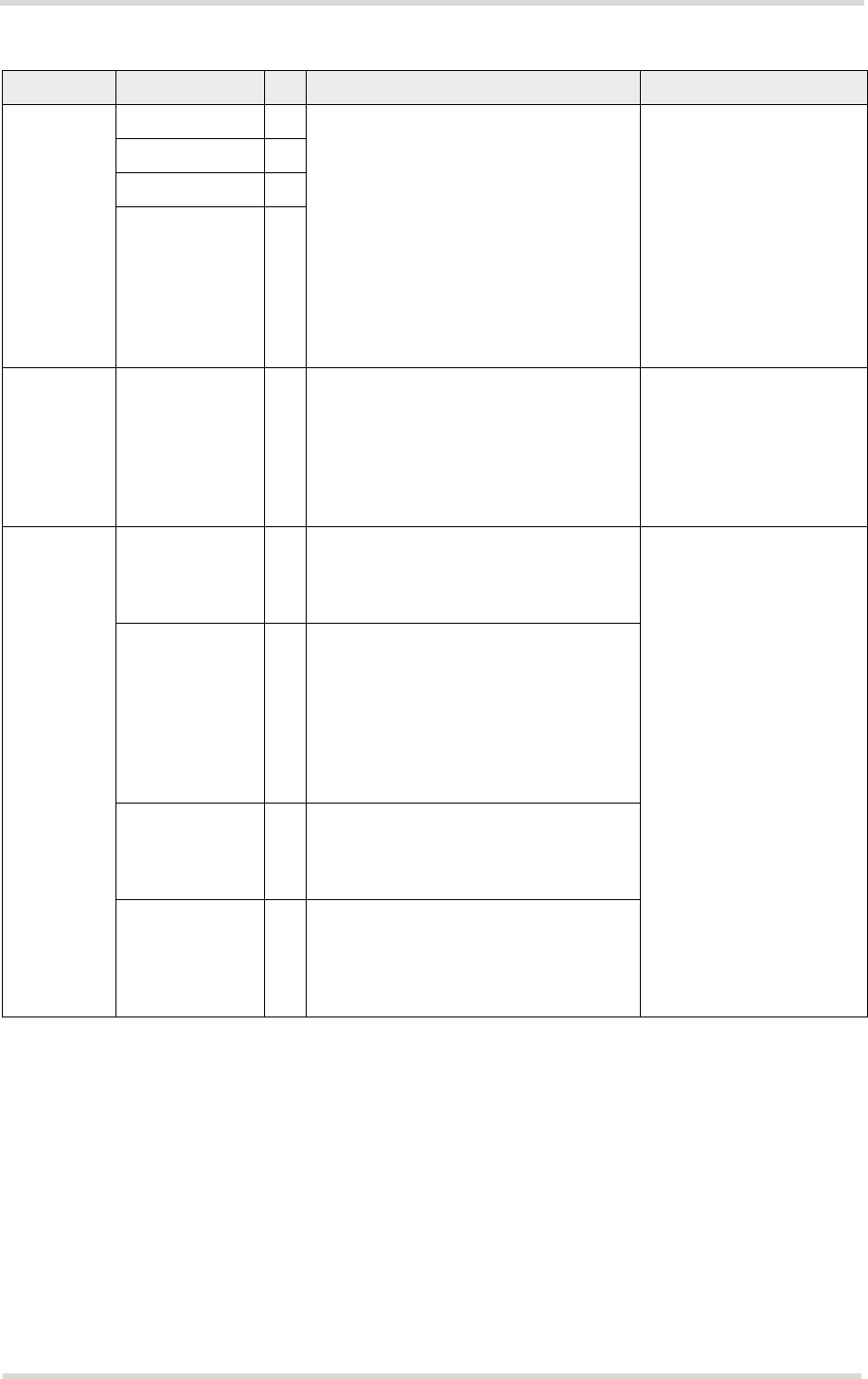

1.3 Circuit Concept

Figure 2 and Figure 3 show block diagrams of the ELS61-AUS module and illustrate the major

functional components:

Figure 2: ELS61-AUS block diagram

SD1 SD2

SD2

LDOs

PMU

LDOs

ON

Reset_BB

SD3

I2CDAT

I2CCLK

USB

GPIO

SIM

CCIN

LPDDR2

SDRAM

FLASH

VDD

VDD

ADQ0 ~ ADQ15

DDR_CA_0~DDR_CA_9

DDR_DQ_0~DDR_DQ_15

Control

Control

CCIN

SIM

GPIO

ASC0

USB

I2C

ON circuit

ON

EMERG_RST

BATT+BB

BATT+RF

RX/TX

RF control

V180

Baseband

controller

and

Power

management

Cinterion® ELS61-AUS Hardware Interface Description

1.3 Circuit Concept

14

ELS61-AUS_HID_v00.031 2016-06-03

Confidential / Preliminary

Page 14 of 102

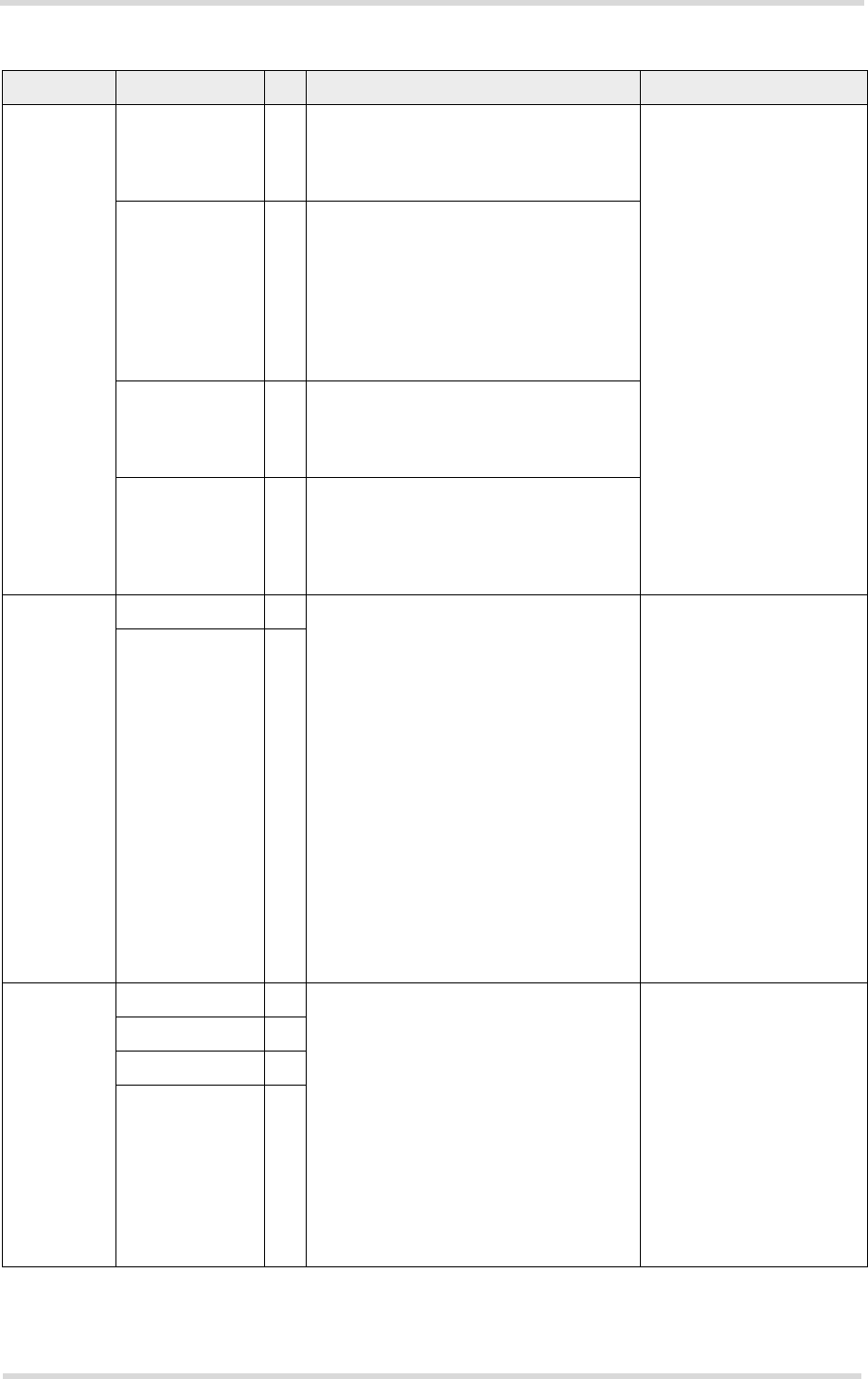

Figure 3: ELS61-AUS RF section block diagram

LTE / UMTS

RF transceiver

SKY77622

SKY13525

SKY13525

Band3

SAW

Filter

Band8

SAW

Filter

Band5

SAW

Filter

Band28

SAW

Filter

Diversity Antenna

Band1

Duplexer

Band8

Duplexer

Band5

Duplexer

Antenna

Coupler

B1_OUT

B8_OUT

B5_OUT

4G_HB_IN

2G/3G_HB_IN

4G_LB_IN

2G/3G_LB_IN

TQ_H

TP_H

TQ_L

TP_L

RX_H3

RX_H3X

RX_L2

RX_L2X

RX_L1

RX_L1X

RD_M2

RD_L4

RD_L3

RD_L2

TRX1

TRX4

TRX6

TRX1

TRX6

TRX4

TRX5

PA DCDC

SKY87000

BATT+RF

FBR_RF2 MAIN_FWD

MIPI

26MHz

RX/TX

BATT+BB

V180

RF control

RD_H3X

RD_L4X

RD_L3X

RD_L2X

Band3

Duplexer

RX_M2

RX_M2X TRX5

B3_OUT

Band28A

Duplexer

Band28B

Duplexer

RX_L4

RX_L4X

RX_L3

RX_L3X

TRX2

TRX3

B13_OUT

B17_OUT

Cinterion® ELS61-AUS Hardware Interface Description

2 Interface Characteristics

52

ELS61-AUS_HID_v00.031 2016-06-03

Confidential / Preliminary

Page 15 of 102

2 Interface Characteristics

ELS61-AUS is equipped with an SMT application interface that connects to the external appli-

cation. The SMT application interface incorporates the various application interfaces as well as

the RF antenna interface.

2.1 Application Interface

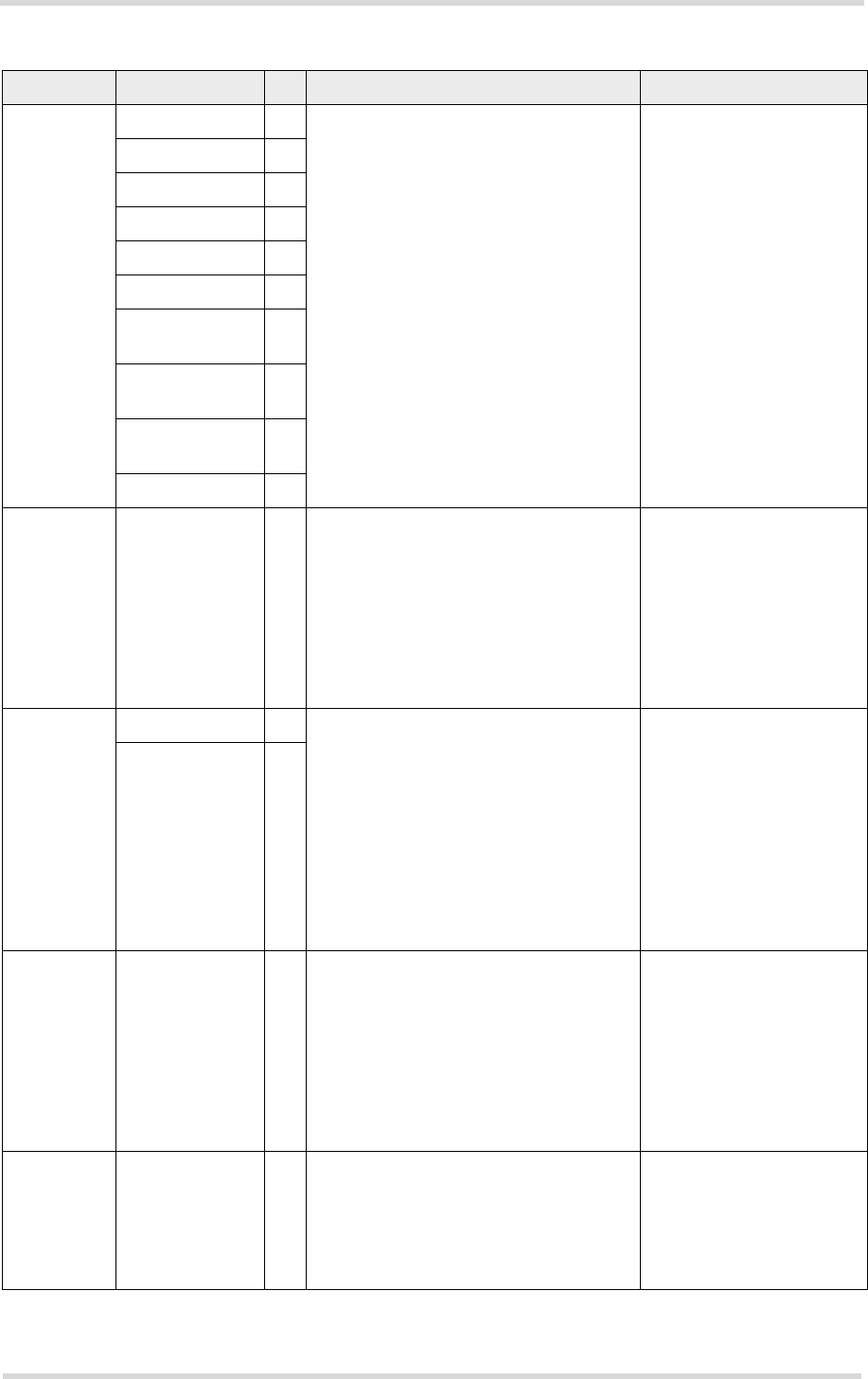

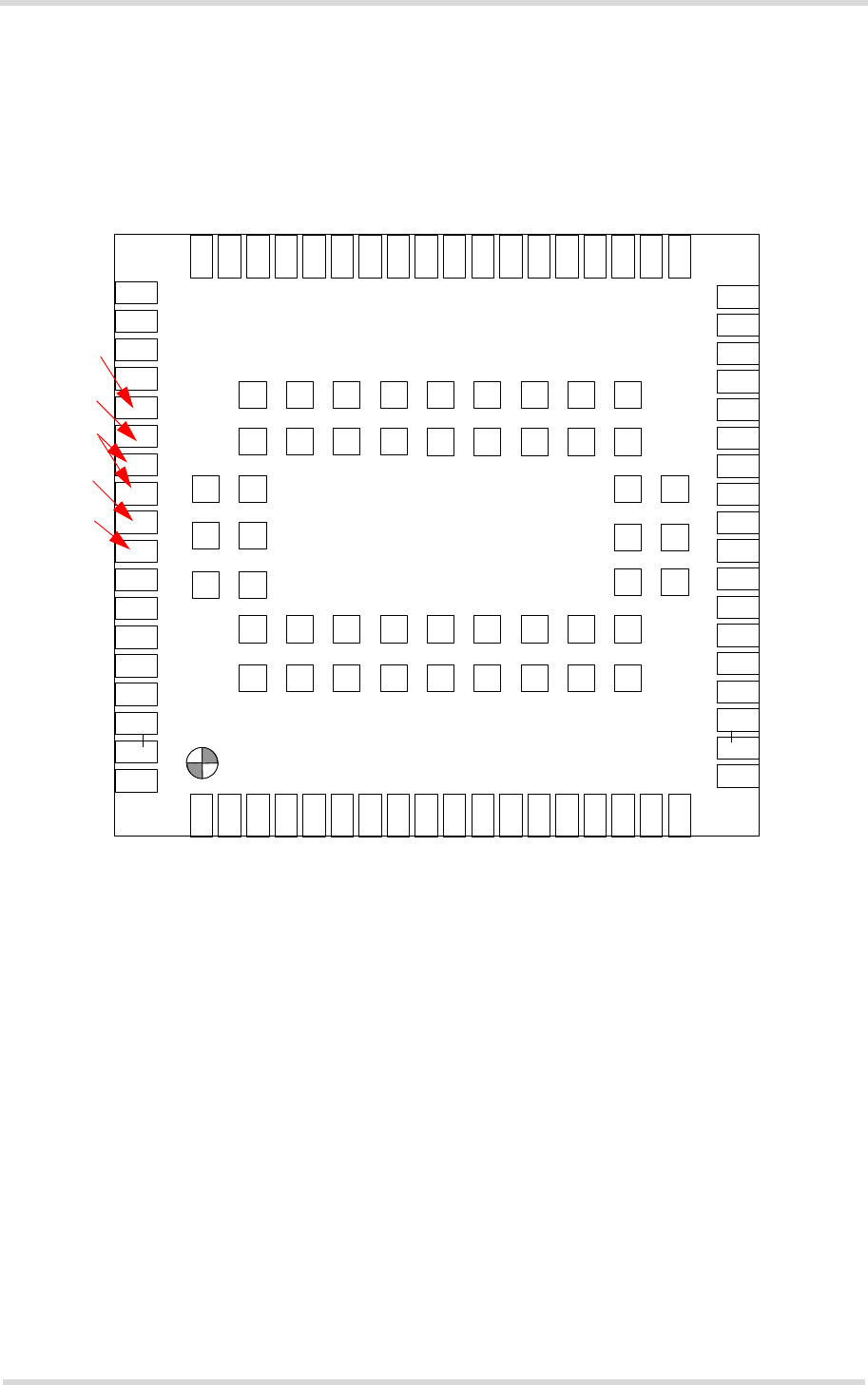

2.1.1 Pad Assignment

The SMT application interface on the ELS61-AUS provides connecting pads to integrate the

module into external applications. Figure 4 shows the connecting pads’ numbering plan, thE

following Table 1 lists the pads’ assignments.

Figure 4: Numbering plan for connecting pads (bottom view)

Supply pads: BATT+

Control pads

GND pads

ASC0 pads Combined GPIO/ASC1/SPI pads

SIM pads

I2C pads

Supply pads: Other

Combined GPIO/Control pads

(LED, PWM, COUNTER, FST_SHDN)

USB pads

GPIO pads

218217216215214213212211210209208

207

206

205204203202201

33

32

31

30

29

28

27

26

25

24

23

22

21

20

53

54

55

56

57

58

59

60

61

62

63

64

65

66

223224225226227228229230231232233234235236237238239240

67 68 69 70 71 72 73

74 75 76 77 78 79 80

93 94 95 96 97 98 99

100 101 102 103 104 105 106

85 86

89 90

81 82

87 88

91 92

83 84

243

244

241

242

222

221

220

219

252

245

250

251

249

248

247

246

RF antenna pads

Do not use

Not connected

Reserved

Combined GPIO/

ASC0/SPI pads

ADC pad

Cinterion® ELS61-AUS Hardware Interface Description

2.1 Application Interface

52

ELS61-AUS_HID_v00.031 2016-06-03

Confidential / Preliminary

Page 16 of 102

Signal pads that are not used should not be connected to an external application.

Please note that the reference voltages listed in Table 2 are the values measured directly on

the ELS61-AUS module. They do not apply to the accessories connected.

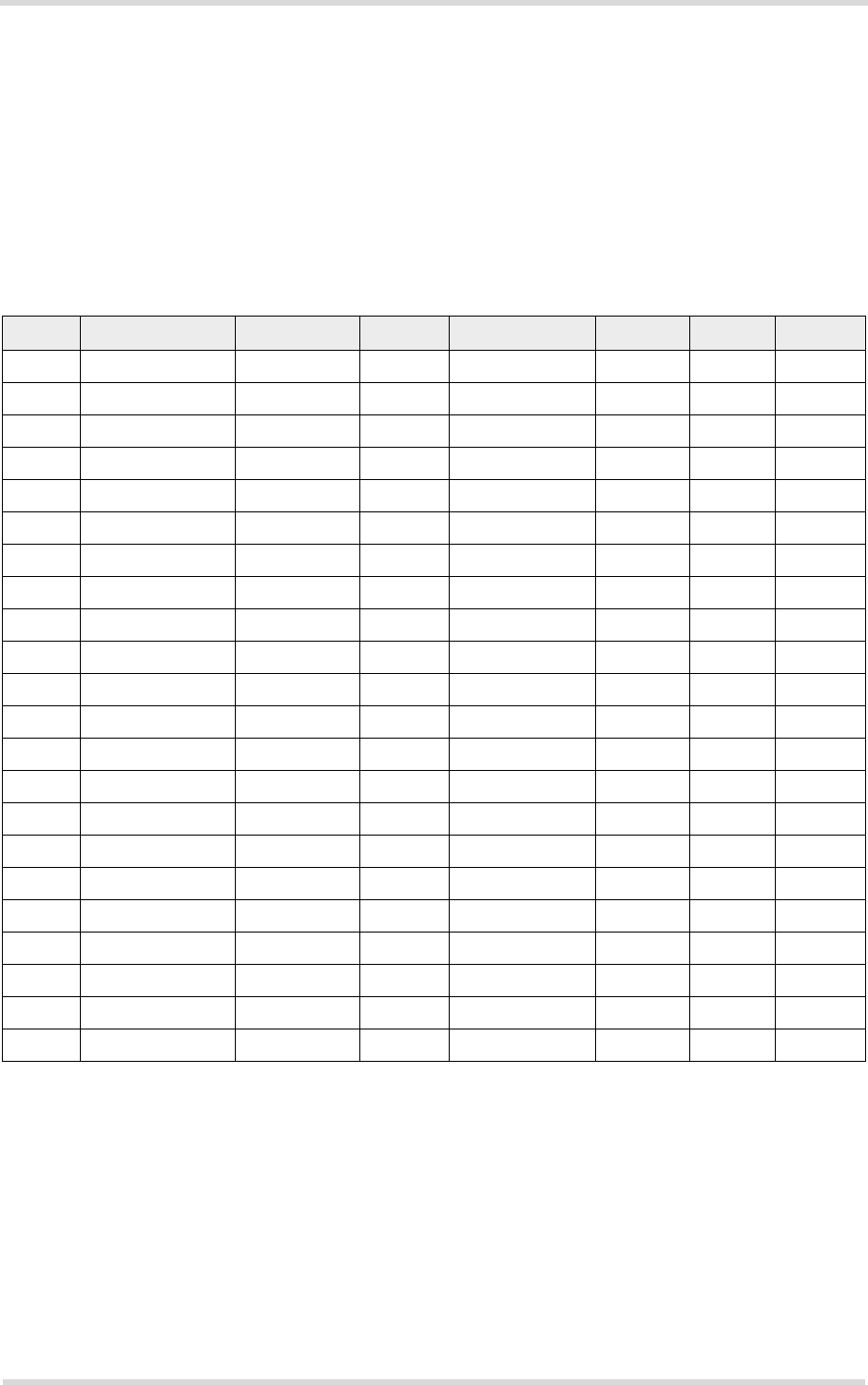

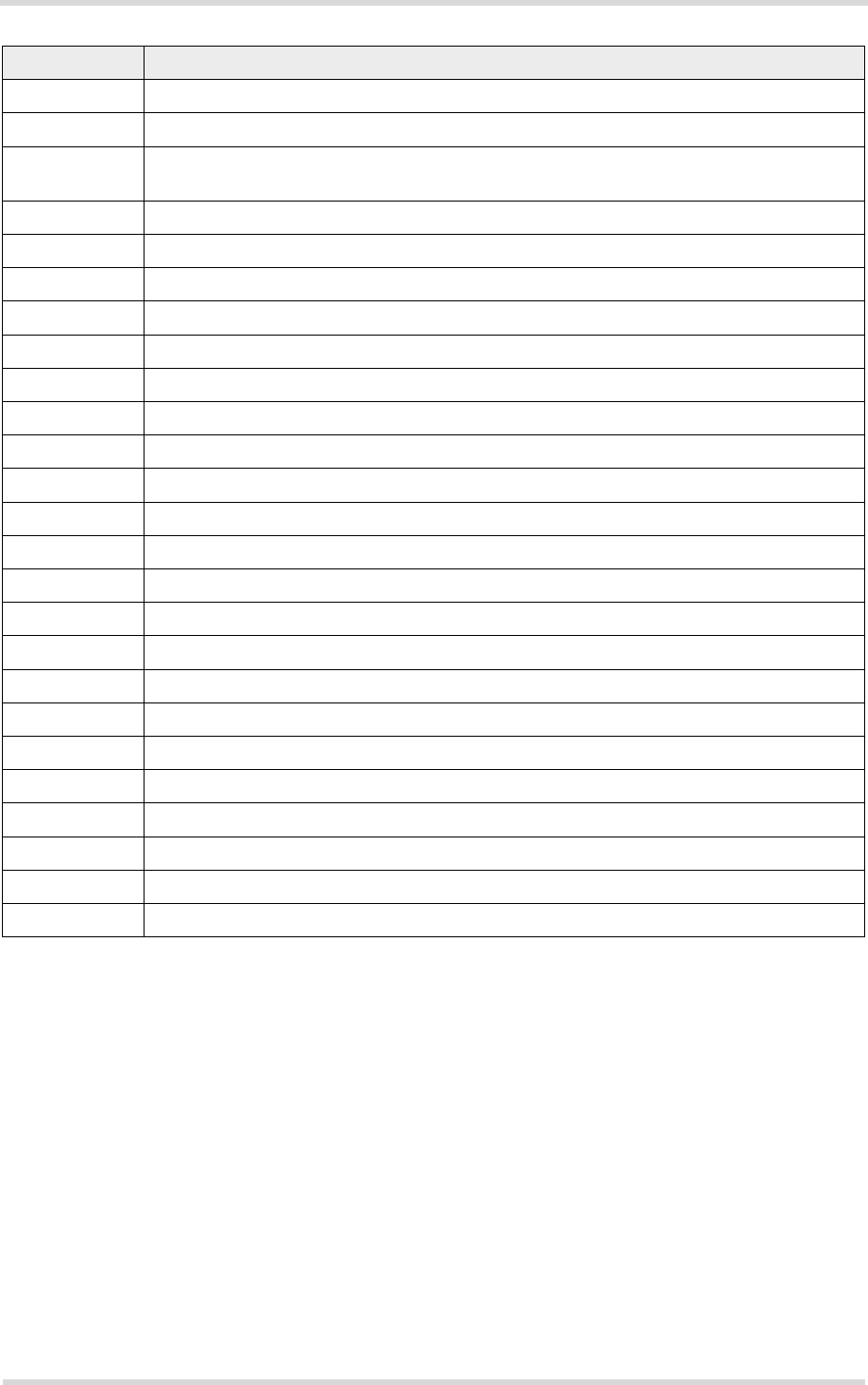

Table 1: Pad assignments

Pad no. Signal name Pad no. Signal name Pad no. Signal name

201 Not connected 24 GPIO22 235 USB_DN

202 Not connected 25 GPIO21 236 Not connected

203 GND 26 GPIO23 237 Not connected

204 BATT+BB 27 I2CDAT 238 GND

205 GND 28 I2CCLK 239 GPIO5/LED

206 ADC1 29 GPIO17/TXD1/MISO 240 GPIO6/PWM2

207 ON 30 GPIO16/RXD1/MOSI 241 GPIO7/PWM1

208 GND 31 GPIO18/RTS1 242 GPIO8/COUNTER

209 V180 32 GPIO19/CTS1/SPI_CS 53 BATT+RF

210 RXD0 33 EMERG_RST 54 GND

211 CTS0 221 GPIO12 55 GND

212 TXD0 222 GPIO11 56 ANT_DRX

213 GPIO24/RING0 223 GND 57 GND

214 RTS0 224 Not connected 58 GND

215 VDDLP 225 GND 59 ANT_MAIN

216 CCRST 226 Not connected 60 GND

217 CCIN 227 GND 61 GND

218 CCIO 228 Not connected 62 GND

219 GPIO14 229 GPIO4/FST_SHDN 63 GND

220 GPIO13 230 GPIO3/DSR0/SPI_CLK 64 GND

20 CCVCC 231 GPIO2/DCD0 65 Not connected

21 CCCLK 232 GPIO1/DTR0 66 Not connected

22 VCORE 233 VUSB 243 Not connected

23 GPIO20 234 USB_DP 244 GPIO15

Centrally located pads

67 Not connected 83 GND 99 GND

68 Not connected 84 GND 100 GND

69 Not connected 85 GND 101 GND

70 Not connected 86 GND 102 GND

71 Not connected 87 Not connected 103 GND

72 Not connected 88 GND 104 Not connected

73 Not connected 89 GND 105 Not connected

74 Do not use 90 GND 106 Not connected

75 Do not use 91 Not connected 245 GND

76 Not connected 92 GND 246 Not connected

77 Not connected 93 GND 247 Not connected

78 Not connected 94 GND 248 Not connected

79 Not connected 95 GND 249 Not connected

80 Not connected 96 GND 250 GND

81 GND 97 GND 251 GND

82 GND 98 GND 252 GND

Cinterion® ELS61-AUS Hardware Interface Description

2.1 Application Interface

52

ELS61-AUS_HID_v00.031 2016-06-03

Confidential / Preliminary

Page 17 of 102

2.1.2 Signal Properties

Table 2: Signal properties

Function Signal name IO Signal form and level Comment

Power

supply

BATT+BB

BATT+RF

IWCDMA activated:

VImax = 4.5V

VInorm = 4.0V

VImin = 3.0V during Transmit active.

Imax = 700mA during Tx

LTE activated:

VImax = 4.5V

VInorm = 4.0V

VImin = 3.0V during Transmit active.

Lines of BATT+ and GND

must be connected in

parallel for supply pur-

poses because higher

peak currents may occur.

Minimum voltage must

not fall below 3.0V includ-

ing drop, ripple, spikes

and not rise above 4.5V.

BATT+BB and BATT+RF

require an ultra low ESR

capacitor:

BATT+BB --> 50µF

BATT+RF --> 150µF

If using Multilayer

Ceramic Chip Capacitors

(MLCC) please take DC-

bias into account.

Power

supply

GND Ground Application Ground

External

supply

voltage

V180 O Normal operation:

VOnorm = 1.80V ±3%

IOmax = -10mA

SLEEP mode Operation:

VOSleep = 1.80V ±5%

IOmax = -10mA

CLmax = 2µF

V180 should be used to

supply level shifters at

the interfaces or to supply

external application cir-

cuits.

VCORE and V180 may

be used for the power

indication circuit.

V180 is sensitive to back

powering. While not used

VImax must be <0.2V.

If unused keep lines

open.

VCORE O VOnorm = 1.2V

IOmax = -10mA

CLmax = 100nF

SLEEP mode Operation:

VOSleep = 0.90V...1.2V ±4%

IOmax = -10mA

Ignition ON I VIHmax = 5V tolerant

VIHmin = 1.3V

VILmax = 0.5V

Slew rate <= 1ms

ON ___|~~~~

This signal switches the

module on, and is rising

edge sensitive triggered.

Emer-

gency

restart

EMERG_RST I RI ≈ 1kΩ, CI ≈ 1nF

VOHmax = VDDLP max

VIHmin = 1.35V

VILmax = 0.3V at ~200µA

~~|___|~~ low impulse width > 10ms

This line must be driven

low by an open drain or

open collector driver con-

nected to GND.

If unused keep line open.

Cinterion® ELS61-AUS Hardware Interface Description

2.1 Application Interface

52

ELS61-AUS_HID_v00.031 2016-06-03

Confidential / Preliminary

Page 18 of 102

Fast

shutdown

FST_SHDN I VILmax = 0.35V

VIHmin = 1.30V

VIHmax = 1.85V

~~|___|~~ low impulse width > 10ms

This line must be driven

low.

If unused keep line open.

Note that the fast shut-

down line is originally

available as GPIO line. If

configured as fast shut-

down, the GPIO line is

assigned as follows:

GPIO4 --> FST_SHDN

RTC

backup

VDDLP I/O VOnorm = 1.8V

IOmax = -25mA

VImax = 1.9V

VImin = 1.0V

IItyp < 1µA

It is recommended to use

a serial resistor between

VDDLP and a possible

capacitor.

If unused keep line open.

USB VUSB_IN I VImin = 3V

VImax = 5.25V

Active and suspend current:

Imax < 100µA

All electrical characteris-

tics according to USB

Implementers' Forum,

USB 2.0 Specification.

If unused keep lines

open.

USB_DN I/O Full and high speed signal characteris-

tics according USB 2.0 Specification.

USB_DP

Serial

Interface

ASC0

RXD0 O VOLmax = 0.25V at I = 1mA

VOHmin = 1.55V at I = -1mA

VOHmax = 1.85V

If unused keep lines

open.

Note that some ASC0

lines are originally avail-

able as GPIO lines. If

configured as ASC0

lines, the GPIO lines are

assigned as follows:

GPIO1 --> DTR0

GPIO2 --> DCD0

GPIO3 --> DSR0

GPIO24 --> RING0

The DSR0 line is also

shared with the SPI inter-

face‘s SPI_CLK signal.

CTS0 O

DSR0 O

DCD0 O

RING0 O

TXD0 I VILmax = 0.35V

VIHmin = 1.30V

VIHmax = 1.85V

RTS0 I Pull down resistor active

VILmax = 0.35V at > 50µA

VIHmin = 1.30V at < 240µA

VIHmax = 1.85V at < 240µA

DTR0 I Pull up resistor active

VILmax = 0.35V at < -200µA

VIHmin = 1.30V at > -50µA

VIHmax = 1.85V

Table 2: Signal properties

Function Signal name IO Signal form and level Comment

Cinterion® ELS61-AUS Hardware Interface Description

2.1 Application Interface

52

ELS61-AUS_HID_v00.031 2016-06-03

Confidential / Preliminary

Page 19 of 102

Serial

Interface

ASC1

RXD1 O VOLmax = 0.25V at I = 1mA

VOHmin = 1.55V at I = -1mA

VOHmax = 1.85V

VILmax = 0.35V

VIHmin = 1.30V

VIHmax = 1.85V

If unused keep line open.

Note that the ASC1 inter-

face lines are originally

available as GPIO lines.

If configured as ASC1

lines, the GPIO lines are

assigned as follows:

GPIO16 --> RXD1

GPIO17 --> TXD1

GPIO18 --> RTS1

GPIO19 --> CTS1

TXD1 I

RTS1 I

CTS1 O

SIM card

detection

CCIN I RI ≈ 110kΩ

VIHmin = 1.45V at I = 15µA,

VIHmax= 1.9V

VILmax = 0.3V

CCIN = High, SIM card

inserted.

For details please refer to

Section 2.1.6.

If unused keep line open.

3V SIM

Card Inter-

face

CCRST O VOLmax = 0.30V at I = 1mA

VOHmin = 2.45V at I = -1mA

VOHmax = 2.90V

Maximum cable length or

copper track to SIM card

holder should not exceed

100mm.

CCIO I/O VILmax = 0.50V

VIHmin = 2.05V

VIHmax = 2.90V

VOLmax = 0.25V at I = 1mA

VOHmin = 2.50V at I = -1mA

VOHmax = 2.90V

CCCLK O VOLmax = 0.25V at I = 1mA

VOHmin = 2.40V at I = -1mA

VOHmax = 2.90V

CCVCC O VOmin = 2.80V

VOtyp = 2.85V

VOmax = 2.90V

IOmax = -30mA

Table 2: Signal properties

Function Signal name IO Signal form and level Comment

Cinterion® ELS61-AUS Hardware Interface Description

2.1 Application Interface

52

ELS61-AUS_HID_v00.031 2016-06-03

Confidential / Preliminary

Page 20 of 102

1.8V SIM

Card Inter-

face

CCRST O VOLmax = 0.25V at I = 1mA

VOHmin = 1.45V at I = -1mA

VOHmax = 1.90V

Maximum cable length or

copper track to SIM card

holder should not exceed

100mm.

CCIO I/O VILmax = 0.35V

VIHmin = 1.25V

VIHmax = 1.85V

VOLmax = 0.25V at I = 1mA

VOHmin = 1.50V at I = -1mA

VOHmax = 1.85V

CCCLK O VOLmax = 0.25V at I = 1mA

VOHmin = 1.50V at I = -1mA

VOHmax = 1.85V

CCVCC O VOmin = 1.75V

VOtyp = 1.80V

VOmax = 1.85V

IOmax = -30mA

I2C I2CCLK IO Open drain IO

VOLmin = 0.35V at I = -3mA

VOHmax = 1.85V

R external pull up min = 560Ω

VILmax = 0.35V

VIHmin = 1.3V

VIHmax = 1.85V

According to the I2C Bus

Specification Version 2.1

for the fast mode a rise

time of max. 300ns is per-

mitted. There is also a

maximum VOL=0.4V at

3mA specified.

The value of the pull-up

depends on the capaci-

tive load of the whole sys-

tem (I2C Slave + lines).

The maximum sink cur-

rent of I2CDAT and

I2CCLK is 4mA.

If lines are unused keep

lines open.

I2CDAT IO

SPI SPI_CLK O VOLmax = 0.25V at I = 1mA

VOHmin = 1.55V at I = -1mA

VOHmax = 1.85V

VILmax = 0.35V

VIHmin = 1.30V

VIHmax = 1.85V

If lines are unused keep

lines open.

Note that the SPI inter-

face lines are originally

available as GPIO lines.

If configured as SPI lines,

the GPIO lines are

assigned as follows:

GPIO3 --> SPI_CLK

GPIO16 --> MOSI

GPIO17 --> MISO

GPIO19 --> SPI_CS

MOSI O

MISO I

SPI_CS O

Table 2: Signal properties

Function Signal name IO Signal form and level Comment

Cinterion® ELS61-AUS Hardware Interface Description

2.1 Application Interface

52

ELS61-AUS_HID_v00.031 2016-06-03

Confidential / Preliminary

Page 21 of 102

GPIO

interface

GPIO1-GPIO3 IO VOLmax = 0.25V at I = 1mA

VOHmin = 1.55V at I = -1mA

VOHmax = 1.85V

VILmax = 0.35V

VIHmin = 1.30V

VIHmax = 1.85V

If unused keep line open.

Please note that most

GPIO lines can be config-

ured by AT command for

alternative functions:

GPIO1-GPIO3: ASC0

control lines DTR0,

DCD0 and DSR0

GPIO4: Fast shutdown

GPIO5: Status LED line

GPIO6/GPIO7: PWM

GPIO8: Pulse Counter

GPIO16-GPIO19: ASC1

or SPI

GPIO24: ASC0 control

line RING0

GPIO4 IO

GPIO5 IO

GPIO6 IO

GPIO7 IO

GPIO8 IO

GPIO11-

GPIO15

IO

GPIO16-

GPIO19

IO

GPIO20-

GPIO23

IO

GPIO24 IO

Status LED LED O VOLmax = 0.25V at I = 1mA

VOHmin = 1.55V at I = -1mA

VOHmax = 1.85V

If unused keep line open.

Note that the LED line is

originally available as

GPIO line. If configured

as LED line, the GPIO

line is assigned as fol-

lows:

GPIO5 --> LED

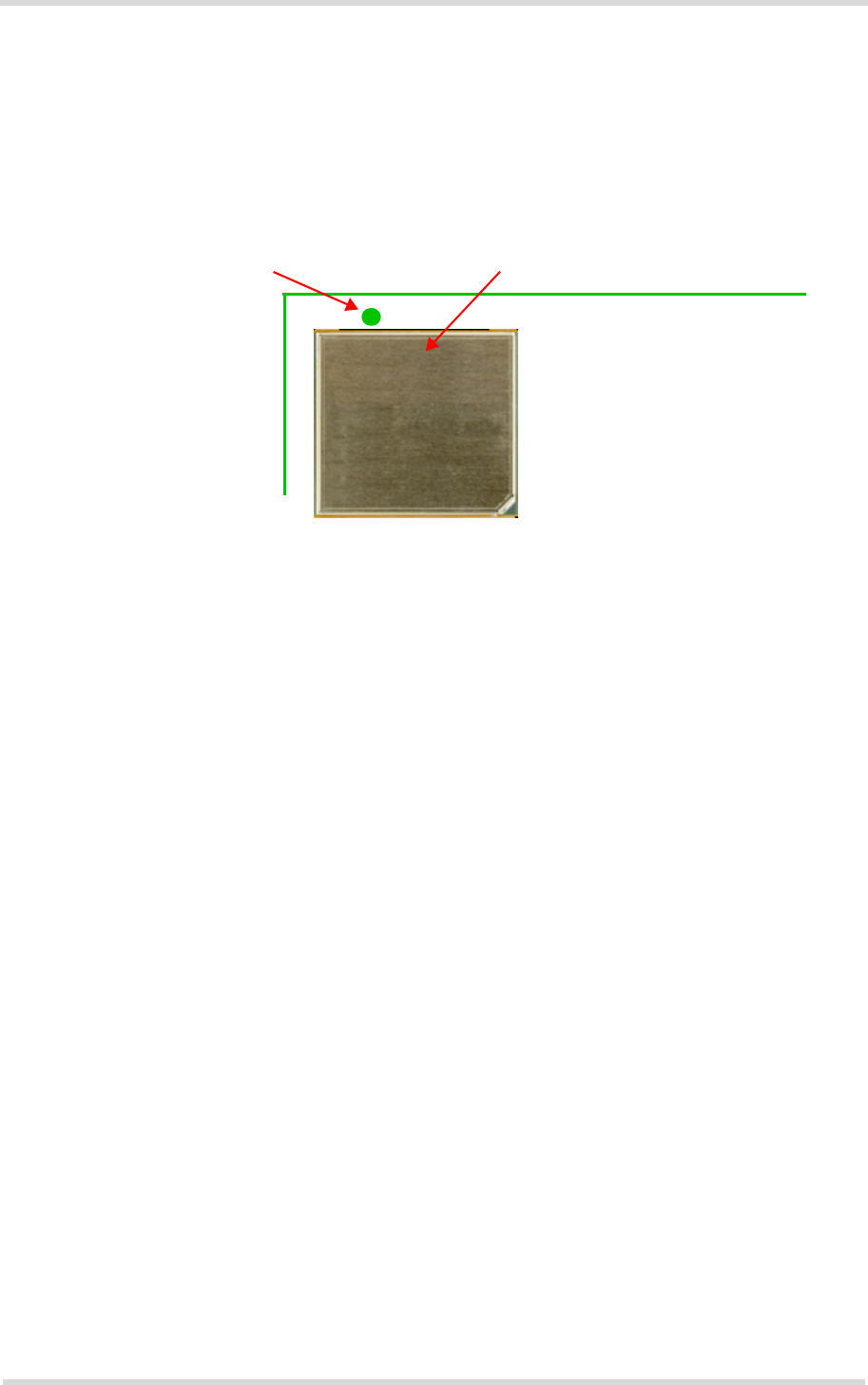

PWM PWM1 O VOLmax = 0.25V at I = 1mA

VOHmin = 1.55V at I = -1mA

VOHmax = 1.85V

If unused keep lines

open.

Note that the PWM lines

are originally available as

GPIO lines. If configured

as PWM lines, the GPIO

lines are assigned as fol-

lows:

GPIO7 --> PWM1

GPIO6 --> PWM2

PWM2 O

Pulse

counter

COUNTER I Internal up resistor active

VILmax = 0.35V at < -200µA

VIHmin = 1.30V at > -50µA

VIHmax = 1.85V

If unused keep line open.

Note that the COUNTER

line is originally available

as GPIO line. If config-

ured as COUNTER line,

the GPIO line is assigned

as follows:

GPIO8 --> COUNTER

ADC

(Analog-to-

Digital Con-

verter)

ADC1 I RI = 1MΩ

VI = 0V ... 1.2V (valid range)

VIH max = 1.2V

Resolution 1024 steps

Tolerance 0.3%

ADC can be used as

input for external mea-

surements.

If unused keep line open.

Table 2: Signal properties

Function Signal name IO Signal form and level Comment

Cinterion® ELS61-AUS Hardware Interface Description

2.1 Application Interface

52

ELS61-AUS_HID_v00.031 2016-06-03

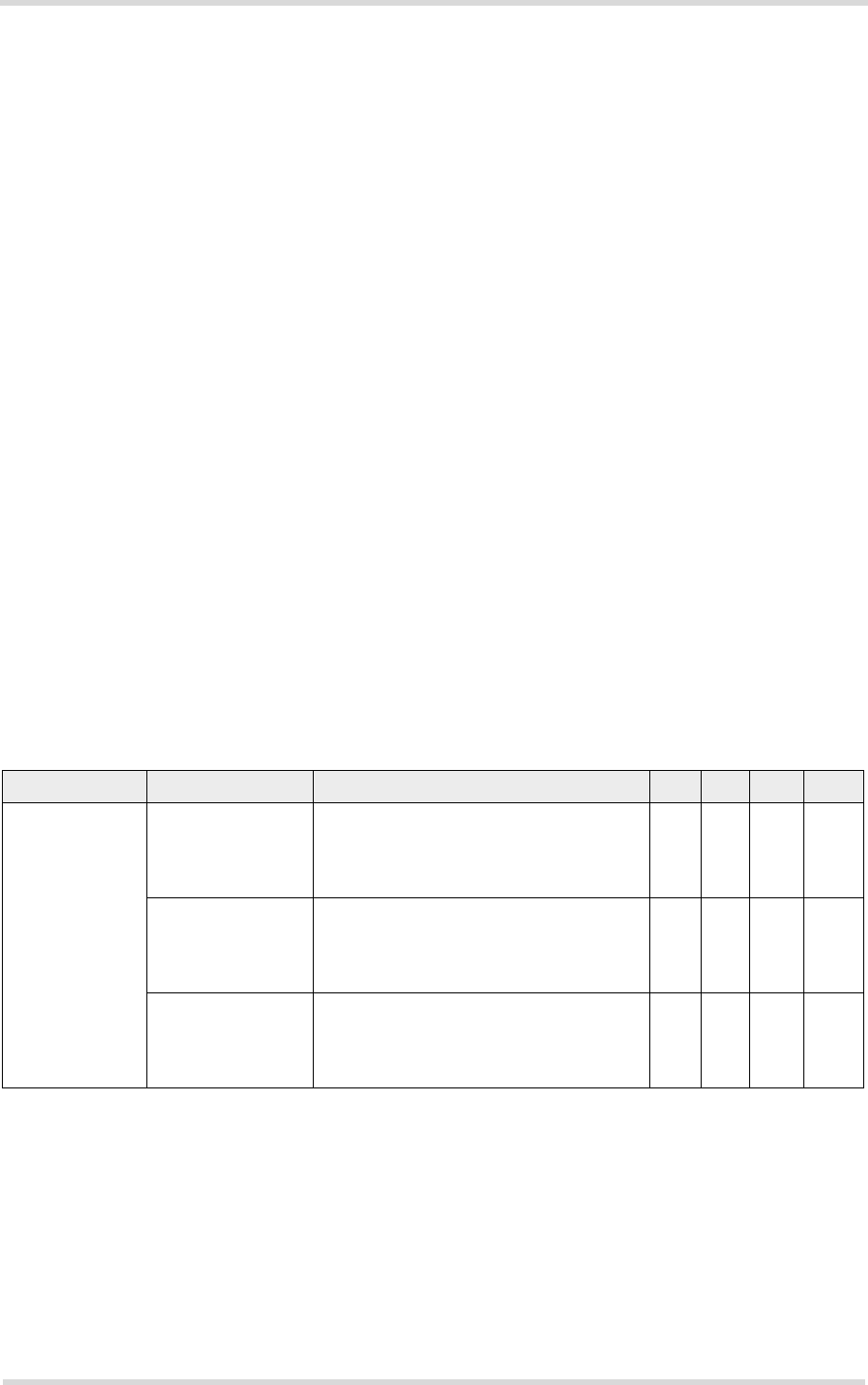

Confidential / Preliminary

Page 22 of 102

2.1.2.1 Absolute Maximum Ratings

The absolute maximum ratings stated in Table 3 are stress ratings under any conditions.

Stresses beyond any of these limits will cause permanent damage to ELS61-AUS.

Table 3: Absolute maximum ratings

Parameter Min Max Unit

Supply voltage BATT+BB, BATT+RF -0.5 +5.5 V

Voltage at all digital lines in Power Down mode -0.3 +0.3 V

Voltage at digital lines in normal operation -0.2 V180 + 0.2 V

Voltage at SIM/USIM interface, CCVCC in normal operation -0.5 +3.3 V

VDDLP input voltage -0.15 2.0 V

Voltage at ADC line in normal operation 0 1.2 V

Voltage at analog lines in Power Down mode -0.3 +0.3 V

V180 in normal operation +1.7 +1.9 V

Current at V180 in normal operation -50 mA

VCORE in normal operation +0.85 +1.25 V

Current at VCORE in normal operation -50 mA

Cinterion® ELS61-AUS Hardware Interface Description

2.1 Application Interface

52

ELS61-AUS_HID_v00.031 2016-06-03

Confidential / Preliminary

Page 23 of 102

2.1.3 USB Interface

ELS61-AUS supports a USB 2.0 High Speed (480Mbit/s) device interface that is Full Speed

(12Mbit/s) compliant. The USB interface is primarily intended for use as command and data in-

terface and for downloading firmware.

The external application is responsible for supplying the VUSB_IN line. This line is used for ca-

ble detection only. The USB part (driver and transceiver) is supplied by means of BATT+. This

is because ELS61-AUS is designed as a self-powered device compliant with the “Universal Se-

rial Bus Specification Revision 2.0”1.

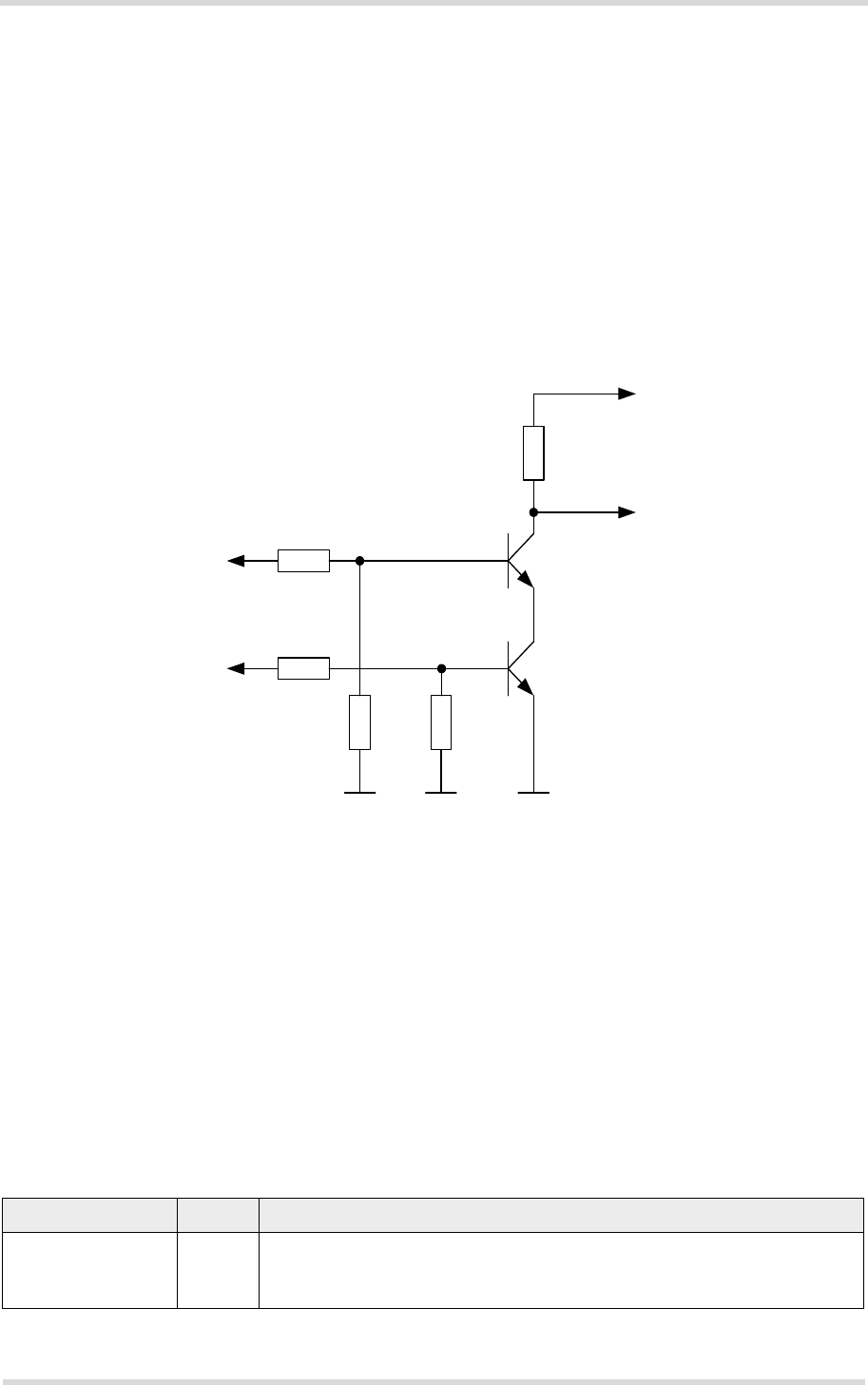

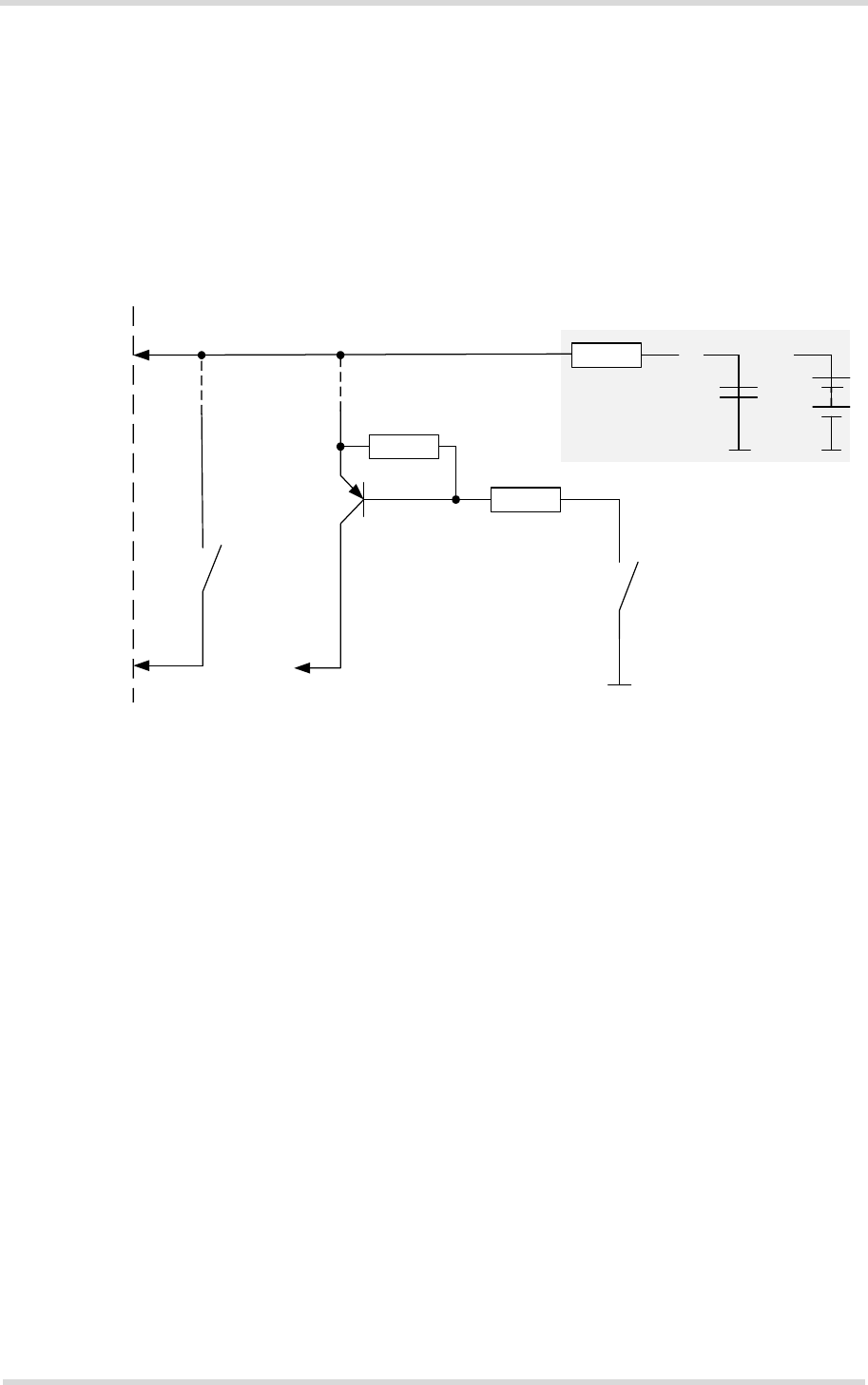

Figure 5: USB circuit

To properly connect the module's USB interface to the external application, a USB 2.0 compat-

ible connector and cable or hardware design is required. For more information on the USB re-

lated signals see Table 2. Furthermore, the USB modem driver distributed with ELS61-AUS

needs to be installed.

1. The specification is ready for download on http://www.usb.org/developers/docs/

VBUS

DP

DN

VREG (3V075)

BATT+

USB_DP2)

lin. reg.

GND

Module

Detection only VUSB_IN

USB part1)

RING0

Host wakeup

1) All serial (including RS) and pull-up resistors for data lines are implemented.

USB_DN2)

2) If the USB interface is operated in High Speed mode (480MHz), it is recommended to take

special care routing the data lines USB_DP and USB_DN. Application layout should in this

case implement a differential impedance of 90 ohms for proper signal integrity.

RS

RS

SMT

Cinterion® ELS61-AUS Hardware Interface Description

2.1 Application Interface

52

ELS61-AUS_HID_v00.031 2016-06-03

Confidential / Preliminary

Page 24 of 102

2.1.3.1 Reducing Power Consumption

While a USB connection is active, the module will never switch into SLEEP mode. Only if the

USB interface is in Suspended state or Detached (i.e., VUSB_IN = 0) is the module able to

switch into SLEEP mode thereby saving power. There are two possibilities to enable power re-

duction mechanisms:

• Recommended implementation of USB Suspend/Resume/Remote Wakeup:

The USB host should be able to bring its USB interface into the Suspended state as

described in the “Universal Serial Bus Specification Revision 2.0“1. For this functionality to

work, the VUSB_IN line should always be kept enabled. On incoming calls and other events

ELS61-AUS will then generate a Remote Wakeup request to resume the USB host control-

ler.

See also [5] (USB Specification Revision 2.0, Section 10.2.7, p.282):

"If USB System wishes to place the bus in the Suspended state, it commands the Host Con-

troller to stop all bus traffic, including SOFs. This causes all USB devices to enter the Sus-

pended state. In this state, the USB System may enable the Host Controller to respond to

bus wakeup events. This allows the Host Controller to respond to bus wakeup signaling to

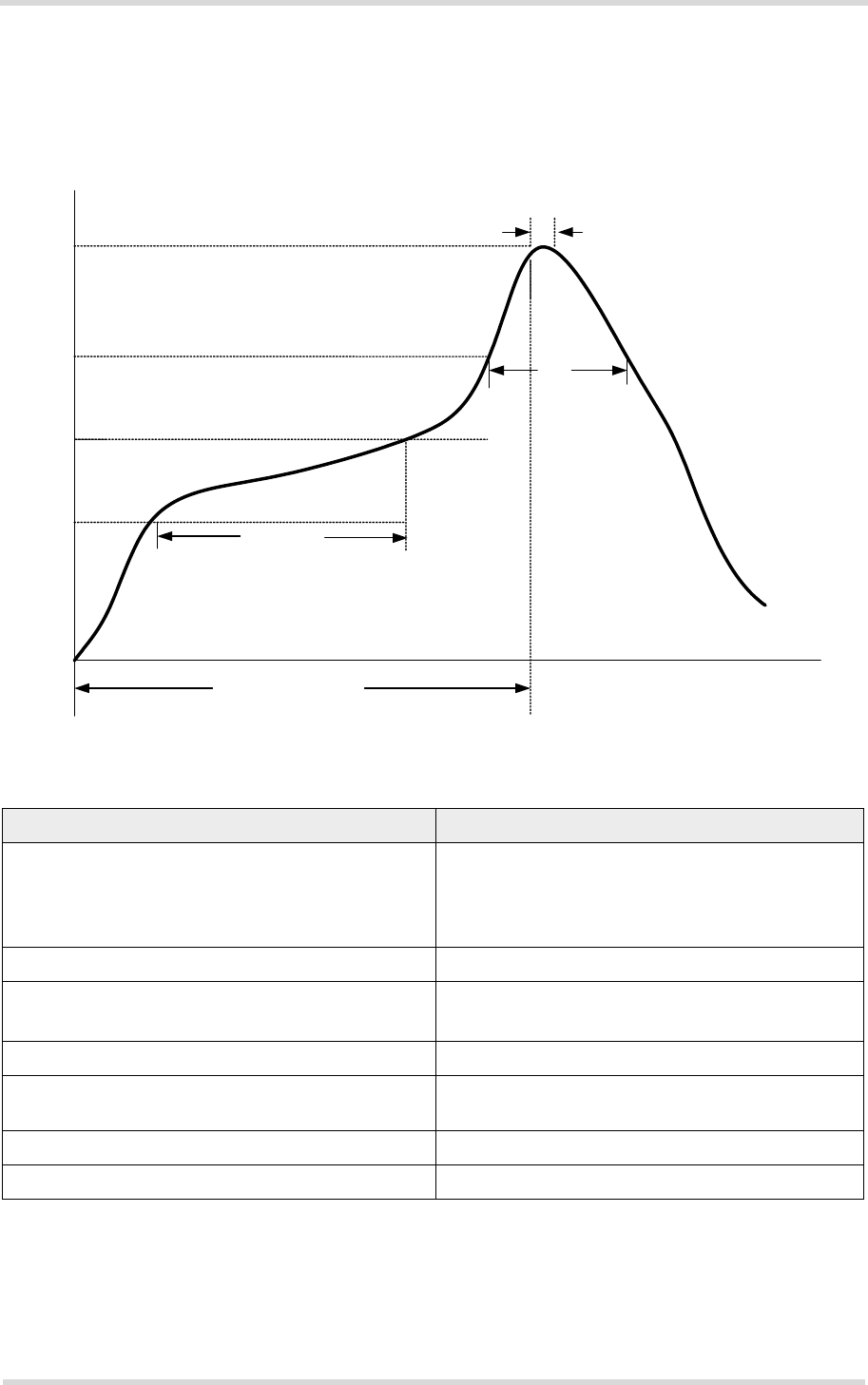

restart the host system."

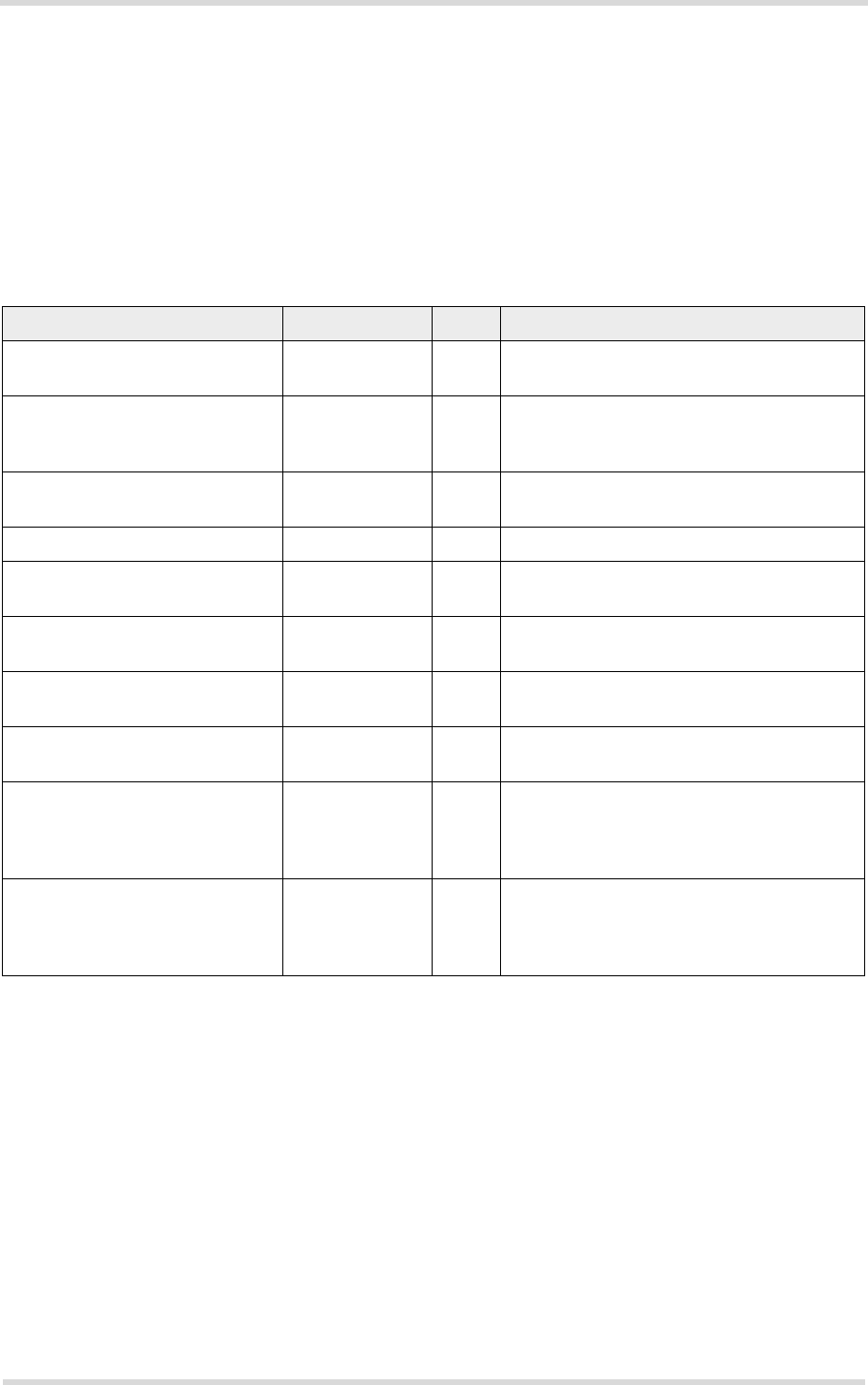

• Implementation for legacy USB applications not supporting USB Suspend/Resume:

As an alternative to the regular USB suspend and resume mechanism it is possible to

employ the RING0 line to wake up the host application in case of incoming calls or events

signalized by URCs while the USB interface is in Detached state (i.e., VUSB_IN = 0). Every

wakeup event will force a new USB enumeration. Therefore, the external application has to

carefully consider the enumeration timings to avoid loosing any signalled events. For details

on this host wakeup functionality see Section 2.1.13.3. To prevent existing data call con-

nections from being disconnected while the USB interface is in detached state (i.e., VUS-

B_IN=0) it is possible to call AT&D0, thus ignoring the status of the DTR line (see also [1]).

1. The specification is ready for download on http://www.usb.org/developers/docs/

Cinterion® ELS61-AUS Hardware Interface Description

2.1 Application Interface

52

ELS61-AUS_HID_v00.031 2016-06-03

Confidential / Preliminary

Page 25 of 102

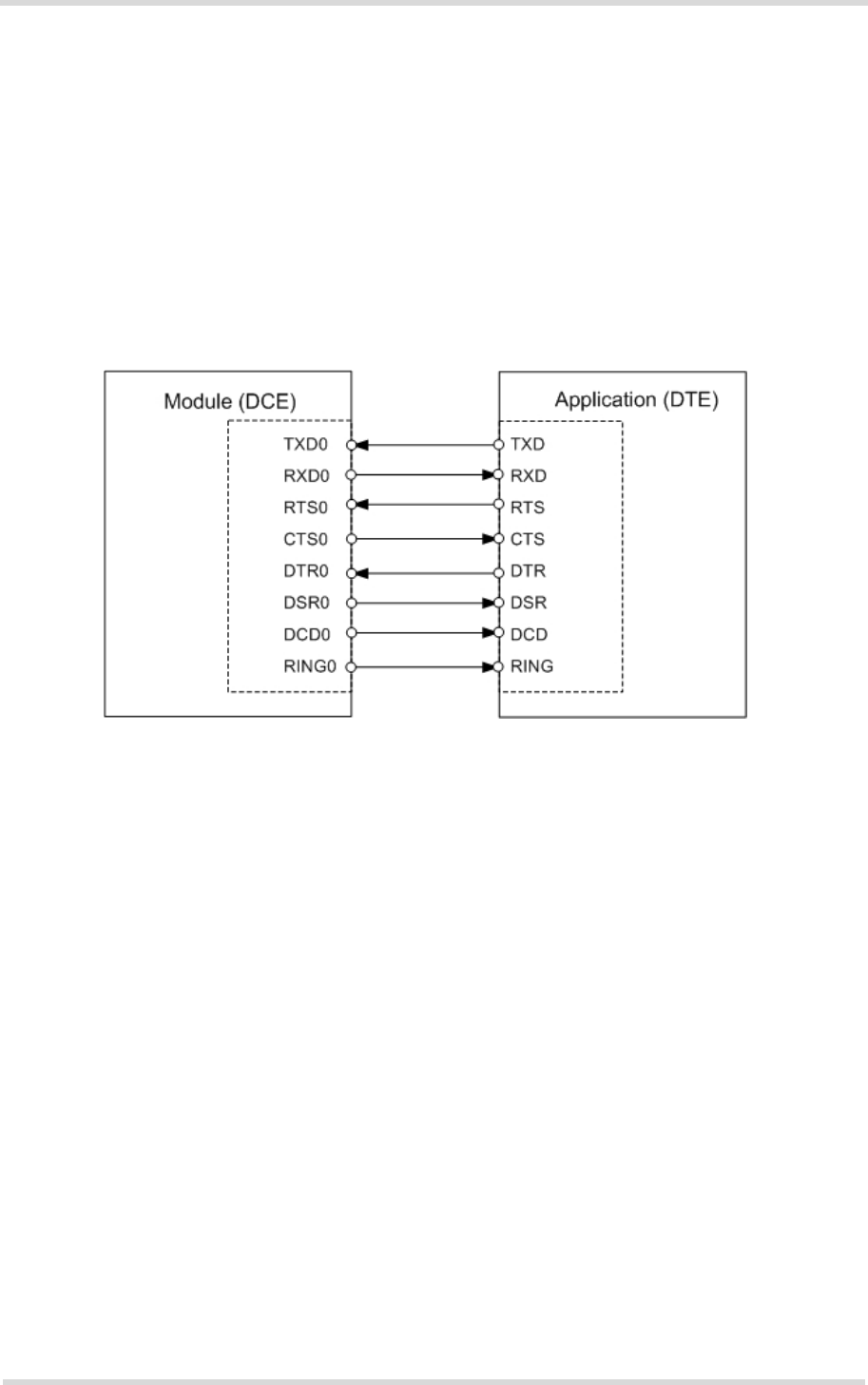

2.1.4 Serial Interface ASC0

ELS61-AUS offers an 8-wire unbalanced, asynchronous modem interface ASC0 conforming to

ITU-T V.24 protocol DCE signalling. The electrical characteristics do not comply with ITU-T

V.28. The significant levels are 0V (for low data bit or active state) and 1.8V (for high data bit

or inactive state). For electrical characteristics please refer to Table 2. For an illustration of the

interface line’s startup behavior see Figure 7.

ELS61-AUS is designed for use as a DCE. Based on the conventions for DCE-DTE connec-

tions it communicates with the customer application (DTE) using the following signals:

• Port TXD @ application sends data to the module’s TXD0 signal line

• Port RXD @ application receives data from the module’s RXD0 signal line

Figure 6: Serial interface ASC0

Features:

• Includes the data lines TXD0 and RXD0, the status lines RTS0 and CTS0 and, in addition,

the modem control lines DTR0, DSR0, DCD0 and RING0.

• The RING0 signal serves to indicate incoming calls and other types of URCs (Unsolicited

Result Code). It can also be used to send pulses to the host application, for example to

wake up the application from power saving state.

• Configured for 8 data bits, no parity and 1 stop bit.

• ASC0 can be operated at fixed bit rates from 1,200bps up to 921,600bps.

• Autobauding supports bit rates from 1,200bps up to 230,400bps.

• Supports RTS0/CTS0 hardware flow control. The hardware hand shake line RTS0 has an

internal pull down resistor causing a low level signal, if the line is not used and open.

Although hardware flow control is recommended, this allows communication by using only

RXD and TXD lines.

• Wake up from SLEEP mode by RTS0 activation (high to low transition; see Section 3.3.3).

Note: The ASC0 modem control lines DTR0, DCD0, DSR0 and RING0 are originally available

as GPIO lines. If configured as ASC0 lines, these GPIO lines are assigned as follows:

GPIO1 --> DTR0, GPIO2 --> DCD0, GPIO3 --> DSR0 and GPIO24 --> RING0. Also, DSR0 is

shared with the SPI_CLK line of the SPI interface and may be configured as such. Configura-

tion is done by AT command (see [1]). The configuration is non-volatile and becomes active

after a module restart.

Cinterion® ELS61-AUS Hardware Interface Description

2.1 Application Interface

52

ELS61-AUS_HID_v00.031 2016-06-03

Confidential / Preliminary

Page 26 of 102

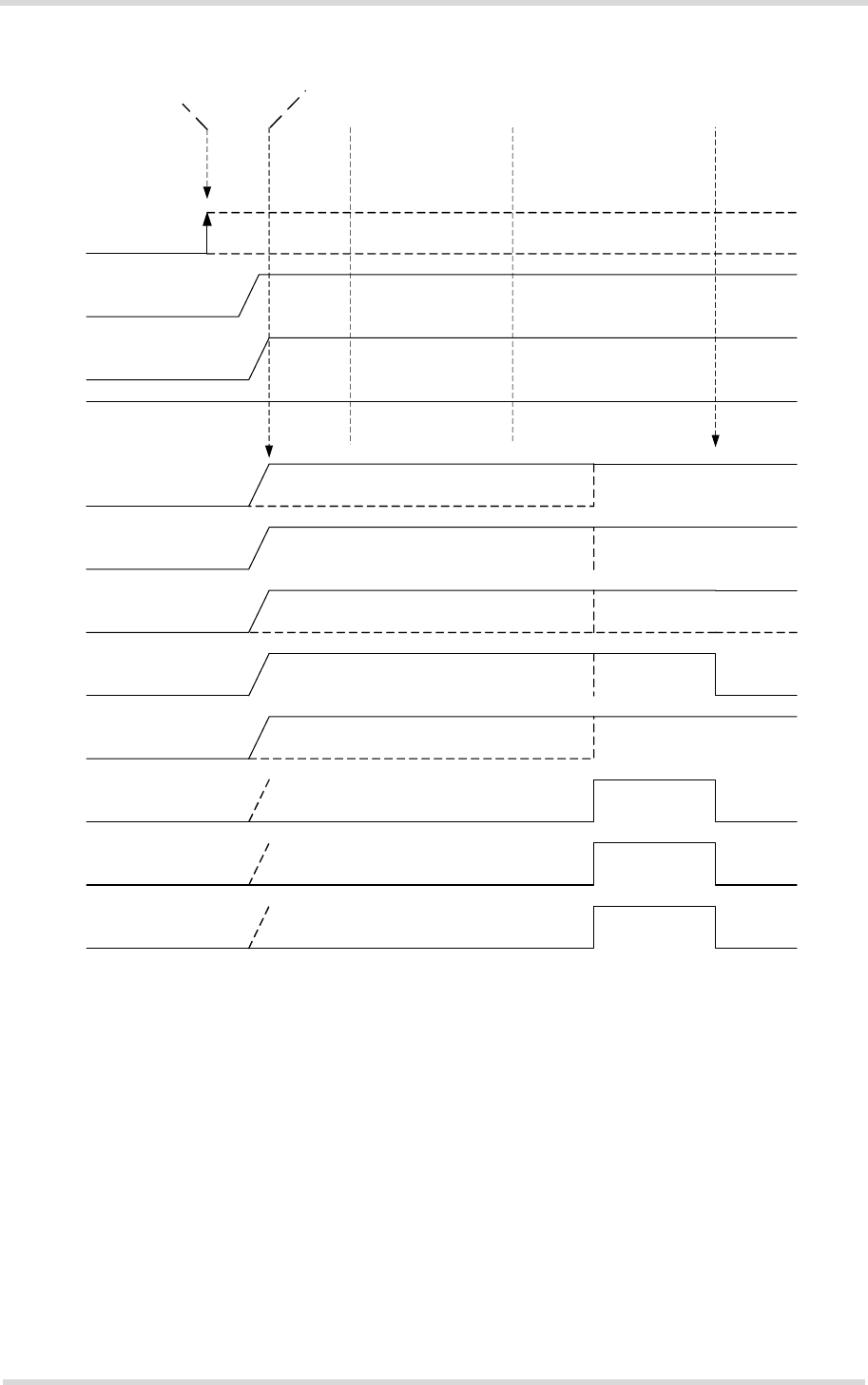

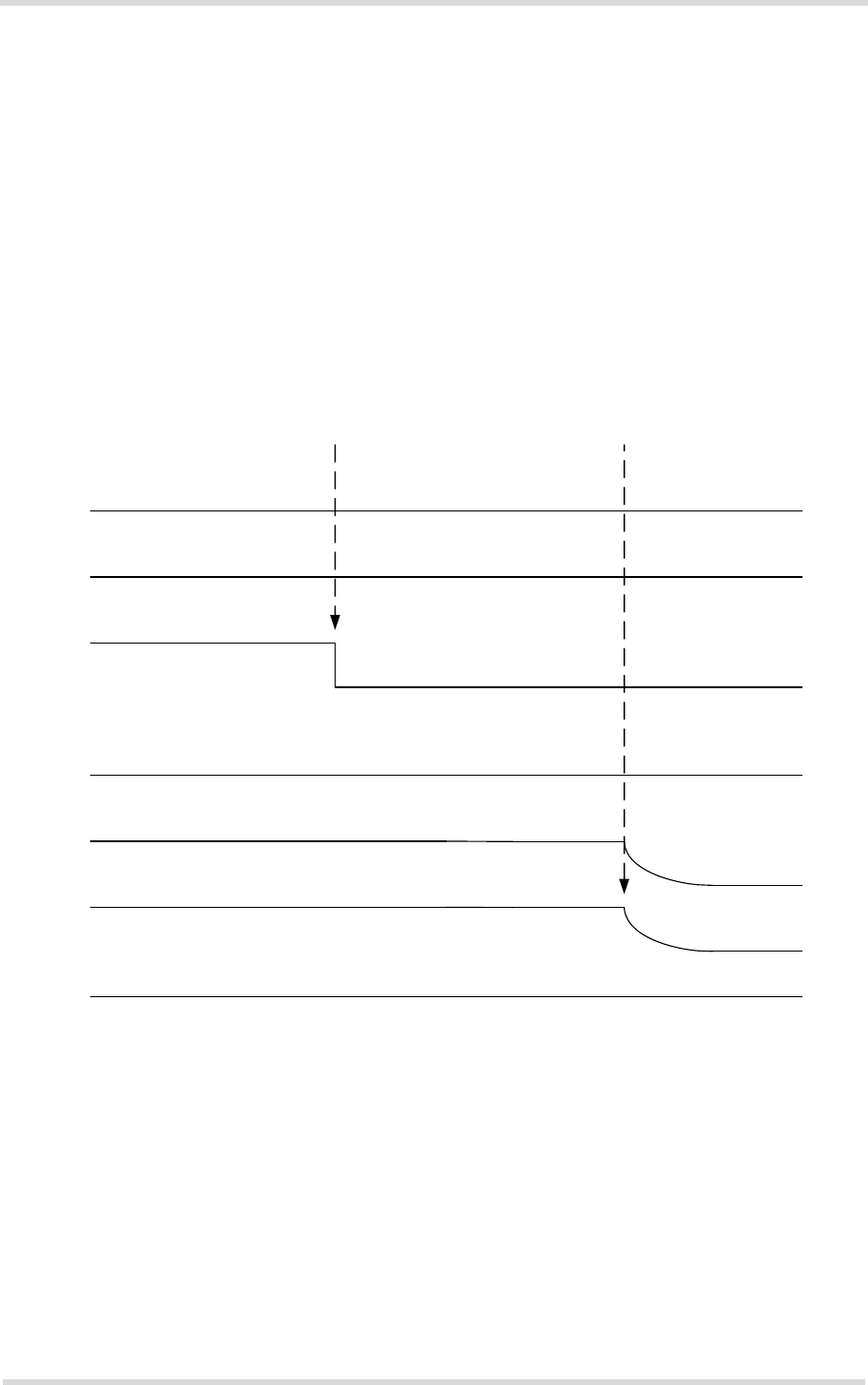

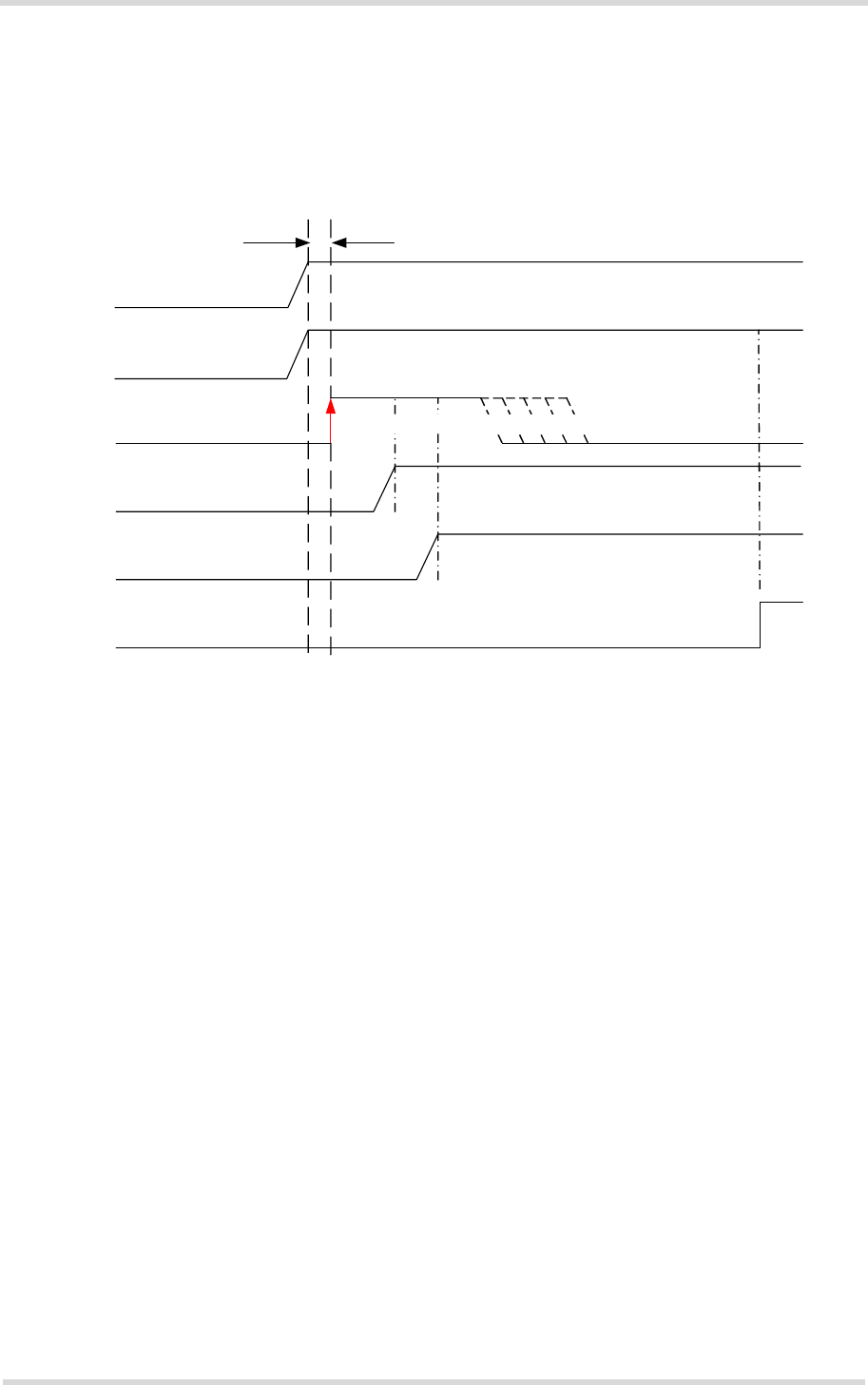

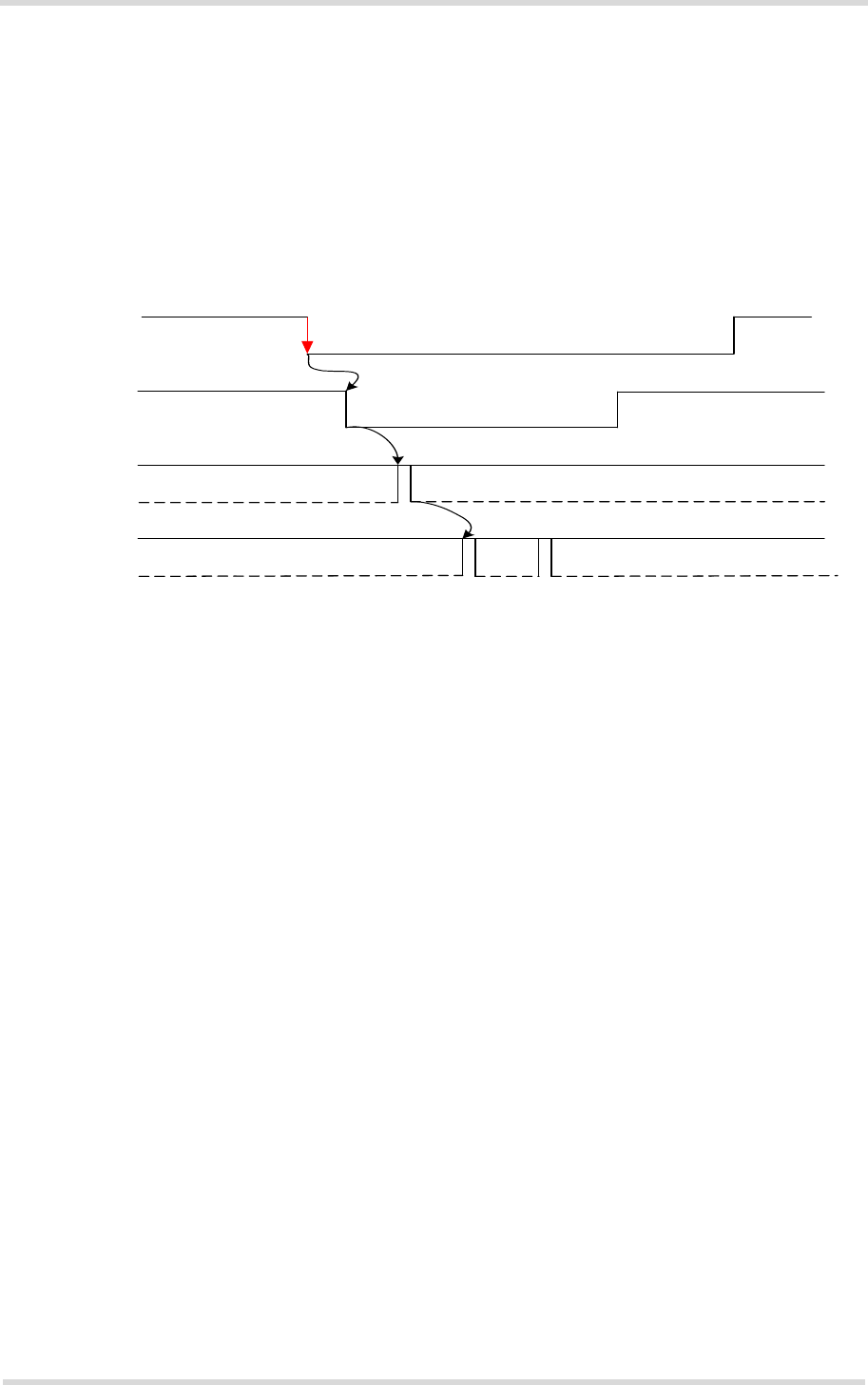

The following figure shows the startup behavior of the asynchronous serial interface ASC0.

For pull-up and pull-down values see Table 10.

Figure 7: ASC0 startup behavior

Notes:

During startup the DTR0 signal is driven active low for 500µs. It is recommended to provide a

470Ω serial resistor for the DTR0 line to prevent shorts.

No data must be sent over the ASC0 interface before the interface is active and ready to re-

ceive data (see Section 3.2.1).

An external pull down to ground on the DCD0 line during the startup phase activates a special

mode for ELS61-AUS. In this special mode the AT command interface is not available and the

module may therefore no longer behave as expected.

TXD0

RXD0

RTS0

CTS0

DTR0/GPIO1

DSR0/GPIO3

DCD0/GPIO2

RING0/GPIO24

ON

EMERG_RST

PU

PD

PD

PD

PD

PU

PD

PU

Power supply active

Start up

Firmware

initialization

Command interface

initialization

Interface

active

Reset

state

V180

VCORE

PD

PU

PU

PU

PD

PD

PD

Cinterion® ELS61-AUS Hardware Interface Description

2.1 Application Interface

52

ELS61-AUS_HID_v00.031 2016-06-03

Confidential / Preliminary

Page 27 of 102

2.1.5 Serial Interface ASC1

Four ELS61-AUS GPIO lines can be configured as ASC1 interface signals to provide a 4-wire

unbalanced, asynchronous modem interface ASC1 conforming to ITU-T V.24 protocol DCE

signalling. The electrical characteristics do not comply with ITU-T V.28. The significant levels

are 0V (for low data bit or active state) and 1.8V (for high data bit or inactive state). For electrical

characteristics please refer to Table 2. For an illustration of the interface line’s startup behavior

see Figure 9.

The ASC1 interface lines are originally available as GPIO lines. If configured as ASC1 lines,

the GPIO lines are assigned as follows: GPIO16 --> RXD1, GPIO17 --> TXD1, GPIO18 -->

RTS1 and GPIO19 --> CTS1. Configuration is done by AT command (see [1]: AT^SCFG). The

configuration is non-volatile and becomes active after a module restart.

ELS61-AUS is designed for use as a DCE. Based on the conventions for DCE-DTE connec-

tions it communicates with the customer application (DTE) using the following signals:

• Port TXD @ application sends data to module’s TXD1 signal line

• Port RXD @ application receives data from the module’s RXD1 signal line

Figure 8: Serial interface ASC1

Features

• Includes only the data lines TXD1 and RXD1 plus RTS1 and CTS1 for hardware hand-

shake.

• On ASC1 no RING line is available.

• Configured for 8 data bits, no parity and 1 or 2 stop bits.

• ASC1 can be operated at fixed bit rates from 1,200 bps to 921,600 bps.

• Autobauding supports bit rates from 1,200bps up to 230,400bps.

• Supports RTS1/CTS1 hardware flow. The hardware hand shake line RTS0 has an internal

pull down resistor causing a low level signal, if the line is not used and open. Although hard-

ware flow control is recommended, this allows communication by using only RXD and TXD

lines.

Cinterion® ELS61-AUS Hardware Interface Description

2.1 Application Interface

52

ELS61-AUS_HID_v00.031 2016-06-03

Confidential / Preliminary

Page 28 of 102

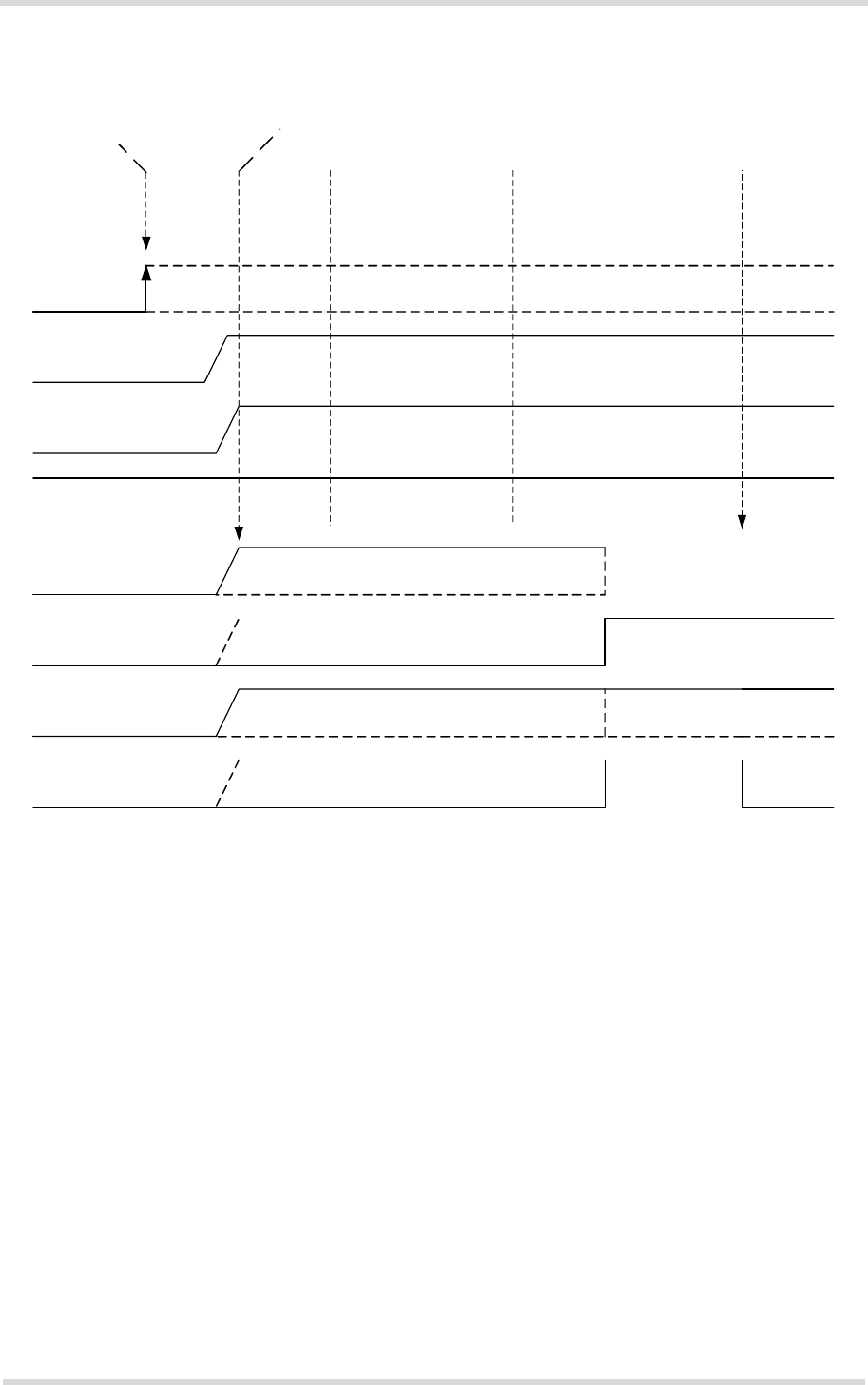

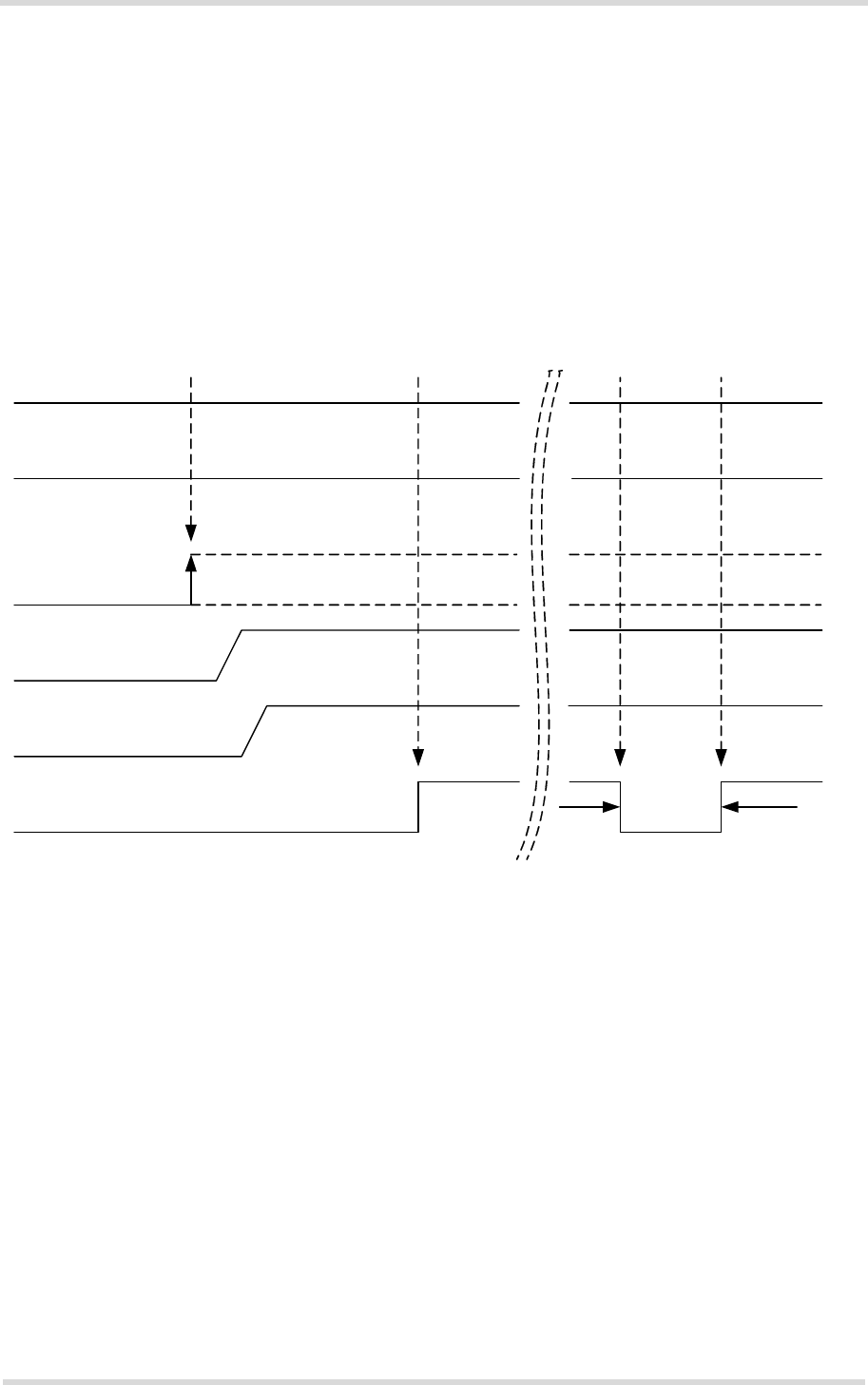

The following figure shows the startup behavior of the asynchronous serial interface ASC1.

*) For pull-down values see Table 10.

Figure 9: ASC1 startup behavior

TXD1/GPIO17

RXD1/GPIO16

RTS1/GPIO18

CTS1/GPIO19

ON

EMERG_RST

PD

PD

PD

PD

Power supply active

Start up

Firmware

initialization

Command interface

initialization

Interface

active

Reset

state

V180

VCORE

PD

Cinterion® ELS61-AUS Hardware Interface Description

2.1 Application Interface

52

ELS61-AUS_HID_v00.031 2016-06-03

Confidential / Preliminary

Page 29 of 102

2.1.6 UICC/SIM/USIM Interface

ELS61-AUS has an integrated UICC/SIM/USIM interface compatible with the 3GPP 31.102

and ETSI 102 221. This is wired to the host interface in order to be connected to an external

SIM card holder. Five pads on the SMT application interface are reserved for the SIM interface.

The UICC/SIM/USIM interface supports 3V and 1.8V SIM cards. Please refer to Table 2 for

electrical specifications of the UICC/SIM/USIM interface lines depending on whether a 3V or

1.8V SIM card is used.

The CCIN signal serves to detect whether a tray (with SIM card) is present in the card holder.

To take advantage of this feature, an appropriate SIM card detect switch is required on the card

holder. For example, this is true for the model supplied by Molex, which has been tested to op-

erate with ELS61-AUS and is part of the Gemalto M2M reference equipment submitted for type

approval. See Section 7.1 for Molex ordering numbers.

Note [1]: No guarantee can be given, nor any liability accepted, if loss of data is encountered after removing

the SIM card during operation. Also, no guarantee can be given for properly initializing any SIM card that

the user inserts after having removed the SIM card during operation. In this case, the application must

restart ELS61-AUS.

Note [2]: On the evaluation board, the CCIN signal is inverted, thus the CCIN signal is by default high and

will change to a low level if a SIM card is inserted.

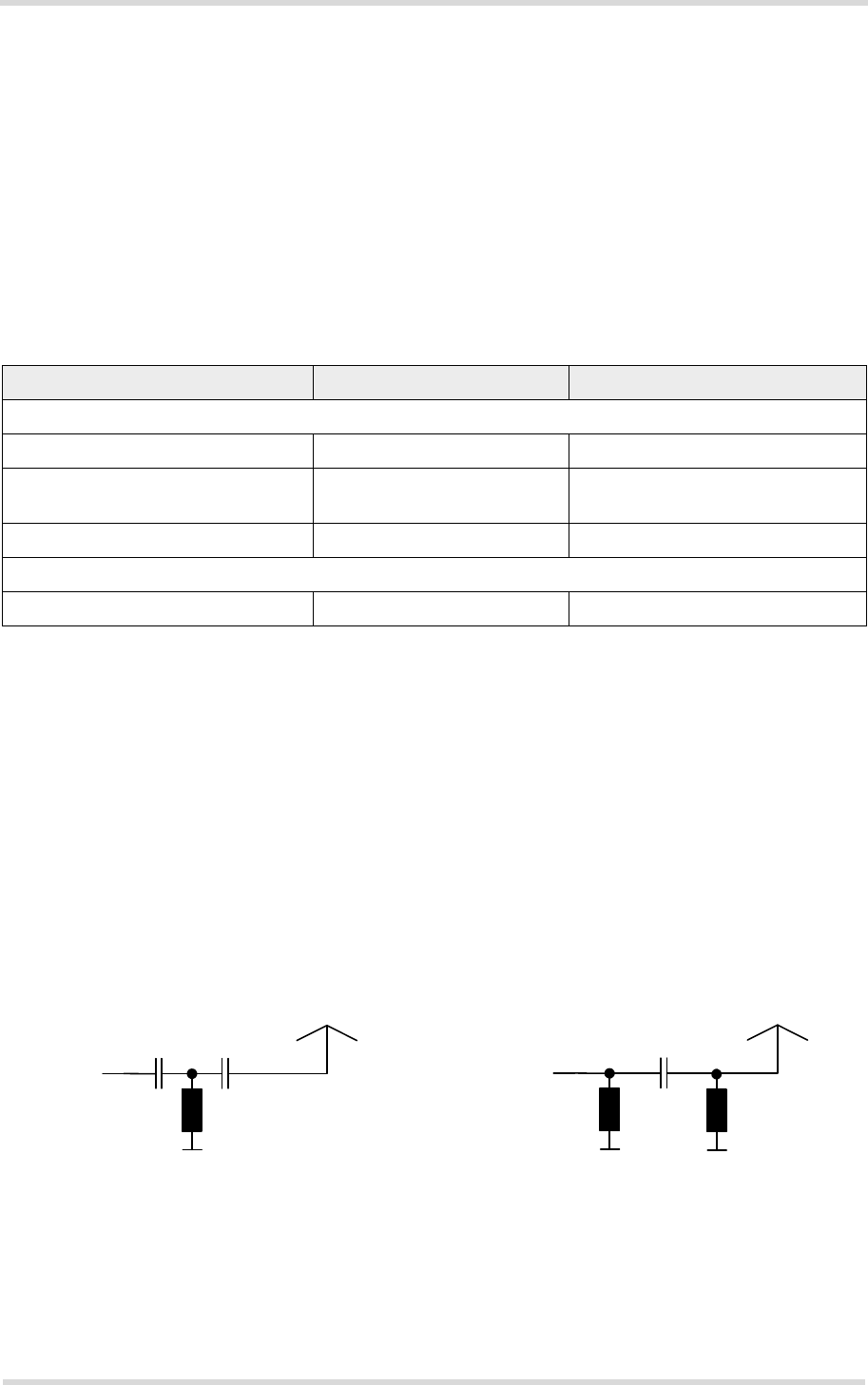

Table 4: Signals of the SIM interface (SMT application interface)

Signal Description

GND Separate ground connection for SIM card to improve EMC.

CCCLK Chipcard clock

CCVCC SIM supply voltage.

CCIO Serial data line, input and output.

CCRST Chipcard reset

CCIN Input on the baseband processor for detecting a SIM card tray in the holder. If the SIM is

removed during operation the SIM interface is shut down immediately to prevent destruc-

tion of the SIM. The CCIN signal is by default low and will change to high level if a SIM card

is inserted.

The CCIN signal is mandatory for applications that allow the user to remove the SIM card

during operation.

The CCIN signal is solely intended for use with a SIM card. It must not be used for any other

purposes. Failure to comply with this requirement may invalidate the type approval of

ELS61-AUS.

Cinterion® ELS61-AUS Hardware Interface Description

2.1 Application Interface

52

ELS61-AUS_HID_v00.031 2016-06-03

Confidential / Preliminary

Page 30 of 102

The figure below shows a circuit to connect an external SIM card holder.

Figure 10: External UICC/SIM/USIM card holder circuit

The total cable length between the SMT application interface pads on ELS61-AUS and the

pads of the external SIM card holder must not exceed 100mm in order to meet the specifica-

tions of 3GPP TS 51.010-1 and to satisfy the requirements of EMC compliance.

To avoid possible cross-talk from the CCCLK signal to the CCIO signal be careful that both

lines are not placed closely next to each other. A useful approach is using a GND line to shield

the CCIO line from the CCCLK line.

An example for an optimized ESD protection for the SIM interface is shown in Section 2.1.6.1.

SIM

CCVCC

CCRST

CCIO

CCCLK

220nF

1nF

CCIN

V180

Cinterion® ELS61-AUS Hardware Interface Description

2.1 Application Interface

52

ELS61-AUS_HID_v00.031 2016-06-03

Confidential / Preliminary

Page 31 of 102

2.1.6.1 Enhanced ESD Protection for SIM Interface

To optimize ESD protection for the SIM interface it is possible to add ESD diodes to the SIM

interface lines as shown in the example given in Figure 11.

The example was designed to meet ESD protection according ETSI EN 301 489-1/7: Contact

discharge: ± 4kV, air discharge: ± 8kV.

Figure 11: SIM interface - enhanced ESD protection

CCRST

CCCLK

CCIO

CCVCC

CCIN GND

123

654

SIM_RST

SIM_CLK

SIM_IO

SIM_VCC

SIM_DET

Module

Cinterion® ELS61-AUS Hardware Interface Description

2.1 Application Interface

52

ELS61-AUS_HID_v00.031 2016-06-03

Confidential / Preliminary

Page 32 of 102

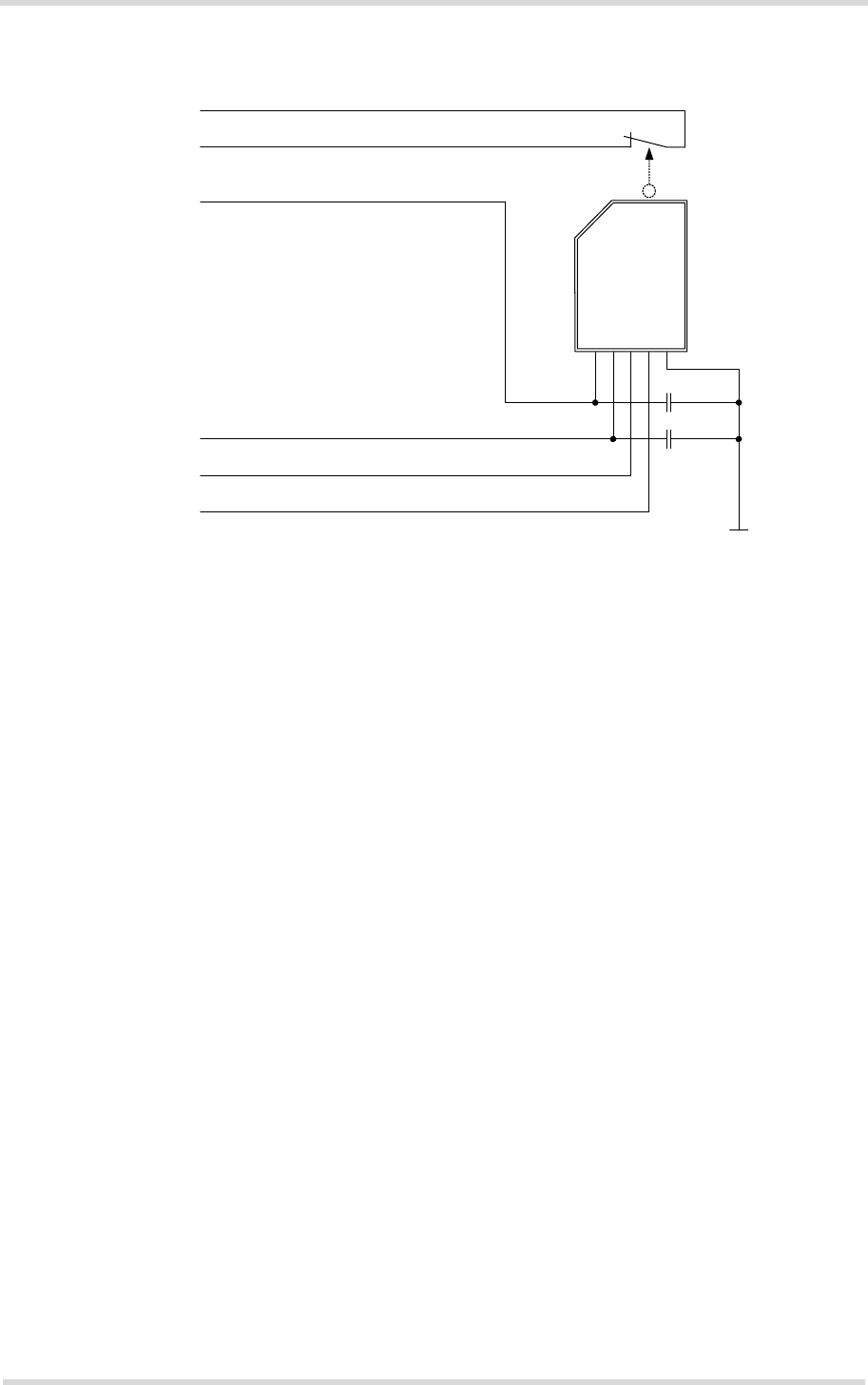

2.1.7 RTC Backup

The internal Real Time Clock of ELS61-AUS is supplied from a separate voltage regulator in

the power supply component which is also active when ELS61-AUS is in Power Down mode

and BATT+ is available. An alarm function is provided that allows to wake up ELS61-AUS with-

out logging on to the UMTS network.

In addition, you can use the VDDLP pad to backup the RTC from an external capacitor. The

capacitor is charged from the internal LDO of ELS61-AUS. If the voltage supply at BATT+ is

disconnected the RTC can be powered by the capacitor. The size of the capacitor determines

the duration of buffering when no voltage is applied to ELS61-AUS, i.e. the greater the capac-

itor the longer ELS61-AUS will save the date and time. The RTC can also be supplied from an

external battery (rechargeable or non-chargeable). In this case the electrical specification of

the VDDLP pad (see Section 2.1.2) has to be taken in to account.

Figure 12 shows an RTC backup configuration. A serial 1kΩ resistor has to be placed on the

application next to VDDLP. It limits the input current of an empty capacitor or battery.

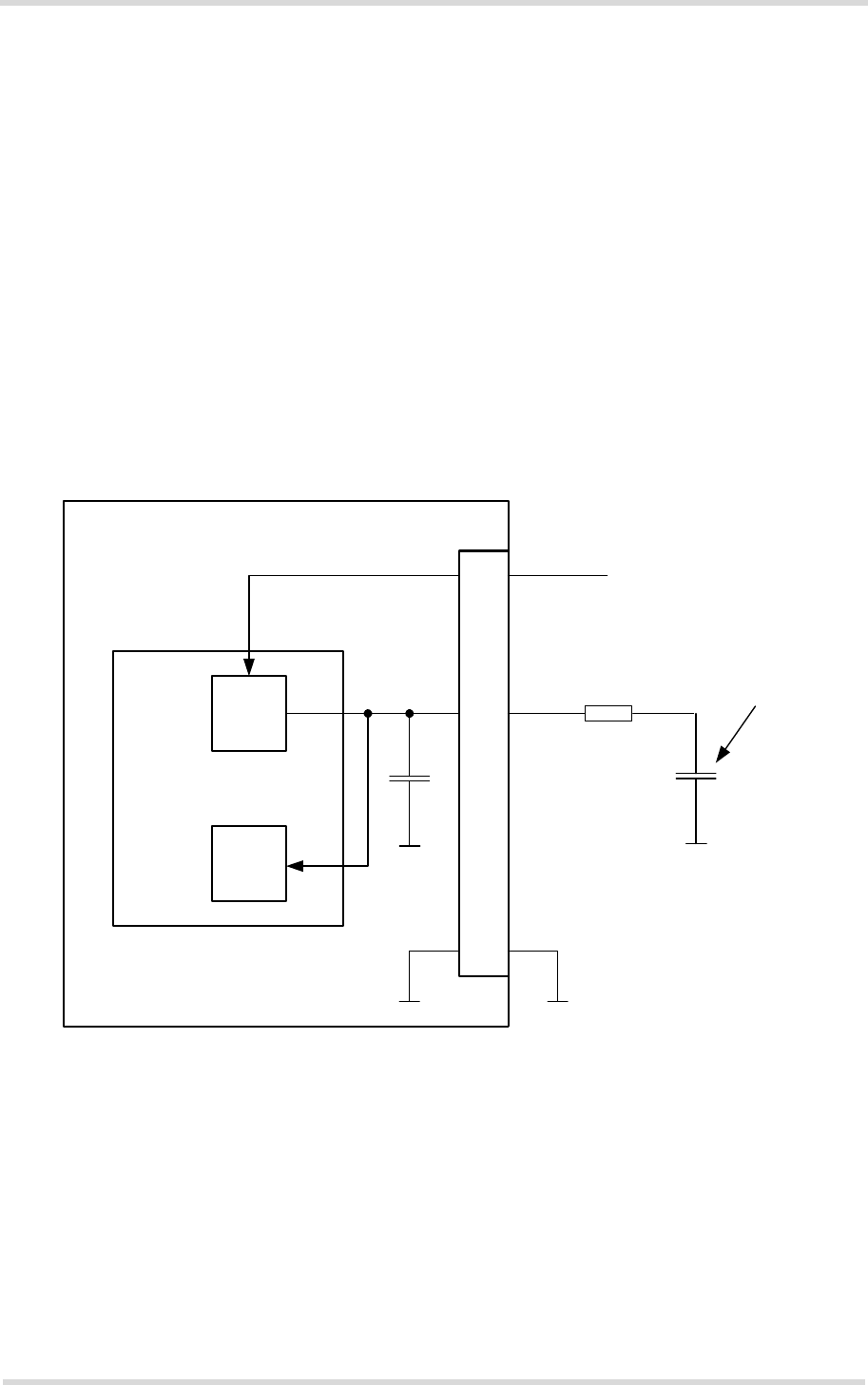

Figure 12: RTC supply variants

Capacitor

VDDLP

GSM processor and

power management

LRTC

RTC

Application interface

BATT+

Module

1k

GND

Cinterion® ELS61-AUS Hardware Interface Description

2.1 Application Interface

52

ELS61-AUS_HID_v00.031 2016-06-03

Confidential / Preliminary

Page 33 of 102

2.1.8 GPIO Interface

ELS61-AUS offers a GPIO interface with 22 GPIO lines. The GPIO lines are shared with other

interfaces or functions: Fast shutdown (see Section 2.1.13.4), status LED (see Section

2.1.13.1), the PWM functionality (see Section 2.1.11), an pulse counter (see Section 2.1.12),

ASC0 (see Section 2.1.4), ASC1 (see Section 2.1.5), an SPI interface (see Section 2.1.10).

The following table shows the configuration variants for the GPIO pads. All variants are mutu-

ally exclusive, i.e. a pad configured for instance as Status LED is locked for alternative usage.

After startup, the above mentioned alternative GPIO line assignments can be con-

figured using AT commands (see [1]). The configuration is non-volatile and available after mod-

ule restart.

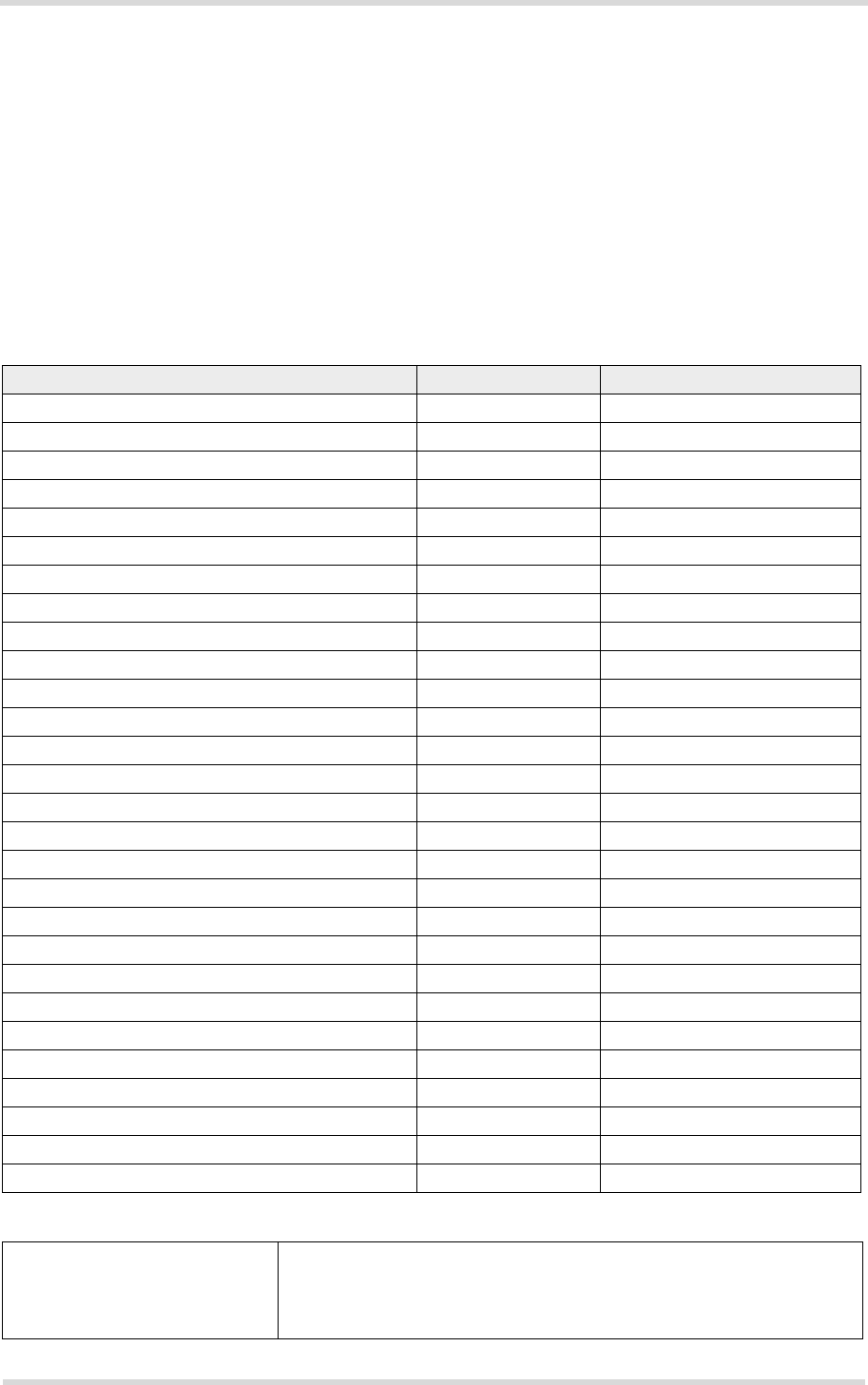

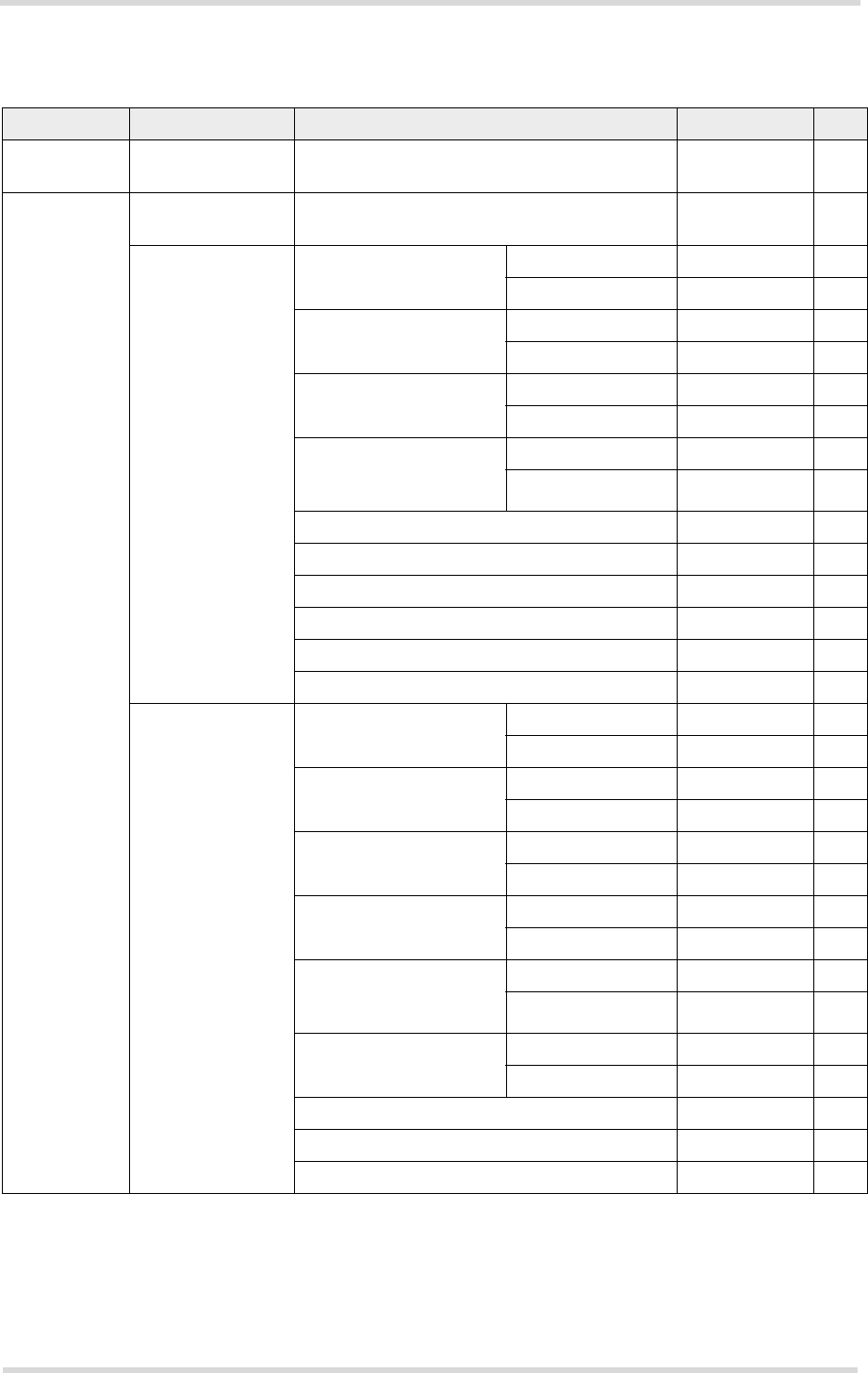

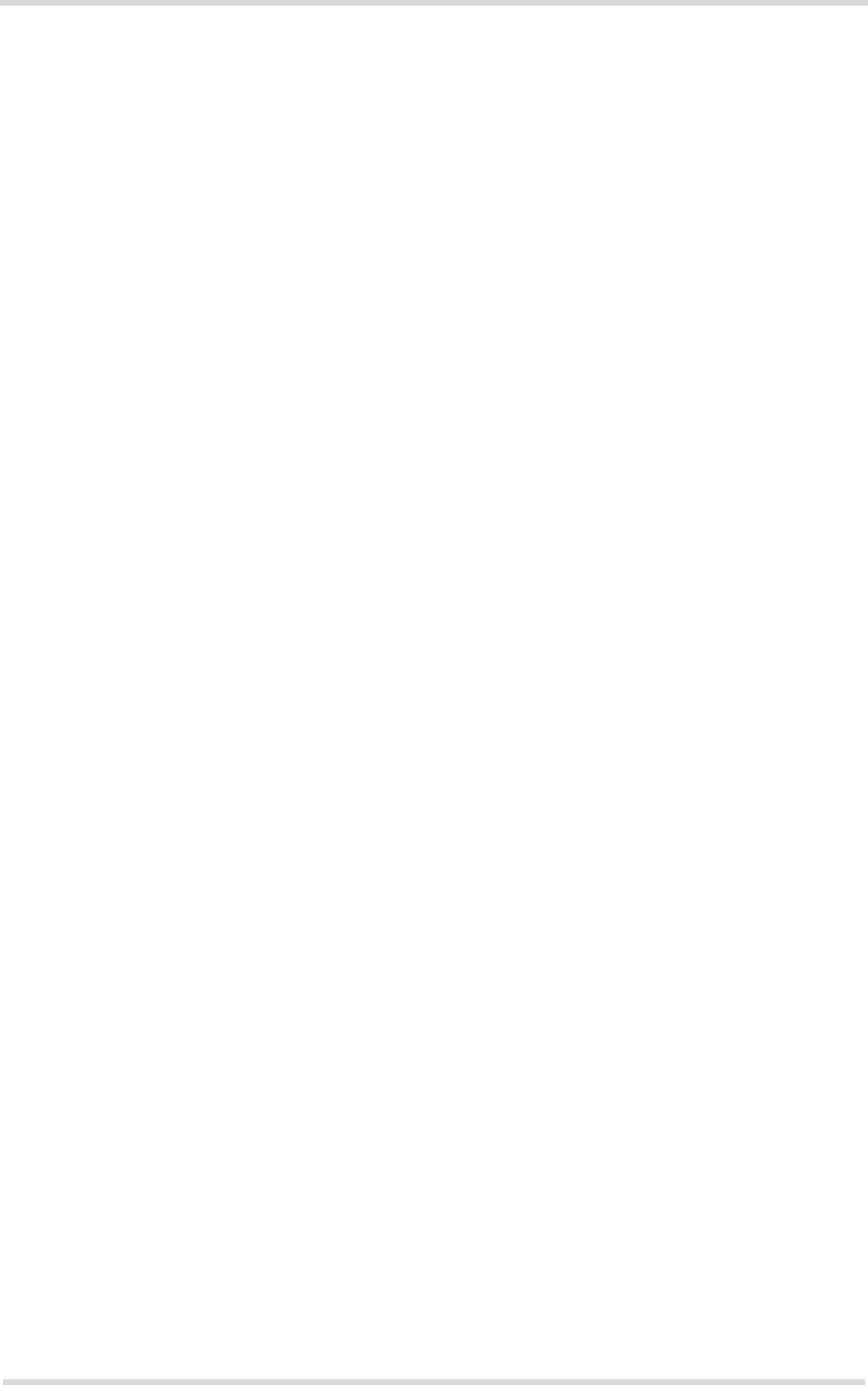

Table 5: GPIO lines and possible alternative assignment

GPIO Fast Shutdown Status LED PWM Pulse Counter ASC0 ASC1 SPI

GPIO1 DTR0

GPIO2 DCD0

GPIO3 DSR0 SPI_CLK

GPIO4 FST_SHDN

GPIO5 Status LED

GPIO6 PWM2

GPIO7 PWM1

GPIO8 COUNTER

GPIO11

GPIO12

GPIO13

GPIO14

GPIO15

GPIO16 RXD1 MOSI

GPIO17 TXD1 MISO

GPIO18 RTS1

GPIO19 CTS1 SPI_CS

GPIO20

GPIO21

GPIO22

GPIO23

GPIO24 RING0

Cinterion® ELS61-AUS Hardware Interface Description

2.1 Application Interface

52

ELS61-AUS_HID_v00.031 2016-06-03

Confidential / Preliminary

Page 34 of 102

The following figure shows the startup behavior of the GPIO interface. With an active state of

the ASC0 interface (i.e. CTS0 is at low level) the initialization of the GPIO interface lines is also

finished.

*) For pull down values see Table 10.

Figure 13: GPIO startup behavior

GPIO1 - 8 PD

CTS0

ON

EMERG_RST

Power supply active

Start up

Firmware

initialization

Command interface

initialization

Interface

active

Reset

state

V180

VCORE

GPIO11 - 24 PD

Cinterion® ELS61-AUS Hardware Interface Description

2.1 Application Interface

52

ELS61-AUS_HID_v00.031 2016-06-03

Confidential / Preliminary

Page 35 of 102

2.1.9 I2C Interface

I2C is a serial, 8-bit oriented data transfer bus for bit rates up to 400kbps in Fast mode. It con-

sists of two lines, the serial data line I2CDAT and the serial clock line I2CCLK. The module acts

as a single master device, e.g. the clock I2CCLK is driven by the module. I2CDAT is a bi-direc-

tional line. Each device connected to the bus is software addressable by a unique 7-bit ad-

dress, and simple master/slave relationships exist at all times. The module operates as master-

transmitter or as master-receiver. The customer application transmits or receives data only on

request of the module.

To configure and activate the I2C bus use the AT^SSPI command. Detailed information on the

AT^SSPI command as well explanations on the protocol and syntax required for data transmis-

sion can be found in [1].

The I2C interface can be powered via the V180 line of ELS61-AUS. If connected to the V180

line, the I2C interface will properly shut down when the module enters the Power Down mode.

In the application I2CDAT and I2CCLK lines need to be connected to a positive supply voltage

via a pull-up resistor. For electrical characteristics please refer to Table 2.

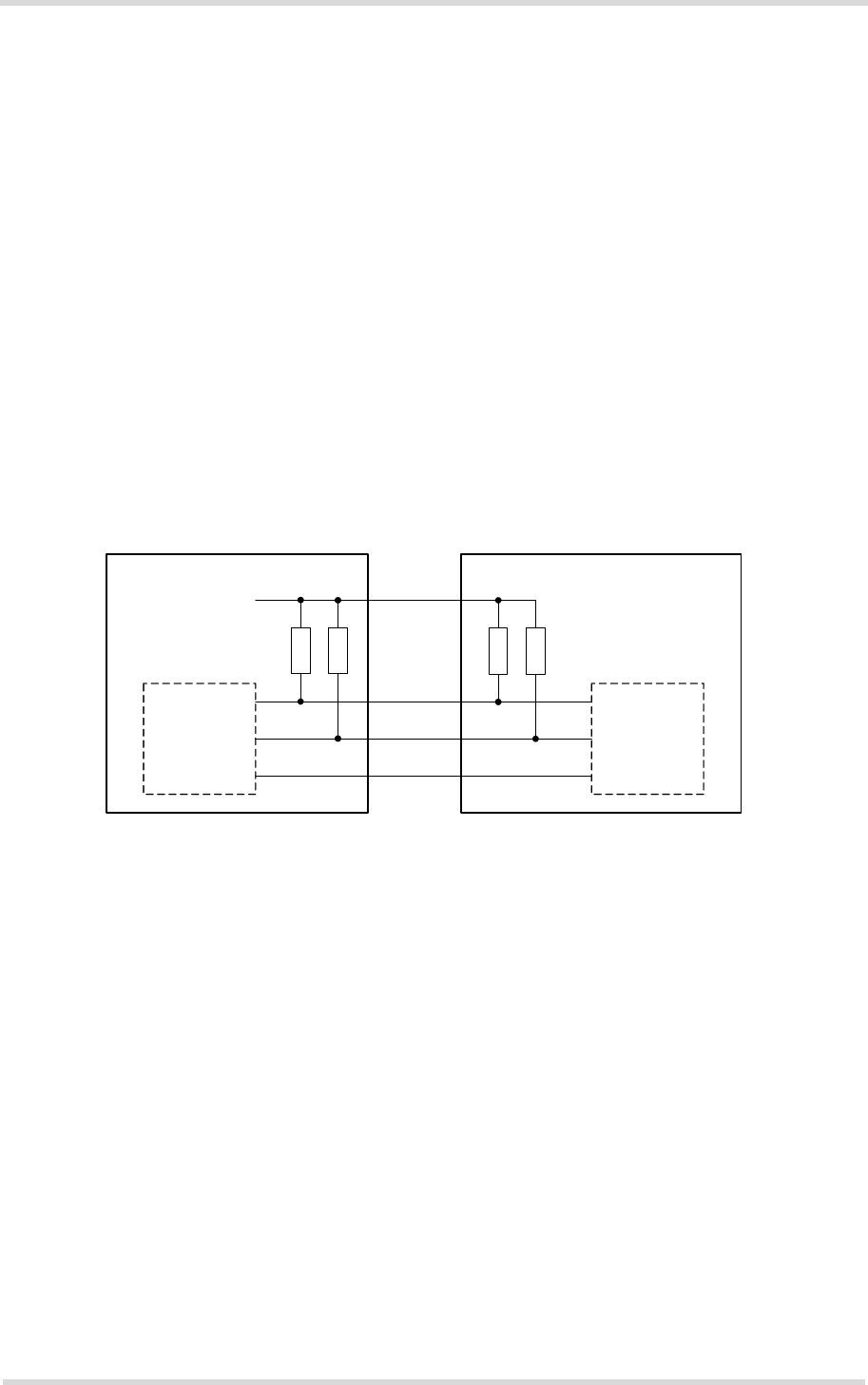

Figure 14: I2C interface connected to V180

Note: Good care should be taken when creating the PCB layout of the host application: The

traces of I2CCLK and I2CDAT should be equal in length and as short as possible.

I2CCLK

I2CDAT

GND

I2CCLK

I2CDAT

GND

Module Application

V180

R pull up

R pull up

R pull up

R pull up

Cinterion® ELS61-AUS Hardware Interface Description

2.1 Application Interface

52

ELS61-AUS_HID_v00.031 2016-06-03

Confidential / Preliminary

Page 36 of 102

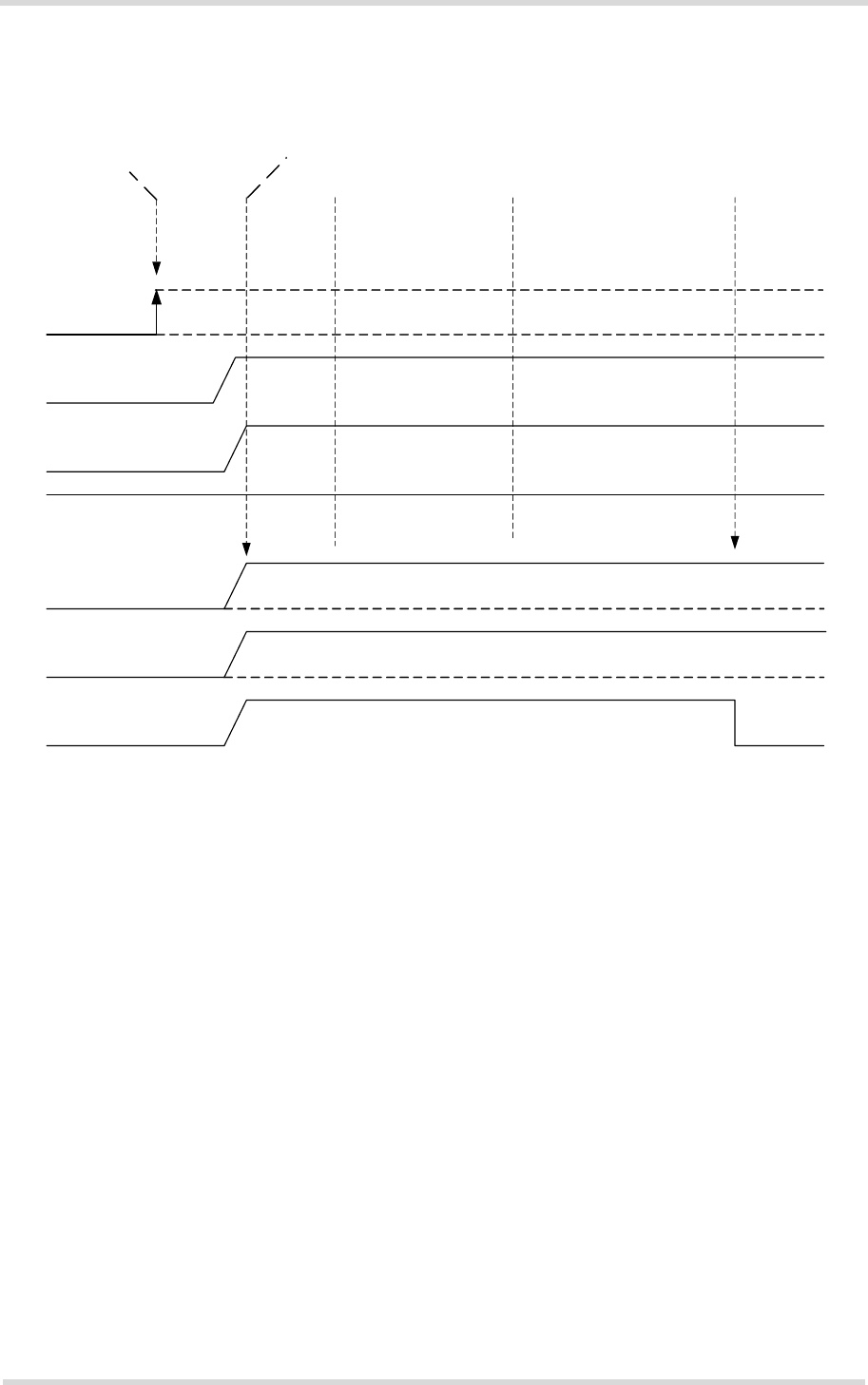

The following figure shows the startup behavior of the I2C interface. With an active state of the

ASC0 interface (i.e. CTS0 is at low level) the initialization of the I2C interface is also finished.

Figure 15: I2C startup behavior

I2CCLK

I2CDAT

Open Drain

Open Drain

(external pull up)

(external pull up)

CTSx

ON

EMERG_RST

Power supply active

Start up

Firmware

initialization

Command interface

initialization

Interface

active

Reset

state

V180

VCORE

Cinterion® ELS61-AUS Hardware Interface Description

2.1 Application Interface

52

ELS61-AUS_HID_v00.031 2016-06-03

Confidential / Preliminary

Page 37 of 102

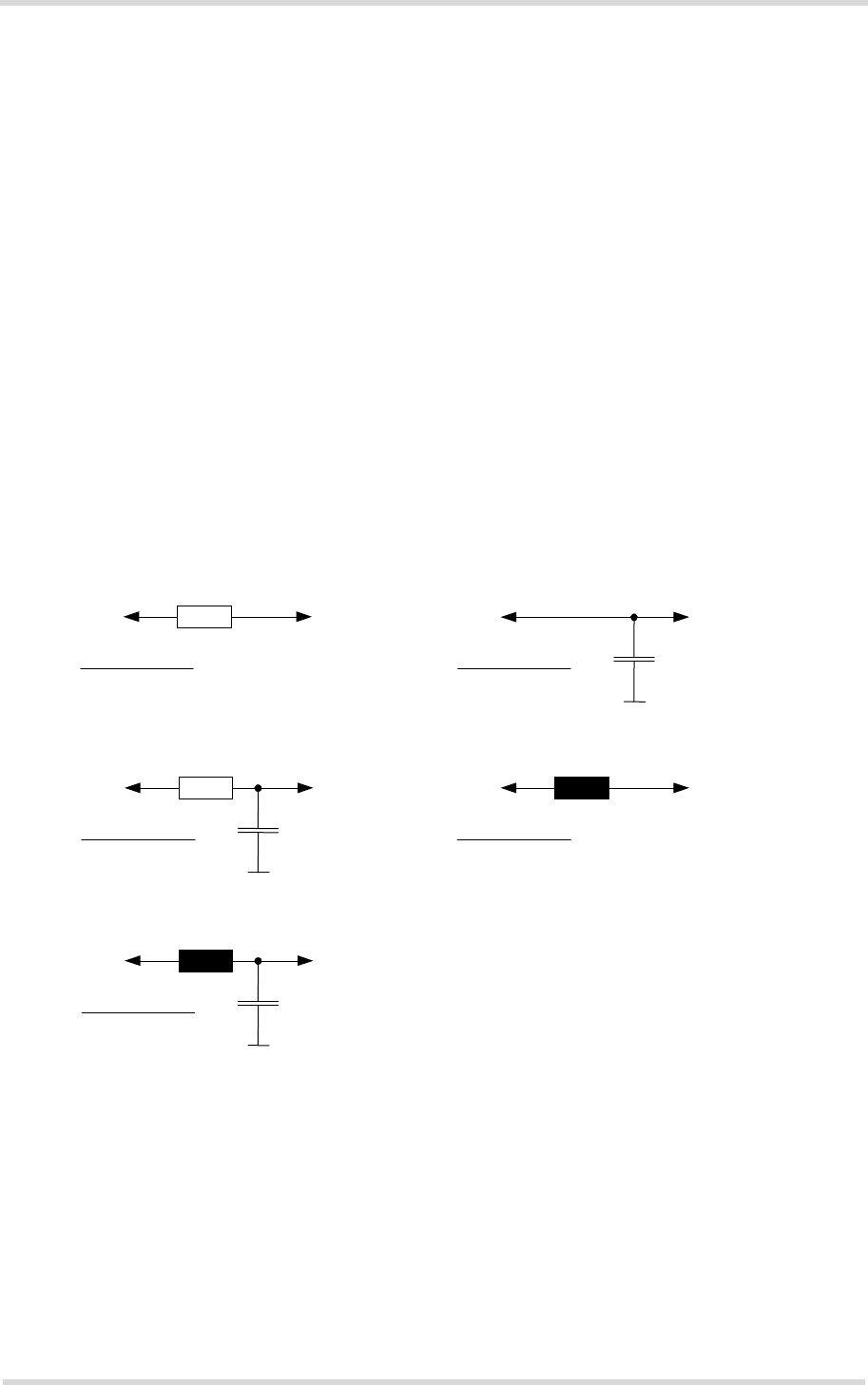

2.1.10 SPI Interface

Four ELS61-AUS GPIO interface lines can be configured as Serial Peripheral Interface (SPI).

The SPI is a synchronous serial interface for control and data transfer between ELS61-AUS

and the external application. Only one application can be connected to the SPI and the inter-

face supports only master mode. The transmission rates are up to 6.5Mbit/s. The SPI interface

comprises the two data lines MOSI and MISO, the clock line SPI_CLK a well as the chip select

line SPI_CS.

The four GPIO lines can be configured as SPI interface signals as follows: GPIO3 --> SPI_CLK,

GPIO16 --> MOSI, GPIO17 --> MISO and GPIO19 --> SPI_CS. The configuration is done by

AT command (see [1]). It is non-volatile and becomes active after a module restart.

The GPIO lines are also shared with the ASC1 signal lines and the ASC0 modem status signal

line DSR0.

To configure and activate the SPI interface use the AT^SSPI command. Detailed information

on the AT^SSPI command as well explanations on the SPI modes required for data transmis-

sion can be found in [1].

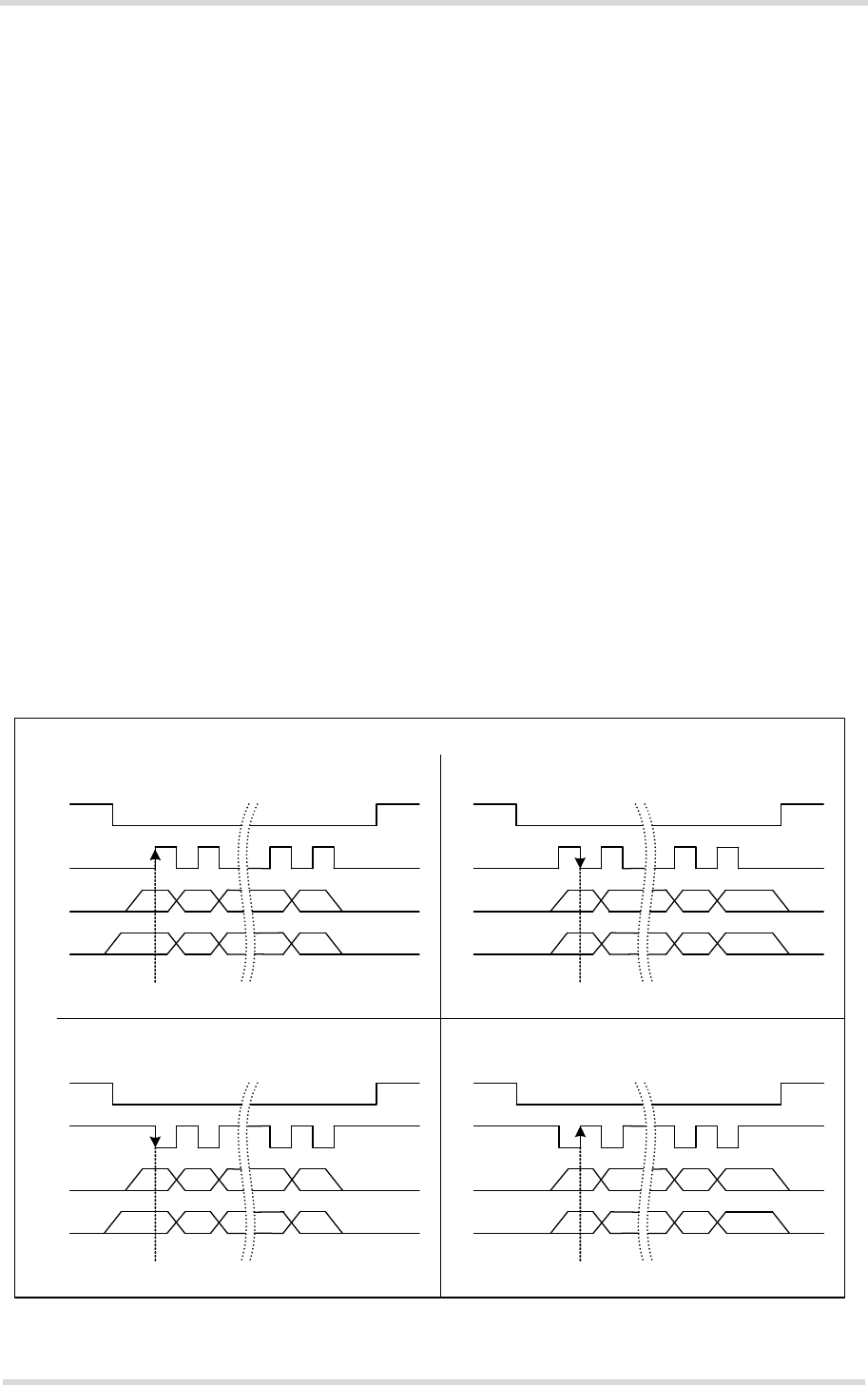

In general, SPI supports four operation modes. The modes are different in clock phase and

clock polarity. The module’s SPI mode can be configured by using the AT command AT^SSPI.

Make sure the module and the connected slave device works with the same SPI mode.

Figure 16 shows the characteristics of the four SPI modes. The SPI modes 0 and 3 are the most

common used modes. For electrical characteristics please refer to Table 2.

Figure 16: Characteristics of SPI modes

SPI MODE 0 SPI MODE 1

SPI MODE 2 SPI MODE 3

Clock phase

Clock polarity

SPI_CS

MOSI

SPI_CLK

MISO

SPI_CS

MOSI

SPI_CLK

MISO

SPI_CS

MOSI

SPI_CLK

MISO

SPI_CS

MOSI

SPI_CLK

MISO

Sample Sample

Sample Sample

Cinterion® ELS61-AUS Hardware Interface Description

2.1 Application Interface

52

ELS61-AUS_HID_v00.031 2016-06-03

Confidential / Preliminary

Page 38 of 102

2.1.11 PWM Interfaces

The GPIO6 and GPIO7 interface lines can be configured as Pulse Width Modulation interface

lines PWM1 and PWM2. The PWM interface lines can be used, for example, to connect buzz-

ers. The PWM1 line is shared with GPIO7 and the PWM2 line is shared with GPIO6 (for GPIOs

see Section 2.1.8). GPIO and PWM functionality are mutually exclusive.

The startup behavior of the lines is shown in Figure 13.

2.1.12 Pulse Counter

The GPIO8 line can be configured as pulse counter line COUNTER. The pulse counter inter-

face can be used, for example, as a clock (for GPIOs see Section 2.1.8).

2.1.13 Control Signals

2.1.13.1 Status LED

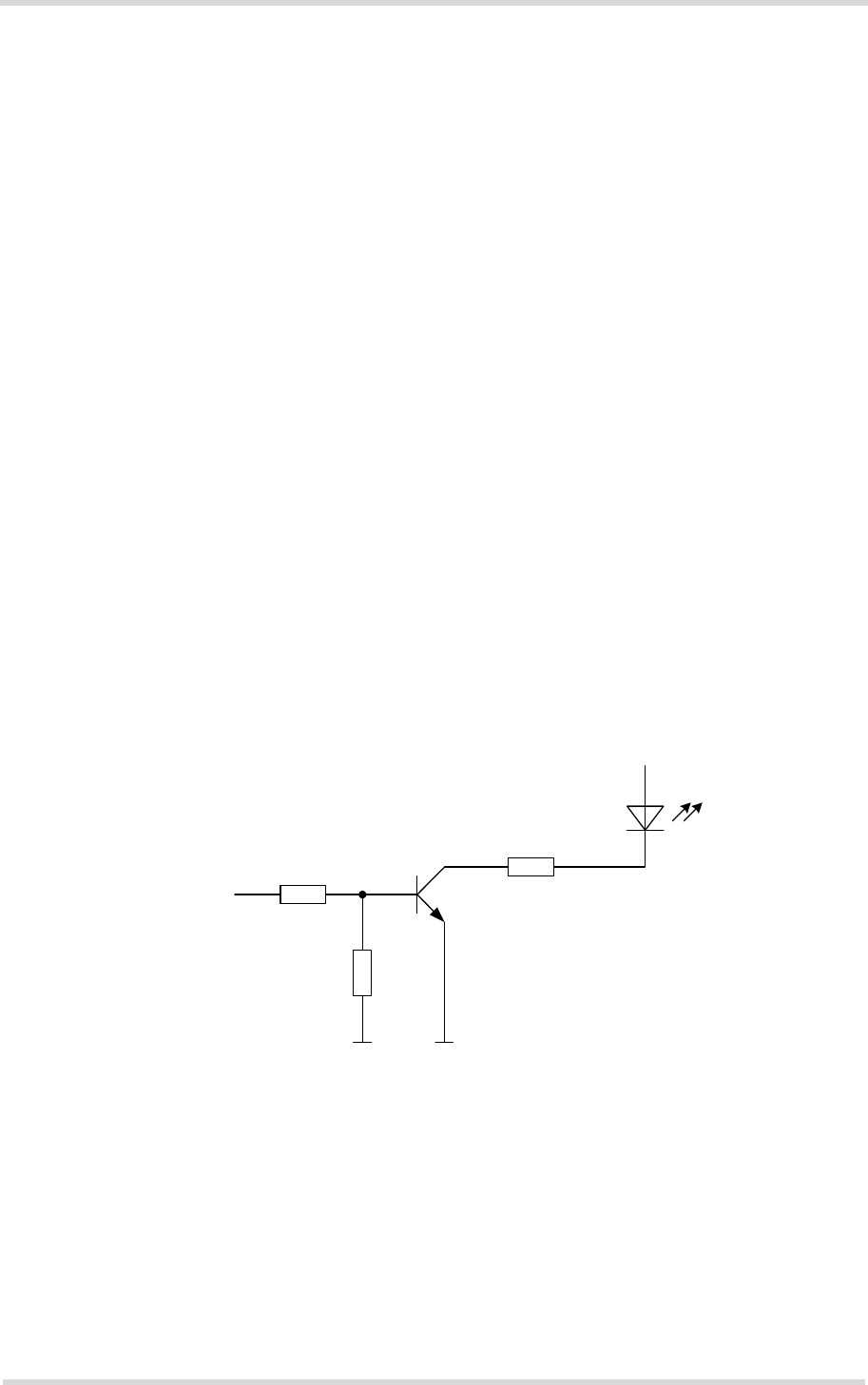

The GPIO5 interface line can be configured to drive a status LED that indicates different oper-

ating modes of the module (for GPIOs see Section 2.1.8). GPIO and LED functionality are mu-

tually exclusive.

To take advantage of this function connect an LED to the GPIO5/LED line as shown in Figure

17.

Figure 17: Status signaling with LED driver

VCC

GPIO5/

LED

LED

GNDGND

R1

R2

R3

Cinterion® ELS61-AUS Hardware Interface Description

2.1 Application Interface

52

ELS61-AUS_HID_v00.031 2016-06-03

Confidential / Preliminary

Page 39 of 102

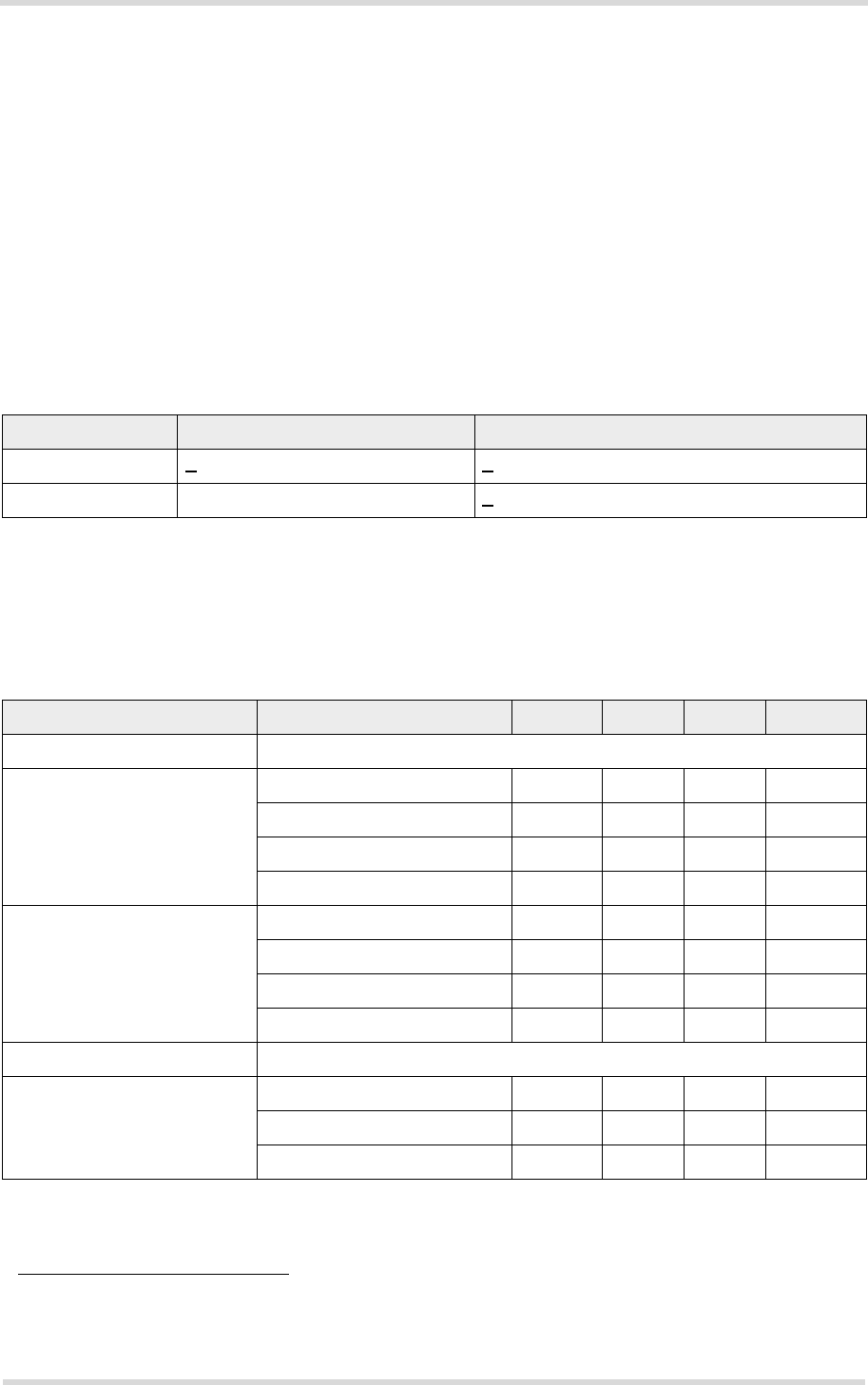

2.1.13.2 Power Indication Circuit

In Power Down mode the maximum voltage at any digital or analog interface line must not ex-

ceed +0.3V (see also Section 2.1.2.1). Exceeding this limit for any length of time might cause

permanent damage to the module.

It is therefore recommended to implement a power indication signal that reports the module’s

power state and shows whether it is active or in Power Down mode. While the module is in

Power Down mode all signals with a high level from an external application need to be set to

low state or high impedance state. The sample power indication circuit illustrated in Figure 18

denotes the module’s active state with a low signal and the module’s Power Down mode with

a high signal or high impedance state.

Figure 18: Power indication circuit

2.1.13.3 Host Wakeup

If no call, data or message transfer is in progress, the host may shut down its own USB inter-

face to save power. If a call or other request (URC’s, messages) arrives, the host can be noti-

fied of these events and be woken up again by a state transition of the ASC0 interface‘s RING0

line. This functionality should only be used with legacy USB applications not supporting the rec-

ommended USB suspend and resume mechanism as described in [5] (see also Section 2.1.3.1).

For more information on how to configure the RING0 line by AT^SCFG command see [1].

Possible RING0 line states are listed in Table 6.

Table 6: Host wakeup lines

Signal I/O Description

RING0 O Inactive to active low transition:

0 = The host shall wake up

1 = No wake up request

22k

10k

100k

100k

4.7k

V180

VCORE

Power

indication

External

power supply

Cinterion® ELS61-AUS Hardware Interface Description

2.1 Application Interface

52

ELS61-AUS_HID_v00.031 2016-06-03

Confidential / Preliminary

Page 40 of 102

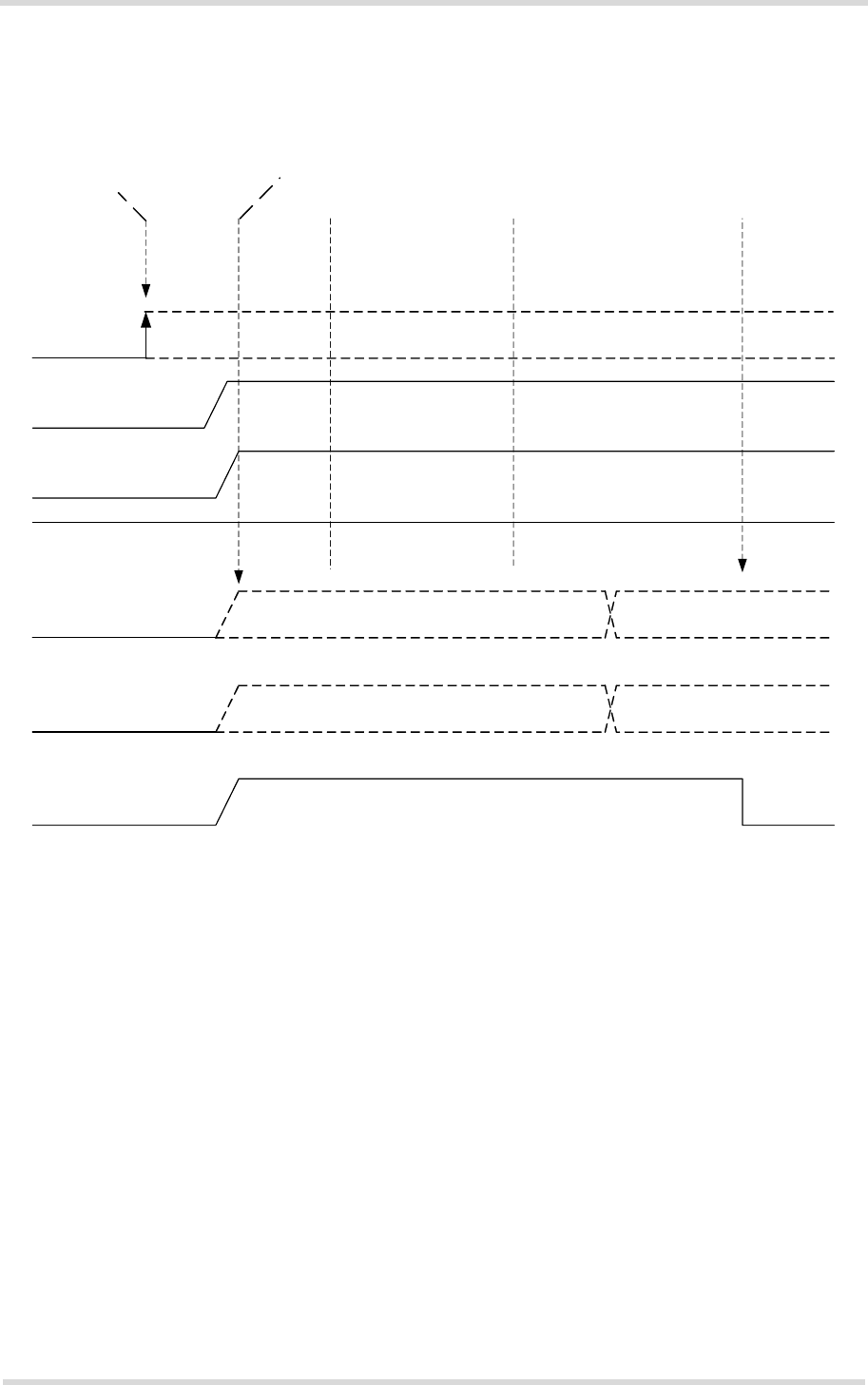

2.1.13.4 Fast Shutdown

The GPIO4 interface line can be configured as fast shutdown signal line FST_SHDN. The con-

figured FST_SHDN line is an active low control signal and must be applied for at least 10 mil-

liseconds. If unused this line can be left open because of a configured internal pull-up resistor.

Before setting the FST_SHDN line to low, the ON signal should be set to low (see Figure 19).

Otherwise there might be back powering at the ON line in Power Down mode.

By default, the fast shutdown feature is disabled. It has to be enabled using the AT command

AT^SCFG "MEShutdown/Fso". For details see [1].

If enabled, a low impulse >10 milliseconds on the FST_SHDN line starts the fast shutdown. The

fast shutdown procedure still finishes any data activities on the module's flash file system, thus

ensuring data integrity, but will no longer deregister gracefully from the network, thus saving

the time required for network deregistration.

Figure 19: Fast shutdown timing

Please note that if enabled, the normal software controlled shutdown using AT^SMSO will also

be a fast shutdown, i.e., without network deregistration. However, in this case no URCs includ-

ing shutdown URCs will be provided by the AT^SMSO command.

BATT+

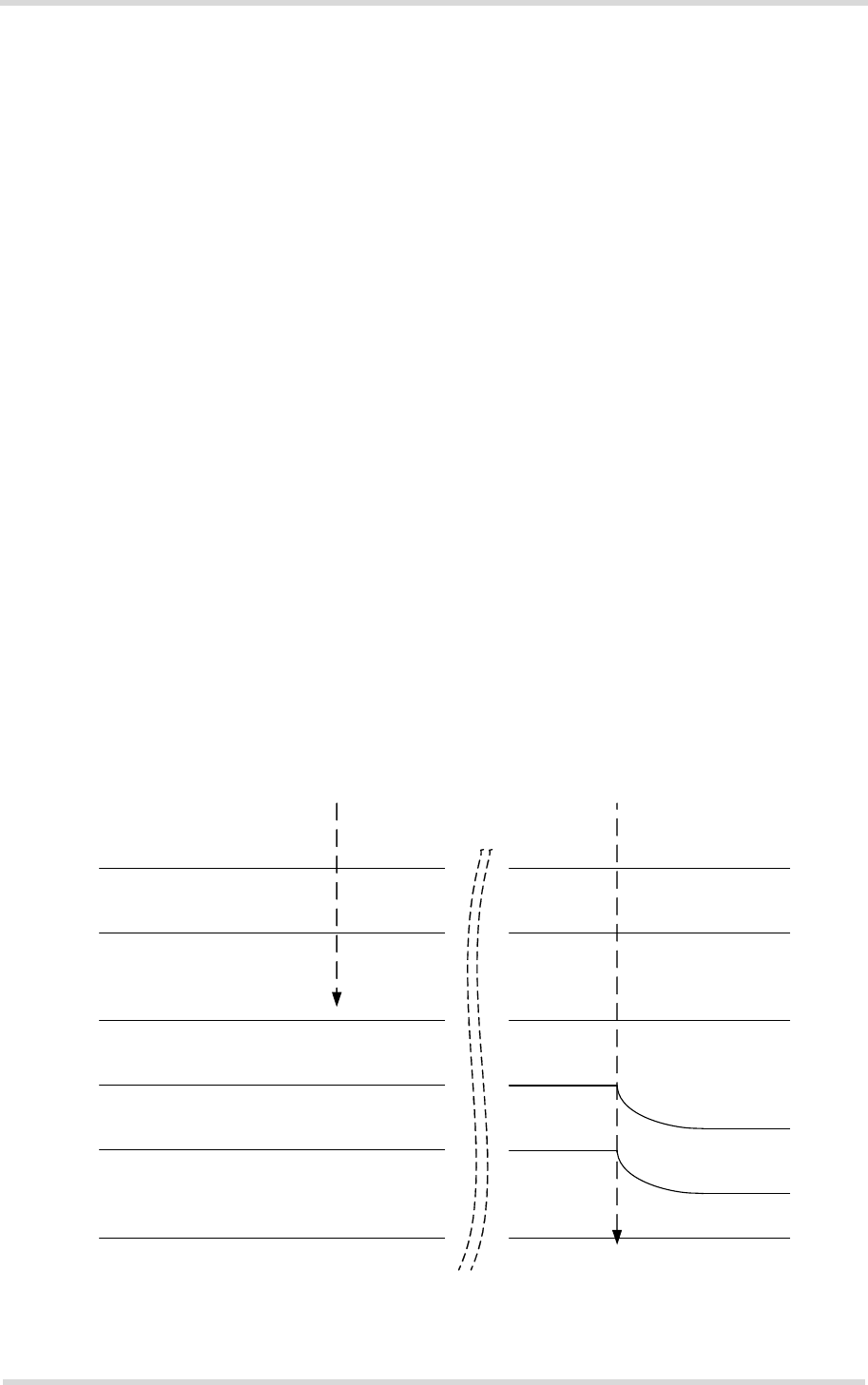

VCORE

V180