u blox LISAU200 3.75G HSPA Wireless Module User Manual LISA U series

u-blox AG 3.75G HSPA Wireless Module LISA U series

u blox >

Contents

- 1. 08 integrators manual

- 2. 08 revised integrators manual

- 3. MANUAL

- 4. Host user guide

- 5. LISA-U2_SysIntegrManual

08 integrators manual

LISA-U series

3.75G HSPA / HSPA+

Wireless Modules

System Integration Manual

Abstract

This document describes the features and the system integration of

LISA-U1 series HSPA and LISA-U2 series HSPA+ wireless modules.

These modules are a complete and cost efficient 3.75G solution

offering up to six-band HSDPA/HSUPA and quad-band GSM/EGPRS

voice and/or data transmission technology in a compact form factor.

locate, communicate, accelerate

33.2 x 22.4 x 2.6 mm

www.u-blox.com

LISA-U series - System Integration Manual

3G.G2-HW-10002-A1

Page 2 of 160

Document Information

Title

LISA-U series

Subtitle

3.75G HSPA / HSPA+

Wireless Modules

Document type

System Integration Manual

Document number

3G.G2-HW-10002-A1

Document status

Advance Information

Document status information

Objective

Specification

This document contains target values. Revised and supplementary data will be published

later.

Advance

Information

This document contains data based on early testing. Revised and supplementary data will

be published later.

Preliminary

This document contains data from product verification. Revised and supplementary data

may be published later.

Released

This document contains the final product specification.

This document applies to the following products:

Name

Type number

Firmware version

PCN / IN

LISA-U100

LISA-U100-00S-00

10.72

3G.G2-SW-11000

LISA-U100-01S-00

11.40

n.a.

LISA-U110

LISA-U110-00S-00

10.72

3G.G2-SW-11000

LISA-U110-01S-00

11.40

n.a.

LISA-U120

LISA-U120-00S-00

10.72

3G.G2-SW-11000

LISA-U120-01S-00

11.40

n.a.

LISA-U130

LISA-U130-00S-00

10.72

3G.G2-SW-11000

LISA-U130-01S-00

11.40

n.a.

LISA-U130-01A-00

11.40

n.a.

LISA-U200

LISA-U200-00S-00

TBD

N/A

LISA-U200-01S-00

TBD

N/A

LISA-U230

LISA-U230-01S-00

TBD

N/A

LISA-U230-01A-00

TBD

N/A

This document and the use of any information contained therein, is subject to the acceptance of the u-blox terms and conditions. They

can be downloaded from www.u-blox.com.

u-blox makes no warranties based on the accuracy or completeness of the contents of this document and reserves the right to make

changes to specifications and product descriptions at any time without notice.

u-blox reserves all rights to this document and the information contained herein. Reproduction, use or disclosure to third parties without

express permission is strictly prohibited. Copyright © 2012, u-blox AG.

u-blox® is a registered trademark of u-blox Holding AG in the EU and other countries.

LISA-U series - System Integration Manual

3G.G2-HW-10002-A1 Advance Information Preface

Page 3 of 160

Preface

u-blox Technical Documentation

As part of our commitment to customer support, u-blox maintains an extensive volume of technical

documentation for our products. In addition to our product-specific technical data sheets, the following manuals

are available to assist u-blox customers in product design and development.

AT Commands Manual: This document provides the description of the supported AT commands by the

LISA-U series modules to verify all implemented functionalities.

System Integration Manual: This Manual provides hardware design instructions and information on how to

set up production and final product tests.

Application Note: document provides general design instructions and information that applies to all u-blox

Wireless modules. See Section Related documents for a list of Application Notes related to your Wireless

Module.

How to use this Manual

The LISA-U series System Integration Manual provides the necessary information to successfully design in and

configure these u-blox wireless modules.

This manual has a modular structure. It is not necessary to read it from the beginning to the end.

The following symbols are used to highlight important information within the manual:

An index finger points out key information pertaining to module integration and performance.

A warning symbol indicates actions that could negatively impact or damage the module.

Questions

If you have any questions about u-blox Wireless Integration, please:

Read this manual carefully.

Contact our information service on the homepage http://www.u-blox.com

Read the questions and answers on our FAQ database on the homepage http://www.u-blox.com

Technical Support

Worldwide Web

Our website (www.u-blox.com) is a rich pool of information. Product information, technical documents and

helpful FAQ can be accessed 24h a day.

By E-mail

Contact the nearest of the Technical Support offices by email. Use our service pool email addresses rather than

any personal email address of our staff. This makes sure that your request is processed as soon as possible. You

will find the contact details at the end of the document.

Helpful Information when Contacting Technical Support

When contacting Technical Support please have the following information ready:

Module type (e.g. LISA-U100) and firmware version

Module configuration

Clear description of your question or the problem

A short description of the application

Your complete contact details

LISA-U series - System Integration Manual

3G.G2-HW-10002-A1 Advance Information Contents

Page 4 of 160

Contents

Preface ................................................................................................................................ 3

Contents .............................................................................................................................. 4

1 System description ....................................................................................................... 7

1.1 Overview .............................................................................................................................................. 7

1.2 Architecture .......................................................................................................................................... 9

1.2.1 Functional blocks ......................................................................................................................... 10

1.2.2 Hardware differences between LISA-U series modules ................................................................. 12

1.3 Pin-out ............................................................................................................................................... 13

1.4 Operating modes ................................................................................................................................ 17

1.5 Power management ........................................................................................................................... 19

1.5.1 Power supply circuit overview ...................................................................................................... 19

1.5.2 Module supply (VCC) .................................................................................................................. 20

1.5.3 Current consumption profiles ...................................................................................................... 28

1.5.4 RTC Supply (V_BCKP) .................................................................................................................. 32

1.5.5 Interface supply (V_INT) ............................................................................................................... 34

1.6 System functions ................................................................................................................................ 35

1.6.1 Module power-on ....................................................................................................................... 35

1.6.2 Module power-off ....................................................................................................................... 39

1.6.3 Module reset ............................................................................................................................... 40

1.7 RF connection ..................................................................................................................................... 42

1.8 (U)SIM interface .................................................................................................................................. 42

1.8.1 (U)SIM functionality ..................................................................................................................... 44

1.9 Serial communication ......................................................................................................................... 45

1.9.1 Serial interfaces configuration ..................................................................................................... 45

1.9.2 Asynchronous serial interface (UART)........................................................................................... 46

1.9.3 USB interface............................................................................................................................... 61

1.9.4 SPI interface ................................................................................................................................ 64

1.9.5 MUX Protocol (3GPP 27.010) ...................................................................................................... 68

1.10 DDC (I2C) interface .......................................................................................................................... 69

1.10.1 Overview ..................................................................................................................................... 69

1.10.2 DDC application circuit ................................................................................................................ 69

1.11 Audio Interface ............................................................................................................................... 74

1.11.1 Analog Audio interface ............................................................................................................... 74

1.11.2 Digital Audio interface ................................................................................................................. 80

1.11.3 Voiceband processing system ...................................................................................................... 85

1.12 General Purpose Input/Output (GPIO) ............................................................................................. 87

1.13 Reserved pins (RSVD) ...................................................................................................................... 96

1.14 Schematic for LISA-U series module integration .............................................................................. 97

1.15 Approvals ........................................................................................................................................ 99

LISA-U series - System Integration Manual

3G.G2-HW-10002-A1 Advance Information Contents

Page 5 of 160

1.15.1 R&TTED and European Conformance CE mark ............................................................................ 99

1.15.2 IC ................................................................................................................................................ 99

1.15.3 Federal communications commission notice .............................................................................. 100

1.15.4 a-tick AUS Certification ............................................................................................................. 103

2 Design-In ................................................................................................................... 104

2.1 Design-in checklist ............................................................................................................................ 104

2.1.1 Schematic checklist ................................................................................................................... 104

2.1.2 Layout checklist ......................................................................................................................... 105

2.1.3 Antenna checklist ...................................................................................................................... 105

2.2 Design Guidelines for Layout ............................................................................................................ 106

2.2.1 Layout guidelines per pin function ............................................................................................. 106

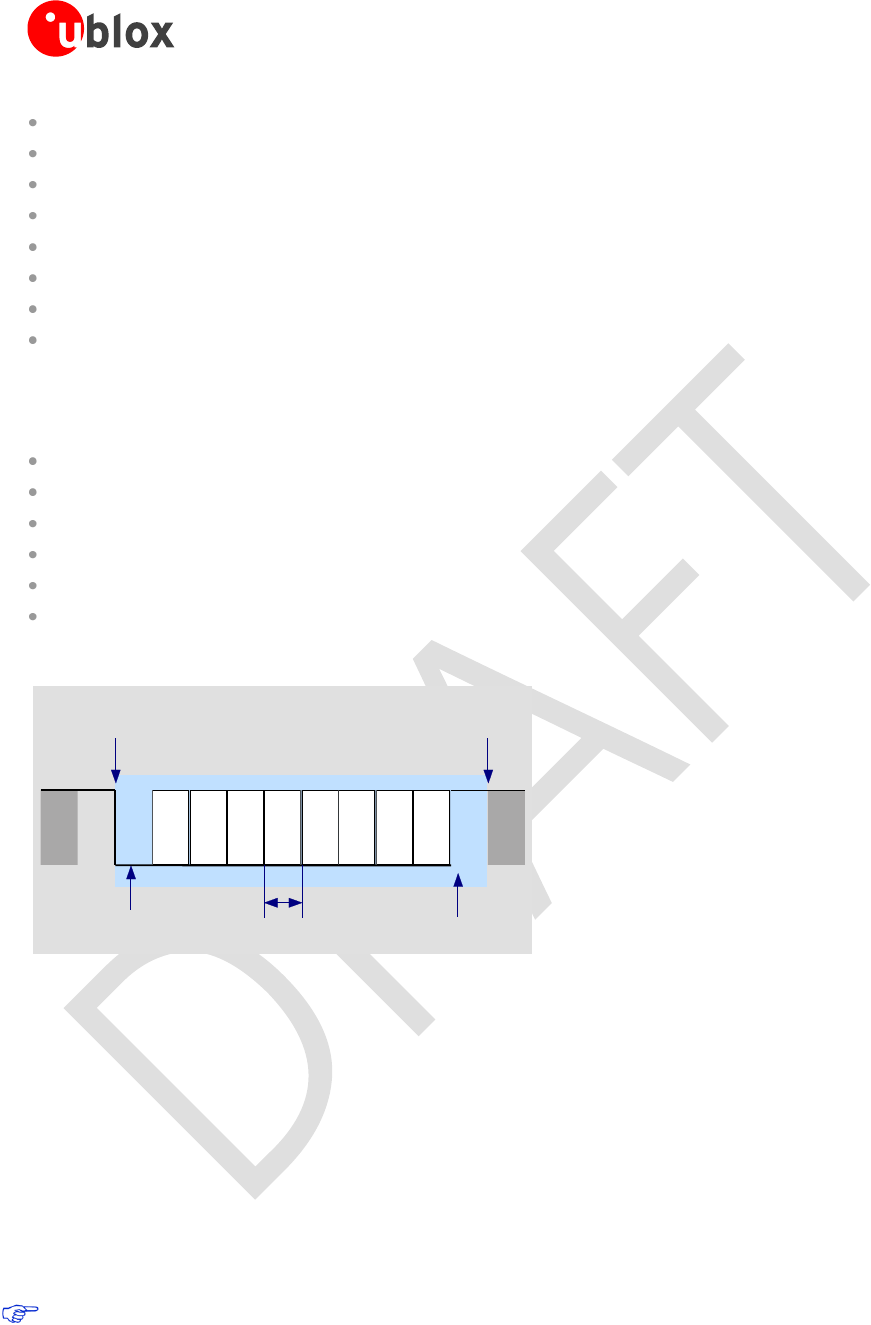

2.2.2 Footprint and paste mask .......................................................................................................... 116

2.2.3 Placement ................................................................................................................................. 118

2.3 Thermal aspects ................................................................................................................................ 119

2.4 Antenna guidelines ........................................................................................................................... 120

2.4.1 Antenna termination ................................................................................................................. 121

2.4.2 Antenna radiation ..................................................................................................................... 122

2.4.3 Antenna detection functionality ................................................................................................ 123

2.5 ESD precautions ................................................................................................................................ 126

2.5.1 ESD immunity test overview ...................................................................................................... 126

2.5.2 ESD immunity test of LISA-U series reference design.................................................................. 126

2.5.3 ESD application circuits .............................................................................................................. 128

3 Features description ................................................................................................. 131

3.1 Firmware (upgrade) Over AT (FOAT) ................................................................................................. 131

3.1.1 Overview ................................................................................................................................... 131

3.1.2 FOAT procedure ........................................................................................................................ 131

3.2 TCP/IP and UDP/IP ............................................................................................................................. 131

3.2.1 Multiple PDP contexts and sockets............................................................................................. 131

3.3 FTP and FTPS .................................................................................................................................... 132

3.4 HTTP and HTTPS ............................................................................................................................... 132

3.5 AssistNow clients and GPS integration .............................................................................................. 132

3.6 Jamming Detection ........................................................................................................................... 132

3.7 In-Band modem ................................................................................................................................ 133

3.8 Smart Temperature Management ..................................................................................................... 133

3.8.1 Smart Temperature Supervisor (STS) .......................................................................................... 134

3.8.2 Threshold Definitions ................................................................................................................. 136

3.9 Hybrid positioning and CellLocate ..................................................................................................... 136

3.9.1 Positioning through cellular information: CellLocate .................................................................. 136

3.9.2 Hybrid positioning ..................................................................................................................... 138

4 Handling and soldering ........................................................................................... 139

4.1 Packaging, shipping, storage and moisture preconditioning ............................................................. 139

4.2 Soldering .......................................................................................................................................... 139

LISA-U series - System Integration Manual

3G.G2-HW-10002-A1 Advance Information Contents

Page 6 of 160

4.2.1 Soldering paste.......................................................................................................................... 139

4.2.2 Reflow soldering ....................................................................................................................... 139

4.2.3 Optical inspection ...................................................................................................................... 141

4.2.4 Cleaning .................................................................................................................................... 141

4.2.5 Repeated reflow soldering ......................................................................................................... 141

4.2.6 Wave soldering.......................................................................................................................... 141

4.2.7 Hand soldering .......................................................................................................................... 141

4.2.8 Rework ...................................................................................................................................... 141

4.2.9 Conformal coating .................................................................................................................... 141

4.2.10 Casting ...................................................................................................................................... 142

4.2.11 Grounding metal covers ............................................................................................................ 142

4.2.12 Use of ultrasonic processes ........................................................................................................ 142

5 Product Testing......................................................................................................... 143

5.1 u-blox in-series production test ......................................................................................................... 143

5.2 Test parameters for OEM manufacturer ............................................................................................ 143

5.2.1 ‘Go/No go’ tests for integrated devices ...................................................................................... 144

5.2.2 Functional tests providing RF operation ..................................................................................... 144

Appendix ........................................................................................................................ 147

A Migration to LISA-U2 series wireless modules ....................................................... 147

A.1 Checklist for migration ..................................................................................................................... 147

A.2 Software migration ........................................................................................................................... 148

A.2.1 Software migration from LISA-U1 series to LISA-U2 series wireless modules .............................. 148

A.3 Hardware migration.......................................................................................................................... 148

A.3.1 Hardware migration from LISA-U1 series to LISA-U2 series wireless modules ............................. 148

A.3.2 Pin-out comparison LISA-U1 series vs. LISA-U2 series ................................................................. 149

A.3.3 Layout comparison LISA-U1 series vs. LISA-U2 series .................................................................. 155

B Glossary .................................................................................................................... 156

Related documents......................................................................................................... 158

Revision history .............................................................................................................. 159

Contact ............................................................................................................................ 160

LISA-U series - System Integration Manual

3G.G2-HW-10002-A1 Advance Information System description

Page 7 of 160

1 System description

1.1 Overview

LISA-U series wireless modules integrate full-feature 3G UMTS/HSxPA and 2G GSM/GPRS/EDGE protocol stack

with Assisted GPS support. These SMT modules come in the compact LISA form factor, featuring Leadless Chip

Carrier (LCC) packaging technology.

3G UMTS/HSDPA/HSUPA Characteristics

2G GSM/GPRS/EDGE Characteristics

Class A User Equipment1

Class B Mobile Station2

UMTS Terrestrial Radio Access (UTRA) Frequency Division Duplex (FDD)

3GPP Release 6 High Speed Packet Access (HSPA) for LISA-U1

series

3GPP Release 7 Evolved High Speed Packet Access (HSPA+) for

LISA-U2 series

Rx Diversity for LISA-U230

GSM EDGE Radio Access (GERA)

3GPP Release 6 for LISA-U1 series

3GPP Release 7 for LISA-U2 series

Rx Diversity for LISA-U230

2-band support for LISA-U100, LISA-U120:

Band II (1900 MHz), Band V (850 MHz)

2-band support for LISA-U110, LISA-U130:

Band I (2100 MHz), Band VIII (900 MHz)

4-band support for LISA-U200-00:

Band I (2100 MHz), Band II (1900 MHz),

Band V (850 MHz), Band VI (800 MHz)

6-band support for LISA-U200-01, LISA-U230:

Band I (2100 MHz), Band II (1900 MHz), Band IV (1700 MHz),

Band V (850 MHz), Band VI (800 MHz), Band VIII (900 MHz)

4-band support

GSM 850 MHz, E-GSM 900 MHz,

DCS 1800 MHz, PCS 1900 MHz

WCDMA/HSDPA/HSUPA Power Class

Power Class 3 (24 dBm) for WCDMA/HSDPA/HSUPA mode

GSM/GPRS Power Class

Power Class 4 (33 dBm) for GSM/E-GSM bands

Power Class 1 (30 dBm) for DCS/PCS bands

EDGE Power Class

Power Class E2 (27 dBm) for GSM/E-GSM bands

Power Class E2 (26 dBm) for DCS/PCS bands

PS (Packet Switched) Data Rate

HSUPA category 6, up to 5.76 Mb/s UL

HSDPA category 8 up to 7.2 Mb/s DL for LISA-U1 series,

LISA-U200

HSDPA category 14 up to 21.1 Mb/s DL for LISA-U230

WCDMA PS data up to 384 kb/s DL/UL

PS (Packet Switched) Data Rate

GPRS multislot class 334, coding scheme CS1-CS4,

up to 107 kb/s DL, 85.6 kb/s UL for LISA-U2 series

GPRS multislot class 124, coding scheme CS1-CS4,

up to 85.6 kb/s DL/UL for LISA-U1 for LISA-U1 series

EDGE multislot class 333, coding scheme MCS1-MCS9,

up to 296 kb/s DL, 236.8 kb/s UL for LISA-U2

EDGE multislot class 124, coding scheme MCS1-MCS9,

up to 236.8 kb/s DL/UL for LISA-U1

CS (Circuit Switched) Data Rate

WCDMA CS data up to 64 kb/s DL/UL

CS (Circuit Switched) Data Rate

GSM CS data up to 9.6 kb/s DL/UL

supported in transparent/non transparent mode

Table 1: LISA-U series UMTS/HSDPA/HSUPA and GSM/GPRS/EDGE characteristics

Operation modes I to III are supported on GSM/GPRS network, with user-defined preferred service selectable

from GSM to GPRS. Paging messages for GSM calls can be optionally monitored during GPRS data transfer in

not-coordinating NOM II-III.

Direct Link mode is supported for TCP / UDP sockets except for LISA-U1xx-00 module versions.

1

Device can work simultaneously in Packet Switch and Circuit Switch mode: voice calls are possible while the data connection is active

2

Device can be attached to both GPRS and GSM services (i.e. Packet Switch and Circuit Switch mode) using one service at a time. If for

example during data transmission an incoming call occurs, the data connection is suspended to allow the voice communication. Once the

voice call has terminated, the data service is resumed.

3

GPRS/EDGE multislot class 33 implies a maximum of 5 slots in DL (reception) and 4 slots in UL (transmission) with 6 slots in total.

4

GPRS/EDGE multislot class 12 implies a maximum of 4 slots in DL (reception) and 4 slots in UL (transmission) with 5 slots in total.

LISA-U series - System Integration Manual

3G.G2-HW-10002-A1 Advance Information System description

Page 8 of 160

Regarding 3G transmit and receive data rate capability, LISA-U series modules implement 3G High-Speed Uplink

Packet Access (HSUPA) category 6, LISA-U1 series and LISA-U200 modules implement 3G High Speed Downlink

Packet Access (HSDPA) category 8, while LISA-U230 modules implement the 3G HSDPA category 14. HSUPA and

HSDPA categories determine the maximum speed at which data can be respectively transmitted and received:

higher categories allowing faster data transfer rates as indicated in Table 1.

The 3G network automatically performs adaptive coding and modulation using a choice of forward error

correction code rate and choice of modulation type, to achieve the highest possible data rate and data

transmission robustness according to the quality of the radio channel.

Regarding 2G transmit and receive data rate capability, LISA-U1 series modules implement GPRS/EGPRS class 12,

while LISA-U2 series modules implement GPRS/EGPRS class 33. GPRS and EGPRS classes determine the maximum

number of timeslots available for upload and download and thus the speed at which data can be transmitted

and received: higher classes typically allowing faster data transfer rates as indicated in Table 1.

The 2G network automatically configures the number of timeslots used for reception or transmission (voice calls

take precedence over GPRS/EGPRS traffic) and channel encoding (from Coding Scheme 1 up to Modulation and

Coding Scheme 9), performing link adaptation to achieve the highest possible data rate.

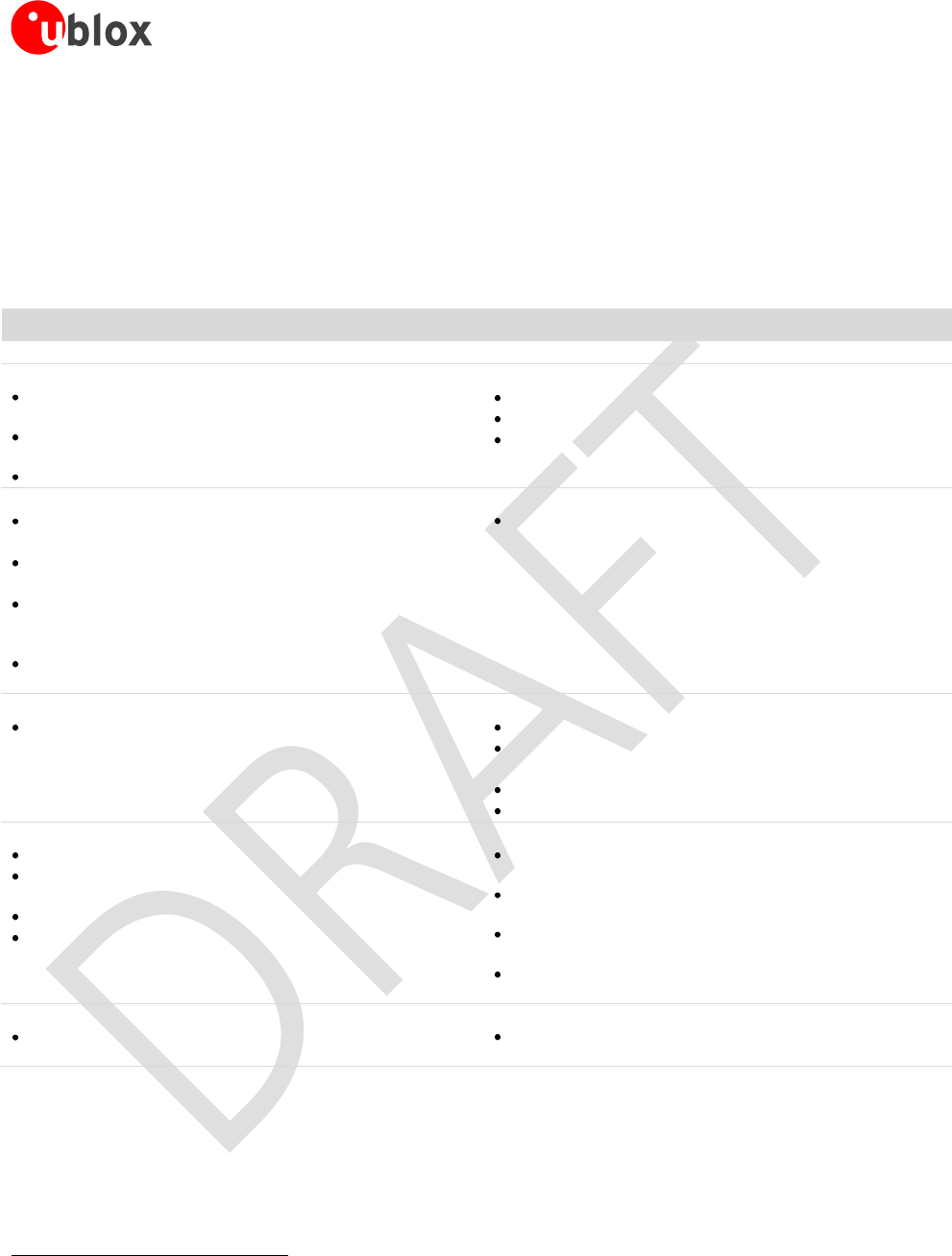

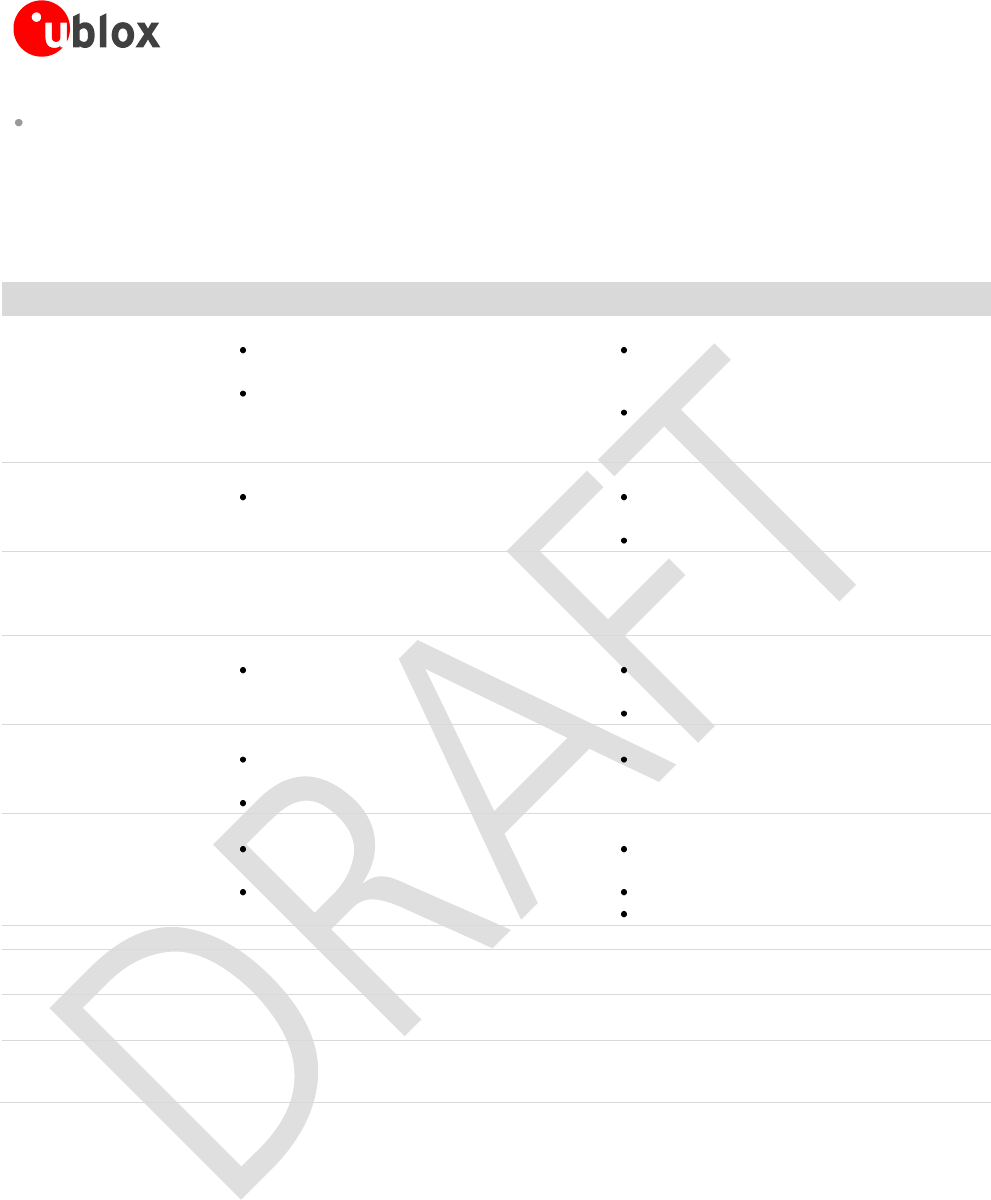

A summary of interfaces and features provided by LISA-U series modules is described in the Table 2. Note that

LISA-U130-01 and LISA-U230-01 are available in standard and automotive quality grade versions.

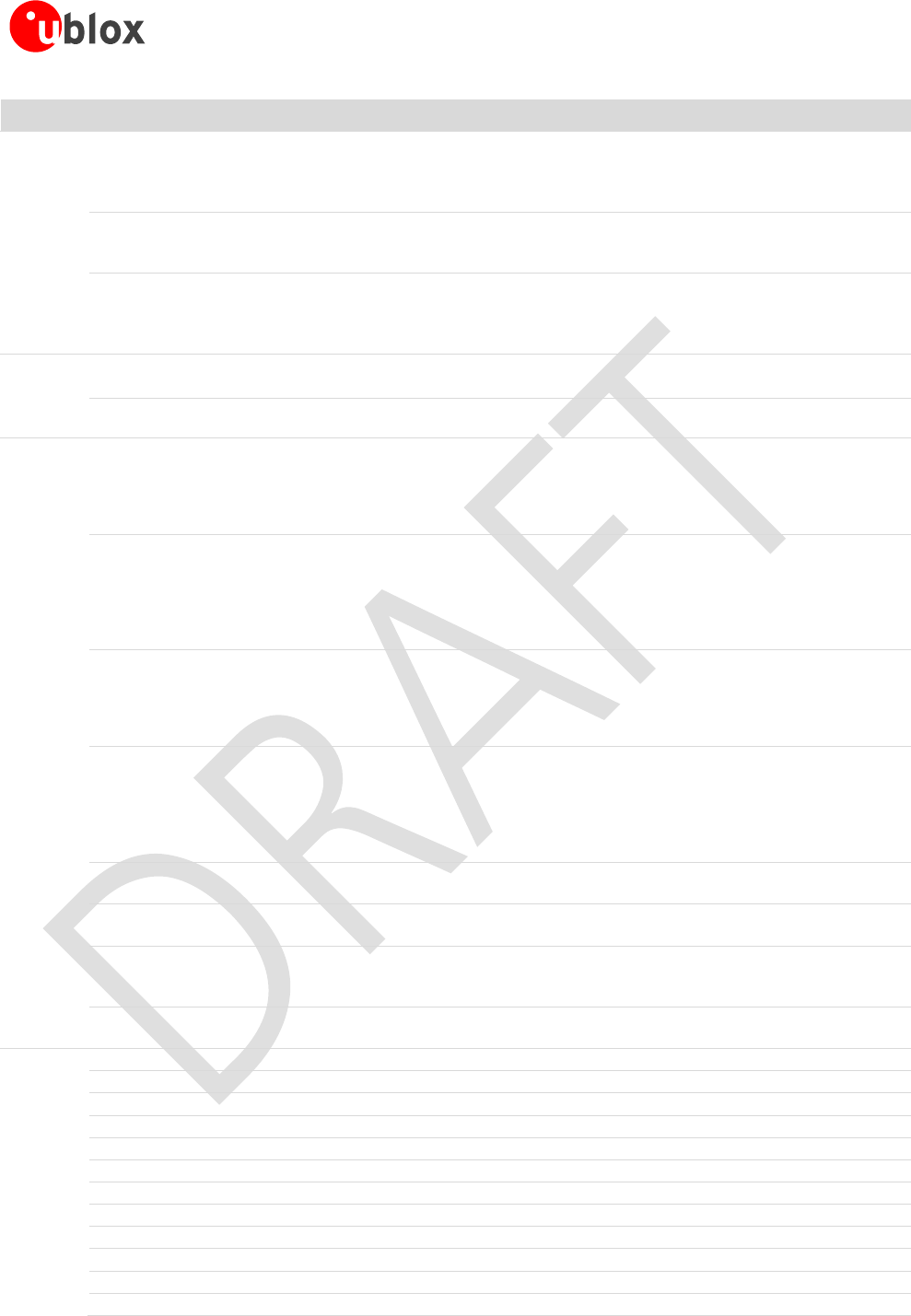

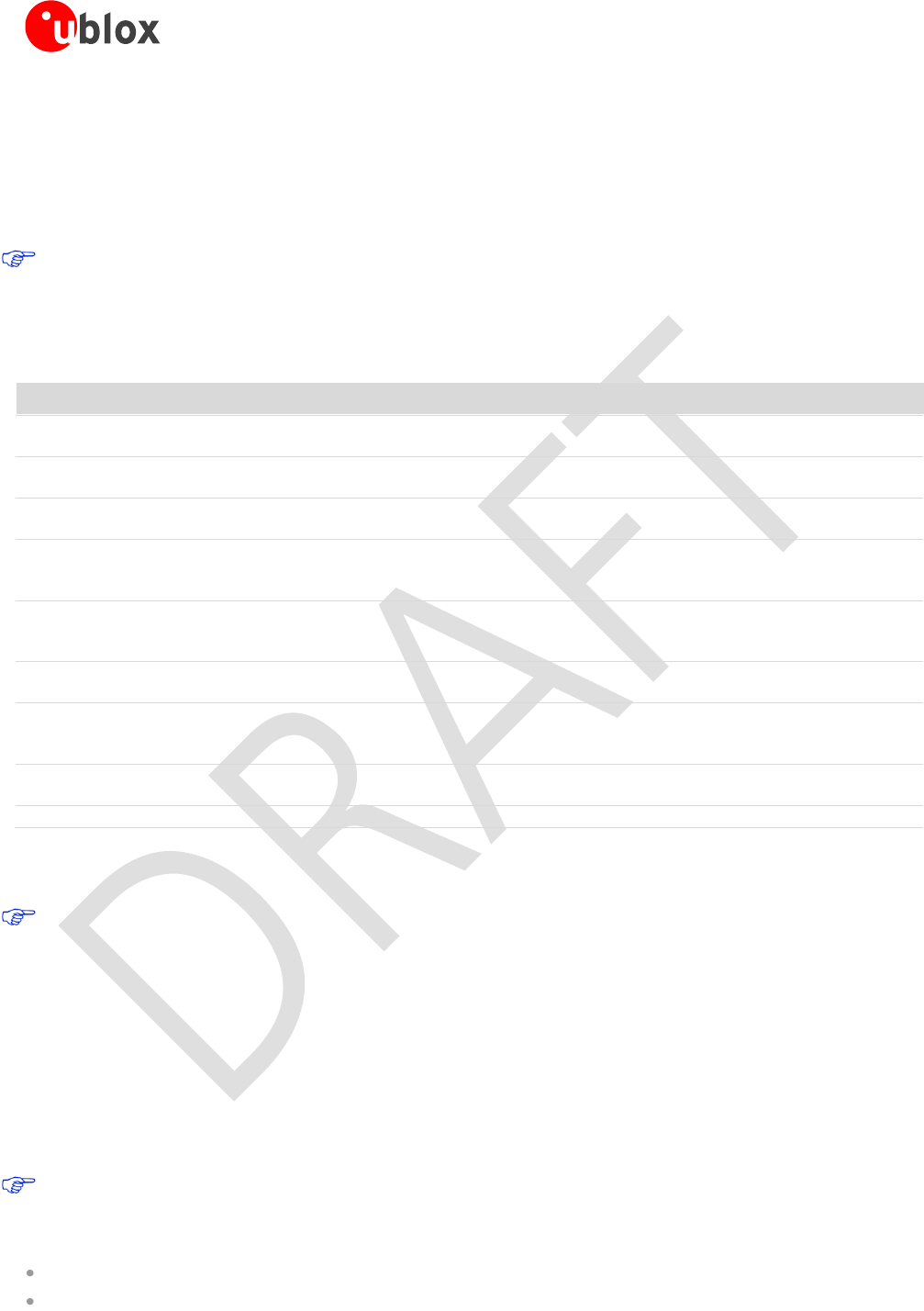

Module

Technology

Bands

Interface

Audio

Functions

HSUPA [Mb/s]

HSDPA [Mb/s]

UMTS/HSPA bands [MHz]

GSM/GPRS/EDGE quad-band

UART

SPI (5 wire)

USB

DDC for u-blox GPS

GPIO

Analog Audio

Digital Audio

Network indication

Antenna Supervisor

Jamming detection

Embedded TCP/UDP stack

HTTP, SSL

GPS via Modem

Embedded AssistNow

FW update over AT (FOAT)

In-band modem

Rx diversity

CellLocate

SIM Access Profile (SAP)

LISA-U100-00

5.76

7.2

850/1900

•

1

1

1

1

5

•

•

•

•

•

LISA-U100-01

5.76

7.2

850/1900

•

1

1

1

1

5

•

•

•

•

•

•

•

•

•

LISA-U110-00

5.76

7.2

900/2100

•

1

1

1

1

5

•

•

•

•

•

LISA-U110-01

5.76

7.2

900/2100

•

1

1

1

1

5

•

•

•

•

•

•

•

•

•

LISA-U120-00

5.76

7.2

850/1900

•

1

1

1

1

5

1

1

•

•

•

•

•

LISA-U120-01

5.76

7.2

850/1900

•

1

1

1

1

5

1

1

•

•

•

•

•

•

•

•

•

LISA-U130-00

5.76

7.2

900/2100

•

1

1

1

1

5

1

1

•

•

•

•

•

LISA-U130-01

5.76

7.2

900/2100

•

1

1

1

1

5

1

1

•

•

•

•

•

•

•

•

•

•

LISA-U200-00

5.76

7.2

800/850/

1900/2100

•

1

1

1

1

14

•

•

•

•

•

•

LISA-U200-01

5.76

7.2

800/850/900/

1700/1900/2100

•

1

1

1

1

14

2

•

•

•

•

•

•

•

•

•

•

•

LISA-U230-01

5.76

21.1

800/850/900/

1700/1900/2100

•

1

1

1

1

14

2

•

•

•

•

•

•

•

•

•

•

•

•

Table 2: LISA-U series features summary

LISA-U series - System Integration Manual

3G.G2-HW-10002-A1 Advance Information System description

Page 9 of 160

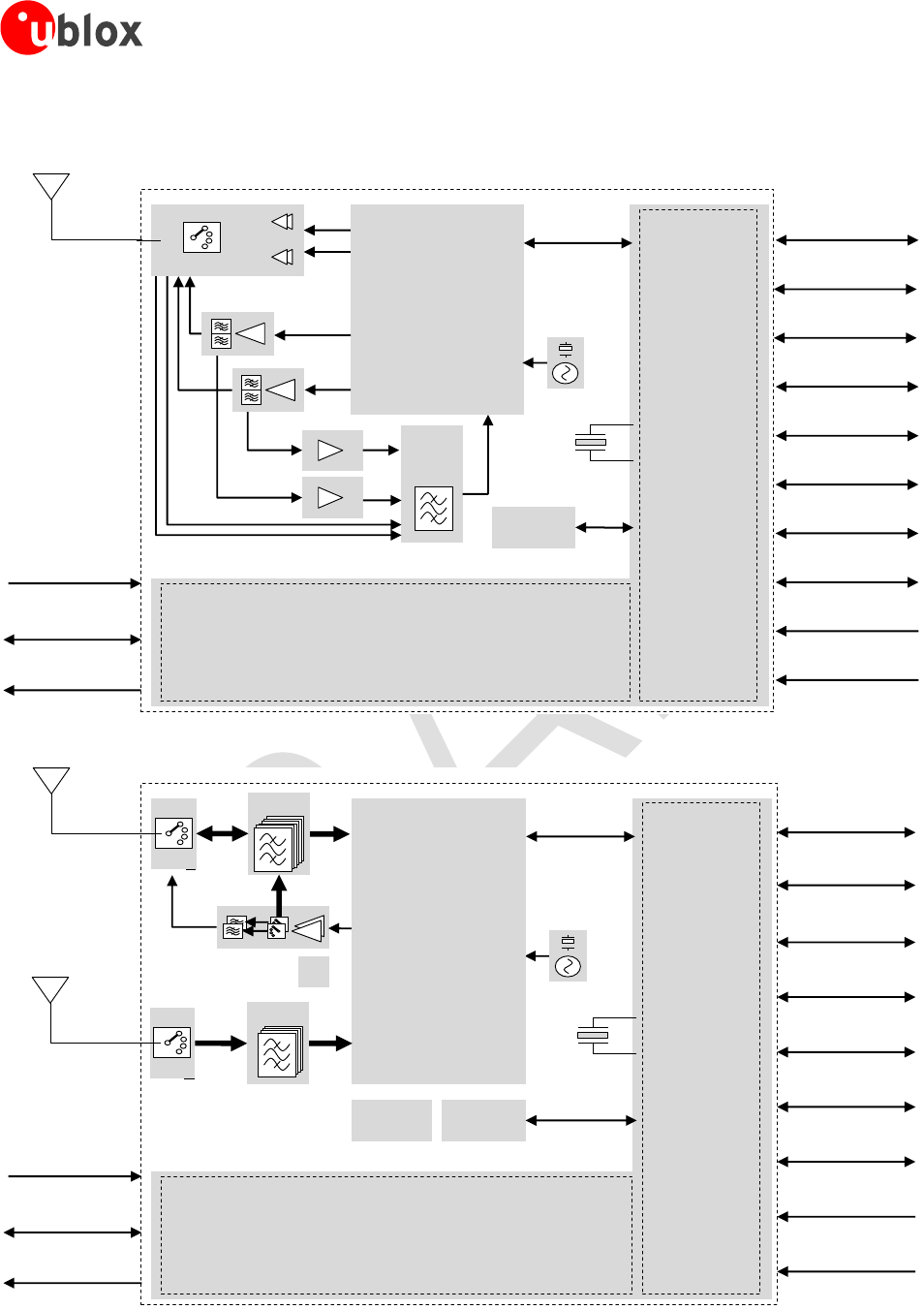

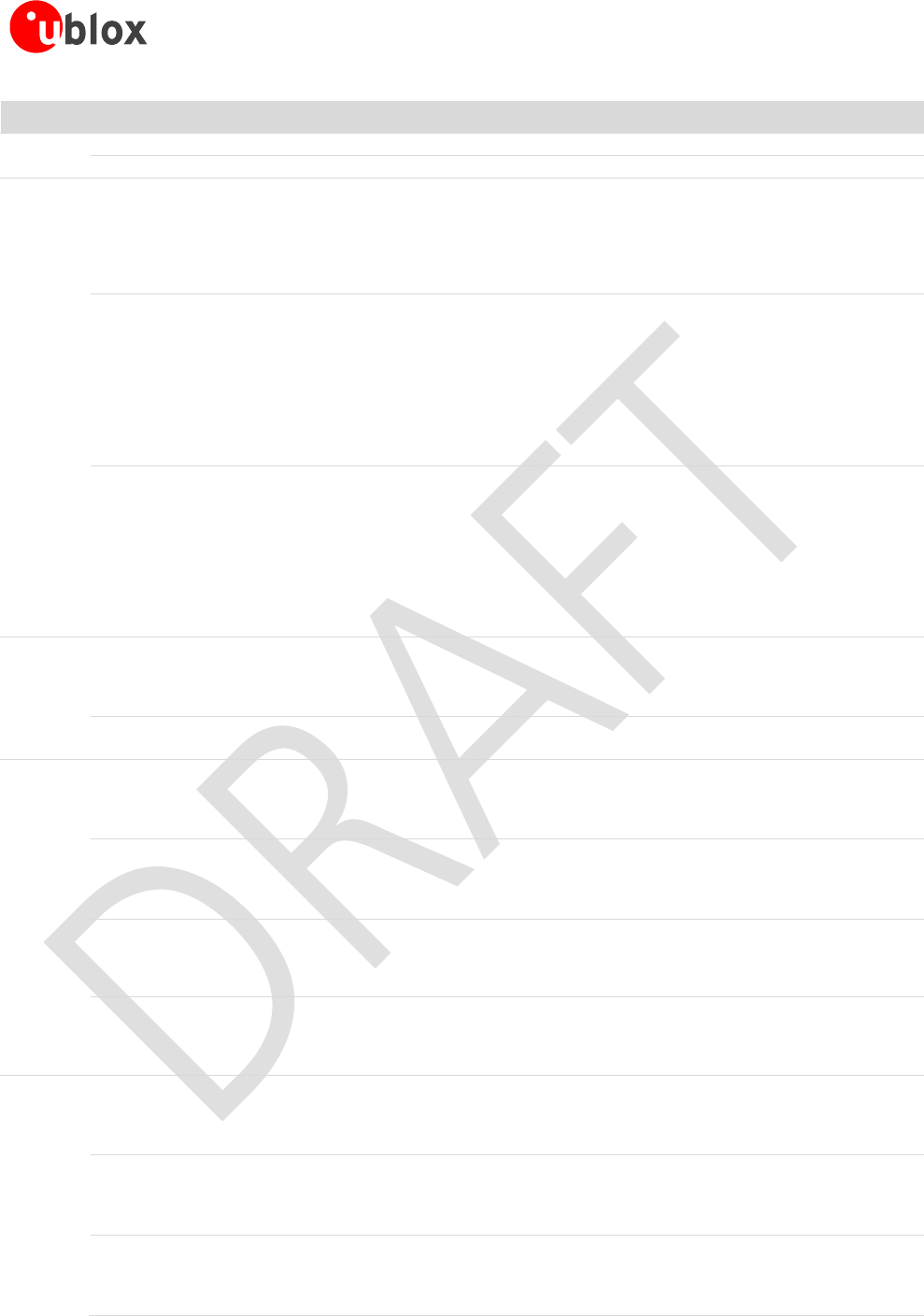

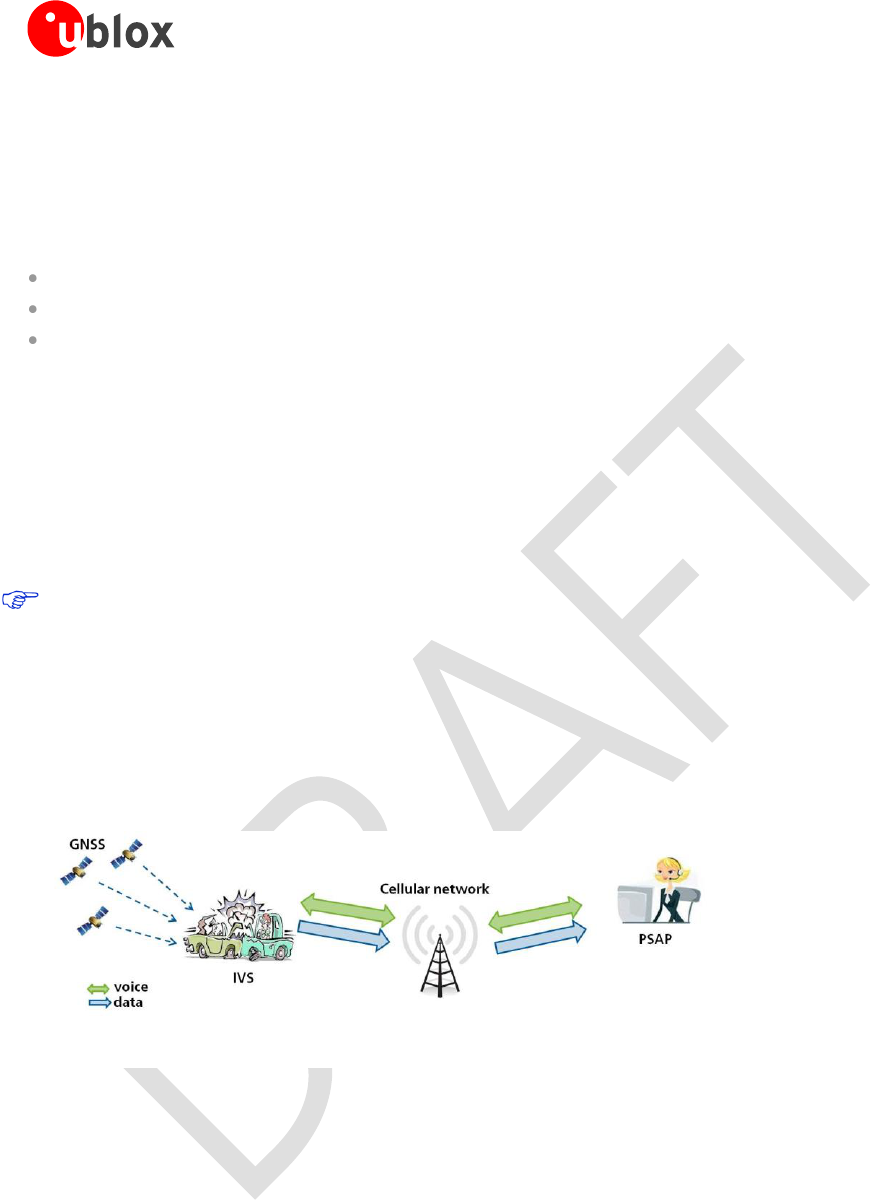

1.2 Architecture

Wireless

Base-band

Processor

Memory

Power Management Unit

RF

Transceiver

26 MHz

32.768 kHz

SAW

Filter

FEM & 2G PA

ANT

LNA

3G PA

LNA

3G PA

DDC (for GPS)

(U)SIM Card

UART

SPI

USB

GPIO(s)

Power On

External Reset

V_BCKP (RTC)

Vcc (Supply)

V_INT (I/O)

Digital Audio (I2S)

AnalogAudio

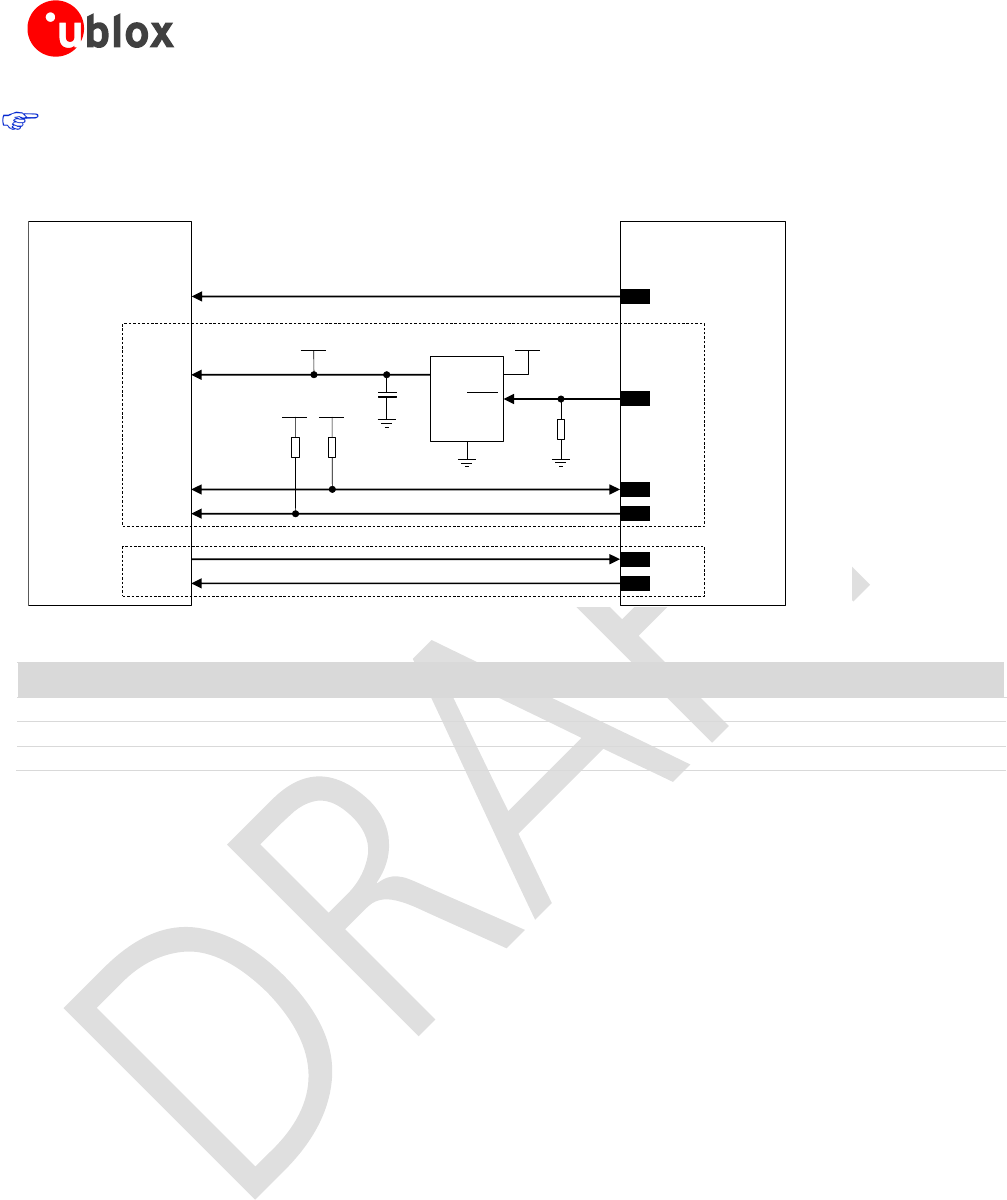

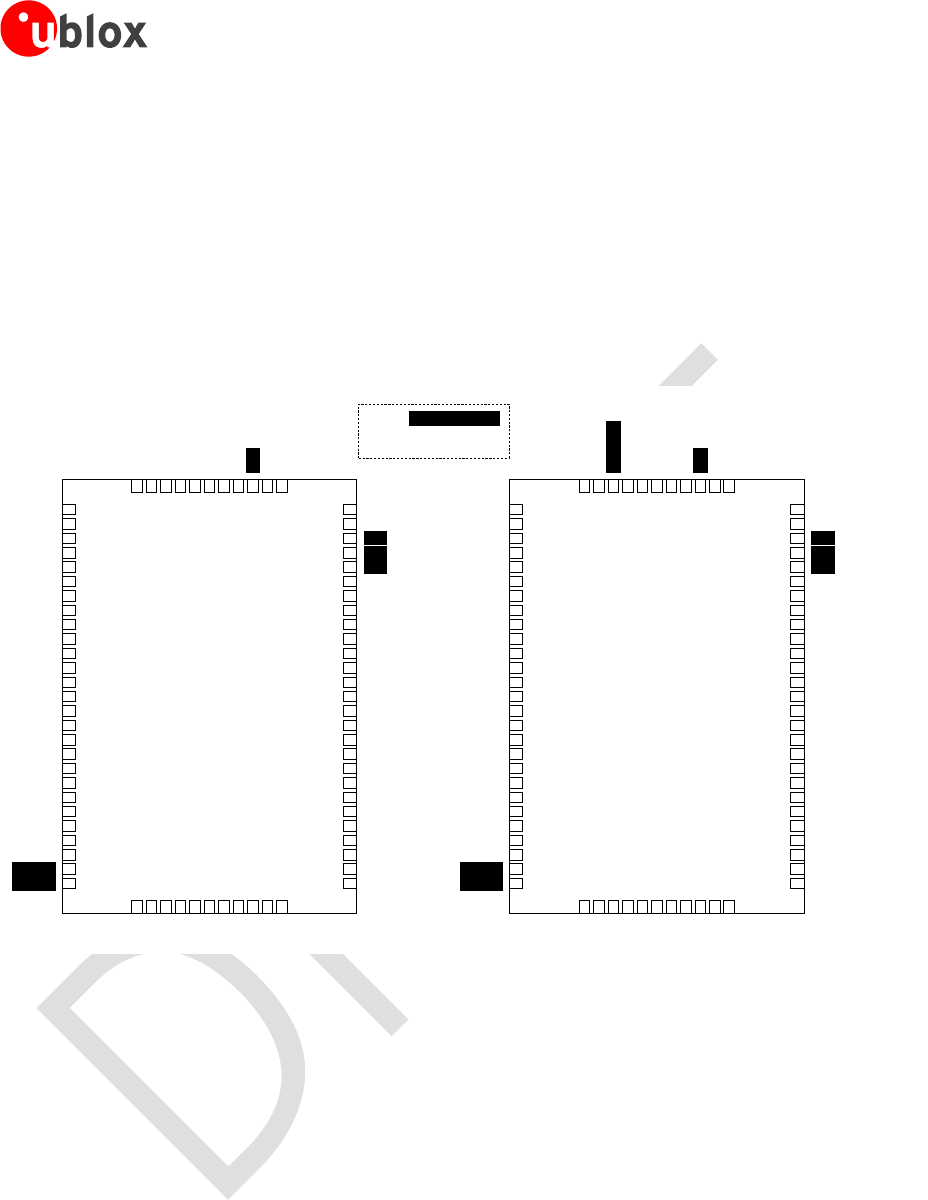

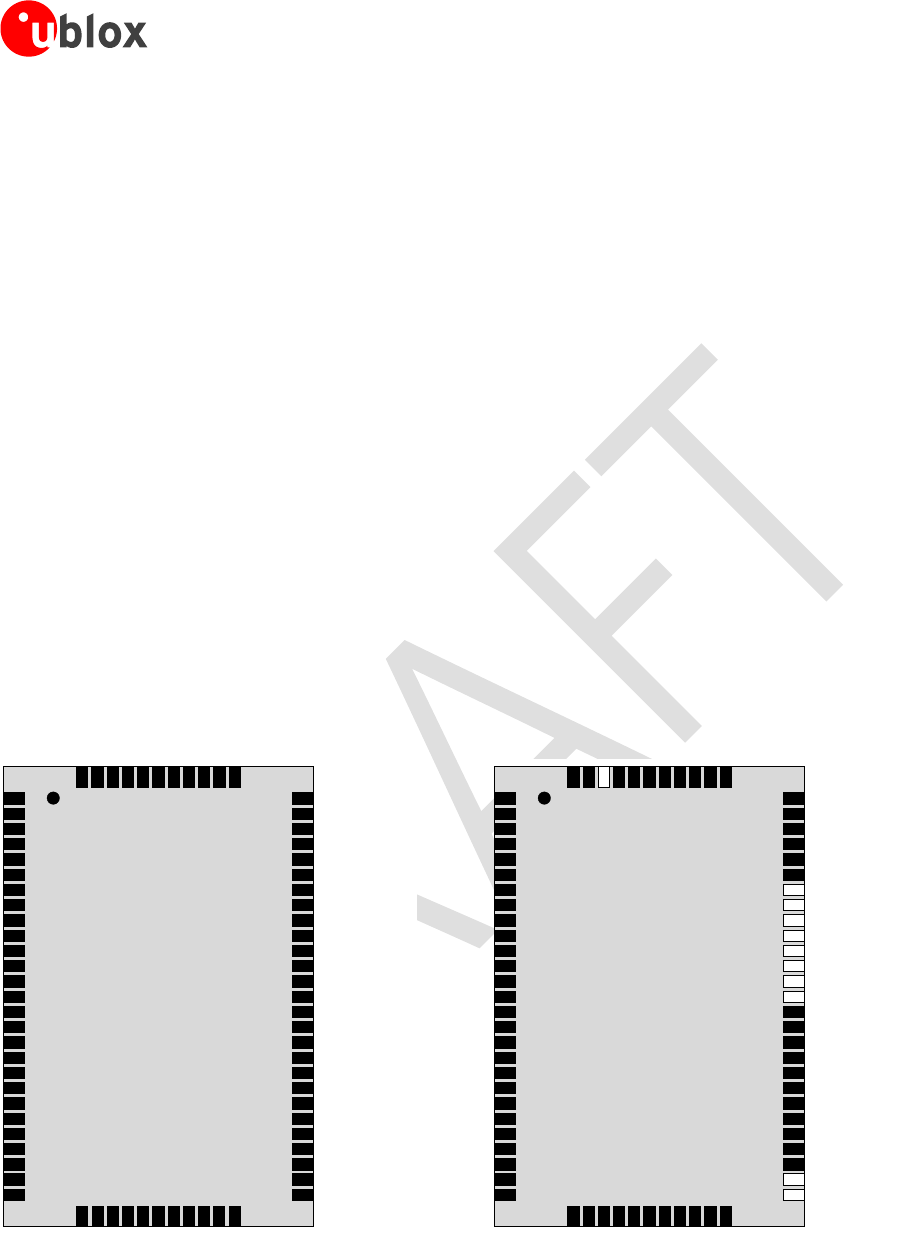

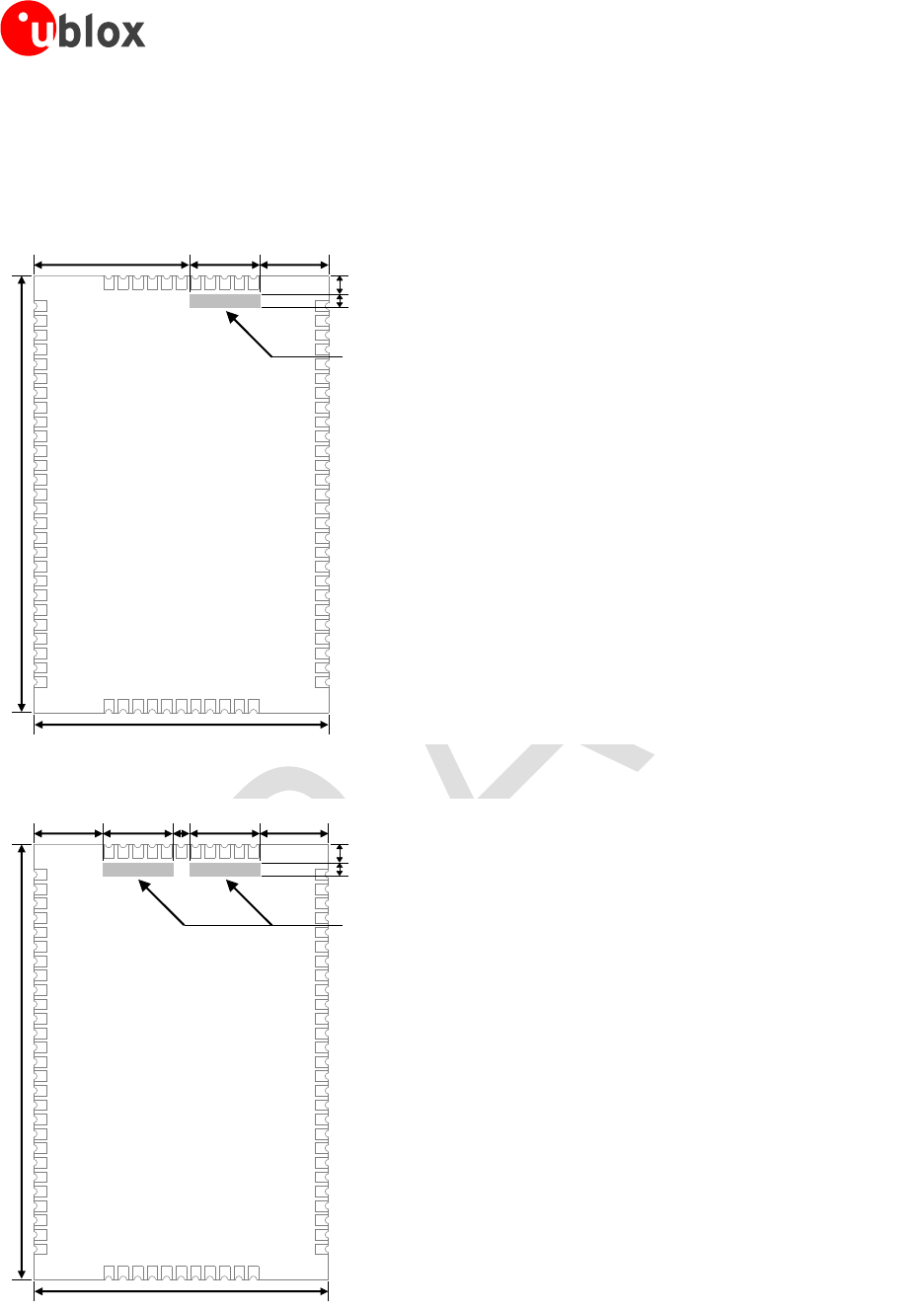

Figure 1: LISA-U1 series block diagram (for available options refer to the product features summary in Table 2)

Wireless

Base-band

Processor

Memory

Power Management Unit

26 MHz

32.768 kHz

ANT

Switch & Multi band & mode PA

DDC (for GPS)

(U)SIM Card

UART

SPI

USB

GPIO(s)

Power On

External Reset

V_BCKP (RTC)

Vcc (Supply)

V_INT (I/O)

Digital Audio (I2S)

RF

SWITCH

RF

Transceiver

Duplexers

& Filters

ANT_DIV

RF

SWITCH

Filter

Bank

PA

PMU

Transceiver

PMU

Figure 2: LISA-U2 series block diagram (for available options refer to the product features summary in Table 2)

LISA-U series - System Integration Manual

3G.G2-HW-10002-A1 Advance Information System description

Page 10 of 160

1.2.1 Functional blocks

LISA-U series modules consist of the following internal functional blocks: RF section, Baseband and Power

Management Unit section.

LISA-U1 series RF section

A shielding box includes the RF high-power signal circuitry, namely:

Front-End Module (FEM) with integrated quad-band 2G Power Amplifier and antenna switch multiplexer

Two single-band 3G HSPA/WCDMA Power Amplifier modules with integrated duplexers

The RF antenna pad (ANT) is directly connected to the FEM, which dispatches the RF signals according to the

active mode. For time-duplex 2G operation, the incoming signal at the active Receiver (RX) slot is applied to

integrated SAW filters for out-of-band rejection and then sent to the appropriate receiver port of the RF

transceiver. During the allocated Transmitter (TX) slots, the low level signal coming from the RF transceiver is

enhanced by the 2G power amplifier module and then directed to the antenna through the FEM. The 3G

transmitter and receiver are instead active at the same time due to frequency-domain duplex operation. The

switch integrated in the FEM connects the antenna port to the passive duplexer which separates the TX and RX

signal paths. The duplexer itself provides front-end RF filtering for RX band selection while combining the

amplified TX signal coming from the fixed gain linear power amplifier.

In the same shielding box that includes the RF high-power signal circuitry there are all the low-level analog RF

components, namely:

Dual-band HSPA/WCDMA and quad-band EDGE/GPRS/GSM transceiver

Voltage Controlled Temperature Compensated 26 MHz Crystal Oscillator (VC-TCXO)

Low Noise Amplifier (LNA) and SAW RF filters for 2G and 3G receivers

While operating in 3G mode, the RF transceiver performs direct up-conversion and down-conversion of the

baseband I/Q signals, with the RF voltage controlled gain amplifier being used to set the uplink TX power. In the

downlink path, the external LNA enhances the RX sensitivity while discrete inter-stage SAW filters additionally

improve the rejection of out-of-band blockers. An internal programmable gain amplifier optimizes the signal

levels before delivering to the analog I/Q to baseband for further digital processing.

For 2G operations, a constant gain direct conversion receiver with integrated LNAs and highly linear RF

quadrature demodulator are used to provide the same I/Q signals to baseband as well. In transmission mode, the

up-conversion is implemented by means of a digital sigma-delta transmitter or polar modulator depending on

the modulation to be transmitted.

In all the modes, a fractional-N sigma-delta RF synthesizer and an on-chip 3.296-4.340 GHz voltage controlled

oscillator are used to generate the local oscillator signal.

The frequency reference to RF oscillators is provided by the 26 MHz VC-TCXO. The same signal is buffered to the

baseband as a master reference for clock generation circuits while operating in active mode.

LISA-U2 series RF section

A shielding box contains the RF high-power signal circuitry, including:

Multimode Single Chain Power Amplifier Module used for 3G HSPA/WCDMA and 2G EDGE/GSM operations

Power Management Unit with integrated DC/DC converter for the Power Amplifier Module

The RF antenna pad (ANT) is directly connected to the main antenna switch, which dispatches the RF signals

according to the active mode. For time-duplex 2G operation, the incoming signal at the active Receiver (RX) slot

is applied by the main antenna switch to the duplexer SAW filter bank for out-of-band rejection and then sent to

the appropriate receiver port of the RF transceiver. During the allocated Transmitter (TX) slots, the low level

signal coming from the RF transceiver is enhanced by the power amplifier and then directed to the antenna pad

through the main antenna switch. The 3G transmitter and receiver are active at the same time due to frequency-

domain duplex operation. The switch integrated in the main antenna switch connects the antenna port to the

duplexer SAW filter bank which separates the TX and RX signal paths. The duplexer itself provides front-end RF

filtering for RX band selection while combining the amplified TX signal coming from the power amplifier.

LISA-U series - System Integration Manual

3G.G2-HW-10002-A1 Advance Information System description

Page 11 of 160

A separated shielding box contains all the other analog RF components, including:

Main Antenna Switch

Duplexer SAW filter bank

Antenna Switch for diversity receiver

SAW filter bank for diversity receiver

Six-band HSPA/WCDMA and quad-band EDGE/GPRS/GSM transceiver

Power Management Unit with integrated DC/DC converter for the Power Amplifier Module

Voltage Controlled Temperature Compensated 26 MHz Crystal Oscillator (VC-TCXO)

While operating in 3G mode, the RF transceiver performs direct up-conversion and down-conversion of the

baseband I/Q signals, with the RF voltage controlled gain amplifier being used to set the uplink TX power. In the

downlink path, the integrated LNA enhances the RX sensitivity while discrete inter-stage SAW filters additionally

improve the rejection of out-of-band blockers. An internal programmable gain amplifier optimizes the signal

levels before delivering to the analog I/Q to baseband for further digital processing.

For 2G operations, a constant gain direct conversion receiver with integrated LNAs and highly linear RF

quadrature demodulator are used to provide the same I/Q signals to the baseband as well. In transmission mode,

the up-conversion is implemented by means of a digital sigma-delta transmitter or polar modulator depending

on the modulation to be transmitted.

The RF antenna pad for the diversity receiver (ANT_DIV) available on LISA-U230 modules is directly connected to

the antenna switch for the diversity receiver, which dispatches the incoming RF signals to the dedicated SAW

filter bank for out-of-band rejection and then to the diversity receiver port of the RF transceiver.

In all the modes, a fractional-N sigma-delta RF synthesizer and an on-chip 3.296-4.340 GHz voltage controlled

oscillator are used to generate the local oscillator signal.

The frequency reference to RF oscillators is provided by the 26 MHz VC-TCXO. The same signal is buffered to the

baseband as a master reference for clock generation circuits while operating in active mode.

LISA-U series modulation techniques

Modulation techniques related to radio technologies supported by LISA-U series modules, are listed as follows:

GSM GSMK

GPRS GMSK

EDGE GMSK / 8-PSK

WCDMA QPSK

HSDPA QPSK / 16-QAM

HSUPA QPSK / 16-QAM

LISA-U series Baseband and Power Management Unit section

Another shielding box of LISA-U series modules includes all the digital circuitry and the power supplies, basically

the following functional blocks:

Wireless baseband processor, a mixed signal ASIC which integrates:

Microprocessor for controller functions, 2G & 3G upper layer software

DSP core for 2G Layer 1 and audio processing

3G coprocessor and HW accelerator for 3G Layer 1 control software and routines

Dedicated HW for interfaces management

Memory system in a Multi-Chip Package (MCP) integrating two devices:

NOR flash non-volatile memory

DDR SRAM volatile memory

Power Management Unit (PMU), used to derive all the system supply voltages from the module supply VCC

LISA-U series - System Integration Manual

3G.G2-HW-10002-A1 Advance Information System description

Page 12 of 160

32.768 kHz crystal, connected to the Real Time Clock (RTC) oscillator to provide the clock reference in idle or

power-off mode

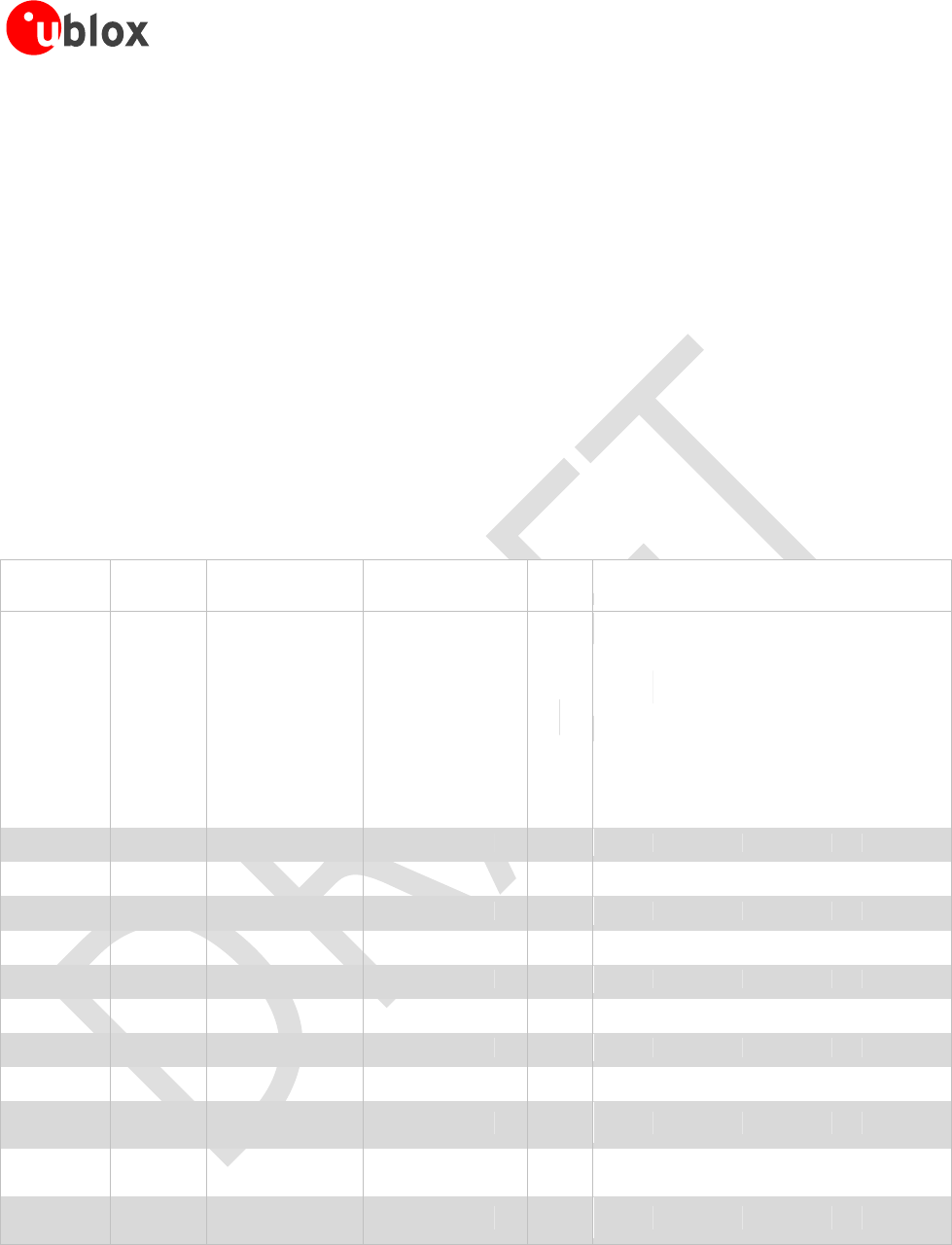

1.2.2 Hardware differences between LISA-U series modules

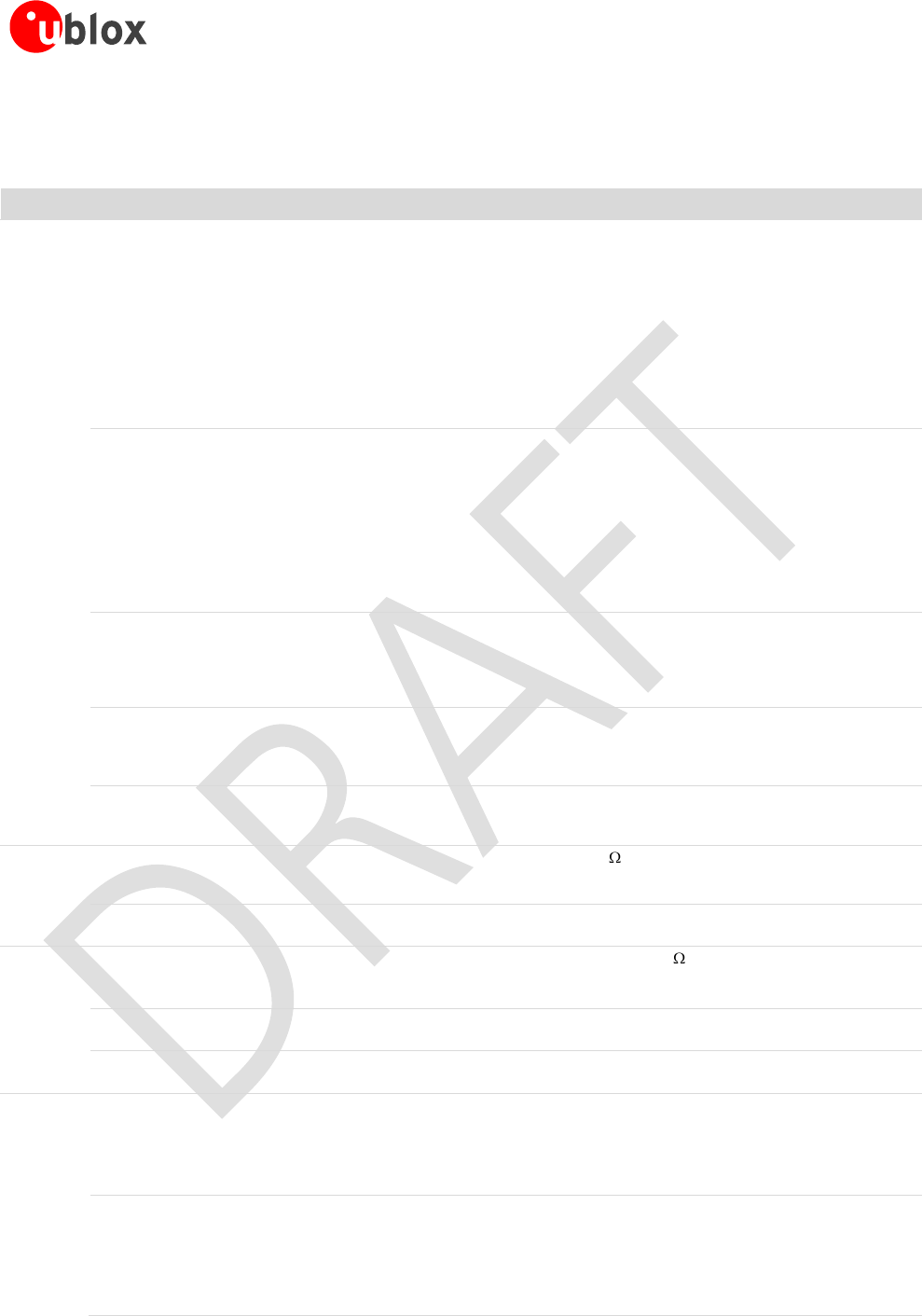

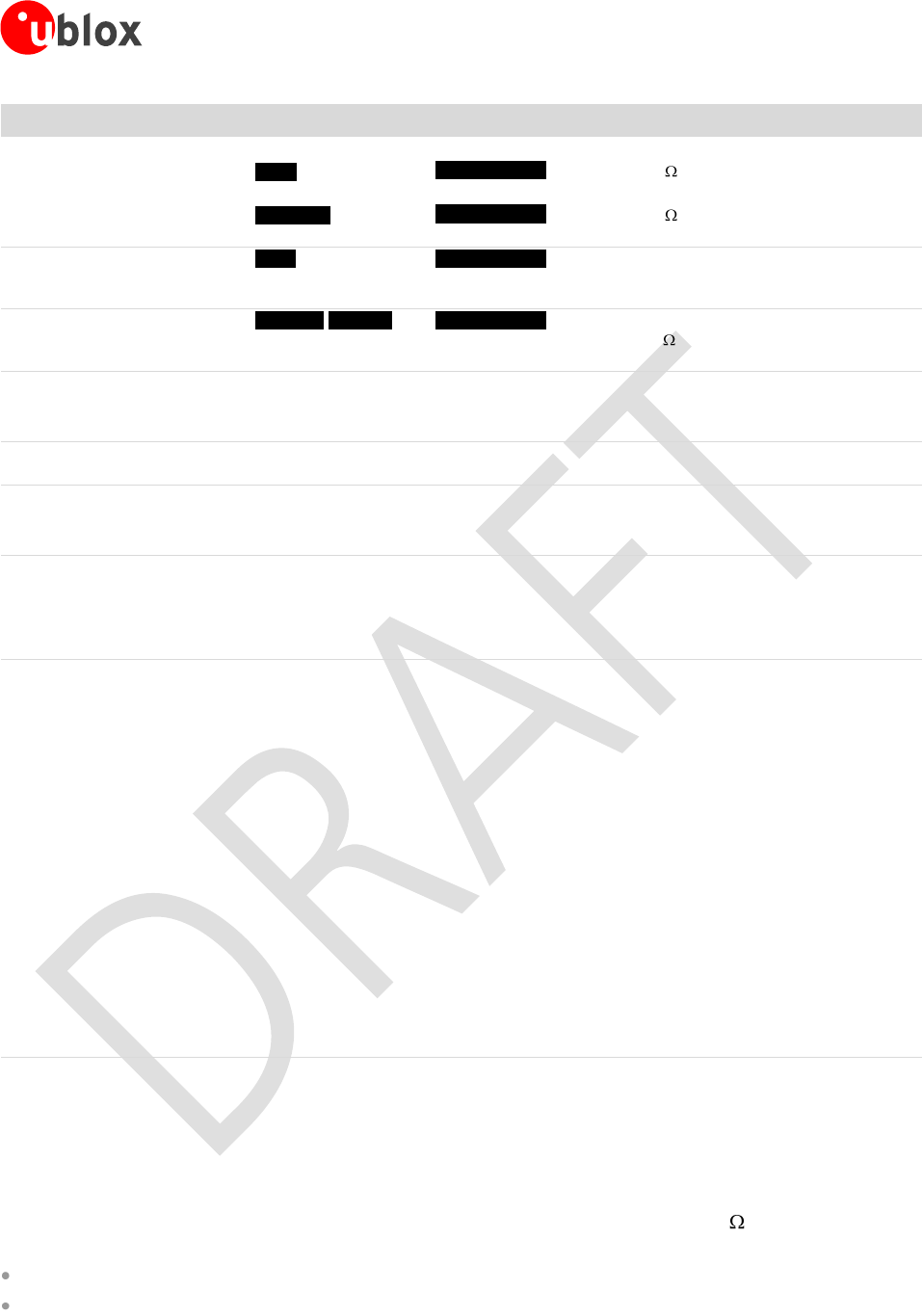

Main hardware differences between the LISA-U series modules are summarized in Table 3.

Characteristic

LISA-U1 series

LISA-U2 series

3G bands

LISA-U100, LISA-U120:

Band II (1900 MHz), Band V (850 MHz)

LISA-U110, LISA-U130:

Band I (2100 MHz), Band VIII (900 MHz)

LISA-U200-00:

Band I (2100 MHz), Band II (1900 MHz),

Band V (850 MHz), Band VI (800 MHz)

LISA-U200-01, LISA-U230:

Band I (2100 MHz), Band II (1900 MHz),

Band IV (1700 MHz), Band V (850 MHz),

Band VI (800 MHz), Band VIII (900 MHz)

HSDPA data rate

LISA-U1 series:

HSDPA category 8, up to 7.2 Mb/s DL

LISA-U200:

HSDPA category 8, up to 7.2 Mb/s DL

LISA-U230:

HSDPA category 14, up to 21.1 Mb/s DL

EDGE/GPRS data rate

EDGE multislot class 12, MCS1-MCS9,

up to 236.8 kb/s DL/UL

GPRS multislot class 12, CS1-CS4,

up to 85.6 kb/s DL/UL

EDGE multislot class 33, MCS1-MCS9,

up to 296 kb/s DL, 236.8 kb/s UL

GPRS multislot class 33, CS1-CS4,

up to 107 kb/s DL, 85.6 kb/s UL

Rx diversity

LISA-U1 series:

Not supported

LISA-U200:

Not supported

LISA-U230:

Supported: ANT_DIV RF input for Rx diversity

Analog audio

LISA-U100, LISA-U110:

Not supported

LISA-U120, LISA-U130:

One differential input, one differential output

LISA-U2 series:

Not supported

Digital audio

LISA-U100, LISA-U110:

Not supported

LISA-U120, LISA-U130:

One 4-wire digital audio interface

LISA-U200-00:

Not supported

LISA-U200-01, LISA-U230:

Two 4-wire digital audio interfaces

CODEC_CLK clock output for external codec

GPIO

5 GPIOs

14 GPIOs

VCC operating range

VCC normal operating range: 3.4 V – 4.2 V

VCC extended operating range: 3.1 V – 4.2 V

VCC normal operating range: 3.3 V – 4.4 V

VCC extended operating range: 3.1 V – 4.5 V

V_BCKP operating range

V_BCKP output: 2.3 V typ.

V_BCKP input: 1.0 V – 2.5 V

V_BCKP output: 1.8 V typ.

V_BCKP input: 1.0 V – 1.9 V

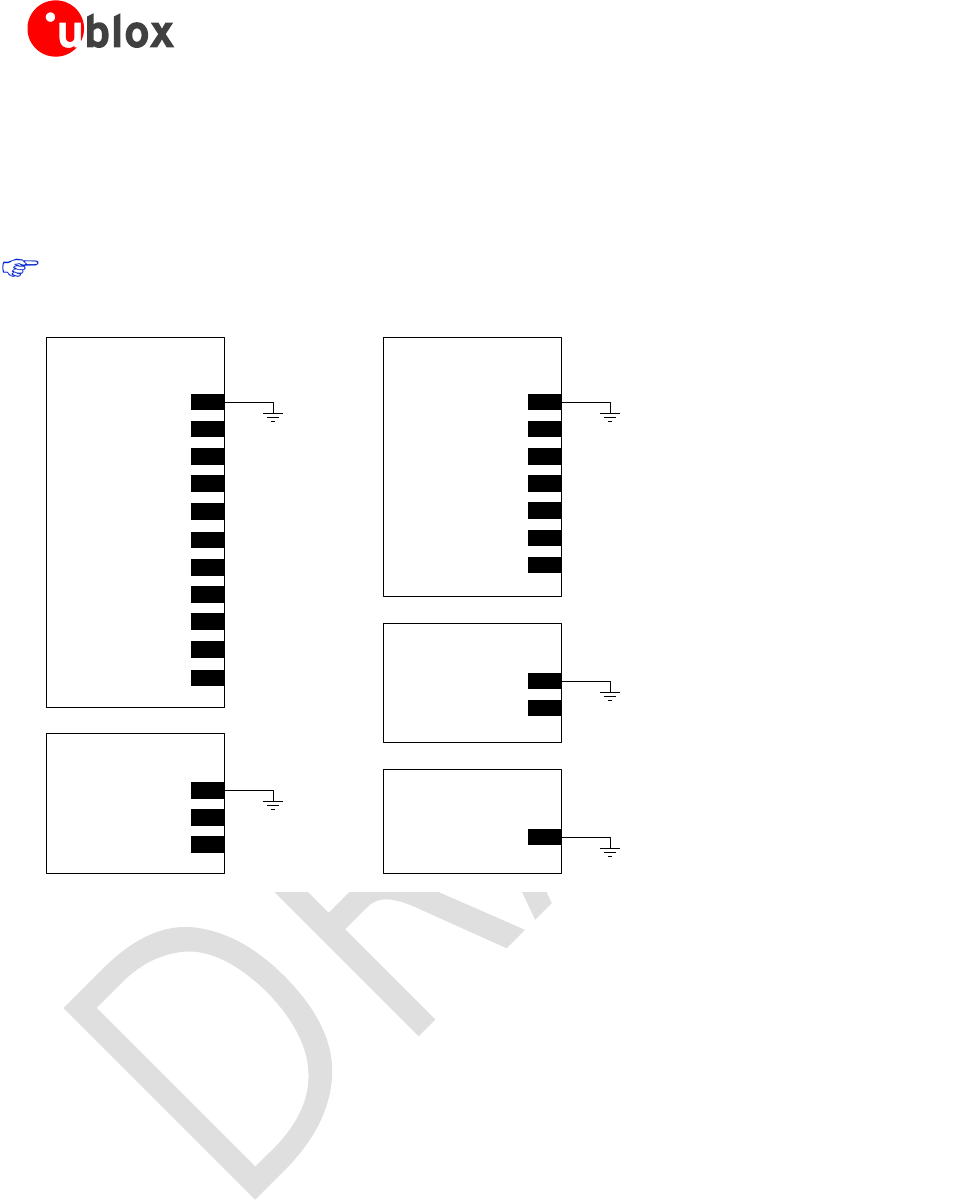

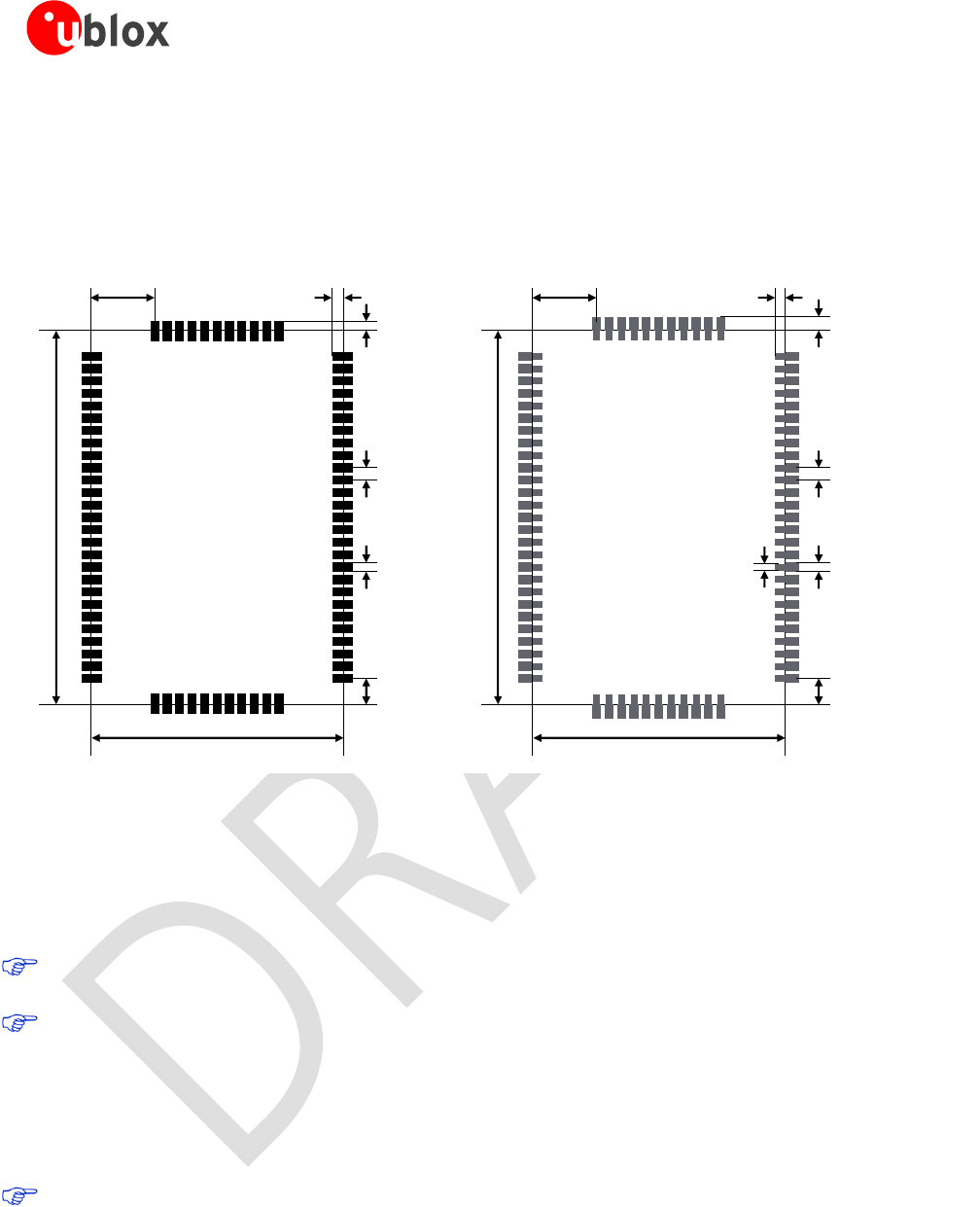

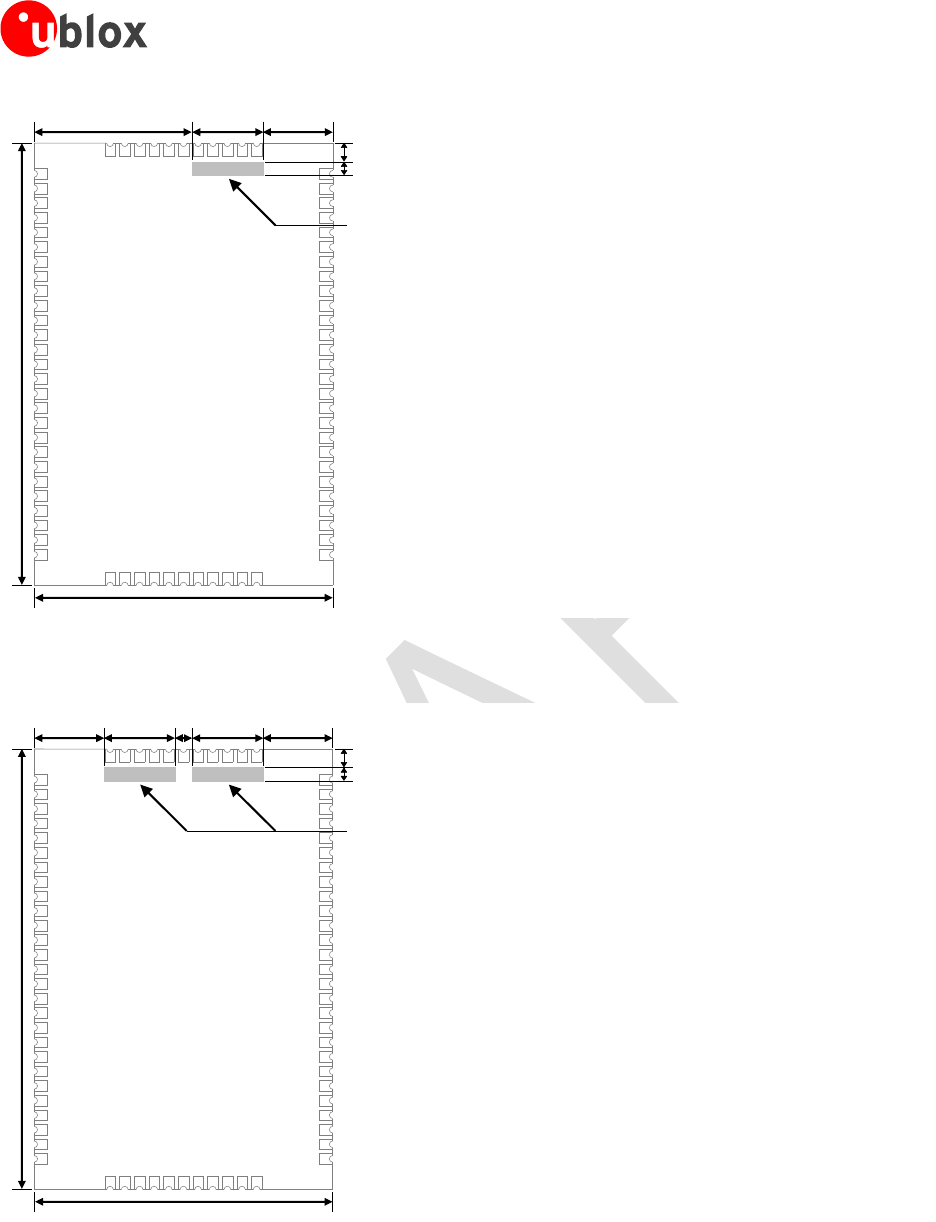

Exposed GND area

One signals keep-out area on the top layer of the

application board, due to one exposed GND area on

the bottom layer of the module (see Figure 61)

Two signals keep-out areas on the top layer of the

application board, due to two exposed GND areas

on the bottom layer of the module (see Figure 62)

Table 3: Main hardware differences between LISA-U series modules

For additional details and minor hardware differences between the LISA-U series modules, refer to section A.3.

LISA-U series - System Integration Manual

3G.G2-HW-10002-A1 Advance Information System description

Page 13 of 160

1.3 Pin-out

Table 4 lists the pin-out of the LISA-U series modules, with pins grouped by function.

Function

Pin

Module

No

I/O

Description

Remarks

Power

VCC

All

61, 62, 63

I

Module supply

input

Clean and stable supply is required: low ripple and

low voltage drop must be guaranteed.

Voltage provided has to be always above the

minimum limit of the operating range.

Consider that there are large current spikes in

connected mode, when a GSM call is enabled.

VCC pins are internally connected, but all the

available pads must be connected to the external

supply in order to minimize power loss due to

series resistance.

See section 1.5.2

GND

All

1, 3, 6, 7,

8, 17, 25,

28, 29, 30,

31, 32, 33,

34, 35, 36,

37, 38, 60,

64, 65, 66,

67, 69, 70,

71, 72, 73,

75, 76

N/A

Ground

GND pins are internally connected but a good

(low impedance) external ground connection can

improve RF performance: all GND pins must be

externally connected to ground.

V_BCKP

All

2

I/O

Real Time Clock

supply

input/output

V_BCKP = 2.3 V (typical) on LISA-U1 series

V_BCKP = 1.8 V (typical) on LISA-U2 series

generated by the module when VCC supply

voltage is within valid operating range.

See section 1.5.4

V_INT

All

4

O

Digital Interfaces

supply output

V_INT = 1.8V (typical) generated by the module

when it is switched-on and the RESET_N (external

reset input pin) is not forced to the low level.

See section 1.5.5

VSIM

All

50

O

SIM supply

output

VSIM = 1.80 V typical or 2.90 V typical generated

by the module according to the SIM card type.

See section 1.8

RF

ANT

All

68

I/O

RF input/output

for main Tx/Rx

antenna

50 nominal impedance.

See section 1.7, section 2.4 and section 2.2.1.1

ANT_DIV

LISA-U230

74

I

RF input for Rx

diversity antenna

50 Ω nominal impedance

See section 1.7, section 2.4 and section 2.2.1.1

SIM

SIM_IO

All

48

I/O

SIM data

Internal 4.7 k pull-up to VSIM.

Must meet SIM specifications.

See section 1.8

SIM_CLK

All

47

O

SIM clock

Must meet SIM specifications.

See section 1.8

SIM_RST

All

49

O

SIM reset

Must meet SIM specifications.

See section 1.8

SPI

SPI_MISO

All

57

O

SPI Data Line

Output

Module Output: module runs as an SPI slave.

Shift data on rising clock edge (CPHA=1).

Latch data on falling clock edge (CPHA=1).

Idle high.

See section 1.9.4

SPI_MOSI

All

56

I

SPI Data Line

Input

Module Input: module runs as an SPI slave.

Shift data on rising clock edge (CPHA=1).

Latch data on falling clock edge (CPHA=1).

Idle high.

Internal active pull-up to V_INT (1.8 V) enabled.

See section 1.9.4

LISA-U series - System Integration Manual

3G.G2-HW-10002-A1 Advance Information System description

Page 14 of 160

Function

Pin

Module

No

I/O

Description

Remarks

SPI_SCLK

All

55

I

SPI Serial Clock

Input

Module Input: module runs as an SPI slave.

Idle low (CPOL=0).

Internal active pull-down to GND enabled.

See section 1.9.4

SPI_SRDY

All

58

O

SPI Slave Ready

Output

Module Output: module runs as an SPI slave.

Idle low.

See section 1.9.4

SPI_MRDY

All

59

I

SPI Master Ready

Input

Module Input: module runs as an SPI slave.

Idle low.

Internal active pull- down to GND enabled.

See section 1.9.4

DDC

SCL

All

45

O

I2C bus clock line

Fixed open drain. External pull-up required.

See section 1.10

SDA

All

46

I/O

I2C bus data line

Fixed open drain. External pull-up required.

See section 1.10

UART

RxD

All

16

O

UART data

output

Circuit 104 (RxD) in ITU-T V.24.

Provide access to the pin for FW update and

debugging if the USB interface is connected to the

application processor.

See section 1.9.2

TxD

All

15

I

UART data input

Circuit 103 (TxD) in ITU-T V.24.

Internal active pull-up to V_INT (1.8 V) enabled.

Provide access to the pin for FW update and

debugging if the USB interface is connected to the

application processor.

See section 1.9.2

CTS

All

14

O

UART clear to

send output

Circuit 106 (CTS) in ITU-T V.24.

Provide access to the pin for debugging if the USB

interface is connected to the application

processor.

See section 1.9.2

RTS

All

13

I

UART ready to

send input

Circuit 105 (RTS) in ITU-T V.24.

Internal active pull-up to V_INT (1.8 V) enabled.

Provide access to the pin for debugging if the USB

interface is connected to the application

processor.

See section 1.9.2

DSR

All

9

O

UART data set

ready output

Circuit 107 (DSR) in ITU-T V.24.

See section 1.9.2

RI

All

10

O

UART ring

indicator output

Circuit 125 (RI) in ITU-T V.24.

See section 1.9.2

DTR

All

12

I

UART data

terminal ready

input

Circuit 108/2 (DTR) in ITU-T V.24.

Internal active pull-up to V_INT (1.8 V) enabled.

See section 1.9.2

DCD

All

11

O

UART data carrier

detect output

Circuit 109 (DCD) in ITU-T V.24.

See section 1.9.2

GPIO

GPIO1

All

20

I/O

GPIO

See section 1.12

GPIO2

All

21

I/O

GPIO

See section 1.12

GPIO3

All

23

I/O

GPIO

See section 1.12

GPIO4

All

24

I/O

GPIO

See section 1.12

GPIO5

All

51

I/O

GPIO

See section 1.12

GPIO6

LISA-U2

39

I/O

GPIO

See section 1.12

GPIO7

LISA-U2

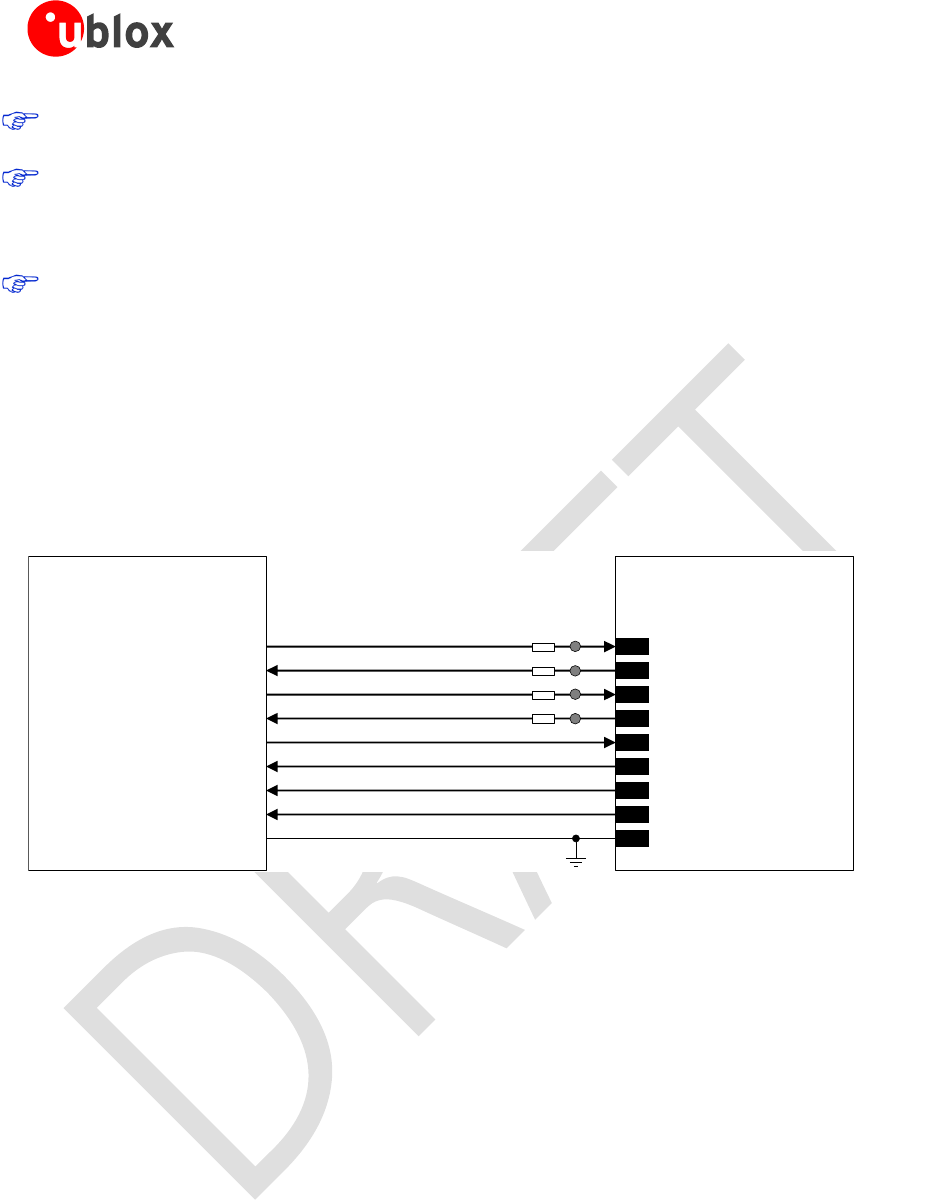

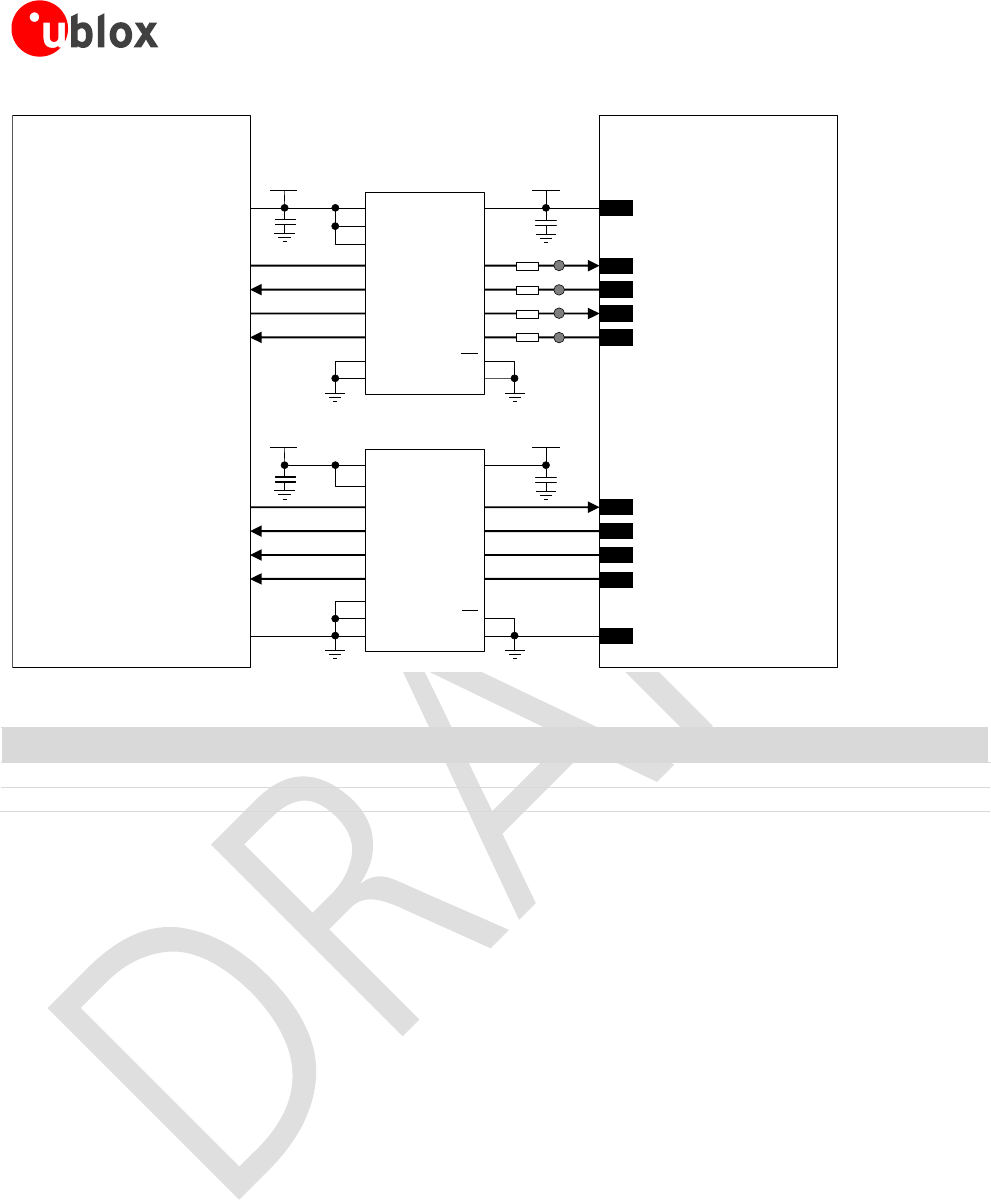

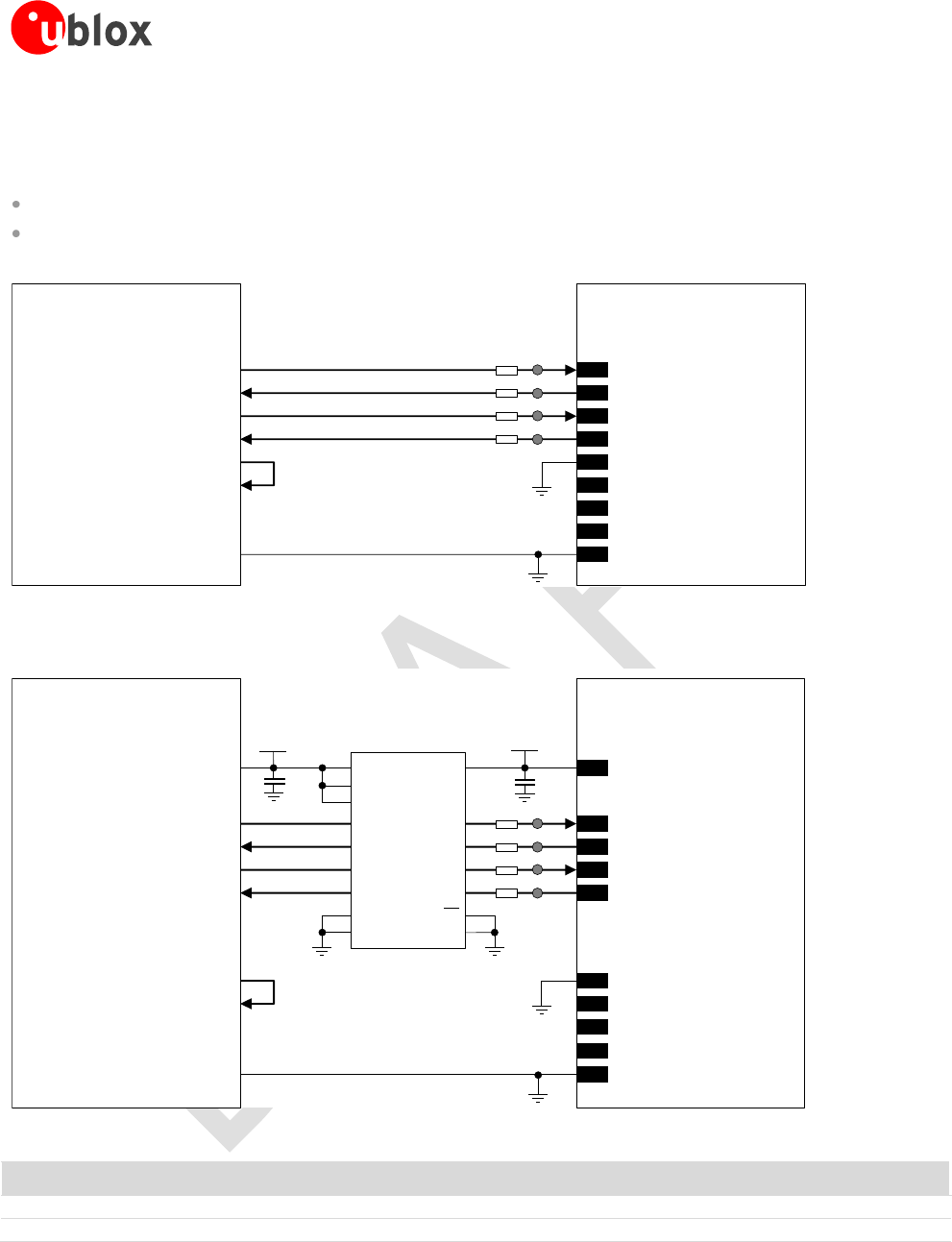

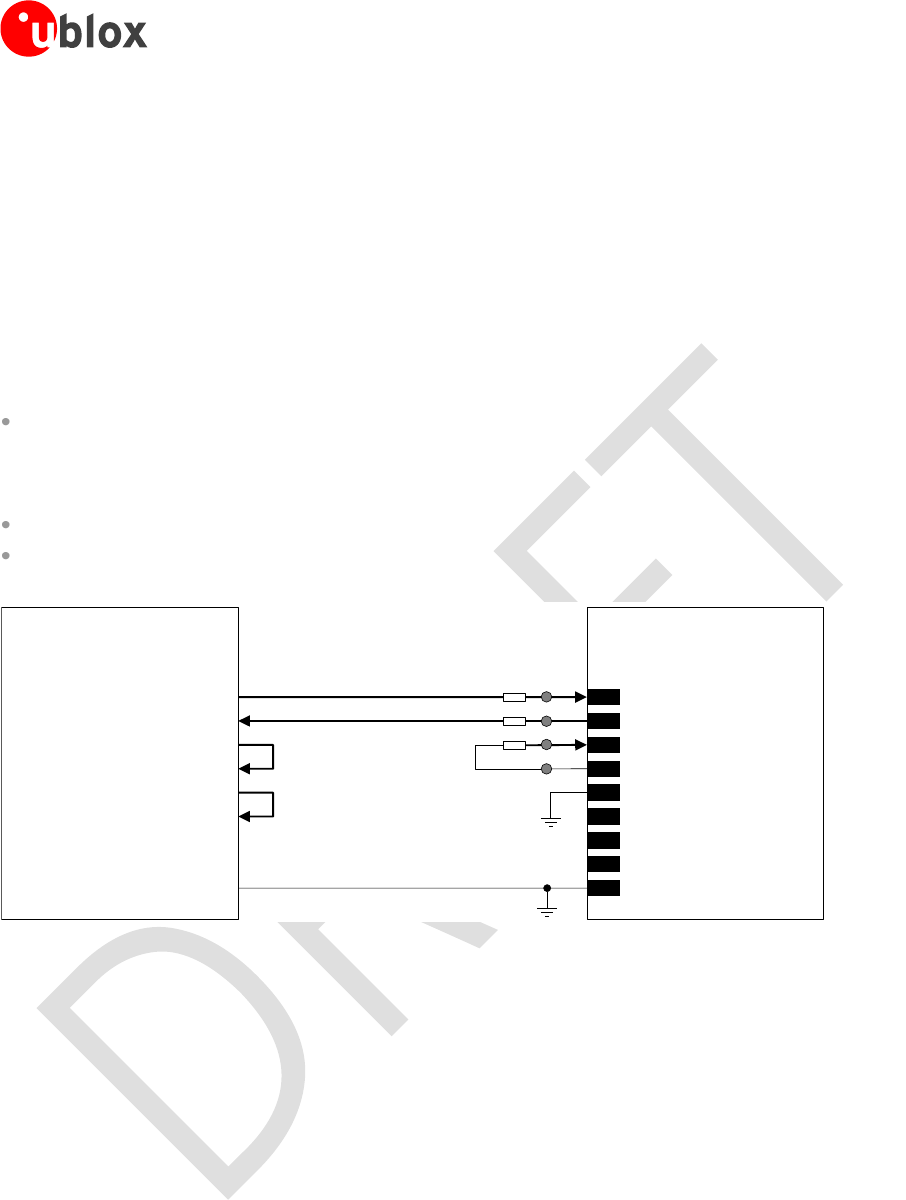

40

I/O

GPIO

See section 1.12

GPIO8

LISA-U2

53

I/O

GPIO

See section 1.12

GPIO9

LISA-U2

54

I/O

GPIO

See section 1.12

GPIO10

LISA-U2

55

I/O

GPIO

See section 1.12

GPIO11

LISA-U2

56

I/O

GPIO

See section 1.12

GPIO12

LISA-U2

57

I/O

GPIO

See section 1.12

LISA-U series - System Integration Manual

3G.G2-HW-10002-A1 Advance Information System description

Page 15 of 160

Function

Pin

Module

No

I/O

Description

Remarks

GPIO13

LISA-U2

58

I/O

GPIO

See section 1.12

GPIO14

LISA-U2

59

I/O

GPIO

See section 1.12

USB

VUSB_DET

All

18

I

USB detect input

Input for VBUS (5 V typical) USB supply sense to

enable USB interface.

Provide access to the pin for FW update and

debugging if the USB interface is not connected to

the application processor.

See section 1.9.3

USB_D-

All

26

I/O

USB Data Line D-

90 Ω nominal differential impedance

Pull-up or pull-down resistors and external series

resistors as required by the USB 2.0 high-speed

specification [8] are part of the USB pad driver and

need not be provided externally.

Provide access to the pin for FW update and

debugging if the USB interface is not connected to

the application processor.

See section 1.9.3

USB_D+

All

27

I/O

USB Data Line

D+

90 Ω nominal differential impedance

Pull-up or pull-down resistors and external series

resistors as required by the USB 2.0 high-speed

specification [8] are part of the USB pad driver and

need not be provided externally.

Provide access to the pin for FW update and

debugging if the USB interface is not connected to

the application processor.

See section 1.9.3

System

PWR_ON

All

19

I

Power-on input

PWR_ON pin has high input impedance.

Do not keep floating in noisy environment:

external pull-up required.

See section 1.6.1

RESET_N

All

22

I

External reset

input

Internal 10 kΩ pull-up to V_BCKP.

See section 1.6.3

Analog

Audio

MIC_N

LISA-U120

LISA-U130

39

I

Differential

analog audio

input (negative)

Differential analog input shared for all analog path

modes: handset, headset, hands-free mode.

Internal DC blocking capacitor.

See section 1.11.1

MIC_P

LISA-U120

LISA-U130

40

I

Differential

analog audio

input (positive)

Differential analog input shared for all analog path

modes: handset, headset, hands-free mode.

Internal DC blocking capacitor.

See section 1.11.1

SPK_P

LISA-U120

LISA-U130

53

O

Differential

analog audio

output (positive)

Differential analog audio output shared for all

analog path modes: earpiece, headset and

loudspeaker mode.

See section 1.11.1

SPK_N

LISA-U120

LISA-U130

54

O

Differential

analog audio

output (negative)

Differential analog audio output shared for all

analog path modes: earpiece, headset and

loudspeaker mode.

See section 1.11.1

Digital

Audio

I2S_CLK

LISA-U120

LISA-U130

LISA-U200-01

LISA-U230

43

I/O

First I2S clock

Check device specifications to ensure compatibility

to module supported modes.

See section 1.11.2.

I2S_RXD

LISA-U120

LISA-U130

LISA-U200-01

LISA-U230

44

I

First I2S receive

data

Internal active pull-down to GND enabled.

Check device specifications to ensure compatibility

to module supported modes.

See section 1.11.2.

I2S_TXD

LISA-U120

LISA-U130

LISA-U200-01

LISA-U230

42

O

First I2S transmit

data

Check device specifications to ensure compatibility

to module supported modes.

See section 1.11.2.

LISA-U series - System Integration Manual

3G.G2-HW-10002-A1 Advance Information System description

Page 16 of 160

Function

Pin

Module

No

I/O

Description

Remarks

I2S_WA

LISA-U120

LISA-U130

LISA-U200-01

LISA-U230

41

I/O

First I2S word

alignment

Check device specifications to ensure compatibility

to module supported modes.

See section 1.11.2.

I2S1_CLK

LISA-U200-01,

LISA-U230

53

I/O

Second I2S clock

Check device specifications to ensure compatibility

to module supported modes.

See section 1.11.2.

I2S1_RXD

LISA-U200-01

LISA-U230

39

I

Second I2S

receive data

Internal active pull-down to GND enabled.

Check device specifications to ensure compatibility

to module supported modes.

See section 1.11.2.

I2S1_TXD

LISA-U200-01

LISA-U230

40

O

Second I2S

transmit data

Check device specifications to ensure compatibility

to module supported modes.

See section 1.11.2.

I2S1_WA

LISA-U200-01

LISA-U230

54

I/O

Second I2S word

alignment

Check device specifications to ensure compatibility

to module supported modes.

See section 1.11.2.

CODEC_CLK

LISA-U200-01

LISA-U230

52

O

Clock output

Digital clock output for external audio codec

See section 1.11.2.

Reserved

RSVD

All

5

N/A

RESERVED pin

This pin must be connected to ground

See section 1.13

RSVD

LISA-U1

LISA-U200-00

52

N/A

RESERVED pin

Pad disabled

See section 1.13

RSVD

LISA-U1

LISA-U200

74

N/A

RESERVED pin

Do not connect

See section 1.13

RSVD

LISA-U100

LISA-U110

LISA-U200-00

43

N/A

RESERVED pin

Pad disabled

See section 1.13

RSVD

LISA-U100

LISA-U110

LISA-U200-00

44

N/A

RESERVED pin

Pad disabled

See section 1.13

RSVD

LISA-U100

LISA-U110

LISA-U200-00

42

N/A

RESERVED pin

Pad disabled

See section 1.13

RSVD

LISA-U100

LISA-U110

LISA-U200-00

41

N/A

RESERVED pin

Pad disabled

See section 1.13

RSVD

LISA-U100

LISA-U110

39

N/A

RESERVED pin

Do not connect

See section 1.13

RSVD

LISA-U100

LISA-U110

40

N/A

RESERVED pin

Do not connect

See section 1.13

RSVD

LISA-U100

LISA-U110

53

N/A

RESERVED pin

Do not connect

See section 1.13

RSVD

LISA-U100

LISA-U110

54

N/A

RESERVED pin

Do not connect

See section 1.13

Table 4: LISA-U series modules pin definition, grouped by function

LISA-U series - System Integration Manual

3G.G2-HW-10002-A1 Advance Information System description

Page 17 of 160

1.4 Operating modes

LISA-U series modules have several operating modes. Table 5 summarizes the various operating modes and

provides general guidelines for operation.

Operating Mode

Description

Features / Remarks

Transition condition

General Status: Power-down

Not-Powered

Mode

VCC supply not present or

below operating range.

Microprocessor switched off

(not operating).

RTC only operates if supplied

through V_BCKP pin.

Module is switched off.

Application interfaces are not accessible.

Internal RTC timer operates only if a valid

voltage is applied to V_BCKP pin.

Module cannot be switched on by a

falling edge provided on the PWR_ON

input, or by a preset RTC alarm or by a

rising edge provided on the RESET_N

input.

Module can be switched on applying

VCC supply.

Power-Off Mode

VCC supply within operating

range.

Microprocessor switched off

(not operating).

Only RTC runs.

Module is switched off: normal shutdown

by AT+CPWROFF command (refer to

u-blox AT Commands Manual [3]), or by

PWR_ON held low for more than 1 s

(LISA-U2 series only).

Application interfaces are not accessible.

Only the internal RTC timer in operation.

Module can be switched on by a falling

edge on the PWR_ON input, or by a

preset RTC alarm, or by a rising edge on

the RESET_N input.

General Status: Normal Operation

Idle-Mode

Microprocessor runs with

32 kHz as reference oscillator.

Module does not accept data

signals from an external

device.

If power saving is enabled, the module

automatically enters idle-mode whenever

possible.

Application interfaces are disabled.

If hardware flow control is enabled, the

CTS line to ON state indicates that the

module is in active mode and the UART

interface is enabled: the line is driven in

the OFF state when the module is not

prepared to accept data by the UART

interface.

If hardware flow control is disabled, the

CTS line is fixed to ON state.

Module by default is not set to

automatically enter idle-mode whenever

possible, unless power saving

configuration is enabled by appropriate

AT command (refer to u-blox AT

Commands Manual [3], AT+UPSV).

Module enters automatically idle-mode

when power saving is enabled and

there is no activity for the defined time

interval:

Module registered with the

network and power saving

enabled. Periodically wakes up to

active mode to monitor the paging

channel for the paging block

reception according to network

indication

Module not registered with the

network and power saving is

enabled. Periodically wakes up to

monitor external activity

Module wakes up from idle-mode to

active-mode in the following events:

Incoming voice or data call

RTC alarm occurs

Data received on UART interface

(refer to 1.9.2)

RTS input line set to the ON state

by the DTE if the AT+UPSV=2

command is sent to the module

(refer to 1.9.2)

USB detection, applying 5 V (typ.)

to the VUSB_DET pin

The connected USB host forces a

remote wakeup of the module as

USB device (refer to 1.9.3)

The connected SPI master indicates

to the module that it is ready for

transmission or reception, by the

SPI/IPC SPI_MRDY input signal

(refer to 1.9.4)

LISA-U series - System Integration Manual

3G.G2-HW-10002-A1 Advance Information System description

Page 18 of 160

Operating Mode

Description

Features / Remarks

Transition condition

Active-Mode

Microprocessor runs with

26 MHz as reference

oscillator.

The module is prepared to

accept data signals from an

external device.

Module is switched on and is fully active.

The application interfaces are enabled,

unless power saving configuration is

enabled by the AT+UPSV command (refer

to sections 1.9.2.3, 1.9.3.2, 1.9.4.2 and

u-blox AT Commands Manual [3]).

Power saving is not enabled by default: it

can be enabled by the AT+UPSV

command (see u-blox AT Commands

Manual [3]).

If power saving is enabled, the module

automatically enters idle-mode and

application interfaces are disabled

whenever possible (refer to sections

1.9.2.3, 1.9.3.2, 1.9.4.2 and u-blox AT

Commands Manual [3], AT+UPSV).

Connected-Mode

Voice or data call enabled.

Microprocessor runs with

26 MHz as reference

oscillator.

The module is prepared to

accept data signals from an

external device.

The module is switched on and a voice

call or a data call (2G/3G) is in progress.

Module is fully active.

The application interfaces are enabled,

unless power saving configuration is

enabled by the AT+UPSV command (see

section 1.9.2.3, 1.9.3.2, 1.9.4.2 and the

u-blox AT Commands Manual [3]).

When call terminates, the module

returns to the active operating mode.

Table 5: Module operating modes summary

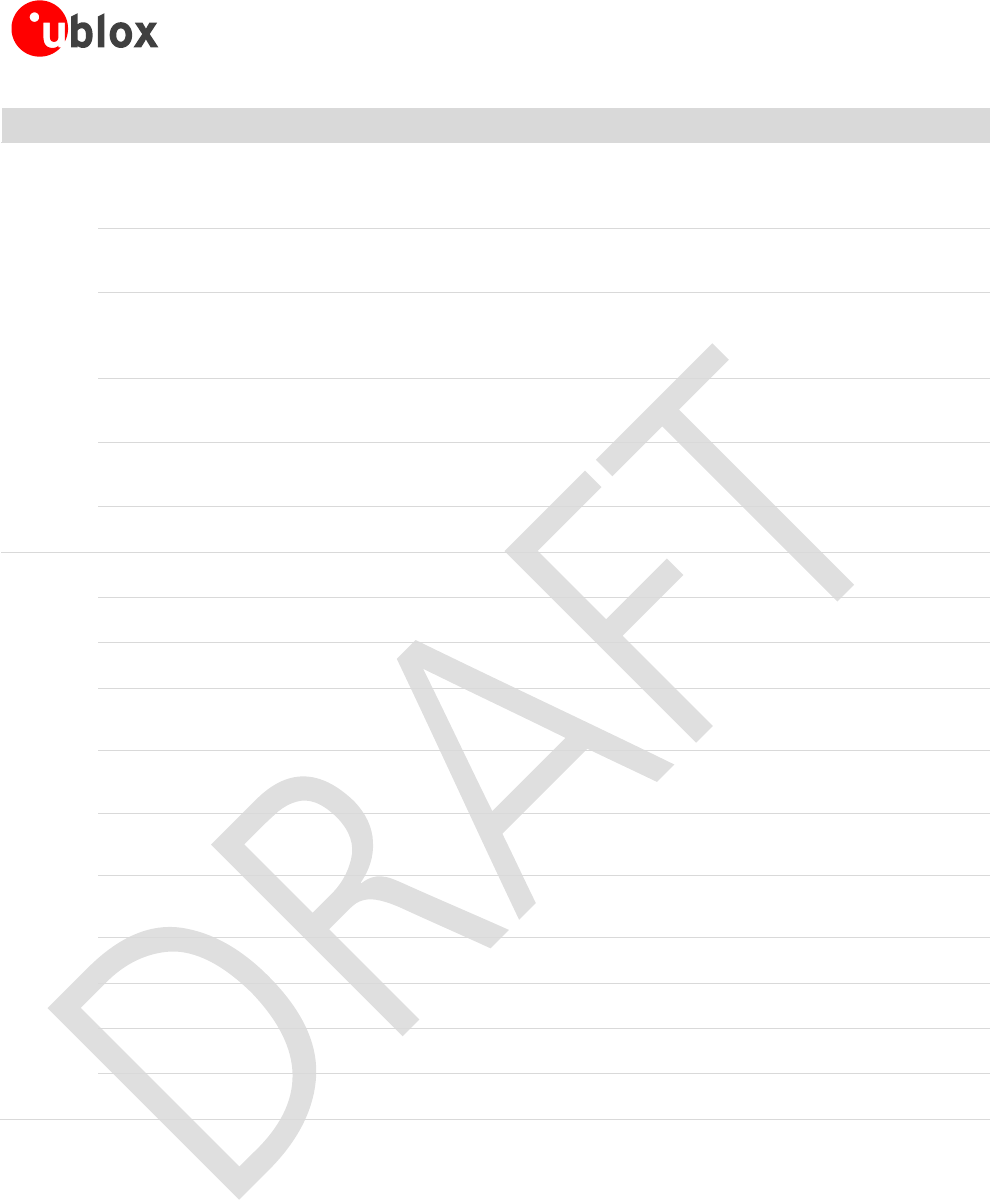

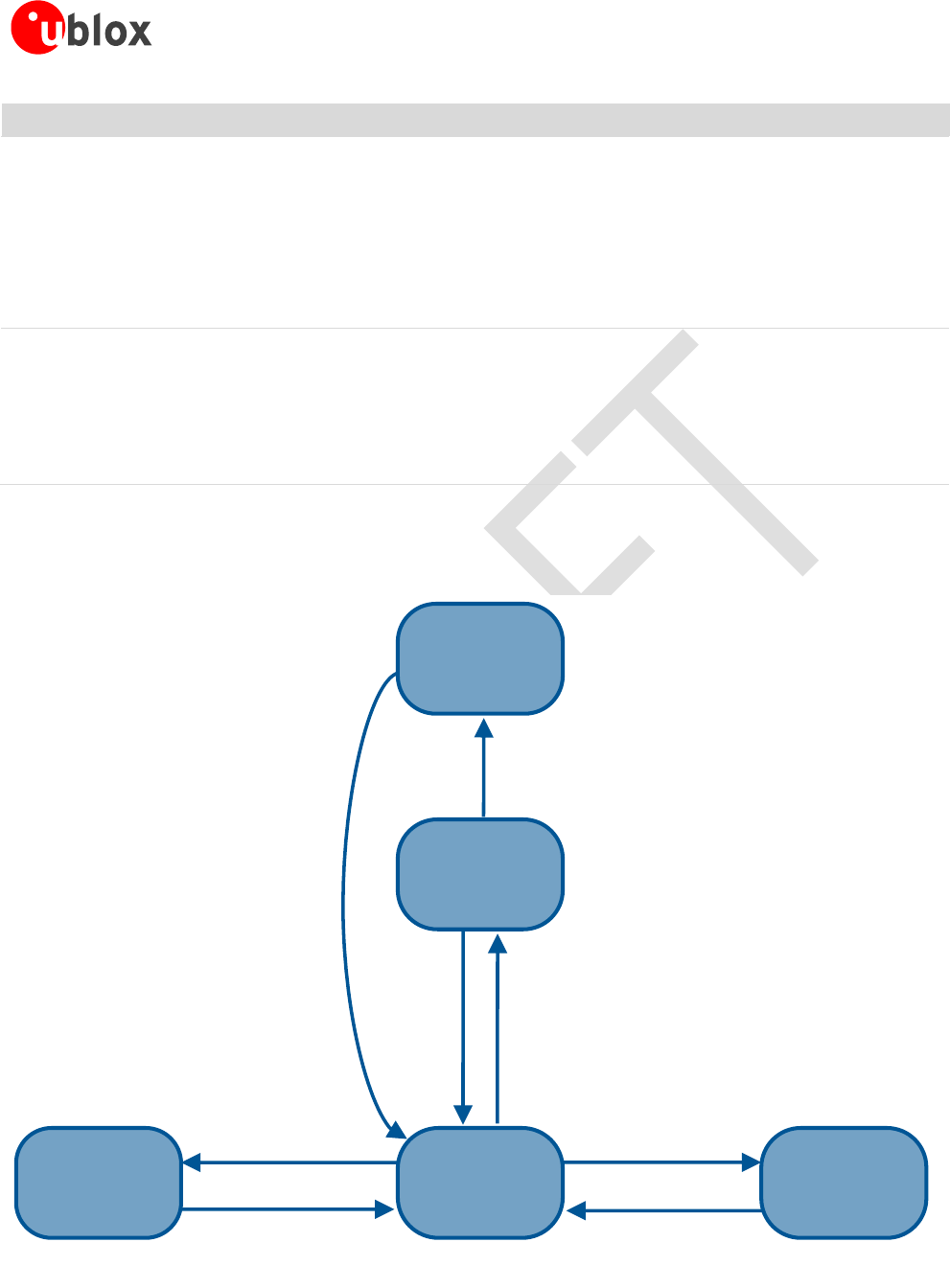

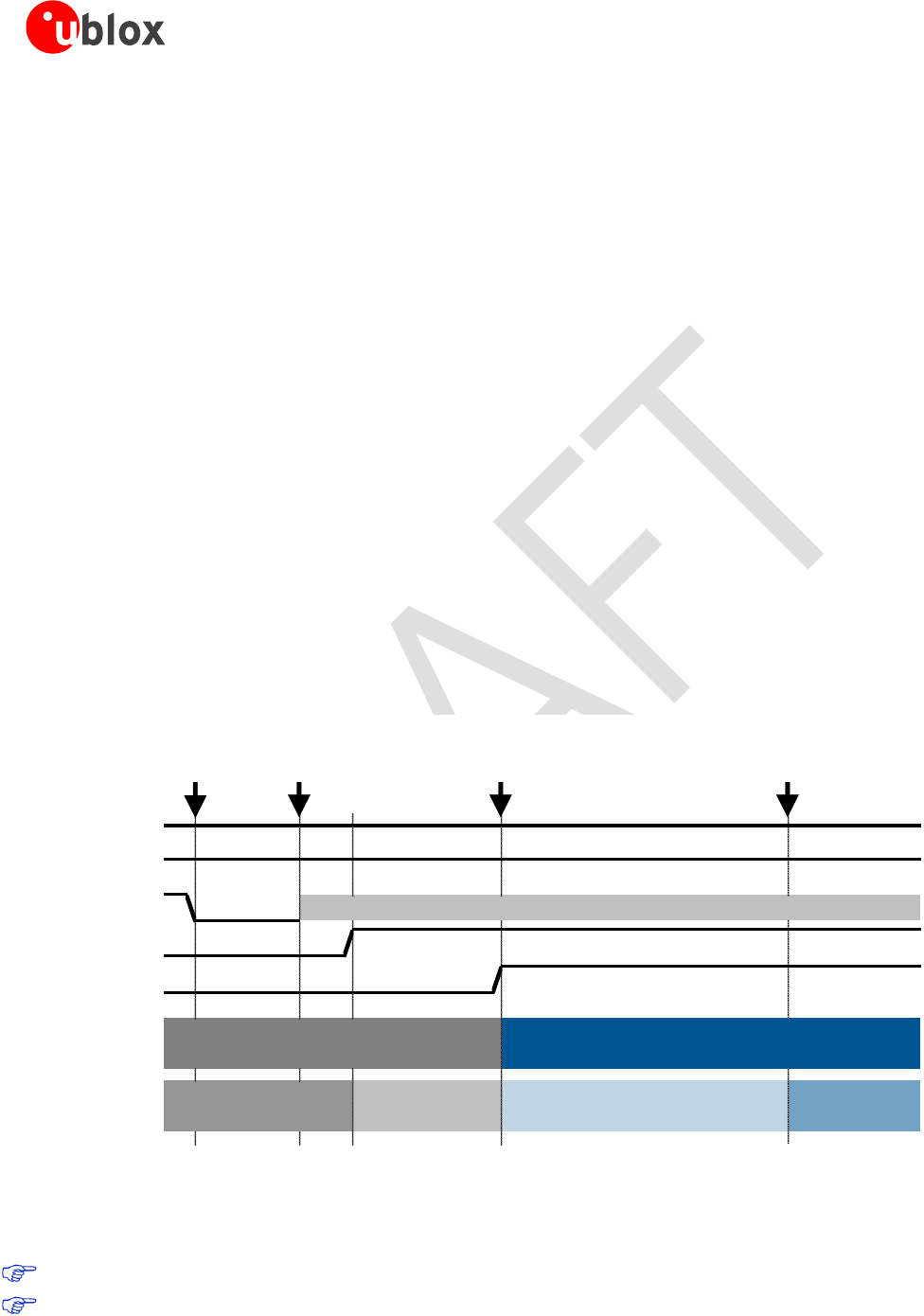

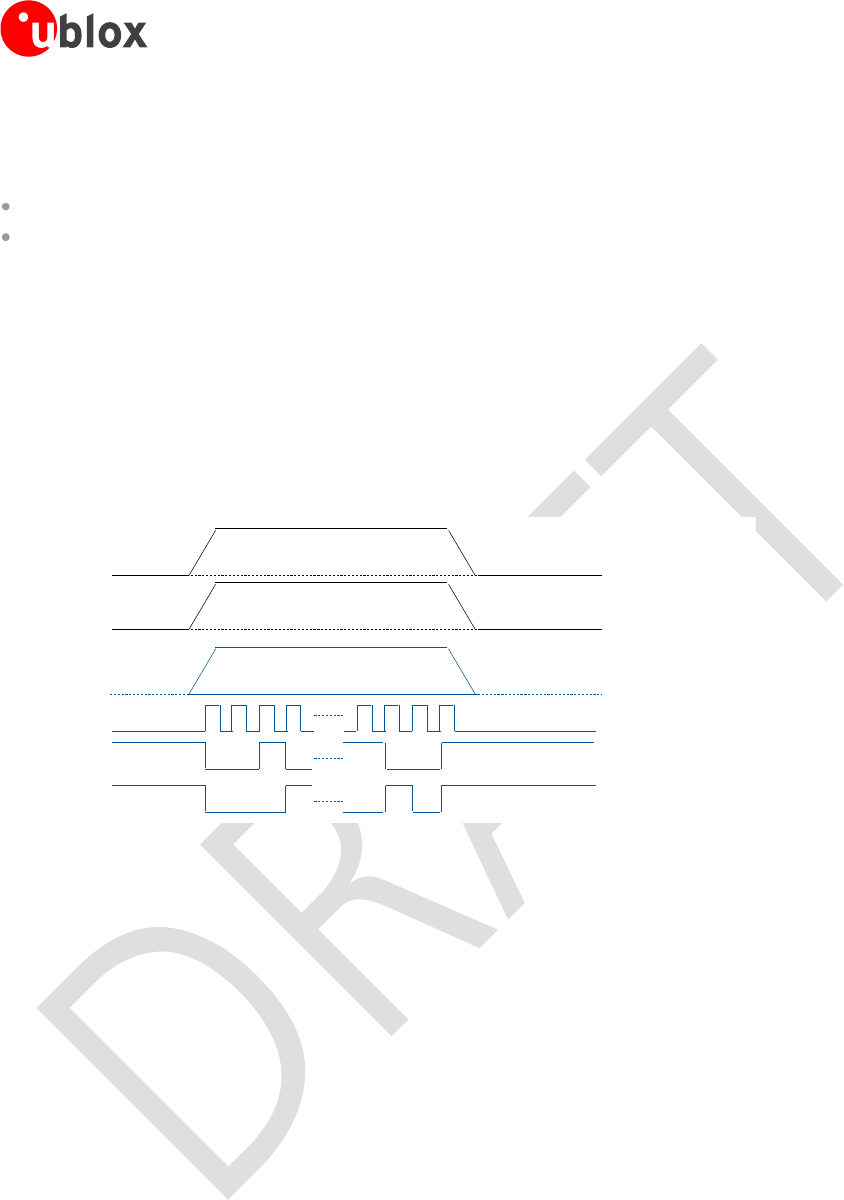

Transition between the different modes is described in Figure 3.

Switch ON:

•Apply VCC

If power saving is enabled

and there is no activity for

a defined time interval

Any wake up event described

in the module operating

modes summary table above

Incoming/outgoing call or

other dedicated device

network communication

Call terminated,

communication dropped

Remove VCC

Switch ON:

•PWR_ON

•RESET_N

•RTC Alarm

Not

powered

Power off

ActiveConnected Idle

Switch OFF:

•AT+CPWROFF

•PWR_ON (LISA-U2 only)

Figure 3: Operating modes transition

LISA-U series - System Integration Manual

3G.G2-HW-10002-A1 Advance Information System description

Page 19 of 160

1.5 Power management

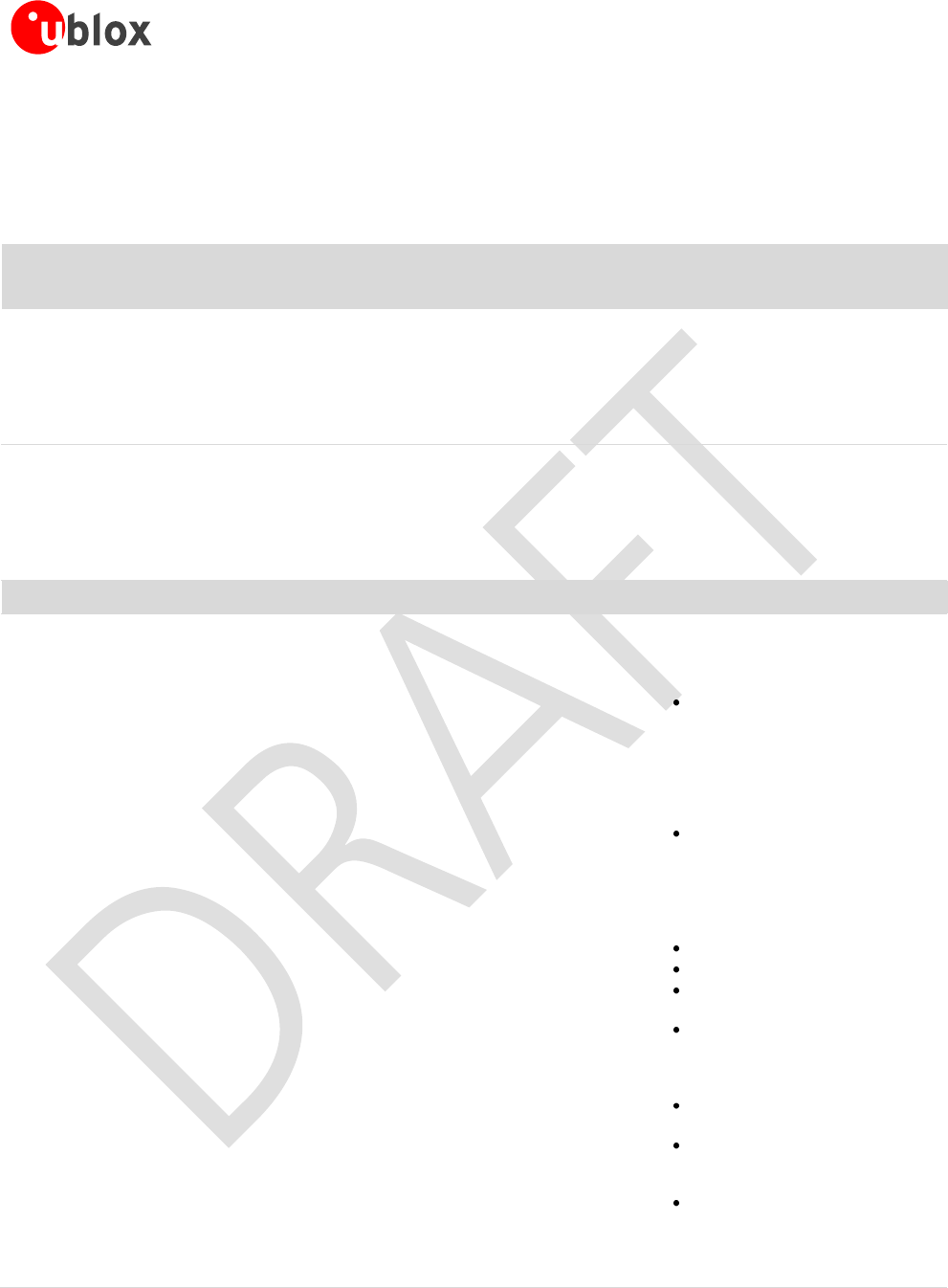

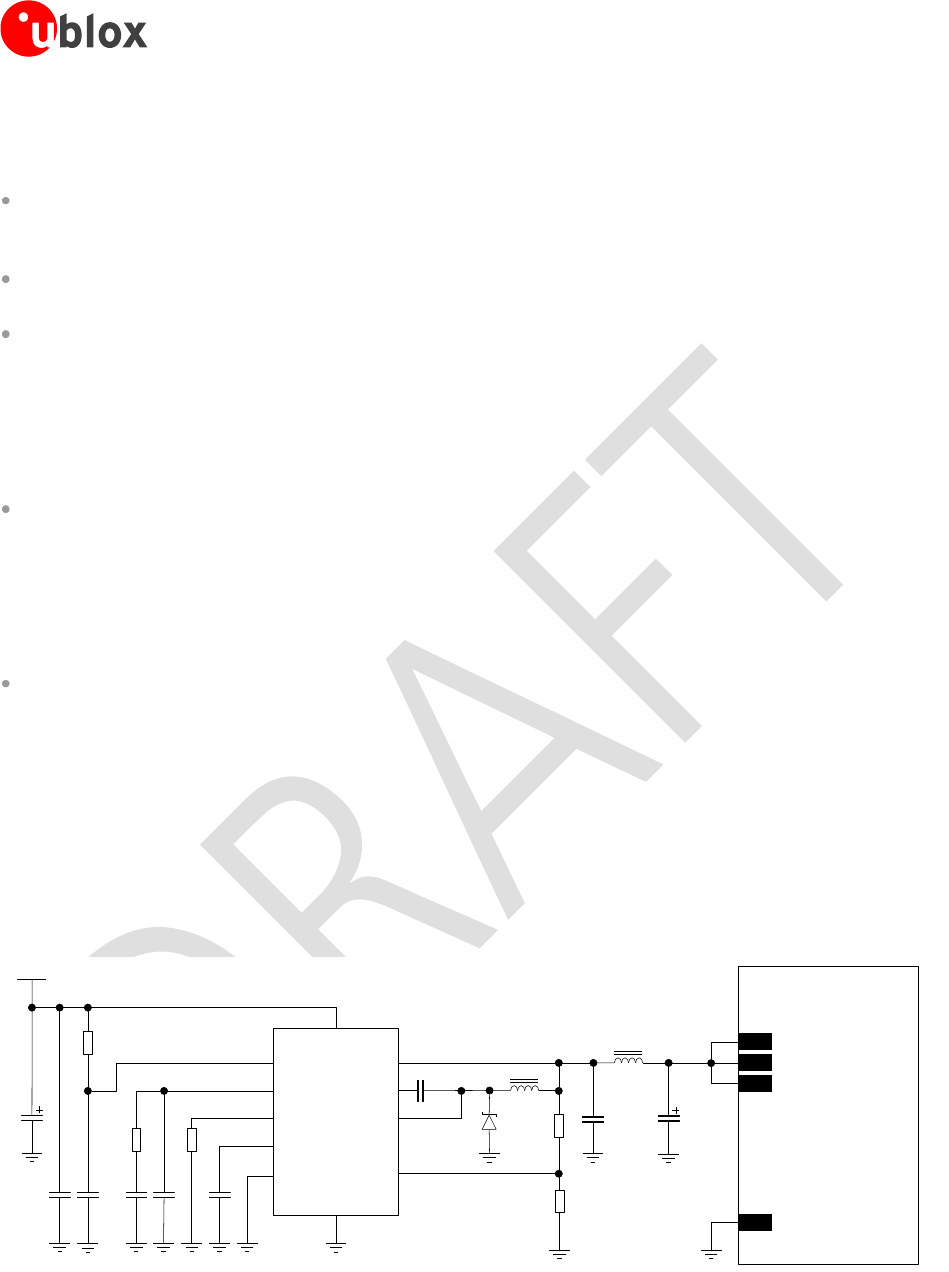

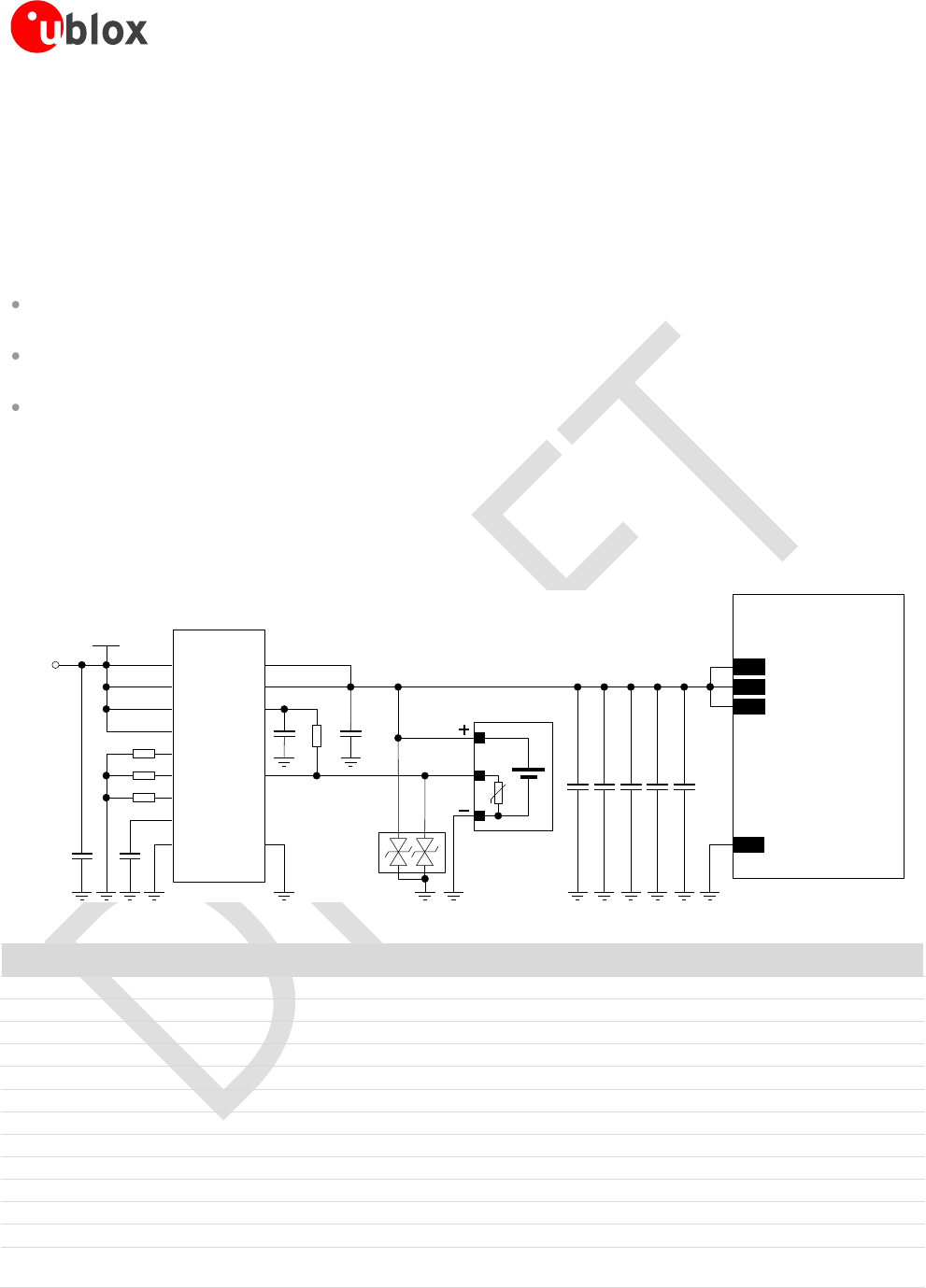

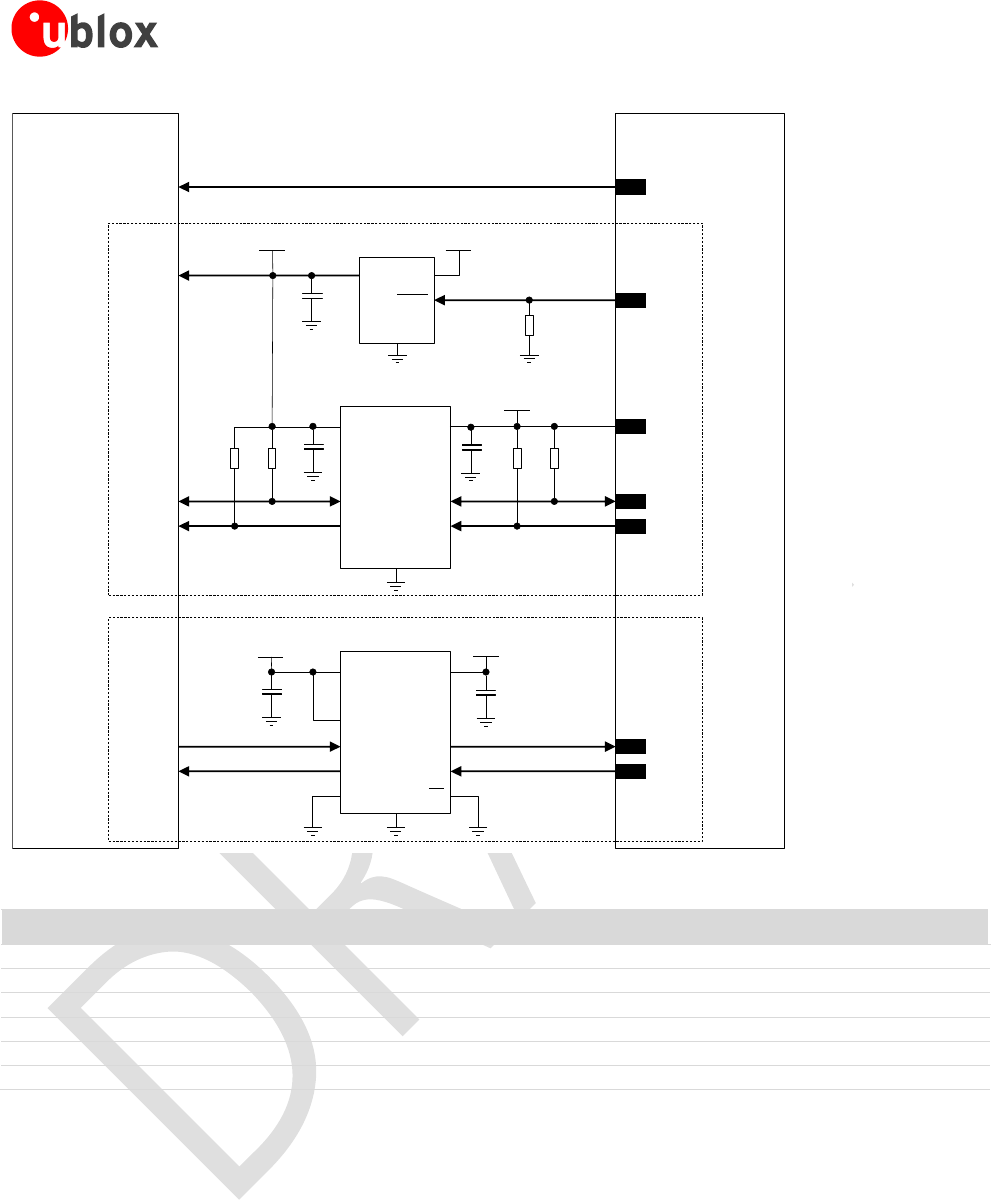

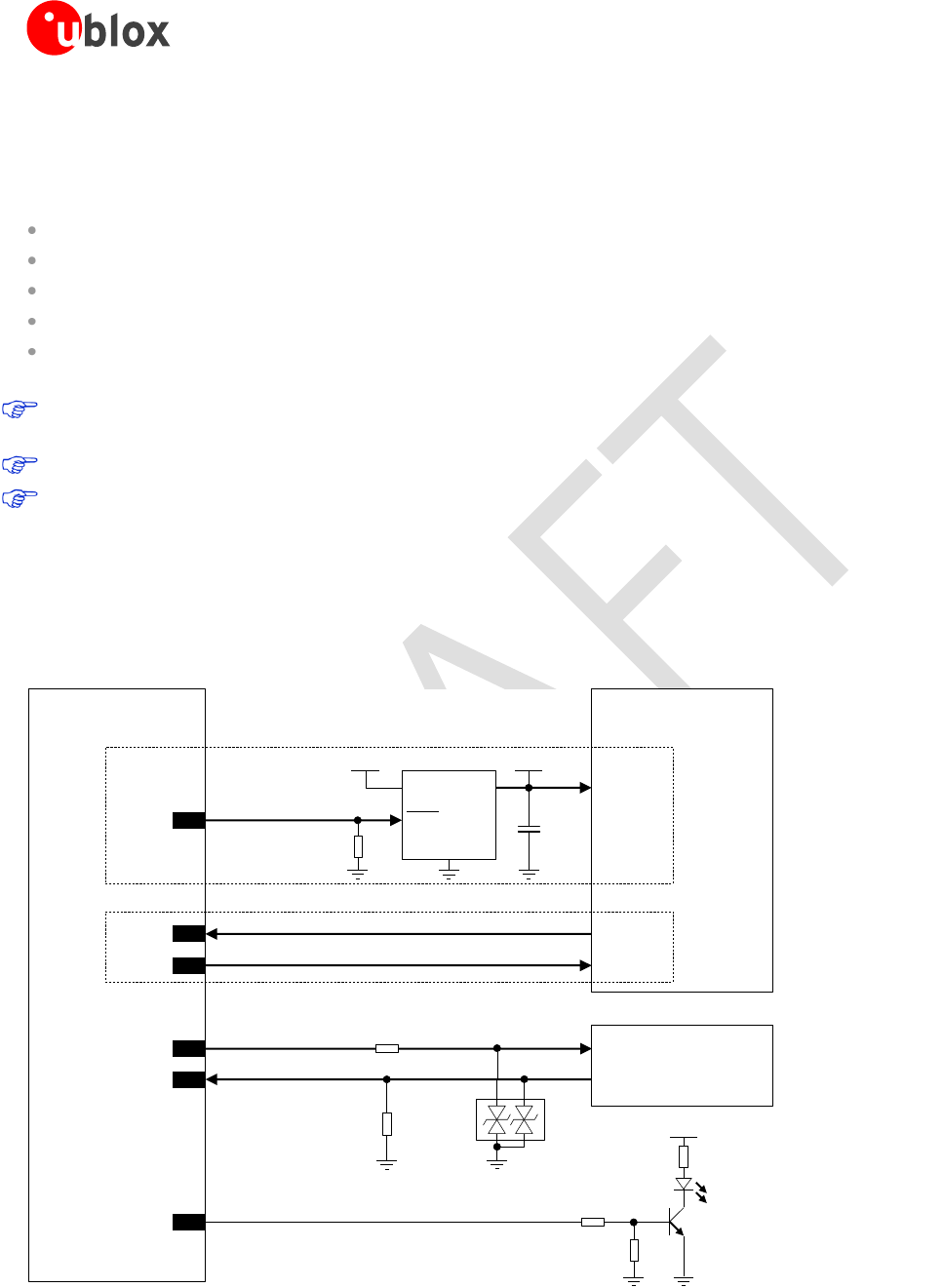

1.5.1 Power supply circuit overview

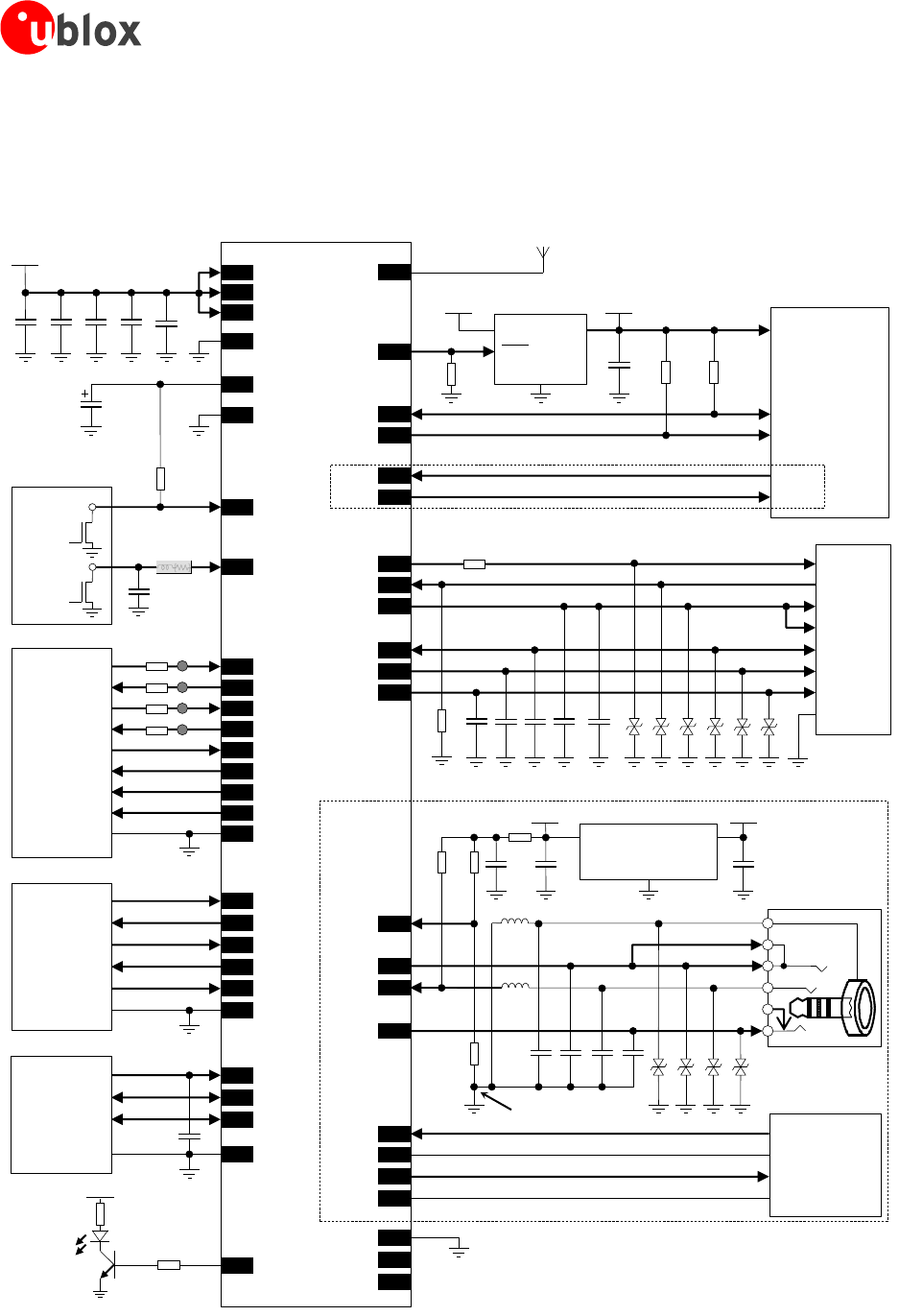

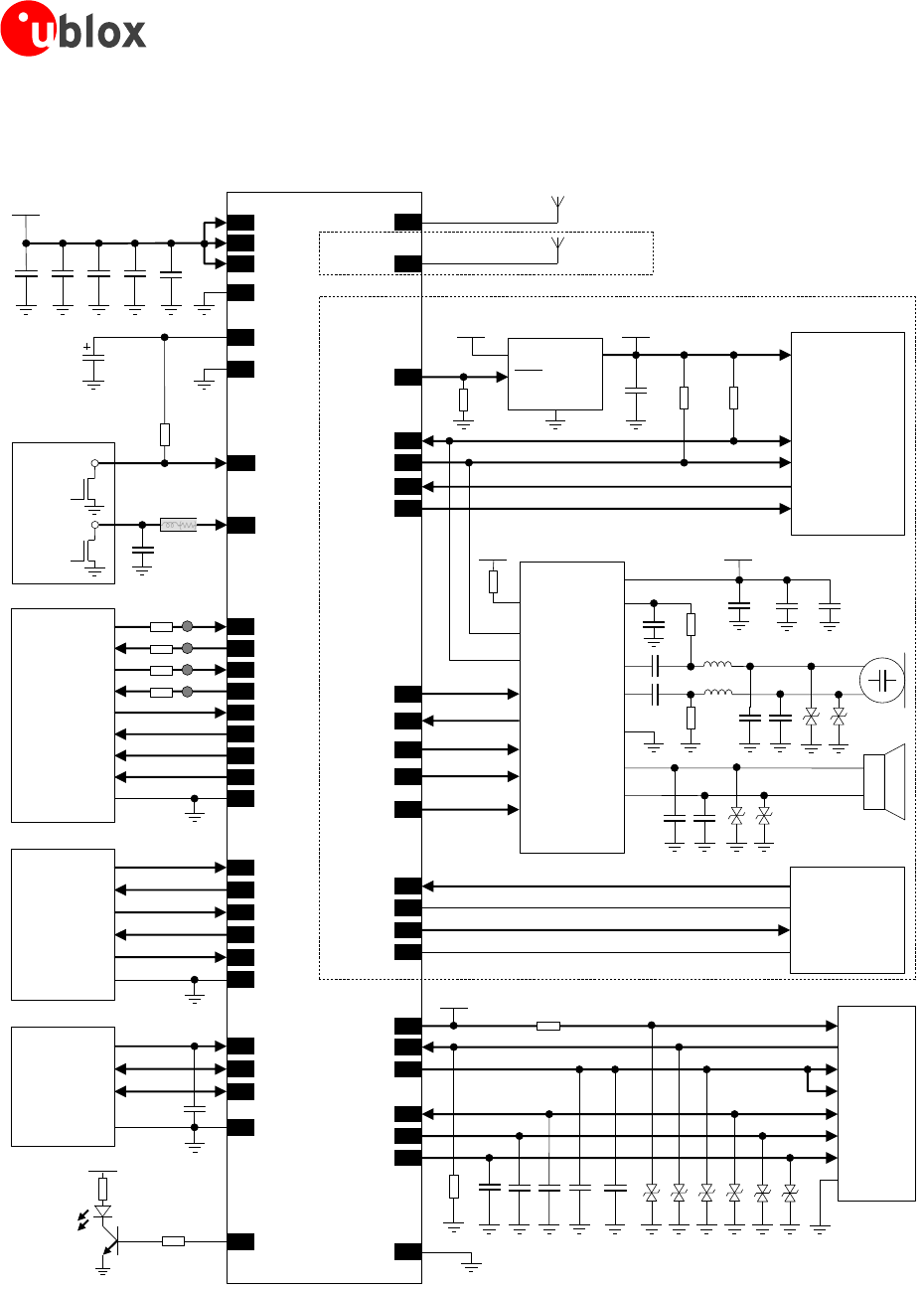

LISA-U series modules feature a power management concept optimized for the most efficient use of supplied

power. This is achieved by hardware design utilizing a power efficient circuit topology (Figure 4), and by power

management software controlling the module’s power saving mode.

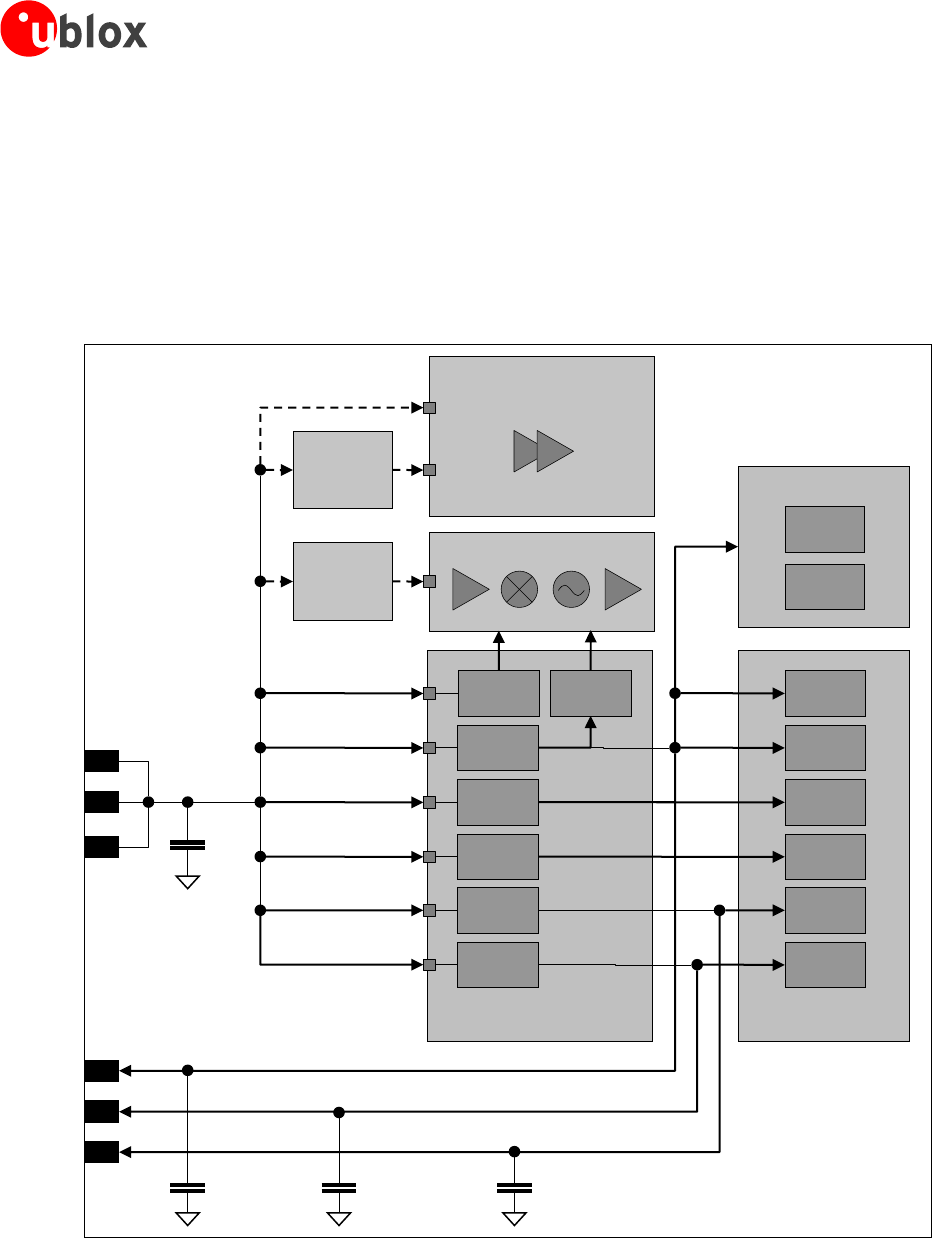

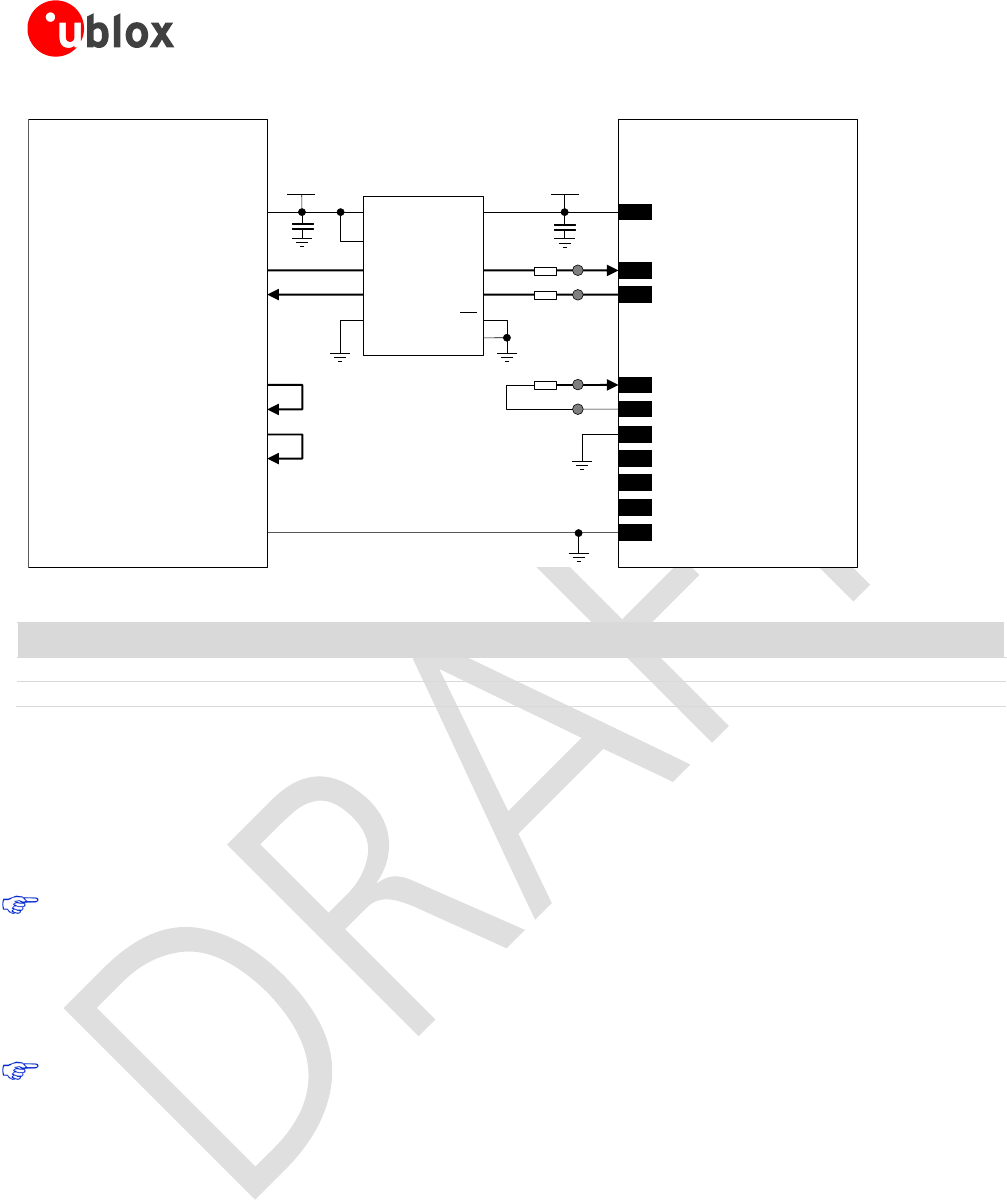

Baseband Processor

2G/3G

Power Amplifier(s)

Switching

Step-Down

5 x 10 µF

61

VCC

62

VCC

63

VCC

50

VSIM

2

V_BCKP

4

V_INT

Linear

LDO

Linear

LDO

Switching

Step-Down

Linear

LDO

Linear

LDO

Linear

LDO

I/O

EBU

CORE

Analog

SIM

RTC

NOR Flash

DDR SRAM

RF Transceiver

Memory

Power Management Unit

22 µF 10 µF (LISA-U1)

220 nF (LISA-U2) 220 nF

2G/3G PA

PMU

(LISA-U2)

Transceiver

PMU

(LISA-U2)

(LISA-U1)

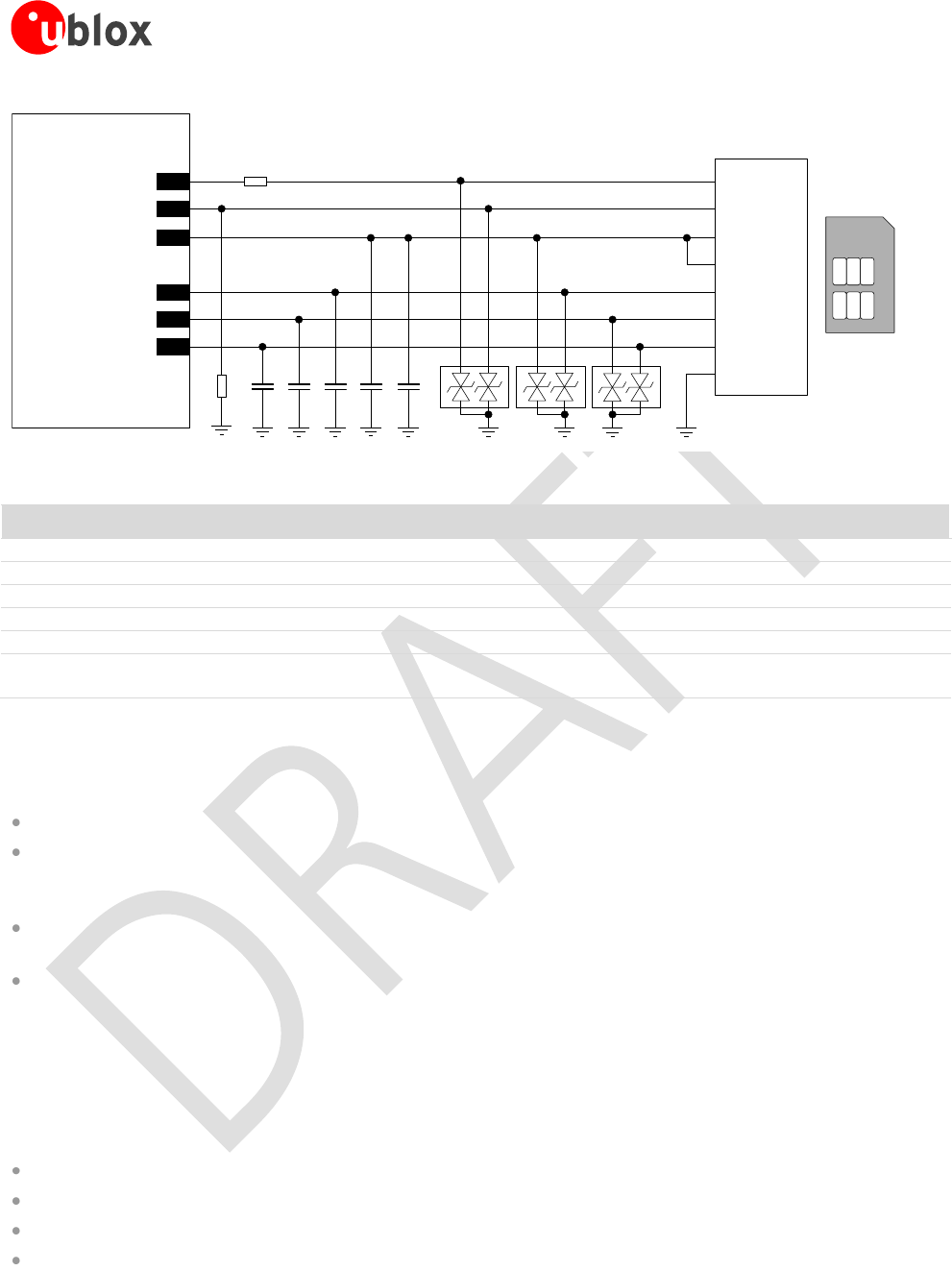

Figure 4: LISA-U series power management simplified block diagram

Pins with supply function are reported in Table 6, Table 11 and Table 14.

LISA-U series modules must be supplied via the VCC pins. There is only one main power supply input, available

on the three VCC pins that must be all connected to the external power supply

LISA-U series - System Integration Manual

3G.G2-HW-10002-A1 Advance Information System description

Page 20 of 160

The VCC pins are directly connected to the RF power amplifiers and to the integrated Power Management Unit

(PMU) within the module: all supply voltages needed by the module are generated from the VCC supply by

integrated voltage regulators.

V_BCKP is the Real Time Clock (RTC) supply. When the VCC voltage is within the valid operating range, the

internal PMU supplies the Real Time Clock and the same supply voltage will be available to the V_BCKP pin. If

the VCC voltage is under the minimum operating limit (for example, during not powered mode), the Real Time

Clock can be externally supplied via the V_BCKP pin (see section 1.5.4).

When a 1.8 V or a 3 V SIM card type is connected, LISA-U series modules automatically supply the SIM card via

the VSIM pin. Activation and deactivation of the SIM interface with automatic voltage switch from 1.8 to 3 V is

implemented, in accordance to the ISO-IEC 7816-3 specifications.

The same voltage domain used internally to supply the digital interfaces is also available on the V_INT pin, to

allow more economical and efficient integration of the LISA-U series modules in the final application.

The integrated Power Management Unit also provides the control state machine for system start up and system

reset control.

1.5.2 Module supply (VCC)

The LISA-U series modules must be supplied through the VCC pins by a DC power supply. Voltages must be

stable: during operation, the current drawn from VCC can vary by some orders of magnitude, especially due to

surging consumption profile of the GSM system (described in the section 1.5.3). It is important that the system

power supply circuit is able to support peak power (refer to LISA-U1 series Data Sheet [1] and LISA-U2 series

Data Sheet [2] for the detailed specifications).

Name

Description

Remarks

VCC

Module power supply input

VCC pins are internally connected, but all the available pads

must be connected to the external supply in order to

minimize the power loss due to series resistance.

Clean and stable supply is required: low ripple and low

voltage drop must be guaranteed.

Voltage provided must always be above the minimum limit of

the operating range.

Consider that during a GSM call there are large current spikes

in connected mode.

GND

Ground

GND pins are internally connected but a good (low

impedance) external ground can improve RF performance: all

available pads must be connected to ground.

Table 6: Module supply pins

VCC pins ESD sensitivity rating is 1 kV (Human Body Model according to JESD22-A114F). Higher

protection level can be required if the line is externally accessible on the application board. Higher

protection level can be achieved by mounting an ESD protection (e.g. EPCOS CA05P4S14THSG varistor

array) on the line connected to this pin, close to accessible point.

The voltage provided to the VCC pins must be within the normal operating range limits as specified in the

LISA-U1 series Data Sheet [1] and LISA-U2 series Data Sheet [2]. Complete functionality of the module is only

guaranteed within the specified minimum and maximum VCC voltage normal operating range.

The module cannot be switched on if the VCC voltage value is below the specified normal operating

range minimum limit: ensure that the input voltage at VCC pins is above the minimum limit of the

normal operating range for more than 1 s after the start of the switch-on of the module.

LISA-U series - System Integration Manual

3G.G2-HW-10002-A1 Advance Information System description

Page 21 of 160

When LISA-U series modules are in operation, the voltage provided to VCC pins can go outside the normal

operating range limits but must be within the extended operating range limits specified in LISA-U1 series Data

Sheet [1] and LISA-U2 series Data Sheet [2]. Occasional deviations from the ETSI specifications may occur when

the input voltage at VCC pins is outside the normal operating range and is within the extended operating range.

LISA-U series modules switch off when VCC voltage value drops below the specified extended operating

range minimum limit: ensure that the input voltage at VCC pins never drops below the minimum limit of

the extended operating range when the module is switched on, not even during a GSM transmit burst,

where the current consumption can rise up to maximum peaks of 2.5 A in case of a mismatched

antenna load.

Operation above the normal operating range maximum limit is not recommended and

extended exposure beyond it may affect device reliability.

Stress beyond the VCC absolute maximum ratings can cause permanent damage to the

module: if necessary, voltage spikes beyond VCC absolute maximum ratings must be restricted

to values within the specified limits by using appropriate protection.

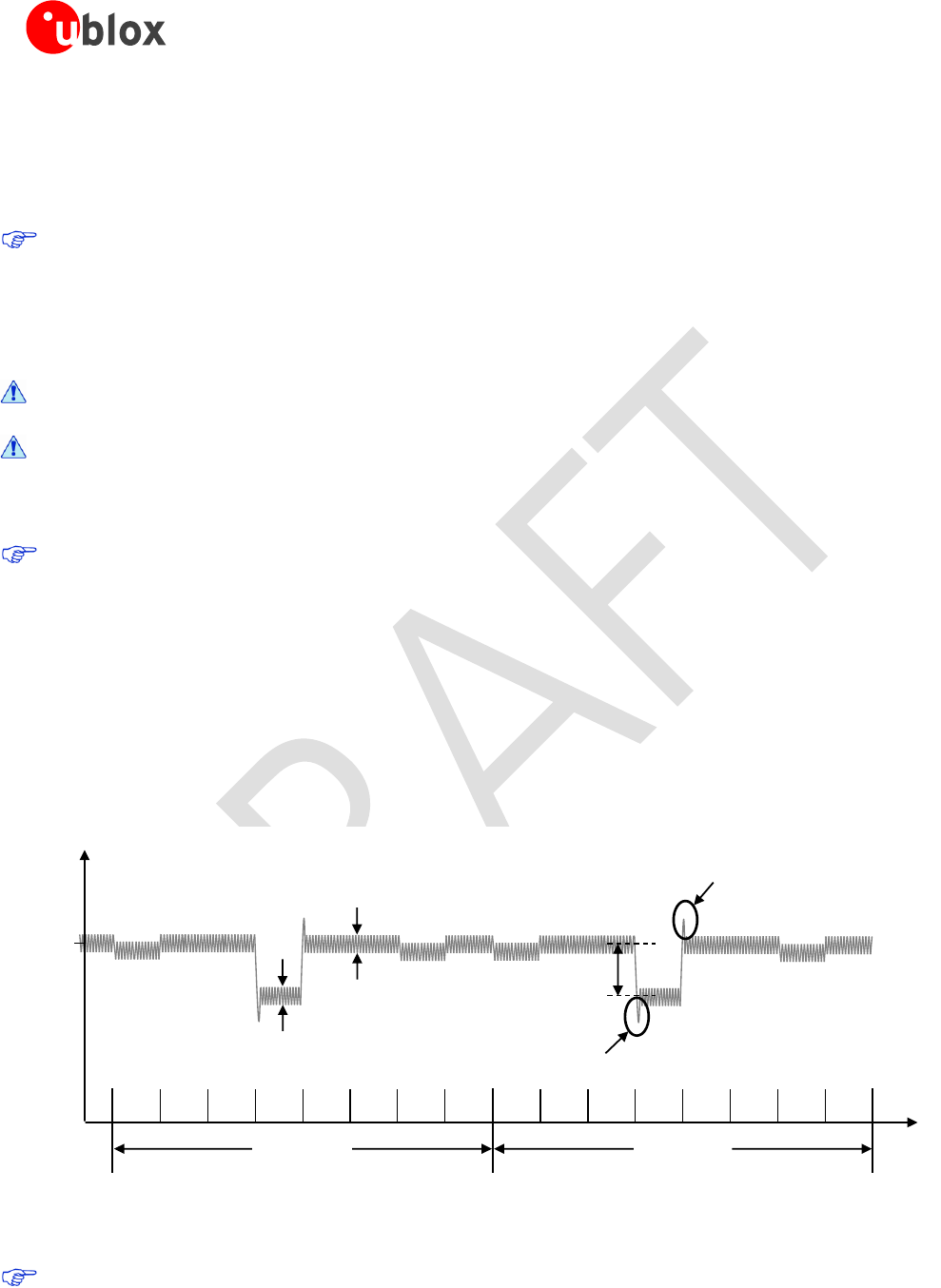

When designing the power supply for the application, pay specific attention to power losses and

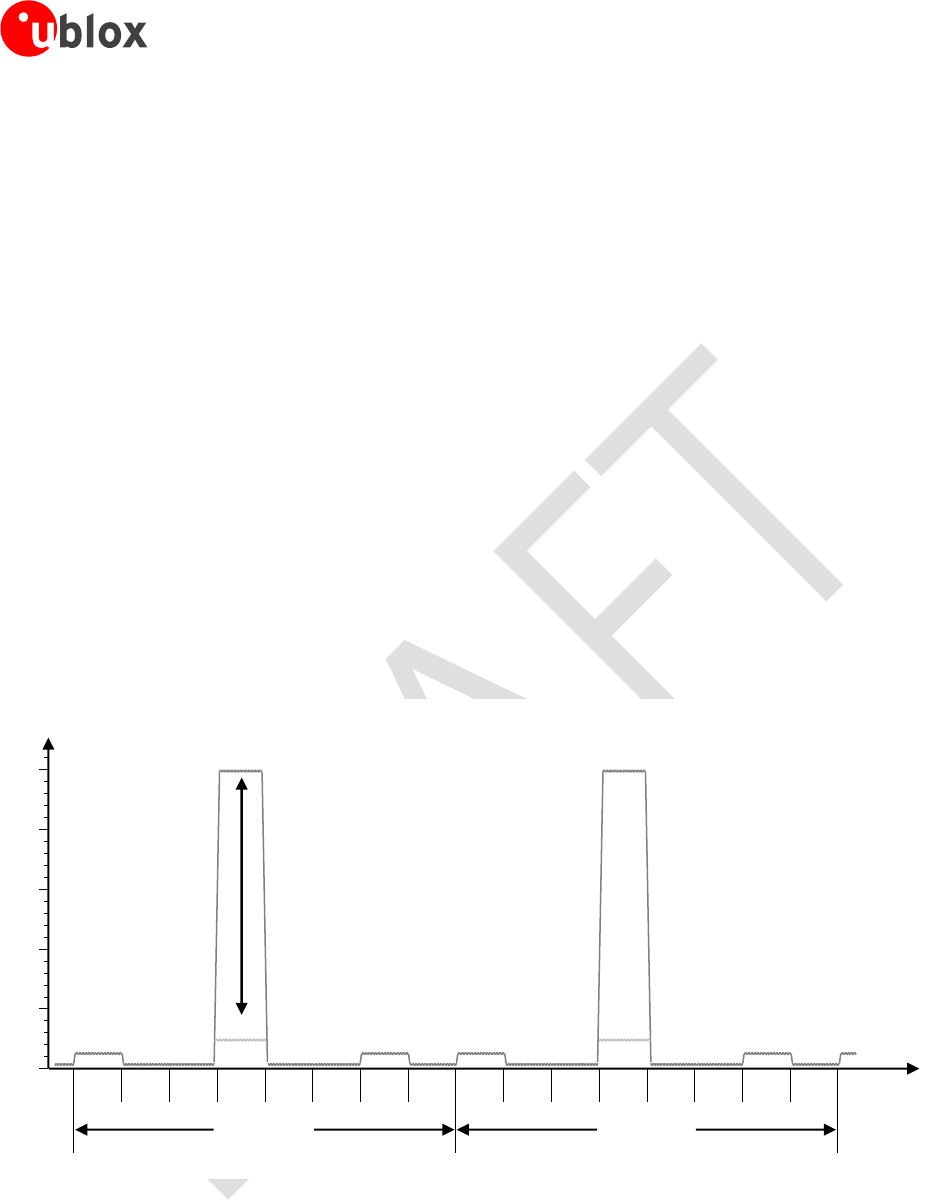

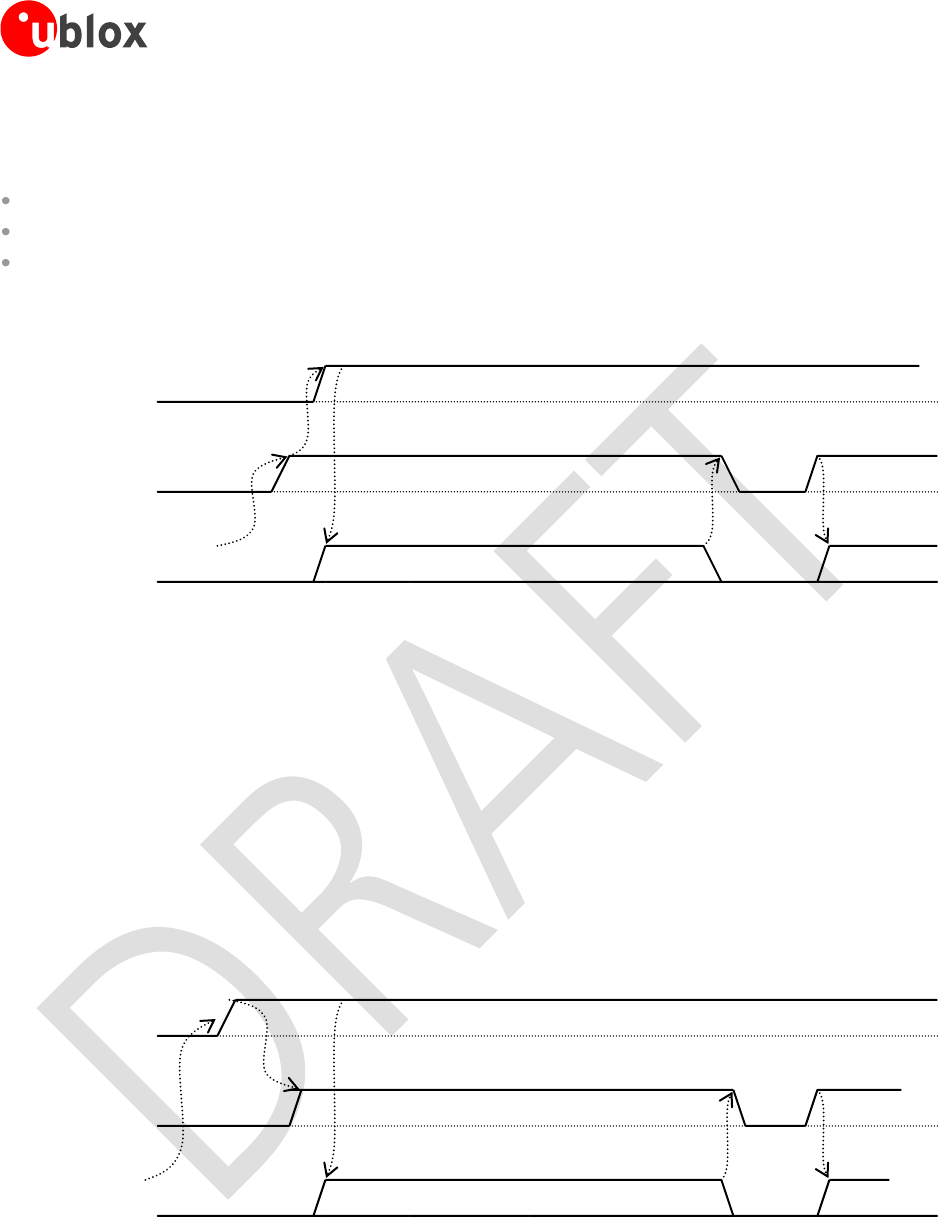

transients. The DC power supply must be able to provide a voltage profile to the VCC pins with the

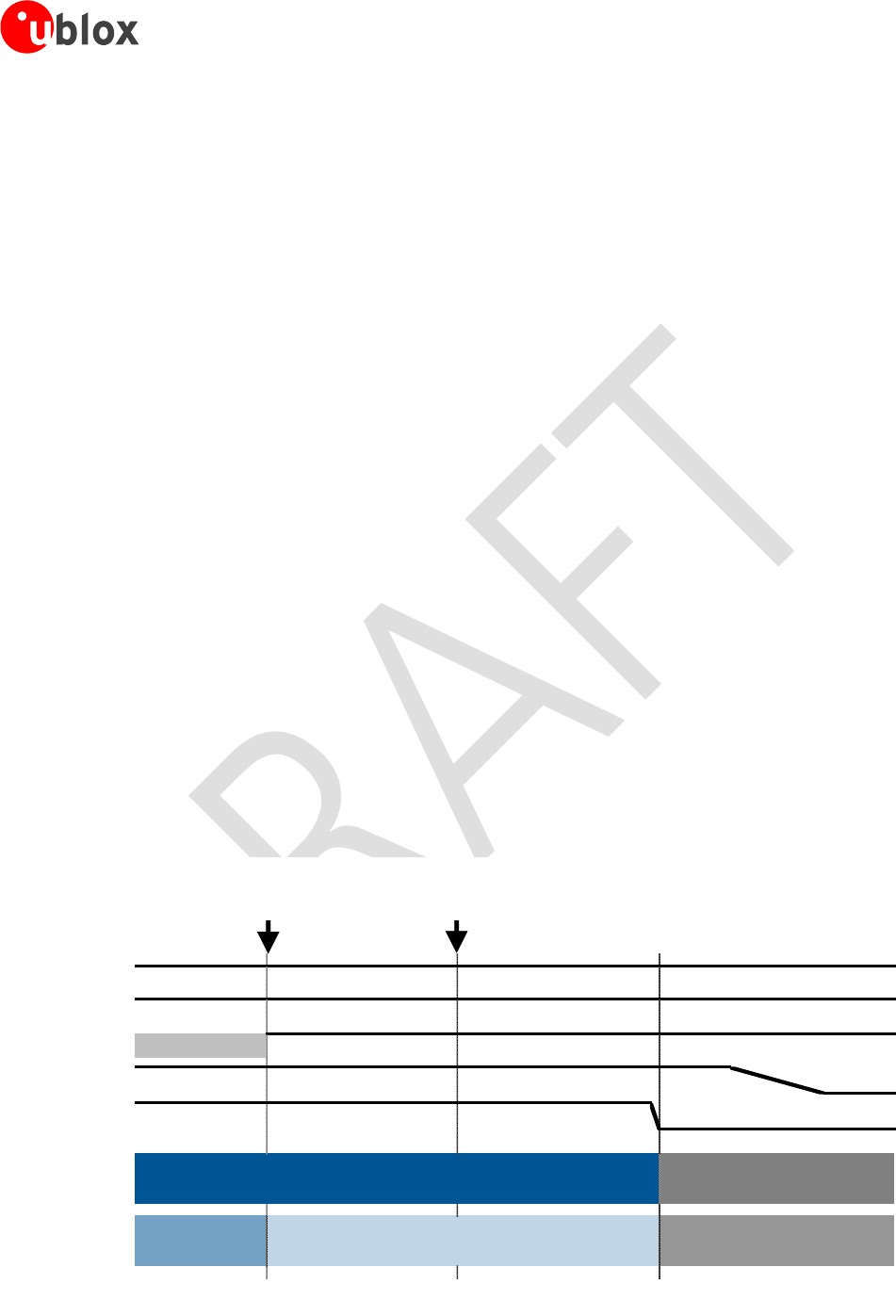

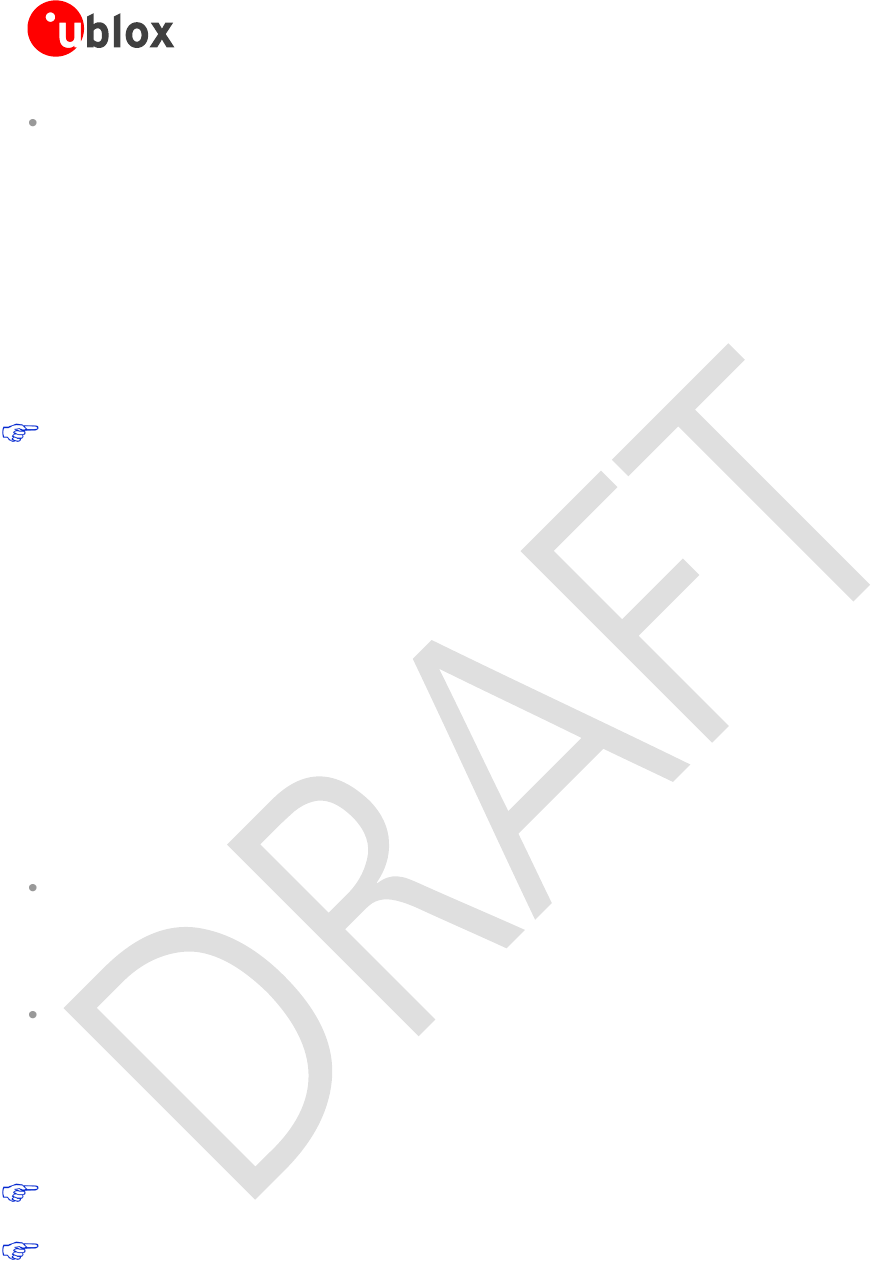

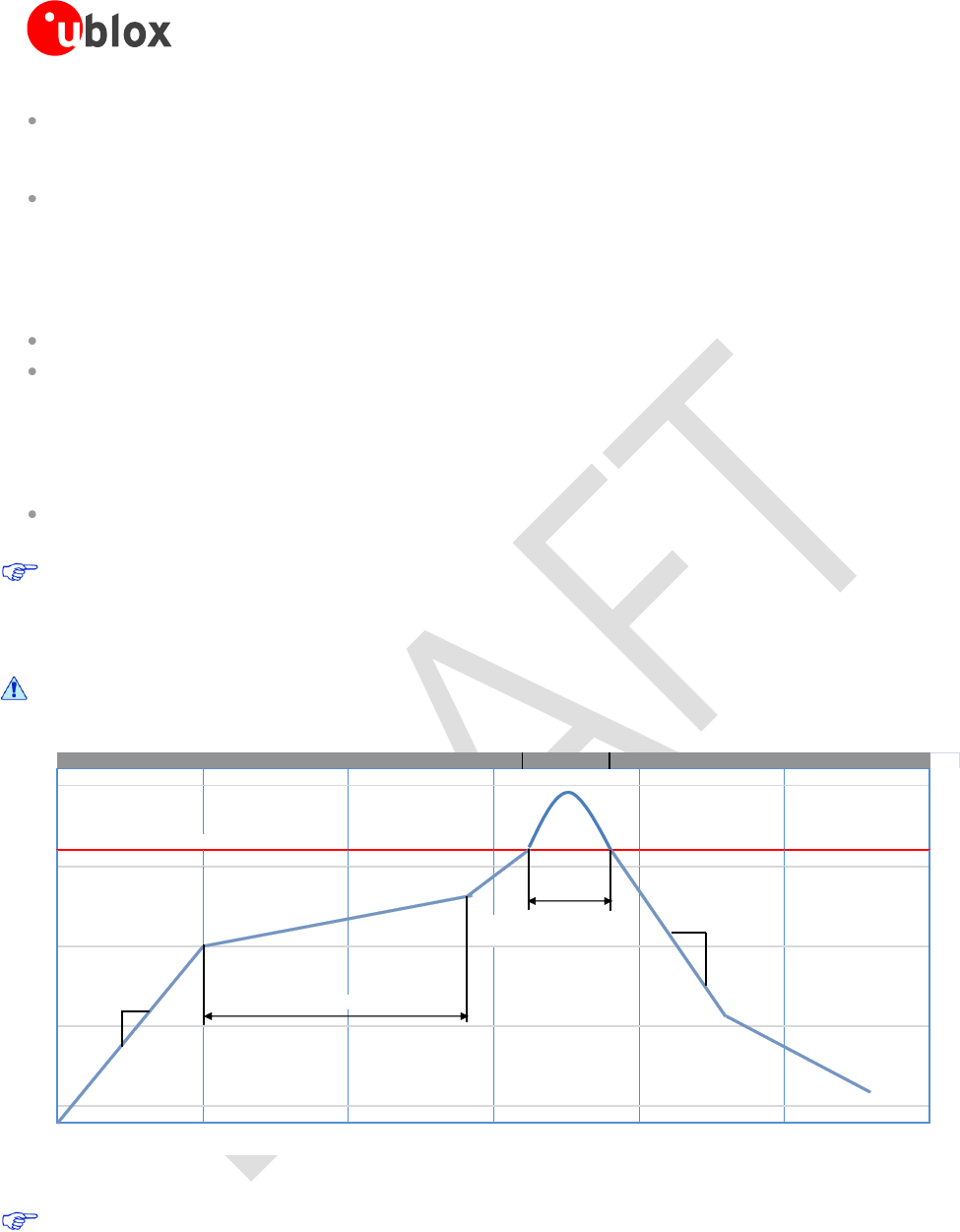

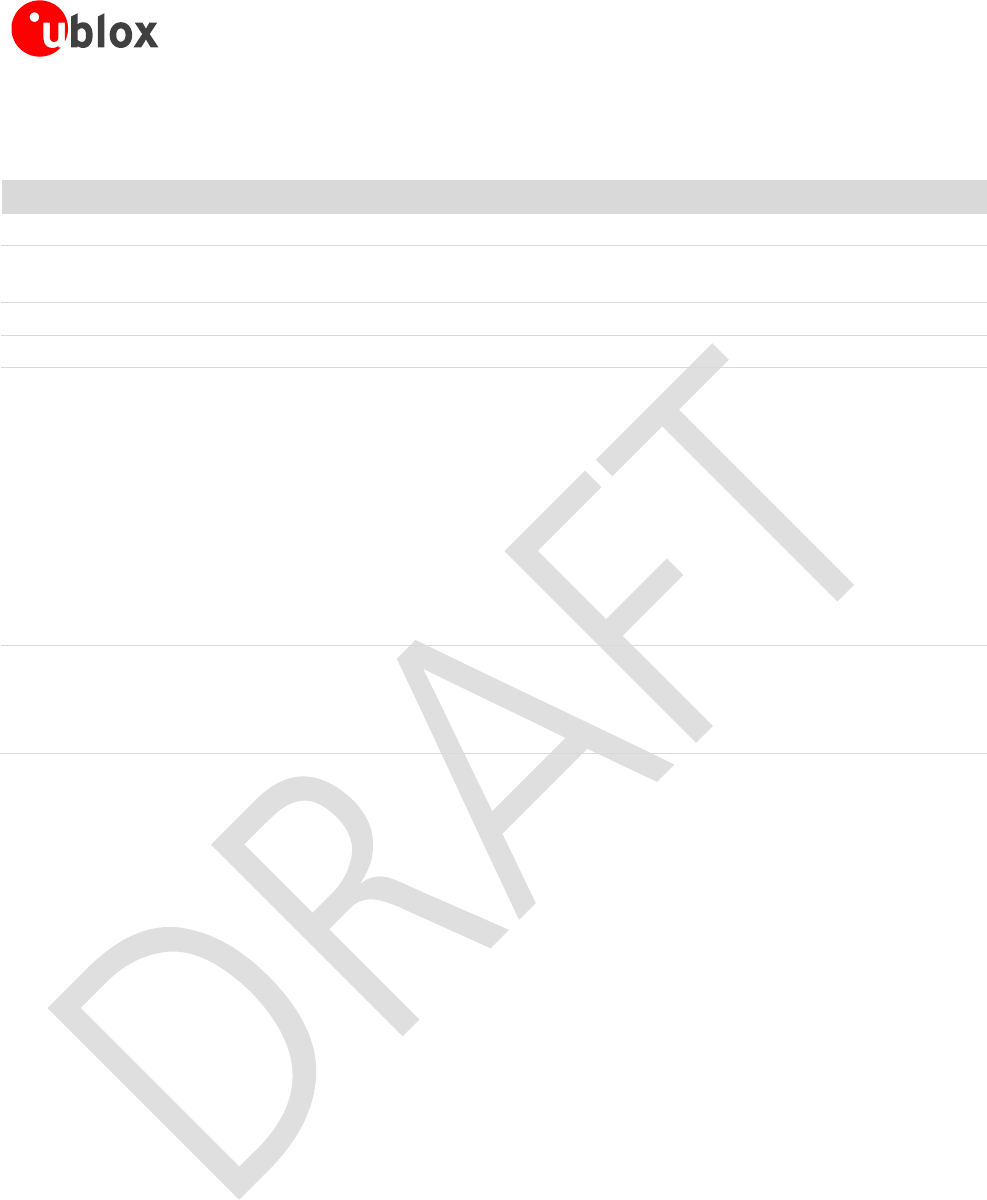

following characteristics:

o Voltage drop during transmit slots must be lower than 400 mV

o No undershoot or overshoot at the start and at the end of transmit slots

o Voltage ripple during transmit slots must be minimized:

lower than 70 mVpp if fripple ≤ 200 kHz

lower than 10 mVpp if 200 kHz < fripple ≤ 400 kHz

lower than 2 mVpp if fripple > 400 kHz

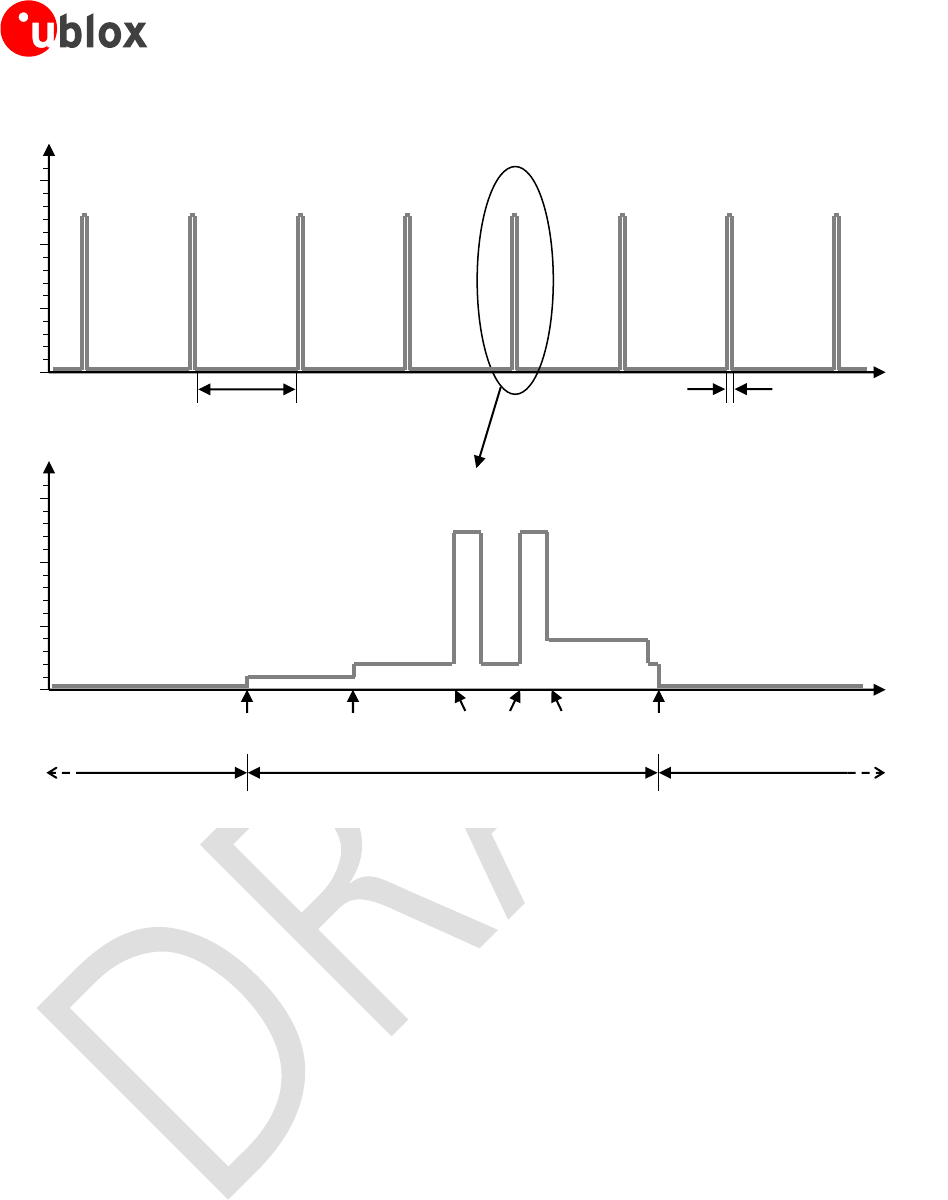

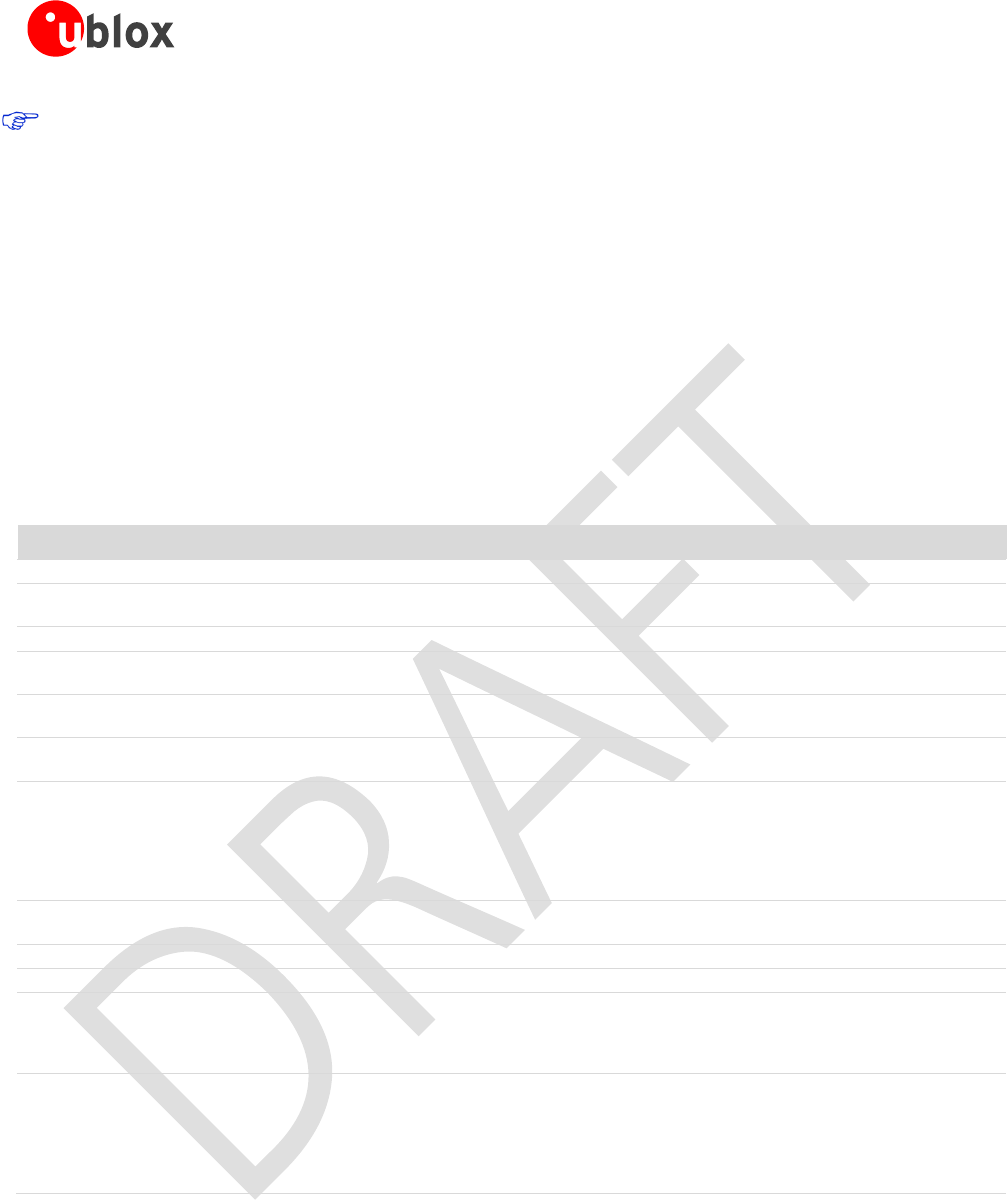

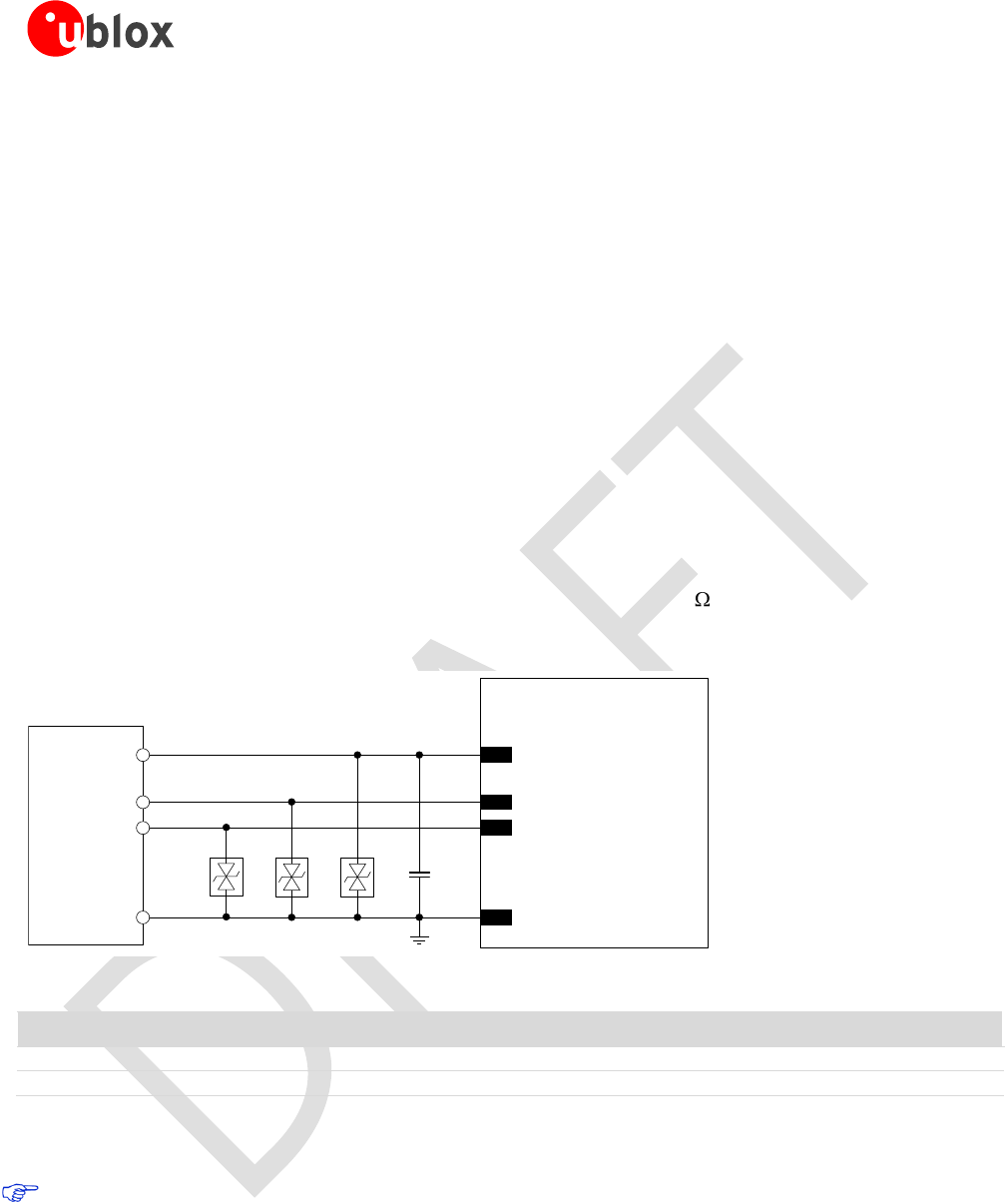

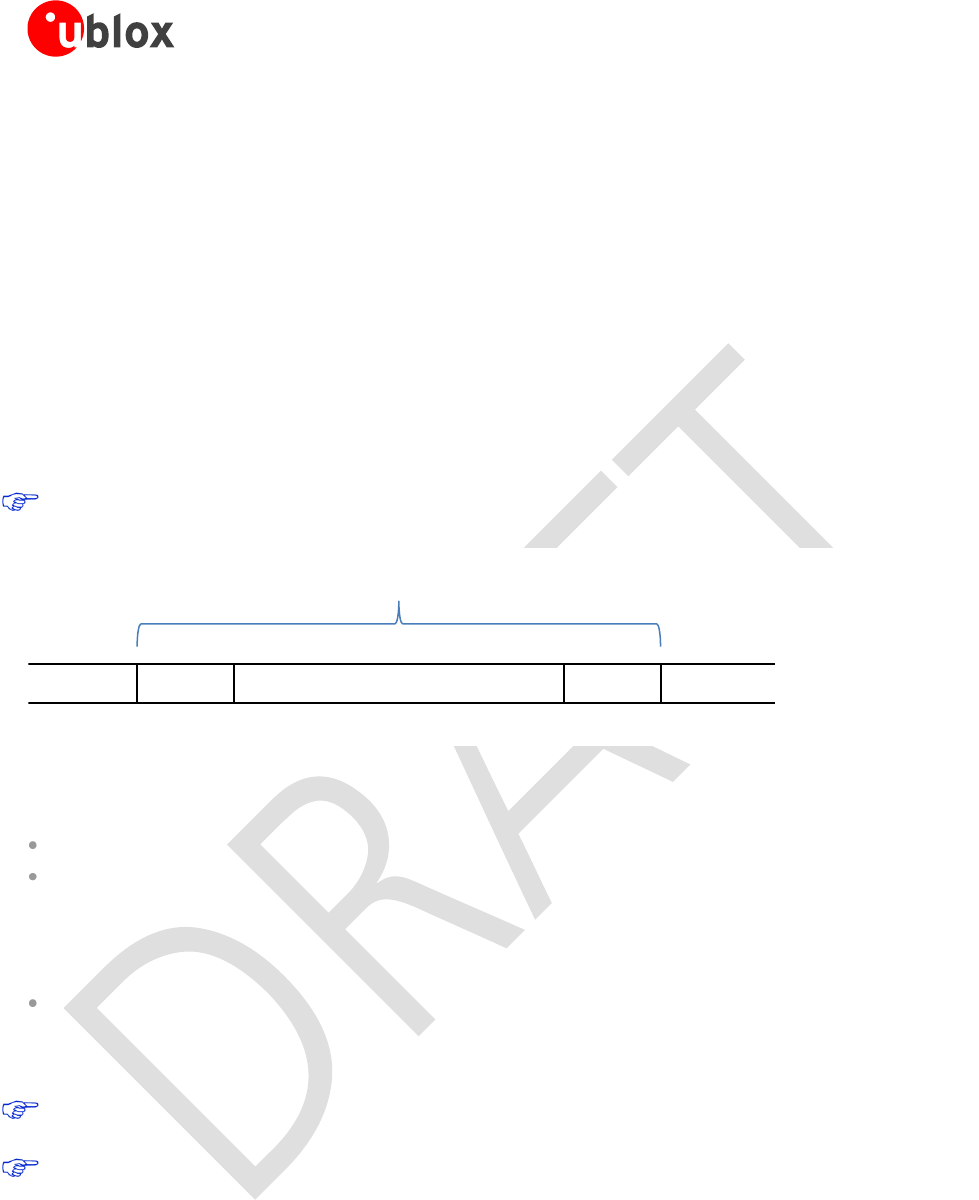

Time

undershoot

overshoot

ripple

ripple

drop

Voltage

3.8 V

(typ)

RX

slot

unused

slot

unused

slot

TX

slot

unused

slot

unused

slot

MON

slot

unused

slot

RX

slot

unused

slot

unused

slot

TX

slot

unused

slot

unused

slot

MON

slot

unused

slot

GSM frame

4.615 ms

(1 frame = 8 slots)

GSM frame

4.615 ms

(1 frame = 8 slots)

Figure 5: Description of the VCC voltage profile versus time during a GSM call

Any degradation in power supply performance (due to losses, noise or transients) will directly affect the

RF performance of the module since the single external DC power source indirectly supplies all the

digital and analog interfaces, and also directly supplies the RF power amplifier (PA).

LISA-U series - System Integration Manual

3G.G2-HW-10002-A1 Advance Information System description

Page 22 of 160

The voltage at the VCC pins must ramp from 2.5 V to 3.2 V within 1 ms. This VCC slope allows a proper

switch on of the module, that is switched on when the voltage rises to the VCC normal operating range

starting from a voltage value lower than 2.25 V.

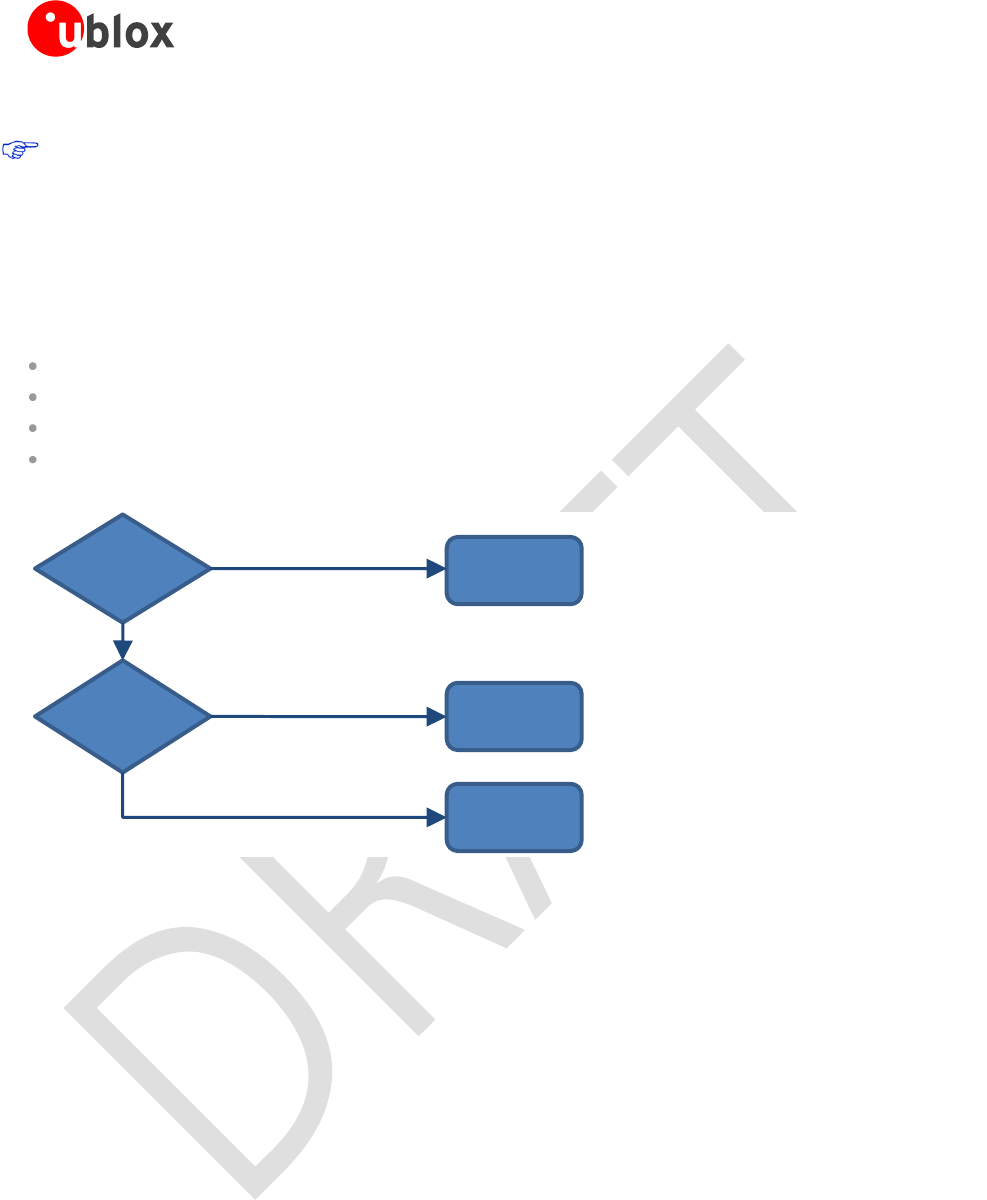

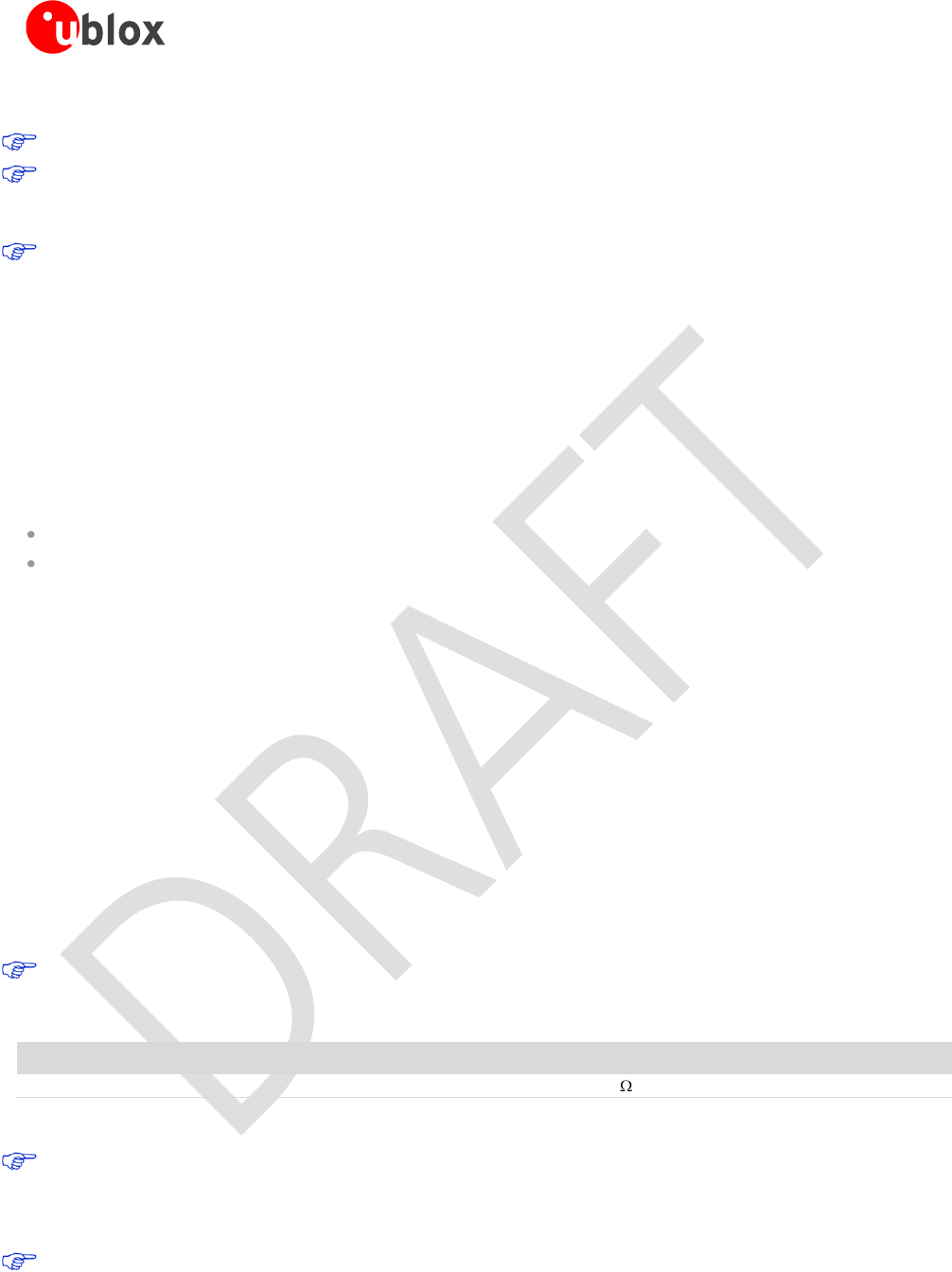

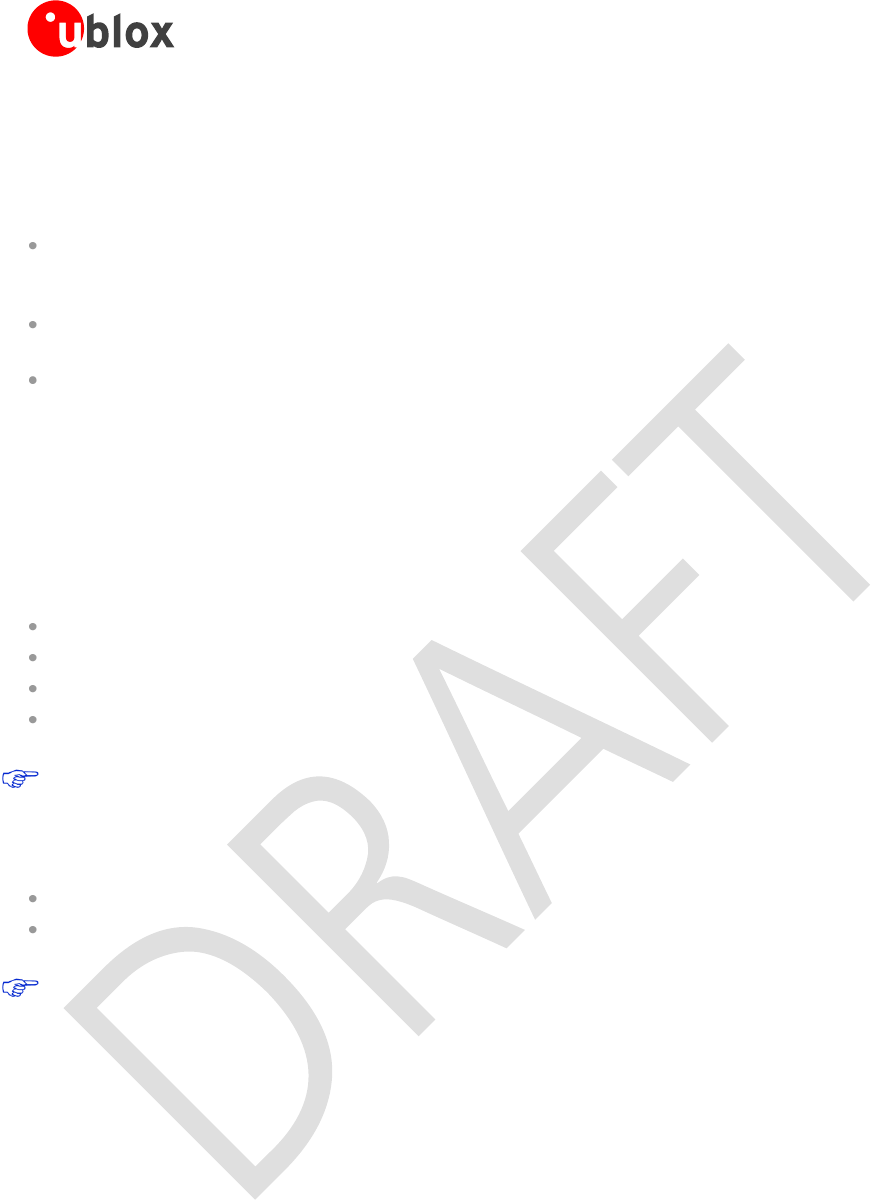

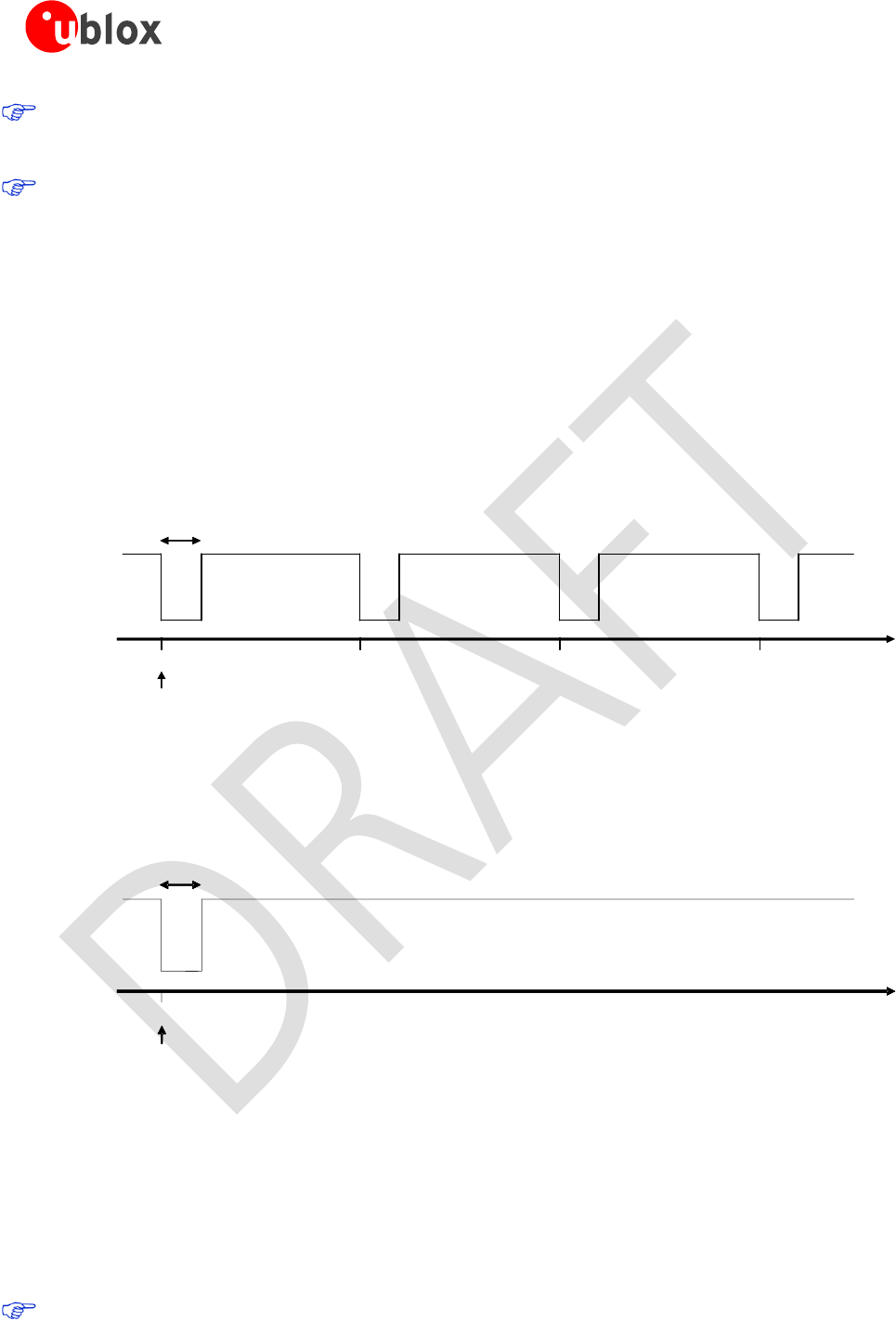

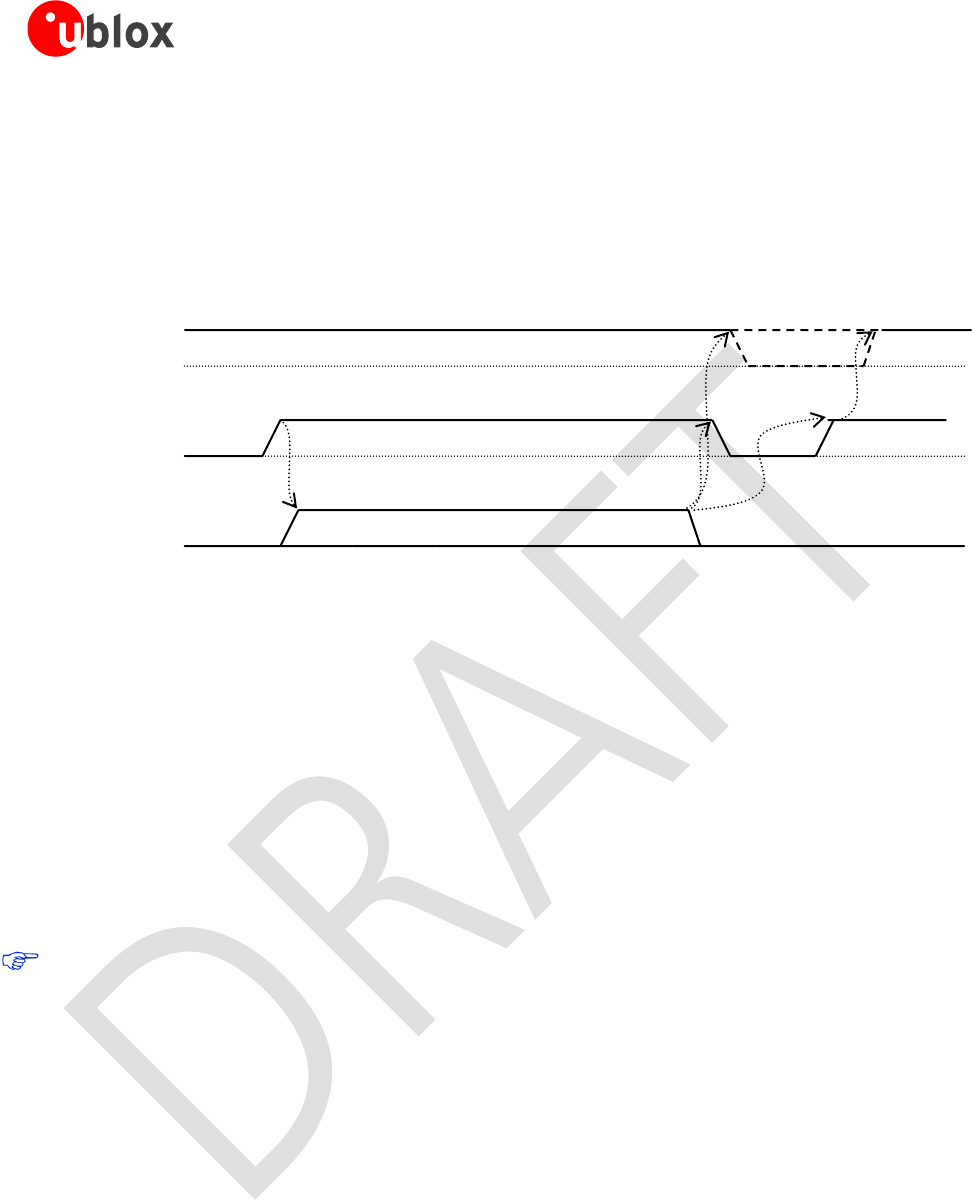

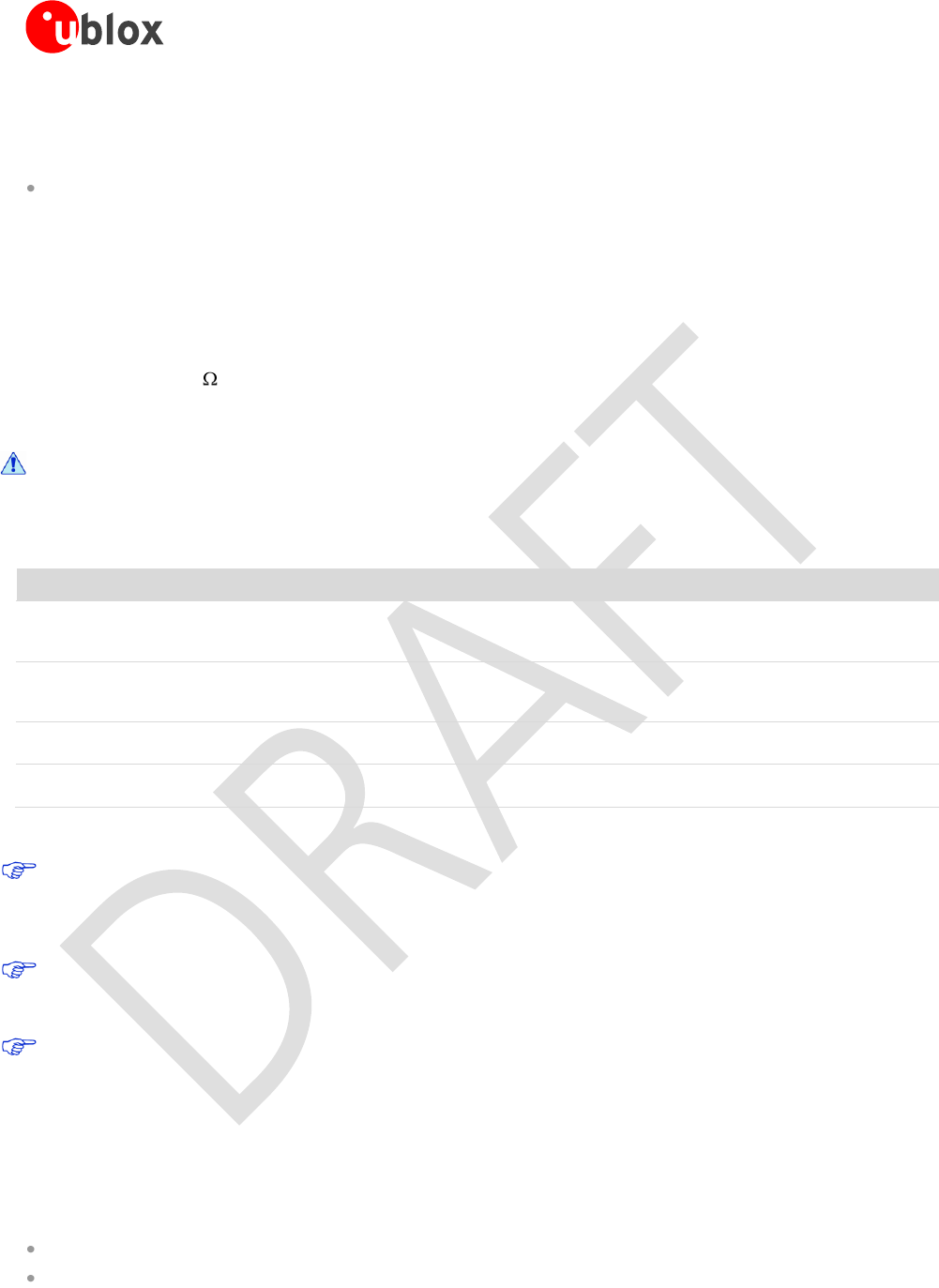

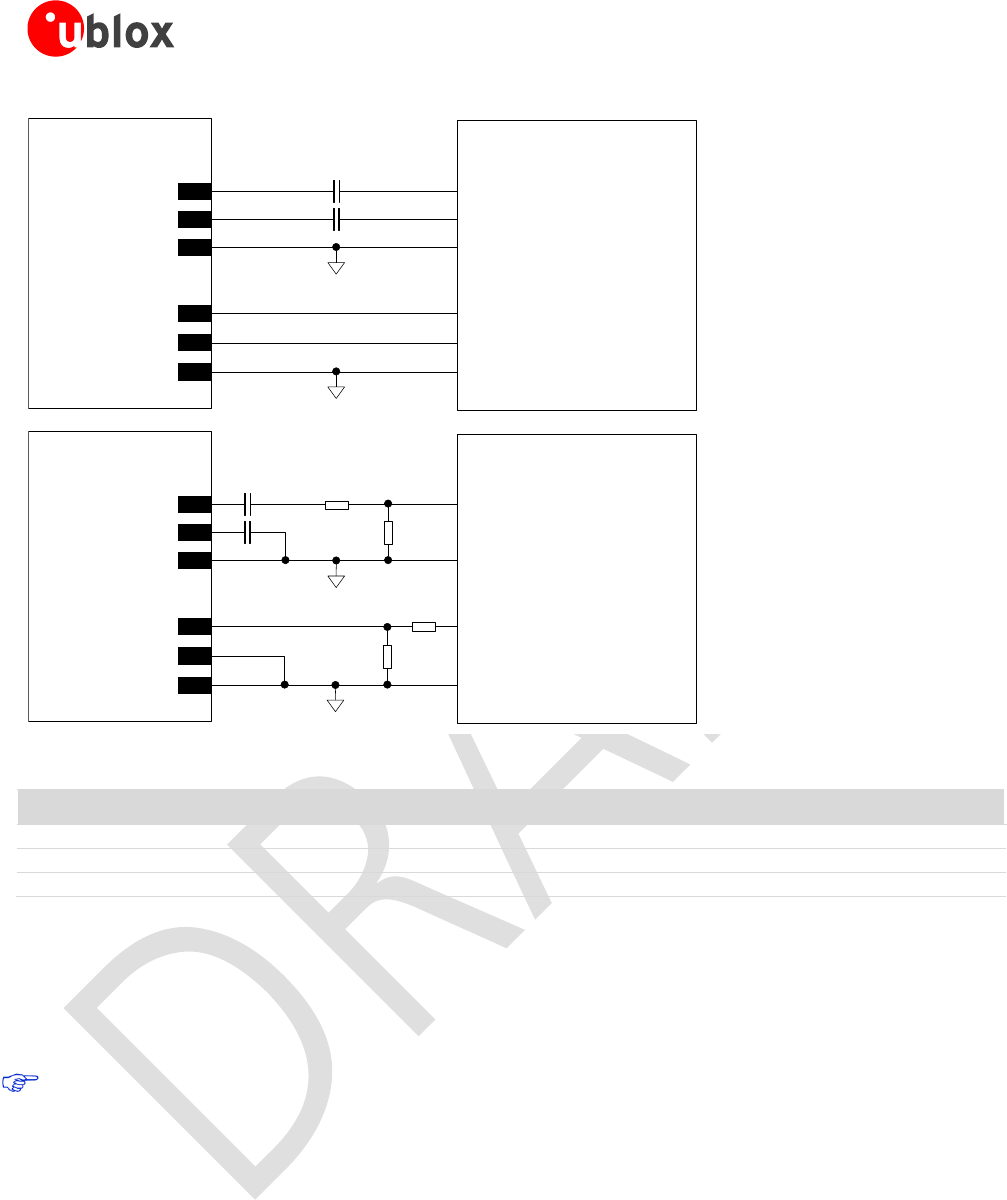

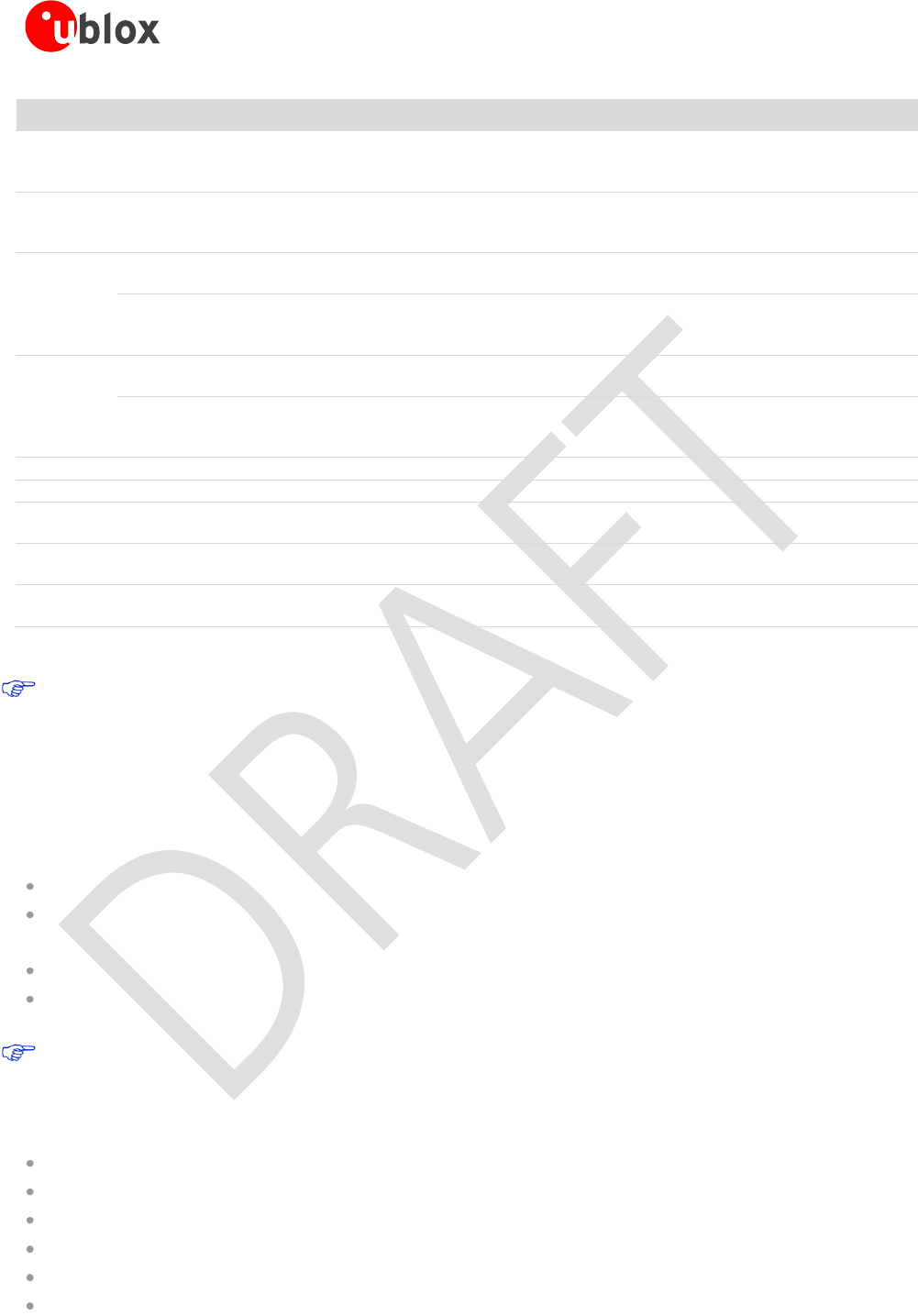

1.5.2.1 VCC application circuits

LISA-U series modules must be supplied through the VCC pins by one (and only one) proper DC power supply

that must be one of the following:

Switching regulator

Low Drop-Out (LDO) linear regulator

Rechargeable Lithium-ion (Li-Ion) or Lithium-ion polymer (Li-Pol) battery

Primary (disposable) battery

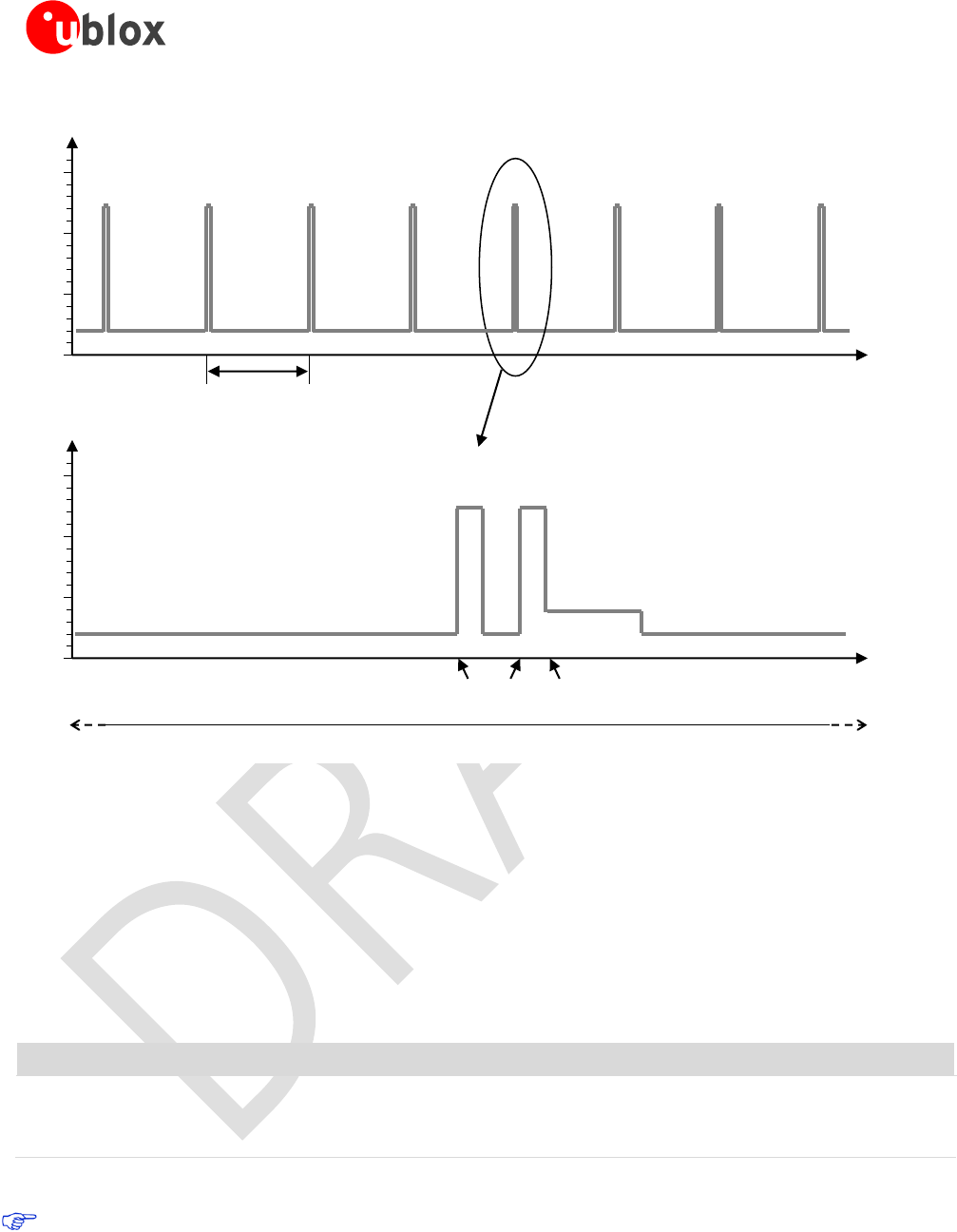

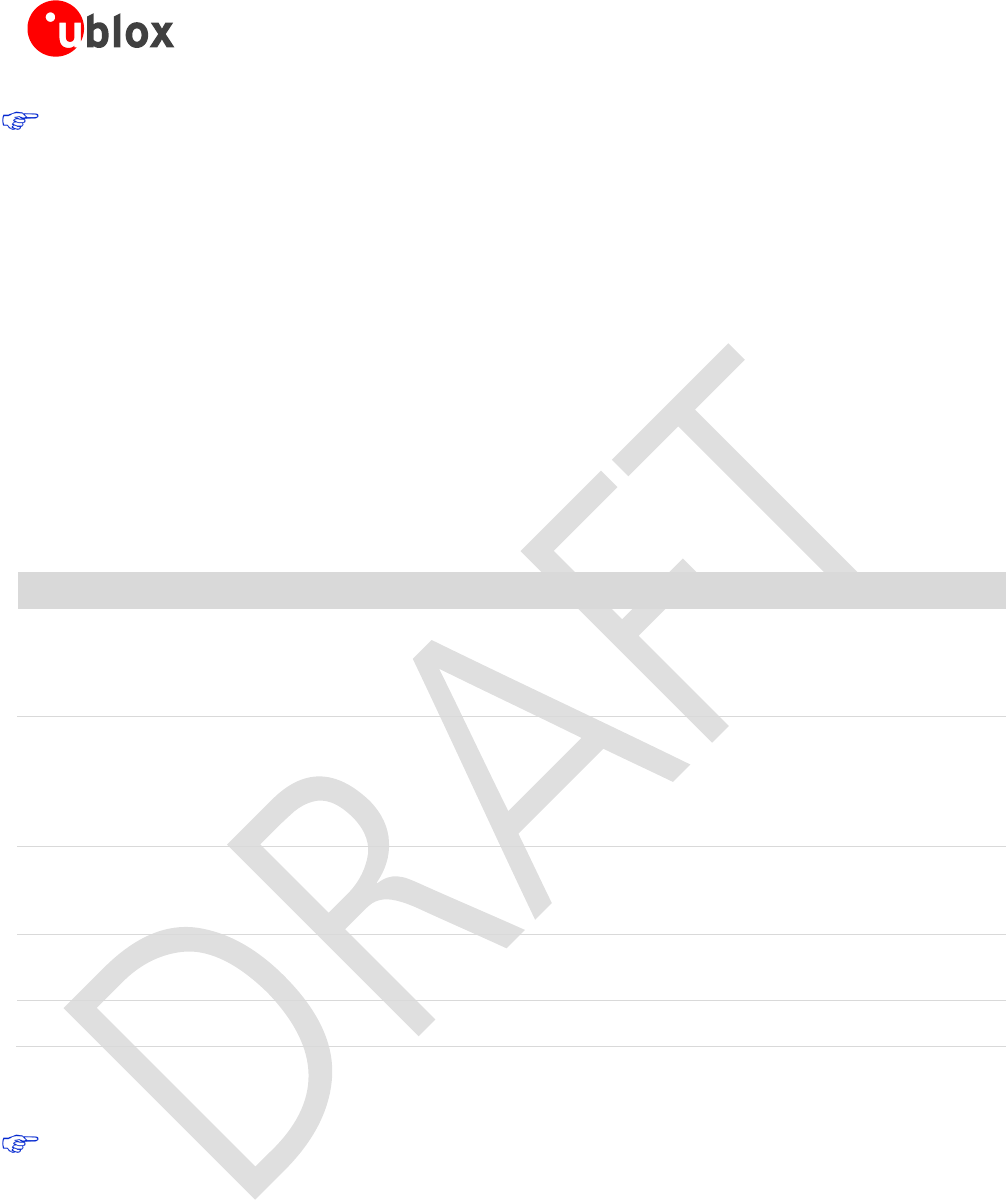

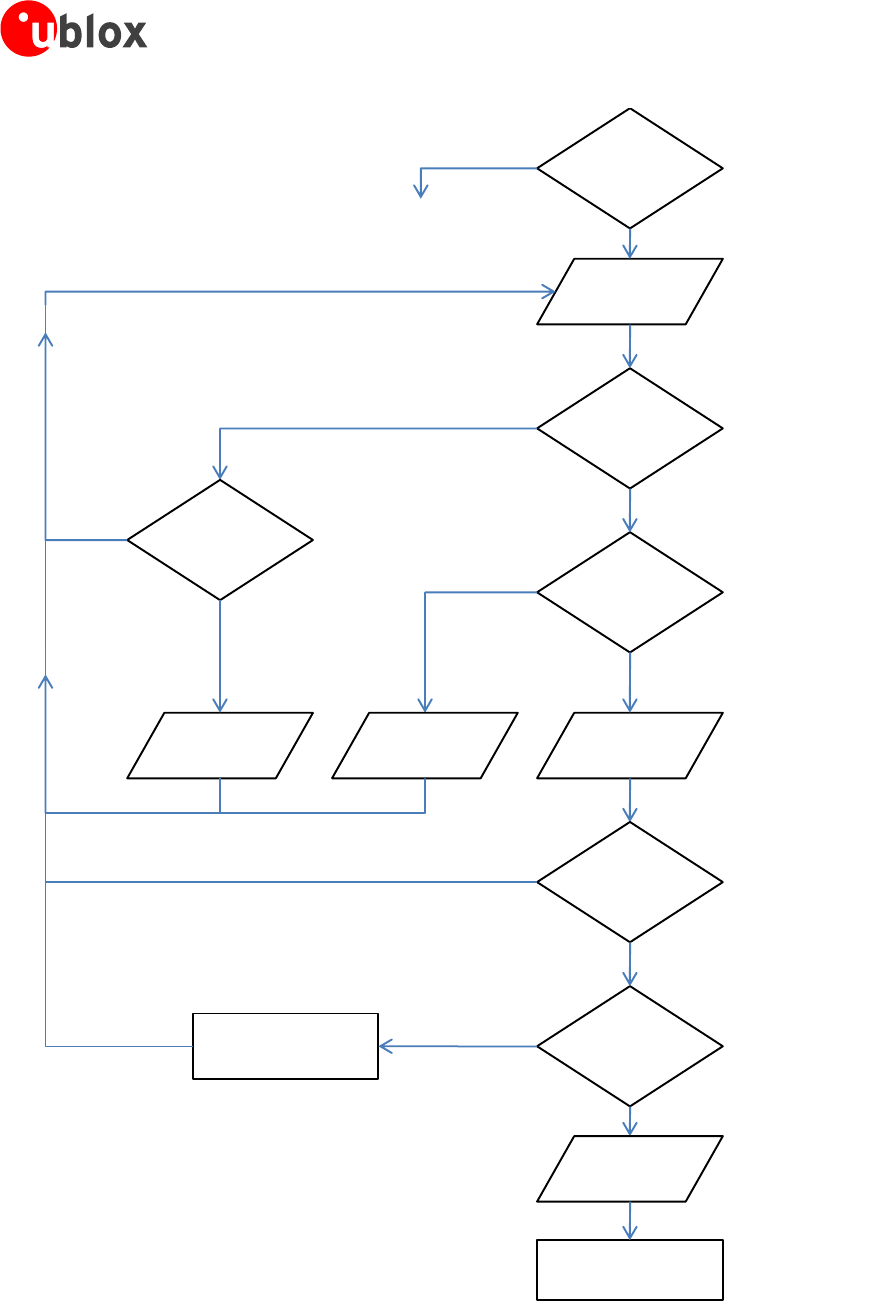

Main Supply

Available?

Battery

Li-Ion 3.7 V

Linear LDO

Regulator

Main Supply

Voltage

>5 V?

Switching

Step-Down

Regulator

No, portable device

No, less than 5 V

Yes, greater than 5 V

Yes, always available

Figure 6: VCC supply concept selection

The switching step-down regulator is the typical choice when the available primary supply source has a nominal

voltage much higher (e.g. greater than 5 V) than the LISA-U series modules operating supply voltage. The use of

switching step-down provides the best power efficiency for the overall application and minimizes current drawn

from the main supply source.

The use of an LDO linear regulator becomes convenient for a primary supply with a relatively low voltage (e.g.

less than 5 V). In this case the typical 90% efficiency of the switching regulator will diminish the benefit of

voltage step-down and no true advantage will be gained in input current savings. On the opposite side, linear

regulators are not recommended for high voltage step-down as they will dissipate a considerable amount of

energy in thermal power.

If LISA-U series modules are deployed in a mobile unit where no permanent primary supply source is available,

then a battery will be required to provide VCC. A standard 3-cell Li-Ion or Li-Pol battery pack directly connected

to VCC is the usual choice for battery-powered devices. During charging, batteries with Ni-MH chemistry

typically reach a maximum voltage that is above the maximum rating for VCC, and should therefore be avoided.

The use of primary (not rechargeable) battery is uncommon, since the most cells available are seldom capable of

delivering the burst peak current for a GSM call due to high internal resistance.

Keep in mind that the use of batteries requires the implementation of a suitable charger circuit (not included in

LISA-U series modules). The charger circuit should be designed in order to prevent over-voltage on VCC beyond

the upper limit of the absolute maximum rating.

The following sections highlight some design aspects for each of the supplies listed above.

LISA-U series - System Integration Manual

3G.G2-HW-10002-A1 Advance Information System description

Page 23 of 160

Switching regulator

The characteristics of the switching regulator connected to VCC pins should meet the following requirements:

Power capability: the switching regulator with its output circuit must be capable of providing a voltage

value to the VCC pins within the specified operating range and must be capable of delivering 2.5 A current

pulses with 1/8 duty cycle to the VCC pins

Low output ripple: the switching regulator together with its output circuit must be capable of providing a

clean (low noise) VCC voltage profile

High switching frequency: for best performance and for smaller applications select a switching frequency

≥ 600 kHz (since L-C output filter is typically smaller for high switching frequency). The use of a switching

regulator with a variable switching frequency or with a switching frequency lower than 600 kHz must be

carefully evaluated since this can produce noise in the VCC voltage profile and therefore negatively impact

GSM modulation spectrum performance. An additional L-C low-pass filter between the switching regulator

output to VCC supply pins can mitigate the ripple on VCC, but adds extra voltage drop due to resistive

losses on series inductors

PWM mode operation: select preferably regulators with Pulse Width Modulation (PWM) mode. While in

active mode Pulse Frequency Modulation (PFM) mode and PFM/PWM mode transitions must be avoided to

reduce the noise on the VCC voltage profile. Switching regulators able to switch between low ripple PWM

mode and high efficiency burst or PFM mode can be used, provided the mode transition occurs when the

module changes status from idle/active mode to connected mode (where current consumption increases to a

value greater than 100 mA): it is permissible to use a regulator that switches from the PWM mode to the

burst or PFM mode at an appropriate current threshold (e.g. 60 mA)

Output voltage slope: the use of the soft start function provided by some voltage regulator must be

carefully evaluated, since the voltage at the VCC pins must ramp from 2.5 V to 3.2 V within 1 ms to allow a

proper switch-on of the module

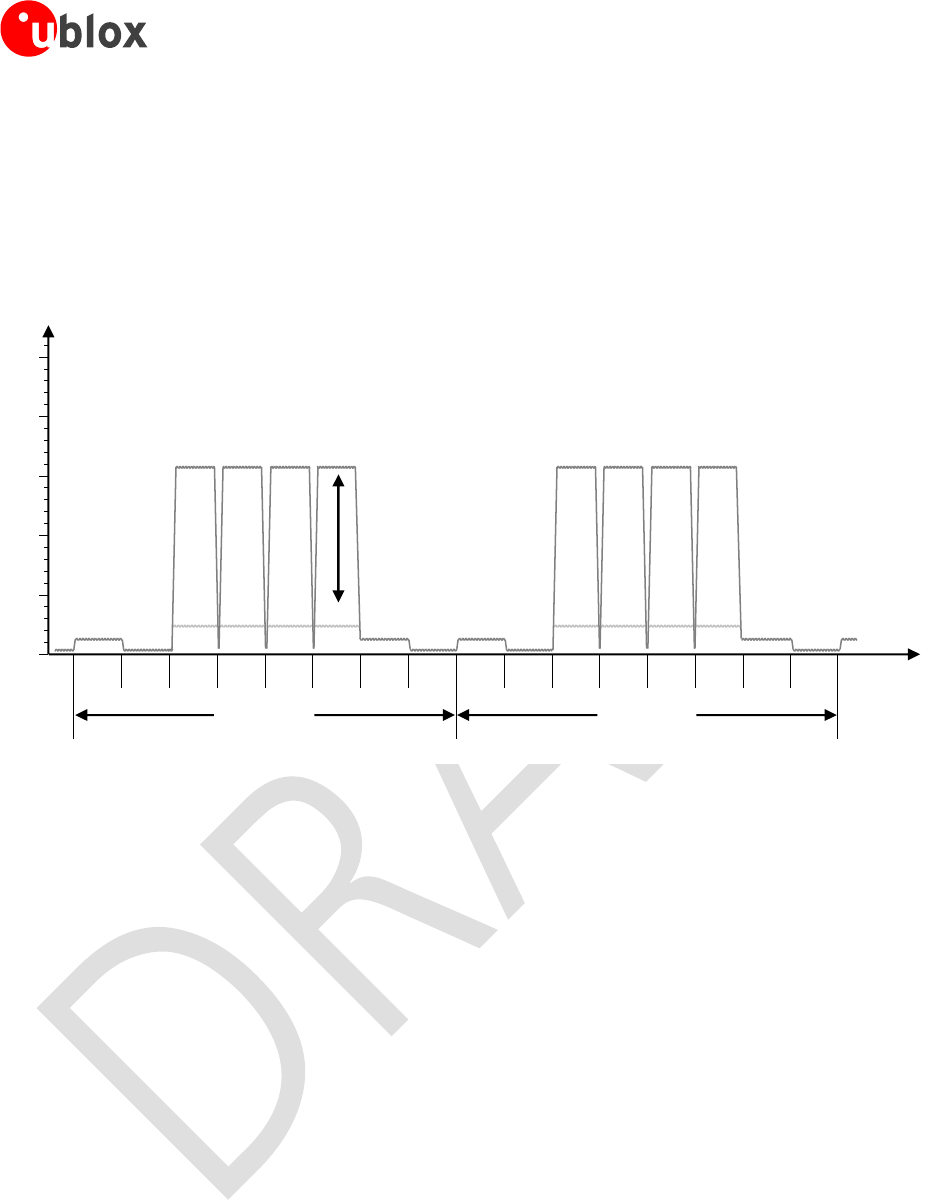

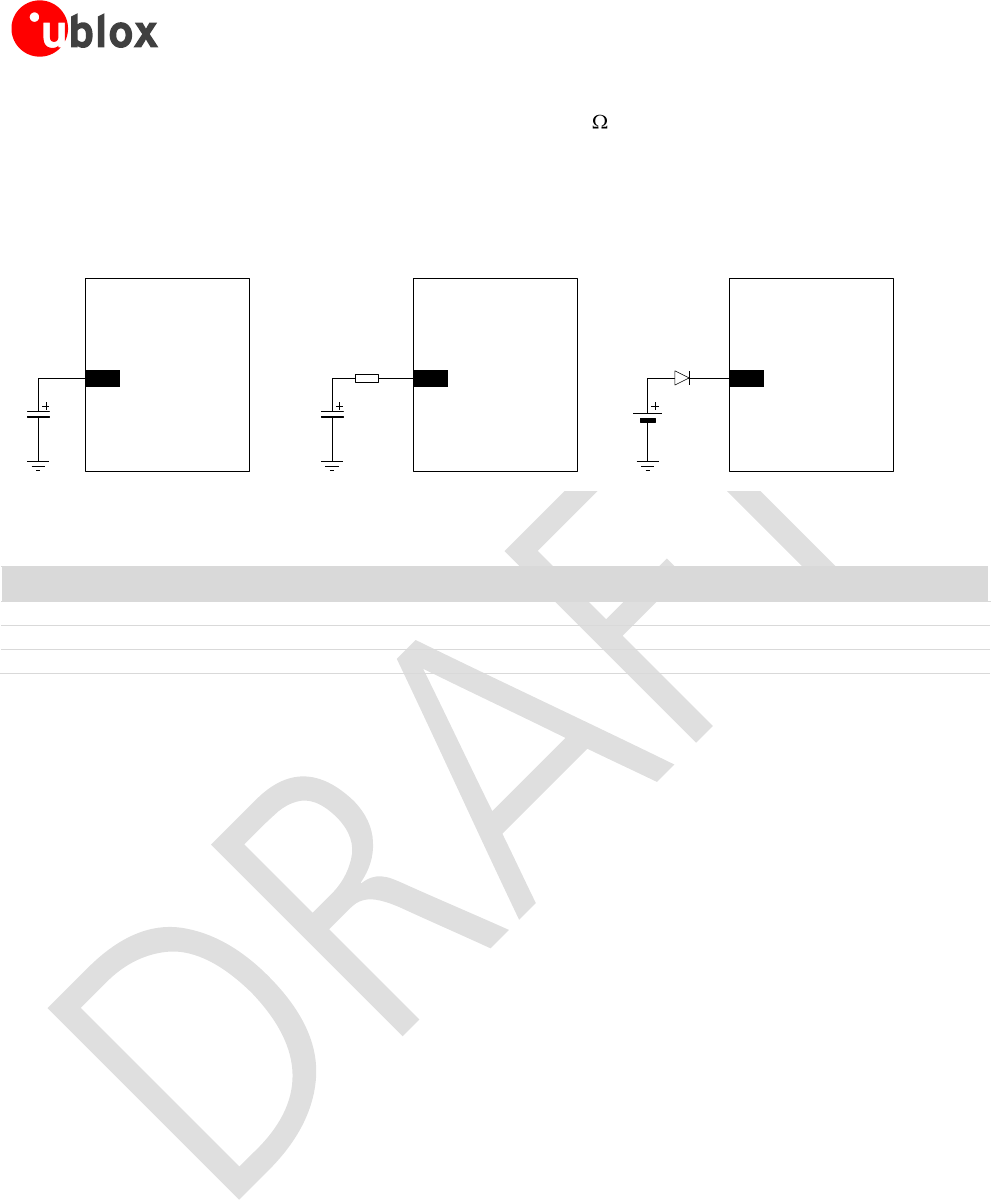

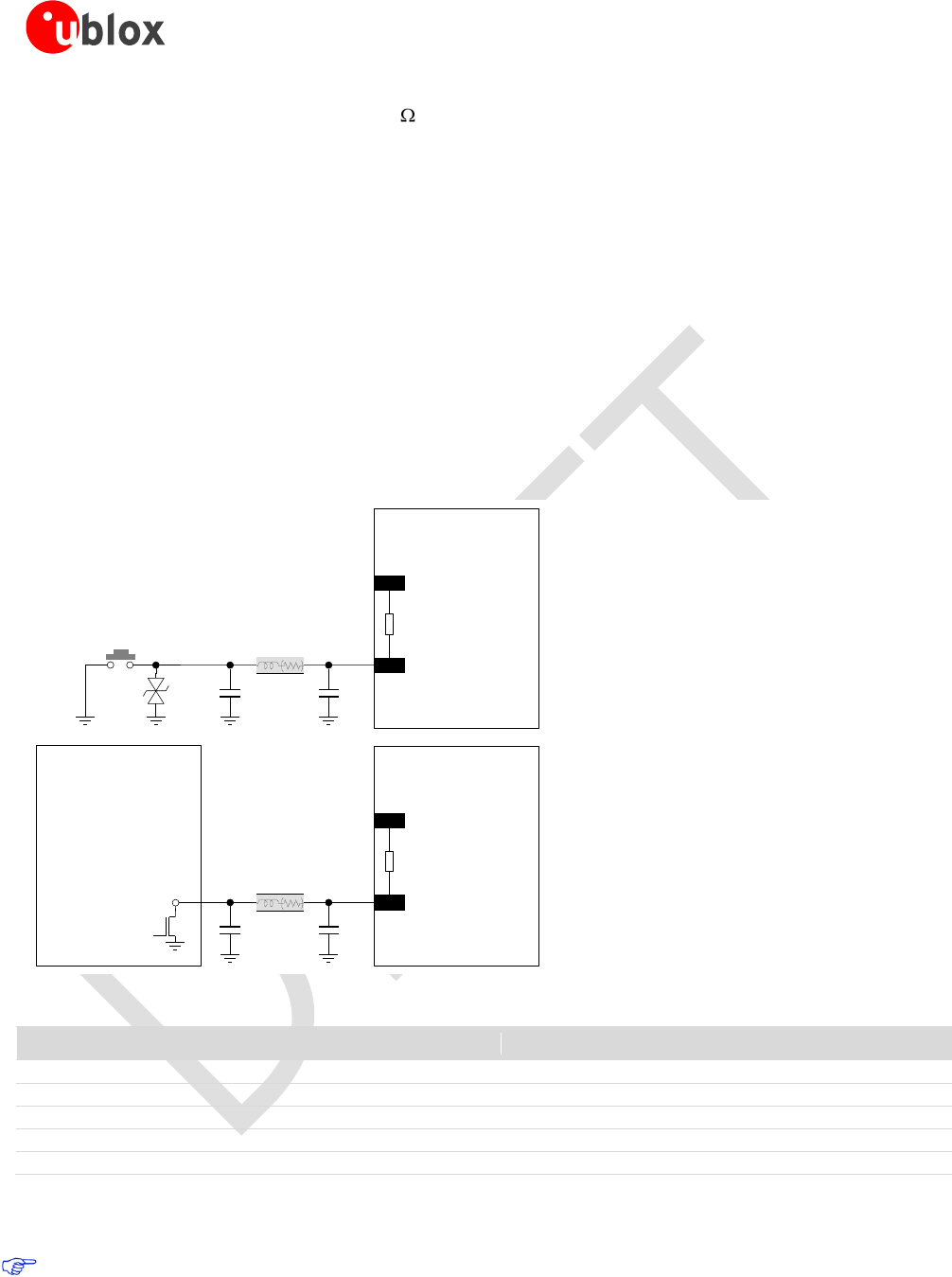

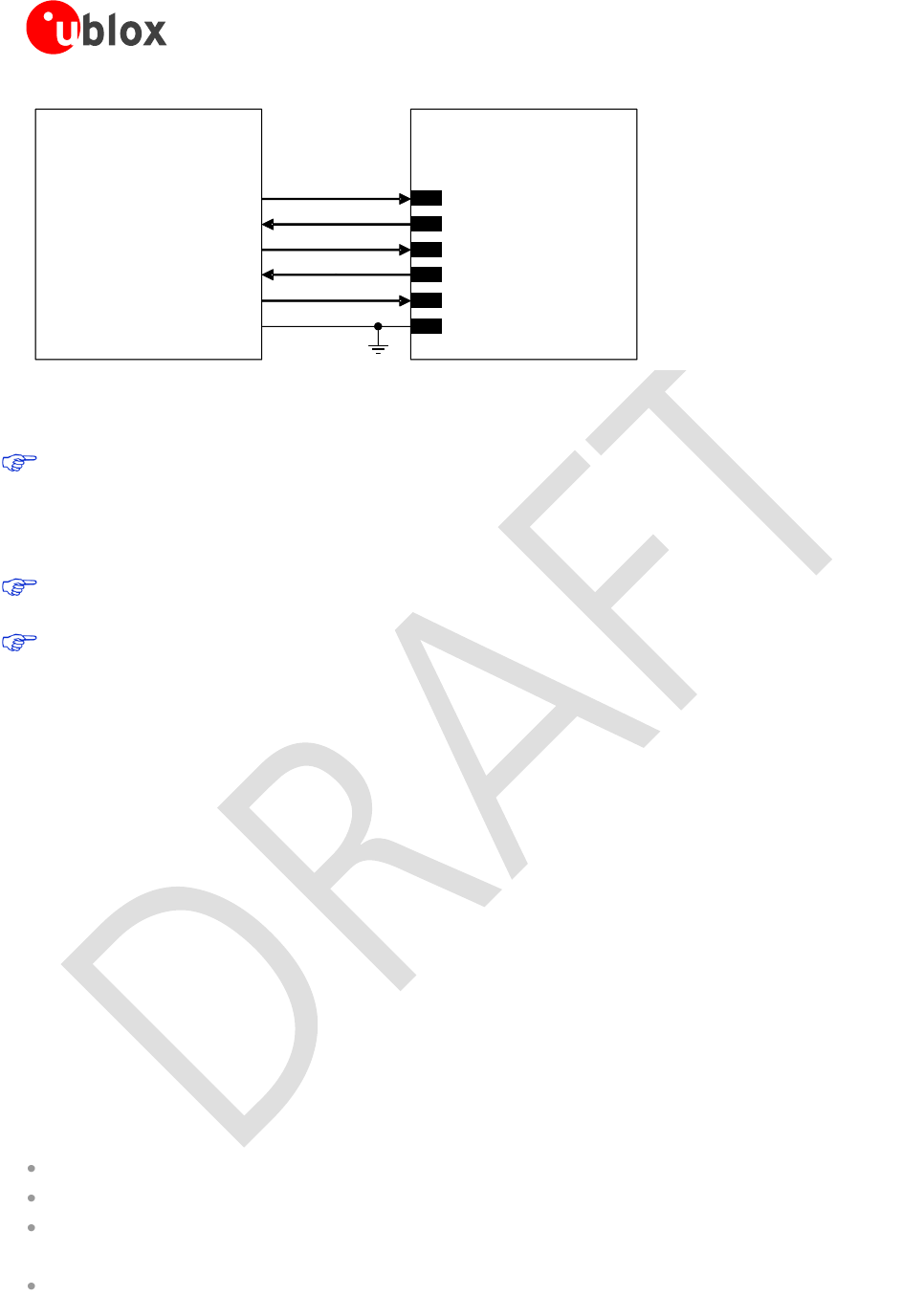

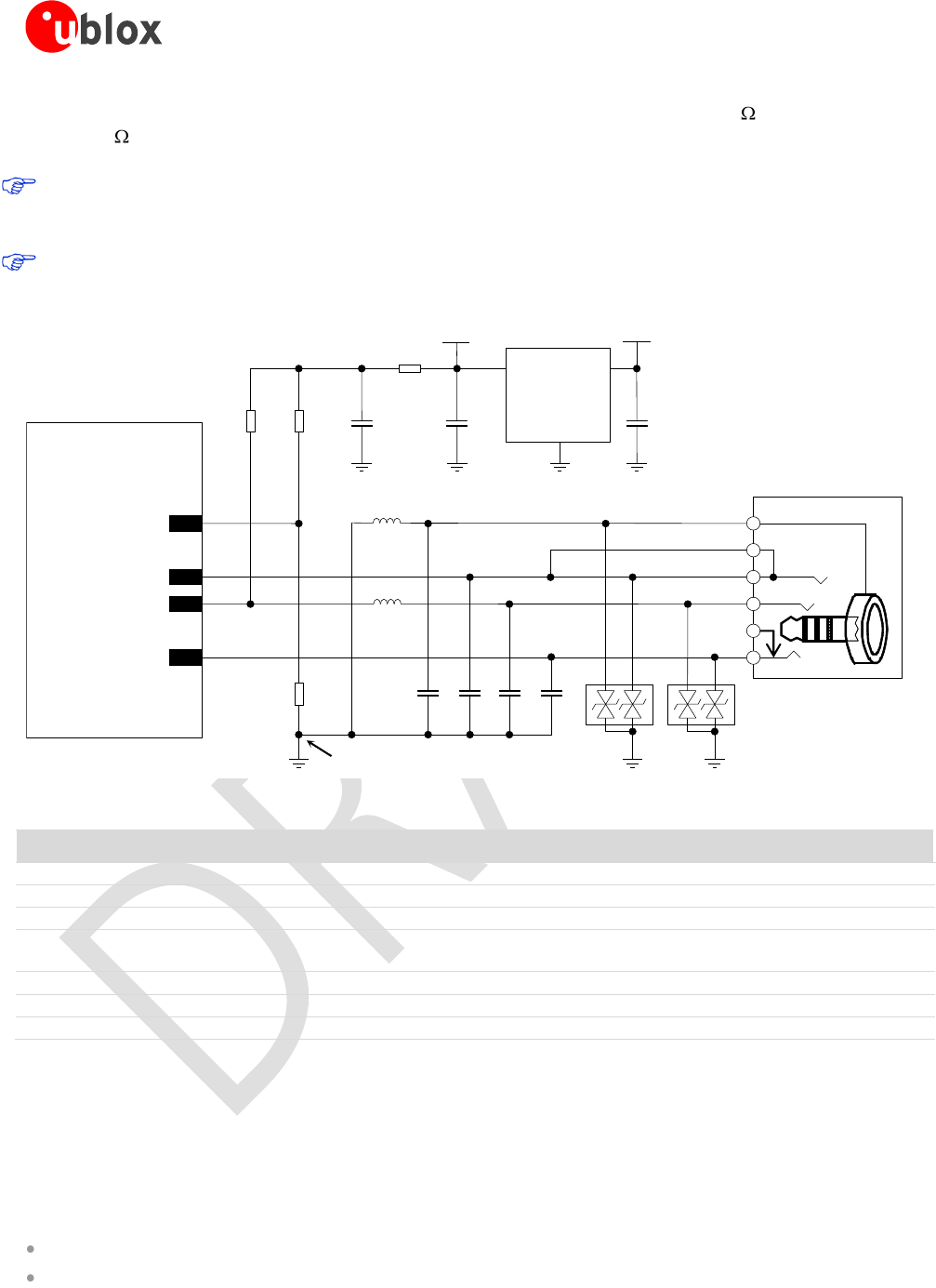

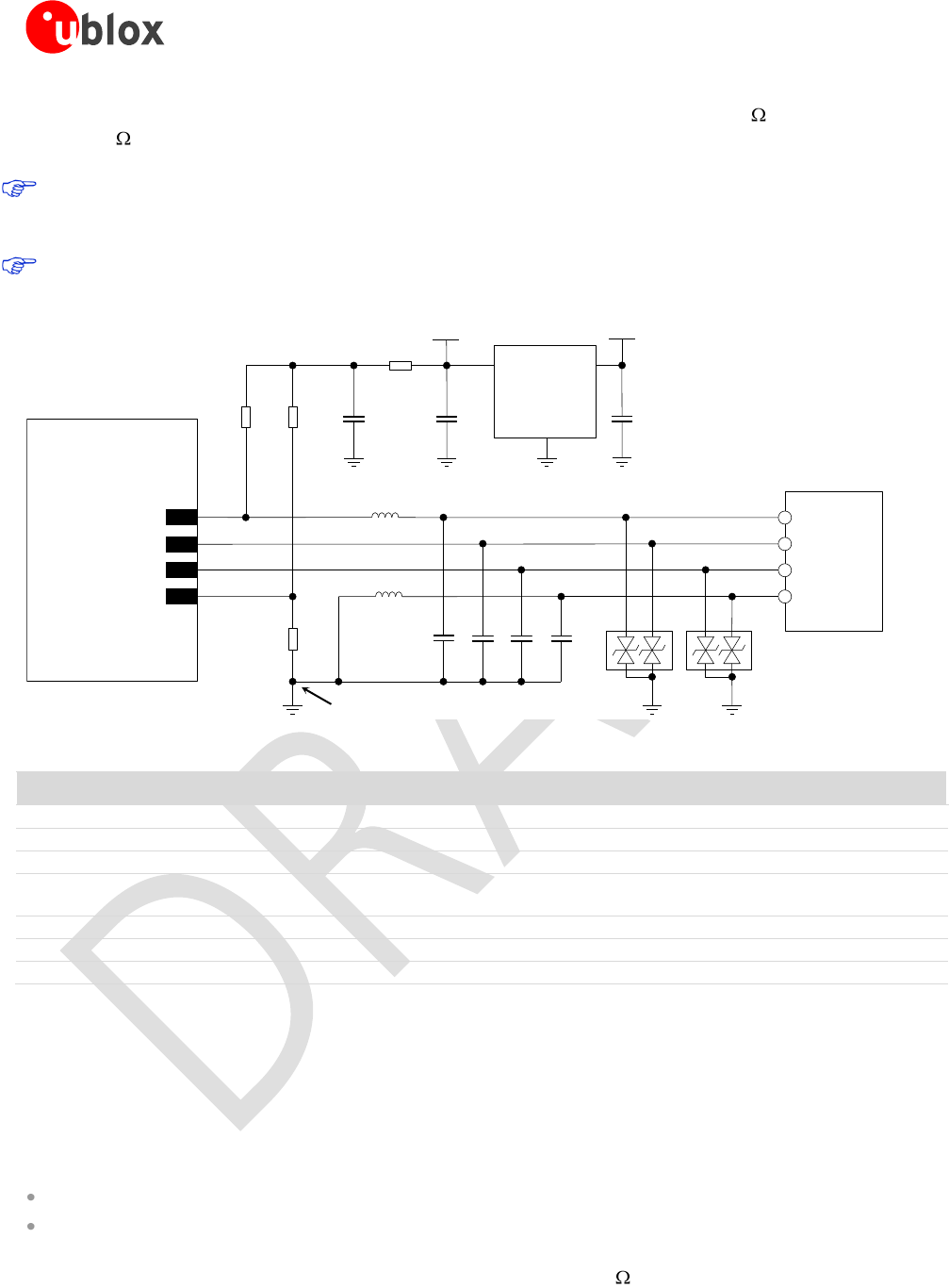

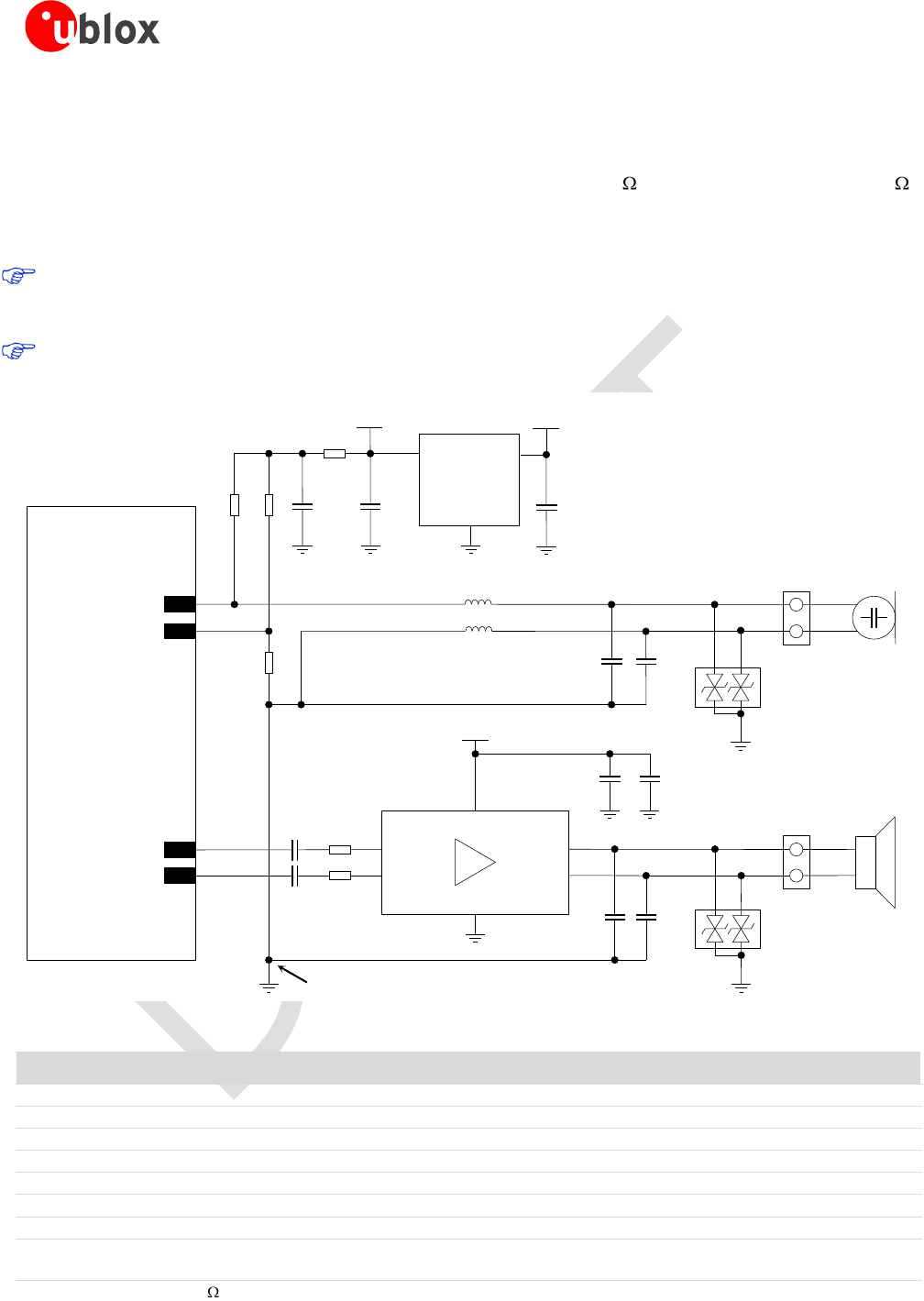

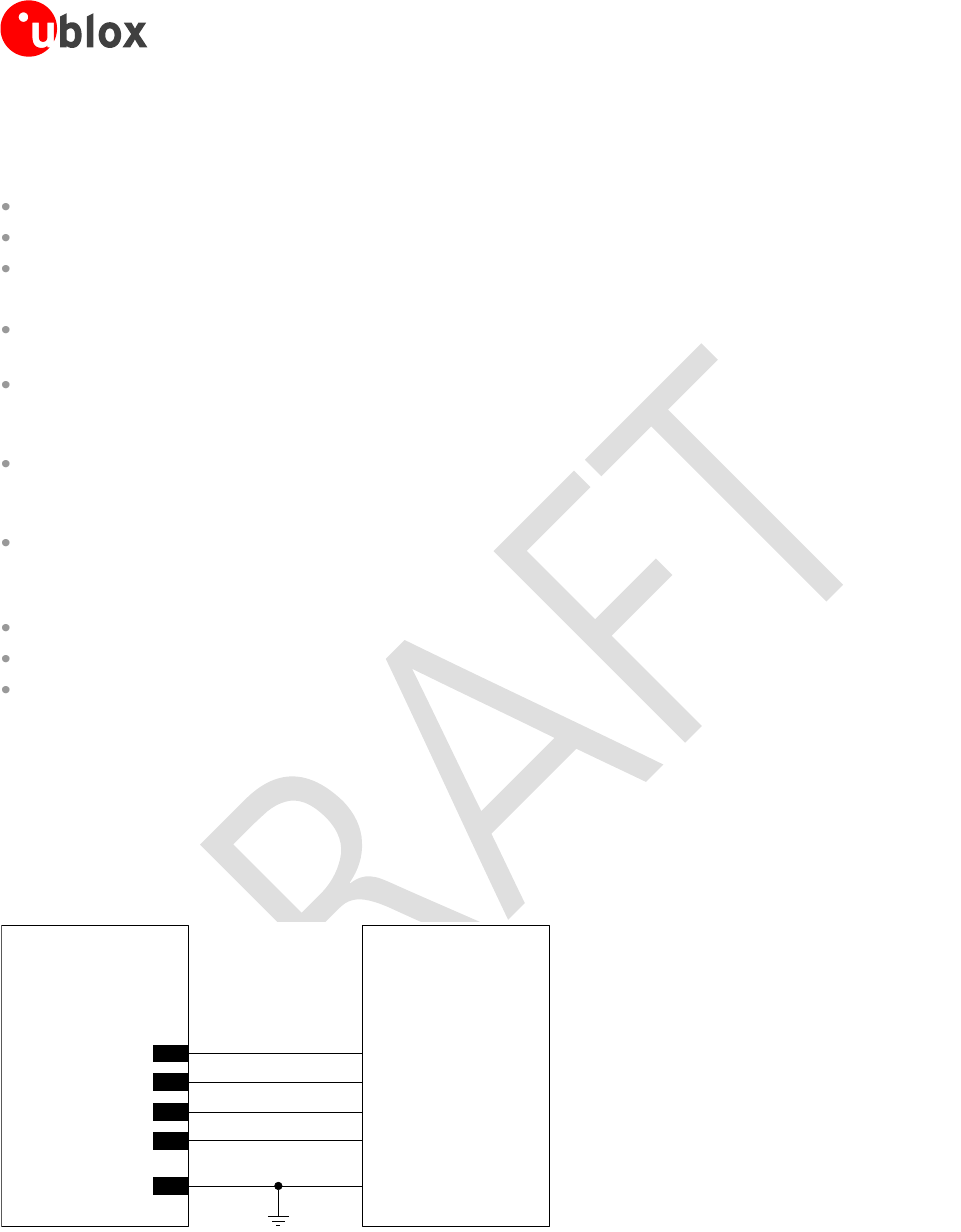

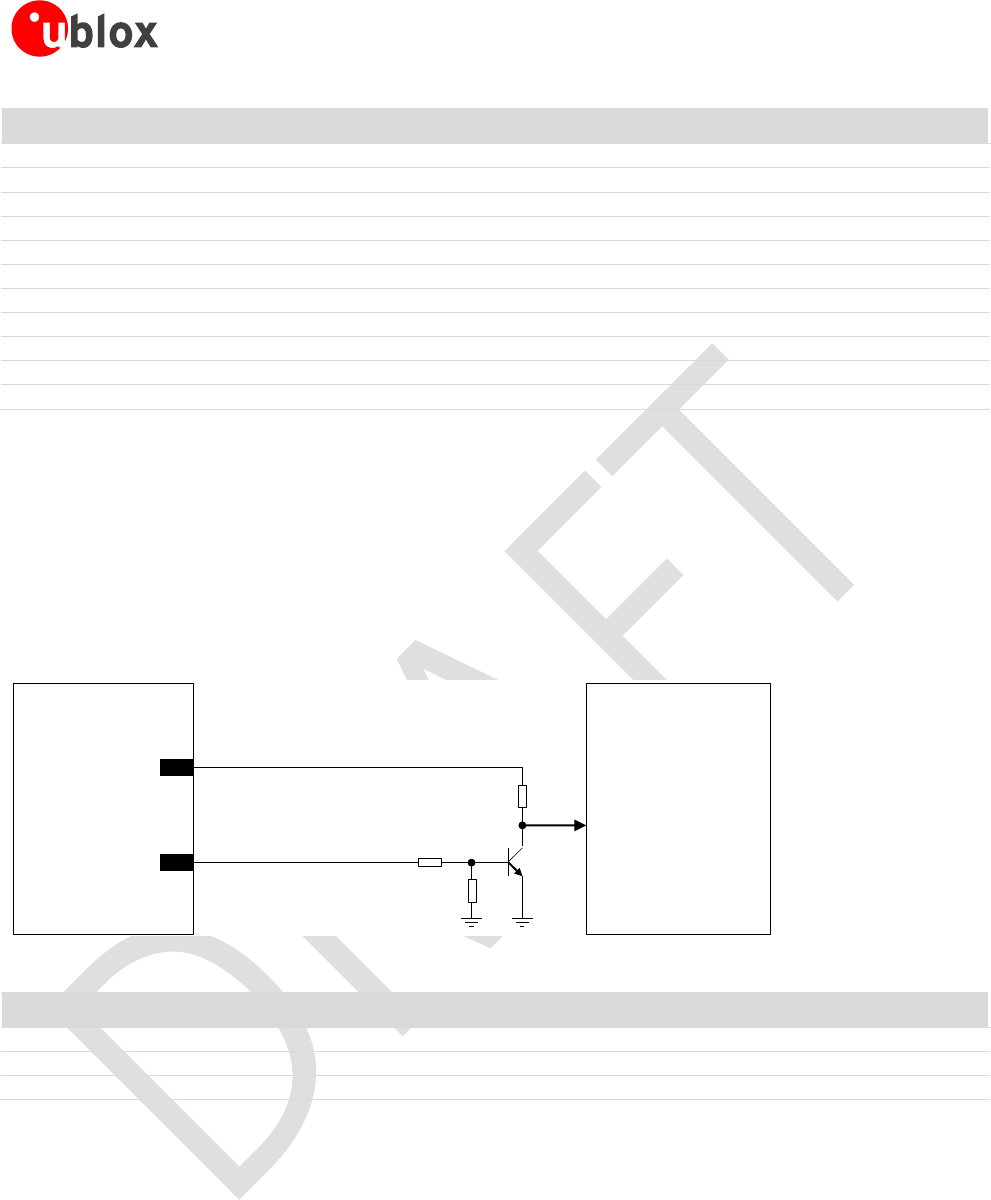

Figure 7 and the components listed in Table 7 show an example of a high reliability power supply circuit, where

the module VCC is supplied by a step-down switching regulator capable of delivering 2.5 A current pulses with

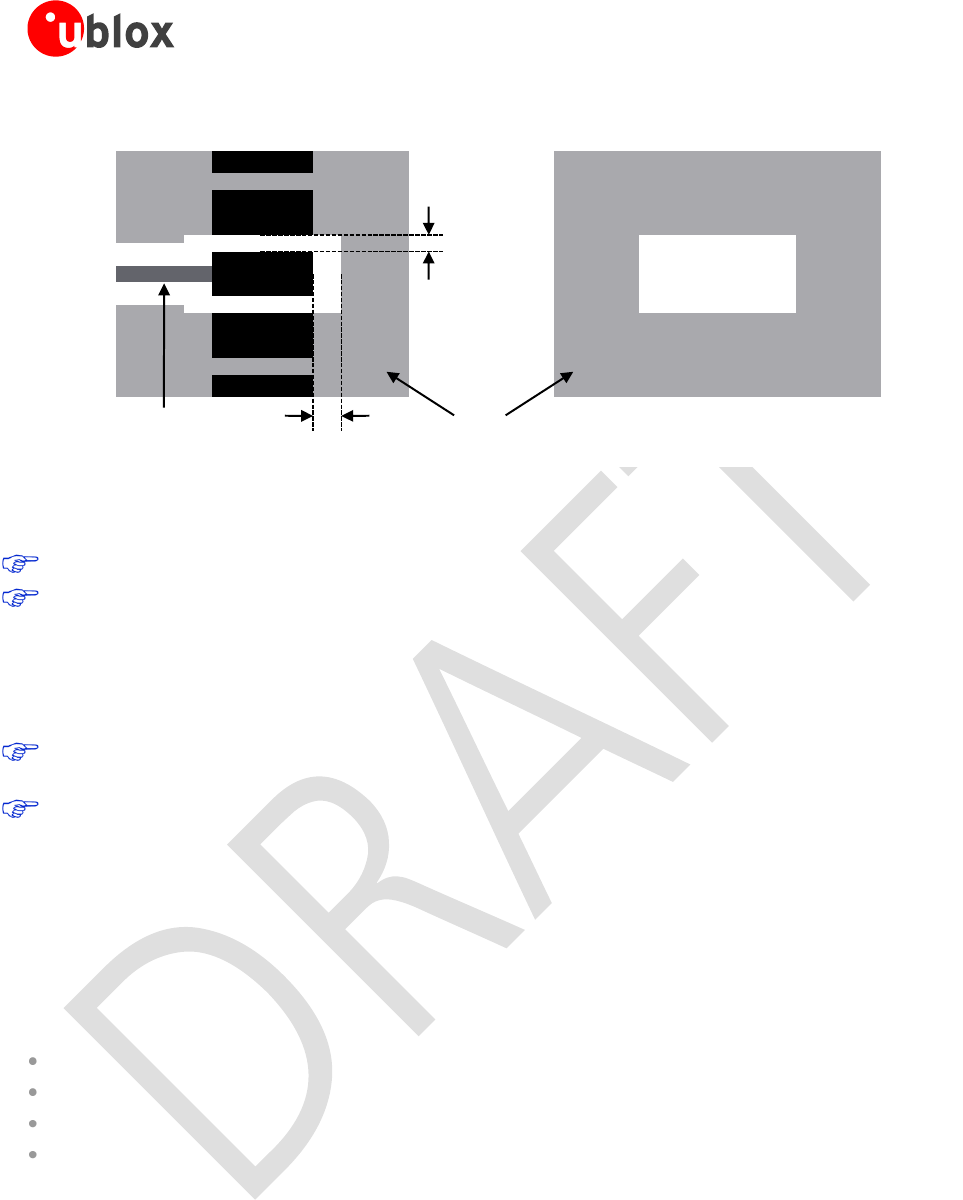

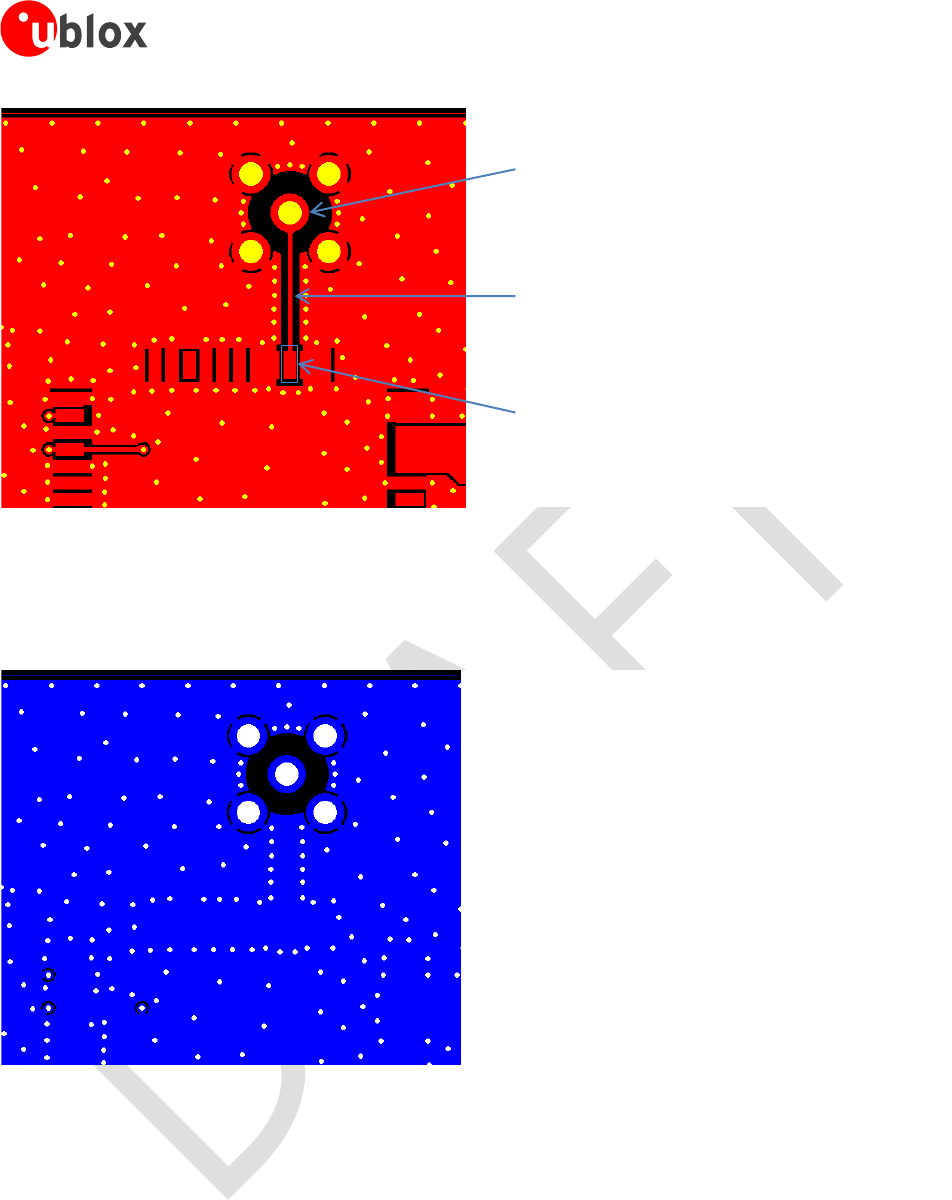

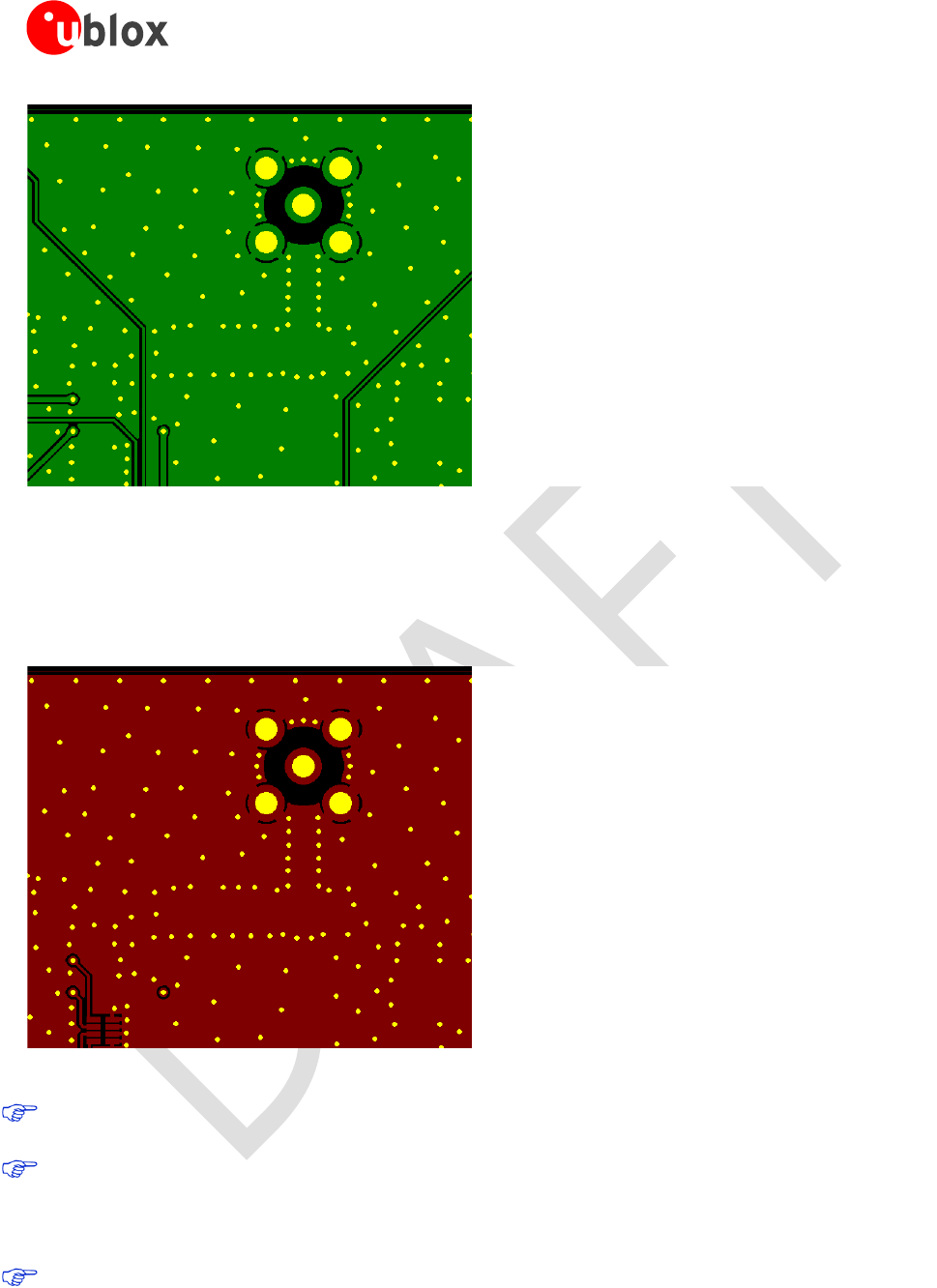

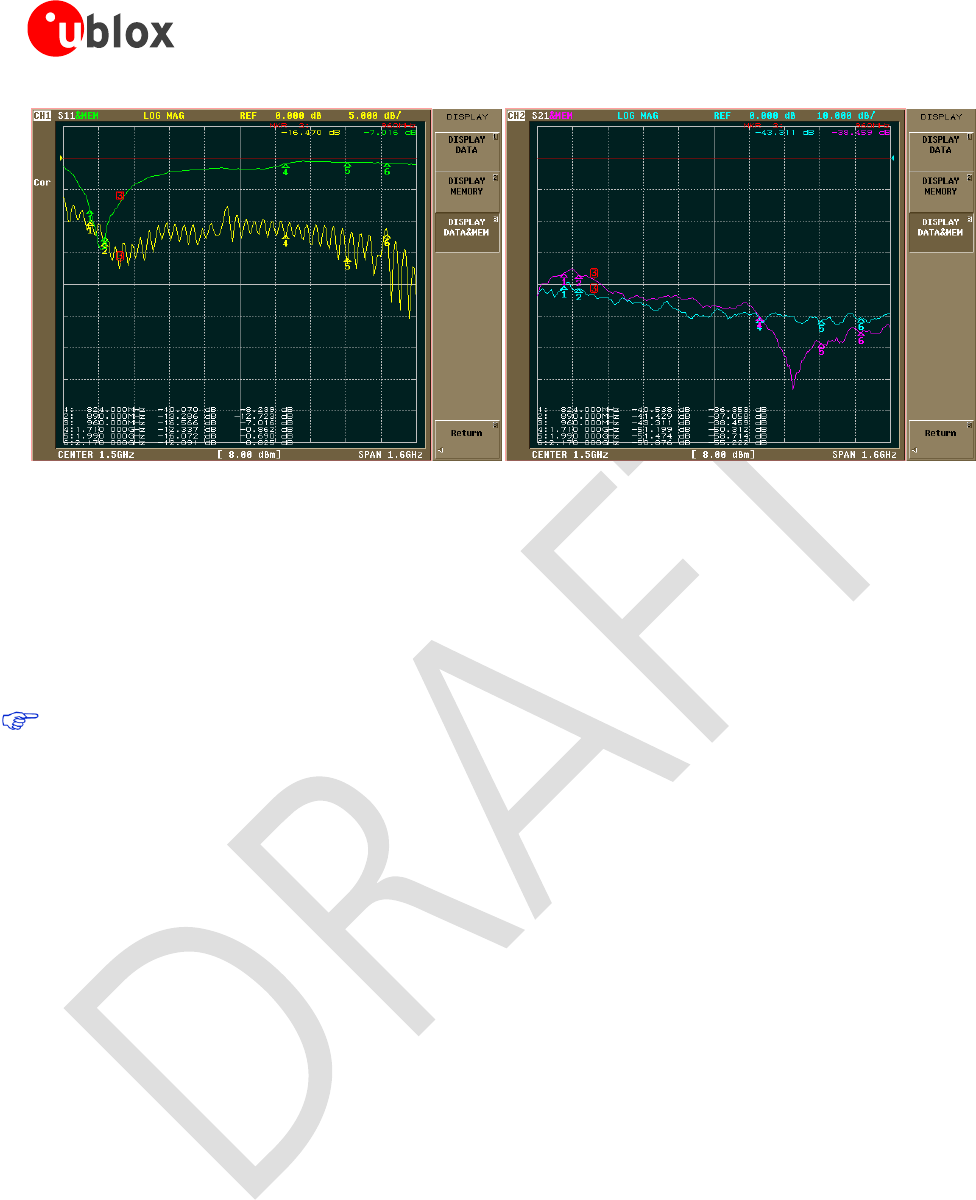

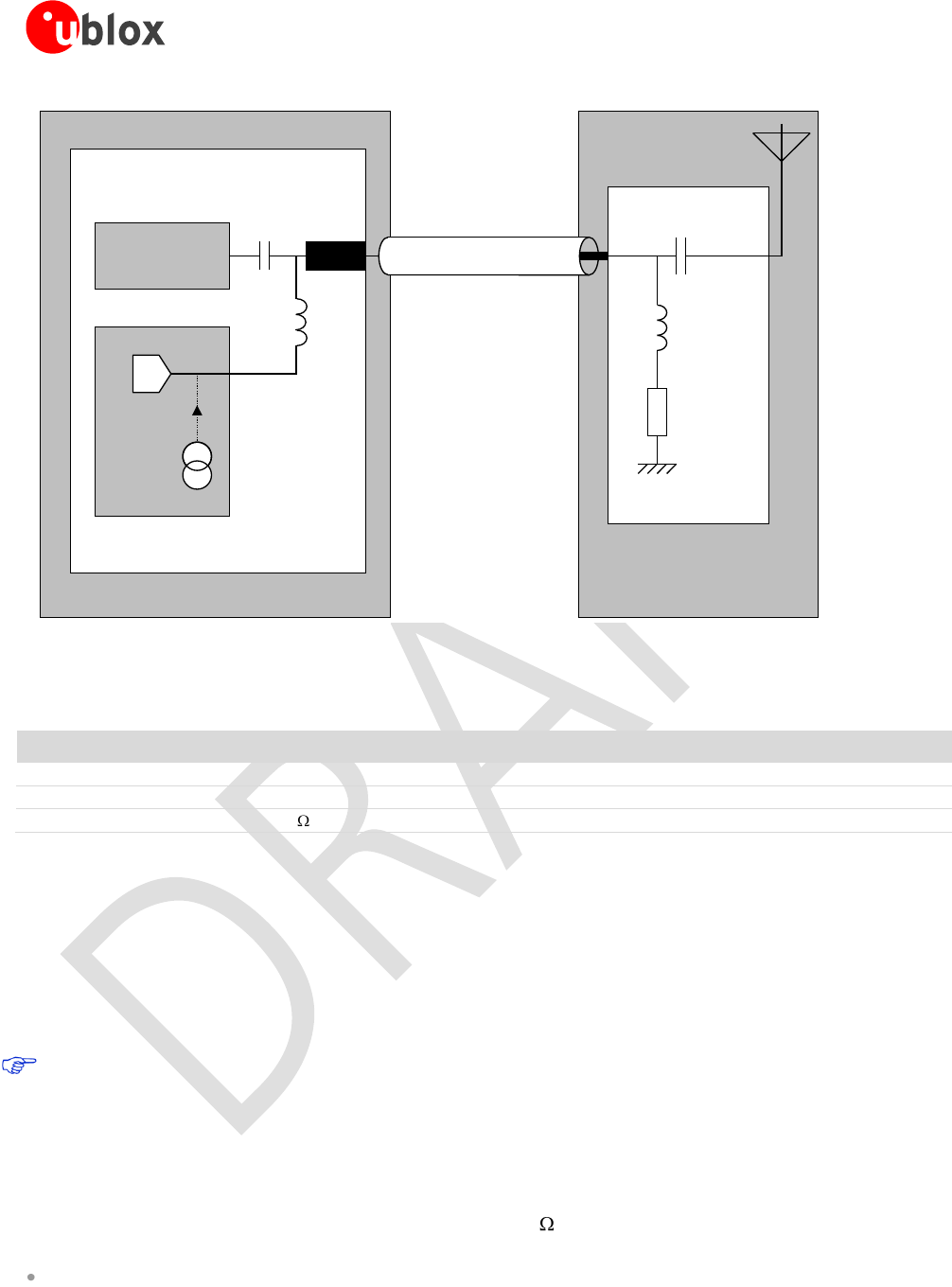

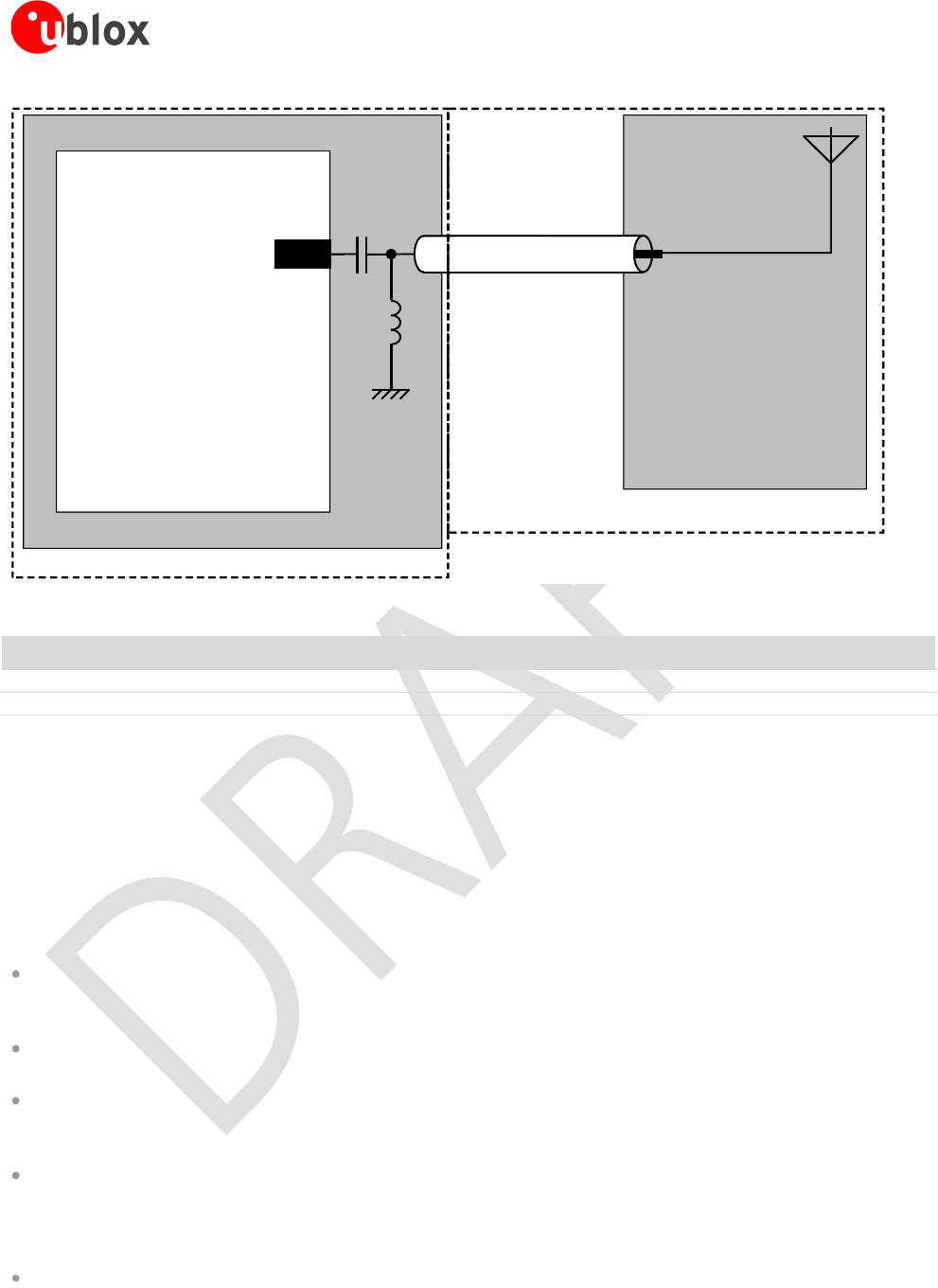

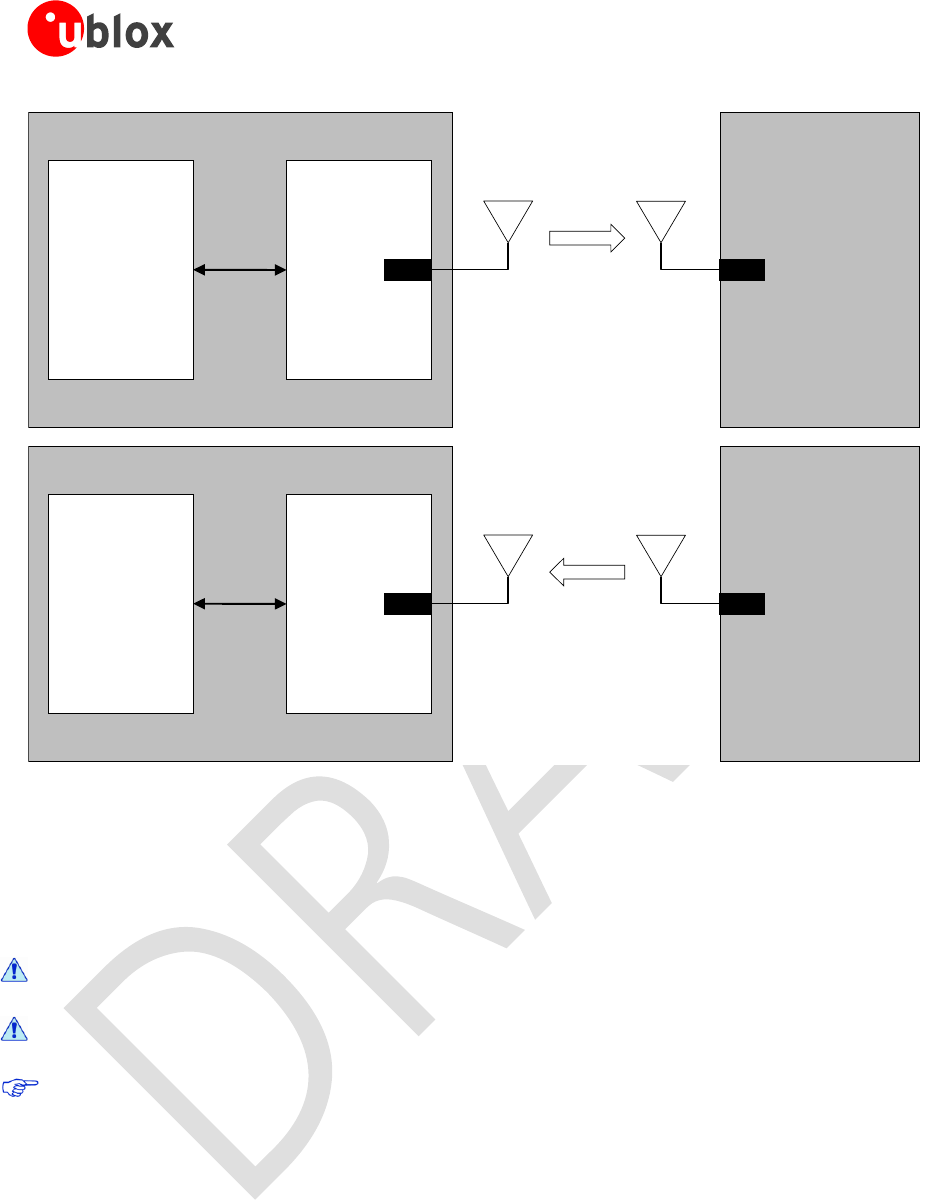

low output ripple and with fixed switching frequency in PWM mode operation greater than 1 MHz. The use of a