u blox TOBYL210 GSM/UMTS/LTE Data Module User Manual TOBY L2 series

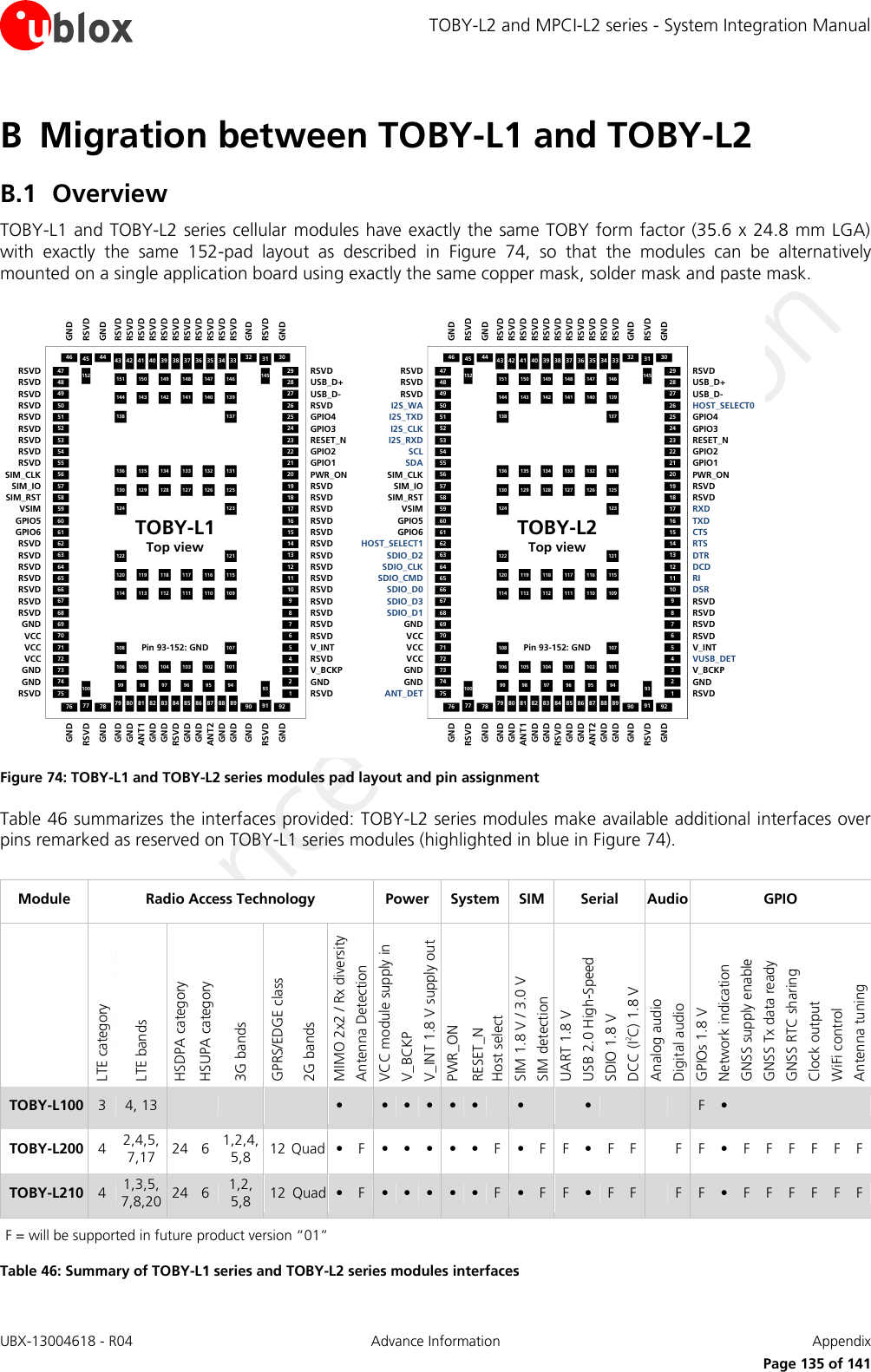

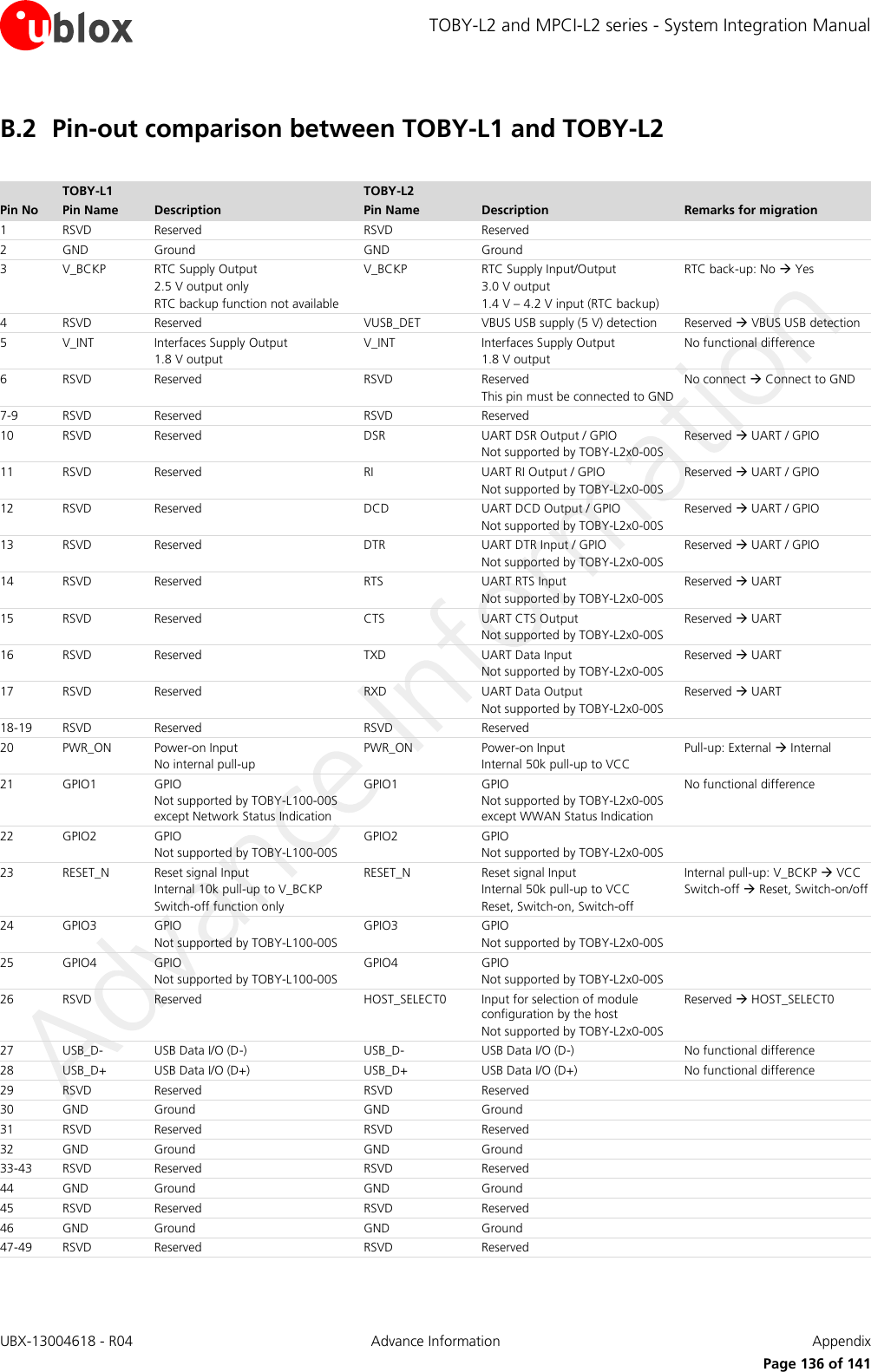

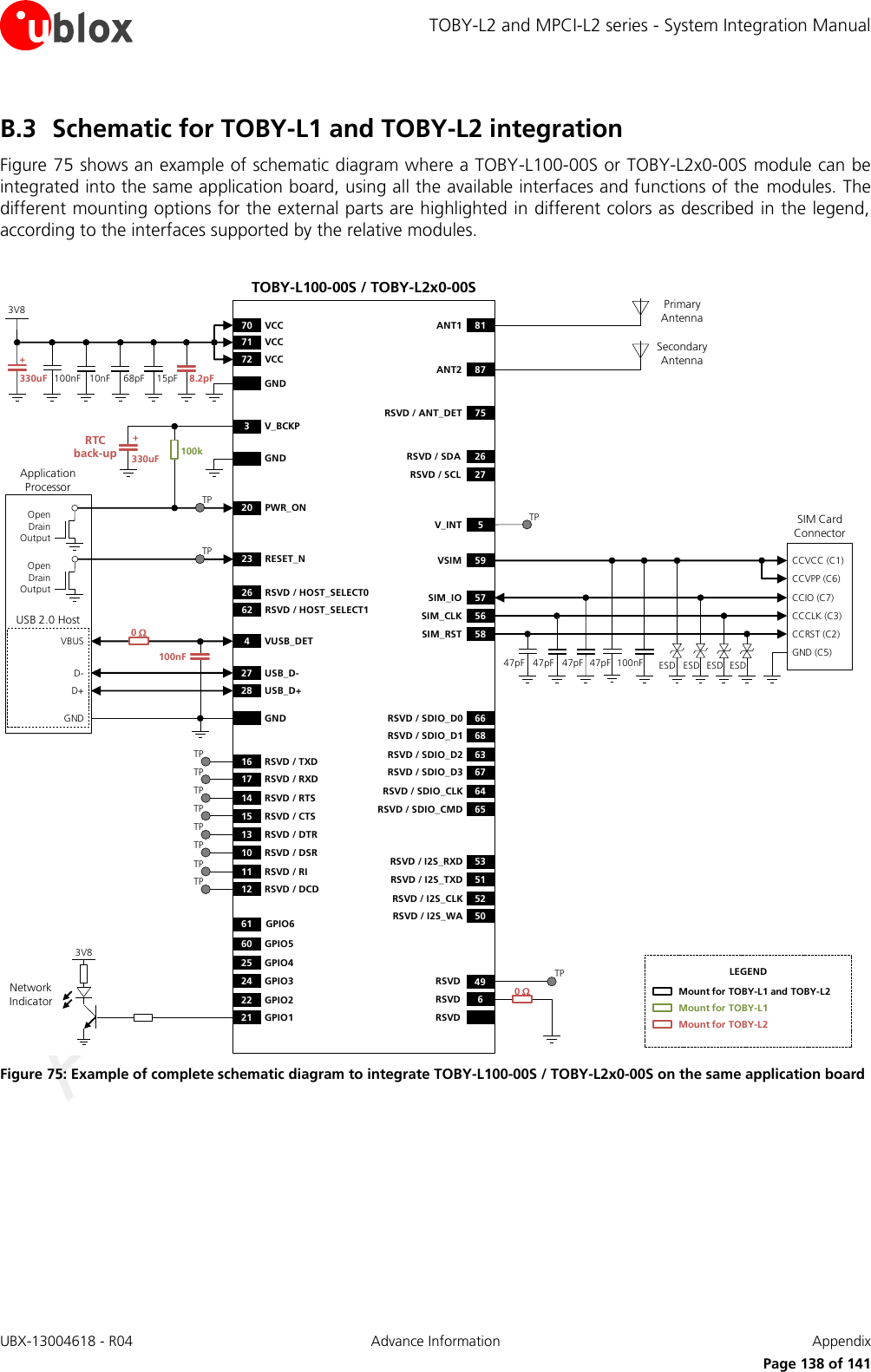

u-blox AG GSM/UMTS/LTE Data Module TOBY L2 series

u blox >

Contents

- 1. System Integration Manual

- 2. TempConfidential_TOBY-L2-MPCI-L2_SysIntegrManual_UBX-13004618

System Integration Manual

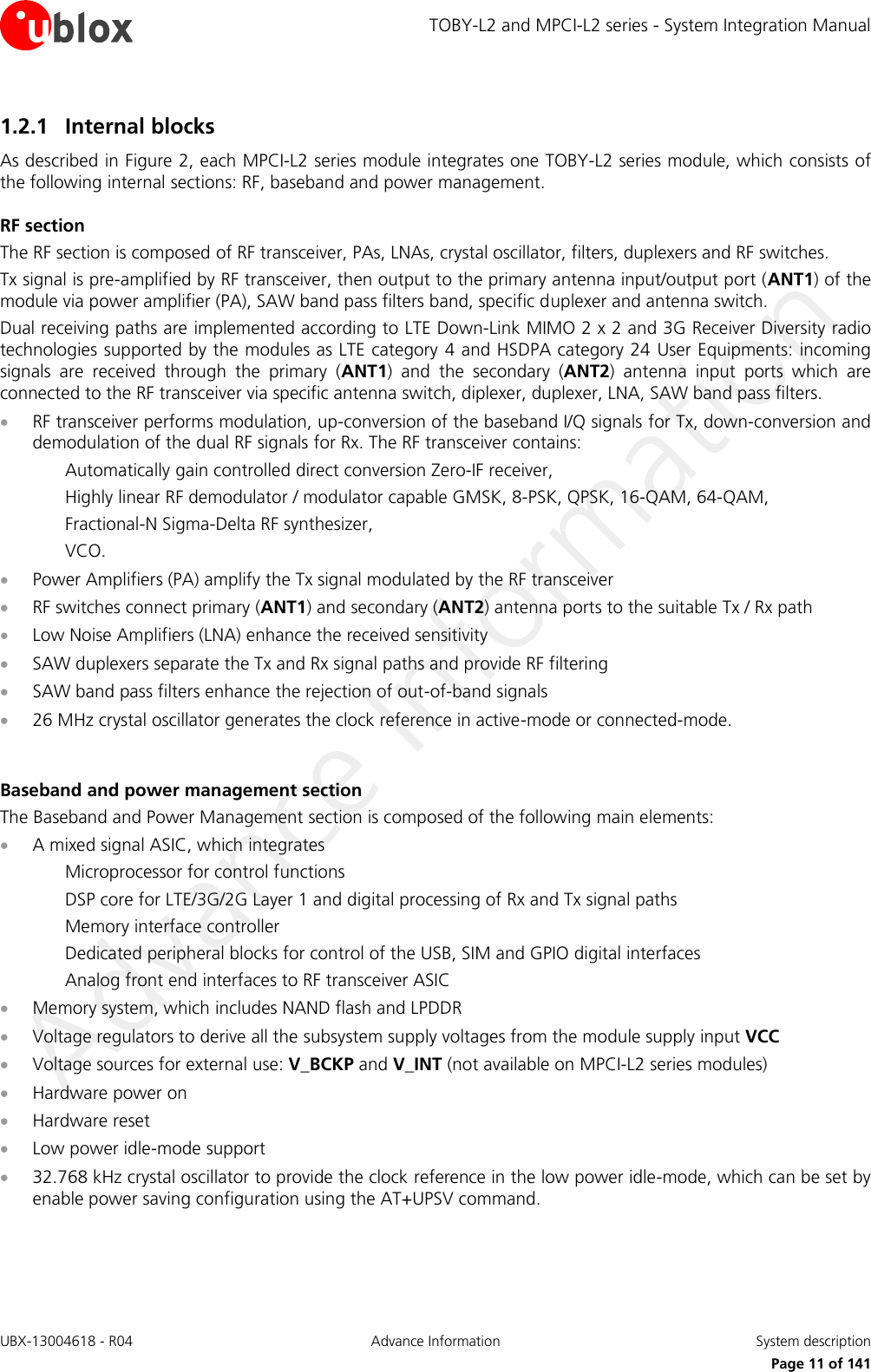

![TOBY-L2 and MPCI-L2 series - System Integration Manual UBX-13004618 - R04 Advance Information System description Page 13 of 141 Function Pin Name Pin No I/O Description Remarks SIM VSIM 59 O SIM supply output VSIM = 1.8 V / 3 V automatically generated according to the connected SIM type. See section 1.8 for functional description. See section 2.5 for external circuit design-in. SIM_IO 57 I/O SIM data Data input/output for 1.8 V / 3 V SIM Internal 4.7 k pull-up to VSIM. See section 1.8 for functional description. See section 2.5 for external circuit design-in. SIM_CLK 56 O SIM clock 3.25 MHz clock output for 1.8 V / 3 V SIM See section 1.8 for functional description. See section 2.5 for external circuit design-in. SIM_RST 58 O SIM reset Reset output for 1.8 V / 3 V SIM See section 1.8 for functional description. See section 2.5 for external circuit design-in. USB VUSB_DET 4 I USB detect input Input for VBUS (5 V typical) USB supply sense. See section 1.9.1 for functional description. See section 2.6.1 for external circuit design-in. USB_D- 27 I/O USB Data Line D- USB interface for AT commands, data communication, FOAT, FW update by u-blox EasyFlash tool and diagnostic. 90 nominal differential impedance (Z0) 30 nominal common mode impedance (ZCM) Pull-up or pull-down resistors and external series resistors as required by the USB 2.0 specifications [4] are part of the USB pad driver and need not be provided externally. See section 1.9.1 for functional description. See section 2.6.1 for external circuit design-in. USB_D+ 28 I/O USB Data Line D+ USB interface for AT commands, data communication, FOAT, FW update by u-blox EasyFlash tool and diagnostic. 90 nominal differential impedance (Z0) 30 nominal common mode impedance (ZCM) Pull-up or pull-down resistors and external series resistors as required by the USB 2.0 specifications [4] are part of the USB pad driver and need not be provided externally. See section 1.9.1 for functional description. See section 2.6.1 for external circuit design-in. UART RXD 17 O UART data output Note: UART not supported by TOBY-L2x0-00S. 1.8 V output, Circuit 104 (RXD) in ITU-T V.24, for AT command, data communication, FOAT. Add Test-Point and series 0 to access for diagnostic. See section 1.9.2 for functional description. See section 2.6.2 for external circuit design-in. TXD 16 I UART data input Note: UART not supported by TOBY-L2x0-00S. 1.8 V input, Circuit 103 (TXD) in ITU-T V.24, for AT command, data communication, FOAT. Add Test-Point and series 0 to access for diagnostic. See section 1.9.2 for functional description. See section 2.6.2 for external circuit design-in. CTS 15 O UART clear to send output Note: UART not supported by TOBY-L2x0-00S. 1.8 V output, Circuit 106 (CTS) in ITU-T V.24. Add Test-Point and series 0 to access for diagnostic. See section 1.9.2 for functional description. See section 2.6.2 for external circuit design-in. RTS 14 I UART ready to send input Note: UART not supported by TOBY-L2x0-00S. 1.8 V input, Circuit 105 (RTS) in ITU-T V.24. Add Test-Point and series 0 to access for diagnostic. See section 1.9.2 for functional description. See section 2.6.2 for external circuit design-in.](https://usermanual.wiki/u-blox/TOBYL210.System-Integration-Manual/User-Guide-2425113-Page-13.png)

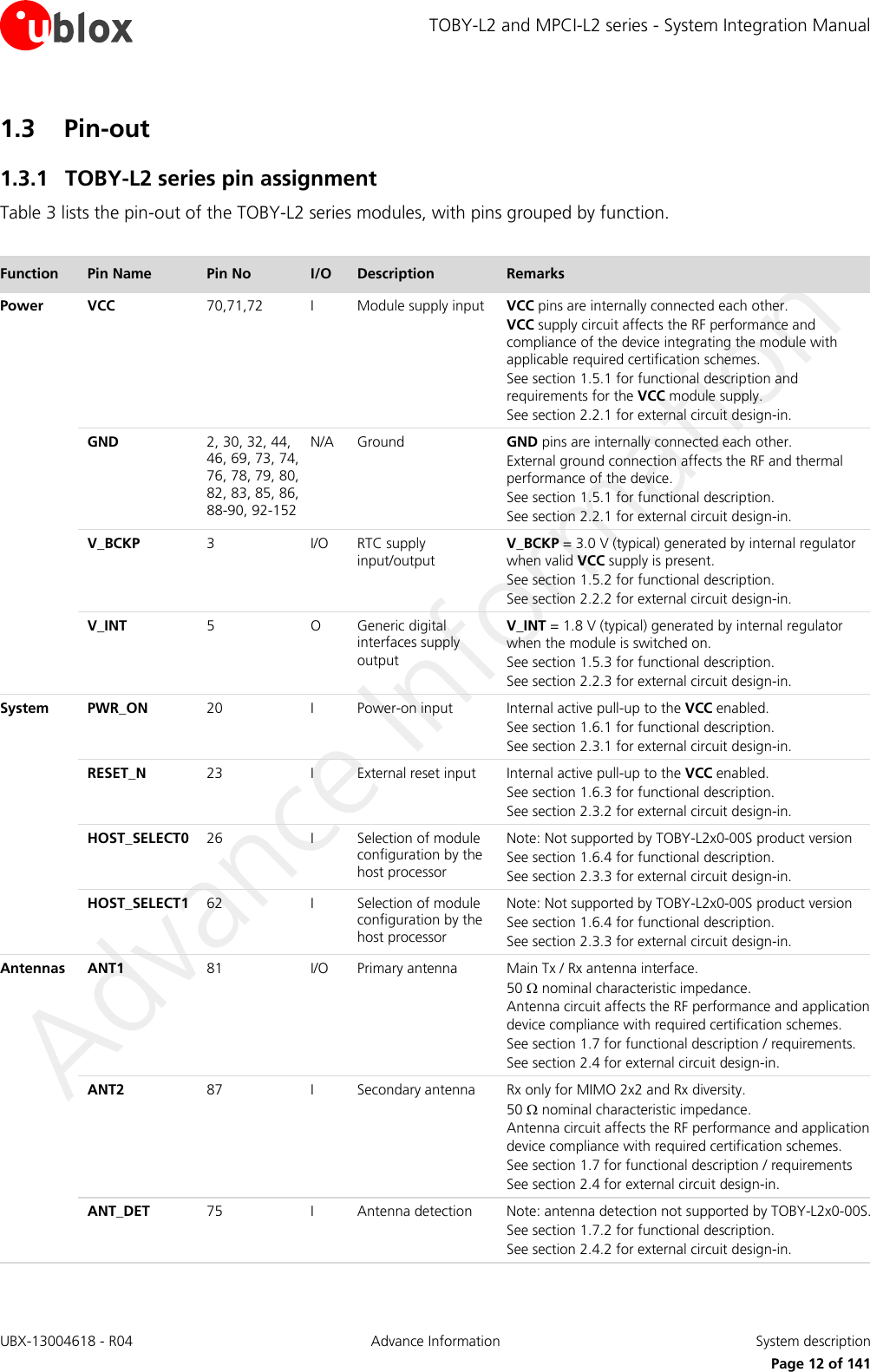

![TOBY-L2 and MPCI-L2 series - System Integration Manual UBX-13004618 - R04 Advance Information System description Page 14 of 141 Function Pin Name Pin No I/O Description Remarks DSR 10 O / I/O UART data set ready output / GPIO Note: UART / GPIO not supported by TOBY-L2x0-00S. 1.8 V, Circuit 107 in ITU-T V.24, configurable as GPIO. Add Test-Point and series 0 to access for diagnostic. See section 1.9.2 and 1.11 for functional description. See section 2.6.2 and 2.8 for external circuit design-in. RI 11 O / I/O UART ring indicator output / GPIO Note: UART / GPIO not supported by TOBY-L2x0-00S. 1.8 V, Circuit 125 in ITU-T V.24, configurable as GPIO. Add Test-Point and series 0 to access for diagnostic. See section 1.9.2 and 1.11 for functional description. See section 2.6.2 and 2.8 for external circuit design-in. DTR 13 I / I/O UART data terminal ready input / GPIO Note: UART / GPIO not supported by TOBY-L2x0-00S. 1.8 V, Circuit 108/2 in ITU-T V.24, configurable as GPIO. Add Test-Point and series 0 to access for diagnostic. See section 1.9.2 and 1.11 for functional description. See section 2.6.2 and 2.8 for external circuit design-in. DCD 12 O / I/O UART data carrier detect output / GPIO Note: UART / GPIO not supported by TOBY-L2x0-00S. 1.8 V, Circuit 109 in ITU-T V.24, configurable as GPIO. Add Test-Point and series 0 to access for diagnostic. See section 1.9.2 and 1.11 for functional description. See section 2.6.2 and 2.8 for external circuit design-in. DDC SCL 54 O I2C bus clock line Note: I2C not supported by TOBY-L2x0-00S. 1.8 V open drain, for communication with u-blox GNSS receivers and other I2C-slave devices as an audio codec. External pull-up required. See section 1.9.3 for functional description. See section 2.6.3 for external circuit design-in. SDA 55 I/O I2C bus data line Note: I2C not supported by TOBY-L2x0-00S. 1.8 V open drain, for communication with u-blox GNSS receivers and other I2C-slave devices as an audio codec. External pull-up required. See section 1.9.3 for functional description. See section 2.6.3 for external circuit design-in. SDIO SDIO_D0 66 I/O SDIO serial data [0] Note: SDIO not supported by TOBY-L2x0-00S. SDIO interface for communication with external Wi-Fi chip See section 1.9.4 for functional description. See section 2.6.4 for external circuit design-in. SDIO_D1 68 I/O SDIO serial data [1] Note: Not supported by TOBY-L2x0-00S. SDIO interface for communication with external Wi-Fi chip See section 1.9.4 for functional description. See section 2.6.4 for external circuit design-in. SDIO_D2 63 I/O SDIO serial data [2] Note: SDIO not supported by TOBY-L2x0-00S. SDIO interface for communication with external Wi-Fi chip See section 1.9.4 for functional description. See section 2.6.4 for external circuit design-in. SDIO_D3 67 I/O SDIO serial data [3] Note: SDIO not supported by TOBY-L2x0-00S. SDIO interface for communication with external Wi-Fi chip See section 1.9.4 for functional description. See section 2.6.4 for external circuit design-in. SDIO_CLK 64 O SDIO serial clock Note: SDIO not supported by TOBY-L2x0-00S. SDIO interface for communication with external Wi-Fi chip See section 1.9.4 for functional description. See section 2.6.4 for external circuit design-in.](https://usermanual.wiki/u-blox/TOBYL210.System-Integration-Manual/User-Guide-2425113-Page-14.png)

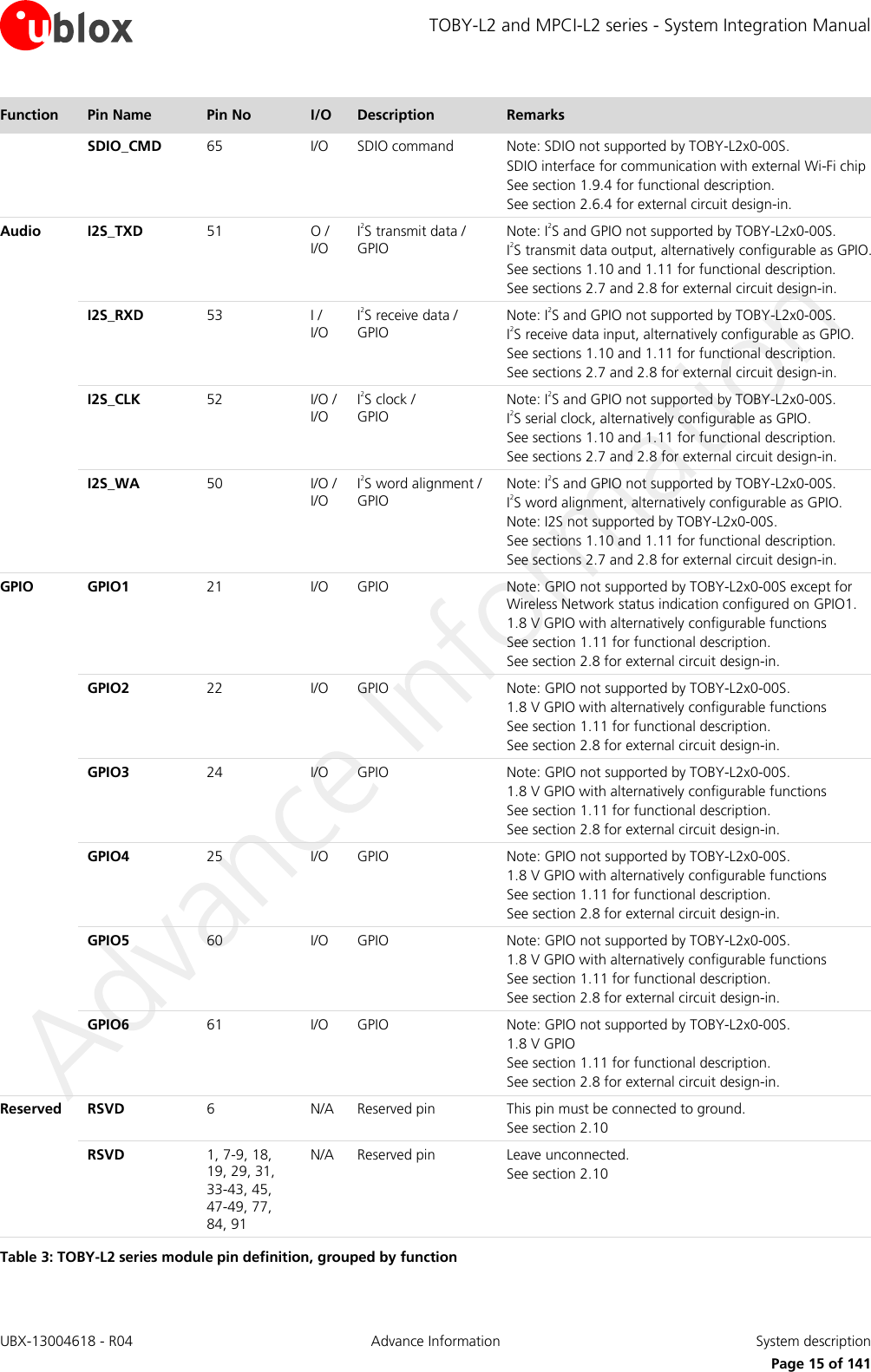

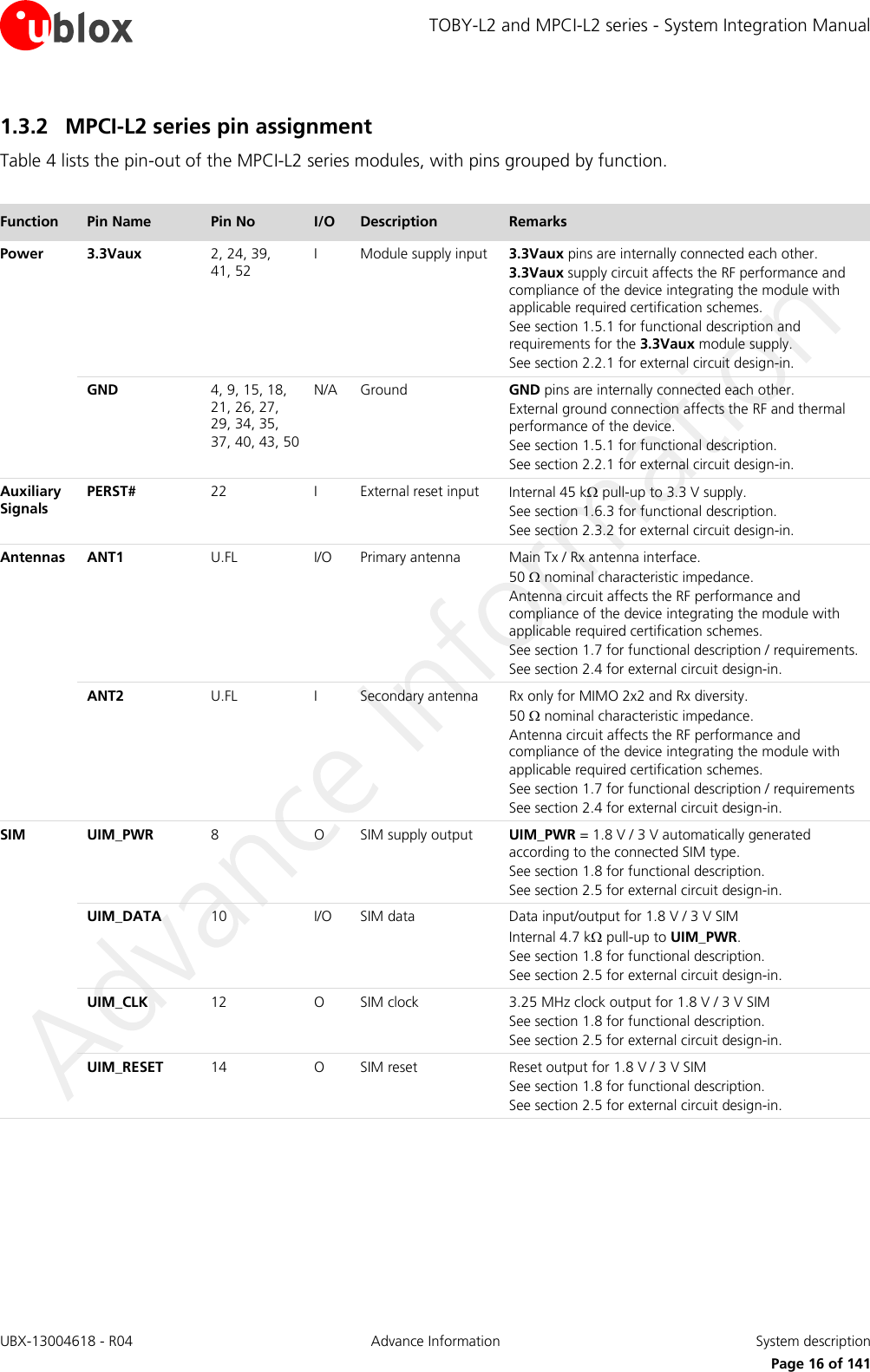

![TOBY-L2 and MPCI-L2 series - System Integration Manual UBX-13004618 - R04 Advance Information System description Page 17 of 141 Function Pin Name Pin No I/O Description Remarks USB USB_D- 36 I/O USB Data Line D- USB interface for AT commands, data communication, FOAT, FW update by u-blox EasyFlash tool and diagnostic. 90 nominal differential impedance (Z0) 30 nominal common mode impedance (ZCM) Pull-up or pull-down resistors and external series resistors as required by the USB 2.0 specifications [4] are part of the USB pad driver and need not be provided externally. See section 1.9.1 for functional description. See section 2.6.1 for external circuit design-in. USB_D+ 38 I/O USB Data Line D+ USB interface for AT commands, data communication, FOAT, FW update by u-blox EasyFlash tool and diagnostic. 90 nominal differential impedance (Z0) 30 nominal common mode impedance (ZCM) Pull-up or pull-down resistors and external series resistors as required by the USB 2.0 specifications [4] are part of the USB pad driver and need not be provided externally. See section 1.9.1 for functional description. See section 2.6.1 for external circuit design-in. Specific Signals LED_WWAN# 42 O LED indicator output Open drain active low output. See section 1.12 for functional description. See section 2.9 for external circuit design-in. W_DISABLE# 20 I Wireless radio disable input Internal 22 k pull-up to 3.3Vaux. See section 1.12 for functional description. See section 2.9 for external circuit design-in. Not Connected NC 1, 3, 5-7, 11, 13, 16, 17, 19, 23, 25, 28, 30-33, 44-46, 47-49, 51 N/A Not connected Internally not connected. See section 1.14 for the description. Table 4: MPCI-L2 series module pin definition, grouped by function](https://usermanual.wiki/u-blox/TOBYL210.System-Integration-Manual/User-Guide-2425113-Page-17.png)

![TOBY-L2 and MPCI-L2 series - System Integration Manual UBX-13004618 - R04 Advance Information System description Page 18 of 141 1.4 Operating modes TOBY-L2 and MPCI-L2 series modules have several operating modes. The operating modes are defined in Table 5 and described in detail in Table 6, providing general guidelines for operation. General Status Operating Mode Definition Power-down Not-Powered Mode VCC or 3.3Vaux supply not present or below operating range: module is switched off. Power-Off Mode VCC or 3.3Vaux supply within operating range and module is switched off. Normal Operation Idle-Mode Module processor core runs with 32 kHz reference generated by the internal oscillator. Active-Mode Module processor core runs with 26 MHz reference generated by the internal oscillator. Connected-Mode RF Tx/Rx data connection enabled and processor core runs with 26 MHz reference. Table 5: TOBY-L2 and MPCI-L2 series modules operating modes definition Operating Mode Description Transition between operating modes Not-Powered Mode Module is switched off. Application interfaces are not accessible. When VCC or 3.3Vaux supply is removed, the modules enter not-powered mode. When in not-powered mode, TOBY-L2 modules cannot be switched on by PWR_ON, RESET_N or RTC alarm and enter active-mode after applying VCC supply (see 1.6.1). When in not-powered mode, MPCI-L2 modules cannot be switched on by RTC alarm and enter active-mode after applying 3.3Vaux supply (see 1.6.1). Power-Off Mode Module is switched off: normal shutdown by an appropriate power-off event (see 1.6.2). Application interfaces are not accessible. MPCI-L2 modules do not support Power-Off Mode but halt mode (see 1.6.2 and u-blox AT Commands Manual [3], AT+CFUN=127 command). When the modules are switched off by an appropriate power-off event (see 1.6.2), the modules enter power-off mode from active-mode. When in power-off mode, TOBY-L2 modules can be switched on by PWR_ON, RESET_N or an RTC alarm. When in power-off mode, TOBY-L2 modules enter the not-powered mode after removing VCC supply. Idle-Mode Module is switched on with application interfaces disabled or suspended: the module is temporarily not ready to communicate with an external device by means of the application interfaces as configured to reduce the current consumption. The module enters the low power idle-mode whenever possible if power saving is enabled by AT+UPSV (see u-blox AT Commands Manual [3]) reducing current consumption (see 1.5.1.5). Power saving configuration is not enabled by default: it can be enabled by the AT+UPSV command (see the u-blox AT Commands Manual [3]). The modules automatically switch from active-mode to low power idle-mode whenever possible if power saving is enabled (see sections 1.5.1.5, 1.9.1.4, 1.9.2.4 and u-blox AT Commands Manual [3], AT+UPSV). The modules wake up from idle-mode to active-mode in the following events: Automatic periodic monitoring of the paging channel for the paging block reception according to network conditions (see 1.5.1.5) The connected USB host forces a remote wakeup of the module as USB device (see 1.9.1.4) A preset RTC alarm occurs (see u-blox AT Commands Manual [3], AT+CALA) Active-Mode Module is switched on with application interfaces enabled or not suspended: the module is ready to communicate with an external device by means of the application interfaces unless power saving configuration is enabled by AT+UPSV (see 1.9.1.4, 1.9.2.4 and u-blox AT Commands Manual [3]). When the modules are switched on by an appropriate power-on event (see 1.6.1), the module enter active-mode from power-off mode. If power saving configuration is enabled by the AT+UPSV command, the module automatically switches from active to idle-mode whenever possible and the module wakes up from idle to active-mode in the events listed above (see idle-mode to active-mode transition description above). When a RF Tx/Rx data connection is initiated or when RF Tx/Rx is required due to a connection previously initiated, the module switches from active to connected-mode.](https://usermanual.wiki/u-blox/TOBYL210.System-Integration-Manual/User-Guide-2425113-Page-18.png)

![TOBY-L2 and MPCI-L2 series - System Integration Manual UBX-13004618 - R04 Advance Information System description Page 19 of 141 Operating Mode Description Transition between operating modes Connected-Mode RF Tx/Rx data connection is in progress. The module is prepared to accept data signals from an external device unless power saving configuration is enabled by AT+UPSV (see sections 1.9.1.4, 1.9.2.4 and u-blox AT Commands Manual [3]). When a data connection is initiated, the module enters connected-mode from idle-mode. If power saving configuration is enabled by the AT+UPSV command, the module automatically switches from connected to active and then idle-mode whenever possible and the module wakes up from idle to active and then connected mode if RF Transmission/Reception is necessary. When a data connection is terminated, the module returns to the active-mode. Table 6: TOBY-L2 and MPCI-L2 series modules operating modes description Figure 3 describes the transition between the different operating modes. TOBY-L2 Switch ON:•Apply VCCMPCI-L2 Switch ON:•Apply 3.3VauxIf power saving is enabled and there is no activity for a defined time intervalAny wake up event described in the module operating modes summary table aboveIncoming/outgoing call or other dedicated device network communicationNo RF Tx/Rx in progress, Call terminated, Communication droppedTOBY-L2x0 Switch ON:•PWR_ON•RESET_N•RTC alarmNot poweredPower offActiveConnected IdleTOBY-L2x0 Switch OFF:•AT+CPWROFF•RESET_NMPCI-L2:•Remove 3.3VauxTOBY-L2:•Remove VCC Figure 3: TOBY-L2 and MPCI-L2 series modules operating modes transition](https://usermanual.wiki/u-blox/TOBYL210.System-Integration-Manual/User-Guide-2425113-Page-19.png)

![TOBY-L2 and MPCI-L2 series - System Integration Manual UBX-13004618 - R04 Advance Information System description Page 20 of 141 1.5 Supply interfaces 1.5.1 Module supply input (VCC or 3.3Vaux) TOBY-L2 modules are supplied via the three VCC pins, and MPCI-L2 modules are supplied via the five 3.3Vaux pins. All supply voltages used inside the modules are generated from the VCC or the 3.3Vaux supply input by integrated voltage regulators, including the V_BCKP RTC supply, the V_INT generic digital interface supply, and the VSIM or UIM_PWR SIM interface supply. The current drawn by the TOBY-L2 and MPCI-L2 series modules through the VCC or 3.3Vaux pins can vary by several orders of magnitude depending on radio access technology, operation mode and state. It is important that the supply source is able to support both the high peak of current consumption during 2G transmission at maximum RF power level (as described in the section 1.5.1.2) and the high average current consumption during 3G and LTE transmission at maximum RF power level (as described in the sections 1.5.1.3 and 1.5.1.4). 1.5.1.1 VCC or 3.3Vaux supply requirements Table 7 summarizes the requirements for the VCC or 3.3Vaux modules supply. See section 2.2.1 for suggestions to properly design a VCC or 3.3Vaux supply circuit compliant with the requirements listed in Table 7. The supply circuit affects the RF compliance of the device integrating TOBY-L2 and MPCI-L2 series modules with applicable required certification schemes as well as antenna circuit design. Compliance is guaranteed if the requirements summarized in the Table 7 are fulfilled. Item Requirement Remark VCC or 3.3Vaux nominal voltage Within VCC or 3.3Vaux normal operating range: See “Supply/Power pins” section in the TOBY-L2 Data Sheet [1] or in the MPCI-L2 Data Sheet [2]. The modules cannot be switched on if the supply voltage is below the normal operating range minimum limit. VCC or 3.3Vaux voltage during normal operation Within VCC or 3.3Vaux extended operating range: See “Supply/Power pins” section in the TOBY-L2 Data Sheet [1] or in the MPCI-L2 Data Sheet [2]. The modules may switch off if the supply voltage drops below the extended operating range minimum limit. VCC or 3.3Vaux average current Support with adequate margin the highest averaged current consumption value in connected-mode conditions specified for VCC in TOBY-L2 Data Sheet [1] or specified for 3.3Vaux in MPCI-L2 Data Sheet [2]. The maximum average current consumption can be greater than the specified value according to the actual antenna mismatching, temperature and supply voltage. Sections 1.5.1.2, 1.5.1.3 and 1.5.1.4 describe current consumption profiles in 2G, 3G and LTE connected-mode. VCC or 3.3Vaux peak current Support with margin the highest peak current consumption value in 2G connected-mode conditions specified for VCC in TOBY-L2 Data Sheet [1] or specified for 3.3Vaux in MPCI-L2 Data Sheet [2]. The specified maximum peak of current consumption occurs during GSM single transmit slot in 850/900 MHz connected-mode, in case of mismatched antenna. Section 1.5.1.2 describes 2G Tx peak/pulse current. VCC or 3.3Vaux voltage drop during 2G Tx slots Lower than 400 mV Supply voltage drop values greater than recommended during 2G TDMA transmission slots directly affect the RF compliance with applicable certification schemes. Figure 5 describes supply voltage drop during 2G Tx slots. VCC or 3.3Vaux voltage ripple during RF transmission Noise in the supply has to be minimized High supply voltage ripple values during LTE/3G/2G RF transmissions in connected-mode directly affect the RF compliance with applicable certification schemes. Figure 5 describes supply voltage ripple during RF Tx. VCC or 3.3Vaux under/over-shoot at start/end of Tx slots Absent or at least minimized Supply voltage under-shoot or over-shoot at the start or the end of 2G TDMA transmission slots directly affect the RF compliance with applicable certification schemes. Figure 5 describes supply voltage under/over-shoot Table 7: Summary of VCC or 3.3Vaux modules supply requirements](https://usermanual.wiki/u-blox/TOBYL210.System-Integration-Manual/User-Guide-2425113-Page-20.png)

![TOBY-L2 and MPCI-L2 series - System Integration Manual UBX-13004618 - R04 Advance Information System description Page 21 of 141 1.5.1.2 VCC or 3.3Vaux current consumption in 2G connected-mode When a GSM call is established, the VCC or 3.3Vaux module current consumption is determined by the current consumption profile typical of the GSM transmitting and receiving bursts. The peak of current consumption during a transmission slot is strictly dependent on the RF transmitted power, which is regulated by the network. The transmitted power in the transmit slot is also the more relevant factor for determining the average current consumption. If the module is transmitting in 2G single-slot mode in the 850 or 900 MHz bands, at the maximum RF power level (approximately 2 W or 33 dBm in the allocated transmit slot/burst) the current consumption can reach an high peak (see the “Current consumption” section in the TOBY-L2 Data Sheet [1] or the MPCI-L2 Data Sheet [2]) for 576.9 µs (width of the transmit slot/burst) with a periodicity of 4.615 ms (width of 1 frame = 8 slots/burst), so with a 1/8 duty cycle according to GSM TDMA (Time Division Multiple Access). If the module is transmitting in 2G single-slot mode in the 1800 or 1900 MHz bands, the current consumption figures are quite less high than the one in the low bands, due to 3GPP transmitter output power specifications. During a GSM call, current consumption is not so significantly high in receiving or in monitor bursts and is low in the inactive unused bursts. Figure 4 shows an example of the module current consumption profile versus time in 2G single-slot mode. Time [ms]RX slotunused slotunused slotTX slotunused slotunused slotMON slotunused slotRX slotunused slotunused slotTX slotunused slotunused slotMON slotunused slotGSM frame 4.615 ms (1 frame = 8 slots)Current [A]200 mA60-120 mA1900 mAPeak current depends on TX power and actual antenna loadGSM frame 4.615 ms (1 frame = 8 slots)60-120 mA10-40 mA0.01.51.00.52.02.5 Figure 4: VCC or 3.3Vaux current consumption profile versus time during a 2G single-slot call (1 TX slot, 1 RX slot) Figure 5 illustrates VCC or 3.3Vaux voltage profile versus time during a 2G single-slot call, according to the relative VCC or 3.3Vaux current consumption profile described in Figure 4. Time [ms]undershootovershootrippledropVoltage [mV]3.8 V (typ)RX slotunused slotunused slotTX slotunused slotunused slotMON slotunused slotRX slotunused slotunused slotTX slotunused slotunused slotMON slotunused slotGSM frame 4.615 ms (1 frame = 8 slots)GSM frame 4.615 ms (1 frame = 8 slots) Figure 5: VCC or 3.3Vaux voltage profile versus time during a 2G single-slot call (1 TX slot, 1 RX slot)](https://usermanual.wiki/u-blox/TOBYL210.System-Integration-Manual/User-Guide-2425113-Page-21.png)

![TOBY-L2 and MPCI-L2 series - System Integration Manual UBX-13004618 - R04 Advance Information System description Page 22 of 141 When a GPRS connection is established, more than one slot can be used to transmit and/or more than one slot can be used to receive. The transmitted power depends on network conditions, which set the peak current consumption, but following the 3GPP specifications the maximum Tx RF power is reduced if more than one slot is used to transmit, so the maximum peak of current is not as high as can be in case of a 2G single-slot call. If the module transmits in GPRS class 12 in the 850 or 900 MHz bands, at the maximum RF power control level, the current consumption can reach a quite high peak but lower than the one achievable in 2G single-slot mode. This happens for 2.307 ms (width of the 4 transmit slots/bursts) with a periodicity of 4.615 ms (width of 1 frame = 8 slots/bursts), so with a 1/2 duty cycle, according to 2G TDMA. If the module is in GPRS connected mode in the 1800 or 1900 MHz bands, the current consumption figures are quite less high than the one in the low bands, due to 3GPP transmitter output power specifications. Figure 6 reports the current consumption profiles in GPRS class 12 connected mode, in the 850 or 900 MHz bands, with 4 slots used to transmit and 1 slot used to receive. Time [ms]RX slotunused slotTX slotTX slotTX slotTX slotMON slotunused slotRX slotunused slotTX slotTX slotTX slotTX slotMON slotunused slotGSM frame 4.615 ms (1 frame = 8 slots)Current [A]200mA60-130mAPeak current depends on TX power and actual antenna loadGSM frame 4.615 ms (1 frame = 8 slots)1600 mA0.01.51.00.52.02.5 Figure 6: VCC or 3.3Vaux current consumption profile during a 2G GPRS/EDGE multi-slot connection (4 TX slots, 1 RX slot) In case of EDGE connections the VCC current consumption profile is very similar to the GPRS current profile, so the image shown in Figure 6, representing the current consumption profile in GPRS class 12 connected mode, is valid for the EDGE class 12 connected mode as well.](https://usermanual.wiki/u-blox/TOBYL210.System-Integration-Manual/User-Guide-2425113-Page-22.png)

![TOBY-L2 and MPCI-L2 series - System Integration Manual UBX-13004618 - R04 Advance Information System description Page 23 of 141 1.5.1.3 VCC or 3.3Vaux current consumption in 3G connected mode During a 3G connection, the module can transmit and receive continuously due to the Frequency Division Duplex (FDD) mode of operation with the Wideband Code Division Multiple Access (WCDMA). The current consumption depends again on output RF power, which is always regulated by network commands. These power control commands are logically divided into a slot of 666 µs, thus the rate of power change can reach a maximum rate of 1.5 kHz. There are no high current peaks as in the 2G connection, since transmission and reception are continuously enabled due to FDD WCDMA implemented in the 3G that differs from the TDMA implemented in the 2G case. In the worst scenario, corresponding to a continuous transmission and reception at maximum output power (approximately 250 mW or 24 dBm), the average current drawn by the module at the VCC pins is high (see the “Current consumption” section in TOBY-L2 Data Sheet [1] or in MPCI-L2 Data Sheet [2]). Even at lowest output RF power (approximately 0.01 µW or -50 dBm), the current is still not so low due to module baseband processing and transceiver activity. Figure 7 shows an example of current consumption profile of the module in 3G WCDMA/DC-HSPA+ continuous transmission mode. Time [ms]3G frame 10 ms (1 frame = 15 slots)Current [mA]Current consumption value depends on TX power and actual antenna load170 mA1 slot 666 µs850 mA0300200100500400600700800 Figure 7: VCC or 3.3Vaux current consumption profile versus time during a 3G connection (TX and RX continuously enabled)](https://usermanual.wiki/u-blox/TOBYL210.System-Integration-Manual/User-Guide-2425113-Page-23.png)

![TOBY-L2 and MPCI-L2 series - System Integration Manual UBX-13004618 - R04 Advance Information System description Page 24 of 141 1.5.1.4 VCC or 3.3Vaux current consumption in LTE connected-mode During a LTE connection, the module can transmit and receive continuously due to LTE radio access technology. The current consumption is strictly dependent on the transmitted RF output power, which is always regulated by network commands. These power control commands are logically divided into a slot of 0.5 ms (time length of one Resource Block), thus the rate of power change can reach a maximum rate of 2 kHz. Figure 8 shows an example of the module current consumption profile versus time in LTE connected-mode. Detailed current consumption values can be found in TOBY-L2 Data Sheet [1] and in MPCI-L2 Data Sheet [2]. Time [ms]Current [mA]Current consumption value depends on TX power and actual antenna load1 Slot1 Resource Block (0.5 ms) 1 LTE Radio Frame (10 ms)0300200100500400600700800 Figure 8: VCC or 3.3Vaux current consumption profile versus time during LTE connection (TX and RX continuously enabled)](https://usermanual.wiki/u-blox/TOBYL210.System-Integration-Manual/User-Guide-2425113-Page-24.png)

![TOBY-L2 and MPCI-L2 series - System Integration Manual UBX-13004618 - R04 Advance Information System description Page 25 of 141 1.5.1.5 VCC or 3.3Vaux current consumption in cyclic idle/active mode (power saving enabled) The power saving configuration is by default disabled, but it can be enabled using the AT+UPSV command (see the u-blox AT Commands Manual [3]). When power saving is enabled, the module automatically enters the low power idle-mode whenever possible, reducing current consumption. During low power idle-mode, the module processor runs with 32 kHz reference clock frequency. When the power saving configuration is enabled and the module is registered or attached to a network, the module automatically enters the low power idle-mode whenever possible, but it must periodically monitor the paging channel of the current base station (paging block reception), in accordance to the 2G/3G/LTE system requirements, even if connected-mode is not enabled by the application. When the module monitors the paging channel, it wakes up to the active-mode, to enable the reception of paging block. In between, the module switches to low power idle-mode. This is known as discontinuous reception (DRX). The module processor core is activated during the paging block reception, and automatically switches its reference clock frequency from 32 kHz to the 26 MHz used in active-mode. The time period between two paging block receptions is defined by the network. This is the paging period parameter, fixed by the base station through broadcast channel sent to all users on the same serving cell. In case of 2G radio access technology, the paging period can vary from 470.76 ms (DRX = 2, length of 2 x 51 2G frames = 2 x 51 x 4.615 ms) up to 2118.42 ms (DRX = 9, length of 9 x 51 2G frames = 9 x 51 x 4.615 ms). In case of 3G radio access technology, the paging period can vary from 640 ms (DRX = 6, i.e. length of 26 3G frames = 64 x 10 ms) up to 5120 ms (DRX = 9, length of 29 3G frames = 512 x 10 ms). In case of LTE radio access technology, the paging period can vary from 320 ms (DRX = 5, length of 25 LTE frames = 32 x 10 ms) up to 2560 ms (DRX = 8, length of 28 LTE frames = 256 x 10 ms). Figure 9 illustrates a typical example of the module current consumption profile when power saving is enabled. The module is registered with network, automatically enters the low power idle-mode and periodically wakes up to active-mode to monitor the paging channel for the paging block reception. Detailed current consumption values can be found in TOBY-L2 Data Sheet [1] and in MPCI-L2 Data Sheet [2]. ~50 msIDLE MODE ACTIVE MODE IDLE MODEActive Mode EnabledIdle Mode Enabled2G case: 0.44-2.09 s 3G case: 0.61-5.09 s LTE case: 0.27-2.51 sIDLE MODE~50 msACTIVE MODETime [s]Current [mA]Time [ms]Current [mA]RX Enabled01000100 Figure 9: VCC or 3.3Vaux current consumption profile with power saving enabled and module registered with the network: the module is in idle-mode and periodically wakes up to active-mode to monitor the paging channel for paging block reception](https://usermanual.wiki/u-blox/TOBYL210.System-Integration-Manual/User-Guide-2425113-Page-25.png)

![TOBY-L2 and MPCI-L2 series - System Integration Manual UBX-13004618 - R04 Advance Information System description Page 26 of 141 1.5.1.6 VCC or 3.3Vaux current consumption in fixed active-mode (power saving disabled) When power saving is disabled, the module does not automatically enter the low power idle-mode whenever possible: the module remains in active-mode. Power saving configuration is by default disabled. It can also be disabled using the AT+UPSV command (see u-blox AT Commands Manual [3] for detail usage). The module processor core is activated during idle-mode, and the 26 MHz reference clock frequency is used. It would draw more current during the paging period than that in the power saving mode. Figure 10 illustrates a typical example of the module current consumption profile when power saving is disabled. In such case, the module is registered with the network and while active-mode is maintained, the receiver is periodically activated to monitor the paging channel for paging block reception. ACTIVE MODE2G case: 0.44-2.09 s 3G case: 0.61-5.09 sLTE case: 0.32-2.56 sPaging periodTime [s]Current [mA]Time [ms]Current [mA]RX Enabled01000100 Figure 10: VCC or 3.3Vaux current consumption profile with power saving disabled and module registered with the network: active-mode is always held and the receiver is periodically activated to monitor the paging channel for paging block reception](https://usermanual.wiki/u-blox/TOBYL210.System-Integration-Manual/User-Guide-2425113-Page-26.png)

![TOBY-L2 and MPCI-L2 series - System Integration Manual UBX-13004618 - R04 Advance Information System description Page 27 of 141 1.5.2 RTC supply input/output (V_BCKP) The RTC supply V_BCKP pin is not available on MPCI-L2 series modules. The V_BCKP pin of TOBY-L2 series modules connects the supply for the Real Time Clock (RTC). A linear LDO regulator integrated in the Power Management Unit internally generates this supply, as shown in Figure 11, with low current capability (see the TOBY-L2 series Data Sheet [1]). The output of this regulator is always enabled when the main module voltage supply applied to the VCC pins is within the valid operating range. Baseband Processor70VCC71VCC72VCC3V_BCKPLinear LDOPower ManagementTOBY-L2 series32 kHzRTC Figure 11: TOBY-L2 series RTC supply (V_BCKP) simplified block diagram The RTC provides the module time reference (date and time) that is used to set the wake-up interval during the low power idle-mode periods, and is able to make available the programmable alarm functions. The RTC functions are available also in power-down mode when the V_BCKP voltage is within its valid range (specified in the “Input characteristics of Supply/Power pins” table in TOBY-L2 series Data Sheet [1]). The RTC can be supplied from an external back-up battery through the V_BCKP, when the main module voltage supply is not applied to the VCC pins. This lets the time reference (date and time) run until the V_BCKP voltage is within its valid range, even when the main supply is not provided to the module. Consider that the module cannot switch on if a valid voltage is not present on VCC even when the RTC is supplied through V_BCKP (meaning that VCC is mandatory to switch on the module). The RTC has very low current consumption, but is highly temperature dependent. For example, V_BCKP current consumption at the maximum operating temperature can be higher than the typical value at 25 °C specified in the “Input characteristics of Supply/Power pins” table in the TOBY-L2 series Data Sheet [1]. If V_BCKP is left unconnected and the module main supply is not applied to the VCC pins, the RTC is supplied from the bypass capacitor mounted inside the module. However, this capacitor is not able to provide a long buffering time: within few milliseconds the voltage on V_BCKP will go below the valid range (1.4 V min). This has no impact on cellular connectivity, as all the module functionalities do not rely on date and time setting.](https://usermanual.wiki/u-blox/TOBYL210.System-Integration-Manual/User-Guide-2425113-Page-27.png)

![TOBY-L2 and MPCI-L2 series - System Integration Manual UBX-13004618 - R04 Advance Information System description Page 28 of 141 1.5.3 Generic digital interfaces supply output (V_INT) The generic digital interfaces supply V_INT pin is not available on MPCI-L2 series modules. The V_INT output pin of the TOBY-L2 series modules is connected to an internal 1.8 V supply with current capability specified in the TOBY-L2 series Data Sheet [1]. This supply is internally generated by a switching step-down regulator integrated in the Power Management Unit and it is internally used to source the generic digital I/O interfaces of the TOBY-L2 module, as described in Figure 12. The output of this regulator is enabled when the module is switched on and it is disabled when the module is switched off. Baseband Processor70VCC71VCC72VCC5V_INTSwitchingStep-DownPower ManagementTOBY-L2 seriesDigital I/O Figure 12: TOBY-L2 series generic digital interfaces supply output (V_INT) simplified block diagram The switching regulator operates in Pulse Width Modulation (PWM) mode for greater efficiency at high output loads and it automatically switches to Pulse Frequency Modulation (PFM) power save mode for greater efficiency at low output loads. The V_INT output voltage ripple is specified in the TOBY-L2 series Data Sheet [1].](https://usermanual.wiki/u-blox/TOBYL210.System-Integration-Manual/User-Guide-2425113-Page-28.png)

![TOBY-L2 and MPCI-L2 series - System Integration Manual UBX-13004618 - R04 Advance Information System description Page 29 of 141 1.6 System function interfaces 1.6.1 Module power-on The PWR_ON input pin is not available on MPCI-L2 series modules. When the TOBY-L2 and MPCI-L2 series modules are in the not-powered mode (switched off, i.e. the VCC or 3.3Vaux module supply is not applied), they can be switched on as following: Rising edge on the VCC or 3.3Vaux supply input to a valid voltage for module supply, so that the module switches on applying a proper VCC or 3.3Vaux supply within the normal operating range. Alternately, the RESET_N or PERST# pin can be held to the low level during the VCC or 3.3Vaux rising edge, so that the module switches on releasing the RESET_N or PERST# pin when the VCC or 3.3Vaux module supply voltage stabilizes at its proper nominal value within the normal operating range. The status of the PWR_ON input pin of TOBY-L2 modules while applying the VCC module supply is not relevant: during this phase the PWR_ON pin can be set high or low by the external circuit. When the TOBY-L2 modules are in the power-off mode (i.e. switched off with valid VCC module supply applied), they can be switched on as following: Low level on the PWR_ON pin, which is normally set high by an internal pull-up, for a valid time period. Low level on the RESET_N pin, which is normally set high by an internal pull-up, for a valid time period. RTC alarm, i.e. pre-programmed alarm by AT+CALA command (see u-blox AT Commands Manual [3]). As described in Figure 13, the TOBY-L2 series PWR_ON input is equipped with an internal active pull-up resistor to the VCC module supply: the PWR_ON input voltage thresholds are different from the other generic digital interfaces. Detailed electrical characteristics are described in TOBY-L2 series Data Sheet [1]. Baseband Processor20PWR_ONTOBY-L2 seriesVCCPower-onPower ManagementPower-on50k Figure 13: TOBY-L2 series PWR_ON input description For more pin information and electrical characteristics, see the TOBY-L2 Data Sheet [1] and MPCI-L2 Data Sheet [2].](https://usermanual.wiki/u-blox/TOBYL210.System-Integration-Manual/User-Guide-2425113-Page-29.png)

![TOBY-L2 and MPCI-L2 series - System Integration Manual UBX-13004618 - R04 Advance Information System description Page 30 of 141 Figure 14 shows the module power-on sequence from the not-powered mode, describing the following phases: The external supply is applied to the VCC or 3.3Vaux module supply inputs, representing the start-up event. The PWR_ON and the RESET_N or PERST# pins suddenly rise to high logic level due to internal pull-ups. The V_BCKP RTC supply output is suddenly enabled by the module as VCC reaches a valid voltage value. All the generic digital pins of the module are tri-stated until the switch-on of their supply source (V_INT). The internal reset signal is held low: the baseband core and all the digital pins are held in the reset state. The reset state of all the digital pins is reported in the pin description table of TOBY-L2 Series Data Sheet [1]. When the internal reset signal is released, any digital pin is set in a proper sequence from the reset state to the default operational configured state. The duration of this pins’ configuration phase differs within generic digital interfaces and the USB interface due to host / device enumeration timings (see section 1.9.1). The module is fully ready to operate after all interfaces are configured. VCC or 3.3VauxV_BCKPPWR_ONRESET_N or PERST#V_INTInternal ResetSystem StateBB Pads StateInternal Reset → Operational OperationalTristate / Floating Internal ResetOFFON0 ms~10 ms~20 sStart of interface configurationModule interfaces are configuredStart-up event~5 ms Figure 14: TOBY-L2 and MPCI-L2 series power-on sequence description The Internal Reset signal is not available on a module pin, but the host application can monitor: The V_INT pin to sense the start of the TOBY-L2 module power-on sequence. The USB interface to sense the start of the MPCI-L2 module power-on sequence: the module, as USB device, informs the host of the attach event via a reply on its status change pipe for proper bus enumeration process according to Universal Serial Bus Revision 2.0 specification [6]. Before the switch-on of the generic digital interface supply source (V_INT) of the module, no voltage driven by an external application should be applied to any generic digital interface of TOBY-L2 module. Before the TOBY-L2 and MPCI-L2 series module is fully ready to operate, the host application processor should not send any AT command over the AT communication interfaces (USB, UART) of the module.](https://usermanual.wiki/u-blox/TOBYL210.System-Integration-Manual/User-Guide-2425113-Page-30.png)

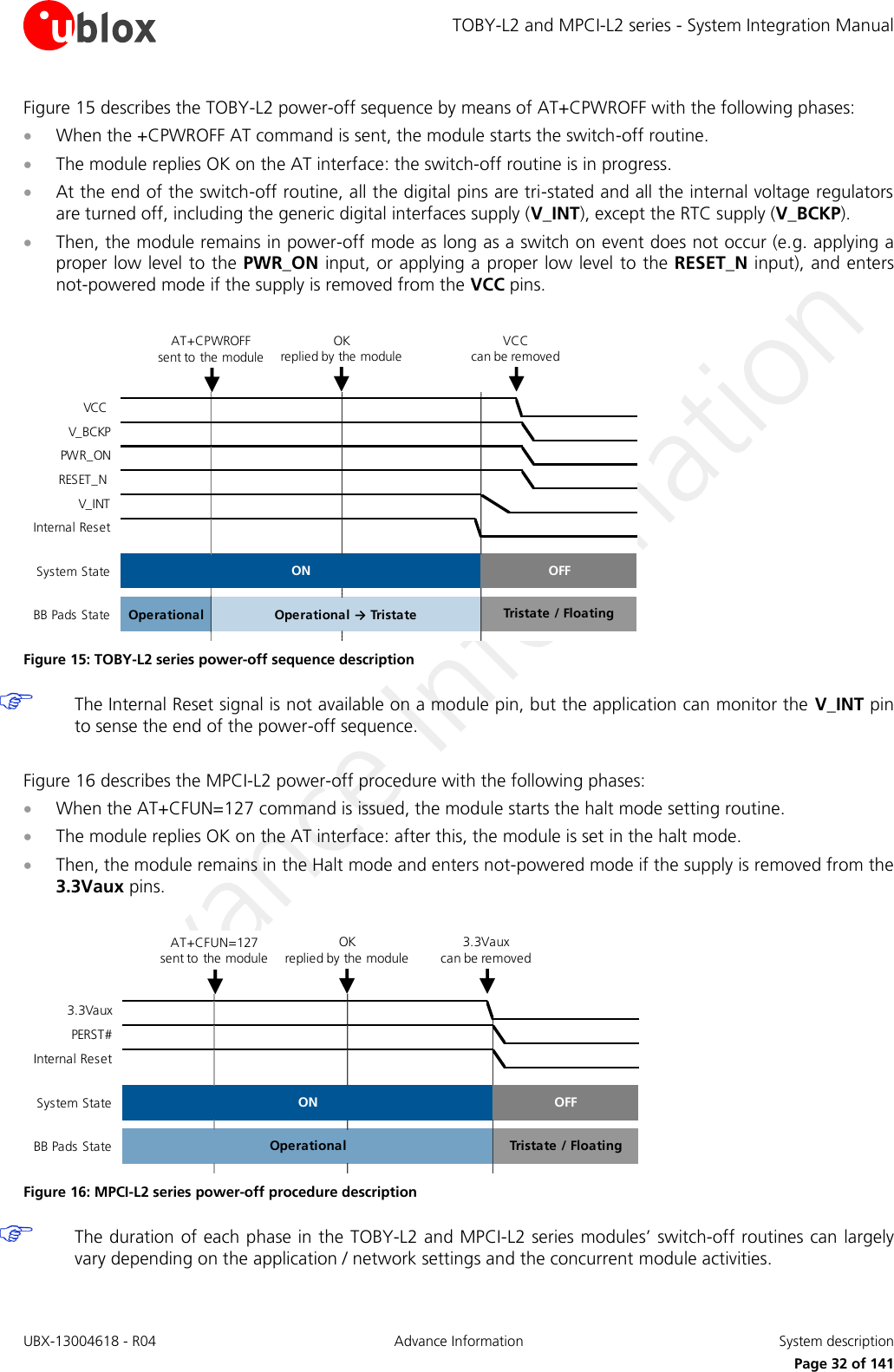

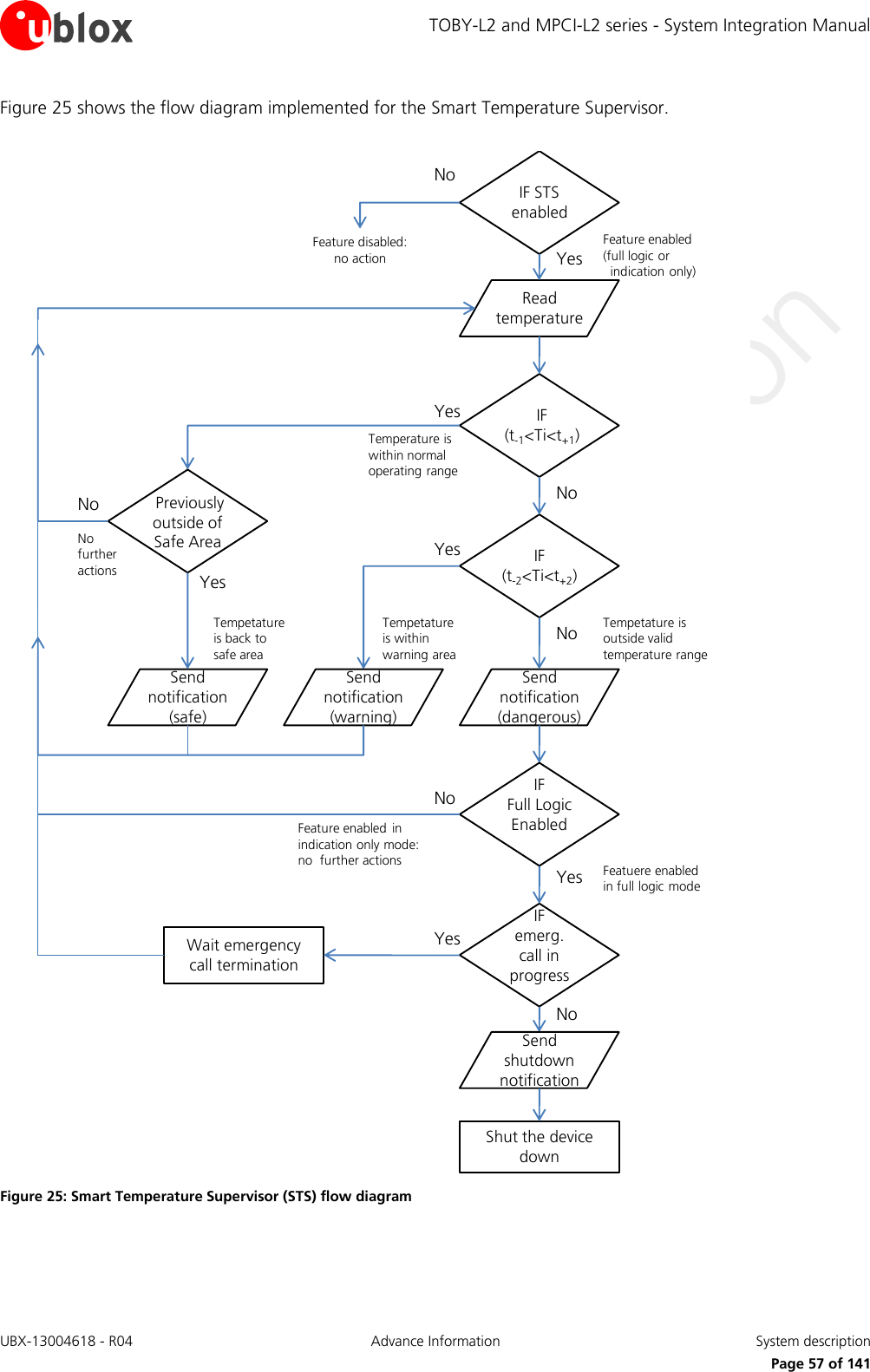

![TOBY-L2 and MPCI-L2 series - System Integration Manual UBX-13004618 - R04 Advance Information System description Page 31 of 141 1.6.2 Module power-off TOBY-L2 series can be properly switched off by: AT+CPWROFF command (see u-blox AT Commands Manual [3]). The current parameter settings are saved in the module’s non-volatile memory and a proper network detach is performed. The MPCI-L2 series modules do not switch off by the AT+CPWROFF command as the TOBY-L2 modules, but the AT+CPWROFF command causes a reset (reboot) of the module due to the MPCI-L2 module’s internal configuration: the command stores the actual parameter settings in the non-volatile memory of MPCI-L2 modules and performs a network detach, with a subsequent reset (reboot) of the module. An abrupt under-voltage shutdown occurs on TOBY-L2 and MPCI-L2 series modules when the VCC or 3.3Vaux module supply is removed. If this occurs, it is not possible to perform the storing of the current parameter settings in the module’s non-volatile memory or to perform the proper network detach. It is highly recommended to avoid an abrupt removal of the VCC supply during TOBY-L2 modules normal operations: the power off procedure must be started by the AT+CPWROFF command, waiting the command response for a proper time period (see u-blox AT Commands Manual [3]), and then a proper VCC supply has to be held at least until the end of the modules’ internal power off sequence, which occurs when the generic digital interfaces supply output (V_INT) is switched off by the module. It is highly recommended to avoid an abrupt removal of the 3.3Vaux supply during MPCI-L2 modules normal operations: the power off procedure must be started by setting the MPCI-L2 module in the halt mode by the AT+CFUN=127 command (which stores the actual parameter settings in the non-volatile memory of the module and performs a network detach), waiting the command response for a proper time period (see the u-blox AT Commands Manual [3]), and then the 3.3Vaux supply can be removed. An abrupt hardware shutdown occurs on TOBY-L2 series modules when a low level is applied on the RESET_N pin for a specific time period. In this case, the current parameter settings are not saved in the module’s non-volatile memory and a proper network detach is not performed. It is highly recommended to avoid an abrupt hardware shutdown of the module by forcing a low level on the RESET_N input pin during module normal operation: the RESET_N line should be set low only if reset or shutdown via AT commands fails or if the module does not reply to a specific AT command after a time period longer than the one defined in the u-blox AT Commands Manual [3]. An over-temperature or an under-temperature shutdown occurs on TOBY-L2 and MPCI-L2 series modules when the temperature measured within the cellular module reaches the dangerous area, if the optional Smart Temperature Supervisor feature is enabled and configured by the dedicated AT command. For more details see u-blox AT Commands Manual [3], +USTS AT command. The Smart Temperature Supervisor feature is not supported by the TOBY-L2x0-00S and MPCI-L2x0-00S product versions.](https://usermanual.wiki/u-blox/TOBYL210.System-Integration-Manual/User-Guide-2425113-Page-31.png)

![TOBY-L2 and MPCI-L2 series - System Integration Manual UBX-13004618 - R04 Advance Information System description Page 33 of 141 1.6.3 Module reset TOBY-L2 and MPCI-L2 series modules can be properly reset (rebooted) by: AT+CFUN command (see u-blox AT Commands Manual [3]). MPCI-L2 series modules can be additionally properly reset (rebooted) by: AT+CPWROFF command (see u-blox AT Commands Manual [3]): the behavior differs than TOBY-L2 series, as MPCI-L2 modules will reboot rather than remain switched off due to modules’ internal configuration. In the cases listed above an “internal” or “software” reset of the module is executed: the current parameter settings are saved in the module’s non-volatile memory and a proper network detach is performed. An abrupt hardware reset occurs on TOBY-L2 and MPCI-L2 series modules when a low level is applied on the RESET_N or PERST# input pin for a specific time period. In this case, the current parameter settings are not saved in the module’s non-volatile memory and a proper network detach is not performed. It is highly recommended to avoid an abrupt hardware reset of the module by forcing a low level on the RESET_N or PERST# input during modules normal operation: the RESET_N or PERST# line should be set low only if reset or shutdown via AT commands fails or if the module does not provide a reply to a specific AT command after a time period longer than the one defined in the u-blox AT Commands Manual [3]. As described in Figure 17, the RESET_N and PERST# input pins are equipped with an internal pull-up to the VCC supply in the TOBY-L2 series and to the 3.3 V in the MPCI-L2 series. Baseband Processor23RESET_NTOBY-L2 seriesVCCResetPower ManagementReset50kBaseband Processor22PERST#MPCI-L2 seriesResetPower ManagementReset45k3.3 V Figure 17: TOBY-L2 and MPCI-L2 series RESET_N and PERST# input equivalent circuit description For more electrical characteristics details see TOBY-L2 Data Sheet [1] and MPCI-L2 Data Sheet [2]. 1.6.4 Module configuration selection by host processor The HOST_SELECT0 and HOST_SELECT1 pins are not available on MPCI-L2 series modules. The functionality of the HOST_SELECT0 and HOST_SELECT1 pins is not supported by TOBY-L2x0-00S. TOBY-L2 series modules include two input pins (HOST_SELECT0 and HOST_SELECT1) for the selection of the module configuration by the host application processor.](https://usermanual.wiki/u-blox/TOBYL210.System-Integration-Manual/User-Guide-2425113-Page-33.png)

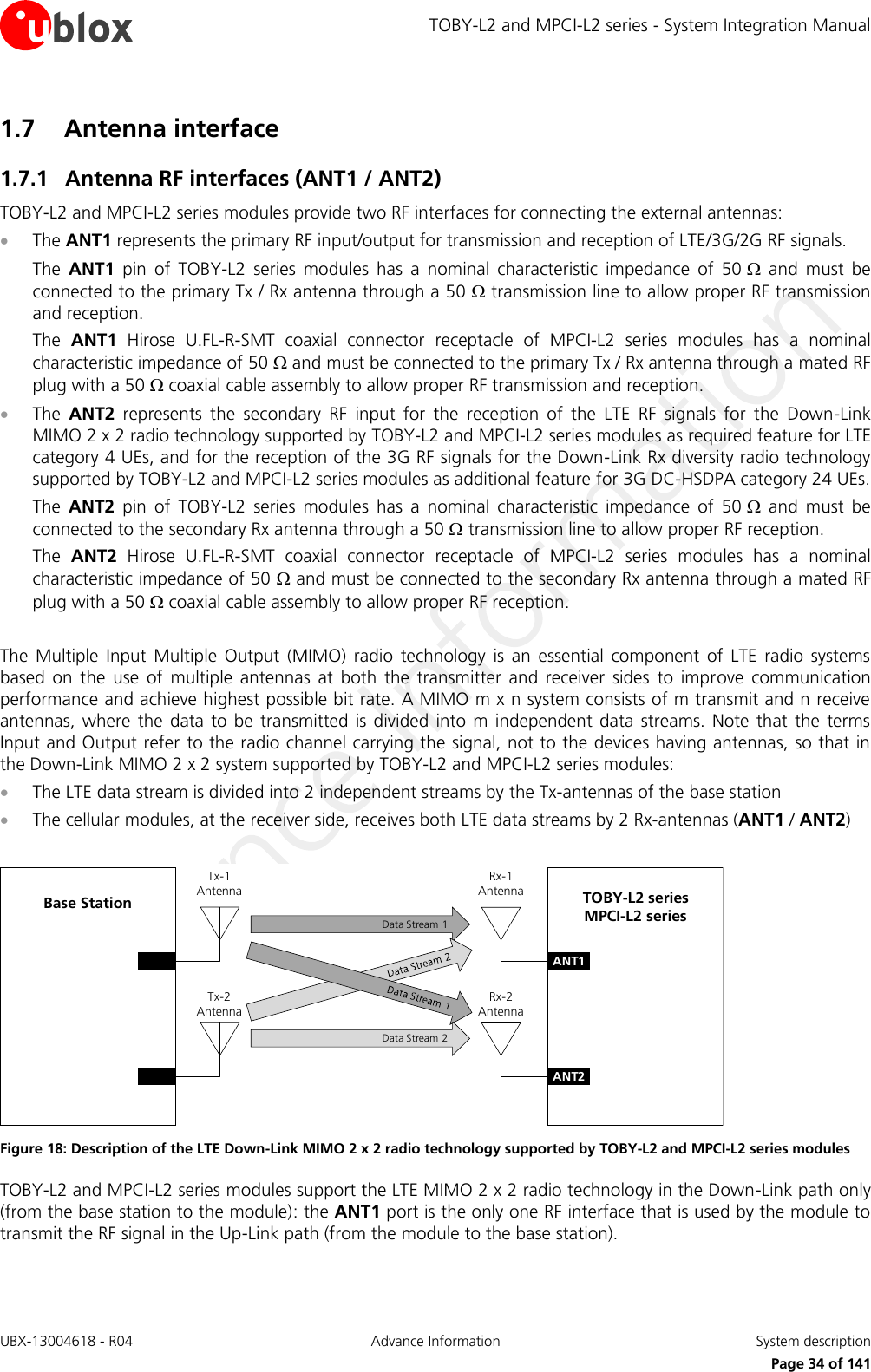

![TOBY-L2 and MPCI-L2 series - System Integration Manual UBX-13004618 - R04 Advance Information System description Page 35 of 141 1.7.1.1 Antenna RF interfaces requirements Table 8, Table 9 and Table 10 summarize the requirements for the antennas RF interfaces (ANT1 / ANT2). See section 2.4.1 for suggestions to properly design antennas circuits compliant with these requirements. The antenna circuits affect the RF compliance of the device integrating TOBY-L2 and MPCI-L2 series modules with applicable required certification schemes (for more details see section 4). Compliance is guaranteed if the antenna RF interfaces (ANT1 / ANT2) requirements summarized in Table 8, Table 9 and Table 10 are fulfilled. Item Requirements Remarks Impedance 50 nominal characteristic impedance The impedance of the antenna RF connection must match the 50 impedance of the ANT1 port. Frequency Range See the TOBY-L2 series Data Sheet [1] and the MPCI-L2 series Data Sheet [2] The required frequency range of the antenna connected to ANT1 port depends on the operating bands of the used cellular module and the used mobile network. Return Loss S11 < -10 dB (VSWR < 2:1) recommended S11 < -6 dB (VSWR < 3:1) acceptable The Return loss or the S11, as the VSWR, refers to the amount of reflected power, measuring how well the primary antenna RF connection matches the 50 characteristic impedance of the ANT1 port. The impedance of the antenna termination must match as much as possible the 50 nominal impedance of the ANT1 port over the operating frequency range, reducing as much as possible the amount of reflected power. Efficiency > -1.5 dB ( > 70% ) recommended > -3.0 dB ( > 50% ) acceptable The radiation efficiency is the ratio of the radiated power to the power delivered to antenna input: the efficiency is a measure of how well an antenna receives or transmits. The radiation efficiency of the antenna connected to the ANT1 port needs to be enough high over the operating frequency range to comply with the Over-The-Air (OTA) radiated performance requirements, as Total Radiated Power (TRP) and the Total Isotropic Sensitivity (TIS), specified by applicable related certification schemes. Maximum Gain According to radiation exposure limits The power gain of an antenna is the radiation efficiency multiplied by the directivity: the gain describes how much power is transmitted in the direction of peak radiation to that of an isotropic source. The maximum gain of the antenna connected to ANT1 port must not exceed the herein stated value to comply with regulatory agencies radiation exposure limits. For additional info see the section 4.2.2. Input Power > 33 dBm ( > 2 W ) The antenna connected to the ANT1 port must support with adequate margin the maximum power transmitted by the modules. Table 8: Summary of primary Tx/Rx antenna RF interface (ANT1) requirements](https://usermanual.wiki/u-blox/TOBYL210.System-Integration-Manual/User-Guide-2425113-Page-35.png)

![TOBY-L2 and MPCI-L2 series - System Integration Manual UBX-13004618 - R04 Advance Information System description Page 36 of 141 Item Requirements Remarks Impedance 50 nominal characteristic impedance The impedance of the antenna RF connection must match the 50 impedance of the ANT2 port. Frequency Range See the TOBY-L2 series Data Sheet [1] and the MPCI-L2 series Data Sheet [2] The required frequency range of the antennas connected to ANT2 port depends on the operating bands of the used cellular module and the used Mobile Network. Return Loss S11 < -10 dB (VSWR < 2:1) recommended S11 < -6 dB (VSWR < 3:1) acceptable The Return loss or the S11, as the VSWR, refers to the amount of reflected power, measuring how well the secondary antenna RF connection matches the 50 characteristic impedance of the ANT2 port. The impedance of the antenna termination must match as much as possible the 50 nominal impedance of the ANT2 port over the operating frequency range, reducing as much as possible the amount of reflected power. Efficiency > -1.5 dB ( > 70% ) recommended > -3.0 dB ( > 50% ) acceptable The radiation efficiency is the ratio of the radiated power to the power delivered to antenna input: the efficiency is a measure of how well an antenna receives or transmits. The radiation efficiency of the antenna connected to the ANT2 port needs to be enough high over the operating frequency range to comply with the Over-The-Air (OTA) radiated performance requirements, as the TIS, specified by applicable related certification schemes. Table 9: Summary of secondary Rx antenna RF interface (ANT2) requirements Item Requirements Remarks Efficiency imbalance < 0.5 dB recommended < 1.0 dB acceptable The radiation efficiency imbalance is the ratio of the primary (ANT1) antenna efficiency to the secondary (ANT2) antenna efficiency: the efficiency imbalance is a measure of how much better an antenna receives or transmits compared to the other antenna. The radiation efficiency of the secondary antenna needs to be roughly the same of the radiation efficiency of the primary antenna for good RF performance. Envelope Correlation Coefficient < 0.4 recommended < 0.5 acceptable The Envelope Correlation Coefficient (ECC) between the primary (ANT1) and the secondary (ANT2) antenna is an indicator of 3D radiation pattern similarity between the two antennas: low ECC results from antenna patterns with radiation lobes in different directions. The ECC between primary and secondary antenna needs to be enough low to comply with radiated performance requirements specified by related certification schemes. Isolation > 15 dB recommended > 10 dB acceptable The antenna to antenna isolation is the loss between the primary (ANT1) and the secondary (ANT2) antenna: high isolation results from low coupled antennas. The isolation between primary and secondary antenna needs to be high for good RF performance. Table 10: Summary of primary (ANT1) and secondary (ANT2) antennas relationship requirements](https://usermanual.wiki/u-blox/TOBYL210.System-Integration-Manual/User-Guide-2425113-Page-36.png)

![TOBY-L2 and MPCI-L2 series - System Integration Manual UBX-13004618 - R04 Advance Information System description Page 37 of 141 1.7.2 Antenna detection interface (ANT_DET) Antenna detection interface (ANT_DET) is not available on MPCI-L2 series modules. Antenna detection interface (ANT_DET) is not supported by the TOBY-L2x0-00S product version. The antenna detection is based on ADC measurement. The ANT_DET pin is an Analog to Digital Converter (ADC) provided to sense the antenna presence. The antenna detection function provided by ANT_DET pin is an optional feature that can be implemented if the application requires it. The antenna detection is forced by the +UANTR AT command. See the u-blox AT Commands Manual [3] for more details on this feature. The ANT_DET pin generates a DC current (for detailed characteristics see the TOBY-L2 series Data Sheet [1]) and measures the resulting DC voltage, thus determining the resistance from the antenna connector provided on the application board to GND. So, the requirements to achieve antenna detection functionality are the following: an RF antenna assembly with a built-in resistor (diagnostic circuit) must be used an antenna detection circuit must be implemented on the application board See section 2.4.2 for antenna detection circuit on application board and diagnostic circuit on antenna assembly design-in guidelines. 1.8 SIM interface 1.8.1 SIM interface TOBY-L2 and MPCI-L2 series modules provide high-speed SIM/ME interface including automatic detection and configuration of the voltage required by the connected SIM card or chip. Both 1.8 V and 3 V SIM types are supported. Activation and deactivation with automatic voltage switch from 1.8 V to 3 V are implemented, according to ISO-IEC 7816-3 specifications. The VSIM or UIM_PWR supply output provides internal short circuit protection to limit start-up current and protect the SIM to short circuits. The SIM driver supports the PPS (Protocol and Parameter Selection) procedure for baud-rate selection, according to the values determined by the SIM card or chip. 1.8.2 SIM detection interface SIM detection interface (GPIO5) is not available on MPCI-L2 series modules. SIM detection interface (GPIO5) is not supported by the TOBY-L2x0-00S product version. The GPIO5 pin is by default configured to detect the SIM card mechanical / physical presence. The pin is configured as input with an internal active pull-down enabled, and it can sense SIM card presence only if properly connected to the mechanical switch of a SIM card holder as described in section 2.5: Low logic level at GPIO5 input pin is recognized as SIM card not present High logic level at GPIO5 input pin is recognized as SIM card present The SIM card detection function provided by GPIO5 pin is an optional feature that can be implemented / used or not according to the application requirements: an Unsolicited Result Code (URC) is generated each time that there is a change of status (for more details see the u-blox AT Commands Manual [3]). The optional function “SIM card hot insertion/removal” can be additionally enabled on the GPIO5 pin by specific AT command (see the u-blox AT Commands Manual [3]).](https://usermanual.wiki/u-blox/TOBYL210.System-Integration-Manual/User-Guide-2425113-Page-37.png)

![TOBY-L2 and MPCI-L2 series - System Integration Manual UBX-13004618 - R04 Advance Information System description Page 38 of 141 1.9 Data communication interfaces TOBY-L2 and MPCI-L2 series modules provide the following serial communication interface: USB interface: High-Speed USB 2.0 compliant interface available for the communication with an external host application processor, for AT commands, data communication, FW upgrade by means of the FOAT feature, FW upgrade by means of the u-blox EasyFlash tool and for diagnostic purpose (see section 1.9.1 for functional description) TOBY-L2 series modules additionally provide the following serial communication interfaces: UART interface: asynchronous serial interface available for the communication with an external host application processor, for AT commands, data communication, FW upgrade by means of the FOAT feature (see section 1.9.2 for functional description) DDC interface: I2C bus compatible interface available for the communication with u-blox GNSS positioning chips/modules and with external I2C devices as an audio codec (see section 1.9.3 for functional description) SDIO interface: Secure Digital Input Output interface available for the communication with an external Wi-Fi chip or module (see section 1.9.4 for functional description) 1.9.1 Universal Serial Bus (USB) 1.9.1.1 USB features TOBY-L2 and MPCI-L2 series modules include a High-Speed USB 2.0 compliant interface with maximum data rate of 480 Mb/s, representing the main interface for transferring high speed data with a host application processor: the USB interface is available for AT commands, data communication, FW upgrade by means of the FOAT feature, FW upgrade by means of the u-blox EasyFlash tool and for diagnostic purpose.The module itself acts as a USB device and can be connected to a USB host such as a Personal Computer or an embedded application microprocessor equipped with compatible drivers. The USB_D+ / USB_D- lines carry the USB serial bus data and signaling, providing all the functionalities for the bus attachment, configuration, enumeration, suspension or remote wakeup according to the Universal Serial Bus Revision 2.0 specification [6] The additional VUSB_DET input pin is available on TOBY-L2 series modules as optional feature to sense the USB VBUS supply (5.0 V typical) from the host, providing the complete bus detach functionality for further reduction of the module current consumption in particular during low-power idle mode with power saving enabled: TOBY-L2 series modules disable the USB interface when a low logic level is sensed after a high-to-low logic level transition on the VUSB_DET input pin, reducing the current consumption. The VUSB_DET pin is not available on MPCI-L2 series modules. The USB interface is controlled and operated with: AT commands according to 3GPP TS 27.007 [8], 3GPP TS 27.005 [9], 3GPP TS 27.010 [10] u-blox AT commands For the complete list of supported AT commands and their syntax see u-blox AT Commands Manual [3].](https://usermanual.wiki/u-blox/TOBYL210.System-Integration-Manual/User-Guide-2425113-Page-38.png)

![TOBY-L2 and MPCI-L2 series - System Integration Manual UBX-13004618 - R04 Advance Information System description Page 39 of 141 TOBY-L2 and MPCI-L2 modules provide by default the following USB profile with the listed set of USB functions: 1 RNDIS for Ethernet-over-USB connection 1 CDC-ACM for AT commands and data communication The USB profile of TOBY-L2 and MPCI-L2 modules identifies itself by its VID (Vendor ID) and PID (Product ID) combination, included in the USB device descriptor according to the USB 2.0 specifications [6]. The VID and PID of the default USB profile configuration with the set of functions described above (1 RNDIS for Ethernet-over-USB and 1 CDC-ACM for AT commands and data) are the following: VID = 0x1546 PID = 0x1146 Figure 19 summarizes the USB end-points available with the default USB profile configuration. Default profile configurationInterface 0 Wireless Controller –Remote NDISInterface 1 Communication DataEndPoint Transfer: InterruptEndPoint Transfer: BulkEndPoint Transfer: BulkInterface 2 Communication Control –AT commandsEndPoint Transfer: InterruptInterface 3 Communication DataEndPoint Transfer: BulkEndPoint Transfer: BulkFunction RNDISFunction CDC Serial Figure 19: TOBY-L2 and MPCI-L2 series USB End-Points summary for the default USB profile configuration The USB of the modules can be configured by the AT+UUSBCONF command (for more details see the u-blox AT Commands Manual [3]) to select different sets of USB functions available in mutually exclusive way, selecting the active USB profile consisting of a specific set of functions with various capabilities and purposes, such as: CDC-ACM for AT commands and data CDC-ACM for GNSS tunneling CDC-ACM for SIM Access Profile (SAP) CDC-ACM for diagnostic RNDIS for Ethernet-over-USB CDC-ECM for Ethernet-over-USB CDC-NCM for Ethernet-over-USB MBIM for Ethernet-over-USB CDC-ACM for GNSS tunneling, CDC-ACM for SIM Access Profile (SAP), and CDC-NCM and MBIM functions are not supported by the TOBY-L2x0-00S and MPCI-L2x0-00S product versions.](https://usermanual.wiki/u-blox/TOBYL210.System-Integration-Manual/User-Guide-2425113-Page-39.png)

![TOBY-L2 and MPCI-L2 series - System Integration Manual UBX-13004618 - R04 Advance Information System description Page 40 of 141 For example, the default USB profile configuration which provides 2 functions (1 RNDIS for Ethernet-over-USB and 1 CDC-ACM for AT commands and data) can be changed by means of the AT+UUSBCONF command switching to a USB profile configuration which provides the following 6 functions: 3 CDC-ACM for AT commands and data 1 CDC-ACM for GNSS tunneling 1 CDC-ACM for SIM Access Profile (SAP) 1 CDC-ACM for diagnostic As each USB profile of TOBY-L2 and MPCI-L2 modules identifies itself by its specific VID and PID combination included in the USB device descriptor according to the USB 2.0 specifications [6], the VID and PID combination changes as following by switching the active USB profile configuration to the set of 6 functions described above: VID = 0x1546 PID = 0x1141 Alternatively, as another example, the USB profile configuration can be changed by means of the AT+UUSBCONF command switching to a USB profile configuration which provides the following 4 functions: 1 CDC-ECM for Ethernet-over-USB 3 CDC-ACM for AT commands and data In case of this USB profile with the set of 4 functions described above, the VID and PID are the following: VID = 0x1546 PID = 0x1143 The switch of the active USB profile selected by the AT+UUSBCONF command is not performed immediately. The settings are saved in the non-volatile memory of the module at the power off, and the new configuration is effective at the subsequent reboot of the module. If the USB is connected to the host before the module is switched on, or if the module is reset (rebooted) with the USB connected to the host, the VID and PID are automatically updated during the boot of the module. First, VID and PID are the following: VID = 0x1546 PID = 0x1140 This VID and PID combination identifies a USB profile where no USB function described above is available: AT commands must not be sent to the module over the USB profile identified by this VID and PID combination. Then, after a time period (roughly 20 s, depending on the host / device enumeration timings), the VID and PID are updated to the ones related to the USB profile selected by the AT+UUSBCONF command. For more details regarding the TOBY-L2 and MPCI-L2 series modules USB configurations and capabilities, see the u-blox AT Commands Manual [3], +UUSBCONF AT command.](https://usermanual.wiki/u-blox/TOBYL210.System-Integration-Manual/User-Guide-2425113-Page-40.png)

![TOBY-L2 and MPCI-L2 series - System Integration Manual UBX-13004618 - R04 Advance Information System description Page 41 of 141 1.9.1.2 USB in Windows The USB drivers (INF files) are provided for Windows systems and should be installed properly by following the step-by-step instruction in EVK-L20 / EVK-L21 User Guide [4]. USB drivers are available for the following operating system platforms: Windows Vista Windows 7 Windows 8 Windows 8.1 Windows Embedded Compact 7 The module firmware can be upgraded over the USB interface by means of the FOAT feature, or using the u-blox EasyFlash tool (for more details see Firmware Update Application Note [4]). 1.9.1.3 USB in Linux/Android It is not required to install a specific driver for each Linux-based or Android-based operating system (OS) to use the module USB interface, which is compatible with standard Linux/Android USB kernel drivers. The full capability and configuration of the module USB interface can be reported by running ‘lsusb –v’ or an equivalent command available in the host operating system when the module is connected. 1.9.1.4 USB and power saving If power saving is enabled by the AT+UPSV command, the modules automatically enter the USB suspended state when the device has observed no bus traffic for a specific time period according to the USB 2.0 specification [6]. In suspended state, the module maintains any USB internal status as device. In addition, the module enters the suspended state when the hub port it is attached to is disabled. This is referred to as USB selective suspend. The module exits suspend mode when there is bus activity. If the USB is connected and not suspended, the module is forced to stay in active-mode, therefore the AT+UPSV settings are overruled but they have effect on the power saving configuration of the other interfaces. The modules are capable of USB remote wake-up signaling: i.e. it may request the host to exit suspend mode or selective suspend by using electrical signaling to indicate remote wake-up. This notifies the host that it should resume from its suspended mode, if necessary, and service the external event. Remote wake-up is accomplished using electrical signaling described in the USB 2.0 specifications [6]. For the module current consumption description with power saving enabled and USB suspended, or with power saving disabled and USB not suspended, see the sections 1.5.1.5, 1.5.1.6 and the TOBY-L2 Data Sheet [1] or the MPCI-L2 Data Sheet [2]. The additional VUSB_DET input pin available on TOBY-L2 series modules provides the complete bus detach functionality: the modules disable the USB interface when a low logic level is sensed after a high-to-low logic level transition on the VUSB_DET input pin. This allows a further reduction of the module current consumption, in particular as compared to the USB suspended status during low-power idle mode with power saving enabled.](https://usermanual.wiki/u-blox/TOBYL210.System-Integration-Manual/User-Guide-2425113-Page-41.png)

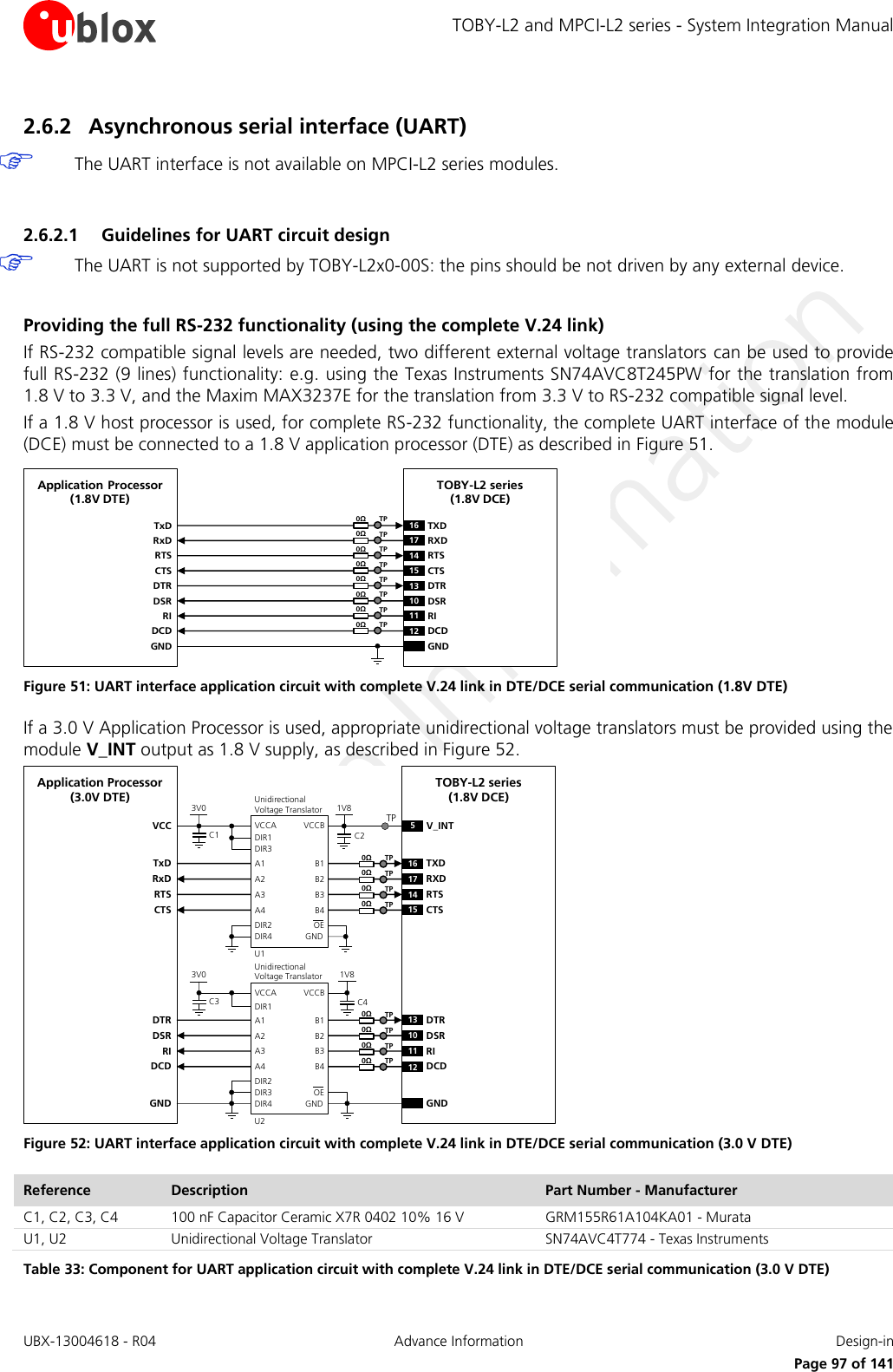

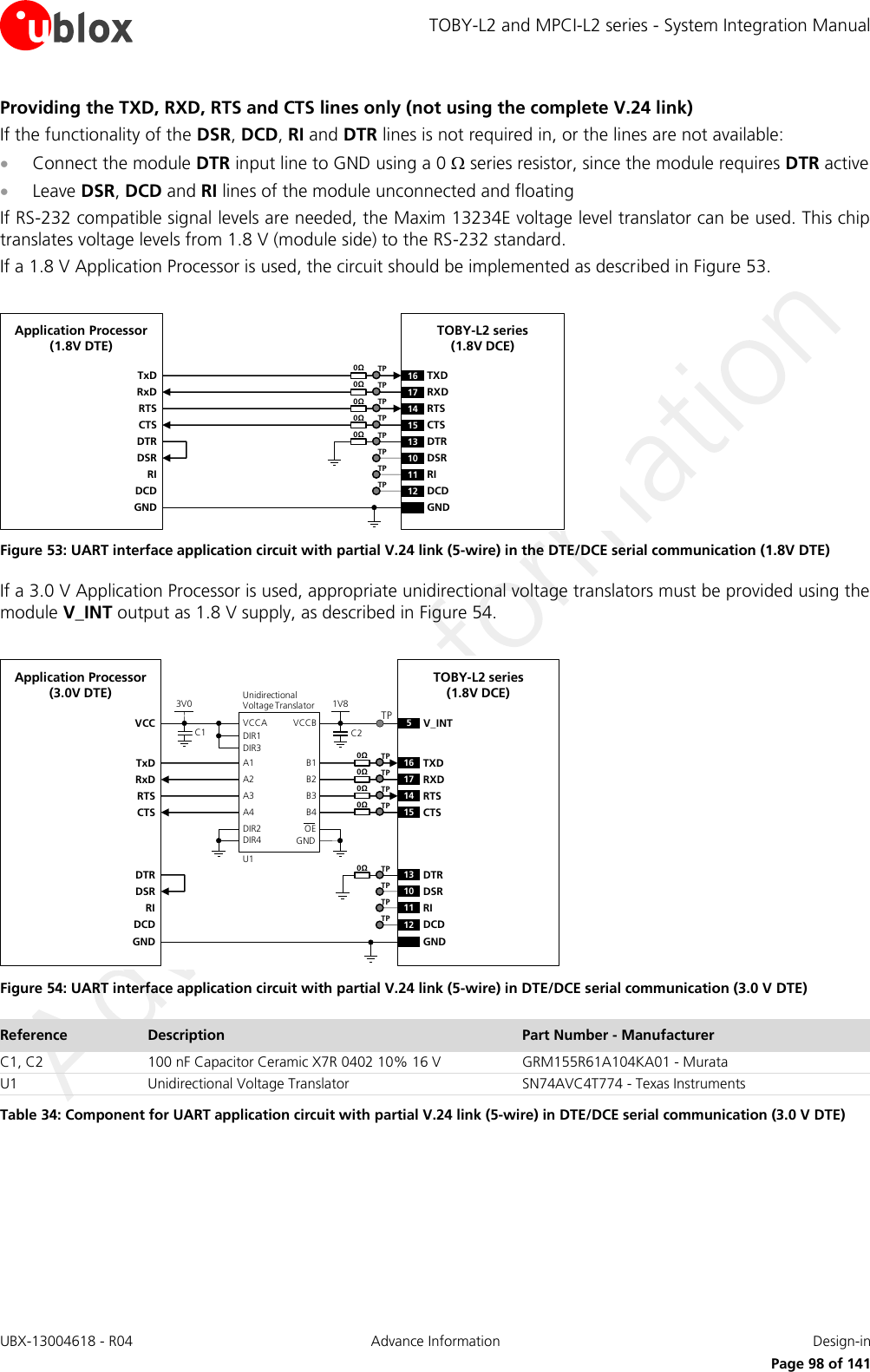

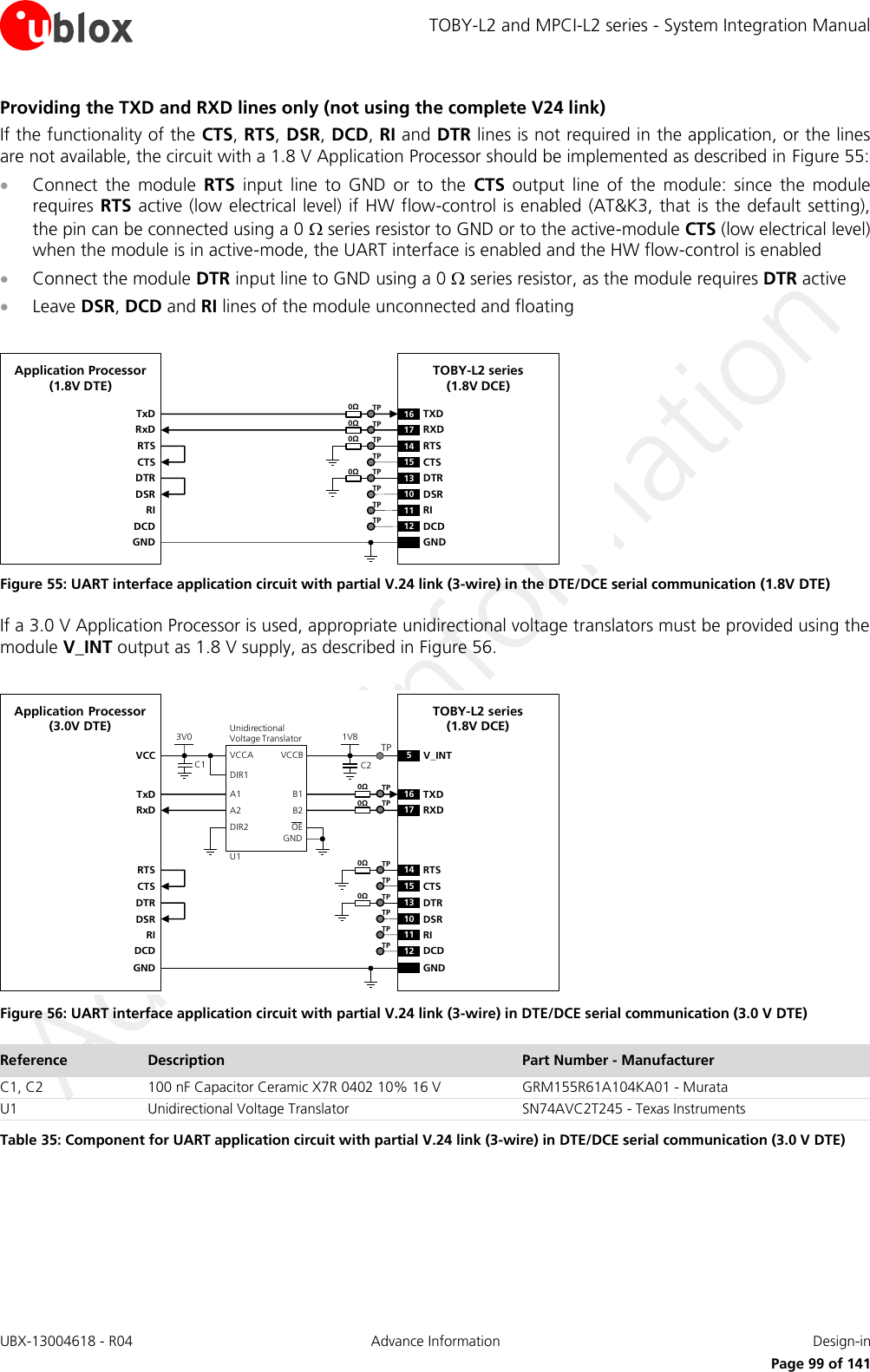

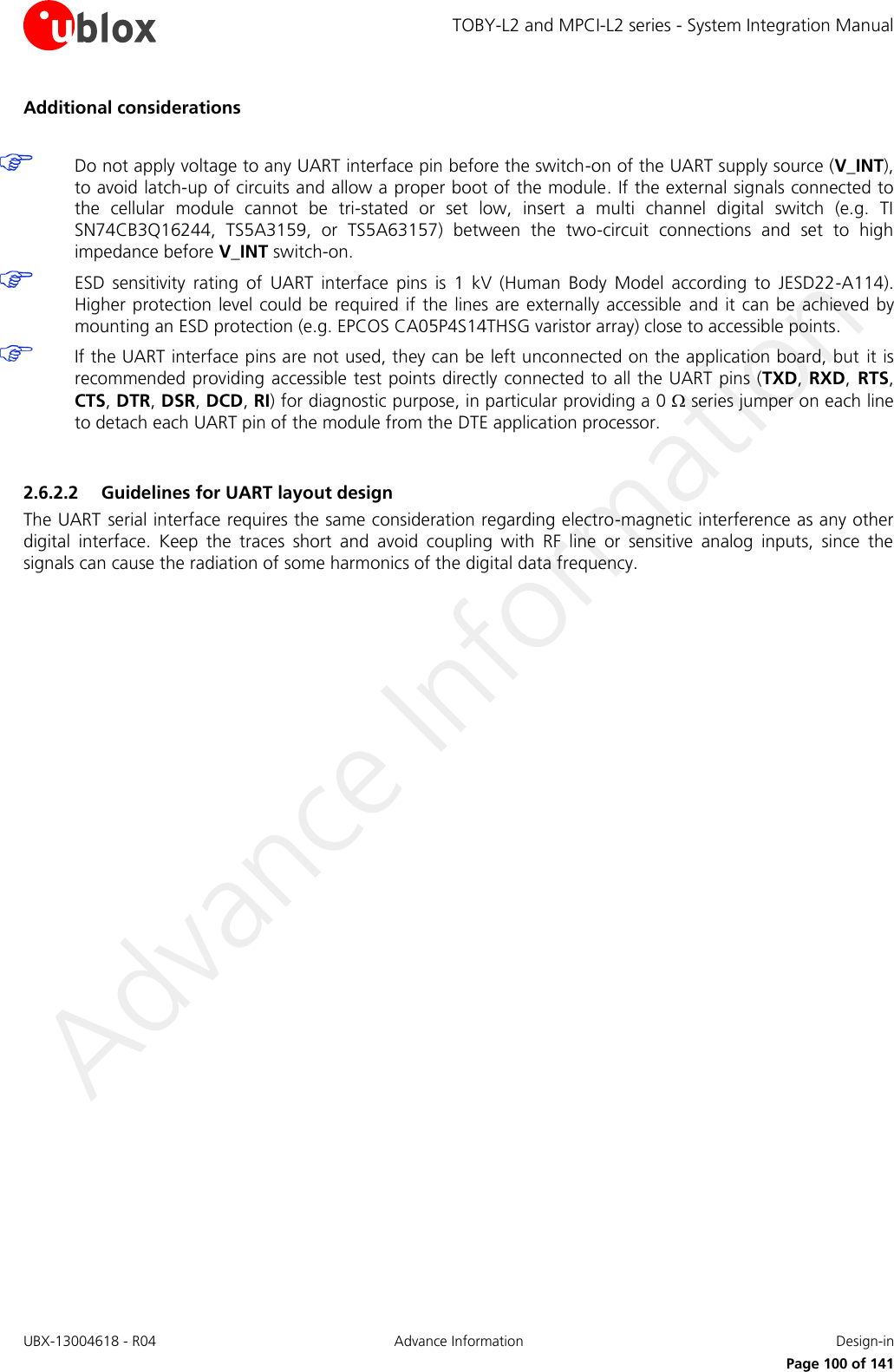

![TOBY-L2 and MPCI-L2 series - System Integration Manual UBX-13004618 - R04 Advance Information System description Page 42 of 141 1.9.2 Asynchronous serial interface (UART) The UART interface is not available on MPCI-L2 series modules. The UART interface is not supported by the TOBY-L2x0-00S product version. 1.9.2.1 UART features The UART interface is a 9-wire 1.8 V unbalanced asynchronous serial interface (UART) that can be connected to an application host processor for AT commands and data communication. The module firmware can be upgraded over the UART interface by means of the Firmware upgrade over AT (FOAT) feature only: for more details see section 1.15 and Firmware update application note [4]. UART interface provides RS-232 functionality conforming to the ITU-T V.24 Recommendation (more details available in ITU Recommendation [7]), with CMOS compatible signal levels: 0 V for low data bit or ON state, and 1.8 V for high data bit or OFF state. For detailed electrical characteristics see TOBY-L2 Data Sheet [1]. TOBY-L2 modules are designed to operate as LTE/3G/2G cellular modems, i.e. the data circuit-terminating equipment (DCE) is according to the ITU-T V.24 Recommendation [7]. A customer application processor connected to the module through the UART interface represents the data terminal equipment (DTE). The signal names of the UART interface of the TOBY-L2 series modules conform to the ITU-T V.24 Recommendation [7]: e.g. TXD line represents the data transmitted by the DTE (application processor data output) and received by the DCE (module data input). The UART interface is controlled and operated with: AT commands according to 3GPP TS 27.007 [8], 3GPP TS 27.005 [9], 3GPP TS 27.010 [10] u-blox AT commands For the complete list of supported AT commands and their syntax see u-blox AT Commands Manual [3]. 1.9.2.2 UART interface configuration The UART interface of TOBY-L2 series modules is configured as described in Table 11 (for information about further settings, see the u-blox AT Commands Manual [3]). Interface AT Settings Comments UART interface AT interface: enabled AT command interface is enabled by default on the UART physical interface MUX protocol: disabled Multiplexing mode is disabled by default and it can be enabled by AT+CMUX command. For more details, see the Mux Implementation Application Note [11]. The following virtual channels are defined: Channel 0: Control channel Channel 1 – 5: AT commands / data connection Channel 6: GNSS tunneling Channel 7: SIM Access Profile Table 11: Default UART interface configuration](https://usermanual.wiki/u-blox/TOBYL210.System-Integration-Manual/User-Guide-2425113-Page-42.png)

![TOBY-L2 and MPCI-L2 series - System Integration Manual UBX-13004618 - R04 Advance Information System description Page 43 of 141 1.9.2.3 UART signals behavior At the module switch-on, before the UART interface initialization (as described in the power-on sequence reported in Figure 14), each pin is first tri-stated and then is set to its relative internal reset state. At the end of the boot sequence, the UART interface is initialized, the module is by default in active-mode, and the UART interface is enabled. 1.9.2.4 UART and power-saving The power saving configuration is controlled by the AT+UPSV command (for the complete description, see the u-blox AT Commands Manual [3]). When power saving is enabled, the module automatically enters low power idle-mode whenever possible, and otherwise the active-mode is maintained by the module (see section 1.4 for definition and description of module operating modes referred to in this section). The AT+UPSV command configures both the module power saving and also the UART behavior in relation to the power saving. The conditions for the module entering low power idle-mode also depend on the UART power saving configuration, as the module does not enter the low power idle-mode according to any required activity related to the network (within or outside an active call) or any other required concurrent activity related to the functions and interfaces of the module, including the UART interface. 1.9.2.5 UART multiplexer protocol TOBY-L2 series modules have a software layer with multiplexer functionality as per 3GPP TS 27.010 Multiplexer Protocol [10], available on the UART physical link. This is a data link protocol (layer 2 of OSI model) which uses HDLC-like framing and operates between the module (DCE) and the application processor (DTE) and allows a number of simultaneous sessions over the used physical link (the UART interface): the user can concurrently use AT command interface on one MUX channel and data communication on another multiplexer channel. The following virtual channels are defined: Channel 0: control channel Channel 1 – 5: AT commands / data connection Channel 6: GNSS tunneling Channel 7: SIM Access Profile For more details, see Mux implementation Application Note [11].](https://usermanual.wiki/u-blox/TOBYL210.System-Integration-Manual/User-Guide-2425113-Page-43.png)

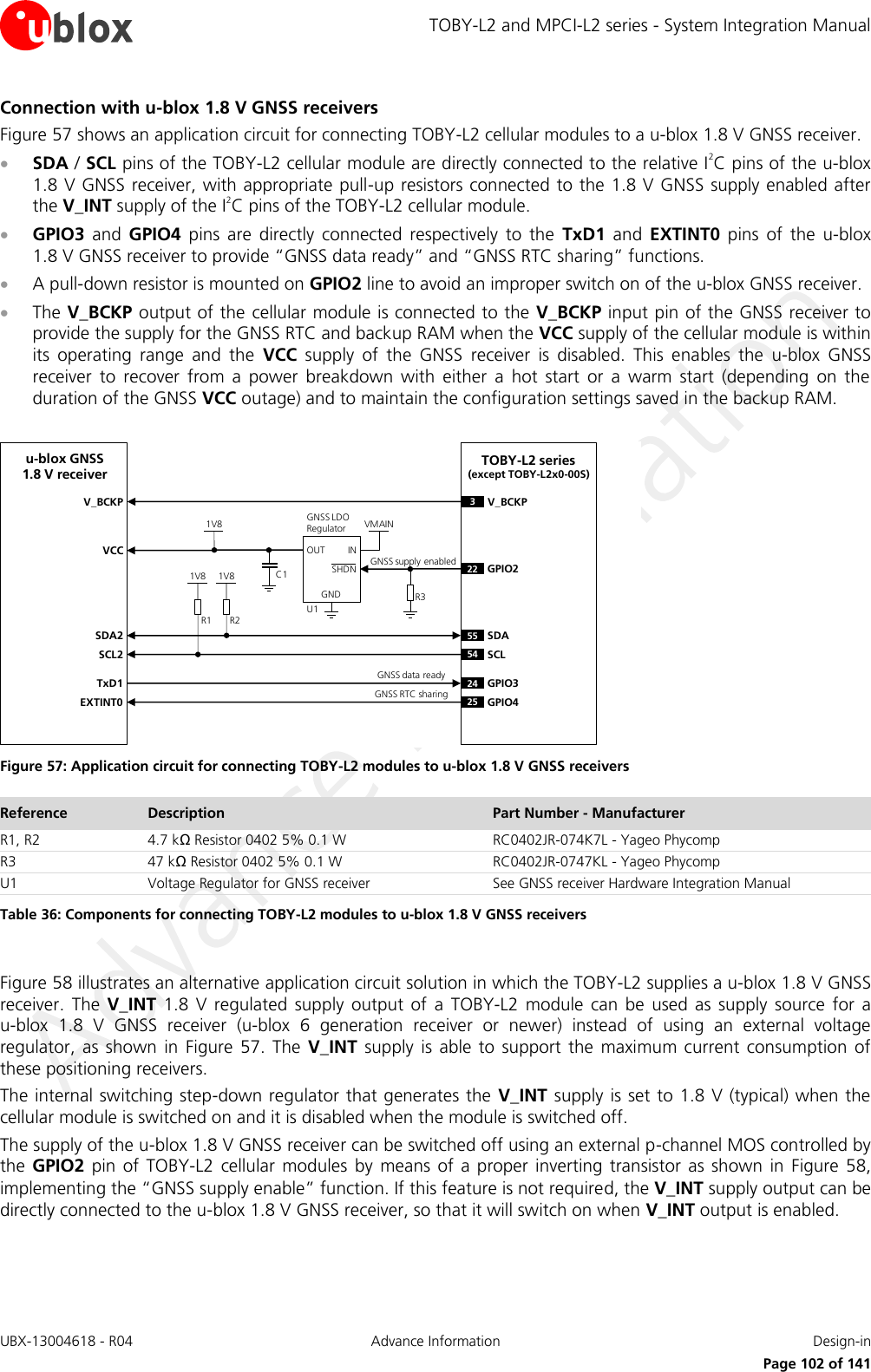

![TOBY-L2 and MPCI-L2 series - System Integration Manual UBX-13004618 - R04 Advance Information System description Page 44 of 141 1.9.3 DDC (I2C) interface The I2C bus compatible Display Data Channel interface is not available on the MPCI-L2 series modules, as AssistNow embedded GNSS positioning aiding, CellLocate® positioning through cellular information and custom functions over GPIOs for the integration with u-blox positioning chips / modules. The I2C bus compatible Display Data Channel interface is not supported by the TOBY-L2x0-00S product version, as AssistNow embedded GNSS positioning aiding, CellLocate® positioning through cellular information and custom functions over GPIOs for the integration with u-blox positioning chips / modules. The SDA and SCL pins of TOBY-L2 series modules represent an I2C bus compatible Display Data Channel (DDC) interface for the communication with u-blox GNSS receivers and with other external I2C devices as audio codecs: an I2C master can communicate with more I2C slaves in accordance to the I2C bus specifications [12]. The DDC (I2C) interface is the only one interface dedicated for communication between u-blox cellular module and u-blox positioning receivers. The AT commands interface is not available on the DDC (I2C) interface. The DDC (I2C) interface pads of the module, serial data (SDA) and serial clock (SCL), are open drain output and external pull up resistors must be used conforming to the I2C bus specifications [12]. u-blox has implemented special features in the cellular modules to ease the design effort for the integration of a u-blox cellular module with a u-blox GNSS receiver (details in GNSS Implementation Application Note [13]). Combining a u-blox cellular module with a u-blox GNSS receiver allows designers to full access the GNSS receiver directly via the cellular module: it relays control messages to the GNSS receiver via a dedicated DDC (I2C) interface. A 2nd interface connected to the GNSS receiver is not necessary: AT commands via the AT interfaces of the cellular module (UART, USB) allows a full control of the GNSS receiver from any host processor. u-blox cellular modules feature embedded GNSS aiding that is a set of specific features developed by u-blox to enhance GNSS performance, decreasing Time To First Fix (TTFF), thus allowing to calculate the position in a shorter time with higher accuracy. Additional custom functions over GPIO pins are designed to improve the integration with u-blox GNSS receivers: GNSS receiver power-on/off: “GNSS supply enable” function over the GPIO2 pin improves the positioning receiver power consumption. When the GNSS functionality is not required, the positioning receiver can be completely switched off by the cellular module controlled by the application processor over AT commands The wake up from idle-mode when the GNSS receiver is ready to send data: “GNSS data ready” function over the GPIO3 pin improves the cellular module power consumption. When power saving is enabled in the cellular module by the AT+UPSV command and the GNSS receiver does not send data by the DDC (I2C) interface, the module automatically enters idle-mode whenever possible. With the “GNSS data ready” function the GNSS receiver can indicate to the cellular module that it is ready to send data: the positioning receiver can wake up the cellular module to avoid data loss even if power saving is enabled. The RTC synchronization signal to the GNSS receiver: “GNSS RTC sharing” function over the GPIO4 pin improves GNSS receiver performance, decreasing the Time To First Fix (TTFF), and thus allowing to calculate the position in a shorter time with higher accuracy. When GNSS local aiding is enabled, the cellular module automatically uploads data such as position, time, ephemeris, almanac, health and ionospheric parameter from the positioning receiver into its local memory, and restores this to the GNSS receiver at the next power up of the positioning receiver](https://usermanual.wiki/u-blox/TOBYL210.System-Integration-Manual/User-Guide-2425113-Page-44.png)

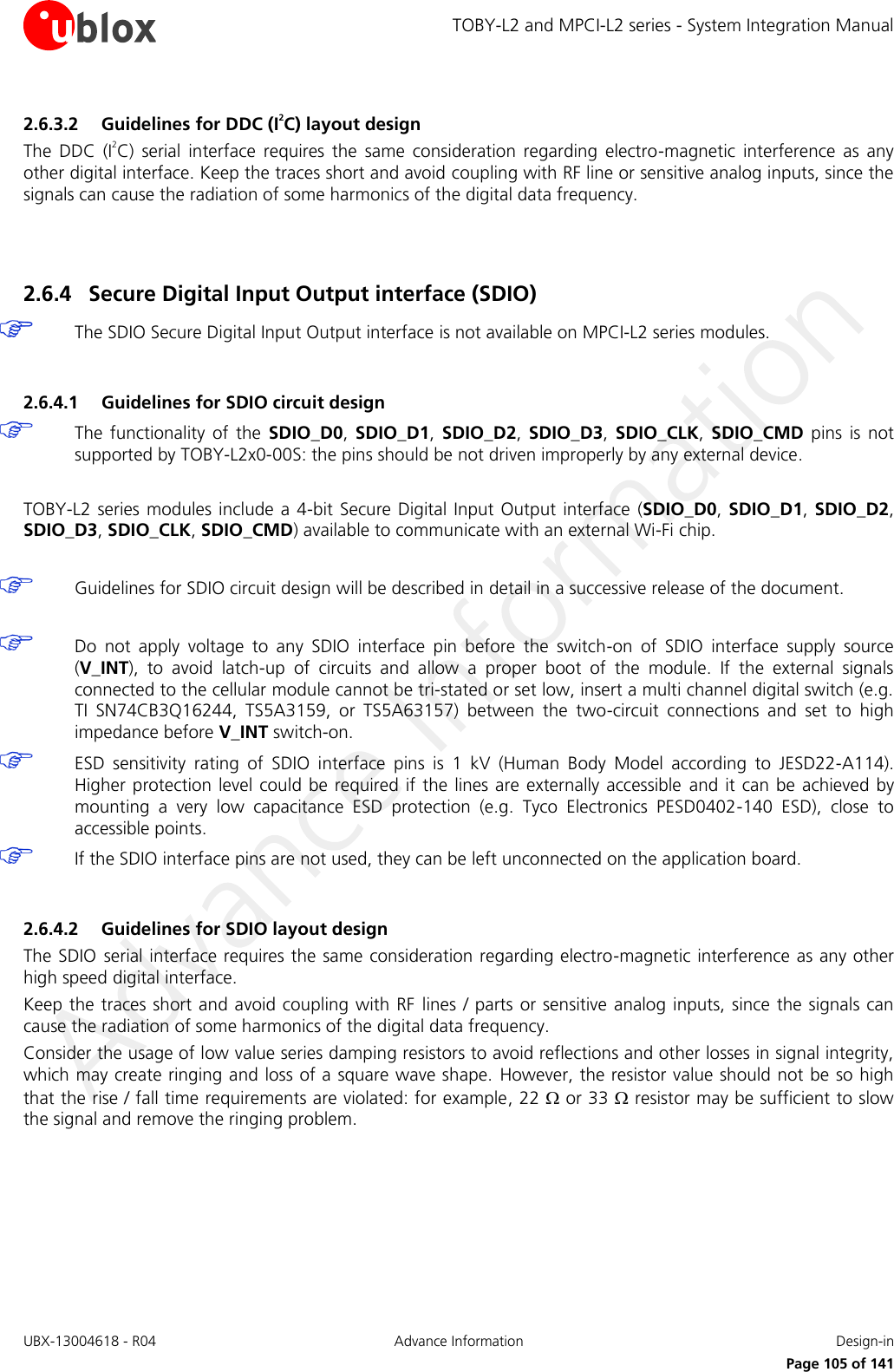

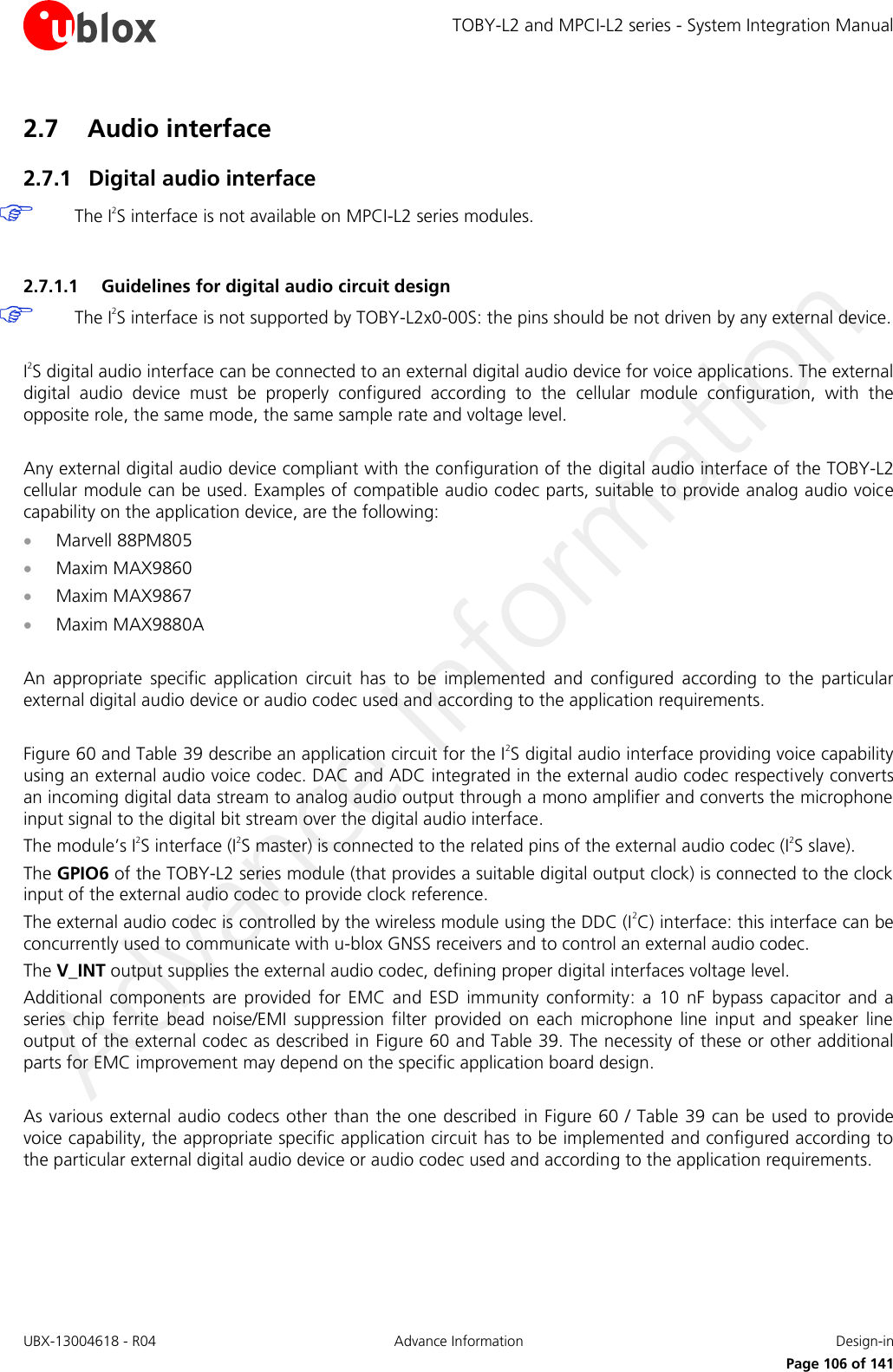

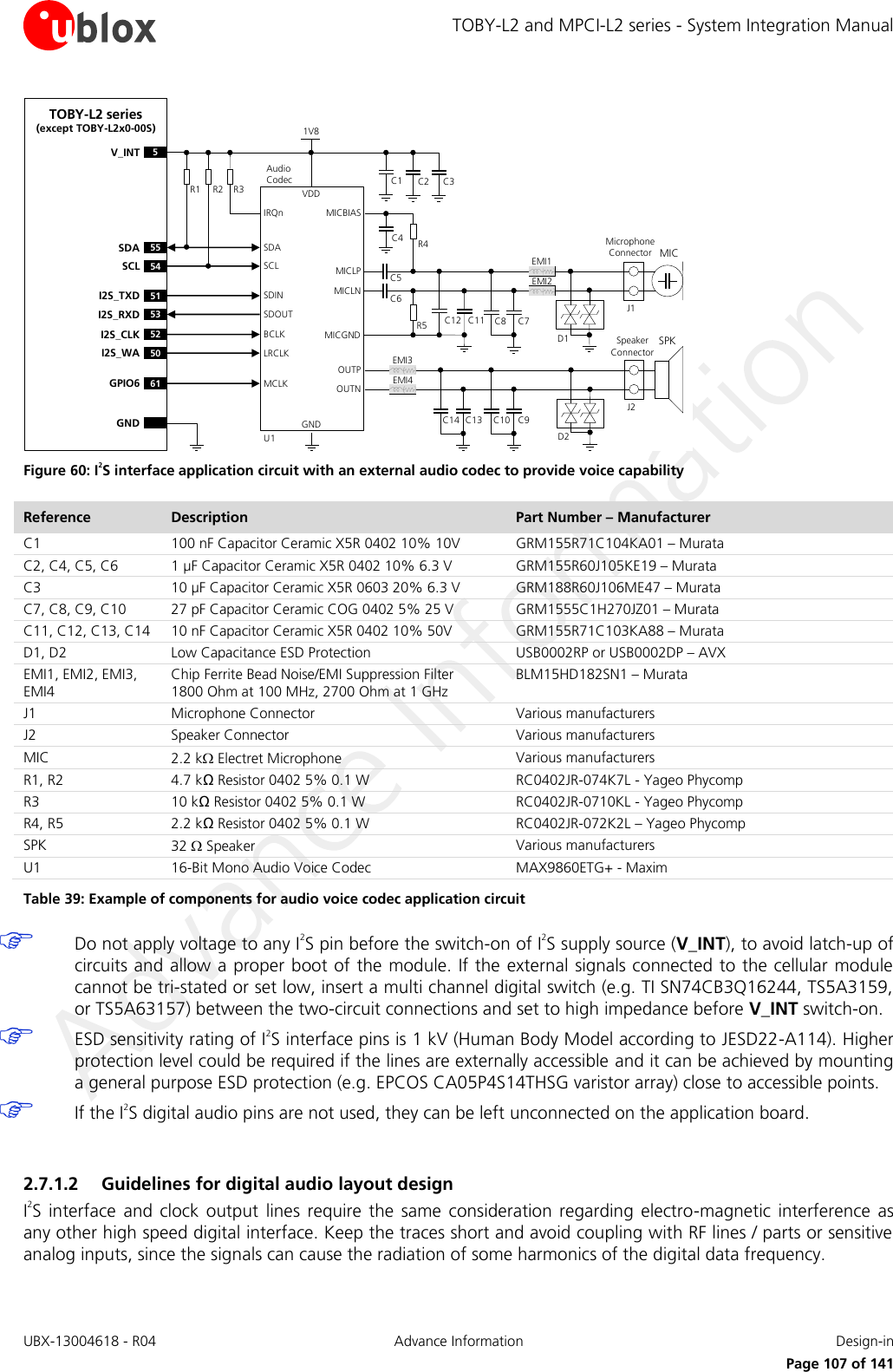

![TOBY-L2 and MPCI-L2 series - System Integration Manual UBX-13004618 - R04 Advance Information System description Page 45 of 141 1.9.4 Secure Digital Input Output interface (SDIO) Secure Digital Input Output interface is not available on MPCI-L2 series modules. Secure Digital Input Output interface is not supported by the TOBY-L2x0-00S product version. TOBY-L2 series modules include a 4-bit Secure Digital Input Output interface (SDIO_D0, SDIO_D1, SDIO_D2, SDIO_D3, SDIO_CLK, SDIO_CMD) designed to communicate with an external Wi-Fi chip. 1.10 Audio 1.10.1 Digital audio over I2S interface Digital audio over I2S interface is not available on MPCI-L2 series modules. Digital audio over I2S interface is not supported by the TOBY-L2x0-00S product version. TOBY-L2 series modules include a 4-wire I2S digital audio interface (I2S_TXD, I2S_RXD, I2S_CLK, I2S_WA) that can be configured by AT command to transfer digital audio data with an external device as an audio codec (for more details see u-blox AT Commands Manual [3]).](https://usermanual.wiki/u-blox/TOBYL210.System-Integration-Manual/User-Guide-2425113-Page-45.png)

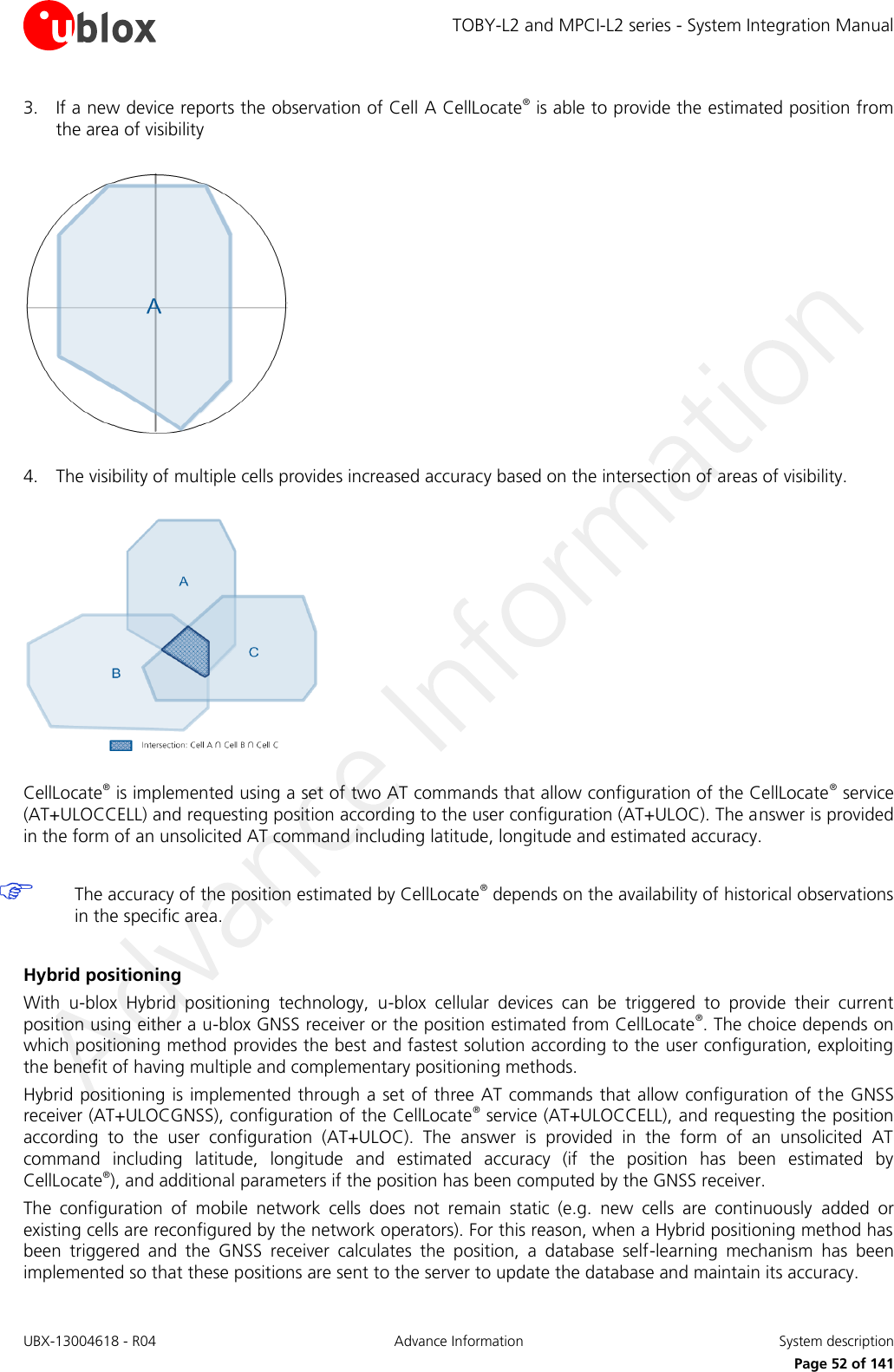

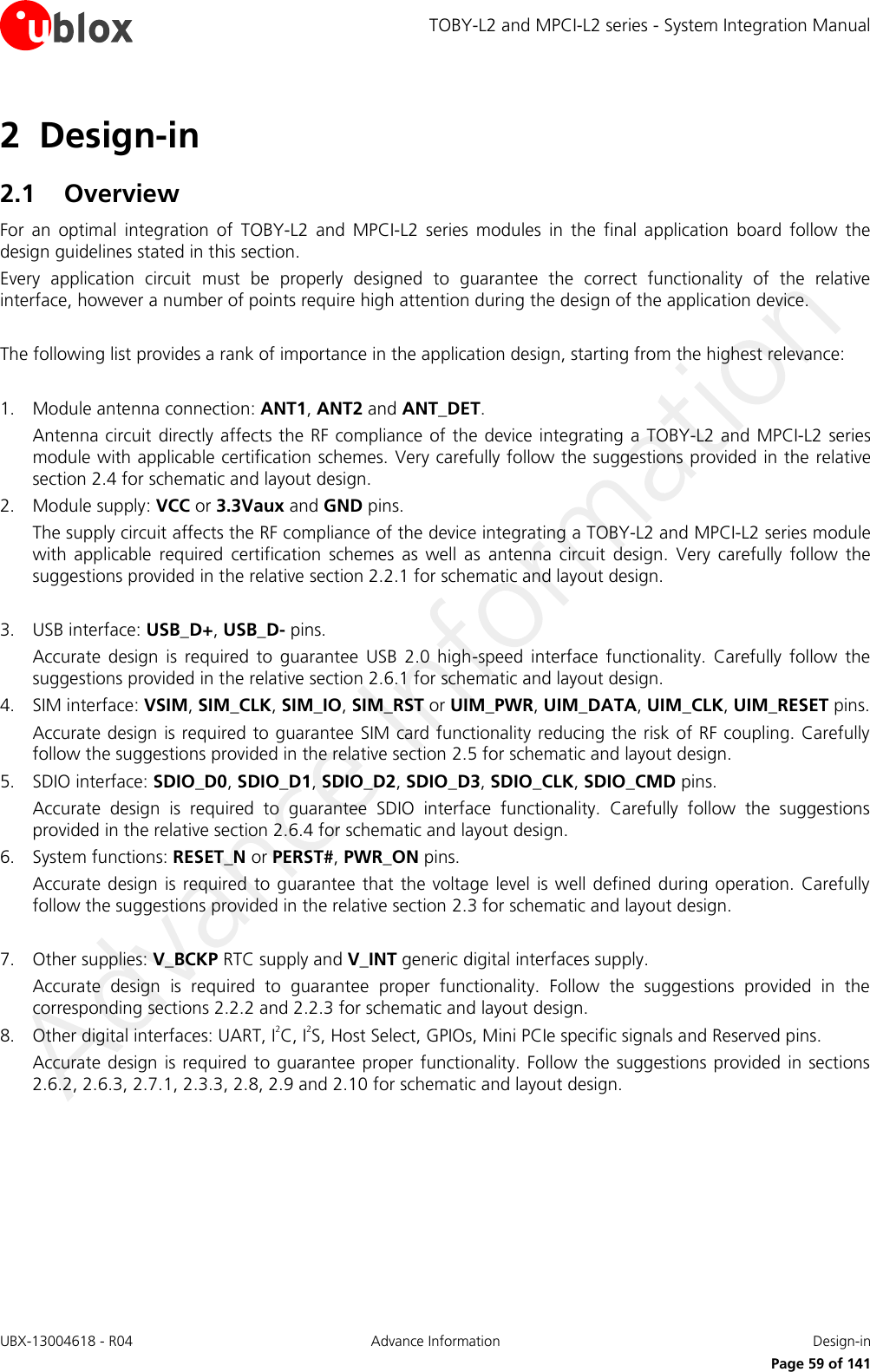

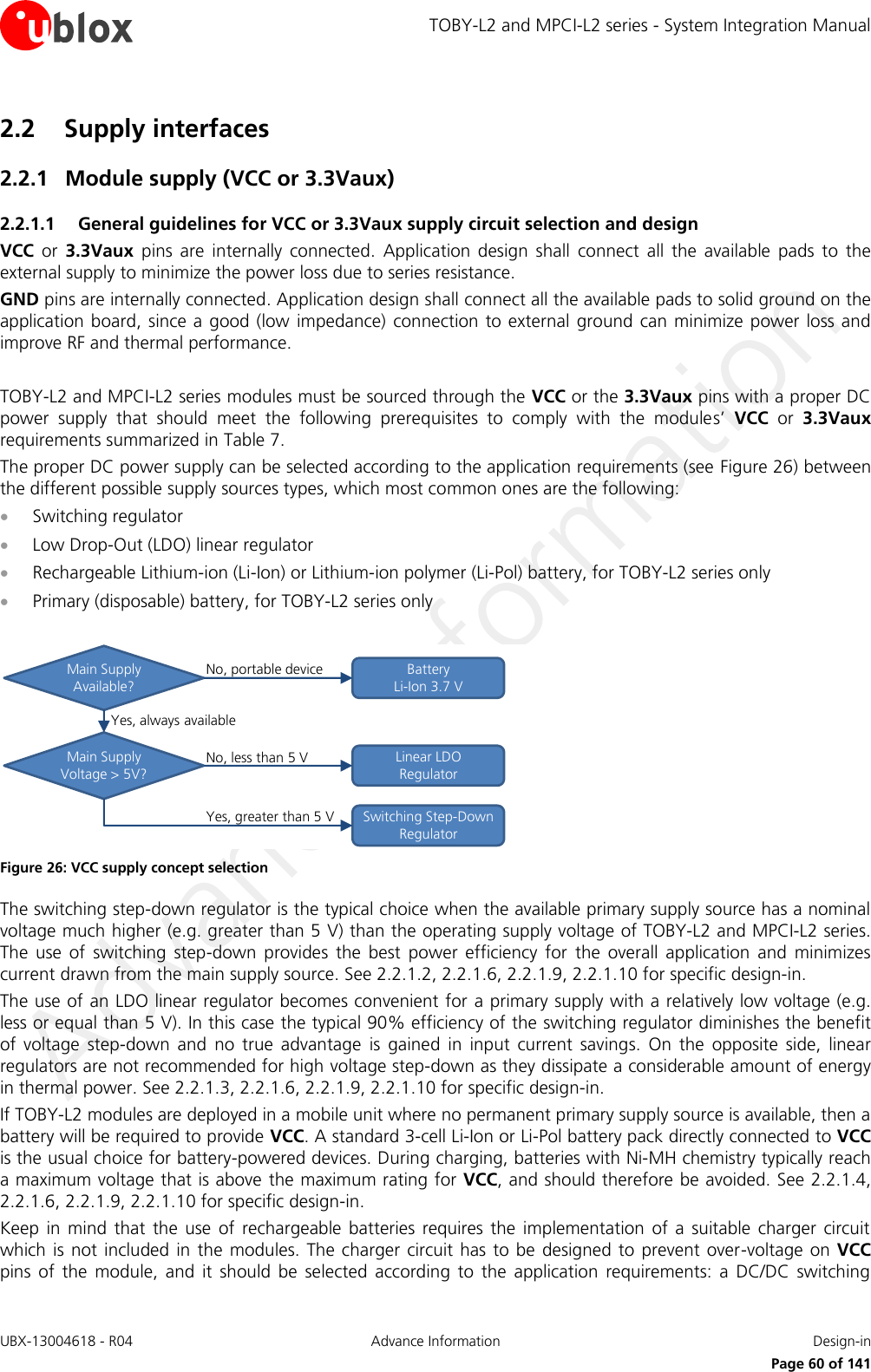

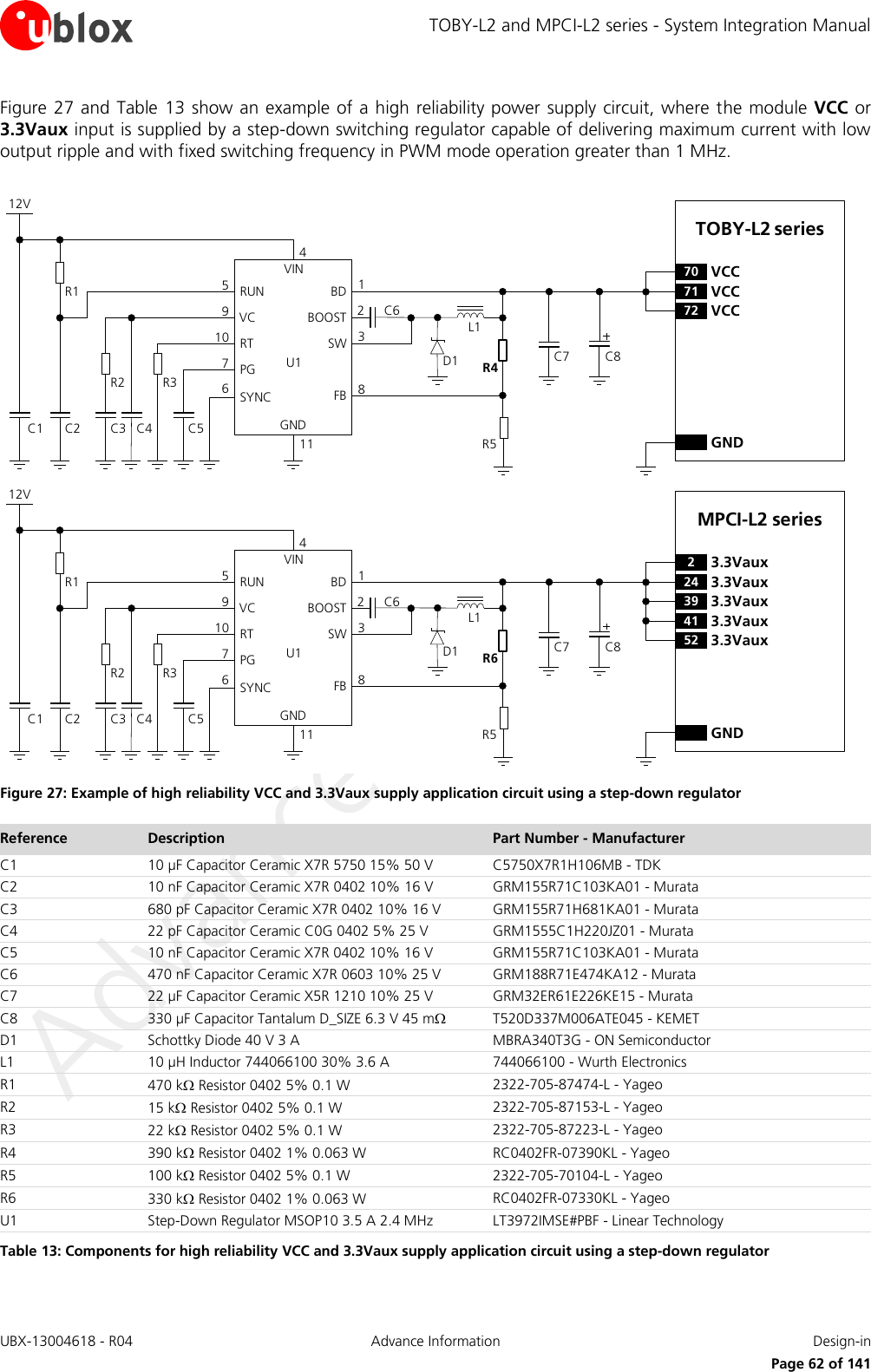

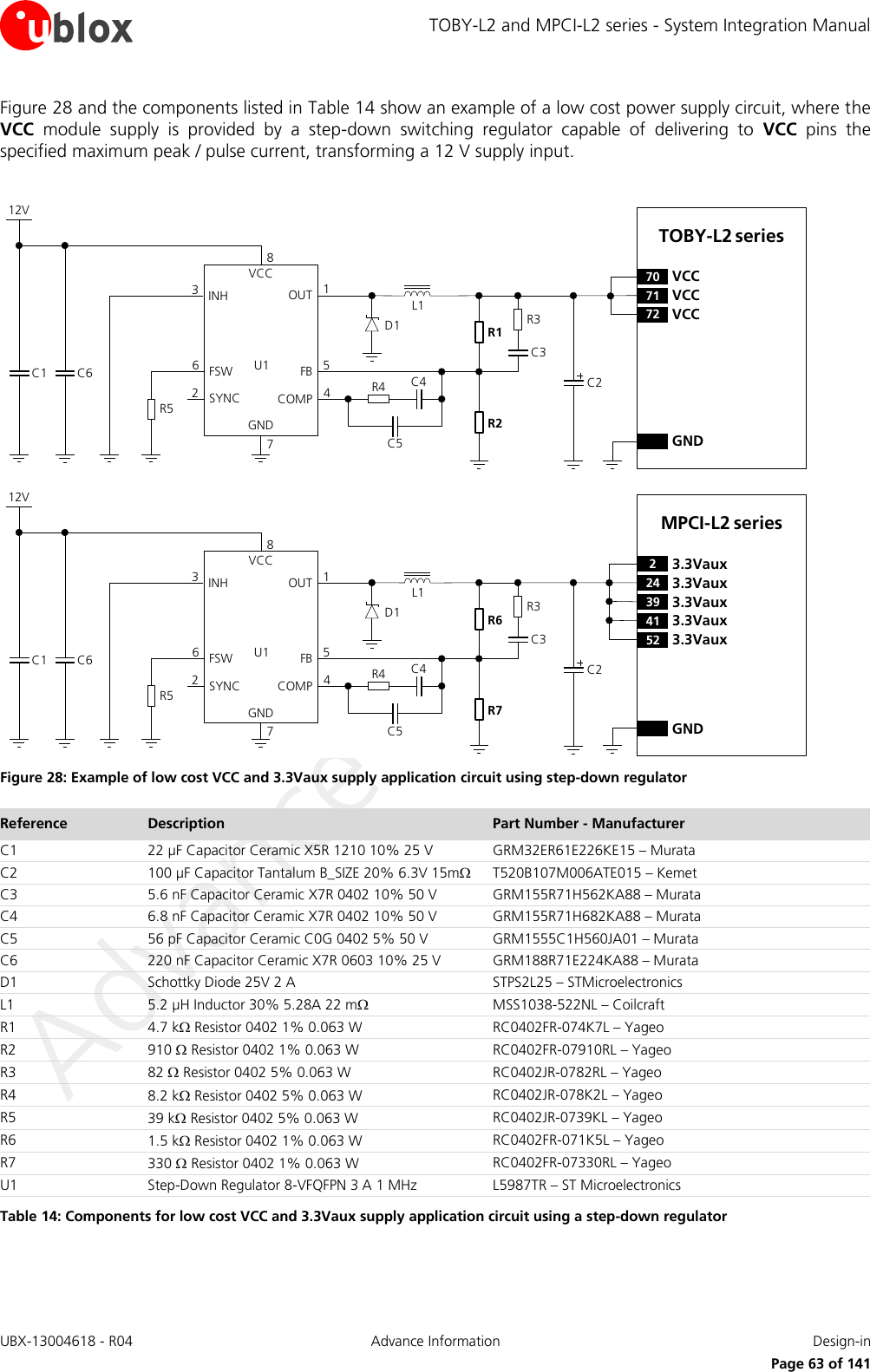

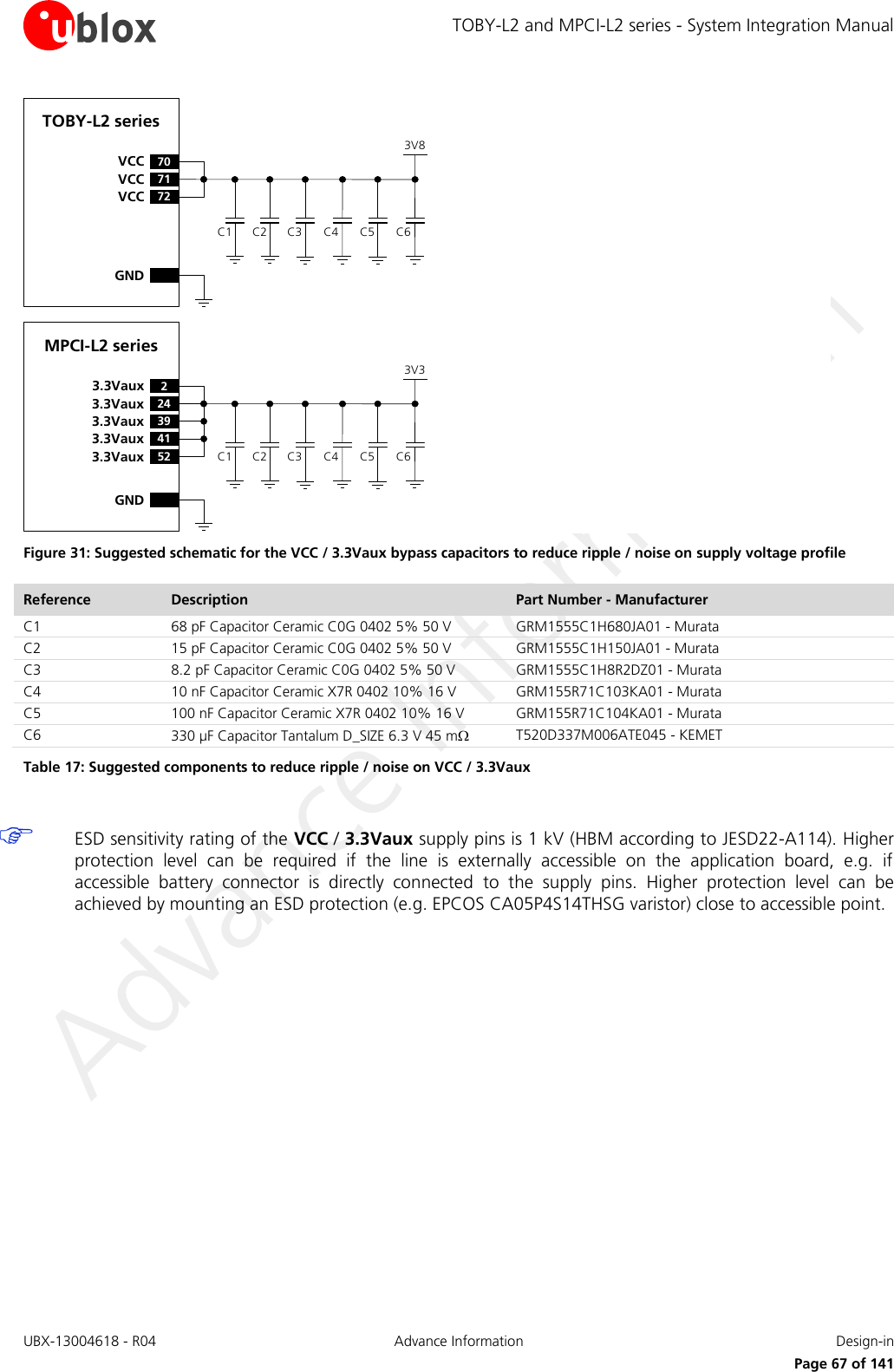

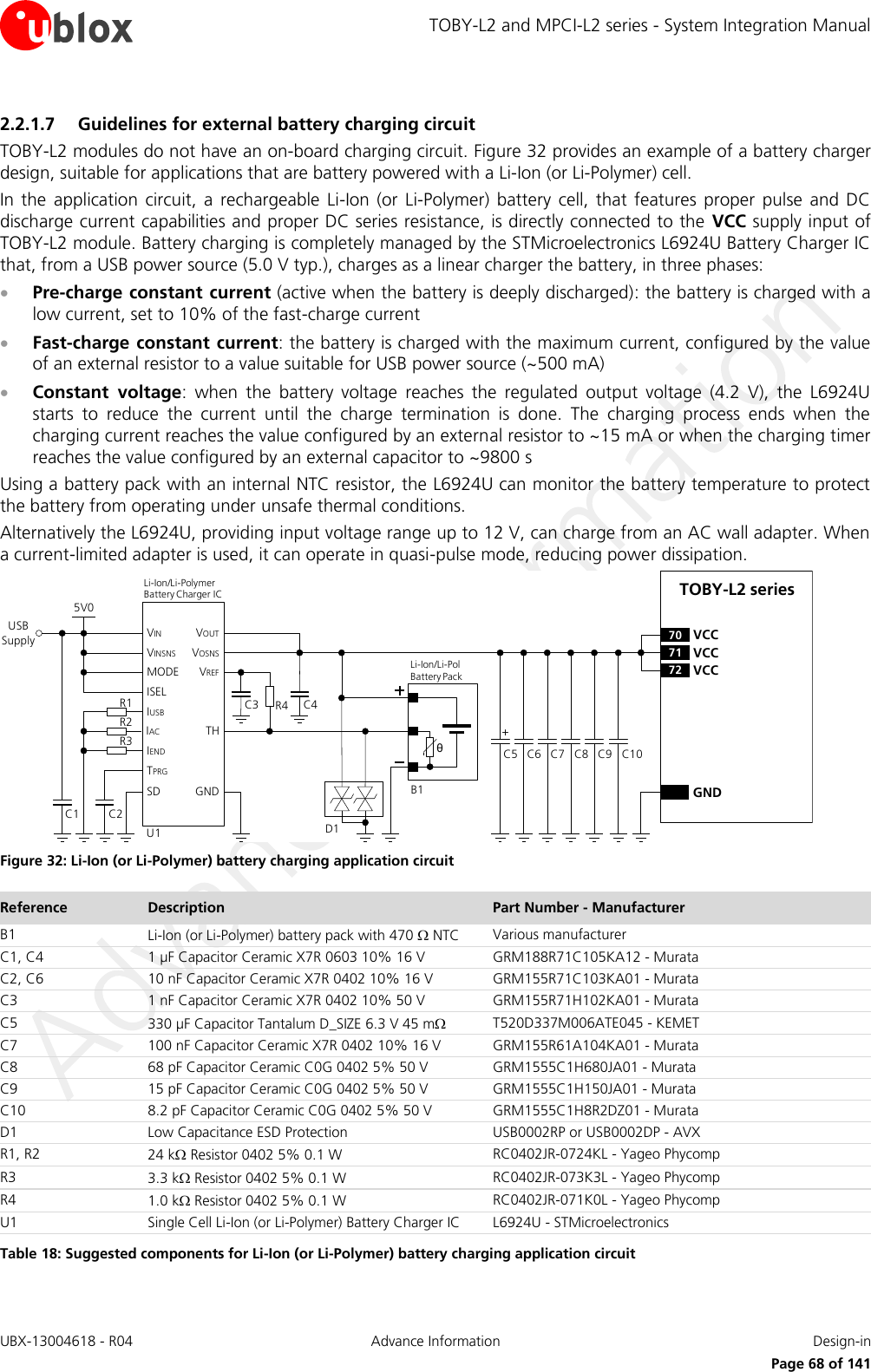

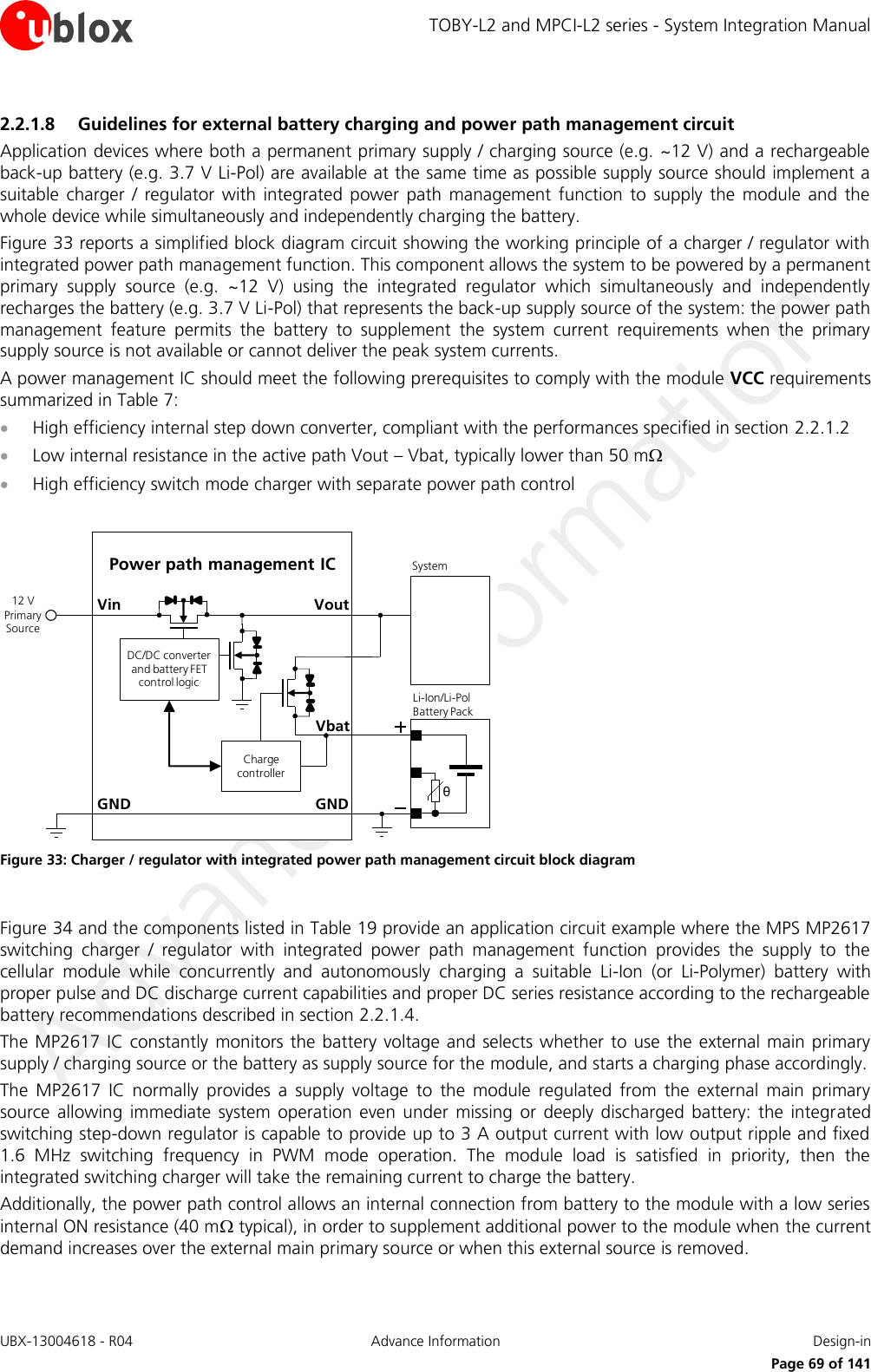

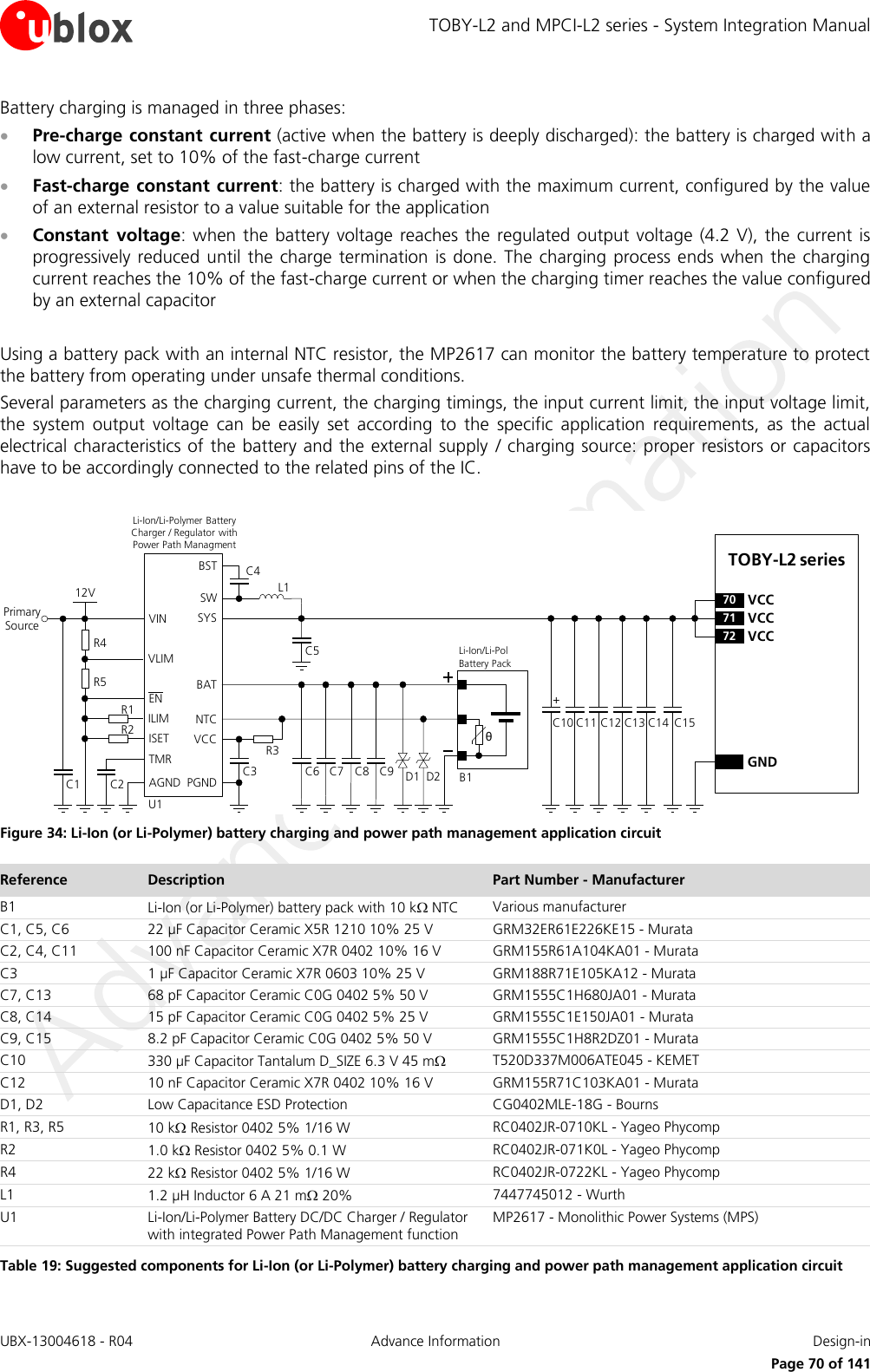

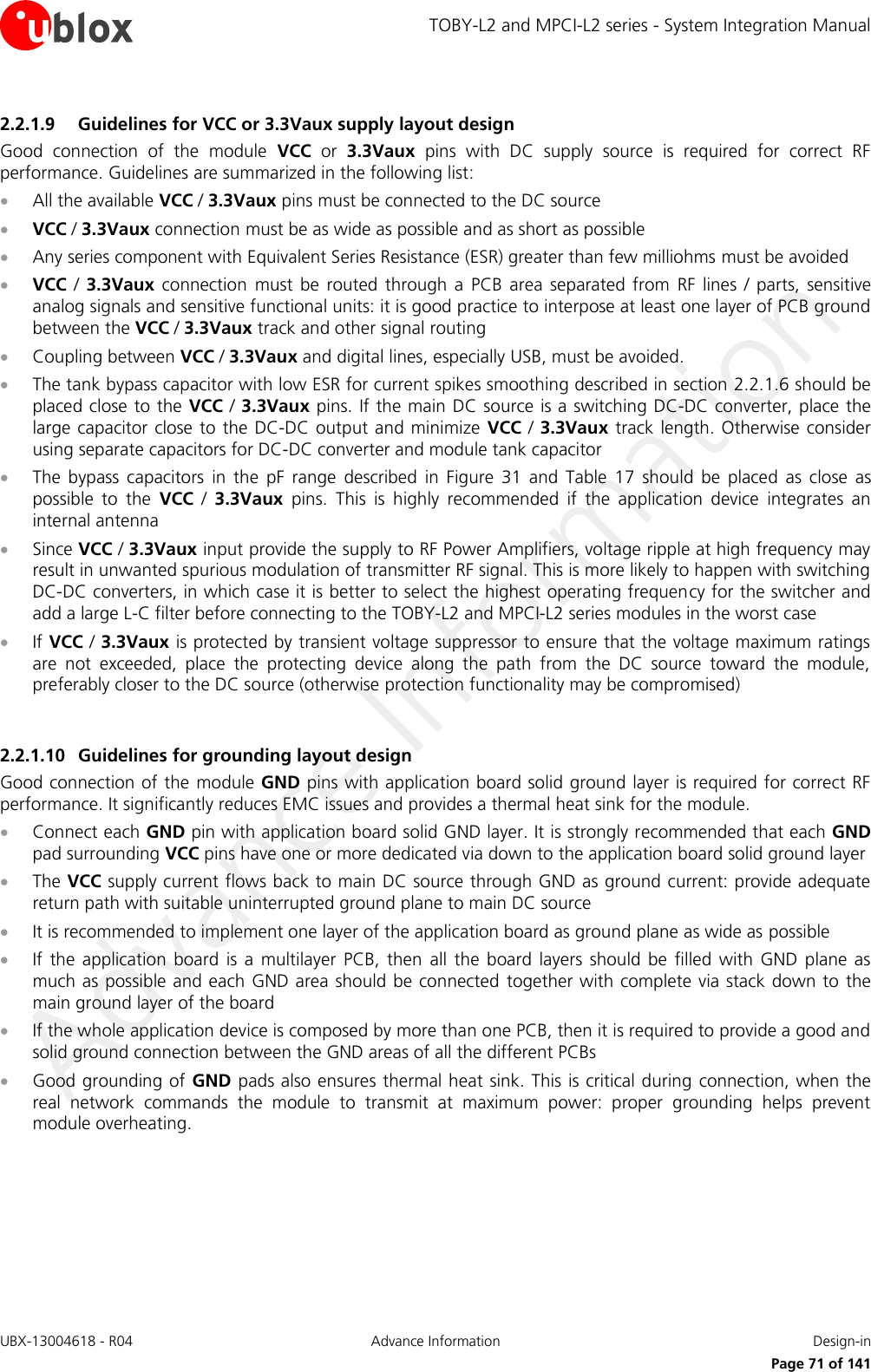

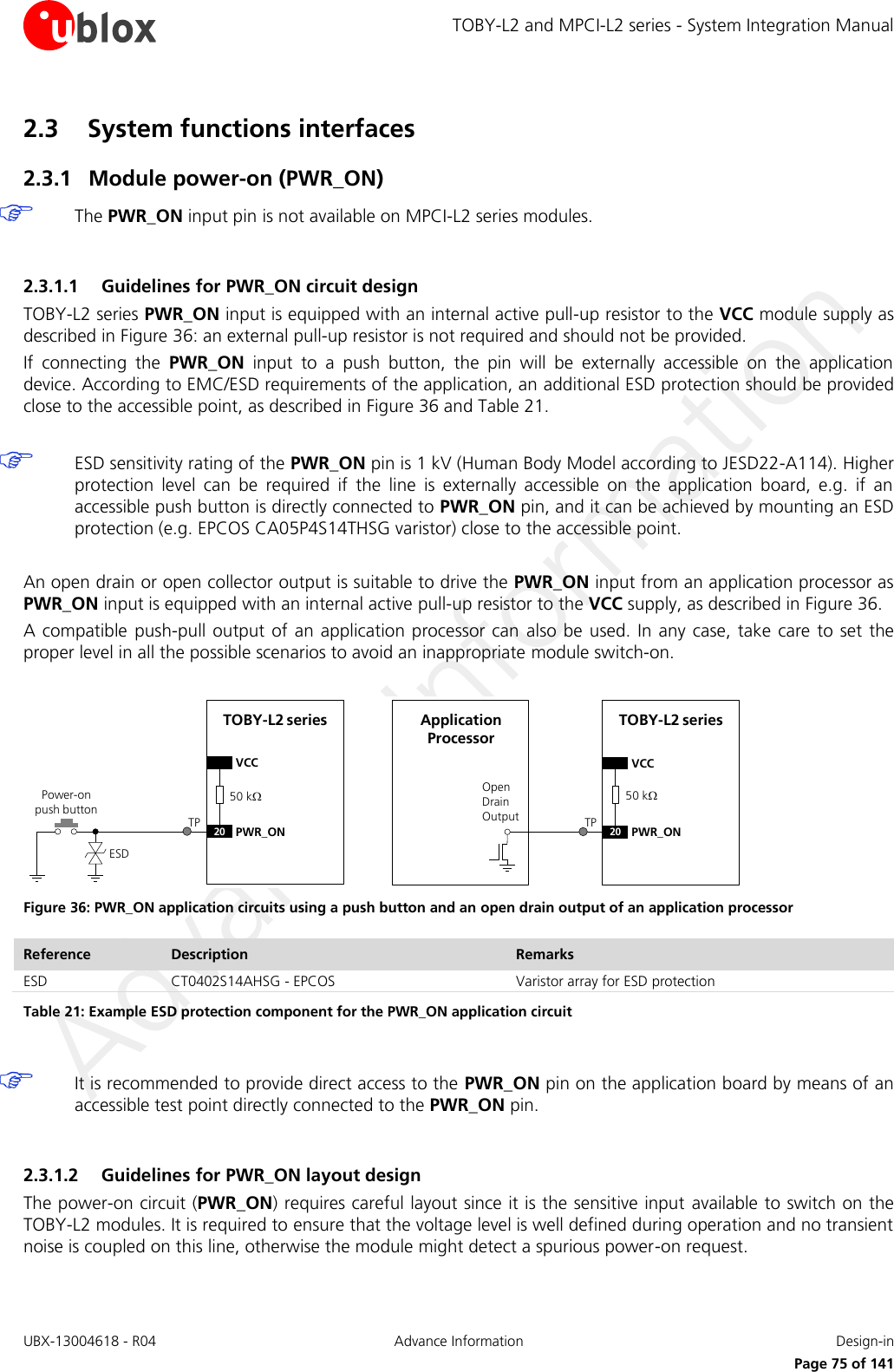

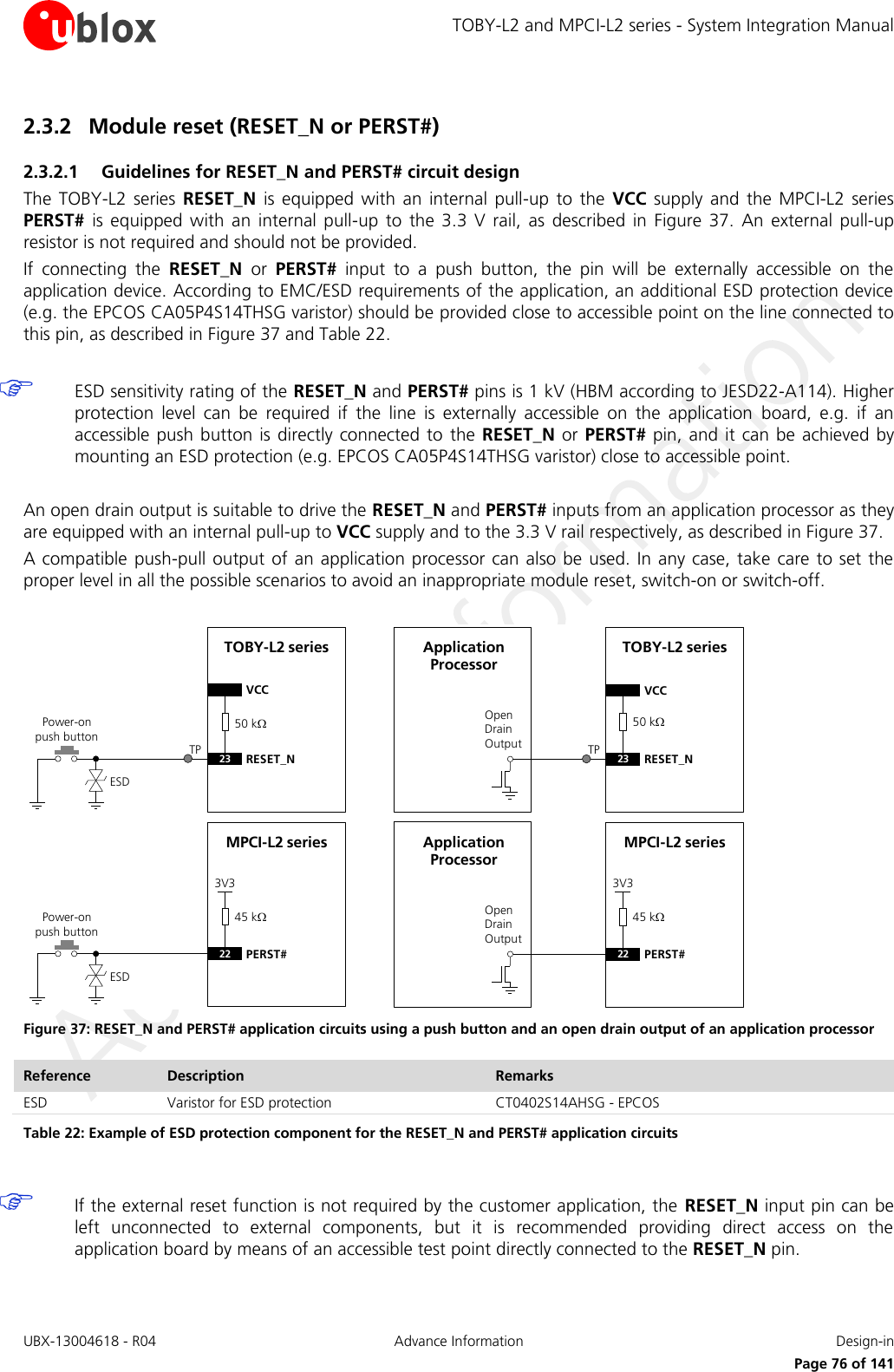

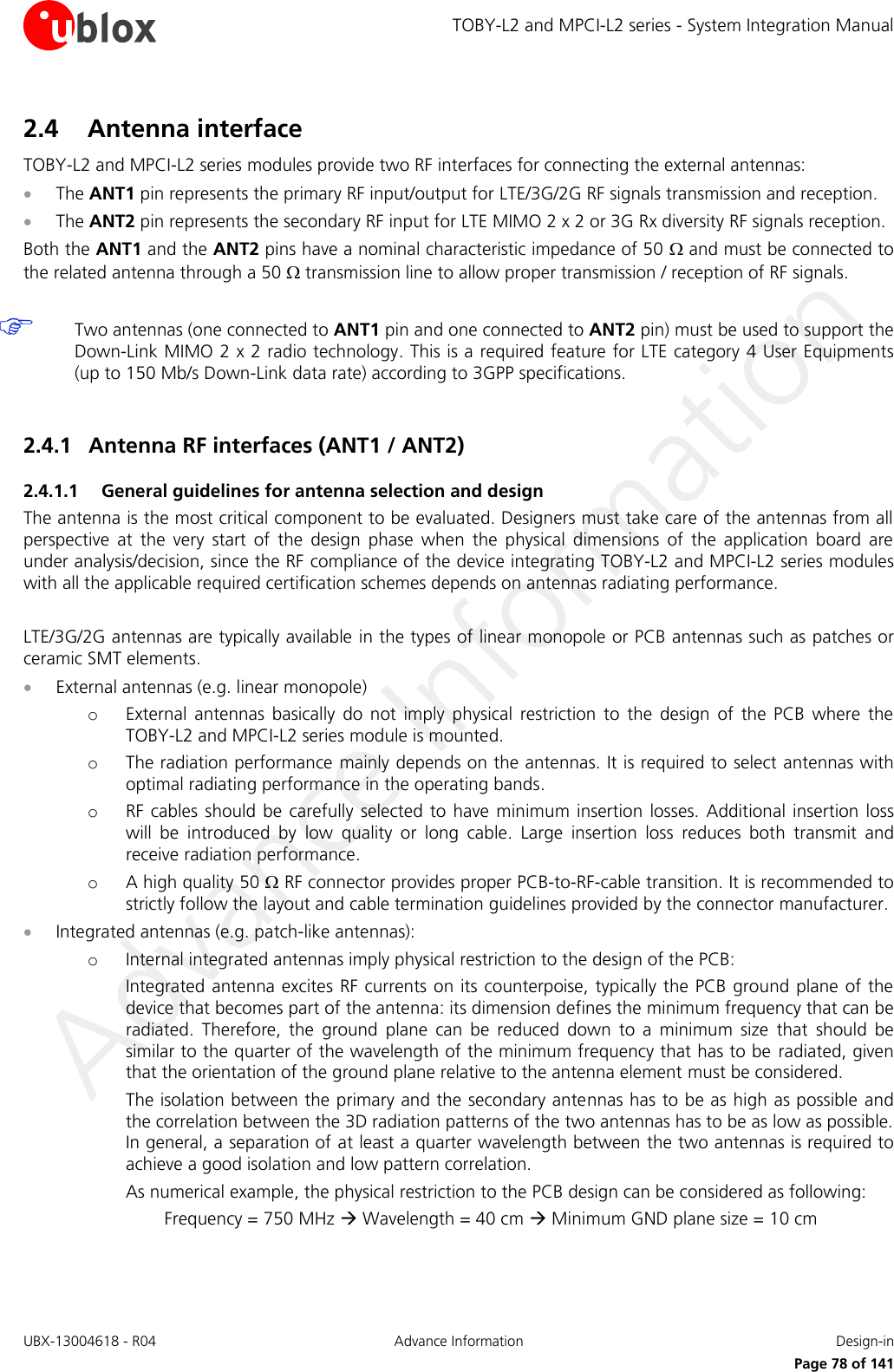

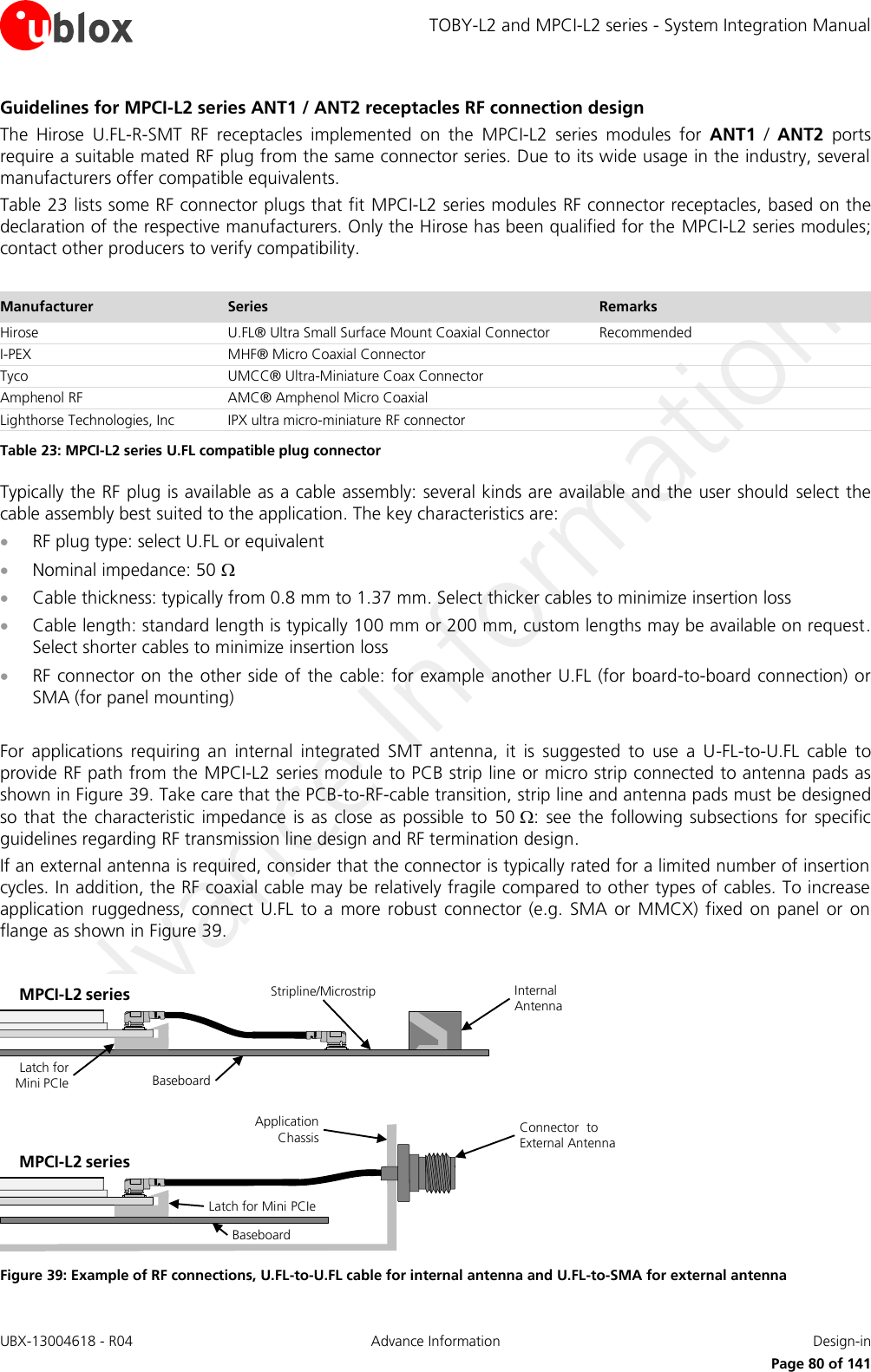

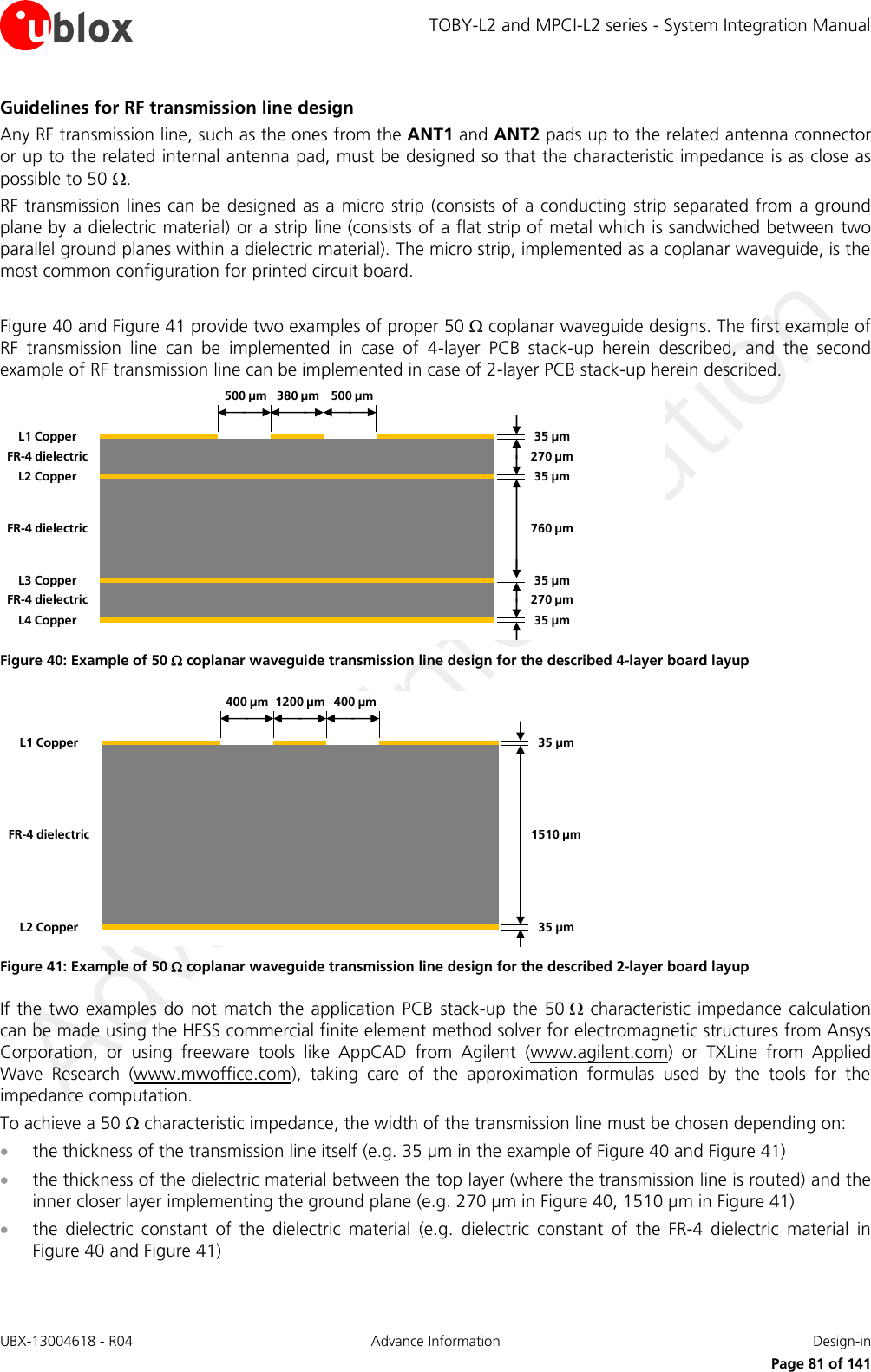

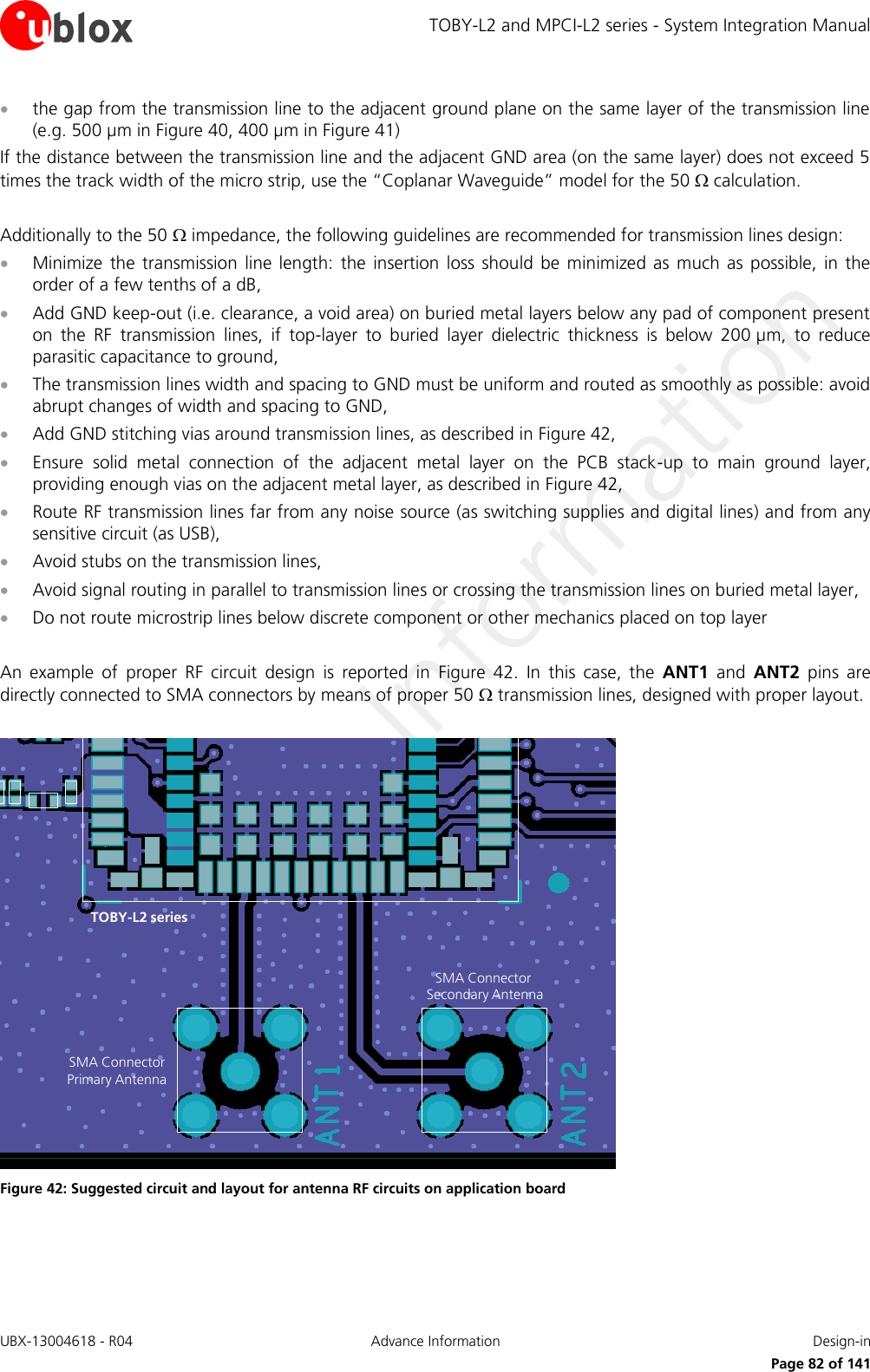

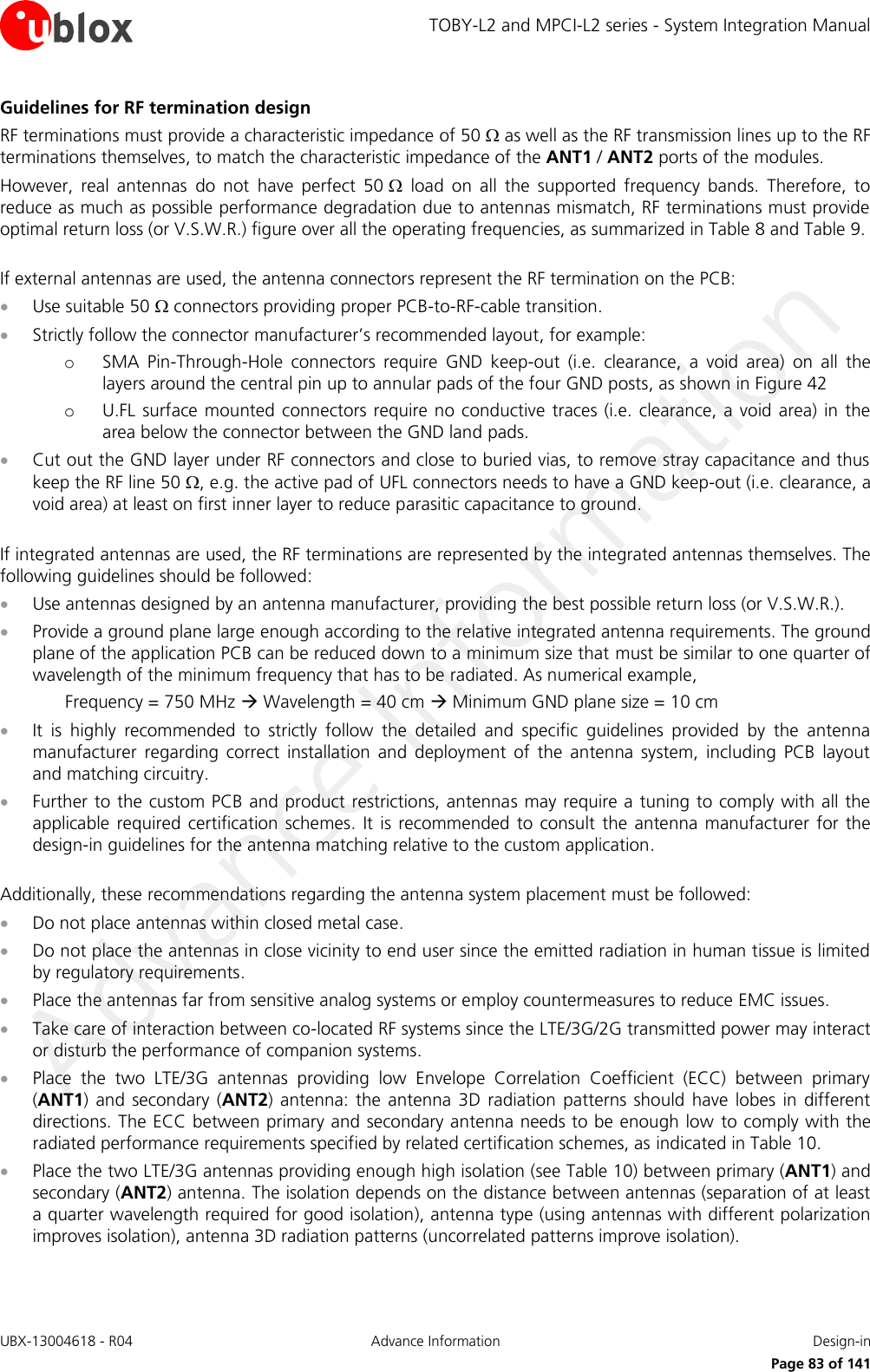

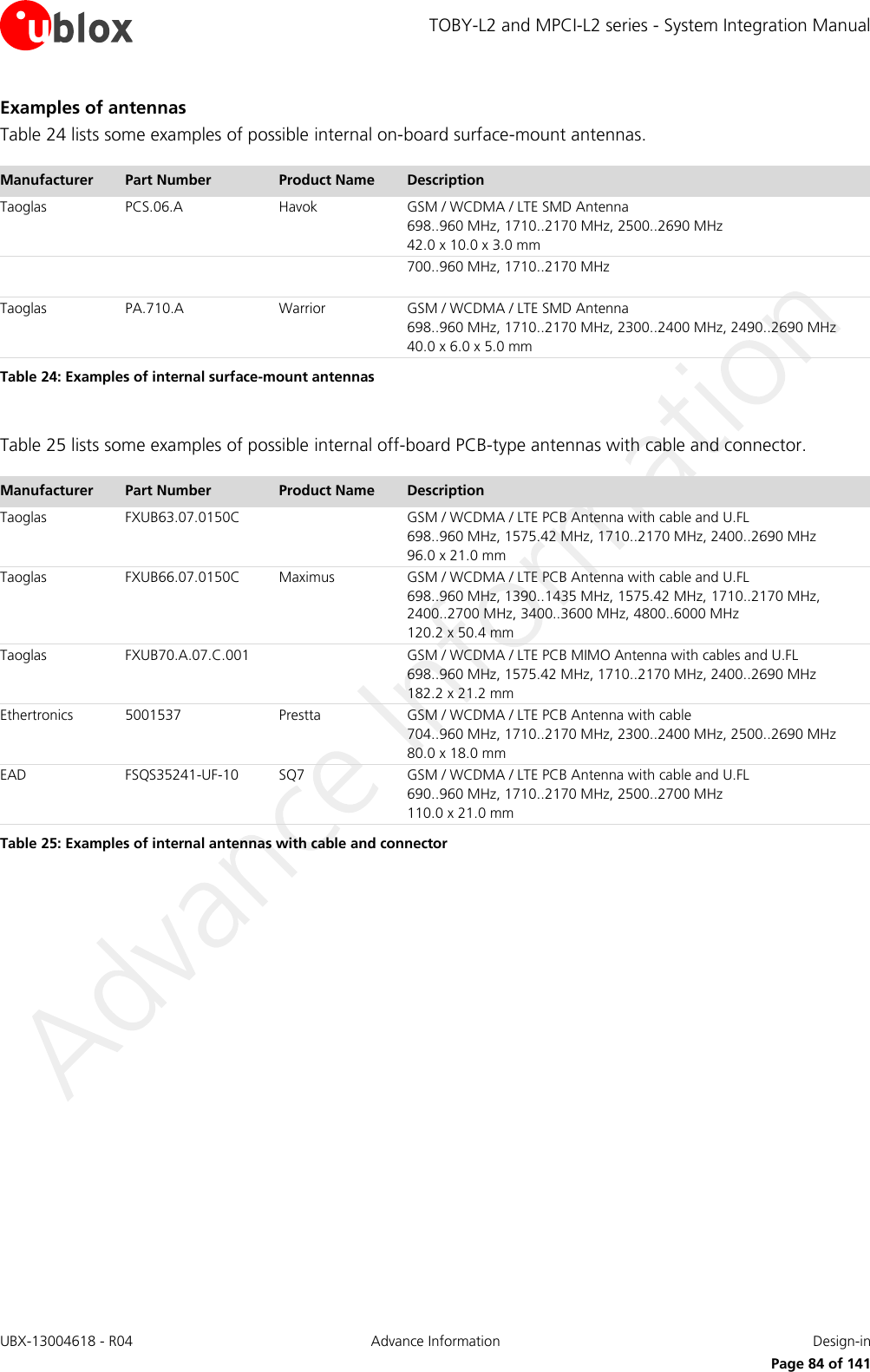

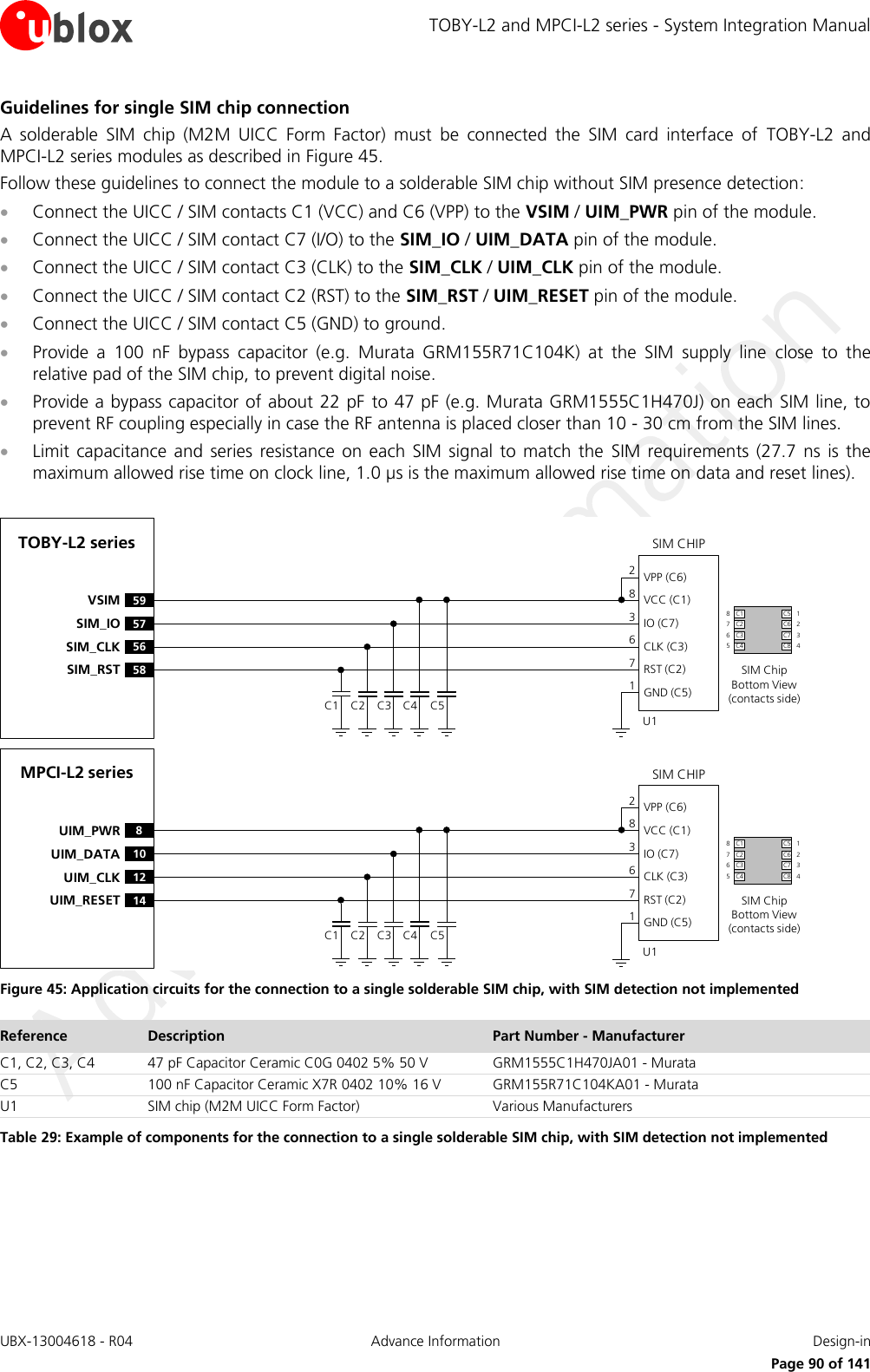

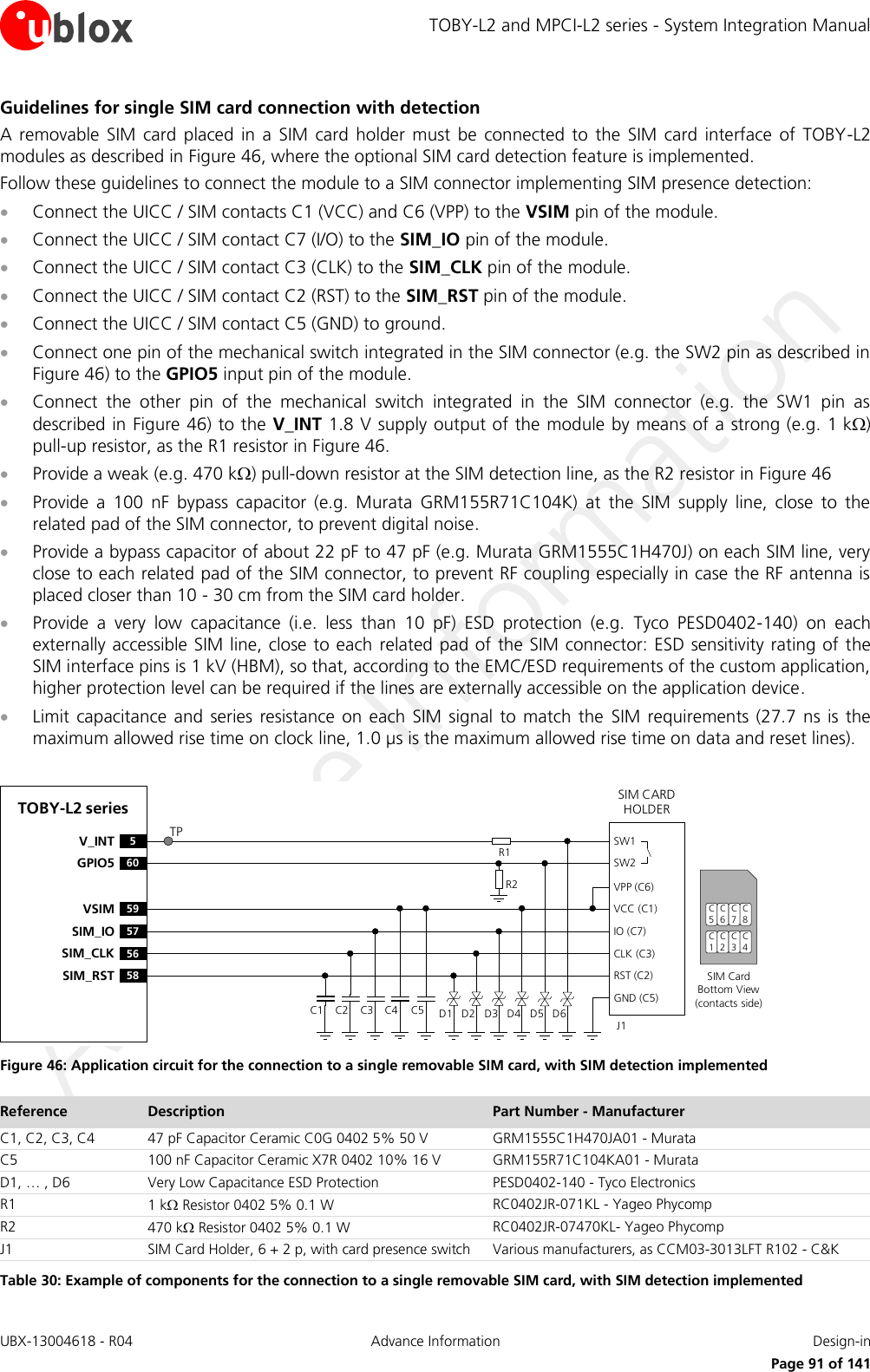

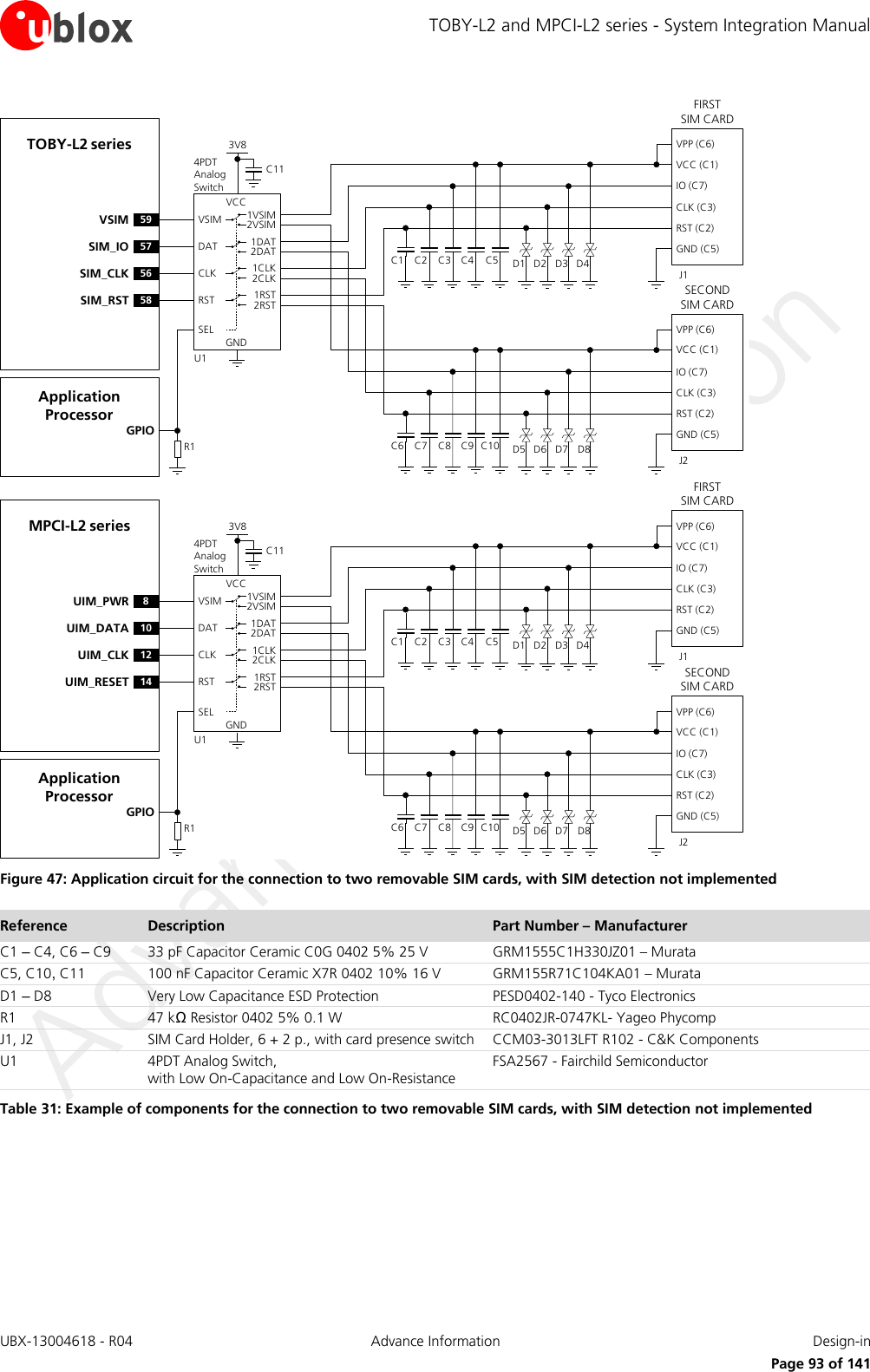

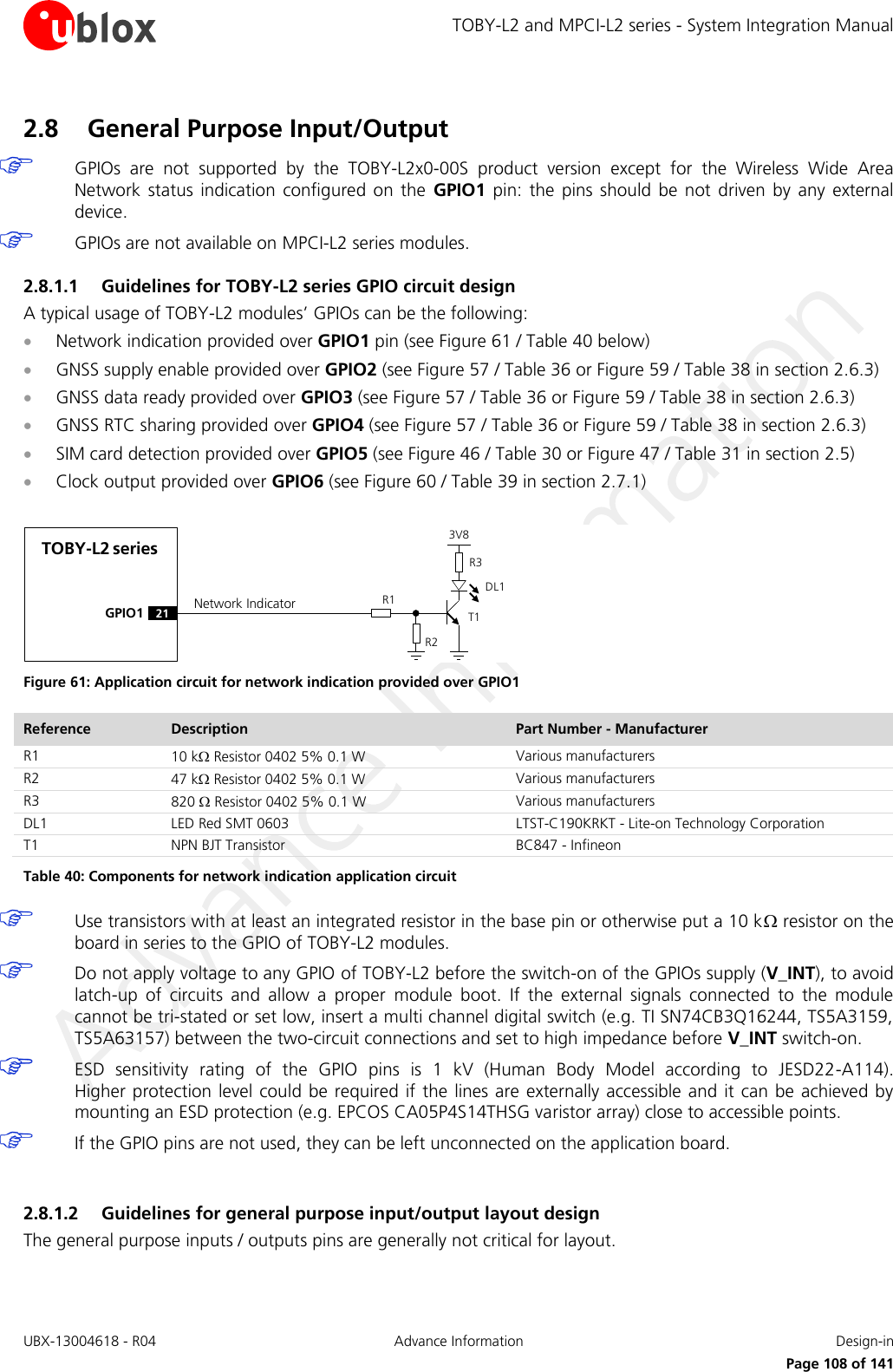

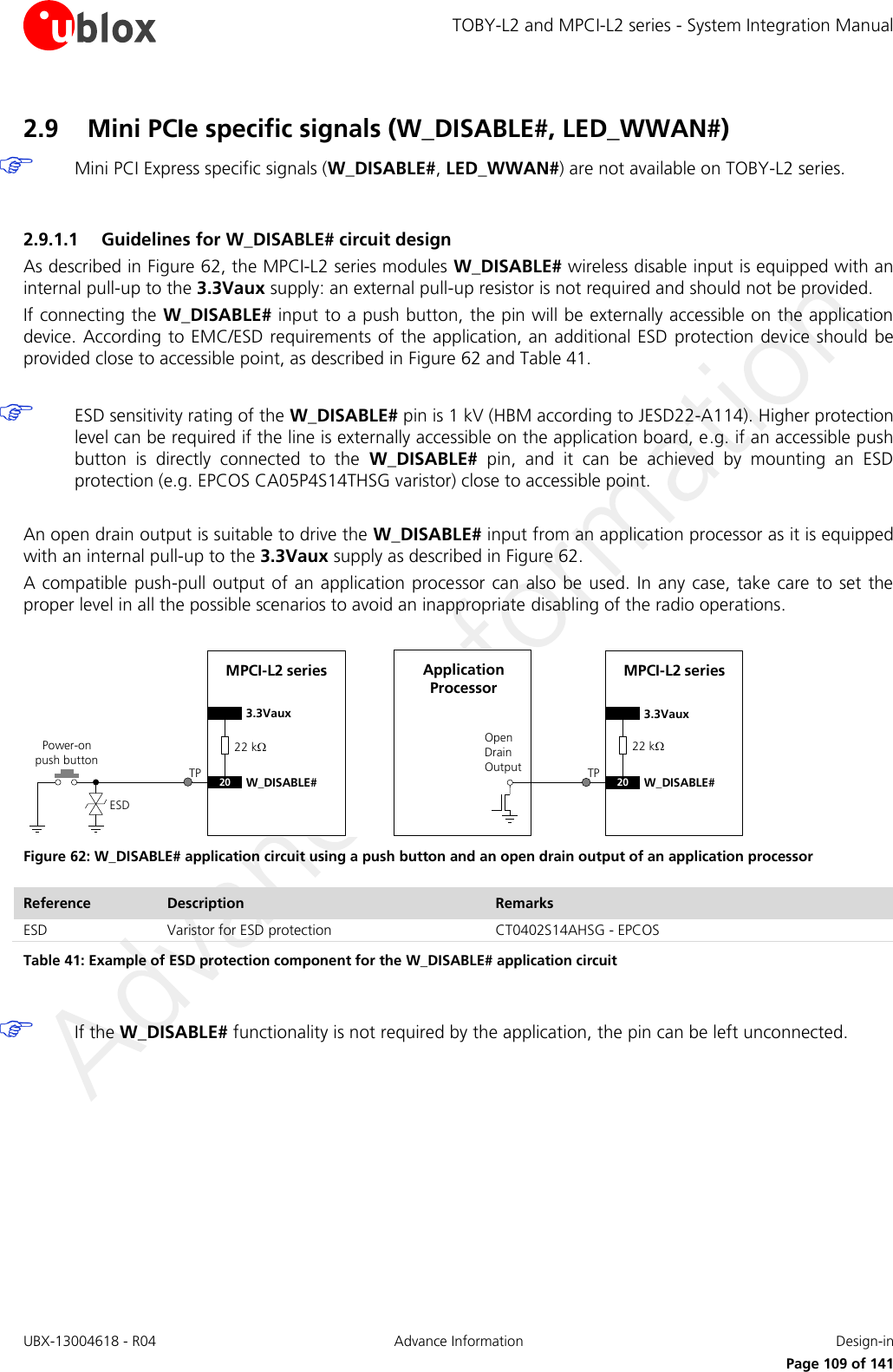

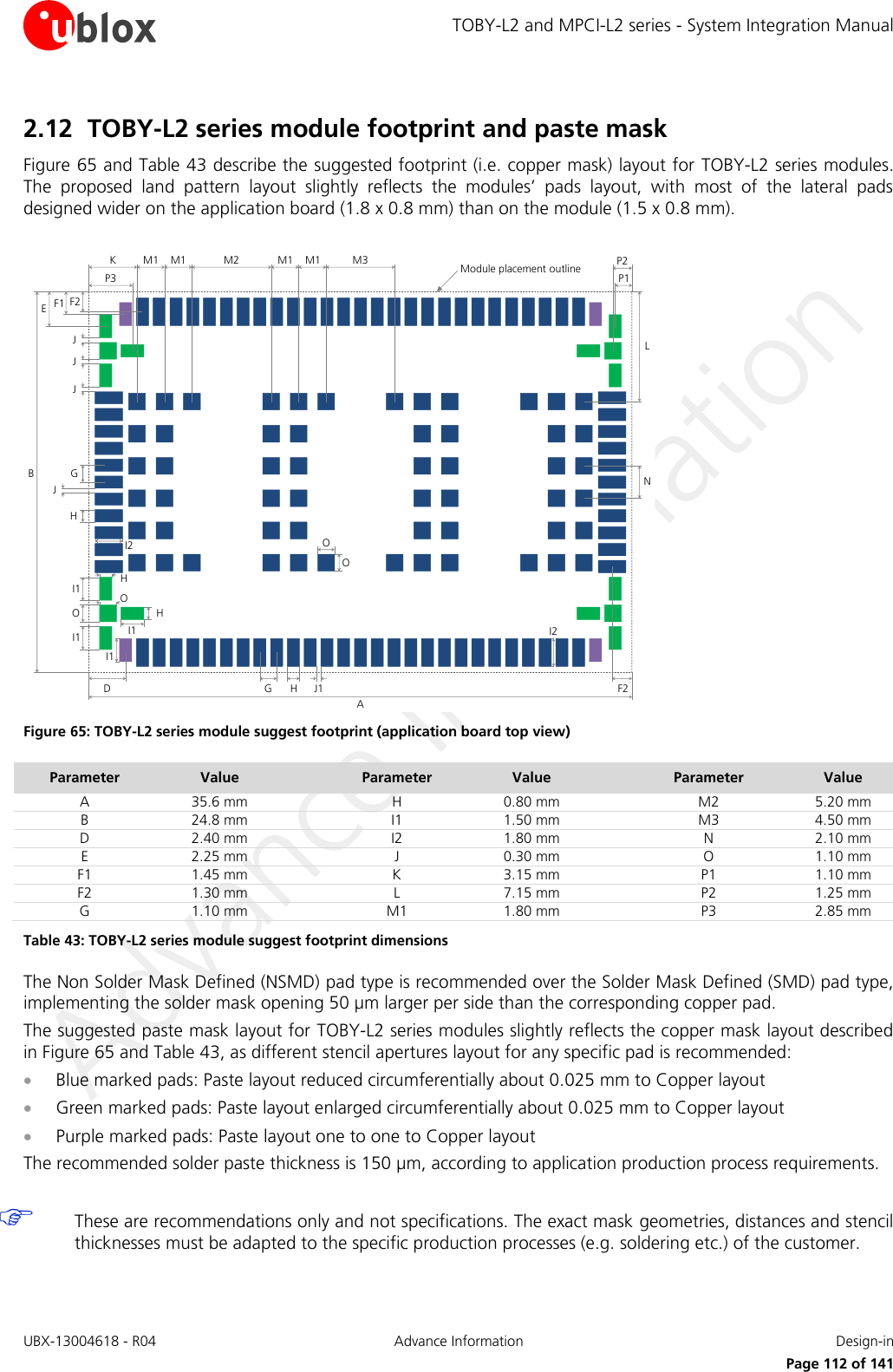

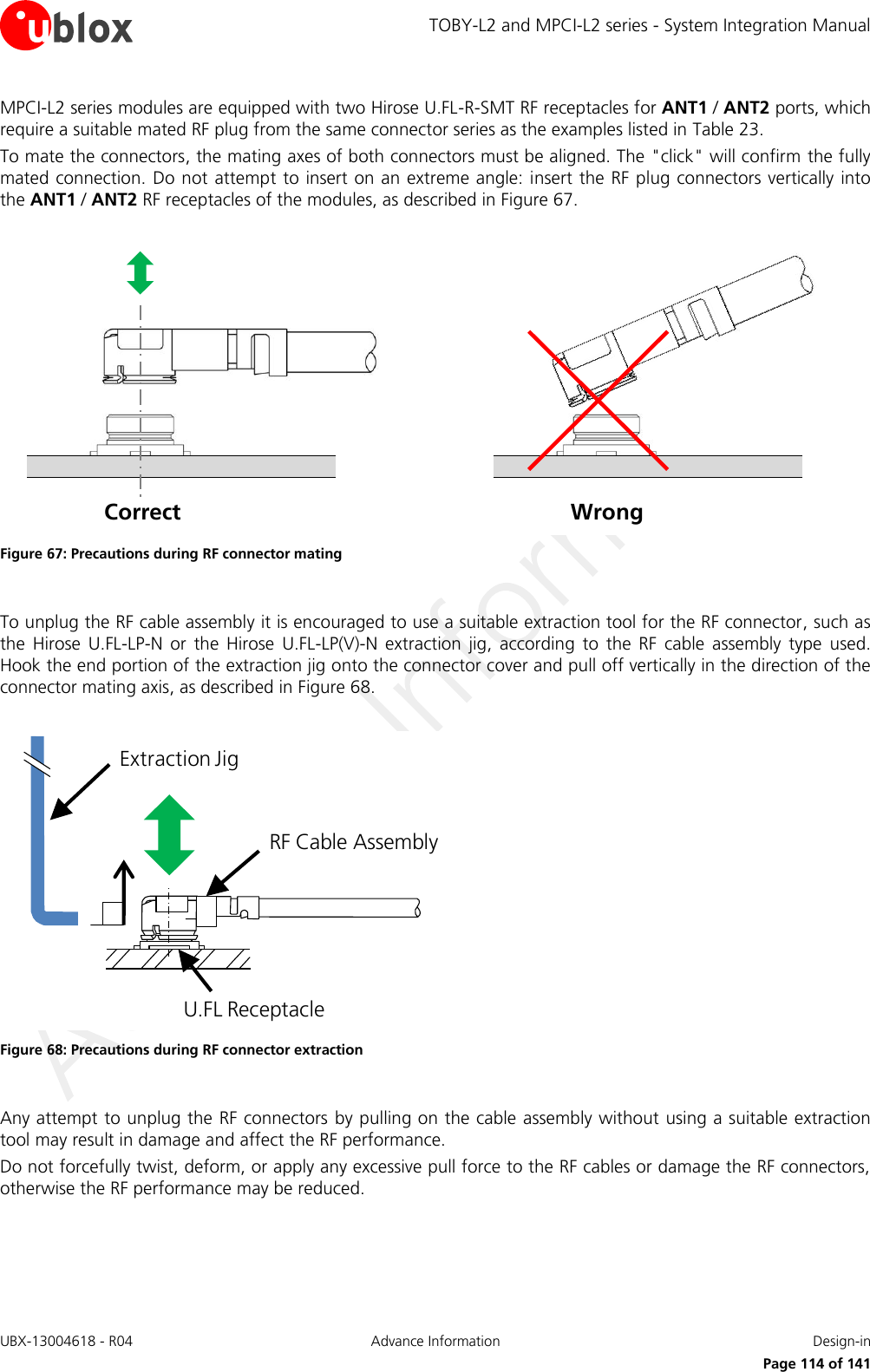

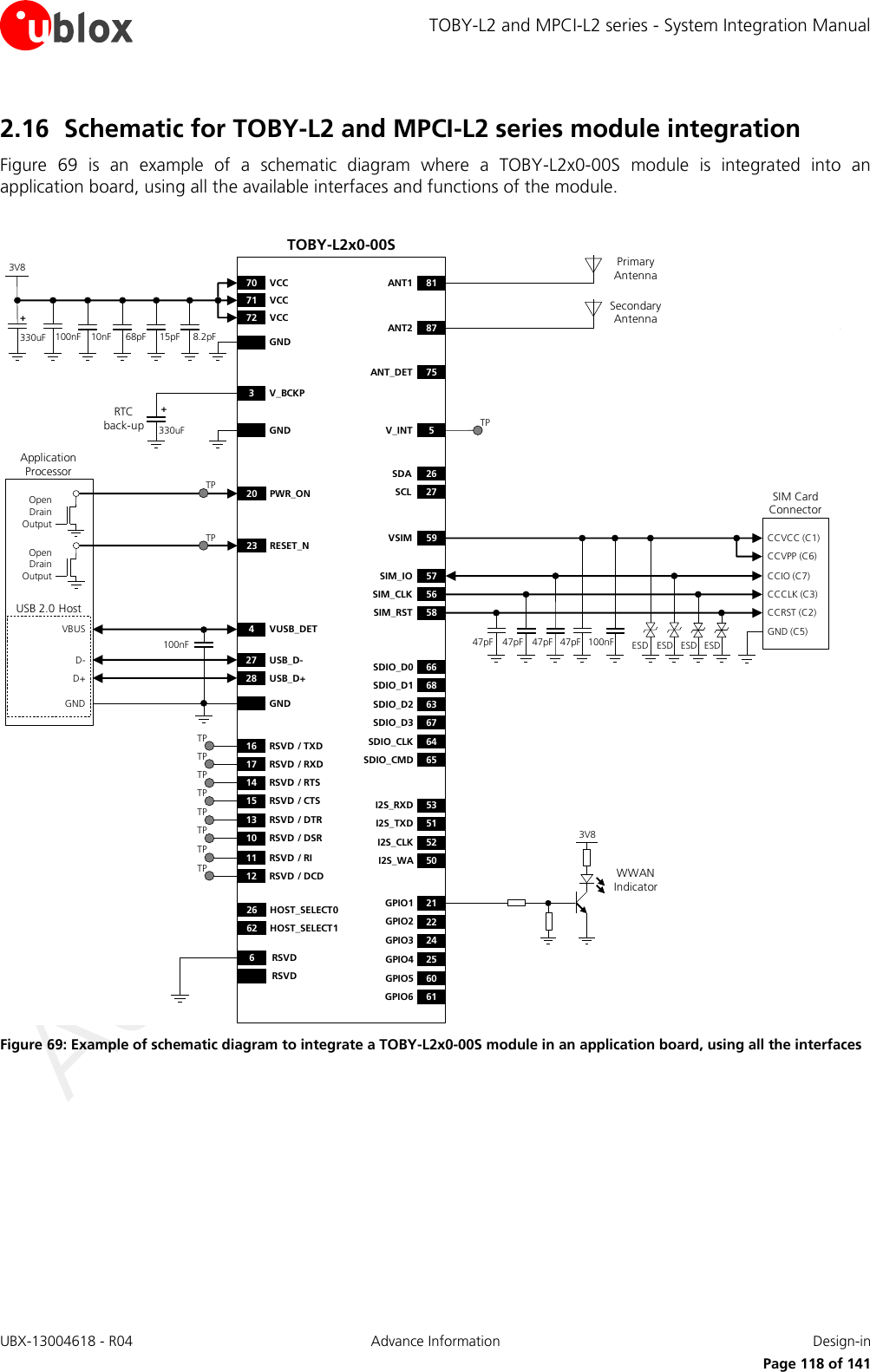

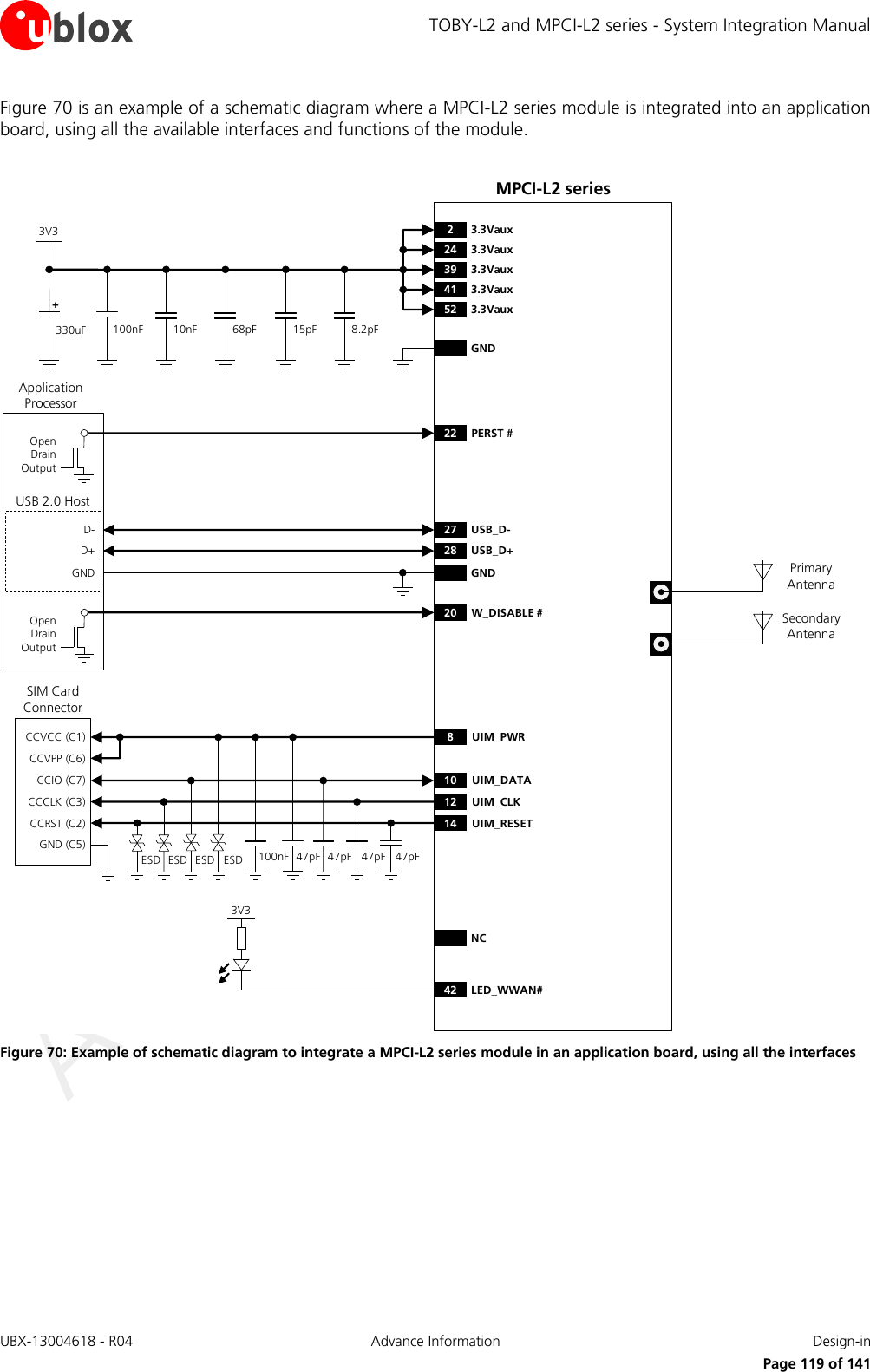

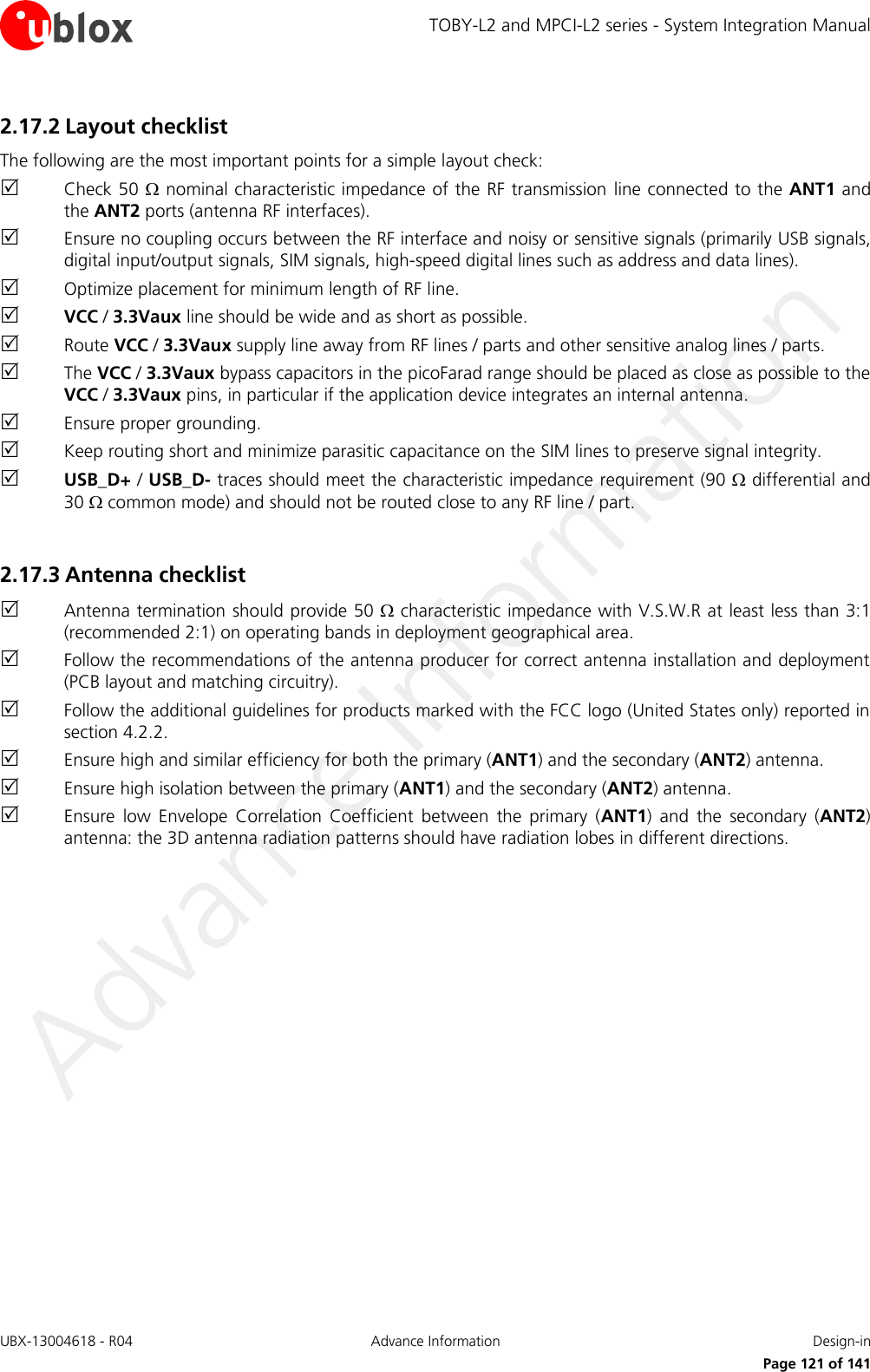

![TOBY-L2 and MPCI-L2 series - System Integration Manual UBX-13004618 - R04 Advance Information System description Page 46 of 141 1.11 General Purpose Input/Output General Purpose Input / Output pins are not supported by the TOBY-L2x0-00S product version except for the Wireless Wide Area Network status indication configured on the GPIO1 pin. General Purpose Input / Output pins are not available on MPCI-L2 series modules. TOBY-L2 series modules include 14 pins (GPIO1-GPIO6, I2S_TXD, I2S_RXD, I2S_CLK, I2S_WA, DTR, DSR, DCD, RI) that can be configured as General Purpose Input/Output or to provide custom functions via u-blox AT commands (see the u-blox AT Commands Manual [3]), as summarized in Table 12. Function Description Default GPIO Configurable GPIOs Network status indication Network status: registered home network, registered roaming, data transmission, no service GPIO1 GPIO1 GNSS supply enable Enable/disable the supply of u-blox GNSS receiver connected to cellular module GPIO2 GPIO2 GNSS data ready Sense when u-blox GNSS receiver connected to the module is ready for sending data by the DDC (I2C) GPIO3 GPIO3 GNSS RTC sharing Real Time Clock synchronization signal to u-blox GNSS receiver connected to cellular module GPIO4 GPIO4 SIM card detection SIM card physical presence detection GPIO5 GPIO5 SIM card hot insertion/removal SIM card hot insertion/removal -- GPIO5 I2S digital audio interface I2S digital audio interface I2S_RXD, I2S_TXD, I2S_CLK, I2S_WA I2S_RXD, I2S_TXD, I2S_CLK, I2S_WA 26 MHz clock output 26 MHz clock output for an external audio codec or an external Wi-Fi chip/module GPIO6 GPIO6 Wi-Fi enable Enable/disable the supply of the external Wi-Fi chip or module connected to the cellular module -- GPIO1, GPIO4, DSR Wi-Fi data ready Sense when the external Wi-Fi chip/module connected to the cellular module is ready for sending data by the SDIO, waking up the cellular module from low power idle mode -- GPIO3, DTR Wi-Fi reset Reset the external Wi-Fi chip or module connected to the cellular module -- GPIO3, DCD Wi-Fi power saving Enable/disable the low power mode of the external Wi-Fi chip/module connected to the cellular module -- GPIO2, RI 32 kHz clock output 32 kHz clock output for an external Wi-Fi chip or module -- GPIO4 Antenna tuning 4-bit tunable antenna control signals mapping the actual operating RF band over a 4-pin interface provided for the implementation of external antenna tuning solutions -- I2S_RXD, I2S_TXD, I2S_CLK, I2S_WA DSR, DTR, DCD, RI DSR UART data set ready output DSR DSR DTR UART data terminal ready input DTR DTR DCD UART data carrier detect output DCD DCD RI UART ring indicator output RI RI General purpose input Input to sense high or low digital level -- All General purpose output Output to set the high or the low digital level -- All Pin disabled Tri-state with an internal active pull-down enabled -- All Table 12: TOBY-L2 series GPIO custom functions configuration](https://usermanual.wiki/u-blox/TOBYL210.System-Integration-Manual/User-Guide-2425113-Page-46.png)