Cover U DV4100 14101513564522

User Manual: DV4100

Open the PDF directly: View PDF ![]() .

.

Page Count: 143 [warning: Documents this large are best viewed by clicking the View PDF Link!]

Service

Manual

Please use this service manual with referring to the user guide (D.F.U) without fail.

302W855010 AO

3120 785 22440

First Issue:2000.11

DV4100/A1B, /N1B, /S1G, /U1B

DVD Player

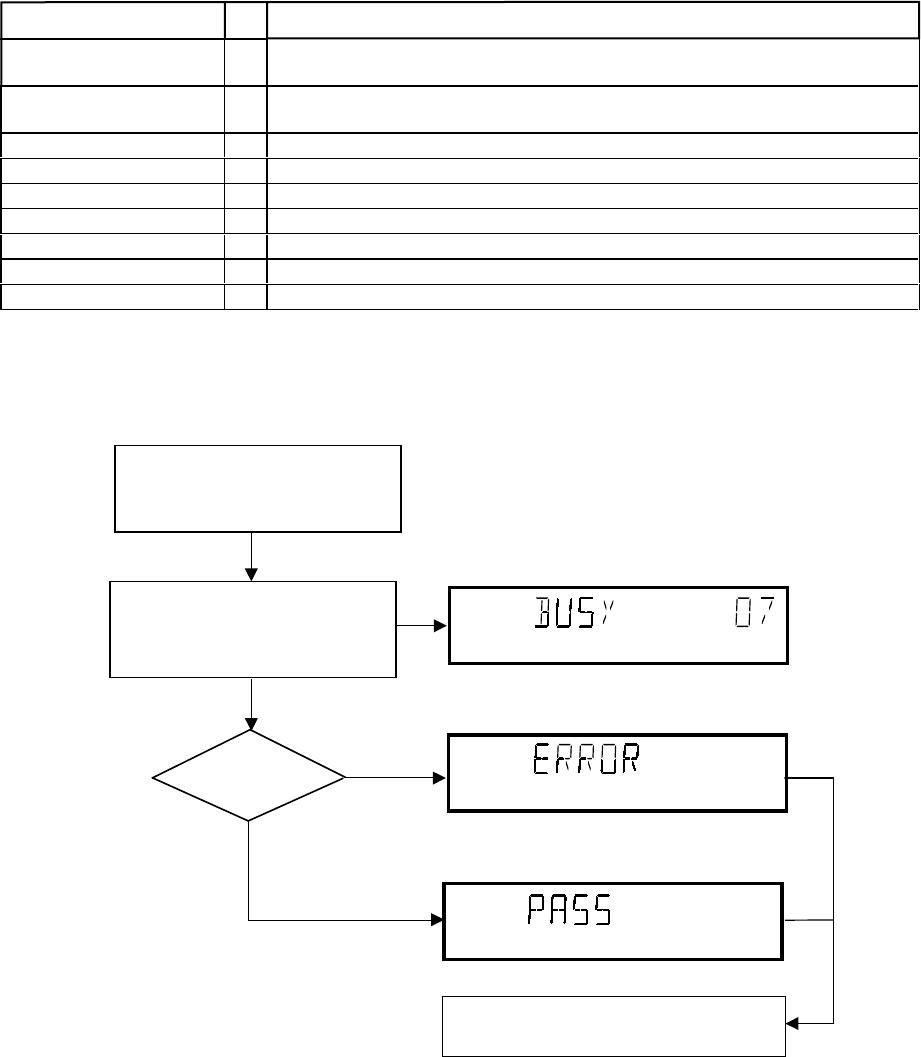

DV4100

TABLE OF CONTENTS

1. TECHNICAL SPECIFICATION ...............................................................................1

2. CONNECTION FACILITIES ....................................................................................3

3. INFORMATIONS ..................................................................................................... 4

4. SERVICING HINT ...................................................................................................5

5. WARNING AND LASER SAFETY INSTRUCTIONS ............................................... 6

6. SERVICE HINTS ....................................................................................................8

7. BLOCK DIAGRAM ..................................................................................................9

8. WIRING DIAGRAM ............................................................................................... 13

9. DISMANTLING INSTRUCTIONS .........................................................................15

10. EXPLODED VIEW AND PARTS LIST...................................................................17

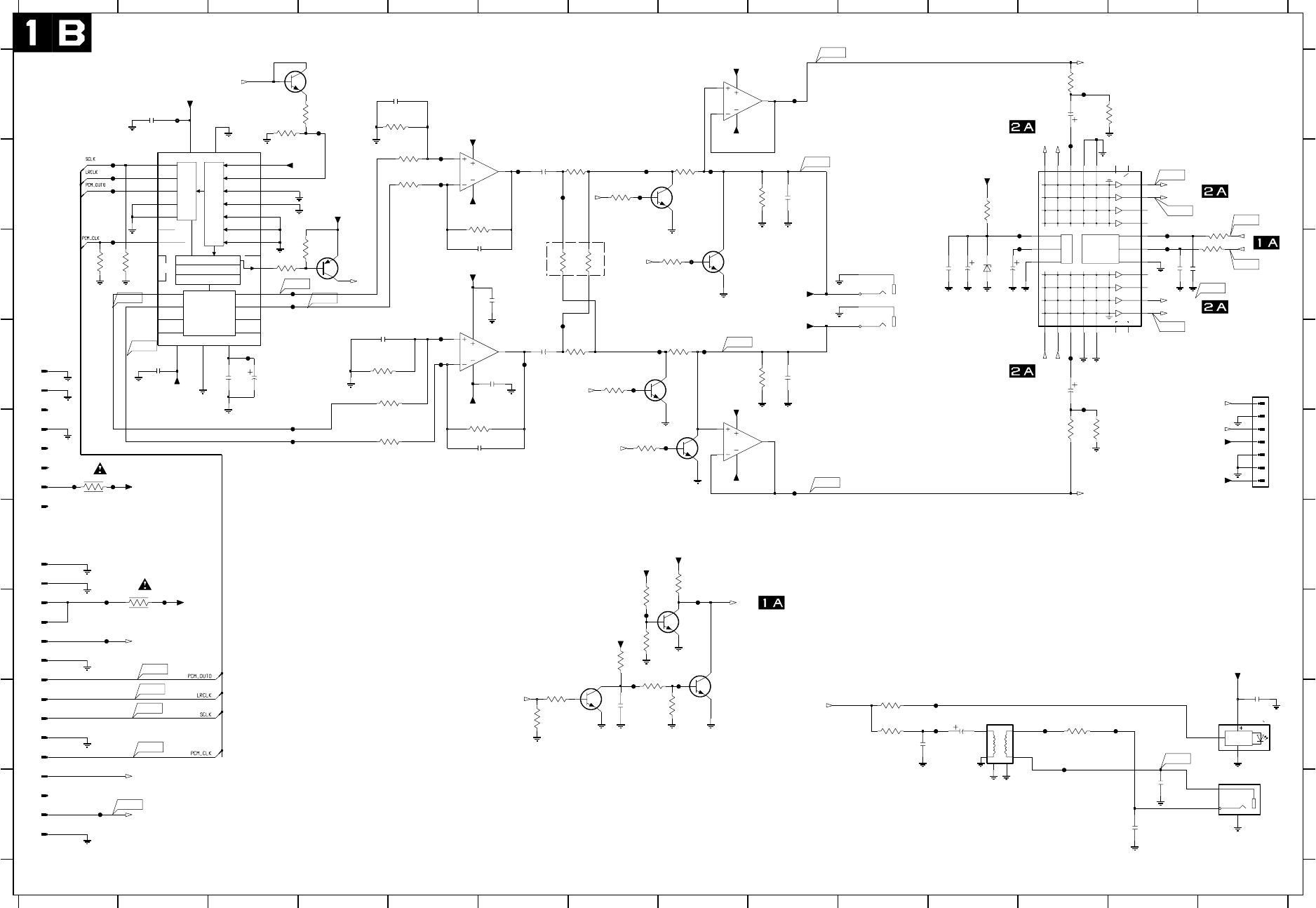

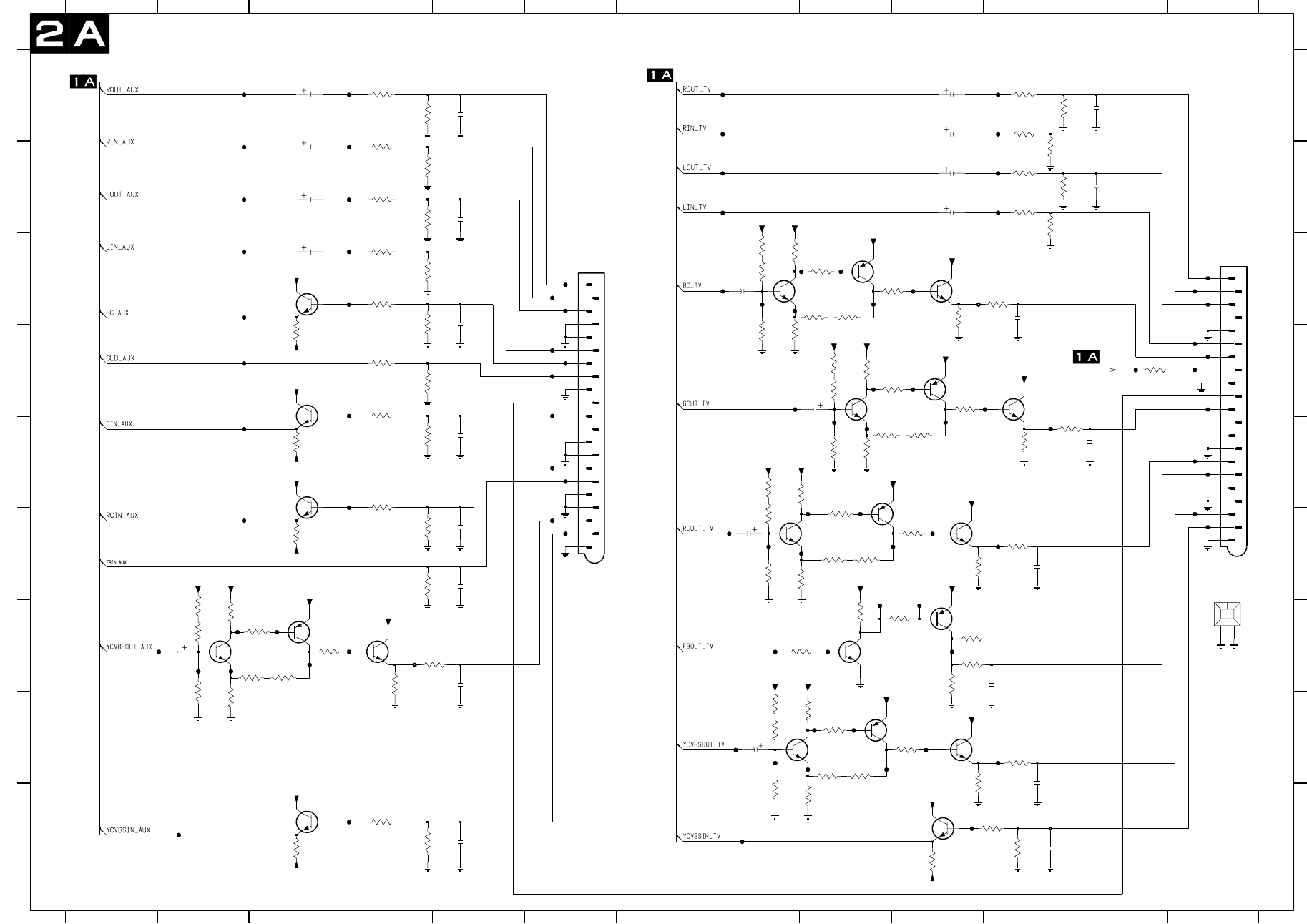

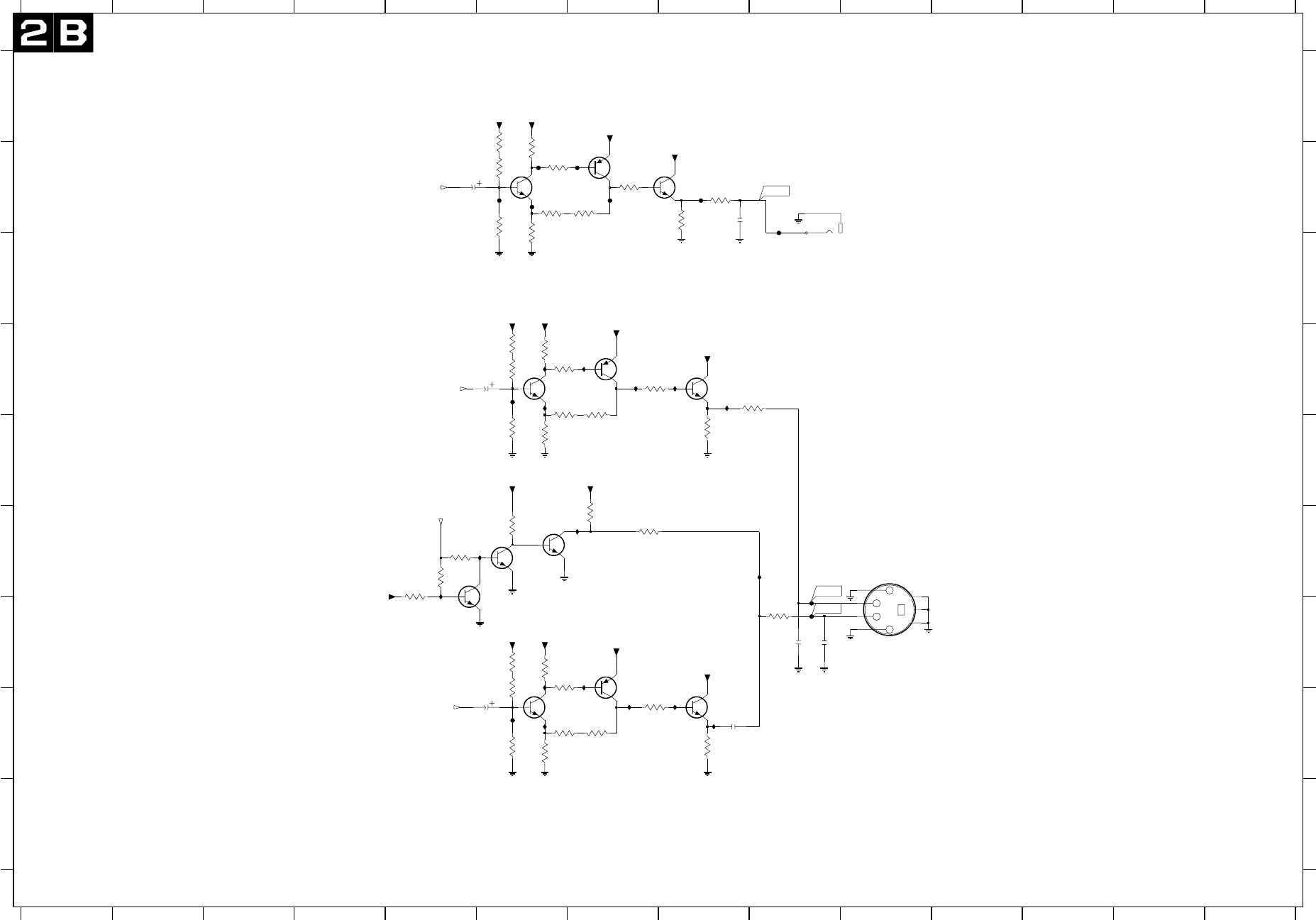

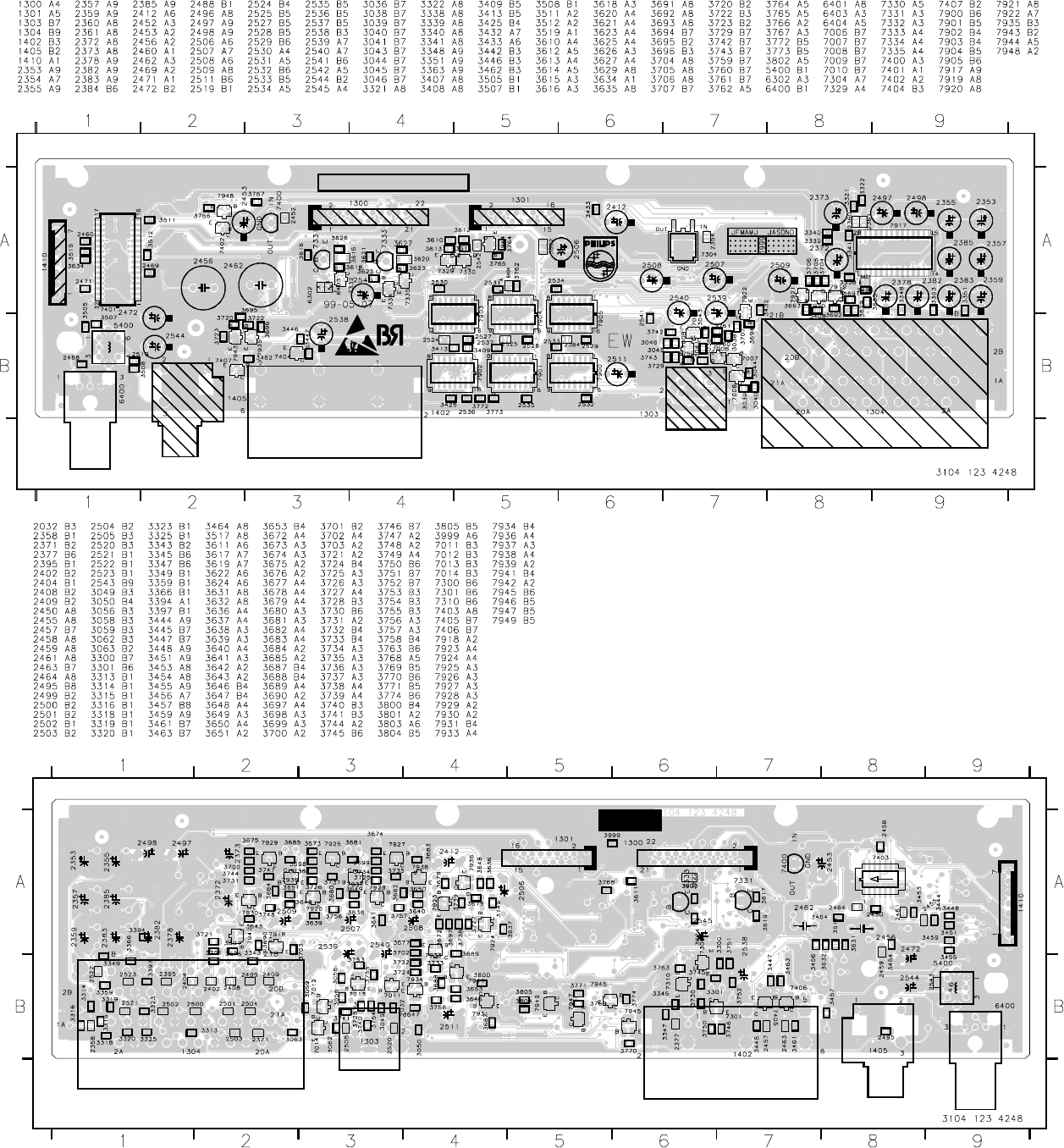

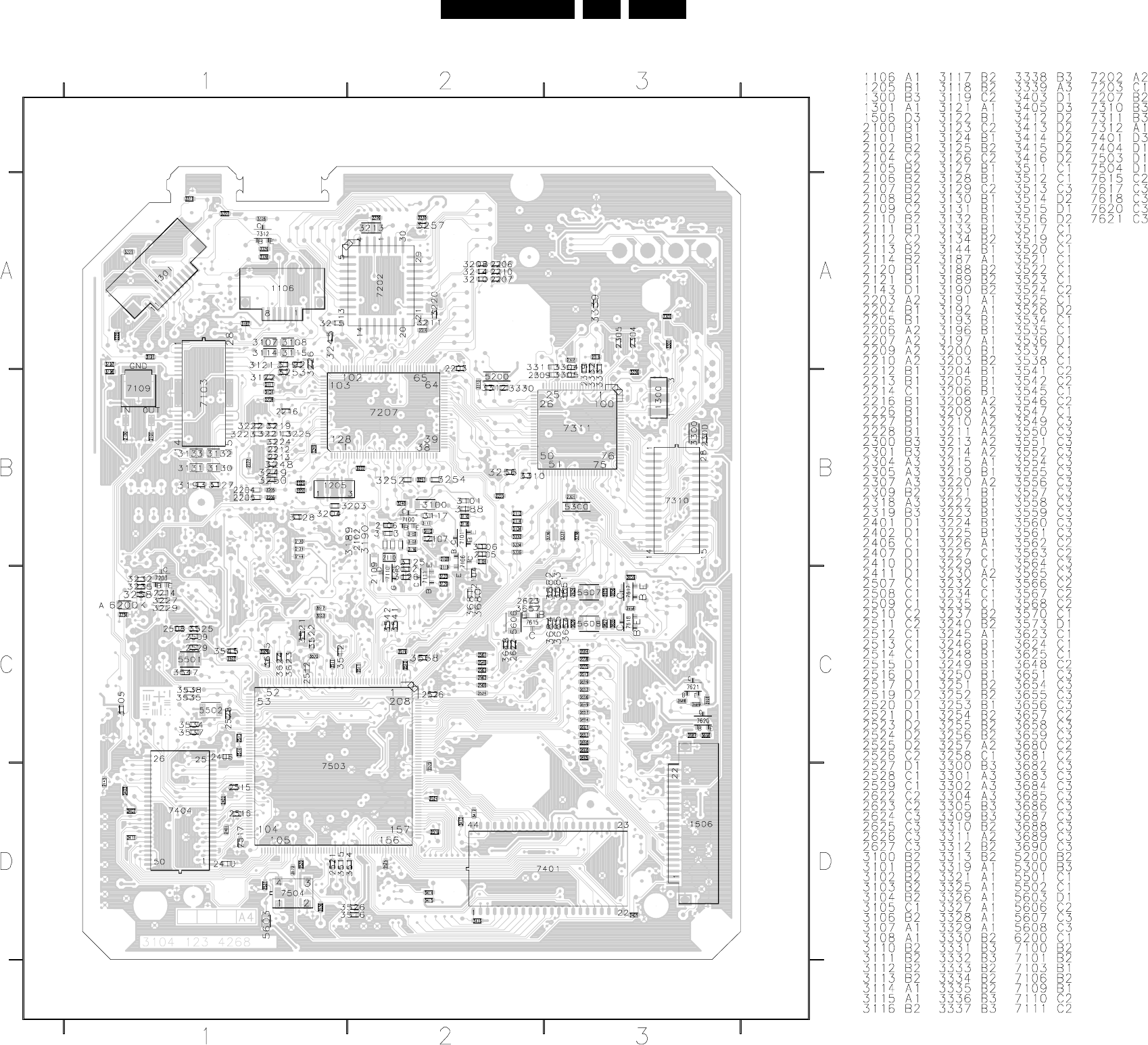

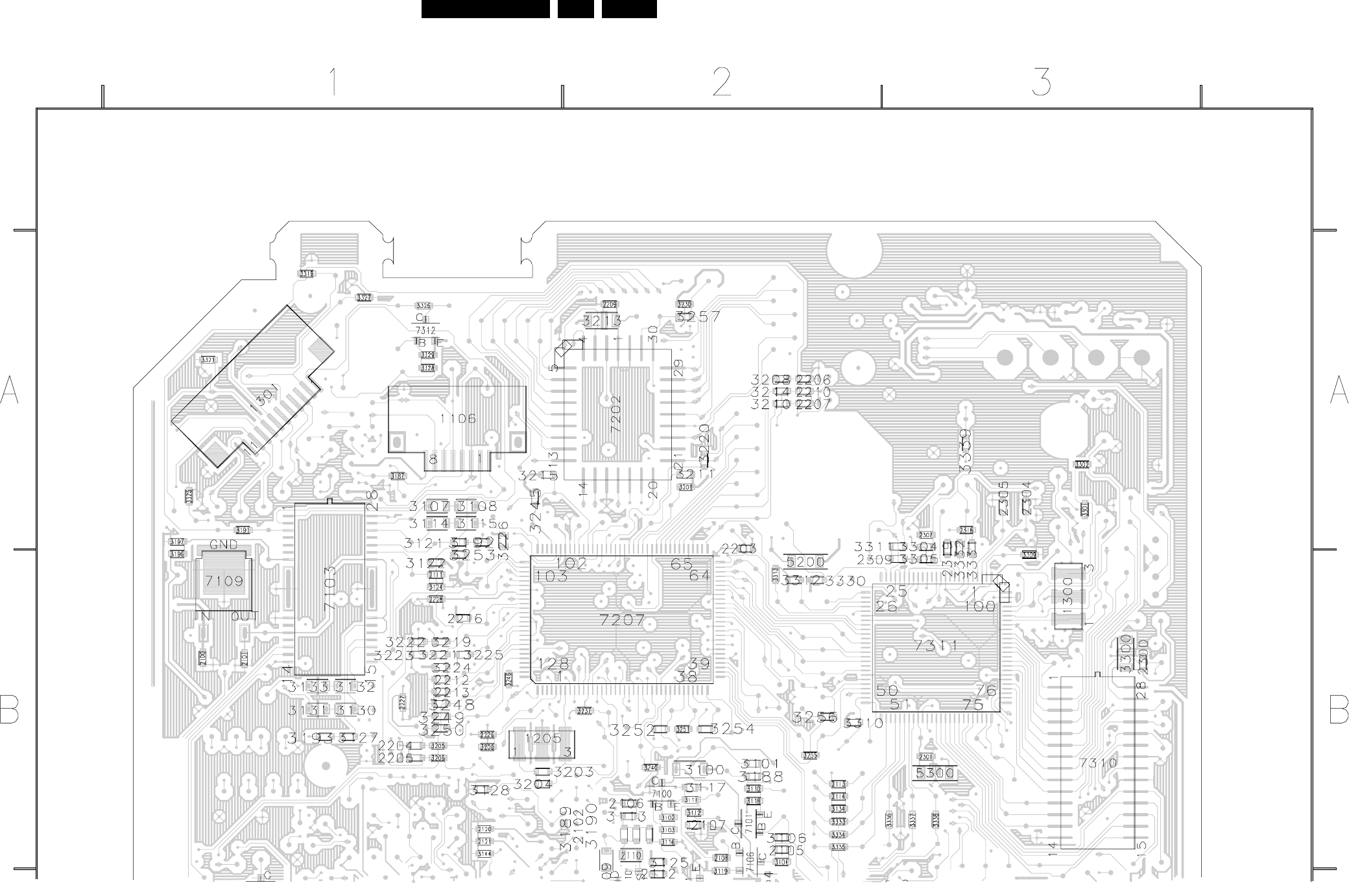

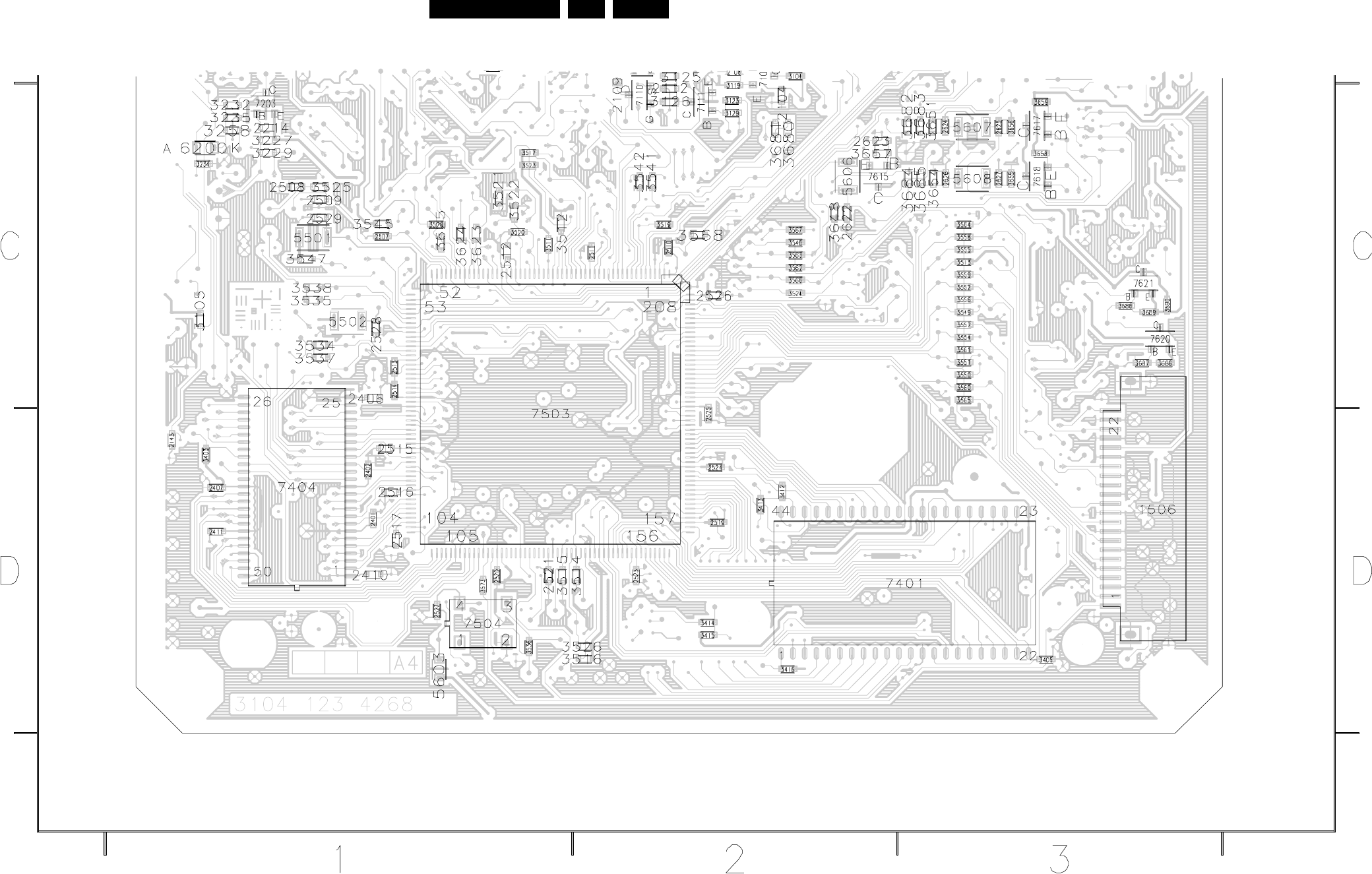

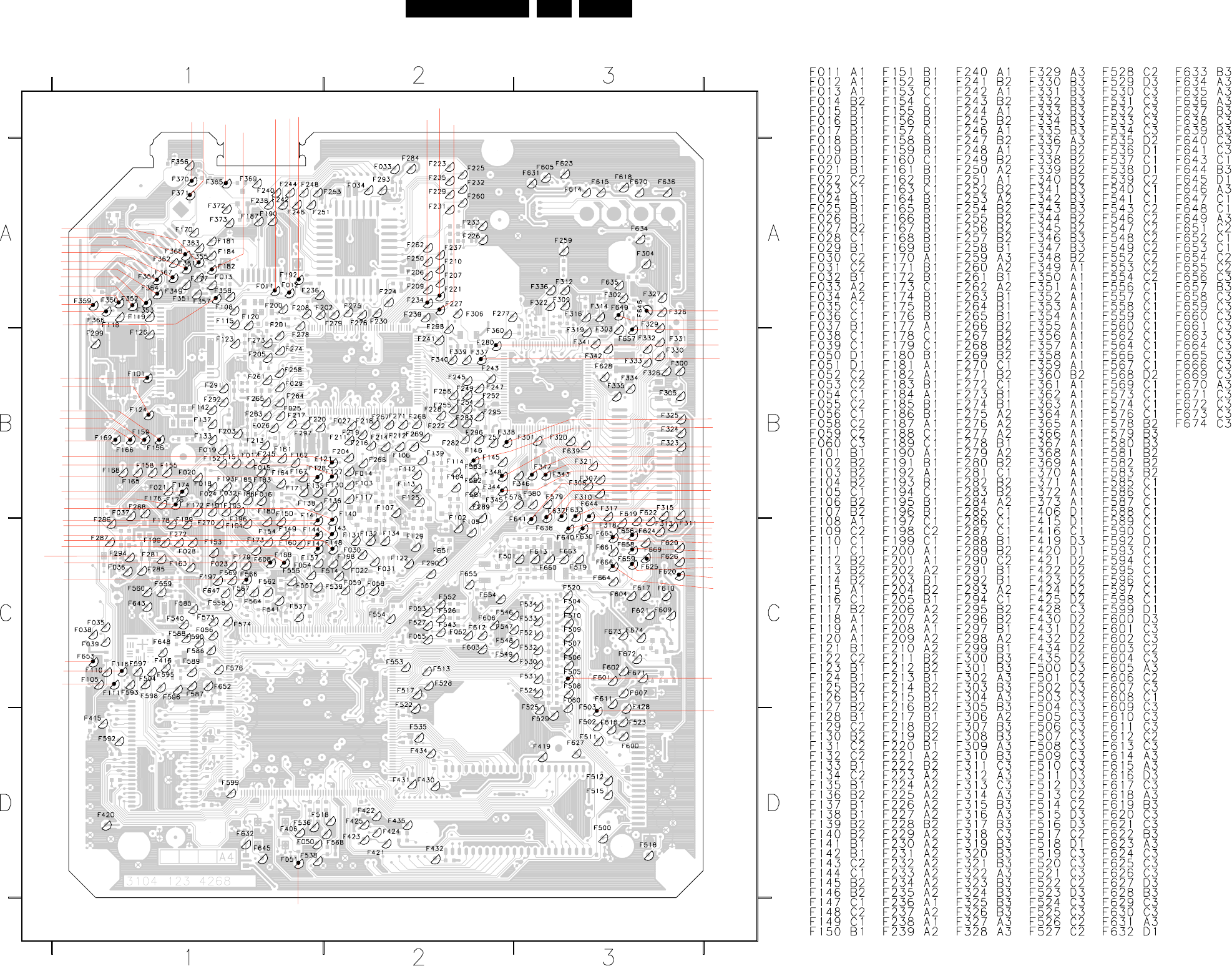

11. SCHEMATIC DIAGRAM AND PARTS LOCATION ...............................................21

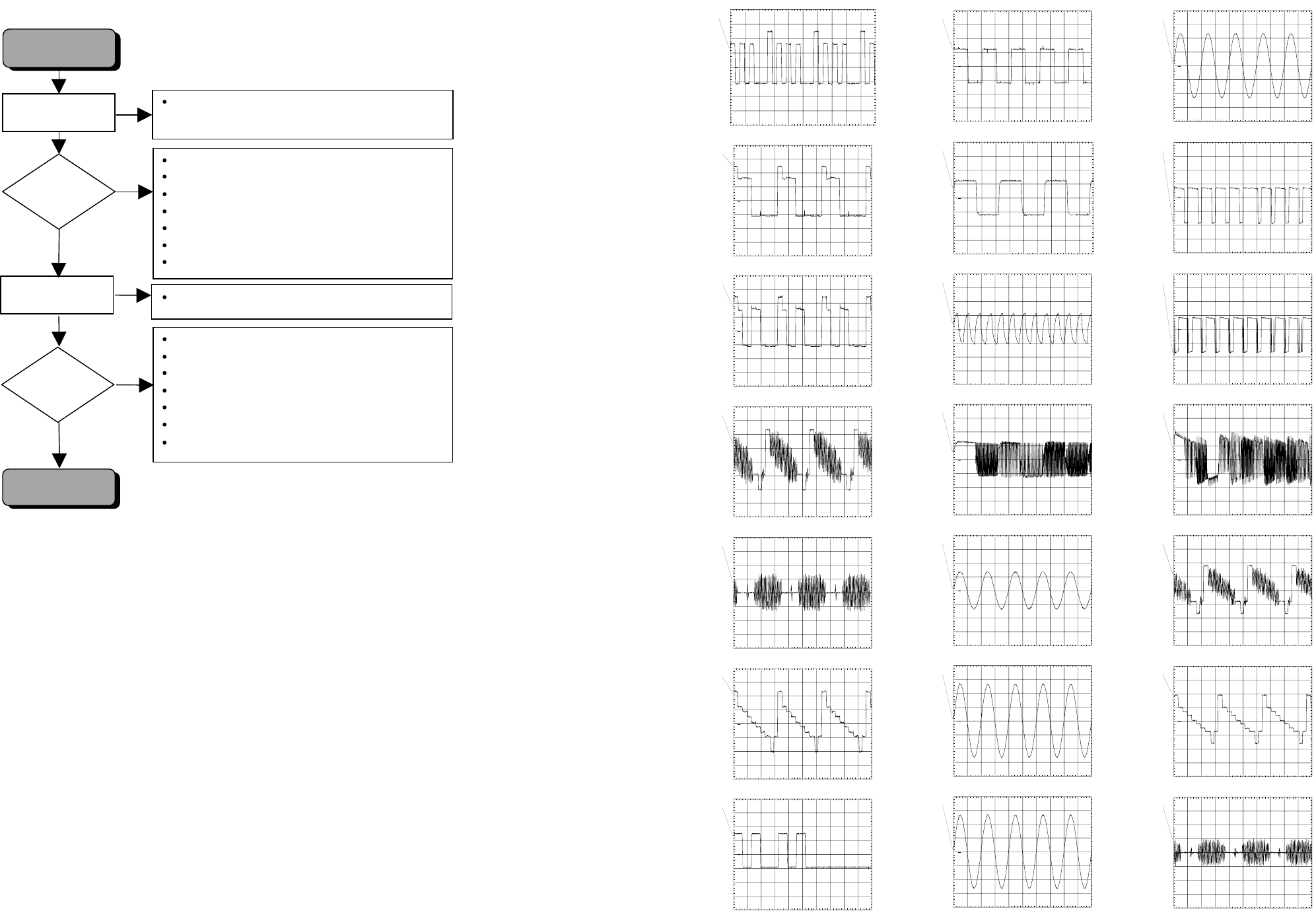

12. TROUBLESHOOTING ..........................................................................................47

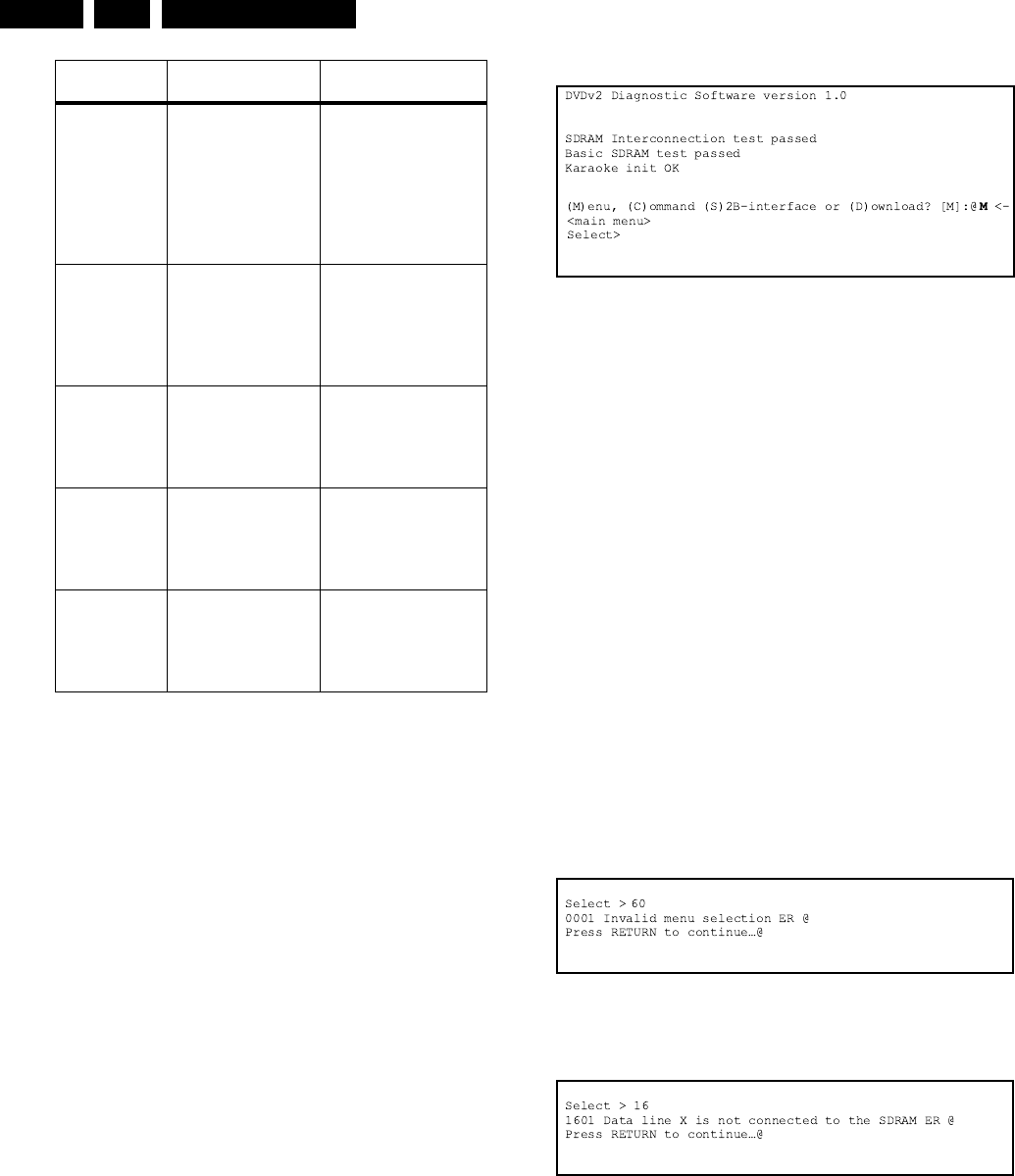

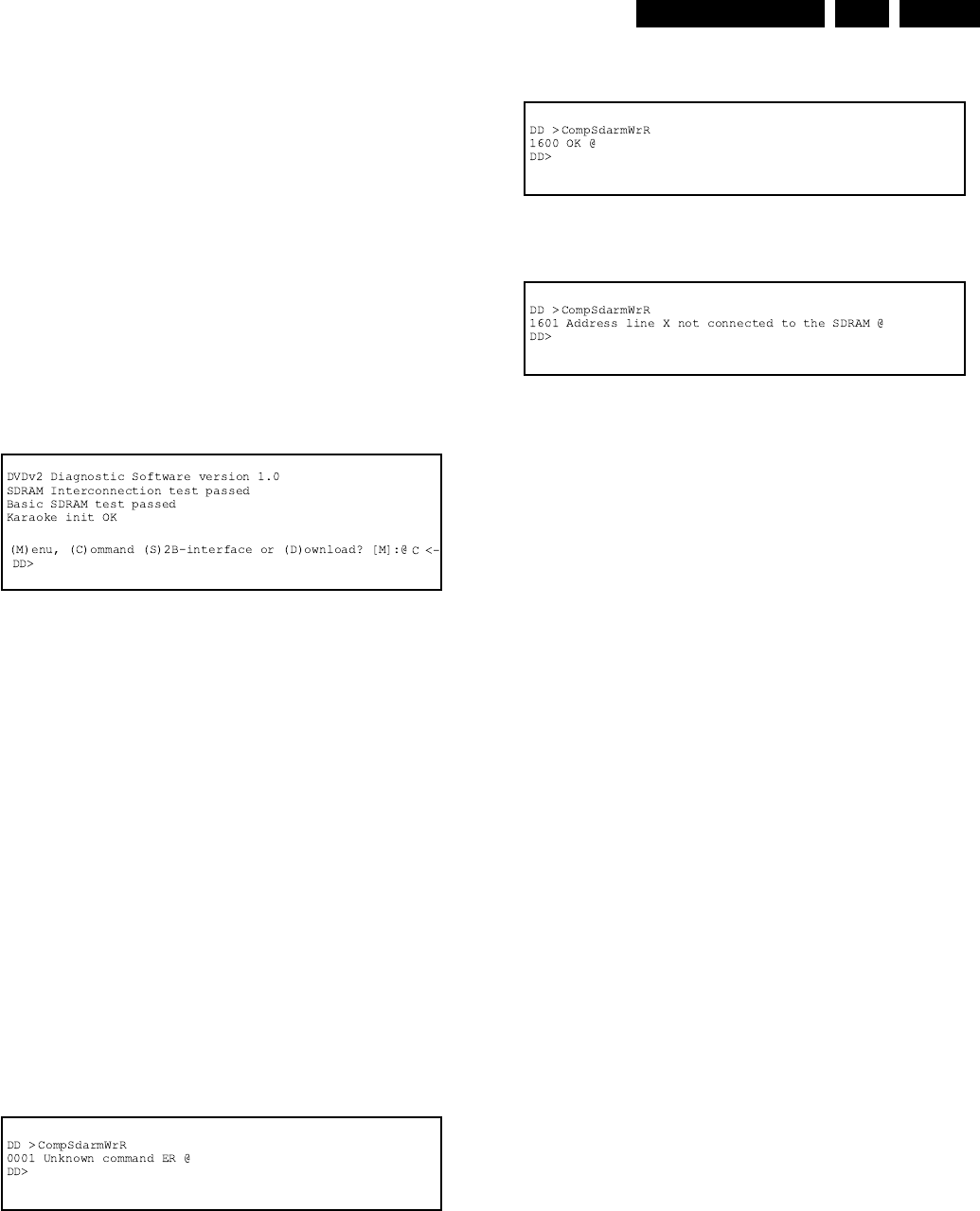

13. DIAGNOSTIC SOFWARE : SCRIPT INTERFACES ............................................. 53

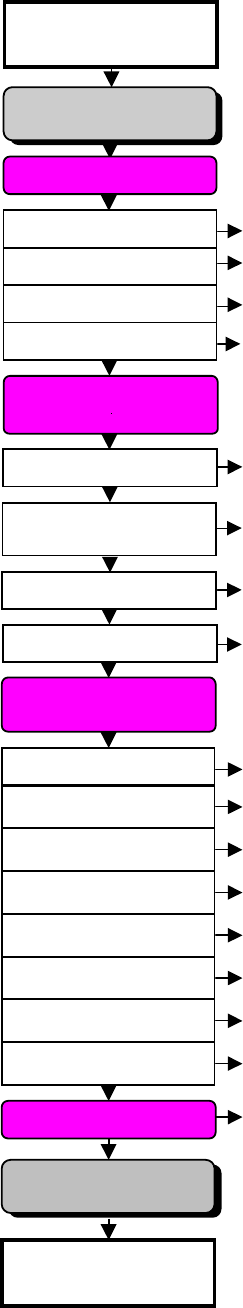

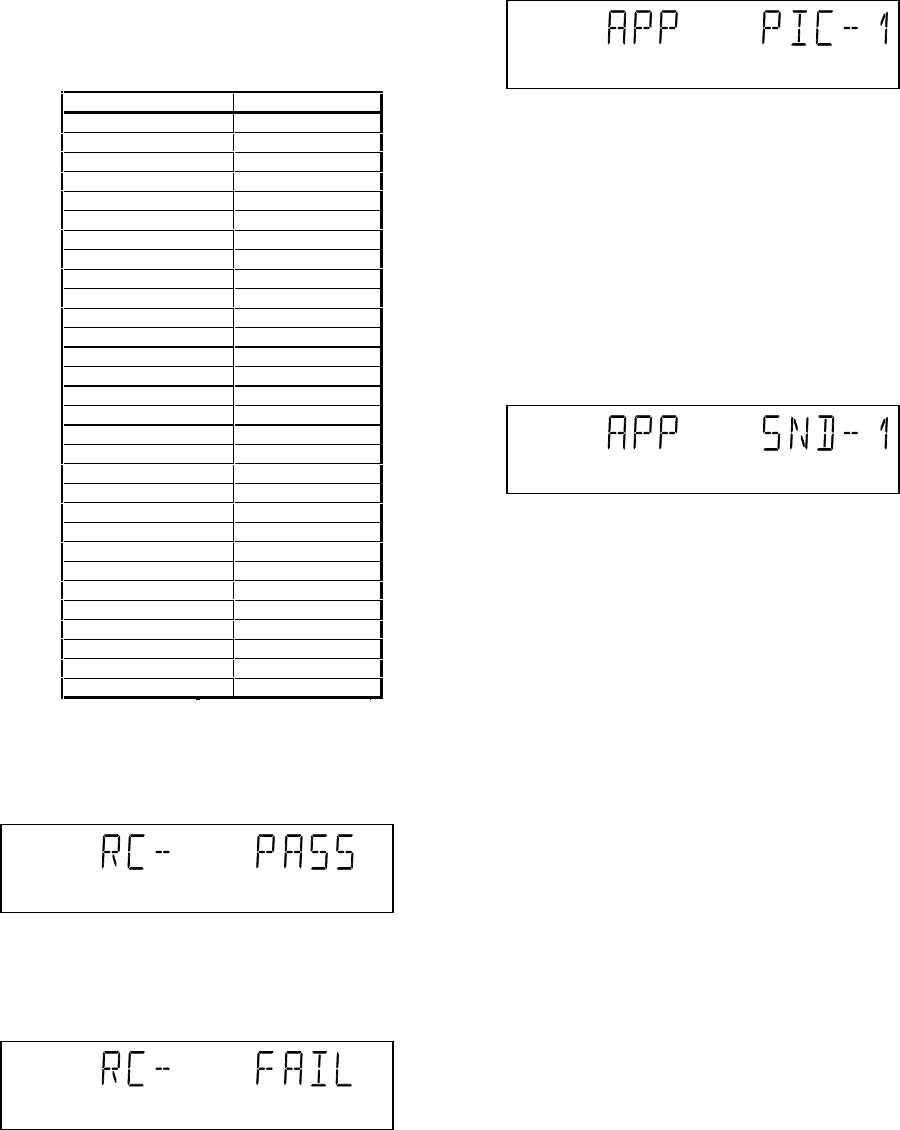

14. INTERACTIVE TESTS.......................................................................................... 55

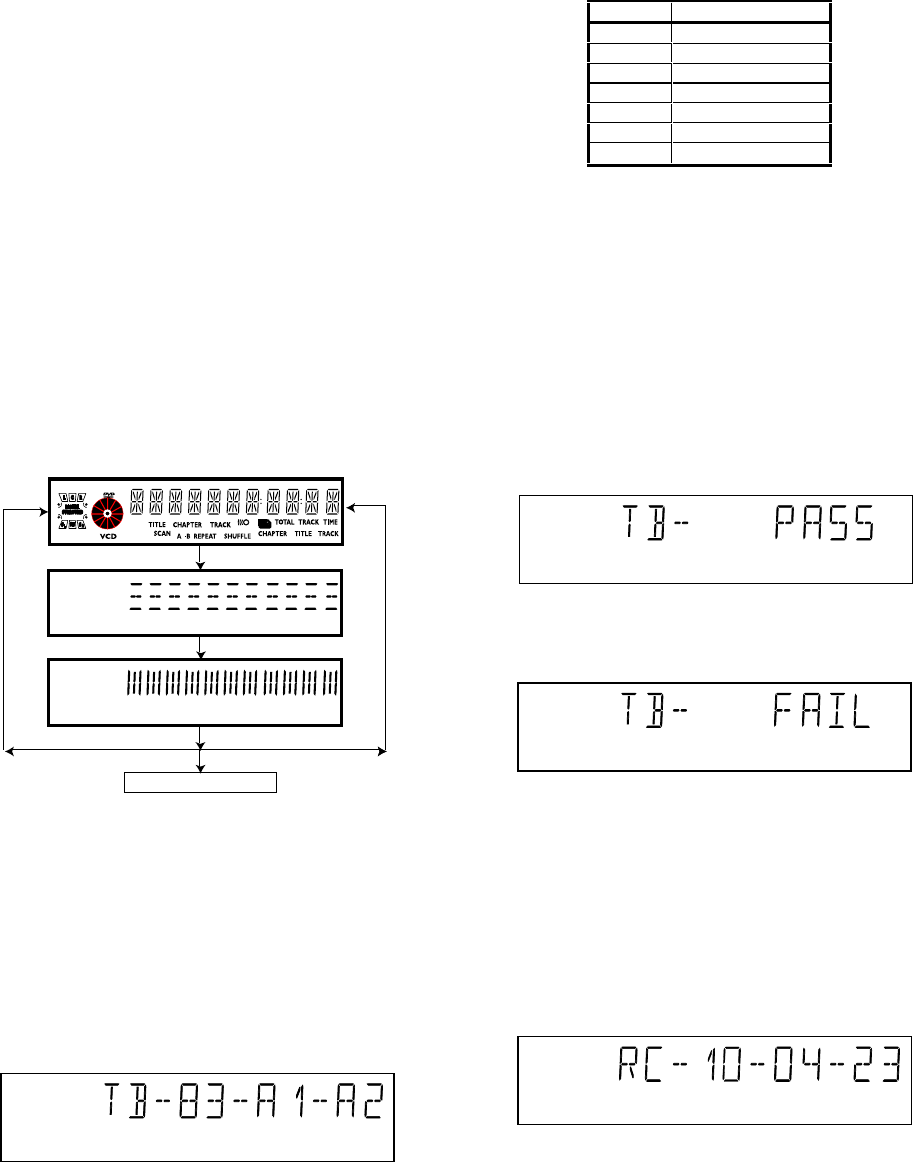

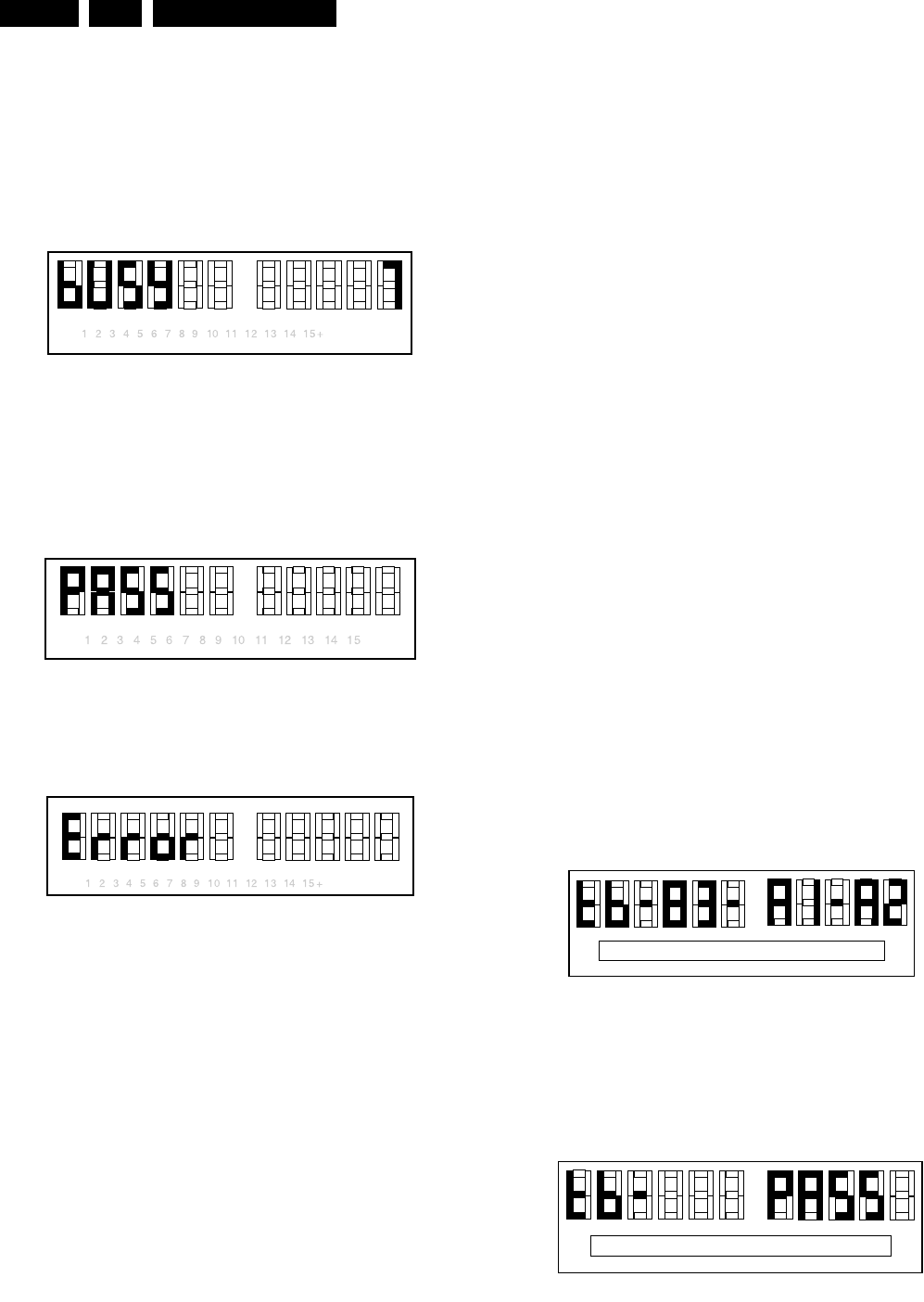

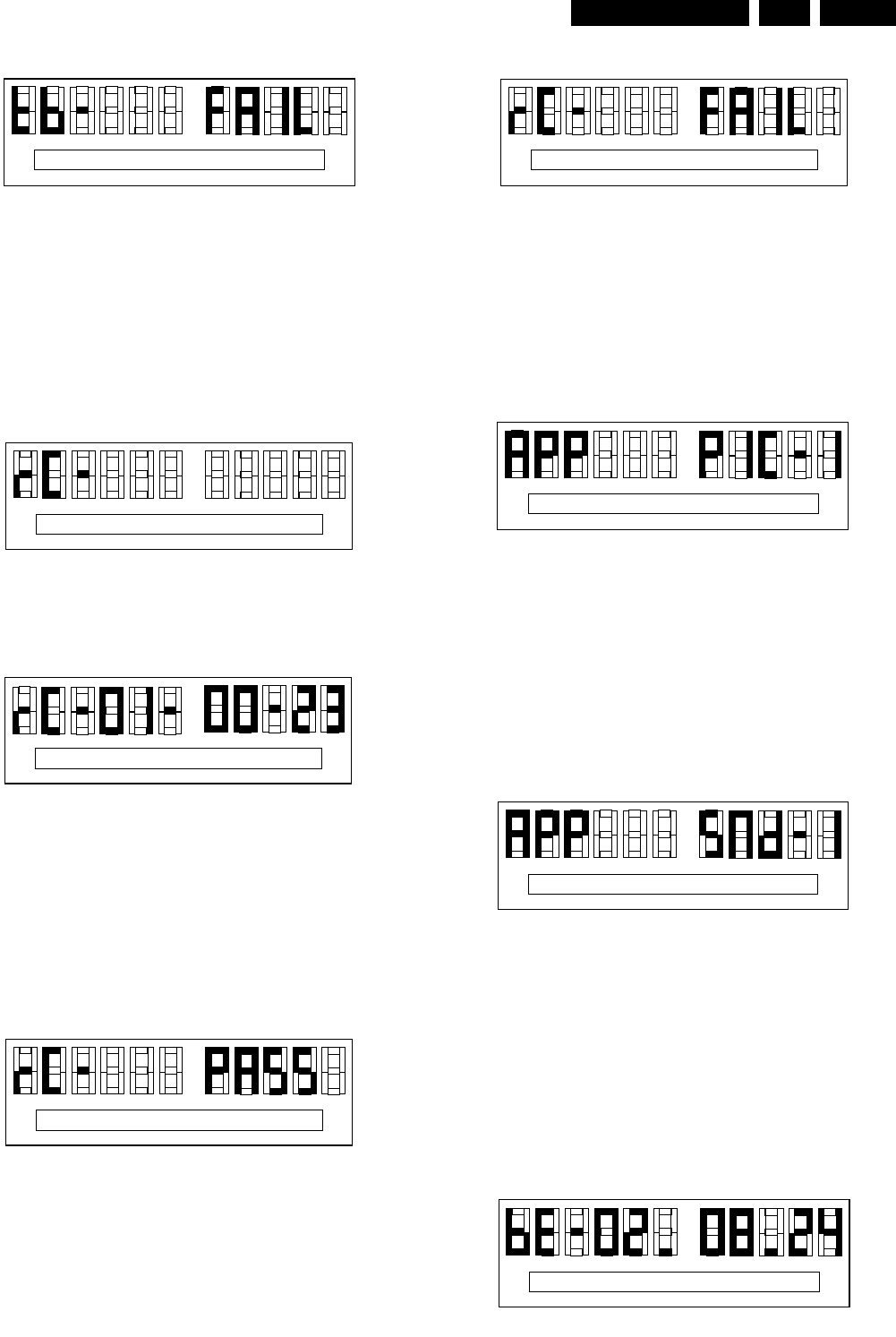

15. TEST INSTRUCTIONS DISPLAY BOARD ...........................................................62

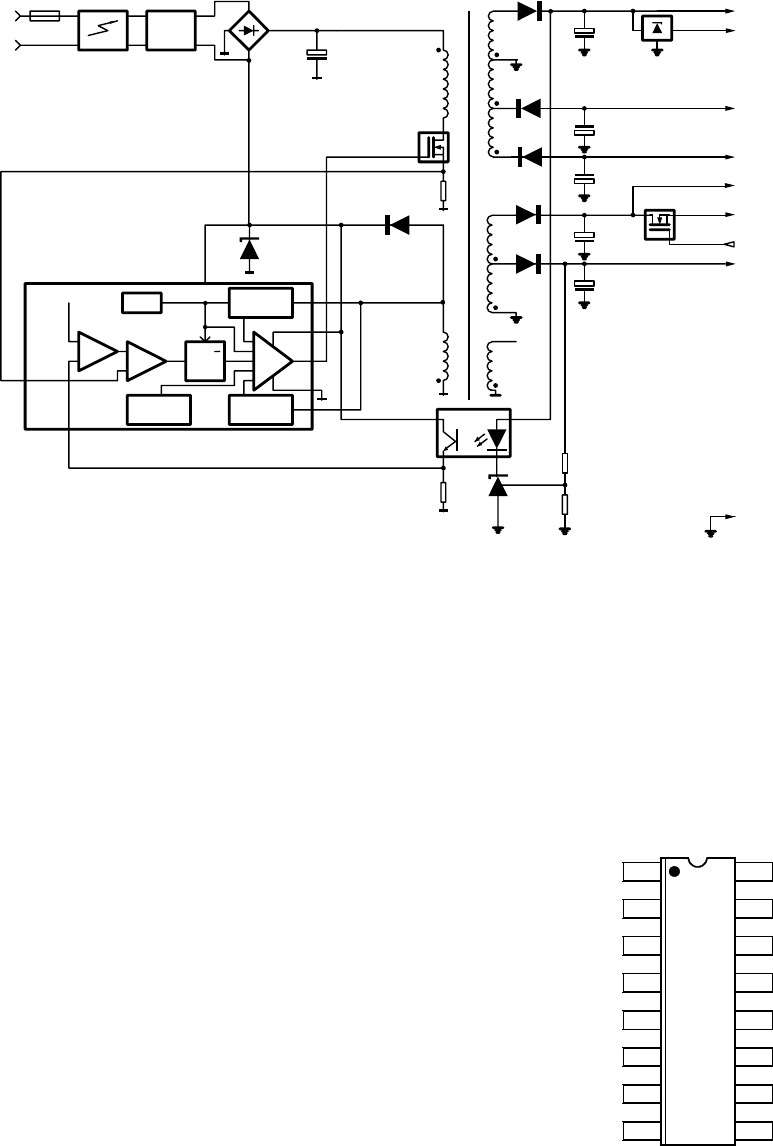

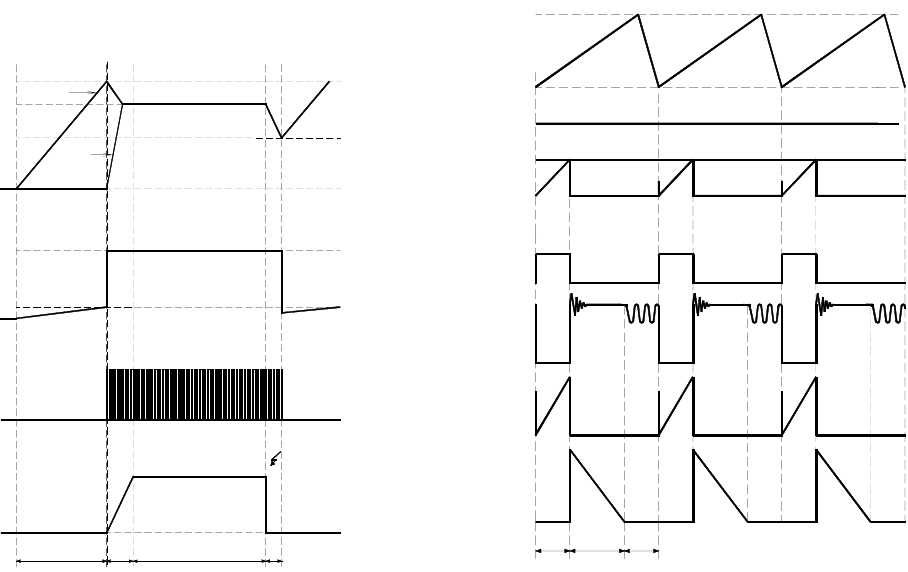

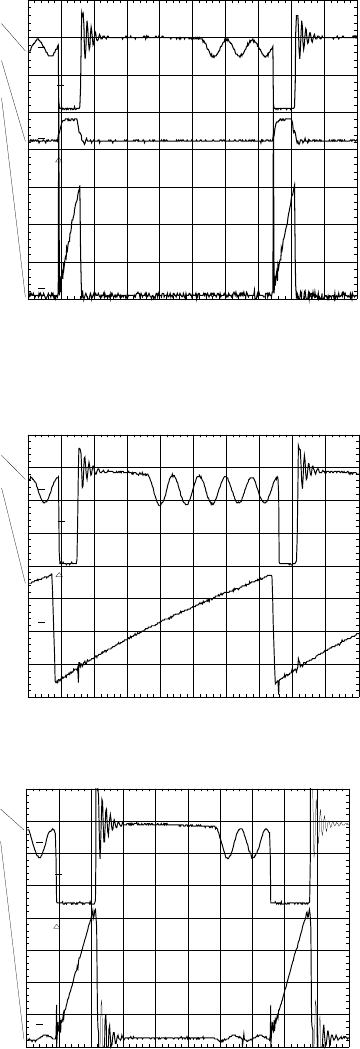

16. CURRENT MODE POWER SUPPLY 20PS203 ...................................................64

17. CIRCUIT DESCRIPTIONS AND ABBREVIATIONS.............................................. 68

18. ELECTRICAL PARTS LIST ................................................................................... 70

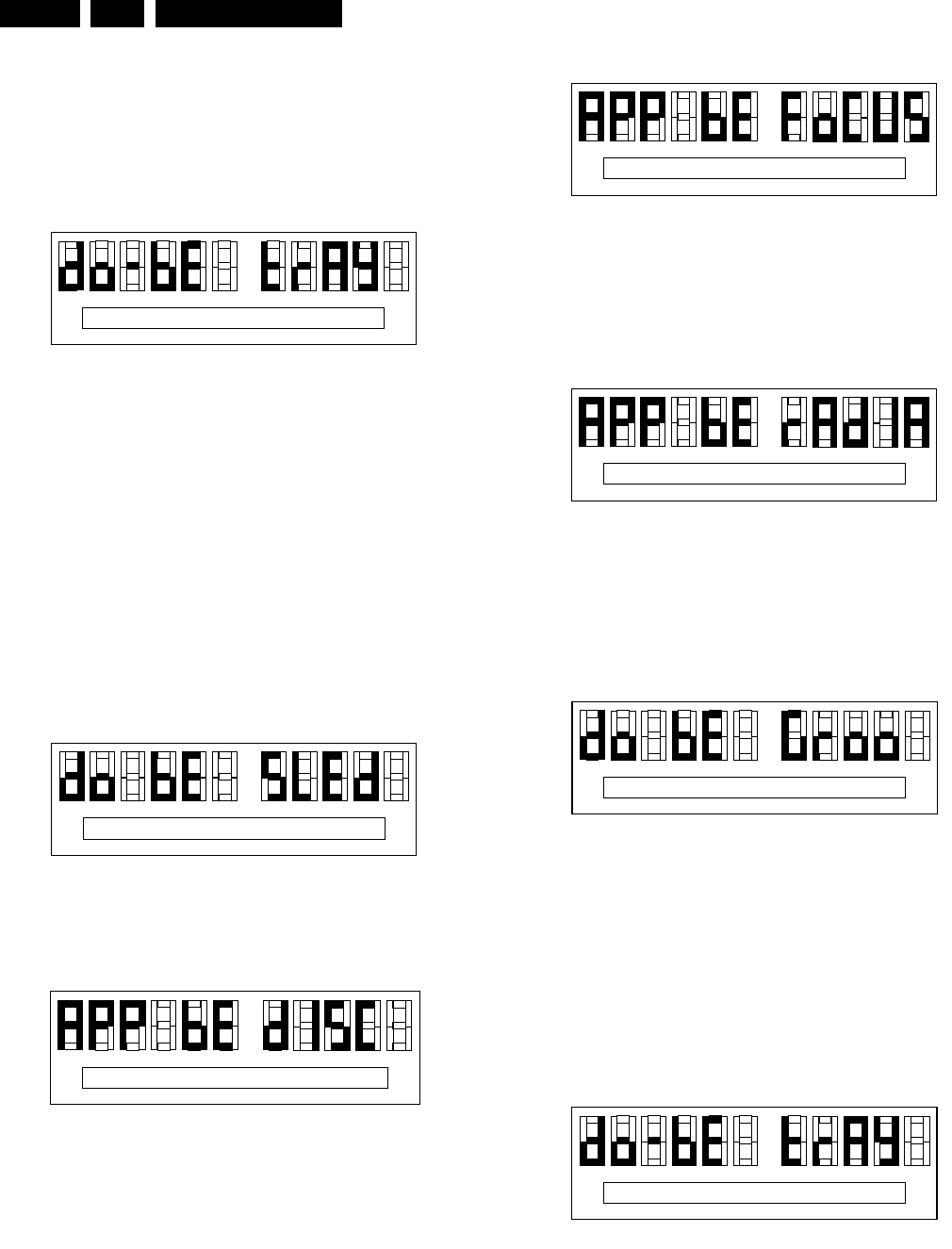

STOP

SOUND

PAUSE

OPEN/CLOSE

ON/OFF

STANDBY

POWER

DVD PLAYER DV4100

PLAY

Printed in Japan

DV4100

MARANTZ DESIGN AND SERVICE

Using superior design and selected high grade components, MARANTZ company has created the ultimate in stereo sound.

Only original MARANTZ parts can insure that your MARANTZ product will continue to perform to the specifications for which

it is famous.

Parts for your MARANTZ equipment are generally available to our National Marantz Subsidiary or Agent.

ORDERING PARTS :

Parts can be ordered either by mail or by Fax.. In both cases, the correct part number has to be specified.

The following information must be supplied to eliminate delays in processing your order :

1. Complete address

2. Complete part numbers and quantities required

3. Description of parts

4. Model number for which part is required

5. Way of shipment

6. Signature : any order form or Fax. must be signed, otherwise such part order will be considered as null and void.

SHOCK, FIRE HAZARD SERVICE TEST :

CAUTION : After servicing this appliance and prior to returning to customer, measure the resistance between either primary AC

cord connector pins ( with unit NOT connected to AC mains and its Power switch ON ), and the face or Front Panel of product and

controls and chassis bottom.

Any resistance measurement less than 1 Megohms should cause unit to be repaired or corrected before AC power is applied, and

verified before it is return to the user/customer.

Ref. UL Standard No. 1492.

In case of difficulties, do not hesitate to contact the Technical

Department at above mentioned address.

001120 A.O

USA

MARANTZ AMERICA, INCMARANTZ AMERICA, INC.

440 MEDINAH ROAD

ROSELLE, ILLINOIS 60172

USA

PHONE : 630 - 307 - 3100

FAX : 630 - 307 - 2687

BRAZIL

PHILIPS DA AMAZONIA IND. ELET. ITDA

CENTRO DE INFORMACOES AO

CEP 04698-970

SAO PAULO, SP, BRAZIL

PHONE : 0800 - 123123(Discagem Direta Gratuita)

FAX : +55 11 534. 8988

JAPAN

Technical

MARANTZ JAPAN, INC.

35- 1, 7- CHOME, SAGAMIONO

SAGAMIHARA - SHI, KANAGAWA

JAPAN 228-8505

PHONE : +81 42 748 1013

FAX : +81 42 741 9190

EUROPE / TRADING

MARANTZ EUROPE B.V.

P.O.BOX 80002, BUILDING SFF2

5600 JB EINDHOVEN

THE NETHERLANDS

PHONE : +31 - 40 - 2732241

FAX : +31 - 40 - 2735578

TECHNICAL AUDIO GROUP PTY, LTD

558 DARLING STREET,

BALMAIN, NSW 2041,

AUSTRALIA

PHONE : 61 - 2 - 9810 - 5300

FAX : 61 - 2 - 9810 - 5355

CANADA

LENBROOK INDUSTRIES LIMITED

633 GRANITE COURT,

PICKERING, ONTARIO L1W 3K1

CANADA

PHONE : 905 - 831 - 6333

FAX : 905 - 831 - 6936

AUSTRALIA

QualiFi Pty Ltd,

24 LIONEL ROAD,

MT. WAVERLEY VIC 3149

AUSTRALIA

PHONE : +61 - (0)3 - 9543 - 1522

FAX : +61 - (0)3 - 9543 - 3677

NEW ZEALAND

WILDASH AUDIO SYSTEMS NZ

14 MALVERN ROAD MT ALBERT

AUCKLAND NEW ZEALAND

PHONE : +64 - 9 - 8451958

FAX : +64 - 9 - 8463554

THAILAND

MRZ STANDARD CO.,LTD

746 - 754 MAHACHAI ROAD.,

WANGBURAPAPIROM, PHRANAKORN,

BANGKOK, 10200 THAILAND

PHONE : +66 - 2 - 222 9181

FAX : +66 - 2 - 224 6795

TAIWAN

PAI- YUING CO., LTD.

6 TH FL NO, 148 SUNG KIANG ROAD,

TAIPEI, 10429, TAIWAN R.O.C.

PHONE : +886 - 2 - 25221304

FAX : +886 - 2 - 25630415

MALAYSIA

WO KEE HONG ELECTRONICS SDN. BHD.

SUITE 8.1, LEVEL 8, MENARA GENESIS,

NO. 33, JALAN SULTAN ISMAIL,

50250 KUALA LUMPUR, MALAYSIA

PHONE : +60 3 - 2457677

FAX : +60 3 - 2458180

AMERICAS

SUPERSCOPE TECHNOLOGIES, INC.

MARANTZ PROFESSIONAL PRODUCTS

2640 WHITE OAK CIRCLE, SUITE A

AURORA, ILLINOIS 60504 USA

PHONE : 630 - 820 - 4800

FAX : 630 - 820 - 8103

AUSTRALIA

KOREA

MK ENTERPRISES LTD.

ROOM 604/605, ELECTRO-OFFICETEL, 16-58,

3GA, HANGANG-RO, YONGSAN-KU, SEOUL

KOREA

PHONE : +822 - 3232 - 155

FAX : +822 - 3232 - 154

SINGAPORE

WO KEE HONG DISTRIBUTION PTE LTD

130 JOO SENG ROAD

#03-02 OLIVINE BUILDING

SINGAPORE 368357

PHONE : +65 858 5535 / +65 381 8621

FAX : +65 858 6078

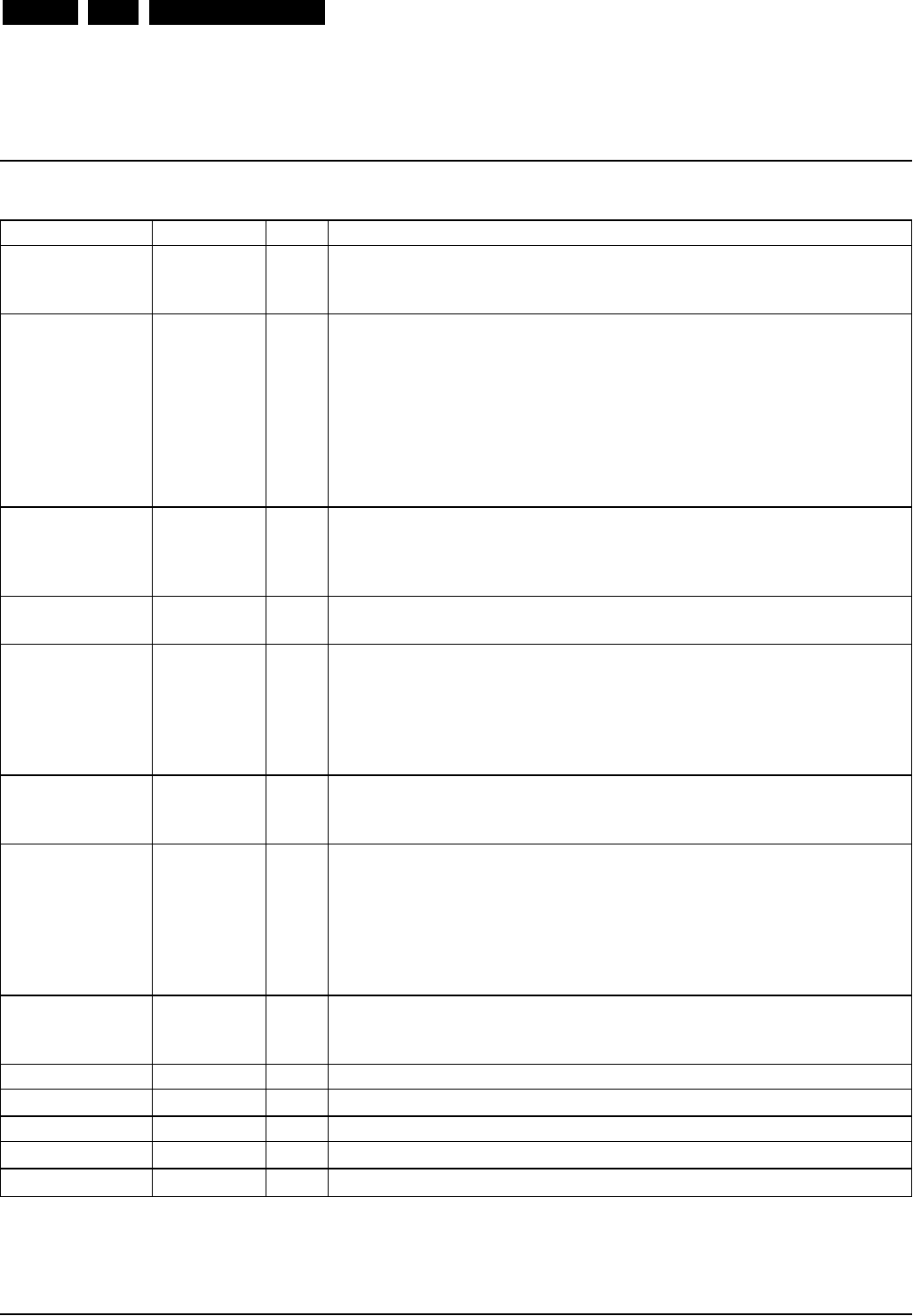

1

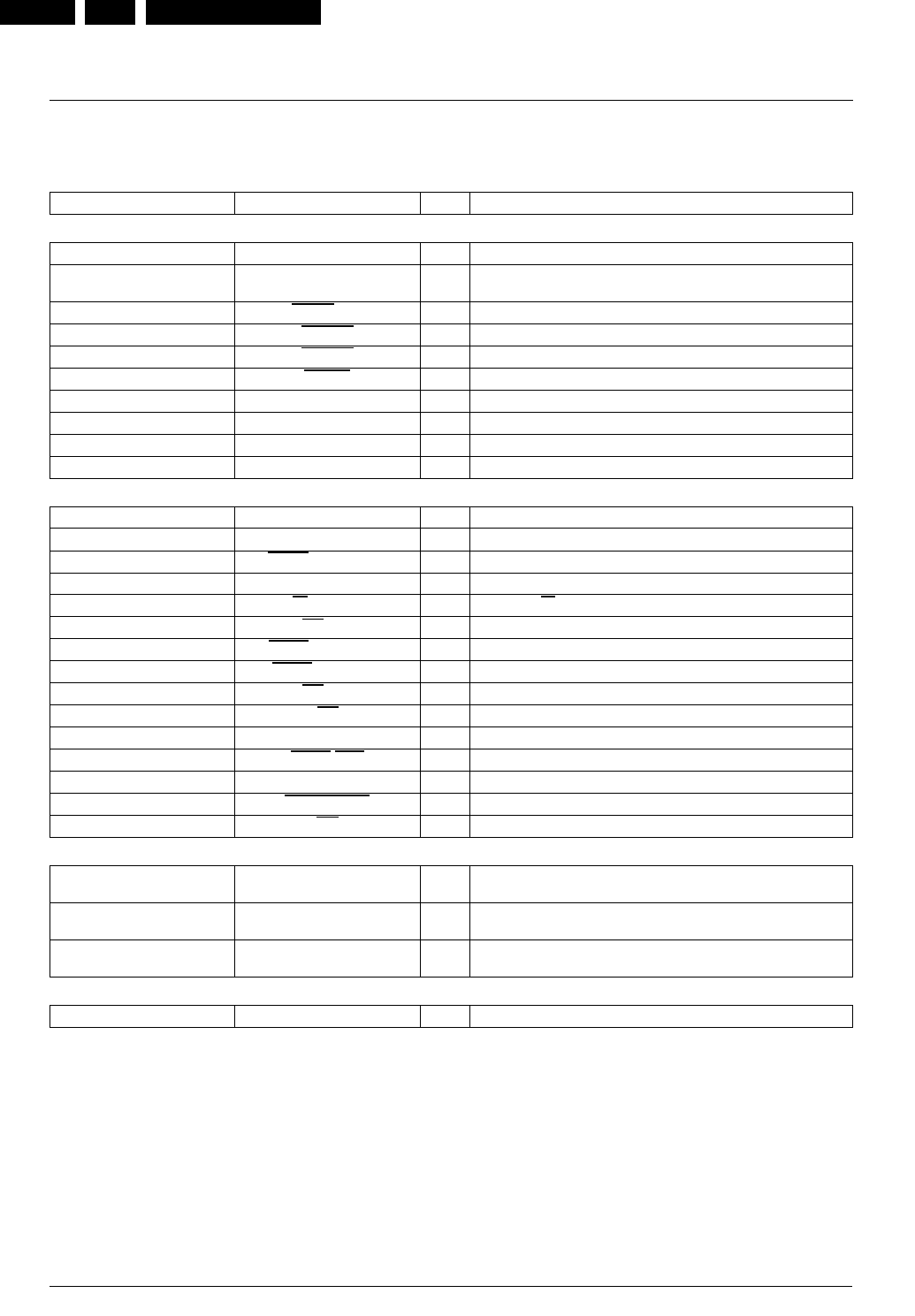

PLAYBACK SYSTEM

DVD-Video

Video CD

CD (CD-R and CD-RW)

OPTICAL READOUT SYSTEM

Lasertype Semiconductor AlGaAs

Numerical Aperture 0.60 (DVD)

0.45 (VCD/CD)

Wavelength 650 nm (DVD)

780 nm (VCD/CD)

DVD DISC FORMAT

Medium Optical Disc

Diameter 12cm (8cm)

Playing time One layer 2.15 h*

(12cm) Dual layer 4 h*

Two side 4.30 h*

Single layer

Two side 8 h*

Dual layer

TV STANDARD EUROPE USA

(PAL/50Hz) (NTSC/60Hz)

Number of lines 625 525

Playback Multistandard (PAL/NTSC)

VIDEO FORMAT

DA Converter 10 bits

Signal handling Components

Digital Compression MPEG2 for DVD,

MPEG1 for VCD

DVD

Horiz. Resolutio 720 pixels** 720 pixels**

Vertical Resolution 576 lines 480 lines

VCD

Horiz. Resolution 352 pixels 352 pixels

Vertical Resolution 288 lines 240 lines

VIDEO PERFORMANCE

Video output 1 Vpp into 75 ohm

S-Video output Y: 1 Vpp into 75 ohm

C: 0.3 Vpp into 75 ohm

RGB output 1 Vpp into 75 ohm

Black Level Shift On/Off

Video Shift Left/Right

AUDIO FORMAT

Digital MPEG Compressed Digital

DTS/AC-3

PCM 16, 20, 24 bits

fs, 44.1, 48, 96 kHz

Analog Sound Stereo

Dolby Pro Logic downmix from AC-3 multi-channel sound

3D Sound for virtual 5.1 channel sound on 2 speakers

AUDIO PERFORMANCE

DA Converter 24 bits

DVD fs 96 kHz 4 Hz - 22kHz

fs 48 kHz 4 Hz - 22 kHz

Video CD fs 48 kHz 4 Hz - 22 kHz

CD fs 44.1 kHz 4 Hz - 20 kHz

Signal-Noise (1kHz) 95 dB

Dynamic Range (1kHz) 90 dB

Crosstalk (1kHz) 110 dB

Distortion and Noise (1kHz) 85 dB

CONNECTIONS

SCART Euroconnector 2x

S-Video Output Mini DIN, 4 pins

Video Output Cinch (yellow)

Audio L+R output Cinch (white/red)

Digital Output 1 coaxial, 1 optical

IEC958 for CDDA / LPCM

IEC1937 for MPEG1/2,

AC-3 and DTS

CABINET

Dimensions(w x h x d) 440 x 92 x 305 mm

Weight Approx. 3.8 Kg

PACKAGE CONTENTS

DVD-Video Player

Remote Control & Batteries

AC Power cable

User Manual

SCART cable (Euroconnector)

Audio/Video cable

GENERAL FUNCTIONALITY

Stop / Play / Pause

Fast Forward / Backward

Time search

Step Forward / Backward

Slow

Title / Chapter / Track Select

Skip Next / Skip Previous

Repeat (Chapter / Title / All) or (Track / All)

A-B Repeat

Shuffle

Enhanced ease of use graphical interface

Perfect Still with digital multi-tap filter

Zoom (x1.33, x2, x4) with picture enhancement

3D Sound

Virtual jog shuttle

Audio and video bit rate indicator

(only available in certain countries)

DVD FUNCTIONALITY

Multi-angle Selection

Audio Selection (1 out of max. 8 languages)

Subtitles Selection (1 out of max. 32 languages)

Aspect Ratio conversion (16:9, 4:3 Letterbox, 4:3 Pan Scan)

Parental Control and Disk Lock

Disc Menu support (Title Menu and Root Menu)

Resume (5 discs) after stop / standby

Screen Saver (Dim 75% after 15 min.)

Programming Titles/chapters with Favorite Selection

VIDEO CD FUNCTIONALITY

Playback Control for VCD 2.0 discs

Parental Control and Disc lock

Resume (5 discs) after stop / standby

Screen Saver (Dim 75% after 15 min.)

Programming Tracks with Favorite Selection

AUDIO CD FUNCTIONALITY

Time Display (Total / Track )

Full audio functionality with remote control

Programming with Favorite Track Selection

* typical playing time for movie with 2 spoken languages and 3 subtitle languages.

** equivalent to 500 lines on your TV

Specifications subject to change without prior notice

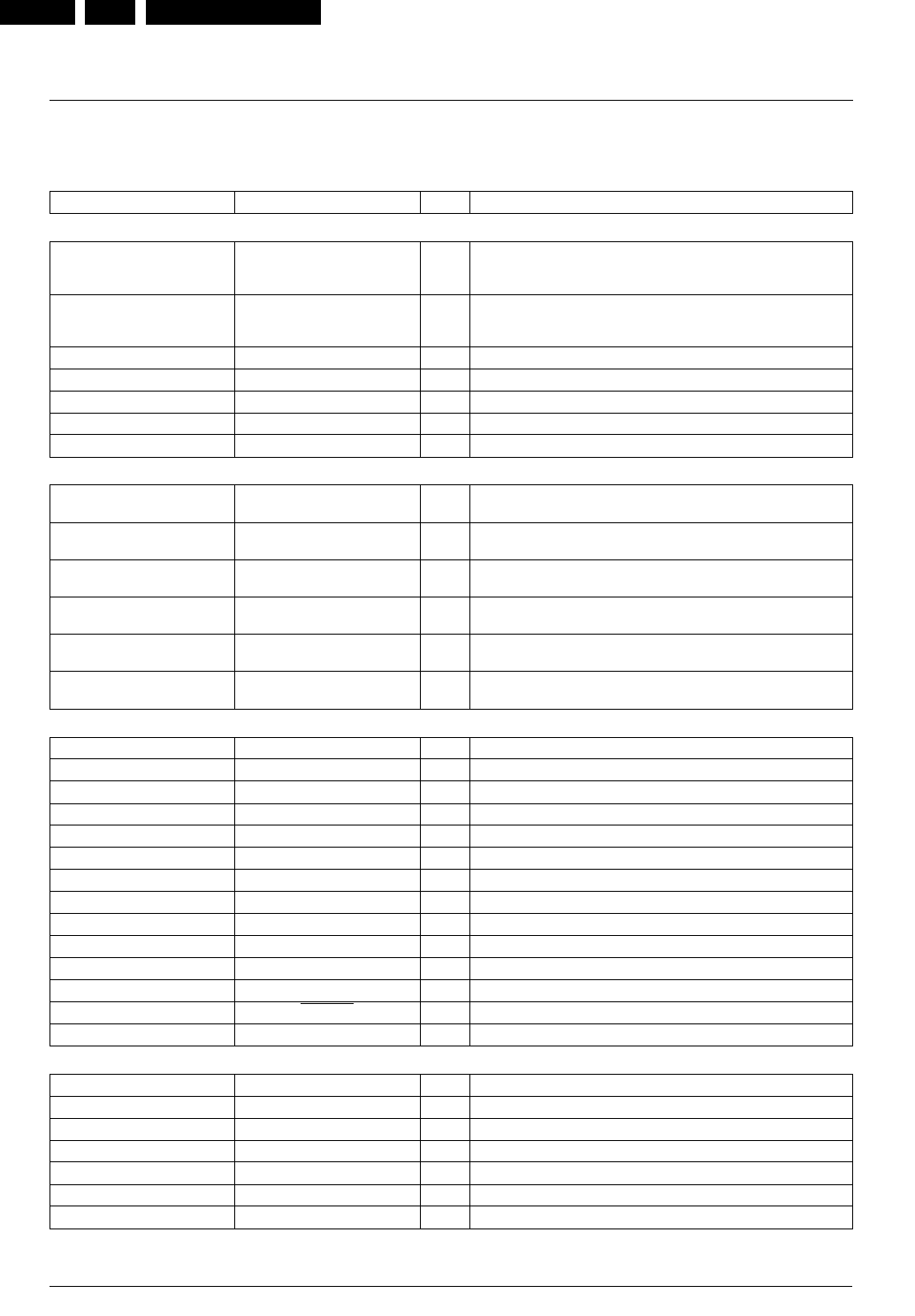

1. TECHHNICAL SPECIFICATIONS (/N1B)

PLAYBACK SYSTEM

DVD-Video

Video CD

CD (CD-R and CD-RW)

OPTICAL READOUT SYSTEM

Lasertype Semiconductor AlGaAs

Numerical Aperture 0.60 (DVD)

0.45 (VCD/CD)

Wavelength 650 nm (DVD)

780 nm (VCD/CD)

DVD DISC FORMAT

Medium Optical Disc

Diameter 12cm (8cm)

Playing time One layer 2.15 h*

(12cm) Dual layer 4 h*

Two side 4.30 h*

Single layer

Two side 8 h*

Dual layer

TV STANDARD EUROPE USA

(PAL/50Hz) (NTSC/60Hz)

Number of lines 625 525

Playback Multistandard (PAL/NTSC)

VIDEO FORMAT

DA Converter 10 bits

Signal handling Components

Digital Compression MPEG2 for DVD,

MPEG1 for VCD

DVD

Horiz. Resolution 720 pixels* 720 pixels**

Vertical Resolution 576 line 480 lines

VCD

Horiz. Resolution 352 pixel 352 pixels

Vertical Resolution 288 line 240 lines

VIDEO PERFORMANCE

Video output 1 Vpp into 75 ohm

S-Video output Y: 1 Vpp into 75 ohm

C: 0.3 Vpp into 75 ohm

Y 1 Vpp into 75 ohm

C

R

0.7 Vpp into 75 ohm

C

B

0.7 Vpp into 75 ohm

Black Level Shift On/Off

Video Shift Left/Right

AUDIO FORMAT

Digital MPEG Compressed

DTS/AC-3

PCM 16, 20, 24 bits

fs, 48, 96 kHz

Analog Sound Stereo

Dolby Pro Logic downmix from AC-3 multi-channel sound

3D Sound for virtual 5.1 channel sound on 2 speakers

AUDIO PERFORMANCE

DA Converter 24 bits

DVD fs 96 kHz 4 Hz - 44 kHz

fs 48 kHz 4 Hz - 22 kHz

Video CD fs 48 kHz 4 Hz - 22 kHz

CD fs 44.1 kHz 4 Hz - 20 kHz

Signal-Noise (1kHz) 95 dB

Dynamic Range (1kHz) 90 dB

Crosstalk (1kHz) 110 dB

Distortion and Noise (1kHz) 85 dB

CONNECTIONS

S-Video Output Mini DIN, 4 pins

Component Video Y Cinch (green)

U (C

R

) Cinch (blue)

V (C

B

) Cinch (red)

Video Output Cinch (yellow) 2x

Audio L+R output Cinch (white/red) 2x

Digital Output 1 coaxial, 1 optical

IEC958 for CDDA / LPCM

IEC1937 for MPEG1/2,

AC-3 and DTS

CABINET

Dimensions (w x h x d) 440 x 92 x 305mm

Weight Approx. 3.8 Kg

PACKAGE CONTENTS

DVD-Video Player

Remote Control & Batteries

AC power cord

User Manual

Audio/Video cord

GENERAL FUNCTIONALITY

Stop / Play / Pause

Fast Forward / Backward

Time search

Step Forward / Backward

Title / Chapter / Track Select

Skip Next / Skip Previous

Repeat (Chapter / Title / All) or (Track / All)

A-B Repeat

Shuffle

Enhanced ease of use graphical interface

Perfect Still with digital multi-tap filter

Zoom (x1.33 x2. x4) with picture enhancement

3D Sound

Virtual Jog Shuttle

Audio and video bit rate indicator

(only available in certain countries)

DVD FUNCTIONALITY

Multi-angle Selection

Audio Selection (1 out of max. 8 languages)

Subtitles Selection (1 out of max. 32 languages)

Aspect Ratio conversion (16:9, 4:3 Letterbox, 4:3 Pan Scan)

Parental Control and Disk Lock

Disc Menu support (Title Menu and Root Menu)

Resume (5 discs) after stop / standby

Screen Saver (Dim 75% after 15 min.)

Programming Titles/chapters with Favorite Selection

VIDEO CD FUNCTIONALITY

Playback Control for VCD 2.0 discs

Parental Control and Disc lock

Resume (5 discs) after stop / standby

Screen Saver (Dim 75% after 15 min.)

Programming Tracks with Favorite Selection

AUDIO CD FUNCTIONALITY

Time Display (Total / Track )

Full audio functionality with remote control

Programming with Favorite Track Selection

* typical playing time for movie with 2 spoken languages and 3 subtitle languages.

** equivalent to 500 lines on your TV

Specifications subject to change without prior notice

2

(/A1B, /S1G, /U1B)

1 2

2

2

5

5

4

4

3

6

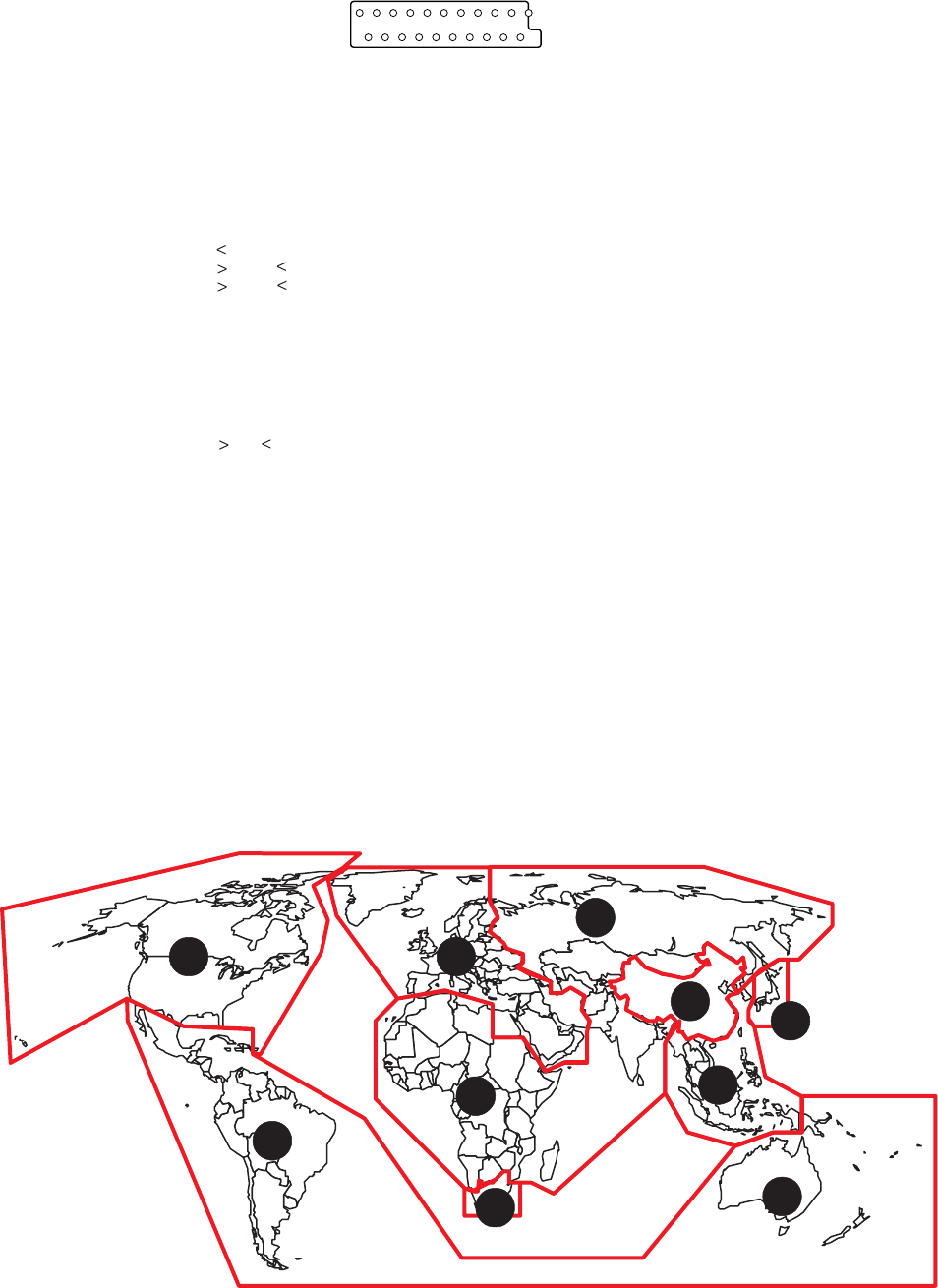

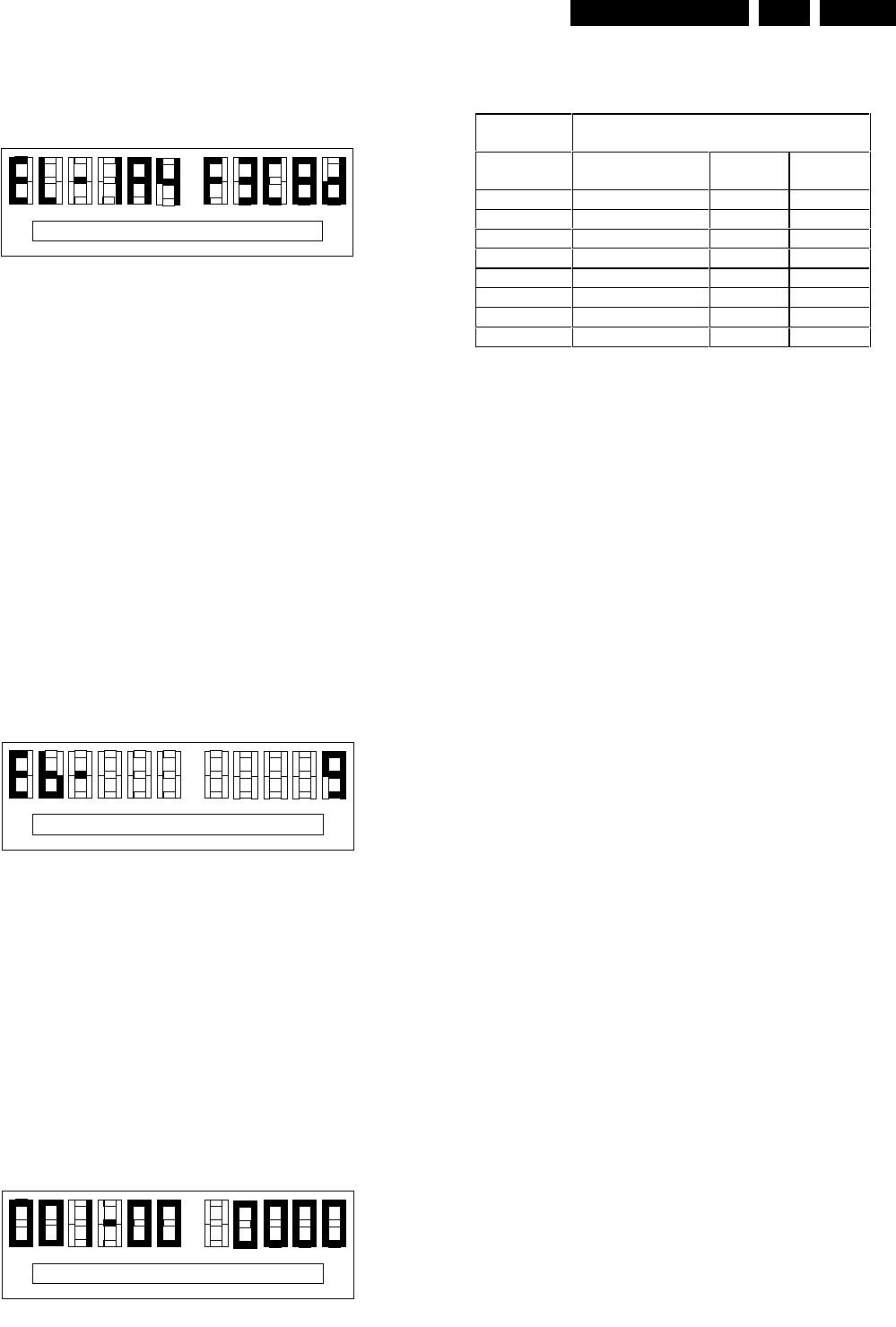

Map of DVD Regions

What are "regional codes"?

Motion picture studios want to control the home release of movies in different countries because theater releases arenít

simultaneous (a movie may come out on DVD in the US when itís just hitting screens in Europe). Therefore they have

required that the DVD standard include codes which can be used to lock out the playback of certain discs in certain geo-

graphical regions. Players sold in each region will have that regionís code built into the player. The player will refuse to play

these "region coded" discs which are not allowed in the region. However, regional codes are entirely optional. Discs without

codes will play on any player in any country. Some studios have already announced that only their new releases will have

regional codes. There are six regions:

1. United States and Canada

2. Europe and Japan

3. Far East (except Japan & China)

4. South America and Oceania

5. Africa and the Middle East

6. China (except Hong Kong)

3

2. CONNECTION FACILITIES

1 3 5 7 9 11 13 15 17 19

21

2 4 6 8 10 12 14 16 18 20

2-1 Video performance (/N1B only)

SCART (/N1B versions only)

Full according PQR3 IMS

Connector implementation according EN50049-1; color = black; dual SCART

Fully according to prEN1057-2-1

Signal switching is P50 controlled; supported features of mode 3 see survey of applicable standards.

2-1-1 SCART II (connected to TV)

Pin signals:

1 Output Audio R 1.8V RMS

2 Input Audio R

3 Output Audio L 1.8V RMS

4 Audio GND

5 Blue/Chroma GND

6 Input Audio L

7 Bi-dir Blue out/Chroma in 0.7pp +/-0.1V into 75 Ohm (*)

8 Output Function switch 2V = TV

4.5V / 7V = asp. ratio 16:9 DVD

9.5V / 12V = asp. ratio 4:3 DVD

9 Green GND

10 Bi-dir P50 control

11 Output Green 0.7Vpp +/-0.1V into 75 Ohm (*)

12 not connected

13 Red/Chroma GND

14 fast switch GND

15 Output Red out/Chroma out 0.7Vpp +/-0.1V into 75 Ohm (*)

+/-3dB 0.3Vpp in case of Chroma

16 Output fast switch RGB 1V / 3V into 75 Ohm = RGB

/CVBS or Y

0.4V into 75 Ohm = CVBS

17 Y/CVBS GND

18 fast switching GND

19 Output CVBS/Y/RGB sync 1Vpp +/-0.1V into 75 Ohm (*)

20 Input CVBS/Y

21 Shield

SCART I (connected to AUX)

Pin signals:

1 Output Audio R 1.8V RMS

2 Input Audio R

3 Output Audio L 1.8V RMS

4 Audio GND

5 Blue/Chroma GND

6 Input Audio L

7 Bi-dir Blue in/Chroma out +/-3dB 0.3Vpp Chroma

8 Input Function switch

9 Green GND

10 Bi-dir P50 control

11 Input Green

12 not connected

13 Red/Chroma GND

14 fast switch GND

15 Input Red in/Chroma in

16 Input fast switch RGB/CVBS or Y

17 CVBS GND

18 fast switching GND

19

20 Input CVBS/Y

21 Shield

(*) for 100% white

4

3. INFORMATIONS

REGION CODE

THE DISCS THAT THE DV4100 CAN HANDLE

The following discs can be played back with a DV4100.

Note: The regional code of the discs must meet to the regional

code of the DV4100.

DVD INFORMATION

Below is a glossary of the new terms related to DVD.

Title:

A disc may have more than one story/movie on it, so each

story/movie is called a “title”.

For example, if there are 2 movies on the disc, they are

separated into Title 1 and Title 2.

Chapter:

A title may also be separated into chapters.

For example, a movie (title) may be separated into 3 scenes

(chapters).

Subtitles:

DVDs are recorded with up to 32 different subtitle languages.

If a disc has more than one subtitle language, you can select

the subtitle language that you want to read.

Soundtrack language:

DVDs are recorded with up to 8 different soundtrack languages.

If a disc has more than one language, you can select the

soundtrack language that you want to listen to.

disc mark playback capability size side

DVD Audio/Video 12 cm single/double

8 cm

CD Audio 12 cm single

8 cm

12 cm

VCD Audio/Video single

8 cm

VERSION REGION CODE COUNTRY

/N1B 2 EUROPE

/S1G 3 ASIAN PACIFIC

/U1B 1 USA/CANADA

/A1B 4 AUSTRALIA

Multi-angles:

On some DVDs, scenes have been filmed from different angles

(up to a maximum of 9). On these discs, you can select the

angle that you want to watch. Please refer to the DVD’s manual

to see which scenes have multi-angles.

Title 1 Title 2

Chapter

3Chapter

1Chapter

2Chapter

3

Chapter

1Chapter

2

It is important to note that CD-R, CD-RW discs must be

FINALIZED before they can be played on this player. The disc

types which run on the player feature one or more of these

logos on the disc packaging.

5

4. SERVICING HINT

SERVICE TOOLS

Audio signals disc 4822 397 30184

Disc without errors (SBC444)+

Disc with DO errors, black spots and fingerprints (SBC444A) 4822 397 30245

Disc (65 min 1kHz) without no pause 4822 397 30155

Max. diameter disc (58.0 mm) 4822 397 60141

Torx screwdrivers

Set (straight) 4822 395 50145

Set (square) 4822 395 50132

13th order filter 4822 395 30204

DVD test disc

TEST software for PC : ComPair V1. 2

ComPair V1. 3

Connection Cable

4822 397 10131

4822 727 21634

4822 727 21637

3122 785 90017

SERVICE HINTS

6

5. WARNING AND LASER SAFETY INSTRUCTIONS

SHOCK, FIRE HAZARD SERVICE TEST:

CAUTION: After servicing this appliance and prior to returning to customer, measure the resistance between

either primary AC cord connector pins (with unit NOT connected to AC mains and its Power switch ON), and the

face or Front Panel of product and controls and chassis bottom,

Any resistance measurement less than 1 Megohms should cause unit to be repaired or corrected before AC

power is applied, and verified before return to user/customer.

Ref.UL Standard NO.1492.

NOTE ON SAFETY:

Symbol : Fire or electrical shock hazard. Only original parts should be used to replace any part with symbol

Any other component substitution(other than original type), may increase risk or fire or electrical shock hazard.

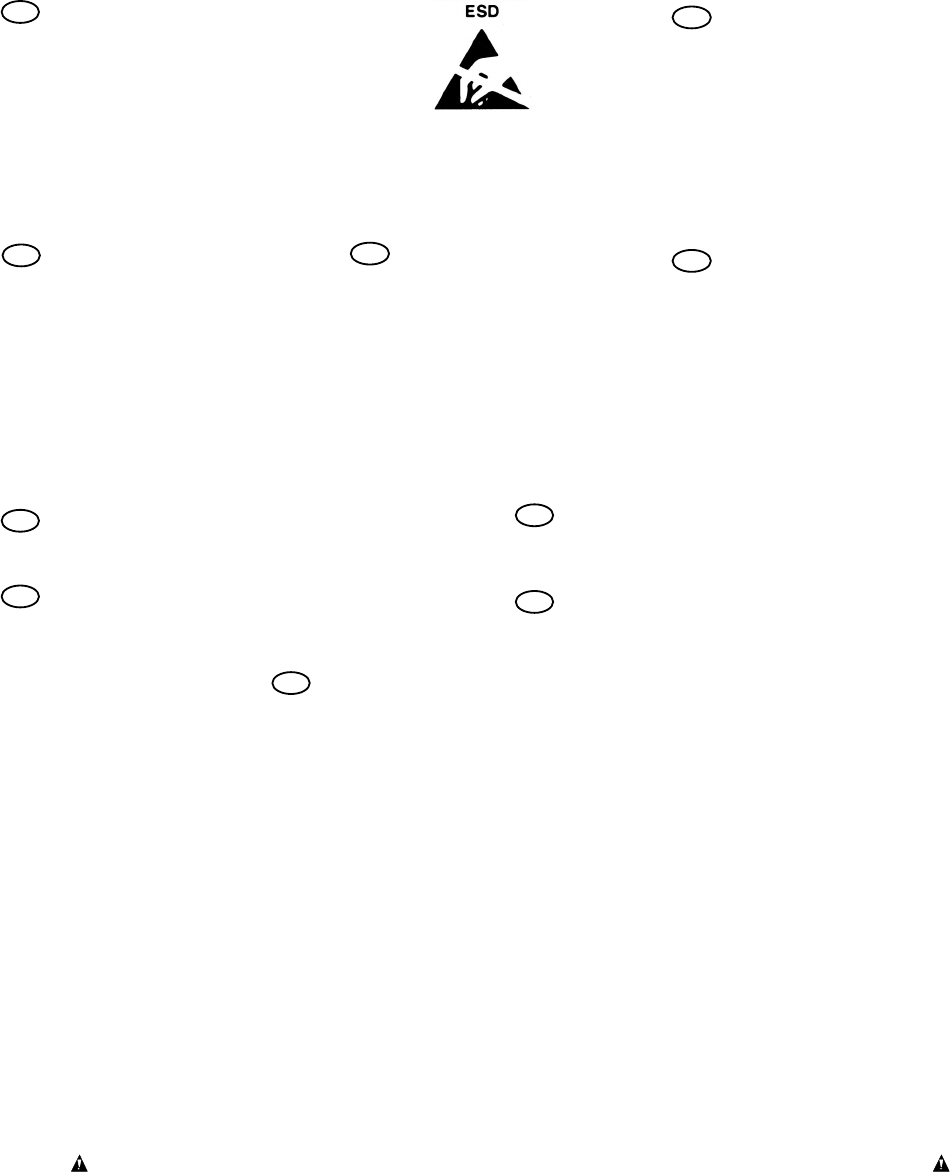

FATTENTION

Tous les IC et beaucoup d’autres semi-

conducteurs sont sensibles aux décharges

statiques (ESD).

Leur longévité pourrait être considérablement

écourtée par le fait qu’aucune précaution

n’est prise a leur manipulation.

Lors de réparations, s’assurer de bien être

relié au même potentiel que la masse de

l’appareil et enfiler le bracelet serti d’une

résistance de sécurité.

Veiller a ce que les composants ainsi que les

outils que l’on utilise soient également a ce

potentiel.

DWARNUNG

Alle IC und viele andere Halbleiter sind

empfindlich gegen elektrostatische

Entladungen (ESD).

Unsorgfältige Behandlung bei der Reparatur

kann die Lebensdauer drastisch vermindern.

Sorgen sie dafür, das Sie im Reparaturfall

über ein Pulsarmband mit Widerstand mit

dem Massepotential des Gerätes verbunden

sind.

Halten Sie Bauteile und Hilfsmittel ebenfalls

auf diesem Potential.

WAARSCHUWING

Alle IC’s en vele andere halfgeleiders zijn

gevoelig voor elektrostatische ontladingen

(ESD).

Onzorgvuldig behandelen tijdens reparatie

kan de levensduur drastisch doen

verminderen.

Zorg ervoor dat u tijdens reparatie via een

polsband met weerstand verbonden bent met

hetzelfde potentiaal als de massa van het

apparaat.

Houd componenten en hulpmiddelen ook op

ditzelfde potentiaal.

AVVERTIMENTO

Tutti IC e parecchi semi-conduttori sono

sensibili alle scariche statiche (ESD).

La loro longevita potrebbe essere fortemente

ridatta in caso di non osservazione della piu

grande cauzione alla loro manipolazione.

Durante le riparazioni occorre quindi essere

collegato allo stesso potenziale che quello

della massa dell’apparecchio tramite un

braccialetto a resistenza.

Assicurarsi che i componenti e anche gli

utensili con quali si lavora siano anche a

questo potenziale.

All ICs and many other semi-conductors are

susceptible to electrostatic discharges (ESD).

Careless handling during repair can reduce

life drastically.

When repairing, make sure that you are

connected with the same potential as the

mass of the set via a wrist wrap with

resistance.

Keep components and tools also at this

potential.

WARNING

Safety regulations require that the set be restored to its original condition

and that parts which are identical with those specified be used.

Veiligheidsbepalingen vereisen, dat het apparaat in zijn oorspronkelijke

toestand wordt terug gebracht en dat onderdelen, identiek aan de

gespecifieerde worden toegepast.

Bei jeder Reparatur sind die geltenden Sicherheitsvorschriften zu beachten.

Der Originalzustand des Gerats darf nicht verandert werden.

Fur Reparaturen sind Original-Ersatzteile zu verwenden.

Le norme di sicurezza esigono che l’apparecchio venga rimesso nelle

condizioni originali e che siano utilizzati pezzi di ricambiago idetici a quelli

specificati.

Les normes de sécurité exigent que l’appareil soit remis a l’état d’origine et

que soient utilisées les pièces de rechange identiques à celles spécifiées.

GB NL

I

D

I

F

GB

NL

7

LASER SAFETY

This

this unit employs a laser. Only a qualified service person should remove the cover or attempt to service

device, due to possible eye injury.

LASER DEVICE UNIT

Type: Semiconductor laser GaAlAs

Wave length: 650 nm (DVD)

780 nm (VCD/CD)

Output Power: 7 mW (DVD)

10 mW (VCD/CD)

Beam divergence: 60 degree

USE OF CONTROLS OR ADJUSTMENTS OR PERFORMANCE OF PROCEDURE OTHER THAN

THOSESPECIFIED HEREIN MAY RESULT IN HAZARDOUS RADIATION EXPOSURE.

AVOID DIRECT EXPOSURE TO BEAM

WARNING

The use of optical instruments with this product will increase eye hazard.

Repair handling should take place as much as possible with a disc loaded inside the player

WARNING LOCATION: INSIDE ON LASER COVERSHIELD

CAUTION VISIBLE AND INVISIBLE LASER RADIATION WHEN OPEN AVOID EXPOSURE TO BEAM

ADVARSEL SYNLIG OG USYNLIG LASERSTRÅLING VED ÅBNING UNDGÅ UDSÆTTELSE FOR STRÅLING

ADVARSEL SYNLIG OG USYNLIG LASERSTRÅLING NÅR DEKSEL ÅPNES UNNGÅ EKSPONERING FOR STRÅLEN

VARNING SYNLIG OCH OSYNLIG LASERSTRÅLNING NÄR DENNA DEL ÄR ÖPPNAD BETRAKTA EJ STRÅLEN

VARO! AVATT AESSA OLET ALTTIINA NÄKYVÄLLE JA NÄKYMÄTTÖMÄLLE LASER SÄTEILYLLE. ÄLÄ KATSO SÄTEESEEN

VORSICHT SICHTBARE UND UNSICHTBARE LASERSTRAHLUNG WENN ABDECKUNG GEÖFFNET NICHT DEM STRAHL AUSSETSEN

DANGER VISIBLE AND INVISIBLE LASER RADIATION WHEN OPEN AVOID DIRECT EXPOSURE TO BEAM

ATTENTION RAYO NNEMENT LASER VISIBLE ET INVISIBLE EN CAS D'OUVERTURE EXPOSITION DANGEREUSE AU FAISCEAU

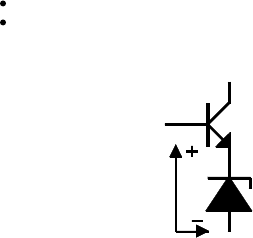

Warning for powersupply on position 1005

The primary side of the powersupply including the heatsink carrieslive mains voltage when the

player is connected to the mains even when the player is swiched off !

This primary area is not shielded so it is possible to touc h copper tracks and/or components when

servicing the player. Service personnel have to take precautions to prevent touching this area or

components in this area .

The primary side of the powersupply has been indicated with a lightning stroke and a stripe-marked

printed on the printed wiring board

Note:

The screws on the basic Engine (position 218 in on the exploded view drawing) may never be

touched removed or re-adjusted.

Handle the Basic engine with care when the unit has to be exchanged!

The mechanism of the basic engine is very sensative for droping or shocks

!

6. SERVICE HINTS

8

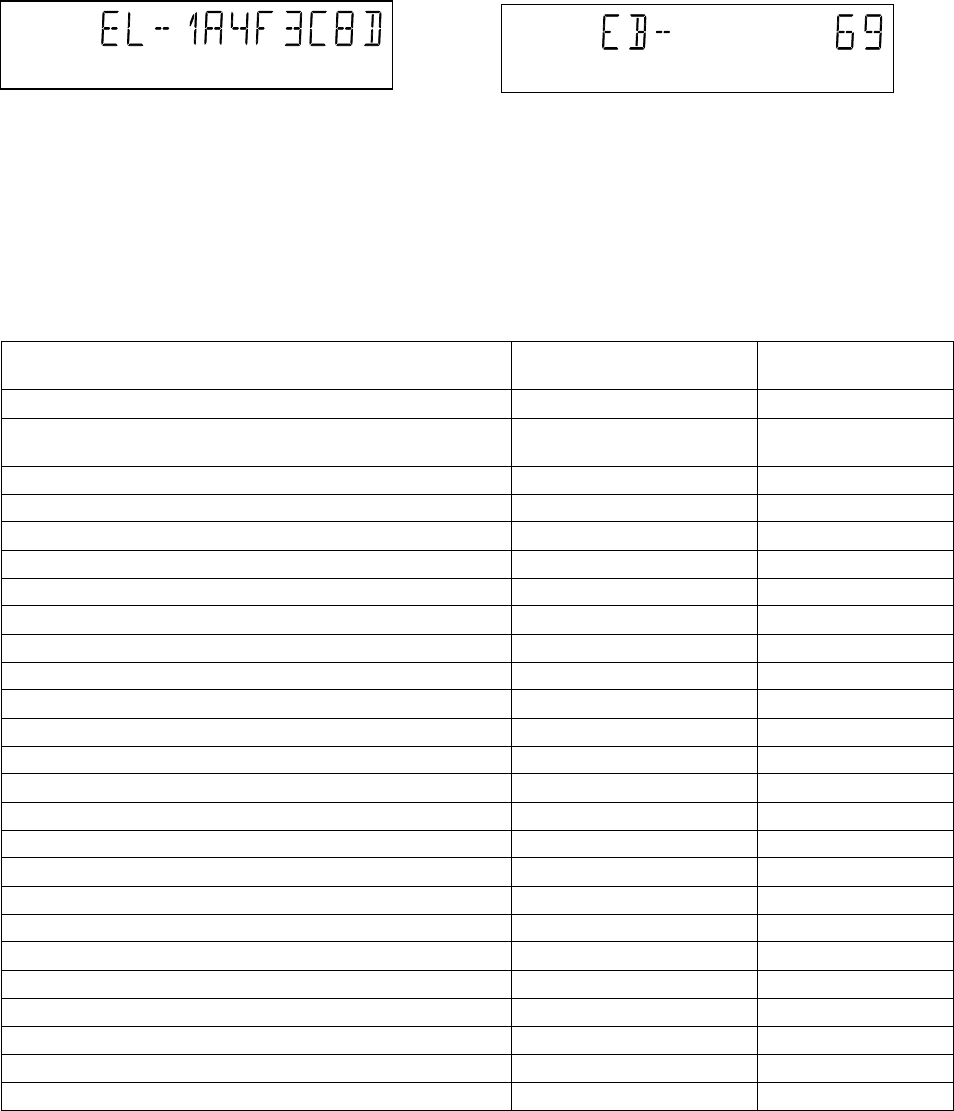

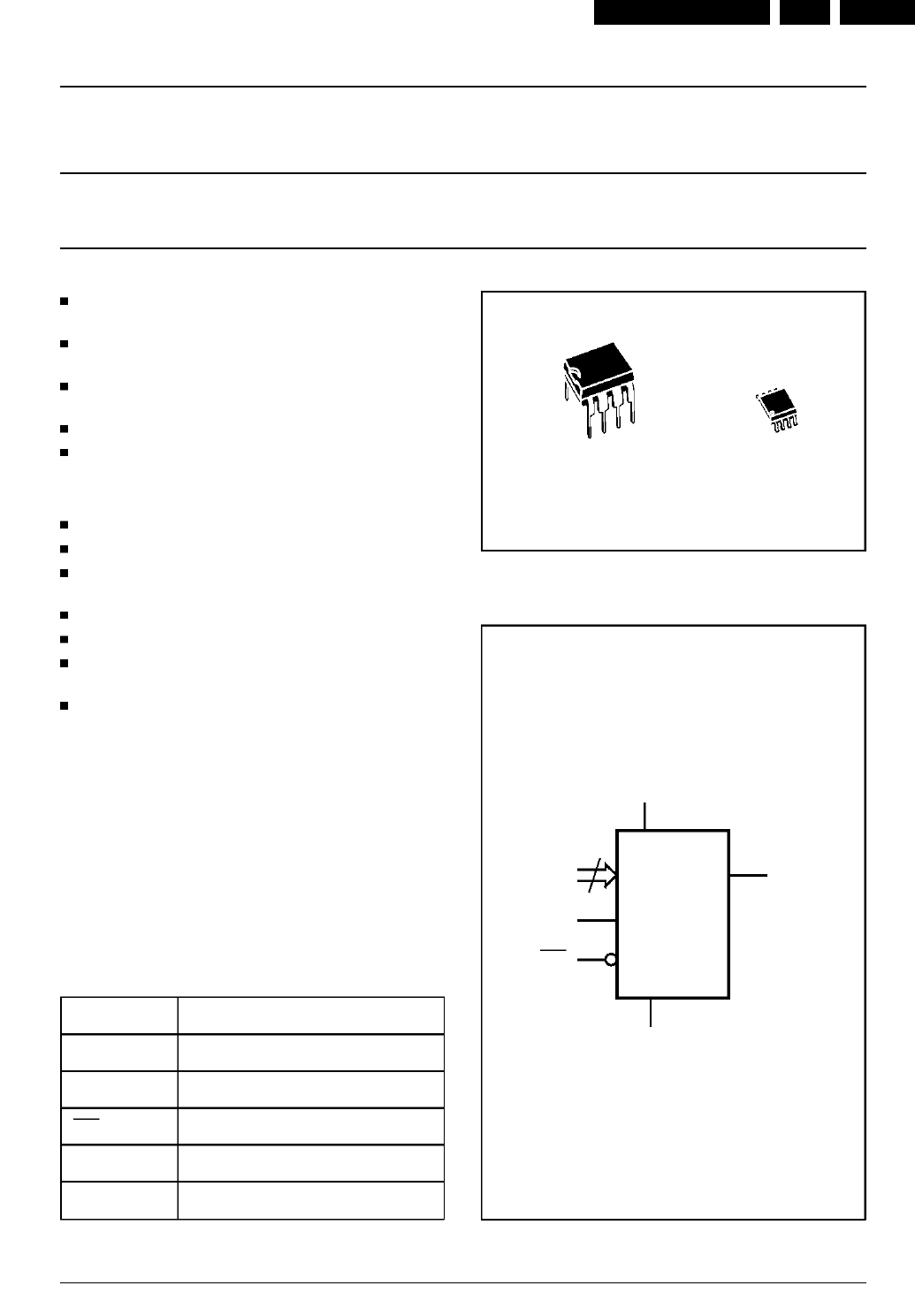

6.1 DVD-Module 218

The DVD mechanism has to be exchanged completely in case

of failure. A new or repaired mechanism can be ordered with

codenumber 9305 023 61001.

Return the defective unit complete assembled in original

package to Philips Consumer Service in Eindhoven.

The monoboard has to be repaired on component level.

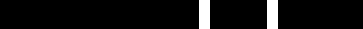

6.2 Diagnostic software

In chapter “Diagnostic software” some tests are refering to the

SCART functionality.

These tests are for sets with RGB-output.

For sets without RGB-output no SCART connector is mounted.

In these sets the SCART tests will automatically be skipped

6.3 Power Supply options

6.4 Compair

For assistance with the repair process of the monoboard an

electronic Fault finding guidance has been developed , this

program is called COMPAIR.

This COMPAIR program is available on CDROM.

The Version of the CDROM for repair of the monoboard is V1.3

and can be ordered with codenumber : 4822 727 21637.

This is an update CDROM , so when the COMPAIR CDROM is

used for the first time , one has to install the COMPAIR

ENGINE CDROM V1.2 first.

The V1.2 CDROM can be ordered with codenumber 4822 727

634 and has to registered after installation , the procedure for

registration is explained in the help file of the program and in

the booklet from the CDROM.

The cable to connect the monoboard with a PC can be ordered

with codenumber 3122 785 90017.

All the hardware and software requirements of the systems

necessary for working with COMPAIR is described on the

CDROM.

6.5 Monoboard repair

For repair of the monoboard the service manual 3122 785

10045 must be used.

3122 427 21750 3122 427 21370 3122 427 21760

110V USA 220V Europe China Multi voltage A/P

2261 CAP 330pF 2121 ELCO 100uF 385V 2261 CAP 330pF

2121 ELCO 150uF 250V 2121 ELCO 150uF 400V

3133 Resistor 10M

910

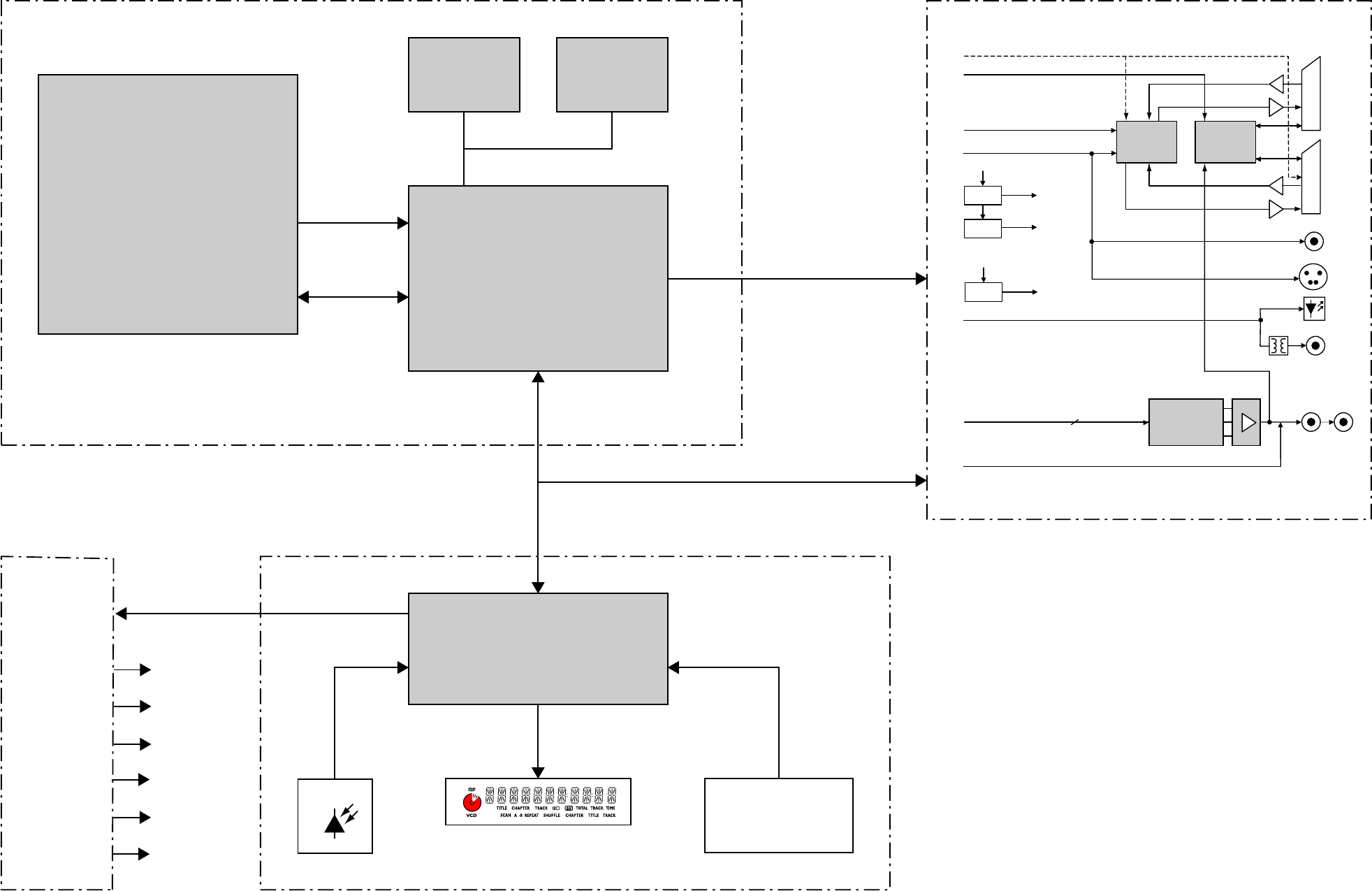

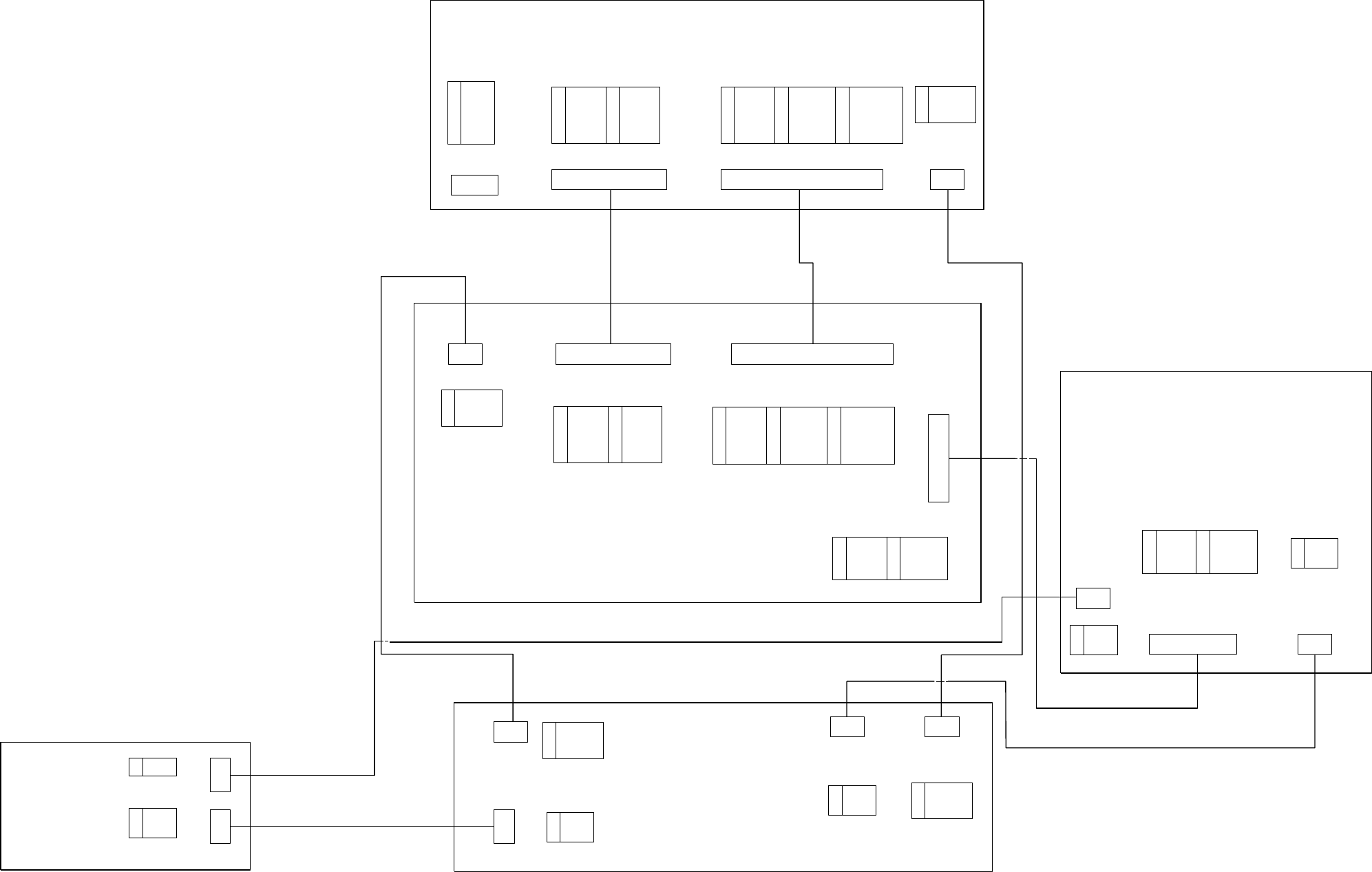

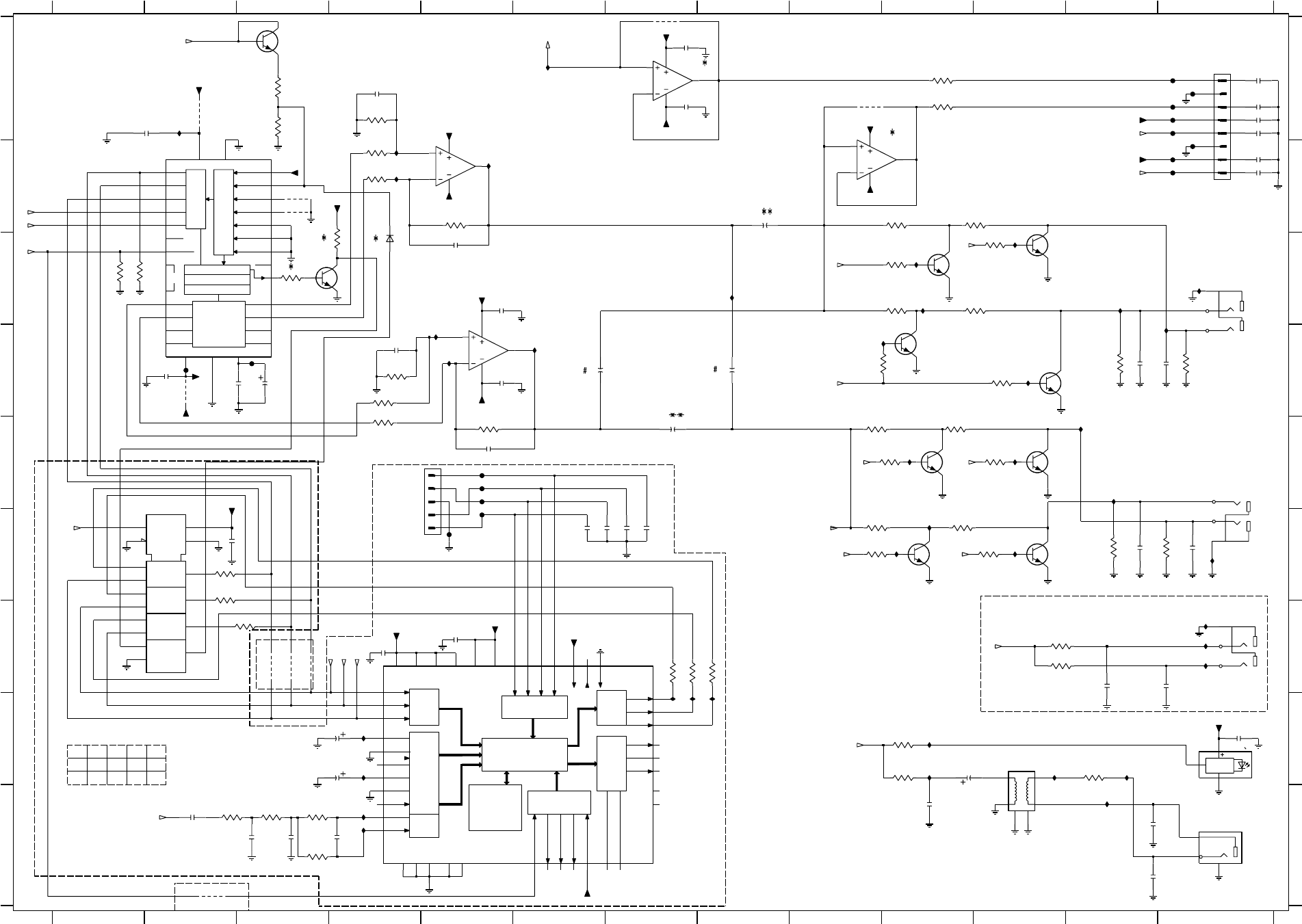

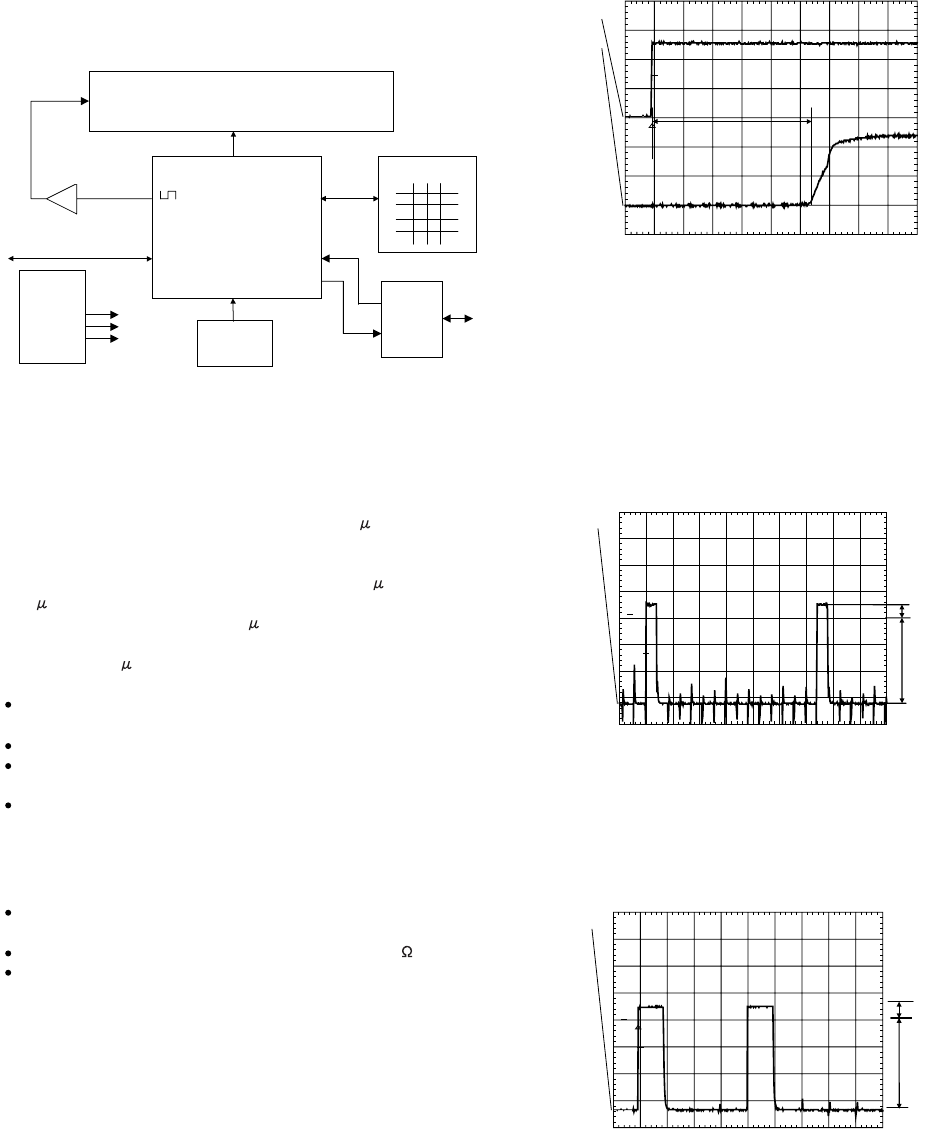

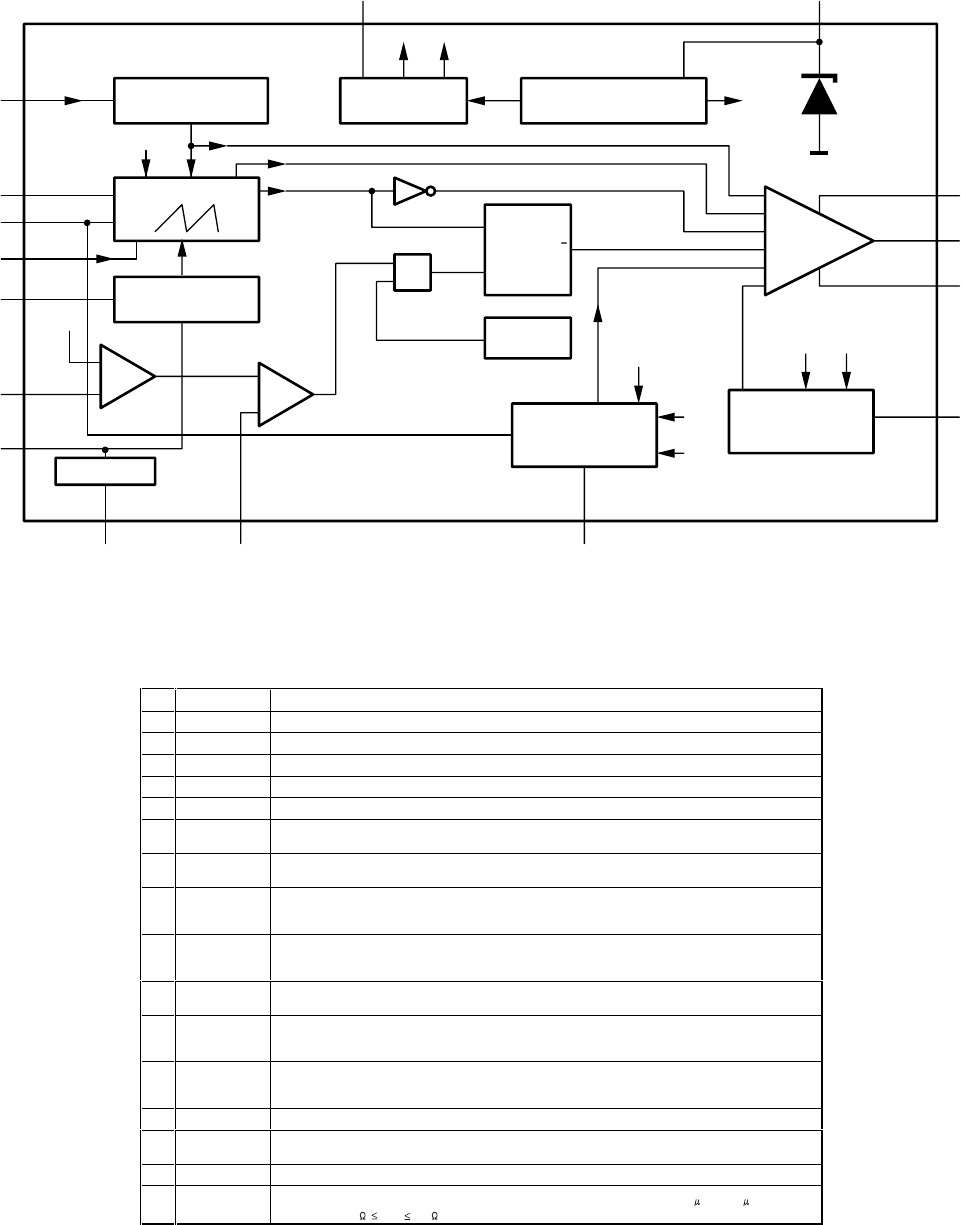

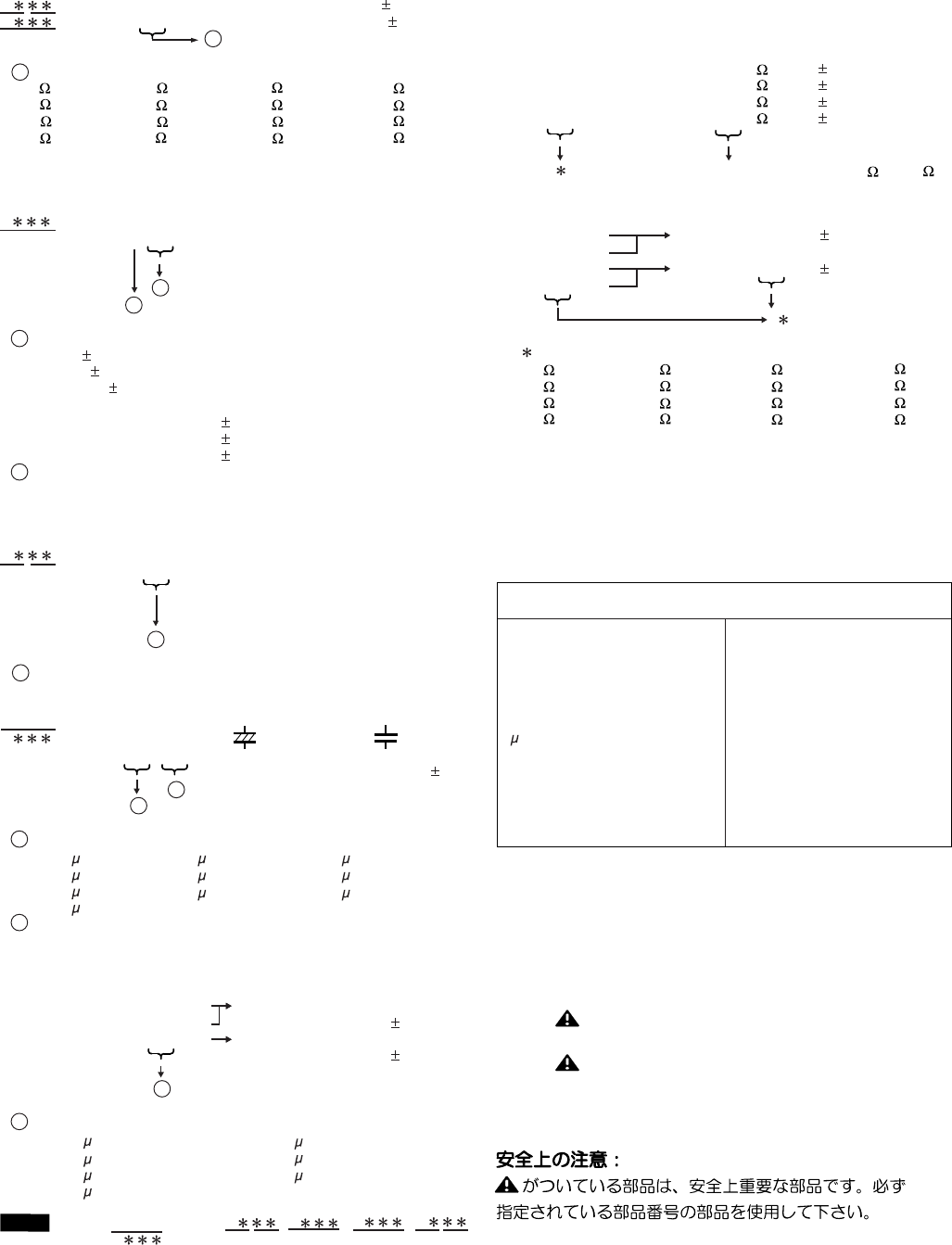

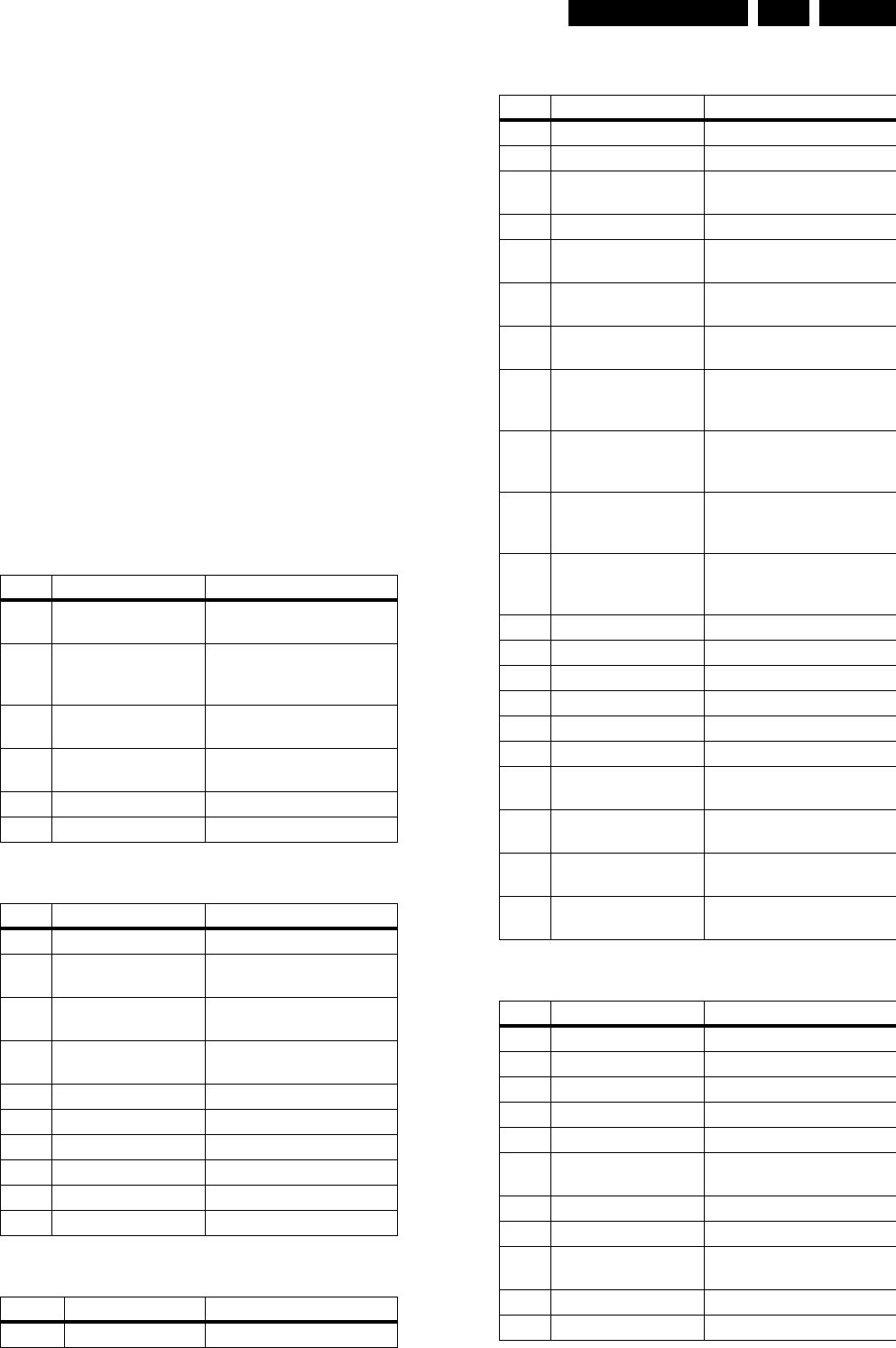

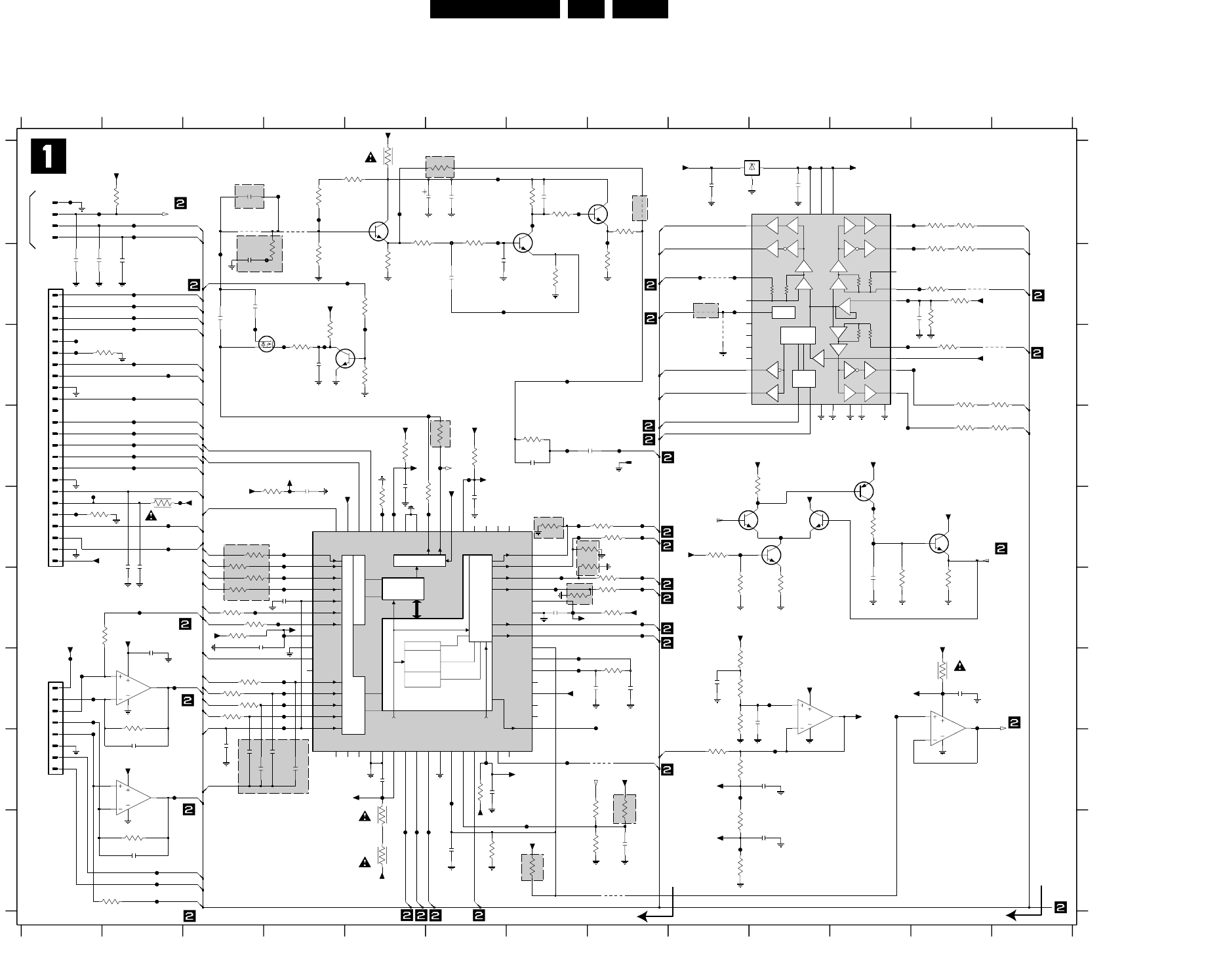

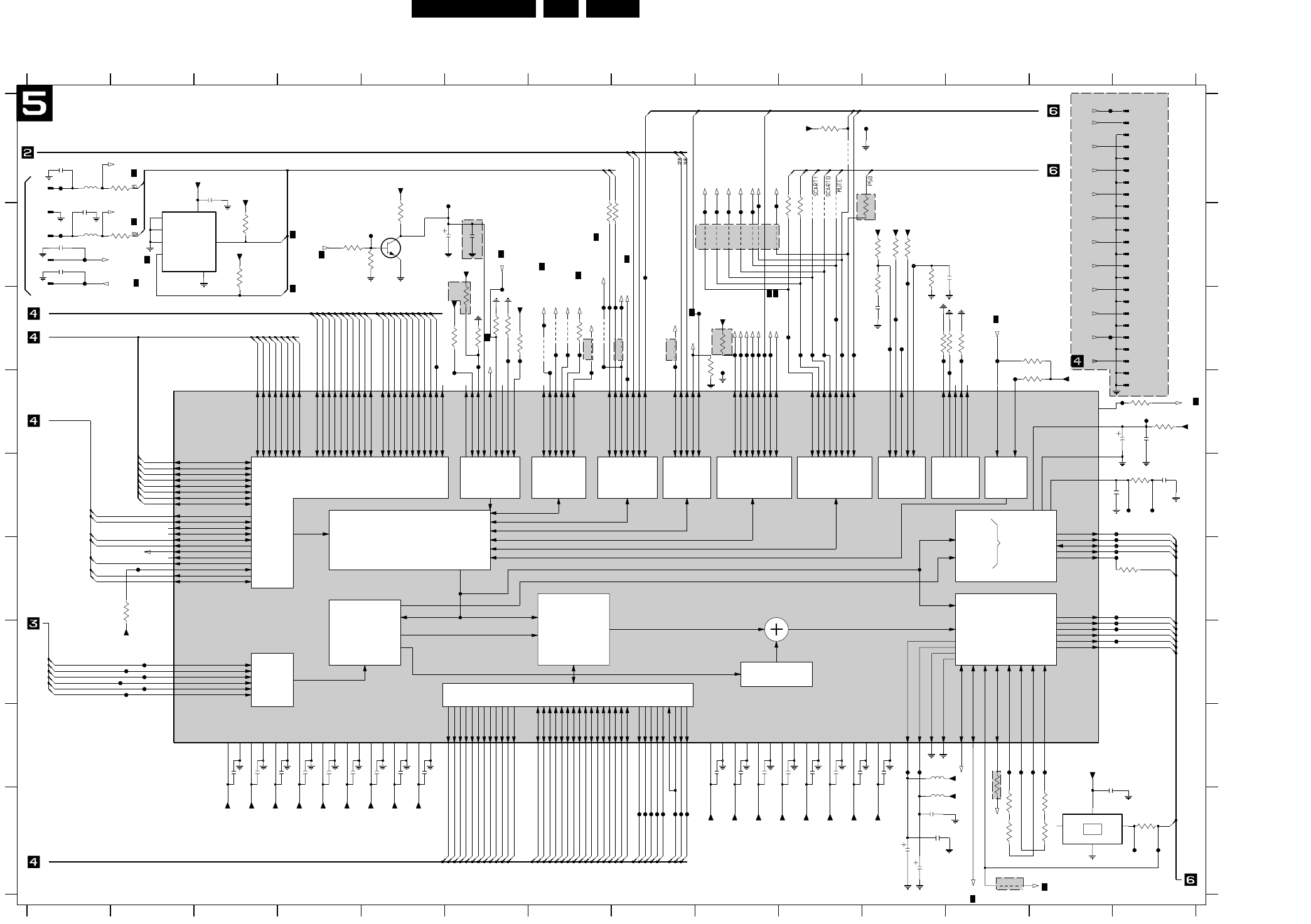

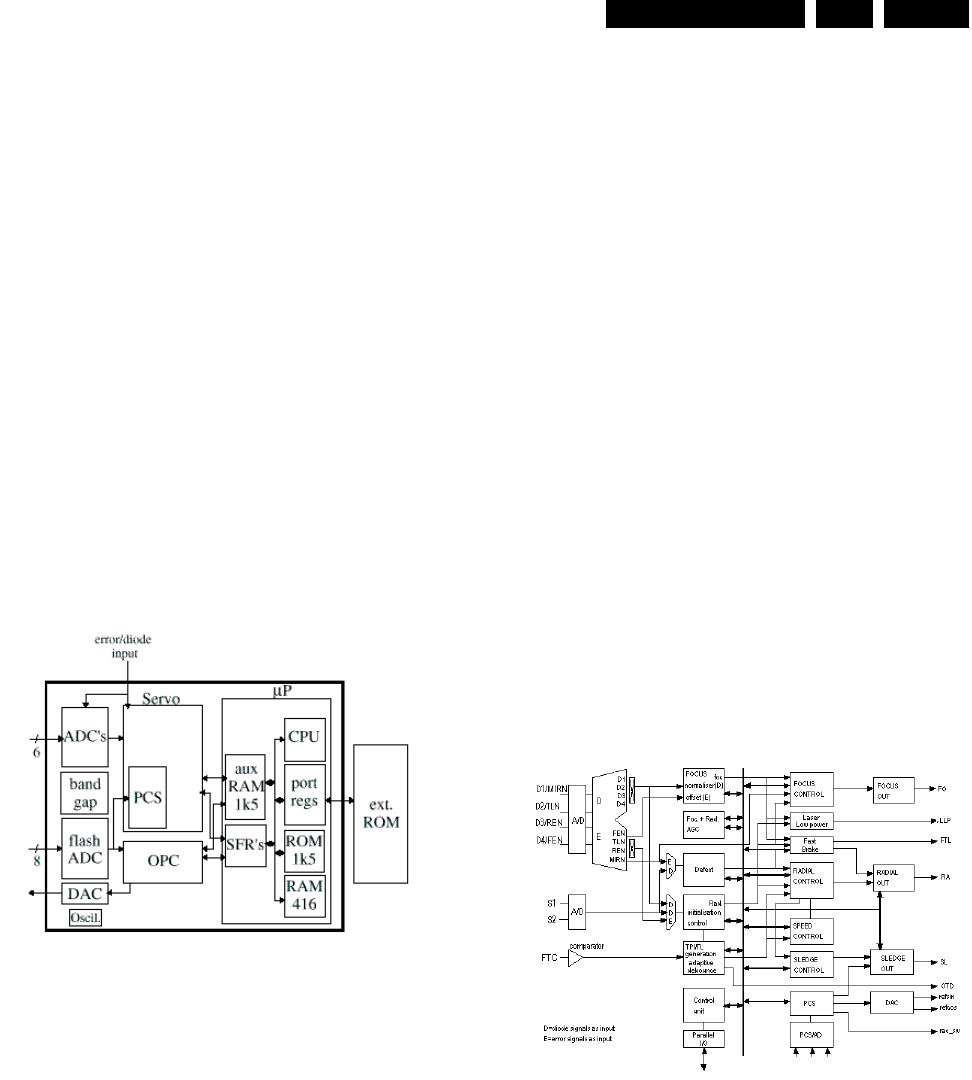

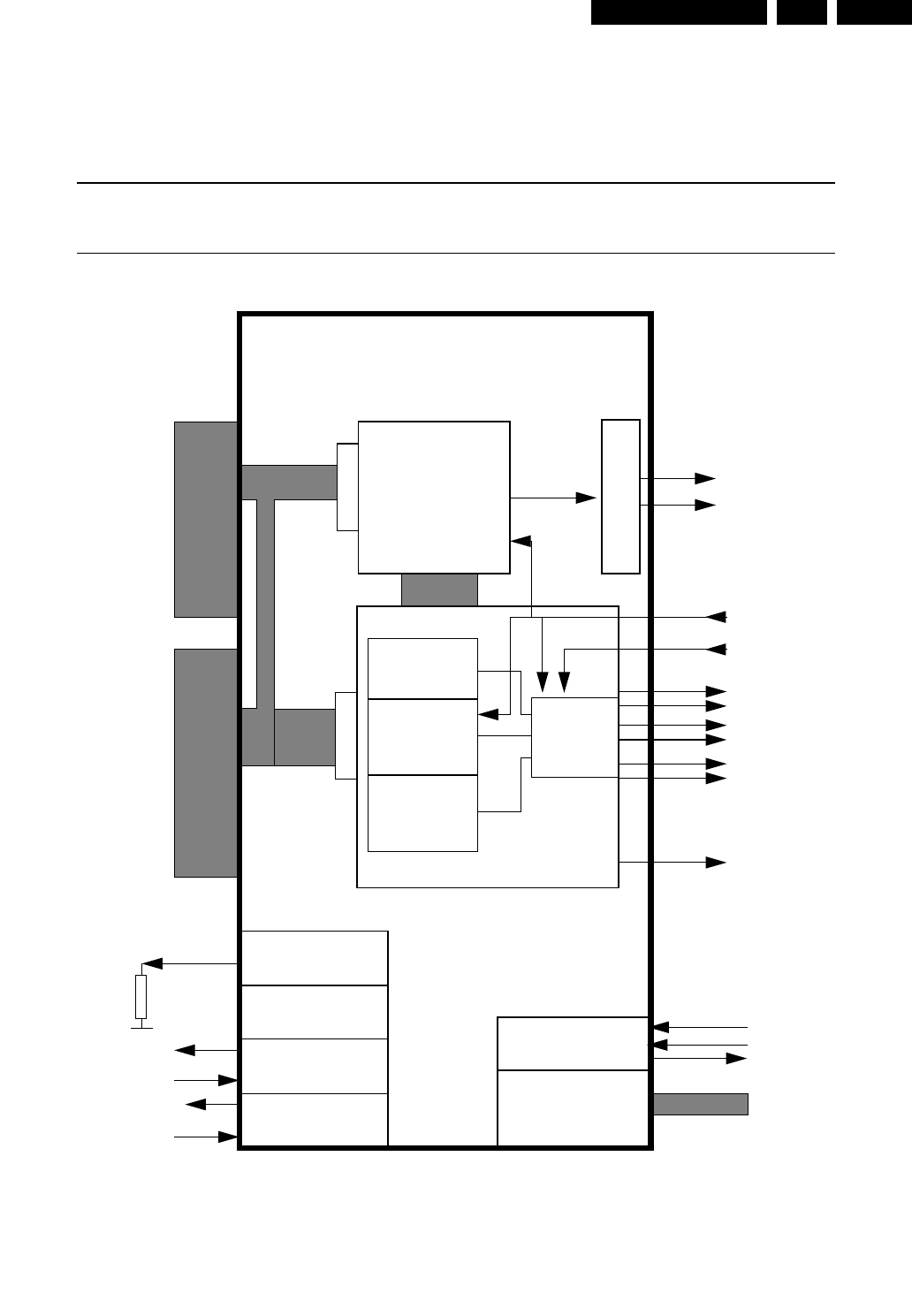

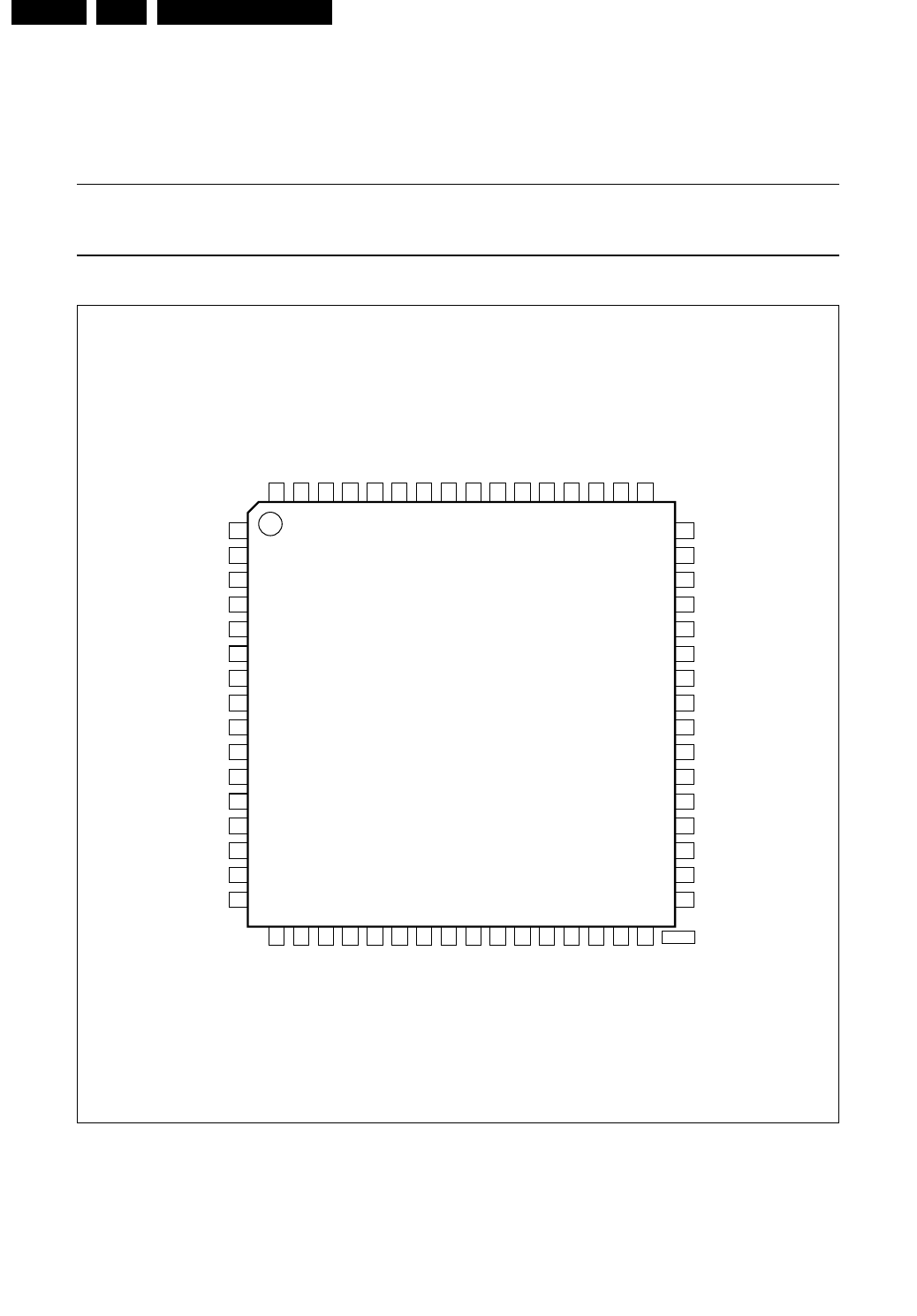

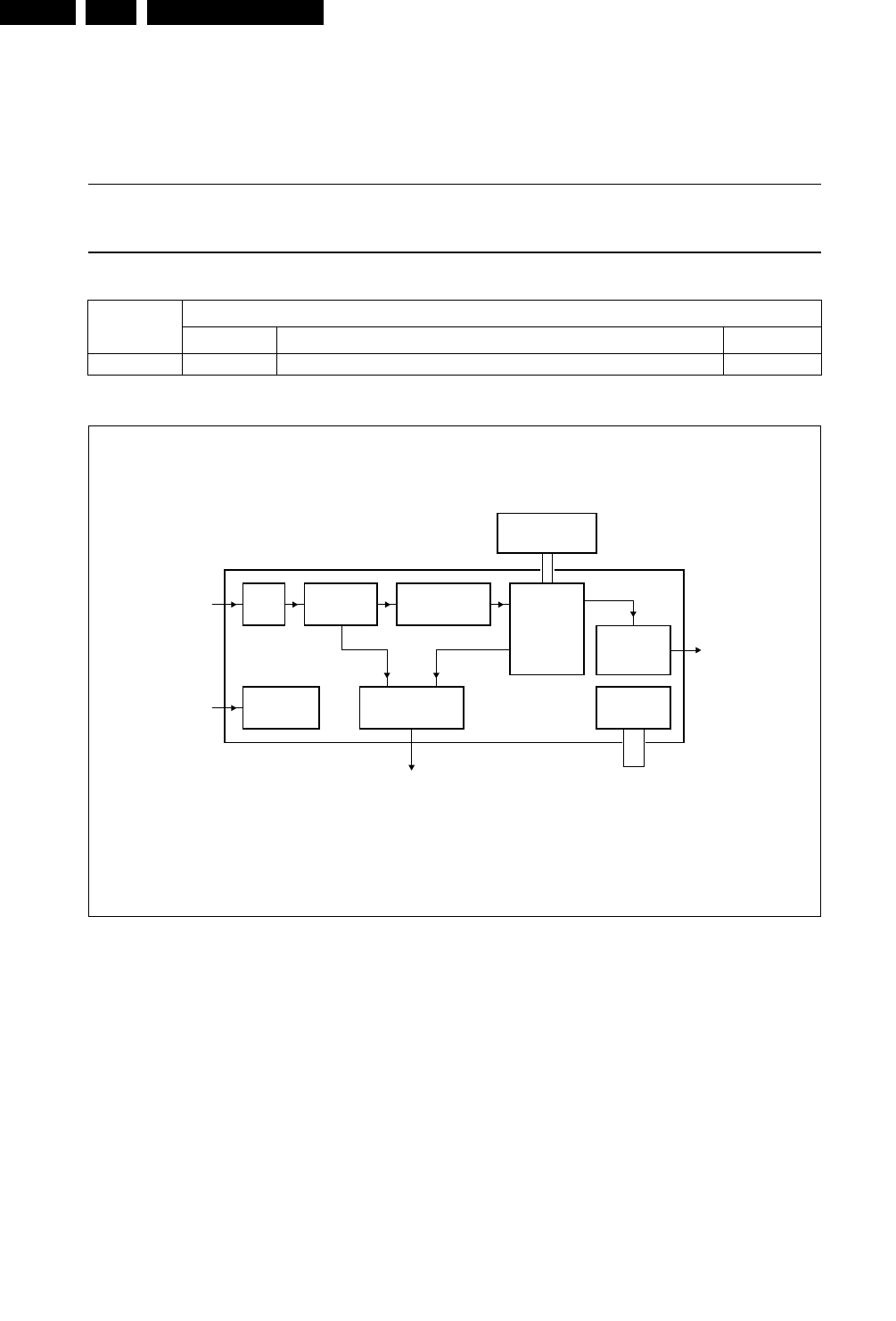

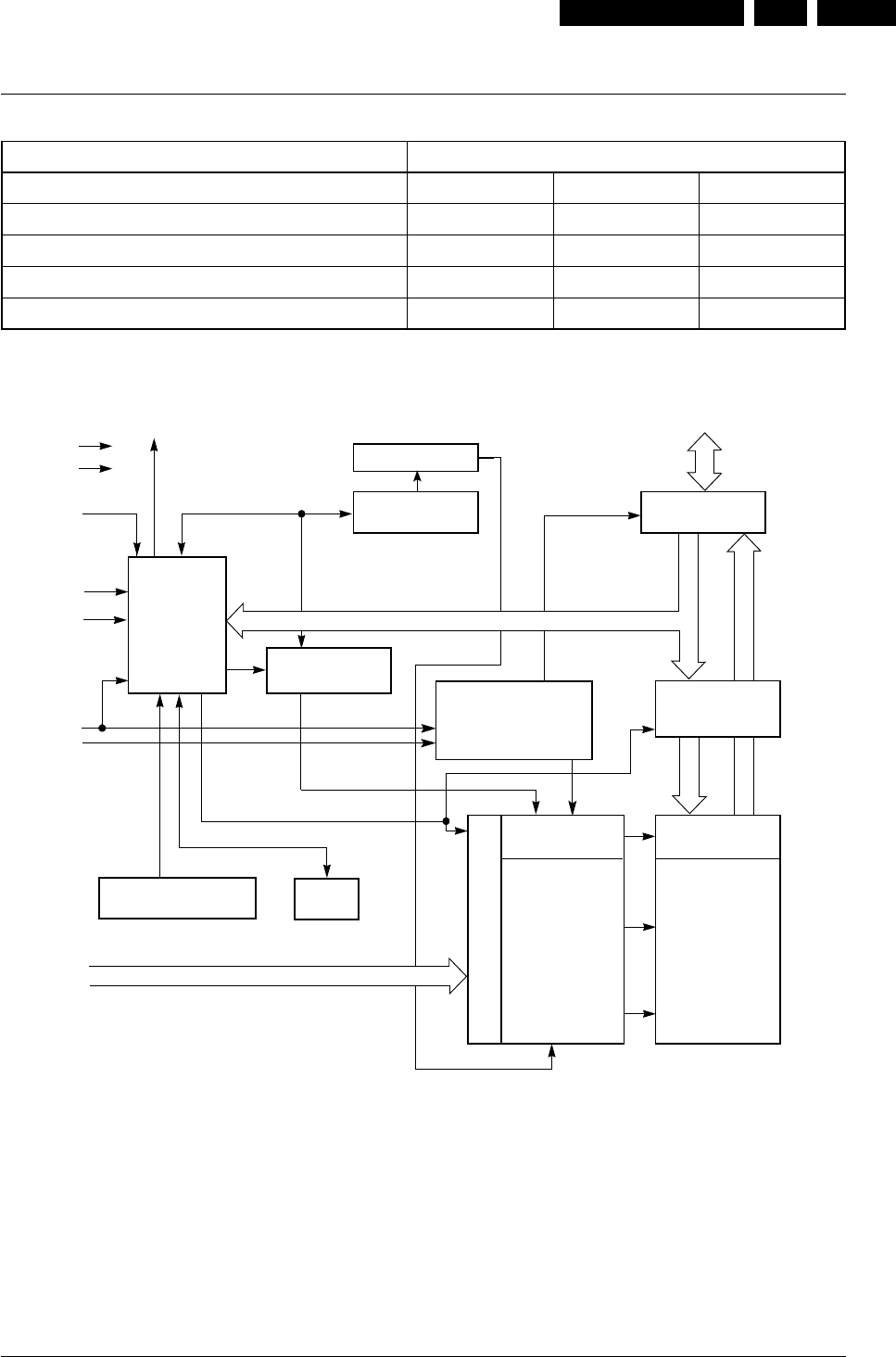

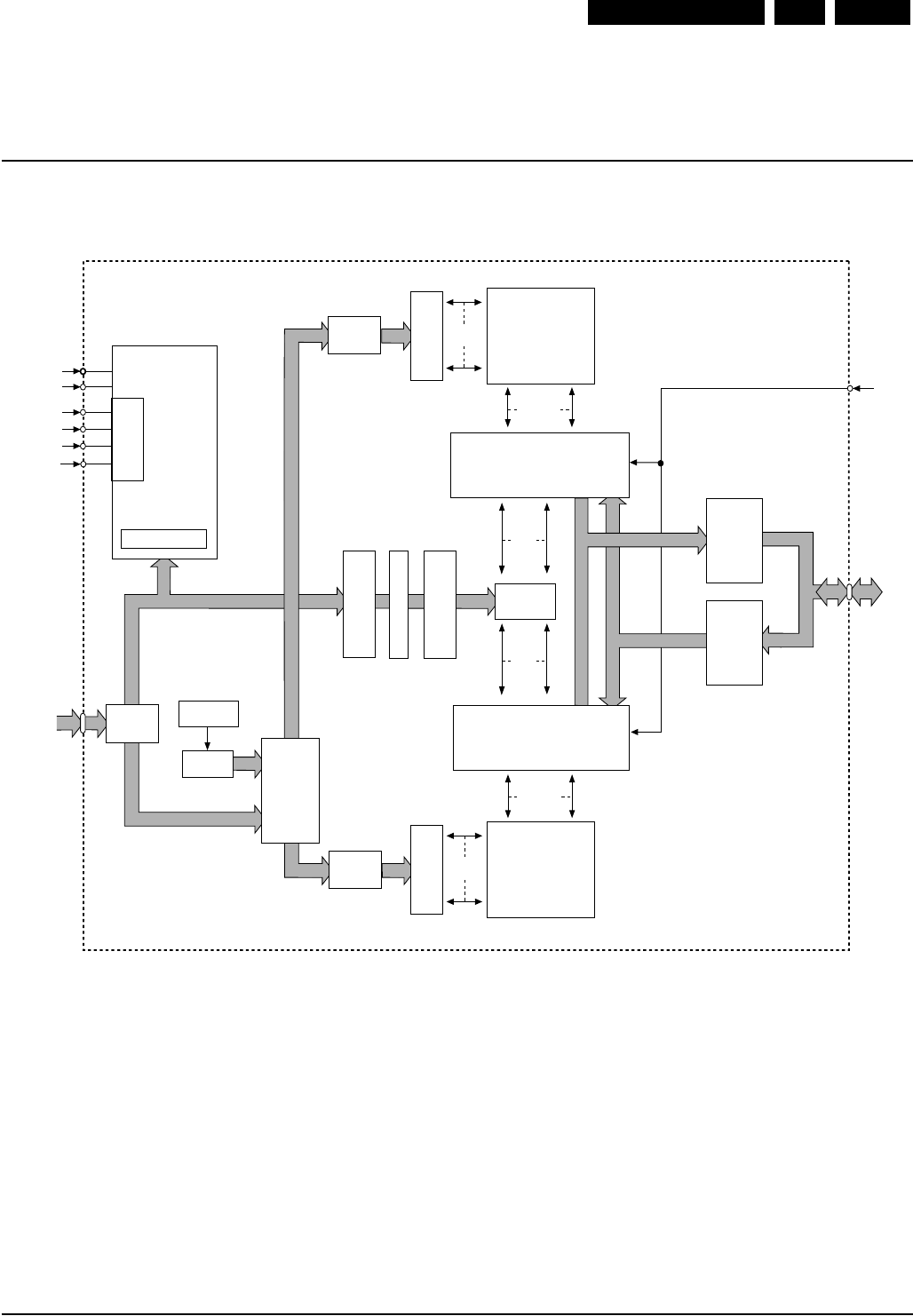

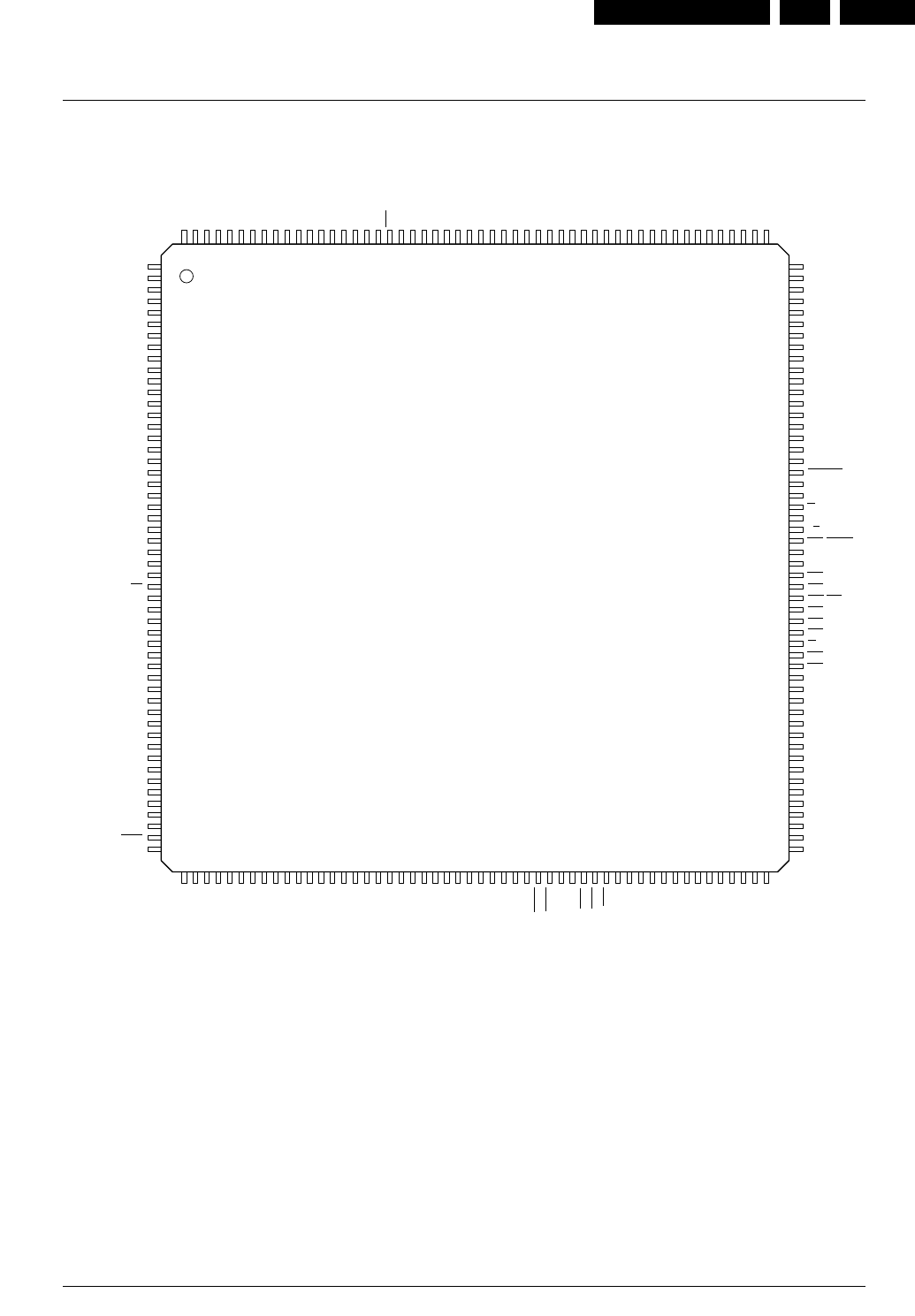

7. BLOCK DIAGRAM (/N1B)

SLAVE PROCESSOR

KEYBOARD

SPMS

St_by

AUDIO/VIDEO BACKEND BOARD

JBE

(servo)

RAM ROM

HOST

Sti5505

I2S

S2B

MONO BOARD

A/V signals

I2C

SCART

SWITCHING

AUX

TV

Y/C

CVBS(/YC not on SCART)

CVBS

CVBS

0/6/12V

RGB

UDA1328T

3

Kill

8Vstab

3V3stab

+12Vstby

Video

IC's and

audio

buffers

DAC

RGB/CVBS

RGB/CVBS

CVBS

AUDIO

AUDIO

AUDIO

L + R

DAC

SCART

SCART

DISPLAY BOARD

RGB/CVBS

L+R

I2C

DIG_OUT

I2S Audio

-5Vstab

-8Vstby

Switches

OPTICAL

OUTPUT

DIGITAL

OUTPUT

RC

7104

1113

TEA6420

AUDIO SCART

SWITCHING

7917

7401 7403

7900-7905

+12V stby

+5V stby

-8V stby

-40V

+5V

+3V3

11 12

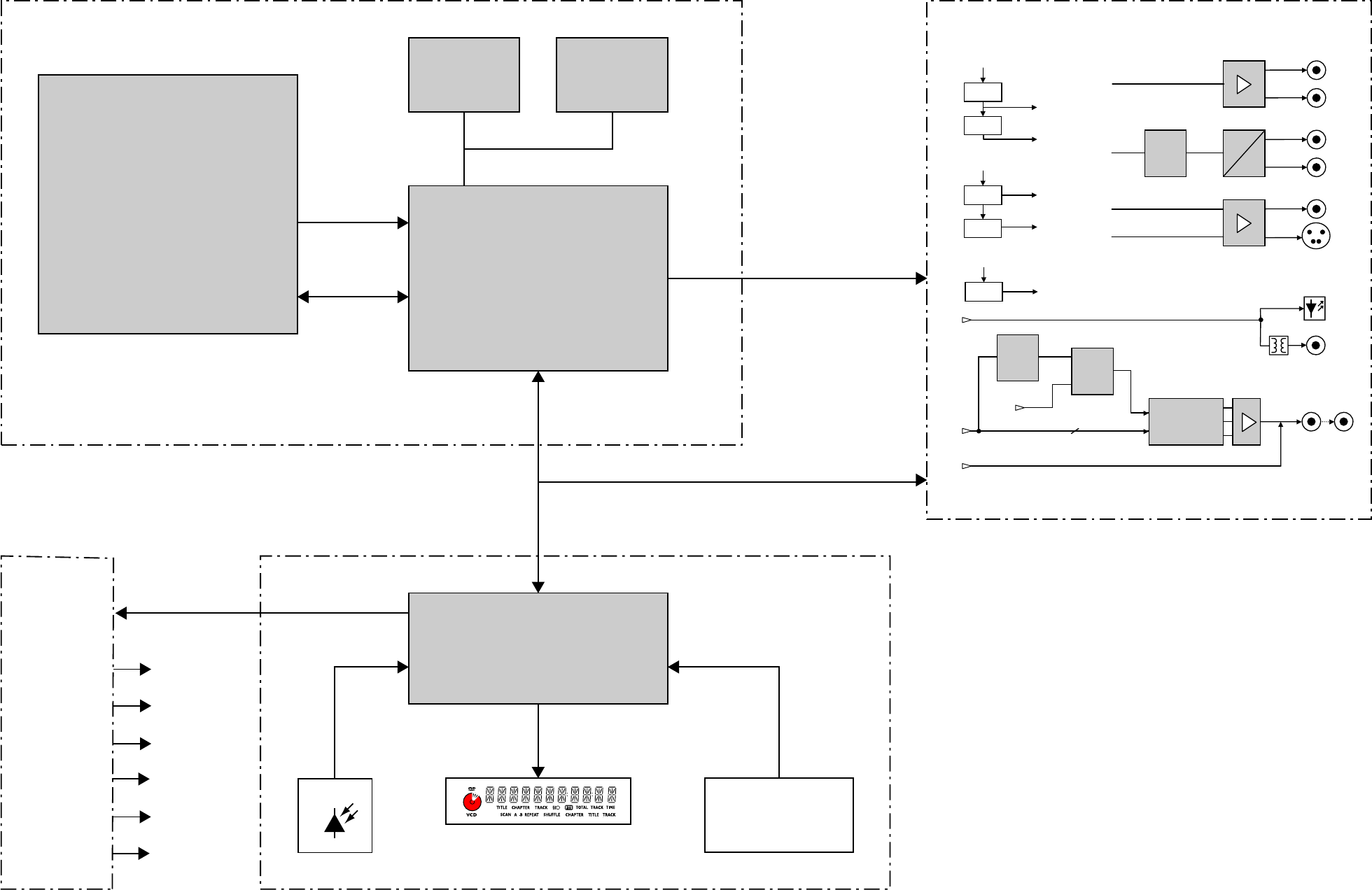

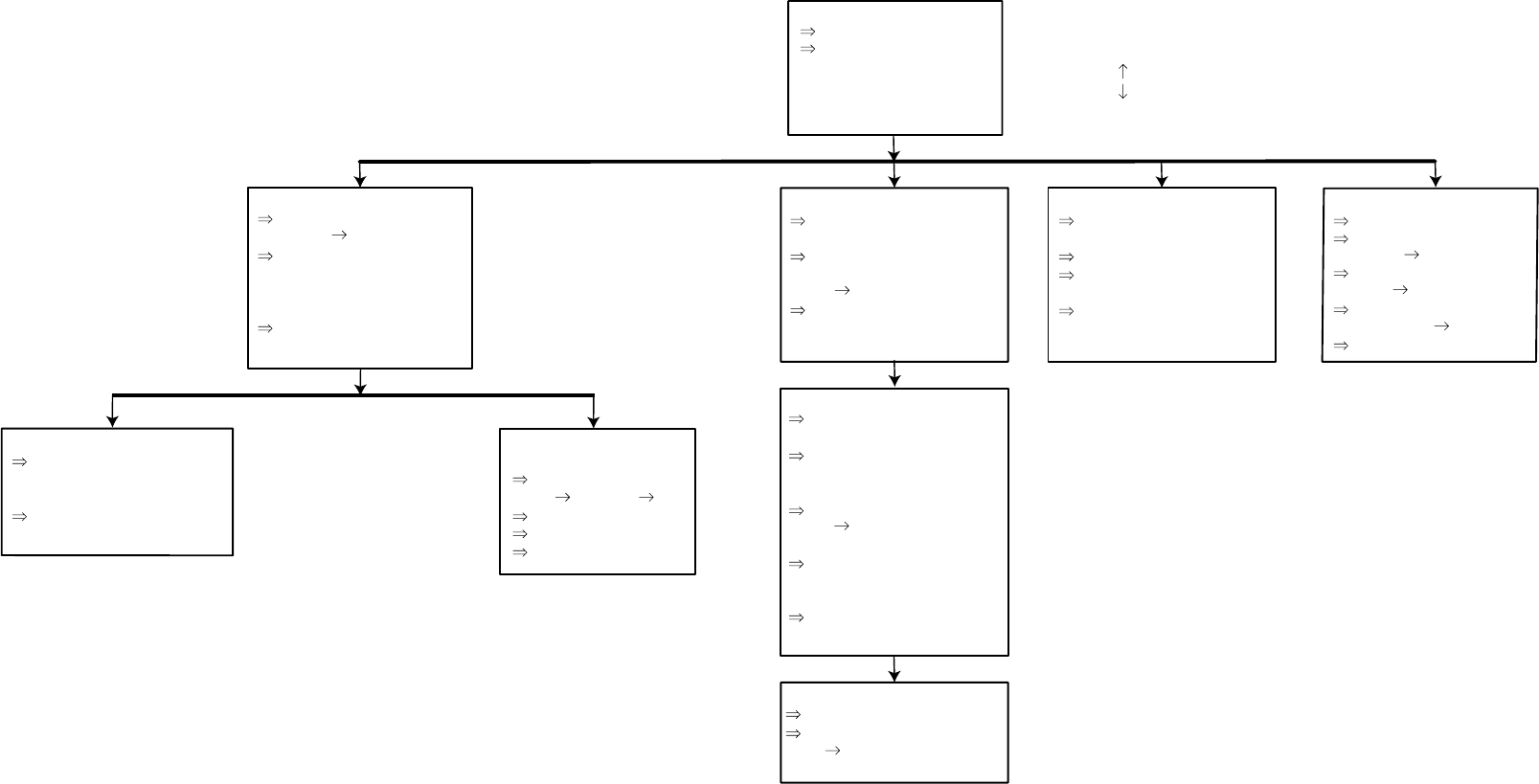

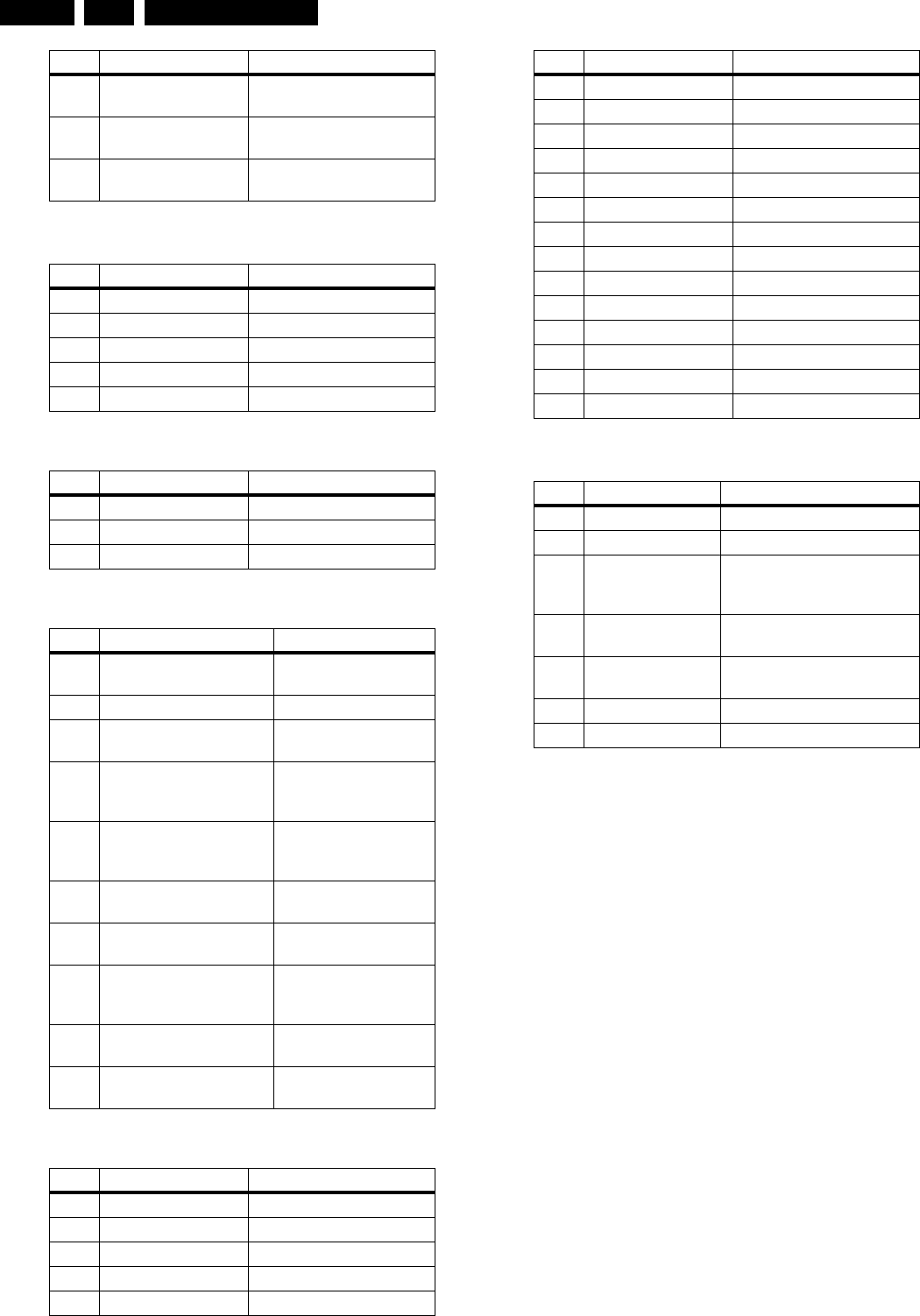

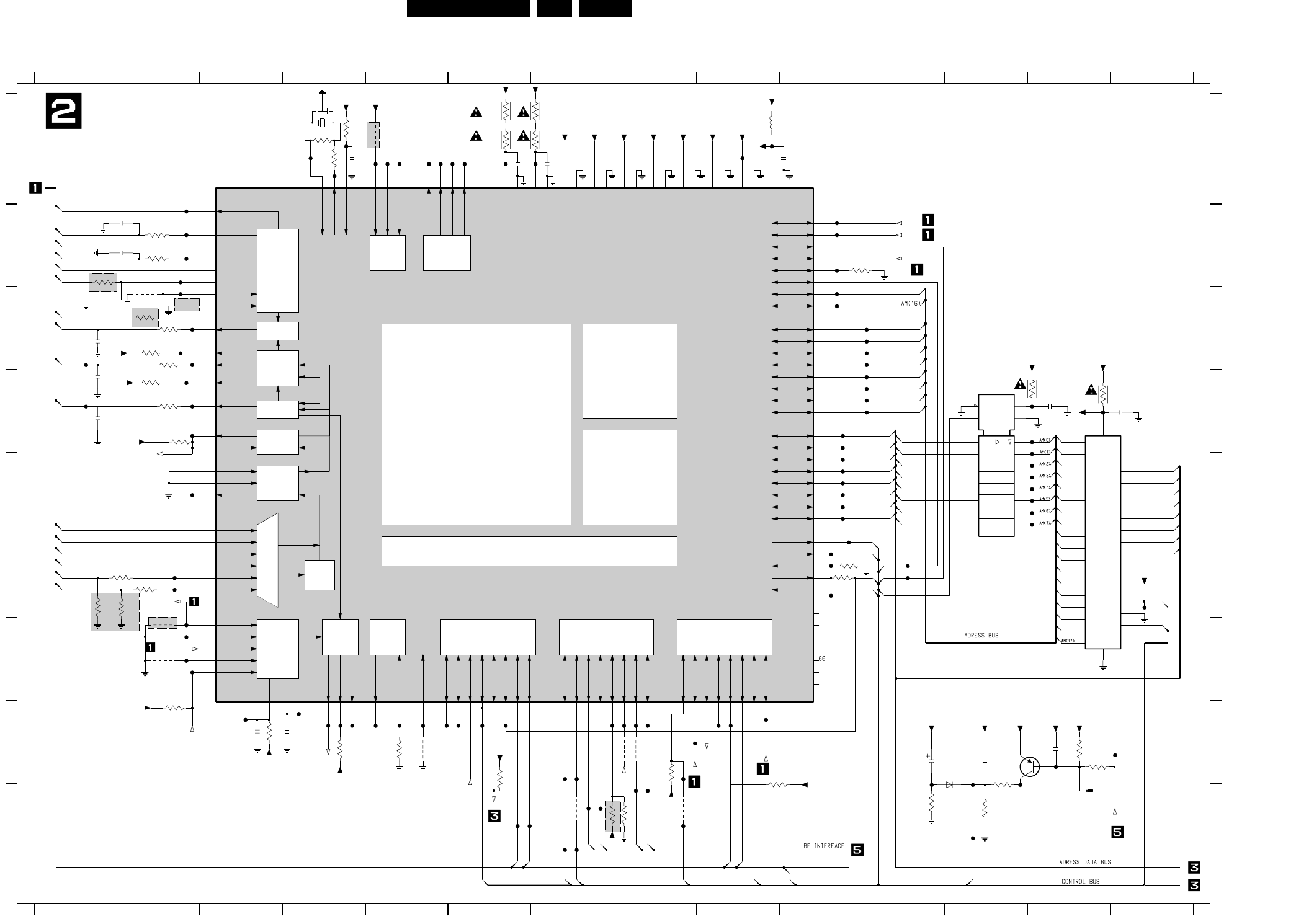

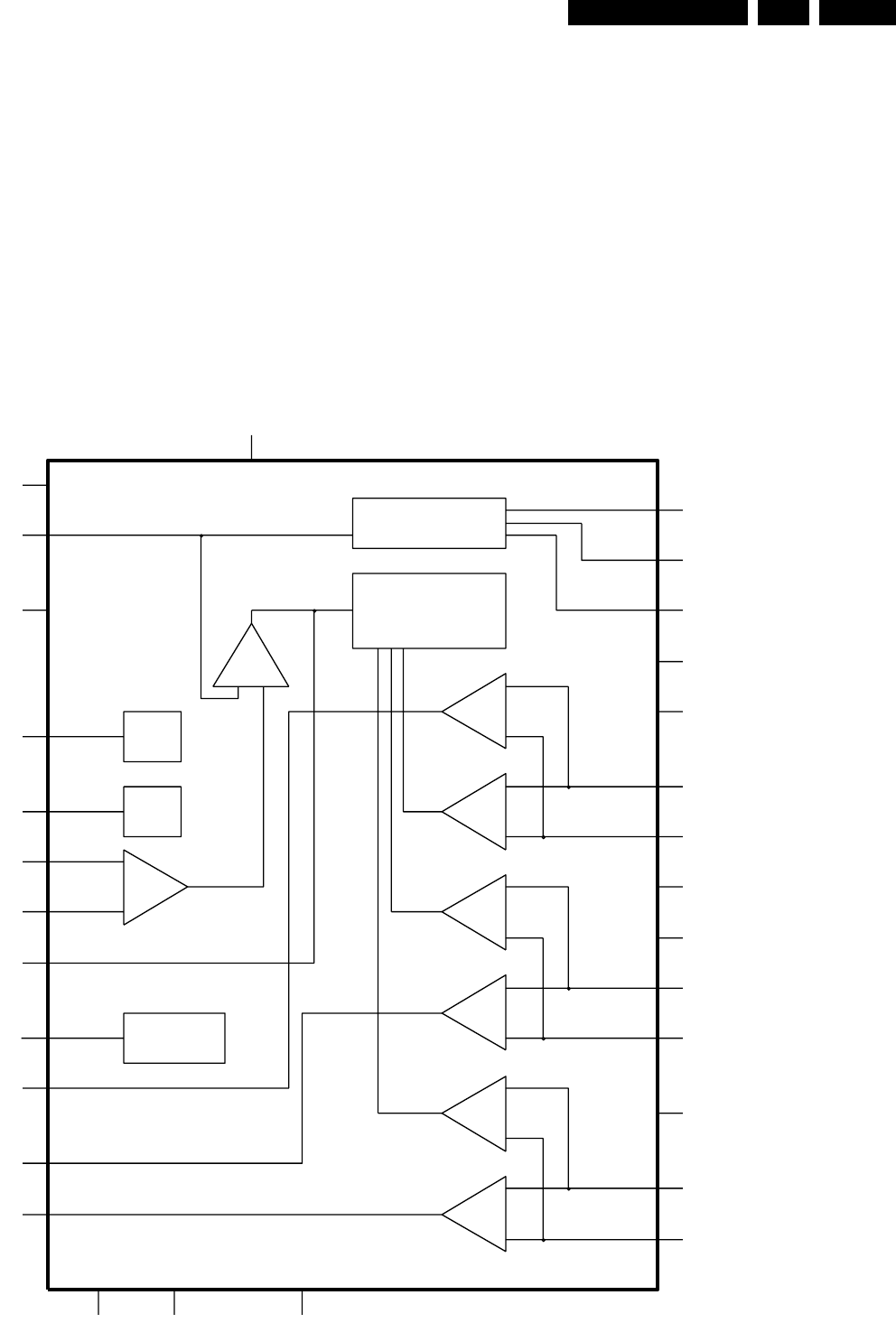

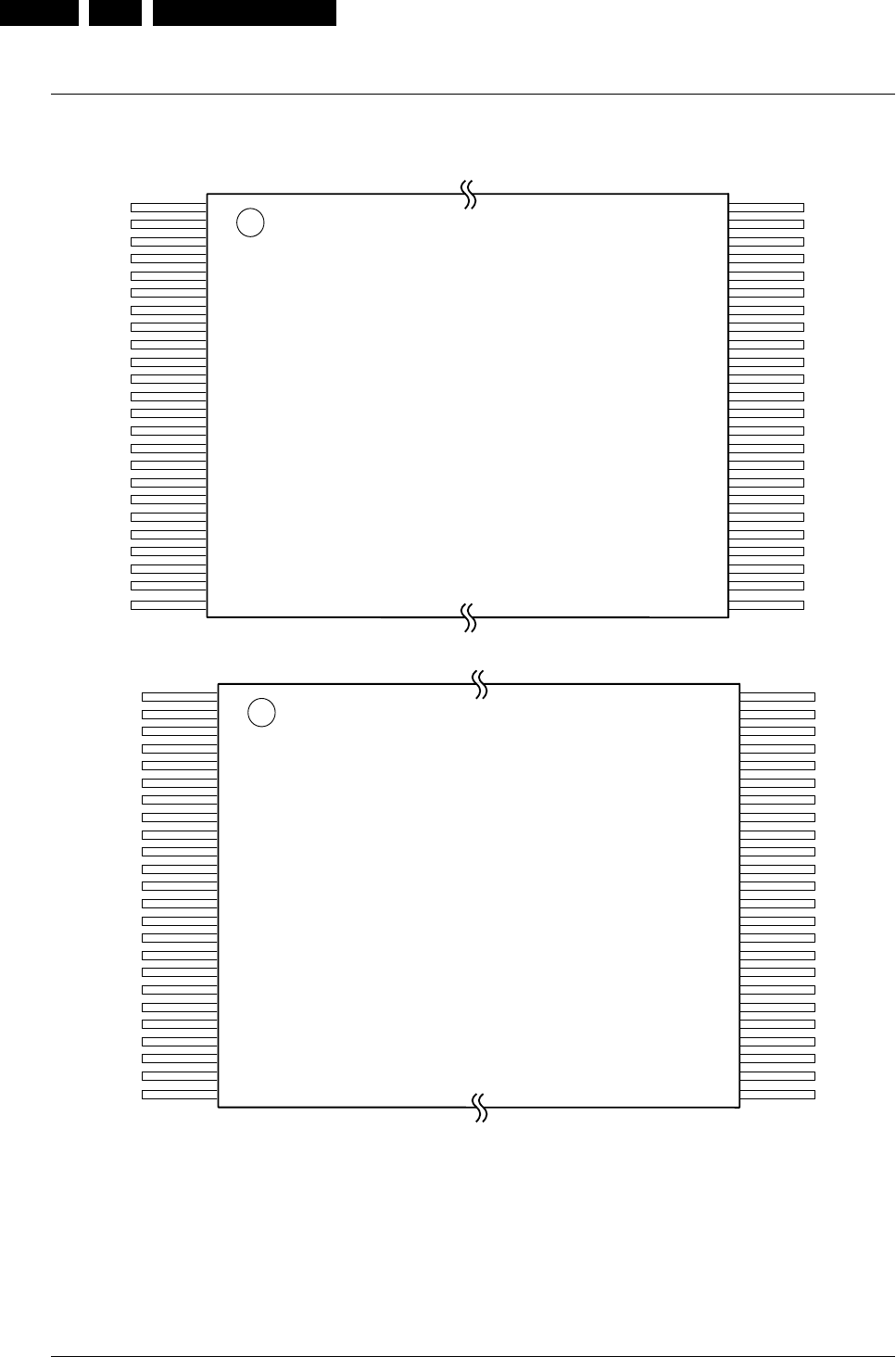

(/A1B, /S1G, /U1B)

SLAVE PROCESSOR

KEYBOARD

SPMS St_by

AUDIO/VIDEO BACKEND BOARD

JBE

(servo)

RAM ROM

HOST

Sti5505

I2S

S2B

MONO BOARD

A/V signals

I2C

Y/C

Y

UDA1328T

3

KILL

8Vstab

3V3stab

+12Vstby

Video

IC's and

audio

buffers

DAC

Headphone out

L + R

(ONLY DVD751)

2x

DAC

DISPLAY BOARD

DIG_OUT

I2S Audio

MICRO

-5Vstab

-8Vstby

Switches

-8V

-5V

-8V

OPTICAL

OUTPUT

DIGITAL

OUTPUT

RC

7104

1113

7400

7405 # # DVD732 ONLY

7403 #

7008

7002

CVBS1

CVBS

RGB

Y

C

CVBS2

7020 : 7023

+12V stby

+5V stby

-8V stby

-40V

+5V

+3V3

CB

CR

TDA 4780

KOK

TC9409

-5V

13 14

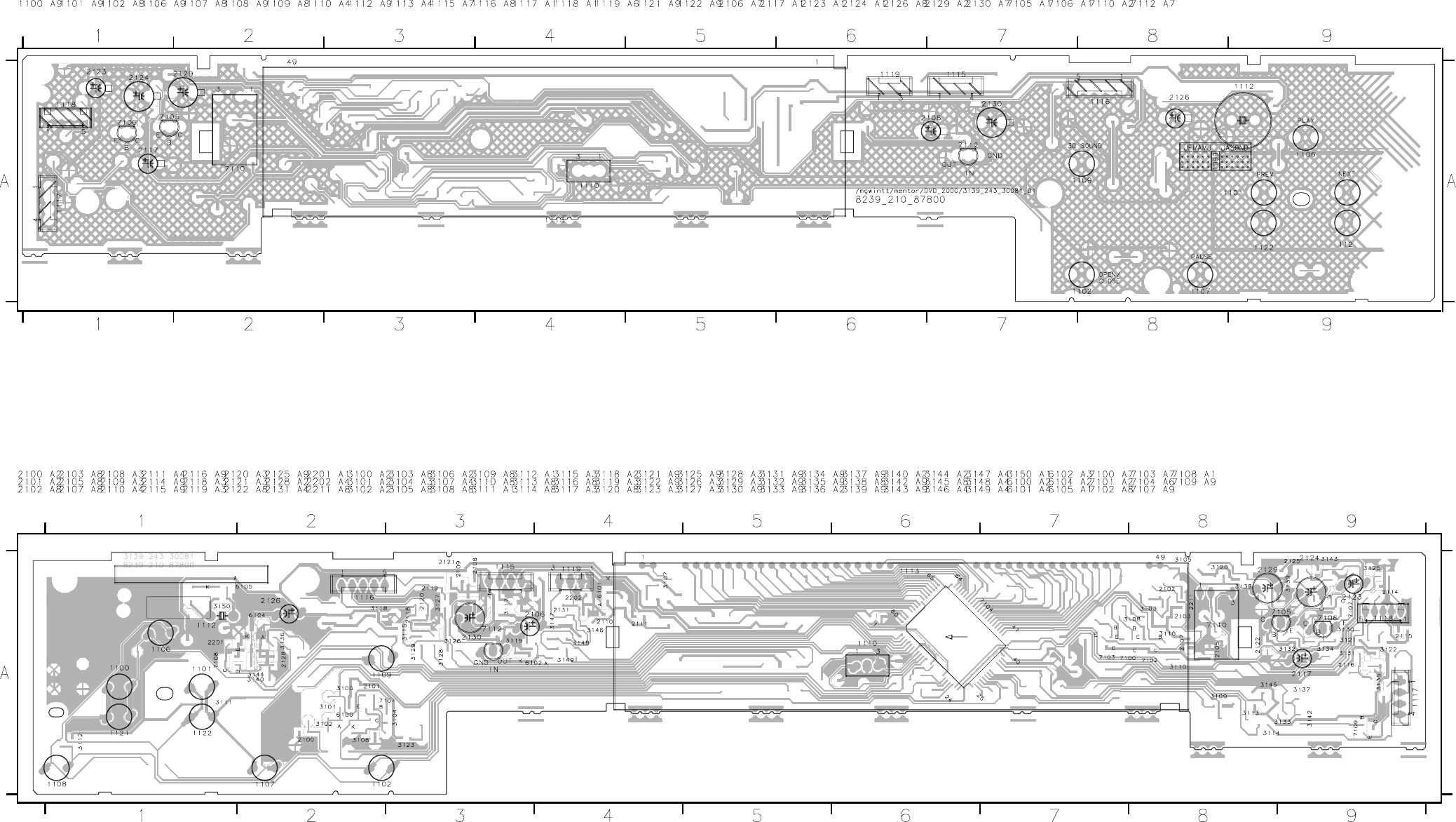

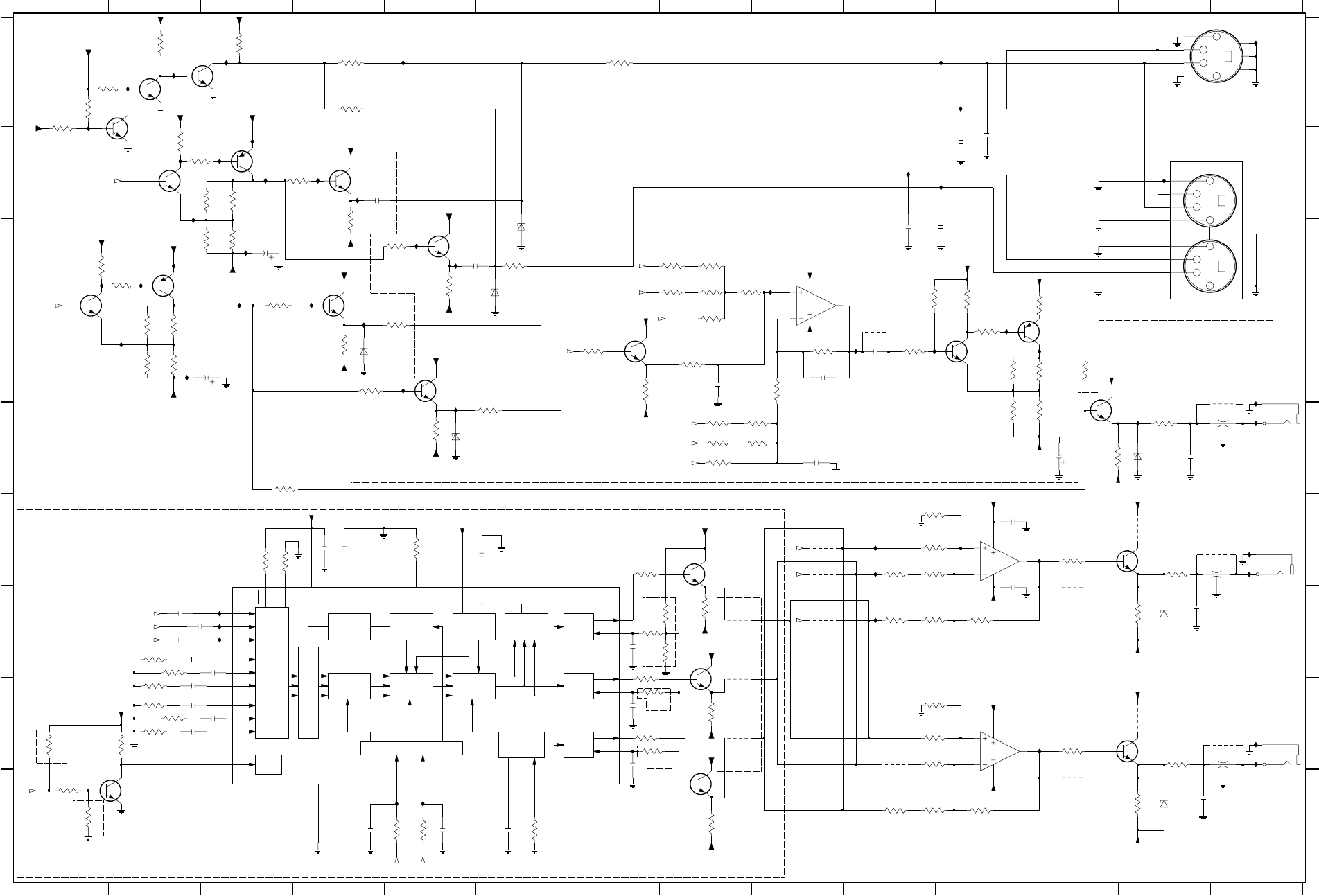

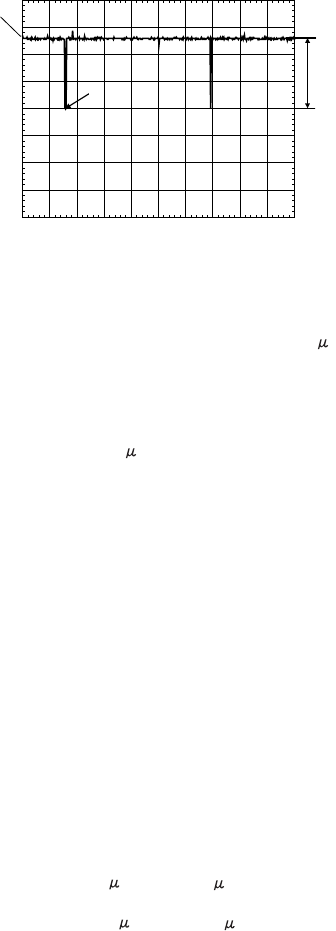

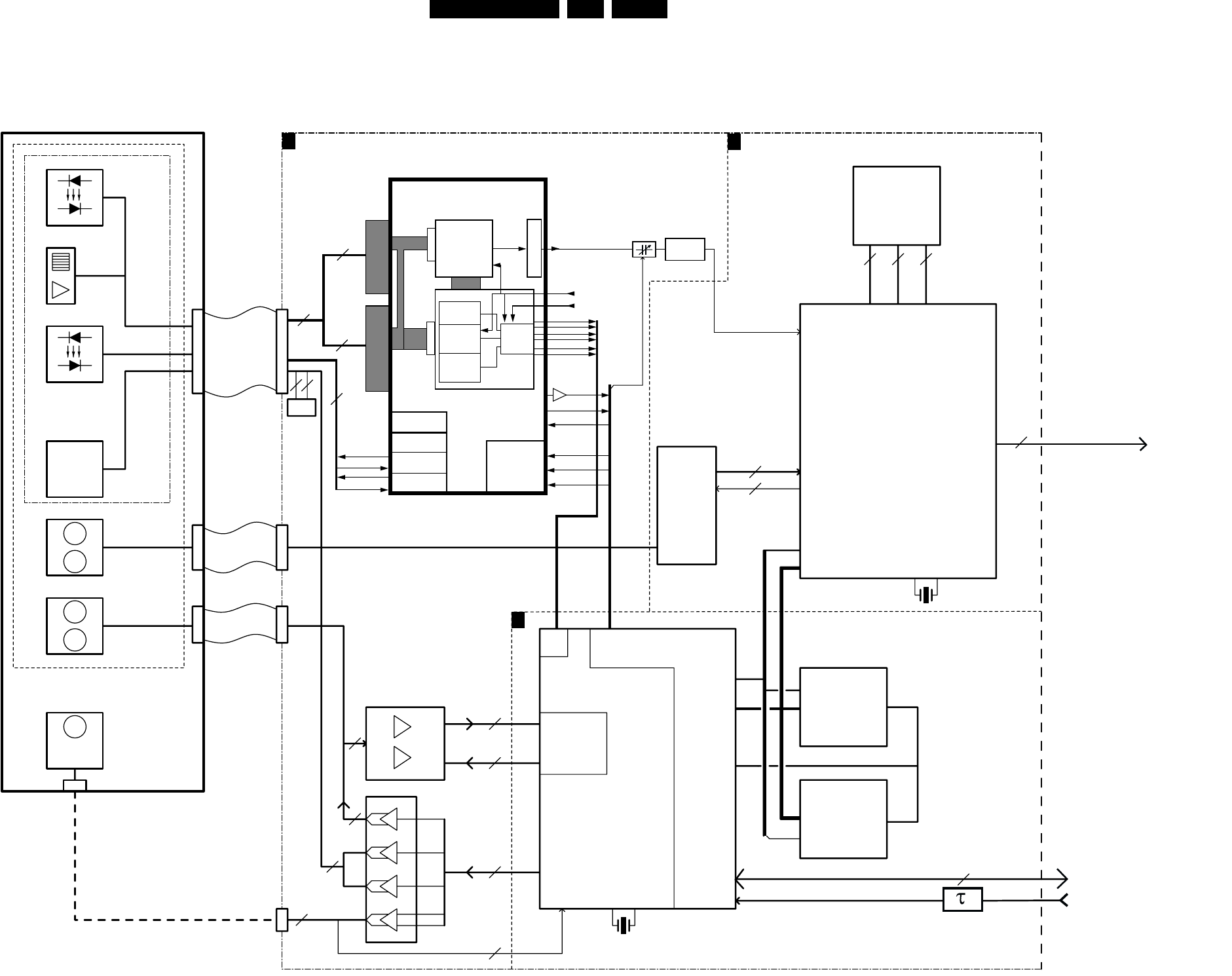

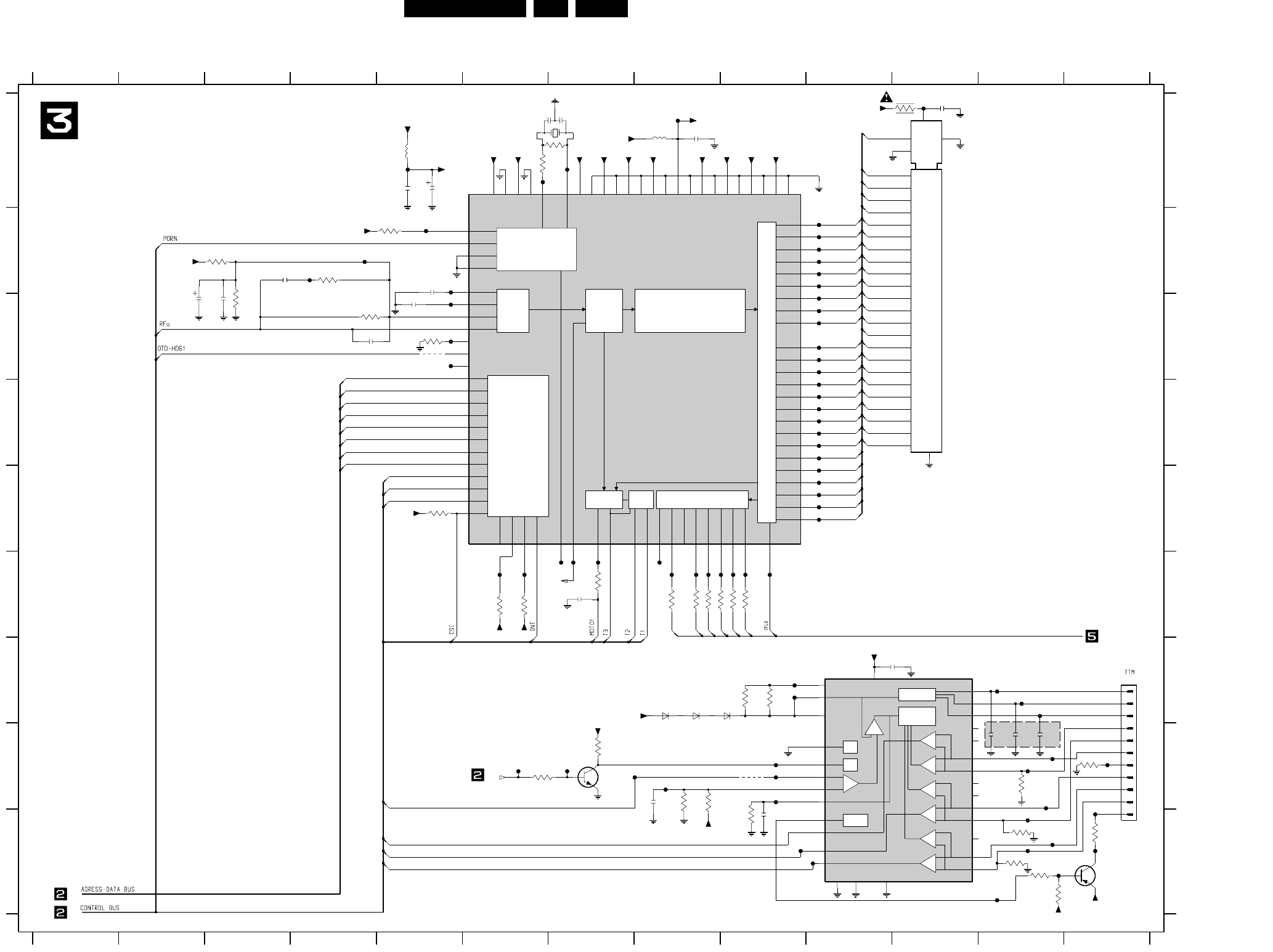

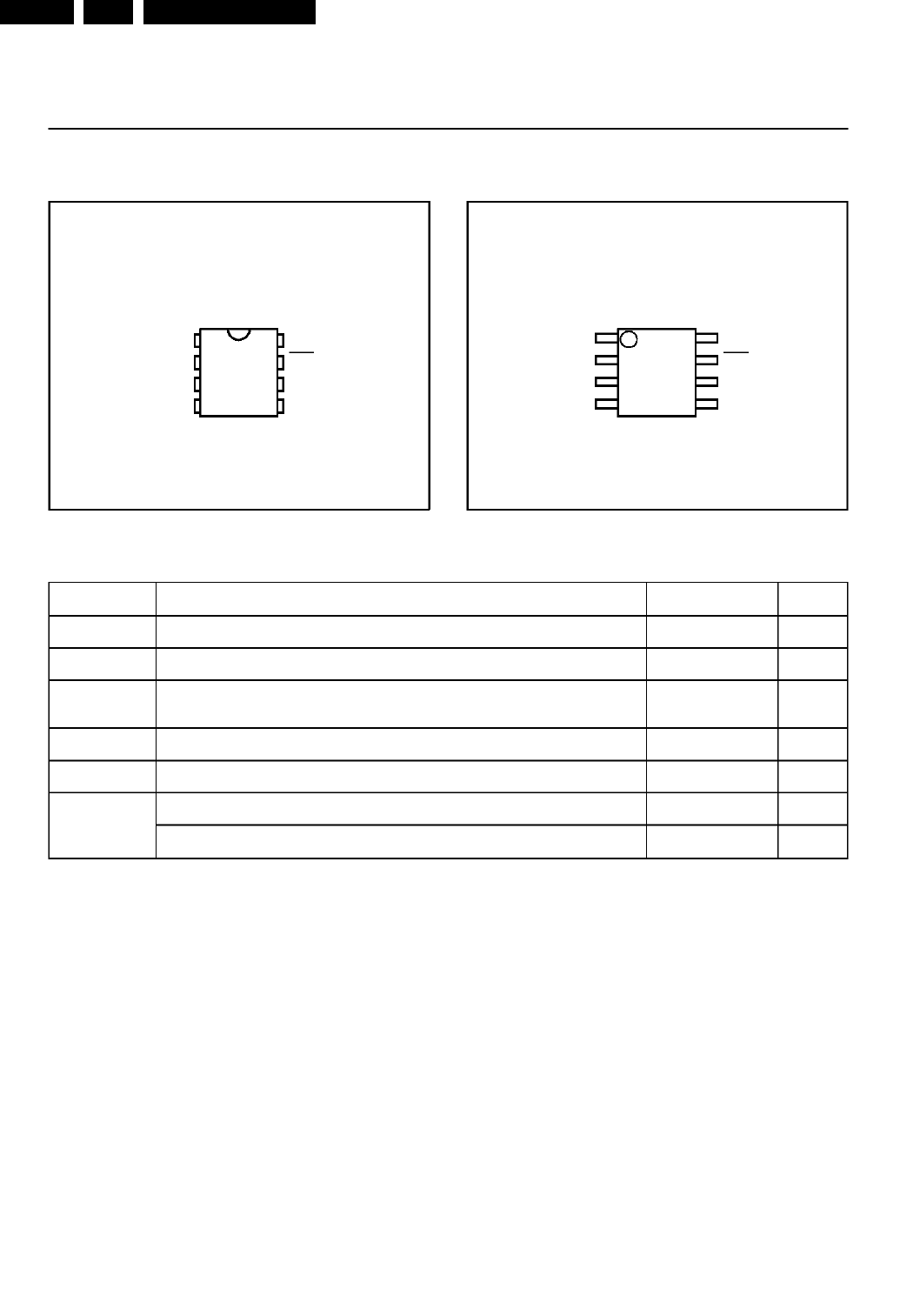

8. WIRING DIAGRAM

Non Euro model only

EH

1

2

20

1

2STBKEY+

STBKEY-

105MM -----> 105MM -----> 400MM ----->

3139 110 38371

----->

100MM

3139 110 37201

----->

400MM

Non Euro model only

5

ADJA_OUT

ADJA_IN

ADJB_OUT

1

2

3

4

5

6

7

HP_L

MIC GND

HP_R

+12V

MIC_A

EH

GND

+12V

GND

+5VSTBY

STBKEY-

EH EH

EH

PH

*

4

1

1205

1

2

3

4

+5VSTBY

STBLED

STBKEY+

STBKEY-

STANDBY

BOARD

4

1115 15 1116

1

2

4

GND

C

GND

Y

ADJB_IN

MIC GND

DISPLAY

BOARD

1

4

1117

1

2

3

4

+12V

GND

+5VSTBY

-40V

1

2

3

4

+5V

+5VSTBY

+6VSTBY

GND

GND

GND

-8VSTBY

2

+12VSTBY

CENTER_ON

STEREO_MUTE

DIG_OUT

GND

1

2

3

4

5

6

7

8

9

10

11

12

1

2

3

4

0207

3V3

3V3

PCM_OUT2

GND

PCM_OUT1

-8VSTBY

SCL

+12VSTBY

SDA

STBCONTROL

3V3A

9

10

11

12

1

2

3

4

5

6

7

8

9

10

11

12

3V3

3V3

+5V

+5VSTBY

+6VSTBY

GND

GND

+5VD

+5WD

KILL

GND

PCM_OUT0

LRCLK

SCLK

FFC

PCM_CLK

MIC GND

1

2

31

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

GND

H_SYNC

GND

MONO BOARD

1

2

3

4

5

6

+6VSTBY

8

CVBS

GND

0|6|12

-8V

13

14

15

16

17

18

19

20

21

22

P50

B

G

GND

R

CVBS

GND

0|6|12

-8V

1

2

3

4

5

ADJA_OUT

ADJA_IN

GND

ADJB_IN

8 1

16 1

4

5

15 116 122

1

12

1501 1604 1603

1600

SCL

GND

SCA

STBCONTROL

P50

GND

C

GND

Y

P50

B

G

7

R

280MM

GND

-8V

8

+5VD

+5WD

KILL

GND

PCM_OUT0

LRCLK

SCLK

GND

PCM_CLK

CENTER_ON

STEREO_MUTE

DIG_OUT

GND

A/V BOARD

EH

EH FFC FFC

*

15

16

17

18

19

20

21

ADJB_OUT

122 15

1002 1000 1001 1003

GND

H_SYNC

GND

PCM_OUT2

GND

PCM_OUT1

-8VSTBY

SCL

+12VSTBY

SDA

+6VSTBY

3V3A

1

2

3

4

5

6

7

GND

<-----

1

GND

-8VSTBY

STBCONTROL

KILL 8

9

10

11

12

13

14

15

16

1

2

3

4

5

6

7

8

9

10

11

12

13

14 22

PH

5

SCL

GND

SCA

STBCONTROL

P50

1

3

4

+5VSTBY

STBLED

-40V

POWER SUPPLY

BOARD

EHHR

41

0205 121

3

FFCPH

GND

+12VSTBY

15 1118

<----- 280MM

<----- 400MM

----->

100MM

3139 110 38831

3139 110 34221

3139 110 34321

3103 308 91150

3139 110 38631

3139 110 38681

3139 110 34251

STBKEY+

1

2

STBKEY+

STBKEY -

EH

1

2 CN4

15 16

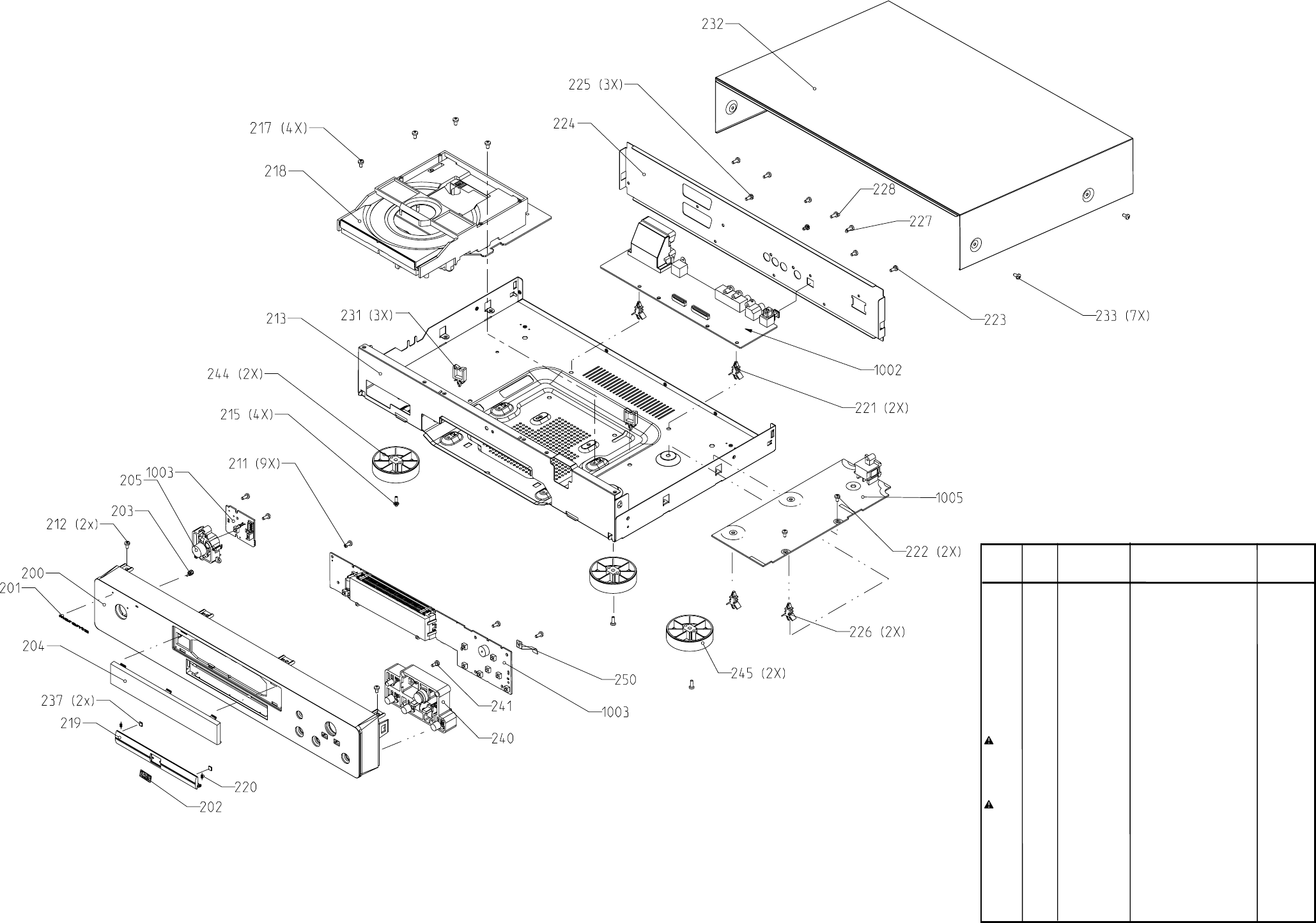

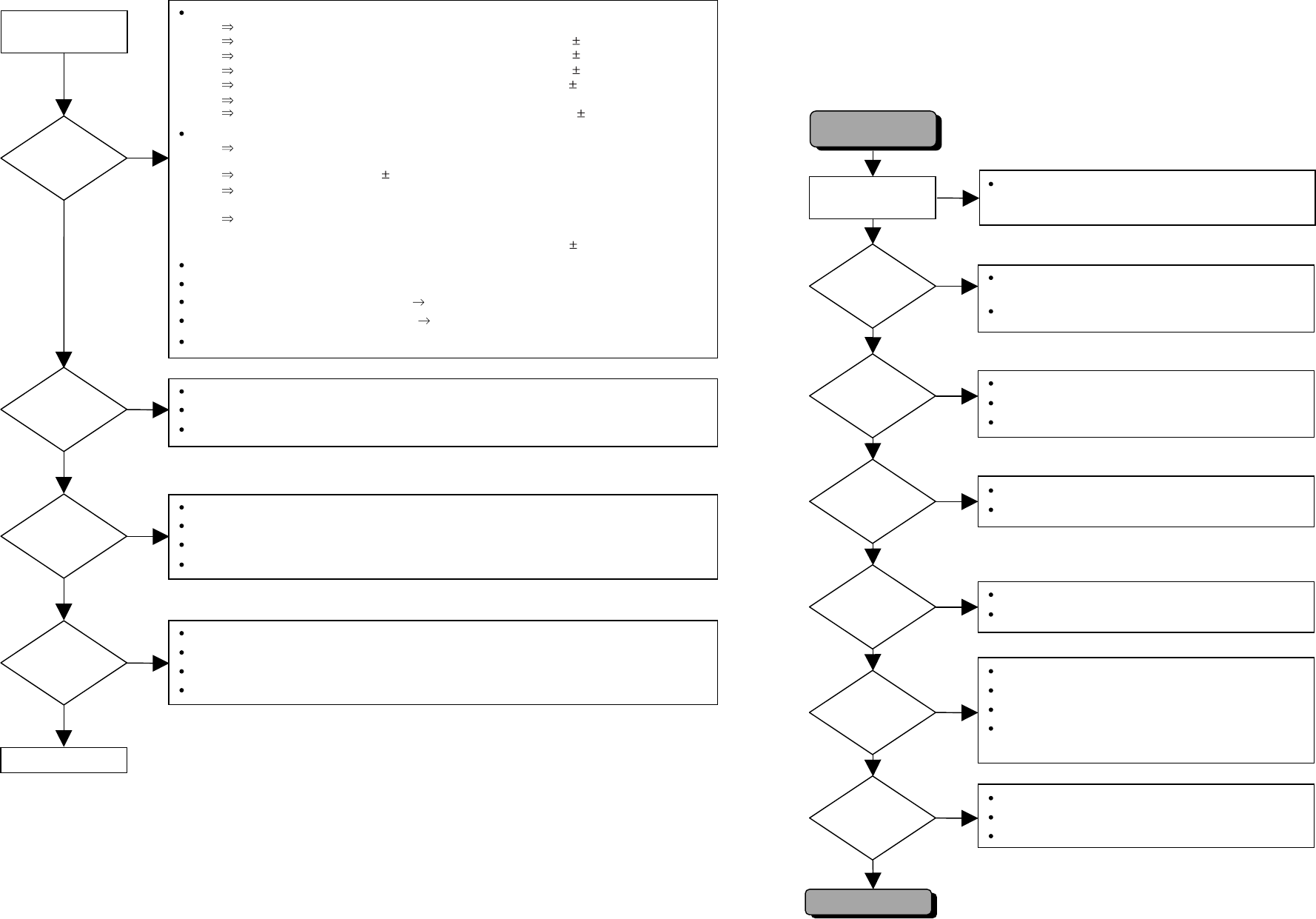

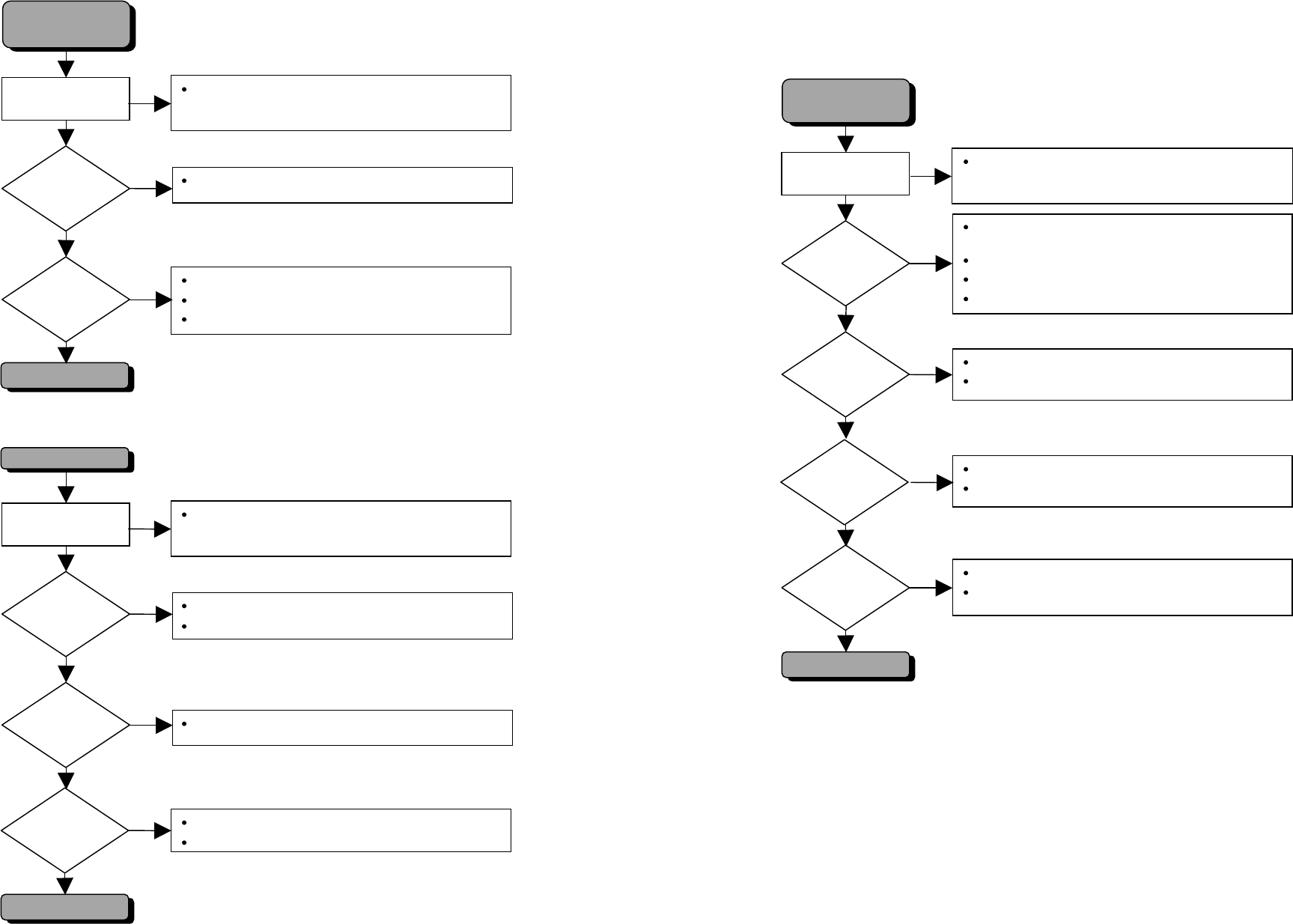

9. DISMANTLING INSTRUCTIONS

Cover 151

Remove 7 screws 233

Lift cover at rearside to

remove

Front assy 1

remove 2 screws 212

(front 1 frame 213)

unlock front from frame by

releasing successively 3

snaps (on the left, in the

middle and on the right)

put front assy in front of the

set(service position)

DVD MODULE 218

Remove connections to

Mono board

remove 4 screws

217 (loader bracket

2 frame 213)

demount module

DVD MONO Board 7

See also exploded view of

DVD module

Remove flex connections to

turntable motor and sledge

motor.

remove 4 screws

10 13(mono board 7

loader bracket 2)

remove carefully flex

connection to OPU and wire

connection to tray motor.

demount board.

LOADER VAL3000 1

Remove 2 screws 8,9

Remove 4 suspensions

3 6 from loader bracket

Standby board 1003 and

switch assy

Remove 2 screws

25 26(board front)

demount board

Remove 1 screw 207

Take out switch assy

Display board 1002

Remove 7 screws

203(board front), pay

attention to earth spring 300.

demount board

AV board 1002

remove flex connections to

Mono board

remove 7 screws 227

release snaps of 2 spacers

221

demount board

Power supply unit 1005

remove connections

remove 2 screws 222

(board frame)

remove screw 225 (mains

inled backplate)

release snaps of spacers

226 (board frame)

demount board

mounting

demounting

17 18

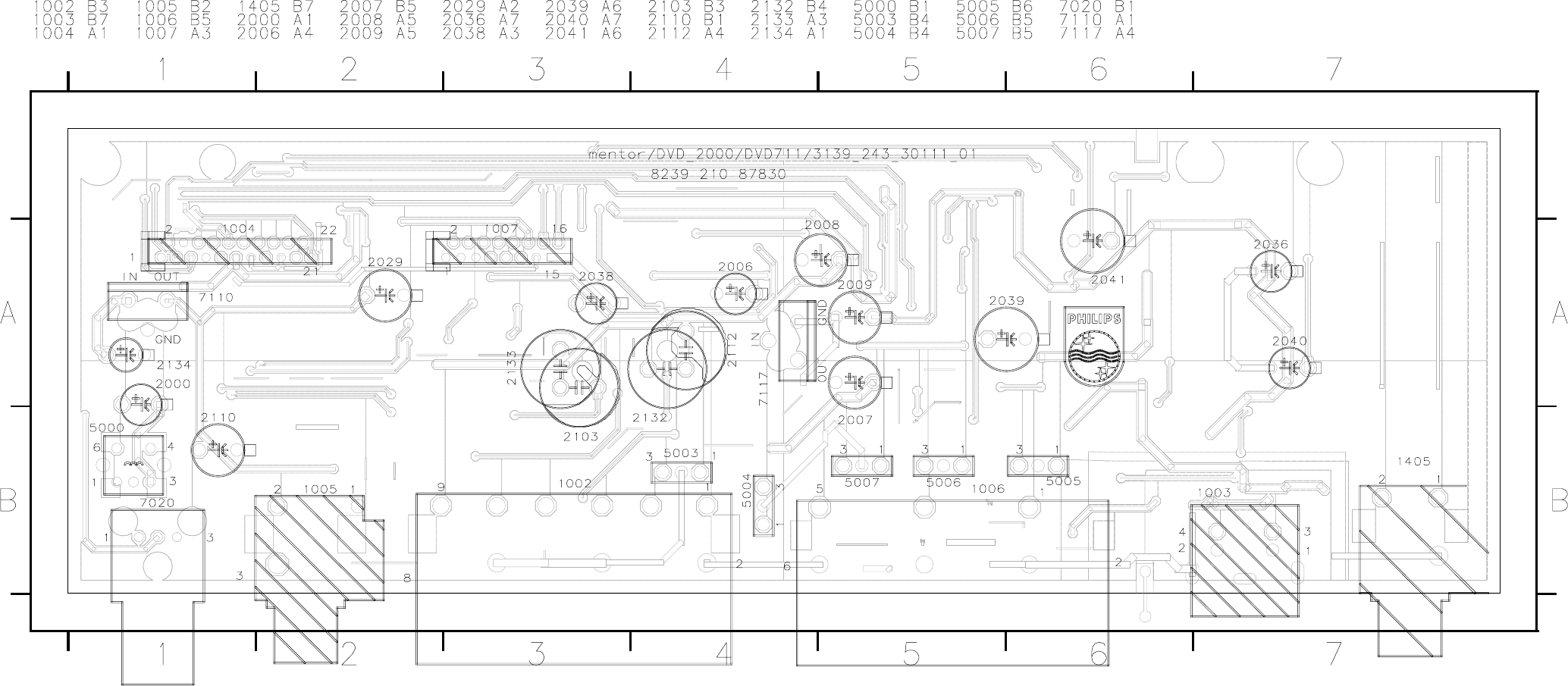

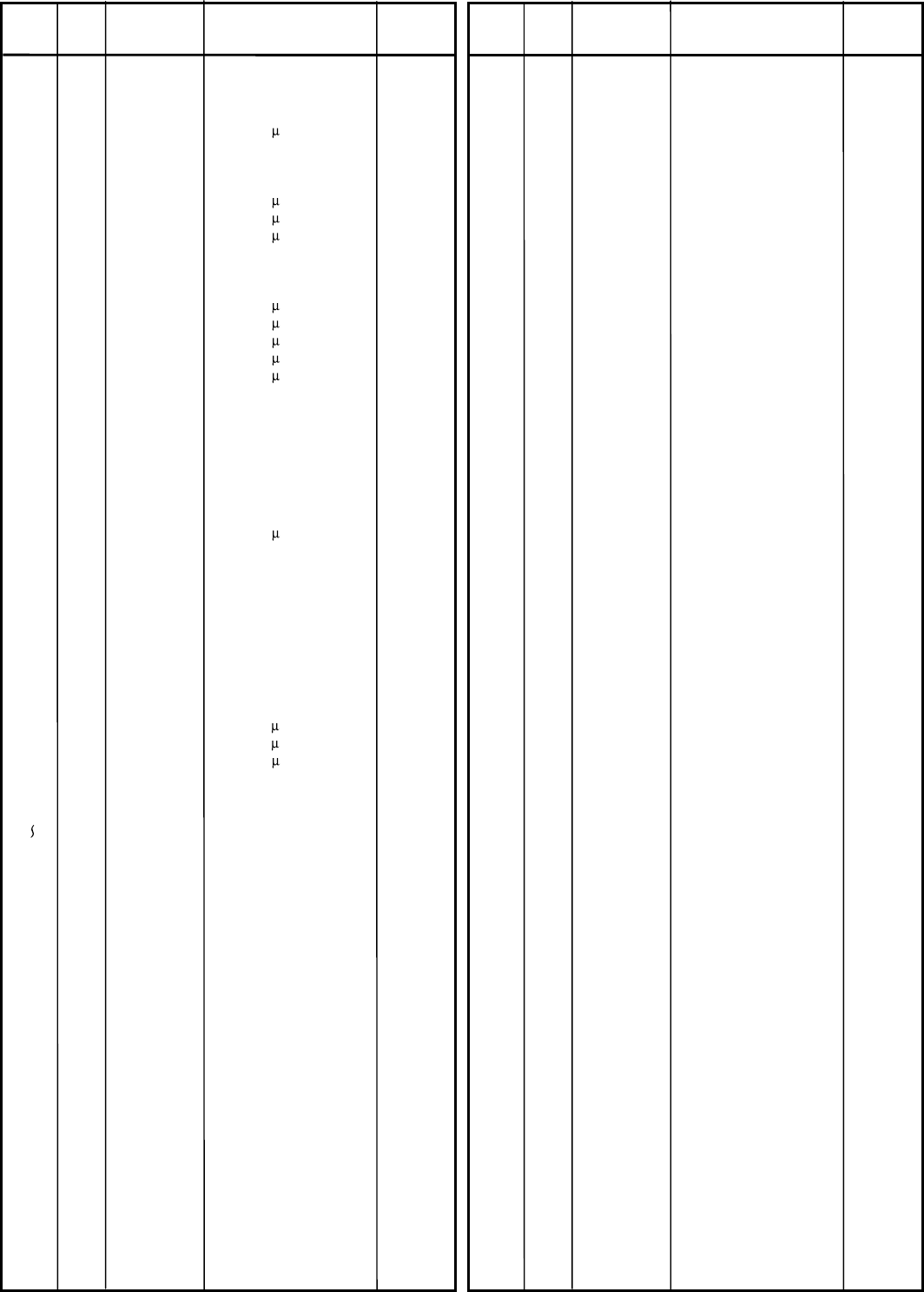

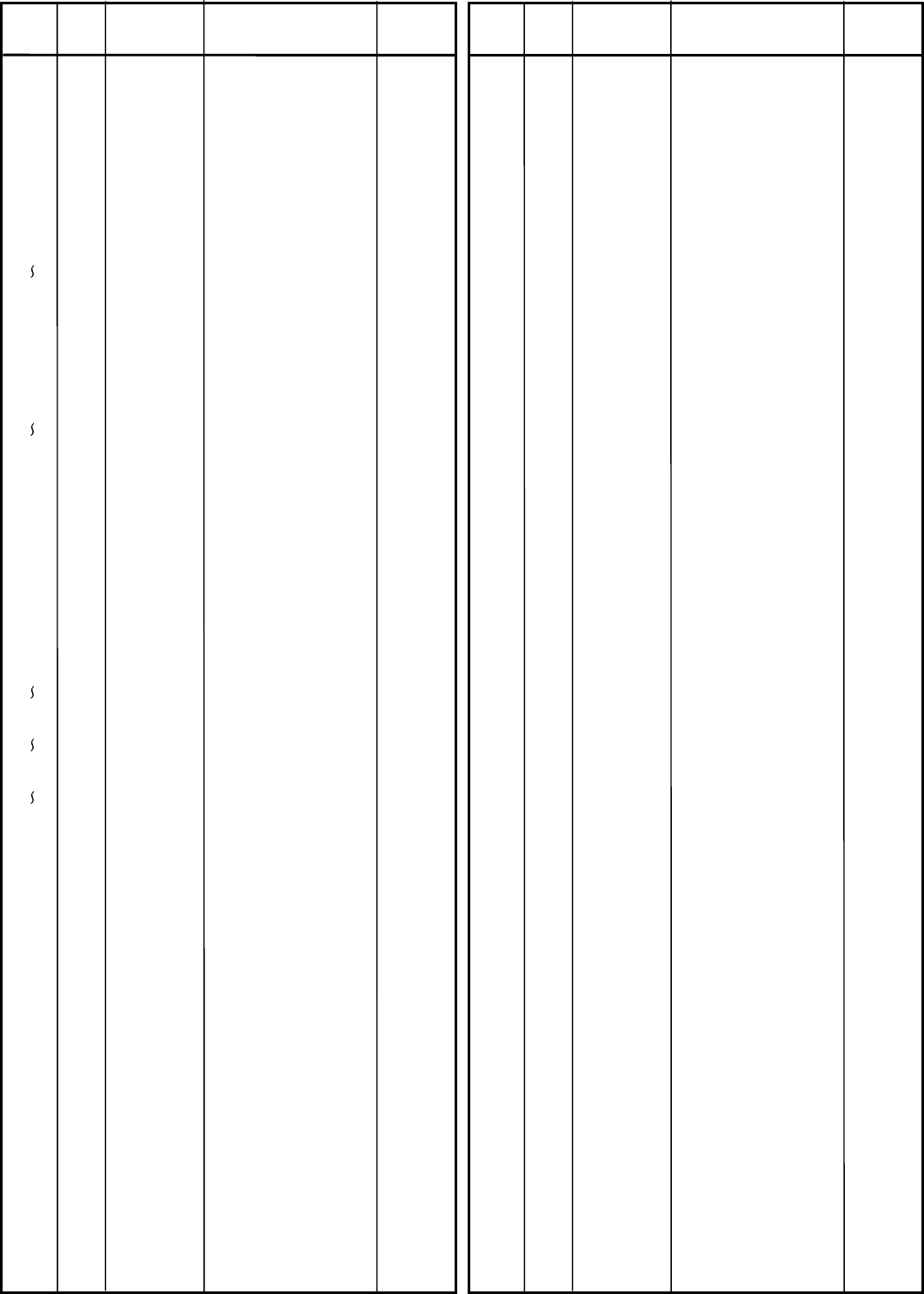

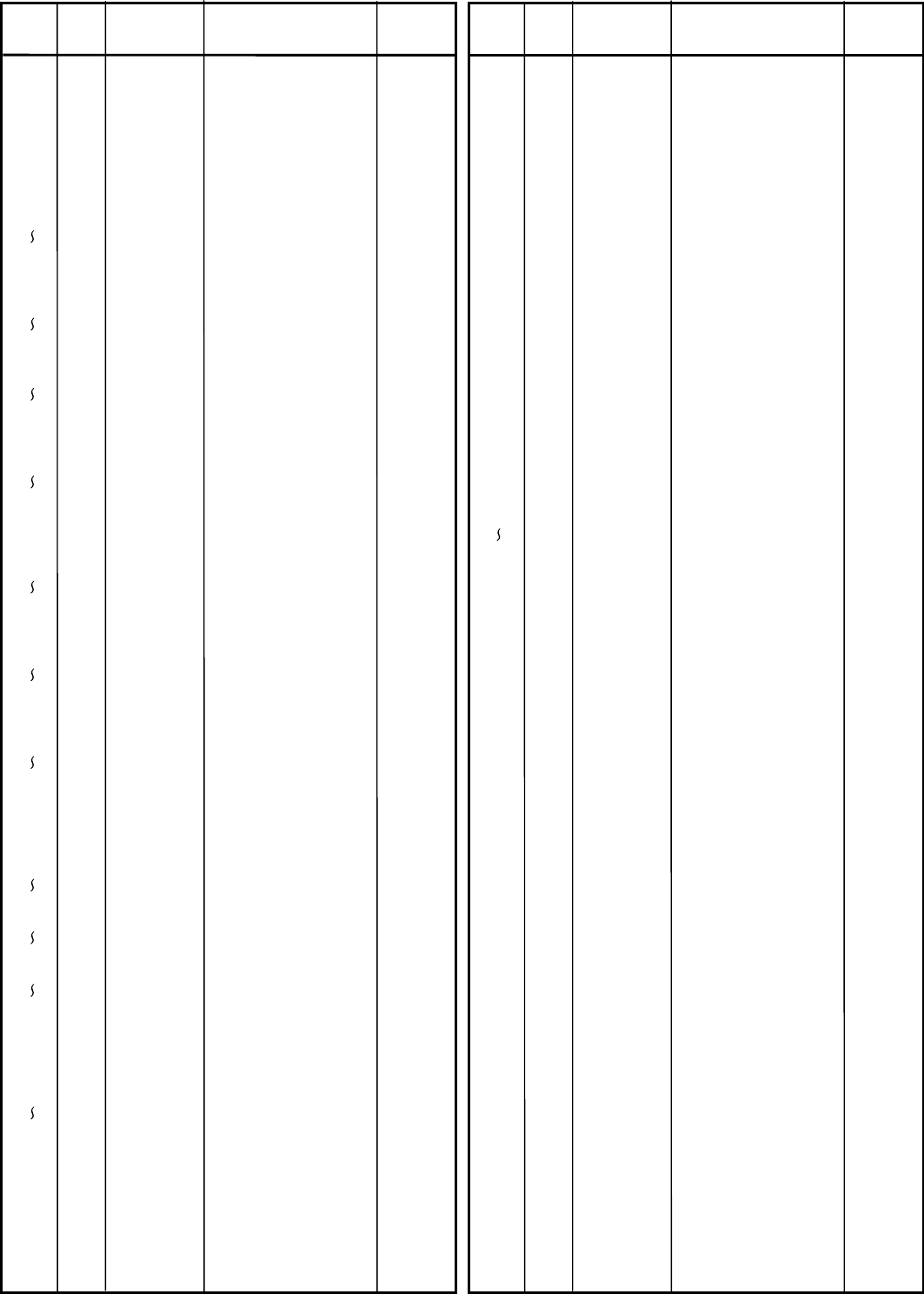

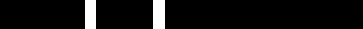

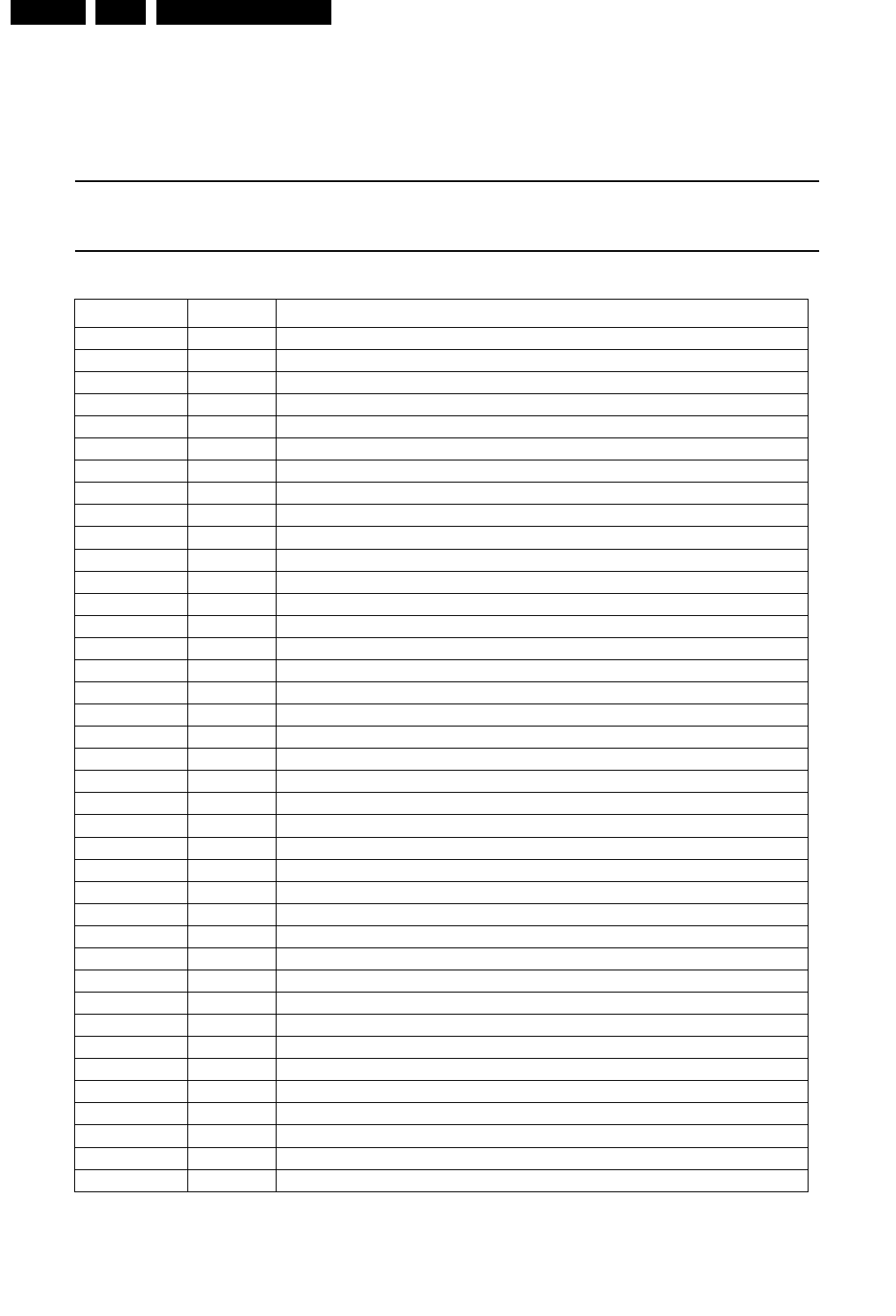

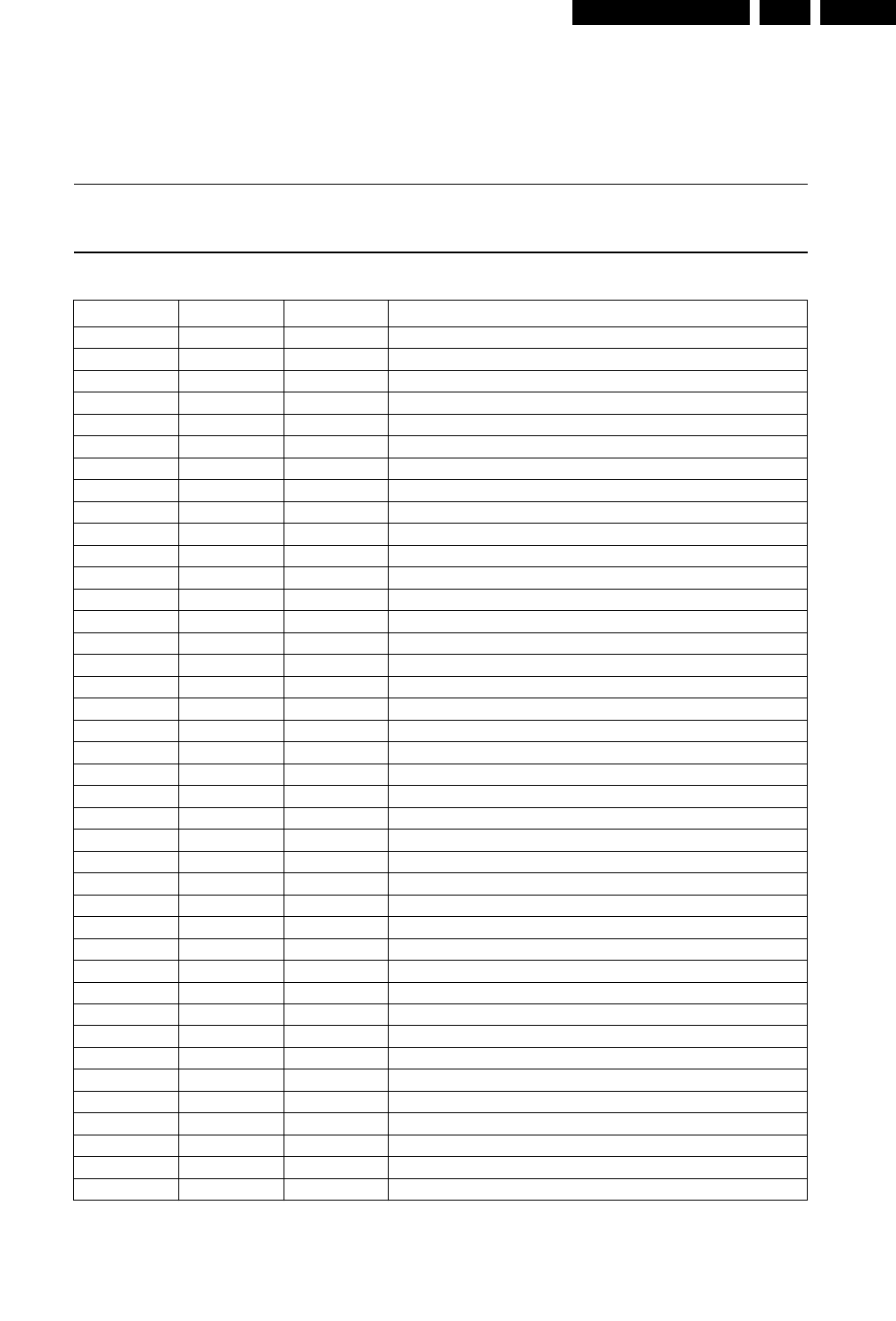

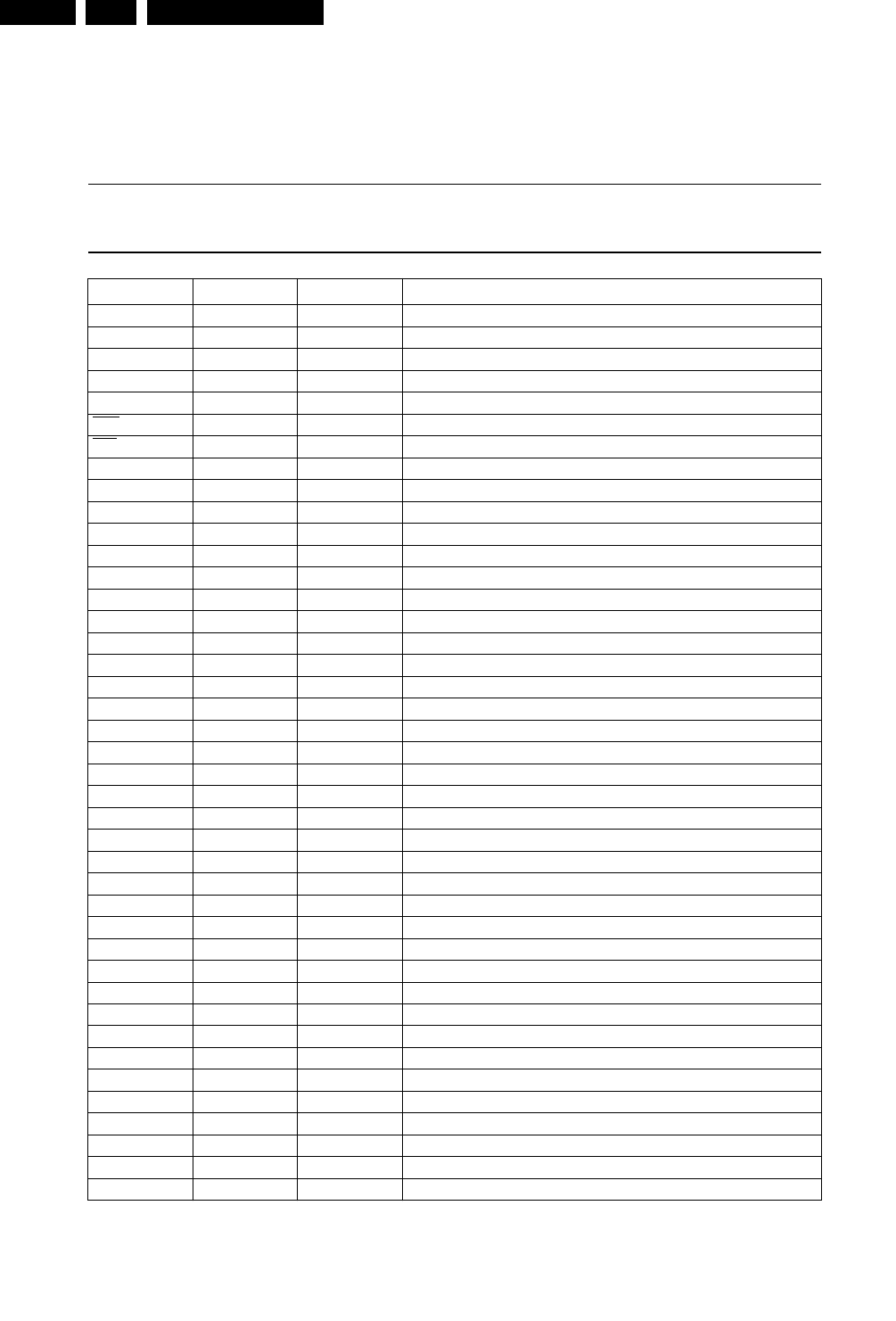

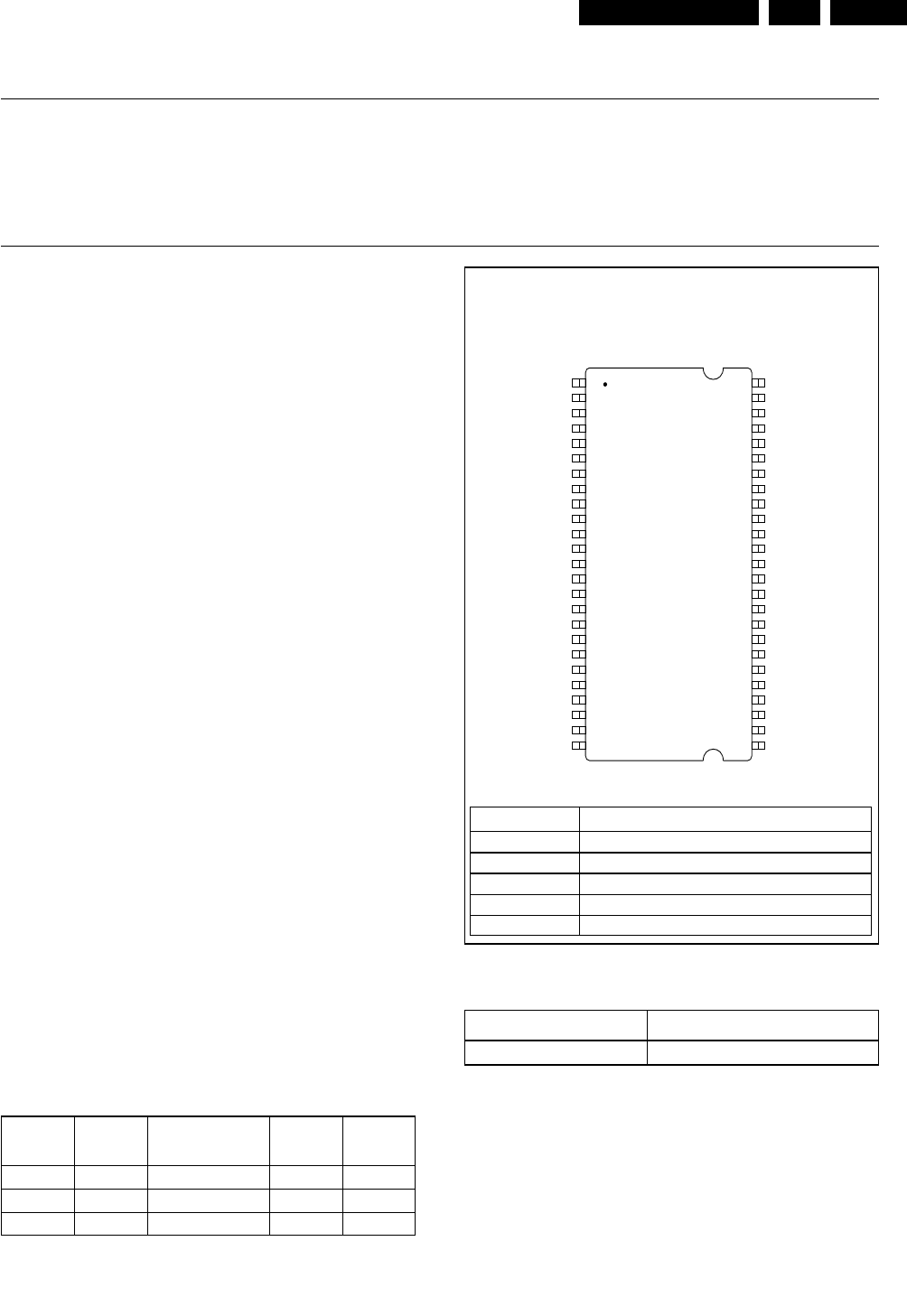

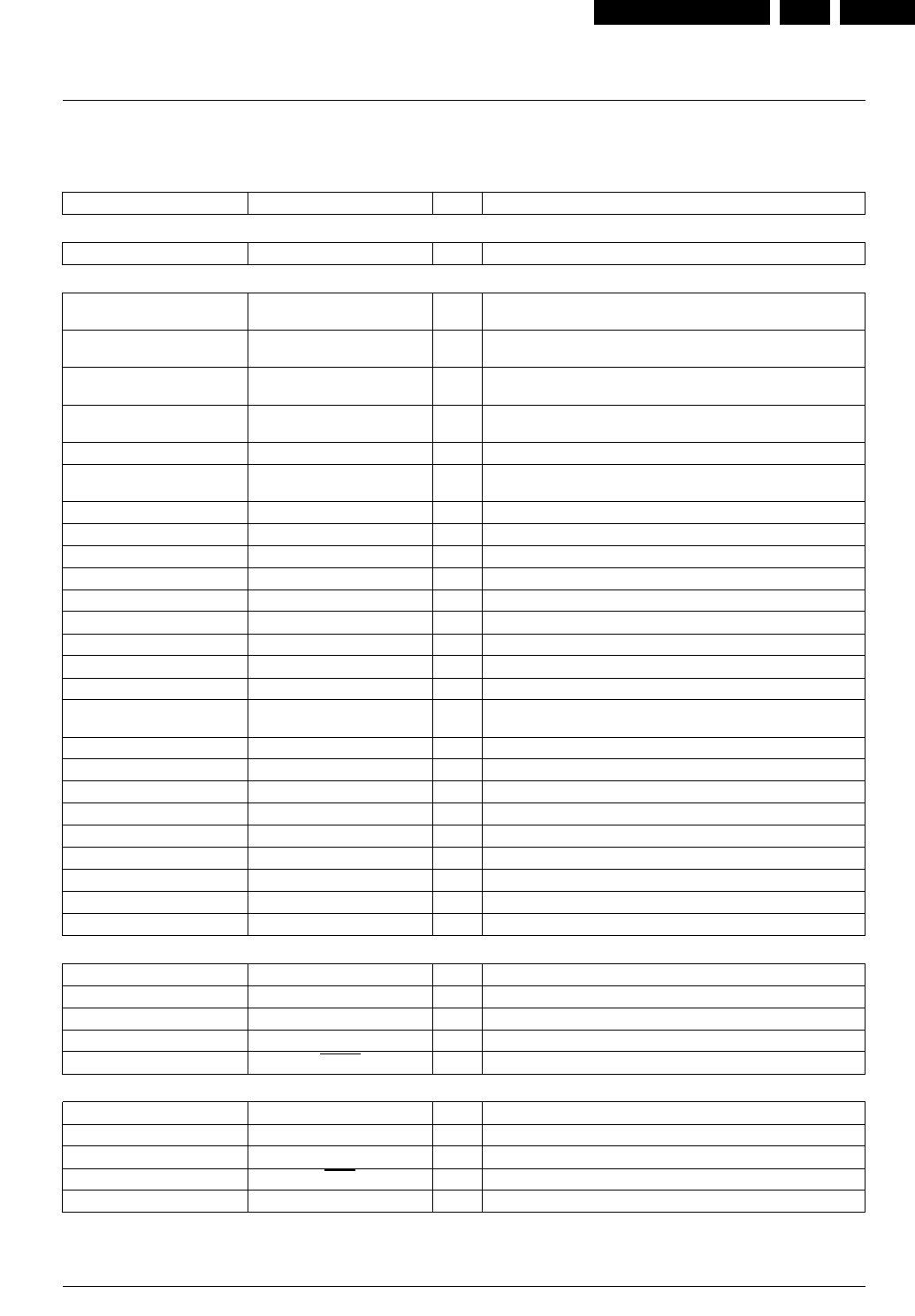

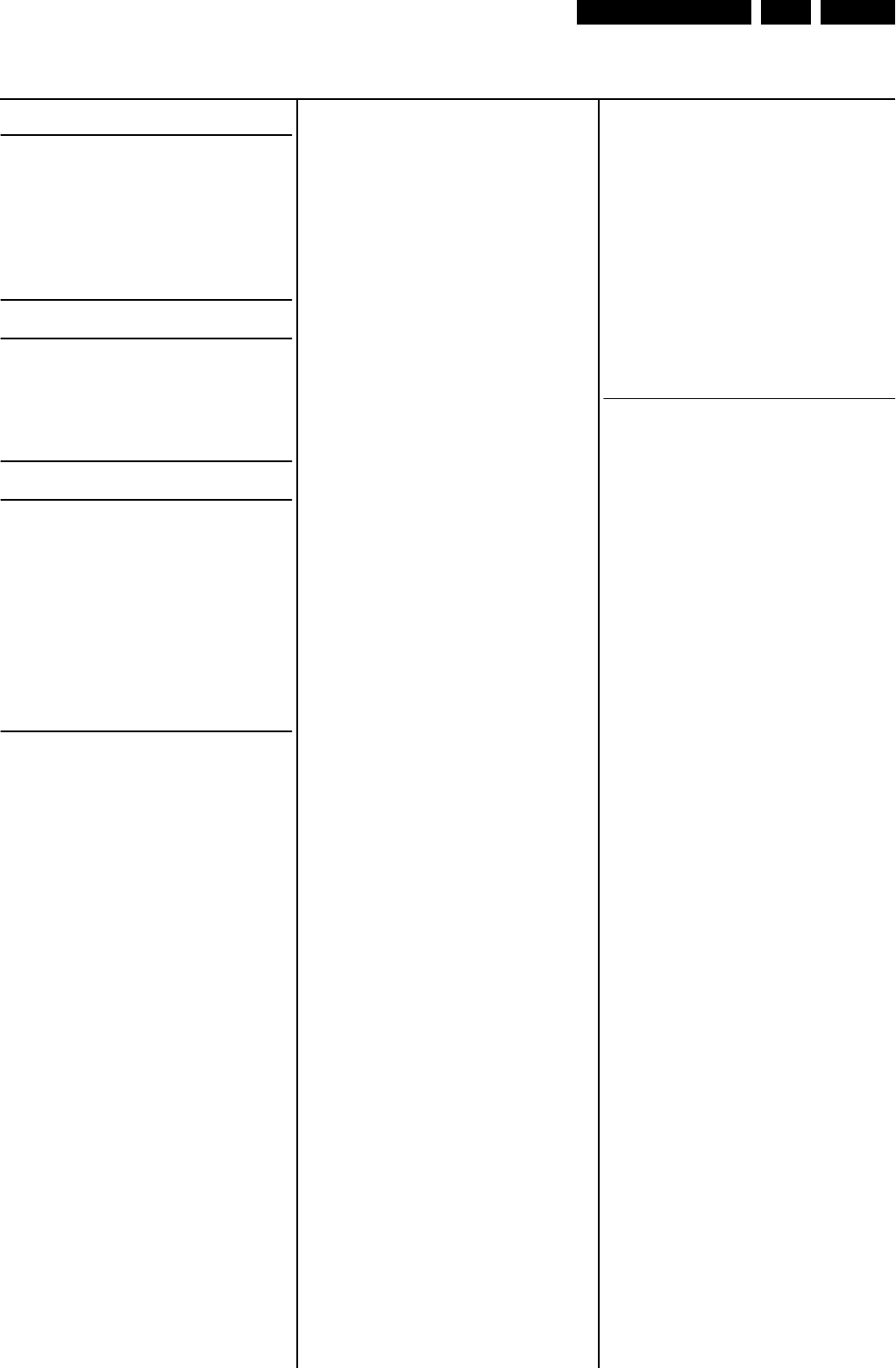

10. EXPLODED VIEW AND PARTS LIST (/N1B)

POS.

NO VERS.

COLOR PART NO.

(PCS) DESCRIPTION PART NO.

(MJI)

0200 3139 247 51280 FRONT PANEL (BLACK) QT24751280

0201 3120 001 00051 BADGE MARANTZ QZ00100051

0202 3139 247 51310 BADGE DVD QT24751310

0204 3139 244 00550 WINDOW QT24400550

0205 3139 244 00560 BUTTON STANDBY QT24400560

0219 3139 244 00590 DOOR QT24400590

0220 3139 241 20110 SPRING DOOR QT24120110

0240 3139 247 51410 BUTTON CONTROL QT24751410

0244 3139 247 51461 FOOT QT24751461

0245 3139 247 51461 FOOT QT24751461

1005 3122 427 22300 PSU PCB ASSY

DVD2B+ 20PS223

1014 3104 157 11190 CWAS FLEX DVD 22 130 32S QW15711190

1018 3104 157 11200 CWAS FLEX DVD 16 130 32S QW15711200

0385 4822 321 10249 MAINS CORD QP32110249

0384 3139 228 85500 REMOTE CONTROL QT22885500

0387 3139 246 10340 USER GUIDE (/N1B) QT24610340

19 20

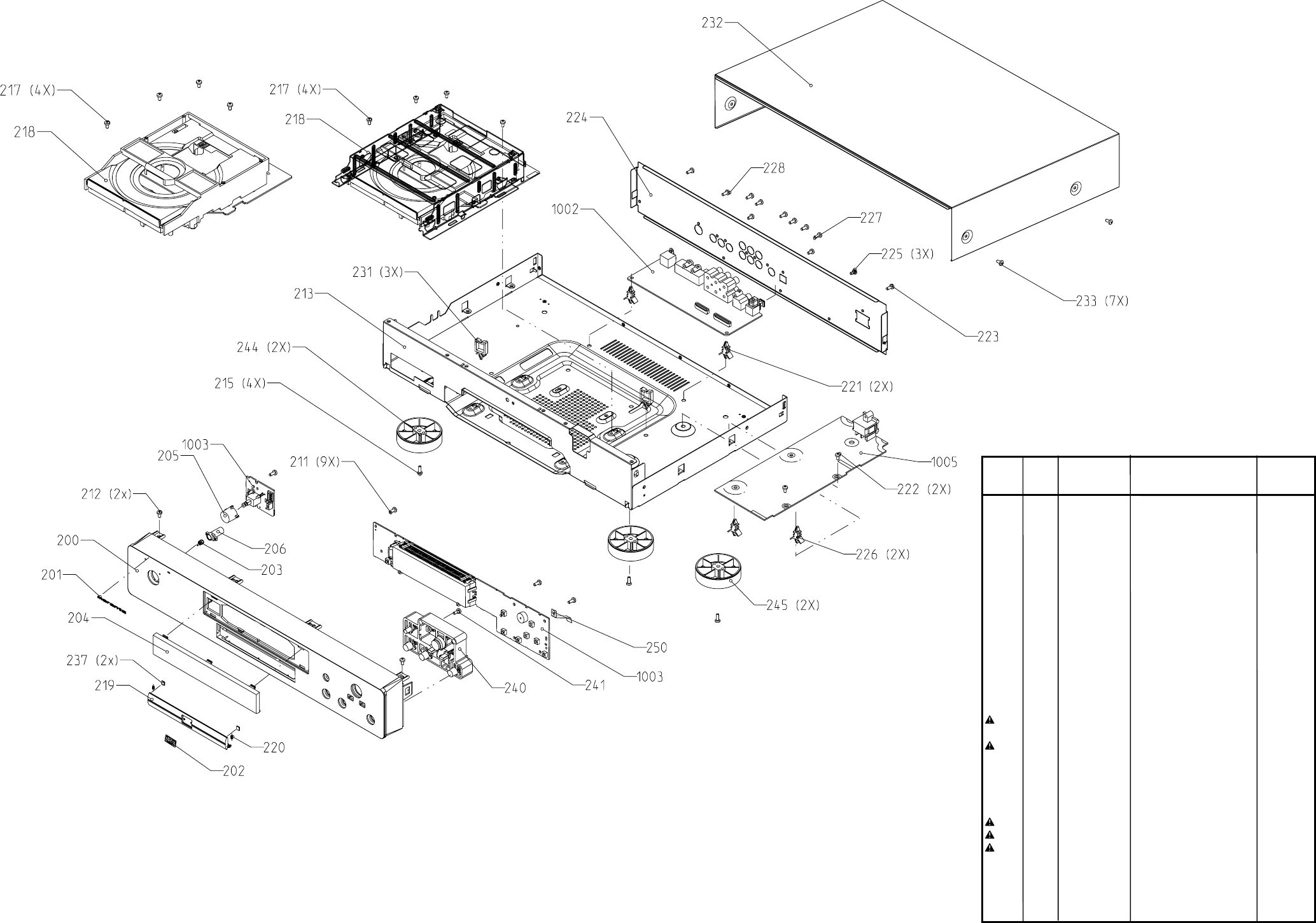

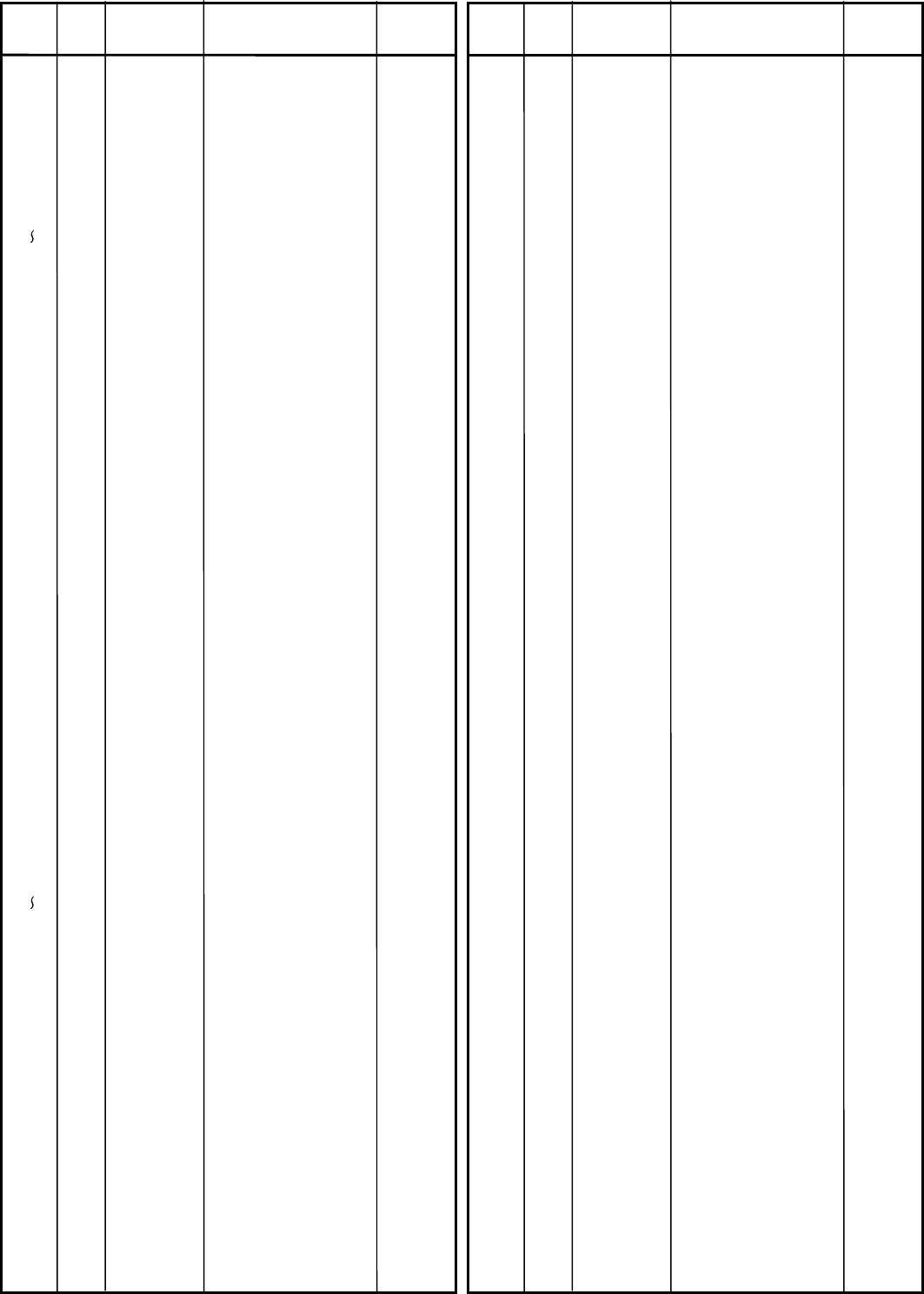

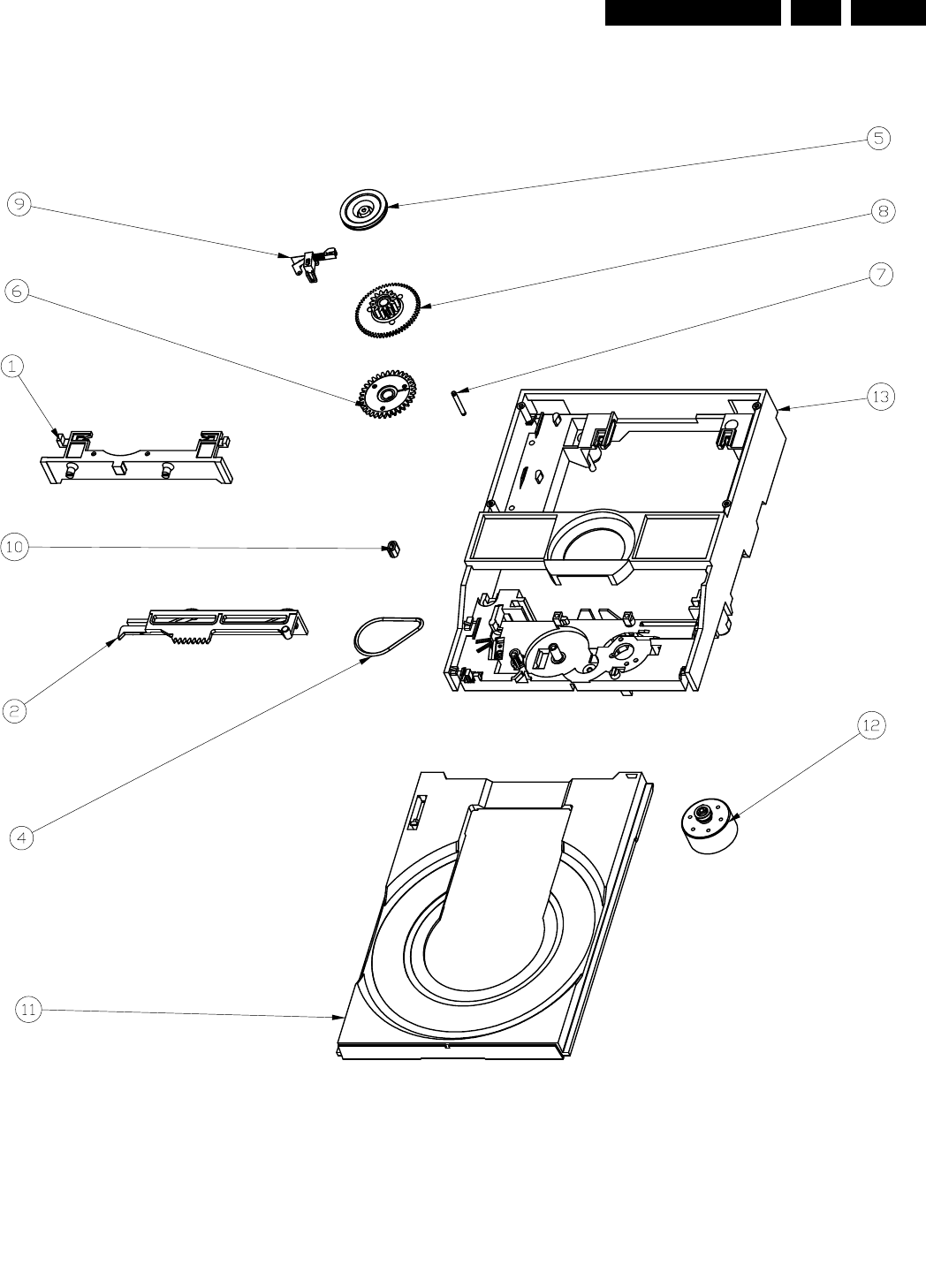

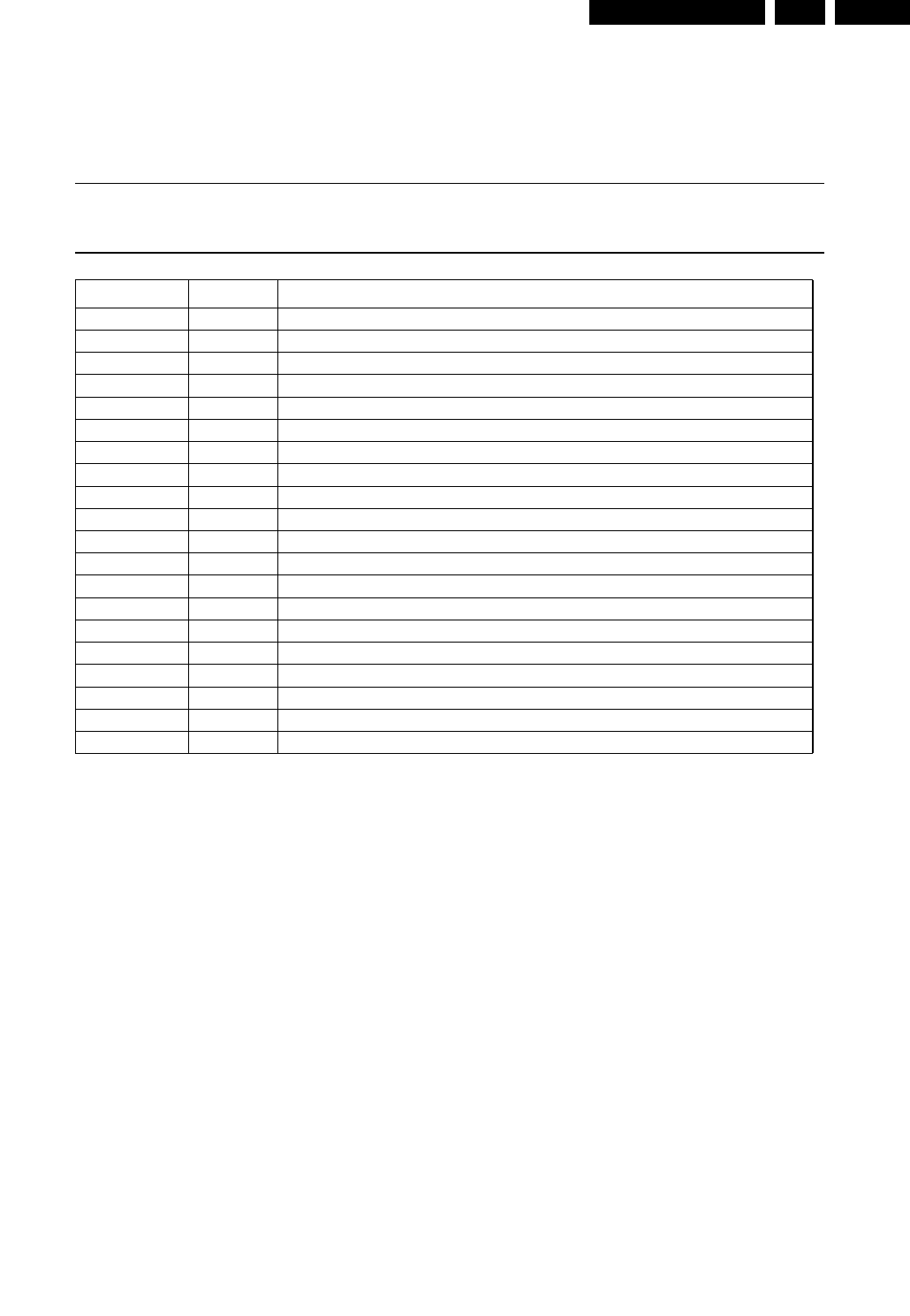

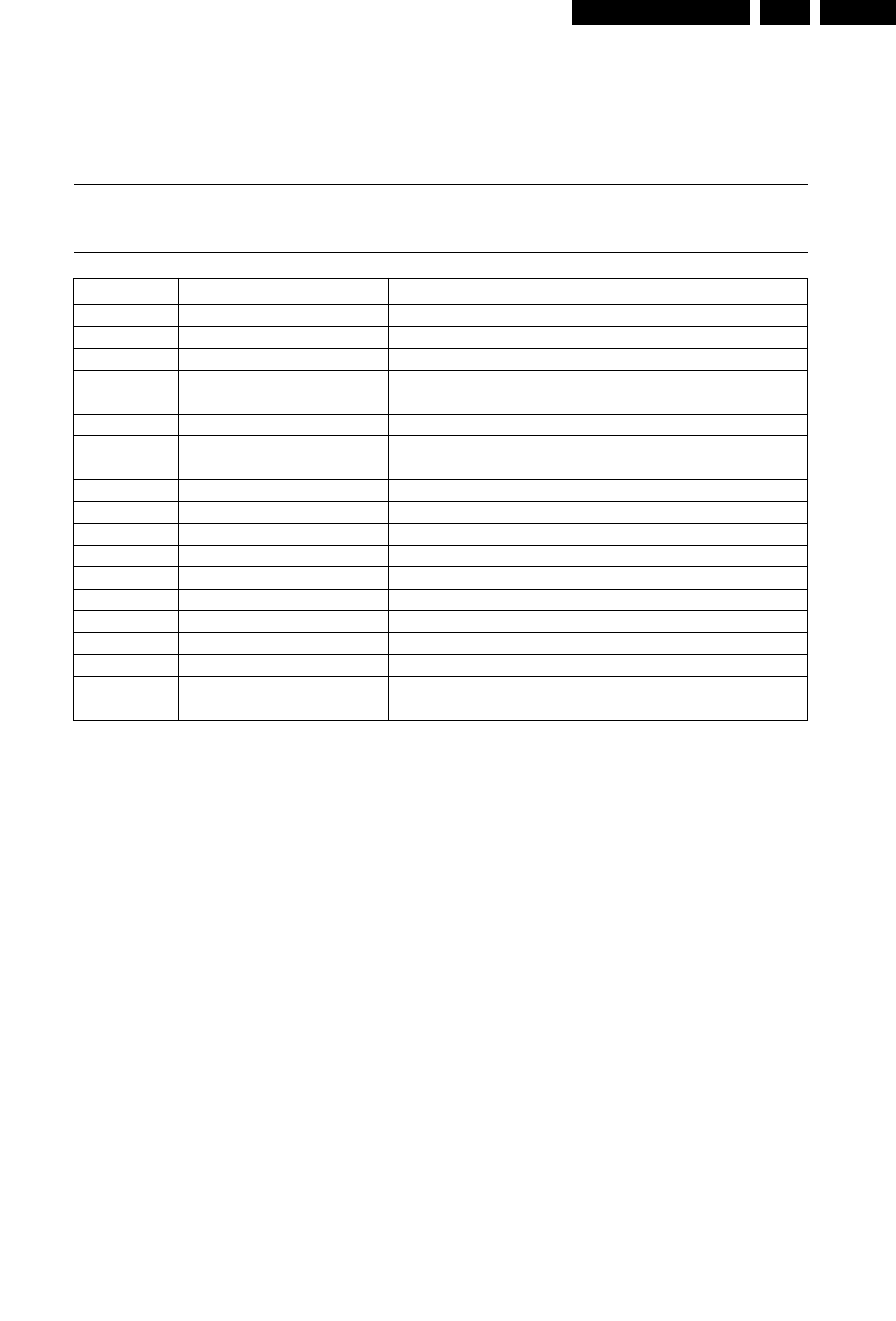

(/A1B, /S1G, /U1B)

For /A1B, /S1G and /U1B new

For /U1B old

POS.

NO VERS.

COLOR PART NO.

(PCS) DESCRIPTION PART NO.

(MJI)

0200

/A1B,/U1B

3139 247 51290 FRONT PANEL (BLACK) QT24751290

0200 /S1G 3139 247 51302 FRONT PANEL (GOLD) QT24751302

0201 4822 454 11825 BADGE MARANTZ QP45411825

0202

/A1B,/U1B

3139 247 51310 BADGE DVD (BLACK) QT24751310

0202 /S1G 3139 247 51321 BADGE DVD (GOLD) QT24751321

0204 3139 244 00550 WINDOW QT24400550

0205

/A1B,/U1B

3139 244 00570 BUTTON POWER (BLACK) QT24400570

0205 /S1G 3139 247 51331 BUTTON POWER (GOLD) QT24751331

0219

/A1B,/U1B

3139 244 00590 DOOR (BLACK) QT24400590

0219 /S1G 3139 247 51341 DOOR (GOLD) QT24751341

0220 3139 241 20110 SPRING DOOR QT24120110

0240

/A1B,/U1B

3139 247 51410 BUTTON CONTROL (BLACK) QT24751410

0240 /S1G 3139 247 51421 BUTTON CONTROL (GOLD) QT24751421

0244 3139 247 51451 FOOT QT24751451

0245 3139 247 51271 FOOT QT24751271

1005

/A1B,/S1G

3139 248 80390 PSU PCB ASSY DVD2000

(OVS) QT24880390

1005 /U1B 3139 248 80380 PSU PCB ASSY DVD2000

(USS) QT24880380

1014 3139 110 34220 FFC FOIL 22P/105/22P BD B QT11034220

1018 3139 110 34230 FFC FOIL 16P/105/16P BD B QT11034230

0384 3139 228 85500 REMOTE CONTROL QT22885500

0385 /A1B 3139 118 73040 MAINS CORD (/A1B) QT11873040

0385 /S1G 4822 321 10249 MAINS CORD (/S1G) QP32110249

0385 /U1B 4822 321 11466 MAINS CORD (/U1B) QP32111466

0387 /U1B 3139 246 10350 USER GUIDE (/U1B) QT24610350

0387

/A1B,/U1B

3139 246 10521 USER GUIDE (/A1B,/S1G) QT24610521

21 22

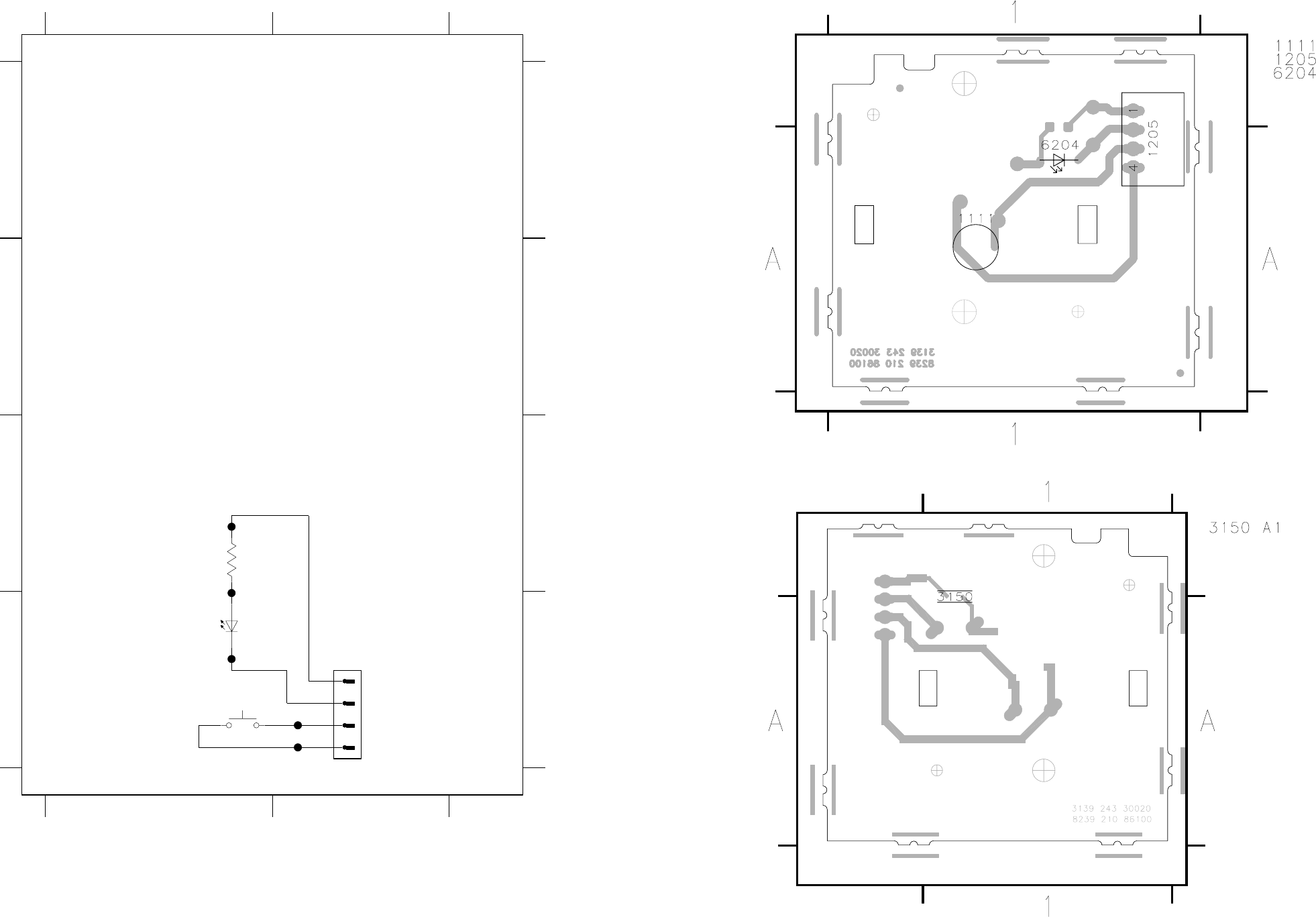

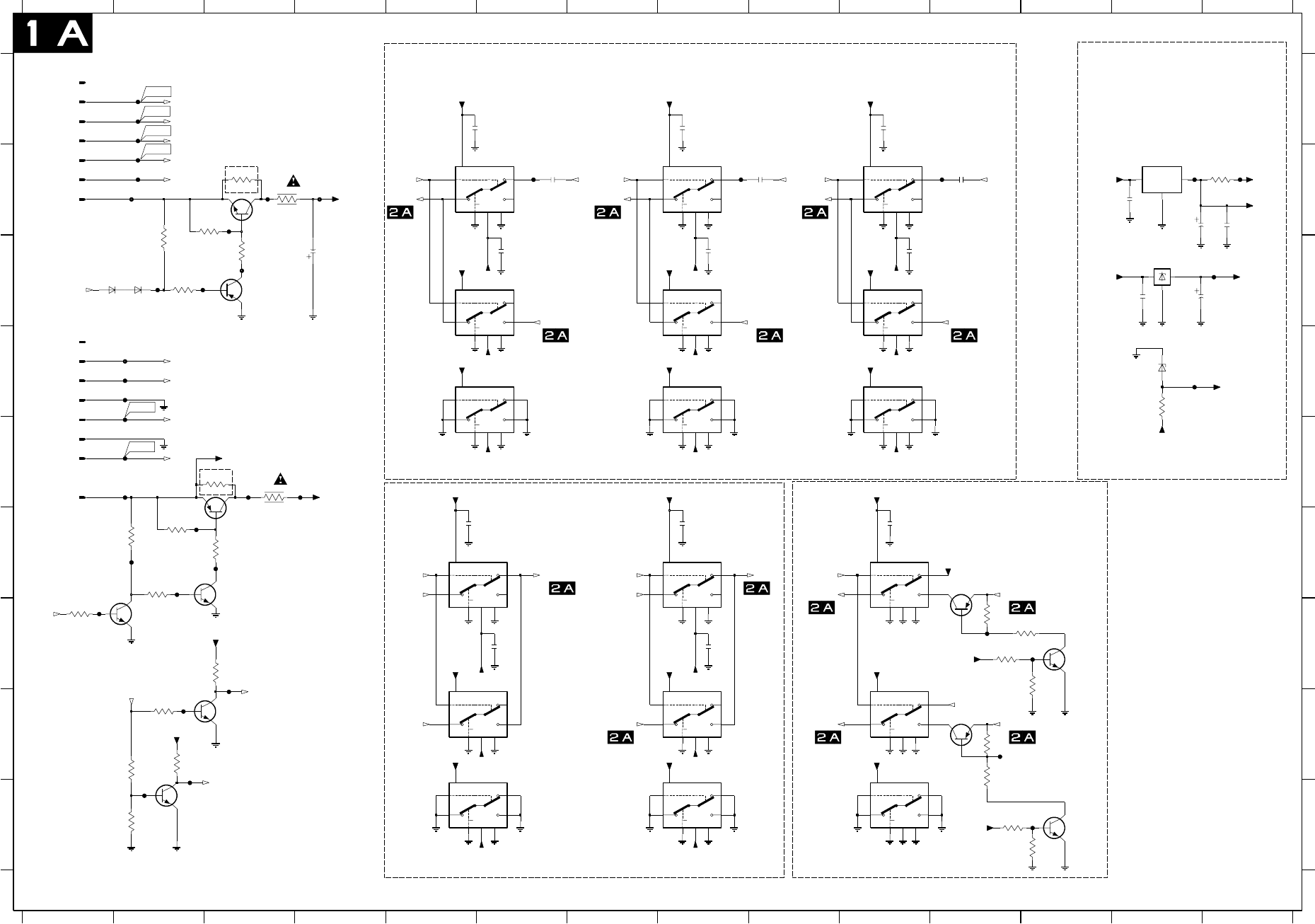

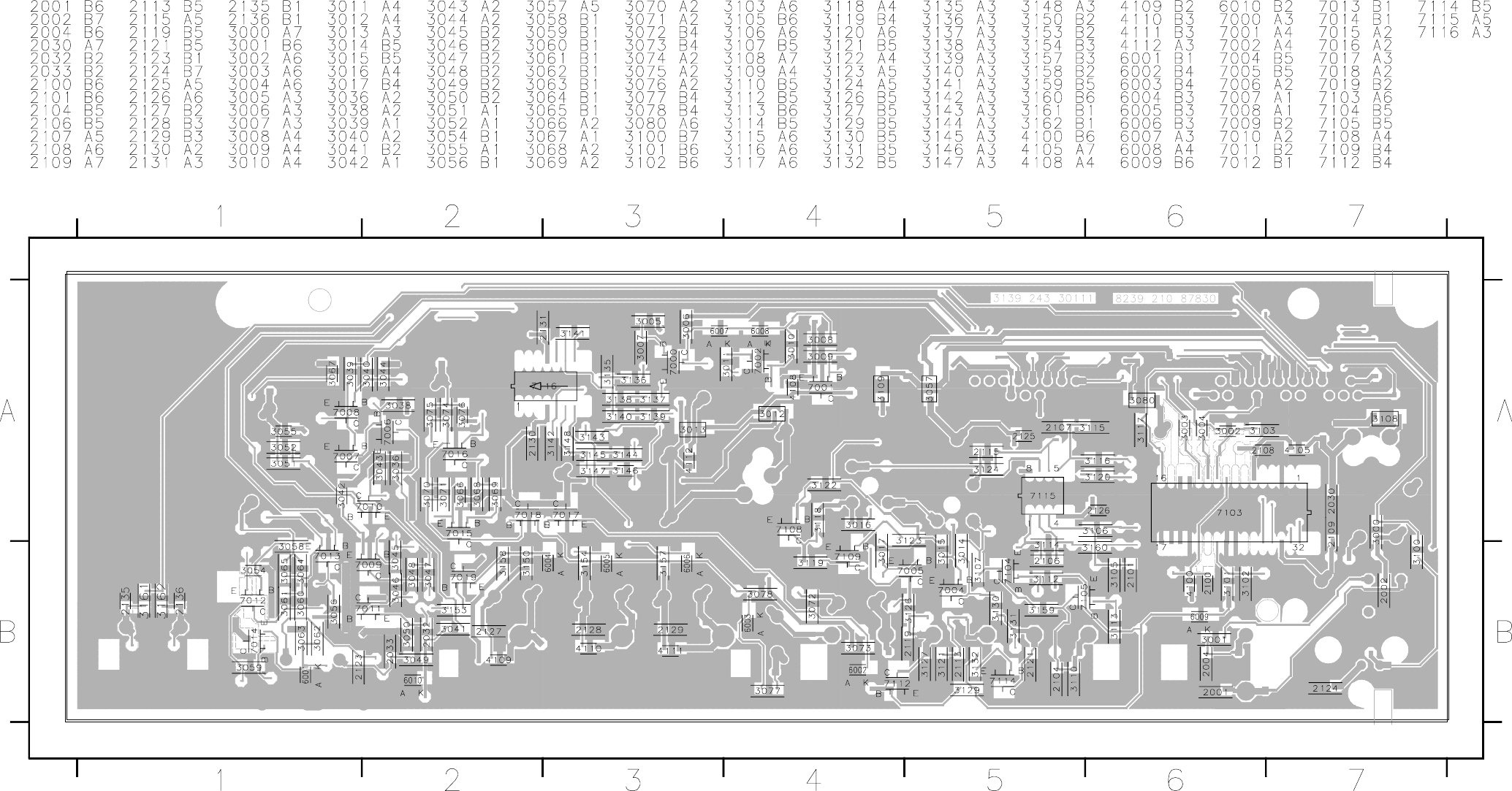

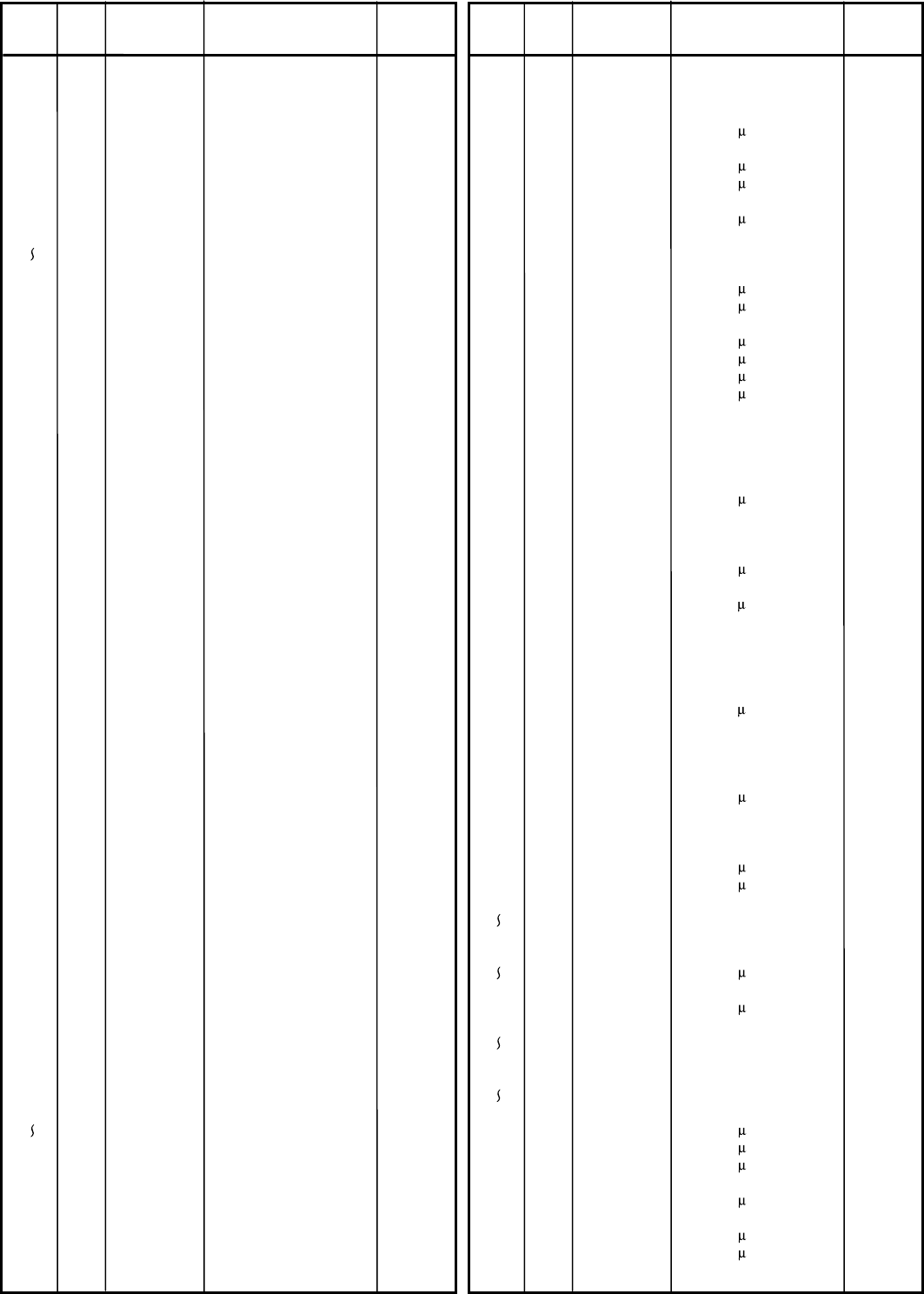

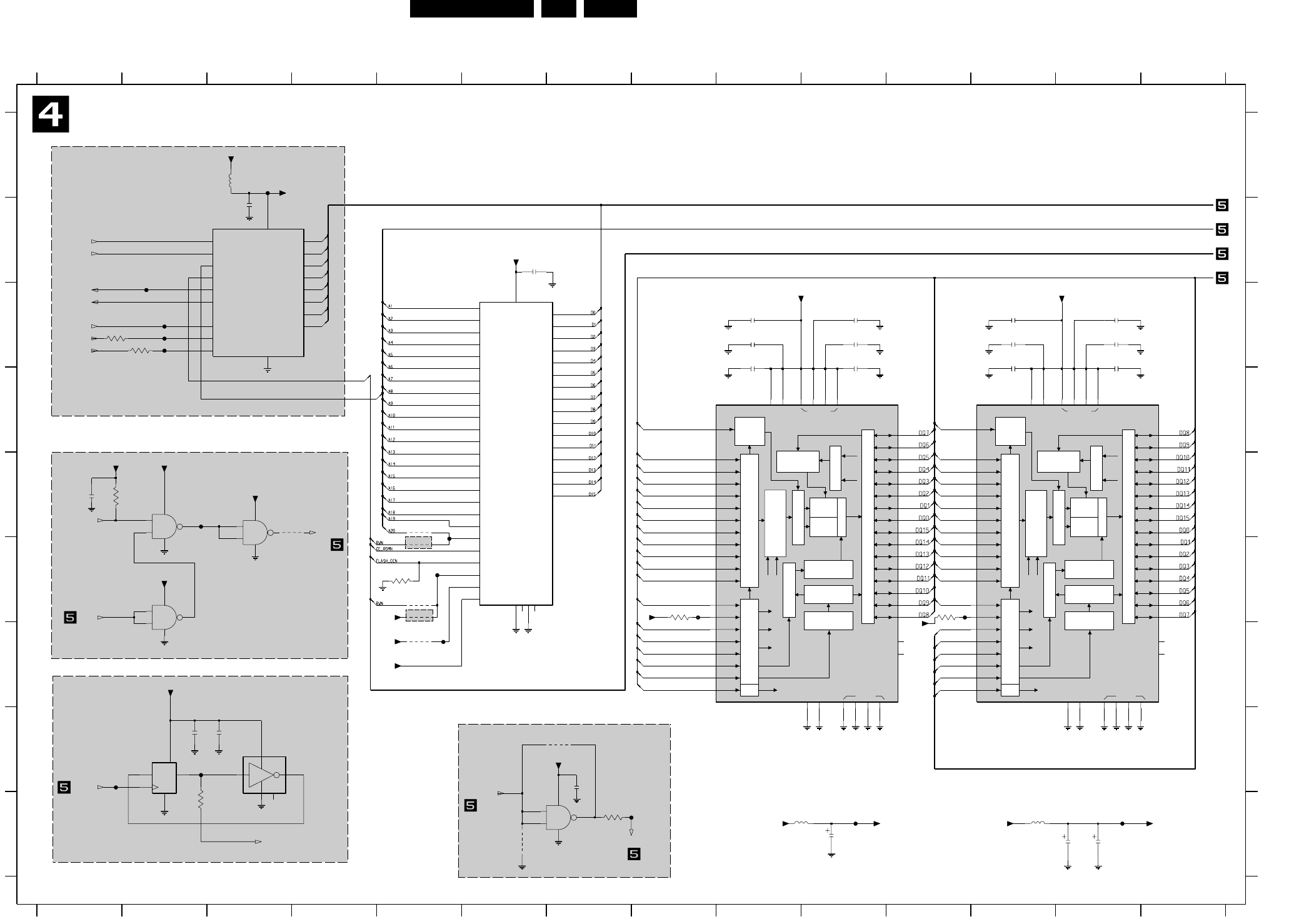

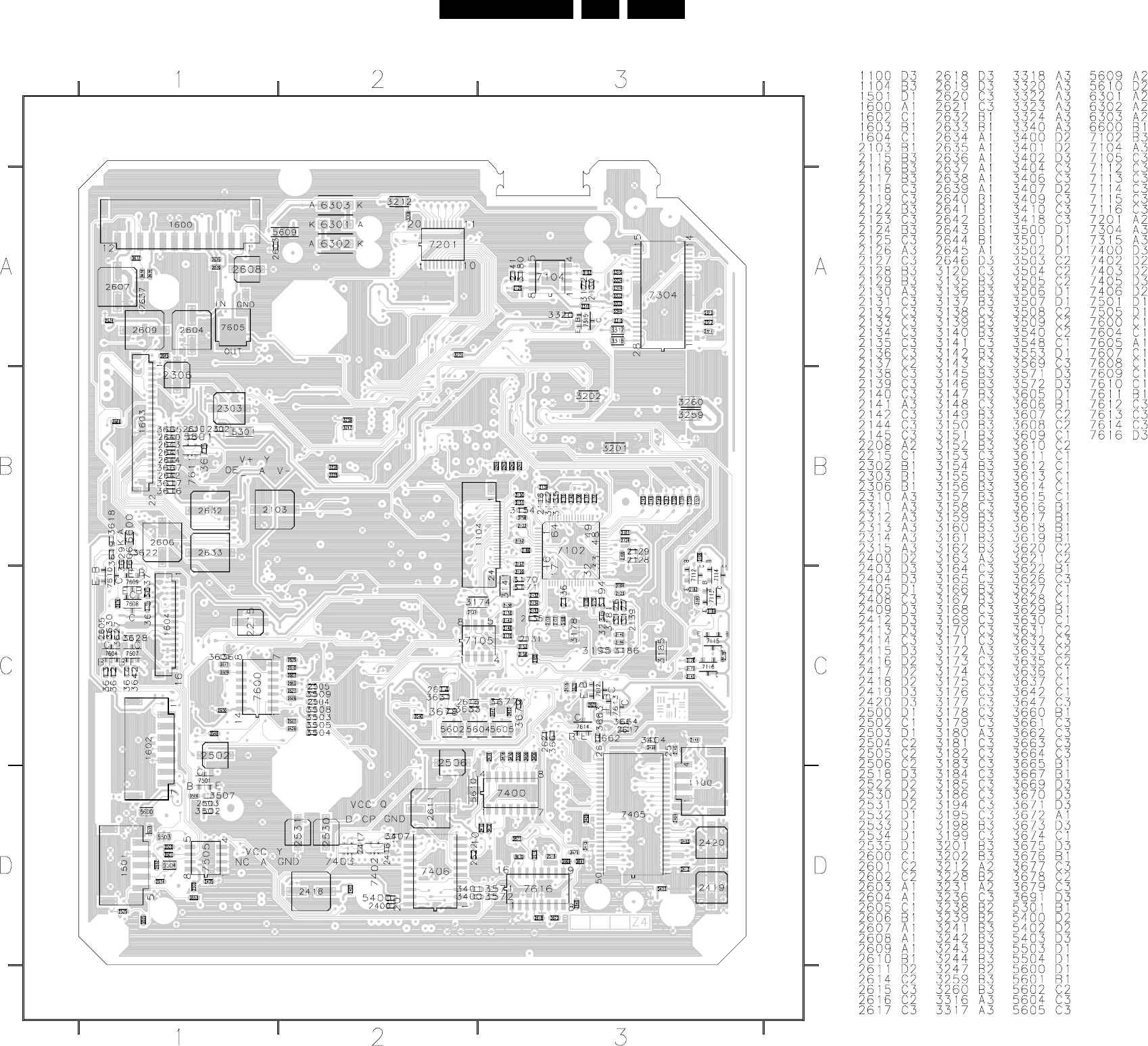

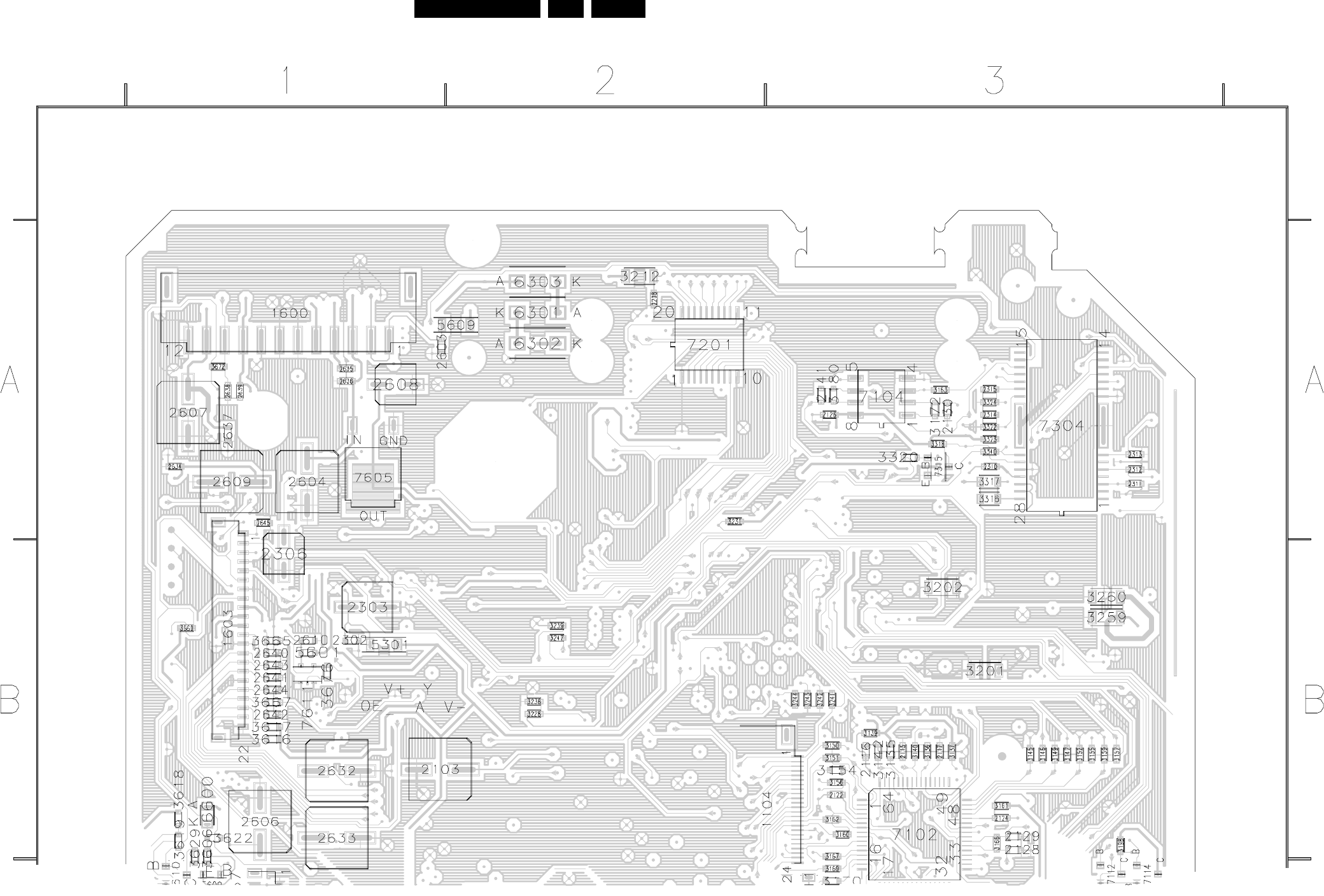

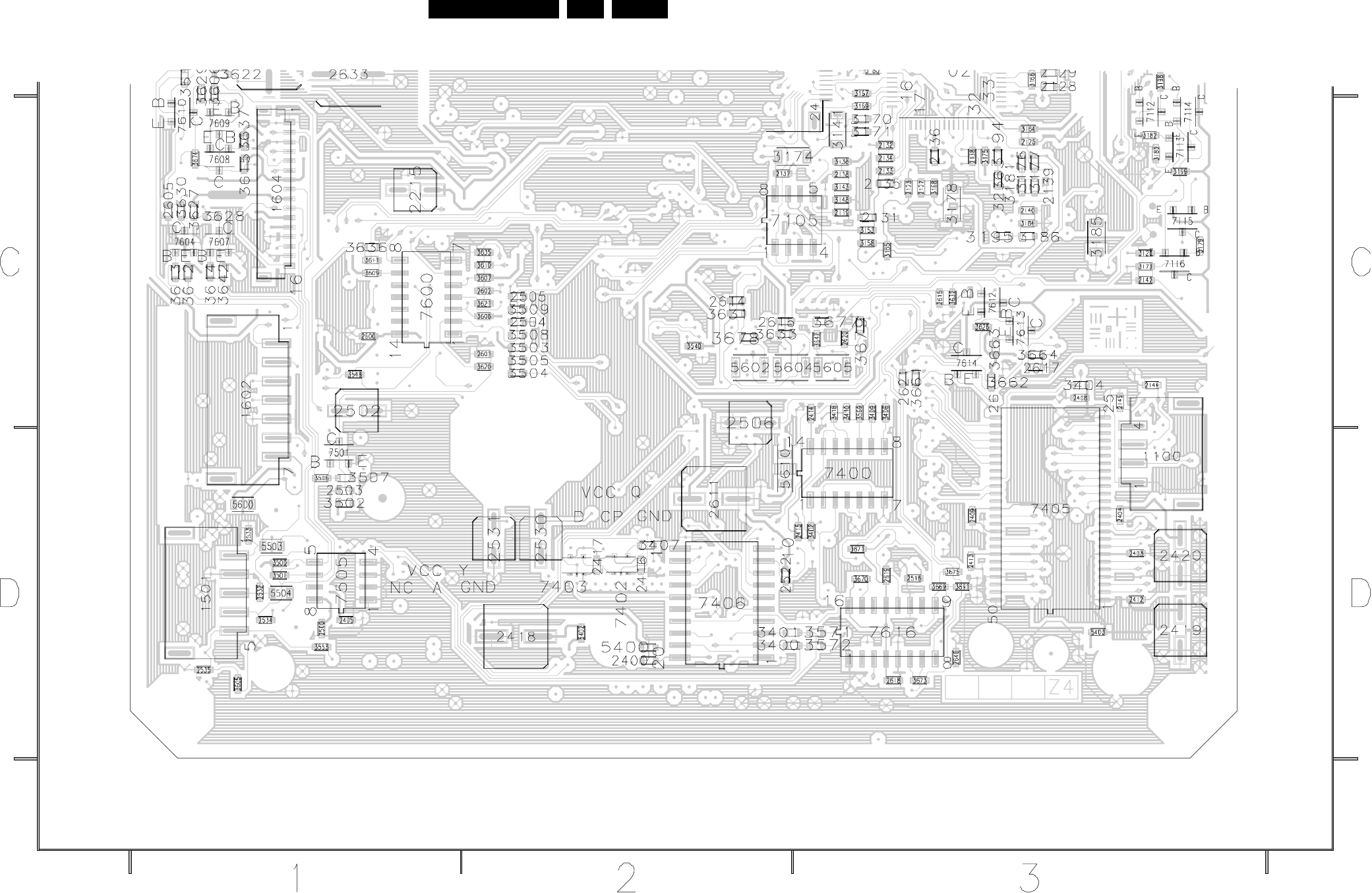

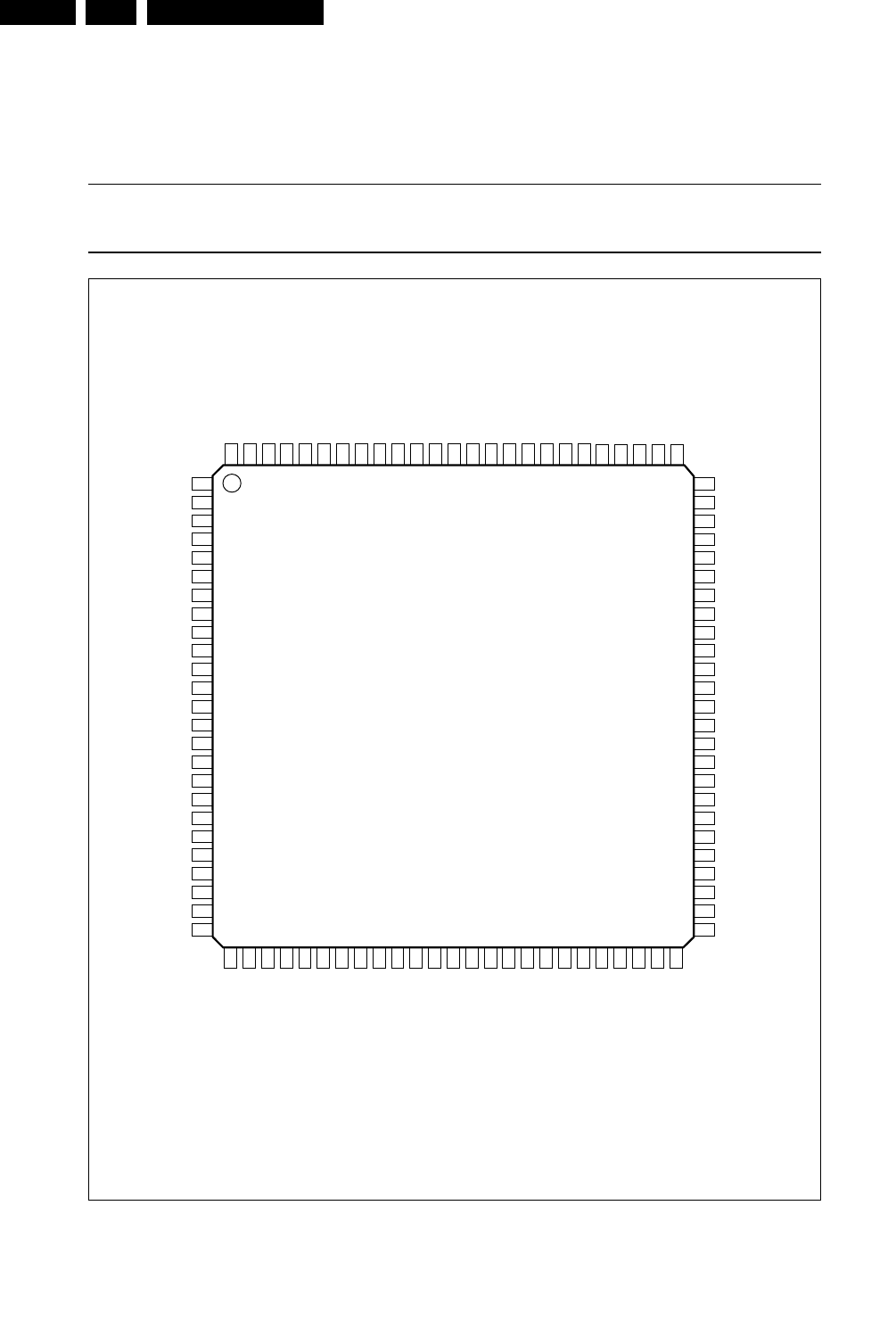

12. SCHEMATIC DIAGRAM AND PARTS LOCATION

1111 D1

1205 D2

3150 C1

6204 D1

T134 C1

T135 D1

T136 D1

T137 D2

T138 D2

1

2

3

4

GEEN SYMBOOL

CQW10

STANDBY

D1: Standby PCB (N1B)

To Con 1117 of Display PCB

12

12

A

B

C

D

A

B

C

D

SKQNAB

1111

1205 EH-S

T134

LTL-1CHPE

6204

3150

100R

T137

T138

T136

T135

Volume / Standby PWB

23 24

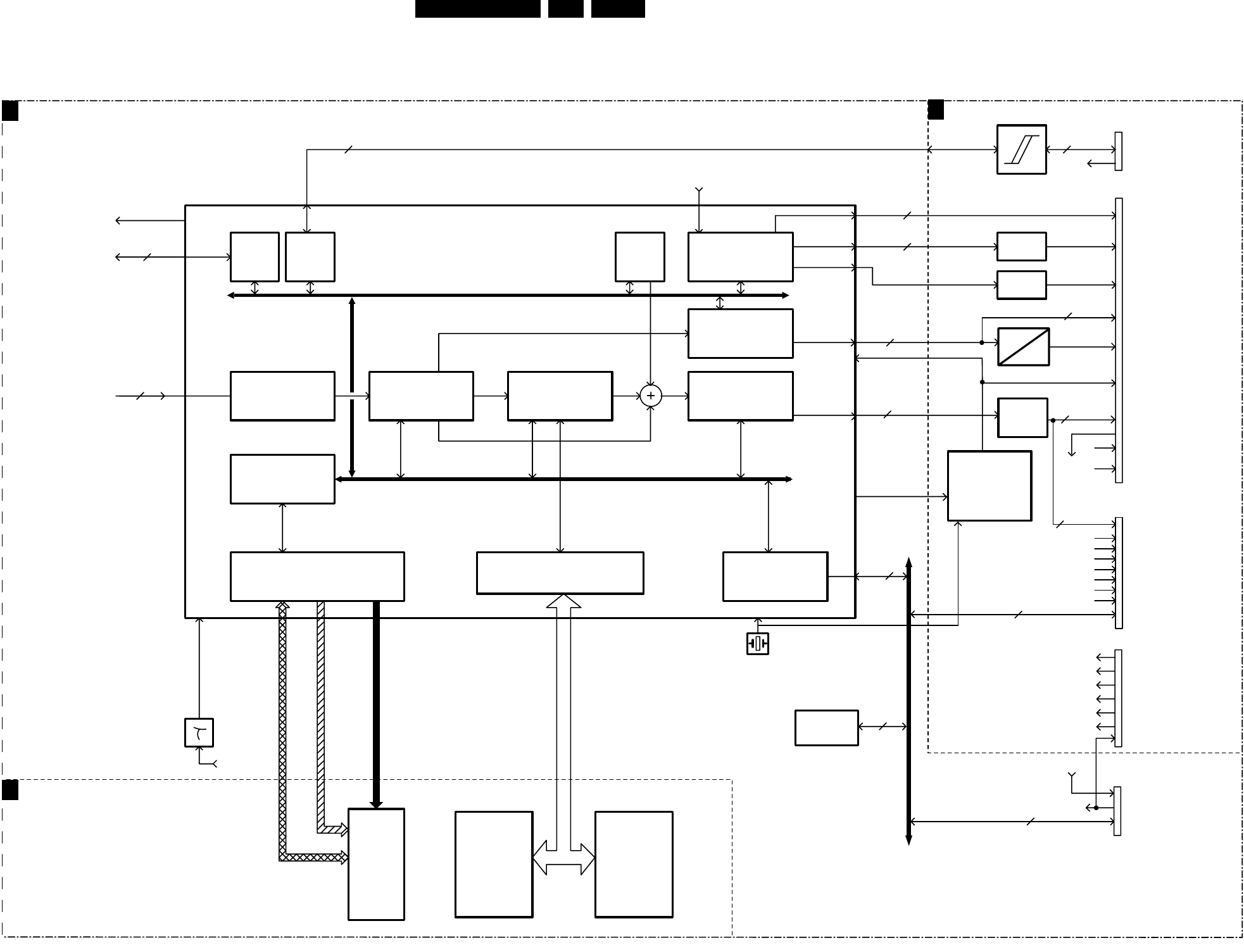

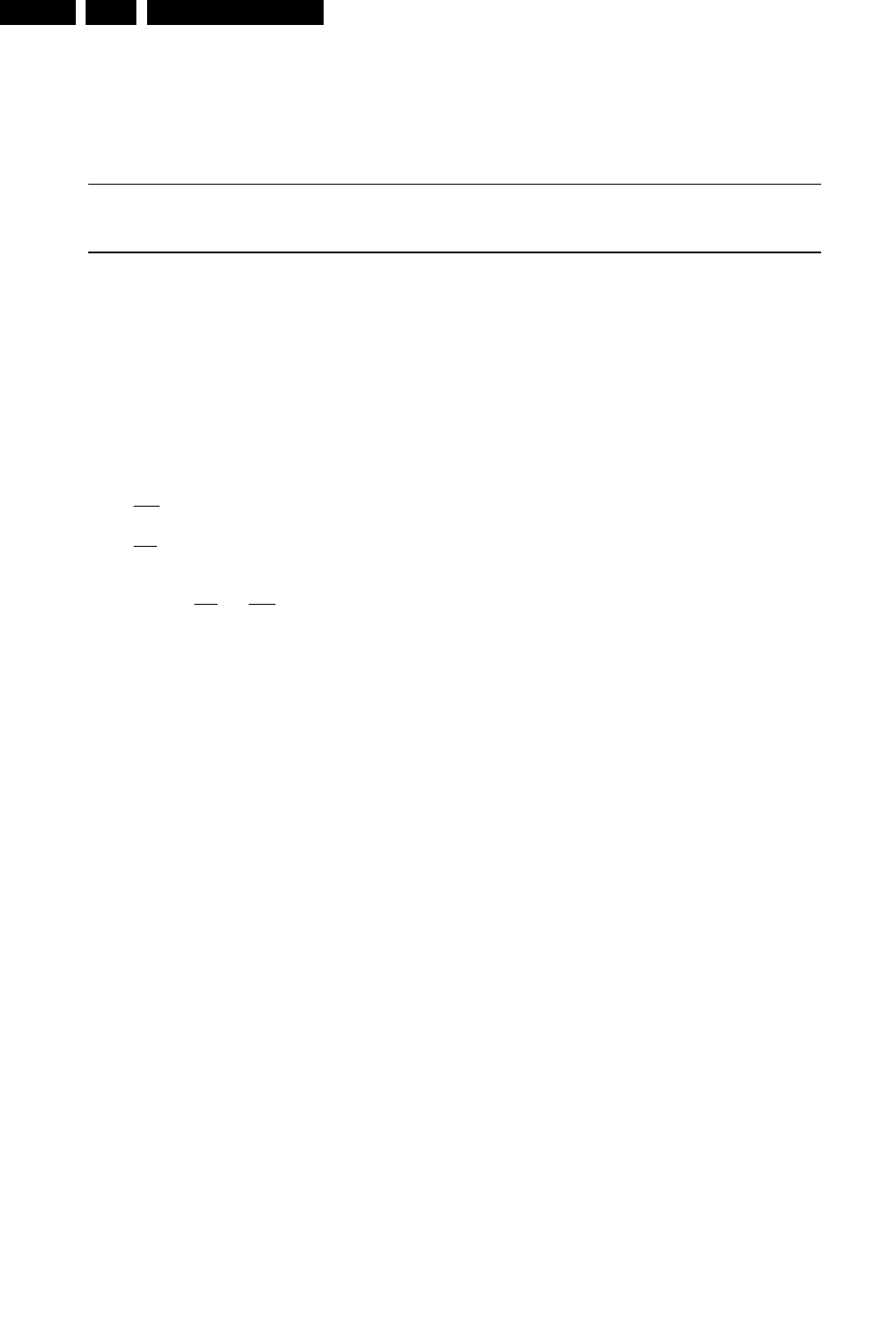

Display

8-Bit A/D

Converter

Counter

VFT driver circuit (automatic display)

80k pull

down

8-Bit h.break. v.

out w. latch P8

8-Bit high breakdown voltage

output part ewith latch P7

8-Bit high breakdown v.

output port with latch P6

4-Bit In/Output

sink open drain

out. port w. latch P9

5-Bit h. breakd. v.

out w. latch PD

8-Bit Input/Output

(tri-state) P0 3-Bit In/Output

with latch P2

8-Bit Input/Output

(tri-state) P0

3-B. I/O P3

sink o.drain

RAM ROM

Program

CPU

V24

V25

V26

V27

V28

V29

V30

V31

V32

V33

80k pull down 80k pull down

P6-P9 source open drain 80k pull down

source open

drain 80k p.d.

VDD

VAREF

VASS

AIN13

AIN12

AIN11

AIN10

AIN7

AIN6

AIN5

AIN4

AIN3

AIN2

AIN1

AIN0

SCK0

V7

V6

V5

V4

V3

V2

V1

V0

SO1

P03

(tri-state) P5

8-Bit Input/Output

(tri-state) P4

8-Bit h. breakdown v.

XIN

-RESET

XTOUT

XTIN

TEST

-STOP

-INT0

-INT1

TC2

-DV0

TC4

TC1

INT2

INT4

SCL

SCA

P04

P05

P06

P07

VSS

XOUT

V34

V35

V36

VKK

-SCK1

SI1

V23

V22

V21

V20

V19

V18

V17

V16

V15

V14

V13

V12

V11

V10

V9

V8

VCD

D

SHUFFLE

CHAPTER TRACK

SCAN A-B

FTS TOTAL TRACK

TRACKTITLE

TIME

CHAPTER

VD

TITLE

WREPEAT

L

DIGITAL

SURROUND

L

R

CR

SSS

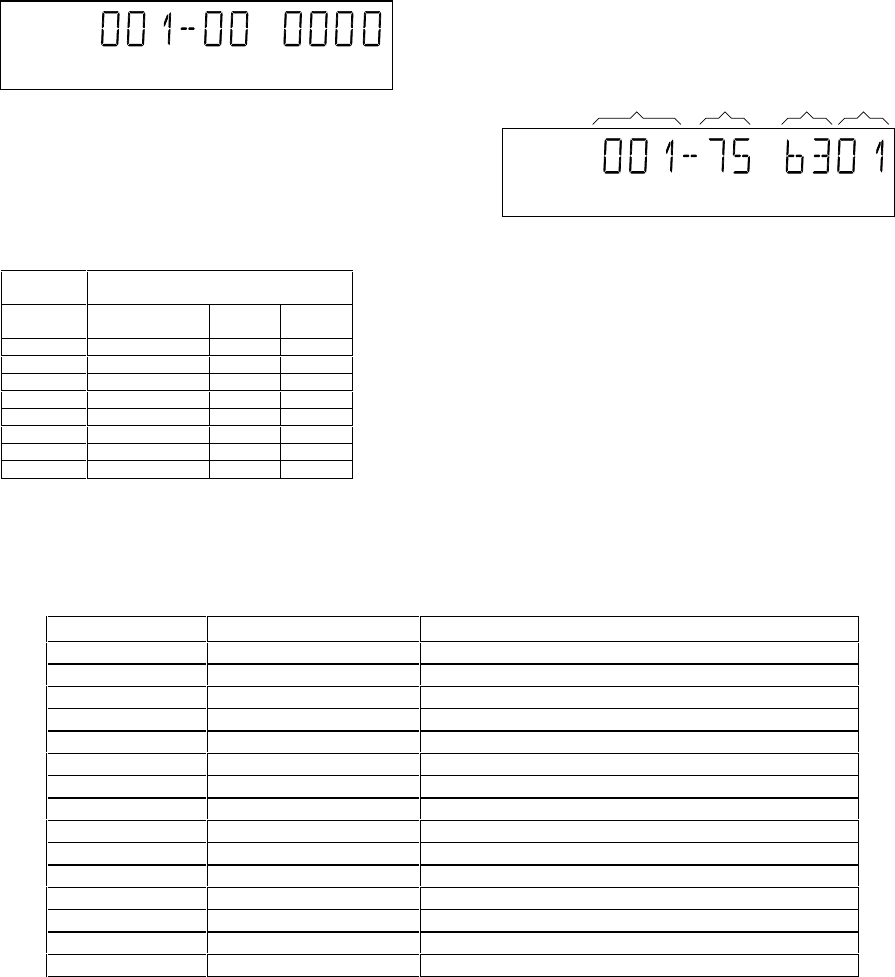

A1 : FRONT DISPLAY PCB

TMP87CH74

7104

11 12 19

VFD GRID14

PLAY

65

PAUSE

to scart

54 46

53

MICRO-

P50

5056 49

17

TO 1205

F127

For DVD732 only

scart PIN 10

INFO : FIL2-FIL1=4.8Vac-RMS

MICRO+

38

30

29

28

27

26

25

42

F126

41

F128

STOP

F116

+5V stb

F117

OPEN / CLOSE

3D SOUND

OPTION

4

PREVNEXT

89 2216 21

39

80

79

STBY - LEDCONTROL

37

36

35

OPTION

7

-40V

1

STBY control

10

VFD GRID 12

34

23 13

5152

63 62 61

70

69

71

72

73

55

75

P50

interface

68

67

(-40V)

33

32

31

10 11 12 13 14

123456

45 44 4348 47

40

OPTION

F118

+12V

GND

20

SCL

SCA

64

66

For DVD 751

only

76

77

5614 15

59

60

24

78

23

VFD GRID 13

18

P50

74

58

123456789

7 8 9 10111213 14

A

B

For models with P50 only

D

E

F

G

H

I

57

C

6789333435363738394041424344454849 5212223242526272829303132

1113 110111213141516171819 220

F204

14-MT-26GNK

F165

F166

2107

33n

F217

F168

3134

330R

27K

3101

F120

3118

10K

F129

F161

F216

F119

F181

2211

BAS216

6100

3107

0R

100p

F121

10K

3140

2128

1n

22u

2130

3100

22K

2119

22p

3145

10K

F153

VKK

2114

22p

3109

SKQNAB

1101

4K7

3126

10R

10R

3128

F164

3138

470R

3105

0R

2131

1n

+5Vstb

2202

1n

+5Vstb

22p

2121

F202

10R

3133

F212

1110

VKK

6101

BZX284-C8V2

3114

10R

3120

470R

2110

33n

F211

F149

VKK

F229 F147

F228

1115

EH-B

1

2

3

4

F232

F187 SKQNAB

1109

22p

2118

F141

33n

2108

SKQNAB

3104

1100

3131

4R7

100K

F104

F137

2201

F179

3113

4K7

33n

2125

22p

10K

3143

4K7

3139

BC847B

7108

F203

2105

33n

1108

SKQNAB

1107

SKQNAB

220p

2100

3106

220R

2101

220p

F178

F107

F177

7112

MC79L24

GND

3

IN

2

OUT

1

F219

3119

10K

3144

100K

2111

33n

6104

BAS216

VFIL_DC

VFIL_DC

2106

10u

1102

SKQNAB

F201

F180

F150

F244

F245

F183

+5Vstb

VKK

82K

3108

4K7

3110

F241

F243 10R

F242

F200

3122

7109

BC857B

F109

F108

BAS216

6105

3150

4K7

F176

F227 F175

F167

F230

F138

F139

3130

10R

F171

BC327-25

7106

F170

F173

F102

F103

F234

F223

F235

F213

F124

F210

F209

F133

F208

82K

3103

7102

BC847B

10K

3123

7100

BC847B

VKK

+5Vstb

+5Vstby

+12V

F105

1202

1207

3147

10K10K

3146

SKQNAB

1106

2116

33n 10u

2117

2109

VKK

F130

33n

GND

1

OUT

3

VS

2

2115

22p

4K7

3115

7110

TSOP1736

F163

3102

47K

F159

F157

F160

F155

F152

F169

+5Vstb

2

3

100R

3148

100R

3149

1

2

3

4

5

EH-B

1119

1

3121

4K7

EH-B 1116

F123

F122

F132

2129

7107

BC847B

2123

10u

22u

F101

4R7

3117

F100

22u

10R

3127

2124

BC337-25

7105

3112

4K7

F106

3111

4K7

F113

F135

+5Vstby

F114

F221

22p

2120

F222

3132

330R

+12V

F214

PKM13EPY

1112

3136

F218

33n

2122

1K

PH-B

1118

1

2

3

4

5

10R

3129

7101

BC847B

F231 100p

2103

F131

330R

F186

10K

3137

3142

BC847B

BZX284-C10

6102

F151

7103

F154

4

3135

220R

F184

F205

1117

EH-B

1

2

3

F206

F207

F172

F158

F156

3116

82K

10u

2126

3125

10R

F142

F140

F162

F233

F226

1122

SKQNAB

2102

100p

SKQNAB

1121

7202

F125

STBKEY+ STBKEY-

+5Vstb

V15

G14

G13

G12

OUT_P50 IN_P50

V13V14

V15

V14

IN_P50

OUT_P50

STBKEY+

STBKEY-

K_DATA

K_RESET

K_CLK

K_STROBE

FIL1

FIL2

FIL1FIL2

V13

25 26

Display PWB

27 28

Supply and video switching (/N1B)

F276 E4

F277 F2

F278 F2

F279 F3

F280 F2

F281 G1

F401 C14

F500 G11

F501 G12

F502 H11

F503 I12

U182 B6

U183 B8

U185 D13

U228 H2

U229 G3

U230 H2

U275 I2

7901-B G8

7901-C H8

7902-A F10

7902-B G10

7904-A B8

7904-B C8

7904-C D8

7905-A B10

7943 I2

7945 F11

7946 H11

F109 A2

F110 A2

F112 B2

F113 B2

F120 B13

F121 B14

F130 D2

F135 E2

F138 D2

F142 D2

F144 D2

3624 F2

3625 G1

3626 B3

3627 E3

F150 E2

F211 B11

F260 B2

F269 B3

3723 I2

3762 D13

3769 G12

3770 G11

F270 B4

F271 B3

F272 C3

3774 H11

3804 G11

3805 G12

F273 C2

F274 C2

F275 E3

7304 B13

7331 B3

7332 C3

7333 F3

7334 F3

7335 G2

7400 C13

7900-A F6

7900-B G6

7900-C H6

7901-A F8

RGB switching

D

E

F

7902-C H10

7903-A B6

7903-B C6

7903-C D6

B

C

D

E

7905-B C10

7905-C D10

7935 H3

I

1300-1 A1

1300-2 A1

7947 I12

7949 G12

F106 A2

1300-8 B1

1300-9 B1

1301-10 D1

1301-13 D1

1301-14 D1

1301-15 E1

1301-16 E1

1301-2 D1

1301-8 D1

1301-9 E1

2354 B13

VIDEO SWITCHING

123

3695 H2

3696 G3

3720 H2

3722 H2

8 9 10 11

3771 H11

3772 I11

3773 I12

123

6302 C2

6403 C1

6404 D13

7 8 9 1011121314

A

B

C

BLANKING

CVBS SWITCHING

supply

2384 B11

G

H

I

A

2412 B14

2452 C13

2453 C14

2524 B6

F

G

H

2525 B9

2527 A6

2528 A8

1300-3 A1

1300-5 A1

1300-6 B1

2529 A10

2530 C6

2531 C8

2532 F6

2533 G6

2534 C10

2535 F8

2536 F10

2537 G8

2541 B14

2545 C4

3433 B14

3615 B3

3616 B3

3617 C2

3618 C3

3619 C2

3620 E3

3621 F2

3622 F2

3623 F3

4567

SUPPLY &

12 13 14

456

F113

E

6

S

10

Vdd

16

Vee

7

Vss

8

Y0

2

Y1

1

Z

15

F276

HEF4053BT

7903-B

+6V

-5V

10

3695

10K

1301-10

1301-16

16

L78L33

7400

2

13

+6V

F272

3626

0R

Vdd

16

Vee

7

Vss

8

Y0

12

Y1

13

Z

14

F271

+6V

HEF4053BT

7902-A

E

6

S

11

U228

U229 7902-B

HEF4053BT

6

E

10

S

16

Vdd

7

Vee

8

Vss

2

Y0

1

Y1

15

Z

1301-2

2

7943

BC847B

10K

3622

F260

+8VAud

3773

10K

6

E

10

S

16

Vdd

7

Vee

8

Vss

2

Y0

1

Y1

15

Z

BAS216

6302 7904-B

HEF4053BT

7332

BC857B

F278

F279

F121

56K

3720

2

GND

1IN 3

OUT

+12Vstby

7905-A

HEF4053BT

6

E

11

S

16

Vdd

7

Vee

8

Vss

12

Y0

13

Y1

14

Z

LF80C

7304

1300-9

9

1300-6

6

1300-8

8

1300-3

3

1300-5

5

100n

1301-9

9

3433

0R

2541

U182

F138

22n

25282527

22n

22n

2536

47K

3770

47u

+12Vstby

2453

F273

F503

F274

F269 F270

3V3

-8Vstby

4R7

3615

+12Vstby

3618

1K

10K

3619

10K

3617

2534

22n

7331

BC547B

+6V

220n

2384

E

6

S

10

Vdd

16

Vee

7

Vss

8

Y0

2

Y1

1

Z

15

F281

HEF4053BT

7905-B

22n

2530

BC847B

7935

F130

1300-2

2

6404

BZX284-C5V1

270R

3762

E

6

S

9

Vdd

16

Vee

7

Vss

8

Y0

5

Y1

3

Z

4

U185

HEF4053BT

7905-C

14 U183

HEF4053BT

7904-A

E

6

S

11

Vdd

16

Vee

7

Vss

8

Y0

12

Y1

13

Z

3805

10K

F502

BC847B

7334

14

F501

F500

1301-14

+12Vstby

4K7

3616

BC327-25

F135 F275

7333

3696

10K

+6V

3627

0R

Vdd

16

Vee

7

Vss

8

Y0

5

Y1

3

Z

4

+6V

HEF4053BT

7902-C

E

6

S

9

F280

3621

4K7

F142

E

6

S

9

Vdd

16

Vee

7

Vss

8

Y0

5

Y1

3

Z

4

+8VAud

HEF4053BT

7903-C

220n

2524

3769

47K

+12Vstby

+8Vstby

1K

3625

1301-15

15

+12Vstby

BC847B

7949

F120

56K

2531

22n

+6V

3723

10K

3624

U275

+6V F401

Z

4

7900-C

HEF4053BT

E

6

S

9

Vdd

16

Vee

7

Vss

8

Y0

5

Y1

3

7946

BC857B

BC847B

7947

3772

47K

3774

47K47K

3771

BC857B

7945

+12V

7900-A

HEF4053BT

E

6

S

11

Vdd

16

Vee

7

Vss

8

Y0

12

Y1

13

Z

14

Vdd

7

Vee

8

Vss

12

Y0

13

Y1

14

Z

1300-1

1

7903-A

HEF4053BT

6

E

11

S

16

3623

4K7

7335

BC847B

+6V

-8Vstby

+12Vstby

22n

2533

22n

2535

22n

2532

47K

3804

+12Vstby

U230

8

1301-8

S

16

Vdd

7

Vee

8

Vss

5

Y0

3

Y1

4

Z

2452

220n

Vee

7

Vss

8

Y0

2

Y1

1

Z

15

HEF4053BT

7901-C

6

E

9

7

Vee

8

Vss

12

Y0

13

Y1

14

Z

7901-B

HEF4053BT

E

6

S

10

Vdd

16

HEF4053BT

7901-A

6

E

11

S

16

Vdd

47u

2412

2545

47u

+6V

2525

220n

7904-C

HEF4053BT

6

E

9

S

16

Vdd

7

Vee

8

Vss

5

Y0

3

Y1

4

Z

220n

2354

4R7

3620

+6V +6V

BAS216

+6V +6V

+6V

6403

13

F211

2529

22n

1301-13

56K

3722

F277

+5V

7900-B

6

E

10

S

16

Vdd

7

Vee

8

Vss

2

Y0

1

Y1

15

Z

HEF4053BT

+6V

22n

2537

DC_OFF

YCVBSOUT_AUX

-5V

-5V

-5V

-5V

-5V

-5V

YCVBSIN_TV

CVBS

SELECT

YCVBSIN_AUX

YCVBSOUT_TV

CVBS

SELECT

0|6|12

FBIN_AUX

SLB_AUX

B

G

R

CVBS

0|6|12

RCOUT_TV

-5V

-5V

-5V

-5V

-5V

-5V

-5V

-5V -5V

SELECT_HIGH

SELECT_HIGH

G

SELECT

GOUT_TV

GIN_AUX

B

SELECT

BC_TV

BC_AUX

SELECT

SDA

SCL

R

Y_ENC

DC_OFF

SELECT

C_ENC

FBOUT_TV

SLB_TV

0|6|12

RCIN_AUX

-9.5V

-9.2V

-8.6V

-0.6V

0V

-1.2V

0V

+11.5V

+11.2V

+10.8V

0V

0.7V

0V

+6V

0V

0.7V

0.7V

0V

11.4V 8V

8V 3.3V

-5.2V

SELECT:

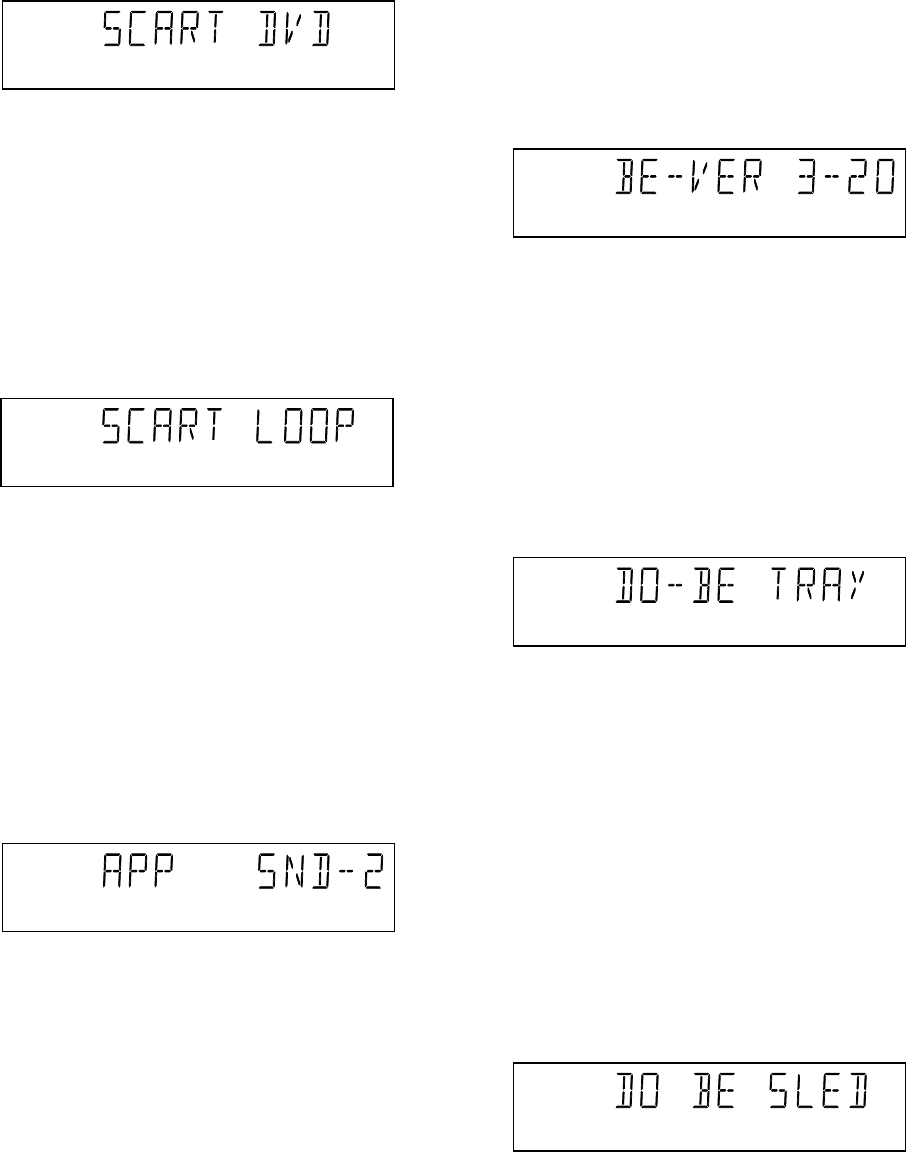

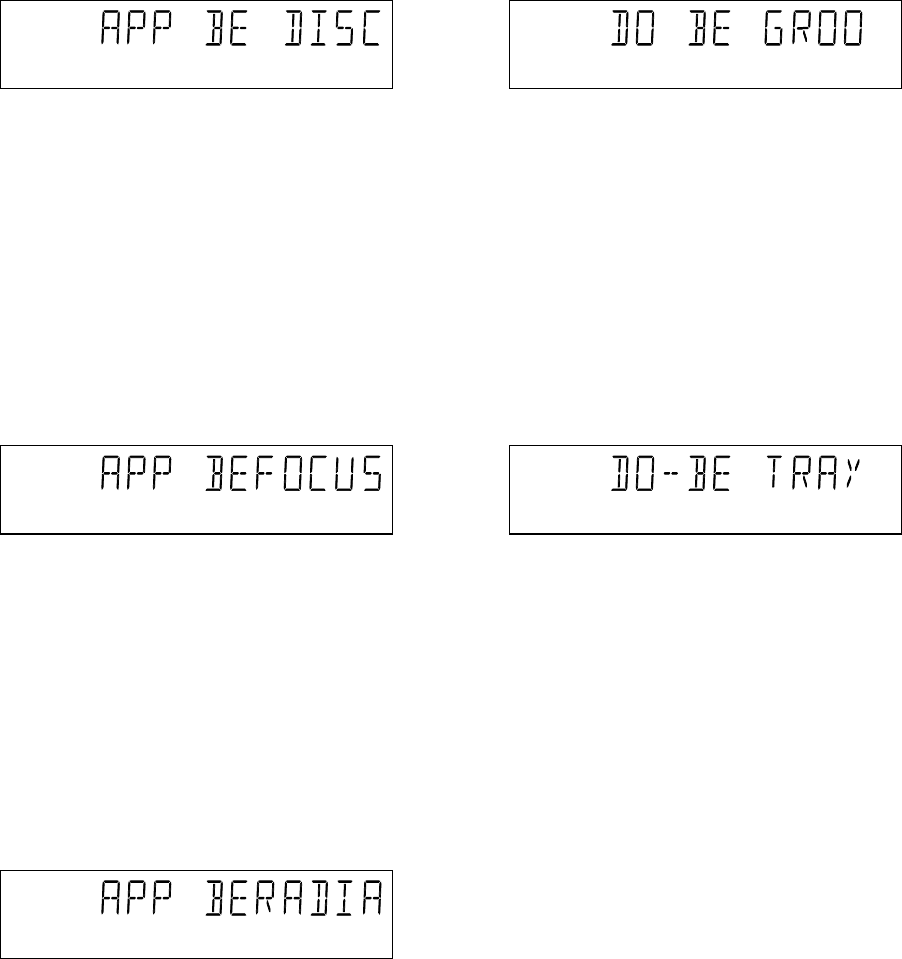

0V DURING PLAYER SCRIPT: "SCART DVD"

6V DURING PLAYER SCRIPT: "SCART LOOP"

SELECT HIGH:

0V DURING PLAYER SCRIPT: "SCART DVD"

12V DURING PLAYER SCRIPT: "SCART LOOP"

ALL DC VOLTAGES MEASURED

IN STOP MODE.

TP1

TP2

TP3

TP4

TP5

TP6

29 30

Audio A/V MUX (/N1B)

NC

NC

DECODER

BUS

SUPPLY

DRIVER

CONTROL

INTERFACE

DAC’S

VOL/MUTE/DEEMPH

INTERPOL FILTER

NOISE SHAPER

NC

DIGITAL

INTERFACE

U191 E3

U226 C12

U227 D7

F267 H8

F268 G7

F400 A9

F406 B8

F408 B5

F410 B7

F414 A2

F415 D5

F416 D8

F421 D6

F422 B1

F423 D7

F424 E8

F425 B1

F432 C1

F437 D3

F448 G1

F455 G1

F478 I1

F486 H11

F487 H11

F488 H12

F489 H13

3765 H6

3766 C3

3767 C4

F490 H12

F497 E1

F504 E1

5400 H11

6400 H14

6401 C11

F505 G2

U186 C12

U187 B7

7402 A4

7403-A B6

7403-B D6

U188 C3

U189 C3

U190 E3

7405 E8

7406 C8

7407 B8

7917 B12

7944 G7

7948 C4

F139 C13

F141 C13

F176 D12

F177 B12

F180 A12

F181 D12

F265 G8

F266 H7

3445 D9

3446 D7

3447 E7

F403 B5

F404 B6

F405 B8

3454 A5

3455 B5

3456 B7

F411 C8

F412 A4

F413 E9

3462 B7

3463 C8

3464 B6

F417 D8

F418 D5

F419 B1

3511 C1

3512 C2

3517 C7

3519 A3

3610 F8

3611 G7

3612 H7

3613 G7

3614 H8

3631 D7

3632 C6

3634 A4

3635 B11

3764 H6

2373 A12

2450 C6

2455 D4

3768 G7

3802 E1

3803 G2

2459 A5

2460 A2

2461 E6

7329 G8

7330 H8

7401 B2

2469 D2

2471 D3

2472 D3

7403-C A9

7403-D E9

7404 D8

2497 C11

2498 C11

2519 I13

2542 H7

2543 H10

2544 H11

3321 C14

3322 C14

3338 E13

3339 E12

3340 A12

3341 A13

3442 D8

3444 D4

AUDIO SCART SWITCHING

Option L/R

1300-10 G1

3448 D5

3451 E5

3453 E6

1300-14 G1

1300-15 H1

1300-16 H1

3457 B8

3459 B5

3461 B9

1300-20 I1

1300-21 I1

1300-22 I1

3505 H10

3507 H10

3508 H12

1301-11 E1

1301-12 F1

1301-3 D1

1301-4 D1

1301-5 E1

1301-6 E1

1301-7 E1

1402-B D10

1402-C C10

1405 I14

1410 D14

2360 C14

2361 C13

2372 D12

123

2456 D6

2457 D9

2458 D6

789

2462 B6

2463 B9

2464 C6

13 14

1

2488 H14

2495 I13

2496 C11

4567891011121314

A

B

C

D

E

F

1300-11 G1

1300-12 G1

1300-13 G1

G

H

I

1300-17 H1

1300-18 H1

1300-19 I1

A

B

C

1300-4 F1

1300-7 F1

1301-1 D1

D

E

F

G

H

I

456 101112

AUDIO

23

U227

F176

U187

3632

100R

3634

2K2

3519

5K6

100R

3631

10K

100U

2456

3444

10K

3451

3453

F432

10K

F422

F425

F412

F419

12

13

14

4

11

F414

3613

2K7

MC33079

7403-D

BC817-25

7402

3611

4K7

F423

F415

F418

-8Vstby

F411

F405

F410

F406

F400

F408

F404

F478

2463

10K

3461

24573445

10K

1n

1n

3511

10K

10K

3512

BC817-40

7404

7406

2472

47u

BC817-40

100n

2471

100R

3457

2K7

3463

3447

2K7

100R

3517

6

5

STEREO_R

STEREO_L

YKC21-3930

1402-B

4

3

YKC21-3930

1402-C

+5V

12

F177

BC847B

7329

F141

52030

1300-12

F139

F416

F437

F424

F417

F413

F421

2360

50

2373

4u7

47p

100R

3322

47p

2361

1K

3339

3321

100R

F403

2372

50

4u7

3767

22K

3V3

22K

3766

U191

7948

BC857B

U189

U190

F505

-8Vstby

4R7

3803

F448

F455

2464

+5V

100p

2461

100p

100p

2455

100p

2459

7405

BC817-40

BC817-40

7407

2496

22n

3635

220R

6401

BZX284-C9V1

100u

2498

100R

3442

2497

22u

23

R4

20

R5

19

RO1 12

RO2 14

RO3 16

RO4 18

SCL 27

SDA 28VS3

L1

4

L2

5

L3

6

L4

9

L5

10

LO1 11

LO2 13

LO3 15

LO4 17

78

2122

R1

25

R2

24

R3

1300-15

52030 15

TEA6420

7917

ADDR 26

C2

GND1

1300-13

52030 13

52030

1300-14

14

1300-11

52030 11

52030

1300-18

18

7

52030

1300-10

10

F504

52030

1300-7

1300-4

52030 4

F180

100n

2488

2

34

6

78

3505

100R

+5V

5400

7CHA

1

100n

2495

68R

3508

6400

GP1F32T

3

1

2

F489

F490

2519

100n

2u2

2542

7

47K

3768

1410 EH-B

1

2

3

4

5

6

+8VAud

7330

BC847B

+12V

F488

52030

1300-22

22

2543

47p

2544

10u

3765

10K

21

10K

3764

BC847B

7944

52030

1300-20

20

1300-21

52030

17

1300-19

52030 19

52030

1300-16

16

1300-17

52030

U186

U226

3341

47K

3338

47K

3340

+8VAud

F181

1K

F497

1301-6

52030 6

1301-7

52030 7

52030

1301-5

5

F265

100R

3507

F266

F268

F267

+6V

3455

10K

3610

4K7

3614

22K

52030

1301-3

3

3612

47K

52030

1301-12

12

1301-1

52030 1

1301-11

52030 11

+6V

4R7

3802

2K7

3446

3V3

3448

10K

3V3

2469

22n

+12Vstby

2460

22n

1

3

2

F486

YKC21-3416

1405

VO1P

31VO2N

32VO2P

1VO3 2VO4

4VO5 5VO6

30

VREFA

3

VSSA

20

VSSD

11 WS

3V3

DS

18L3CLK

19L3DATA

17L3MODE

23MUTE

7

8

15

9STATIC

16 SYSCLK

27 TST1

22TST2

6

VDDA

21

VDDD

29 VO1N

28

7

4

11

7401

UDA1328T

10 BCK

25DEEM0

24DEEM112 DI12

13 DI34

14 DI56

26

2458

7403-B

MC33079

5

6

22n

+8VAud

22n

2450

11

7403-C

MC33079

10

9

8

4

11

+8VAud

MC33079

7403-A

3

2

1

4

-8Vstby

+8VAud

1301-4

52030 4

3456

-8Vstby

-8Vstby

2462

100U 100R

10K

3459

10K

3464

3462

3454

10K

F487

2K7

HP_L HP_L

HP_R HP_R

{PCM_OUT0,PCM_OUT1,PCM_OUT2,SCLK,LRCLK,PCM_CLK,DEEM0,DEEM1}

DIG_OUTSTANDBY

KILL

STANDBY

DIG_OUT

HP_L

HP_R

SCL

LIN_TV

LOUT_TV

LIN_AUX

LOUT_AUX

ROUT_TV

ROUT_AUX

RIN_AUX

RIN_TV

SDA

DC_OFF

KILL

KILL

KILL

KILL

KILL

KILL

TP7

TP8

TP9

TP10

TP11

TP12

TP13

TP14

TP15

TP16

TP17

TP18

KILL:

-8V DURING PLAY

+4.8V DURING STOP, NEXT, PREVIOUS

+1.6V

0V

6V

0.6V

0.7V

0V

9.2V

4.6V

TP12

TP12

TP12

TP13

TP14

TP15

TP15

TP15

31 32

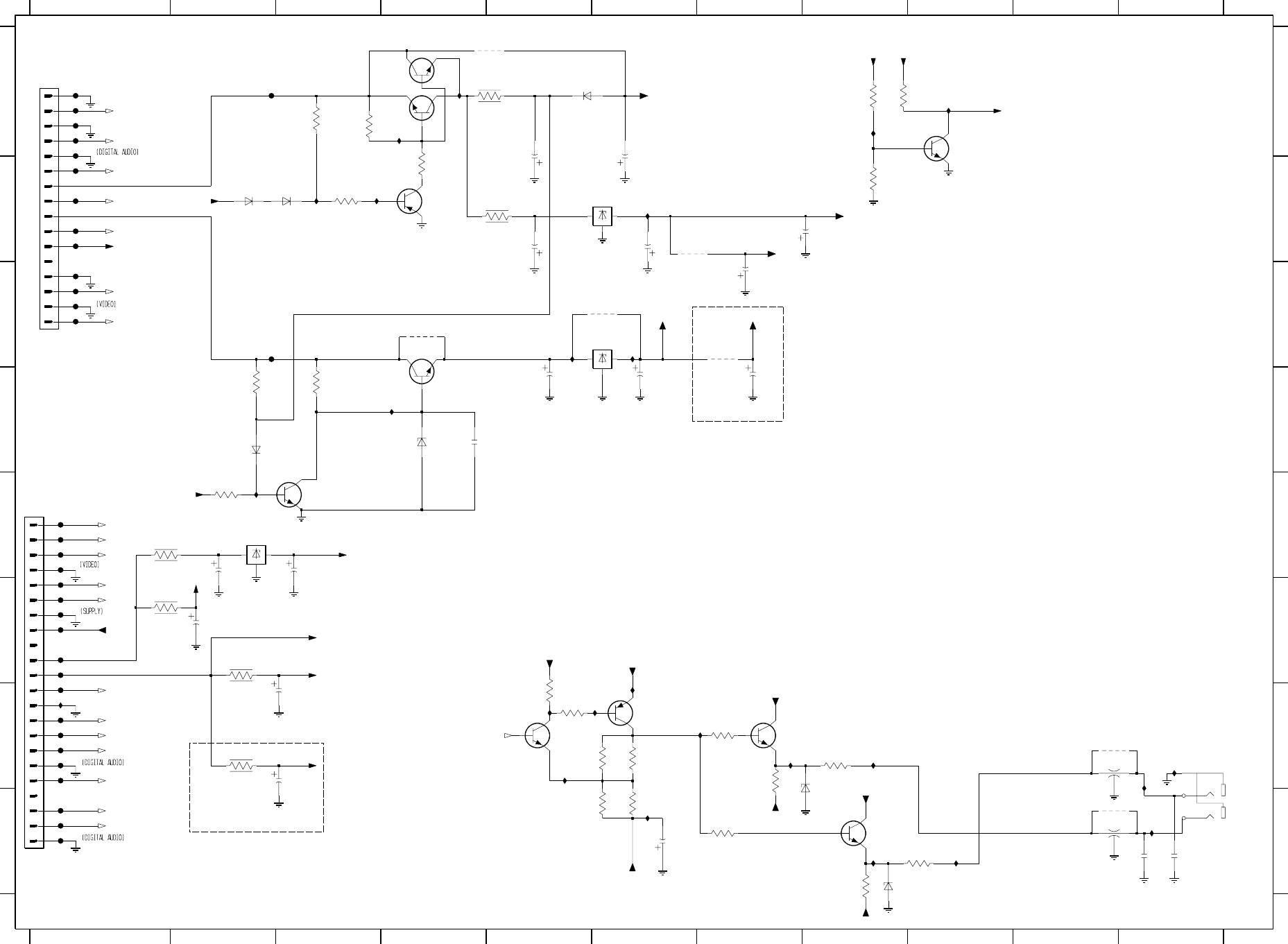

Scart panel (N1B)

2383 B3

2385 C3

2395 C5

2402 F5

2404 E5

2408 F5

2409 I5

C

2509 C8

2511 H8

2521 B12

2522 A5

2523 B5

TV-SCART

AUX-SCART

1 10 11 12 13

12

3349 A5

3351 B4

3359 B5

3363 B4

3366 B5

3394 C4

3397 C5

43 11 12 13

A

B

C

D

3638 D9

3639 E9

3640 E8

3641 F8

3642 C8

1304-1 C13

1304-2 C6

1304-3 G13

E

F

G

H

I

A

B

SCART

3675 C11

3676 G10

3677 H11

3678 G3

3679 G3

3680 D10

3681 D10

2499 G5

D

E

F

G

H

I

2507 D9

2508 F8

3692 D4

3693 E4

3694 I4

3697 G4

3698 E11

3313 D12

3314 A11

3315 A11

23456789

3725 F9

3726 E9

3727 G3

3731 C9

3732 I9

3733 H9

3734 F8

3407 E5

5678910

3636 G2

3637 G2

3756 D9

3757 F8

3758 H8

3800 G9

3801 G10

3643 D8

3646 H8

3647 I8

2353 A10

2355 A10

2357 B10

2358 A12

2359 B10

2371 I11

2378 A3

2382 A3

7929 C10

7930 C8

7931 G9

7933 H10

7934 H9

7936 G3

7937 D10

3682 F9

2500 E12

2501 F11

2502 C11

2503 G11

2504 H11

2506 G2

3690 I11

3691 C4

F134 C13

F137 C13

F140 C13

F145 D13

F148 D12

3699 F10

3700 C10

3701 G10

3316 A12

3318 B11

3319 B11

3320 B12

3323 B11

3325 B11

3343 I11

3348 A4

F234 D6

F247 E6

F259 F6

U131 G3

U132 E10

U133 F10

U134 C9

3735 F9

3408 F4

3409 D4

3413 D4

3425 F5

3432 I4

3629 C5

3748 C8

3749 G2

U145 D10

U146 D9

U147 E9

U148 E13

U149 F11

7918 I10

7919 C3

7920 D3

3648 G2

3649 D9

3650 E8

3651 C8

3653 H9

3672 G5

3673 E11

3674 F11

U161 C8

U162 G10

U163 G9

U167 H11

U168 H10

U169 H9

U170 H9

7938 F10

3683 F10

3684 C9

3685 C10

3687 G9

3688 H9

3689 H10

F127 B11

F133 B11

U201 E4

U202 E2

U203 F2

U204 E6

U205 G2

F149 D13

F183 F13

F193 A4

3702 I10

3703 I10

3704 D3

3705 E3

3706 F3

3707 I3

3721 G10

3724 H9

U213 F8

U214 F8

U215 D9

U216 D8

U217 C8

U218 C8

U219 B8

U136 F6

3736 E9

3737 E10

3738 H2

3739 G3

3744 D8

3747 C9

U143 E11

U144 D11

U222 G2

U223 A8

U225 D6

U278 G8

U279 G9

U150 F10

U151 F9

U152 F9

7921 E3

7922 I3

7923 G4

7924 G2

7925 D11

7926 D9

7927 F10

7928 F9

U159 C9

U160 C9

U184 H8

U193 A2

U194 B2

U195 B2

U196 C2

U197 C2

7939 C9

7941 H9

7942 G10

F103 H10

F114 A11

F115 A11

U199 D4

U200 C4

U198 D2

U206 I4

U207 I2

U208 I8

U209 I10

U210 H8

U211 H8

U212 G10

F195 B4

F205 B4

F212 C4

F216 C6

F218 D6

F219 C6

F222 C6

F229 D6

330R

+8Vstby

U137 G4

U138 G4

U139 G3

U140 G2

U141 G2

U142 D13

U220 B8

U221 A8

U153 F8

U154 D13

U155 E13

U156 F13

U157 C10

U158 C10

100R

3689

3653

100R

3688 7941

BC857B

BC847B

7934

2509

2u2

3677

75R

BC847B

7933

3702

1K

U162

U163

U155

U193

2503

220p

100K

3647

U225

100K

3641 100K

3643

100K

3639

7928

BC847B

100K

3646

BC857B

7938

3638

100K

3640 100K

3642

100K

3721

150R

2501

220p

2523

+8Vstby

+8Vstby

220p

100R

330R

3650

3682

100R 3683

U136

1K

3699

75R

3674

+8Vstby

7927

BC847B

+8Vstby

330R

3732

2507

2u2

U223

U220

U221

+8Vstby

U219

U216

U214

U215

U212

U213

U210

U211

+8Vstby

U209

3673

75R

BC847B

7925

3698

1K

3704

6K8

+8Vstby

7919

BC847B

U159

U160

U161 U134

U157

U158

U154

330R

3736

22R

3726

330R

37353725

22R

100K

3636

100K

3637

100K

3758

100K

3749

3756

100K

3757 100K

3748

100K

330R

3739

U141 3727

22R

U140

U131

U139

F137

U137

U138

F115

+8Vstby

+8Vstby

220p

2499

330R

3648

3678

100R 3679

100R

7924

BC847B

BC857B

7936

U218

U217

U279

4K7

3800

U278

+6V

4K7

3801

3705

7920

BC847B

6K8

1K

3692

75R

3432

1K

3691

3409

220R

6K8

3703

3690

7918

BC847B

75R

1K

7942

BC857B

3629

U206

470R

3701

U205

U204

U222

U202

U203

U200

U201

U199

3731

22R

U198

3744

330R

F149

3737

330R

F145

F148

F133

50

2357

F140

F127

1K

3319

4u7

F114

F134

220p

220p

2409

3738

330R

2408

220p

330R

3747

+8Vstby

2521

U184

2511

2u2

U169

U170

U168

F103

U167

3733

330R

3734

330R

22R

3724

75R

3425

3413

47K75R

3408

75R

3407

50

2385

47K

3397

3394

470R

4u7

U208

3676

150R

+8Vstby

U207

BC847B

7931

2u2

2508

+8Vstby

U153 U133

U151

U152

U196

U197

U195

3325

47K

U194

2359

4u7

50

3323

470R

47K

3320

2522

220p

U145

U144

U132

U142

U143

+8Vstby

2500

220p

3649

330R

+8Vstby

U156

47K

+8Vstby

2504

220p

4u7

2383

50 3366

3318

47K

470R

3315

4u7

2355

50

47K

3316

3314

1K

4u7

2353

50

16B

17B

18B

19B

2B

20B

21B

3B

4B

5B

6B

7B

8B

9B

1304-2

1B

10B

11B

12B

13B

14B

15B 15A

16A

17A

18A

19A

2A

20A

21A

3A

4A

5A

6A

7A

8A

9A

1304-1

1A

10A

11A

12A

13A

14A

4K7

3687

3685

3651

330R

+8Vstby

100R

3684

100R

BC847B

7930

+8Vstby

7939

BC857B

3675

75R

U150

3700

1K

U148

U149

2402

220p

220R

3313

U146

U147

75R

3672

1K

3697

7923

BC847B

7922

BC847B

6K8

3707

1K

3694

100R

3681

100R

3680 7937

BC857B

BC847B

7926

3363

1K

2382

4u7

50 47K

3359

470R

3351

50

4u7

2378

47K

3349

1K

3348

F193

F219

F183

F216

+8Vstby

2502

220p

1304-3

0350808190

MT1 MT2

F247

F259

F212

F229

F234

F218

F205

F195

F222

+8Vstby

BC847B

7929

2u2

2506

220p

+8Vstby

2395

220p

2404

2371

220p

220p

2358

6K8

3343

75R

7921

3706

3693

1K

BC847B

-8Vstby

SLB_TV

+8Vstby

-8Vstby

+8Vstby

-8Vstby

+8Vstby

-8Vstby

+8Vstby

-8Vstby

+8Vstby

{ROUT_AUX,RIN_AUX,LOUT_AUX,LIN_AUX,BC_AUX,SLB_AUX,GIN_AUX,RCIN_AUX,FBIN_AUX,YCVBSOUT_AUX,YCVBSIN_AUX}

2.2V

7.4V 7.4V

1.6V

2.6V

2.6V

2V

2.2V

7.4V 7.4V

1.6V

2.6V

2.6V

2V

2.2V

7.4V 7.4V

1.6V

2.6V

2.6V

2V

2.2V

7.4V

7.4V

1.6V

2.6V

2.6V

2V

2.2V

7.4V 7.4V

1.6V

2.6V

2.6V

2V

-0.6V

-0.6V

-0.6V

-0.6V

-0.6V

33 34

CVBS / YC panel (/N1B)

I221 H6

I241 D7

I242 D6

I245 D7

I246 D8

I247 D8

I251 D6

U130 B7

U192 G9

U224 G9

U276 B6

U277 D6

3750 B6

3751 A6

3752 B6

3759 H6

3760 G6

3761 G6

7006 F6

7007 F6

7010 H6

7011 H8

7012 D7

7013 D6

7014 D8

7300 B7

7301 B6

7310 B8

F100 B6

F101 B7

F104 B8

F107 B6

F108 B9

F600 H6

I189 F7

I191 F6

I196 F6

2538 B5

2539 D6

2540 H6

I200 G5

I208 F9

I210 G7

3040 F5

3041 F7

3043 G6

I211 G6