Presentation ER 4096B 20120823 S203C Chevallier

User Manual: ER 4096B

Open the PDF directly: View PDF ![]() .

.

Page Count: 21

© 2012 Rambus Inc.

Christophe Chevallier

Rambus Inc.

August 22, 2012

1

Tuesday, August 28, 12

© 2012 Rambus Inc.

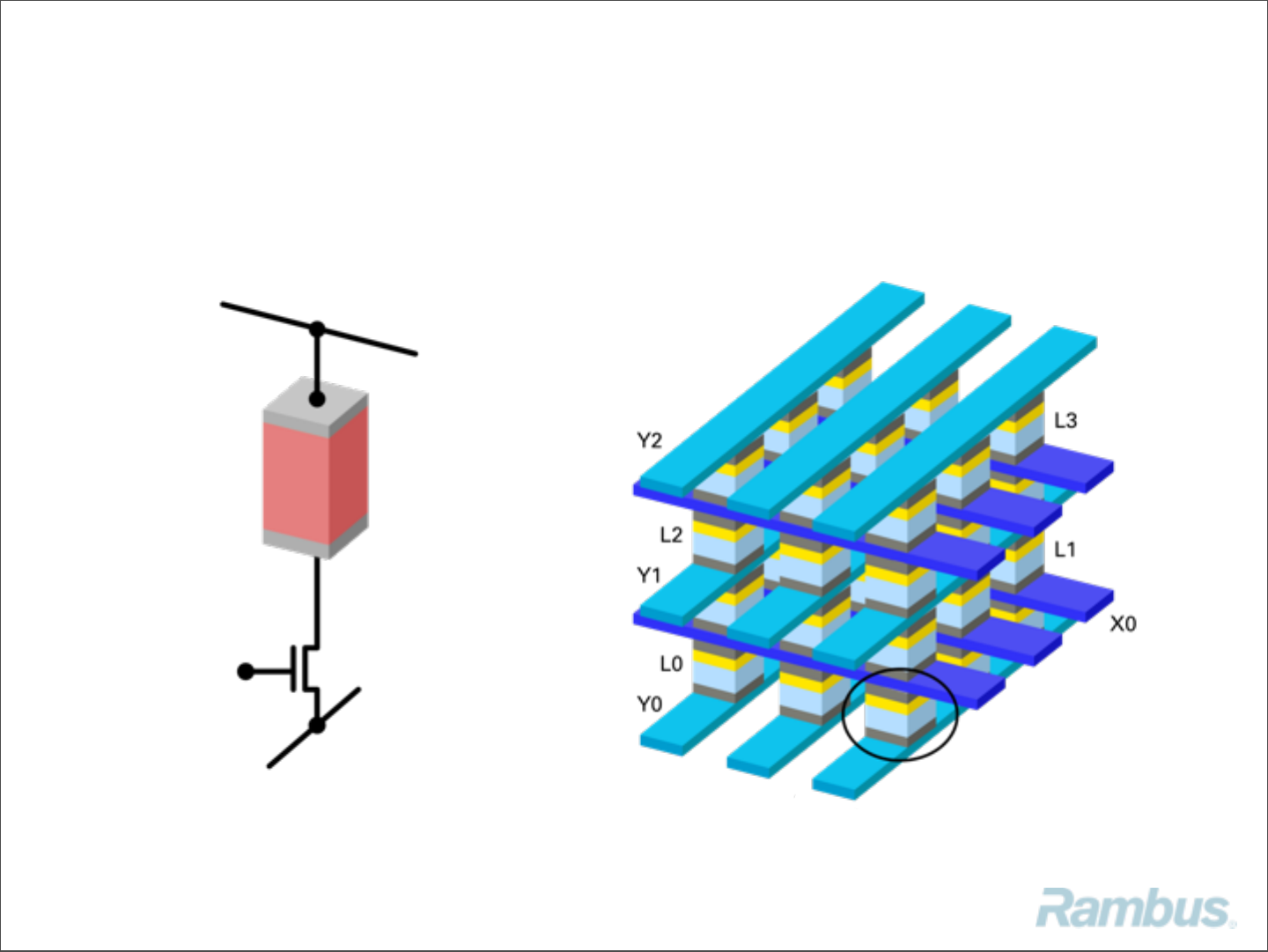

True Cross Point Arrays, without a transistor per

cell, are necessary to achieve high density

memories. Can they be fast too?

2

Typical RRAM cell has a

transistor as select device

RRAM cell in a cross point for

very high density

Tuesday, August 28, 12

© 2012 Rambus Inc.

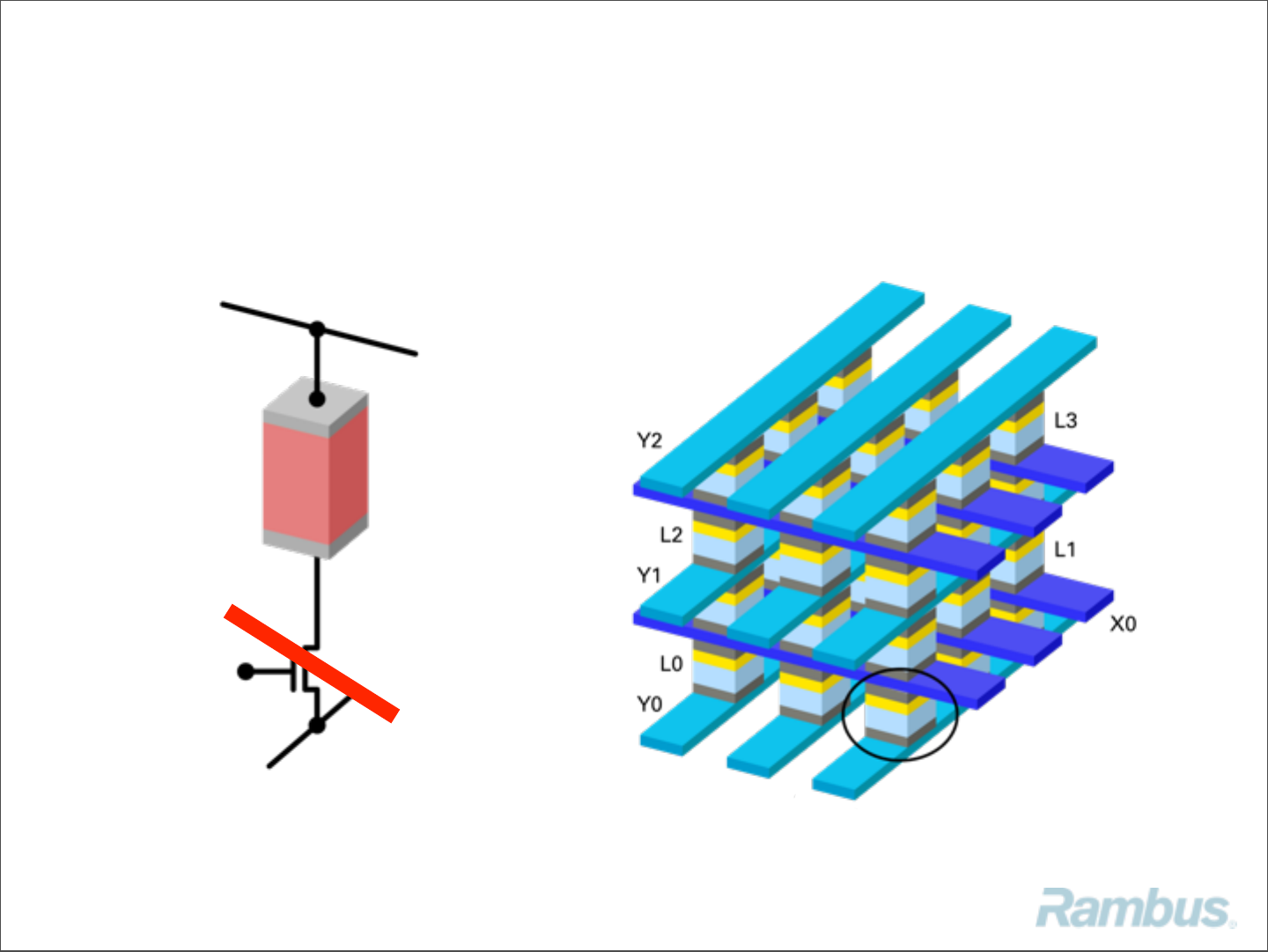

True Cross Point Arrays, without a transistor per

cell, are necessary to achieve high density

memories. Can they be fast too?

2

Typical RRAM cell has a

transistor as select device

RRAM cell in a cross point for

very high density

Tuesday, August 28, 12

© 2012 Rambus Inc.

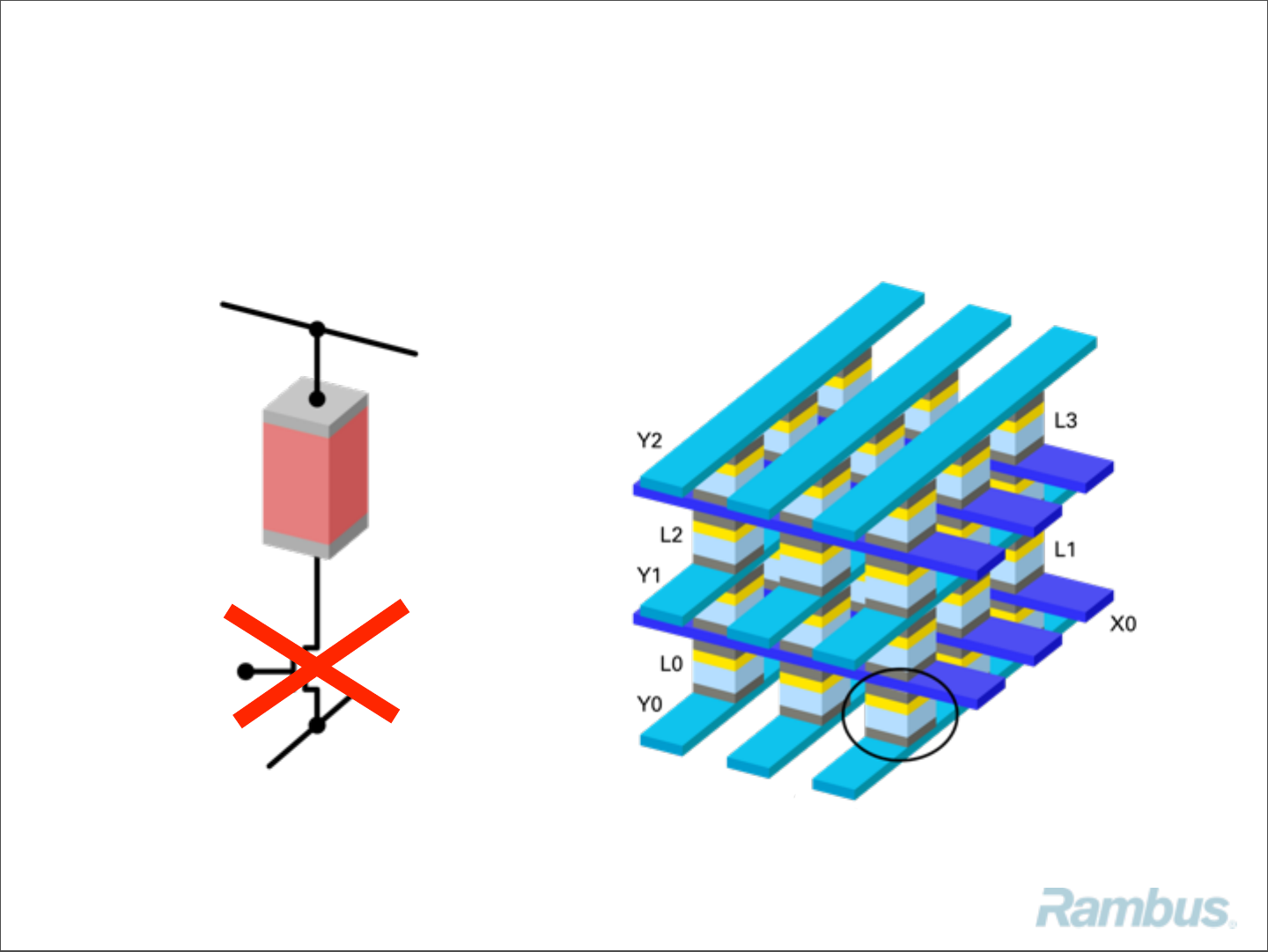

True Cross Point Arrays, without a transistor per

cell, are necessary to achieve high density

memories. Can they be fast too?

2

Typical RRAM cell has a

transistor as select device

RRAM cell in a cross point for

very high density

Tuesday, August 28, 12

© 2012 Rambus Inc.

Cross Point Arrays can achieve high read and

write bandwidth in high density memories

•Techniques:

•Hierarchical Bit Line structure

•IR drop compensation

•Low current cell

•Gain Stage Sensing

•Parallelism

•Impact:

•Improved read / write throughput

•Improved read latency

3

Tuesday, August 28, 12

© 2012 Rambus Inc.

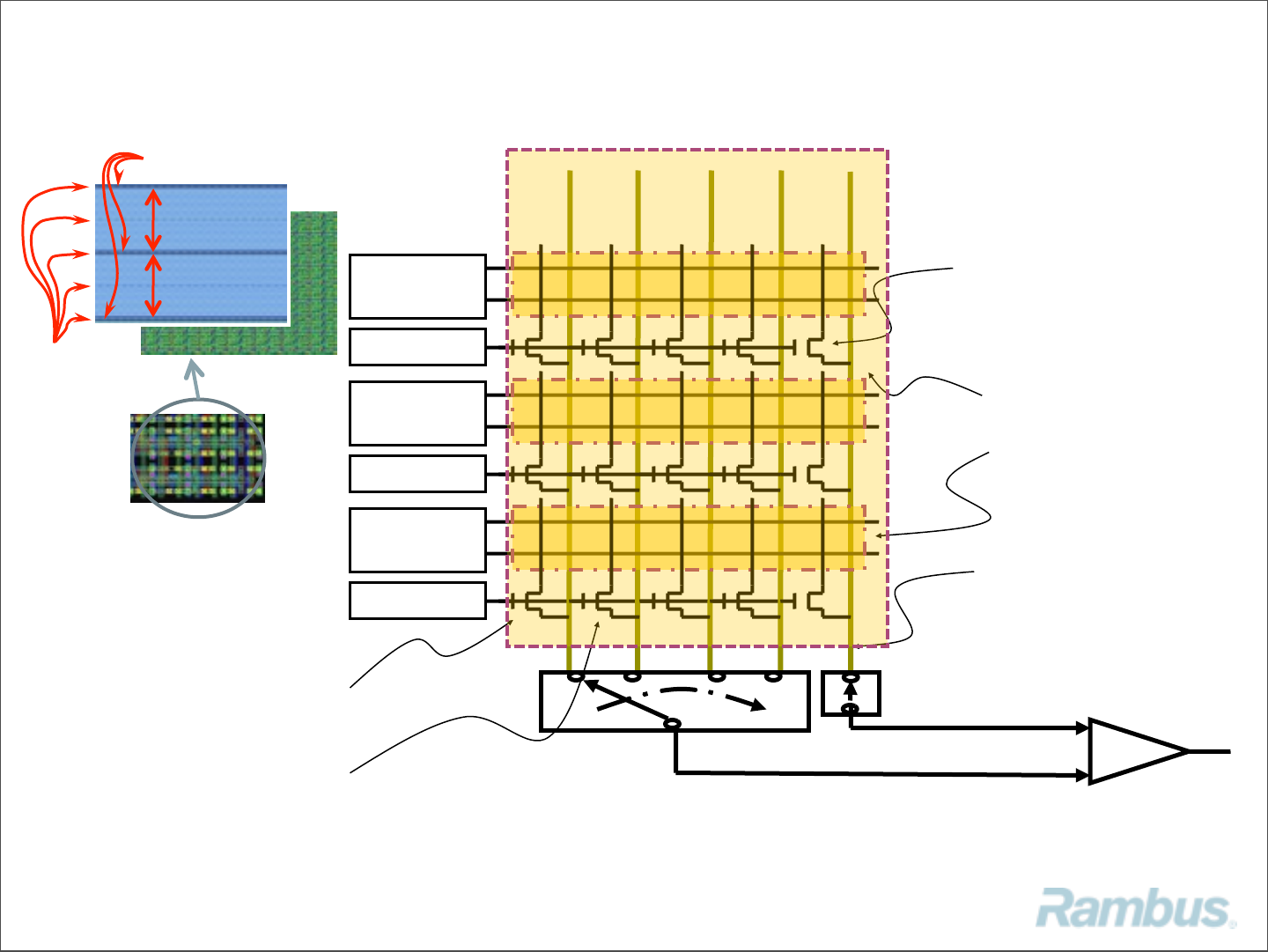

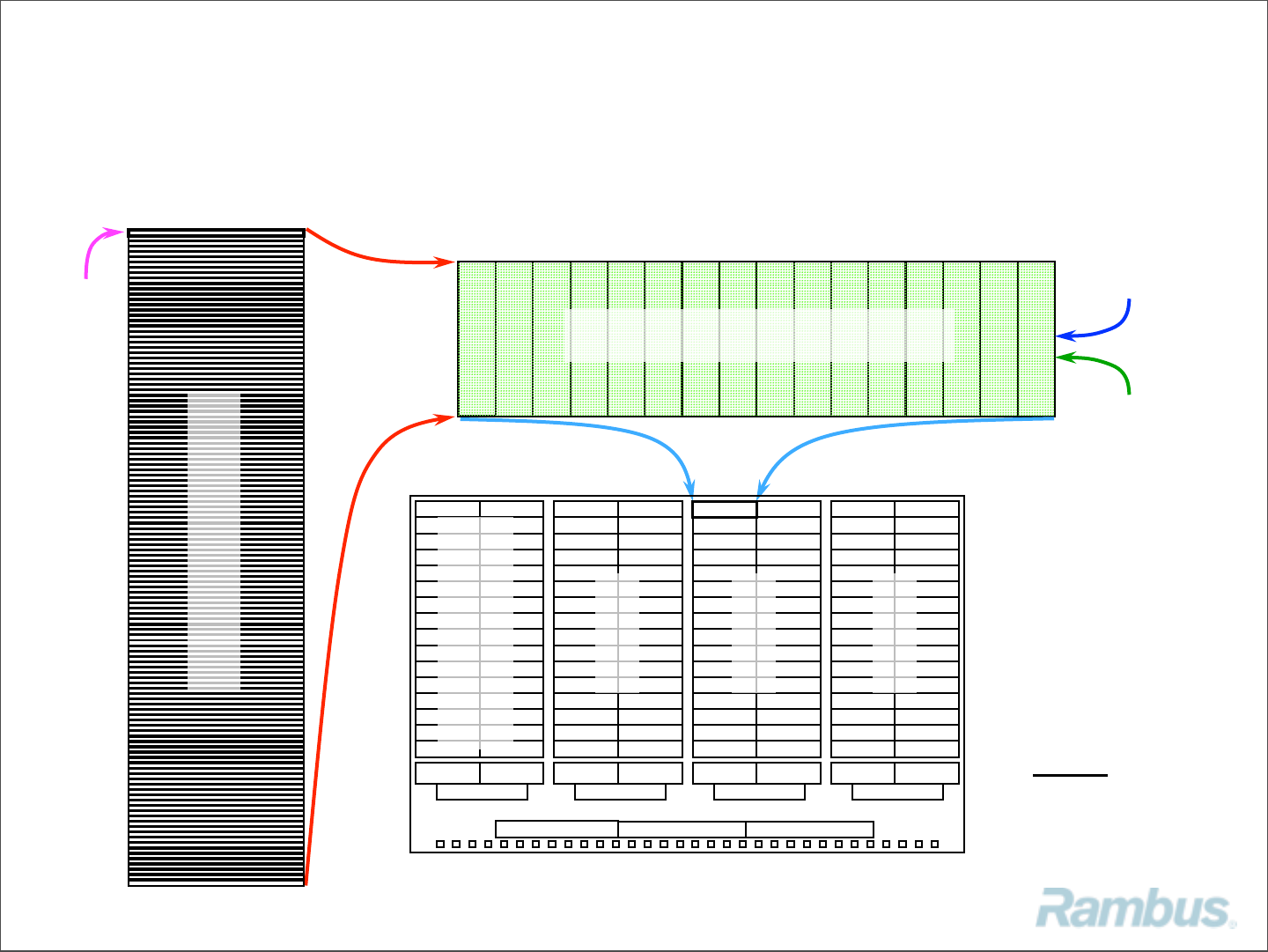

Section 3b: Local Bitline Cross Point Array – Architecture

Local Bitline Architecture

SA

2 Mb arrays

Local Bit Line

select transistor

Global Bit Line Mux

Local Bitline

Global Bitline

Xdecoder

LBL gate drv

256 Mb arrays “Bricks” divided in 2Mb local blocks

Xdecoder

LBL gate drv

Xdecoder

LBL gate drv

. . . . .

. . . . .

. . . . .

4

128 Rows = Local

Bitline

VIA

drops

down to

CMOS

128 Rows = Local

Bitline

Local Bitline

“breaks”

Tuesday, August 28, 12

© 2012 Rambus Inc.

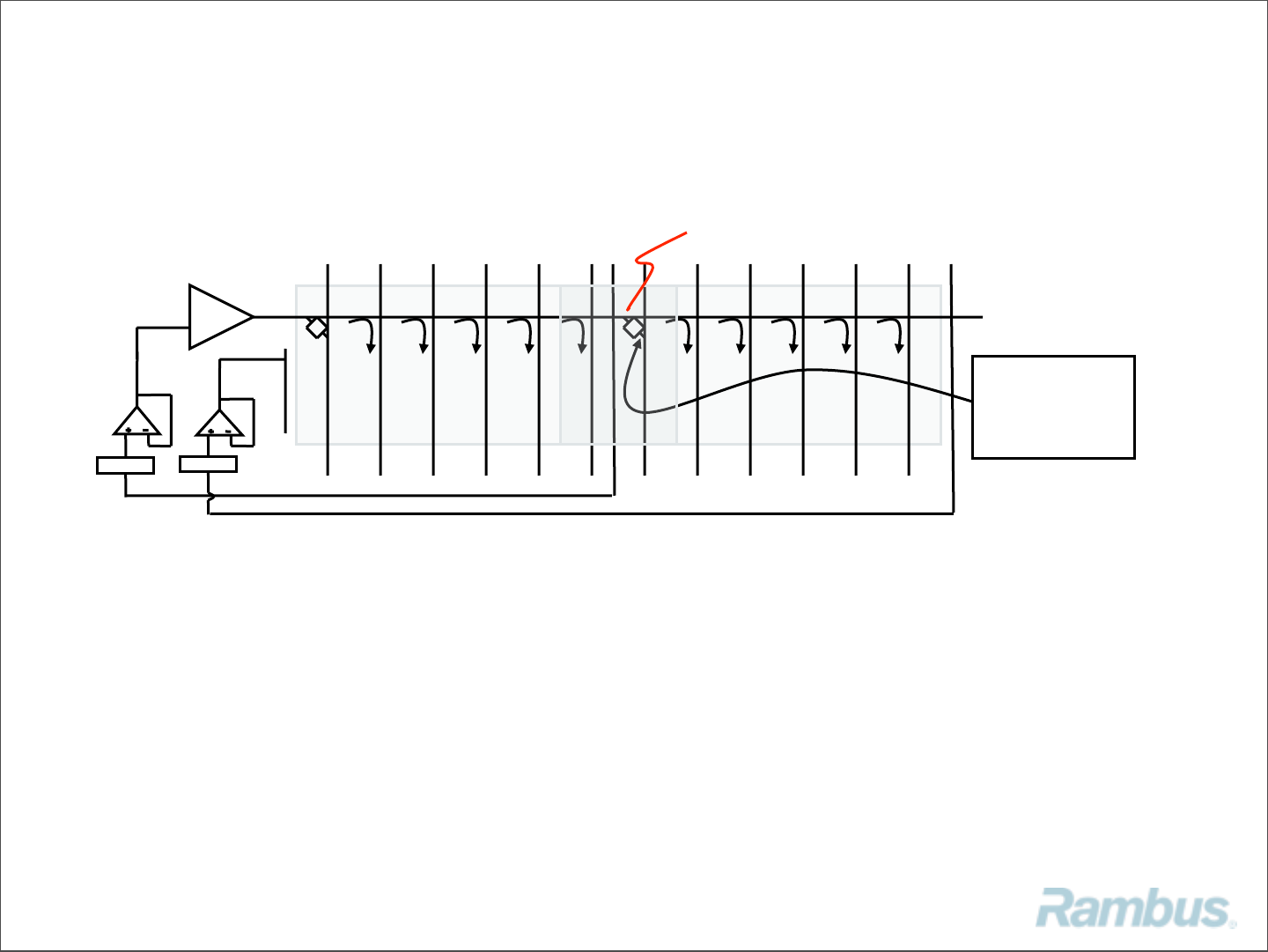

Row IR Drop with ΔV and location

compensation, plus counter bias

•Adjust Driver voltage depending on location of cells being

programmed

•Added bias on unselected Word Lines will bias unselected Bit

Lines

•Total Word Line current around 100 uA

1.6V

-1.0V

2.5V across

cell to be

written

Floating lines

ratio ratio ~0.5V

5

1.5V

Tuesday, August 28, 12

© 2012 Rambus Inc.

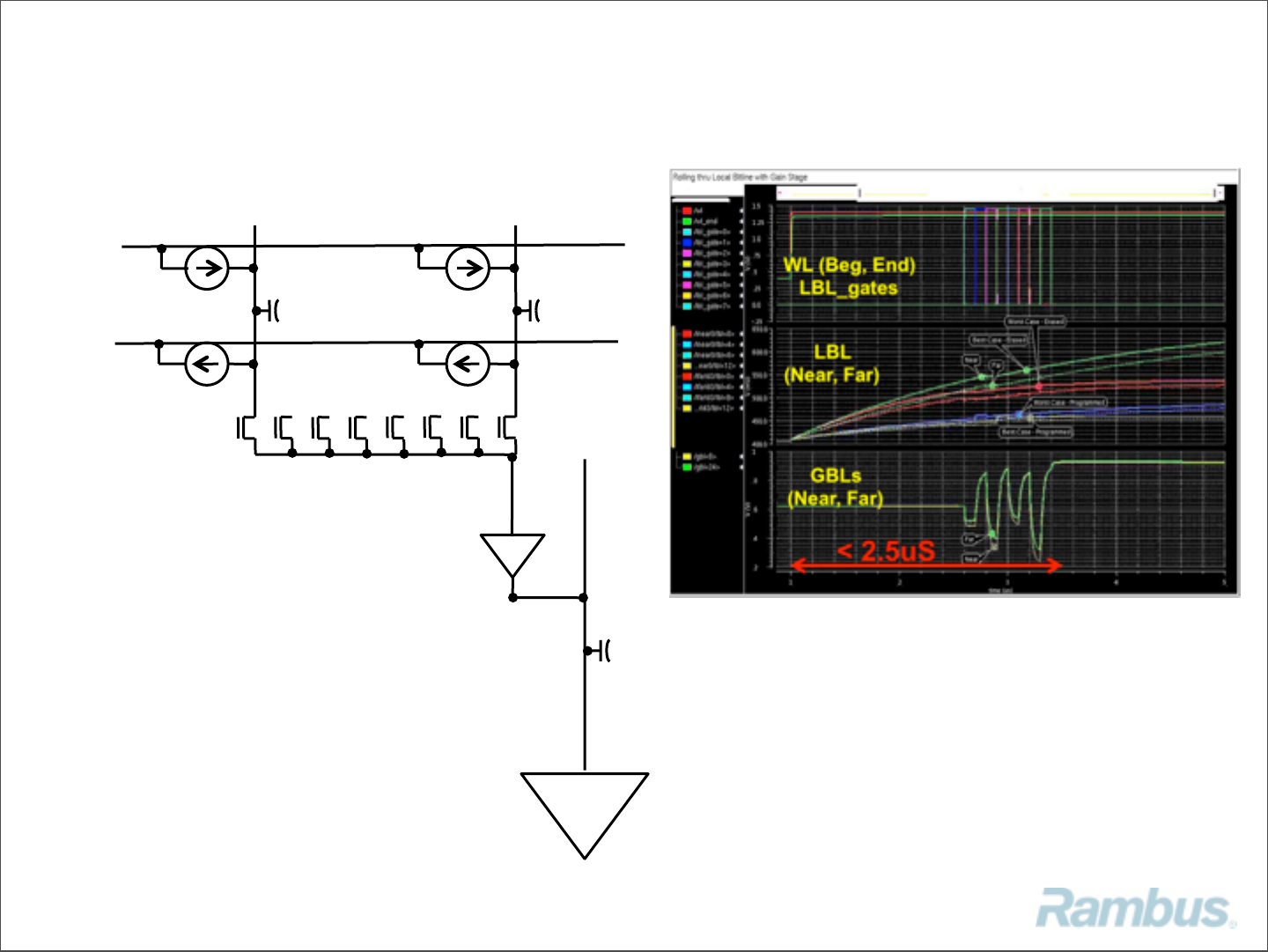

Latency - constrained by sensing

Small array ! shorter latency

Low current ! longer latency

6

Gain Stage Sensing

1)Isolates Local Bit Line from Global

Bit Line capacitance

2)Amplifies LBL signal

3)Bypass for write access

4)Vt offset compensation

5)Reduced Latency from 50 µs to

under 5 µs.

Cell

255 Unselected Cell

Sense-amp

LBL LBL

GBL

Gain Stage

Tuesday, August 28, 12

© 2012 Rambus Inc.

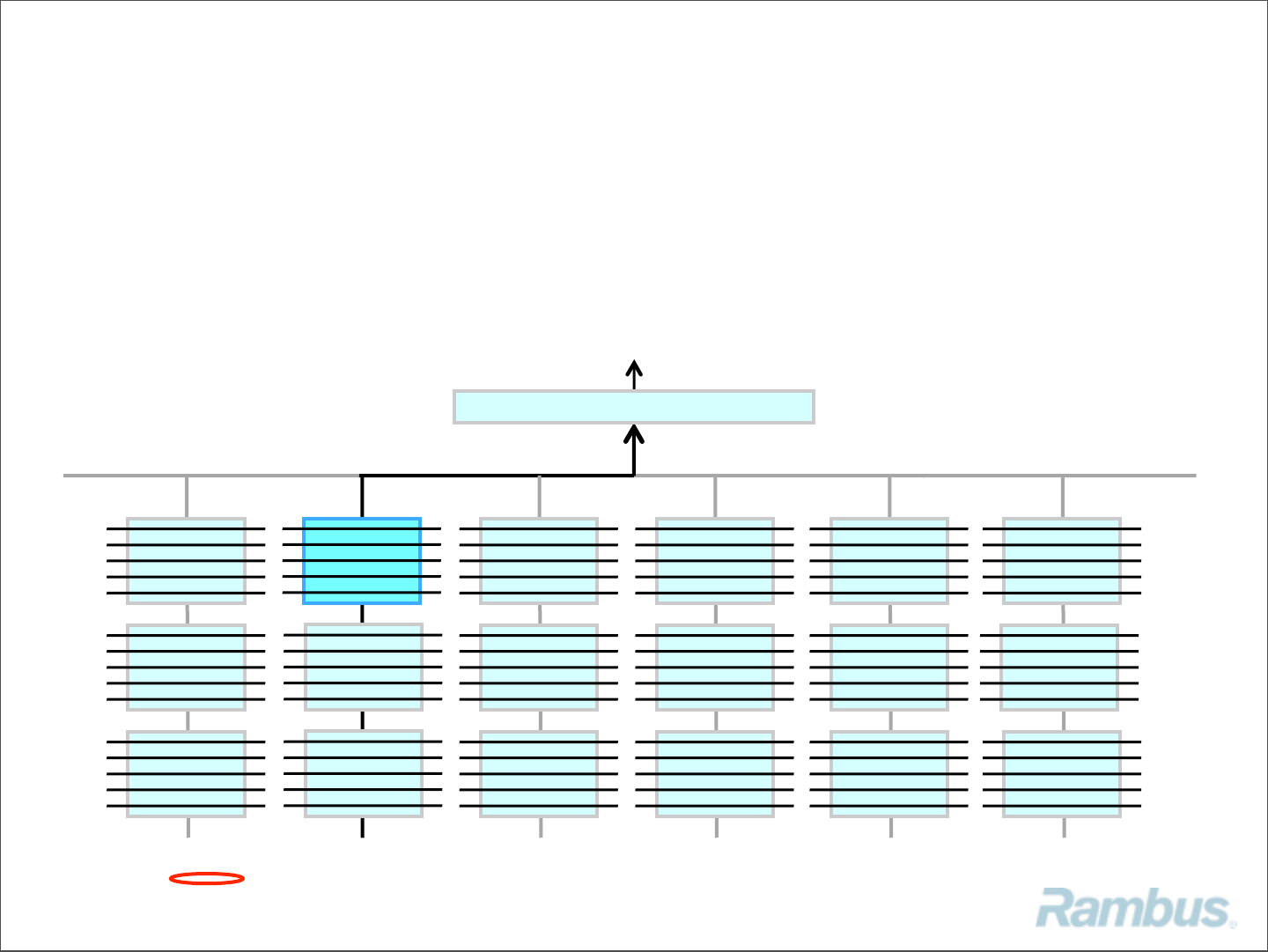

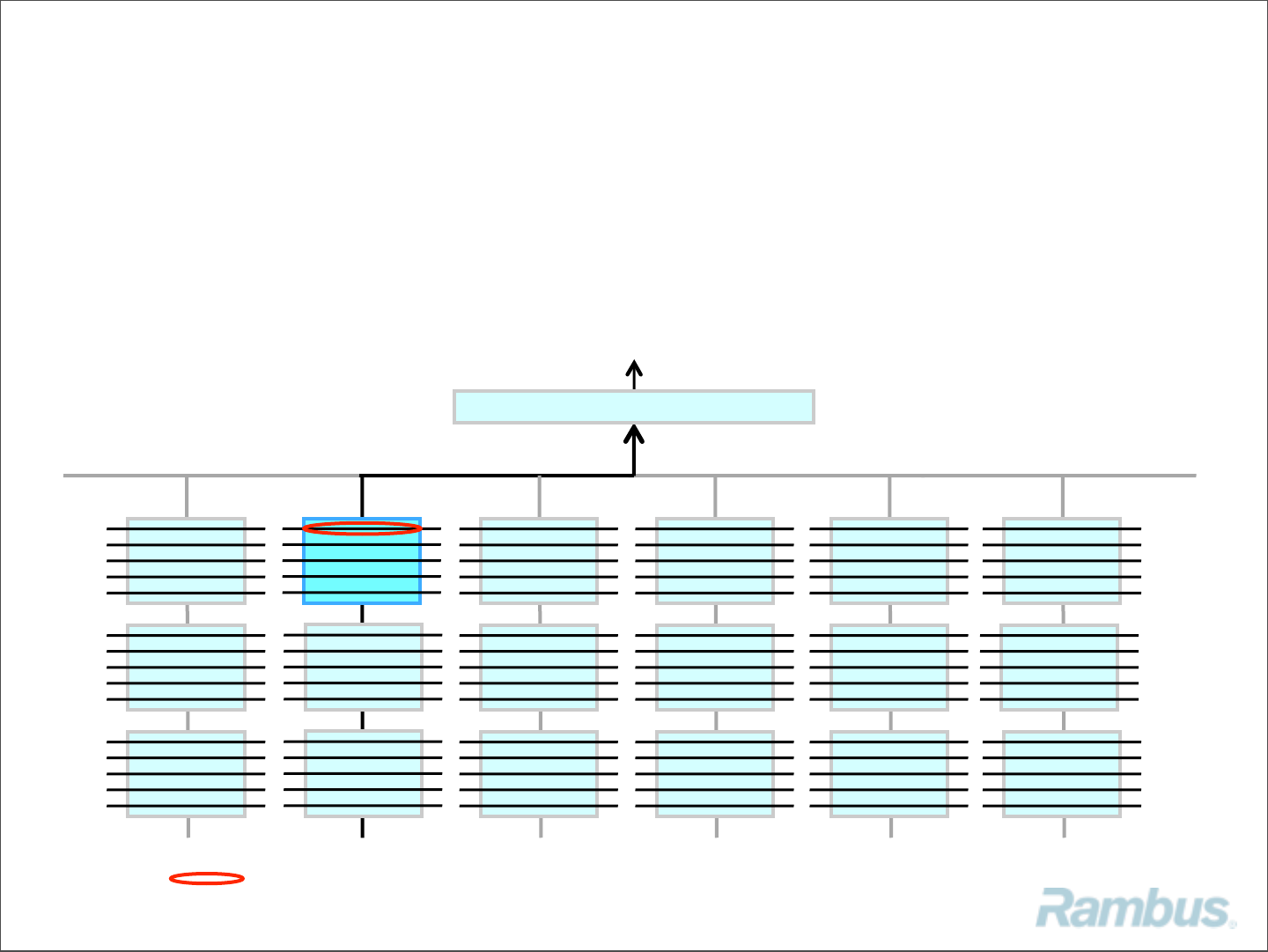

Power and Speed: Single Block Throughput

= 4096b sub-word read from Tile in one 50us sensing cycle

I/O

4096b 4096b 4096b 4096b

4096b

Read 16 rows in 1 Block to fill page buffer

16x50uS = 800µS " 10MB/sec

4096b4096b

8kB Page Buffer

7

Tuesday, August 28, 12

© 2012 Rambus Inc.

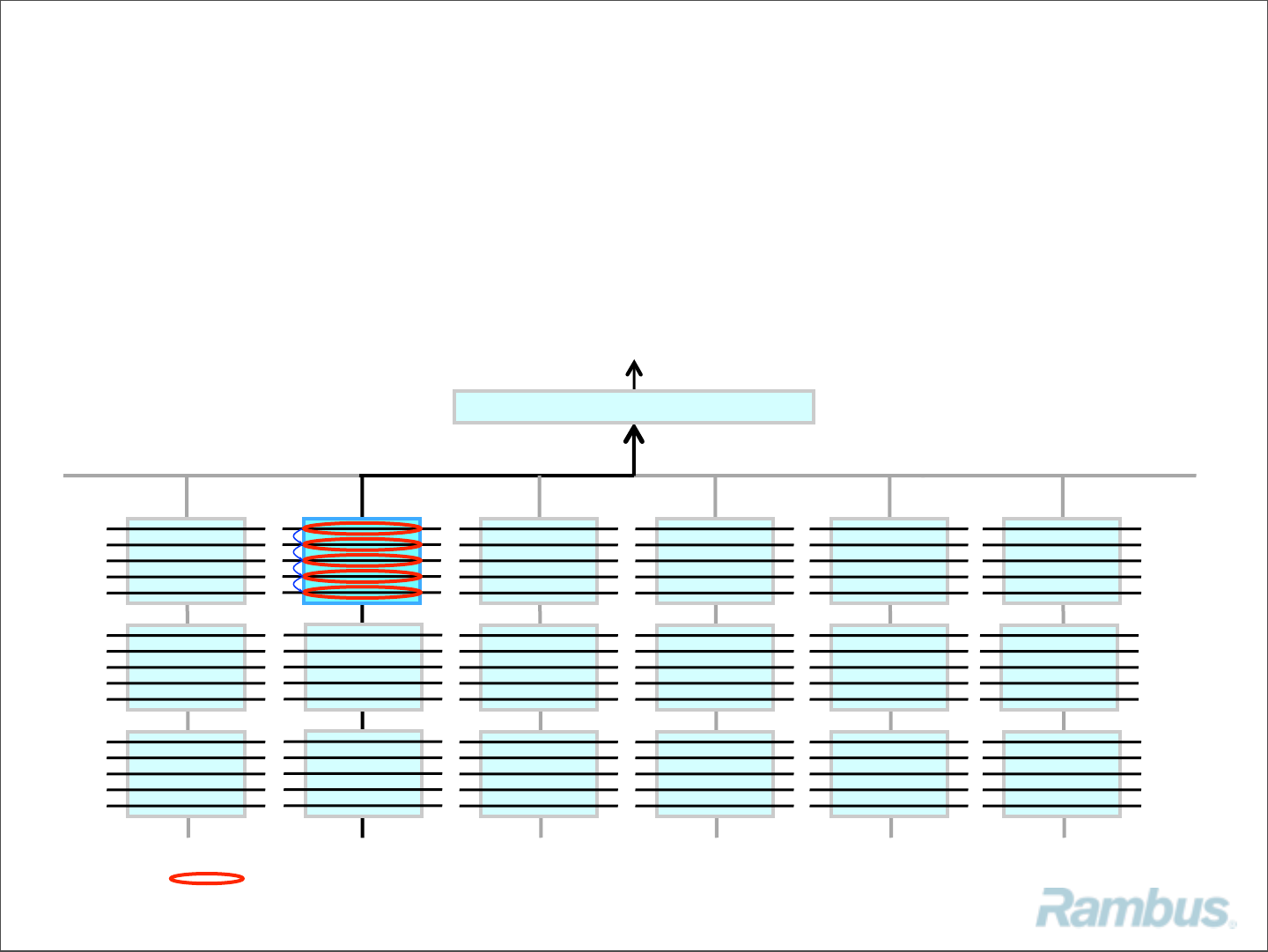

Power and Speed: Single Block Throughput

= 4096b sub-word read from Tile in one 50us sensing cycle

I/O

4096b 4096b 4096b 4096b

4096b

Read 16 rows in 1 Block to fill page buffer

16x50uS = 800µS " 10MB/sec

4096b4096b

8kB Page Buffer

7

Tuesday, August 28, 12

© 2012 Rambus Inc.

Power and Speed: Single Block Throughput

16x

= 4096b sub-word read from Tile in one 50us sensing cycle

I/O

4096b 4096b 4096b 4096b

4096b

Read 16 rows in 1 Block to fill page buffer

16x50uS = 800µS " 10MB/sec

4096b4096b

8kB Page Buffer

7

Tuesday, August 28, 12

© 2012 Rambus Inc.

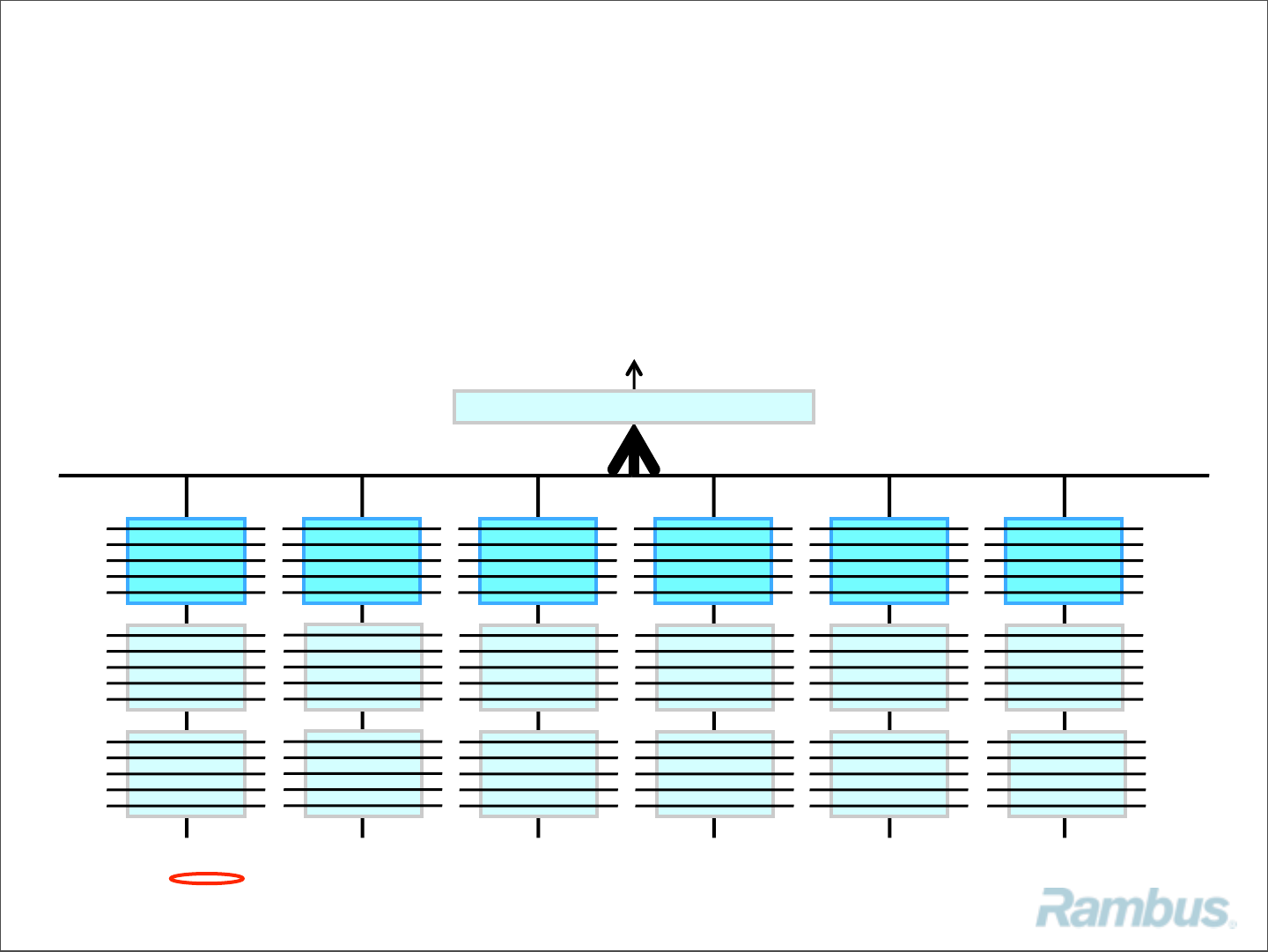

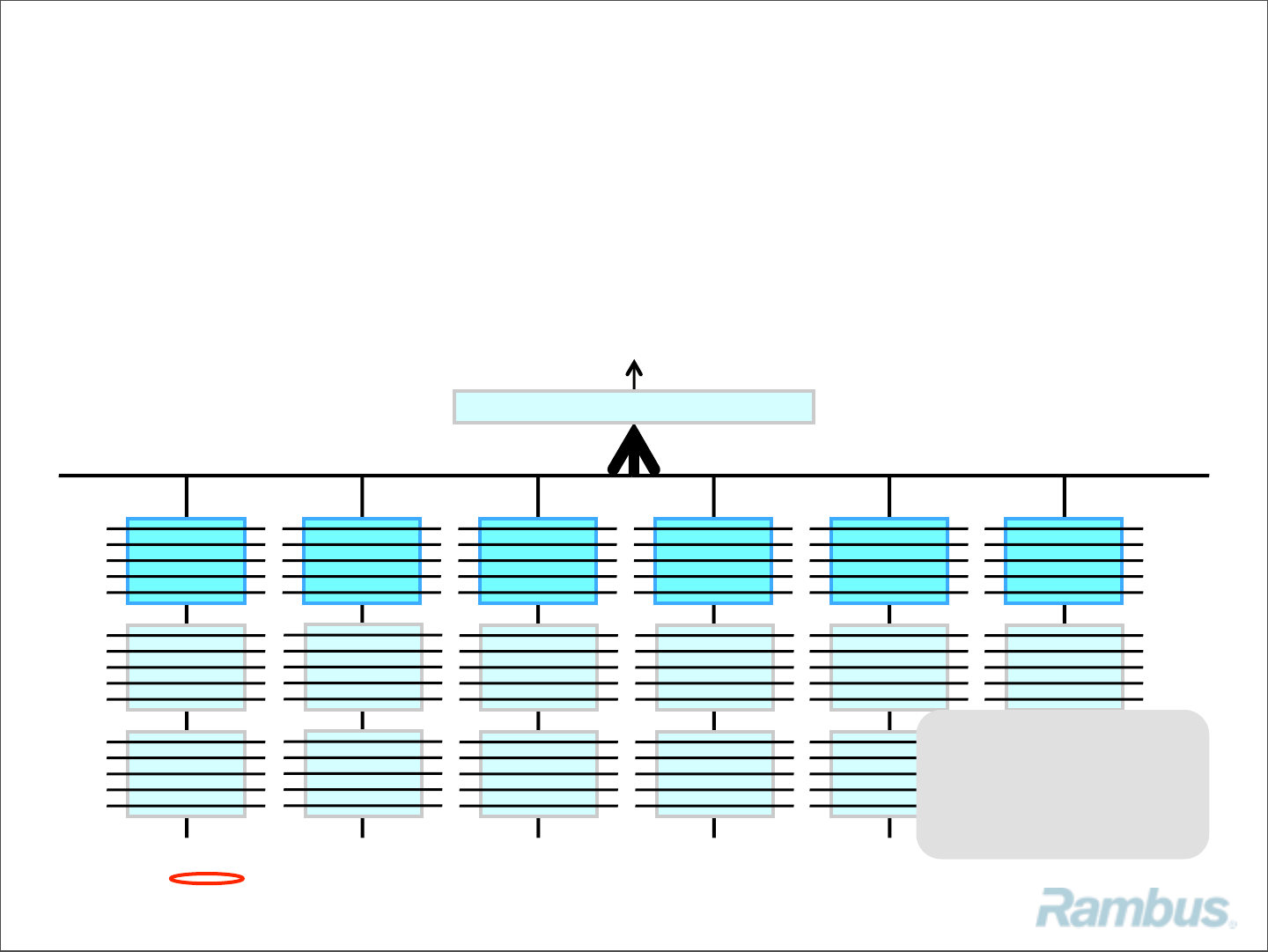

4096b

Power and Speed: 16 Block Throughput

I/O

64kb

Read 1 row in 16 Blocks to fill page buffer

1x50uS = 50uS " 160MB/sec

8kB Page Buffer

4096b 4096b 4096b

= 4096b sub-word read from Tile in one 50us sensing cycle

• • • (+5)

(+5) • • •

4096b 4096b

8

Tuesday, August 28, 12

© 2012 Rambus Inc.

4096b

Power and Speed: 16 Block Throughput

I/O

64kb

Read 1 row in 16 Blocks to fill page buffer

1x50uS = 50uS " 160MB/sec

8kB Page Buffer

4096b 4096b 4096b

= 4096b sub-word read from Tile in one 50us sensing cycle

• • • (+5)

(+5) • • •

4096b 4096b

1x1x 1x1x 1x1x

8

Tuesday, August 28, 12

© 2012 Rambus Inc.

4096b

Power and Speed: 16 Block Throughput

I/O

64kb

Read 1 row in 16 Blocks to fill page buffer

1x50uS = 50uS " 160MB/sec

8kB Page Buffer

4096b 4096b 4096b

= 4096b sub-word read from Tile in one 50us sensing cycle

• • • (+5)

(+5) • • •

4096b 4096b

1x1x 1x1x 1x1x

8

+ Page Erase /

Simplified block

management

Tuesday, August 28, 12

© 2012 Rambus Inc.

512Gb/1Tb Storage Chip with Multi-Plane

Architecture

Sub-Plane = 16 Bricks

Brick = 128 Tiles

(4k x 128 x 4) x 128

= 256Mb per Brick

Tile

[ (4k x 128 x 4) x 128 ] x 16

= 4Gb per Sub-Plane

(4k x 128 x 4)

x 128

x 16

x 32

= 128Gb per Plane

x 4

= 512Gb (SLC)

X2 (MLC)

= 1Tb

(256K Tiles)

PB µC

Ana

PB µC

Ana

PB µC

Ana

PB µC

Ana

Plane 0

(32 Sub-Planes)

Plane 1

Plane 2

Plane 3

Timing Master µCI/F

Page is 1 row of

cells across 16

Blocks/Bricks

“Erase” Block

is 1 row of

Blocks

across 16 Bricks

125MB/s 125MB/s 125MB/s 125MB/s

≥500MB/s DDR

9

Tuesday, August 28, 12

© 2012 Rambus Inc.

Conclusion

from RRAM Cell to System

10

Tuesday, August 28, 12

© 2012 Rambus Inc.

Conclusion

from RRAM Cell to System

10

Self-select

(no select transistor)

Low Current Cell Vertical

Processing

Tuesday, August 28, 12

© 2012 Rambus Inc.

Conclusion

from RRAM Cell to System

10

Small Arrays /

Parallelism

Stackable Cross-Point

Hierarchical BL

Self-select

(no select transistor)

Low Current Cell Vertical

Processing

Tuesday, August 28, 12

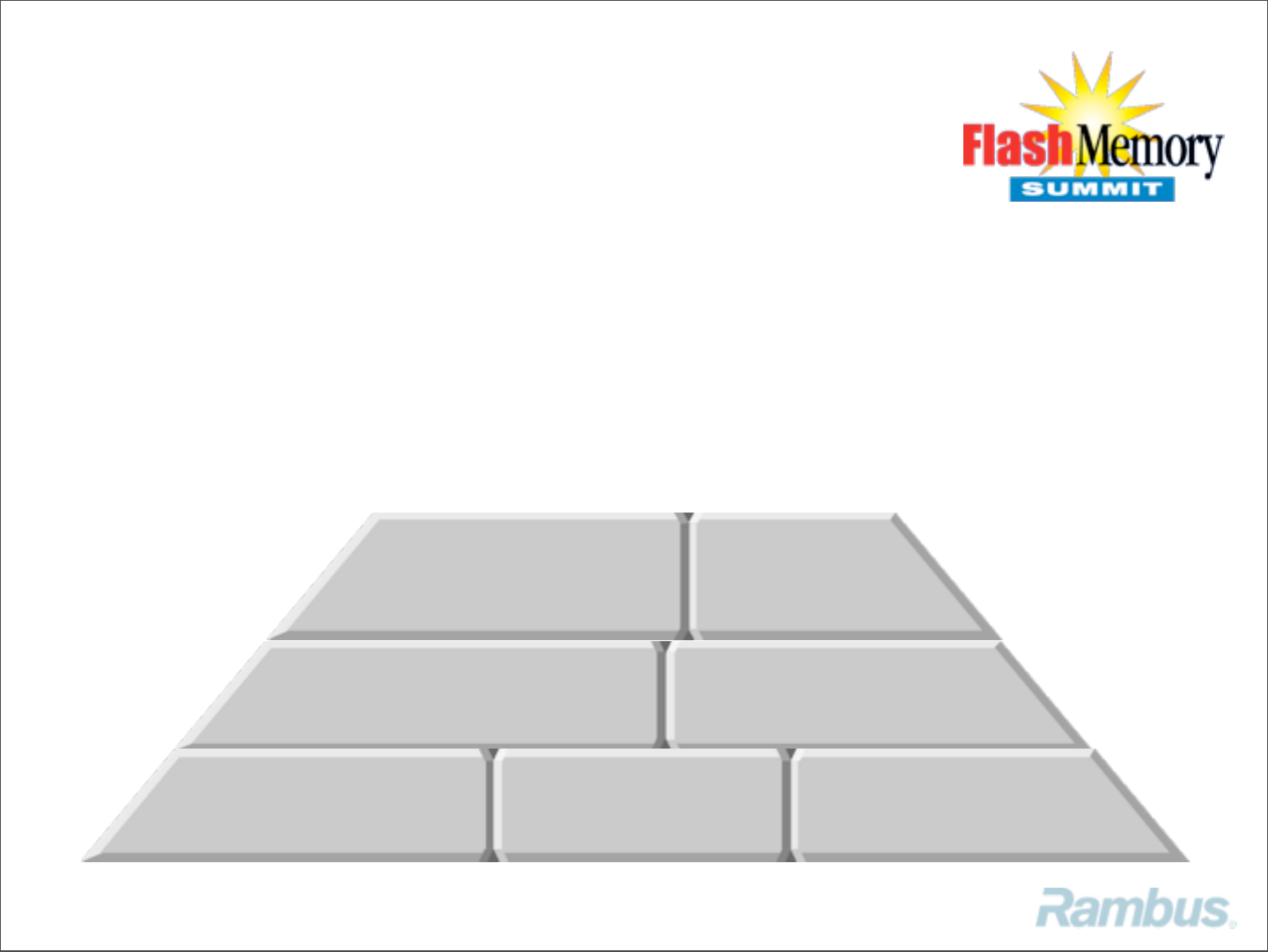

© 2012 Rambus Inc.

Conclusion

from RRAM Cell to System

10

Byte /

Page Erase

WL Control

Gain Stage Sensing

Small Arrays /

Parallelism

Stackable Cross-Point

Hierarchical BL

Self-select

(no select transistor)

Low Current Cell Vertical

Processing

Tuesday, August 28, 12

© 2012 Rambus Inc.

Conclusion

from RRAM Cell to System

10

High Speed

Interface

Low Power

Byte /

Page Erase

WL Control

Gain Stage Sensing

Small Arrays /

Parallelism

Stackable Cross-Point

Hierarchical BL

Self-select

(no select transistor)

Low Current Cell Vertical

Processing

Tuesday, August 28, 12

© 2012 Rambus Inc.

Conclusion

from RRAM Cell to System

10

Tb

Memory,

High System

Bandwidth

High Speed

Interface

Low Power

Byte /

Page Erase

WL Control

Gain Stage Sensing

Small Arrays /

Parallelism

Stackable Cross-Point

Hierarchical BL

Self-select

(no select transistor)

Low Current Cell Vertical

Processing

Tuesday, August 28, 12