C6000 Embedded Design Workshop Student Guide Rev1.20

C6000_Embedded_Design_Workshop_Student_Guide_rev1.20

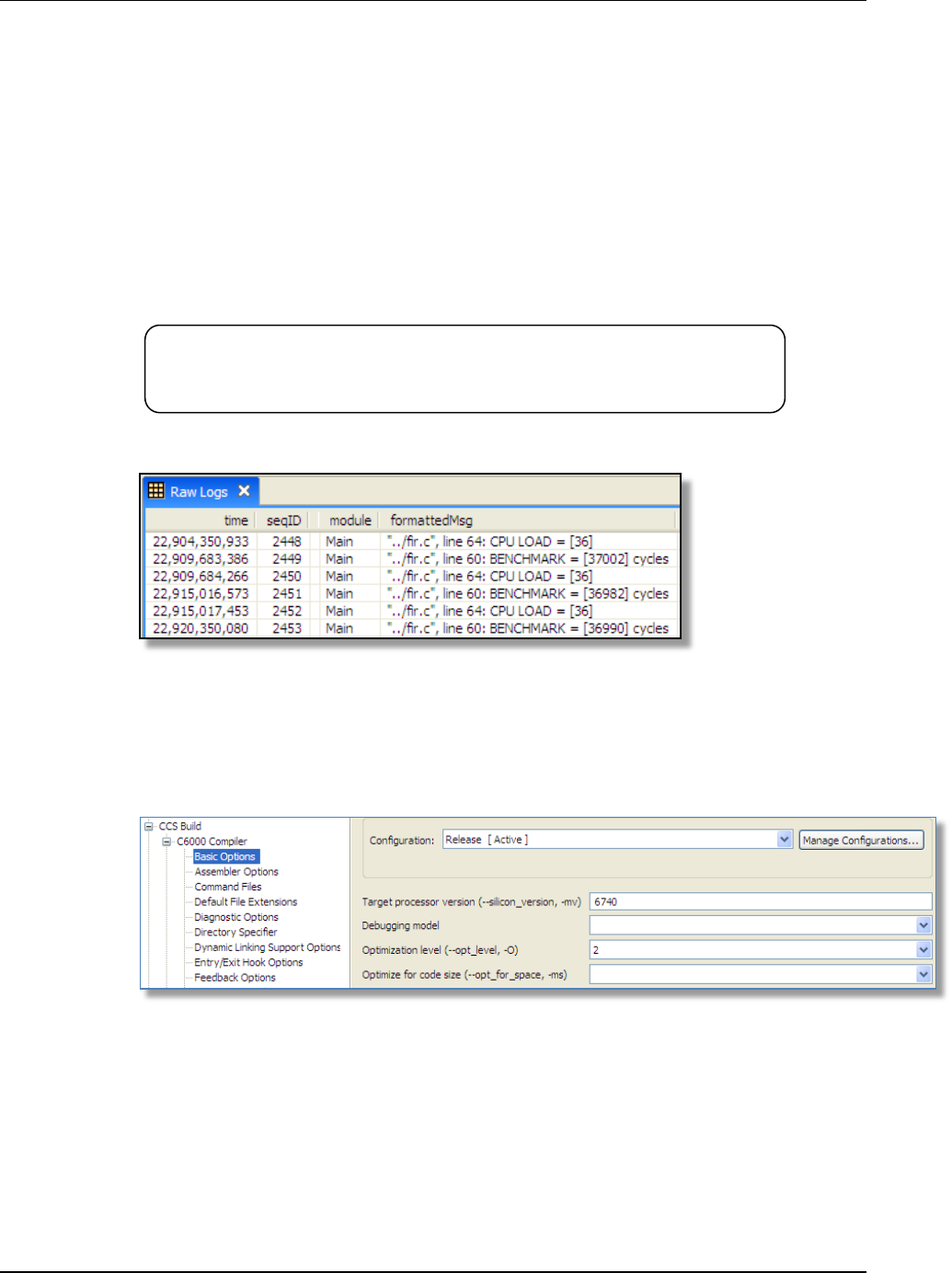

C6000_Embedded_Design_Workshop_Student_Guide_rev1.20

C6000_Embedded_Design_Workshop_Student_Guide_rev1.20

User Manual:

Open the PDF directly: View PDF ![]() .

.

Page Count: 286 [warning: Documents this large are best viewed by clicking the View PDF Link!]

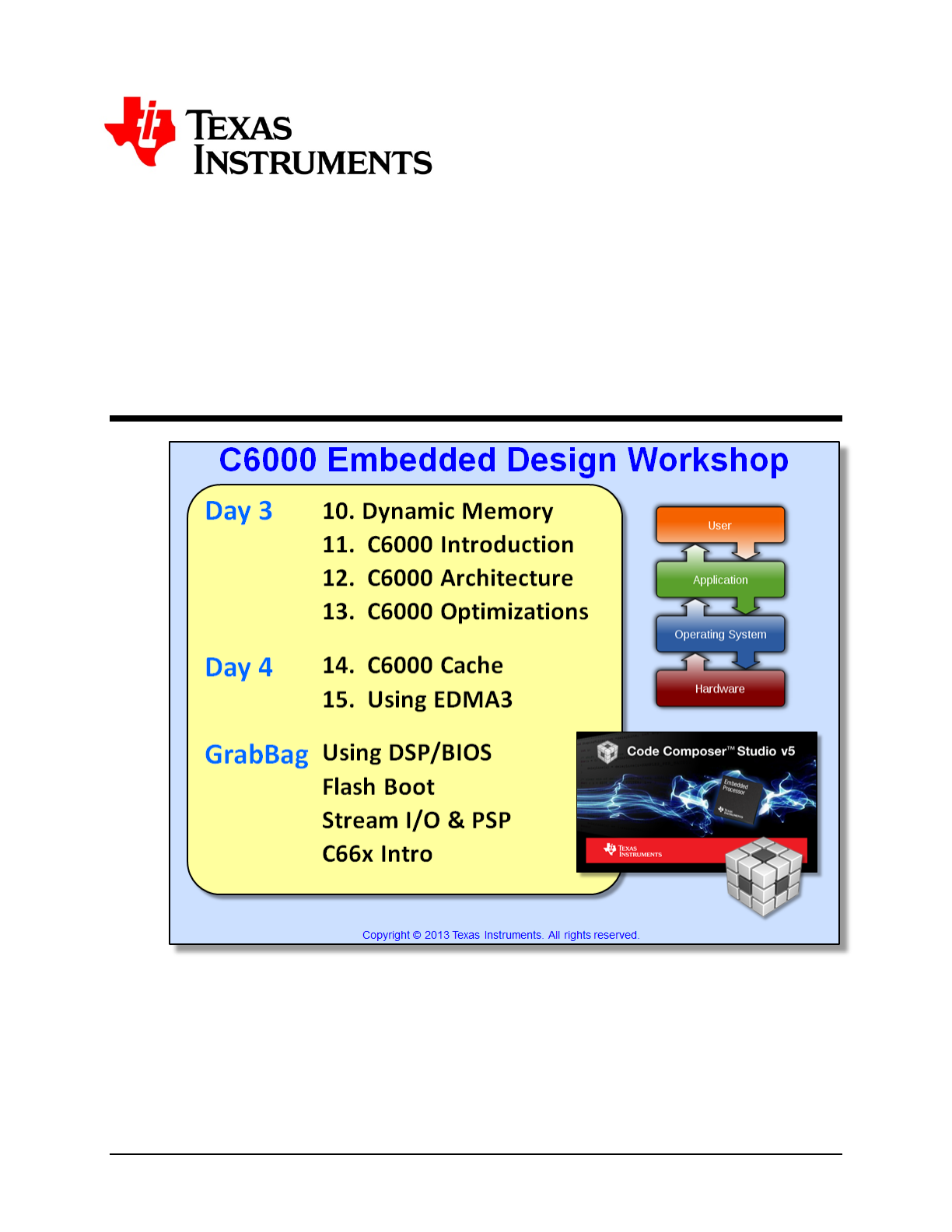

- C6000_2DAY_00_Cover

- C6000_2DAY_10_DynMem

- C6000_2DAY_11_C6000_INTRO

- C6000 Introduction

- Module Topics

- TI EP Product Portfolio

- DSP Core

- Devices & Documentation

- Peripherals

- Example Device: C6748 DSP

- Choosing a Device

- C6000 Arch “Catchup”

- Quiz

- Using Double Buffers

- Lab 11: An Hwi-Based Audio System

- Additional Information

- Notes

- C6000 Introduction

- C6000_2DAY_12_C6000_ARCH

- C6000_2DAY_13_OPT

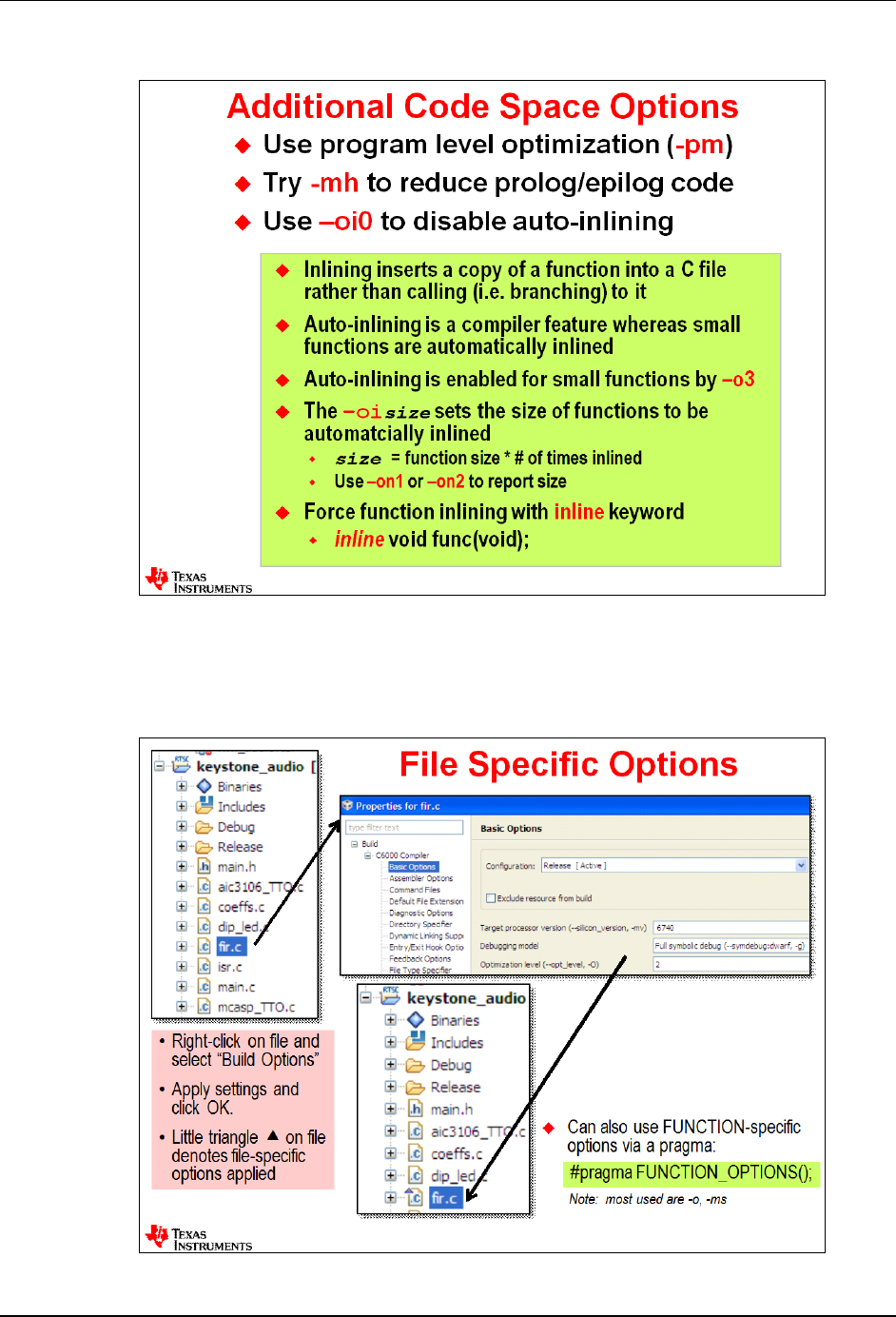

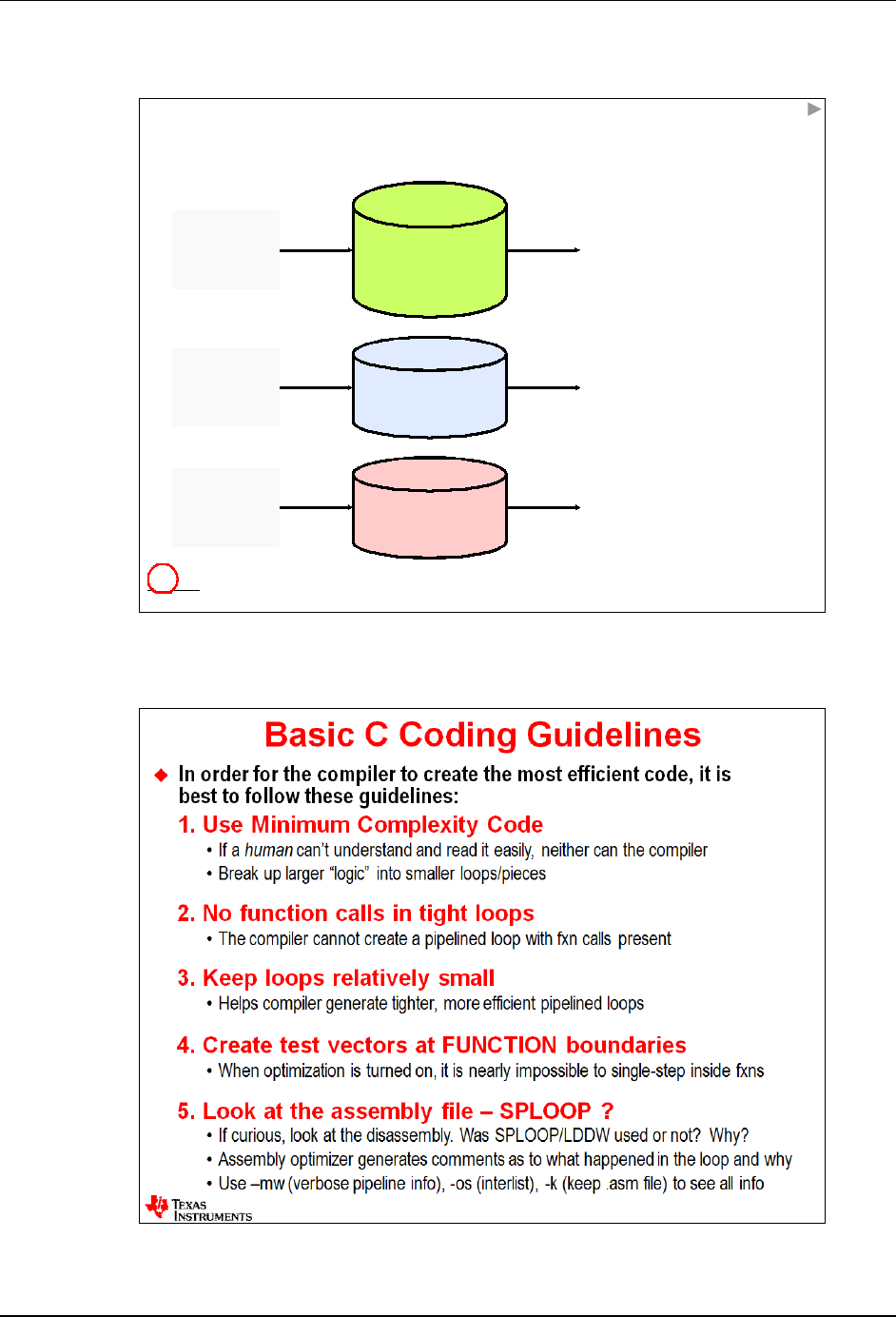

- C and System Optimizations

- Module Topics

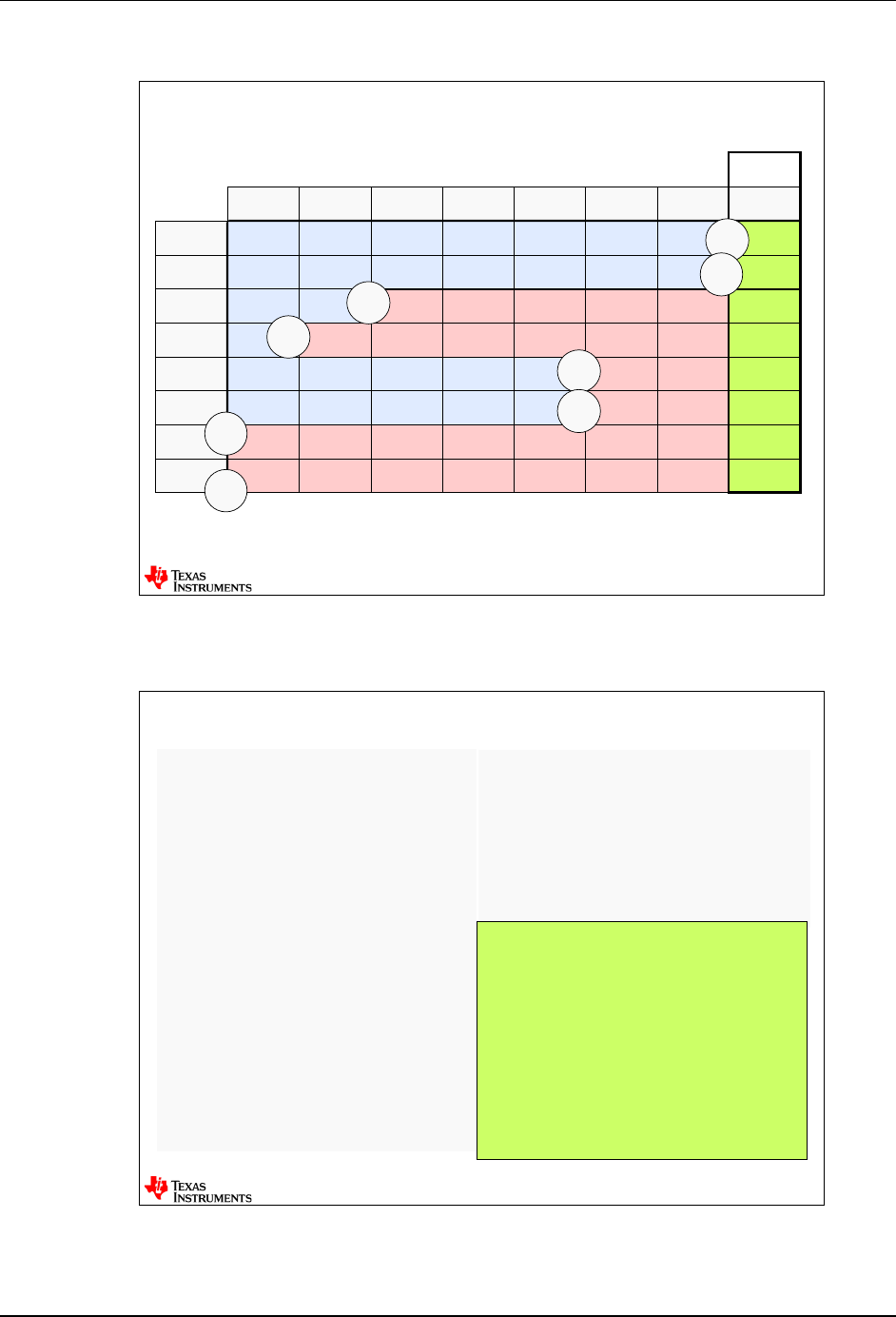

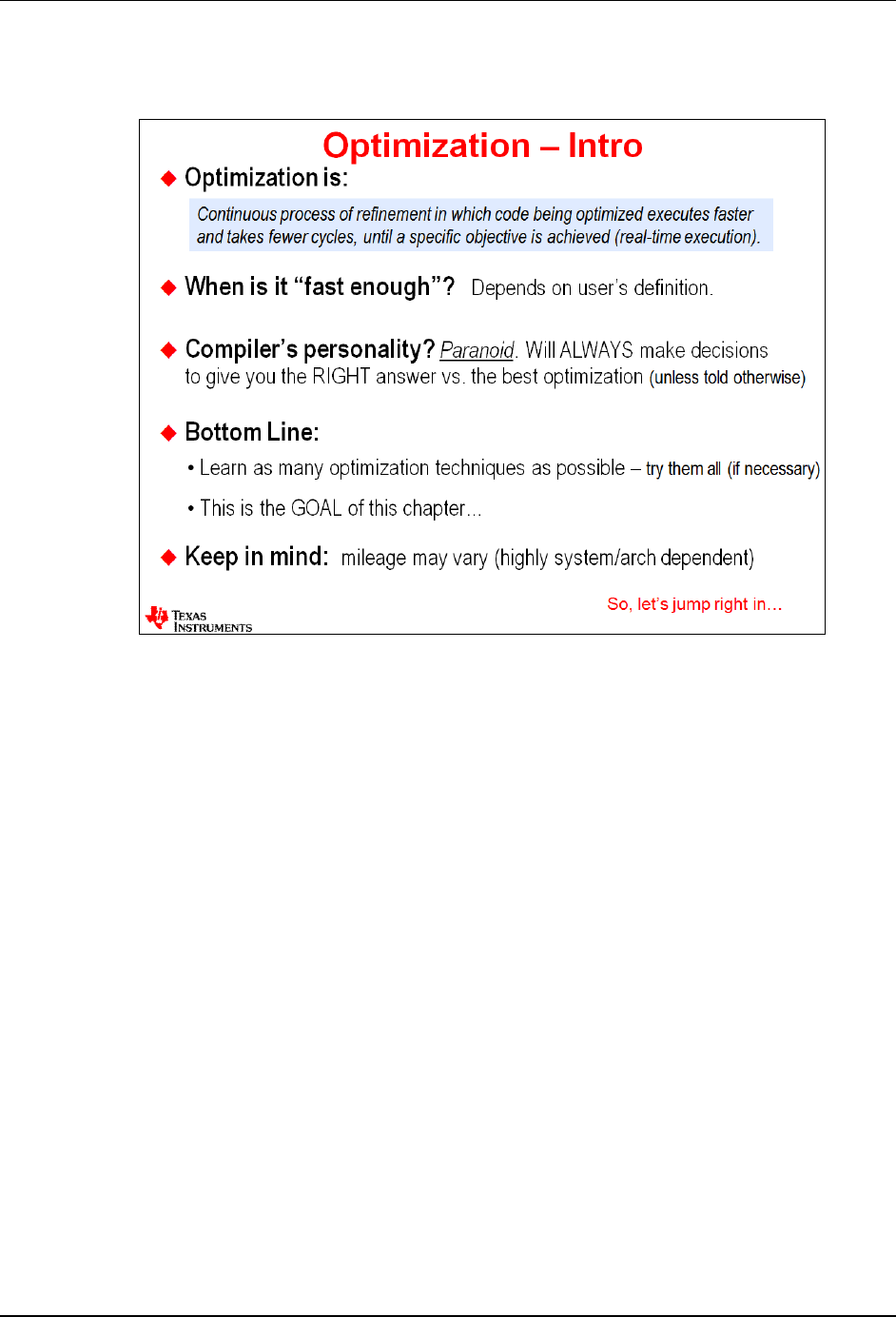

- Introduction – “Optimal” and “Optimization”

- C Compiler and Optimizer

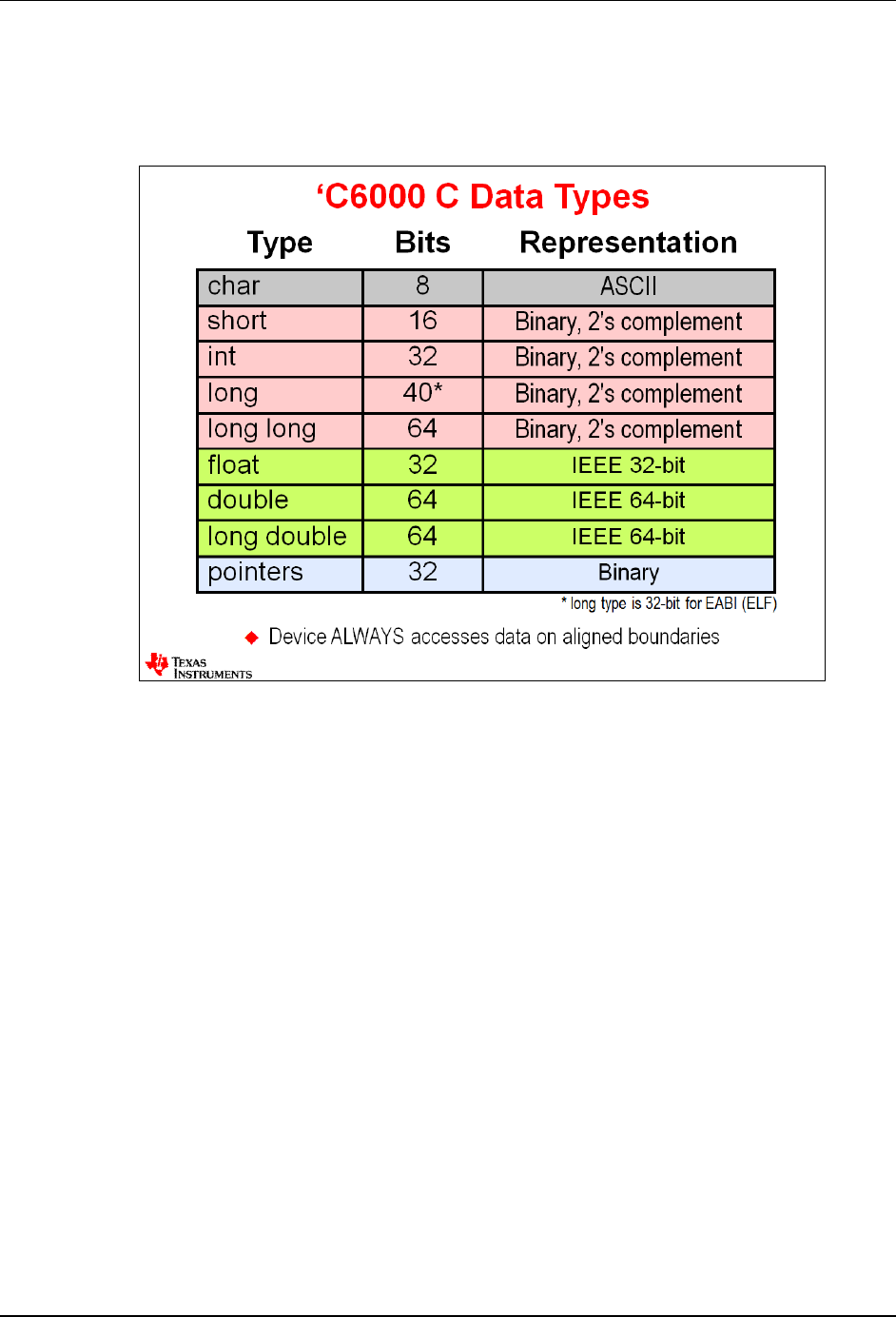

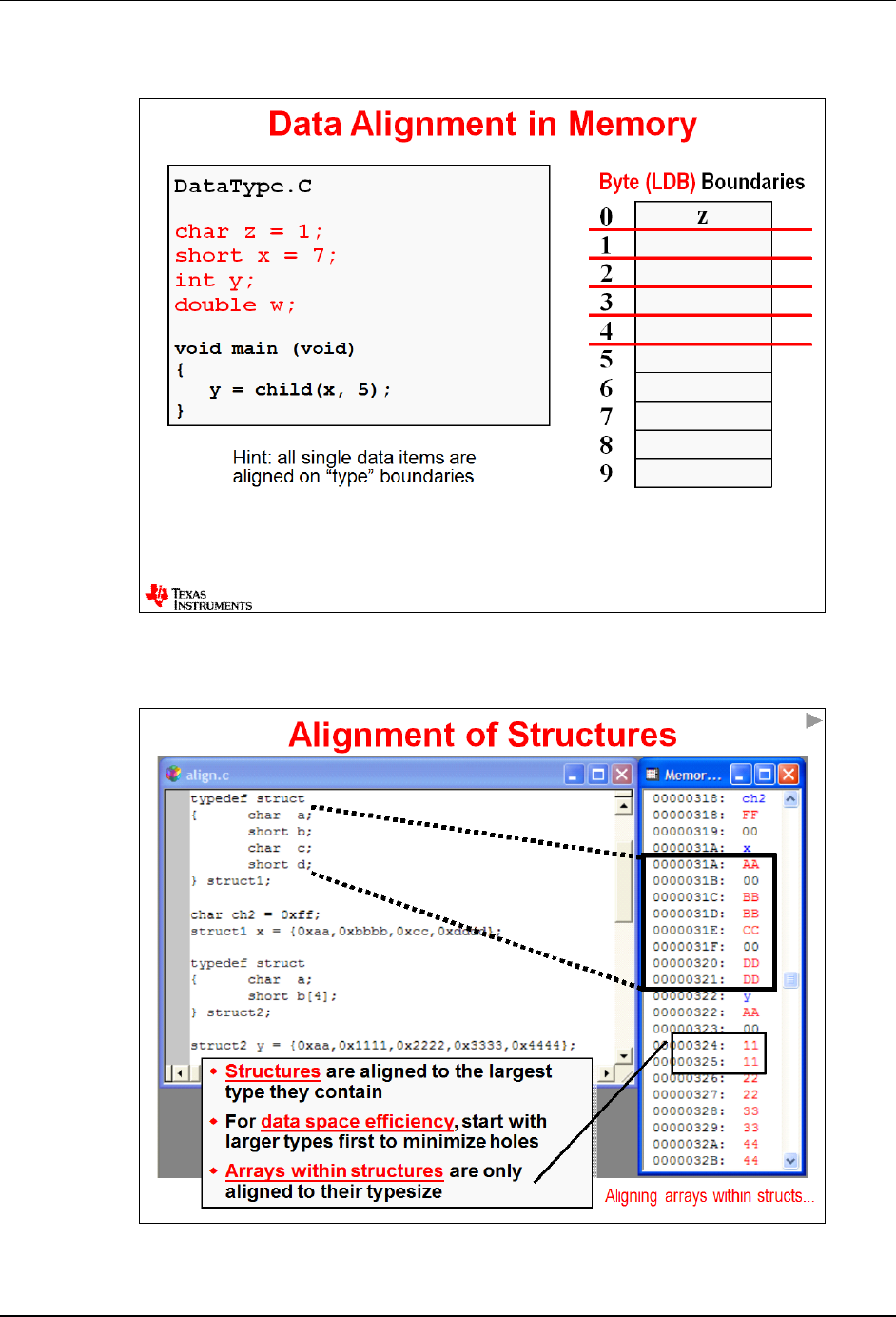

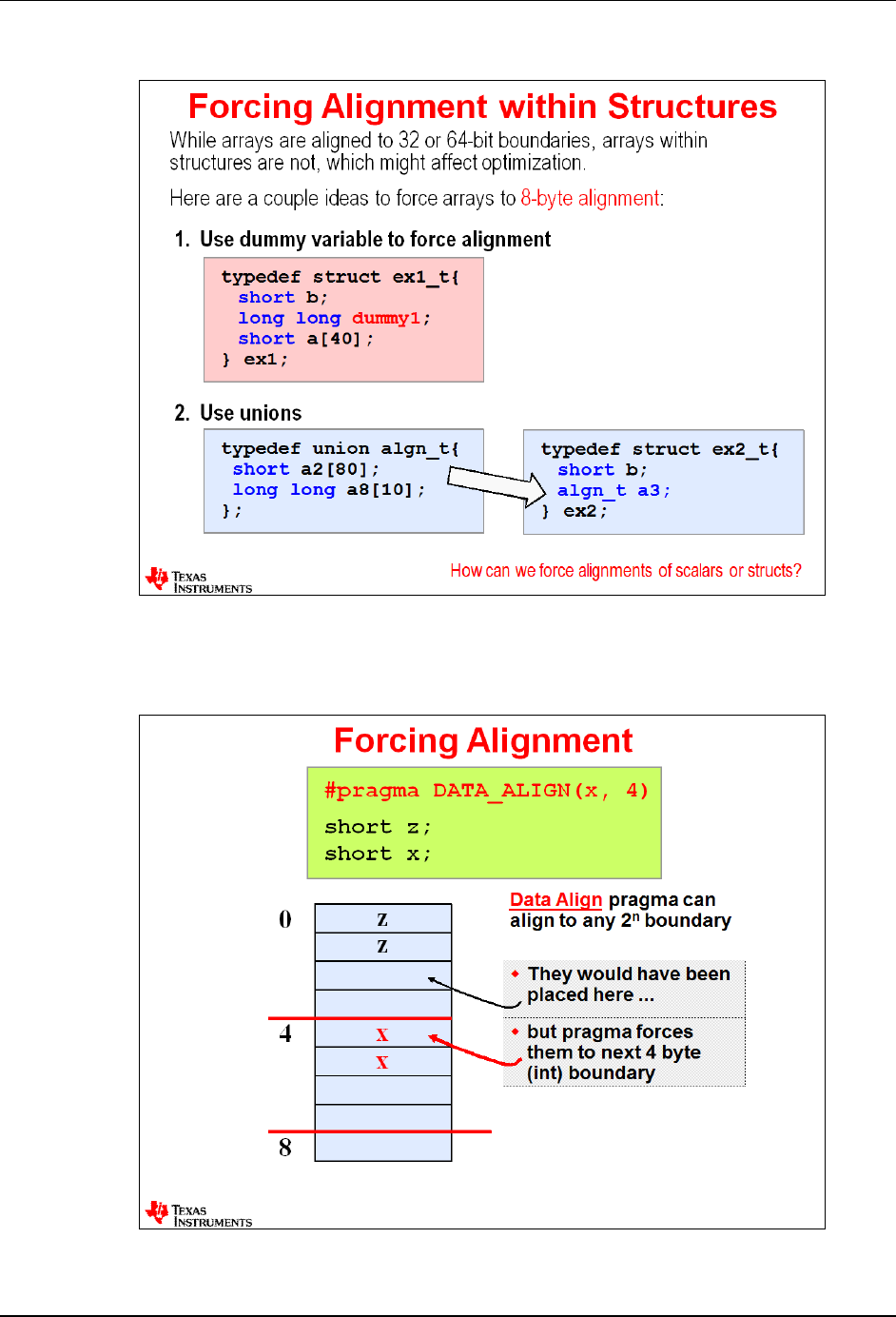

- Data Types and Alignment

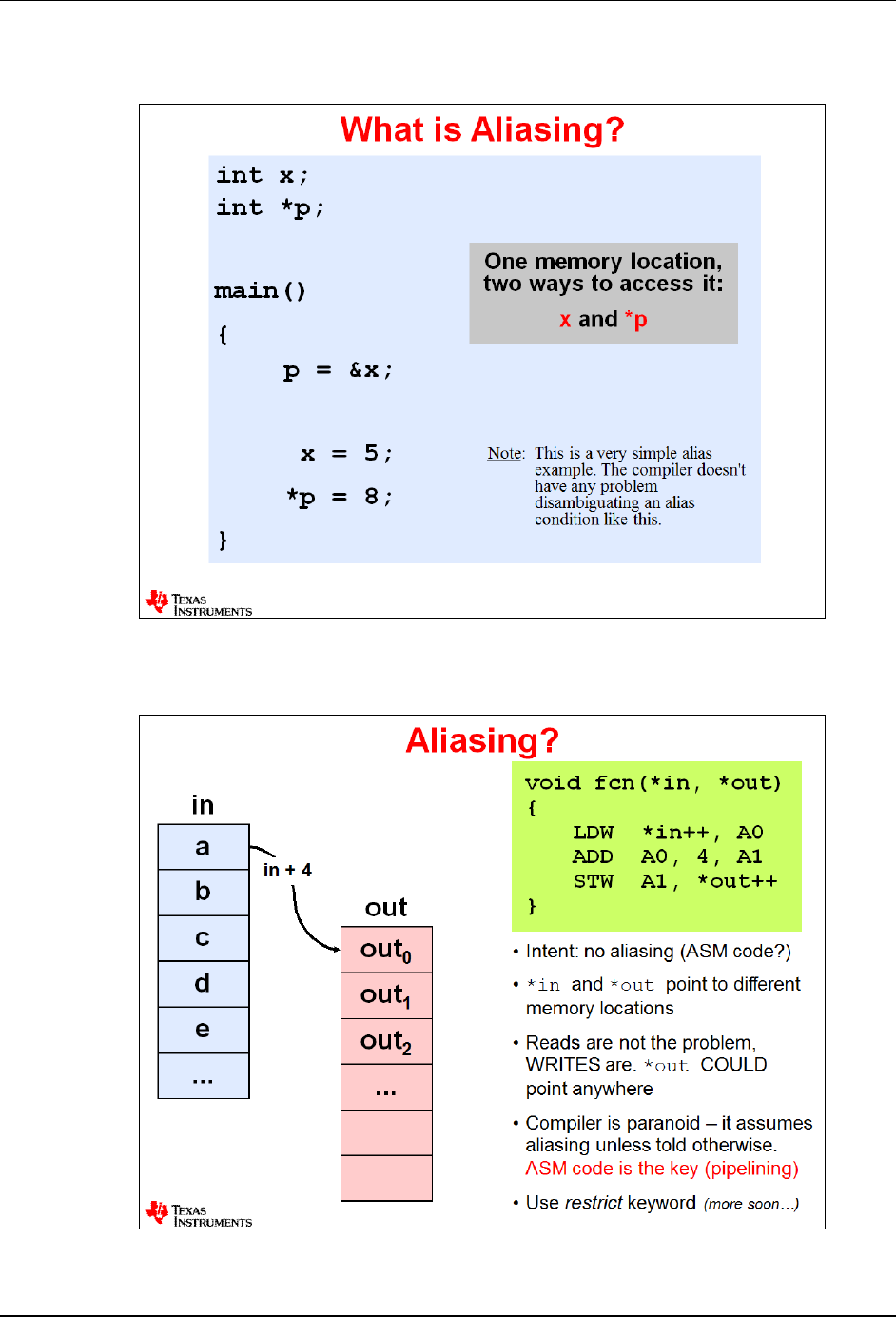

- Restricting Memory Dependencies (Aliasing)

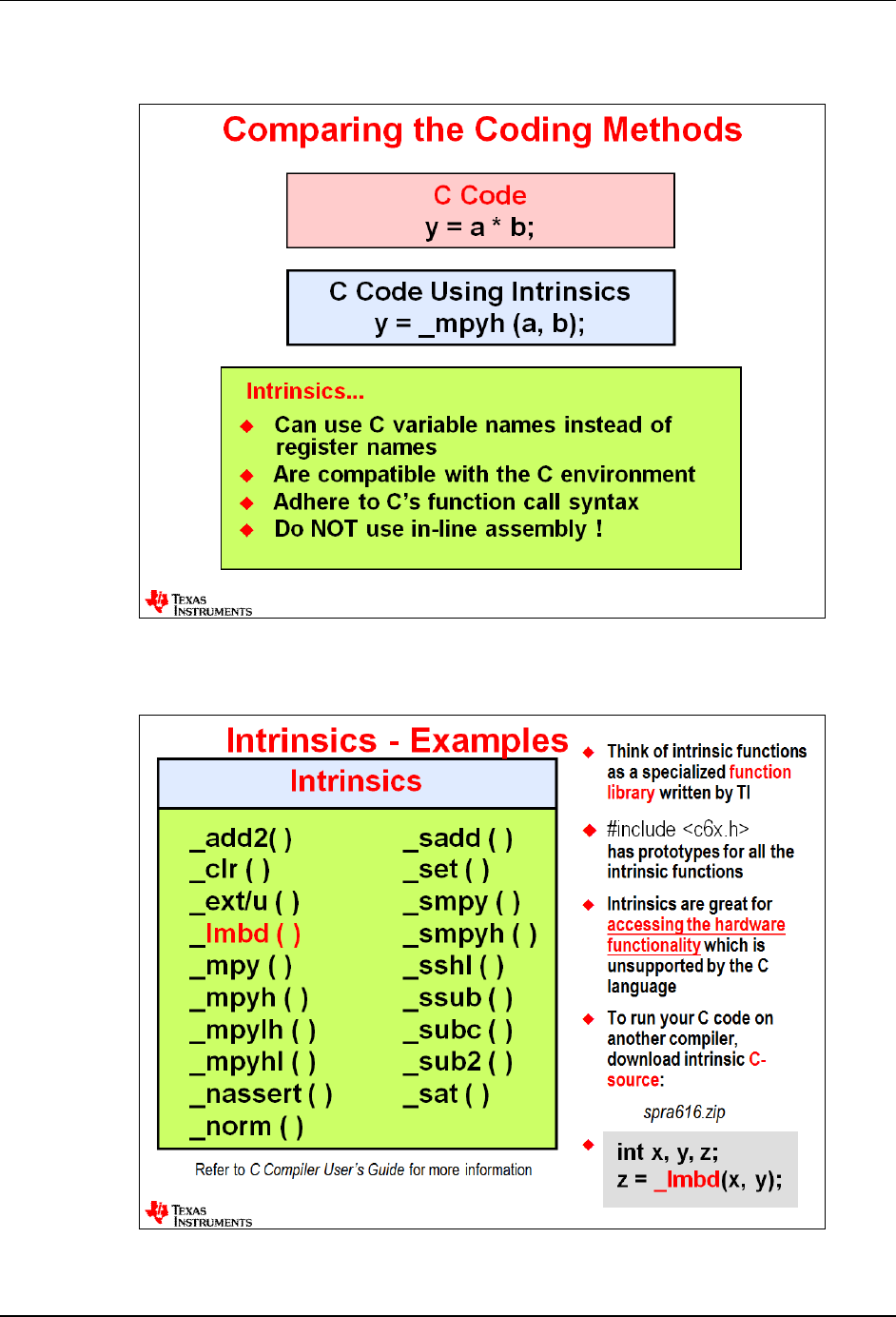

- Access Hardware Features – Using Intrinsics

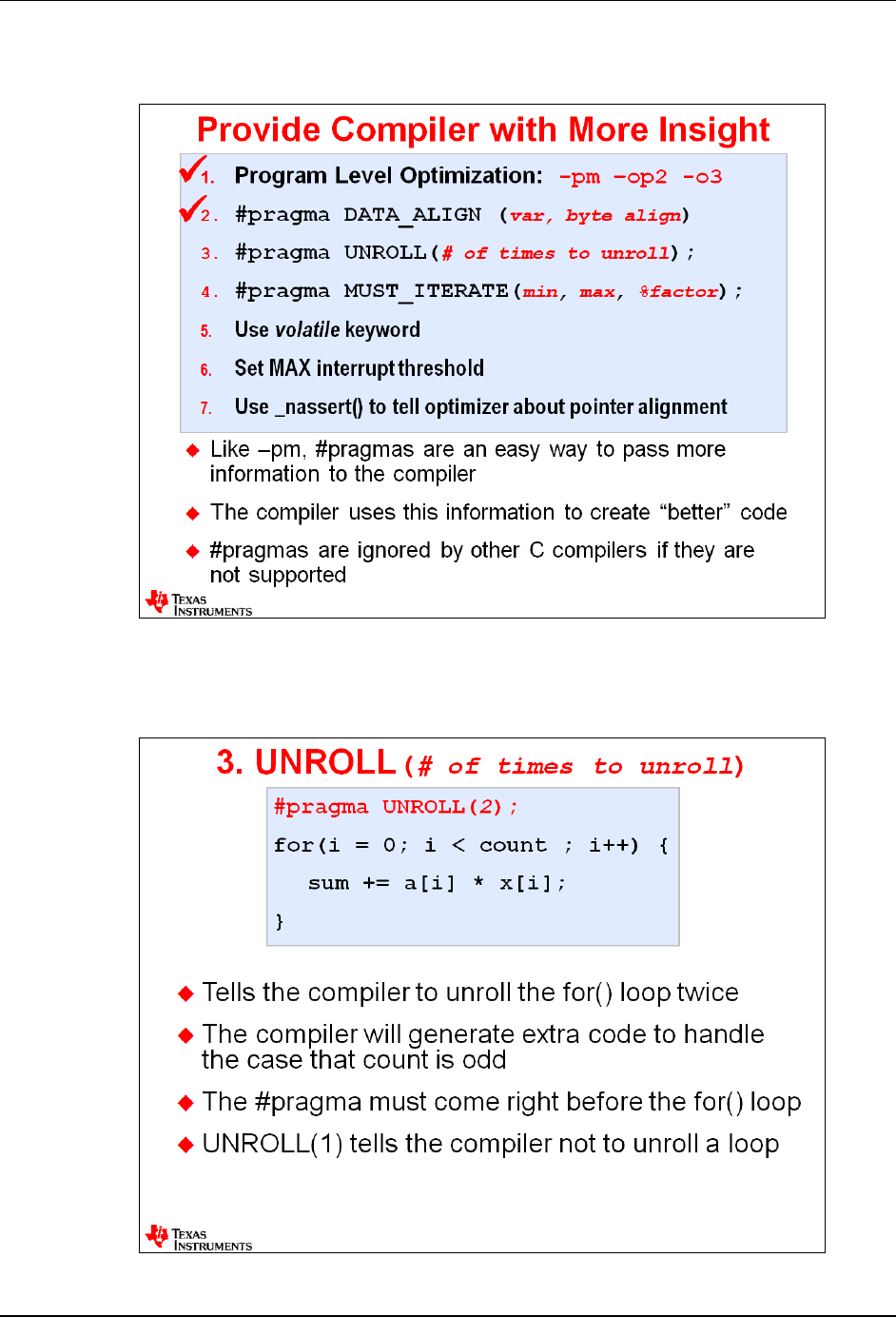

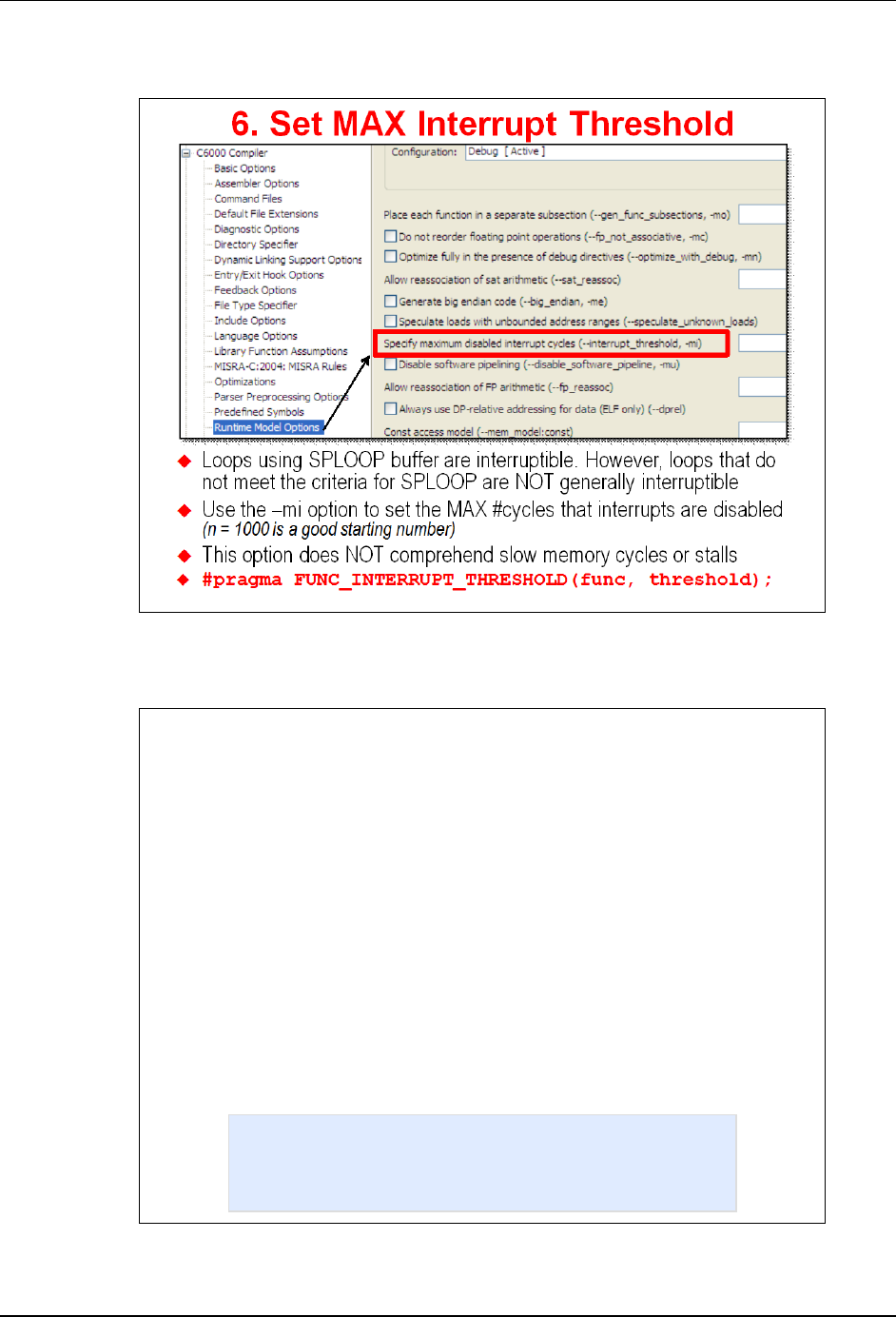

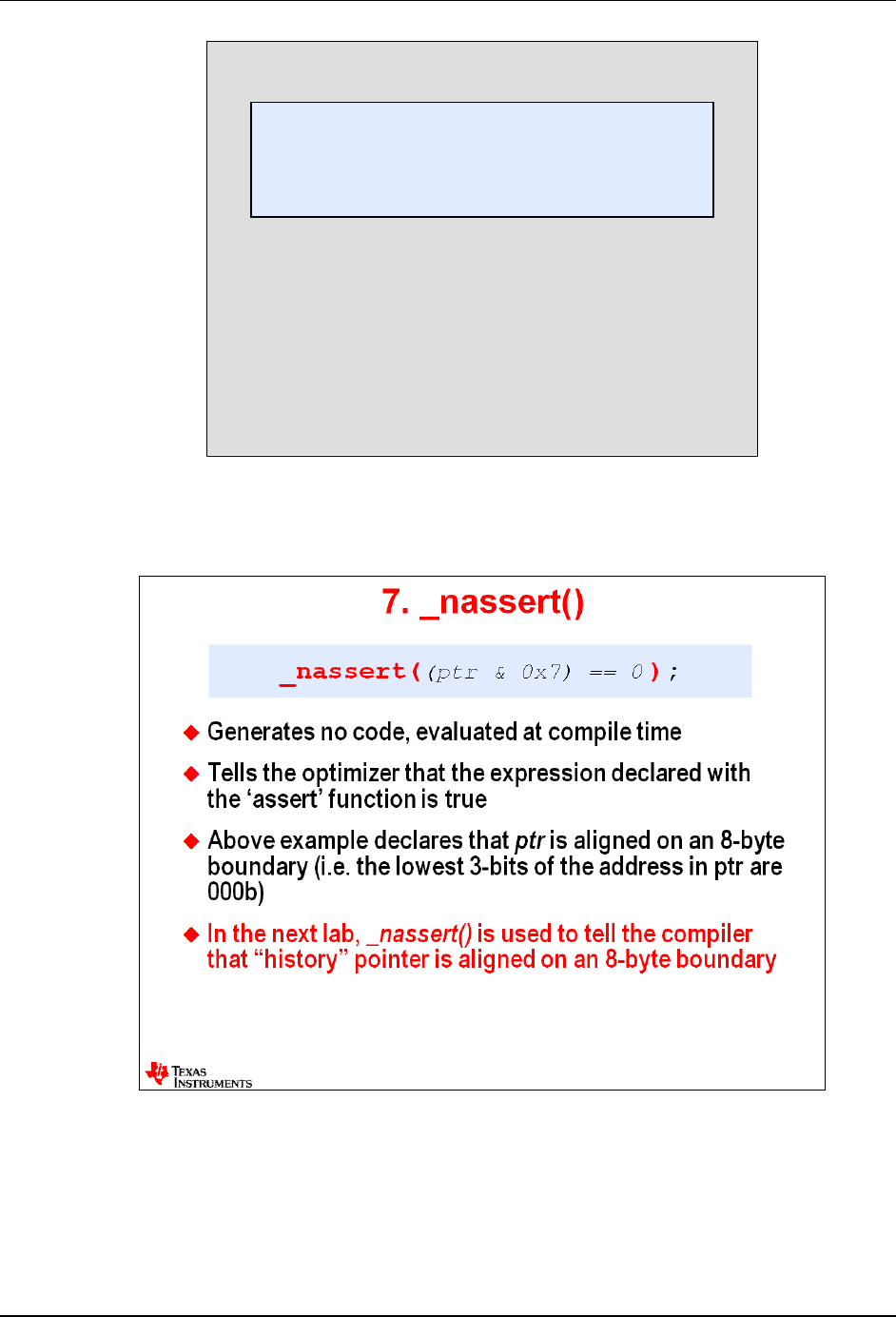

- Give Compiler MORE Information

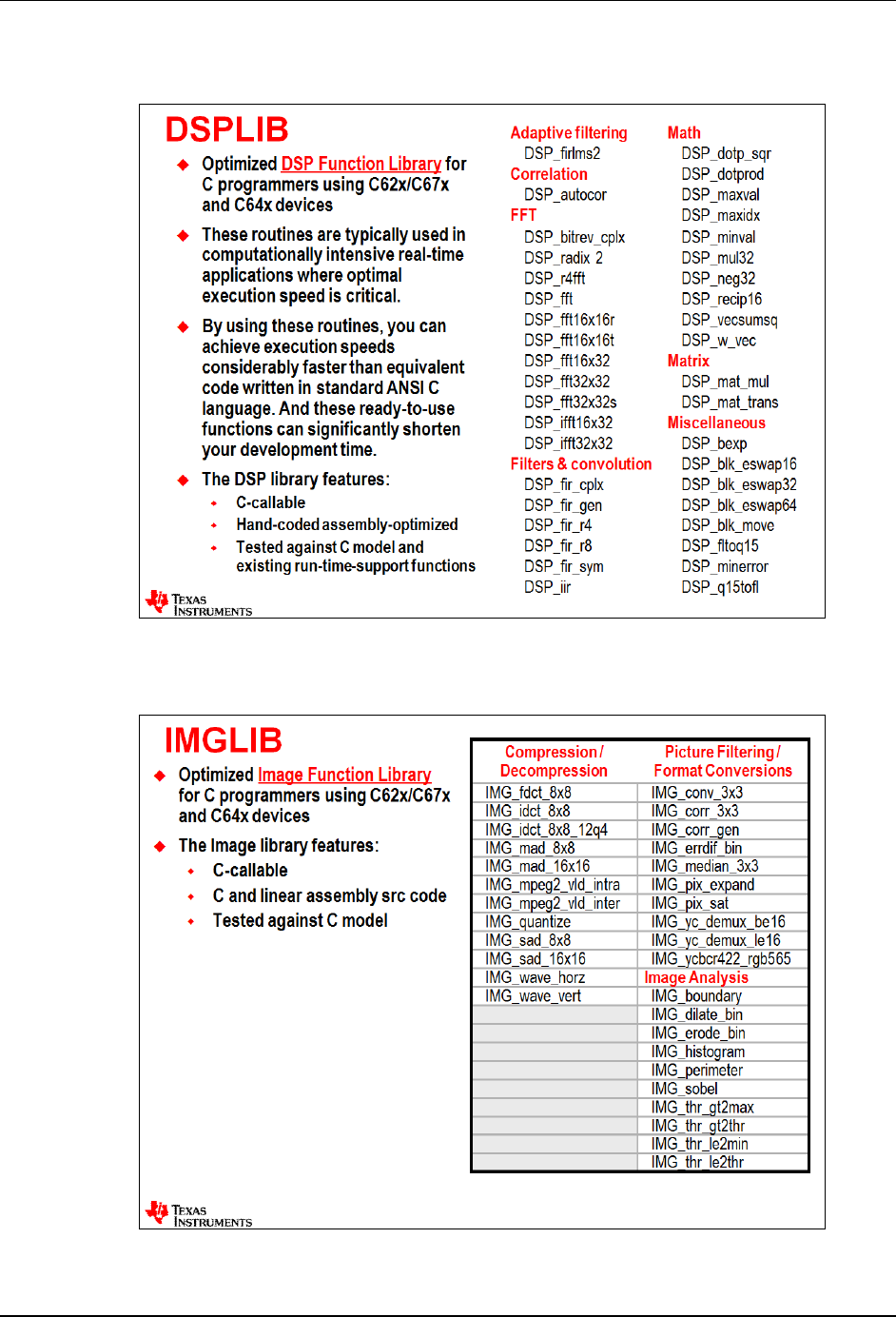

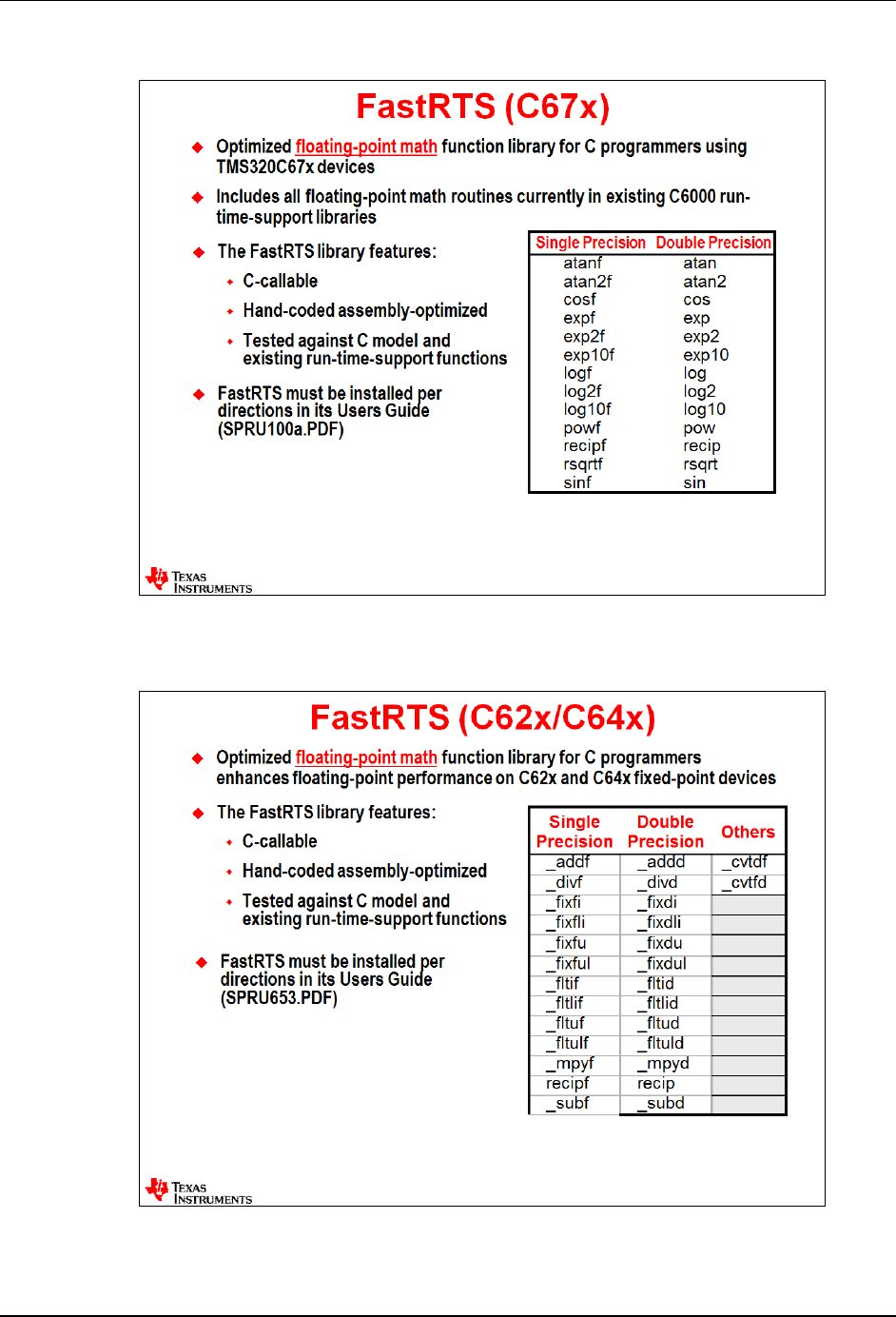

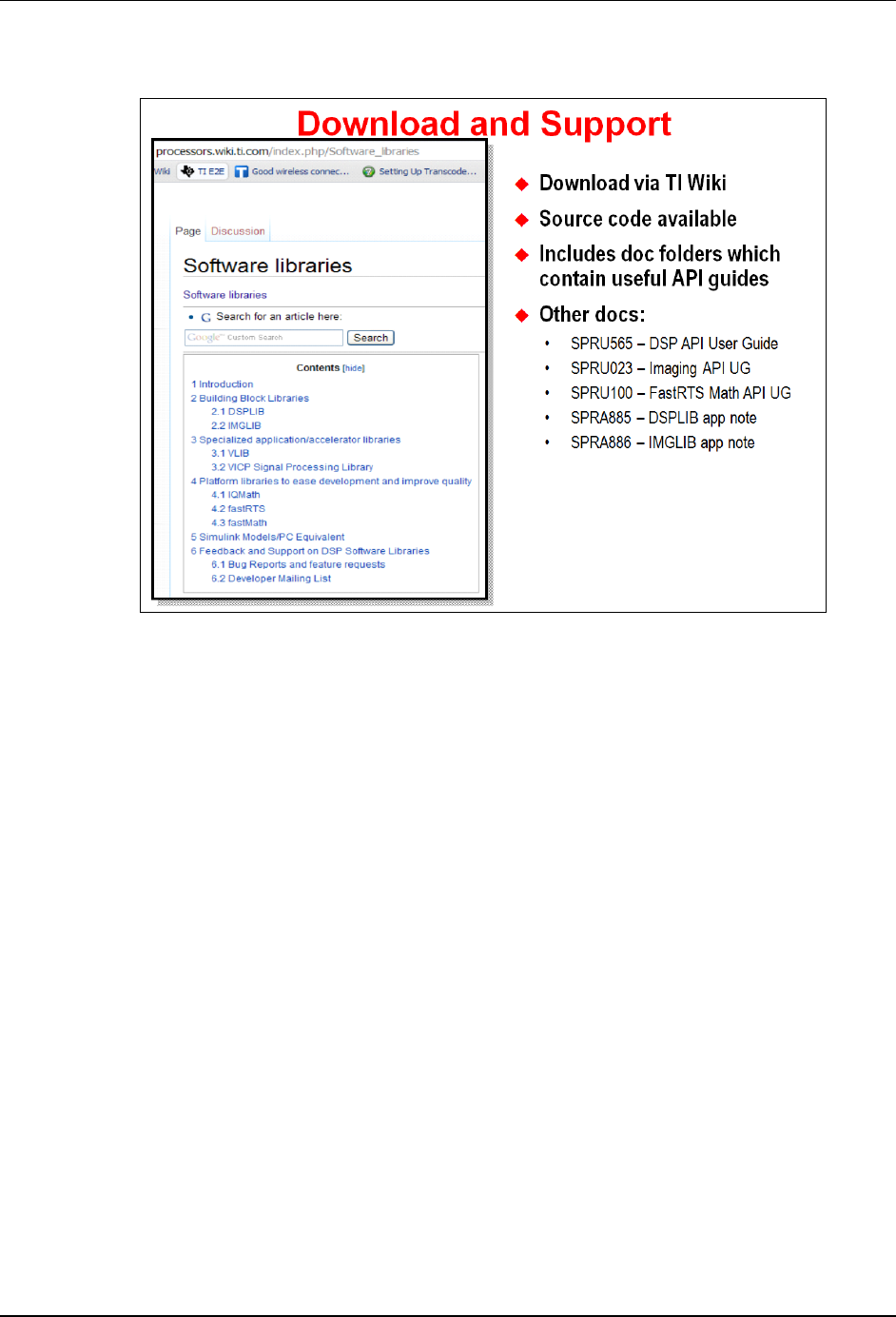

- Using Optimized Libraries

- System Optimizations

- Chapter Quiz

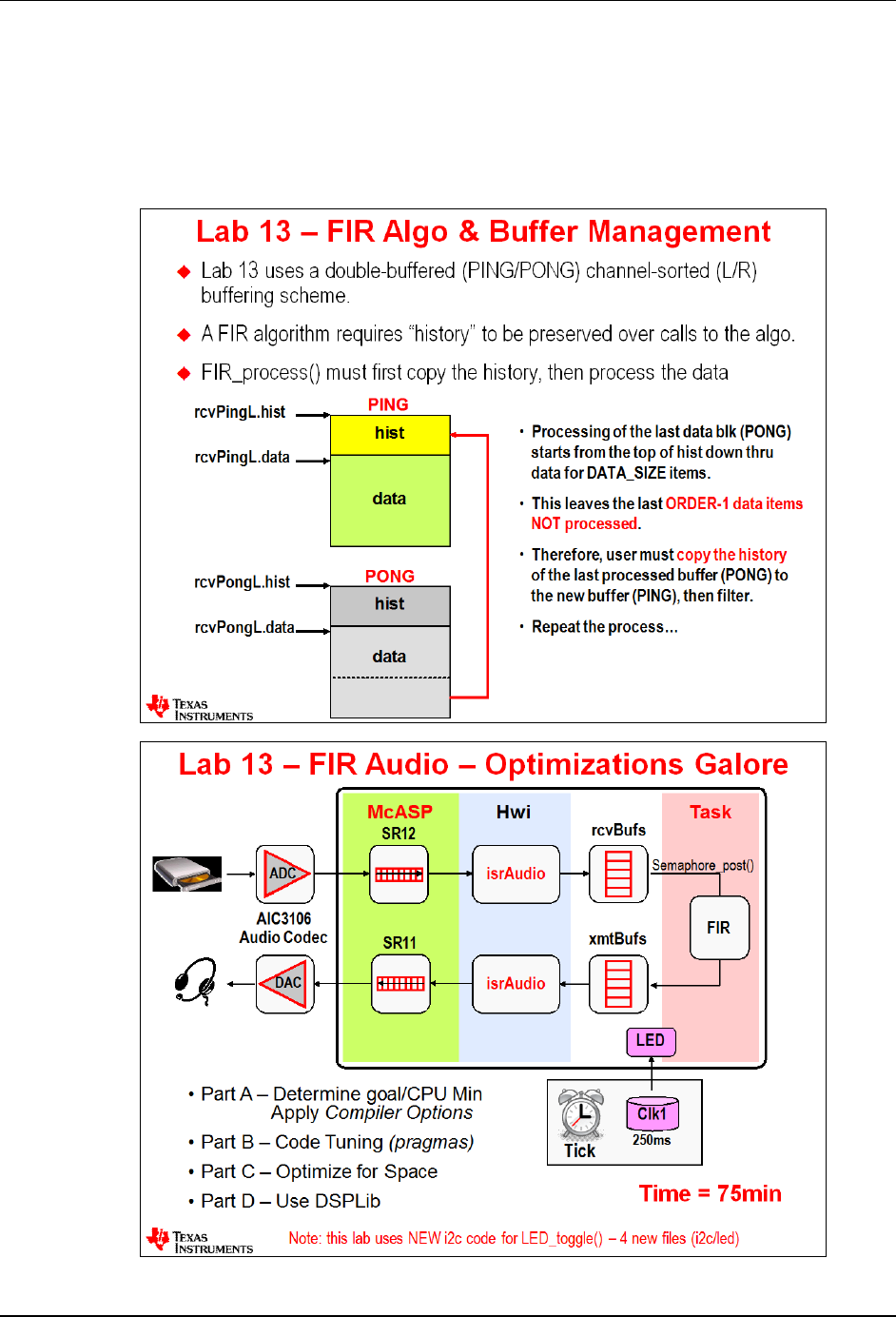

- Lab 13 – C Optimizations

- Lab 13 – C Optimizations – Procedure

- Additional Information

- Notes

- C and System Optimizations

- C6000_2DAY_14_CACHE

- C6000_2DAY_15_EDMA3_Basics

- C6000_2DAY_16_GrabBag_key

- C6000_2DAY_16a_DSPBIOS

- C6000_2DAY_16b_Flash

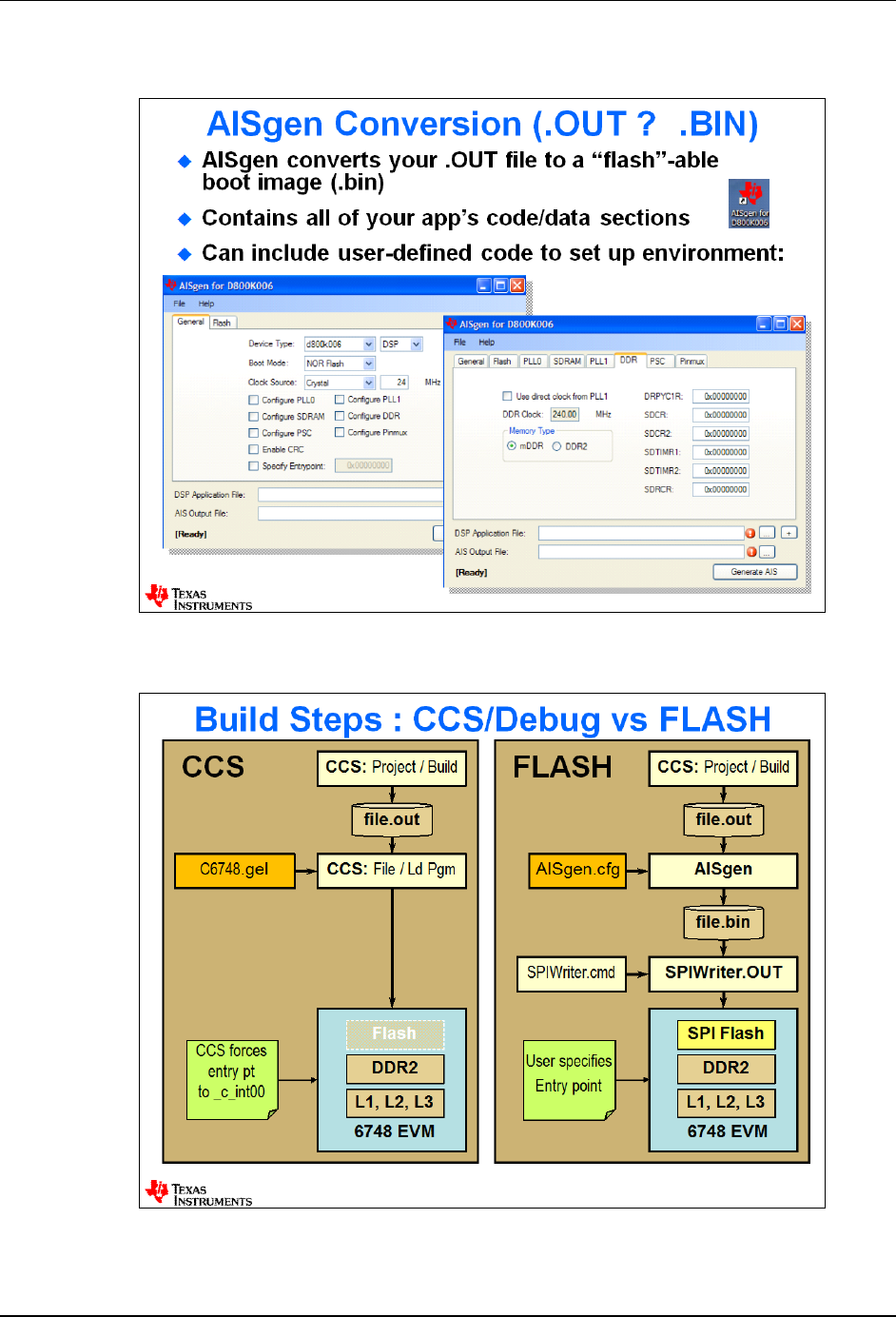

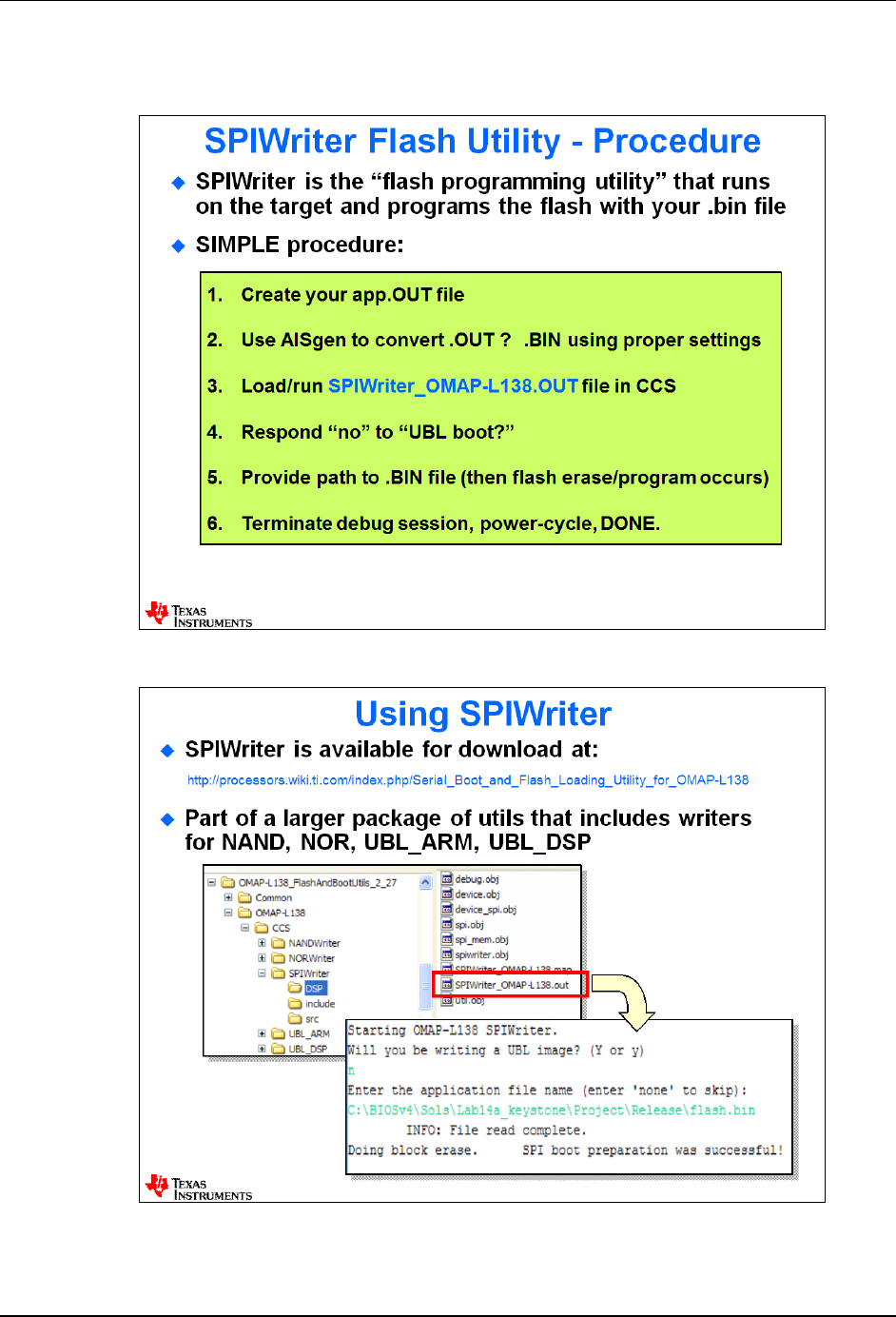

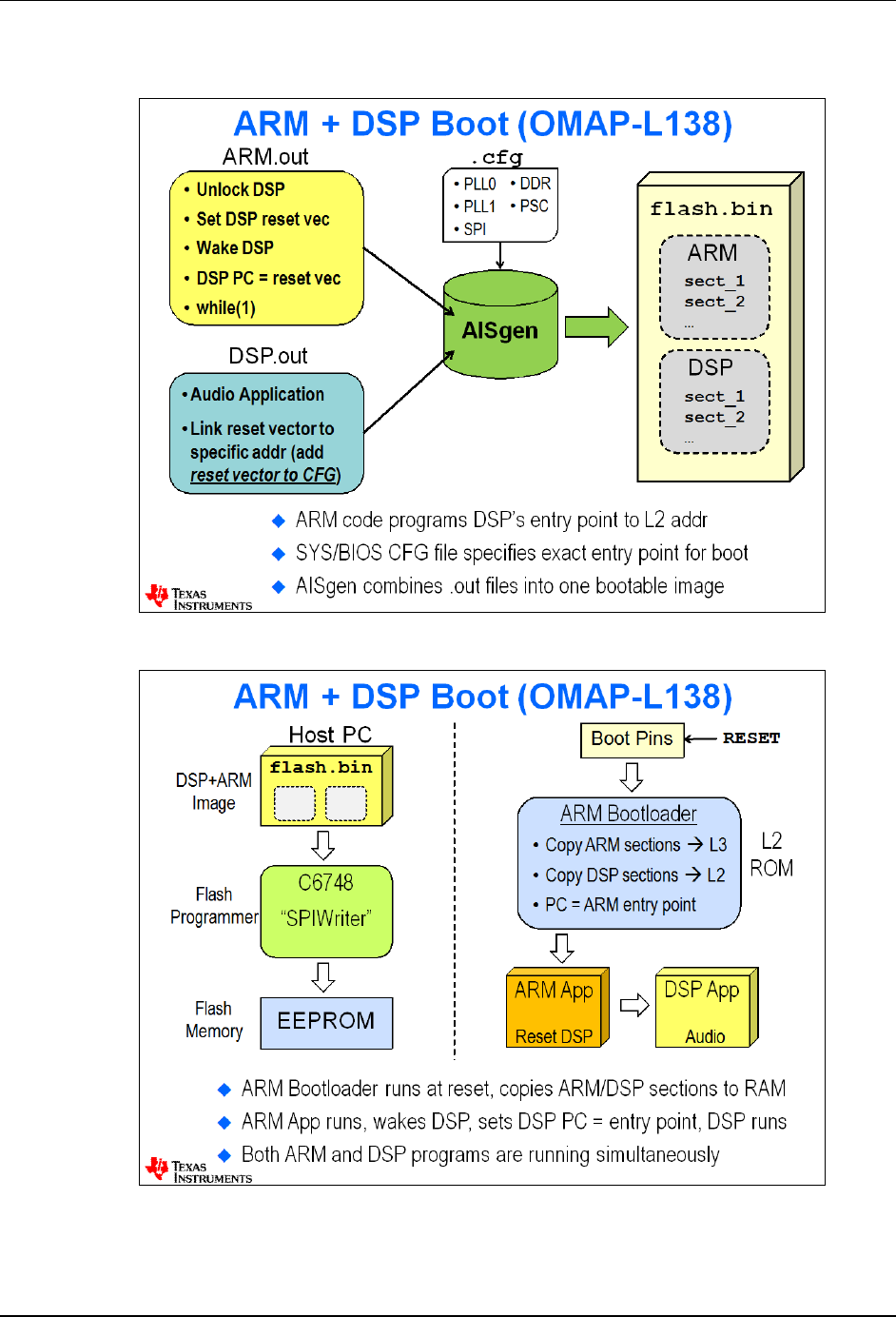

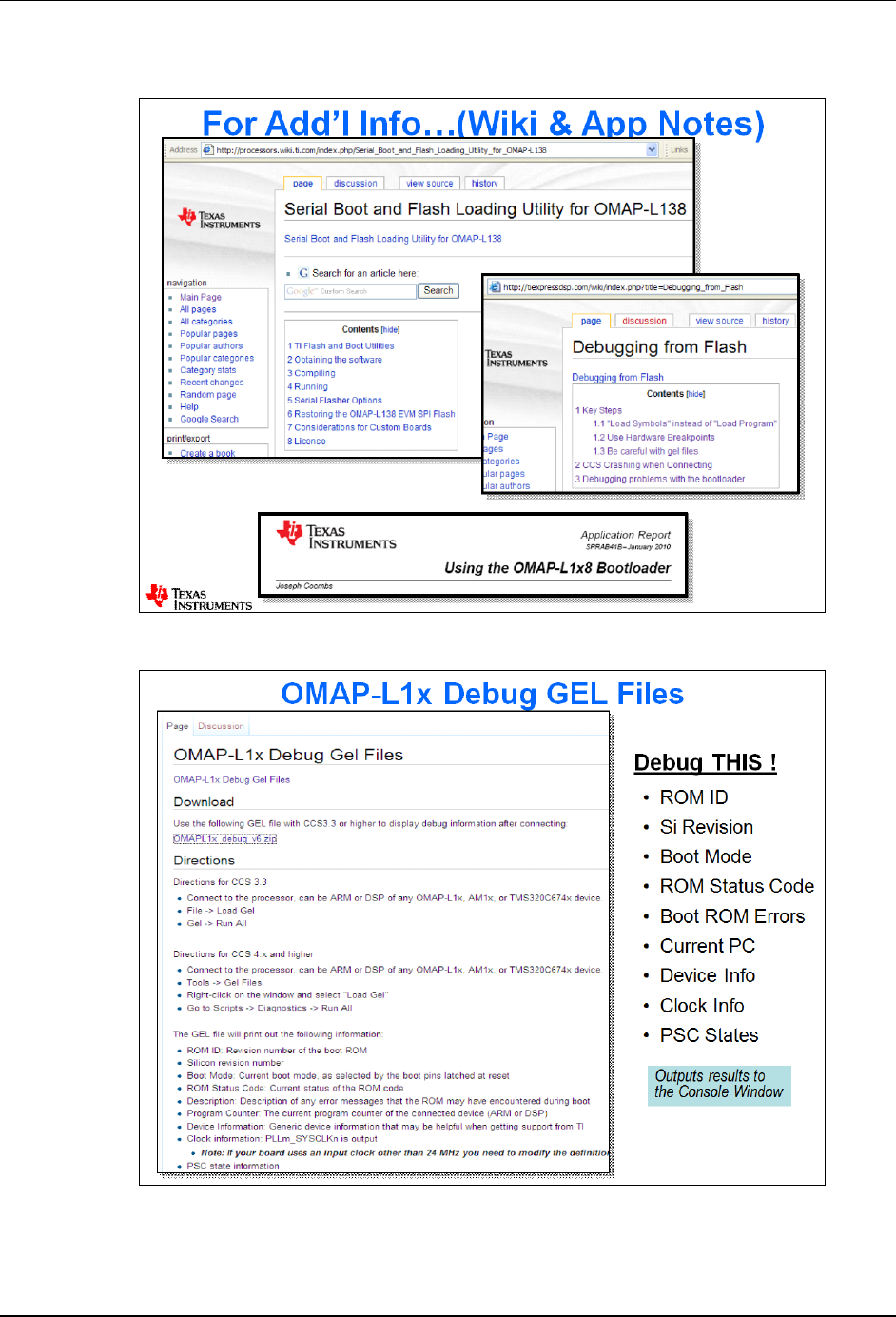

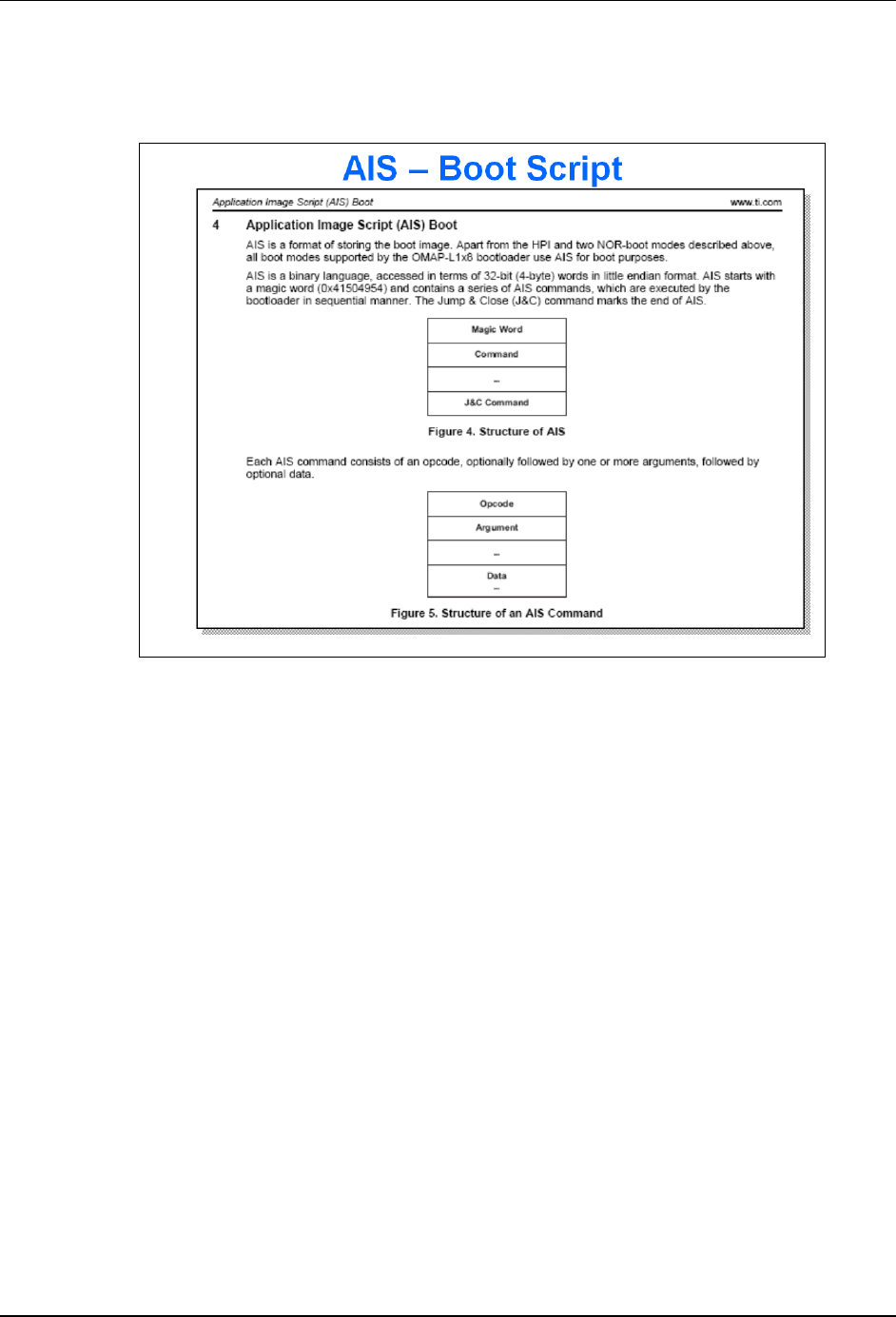

- Booting From Flash

- Module Topics

- Booting From Flash

- Lab 16b: Booting From Flash

- Additional Information

- Notes

- Booting From Flash

- C6000_2DAY_16c_SIO_PSP

- C6000_2DAY_16d_C66x_Intro

Intro to the TI-RTOS Kernel Workshop - Cover 0 - 1

C6000 Embedded Design Workshop

Student Guide

C6000 Embedded Design Workshop

Student Guide, Rev 1.20 – November 2013

Technical Training

Notice

0 - 2 Intro to the TI-RTOS Kernel Workshop - Cover

Notice

Creation of derivative works unless agreed to in writing by the copyright owner is forbidden. No

portion of this publication may be reproduced, stored in a retrieval system or transmitted in any

form or by any means, electronic, mechanical, photocopying, recording or otherwise, without the

prior written permission from the copyright holder.

Texas Instruments reserves the right to update this Guide to reflect the most current product

information for the spectrum of users. If there are any differences between this Guide and a

technical reference manual, references should always be made to the most current reference

manual. Information contained in this publication is believed to be accurate and reliable.

However, responsibility is assumed neither for its use nor any infringement of patents or rights of

others that may result from its use. No license is granted by implication or otherwise under any

patent or patent right of Texas Instruments or others.

Copyright 2013 by Texas Instruments Incorporated. All rights reserved.

Technical Training Organization

Semiconductor Group

Texas Instruments Incorporated

7839 Churchill Way, MS 3984

Dallas, TX 75251-1903

Revision History

Rev 1.00 - Oct 2013 - Re-formatted labs/ppts to fit alongside new TI-RTOS Kernel workshop

Rev 1.10 – Oct 2013 – Added chapter 10 (Dyn Memory) as first optional chapter

Rev 1.20 – Nov 2013 – upgraded all labs to use UIA/SA

TI-RTOS Workshop - Using Dynamic Memory 10 - 1

Using Dynamic Memory

Introduction

In this chapter, you will learn about how to pass data between threads and how to protect

resources during critical sections of code – including using Events, MUTEXs, BIOS “contains”

such as Mailboxes and Queues and other methods of helping threads (mainly Tasks)

communicate with each other.

.

Objectives

Objectives

Compare/contrast static and dynamic systems

Define heaps and describe how to configure the

different types of heaps (std, HeapBuf, etc.)

Describe how to eliminate the drawbacks of

using std heaps (fragments, non-determinism)

Implement dynamic object creation

Lab –Using the previous Task/Sem lab, create

our Semaphores and Tasks dynamically

Module Topics

10 - 2 TI-RTOS Workshop - Using Dynamic Memory

Module Topics

Using Dynamic Memory ....................................................................................................... 10-1

Module Topics.................................................................................................................... 10-2

Static vs. Dynamic .............................................................................................................. 10-3

Dynamic Memory Concepts................................................................................................ 10-4

Using Dynamic Memory.................................................................................................. 10-4

Creating A Heap ............................................................................................................. 10-6

Different Types of Heaps .................................................................................................... 10-7

HeapMem ...................................................................................................................... 10-7

HeapBuf ......................................................................................................................... 10-8

HeapMultiBuf.................................................................................................................. 10-9

Default System Heap .................................................................................................... 10-10

Dynamic Module Creation ................................................................................................ 10-11

Custom Section Placement .............................................................................................. 10-13

Lab 10: Using Dynamic Memory ...................................................................................... 10-15

Lab 10 – Procedure – Using Dynamic Task/Sem .............................................................. 10-16

Import Project ............................................................................................................... 10-16

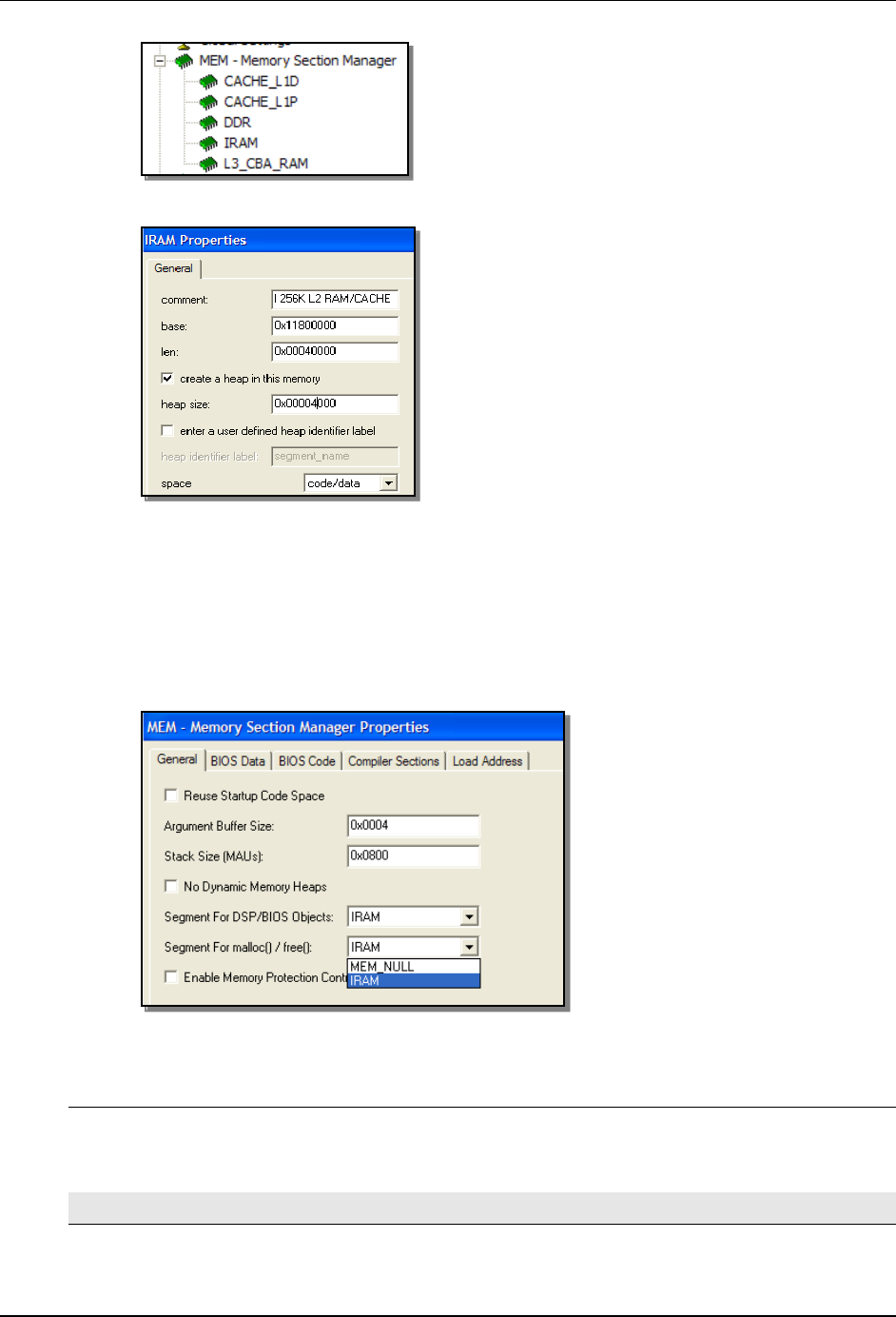

Check Dynamic Memory Settings ................................................................................. 10-17

Inspect New Code in main().......................................................................................... 10-18

Delete the Semaphore and Add It Dynamically ............................................................. 10-18

Build, Load, Run, Verify ................................................................................................ 10-19

Delete Task and Add It Dynamically ............................................................................. 10-20

Additional Information....................................................................................................... 10-22

Notes ............................................................................................................................... 10-23

More Notes… ................................................................................................................... 10-24

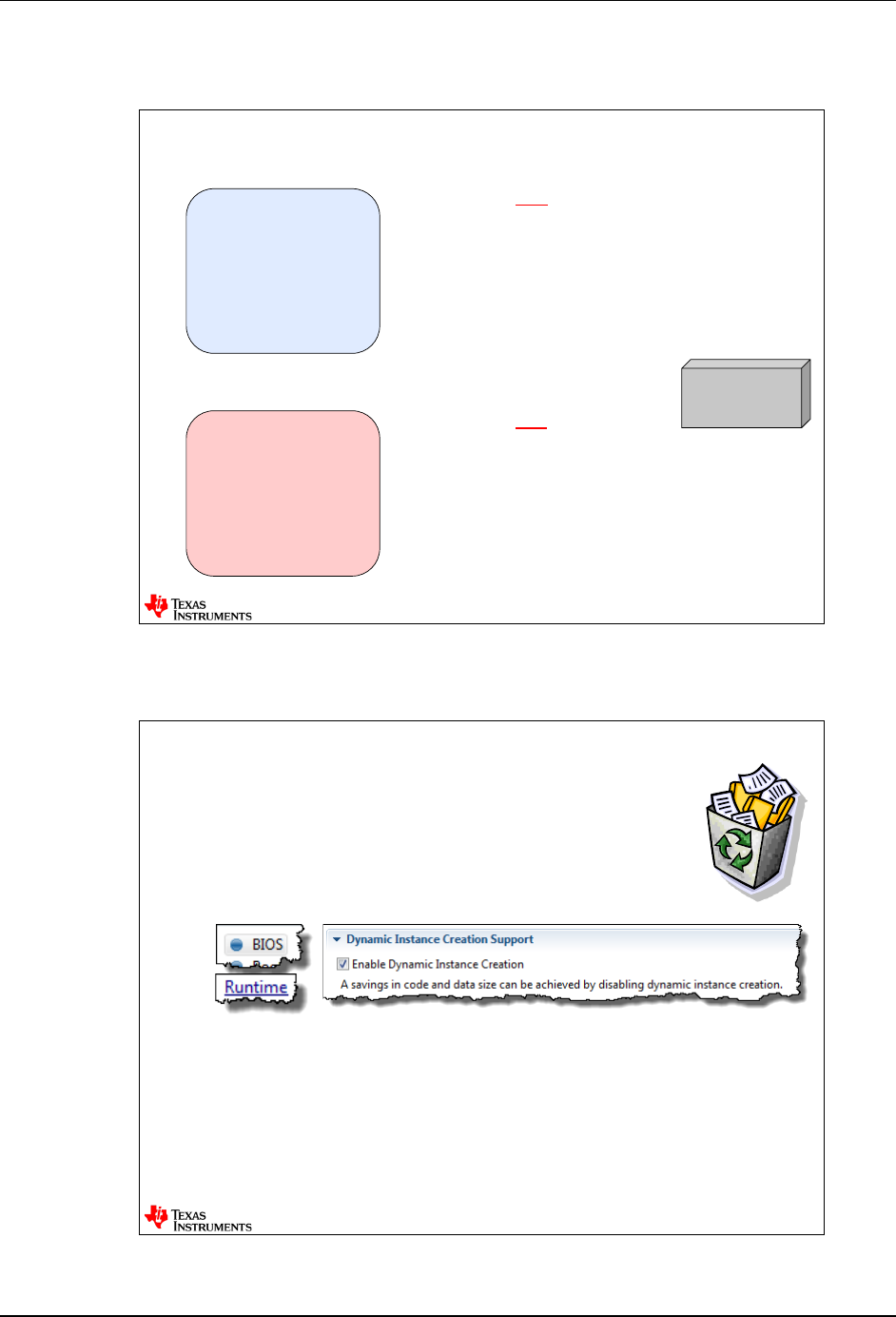

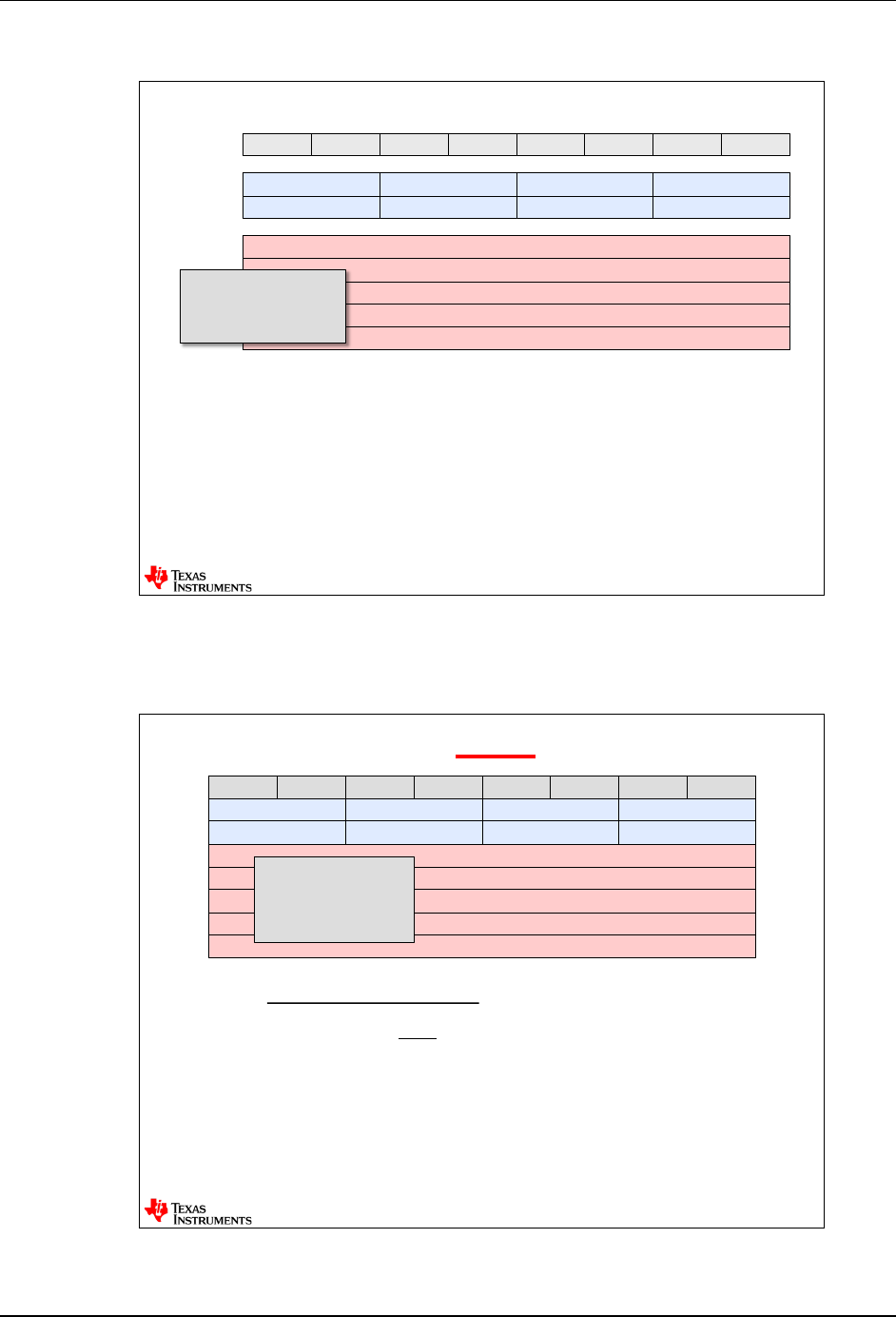

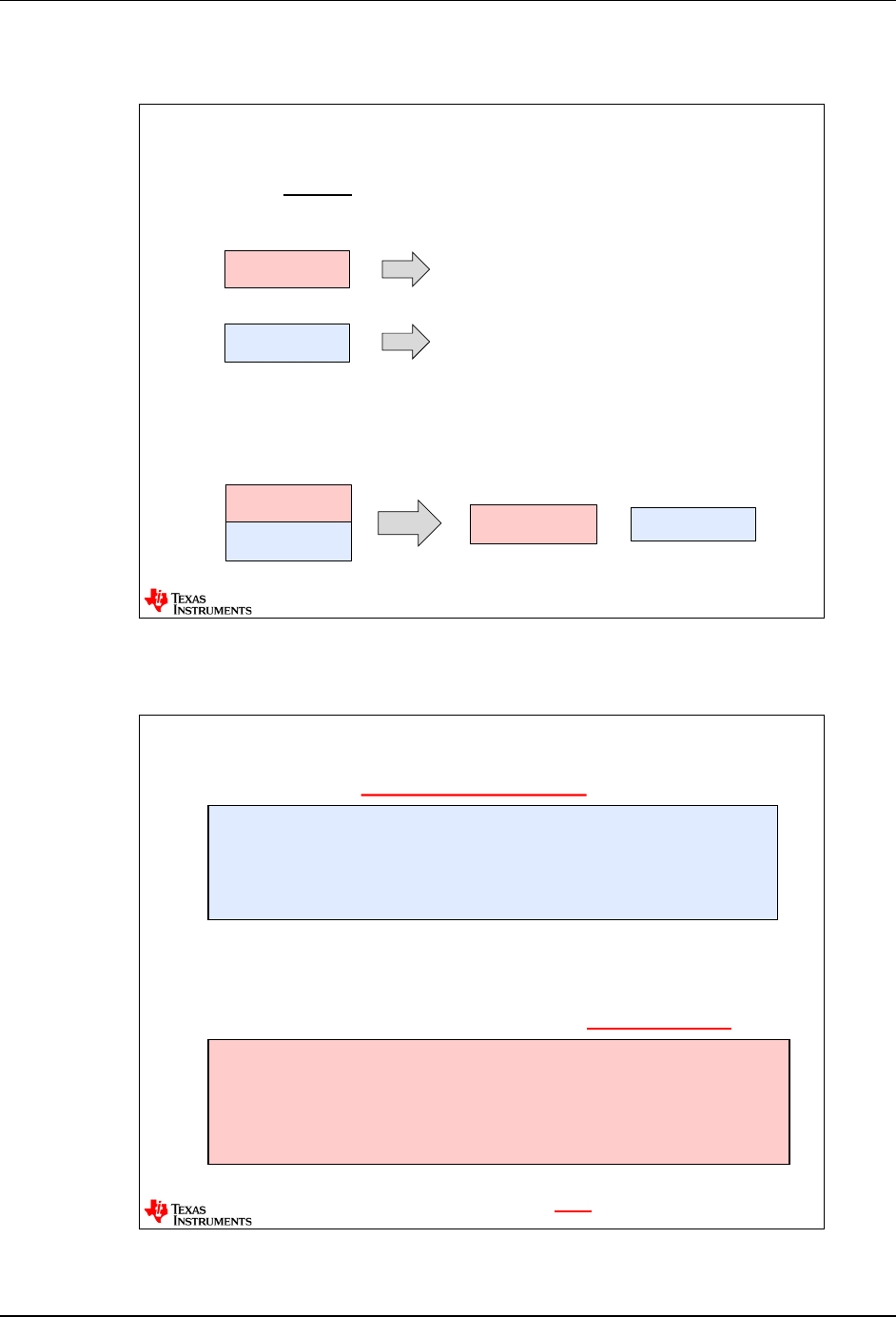

Static vs. Dynamic

TI-RTOS Workshop - Using Dynamic Memory 10 - 3

Static vs. Dynamic

Static vs Dynamic Systems

Link Time:

-Allocate Buffers

Execute:

-Read data

-Process data

-Write data

Allocated at LINK time

+ Easy to manage (less thought/planning)

+ Smaller code size, faster startup

+ Deterministic, atomic (interrupts won’t mess it up)

-Fixed allocation of memory resources

Optimal when most resources needed concurrently

Create:

-Allocate Buffers

Execute:

-R/W & Process

Delete:

-FREE Buffers

Allocated at RUN time

+ Limited resources are SHARED

+ Objects (buffers) can be freed back to the heap

+ Smaller RAM budget due to re-use

-Larger code size, more difficult to manage

-NOT deterministic, NOT atomic

Optimal when multi threads share same resource

or memory needs not known until runtime

SYS/BIOS

allows either

method

Static Memory

Dynamic Memory (HEAP)

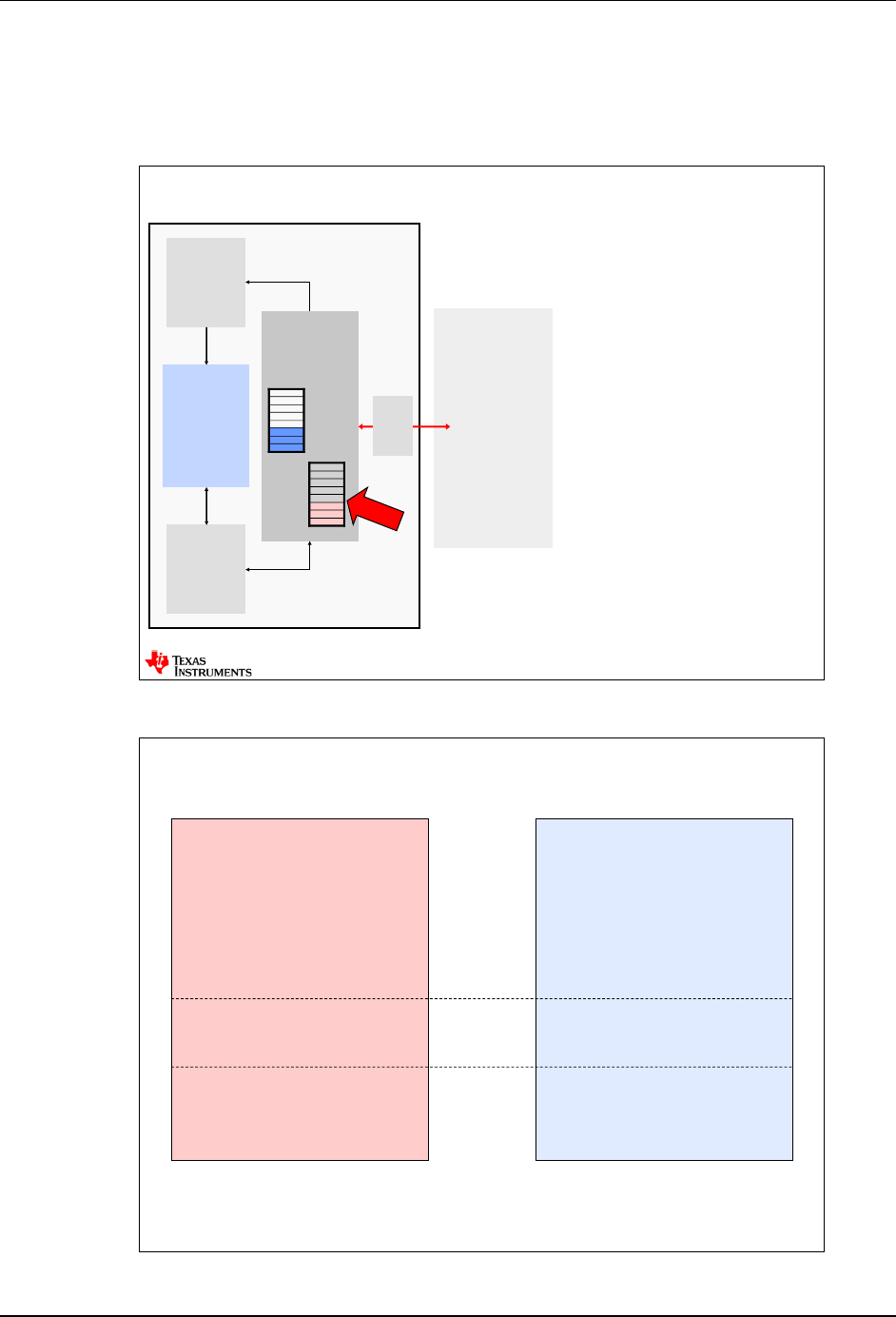

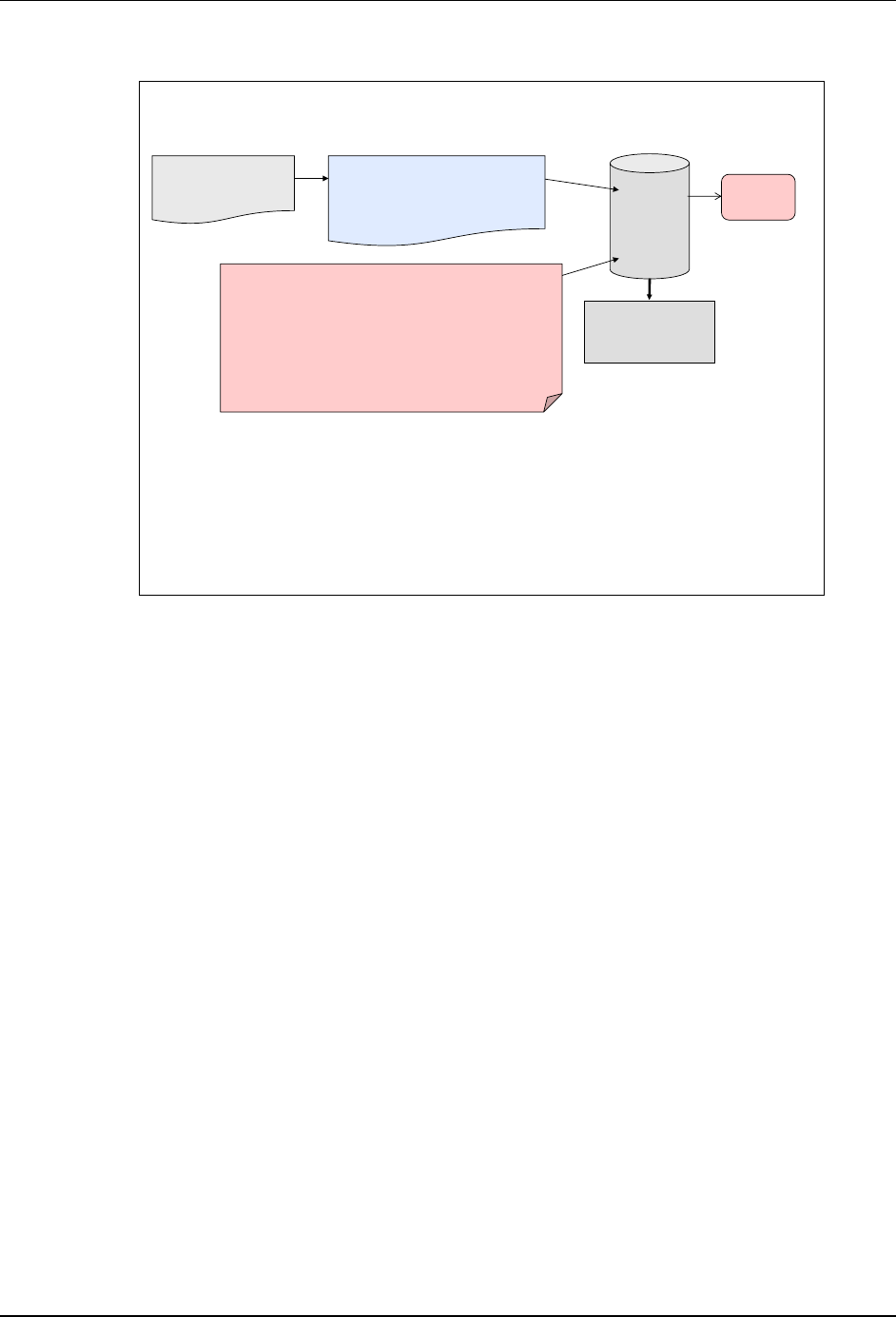

BIOS Runtime Cfg –Dynamic Memory

MAU –Minimum Addressable Unit

•Memory allocation sizes are measured in MAUs

•8 bits: C6000, MSP430, ARM

•16 bits: C28x

Memory Policies –Dynamic or Static?

•Dynamic is the default policy (recommended)

•Static policy can save some code/data memory

•Select via .CFG GUI:

Note: ~5K bytes savings on a C6000

choosing “static only” vs. “dynamic”

Dynamic Memory Concepts

10 - 4 TI-RTOS Workshop - Using Dynamic Memory

Dynamic Memory Concepts

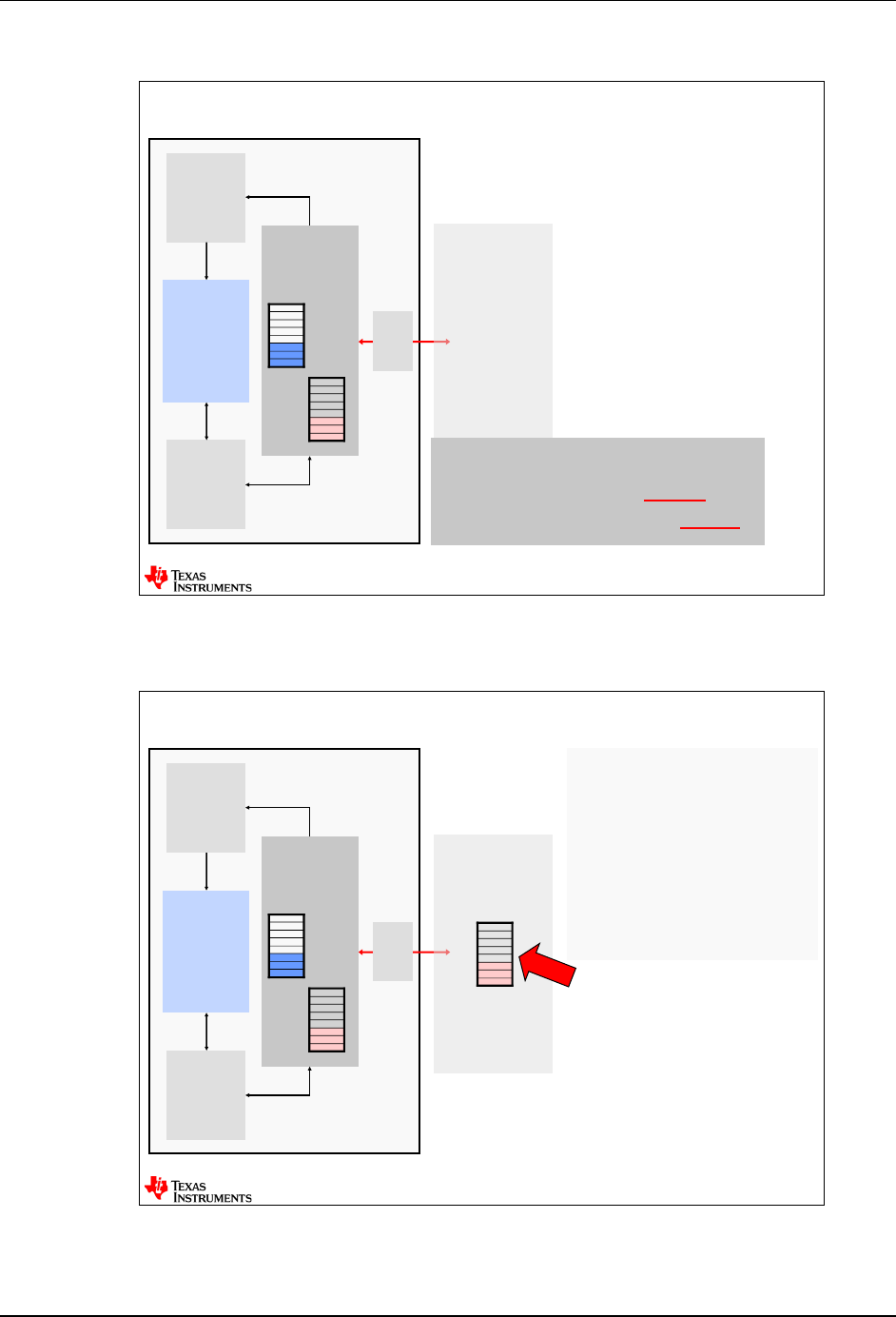

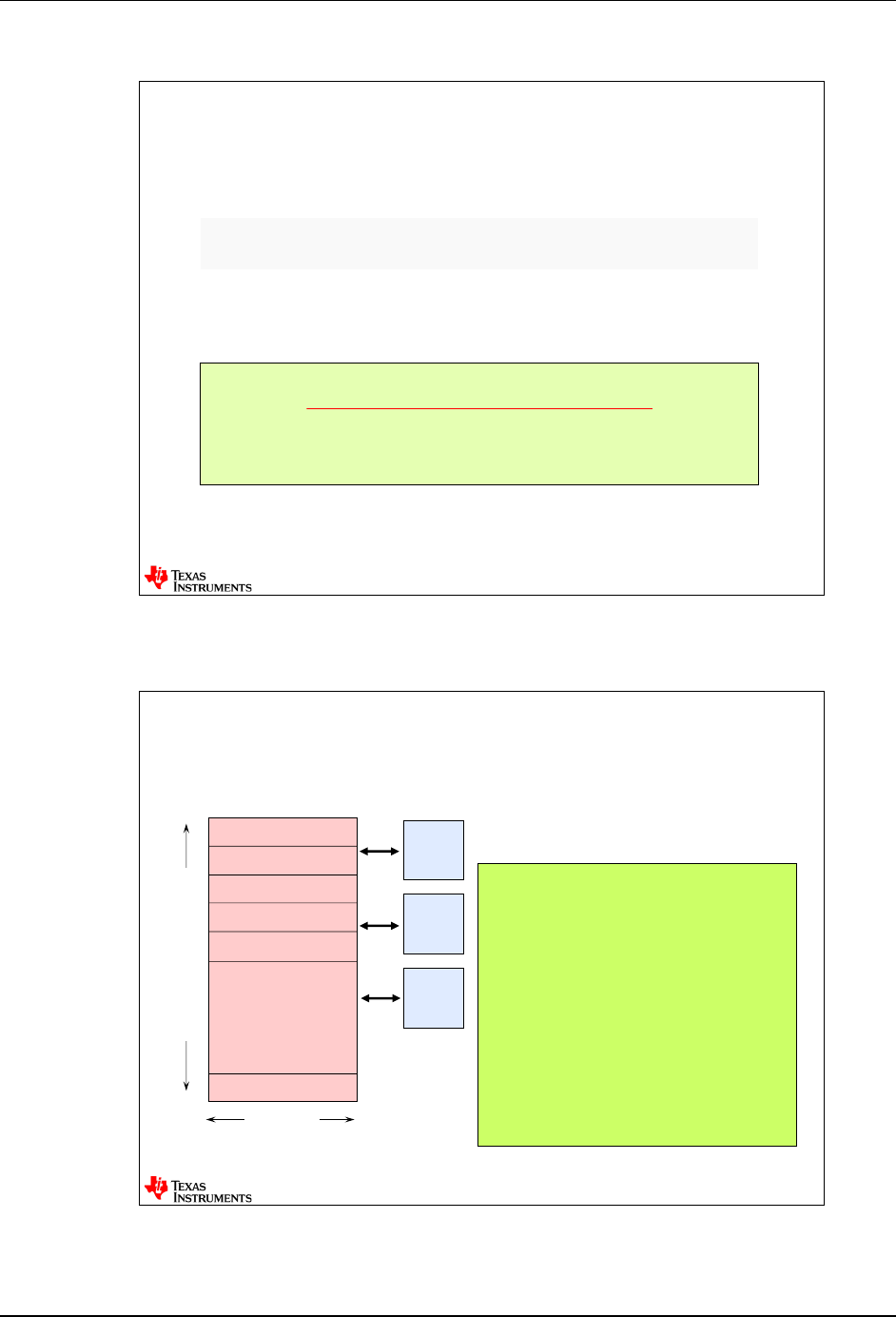

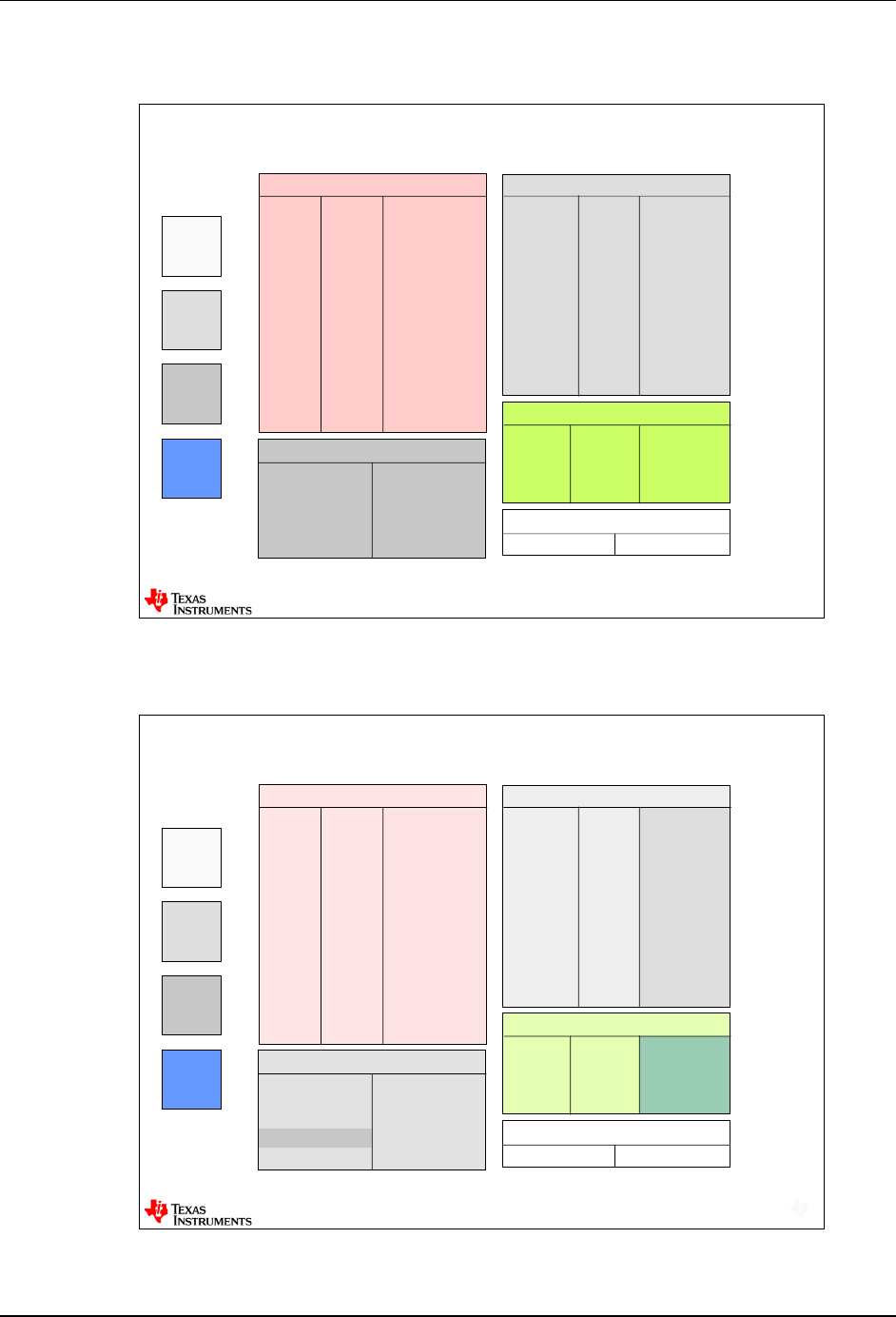

Using Dynamic Memory

External

Memory

Dynamic Memory Usage (Heap)

Internal

SRAM

CPU

Program

Cache

Data

Cache

EMIF

Using Memory Efficiently

Stack

Heap

Common memory reuse

within C language

A Heap (

i.e. system

memory) allocates, then

frees chunks of memory

from a common system

block

Code Example…

Dynamic Example (Heap)

#define SIZE 32

char x[SIZE]; /*allocate*/

char a[SIZE];

x={…}; /*initialize*/

a={…};

filter(…); /*execute*/

“Normal” (static) C Coding

#define SIZE 32

x=malloc(SIZE);

// MAUs

a=malloc(SIZE); // MAUs

x={…};

a={…};

filter(…);

free(x);

free(a);

“Dynamic” C Coding

Create

Execute

Delete

High-performance DSP users have traditionally used static embedded systems

As DSPs and compilers have improved, the benefits of dynamic systems often

allow enhanced flexibility (more threads) at lower costs

Dynamic Memory Concepts

TI-RTOS Workshop - Using Dynamic Memory 10 - 5

Dynamic Memory (Heap)

Internal

SRAM

CPU

Program

Cache

Data

Cache

EMIF

External

Memory

Stack

Heap

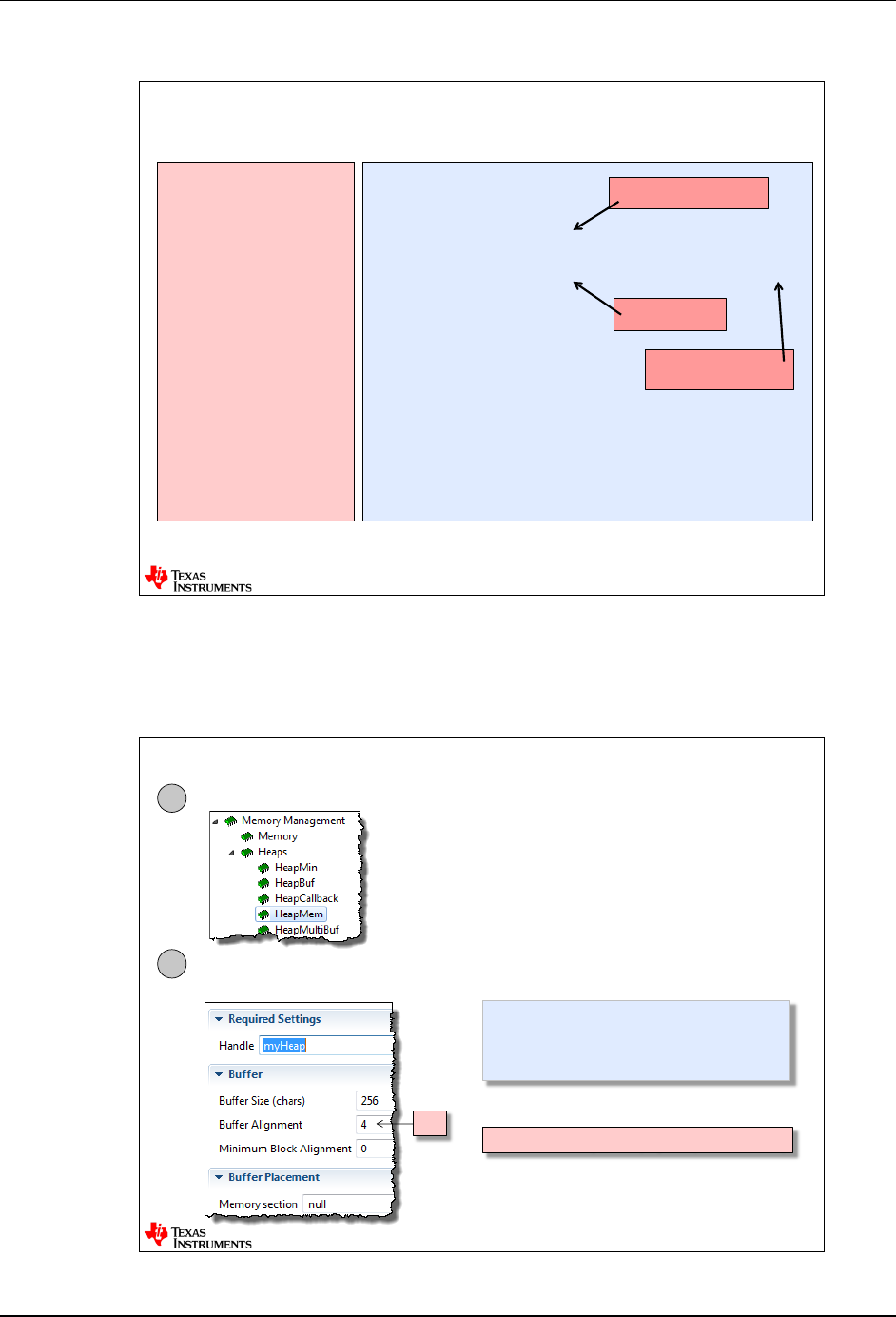

What if I need two heaps?

Say, a big image array off-chip, and

Fast scratch memory heap on-chip?

Using Memory Efficiently

Common memory reuse

within C language

A Heap (i.e. system

memory) allocates, then

frees chunks of memory

from a common system

block

Multiple Heaps

Internal

SRAM

CPU

Program

Cache

Data

Cache

EMIF

External

Memory

Stack

Heap

Heap2

BIOS enables multiple

heaps to be created

Create and name heaps in

.CFG file or via C code

Use Memory_alloc()

function to allocate

memory and specify

which heap

Dynamic Memory Concepts

10 - 6 TI-RTOS Workshop - Using Dynamic Memory

Memory_alloc()

#define SIZE 32

x = Memory_alloc(NULL, SIZE, align, &eb);

a = Memory_alloc(myHeap, SIZE, align, &eb);

x = {…};

a = {…};

filter(…);

Memory_free(NULL,x,SIZE);

Memory_free(myHeap,a,SIZE);

Using Memory functions

#define SIZE 32

x=malloc(SIZE);

a=malloc(SIZE);

x={…};

a={…};

filter(…);

free(a);

free(x);

Standard C syntax

Notes: -malloc(size) API is translated to Memory_alloc(NULL,size,0,&eb) in SYS/BIOS

-Memory_calloc/valloc also available

Default System Heap

Custom heap

Error Block (more

details later)

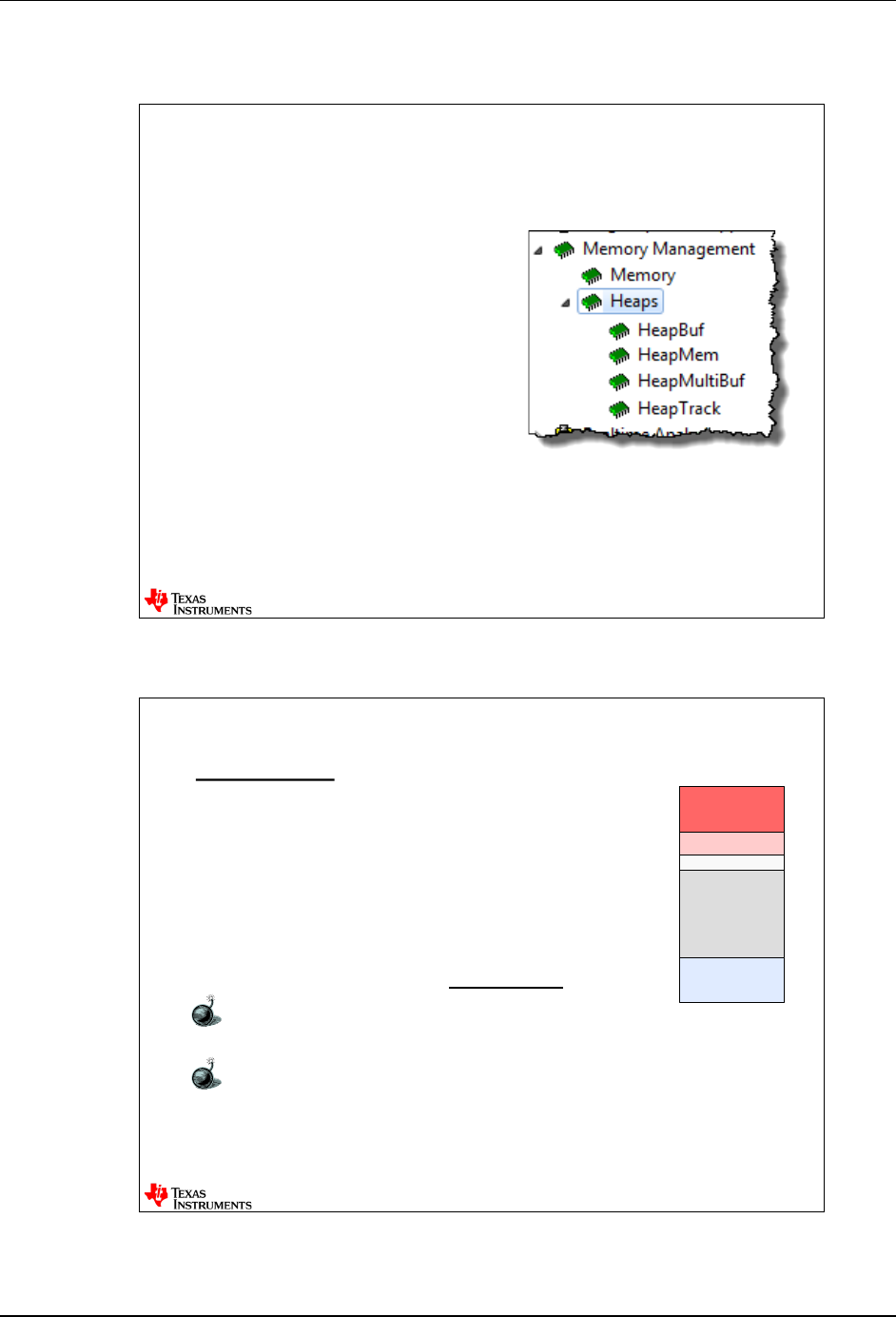

Creating A Heap

Creating A Heap (HeapMem)

1Use HeapMem (Available Products)

2Create HeapMem (myHeap): size, alignment, name

buf1 = Memory_alloc(myHeap, 64, 0, &eb)

HeapMem_Params_init(&prms);

prms.size = 256;

myHeap = HeapMem_create(&prms, &eb);

OR…

Static Dynamic

Usage

2

n

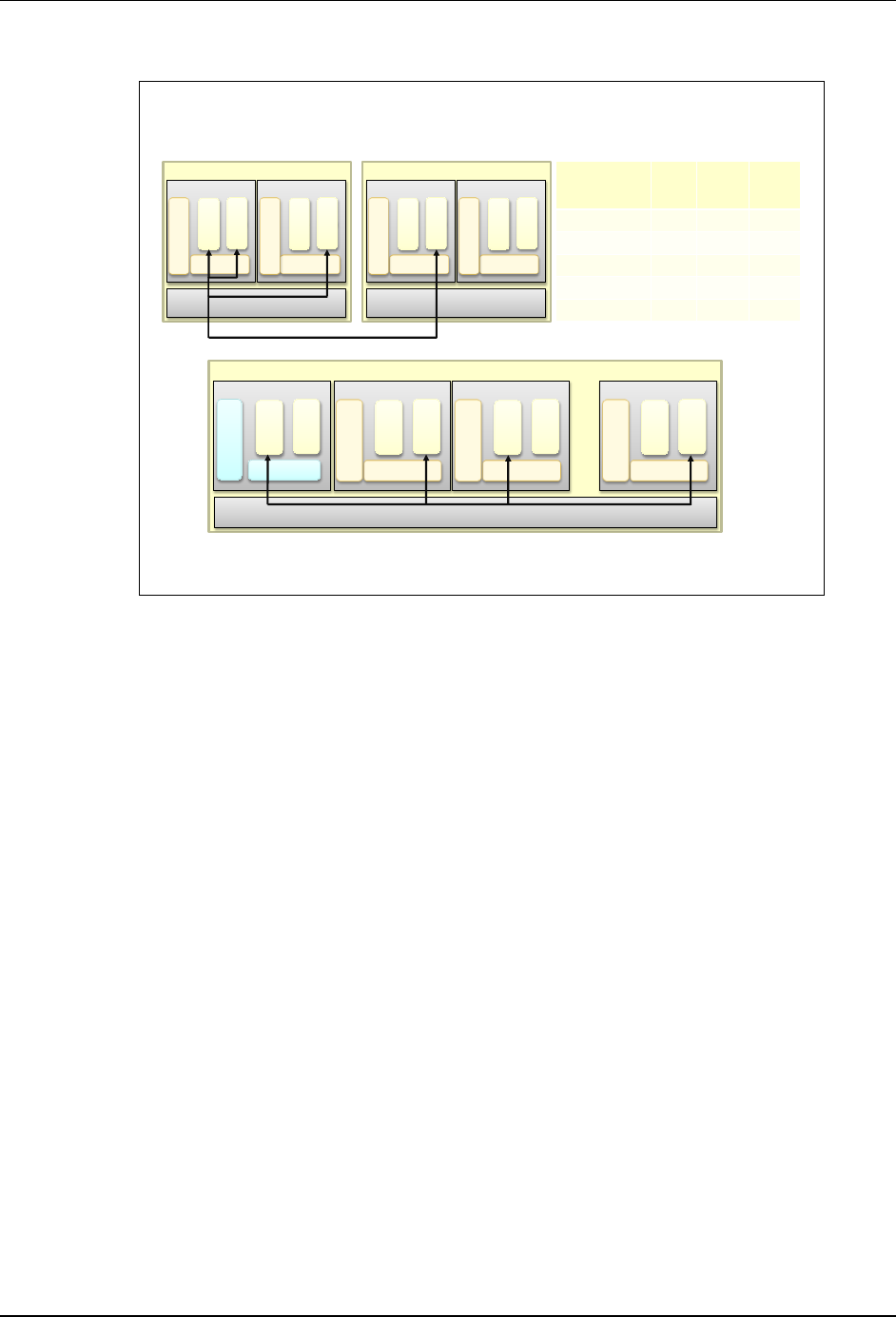

Different Types of Heaps

TI-RTOS Workshop - Using Dynamic Memory 10 - 7

Different Types of Heaps

Heap Types

Users can choose from 3 different types of Heaps:

HeapMem

•Allocate variable-size blocks

•Default system heap type

HeapBuf

•Allocate fixed-size blocks

HeapMultiBuf

•Specify variable-size blocks, but internally,

allocate from a variety of fixed-size blocks

HeapMem

HeapMem

HeapMem

Most flexible –allows allocation of

variable-sized blocks (like malloc())

Ideal when size of memory is not known

until runtime

Creation: .CFG (static) or C code (dynamic)

Like malloc(), there are drawbacks:

NOT Deterministic –Memory Manager traverses

linked list to find blocks

Fragmentation –After frequent allocate/free, fragments occur

Is there a heap type without these drawbacks?

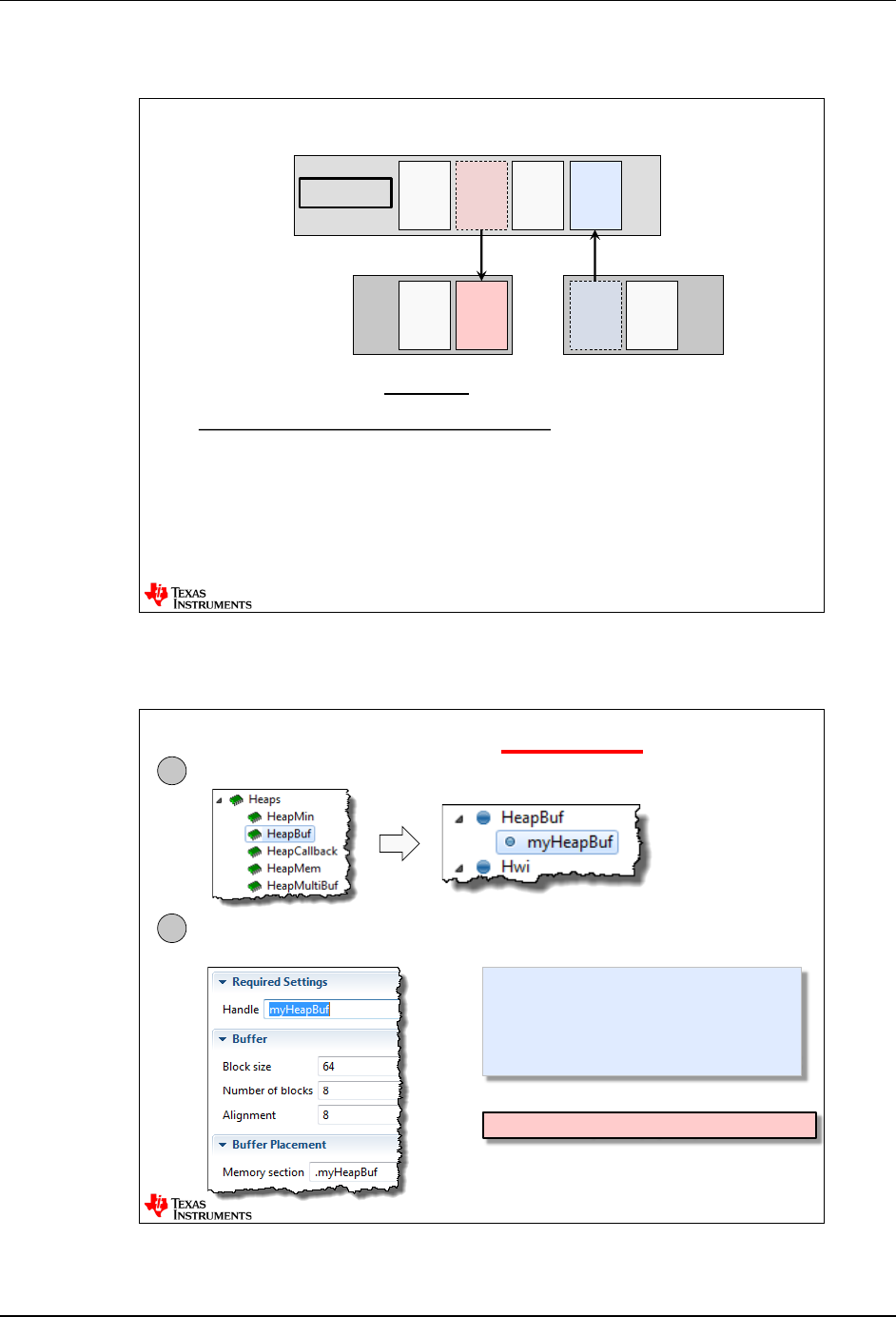

Different Types of Heaps

10 - 8 TI-RTOS Workshop - Using Dynamic Memory

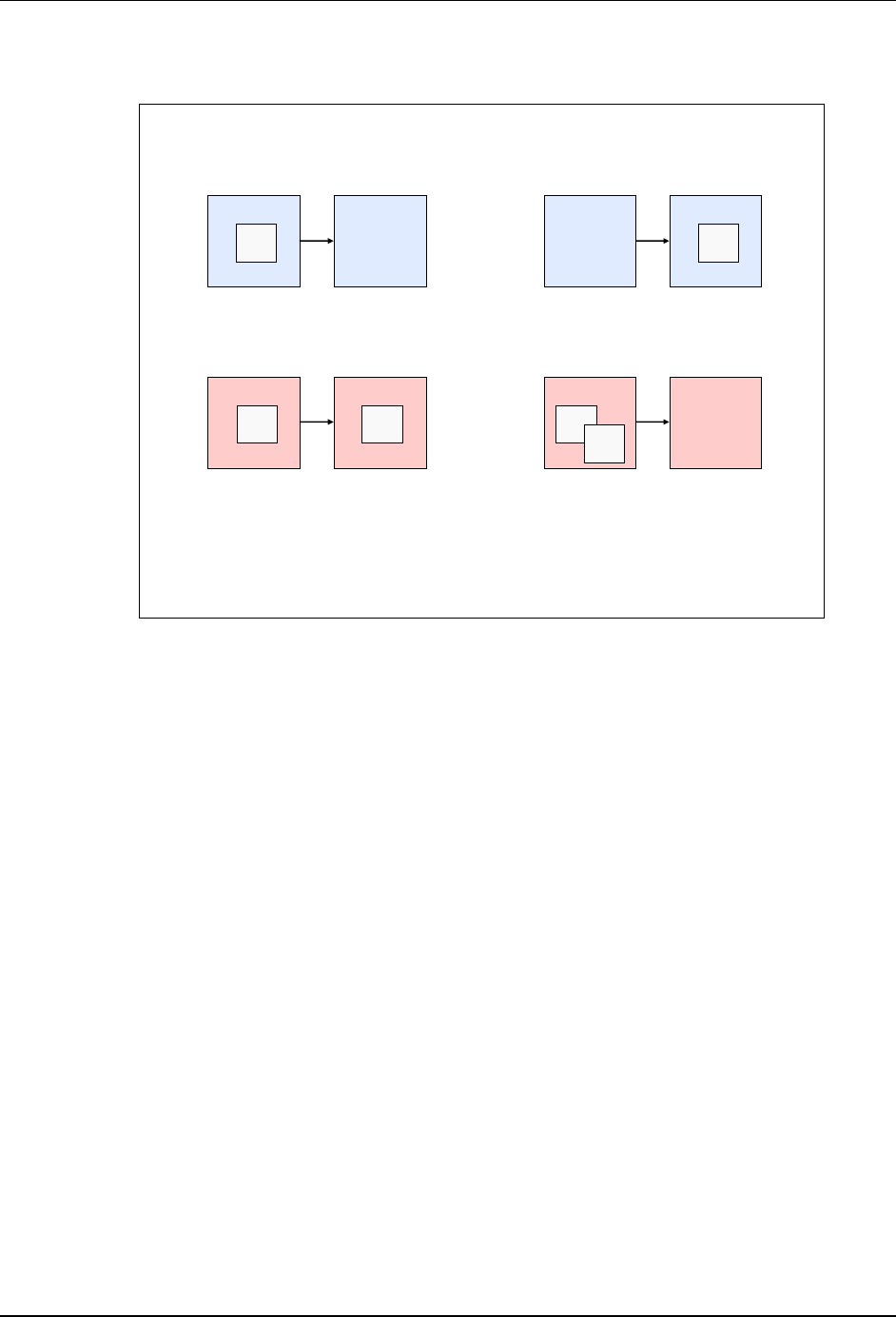

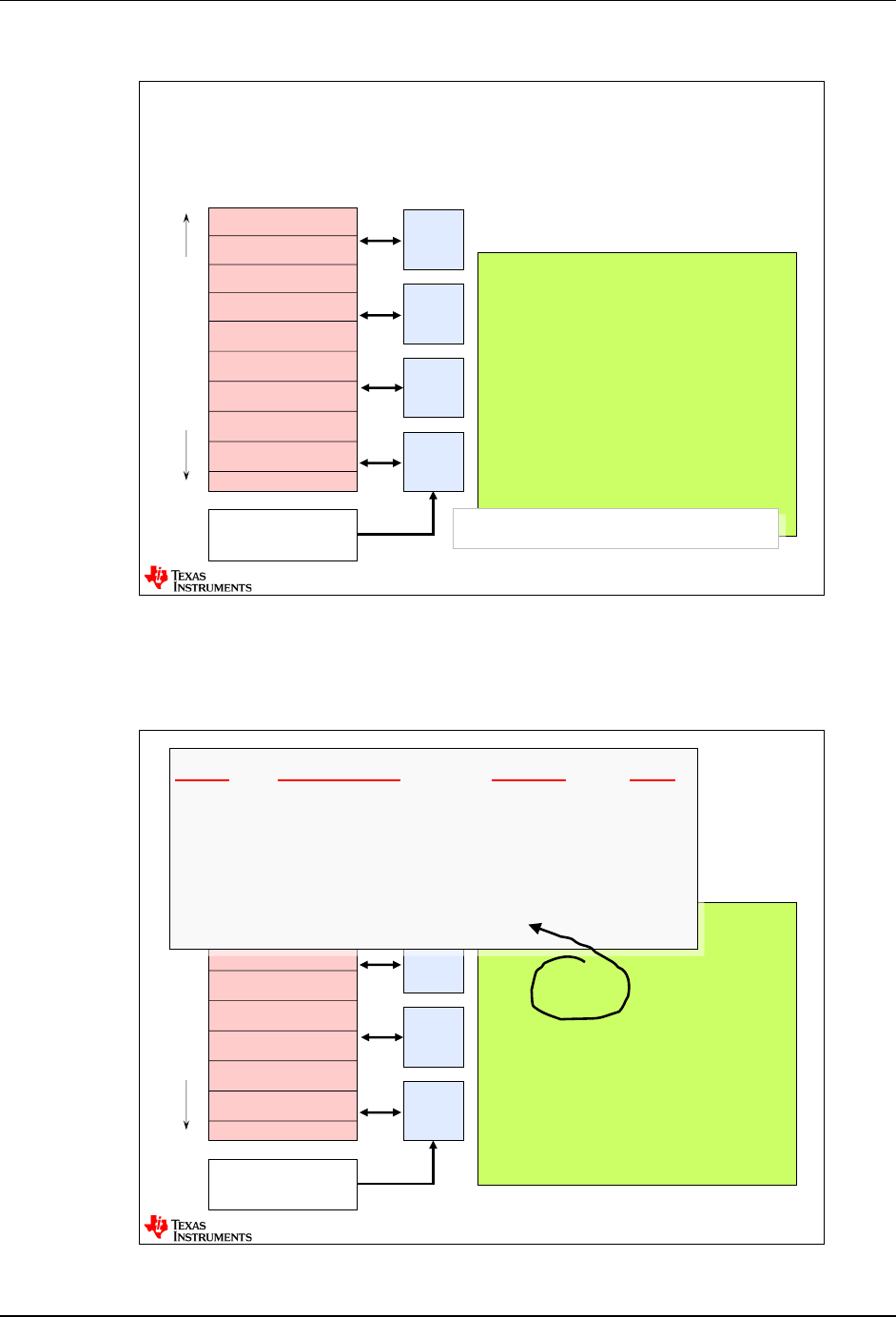

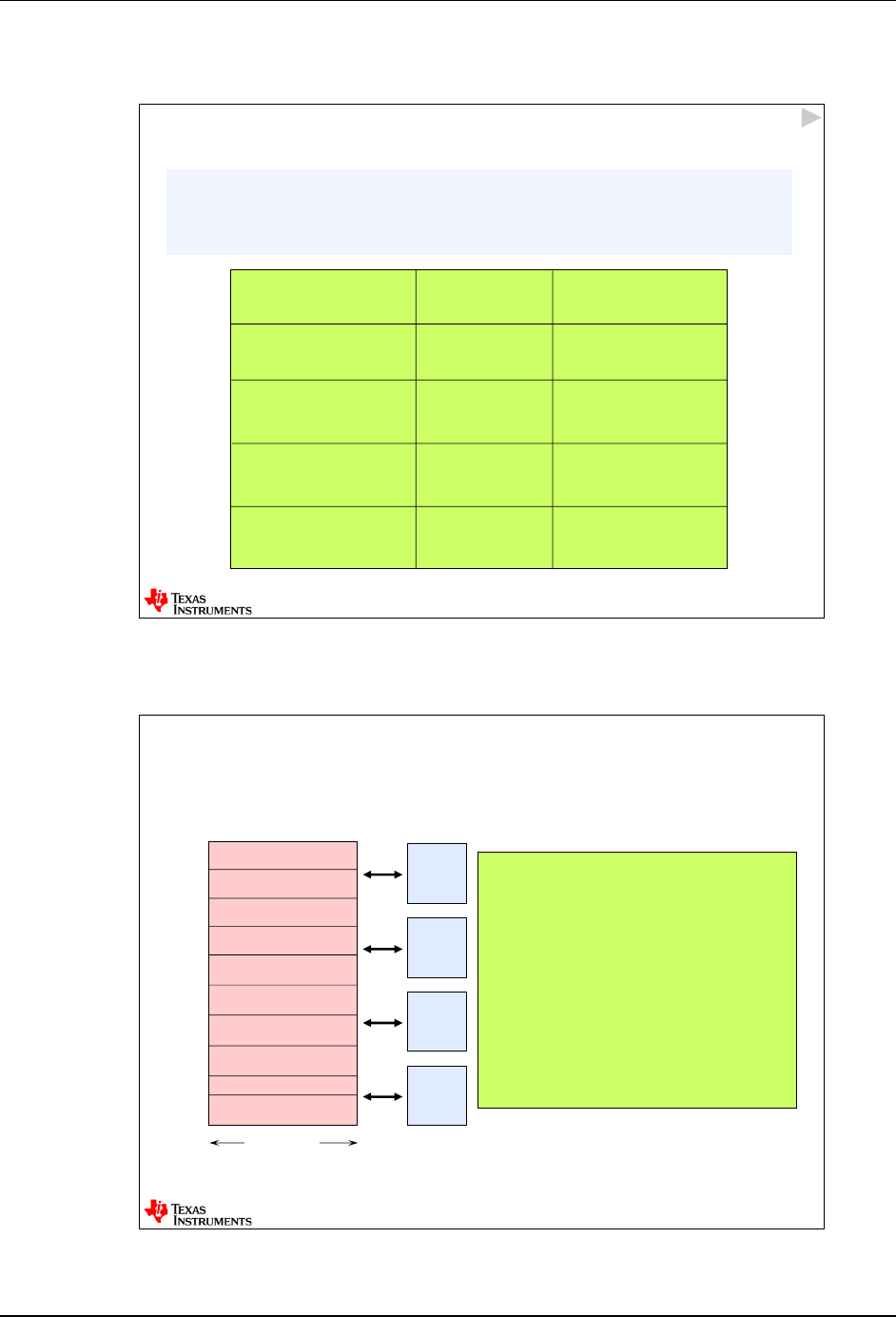

HeapBuf

HeapBuf

Allows allocation of fixed-size blocks (no fragmentation)

Deterministic, no reentrancy problems

Ideal when using a varying number of fixed-size

blocks (e.g. 4-6 buffers of 64 bytes each)

Creation: .CFG (static) or C code (dynamic)

For blockSize=64: Ask for 16, get 64. Ask for 66, get NULL

How do you create a HeapBuf?

BUF BUF BUF BUF

SWI

Memory_alloc()

TSK

Memory_free()

BUF BUF BUF BUF

HeapBuf_create() HeapBuf_delete()

HeapBuf

Creating A HeapBuf

1Use HeapBuf (Available Products)

2Create HeapBuf (myBuf): blk size, # of blocks, name

buf1 = Memory_alloc(myHeapBuf, 64, 0, &eb)

What if I need multiple sizes (16, 32, 128)?

prms.blockSize = 64;

prms.numBlocks = 8;

prms.bufSize = 256;

myHeapBuf = HeapBuf_create(&prms, &eb);

OR…

Static Dynamic

Usage

Different Types of Heaps

TI-RTOS Workshop - Using Dynamic Memory 10 - 9

Multiple HeapBufs

16 16 16 16 16 16 16 16

32 32 32 32

32 32 32 32

128

128

128

128

128

heapBuf1

heapBuf2

heapBuf3

1024 MAUs in 3 HeapBuf’s:

•8 x 16-bytes

•8 x 32-bytes

•5 x 128-bytes

Given this configuration, what happens when we allocate

the 9

th 16-byte location from heapBuf1?

What “mechanism” would you want to exist to avoid the

NULL return pointer?

HeapMultiBuf

HeapMultiBuf

Allows variable-size allocation from a variety of fixed-size blocks

Services requests for ANY memory size, but always returns the

most efficient-sized available block

Can be configured to “block borrow” from the “next size up”

Creation: .CFG (static) or C code (dynamic)

Ask for 17, get 32. Ask for 36, get 128.

16 16 16 16 16 16 16 16

32 32 32 32

32 32 32 32

128

128

128

128

128

1024 MAUs in 3 Buffers:

•8 x 16-byte

•8 x 32-byte

•5 x 128-byte

Different Types of Heaps

10 - 10 TI-RTOS Workshop - Using Dynamic Memory

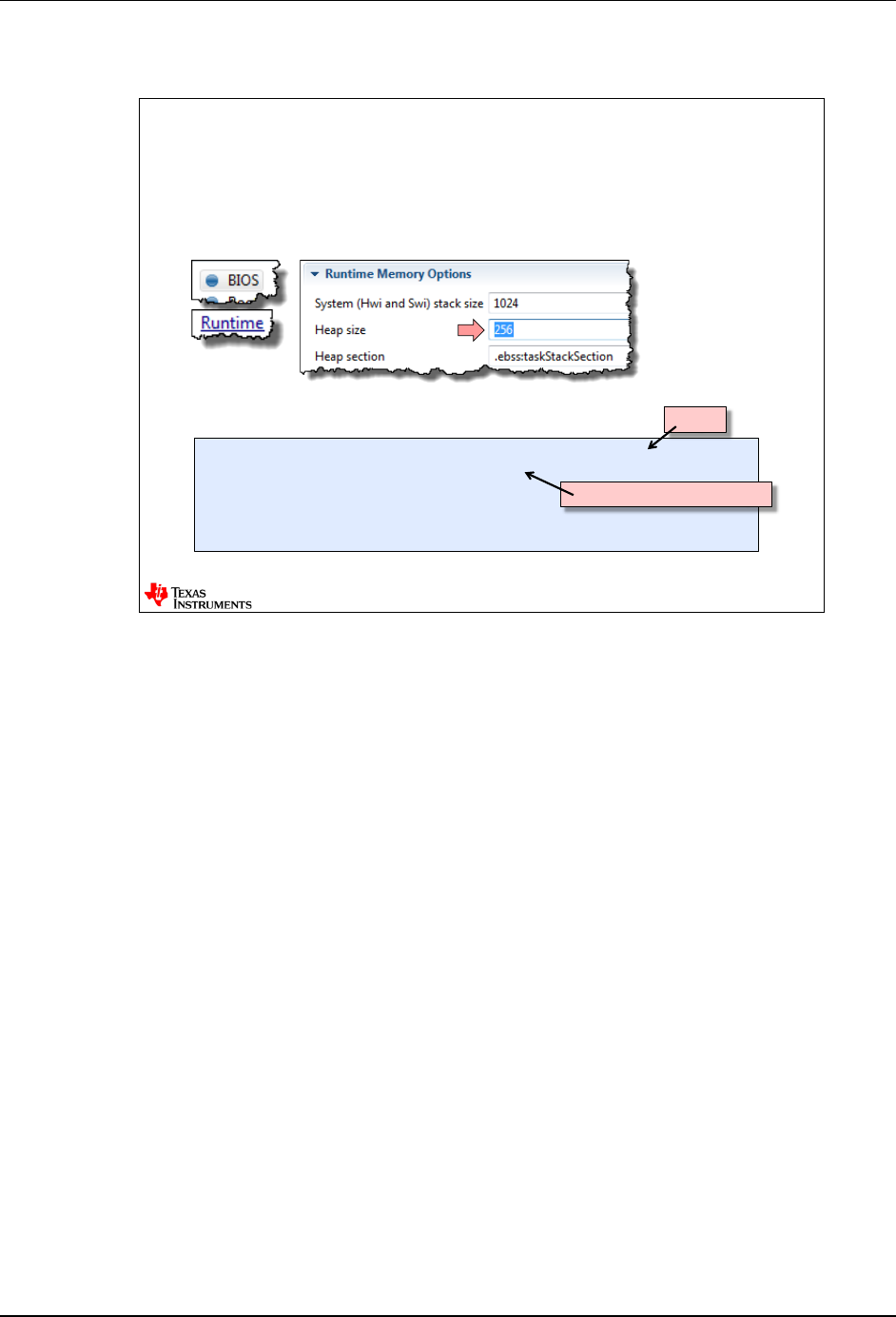

Default System Heap

Default System Heap

BIOS automatically creates a default system heap of type HeapMem

How do you configure the default heap?

In the .CFG GUI, of course:

How to USE this heap?

buf1 = Memory_alloc(NULL, 128, 0, &eb);

myAlgo(buf1);

Memory_free(NULL, buf1, 128);

If NULL, uses default heap

align

Dynamic Module Creation

TI-RTOS Workshop - Using Dynamic Memory 10 - 11

Dynamic Module Creation

#define COUNT 0

Semaphore_Handle hMySem;

hMySem = Semaphore_create(COUNT,NULL,&eb);

Semaphore_post(hMySem);

Semaphore_delete(&hMySem);

Dynamically Creating SYS/BIOS Objects

Module_create

Allocates memory for object out of heap

Returns a Module_Handle to the created object

Module_delete

Frees the object’s memory

Example: Semaphore creation/deletion:

Hwi

Swi

Task

Semaphore

Stream

Mailbox

Timer

Clock

List

Event

Gate

C

X

D

Note: always check return value of _create APIs !

Modules

params

Example –Dynamic Task API

Task_Handle hMyTsk;

Task_Params taskParams;

Task_Params_init(&taskParams);

taskParams.priority = 3;

hMyTsk = Task_create(myCode,&taskParams,&eb);

// “MyTsk” now active w/priority = 3 ...

Task_delete(&hMyTsk);

C

X

D

taskParams includes: heap location, priority, stack ptr/size, environment ptr, name

Dynamic Module Creation

10 - 12 TI-RTOS Workshop - Using Dynamic Memory

What is Error Block ?

buf1 = Memory_alloc (myBuf, 64, 0, &eb)Error_Block eb;

Error_init (&eb);

Setup Code

Most SYS/BIOS APIs that expect an error block also return

a handle to the created object or allocated memory

If NULL is passed instead of an initialized Error_Block and

an error occurs, the application aborts and the error can be

output using System_printf().

This may be the best behavior in systems where an error is

fatal and you do not want to do any error checking

The main advantage of passing and testing Error_block is

that your program controls when it aborts.

Typically, systems pass Error_block and check resource

pointer to see if it is NULL, then make a decision…

Usage

Can check Error_Block using: Error_check()

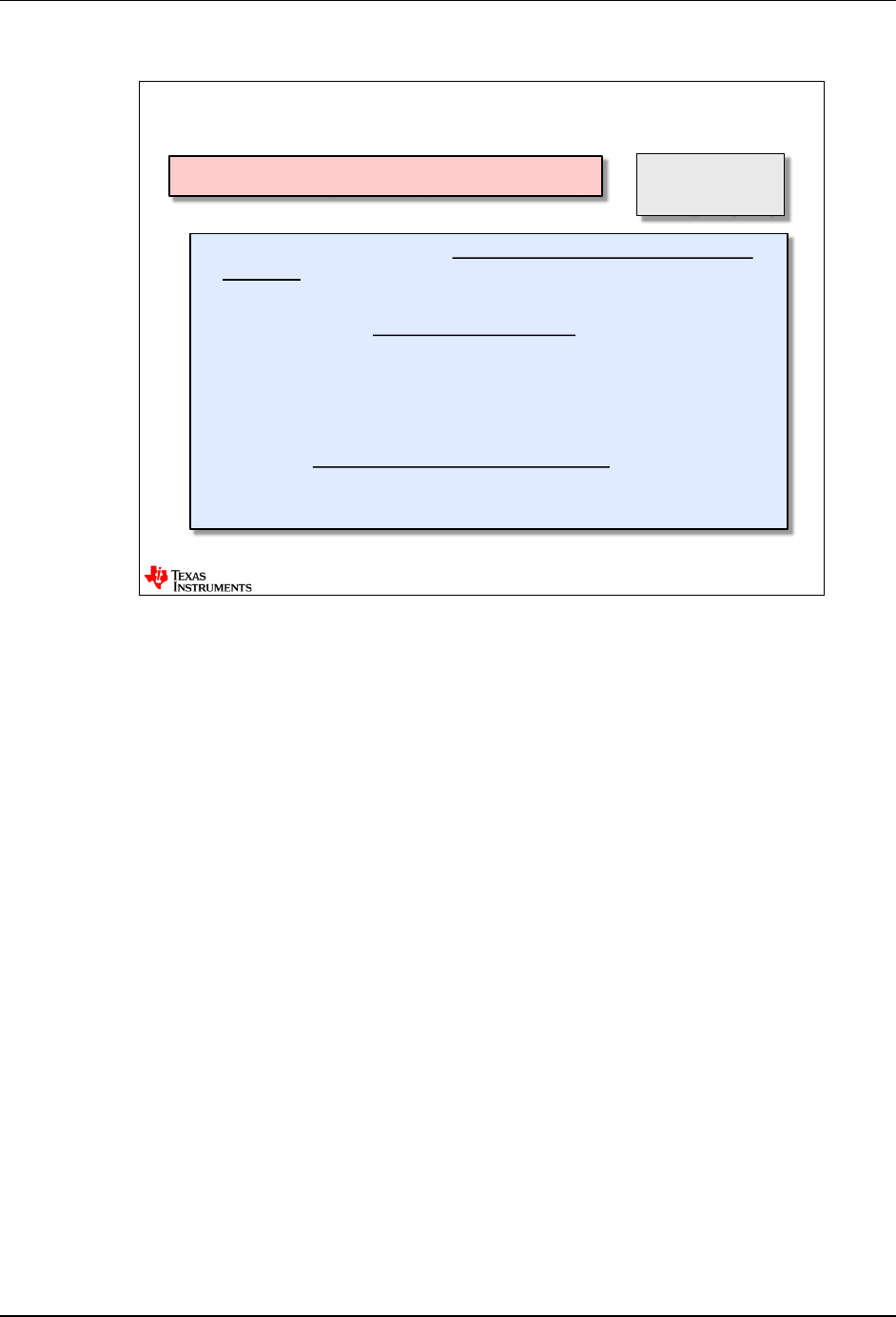

Custom Section Placement

TI-RTOS Workshop - Using Dynamic Memory 10 - 13

Custom Section Placement

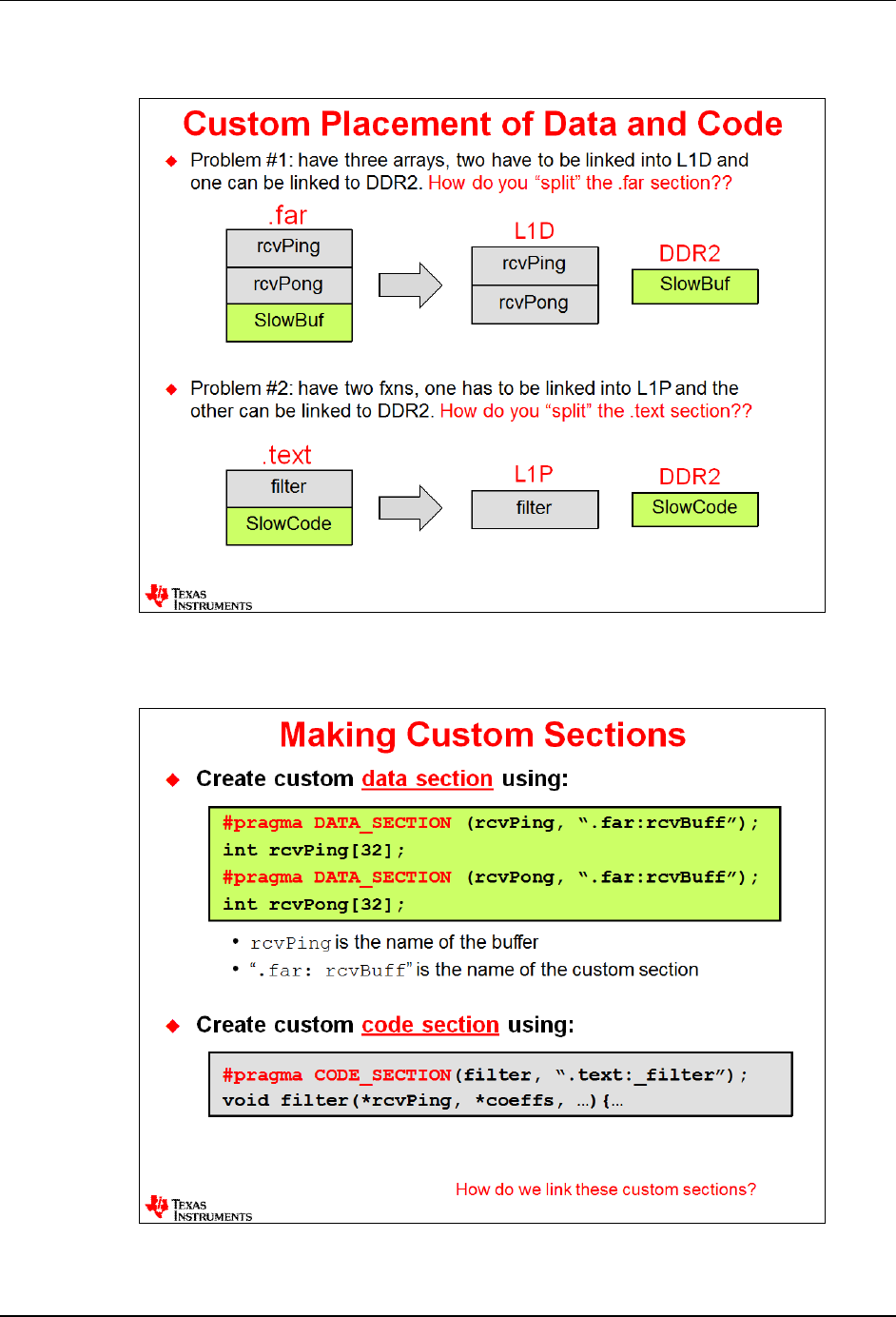

Custom Placement of Data and Code

Problem #1: You have a function or buffer that you want to

place at a specific address in the memory map. How is this

accomplished?

myFxn

myBuffer

.myCode

Mem1

Problem #2: have two buffers, you want one to be linked at Ram1

and the other at Ram2. How do you “split” the .bss (compiler’s

default) section??

buf1

buf2

.bss

buf1 buf2

Ram1 Ram2

.myBuf

Mem2

Making Custom Sections

#pragma CODE_SECTION (myFxn, “.myCode”);

void myFxn(*ptr, *ptr2, …){ };

#pragma DATA_SECTION (myBuffer, “.myBuf”);

int16_t myBuffer[32];

Create custom code & data sections using:

#pragma DATA_SECTION(buf1, “.bss:buf1”);

int16_t buf1[8];

#pragma DATA_SECTION(buf2, “.bss:buf2”);

int16_t buf2[8];

Split default compiler section using SUB sections:

How do you LINK these custom sections?

•

myFxn & myBuffer is the name of the fxn/var

•

“.myCode & .myBuf” are the names of the custom sections

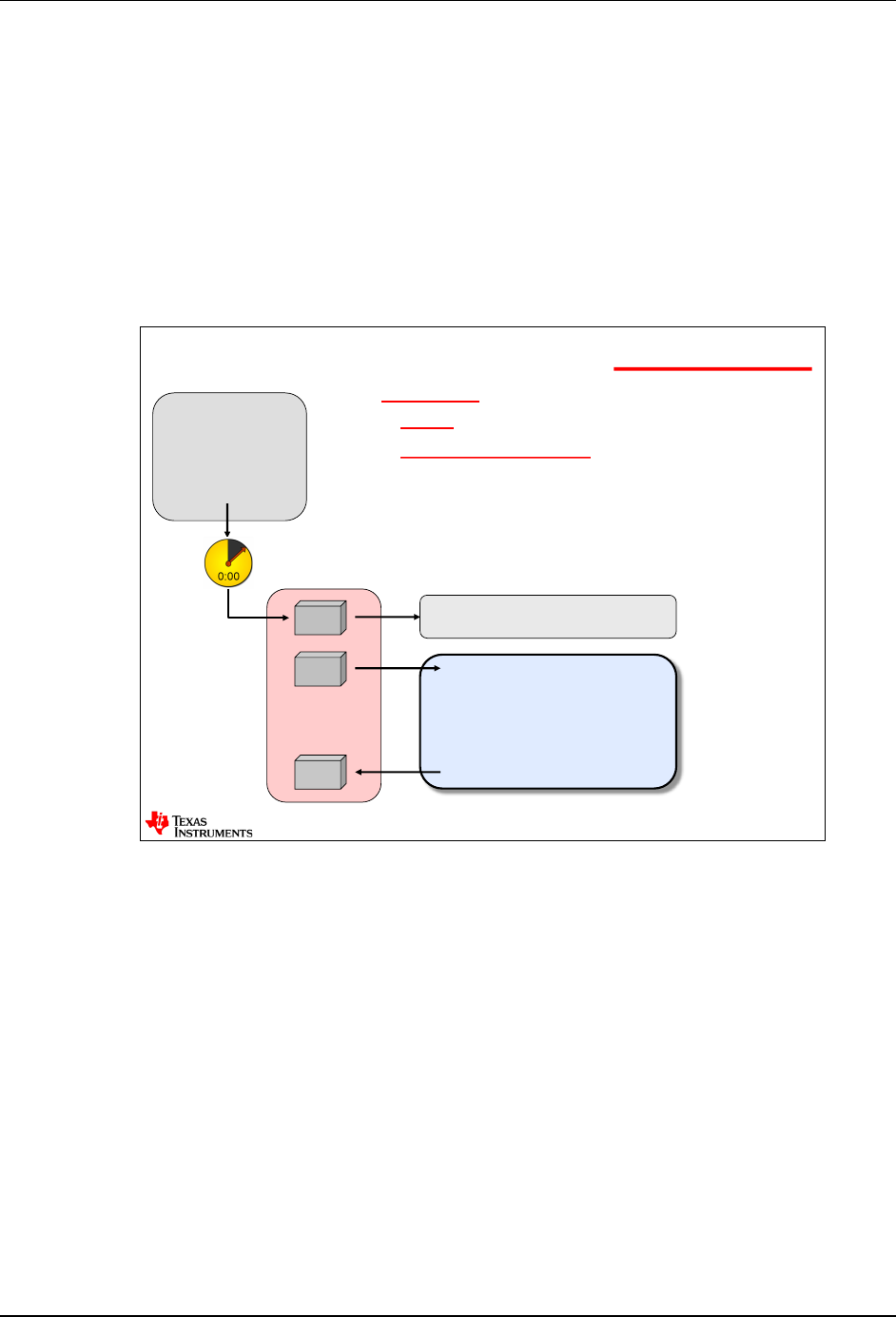

Custom Section Placement

10 - 14 TI-RTOS Workshop - Using Dynamic Memory

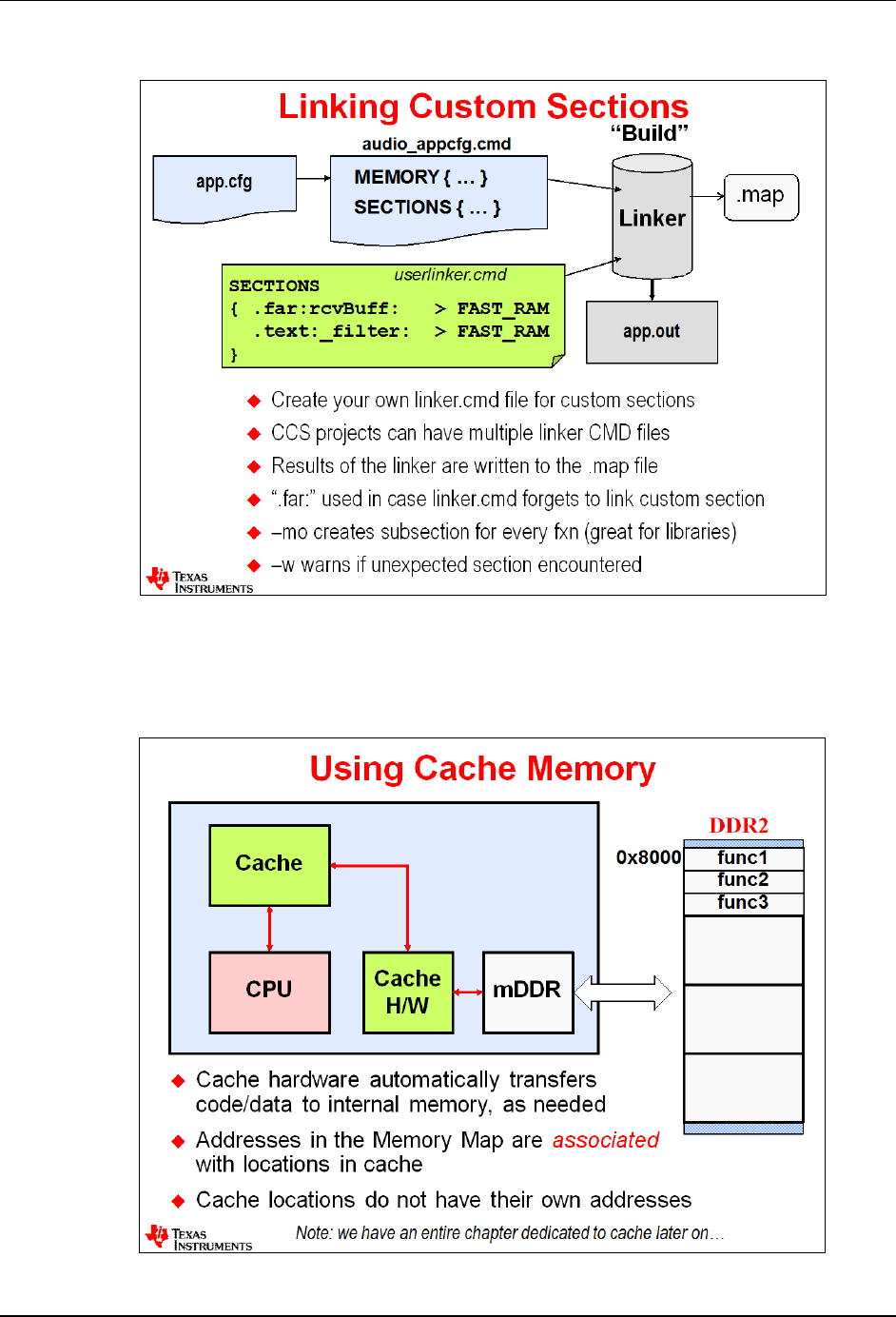

Linking Custom Sections

app.cfg

Linker

app.out

Create your own linker.cmd file for custom sections

CCS projects can have multiple linker CMD files

May need to create custom MEMORY segments also (device-specific)

“.bss:” used as protection against custom section not being linked

–w warns if unexpected section encountered

“Build”

SECTIONS

{ .myCode: > Mem1

.myBuf: > Mem2

.bss:buf1 > Ram1

.bss:buf2 > Ram2

}

M EMORY { … }

SECTIONS { … }

app.cmd

.map

userlinker.cmd

Lab 10: Using Dynamic Memory

TI-RTOS Workshop - Using Dynamic Memory 10 - 15

Lab 10: Using Dynamic Memory

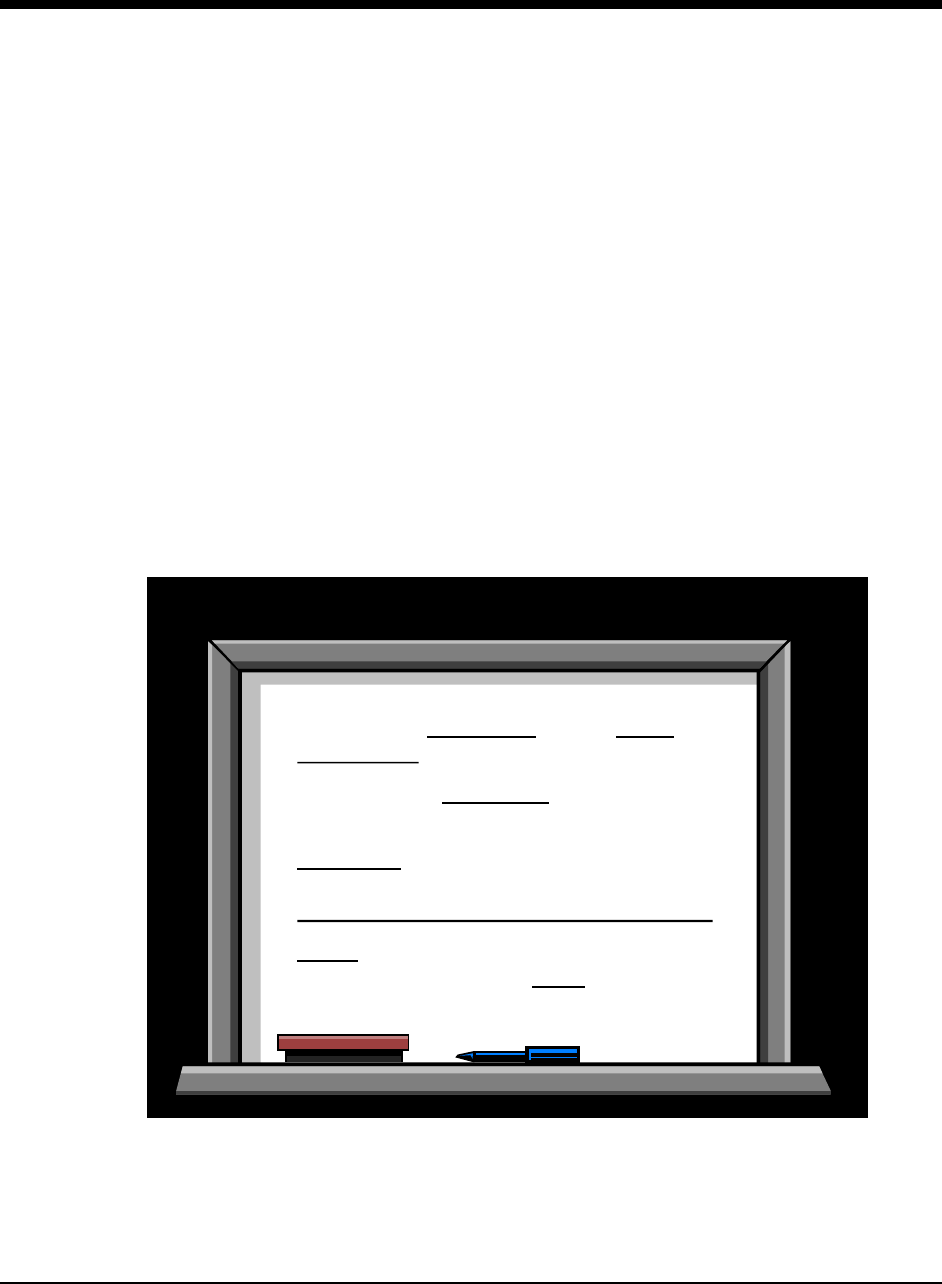

You might notice this system block diagram looks the same as what we used back in Lab 8 –

that’s because it IS.

We’ll have the same objects and events, it’s just that we will create the objects dynamically

instead of statically.

In this lab, you will delete the current STATIC configuration of the Task and Semaphore and

create them dynamically. Then, if your LED blinks once again, you were successful.

Lab 10 –Creating Task/Sem Dynamically

main() {

init_hw();

Timer (500ms)

BIOS_start();

}

main.c

Hwi

Scheduler

Idle

Semaphore_post(LedSem);

Procedure

•Import archived (.zip) project (from Task lab)

•Delete Task/Sem objects (for ledToggle)

•Write code to create Task/Sem Dynamically

•Build, “Play ”, Debug

•Use ROV/UIA to debug/analyze

Time: 30 min

Hwi ISR

ledToggle() {

while(1) {

Semaphore_pend(LedSem);

Toggle_LED;

}

}

Task

ledToggleTas k

Lab 10 – Procedure – Using Dynamic Task/Sem

10 - 16 TI-RTOS Workshop - Using Dynamic Memory

Lab 10 – Procedure – Using Dynamic Task/Sem

In this lab, you will import the solution for the Task lab from before and modify it by DELETING

the static declaration of the Task and Semaphore in the .cfg file and then add code to create

them DYNAMICALLY in main().

Import Project

1. Open CCS and make sure all existing projects are closed.

► Close any open projects (right-click Close Project) before moving on. With many main.c

and app.cfg files floating around, it might be easy to get confused about WHICH file you are

editing.

► Also, make sure all file windows are closed.

2. Import existing project from \Lab10.

Just like last time, the author has already created a project for you and it’s contained in an

archived .zip file in your lab folder.

Import the following archive from your /Lab_10 folder:

Lab_10_TARGET_STARTER_blink_Mem.zip

► Click Finish.

The project “blink_TARGET_MEM” should now be sitting in your Project Explorer. This is the

SOLUTION of the earlier Task lab with a few modifications explained later.

► Expand the project to make sure the contents look correct.

3. Build, load and run the project to make sure it works properly.

We want to make sure the imported project runs fine before moving on. Because this is the

solution from the previous lab, well, it should build and run.

► Build – fix errors.

► Then run it and make sure it works. If all is well, move on to the next step…

If you’re having any difficulties, ask a neighbor for help…

Lab 10 – Procedure – Using Dynamic Task/Sem

TI-RTOS Workshop - Using Dynamic Memory 10 - 17

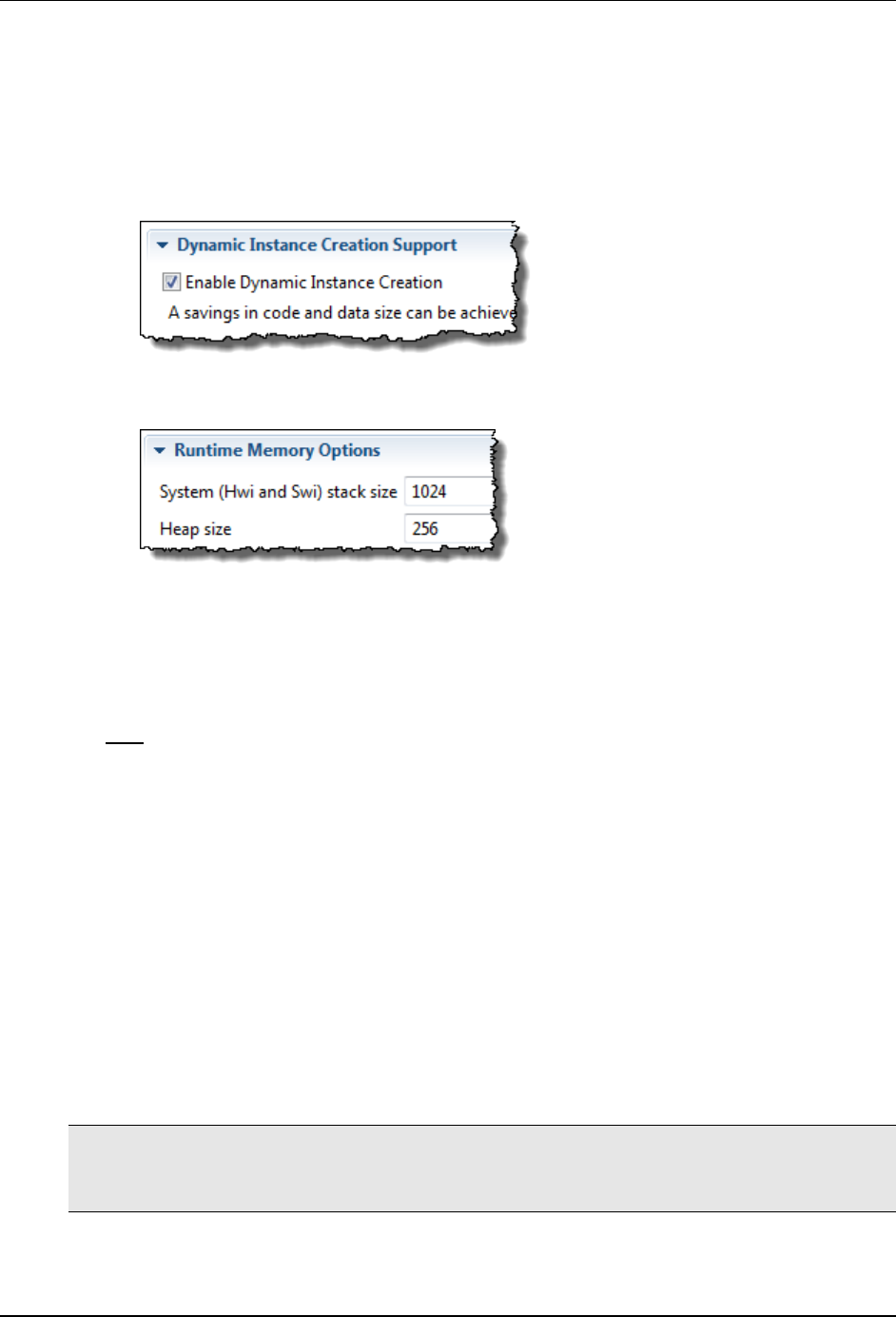

Check Dynamic Memory Settings

4. Open BIOS

Runtime and check settings.

► Open app.cfg and click on BIOS

Runtime.

► Make sure the “Enable Dynamic Instance Creation” checkbox is checked (it should already

be checked):

► Check the Runtime Memory Options and make sure the settings below are set properly for

stack and heap sizes.

We need SOME heap to create the Semaphore and Task out of, so 256 is a decent number

to start with. We will see if it is large enough as we go along.

► Save app.cfg.

The author also wants you to know that there is duplication of these numbers throughout the

.cfg file which causes some confusion – especially for new users. First, BIOS

Runtime is

THE place to change the stack and heap sizes.

Other areas of the app.cfg file are “followers” of these numbers – they reflect these

settings. Sometimes they are displayed correctly in other “modules” and some show “zero”.

No worries, just use the BIOS

Runtime numbers and ignore all the rest.

But, you need to see for yourself that these numbers actually show up in four places in the

app.cfg file. Of course, BIOS

Runtime is the first and ONLY place you should use.

► However, click on the following modules and see where these numbers show up (don’t

modify any numbers – just click and look):

• Hwi

• Memory

• Program

Yes, this can be confusing, but now you know. Just use BIOS

Runtime and ignore the other

locations for these settings.

Hint: If you change the stack or heap sizes in any of these other windows, it may result in a

BIOS CFG warning of some kind. So, the author will say this one more time – ONLY use

BIOS Runtime to change stack and heap sizes.

Lab 10 – Procedure – Using Dynamic Task/Sem

10 - 18 TI-RTOS Workshop - Using Dynamic Memory

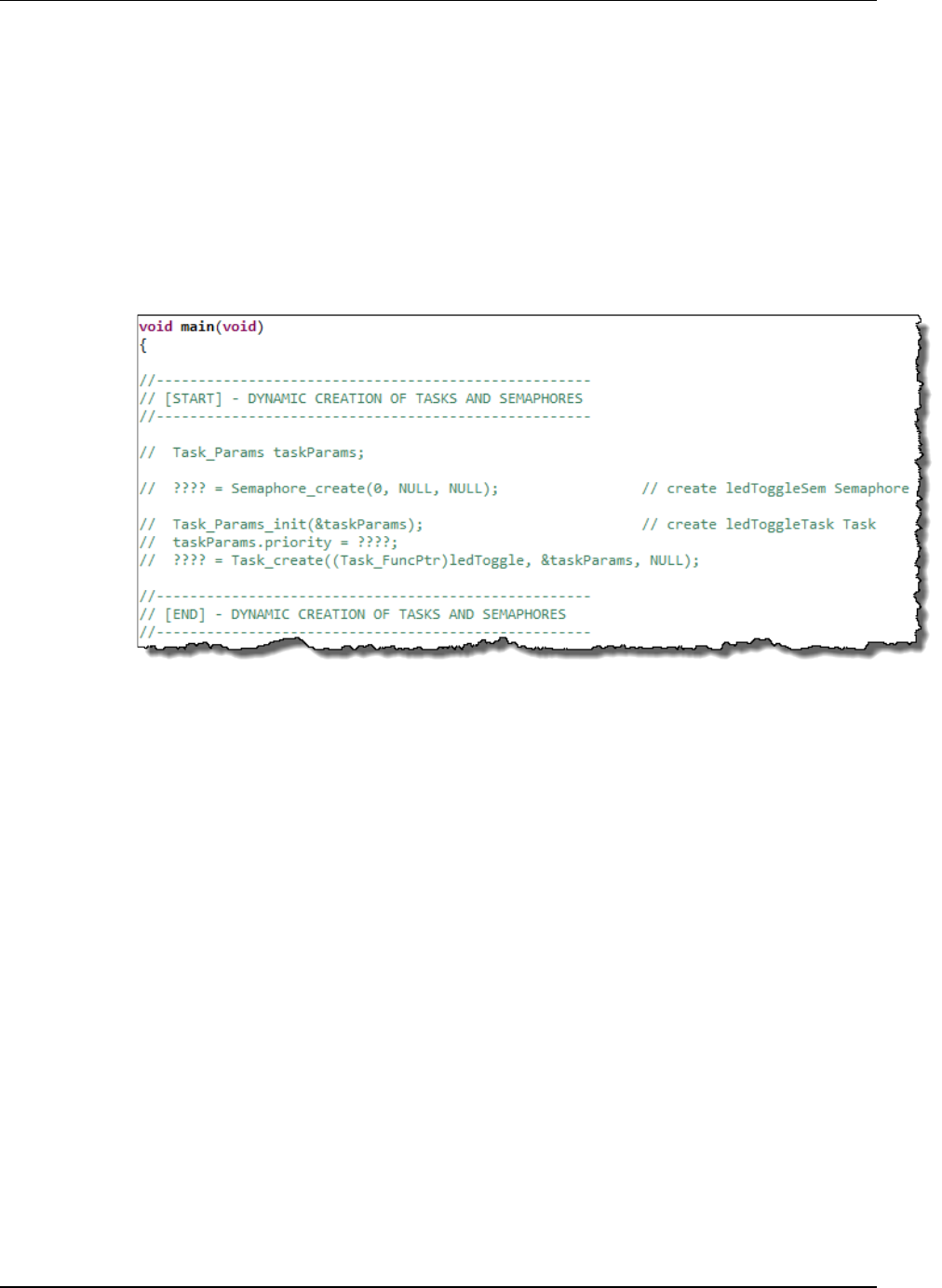

Inspect New Code in main()

5. Open main.c and inspect the new code.

The author has already written some code for you in main(). Why? Well, instead of making

you type the code and make spelling or syntax errors and deal with the build errors, it is just

easier to provide commented code and have you uncomment it. Plus, when you create the

Task dynamically, the casting of the Task function pointer is a bit odd.

► Open main.c and find main().

► Inspect the new code that creates the Semaphore and Task dynamically (DO NOT

UNCOMMENT ANYTHING YET):

As you go through this lab, you will be uncommenting pieces of this code to create the

Semaphore and Task dynamically and you’ll have to fill in the “????” with the proper names

or values. Hey, we couldn’t do ALL the work for you.

Also notice in the global variable declaration area that there are two handles for the

Sempahore and Task also provided.

In order to use functions like Semaphore_create() and Task_create(), you will need to

uncomment the necessary #include for the header files also.

Delete the Semaphore and Add It Dynamically

6. Get rid of the Semaphore in app.cfg.

► Remove ledToggleSem from the app.cfg file and save app.cfg.

7. Uncomment the two lines of code associated with creating ledToggleSem dynamically.

► In the global declaration area above main(), uncomment the line associated with the

handle for the Semaphore and name the Semaphore ledToggleSem.

► In main(), uncomment the line of code for Semaphore_create() and use the same

name for the Semaphore.

► In the #include section near the top of main.c, uncomment the #include for

Semaphore.h.

► Save main.c.

Lab 10 – Procedure – Using Dynamic Task/Sem

TI-RTOS Workshop - Using Dynamic Memory 10 - 19

Build, Load, Run, Verify

8. Build, load and run your code.

► Build the new code, load it and run it for 5 blinks.

Is it working? If not, it is debug time. If it is working, you can move on…

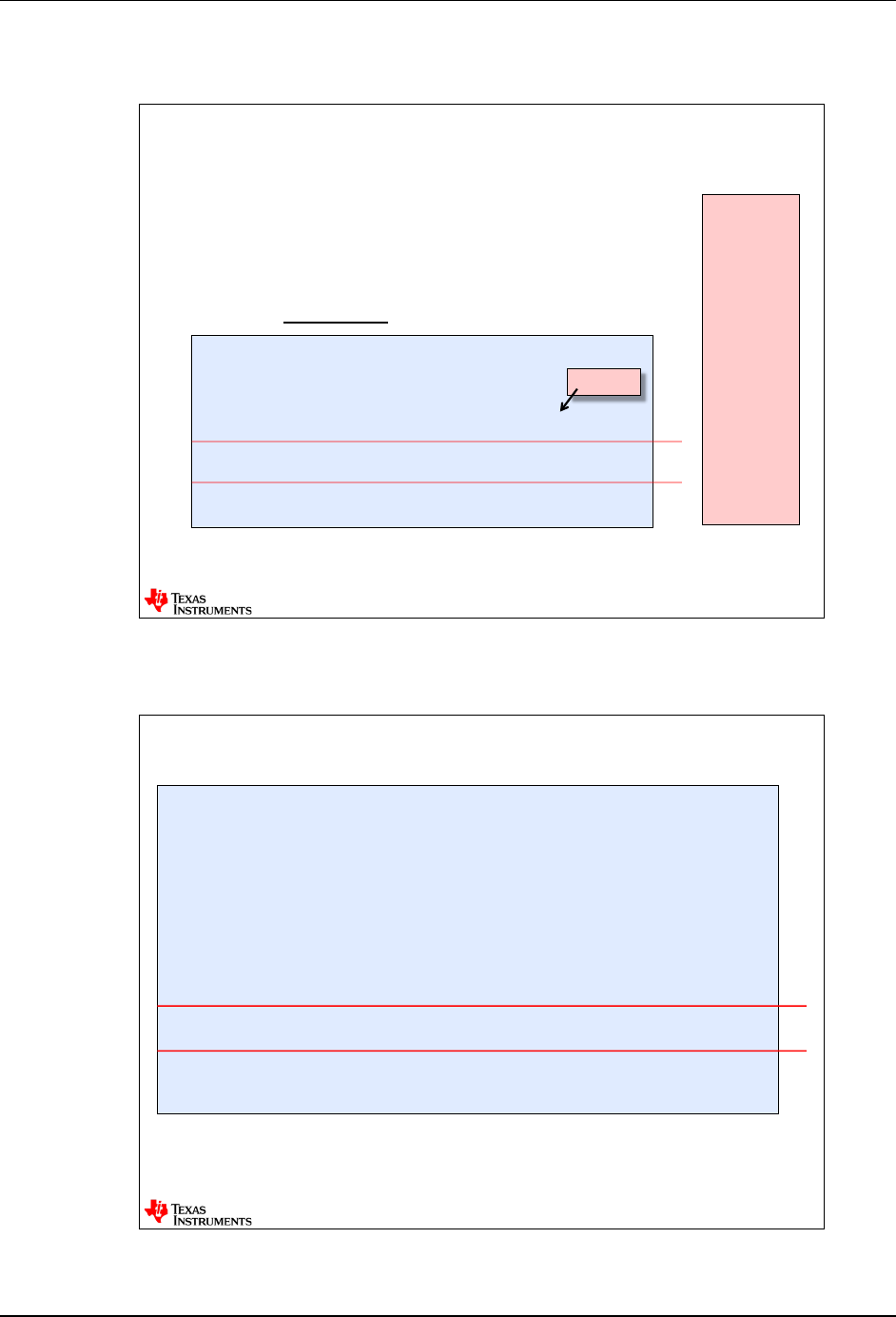

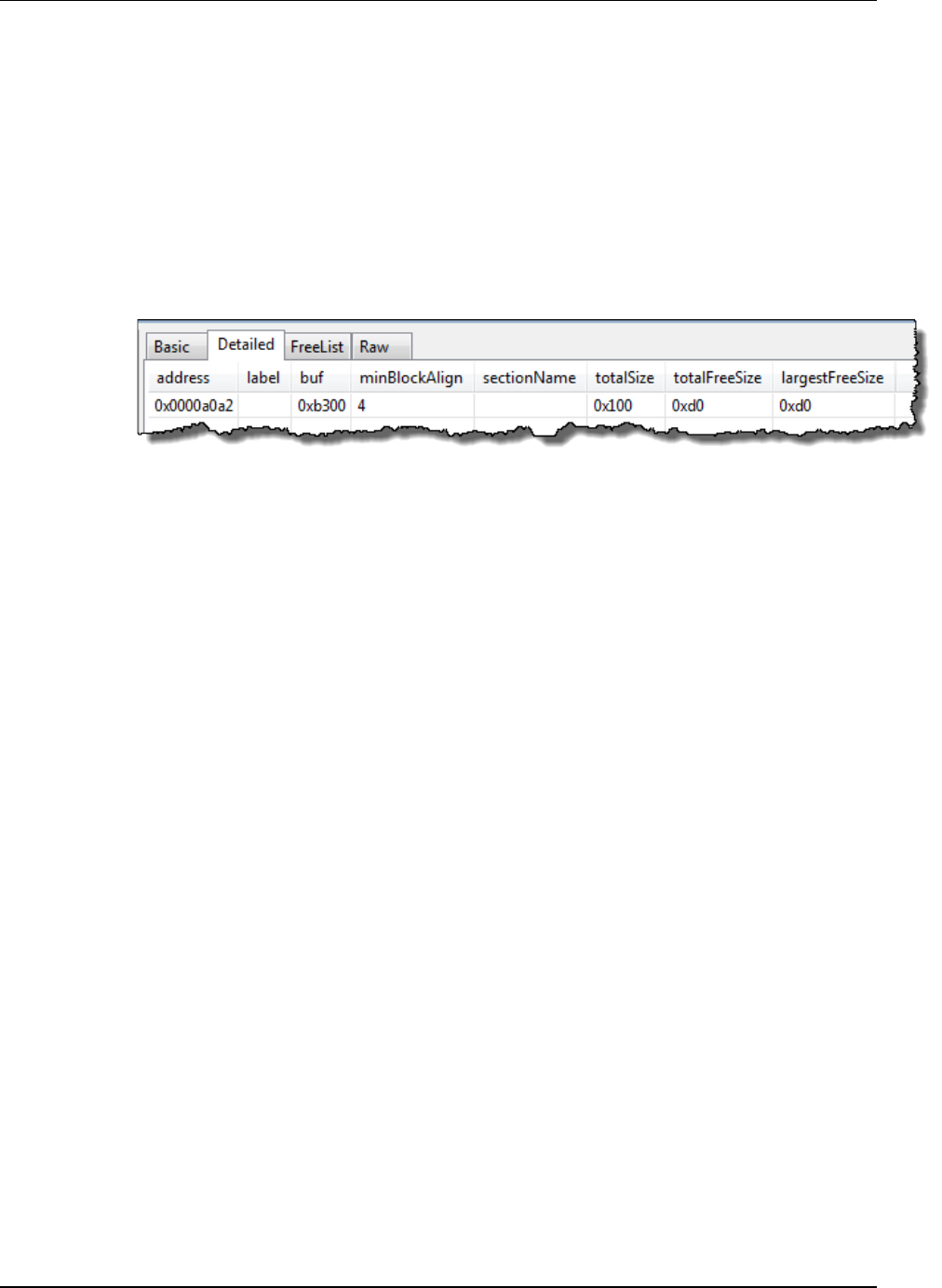

9. Check heap in ROV.

So, how much heap memory does a Semaphore take? Where do you find the heap sizes and

how much was used? ROV, of course…

► Open ROV and click on HeapMem (the standard heap type), then click on Detailed:

So, in this example (C28x), the starting heap size was 0x100 (256) and 0xd0 is still free

(208), so the Semaphore object took 48 16-bit locations on the C28x (assuming nothing else

is on the heap). Ok. So, we didn’t run out of heap. Good thing.

► Write down how many bytes your Semaphore required here: _____________

► How much free size do you have left over? ____________

So, when you create a Task, which has its own stack, if you create it with a stack larger than

the free size left over, what might happen?

_______________________________________________________

Well, let’s go try it…

Lab 10 – Procedure – Using Dynamic Task/Sem

10 - 20 TI-RTOS Workshop - Using Dynamic Memory

Delete Task and Add It Dynamically

10. Delete the Task in app.cfg.

Remove the Task from the app.cfg file and save app.cfg.

11. Uncomment some lines of code and declarations.

► Uncomment the #include for Task.h.

► Uncomment the declaration of the Task_Handle.

► Uncomment the code in main() that creates the Task (ledToggleTask) and fill in the

???? properly.

► Create the Task at priority 2.

► Save main.c.

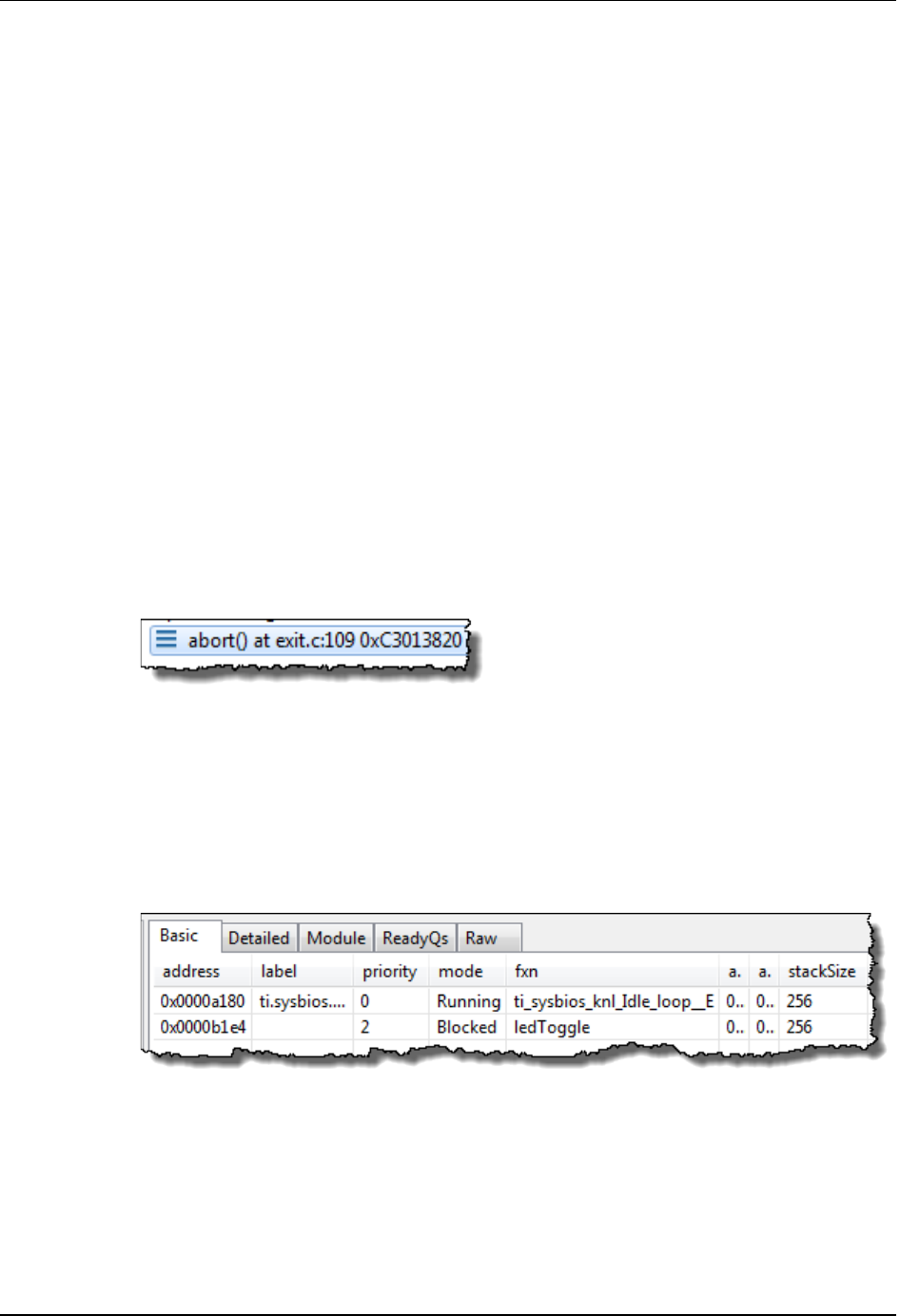

12. Build, load, run, verify.

► Build and run your code for five blinks. No blink? Read further…

► Halt your code.

Your code probably is probably sitting at abort(). How would the author know that? Well,

when you create a Task, it needs a stack. On the C6000, the default stack size is 2048 bytes.

For C28x, it is 256.

You probably aborted with a message that looks similar to this:

What happened? Two things. First, your heap is not big enough to create a Task from

because the Task requires a stack that is larger than the entire heap.

Also, did you pass an error block in the Task_create() function? Probably not. So, what

happens if you get a NULL pointer back and you do NOT pass an error block? BIOS aborts.

Well, that’s what it looks like.

13. Open ROV to see the damage.

► Open ROV and click on Task. You should see something similar to this:

► Look at the size of “stackSize” for ledToggle (name may or may not show up). This

screen capture was for C28x, so your size may be different (probably larger).

► What size did you set the heap to in BIOS Runtime? __________ bytes

► What is the size of the stack needed for ledToggle (shown in ROV)? __________ bytes

Get the picture? You need to increase the size of the heap…

Lab 10 – Procedure – Using Dynamic Task/Sem

TI-RTOS Workshop - Using Dynamic Memory 10 - 21

14. Go back and increase the size of the heap.

► Open BIOS

Runtime and use the following heap sizes:

• C28x: 1024

• C6000: 4096

• MSP430: 1024

• TM4C: 4096

We probably don’t need THIS large of a heap for this application – it could be tuned better –

we’re just using a larger number to see the application work.

► Save app.cfg.

15. Wait, what about Error Block?

In a real application, the user has a choice whether to use Error Block or not. For debug

purposes, maybe it is best to leave it off so that your program aborts when the handle to the

requested resource is NULL. If you don’t like that, then use Error Block and check the return

handle and deal with it however you choose – user preference.

In our lab, we chose to ignore Error Block, but at least you know it is there, how to initialize

one and how it works.

16. Rebuild and run again.

Rebuild and run the new project with the larger heap. Run for 5 blinks – it should work fine

now.

17. Terminate your debug session, close the project and close CCS.

You’re finished with this lab. Help a neighbor who is struggling – you know you

KNOW IT when you can help someone else – and it’s being a good neighbor. But, if

you want to be selfish and just leave the room because the workshop is OVER, no

one will look at you funny !!

Additional Information

10 - 22 TI-RTOS Workshop - Using Dynamic Memory

Additional Information

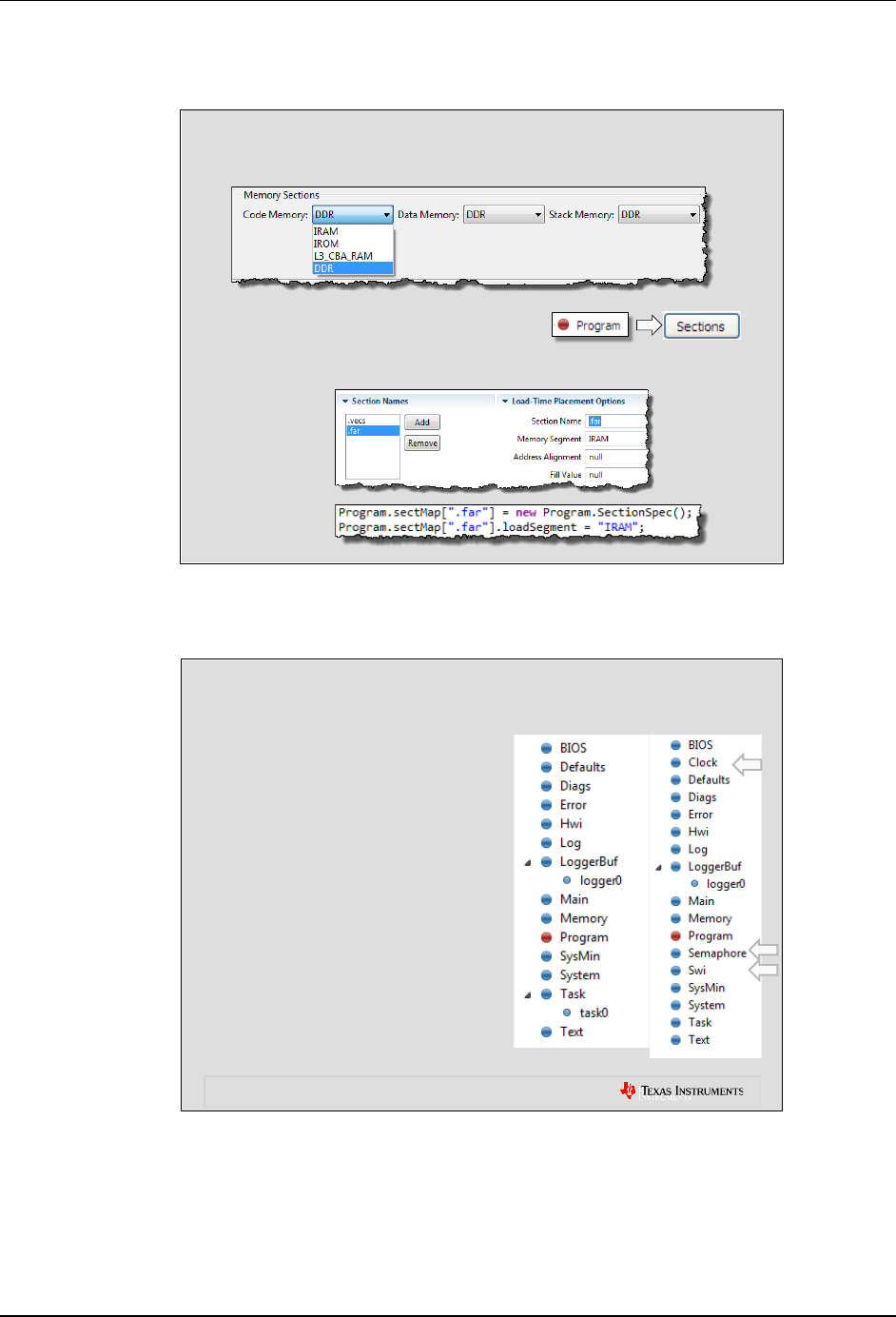

Placing a Specific Section into Memory

•SYS/BIOS GUI now supports specific placements of sections (like .far, .bss, etc.)

into specific memory segments (like IRAM, DDR, etc.):

Via the Platform File (C6000 Only) –hi-level, but works fine:

Via the app.cfg GUI (finer control):

GUI

CFG script

D .text .econst .ebss

TYP 3568 1b4e 11c0

MIN 2940 4BF 752

----------------------------------------------------------------------------

Savings C28(3112) 168F(5775) A6E(2670)

TYP vs. MIN footprints –C28x

SAVINGS –OVERALL

FLASH RAM TOTAL

8887 2670 11557

Notes

TI-RTOS Workshop - Using Dynamic Memory 10 - 23

Notes

More Notes…

10 - 24 TI-RTOS Workshop - Using Dynamic Memory

More Notes…

*** the very end ***

C6000 Embedded Design Workshop - C6000 Introduction 11 - 1

C6000 Introduction

Introduction

This is the first chapter that specifically addresses ONLY the C6000 architecture. All chapters

from here on assume the student has already taken the 2-day TI-RTOS Kernel workshop.

During those past two days, some specific C6000 architecture items were skipped in favor of

covering all TI EP processors with the same focus. Now, it is time to dive deeper into the C6000

specifics.

The first part of this chapter focuses on the C6000 family of devices. The 2nd part dives deeper

into topics already discussed in the previous two days of the TI-RTOS Kernel workshop. In a way,

this chapter is “catching up” all the C6000 users to understand this target environment

specifically.

After this chapter, we plan to dive even deeper into specific parts of the architecture like

optimizations, cache and EDMA.

Objectives

Objectives

Introduce the C6000 Core and the C6748

target device

Highlight a few uncommon pieces of the

architecture –e.g. the SCR and PRU

“Catch up” from the TI-RTOS Kernel

discussions are C6000-specific topics such as

Interrupts, Platforms and Target Config Files

Lab 11 –Create a custom platform and create

an Hwi to respond to the audio interrupts

Module Topics

11 - 2 C6000 Embedded Design Workshop - C6000 Introduction

Module Topics

C6000 Introduction............................................................................................................... 11-1

Module Topics.................................................................................................................... 11-2

TI EP Product Portfolio ....................................................................................................... 11-3

DSP Core........................................................................................................................... 11-4

Devices & Documentation .................................................................................................. 11-6

Peripherals ......................................................................................................................... 11-7

PRU ............................................................................................................................... 11-7

SCR / EDMA3 ............................................................................................................... 11-8

Pin Muxing ..................................................................................................................... 11-9

Example Device: C6748 DSP ........................................................................................... 11-11

Choosing a Device ........................................................................................................... 11-12

C6000 Arch “Catchup” ...................................................................................................... 11-13

C64x+ Interrupts ........................................................................................................... 11-13

Event Combiner............................................................................................................ 11-14

Target Config Files ....................................................................................................... 11-14

Creating Custom Platforms ........................................................................................... 11-15

Quiz ................................................................................................................................. 11-19

Quiz - Answers ............................................................................................................. 11-20

Using Double Buffers ....................................................................................................... 11-21

Lab 11: An Hwi-Based Audio System ............................................................................... 11-23

Lab 11 – Procedure ...................................................................................................... 11-24

Hack LogicPD’s BSL types.h ........................................................................................ 11-24

PART B (Optional) – Using the Profiler Clock................................................................ 11-34

Additional Information....................................................................................................... 11-35

Notes ............................................................................................................................... 11-36

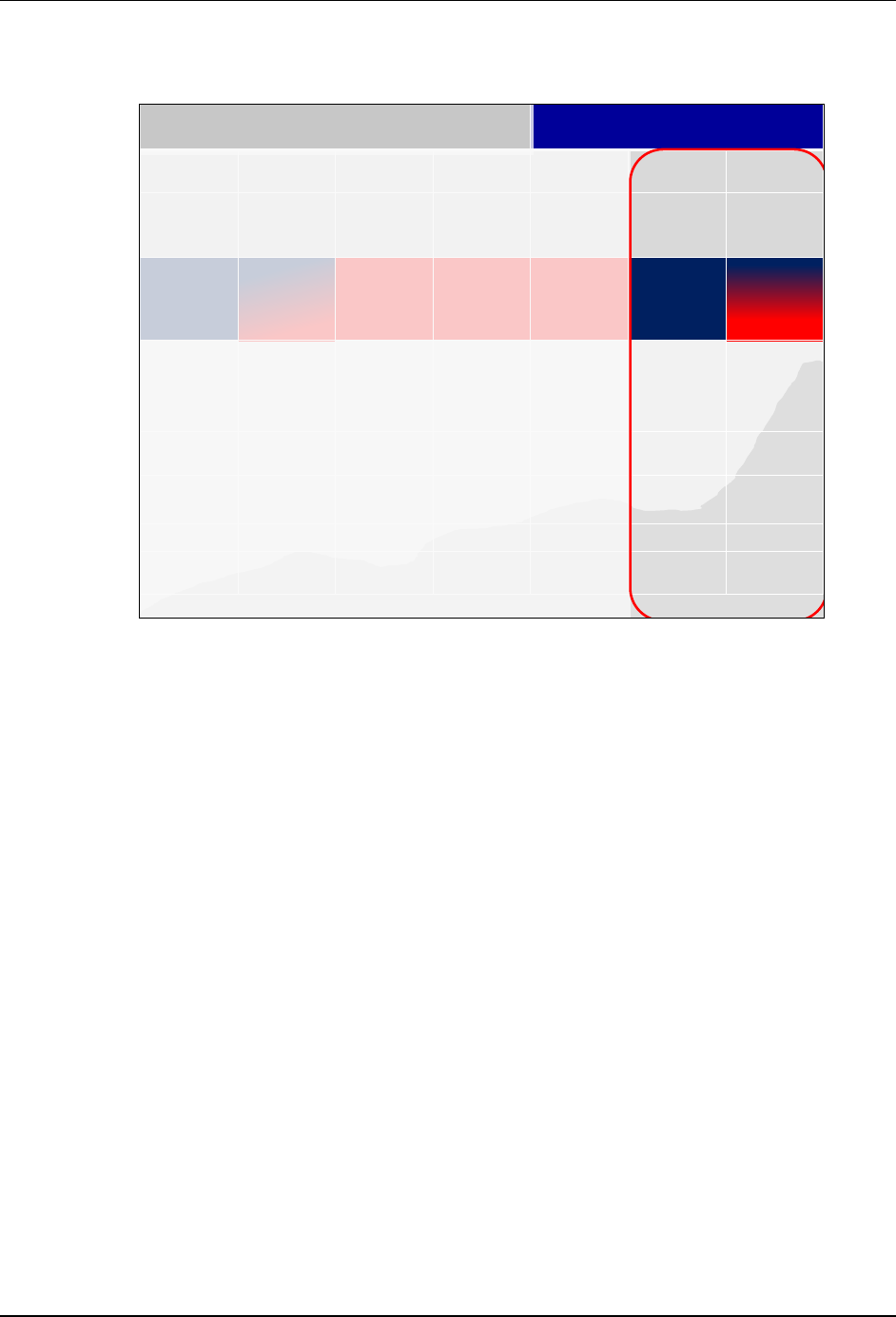

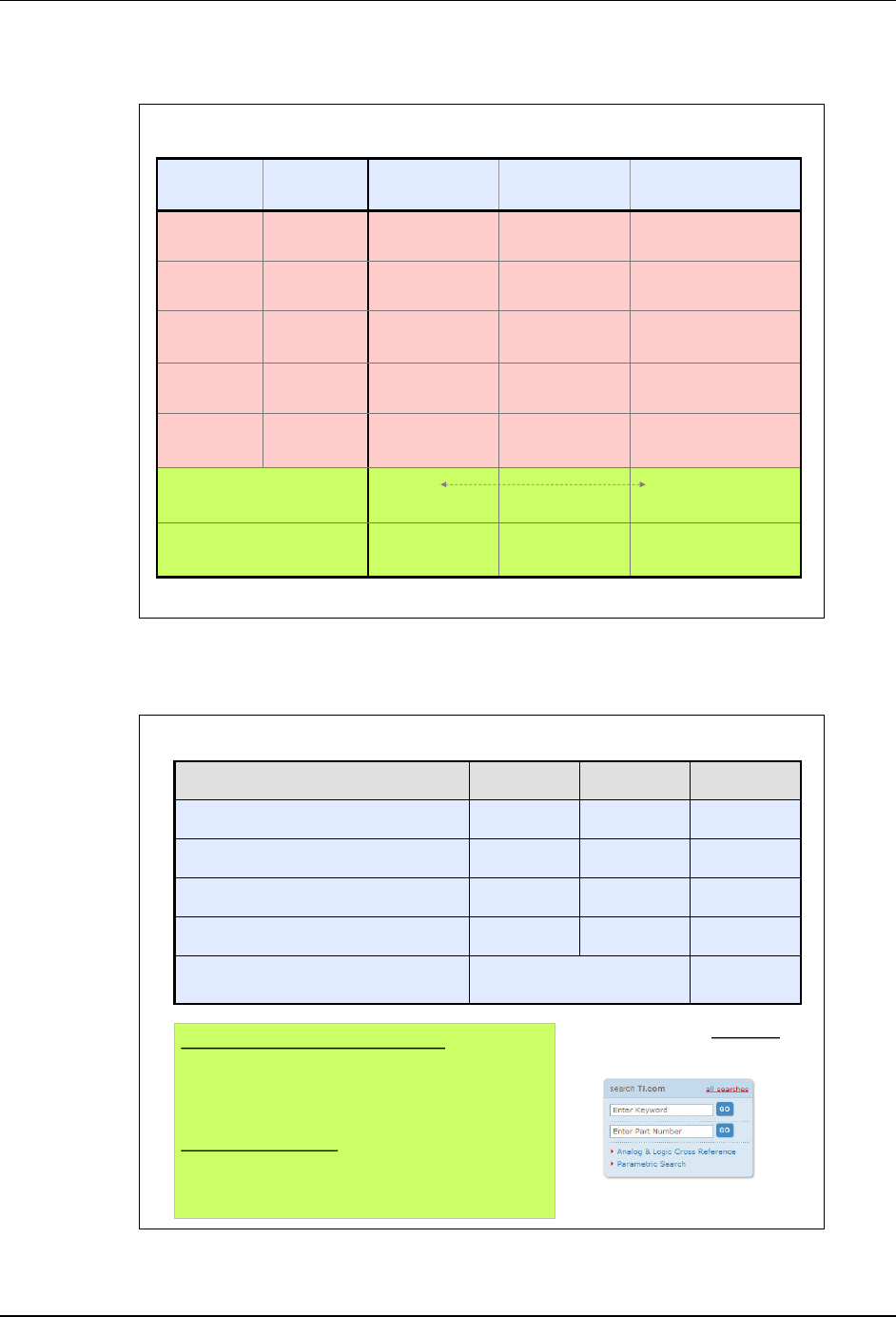

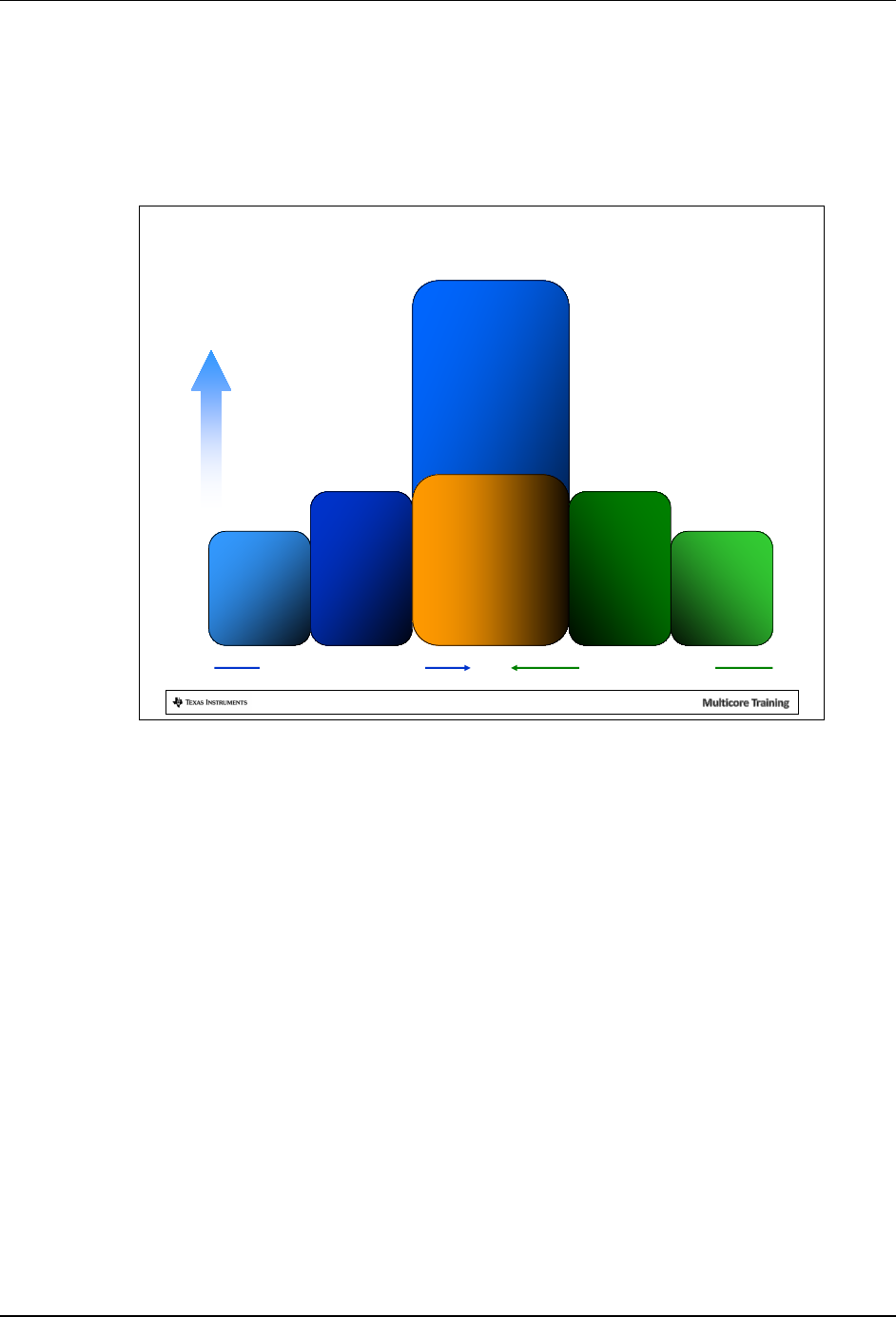

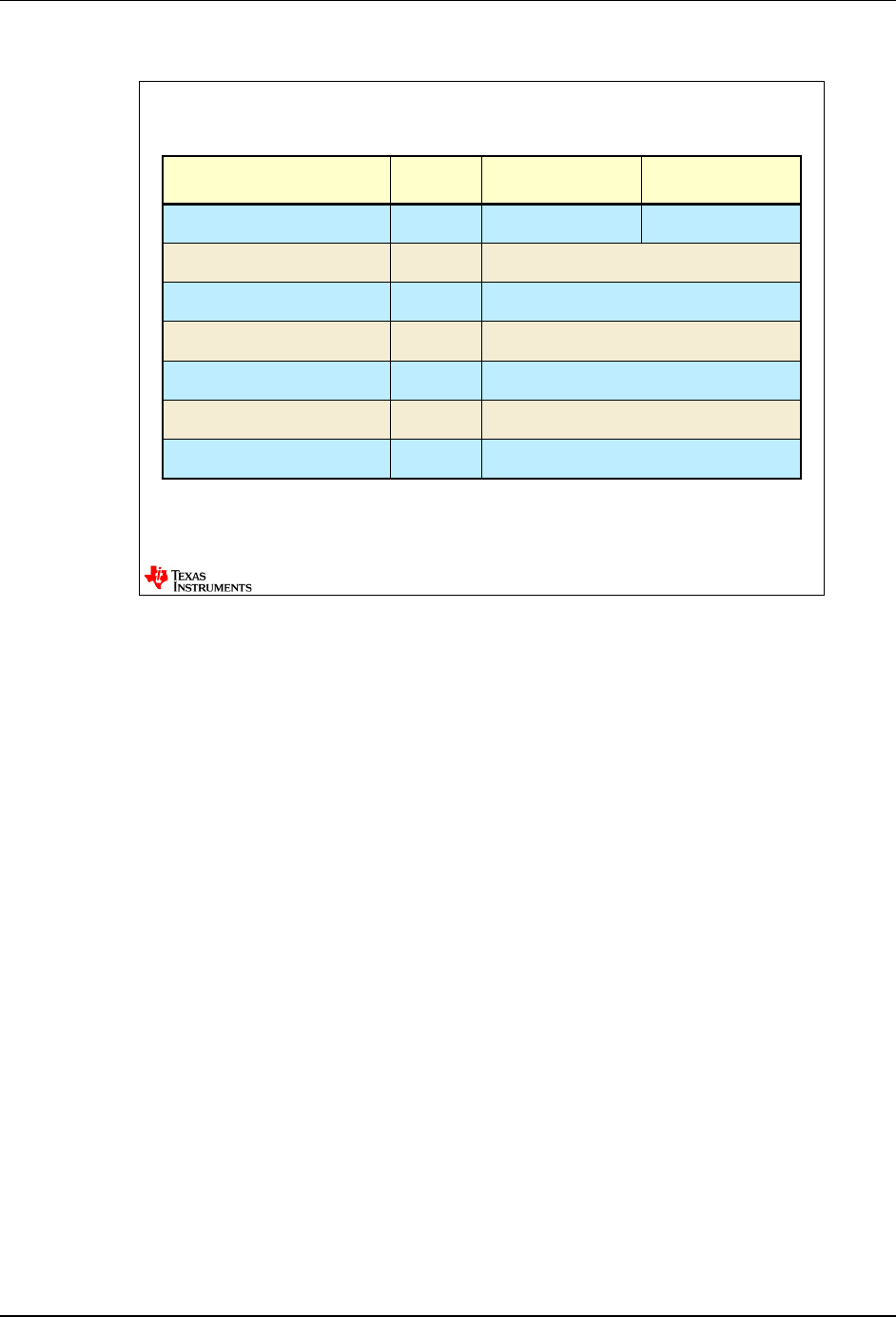

TI EP Product Portfolio

C6000 Embedded Design Workshop - C6000 Introduction 11 - 3

TI EP Product Portfolio

TI’s Embedded Processor Portfolio

Microcontrollers (MCU) Application (MPU)

MSP430

C2000 Tiva-C

Hercules

Sitara DSP

Multicore

16-bit 32-bit 32-bit 32-bit 32-bit 16/32-bit 32-bit

Ultra Low

Power & Cost

Real-time All-around

MCU Safety Linux

Android

All-around

DSP

Massive

Performance

MSP430

ULP RISC

MCU

•

Real-time

C28x MCU

•

ARM

M3+C28

ARM

Cortex

-M3

Cortex

-M4F

ARM

Cortex-

M3

Cortex-R4

ARM

Cortex-A8

Cortex-A9

DSP

C5000

C6000

•

C66 + C66

•

A15 + C66

•

A8 + C64

•ARM9 + C674

•

Low Pwr

Mode

0.1 µA

0.5 µA (RTC)

•

Analog I/F

•

RF430

•

Motor Control

•

Digital Power

•

Precision

Timers/PWM

•

32-bit Float

•Nested Vector

Int Ctrl (NVIC)

•

Ethernet

(MAC+PHY)

•

Lock step

Dual-core R4

•

ECC Memory

•

SIL3 Certified

•

$5 Linux CPU

•

3D Graphics

•

PRU-ICSS

industrial

subsys

•

C5000 Low

Power DSP

•

32-bit fix/float

C6000 DSP

•

Fix or Float

•Up to 12 cores

4 A15 + 8 C66x

•DSP MMAC’s:

352,000

TI RTOS

(SYS/BIOS)

TI RTOS

(SYS/BIOS)

TI RTOS

(SYS/BIOS) N/A

Linux, Android,

SYS/BIOS

C5x: DSP/BIOS

C6x: SYS/BIOS

Linux

SYS/BIOS

Flash: 512K

FRAM: 64K

512K

Flash

512K

Flash

256K to 3M

Flash

L1: 32K x 2

L2: 256K

L1: 32K x 2

L2: 256K

L1: 32K

x 2

L2: 1M + 4M

25 MHz 300 MHz 80 MHz 220 MHz 1.35 GHz 800 MHz 1.4 GHz

$0.25 to

$9.00

$1.85 to

$20.00

$1.00 to

$8.00

$5.00 to

$30.00

$5.00 to

$25.00

$2.00 to

$25.00

$30.00 to

$225.00

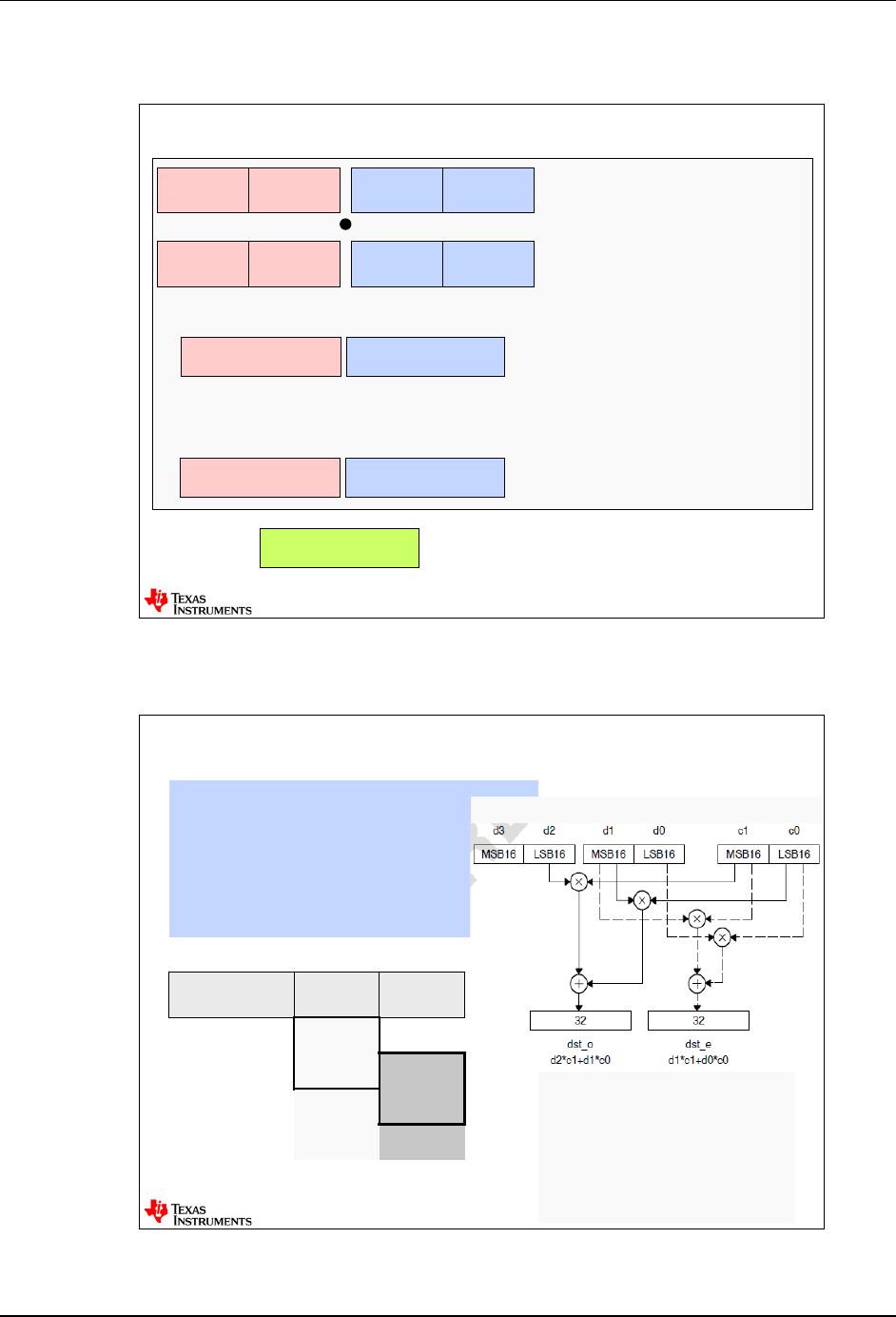

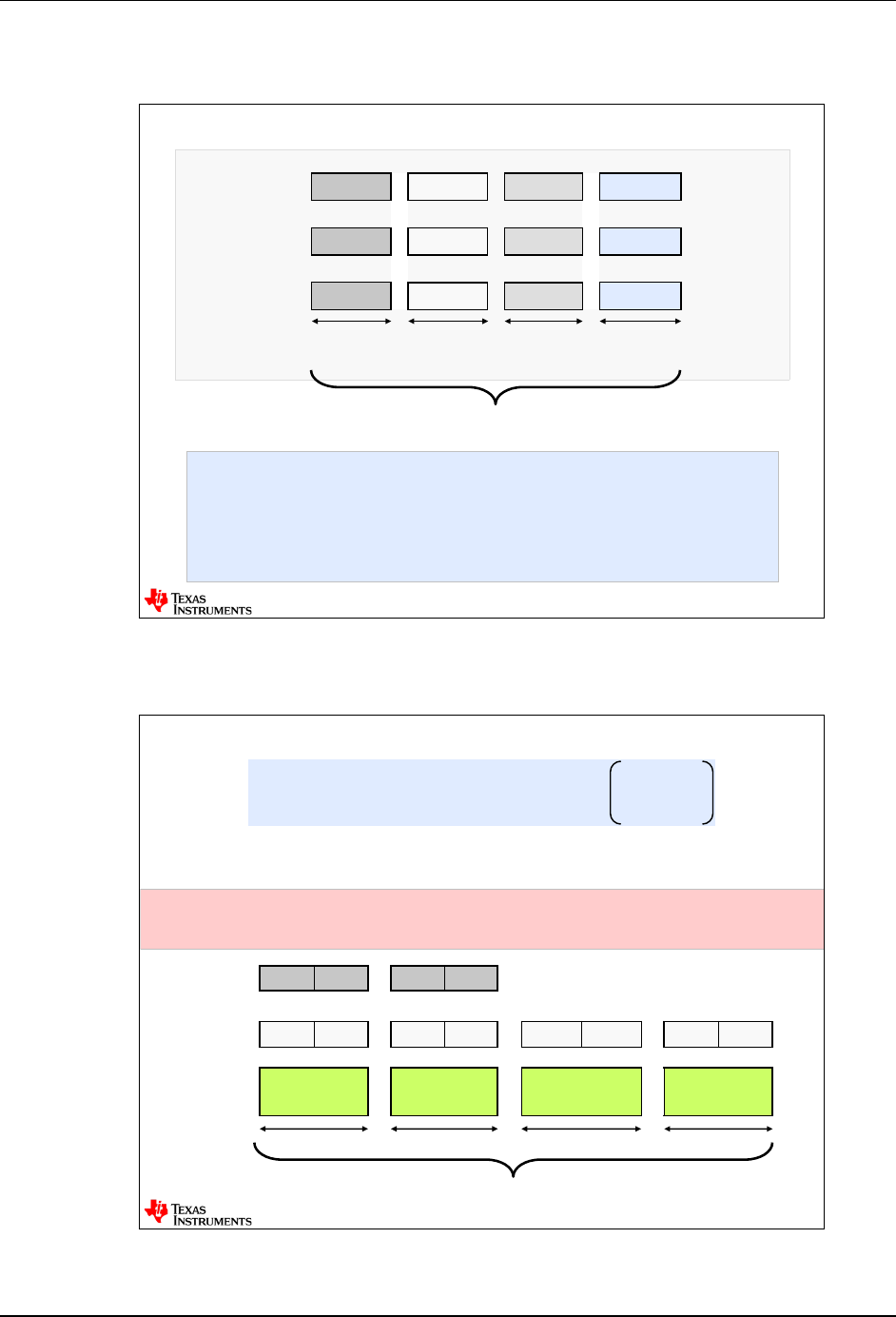

DSP Core

11 - 4 C6000 Embedded Design Workshop - C6000 Introduction

DSP Core

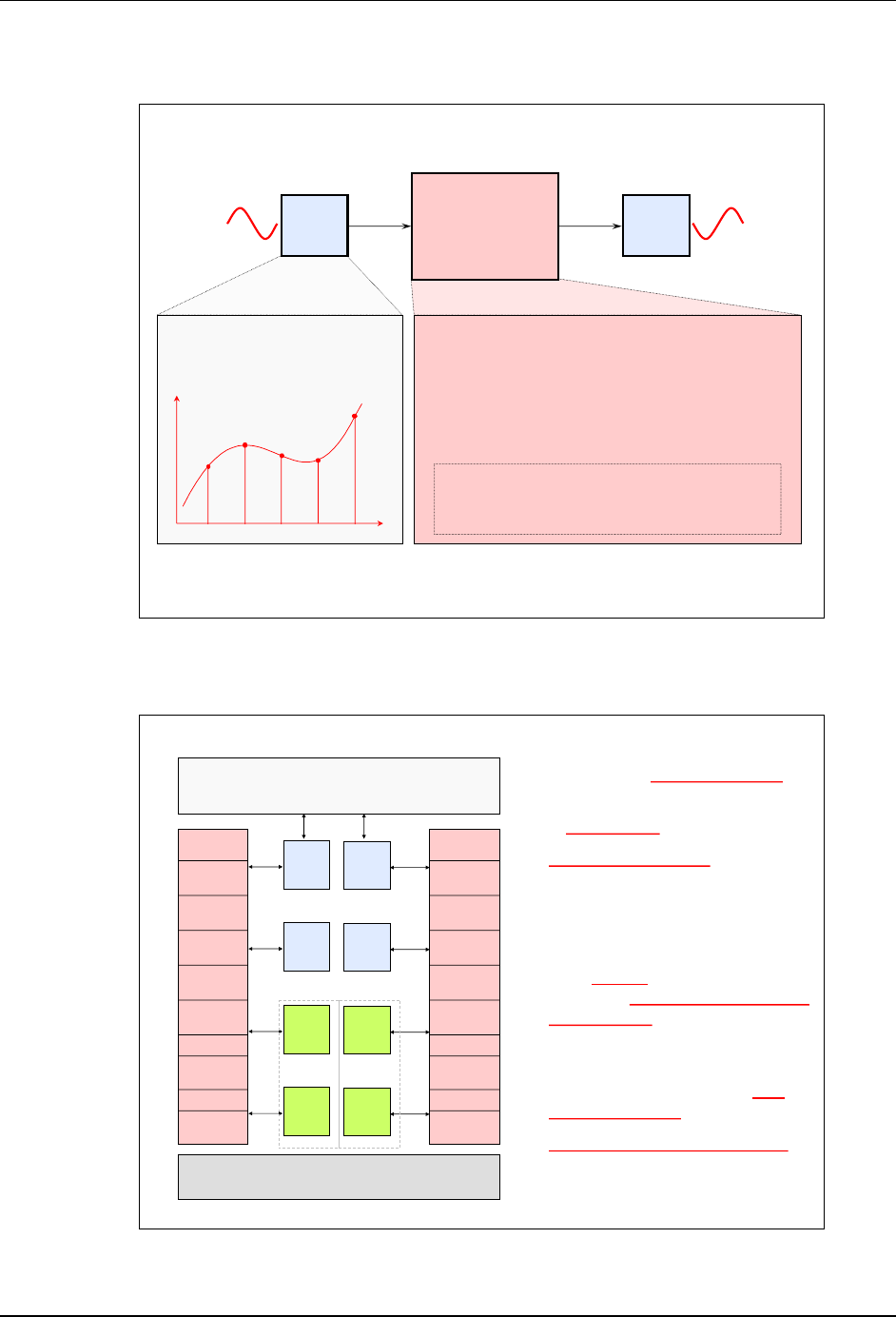

What Problem Are We Trying To Solve?

Digital sampling of

an analog signal:

A

t

Most DSP algorithms can be

expressed with MAC:

count

i = 1

Y = Σcoeffi* xi

for (i = 0; i < count; i++){

Y += coeff[i] * x[i]; }

DAC

x Y

ADC

DSP

How is the architecture designed to maximize computations like this?

'C6x CPU Architecture

Memory

‘C6x Compiler excels at Natural C

Multiplier (.M) and ALU (.L) provide up

to 8 MACs/cycle (8x8

or

16x16)

Specialized instructions accelerate

intensive, non-MAC oriented

calculations. Examples include:

Video compression, Machine

Vision, Reed Solomon, …

While MMACs speed math intensive

algorithms, flexibility of 8 independent

functional units allows the compiler to

quickly perform other types of

processing

‘C6x CPU can dispatch up to eight

parallel instructions each cycle

All ‘C6x instructions are conditional

allowing efficient hardware pipelining

A0

A31

.

.

.S1

.D1

.L1

.S2

.M1 .M2

.D2

.L2

B0

B31

.

.

Controller/Decoder

MACs

Note: More details later…

DSP Core

C6000 Embedded Design Workshop - C6000 Introduction 11 - 5

C66x

C67x

C6000 DSP Family CPU Roadmap

C62x

C64x+ C674

C67x+

C64x

C671x

C621x

Floating Point

Fixed and Floating

Point

Lower power

EDMA3

PRU

L1 RAM/Cache

Compact Instr’s

EDMA3

Video/Imaging

Enhanced

EDMA2

Fixed Point

Available on the most

recent releases

C67x

C6000 DSP Family CPU Roadmap

C62x

C64x+

C66x

C674

C67x+

C64x

1GHz

EDM A (v2 )

2x Register Set

SIM D Instr’s

(Packed Data Proc)

C671x

C621x

EDMA

L1 Cache

L2 Cache/RAM

Lower Cost

DMAX (PRU)

2x Register Set

FFT enhancements

1.2 GHz

EDMA3

SPLOOP

32x32 Int Multiply

Enhanced Instr for

FIR/F FT /Com pl ex

Combined Instr Sets from

C64x+/C67x+

Incr Floating-pt M Hz

Lower power

EDMA3

PRU

L1 RAM and/or Cache

Timestamp Counter

Compact Instr’s

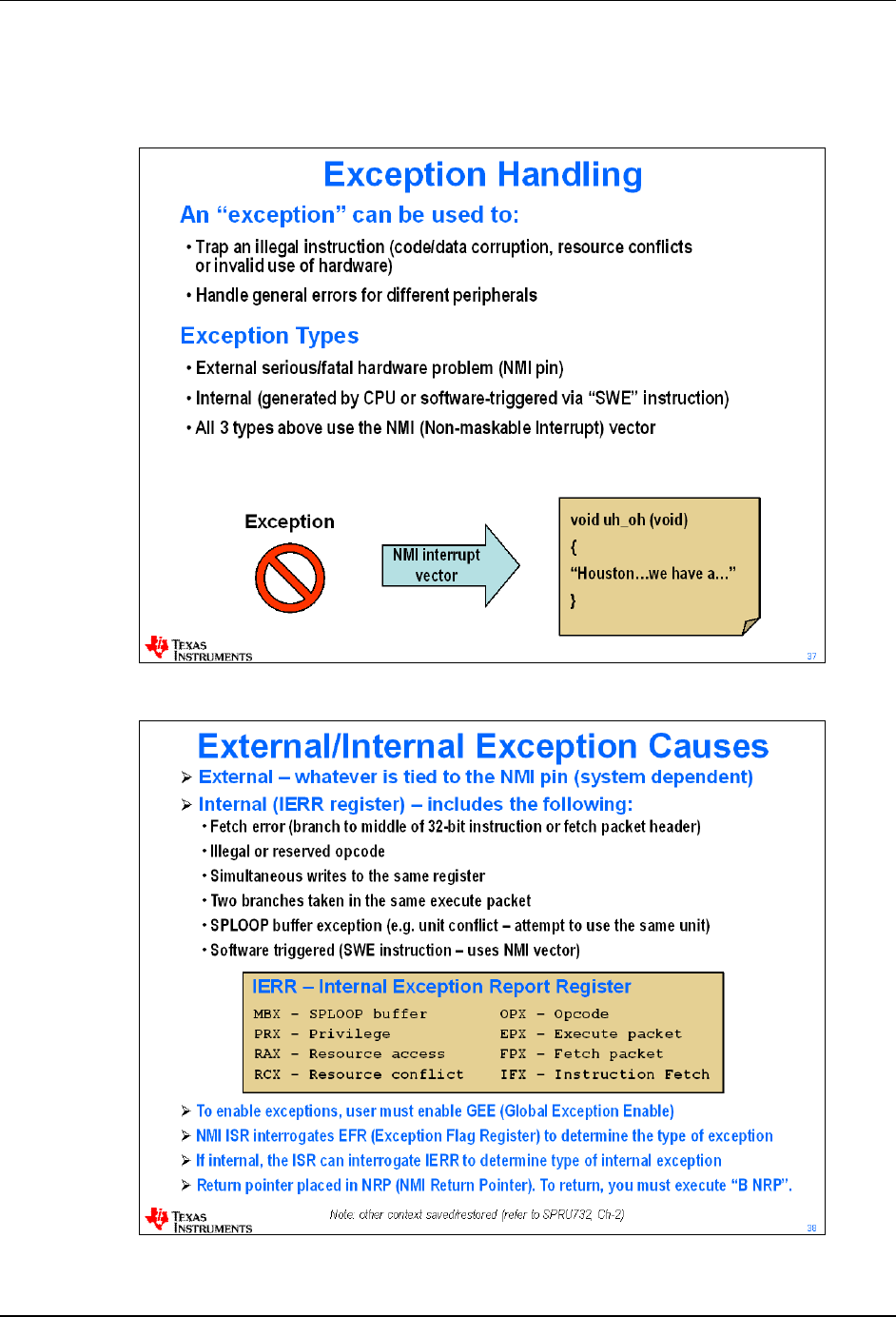

Exceptions

Supervisor/User modes

Devices & Documentation

11 - 6 C6000 Embedded Design Workshop - C6000 Introduction

Devices & Documentation

DSP Generations : DSP and ARM+DSP

Fixed-Point

Cores

Float-Point

Cores DSP DSP+DSP

(Multi-core) ARM+DSP

C62x C67x C620x, C670x

C621x C67x C6211, C671x

C64x C641x

DM642

C67x+ C672x

C64x+ DM643x

C645x C647x

DM64xx,

OMAP35x, DM37x

C674x C6748 OMAP-L138*

C6A8168

C66x Future C667x

C665x (new)

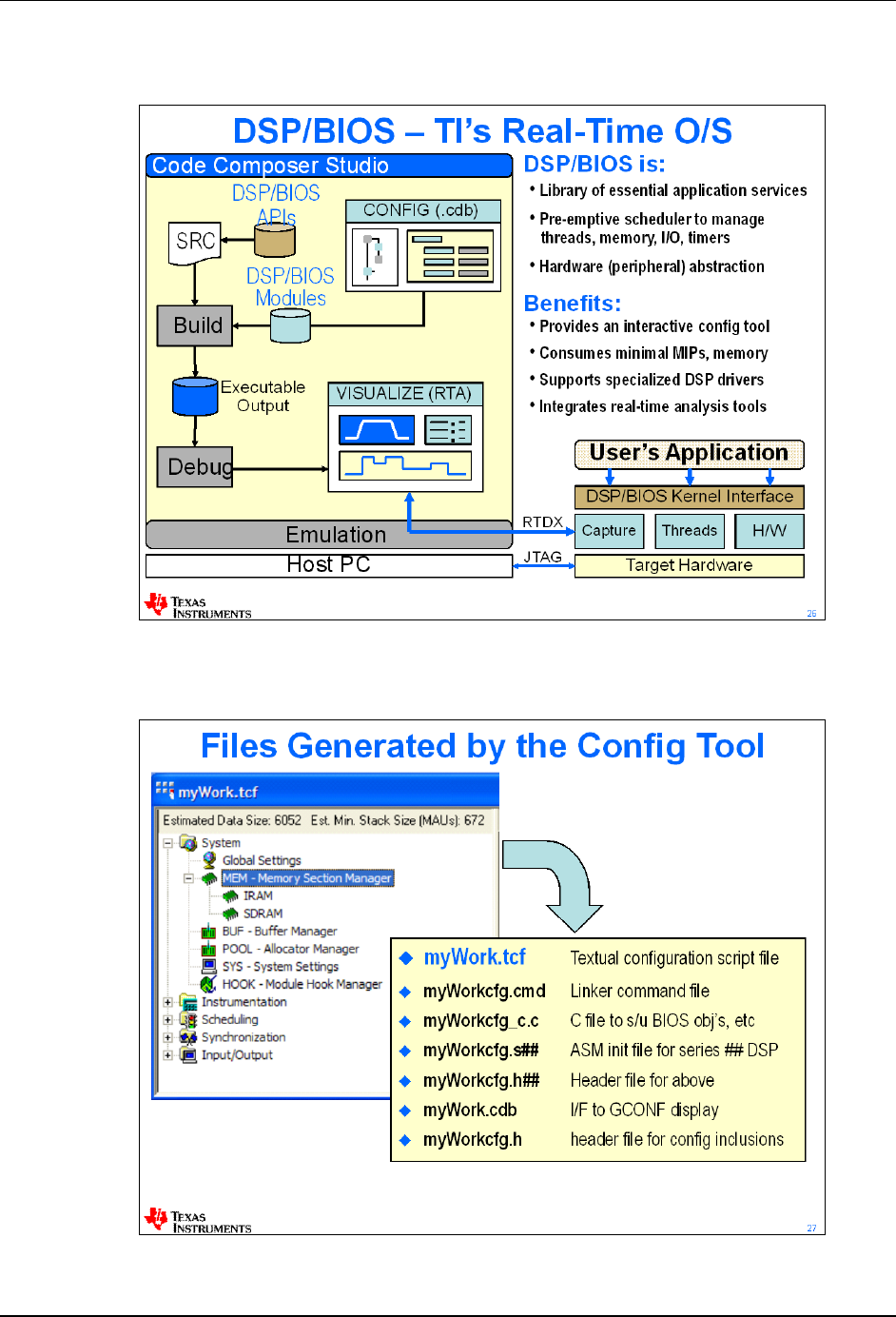

DSP/BIOS Real-Time Operating System

SPRU423 -DSP/BIOS (v5) User’s Guide

SPRU403 -DSP/BIOS (v5) C6000 API Guide

SPRUEX3 -SYS/BIOS (v6) User’s Guide

Code Generation Tools

SPRU186 -Assembly Language Tools User’s Guide

SPRU187 -Optimizing C Compiler User’s Guide

Key C6000 Manuals

C64x/C64x+ C674 C66x

CPU Instruction Set Ref Guide SPRU732 SPRUFE8 SPRUGH7

Megamodule/Corepac Ref Guide SPRU871 SPRUFK5 SPRUGW0

Peripherals Overview Ref Guide SPRUE52 SPRUFK9 N/A

Cache User’s Guide SPRU862 SPRUG82 SPRUGY8

Programmers Guide SPRU198 SPRA198

SPRAB27

To find a manual, at www.ti.com

and enter the document number

in the Keyword field:

or…

www.ti.com/lit/<litnum>

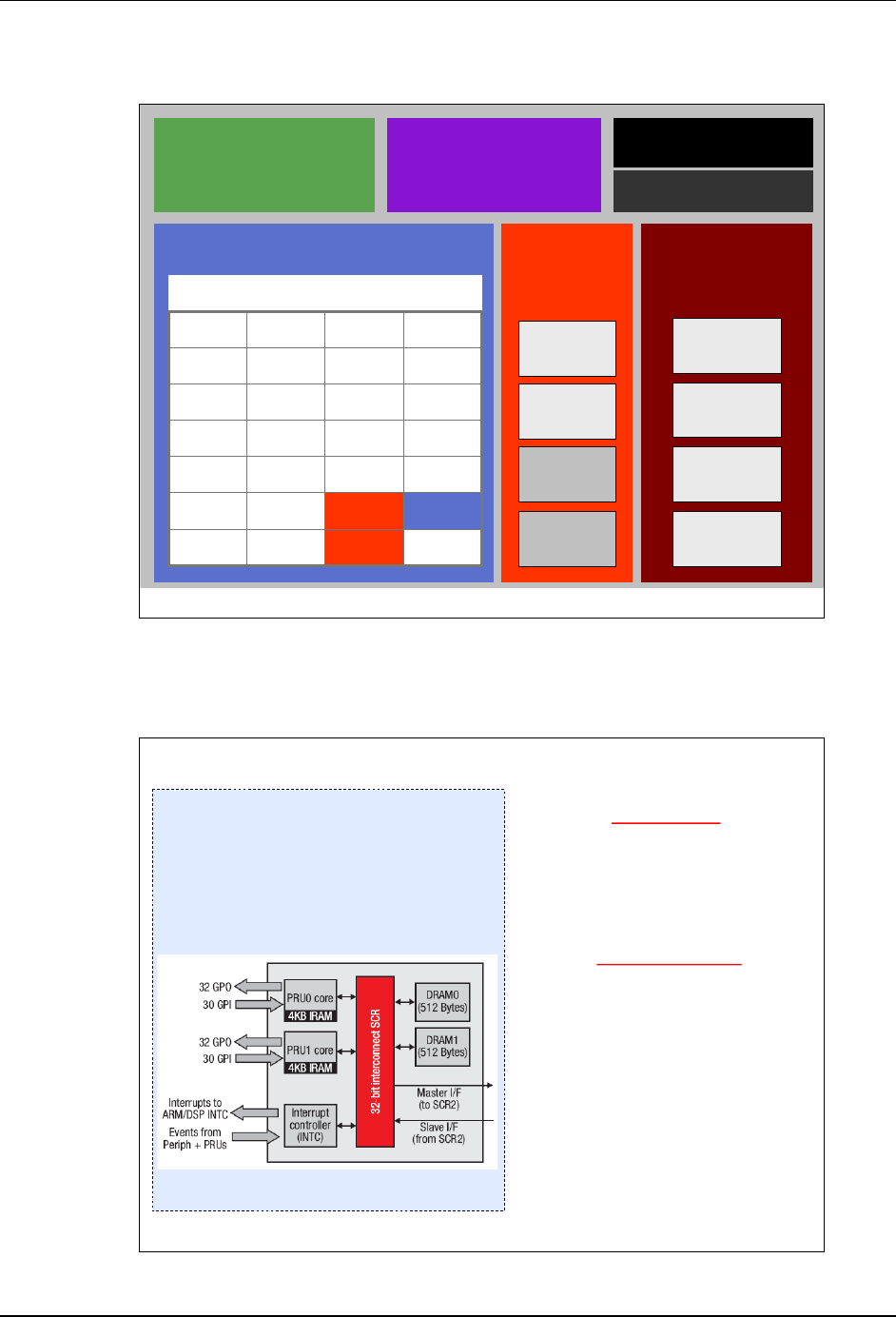

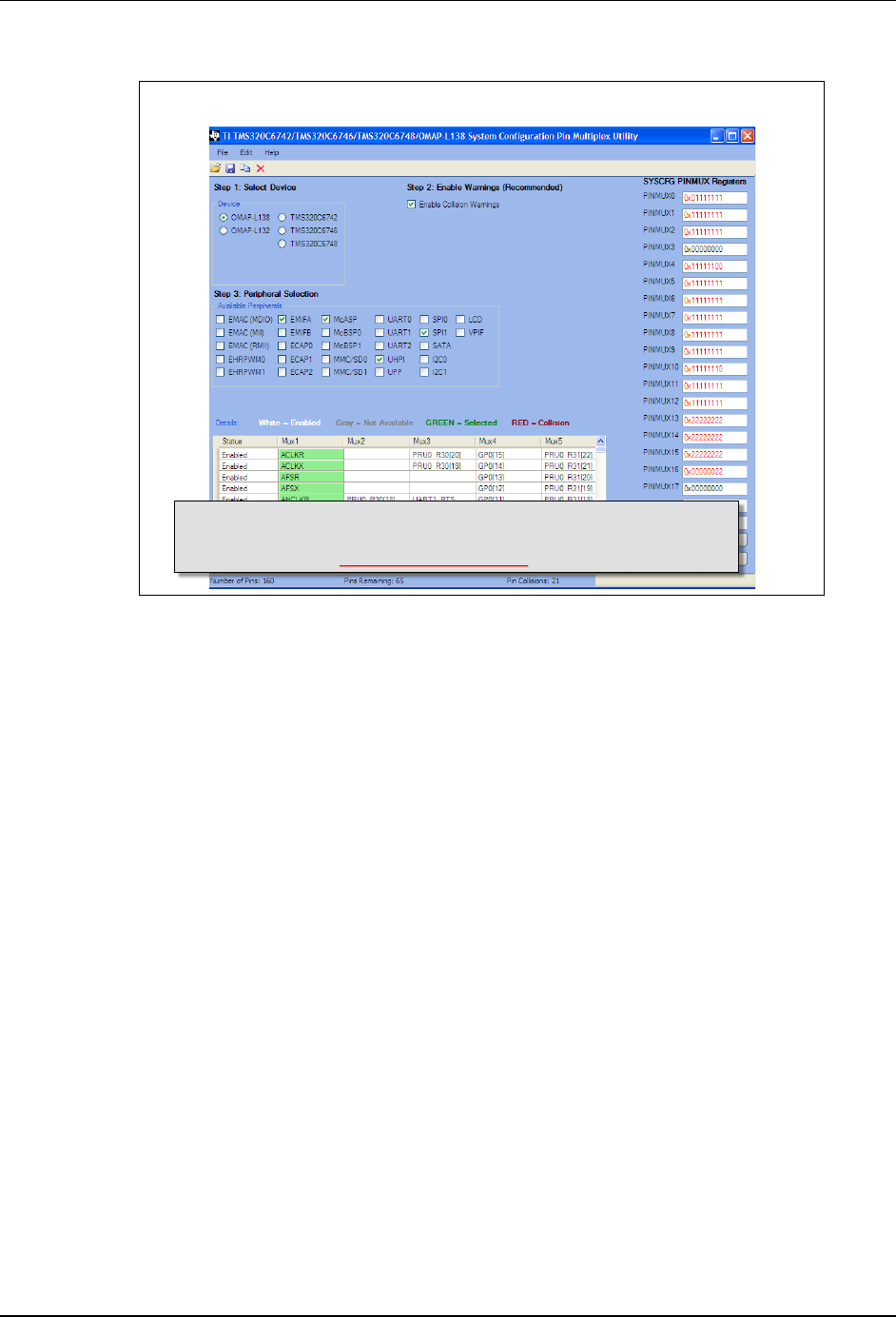

Peripherals

C6000 Embedded Design Workshop - C6000 Introduction 11 - 7

Peripherals

ARM Graphics

Accelerator

C6x DSP

Video Accelerator(s)

Peripherals Video/Display

Subsytem

PRU

(Soft Peripheral)

Capture

Analog

Display

Digital

Display

LCD

Controller

What’s

Next?

DIY…

Serial Storage Master Timing

McBSP DDR2 PCIe Timers

McASP DDR3 USB 2.0 Watch

ASP SDRAM EMAC PWM

UART Async uPP eCAP

SPI SD/MMC HPI RTC

I2C ATA/CF EDMA3

CAN SATA SCR GPIO

UART

CAN

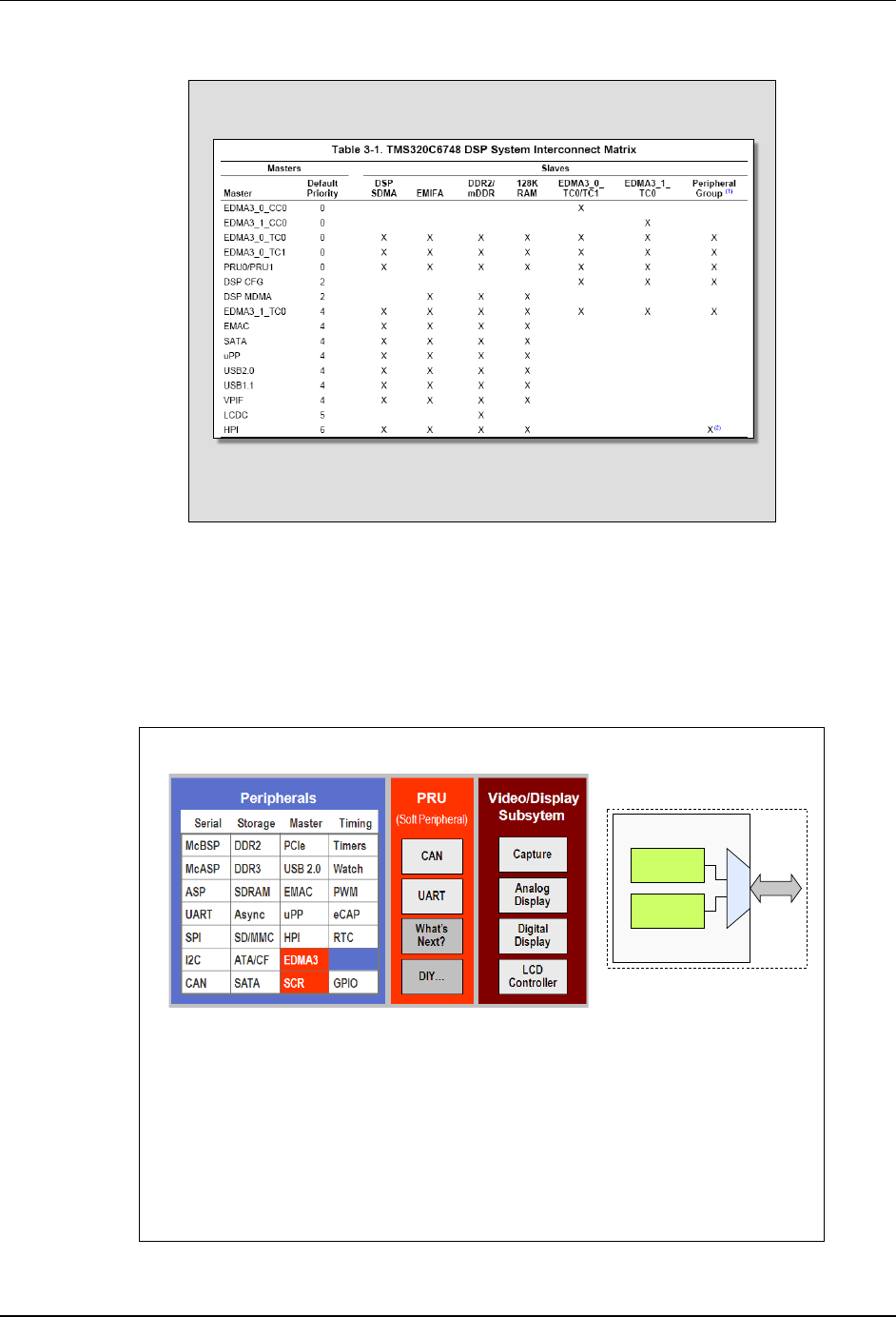

We’ll just look at three of these: PRU and SCR/EDMA3

PRU

Programmable Realtime Unit (PRU)

Use as a soft peripheral to imple-

ment add’l on-chip peripherals

Examples implementations

include:

Soft UART

Soft CAN

Create custom peripherals or

setup non-linear DMA moves.

No C compiler (ASM only)

Implement smart power

controller:

Allows switching off both ARM and

DSP clocks

Maximize power down time by

evaluating system events before

waking up DSP and/or ARM

PRU consists of:

2 Independent, Realtime RISC Cores

Access to pins (GPIO)

Its own interrupt controller

Access to memory (master via SCR)

Device power mgmt control

(ARM/DSP clock gating)

Peripherals

11 - 8 C6000 Embedded Design Workshop - C6000 Introduction

PRU SubSystem : IS / IS-NOT

Is IsNot

Dual 32bit RISC processor specifically

designed for manipulation of packed memory

mapped data structures and implementing

system features that have tight real time

constraints.

Is not a H/W accelerator used to speed up

algorithm computations.

Simple RISC ISA:

Approximately 40 instructions

Logical, arithmetic, and flow control ops all

complete in a single cycle

Is not a general purpose RISC processor:

No multiply hardware/instructions

No cache or pipeline

No C programming

Simple tooling:

Basic commandline assembler/linker

Is not integrated with CCS. Doesn’t include

advanced debug options

Includes example code to demonstrate

various features. Examples can be used as

building blocks.

No Operating System or high-level

application software stack

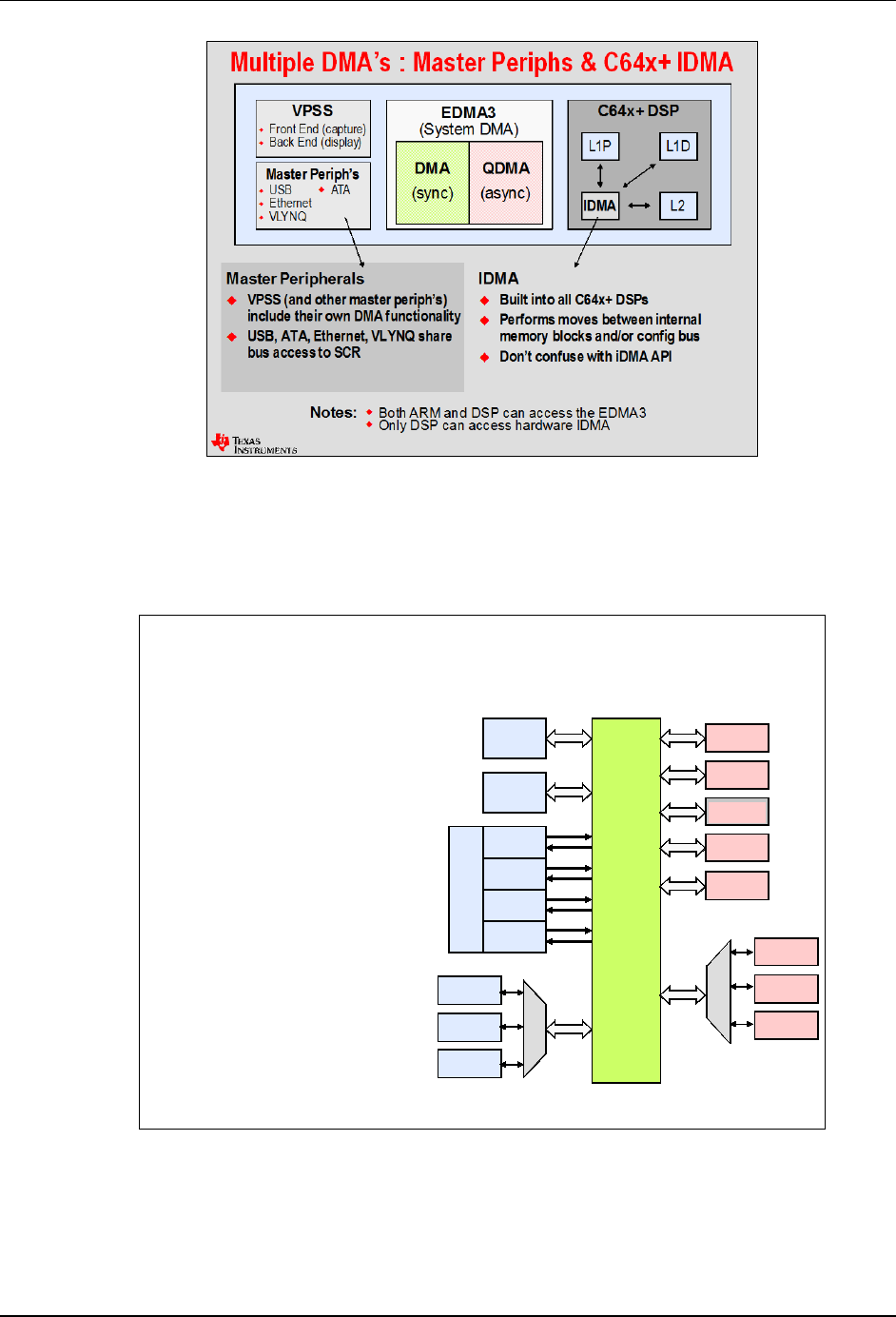

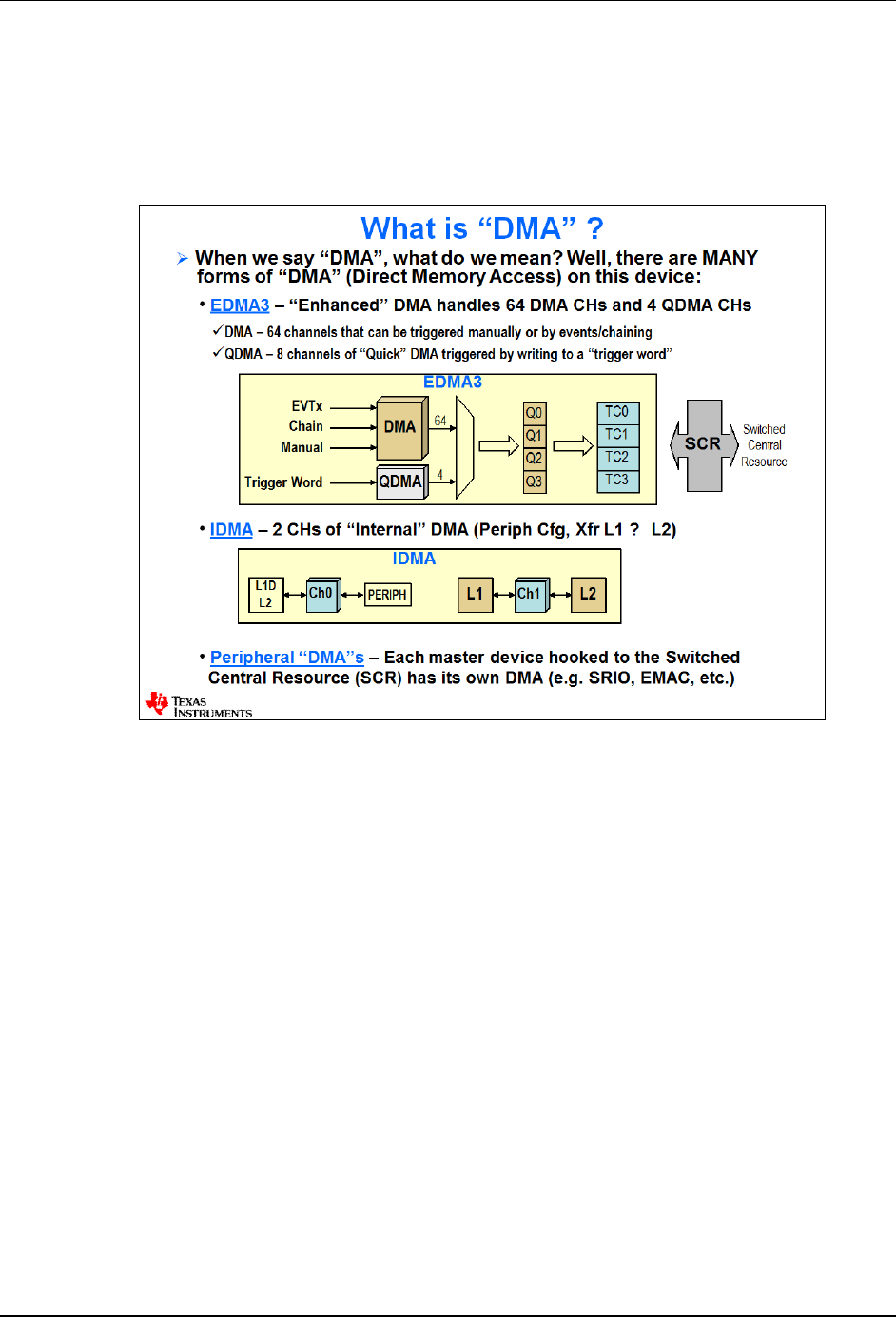

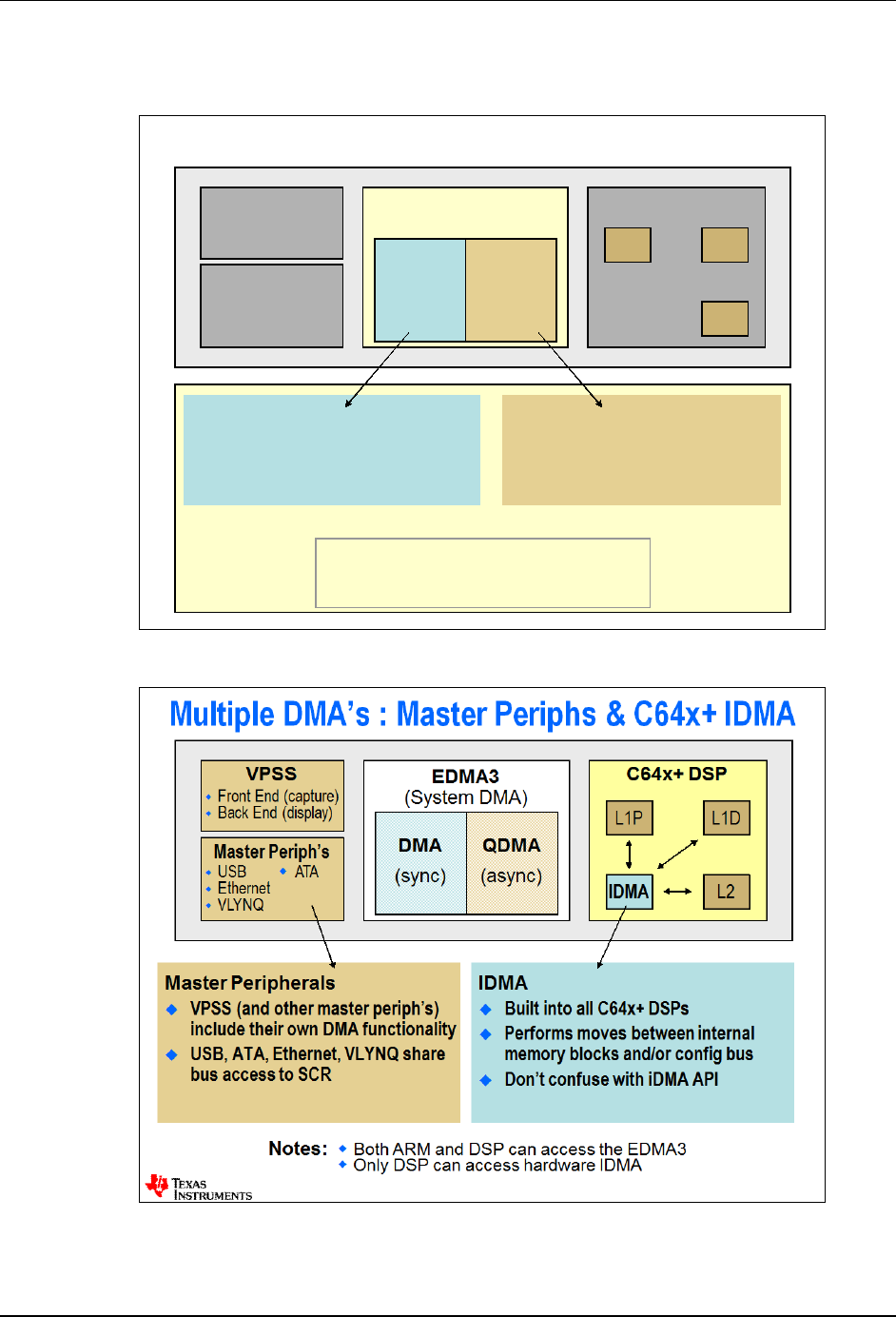

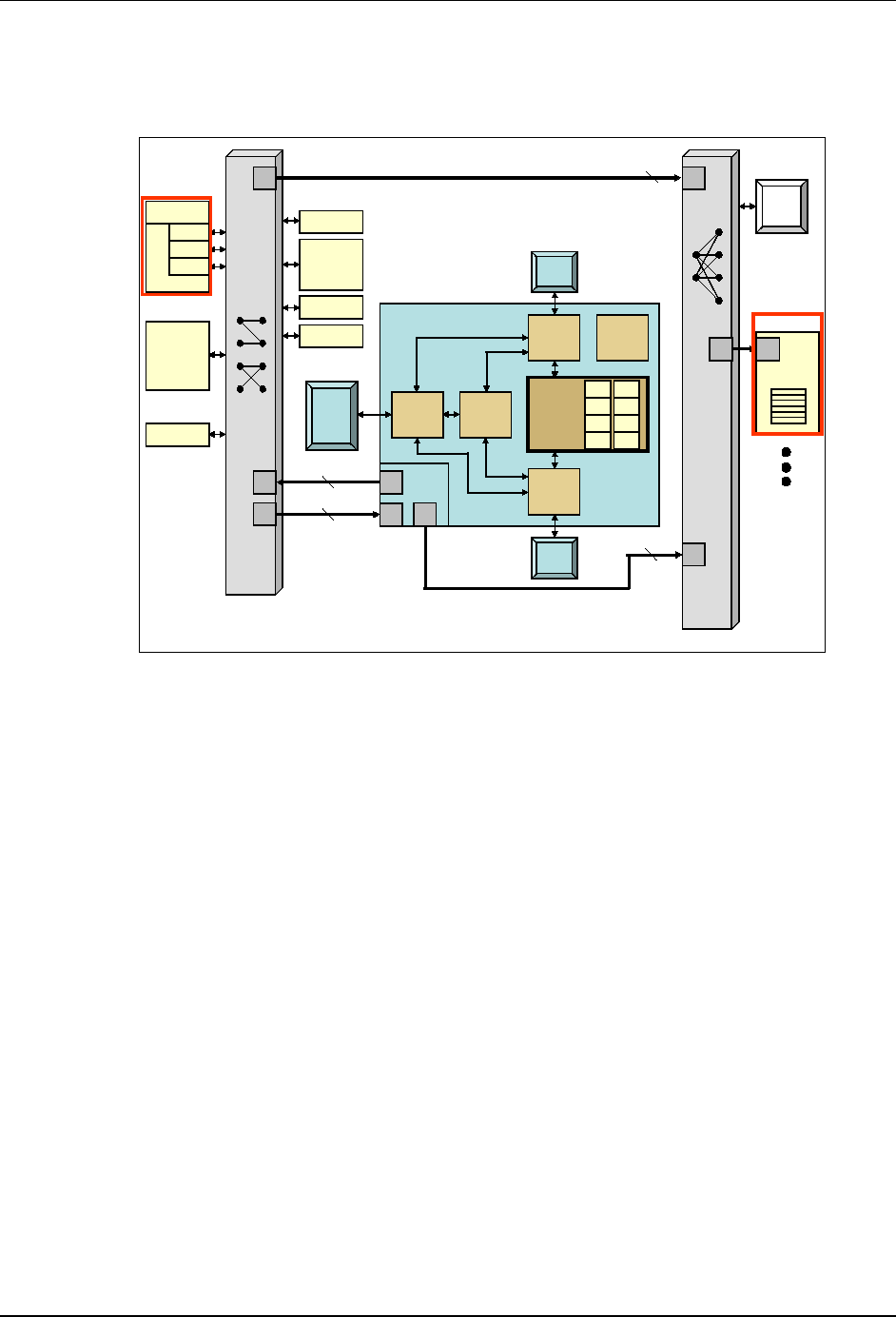

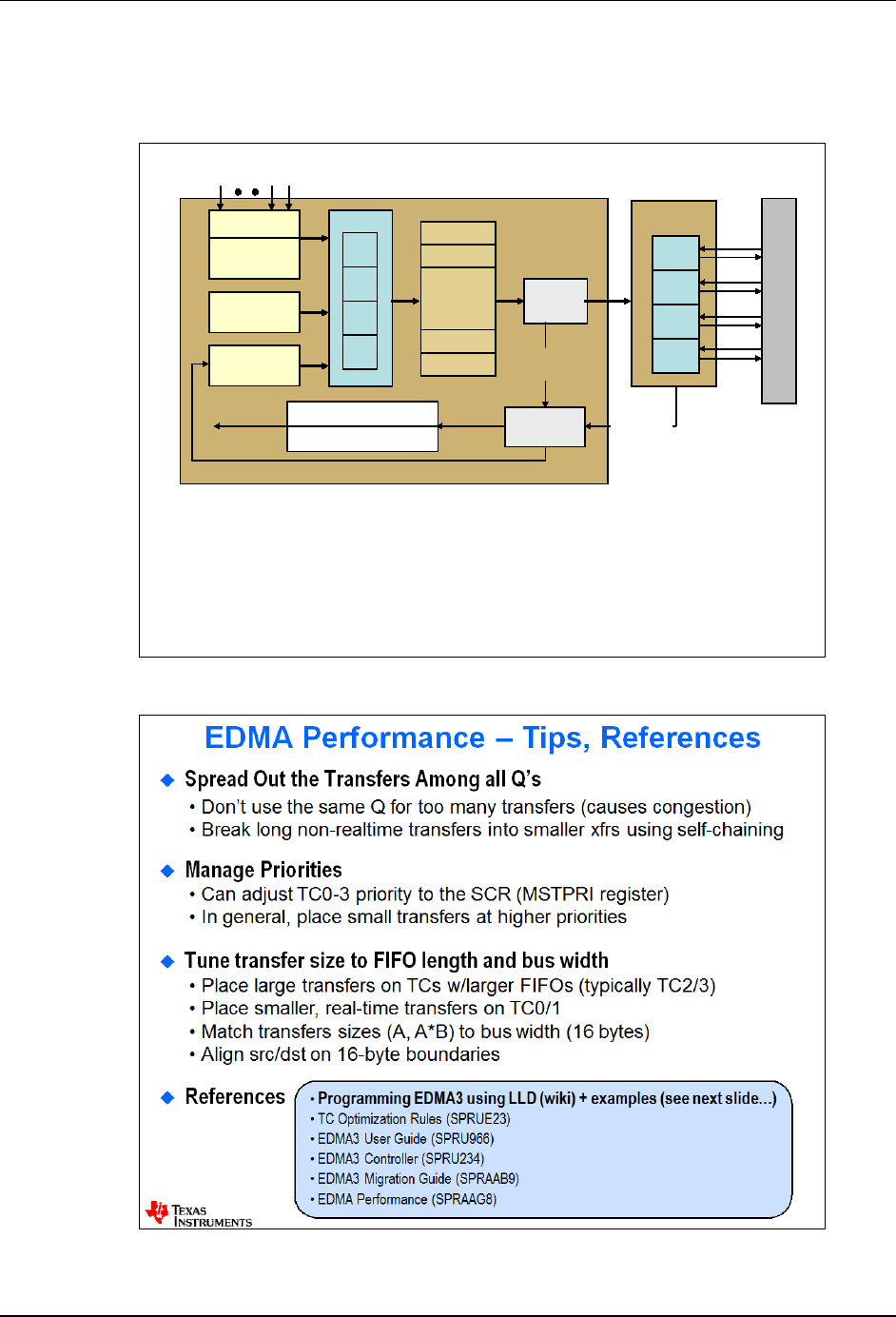

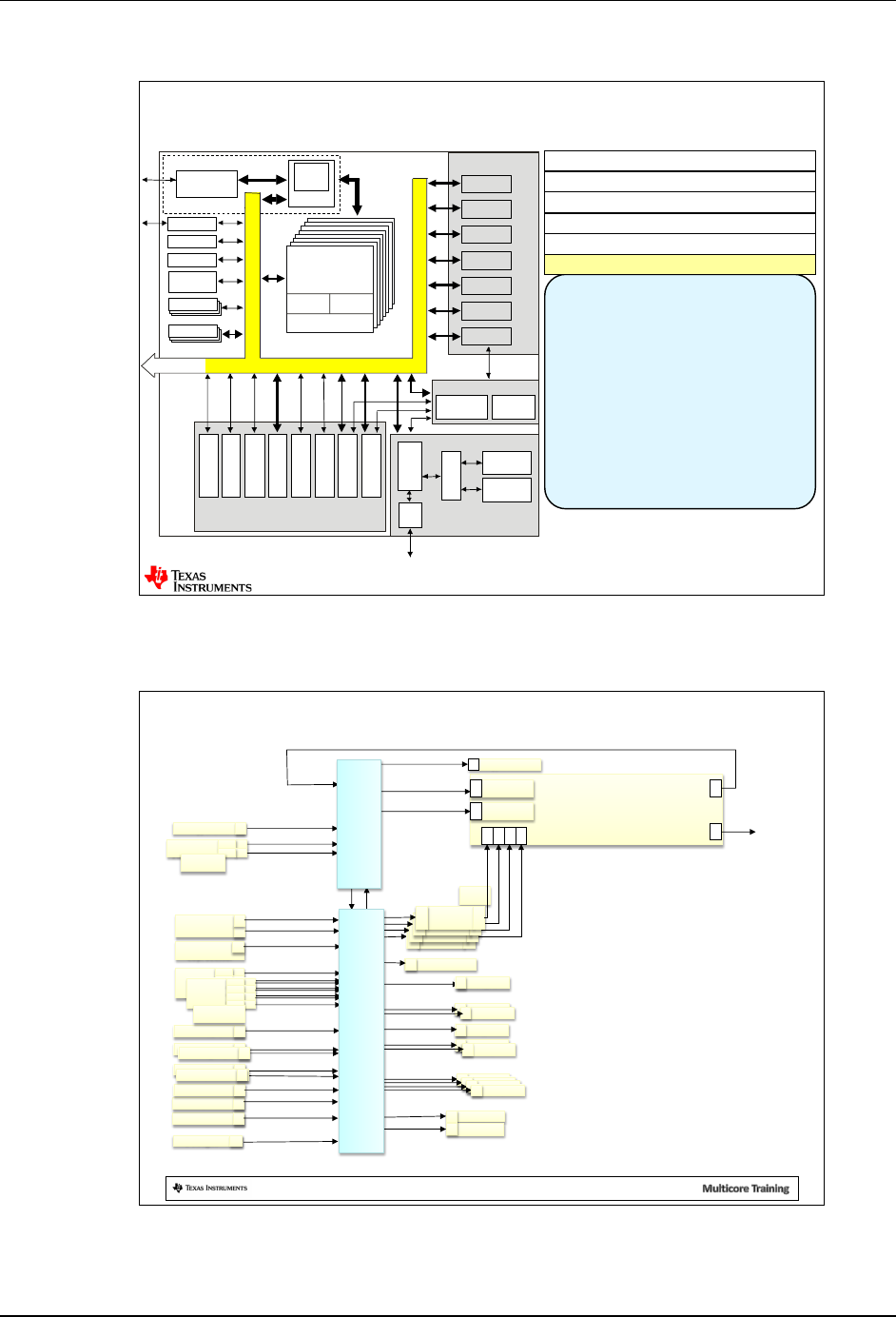

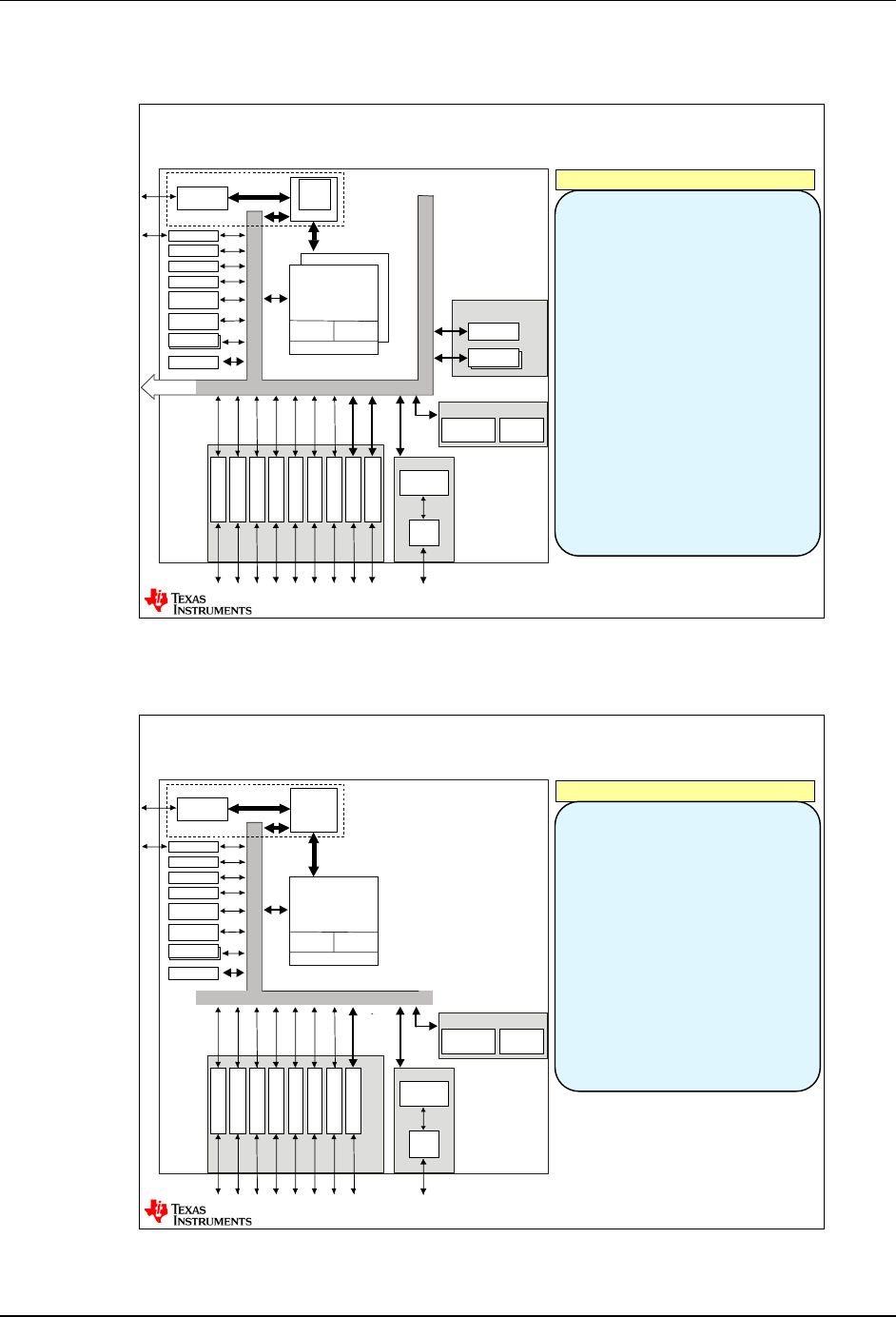

SCR / EDMA3

System Architecture –SCR/EDMA

ARM

DSP

TC0

TC1

TC2

CC

PCI

HPI

EMAC SCR

Switched

Central

Resource

C64 Mem

DDR2

EMIF64

TCP

VCP

PCI

McBSP

Utopia

“Masters” “Slaves”

SCR –Switched Central Resource

Masters initiate accesses to/from

slaves via the SCR

Most Masters (requestors) and Slaves

(resources) have their own port

to the SCR

Lower bandwidth masters (HPI,

PCI66, etc) share a port

There is a default priority (0 to 7) to

SCR resources that can be modified.

EDM A3

Note: this picture is the “general idea”.

Every device has a different scheme

for SCRs and peripheral muxing. In

other words “check your data sheet”.

Peripherals

C6000 Embedded Design Workshop - C6000 Introduction 11 - 9

TMS320C6748 Interconnect Matrix

Note: not ALL connections are valid

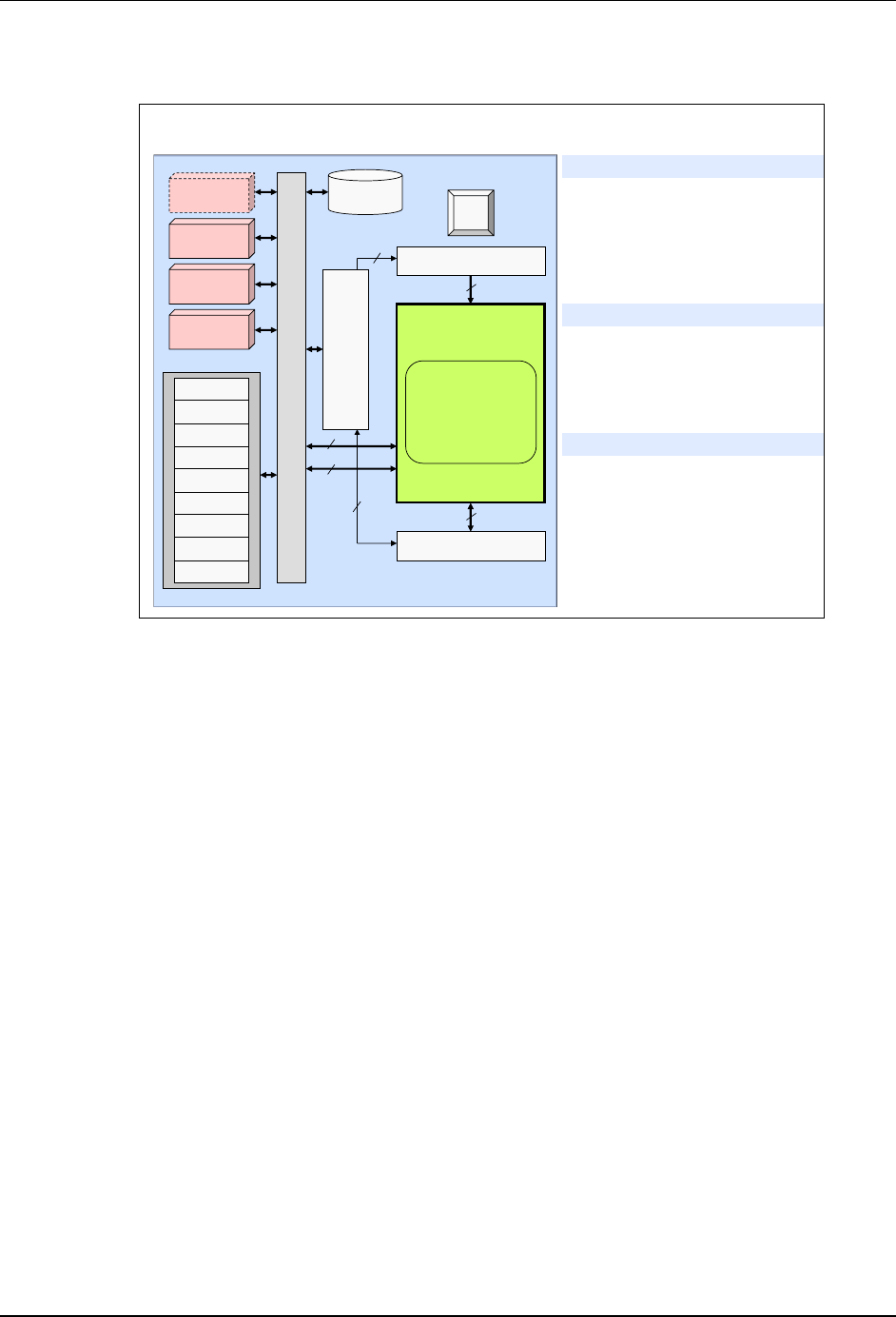

Pin Muxing

What is Pin Multiplexing?

How many pins are on your device?

How many pins would all your peripheral require?

Pin Multiplexing is the answer –only so many peripherals can be used at

the same time … in other words, to reduce costs, peripherals must share

available pins

Which ones can you use simultaneously?

Designers examine app use cases when deciding best muxing layout

Read datasheet for final authority on how pins are muxed

Graphical utility can assist with figuring out pin-muxing…Pin mux utility...

HPI

uPP

Pin Mux Example

Peripherals

11 - 10 C6000 Embedded Design Workshop - C6000 Introduction

Pin Muxing Tools

Graphical Utilities For Determining which Peripherals can be Used Simultaneously

Provides Pin Mux Register Configurations. Warns user about conflicts.

ARM-based devices: www.ti.com/tool/pinmuxtool others: see product page

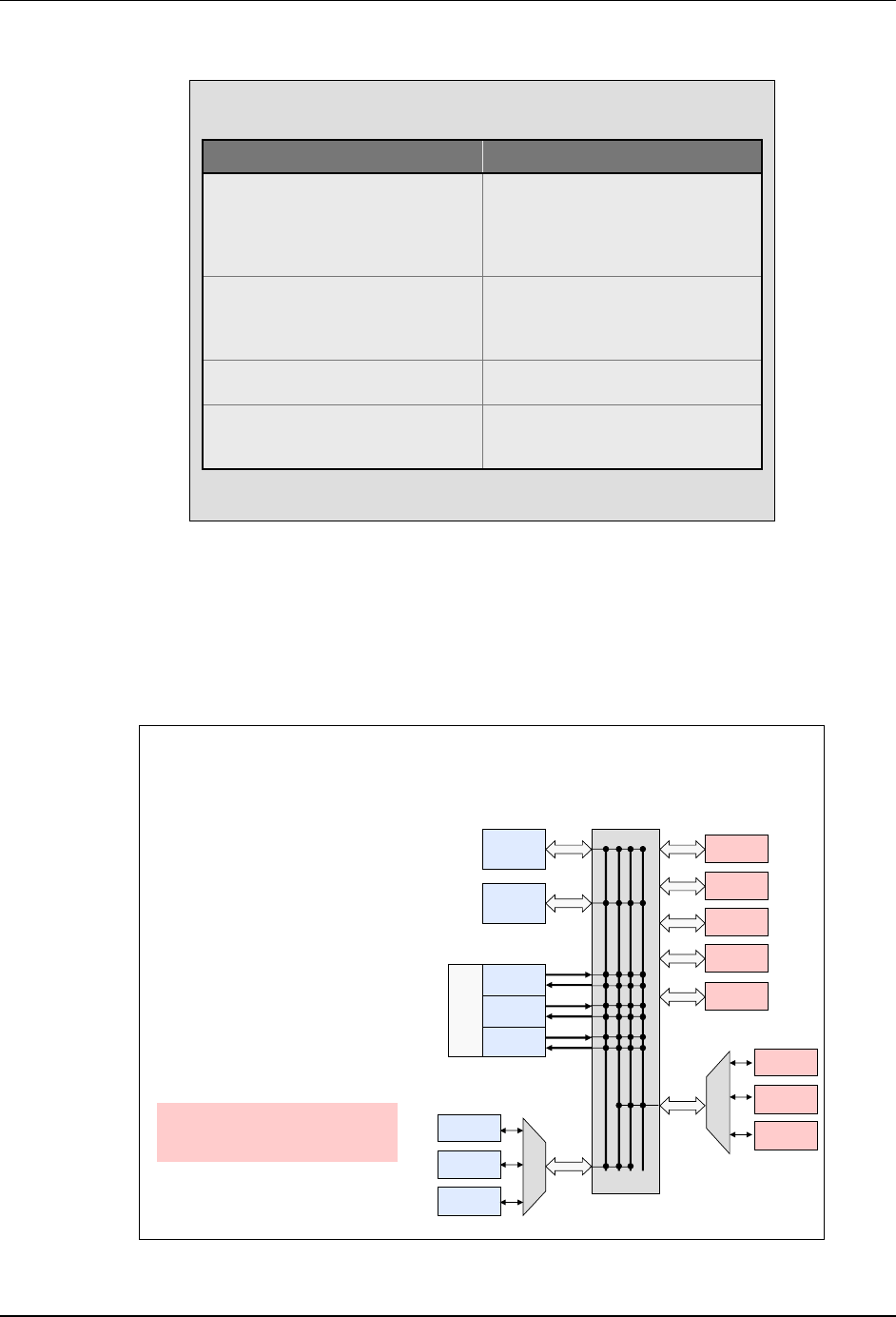

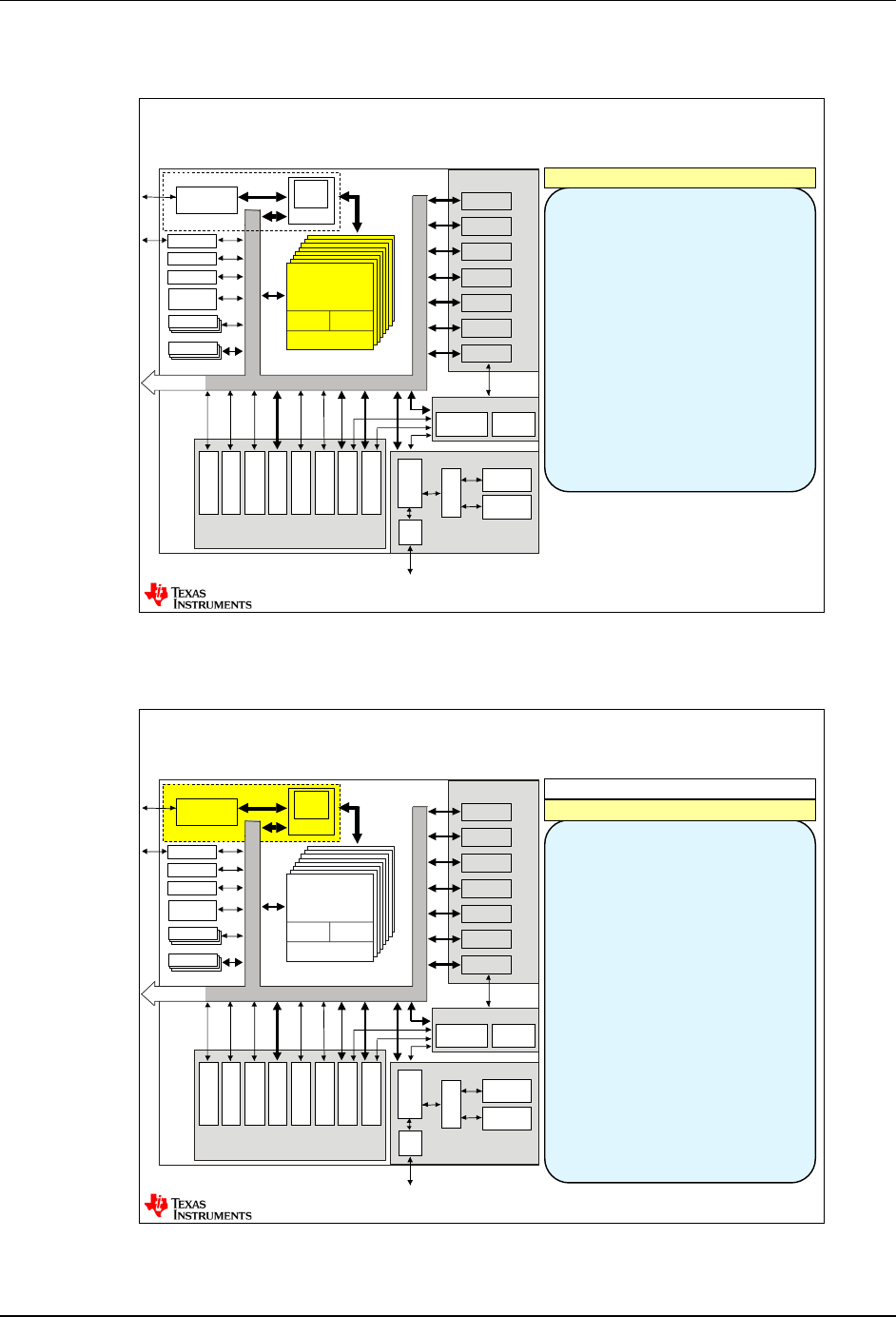

Example Device: C6748 DSP

C6000 Embedded Design Workshop - C6000 Introduction 11 - 11

Example Device: C6748 DSP

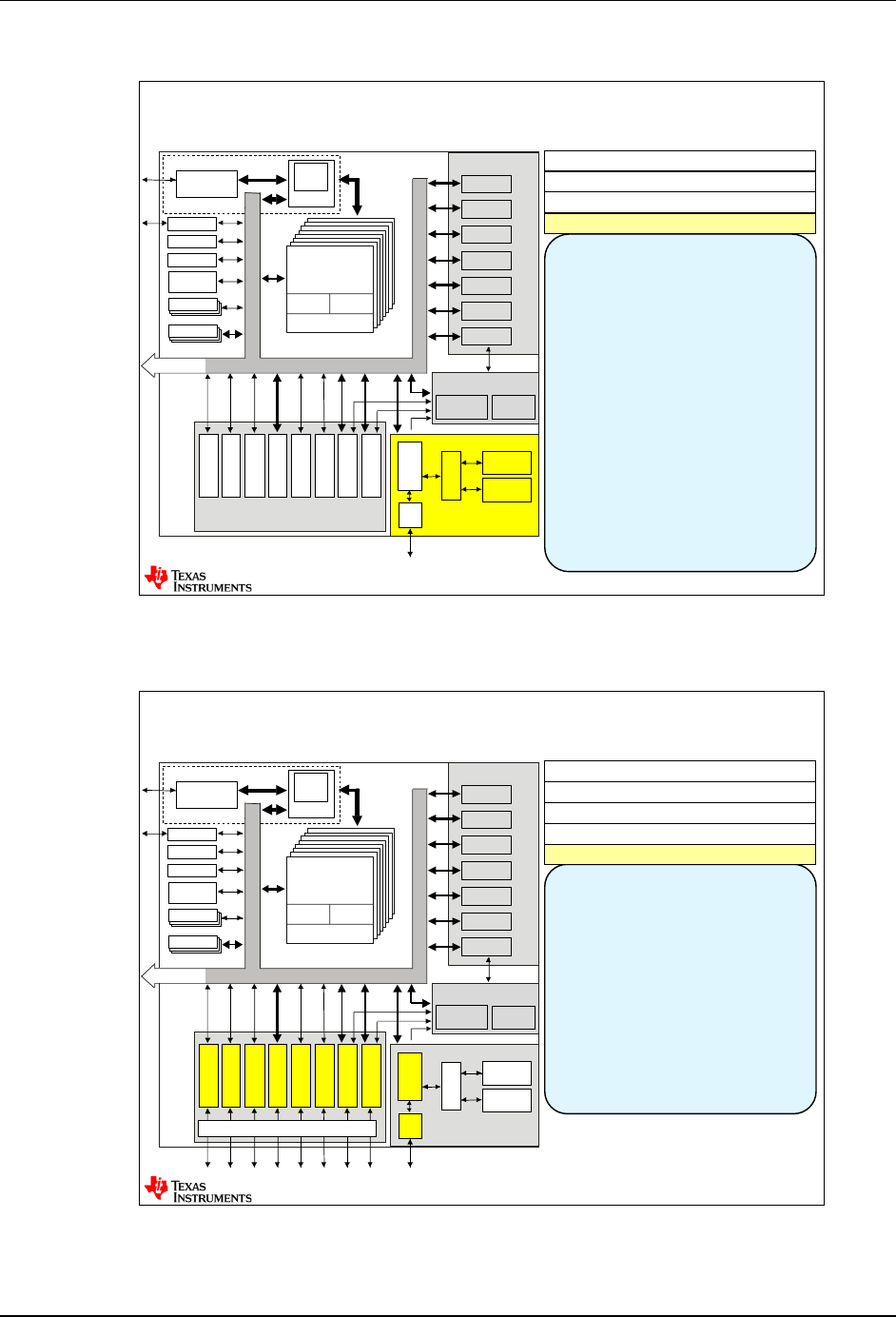

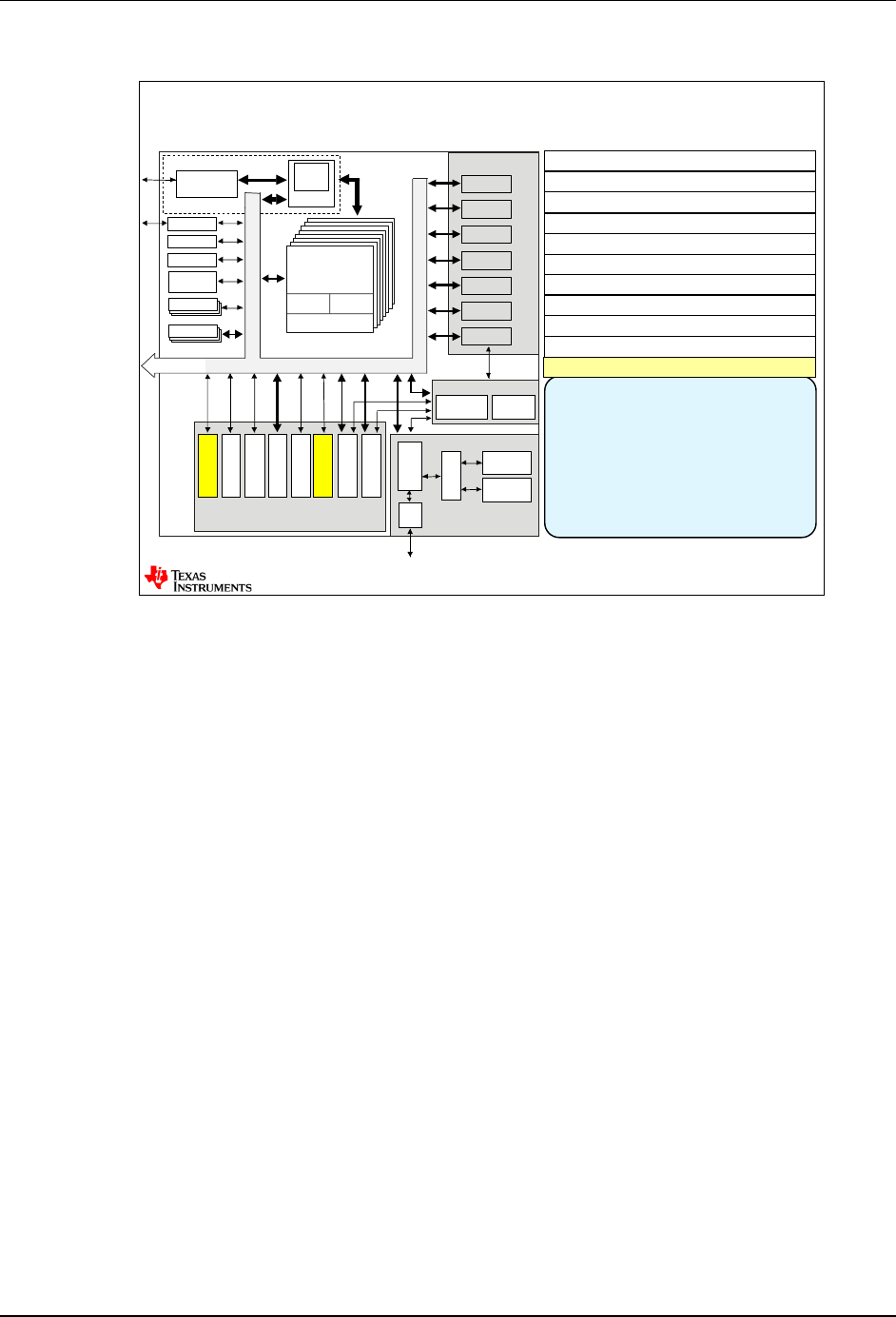

TMS320C674x Architecture -Overview

128K L3

16-bit EMIF

DDR2

mDDR

McASP

MMC/SD

EMAC

HPI

SATA

I2C, SPI, UART

Switched Central Resource (SCR)

256K

L2

EDMA3

C674x+ DSP Core

32KB L1P Cache/SRAM

32KB L1D Cache/SRAM

4-32x

PLL

Performance & Memory

TMS320C6748

128

128

256

128

Communications

•Up to 456MHz

•256K L2 (cache/SRAM)

•32K L1P/D Cache/SRAM

•16-bit DDR2-266

•16-bit EMIF (NAND Flash)

•64-Channel EDMA 3.0

•10/100 EMAC

•USB 1.1 & 2.0

•S ATA

Power/Packaging

•13x13mm nPBGA & 16x16mm

PBGA

•Pin-to-pin compatible w/OMAP

L138 (+ARM9), 361-pin pkg

•Dynamic voltage/freq scaling

•Total Power < 420mW

128

128

USB

Timers

LCD, PWM, eCAP

uPP

Fixed & Floating-Pt

CPU

Choosing a Device

11 - 12 C6000 Embedded Design Workshop - C6000 Introduction

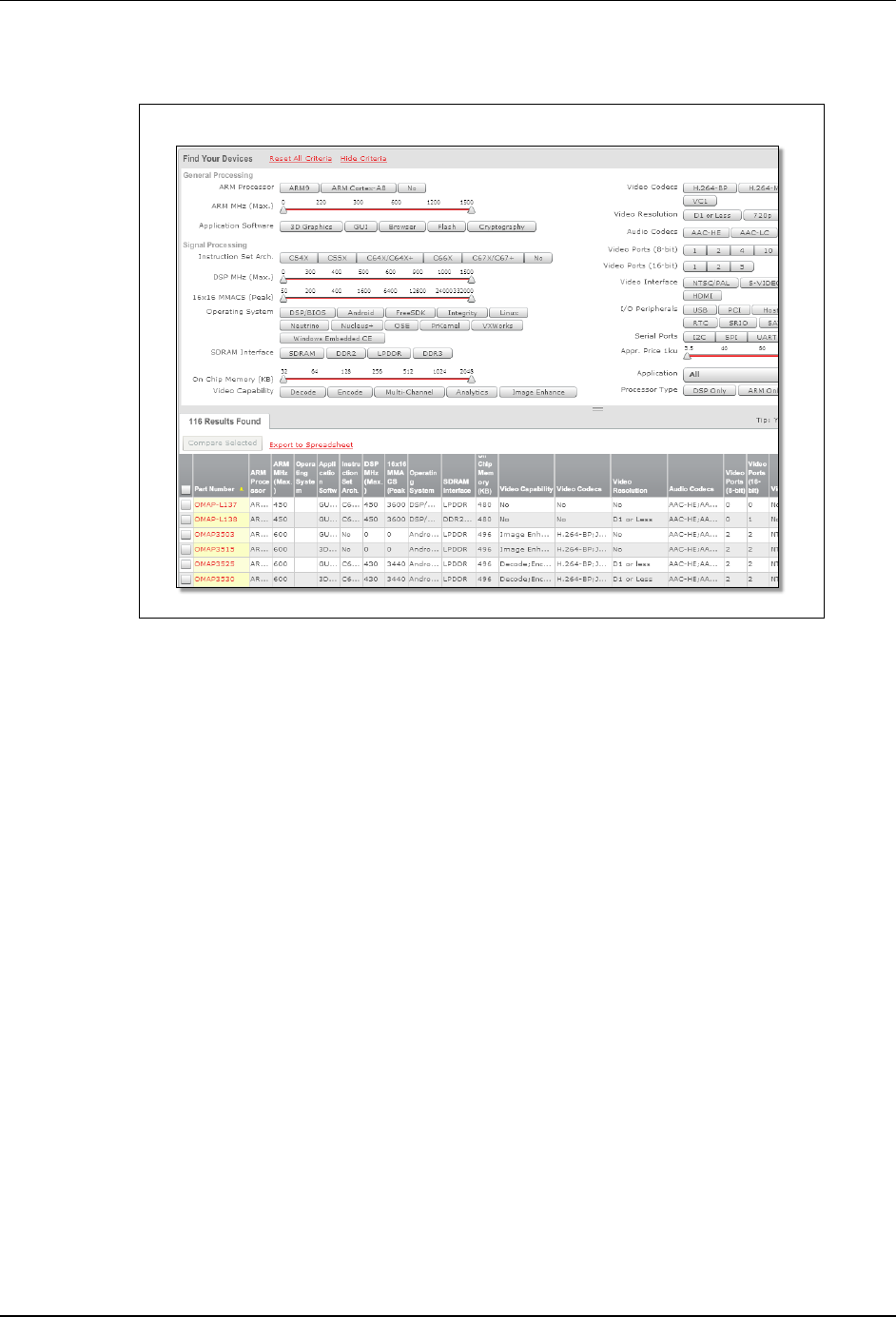

Choosing a Device

DSP & ARM MPU Selection Tool

http://focus.ti.com/en/multimedia/flash/selection_tools/dsp/dsp.html

C6000 Arch “Catchup”

C6000 Embedded Design Workshop - C6000 Introduction 11 - 13

C6000 Arch “Catchup”

C64x+ Interrupts

How do Interrupts Work?

1. An interrupt occurs

•EDMA

•McASP

•Timer

•Ext’l pins

2. Interrupt Selector

124+4

12

3. Sets flag in Interrupt

Flag Register

(IFR)

…

4. Is this specific interrupt

enabled? (IER)

5. Are interrupts globally

enabled? (GIE/NMIE)

6. •CPU Acknowledge

•Auto hardware sequence

•HWI Dispatcher (vector)

•Branch to ISR

7. Interrupt Service Routine (ISR)

•Context Save, ISR, Context Restore

User is responsible for setting up the following:

•#2 –Interrupt Selector (choose which 12 of 128 interrupt sources to use)

•#4 –Interrupt Enable Register (IER) –individually enable the proper interrupt sources

•#5 –Global Interrupt Enable (GIE/NMIE) –globally enable all interrupts

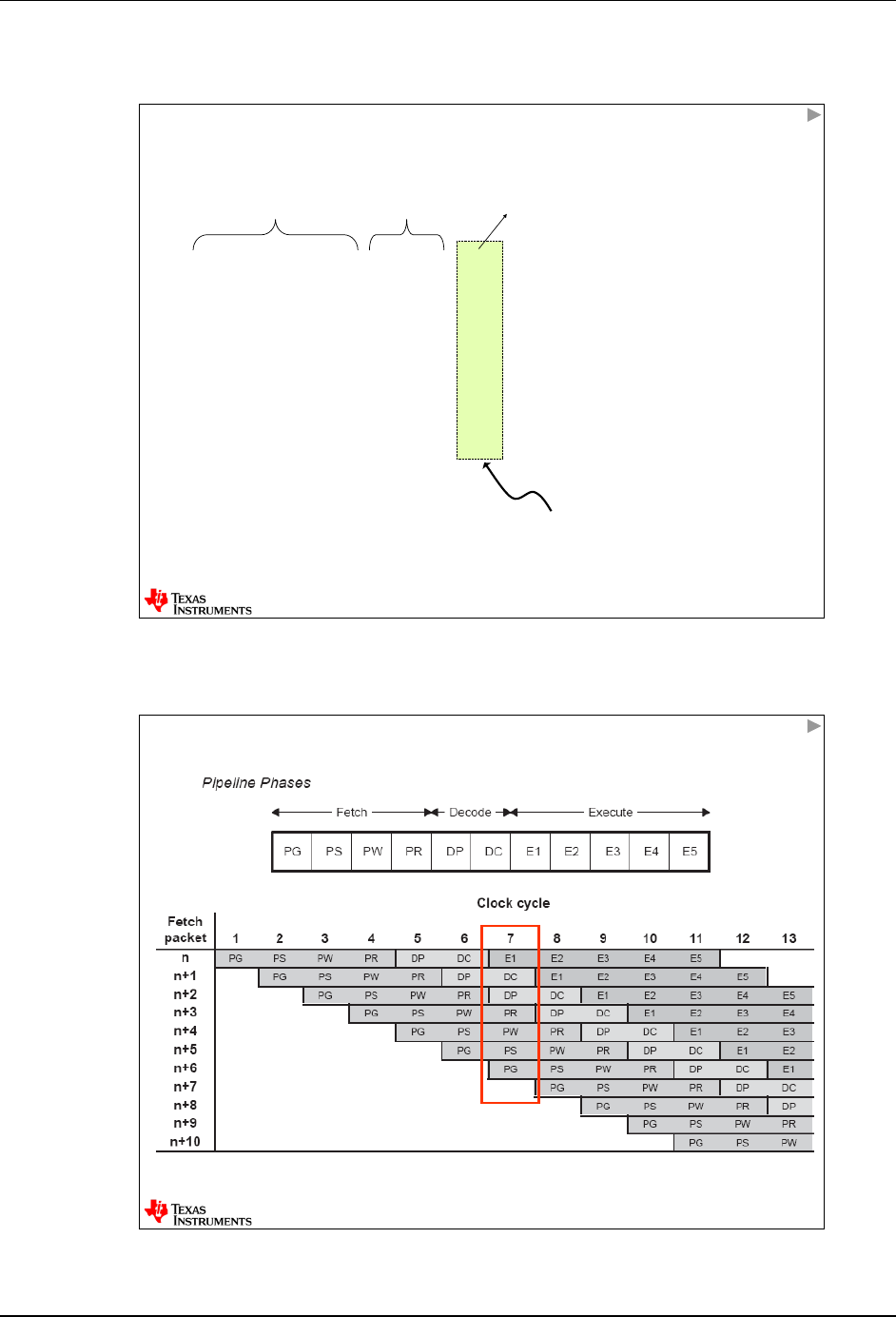

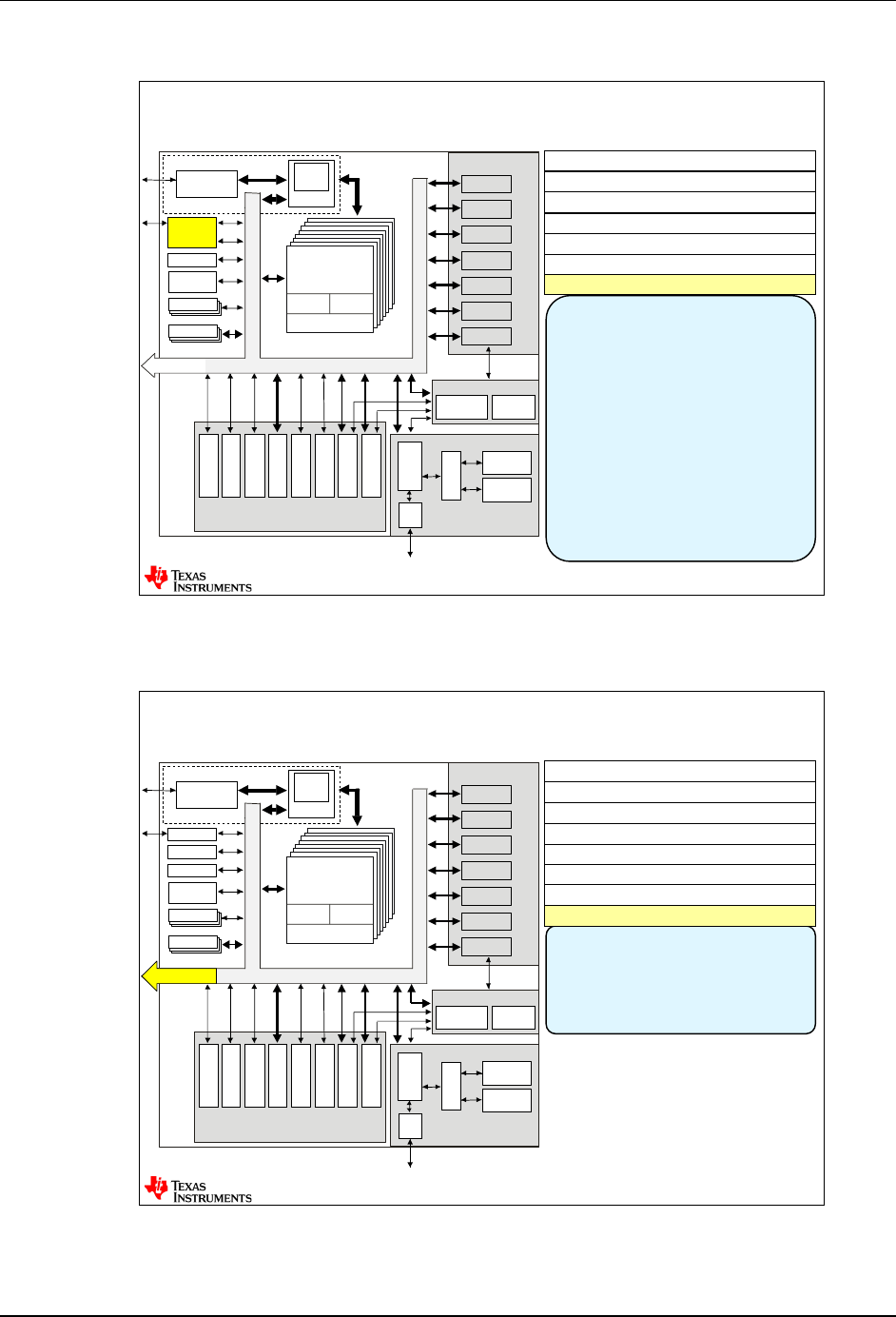

C64x+ Hardware Interrupts

C6748 has 128 possible interrupt sources (but only 12 CPU interrupts)

4-Step Programming:

Interrupt

Selector

0.

.

MCASP0_INT

.

.

127

0

HWI

4

1

HWI

5

0

HWI

15

.

.

.

IFR IER GIE

Vector

Table

1. Interrupt Selector –choose which of the 128 sources are tied to the 12 CPU ints

2. IER –enable the individual interrupts that you want to “listen to” (in BIOS .cfg)

3. GIE –enable global interrupts (turned on automatically if BIOS is used)

4. Note: HWI Dispatcher performs “smart” context save/restore (automatic for BIOS Hwi)

1 2 3 4

Note: NMIE must also be enabled. BIOS automatically sets NMIE=1. If

BIOS is NOT used, the user must turn on both GIE and NMIE manually.

C6000 Arch “Catchup”

11 - 14 C6000 Embedded Design Workshop - C6000 Introduction

Event Combiner

Event Combiner (ECM)

EVT 4-31

EVTFLAG[0]

Interrupt

Selector

C

P

U

128:12

EVT 32-63

EVTFLAG[1]

EVT 64-95

EVTFLAG[2]

EVT 96-127

EVTFLAG[3]

EVTMASK[0]

EVTMASK[1]

EVTMASK[2]

EVTMASK[3]

MEVTFLAG[0]

MEVTFLAG[1]

MEVTFLAG[2]

MEVTFLAG[3]

EVT0

EVT1

EVT2

EVT3

EVT 4-127

Occur? Care? Both Yes?

Use only if you need more than 12 interrupt events

ECM combines multiple events (e.g. 4-31) into one event (e.g. EVT0)

EVTx ISR must parse MEVTFLAG to determine which event occurred

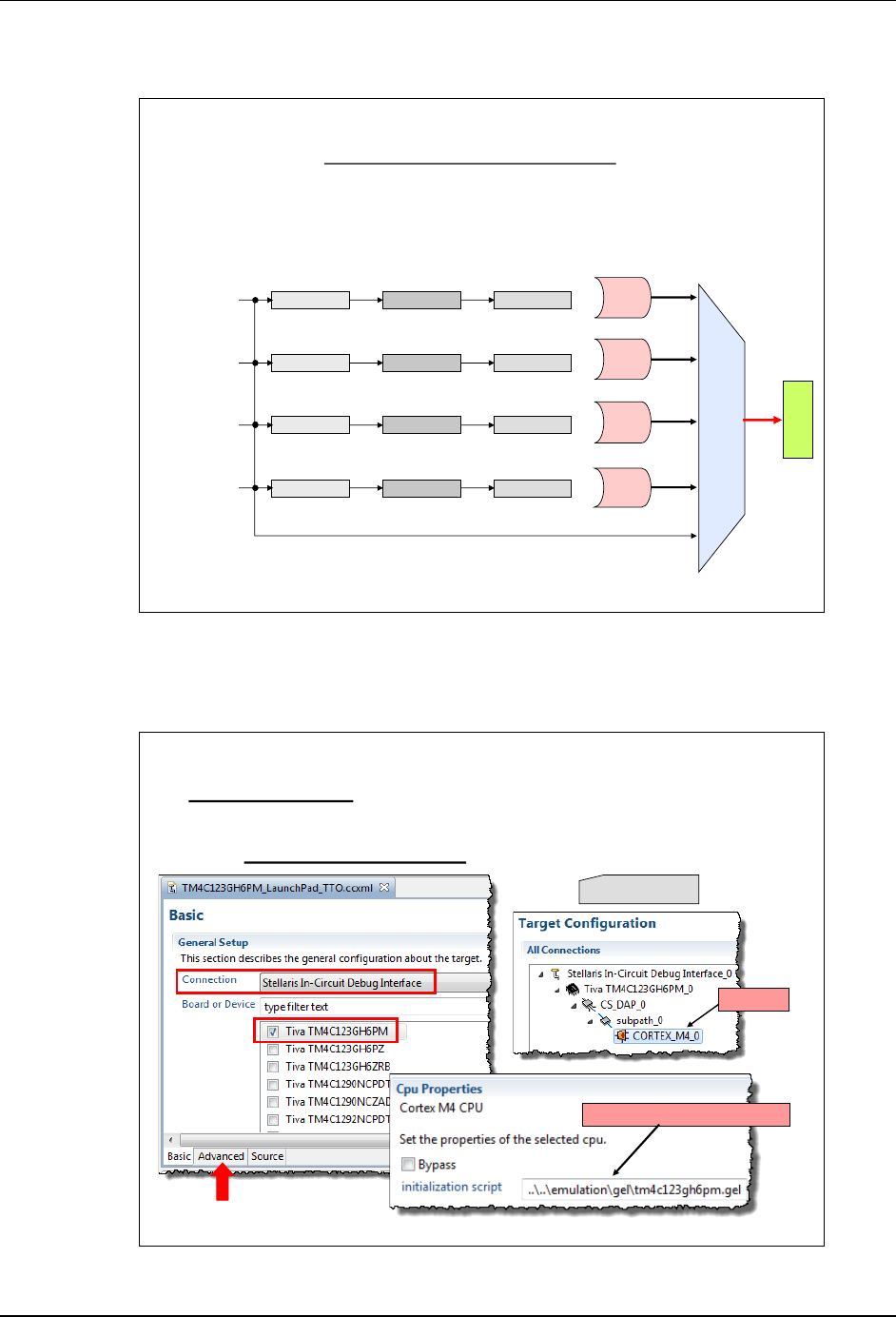

Target Config Files

Creating a New Target Config File (.ccxml)

Target Configuration –defines your “target” –i.e. emulator/device used, GEL

scripts (replaces the old CCS Setup)

Create user-defined configurations (select based on chosen board)

“click”

Advanced Tab

More on GEL files...

Specify GEL script here

C6000 Arch “Catchup”

C6000 Embedded Design Workshop - C6000 Introduction 11 - 15

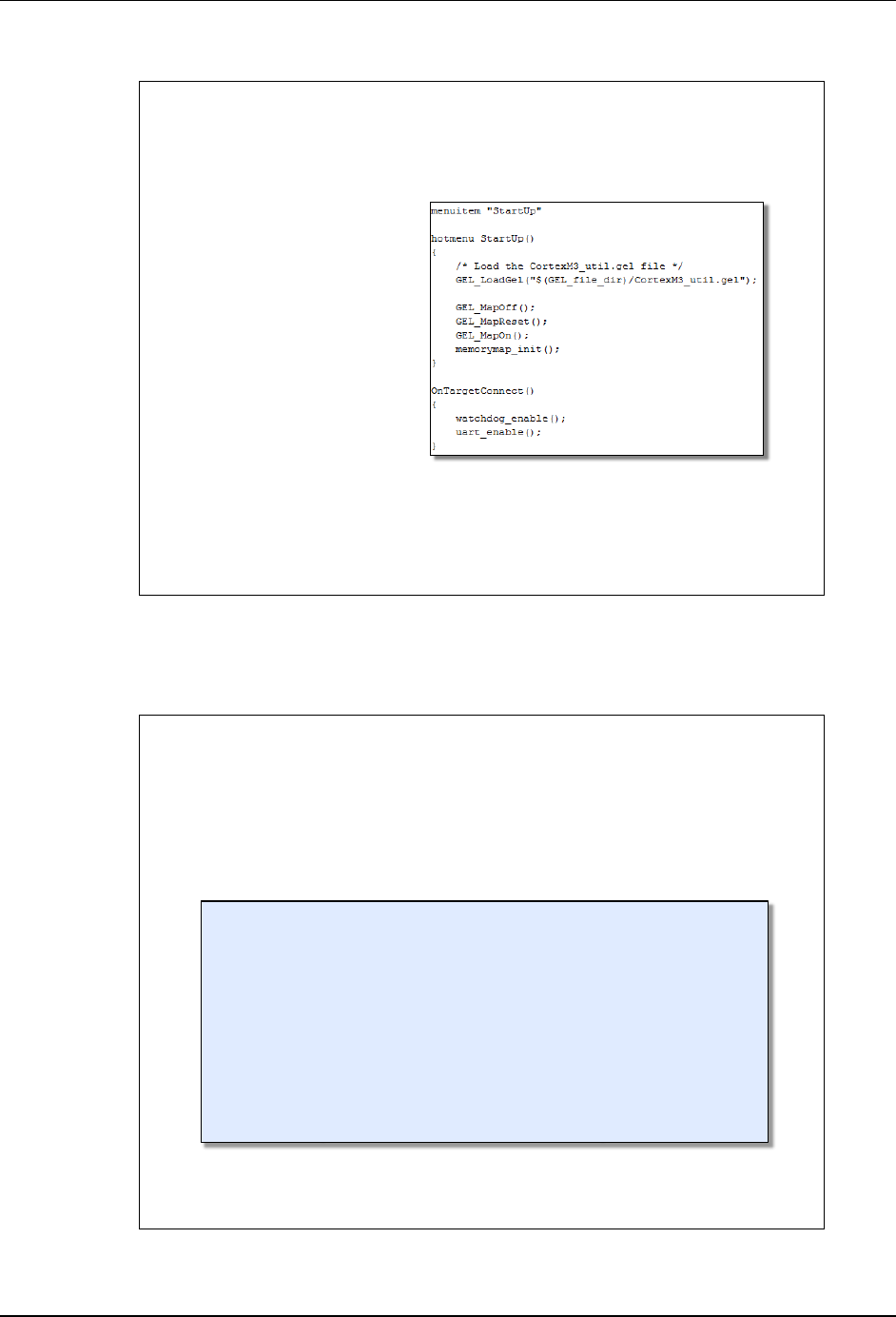

What is a GEL File ?

GEL –General Extension Language (not much help, but there you go…)

A GEL file is basically a “batch file” that sets up the CCS debug

environment including:

•Memory Map

•Watchdog

•UART

•Other periphs

The board manufacturer (e.g. SD or LogicPD) supplies GEL files

with each board.

To create a “stand-alone” or “bootable” system, the user must

write code to perform these actions (optional chapter covers these details)

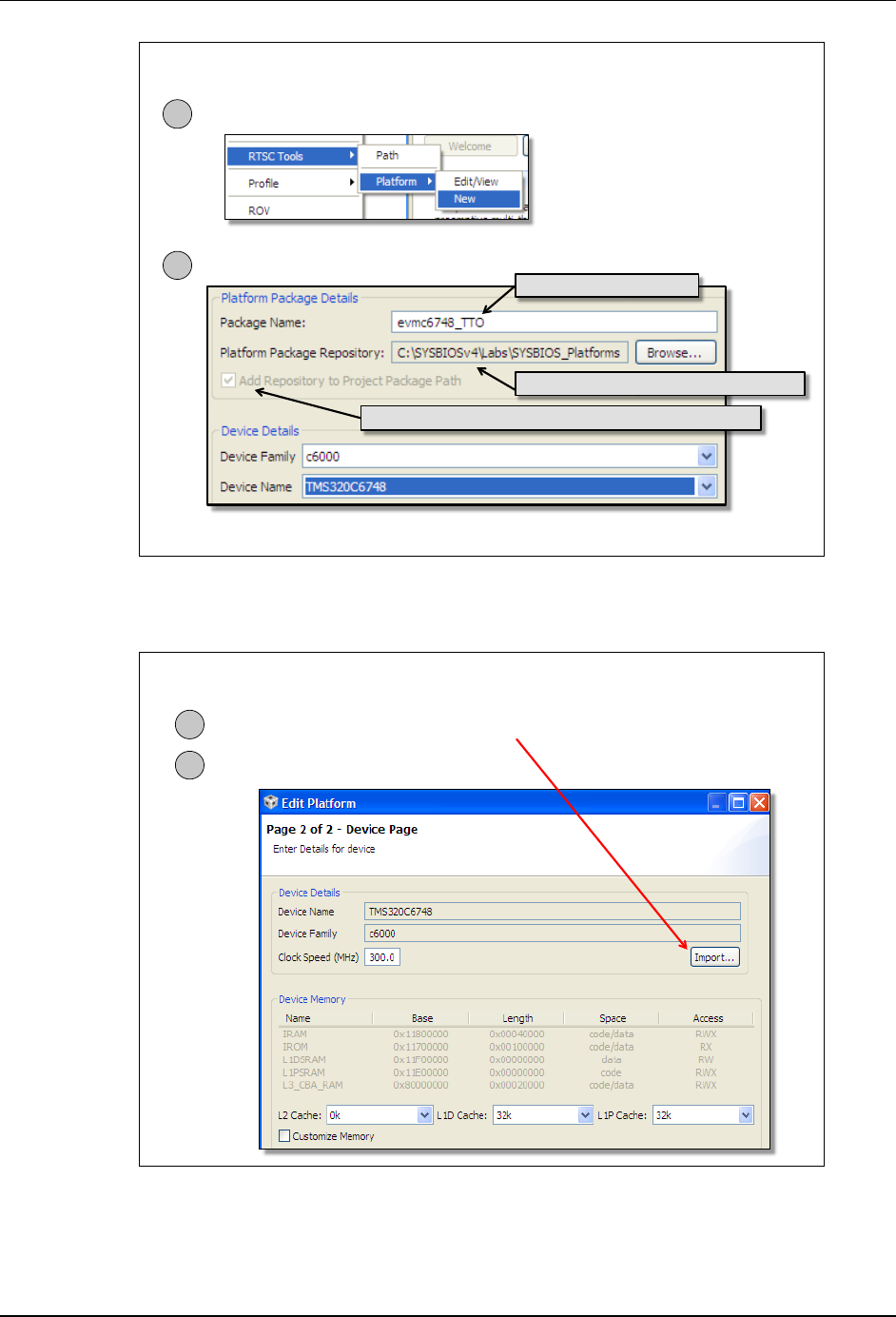

Creating Custom Platforms

Creating Custom Platforms -Procedure

Most users will want to create their own custom

platform package (Stellaris/c28X –maybe not –

they will use a .cmd file directly)

Here is the process:

1. Create a new platform package

2. Select repository, add to project path, select device

3. Import the existing “seed” platform

4. Modify settings

5. [Save] –creates a custom platform pkg

6. Build Options –select new custom platform

C6000 Arch “Catchup”

11 - 16 C6000 Embedded Design Workshop - C6000 Introduction

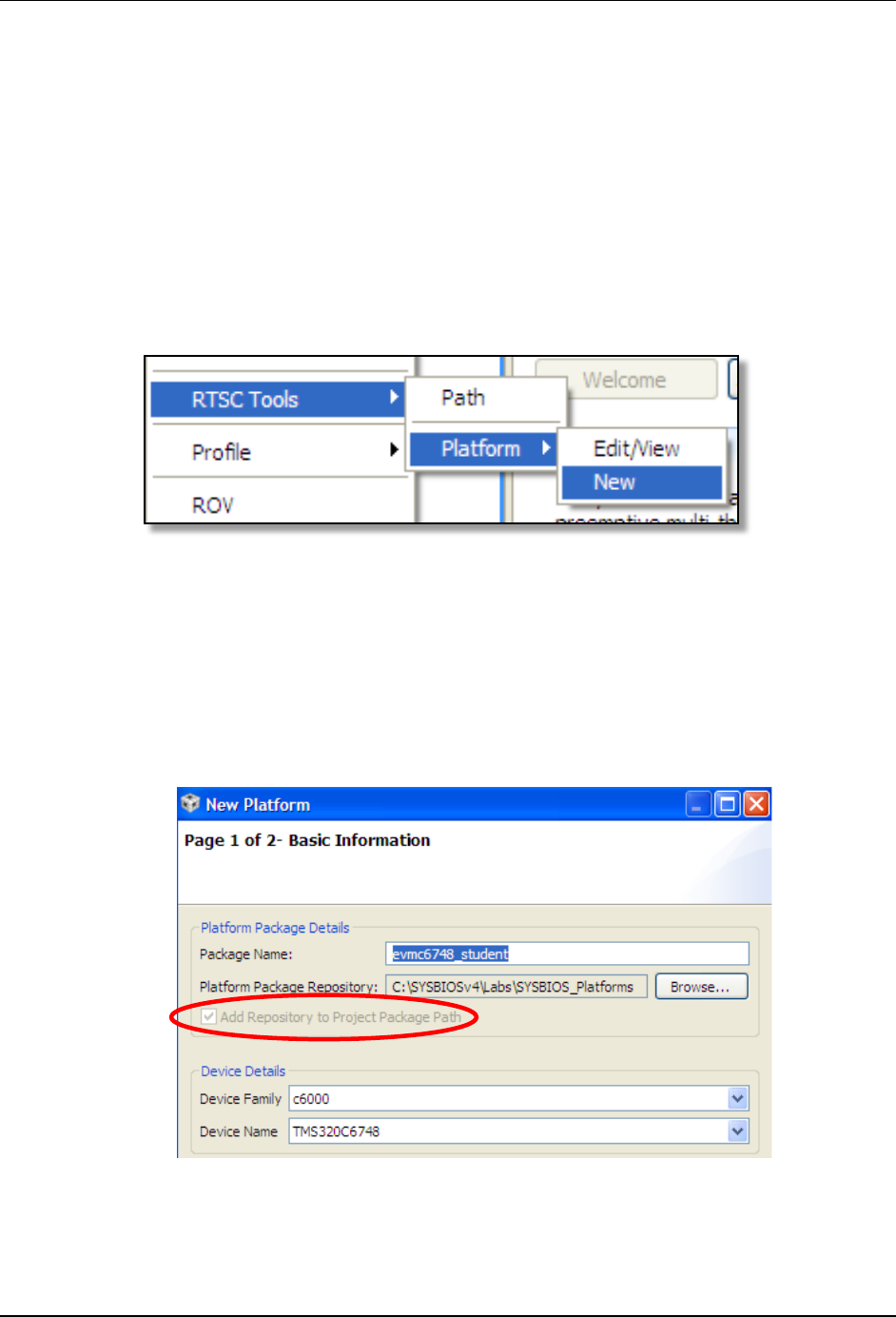

Creating Custom Platforms -Procedure

1Create New Platform (via DEBUG perspective)

2Configure New Platform

“Add Repository to Path” –adds platform path to project path

Custom Repository vs. XDC default location

Platform Package Name

Creating Custom Platforms -Procedure

3New Device Page –Click “Import” (copy “seed” platform)

4Customize Settings

C6000 Arch “Catchup”

C6000 Embedded Design Workshop - C6000 Introduction 11 - 17

Creating Custom Platforms -Procedure

5[SAVE] New Platform (creates custom platform package)

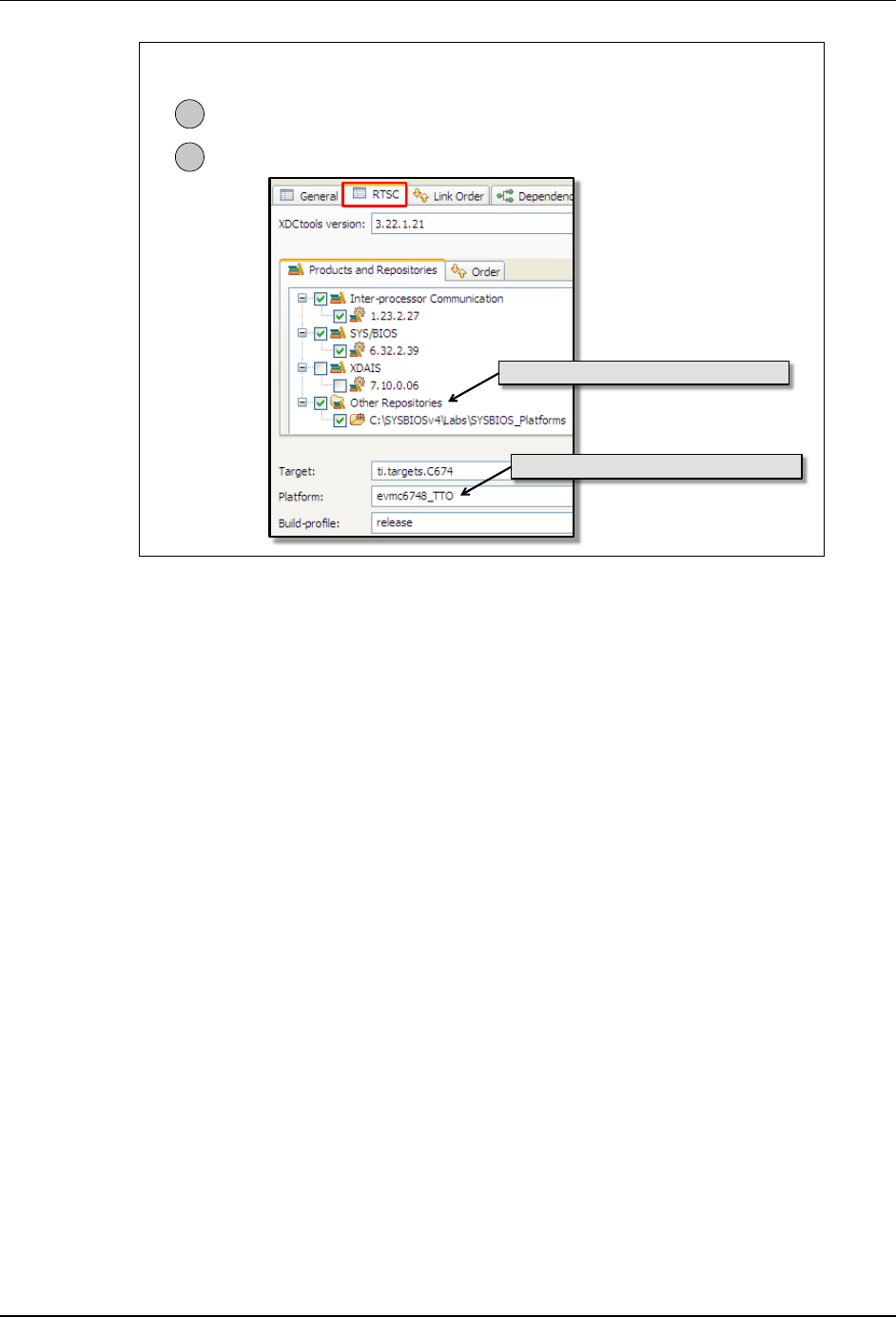

6Select New Platform in Build Options (RTSC tab)

Custom Repository vs. XDC default location

With path added, the tools find new platform

C6000 Arch “Catchup”

11 - 18 C6000 Embedded Design Workshop - C6000 Introduction

*** this page is blank for absolutely no reason ***

Quiz

C6000 Embedded Design Workshop - C6000 Introduction 11 - 19

Quiz

Chapter Quiz

CPU

256

128

1. How many functional units does the C6000 CPU have?

2. What is the size of a C6000 instruction word?

3. What is the name of the main “bus arbiter” in the architecture?

4. What is the main difference between a bus “master” and “slave”?

5. Fill in the names of the following blocks of memory and bus:

Quiz

11 - 20 C6000 Embedded Design Workshop - C6000 Introduction

Quiz - Answers

Chapter Quiz

•8 functional units or “execution units”

•256 bits (8 units x 32-bit instructions per unit)

•Switched Central Resource (SCR)

•Masters can initiate a memory transfer (e.g. EDMA, CPU…)

CPU

256

128

L1P

L1D

L2

S

C

R

1. How many functional units does the C6000 CPU have?

2. What is the size of a C6000 instruction word?

3. What is the name of the main “bus arbiter” in the architecture?

4. What is the main difference between a bus “master” and “slave”?

5. Fill in the names of the following blocks of memory and bus:

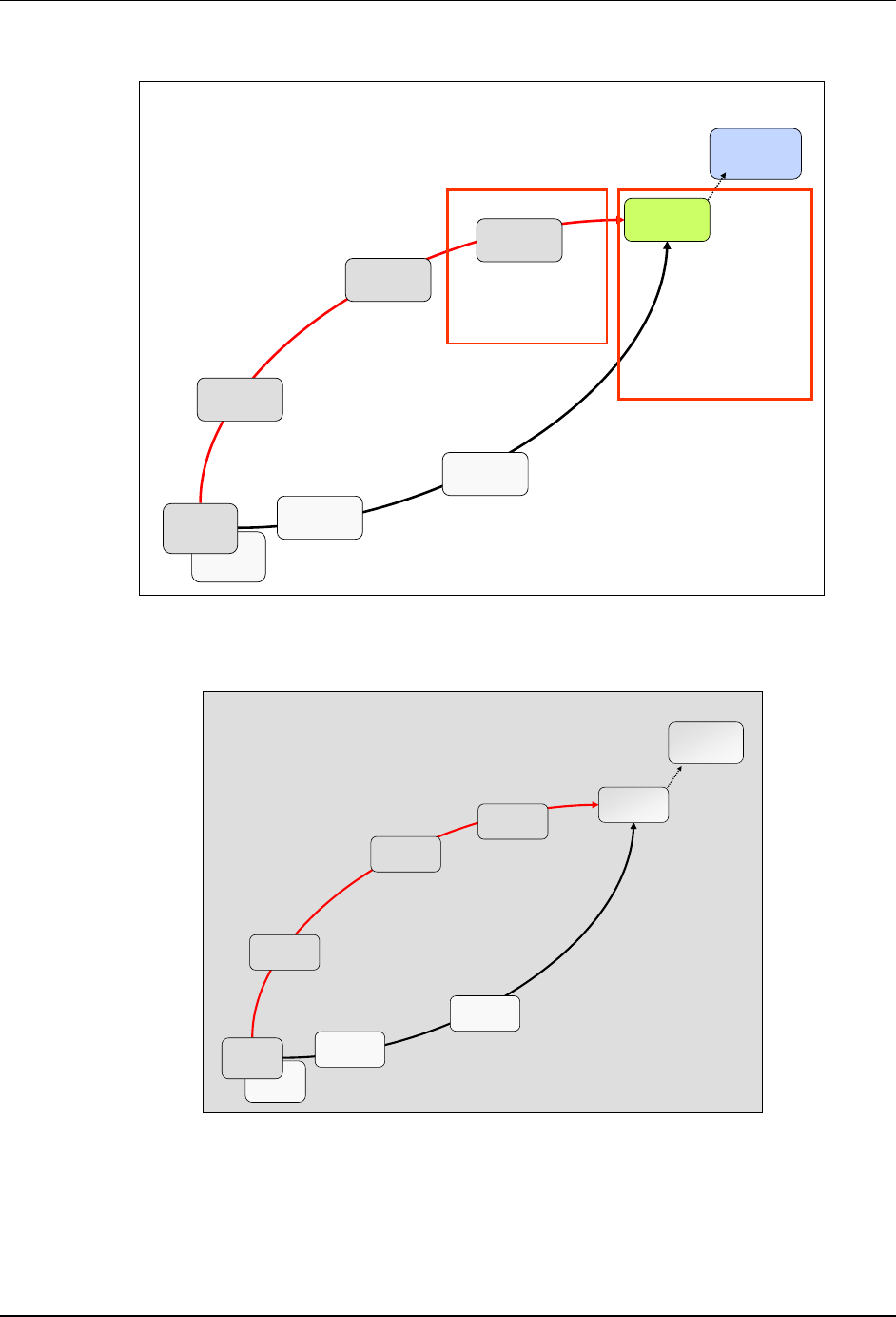

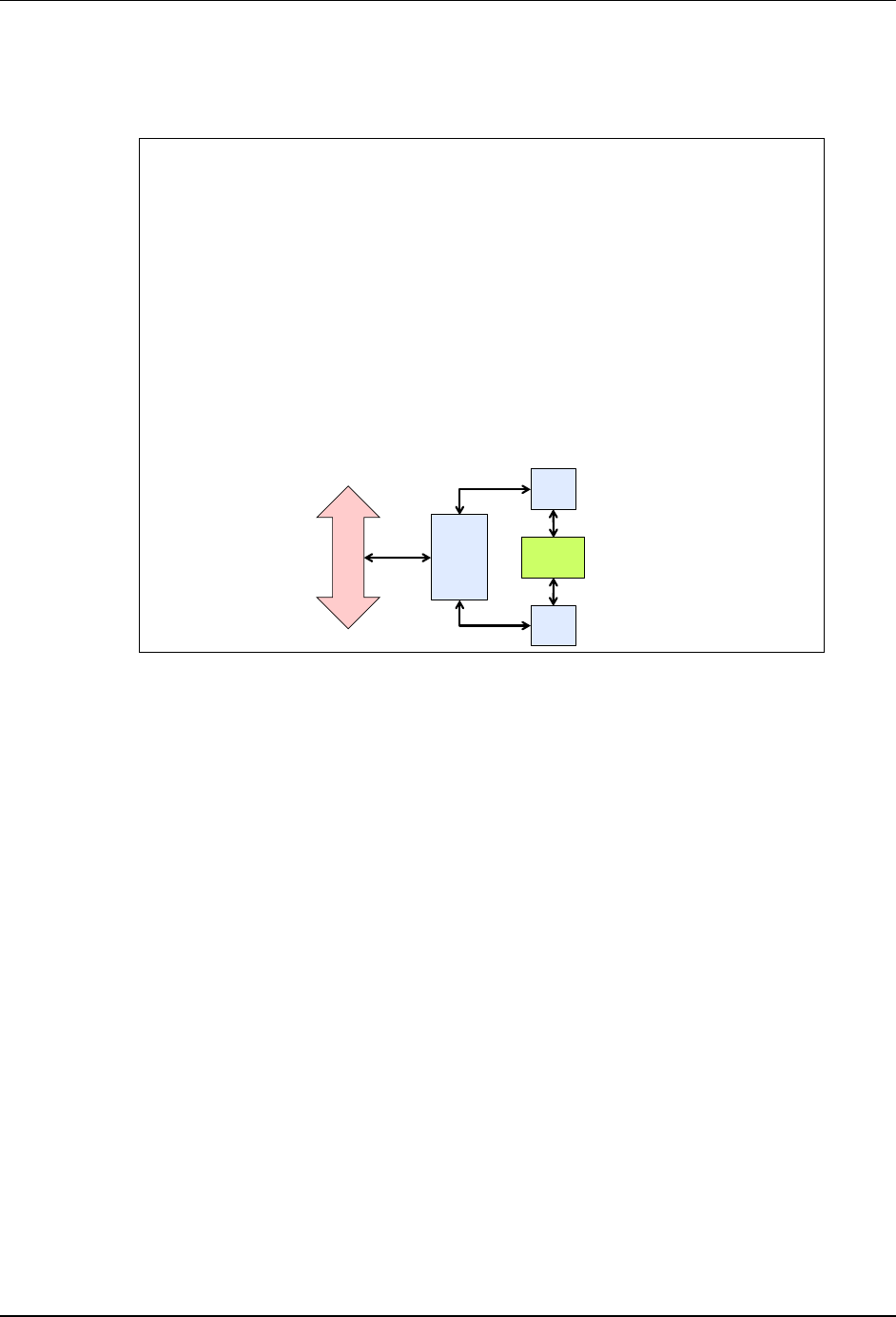

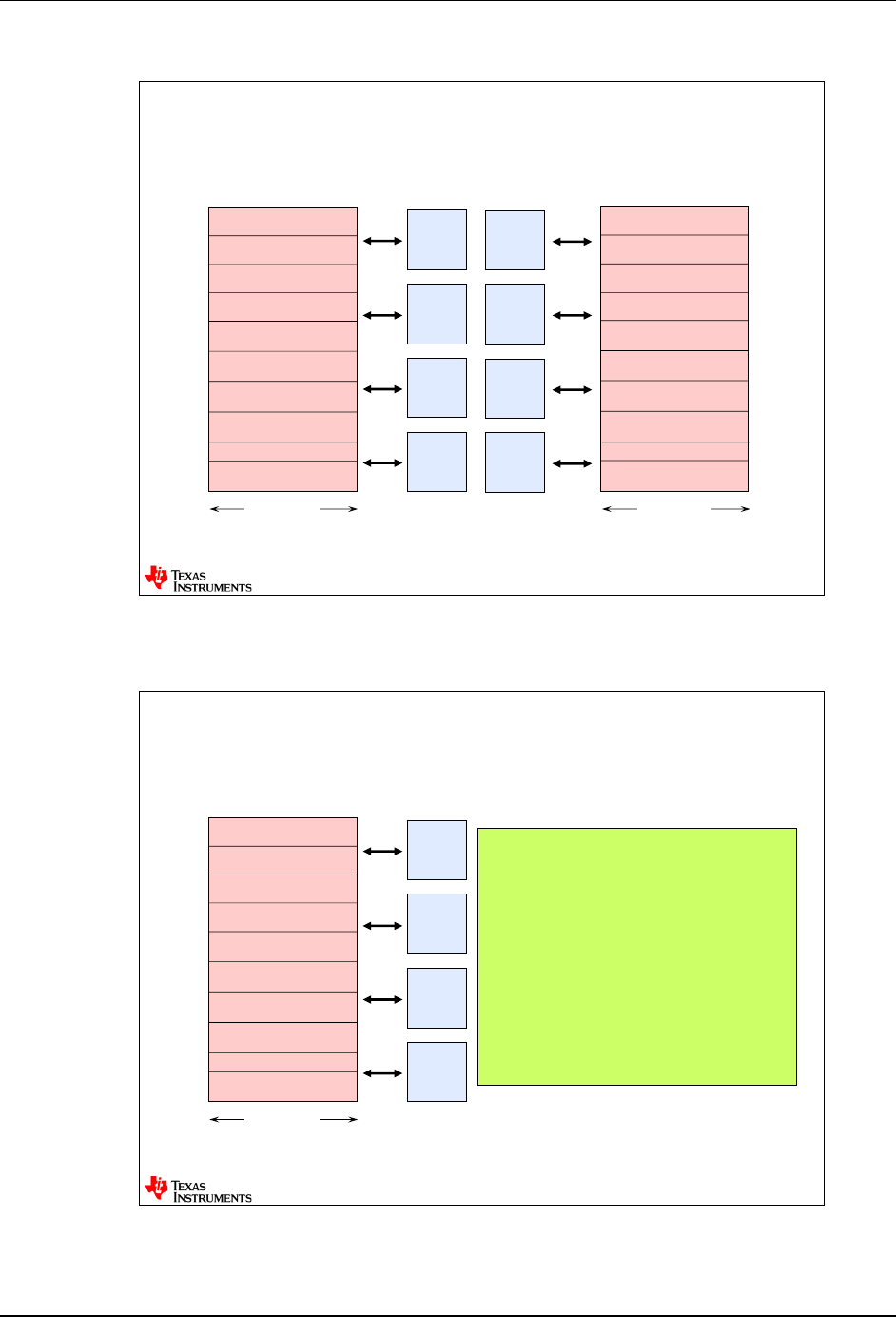

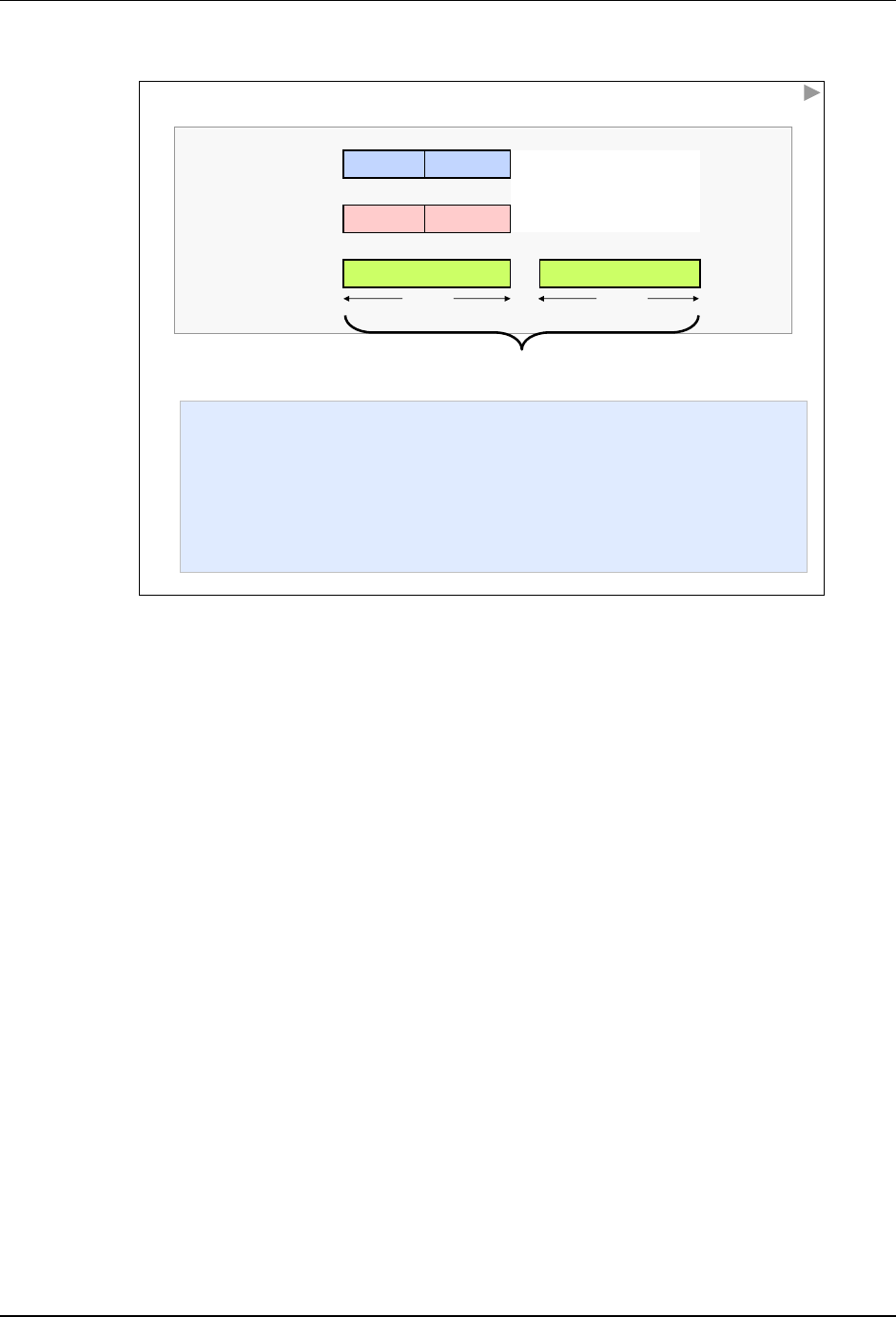

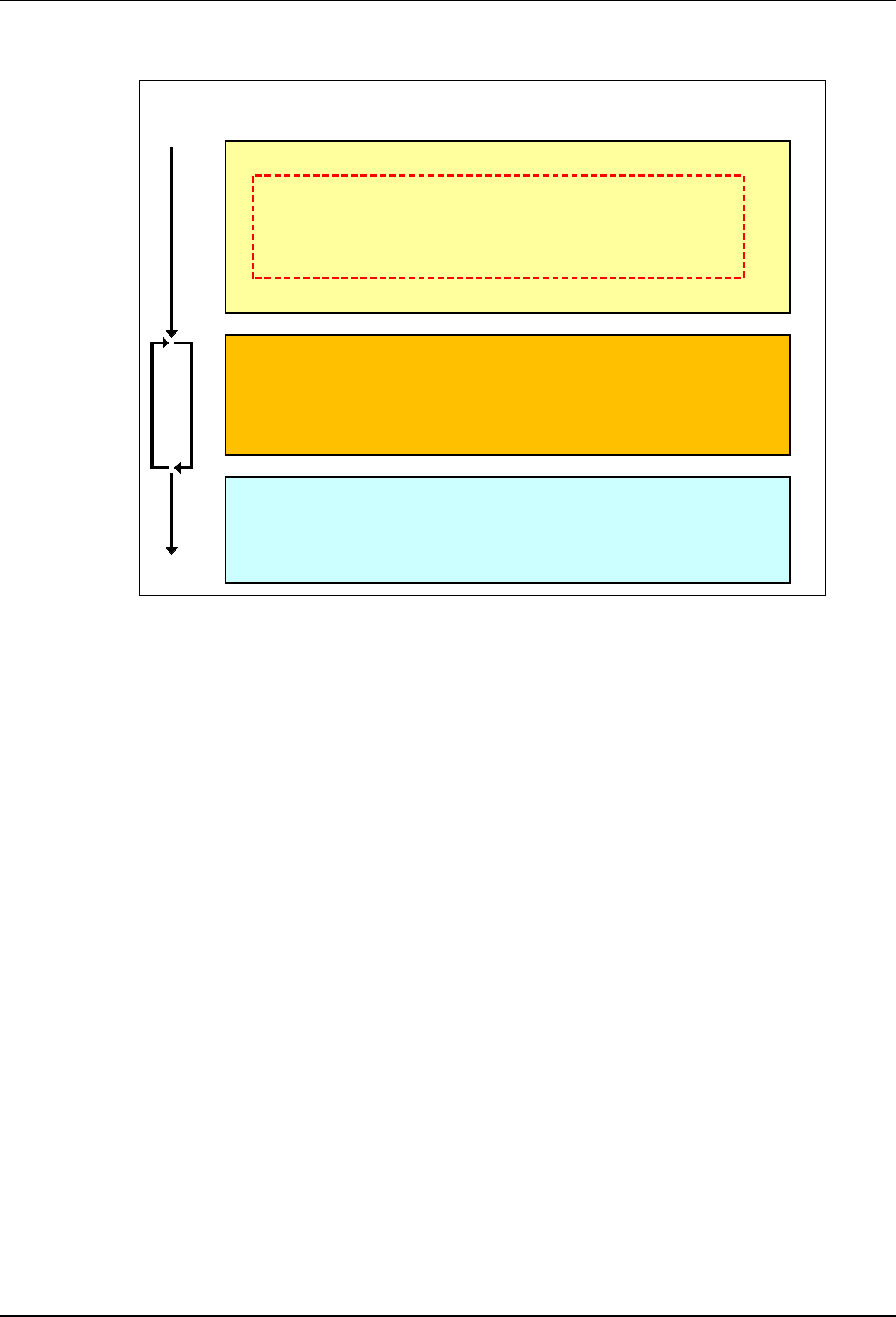

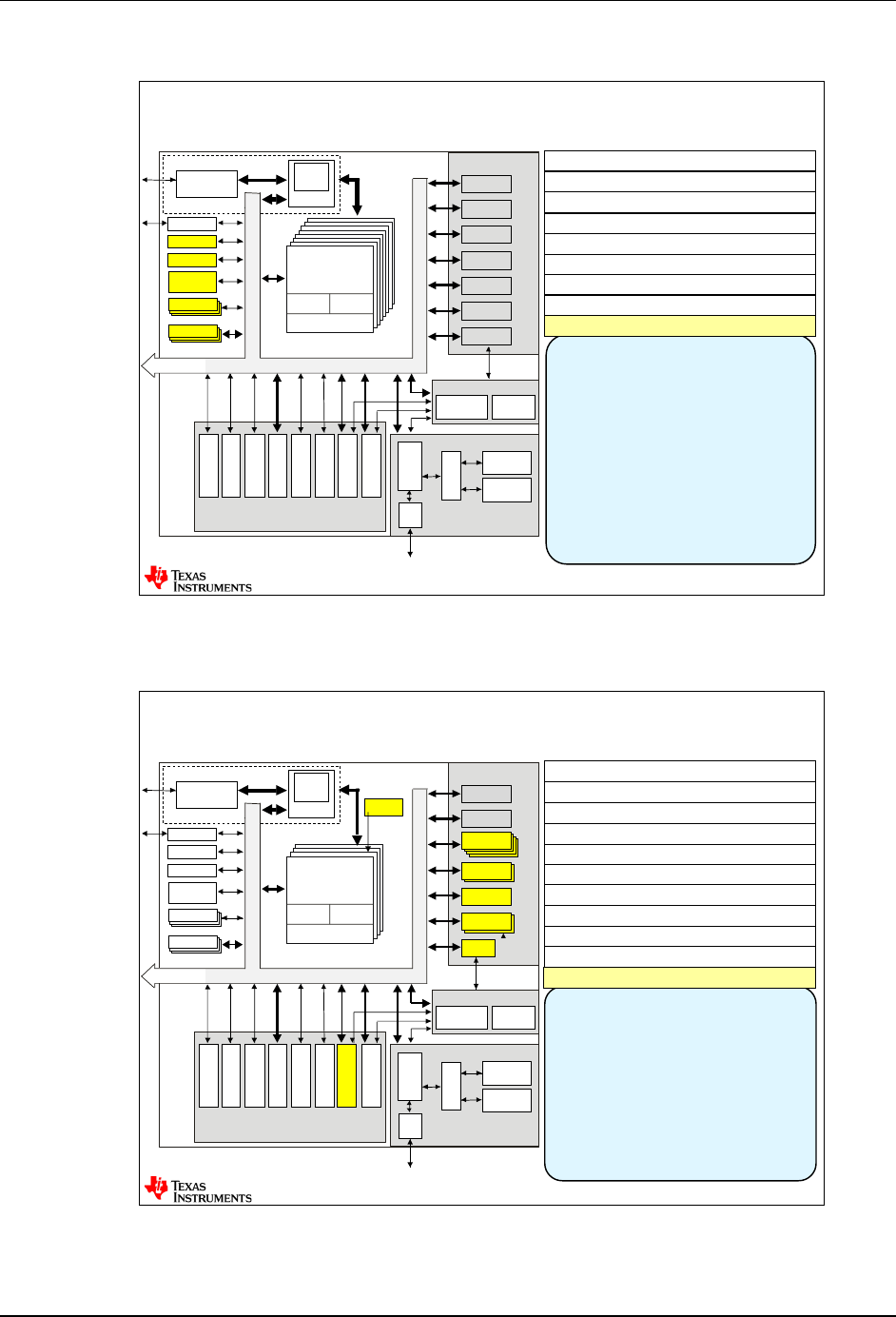

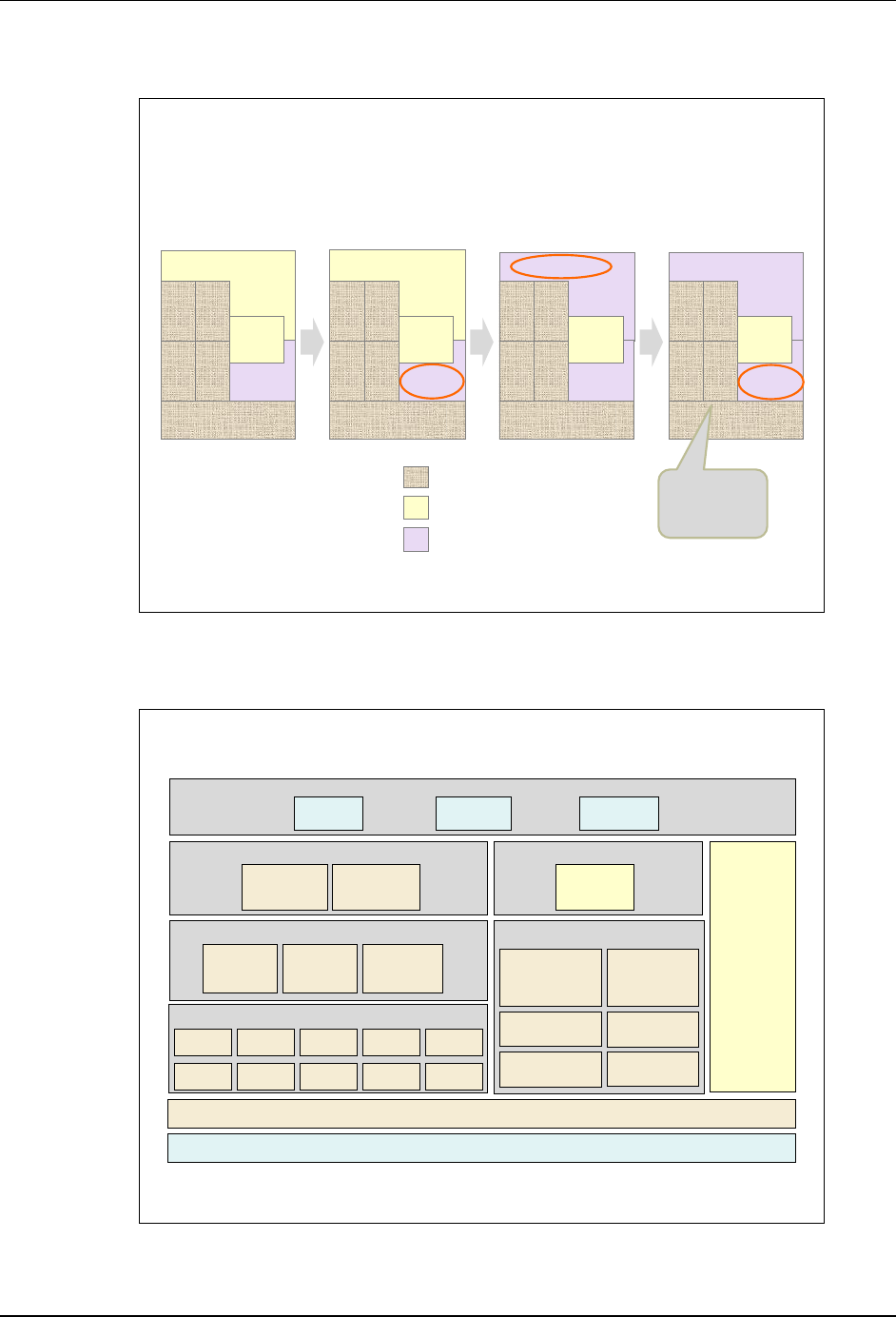

Using Double Buffers

C6000 Embedded Design Workshop - C6000 Introduction 11 - 21

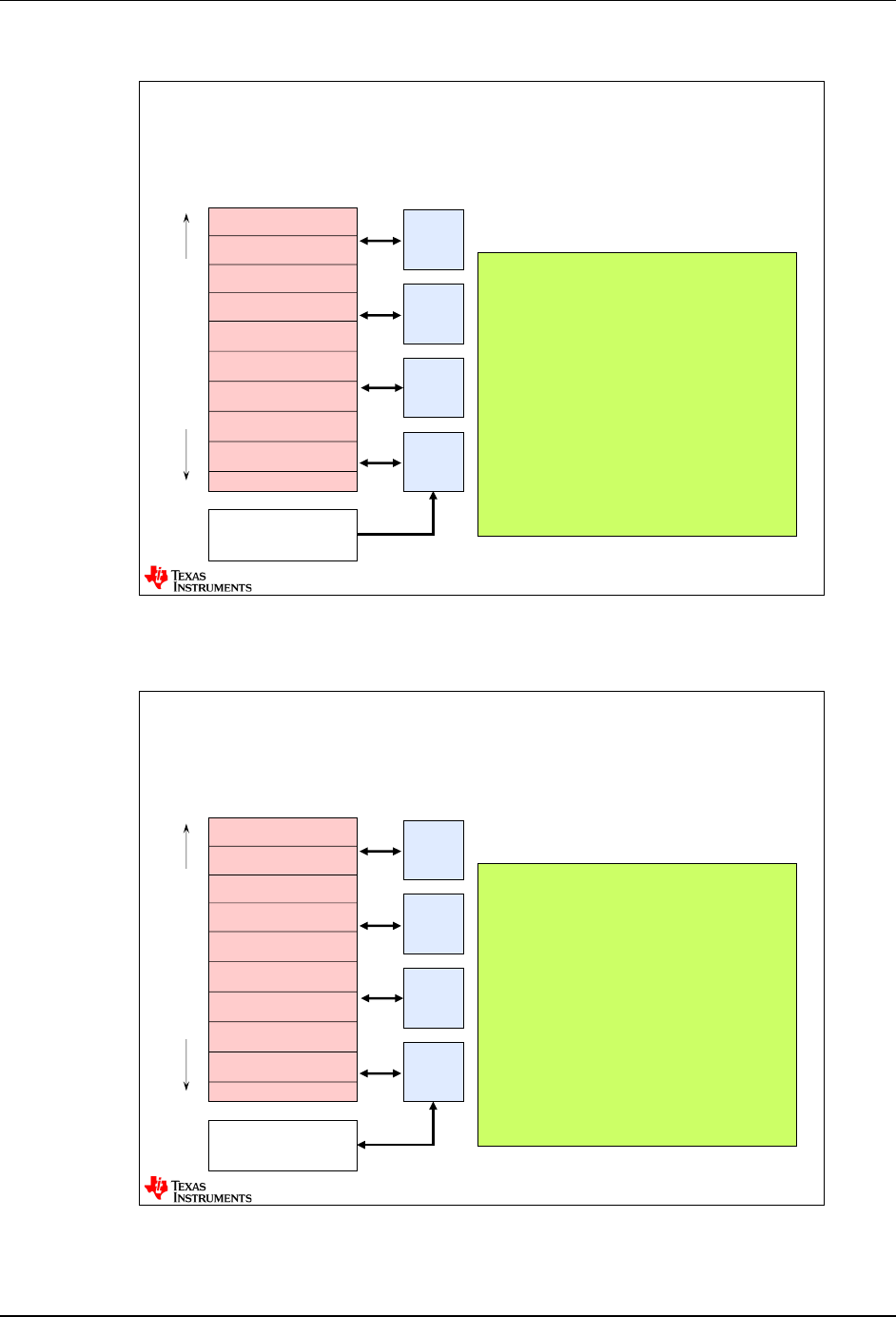

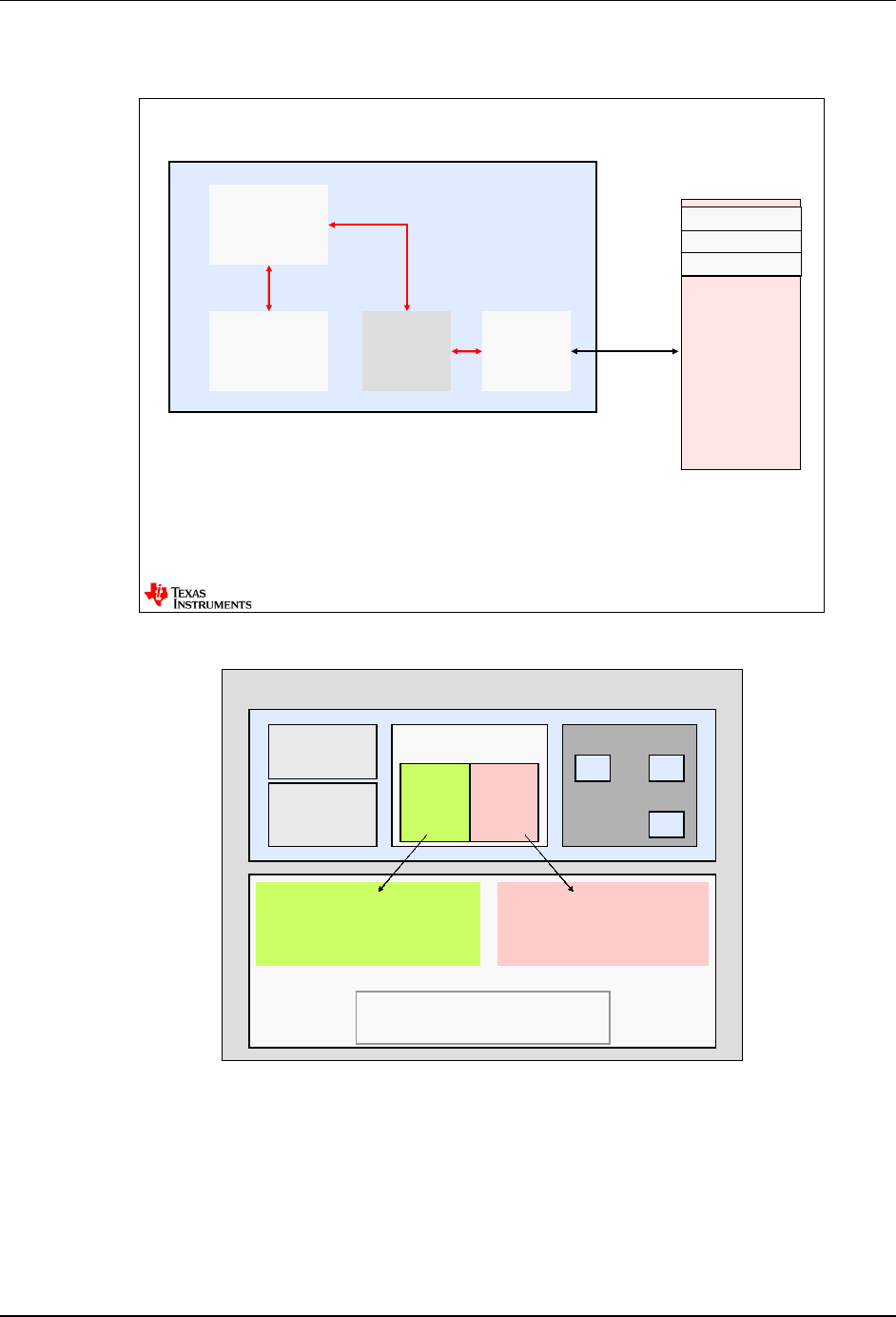

Using Double Buffers

Hwi

Single vs Double Buffer Systems

BUF

Swi/Task Hwi Swi/Task

BUF

Single buffer system: collect data or process data –not both!

Hwi Swi/Task Hwi Swi/Task

BUF

x

Double buffer system: process and collect data –real-time compliant!

BUF

y

BUF

xBUF

y

One buffer can be processed while another is being collected

When Swi/Task finishes buffer, it is returned to Hwi

Task is now ‘caught up’ and meeting real-time expectations

Hwi must have priority over Swi/Task to get new data while prior

data is being processed –standard in SYS/BIOS

Nowhere to store new data when prior data is being processed

Using Double Buffers

11 - 22 C6000 Embedded Design Workshop - C6000 Introduction

*** this page is also blank – please stop staring at blank pages…it is not healthy ***

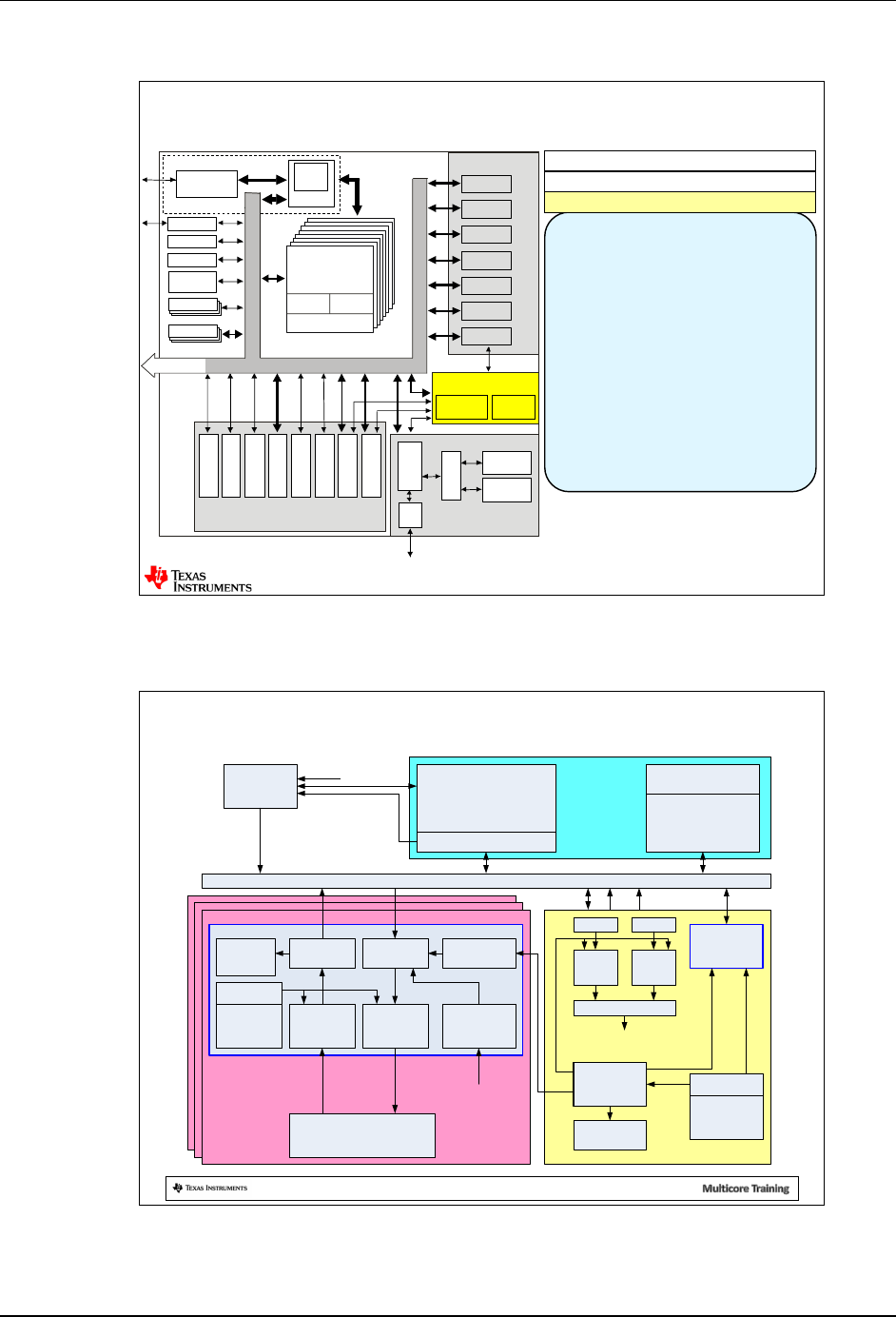

Lab 11: An Hwi-Based Audio System

C6000 Embedded Design Workshop - C6000 Introduction 11 - 23

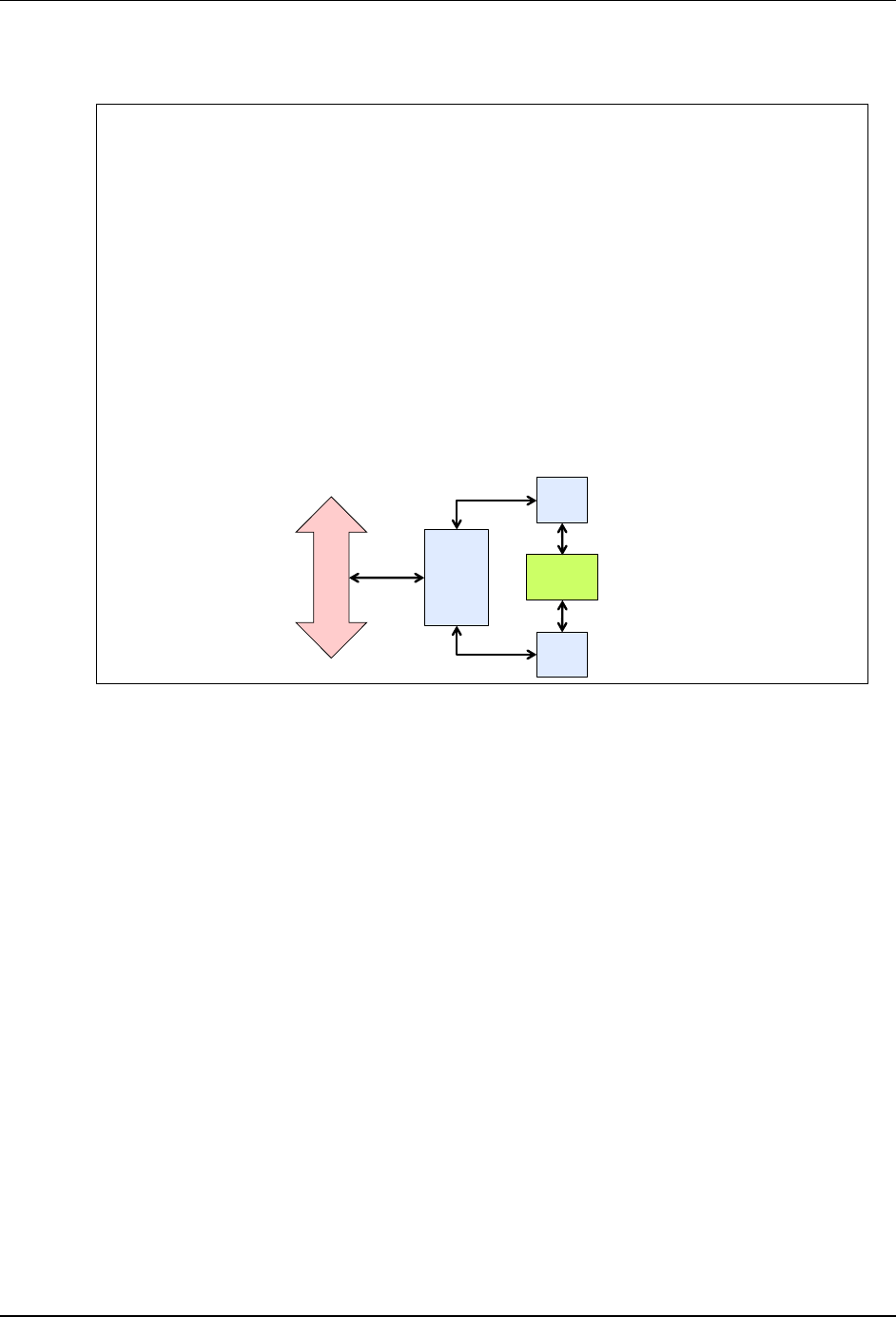

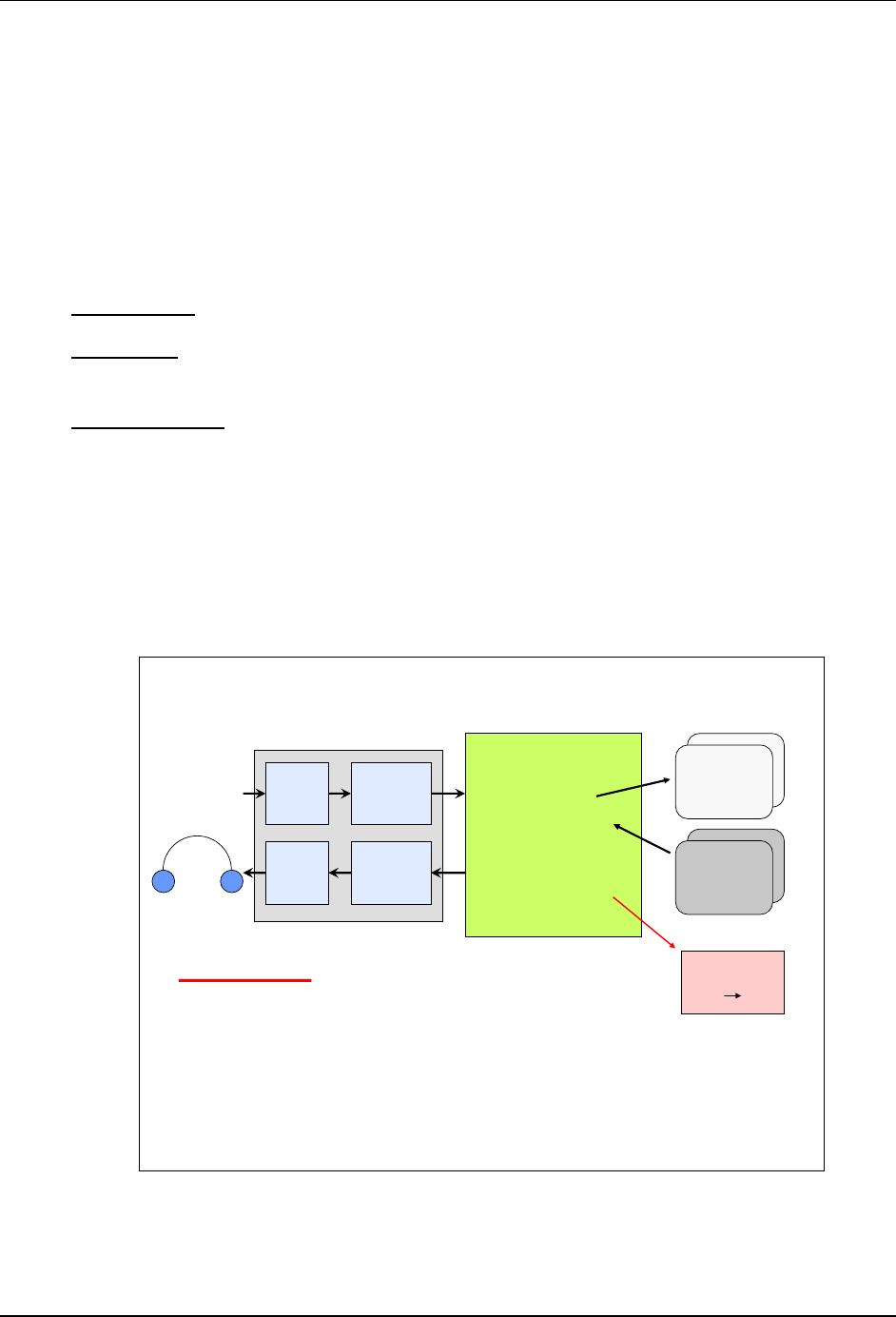

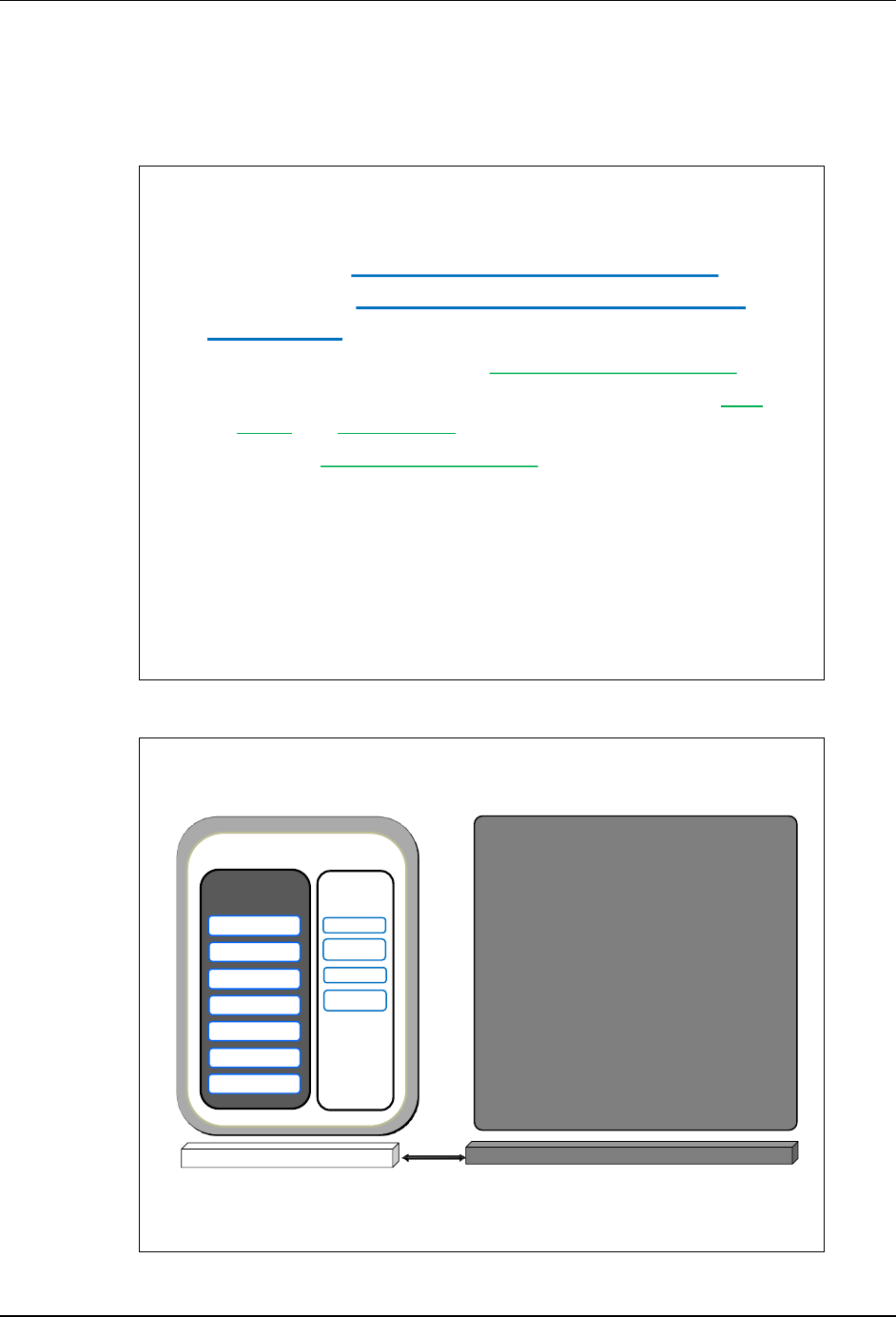

Lab 11: An Hwi-Based Audio System

In this lab, we will use an Hwi to respond to McASP interrupts. The McASP/AIC3106 init code has

already been written for you. The McASP interrupts have been enabled. However, it is your

challenge to create an Hwi and ensure all the necessary conditions to respond to the interrupt are

set up properly.

This lab also employs double buffers – ping and pong. Both the RCV and XMT sides have a ping

and pong buffer. The concept here is that when you are processing one, the other is being filled.

A Boolean variable (pingPong) is used to keep track of which “side” you’re on.

Application: Audio pass-thru using Hwi and McASP/AIC3106

Key Ideas: Hwi creation, Hwi conditions to trigger an interrupt, Ping-Pong

memory management

Pseudo Code:

• main() – init BSL, init LED, return to BIOS scheduler

• isrAudio() – responds to McASP interrupt, read data from RCV XBUF – put in RCV

buffer, acquire data from XMT buffer, write to XBUF. When buffer is full, copy RCV to

XMT buffer. Repeat.

• FIR_process() – memcpy RCV to XMT buffer. Dummy “algo” for FIR later on…

Audio

Output

(48 KHz)

Lab 11 –Hwi Audio

ADC

AIC3106

Audio

Input

(48 KHz)

McASP

XBUF12

DAC

AIC3106

McASP

XBUF11

isrAudio

datIn = XBUF12

pIn[cnt] = datIn

datOut = pOut[cnt]

XBUF11 = datOut

if (cnt >= BUF){

Copy RCV→XMT

}

1. Import existing project (Lab11)

2. Create your own CUSTOM PLATFORM

3. Config Hwi to respond to McASP interrupt

4. Debug Interrupt Problems

mcasp.c

aic3106.c

isr.c

rcvPing

xmtPing

Double Buffers

Time = 45min

COPY

RCV XMT

Hwi

Procedure

Lab 11: An Hwi-Based Audio System

11 - 24 C6000 Embedded Design Workshop - C6000 Introduction

Lab 11 – Procedure

If you can’t remember how to perform some of these steps, please refer back to the previous labs

for help. Or, if you really get stuck, ask your neighbor. If you AND your neighbor are stuck, then

ask the instructor (who is probably doing absolutely NOTHING important) for help.

Import Existing Project

1. Close ALL open projects and files and then open CCS.

2. Import Lab11 project.

► As before, import the archived starter project from:

C:\TI-RTOS\C6000\Labs\Lab_11\

This starter file contains all the starting source files for the audio project including the setup

code for the A/D and D/A on the OMAP-L138 target board. It also has UIA activated.

3. Check the Properties to ensure you are using the latest XDC, BIOS and UIA.

For every imported project in this workshop, ALWAYS check to make sure the latest tools

(XDC, BIOS and UIA) are being used. The author created these projects at time “x” and you

may have updated the tools on your student PC at “x+1” – some time later. The author used

the tools available at time “x” to create the starter projects and solutions which may or may

not match YOUR current set of tools.

Therefore, you may be importing a project that is NOT using the latest versions of the tools

(XDC, BIOS, UIA) or the compiler.

► Check ALL settings for the Properties of the project (XDC, BIOS, UIA) and the compiler

and update the imported project to the latest tools before moving on and save all settings.

Hack LogicPD’s BSL types.h

4. Edit Logic PD’s types.h file (already done for you…but take a look at what the author

did).

Logic PD’s type.h contains typedefs that conflict with BIOS. SO, in order for them to play

together nicely, users need to “hack” this file (like the author did for you already).

► Open the following file via CCS or any editor:

C:\TI_RTOS\Labs\LogicPD_BSL\DSP BSL\inc\types.h

► At the top of the file, notice the following two lines of code:

► Close types.h.

Now that this file is hacked, you will be able to use Logic PD’s types.h for all future labs

without a ton of warnings when you build.

Lab 11: An Hwi-Based Audio System

C6000 Embedded Design Workshop - C6000 Introduction 11 - 25

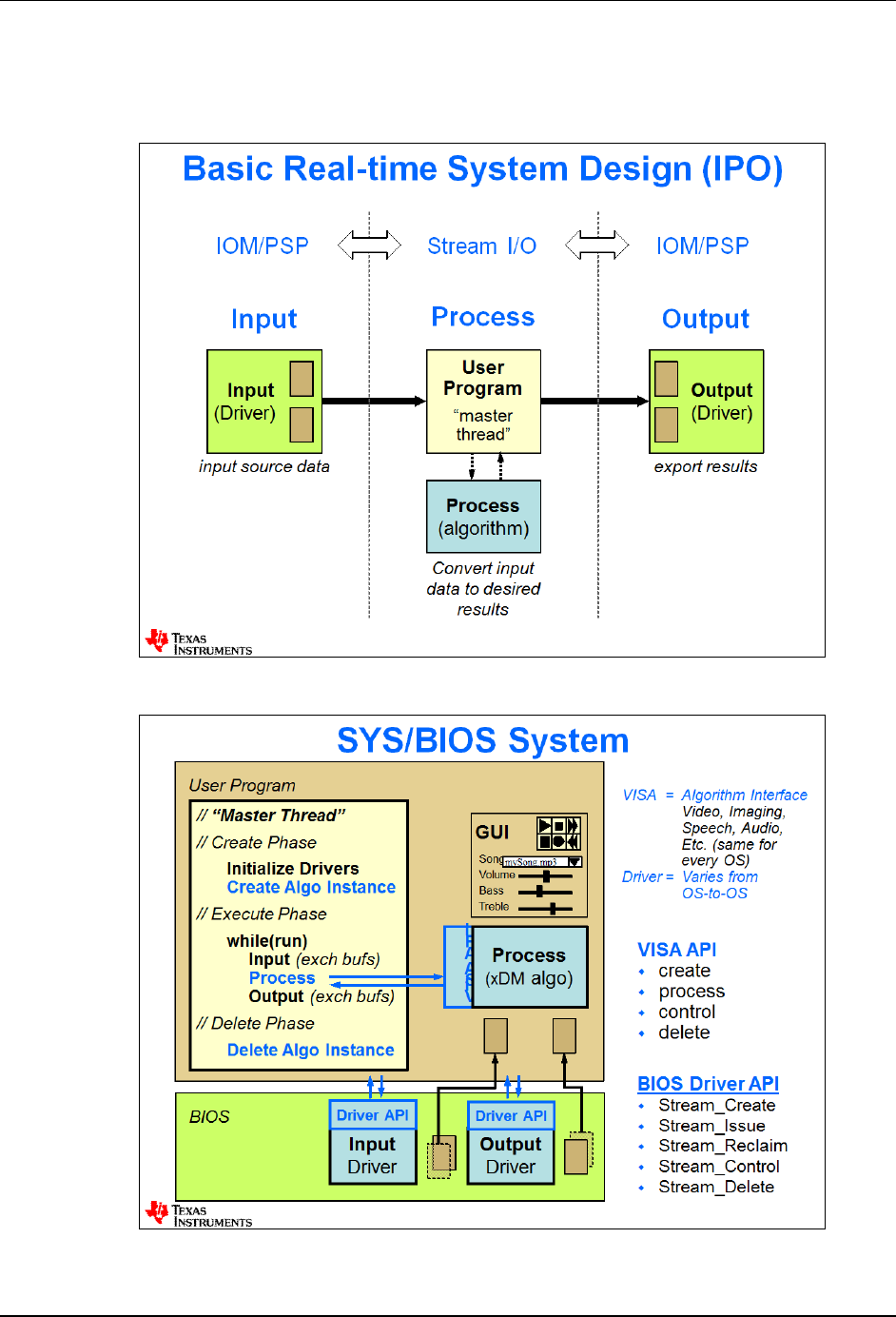

Application (Audio Pass-Thru) Overview

5. Let’s review what this audio pass-thru code is doing.

As discussed in the lab description, this application performs an audio pass-thru. The best

way to understand the process is via I-P-O:

• Input (RCV) – each analog audio sample from the audio INPUT port is converted by the

A/D and sent to the McASP port on the C6748. For each sample, the McASP generates

an interrupt to the CPU. In the ISR, the CPU reads this sample and puts it in a buffer

(RCV ping or pong). Once the buffer fills up (BUFFSIZE), processing begins…

• Process – Our algorithm is very fancy – it is a COPY from the RCV buffer to the XMT

buffer.

• Output (XMT) – When the McASP transmit buffer is empty, it interrupts the CPU and asks

for another sample. In the ISR (same ISR for the RCV side), the CPU reads a sample

from the XMT buffer and writes to the McASP transmit register. The McASP sends this

sample to the D/A and is then tramsitted to the audio OUTPUT port.

Several source files are needed to create this application. Let’s explore those briefly…

Source Code Overview

6. Inspect the source code.

Following is a brief description of the source code. Because this workshop can be targeted at

many processors (MSP430, Stellaris-M3, C28x, C6000, ARM), some of the hardware details

will be minimized and saved for the target-specific chapter.

► Feel free to open any of these files and inspect them as you read…

• main.h – same as before, but contains more function prototypes

• aic3106_TTO.c – initializes the analog interface chip (AIC) on the EVM – this is the A/D

and D/A combo device.

• fir.c – this is a placeholder for the algorithm. Currently, it is simply a copy function – to

copy RCV to XMT buffers.

• isr.c – This is the interrupt service routine (isrAudio). When the interrupt from the

McASP fires (RCV or XMT), the BIOS HWI (soon to be set up) will call this routine to

read/write audio samples.

• main.c – sets up the McASP and AIC and then calls BIOS_start().

• mcasp_TTO.c – init code for the McASP on the C6748 device.

Lab 11: An Hwi-Based Audio System

11 - 26 C6000 Embedded Design Workshop - C6000 Introduction

More Detailed Code Analysis

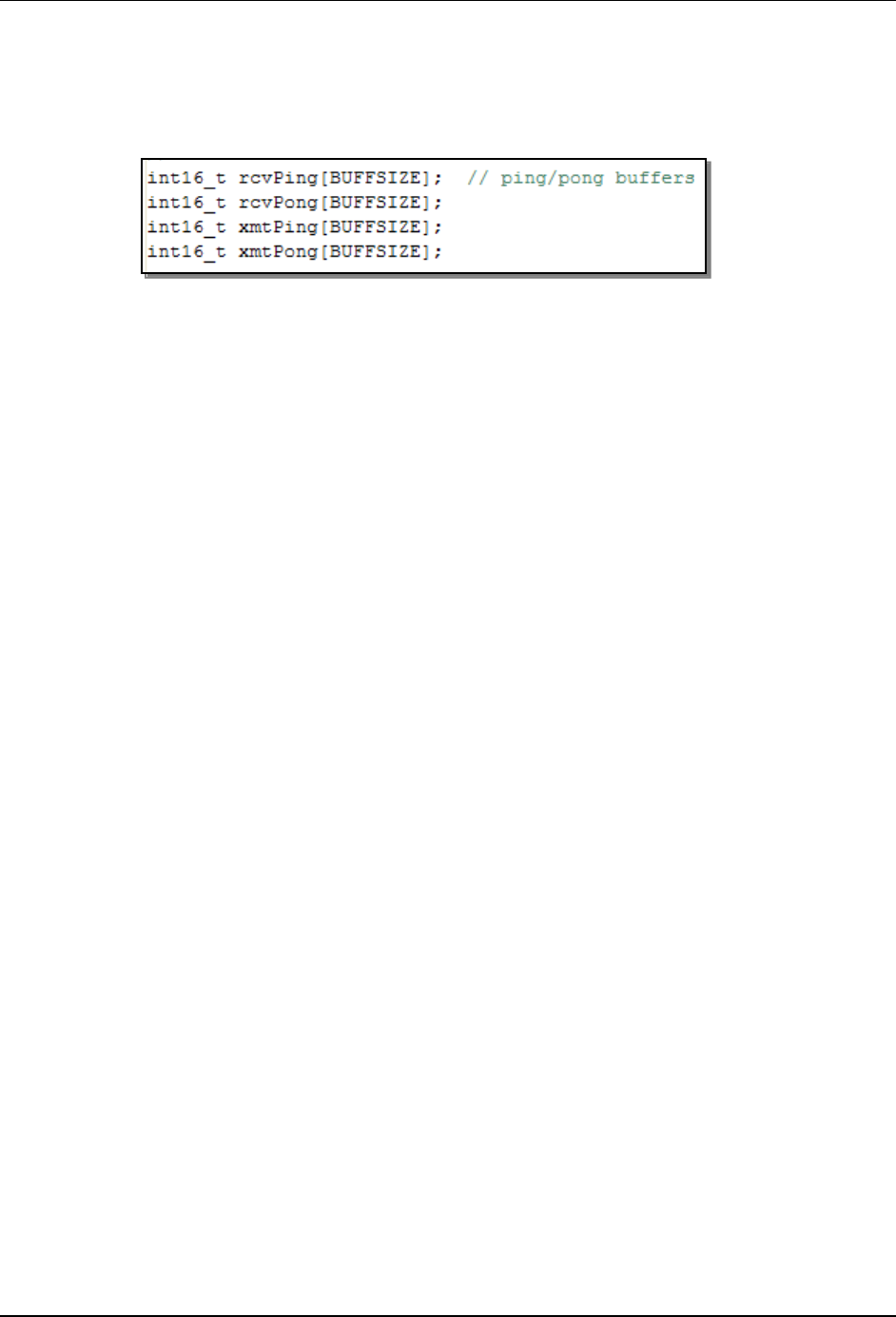

7. Open main.c for editing.

Near the top of the file, you will see the buffer allocations:

Notice that we have separate buffers for Ping and Pong for both RCV and XMT. Where is

BUFFSIZE defined? Main.h. We’ll see him in a minute.

As you go into main(), you’ll see the zeroing of the buffers to provide initial conditions of

ZERO. Think about this for a minute. Is that ok? Well, it depends on your system. If

BUFFSIZE is 256, that means 256 ZEROs will be transmitted to the DAC during the first 256

interrupts. What will that sound like? Do we care? Some systems require solid initial

conditions – so keep that in mind. We will just live with the zeros for now.

Then, you’ll see the calls to the init routines for the McASP and AIC3106. Previously, with

DSP/BIOS, this is where an explicit call to init interrupts was located. However, with

SYS/BIOS, this is done via the GUI. Lastly, there is a call to McASP_Start(). This is where

the McASP is taken out of reset and the clocks start operating and data starts being shifted

in/out. Soon thereafter, we will get the first interrupt.

8. Open mcasp_TTO.c for editing.

This file is responsible for initializing and starting the McASP – hence, two functions (init and

start). In particular, look at line numbers 83 and 84 (approximately). This is where the

serializers are chosen. This specifies XBUF11 (XMT) and XBUF12 (RCV). Also, look at line

numbers 111-114. This is where the McASP interrupts are enabled. So, if they are enabled

correctly, we should get these interrupts to fire to the CPU.

Lab 11: An Hwi-Based Audio System

C6000 Embedded Design Workshop - C6000 Introduction 11 - 27

9. Open isr.c for editing.

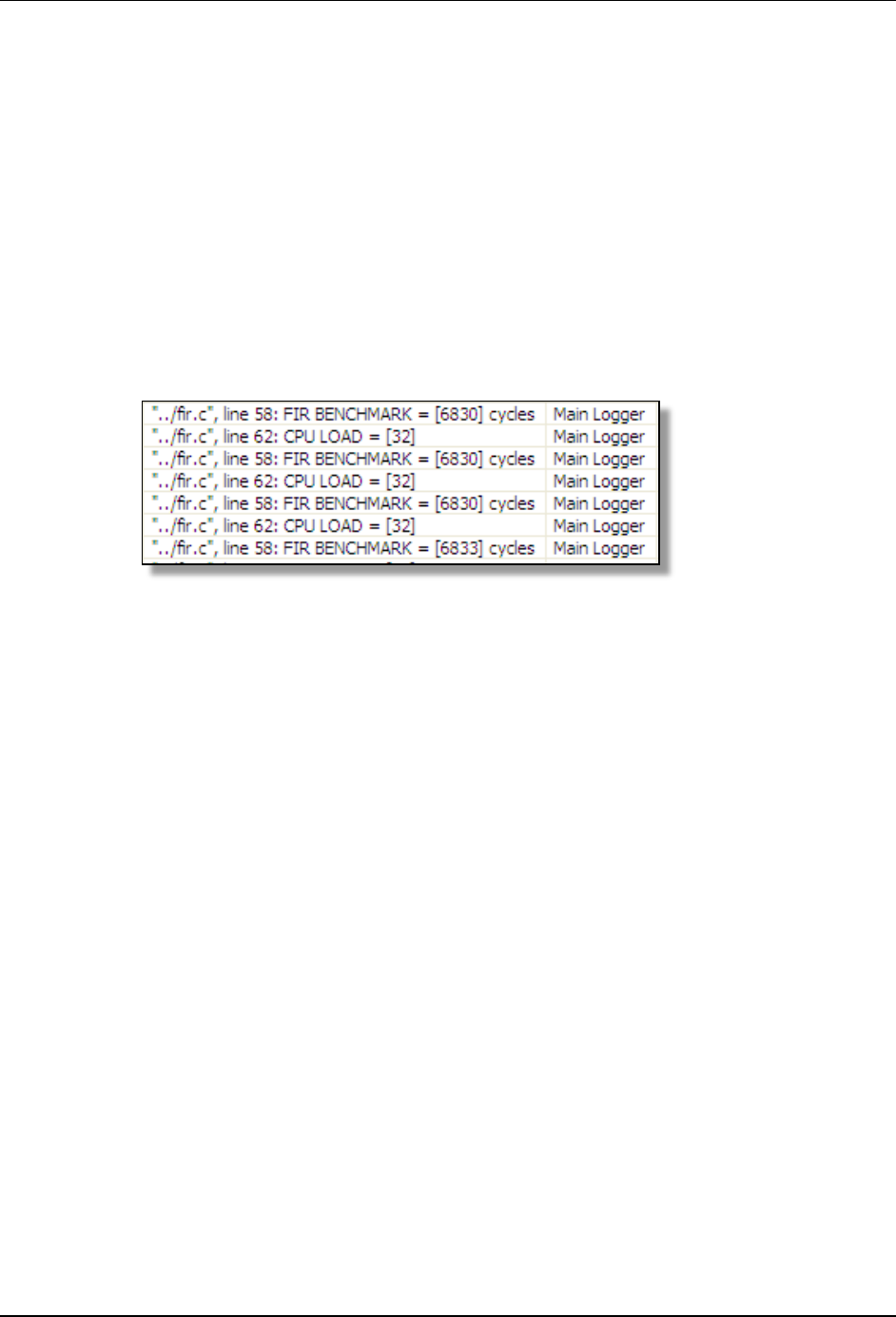

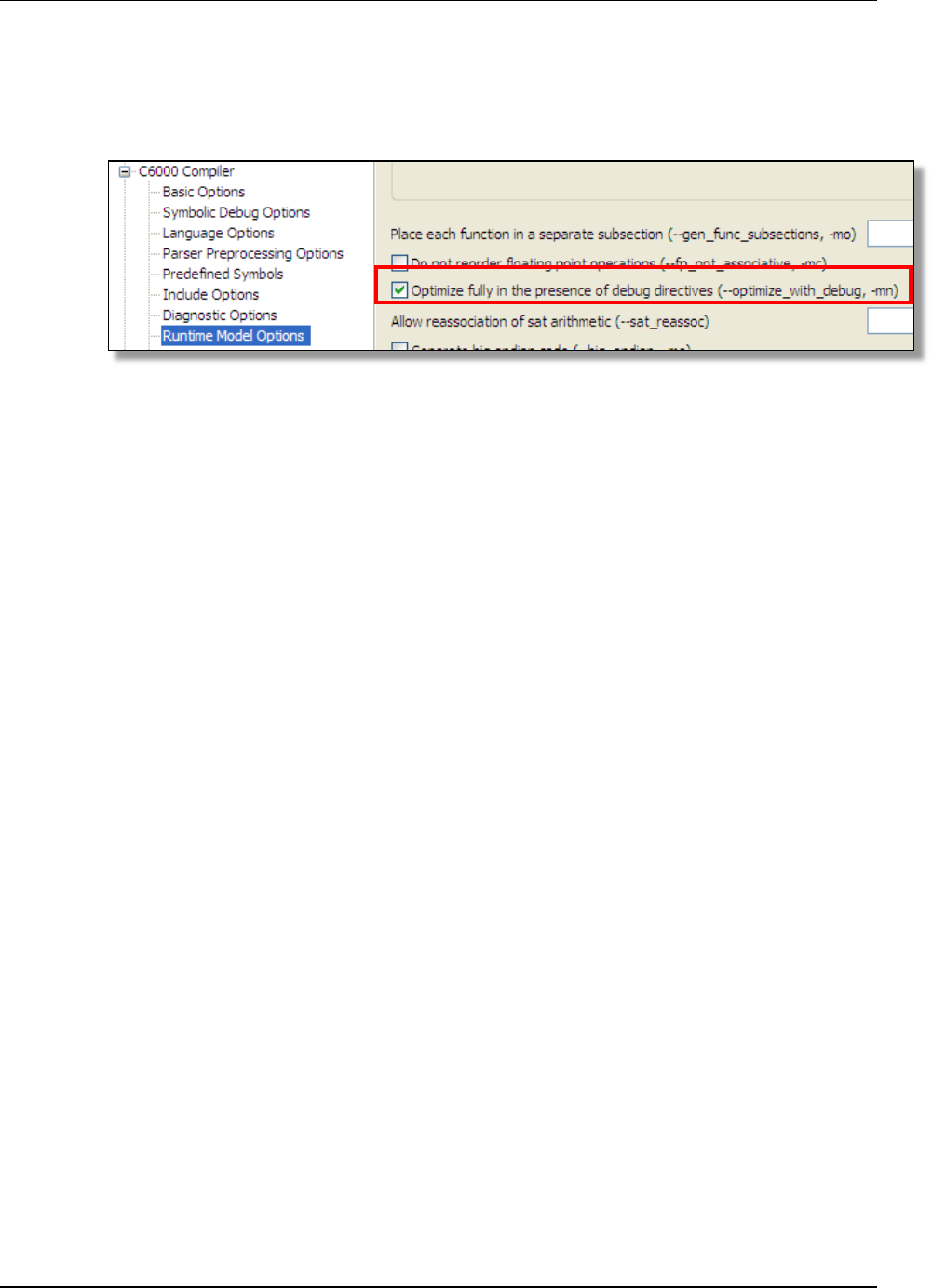

Well, this is where all the real work happens – inside the ISR. This code should look pretty

familiar to you already. There are 3 key concepts to understand in this code:

• Ping/Pong buffer management – notice that two “local” pointers are used to point to the

RCV/XMT buffers. This was done as a pre-cursor to future labs – but works just fine here

too. Notice at the top of the function that the pointers are initialized only if blkCnt is

zero (i.e it is time to switch from ping to pong buffers or vice versa) and we’re done with

the previous block. blkCnt is used as an index into the buffers.

• McASP reads/writes – refer to the read/write code in the middle. When an interrupt

occurs, we don’t know if it was the RRDY (RCV) or XRDY (XMT) bit that triggered the

interrupt. We must first test those bits, then perform the proper read or write accordingly.

On EVERY interrupt, we EITHER read one sample and write one sample. All McASP

reads and writes are 32 bits. Period. Even if your word length is 16 bits (like ours is).

Because we are “MSB first”, the 16-bits of interest land in the UPPER half of the 32-bits.

We turned on ROR (rotate-right) of 16 bits on rcv/xmt to make our code look more

readable (and save time vs. >> 16 via the compiler).

• At the end of the block – what happens? Look at the bottom of the code. When

BUFFSIZE is reached, blkCnt is zero’d and the pingPong Boolean switches. Then, a

call to FIR_process() is made that simply copies RCV buffer to XMT buffer. Then, the

process happens all over again for the “other” (PING or PONG) buffers.

10. Open fir.c for editing.

This is currently a placeholder for a future FIR algorithm to filter our audio. We are simply

“pass through” the data from RCV to XMT. In future labs, a FIR filter written in C will

magically appear and we’ll analyze its performance quite extensively.

11. Open main.h for editing.

main.h is actually a workhorse. It contains all of the #includes for BSL and other items,

#defines for BUFFSIZE and PING/PONG, prototypes for all functions and externs for all

variables that require them. Whenever you are asked to “change BUFFSIZE”, this is the file

to change it in.

Lab 11: An Hwi-Based Audio System

11 - 28 C6000 Embedded Design Workshop - C6000 Introduction

Creating A Custom Platform

12. Create a custom platform file.

In previous labs, we specified a platform file during creation of a new project. In this lab, we

will create our own custom platform that we will use throughout the rest of the labs. Plus, this

is a good skill to know how to do.

Whenever you create your own project, you should always IMPORT the seed platform file for

the specific target board and then make changes. This is what we plan to do next…

► In Debug Perspective, select: Tools

RTSC Tools

Platform

New

When the following dialogue appears:

• ► Give your platform a name: evmc6748_student (the author used _TTO for his)

• ► Point the repository to the path shown (this is where the platform package is stored)

• ► Then select the Device Family/Name as shown

• ► Check the box “Add Repository to Project Package Path” (so we can find it later).

When you check this box, select your current project in the listing that pops up. This also

adds this repository to the list of Repositories in the Properties

General

RTSC tab

dialogue.

► Click Next.

Lab 11: An Hwi-Based Audio System

C6000 Embedded Design Workshop - C6000 Introduction 11 - 29

When the new platform dialogue appears, ► click the IMPORT button to copy the seed file

we used before:

This will copy all of the initial default settings for the board and then we can modify them. A

dialogue box should pop up and select the proper seed file as shown (► select the _TTO

version of the platform file that the author already created for you):

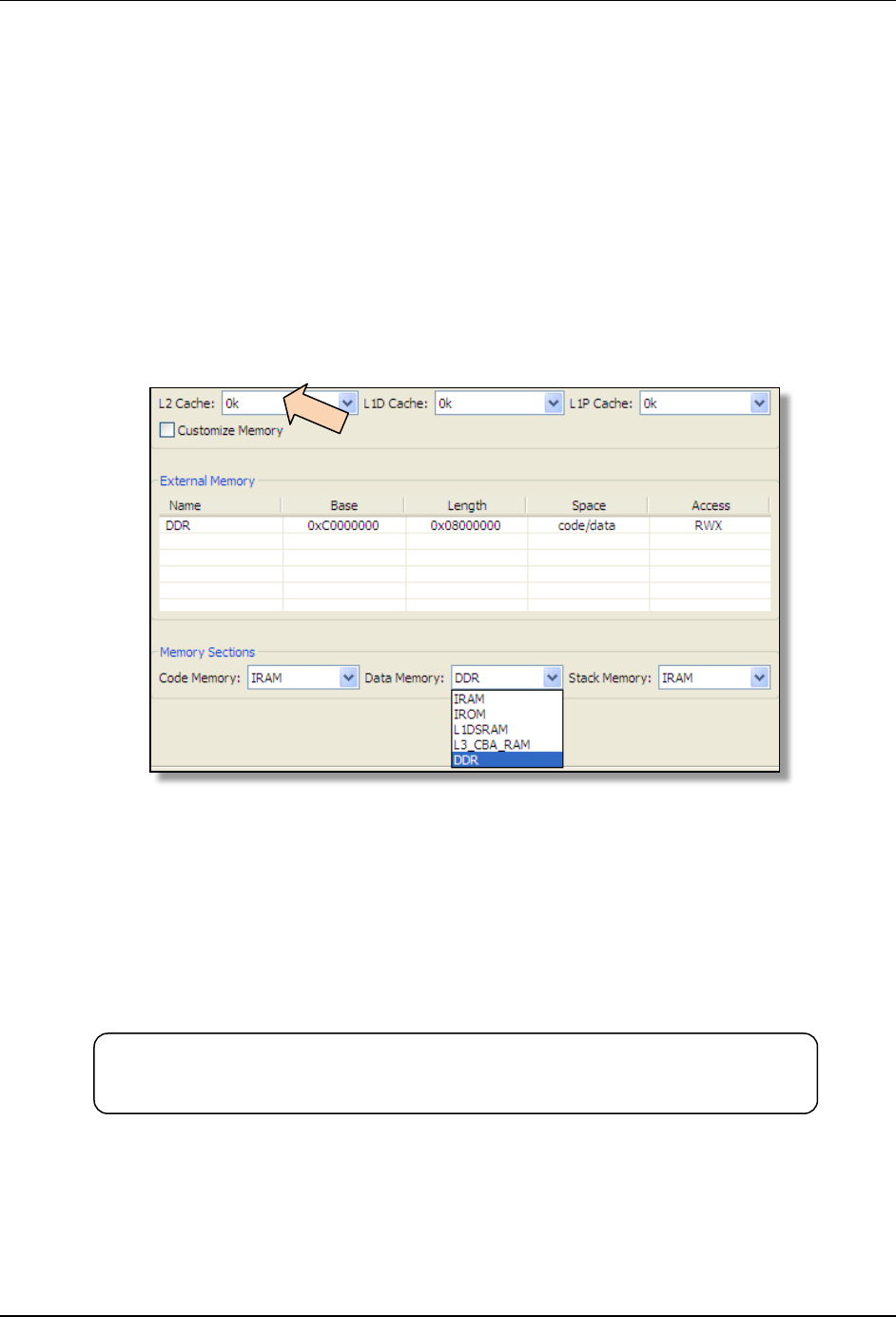

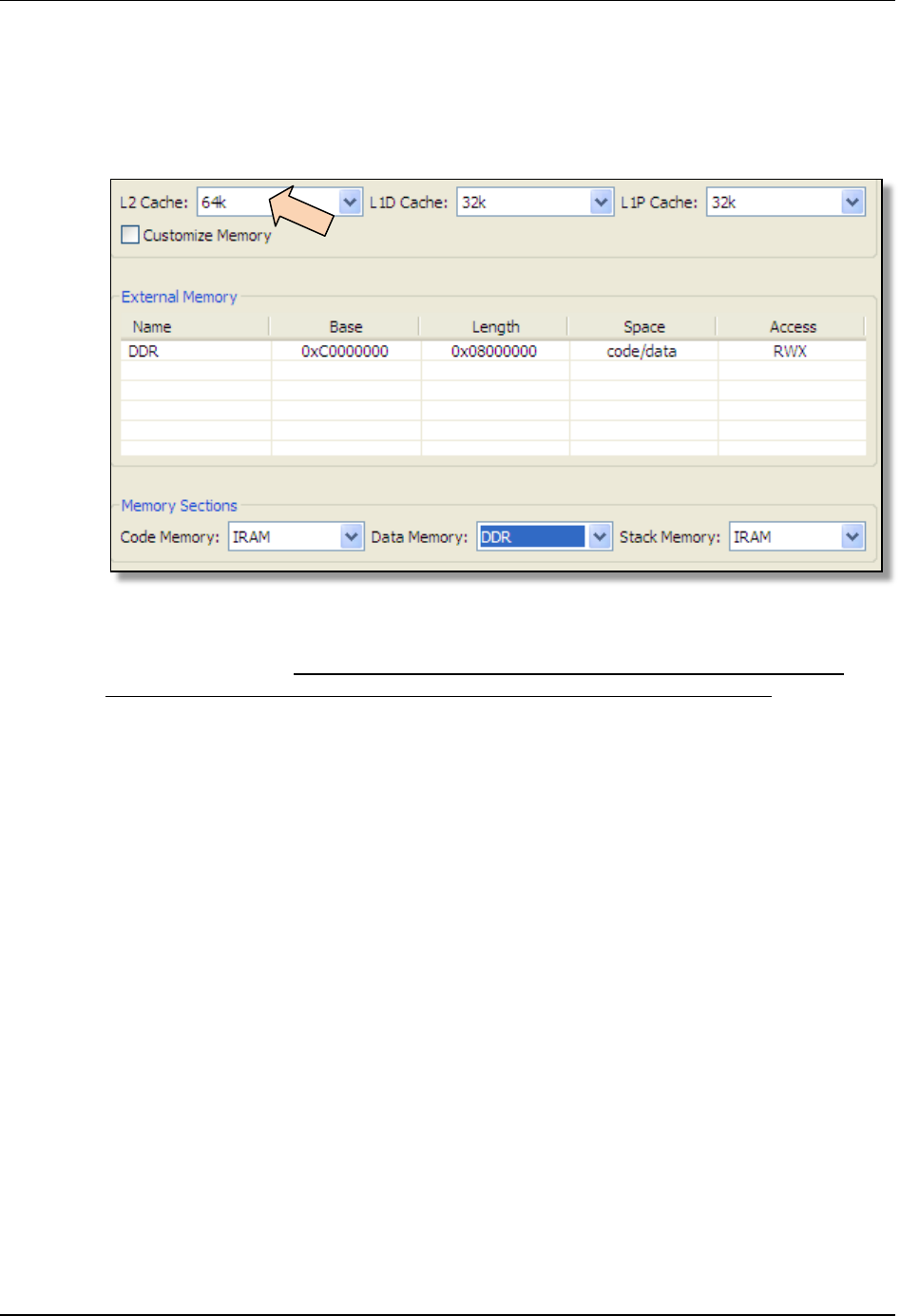

► Modify the memory settings to allocate all code, data and stacks into internal memory

(IRAM) as shown. They may already be SET this way – just double check.

► BEFORE YOU SAVE – HAVE THE INSTRUCTOR CHECK THIS FILE.

► Then save the new platform. This will build a new platform package.

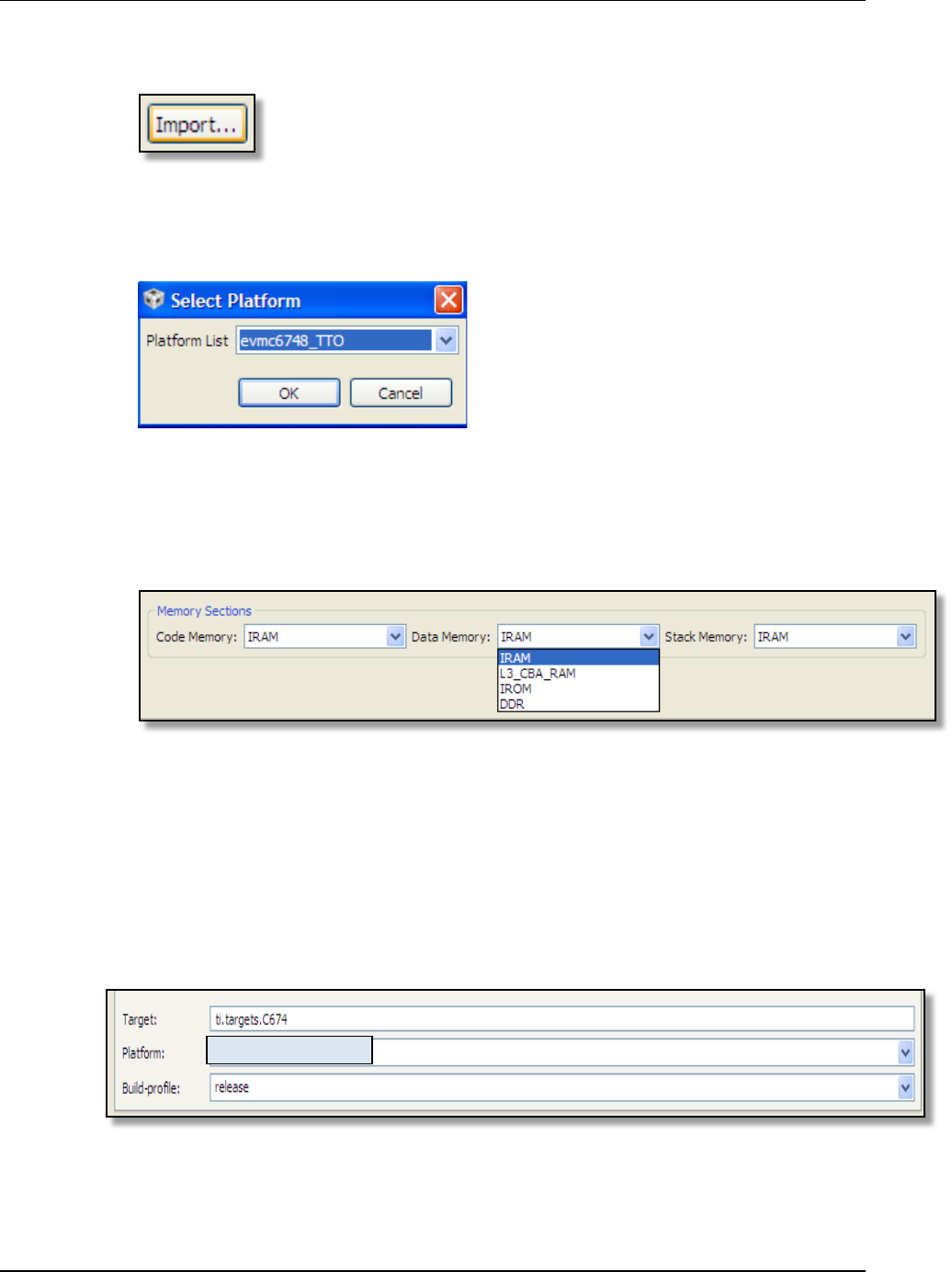

13. Tell the tools to use this new custom platform in your project.

We have created a new platform file, but we have not yet ATTACHED it to our project. When

the project was created, we were asked to specify a platform file and we chose the default

seed platform. How do we get back to the configuration screen?

► Right-click on the project and select Properties

General and then select the RTSC tab.

► Look near the bottom and you’ll see that the default seed platform is still specified. We

need to change this.

► `Click on the down arrow next to the Platform File. The tools should access your new

repository with your new custom platform file: evmc6748_student.

► Select YOUR STUDENT PLATFORM FILE and click Ok. Now, your project is using the

new custom platform. Very nice…

evmc6748_student

Lab 11: An Hwi-Based Audio System

11 - 30 C6000 Embedded Design Workshop - C6000 Introduction

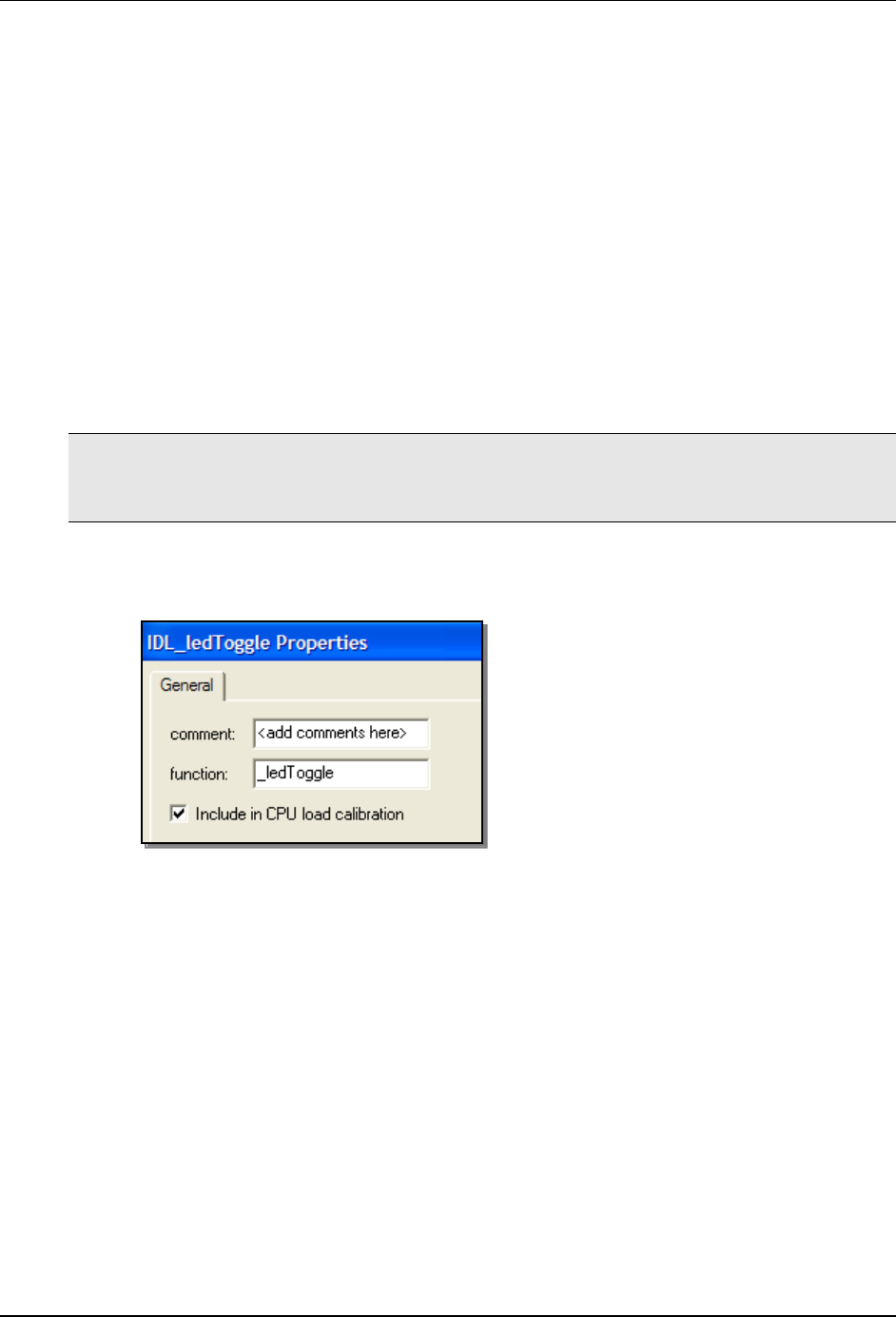

Add Hwi to the Project

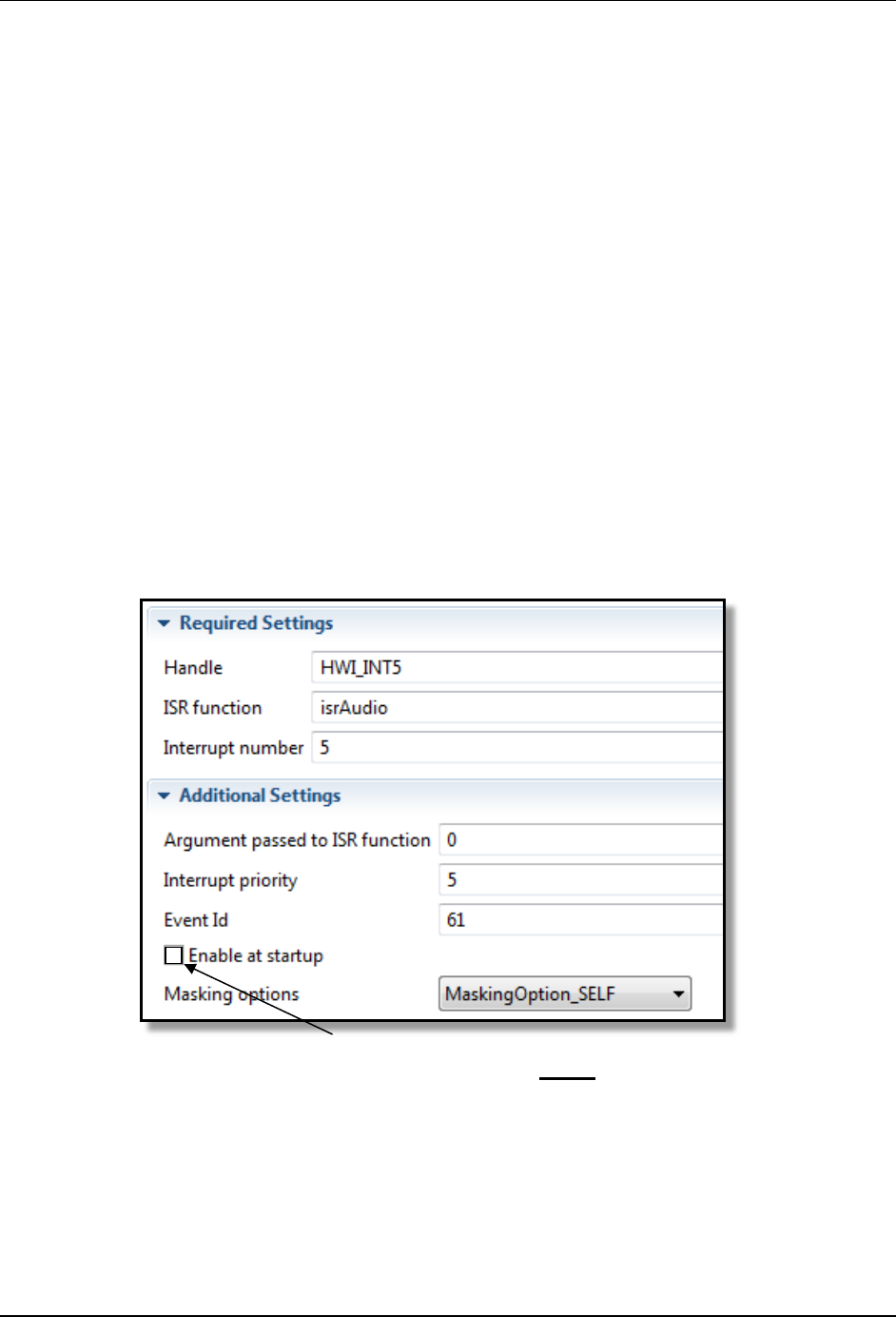

14. Use Hwi module and configure the hardware interrupt for the McASP.

Ok, FINALLY, we get to do some real work to get our code running. For most targets, an

interrupt source (e.g. McASP) will have an interrupt EVENT ID (specified in the datasheet).

This event id needs to be tied to a specific CPU interrupt. The details change based on the

target device.For the C6748, the EVENT ID is #61 and the CPU interrupt we’re using is INT5

(there are 16 interrupts on the C6748 – again, target specific).

So, we need to do two things: (1) tell the tools we want to USE the Hwi BIOS module; (2)

configure a specific interrupt to point to our ISR routine (isrAudio).

During the 2-day TI-RTOS Kernel Workshop, you performed these actions – so this should

be review – but that’s ok. Review is good.

► First, make sure you are viewing the hwi.cfg file.

► In the list of Available Products, locate Hwi, right-click and select “Use Hwi”. It will now

show up on the right-hand Outline View.

► Then, right click on Hwi in the Outline View and select “New Hwi”.

► When the dialogue appears, which is different than what you see below, click OK.

► Then click on the new Hwi (hwi0) (you’ll see a new dialogue like below) and fill in the

following:

Make sure “Enabled at startup” is NOT checked (this sets the IER bit

on the C6748). This will provide us with something to debug later. Once again, you can click

on the new HWI and see the corresponding Source script code.

Lab 11: An Hwi-Based Audio System

C6000 Embedded Design Workshop - C6000 Introduction 11 - 31

Build, Load, Run.

15. Build, load and run the audio pass-thru application.

► Before you Run, make sure audio is playing into the board and your headphones are set

up so you can hear the audio.

► Also, make sure that Windows Media Player is set to REPEAT forever. If the music stops

(the input is air), and you click Run, you might think there is a problem with your code. Nope,

there is no music playing.

► Build and fix any errors. After a successful build, debug the application.

► Once the program is loaded, click Run.

Do you hear audio? If not, it’s debug time – it SHOULD NOT be working (by design). One

quick tip for debug is to place a breakpoint in the isrAudio() routine and see if the program

stops there. If not, no interrupt is being generated. Move on to the next steps to debug the

problem…

Hint: The McASP on the C6748 cannot be restarted after a halt – i.e. you can’t just hit halt,

then Run. Once you halt the code, you must click the restart button and then Play.

Debug Interrupt Problem

As we already know, we decided early on to NOT enable the IER bit in the static configuration of

the Hwi. Ok. But debugging interrupt problems is a crucial skill. The next few steps walk you

through HOW to do this. You may not know WHERE your interrupt problem occurred, so using

these brief debug skills may help in the future.

16. Pause for a moment to reflect on the “dominos” in the interrupt game:

• An interrupt must occur (McASP init code should turn ON this source)

• The individual interrupt must be enabled (IER, BITx)

• Global Interrupts must be turned on (GIE = 1, handled by BIOS)

• HWI Dispatcher must be used to provide proper context save/restore

• Keep this all in mind as you do the following steps…

17. McASP interrupt firing – IFR bit set?

The McASP interrupt is set to fire properly, but is it setting the IFR bit? You configured

HWI_INT5, so that would be a “1” in bit 5 of the IFR.

► Go there now (View → Registers → Core Registers). ► `Look down the list to find the IFR

and IER – the two of most interest at the moment. (author note: could it have been set, then

auto-cleared already?). You can also DISABLE IERbit (as it is already in the CFG file),

build/run, and THEN look at IFR (this is a nice trick).

Write your debug “checkmarks” here:

IFR bit set? □ Yes □ No

Lab 11: An Hwi-Based Audio System

11 - 32 C6000 Embedded Design Workshop - C6000 Introduction

18. Is the IER bit set?

Interrupts must be individually enabled. When you look at IER bit 5, is it set to “1”? Probably

NOT because we didn’t check that “Enable at Start” checkbox.

► Open up the config for HWI_INT5 and check the proper checkbox. Then, hit build and your

code will build and load automatically regardless of which perspective you are in.

IER bit set? □ Yes □ No

Do you hear audio now? You probably should. But let’s check one more thing…

19. Is GIE set?

The Global Interrupt Enable (GIE) Bit is located in the CPU’s CSR register. SYS/BIOS turns

this on automatically and then manages it as part of the O/S. So, no need to check on this.

GIE bit set? □ Yes □ No

Hint: If you create a project that does NOT use SYS/BIOS, it is the responsibility of the user to

not only turn on GIE, but also NMIE in the CSR register. Otherwise, NO interrupts will be

recognized. Ever. Did I say ever?

Other Debug/Analysis Items

20. Using “Load Program After Build” Option and Restart.

Often times, users want to make a minor change in their code and rebuild and run quickly.

After you launch a debug session and connect to the target (which takes time), there is NO

NEED to terminate the session to make code changes. After pausing (halting) the code

execution, make a change to code (using the Edit perspective or Debug perspective) and hit

“Build”. CCS will build and load your new .out file WITHOUT taking the time to launch a new

debug session or re-connecting to the target. This is very handy. TRY THIS NOW.

Because we are using the McASP, any underrun will cause the McASP to crash (no more

audio to the speaker/headphone). So, how can you halt and then start again quickly?

► Halt your code and then select Run

Restart or click the Restart button (arrow with

PLAY):

So, try this now.

► Run your code and halt (pause). Run again. Do you hear audio? Nope. Click the restart

button and run again. Now it should work.

These will be handy tips for all lab steps now and in the future.

Lab 11: An Hwi-Based Audio System

C6000 Embedded Design Workshop - C6000 Introduction 11 - 33

That’s It. You’re Done!!

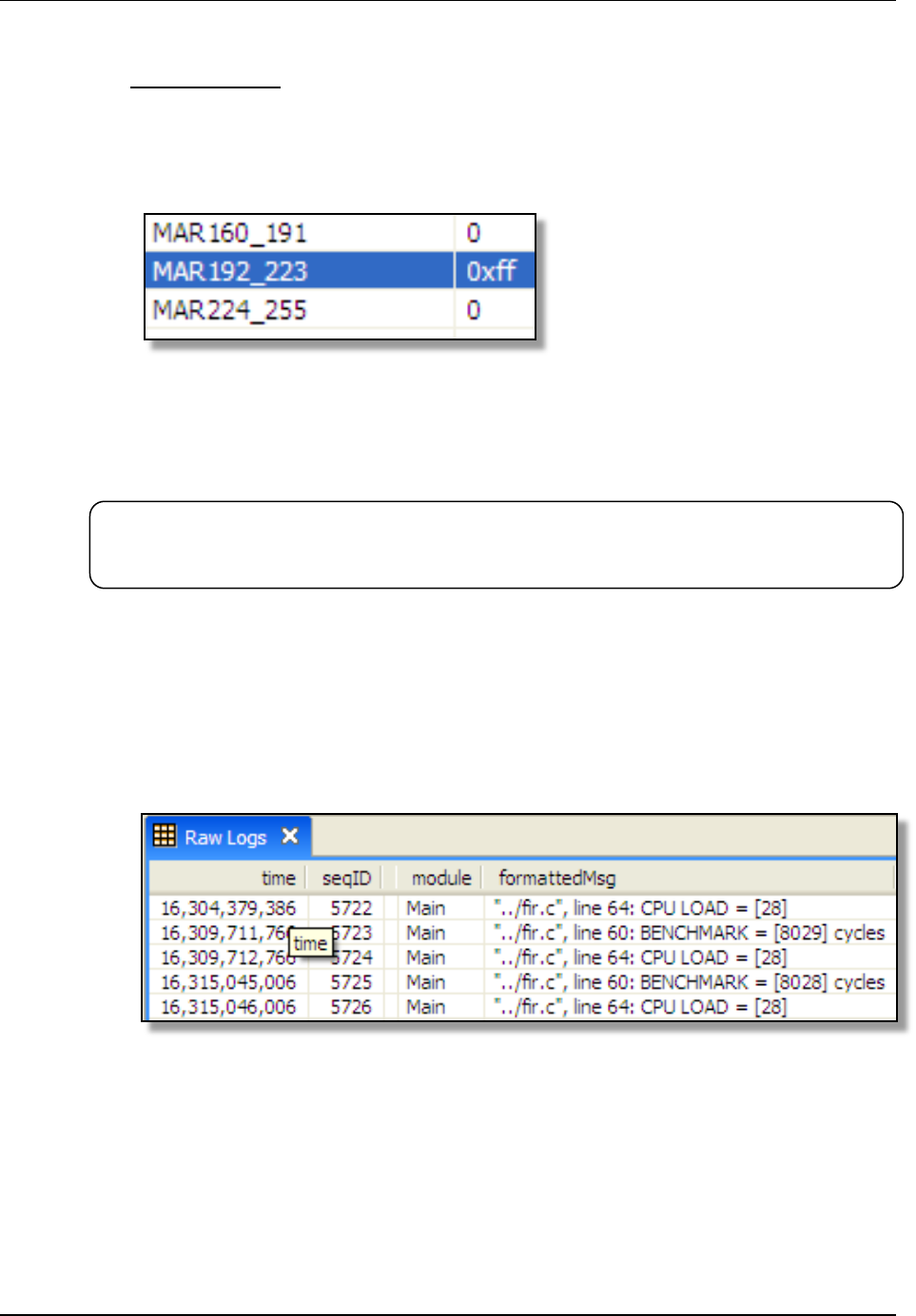

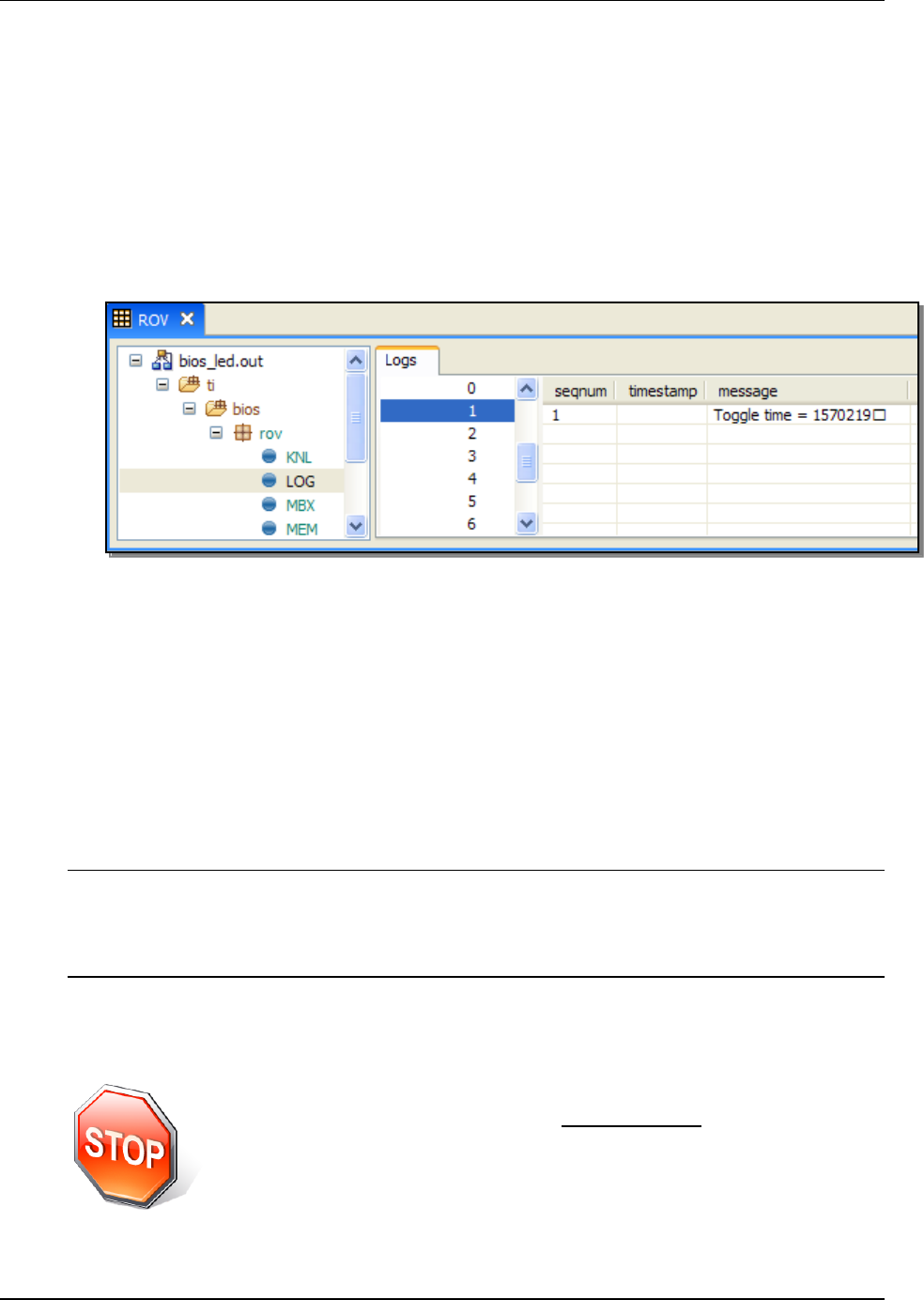

21. Note about benchmarks, UIA and Logs in this lab.

There is really no extra work we can do in terms of UIA and Logs. These services will be

used in all future labs. If you have time and want to add a Log or benchmark using

Timestamp to the code, go ahead.

You spent the past two days in the Kernel workshop playing with these tools. The point of this

lab was to get you up to speed on Platforms and focusing more on C6000 as the specific

target. In the future labs, though, you’ll have more chances to use UIA and Logs to test the

compiler and optimizer and cache settings.

22. Close the project and delete it from the workspace.

Terminate the debug session and close CCS. Power cycle the board.

RAISE YOUR HAND and get the instructor’s attention when you

have completed PART A of this lab. If time permits, you can

quickly do the next optional part…

Lab 11: An Hwi-Based Audio System

11 - 34 C6000 Embedded Design Workshop - C6000 Introduction

PART B (Optional) – Using the Profiler Clock

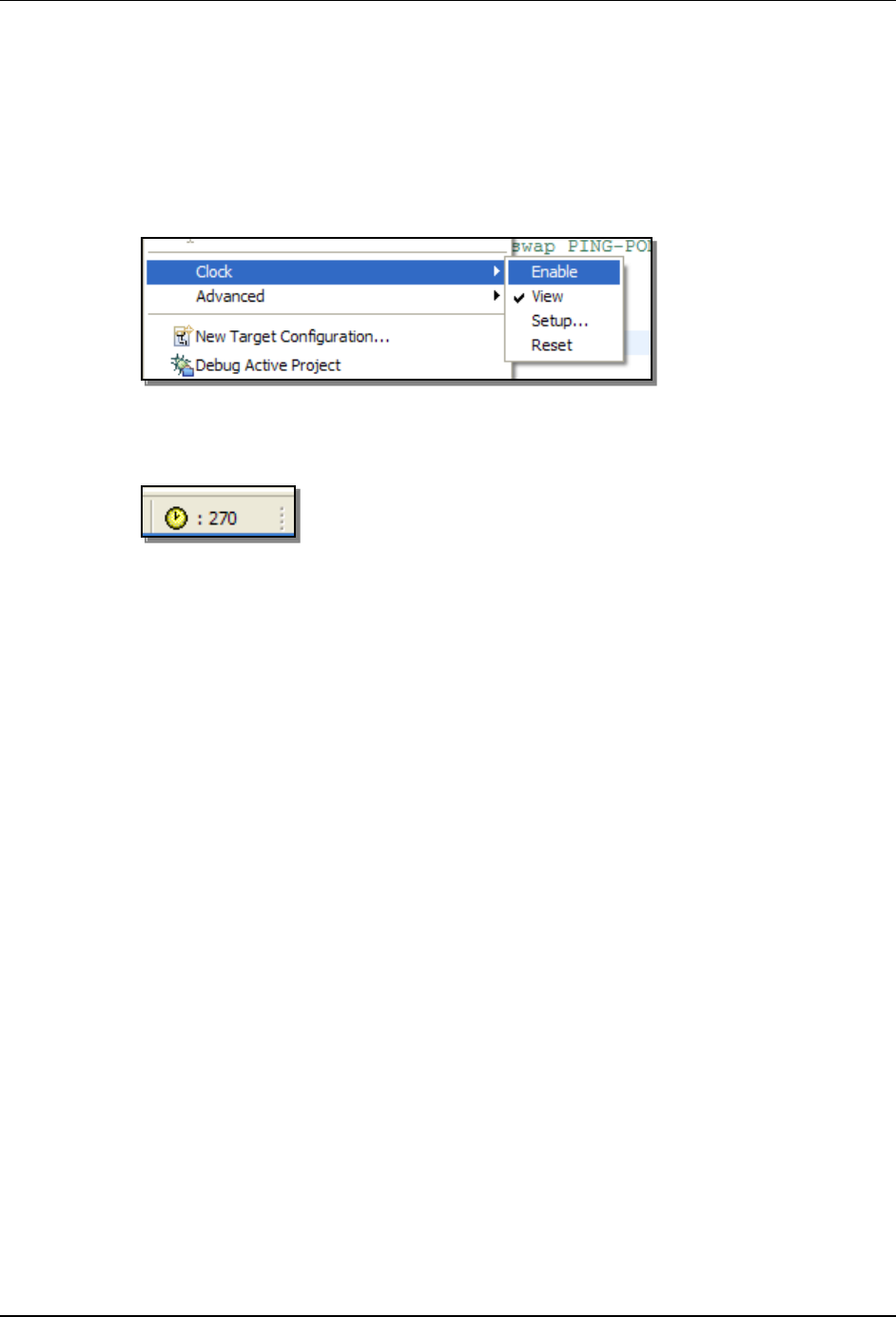

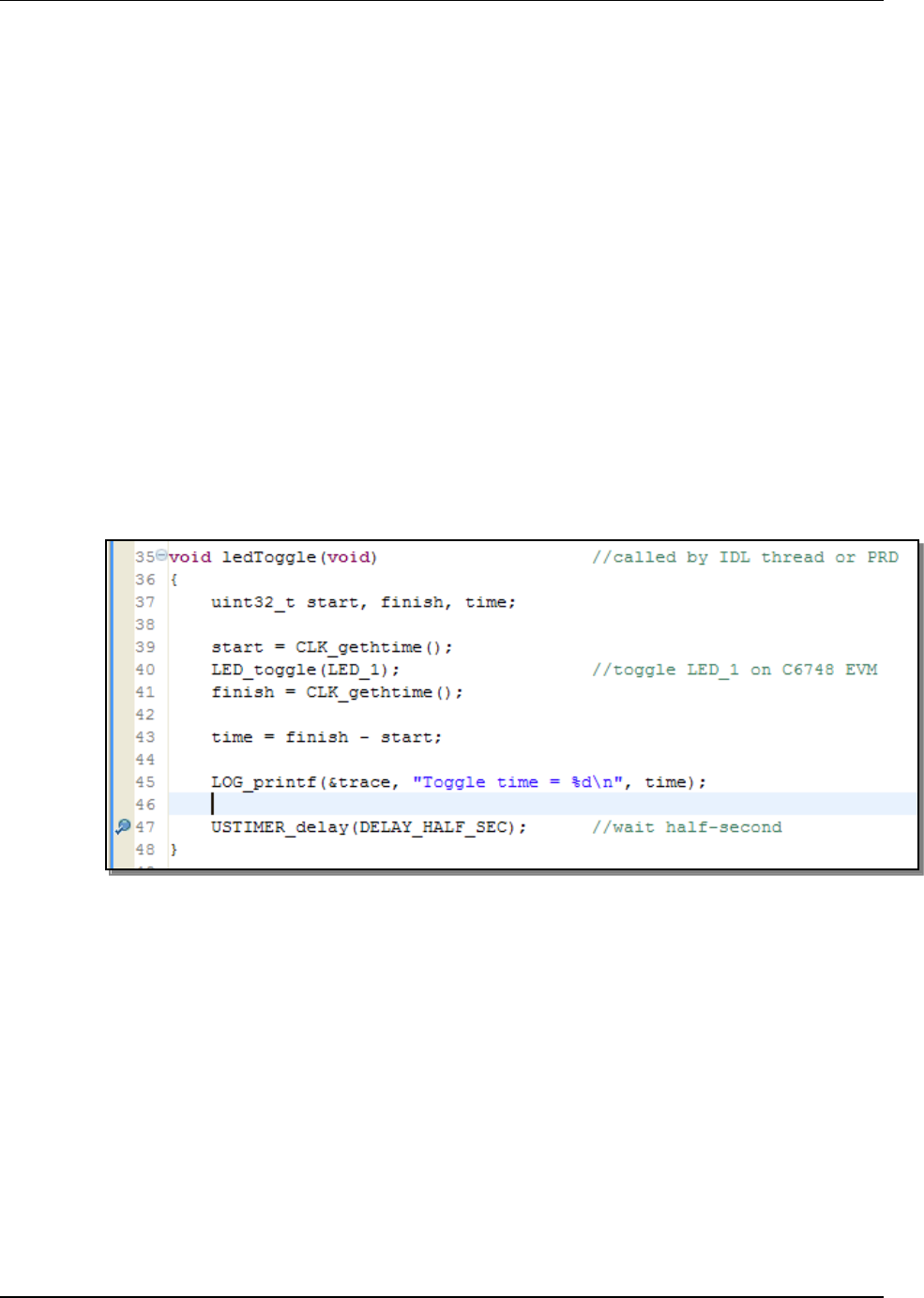

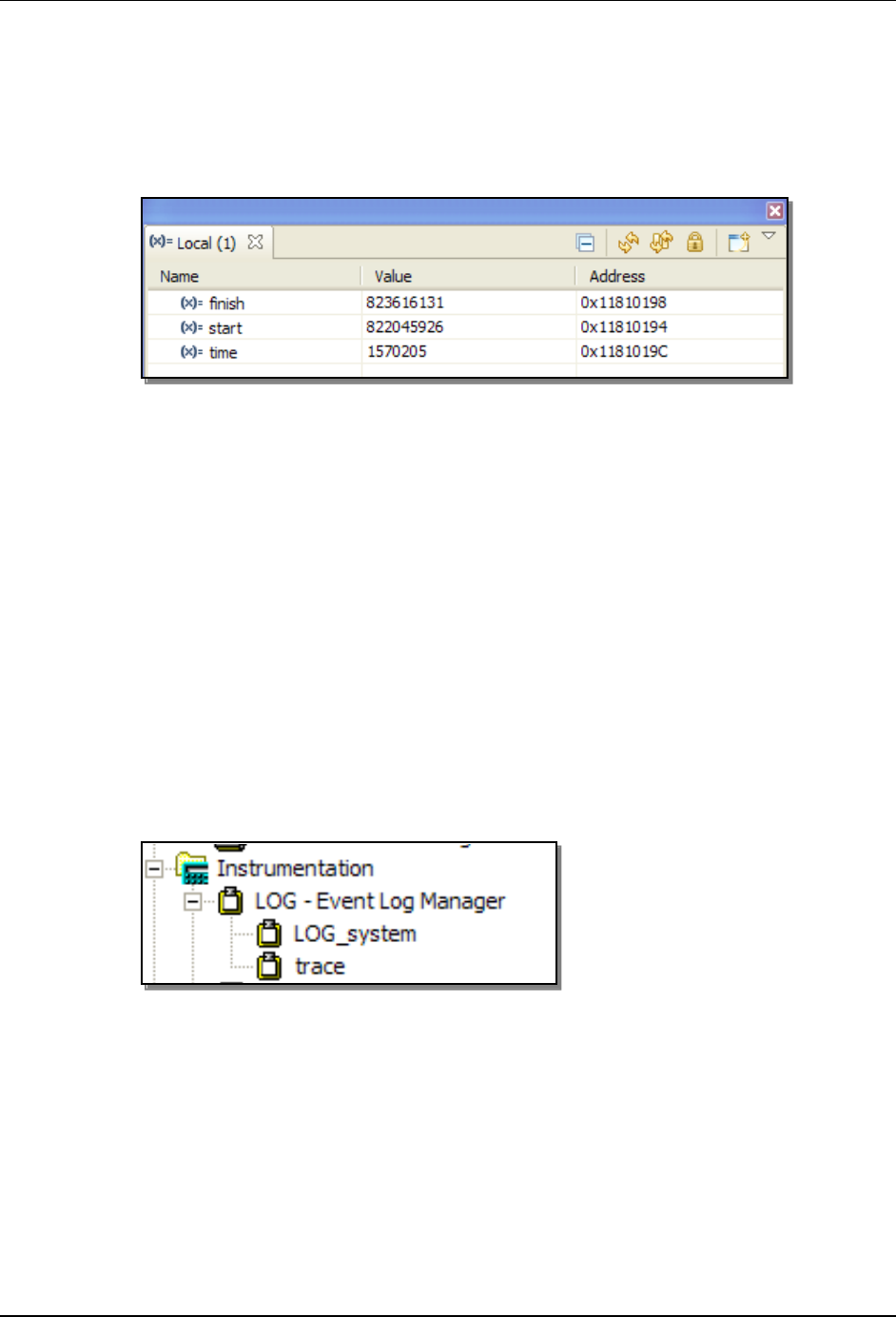

23. Turn on the Profiler Clock and perform a benchmark.

► Set two breakpoints anywhere you like (double click in left pane of code) – one at the

“start” point and another at the “end” point that you want to benchmark.

Turn on the Profiler clock by selecting: Run → Clock → Enable

In the bottom right-hand part of the screen, you should see a little CLK symbol that looks like

this:

Run to the first breakpoint, then double-click on the clock symbol to zero it. Run again and

the number of CPU cycles will display.

Additional Information