CCS_2719_2P2S_Feb82 CCS 2719 2P2S Feb82

CCS_2719_2P2S_Feb82 CCS_2719_2P2S_Feb82

User Manual: CCS_2719_2P2S_Feb82

Open the PDF directly: View PDF ![]() .

.

Page Count: 67

MODEL.2719

2 PARALLEL 1 2

SERIAL

1/0

INTERFACE

.

Reference

Manual

11-,

CaHfoniia

Computer

Systems·

42000096-01

CCS

MODEL

2719

2 PARALLEL / 2 SERIAL

I/O

INTERFACE

Reference

Manual

Rev

B

Manual

#42000095-01

Copyright

1981

California

Computer

Systems

250

Caribbean

Drive

Sunnyvale

CA

94086

Copyright

1981

by

California

Computer

Systems.

All

rights

reserved.

No

part

of

this

publication

may

be

reproduced

in

any

form

or

by

any

means

without

express

permission

of

California

Computer

Systems.

The

information

contained

in

this

manual

is

believed

to

be

correct

at

the

time

of

publication.

However,

CCS

assumes

no

liability

resulting

from

the

use

of

this

publication.

Publication

History:

Revision

A

printed

December

1981

Revision

B

printed

February

1982

Z-80

M

is

a

trademark

of

Zilog,

Inc.

CP/M

M

is

a

trademark

of

Digital

Research,

Inc.

OASIS m

is

a

trademark

of

Phase

One,

Inc.

TABLE

OF

CONTENTS

CHAPTER 1 INTRODUCTION

1.1

GENERAL

DESCRIPTION

.........................•

1-1

1.2

USING

THIS

MANUAL

............................

1-2

1 . 3

SPECIFICAT

IONS

...............................

1-

3

1.4

2719

BLOCK

DIAGRAM

.............•.............

1-4

CHAPTER 2 CONFIGURING

THE

2719

2.1

2.2

2.3

2.4

2.5

2.6

2.7

2.8

2.9

2.10

BASE

ADDRESS

JUMPERS

....•...•............••..

2-1

INTERRUPT

MODE

AND

PRIORITY

CONFIGURATION

.•.•

2-4

2.2.1

Mode 0

Configuration

....••••••.•.••...

2-4

2 . 2 . 2 Mode 1

Configuration

..................

2-4

2.2.3

Mode 2

Configuration

.......•••..•.•...

2-5

SERIAL INTERFACES

..................•..•......

2-7

2.3.1

Synchronous

Conversion

...•.•..•.....•.

2-7

2.3.2

DCE/DTE

Conversion

....••...•.....•..•.

2-7

2.3.3

Non-Standard

Handshaking

...•....•..•..

2-7

2.3.4

Baud

Rate

Source

Jumpers

.•.••..••.....

2-9

2 . 3

.5

Protective

Ground

...........•••.•..•..

2-9

PARALLEL INTERFACE CONFIGURATION

......••....

2-10

2.4.1

Buffer

Direction

Jumpers

•.........•••

2-10

2.4.2

Buffer

Enable

Jumpers

...•......•...•.

2-10

2.4.3

Reversing

Interface

Polarities

•.•..•.

2-10

THE

RESET JUMPER

......................•....•

2-11

INTERRUPT

ACKNOWLEDGE

WAITS

.................

2-11

CLOCK

PHASE

.................................

2-11

DATA

LATCH

ENABLING

AND

DISABLING

...........

2-12

BAUD

RATES

IN

2

MHZ

SYSTEMS

.................

2-12

OPERATION

IN

6

MHZ

SYSTEMS

...•.....••..•.•..

2-12

CHAPTER 3

PROGRAMMING

INFORMATION

3.1

3.2

3.3

3.4

PORT

RELATIVE ADDRESSES

...........••......•..

DART

2719-UNIQUE

PROGRAMMING

.......•.•.......

CTC

2719-UNIQUE

PROGRAMMING

......••.•..•.....

PROGRAMMING

THE

PIA

.........................

.

3.4.1

3.4.2

~.4.3

PIA

Command

Registers

.......••........

PIA

Data

Direction

Registers

.........

.

PIA

Initialization

.............•......

3-1

3-2

3-3

3-4

3-5

3-7

3-7

CHAPTER

4

HARDWARE

DESIGN

4.1

THE

PlAIS

........................•...........

4-1

4 • 2

THE

DART

......•....••...•...•..•..•......•••.

4-

2

4 • 3

THE

eTC

.......•.......•....•.••..............

4-

3

4.4

ADDRESS

AND

CONTROL

LOGIC

....•...............

4-6

4.5

INTERRUPT LOGIC

..............................

4-7

4.6

DATA

BUFFERING

AND

LATCHING

..................

4-9

APPENDIX A TECHNICAL

INFORMATION

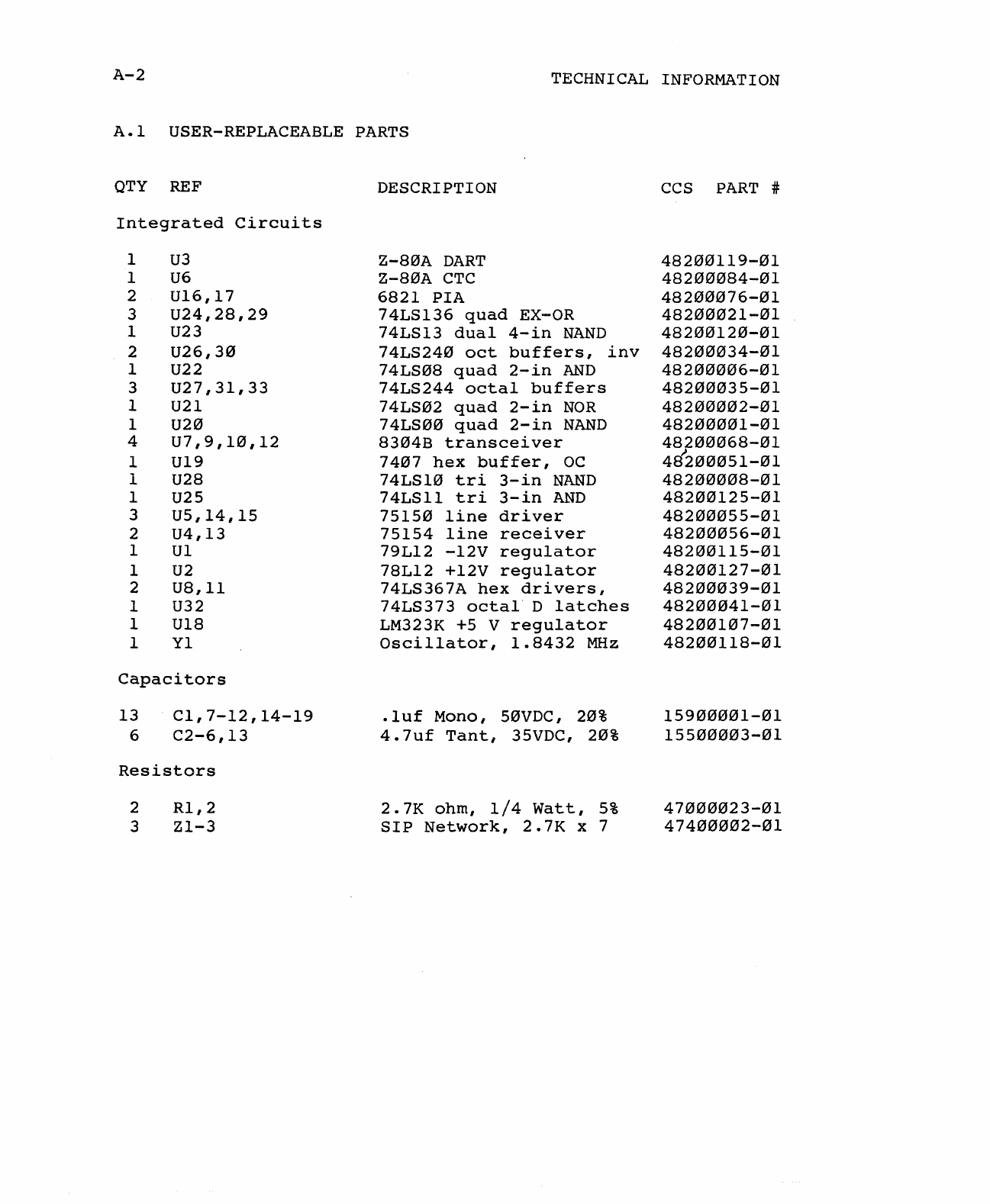

A.l

USER-REPLACEABLE

PARTS

.......................

A-2

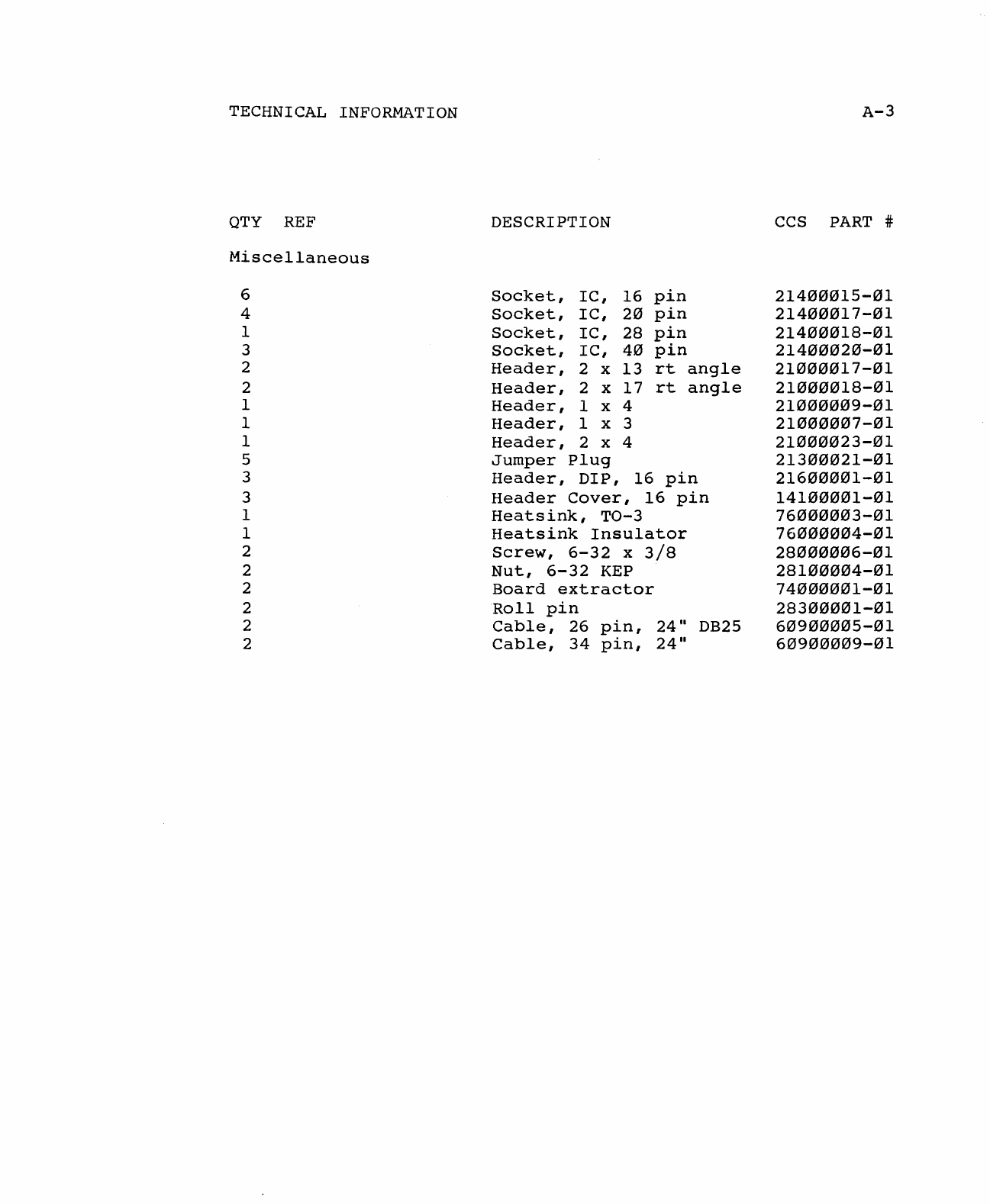

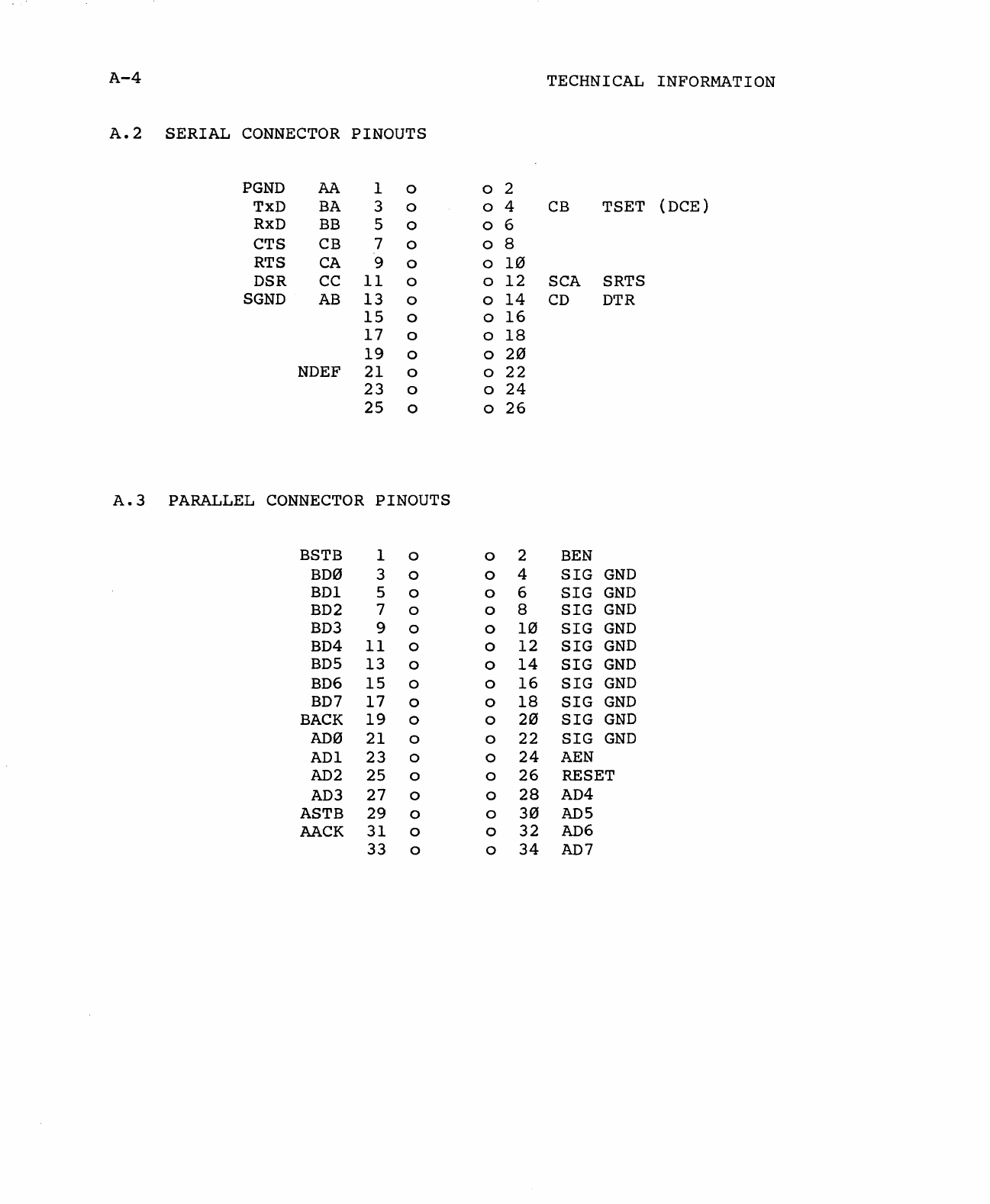

A.2

SERIAL

CONNECTOR

PINOUTS

.....................

A-4

A.3

PARALLEL

CONNECTOR

PINOUTS

...................

A-4

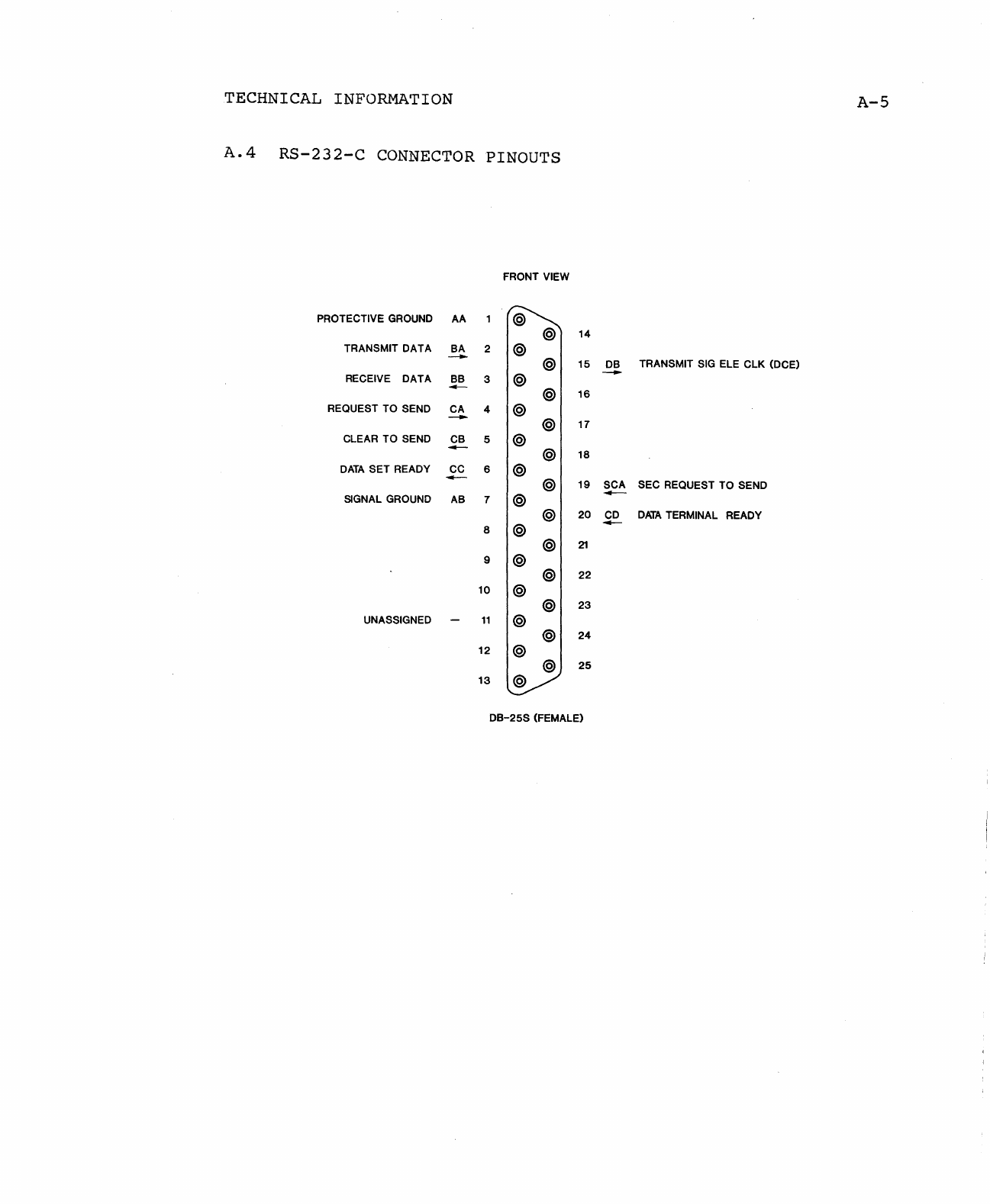

A.4

RS-232-C

CONNECTOR

PINOUTS

...................

A-5

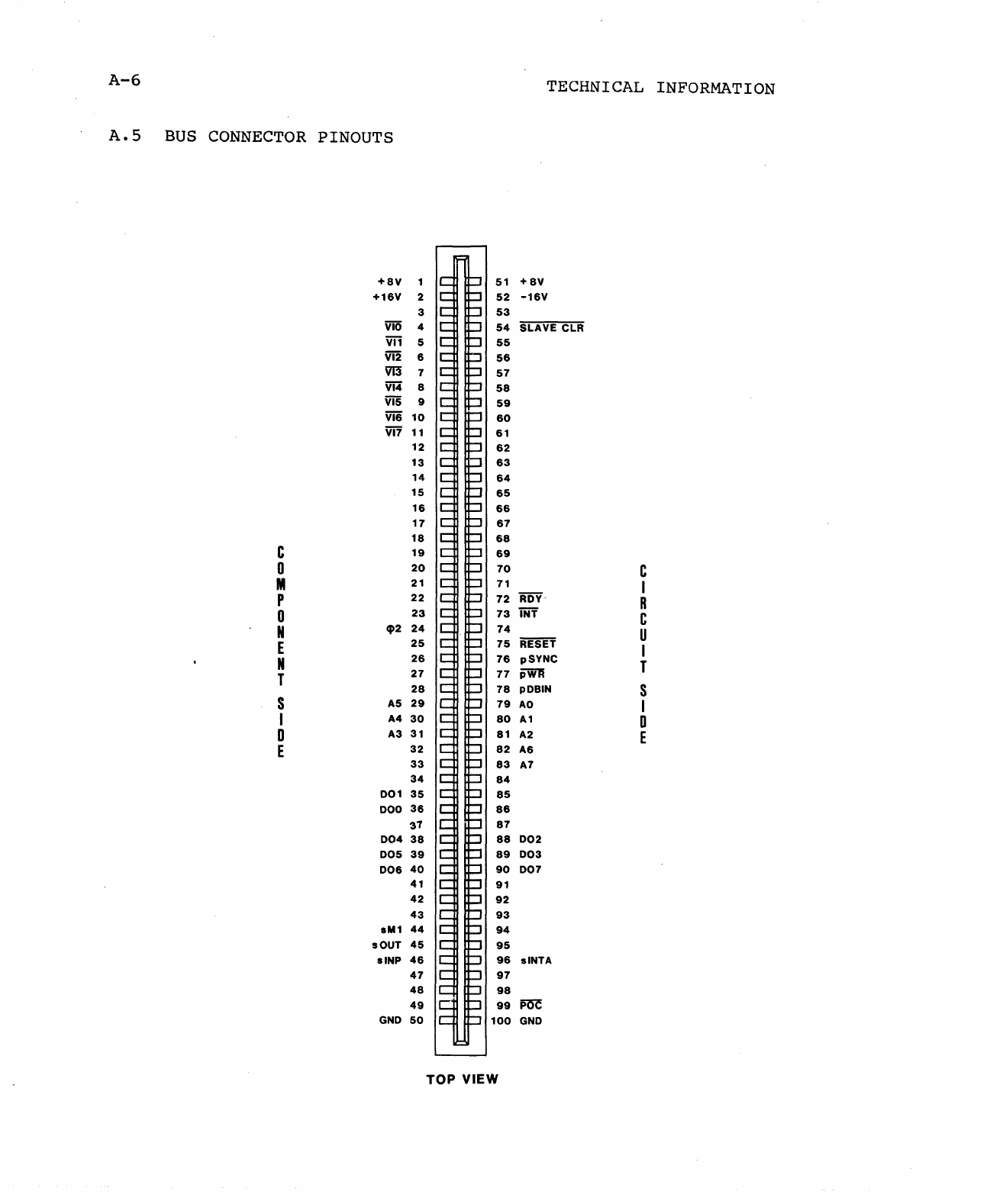

A.5

BUS

CONNECTOR

PINOUTS

........•...............

A-6

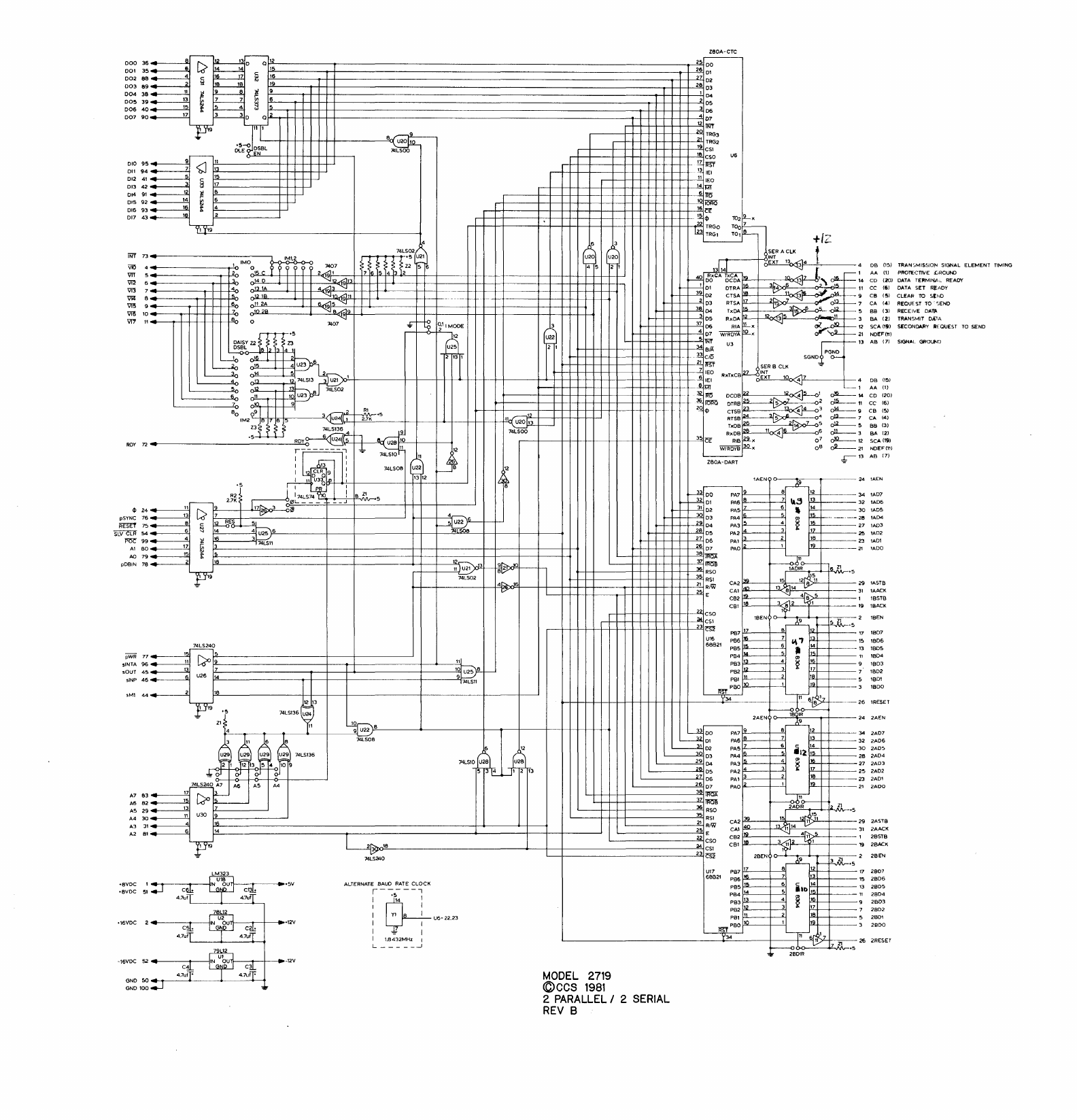

A.6

SCHEMATIC/LOGIC

DIAGRAM

....•.•..•....•..•....

A-7

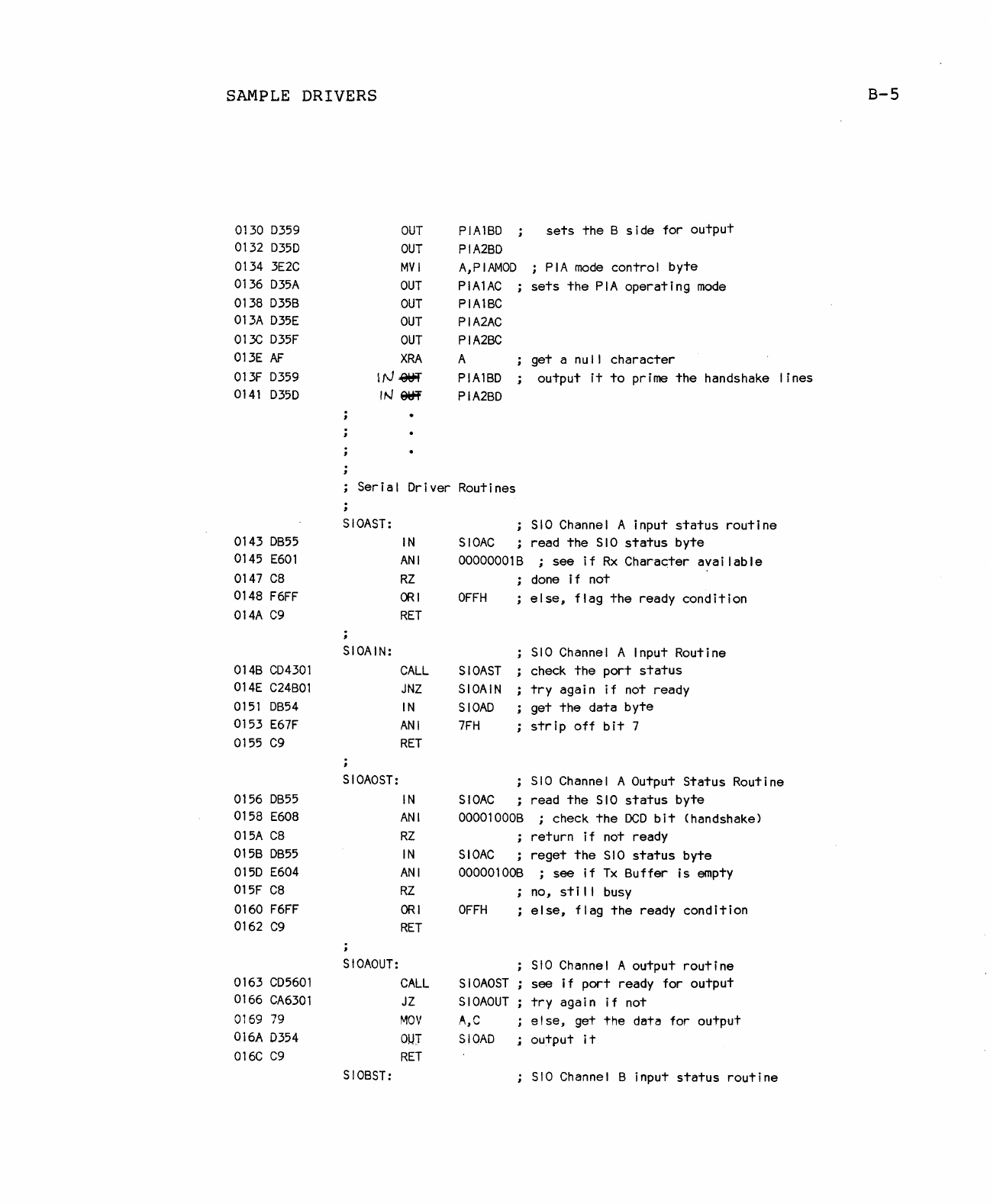

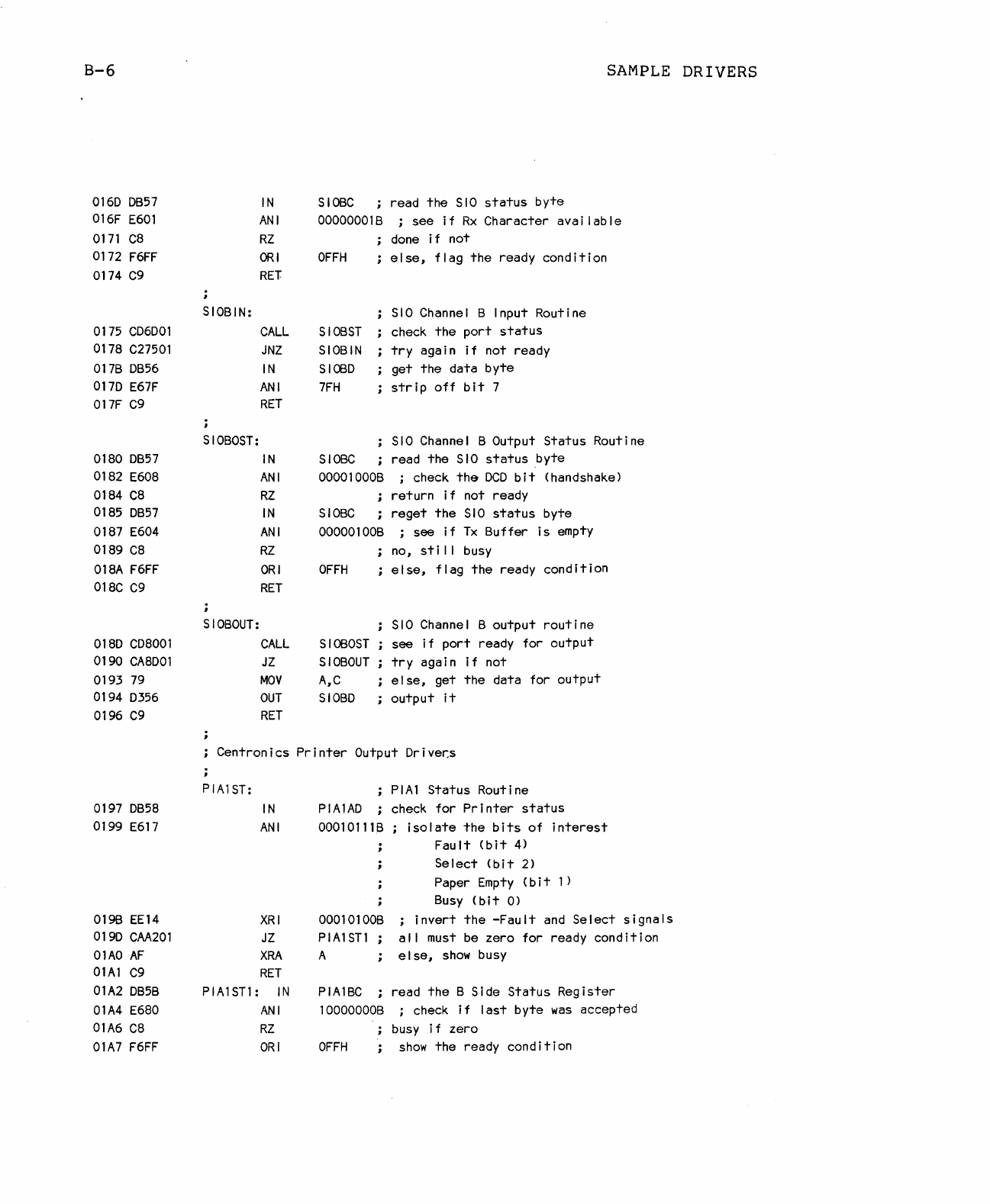

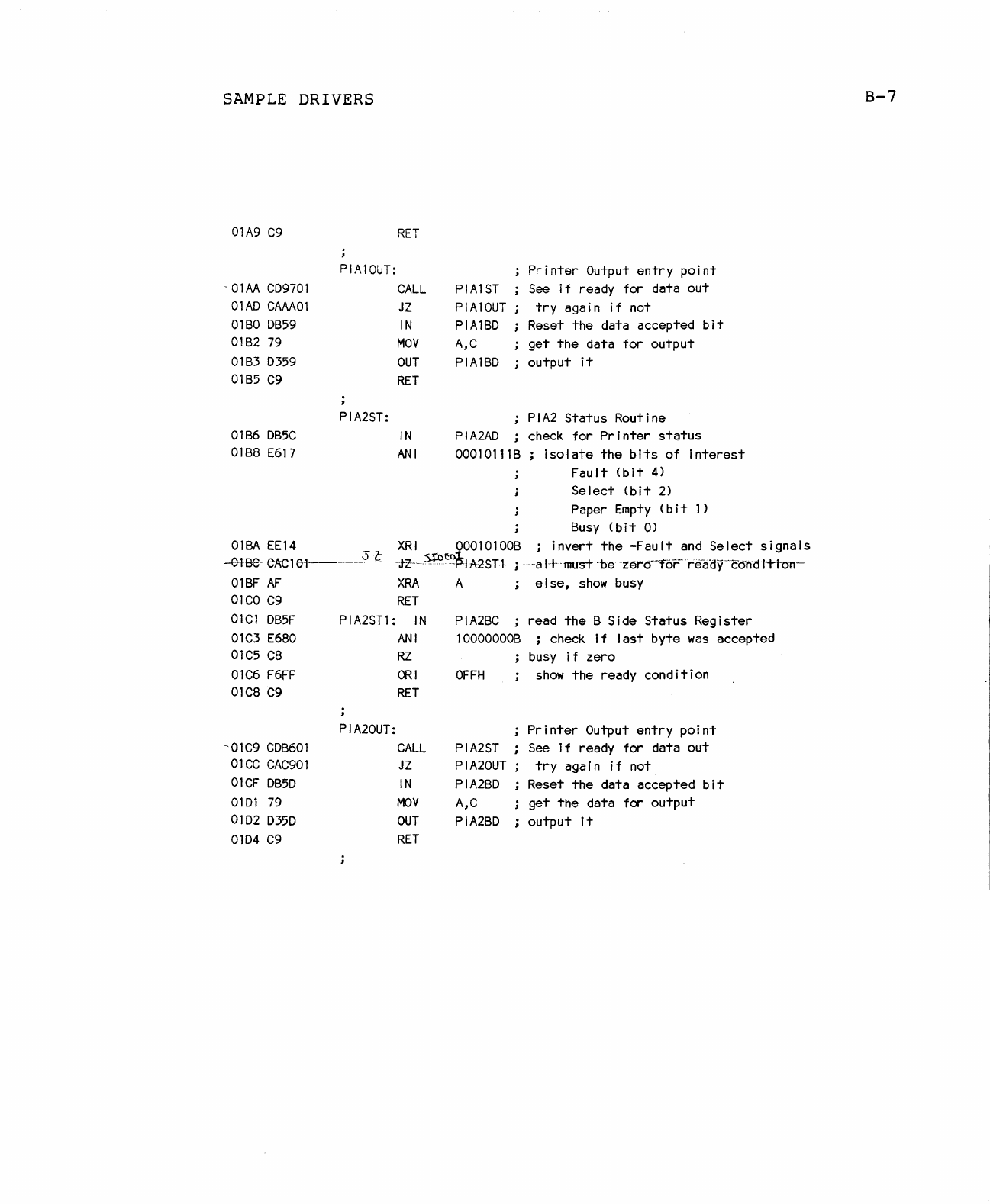

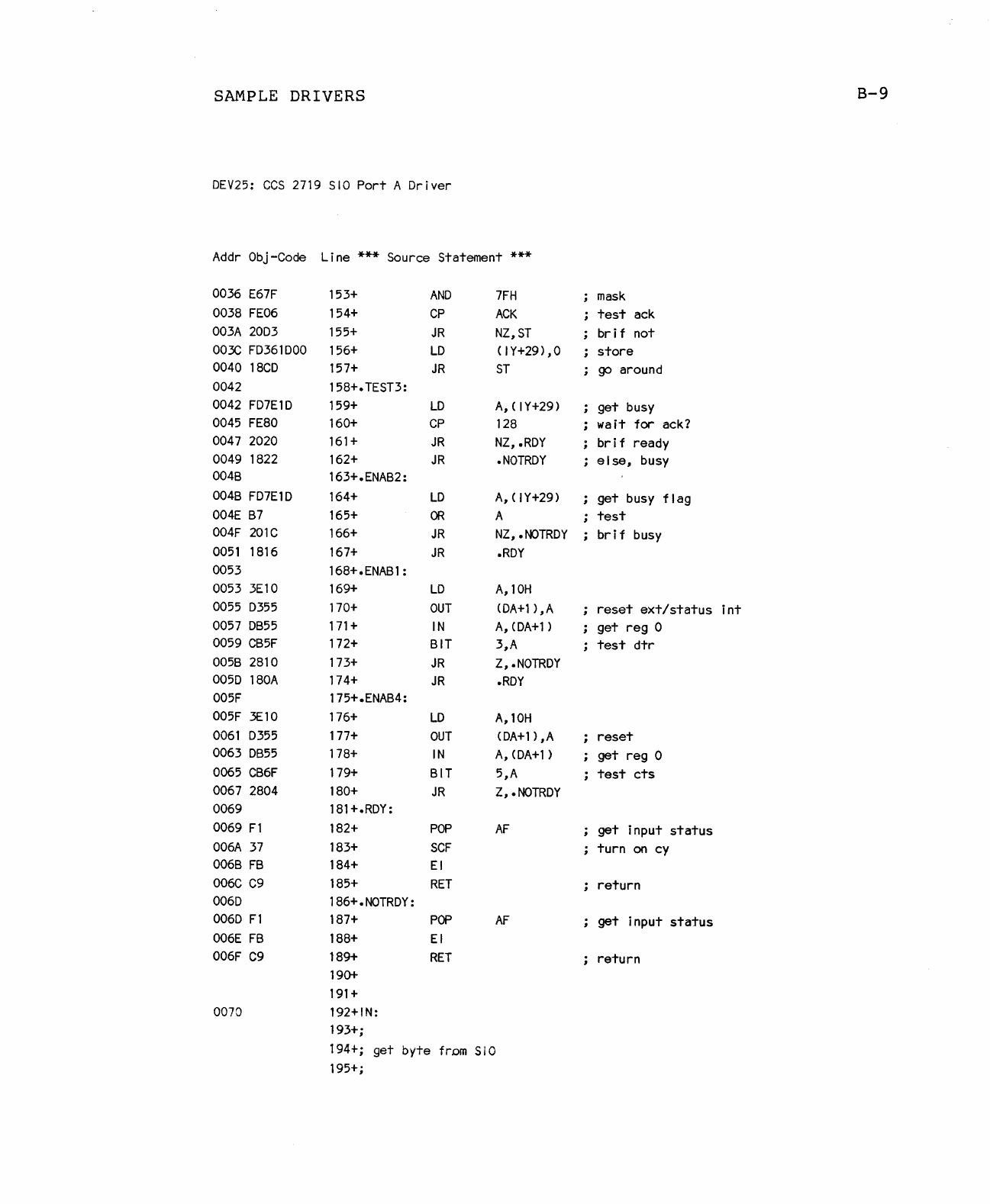

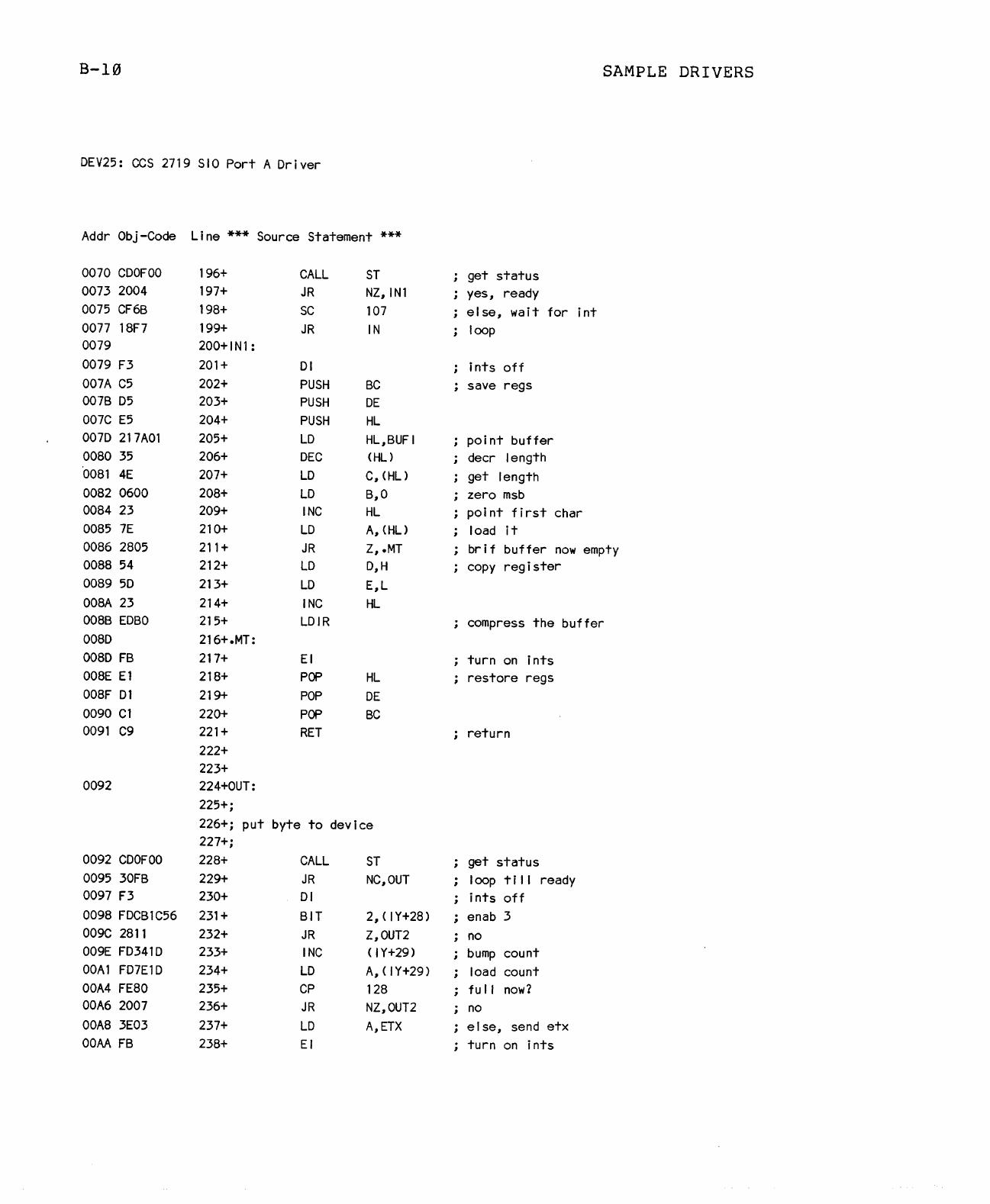

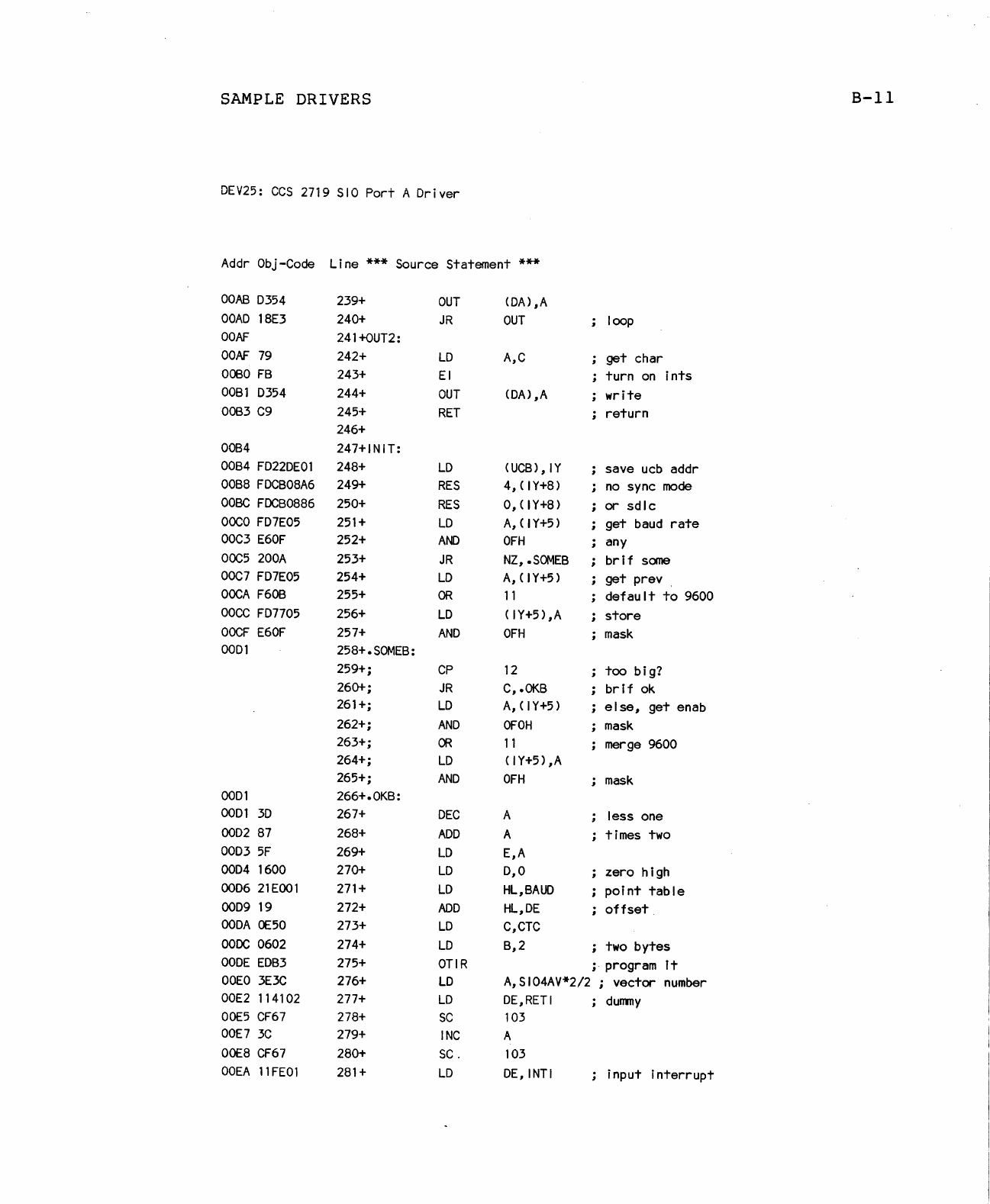

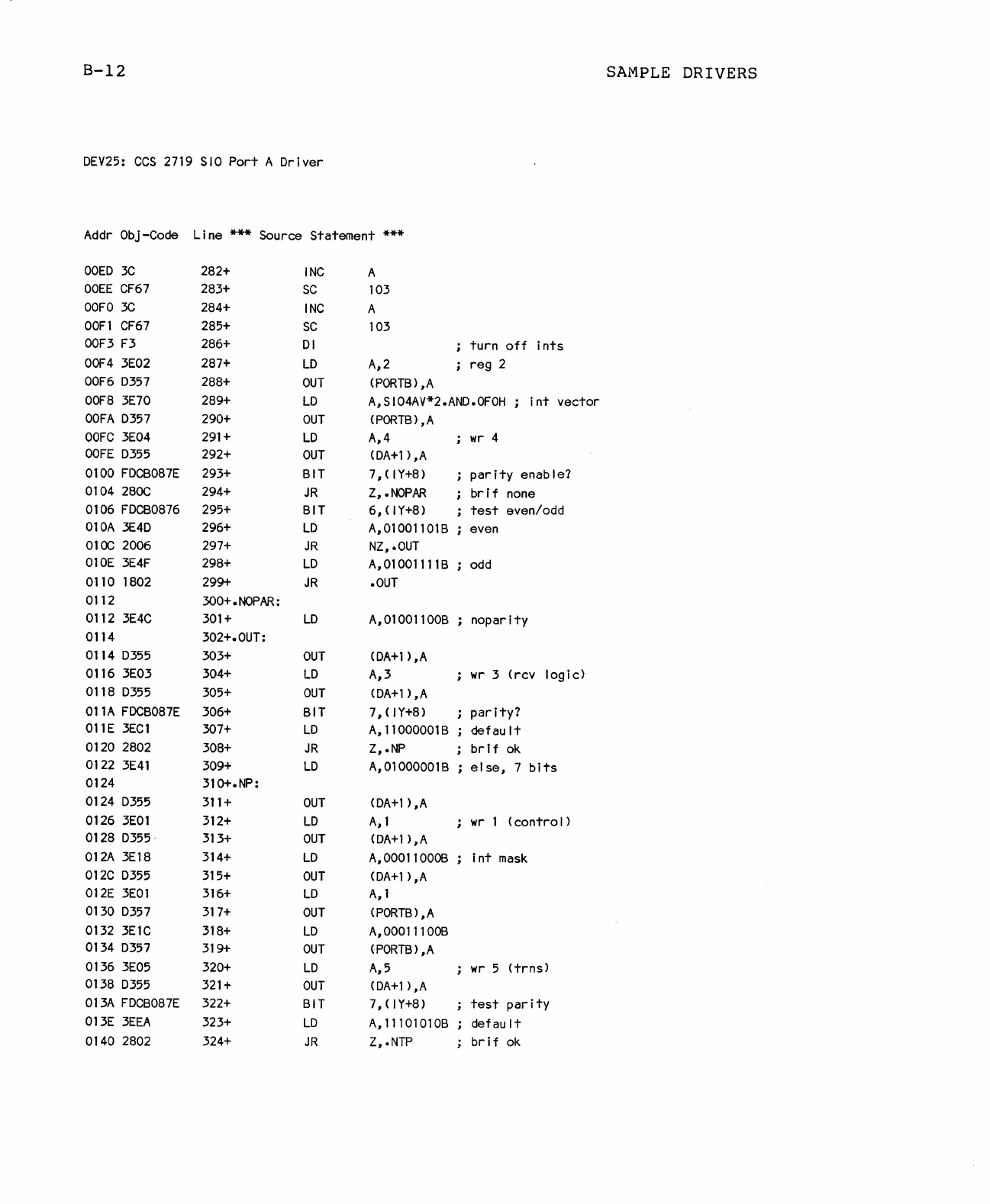

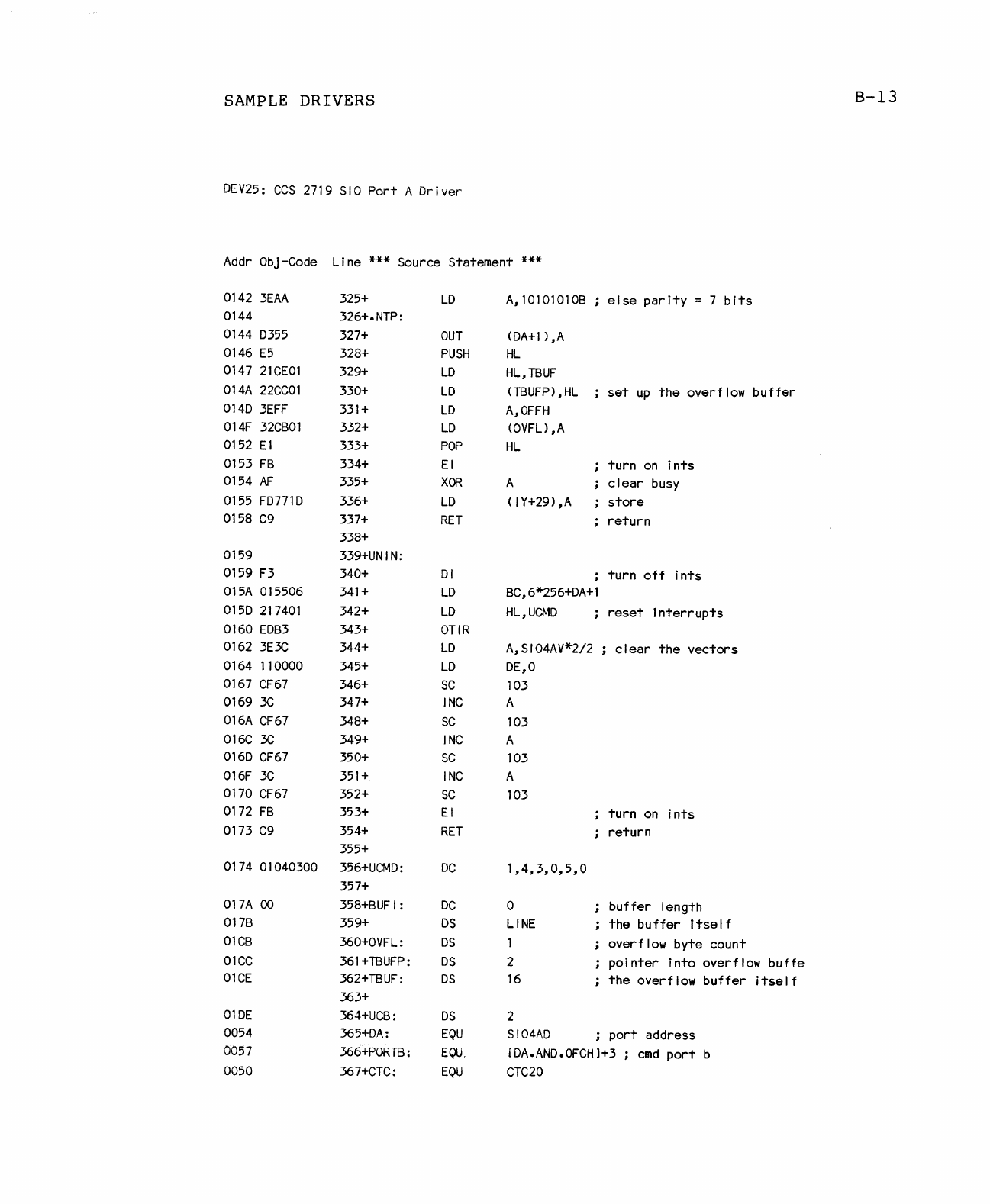

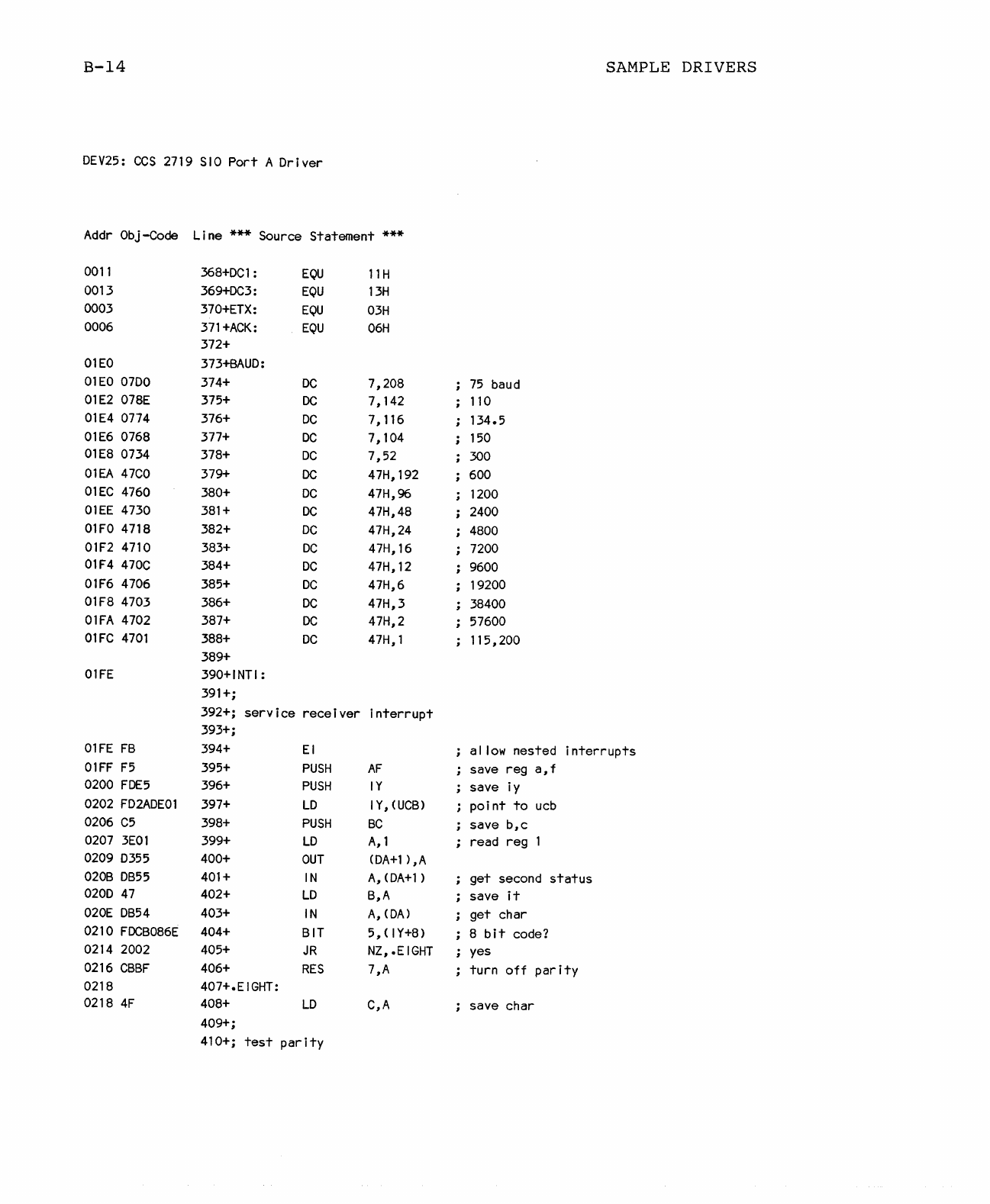

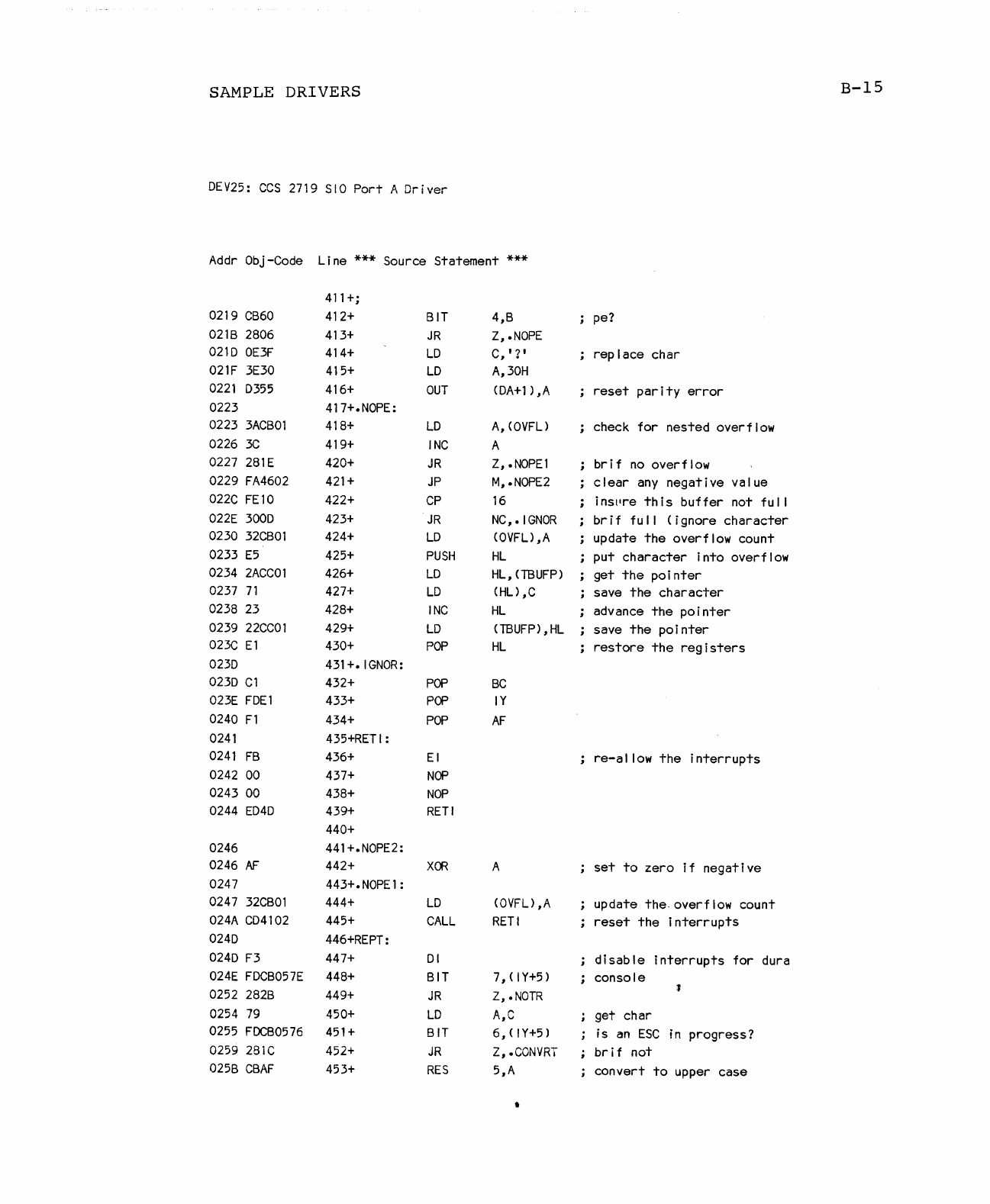

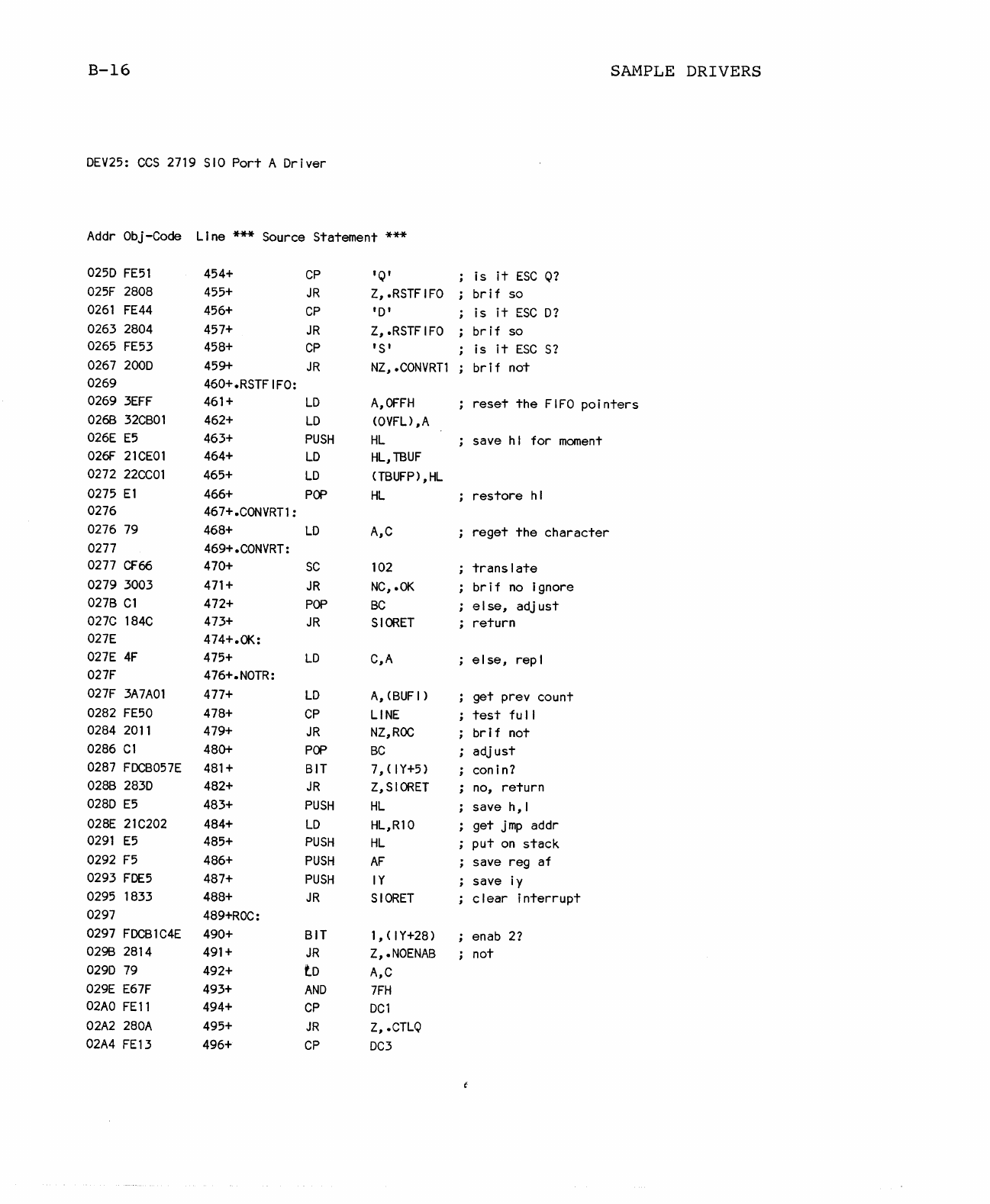

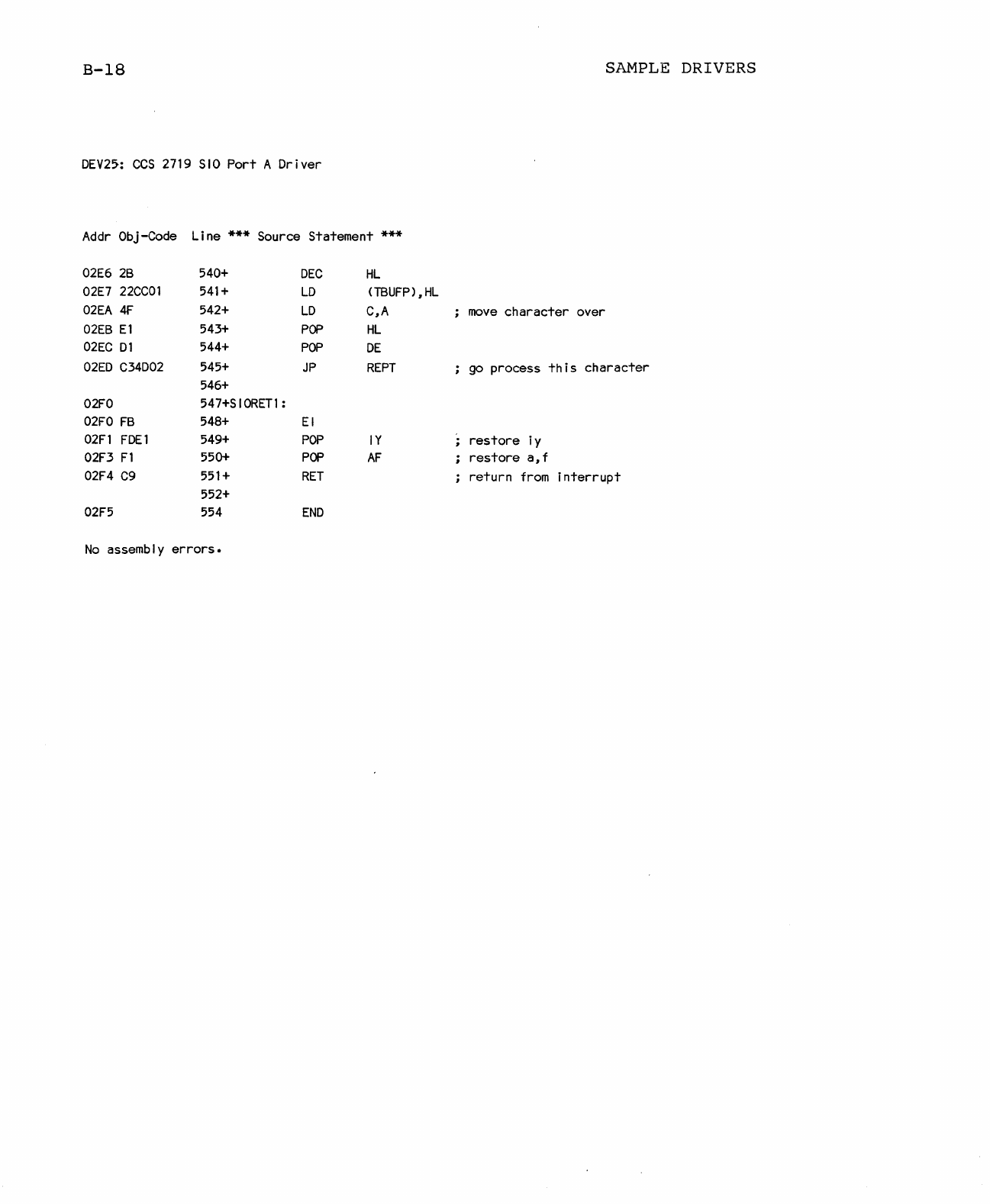

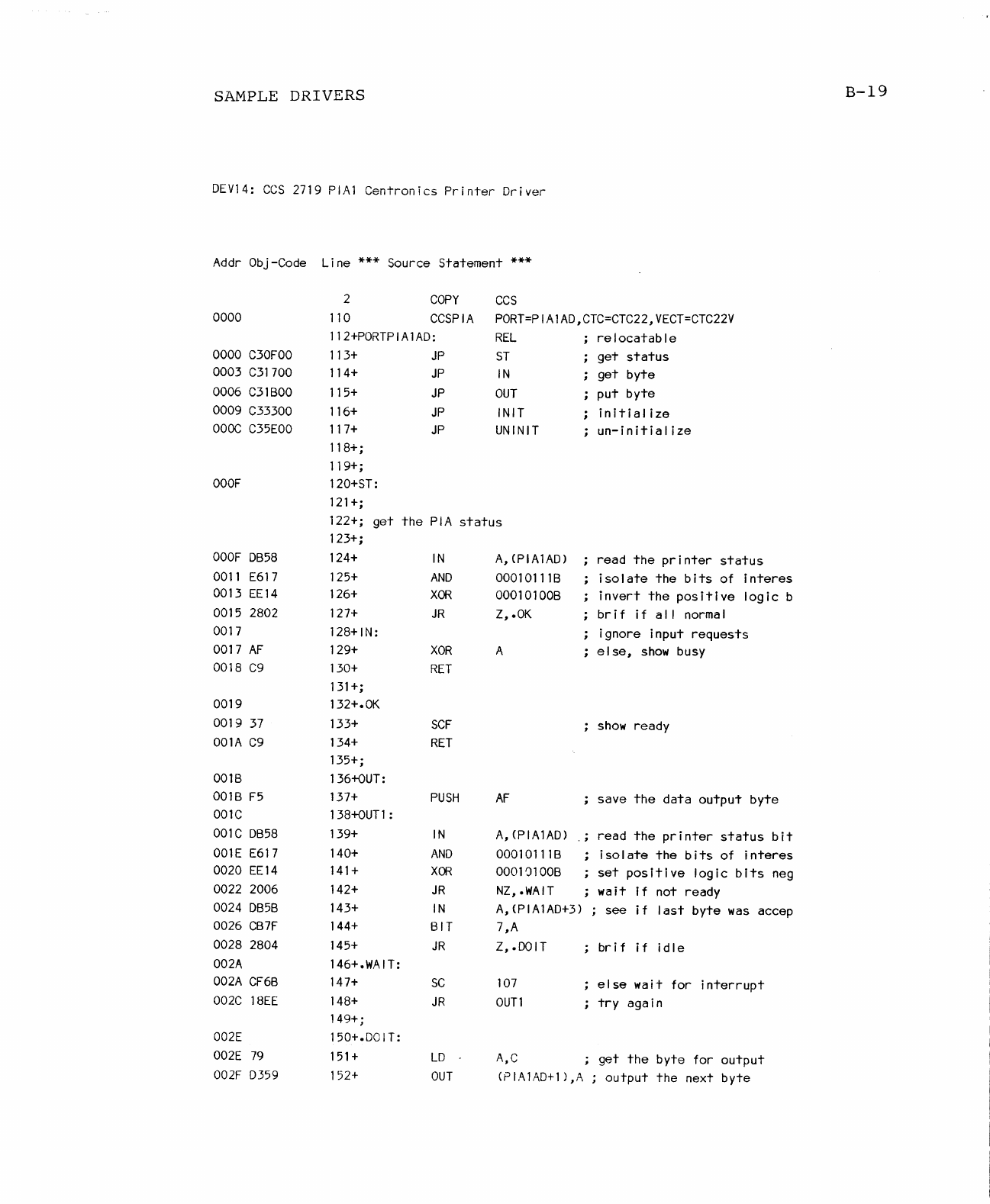

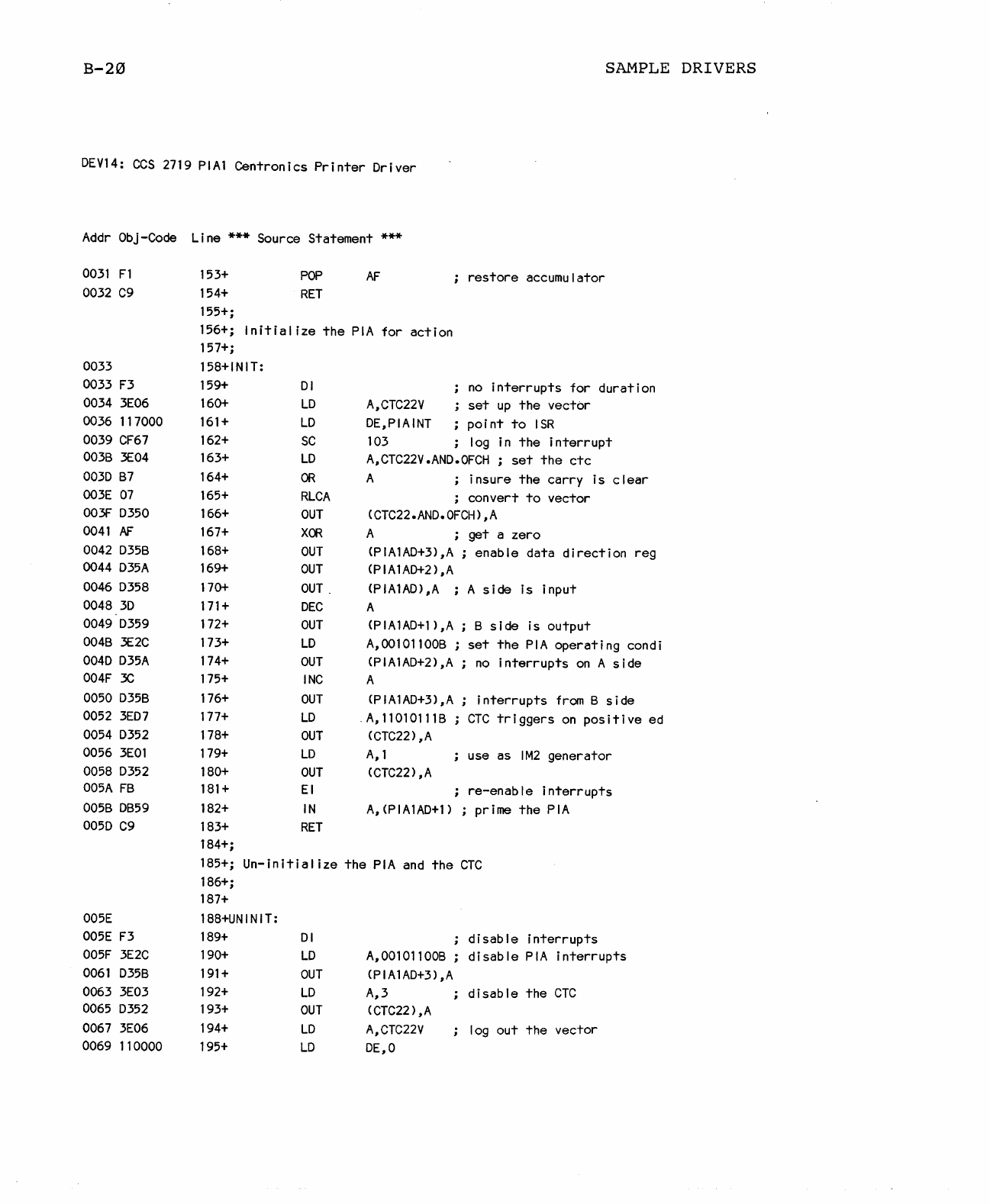

APPENDIX B

SAMPLE

DRIVERS

B

.1

CP/M DRIVER

.".................................

B-2

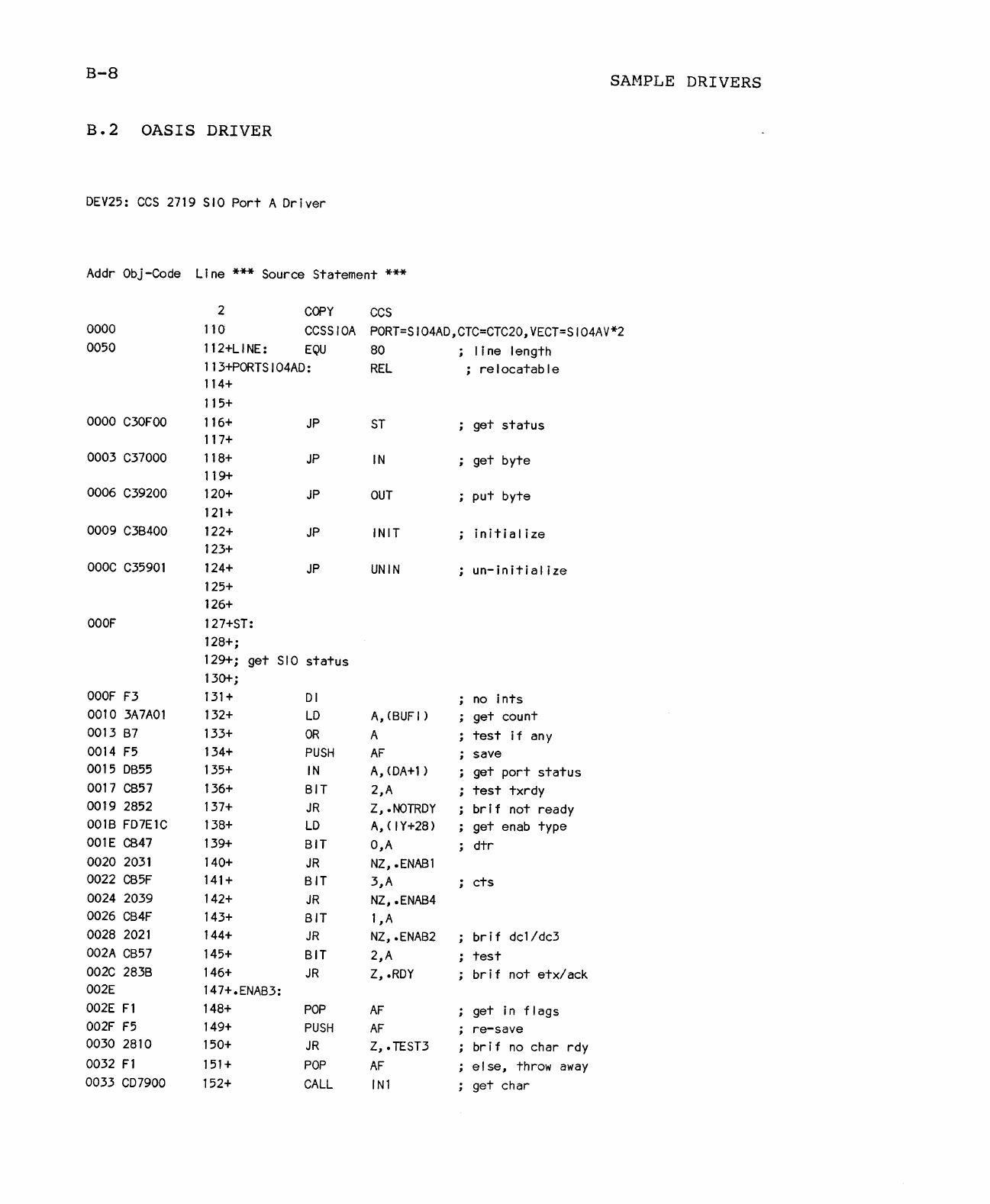

B.2

OASIS DRIVER

..•............•.................

B-8

CHAPTER

1

INTRODUCTION

1.1

GENERAL

DESCRIPTION

The

CCS

Model

2719

is

capable

of

interfacing

a

wide

variety

of

peripheral

equipment

to

Z-80-based

CPUs.

Software

and

hardware

options

give

a

high

degree

of

flexibility

to

the

2719

1s

two

serial

and

two

parallel

I/O

ports.

The

serial

ports

are

controlled

by

a

Z-80

DART

(Dual

Asynchronous

Receiver/Transmitter),

which

handles

asynchronous

serial

data

transfers

in

all

common

formats.

Baud

rates

up

to

11S.2K

are

available.

The

parallel

ports,

each

controlled

by

a

6821

PIA

(peripheral

Interface

Adapter),

are

designed

to

implement

Centronics

interfaces,

but

each

may

also

be

used

as

two

unidirectional

8-bit

ports

with

2-line

handshaking

or

as

one

unidirectional

16-bit

port.

The

2719

fully

supports

the

three

Z-80

interrupt

modes

for

all

ports.

Separate

headers

allow

the

user

to

select

the

Mode 0

or

Mode 2

interrupt

priority

level

and

the

devices

which

will

directly

control

the

INT*

line

for

Mode 1

and

Mode 2

interrupts.

(In

Mode 0

the

INT*

line

is

controlled

by

the

system1s

Interrupt

Controller.)

The

2719

also

supports

CCSls

fast

Mode 2

Interrupt

Daisy

Chain

Look-Ahead

Scheme

as

implemented

in

CCS

Systems

300/400.

Though

designed

especially

for

use

with

CCS

Systems

300/400,

the

2719

is

compatible

with

CCS

System

2210

as

well

as

with

a

majority

of

the

Z-80-based

S-100

systems

presently

available.

The

base

address

of

the

I/O

ports

is

jumper-selectable.

Clock

phase,

Interrupt-Acknowledge

wait,

and

reset

options

allow

the

user

to

meet

the

special

conditions

of

specific

systems.

1-2

INTRODUCTION

1.2

USING THIS

MANUAL

This

manual

is

intended

to

provide

information

required

by

system

integraters,

troubleshooters,

and

programmers.

Chapter

2

deals

with

board

configuration,

including

hardware-configured

serial

and

parallel

interface

options.

Chapter

3

discusses

the

2719-unique

programming

requirements

of

the

DART

and

CTC

and

provides

complete

programming

instructions

for

the

PIAs.

Chapter

4

presents

a

detailed

discussion

of

the

hardware

design

of

the

2719,

and

is

intended

to

be

read

in

conjunction

with

frequent

references

to

the

Schematic/Logic

Diagram

included,

along

with

various

technical

illustrations

and

tables,

in

Appendix

A.

Sample

drivers

for

the

serial

and

parallel

port

drivers

for

CP/M

and

OASIS

operating

systems

are

provided

in

Appendix

B.

INTRODUCTION

1.3

SPECIFICATIONS

I/O

INTERFACES

SERIAL:

Two

Asynchronous

Ports

Meet

EIA

RS-232-C

Standard,

Full

or

Partial

Primary

Channel

Synchronous

Capability

(SIO/0

Plug-Compatible)

Easy

DCE-to-DTE

Reconfiguration

Non-Standard

Handshaking

Options

Programmable

(Z-80

CTC)

or

External

Baud

Rates

PARALLEL:

Two

Centronics-Type

Ports

Hardware

and

Software

Reconfiguration

Options

Port

Buffers

Disabled

When

Cable

Disconnected

SYSTEM

INTERFACE

POWER

S-100:

Complies

with

IEEE

Task

696.l/D2

Supports

All

Three

Z-80

Interrupt

Modes

Supports

CCS's

Mode 2

Interrupt

Extended

Daisy

Chain

Look-Ahead

Scheme

Jumper-Selectable

Board

Base

Address

Full

Buffering

of

Bus-Driving

Outputs,

Schmitt-Trigger

Bus

Receiver

Inputs

+8

Volts

Regul'ated

On-Board

to

+5

Volts

+16

Volts

Regulated

On-Board

to

+12

Volts

-16

Volts

Regulated

On-Board

to

-12

Volts

Consumption:

Heat

Burden:

.75

Amps

at

+8

Volts

.05

Amps

at

+16

Volts

.05

Amps

at

-16

Volts

110

gram-calories/minute

.45

BTU/minute

ENVIRONMENTAL

REQUIREMENTS

Temperature:

Humidity:

o

to

70

C.

(32

to

155

F.)

Up

to

90%

Non-Condensing

1-3

1-4

INTRODUCTION

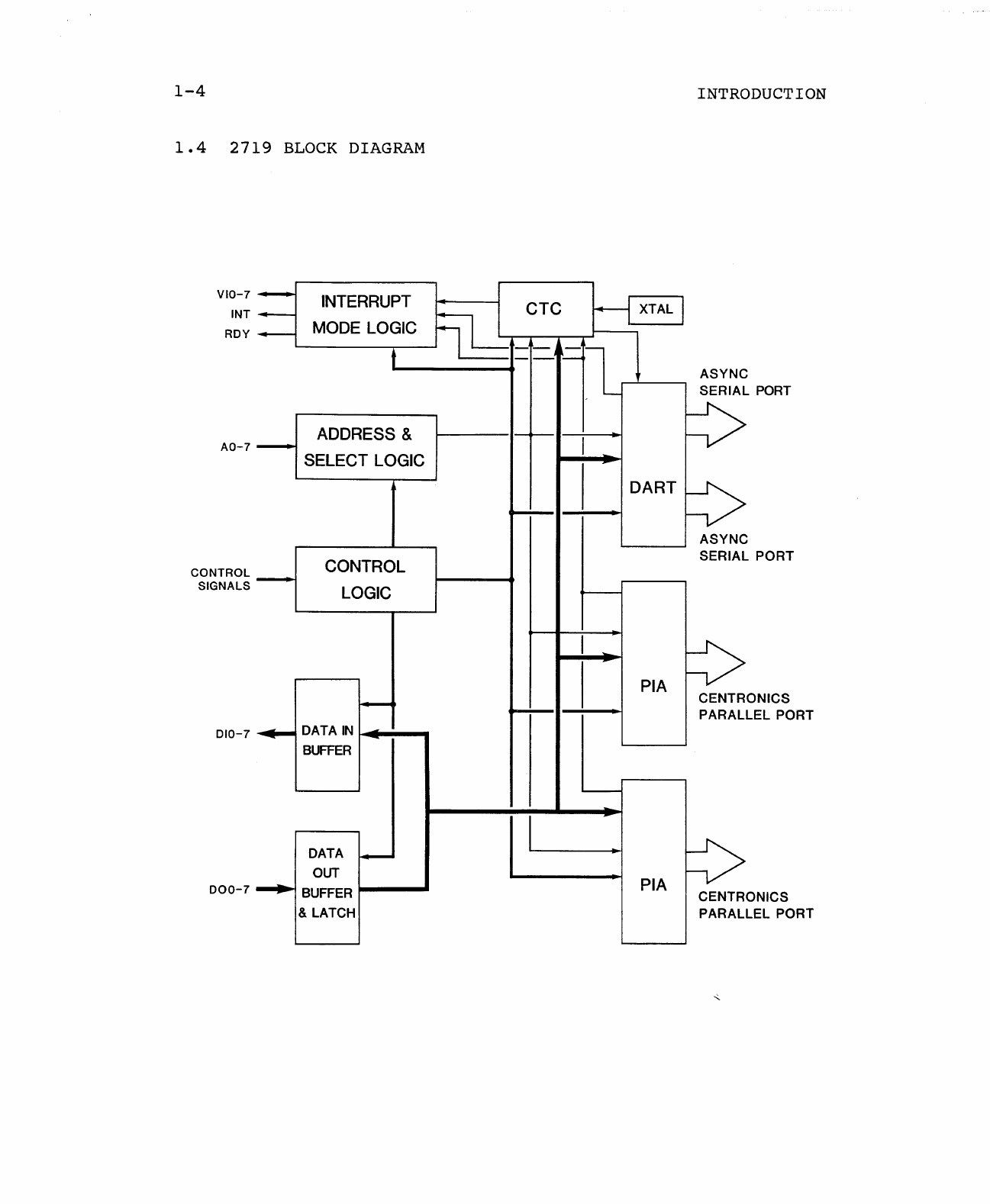

1.4

2719

BLOCK

DIAGRAM

V10-7

-----

INT-

ROY

-

AO-7

----+

INTERRUPT

ru

CTC

H XTAL I

MODE LOGIC

Il

-'"=.J

r='-

I

~

ASYNC

SERIAL

PORT

~

ADDRESS &

SELECT LOGIC

~I--:I-l

DART

~

CONTROL _

SIGNALS

CONTROL

LOGIC

010-7

~

DATA

IN

J.,..~.--

....

BUFFER

DATA

~

OUT

000-7

~

BUFFER

J----

..

& LATCH

PIA

PIA

ASYNC

SERIAL

PORT

~

CENTRONICS

PARALLEL

PORT

CENTRONICS

PARALLEL

PORT

CHAPTER

2

CONFIGURING

THE

2719

The

2719,

while

designed

to

be

flexible,

has

also

been

designed

to

require

as

little

configuration

as

possible

in

its

primary

environment,

CCS

Systems

300/400.

When

the

2719

is

added

to

a

System

300/400,

only

the

1M2

Header

and

Protective

Ground

Jumper

require

configuration.

All

other

headers

and

jumpers

are

shipped

configured

for

a

System

300/400.

However,

if

the

2719

is

used

in

a

CCS

System

2210

or

a

non-CCS

system,

additional

configuration

will

be

required.

This

chapter

includes

configuration

instructions

for

all

board

options.

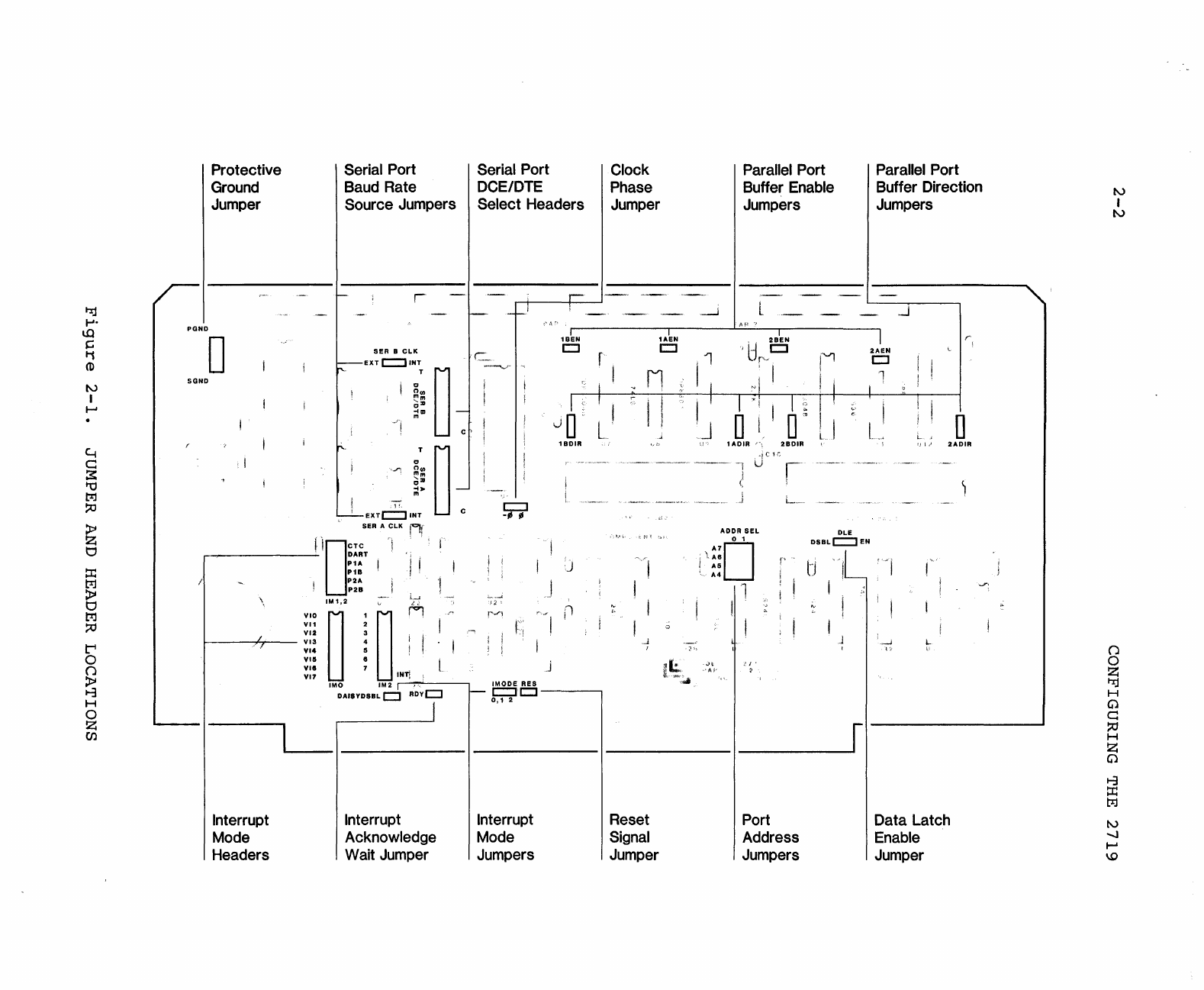

Jumper

and

header

locations

are

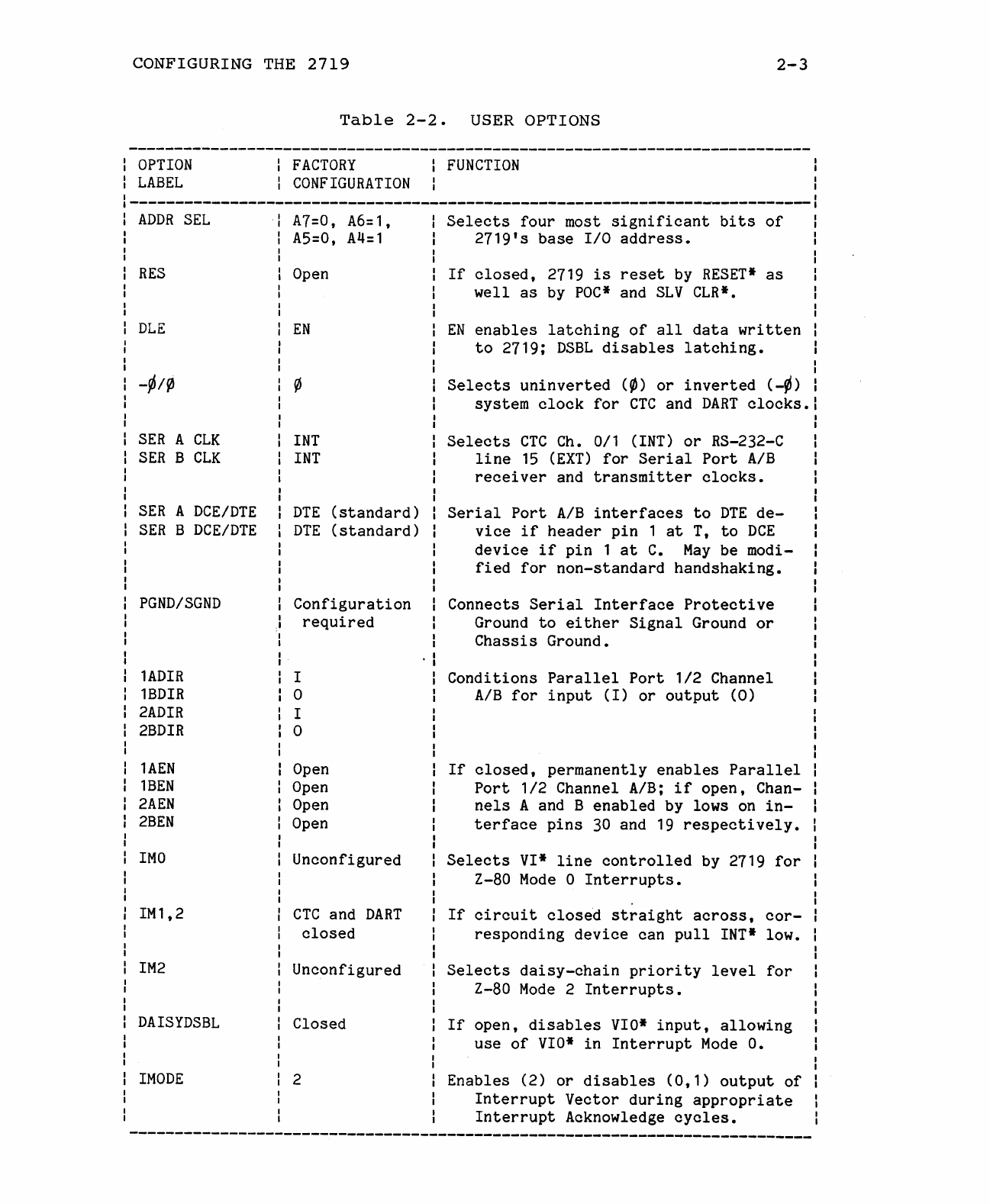

shown

in

Figure

2-1.

Table

2-2

briefly

defines

each

option.

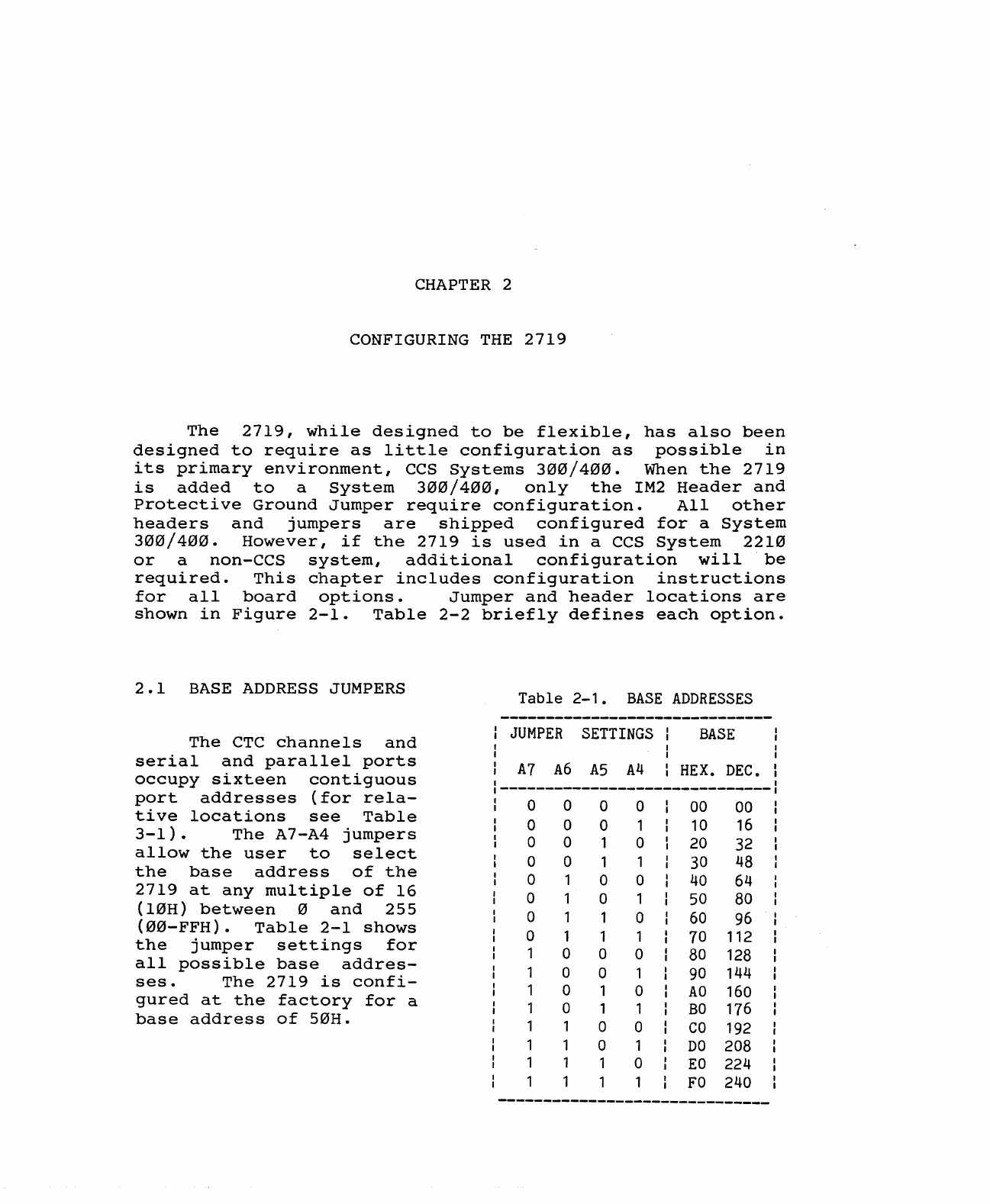

2.1

BASE

ADDRESS

JUMPERS

Table

2-1.

BASE

ADDRESSES

------------------------------

The

CTC

channels

and

JUMPER

SETTINGS

BASE

serial

and

parallel

ports

A7 A6

A5 A4

HEX.

DEC.

occupy

sixteen

contiguous

------------------------------

port

addresses

(for

rela-

0 0 0 0

00 00

tive

locations

see

Table

0 0 0 1

10

16

3-1)

.

The

A7-A4

jumpers

0 0 1 0 20 32

allow

the

user

to

select

0 0 1 1 30

48

the

base

address

of

the

0 1 0 0

40

64

2719

at

any

multiple

of

16

0 1 0 1 50 80

(10H)

between

0

and

255

0 1 1 0

60

96

(00-FFH)

.

Table

2-1

shows

0 1 1 1 70 112

the

jumper

settings

for

1 0 0 0

80

128

all

possible

base

addres-

1 0 0 1

90

144

sese

The

2719

is

confi-

1 0 1 0

AO

160

gured

at

the

factory

for

a 1 0 1 1

BO

176

base

address

of

50H.

1 1 0 0

CO

192

1 1 0 1

DO

208

1 1 1 0

EO

224

1 1 1 1

FO

240

------------------------------

I':tj

1-'-

1O

C

t;

CD

N

I

.....

Y

C

::s:

"'0

I:lj

::0

~

Z

0

::r::

trJ

~

0

trJ

:::0

L'1

0

()

~

8

H

0

Z

CJ)

POND

SOND

Protective

Ground

Jumper

0

I

Serial

Port

Baud

Rate

Source

Jumpers

r

SER

B

CLK

EXT

c::::J

INT

oT

~

(')(1)

'"'"

0:11

;;:111

oT

~

,..r,

~:::

0:11

;;:Joo

"

EXTc::::J

INT

SER A

CLK

i'lf

,..---,..------'

DART

i '

"DcTC

' '

:~:

I I

i

P2A

,

P2B

'.

VI1

1

VI2

~----I-:"---

VI3

VI4

VIS

vie

VI7

INT;

C

VIO

I~M1'2

~

M

IMO

1M

2

~~------,

DAIBYDSBL

D

RDYCJ

Serial

Port

DCE/DTE

Select Headers

1BEN

CJ

1BDIR

c::::J

-II "

'J

{l

I'

j

IMODE

RES

c::::JCJ

0,1

2

Clock

Phase

Jumper

1AEN

D

,.

.J

1

Parallel

Port

Buffer

Enable

Jumpers

'"

I.

'" 1

O

' I 0

~

I

I,

II

1

ADIR

~';

2BDIR

,

-l

C 1

~

U r

ADDR

SEL

DLE

DSBL

c::::J

EN

A7001

lAS

A5

A4

1

,

_____

______________

______________

______________

_

__________

~r

Interrupt

Mode

Headers

Interrupt

Acknowledge

Wait

Jumper

Interrupt

Mode

Jumpers

Reset

Signal

Jumper

Port

Address

Jumpers

Parallel

Port

Buffer

Direction

Jumpers

2AEN

CJ

L , o

.,,;

2ADIR

Data

Latch

Enable

Jumper

CONFIGURING

THE

2719

2-3

:

OPTION

:

LABEL

Table

2-2.

USER

OPTIONS

:

FACTORY

:

FUNCTION

:

CONFIGURATION

,---------------------------------------------------------------------------

ADDR

SEL

RES

DLE

-¢/f/J

SER

A

CLK

SER

B

CLK

SER

A

DCE/DTE

SER

B

DCE/DTE

PGND/SGND

1ADIR

1BDIR

2ADIR

2BDIR

1AEN

1BEN

2AEN

2BEN

IMO

IM1,2

1M2

DAISYDSBL

IMODE

A7=0,

A6=1,

A5=0,

A4=1

Open

EN

INT

INT

DTE

(standard)

DTE

(standard)

Configuration

required

I

o

I

o

Open

Open

Open

Open

Unconfigured

CTC

and

DART

closed

Unconfigured

Closed

2

Selects

four

most

significant

bits

of

2719's

base

I/O

address.

If

closed,

2719

is

reset

by

RESET*

as

well

as

by

POC*

and

SLY

CLR*.

EN

enables

latching

of

all

data

written

to

2719;

DSBL

disables

latching.

Selects

uninverted

(~)

or

inverted

(-~)

system

clock

for

CTC

and

DART

clocks.

Selects

CTC

Ch.

0/1 (INT)

or

RS-232-C

line

15

(EXT)

for

Serial

Port

A/B

receiver

and

transmitter

clocks.

Serial

Port

A/B

interfaces

to

DTE

de-

vice

if

header

pin

1

at

T,

to

DCE

device

if

pin

1

at

C.

May

be modi-

fied

for

non-standard

handshaking.

Connects

Serial

Interface

Protective

Ground

to

either

Signal

Ground

or

Chassis

Ground.

Conditions

Parallel

Port

1/2

Channel

AlB

for

input

(I)

or

output

(0)

If

closed,

permanently

enables

Parallel

Port

1/2

Channel A/B;

if

open,

Chan-

nels

A and B

enabled

by lows

on

in-

terface

pins

30

and

19

respectively.

Selects

VI*

line

controlled

by 2719

for

Z-80

Mode

0

Interrupts.

If

circuit

closed

straight

across,

cor-

responding

device

can

pull

INT*

low.

Selects

daisy-chain

priority

level

for

Z-80

Mode

2

Interrupts.

If

open,

disables

VIO*

input,

allowing

use

of

VIO*

in

Interrupt

Mode

O.

Enables

(2)

or

disables

(0,1)

output

of

Interrupt

Vector

during

appropriate

Interrupt

Acknowledge

cycles.

---------------------------------------------------------------------------

2-4

CONFIGURING

THE

2719

2.2

INTERRUPT

MODE

AND

PRIORITY

CONFIGURATION

Three

header

areas

and

two

jumpers

allow

you

to

tailor

2719

interrupts

to

a

particular

system.

If

the

system

uses

an

interrupt

controller,

you

will

need

to

configure

the

2719

for

Mode 0

interrupts.

If

the

system

does

not

implement

vectored

interrupts,

you

will

need

to

configure

for

Mode

1,

in

which

an

interrupt

causes

an

automatic

restart

at

location

0038H.

If

the

system

supports

the

powerful

Mode 2

Interrupt

Daisy

Chain,

as

CCS

Systems

300/400

do,

you

should

configure

for

Mode

2.

The

three

header

areas

are

labelled

IM0, 1M2,

and

IMl,2

in

accordance

with

the

interrupt

modes

to

which

they

apply.

IMl,2

is

a

2x6

pad

matrix,

hardwired

for

the

standard

configuration,

which

may

be

altered

by

the

installation

of

jumper

wires

or

header

pins

and

shorting

plugs.

IM0

and

1M2

are

socketed

2x8

headers.'

The

Interrupt

Mode (IMODE)

and

Daisy

Chain

Disable

(DAISYDSBL)

Jumpers

are

hardwired

for

Mode

2

and

must

be

reconfigured

for

Mode 0

or

Mode

1.

2.2.1

Mode 0

Configuration

The

first

task

in

configuring

for

Mode 0

is

to

reconfigure

the

IMODE

jumper,

cutting

the

trace

labelled

2

and

installing

a

jumper

in

the

0,1

position.

Next,

cut

the

CTC

and

DART

traces

of

the

IMl,2

Jumpers

and

the

DAISYDSBL

trace.

Finally,

install

the

16

pin

DIP

header

in

the

IM0

socket

and

wire

the

header

cover

to

select

the

VI*

line

by

which

each

device

will

assert

its

interrupt.

Remember

that

the

lower

the

number

of

the

VI*

line,

the

higher

the

interrupt

priority.

The

pins

corresponding

to

the

VI*

lines

are

labelled

0

through

7;

the

six

interrupt

signal

pins

are

labelled

C, D,

lA,

IB,

2A,

and

2B.

Pins

9

and

16

are

not

used.

More

than

one

interrupt

line

may

be

tied

to

one

VI*

line;

it

will

then

be

up

to

the

interrupt

service

routine

called

when

that

VI*

line

is

asserted

to

determine

which

device

generated

the

interrupt.

2.2.2

Mode 1

Configuration

Configuring

for

Mode 1

involves:

1)

leaving

the

IM0

and

1M2

Headers

unconfigured;

2)

reconfiguring

the

IMODE

Jumper

by

cutting

the

trace

labelled

2

and

installing

a

jumper

in

the

0/1

position;

3)

cutting

the

DAISYDSBL

trace;

and

4)

either

leaving

the

IMl,2

Jumpers

as

they

are

or

installing

jumpers,

CONFIGURING

THE

2719

2-5

depending

on

whether

or

not

parallel

port

interrupts

are

to

be

handled

through

the

CTC.

If

they

are

(see

Chapter

3

for

an

explanation

of

how

this

is

done),

the

IM1,2

Jumpers

should

be

left

as

they

are.

If

parallel

port

interrupts

are

to

be

asserted

directly

by

the

parallel

ports,

jumpers

should

be

installed

in

positions

PIA,

PIB,

P2A,

and

P2B.

2.2.3

Mode 2

Configuration

The

Z-80

Mode 2

Interrupt

Daisy

Chain,

when

extended

beyond

four

peripheral

devices,

requires

look-ahead

logic

to

ensure

that

all

devices

are

properly

informed

of

higher-priority

interrupts

within

the

allotted

time.

CCS

Systems

200,

300,

and

400

implement

a

unique

look-ahead

scheme

in

which:

1)

each

board

participating

in

the

daisy

chain

asserts

its

interrupt

priority

by

forcing

a

given

vectored

Interrupt

bus

line

low;

and

2)

a

board

is

prevented

from

interrupting

when

a

lower-numbered

VI*

line

is

low.

Thus

there

are

nine

interrupt

priority

levels,

0-8;

the

priority

0

board

controls

VI0*

and

senses

no

VI*

lines,

while

the

priority

8

board

senses

all

VI*

lines

and

controls

none.

The

1M2

Header

allows

the

user

to

select

the

interrupt

priority

level

of

the

2719

by

selecting

which

VI*

line(s)

the

board

will

be

sensitive

to

and

which

VI*

line

it

will

pull

low.

System

300/400

interrupt

priorities

may

be

determined

at

the

system

implementer's

discretion,

depending

on

system

components

and

application.

However,

the

priority

scheme

shown

below

should

be

appropriate

for

the

majority

of

systems.

The

System

Processor

is

hardwired

for

Level

0;

it

is

the

only

board

whose'priority

is

fixed.

Level

0:

2820

System

Processor

Level

1 :

2805

Wallclock/Terminator

Level

2:

2830

Six-Channel

Serial

I/O

---->

Level

3 :

2719

2

Parallel/2

Serial

I/O

Level

4:

2831

Arithmetic

Processor

Level

5:

2833

GPIB

Interface

Level

7:

2822

Floppy

Disk

Controller

Level

8:

2832

Hard

Di~k

Controller

Note

that

gaps

are

allowed

in

the

priority

structure;

thus,

it

is

not

necessary

to

reconfigure

a

level

3

board

to

level

2

if

there

is

no

level

2

board

in

the

system.

However,

no

priority

level

may

be

occupied

by

more

than

one

board.

2-6

CONFIGURING

THE

2719

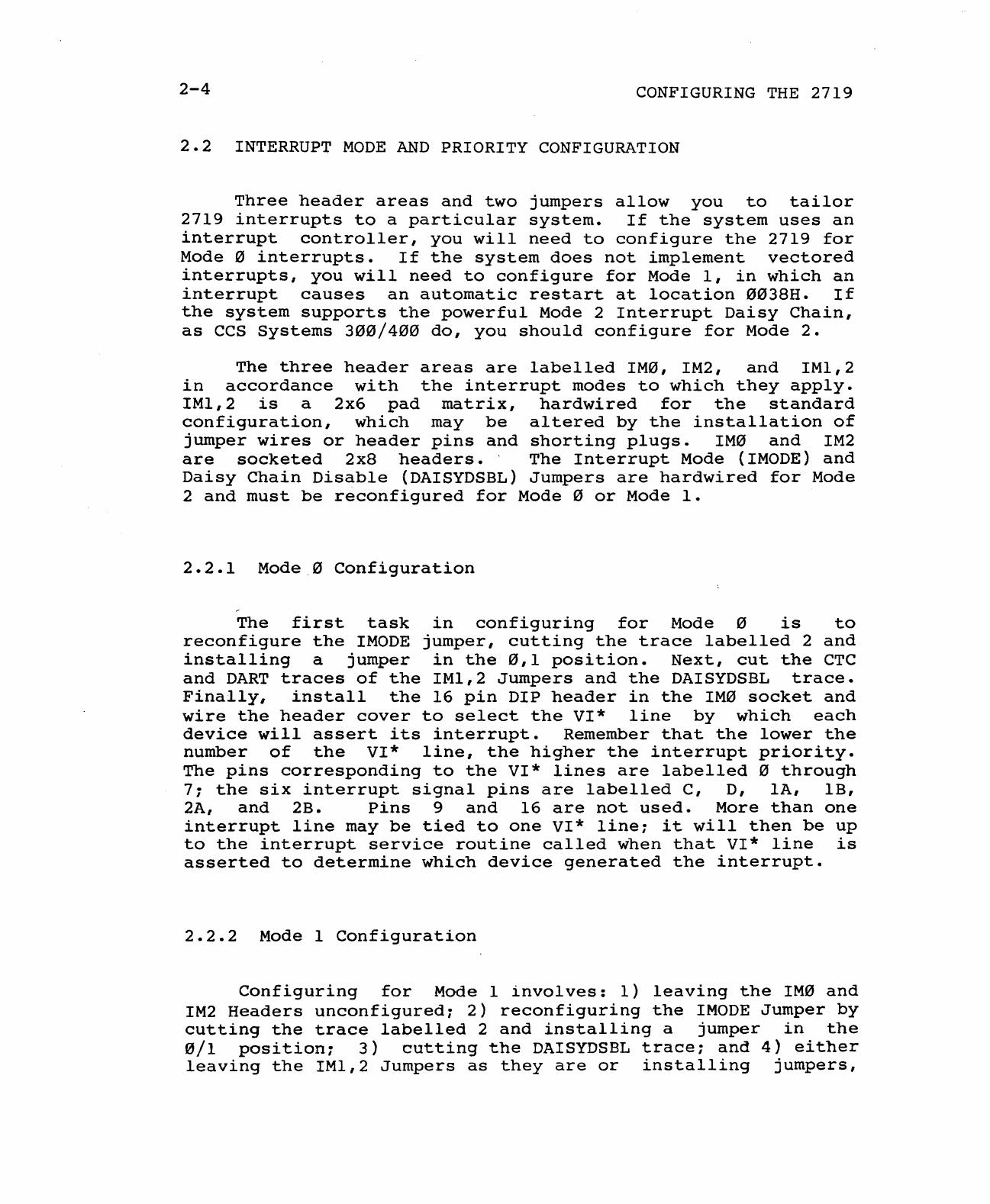

Figure

2-2.

1M2

HEADER

CONFIGURATION

LEVEL

1

LEVEL

2

LEVEL

3

1 1 0 0 1 0 0

2 2 2

0-

3 3 3

4 4 4

5 5 5

6 6 6

7 7 7

INT INT INT

LEVEL

4

LEVEL

5

LEVEL

6

1 0 0 1 0 0 1 0 0

2 0 0 2 0 0 2 0 0

3 0 0 3 0 0 3 0 0

4 N 4 0 0 4 0 0

5 5 N 5 0 0

6 o 0 6 6

~

7 o 0 7 o 0 7

0 INT 0 INT INT

LEVEL

7

LEVEL

8

1 0 0 1 0 0

2 0 0 2 0 0

3 0 0 3 0 0

4 0 0 4 0 0

5 0 0 5 0 0

6 0 0 6 0 0

7

~

7 0 0

INT 0 0 INT

CONFIGURING

THE

2719

2-7

To

configure

the

1M2

Header,

determine

the

priority

level,

then:

1)

tie

all

lower-numbered

left-column

pins

straight

across;

and

2)

tie

the

pin

corresponding

to

the

2719's

priority

level

to

pin

9,

labeled

INT.

Note

that

the

lowest

level

to

which

the

2719

may

be

assigned

is

1:

the

board

is

hardwired

to

sense

the

VI0*

line,

which

is

reserved

as

the

2820

System

Processor's

priority-assertion

line.

Figure

2-2

shows

configuration

of

1M2

for

all

priority

levels.

2.3

SERIAL INTERFACES

2.3.1

Synchronous

Conversion

To

convert

the

2719

serial

communications,

simply

remove

the

it

with

a

Z-80

SIO/0

(neither

the

plug-compatible

with

the

DART).

with

the

board.

2.3.2

DCE/DTE

Conversion

ports

for

synchronous

Z-80

DART

(U3)

and

replace

SIO/l

nor

the

SIO/2

is

The

SIO/0

is

not

supplied

Each

serial

port

interface

includes

a

16-pin

DIP

header

with

cover

for

selecting

whether

the

port-will

interfac~

to

a

DTE

(Data

Terminal

Equipment)

or

DCE

(Data

Communication

Equipment)

device.

Since

most

peripherals

act

as

DTE,

the

2719

is

shipped

configured

to

interface

to

DTE

devices.

To

reconfigure

a

port

to

interface

to

a

DCE

device,

simply

turn

the

port's

DCE/DTE

header

so

that

instead

of

having

pin

1

in

pin

1

of

the

socket

(labeled

T),

pin

1

is

in

pin

9

of

the

socket

(labeled

C).

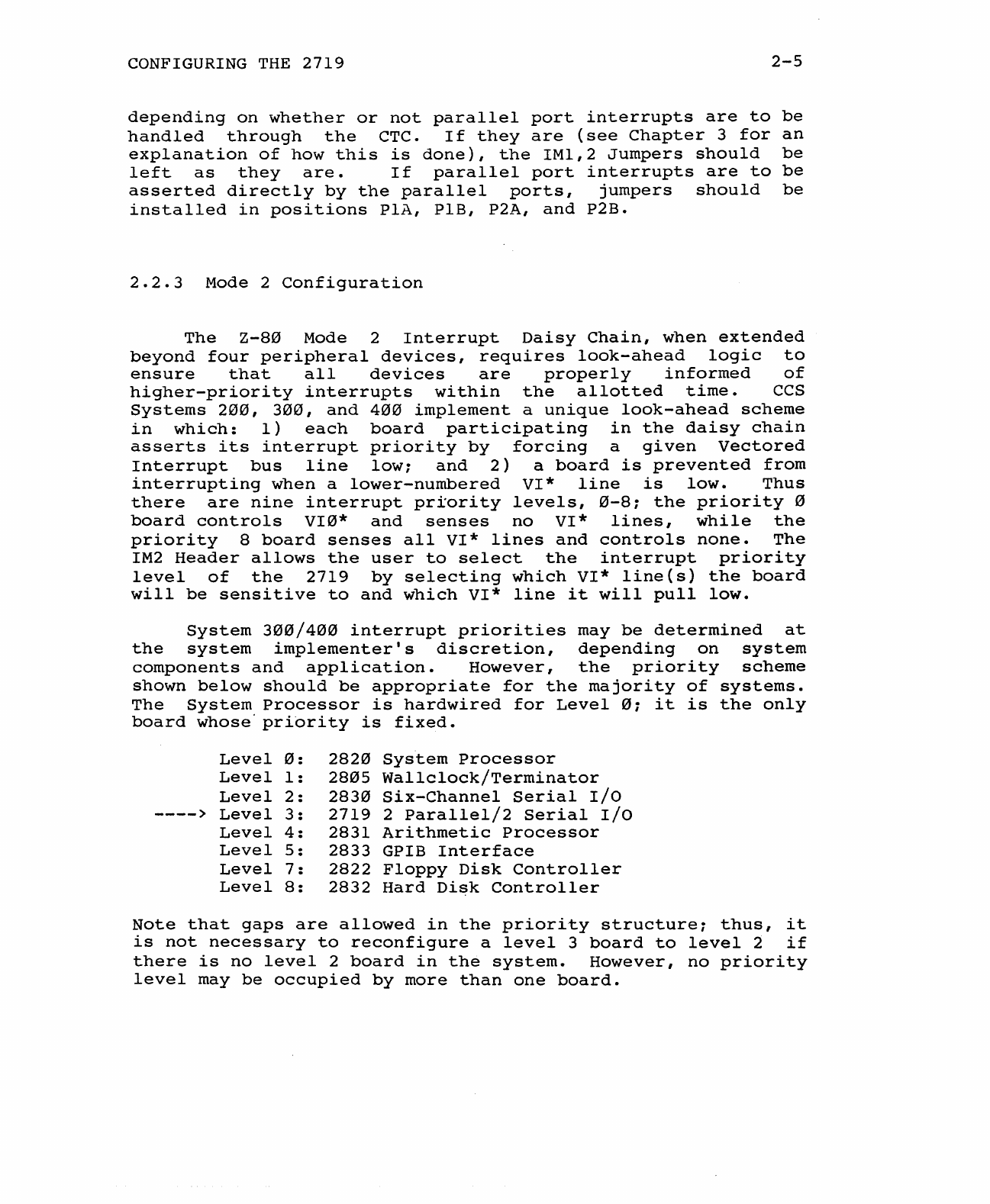

2.3.3

Non-Standard

Handshaking

Some

devices

using

the

RS-232-C

interface,

especially

printers,

use

non-standard

handshaking.

To

interface

such

a

device,

you

will

need

to

reconfigure

a DCE/DTE

Header

according

to

the

requirements

of

the

peripheral.

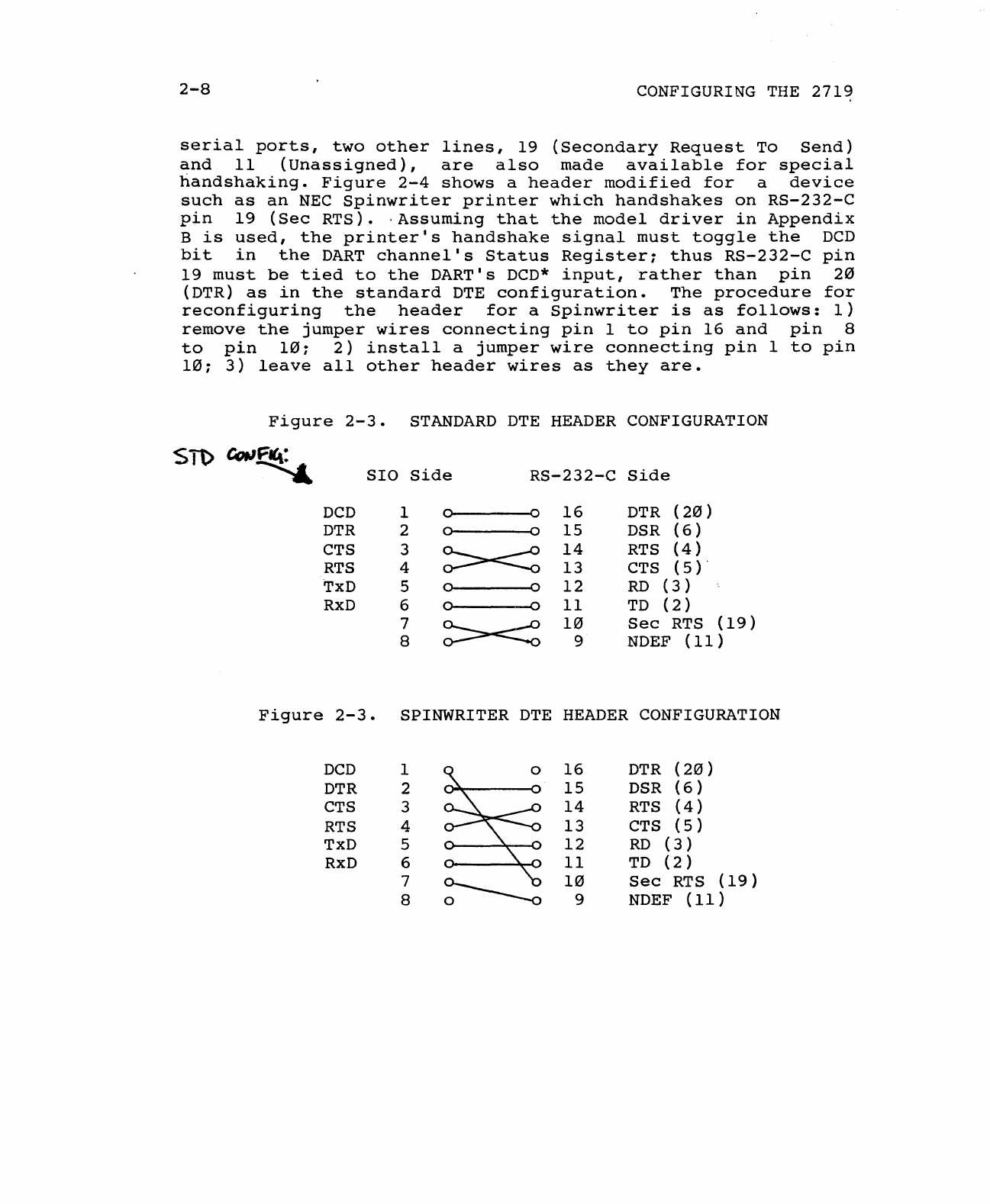

Figure

2-3

shows

the

header

pinouts

and

the

standard

DTE

wiring.

Note

that,

besides

the

RS-232-C

lines

normally

used

by

the

2719's

2-8

CONFIGURING

THE

2719

serial

ports,

two

other

lines,

19

(Secondary

Request

To

Send)

and

11

(Unassigned),

are

also

made

available

for

special

handshaking.

Figure

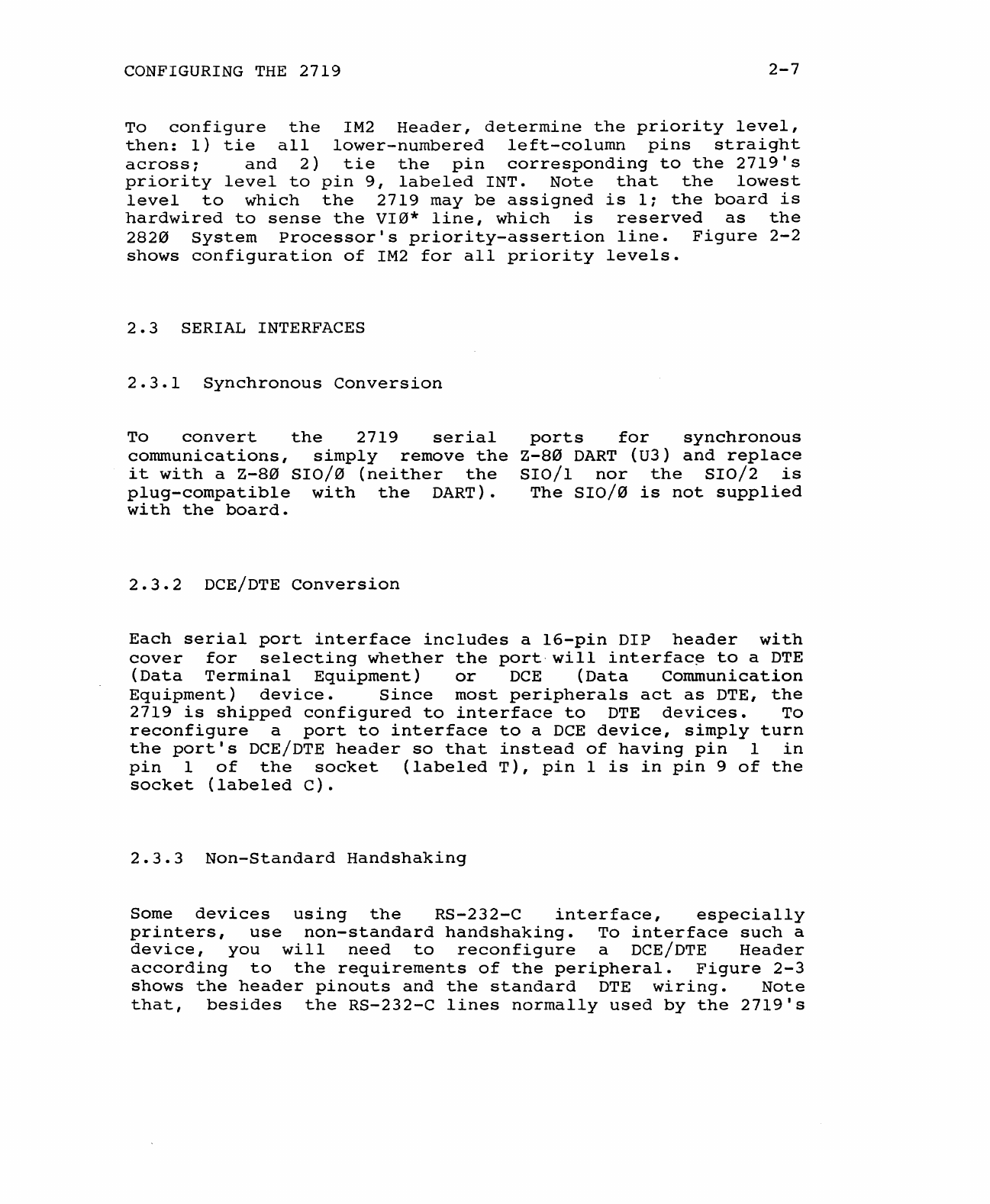

2-4

shows

a

header

modified

for

a

device

such

as

an

NEC

Spinwriter

printer

which

handshakes

on

RS-232-C

pin

19

(Sec

RTS).

-Assuming

that

the

model

driver

in

Appendix

B

is

used,

the

printer's

handshake

signal

must

toggle

the

DCD

bit

in

the

DART

channel's

Status

Register;

thus

RS-232-C

pin

19

must

be

tied

to

the

DART's

DCD*

input,

rather

than

pin

20

(DTR)

as

in

the

standard

DTE

configuration.

The

procedure

for

reconfiguring

the

header

for

a

Spinwriter

is

as

follows:

1)

remove

the

jumper

wires

connecting

pin

1

to

pin

16

and

pin

8

to

pin

10;

2)

install

a

jumper

wire

connecting

pin

1

to

pin

10;

3)

leave

all

other

header

wires

as

they

are.

Figure

2-3.

STANDARD

DTE

HEADER

CONFIGURATION

Sit>

t:w~

SIO

Side

RS-232-C

Side

DCD

1 0 0

16

DTR

(20)

DTR

2 0 0

15

DSR

(6)

CTS 3

><

14

RTS

(4

)

RTS

4

13

CTS

(5

)"

'TxD

5 0 0

12

RD

(3)

RxD

6 0 0

11

TD

(2)

7

><

10

Sec

RTS

(19)

8 9

NDEF

(11)

Figure

2-3.

SPINWRITER

DTE

HEADER

CONFIGURATION

DCD

DTR

CTS

RTS

TxD

RxD

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

DTR

(20)

DSR

(6)

RTS

(4)

CTS

(5)

RD

(3)

TD

(2)

Sec

RTS

(19)

NDEF

(11)

CONFIGURING

THE

2719

2-9

2.3.4

Baud

Rate

Source

Jumpers

If

you

plan

to

use

a

DART

channel

to

interface

a

DCE

device,

you

may

want

that

channel's

baud

rate

clock

to

be

supplied

by

the

DCE

device.

The

Channel

A

and

B

Baud

Rate

Source

Jumpers,

labeled

SER A

CLK

and

SER B CLK,

allow

each

DART

channel's

clocks

to

be

controlled

by

either

the

CTC

or

RS-232-C

li~e

15,

TSEC(DCE),

from

the

peripheral.

The

jumpers

are

hardwired

in

the

INT

position,

selecting

the

internal

(CTC)

baud

rate

sources.

To

select

the

external

(peripheral)

baud

rate

source,

cut

the

INT

trace

and

install

a

jumper

wire

in

the

EXT

position

of

the

appropriate

Baud

Rate

Source

Jumper.

[Please

note

that

because

DART

pins

RxCA

and

TxCA

are

together

on

the

PC

Board,

the

Channel

A

Receiver

transmitter

Clocks

cannot

be

separately

controlled.]

2.3.5

Protective

Ground

tied

and

Protective

Ground

is

defined

as

the

supply

current

return

path,

not

a

signal

current

return

path.

It

is

intended

to

equalize

the

voltage

potential

of

the

terminal

and

the

mainframe,

and

should

be

implemented

whenever

the

terminal

and

the

mainframe

are

connected

to

different

power

sources

which

may

have

different

ground

potentials.

If

both

serial

terminals

interfaced

through

the

2719

are

to

be

connected

to

the

same

outlet

as

the

mainframe,

the

protective

ground

feature

need

not

be

implemented.

At

the

upper

left

corner

of

the

board

are

two

jumper

pads

labeled

PGND

and

SGND.

These

allow

the

user

to

select

one

of

two

implementations

of

the

RS-232-C

Protective

Ground

signals

for

both

ports.

The

recommended

implementation

is

to

run

a

green

wire

from

the

PGND

pad

to

the

mainframe

chassis,

with

an

alligator

clip

or

other

convenient

method

for

connection.

This

conforms

to

the

RS-232

design

specifications,

ensuring

that

terminal

and

mainframe

have

the

same

potentials.

Use

this

method

with

CCS-supplied

terminals.

Some

terminals,

however,

tie

Protective

Ground

and

Signal

Ground

together

or

use

the

Protective

Ground

as

the

Signal

Ground.

If

you

are

using

such

a

terminal

with

the

2719,

you

will

need

to

install

a

100

ohm,

1/2

Watt

resistor

(as

per

EIA

standard

RS-422-A)

between

the

PGND

and

SGND

pads.

2-10

CONFIGURING

THE

2719

2.4

PARALLEL

INTERFACE

CONFIGURATION

2.4.1

Buffer

Direction

Jumpers

Bidirectional

buffers

are

used

on

the

four

parallel

port

data

channels.

The

direction

of

data

flow

is

determined

by

the

Parallel

Port

Buffer

Direction

Jumpers

lADIR,

lBDIR,

2ADIR,

and

2BDIR,

which

are

hardwired

for

the

standard

Centronics-type

interface

configuration.

Channel

B

of

each

port

(Centronics

data

bus)

is

hardwired

in

the

0

position

for

output;

Channel

A

of

each

port

(Centronics

status

bus)

is

hardwired

in

the

I

position

for

input.

To

change

the

direction

of

a

buffer,

cut

the

existing

trace

and

~nstall

a

jumper

wire

in

the

opposite

position.

[Please

note

that

while

each

channel

may

be

used

for

either

input·

or

output,

the

characteristics

of

the

PIA

handshaking

signals

make

Channel

B

more

suited

for

output

and

Channel

A

more

suited

for

input.]

2.4.2

Buffer

Enable

Jumpers

The

parallel

interfaces

are

designed

so

that

lows

on

interface

lines

30

and

19

enable

the

Channel

A

and

Channel

B

interface

buffers

respectively;

otherwise

the

enable

inputs

to

the

buffers

are

pulled

high.

Thus,

the

buffers

will

not

be

enabled

unless

the

interface

cable

is

connected.

On

the

Centronics

interface

lines

30

and

19

are

defined

as

ground

lines.

However,

some

Centronics-type

peripherals

may

not

support

the

lines

as

defined.

If

this

is

the

case,

or

if

the

interface

is

used

in

a

non-Centronics

configuration

and

the

peripheral

does

not

assert

inter£ace

lines

30

and

19

low,

jumper

wires

must

be

installed

between

the

appropriate

Buffer

Enable

Jumper

pads

to

permanently

enable

the

buffers.

The

four

Buffer

Enable

Jumpers

are

labeled

lAEN, lBEN, 2AEN,

and

2BEN.

2.4.3

Reversing

Interface

Polarities

The

parallel

port

buffers

were

selected

to

support

the

Centronics

interface

polarities:

positive

logic

data

and

negative

logic

handshaking.

However,

pin-compatible

buffers

may

be

substituted

for

the

buffers

used

on

the

parallel

ports

CONFIGURING

THE

2719

2-11

if

positive-logic

handshaking

or

negative-logic

data

are

required.

For

negative-logic

data,

replace

the

appropriate

8104/8304

with

an

8103/8303;

for

positive-logic

handshaking,

replace

the

appropriate

74LS367A

with

a

74LS368A.

2.5

THE

RESET

JUMPER

If

the

2719

is

used

in

a

system

which

does

not

automatically

assert

SLVCLR*

when

RESET*

is

asserted,

a

jumper

must

be

installed

between

the

pads

labelled

RES.

This

is

necessary

primarily

when

the

board

is

used

in

Cromemco

systems.

It

is

not

necessary

with

CCS

systems.

If

you

are

uncertain

about

whether

the

Reset

Jumper

is

required,

consult

the

system

documentation;

if

you

remain

uncertain,

call

the

system

manufacturer.

2.6

INTERRUPT

ACKNOWLEDGE

WAITS

If

the

2719

is

used

with

a

CCS

2810

CPU, a

wait

state

is

required

in

all

Interrupt

Acknowledge

cycles

to

ensure

that

the

CTC

has

time

to

put

its

vector

on

the

bus

before

the

CPU

tries

to

read

it.

To

enable

Interrupt

Acknowledge

wait

states,

install

a

jumper

wire

between

the

pads

labeled

ROY.

This

jumper

is

not

required

if

the

2719

is

used

in

a

System

300/400.

If

the

2719

is

used

in

a

non-CCS

system,

this

jumper

mayor

may

not

be

required;

experiment,

and

install

the

jumper

if

necessary.

2.7

CLOCK

PHASE

In

some

systems,

including

the

CCS

2210

(with

the

2810

CPU

board),

the

system

clock

on

bus

pin

24

and

the

CPU

clock

are

of

opposite

phase.

Z-80

devices

in

a

system

must

all

have

clocks

of

the

same

phase

to

work

together.

The

Clock

Phase

Jumper

allows

the

user

to

invert

the

phase

of

the

system

clock

signal

used

on

the

2719

as

necessary.

If

the

2719

is

used

in

a

CCS

System

300/400

or

any

other

system

in

which

the

bus

clock

is

in

phase

with

the

processor

clock,

set

the

Clock

Phase

Jumper

to

the

rightmost

(0)

position.

If

the

2719

is

used

in

a

system

(including

the

CCS

System

2210)

featuring

the

CCS

2810

CPU

board

or

any

other

system

in

which

the

bus

clock

and

processor

clock

are

of

opposite

phase,

set

the

Clock

Phase

Jumper

to

the

leftmost

(-0)

position.

2-12

CONFIGURING

THE

2719

2.8

DATA

LATCH

ENABLING

AND

DISABLING

The

OLE

jumper

has

been

included

on

the

2719

to

allow

disabling

of

the

Data

Out

Latch.

The

jumper

is

hardwired

in

the

EN

position,

which

is

required

if

the

2719

is

used

with

a

CCS

2810

CPU. When

the

2719

is

used

in

a

System

300/400,

the

jumper

may

be

in

either

the

EN

or

DSBL

position.

However,

some

CPU's

may

require

that

data

corning

onto

the

board

not

be

latched.

If

you

are

using

a

non-CCS

CPU,

experiment,

then

disable

the

latching

by

cutting

the

EN

trace

and

installing

a

jumper

wire

in

the

DSBL

position

if

the

2719

cannot

accept

latched

data

from

your

CPU.

2.9

BAUD

RATES

IN

2

MHZ

SYSTEMS

The

CTC

cannot

accept

a CLK/TRG

input

whose

frequency

is

greater

than

half

the

system

clock

frequency.

Thus,

if

you

use

the

2719

in

a 2

MHz

system,

you

must

replace

the

1.8432

MHz

crystal

pack

in

the

lower

right

corner

of

the

board

with

a

74LS74

dual

flip-flop.

The

crystal

pack

is

not

socketed;

you

will

need

to

unsolder

its

four

pins

and

remove

the

solder

from

the

other

pads

before

installing

the

74LS74.

(If

you

install

the

74LS74,

then

at

a

later

date

install

the

2719

in

a 4

MHz

system,

you

need

not

replace

the

crystal

pack

unless

you

want

to

be

able

to

select

baud

rates

greater

than

9600.)

Note

that

installation

of

a

74LS74

will

necessitate

changes

to

the

serial

port

drivers

if

they

have

been

written

for

the

2719

with

the

crystal

pack.

See

Section

3.3.

2.10

OPERATION

IN

6MHZ

SYSTEMS

To

use

"the

2719

in

a 6

MHz

system,

you

must

replace

four

chips:

the

Z-80A

CTC

with

a

Z-80B

CTC;

the

Z-80A

DART

with

a

Z-80B

DART

(or

Z-80B

SIO/0

for

synchronous

capability);

and

both

6821

PIAs

with

68B2l

PIAs.

Some

2719

boards

may

be

shipped

with

68B2l's,

in

which

case

replace

ment

of

the

PIAs

will

not

be

necessary;

check

the

chips

(not

the

silkscreen

labels)

before

replacing

the

PIAs.

Baud

rate

programming

will

not

change

if

the

CTC

is

used

in

the

co~nter

mode

with

the

1.8432

MHz

crystal

pack.

In

the

timer

mode

or

with

a

74LS74

installed

instead

of

the

crystal

pack,

multiply

the

4

MHz

values

in

Table

3-3

by

1.5

(75

baud

will

not

be

available).

CHAPTER

3

PROGRAMMING

INFORMATION

This

section

is

provided

for

those

who

wish

to

write

their

own

drivers

for

the

2719's

serial

and/or

parallel

ports.

Full

instructions

for

programming"the

PIAs

are

given,

as

they

may

not

be

readily

available.

programming

options

for

the

Z-80

SIO

and

CTC

are

quite

elaborate,

and

are

not

given

in

this

manual.

Complete

instructions

are

given

in

the

Z-80

Family

Programming

Reference

Manual

included

in

CCS

System

300/400

documentation

packages

or

available

separately

from

CCS,

as

well

as

in

a

variety

of

other

publications,

a

few

of

which

are

listed

below.

Only

the

programming

limitations

and

requirements

stemming

from

the

implementation

of

the

SIO

and

CTC

on

the

2T19

are

treated

in

this

chapter.

AN

INTRODUCTION

TO

MICROCOMPUTERS,

Osborne

and

Associates,

Inc.

(Berkeley,

CA:

1978).

ZILOG

MICRCOMPUTER

COMPONENTS

DATA

BOOK,

Zilog,

Inc.

(Cupertino,

CA:

1980).

MOSTEK

MICROCOMPUTER

DATA

BOOK,

Mostek

Corporation

(Carollton,

TX:

1979).

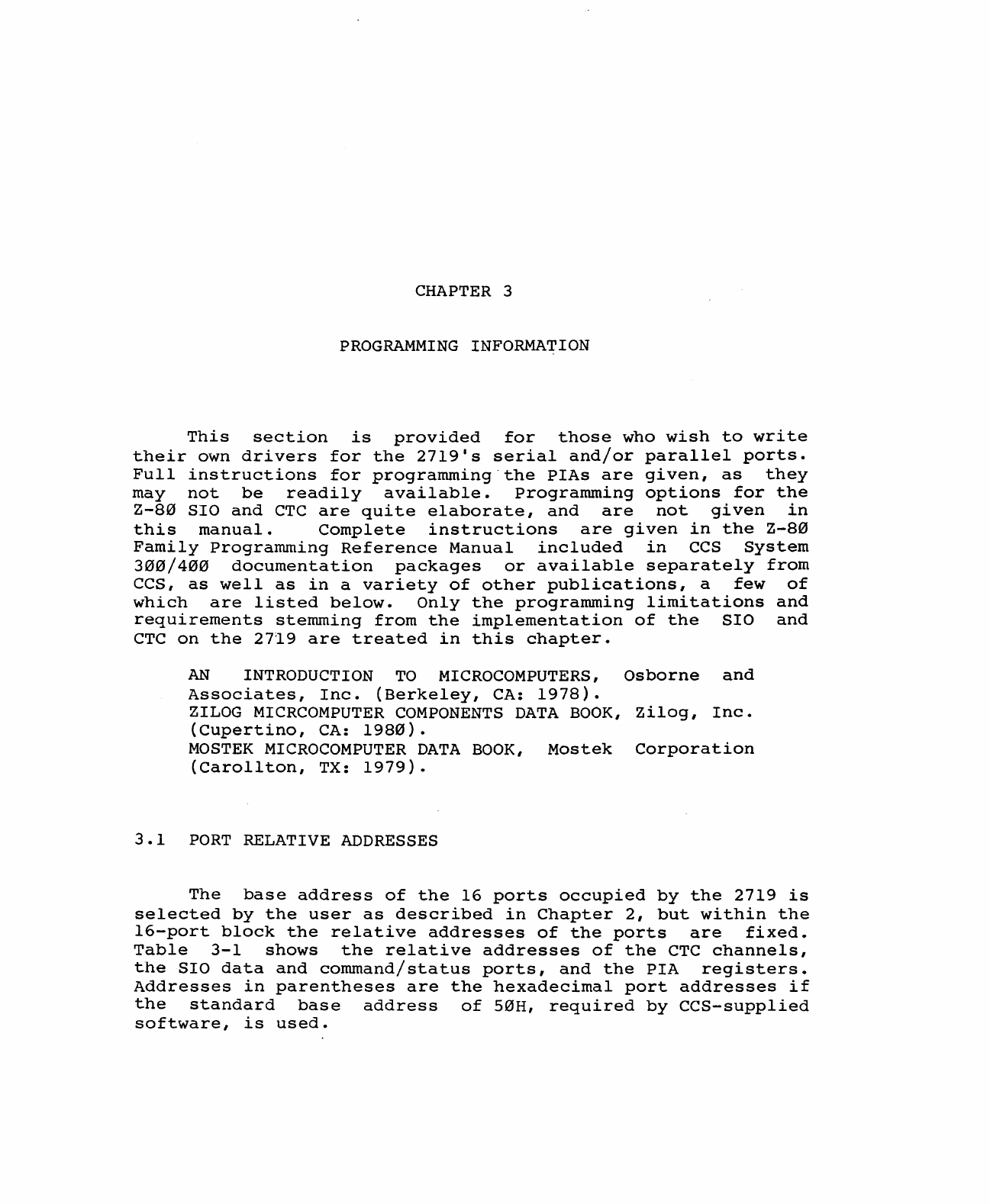

3.1

PORT

RELATIVE

ADDRESSES

The

base

address

of

the

16

ports

occupied

by

the

2719

is

selected

by

the

user

as

described

in

Chapter

2,

but

within

the

l6-port

block

the

relative

addresses

of

the

ports

are

fixed.

Table

3-1

shows

the

relative

addresses

of

the

CTC

channels,

the

SIO

data

and

command/status

ports,

and

the

PIA

registers.

Addresses

in

parentheses

are

the

hexadecimal

port

addresses

if

the

standard

base

address

of

50H,

required

by

CCS-supplied

software,

is

used.

3-2

PROGRAMMING

INFORMATION

Table

3-1.

PORT

RELATIVE

ADDRESSES

-----------------------------------------------------------

1 CTC:

CHANNEL

0

CHANNEL

1

CHANNEL

2

CHANNEL

3

1

Base

(50)

Base+l

(51)

Base+2

(52)

Base+3

(53)

1

1-----------------------------------------------------------1

1

DART:

A

DATA

A

COMMAND

B

DATA

B

COMr~D

1

1

Base+4

(54)

Base+5

(55)

Base+6

(56)

Base+7

(57)

1

1-----------------------------------------------------------1

1

PIAl:

A DATA/DIR B DATA/DIR A

CONTROL

B

CONTROL

1

1

Base+8

(58)

Base+9

(59)

Base+A

(SA)

Base+B

(5B)

1

1-----------------------------------------------------------1

1

PIA2:

A DATA/DIR B DATA/DIR A

CONTROL

B

CONTROL

1

1

Base+C

(5C)

Base+D

(5D)

Base+E

(5E)

Base+F

(SF)

1

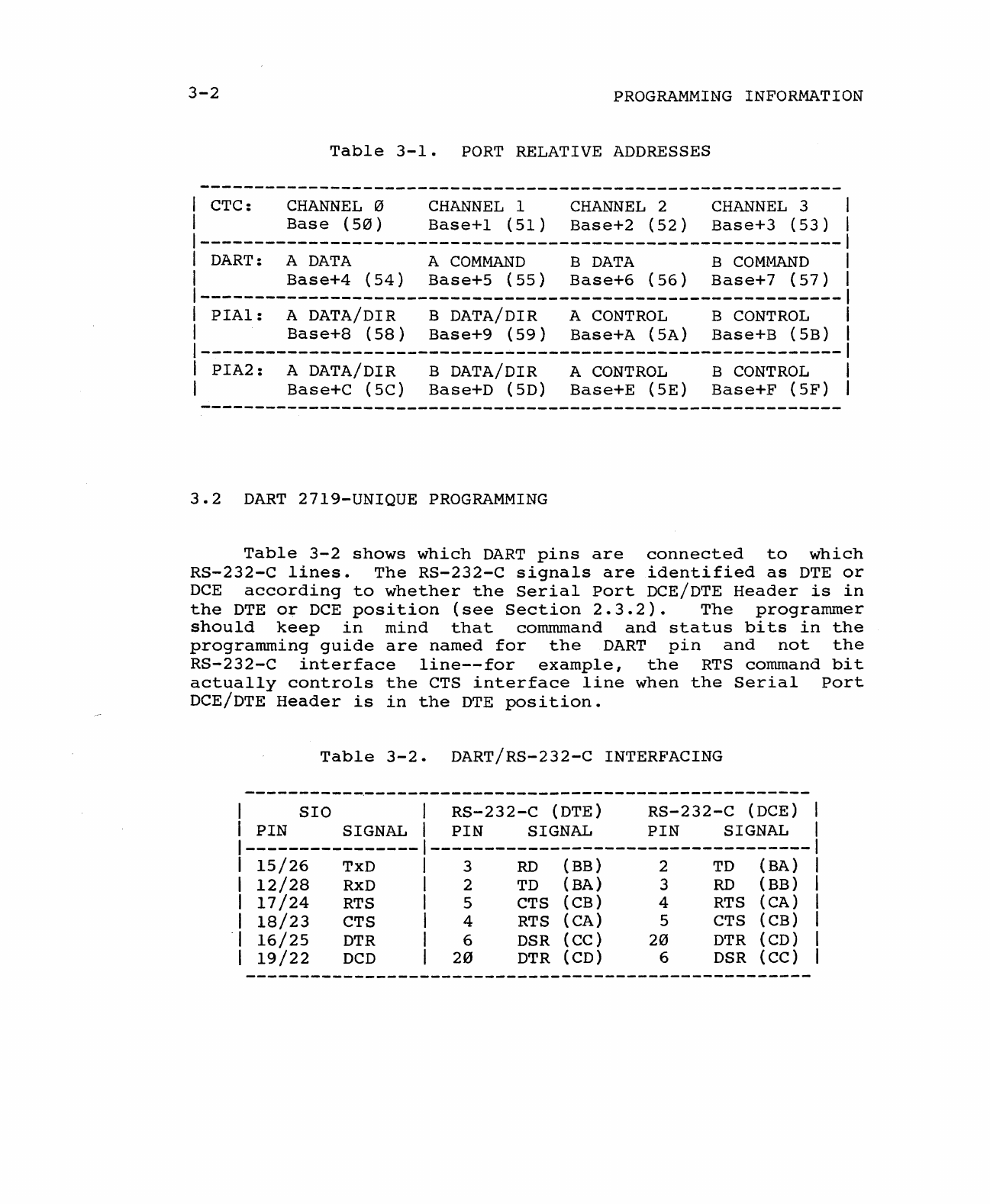

3.2

DART

2719-UNIQUE

PROGRAMMING

Table

3-2

shows

which

DART

pins

are

connected

to

which

RS-232-C

lines.

The

RS-232-C

signals

are

identified

as

DTE

or

DCE

according

to

whether

the

Serial

Port

DCE/DTE

Header

is

in

the

DTE

or

DCE

position

(see

Section

2.3.2).

The

programmer

should

keep

in

mind

that

commmand

and

status

bits

in

the

programming

guide

are

named

for

the

DART

pin

and

not

the

RS-232-C

interface

line--for

example,

the

RTS

command

bit

actually

controls

the

CTS

interface

line

when

the

Serial

Port

DCE/DTE

Header

is

in

the

DTE

position.

Table

3-2.

DART/RS-232-C

INTERFACING

SIO

1

RS-232-C

(DTE)

RS-232-C

(DCE) 1

1 PIN SIGNAL I PIN SIGNAL

PIN

SIGNAL 1

1----------------1-----------------------------------1

1

15/26

TxD 1 3

RD

(BB) 2

TD

(BA) 1

1

12/28

RxD

1 2

TD

(BA) 3

RD

(BB) 1

1

17/24

RTS

1 5

CTS

(CB) 4

RTS

{cAl

1

1

18/23

CTS

1 4

RTS

{cAl

5

CTS

(CB) 1

-I

16/25

DTR

1 6

DSR

(CC) 20

DTR

(CD) 1

I

19/22

DCD

1

20

DTR

(CD) 6

DSR

(CC) 1

PROGRAMMING

INFORMATION

3-3

Programming

limitations

of

the

DART

are

listed

below.

They

result

from

the

fact

that

pins

W/RDYA*, W/RDYB*,

RIA*,

and

RIB*

are

not

connected

on

the

PC

Board.

1.

Bit

7

of

Command

Register

I

(Wait/Ready

Enable)

should

be

0.

Bits

6

and

5

are

don't-care

bits.

2.

Bit

4

of

Status

Register

0

will

always

be

low.

This

will

not

affect

External

Status

Interrupts.

3.3

CTC

2719-UNIQUE

PROGRAMMING

The

CTC

on

the

2719

is

used

to

provide

programmable

clock

signals

for

the

DART

and

to

generate

Mode 2

interrupts

for

the

PIAs.

In

the

factory

configuration,

Channel

0

provides

the

clocks

for

Serial

Port

A,

Channel

1

provides

the

clocks

for

Serial

Port

B,

Channel

2

interrupts

for

PIAl,

and

Channel

3

interrupts

for

PIA2.

Please

note

that,

for

each

serial

port,

both

the

Receiver

Clock

and

the

Transmitter

Clock

are

controlled

by

the

same

CTC

signal

and

therefore

cannot

be

independently

programmed.

The

specific

programming

requirements

for

the

CTC

on

the

2719

are

listed

below.

1.

Channels

0

and

1,

which

determine

the

serial

port

baud

rates,

may

be

programmed

in

either

the

counter

mode

or

the

timer

mode.

Interrupts

should

be

disabled.

Table

3-3

shows

programming

options

for

common

baud

rates.

2.

If

Mode 2

interrupts

from

the

PIAs

are

desired,

Channels

2

and

3

must

be

progran~ed

in

the

counter

mode

with

interrupts

enabled,

rising

edges

counted,

and

a

time

constant

of

1.

Thus

the

two

bytes

sent

after

the

interrupt

vector

to

initialize

Channel

2

or

3

are

D7H

followed

by

0lH.

3-4

PROGRAMMING

INFORMATION

Table

3-3.

TIME

CONSTANTS

FOR

COMMON

BAUD

RATES

TIME

CONSTANTS

---------

----------------------------------------

BAUD

RATE

75

110

134.5

150

300

600

1200

2400

4800

7200

9600

19.2K

38.4K

57.6K

115.2K

CRYSTAL

4

MHZ

C T

192

96

48

24

16

12

6

3

2

1

208

142

116

104

52

26

13

FLIP-FLOP

2

MHZ

C T

104

52

26

13

104

71

58

52

26

13

4

MHZ

C T

208

104

52

26

17

13

208

142

116

104

52

26

13

C =

Counter

Mode (Command

Byte

= 47H)

T =

Timer

Mode,

Prescaler

of

16

(Command =

07H)

DART

Clock

Rate

is

assumed

to

be

16x

3.4

PROGRAMMING

THE

PIA

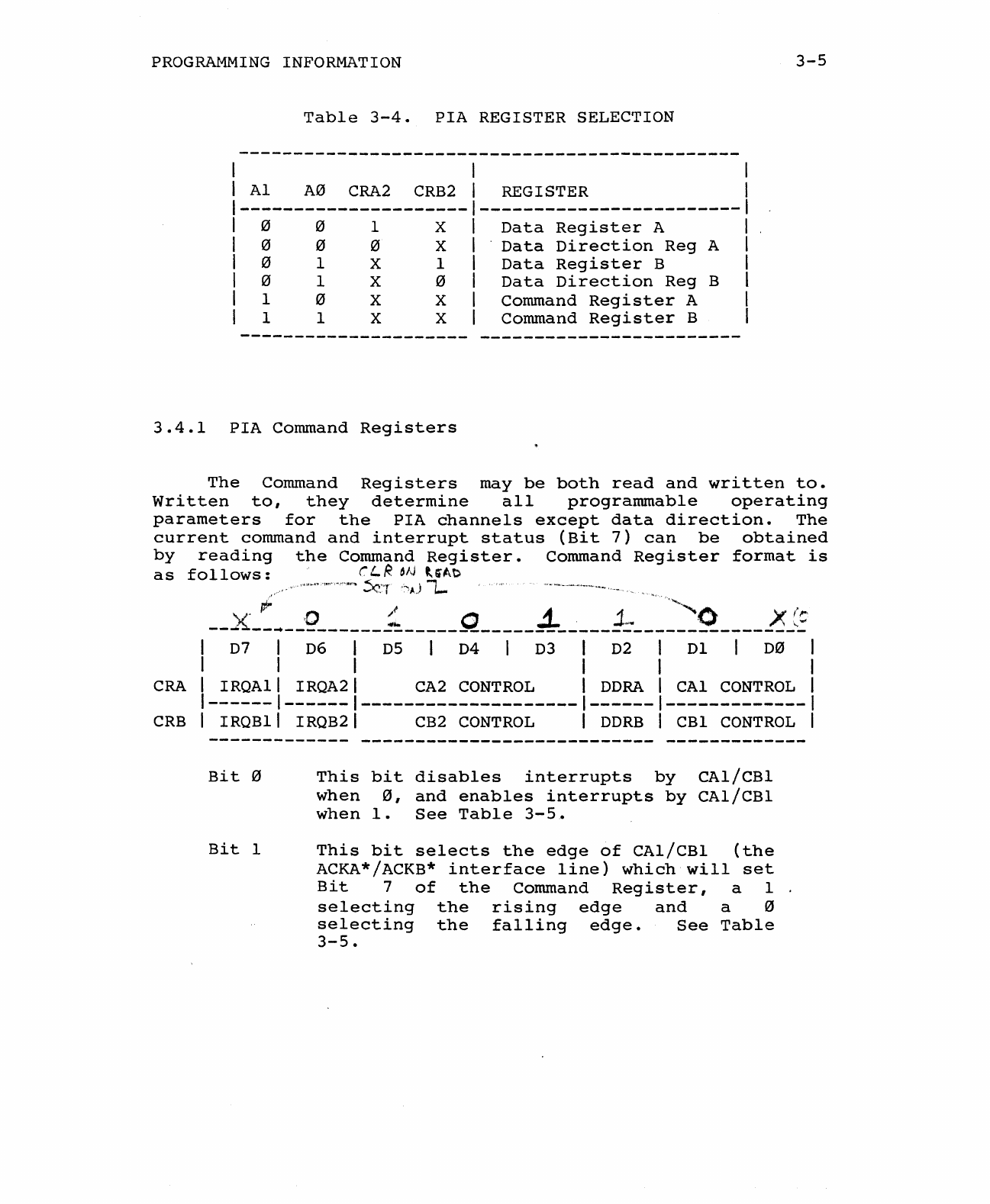

Each

PIA

has

six

accessible

(read

and

write)

registers:

two

Data

Registers,

two

Data

Direction

Registers,

and

two

Command

Registers.

Register

selection

is

determined

by

two

Register

Select

inputs

(RS0,

RS1)

controlled

by

A0

and

Al

and

by

Bit

2

of

the

Command

Register.

Table

3-4

shows

how

each

register

is

selected.

PROGRAt'1MING

INFORMATION

3-5

Table

3-4.

PIA

REGISTER SELECTION

I 1 I

1

Al

A0

CRA2

CRB2

1 REGISTER 1

1---------------------1------------------------1

I 0 0 1 X 1

Data

Register

A I

1 0 0 0

xl'

Data

Direction

Reg A 1

1 0 1

XII

Data

Register

B 1

1 0 1 X 0 I

Data

Direction

Reg B I

1 1 0 X X 1 Command

Register

A 1

1 1 1 X X 1 Command

Register

B 1

---------------------

------------------------

3.4.1

PIA

Command

Registers

The

Command

Registers

may

be

both

read

and

written

to.

Written

to,

they

determine

all

programmable

operating

parameters

for

the

PIA

channels

except

data

direction.

The

current

command

and

interrupt

status

(Bit

7)

can

be

obtained

by

reading

the

Command

Register.

Command

Register

format

is

as

follows:

.'

r L R

61J

t"At>

,

.......

'

......

"

..

"'>~'-

..•

r.~'"'

.:5<::·'r

"~'i\J

~

'

..

'

...

'.--

...

~

..•

- . "

..

,

".

--2{~~-~p

_______

~

_____

~

_____

~_~

___

~

___

~::~

____

~J?

1

D7

1

D6

I

D5

I

D4

I

D3

I

D2

I

Dl

I

D0

1

1 1 I I I I

CRA

1

IRQAll

IRQA21

CA2

CONTROL

I

DDRA

1 CAl

CONTROL

I

1------1------1--------------------1------1-------------I

CRB

1

IRQBll

IRQB21

CB2

CONTROL

I

DDRB

I CBl

CONTROL

I

Bit

0

Bit

1

This

bit

disables

interrupts

by

CAl/CBl

when

0,

and

enables

interrupts

by

CAl/CBl

when

1.

See

Table

3-5.

This

bit

selects

the

edge

of

CAl/CBl

(the

ACKA*/ACKB*

interface

line)

which

will

set

Bit

7

of

the

Command

Register,

a 1 .

selecting

the

rising

edge

and

a 0

selecting

the

falling

edge.

See

Table

3-5.

3-6

PROGRAMMING

INFORMATION

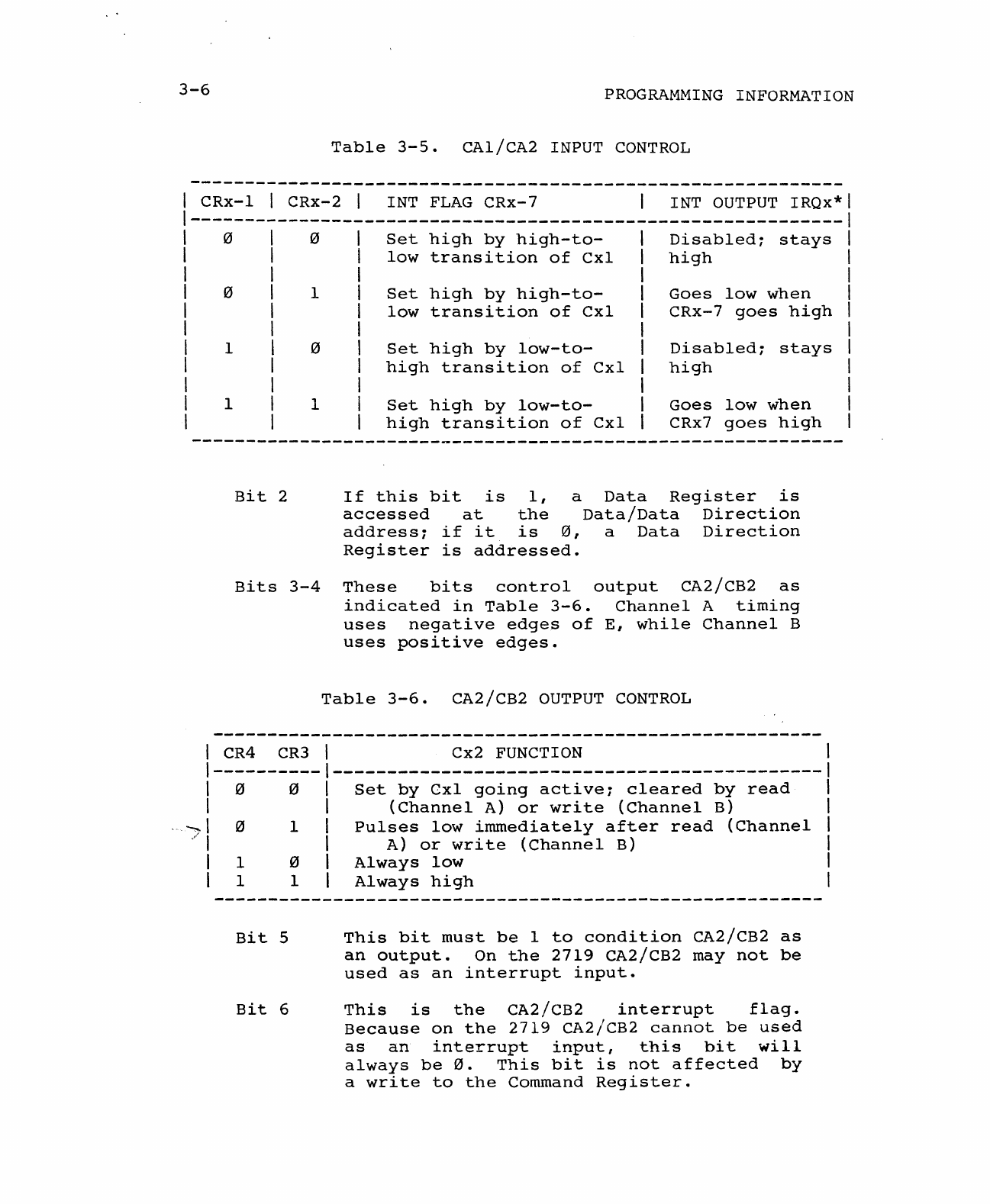

Table

3-5.

CAl/CA2

INPUT

CONTROL

------------------------------------------------------------

CRx-l

I

CRx-2

lINT

FLAG

CRx-7

lINT

OUTPUT

IRQx*

------------------------------------------------------------

o 0

Set

high

by

high-to-

I

Disabled:

stays

low

transition

of

Cxl

1

high

I

o 1

Set

high

by

high-to-

I

Goes

low

when

low

transition

of

Cxl

I

CRx-7

goes

high

I

1 0

Set

high

by

low-to-

1

Disabled:

stays

high

transition

of

Cxl

1

high

I

1 1

Set

high

by

low-to-

1

Goes

low

when

high

transition

of

Cxl

1 CRx7

goes

high

Bit

2

If

this

bit

is

1,

a

Data

Register

is

accessed

at

the

Data/Data

Direction

address:

if

it

is

0,

a

Data

Direction

Register

is

addressed.

Bits

3-4

These

bits

control

output

CA2/CB2

as

indicated

in

Table

3-6.

Channel

A

timing

uses

negative

edges

of

E,

while

Channel

B

uses

positive

edges.

Table

3-6.

CA2/CB2

OUTPUT

CONTROL

1

CR4

CR3

I Cx2 FUNCTION 1

1----------1---------------------------------------------I

1 0 0 1

Set

by

exl

going

active:

cleared

by

read

1

1 I

(Channel

A)

or

write

(Channel

B) I

~I

0 1 I

Pulses

low

immediately

after

read

(Channell

.'

1 1 A)

or

write

(Channel

B) I

I 1 0 1

Always

low

1

1 1 1 I

Always

high

I

Bit

5

Bit

6

This

bit

must

be

1

to

condition

CA2/CB2

as

an

output.

On

the

2719

CA2/CB2 may

not

be

used

as

an

interrupt

input.

This

is

the

CA2/CB2

interrupt

flag.

Because

on

the

2719

CA2/CB2

cannot

be

used

as

an

interrupt

input,

this

bit

will

always

be

0.

This

bit

is

not

affected

by

a

write

to

the

Command

Register.

PROGRAMMING

INFORMATION

Bit

7

This

is

the

CAllcBl

interrupt

flag.

When

this

bit

is

1,

IRQA*/IRQB*

has

been

asserted

by

the

appropriate

transition

of

CAl/cBl.

This

bit

is

cleared

when

the

channel1s

Data

Register

is

read

and

is

not

affected

by

a

write

to

the

Command

Register.

3.4.2

PIA

Data

Direction

Registers

3-7

Bits

0-7

of

the

Data

Direction

Register

control

the

direction

of

data

lines

0-7

respectively.

If

a

bit

is

0,

the

corresponding

data

line

is

an

input;

if

a

bit

is

1,

the

corresponding

data

line

is

an

output.

A

Data

Direction

Register

can

be

accessed

only

if

Bit

2

of

the

Command

Register

for

the

same

channel

is

0.

Because

of

the

way

the

PIA

data

lines

are

buffered

on

the

2719,

ALL

BITS

OF

A

CHANNEL

MUST

BE

PROGRAMMED

FOR

THE

SAME

DIRECTION

and

the

data

direction

programmed

for

a

channel

must

agree

with

the

setting

of

the

corresponding

Parallel

Port

Data

Direction

Jumper

as

described

in

Section

2.4.1.

3.4.3

PIA

INITIALIZATION:

CENTRONICS

CONFIGURATION

The

following

sequence

initializes

a

parallel

port

in

the

standard

Centronics

configuration.

a.

Output

00H

to

both

Ch.

A

and

Ch.

B

Control

Ports

to

select

DDR.

b.

Output

to

Data/Dir

Ports

(00H

to

Ch.

A

and

0FFH

to

Ch.

B)

to

select

direction.

c.

Output

2CH

(or

2DH

for

interrupts)

to

both

Ch.

A

and

Ch.

B

Control

Ports

to

set

the

PIA

mode.

d.

Input

from

both

Ch.

A

and

Ch.

B

Data/Dir

Ports

to

clear

the

status

bits.

CHAPTER

4

HARDWARE

DESIGN

Two

6821

PIAs

and

a

Z-80

DART

provide

the

two

parallel

and

two

serial

ports

of

the

2719.

Most

of

the

interface

functions

are

provided

by

these

three

chips.

A

Z-80

CTC

is

employed

to

generate

baud

rate

clocks

for

the

two

DART

channels

and

Mode 2

interrupts

for

the

two

PIAs.

Additional

logic

supports

interrupt

capability

in

all

three

Z-80

modes,

addresses

and

controls

the

CTC,

DART,

and

PIAs,

and

controls

data

buffering.

Thus

the

2719

can

be

divided

into

six

functional

elements:

the

PIAs,

the

DART,

the

CTC,

the

interrupt

logic,

the

address/control

logic,

and

data

buffering.

Each

element

is

separately

described

below.

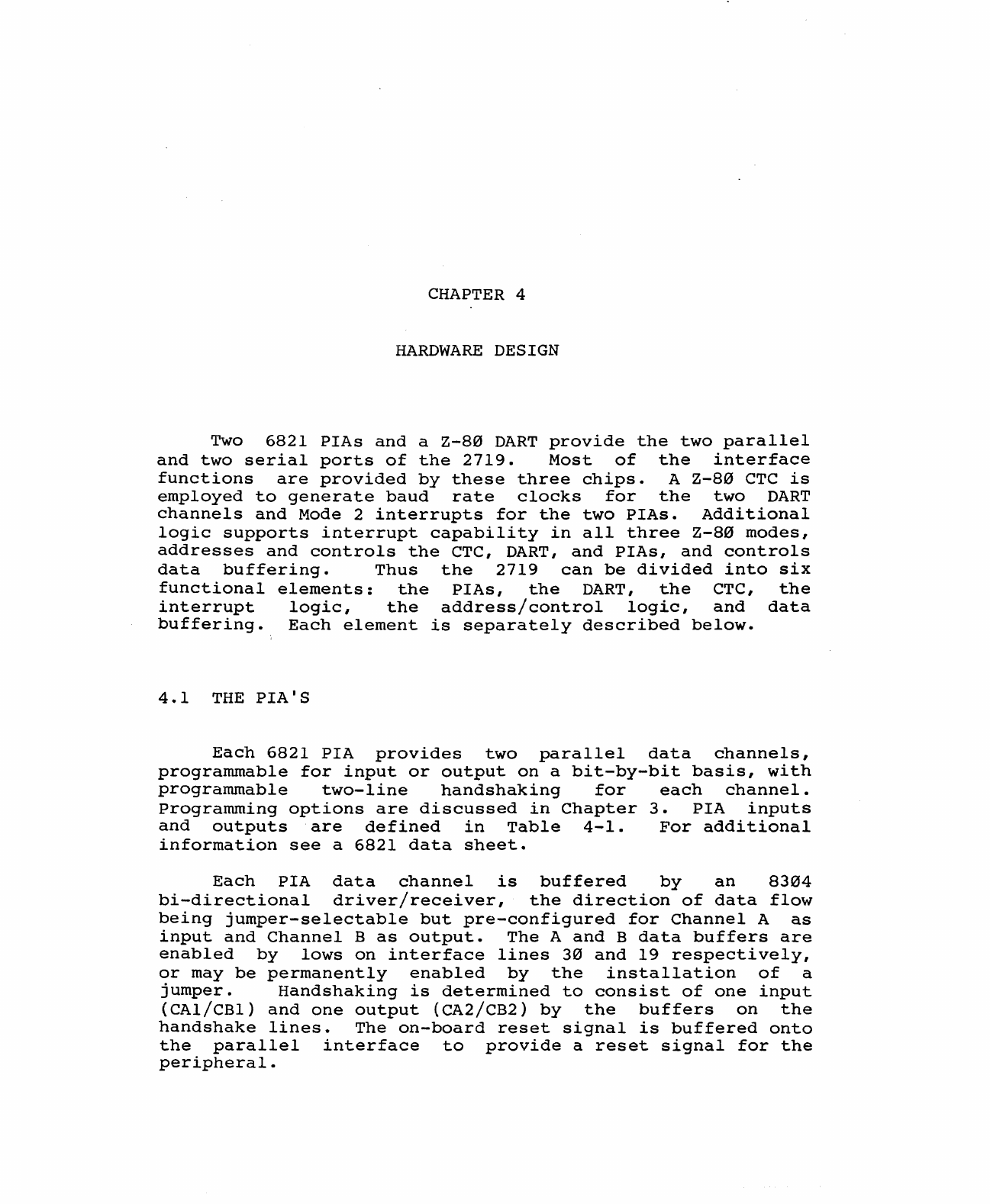

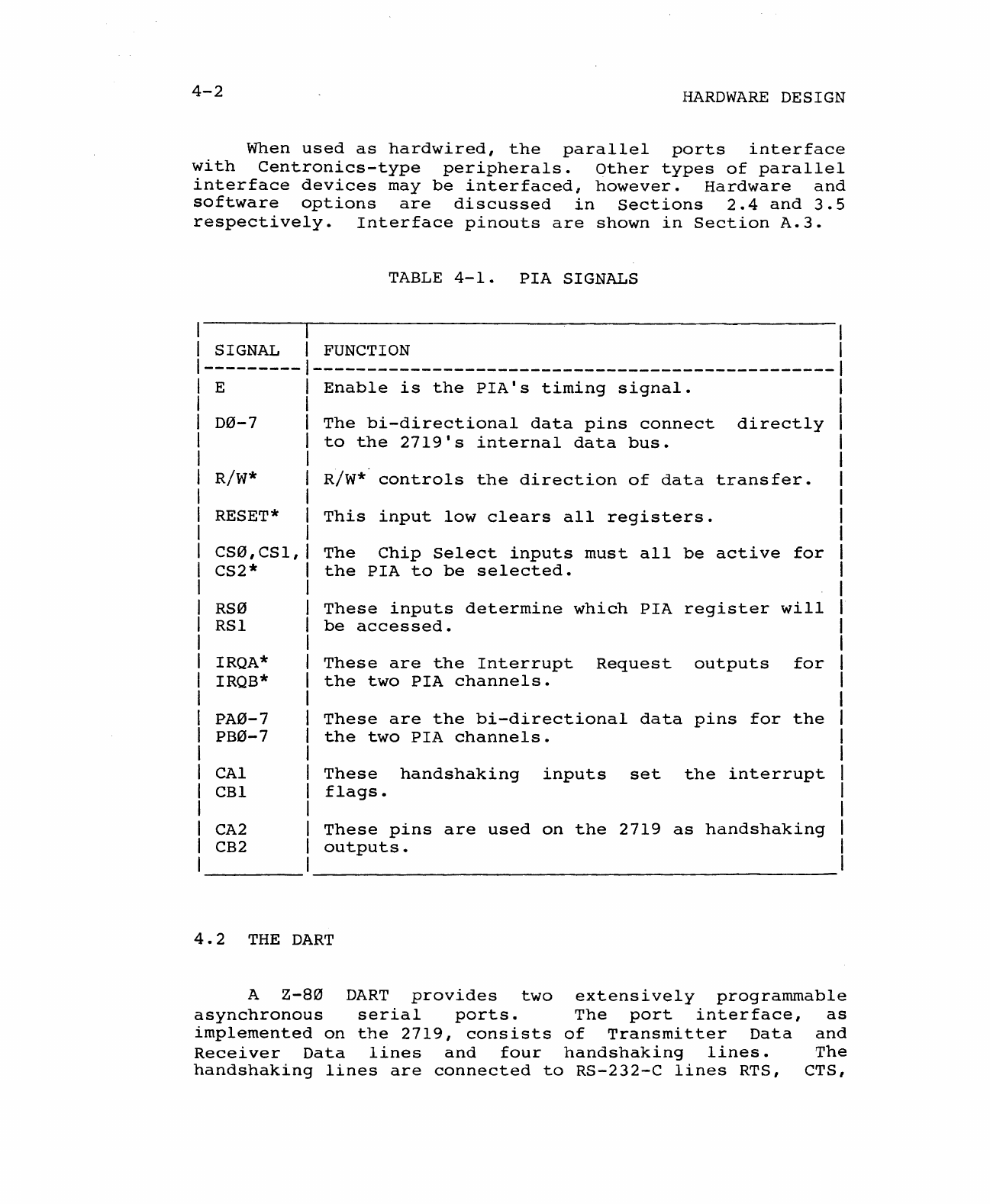

4.1

THE

PIA'S

Each

6821

PIA

provides

two

parallel

data

channels,

programmable

for

input

or

output

on

a

bit-by-bit

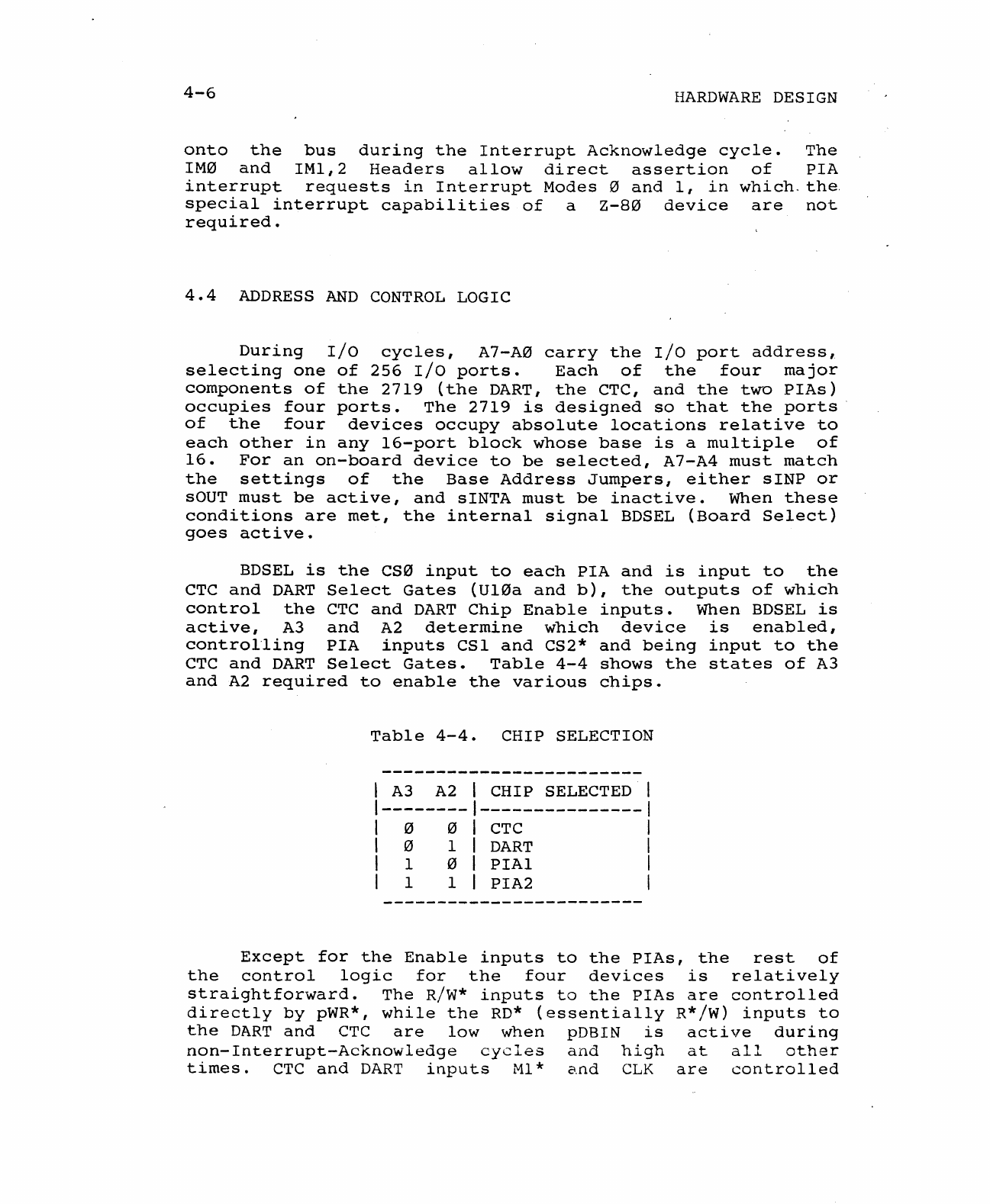

basis,