Acrobat Distiller, Job 9 DVDR980

User Manual: DVDR980

Open the PDF directly: View PDF ![]() .

.

Page Count: 335 [warning: Documents this large are best viewed by clicking the View PDF Link!]

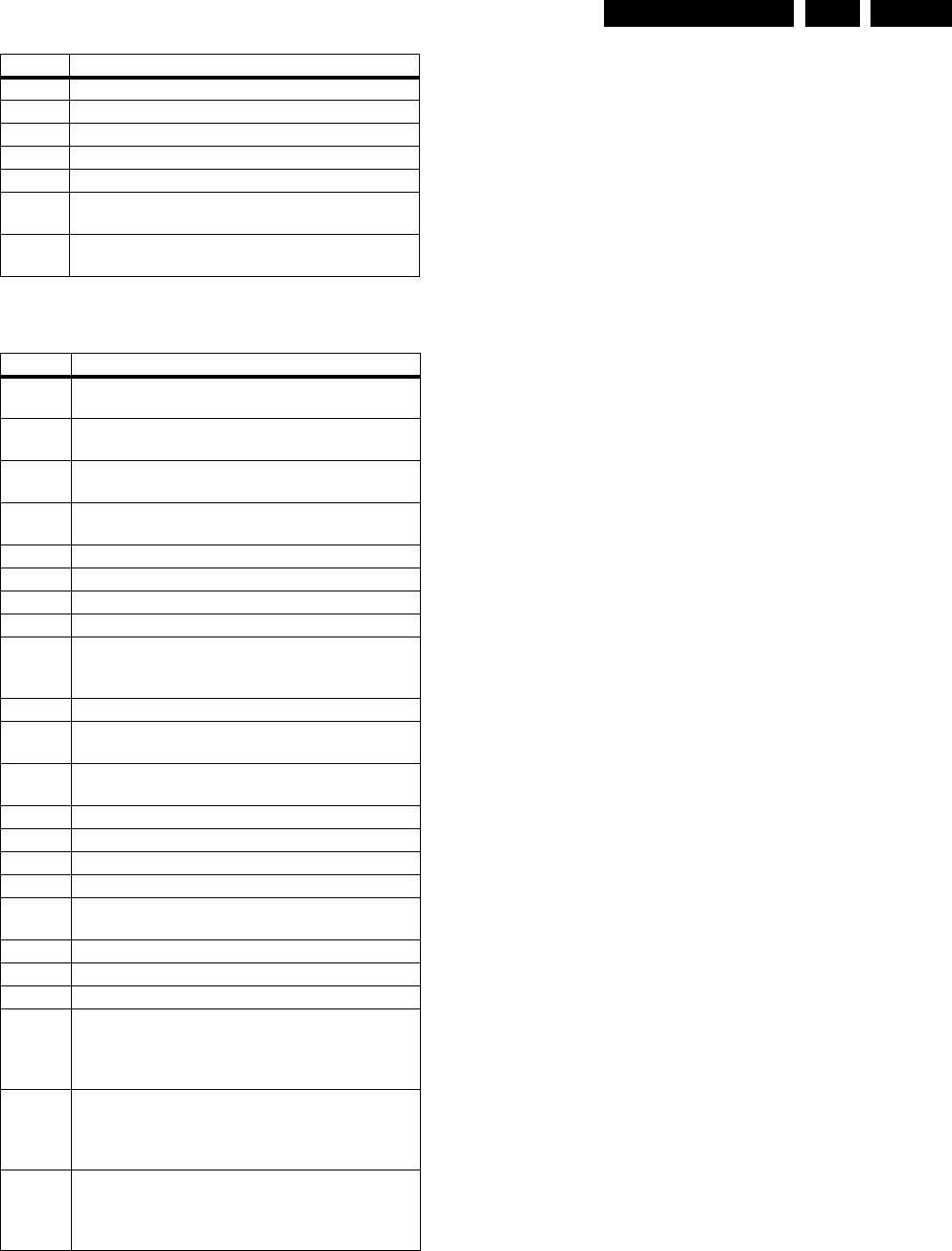

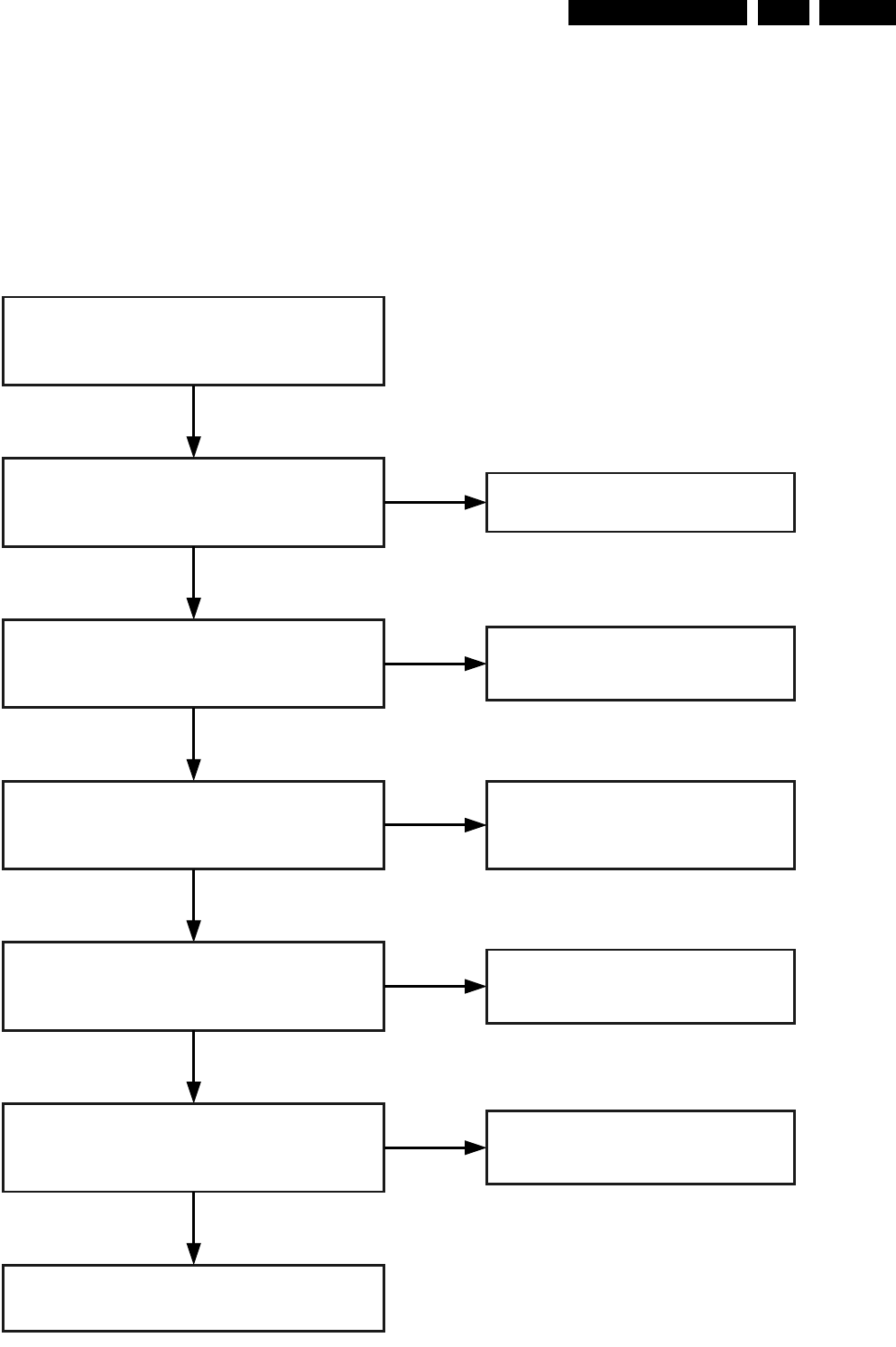

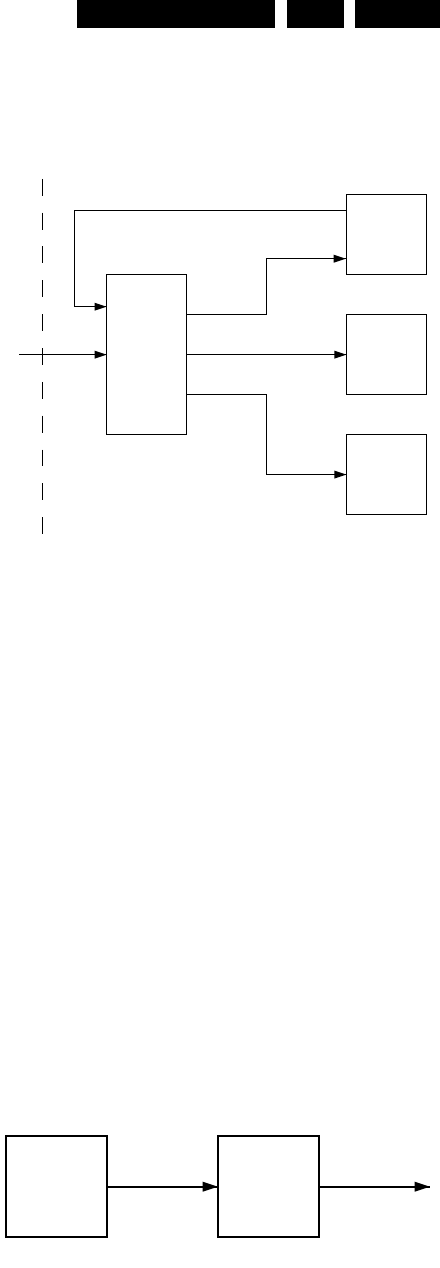

- 1. Technical Specifications and Connection Facilities

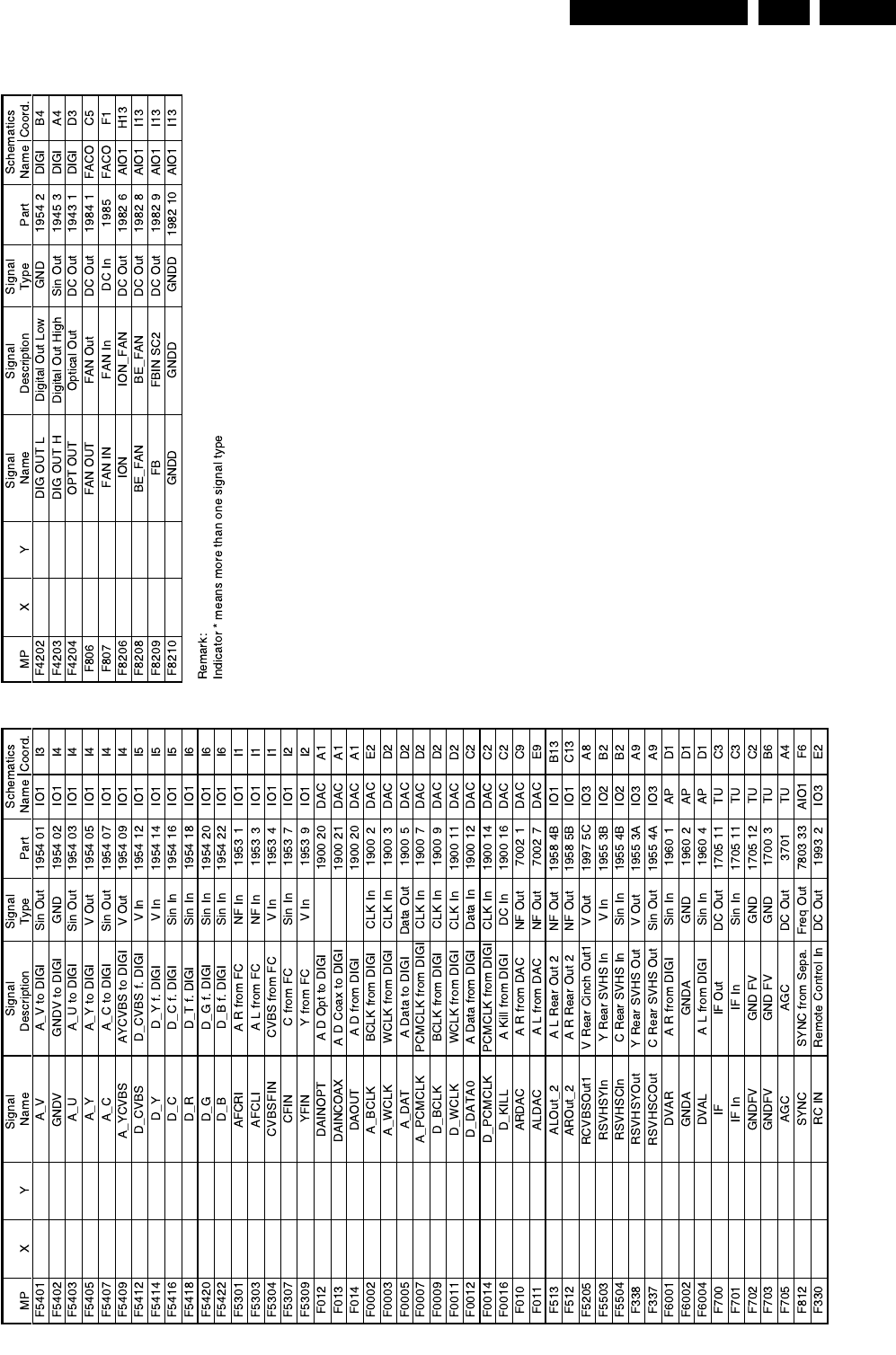

- 2. Safety Instructions, Warnings, Notes, and Service Hints

- 3. Directions For Use

- 4. Mechanical Instructions

- 5. Diagnostic Software and Faultfinding Trees

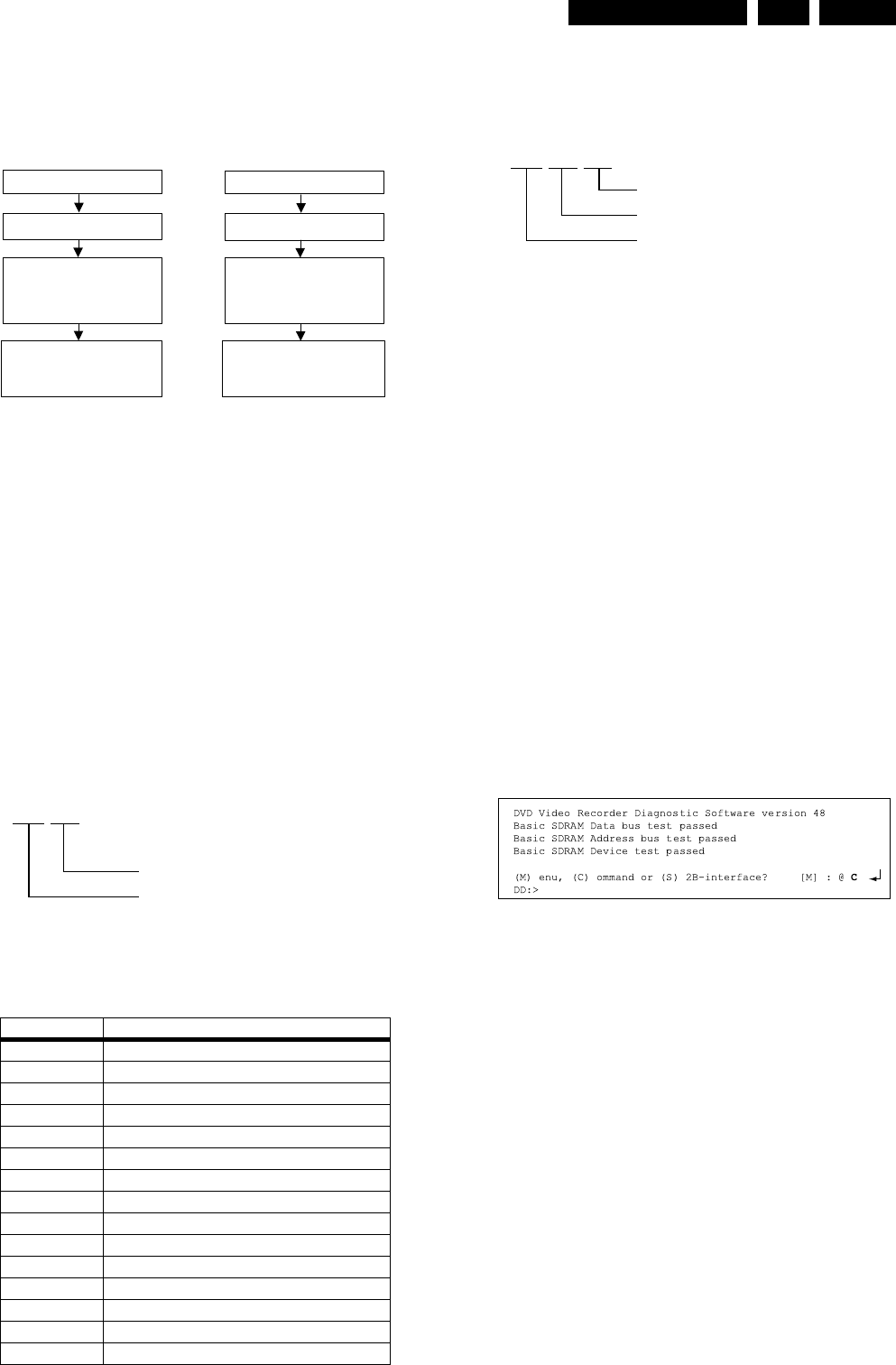

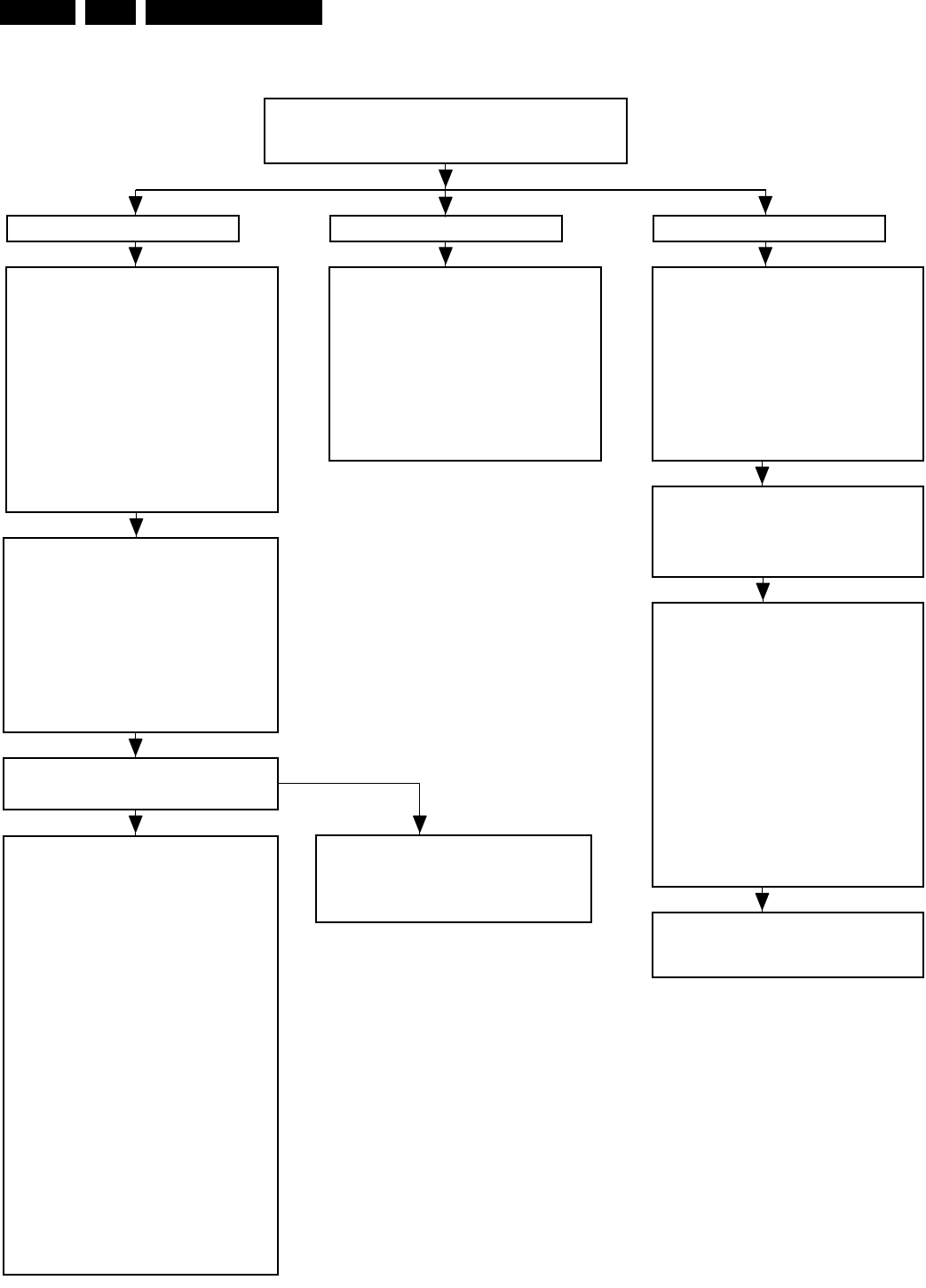

- 5.1 End User/Dealer Script Interface

- 5.2 Player Script Interface

- 5.3 Menu and Command Mode Interface

- 5.3.1 Nuclei Numeration

- 5.3.2 Error Handling

- 5.3.3 Command Mode Interface

- 5.3.4 Menu Mode Interdace

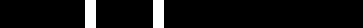

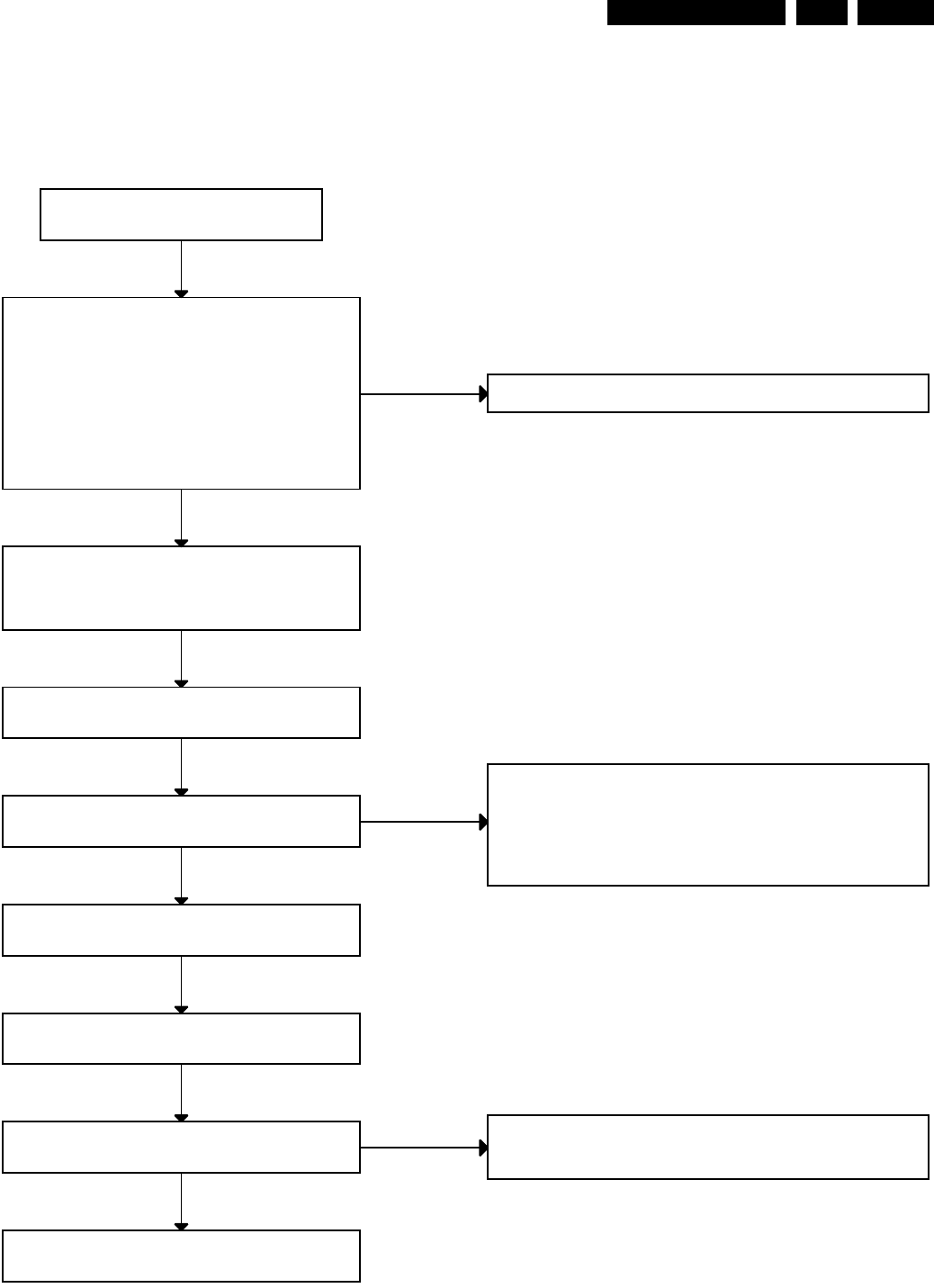

- Activation

- Menu Structure

- Main Menu

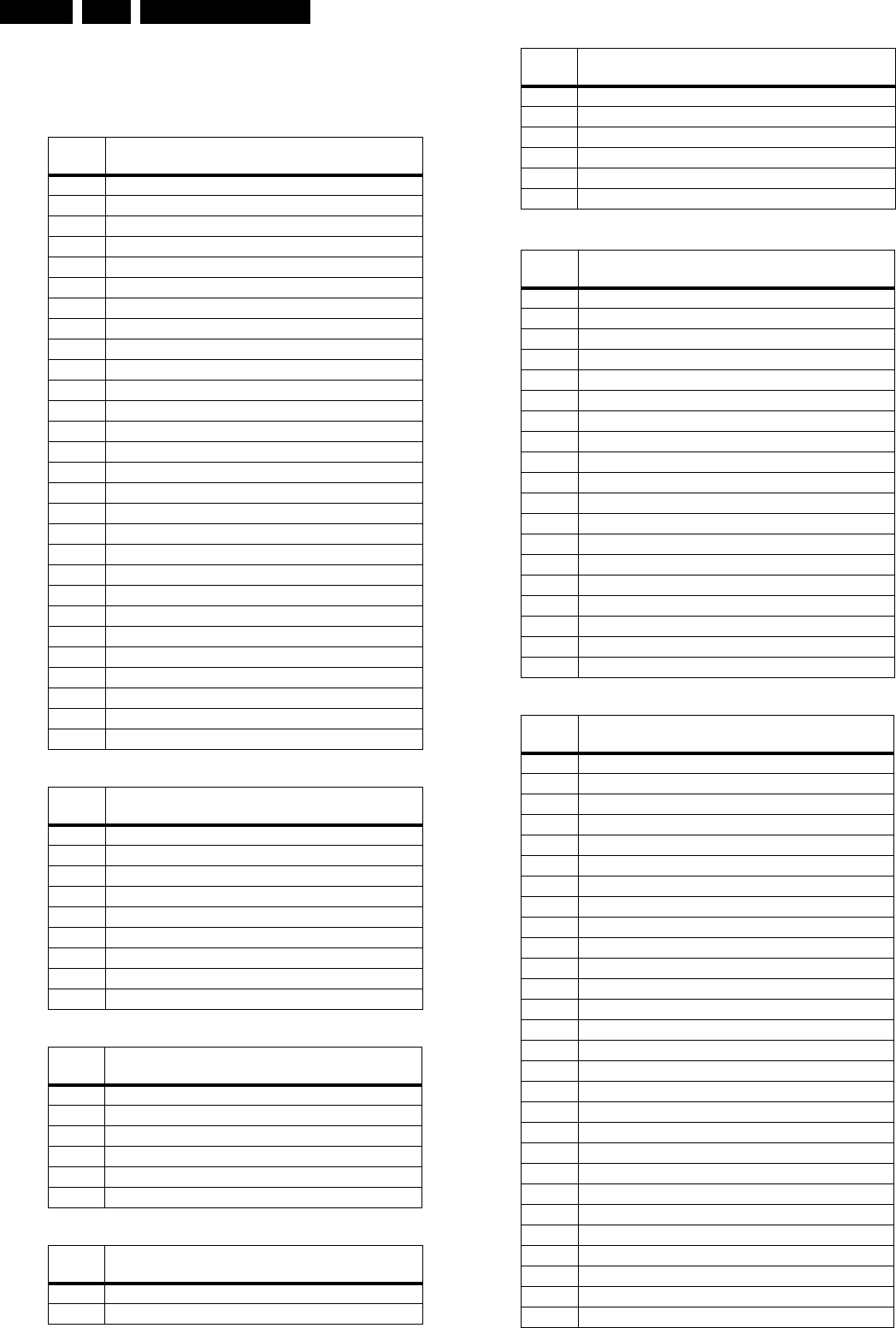

- Digital Board Menu

- Host Decoder Menu

- Digital Board Versions Menu

- Audio Mute Menu

- Colourbar Menu

- Pink Noise Menu

- Sine Generate Menu

- VSM Menu

- AVENC Menu

- Empress Menu

- Video Input Processors Menu

- NVRAM Menu

- Analogue Board Menu

- Analogue Board Versions Menu

- Analogue Components Menu

- Analogue Board Re-virginize Menu

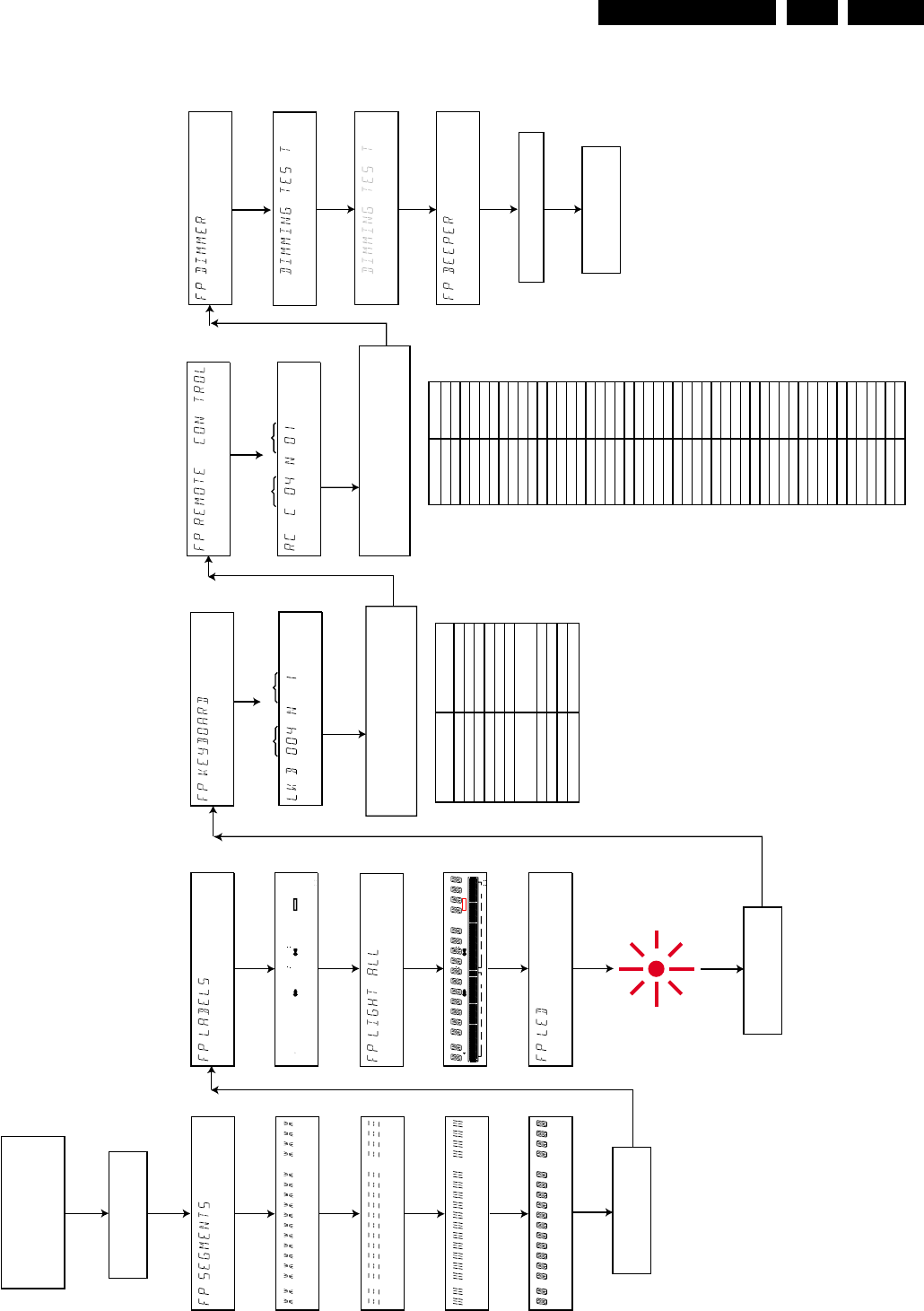

- Front Panel Menu

- Flap Control Menu

- Segment Test Menu

- Basic Engine Menu

- Basic Engine Error Log

- Basic Engine Spindle Motor Menu

- Basic Engine Radial Menu

- Basic Engine Sledge Menu

- Basic Engine Tray Menu

- DVIO Menu

- DVIO Led Menu

- Progressive Scan Board Menu

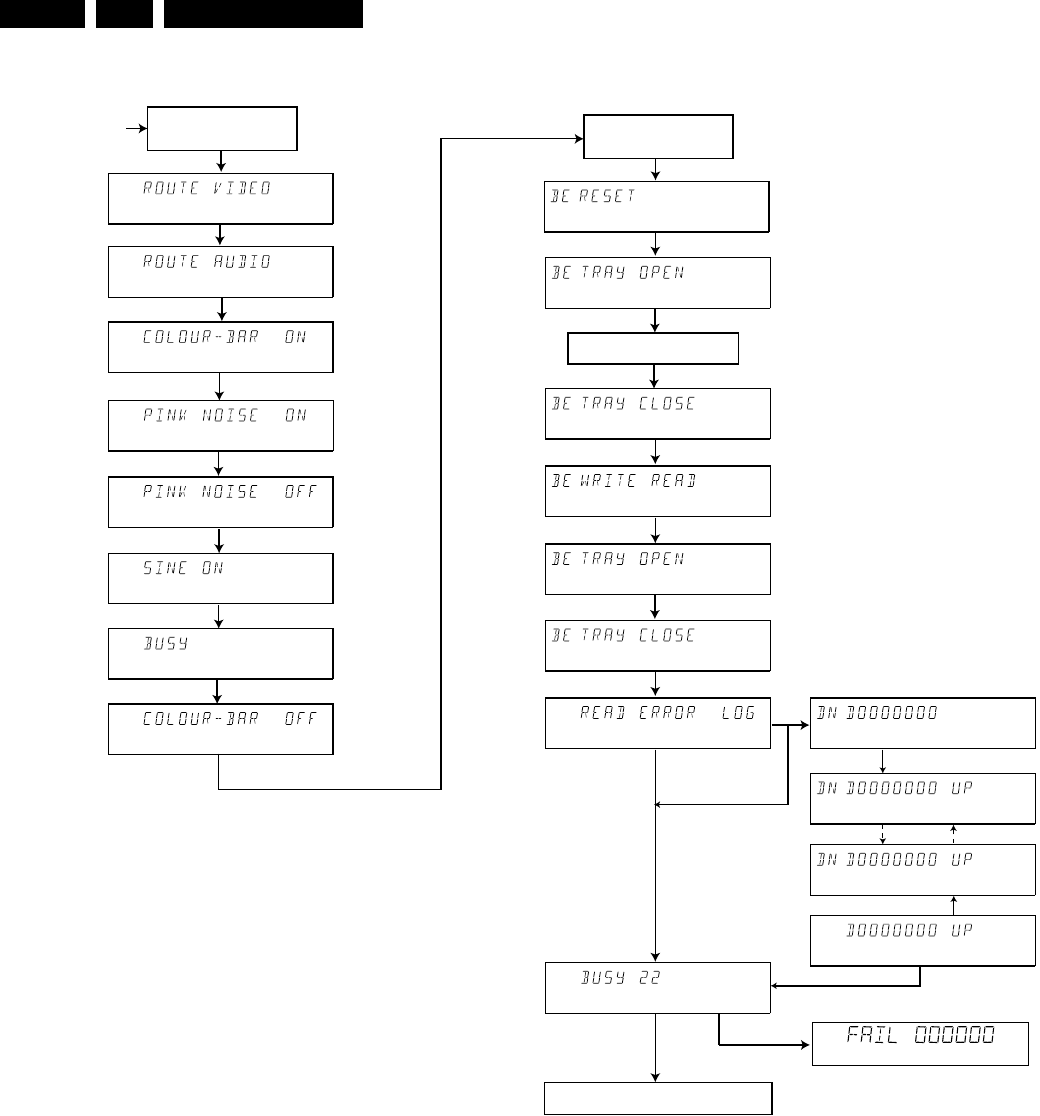

- Loop Tests Menu

- Digital Board Loops Menu

- User/Dealer Loops Menu

- System Loops Menu

- Basic Engine Loops Menu

- Log Menu

- Script Menu

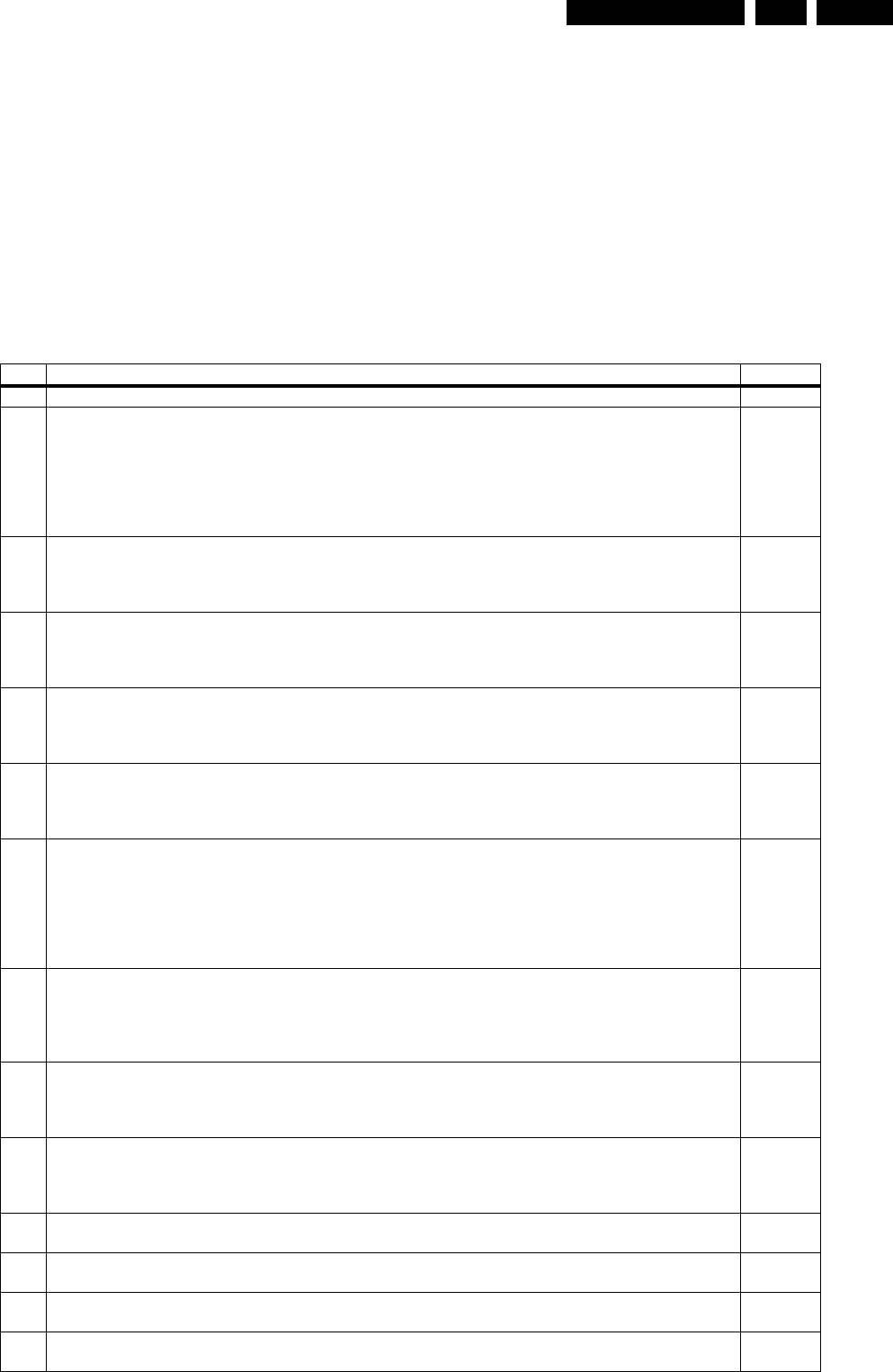

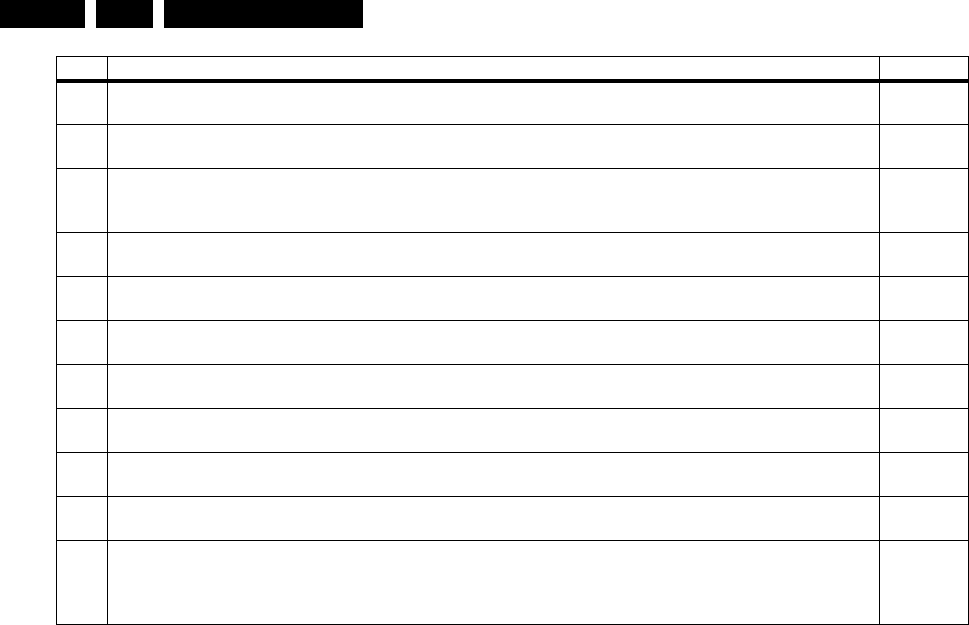

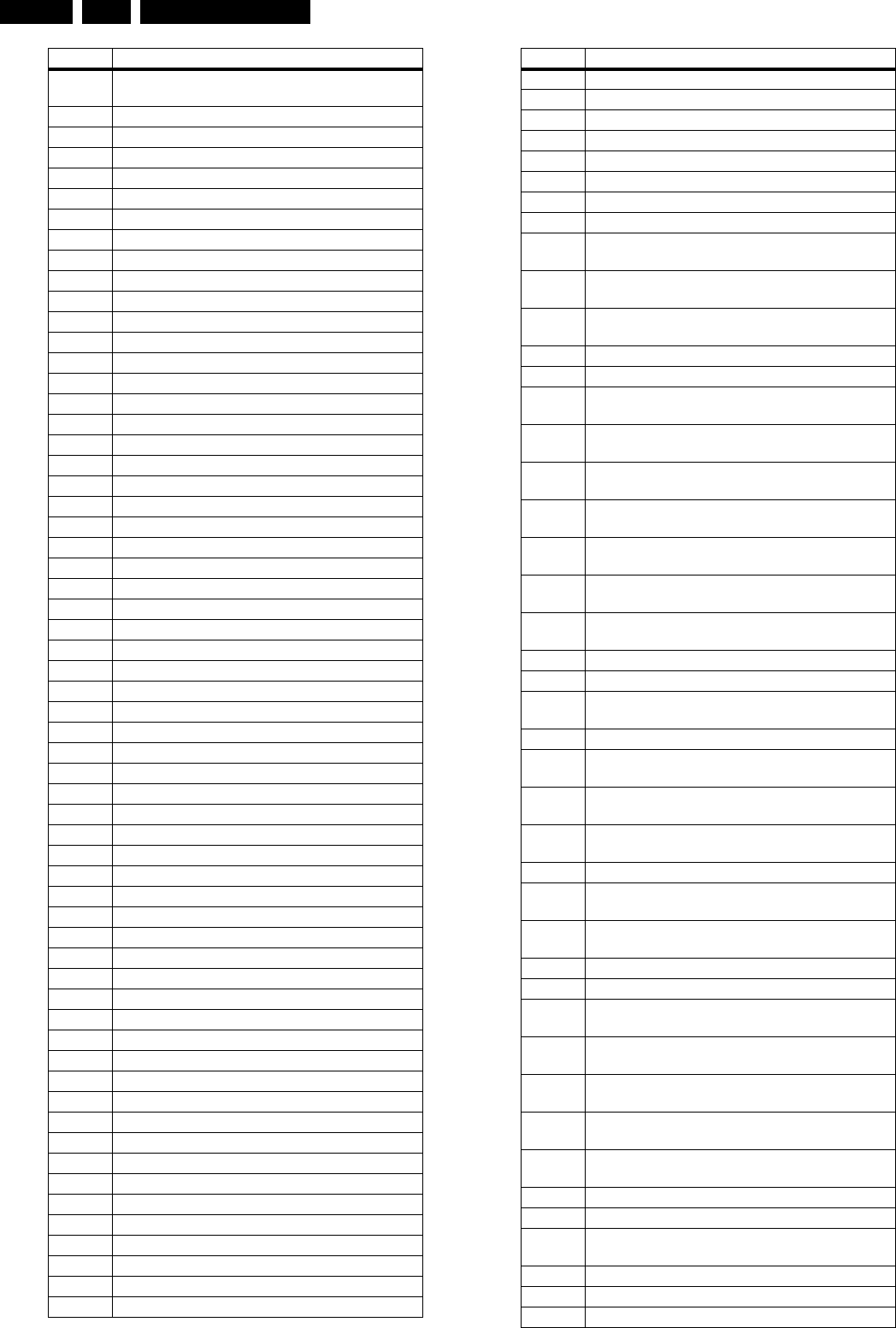

- 5.4 Nuclei Error Codes

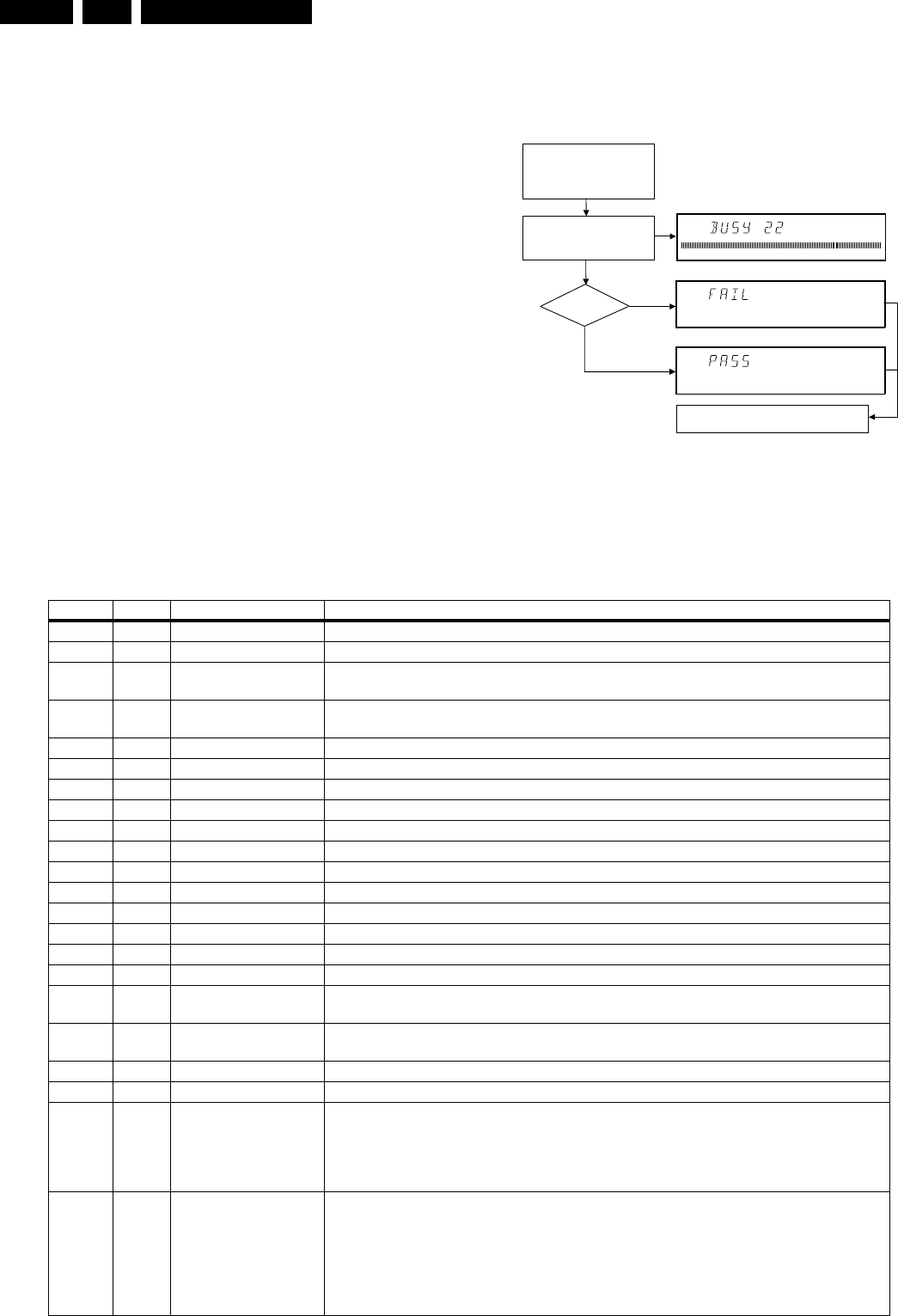

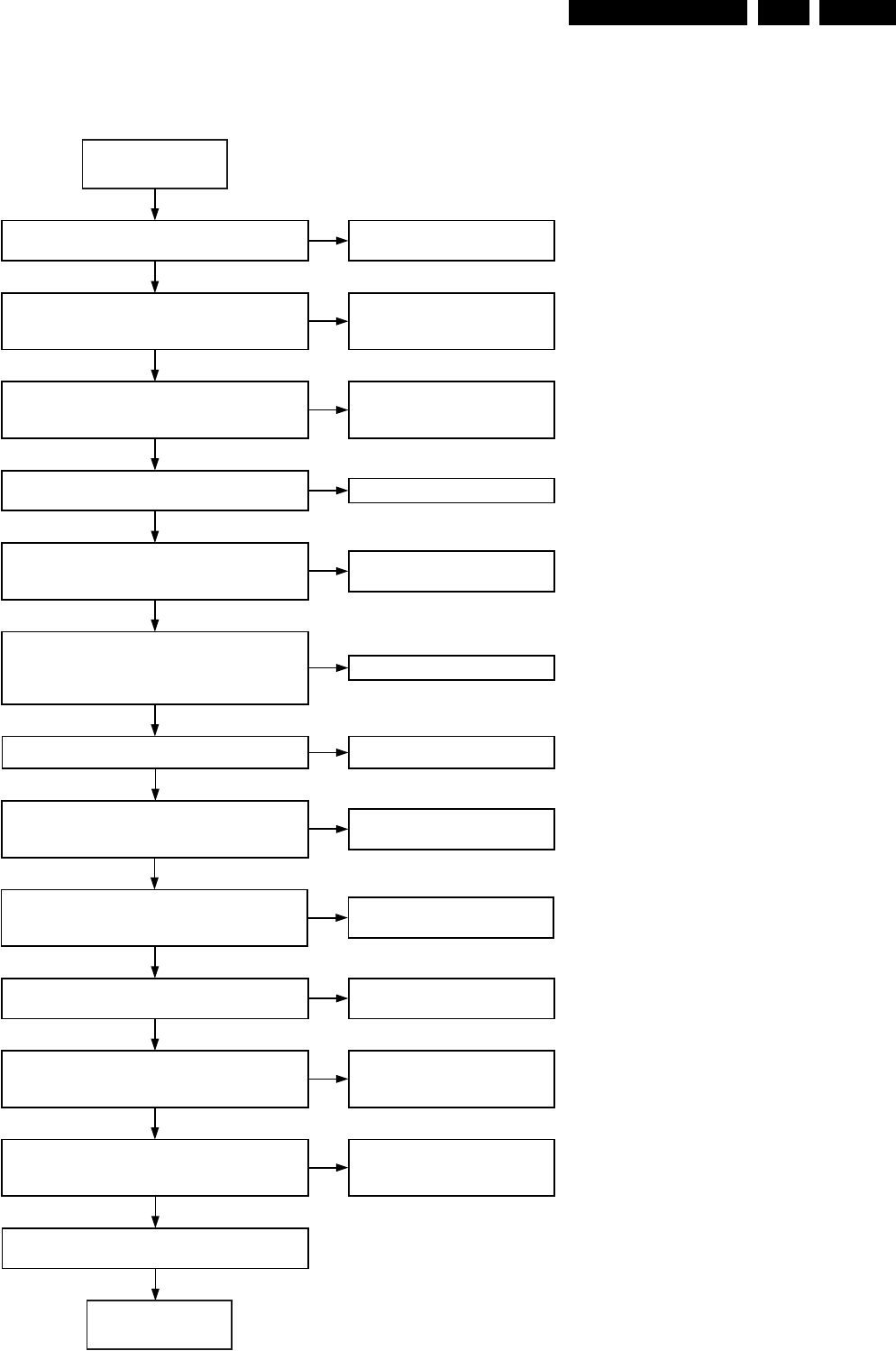

- 5.5 Loop tests

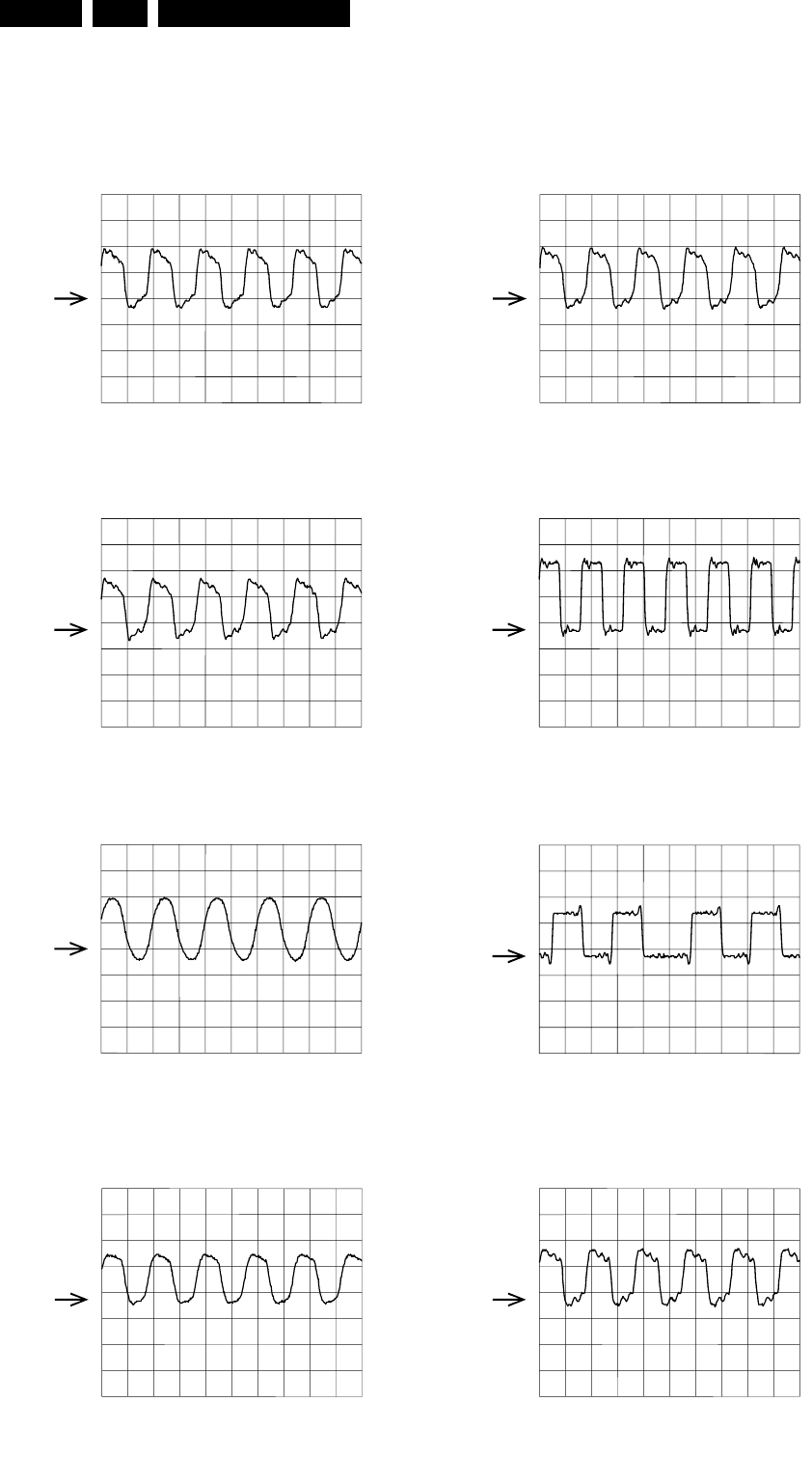

- 5.5.1 Nucleus 900: Digital Audio Loop

- 5.5.2 Nucleus 901: Audio User Dealer Loop

- 5.5.3 Nucleus 902: Digital Video Loop

- 5.5.4 Nucleus 903: Digital Video VBI Loop

- 5.5.5 Nucleus 904: System Video Loop

- 5.5.6 Nucleus 905: System Video VBI Loop

- 5.5.7 Nucleus 906: Video User Dealer Loop

- 5.5.8 Nucleus 907: Video VBI User Dealer Loop

- 5.5.9 Nucleus 908: System Audio Loop Scart (Europe)

- 5.5.10 Nucleus 909: System Audio Loop CINCH (Nafta)

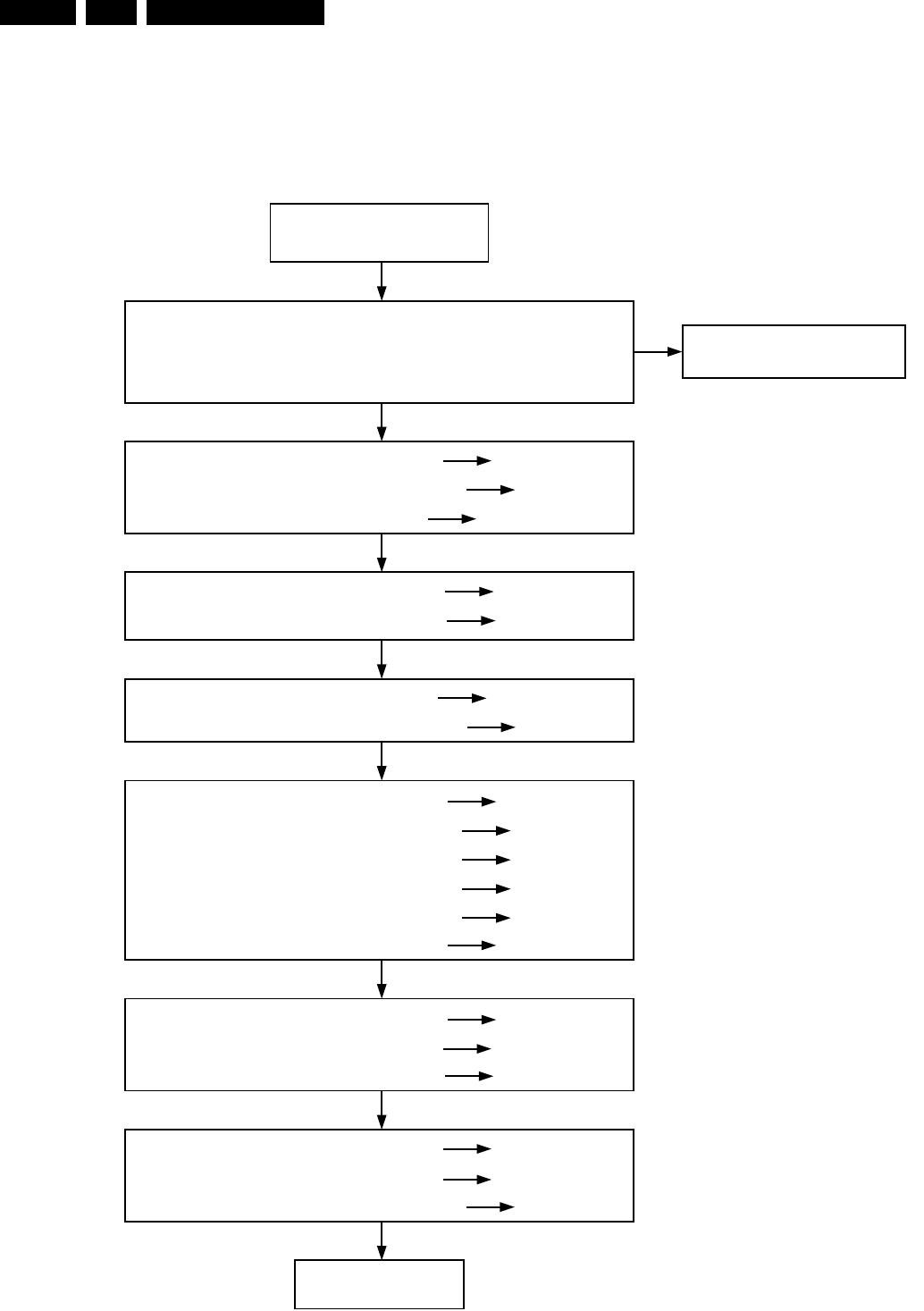

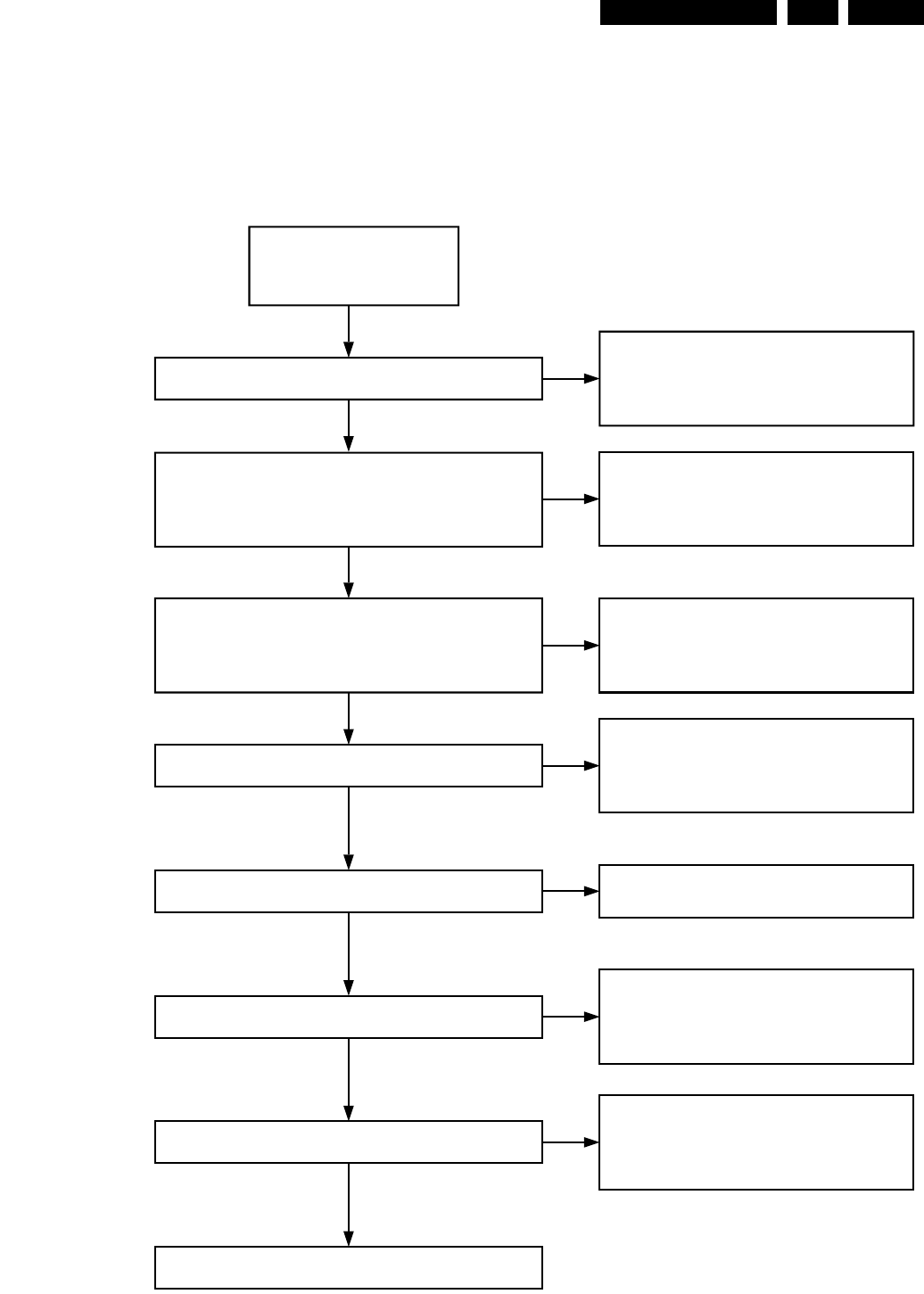

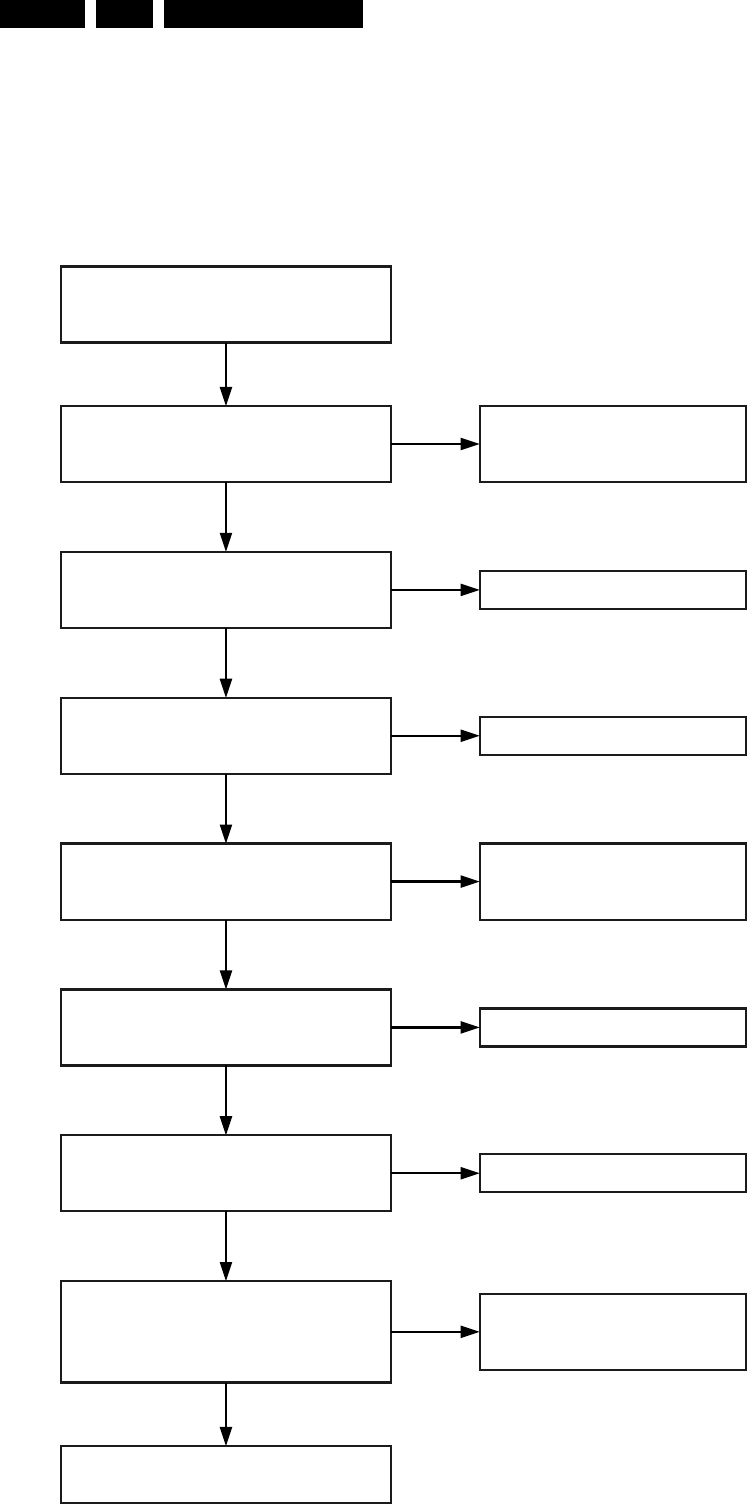

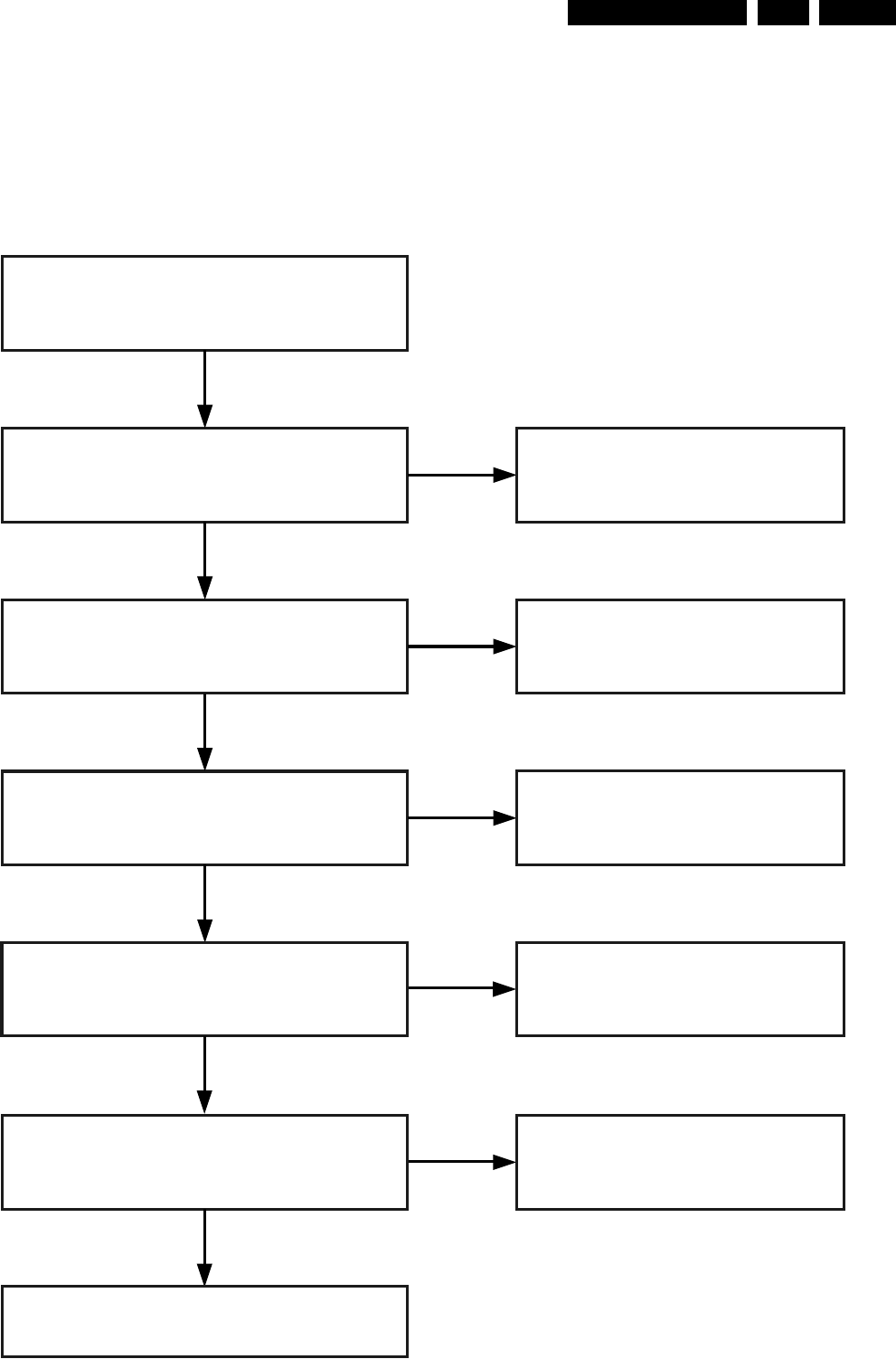

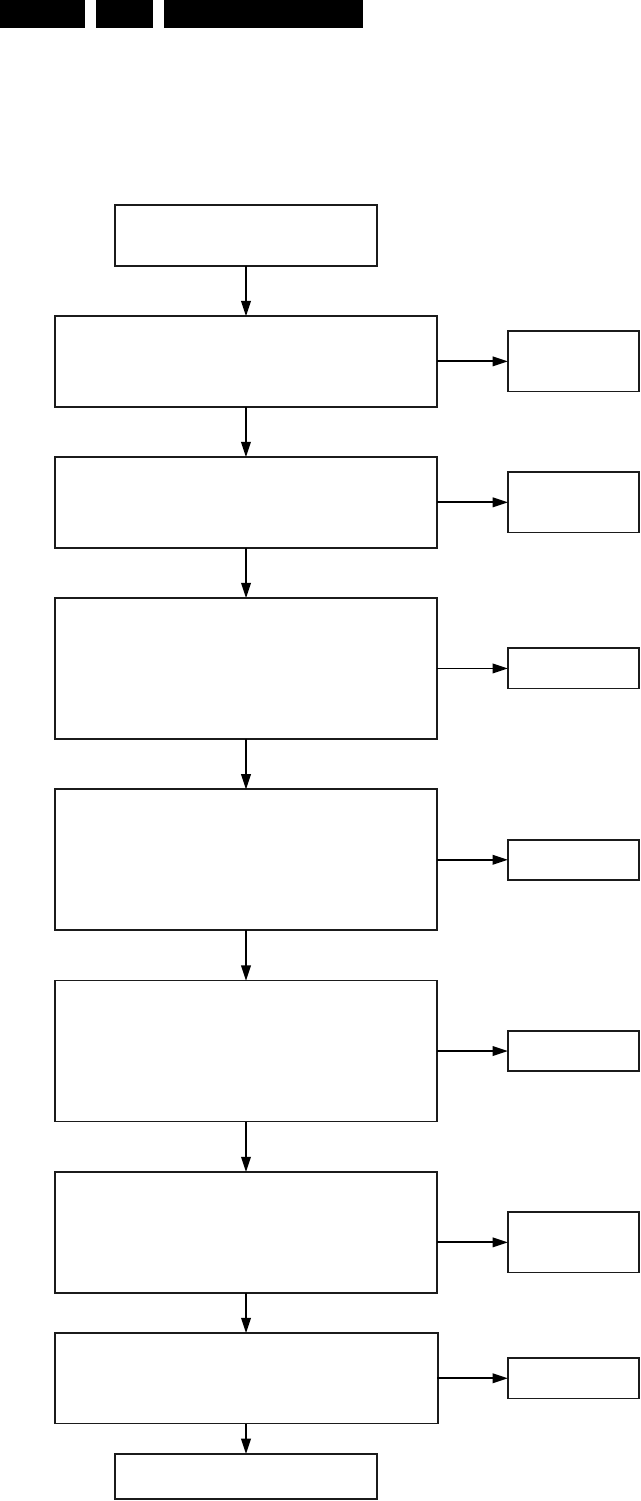

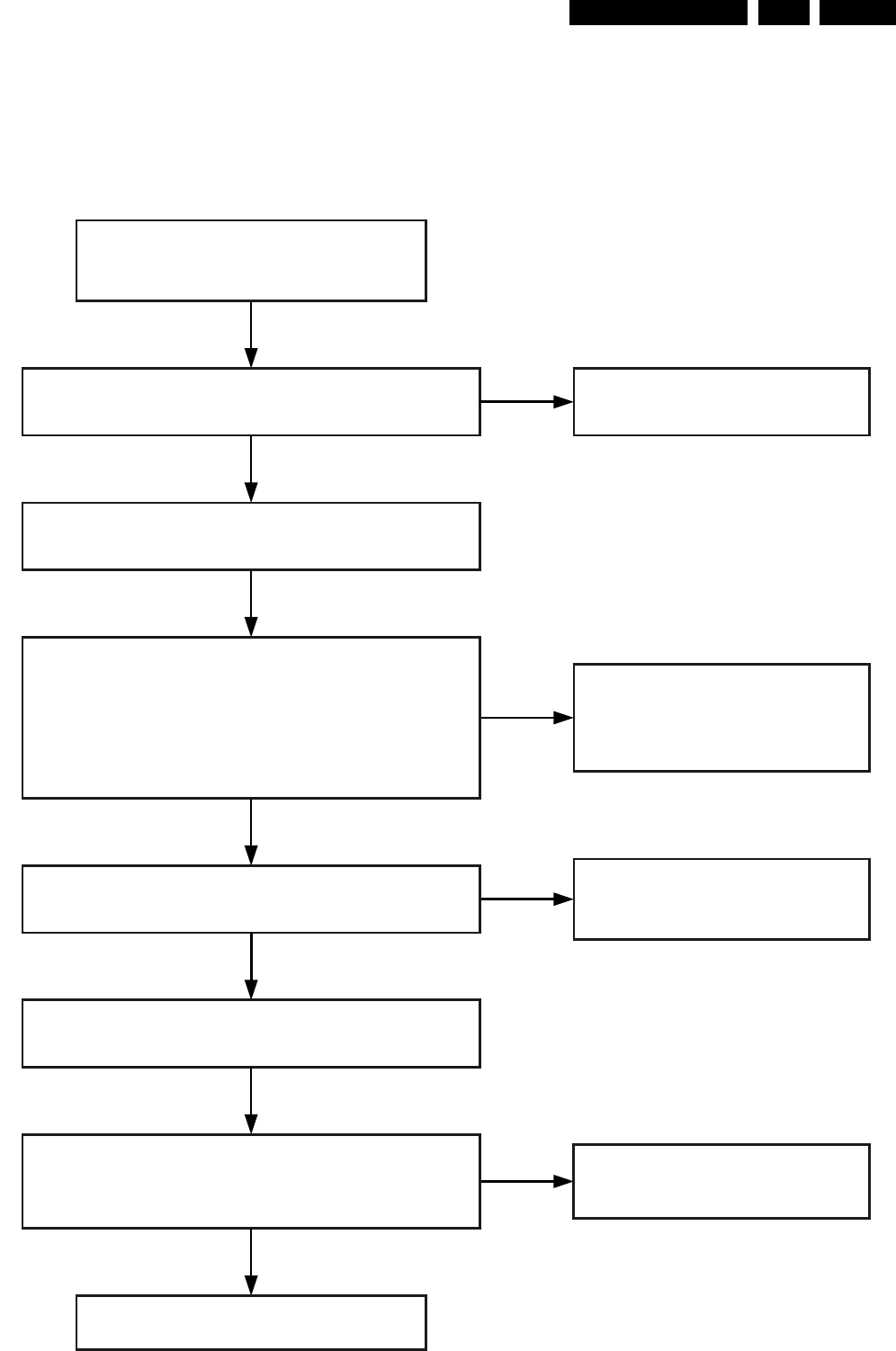

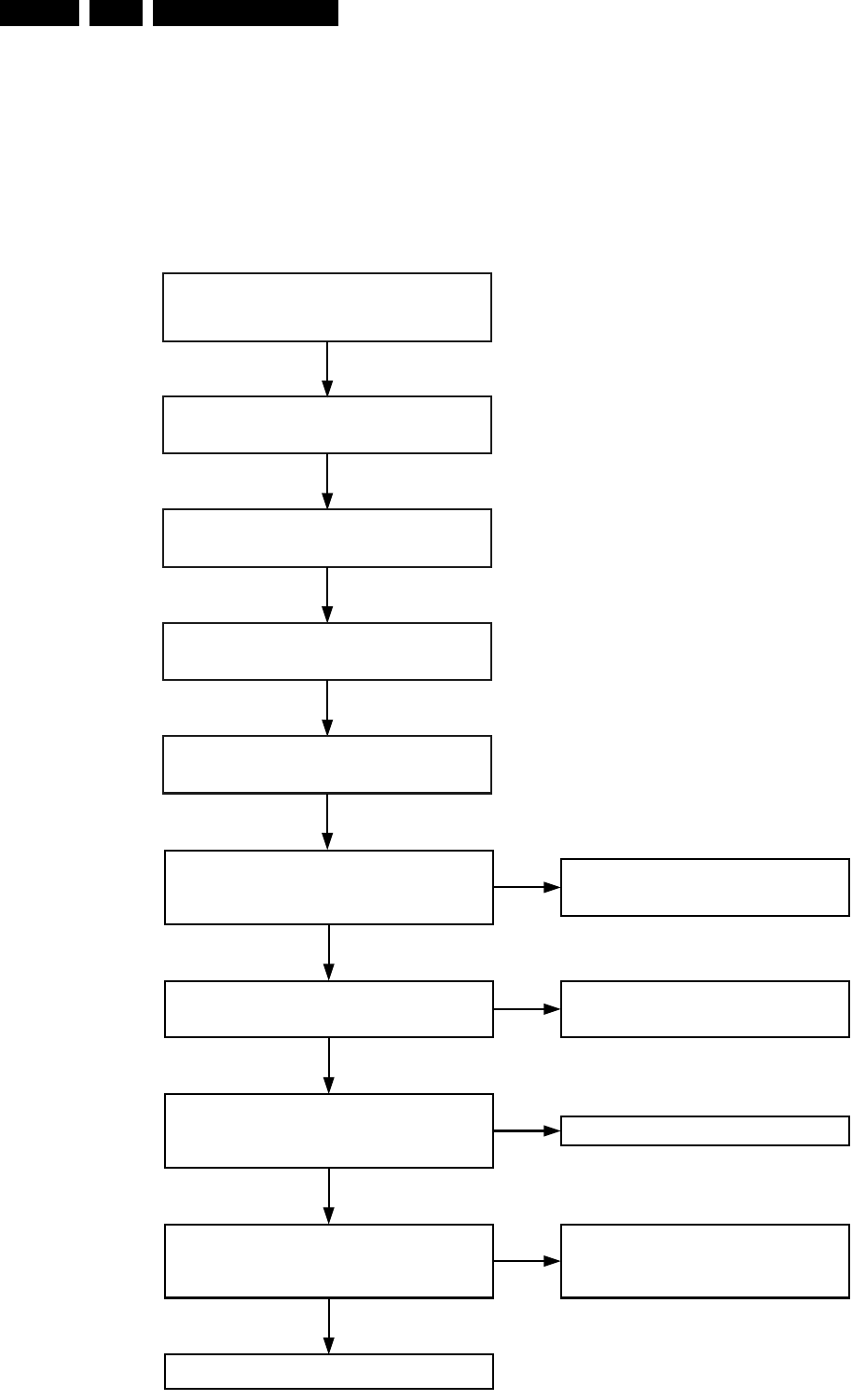

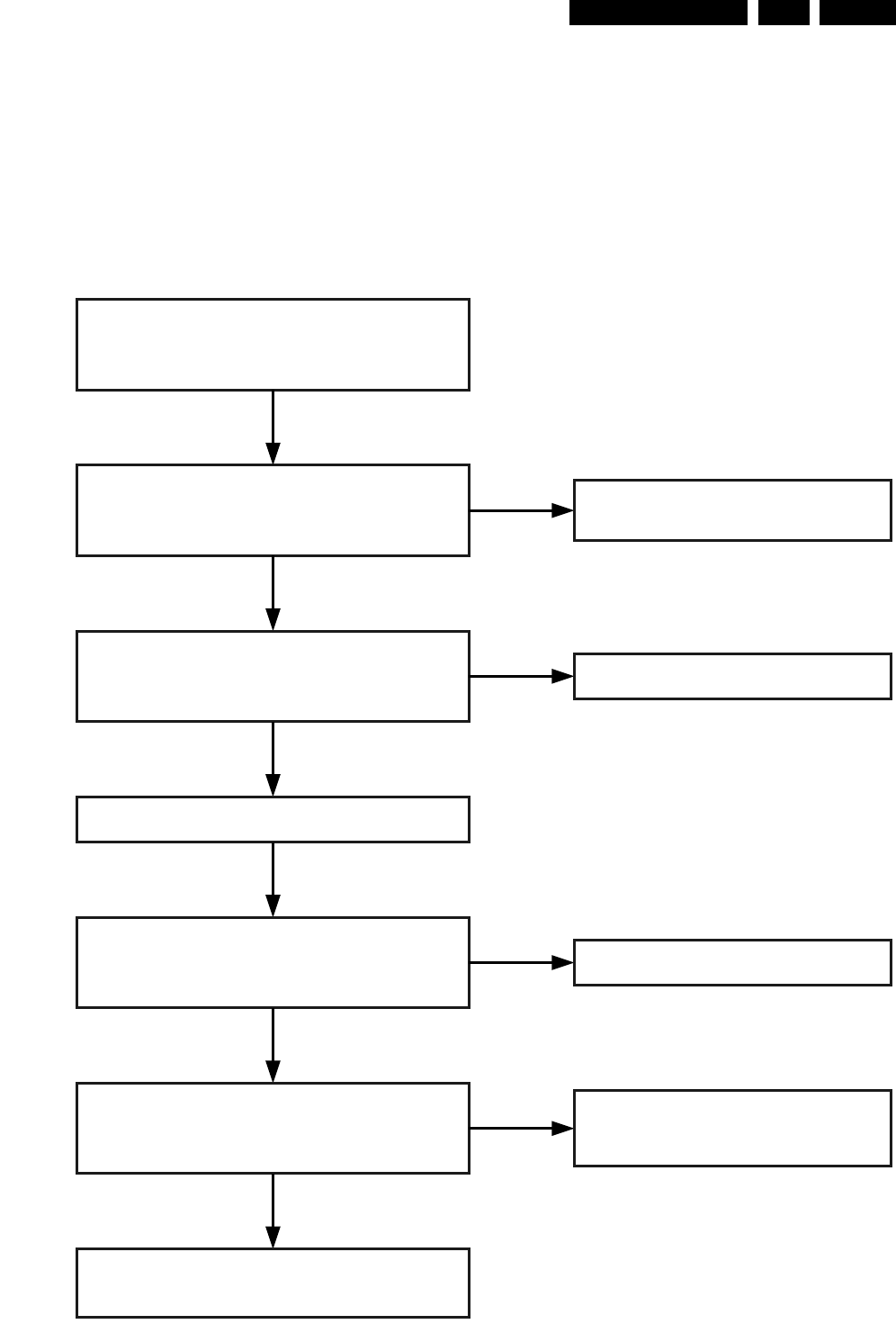

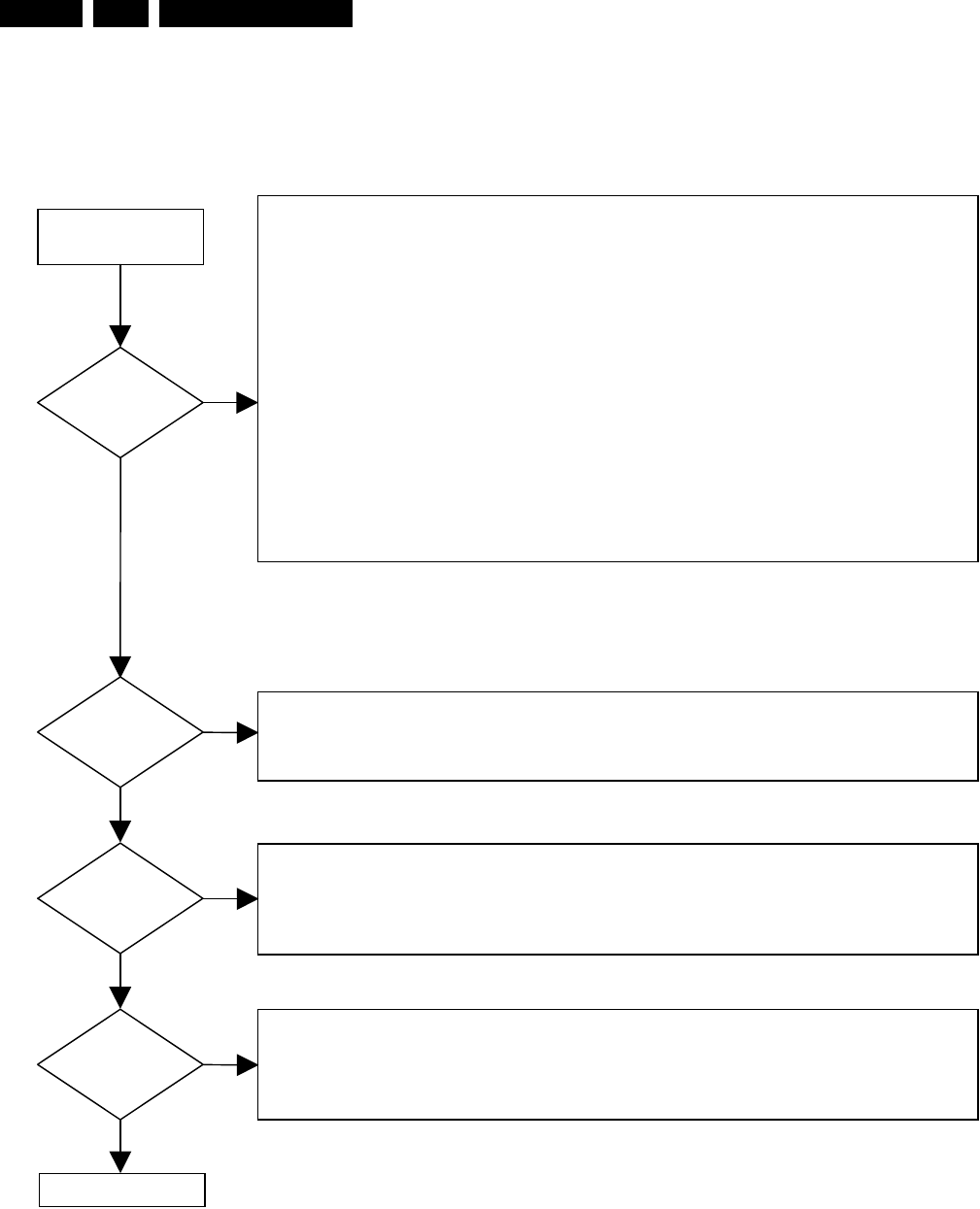

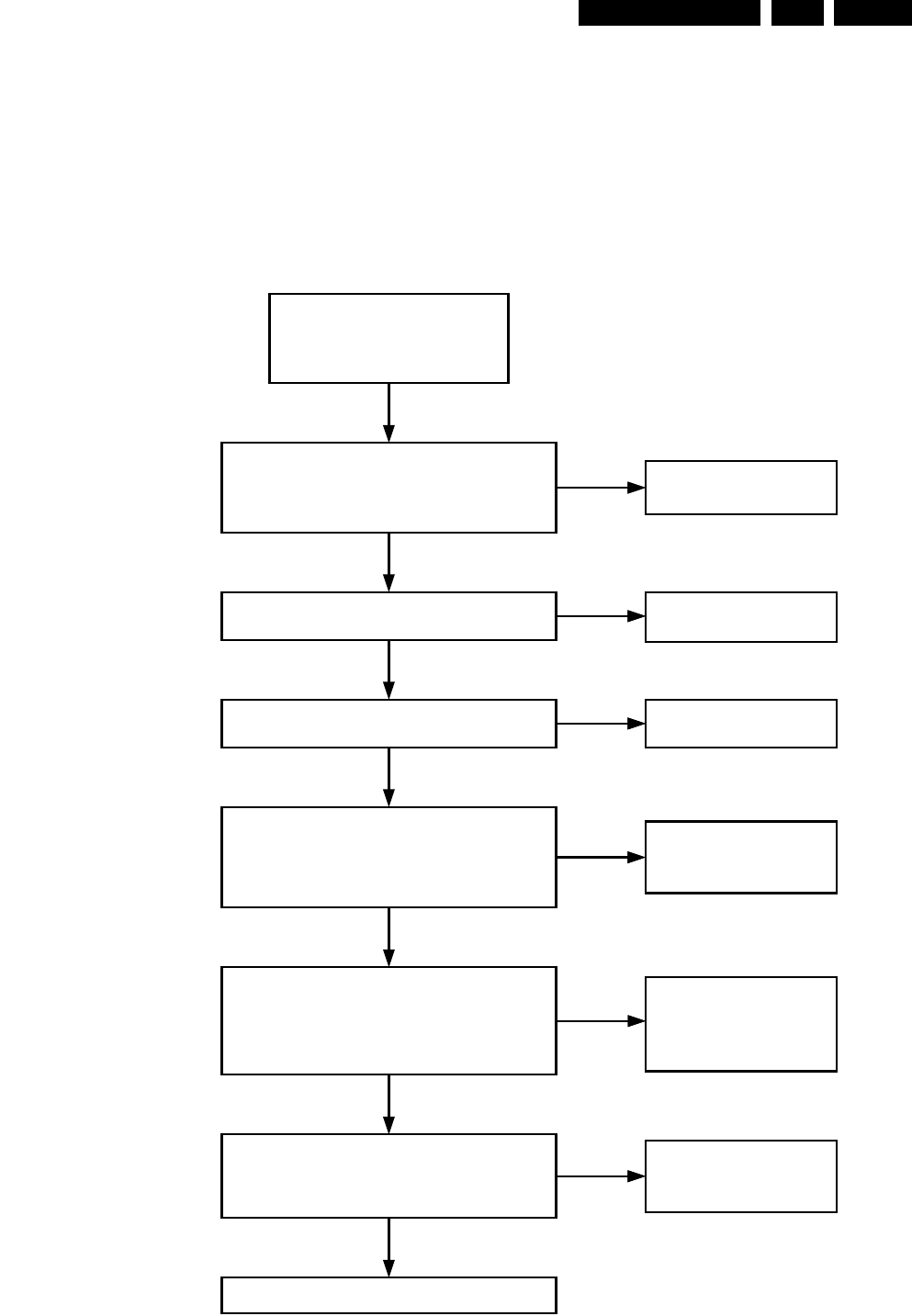

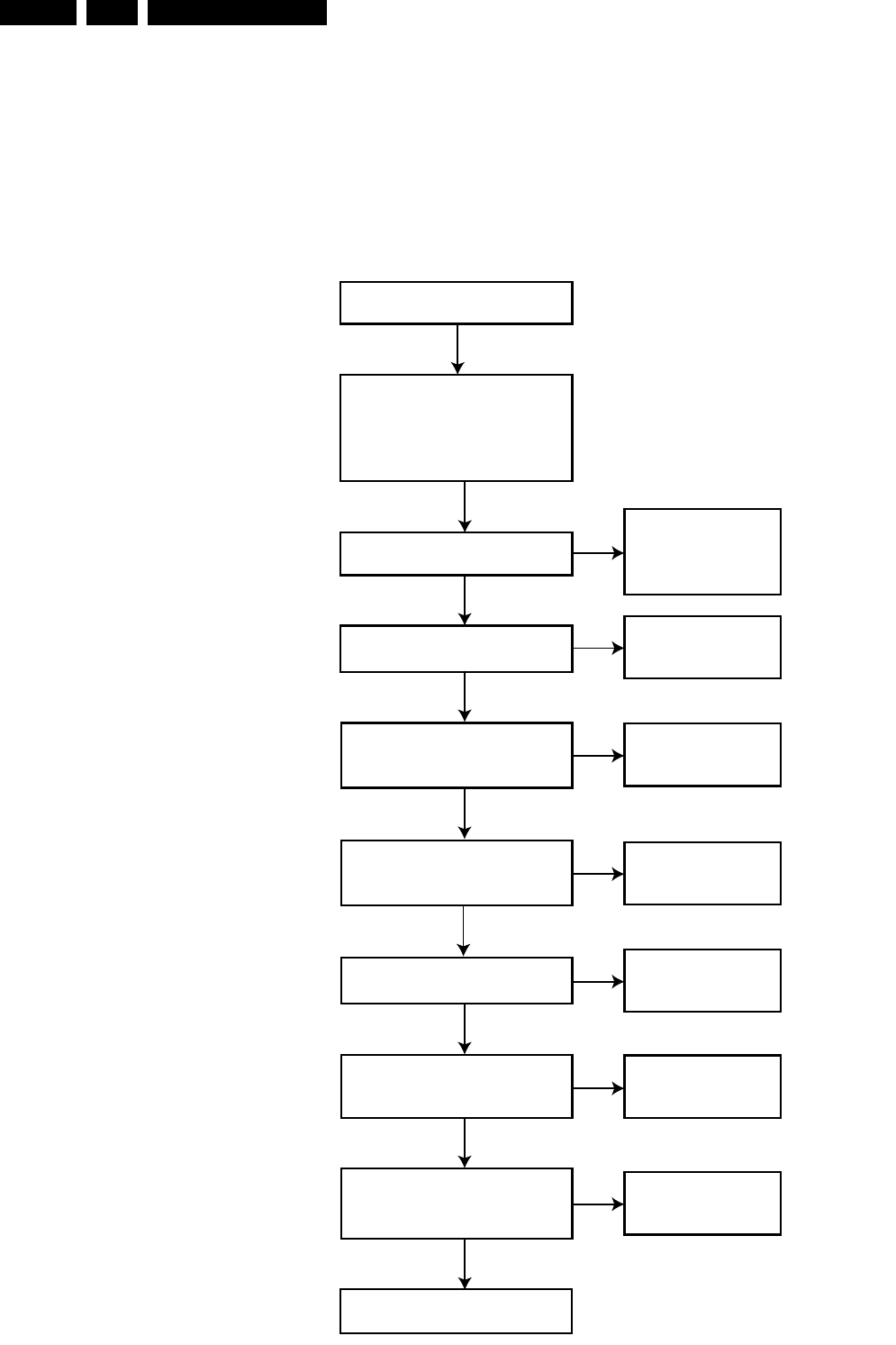

- 5.6 Faultfinding trees

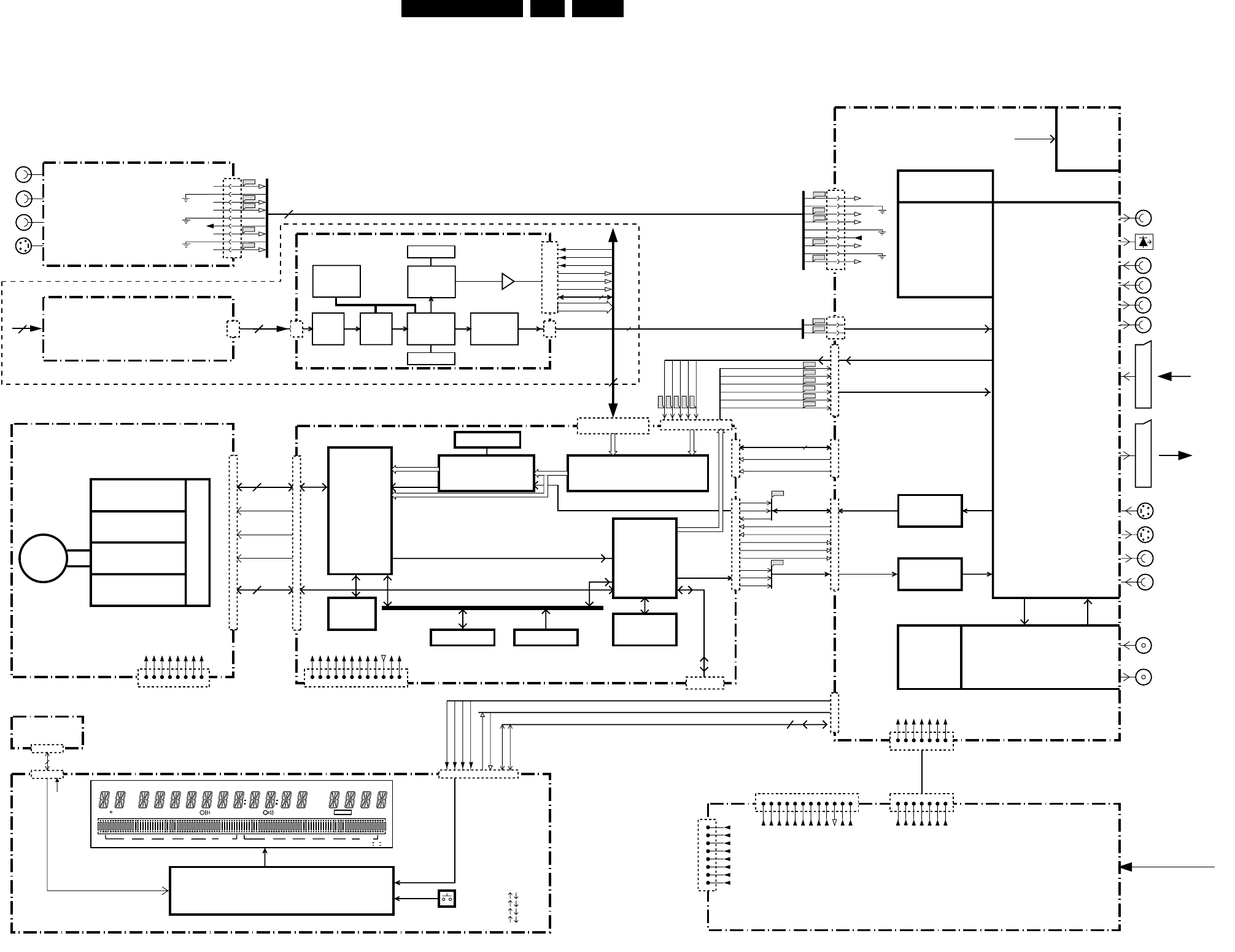

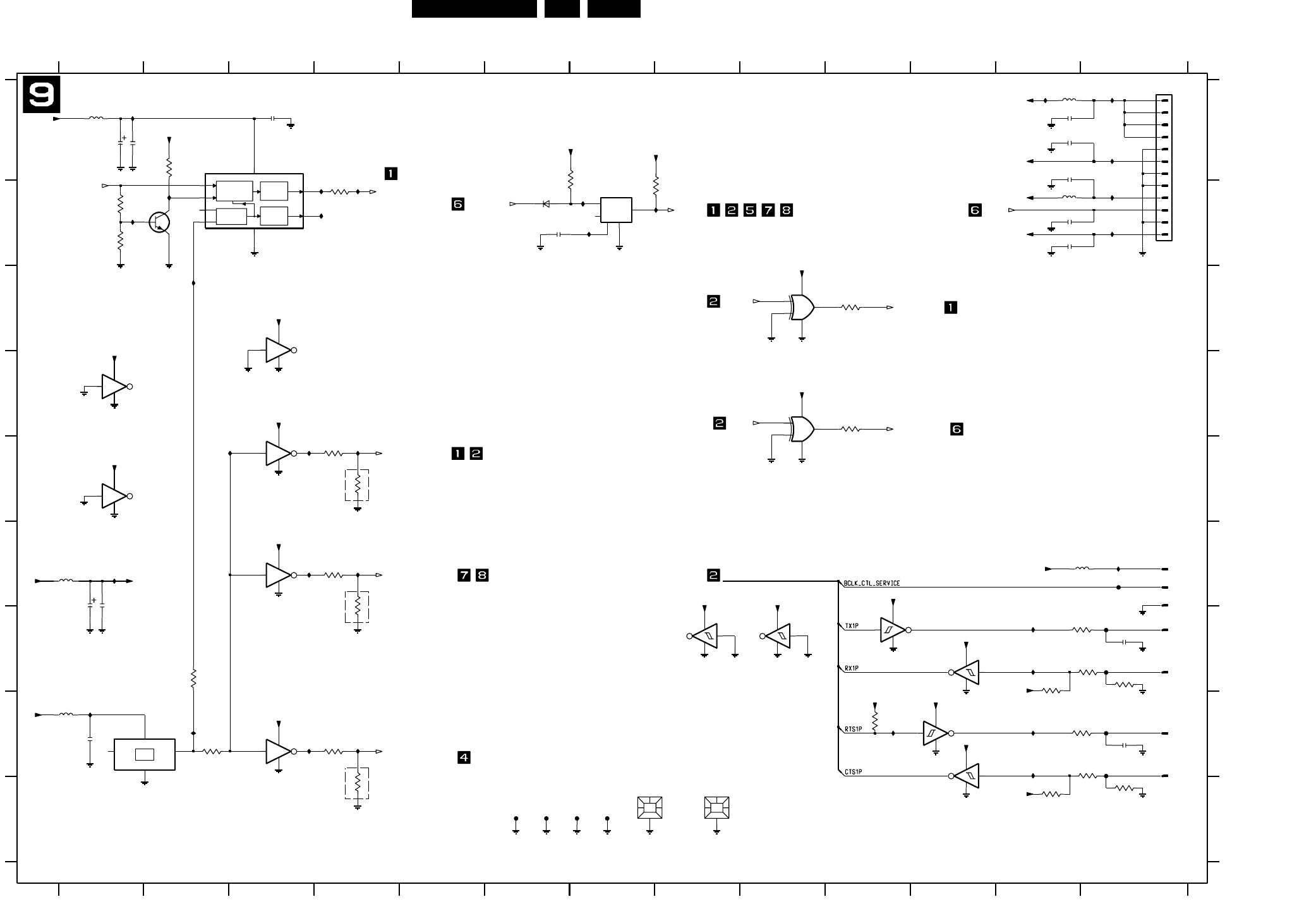

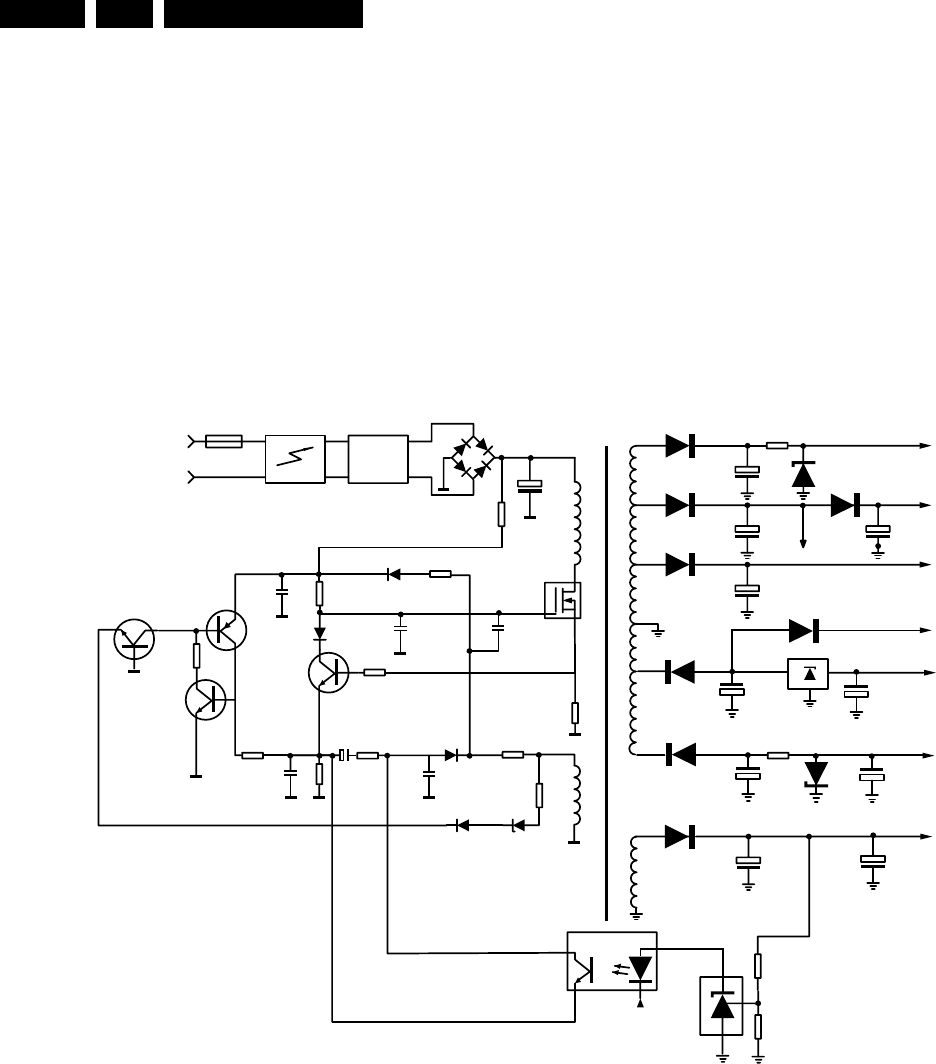

- 6. Block and Wiring Diagram.

- 7. Electrical Diagrams and Print-Layouts

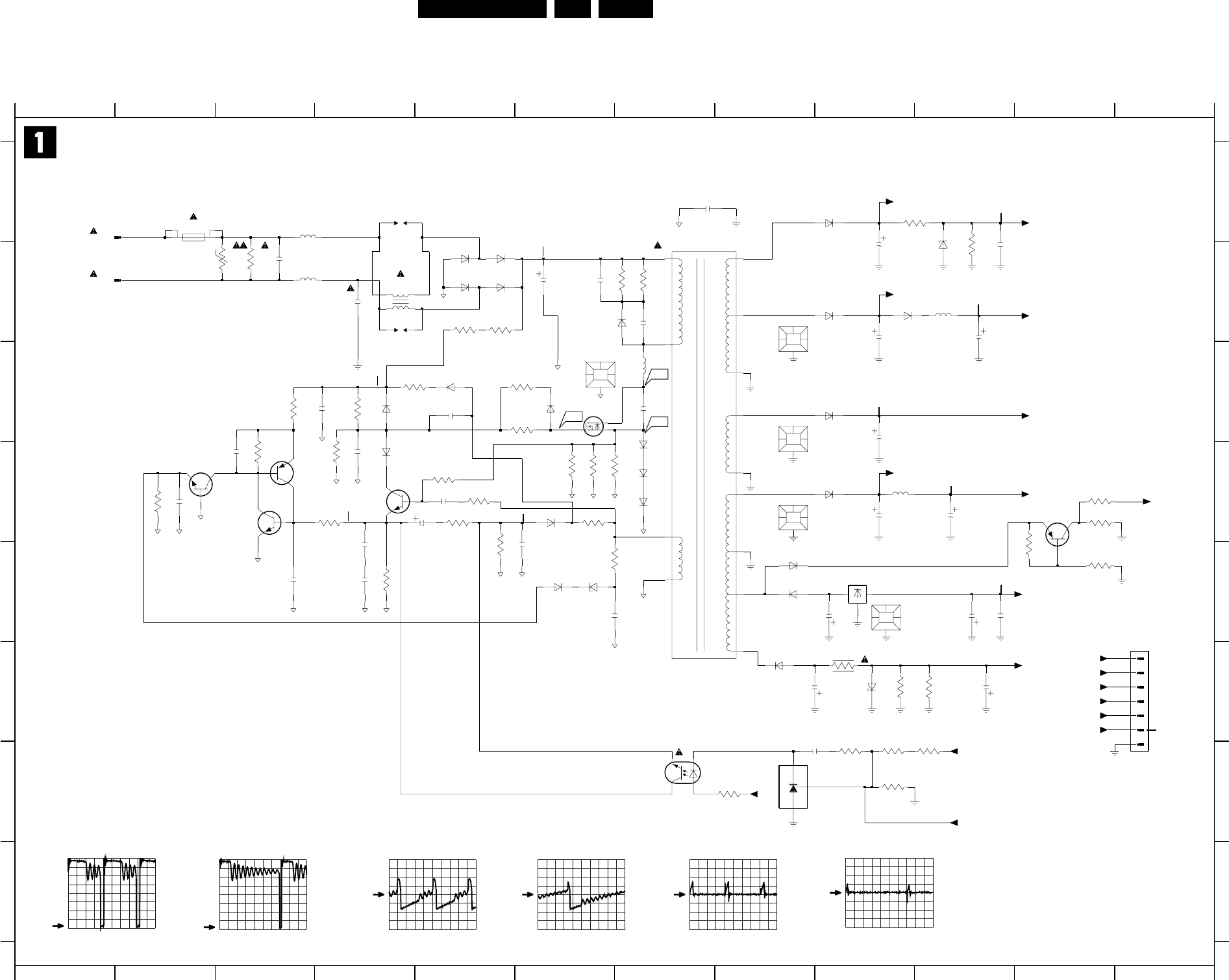

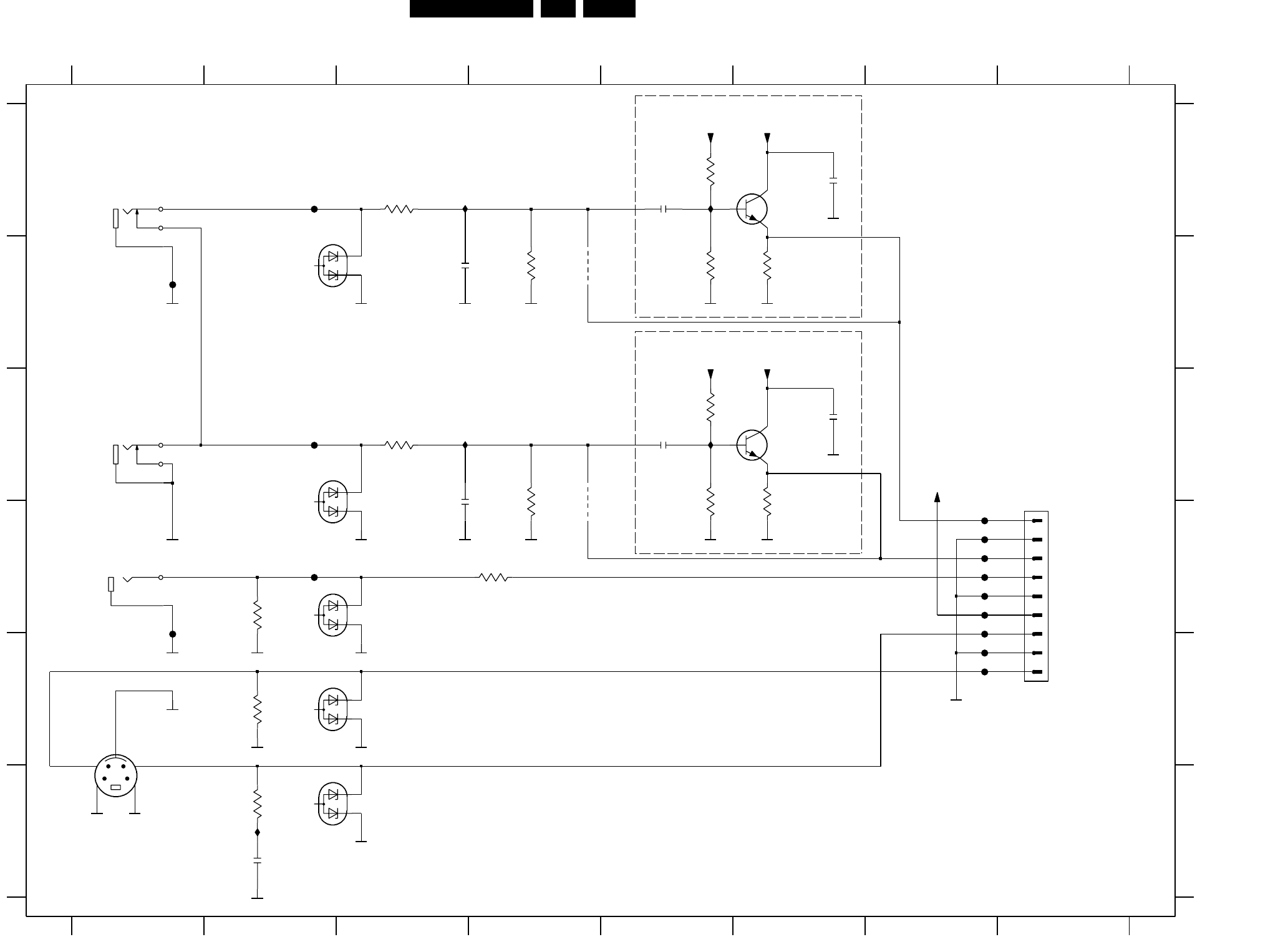

- Power Supply

- Power Supply

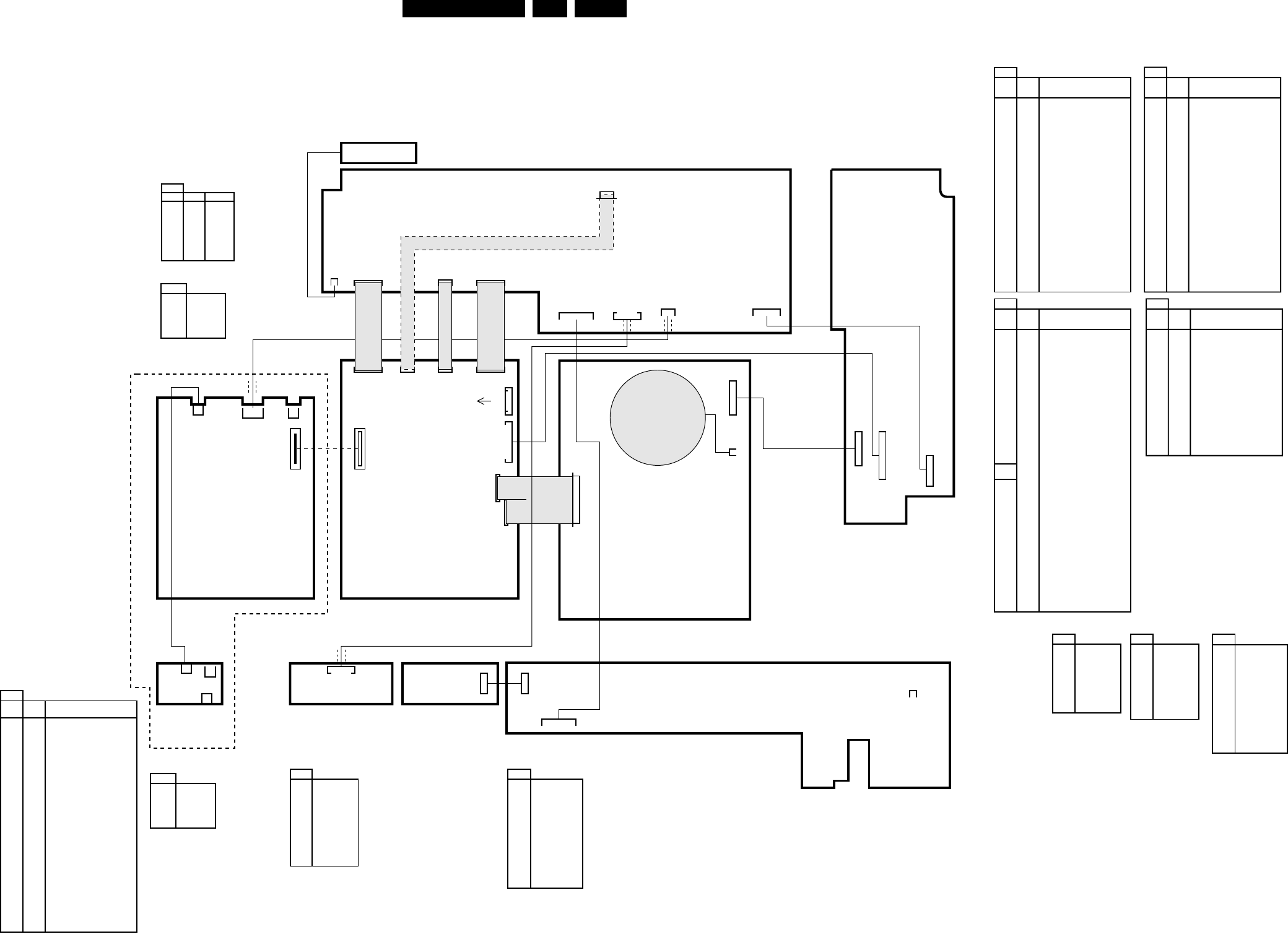

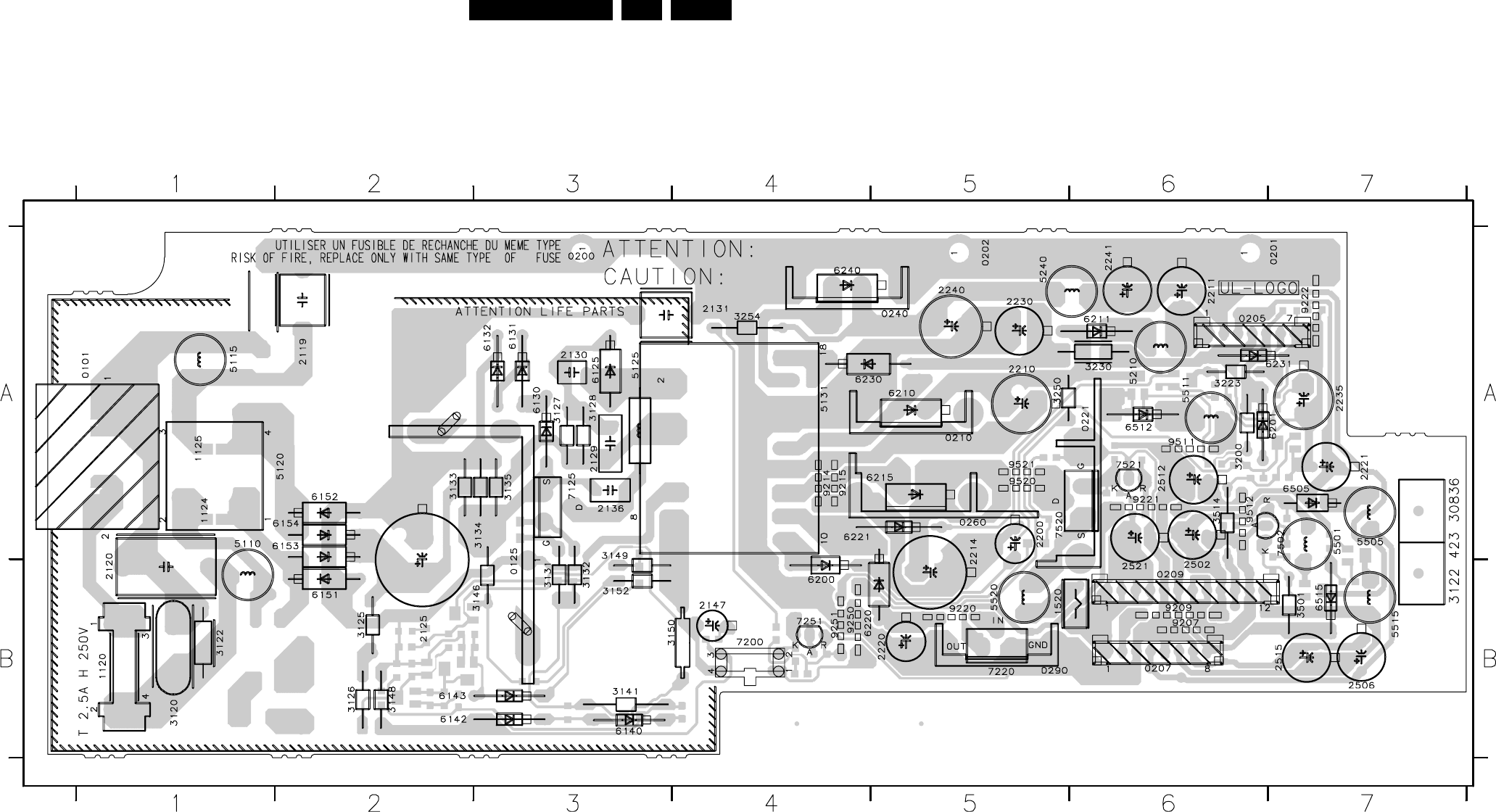

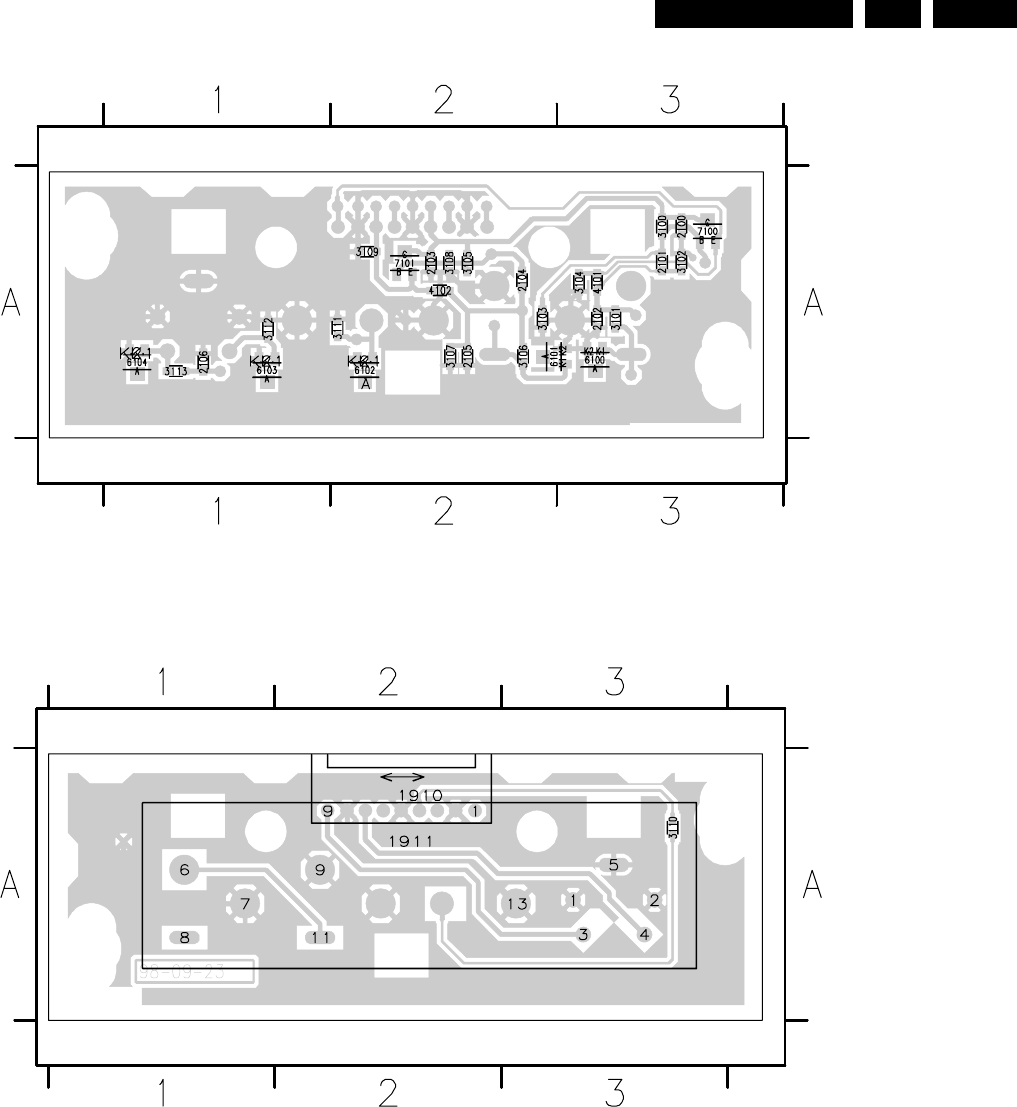

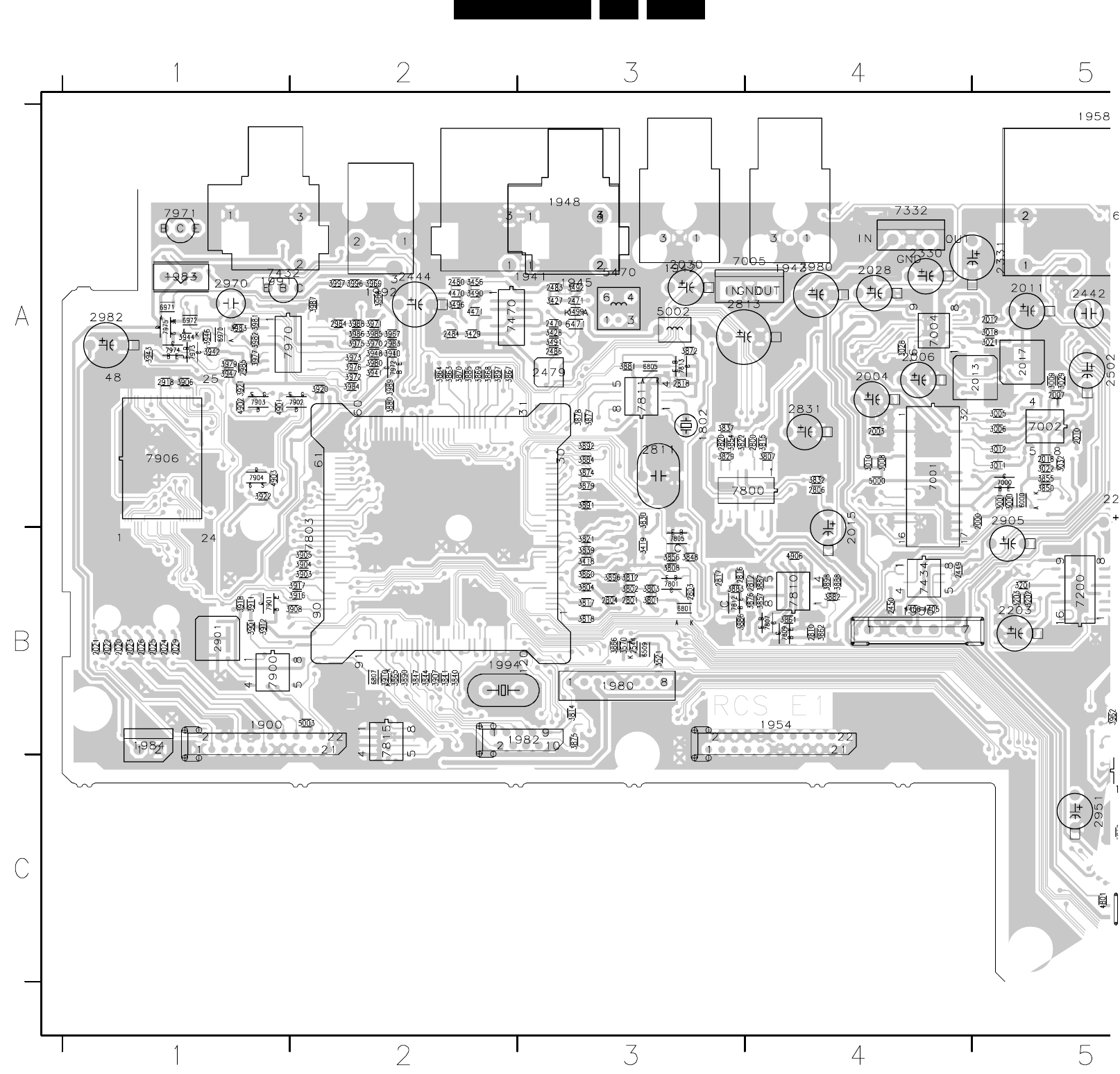

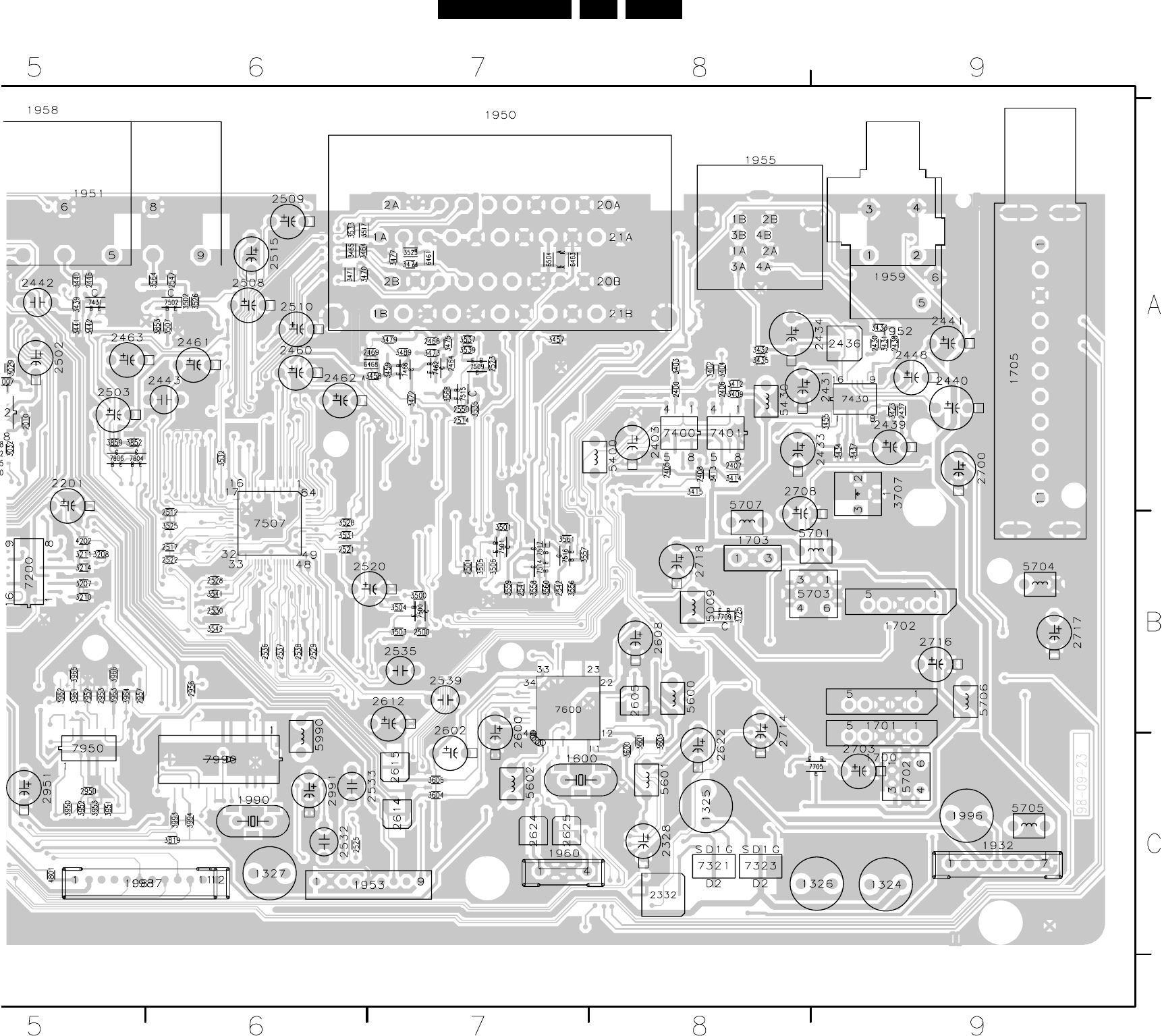

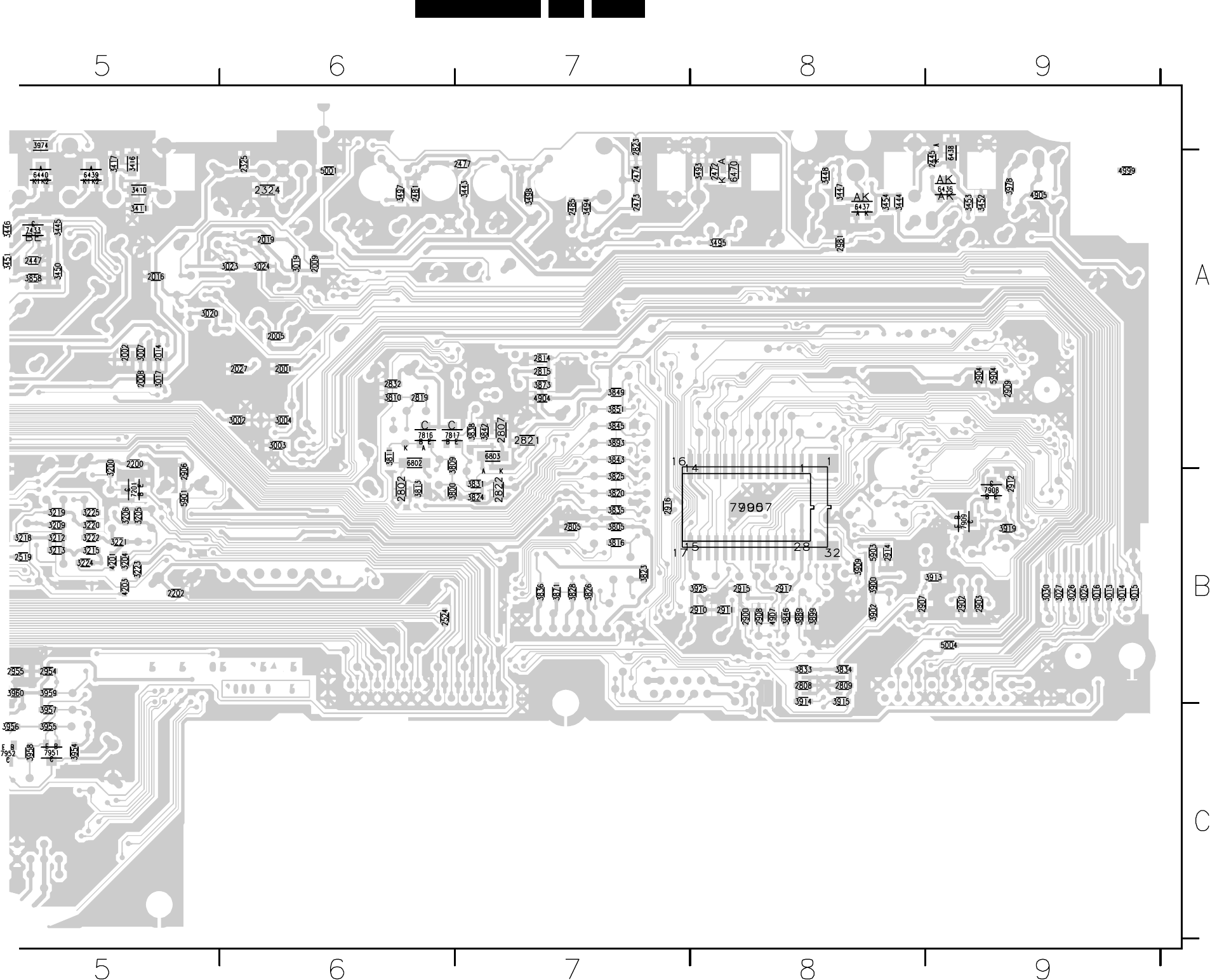

- Layout Power Supply (Top View)

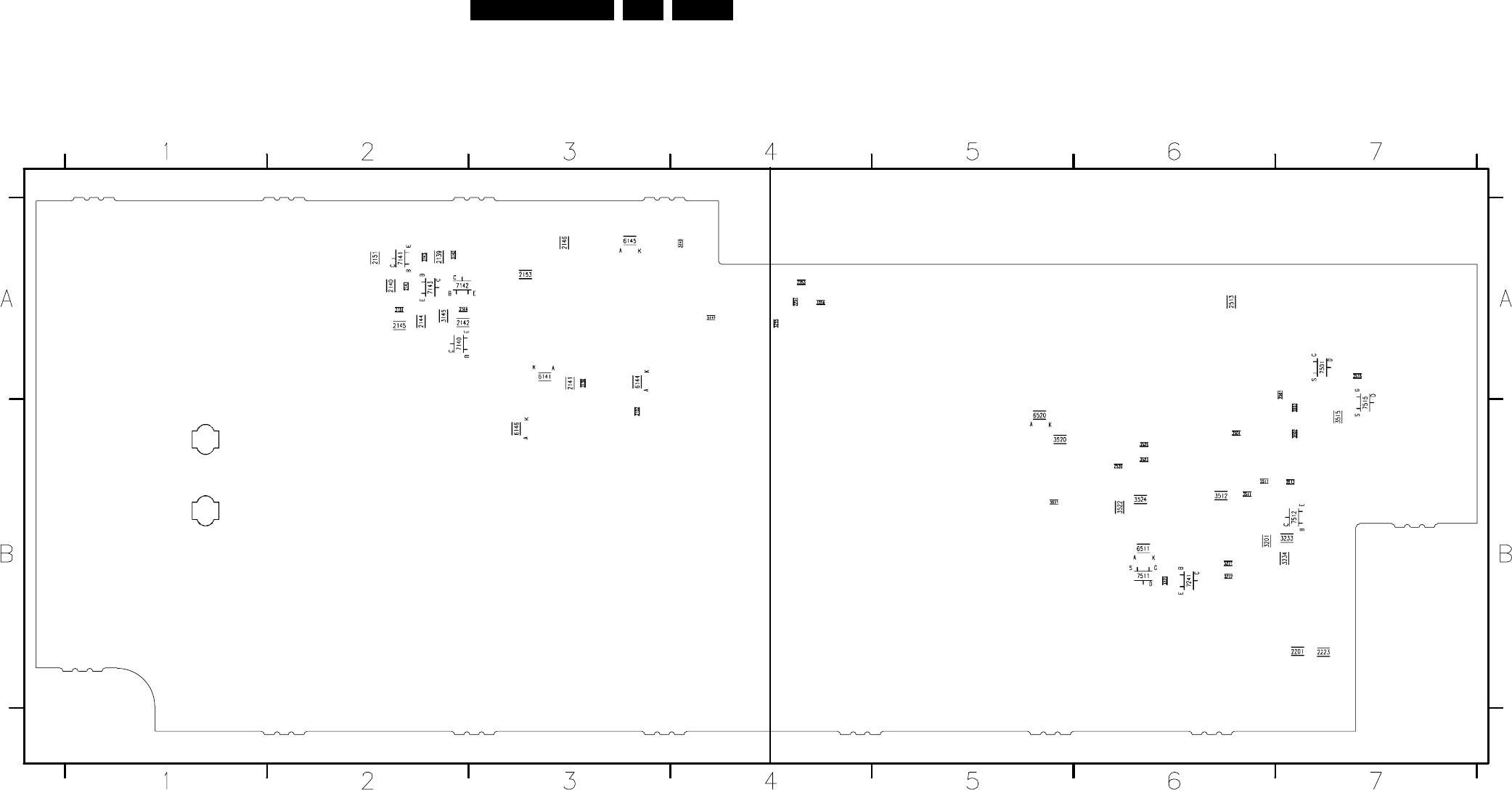

- Layout Power Supply (Overview Bottom View)

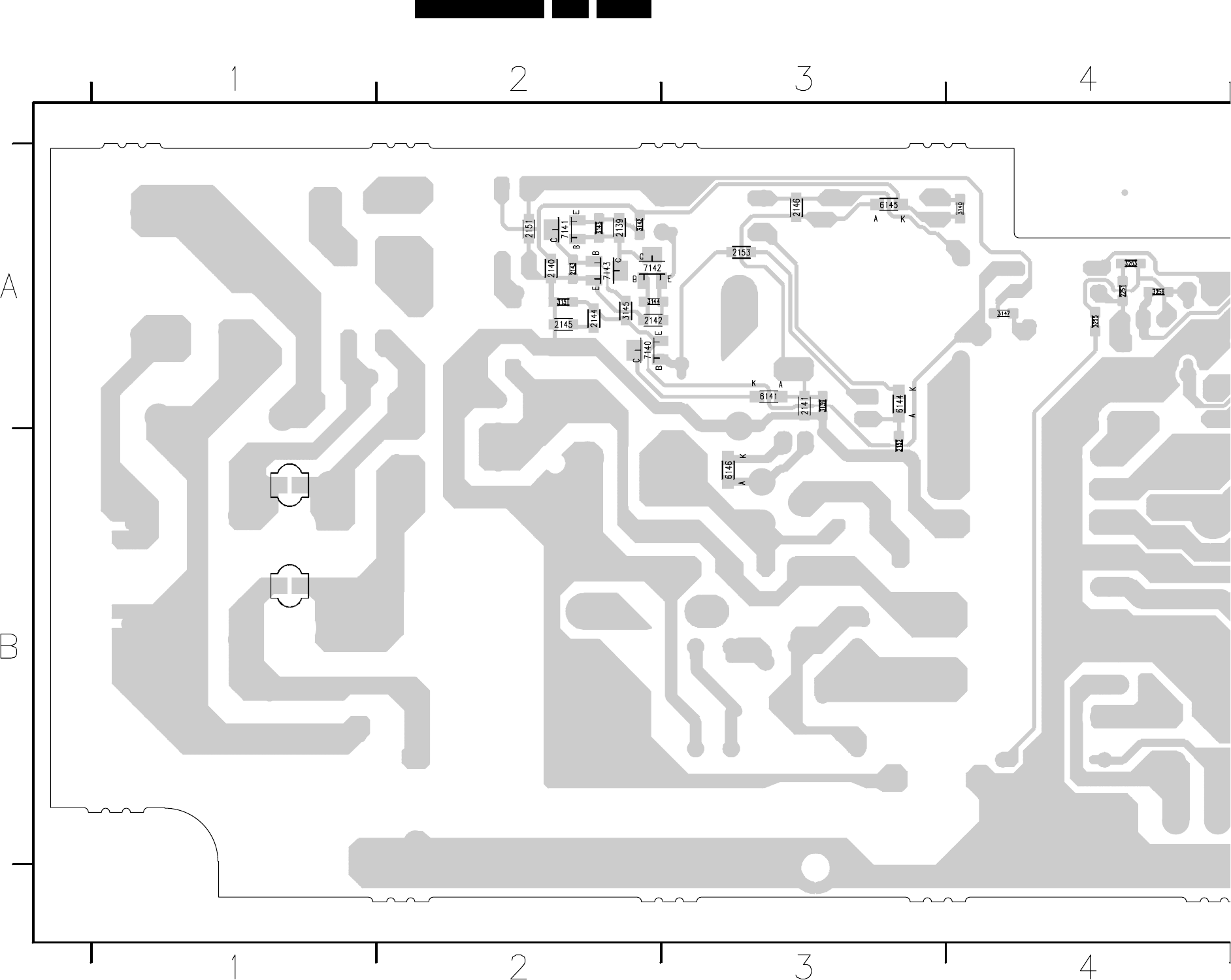

- Layout Power Supply (Part 1 Bottom View)

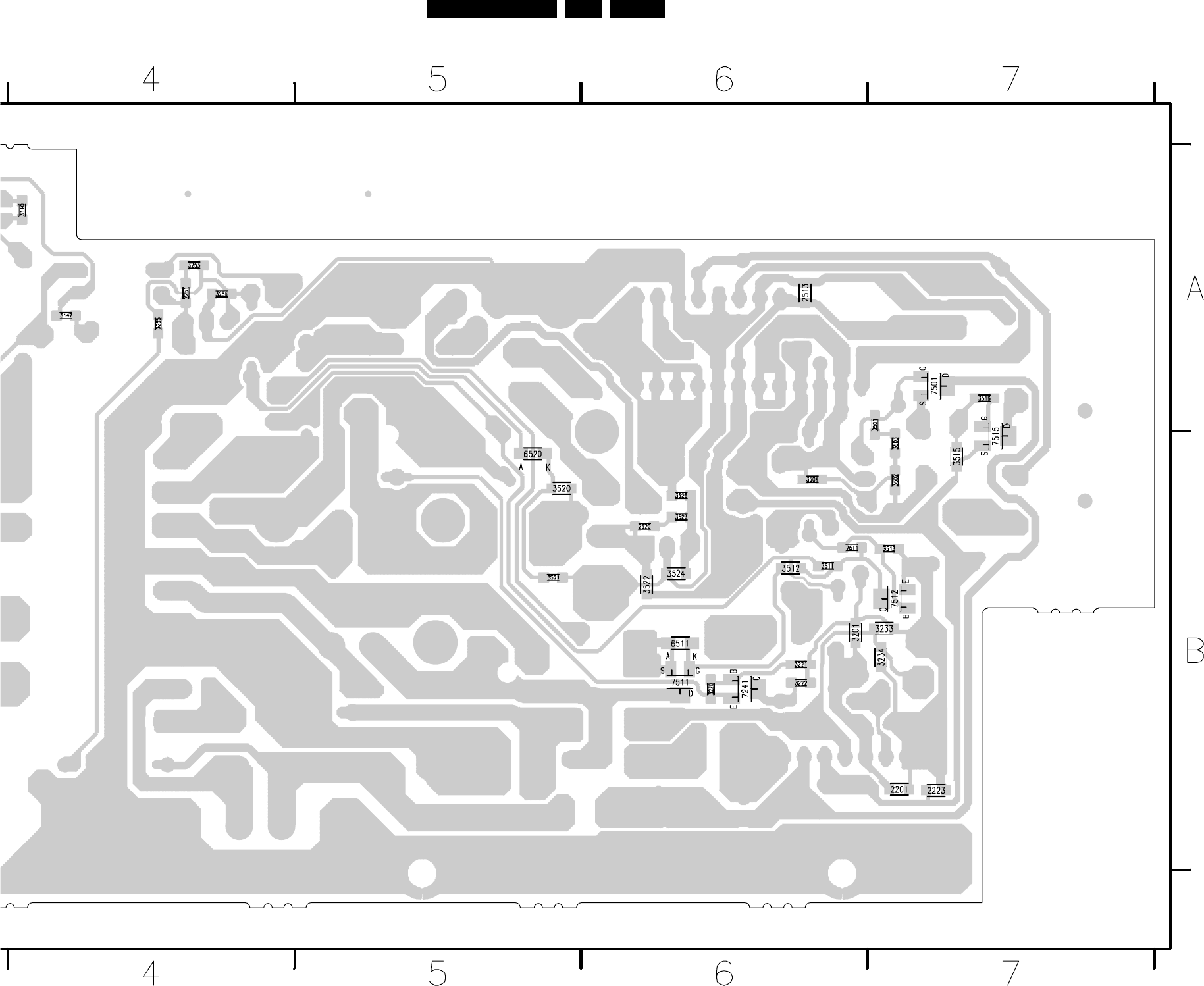

- Layout Power Supply (Part 2 Bottom View)

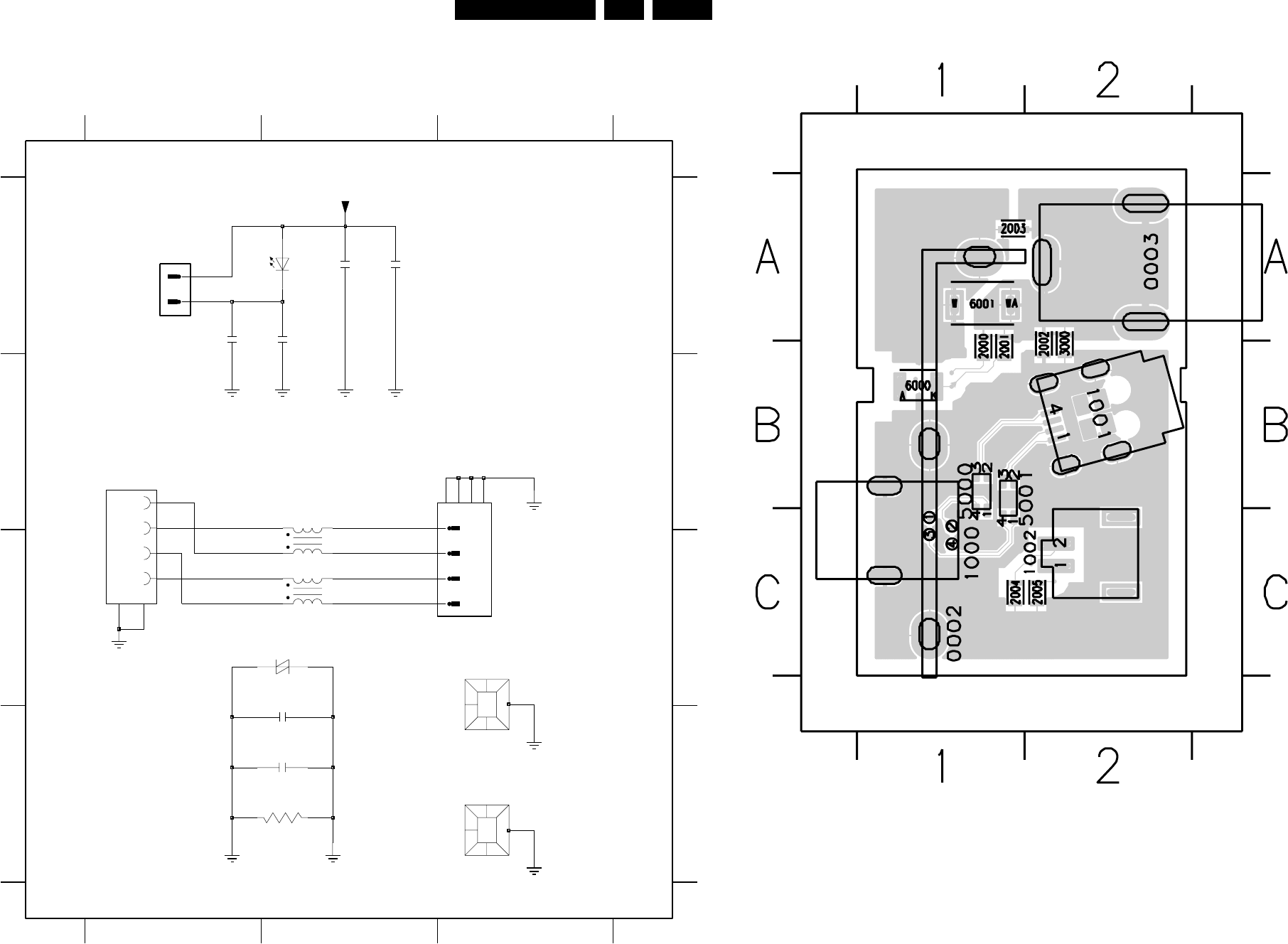

- Display Panel

- Layout Display Panel (Top View)

- Layout Display Panel (Overview Bottom View)

- Layout Display Panel (Part 1 Bottom View)

- Layout Display Panel (Part 2 Bottom View)

- Front AV Part

- Layout Front AV Part

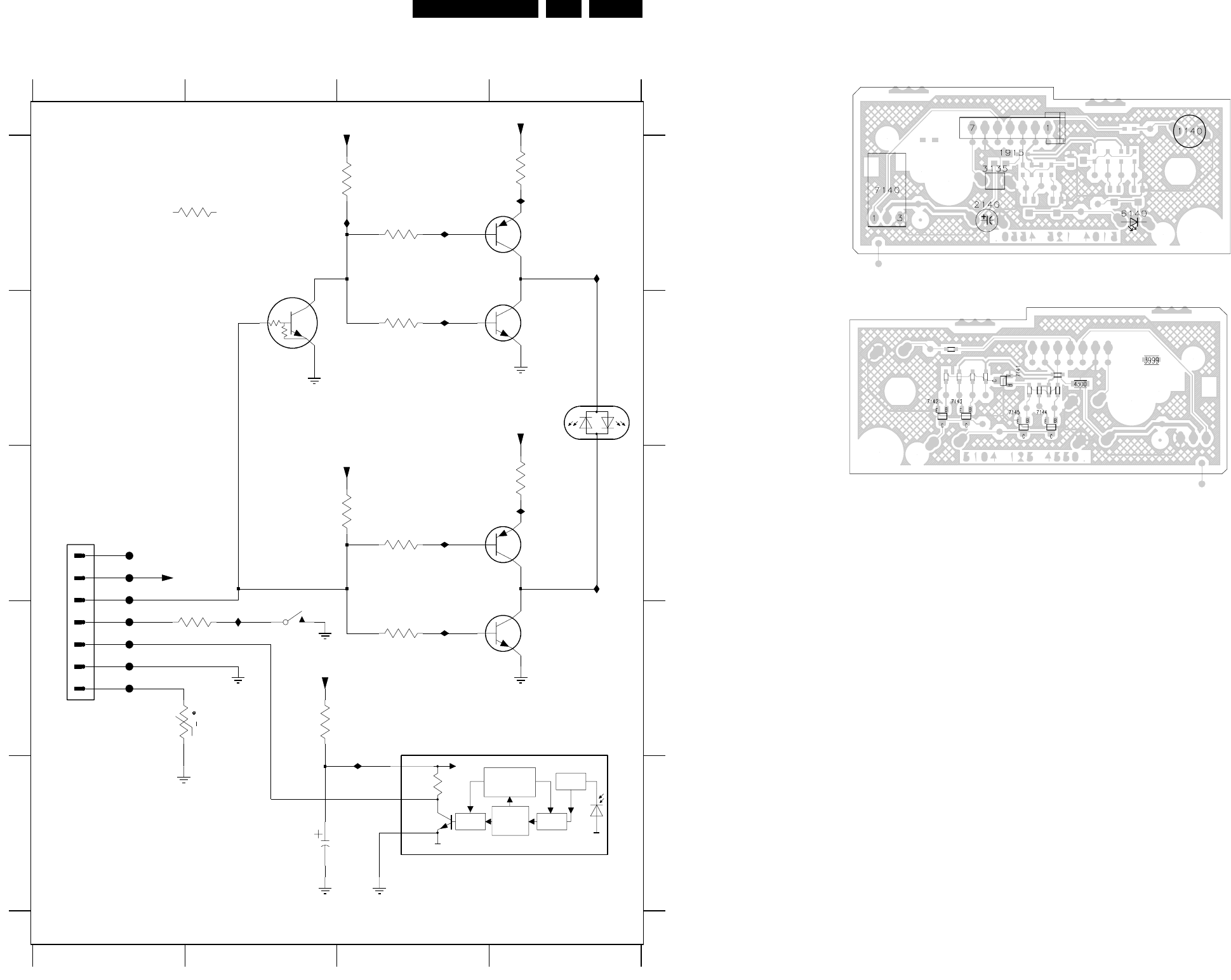

- IR and Standby Panel

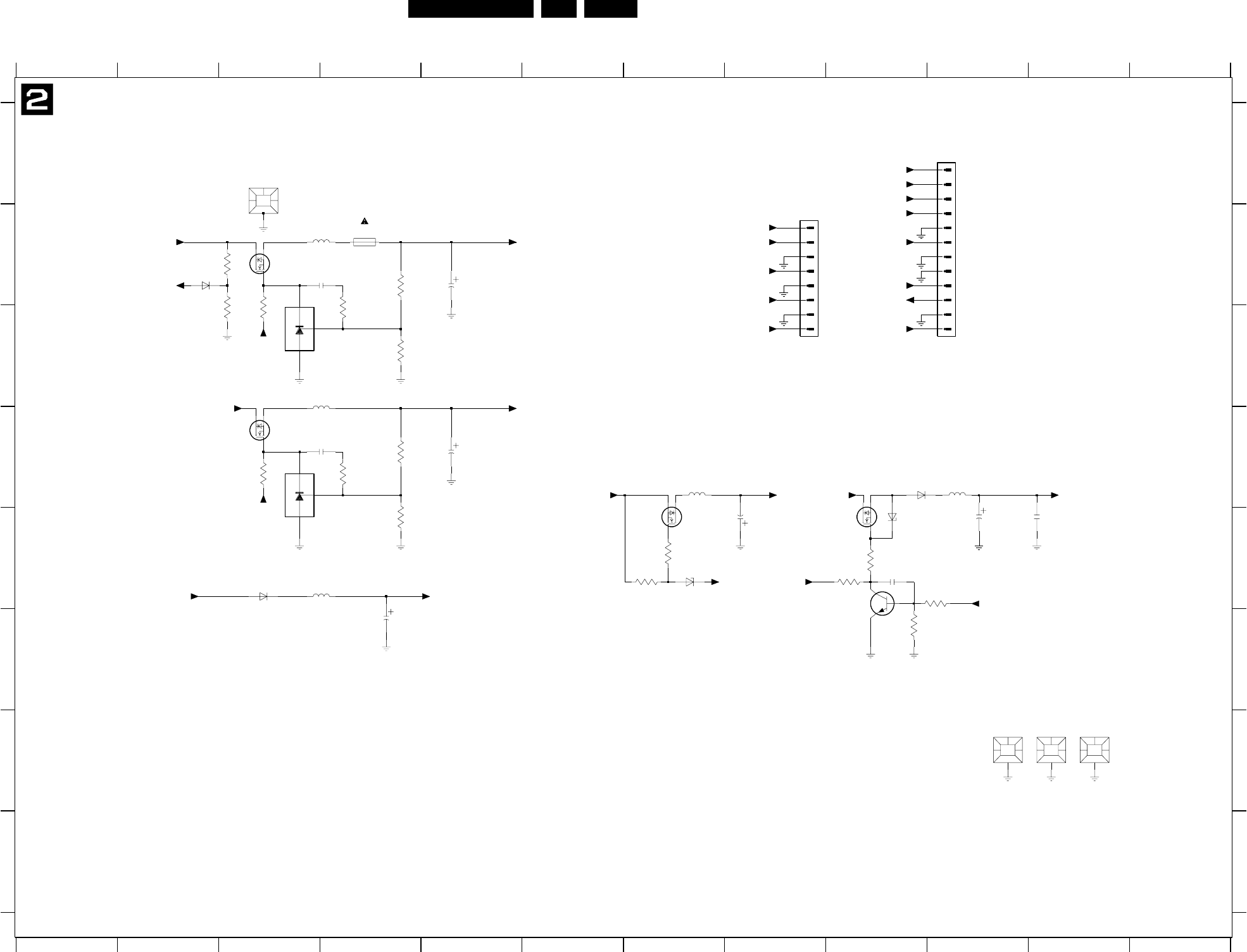

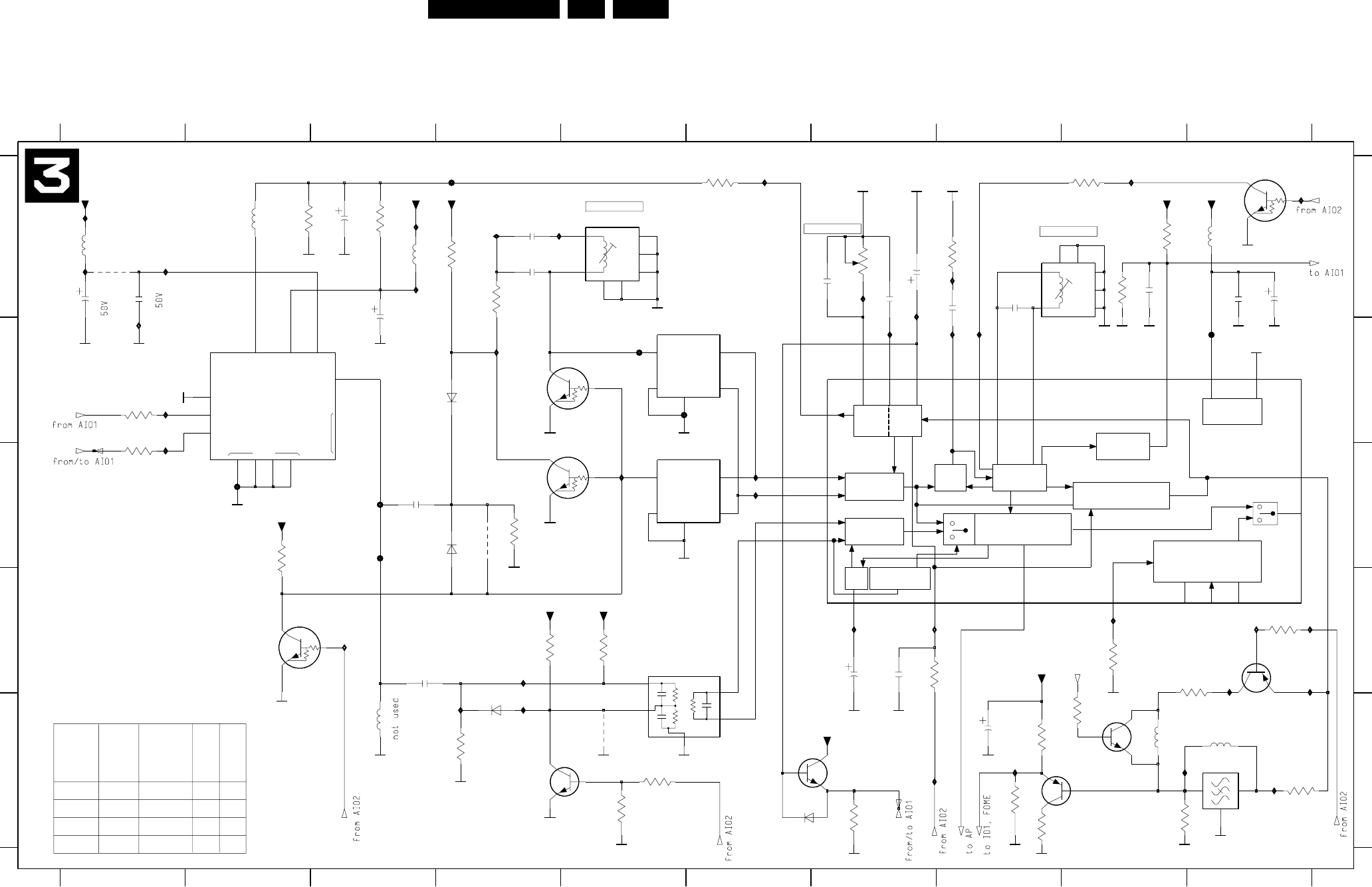

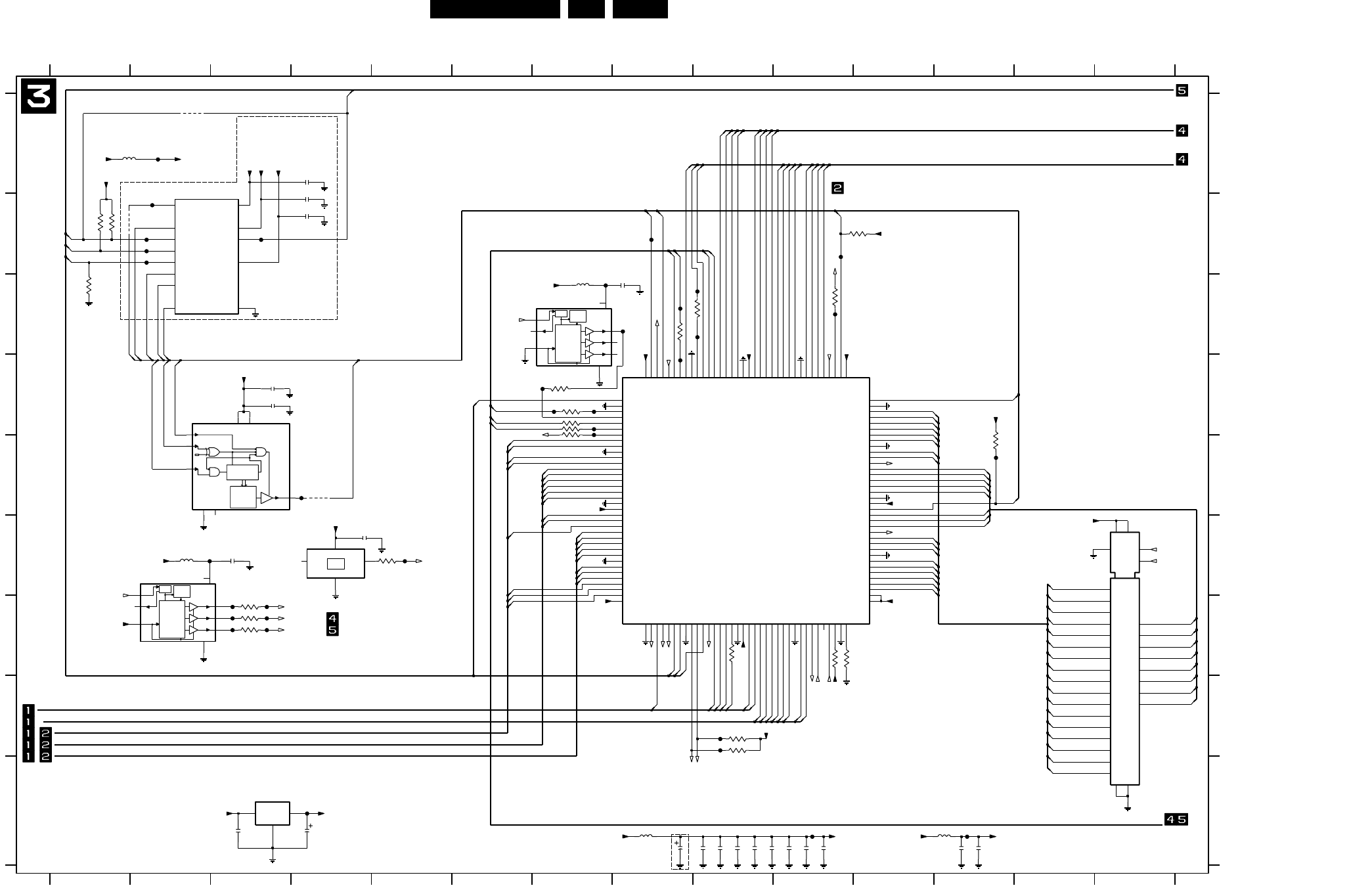

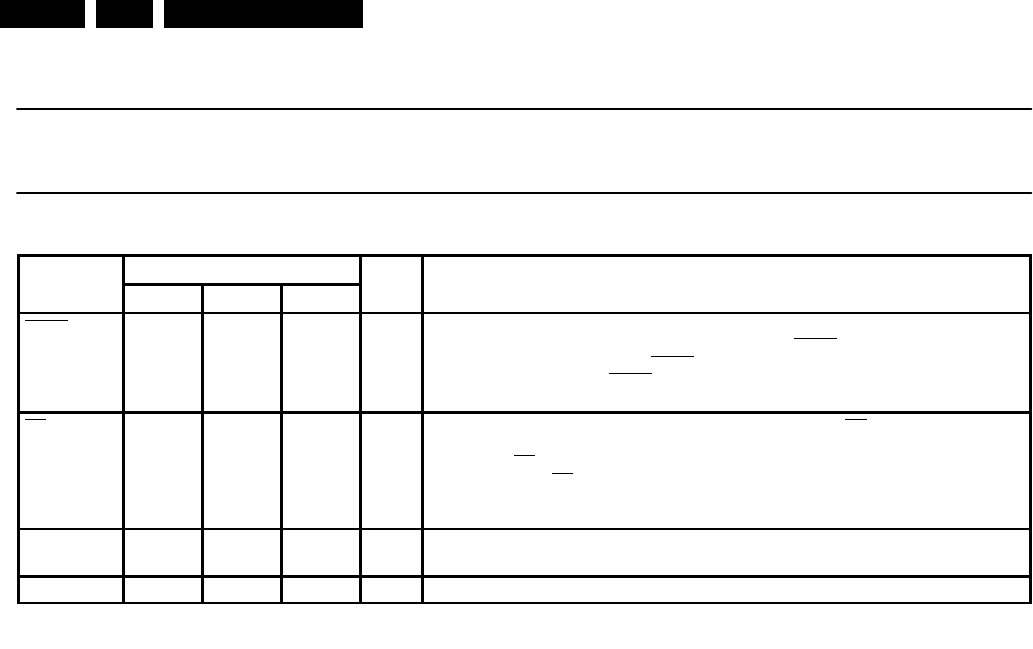

- Analog Board: All in One 1

- Analog Board: All in One 2

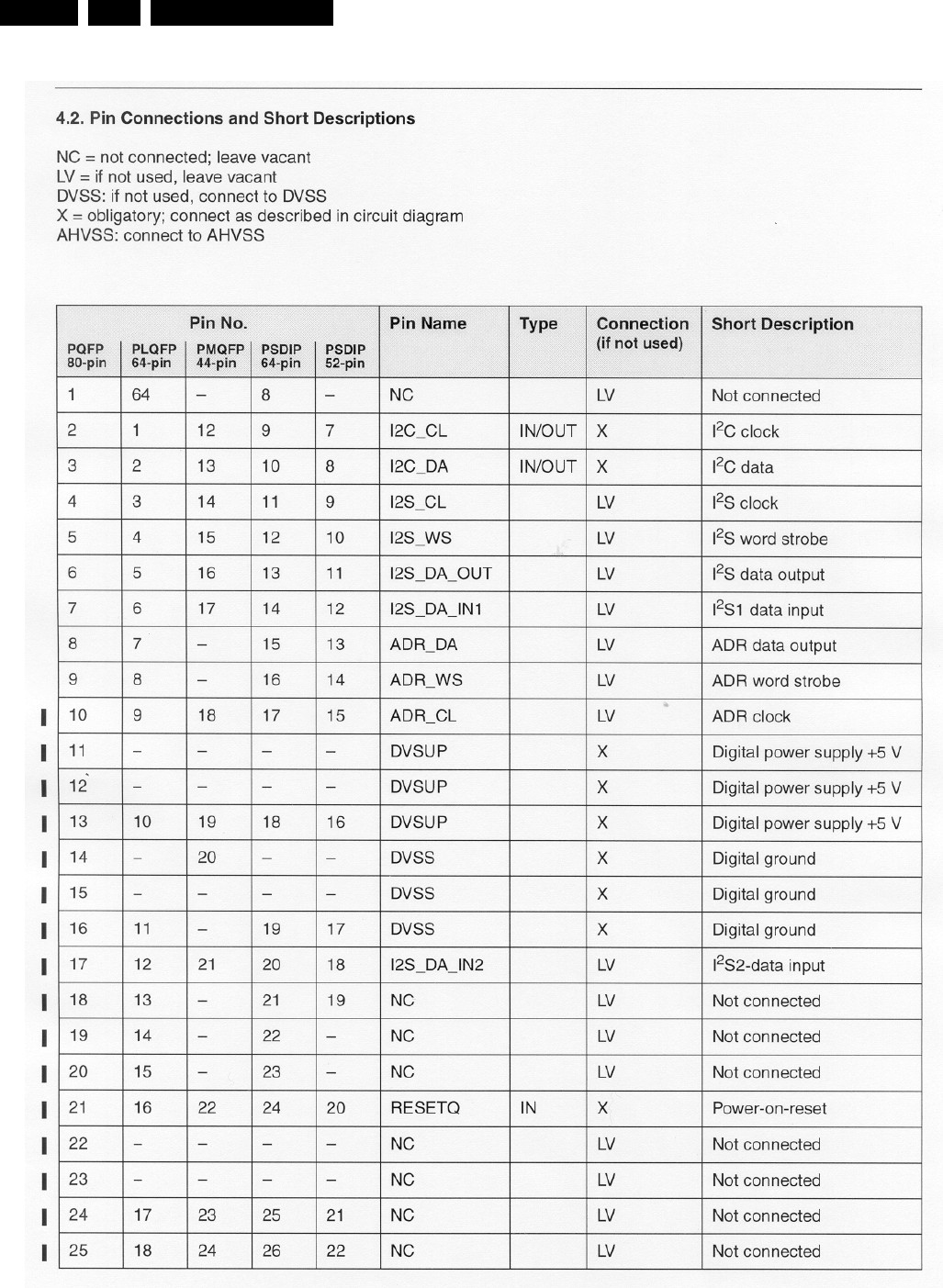

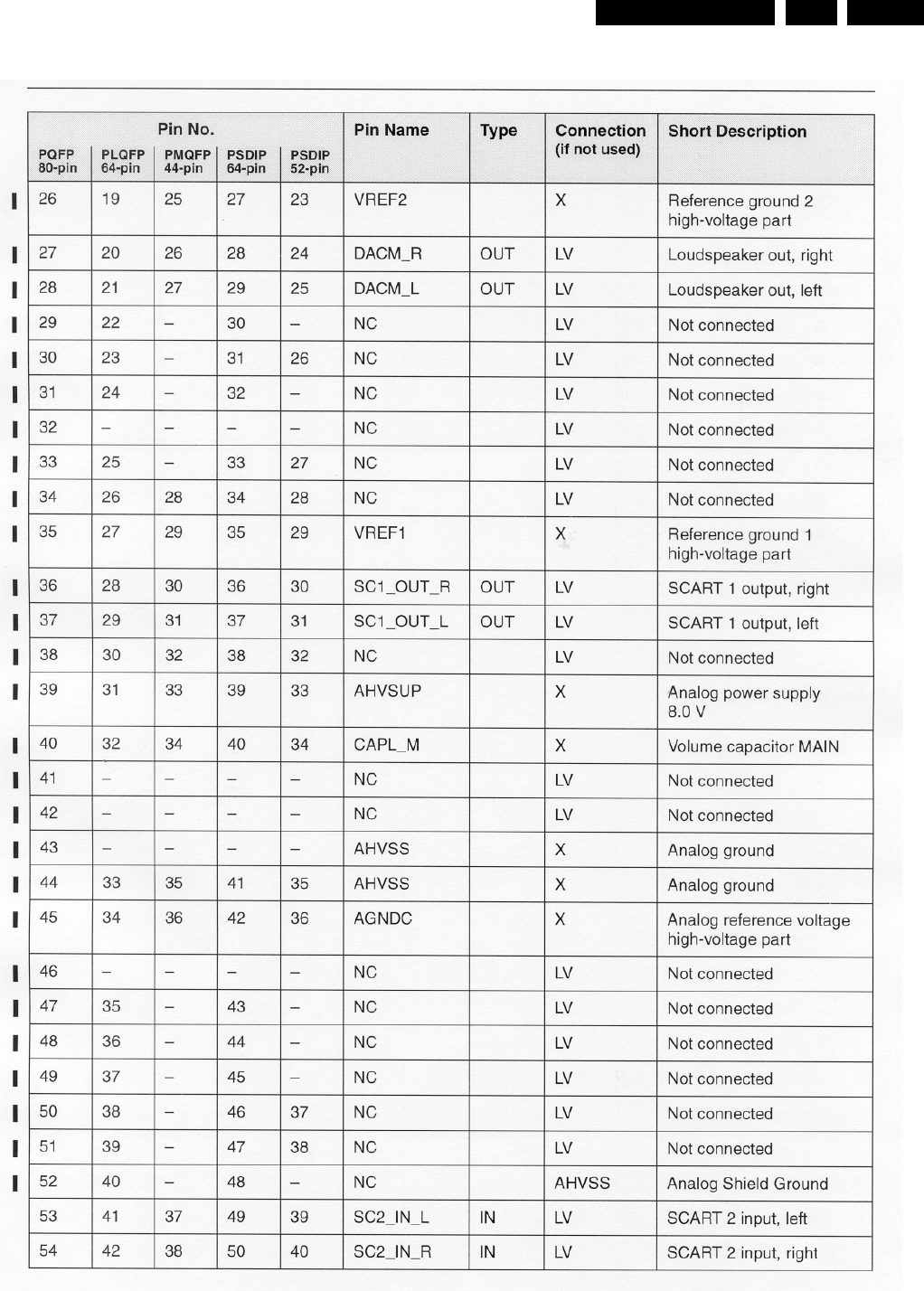

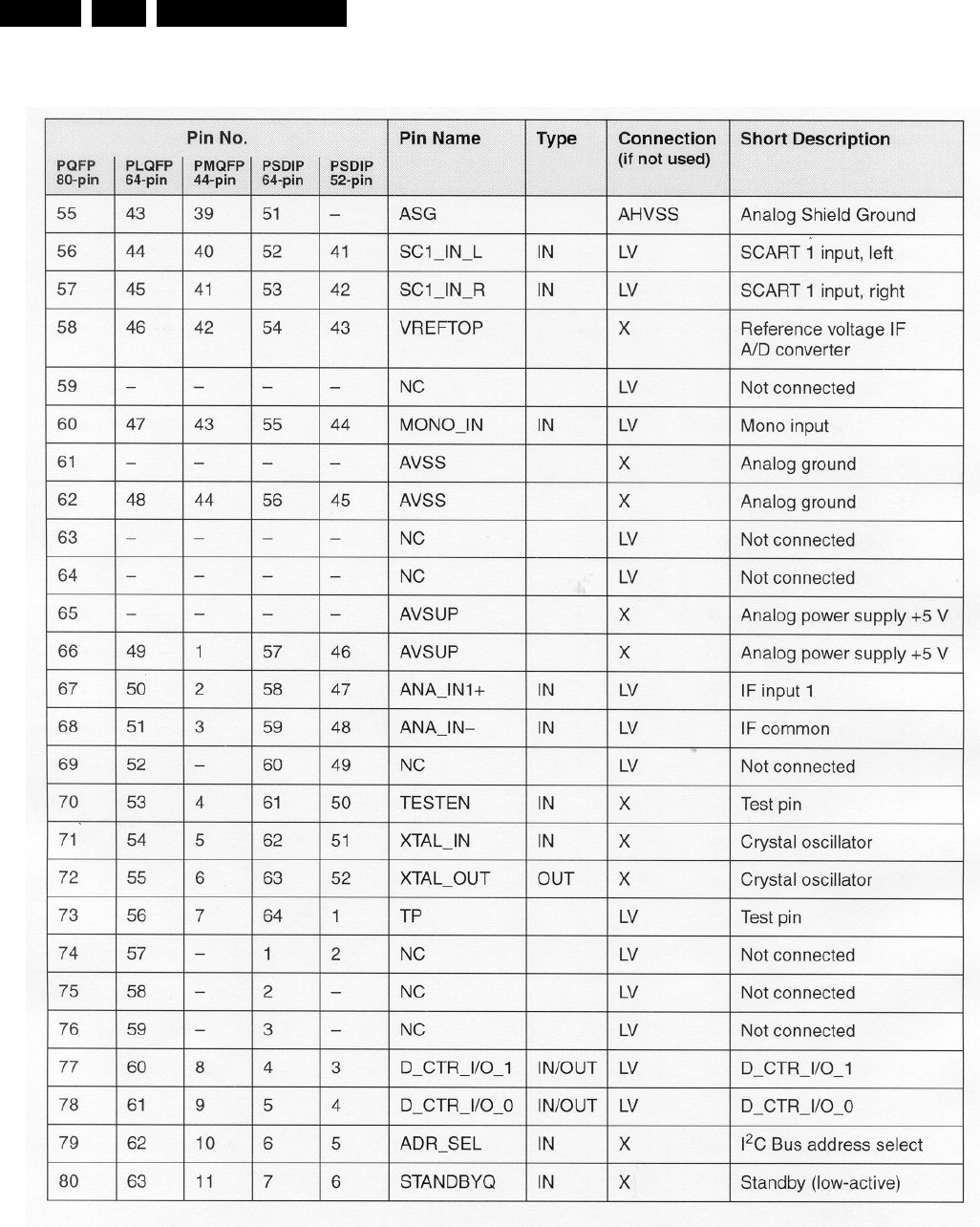

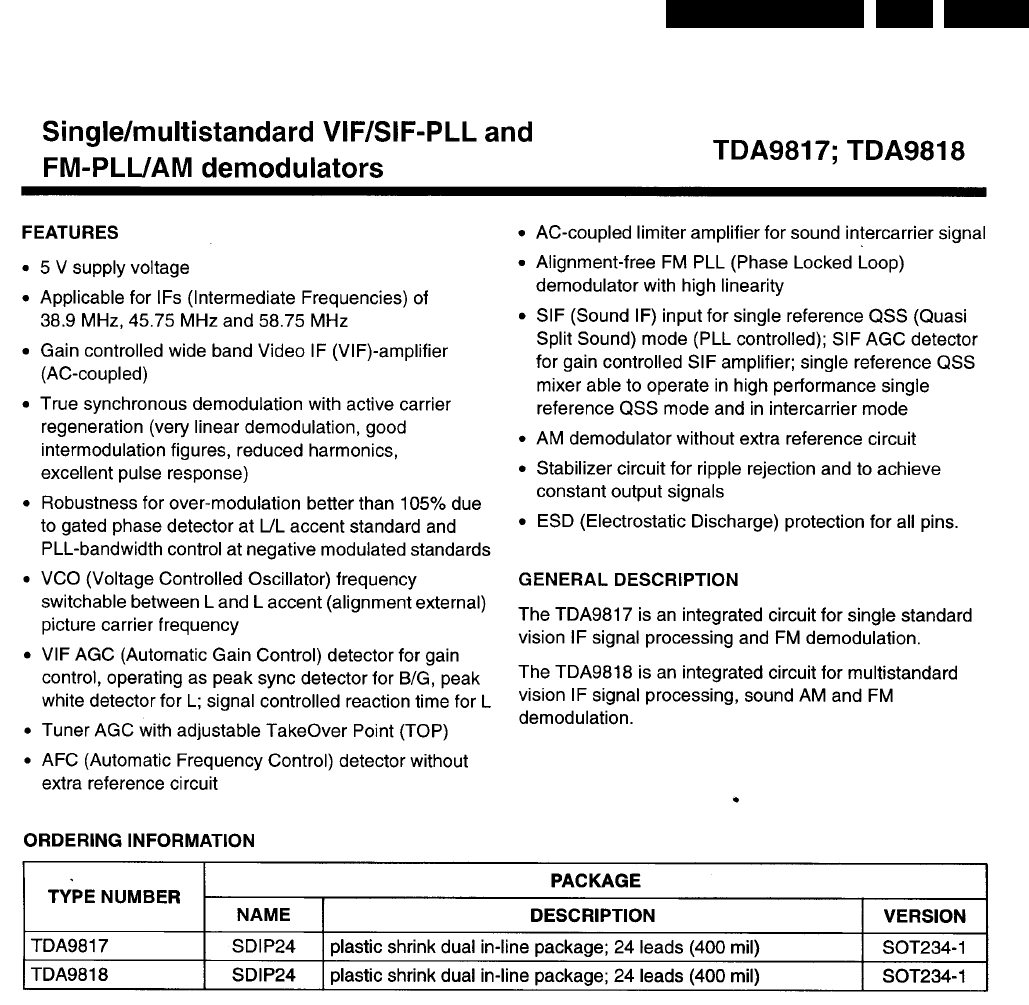

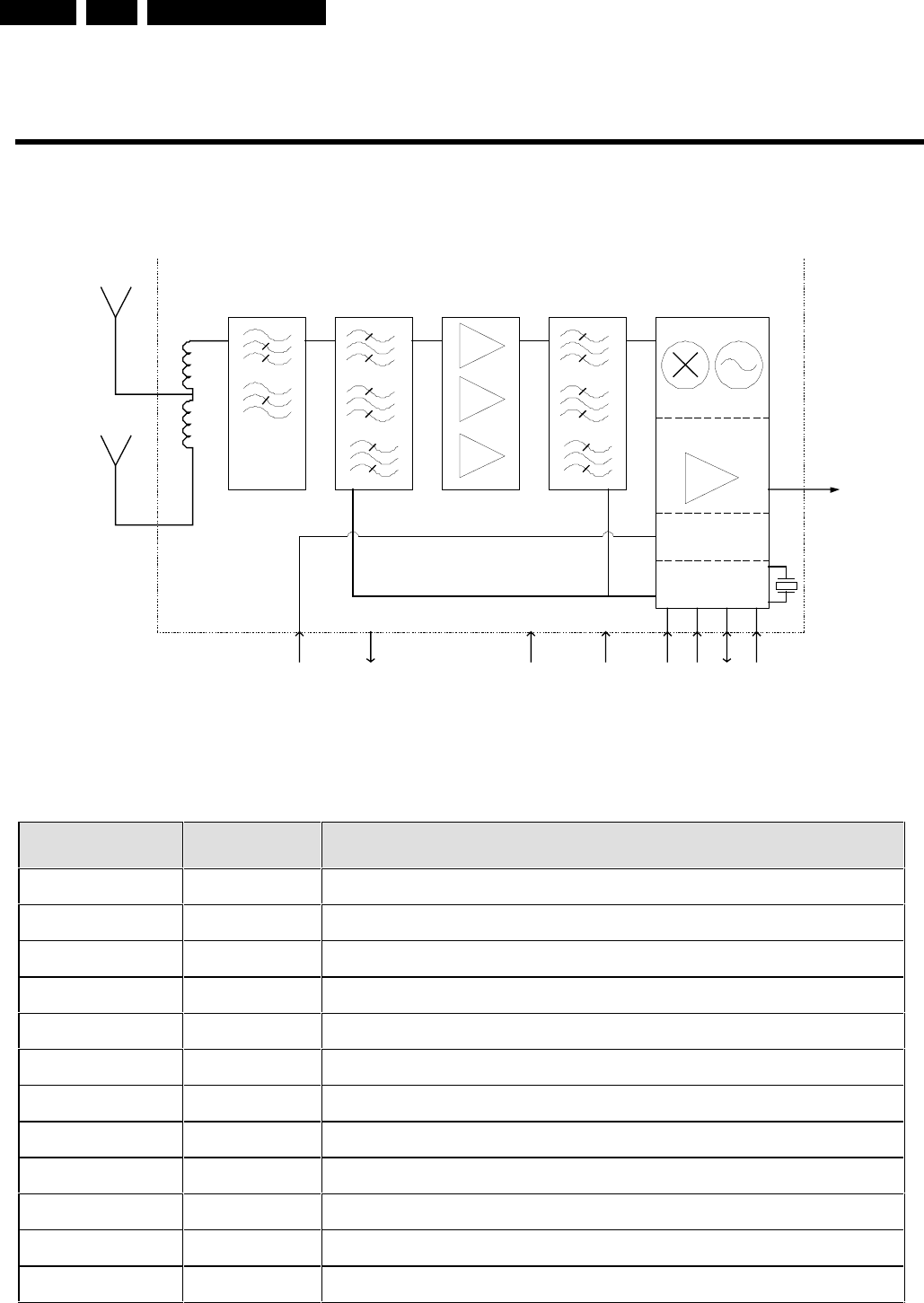

- Analog Board: Tuner / Demodulator

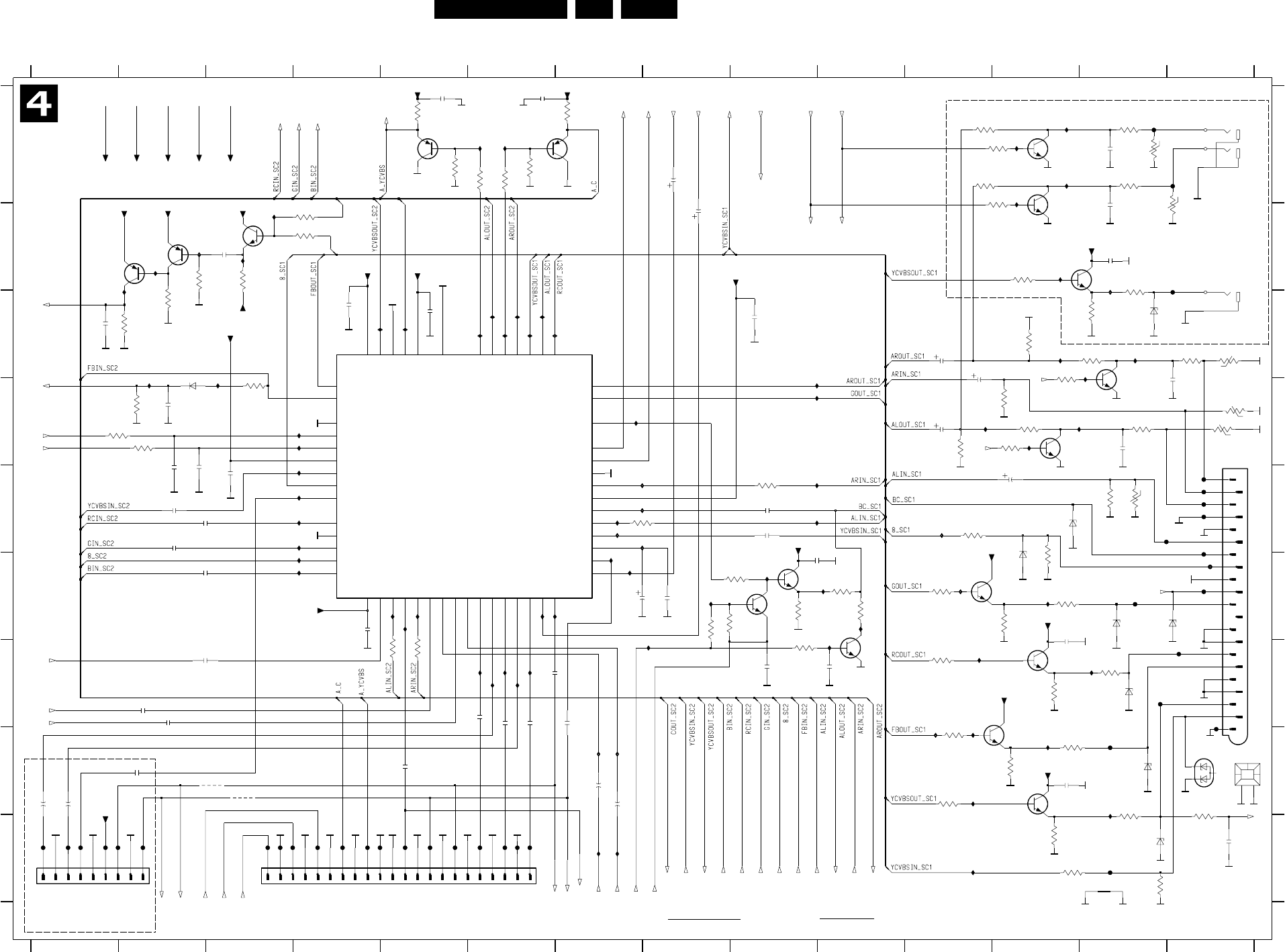

- Analog Board: In / Out 1

- Analog Board: In / Out 2

- Analog Board: In / Out 3

- Analog Board: In / Out 4

- Analog Board: Sound Processing

- Analog Board: Follow Me

- Analog Board: VPS

- Analog Board: Power Supply

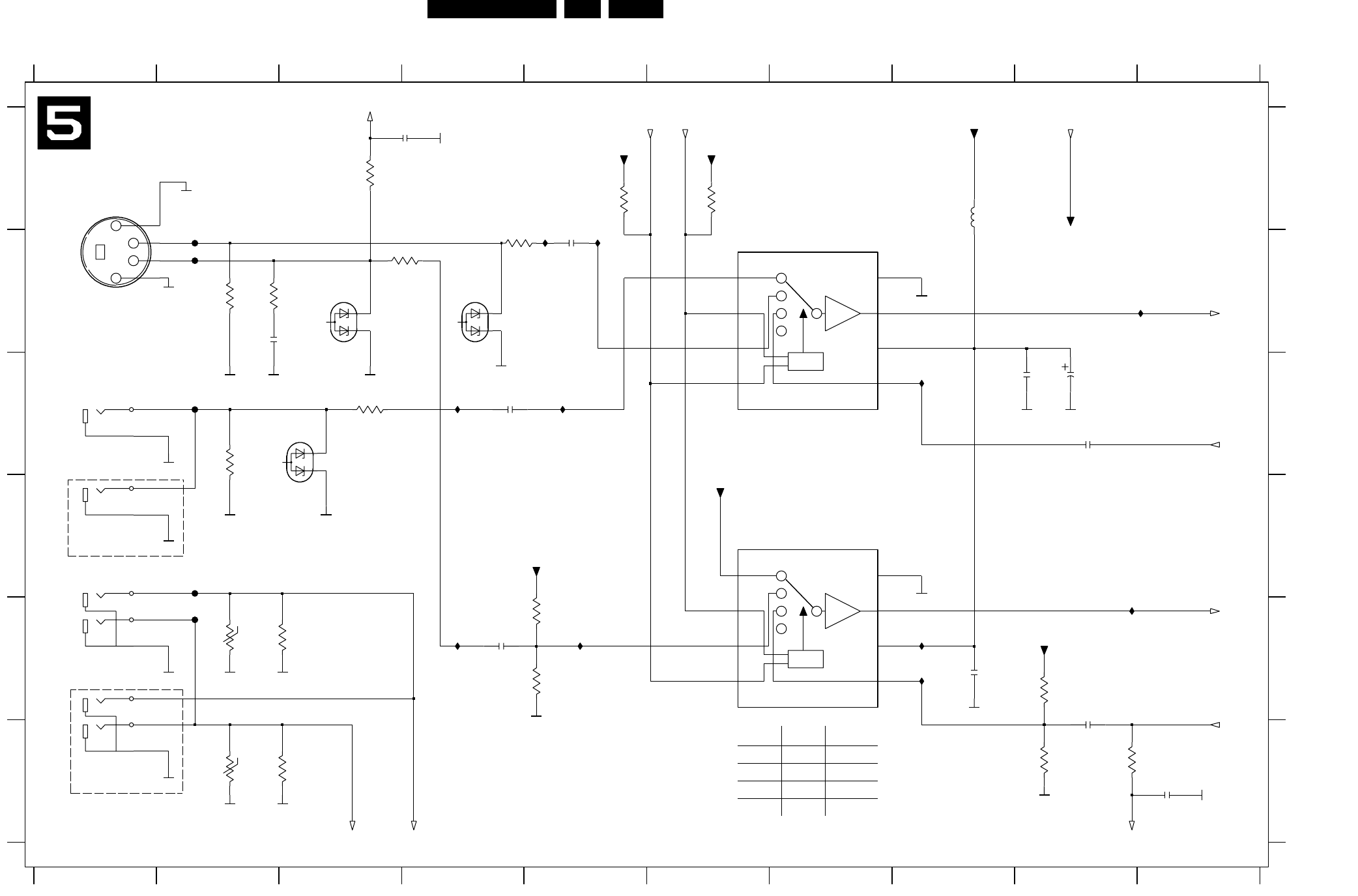

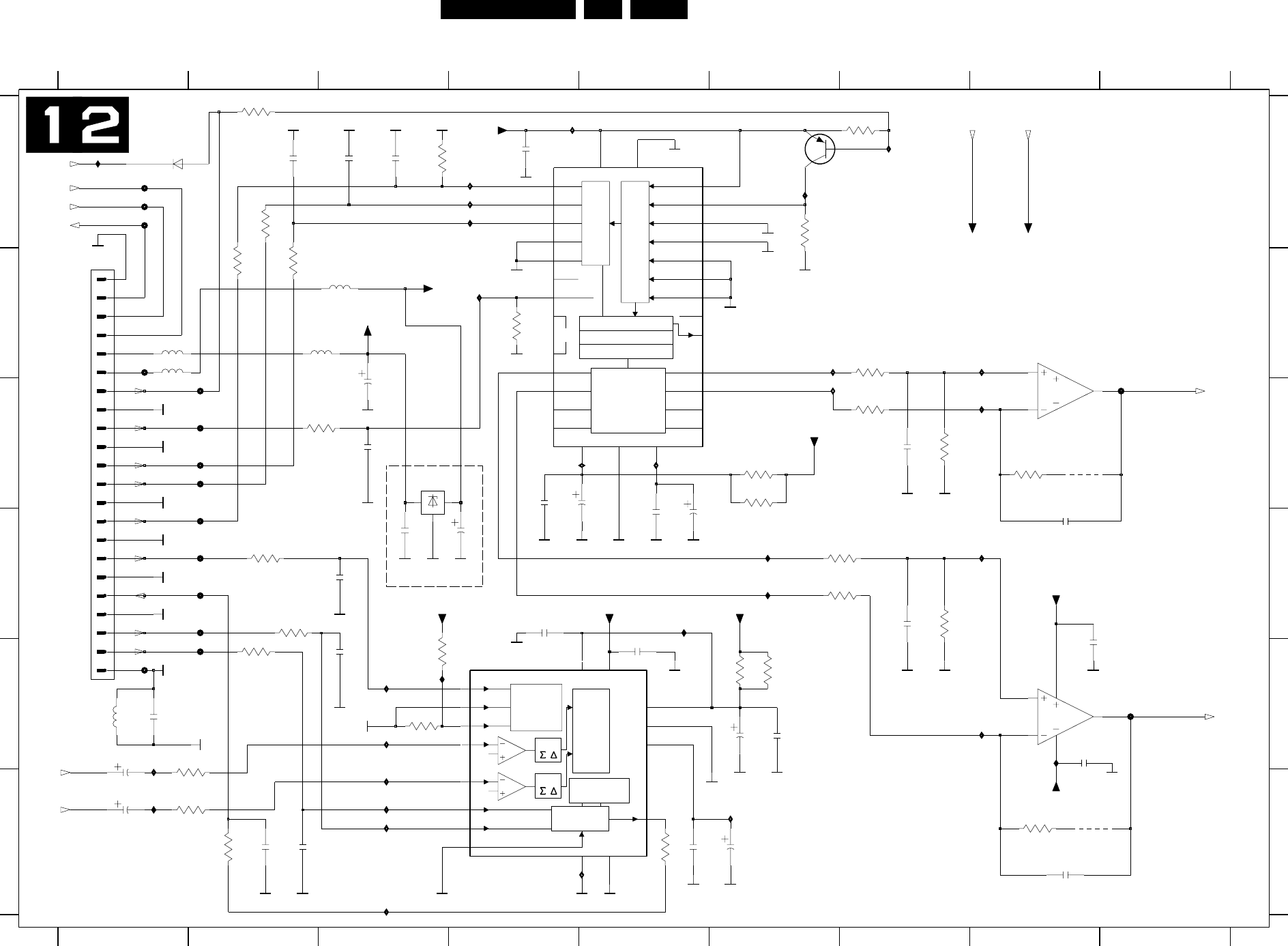

- Analog Board: Audio Converter

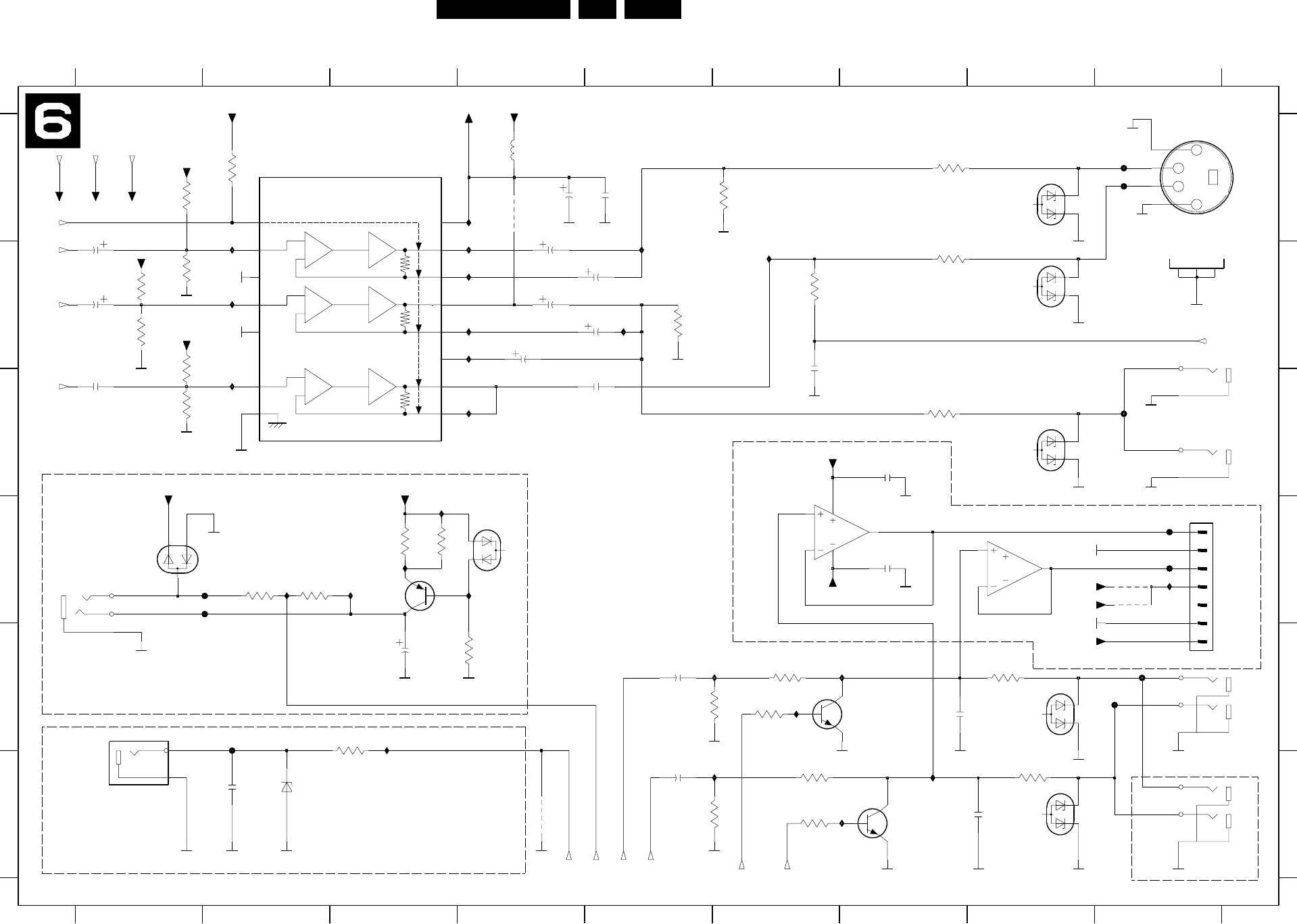

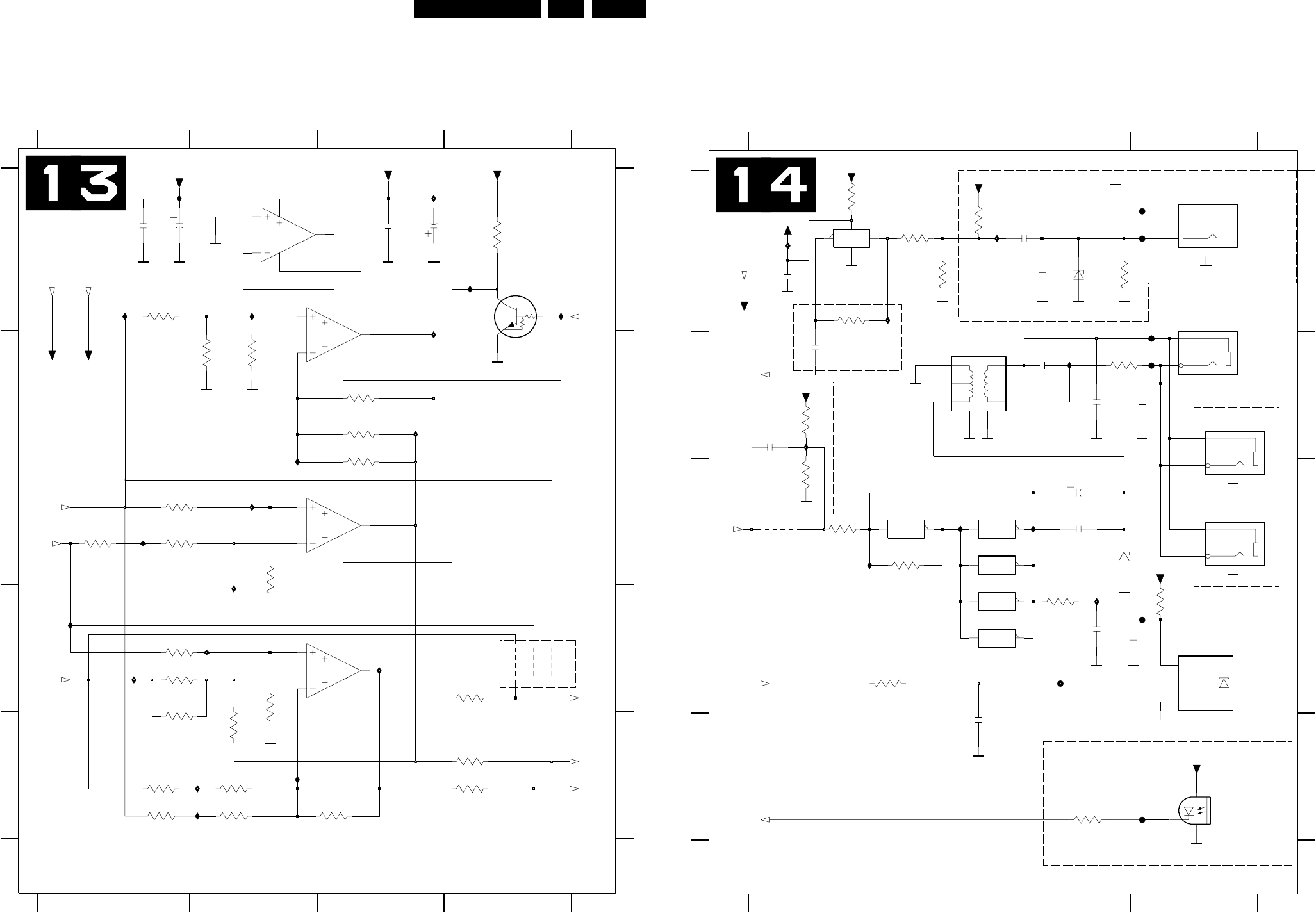

- Analog Board: RGB-YUV-Converter

- Analog Board: Digital In / Out

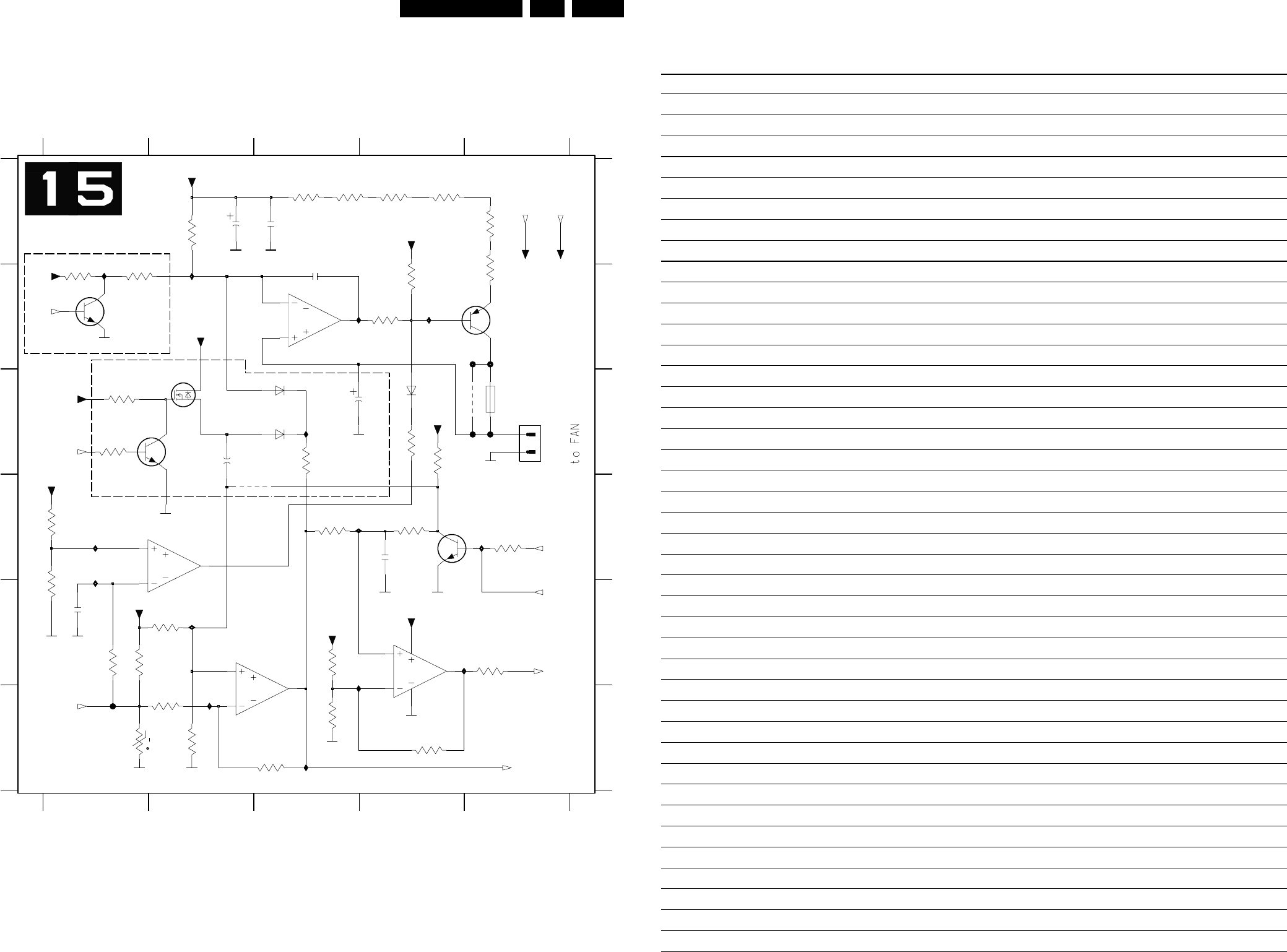

- Analog Board: Fan Control

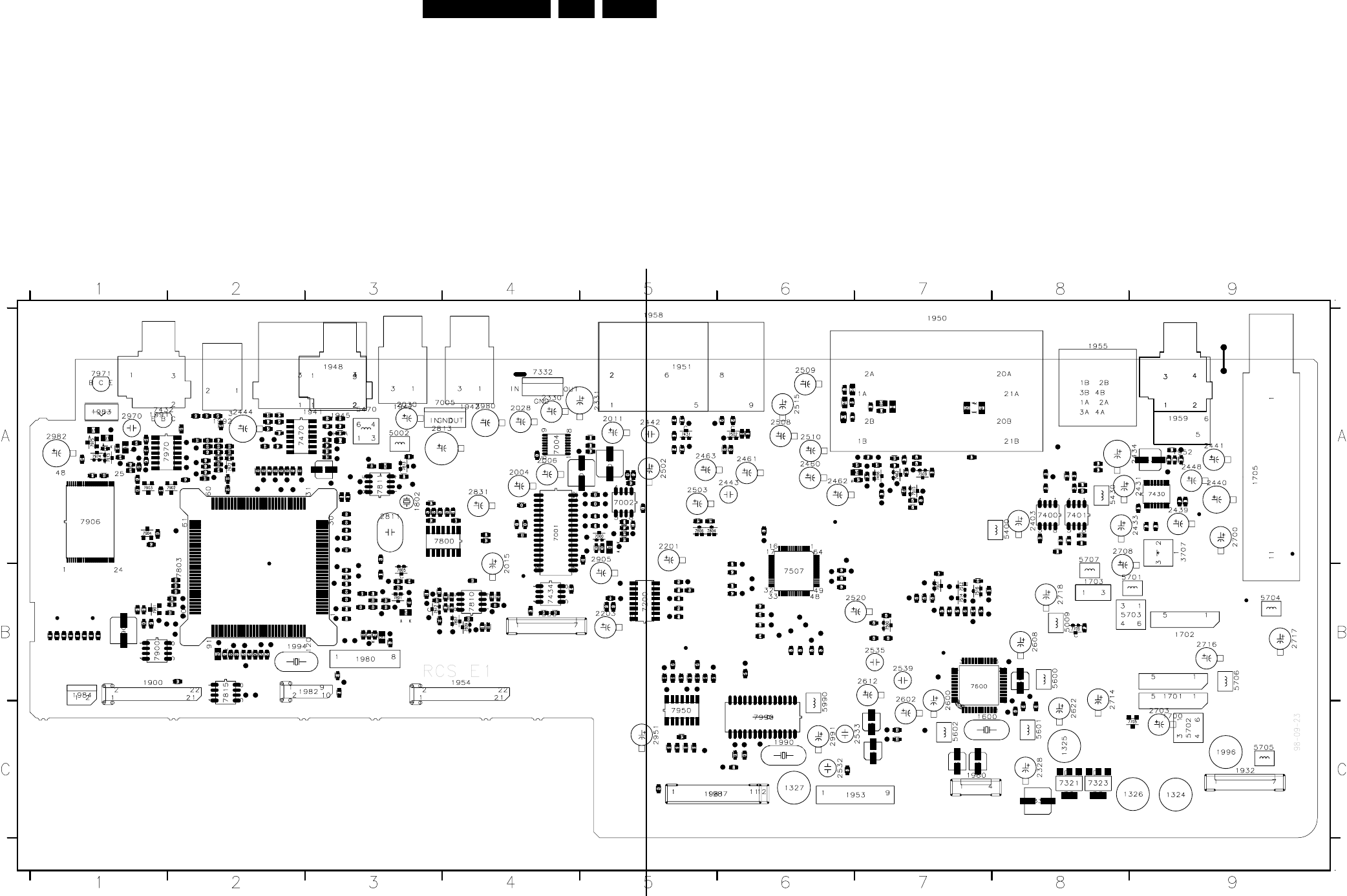

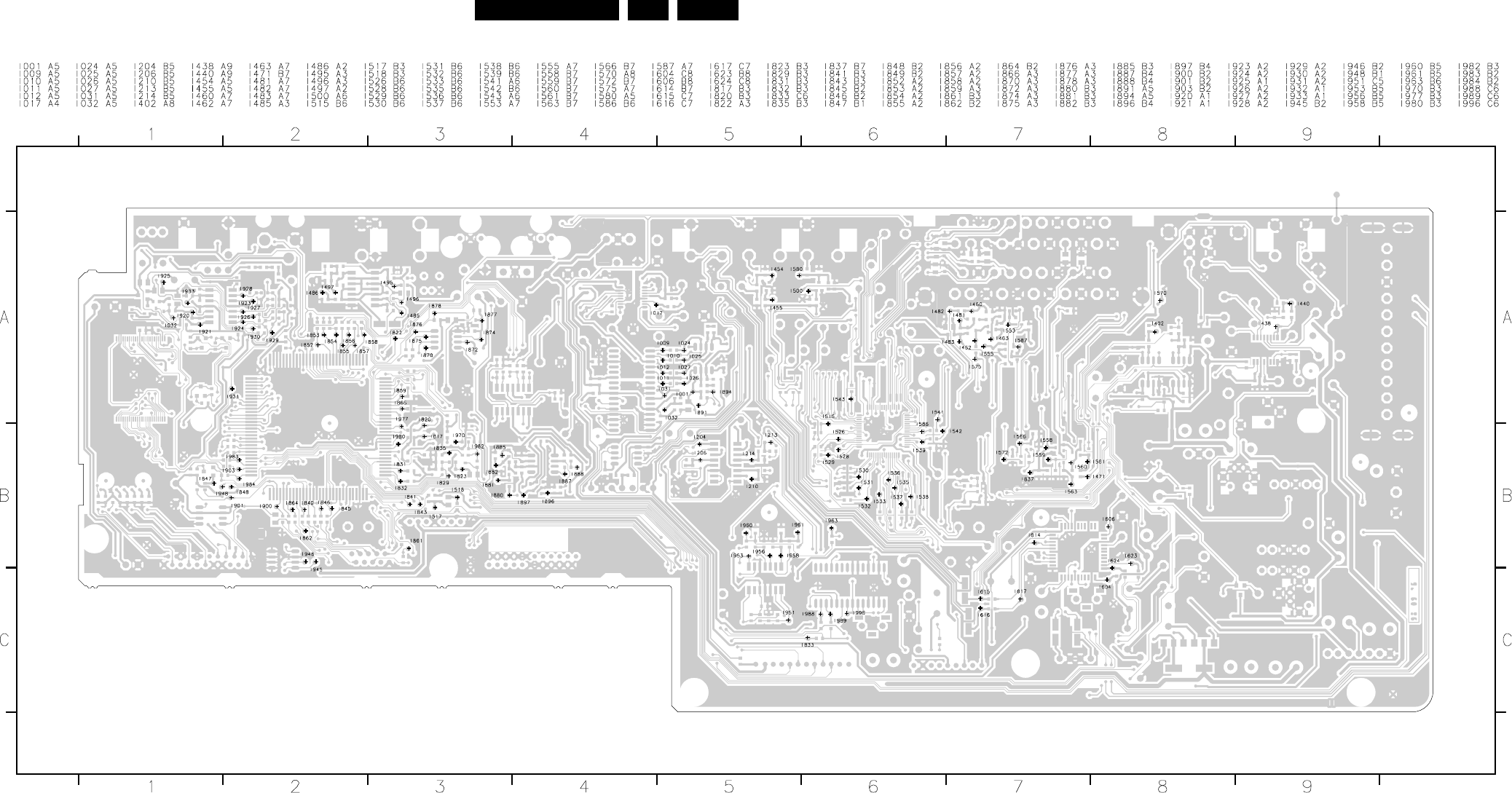

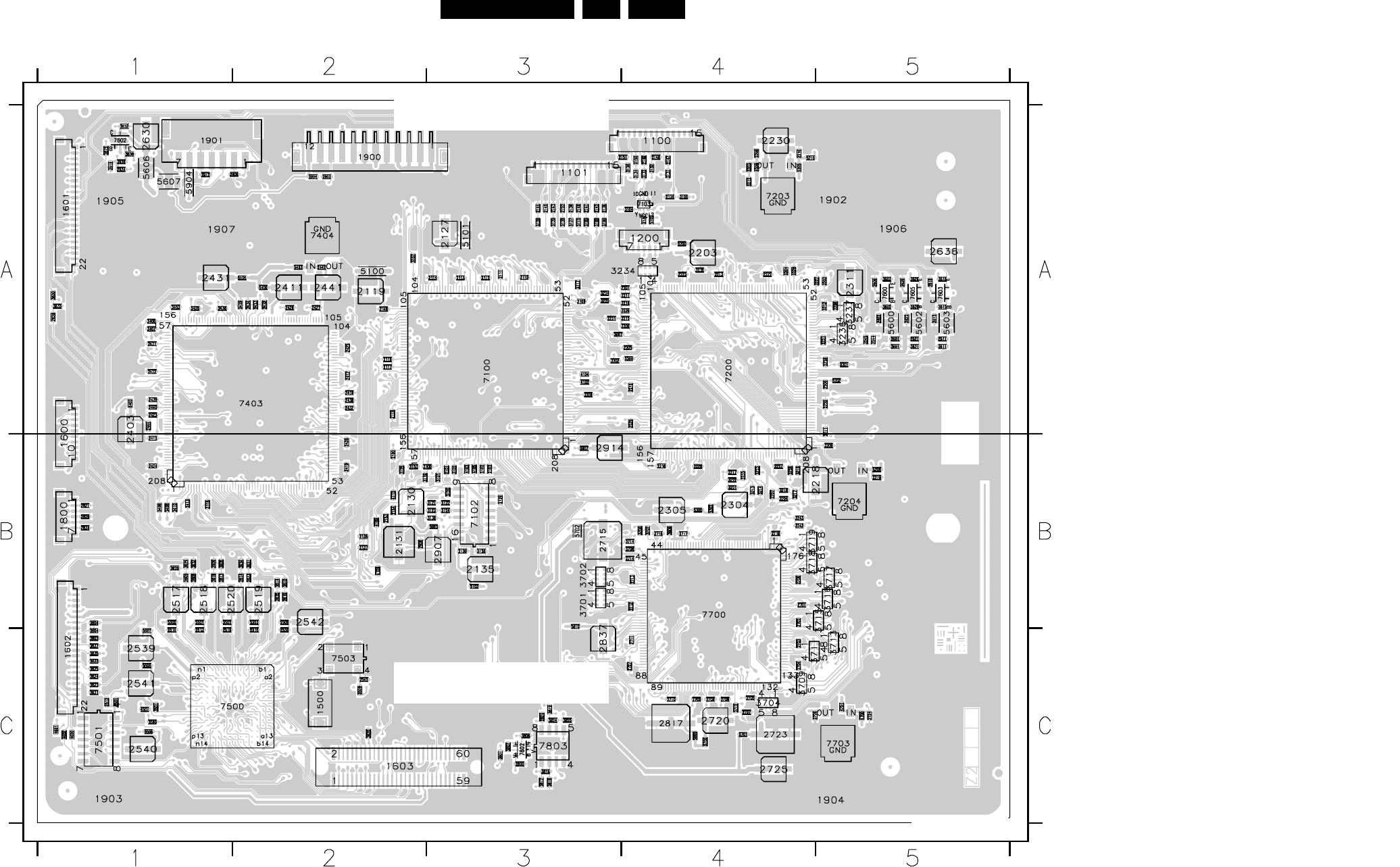

- Layout Analog Board (Overview Top View)

- Layout Analog Board (Part 1 Top View)

- Layout Analog Board (Part 2 Top View)

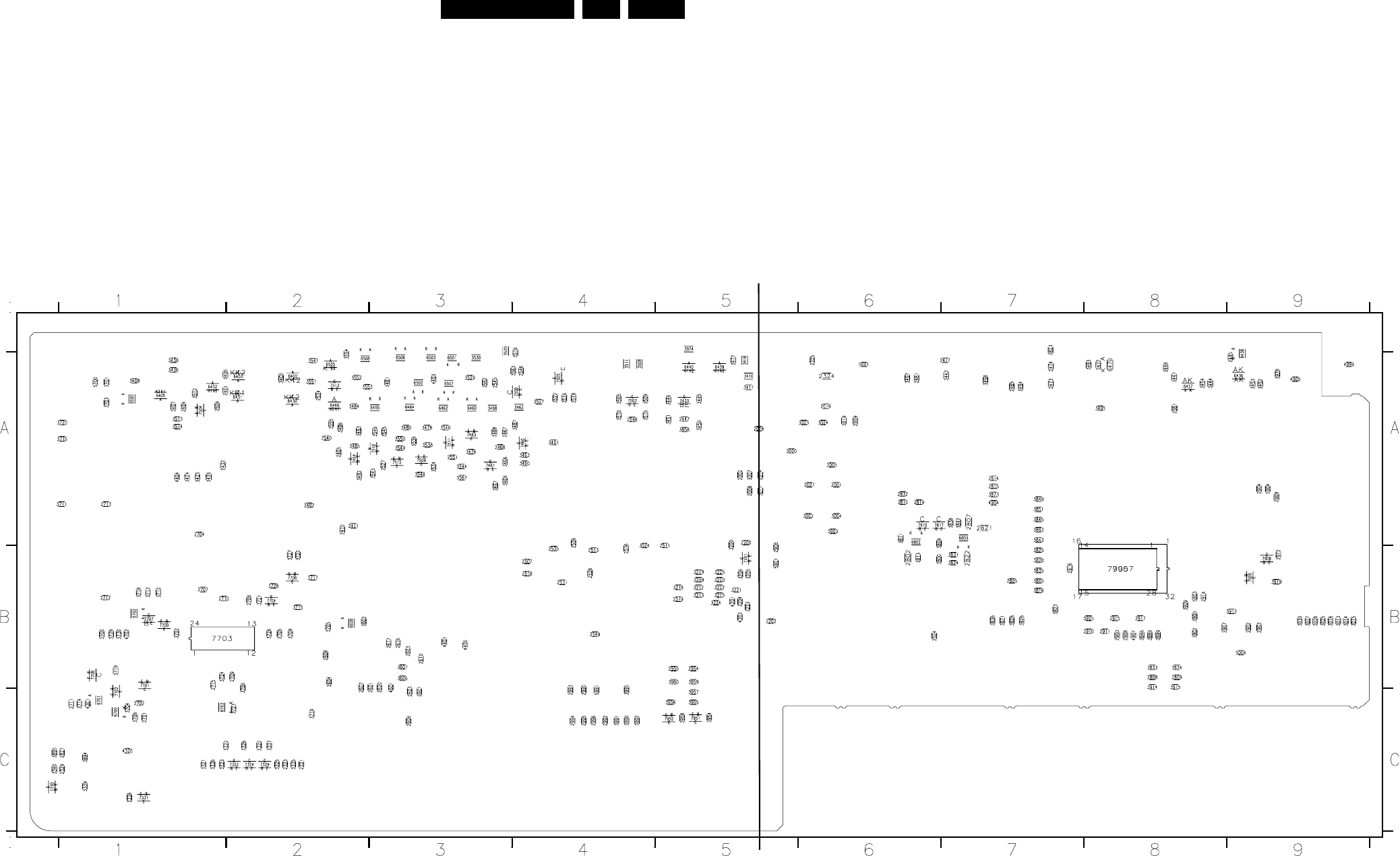

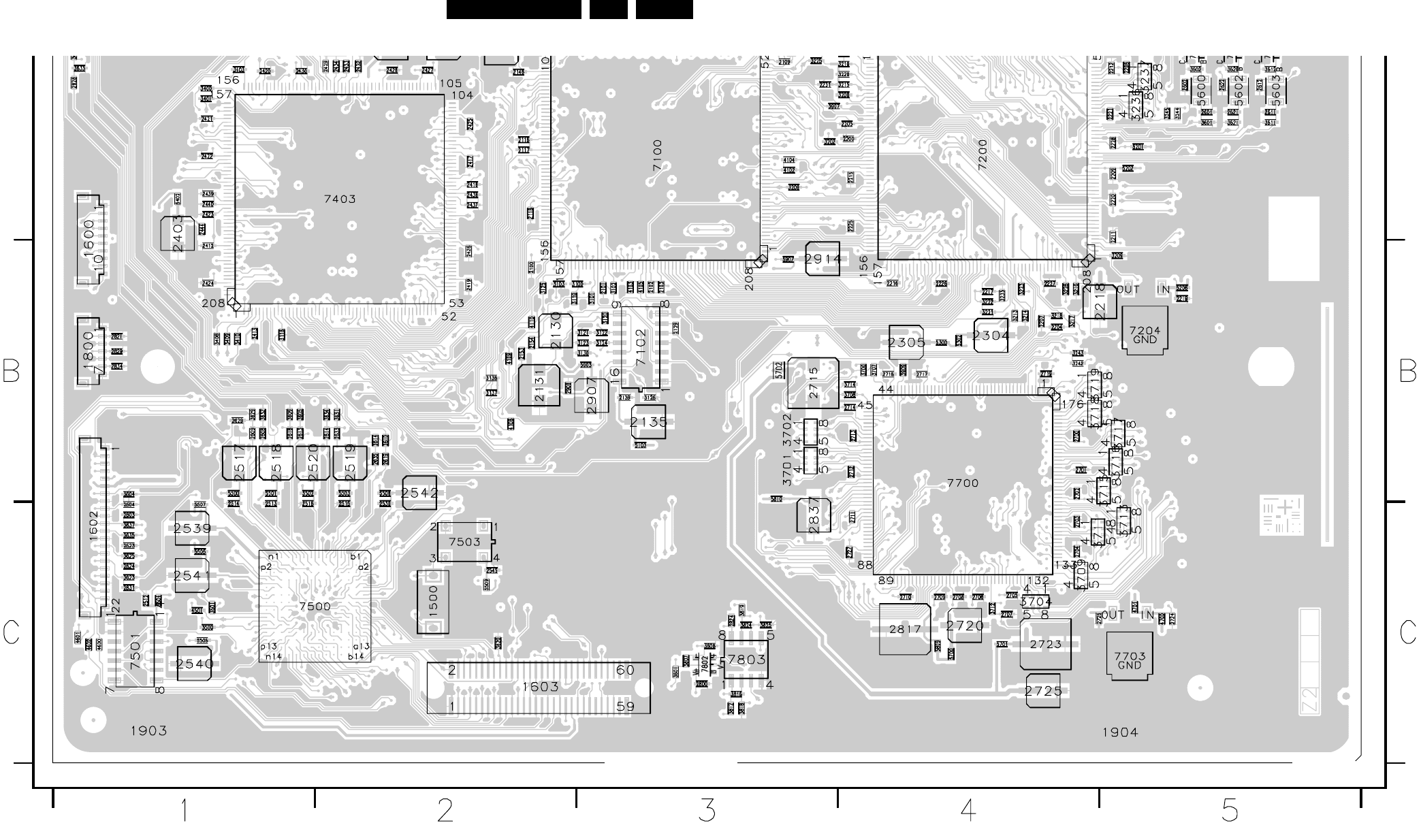

- Layout Analog Board (Overview Bottom View)

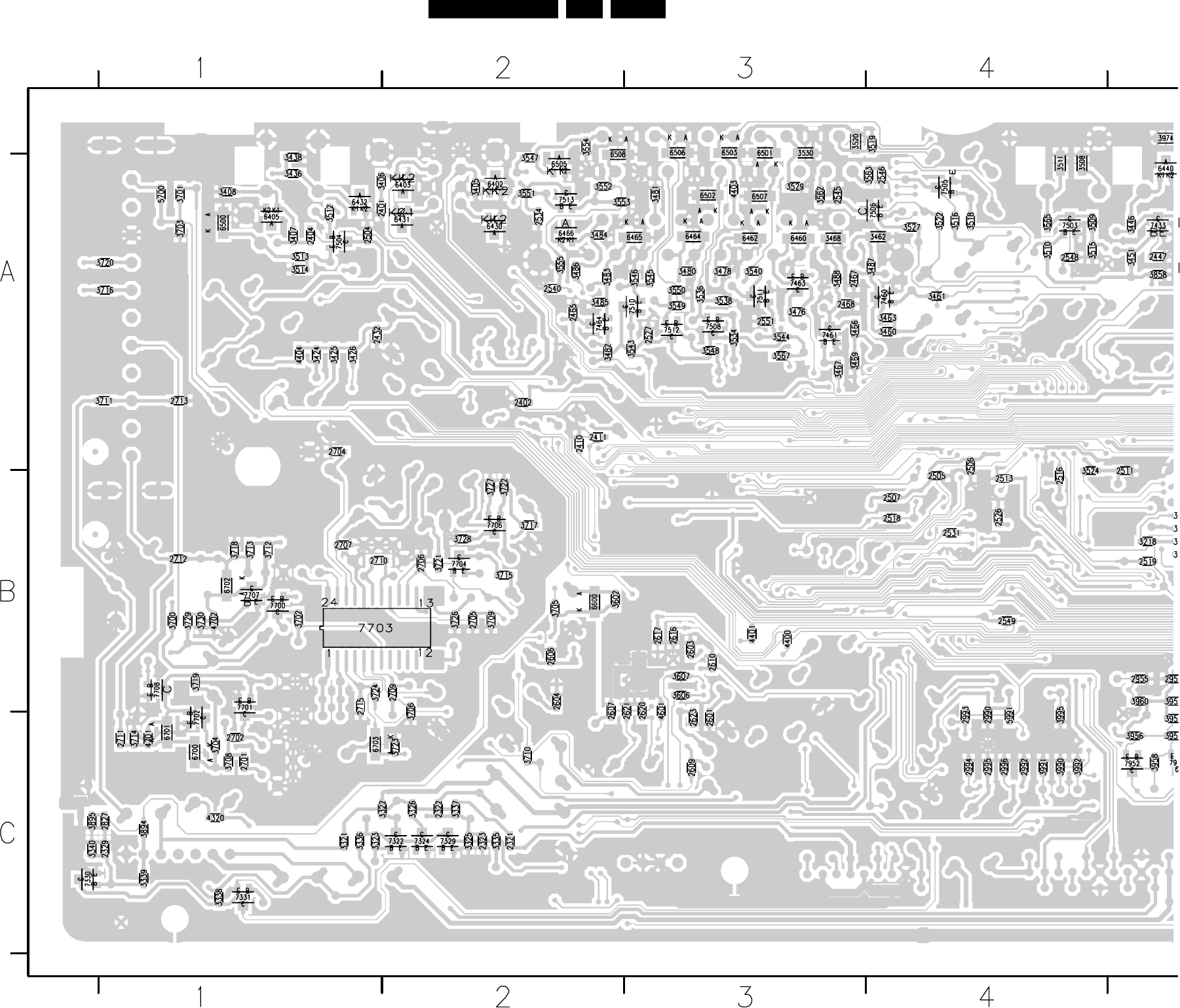

- Layout Analog Board (Part 1 Bottom View)

- Layout Analog Board (Part 2 Bottom View)

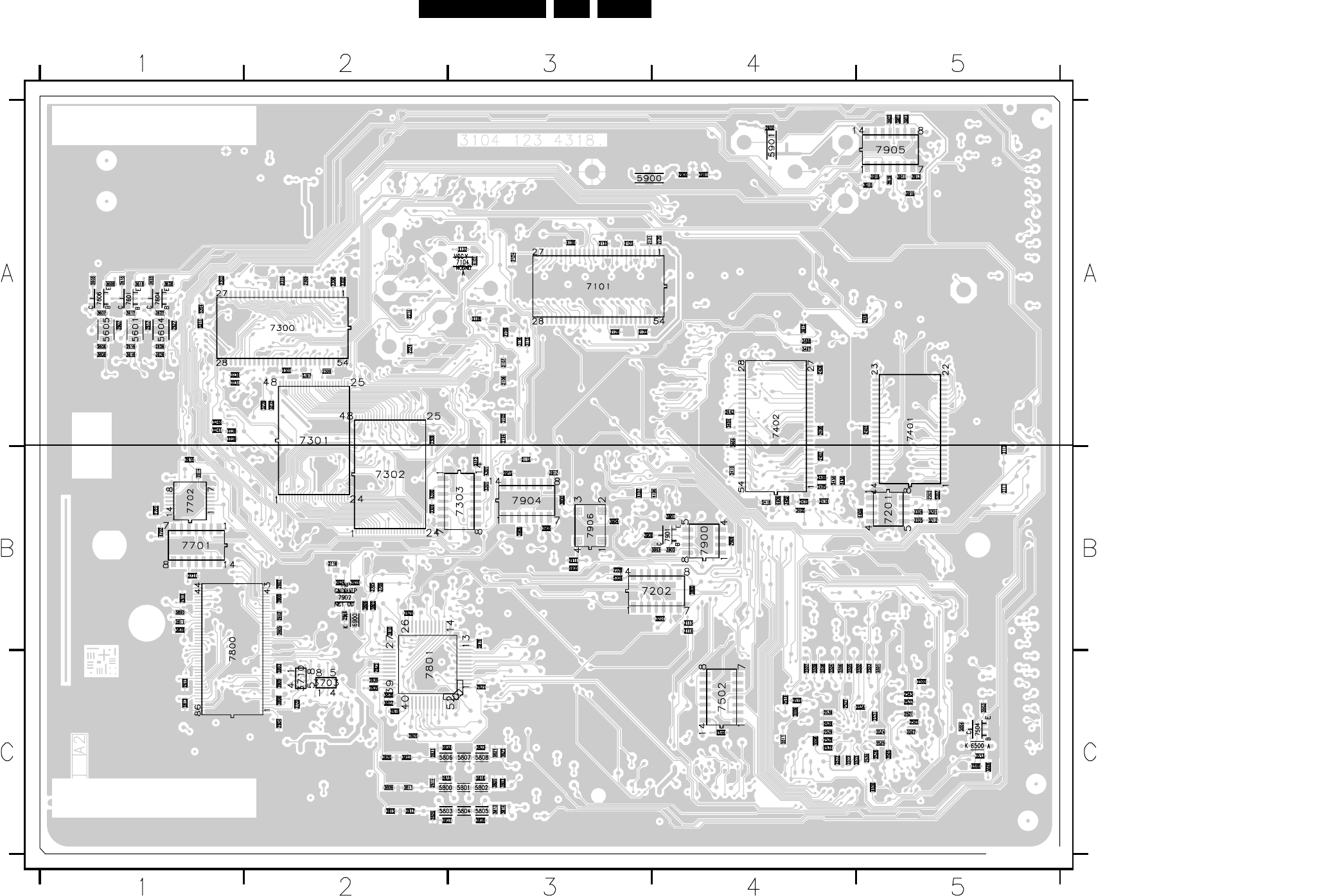

- Layout Analog Board (Testlands Top View)

- Layout Analog Board (Testlands Bottom View)

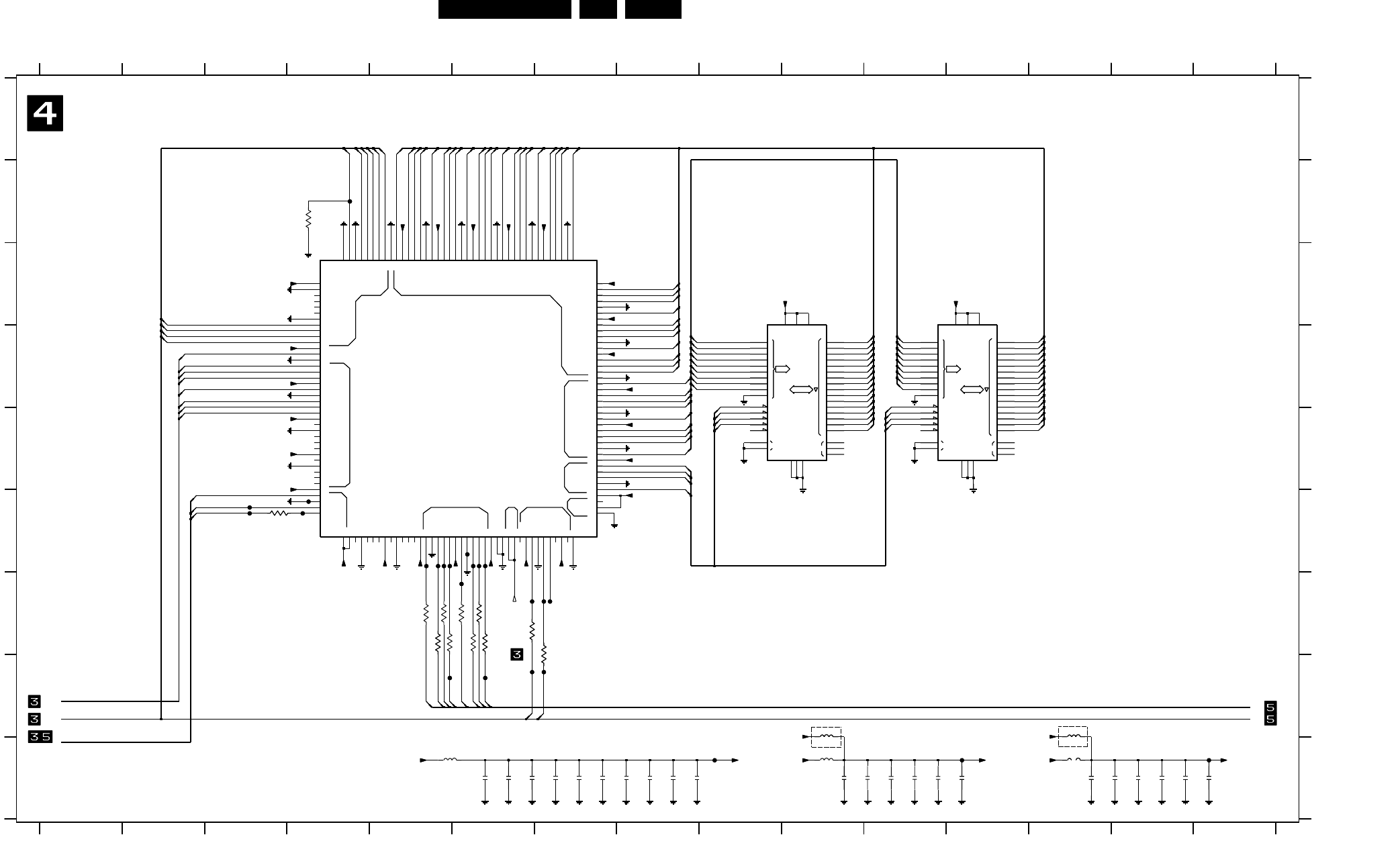

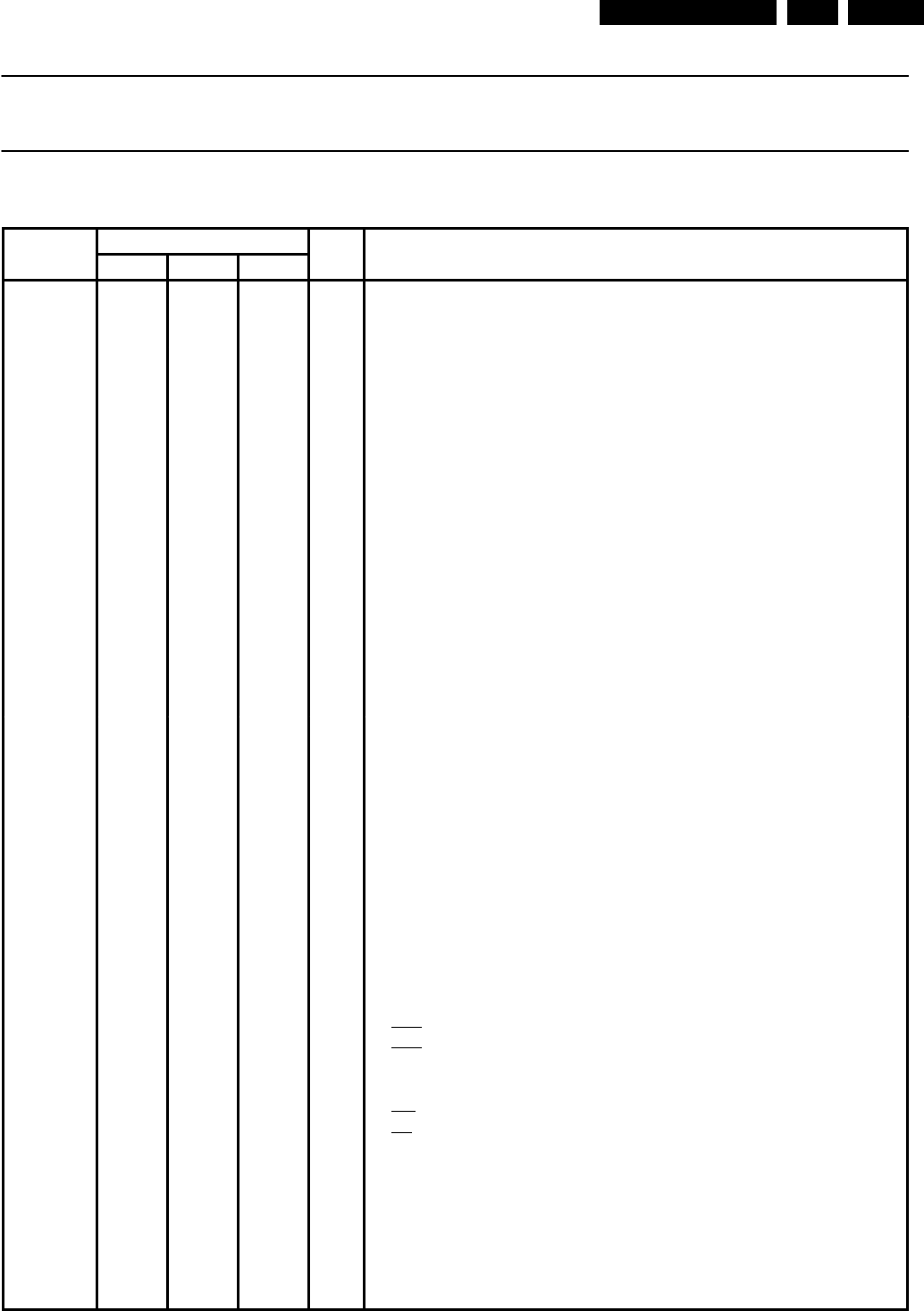

- DVIO Front Board

- Layout DVIO Front Board

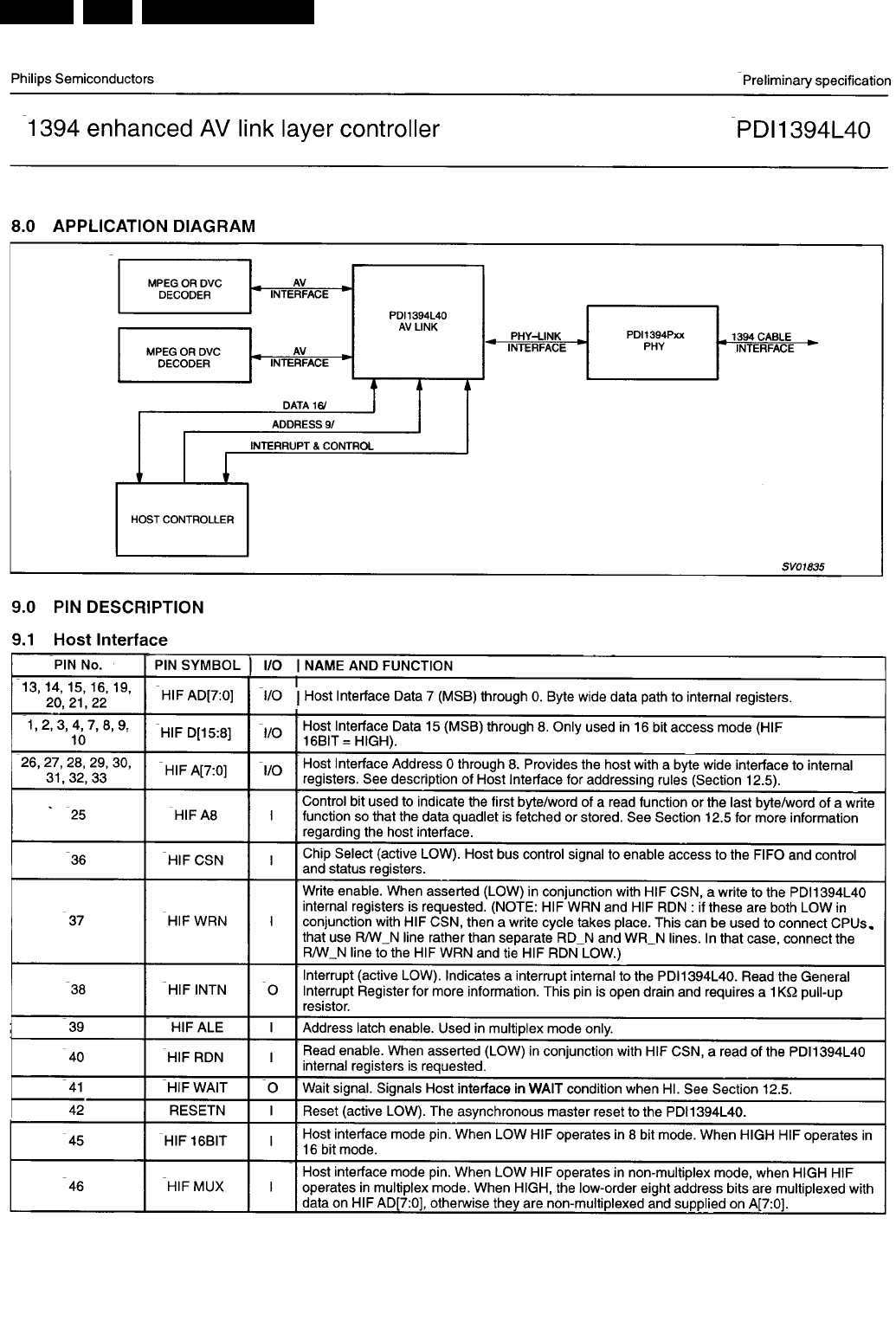

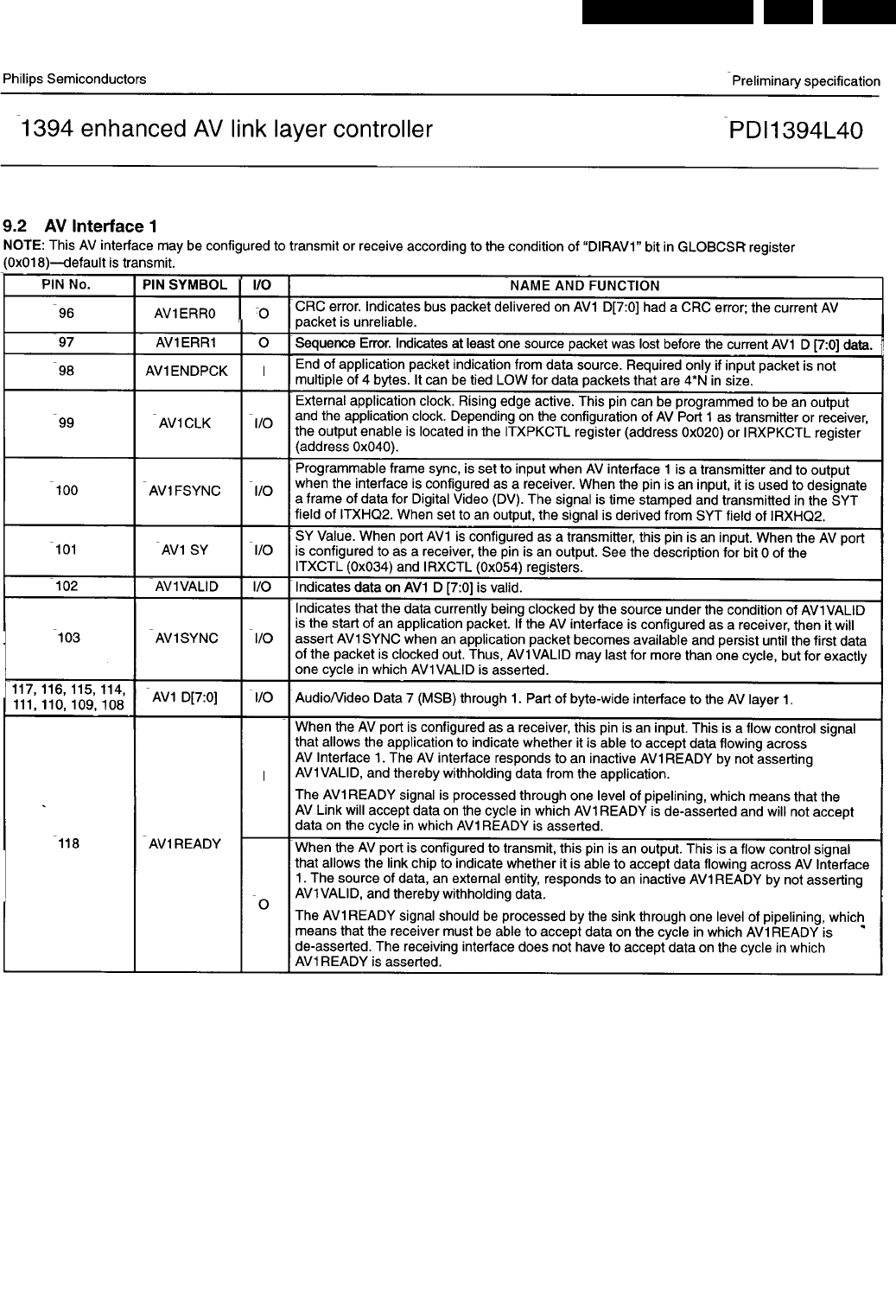

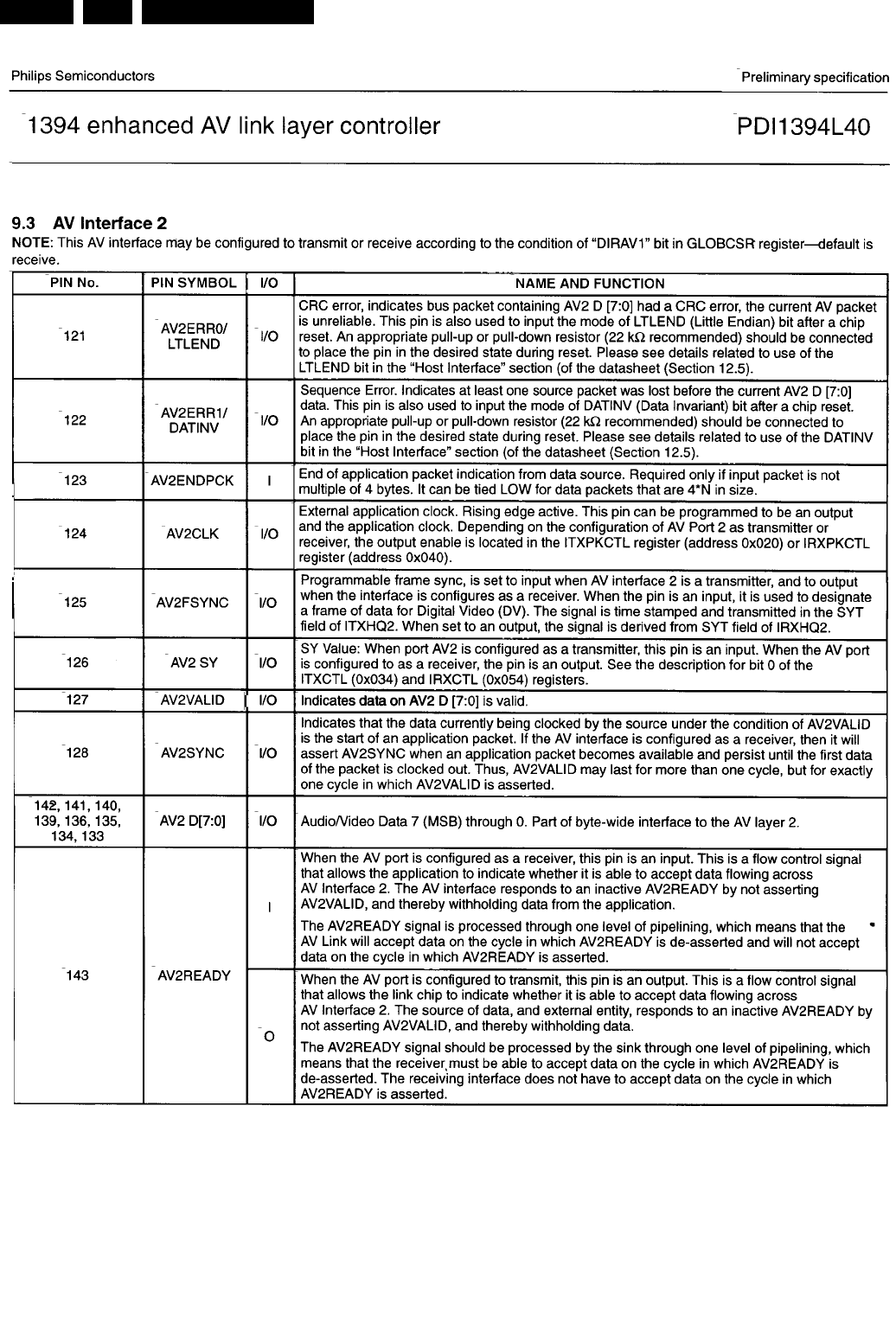

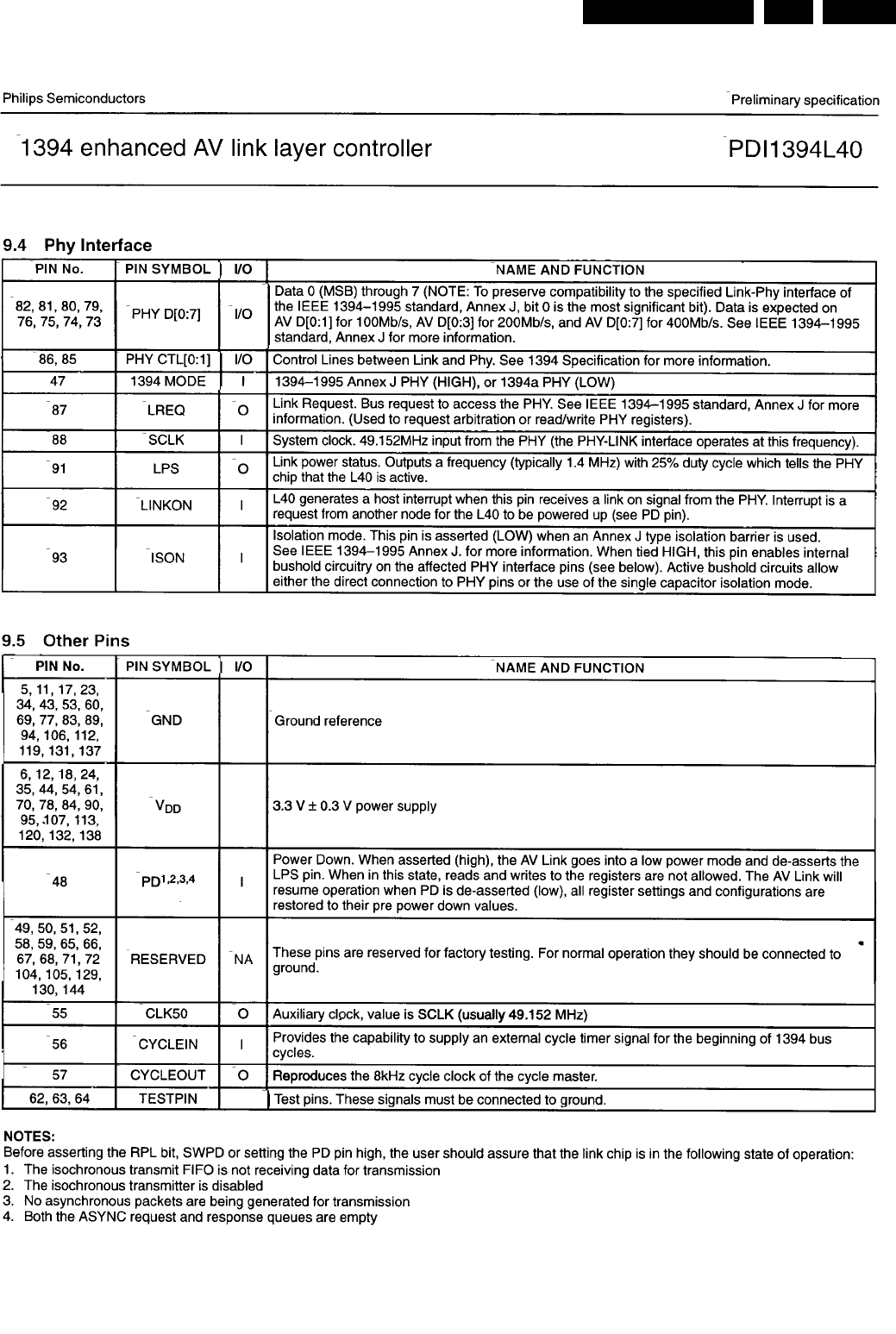

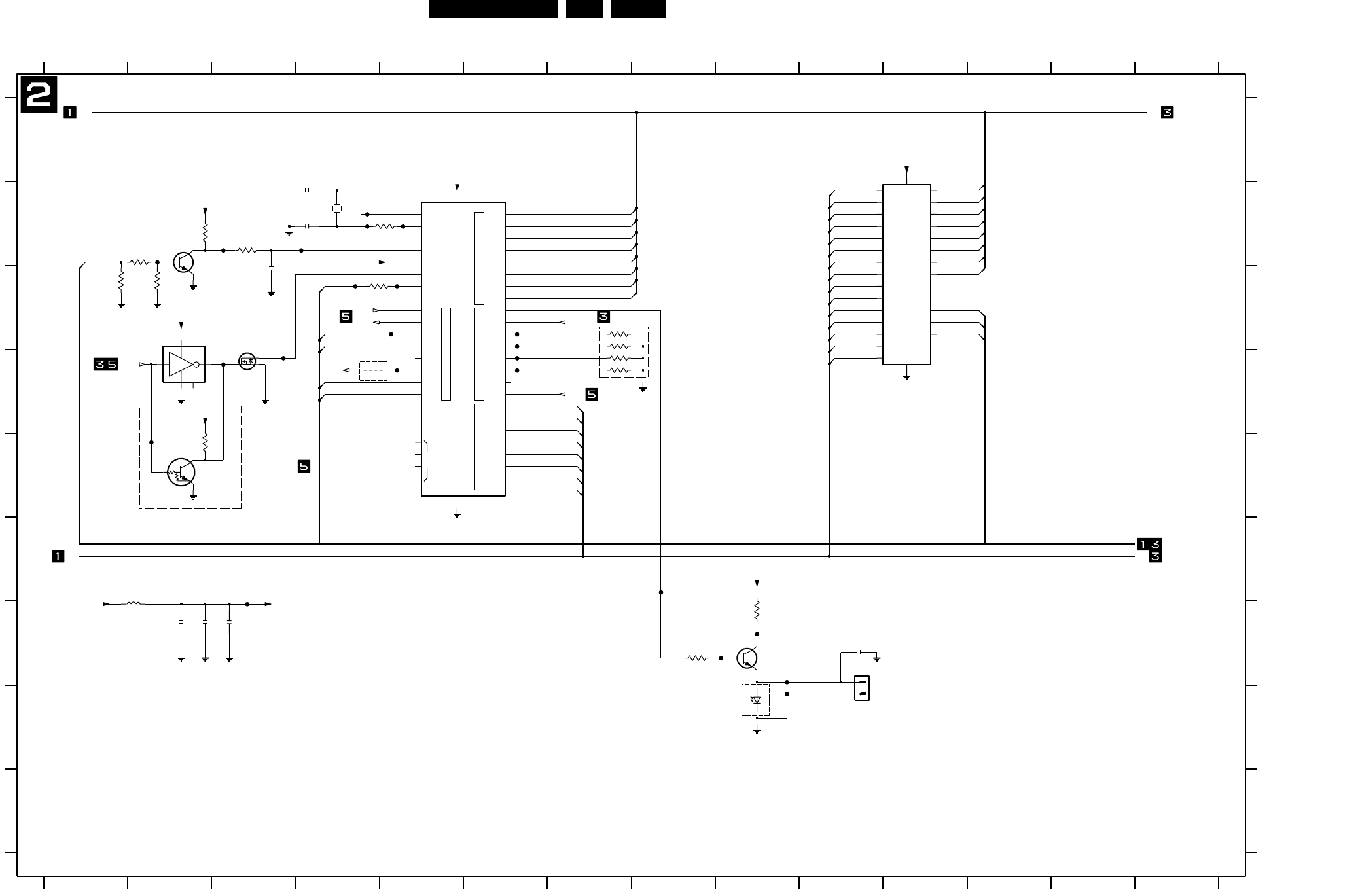

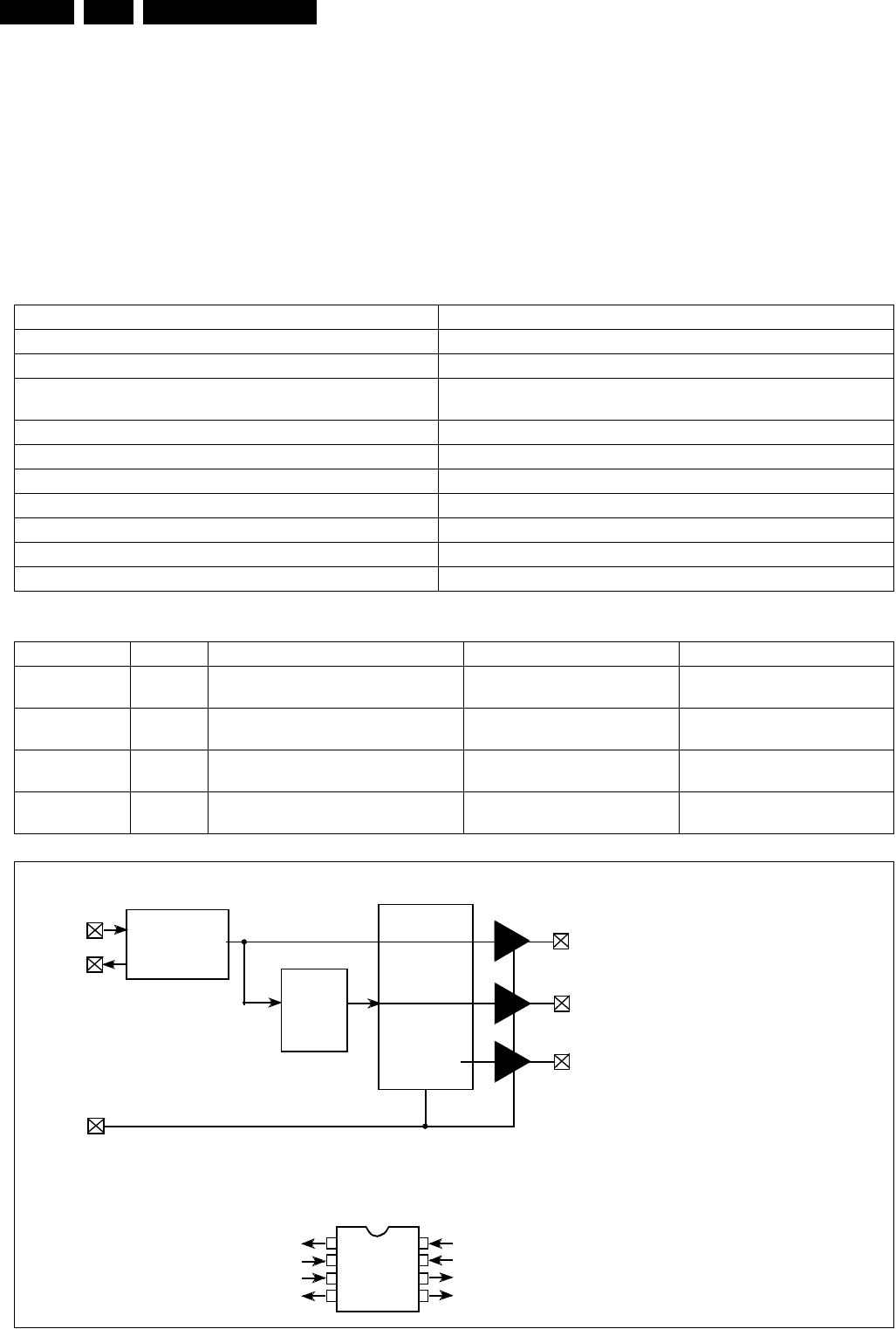

- DVIO Board: 1394 Interface

- DVIO Board: Microprocessor

- DVIO Board: Fifo & Control

- DVIO Board: DVCODEC

- DVIO Board: Audio & Video Output

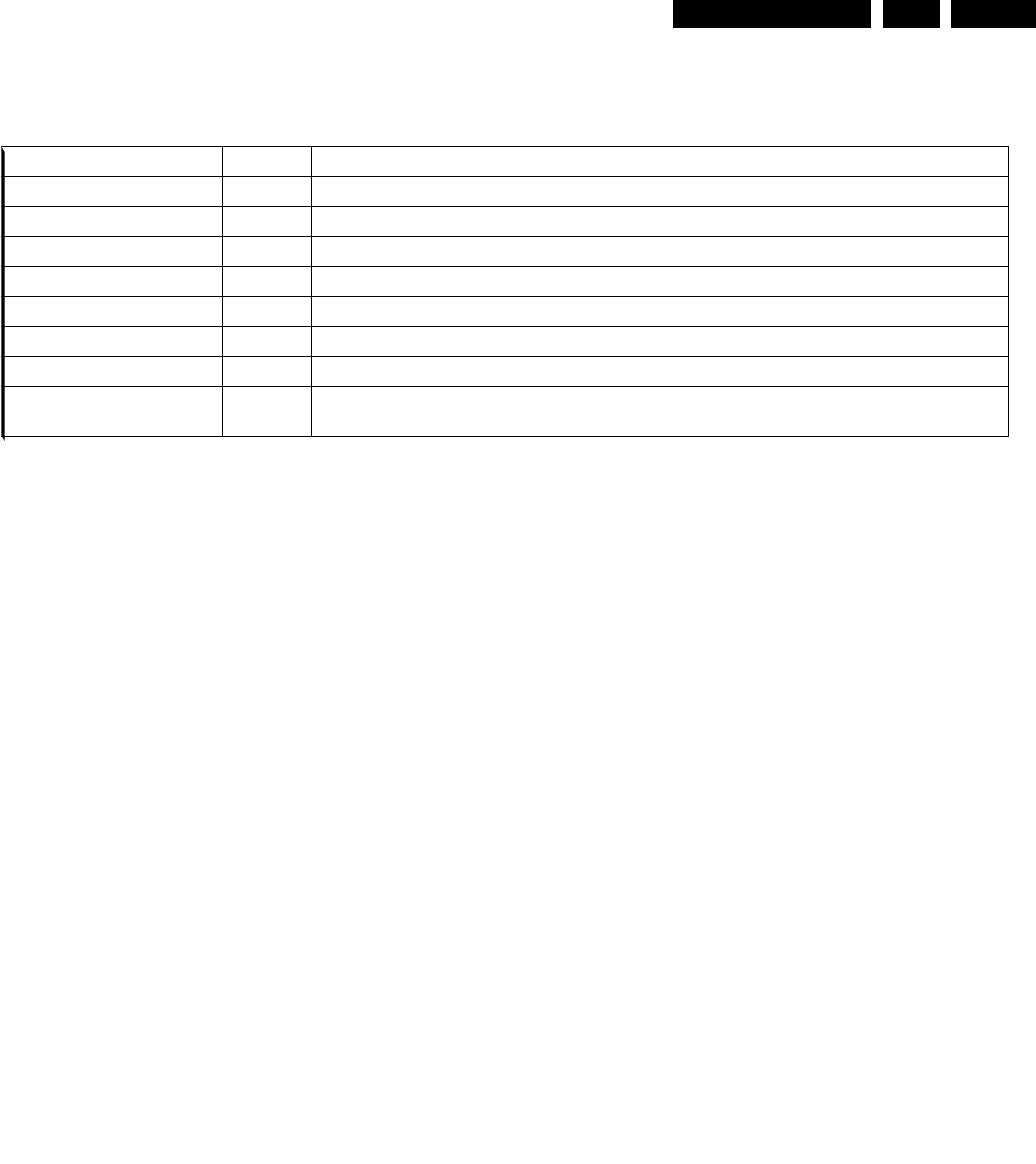

- Layout DVIO Board (Overview Top View)

- Layout DVIO Board (Part 1 Top View)

- Layout DVIO Board (Part 2 Top View)

- Layout DVIO Board (Testlands Bottom View)

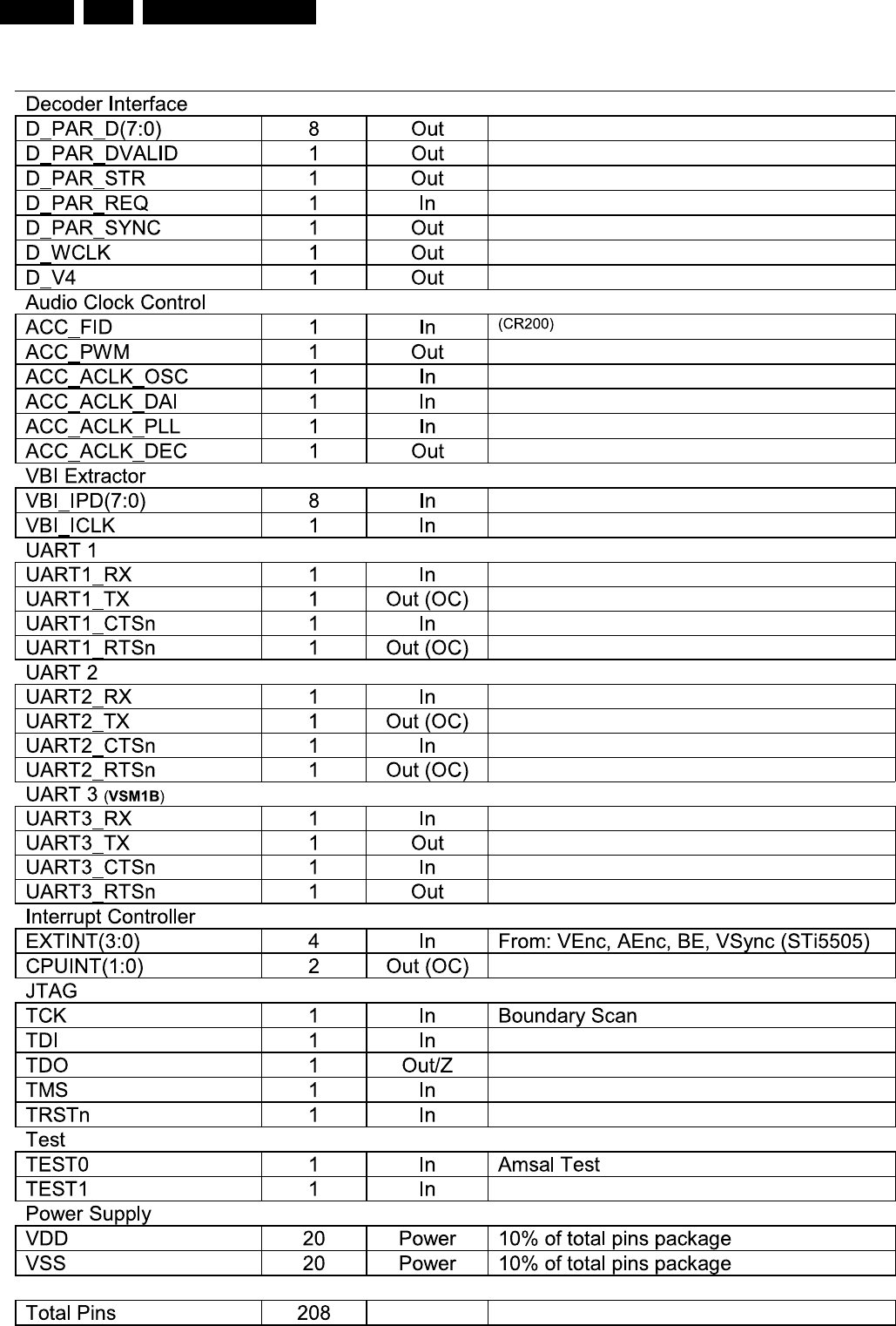

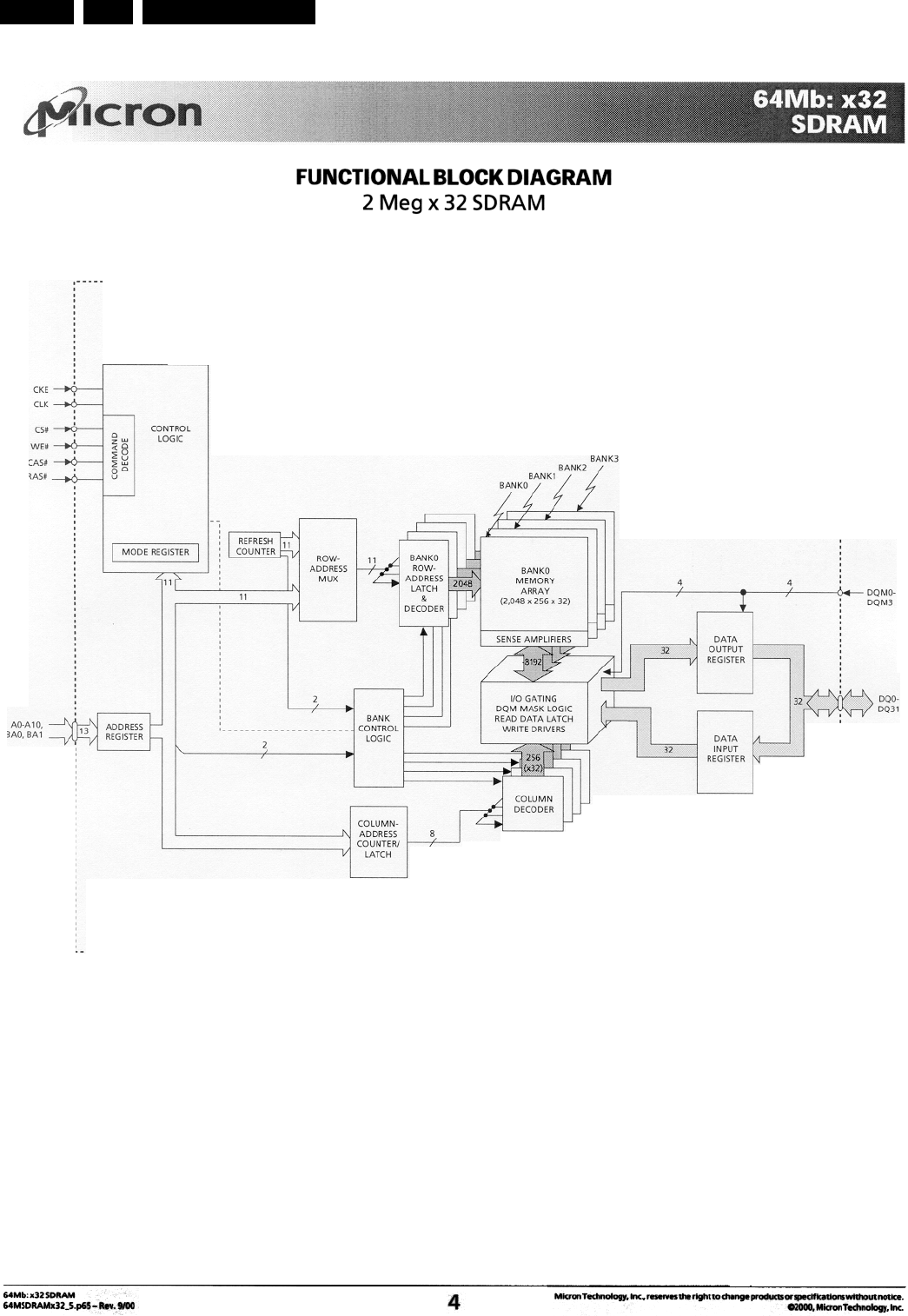

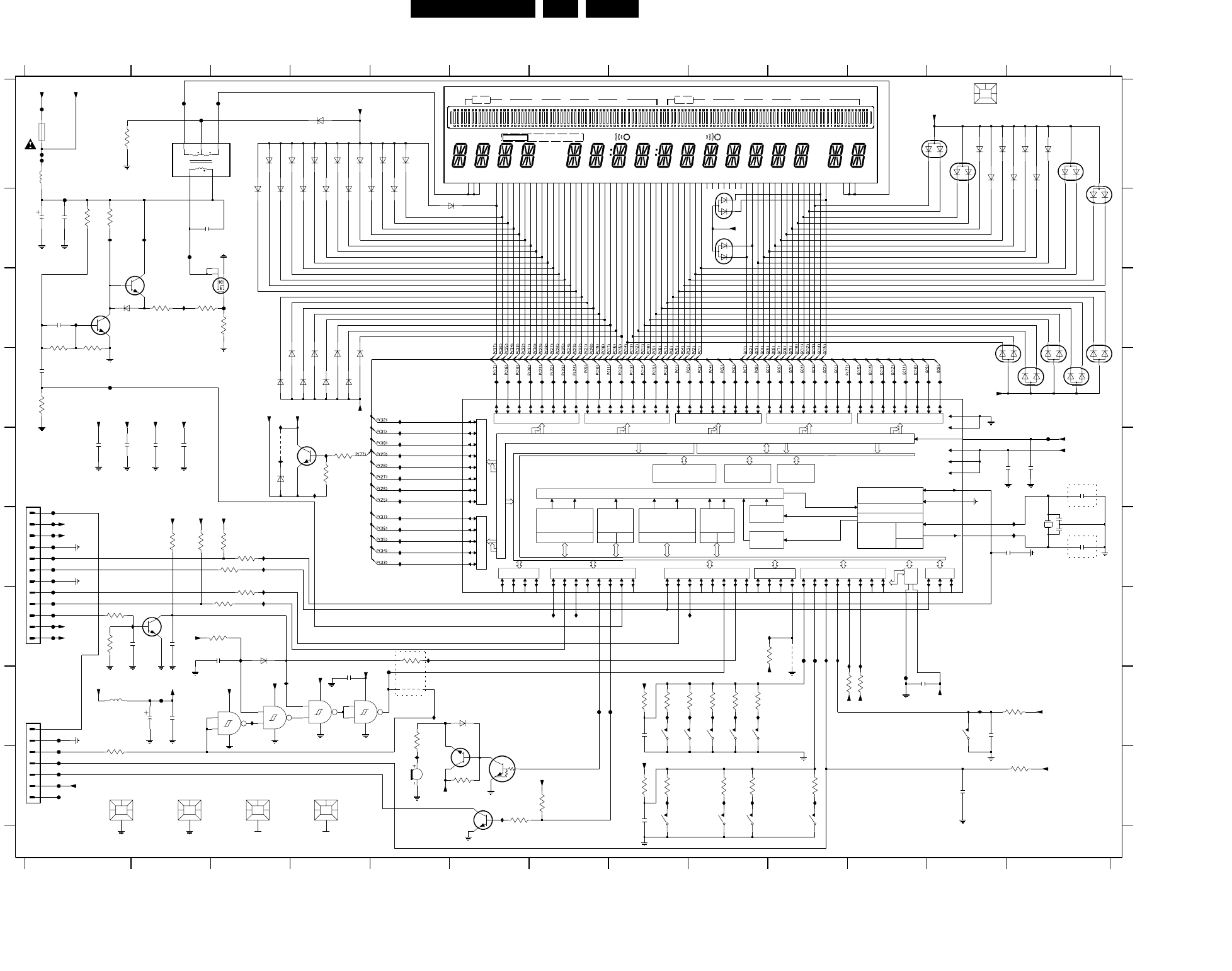

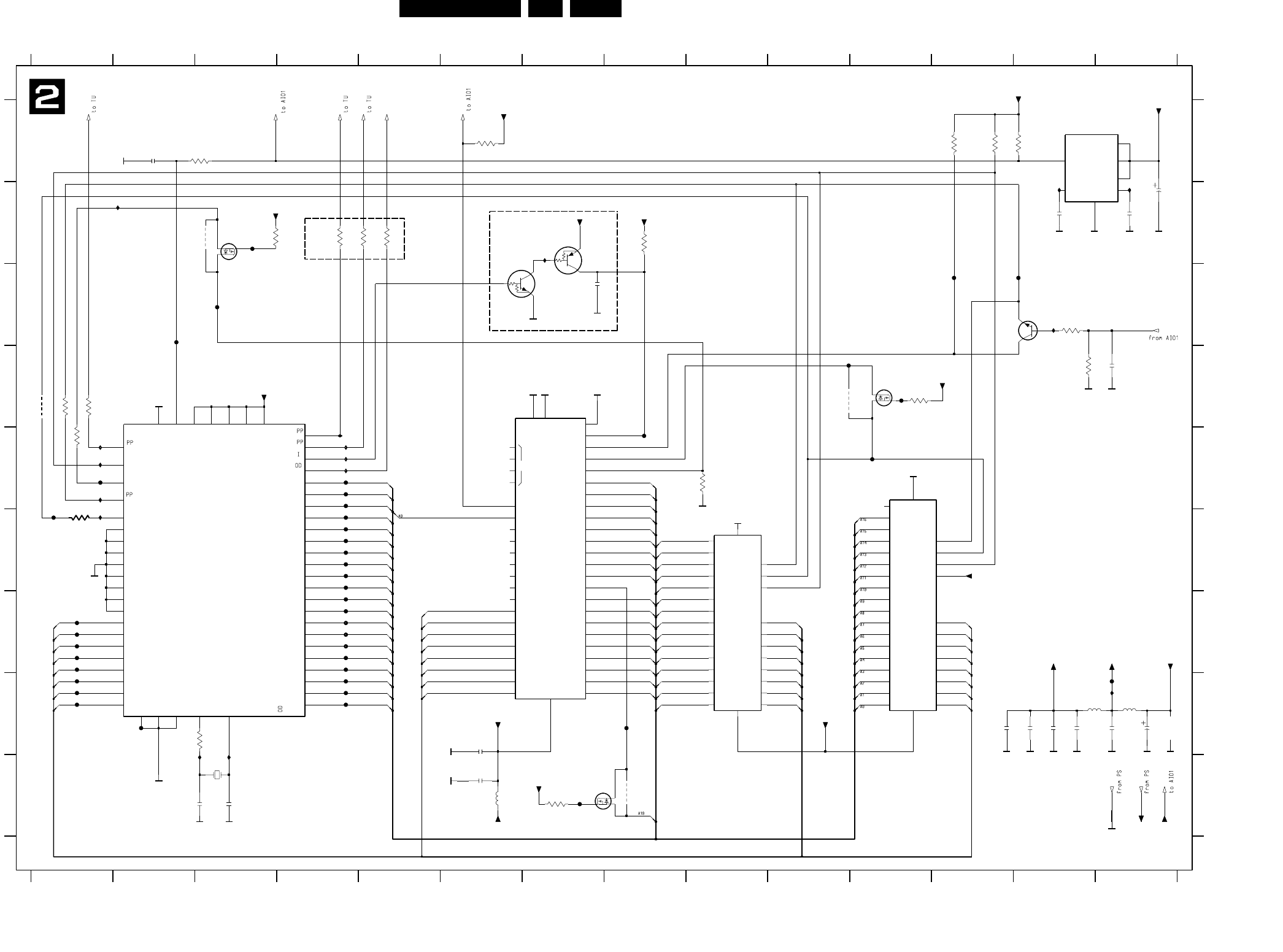

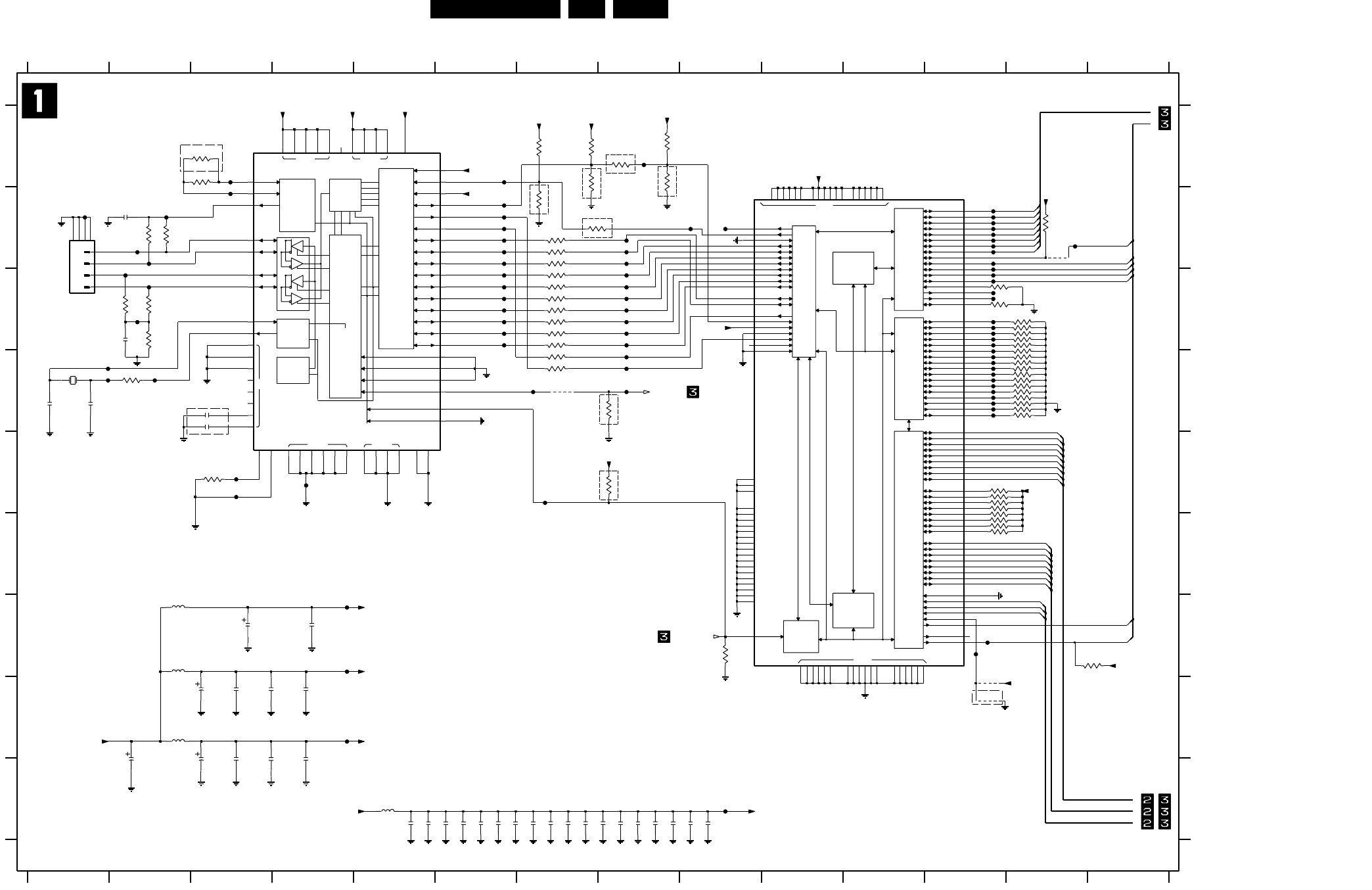

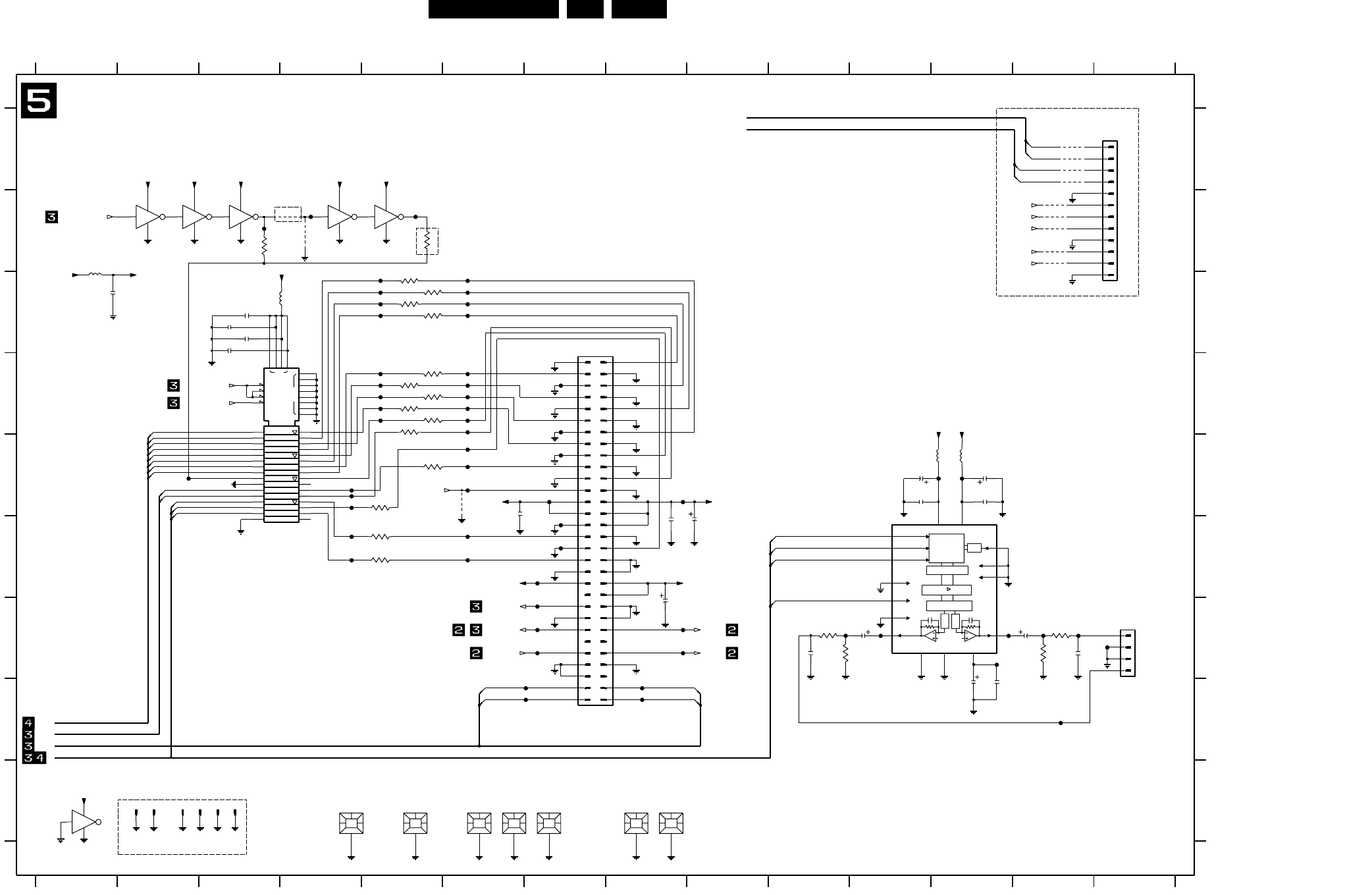

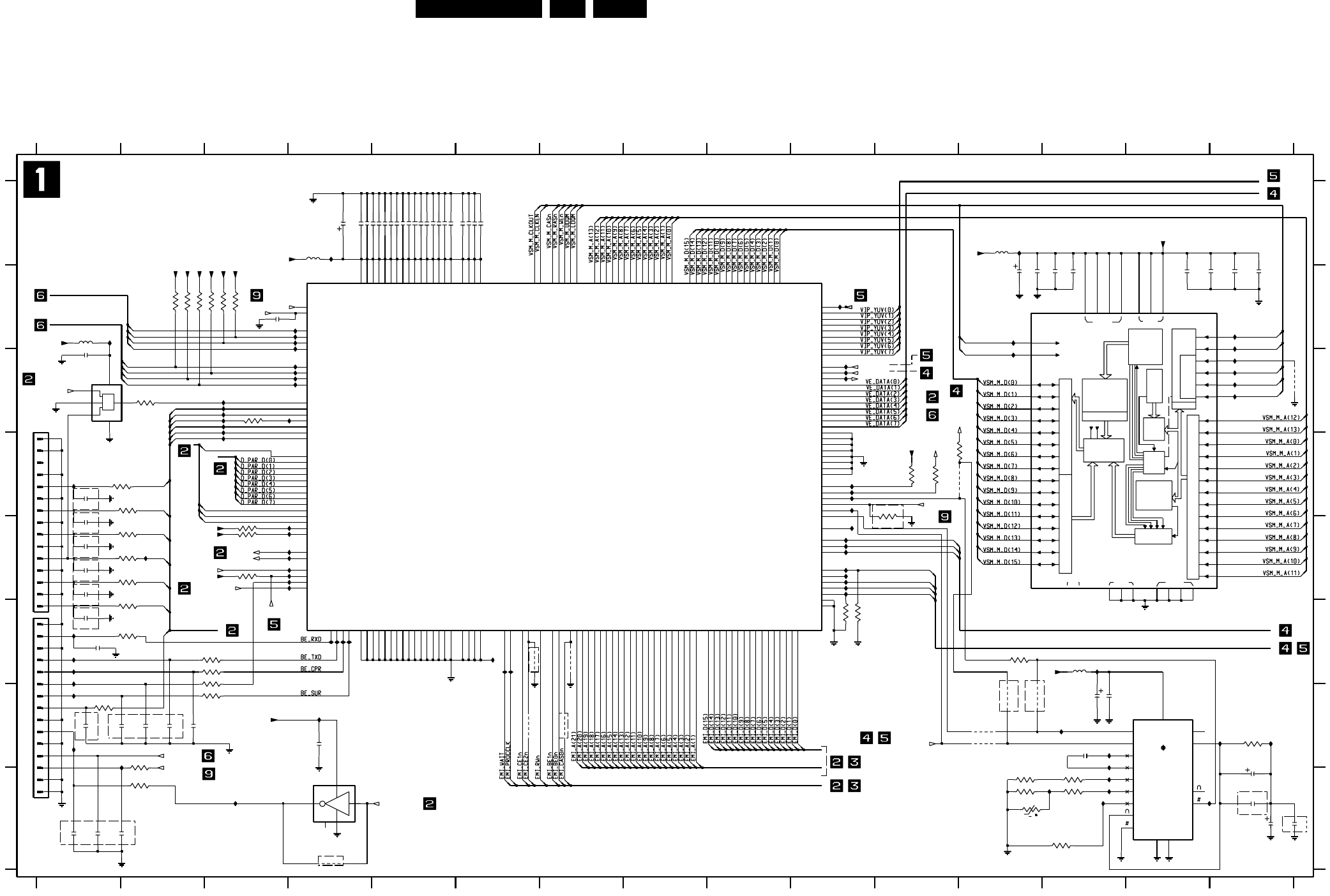

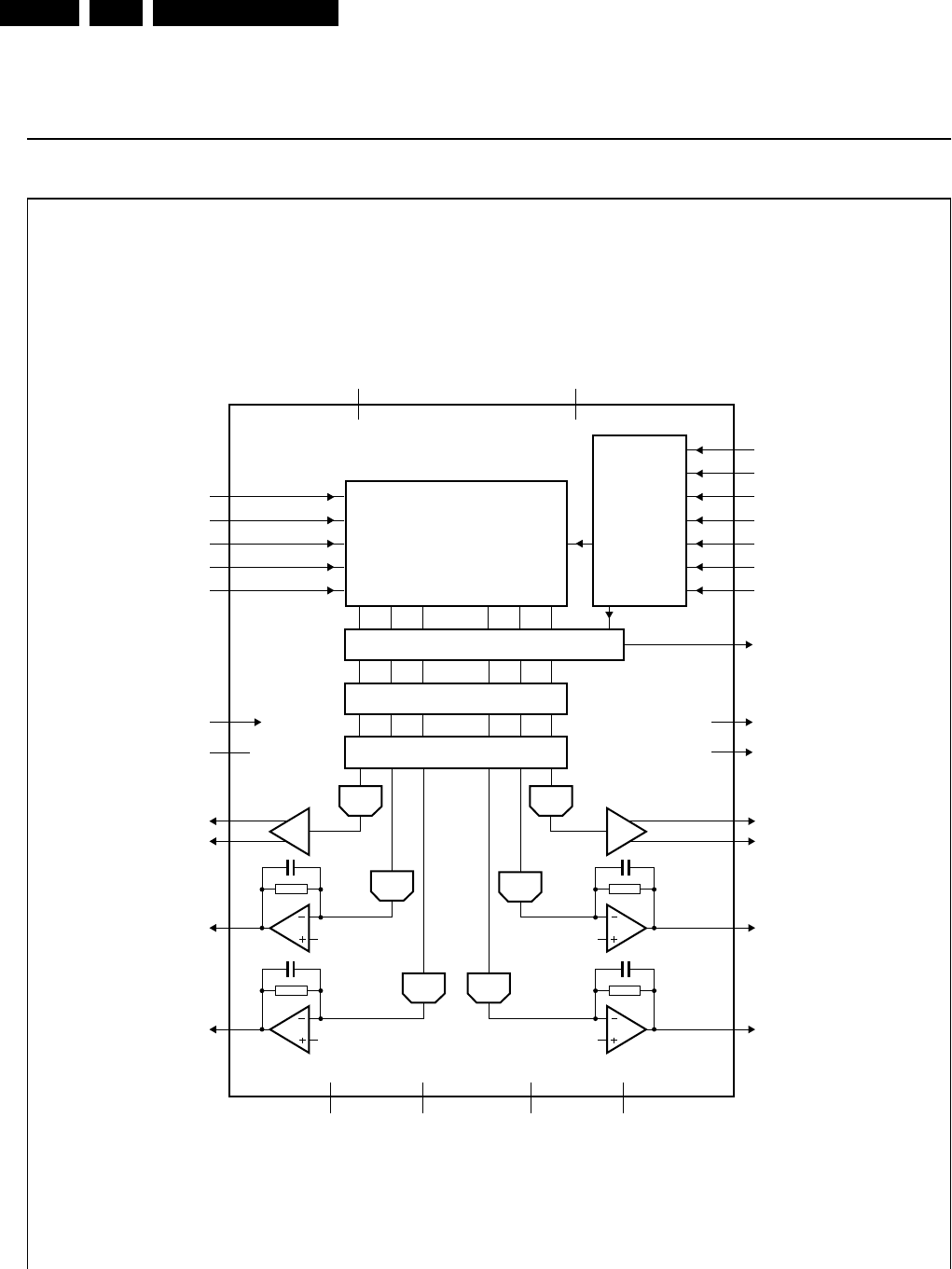

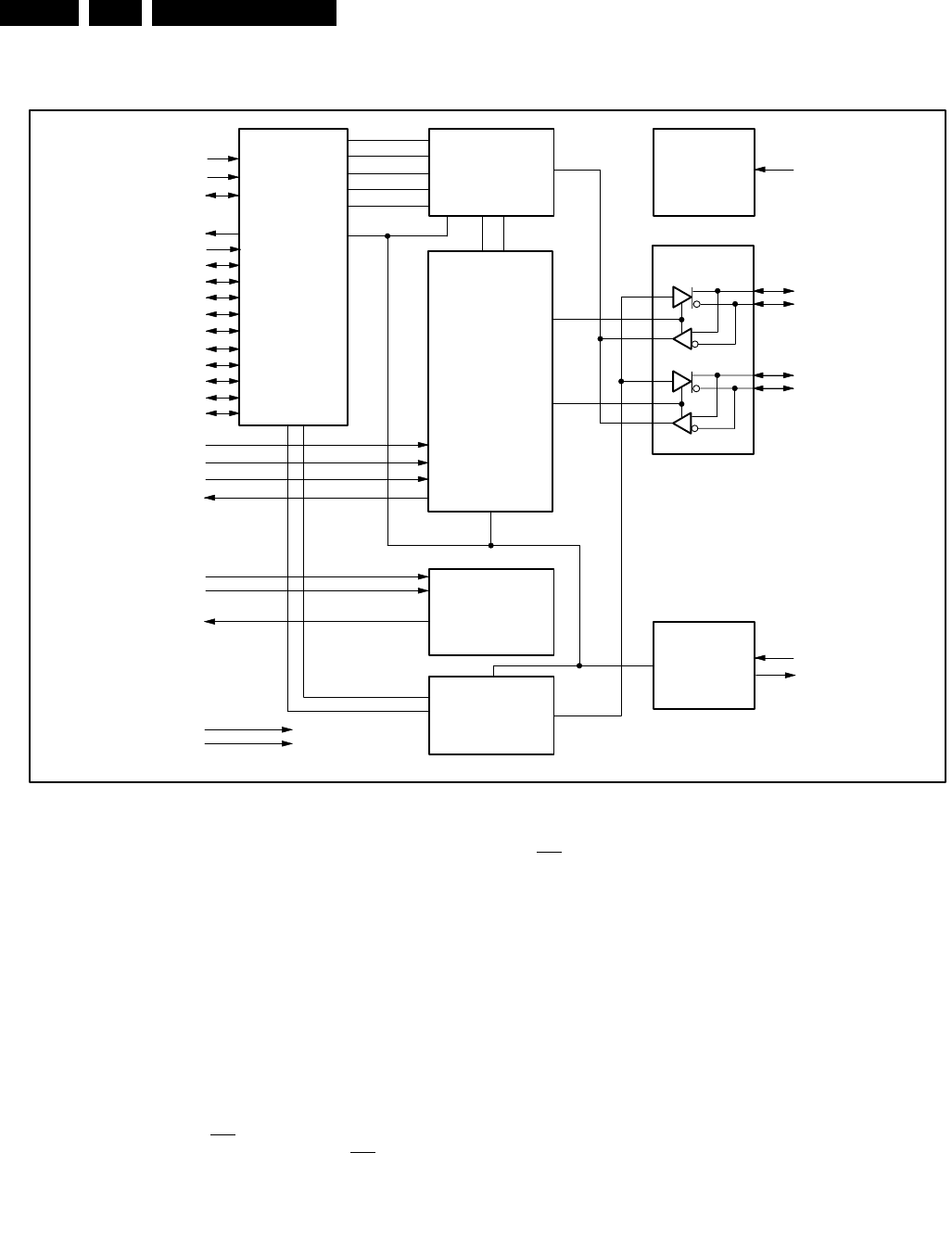

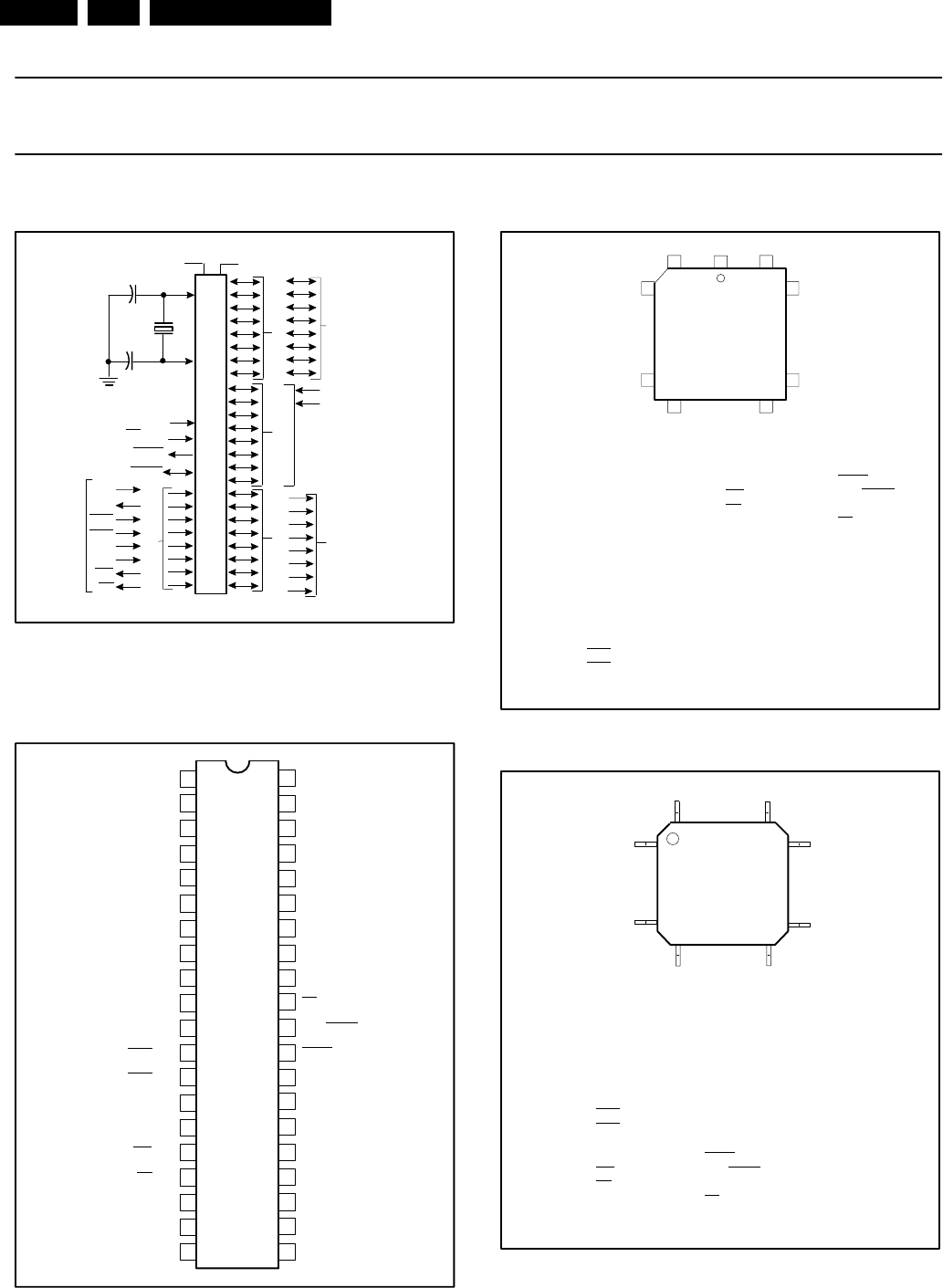

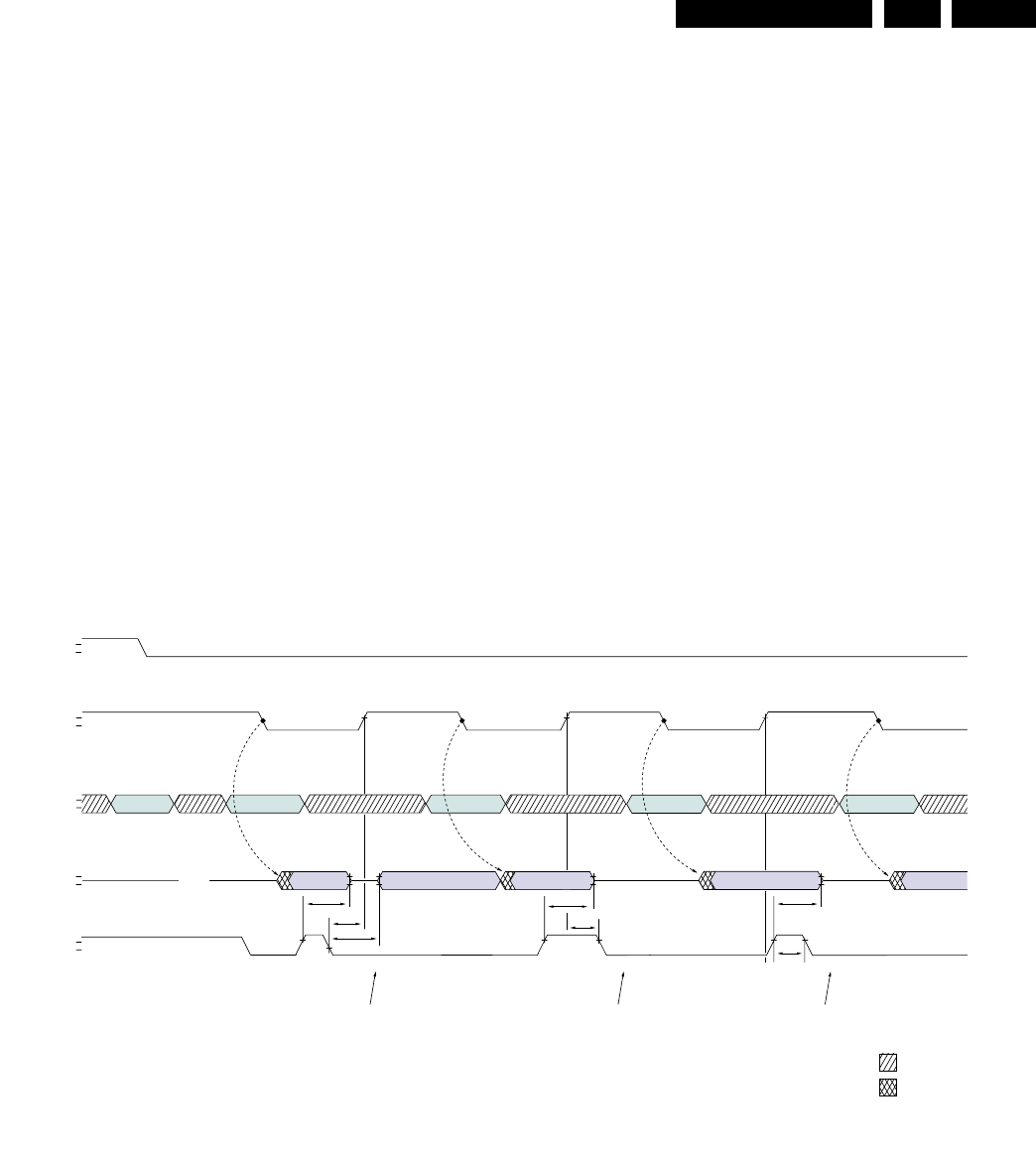

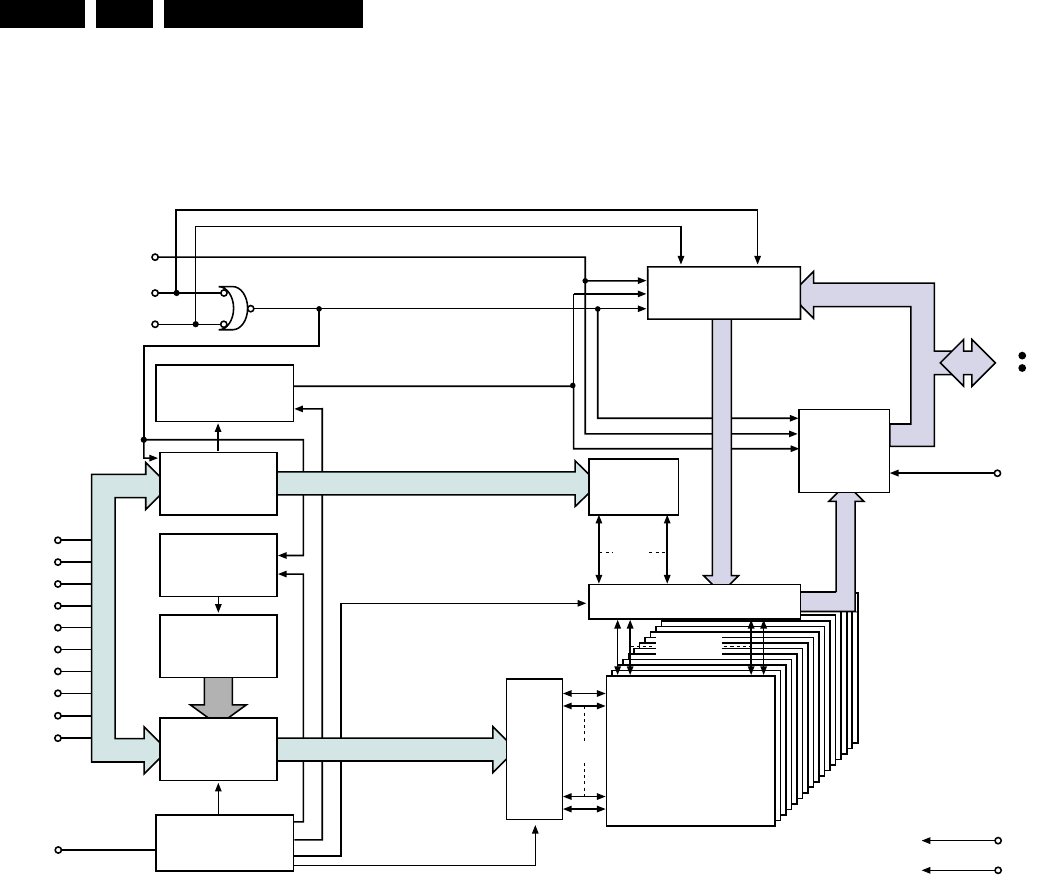

- Digital Board: VSM, Buffer Memory and Bit Engine Interface

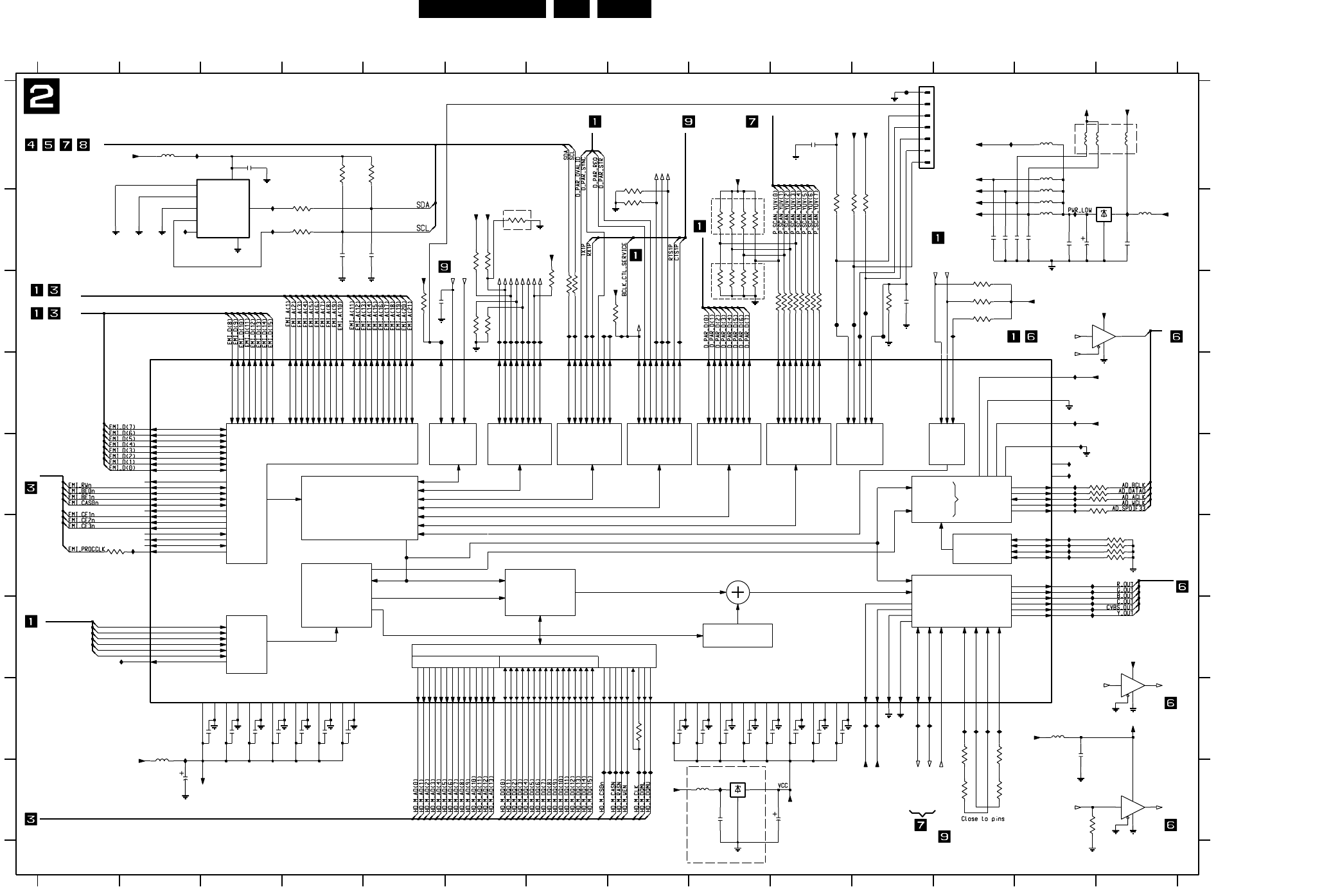

- Digital Board: AV Decoder STI5508

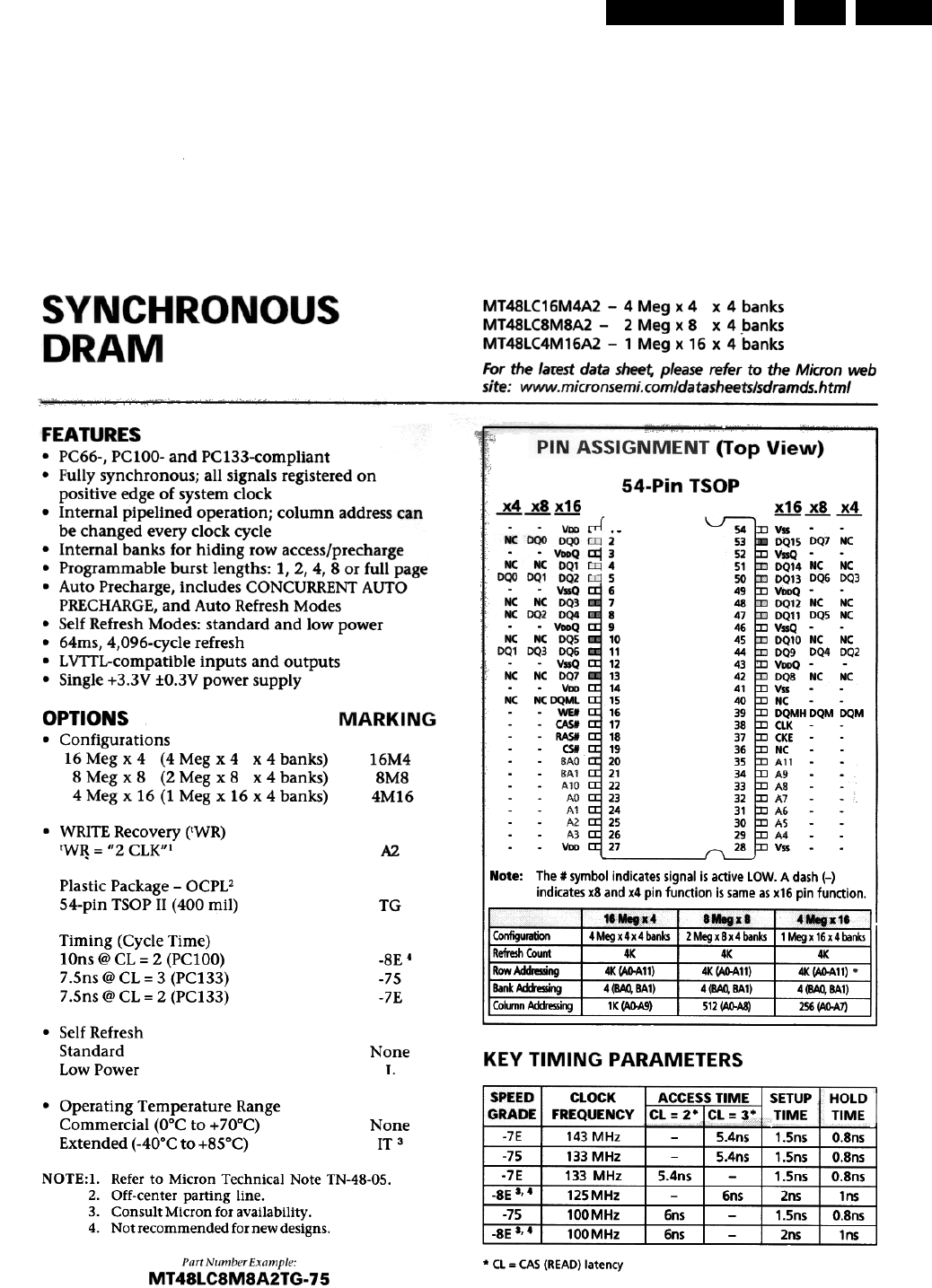

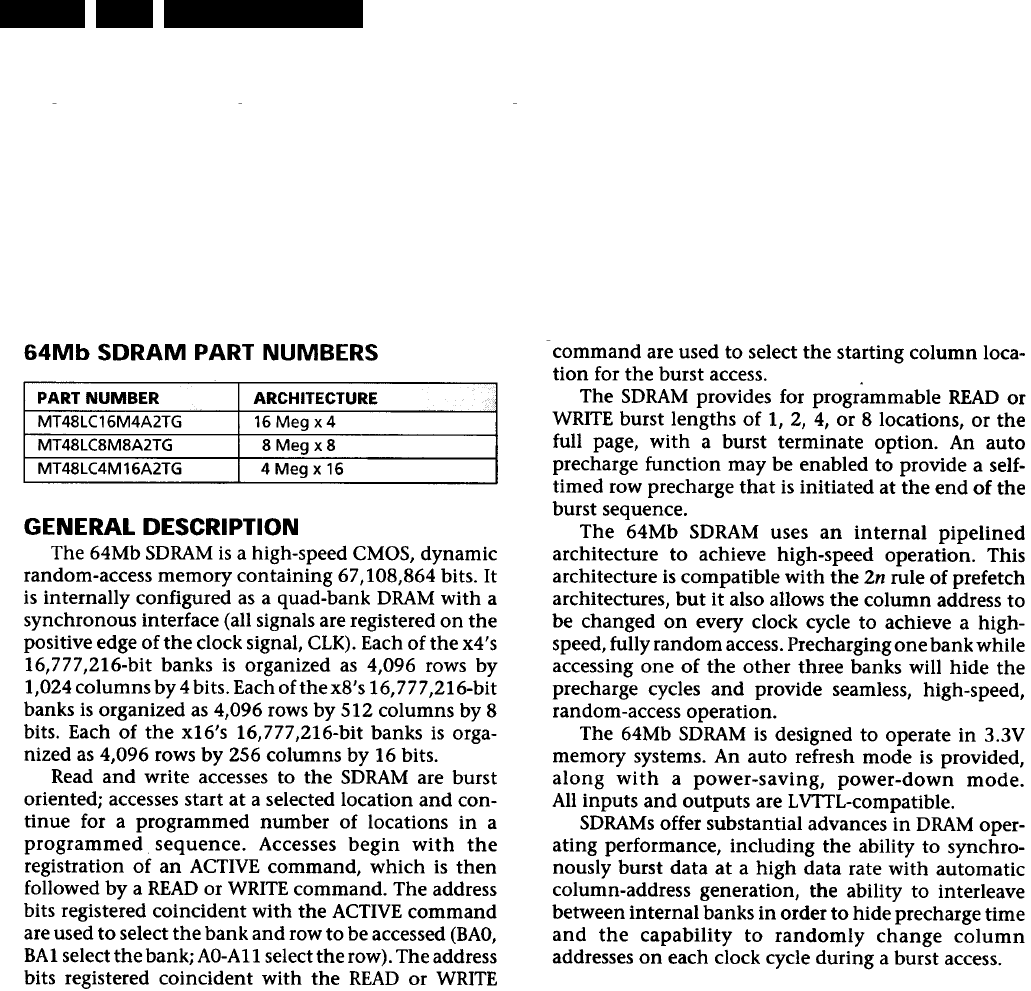

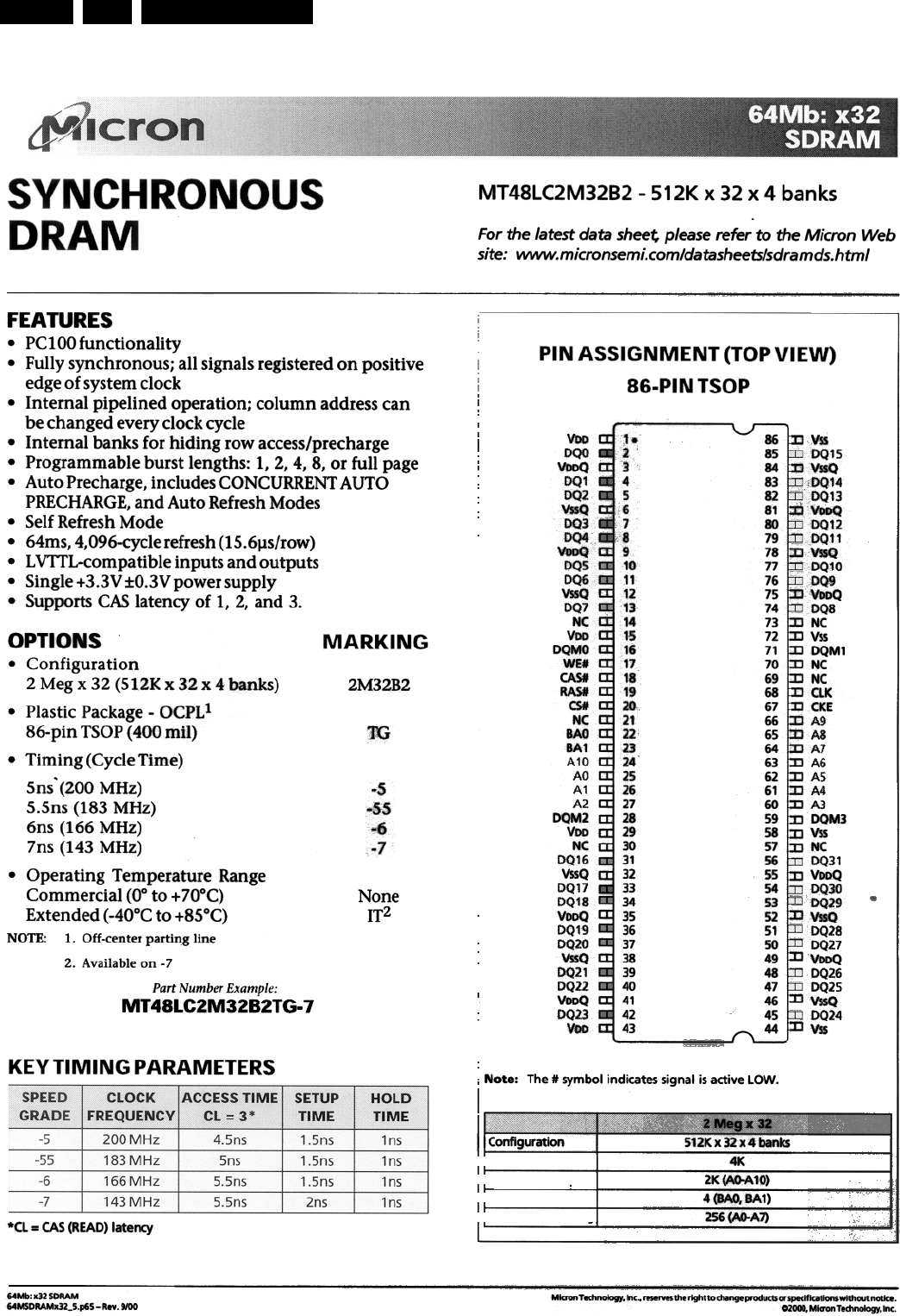

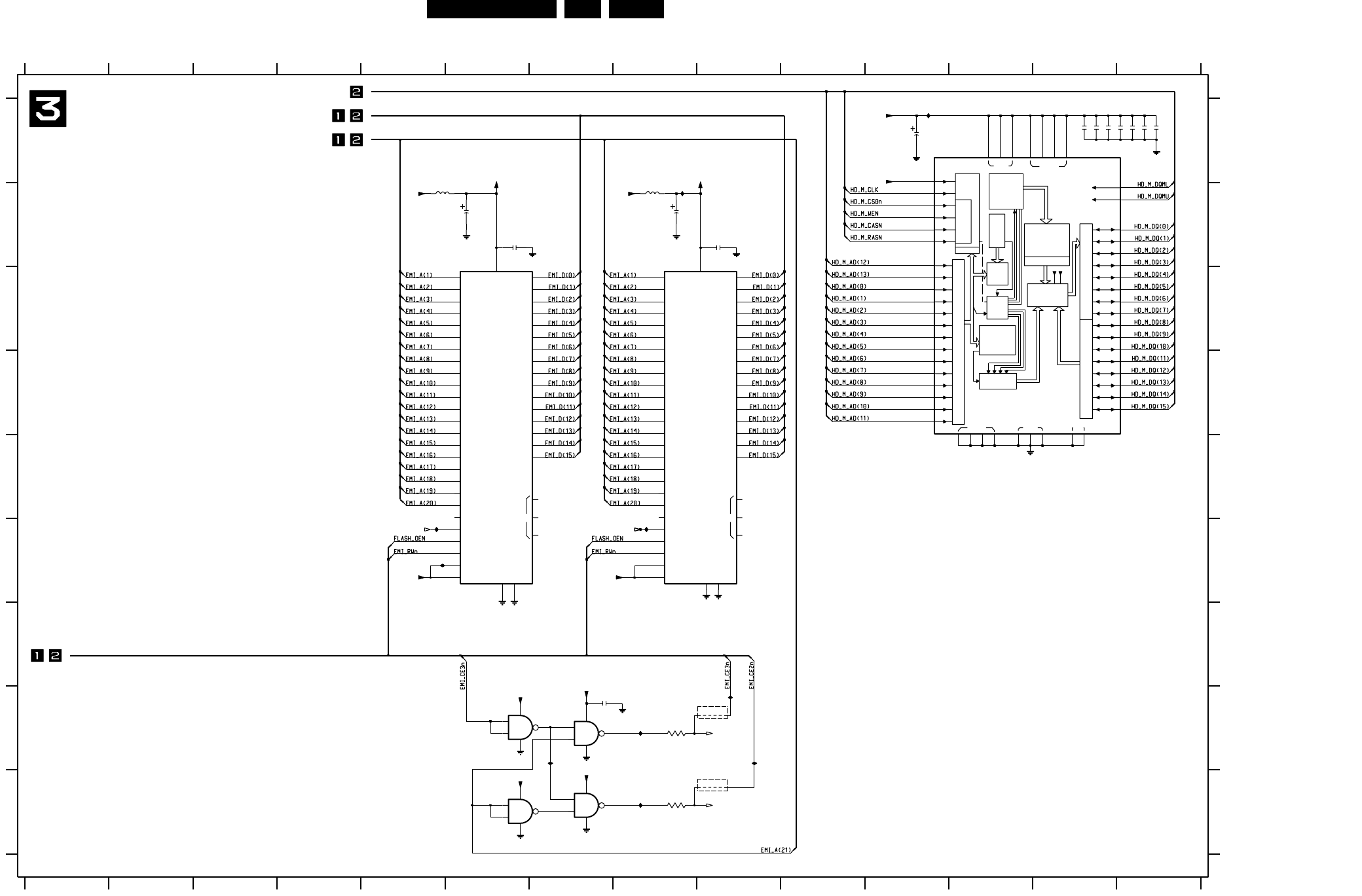

- Digital Board: AV Decoder Memory

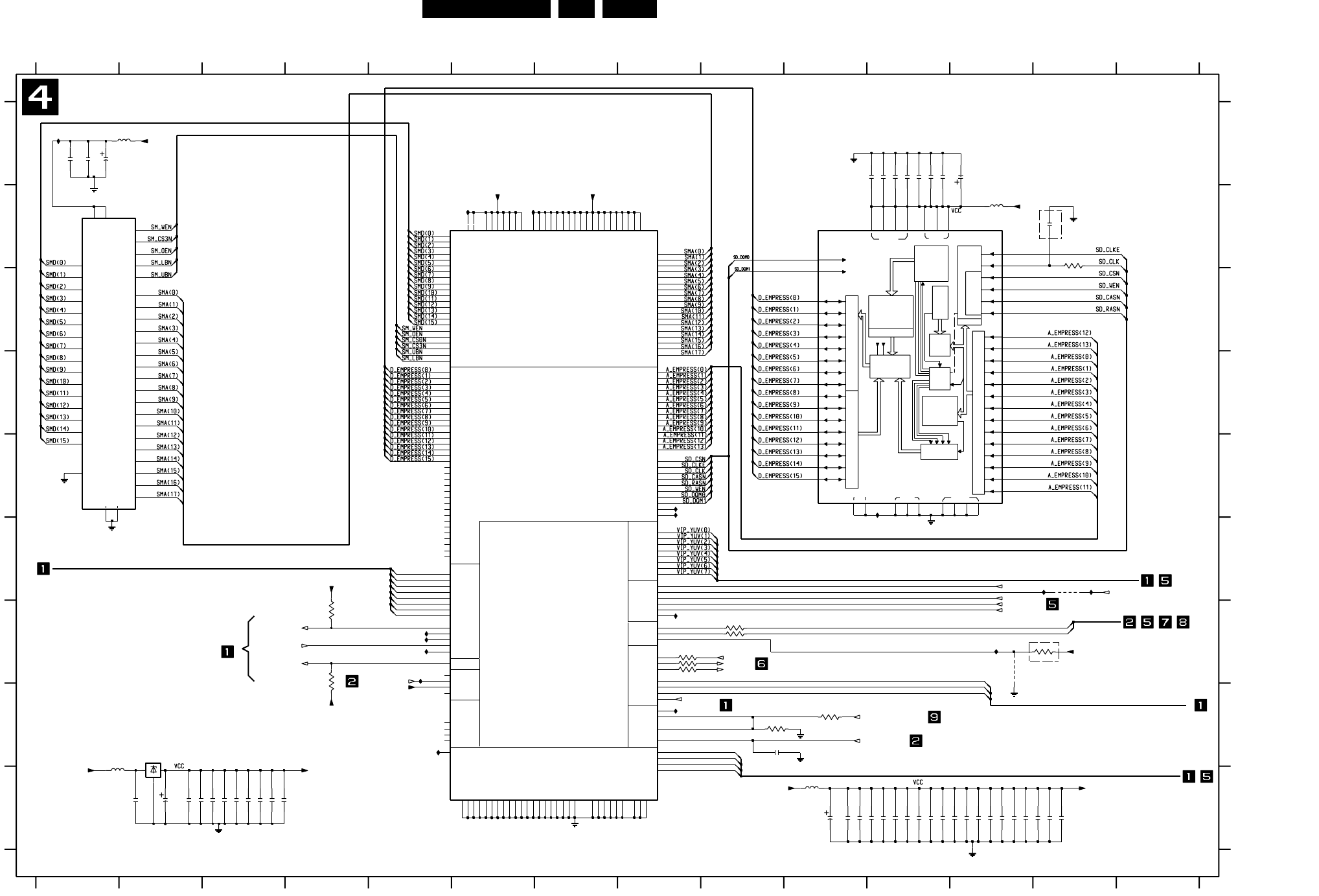

- Digital Board: Video Encoder, Empress

- Digital Board: VIP CVBS Y/C Video Input

- Digital Board: Analog Board Cons. Video In / Output

- Digital Board: Progressive Scan

- Digital Board: Progressive Scan

- Digital Board: Power, Clock, and Reset Audio Clock

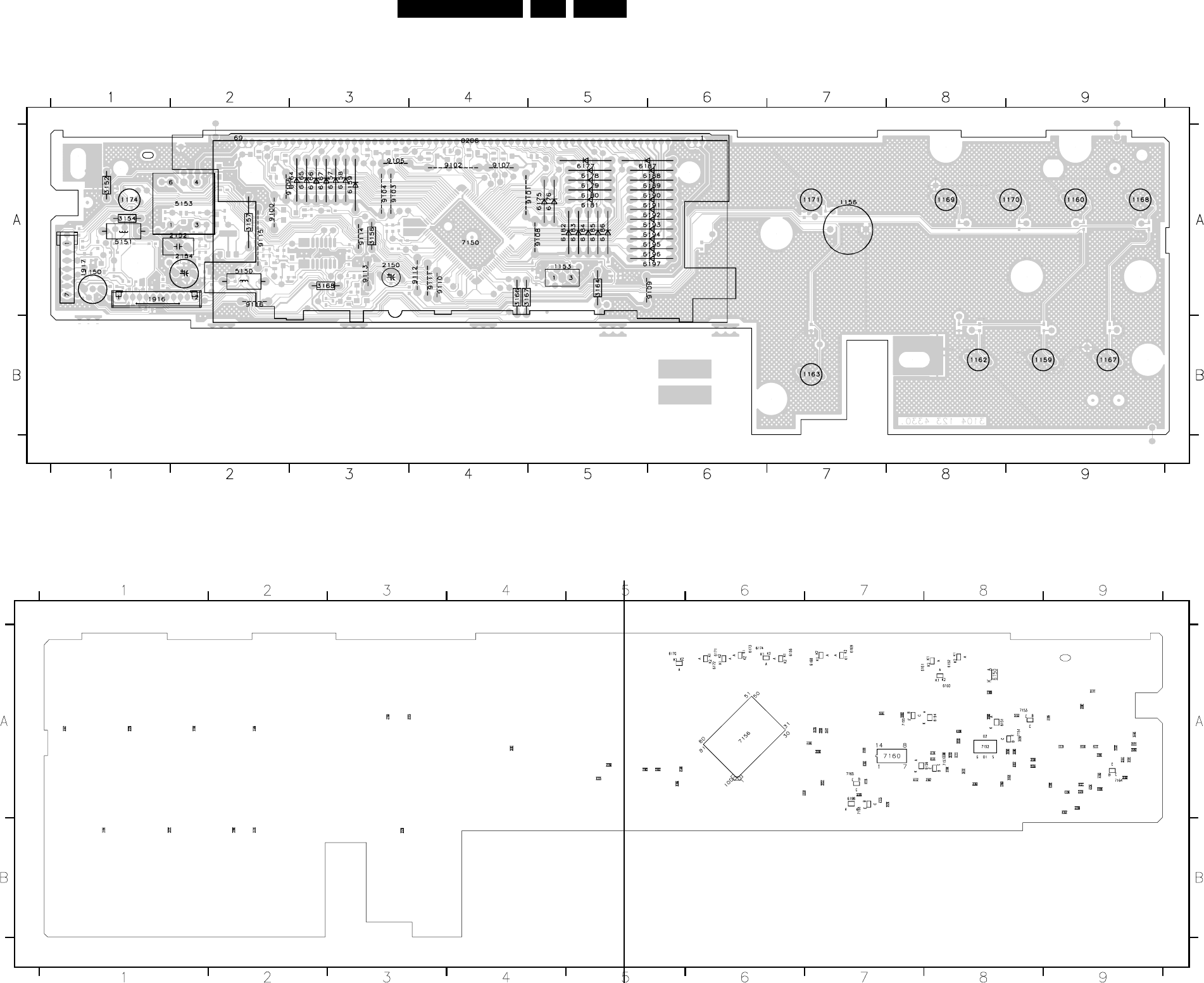

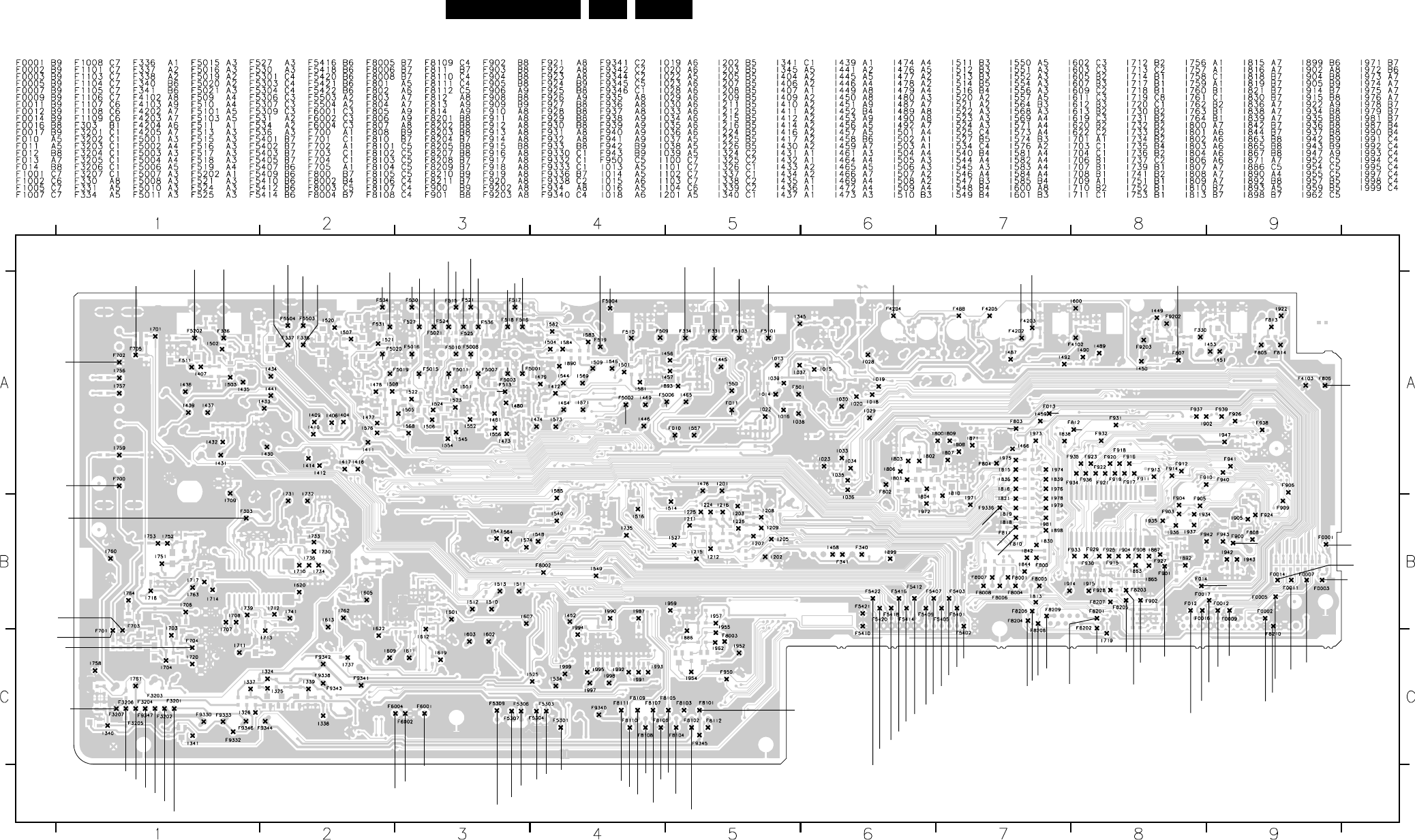

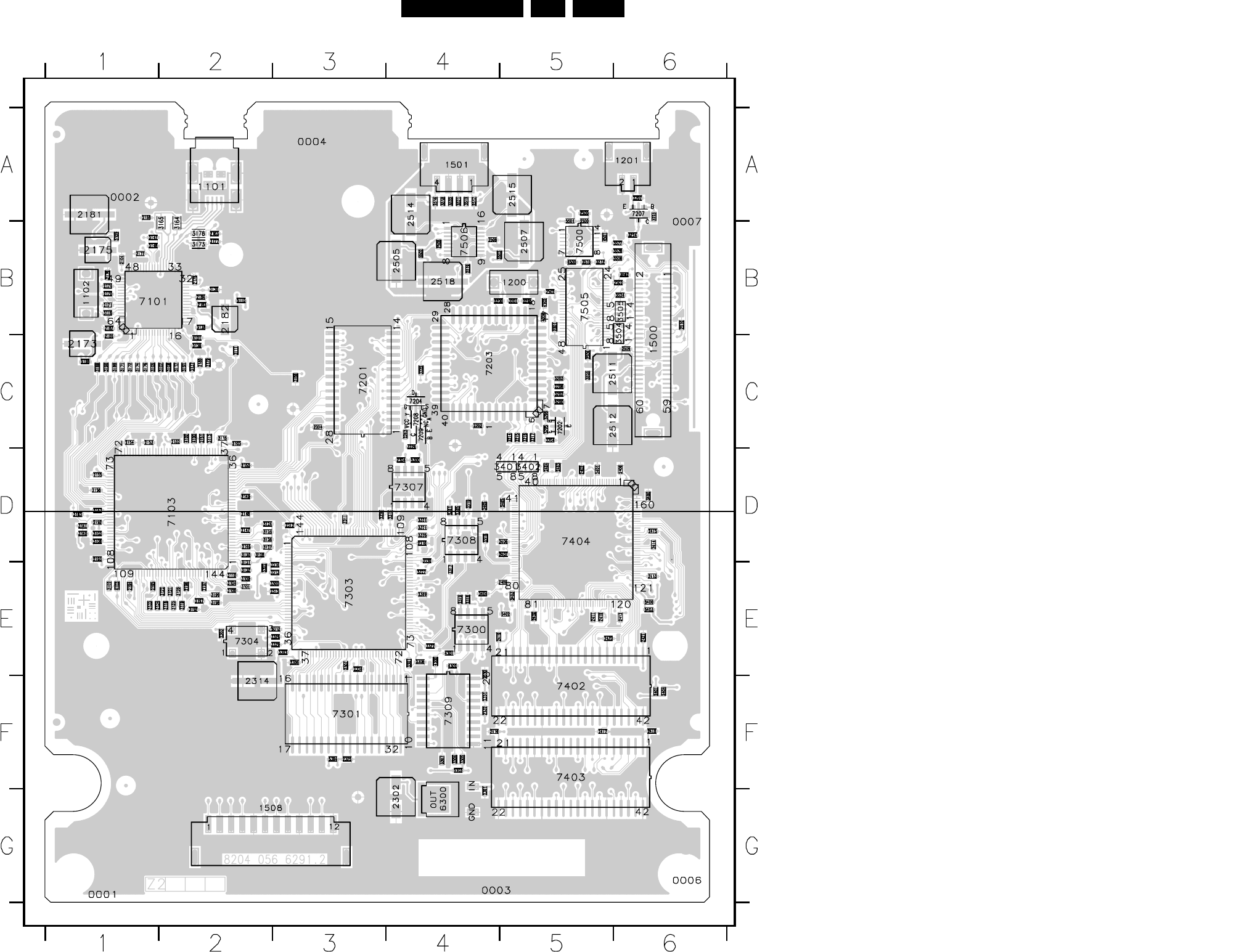

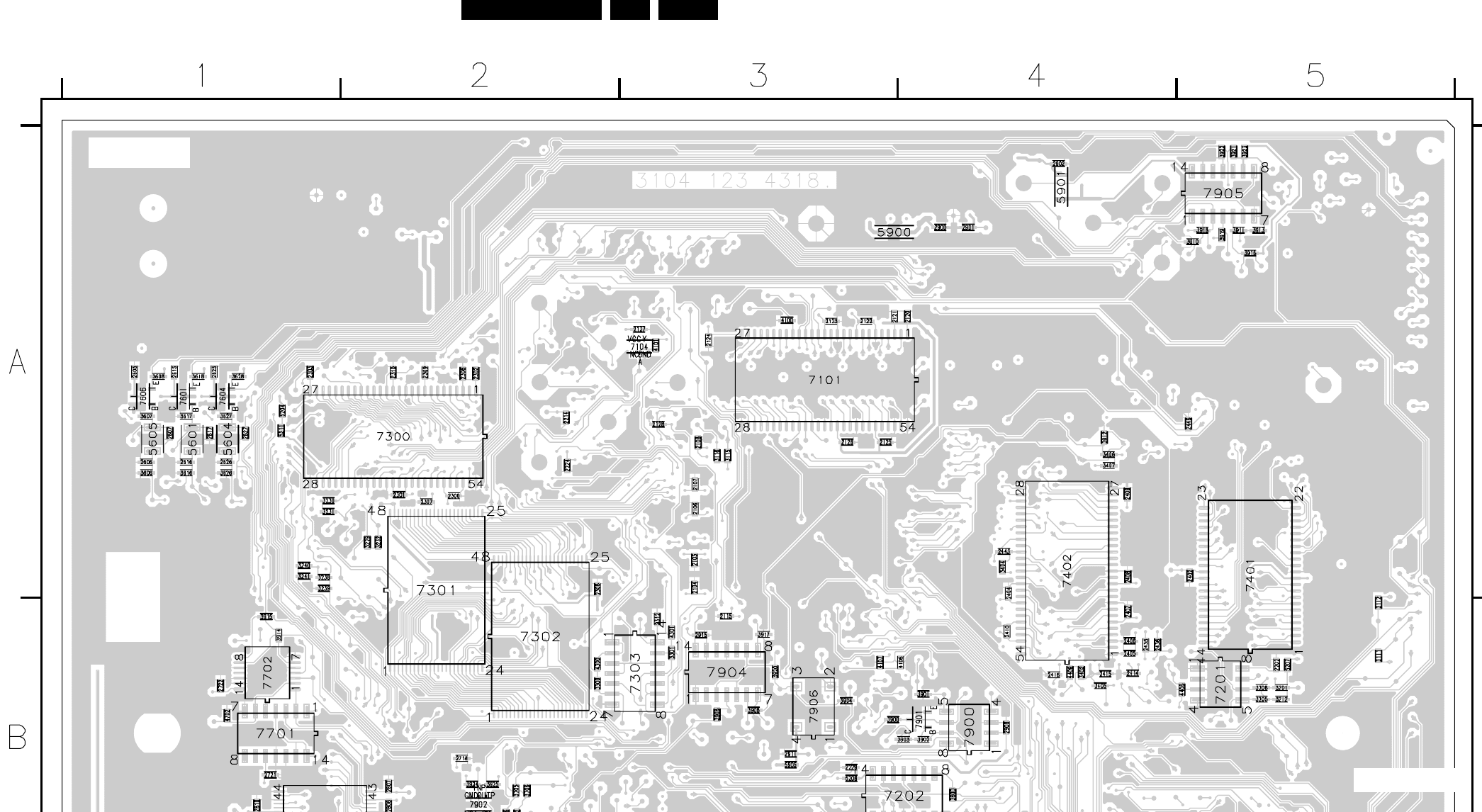

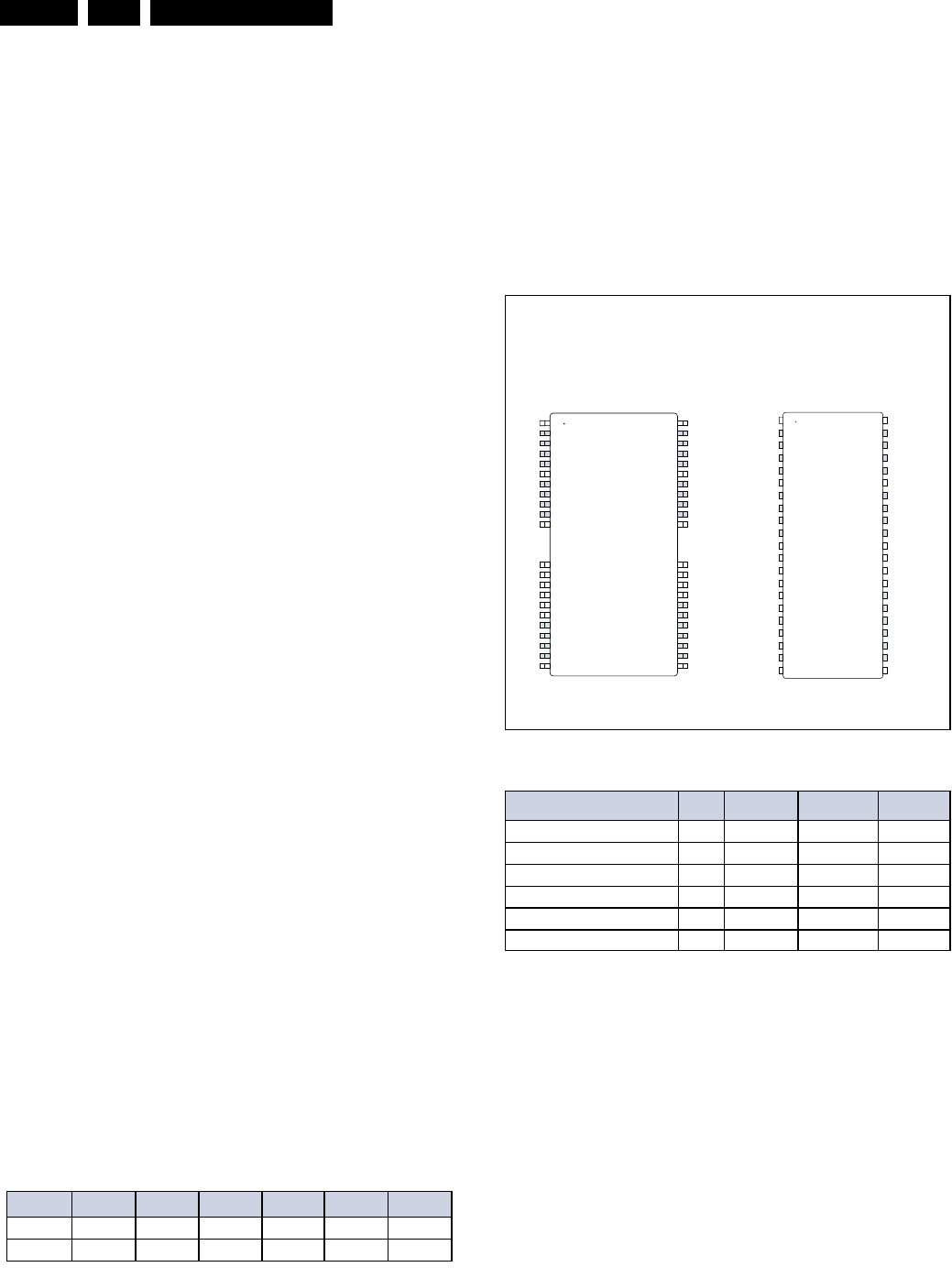

- Layout Digital Board (Overview Top View)

- Layout Digital Board (Part 1 Top View)

- Layout Digital Board (Part 2 Top View)

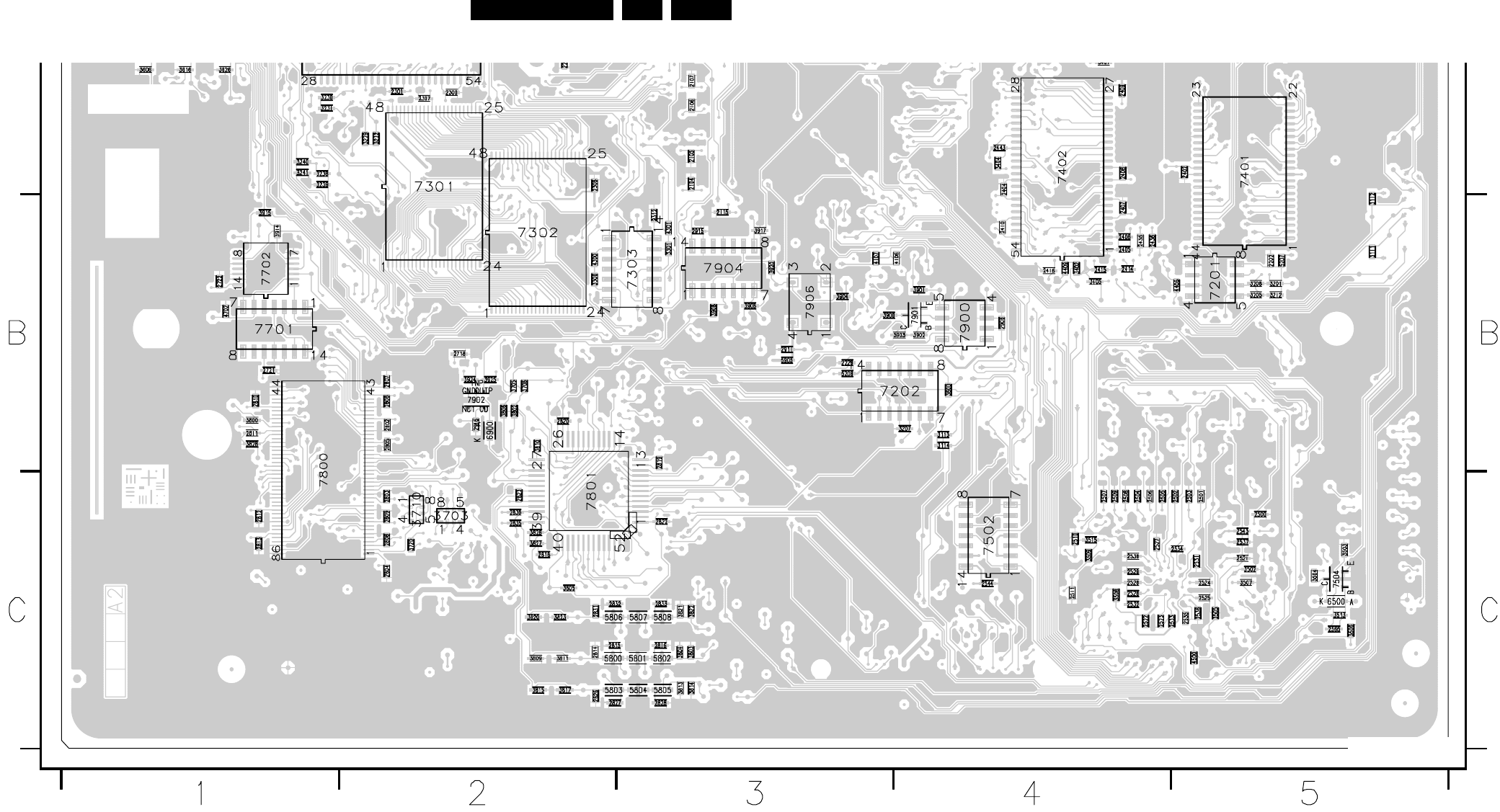

- Layout Digital Board (Overview Bottom View)

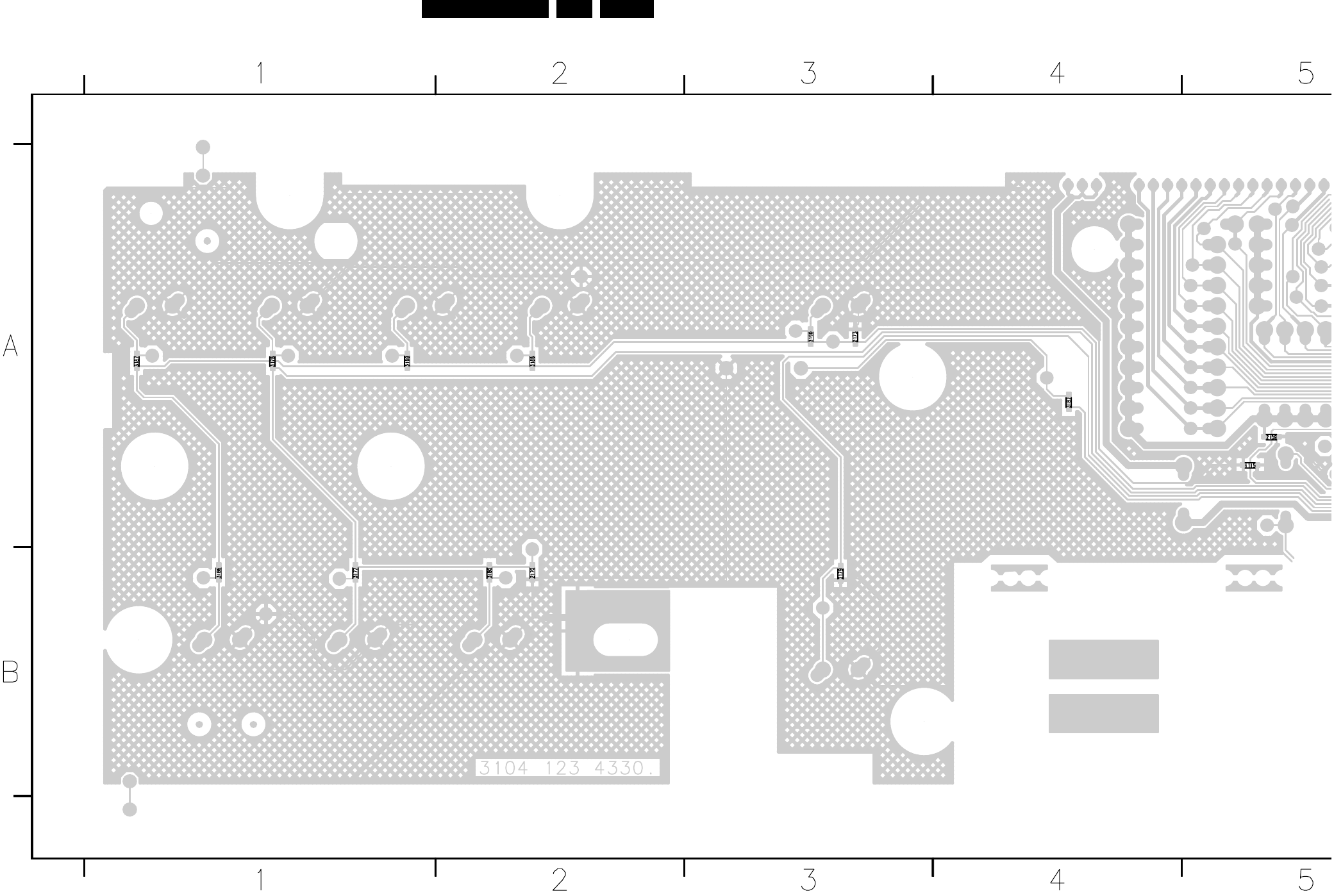

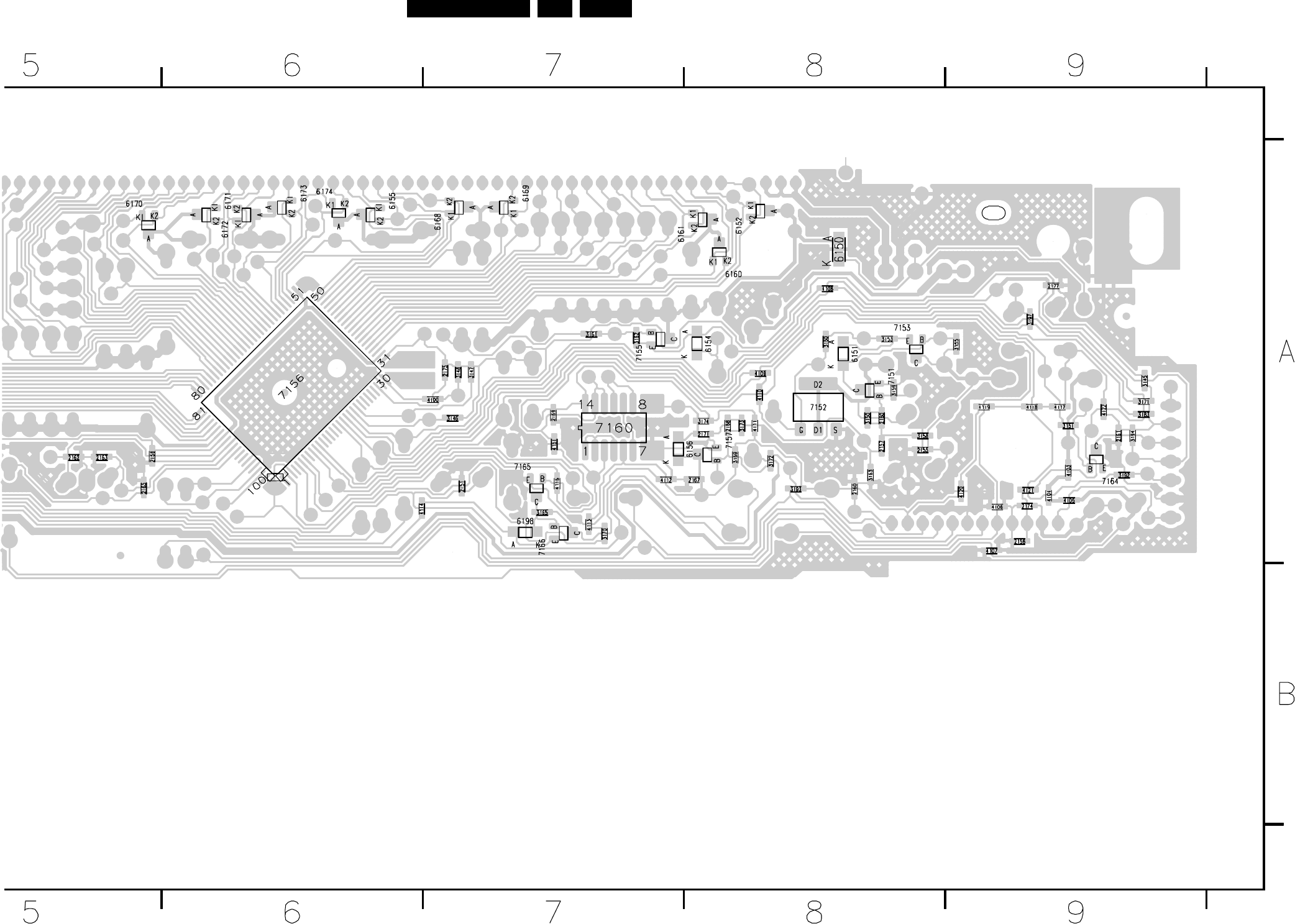

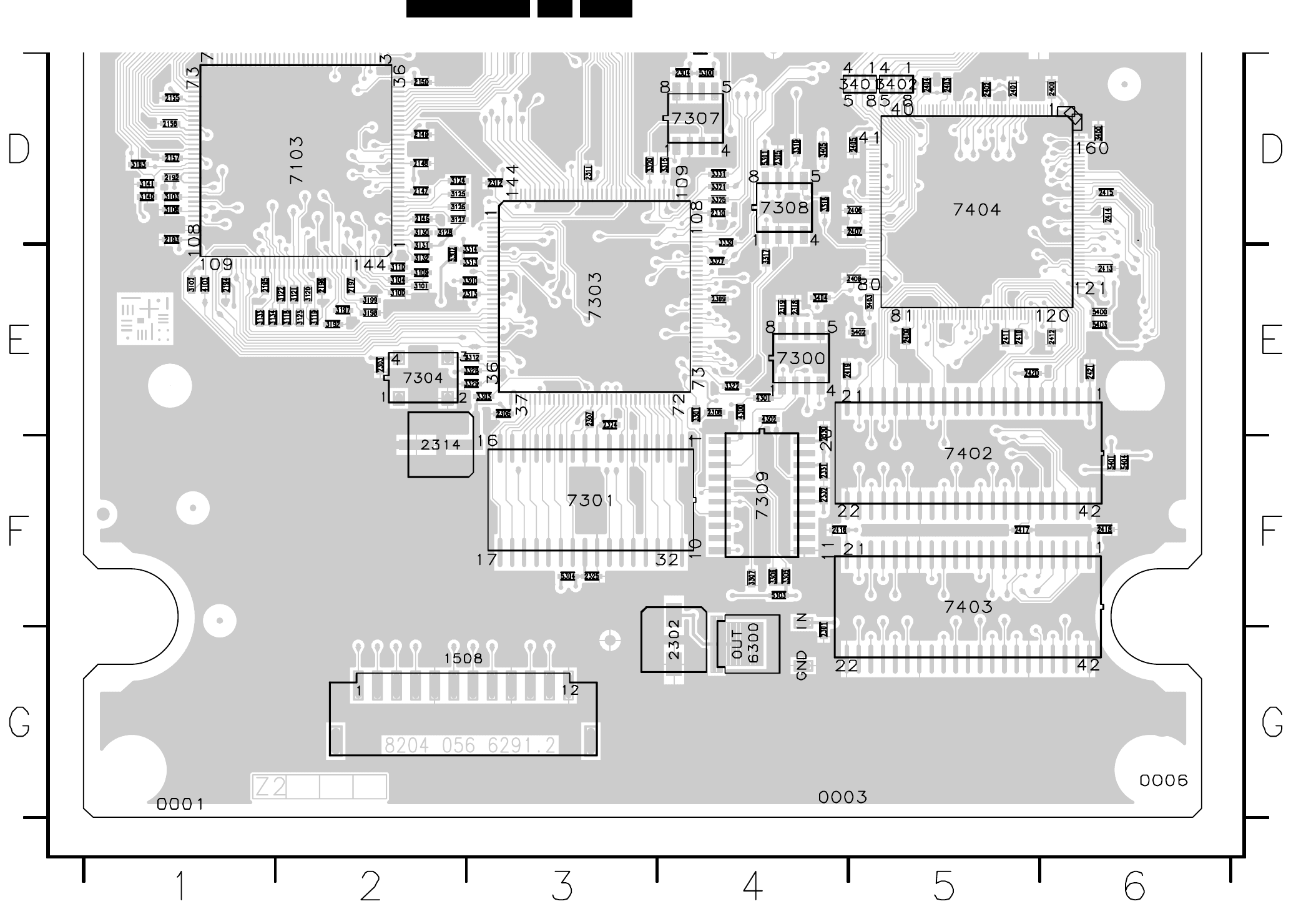

- Layout Digital Board (Part 1 Bottom View)

- Layout Digital Board (Part 2 Bottom View)

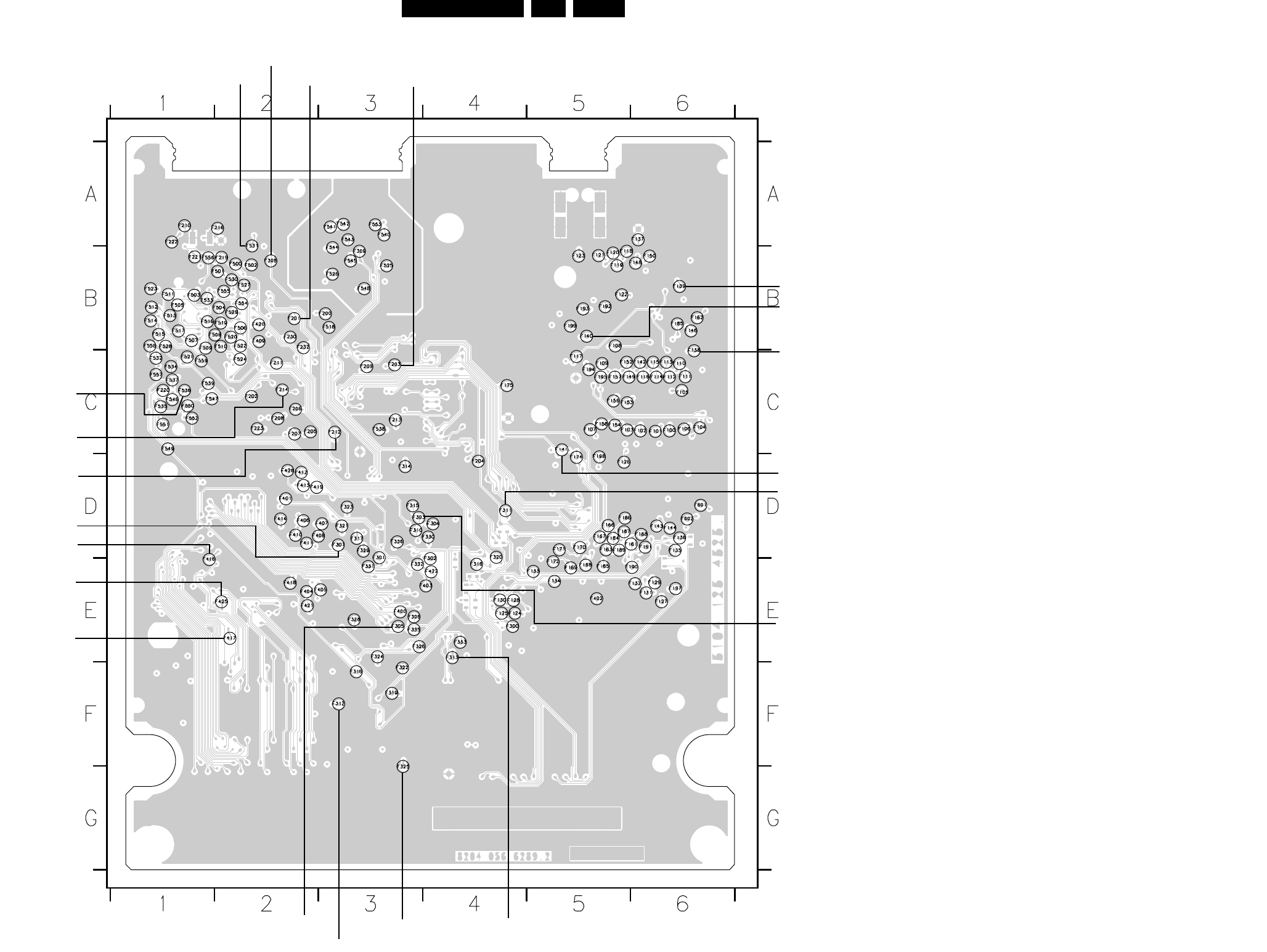

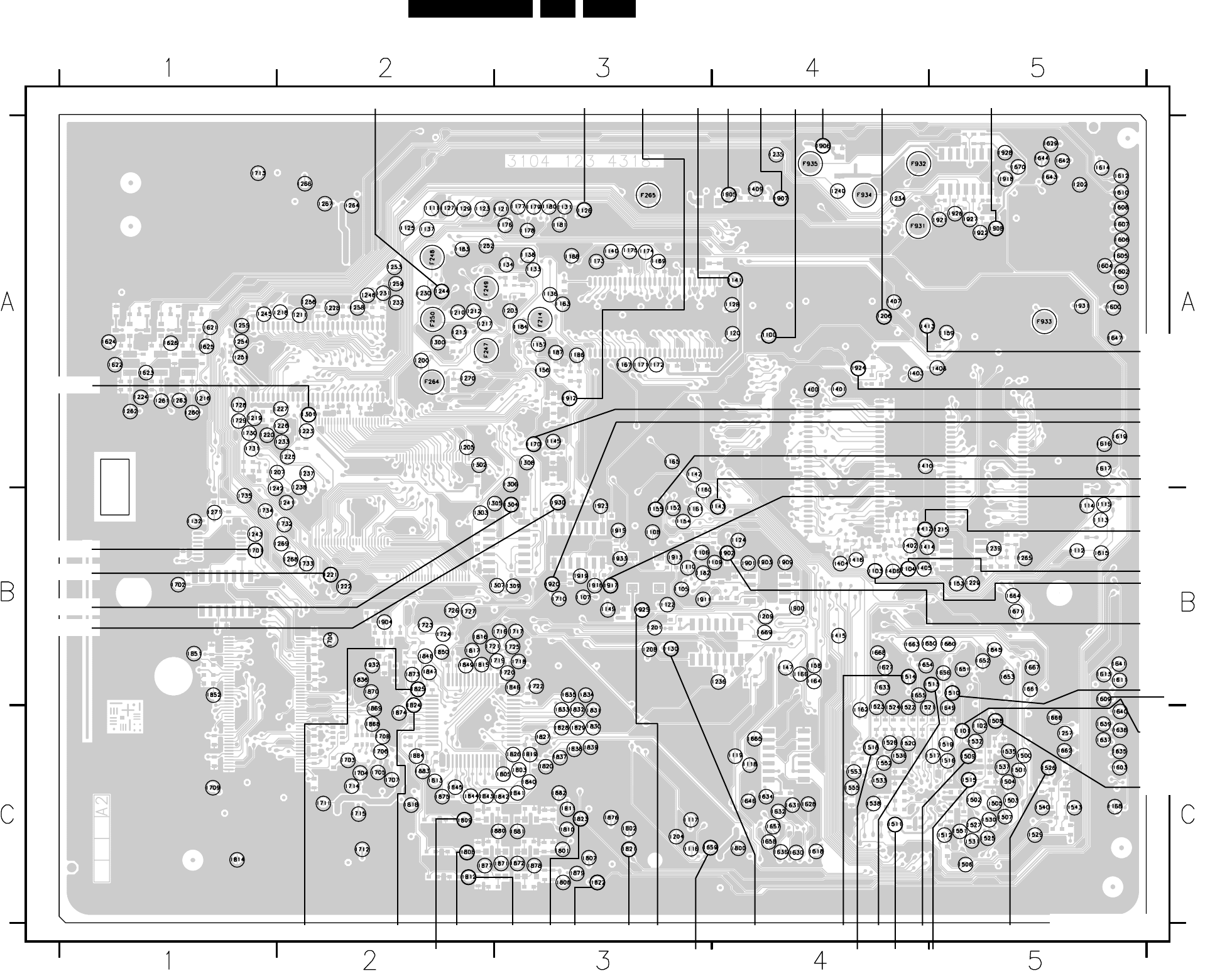

- Layout Digital Board (Testlands Bottom View)

- Layout Digital Board (Mapping Testlands )

- 8. Alignments

- 9. Circuit-, IC Descriptions and List of Abbreviations

- 9.1 Multi-Mode SOPS 50PS203

- 9.2 Display Board

- 9.3 Analogue Board Europe

- 9.4 Analog Board Nafta version

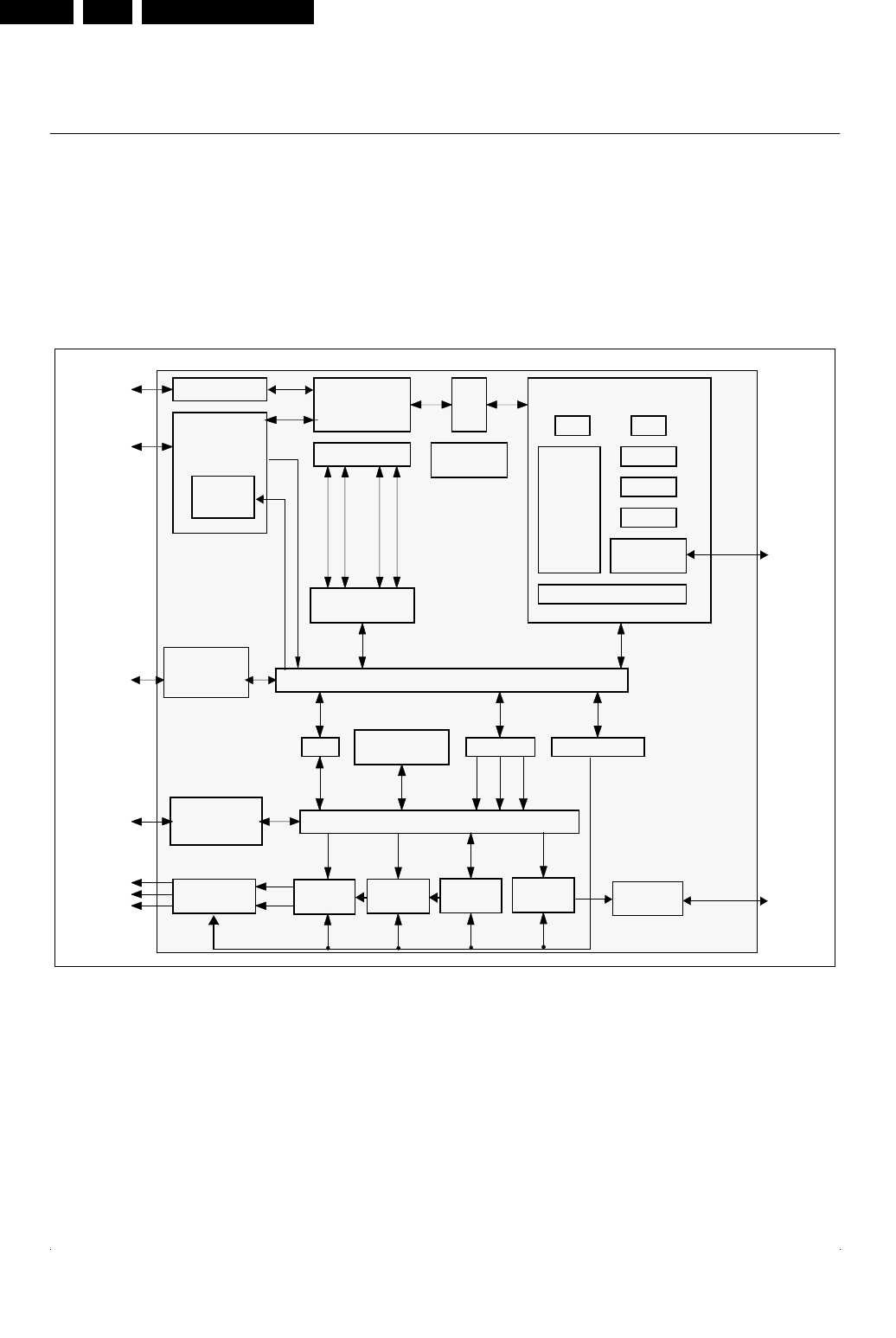

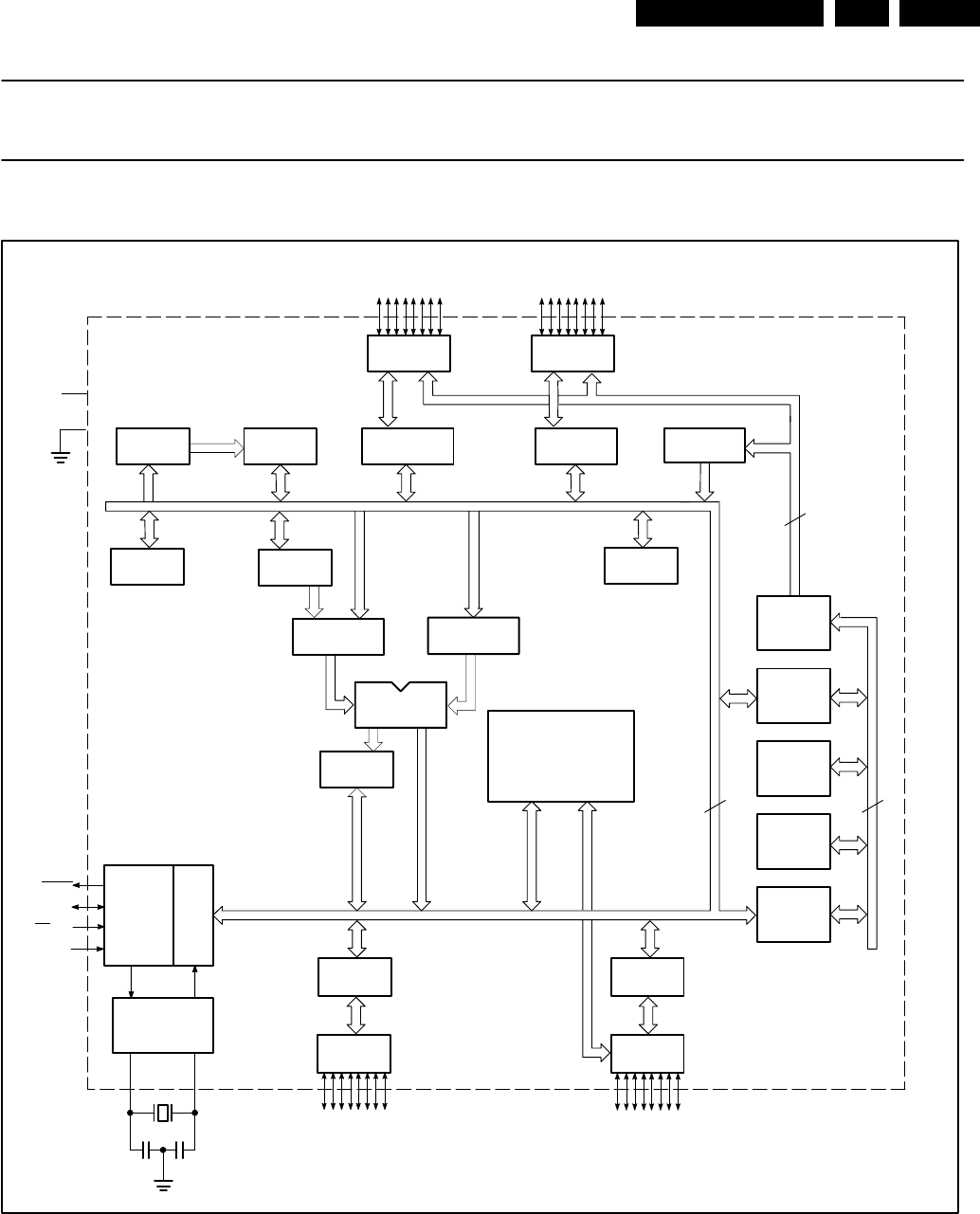

- 9.5 Digital Board

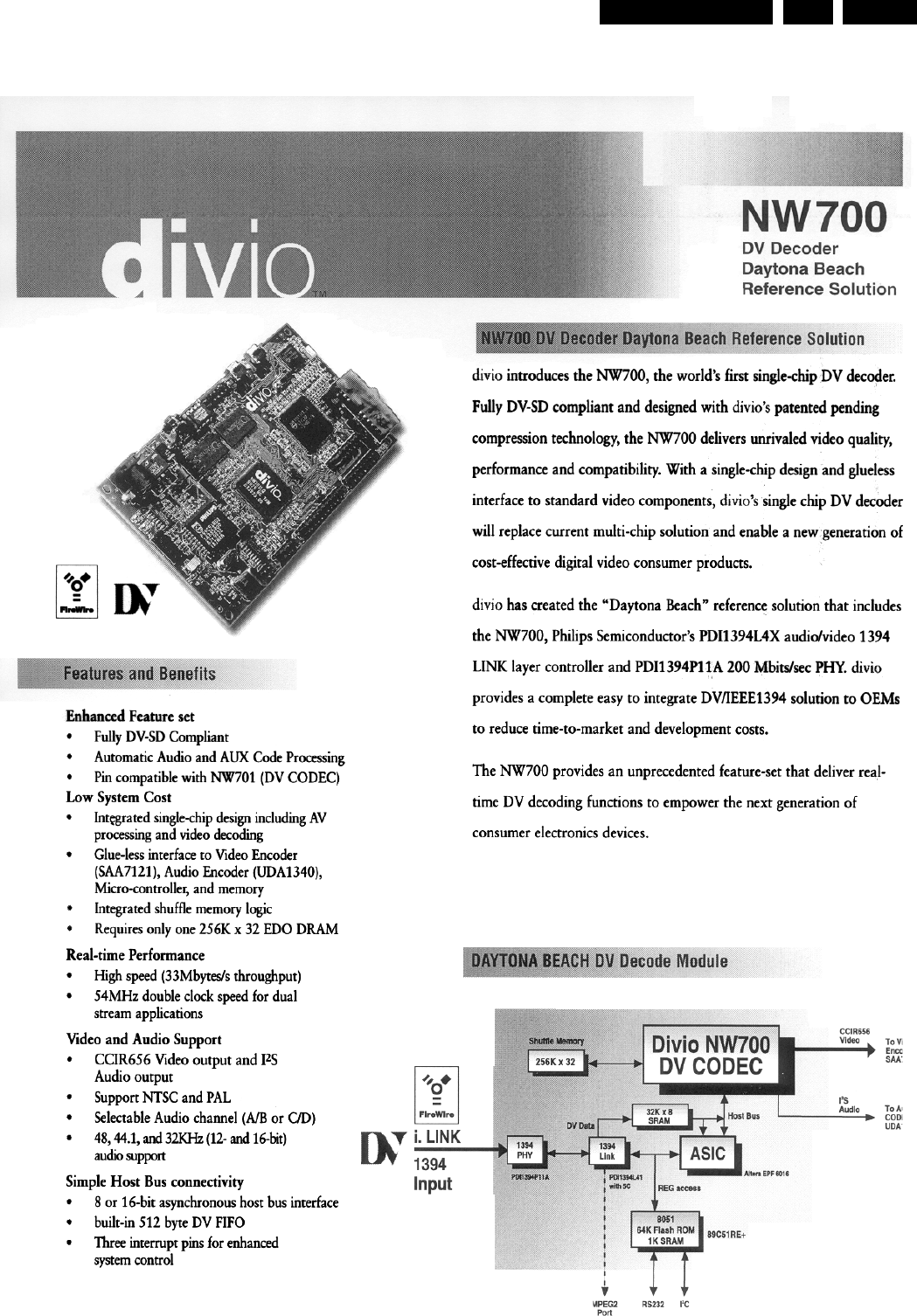

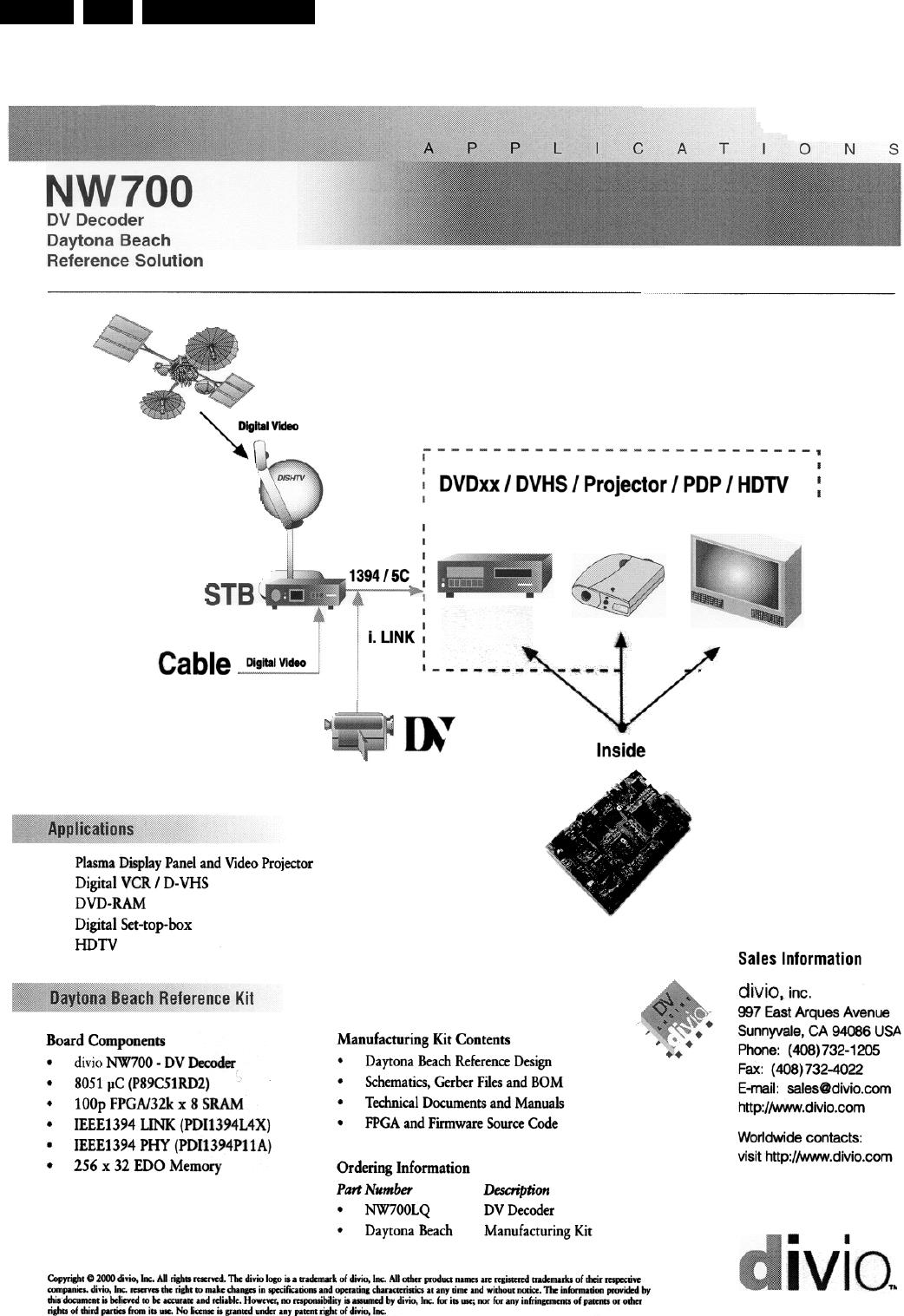

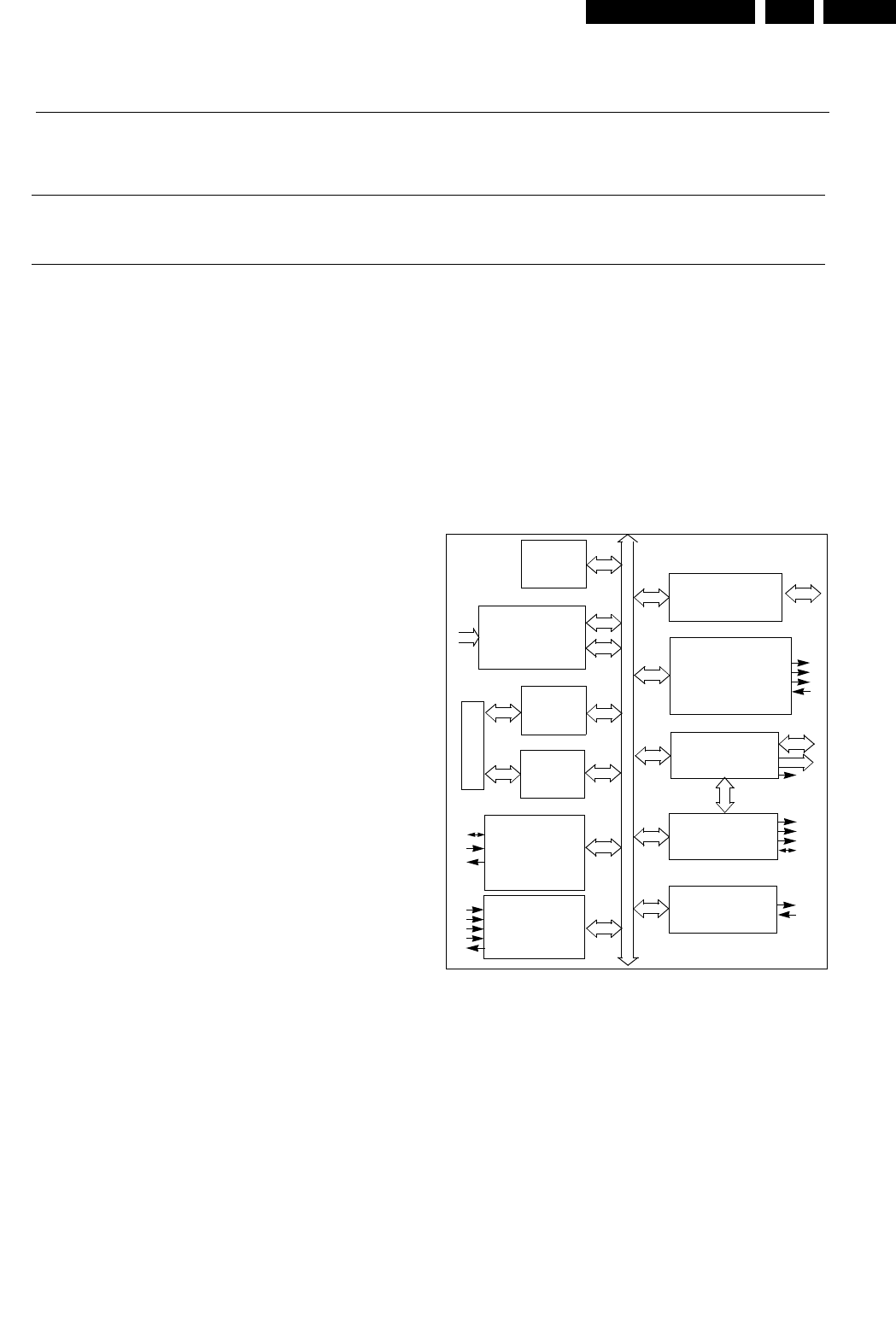

- 9.6 Divio Board

- 9.7 IC’s Analog Board

- 9.8 IC’s Digital Board

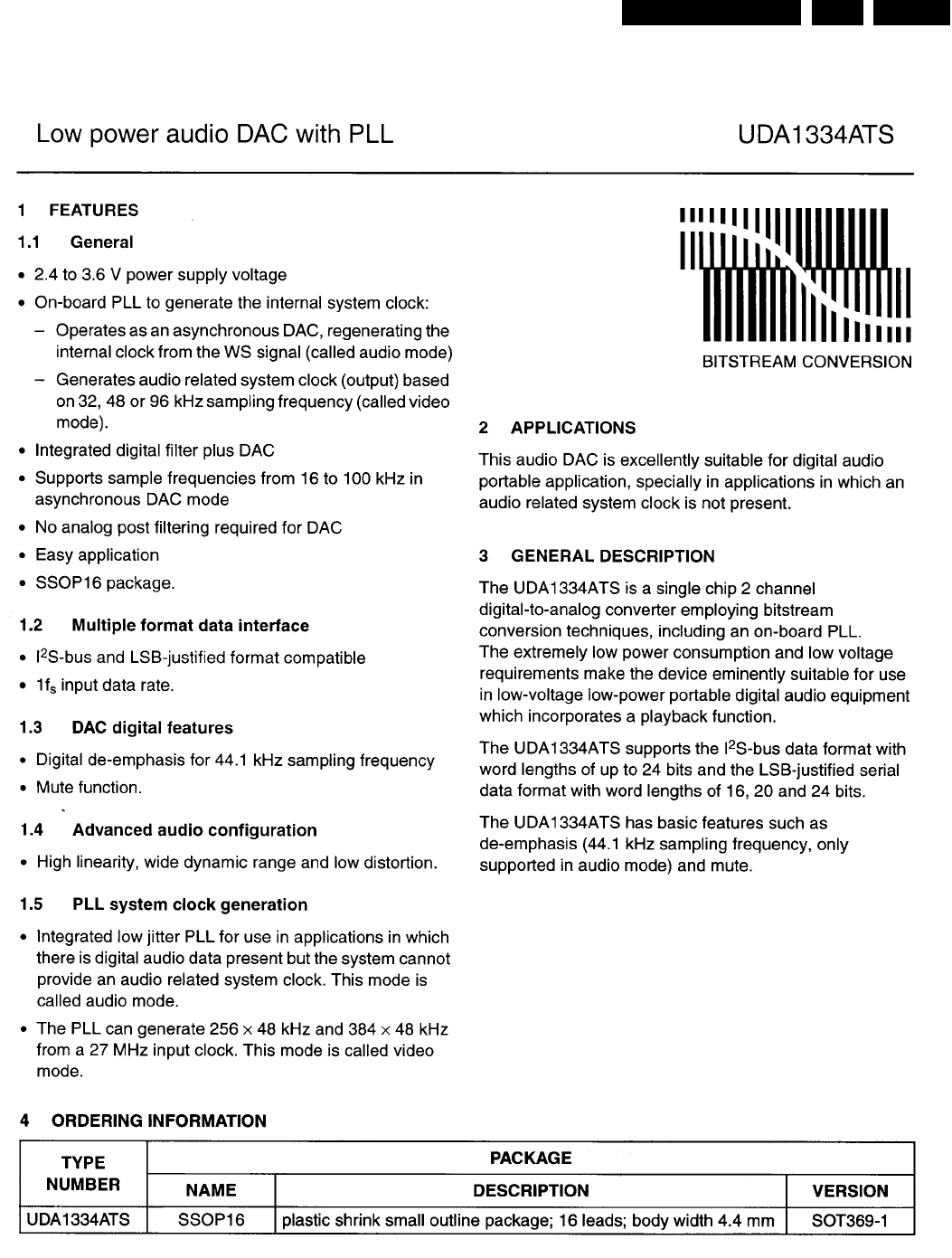

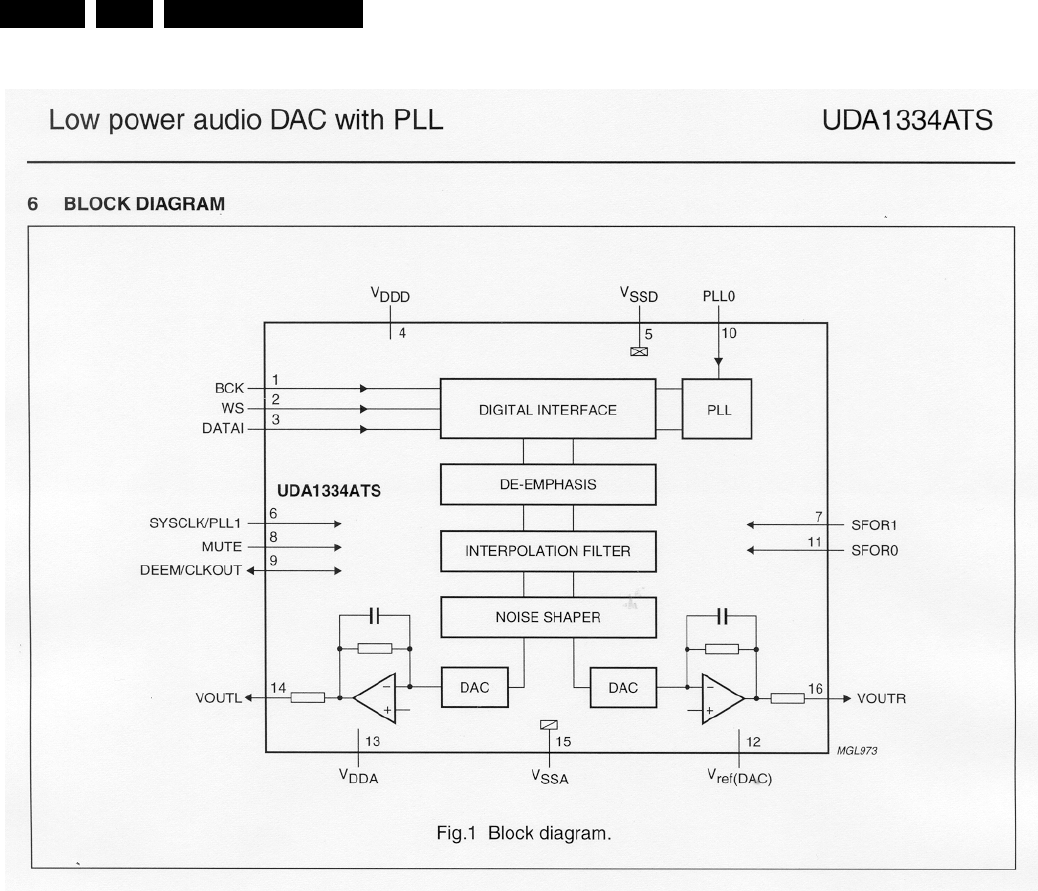

- 9.9 IC’s Divio

- 9.10 List of Abbreviations

- 10. Spare Parts List

Published by MT 0261 Service PaCE Printed in the Netherlands Subject to modification EN 3122 785 11970

©

Copyright 2002 Philips Consumer Electronics B.V. Eindhoven, The Netherlands.

All rights reserved. No part of this publication may be reproduced, stored in a

retrieval system or transmitted, in any form or by any means, electronic,

mechanical, photocopying, or otherwise without the prior permission of Philips.

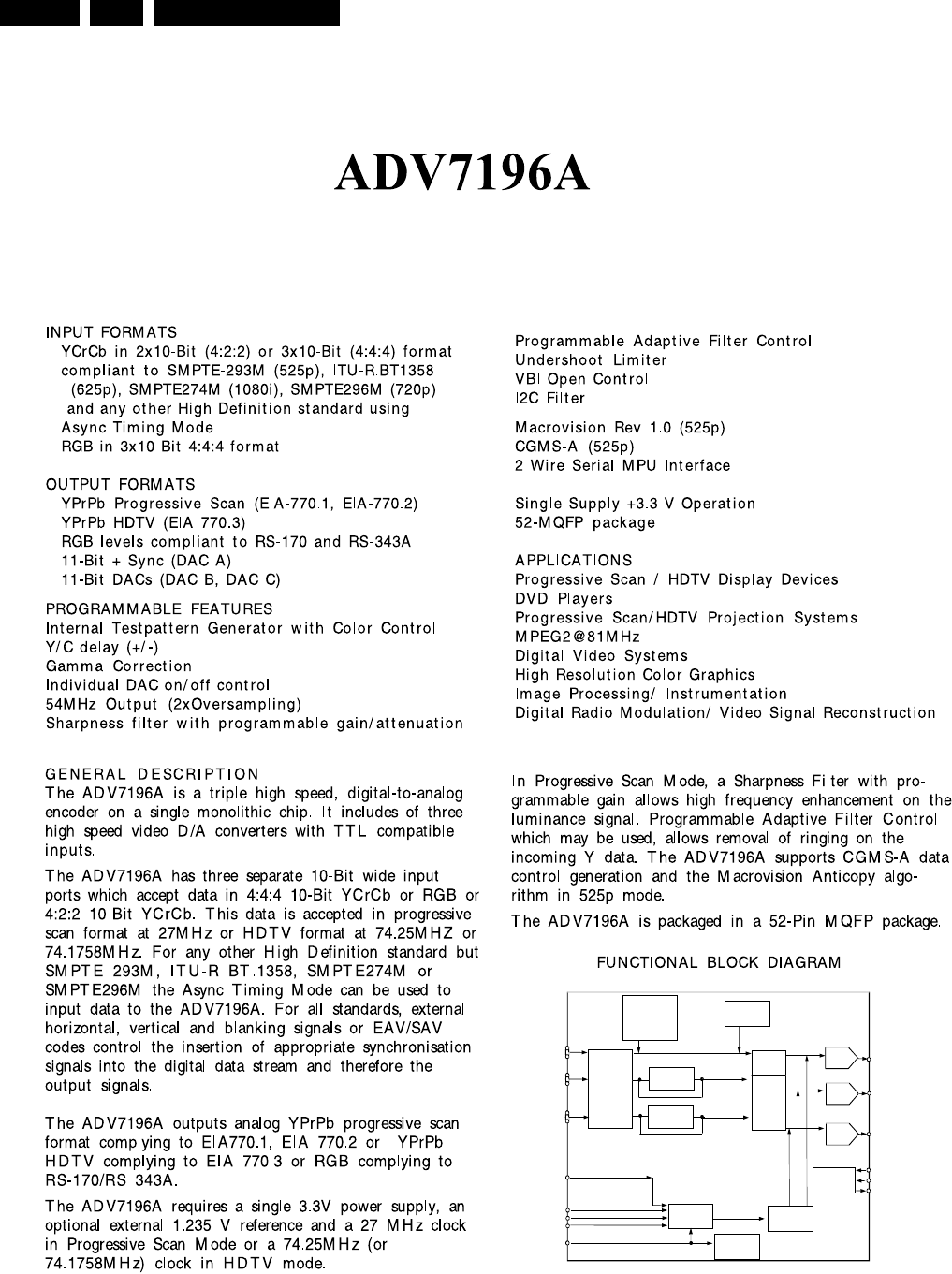

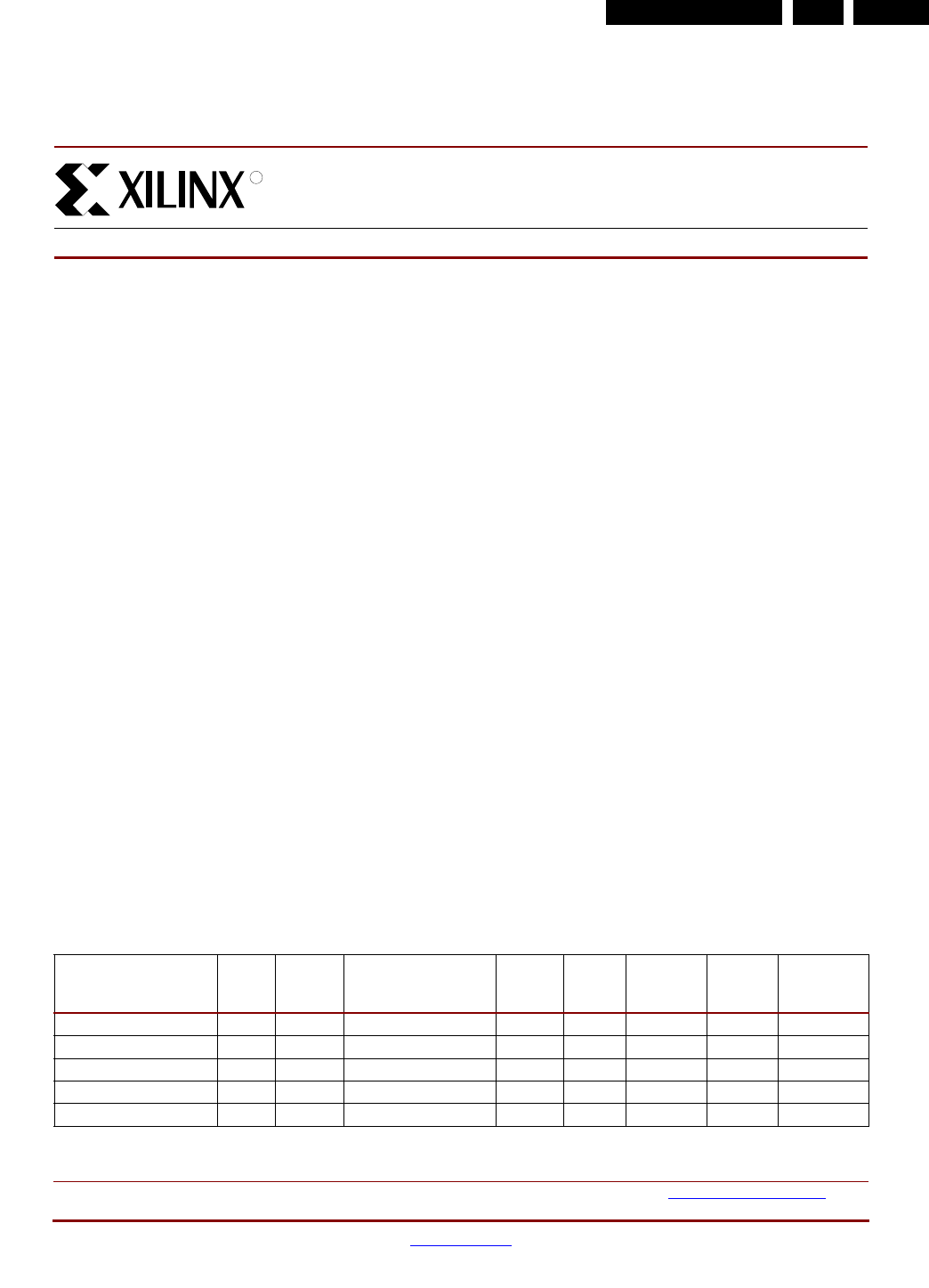

DVD-Video Recorder DVDR980 & DVDR985

/001 /021 /051

CL 26532011_000.eps

160102

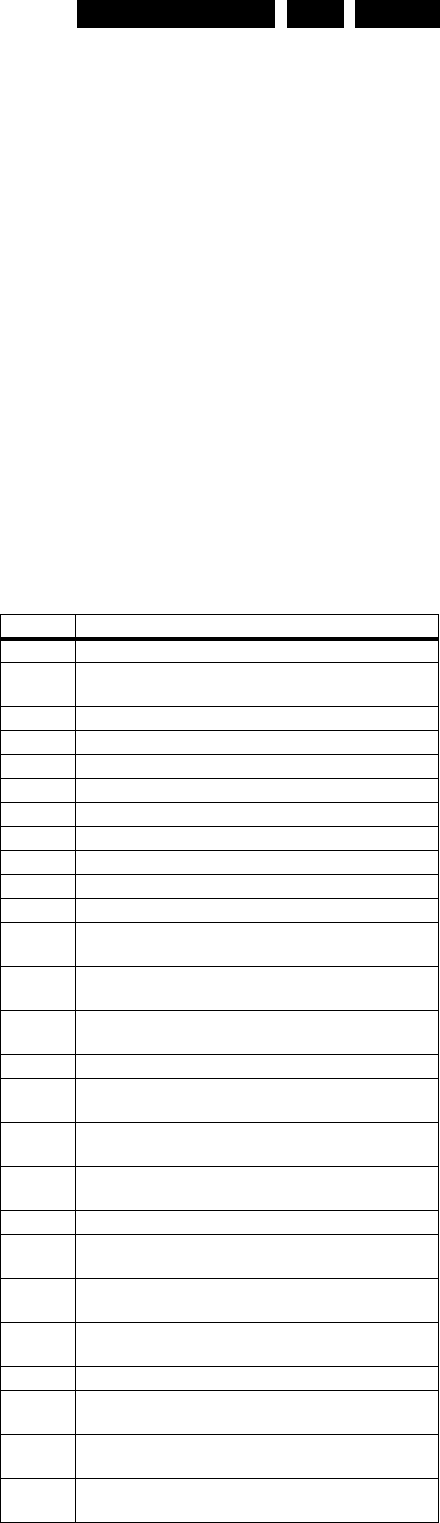

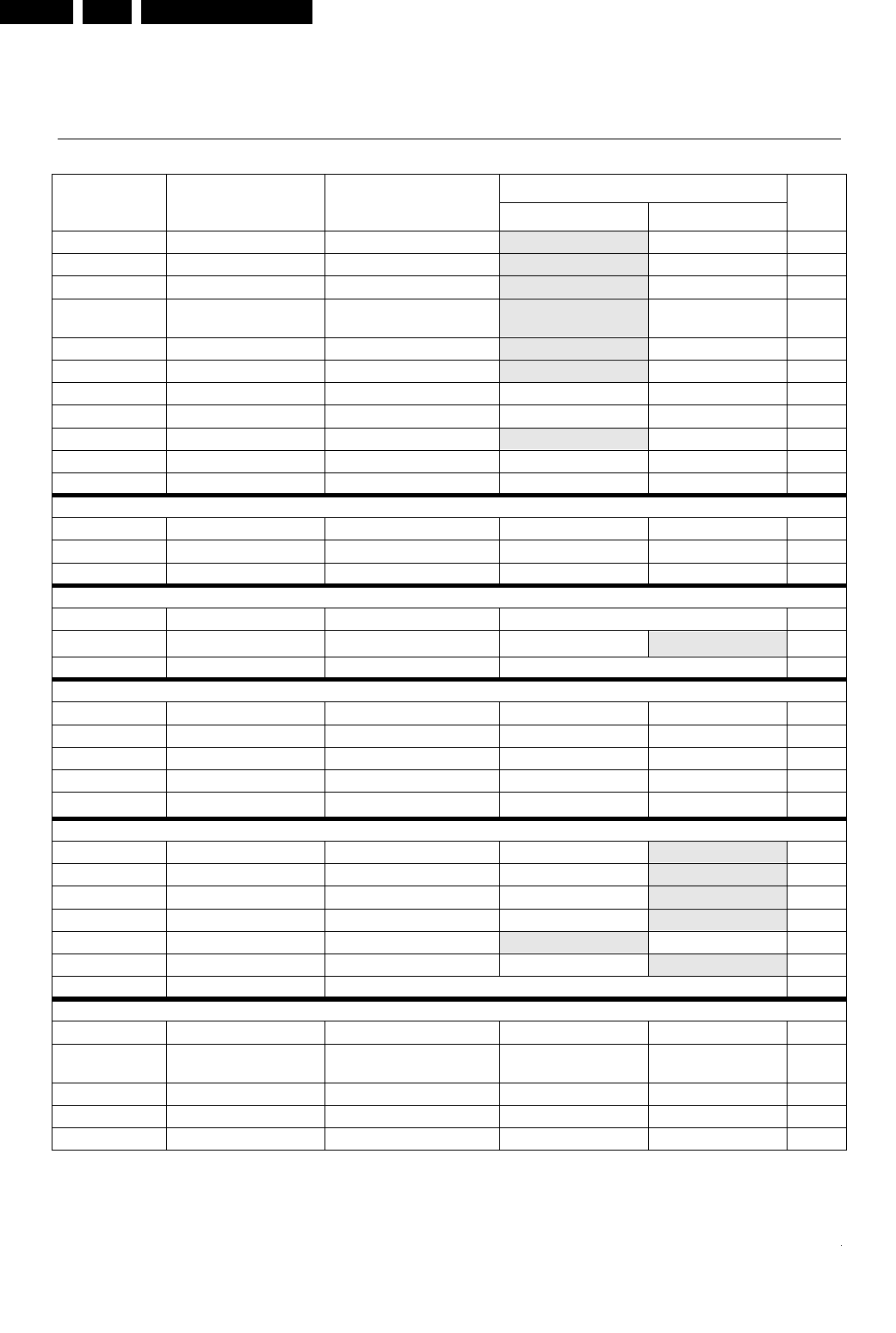

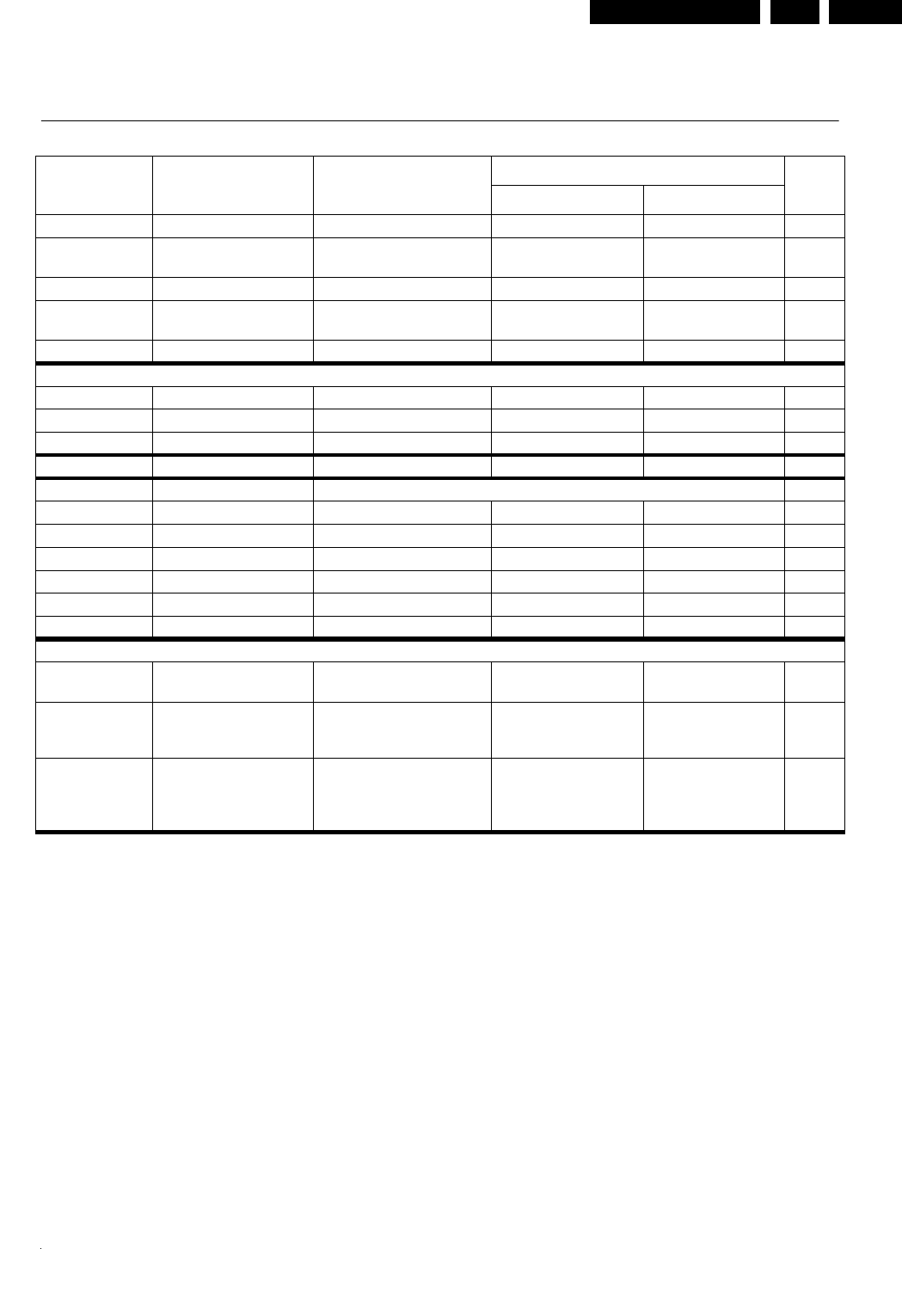

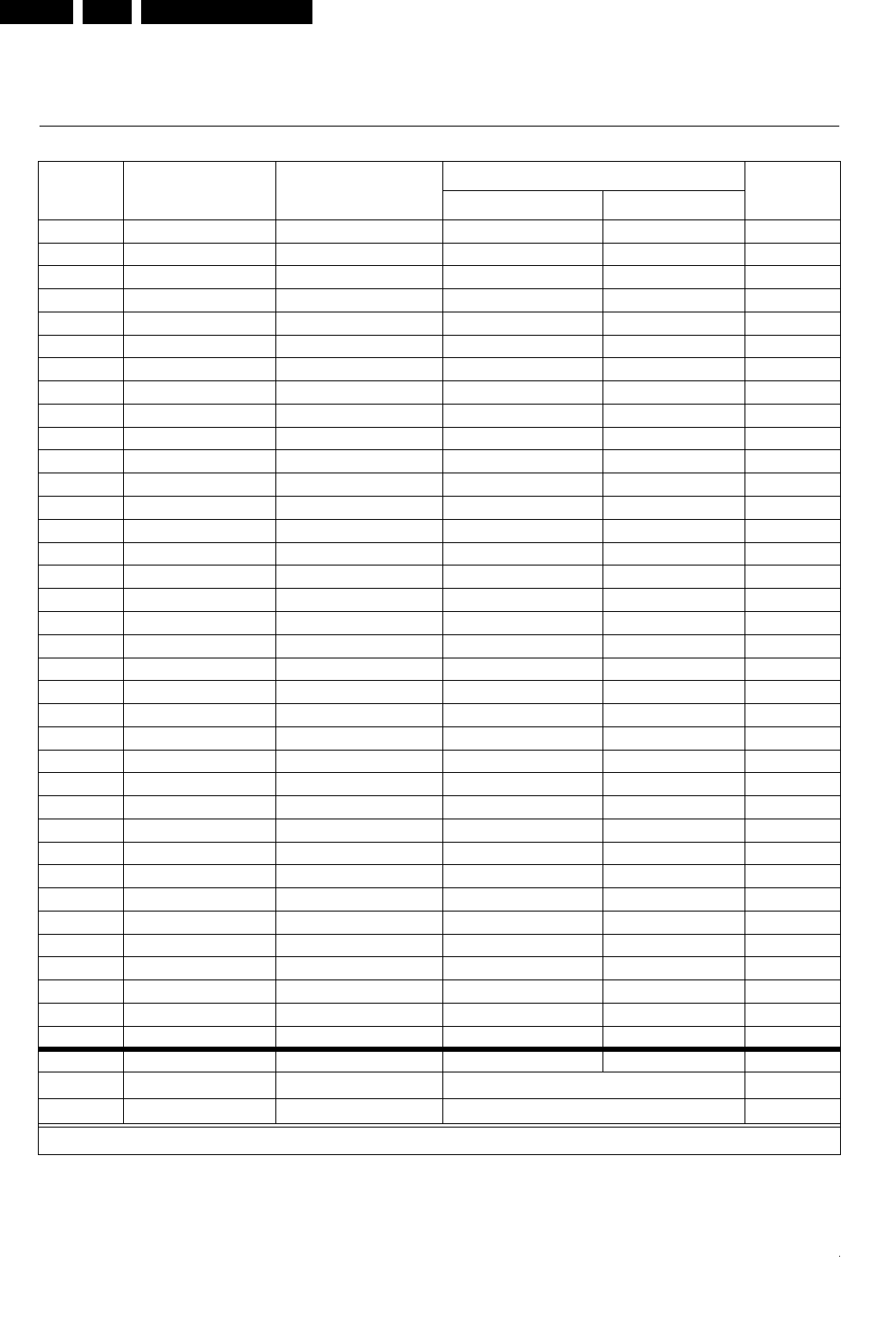

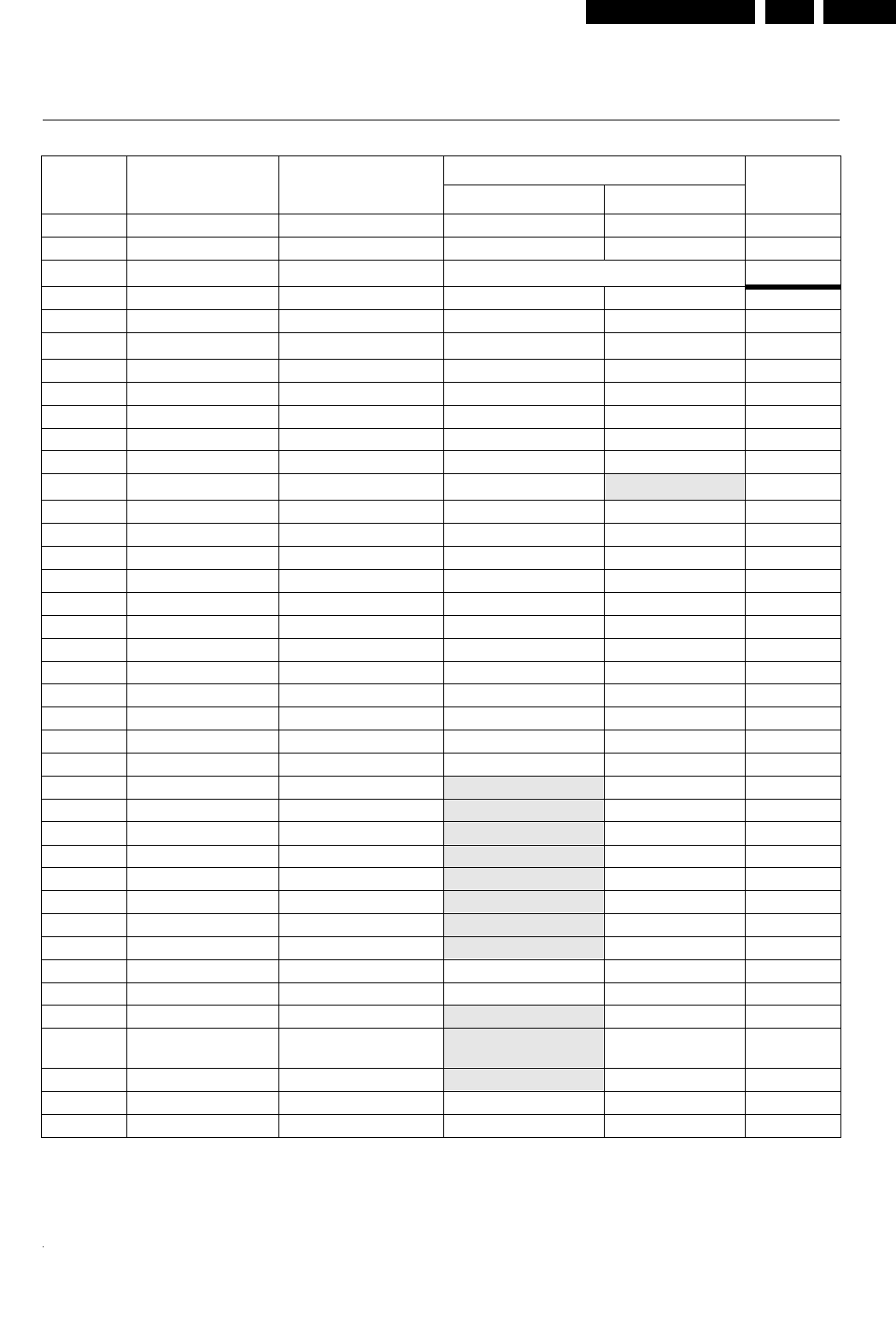

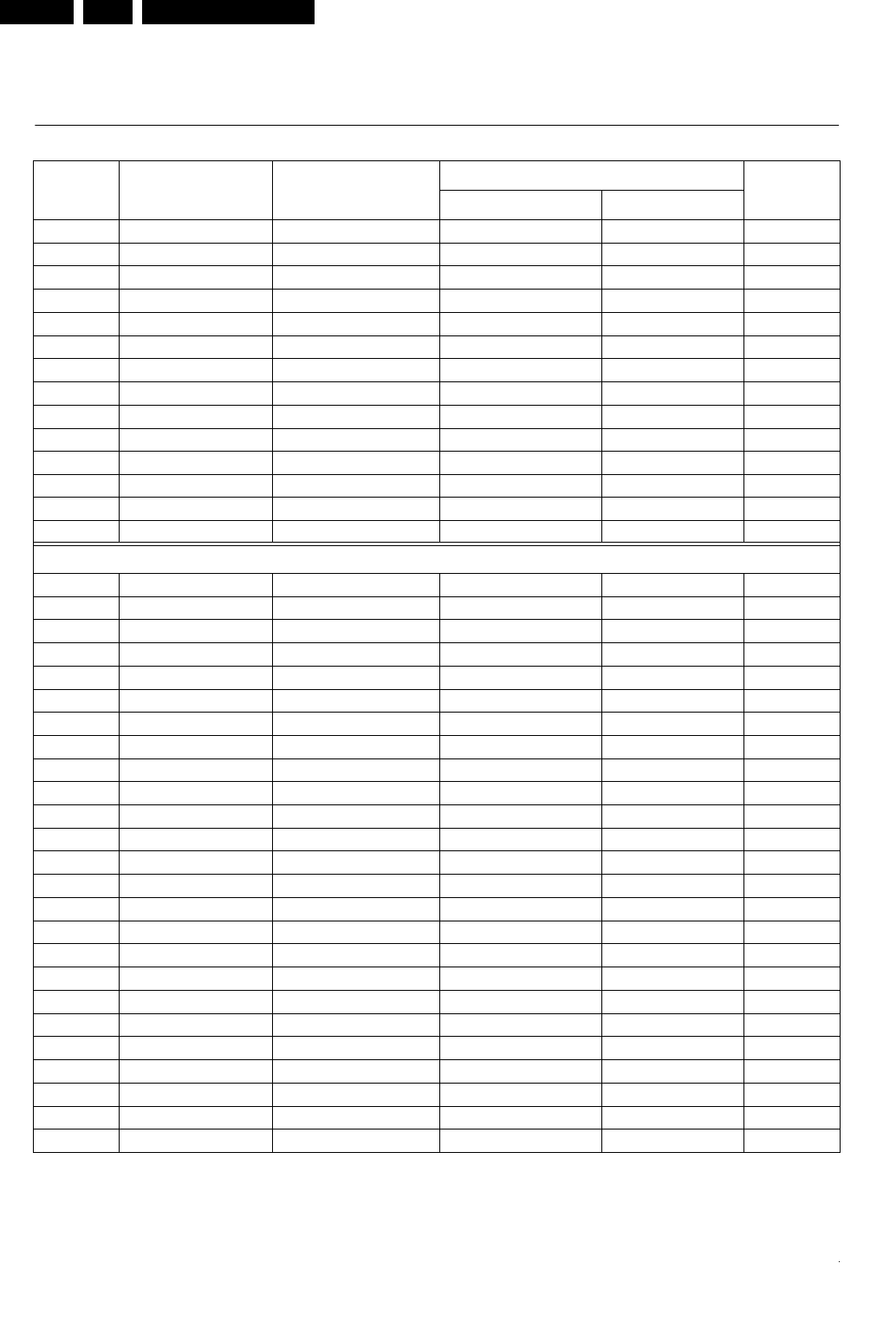

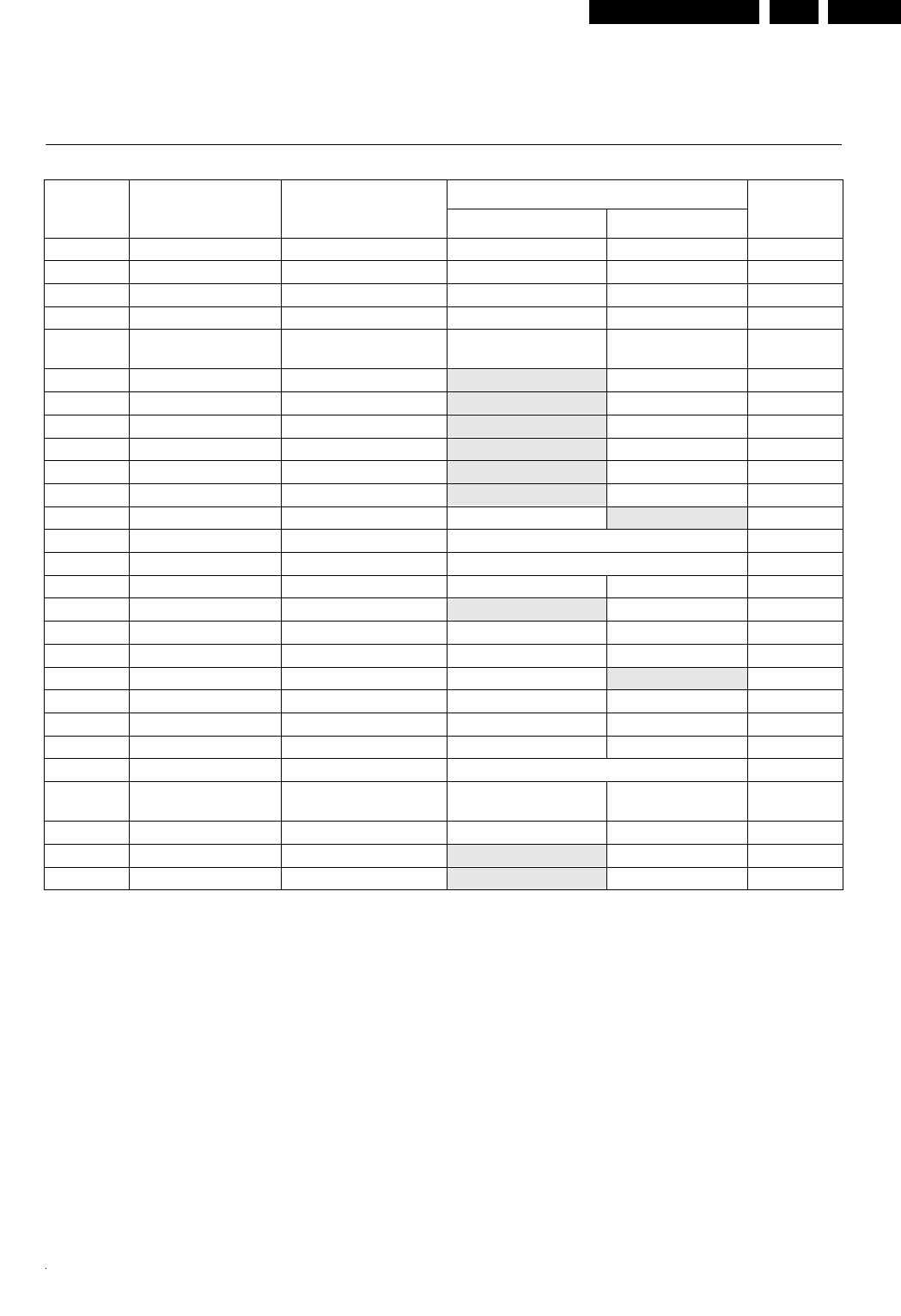

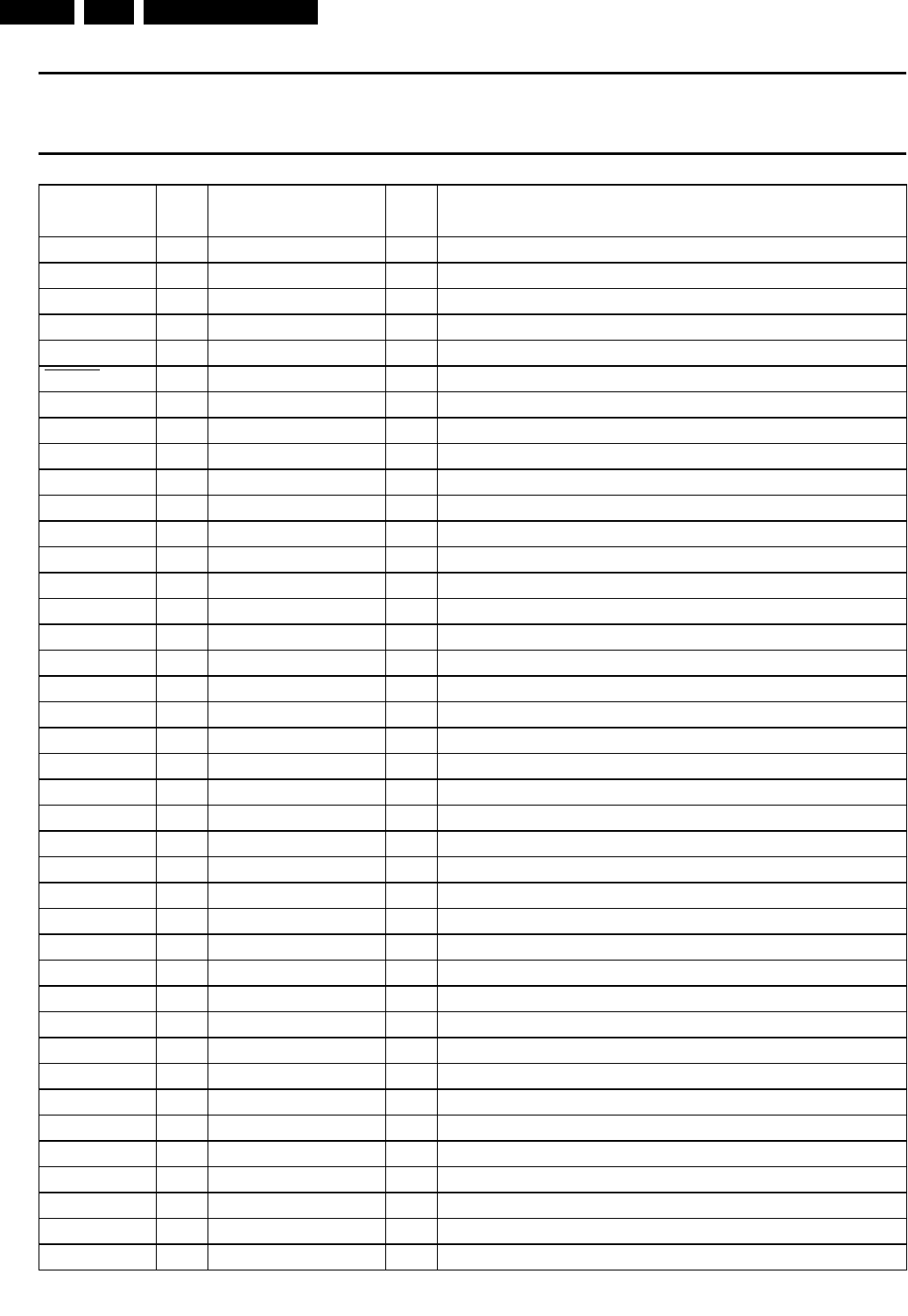

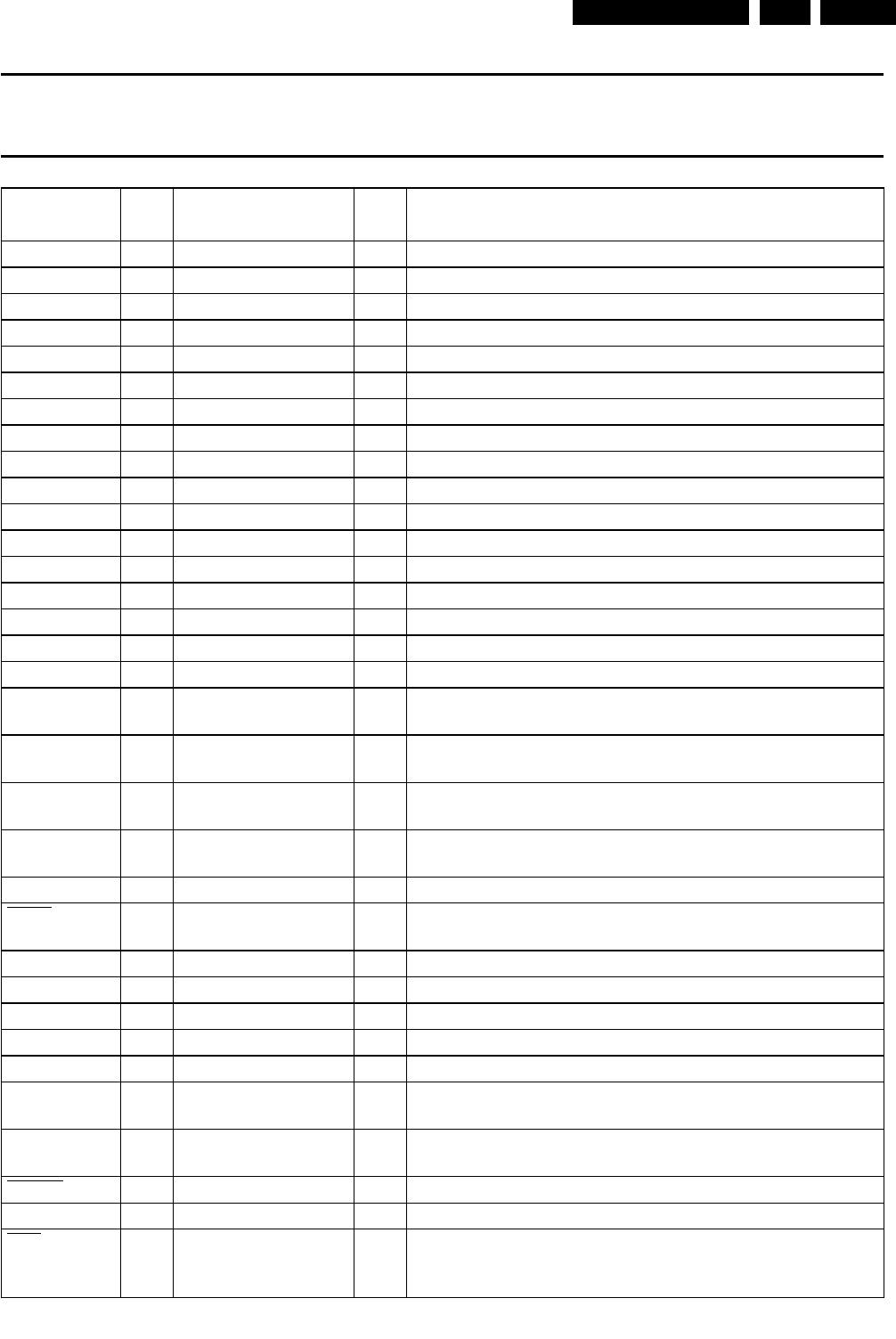

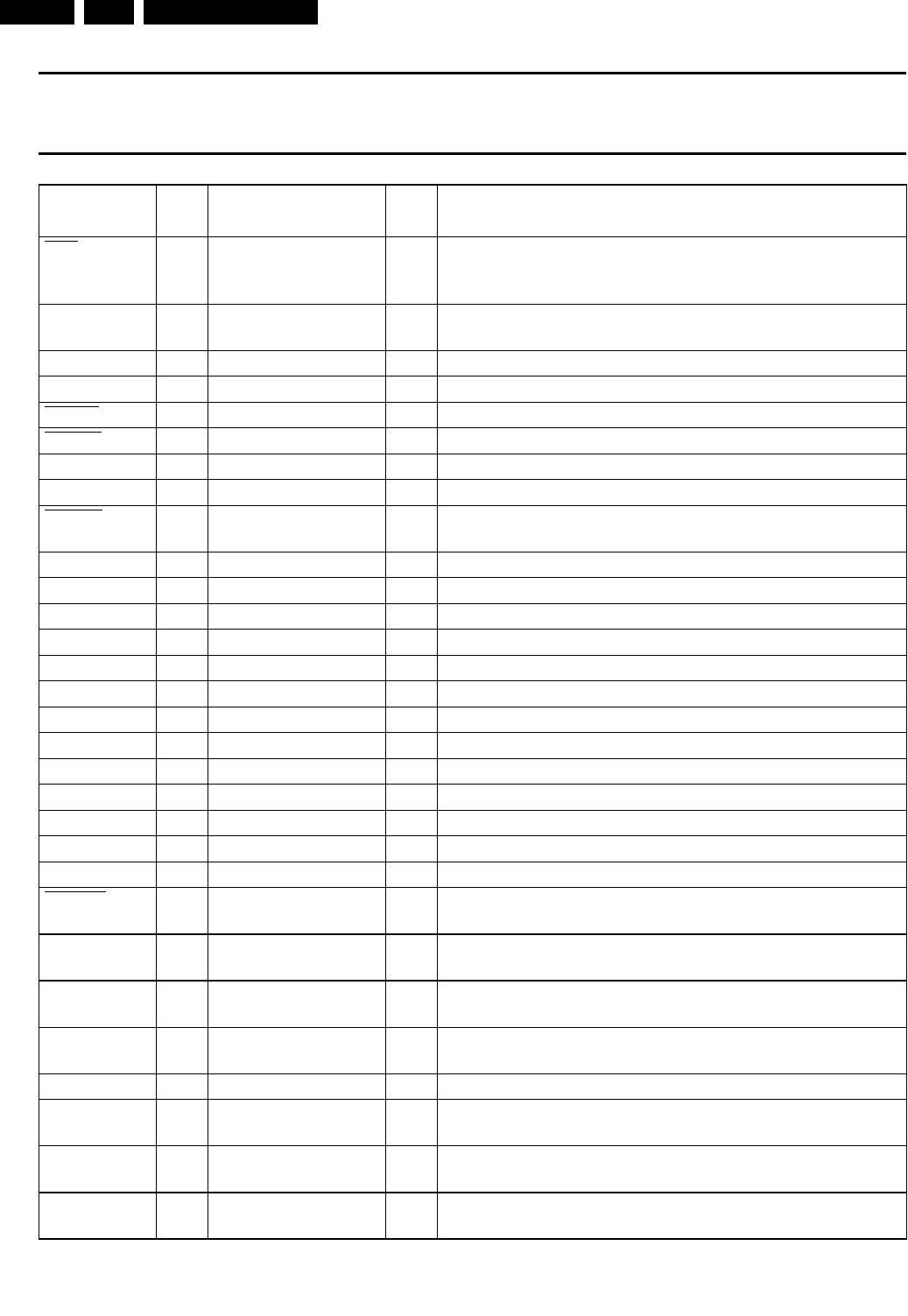

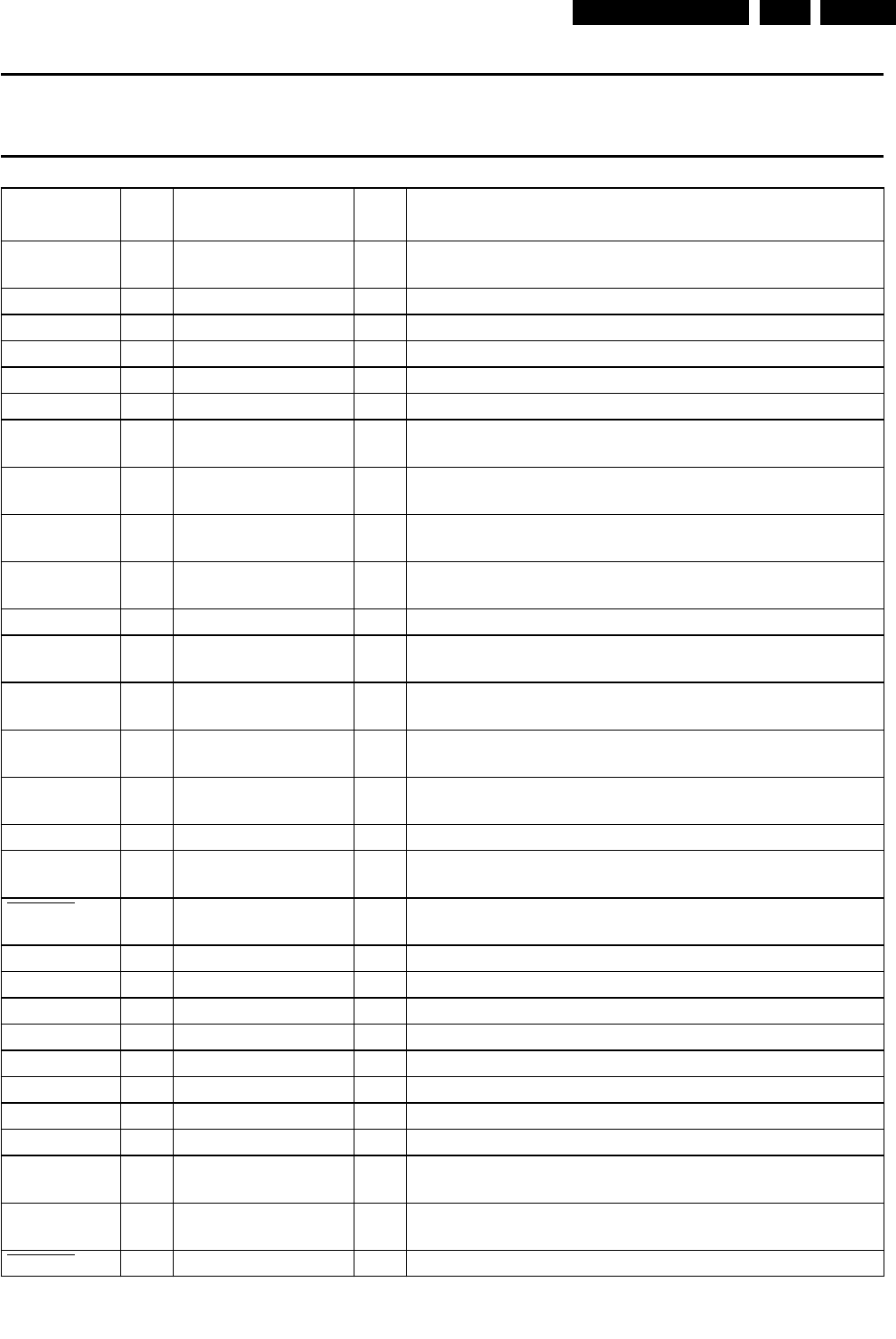

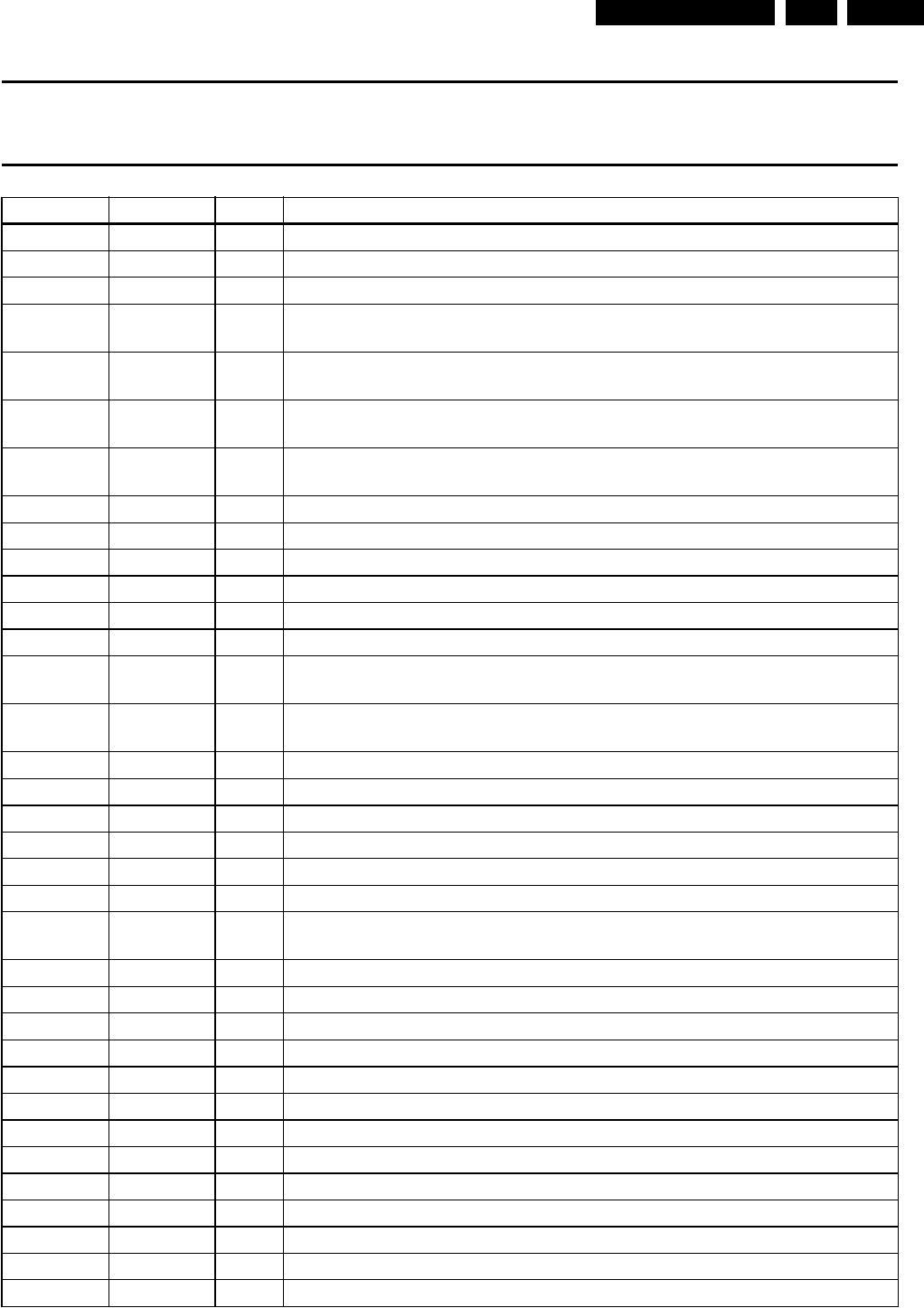

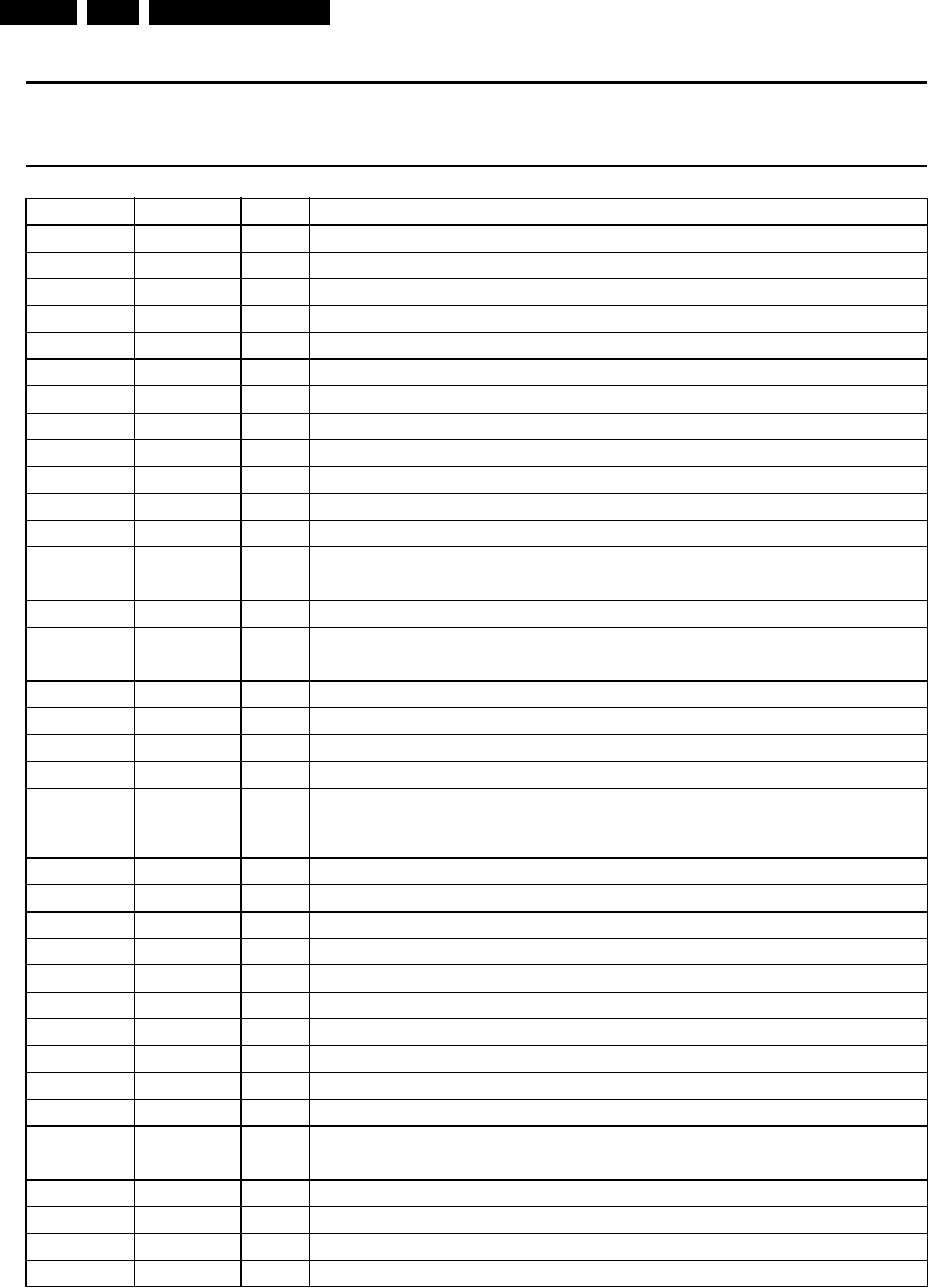

Contents Page Contents Page

1 Technical Specifications and

Connection Facilities 2

2 Warnings, Laser Safety Instructions and Notes 5

3 Directions for Use 7

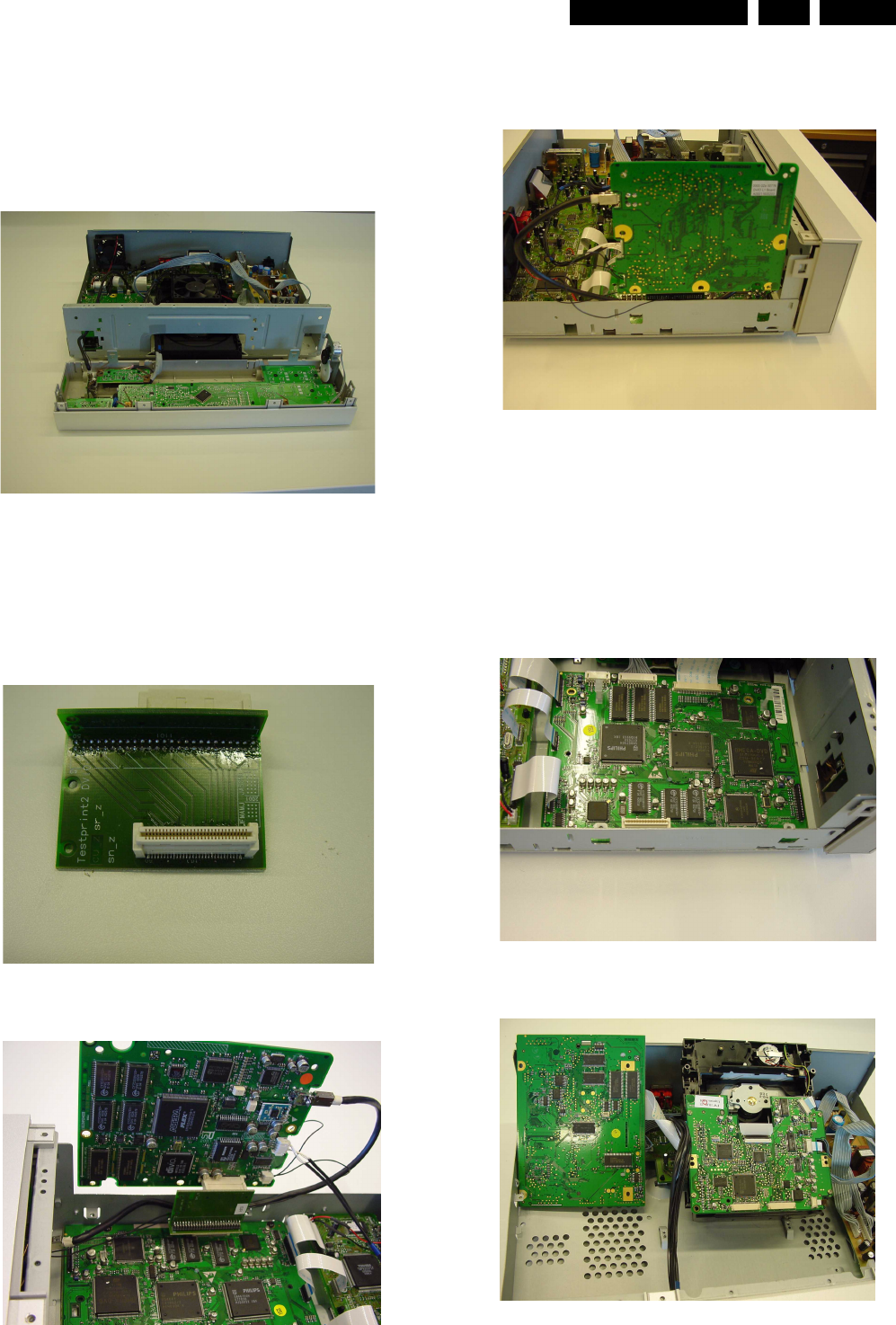

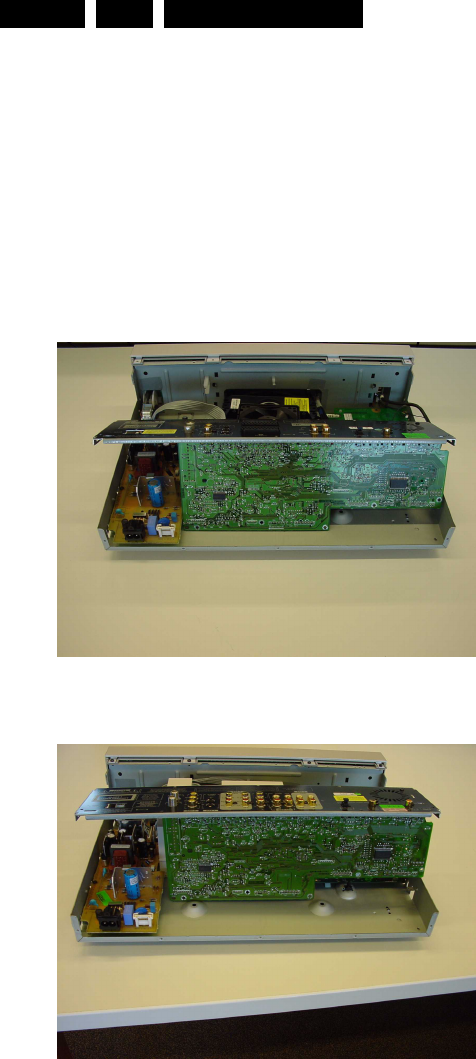

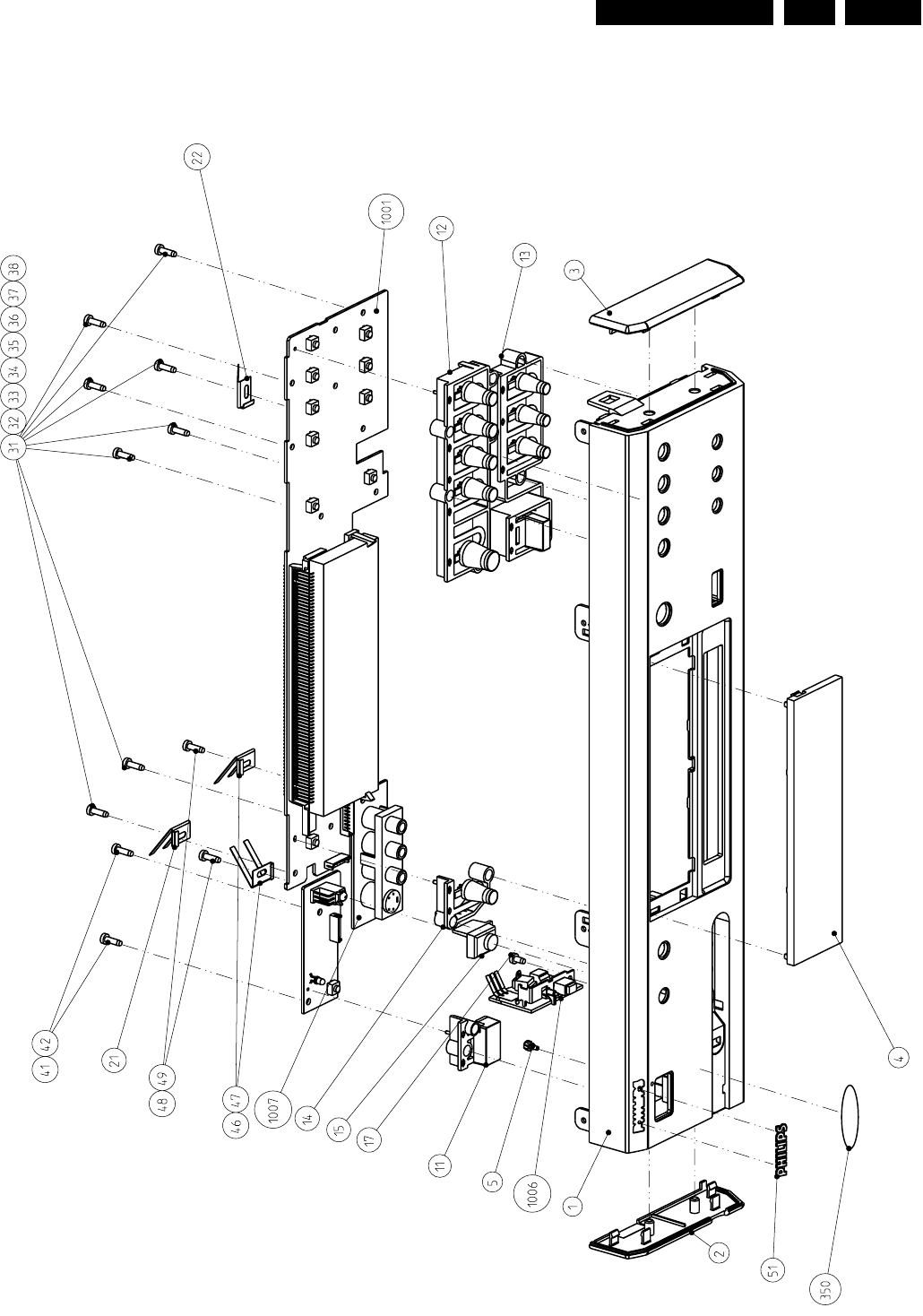

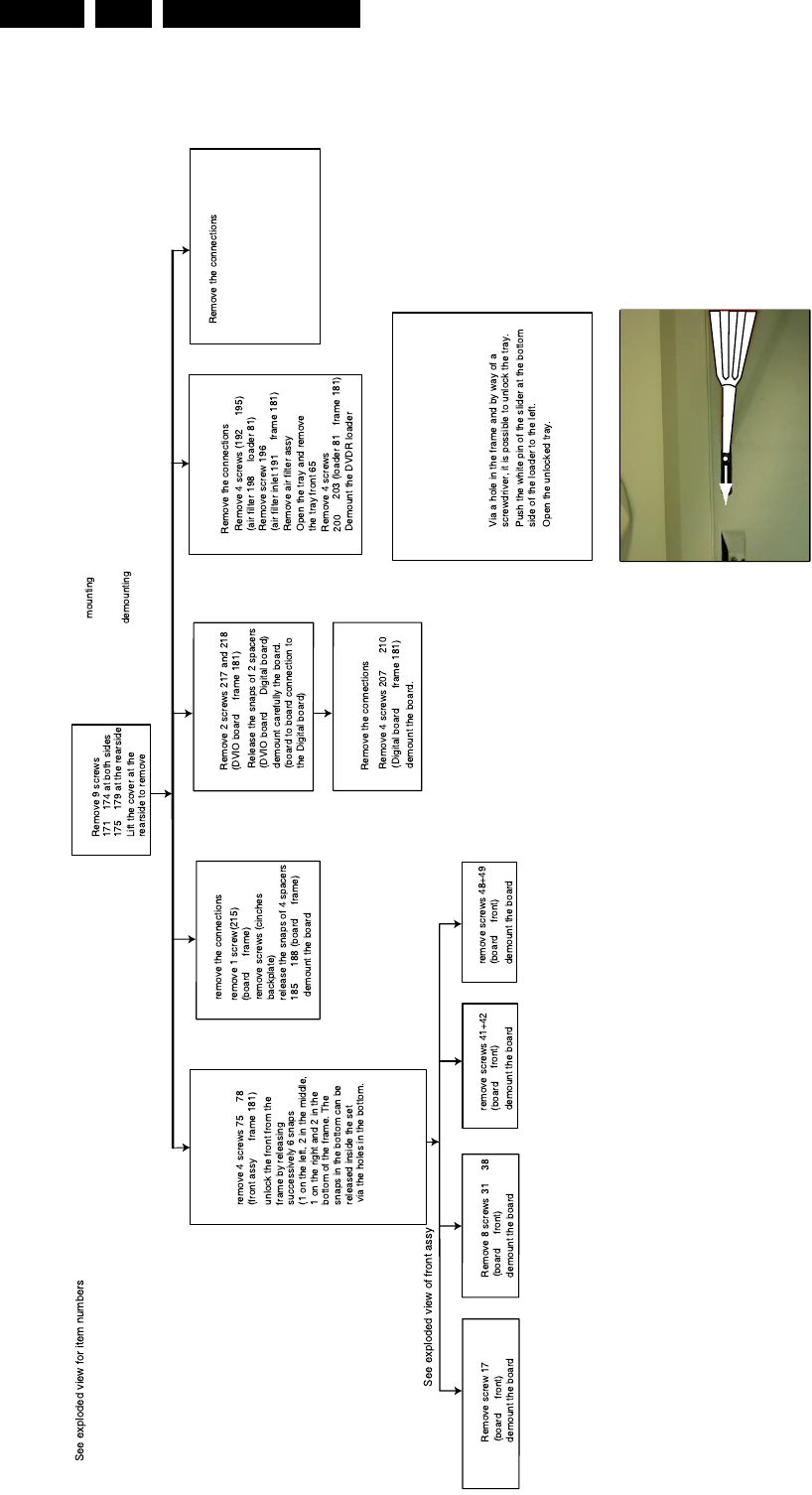

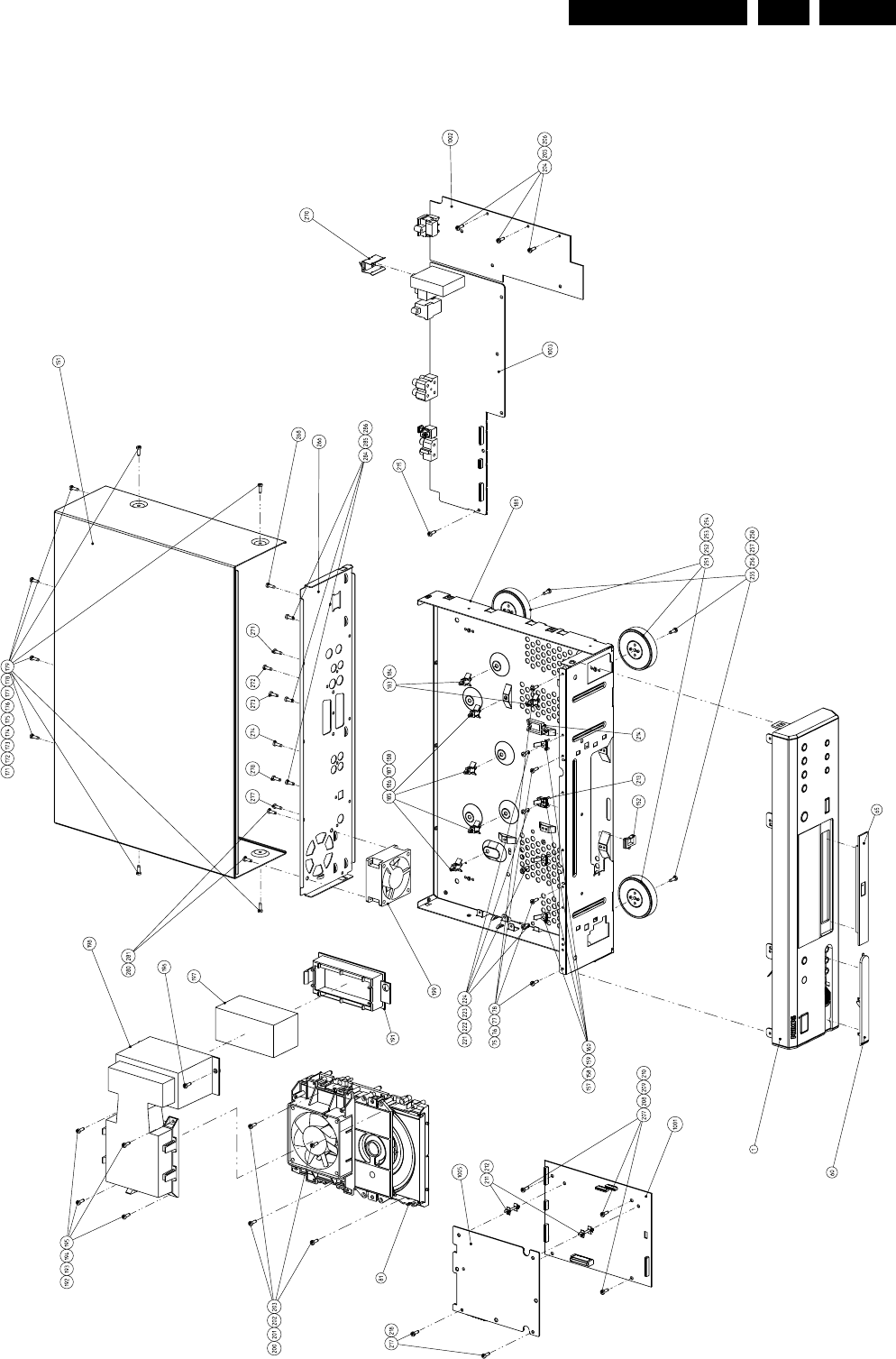

4 Mechanical Instructions and Exploded Views 33

5 Diagnostic Software Descriptions and

Troubleshooting 38

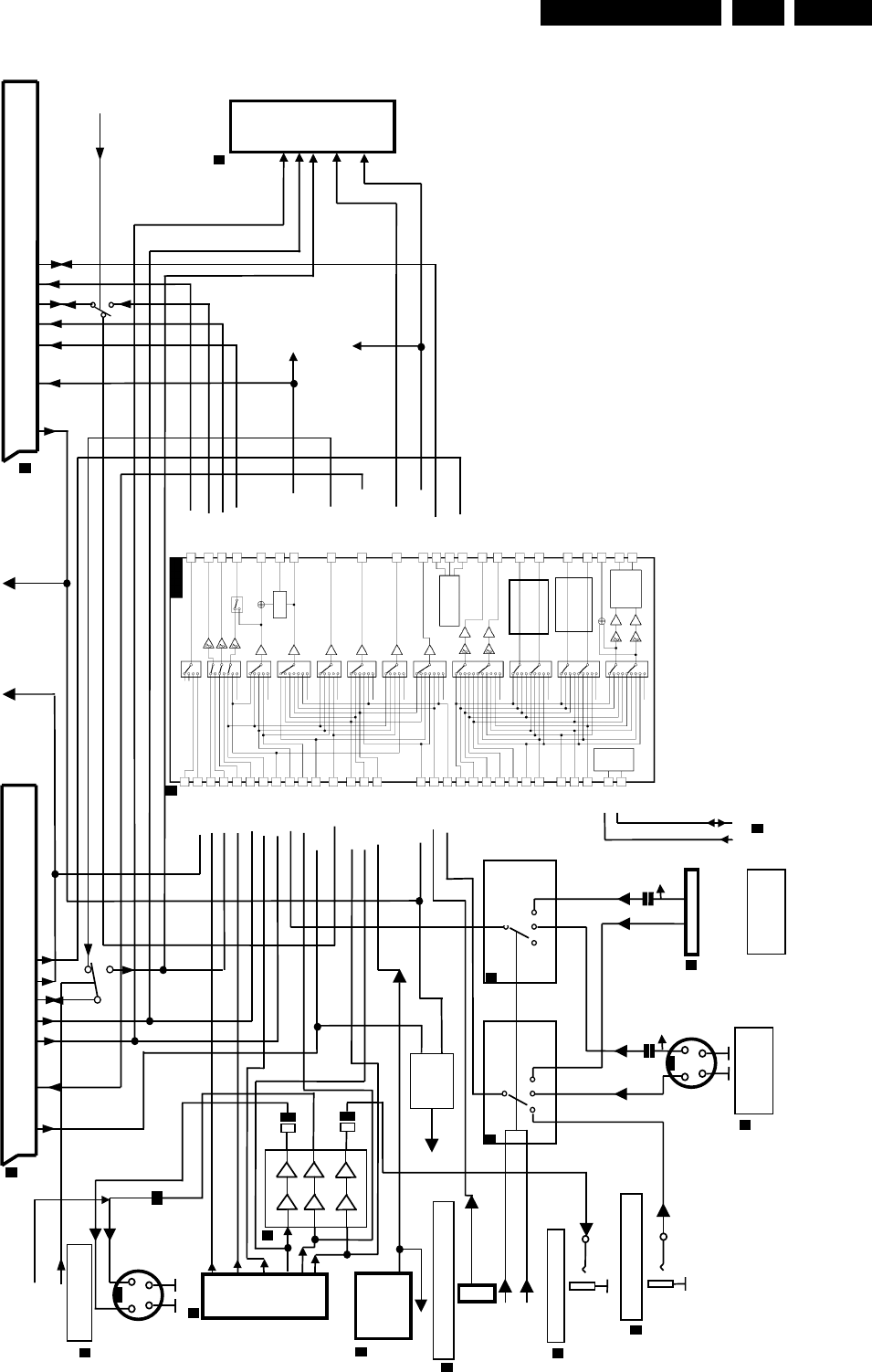

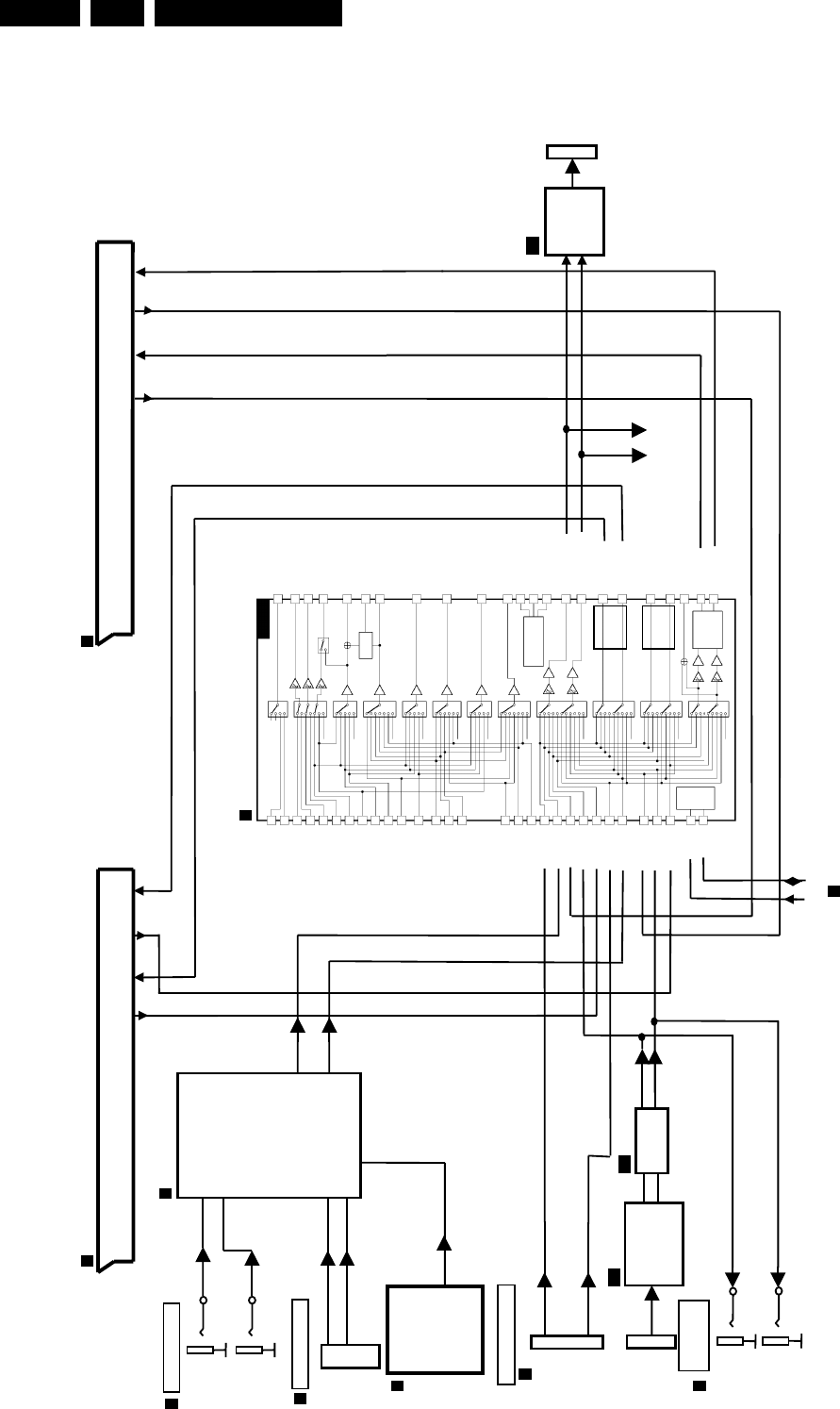

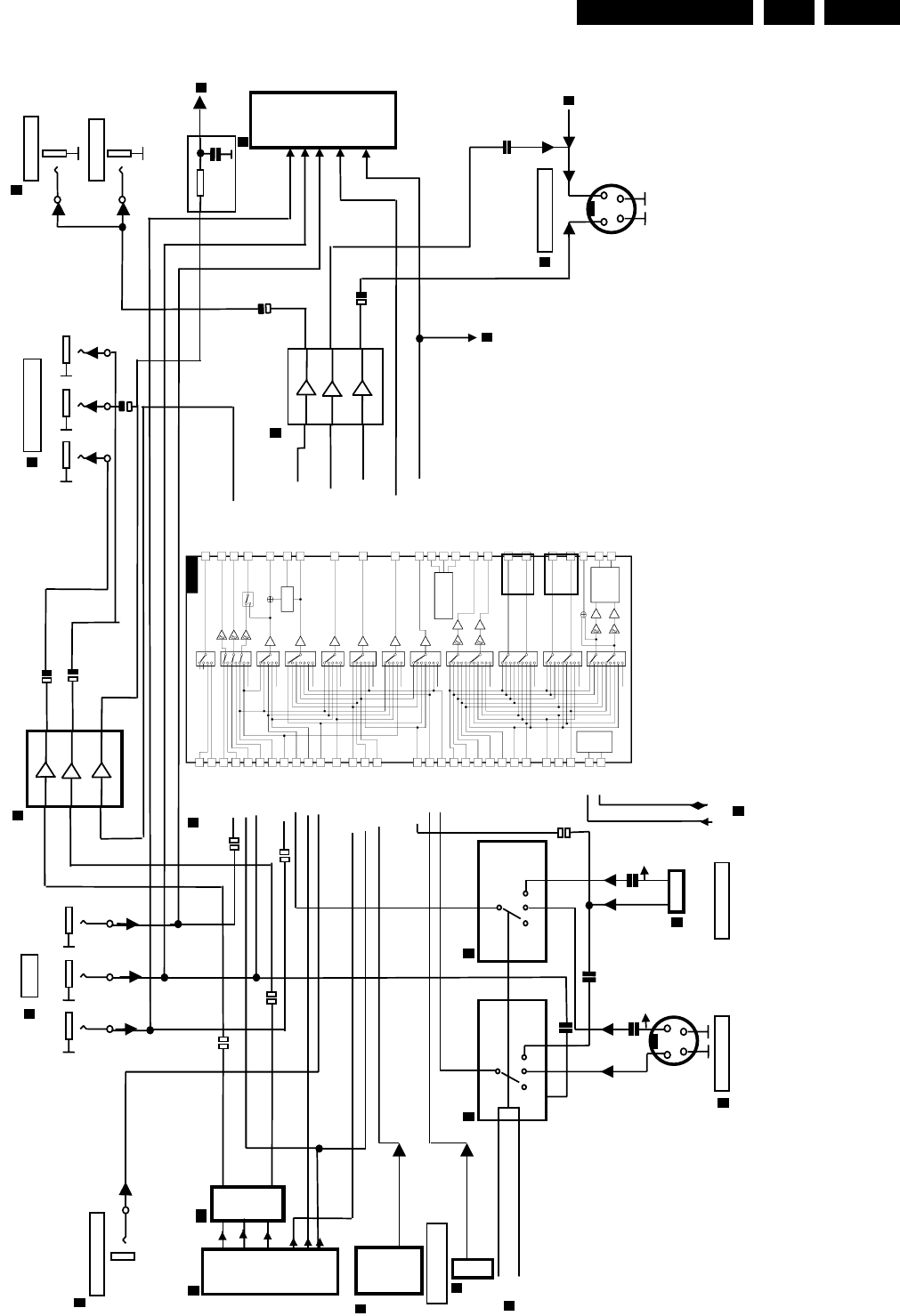

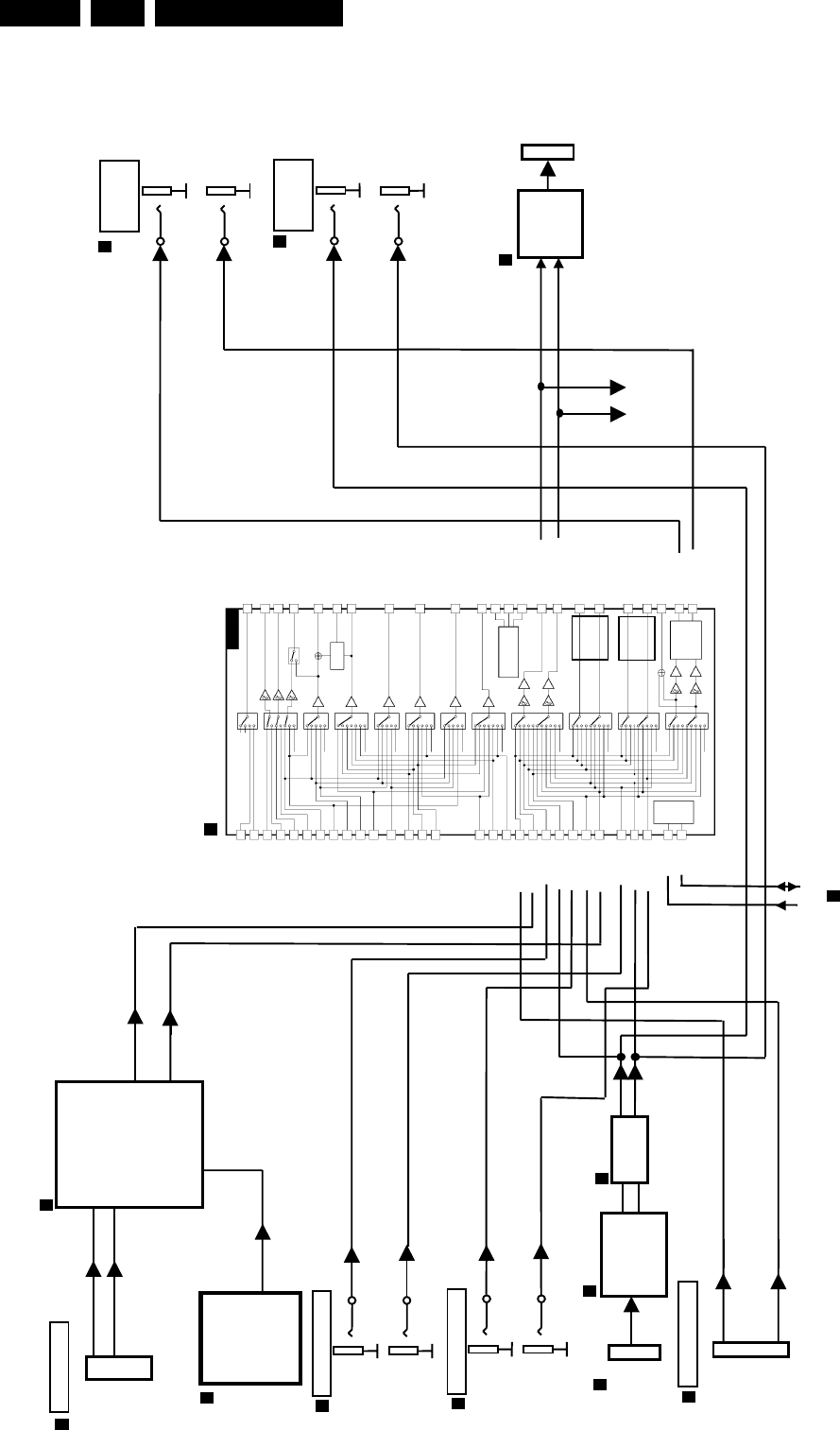

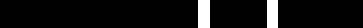

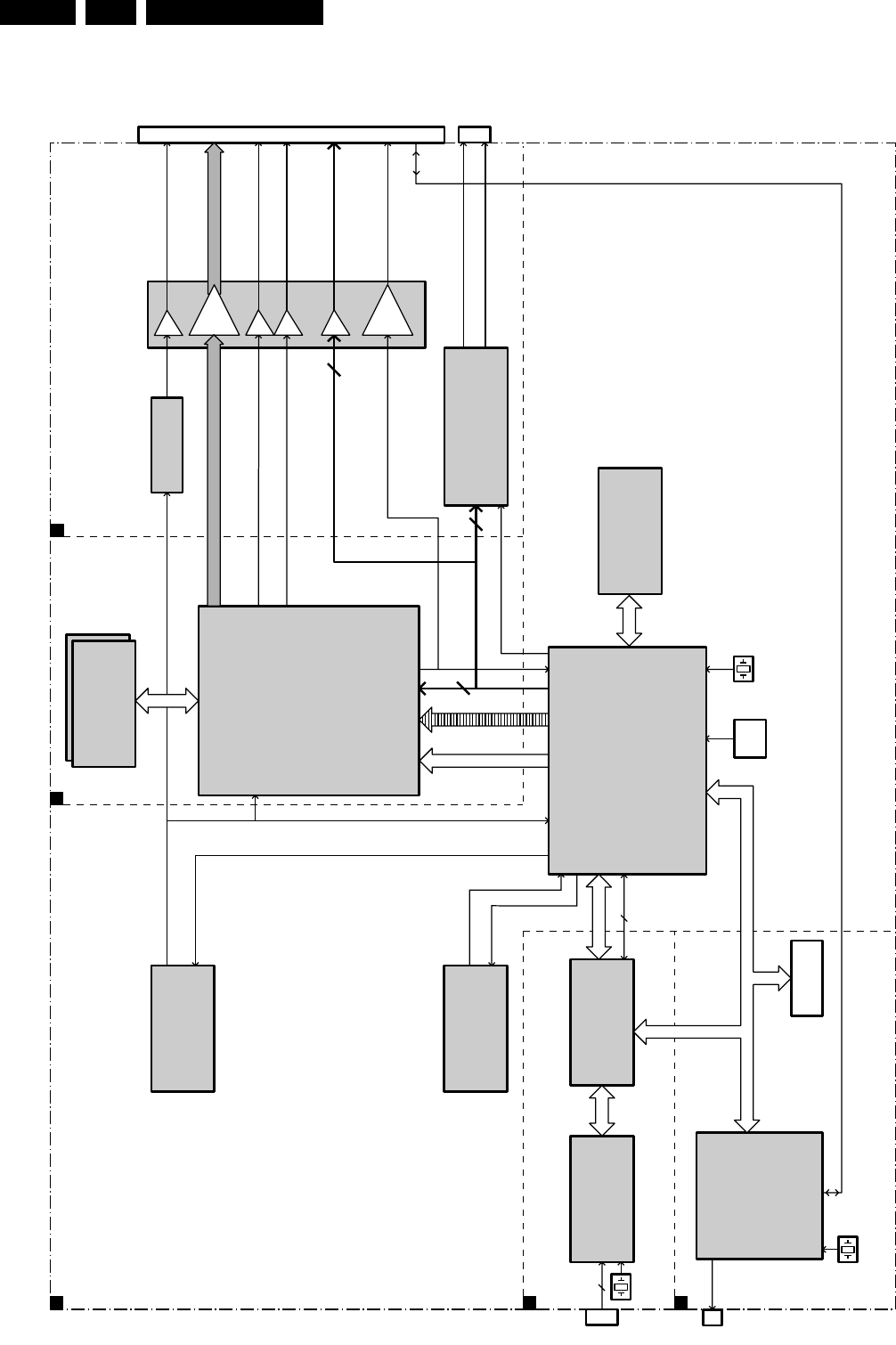

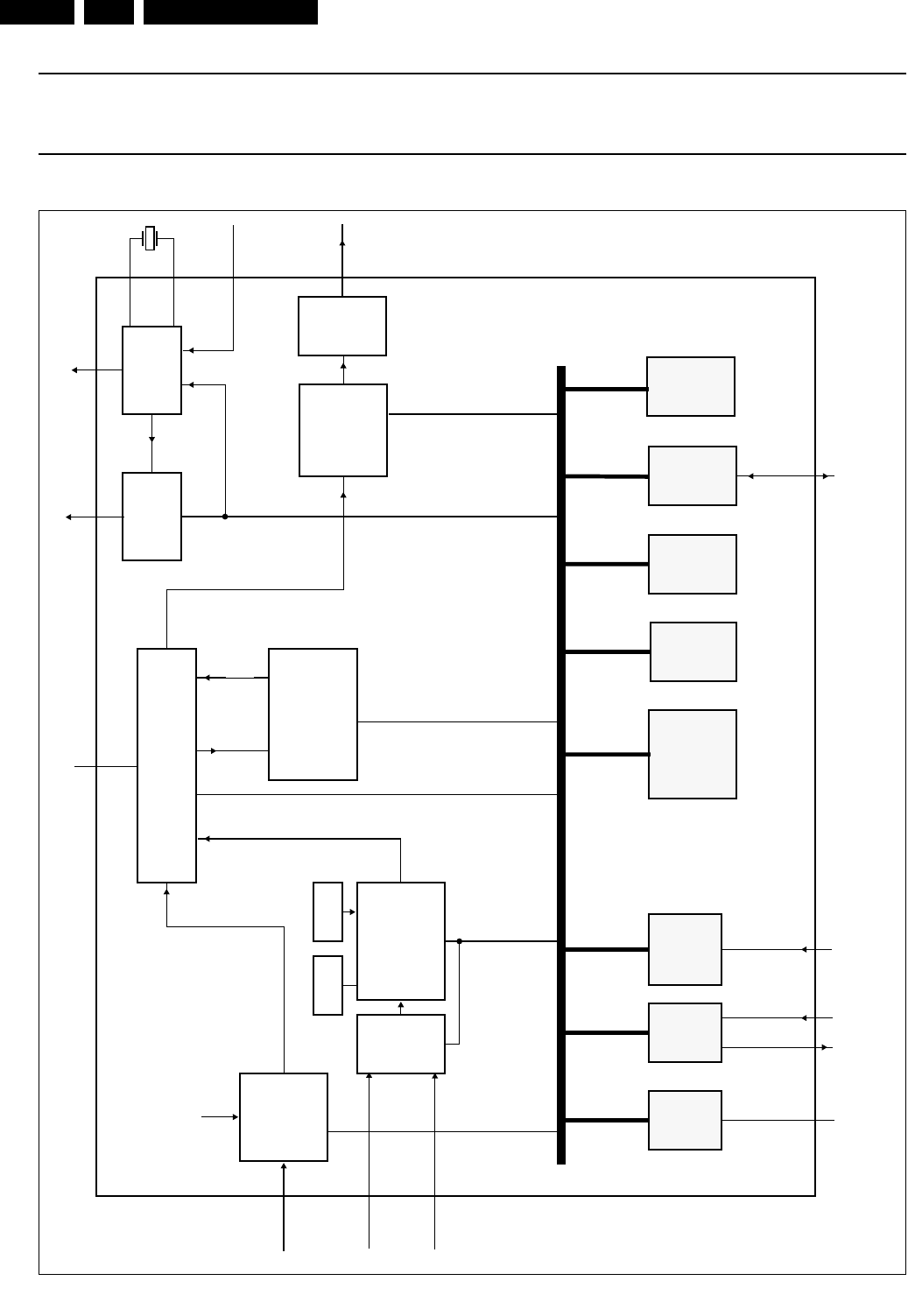

6Block and Wiring Diagram

Block Diagram 93

Wiring Diagram 94

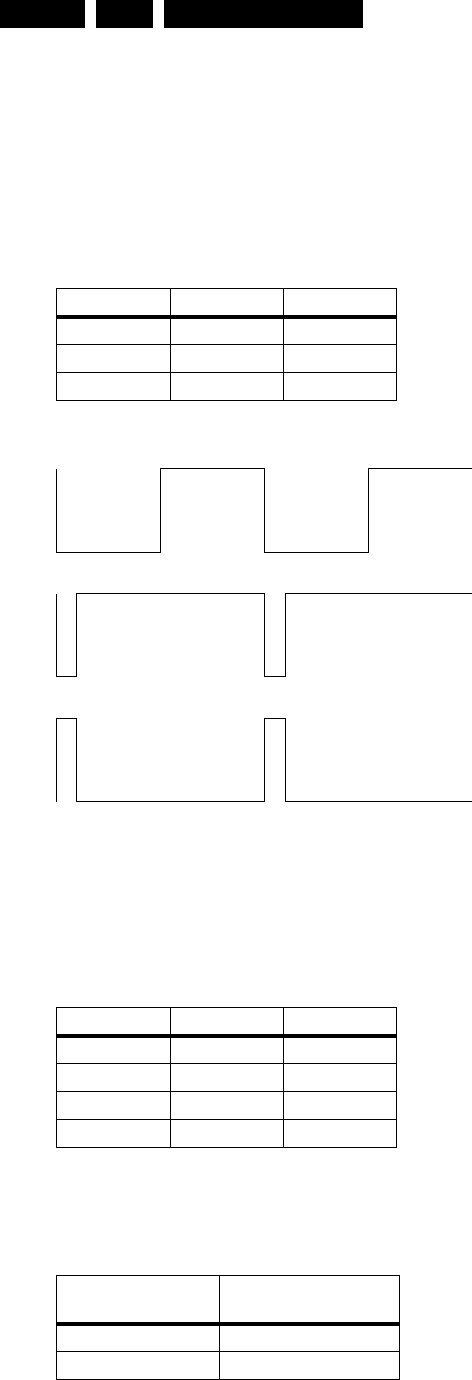

7Electrical Diagrams And Print-Layouts Diagram PWB

Power Supply (Diagram 1) 95 97-100

Power Supply (Diagram 2) 96 97-100

Display Panel (Diagram 1) 101 102->

Front AV Part 105 106

IR & Standby Panel 107 107

Analog Board: All In One 1 (Diagram 1) 108 121->

Analog Board: All In One 2 (Diagram 2) 109 121->

Analog Board: Tuner / Demodul. (Diagram 3) 110 121->

Analog Board: In / Out 1 (Diagram 4) 111 121->

Analog Board: In / Out 2 (Diagram 5) 112 121->

Analog Board: In / Out 3 (Diagram 6) 113 121->

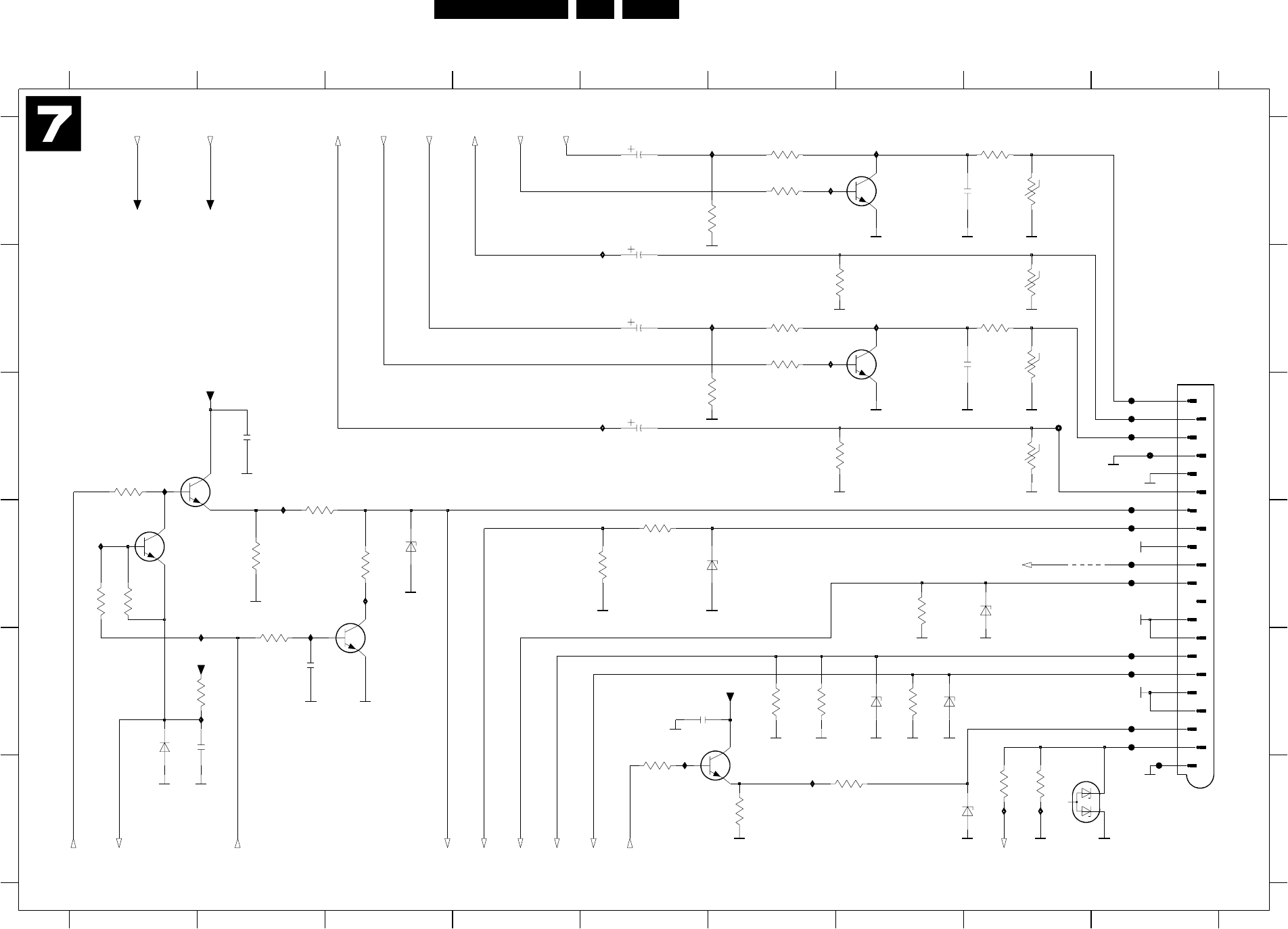

Analog Board: In / Out 4 (Diagram 7) 114 121->

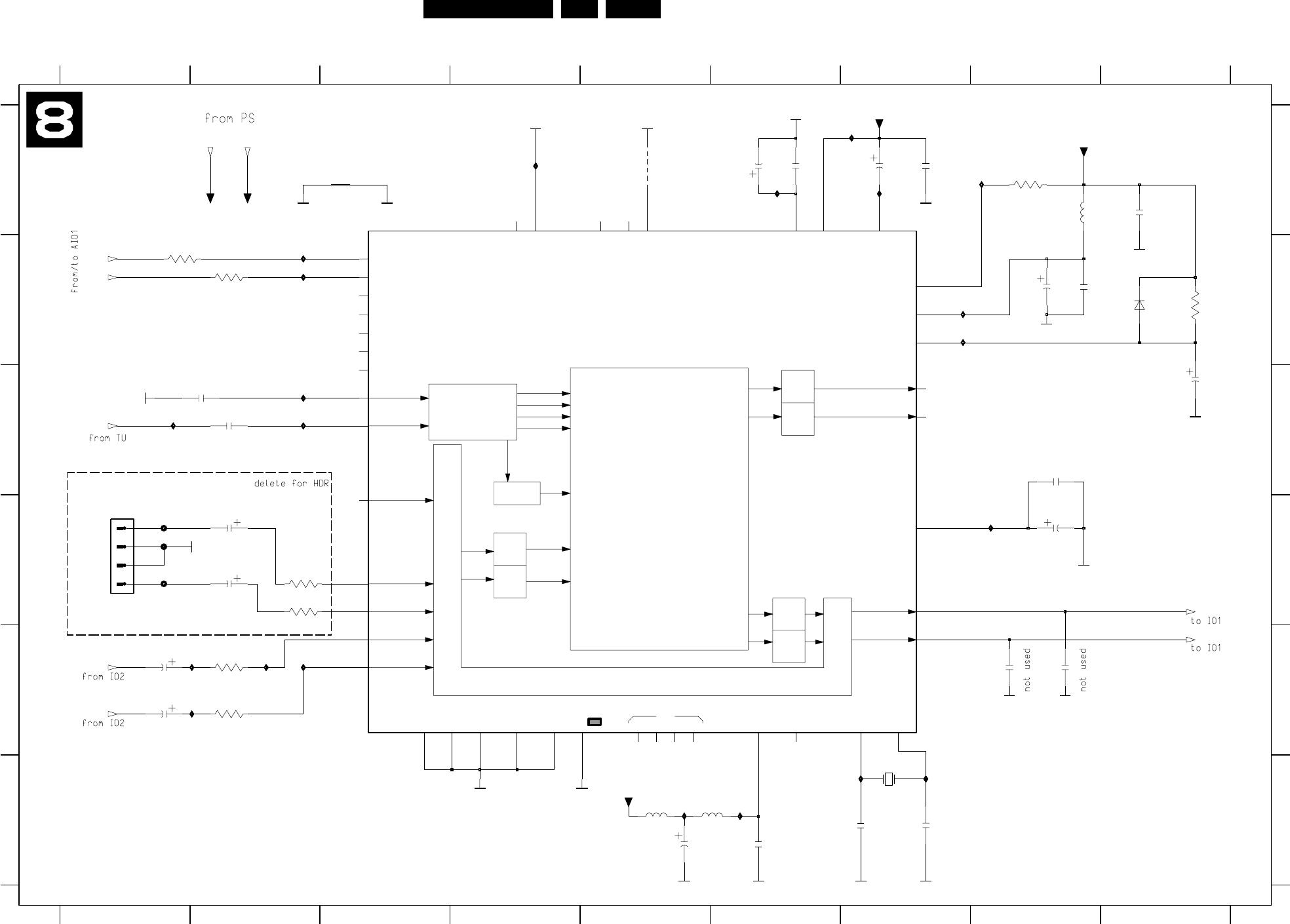

Analog Board: Sound Processing (Diagram 8) 115 121->

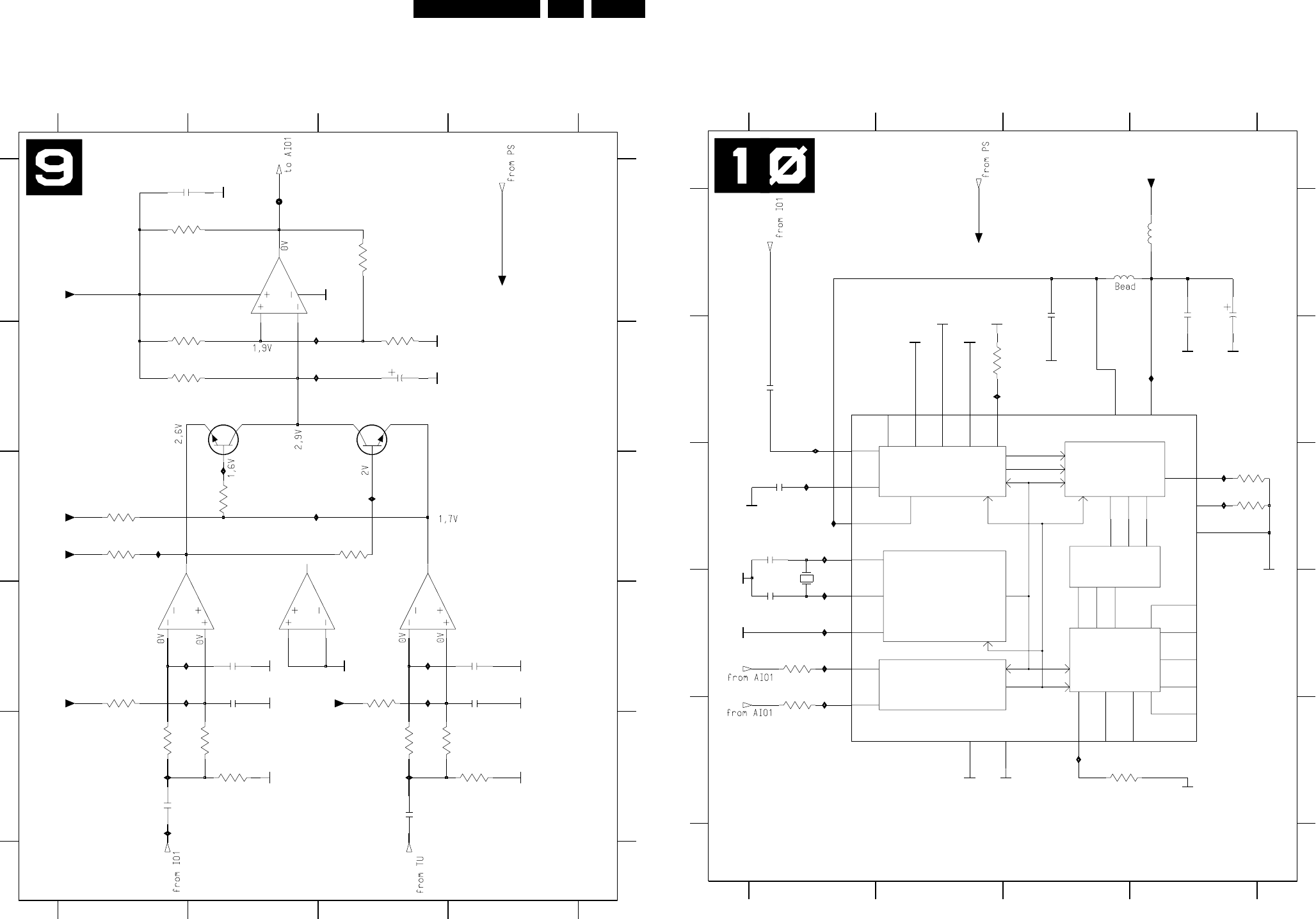

Analog Board: Follow Me (Diagram 9) 116 121->

Analog Board: VPS (Diagram 10) 116 121->

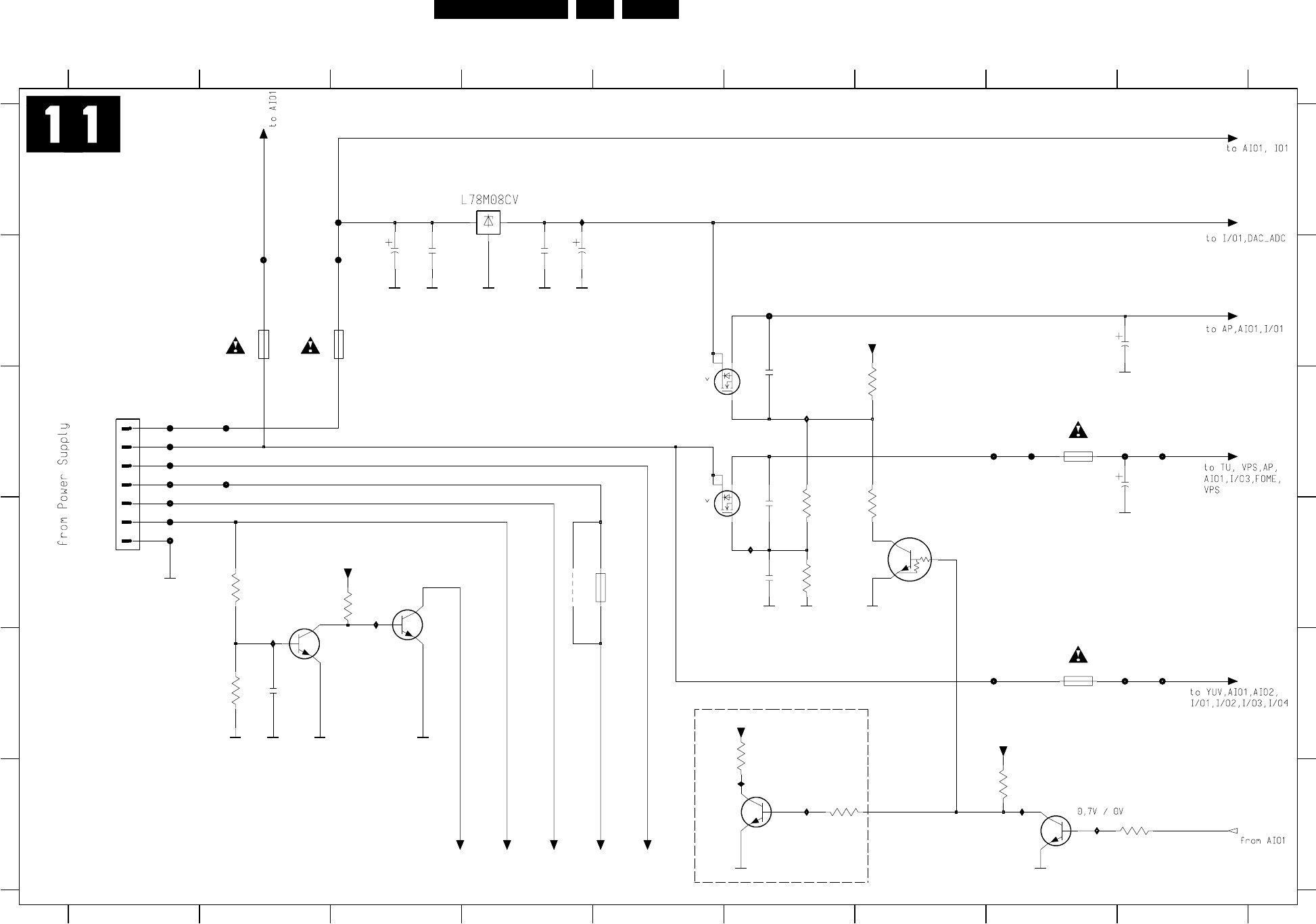

Analog Board: Power Supply (Diagram 11) 117 121->

Analog Board: Audio Converter (Diagram 12) 118 121->

Analog Board: RGB-YUV Conv. (Diagram 13) 119 121->

Analog Board: Digital In / Out (Diagram 14) 119 121->

Analog Board: Fan Control (Diagram 15) 120 121->

DVIO Front Board 129 129

DVIO Board: 1394 Interface (Diagram 1) 130 135->

DVIO Board: Microprocessor (Diagram 2) 131 135->

DVIO Board: FIFO & Control (Diagram 3) 132 135->

DVIO Board: DVCODEC (Diagram 4) 133 135->

DVIO Board: A/V Output (Diagram 5) 134 135->

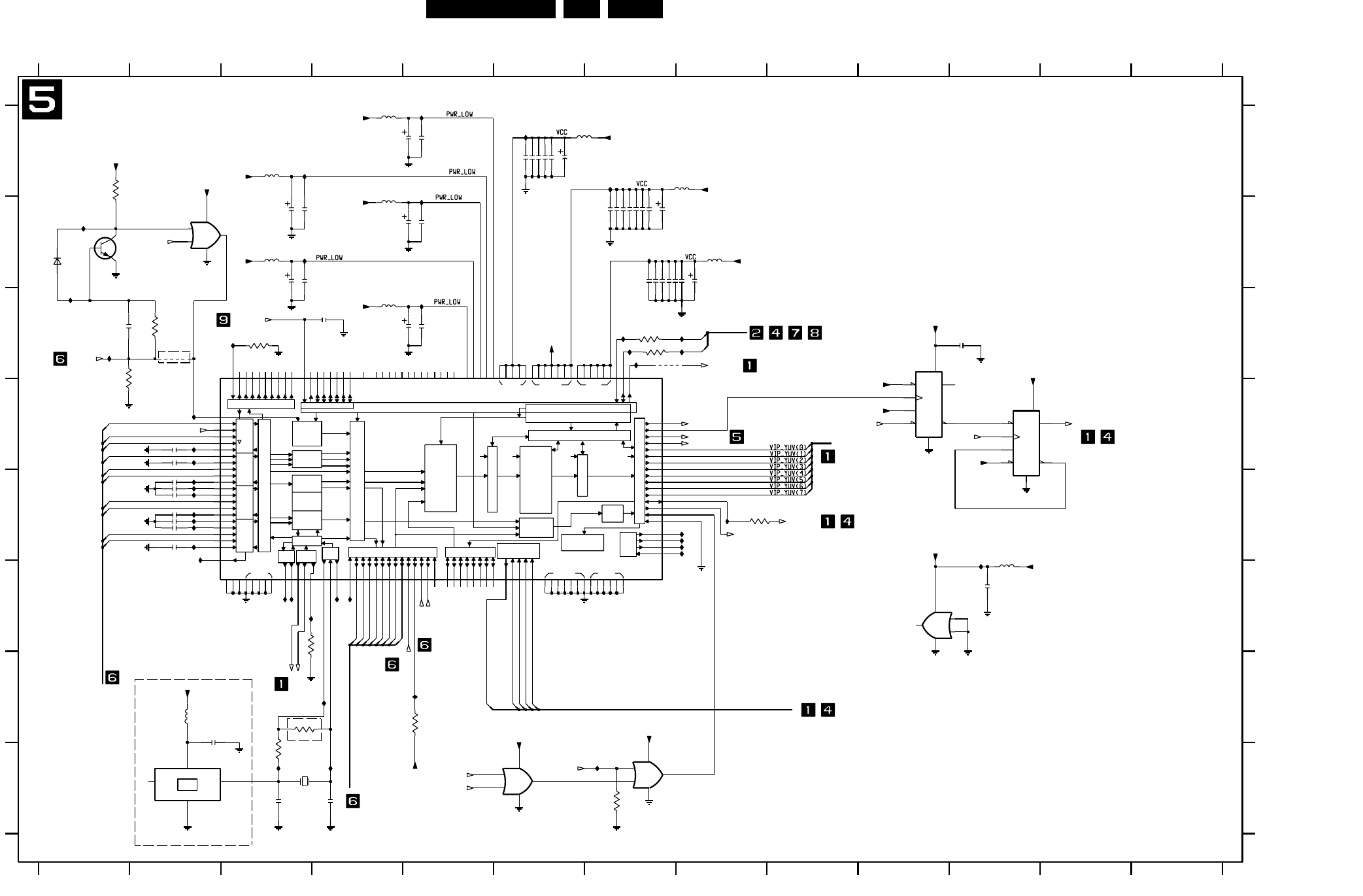

Digital Board: VSM Buffer Mem. (Diagram 1) 139 148->

Digital Board: AV Dec. STI5508 (Diagram 2) 140 148->

Digital Board: AV Decoder Mem. (Diagram 3) 141 148->

Digital Board: Video Enc. Empress(Diagram 4) 142 148->

Digital Board: VIP CVBS Y/C (Diagram 5) 143 148->

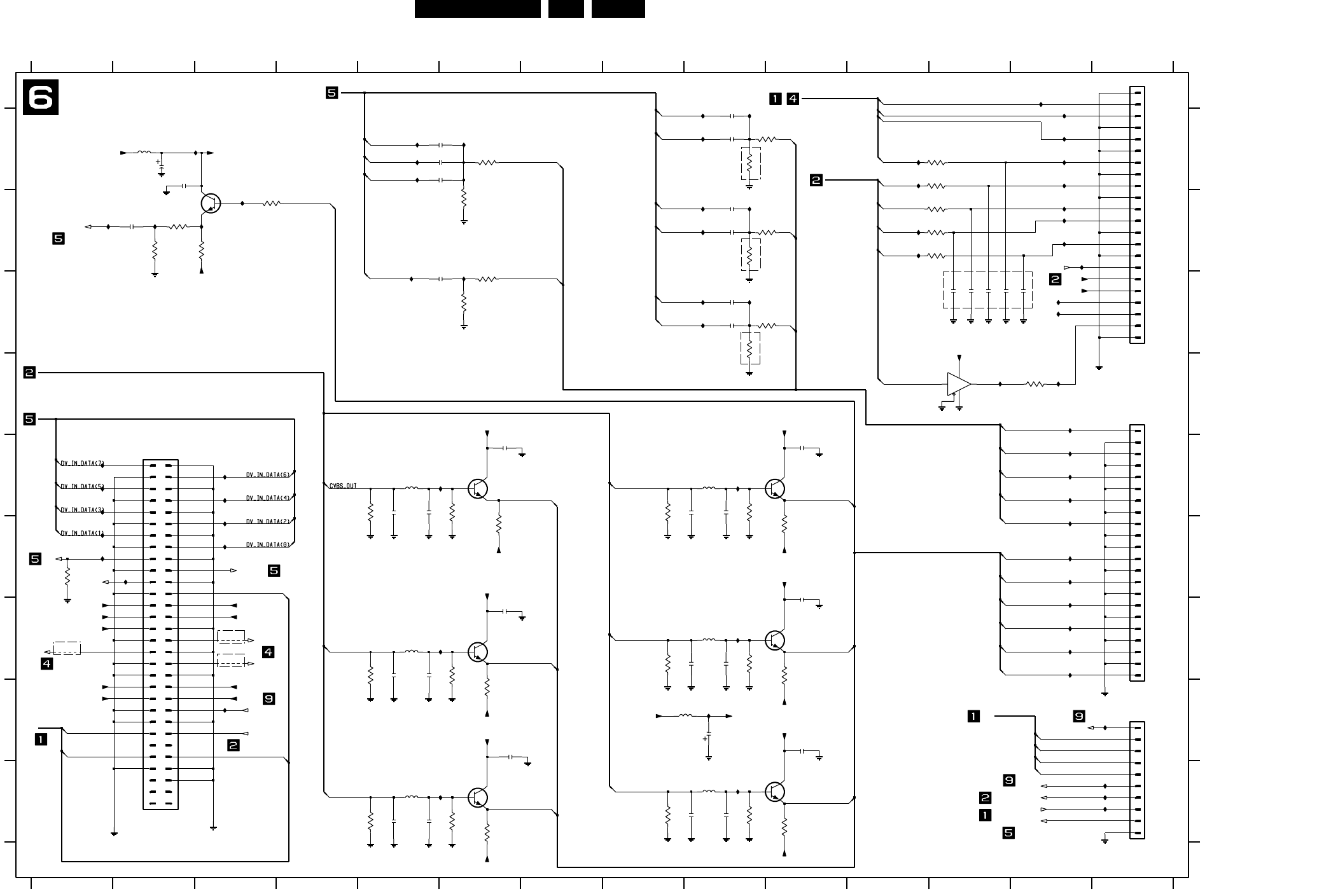

Digital Board: Video In/Out (Diagram 6) 144 148->

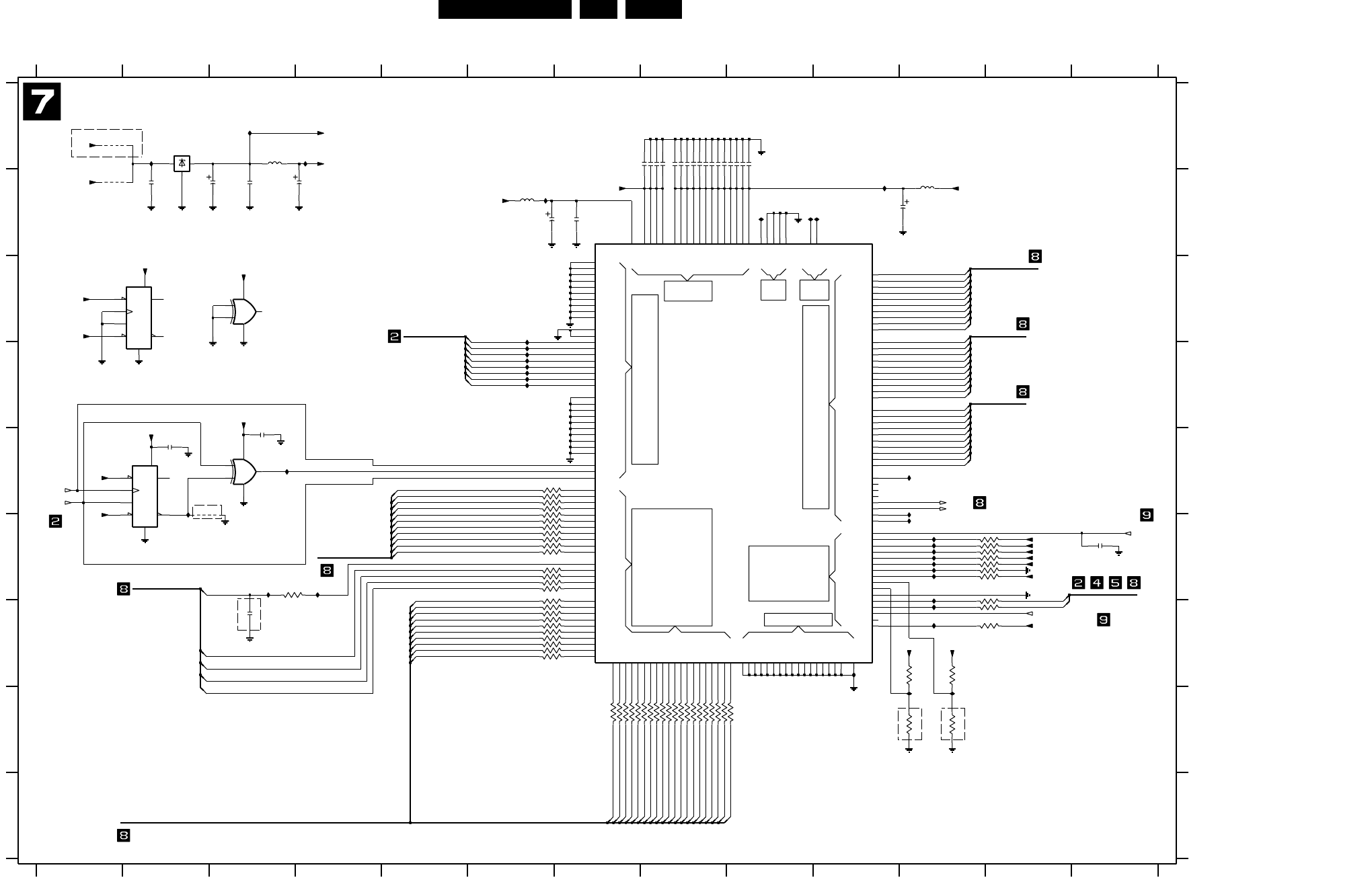

Digital Board: Progressive Scan (Diagram 7) 145 148->

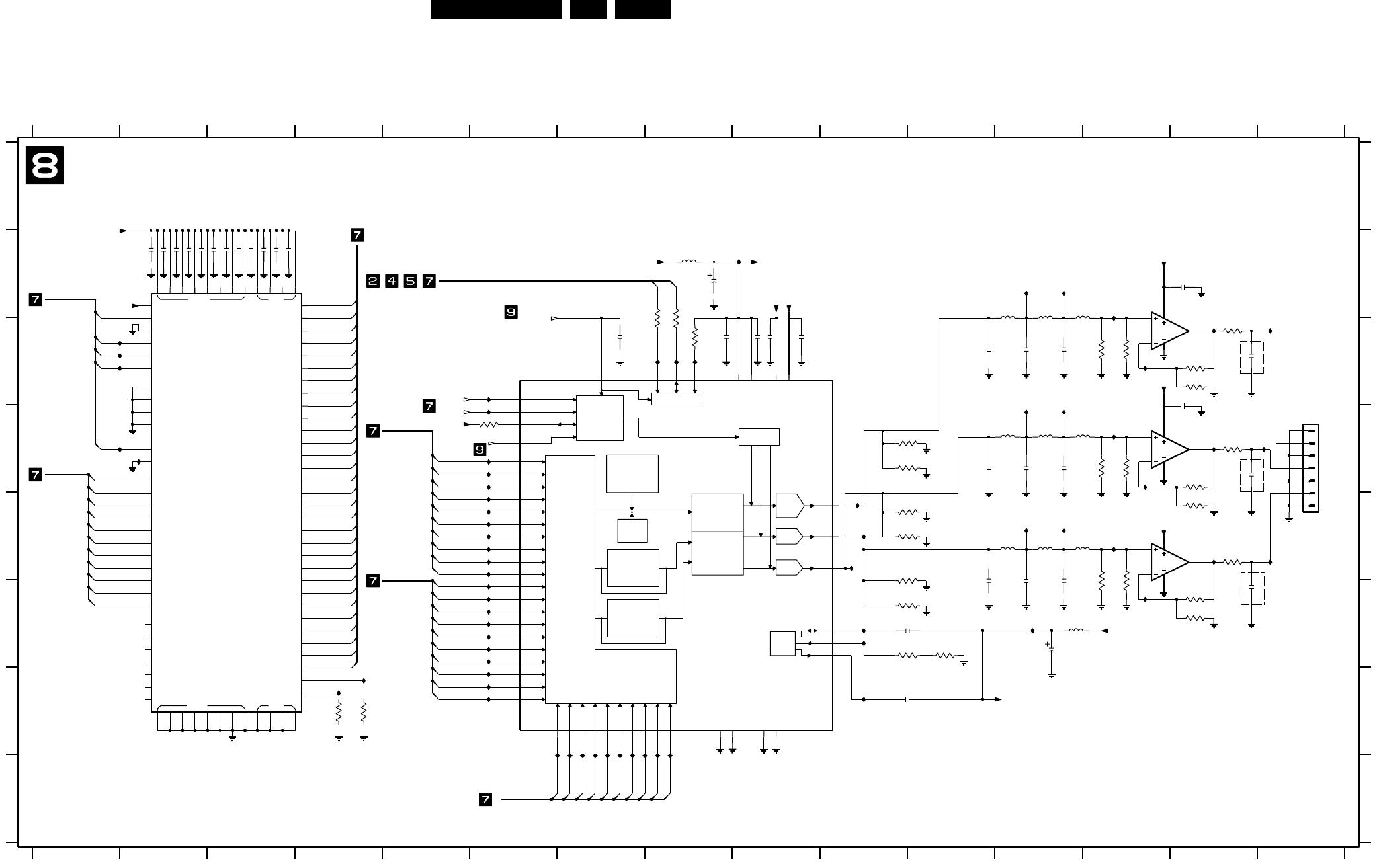

Digital Board: Progressive Scan (Diagram 8) 146 148->

Digital Board: Audio Clock (Diagram 9) 147 148->

8 Electrical Alignments 157

9 Circuit Descriptions and 160

List of Abbreviations 322

10 Spare Part List 327

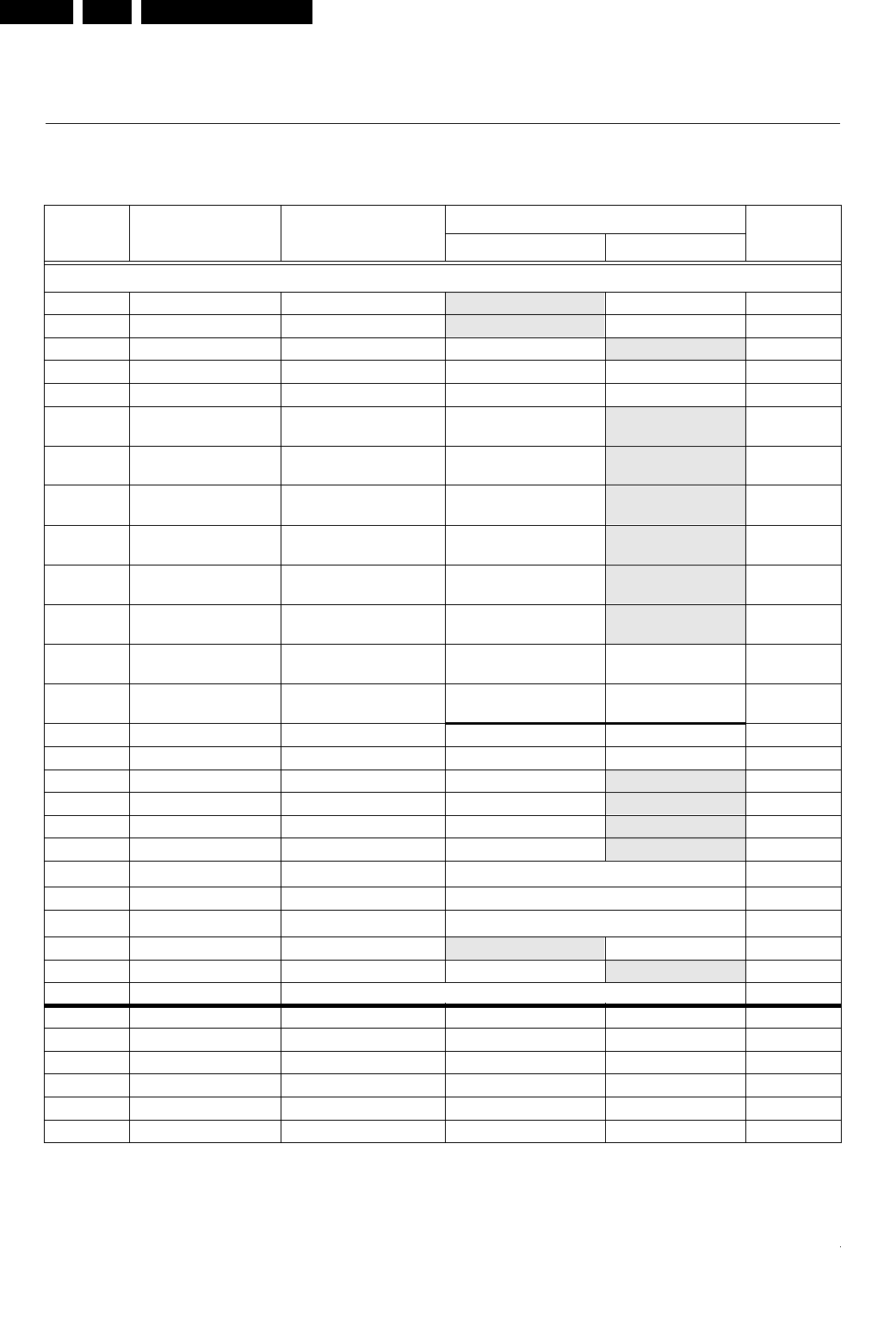

Technical Specifications and Connection Facilities

EN 2 DVDR980-985 /0X11.

1. Technical Specifications and Connection Facilities

1.1 General:

Mains voltage : 220V-240V (198 -

264V AC) for Europe/

Asia

Mains frequency : 50 Hz - 60Hz

Power consumption mains : 32 W

Power consumption standby : < 7 W

Power consumption low power

stand-by : < 3 W

1.2 RF Tuner

Test equipment:Fluke 54200 TV Signal generator

Test streams:PAL BG Philips Standard test pattern

1.2.1 System:

PAL B/G, PAL D/K, SECAM L/L’, PAL I

1.2.2 RF - Loop Through:

Frequency range : 45 MHz - 860 MHz

Gain: (ANT IN - ANT OUT) : -4 dB /±2 dB

1.2.3 Radio Interference:

input voltage /3 tone method (+40

dB min) : typ. 80 dBµV at 75Ω

1.2.4 Receiver:

PLL tuning with AFC for optimum reception

Frequency range: : 45.25 MHz - 860 MHz

Sensitivity at 40 dB S/N : ≥ 60dBµV at 75Ω

(video unweighted )

1.2.5 Video Performance:

Channel 25 / 503,25 MHz,

Test pattern: PAL BG PHILIPS standard test pattern,

RF Level 74 dBV

Measured on SCART 1

Frequency response: : 1 MHz - 4.00 MHz ±

2 dB

Group delay ( 0.1 MHz - 4.4 MHz ) : 0 nsec ± 30 nsec

1.2.6 Audio Performance:

Audio Performance Analogue - HiFi:

Frequency response at SCART 1

(L+R) output: : 40 Hz - 15 kHz / ± 1.5

dB

S/N according to DIN 45405, 7, 1967 :

and PHILIPS standard test pattern

video signal: : -50 dB unweighted

Harmonic distortion ( 1 kHz, ± 25

kHz deviation ): : 0.5 %

Audio Performance NICAM:

Frequency response at SCART

1(L+R) output: : 40 Hz - 15 kHz ± 1.5

dB

S/N according to DIN 45405, 7, 1967 :

and PHILIPS standard test pattern

video signal: : -60 dB unweighted

Harmonic distortion (1 kHz): : 0.1 %

1.2.7 Tuning

Automatic Search Tuning

scanning time without antenna : 2.5 min. PAL

stop level (vision carrier) : 75 V, 75

Maximum tuning error of a recalled

program : ± 62.5 kHz

Maximum tuning error during

operation : ± 100 kHz

Tuning Principle

automatic B,G, I, DK and L/L’detection

manual selection in "STORE" mode

1.3 Analogue Inputs

1.3.1 SCART 1 (Connected to TV)

Pin Signals:

1 - Audio R 1.8V RMS

2 - Audio R

3 - Audio L 1.8V RMS

4 - Audio GND ,

5 - Blue/Chroma

GND ,

6 - Audio L

7 - Blue out/

Chroma in 0.7Vpp ± 0.1V into 75 Ohm (*)

8 - Function

switch <2V = TV

>4.5V / <7V = asp. ratio 16:9 DVD

>9.5V / <12V = asp. ratio 4:3 DVD

9 - Green GND ,

10 - P50 control

11 - Green 0.7Vpp ± 0.1V into 75 Ohm (*)

12 - Nc

13 - Red/Chroma

GND ,

14 - fast switch

GND ,

15 - Red out/

Chroma out 0.7Vpp ± 0.1V into 75 Ohm (*)

± 3dB 0.3Vpp Chroma (burst)

16 - fast switch

RGB/ CVBS or Y <0.4V into 75 Ohm = CVBS

>1V / <3V into 75 Ohm = RGB

17 - Y/CVBS GND

OUT ,

18 - Y/CVBS GND

IN ,

19 - CVBS/Y 1Vpp ± 0.1V into 75 Ohm (*)

20 - CVBS/Y

21 - Shield ,

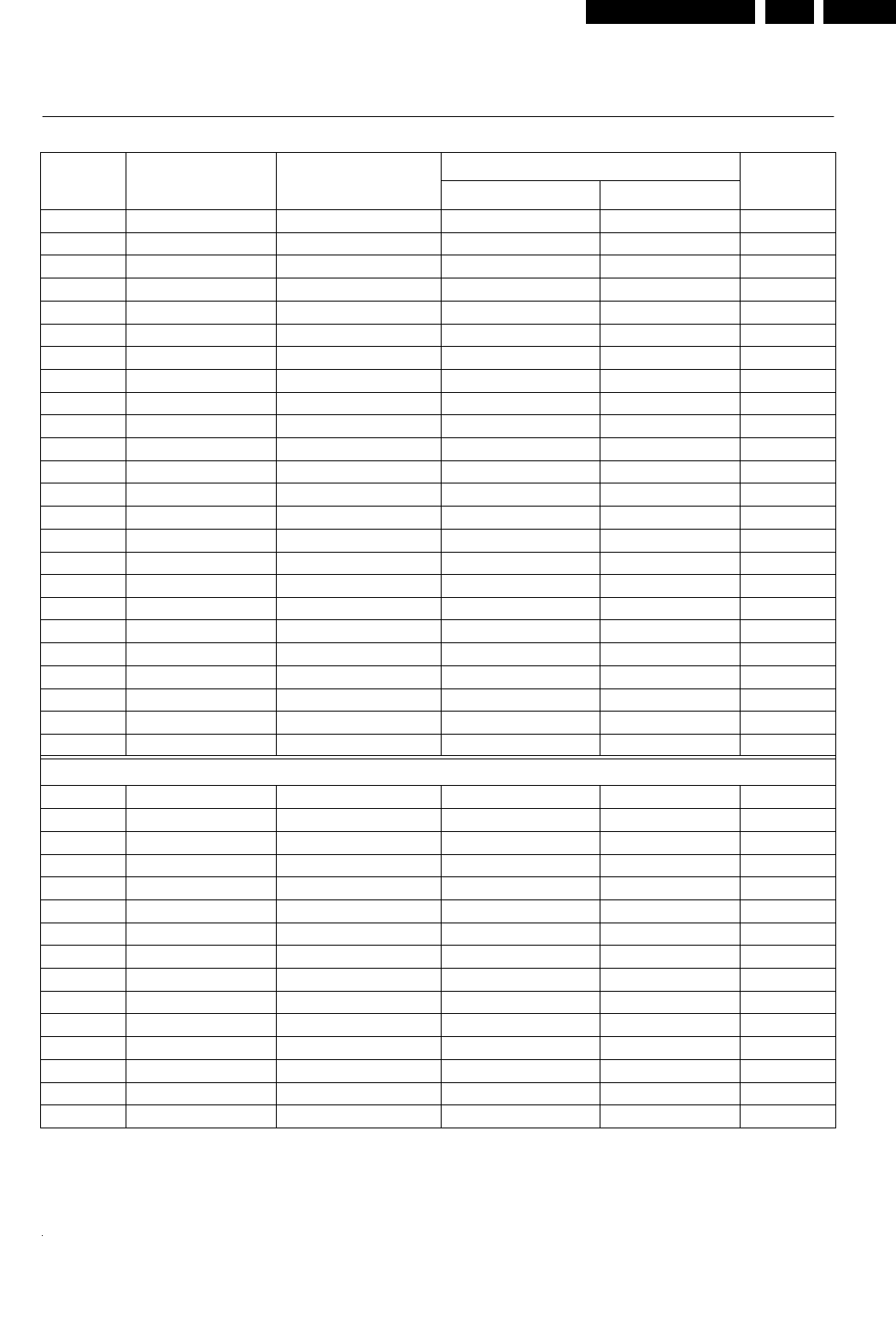

1.3.2 SCART 2 (Connected to AUX)

Pin Signals:

1 -Audio R 1.8V RMS

2 -Audio R

3 -Audio L 1.8V RMS

4 -Audio GND ,

5 -Blue/Chroma

GND ,

6 -Audio L

7 -Blue in/

Chroma out ± 3dB 0.3Vpp Chroma (burst)

8 -Function

switch

9 -Green GND ,

10 -P50 control

Technical Specifications and Connection Facilities EN 3DVDR980-985 /0X1 1.

11 -Green

12 -Nc

13 -Red/Chroma

GND ,

14 -fast switch

GND ,

15 -Red in/

Chroma in

16 -fast switch

RGB/ CVBS or

Y

17 -CVBS GND

OUT ,

18 -CVBS GND

IN ,

19 -CVBS/Y/RGB

sync 1Vpp ± 0.1V into 75 Ohm (*)

20 -CVBS/Y

21 -Shield ,

(*) for 100% white

1.3.3 Audio/Video Front Input Connectors

Audio

Input voltage : 2 Vrms

Input impedance : >10kΩ

Video - Cinch

Input voltage : 1 Vpp ± 0.1V

Input impedance : 75 Ω

Video - YC (Hosiden)

Input voltage Y : 1Vpp ± 0.1V

Input impedance Y : 75 Ω

Input voltage C : burst 300 mVpp ± {x}

dB

Input impedance C : 75 Ω

1.3.4 Cinch Audio/Video Line Input Rear

Audio (EXT1)

Input voltage : 2 Vrms

Input impedance : >10k Ω

Video (EXT4)

Input voltage : 1 Vpp ± 0.1V

Input impedance : 75 Ω

1.3.5 YC Input Rear (Hosiden; EXT3)

1-GND !

2 -GND !

3-Input voltage Y 1Vpp ± 0.1V/ 75 Ω

4-Input voltage C Burst 300 mVpp ± {x} dB/ 75 Ω

1.4 Video Performance

All outputs loaded with 75 Ohm

SNR measurements over full bandwidth without weighting.

1.4.1 CVBS Output Rear (EXT4)

SNR Luminance : > -65 dB

SNR Chrominance AM : > -65 dB

SNR Chrominance PM : > -65 dB

Bandwidth Luminance : 5 MHz ± 1 dB

1.4.2 YC Output Rear (Hosiden ; EXT3)

SNR : > -65 dB

SNR C - AM : > -65 dB

SNR C - PM : > -65 dB

Bandwidth Y : 5 MHz ± 1 dB

1.4.3 SCART (RGB)

SNR : > -65 dB on all output

Bandwidth : 5 MHz ± 1 dB

1.5 Audio Performance

1.5.1 Cinch Output Rear

Output voltage 2 channel mode : 2Vrms ± 1.5dB

Output voltage 5.1 channel Dolby : 1.41Vrms ± 1.5dB

Channel unbalance (1kHz) : <0.85dB

Crosstalk 1kHz : >105dB

Crosstalk 20Hz-20kHz : > 95dB

Frequency response 20Hz- 20kHz : ± 0.1dB max

Signal to noise ratio : >100 dB

Dynamic range 1kHz : >90dB

Dynamic range 20Hz-20kHz : >88dB

Distortion and noise 1kHz : >90dB

Distortion and noise20Hz-20kHz : >80dB

Intermodulation distortion : >87dB

Phase non linearity : ± 1ο max.

Level non linearity : ± 0.5dB max.

Mute (spin-up, pause, access) : >100dB

Outband attenuation: : > 50dB above 25kHz

1.5.2 Scart Audio

Output voltage 2 channel mode : 2Vrms ± 1.5dB

Output voltage 5.1 channel Dolby : 1.41Vrms ± 1.5dB

Channel unbalance (1kHz) : <0.85dB

Crosstalk 1kHz : >105dB

Crosstalk 20Hz-20kHz : > 95dB

Frequency response 20Hz- 20kHz : ± 0.1dB max

Signal to noise ratio : >100 dB

Dynamic range 1kHz : >90dB

Dynamic range 20Hz-20kHz : >88dB

Distortion and noise 1kHz : >90dB

Distortion and noise20Hz-20kHz : >80dB

Intermodulation distortion : >87dB

Phase non linearity : ± 1o max

Level non linearity : ± 0.5dB max

Mute (spin-up, pause, access) : >100dB

Outband attenuation: : > 50dB above 25kHz

1.6 Digital Output

1.6.1 Coaxial

CDDA/ LPCM (incl MPEG1) : according IEC958

MPEG2, AC3 audio : according IEC1937

DTS : according IEC1937,

amendment 1

1.6.2 Optical

identical to coaxial

1.7 Digital Video Input (IEEE 1394)

1.7.1 Applicable Standards

Implementation according:

IEEE Std 1394-1995

IEC 61883 - Part 1

IEC 61883 - Part 2 SD-DVCR (02-01-1997)

Technical Specifications and Connection Facilities

EN 4 DVDR980-985 /0X11.

Specification of consumer use digital VCR’s using 6.3 mm

magnetic tape - dec.1994

Mechanical connection according:

Annex A of 61883-1

1.7.2 Audio Quality

Output voltage 2 channel mode : 2Vrms +/- 1.5dB

Channel unbalance (1kHz) : Tbd

Crosstalk 1kHz : > 85 dB

Crosstalk 20Hz-20kHz : > 95 dB

Frequency response 20Hz- 12kHz : +/- 1dB max

Signal to noise ratio : >95 dB

Dynamic range 1kHz : tbd

Dynamic range 20Hz-20kHz : Tbd

Distortion and noise 1kHz : >65dB

Distortion and noise 20Hz-20kHz : >65dB

Intermodulation distortion : >80dB

Phase non linearity : tbd

Level non linearity : tbd

Outband attenuation : tbd

1.8 P50 System Control

Via SCART pin nr 10

1.9 Dimensions and Weight

Height of feet : 12mm

Apparatus tray closed : WxDxH :435 x 325 x

107

Apparatus tray open : WxDxH :435 x 465 x

107

Weight without packaging : 5.67 Kg

Weight accesoiries : 1.675 Kg

1.10 Laser Output Power & Wavelength

1.10.1 DVD

Output power during reading : 0.8mW

Output power during writing : 20mW

Wavelength : 660nm

1.10.2 CD

Output power : 0.3mW

Wavelength : 780nm

Safety Instructions, Warnings, Notes, and Service Hints EN 5DVDR980-985 /0X1 2.

2. Safety Instructions, Warnings, Notes, and Service Hints

2.1 Safety Instructions

2.1.1 General Safety

Safety regulations require that during a repair:

•Connect the unit to the mains via an isolation transformer.

•Replace safety components, indicated by the symbol ,

only by components identical to the original ones. Any

other component substitution (other than original type) may

increase risk of fire or electrical shock hazard.

Safety regulations require that after a repair, you must return

the unit in its original condition. Pay, in particular, attention to

the following points:

•Route the wires/cables correctly, and fix them with the

mounted cable clamps.

•Check the insulation of the mains lead for external

damage.

•Check the electrical DC resistance between the mains plug

and the secondary side:

1. Unplug the mains cord, and connect a wire between

the two pins of the mains plug.

2. Set the mains switch to the 'on' position (keep the

mains cord unplugged!).

3. Measure the resistance value between the mains plug

and the front panel, controls, and chassis bottom.

4. Repair or correct unit when the resistance

measurement is less than 1 MΩ.

5. Verify this, before you return the unit to the customer/

user (ref. UL-standard no. 1492).

6. Switch the unit ‘off’, and remove the wire between the

two pins of the mains plug.

2.1.2 Laser Safety

This unit employs a laser. Only qualified service personnel may

remove the cover, or attempt to service this device (due to

possible eye injury).

Laser Device Unit

Type : Semiconductor laser

GaAlAs

Wavelength : 650 nm (DVD)

: 780 nm (VCD/CD)

Output Power : 20 mW

(DVD+RW writing)

:0.8 mW

(DVD reading)

:0.3 mW

(VCD/CD reading)

Beam divergence : 60 degree

Figure 2-1

Note: Use of controls or adjustments or performance of

procedure other than those specified herein, may result in

hazardous radiation exposure. Avoid direct exposure to beam.

2.2 Warnings

2.2.1 General

•All ICs and many other semiconductors are susceptible to

electrostatic discharges (ESD, "). Careless handling

during repair can reduce life drastically. Make sure that,

during repair, you are at the same potential as the mass of

the set by a wristband with resistance. Keep components

and tools at this same potential.

Available ESD protection equipment:

–Complete kit ESD3 (small tablemat, wristband,

connection box, extension cable and earth cable) 4822

310 10671.

–Wristband tester 4822 344 13999.

•Be careful during measurements in the live voltage section.

The primary side of the power supply (pos. 1005), including

the heatsink, carries live mains voltage when you connect

the player to the mains (even when the player is 'off'!). It is

possible to touch copper tracks and/or components in this

unshielded primary area, when you service the player.

Service personnel must take precautions to prevent

touching this area or components in this area. A 'lightning

stroke' and a stripe-marked printing on the printed wiring

board, indicate the primary side of the power supply.

•Never replace modules, or components, while the unit is

‘on’.

2.2.2 Laser

•The use of optical instruments with this product, will

increase eye hazard.

•Only qualified service personnel may remove the cover or

attempt to service this device, due to possible eye injury.

•Repair handling should take place as much as possible

with a disc loaded inside the player.

•Text below is placed inside the unit, on the laser cover

shield:

Figure 2-2

2.2.3 Notes

Dolby

Manufactered under licence from Dolby Laboratories. “Dolby”,

“Pro Logic” and the double-D symbol are trademarks of Dolby

Laboratories. Confidential Unpublished Works.

©1992-1997 Dolby Laboratories, Inc. All rights reserved.

Figure 2-3

Trusurround

TRUSURROUND, SRS and symbol (fig 2-4) are trademarks of

SRS Labs, Inc. TRUSURROUND technology is manufactured

under licence frm SRS labs, Inc.

Figure 2-4

CAUTION VISIBLE AND INVISIBLE LASER RADIATION WHEN OPEN AVOID EXPOSURE TO BEAM

ADVARSEL SYNLIG OG USYNLIG LASERSTRÅLING VED ÅBNING UNDGÅ UDSÆTTELSE FOR STRÅLING

ADVARSEL SYNLIG OG USYNLIG LASERSTRÅLING NÅR DEKSEL ÅPNES UNNGÅ EKSPONERING FOR STRÅLEN

VARNING SYNLIG OCH OSYNLIG LASERSTRÅLNING NÄR DENNA DEL ÄR ÖPPNAD BETRAKTA EJ STRÅLEN

VARO! AVATT AESSA OLET ALTTIINA NÄKYVÄLLE JA NÄKYMÄTTÖMÄLLE LASER SÄTEILYLLE. ÄLÄ KAT SO SÄT EESEEN

VORSICHT SICHTBARE UND UNSICHTBARE LASERSTRAHLUNG WENN ABDECKUNG GEÖFFNET NICHT DEM STRAHL AUSSETSEN

DANGER VISIBLE AND INVISIBLE LASER RADIATI ON WHEN OPEN AVOID DIRECT EXPOSURE TO BEAM

AT TENTION RAYONNEMENT LASER VISIBLE ET INVISIBLE EN CAS D'OUVERTURE EXPOSITION DANGEREUSE AU FAISCEAU

!

Safety Instructions, Warnings, Notes, and Service Hints

EN 6 DVDR980-985 /0X12.

Video Plus

“Video Plus+” and “PlusCode” are registered trademarks of the

Gemstar Development Corporation. The “Video Plus+” system

is manufactored under licence from the Gemstar Development

Corporation.

Figure 2-5

Macrovision

This product incorporates copyright protection technology that

is protected by method claims of certain U.S. patents and other

intellectual property rights owned by Macrovision Corporation

and other rights owners.

Use of this copyright protection technology must be autorized

by Macrovision Corporation, and is intended for home and

other limited viewing uses only unless otherwise authorized by

Macrovision Corporation. Reverse engineering or disassembly

is prohibited.

Directions For Use EN 7DVDR980-985 /0X1 3.

3. Directions For Use

English

INTRODUCTION 7

Box contents

First check and identify the contents of your DVD

recorder package, as listed below:

- DVD recorder

- Remote Control Handset with separately-packed

batteries

- 2-core power cord

-

SCART

cable

- S-video cable

- Antenna (aerial) cable

- Audio cable

- Video cable

- DVD+RW disc

- User Manual

- Warranty card

If any item should be damaged or missing, please inform

your supplier without delay.

Keep the packaging materials; you may need them to

transport your recorder in the future.

Placement

lPlace the recorder on a firm, flat surface.

lKeep away from domestic heating equipment and

direct sunlight.

lIn a cabinet, allow about 2.5 cm (1 inch) of free

space all around the recorder for adequate

ventilation.

lThe lense may cloud over when the DVD recorder

is suddenly moved from cold to warm surroundings.

Playing a CD/DVD is not possible then. Leave the

DVD recorder in a warm environment for two

hours before use, so the moisture can evaporate.

lThe recorder should not be exposed to dripping or

splashing, no objects filled with liquids, such as vases,

should be placed on the recorder.

Cleaning discs

Some problems may occur because the disc inside the

recorder is dirty. To avoid these problems clean your

discs regularly, in the following way:

lWhen a disc becomes dirty, clean it with a cleaning

cloth. Wipe the disc from the centre out.

Caution:

Do not use solvents such as benzine, thinner,

commercially available cleaners, or anti-static

spray intended for analogue discs.

Do not use commercially available cleaning discs

to clean the lens, as these discs may damage the

optical unit.

Remote control

Loading the batteries

lOpen the battery compartment cover.

lInsert two 'AA' (LR-6) batteries as indicated inside

the battery compartment.

lClose the cover.

Caution:

Do not mix old and new batteries. Never mix

different types of batteries (standard, alkaline,

etc.). This may reduce the lifetime of the

batteries.

English

6INTRODUCTION

Introduction

DVD Video Recorder

DVD (Digital Versatile Disc) is the new storage medium

that combines the convenience of the Compact Disc

with the latest advanced digital video technology.

DVD-Video uses state-of-the-art MPEG2 data

compression technology to register an entire movie on a

single 5-inch disc. DVD’s variable bitrate compression,

running at up to 9.8 Mbits/second, captures even the

most complex pictures in their original quality.

The crystal-clear digital pictures have a horizontal

resolution of over 500 lines, with 720 pixels (picture

elements) to each line. This resolution is more than

double that of VHS, superior to Laser Disc, and entirely

comparable with digital masters made in recording

studios.

DVD recording is the next step in video technology.

DVD+ReWritable (DVD+RW) uses phase-change media,

the same technology that formed the basis for CD-

ReWritable. A high-power laser is used to change the

reflectivity of the recording layer. This process can be

repeated more than a thousand times. DVD+Recordable

(DVD+R) uses discs based on an organic dye, a

technology pioneered with the successful CD-

Recordable format, to produce discs that keep your data

for a lifetime.

Your Philips DVD recorder is a recorder and player

for digital video discs, with a two-way compatibility

to the universal DVD-Video standard. This means that:

- existing pre-recorded DVD-Video discs can be

played on your Philips DVD recorder and

- recordings, made on your Philips DVD recorder, can

be played on most DVD-Video players and

DVD-ROM drives.

With it, you will be able to record TV programmes or

to edit and archive your own camcorder recordings.

Superb digital picture and sound quality, quick access to

the tracks you have recorded and extensive playback

features contribute to a completely new video

experience.

From now on you will enjoy full-length movies with true

cinema picture quality, and stereo or Multi-channel

sound (depending on the disc, and on your playback set-

up).You will find your recorder remarkably easy to use,

by way of the On-Screen Display on your TV and the

display on the DVD recorder, in combination with the

remote control.

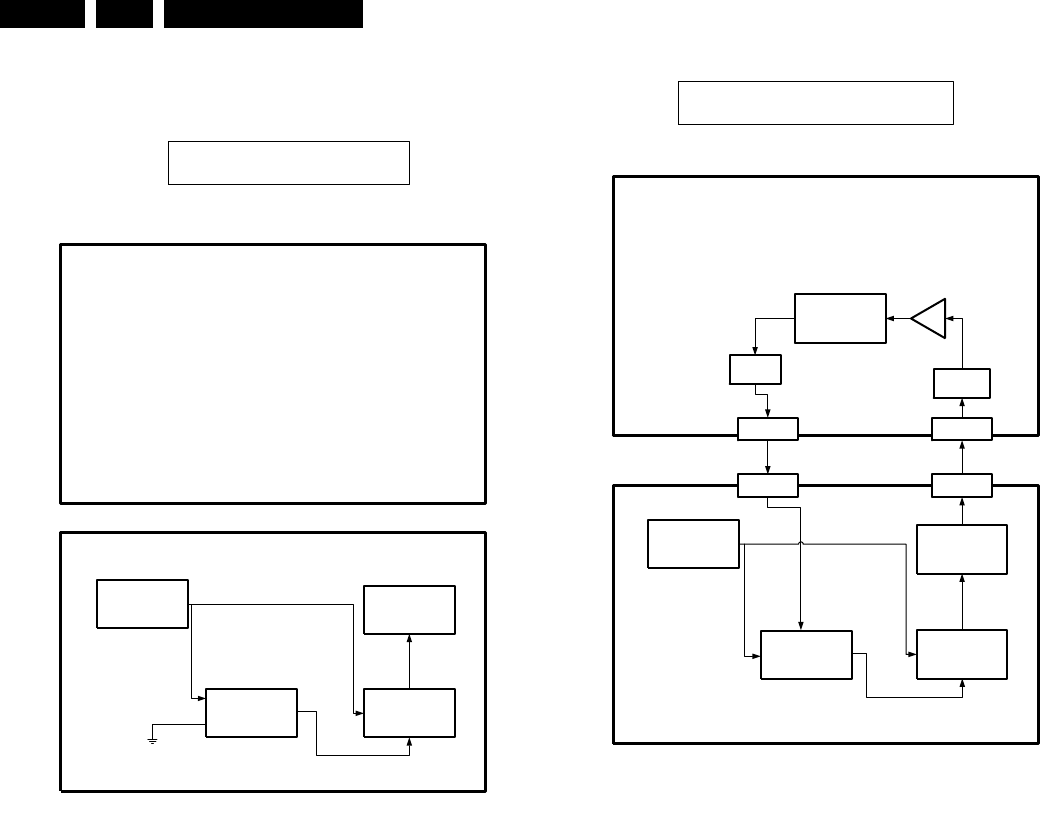

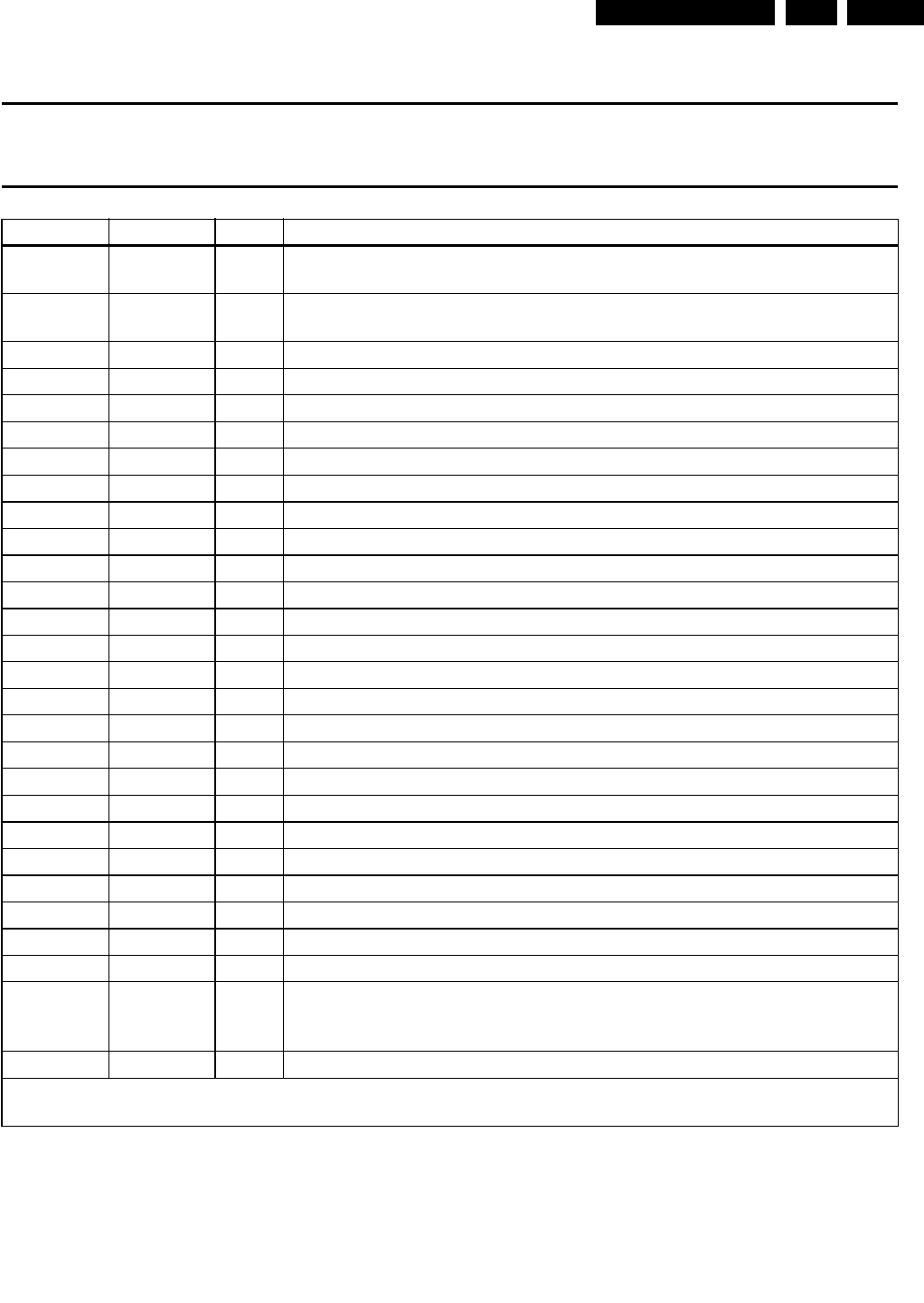

pre-recorded DVD DVD+R(W)

DVD Video

player

Philips DVD

recorder

Directions For Use

EN 8 DVDR980-985 /0X13.

English

INSTALLATION 9

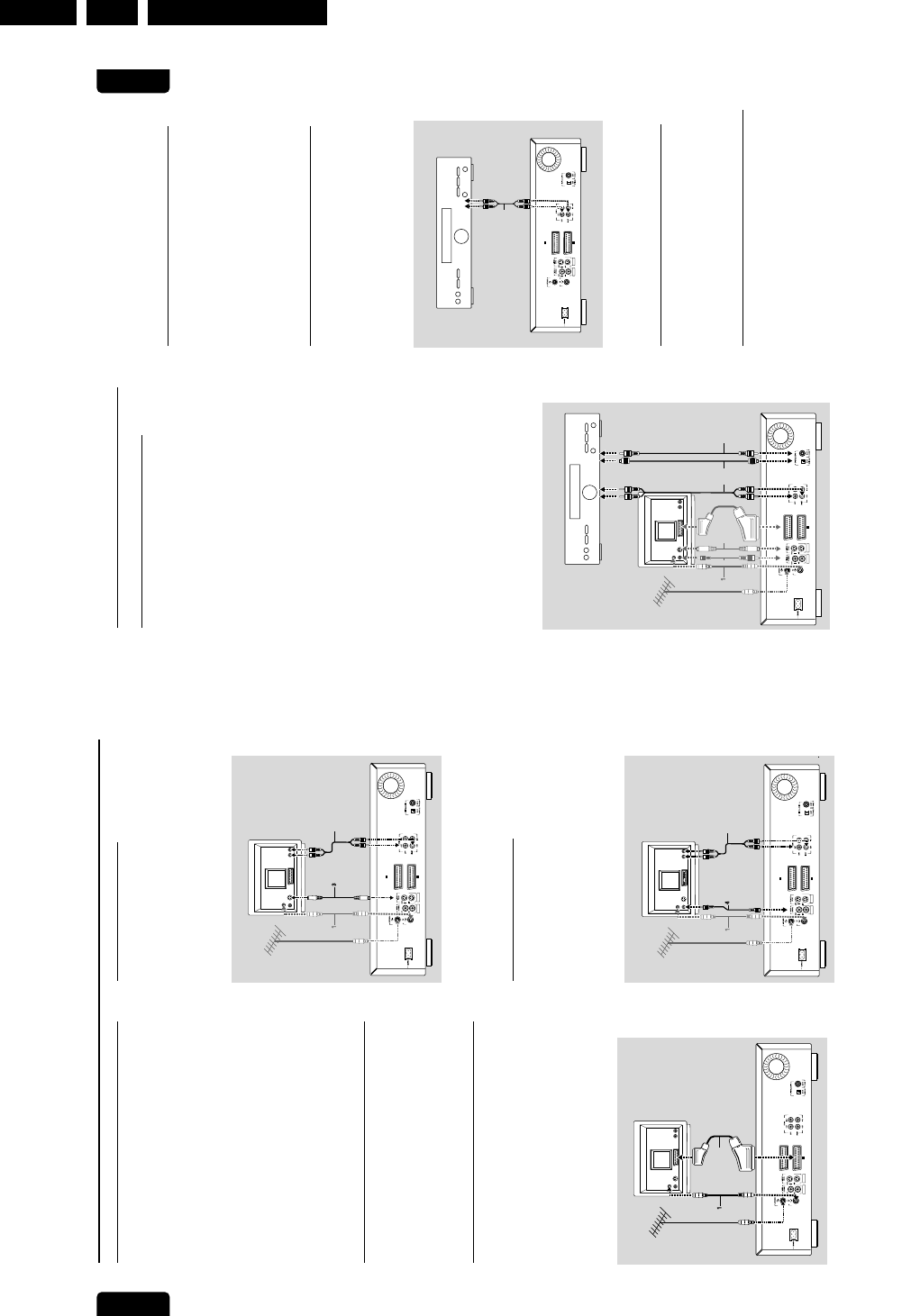

Connecting to audio equipment

Connecting to A/V receiver or A/V

amplifier with digital Multi-channel

decoder

The best possible sound quality is obtained by

connecting your DVD recorder to an A/V receiver with

Multi-channel decoder (Dolby Digital, MPEG 2 and DTS).

Digital Multi-channel sound

Digital Multi-channel connection provides the optimum

sound quality. For this you need a Multi-channel A/V

receiver that supports one or more of the audio types

supported by your DVD recorder (MPEG 2, Dolby

Digital and DTS). For this you can check the receiver

manual and the logos on the front of the receiver.

lConnect the recorder’s digital audio output to the

corresponding input on the receiver. Use a digital

coaxial cable (7) or a digital optical audio cable (8).

If you do not own a digital coaxial audio cable (not

supplied), you may use the supplied video cable (4).

Note:

If the audio type of the digital output does not match the

capabilities of your receiver, the receiver will produce a

strong, distorted sound. The audio type of the DVD disc in

play is displayed in the Status Window, when changing the

language. 6 Channel Digital Surround Sound via digital

connection can only be obtained if your receiver is equipped

with a Digital Multi-channel decoder.

If you cannot connect your DVD recorder to an A/V

receiver with Multi-channel decoder, choose one of the

following alternatives.

Connecting to a receiver equipped with

two channel digital stereo (PCM)

lConnect the recorder’s digital audio output to the

corresponding input on your receiver. Use the

supplied video (CVBS) cable (7) or an optional

digital optical audio cable (8).

lAfter installation you will need to activate PCM on

the DVD recorder’s digital output (see ‘User

Preferences’).

Connecting to a receiver equipped with

Dolby Pro Logic

lConnect the recorder to the TV set and connect the

recorder’s audio Left and Right output sockets to the

corresponding inputs on the Dolby Pro Logic

Audio/Video receiver, using the audio cable supplied (6).

lMake the appropriate Sound settings for Analogue

Output in the user preferences menu.

Connecting to a TV set equipped with a

Dolby Pro Logic decoder

lConnect the recorder to the TV set as described in

chapter ‘Connecting to a TV set’.

Connecting to a receiver with two channel

analogue stereo

lIf you have a receiver with two-channel analogue

stereo without any of the above mentioned sound

systems, connect the audio Left and Right output

sockets to the corresponding sockets on your

receiver, amplifier or stereo system. Use the audio

cable supplied (6).

AUX- I/0

EXT 2

TO TV I/0

EXT 1

EXT 4 EXT 3

AMPLIFIER

6

AMPLIFIER

AUX- I/0

EXT 2

TO TV I/0

EXT 1

TV

643 87

EXT 4 EXT 3

English

8INSTALLATION

Installation

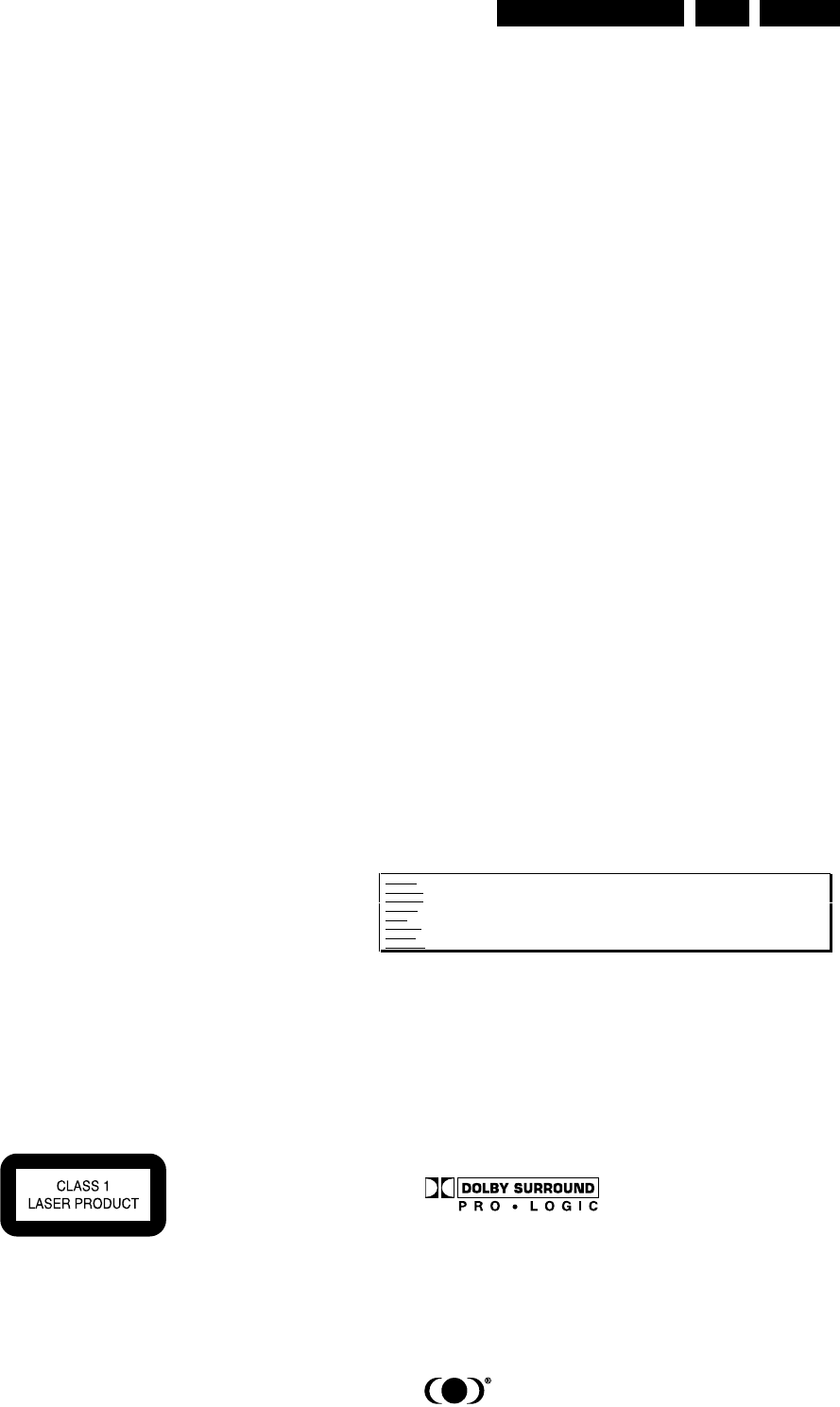

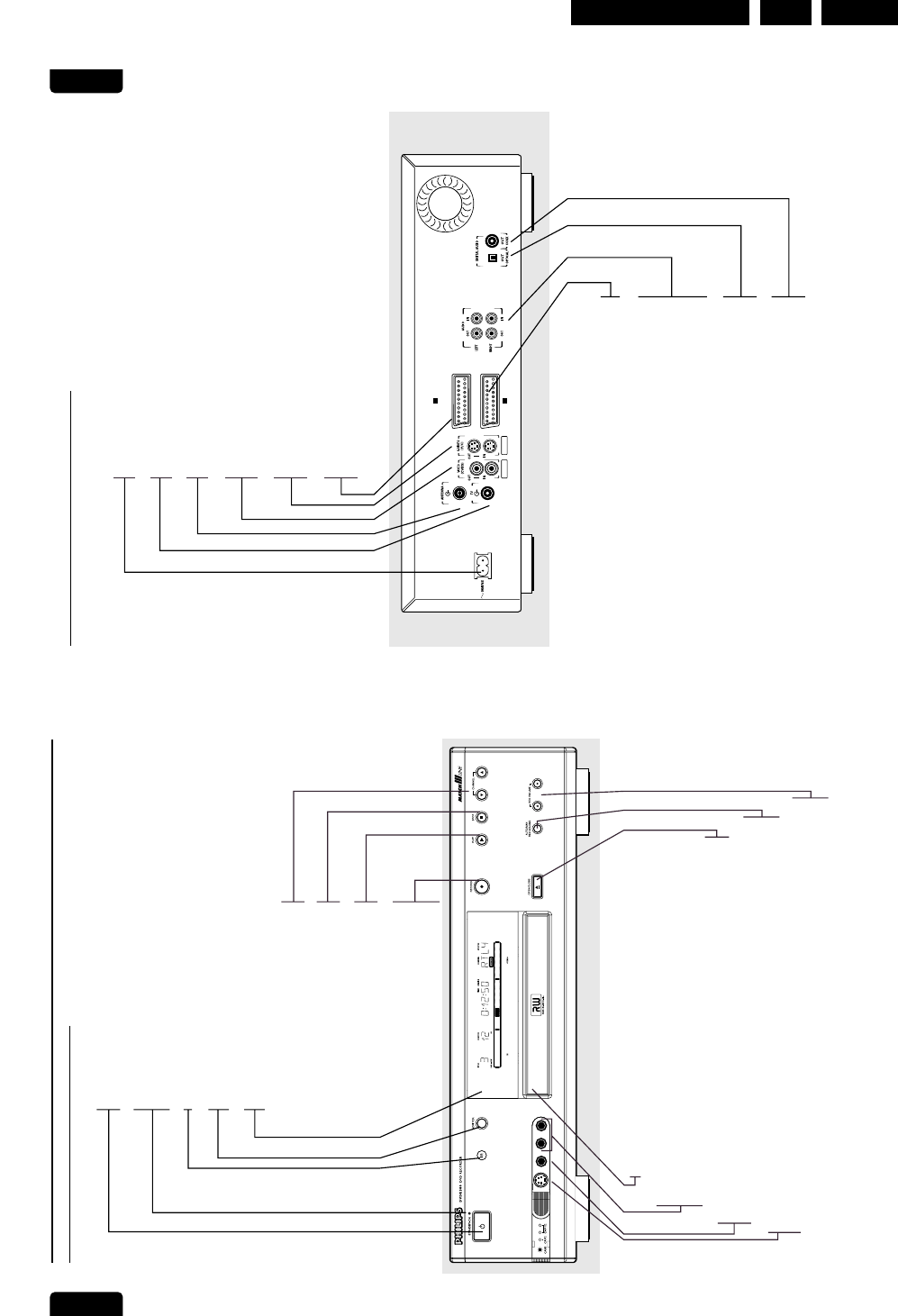

Connections - back side of your

DVD recorder

- Please refer to your TV set, VCR, Stereo System and

any other User Manual(s) as necessary to make the

optimal connections.

- Do not connect the power until all other connections

are made.

- Do not connect your DVD recorder to your TV set

via your VCR, because the video quality could be

distorted by the copy protection system.

- For better sound reproduction you can connect the

recorder audio outputs to your amplifier, receiver,

stereo system or A/V equipment. For this see

‘Connecting to A/V receiver or A/V amplifier’.

Caution:

Do not connect the recorder’s audio output to

the phono input of your audio system in order to

avoid damage to your equipment.

Connecting to the antenna

lRemove the antenna (aerial) cable plug from your

TV set and insert it into the antenna socket at the

back of the DVD recorder.

lPlug one end of the antenna (aerial) cable supplied (1)

into the TV socket on the DVD recorder and the other

end into the antenna input socket on your TV set.

Connecting to a TV set

To obtain the highest possible picture and sound quality

from your TV set it is recommended to use the

SCART

connector on both DVD recorder and TV set.

lConnect the bottom

SCART

connector (EXT 1) to

the TV set, using the

SCART

cable supplied (2) as

shown in the drawing. If your TV set is equipped

with EasyLink or Cinema Link, make sure you use

the correct

SCART

connector. For this refer to the

user manual of your TV set.

If your TV set is not equipped with a

SCART

connector,

you can connect the DVD recorder with the S-video

(Y/C) sockets.

S-video (Y/C) connection

lConnect the S-video output socket to the

corresponding input socket on the TV set, using the

supplied S-video cable (3).

lConnect the audio Left (white) and Right (red)

output sockets to the corresponding sockets on the

TV set using the audio cable supplied (5).

If your TV set is not equipped with S-video sockets, then

connect the DVD recorder with the CVBS sockets to

your TV set.

Video (CVBS) connection

lConnect the Video (CVBS) output socket (yellow)

to the corresponding input socket on the TV set

using the video cable supplied (4).

lConnect the audio Left (white) and Right (red)

output sockets to the corresponding sockets on the

TV set using the audio cable supplied (5).

AUX- I/0

EXT 2

TO TV I/0

EXT 1

5

TV

EXT 4 EXT 3

AUX- I/0

EXT 2

TO TV I/0

EXT 1

5

TV

EXT 4 EXT 3

AUX- I/0

EXT 2

TO TV I/0

EXT 1

2

TV

EXT 4 EXT 3

Directions For Use EN 9DVDR980-985 /0X1 3.

English

INSTALLATION 11

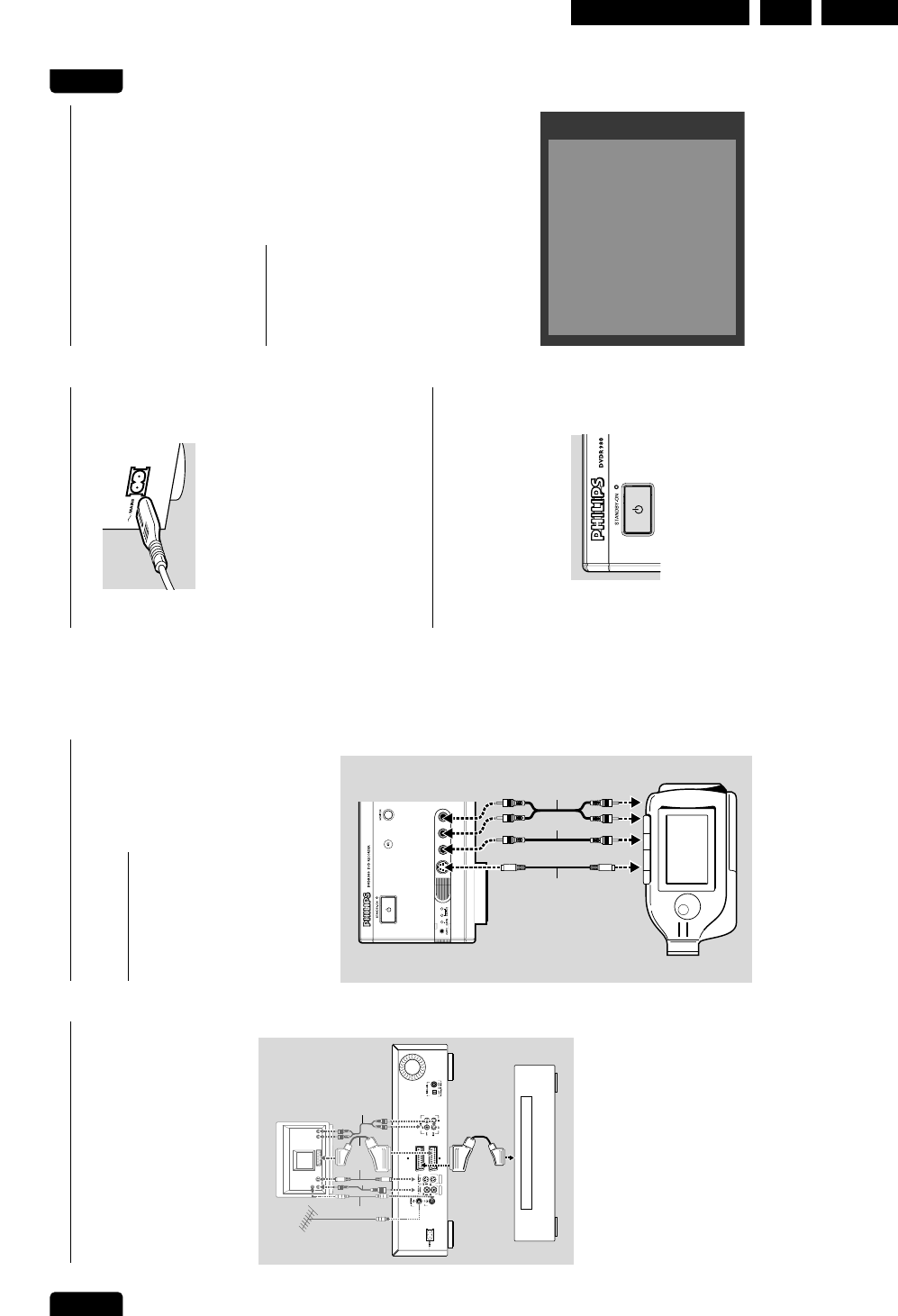

Power supply

lMake sure that all necessary connections are made

before connecting the DVD recorder to the power

supply.

lPlug the power cable supplied into the Power

connector on the rear of the recorder.

lPlug the mains plug into an AC outlet.

Note:

Always check if the local mains voltage matches the required

220V - 240V.

When the recorder is in the Standby position, it is still

consuming some power.

If you wish to disconnect your DVD recorder completely from

the mains, withdraw the plug from the AC Outlet.

When the DVD recorder is disconnected from the mains, TV

channels and timer data will be stored typically 1 year.

Switching on

lSwitch on the TV set and select the programme

number that you have chosen for video playback

(see operating manual for your TV set).

lPress BSTANDBY/ON.

‰The recorder display lights up. If you have not yet

installed your DVD recorder, it will enter ‘virgin

mode’. In this mode you will have to set your

personal preferences.

First time set-up: virgin mode

After switching on the DVD recorder for the very first

time the ‘virgin mode screen’ will appear.

In ‘virgin mode’ you may have to set your preferences

for some of the recorder features.

If the ‘virgin mode screen’ does not appear, your DVD

recorder has been installed already. You may still change

the settings via the ‘installation menu’.

Depending on the kind of TV set, preferences will have

to be set manually or they will be taken over

automatically from the TV set.

Automatic setting

When your TV set is equipped with EasyLink

TM

, Cinema

Link

TM

, N

EX

TV

IEW

Link

TM

, SmartLink

TM

, Q-Link

TM

or

MegaLogic

TM

, the TV settings will be taken over from the

TV set but they cannot be changed manually afterwards.

When preferences are taken over from your TV set, the

message ‘

Easy Link loading data from TV

-

please

wait

’ will appear.

Menus for which no preferences are available will be

displayed. They have to be set manually.

Note:

Preferences have to be set in the order in which the item

menus will appear on the screen.

If the recorder is switched off while setting user preferences,

all preferences have to be set again after switching the

recorder on again.

The ‘virgin mode’ will only be concluded after the

preferences for the last item have been confirmed.

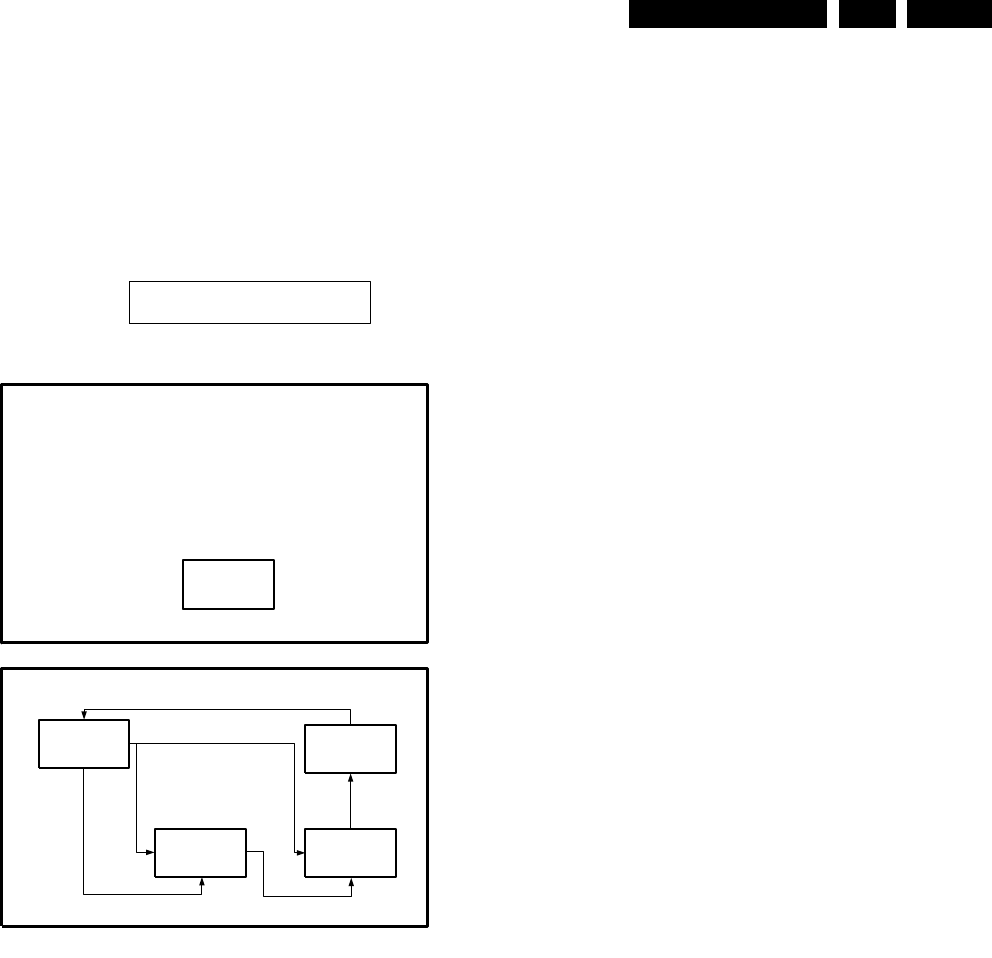

Follow TV

Easy Link

loading data from TV -

please wait

English

10 INSTALLATION

Connecting to other equipment

Use the top

SCART

connector (EXT 2) on your DVD

recorder to make connections to a:

- Satellite receiver or Set top box,

- VCR,

- DVD-Video player

Most pre-recorded video cassettes and DVD discs are

copy protected. If you try to copy them the display

shows ‘COPY PROTECT’.

For installation of a decoder, see ‘User Preferences’ -

‘Installation’.

Notes:

- If the power is off or Low Power Standby is selected (see

User Preferences - features), the signal from EXT 2 will not

be passed on to the TV set on EXT 1.

- EasyLink functionality will not be available to devices

connected via the DVD recorder’s EXT 2

SCART

connector.

Connections - frontside of your

DVD recorder

Camcorder connection

lIf you have a DV, Digital 8, Hi-8 or S-VHS(C)

camcorder, connect the S-video input socket to the

corresponding output socket on the camcorder,

using the S-video cable supplied (1) and connect the

audio cable (3) supplied.

lOtherwise connect the Video input socket (yellow)

to the corresponding output socket on the

camcorder using the video cable supplied (2) and

connect the audio Left (white) and Right (red) input

sockets to the corresponding sockets on the

camcorder using the audio cable supplied (3).

lIf your camcorder has mono sound, use only the left

audio connector. In this case the sound will be

recorded on both audio channels.

AUDIOS-VIDEO VIDEO LR

32

1

Camcorder

Camcorder

TV

Set top box

432 5

1

AUX- I/0

EXT 2

TO TV I/0

EXT 1

EXT 4 EXT 3

Directions For Use

EN 10 DVDR980-985 /0X13.

English

INSTALLATION 13

Country

Select your country. This is used as input for the

‘Parental Control’ feature (see ‘Access Control’) as well

as the searching of TV channels.

Auto TV Channel Search

Make sure the antenna is connected. See ‘Connecting to

the antenna’. Your DVD recorder will search for all TV

channels.

It stores channels in the sequence they are found.

lConfirm with OK.

‰Auto search starts. This can take several minutes.

‰When Auto search is completed ‘

Autom.

search complete

-

XX channels found

’ appears

on the TV screen.

After Auto channel search you can have TV channels

stored automatically in the same order as your TV set.

See ‘User preferences installation’ - ‘Follow TV’.

Time/Date

When Channel auto search is completed the actual Time

and Date are also set automatically.

If the time in the DVD recorder display is not correct,

the clock must be set manually.

lAdjust ’

Time

’, ’

Year

’, ’

Month

’, ’

Date

’ if required,

with the w(down cursor) or v(up cursor) key.

lChange values with the the t(left cursor) or u

(right cursor) key or the digit keys 0-9.

lTo end, press OK.

Note:

All these items may have to be set after first start up (‘virgin

mode’). After that they can always be adapted in the user

preferences menu. When your TV set is equipped with

EasyLink the TV set presets will be taken over from the TV

set but they cannot be changed manually afterwards.

Virgin mode settings are now completed.

All settings can still be changed. See ‘User preferences’.

Autom.search

To continue

Press OK

Autom.search complete

XX channels found

Time

Year

Month

Date

09: 40

2001

02

09

Please wait

Autom.search

Searching for TV channels

XX channels found

Virgin mode

Country

Press OK to continue

Austria

Belgium

Denmark

Finland

France

English

12 INSTALLATION

Manual setting

When a menu is displayed:

lUse the wv (down up cursor) keys to go through

the options in the menu. The icon of the selected

option will be highlighted.

lUse OK to confirm your selection and to select the

next menu.

The following items may have to be set in virgin mode:

Menu language

The on-screen menus of DVD-Video discs will be

displayed in the language you choose.

Audio language

The sound of DVD-Video discs will be in the language

you choose, provided this is available on the disc in play.

If not, speech will revert to the first spoken language on

the disc. Also the DVD-Video disc menu will be in the

language you choose, provided this is available on the disc.

Subtitle language

The subtitles of DVD-Video discs will be in the language

you choose provided this is available on the disc in play. If

not, subtitles will revert to the first subtitle language on

the disc.

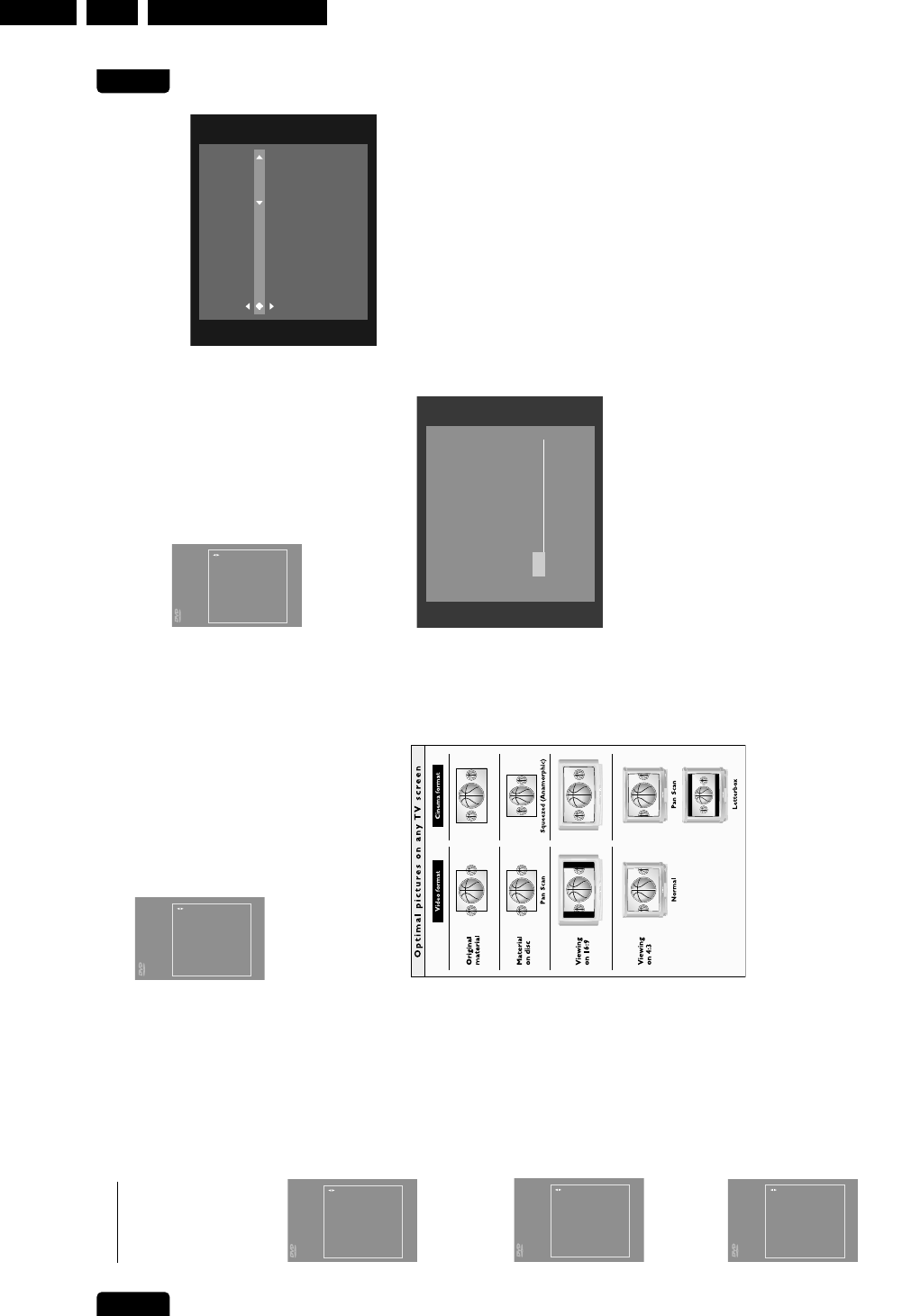

TV Shape

You can choose:

-

16:9

if you have a wide screen (16:9) TV set.

-

4:3

if you have a regular (4:3) TV set. In this case you

can also choose between:

-

Letterbox

for a ‘wide-screen’ picture with black

bars at the top and bottom,

-

Pan Scan

, for a full-height picture with the sides

trimmed. If a disc has Pan Scan, the picture then

moves (pans) horizontally to keep the main action

on the screen.

Virgin mode

TV Shape

Press OK to continue

4:3 letterbox

4:3 panscan

16:9

Virgin mode

Subtitle language

Press OK to continue

English

Español

Français

Português

Italiano

Virgin mode

Audio language

Press OK to continue

English

Español

Français

Português

Italiano

Virgin mode

Menu language

Press OK to continue

English

Español

Français

Italiano

Deutsch

Directions For Use EN 11DVDR980-985 /0X1 3.

English

FUNCTIONAL OVERVIEW 15

Apparatus Claims of U. S. Patent Nos.

4,631,603, 4,577,216, 4,819,098, and 4,907,093

licensed for limited viewing uses only.

AUX- I/0

EXT 2

TO TV I/0

EXT 1

EXT 4 EXT 3

MAINS

- connection to the mains

TV

- RF connection to TV set

ANTENNA

- RF connection to antenna/cable TV signal

Video (CVBS)

- OUT: for connection to a TV, receiver or amplifier with CVBS video inputs

- IN: for connecting a video source with CVBS outputs

S-video (Y/C)

- OUT: for connection to a TV, receiver or amplifier with S-video (Y/C) inputs

- IN: for connecting a video source with S-video (Y/C) outputs

AUX I/O (EXT II)

- for connection to a satellite receiver, decoder, video recorder, set top box

etc. via

SCART

TO TV I/O (EXT I)

- for connection to a TV with

SCART

AUDIO OUT L/R

- connection to an amplifier, receiver, stereo system or

to a TV that is not equipped with a

SCART

connector

AUDIO IN L/R

- connection to the audio output of a video source that

is not equipped with a

SCART

connector

OUT OPTICAL

- connection to an amplifier, receiver or stereo system

with a digital (optical) audio input

OUT COAX

- connection to an amplifier, receiver or stereo system

with a digital (coaxial) audio input

Rear of recorder

English

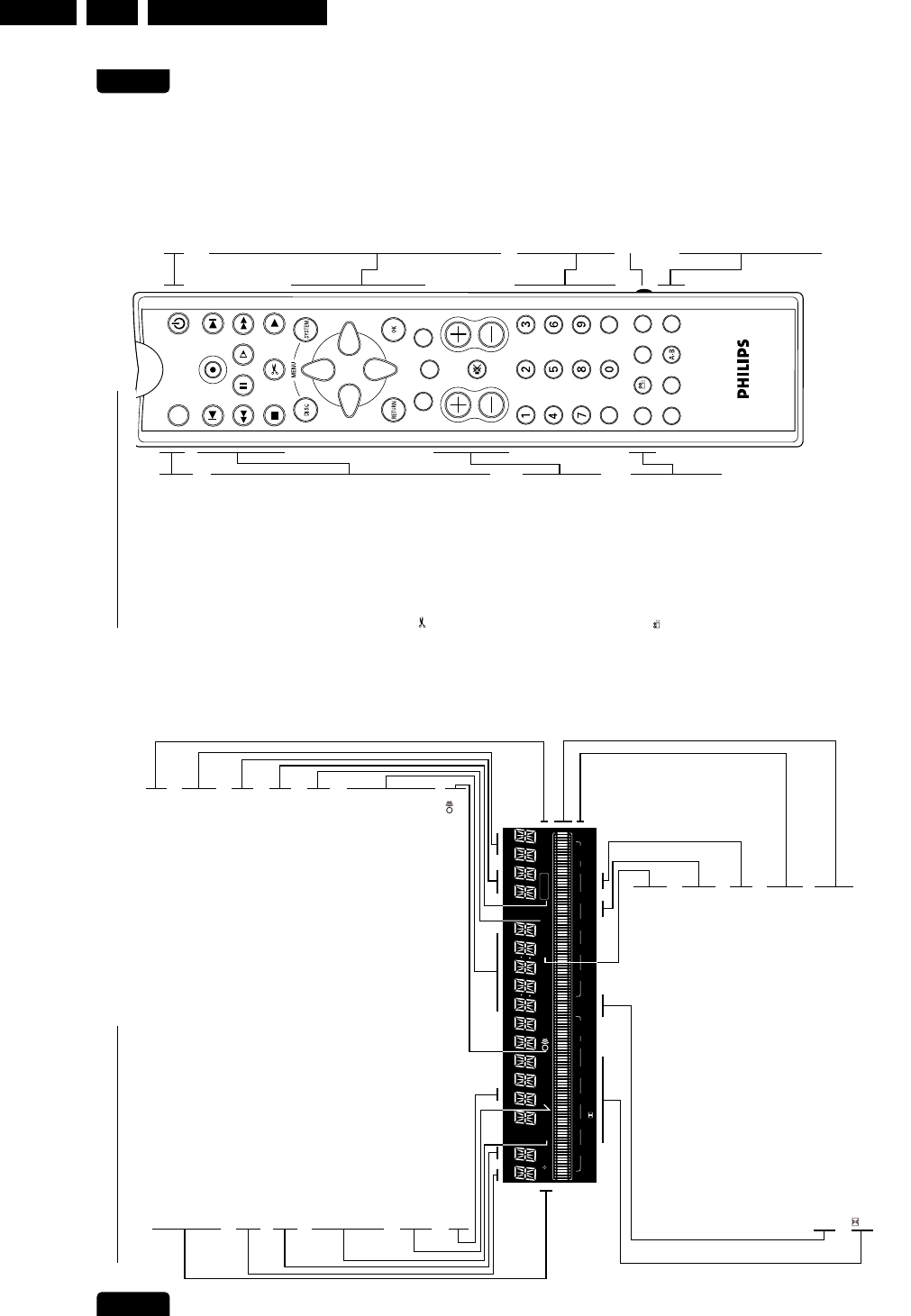

Functional overview

14 FUNCTIONAL OVERVIEW

AUDIOS-VIDEO VIDEO LR

DIGITAL

B STANDBY/ON

- switches the recorder to power/standby mode

Standby indicator

- lights up red when the recorder is in standby mode

- lights up green when the recorder is operative

Infrared remote control receiver

MONITOR

- switches between disc mode and monitor mode

Display

- displays the current status of the recorder

CHANNEL

- to select channels manually

9 STOP

- stops video/audio play or recording

2 PLAY

- starts video/audio play

0 RECORD

- direct recording of the selected programme

on TV or the recorder (depending on the

DIRECT RECORD setting)

Disc loading tray

AUDIO (Left/Right)

- Audio input socket left/right to

connect a camcorder or video

recorder

VIDEO (CVBS)

- Video input socket to connect a

camcorder or video recorder

S-VIDEO

- Video input socket to connect a

camcorder or video recorder

/ OPEN/CLOSE

- opens/closes the disc tray

AUTO/MAN REC VOLUME

- to adjust the recording level

automatically or manually

MANUAL

- 3 4 to increase/decrease

the recording level

Front of recorder

Directions For Use

EN 12 DVDR980-985 /0X13.

English

FUNCTIONAL OVERVIEW 17

MONITOR ON/OFF

REC/OTR

PLAYSTOP FSS

FORWARDREVERSE

NEXT PREVIOUS

PAUSE SLOW

CLEAR

CH

VOL

SELECT

TIMER

MUTE

T/C

ZOOM ANGLE SUBTITLE AUDIO

DIM REPEAT REPEAT SCAN

A/CH

ZYa

ON/OFF B

DISC MENU

- displays DVD disc menu or index

picture screen

SYSTEM MENU

- displays recorder system menu

bar

w v u t

- down/up/right/left cursor

movement

RETURN

- return to previous menu on

(S)VCD disc

CLEAR

- delete last entry/clear timer

TIMER

- displays the ‘timer menu’

SELECT

- switches between different values

in a menu

- switches between record modes

in the Index Picture Screen and in

monitor mode

OK

- acknowledge menu selection

0-9

- numerical key pad

T/C

- select title

- select chapter

A/CH Alternate Channel

- switches to the previous TV

channel

SIDE SWITCH

- enables other keys to operate

the TV set (see Appendix)

DIM

- changes brightness setting of

display

REPEAT

- repeat chapter, track, title, disc

REPEAT A-B

- repeat sequence

SCAN

- playback of the first 10 seconds

of each chapter within a title

(DVD) or the first 10 seconds of

each track on a disc

(

VCD/CD

)

MONITOR

- switches between disc mode and

monitor mode

J

- previous chapter, track or title

0

- direct recording of the currently

selected programme

K

- next chapter, track or title

Q

- search backward

;

- pause

H

- slow motion

R

- search forward

9

- stop

FSS

- displays Favorite Scene Selection

menu for DVD+RW or DVD+R

disc

2

- play

VOL +/–

- TV volume up/down

c

- TV Mute ON/OFF

CH +/–

- programme up/down

a ZOOM

- enlarge video image

ANGLE

- select DVD camera angle

Z SUBTITLE

- subtitle language selector

Y AUDIO

- audio language selector

Remote control

English

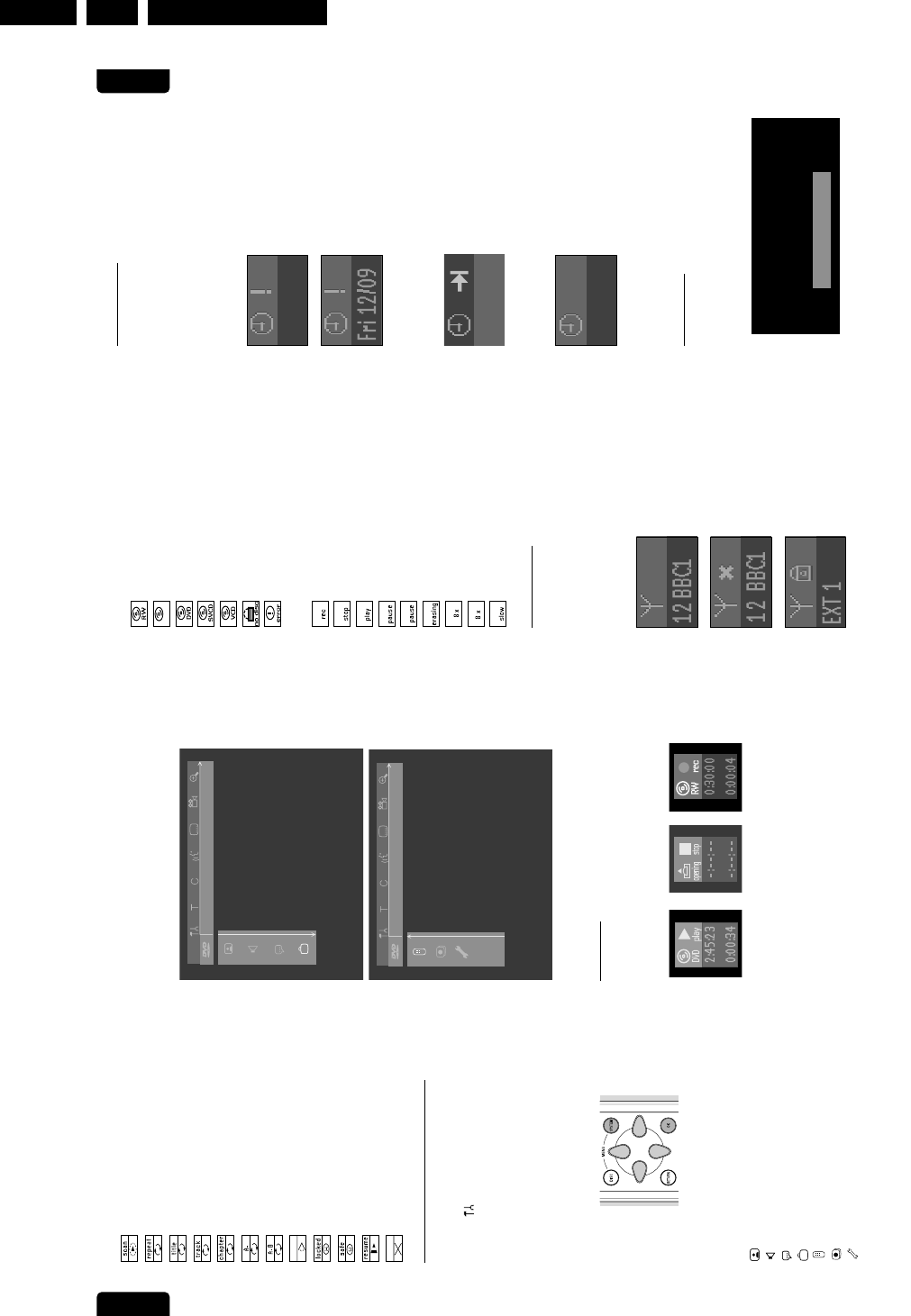

16 FUNCTIONAL OVERVIEW

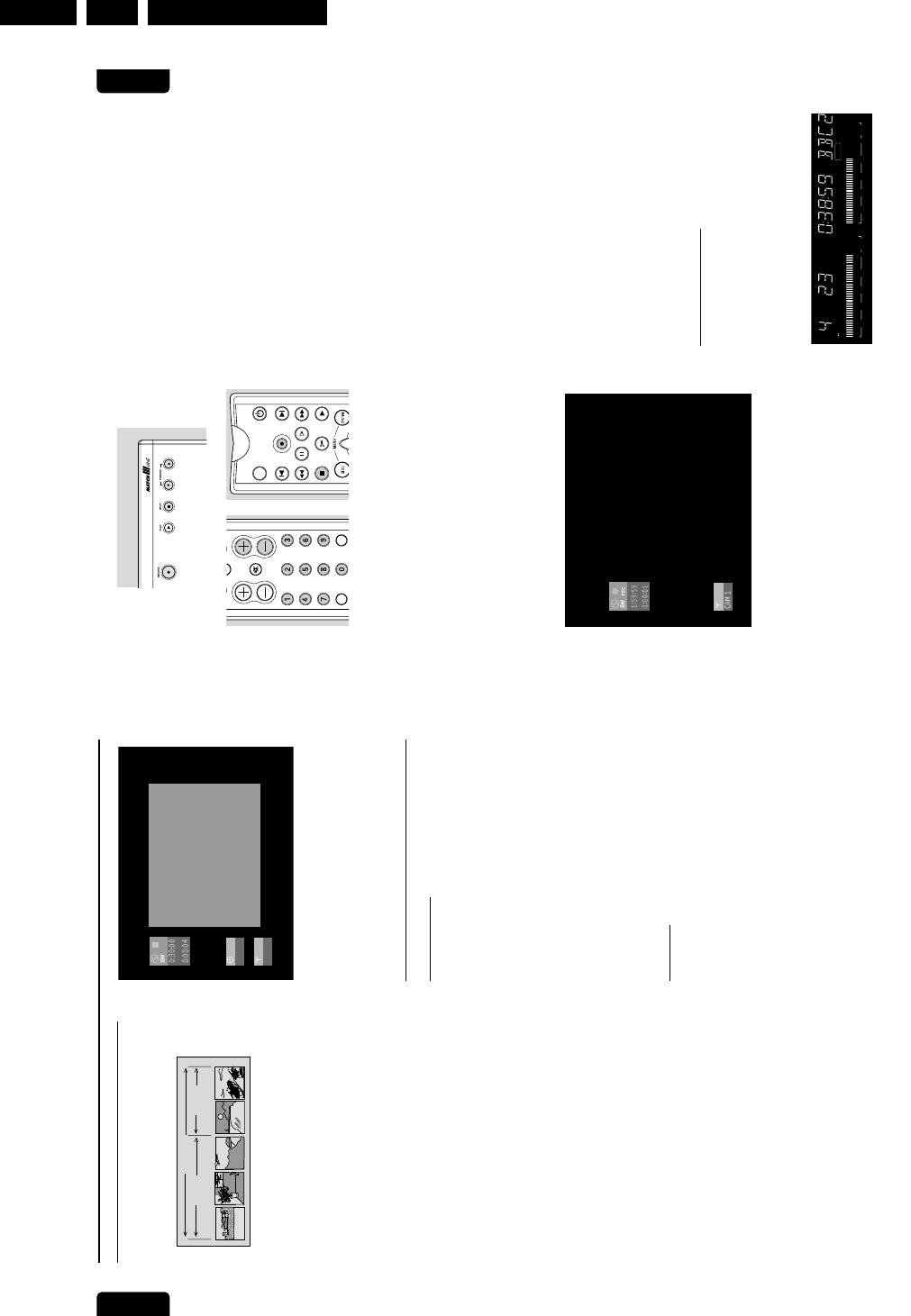

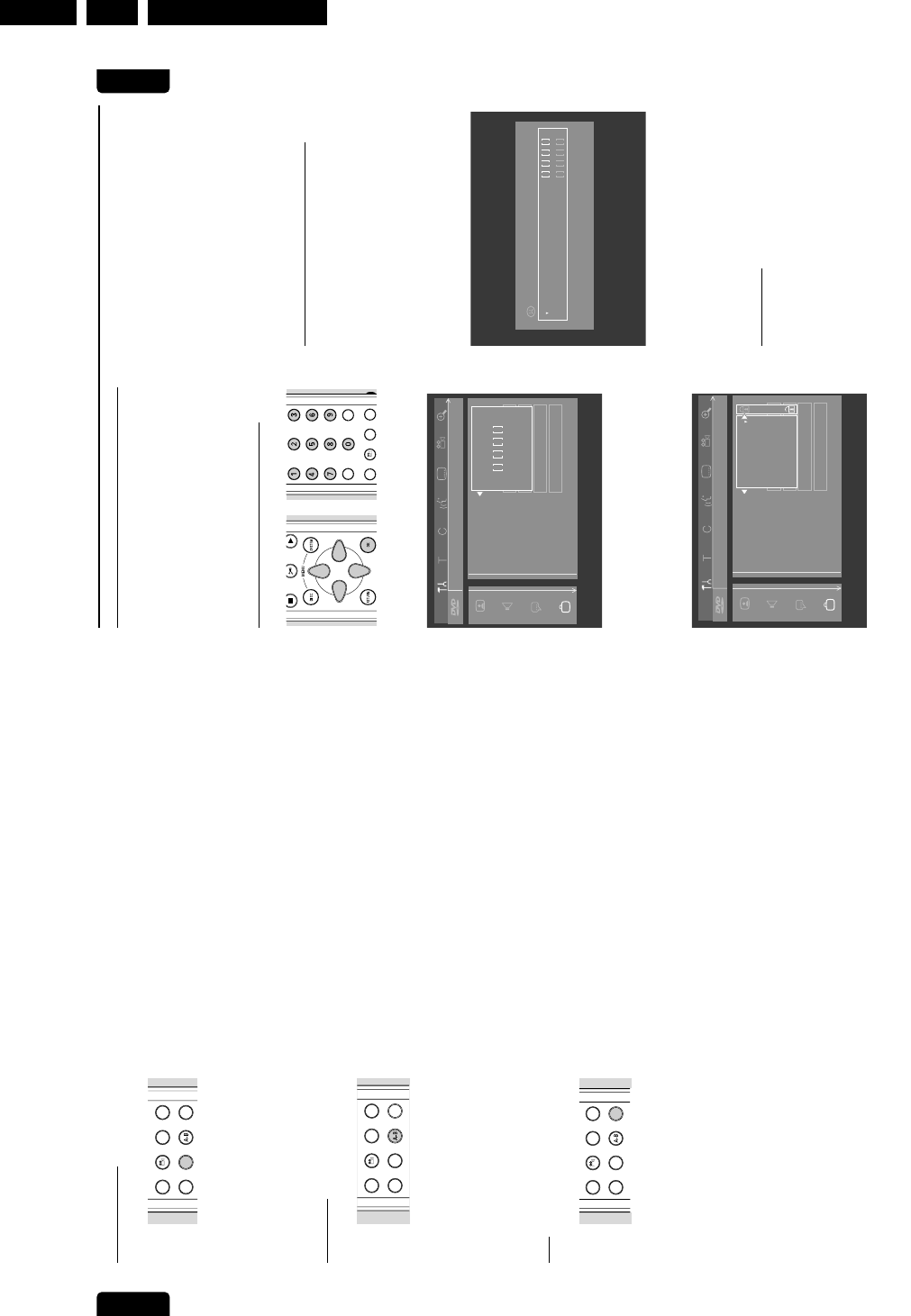

PCMDTS DIGITALMPEG

HQ SP LP EP+

VPS/PDC

DECODER

CHANNEL

DVD CDVRW

TITLE TRACK CHAPTER TOTAL TIME REMAINTRACK

MANUAL

TIMER

SAT

-30-40 -10-20 0

OVER

-30-40 -10-20 0

OVER

SA

NICAM STEREO

RECORD

DVD

- DVD Video disc inserted

DVD+R

- DVD+Recordable disc inserted

DVD+RW

- DVD+Rewritable disc inserted

TITLE

- DVD title number

TRACK

- VCD/CD track number

VCD

- Video CD inserted

CD

- Audio CD inserted

SVCD

- Super Video CD inserted

HQ - SP - LP - EP

- Selected recording mode: High Quality,

Standard Play, Long Play or Extended Play

CHAPTER

- DVD chapter number

DECODER

- Decoder activated for current preset

VPS/PDC

- Video Programming System/Programme

Delivery Control active on current preset

CHANNEL

- Preset name or number

RECORD

- Recording in progress

TIMER

- Timer programmed or active

TRACK TIME

- Track time in minutes and seconds

TOTAL TIME

- Total playback or recording time in hours,

minutes and seconds

TOTAL REMAIN

- Total remaining playback or recording time

in hours, minutes and seconds

- Remote control active (flashing)

SAT

- Recorder prepared for or engaged in satellite

recording

NICAM

- NICAM digital stereo sound on current

preset

STEREO

- Stereo sound from tuner

dB scale

- indicates recording volume when using

manual level control

Disc bar

- Displays disc content, recording level or

formatting progress

MANUAL

- Manual recording level control

DIGITAL - DTS - MPEG - PCM

- Active audio format

Display

Directions For Use EN 13DVDR980-985 /0X1 3.

English

OPERATION 19

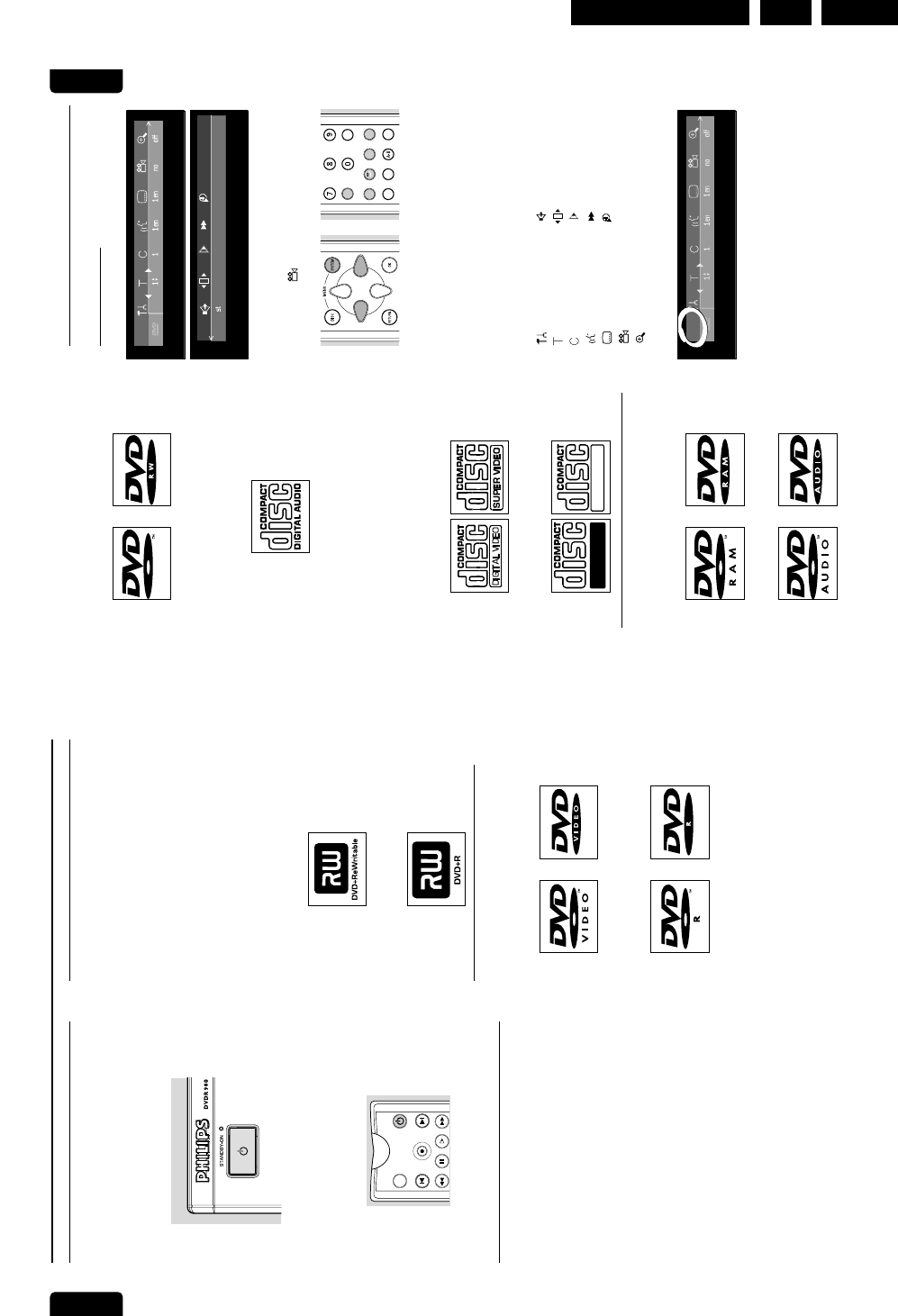

DVD-RW

Only plays if it is recorded in Video mode and has been

finalized.

CD Digital Audio

You can play digital audio CDs in conventional style

through a stereo system, using the keys on the remote

control and/or front panel, or via the TV set using the

on-screen display (OSD).

Super Audio CD

Of hybrid SACD discs, the CD layer can be played.

(Super) Video CD

Depending on the material on the disc (a movie, video

clips, a drama series, etc.) these discs may have one or

more tracks, and tracks may have one or more indexes,

as indicated on the disc case. To make access easy and

convenient, your recorder lets you move between

tracks, and between indexes.

CD-R/CD-RW

Plays if it contains Audio CD.

The following disc types cannot be used at

all, neither for recording nor for playback:

DVD-RAM

DVD-Audio

On-screen display information

System menu bar

The system menu bar can be called up by pressing any of

the following keys on the remote control: SYSTEM

MENU, T/C,ANGLE, ZSUBTITLE, Y

AUDIO and aZOOM.

Widescreen (16:9) TV sets may show only part of the

system menu bar in certain screen modes. Select a

different screen mode on the TV to see the full menu.

A number of recorder functions can be controlled via

the system menu bar. You can navigate between the two

parts of the system menu bar with the t(left cursor)

and the u(right cursor) key.

System menu bar icons

PART 1 PART 2

User preference Sound

Title/Track Step motion

Chapter/Index Slow motion

Audio language Fast motion

Subtitle language Time search

Angle

Zoom

Temporary Feedback Field

The system menu bar contains a ‘Temporary Feedback

Field’ with information concerning prohibited actions,

playback modes, available angles, etc.

T/C

ZOOM ANGLE SUBTITLE AUDIO

DIM REPEAT REPEAT SCAN

A/CH

ZYa

ReWritable

Recordable

RW

English

18 OPERATION

Important notes for operation

You can switch on the DVD recorder with the

BSTANDBY/ON key. Keep your DVD recorder

connected to the mains at all times to ensure that

programmed recordings can be made and that the

television functions normally.

Both the DVD recorder and the remote control have an

’Emergency interrupt’ button. You can use the

BSTANDBY/ON button to interrupt a function.

When you have an operating problem, you can interrupt

the function and start again.

When you switch off the DVD recorder, the display will

briefly show ‘WAIT’.

Loading discs

1Press / OPEN/CLOSE on the front of the

recorder. The disc loading tray opens.

2Lay your chosen disc in the tray, label side up.

Make sure it is sitting properly in the correct recess.

3Press / Open/Close, to close the tray.

‰‘READING’ appears in the status box and on the

recorder display. If the inserted disc is pre-recorded

or write-protected, playback always starts

automatically.

You can always unload a disc by pressing

/OPEN/CLOSE again or pressing 9STOP on the

remote control for two seconds.

Note:

If ‘Child Lock’ is set to ON and the disc inserted is not in the

‘child safe’ list (not authorized), the PIN code must be entered

and/or the disc has to be authorized. (see ‘Access Control’)

Disc types

You will recognize the different types of discs, that can

be used in your DVD recorder by the logo. Depending

on the disc type you can either use it for recording and

playback or playback only. Some discs are not suitable at

all to be used in the DVD recorder.

In the next table a summary is given of all excisting disc

types and their DVD recorder compatibility.

The following disc types can be used for

recording and playback:

DVD+RW

Records and plays; In case of a new blank disc, after the

first recording, some more time (up to two minutes) is

needed to make the disc compatible with DVD-Video

players.

DVD+R

Records and plays.

The following disc type can be used for

playback only:

DVD-Video

DVD-R

Only plays if it contains DVD-Video.

MONITOR ON/OFF

REC/OTR NEXTPREVIOUS

FORWARDREVERSE PAUSE SLOW

Operation

Directions For Use

EN 14 DVDR980-985 /0X13.

English

OPERATION 21

Disc type icons

DVD+RW

DVD+R

DVD-Video

Super Video-CD

Video-CD

no disc

disc error

Disc status icons

recording

stop

playing

pause play

record pause

erasing

fast forward

fast reverse

slow motion

Tuner info box

The tuner info box is located at the bottom left of the

screen and is displayed in monitor mode (See: Recording

Checking input). It displays the currently selected input.

When the tuner is selected it shows programme number

and/or channel name.

Current channel

No signal

Copy-protected signal

Timer info box

The timer info box is located above the tuner info box

and is displayed in monitor mode. It displays the current

status of the timer.

When a timer is programmed it shows a timer indication

and the start time or date of the first programmed

recording.

Timer event due today

Timer event due on another day

When an OTR recording is in progress it shows the end

time.

OTR recording in progress

When no timer is programmed it displays the current

time.

Current time

Note:

Tuner info box and timer info box disappear during playback

and after recording is started.

Warning box

The warning box will be displayed near the bottom of

the screen when appropriate. For instance: ‘

Disc locked

’.

Disc locked

10: 13 h r

10: 15h r

10: 13 h r

H

Q

R

0

0 ;

;

2

9

0

DVD+R

English

20 OPERATION

Scan

Repeat All

Repeat Title

Repeat Track

Repeat Chapter

Repeat A to end

Repeat A-B

Angle

Child Lock On

Child Safe

Resume

Action prohibited

User preference menu operation

lPress SYSTEM MENU on the remote control.

lSelect in the system menu bar and press w

(down cursor).

‰The user preferences menu appears.

lUse the t u v w (left right up down cursor) keys

to toggle through the menus, sub menus and

submenu options.

‰When a menu item is selected, the cursor keys

(on the remote control) to operate the item are

displayed next to the item.

lPress OK to confirm and return to the main menu.

The following functions can be operated via the user

preference menu.

User preference menu icons

Picture settings

Sound settings

Language settings

Feature settings

Remote control settings

Record settings

Installation

lYou can navigate between the various items of the

user preferences menu with the v(up cursor) and

the w(down cursor) key. To select an item press u

(right cursor) key.

lBy pressing SYSTEM MENU the system menu bar

will disappear from the screen.

Status box

The status box on the left hand side of the screen

displays the current status of the recorder and the disc

type loaded for several seconds.

-- --- off on off

-- --- off on off

Directions For Use EN 15DVDR980-985 /0X1 3.

English

OPERATION 23

User preferences

Setting user preferences

You can set your user preferences for some of the

recorder features. (See ‘Operation’ - ‘User preferences

menu operation’)

The following items can be adapted:

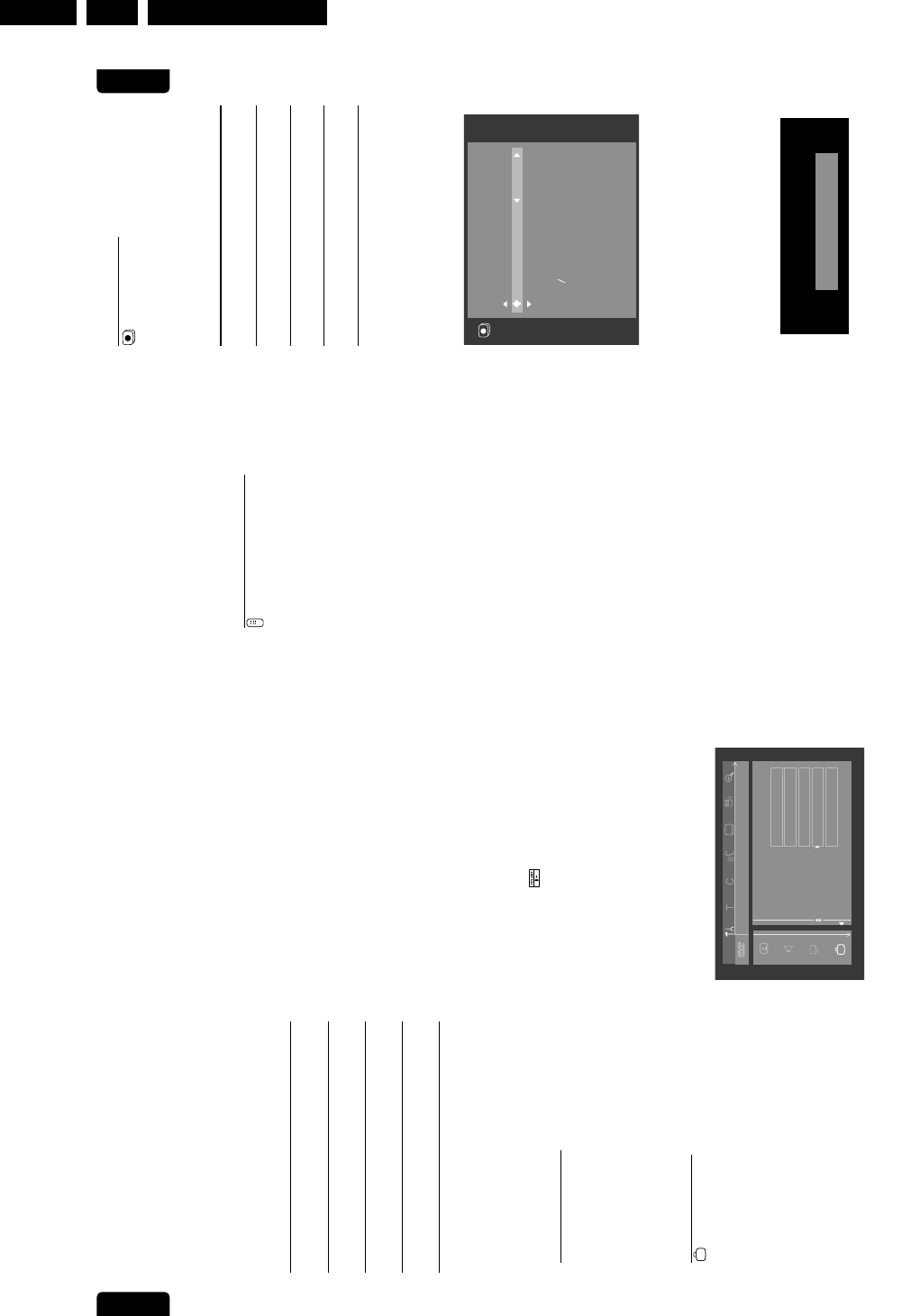

Picture settings

TV Shape

With TV Shape you can adjust the output of your DVD

Recorder to optimally fit your TV screen. You can

choose:

-

16:9

if you have a wide screen (16:9) TV set.

-

4:3

if you have a regular (4:3) TV set. In this case you

can also choose between:

-

Letterbox

: for a ‘wide-screen’ picture with black

bars at the top and bottom,

-

Pan Scan

: for a full-height picture with the sides

trimmed. If a disc has Pan Scan, the picture then

moves (pans) horizontally to keep the main action

on the screen.

Black level shift (NTSC only)

Adapts the colour dynamics to obtain richer contrasts.

Select ‘

On

’ or ‘

Off

’.

Video shift

Factory setting is such that the video will be centered on

your screen. Use this setting to adjust the position of

the picture on your TV set by scrolling it to the left or

right.

SCART

Video

Factory setting is RGB. Select ‘

S

-

video

’ (Y/C) via

SCART

when connecting to an S-VHS recorder.

Sound settings

Digital output

Factory setting ‘

All

’ means that both coaxial and optical

outputs are switched on, and that Dolby Digital Multi-

channel is fed to the outputs as such MPEG audio is

converted to PCM. If your equipment doesn’t include a

digital Multi-channel decoder, set the digital output to

‘

PCM only

’ (Pulse Code Modulation). Both coaxial and

optical outputs are then switched on, and Dolby Digital

and MPEG audio are converted to PCM. If you are not

connecting equipment with a digital input, change the

setting to ‘

Off

’.

Analogue output

Select ‘

Stereo

’, ‘

Surround

’ or ‘

3D Sound

’. Factory

setting is Stereo.

Digital output

Analogue output

Night mode

Sound

-- --- off on off

Stereo

Surround

3D sound

TV shape

Black Level shift

Video shift

SCART video

Picture

OK to exit

-- --- off on off

English

22 OPERATION

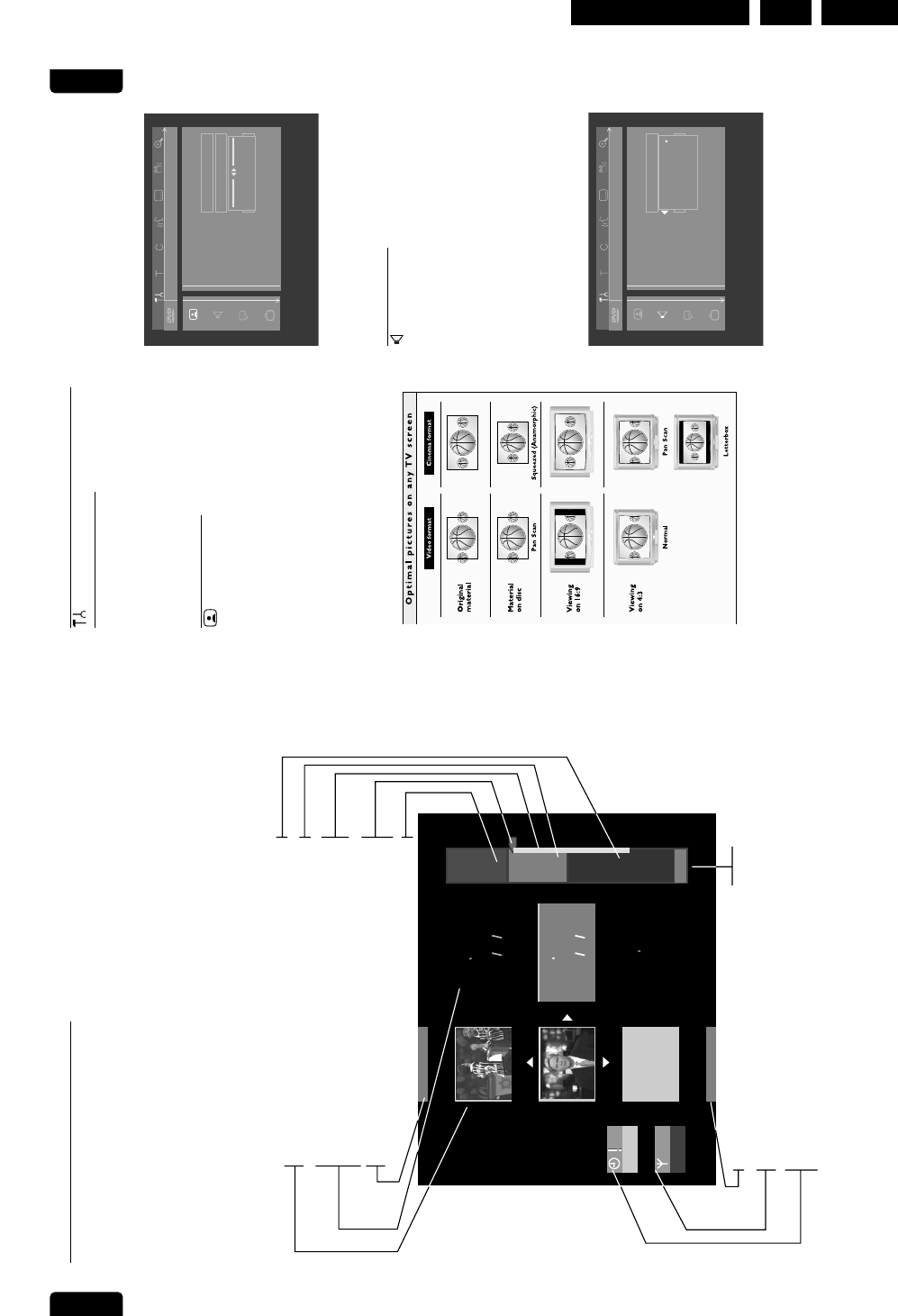

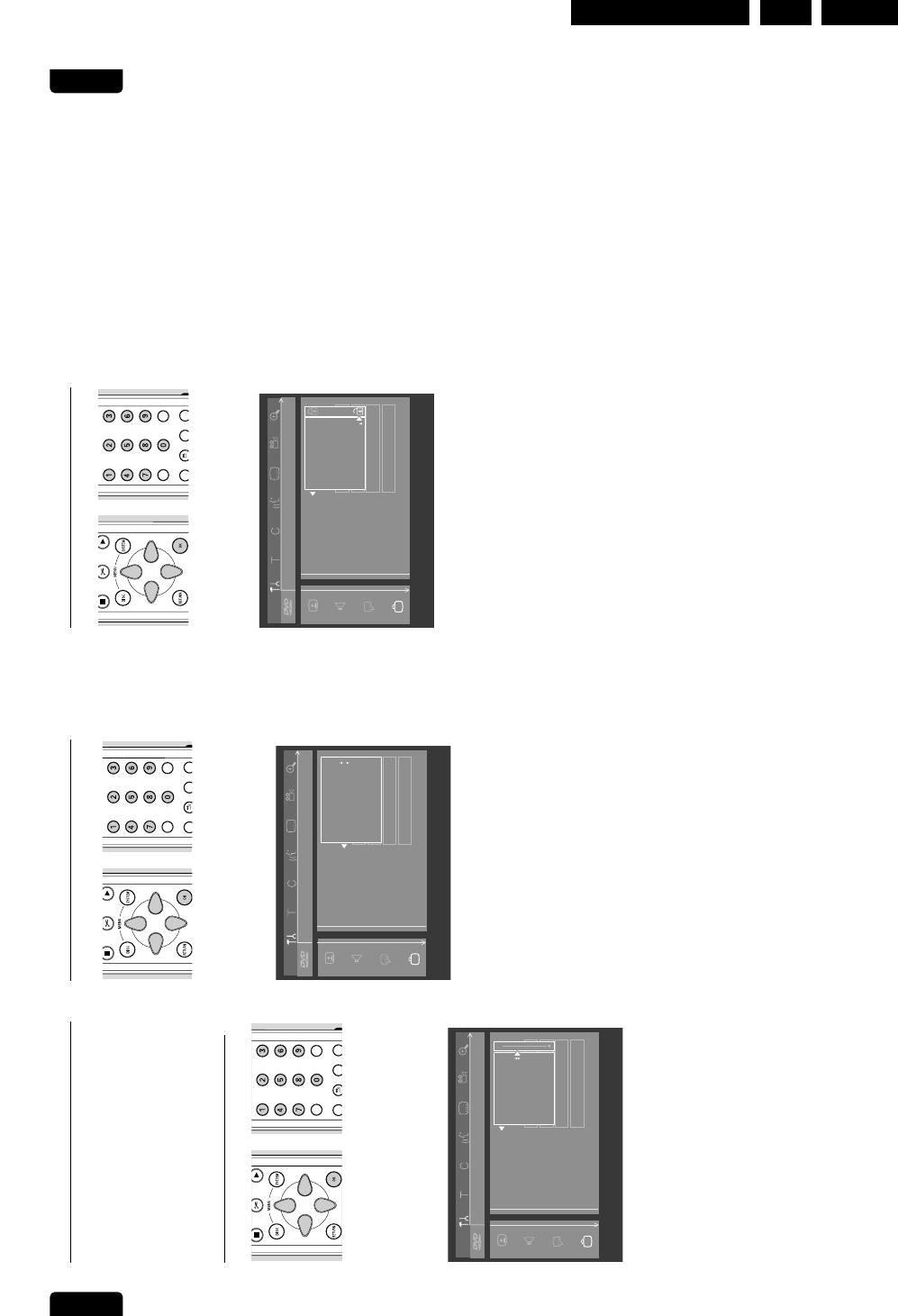

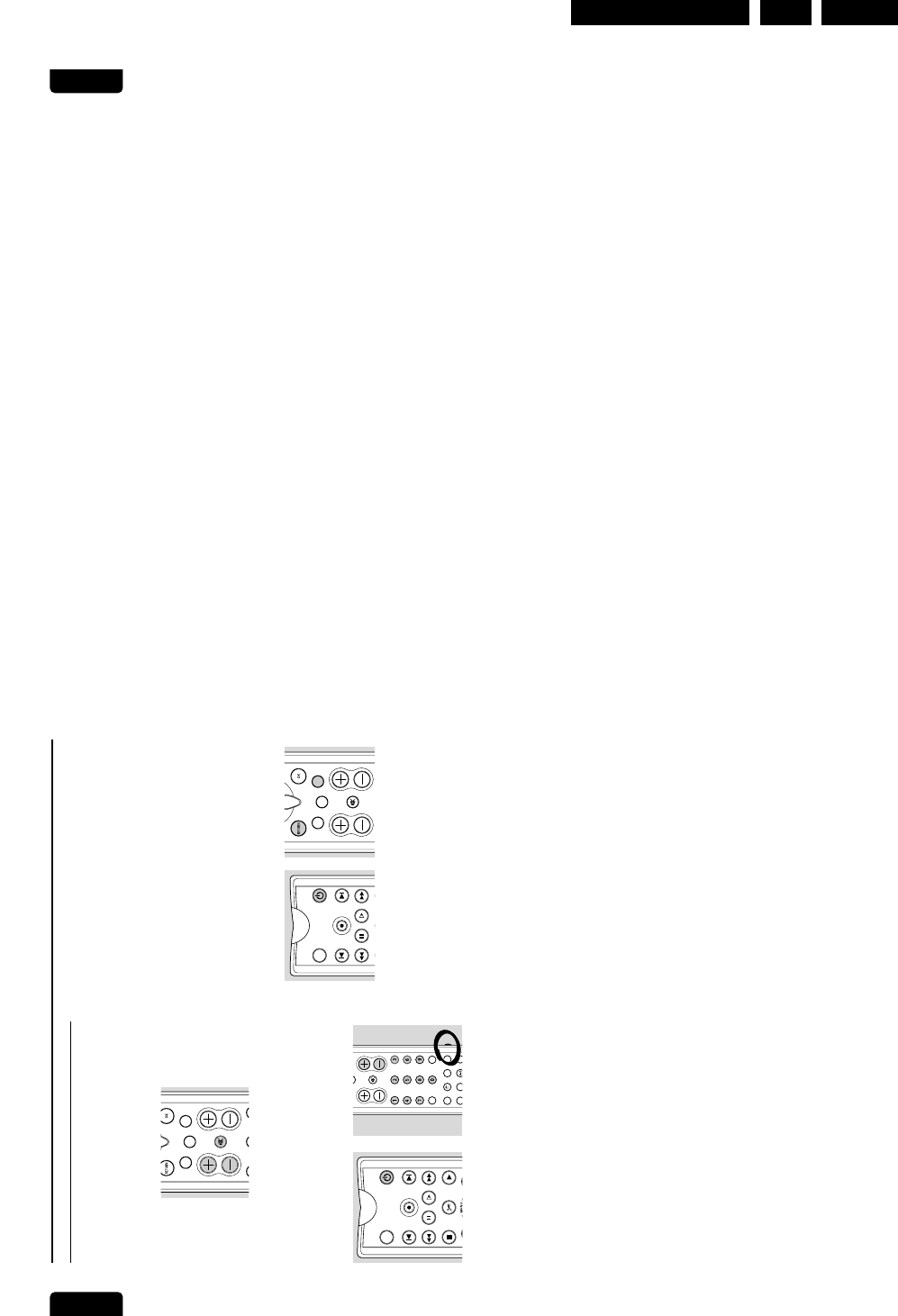

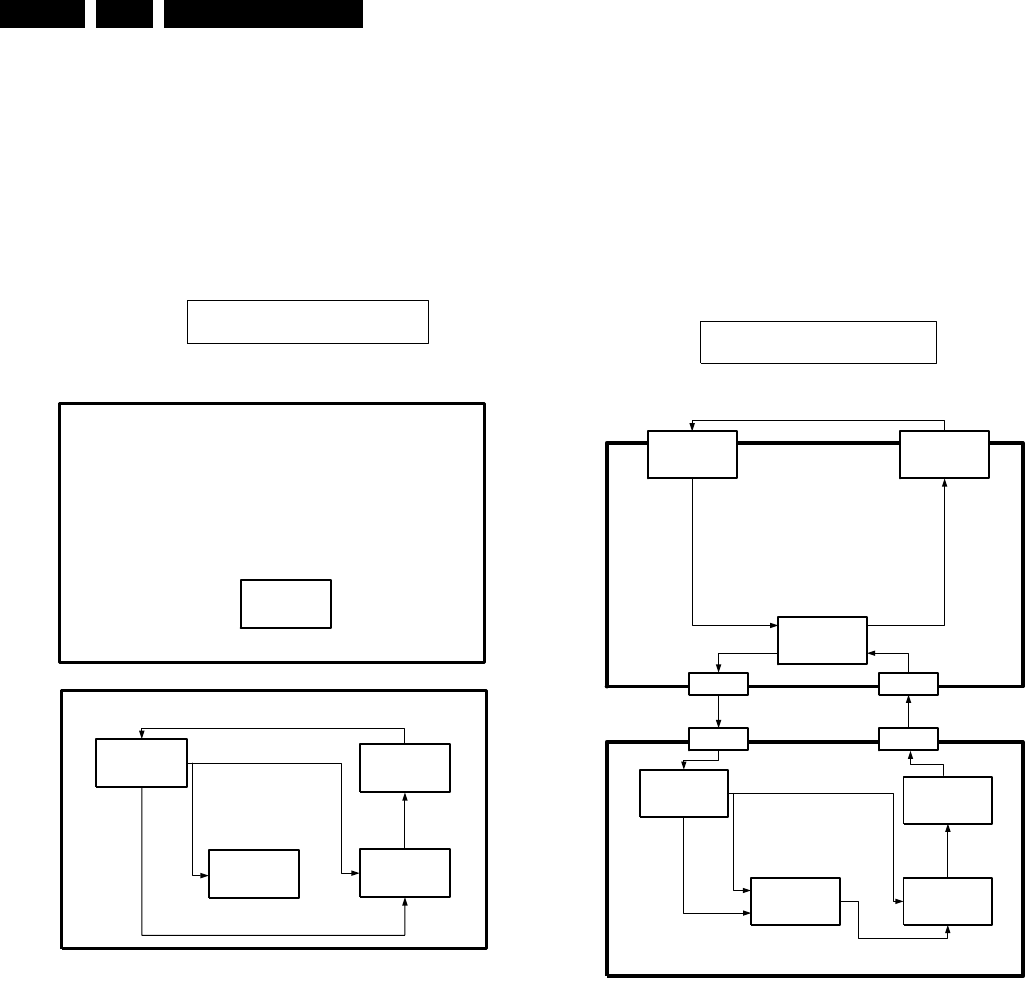

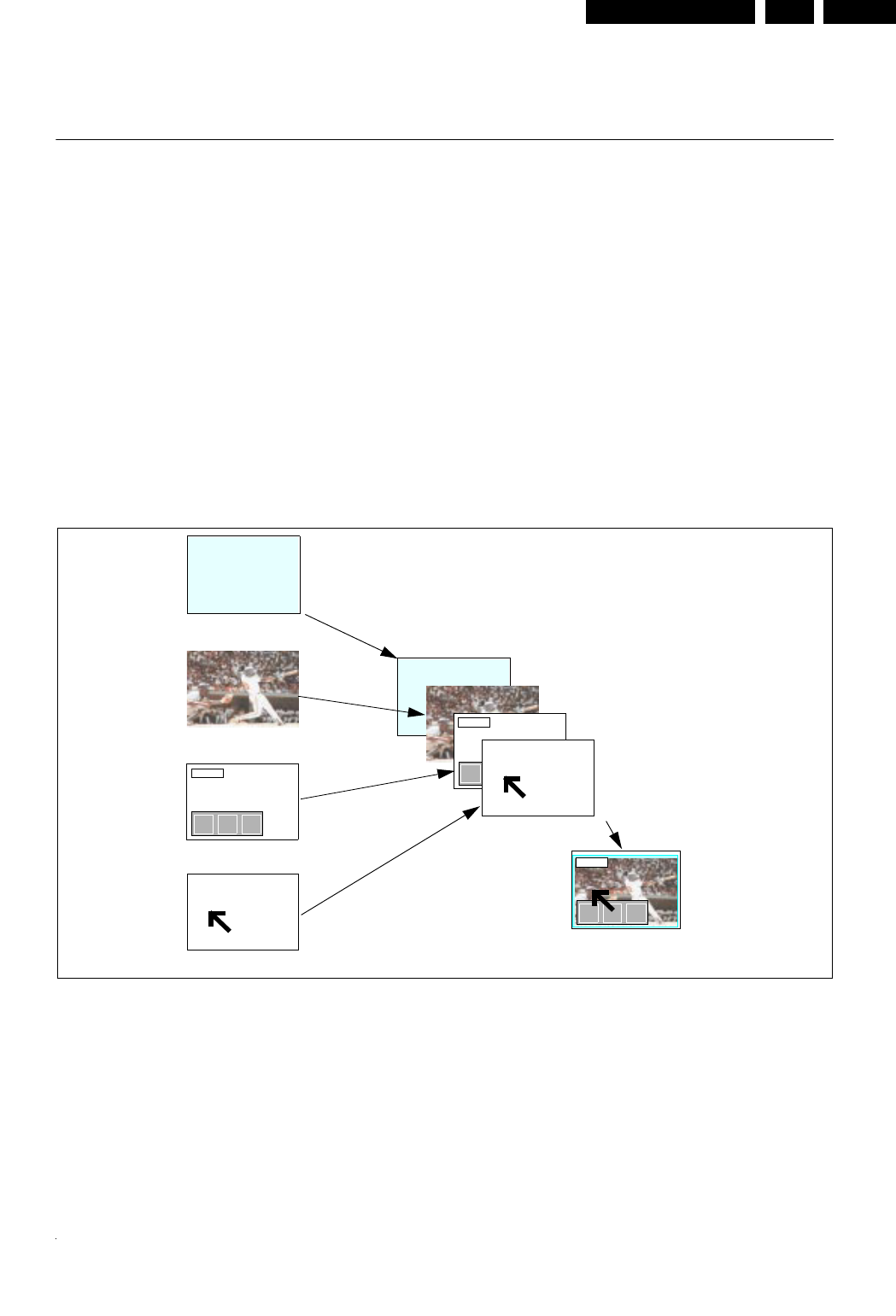

Index Picture Screen

The Index Picture Screen displays an overview of the

titles recorded on the disc. Each title is represented by

an index picture. Next to the index picture the

programme name, duration, recording mode and

recording date of the title are shown. If no name is

known, the DVD recorder will fill in the source and the

time of the recording instead.

Empty spaces (erased titles, or blank space at the end of

the disc) are also shown as such.

lAt maximum three titles will be shown on the

screen at once. If more titles are present, you can

navigate to those with the wv (down up cursor)

keys.

lOn the right hand side of the Index Picture Screen,

you can see the disc bar. This gives an overview of

all titles on the disc, as well as any empty spaces.

On the disc bar, an arrow – the disc pointer –

indicates your current position on the disc. From

this point you may resume playback or recording.

lIf you navigate trough the list of titles with wv

(down up cursor) or J PREVIOUS / KNEXT, the

disc pointer will move along.

lPress 9STOP to reset the disc pointer to the

beginning of the disc.

lTo move the disc pointer to the end of the last title,

keep KNEXT pressed.

lIf you navigate from an Index Picture to the box

right next to it (containing name, rec mode, etc.),

you enter the title settings menu (see under

‘Managing disc content - Title settings’).

ZDF 11:11

00: 00: 55 -SP

T h u 08 02 2001

Empty title

00: 00: 59-SP

1: 15

hr

01 Z D F

VRT 11:13

00: 00: 57 -SP

T h u 08 02 2001

2

4

Index Picture

- image that represents a recorded title

Title description

- programme name

- duration + recording mode

- recording date

Cue to go to Disc Info Screen

or to title on previous screen

Empty title

Current title

Indication what disc area

will be overwritten by

upcoming timer event

Disc Pointer

- shows number and place

of current title on disc

Other title

Cue to go to title on next screen

Tuner Info Box

- displays the selected channel

Timer Info Box

- displays the current time or time/date

of the next timer programme

Disc Bar

- shows an overview of

all titles on disc

Directions For Use

EN 16 DVDR980-985 /0X13.

English

PBC

This feature is only available when a (Super) Video CD is

loaded. It allows you to disable or enable the PBC

(Playback Control) menu of VCD discs. See under

‘Special VCD features’: Factory settings is ‘

On

’.

Finalise disc

This option is only available on unfinalised DVD+R discs.

See ‘Managing disc content - Finalising a DVD+R disc’.

Remote Control settings

Key sound

The recorder makes a ‘beep’ sound upon every key

command given via recorder or remote control keys.

Select ‘

Off

’ to disable this sound. Factory setting is ‘

On

’.

Remote control used

If you want to use the remote control of a Philips DVD

player instead of the standard DVD recorder remote

control, select ‘

DVD player

’. Factory setting is ‘

DVD

recorder

’.

System information

When you move further down in the Remote Control

settings menu, the system status screen will appear.

Press v(cursor up) to go back.

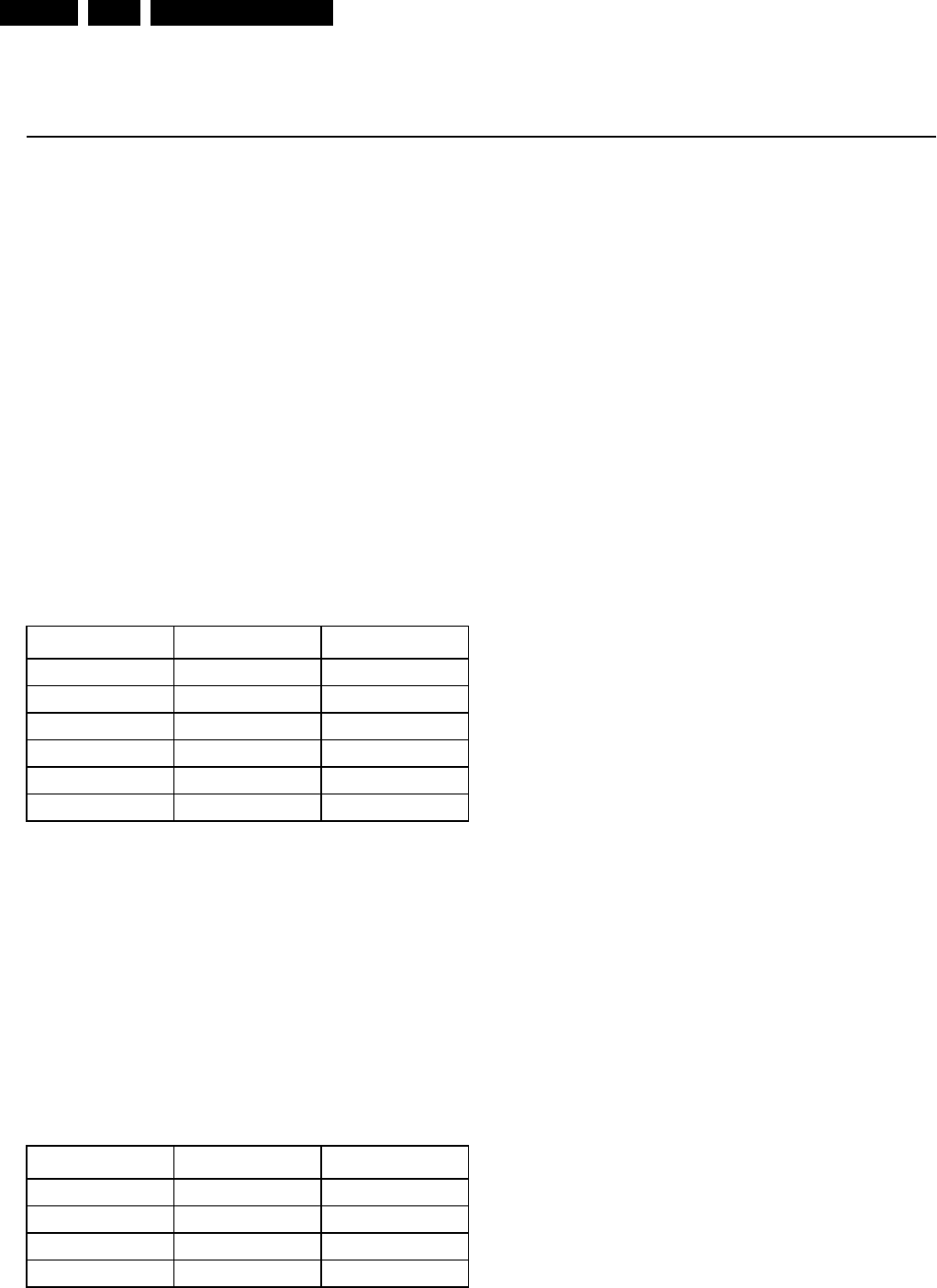

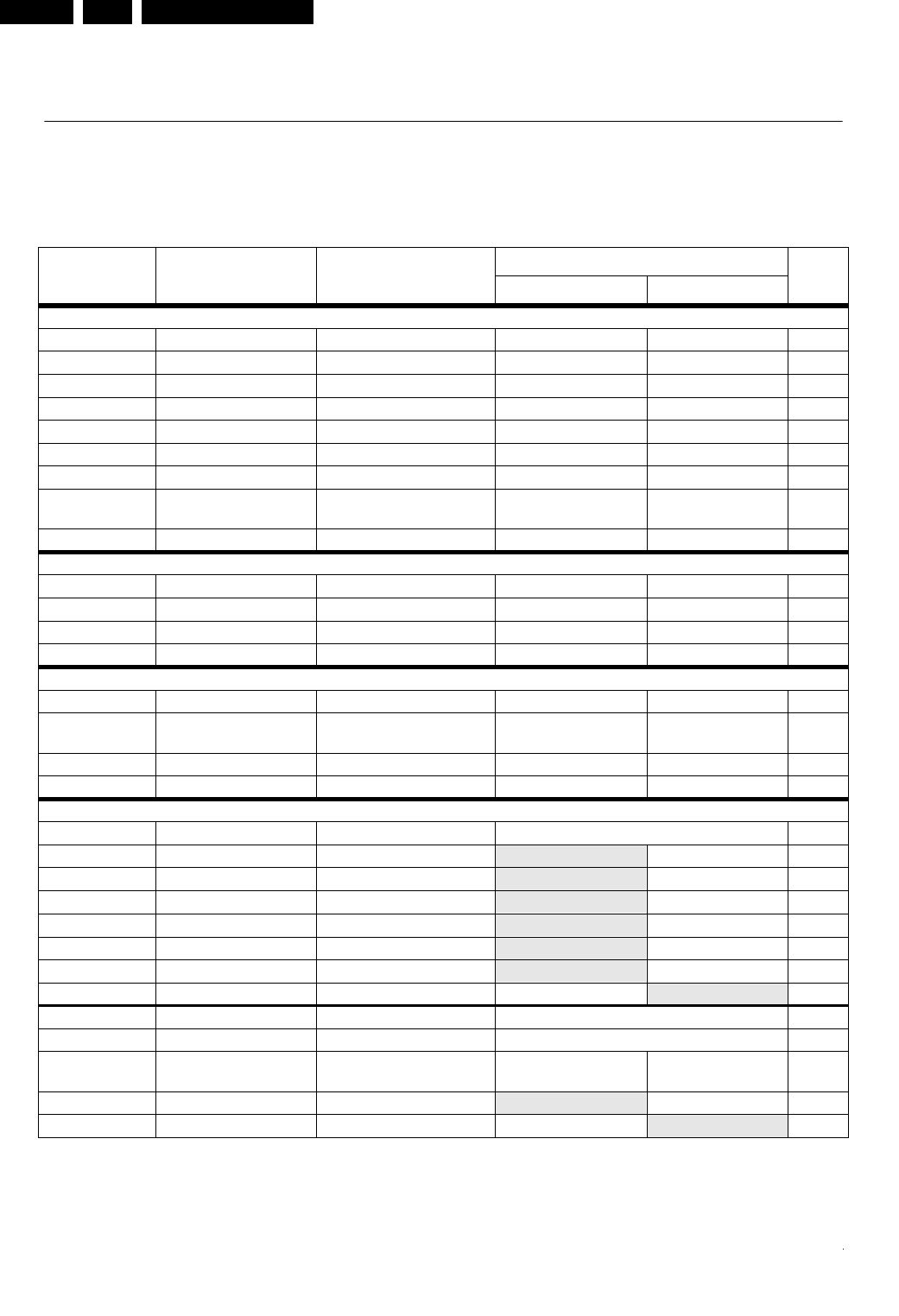

Record Settings

Record mode

By selecting a recording mode you define picture quality

of recordings and maximum recording time for a disc.

Mode Picture quality Total recording

time

HQ best possible 60 minutes

(High Quality) picture quality

SP pre-recorded 120 minutes

(Standard Play) DVD quality

LP better than 180 minutes

(Long Play) S-VHS picture quality

EP better than 240 minutes

(Extended Play) VHS picture quality

In practice, the DVD recorder may record a few

minutes more than indicated. For playback, the correct

recording mode will automatically be selected.

The HQ mode is optimised for recording via the

external inputs. For tuner recordings it is recommended

to use SP, LP or EP.

lIn the record settings menu, select ‘

Record mode

’.

lAlter the recording mode with tor u(left right

cursor).

lConfirm with the OK key.

lTo end, press SYSTEM MENU.

An alternative way to select the record mode is available

in the Index Picture Screen and in monitor mode:

lPress SELECT.

‰The new record mode appears on the screen and

the display.

It is not possible to switch record modes during

recording.

Record Mode: LP

Record settings

To exit press

SYSTEM MENU

Record mode

Direct record

Sat record

Auto chapters

LP/EP rec mode Stndrd

SP

Off

Off

On

OPERATION 25

English

24 OPERATION

Surround: Select this setting when using equipment

with a Dolby Surround Pro Logic decoder.

In this setting the 5.1 audio channels (Dolby

Digital, MPEG-2) are downmixed to a

Surround-compatible 2-channel output.

3D Sound: In a set-up without rear speakers (analogue

stereo output), this option remixes the six

channels of digital surround (Dolby Digital,

MPEG-2) into a two speaker output, while

retaining all of the original audio information.

The result is the listening sensation of being

surrounded by multiple speakers.

Connected audio system Digital out Analogue out

Amplifier or TV with two channel Off Stereo

analogue stereo

Amplifier or TV with Dolby Surround Off Surround

or Dolby Pro Logic

Amplifier with two channel digital PCM only Stereo

stereo

A/V receiver with Multi-channel All Stereo or

decoder (Dolby Digital, MPEG, DTS) Surround

Multi-channel A/V receiver with Off Surround

6-ch connectors

Night Mode

Night mode optimizes the dynamics of the sound with

low volume playback for less disturbance in quiet

environments. This only works for Dolby Digital audio

on DVD-Video discs.

r

Language settings

The preferred language can be adapted via the system

menu bar. Also see ‘virgin mode’. Settings can be

changed for:

- Playback audio language

- Subtitle language

- Menu language

- Country setting.

Feature settings

Access Control

Access Control contains the following features:

Child Lock - When Child Lock is set on, a 4-digit code

needs to be entered in order to play discs.

Parental Level - Allows the conditional presentation of

DVD discs containing Parental Level information.

Change country - Allows conditional presentation of

DVD-Video discs containing country information.

Change code - To change the pin code.

See ‘Acces Control’.

Adapt disc format

This option is only available when a DVD+RW or

DVD+R disc recorded on a different brand of recorder

is loaded. You can adapt the menu to your own

recorder.

A DVD+RW video disc that has been recorded on a

different type or brand of recorder can be played, but

may not provide all features commonly available to

DVD+RW discs, such as the on-screen disc bar, the disc

settings menu, the title settings menu, and editing. If the

disc is not write-protected, the disc format can be

adapted to the own recorder, after which these

functions are available.

Status box

The status box displays the current status of the recorder

and the disc type loaded (See ‘Operation’ - ‘On-screen

display information’). You can switch it On or Off.

Off

= always Off.

On

= displayed together with the system menu bar or

displayed temporarily (disappears after time-out)

when changing the playback or record status.

Factory setting is ‘

On

’.

Auto resume

The Auto resume setting only applies to pre-recorded

DVD-video and Video CD discs only - not only to the

disc in the recorder but also to the last twenty discs you

have played.

If ‘

Auto resume

’ is set to ‘

On

’, playback will start from

the point where it was stopped the last time the disc

was played.

When ‘

Auto resume

’ is set to ‘

Off

’, the recorder will

start playing from the beginning of a disc. In this case you

can still resume when appears on screen by

pressing 2PLAY. Factory setting is ‘

On

’.

Low power standby

If low power standby is ‘

On

’, the recorder will consume

minimum power in standby mode.

Factory setting is ‘

Off

’.

Notes:

When the recorder is in low power standby mode:

- the output of the equipment connected to EXT 2 will not

be passed through to the TV set on EXT 1,

- the Display will be Off,

- the Standby indicator on the recorder will still light up in

standby mode.

Access control

Status box

Autoresume

Low power standby

PBC

Features

Enter code...

On

Off

Off

Off

-- --- off on off

Directions For Use EN 17DVDR980-985 /0X1 3.

English

OPERATION 27

Manual TV channel search

You can perform a search to select and store TV

channels manually. If the DVD recorder is connected via

EasyLink, this function is not available.

lPress SYSTEM MENU.

lSelect ‘

Installation

’.

lSelect ‘

Manual search

’.

lIn the line ‘

Channel

/

freq

.’ select the display for:

Freq.

: frequency

CH

: channel

S

-

CH

: special channel

lIf you know the frequency or channel of the desired

TV channel, you can enter the data in line

‘

Entry

/

search

’ with the digit keys 0-9. If you don’t

know the frequency or channel of the TV channel of

your choice, press u(right cursor) to start channel

search.

lIn the line ‘

Programme number

’ select the

programme number you want, using tor u (left

right cursor) or digit keys 0-9.

lIf you want to change the TV channel name, press

the u(right cursor) key in line ‘

TV channel name

’.

lSelect the character you want to change with the t

(left cursor) or u(right cursor) key.

lChange the character with the w(down cursor) or

v(up cursor) key.

lPress OK to confirm.

This DVD recorder can receive HiFi sound transmissions

in NICAM Stereo. However, if sound distorsion occurs,

due to poor reception, you can switch off NICAM:

lIn the line ‘

NICAM

’ select ‘

On

’ or ‘

Off

’ with the t

(left cursor) or u(right cursor) key.

If you want to change the automatic TV channel setting,

select the line ‘

Fine tuning

’. With the t(left cursor) or

u(right cursor) key you can vary the automatic TV

channel setting.

Important: This re-tuning is only necessary and useful

in special cases, e.g. when stripes appear on your TV

screen when using a cable-TV system.

lPress OK to store the TV channel.

lTo end, press SYSTEM MENU.

Connecting a decoder:

lSwitch on the TV set and select the programme

number for the DVD recorder.

lSelect the TV programme you wish to link with the

decoder function with CH+ or CH-.

lPress SYSTEM MENU

lSelect ‘

Installation

’.

lSelect ‘

Manual search

’.

lSelect ‘

Decoder

’.

lSelect ‘

On

’ with t(left cursor) or u (right cursor).

lConfirm with OK.

‰‘

DECODER

’ apperars on the display.

lTo end, press SYSTEM MENU.

Sort/Clear TV channels manually

lIf the DVD recorder is connected to the TV set

with EasyLink or a similar system, manual sort

cannot be executed. In all other cases, you can

select.

lPress SYSTEM MENU.

lSelect the line ’

Installation

’.

lSelect the line ’

Sort TV channels

’.

lSelect the TV channel to which you want to allocate

a programme number (starting with ‘

P01

’) with the

v(up cursor) or w(down cursor) key and press the

u(right cursor) key.

lSelect the desired position with vor w(up down

cursor) key.

lTo store, press OK.

lTo end, press SYSTEM MENU.

Time/Date

To adjust ‘

Time

’, ‘

Year

’, ‘

Month

’ and ‘

Date

’ with the

digit keys 0-9. Switch between fields with the wv

(down up cursor) keys.

Installation

To exit press

SYSTEM MENU

Time/Date

Time

Year

Month

Date

09: 38

2001

02

09

Installation

To sort

Press To exit press

SYSTEM MENU

Sort TV channels

PO1 NED 1

...

...

PO2 NED 2

PO3 NED 3

PO4 RTL 4

PO5 RTL 5

PO6 VERON

English

26 OPERATION

Direct record

With the Direct Record function switched ‘

On

’ and the

DVD recorder switched to standby, the channel number

selected on your television will be automatically taken

over by the DVD recorder, at the moment it starts

recording. This only applies for televisions connected via

SCART

, which have video output via

SCART

or which have

EasyLink. Factory setting is ‘

Off’

.

lIn the record settings menu, select ‘

Direct record

’.

lSelect ‘

On

’. If you select ‘

Off

’, the function will be

switched off.

lConfirm with OK.

lTo end, press SYSTEM MENU.

Sat record

You can only use this function, when you have a satellite

receiver, which can control other equipment by a

’programming’ function. In this mode your DVD

recorder starts recording when the satellite receiver

releases a signal. The start and end of the recording is

controlled via one of the

SCART

sockets.

lIn the record settings menu, select ‘

Sat record

’.

lSelect the

SCART

socket to which the satellite

receiver is connected with tor u(left right cursor).

lConfirm with OK.

lInsert a recordable DVD+RW disc.

lPress BSTANDBY/ON.

‰When this function is switched on,

SAT

appears

on the display.

‰The DVD recorder is now prepared for

recording.

Factory setting is ‘

Off

’.

Auto chapters

If autochapters is ‘

On

’ every five to six minutes a

chapter marker (beginning of a new chapter) is inserted

during recording. This enables easy navigation through a

title during playback. In either case you can manually

insert chapter markers afterwards. (See ‘Managing disc

content’ - ‘Edit in playback mode’.)

LP/EP rec mode

In long play or extended play recording mode you can

select the ‘

Sport

’ setting to optimize the video

recording for images that contain fast movements, like

sports programmes. The setting does not influence high

quality or standard play recording mode.

Factory setting is ‘

Stndrd

’.

Installation

Auto TV Channel Search

Your DVD recorder will search for all TV channels.

It stores channels in the sequence they are found. (See

‘Installation - First time Set-up’)

Note:

All channels stored so far will be erased.

Follow TV

With Follow TV you can programme the same channel

sequence on the DVD recorder as on the TV set.

This only functions if the recorder socket (EXT1) and

the TV set are connected with a

SCART

cable. Additional

equipment connected to socket EXT2 must be switched

off.

lPress OK.

‰If the DVD recorder recognizes that the TV set

has been connected with a

SCART

cable, ‘TV01’

appears on the display.

‰When ‘NOTV’ (no signal from TV set) appears on

the display, the TV channels can not be allocated

automatically. In this case read ‘Manual TV channel

search’.

lSelect programme number ‘1’ on the TV set.

lConfirm with OK on the remote control of the

DVD recorder.

‰The DVD recorder compares the TV channels on

the TV set and the DVD recorder. If the channels

match, this channel is stored at ‘P01’.

lWait until 'TV02’ appears and repeat the previous

two steps for programme number 2 and the rest of

the channels you want to store.