LG KS10 Manual

User Manual: LG-KS10-Manual

Open the PDF directly: View PDF ![]() .

.

Page Count: 247 [warning: Documents this large are best viewed by clicking the View PDF Link!]

Date: July, 2007 / Issue 1.0

Service Manual Model : KS10

Service Manual

KS10

- 3 -

1. INTRODUCTION.................................. 5

1.1 Purpose ...................................................... 5

1.2 Regulatory Information ............................... 5

2. PERFORMANCE ..................................7

2.1 System Overview.........................................7

2.2 Usable environment.....................................8

2.3 Radio Performance......................................8

2.4 Current Consumption.................................14

2.5 RSSI BAR ..................................................14

2.6 Battery BAR ...............................................15

2.7 Sound Pressure Level ...............................16

2.8 Charging ....................................................16

3. TECHNICAL BRIEF............................17

3.1 General Description ...................................17

3.2 GSM Mode.................................................19

3.3 UMTS Mode...............................................23

3.4 LO Phase-locked Loop ..............................26

3.5 Off-chip RF Components ...........................29

3.6 Digital Baseband

(Stn8810 / MSM6275)................................34

3.7. Hardware Architecture ..............................36

3.8. Subsystem of STn8810 ............................39

3.9. Hardware Peripheral system of

Stn8810 ....................................................42

3.10. Subsystem of MSM6275.........................47

3.11. External memory interface......................50

3.12. Hardware sub system of MSM6275........51

3.13. Audio and sound.....................................61

3.14. Camera interface ....................................67

3.15 Bluetooth..................................................76

3.16 Main Features..........................................77

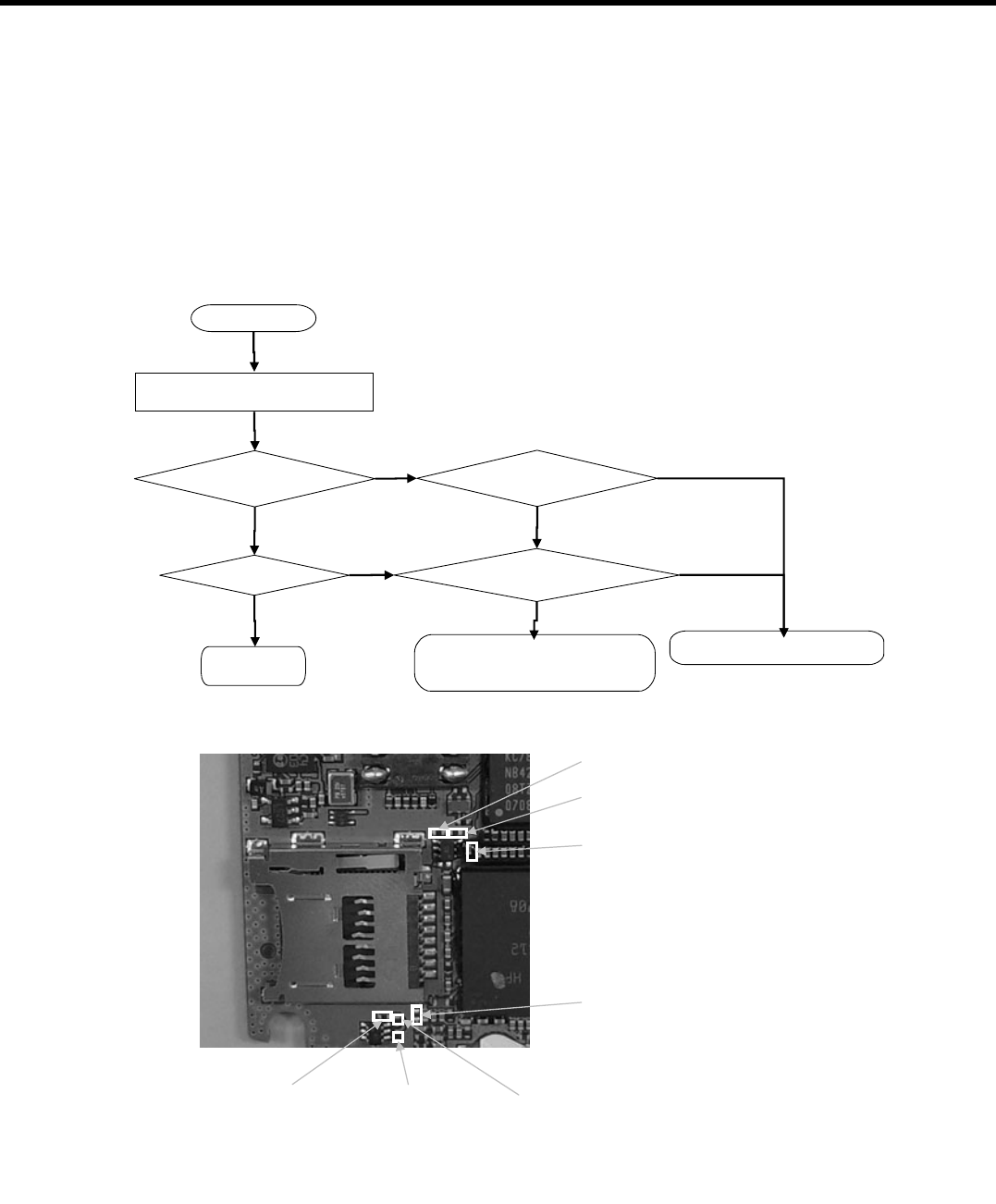

4. TROUBLE SHOOTING.......................83

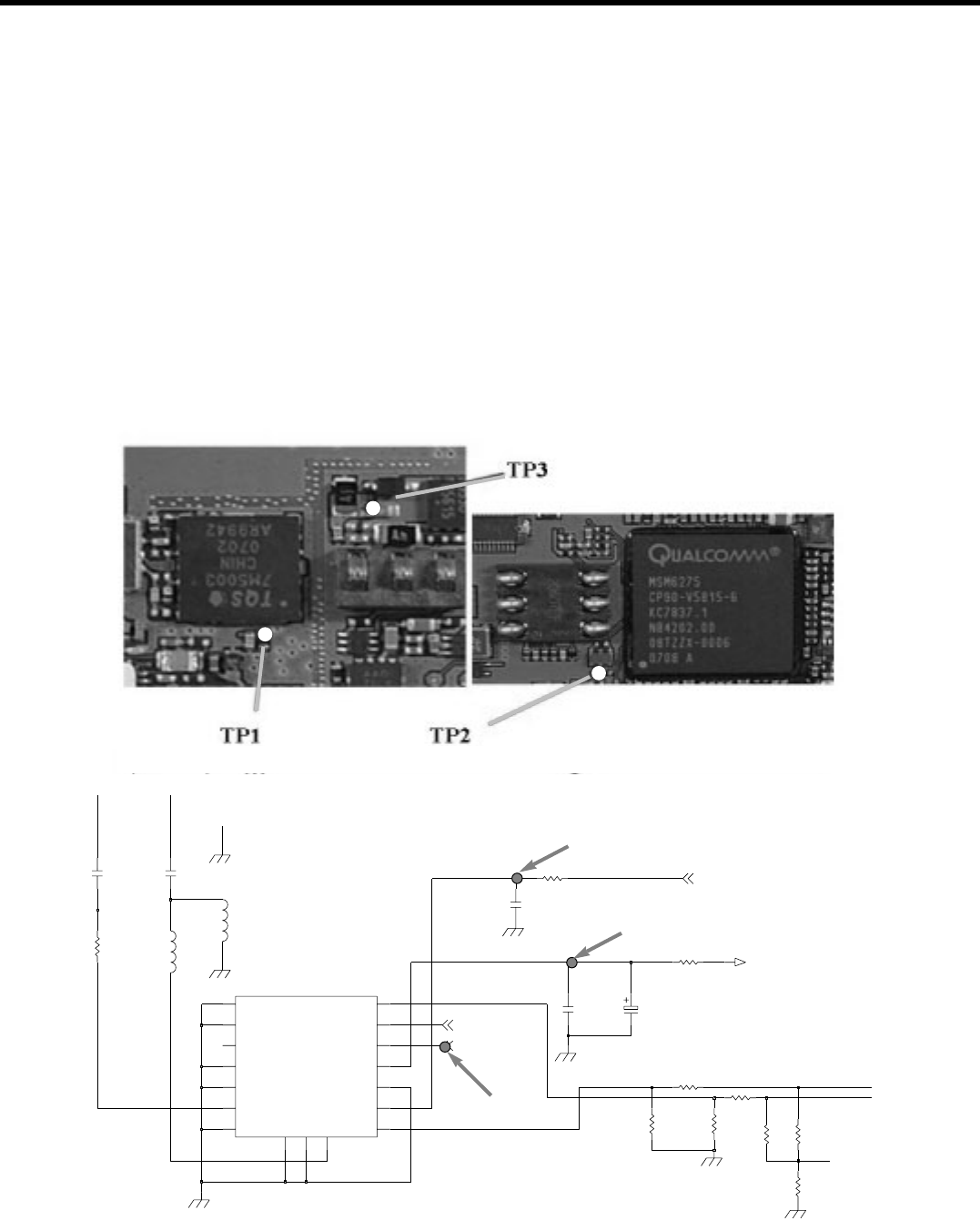

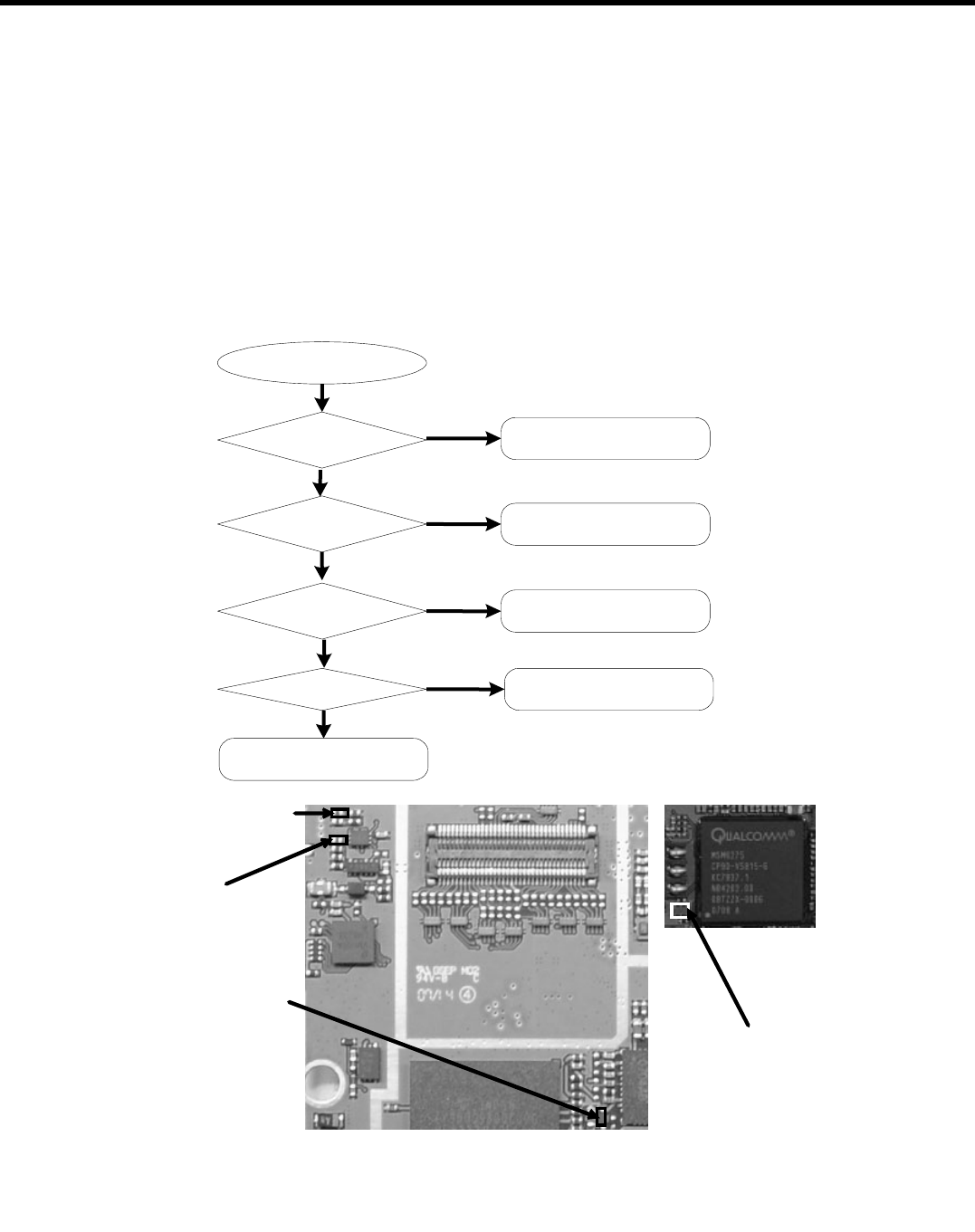

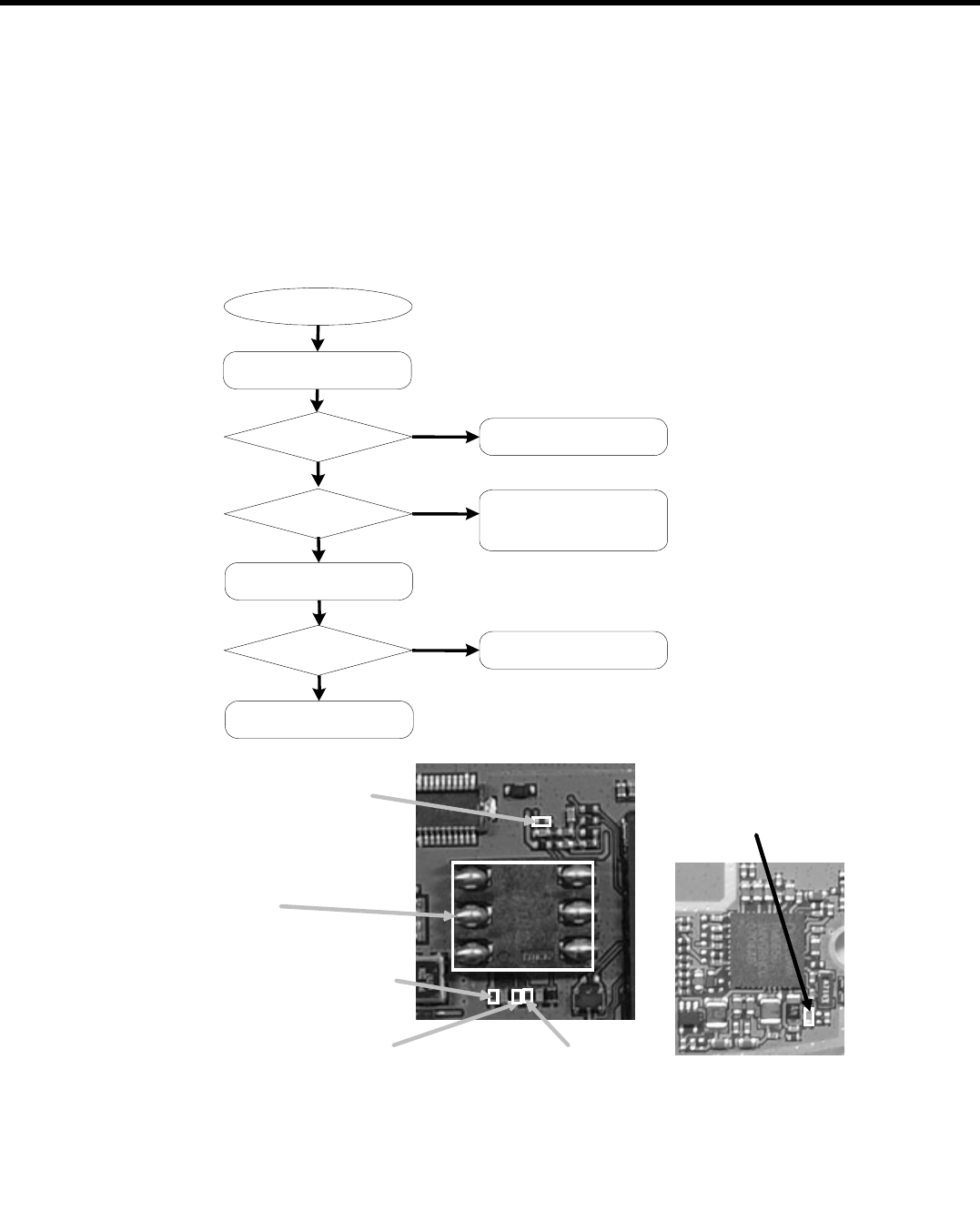

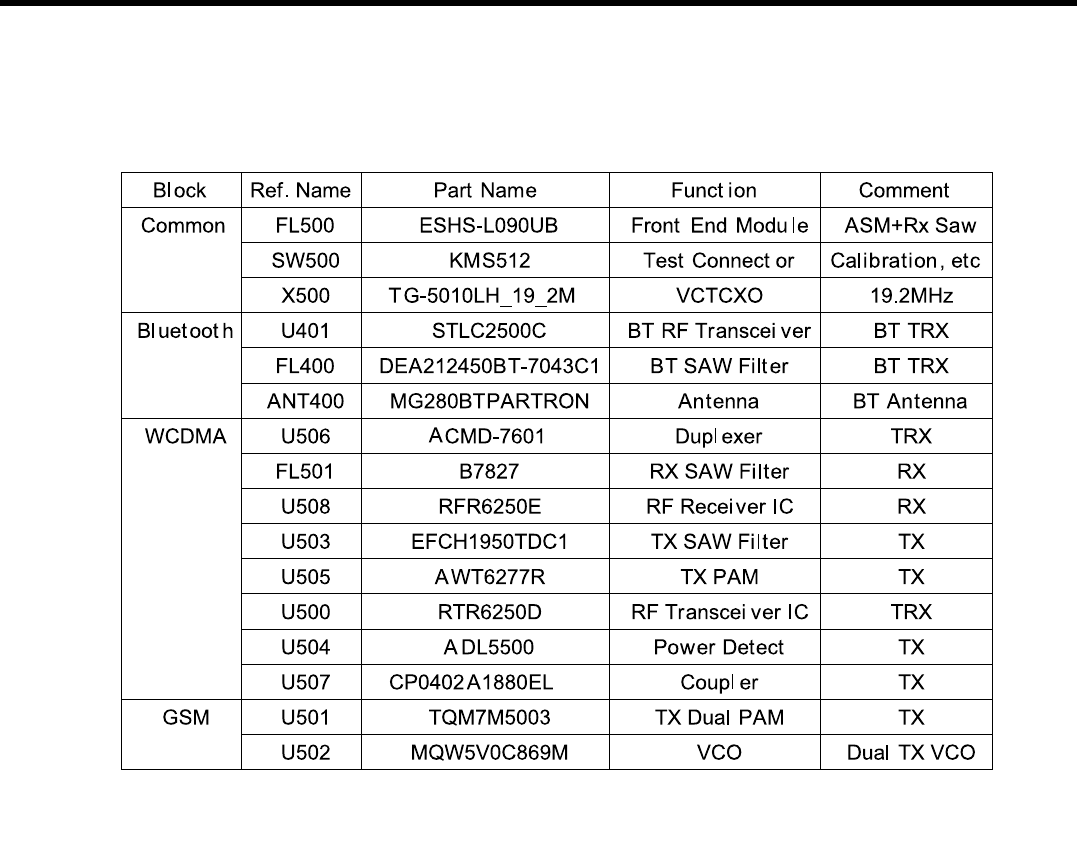

4.1 RF Component ..........................................83

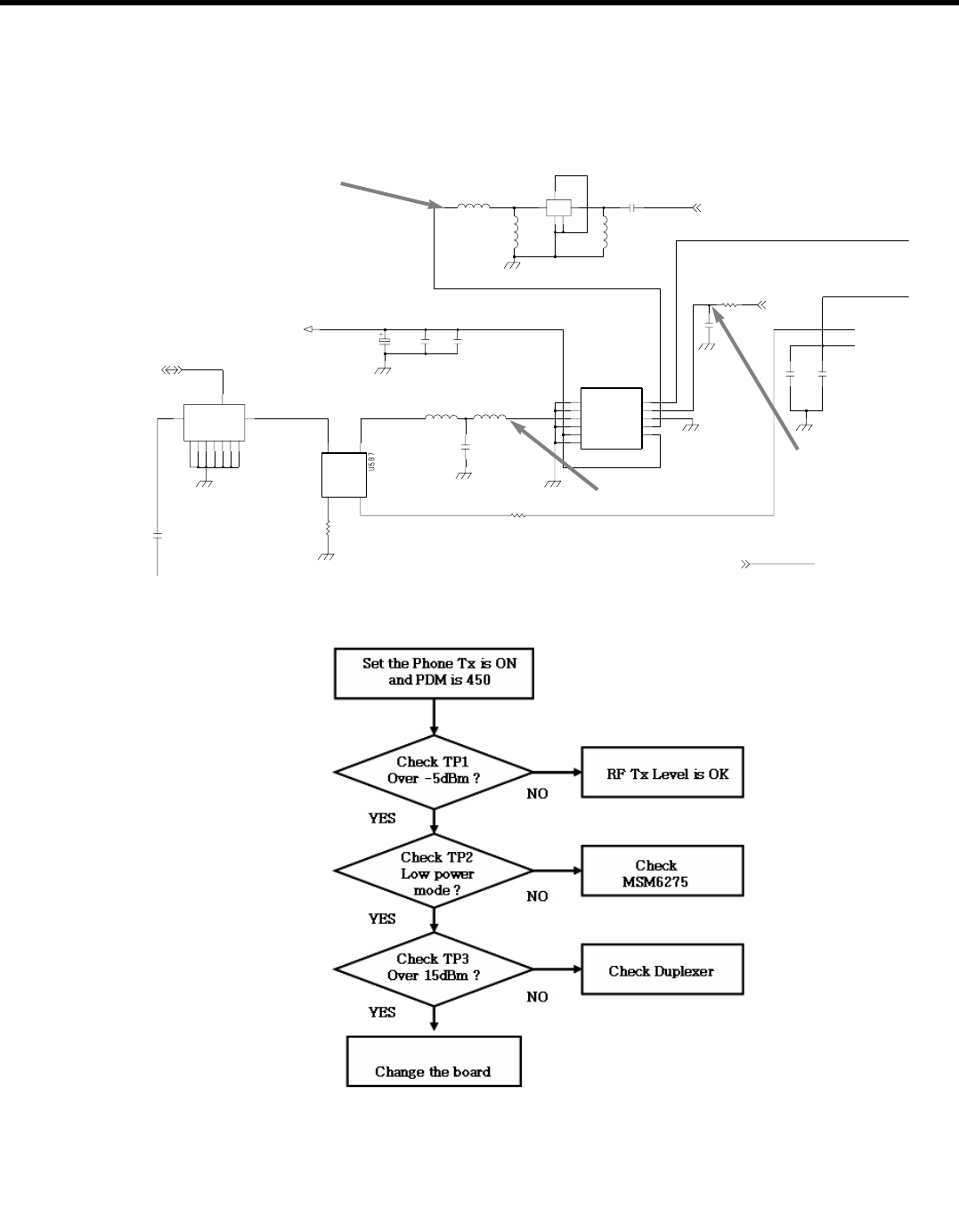

4.2 SIGNAL PATH ...........................................85

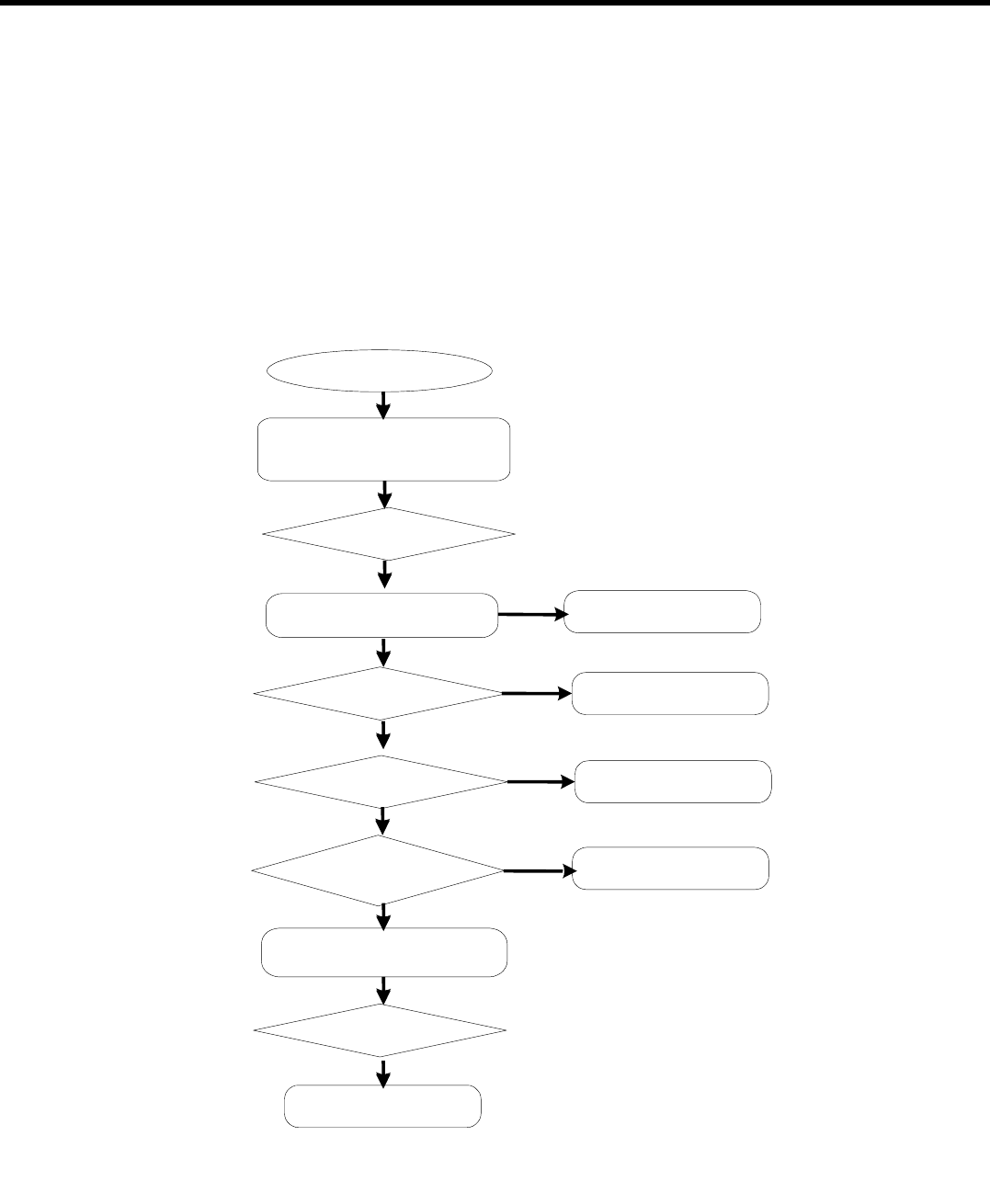

4.3 Checking VCXO Block...............................87

4.4 Checking Ant. Switch Module Block ..........91

4.5 Checking WCDMA Block ...........................93

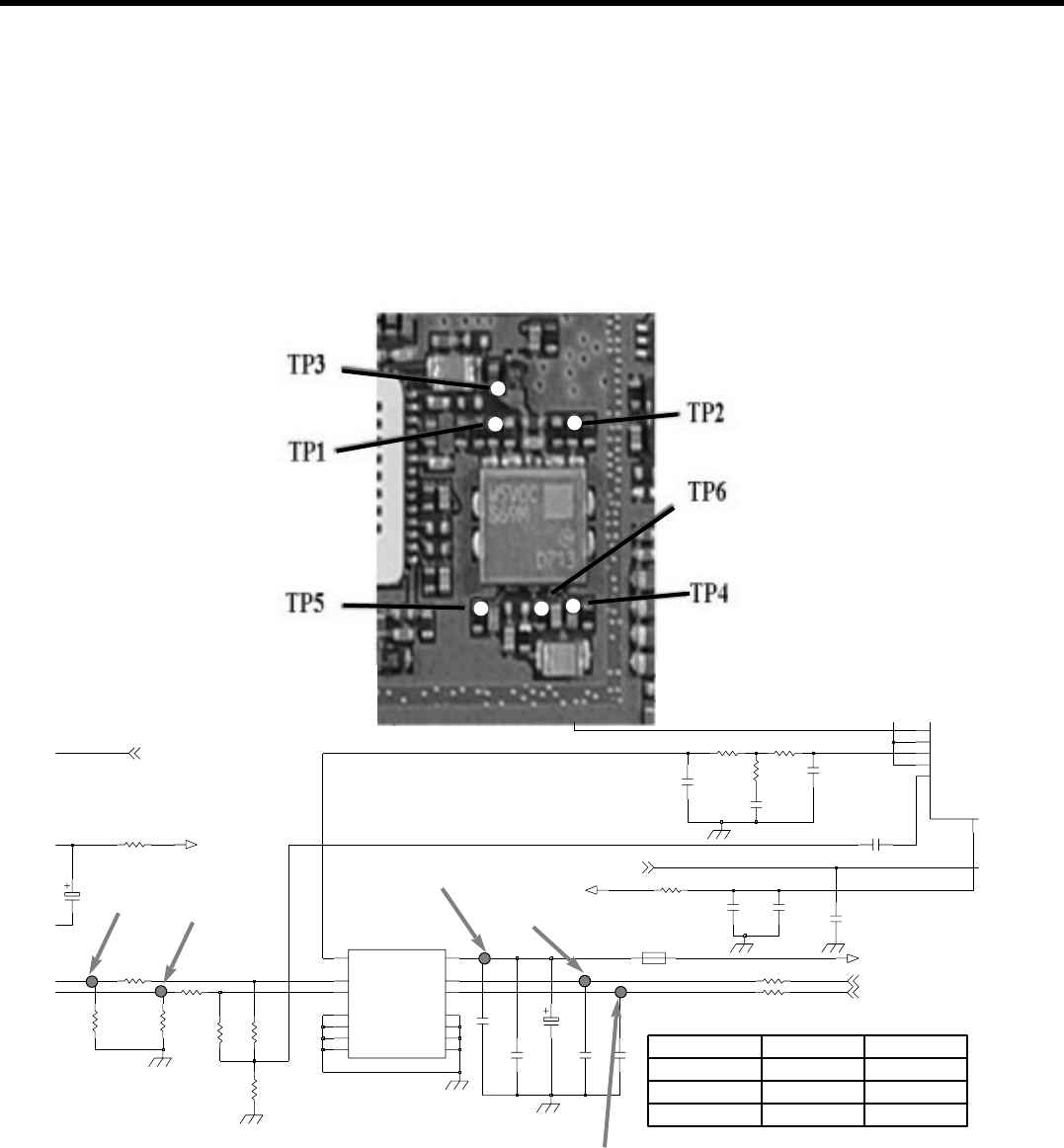

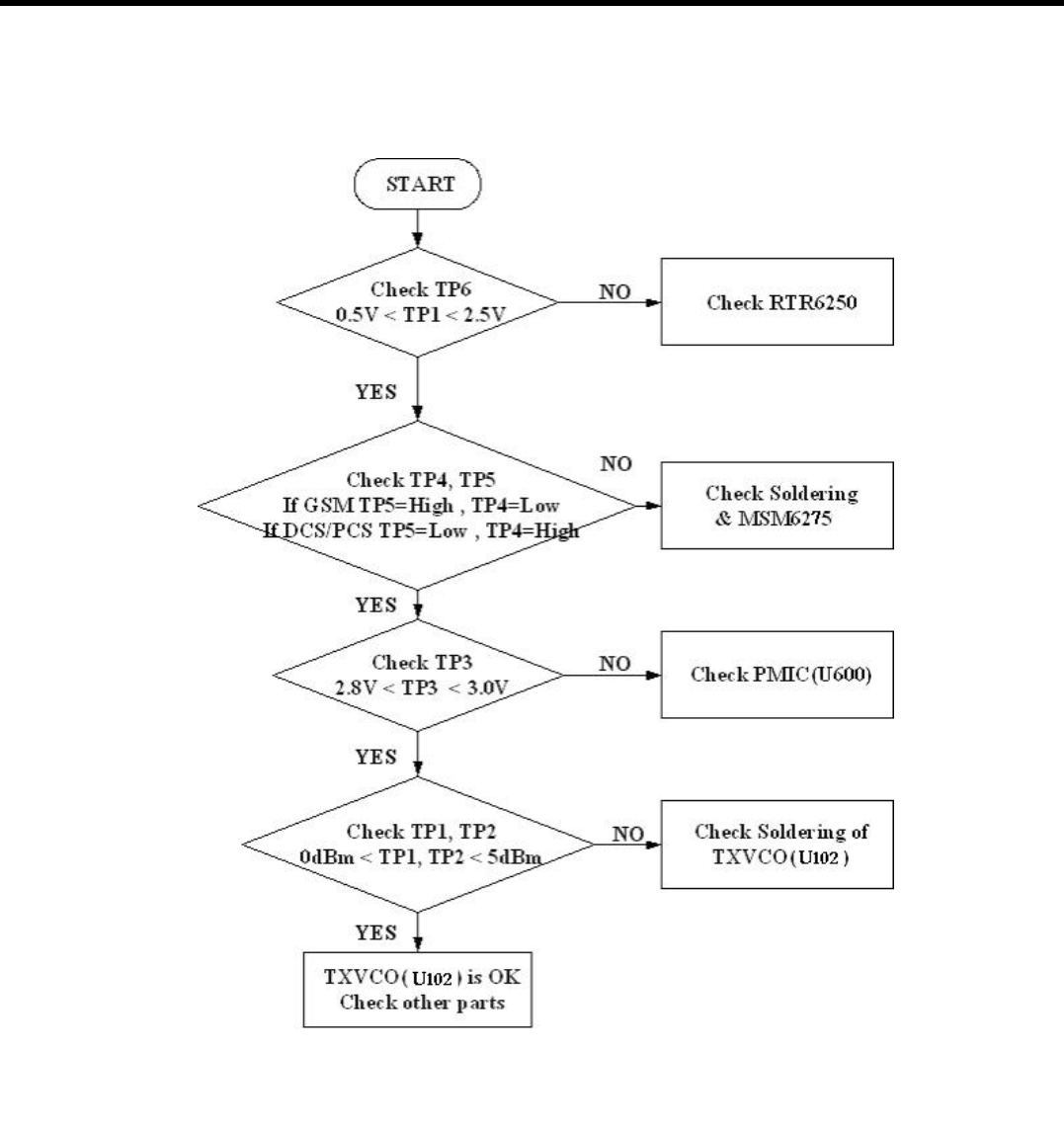

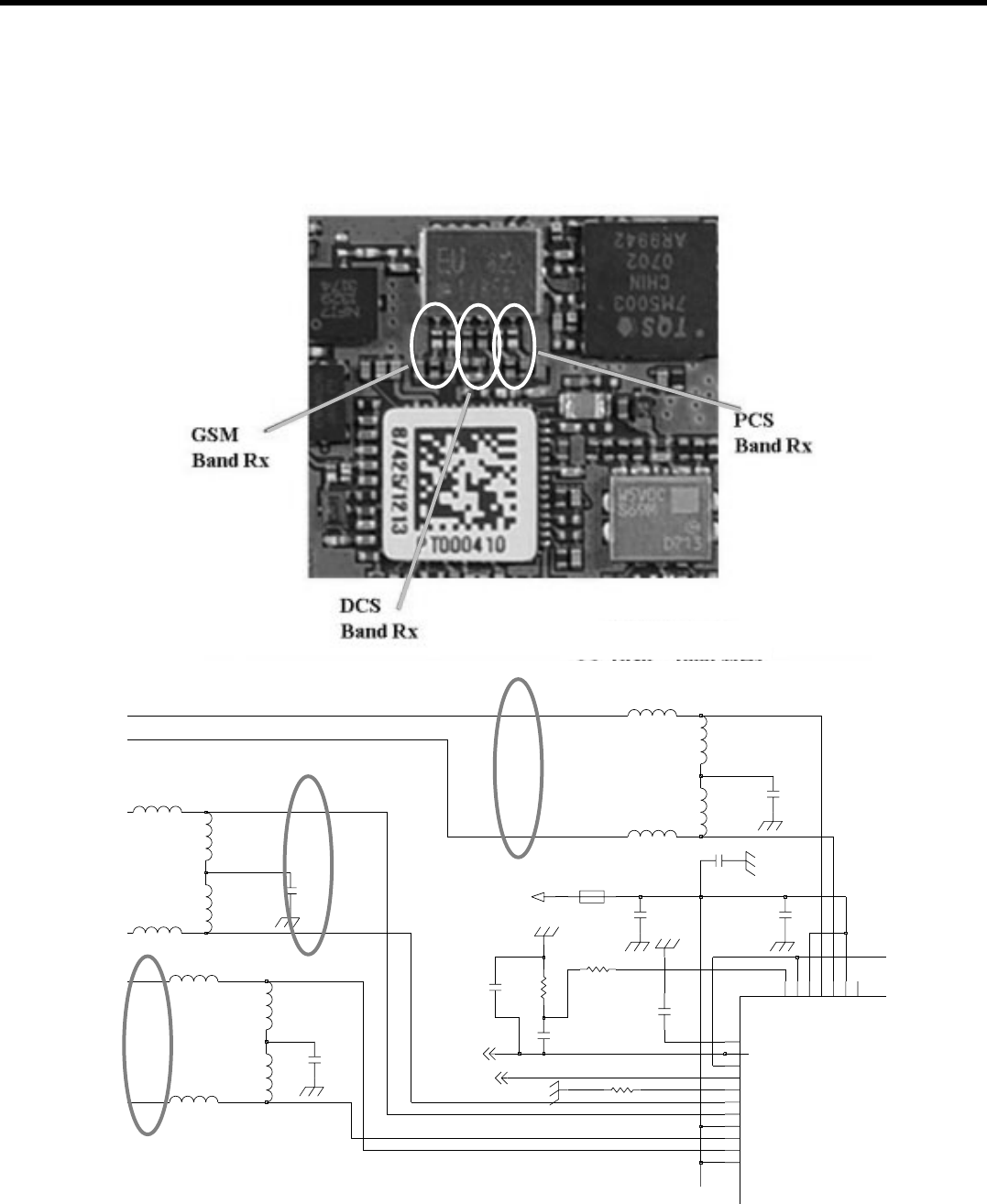

4.6 Checking GSM Block...............................103

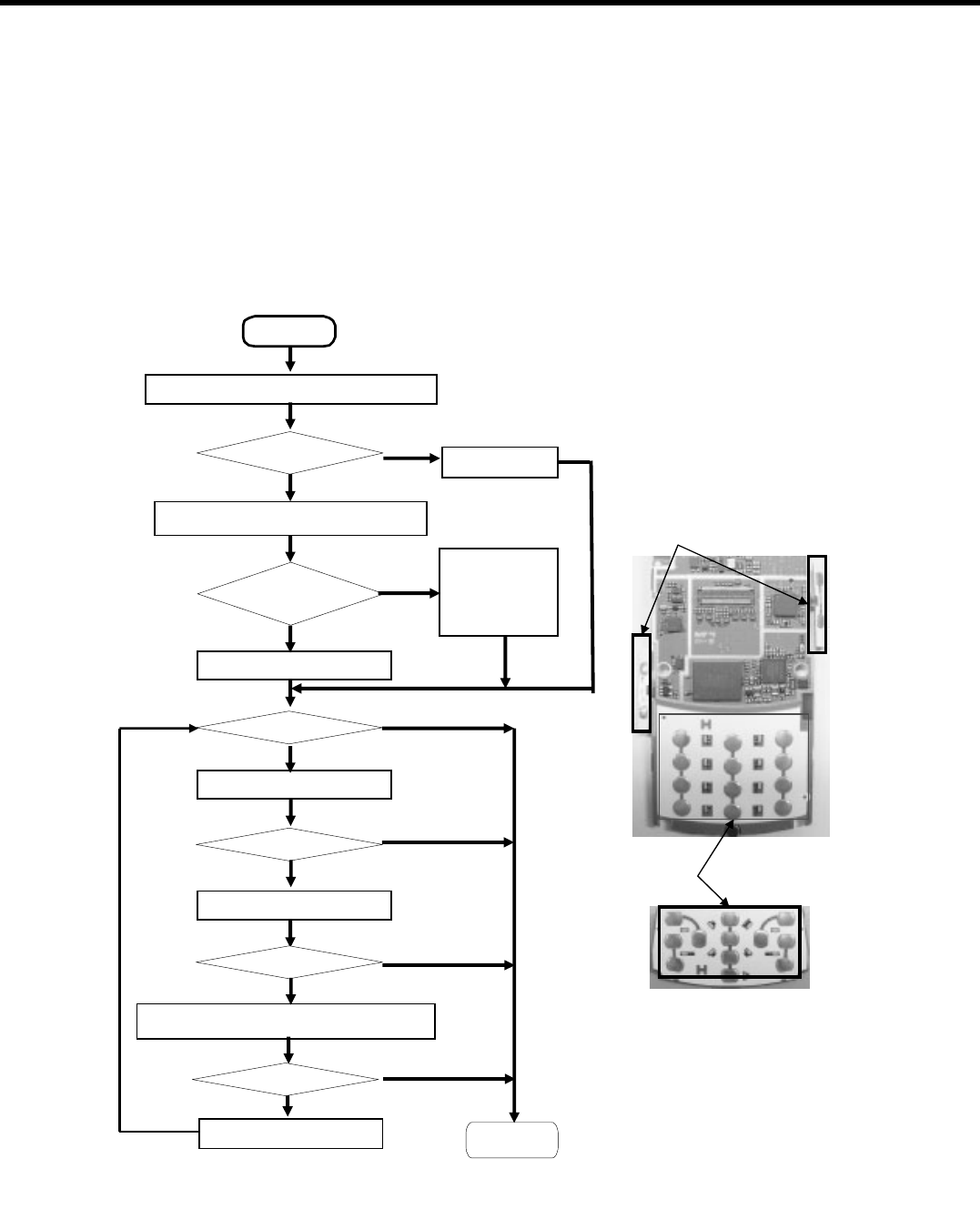

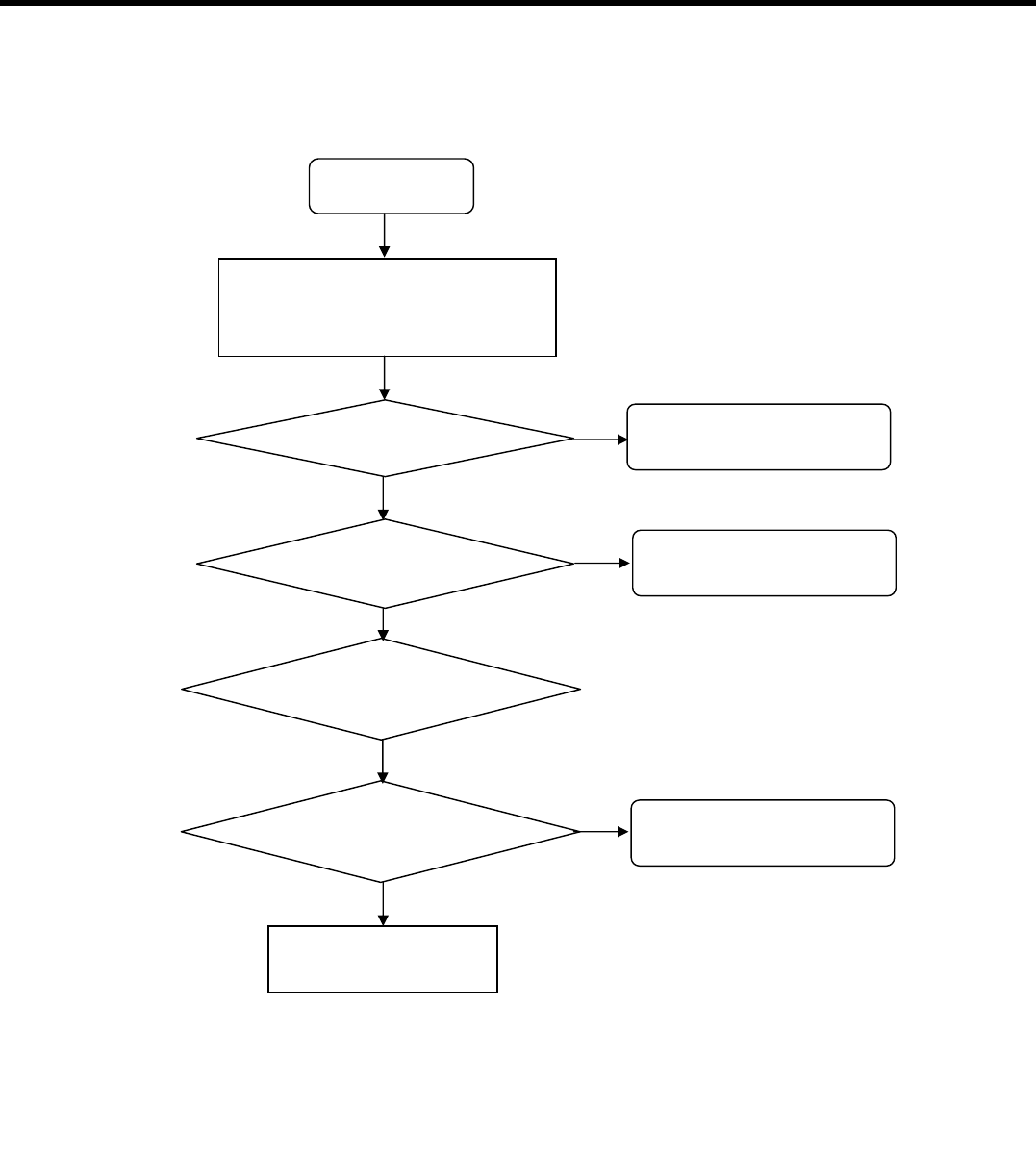

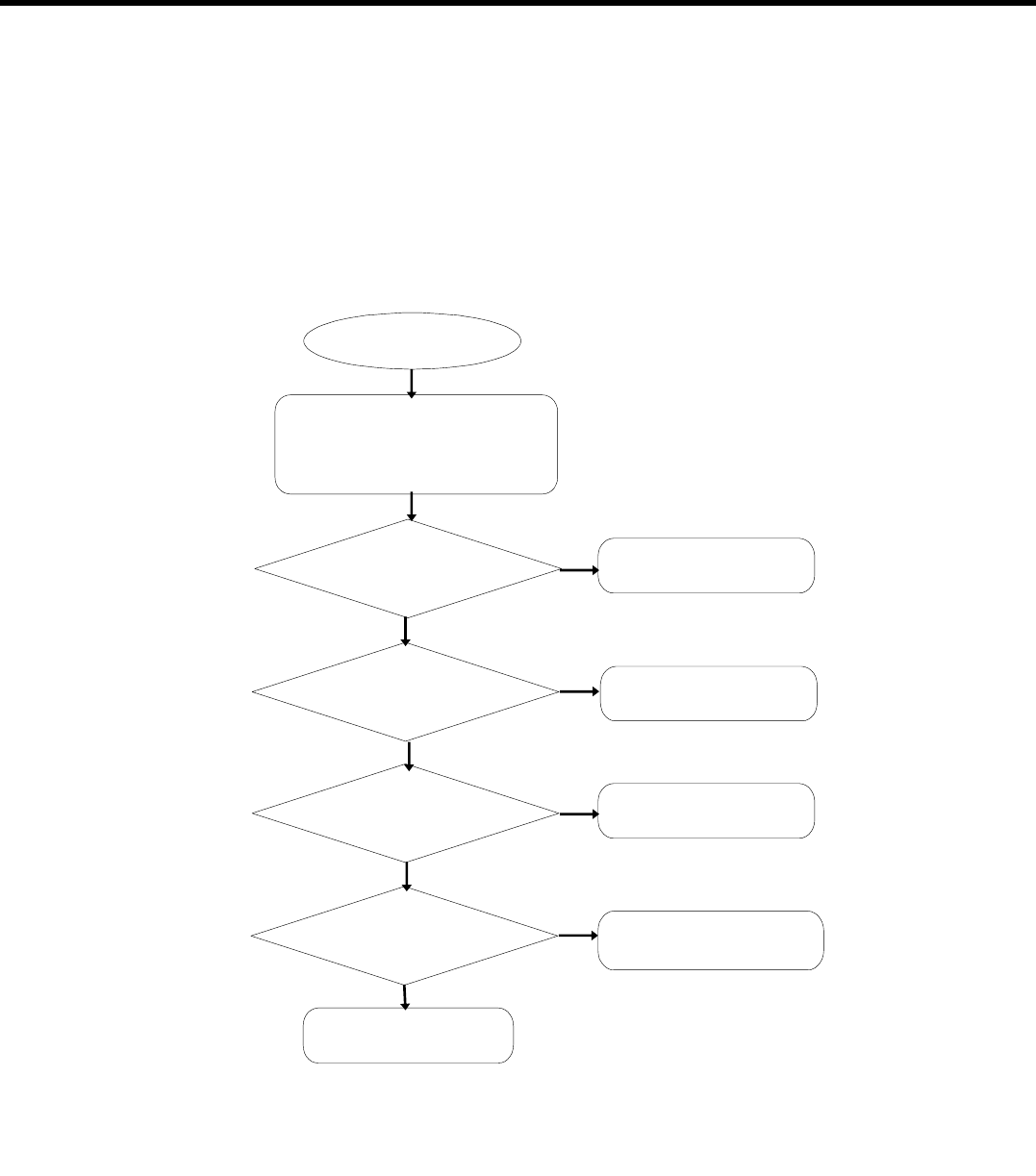

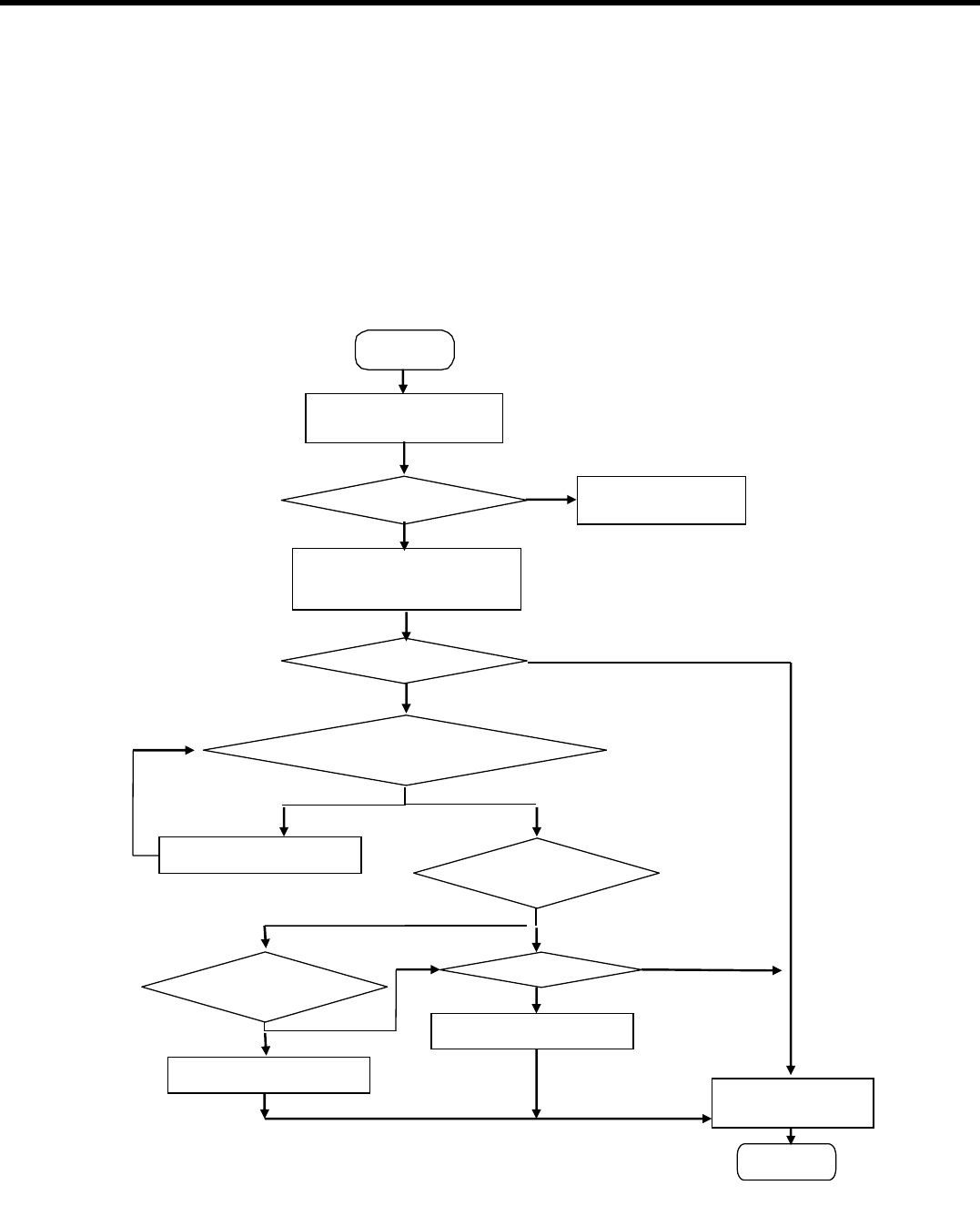

4.7 Power on trouble......................................111

4.8 USB trouble .............................................114

4.9 SIM detect trouble....................................115

4.10 Key sense trouble ..................................116

4.11 Keypad backlight trouble .......................118

4.12 Folder on/off trouble...............................120

4.13 Micro SD trouble ....................................122

4.14 Charging trouble ....................................124

4.15 Audio trouble..........................................127

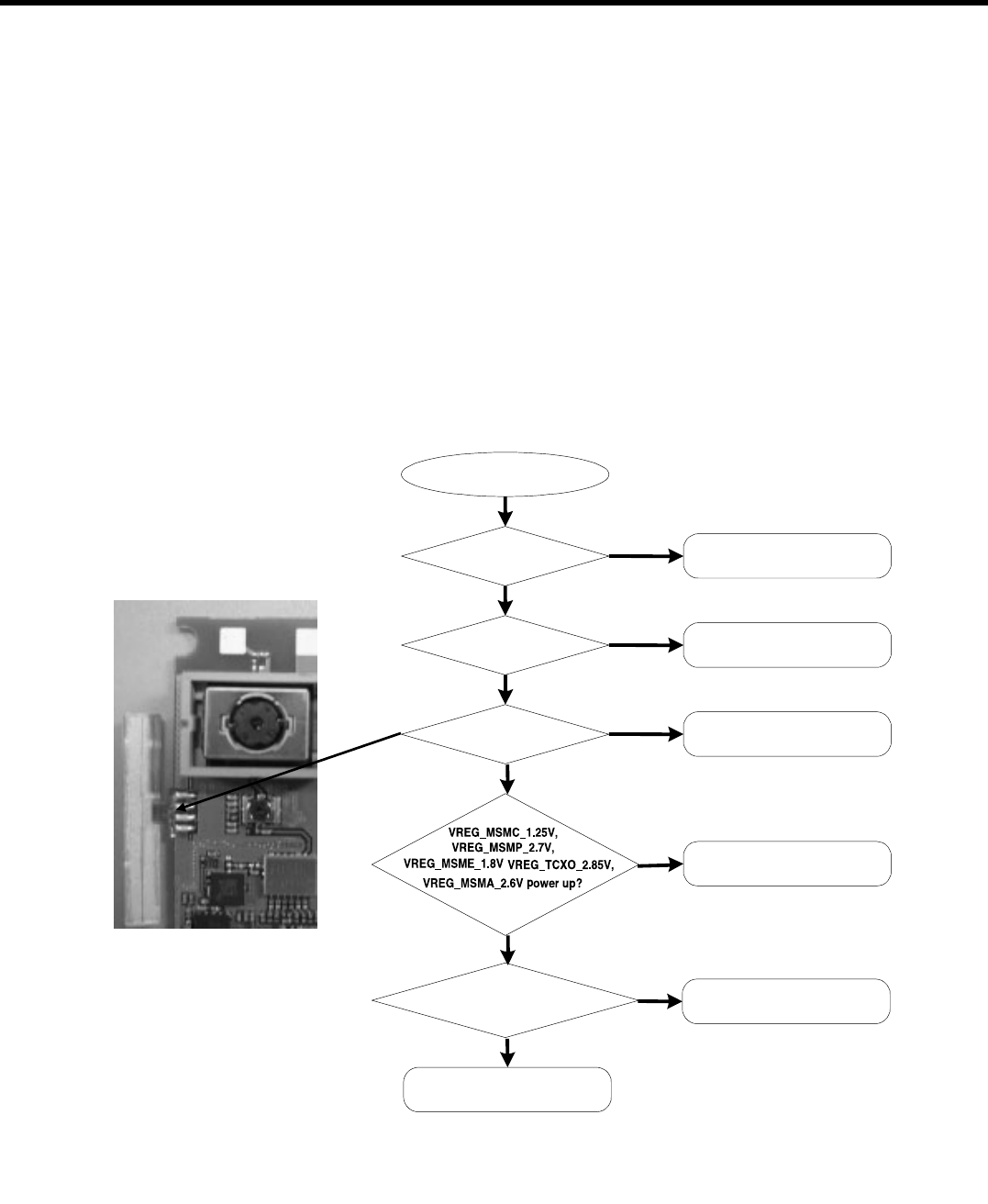

4.16 Camera trouble ......................................143

4.17 Main LCD trouble...................................149

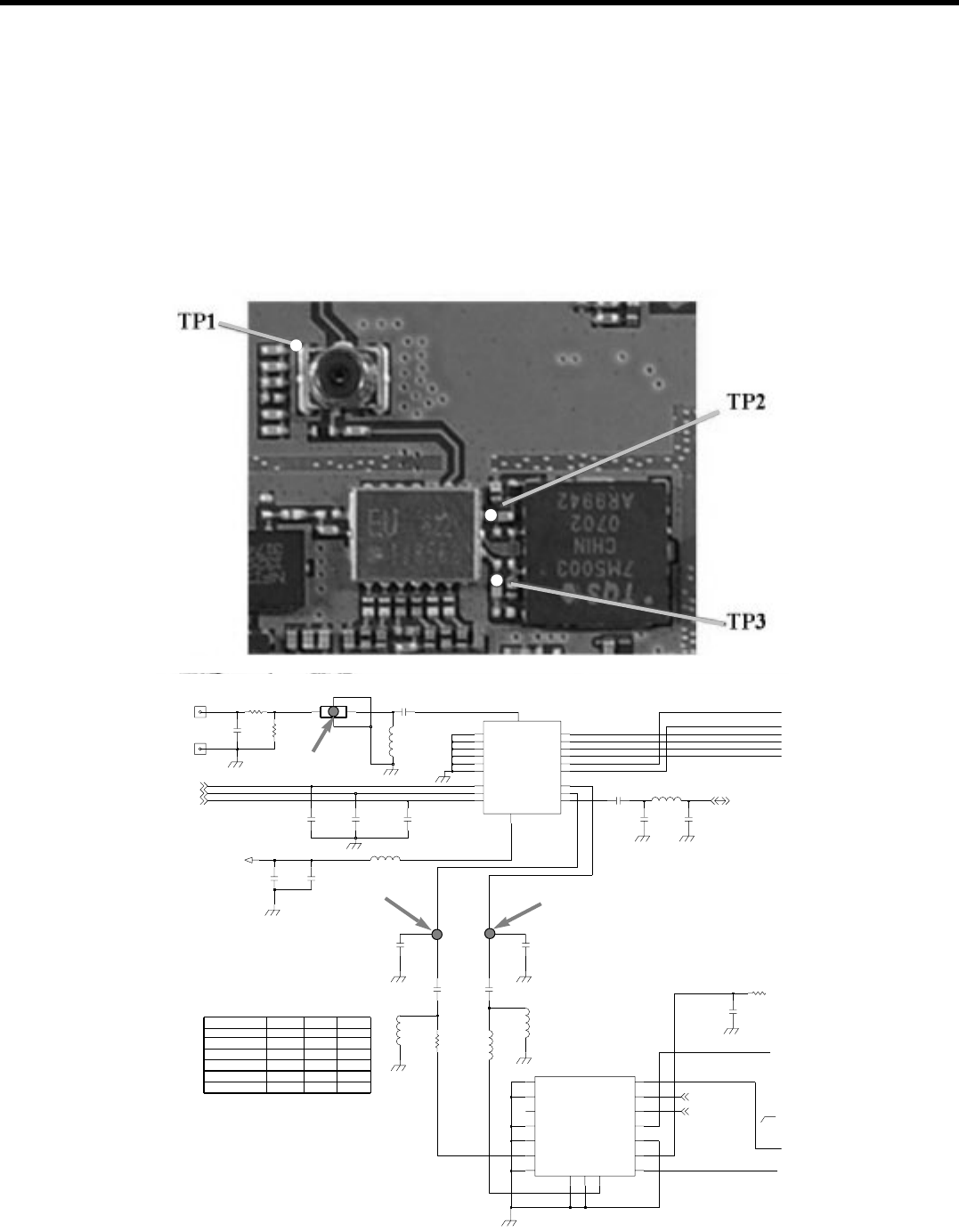

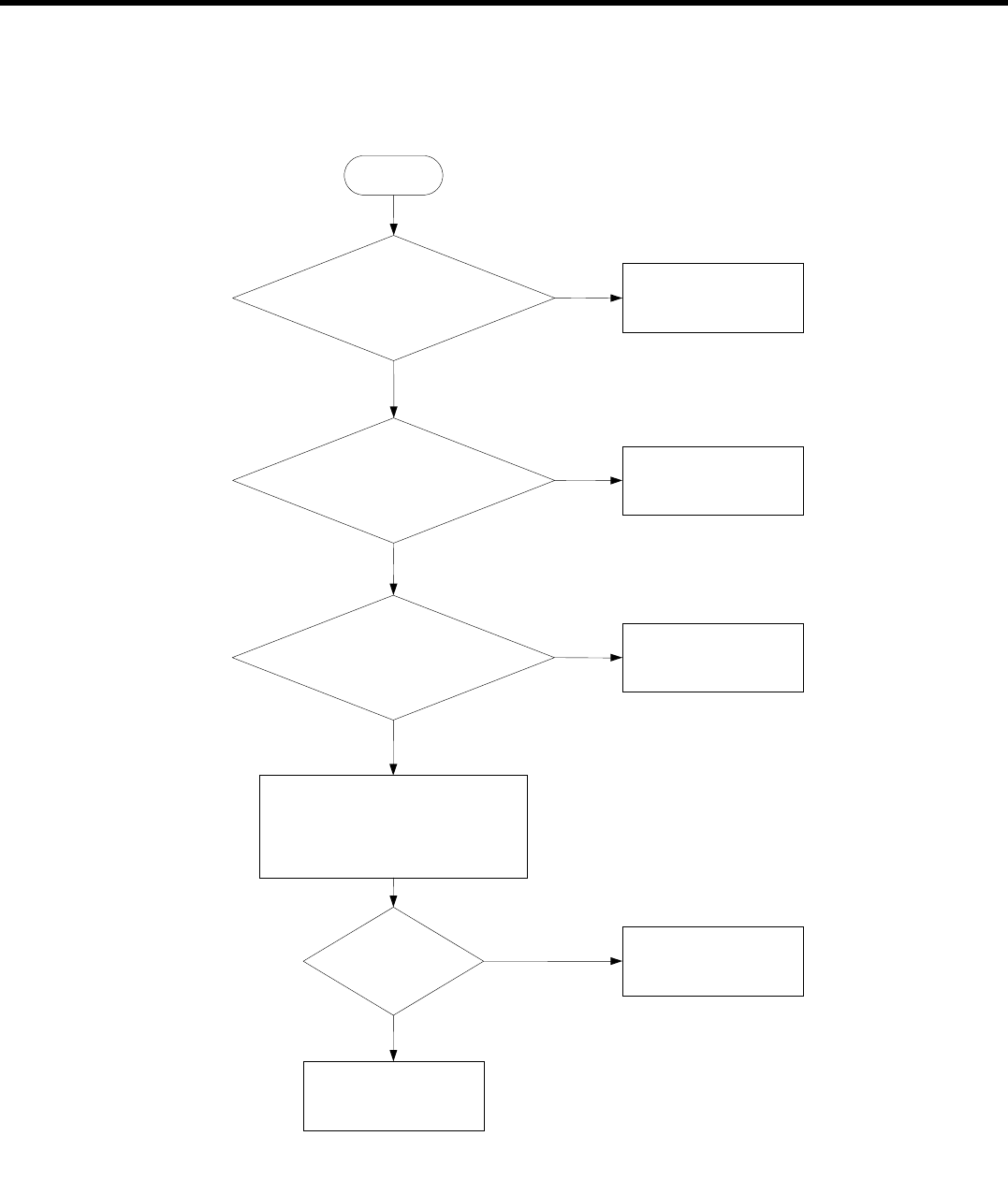

4.18 Bluetooth trouble....................................152

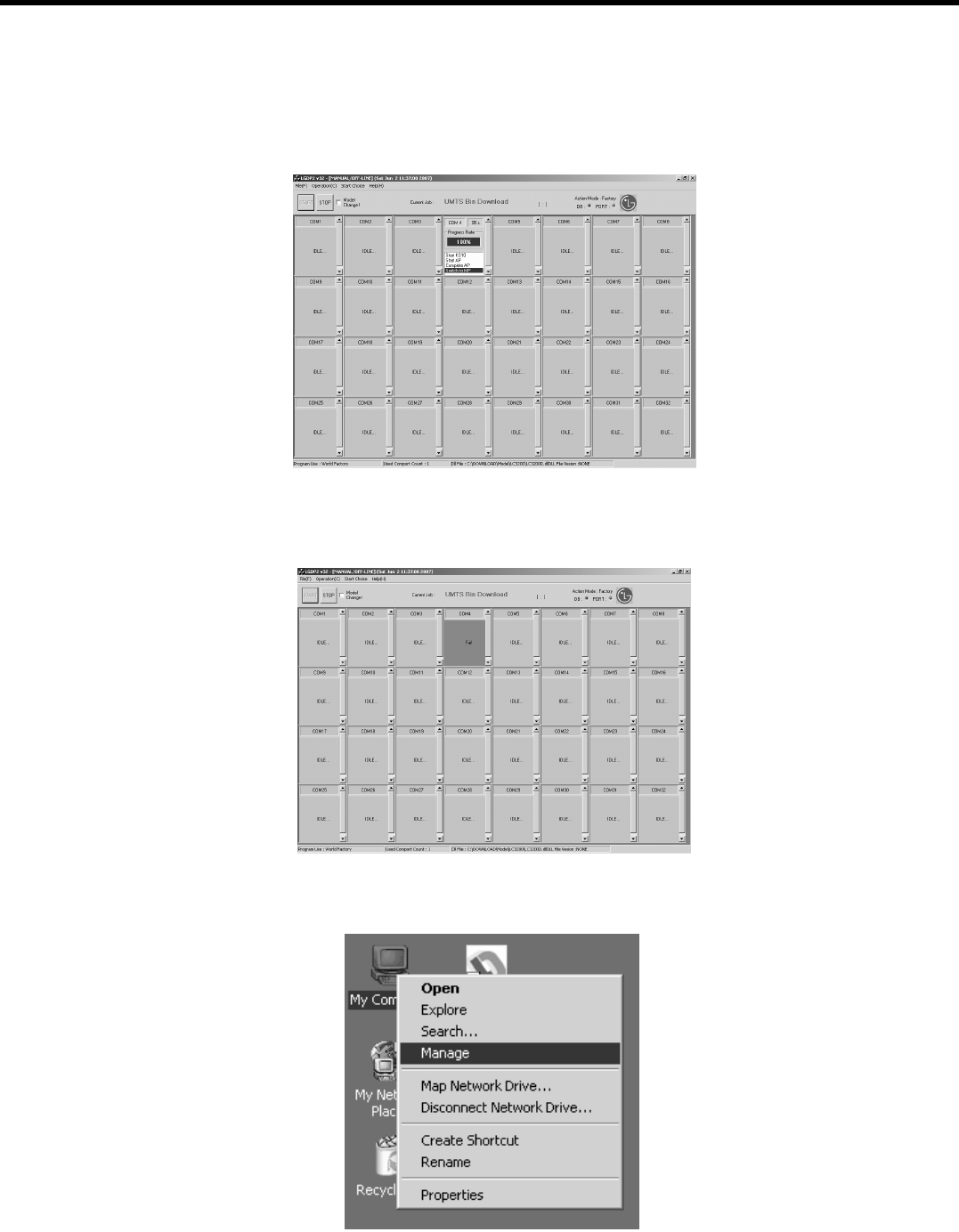

5. DOWNLOAD.....................................155

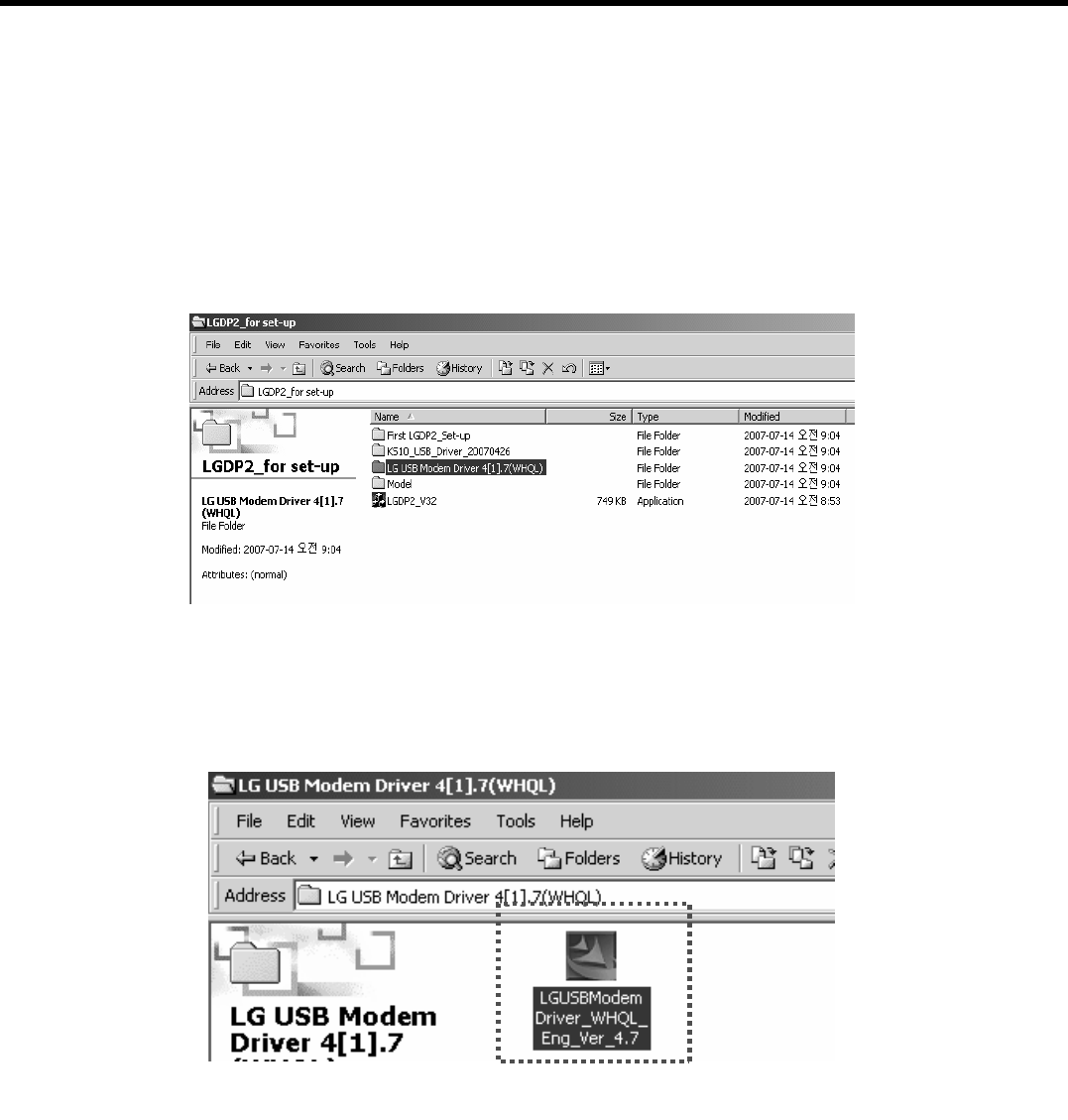

5.1 Composition omposition ..........................155

5.2 LGDP2 Program install LGDP2 Program

install........................................................156

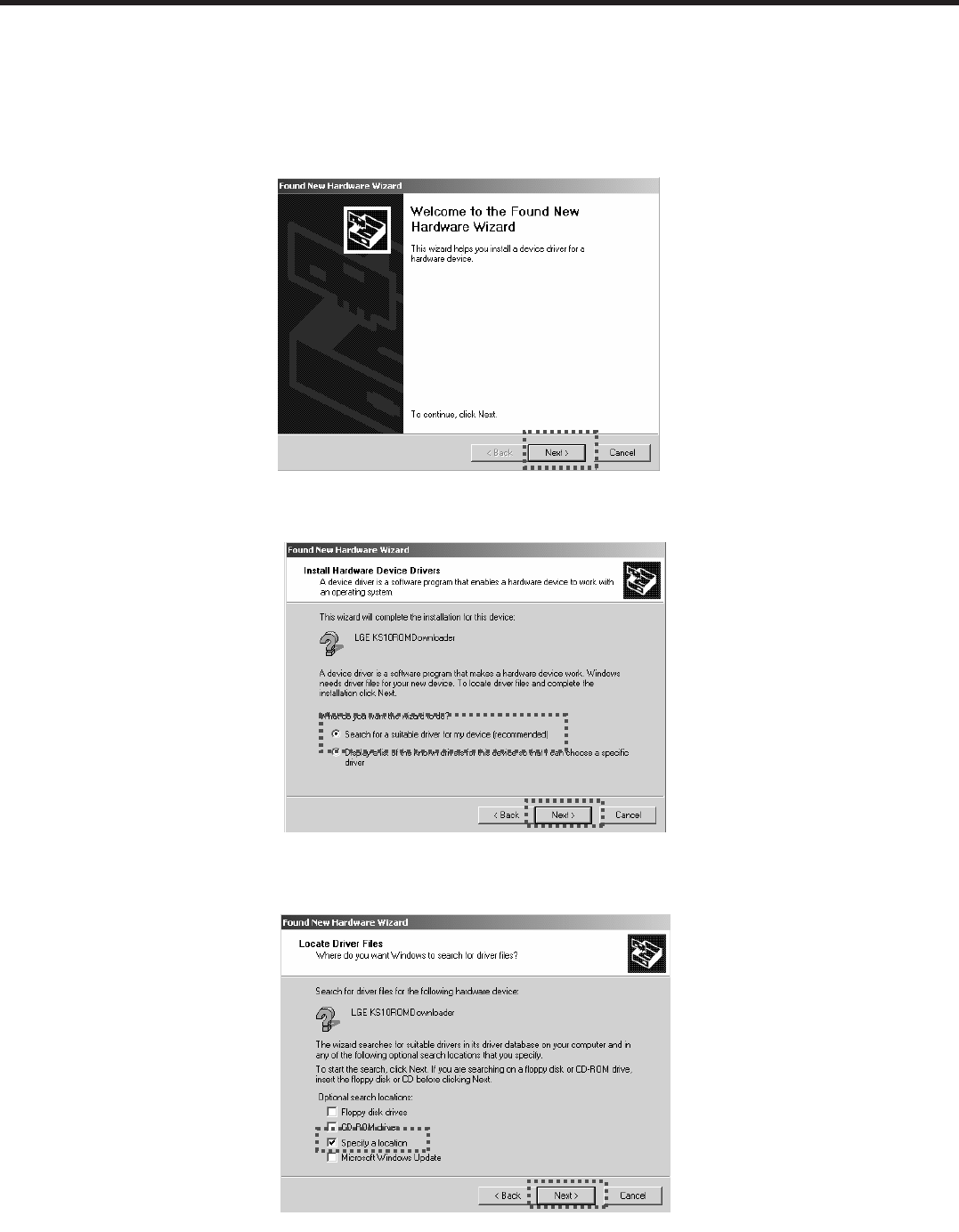

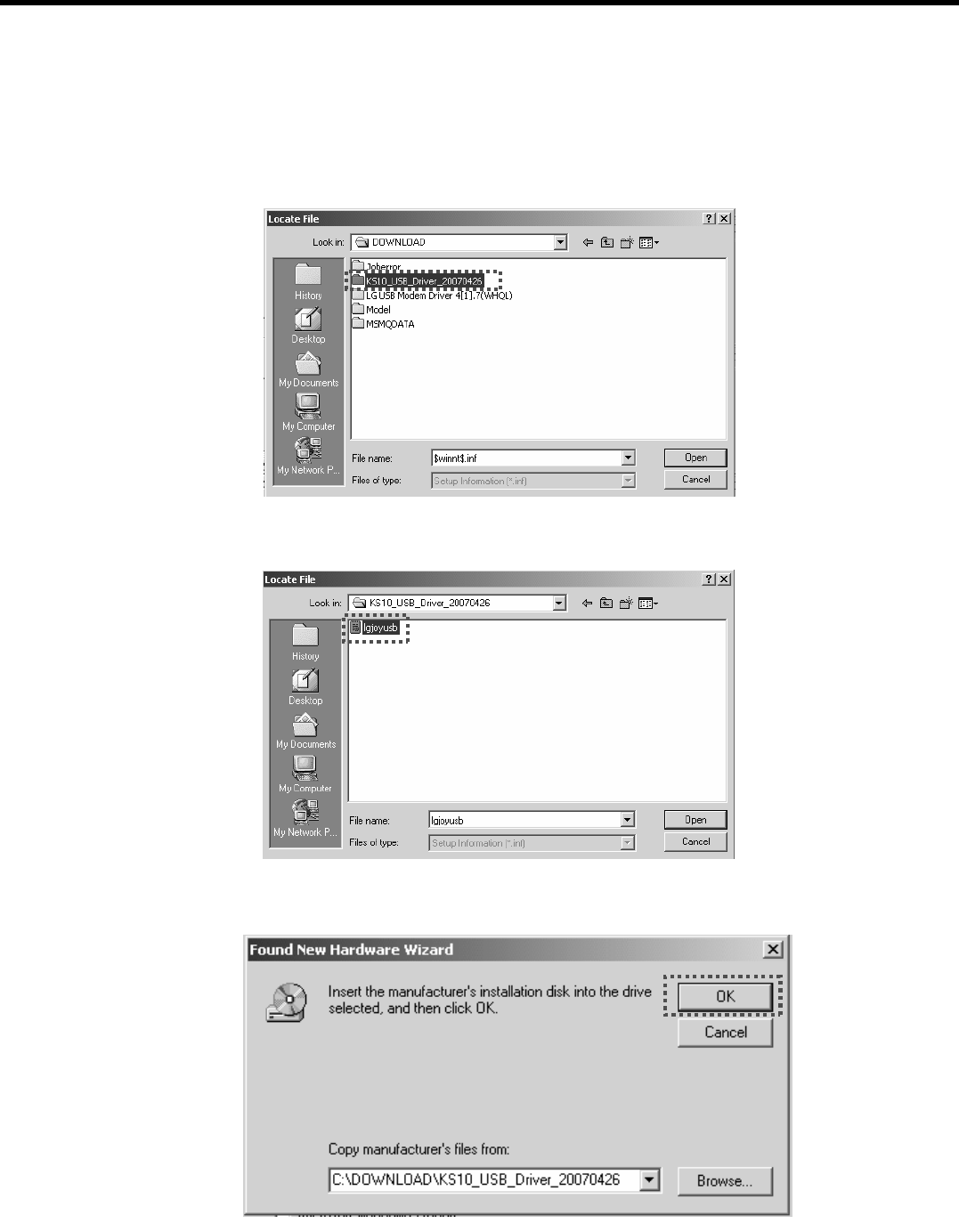

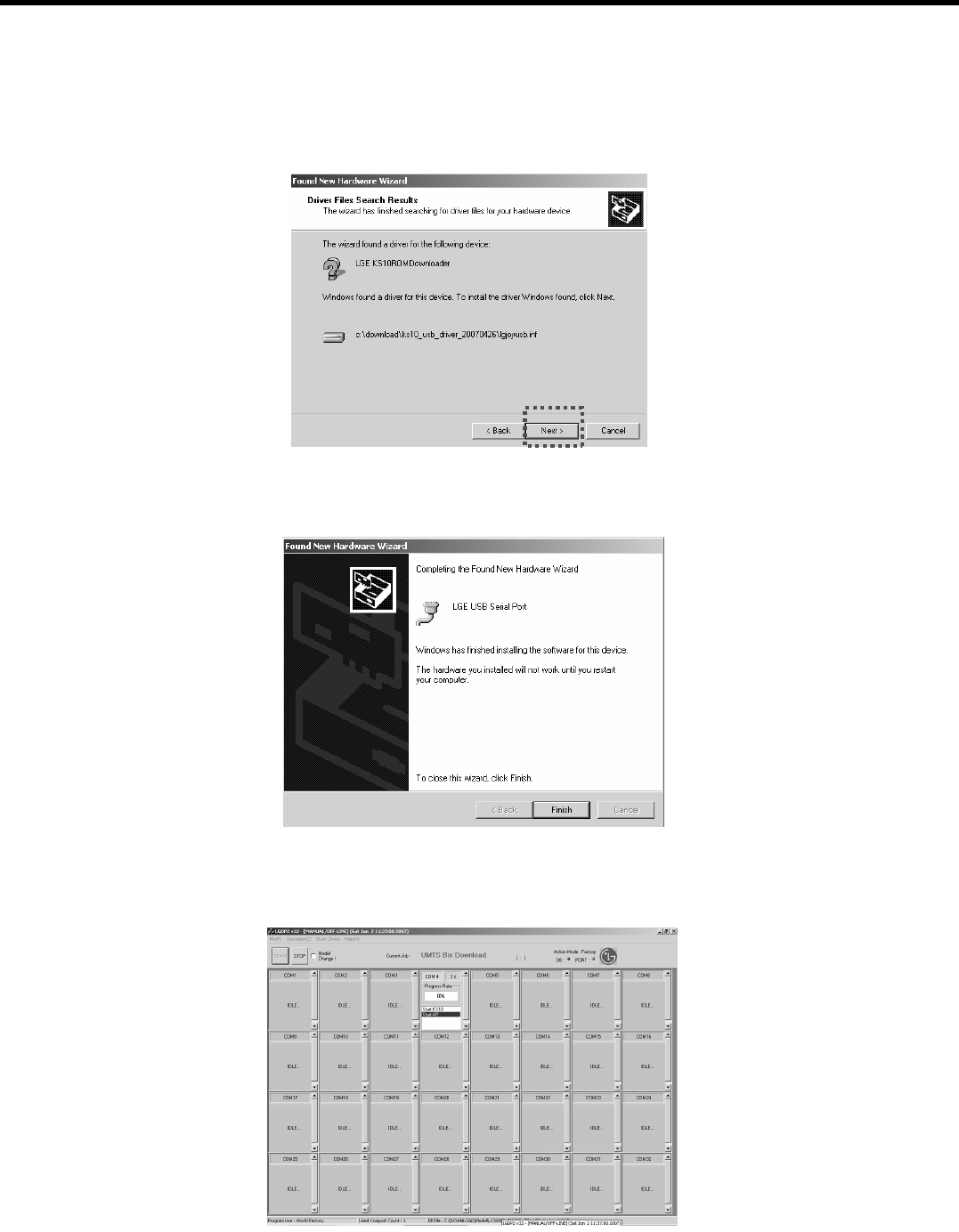

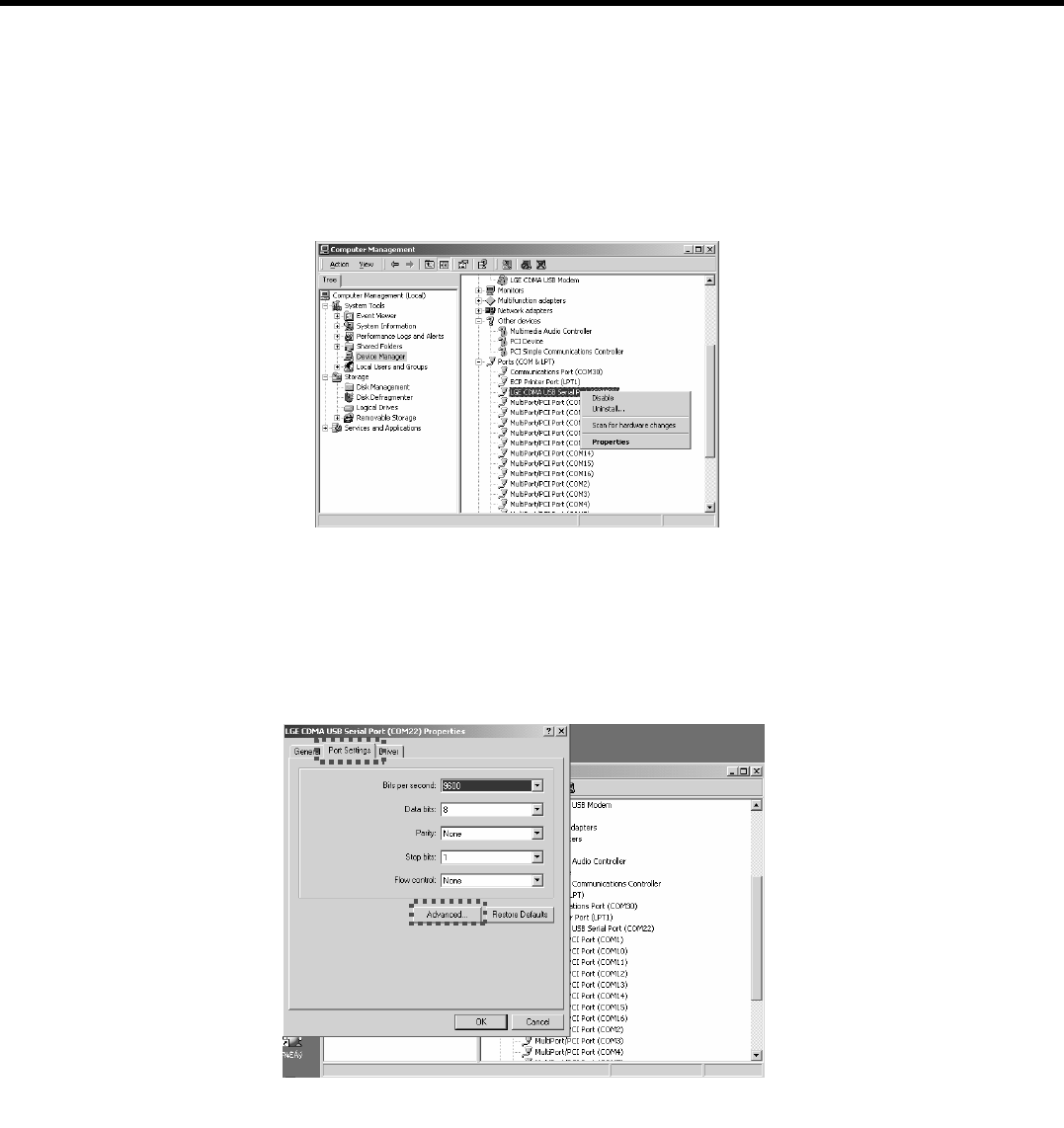

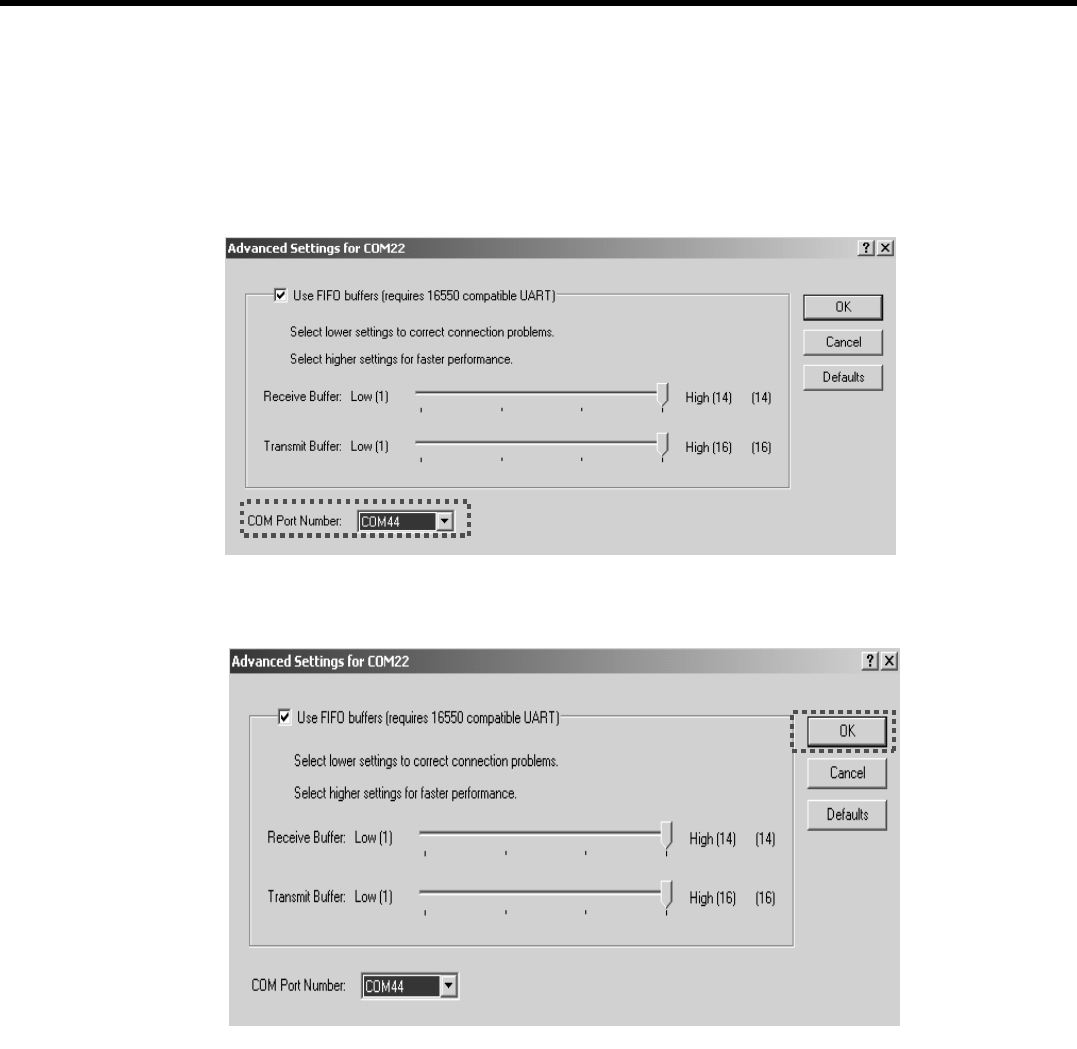

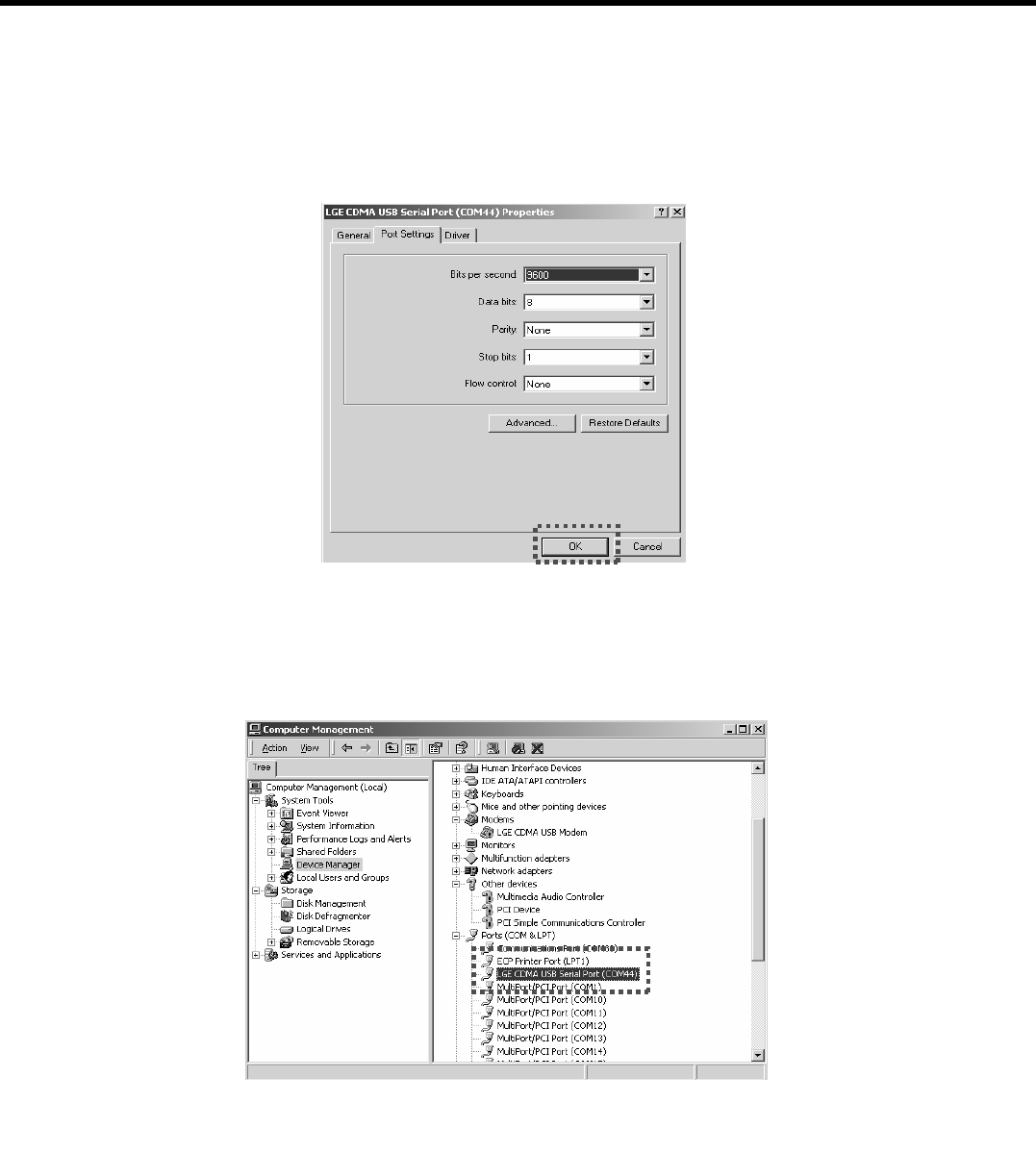

5.3 USB Driver setup USB Driver setup ........159

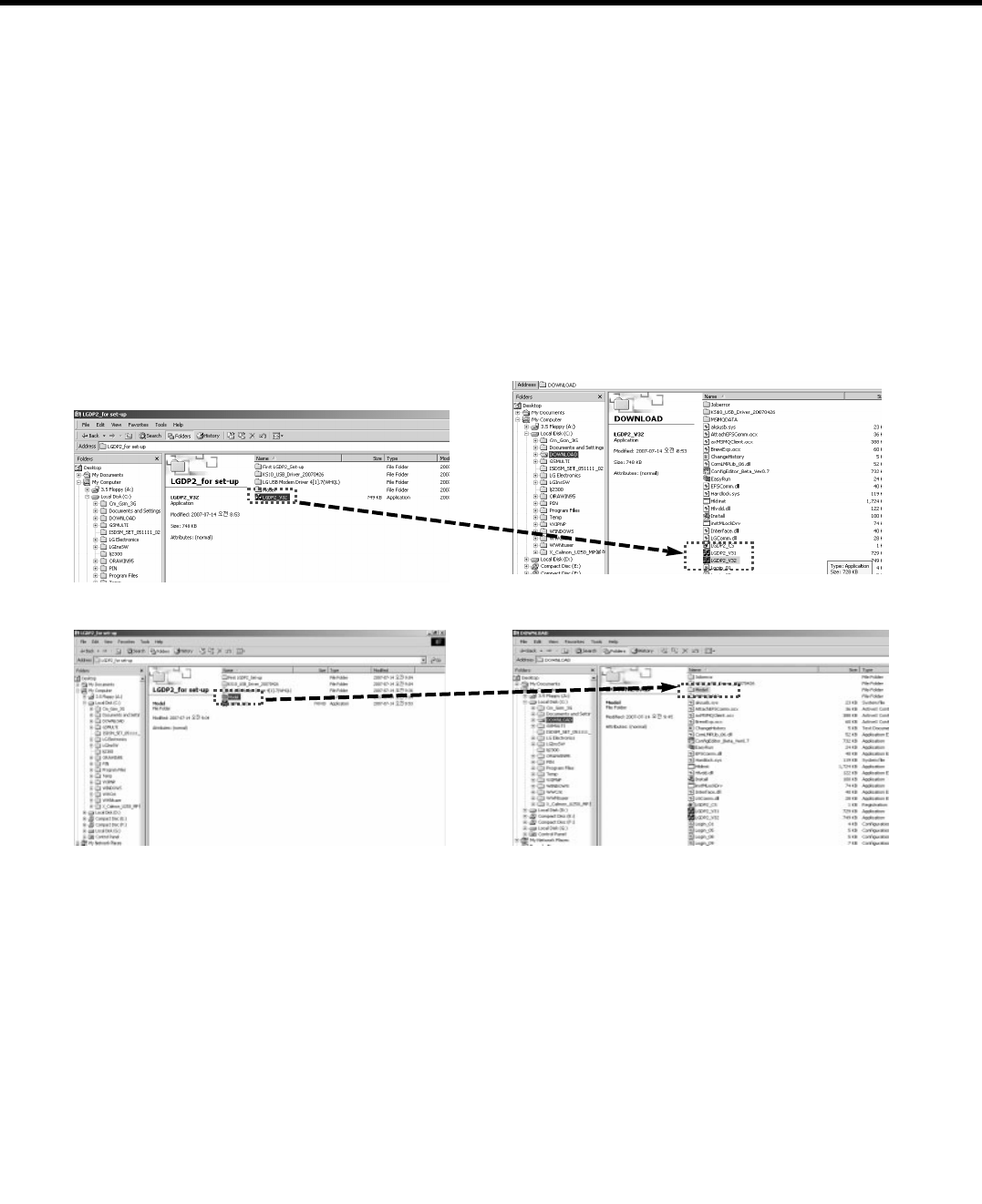

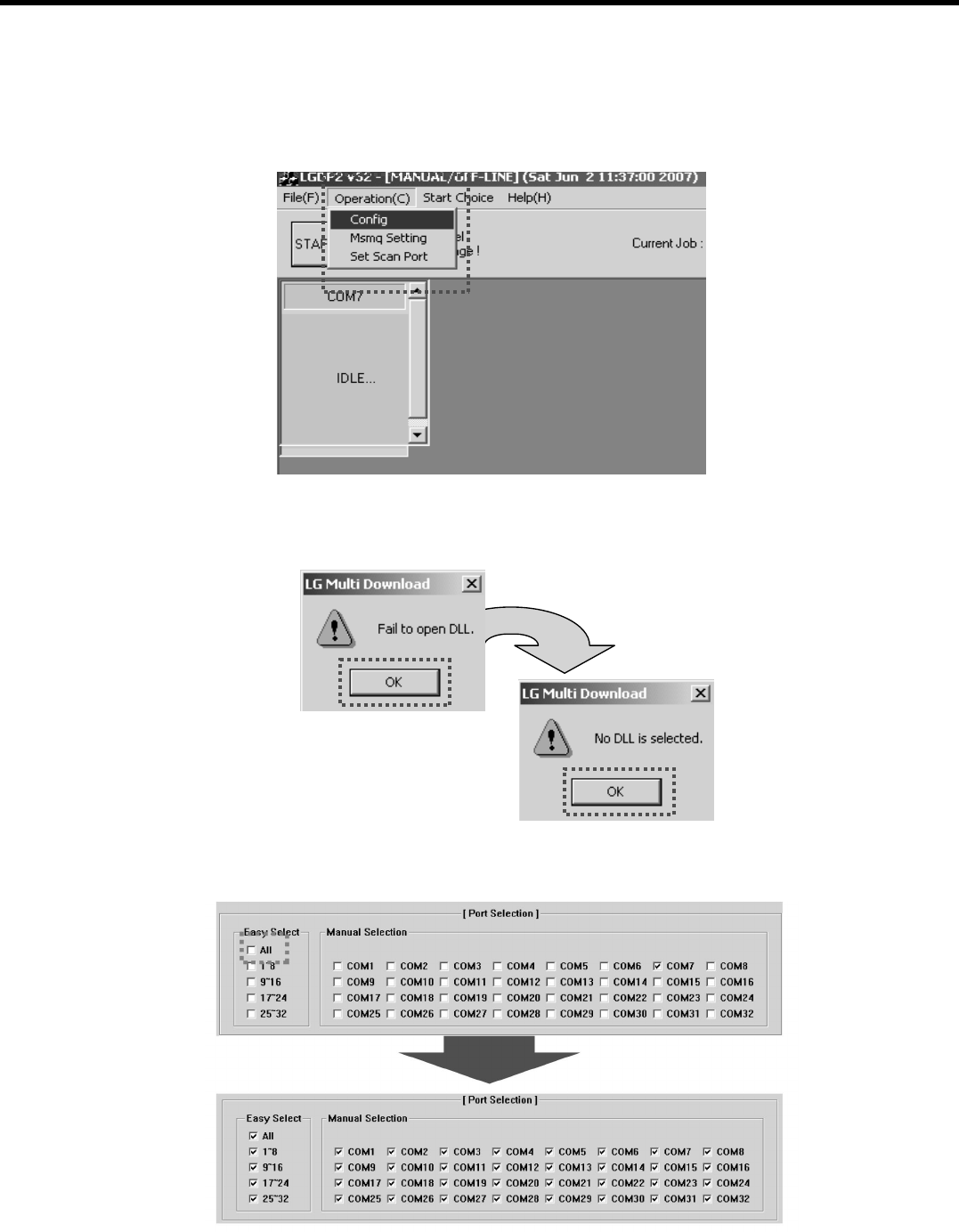

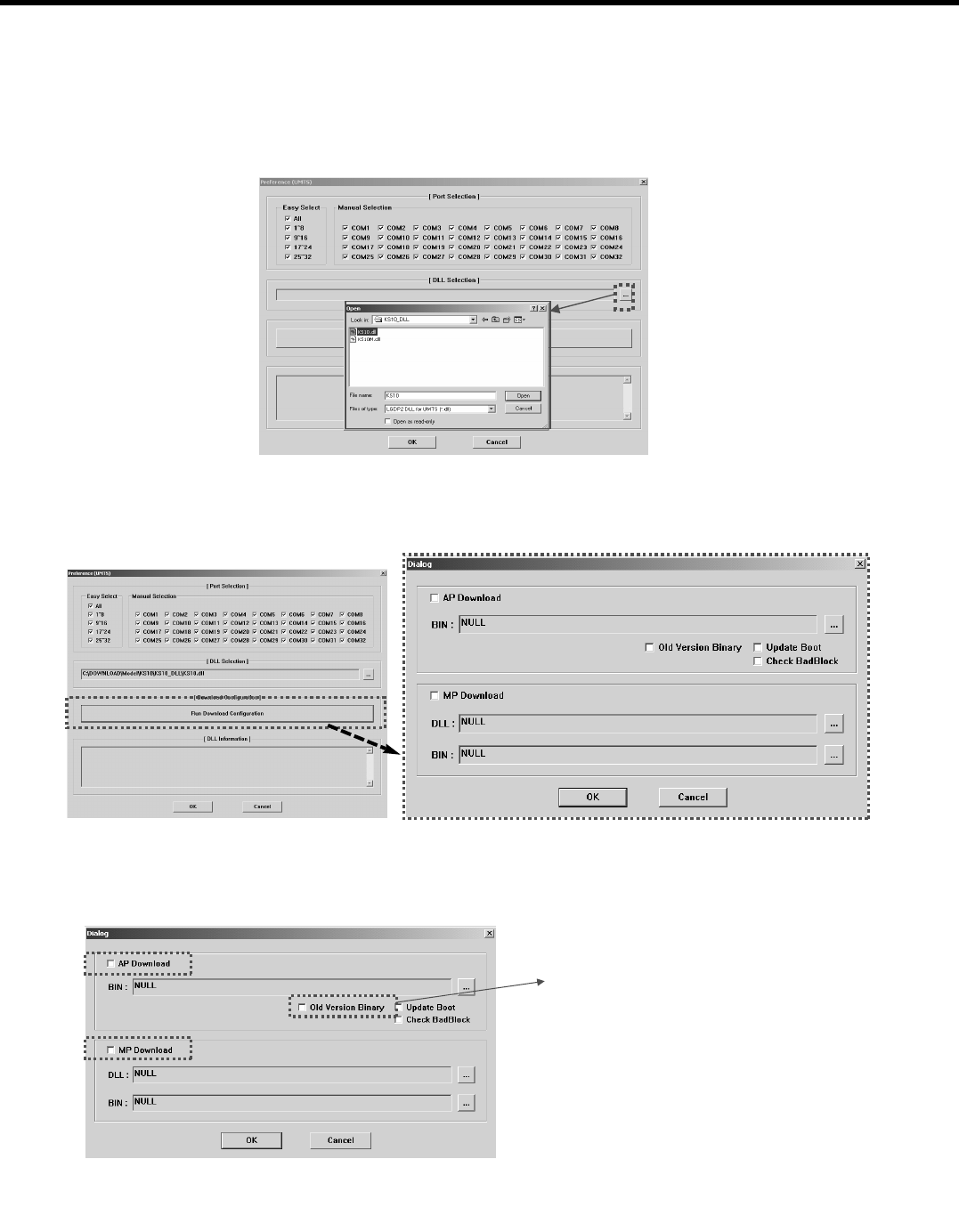

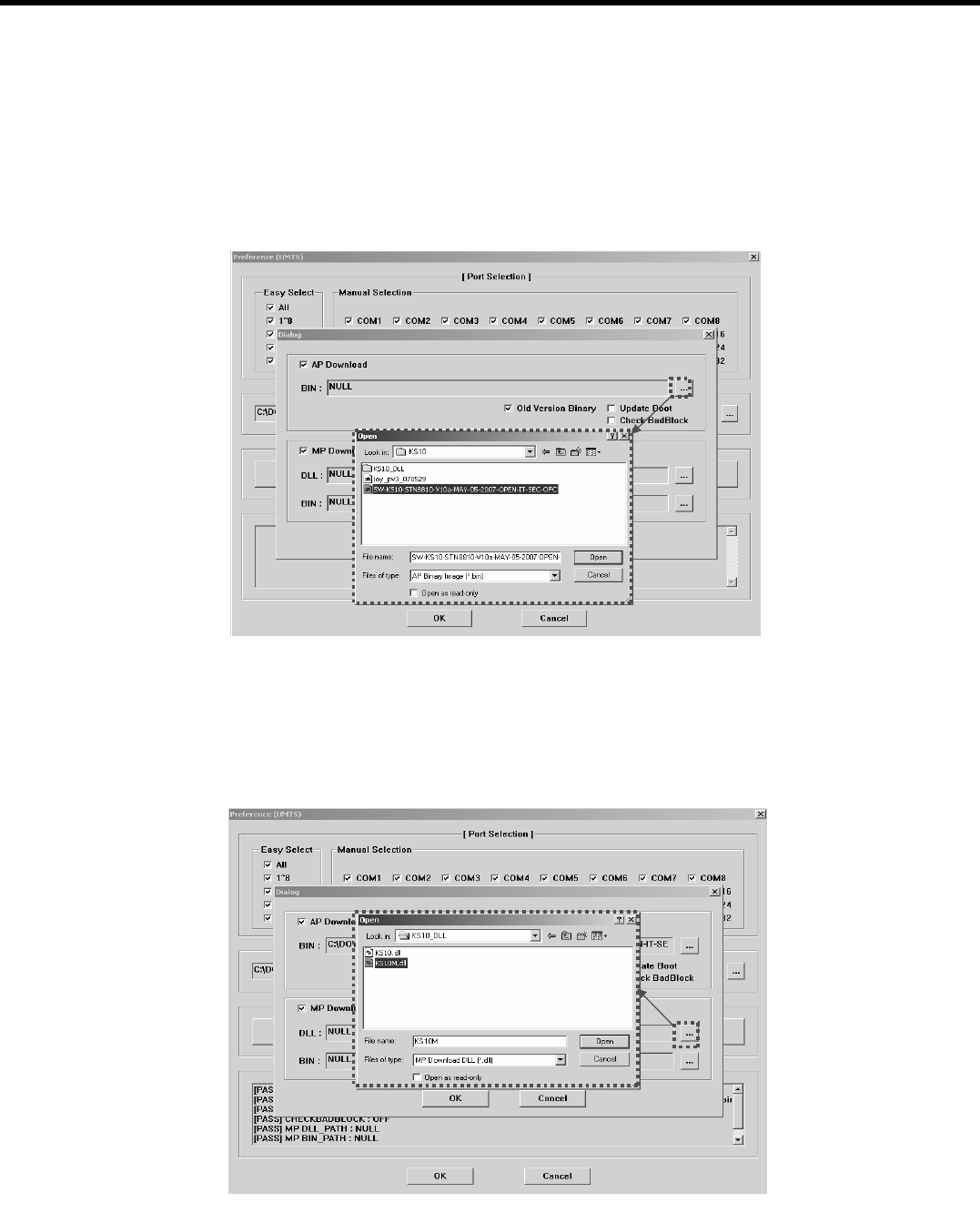

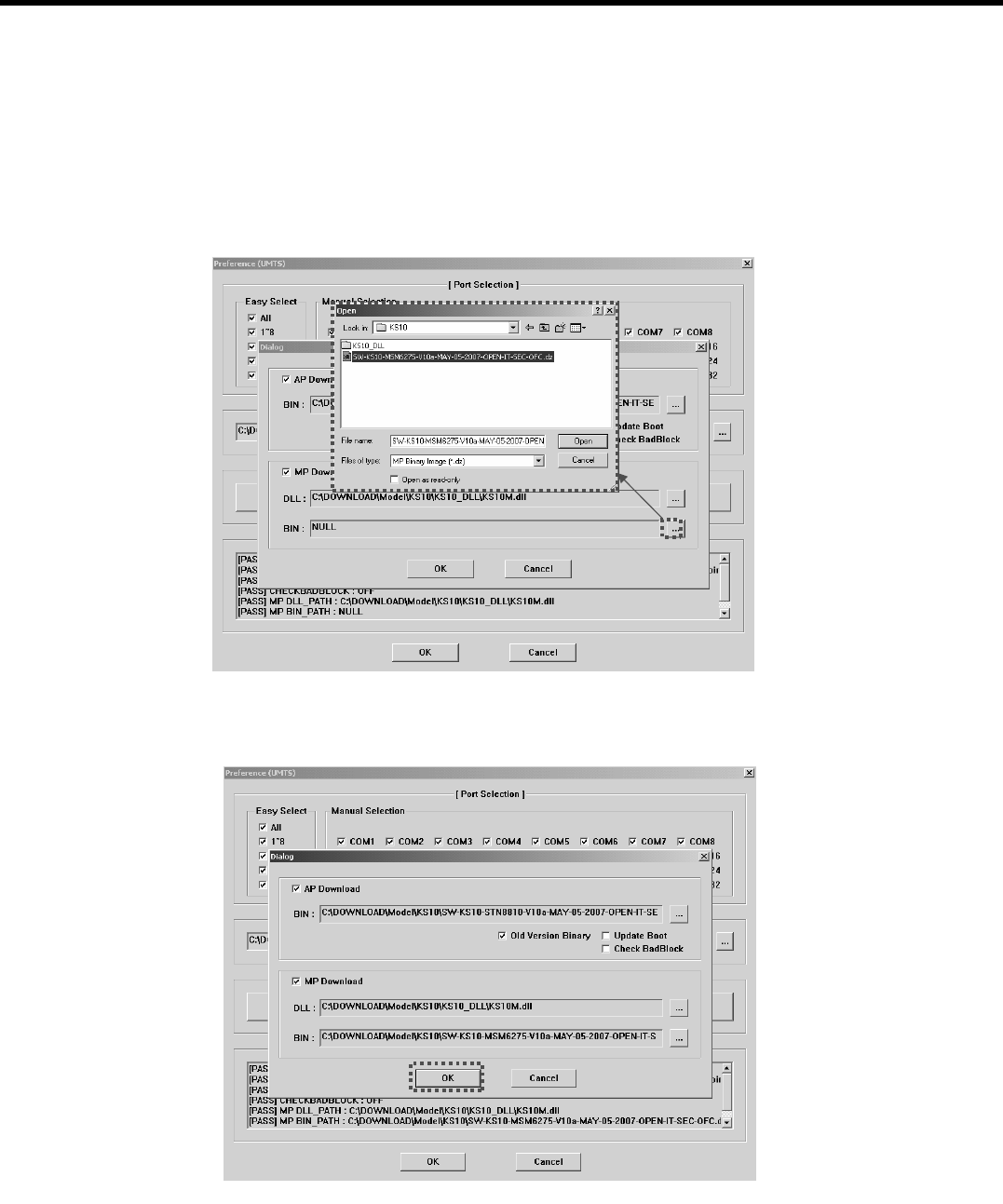

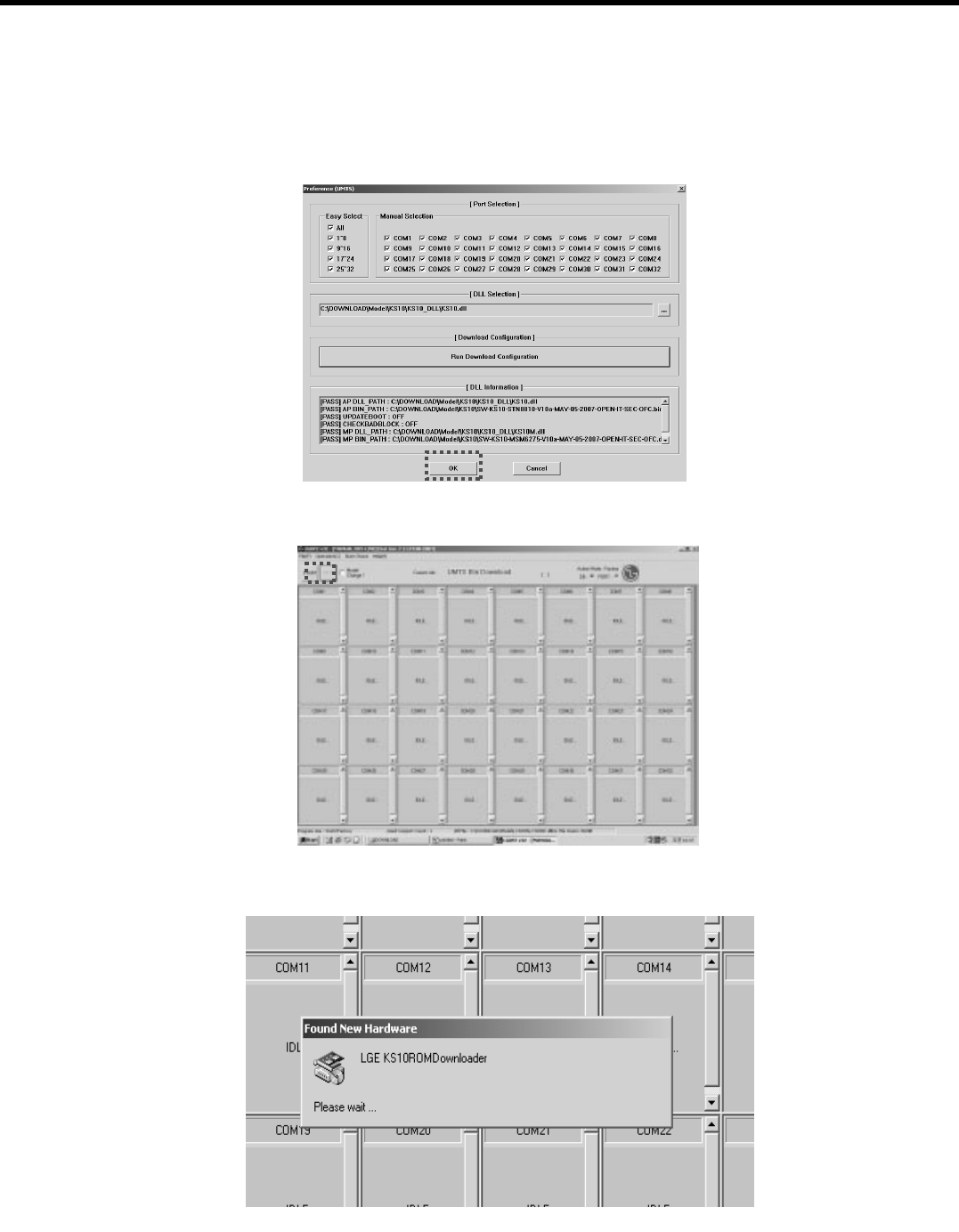

5.4 KS10 LGDP2 run file & DLL file setup .....162

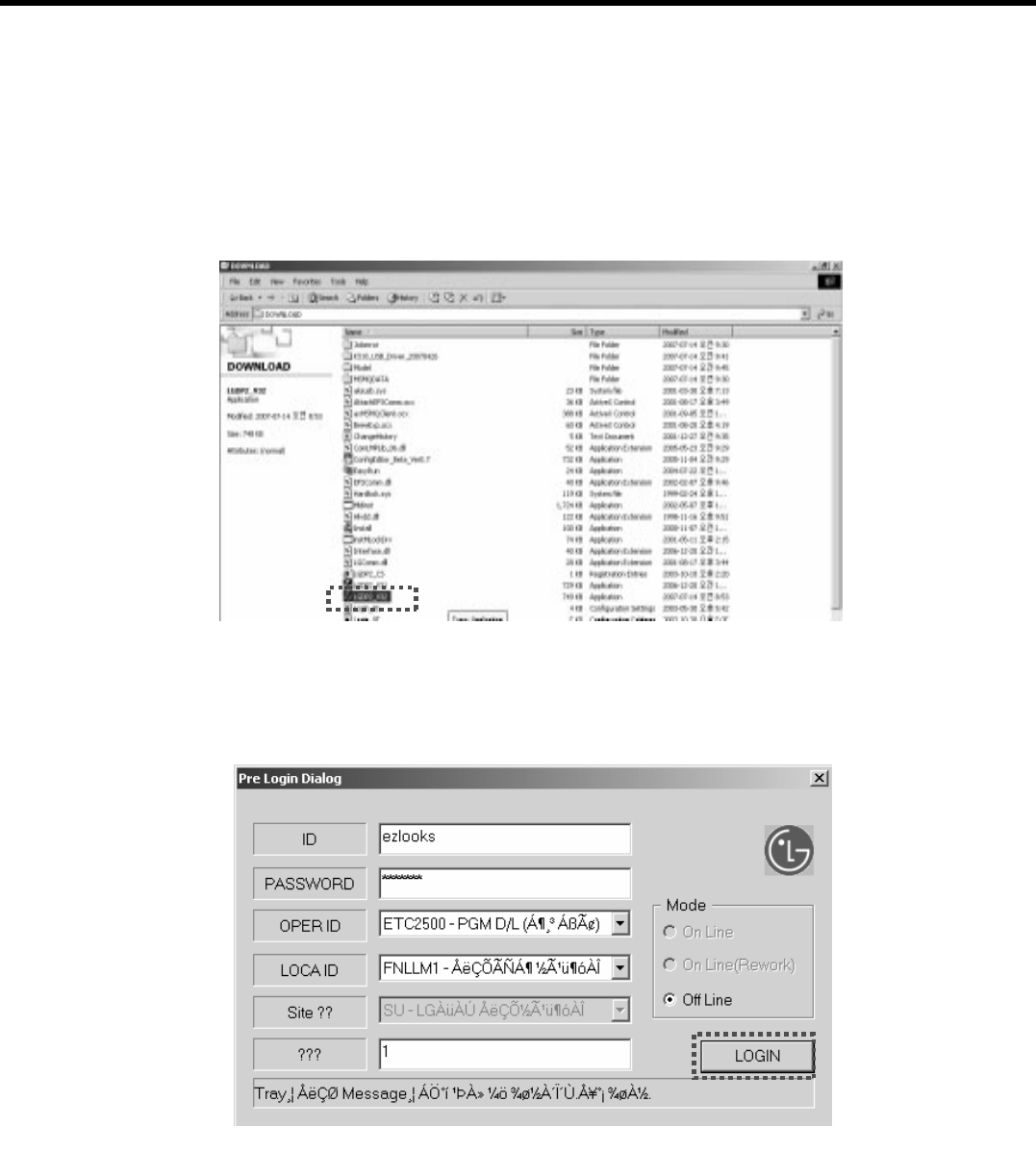

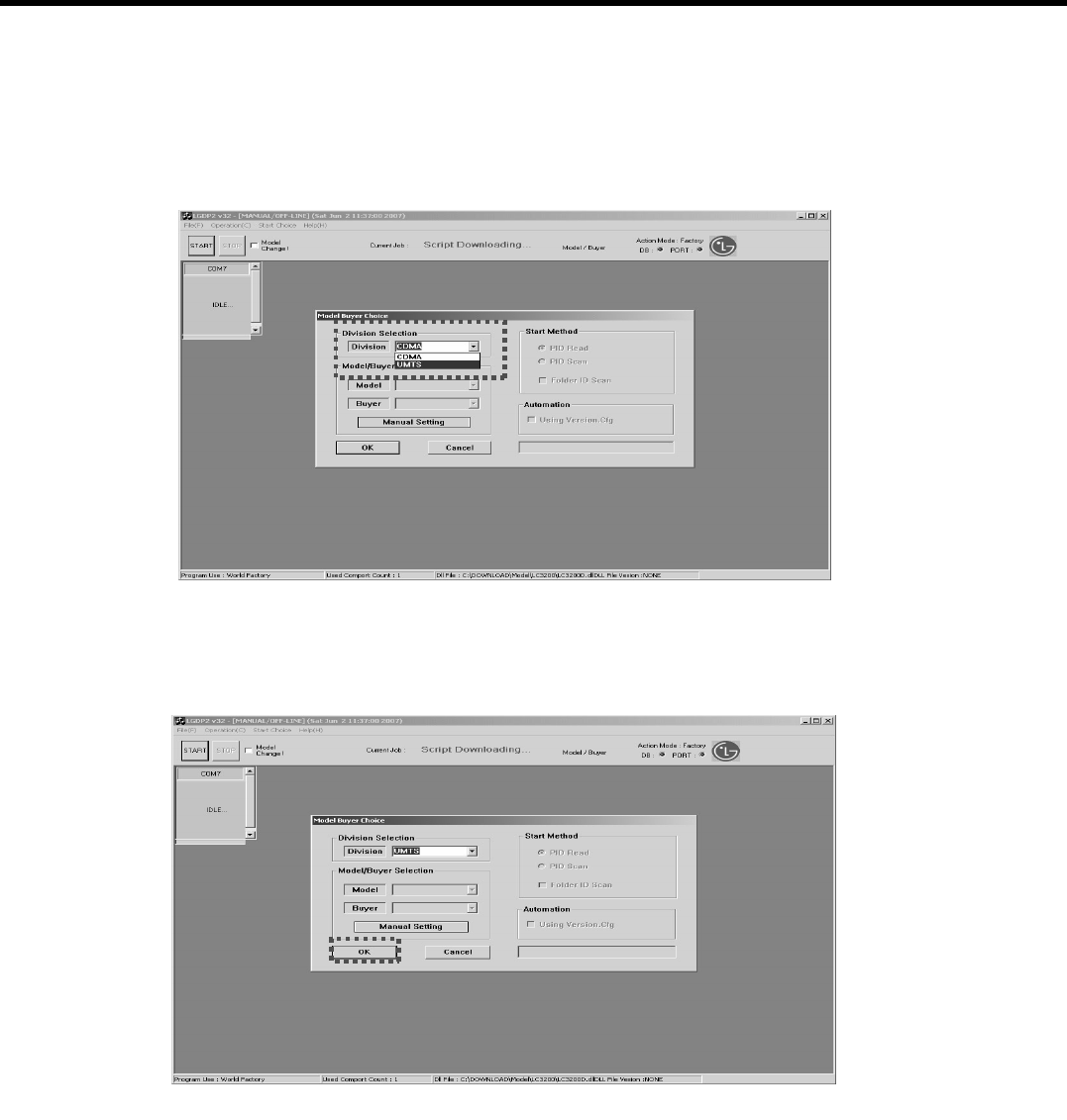

5.5 Execute LGDP2 program.........................163

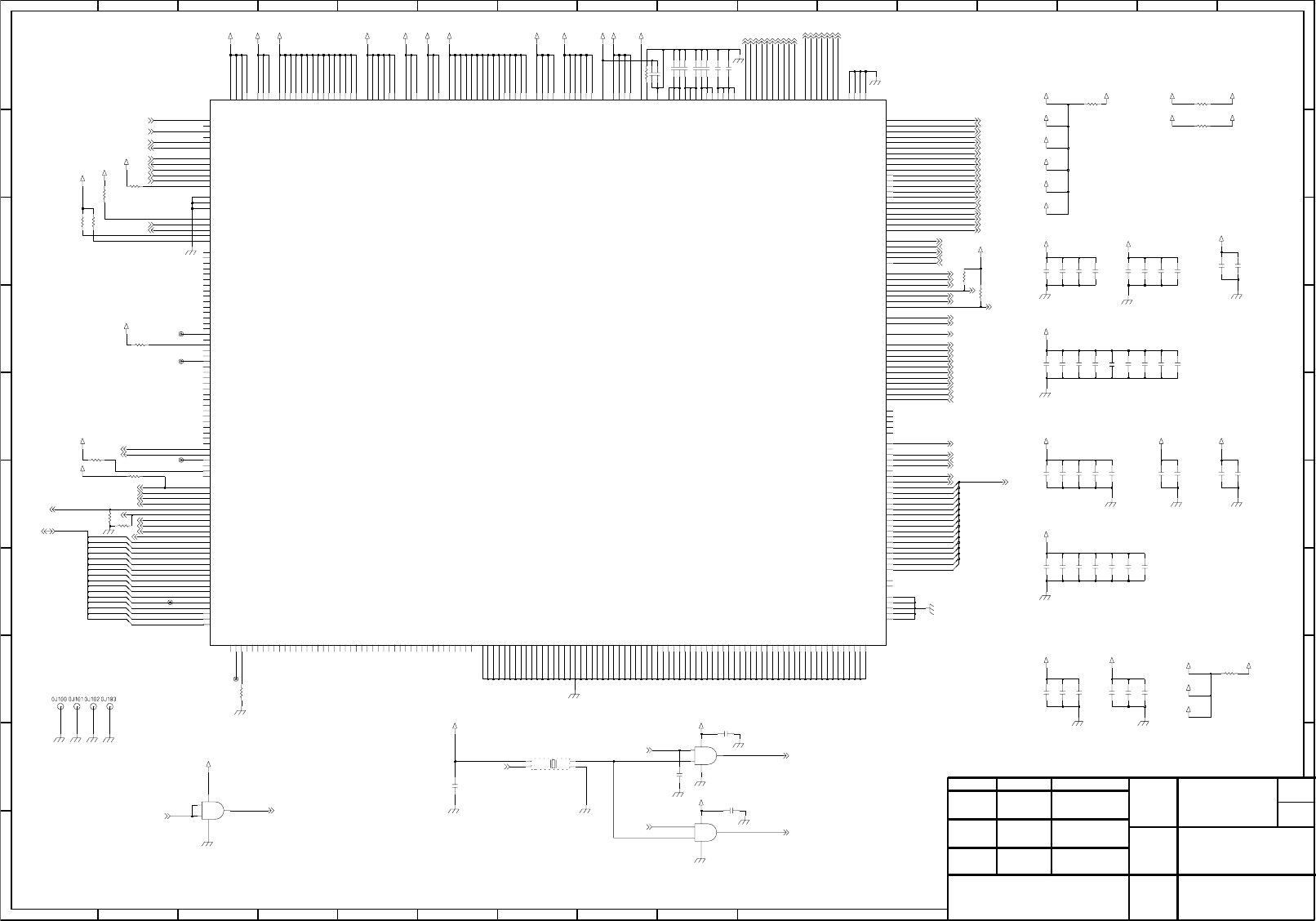

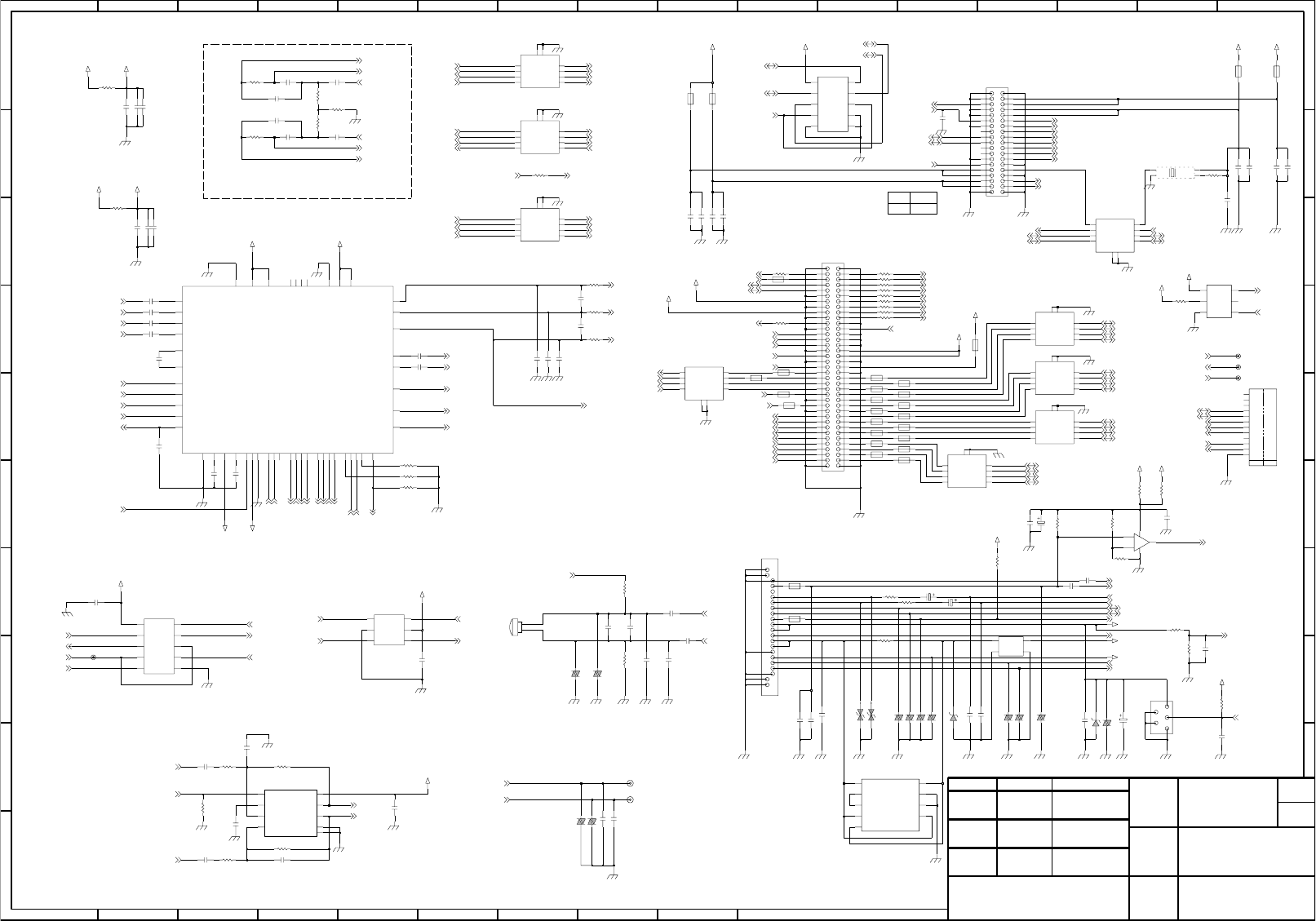

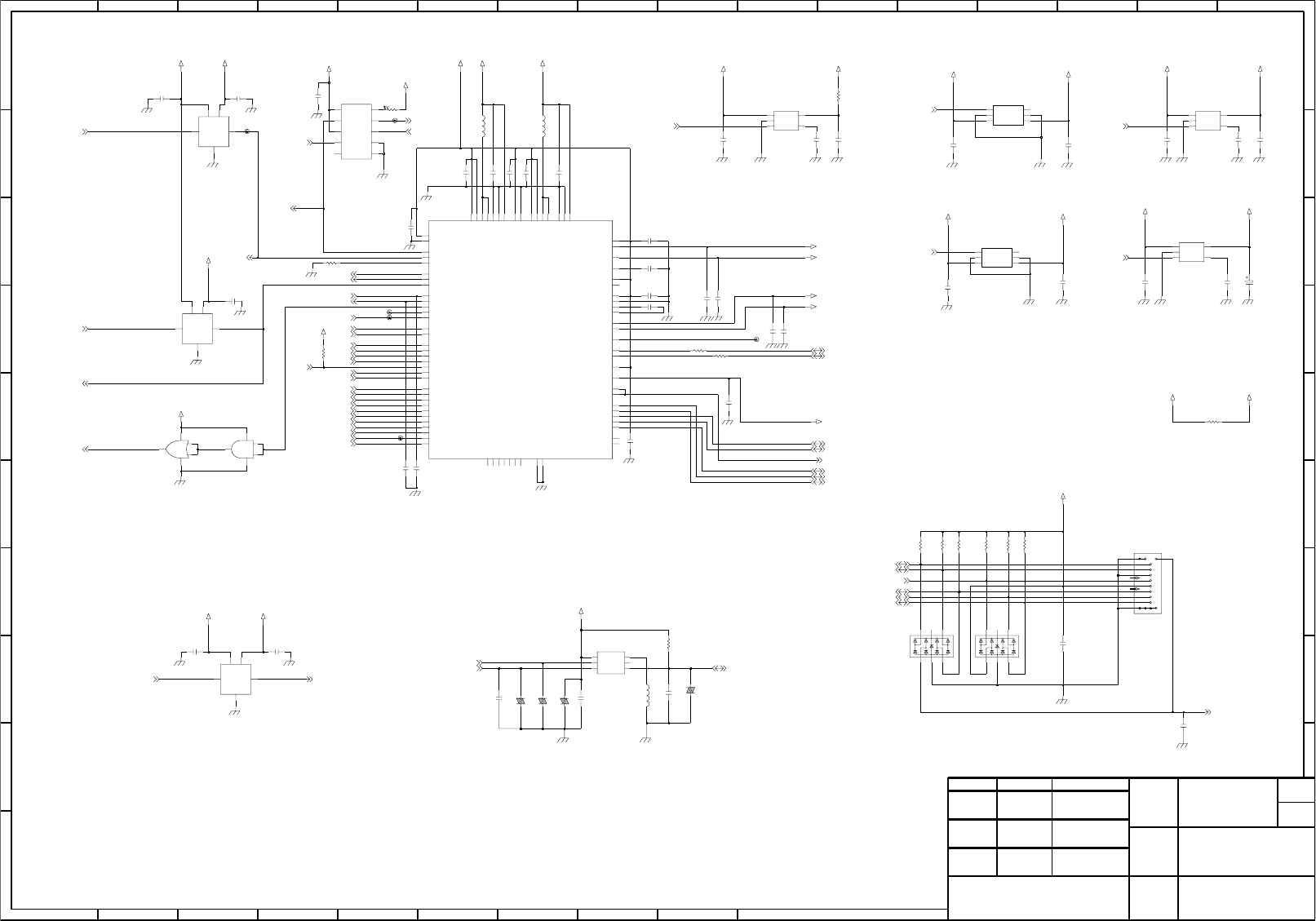

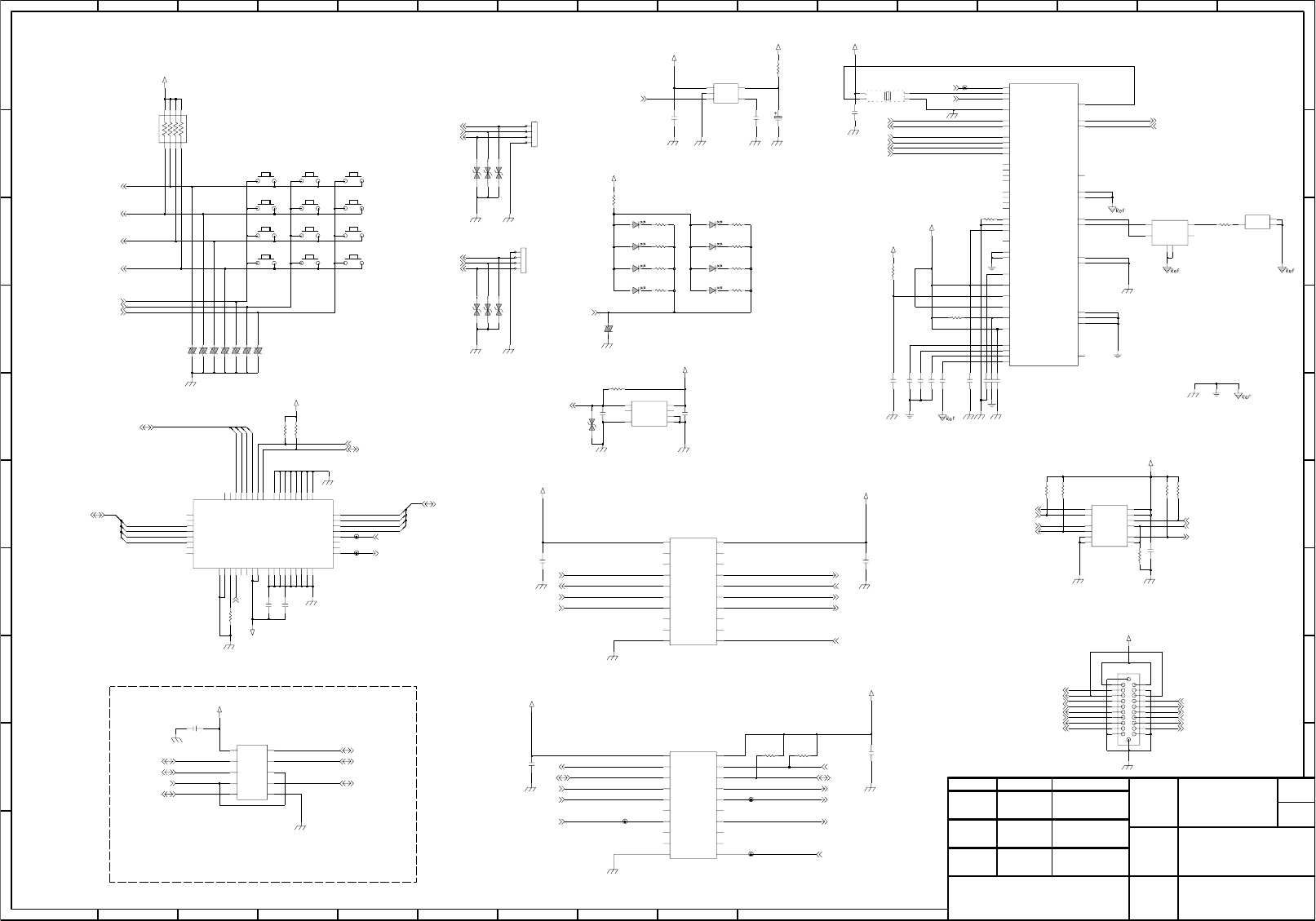

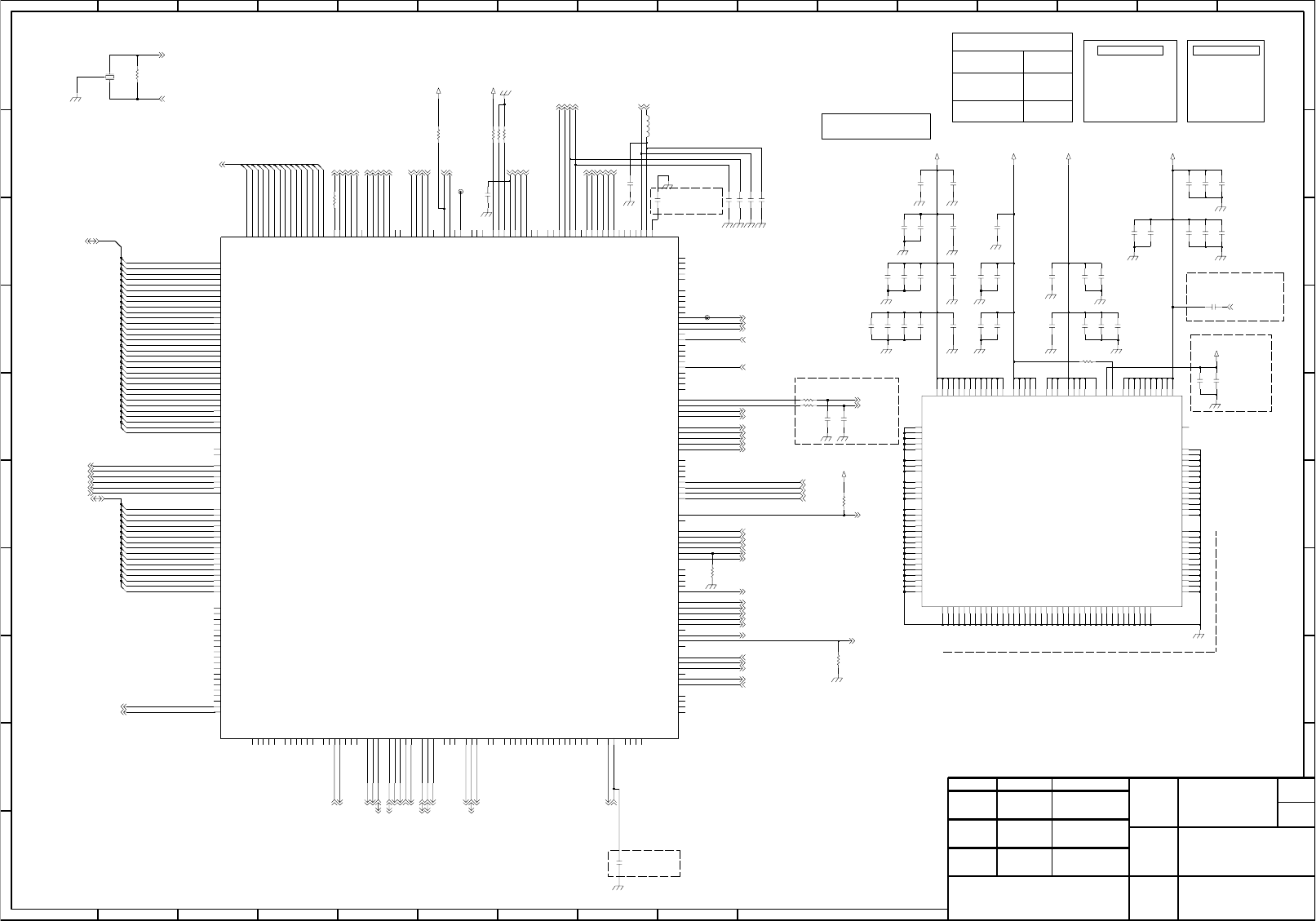

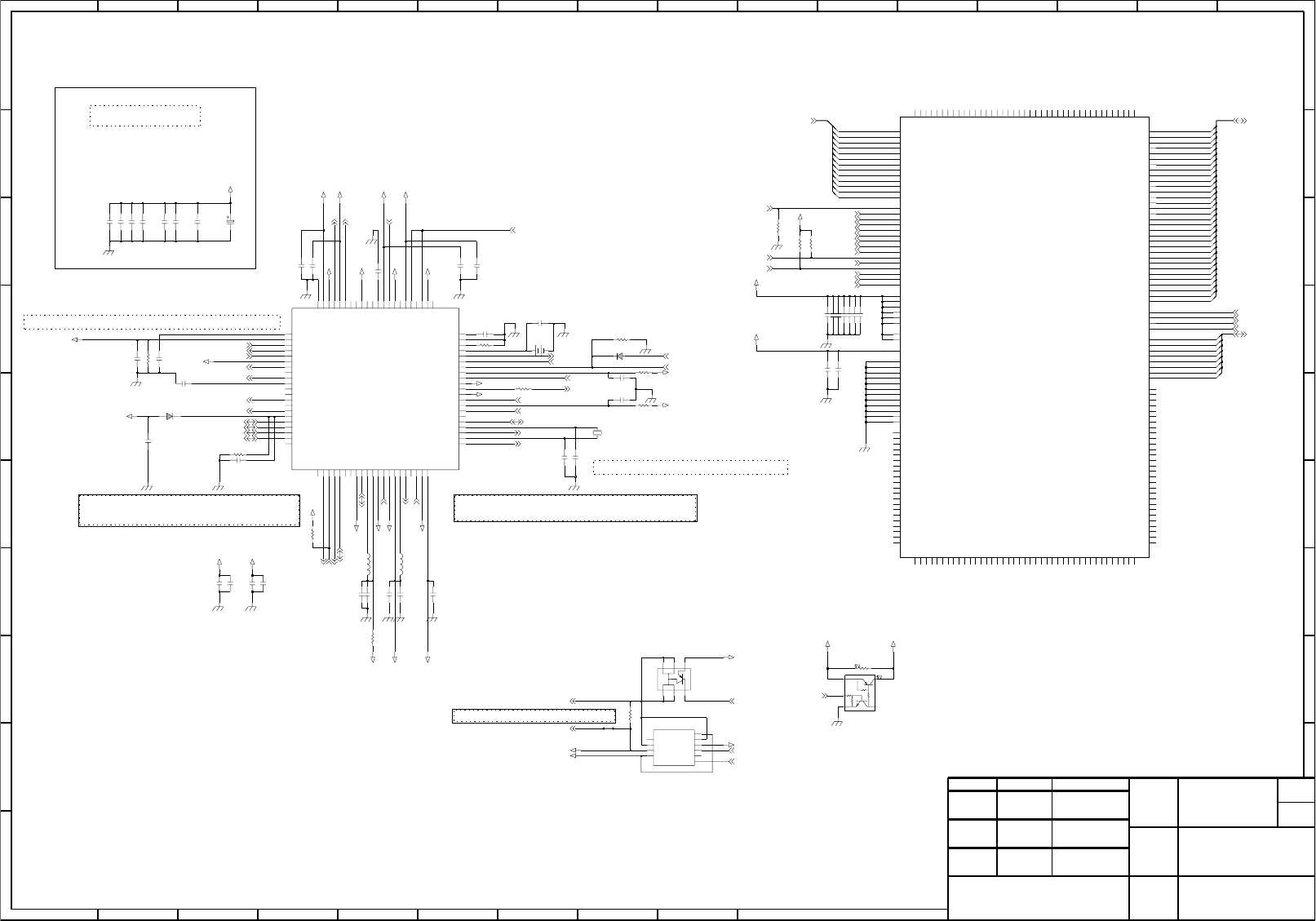

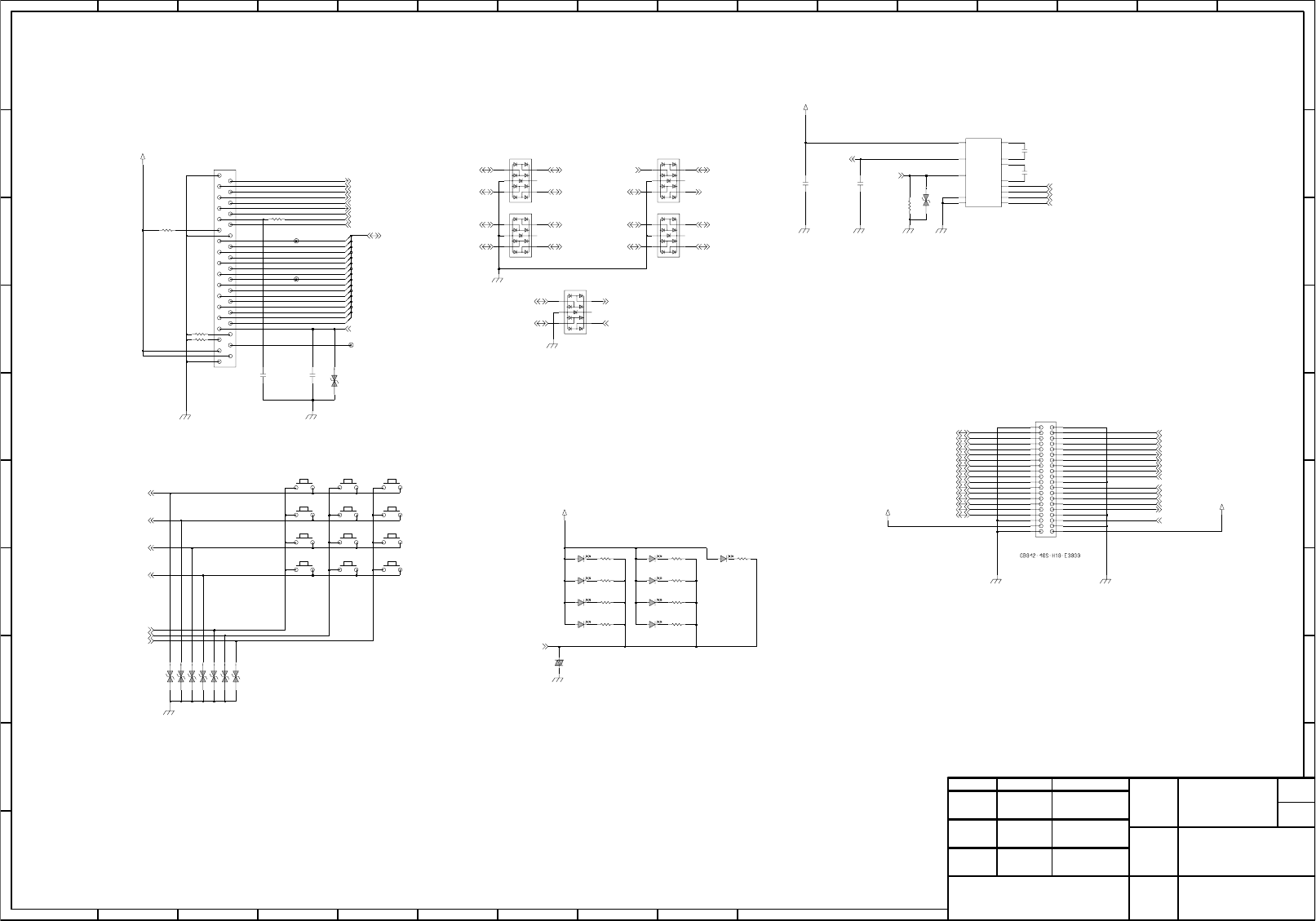

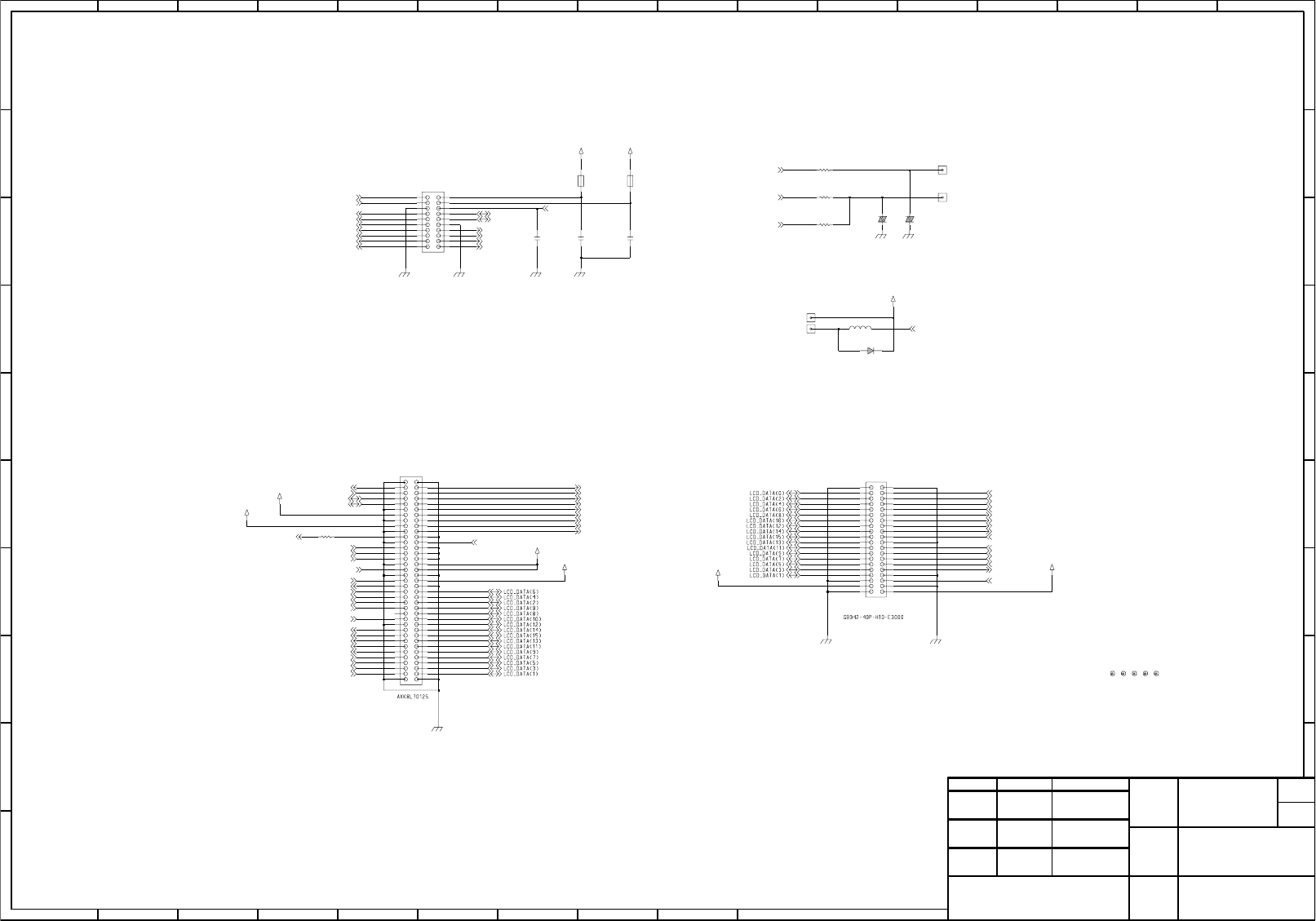

6. BLOCK DIAGRAM ...........................178

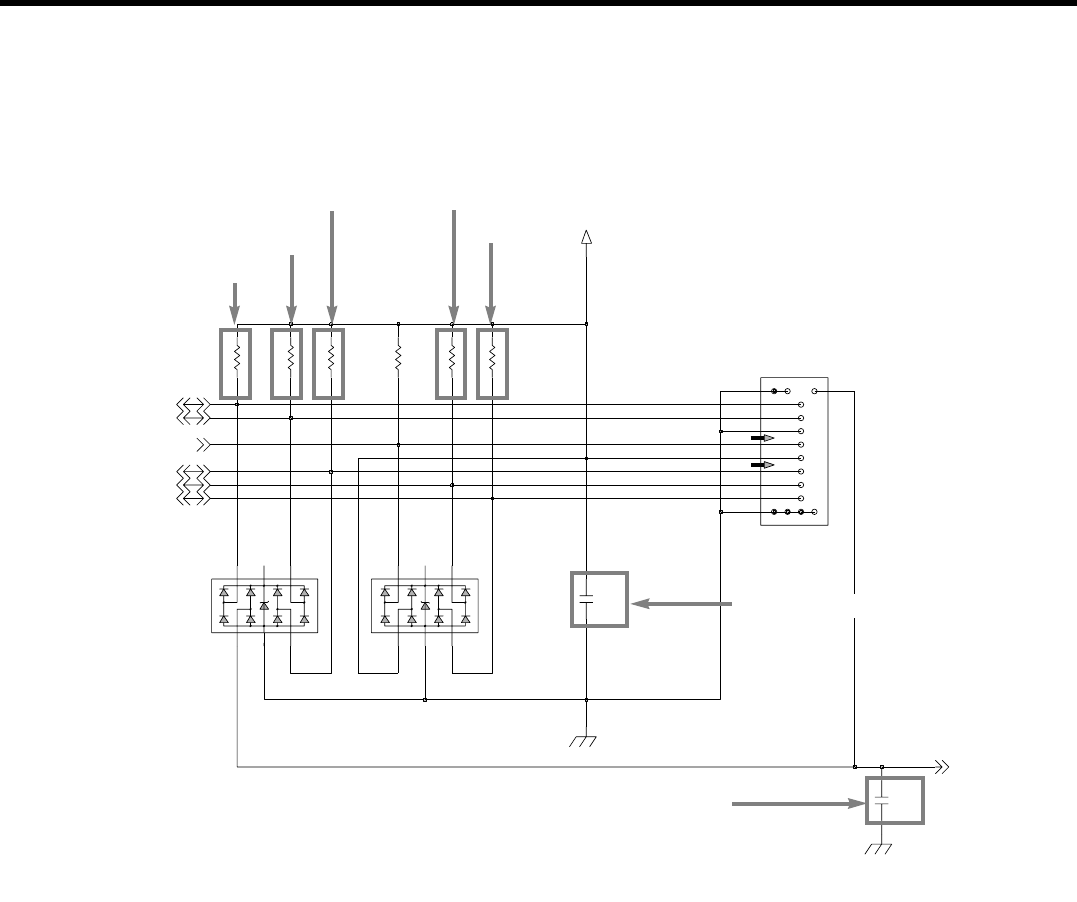

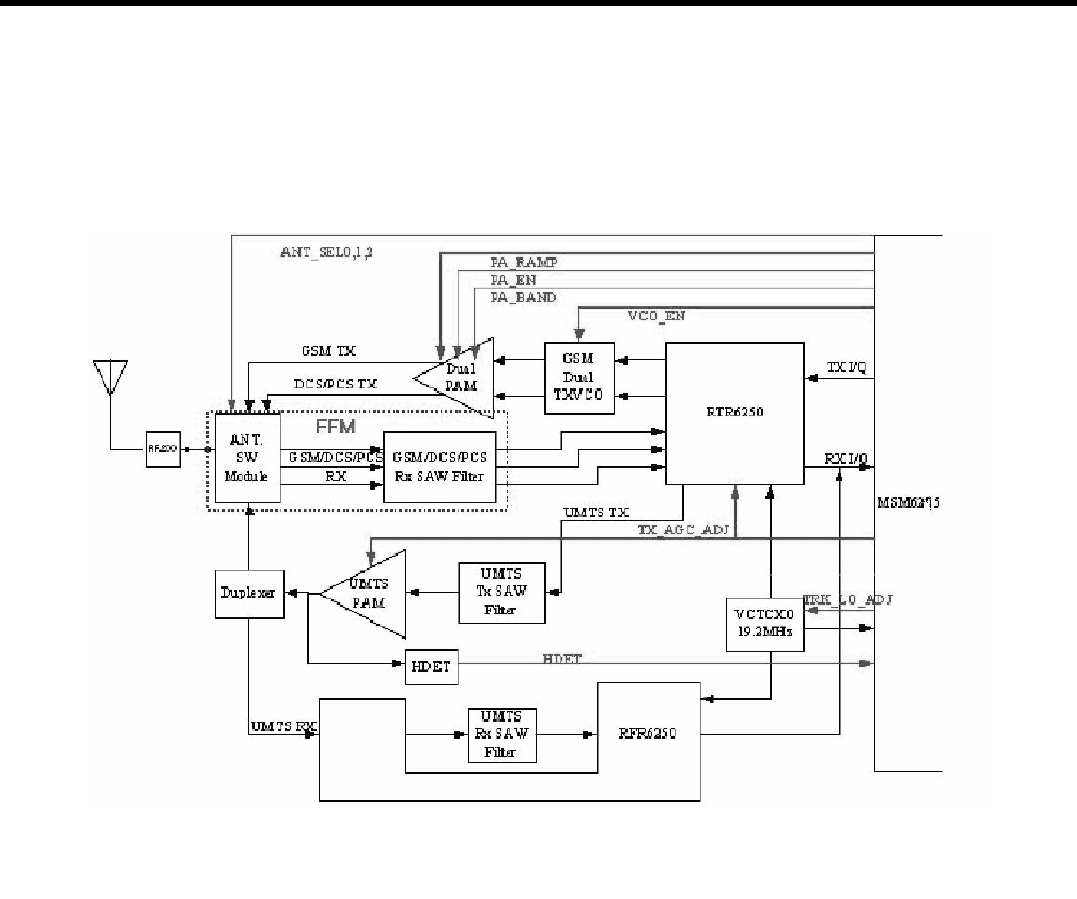

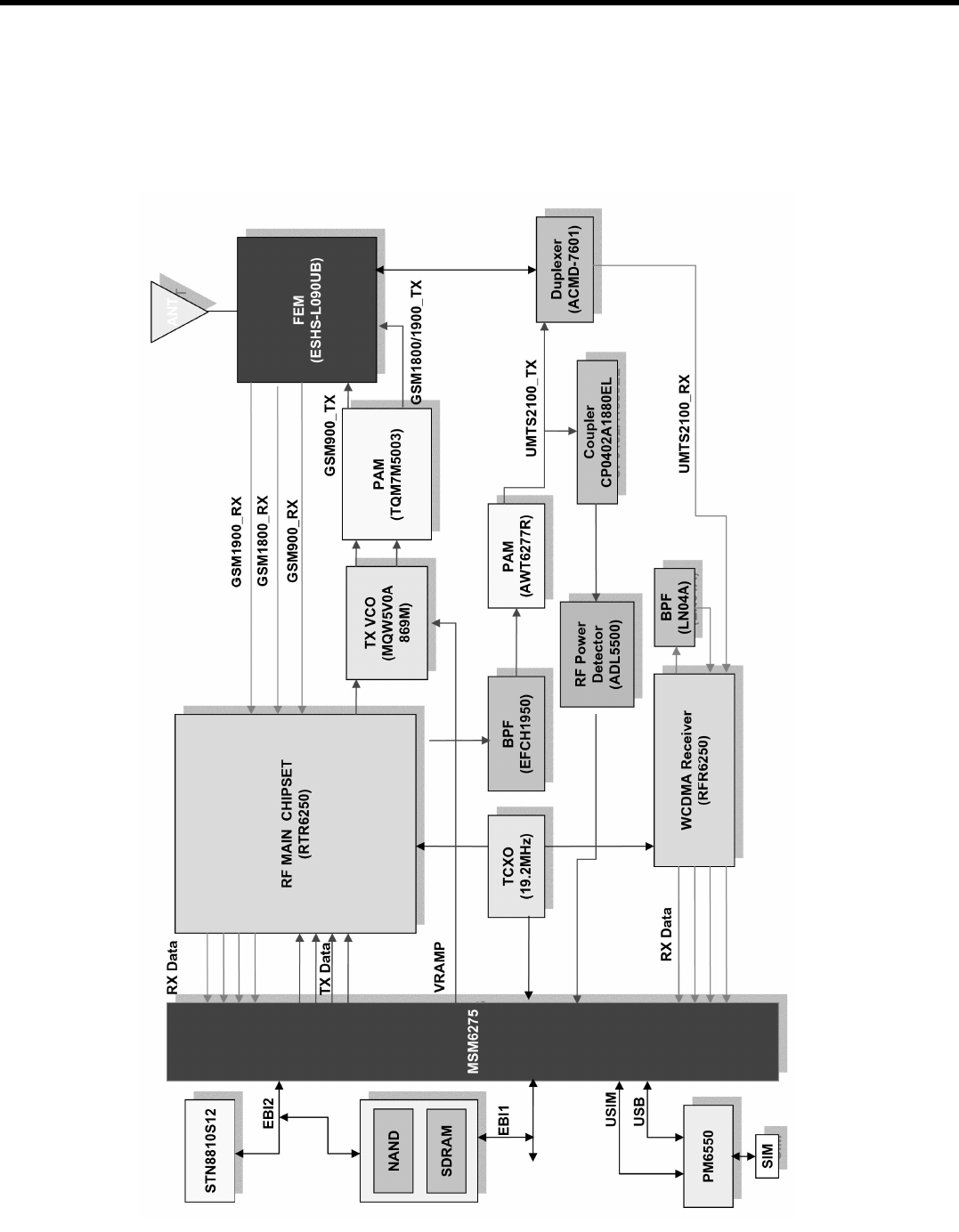

6.1 GSM & WCDMA RF Block.......................178

6.2 Interface Diagram ....................................180

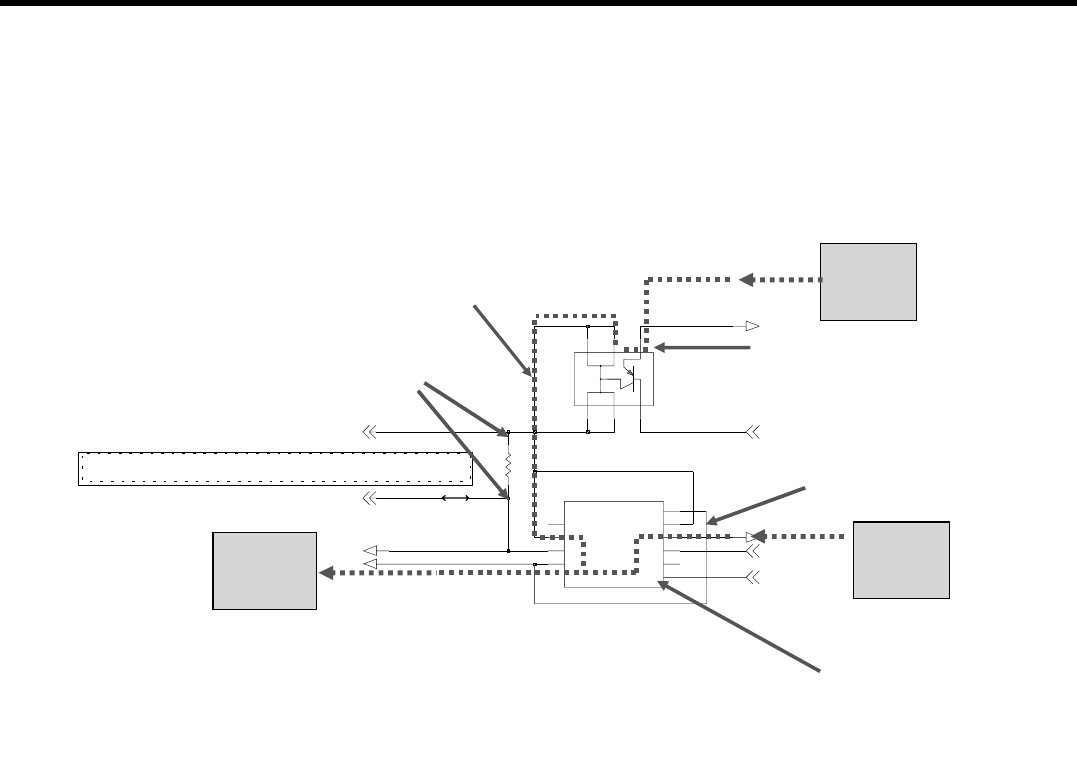

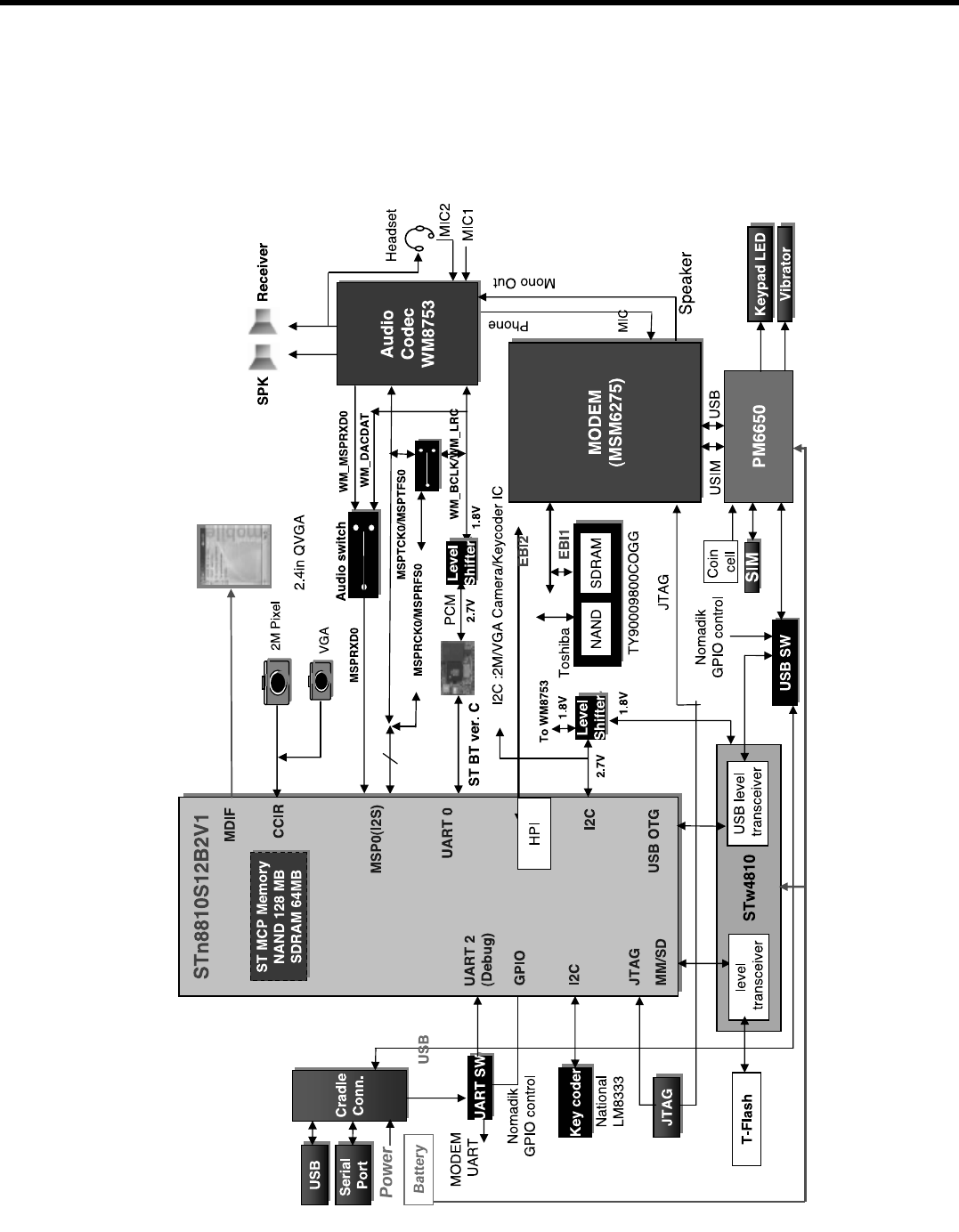

6.3 KS10 Modem & Baseband

Block Diagram .........................................184

6.4 KS10 Application Processor Block

Diagram ...................................................185

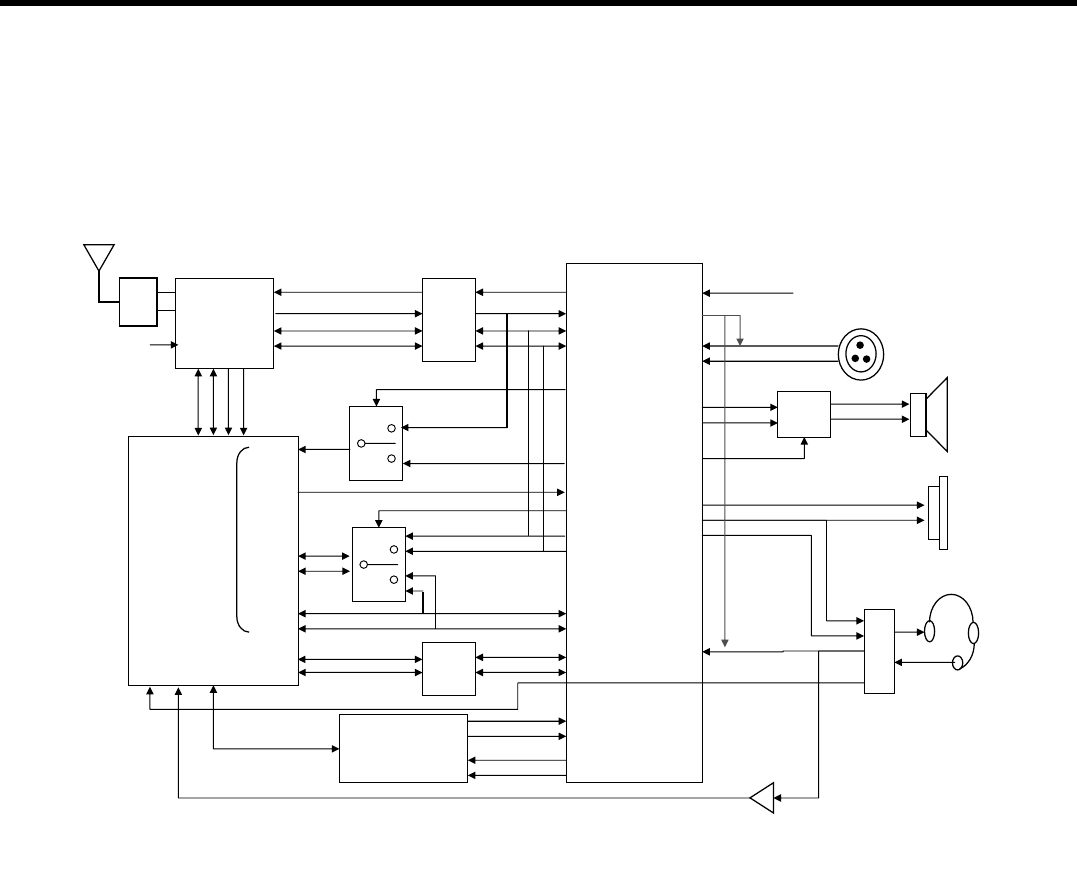

6.5 KS10 Audio & BT Block Diagram ............186

Table Of Contents

LGE Internal Use Only

Copyright © 2007 LG Electronics. Inc. All right reserved.

Only for training and service purposes

- 4 -

6.6 KS10 Camera Block Diagram .................187

6.7 KS10 LCD Block Diagram ......................188

6.8 KS10 Power Distribution Diagram ...........189

6.9 KS10 Clock Distribution Diagram ...........190

7. Circuit Diagram................................177

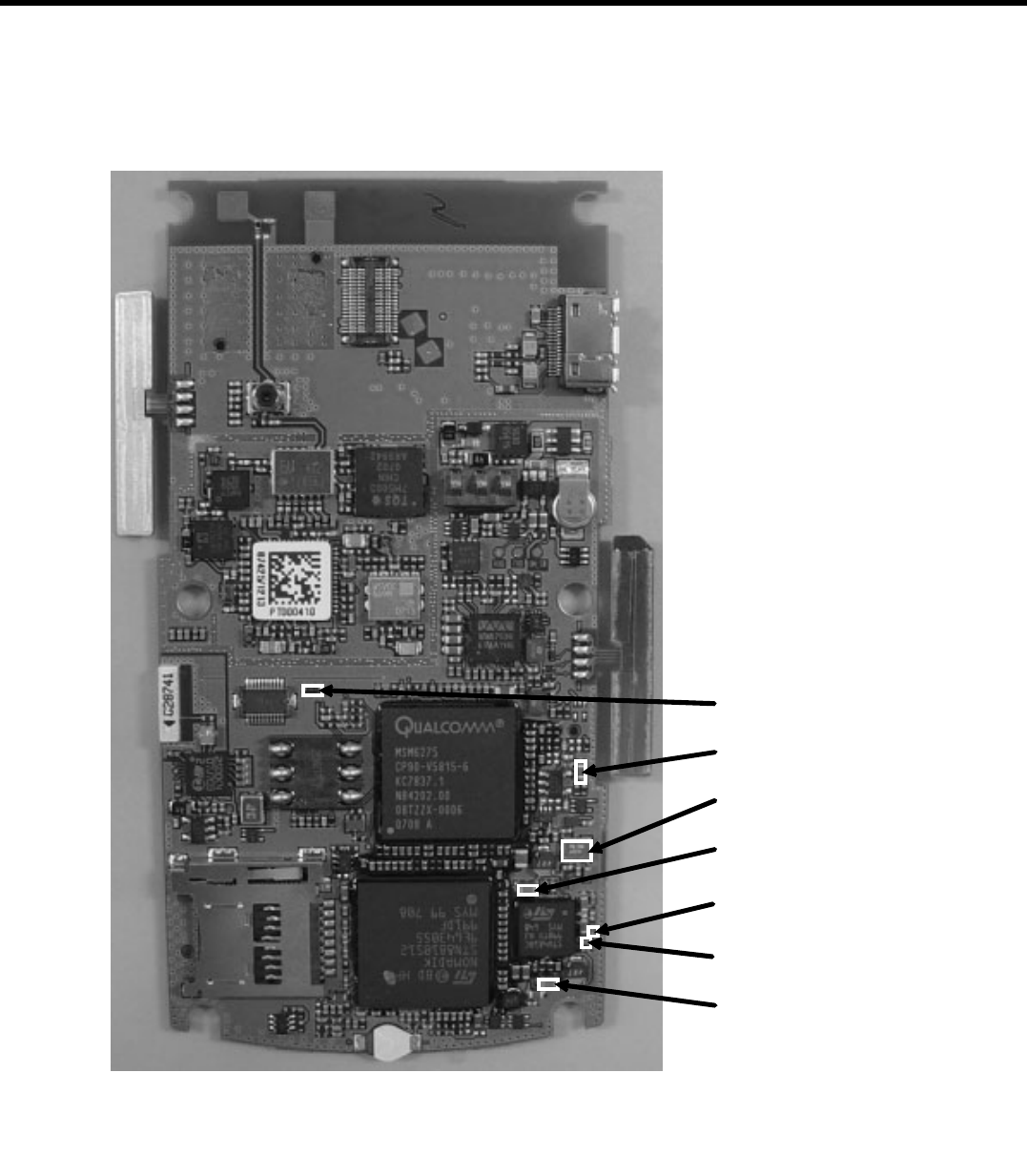

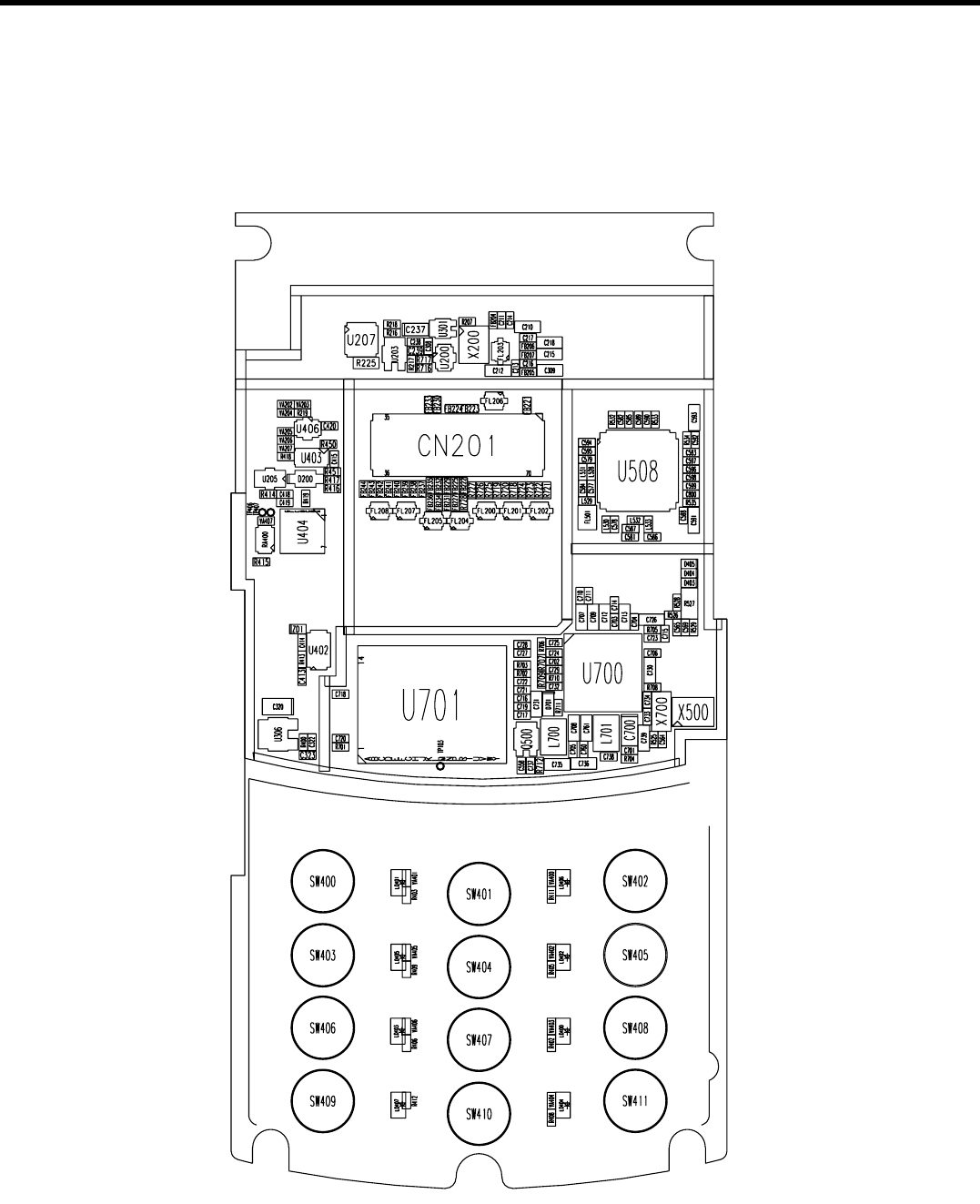

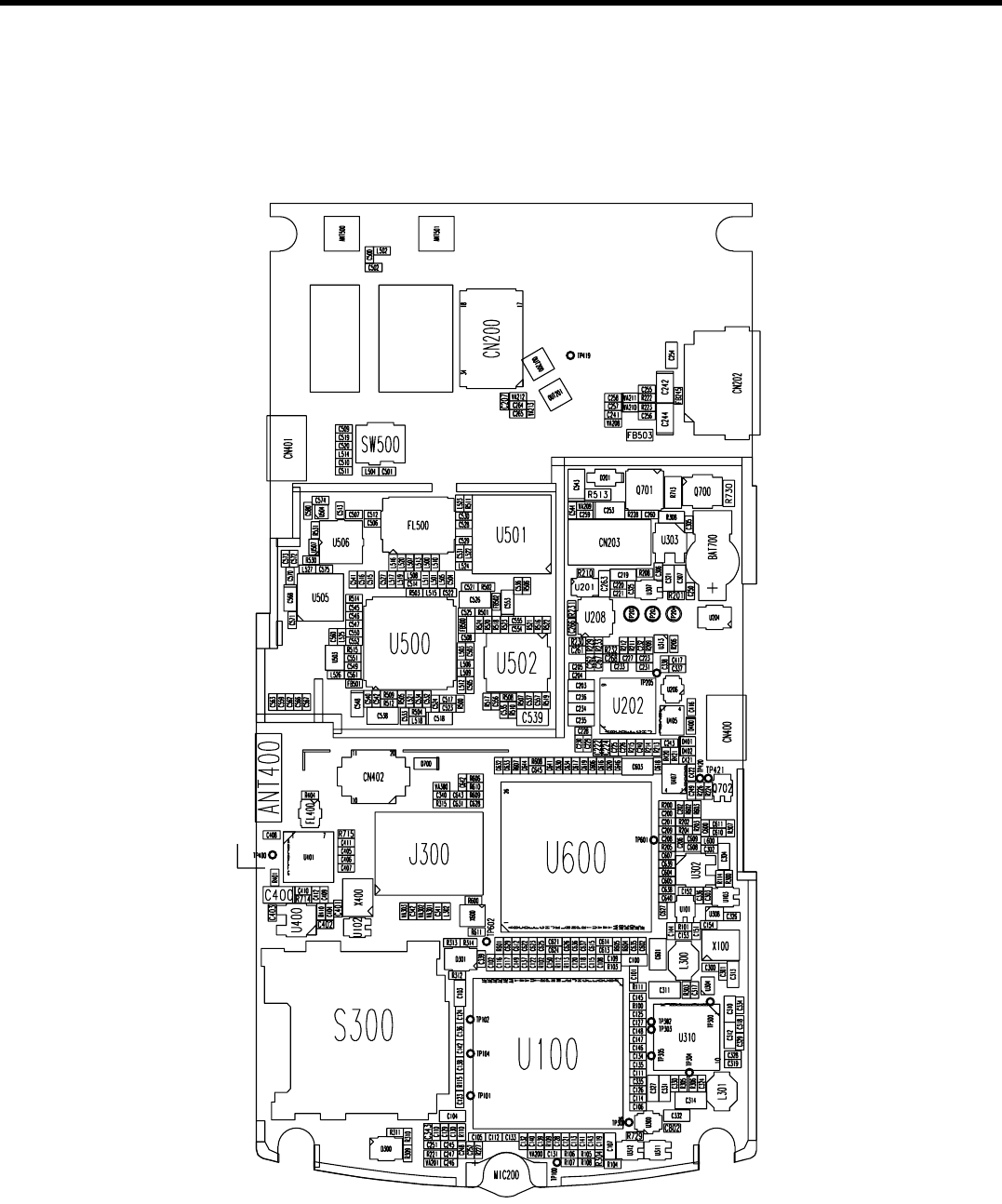

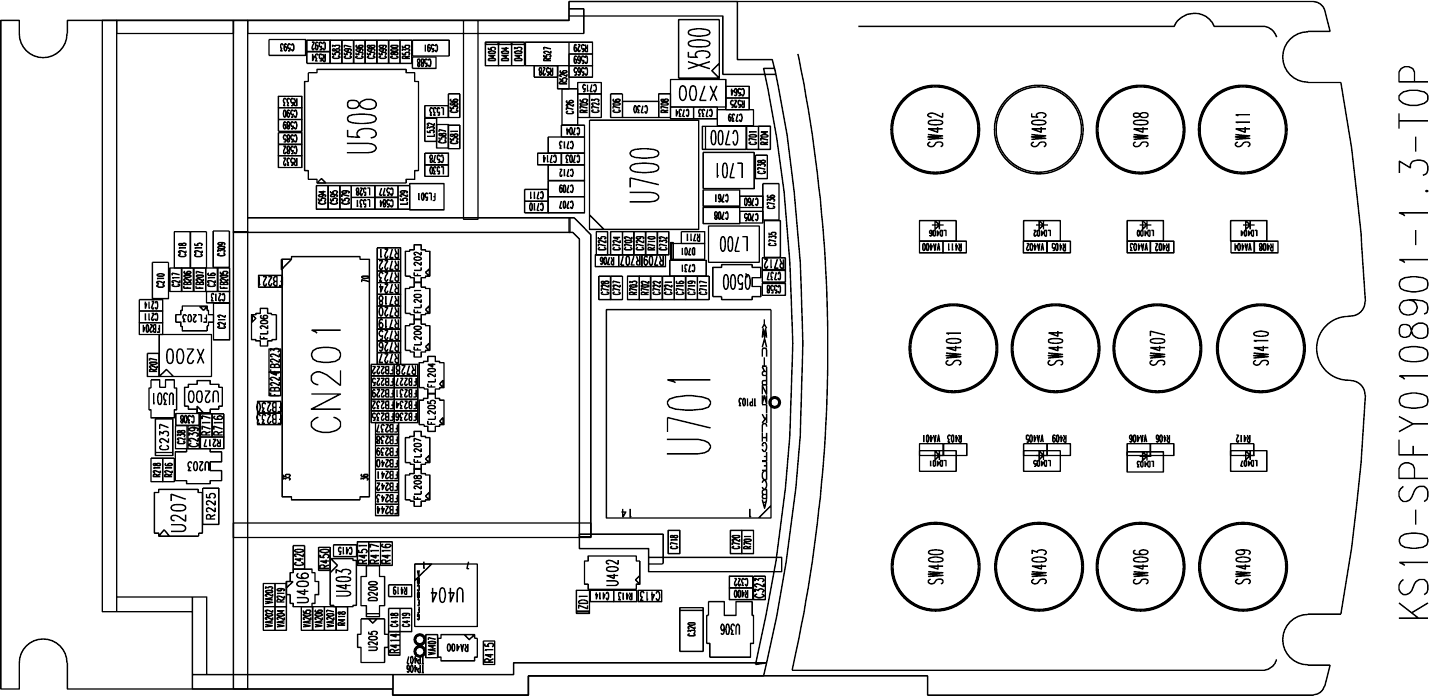

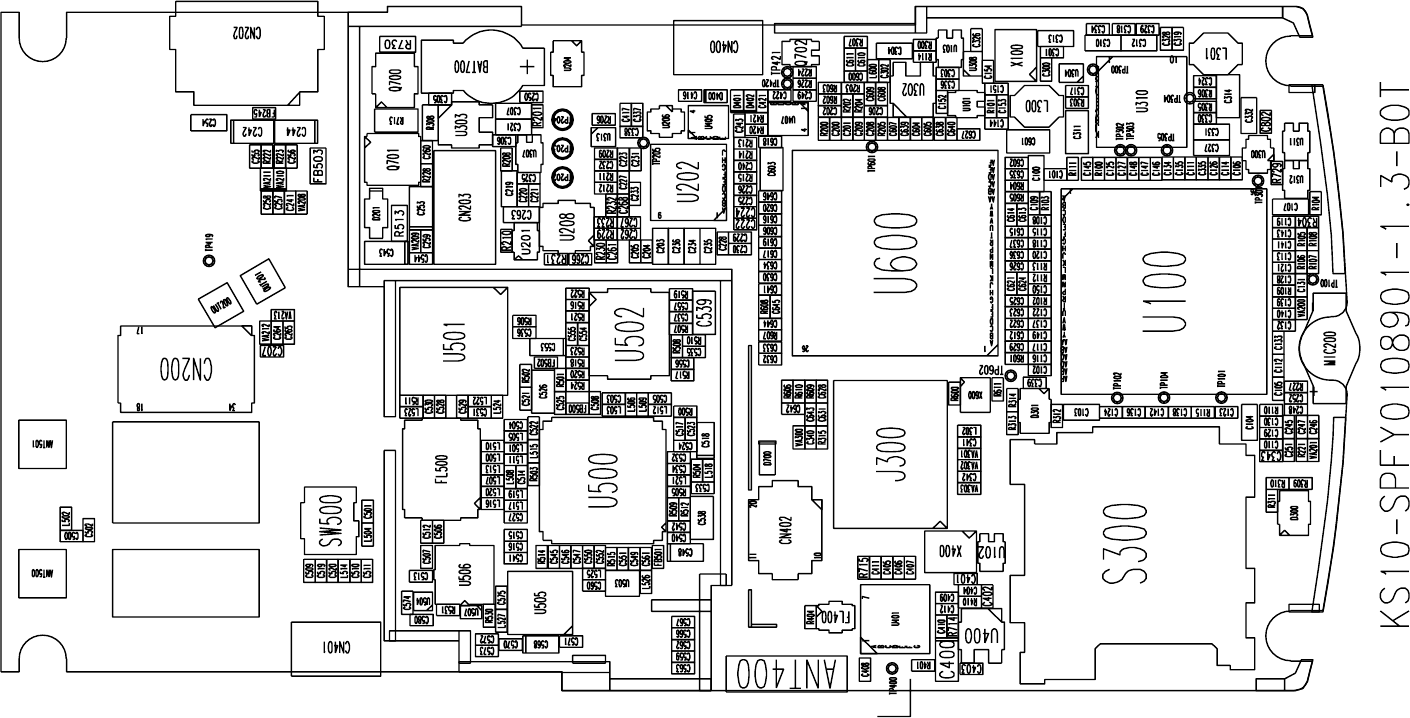

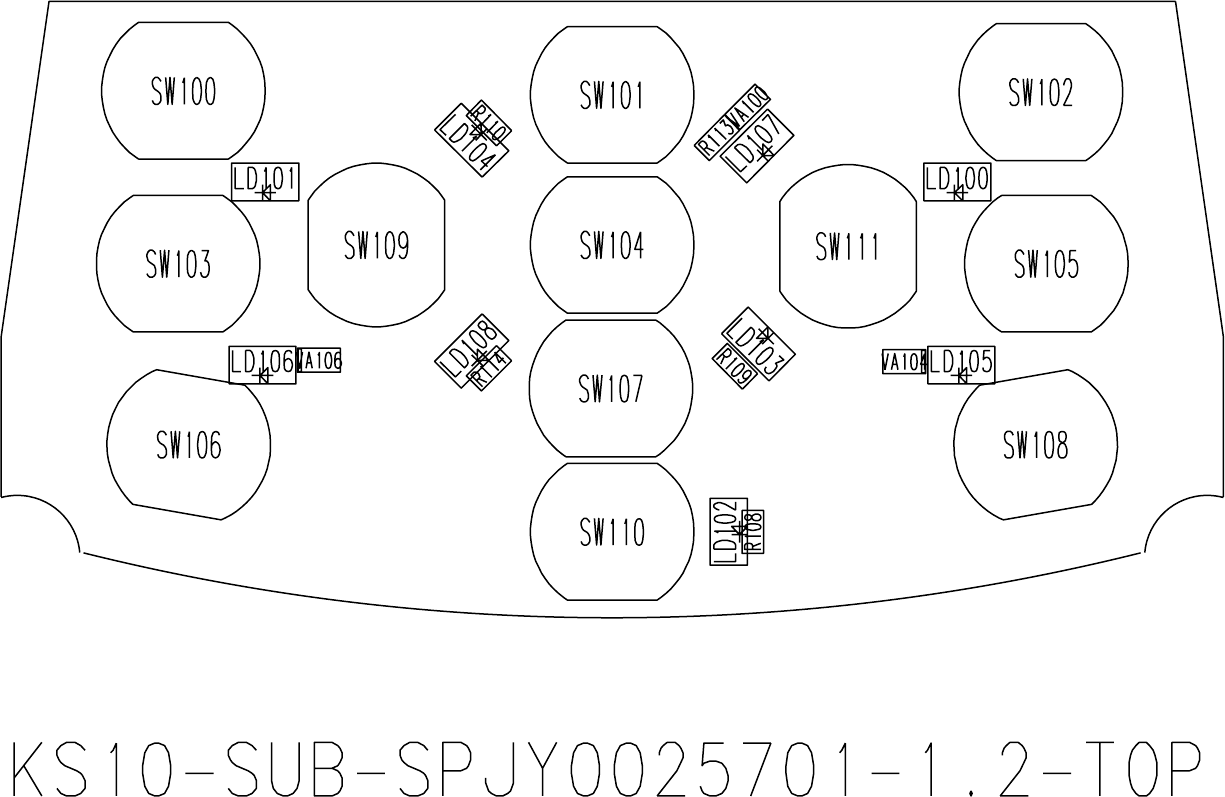

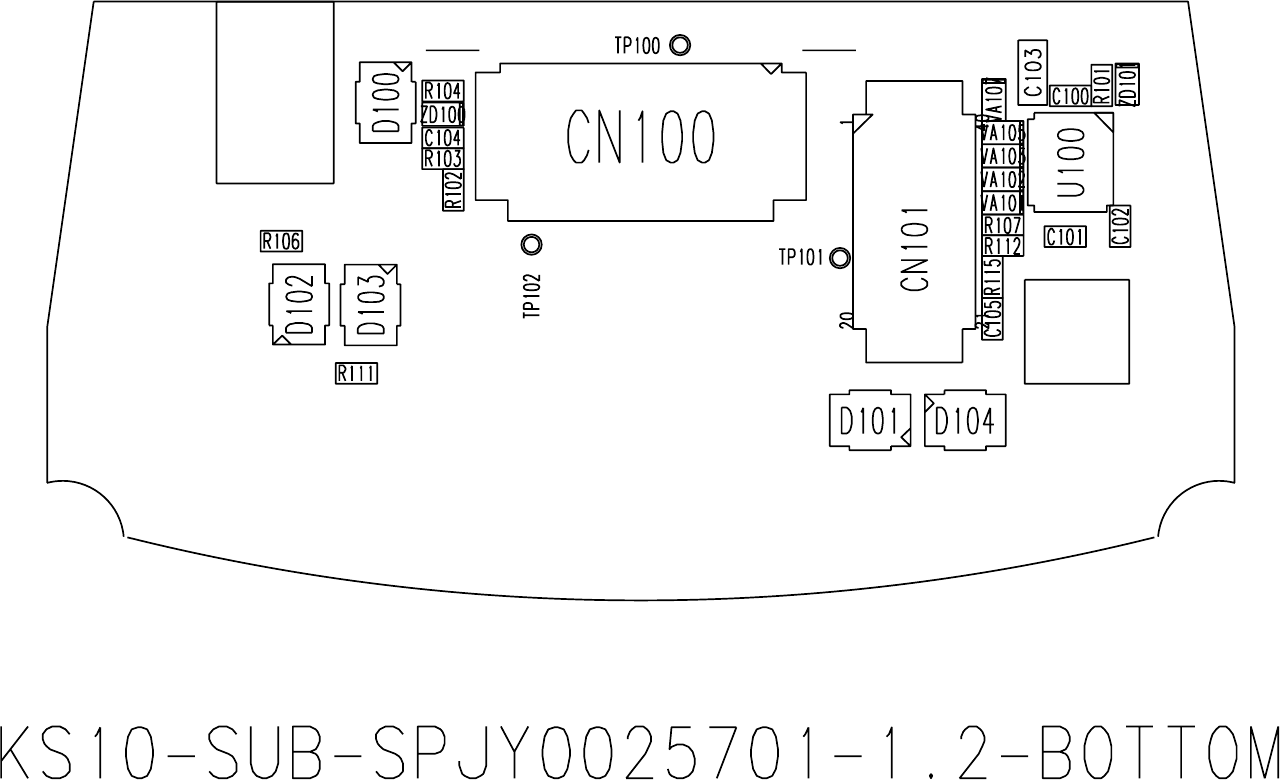

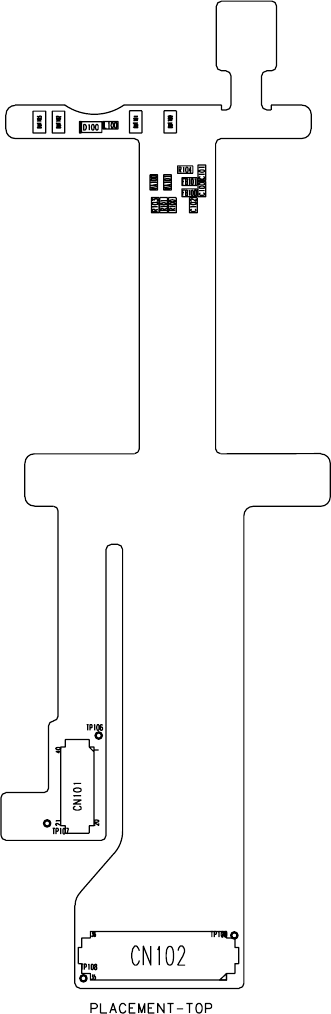

8. PCB LAYOUT ...................................202

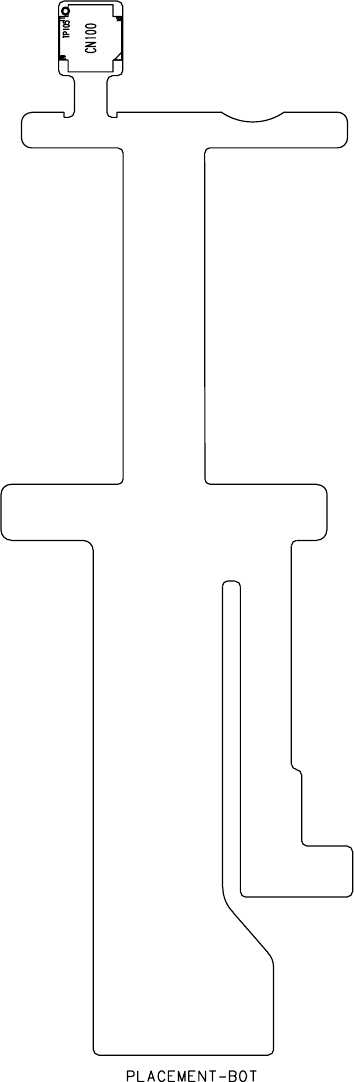

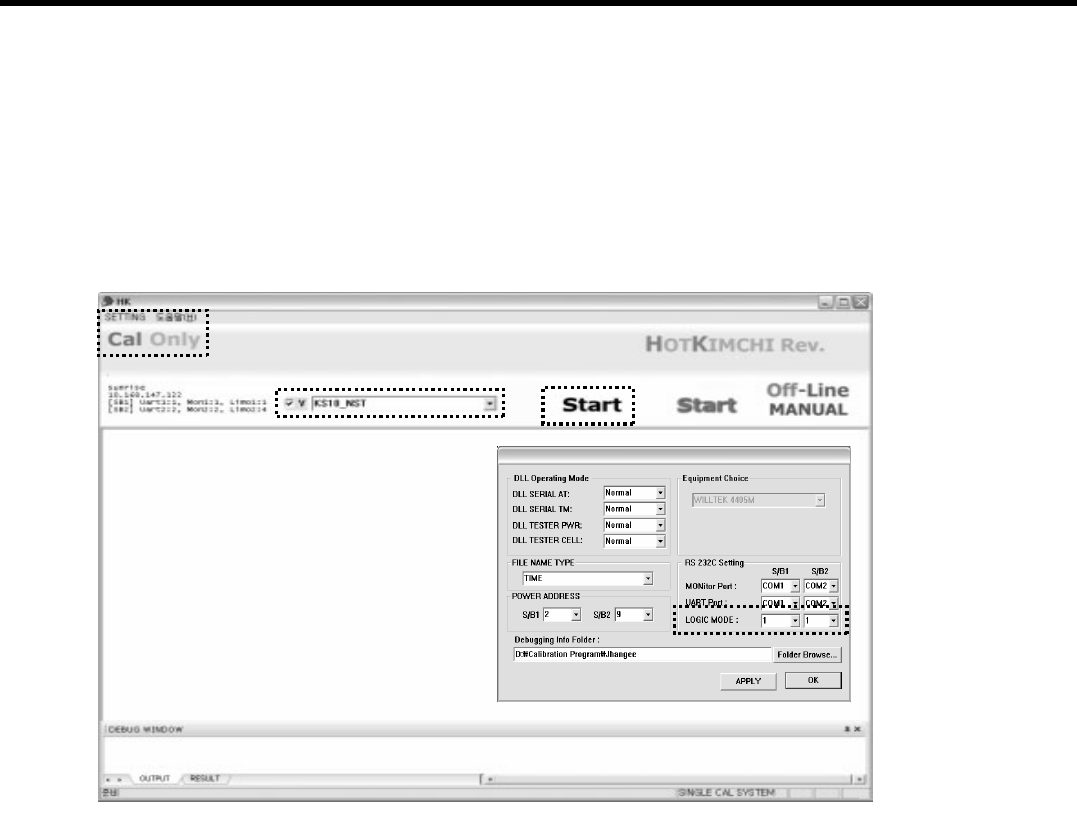

9. Usage of Hot-Kimchi .......................209

9.1 Usage of Hot-Kimchi................................195

10. Engineering Mode .........................212

10.1 Version Info............................................213

10.2 Device Test............................................213

10.3 Factory Reset ........................................214

10.4 MTC .......................................................214

10.5 Save Log................................................214

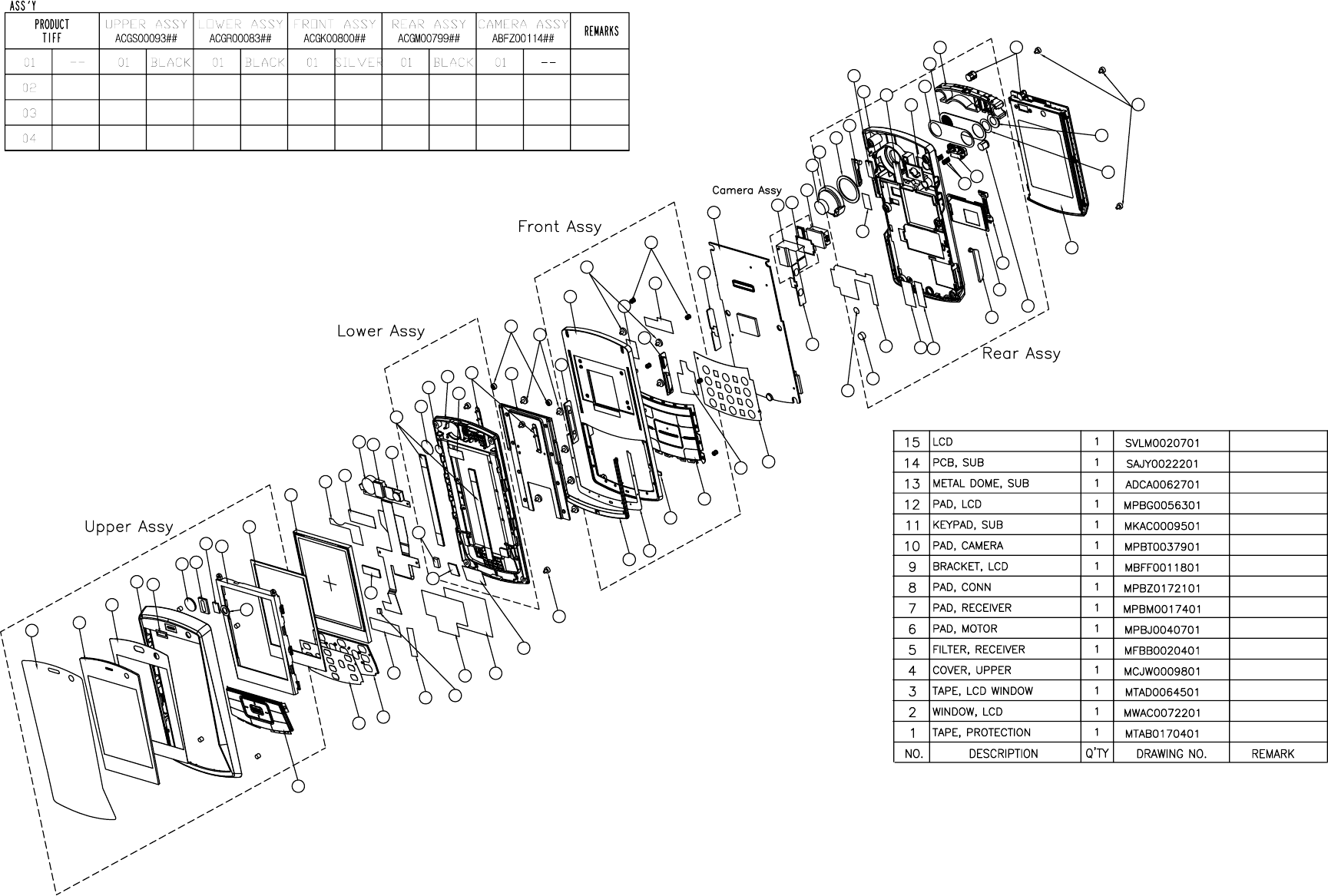

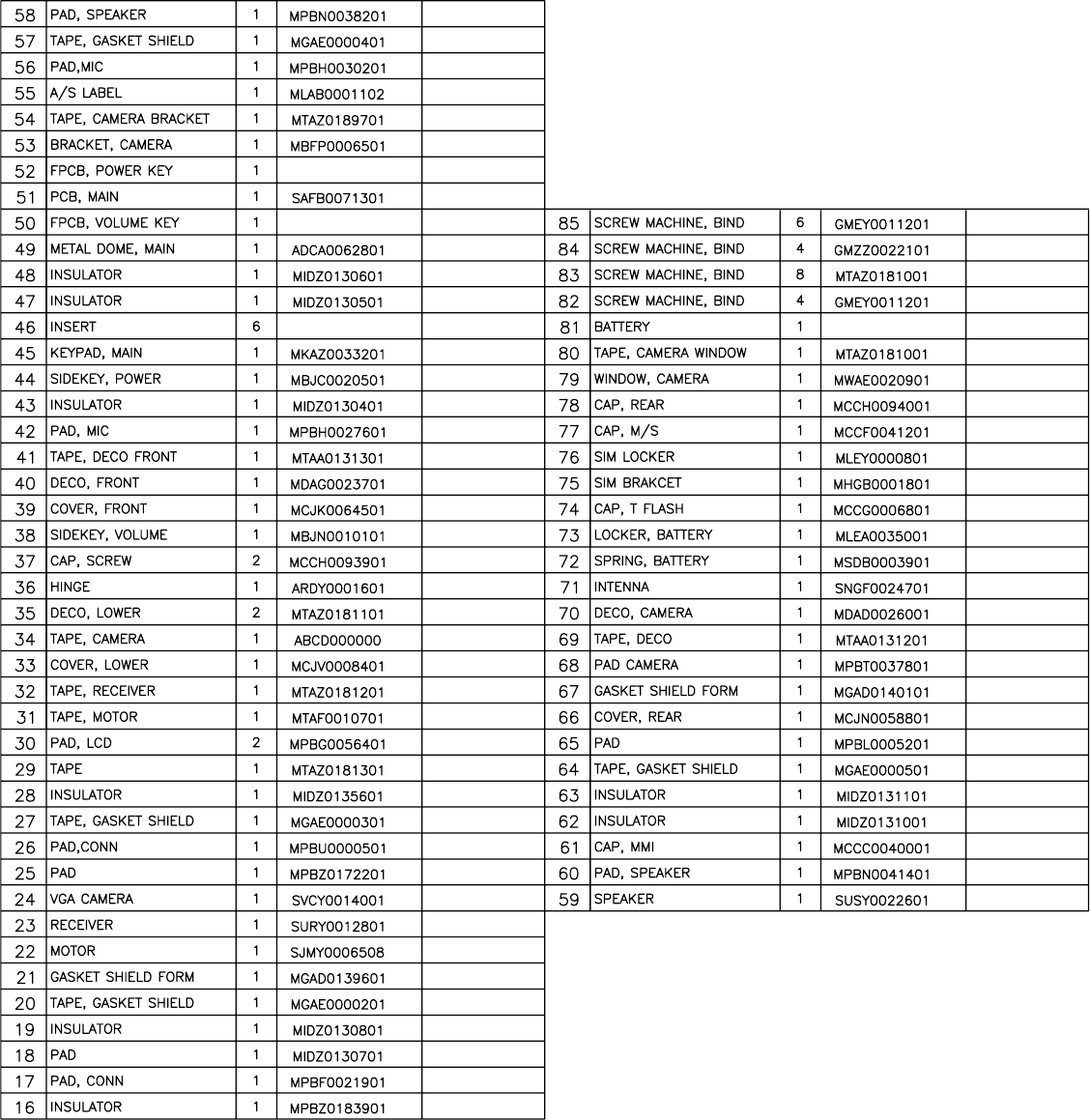

11. EXPLODED VIEW & REPLACEMENT

PART LIST ..................................... 216

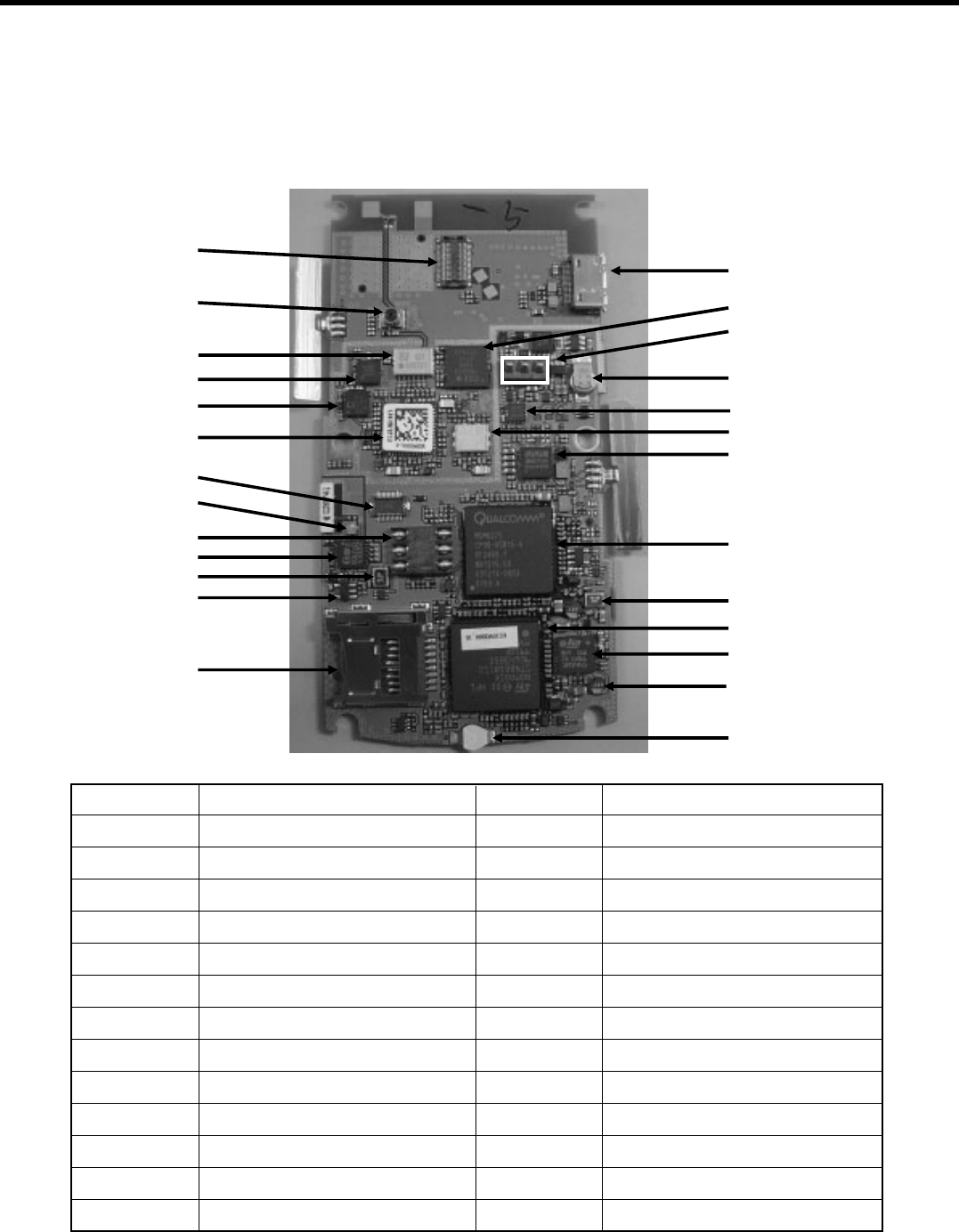

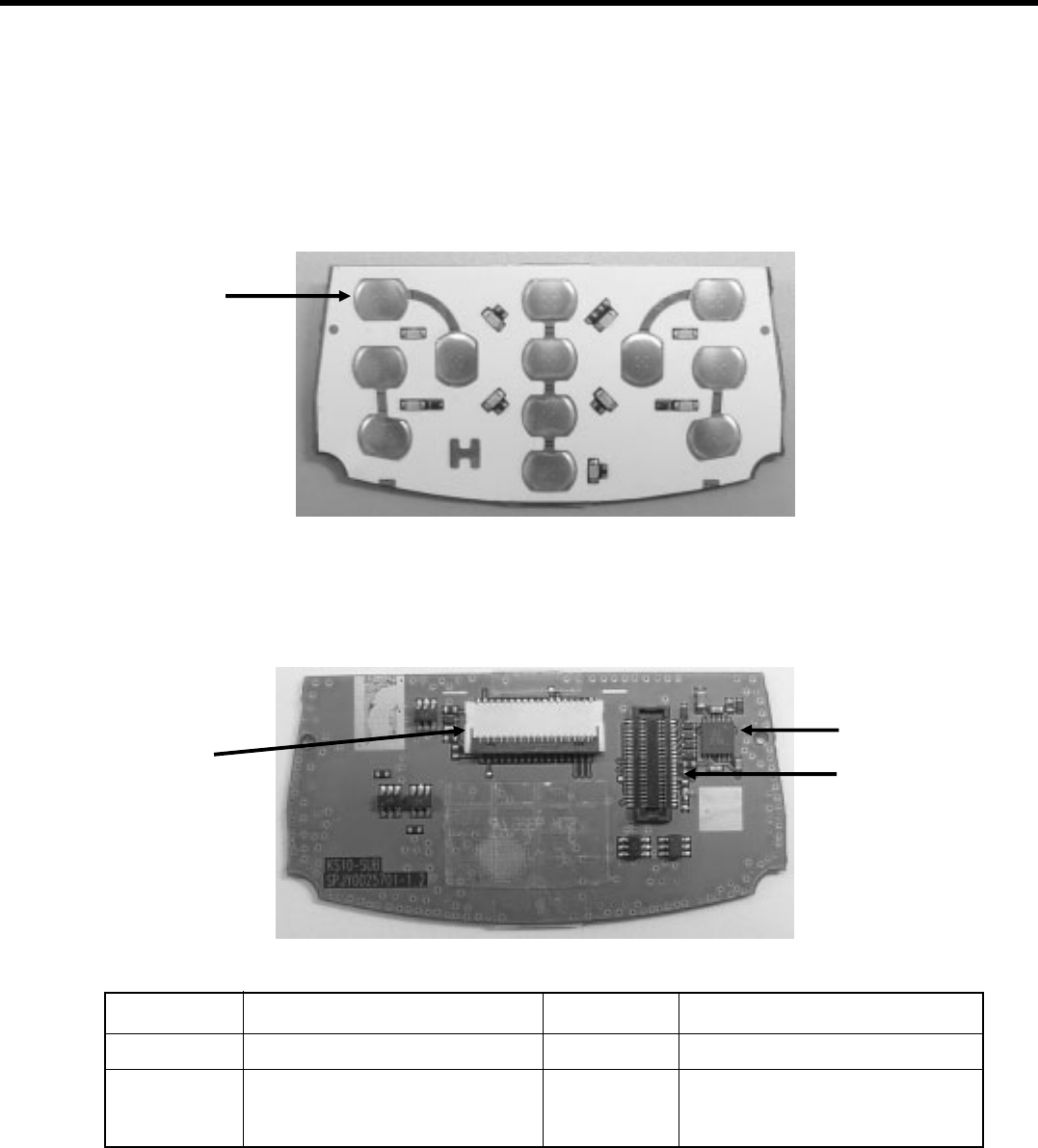

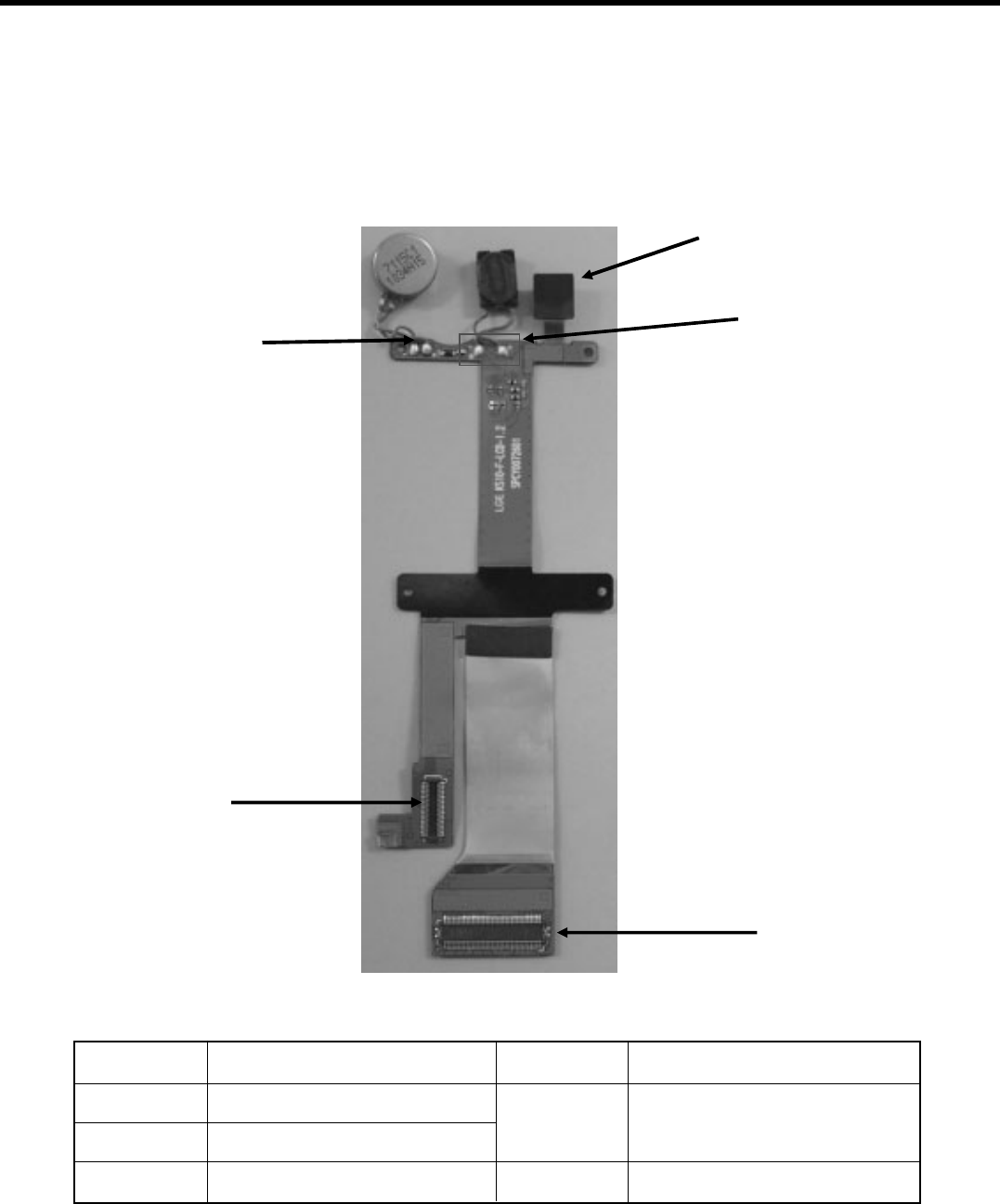

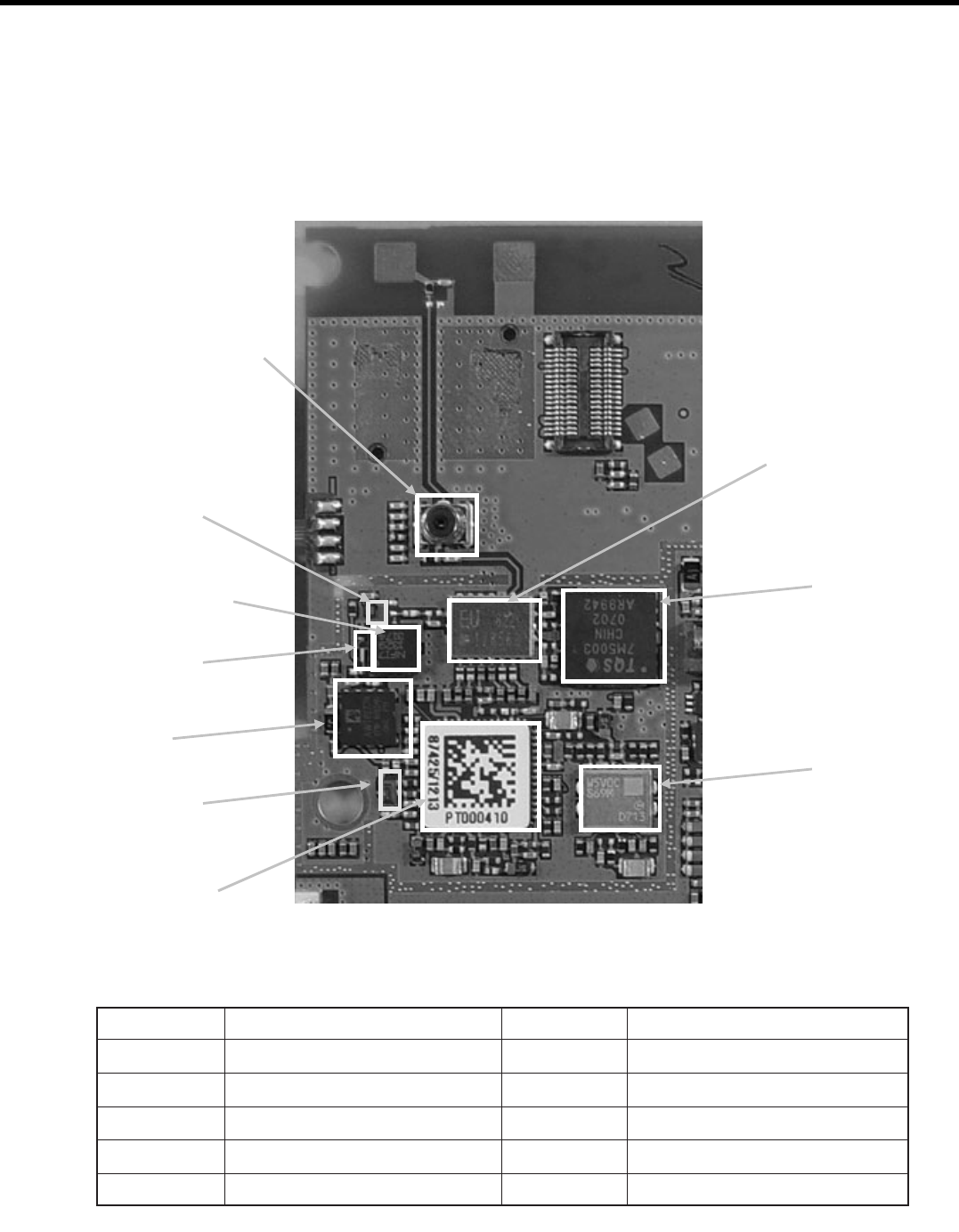

10.1 EXPLODED VIEW ................................ 216

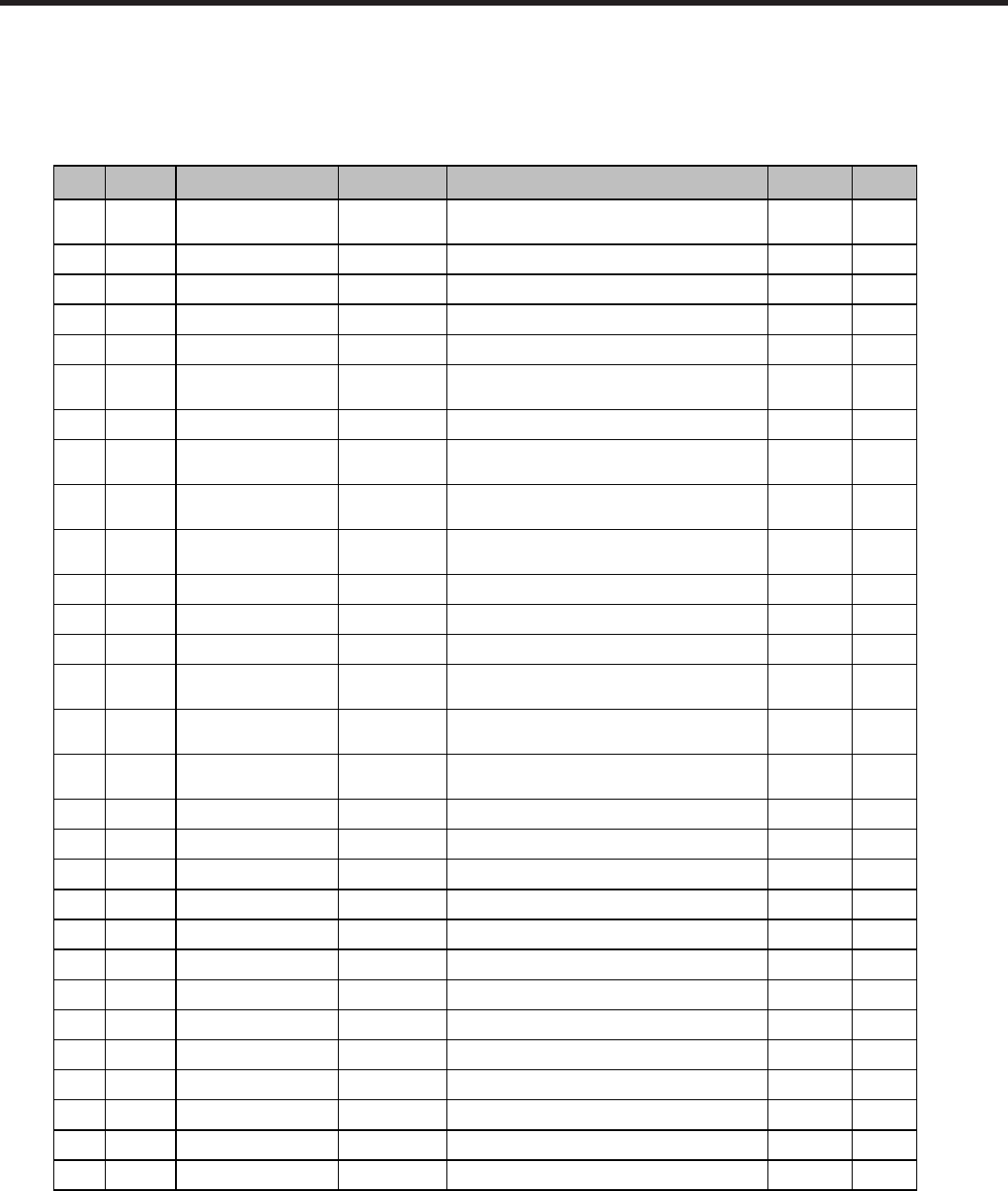

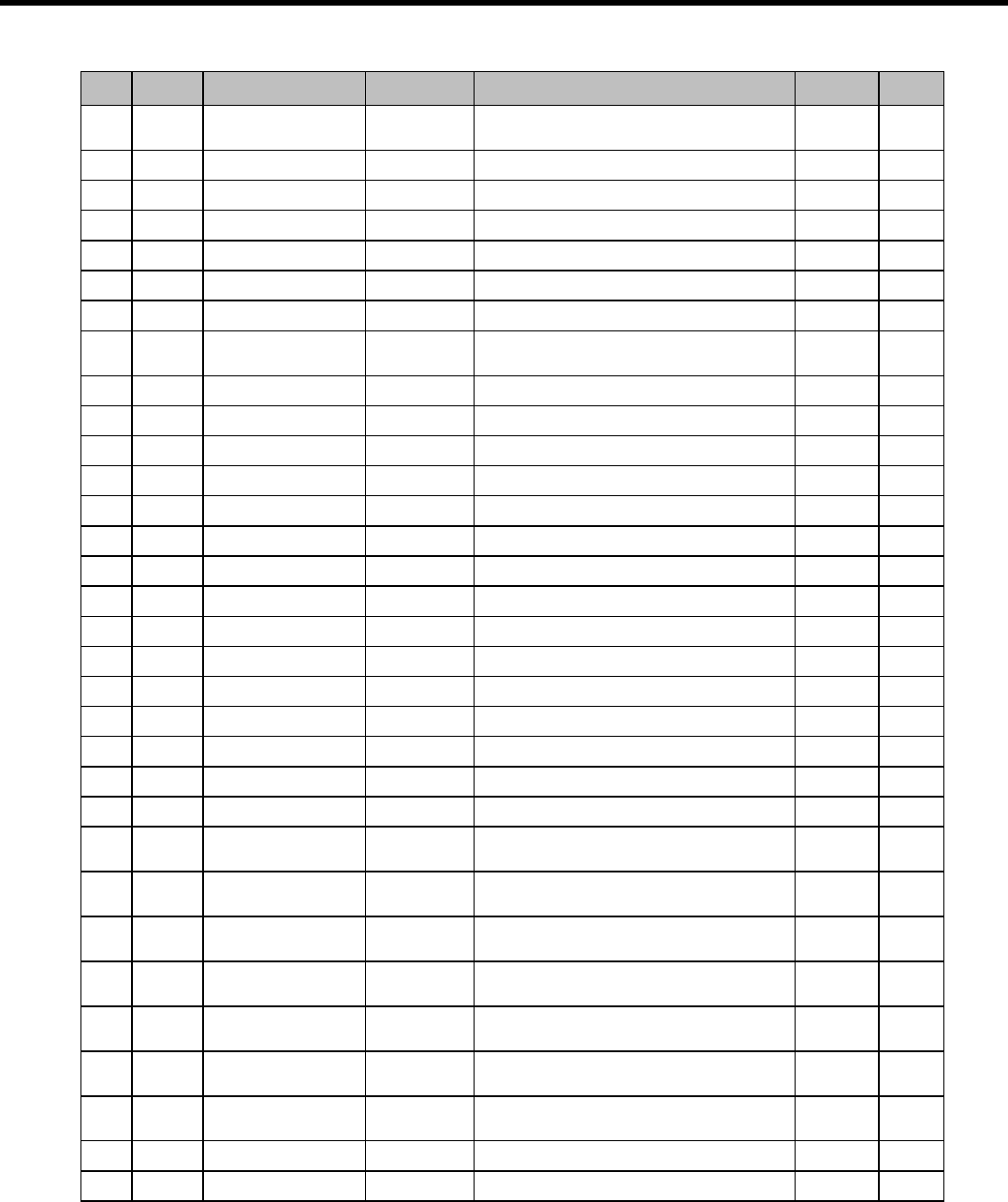

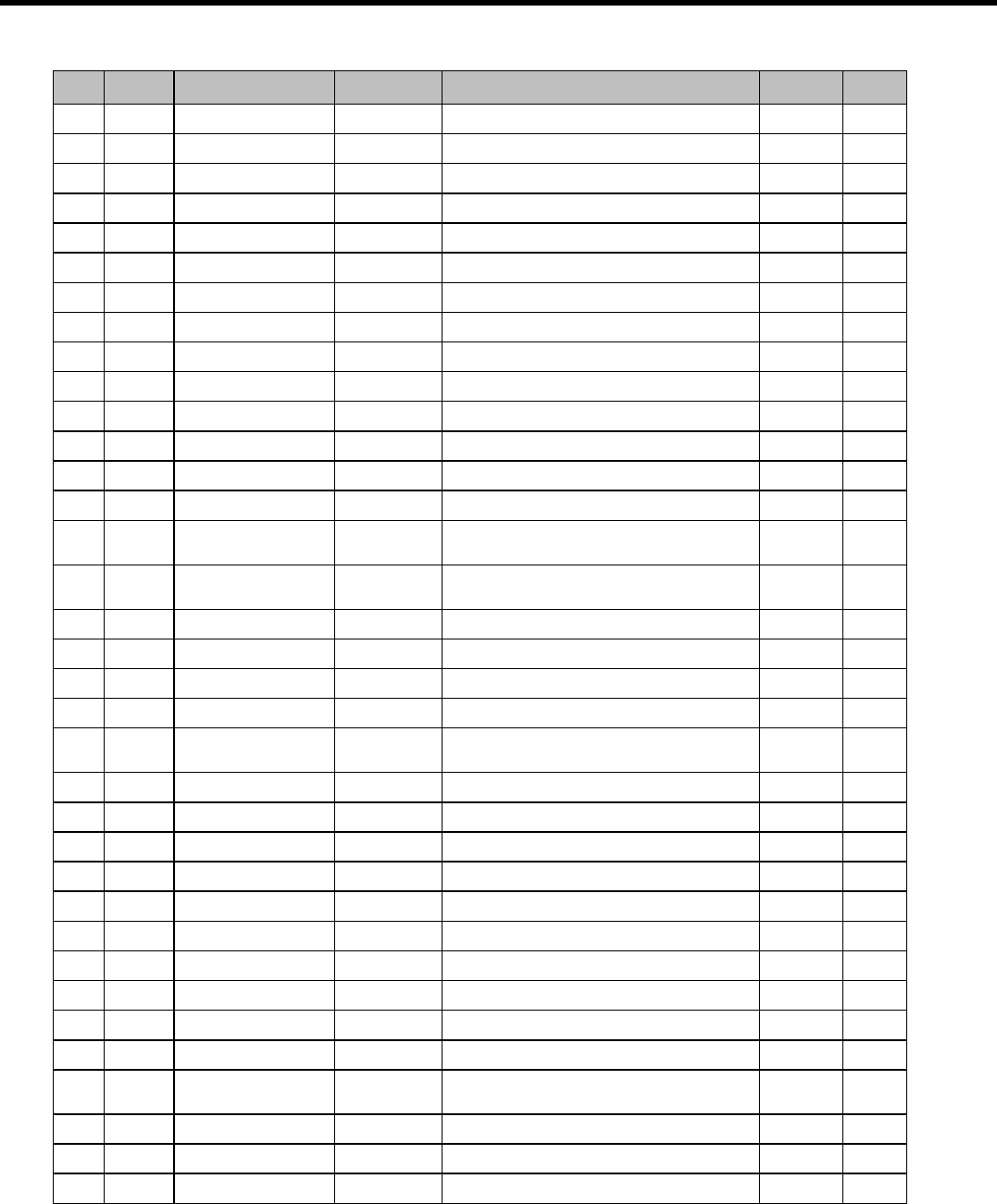

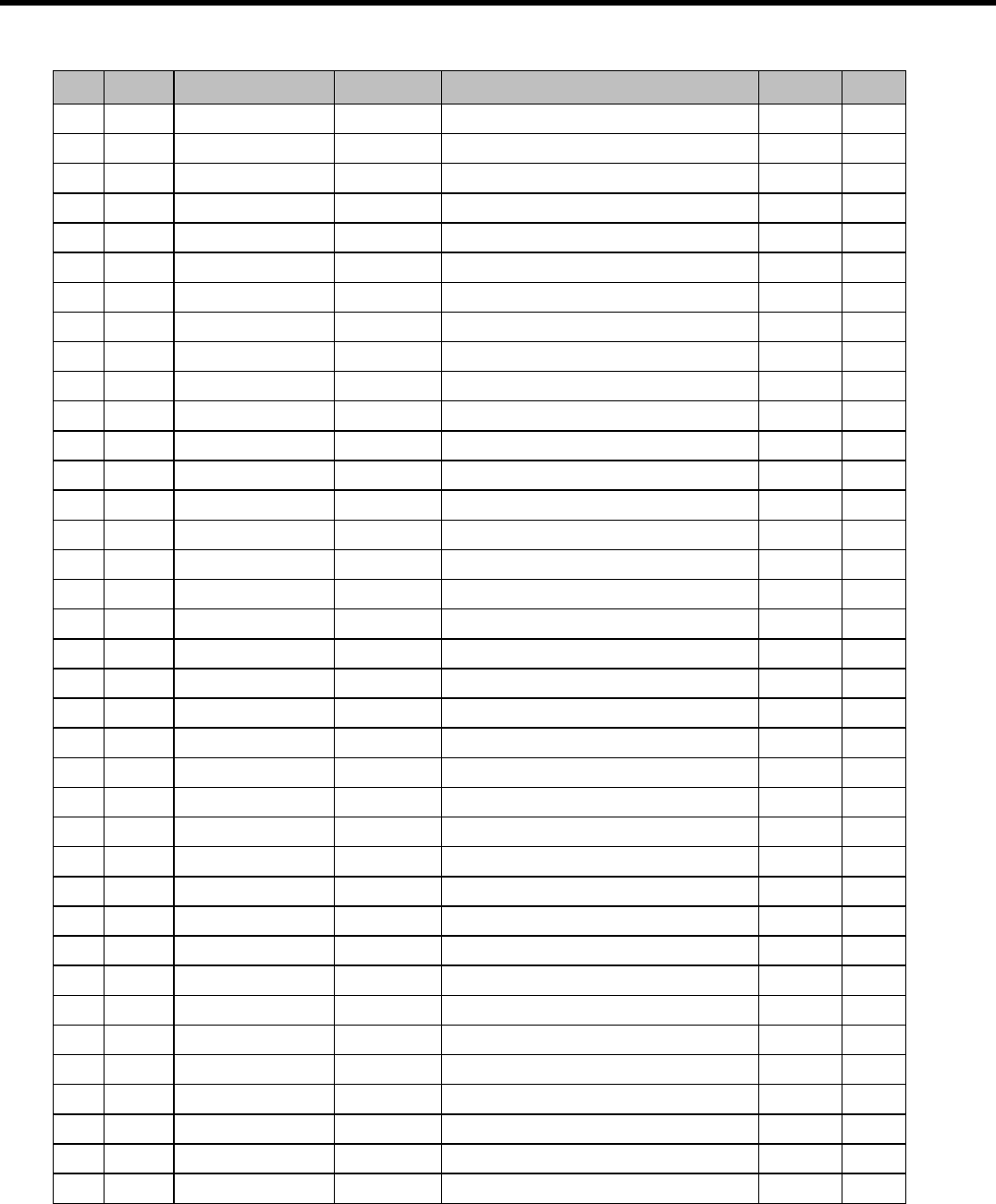

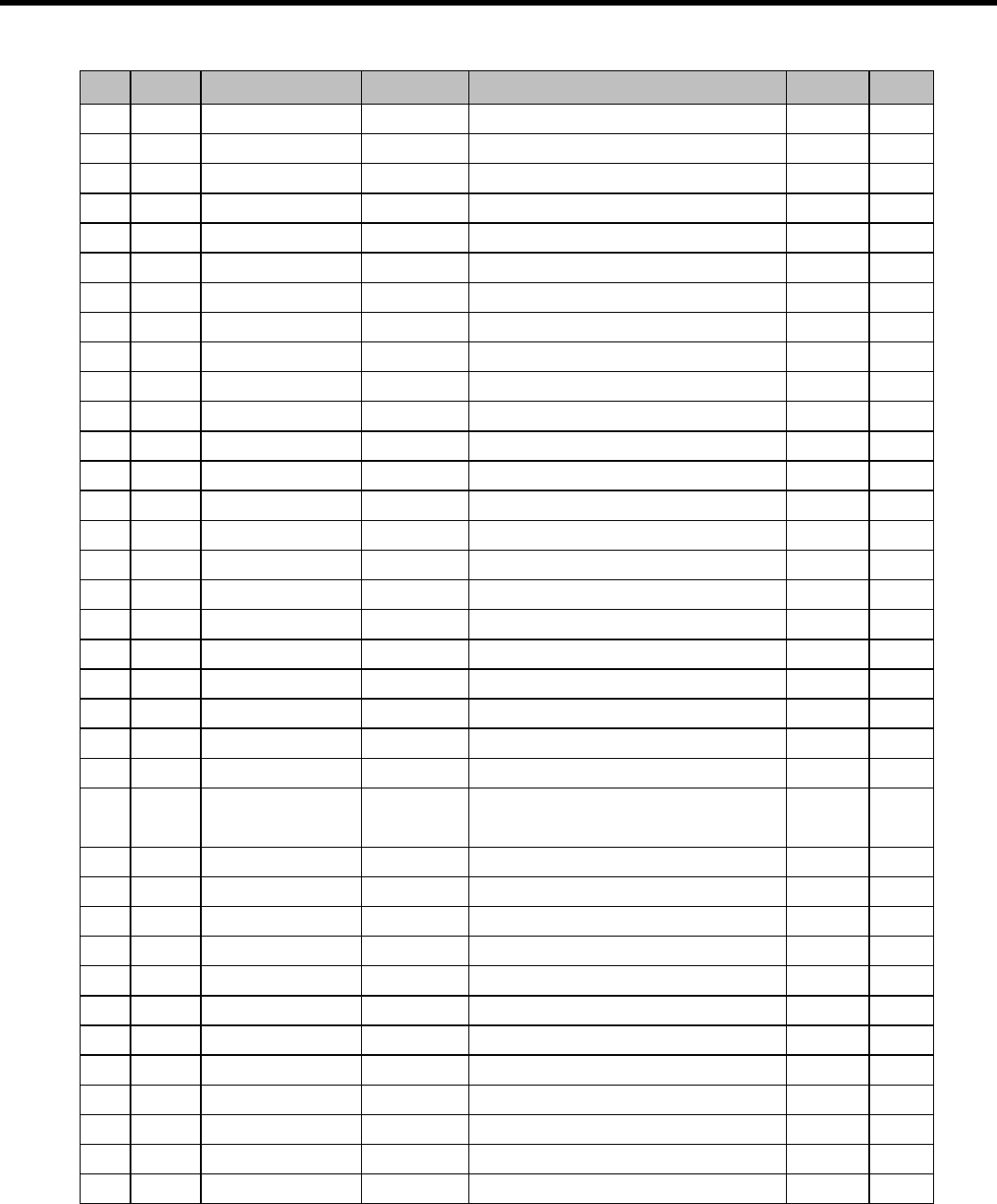

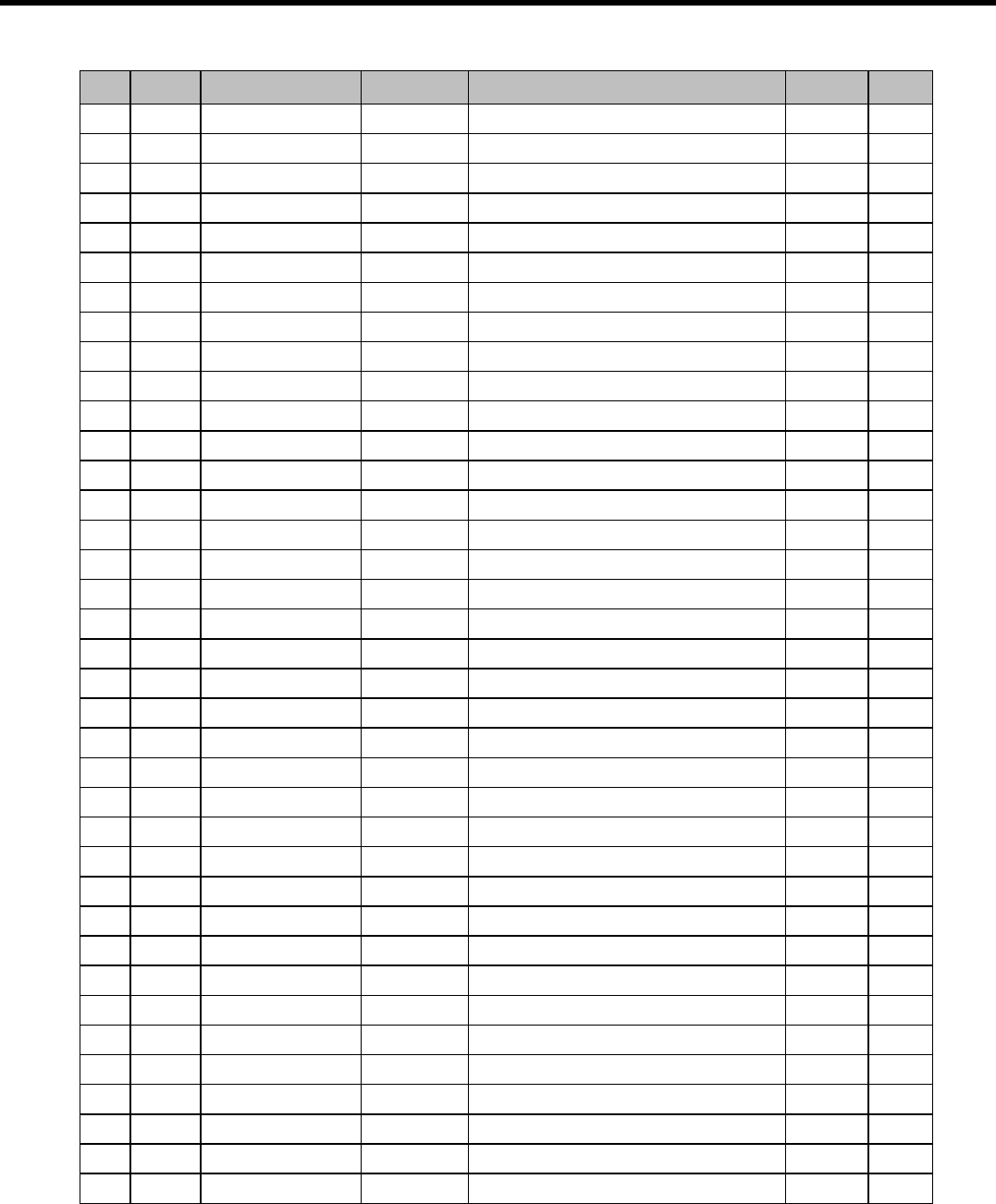

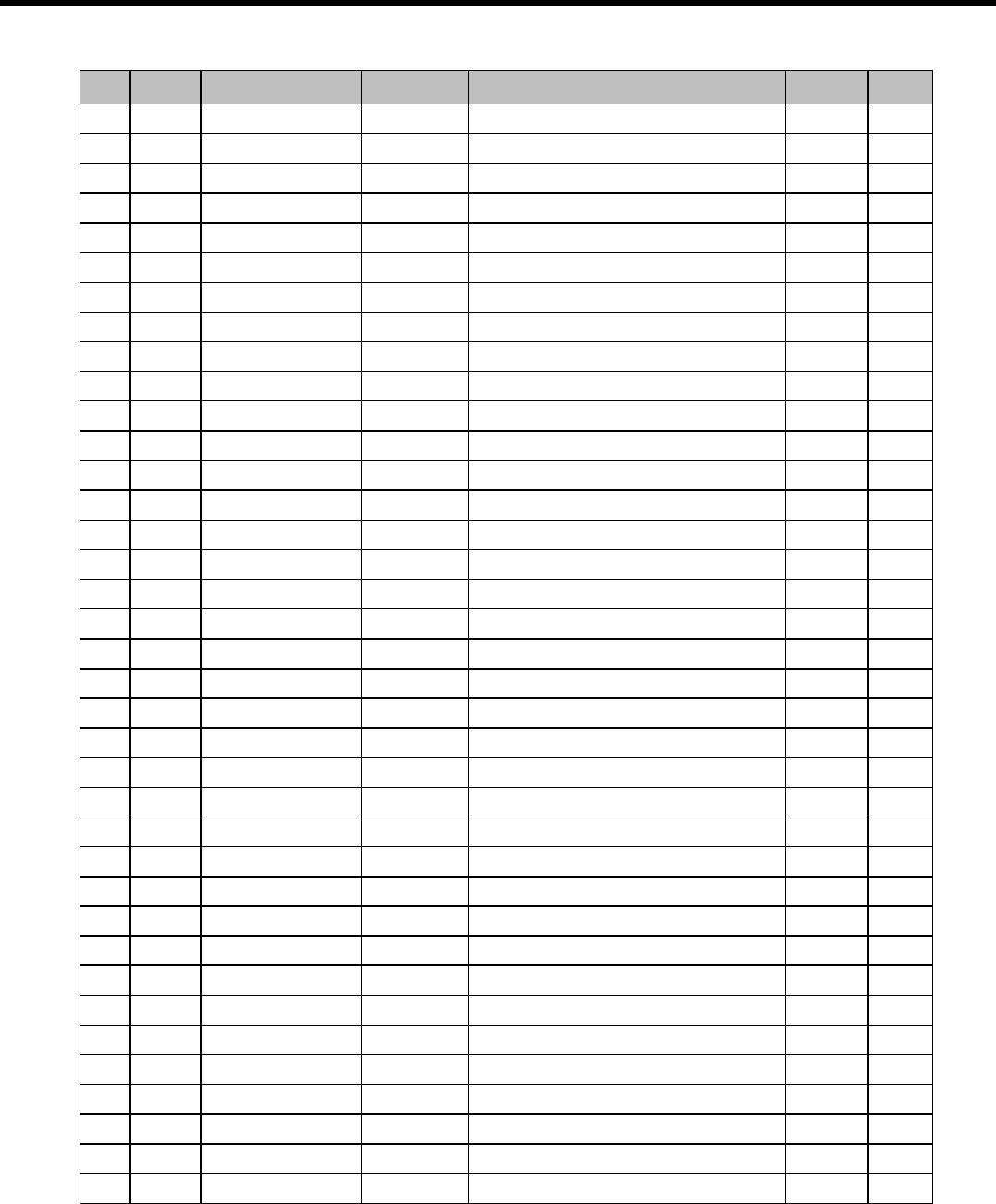

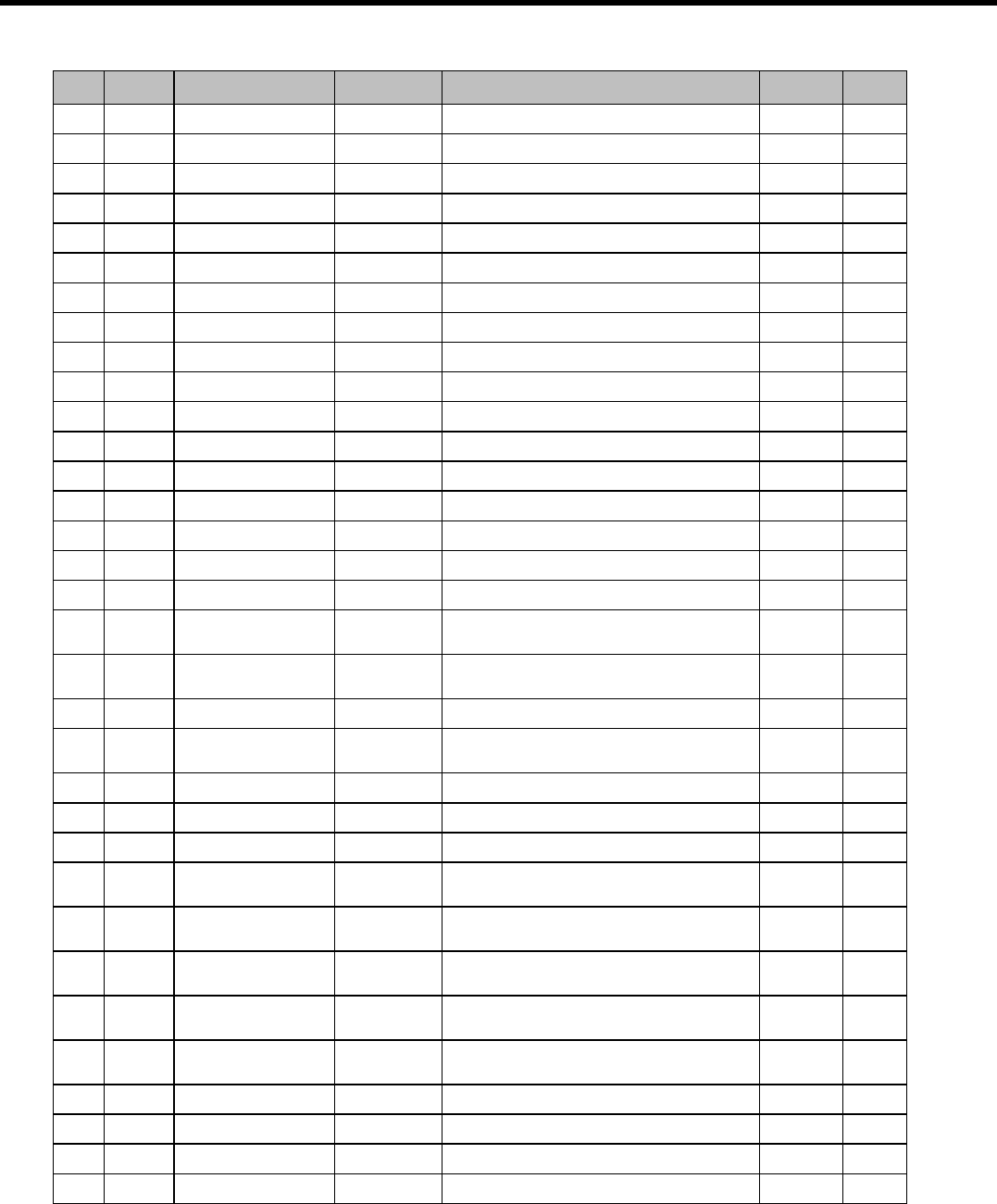

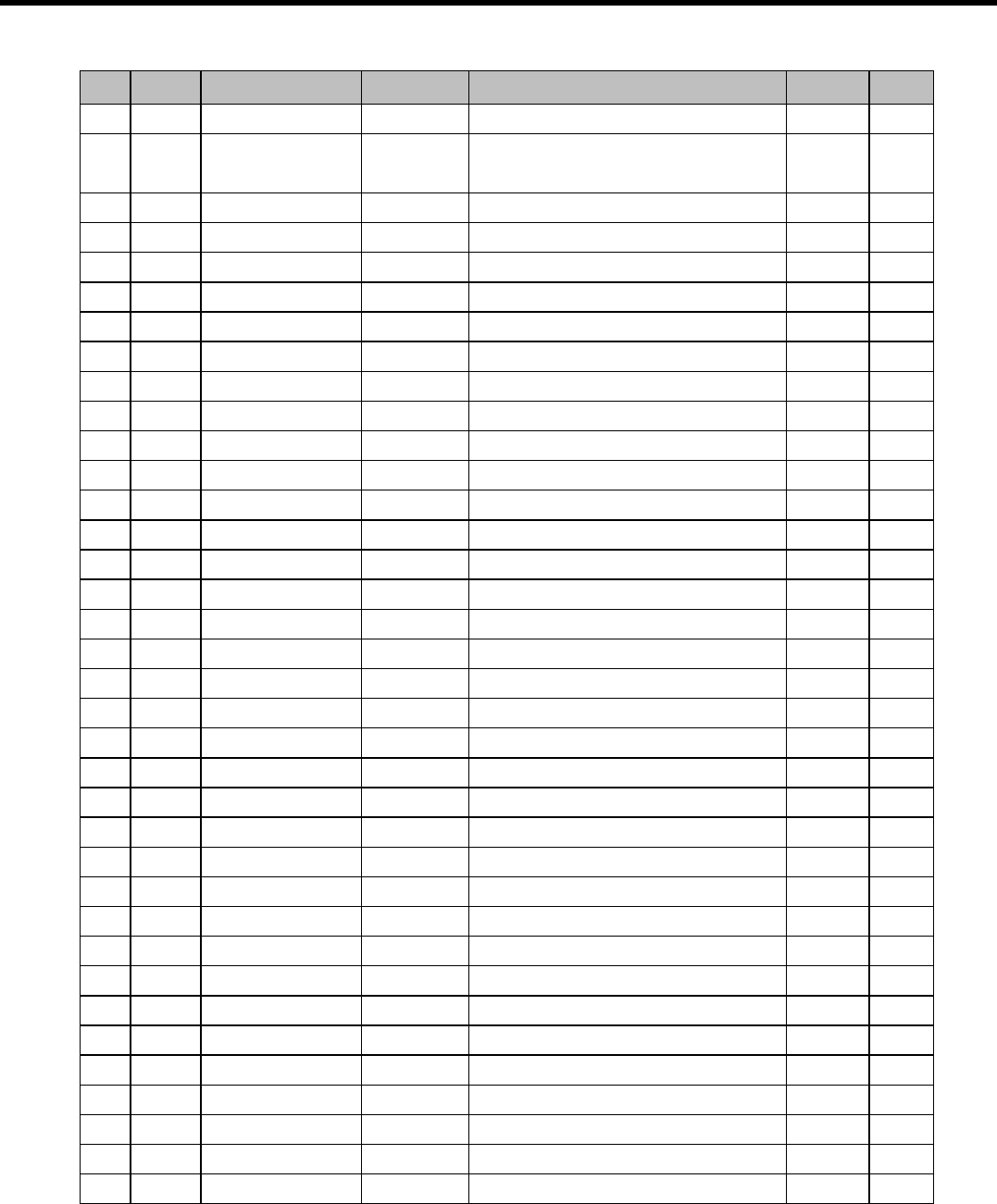

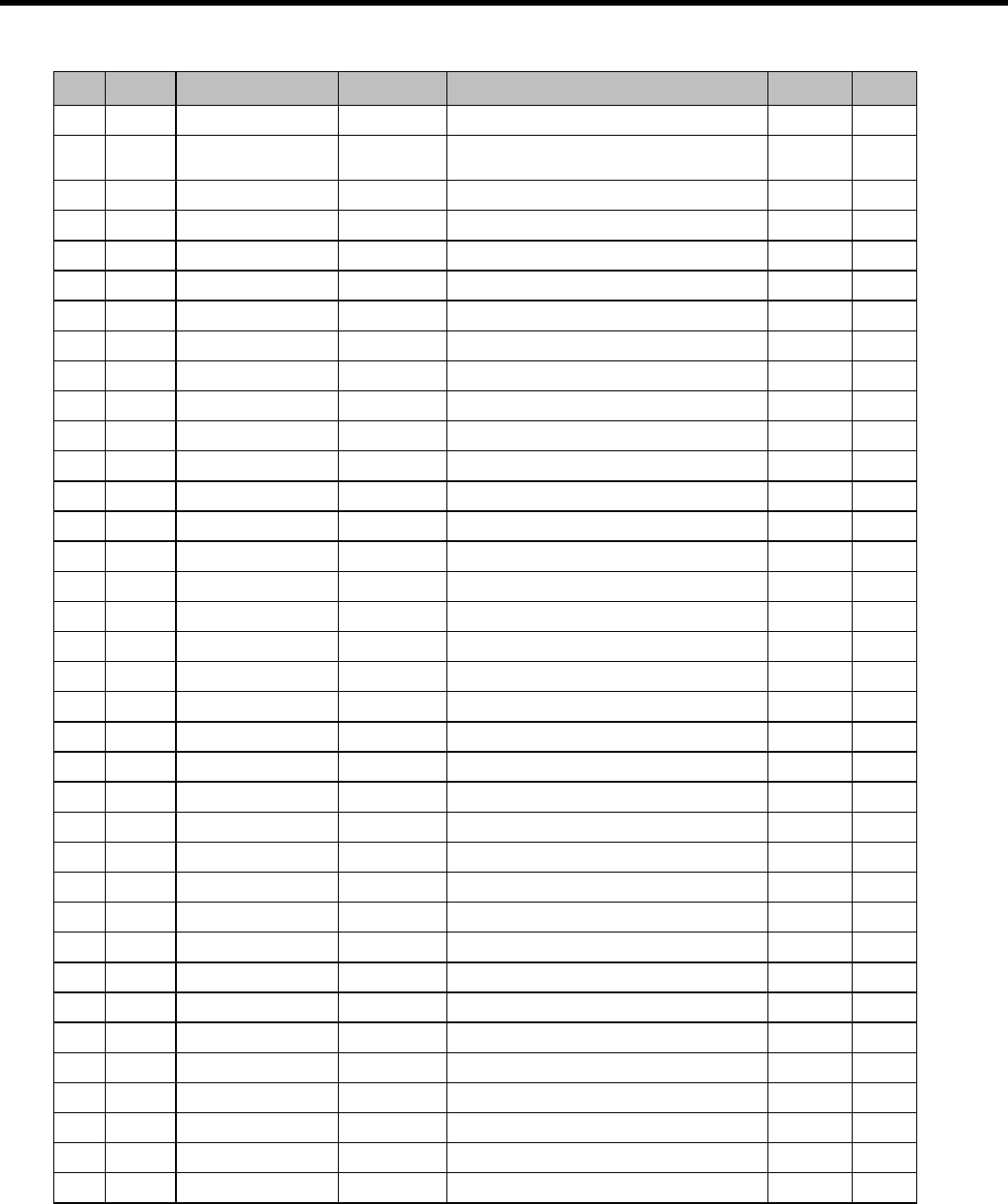

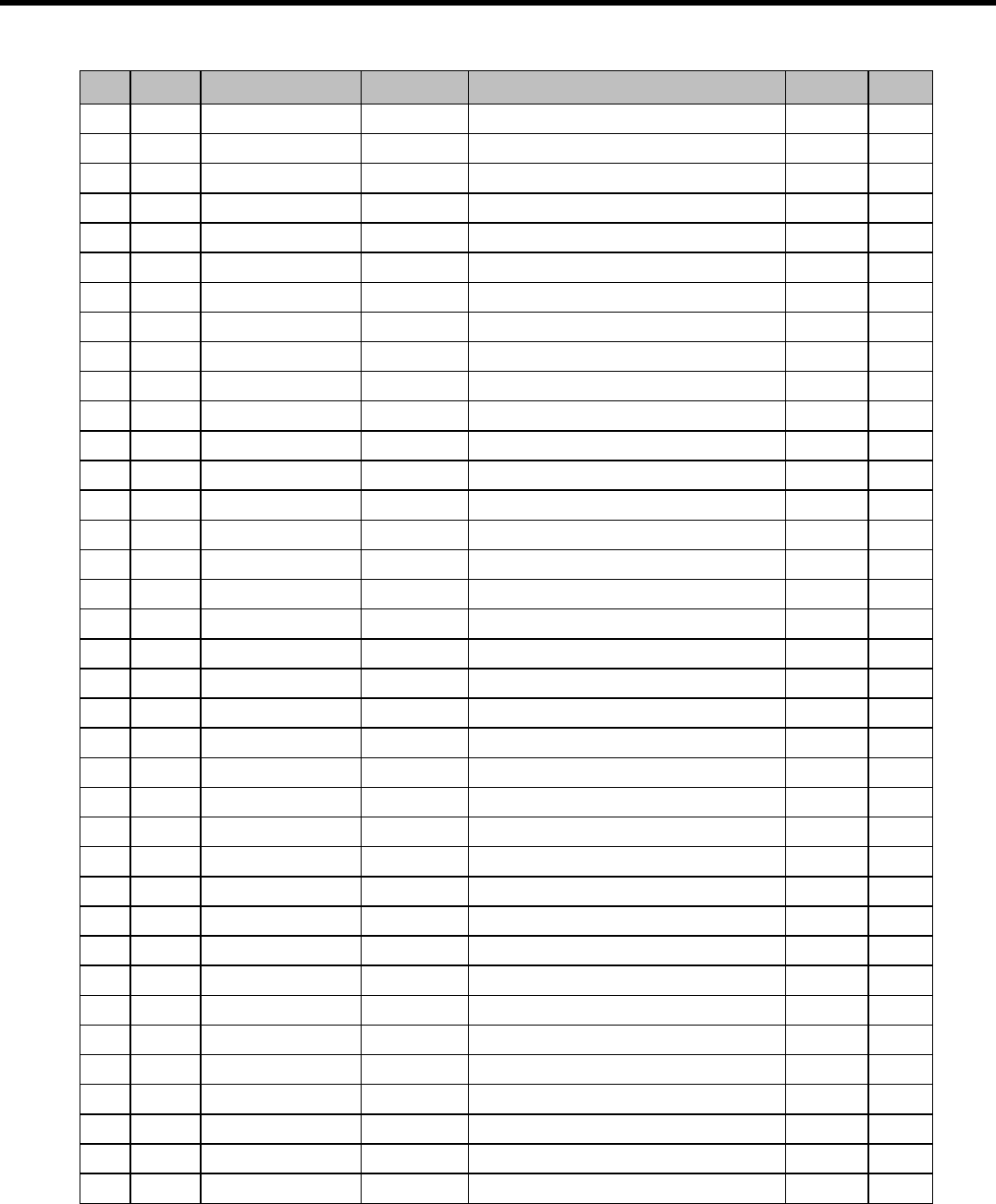

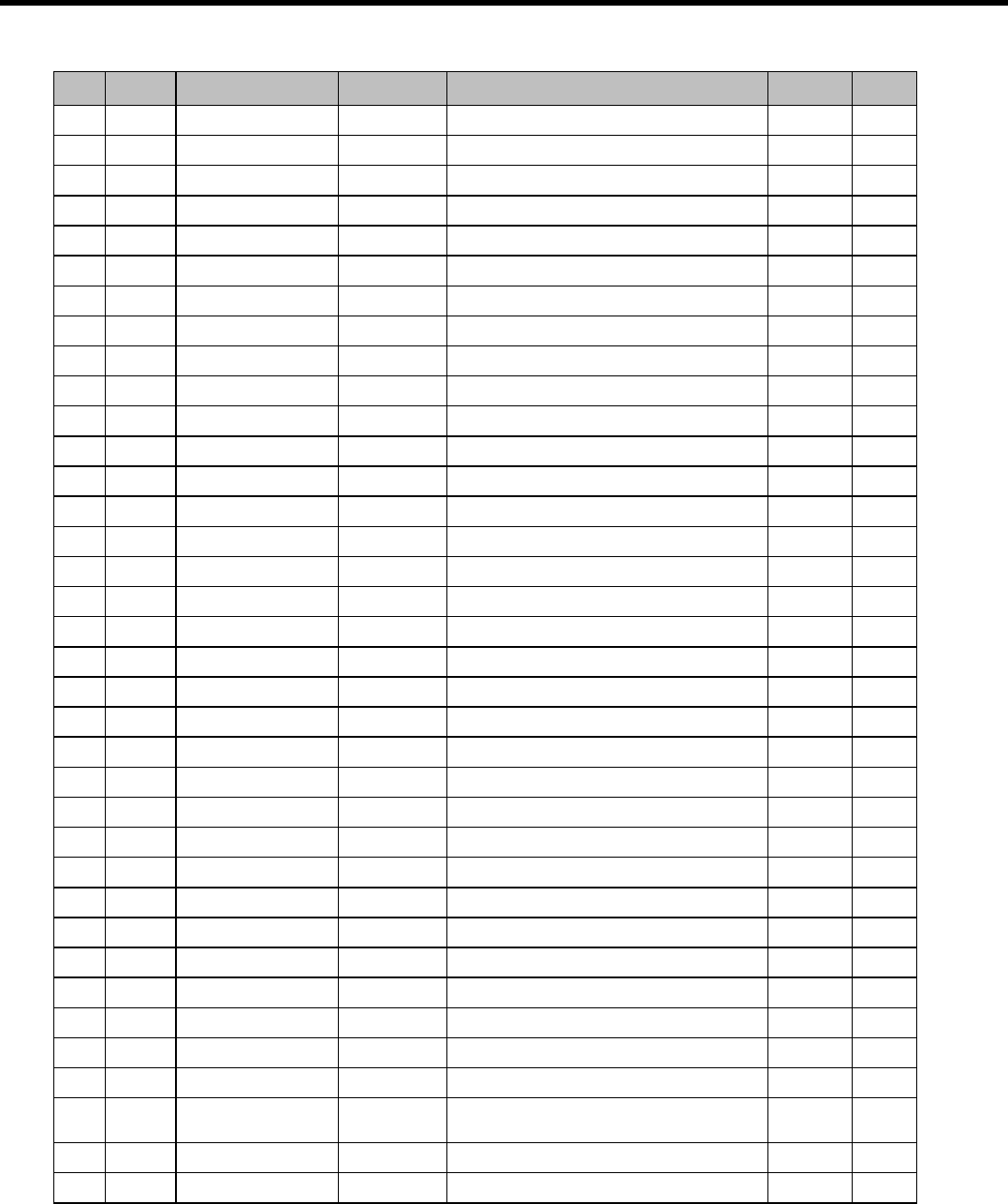

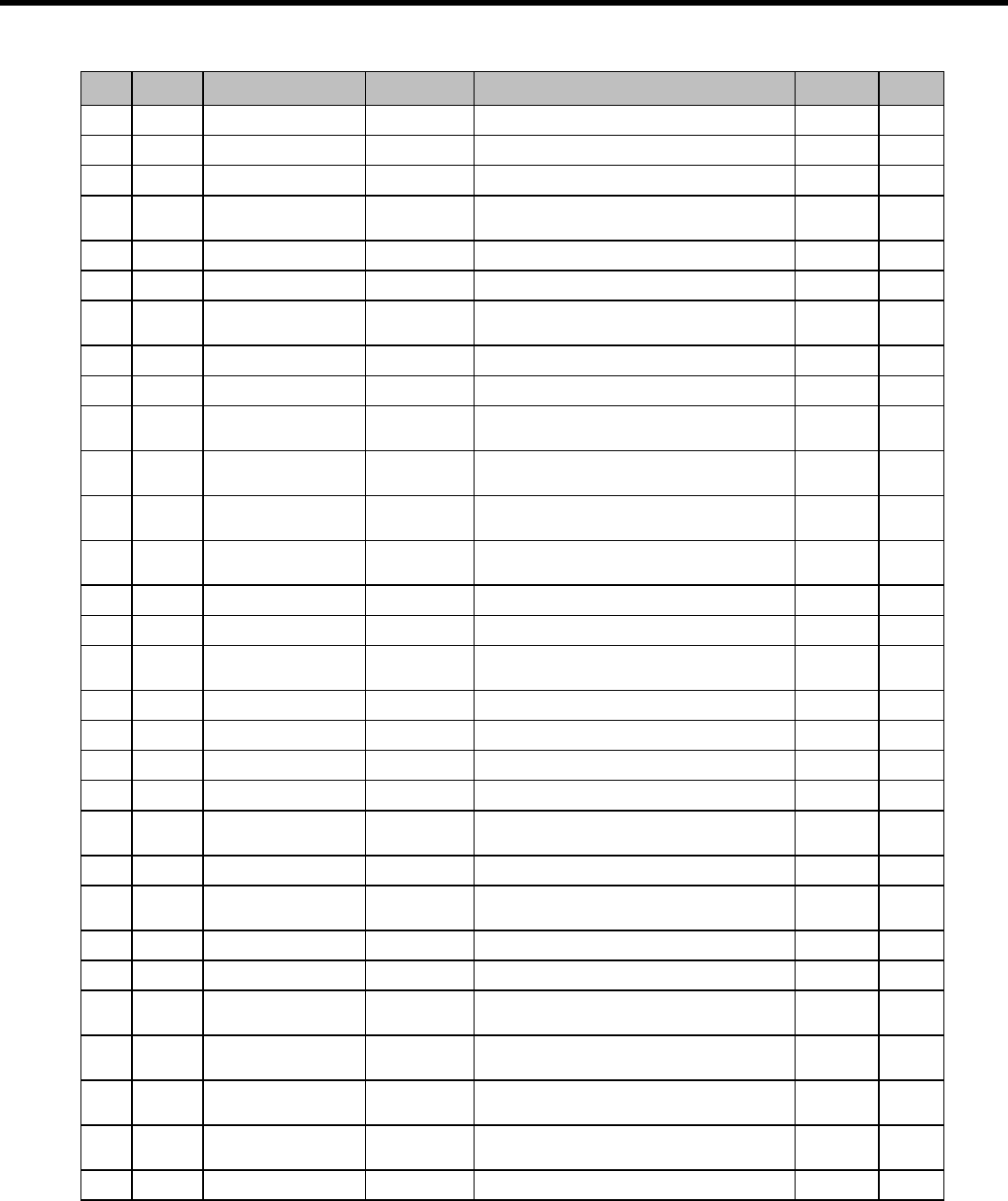

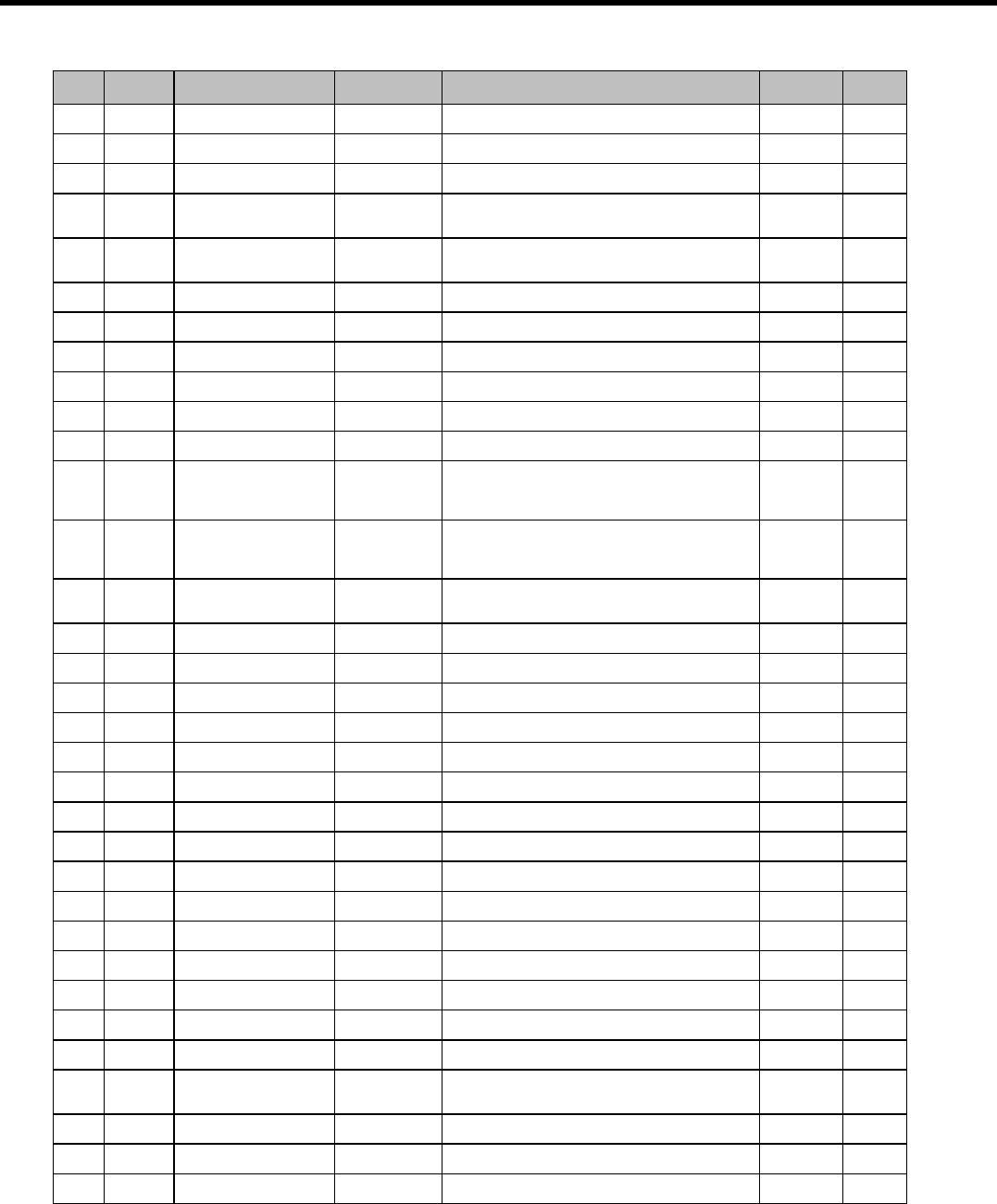

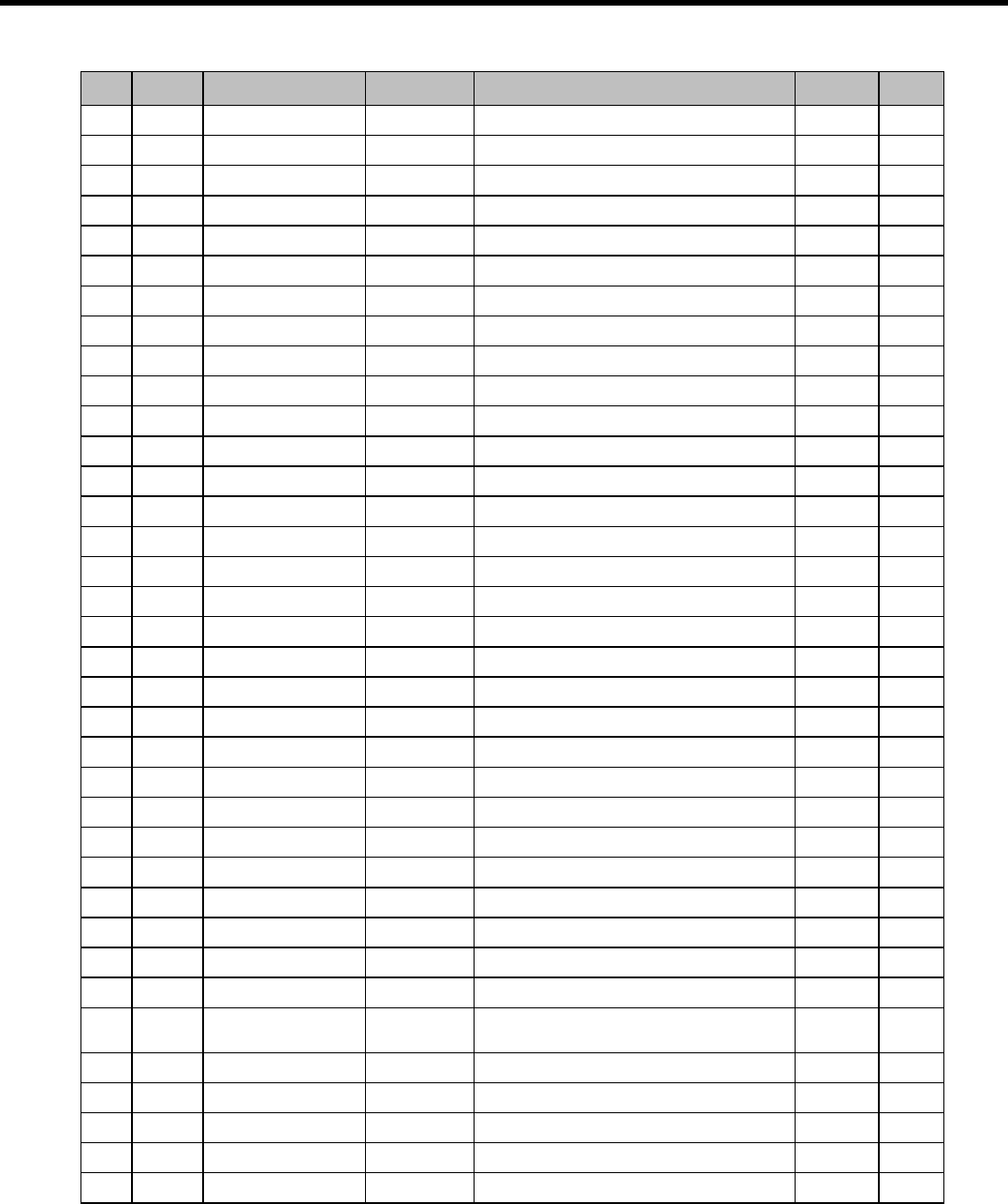

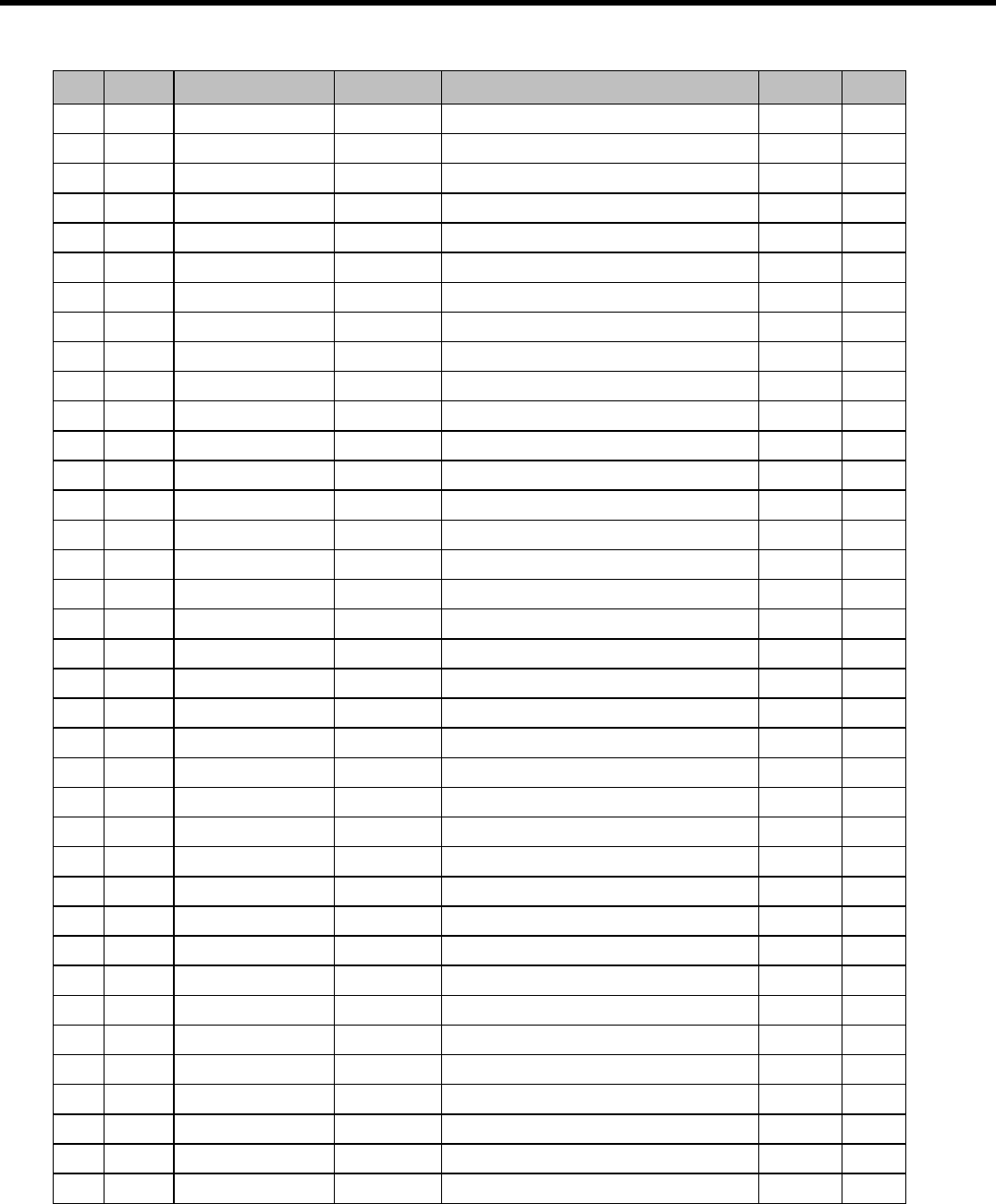

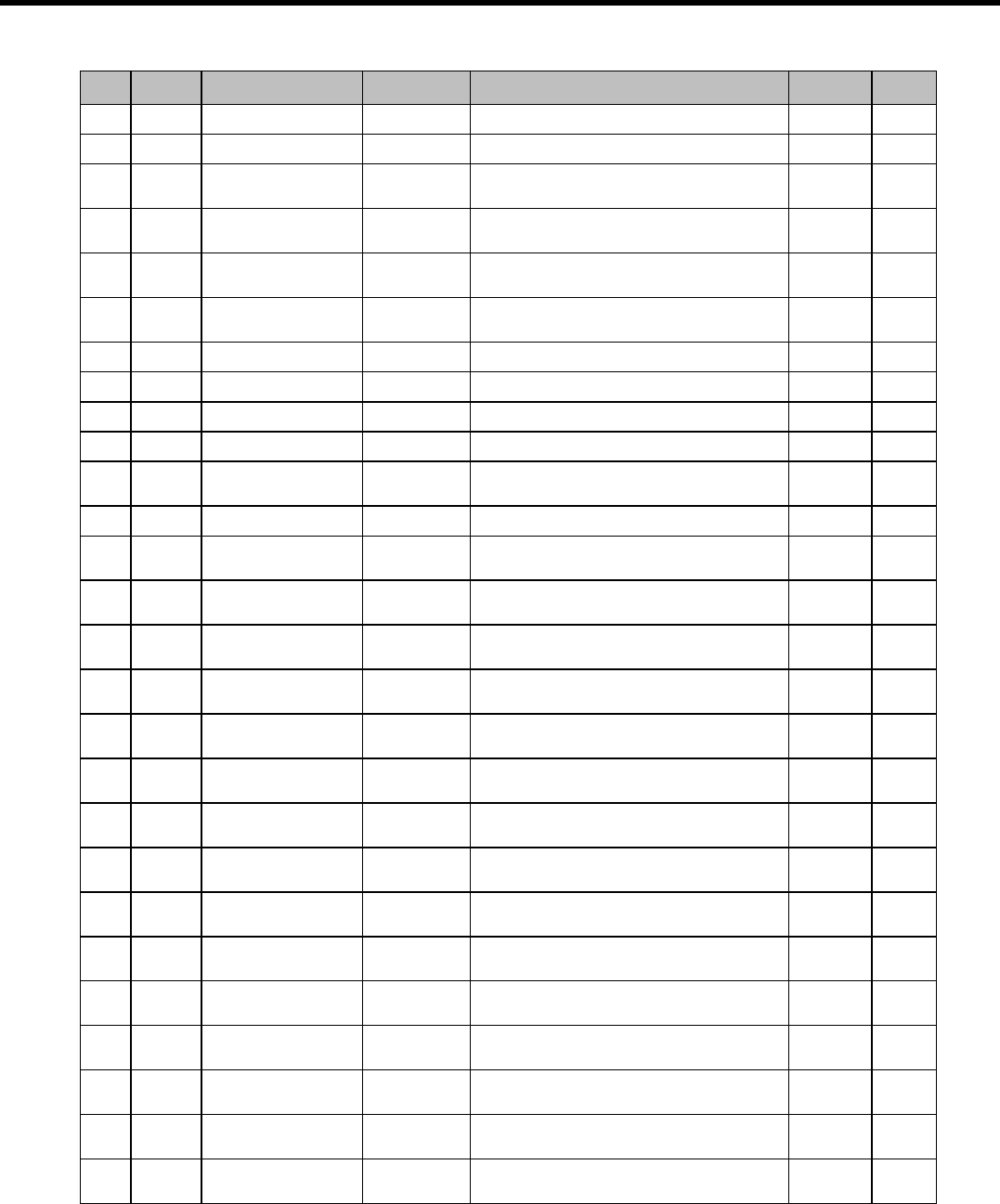

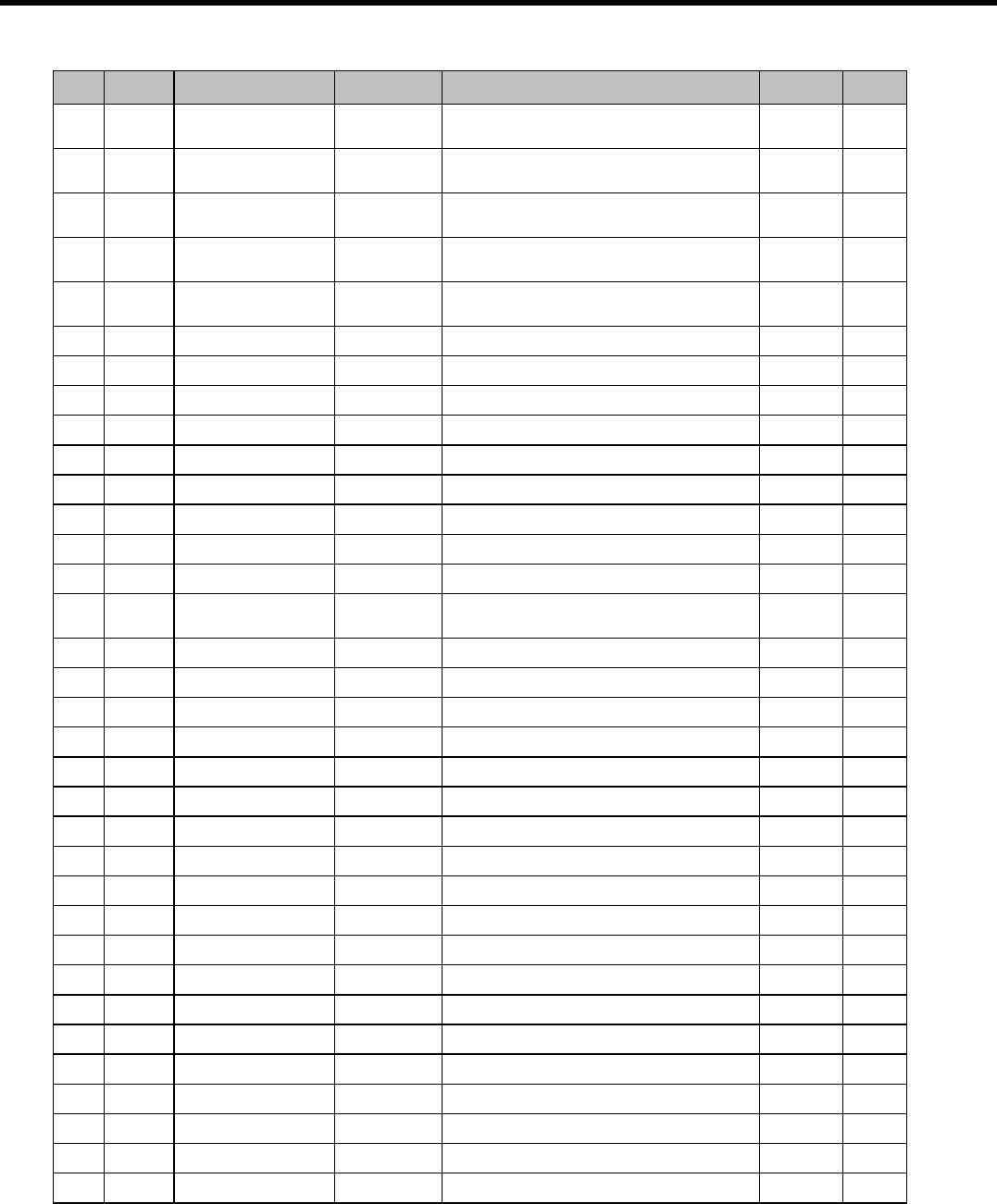

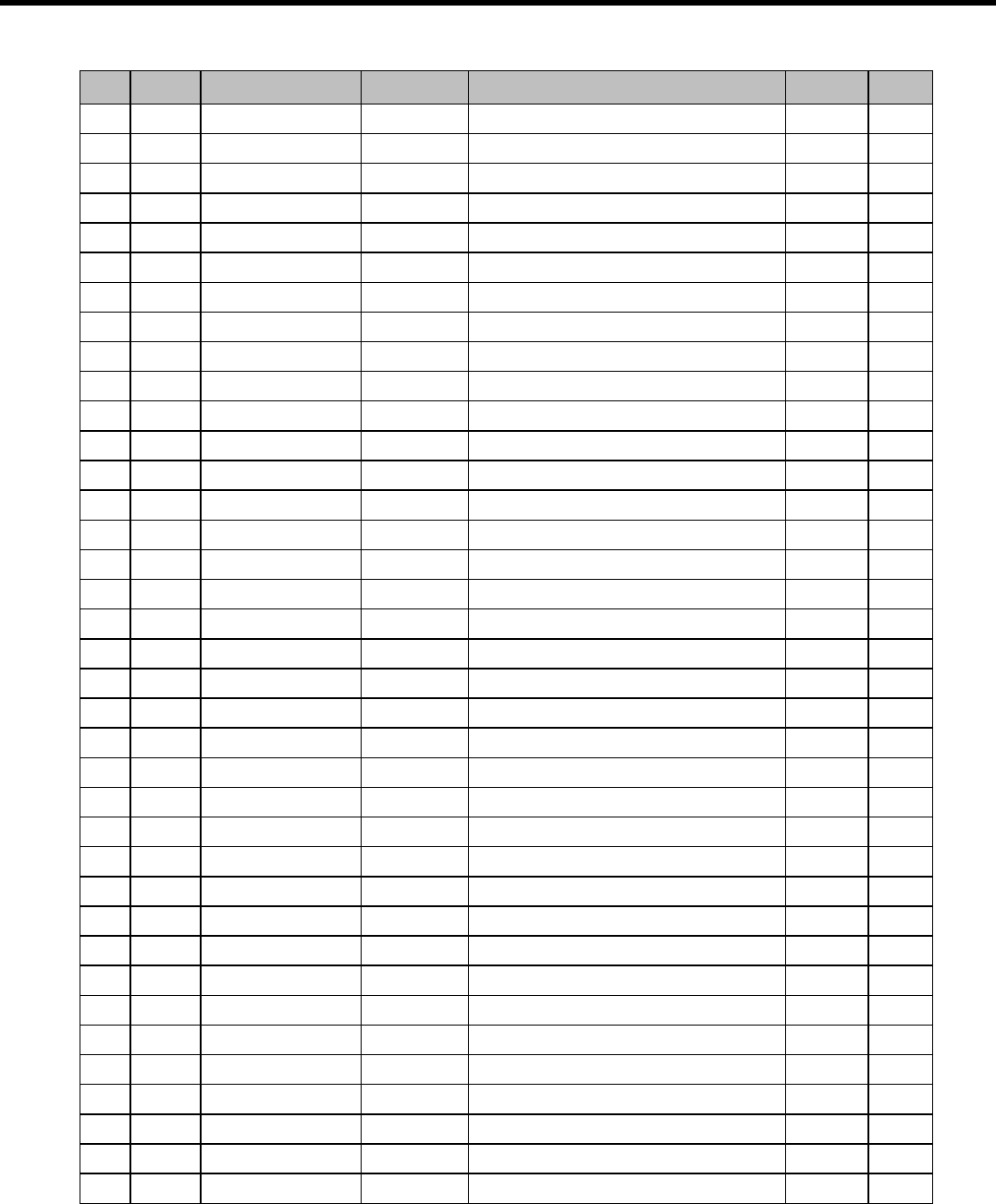

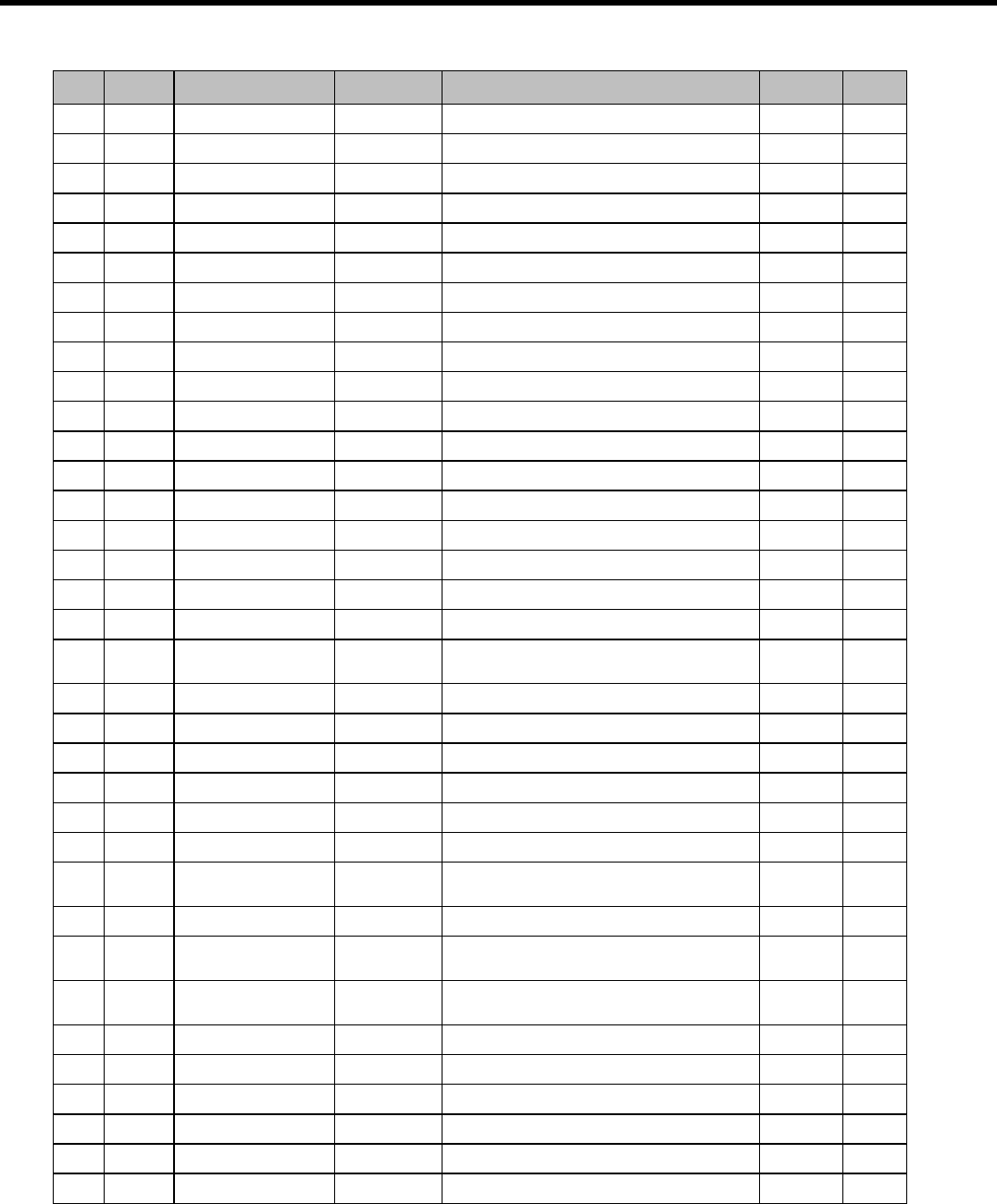

10.2 Replacement Parts

<Mechanic component> ....................... 219

<Main component> ............................... 222

10.3 Accessory ............................................. 246

LGE Internal Use Only

Copyright © 2007 LG Electronics. Inc. All right reserved.

Only for training and service purposes

- 5 -

LGE Internal Use Only

Copyright © 2007 LG Electronics. Inc. All right reserved.

Only for training and service purposes

1.1 Purpose

This manual provides the information necessary to repair, calibration, description and download the

features of this model.

1.2 Regulatory Information

A. Security

Toll fraud, the unauthorized use of telecommunications system by an unauthorized part (for example,

persons other than your company’s employees, agents, subcontractors, or person working on your

company’s behalf) can result in substantial additional charges for your telecommunications services.

System users are responsible for the security of own system.

There are may be risks of toll fraud associated with your telecommunications system. System users

are responsible for programming and configuring the equipment to prevent unauthorized use. The

manufacturer does not warrant that this product is immune from the above case but will prevent

unauthorized use of commoncarrier telecommunication service of facilities accessed through or

connected to it. The manufacturer will not be responsible for any charges that result from such

unauthorized use.

B. Incidence of Harm

If a telephone company determines that the equipment provided to customer is faulty and possibly

causing harm or interruption in service to the telephone network, it should disconnect telephone

service until repair can be done. A telephone company may temporarily disconnect service as long as

repair is not done.

C. Changes in Service

A local telephone company may make changes in its communications facilities or procedure. If these

changes could reasonably be expected to affect the use of the phones or compatibility with the net

work, the telephone company is required to give advanced written notice to the user, allowing the user

to take appropriate steps to maintain telephone service.

D. Maintenance Limitations

Maintenance limitations on the phones must be performed only by the manufacturer or its authorized

agent. The user may not make any changes and/or repairs expect as specifically noted in this manual.

Therefore, note that unauthorized alternations or repair may affect the regulatory status of the system

and may void any remaining warranty.

1. INTRODUCTION

1. INTRODUCTION

- 6 -

LGE Internal Use Only

Copyright © 2007 LG Electronics. Inc. All right reserved.

Only for training and service purposes

E. Notice of Radiated Emissions

This model complies with rules regarding radiation and radio frequency emission as defined by local

regulatory agencies. In accordance with these agencies, you may be required to provide information

such as the following to the end user.

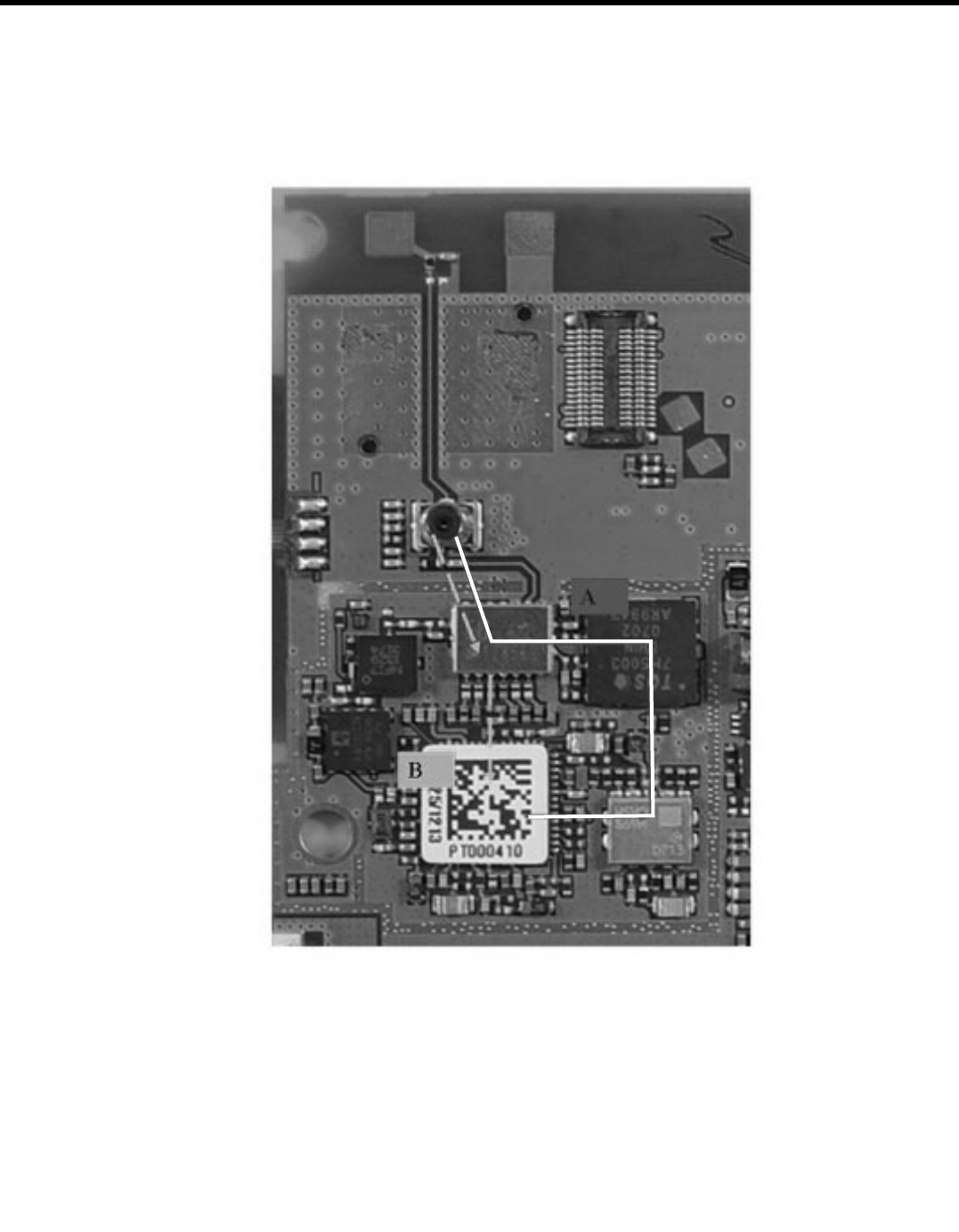

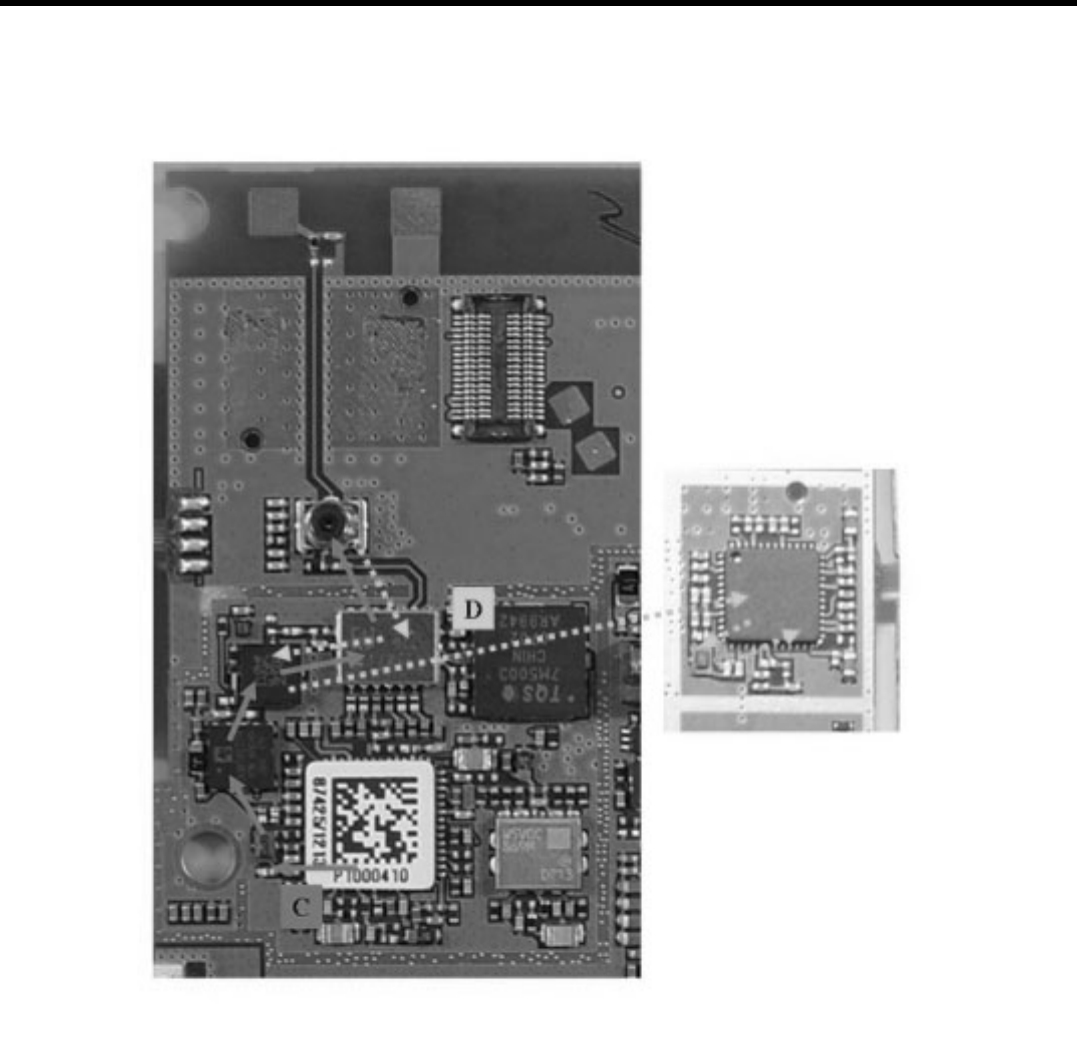

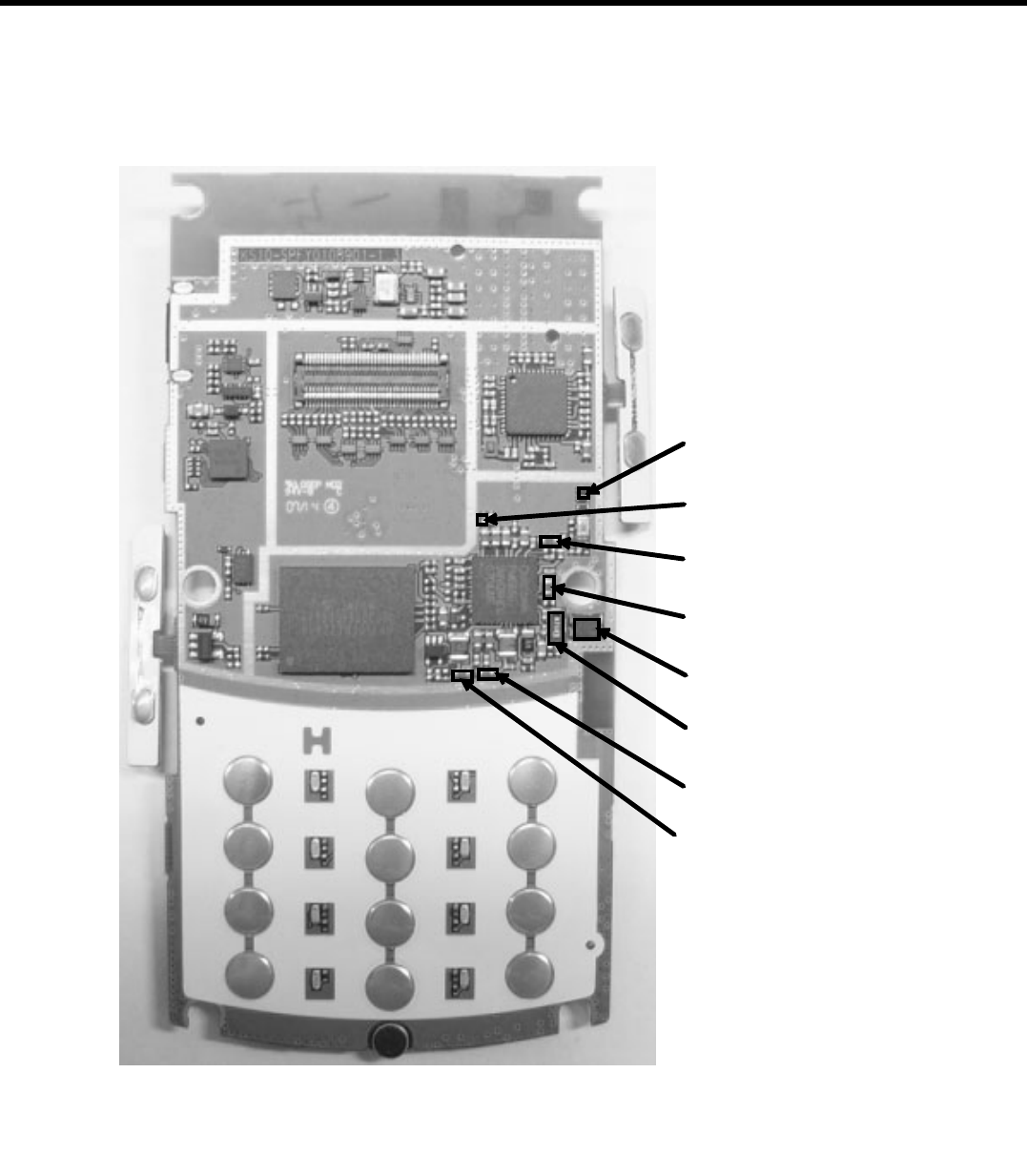

F. Pictures

The pictures in this manual are for illustrative purposes only; your actual hardware may look slightly

different.

G. Interference and Attenuation

A phone may interfere with sensitive laboratory equipment, medical equipment, etc. Interference from

unsuppressed engines or electric motors may cause problems.

H. Electrostatic Sensitive Devices

ATTENTION

Boards, which contain Electrostatic Sensitive Device (ESD), are indicated by the sign.

Following information is ESD handling:

• Service personnel should ground themselves by using a wrist strap when exchange system boards.

• When repairs are made to a system board, they should spread the floor with anti-static mat which is

also grounded.

• Use a suitable, grounded soldering iron.

• Keep sensitive parts in these protective packages until these are used.

• When returning system boards or parts like EEPROM to the factory, use the protective package as

described.

1. INTRODUCTION

- 7 -

LGE Internal Use Only

Copyright © 2007 LG Electronics. Inc. All right reserved.

Only for training and service purposes

2. PERFORMANCE

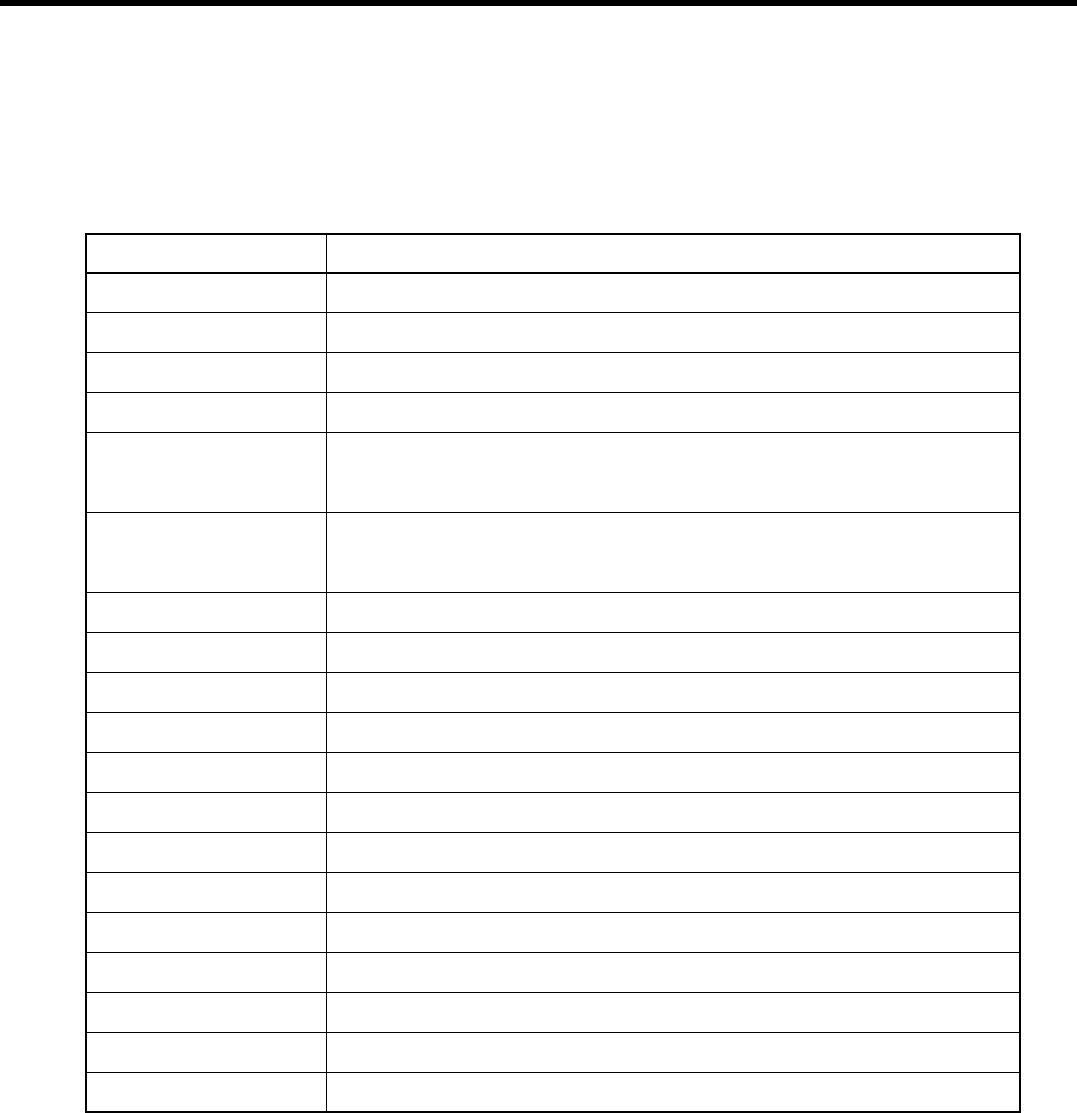

2.1 System Overview

2. PERFORMANCE

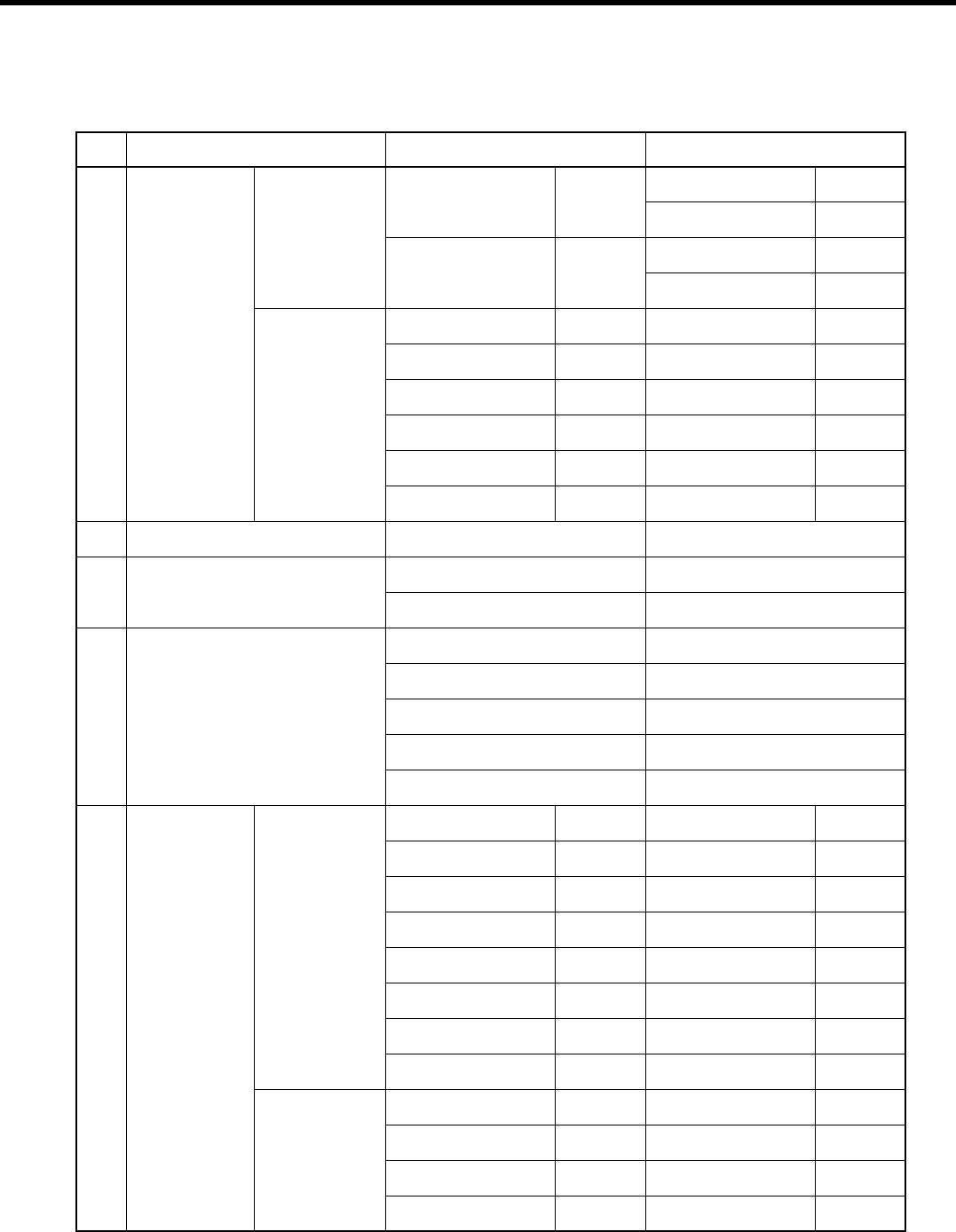

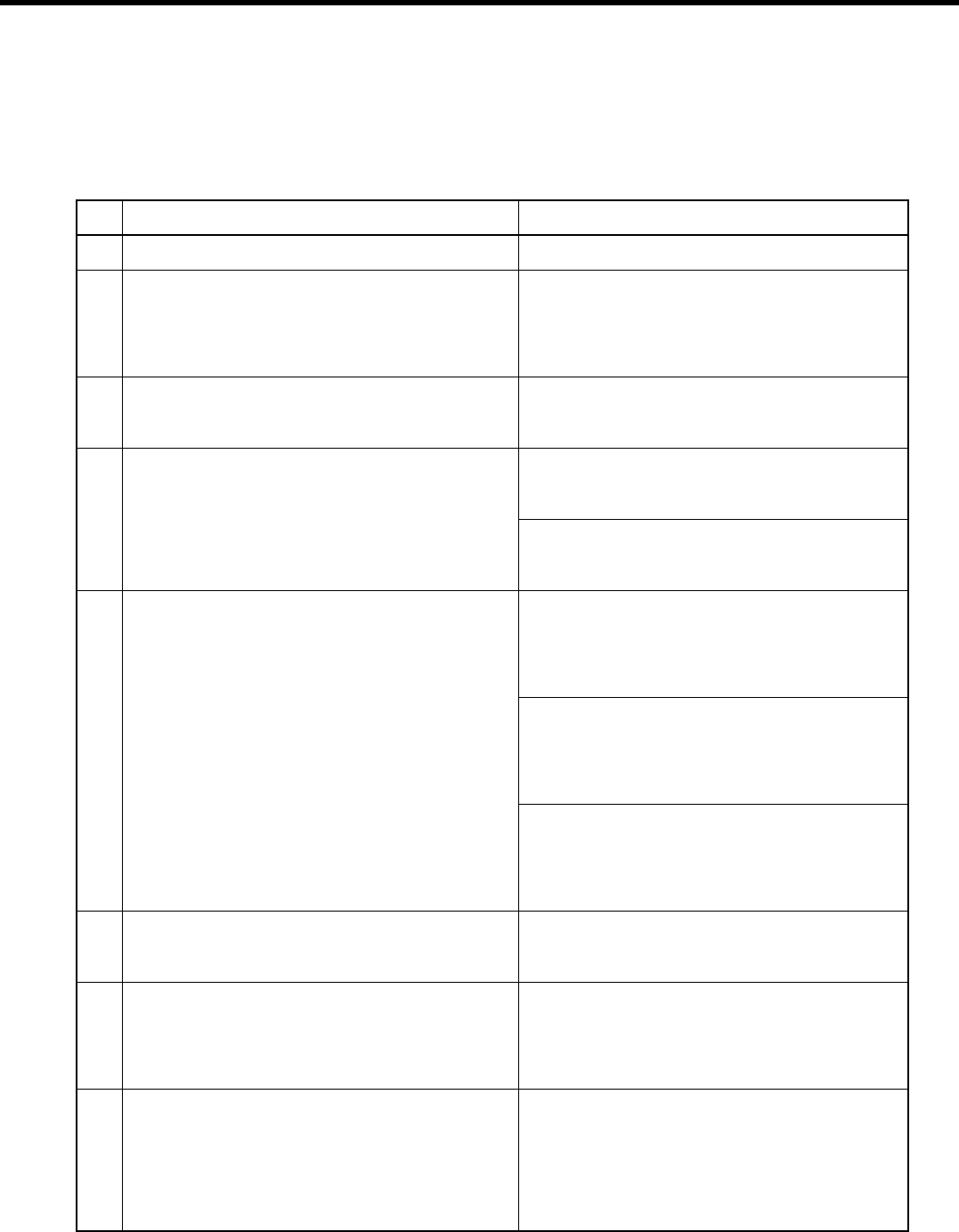

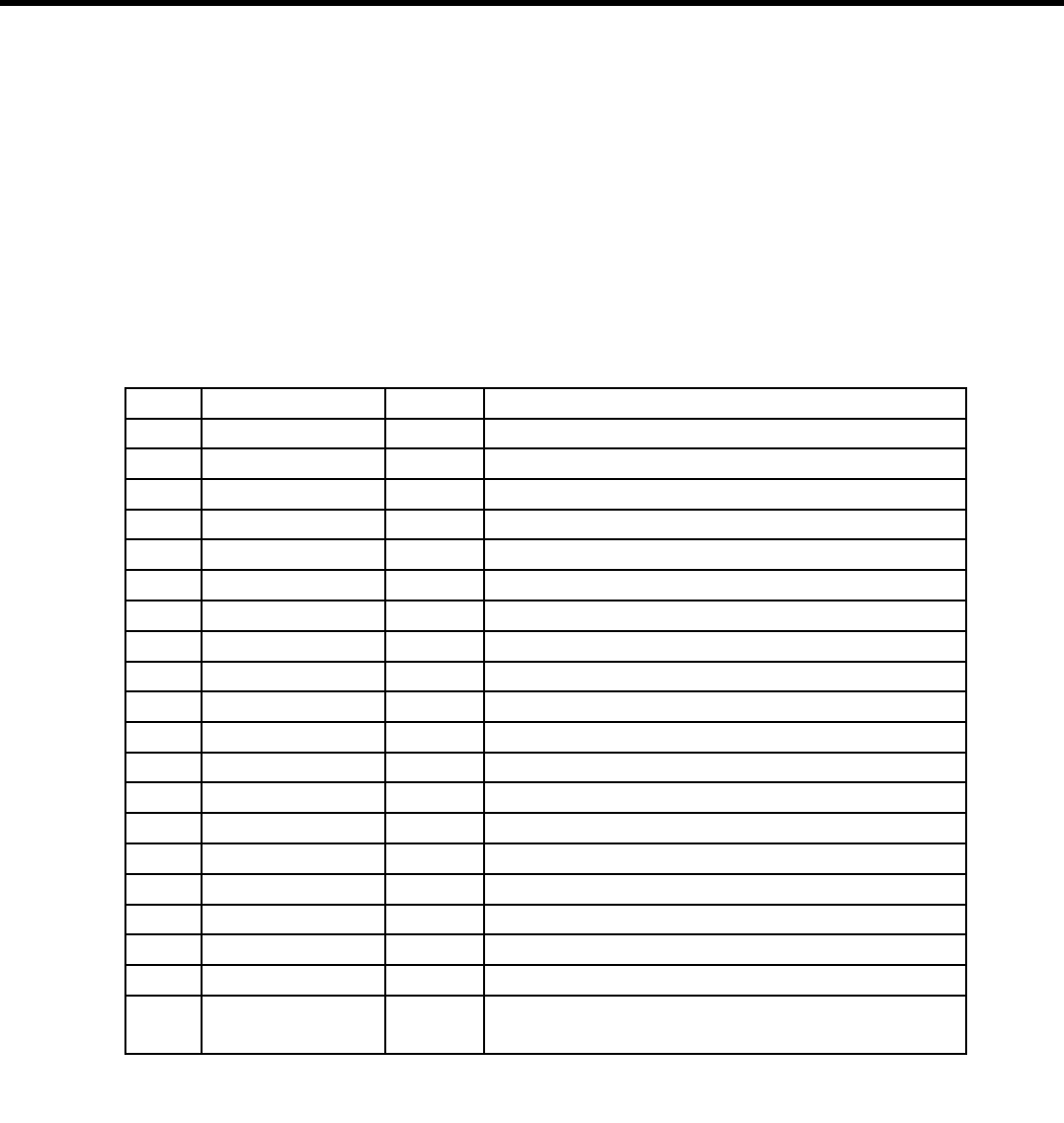

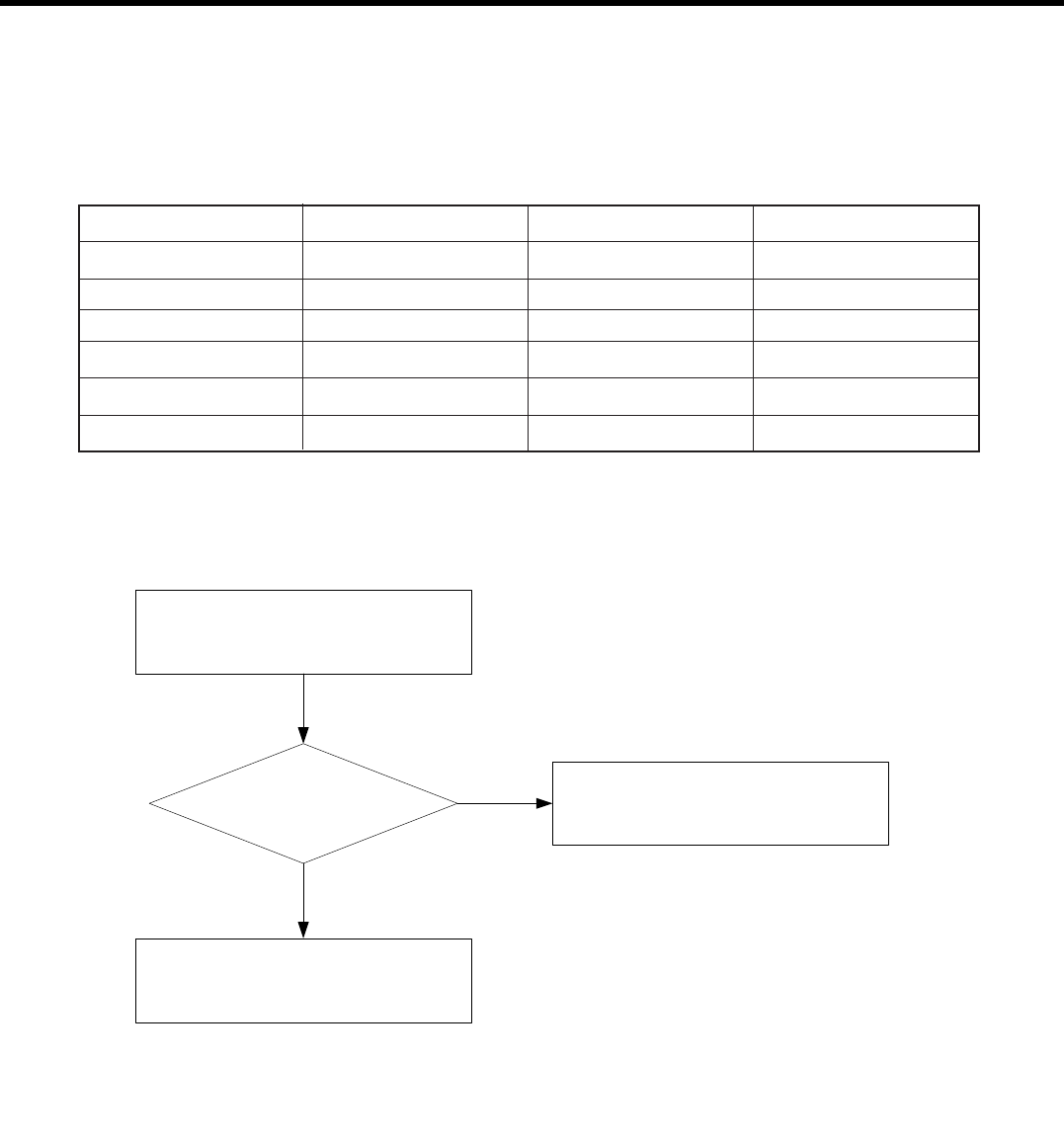

Item Specification

Shape GSM900/1800/1900 and WCDMA Slide Handset

Size 104 X 52 X 18.9 mm

Weight 118 g (with 950mAh Battery)

Power 3.7V normal, 950 mAh Li-Polymer

Talk Time Over 150 min (WCDMA, Tx=12 dBm, Voice)

(with 950mAh) Over 175 min (GSM, Tx=Max, Voice)

Standby Time Over 200 Hrs (WCDMA, DRX=1.28)

(with 950mAh) Over 220 Hrs (GSM, Paging period=9)

Antenna Internal type and Antenna

LCD Main 240 X 320 pixel TFT (QVGA LCD Module)

LCD Backlight Blue LED Back Light (main only)

Camera Dual Camera ; 1.3 Mega pixel (CMOS), VGA Camera (CMOS)

Vibrator Yes (Cylinder Type)

LED Indicator No

MIC Yes

Receiver Yes

Earphone Jack Yes

Connectivity Bluetooth, USB

Volume Key Push Type(+, -)

External Memory Micro-SD

I/O Connect 18 Pin

- 8 -

LGE Internal Use Only

Copyright © 2007 LG Electronics. Inc. All right reserved.

Only for training and service purposes

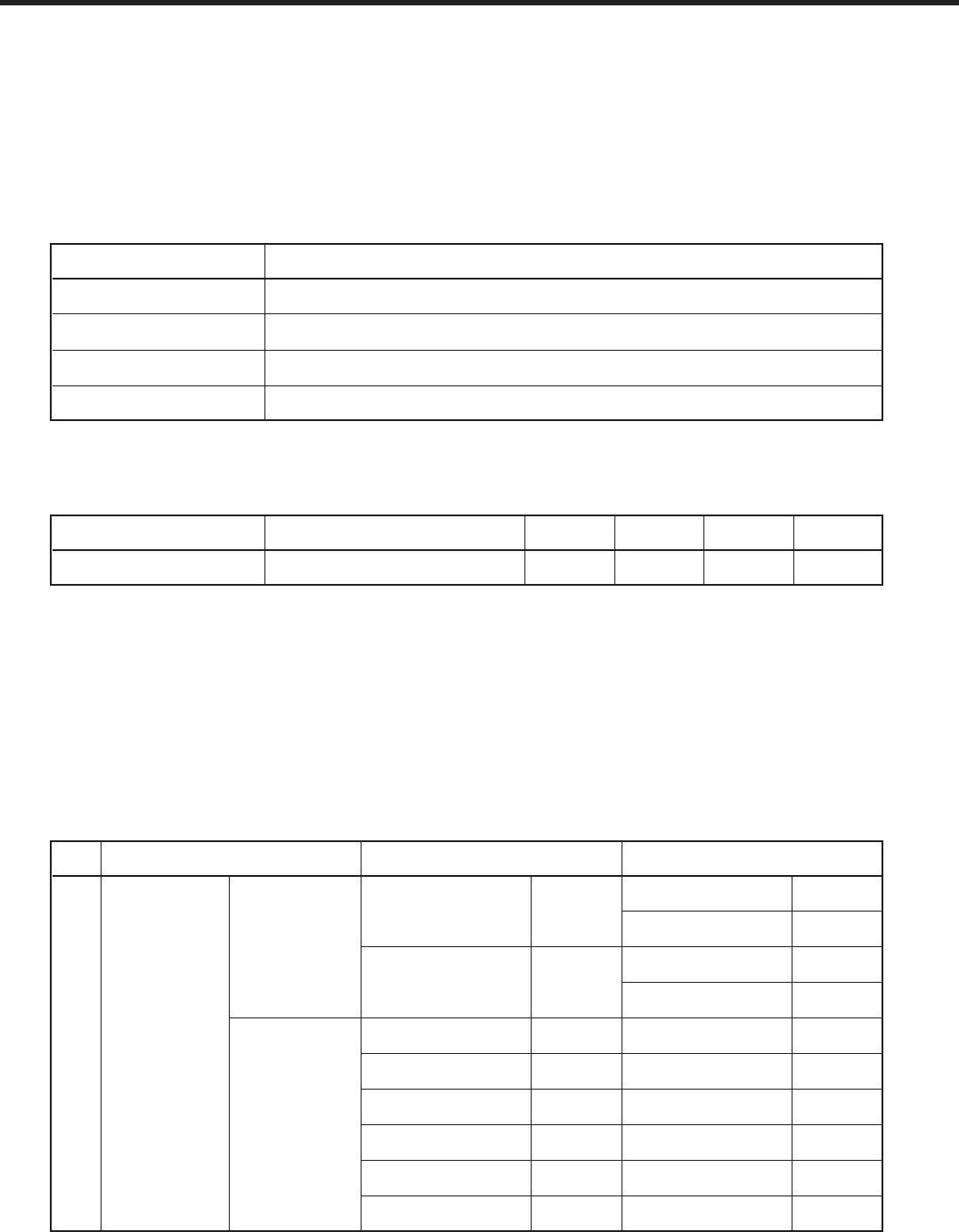

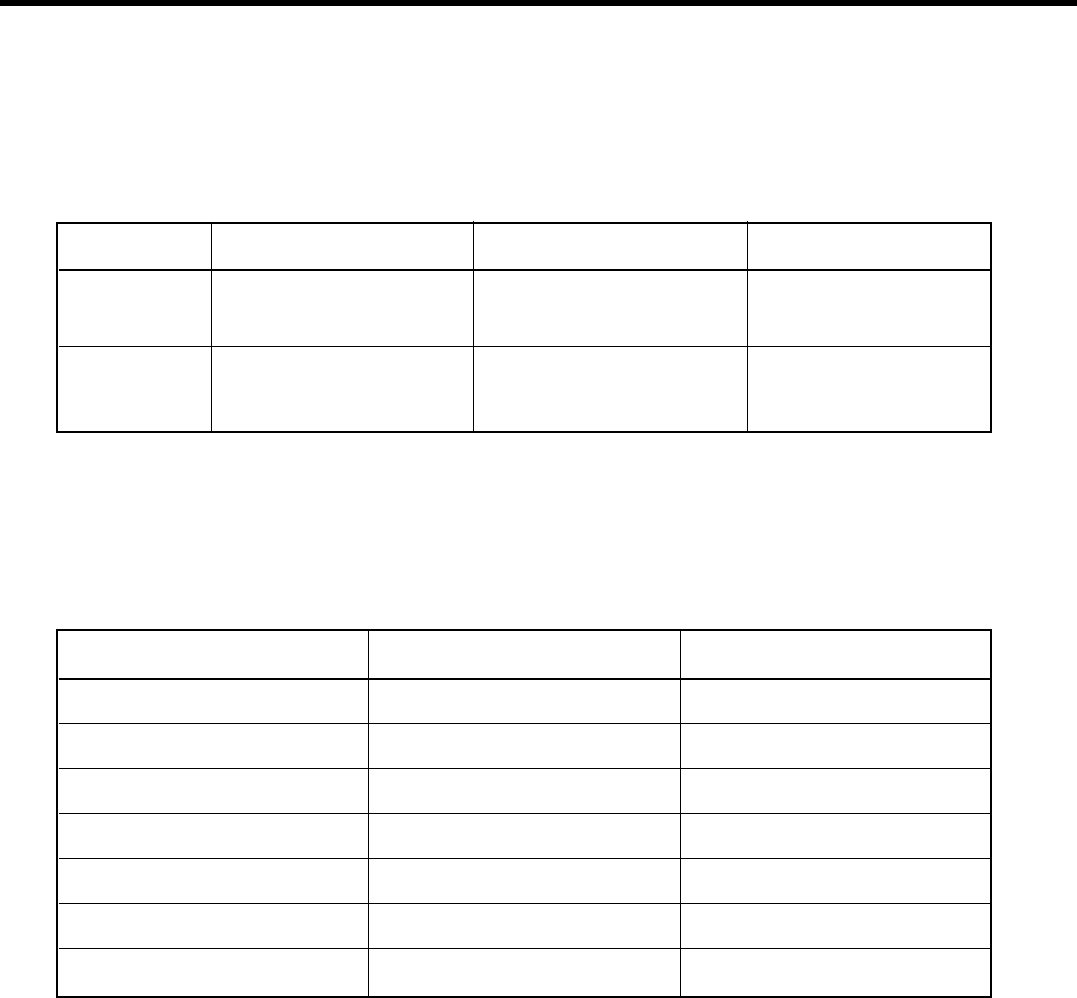

2.2 Usable environment

1) Environment

2) Environment (Accessory)

* CLA : 12 ~ 24 V(DC)

2.3 Radio Performance

1) Transmitter - GSM Mode

* In case of DCS : [A] -> 1710, [B] -> 1785 * In case of PCS : [A] -> 1850, [B] -> 1910

2. PERFORMANCE

Item Specification

Voltage 3.7 V(Typ), [Shut Down : 3.22 V]

Operation Temp -20 ~ +60°C

Storage Temp -20 ~ +70°C

Humidity 85 % (Max)

Reference Spec. Min Typ. Max Unit

TA Power Available power 100 220 240 Vac

No Item GSM DCS & PCS

100k~1GHz -39dBm

9k ~ 1GHz -39dBm

MS allocated 1G~[A]MHz -33dBm

Channel

1G~12.75GHz -33dBm

[A]M~[B]MHz -39dBm

Conducted [B]M~12.75GHz -33dBm

1Spurious 100k~880MHz -60dBm 100k~880MHz -60dBm

Emission 880M~915MHz -62dBm 880M~915MHz -62dBm

Idle Mode

915M~1GHz -60dBm 915M~1GHz -60dBm

1G~[A]MHz -50dBm 1G~[A]MHz -50dBm

[A]M~[B]MHz -56dBm [A]M~[B]MHz -56dBm

[B]M~12.5GHz -50dBm [B]M~12.5GHz -50dBm

- 9 -

LGE Internal Use Only

Copyright © 2007 LG Electronics. Inc. All right reserved.

Only for training and service purposes

2. PERFORMANCE

* In case of DCS : [A] -> 1710, [B] -> 1785 * In case of PCS : [A] -> 1850, [B] -> 1910

No Item GSM DCS & PCS

30M ~ 1GHz -36dBm

30M~1GHz -36dBm

MS allocated 1G~[A]MHz -30dBm

Channel

1G ~ 4GHz -30dBm

[A]M~[B]MHz -36dBm

Radiated [B]M~4GHz -30dBm

2Spurious 30M ~ 880MHz -57dBm 30M~880MHz -57dBm

Emission 880M ~ 915MHz -59dBm 880M~915MHz -59dBm

Idle Mode

915M~1GHz -57dBm 915M~1GHz -57dBm

1G~[A]MHz -47dBm 1G~[A]MHz -47dBm

[A]M~[B]MHz -53dBm [A]M~[B]MHz -53dBm

[B]M~4GHz -47dBm [B]M~4GHz -47dBm

3Frequency Error ±0.1ppm ±0.1ppm

4Phase Error

±5(RMS) ±5(RMS)

±20(PEAK) ±20(PEAK)

3dB below reference sensitivity 3dB below reference sensitivity

Frequency Error RA250 : ±200Hz RA250: ±250Hz

5Under Multipath and HT100 : ±100Hz HT100: ±250Hz

Interference Condition TU50 : ±100Hz TU50: ±150Hz

TU3 : ±150Hz TU1.5: ±200Hz

0 ~ 100kHz +0.5dB 0 ~ 100kHz +0.5dB

200kHz -30dB 200kHz -30dB

250kHz -33dB 250kHz -33dB

Due to 400kHz -60dB 400kHz -60dB

Output RF

modulation 600 ~ 1800kHz -60dB 600 ~ 1800kHz -60dB

61800 ~ 3000kHz -63dB 1800 ~ 6000kHz -65dB

Spectrum

3000 ~ 6000kHz -65dB ≥6000kHz -73dB

≥6000kHz -71dB

Due to

400kHz -19dB 400kHz -22dB

Switching

600kHz -21dB 600kHz -24dB

transient

1200kHz -21dB 1200kHz -24dB

1800kHz -24dB 1800kHz -27dB

- 10 -

LGE Internal Use Only

Copyright © 2007 LG Electronics. Inc. All right reserved.

Only for training and service purposes

2. PERFORMANCE

No Item GSM DCS & PCS

Frequency offset 800kHz

7Intermodulation attenuation –

Intermodulation product should

be Less than 55dB below the

level of Wanted signal

Power control

Power Tolerance

Power control

Power Tolerance

Level (dBm) (dB) Level (dBm) (dB)

533±3 030±3

631±3 128±3

729±3 226±3

827±3 324±3

925±3 422±3

10 23 ±3 5 20 ±3

8Transmitter Output Power 11 21 ±3 6 18 ±3

12 19 ±3 7 16 ±3

13 17 ±3 8 14 ±3

14 15 ±3 9 12 ±4

15 13 ±3 10 10 ±4

16 11 ±5 11 8 ±4

17 9 ±5 12 6 ±4

18 7 ±5 13 4 ±4

19 5 ±5 14 2 ±5

15 0 ±5

9Burst timing Mask IN Mask IN

- 11 -

LGE Internal Use Only

Copyright © 2007 LG Electronics. Inc. All right reserved.

Only for training and service purposes

2. PERFORMANCE

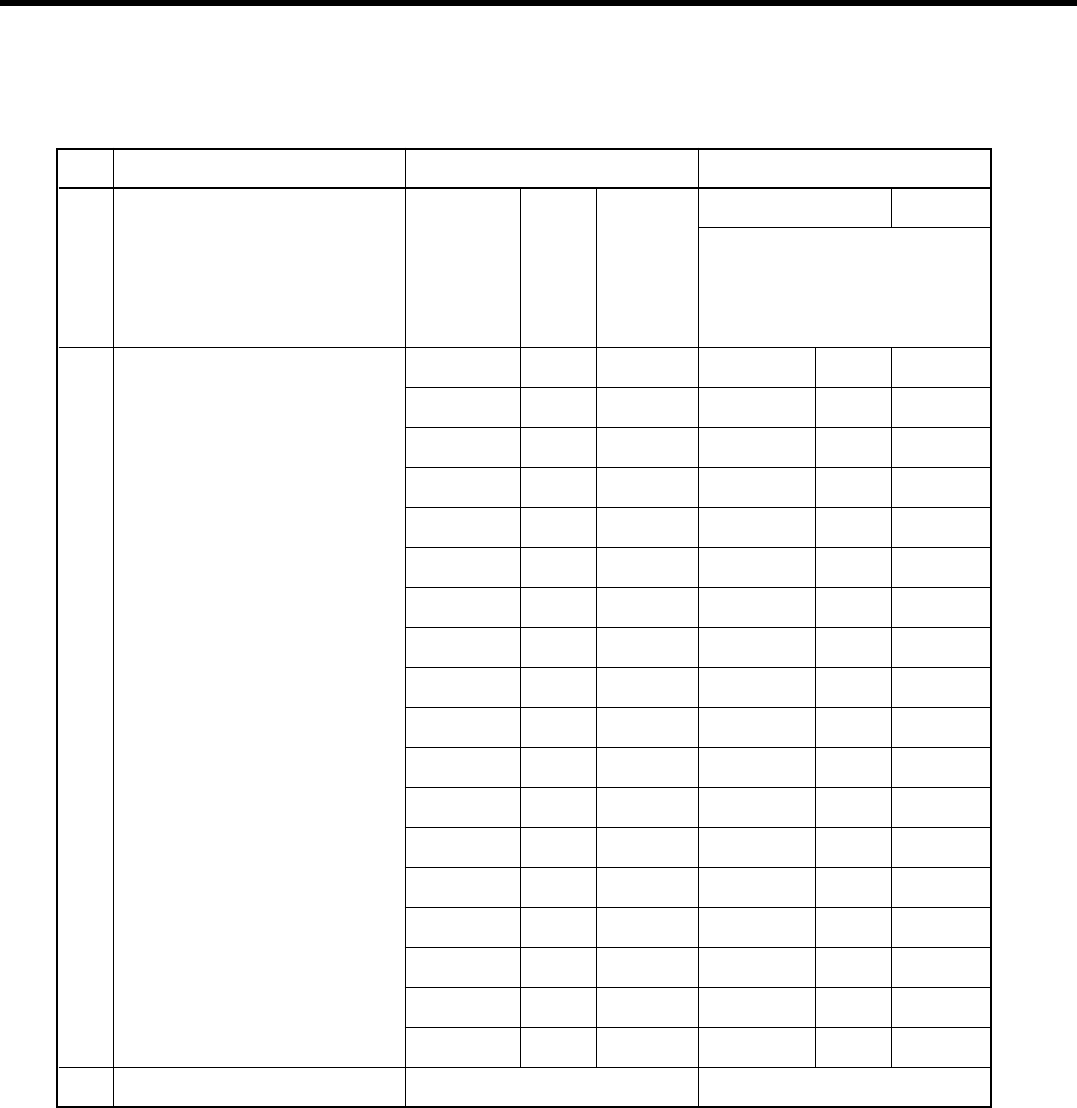

2) Transmitter - WCDMA Mode

No Item Specification

1Maximum Output Power Class 3 : +24dBm(+1/-3dB)

Class 4 : +21dBm(±2dB)

2Frequency Error ±0.1ppm

3Open Loop Power control in uplink ±9dB@normal, ±12dB@extreme

Adjust output(TPC command)

cmd 1dB 2dB 3dB

+1 +0.5/1.5 +1/3 +1.5/4.5

4Inner Loop Power control in uplink 0 -0.5/+0.5 -0.5/+0.5 -0.5/+0.5

-1 -0.5/-1.5 -1/-3 -1.5/-4.5

Group (10 equel command group)

+1 +8/+12 +16/+24

5Minimum Output Power -50dBm(3.84MHz)

Qin/Qout : PCCH quality levels

6Out-of-synchronization handling of output power Toff@DPCCH/Ior : -22 -> -28dB

Ton@DPCCH/Ior : -24 -> -18dB

7Transmit OFF Power -56dBm(3.84MHz)

8Transmit ON/OFF Time Mask

±25us

PRACH,CPCH,uplinlk compressed mode

±25us

9Change of TFC

Power varies according to the data rate

DTX : DPCH off

(minimize interference between UE)

10 Power setting in uplink compressed ±3dB(after 14slots transmission gap)

11 Occupied Bandwidth(OBW) 5MHz(99%)

-35-15*(∆f-2.5)dBc@∆f=2.5~3.5MHz,30k

12 Spectrum emission Mask

-35-1*(∆f-3.5)dBc@∆f=3.5~7.5MHz,1M

-39-10*(∆f-7.5)dBc@∆f=7.5~8.5MHz,1M

-49dBc@∆f=8.5~12.5MHz,1M

- 12 -

LGE Internal Use Only

Copyright © 2007 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3)Receiver - GSM Mode

2. PERFORMANCE

No Item Specification

13 Adjacent Channel Leakage Ratio(ACLR)

33dB@5MHz, ACP>-50dBm

43dB@10MHz, ACP>-50dBm

-36dBm@f=9~150KHz, 1K BW

-36dBm@f=50KHz~30MHz, 10K BW

-36dBm@f=30MHz~1000MHz, 100K BW

14

Spurious Emissions -30dBm@f=1~12.5GHz, 1M BW

(*: additional requirement) (*)-41dBm@f=1893.5~1919.6MHz, 300K

(*)-67dBm@f=925~935MHz, 100K BW

(*)-79dBm@f=935~960MHz, 100K BW

(*)-71dBm@f=1805~1880MHz, 100K BW

15 Transmit Intermodulation

-31dBc@5MHz,Interferer -40dBc

-41dBc@10MHz, Interferer -40dBc

16 Error Vector Magnitude (EVM)

17.5%(>-20dBm)

(@12.2K, 1DPDCH+1DPCCH)

17 Transmit OFF Power

-15dB@SF=4.768Kbps, Multi-code

transmission

No Item GSM DCS & PCS

1

Sensitivity (TCH/FS Class II) -105dBm -105dBm

2

Co-Channel Rejection

C/Ic=7dB Storage -30 ~ +85

(TCH/FS Class II, RBER, TU high/FH)

3Adjacent Channel 200kHz C/Ia1=-12dB C/Ia1=-12dB

Rejection 400kHz C/Ia2=-44dB C/Ia2=-44dB

Wanted Signal :-98dBm Wanted Signal :-96dBm

4

Intermodulation Rejection 1st interferer:-44dBm 1st interferer:-44dBm

2nd interferer:-45dBm 2nd interferer:-44dBm

5

Blocking Response Wanted Signal :-101dBm Wanted Signal :-101dBm

(TCH/FS Class II, RBER)

Unwanted : Depend on Frequency Unwanted : Depend on Frequency

- 13 -

LGE Internal Use Only

Copyright © 2007 LG Electronics. Inc. All right reserved.

Only for training and service purposes

2. PERFORMANCE

4) Receiver - WCDMA Mode

No Item Specification

1Reference Sensitivity Level -106.7 dBm(3.84 MHz)

-25dBm(3.84MHz)

2Maximum Input Level -44dBm/3.84MHz(DPCH_Ec)

UE@+20dBm output power(Class3)

3Adjacent Channel Selectivity (ACS)

33dB

UE@+20dBm output power(Class3)

-56dBm/3.84MHz@10MHz

4In-band Blocking UE@+20dBm output power(Class3)

-44dBm/3.84MHz@15MHz

UE@+20dBm output power(Class3)

-44dBm/3.84MHz@f=2050~2095 and

2185~2230MHz

UE@+20dBm output power(Class3)

-30dBm/3.84MHz@f=2025~2050 and

5Out-band Blocking 2230~2255MHz

UE@+20dBm output power(Class3)

-15dBm/3.84MHz@f=1~2025 and

2255~12500MHz

UE@+20dBm output power(Class3)

6Spurious Response

-44dBm CW

UE@+20dBm output power(Class3)

-46dBm CW@10MHz

7Intermodulation Characteristic -46dBm/3.84MHz@20MHz

UE@+20dBm output power(Class3)

-57dBm@f=9KHz~1GHz, 100K BW

8Spurious Emissions -47dBm@f=1~12.5GHz, 1M BW

-60dBm@f=1920MHz~1980MHz, 3.84M BW

-60dBm@f=2110MHz~2170MHz, 3.84M BW

- 14 -

LGE Internal Use Only

Copyright © 2007 LG Electronics. Inc. All right reserved.

Only for training and service purposes

2. PERFORMANCE

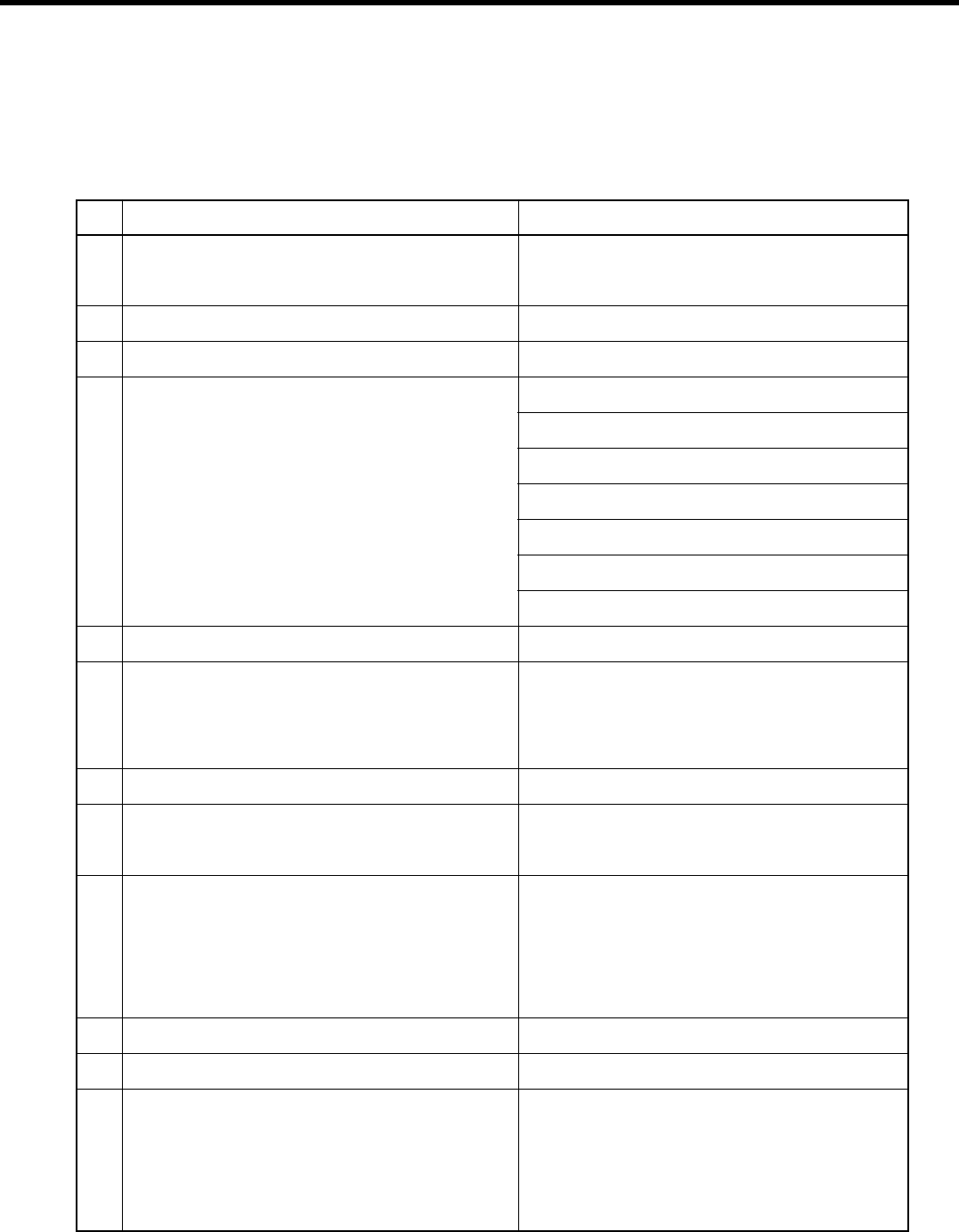

2.4 Current Consumption

(Stand by Test Condition : Bluetooth off, LCD backlight off)

(Call Test Condition : Bluetooth off, LCD backlight dimming mode)

(VT Test Condition : Speaker off, LCD backlight On)

2.5 RSSI BAR

Stand by Voice Call VT

WCDMA

Under 4.32 mA Under 335 mA Under 569mA

(DRX=1.28) (Tx=10dBm -Low power) (Tx=10dBm -Low power)

Under 4.32 mA Under 380 mA

GSM (Paging=5period) (Tx=Max power)

Level Change WCDMA GSM

BAR 7 → 6-86 ±2 dBm -82 ±2dBm

BAR 6 → 5-90 ±2 dBm -86 ±2dBm

BAR 5 → 4-94 ±2 dBm -90 ±2dBm

BAR 4 → 3-98 ±2 dBm -94 ±2dBm

BAR 3 → 2-102 ±2 dBm -98 ±2dBm

BAR 2 → 1-106 ±2 dBm -102 ±2dBm

BAR 1 → 0-110 ±2 dBm -106 ±2dBm

- 15 -

LGE Internal Use Only

Copyright © 2007 LG Electronics. Inc. All right reserved.

Only for training and service purposes

2.6 Battery BAR

2. PERFORMANCE

Indication Standby

Bar 7 3.96 ± 0.05V

Bar 7 →63.95 ± 0.05V

Bar 6 →53.86 ± 0.05V

Bar 5 →43.78 ± 0.05V

Bar 4 →33.74 ± 0.05V

Bar 3 →23.69 ± 0.05V

Bar 2 →13.63 ± 0.05V

Bar 1 →Empty 3.50 ± 0.05V

Low Voltage, 3.63,3.50 ± 0.05V (Stand-by) / 3.63, 3.50 ± 0.05V (Talk)

Warning message + tone Bar 2 → 1 / Bar 1 →Empty

Power Off 3.20 ± 0.05V

- 16 -

LGE Internal Use Only

Copyright © 2007 LG Electronics. Inc. All right reserved.

Only for training and service purposes

2. PERFORMANCE

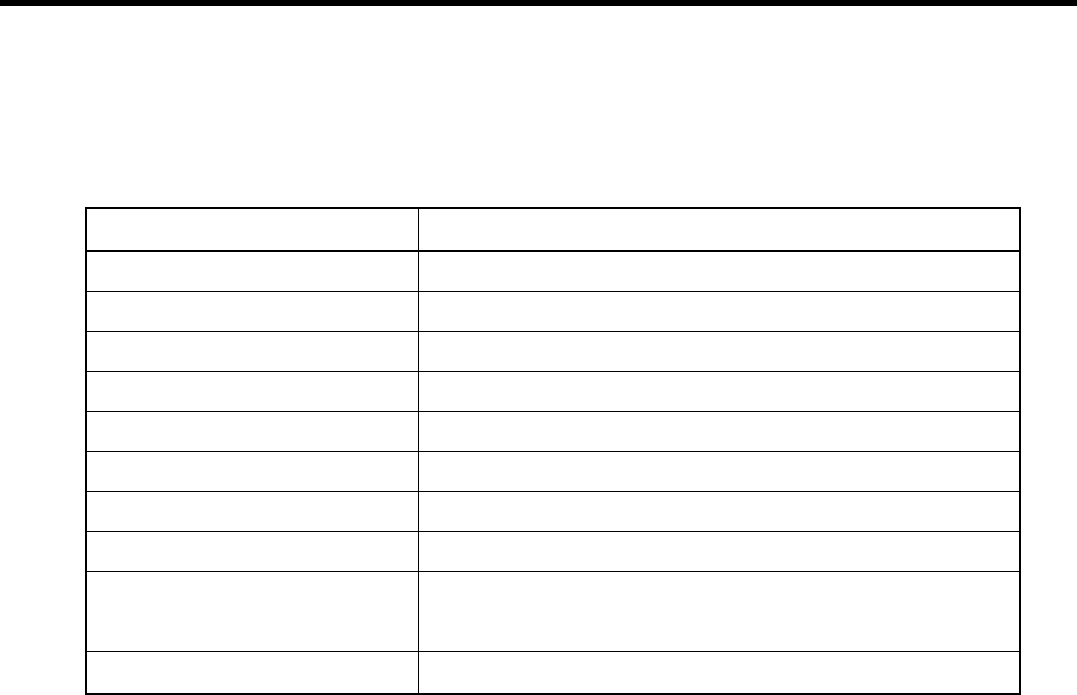

2.7 Sound Pressure Level

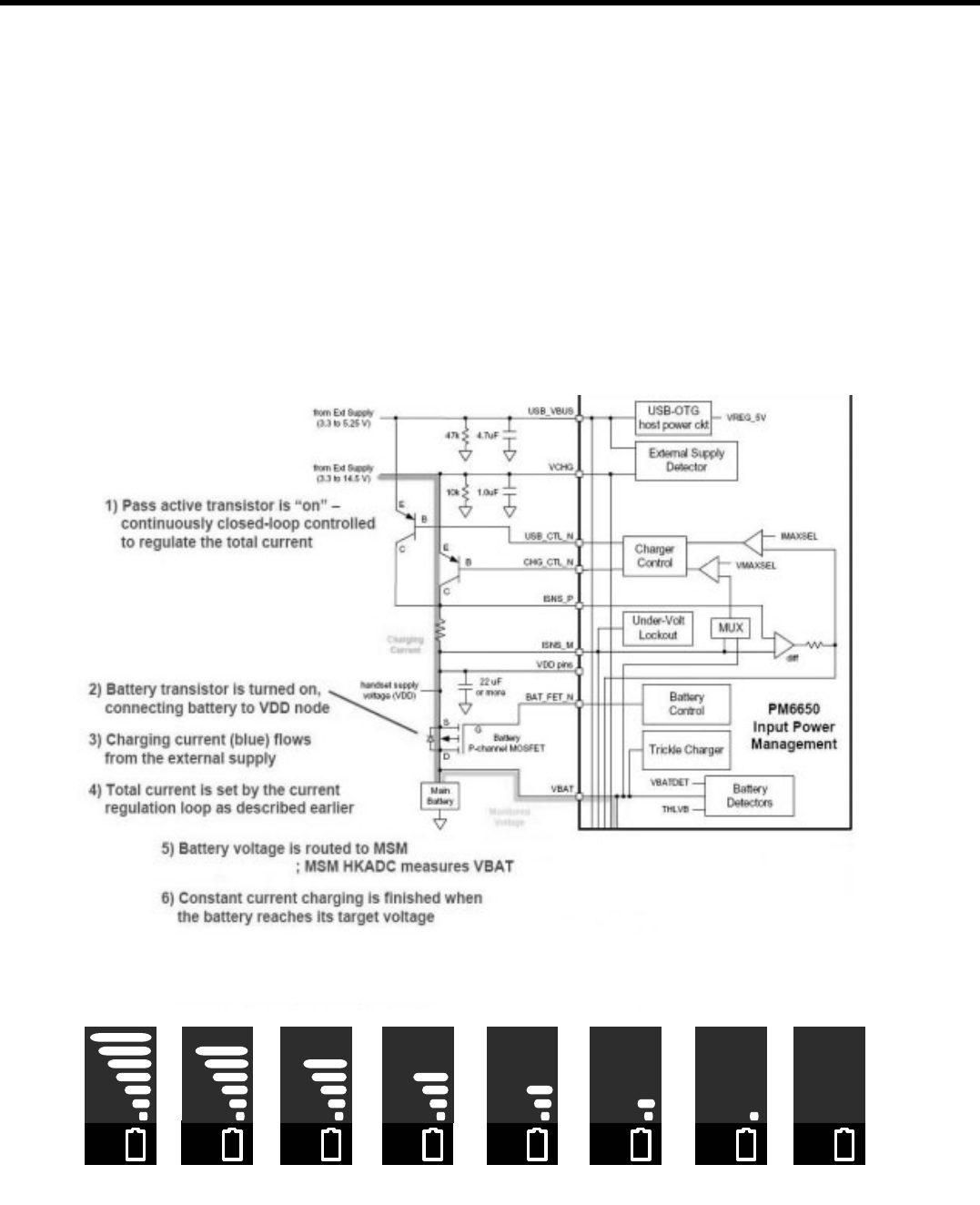

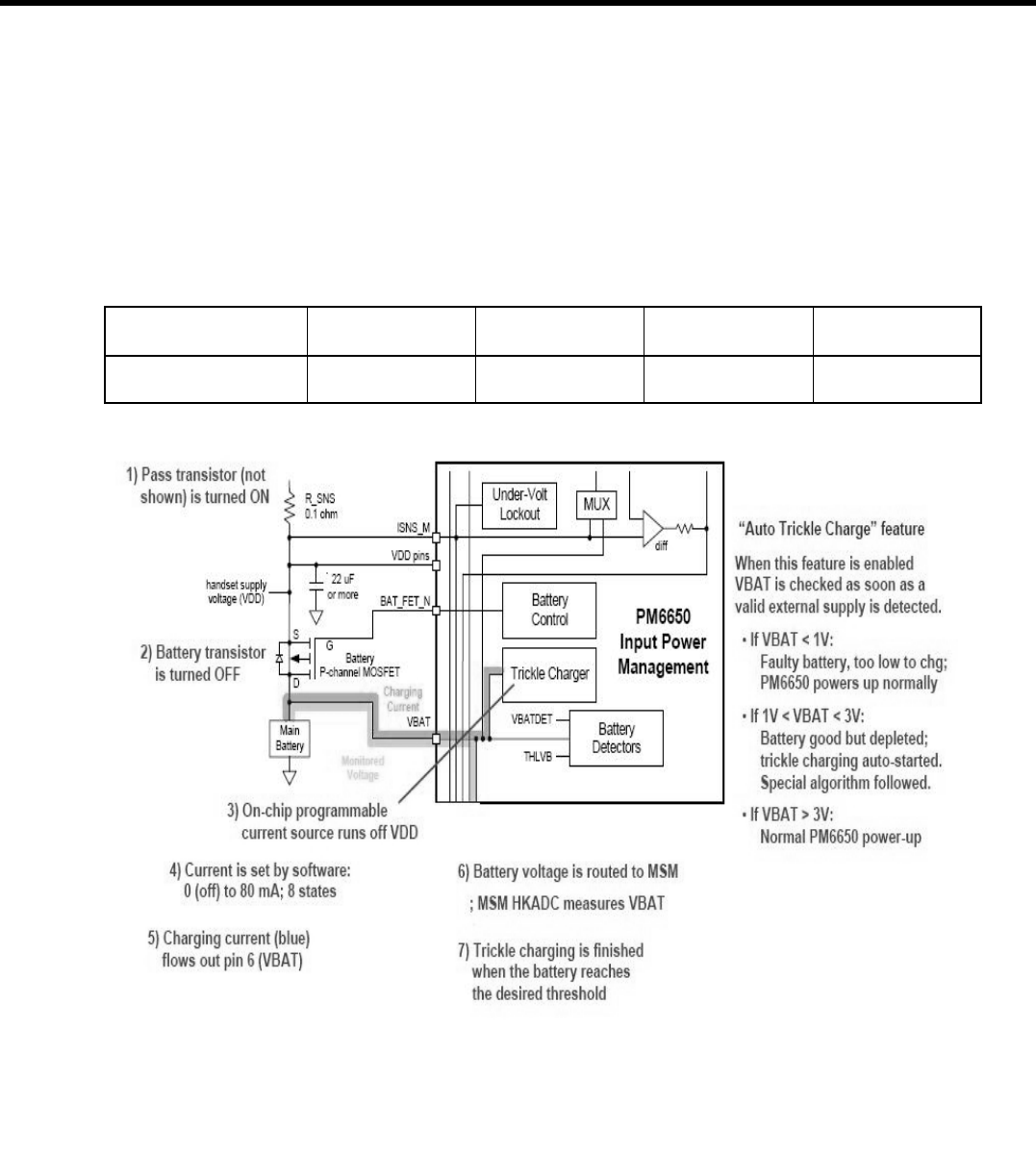

2.8 Charging

- Charging Method : CC & CV (Constant Current & Constant Voltage)

- Maximum Charging Voltage : 4.2V

- Maximum Charging Current : 650mA

- Nominal Battery Capacity : 950 mAh

- Charger Voltage : 4.8V

- Charging time : Max 3 h (Except time trickle charging)

- Full charge indication current (icon stop current) : 60mA

- Low battery POP UP : 3.48V

- Low battery alarm interval : Idle - 3 min, Dedicated - 1min

- Cut-off voltage : 3.22V

No Test Item Specification

1Sending Loudness Rating (SLR) 8 ±3 dB

2Receiving Loudness Rating (RLR) Nor -4 ± 3 dB

Max -15 ± 3 dB

3Side Tone Masking Rating (STMR) Min 17 dB

4Echo Loss (EL) Min 40 dB

5Sending Distortion (SD) Refer to Table 30.3

6Receiving Distortion (RD) Refer to Table 30.4

7Idle Noise-Sending (INS) Max -64 dBm0p

8Idle Noise-Receiving (INR) Nor Under -47 dBPA

Max Under -36 dBPA

9Sending Loudness Rating (SLR) 8±3dB

10 Receiving Loudness Rating (RLR) Nor -1 ±3 dB

Max -12 ±3 dB

11 Side Tone Masking Rating (STMR) Min 25 dB

12 Echo Loss (EL) Min 40 dB

13 Sending Distortion (SD) Refer to Table 30.3

14 Receiving Distortion (RD) Refer to Table 30.4

15 Idle Noise-Sending (INS) Max -55 dBm0p

16 Idle Noise-Receiving (INR) Nor Under -45 dBPA

Max Under -40 dBPA

TDMA Noise

-. GSM : Power Level : 5

DCS/PCS : Power Level : 0

(Cell Power : -90 ~ -105 dBm)

17

-. Acoustic (Max Vol.)

MS/Headset SLR : 8

±

3dB

MS/Headset RLR : -15 ± 3dB/-12dB

(SLR/RLR : Mid-value setting)

MS

Headset

MS and

Headset

Max Under -62 dBm

- 17 -

LGE Internal Use Only

Copyright © 2007 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3. TECHNICAL BRIEF

3.1 General Description

The KS10 supports UMTS-2100 DS-WCDMA, EGSM-900, DCS-1800, and PCS-1900. All receivers

and the UMTS transmitter use the radio One1Zero-IF architecture to eliminate intermediate

frequencies, directly converting signals between RF and baseband. The EGSM, DCS1800 and

PCS1900 transmitters use a baseband-to-IF up-conversion followed by an offset phase-locked loop

that translates the GMSK-modulated signal to RF.

1QUALCOMM’s branded chipset that implements a Zero-IF radio architecture.

3. TECHNICAL BRIEF

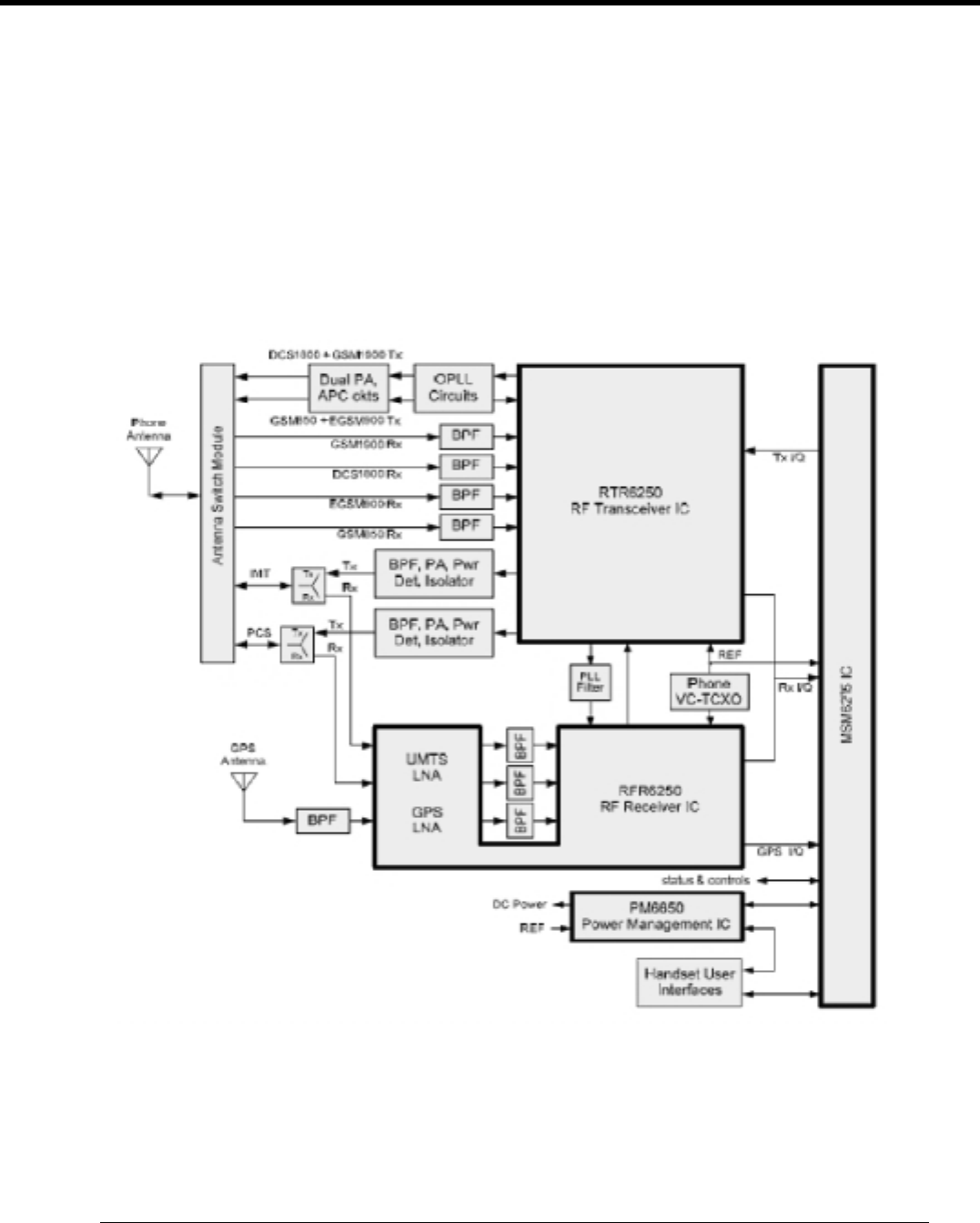

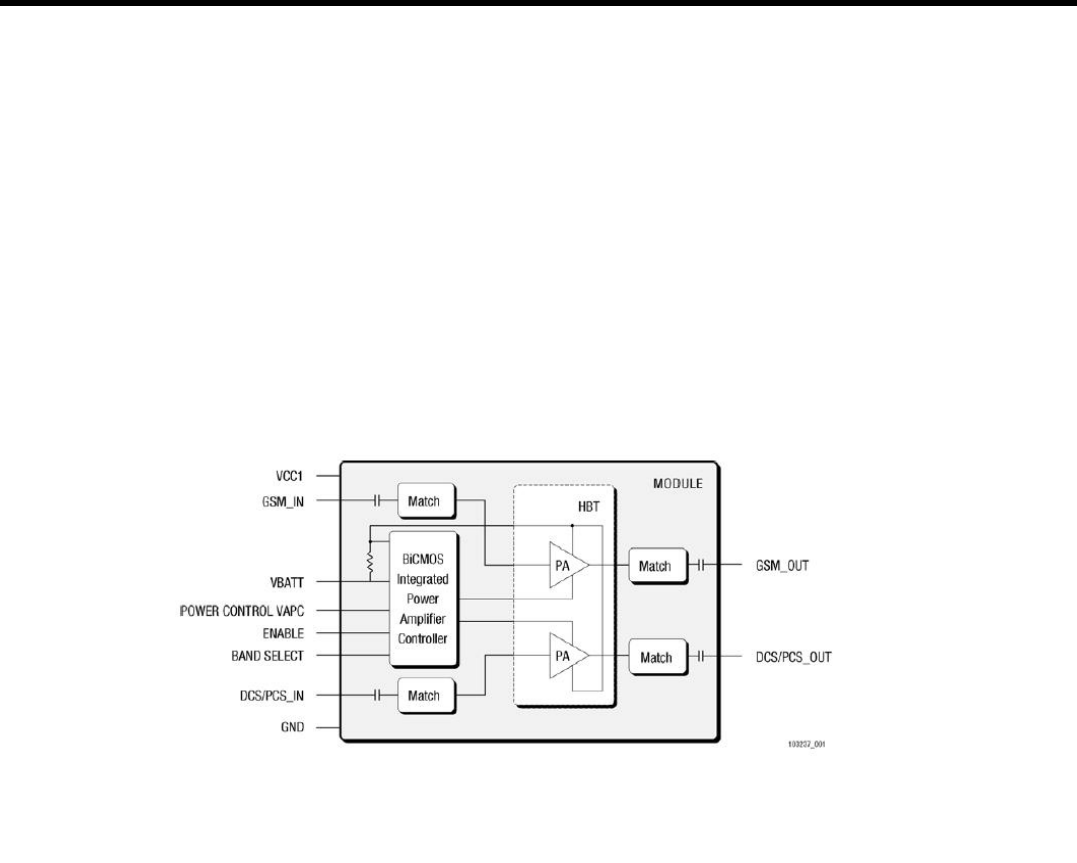

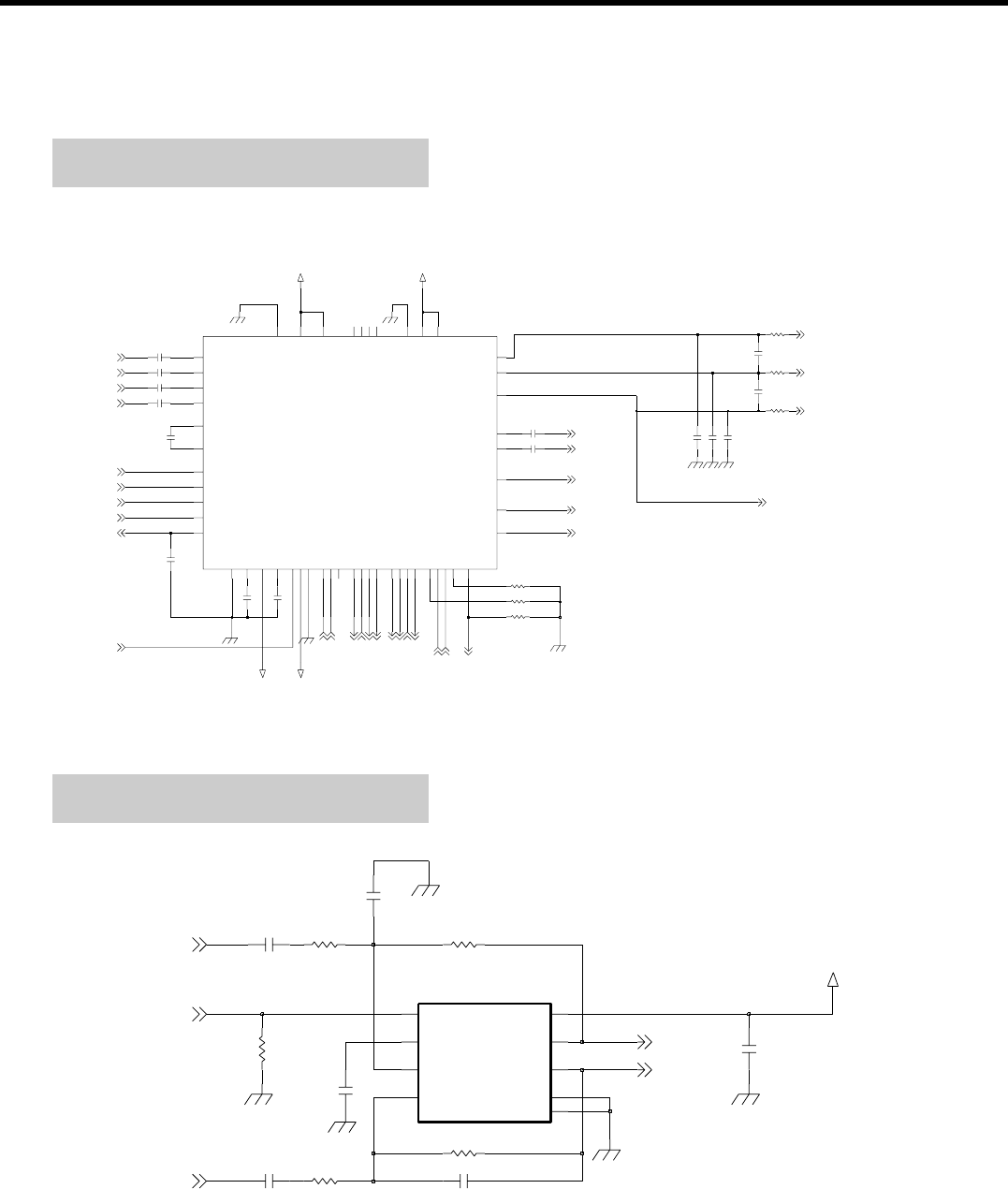

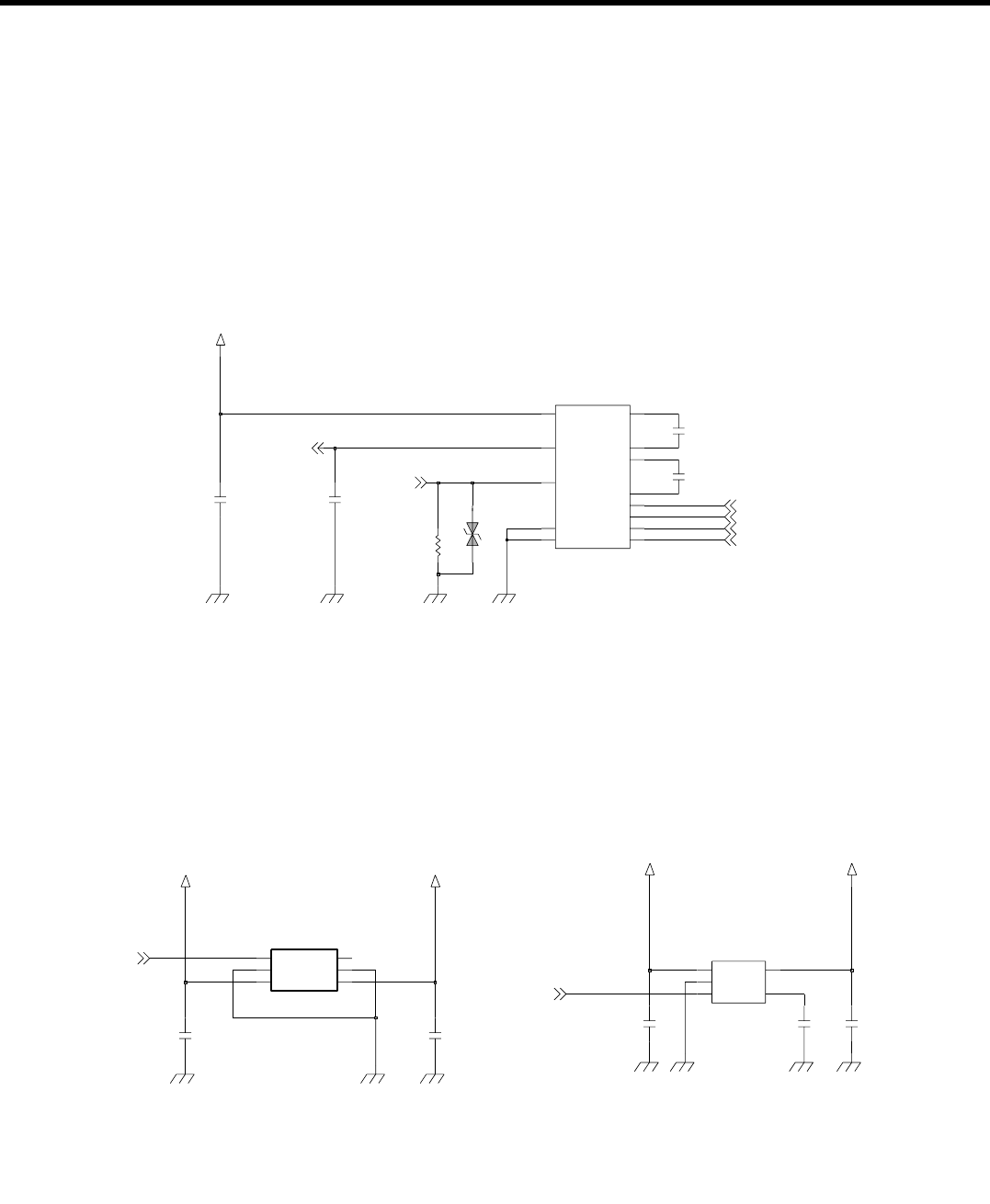

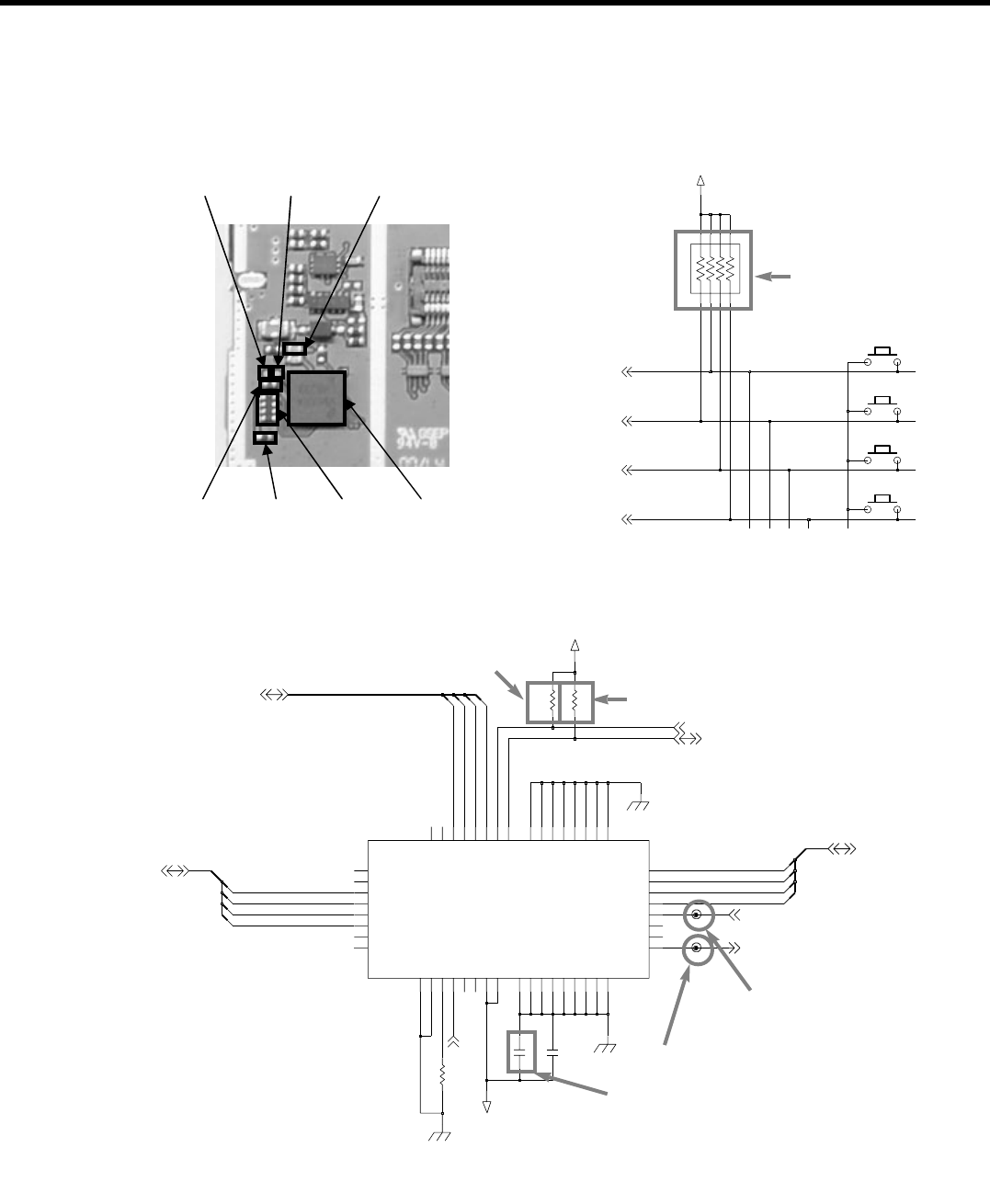

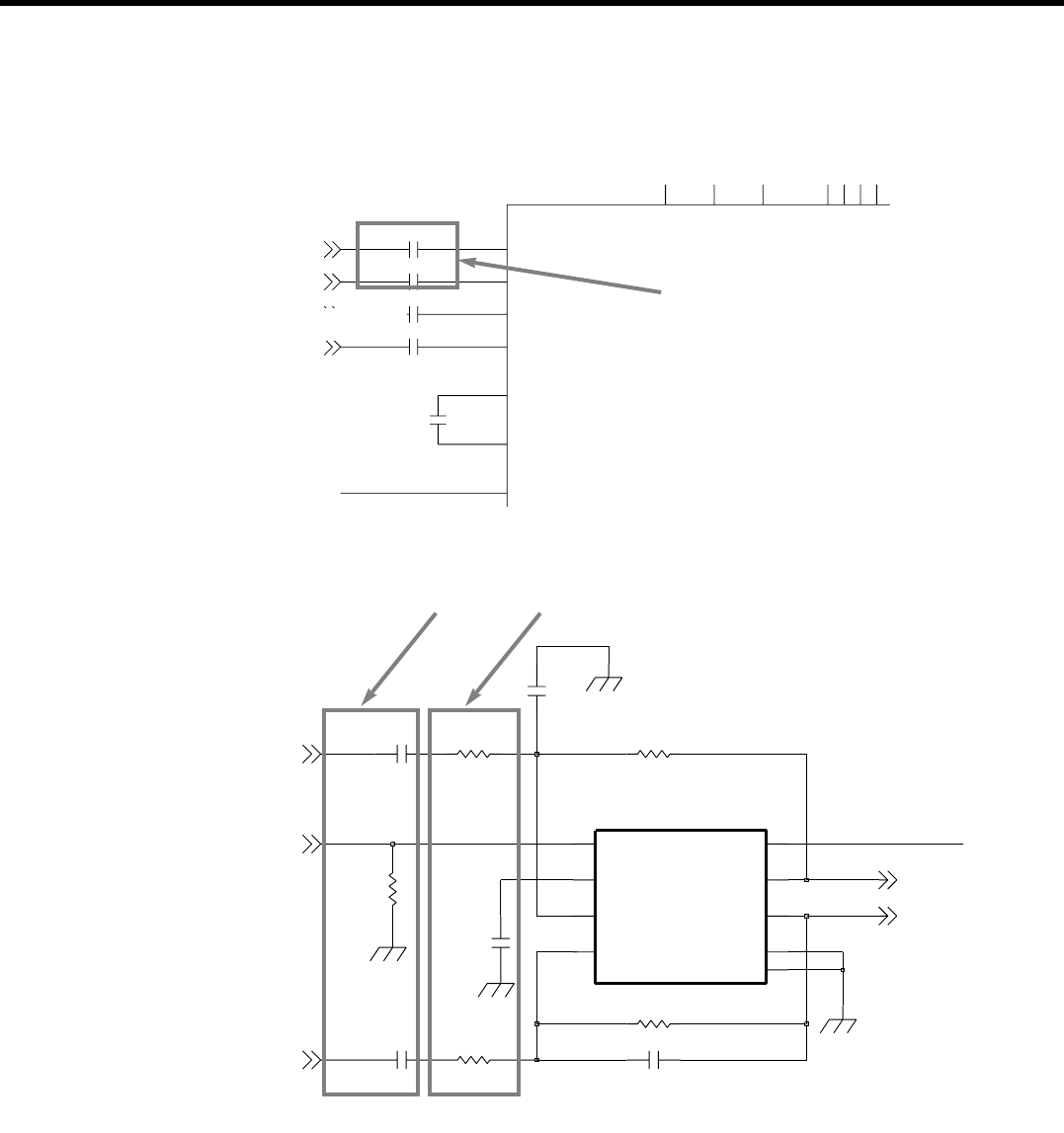

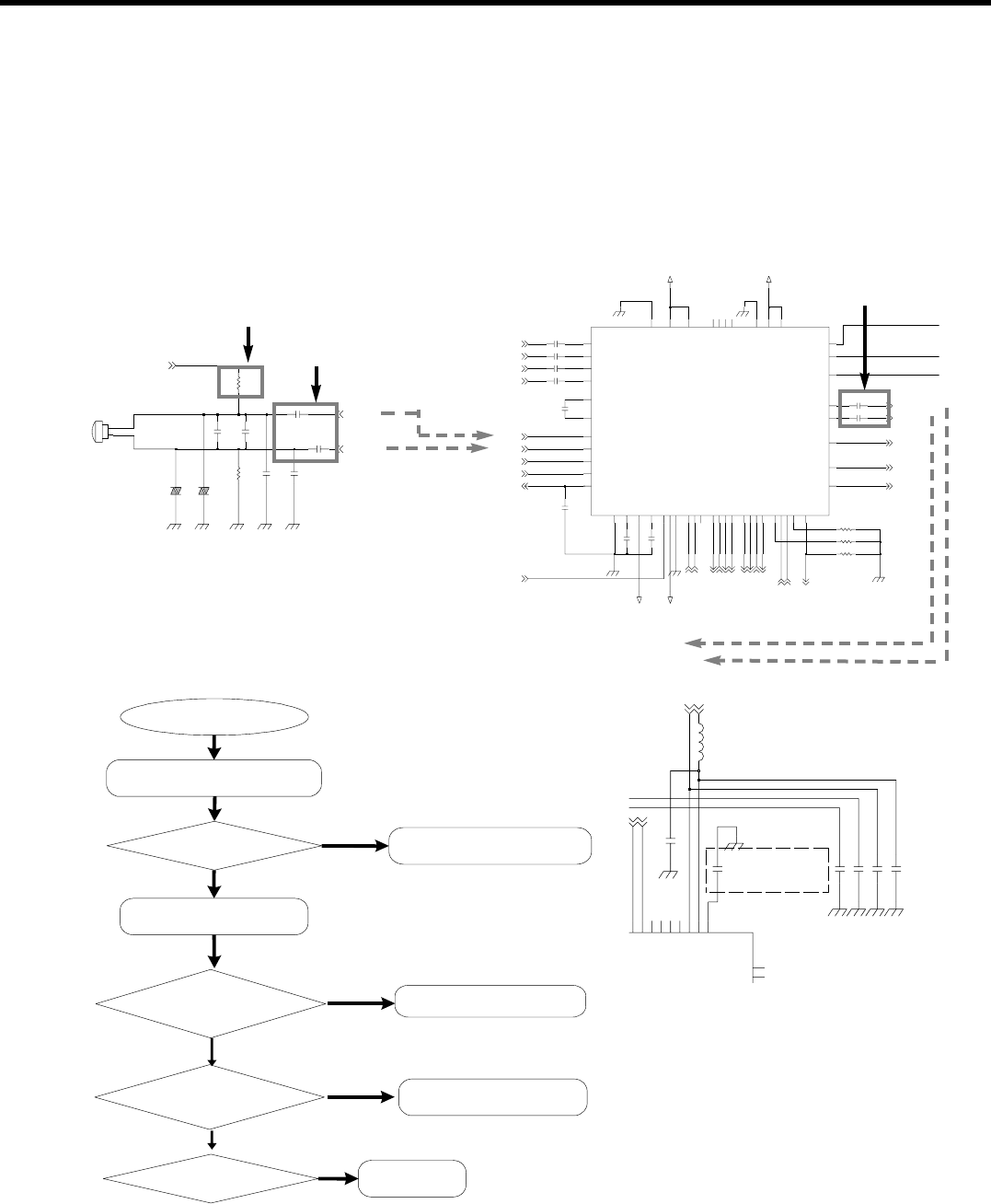

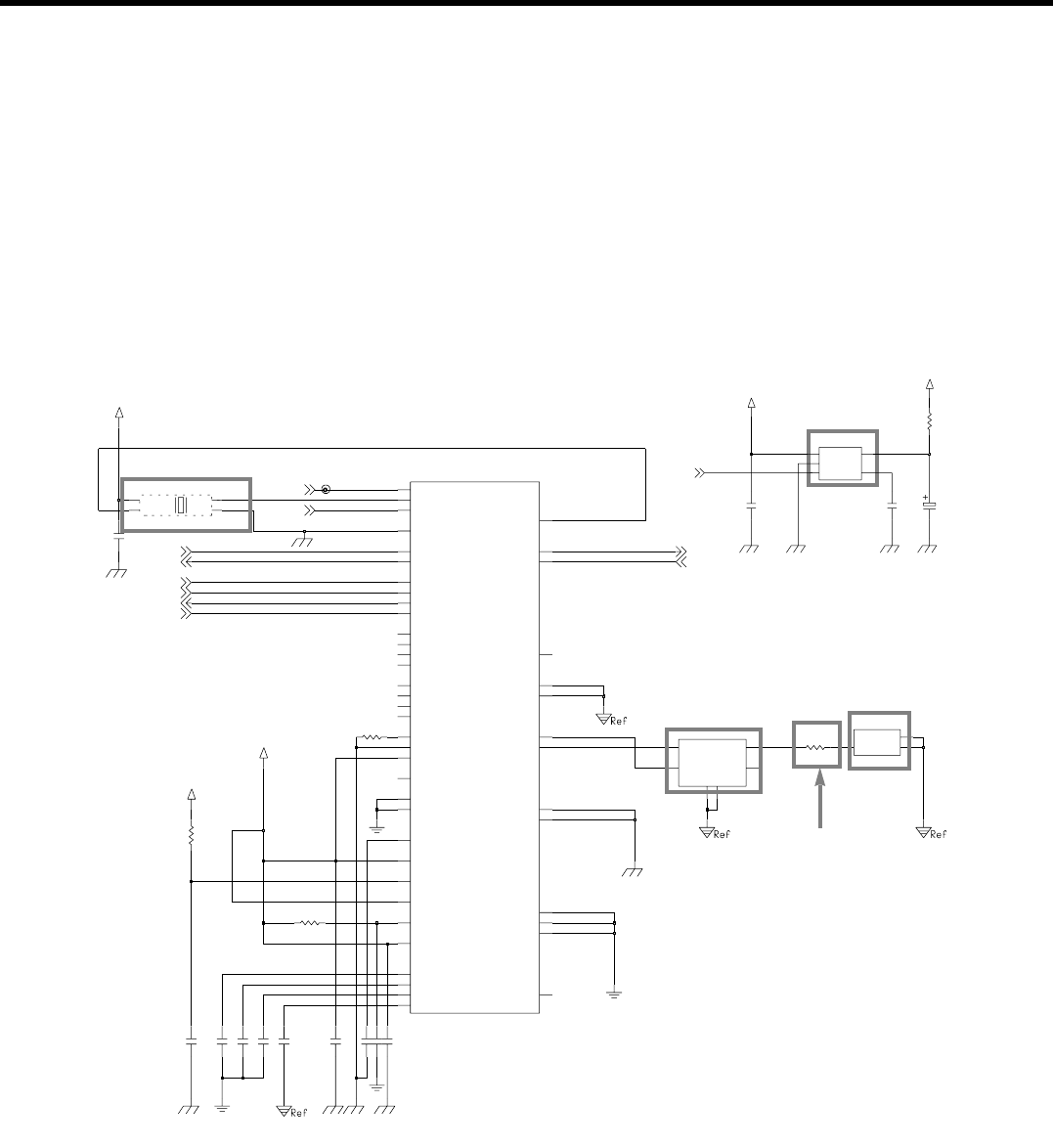

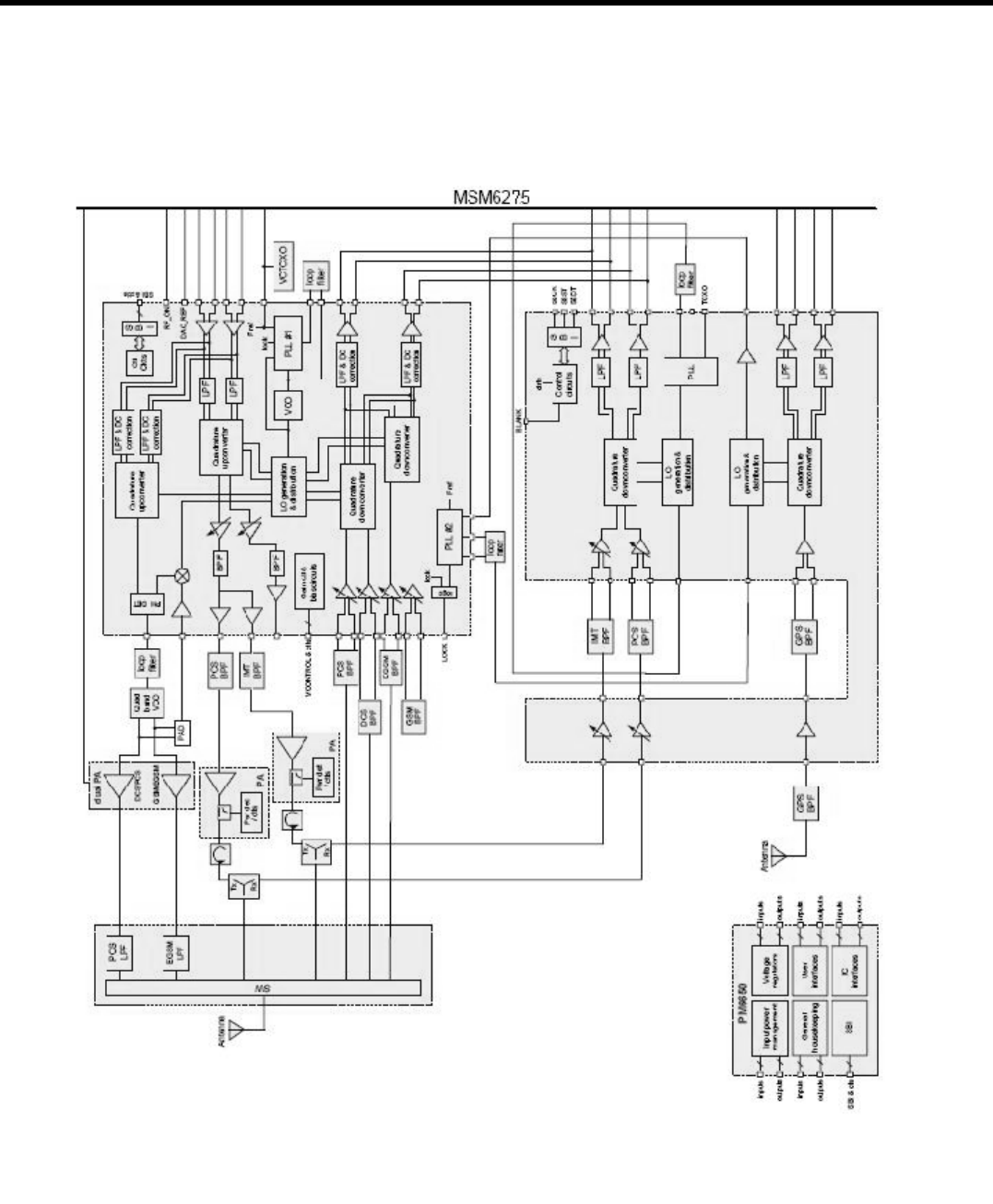

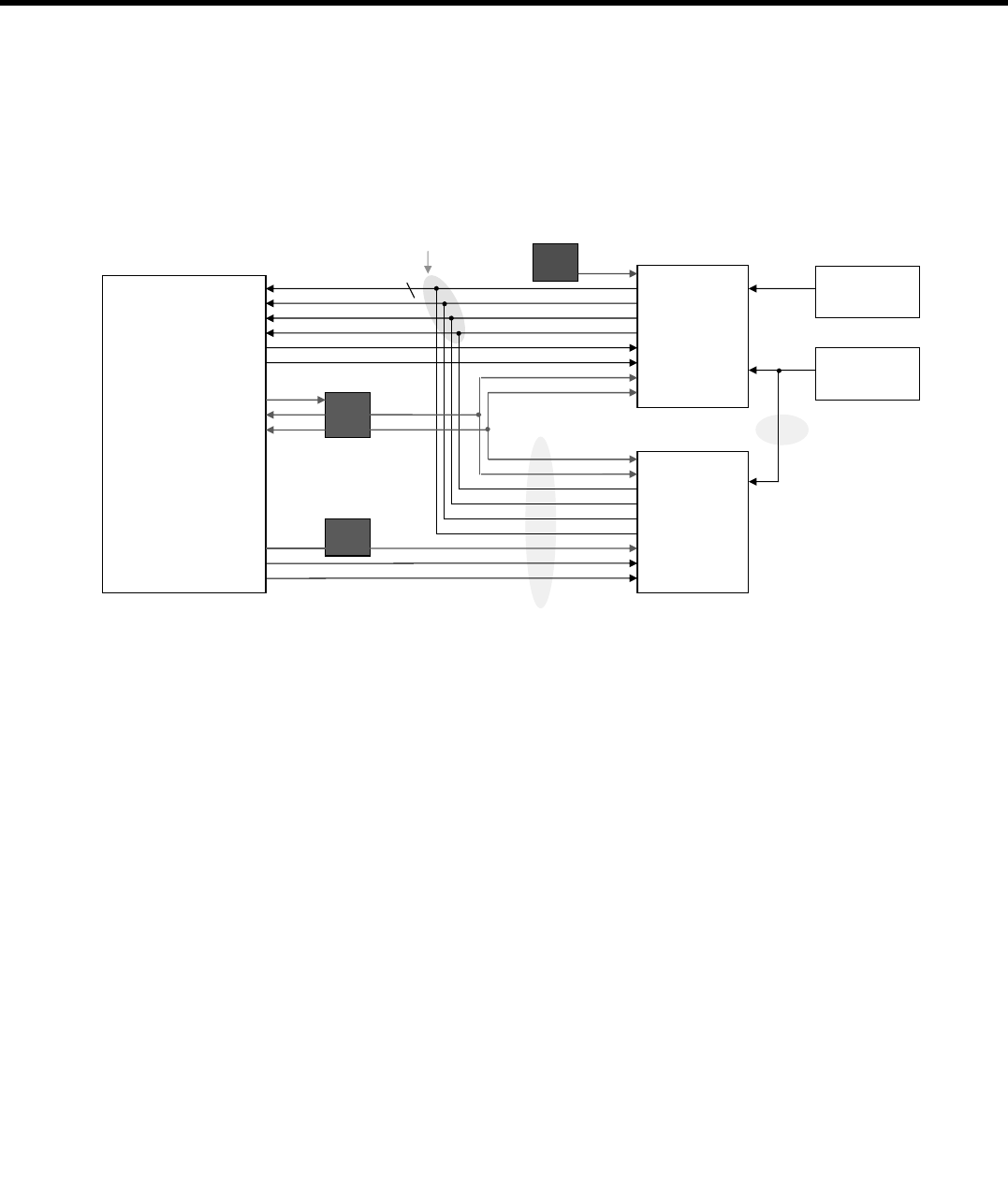

KS10 high-level RF functional block diagram

- 18 -

LGE Internal Use Only

Copyright © 2007 LG Electronics. Inc. All right reserved.

Only for training and service purposes

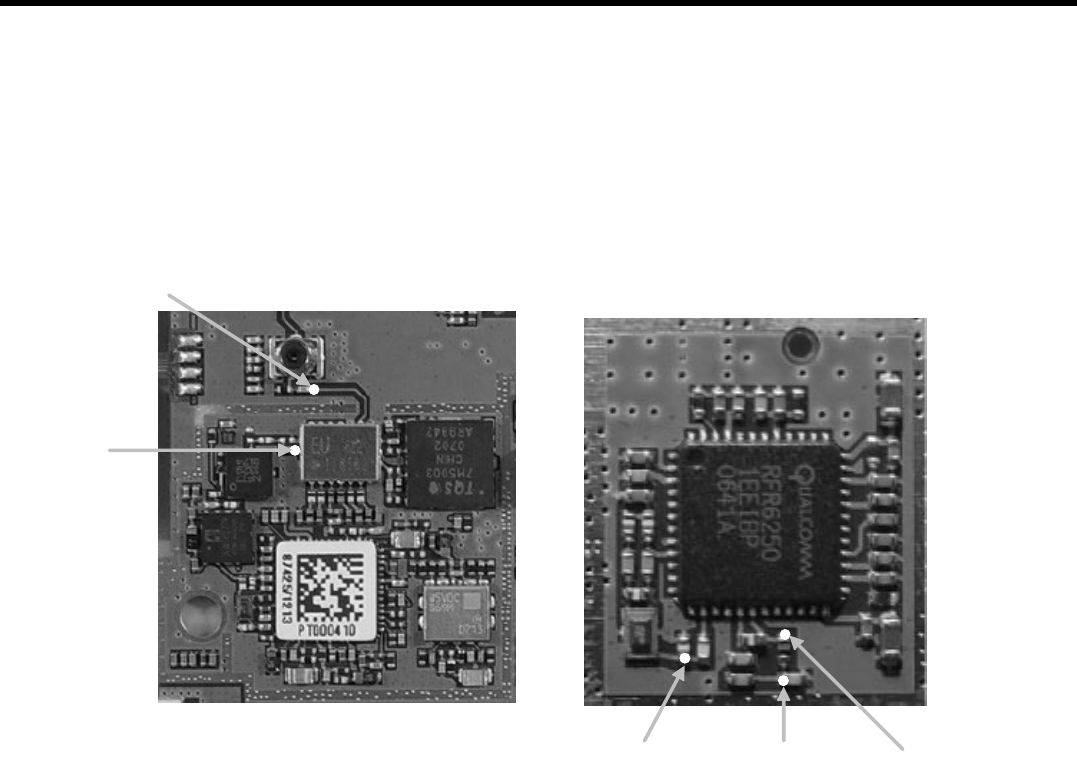

A generic, high-level functional block diagram of KS10 is shown in Figure 1-1. One antenna collects

base station forward link signals and radiates handset reverse link signals. The antenna connects with

receive and transmit paths through a switch module (plus a duplexer for UMTS-2100 operation).

UMTS band signals at the antenna are switched to the relevant UMTS duplexer. The UMTS receive

band signals are amplified by the front-end LNAs of the RFR6250 IC before passing through a band-

pass filter and being applied to the mixer inputs of the RFR6250 IC. On-chip circuits down-convert the

received signal directly from RF to baseband using radioOne Zero-IF techniques. Generation and

distribution of the UMTS LO, for the down-converter, is performed entirely on-chip (except for the loop

filter). The RFR6250 IC outputs analog baseband signals for processing by the MSM device. This

baseband interface is shared with the RTR6250 GSM receiver outputs, but is separate from the GPS

baseband interface.

EGSM, DCS and PCS receive signals from the antenna switch module pass through their band-pass

filters, then are applied to the RTR6250 IC. In a similar fashion to the UMTS paths, RTR6250 IC

circuits down-convert the received signals directly from RF to baseband. The GSM LO for multiband

down conversion is entirely generated within the RTR6250 IC (PLL and distribution functions) with

exception of the off-chip loop filter. The RTR analog baseband outputs are routed to the MSM6275 IC

for further processing (an interface shared with the RFR UMTS receive paths).

The UMTS transmit path begins with analog baseband signals from the MSM device that drive the

RTR6250 IC. Integrated PLL and VCO circuits generate the Tx LO used in the quadrature upconverter

that translates baseband signals directly to RF. The RTR6250 output driver stages deliver fairly high-

level signals that are filtered and applied to the power amplifiers (PA). The PA output is routed to the

antenna through a duplexer and switch module.

The shared EGSM-900, DCS-1800, and PCS-1900 transmit path begins with the same baseband

interface from the MSM6275 IC that is used for the UMTS band. A single EGSM/DCS/PCS quadrature

upconverter translates the GMSK-modulated signal to a convenient intermediate frequency (IF) that

forms one input to an offset phase-locked loop (OPLL). OPLL functions are split between the

RTR6250 IC and off-chip loop filter and dual Tx VCO circuits, and translate the GMSK-modulated

signal to the desired EGSM-900, DCS-1800 or PCS-1900 channel frequency. This signal is applied to

a dual power amplifier (only one is active at a time). The enabled path continues with the PA, an

automated power control (APC) circuit that samples the transmit power and adjusts its level, the switch

module (which includes a band-appropriate lowpass filter), and the antenna.

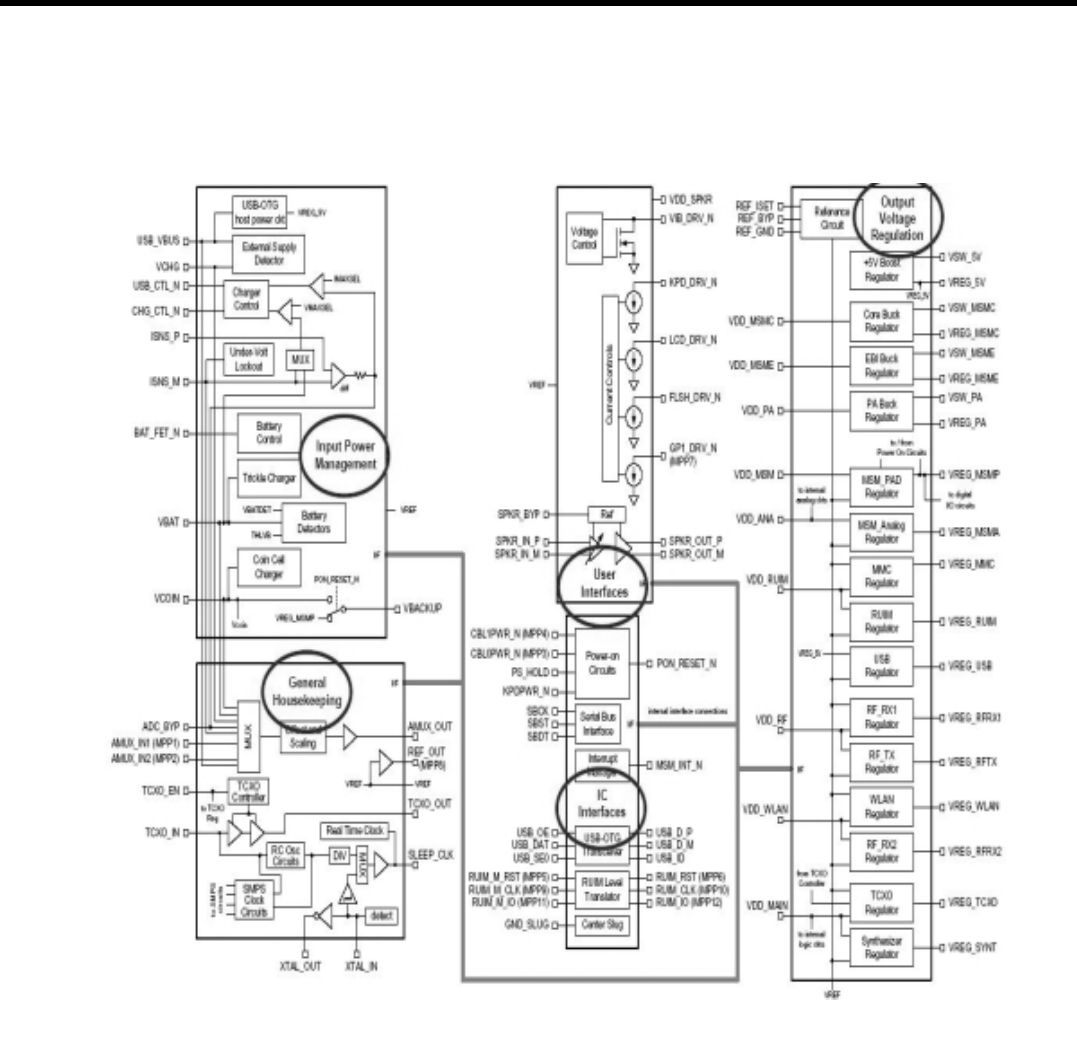

KS10 power supply voltages are managed and regulated by the PM6250 Power Management IC. This

versatile device integrates all wireless handset power management, general housekeeping, and user

interface support functions into a single mixed signal IC. It monitors and controls the external power

source and coordinates battery recharging while maintaining the handset supply voltages using low

dropout, programmable regulators.

The device’s general housekeeping functions include an ADC and analog multiplexer circuit for

monitoring on-chip voltage sources, charging status, and current flow, as well as userdefined off-chip

variables such as temperature, RF output power, and battery ID. Various oscillator, clock, and counter

circuits support IC and higher-level handset functions. Key parameters such as under-voltage lockout

and crystal oscillator signal presence are monitored to protect against detrimental conditions.

3. TECHNICAL BRIEF

- 19 -

LGE Internal Use Only

Copyright © 2007 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3. TECHNICAL BRIEF

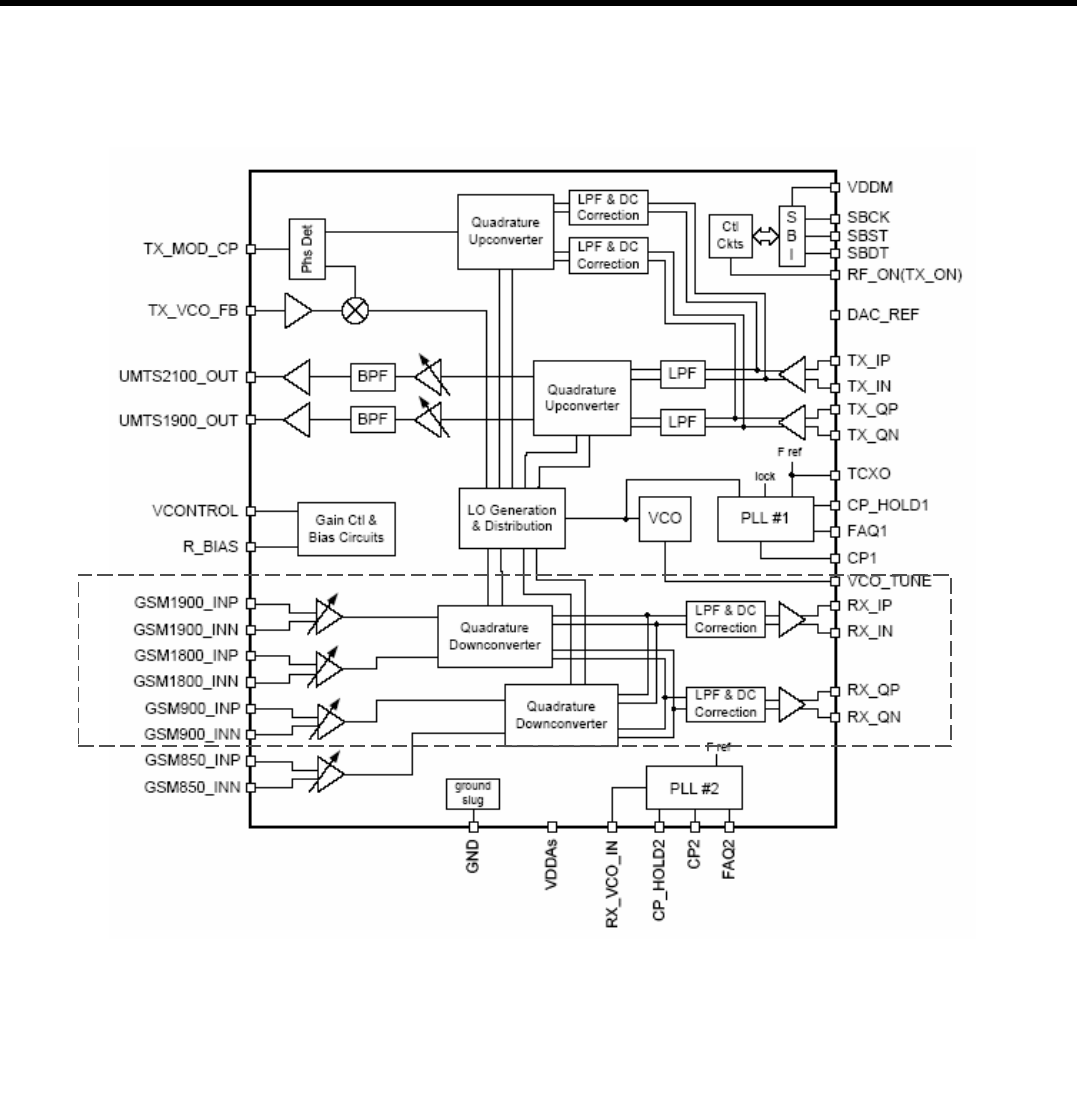

3.2 GSM Mode

3.2.1 GSM Receiver

The Dual-mode KS10’s receiver functions are split between the two RFICs as follows:

• UMTS-2100 operation uses the RFR6250 Receiver ICs to implement the receive signal path,

accepting an RF input and delivering analog baseband outputs (I and Q).

• EGSM-900, DCS-1800, and PCS-1900 modes both use the RTR6250 IC only. Each mode has

independent front-end circuits and down-converters, but they share common baseband circuits (with

only one mode active at a time). All receiver control functions are beginning with SBI2-controlled

parameters.

The EGSM, DCS, and PCS receiver inputs of RTR6250 are connected directly to the transceiver front-

end circuits(filters and antenna switch module). EGSM, DCS, and PCS receiver inputs are similar to

the RFR6250 UMTS Rx input in that they also use differential configurations to improve common-

mode rejection and second-order non-linearity performance.

The balance between the complementary signals is critical and must be maintained from the RF filter

outputs all the way into the IC pins Since EGSM, DCS, and PCS signals are time-division duplex (the

handset can only receive or transmit at one time), switches are used to separate Rx and Tx signals in

place of frequency duplexers - this is accomplished in the switch module.

The EGSM, DCS, and PCS receive signals are routed to the RTR6250 through band selection filters

and matching networks that transform single-ended 50-Ω sources to differential impedances optimized

for gain and noise figure. Similar to the RFR, the RTR input uses a differential configuration to improve

second-order inter-modulation and common mode rejection performance. The RTR6250 input stages

include MSM-controlled gain adjustments that maximize receiver dynamic range.

The amplifier outputs drive the RF ports of the quadrature RF-to-baseband downconverters.

The downconverted baseband outputs are multiplexed and routed to lowpass filters (one I and one Q)

having passband and stopband characteristics suitable for GMSK processing. These filter circuits

include DC offset corrections. The filter outputs are buffered and passed on to the MSM6275 IC for

further processing (an interface shared with the RFR6250 UMTS receiver outputs).

2The RFIC operating modes and circuit parameters are MSM-controlled through the proprietary 3-line Serial Bus Interface (SBI). The Application

Programming Interface (API) is used to implement SBI commands. The API is documented in AMSS Software - please see applicable AMSS

Software documentation for details.

- 20 -

LGE Internal Use Only

Copyright © 2007 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3. TECHNICAL BRIEF

- 21 -

LGE Internal Use Only

Copyright © 2007 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3. TECHNICAL BRIEF

3.2.2 GSM Transmitter

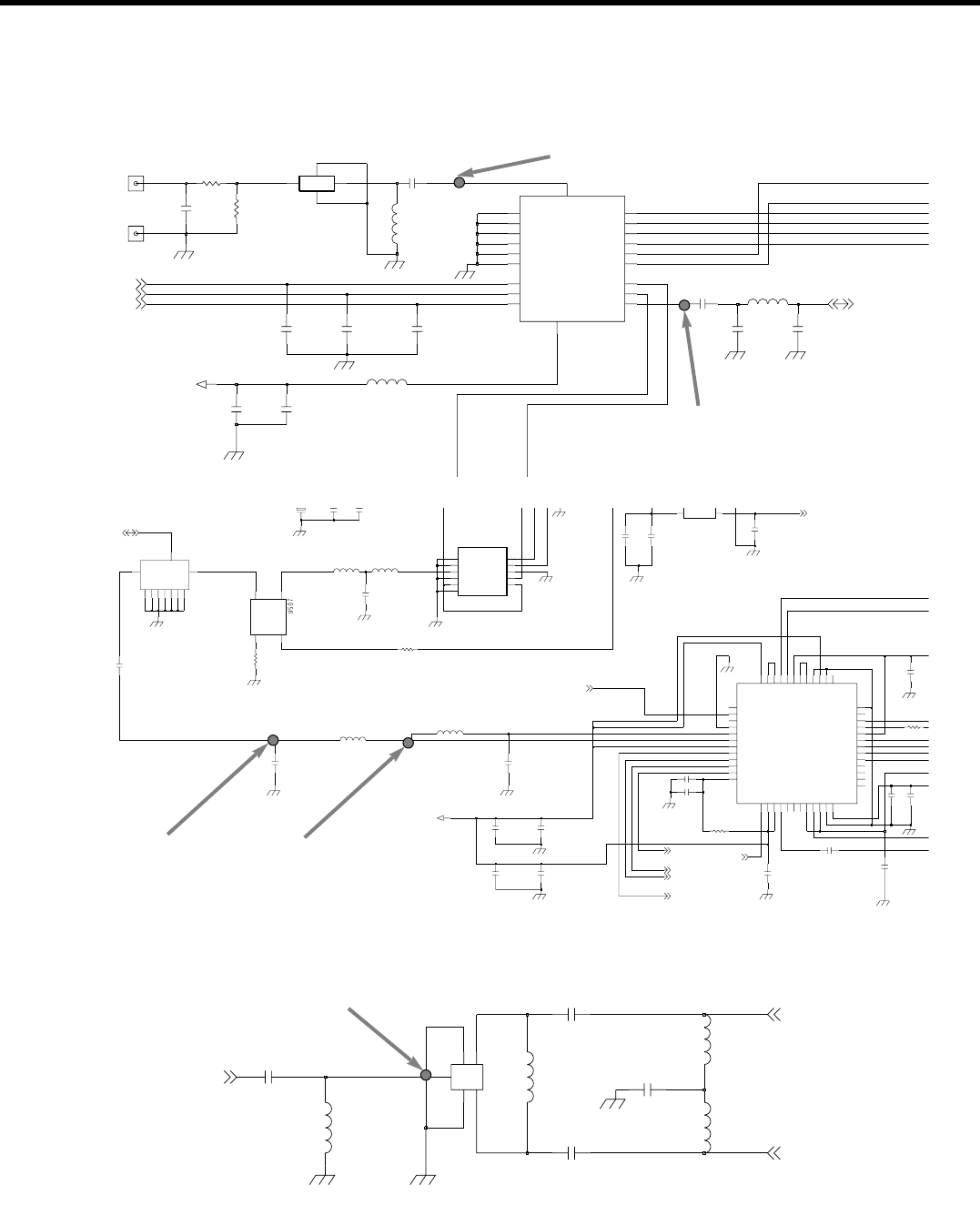

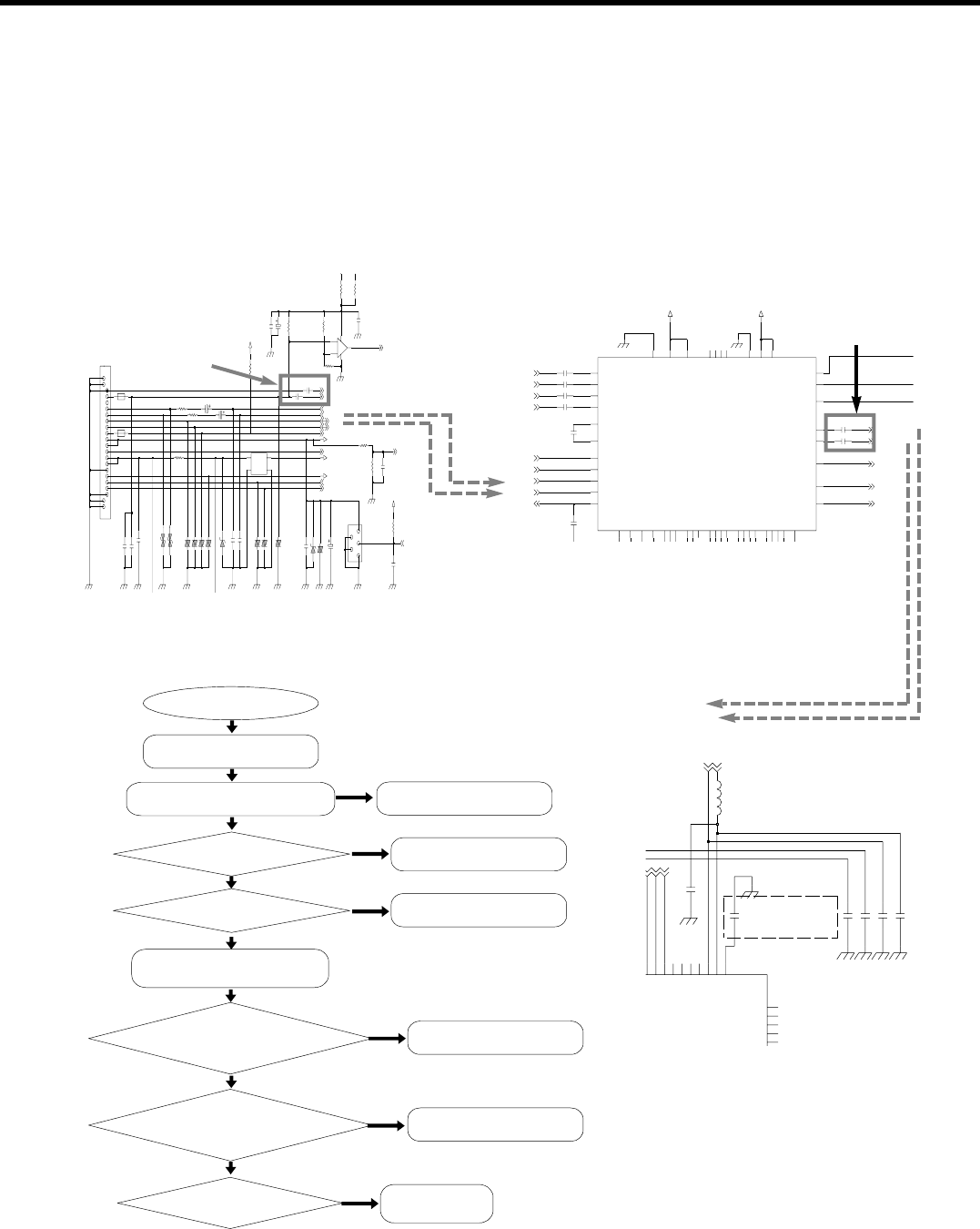

The shared GSM Low-band (EGSM900) and High-band (DCS1800, PCS1900) transmit path begins

with the baseband inputs from the MSM6275 IC. These differential analog input signals are buffered,

lowpass filtered, corrected for DC offsets then applied to the GSM quadrature upconverter. The

upconverter LO signals are generated from the transceiver VCO signal by the LO distribution and

generation circuits within RTR6250. This upconverter translates the GMSK-modulated signal to a

convenient intermediate frequency (IF) that forms one input to a frequency/phase detector circuit. This

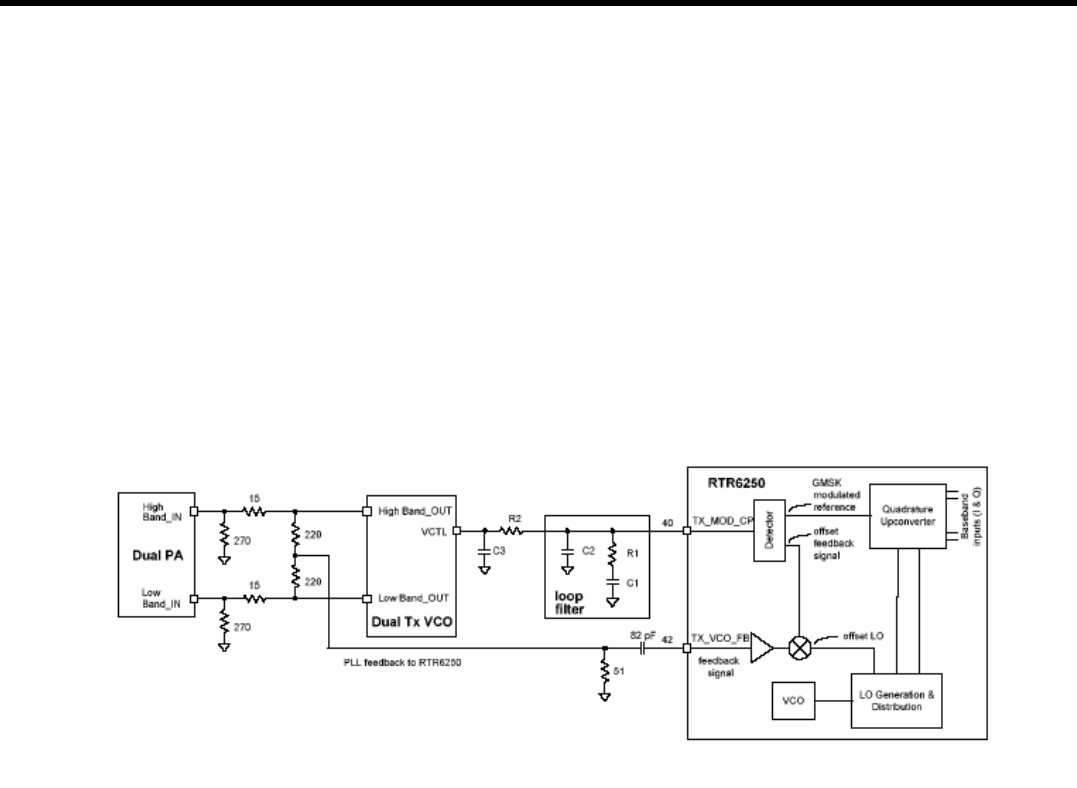

IF signal is the reference input to an offset phase-locked loop (OPLL) circuit as shown in Figure 1.2.2-1.

The feedback path of this OPLL circuit includes a downconversion from the RF output frequency range

to the IF range. The two inputs to this downconversion mixer are formed as follows:

1. The dual Tx VCO output (operating in the desired RF output frequency range) is buffered within the

RTR6250 IC then applied to the mixer RF port.

2. The LO Generation and Distribution circuits that deliver the transmit path.s LO for the baseband-to-IF

upconversion also provides the offset LO signal that is applied to the feedback path.s mixer LO port.

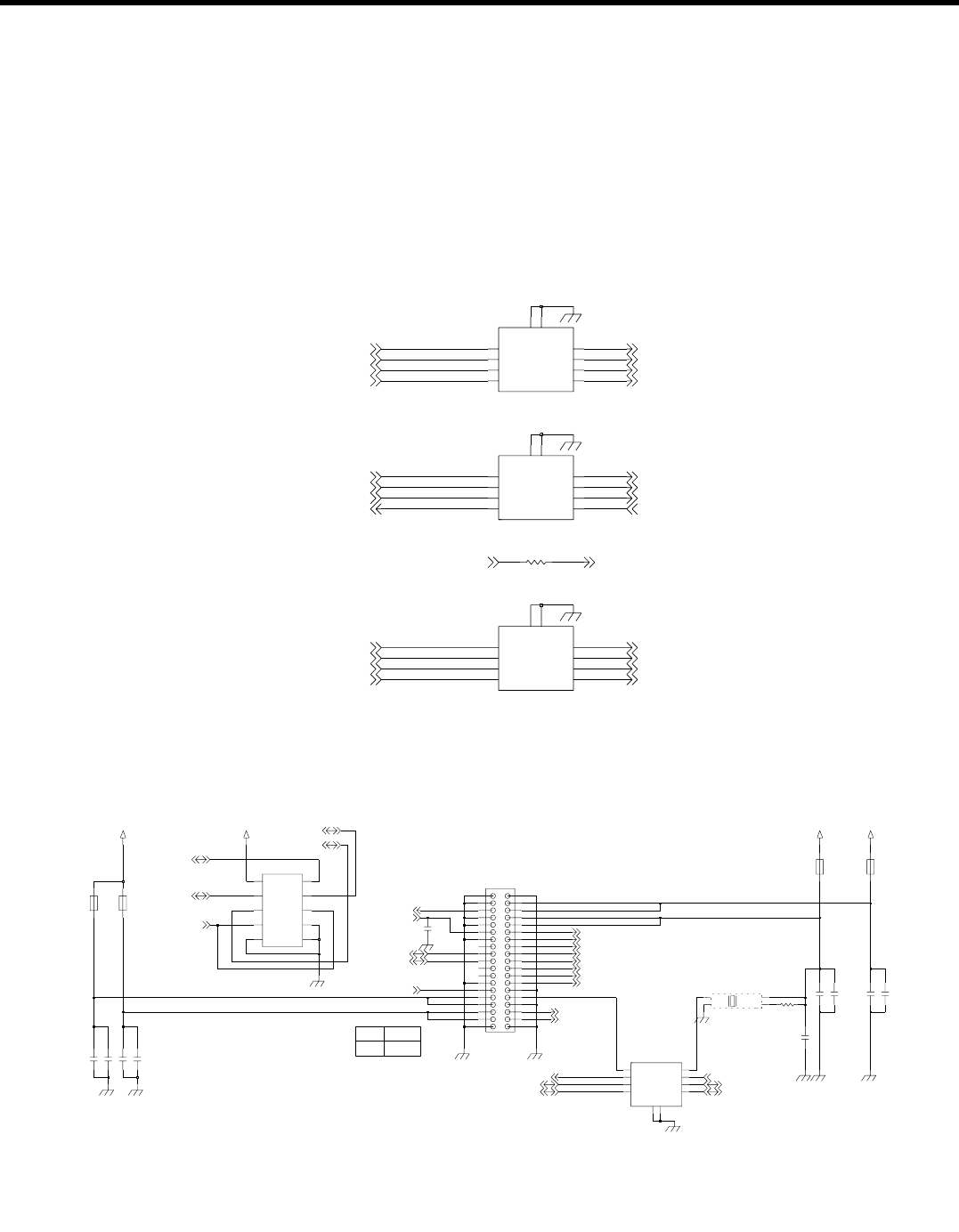

Figure 1.2.2-1 Offset phase-locked loop interfaces

- 22 -

LGE Internal Use Only

Copyright © 2007 LG Electronics. Inc. All right reserved.

Only for training and service purposes

The mixer IF port output is the offset feedback signal - the variable input to the frequency/phase

detector circuit. The detector compares its variable input to its reference input and generates an error

signal that is lowpass filtered by the loop filter and applied to the dual Tx VCO tuning port to force the

VCO output in the direction that minimizes errors. As mentioned earlier, the VCO output is connected to

the feedback path thereby creating a closed-loop control system that will force frequency and phase

errors between the variable and reference inputs to zero.

The waveform at the dual Tx VCO output is the GMSK-modulated signal centered at the desired GSM

channel frequency. A phase-locked loop circuit is used to translate the GMSKmodulated signal from IF

to RF primarily for two reasons:

1. Phase-locked loops provide a lowpass filter function from the reference input to the VCO output.

These results in a bandpass function centered at the desired channel frequency that provides steep,

well-controlled rejection of the out-of-band spectrum.

2. The resulting output bandpass function is virtually unchanged as the transmitter is tuned over

channels spanning the GSM operating band.

The PA is a key component in any transmitter chain and must complement the rest of the transmitter

precisely. For GSM band operation, the closed-loop transmit power control functions add even more

requirements relative to the UMTS PA. In addition to gain control and switching requirements, the usual

RF parameters such as gain, output power level, several output spectrum requirements, and power

supply current are critical. The gain must be sufficient and variable to deliver the desired transmitter

output power given the VCO output level, the subsequent passive devices’ losses, and the control set

point. The maximum and minimum transmitter output power levels depend upon the operating band

class and mobile station class per the applicable standard. Transmitter timing requirements and in-band

and out-of-band emissions, all dominated by the PA, are also specified by the applicable standard.

The active dual Tx VCO output is applied to the dual power amplifier to continue the transmit path, and

feedback to the RTR6250 IC to complete the frequency control loop. The PA operating band (EGSM or

DCS/PCS) is selected by the MSM device GPIO control. (GSM_PA_BAND).

3. TECHNICAL BRIEF

- 23 -

LGE Internal Use Only

Copyright © 2007 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3. TECHNICAL BRIEF

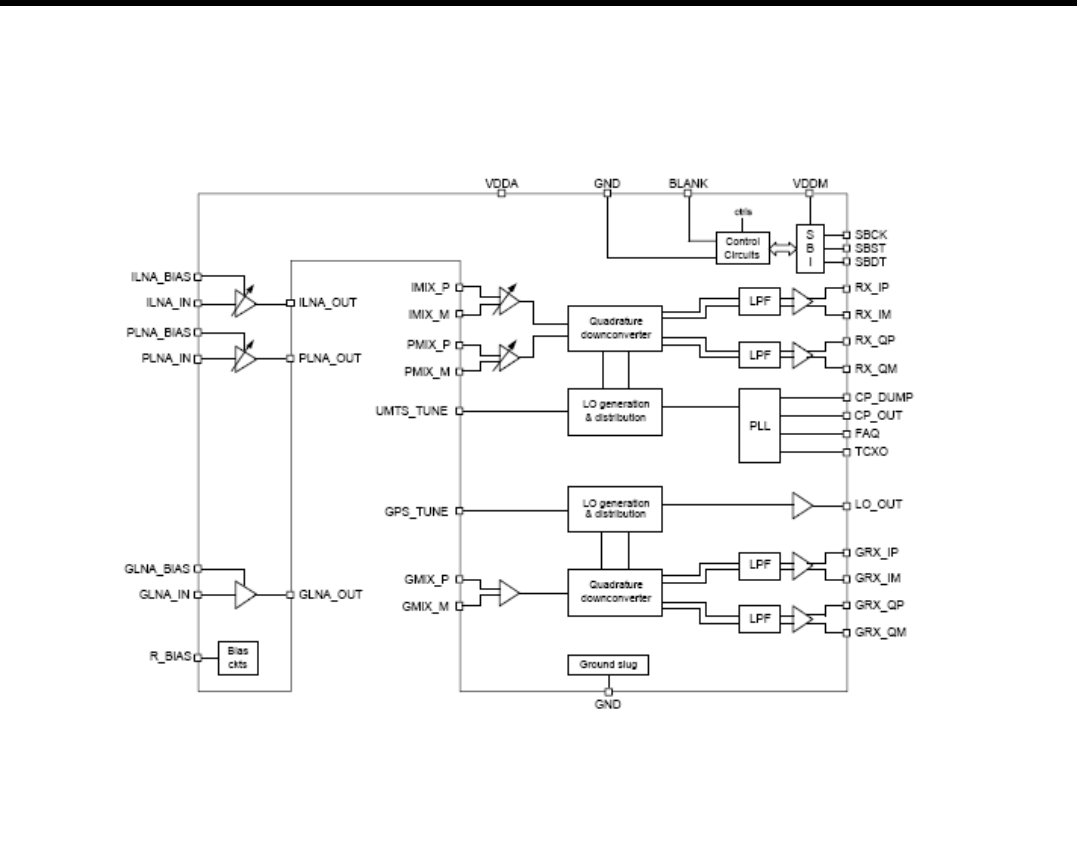

3.3 WCDMA Mode

3.3.1 Receiver

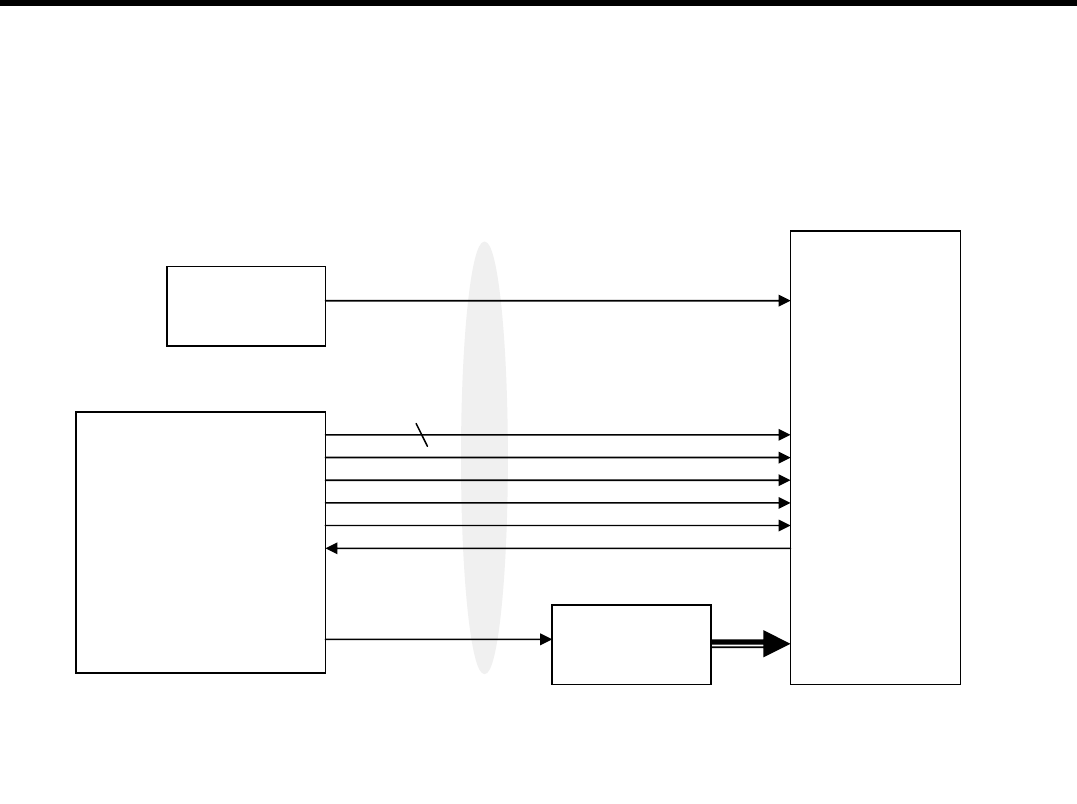

The UMTS duplexer receiver output is routed to LNA circuits within the RFR6250 IC. The LNA gain is

dynamically controlled by the MSM6275 IC to cover full receiver dynamic range and to save current

consumption.

The UMTS LNA output is routed to the down conversion mixer inputs, in the RFR6250 IC, through a

band selection filter that transforms a single-ended 50-Ω source to differential 100-Ω load impedance

that is matched to the RFR6250 IC. The RFR input uses a differential configuration to improve second-

order inter-modulation and common mode rejection performance. The RFR6250 IC input stages include

MSM-controlled gain adjustments that further extend receiver dynamic range.

The amplifier output drives the RF port of the quadrature RF-to-baseband down-converter. The down-

converted baseband outputs are routed to low-pass filters (one I and one Q) having pass-band and

stop-band characteristics suitable for DS-WCDMA processing. The filter outputs are buffered and

passed on to the MSM6275 IC for further processing. This baseband interface is shared with the

RTR6250 GSM receiver outputs.

The RFR6250 IC includes LO generation and distribution circuitry to reduce off-chip component

requirements. The GPS RX LO source is created using the PLL control elements of the RTR6250

PLL2, via a discrete loop filter components, in tandem with the VCO in the RFR6250. Using only this

PLL signal, the RFR6250 LO generation and distribution circuits create the necessary LO signals for

the UMTS quadrature down-converter. By definition, the ZIF down-converter requires FLO equal to FRF,

and the RTR6250/RFR6250 design achieves this without allowing FVCO to equal FRF.

- 24 -

LGE Internal Use Only

Copyright © 2007 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3. TECHNICAL BRIEF

Figure 1.3.1-1 RFR6250 IC functional block diagram

- 25 -

LGE Internal Use Only

Copyright © 2007 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3.3.2 Transmitter

The UMTS transmit path begins with analog baseband signals from the MSM device that drive the

RTR6250 IC. The RTR6250 IC provides all the UMTS transmitter active signalpath circuits except the

power amplifiers. Analog (I and Q) differential signals from the MSM device are buffered, filtered, and

applied to Baseband-to-RF quadrature upconverters. Gain control is implemented on-chip. The RF

outputs include an integrated matching inductor, reducing the off-chip matching network to a single

series capacitor.

The RTR6250 UMTS output is routed to its power amplifier through a bandpass filter, and delivers fairly

high-level signals that are filtered and applied to the PA. The PA device used in KU950 is “Load

Insensitive PA”- no need to use isolator - and routed to the duplexer Tx port directly. Transmit power is

delivered from the duplexer to the antenna through the switch module.

The RTR6250 IC integrates LO generation and distribution circuits on-chip, substantially reducing off-

chip requirements. Various modes and programmable features result in a highly flexible transceiver LO

output that supports not only UMTS transmissions, but all EGSM900 and DCS1800/PCS1900 Rx and

Tx modes as well.

The UMTS Tx LO (PLL1) is generated almost entirely on-chip, requiring only the loop filter off-chip (two

capacitors and two resistors); all UMTS Tx VCO and PLL circuits are on-chip. An internal RTR6250

switch routes the internal VCO signal to the LO generation and distribution circuits to create the

necessary UMTS Tx LO signals.

3. TECHNICAL BRIEF

- 26 -

LGE Internal Use Only

Copyright © 2007 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3.4 LO Phase-locked Loop

Most LO functions are fully integrated on-chip, do not require user adjustment, and need not be

considered by handset designers. QUALCOMM has established and implemented frequency plans

and LO generation schemes that support the radioOne 6250-IIseries chipset while requiring minimal

off-chip design effort. Only one area requires handset designer attention: the loop filters of each

phase-locked loop (PLL).

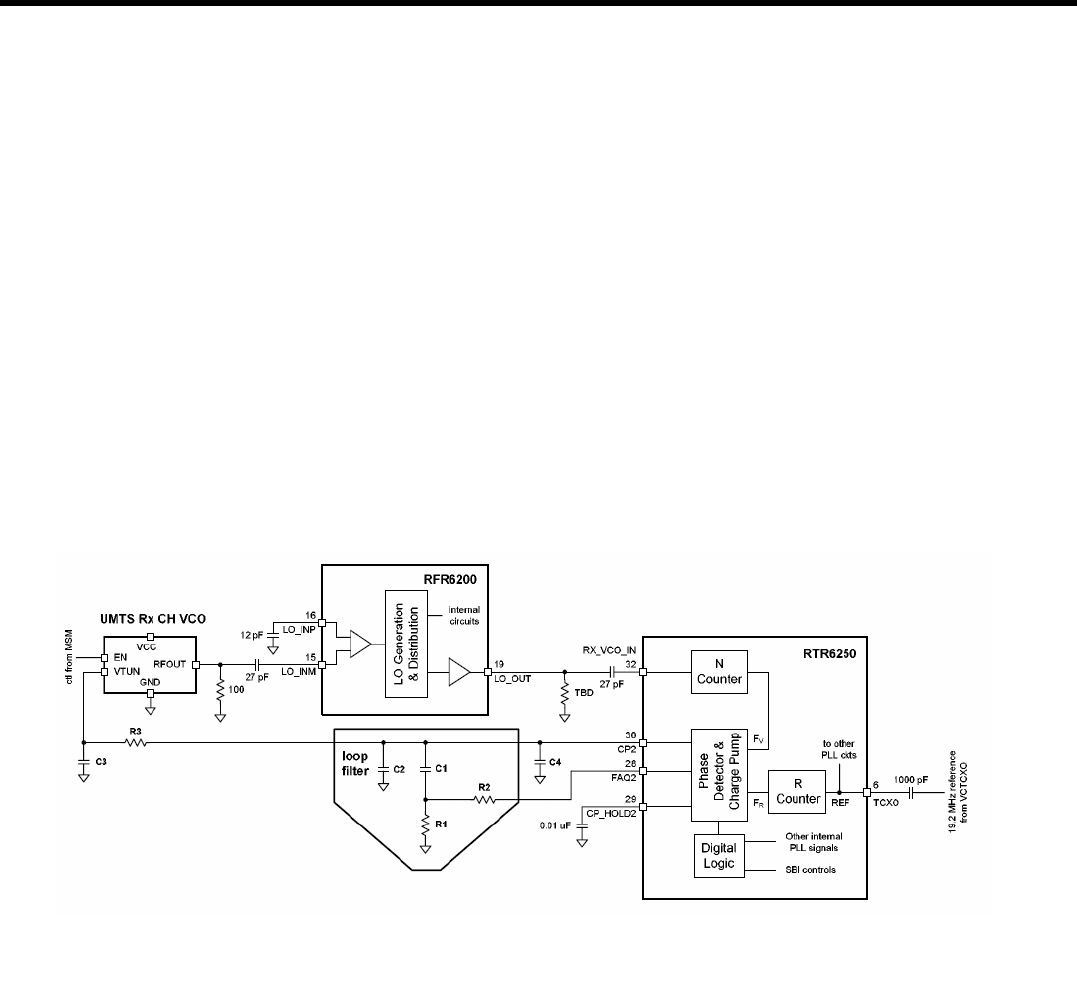

3.4.1 UMTS Rx PLL (PLL2)

UMTS Rx LO functional blocks are distributed between the RFR6250 IC, RTR6250 IC, and external

UMTS_RX_CH_VCO and loop filter components (Figure 1.4.1-1). The external UMTS_RX_CH_VCO

must be enabled for UMTS Rx operation and disabled otherwise; a dedicated MSM6275 IC signal

(UHF_VCO_EN ) enables the VCO.

3. TECHNICAL BRIEF

Figure 1.4.1-1 UMTS Rx PLL functional block diagram

- 27 -

LGE Internal Use Only

Copyright © 2007 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3. TECHNICAL BRIEF

The RFR6250 IC accommodates single-ended or differential LO inputs; if single-ended, either pin can

be active. AC-couple the inactive pin to ground using an appropriately valued capacitor (12 pF is used

in KS10). The 27 pF capacitor should be used to AC-couple the active pin to the VCO signal. Using

only the selected VCO signal, the RFR6250 IC LO generation and distribution circuits create the

necessary LO signals for the active quadrature downconverter.

A sample of the downconverter LO is buffered and routed from RFR6250 IC pin 19 to RTR6250 IC pin

32 (RX_VCO_IN). This signal requires a terminating resistor near the RTR6250 IC input pin and an AC

coupling capacitor that assures the internal RTR6250 IC biasing is not disrupted in the example. Good

microstrip or stripline controlled-impedance techniques must be used.

Most UMTS Rx PLL circuits are included within the RTR6250 IC: reference divider, phase detector,

charge pump, feedback divider, and digital logic that generate LOCK status. The buffered 19.2 MHz

TCXO signal provides the synthesizer input (REF), the frequency reference to which the PLL is phase

and frequency locked. The reference is divided by the RCounter to create a fixed frequency input to

the phase detector, FR. The other phase detector input (FV) varies as the loop acquires lock, and is

generated by dividing the RX_VCO_IN frequency using the feedback path.s N-Counter. The closed

loop will force FV to equal FR when locked. If the loop is not locked the error between FV and FR will

create an error signal at the output of the charge pump. This error signal is filtered by the loop filter

and applied to the VCO, tuning the output frequency such that the error is decreased. Ultimately the

loop forces the error to approach zero and the PLL is phase and frequency locked.

Many key PLL performance characteristics are largely determined by the loop filter design - stability,

transitory response, settling time, and phase noise.

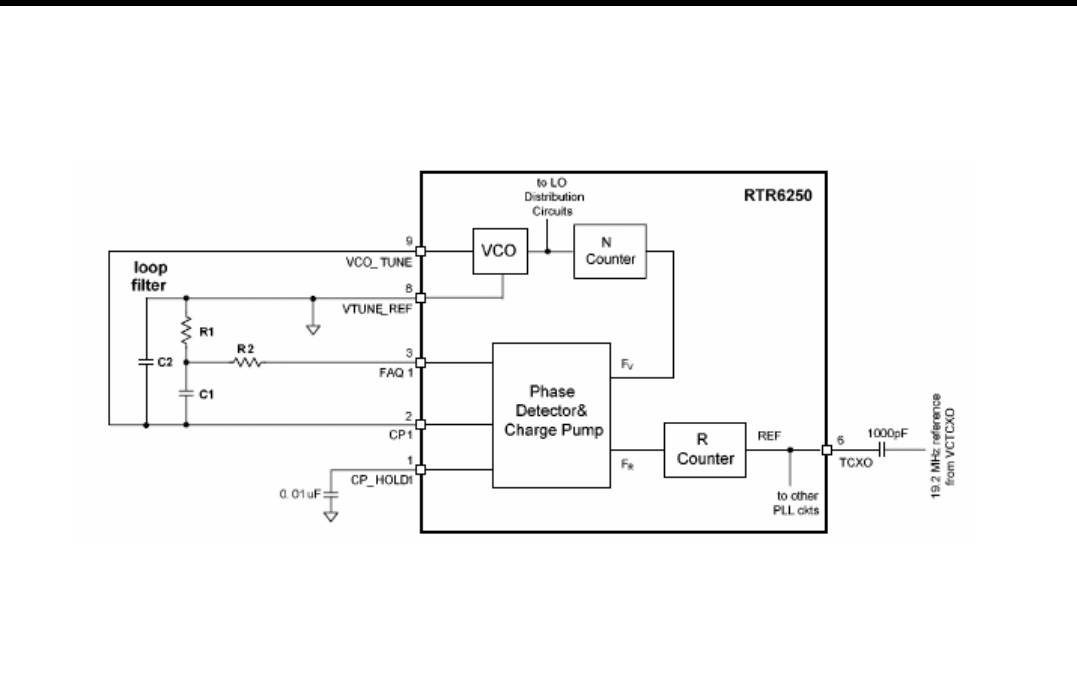

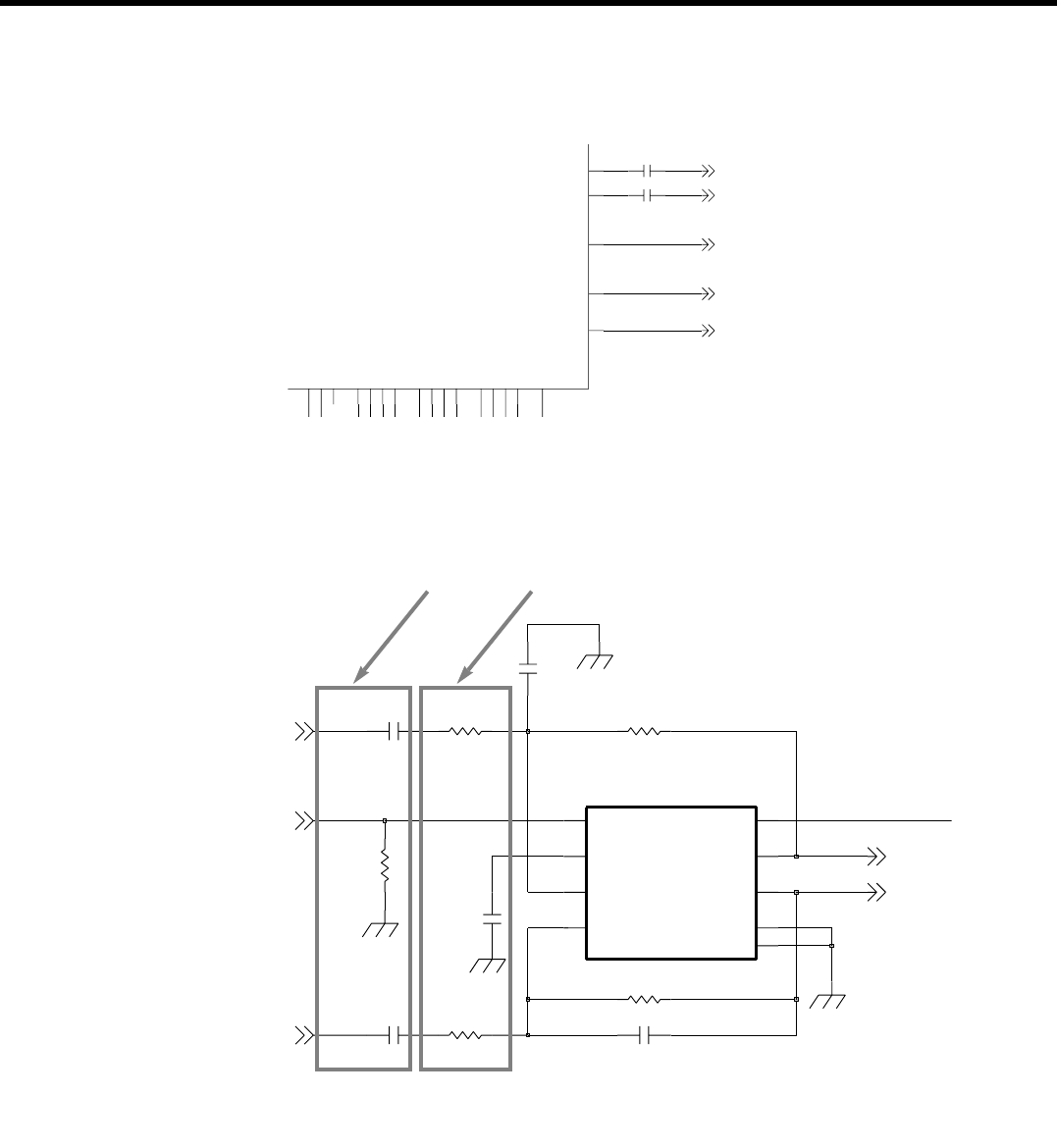

3.4.2 Transceiver PLL (PLL1)

All LO functional blocks for the other handset modes(UMTS Tx, EGSM Tx/Rx, DCS Tx/Rx, PCS

Tx/Rx) are integrated into the RTR6250 IC except the loop filter components (Figure 1.4.2-1). On-chip

circuits include reference divider, phase detector, charge pump, VCO, feedback divider, and digital

logic status. The functional description given in Section 1.4.1 for the UMTS Rx PLL applies to the

Transceiver PLL as well.

- 28 -

LGE Internal Use Only

Copyright © 2007 LG Electronics. Inc. All right reserved.

Only for training and service purposes

The off-chip loop filter allows optimization of key PLL performance characteristics (stability, transitory

response, settling time, and phase noise) for different applications. Guidelines are provided in the next

subsection for proper implementation of this critical circuit.

3. TECHNICAL BRIEF

Figure 1.4.2-1 Transceiver PLL functional block diagram

- 29 -

LGE Internal Use Only

Copyright © 2007 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3. TECHNICAL BRIEF

3.5 Off-chip RF Components

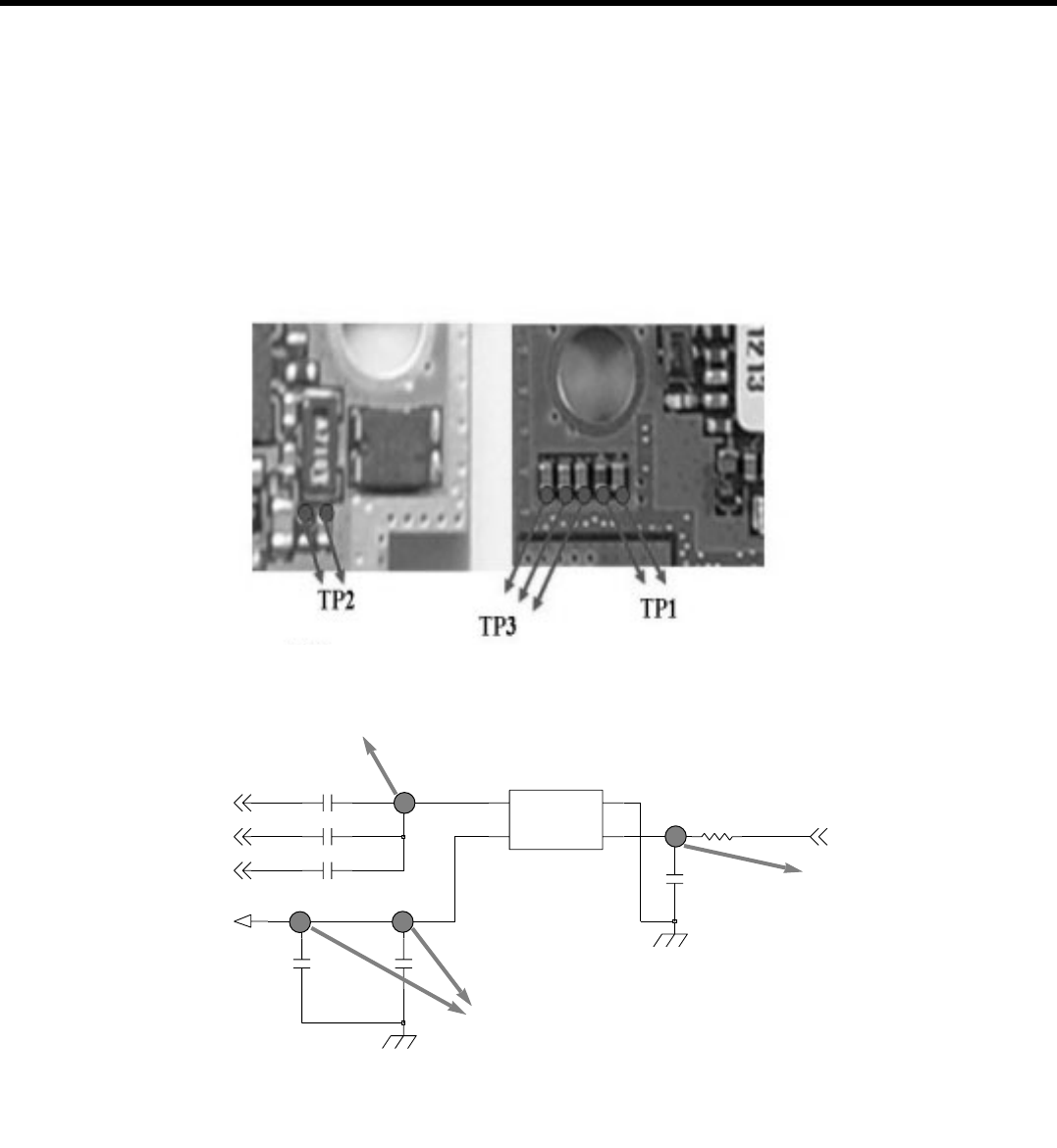

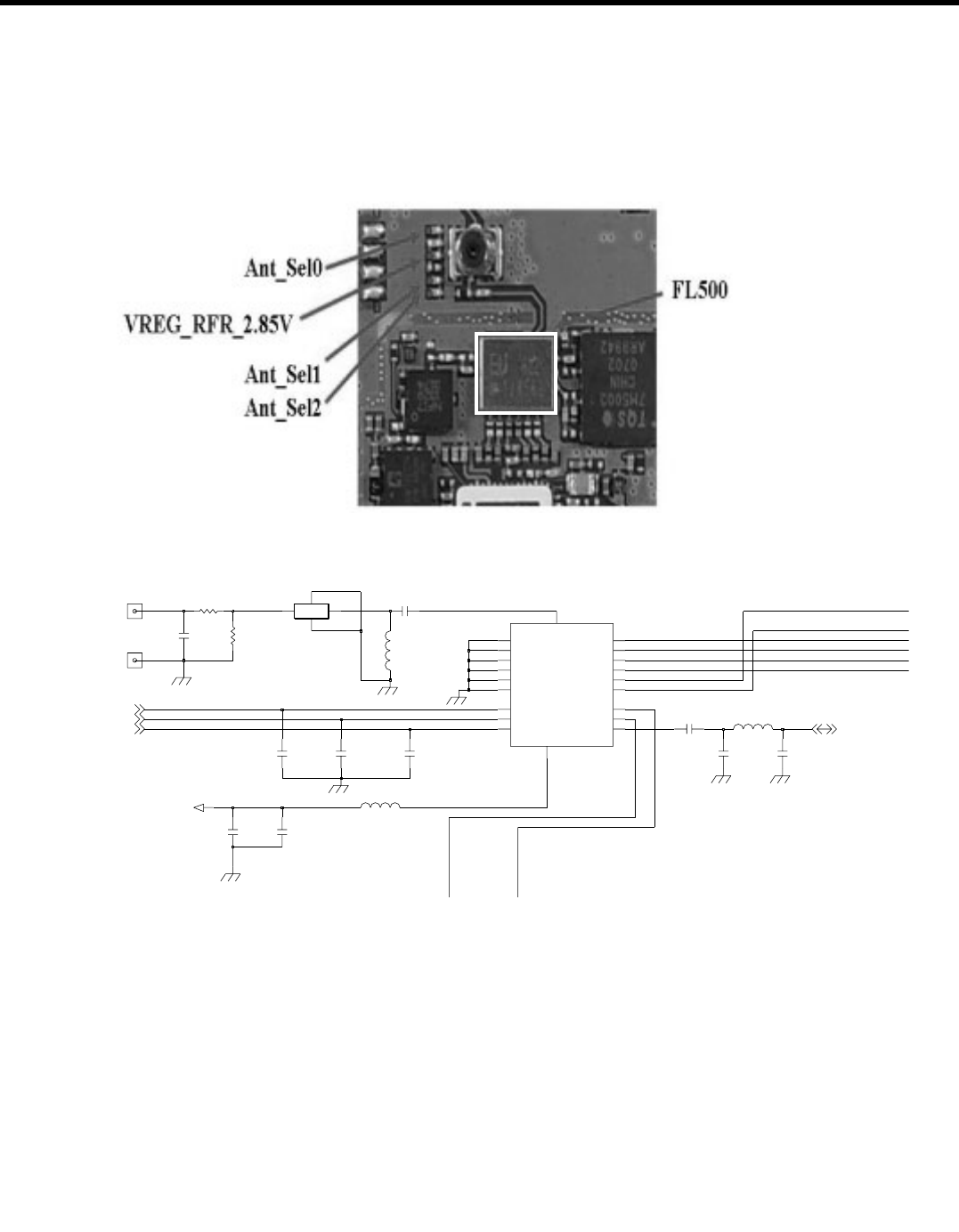

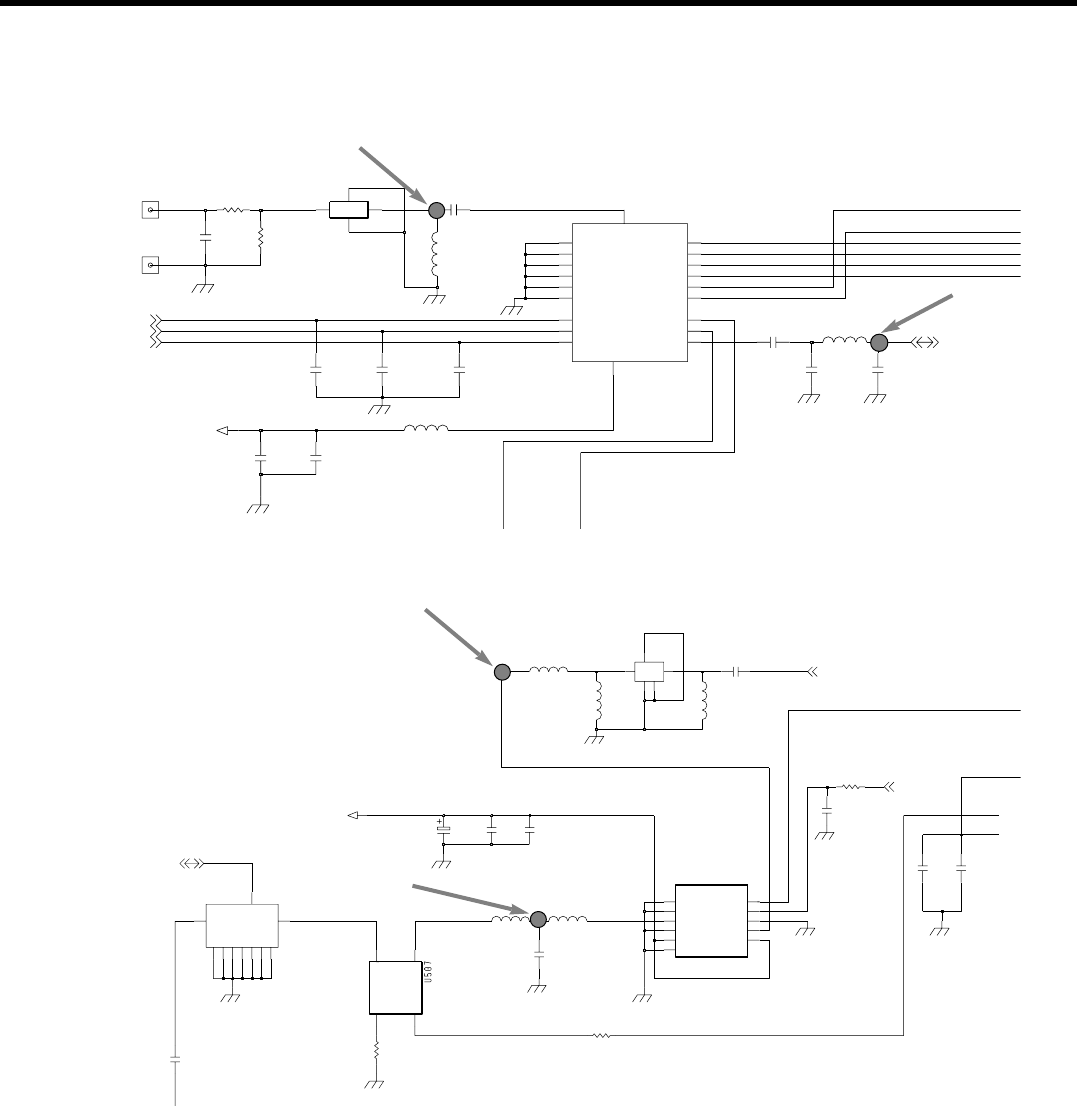

3.5.1 Front End Module(FL500)

Front End module integrates antenna switch module and GSM Rx filter.

The antenna switch module allows multiple operating bands and modes to share the same antenna. In

the KS10 design, a common antenna connects to one of six paths:

1) UMTS-2100 Rx/Tx, 2) EGSM Rx, 3) DCS-1800 Rx, 4) PCS-1900 Rx, 5)EGSM Tx, and 6) DCS-

1800, PCS-1900 Tx. UMTS operation requires simultaneous reception and transmission, so the

UMTS Rx/Tx connection is routed to a duplexer that separates receive and transmit signals. GSM

band of operation is time division duplexed, so only the receiver or transmitter is active at any time

and a frequency duplexer is not required. The module includes lowpass filters for the GSM bands

transmit paths to reduce out-of-band emissions, PA harmonics in particular.

The GSM mode RF filters are located before their LNAs, so their insertion losses are extremely critical

(1.3 dB typical). Other important parameters are:

■Out-of-band rejection or attenuation levels

❏Far out-of-band signals - ranging from DC up to the first band of particular concern and from the

last band of particular concern to beyond three times the highest passband frequency.

❏Frequencies of particular concern . bands known to include other wireless transmitters that may

deliver significant power levels to the receiver input.

❏GSM band receivers operate while the handset transmitters are off so there are no Txband

leakage attenuation requirements.

■Phase and amplitude balance - the UMTS discussion presented above applies for GSM bands as

well. See the data sheet for specific values. Of course, passband ripple and return loss are still

important in all cases for the same reasons explained in the antenna switch module and duplexer

sections.

3.5.2 UMTS duplexer (U506)

A UMTS duplexer splits a single operating band into receive and transmit paths. Important

performance requirements include:

- Insertion loss . this component is also in the receive and transmit paths; In the KS10 typical losses:

UMTS Tx = 1.45 dB, UMTS Rx = 1.86 dB.

- Out-of-band rejection or attenuation . the duplexer provides input selectivity for the receiver, output

filtering for the transmitter, and isolation between the two. Rejection levels for both paths are

specified over a number of frequency ranges. Two Tx-to-Rx isolation levels are critical to receiver

performance:

- Rx-band isolation . the transmitter is specified for out-of-band noise falling into the Rx band. This

noise leaks from the transmit path into the receive path, and must be limited to avoid degrading

receiver sensitivity. The required Rx-band isolation depends on the PA out of-band noise levels and

Rx-band losses between the PA and LNA. Typical duplexer Rx band isolation value is 51 dB.

- 30 -

LGE Internal Use Only

Copyright © 2007 LG Electronics. Inc. All right reserved.

Only for training and service purposes

- Tx-band isolation . the transmit channel power also leaks into the receiver. In this case, the leakage

is outside the receiver passband but at a relatively high level. It combines with Rx band jammers to

create cross-modulation products that fall in-band to desensitize the receiver. The required Tx-band

isolation depends on the PA channel power and Tx-band losses between the PA and LNA. Typical

duplexer Tx-band isolation value is 57 dB.

- Passband ripple . the loss of this fairly narrowband device is not flat across its passband. Passband

ripple increases the receive or transmit insertion loss at specific frequencies, creating performance

variations across the bands channels, and should be controlled.

- Return loss . minimize mismatch losses with typical return losses of 10 dB or more (VSWR <2:1).

- Power handling. high power levels in the transmit path must be accommodated without degraded

performance. The specified level depends on the operating band class and mobile station class (per

the applicable standard), as well as circuit losses and antenna EIRP. Several duplexer characteristics

depend upon its source and load impedances. QUALCOMM strongly recommends an isolator be

used between the UMTS PA and duplexer to assure proper performance.

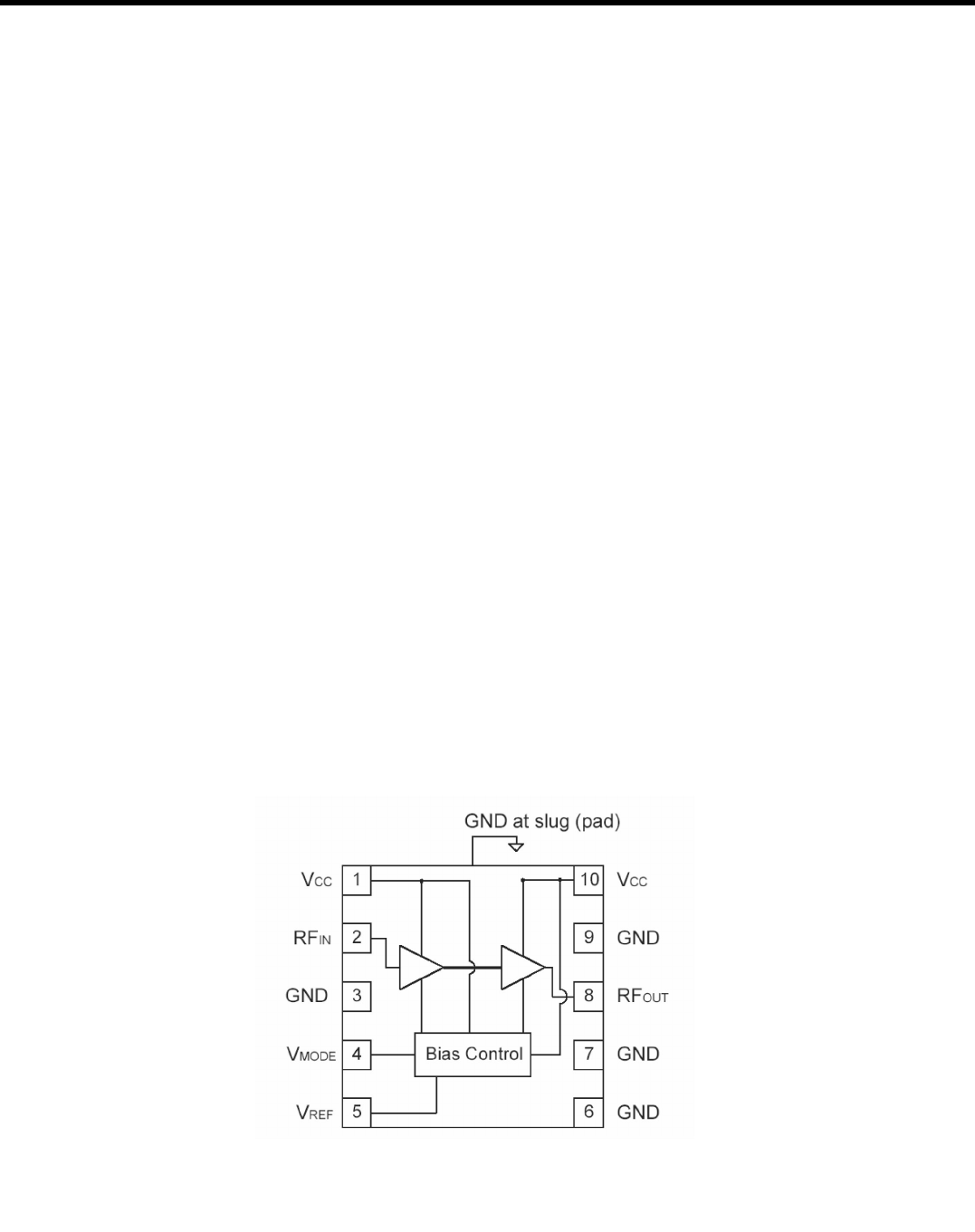

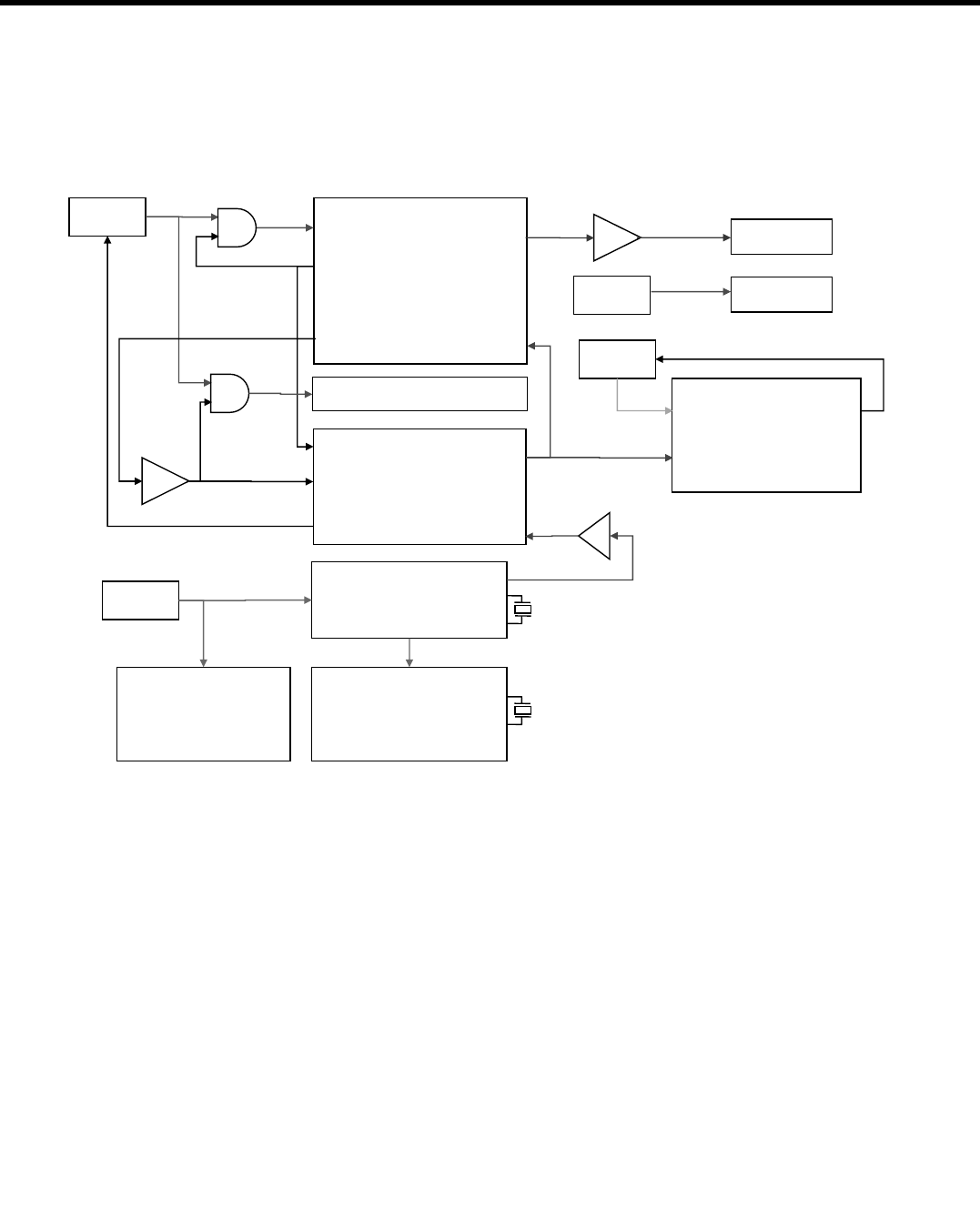

3.5.3 UMTS Power Amplifier (U505)

The AWT6277 meets the increasing demands for higher output power in UMTS handsets. The PA

module is optimized for VREF = +2.85 V, a requirement for compatibility with the Qualcomm® 6250

chipset. The device is manufactured on an advanced InGaP HBT MMIC technology offering state-of-

the-art reliability, temperature stability, and ruggedness. Selectable bias modes that optimize efficiency

for different output power levels, and a shutdown mode with low leakage current, increase handset talk

and standby time. The self-contained 4 mm x 4 mm x 1.1 mm surface mount package incorporates

matching networks optimized for output power, efficiency, and linearity in a 50 Ω system.

3. TECHNICAL BRIEF

Figure 1.5.3-1 UMTS PA functional block diagram

- 31 -

LGE Internal Use Only

Copyright © 2007 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3. TECHNICAL BRIEF

3.5.4 Thermistor (R527)

This thermistor senses temperature variations around UMTS PA to adjust PA gain deviation for

assure compliance with the applicable transmit power control standards. Negative temperature

compensation thermistor is used in the KS10.

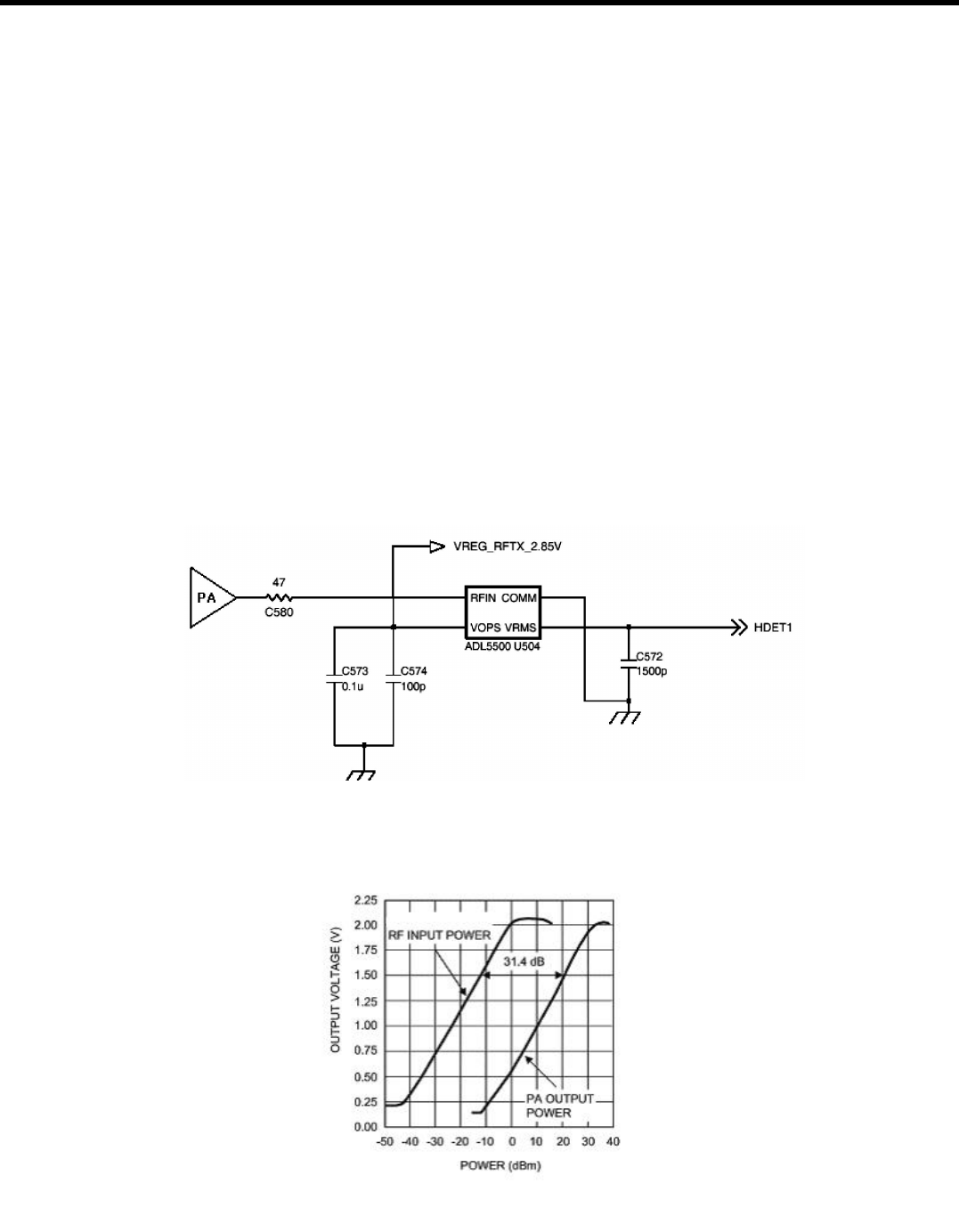

3.5.5. UMTS transmit power detector (U504)

This detector couples PA output power level to calibrate the transmitter characteristic over the channel

variation and temperature. Its detector coupling range and converted voltage is based on diode

sensitivity and transmitter power level.

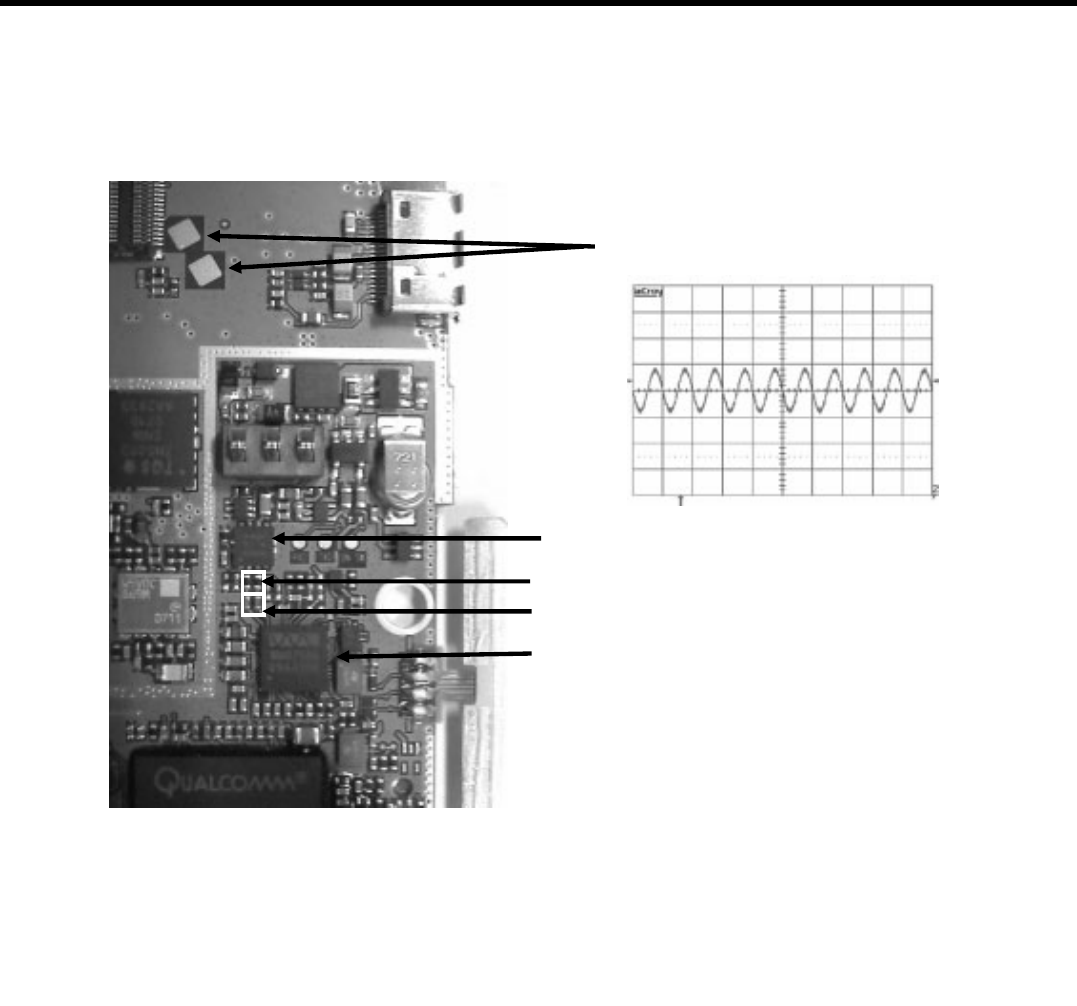

The KS10 uses National Semiconductor ADL5500 power detector IC. In Figure 1.5.5-1, C580 is set to

47ohm&Coupler resulting in an attenuation of 31.4dB. The output voltage is proportional to the

logarithm of the input power. Figure1.5.5-2 shows the output voltage versus PA output power of the

ADL5500 setup as depicted in Figure1.5.5-1

Figure 1.5.5-1 Block diagram of ADL5500 with resistive tap

Figure 1.5.5-2 Power detector response, Vout vs PA output power

- 32 -

LGE Internal Use Only

Copyright © 2007 LG Electronics. Inc. All right reserved.

Only for training and service purposes

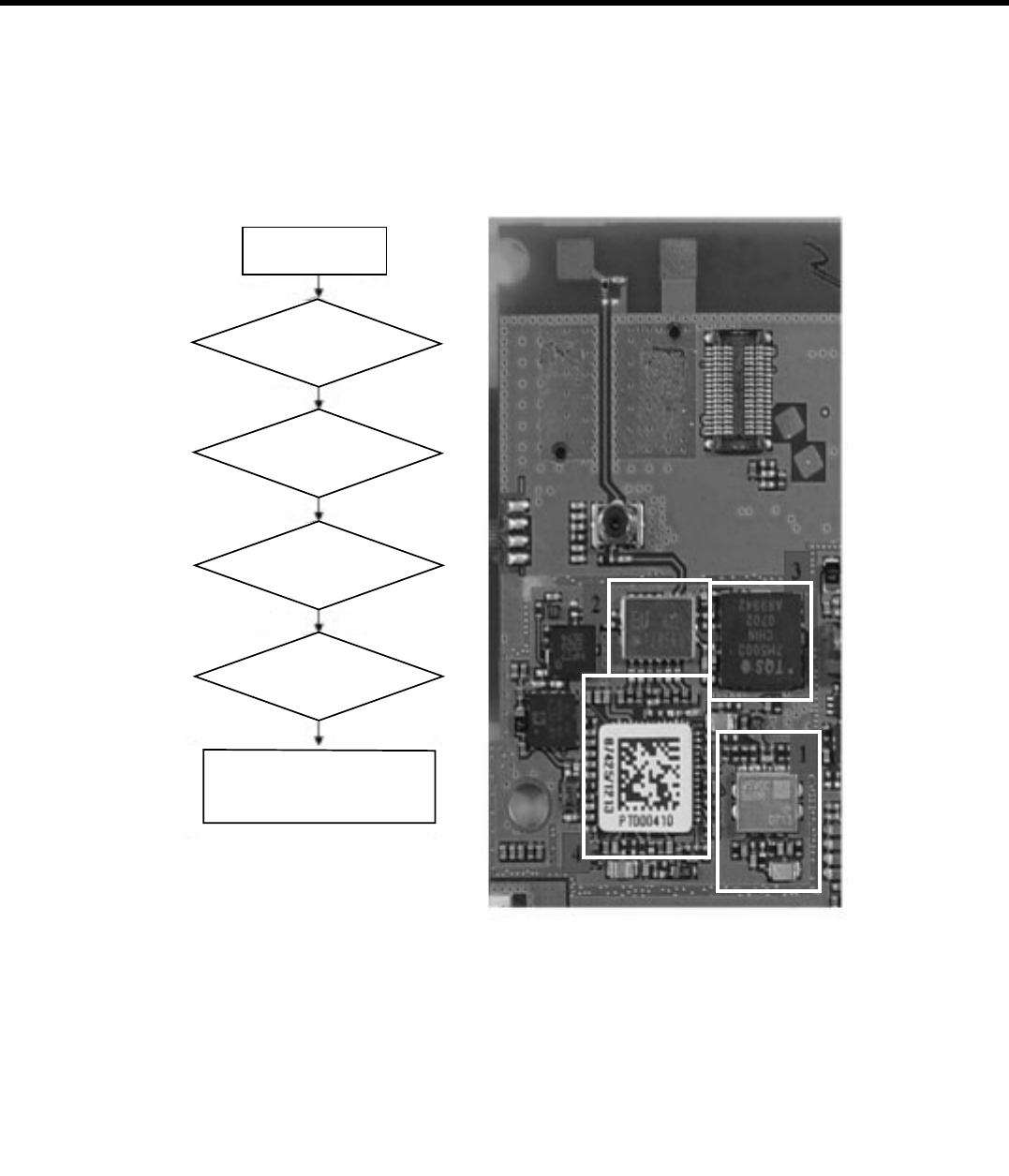

3.5.6 Dual band GSM power amplifier (U501)

The TQM7M5003 is a high-power, high-efficiency power amplifier module with integrated power

control that provides over 50dB of control range. The devices is a self-contained 6mm°ø6mm module

with 50Ω input and output terminals. The device is designed for use as the final RF amplifier in

GSM850, EGSM900, DCS and PCS hand-held digital celluar equipment and other applications in the

824MHz to 849MHz, 880MHz to 915MHz, 1710MHz to 1785MHz and 1850MHz to 1910MHz bands.

The VBATT pin connects to an internal current-sense resistor and interfaces to an integrated power

amplifier control function, which is insensitive to variations in temperature, power supply, process, and

input power. The ENABLE input allows initial turn-on of PAM circuitry to minimize battery drain.

3.5.7 GSM transmit VCO (U502)

The dual Tx VCO is a key component within the GSM OPLL. This VCO performance directly impacts

PLL and transmitter performance. VCO specifications refer to muRata MQW5V0C869M datasheet.

The dual Tx VCO outputs, one for Low-band GSM and one for high band, drive a resistive network

that splits the active signal into two signals: 1) the input to the active PA . this is the low loss path,

and 2) the OPLL feedback signal . this is the high loss path. See Figure 8-1 for recommended

topology and resistor values.

The losses from the VCO outputs to the PA inputs must be factored into the output chain.s power

budget. Each path includes a π-pad that introduces approximately a 3-dB loss. The low band GSM

π-pad is formed by R516 plus R522, R521, and R524; the high band GSM π-pad is formed by R518

plus R523, R520, and R524. One leg of each π-pad is used to couple the VCO output to form the

feedback path as described below.

For a given VCO output drive level, the loss to the RTR6250 input must assure the specified input

level is achieved (-18 to -12 dBm). Large resistors included in the π-pads are used to lightly couple

off the VCO outputs to create the feedback signal. Since the RTR6250 TX_VCO_FB pin presents

fairly high impedance. A series capacitor (82 pF) AC couples the feedback signal into the RTR6250

IC.

3. TECHNICAL BRIEF

Figure 1.5.6-1 GSM PA functional block diagram

- 33 -

LGE Internal Use Only

Copyright © 2007 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3. TECHNICAL BRIEF

3.5.8 UMTS Rx RF filter (FL501)

An RF filter is located between the UMTS LNA and mixer. Insertion loss is important, but not as critical

as losses before the LNA. The most important parameters of this component include:

■Out-of-band rejection or attenuation levels, usually specified to meet these conditions:

❏Far out-of-band signals - ranging from DC up to the first band of particular concern and from the

last band of particular concern to beyond three times the highest passband frequency.

❏Tx-band leakage - the transmitter channel power, although attenuated by the duplexer, still

presents a cross-modulation threat in combination with Rx-band jammers. The RF filter must

provide rejection of this Tx-band leakage.

❏Other frequencies of particular concern . bands known to include other wireless transmitters that

may deliver significant power levels to the receiver input.

■Phase and amplitude balance - the ZIF architecture requires well-balanced differential inputs to the

RFR6250 IC. This is accomplished by the RF filter which takes a single-ended output from the

RFL6250 IC and provides differential outputs having nominal 180 phase separation. Phase and/or

amplitude imbalance causes degraded common-mode rejection and second-order nonlinearity, so

their requirements are specified jointly.

❏±3 degrees and ± 1 dB

❏-12 to + 3 degrees and ± 0.7 dB

Of course, passband ripple and return loss are still important in all cases for the same reasons

explained in the antenna switch module and duplexer sections.

3.5.9 VCTCXO (X500)

The Voltage Controlled Temperature Compensated Crystal Oscillator (VCTCXO) provides the

reference frequency for all RFIC synthesizers as well as clock generation functions within the

MSM6275 IC. The 6275-series chipset requires a 19.2 MHz nominal VCTCXO frequency. The

oscillator frequency is controlled by the MSM6275’s TRK_LO_ADJ pulse density modulated signal in

the same manner as the transmit gain control.

The filtered PDM signal results in an analog control signal into the VCTCXO tuning port whose voltage

is directly proportional to the density of the digital bit stream. The MSM device varies the pulse density

to change the analog control voltage that sets the oscillator frequency - all within a feedback control

loop that minimizes handset frequency drift relative to the network.

- 34 -

LGE Internal Use Only

Copyright © 2007 LG Electronics. Inc. All right reserved.

Only for training and service purposes

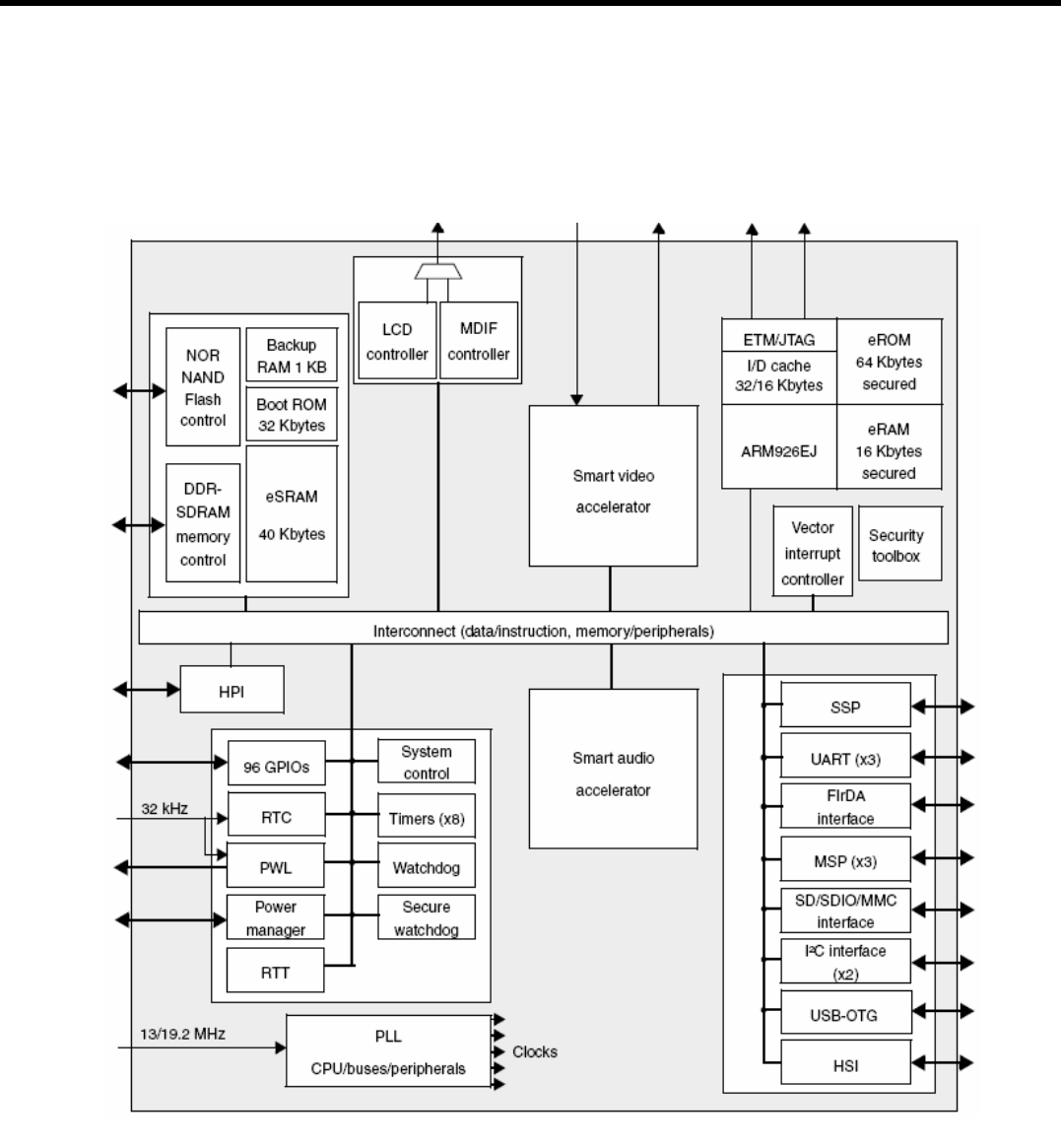

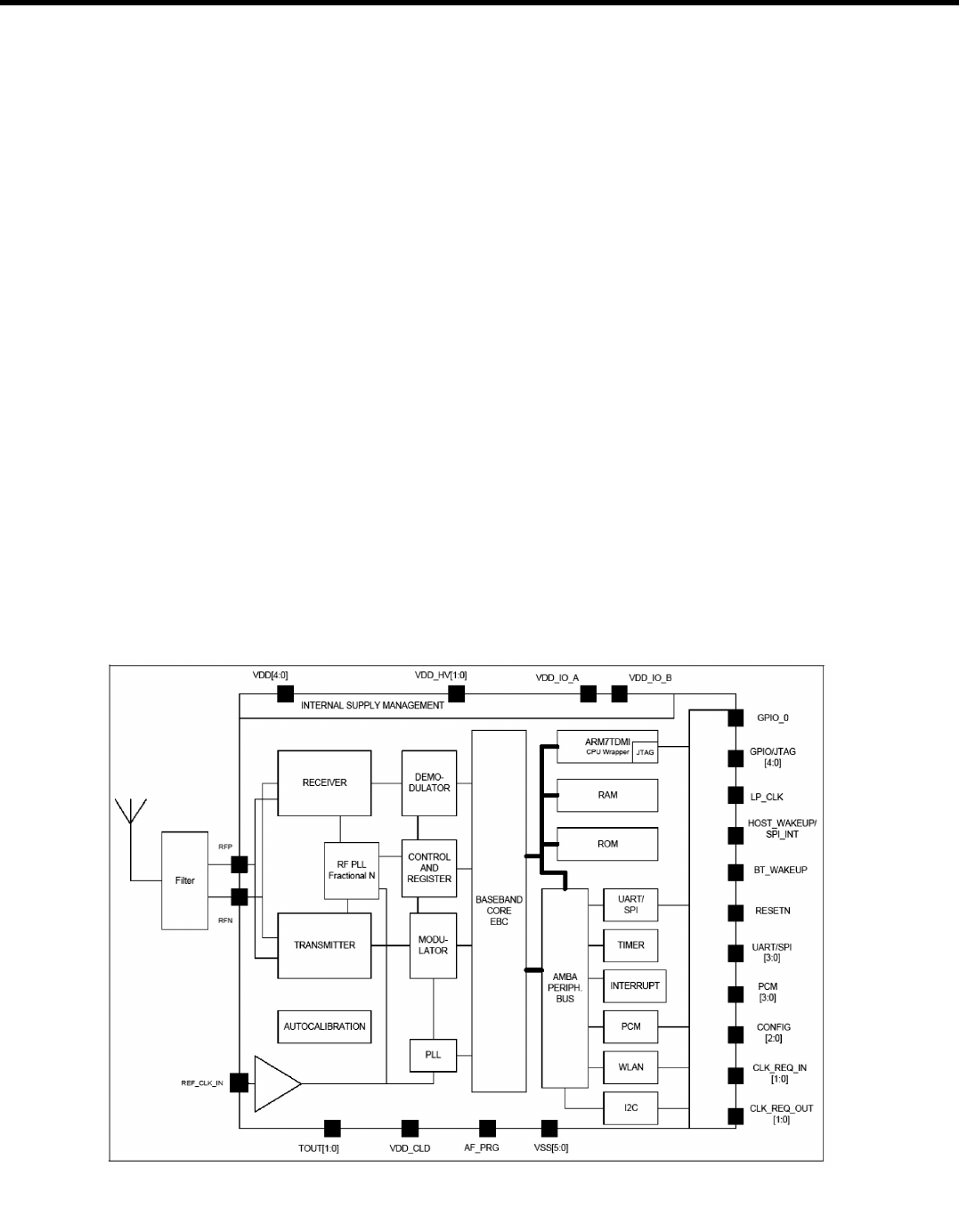

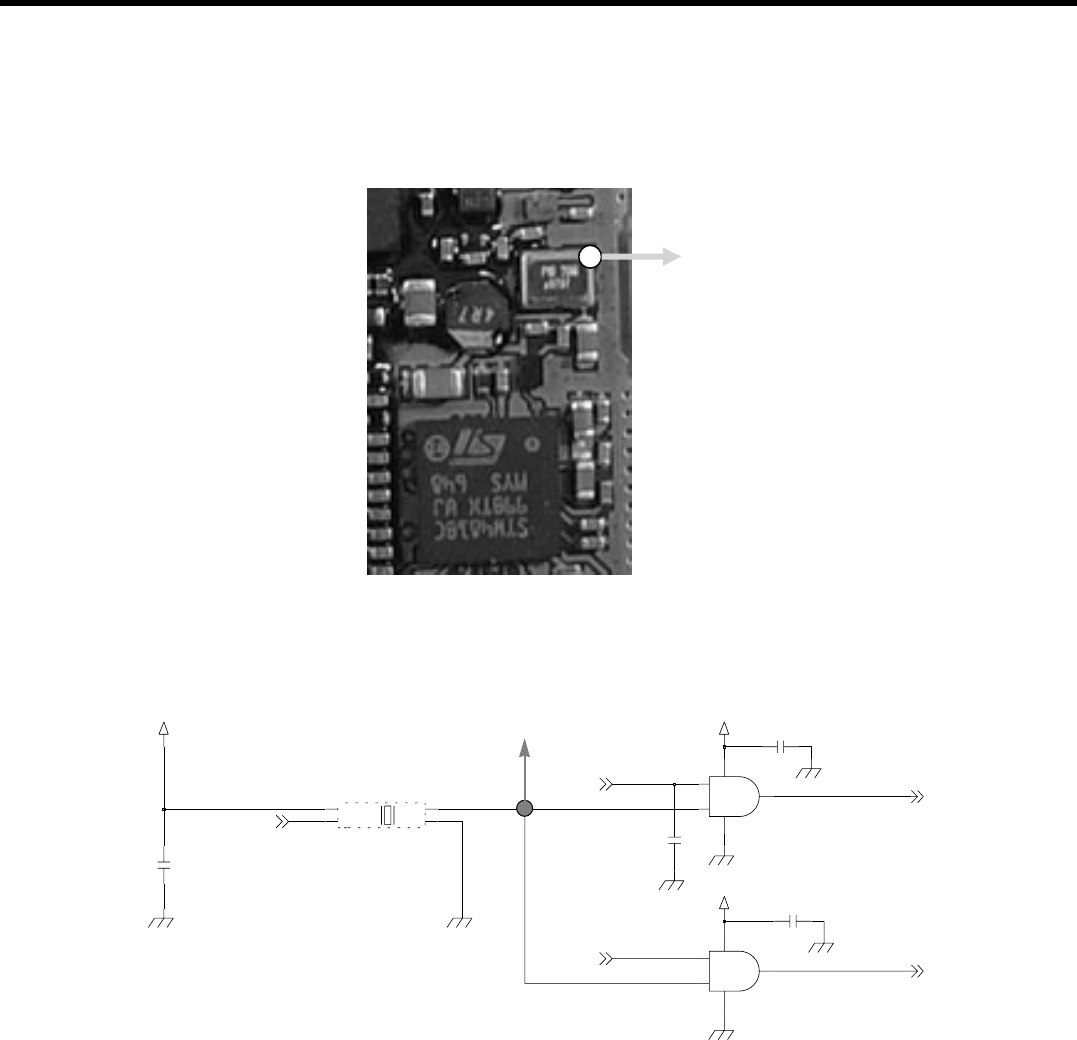

3.6 Digital Baseband (Stn8810 / MSM6275)

3.6.1 General features of Stn8810 device

• Support for Peripheral Device & multimedia function

• Support for high-speed downlink packet access (HSDPA) - 1.8 Mbps

• Minimal support for high-level operating system such as Symbian™, Linux and WinCE® operating

systems (OSs).

• 1-Gbit NAND Flash memory, 512-Mbit DDR mobile RAM Stacked in Package

• Two DSP implementation for multimedia function

- Smart video accelerator : Programmable DSP (MMDSP+) for intermediate level processing,

clocked at 66 MHz,

- Smart audio accelerator : High-performance block, flexible sophisticated audio accelerator based

on the MMDSP+ programmable audio DSP, clocked at 133 MHz,

• ARM926EJ 32-bit RISC CPU at 350MHz

32-Kbyte instruction cache, 16-Kbyte data cache

• MultiMedia Card/SD Card/SDIO host controller

• 96 general-purpose I/Os (muxed with peripheral I/Os)

• Camera interfaces

- Supports high-resolution camera modules up to 4 Mpixels

- Serial camera interface up to 416 Mbit/s (MIPI legacy CSI)

- Parallel camera CCIR-656 interface up to 66 MHz (MIPI legacy CPI)

• Color LCD controller for STN or TFT panels or display interface for display module

- 24-bpp true color

- MIPI legacy DBI and DPI

• Host port interface (HPI)

- 16-bit parallel data bus,

- Multiplexed and non-multiplexed address/data bus,

- Indirect host access,

- Direct host access to a segment of STn8810 memory in multiplexed mode.

- Interface to modem for data communication

• I/O peripherals

- 3 autobaud UARTs (one with modem control signals) up to 3.692 Mbit/s

- 1 synchronous serial port (SSP) up to 24 Mbit/s

- 3 multichannel serial ports (MSP) up to 48 Mbit/s

- 2 I©˜C multi-master/slave interfaces

- One 8-channel, full-duplex high-speed serial interface, 108 Mbit/s

- Host port interface

- JTAG

3. TECHNICAL BRIEF

3. BB Technical Description

- 35 -

LGE Internal Use Only

Copyright © 2007 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3. TECHNICAL BRIEF

3.6.2 General features of MSM6275 device

• Support for multimode operation - WCDMA(UMTS), GSM/GPRS, EDGE

• Support for high-speed downlink packet access (HSDPA) - 1.8 Mbps

• Support for WCDMA (UMTS) uplink data rate up to 384 kbps

• High-performance ARM926EJ-S running at up to 225 MHz

• ARM Jazelle Java hardware acceleration for faster Java-based games and other applets

• QDSP4000 high-performance DSP cores

• Integrated gpsOne position location technology functionality

• Integrated Bluetooth 1.2 baseband processor for wireless connectivity to peripherals

• High-speed, serial mobile display digital interface (MDDI) Type I, which optimizes the interconnection

cost between the MSM device and LCD panel

• Direct interface to digital camera module with video front end (VFE) image processing

• Vocoder support (AMR, FR, EFR, HR)

• Advanced 14x14 mm, 0.5 mm pitch, 409-pin lead-free CSP packaging technology

• WCDMA Access

- Maximum of eight simultaneous transport channels

- Four coded composite transport channels (CCTrCH)

- PS data rates supporting 384kbps DL / 64kbps UL

• GSM/GPRS Access

- GSM/GPRS network signaling (from Layer 1 to 3)

- GSM AMR,EFR,FR

• Operation and Services

- USIM Interfaces

- General Purpose I/O (GPIO) Interface

- Dual Memory Buses (EBI1-SDRAM & EBI2-NAND Flash)

- JTAG

- RTC

• Data Communication

- UARTs (ACB, EDB (RS232))

- Slave USB

- 36 -

3. TECHNICAL BRIEF

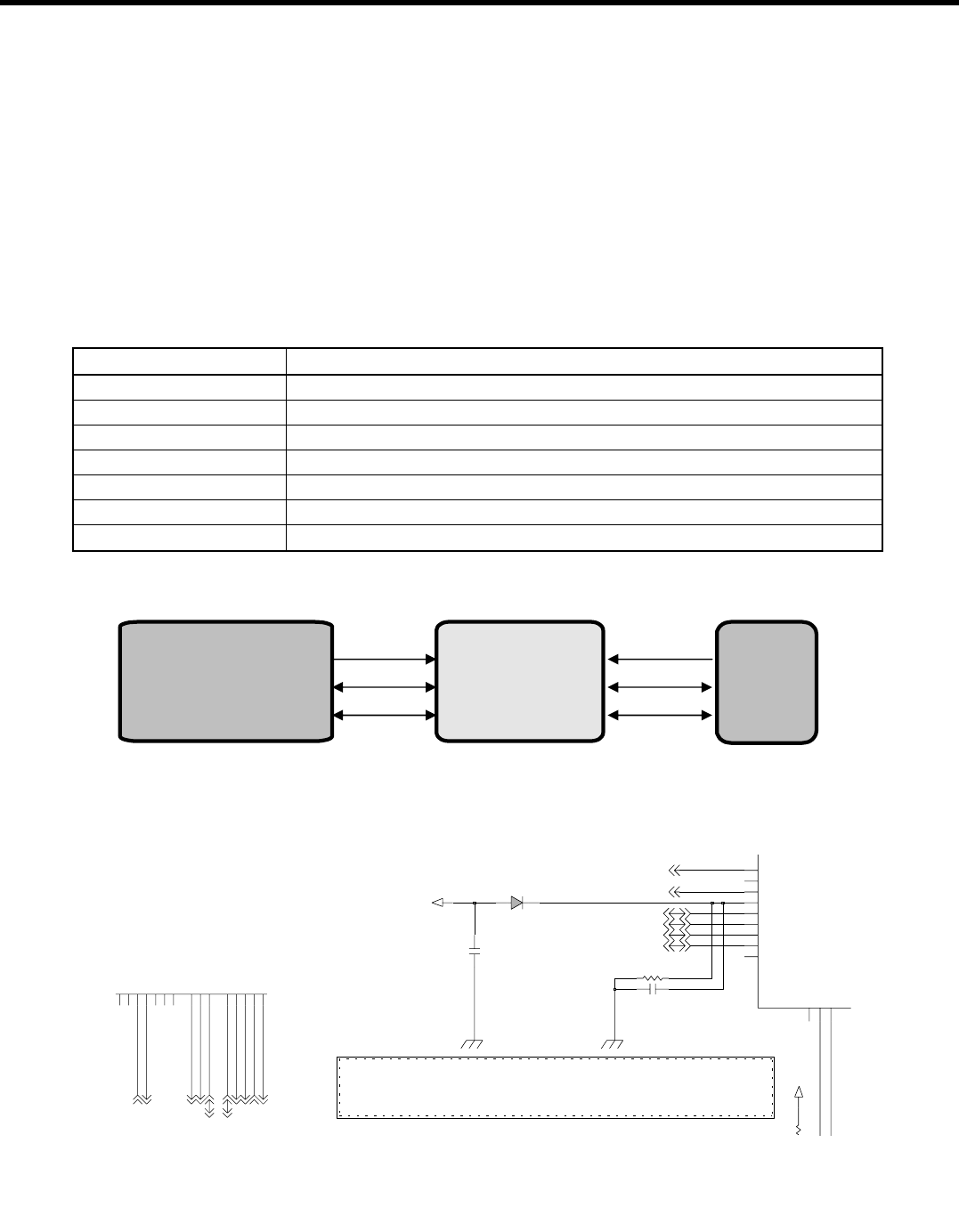

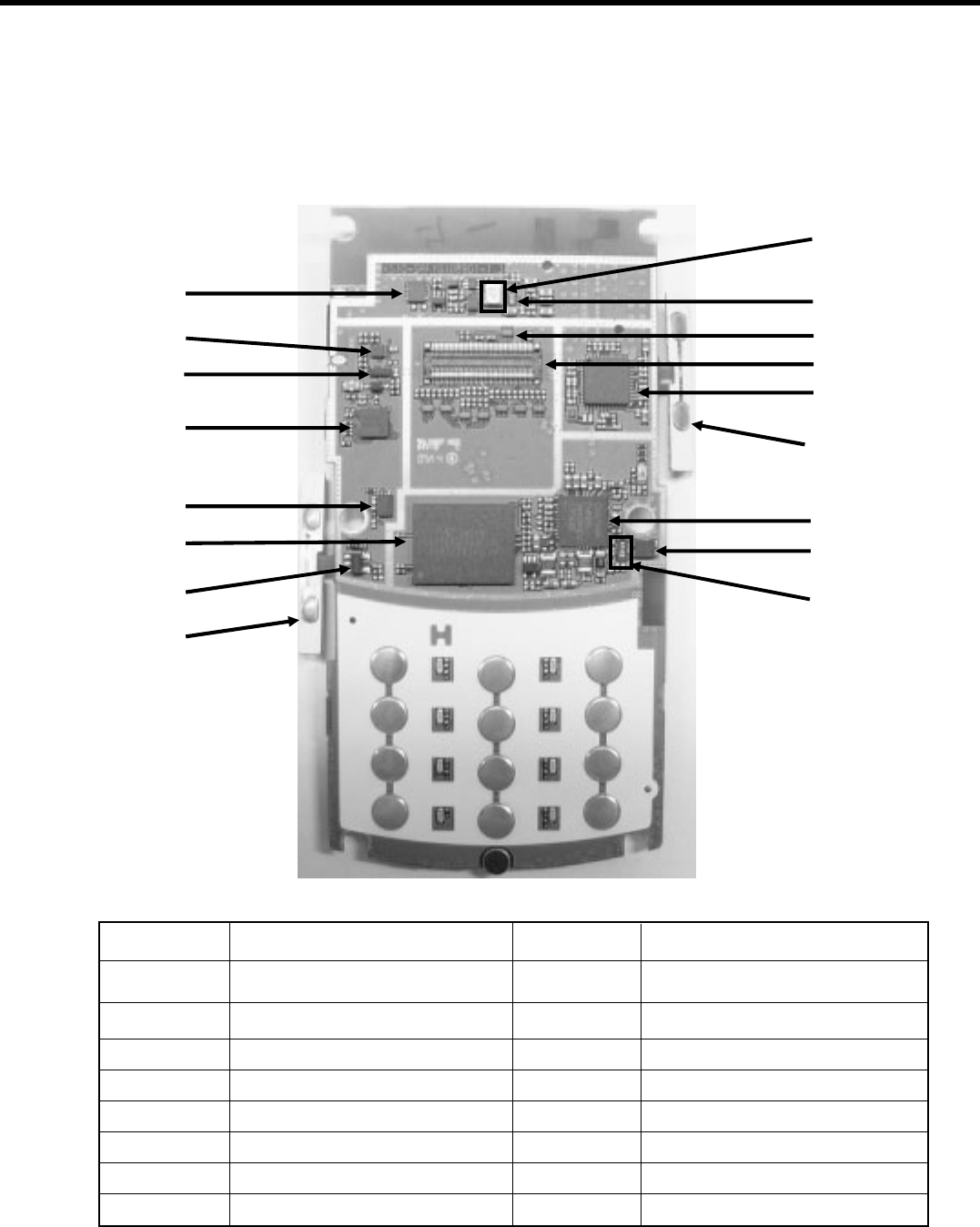

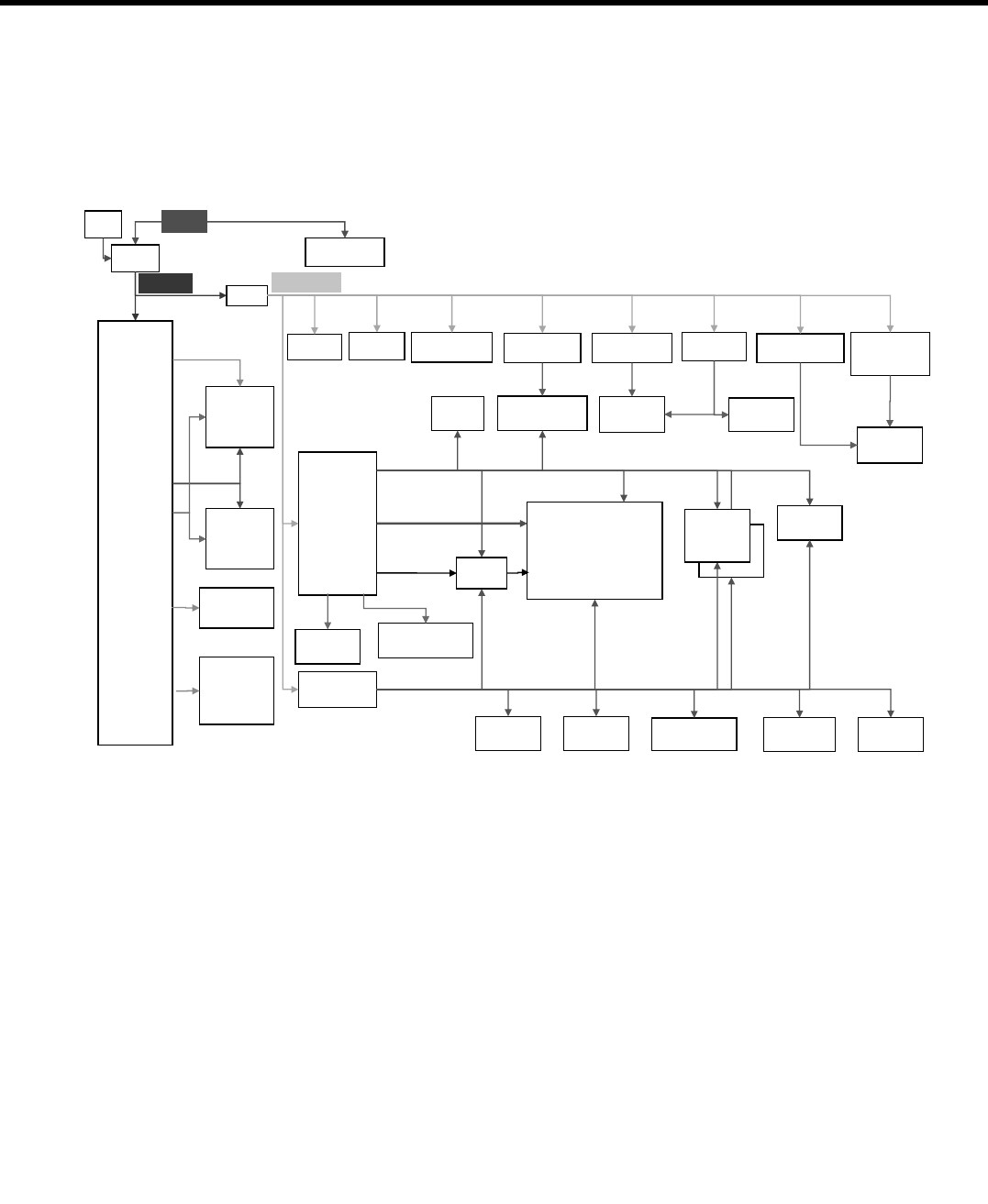

3.7. Hardware Architecture

LGE Internal Use Only

Copyright © 2007 LG Electronics. Inc. All right reserved.

Only for training and service purposes

MSM6275

PM6650

SDRAM

+ NAND

MAIN LCD

GSM

Quadband

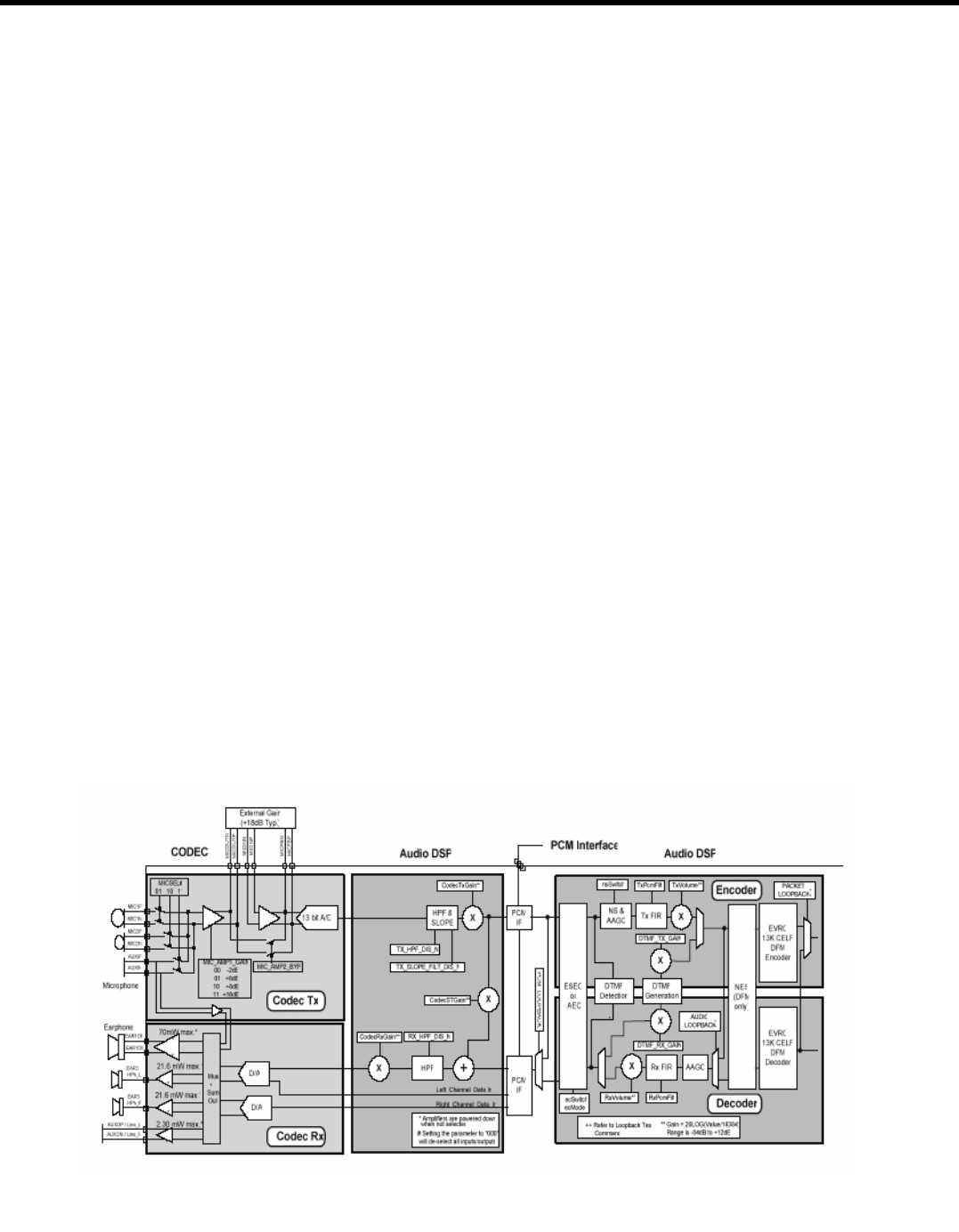

PA

BLUETOOTH

18pin MMI

Connector

18pin MMI

Connector

1.3M CAMERA

Receiver

/SPEAKER

MIC

RFR6250

RTR6250

Micro SD

USIM

GSMQua

d

TX VCO

UMTS

(2100)

PA

WCDMA RX

WCDMA TX

GSM

900/1800/1900

RX FILTER

GSM RX

GSM TX

UMTS

TX

FILTER

D

U

P

L

E

X

E

R

UMTS

RX

FILTER

VGA CAMERA

FEM

STn8810

STw4810

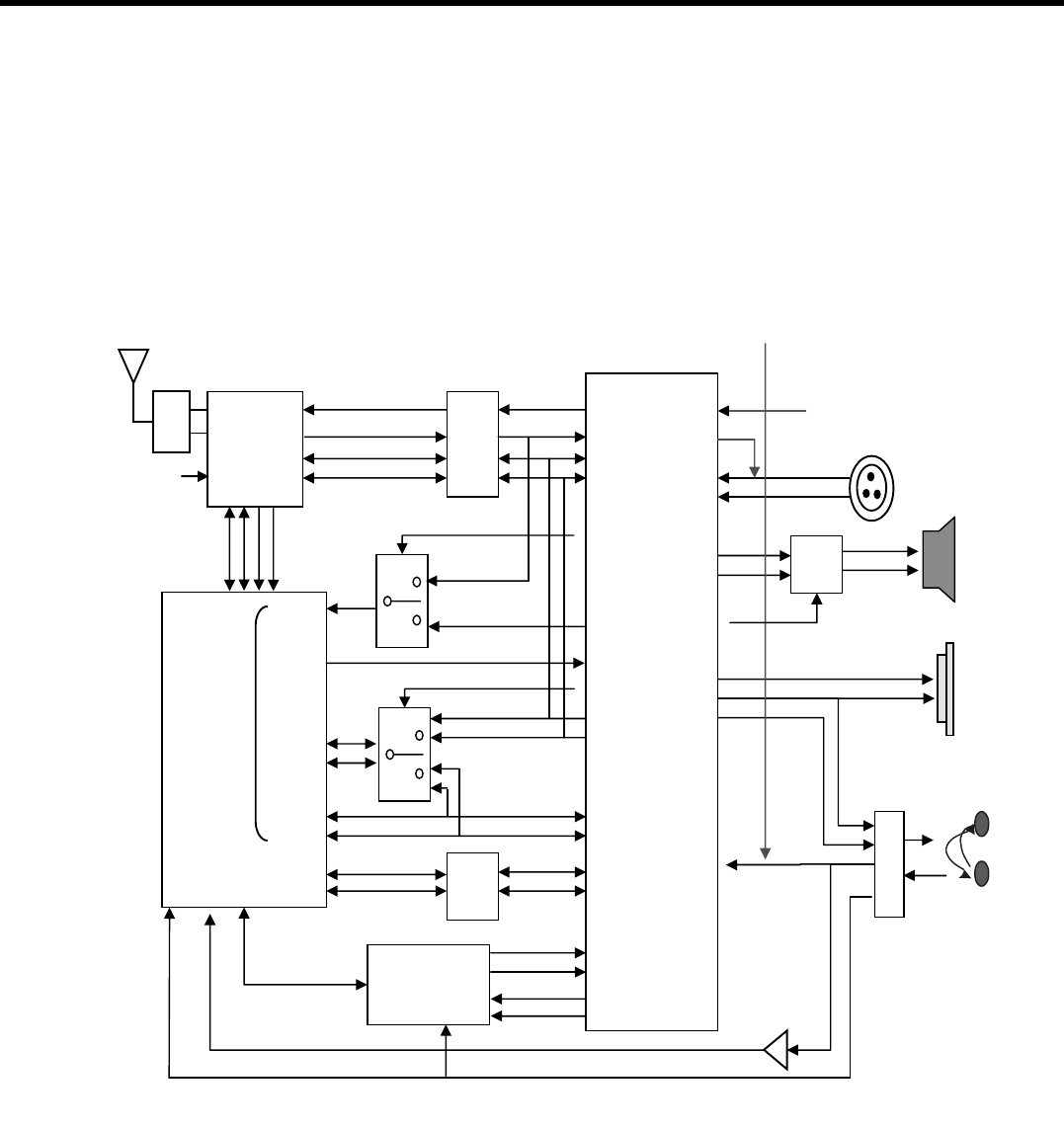

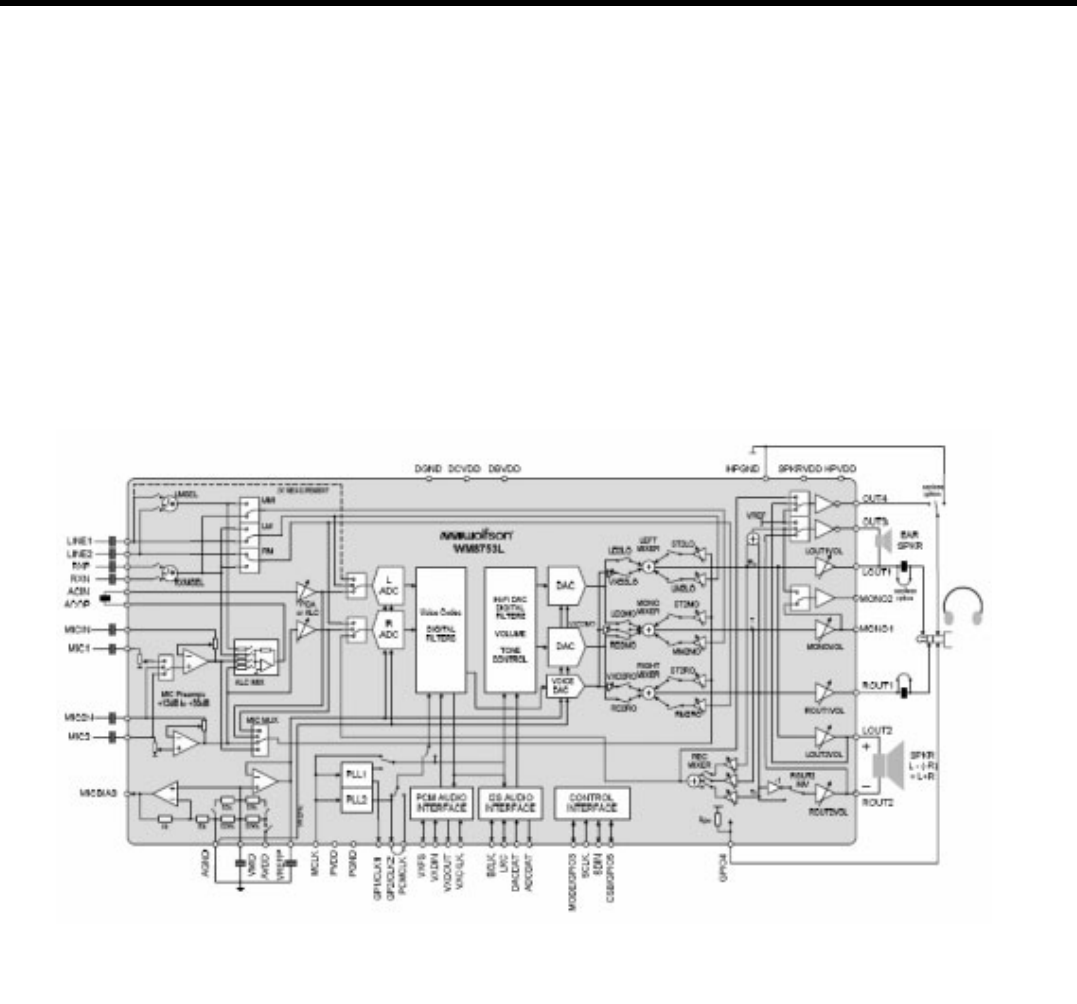

Audio Codec.

(WM8753)

HPI I/F

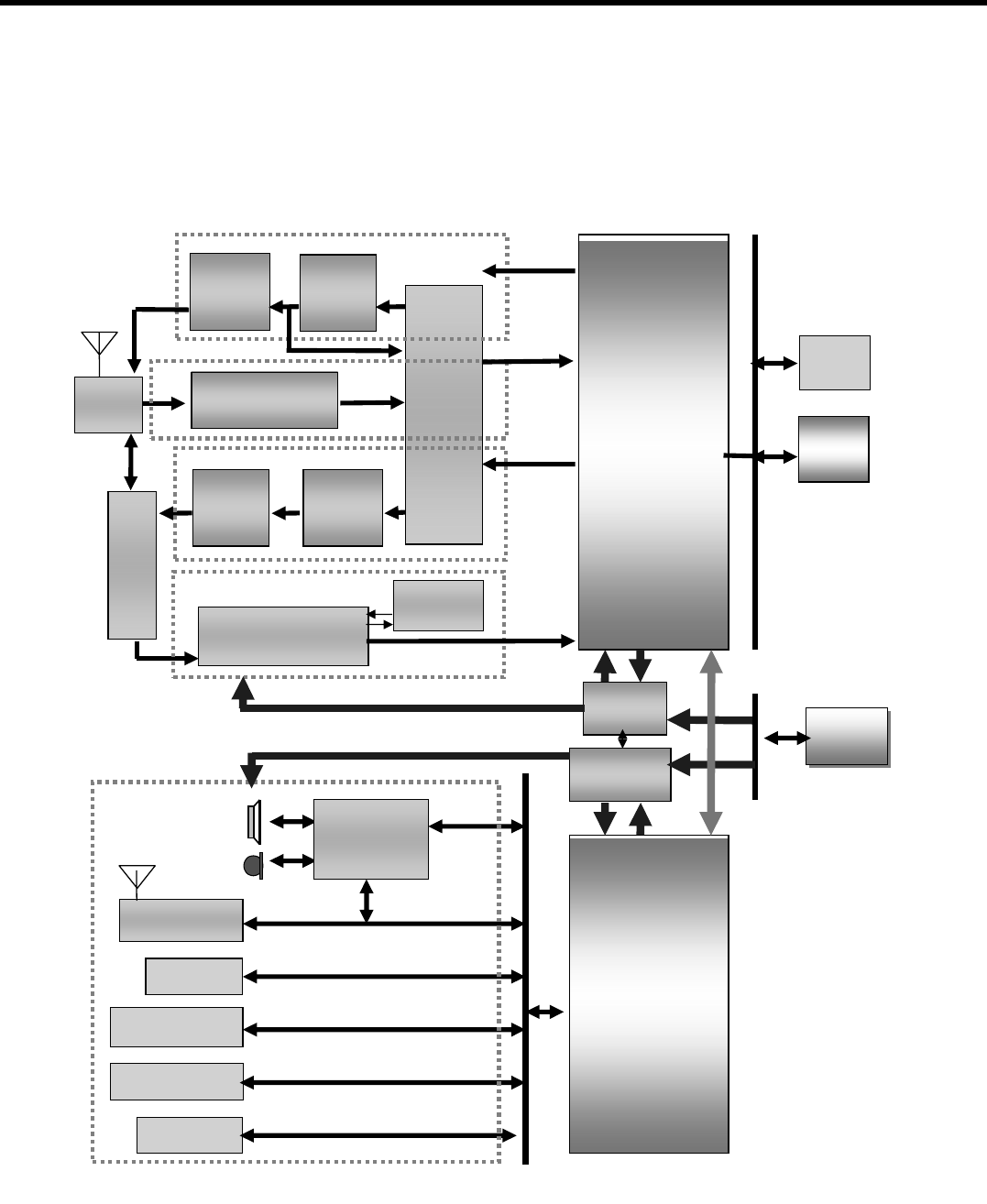

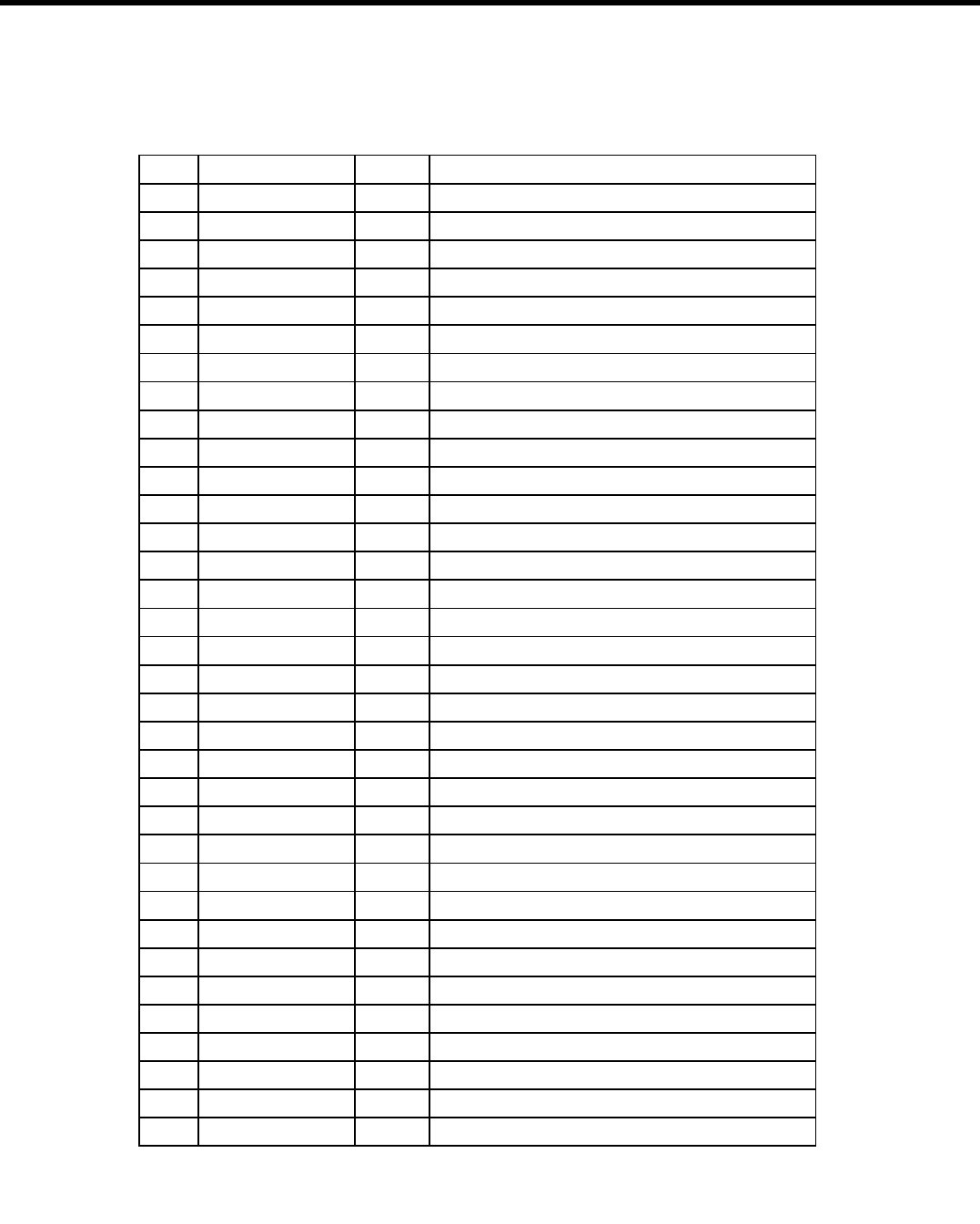

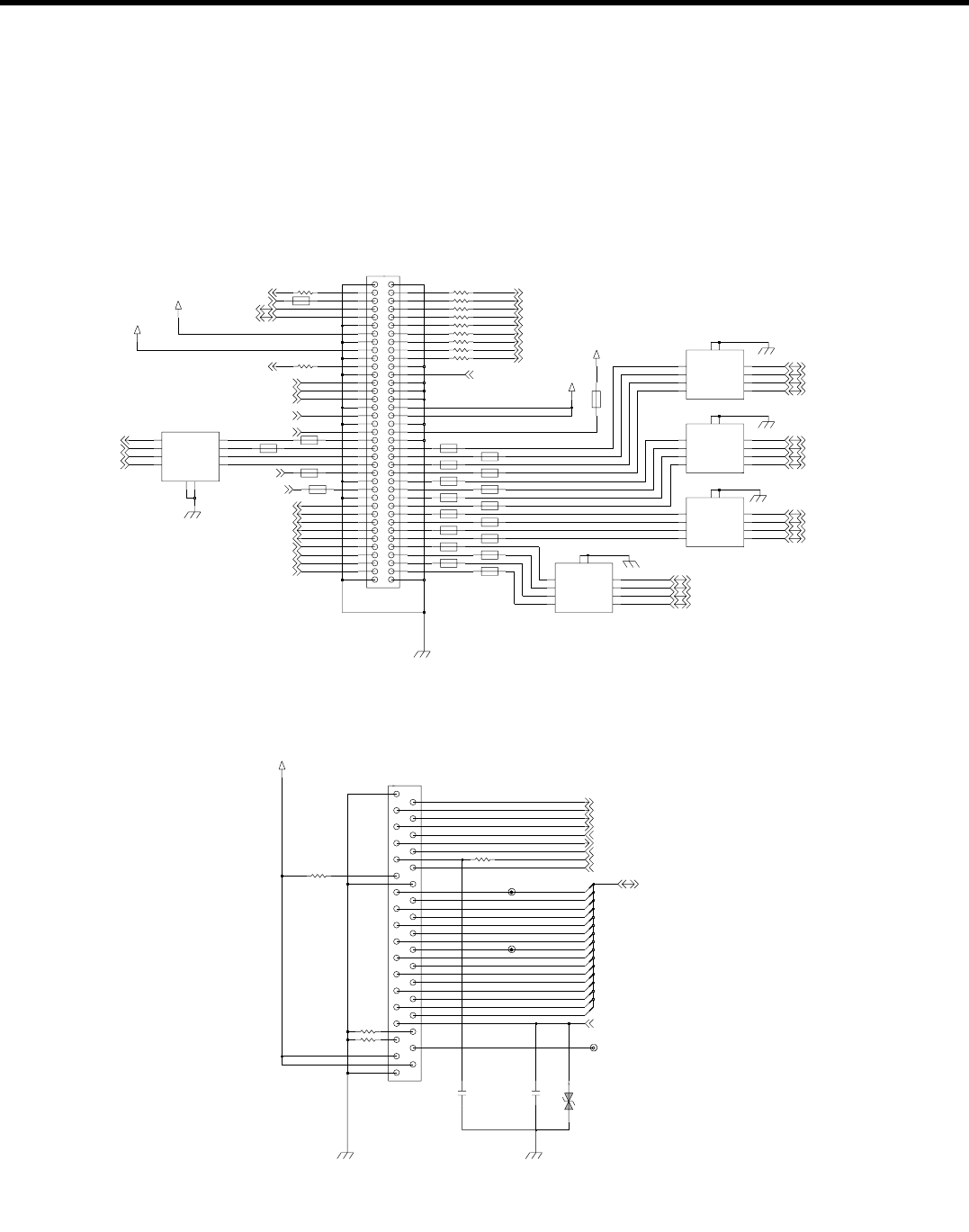

Figure. Simplified Block Diagram

LGE Internal Use Only

Copyright © 2007 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3. TECHNICAL BRIEF

- 37 -

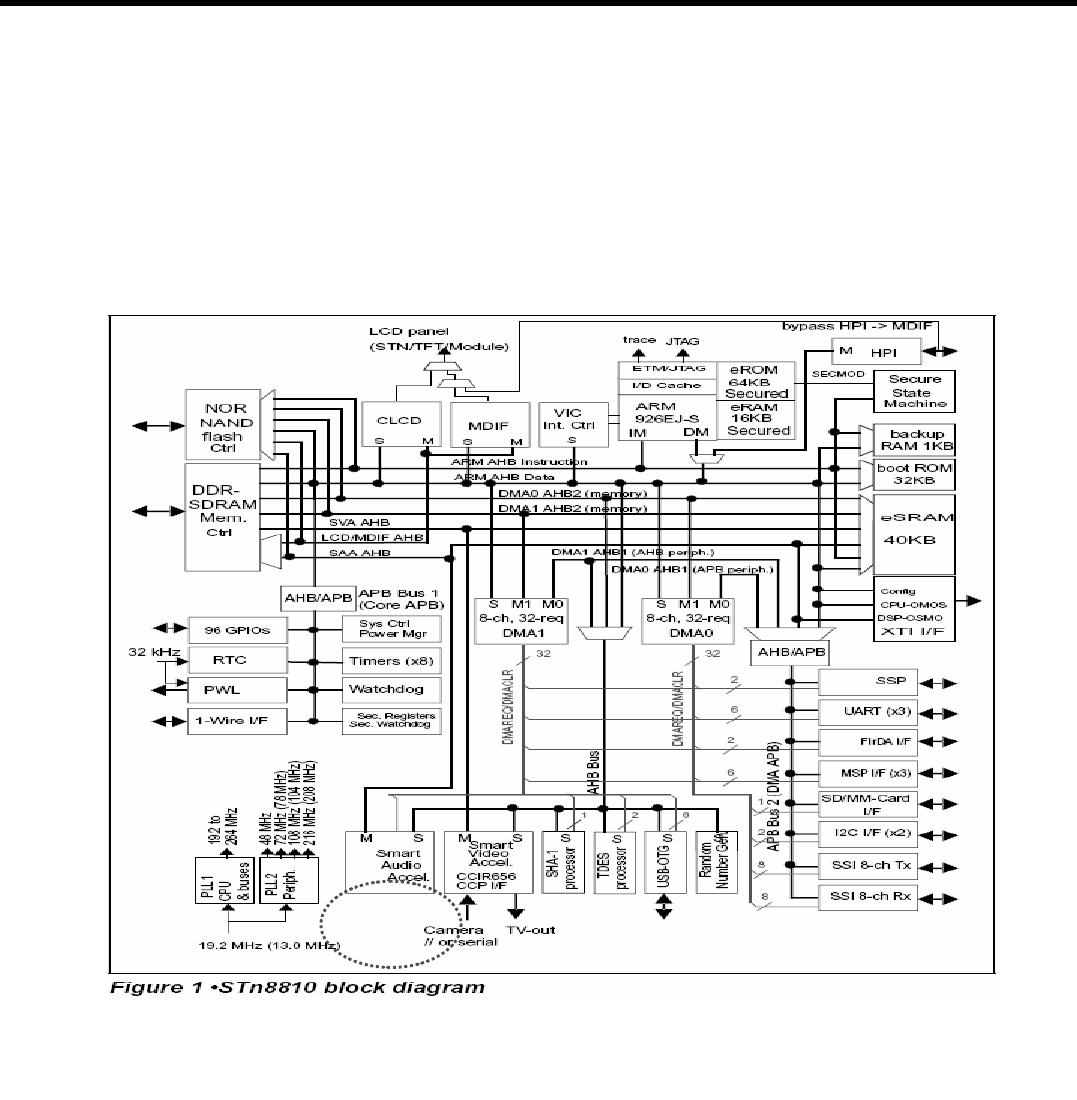

Figure. STn8810 and supported peripherals

3.7.1. STn8810 and supported peripherals

LGE Internal Use Only

Copyright © 2007 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3. TECHNICAL BRIEF

- 38 -

3.7.2. MSM6275 and supported peripherals

Figure. MSM6275 and supported peripherals

LGE Internal Use Only

Copyright © 2007 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3. TECHNICAL BRIEF

- 39 -

3.8. Subsystem of STn8810

3.8.1. ARM926EJ processor

The STn8810 CPU is an ARM926EJ reduced instruction set computer (RISC) processor. This 32-bit

processor core supports 32-bit ARM® and 16-bit Thumb instruction sets, enabling the user to trade off

between high performance and high code density.

The cached ARM CPU features a memory management unit (MMU) and is clocked at 264 MHz.

It has a 32-Kbyte instruction cache and a 16-Kbyte data cache, and supports the Jazelle™ extensions

for Java acceleration. It also includes an embedded trace module (ETM Medium+) for real-time CPU

activity tracing and debugging. It supports 4-bit and 8-bit normal trace mode and 4-bit demultiplexed

trace mode, with normal or half-rate clock.

3.8.2. Smart video accelerator (SVA)

Using leading-edge technology, this block is a low-power, high-performance video accelerator that

supports the following features:

• MPEG-4 simple profile level 3 video encoder and decoder; real time up to VGA 30 fps (encode only

or decode only)

• H.263 profile 3 level 10 video codec; real time subQCIF or QCIF 15 fps for videoconferencing

• H.263 profile 3 level 30 video encoder or decoder; real-time up to CIF 30 fps

• JPEG baseline accelerated encoder or decoder, up to 4080 x 4080 pixels

• Programmable DSP (MMDSP+) for intermediate level processing, clocked at 66 MHz

• Picture pre-/post-processing

• Low-power implementation

3.8.3. Smart audio accelerator (SAA)

This high-performance block is a flexible sophisticated audio accelerator based on the MMDSP+

programmable audio DSP, clocked at 133 MHz, and features:

• 24-bit data path

• Ultra-low power implementation

The audio accelerator features:

• MP3, AAC, AAC+ (SBR) decoding, Midi synthesis, and more

• Speech codecs: AMR (WB, NB), and more

• Audio sample rates of 32 kHz, 44.1 kHz and 48 kHz

• Noise reduction and echo cancelling

• Stereo enhancements and surround effects

LGE Internal Use Only

Copyright © 2007 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3. TECHNICAL BRIEF

- 40 -

3.8.4. Advanced power management unit (PMU)

The dynamic PMU optimizes power consumption of the STn8810. It delivers all the platform clocks,

and handles reset management. It also manages GPIO levels during sleep mode and emergency

self-refresh of SDRAM.

The PMU controls the external voltage regulator, in order to change its settings in different modes.

In deep-sleep mode, only GPIOs, the real-time clock (RTC), system and reset controller (SRC),

PMU and secured RAM remain in operation. The PMU also controls the embedded 1.2 V voltage

switch that switches off the logic supply after the platform has entered sleep mode.

The family of power manager ICs, STw481x companion chips, seamlessly interface with the

Nomadik STn8810 and optimize global system power consumption leveraging on the PMU.

3.8.5. Host port interface (HPI)

The host port interface features:

• 16-bit parallel data bus

• Multiplexed and non-multiplexed address/data bus

• Indirect host access

• Direct host access to a segment of STn8810 memory in multiplexed mode

3.8.6. General purpose inputs/outputs (GPIOs)

The STn8810 provides 96 programmable inputs or outputs that have switchable pull-up and pull-down

resistors and are controllable in two modes:

• Software mode through an APB bus interface

• Hardware mode through a hardware control interface

The GPIO interface provides the following individually programmable functions:

• Any number of pins may be configured as interrupt sources

• Debouncing logic can be enabled for each GPIO to filter out glitches on I/Os

• Any GPIO may be used to wake up the device from sleep mode independent of interrupt

programming, and the input level that triggers wake-up is definable for each enabled GPIO

3.8.7. Universal asynchronous receivers-transmitters (UARTs)

The STn8810 provides three autobaud UARTs, one of which offers all modem control/status signals.

They are enhanced versions of the industry-standard 16C550 UART with a high data rate up to 3.692

Mbit/s.

LGE Internal Use Only

Copyright © 2007 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3. TECHNICAL BRIEF

- 41 -

3.8.8. USB interface

The STn8810 USB interface is USB 2.0 compliant, with On-The-Go standard extension (rev 1.0)

compliance. The USB-OTG features:

• Supports full-speed (12 Mbit/s) and low-speed (1.5 Mbit/s) signaling bit rate

• Supports session request protocol (SRP) and host negotiation protocol (HNP)

• 8 bidirectional endpoints plus control endpoint 0

• Digital interface to external PHY

• Fully compatible with STw4810 power manager companion chip

3.8.9. I2C bus interface

The STn8810 provides two I©˜C bus interfaces that support the following features:

• Slave transmitter/receiver and master transmitter/receiver modes

• Multi-master capability

• 10-bit addressing

• Standard (100 kHz) and fast (400 kHz) speeds

• Compliance with I2C and DDC standards

In addition to receiving and transmitting data, the interface converts data from serial to parallel

format and vice-versa using an interrupt or polled handshake. The interrupts are enabled and

disabled in software.

3.8.10. MultiMediaCard/secure data card interface (MMC/SD/SDIO)

This interface can directly control one SD card (without encryption/decryption logic) or SDIO card, or

one MultiMediaCard. It also supports several of each card type using the GPIOs for card selection.

LGE Internal Use Only

Copyright © 2007 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3. TECHNICAL BRIEF

- 42 -

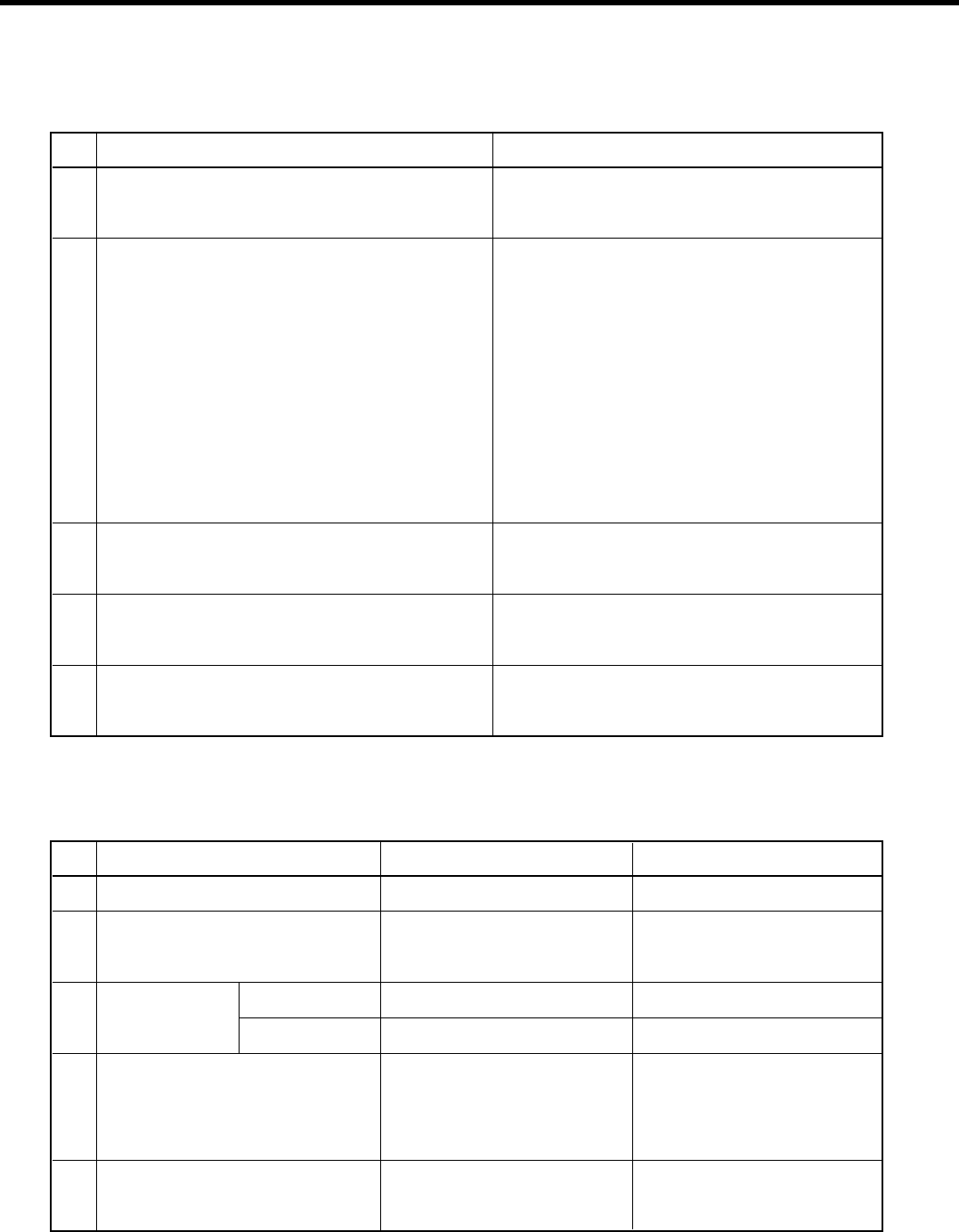

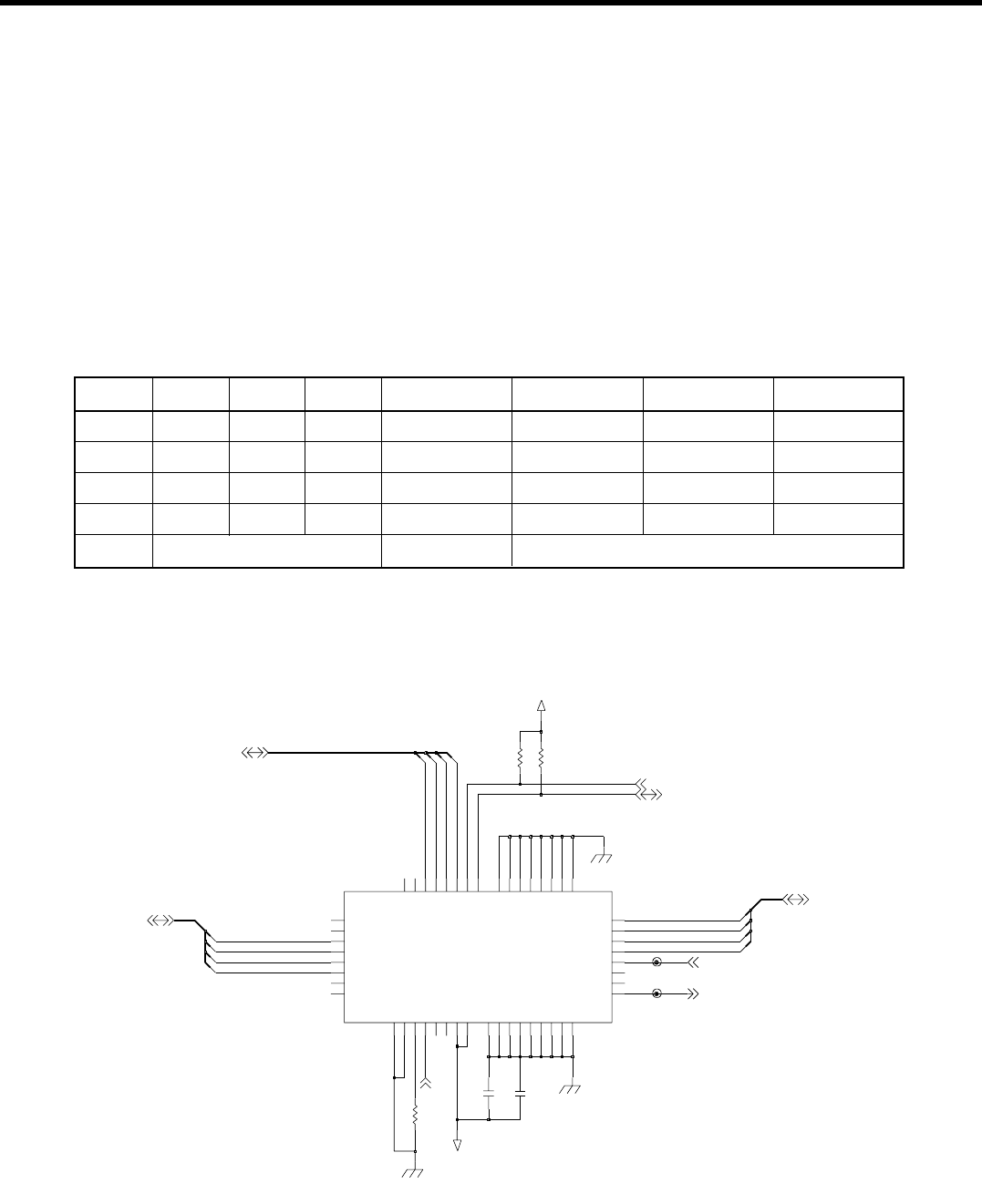

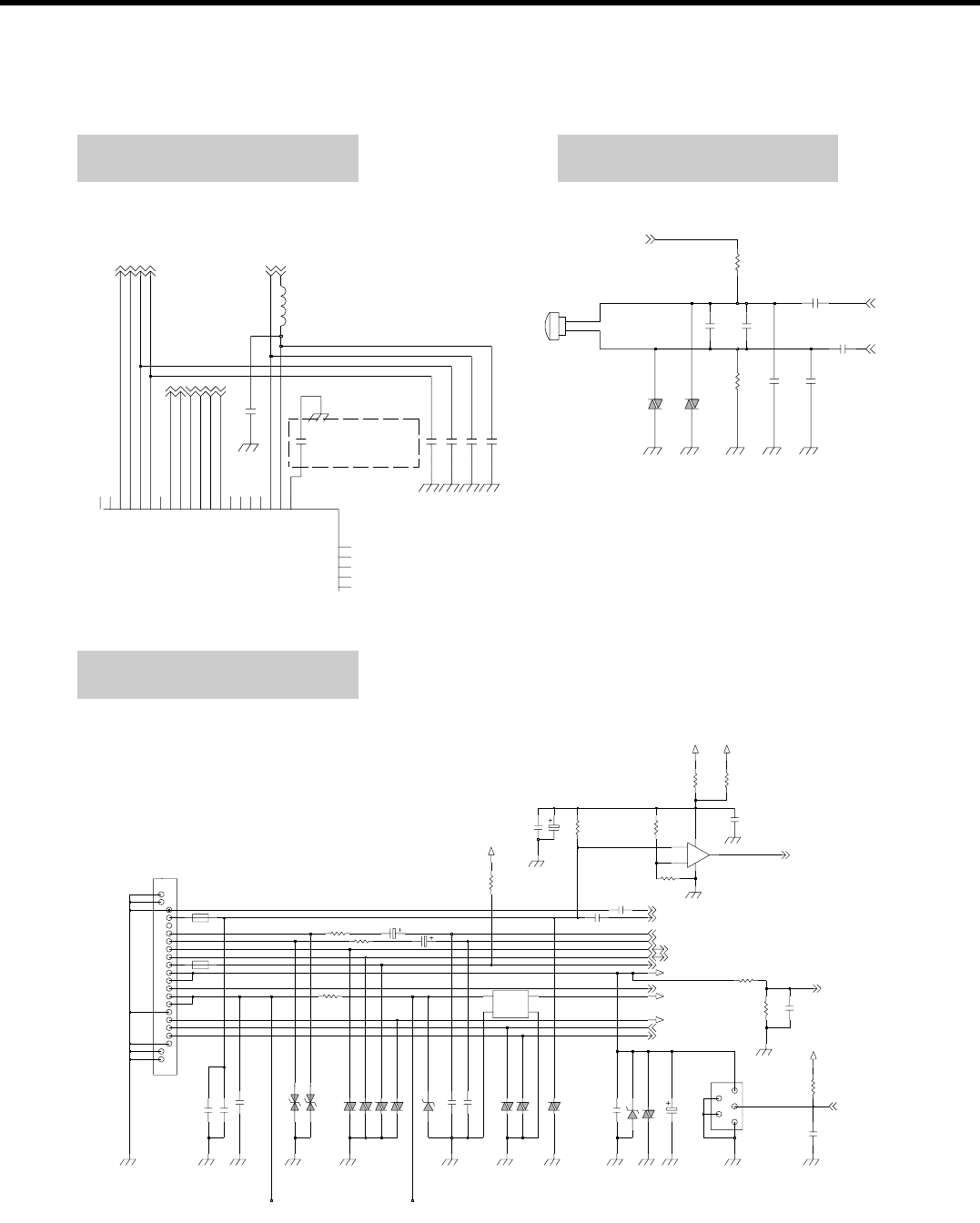

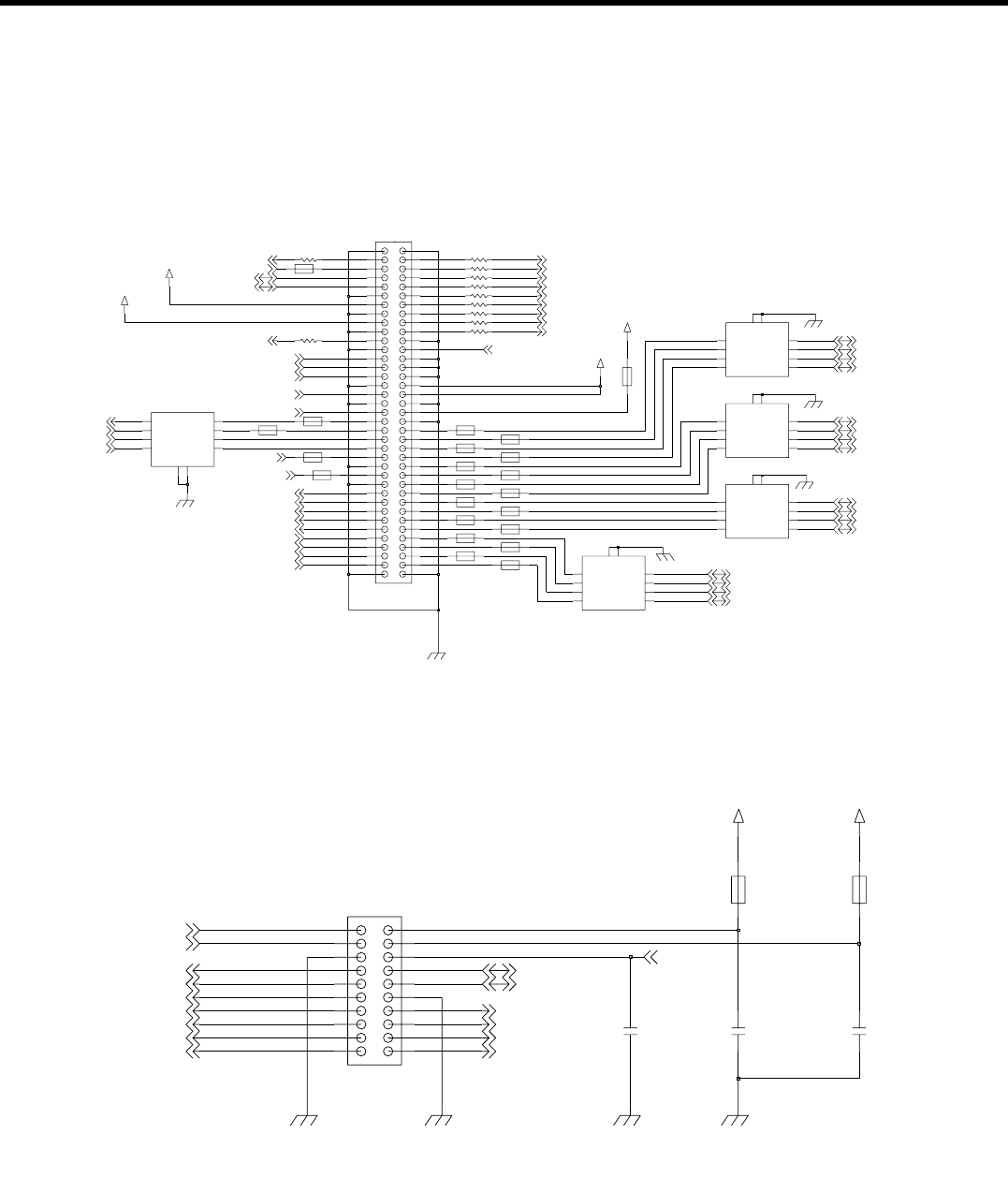

3.9. Hardware Peripheral system of Stn8810

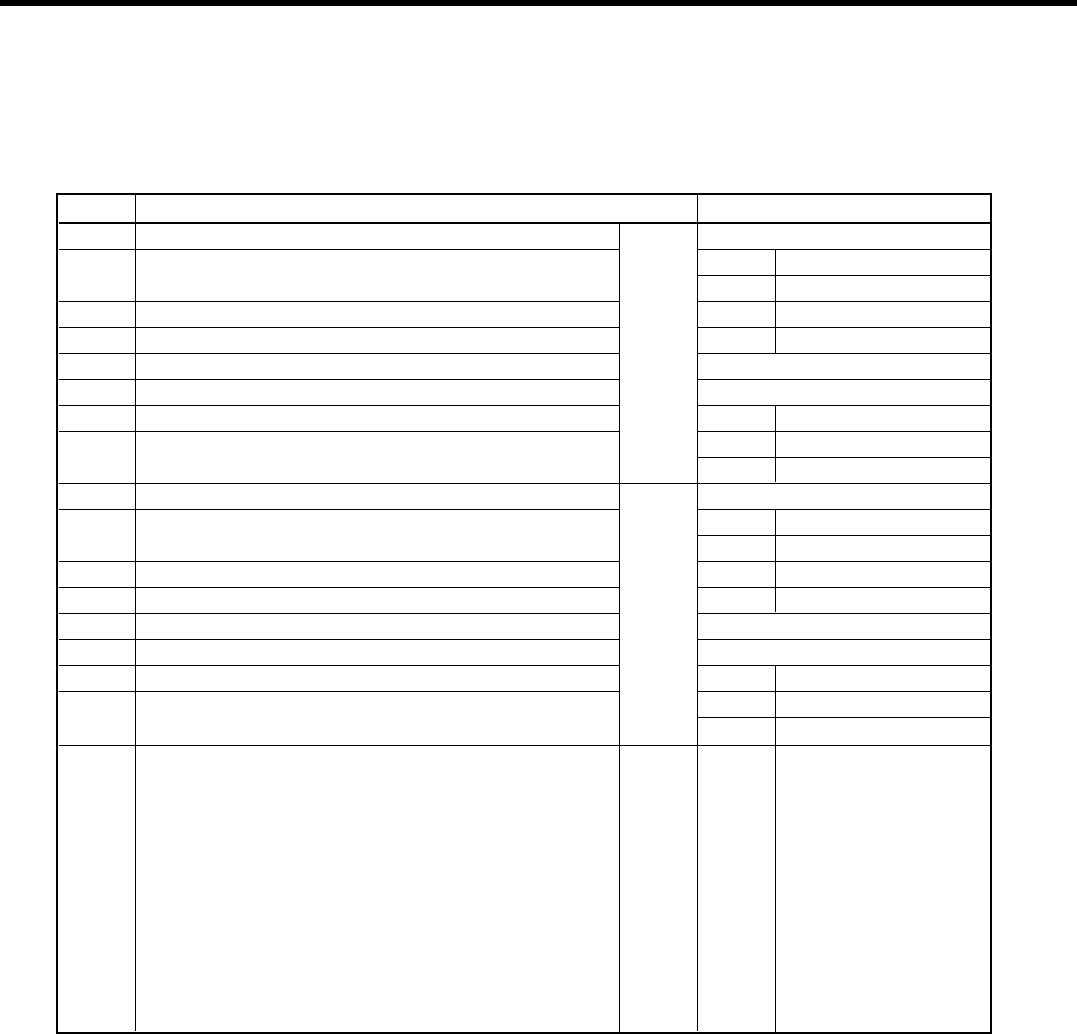

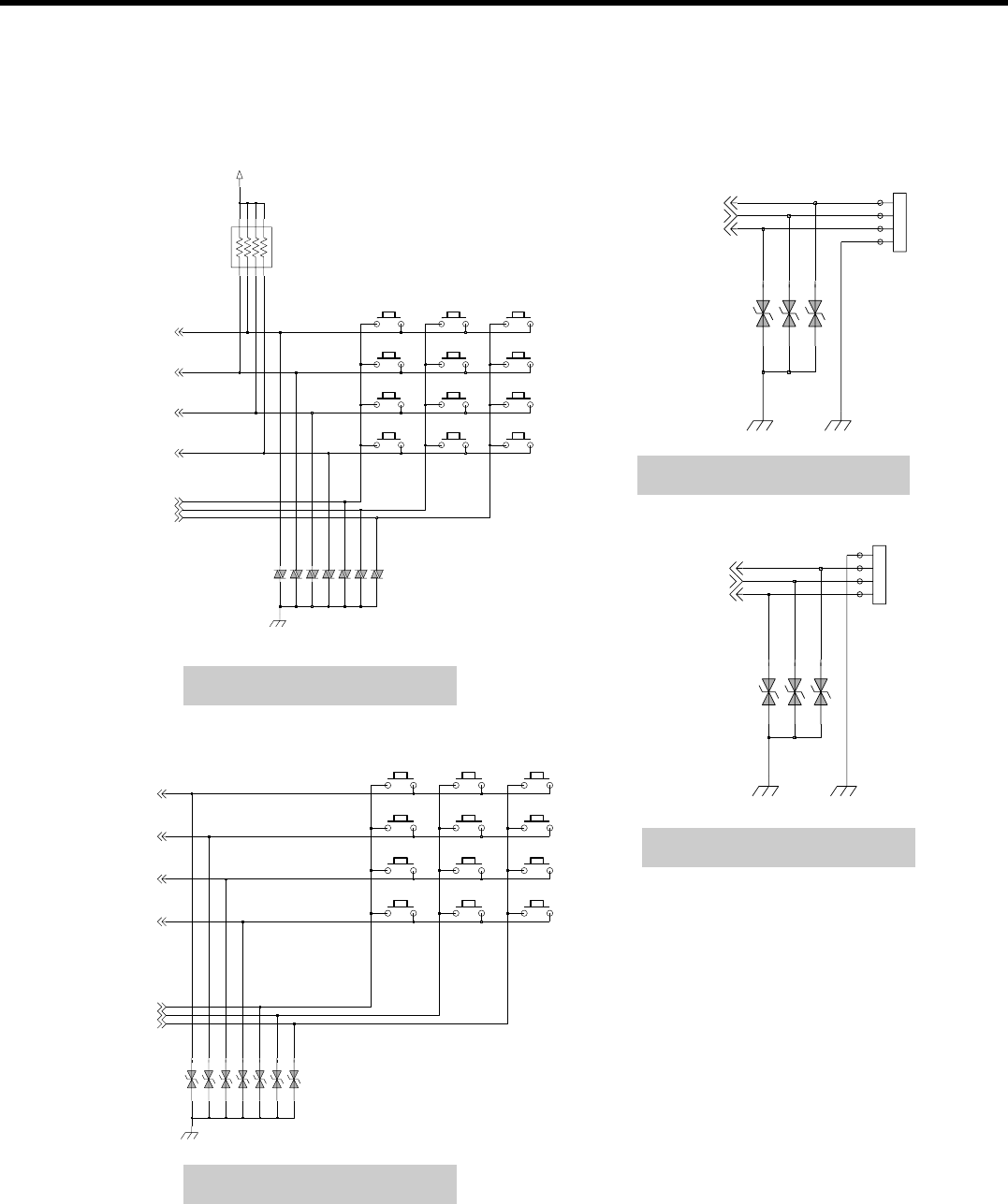

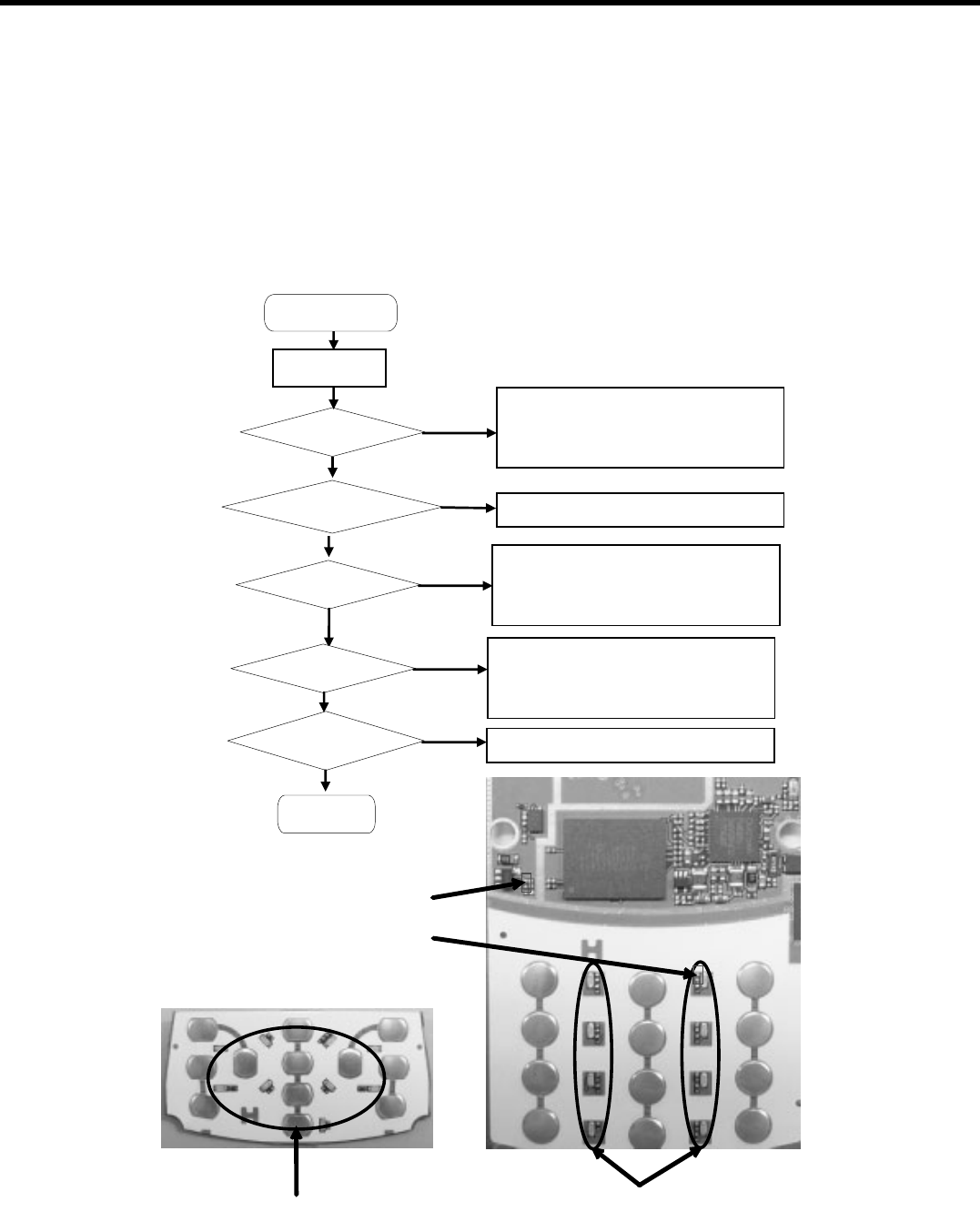

3.9.1. Keypad

KS10 has 28 buttons, 12 function keys in Sub PCB (Folder), 12 numeric keys in main and 4 side keys.

KS10 use key coder IC because Stn8810 has not enough GPIO. Key coder IC use interrupt and I2C

interface for communication with STn8810. Figure shows the Keypad circuit.

°ÆEND’ Key is connected to PM_ON_SW_N to PM6650

Table. Key Matrix Mapping Table

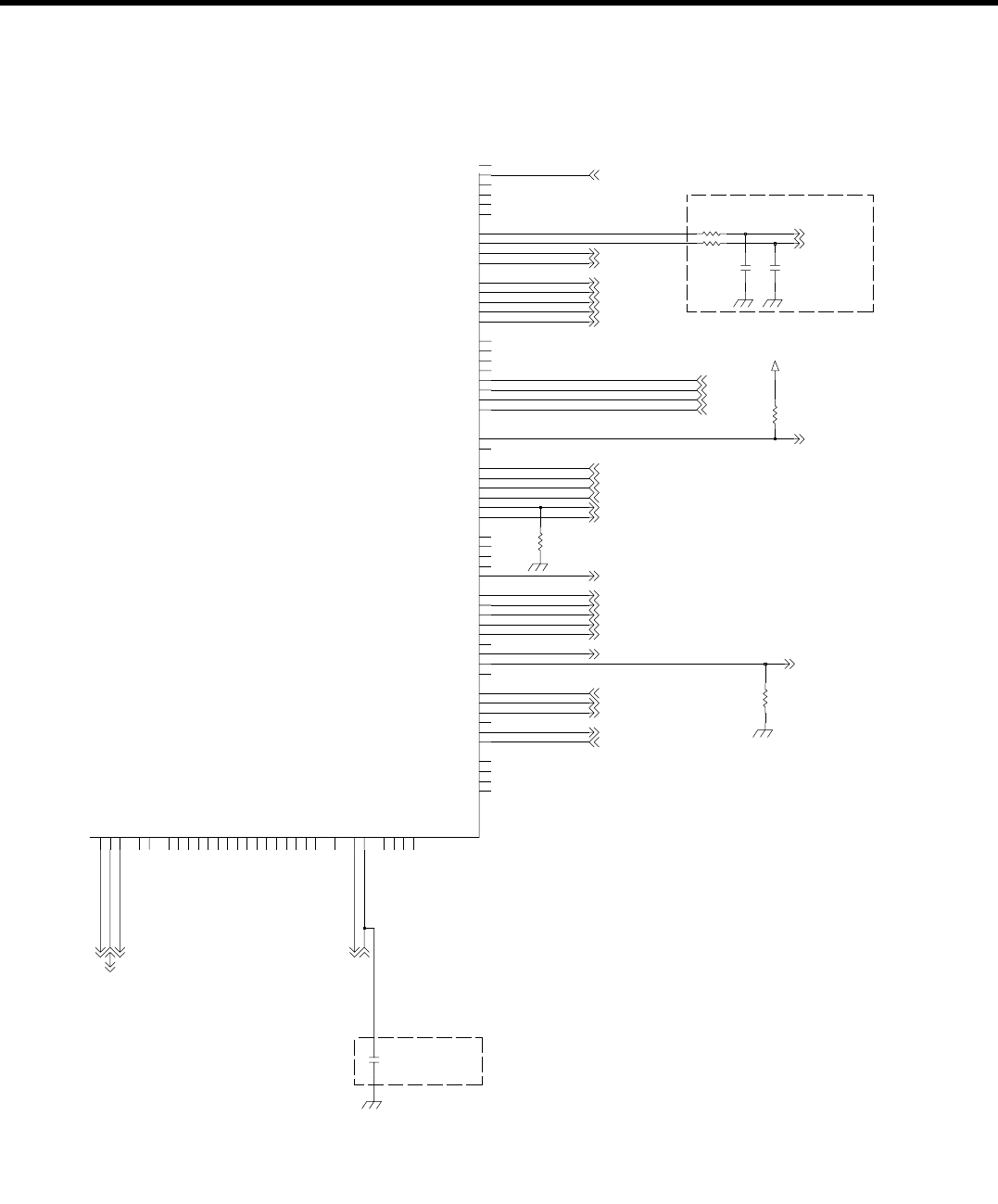

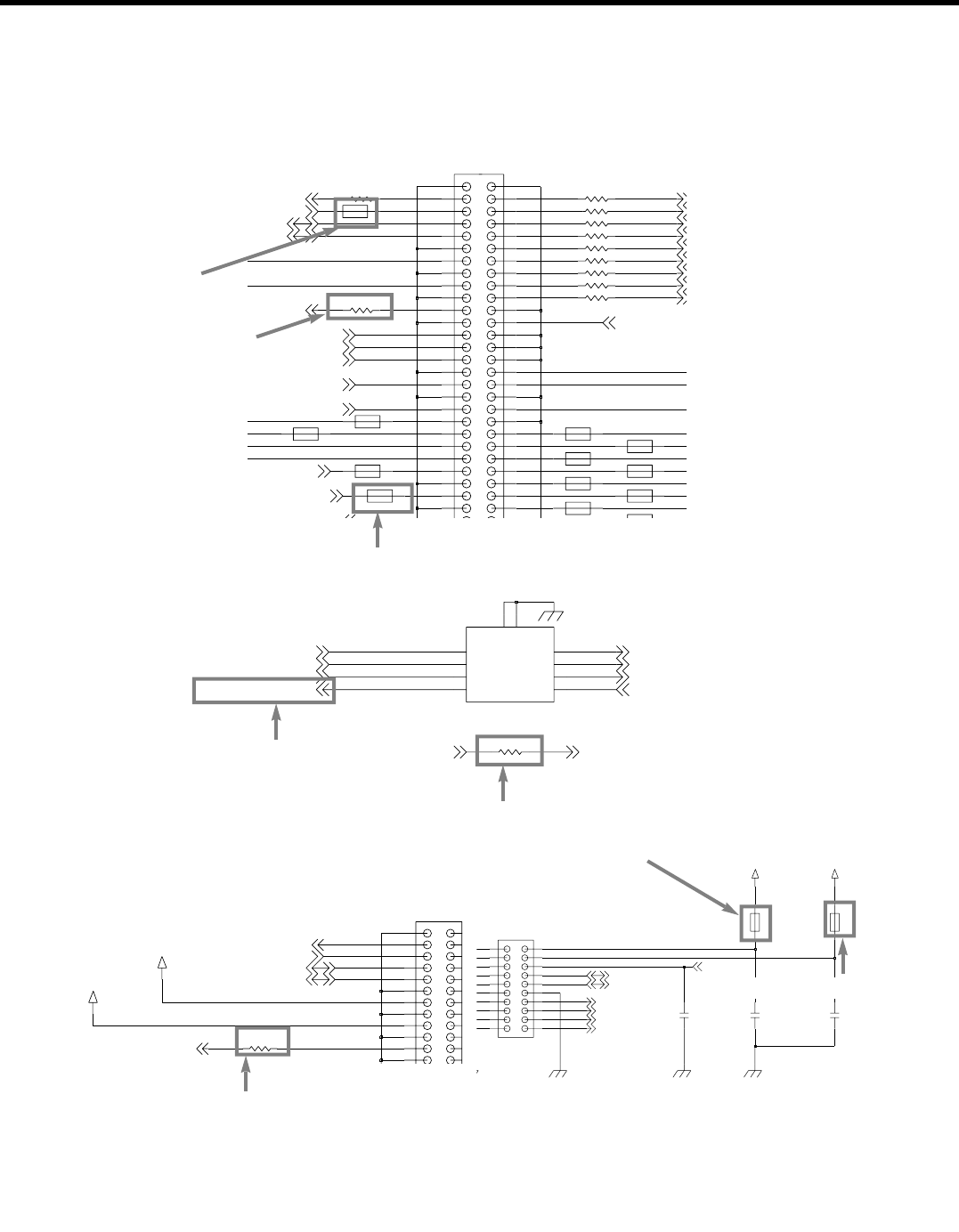

Figure. Schematic of key coder IC

COL0 COL1 COL2 COL3 COL4 COL5 COL6

ROW0 1 2 3 Vol. UP Left Soft Key UP Right Soft Key

ROW1 4 5 6 Vol. DOWN MENU OK CANCEL

ROW2 7 8 9 SHOT SEND DOWN END

ROW3 * 0 # LEFT EDIT RIGHT

Main Side Key Folder

TP407

0.1u

C418

R415

3.3K

TP406

C419

0.1u

3.3K

R414

Wake_INP2 E7

D6

Wake_INP3

B6

Wake_INP4

Wake_INP5 A7

Wake_INP6

A6

B5 Wake_INP7

F3

_RESET

NC1 F5

G6

NC2

NC3 F6

G7

NC4

C2

NC5

NC6 C1

C6

NC7

NC8 B7

F1 PWM

SCL_AB E6

F7

SDA_AB

VCC1

E1

VCC2

E2

G1

WD_Out

Wake_INP0 D7

C7

Wake_INP1Gen_IO_0

D2

D1 Gen_IO_1

Gen_IO_2

B3

Gen_IO_3

A2

A1 Gen_In0

Gen_In1

B2

Int_Rx G2

Int_Tx F2

G3

K_Out0

K_Out1 F4

G4

K_Out2

K_Out3 G5

K_Out4

A5

B4 K_Out5

K_Out6

A4

A3 K_Out7

LM8333GGR8_NOPB

U404

B1 CLK_In

GND1

C3

C4 GND2

C5 GND3

GND4

D3

D4 GND5

GND6

D5

GND7

E3

E4 GND8

GND9

E5

AP_VDD_IO_2.7V

AP_VDD_IO_2.7V

68KR419

FOLDER_DETECT

I2CSCL1

I2CSDA1

KEY_COL(5)

KEY_COL(6)

KEY_COL(7)

KEY_COL(4:7)

KEYCODER_RSTN

KEYCODER_INT

KEY_ROW(0:3)

KEY_ROW(2)

KEY_ROW(3)

KEY_ROW(0)

KEY_ROW(1)

KEY_COL(3)

KEY_COL(2)

KEY_COL(3:0)

KEY_COL(1)KEY_COL(4)

KEY_COL(0)

LGE Internal Use Only

Copyright © 2007 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3. TECHNICAL BRIEF

- 43 -

Figure. Schematic of keypad

SW400

SW411

SW407

VA403 EVLC14S02050

VA405 EVLC14S02050

EVLC14S02050VA404

SW408

VA401 EVLC14S02050

EVLC14S02050VA406

SW401

EVLC14S02050VA402

SW409 SW410

SW402

VA407 EVLC14S02050

SW406

AP_VDD_IO_2.7V

2

4

6

8

1

3

5

7

SW404

RA400 100K

SW405SW403

KEY_COL(1)

KEY_COL(2)

KEY_ROW(0)

KEY_ROW(1)

KEY_ROW(2)

KEY_ROW(3)

KEY_COL(0)

VA102 RSB6.8CST2R

RSB6.8CST2RVA101

SW106 SW108

VA105

VA104

RSB6.8CST2R

RSB6.8CST2R

SW107

VA103

VA107

RSB6.8CST2R

VA106

RSB6.8CST2R

RSB6.8CST2R

SW104 SW105SW103

SW102SW100

SW111SW109

SW101

SW110

KEY_ROW(0)

KEY_ROW(1)

KEY_COL(6)

KEY_COL(4)

KEY_COL(5)

KEY_ROW(3)

KEY_ROW(2)

D402 RSB6.8CST2R

RSB6.8CST2RD401

D400 RSB6.8CST2R

1

2

3

4

CN400

KEY_ROW(0)

KEY_ROW(1)

KEY_COL(3)

RSB6.8CST2RD405

1

2

3

4

CN401

D404 RSB6.8CST2R

RSB6.8CST2RD403

KEY_COL(3)

KEY_ROW(2)

KEY_ON_SW_N

Side Key (Vol. UP/Down)

Side Key (Power/Shot)

Main PCB

Sub PCB

LGE Internal Use Only

Copyright © 2007 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3. TECHNICAL BRIEF

- 44 -

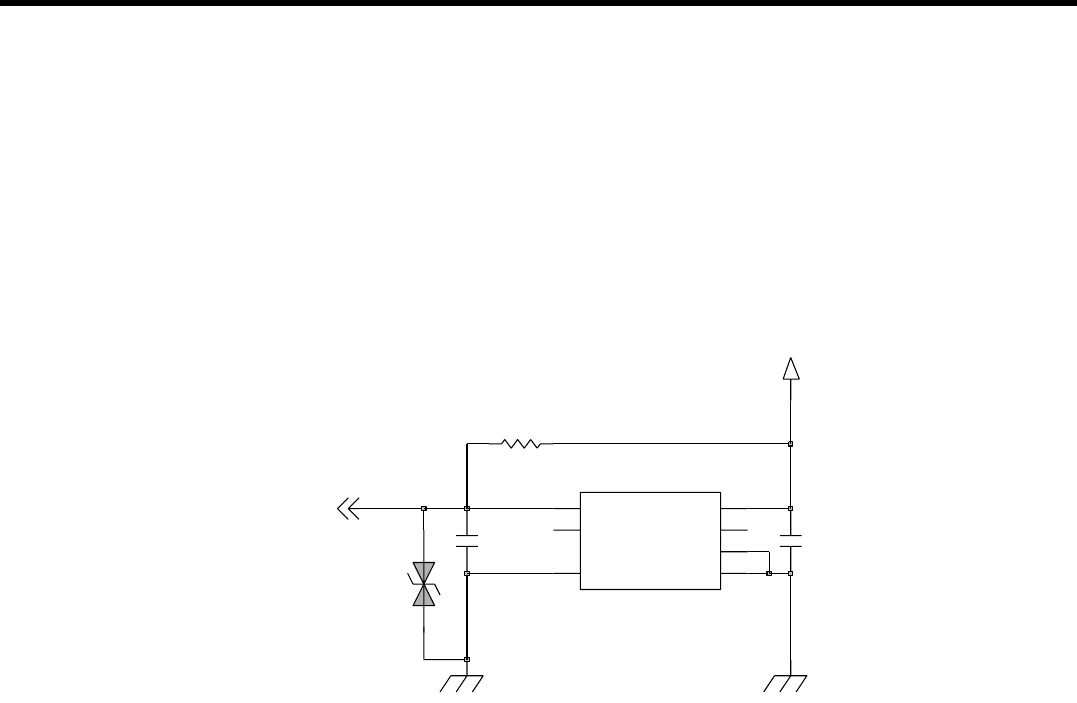

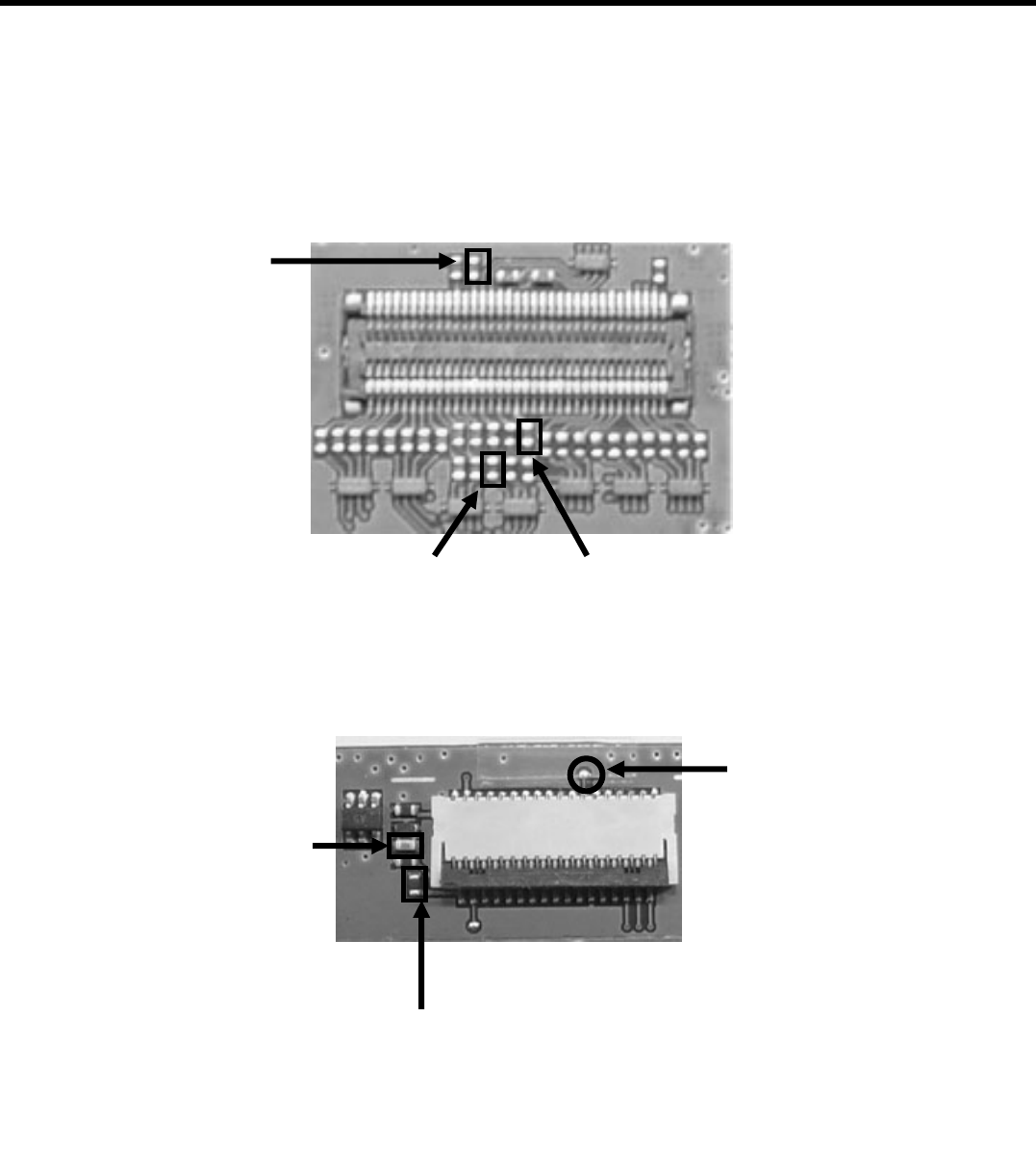

3.9.2. Folder on/off operation

There is a magnet to detect the folder status, opened or closed. If a magnet is close to the hall-effect

switch, the voltage at pin1 of U402 goes to 0V. Otherwise, 2.7V. This folder signal is delivered to

GPIO0 of the Key coder IC .

AP_VDD_IO_2.7V

0.1u

C414

U402 A3212EEH-T

3GND1

GND2 4

2NC1 5

NC2

1OUTPUT

7

PGND

6

VDD

EUSY0200301

R413

100K

C413

1u

ZD1

RSB6.8CST2R

FOLDER_DETECT

Figure. Schematic of folder on/off detection circuit

LGE Internal Use Only

Copyright © 2007 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3. TECHNICAL BRIEF

- 45 -

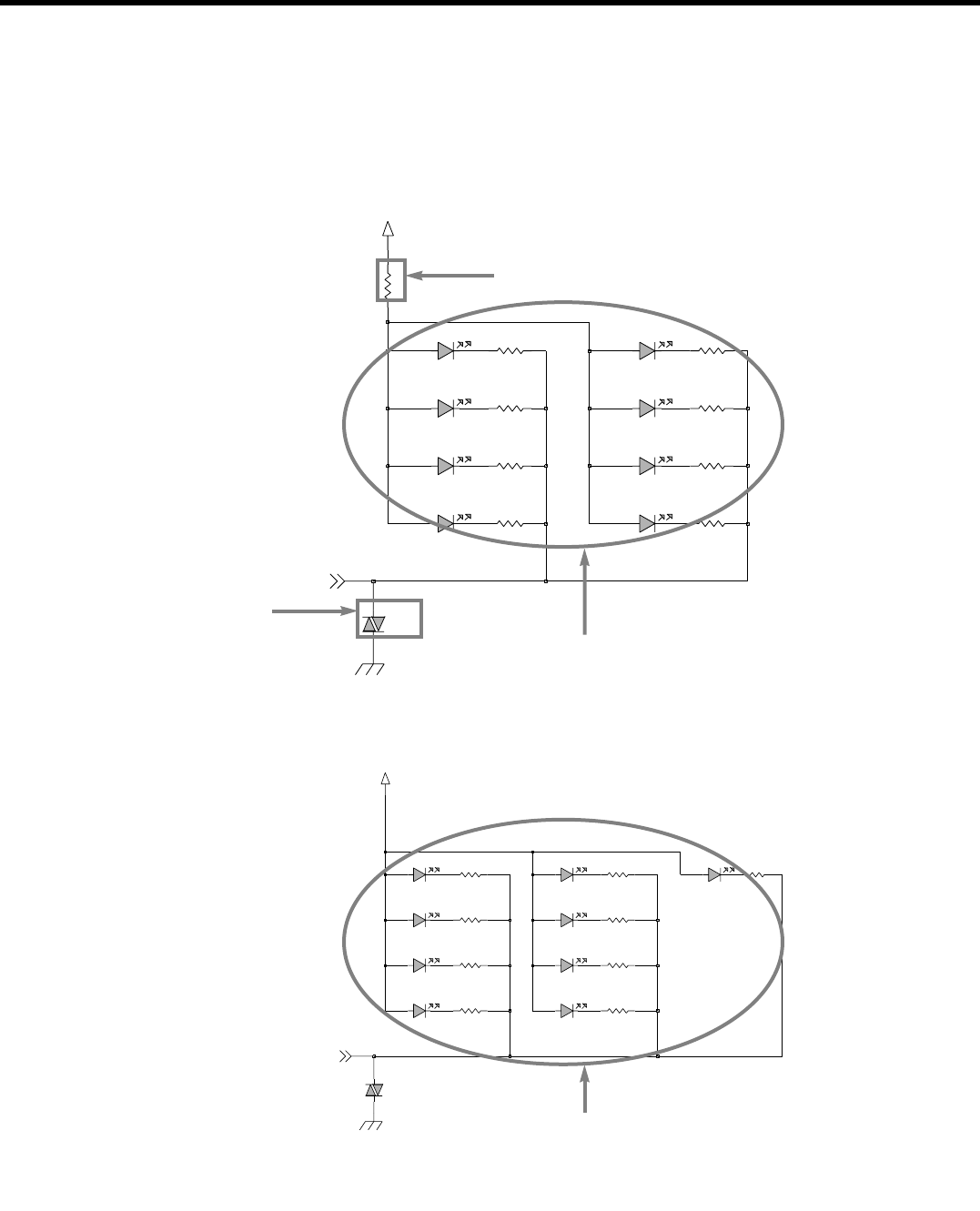

3.9.3. Keypad backlight

There are 8 White LEDs on Top side of Main PCB and 9 White LEDs on Top side of sub PCB in board

backlight circuit and, which are driven by KEYBD_BACKLIGHT line form PM6650. Key Pad backlight

controlled by PM6650.

Figure. Schematic of main PCB keypad backlight circuit

100ohmR411

SSC-TWH104-HLS

LD407

SSC-TWH104-HLS

LD406

SSC-TWH104-HLS

LD402

EVL14K02200

VA400

R409 100ohm

100ohmR412

AP_+VPWR

LD400

SSC-TWH104-HLS

100ohmR406

R400

0

R408 100ohm

SSC-TWH104-HLS

LD401

SSC-TWH104-HLS

LD403

R403 100ohm

SSC-TWH104-HLS

LD405

100ohmR405

R402 100ohm

LD404

SSC-TWH104-HLS

KPD_DRV_N

Figure. Schematic of key PCB keypad backlight circuit

100ohmR109

EVL14K02200

VA100

100ohmR111

100ohmR110

LD108

SSC-TWH104-HLSSSC-TWH104-HLS

LD107

LD104

SSC-TWH104-HLS

AP_+VPWR

SSC-TWH104-HLS

LD103

100ohm

100ohmR113

R112

100ohmR114

LD102

SSC-TWH104-HLS

LD100

SSC-TWH104-HLS

100ohmR107 100ohm R108R106 100ohm

SSC-TWH104-HLS

LD101

LD105

SSC-TWH104-HLS SSC-TWH104-HLS

LD106

KPD_DRV_N

LGE Internal Use Only

Copyright © 2007 LG Electronics. Inc. All right reserved.

Only for training and service purposes

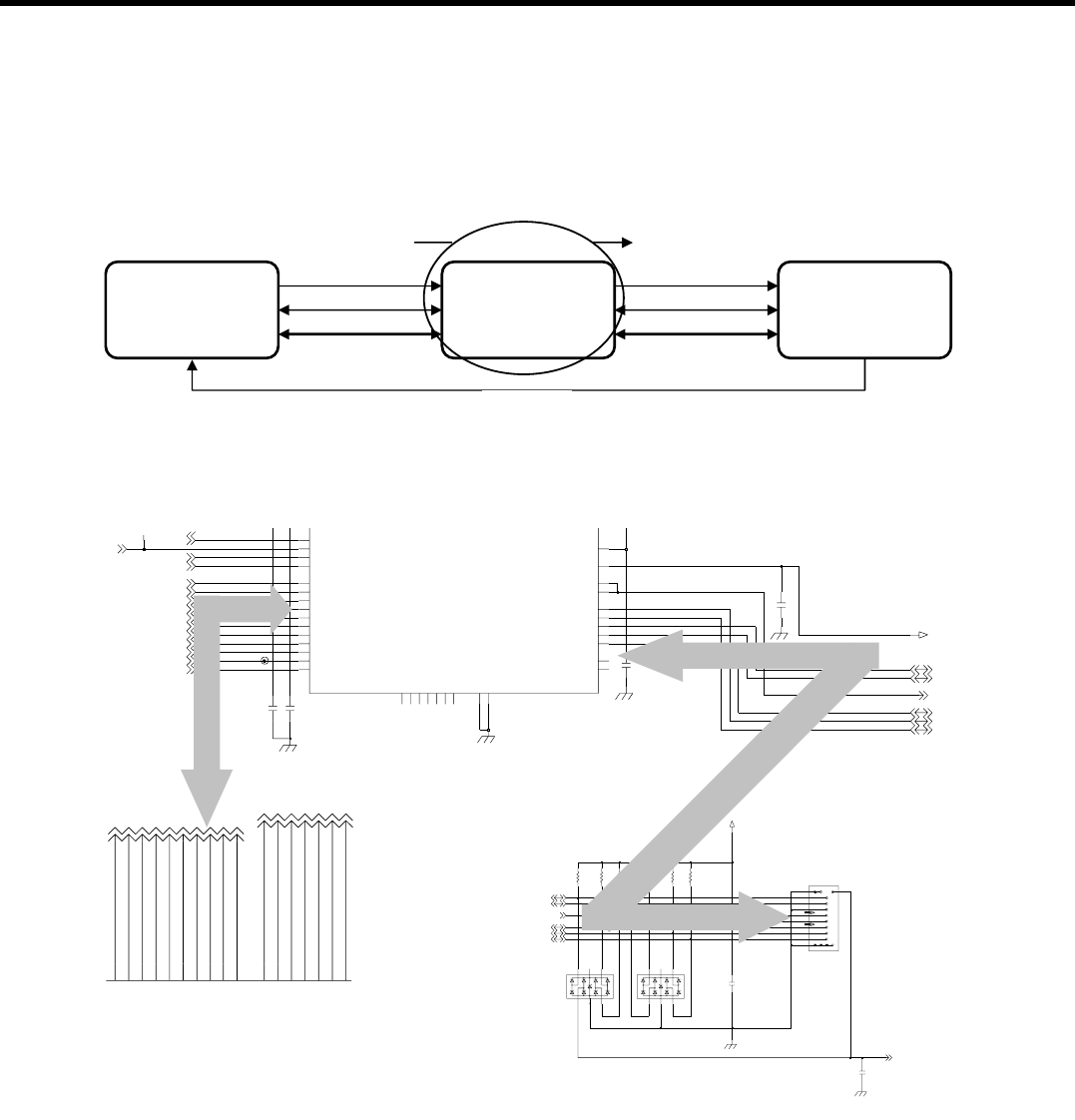

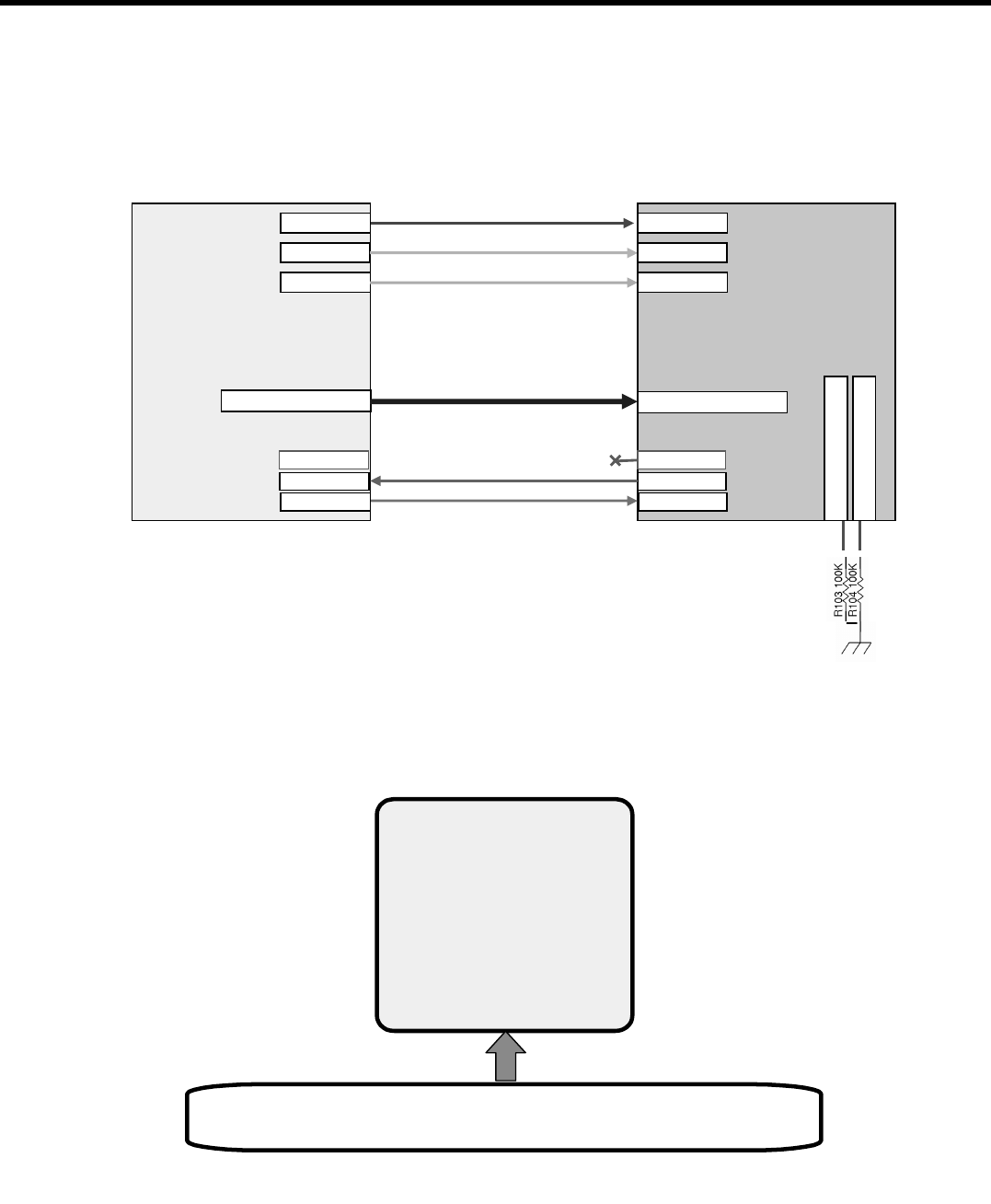

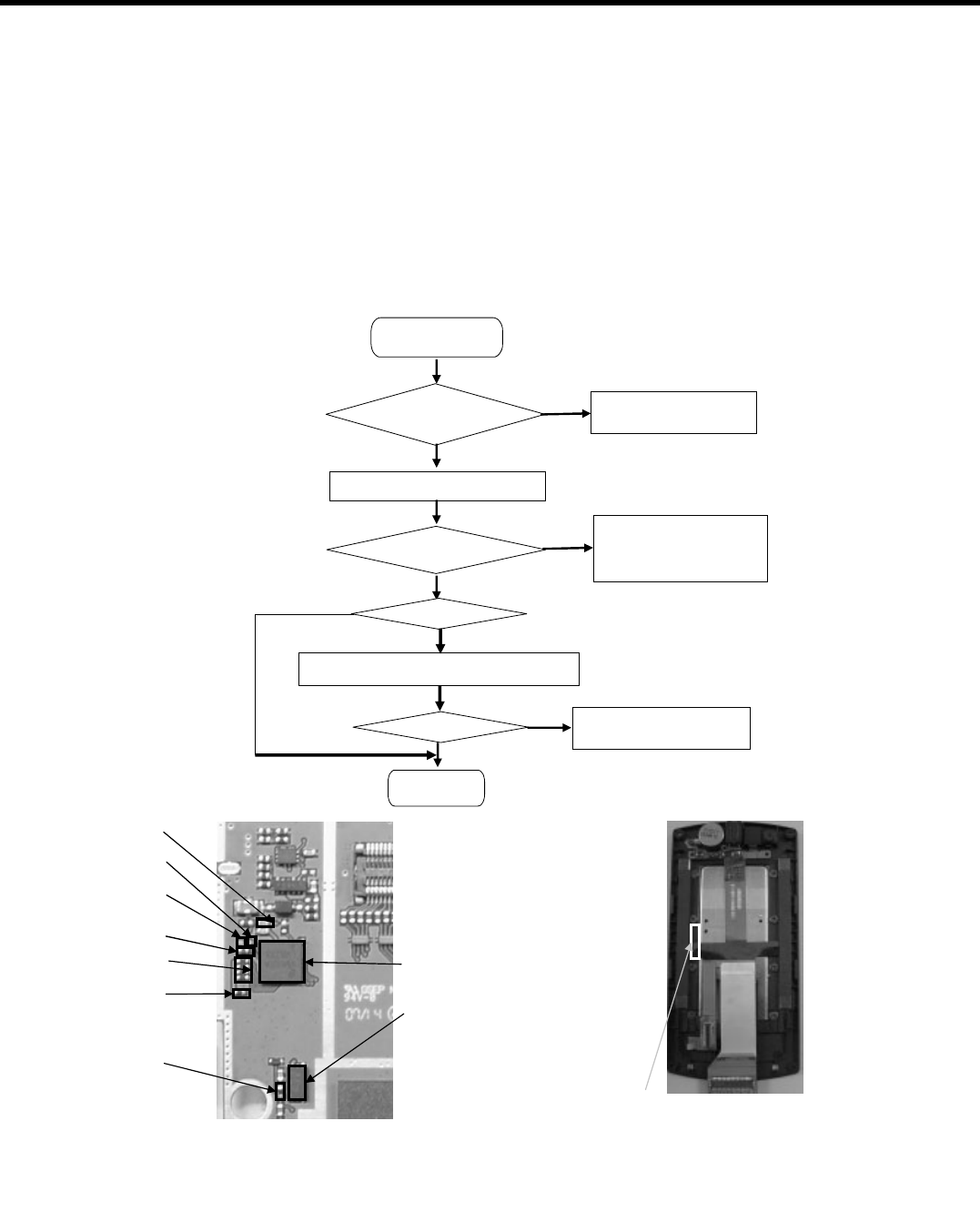

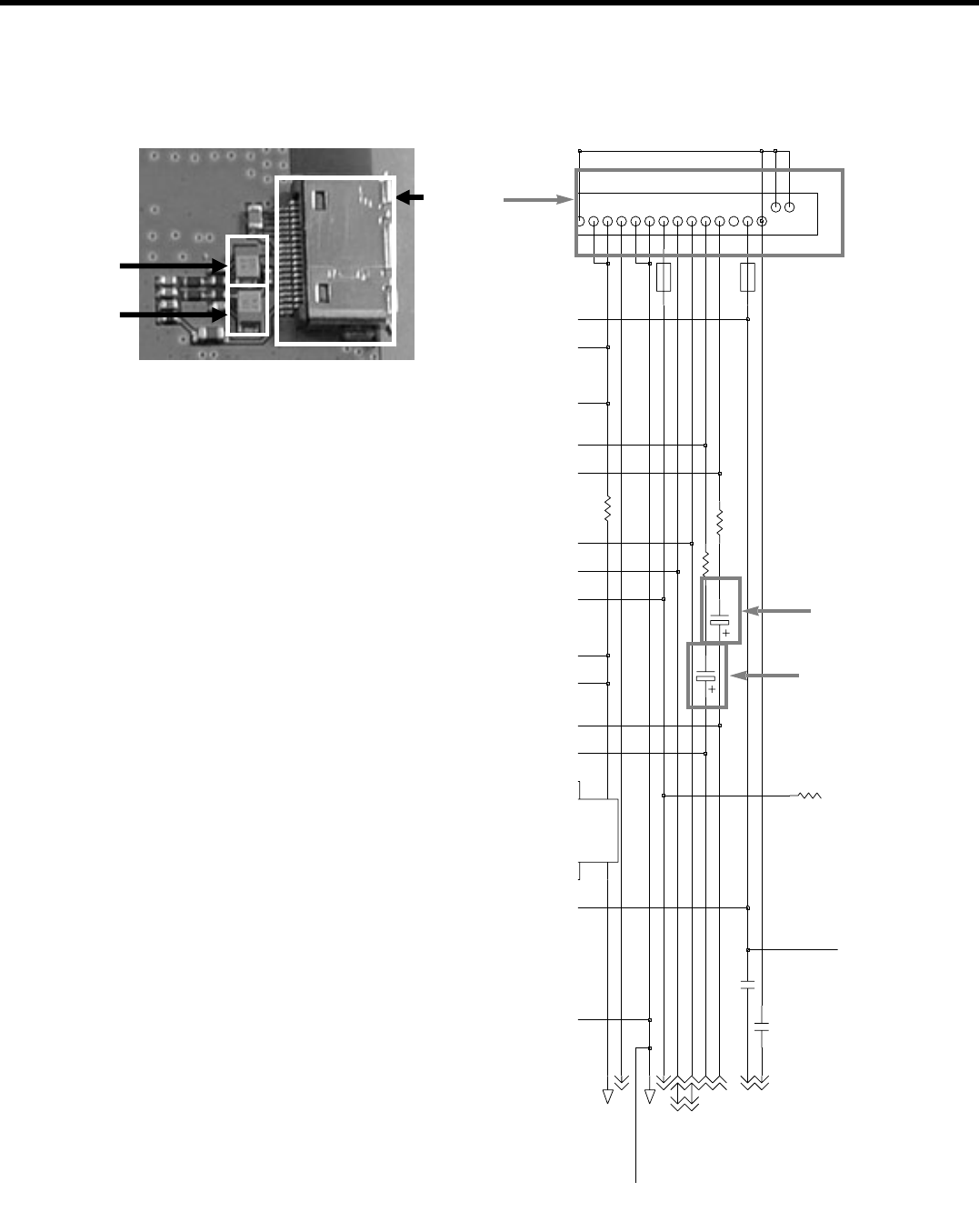

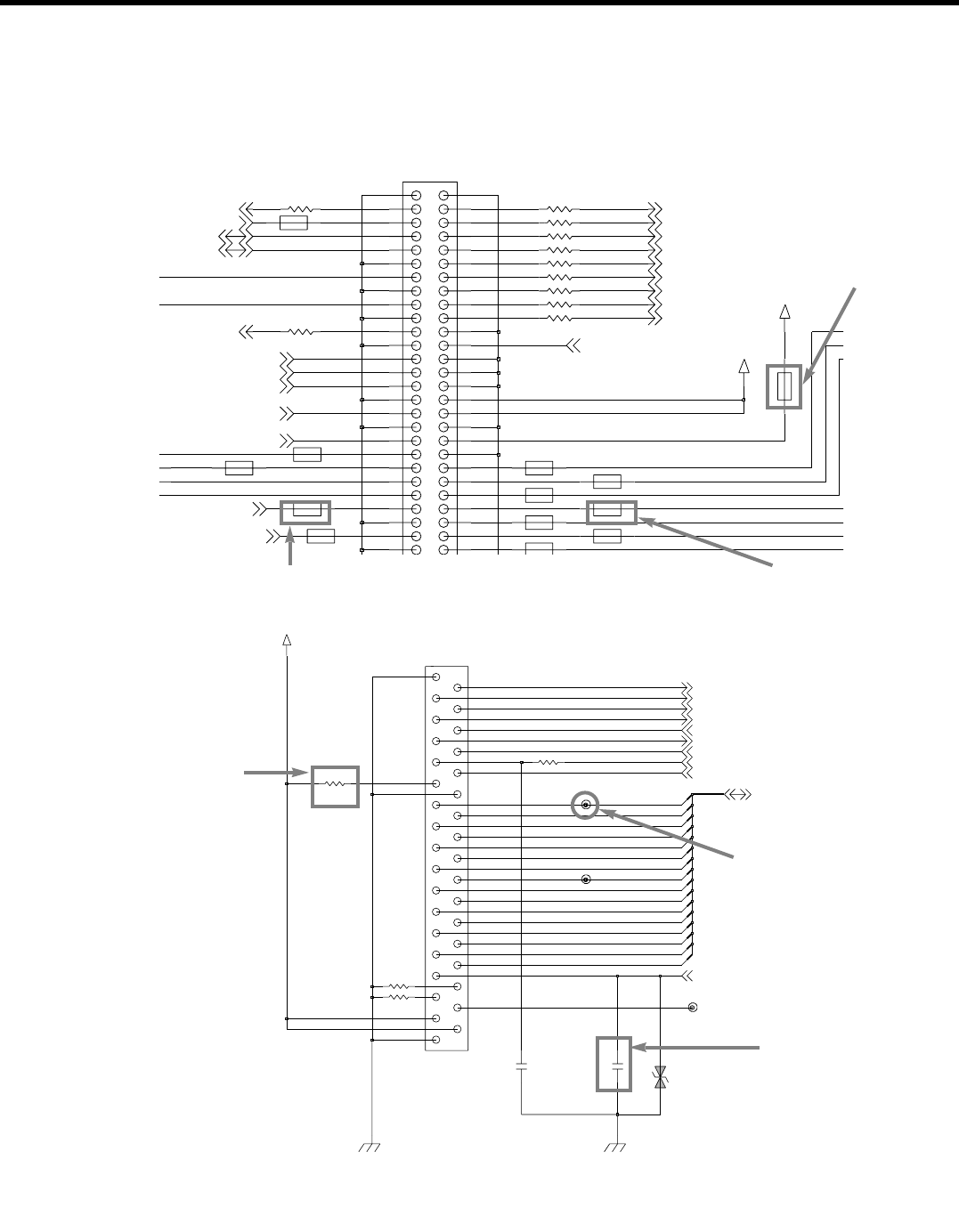

3.9.4. Micro SD

3. TECHNICAL BRIEF

- 46 -

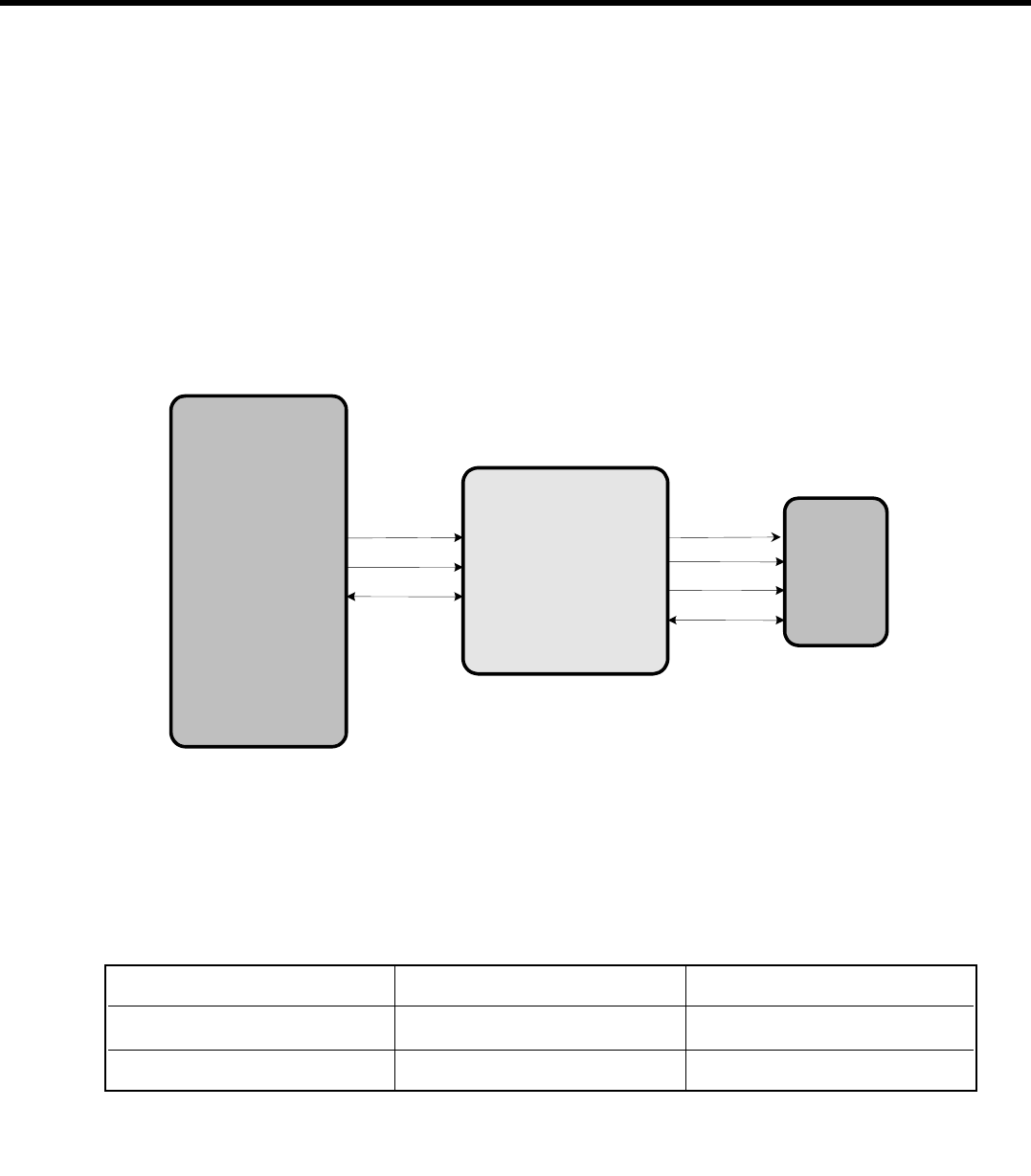

CPU

(ST Micro.)

PMIC

(ST Micro.) SD Socket

Clock Clock

Command Command

Data Data

1.8V Signal 2.85V Signal

Level shifting

SD_INT

VMMC_3.1V

VMMC K5

H8 USBINTN

K7 USBRCV

G9 USBSCL

USBSDA

H9

USBVM

VBAT_MMC J4

MCDATA31DIR

MCFBCLK

H5

B1 NC1

NC2

B7

B8 NC3

NC4

C5

NC5

F8

NC6

G8

NC7

K10

D3

J5

GPO1 K6

GPO2

LATCHCLK F3G2 MCCLK

H1 MCCMD

MCCMDDIR

G3

K2 MCDAT0DIR

K9 MCDAT2DIR

MCDATA0

K1

H3 MCDATA1

J1 MCDATA2

MCDATA3

H2

H4

CLKOUT G1

F2

CMDOUT

E1

DATAOUT0

DATAOUT1 E2

E3

DATAOUT2

DATAOUT3 F1

DN

GND1

B9

GND2

TP305

C335

NA

2.2u

C332

C334

NA

1u

C336

NA

USBINTN

SD_CMD

SD_DAT(2)

SD_CLK

SD_DAT(3)

SD_DAT(1)

MCDAT2DIR

MCDAT31DIR

MCDAT1

MCDAT3

MCDAT2

USBSCL

USBSDA

MCCLK

MCCMDDIR

MCCMD

MCFBCLK

MCDAT0DIR

MCDAT0

SD_DAT(0)

USBVM

USBRCV

D15

F24

MSPTXD2_SMPCE2N

D12

MCCLK

C12

MCCMD

MCCMDDIR E13

MCDAT0 D14

C14

MCDAT0DIR

E14

MCDAT1

MCDAT2 C13

MCDAT3 D13

MCDAT31DIR E15

MCFBCLK E17

E16

MSPRXD0

MSPSCK0 F17

H22

MSPTCK2_SMPIORN

MSPTFS0 C15

G24

MSPTFS2_SMPCE1N

MSPTXD0

MCDAT1

MCDAT0DIR

MCDAT0

MCCMDDIR

MCCMD

MCCLK

REMOTE_PWR_ON_AP

MSPTXD0

SW_RESET

MSPTFS0

SD_INT

MCDAT2DIR

MSPRXD0

MCFBCLK

MCDAT31DIR

MCDAT3

MCDAT2

1u

C339

34

5

6

R310 51K

D301

PLR0504F

1

2

51K

R309

R311 51K

51K

R313

1

2

34

5

6

PLR0504F

D300

R314 51K

NA

C343

NA

R312

5

6

7

8

SWASWBGND

GND

1

2

3

4

GCC110-8S-R-E1000

S300

VMMC_3.1V

SD_INT

SD_DAT(1)

SD_DAT(0)

SD_CLK

SD_CMD

SD_DAT(3)

SD_DAT(2)

PMIC

(ST Micro.)

SD Socket

CPU

(ST Micro.)

LGE Internal Use Only

Copyright © 2007 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3. TECHNICAL BRIEF

- 47 -

3.10. Subsystem of MSM6275

3.10.1. ARM Microprocessor Subsystem

The MSM6275 device uses an embedded ARM926EJ-S microprocessor. This microprocessor,

through the system software, controls most of the functionality for the MSM device, including control of

the external peripherals such as the keypad, LCD, RAM, ROM, and EEPROM devices. Through a

generic serial bus interface (SBI) the ARM926EJ-S configures and controls the functionality of the

RFL6202, RFR6202, RTR6250, RTR6200, and PM6650 devices.

3.10.2. UMTS/HSDPA Subsystem

The UMTS/HSDPA subsystem performs the digital release 99 June 2004 of the WCDMA FDD

standard and release 5 specifications of HSDPA signal processing.

The UMTS Subsystem performs the digital UMTS signal processing. Its components include:

•

Searcher engine

•

Demodulating fingers

•

Combining block

•

Frame deinterleaver

•

Viterbi decoder

•

Up-link subsystem

•

Turbo decoder

On the down-link channel the UMTS subsystem searches, demodulates, and decodes incoming

CPICH, CCPCH, SCH, and Traffic Channel information. It extracts packet data from the downlink

traffic channel and prepares the packet data for processing. For the up-link, the WCDMA subsystem

processes the packet data and modulates the up-link traffic channel (DCH).

3.10.3. GSM/GPRS Subsystem

The GSM/GPRS/EGPRS subsystem reuses the MSM6275 GSM core. It performs the digital GSM

signal processing and PA gain controls for GPRS support. The PA output level is controlled by an

analog signal generated on the MSM. In GSM mode, the power profile ramps up before The burst and

ramps down after the burst. In GPRS mode, at the beginning of each burst (up to Four active transmit

slots), PA must be smoothly ramped up to some desired output power level, Held at that level for the

current slot, smoothly ramped down/up during the transition period and Held to the new level for the

next slot until the last slot. Then it must be smoothly ramped down to near-zero level. The MSM6275

support differential GSM PA power control output.

LGE Internal Use Only

Copyright © 2007 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3.10.4. RF Interface

The RF interface communicates with the mobile station external RF circuits. Signals to these Circuits

control signal gain in the Rx and Tx signal path, control DC offset errors, and maintain the system

frequency reference.

3.10.5. Serial Bus Interface (SBI)

The MSM6275 device’s SBI is designed specifically to be a quick, low pin count control Protocol for

QUALCOMM’s RFL6202, RFR6202, RTR6250, RTR6200, and PM6650 ASICs. Using the SBI, the

RTR6250, RFR6200, RFL6200, and PM6650 devices can be configured for different operating modes

and for minimum power consumption, extending battery life in standby mode. The SBI also controls

DC baseband offset errors.

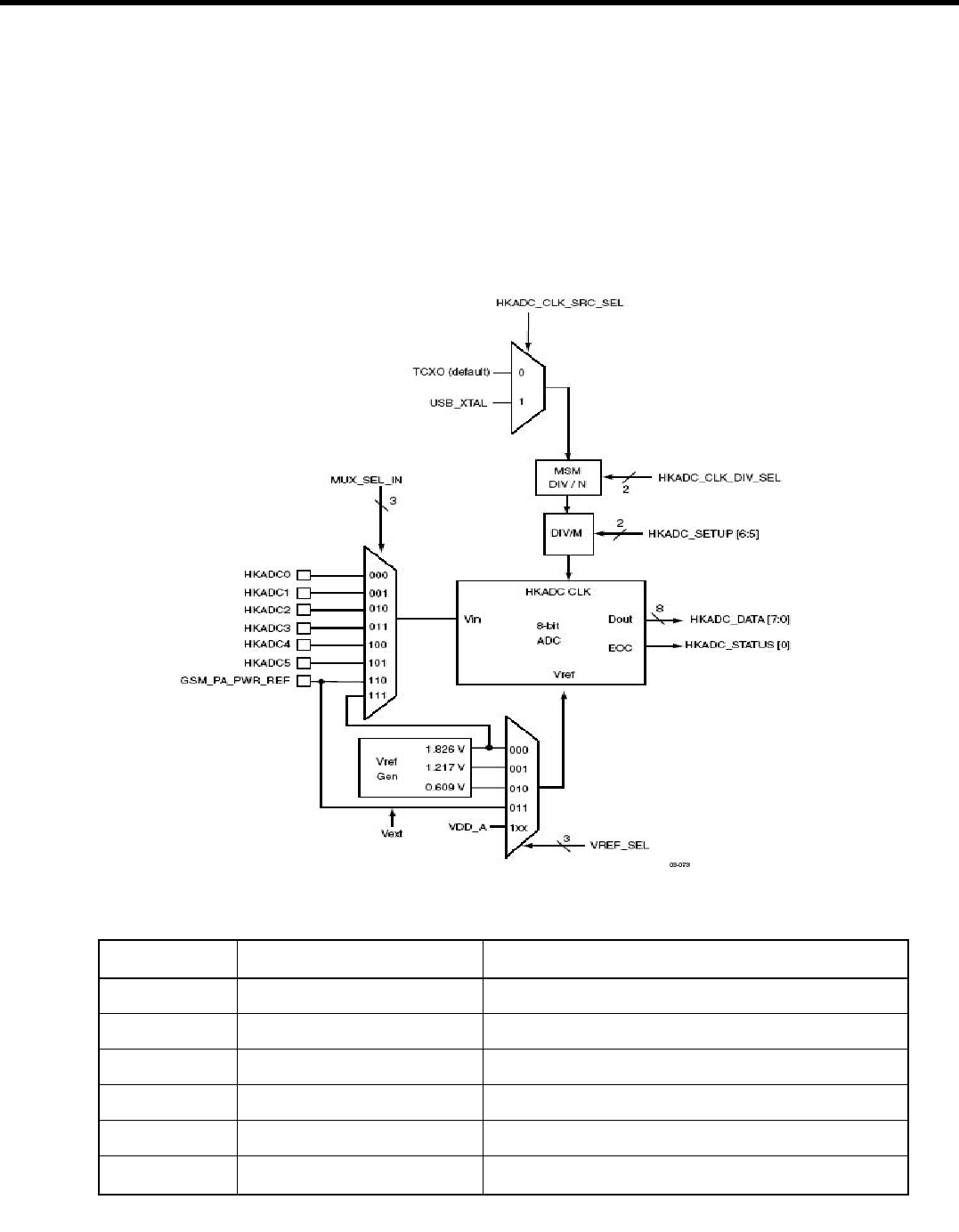

3.10.6. HKADC

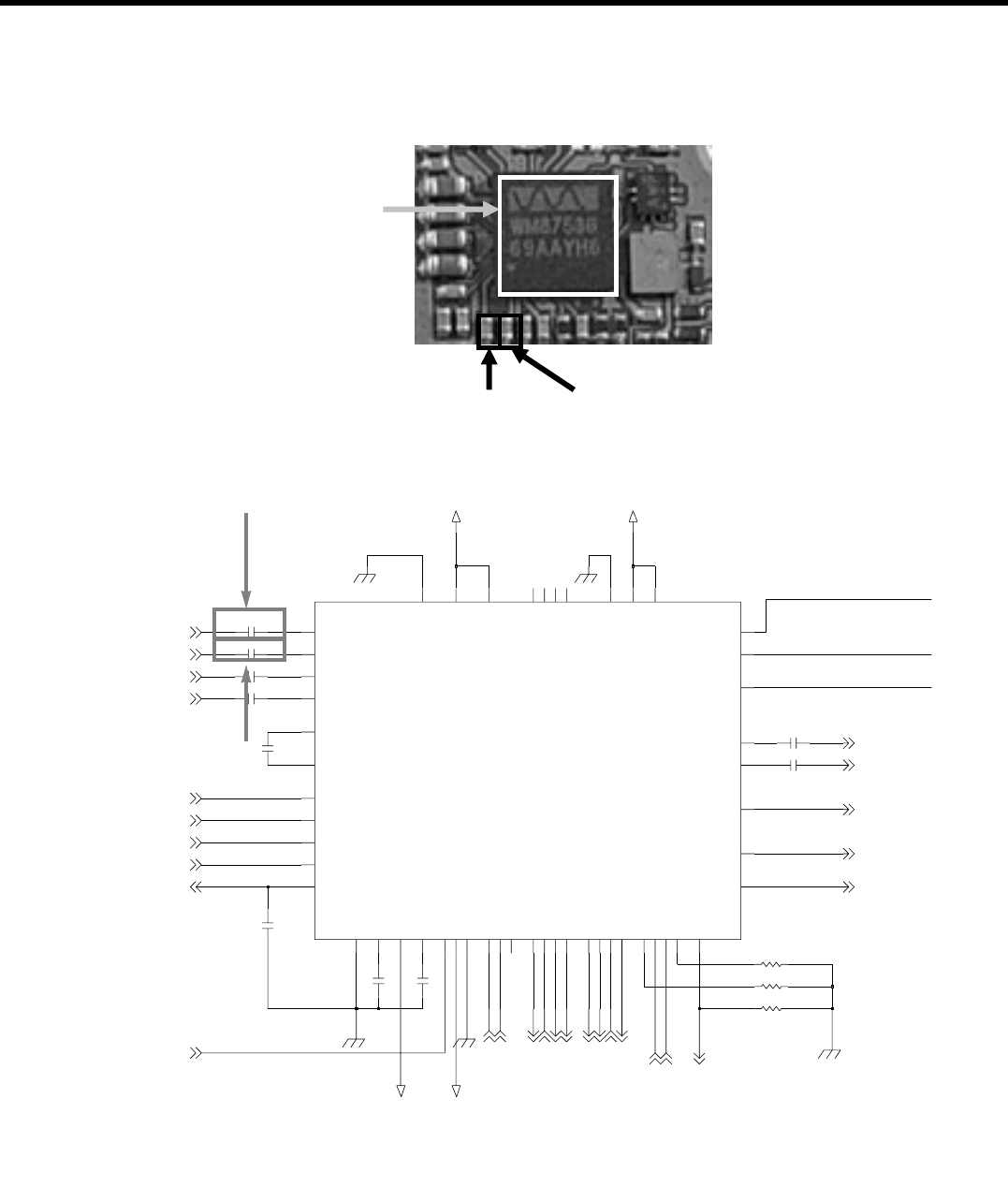

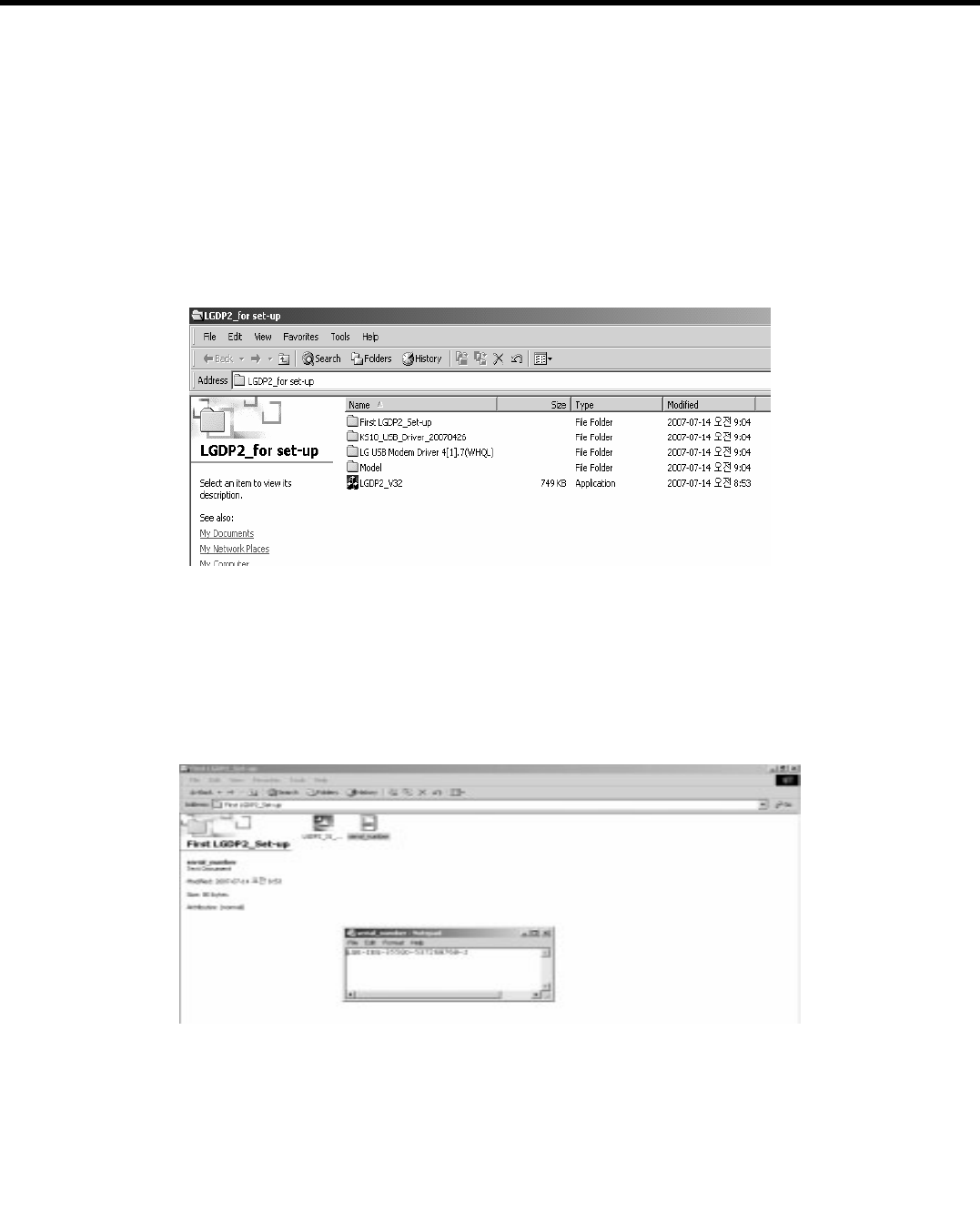

The MSM6275 device has an on-chip 8-bit analog-to-digital converter (HKADC) which is Intended to