Radio Shack Hardware Manual II Technical Reference 1980 Text

User Manual: manual pdf -FilePursuit

Open the PDF directly: View PDF ![]() .

.

Page Count: 204 [warning: Documents this large are best viewed by clicking the View PDF Link!]

TRS-80 MODEL II

TECHNICAL REFERENCE

MANUAL

Catalog Number 26-4921

Radio /hack

jy? ADIVISION OF TANDY CORPORATION

One Tandy Center

Fort Worth, Texas 76102

All rights reserved. Reproduction or use, without express

permission, of editorial or pictorial content, in any manner

is prohibited. No patent liability is assumed with respect to

the use of the information contained herein.

©Copyright 1980, Radio Shack

ADivision of Tandy Corporation

Fort Worth, Texas 76102,

Printed in the United States of America

IMPORTANT NOTICE

This Technical Reference Manual is written for owners of the TRS-80

Model II Microcomputer who have athorough understanding of electronics

and computer circuitry. It is not written to the beginner's level of

comprehension.

Radio Shack will not be liable for any damage caused, or alleged to be

caused, by the customer or any other person using this technical manual to

repair, modify, or alter the TRS-80 Model II Computer in any manner.

Many parts of the computer electronics are very sensitive ana" can be easily

damaged by improper servicing. We strongly suggest that for proper

servicing, the computer be returned to Radio Shack.

While this technical manual has been carefully prepared. Radio Shack will

not be responsible for any errors or omissions and will not be liable for

damages resulting from the use of information contained herein.

Because of the sensitivity of computer equipment, and the potential

problems which can result from improper servicing, the following limitations

apply to services offered by Radio Shack:

1

.

If any of the warranty seals on any Radio Shack computer products are

broken. Radio Shack reserves the right to refuse to service the equipment

or to void any remaining warranty on the equipment.

2. If any Radio Shack computer equipment has been modified so that it is

not within manufacturer's specifications, including, but not limited to,

the installation of any non- Radio Shack parts, components, or replace-

ment boards, then Radio Shack reserves the right to refuse to service the

equipment, void any remaining warranty, remove and replace any

non- Radio Shack part found in the equipment, and perform whatever

modifications are necessary to return the equipment to original factory

manufacturer's specifications.

3. The cost for the labor and parts required to return the Radio Shack

computer equipment to its original manufacturer's specifications will be

charged to the customer in addition to the normal repair charges.

An Overview

This Technical Reference Manual presents acomprehensive theory of

operation for the CPU Module, the FDC, Video/Keyboard, Video Display,

Disk Drives and the Power Supplies. There are also general checkout

procedures to aid you the user in tracing problems down to aspecific sub-

assembly or P. C. Board —but no lower.

This Manual limits repair procedures to replacement of subassemblies only.

Aparts list containing part numbers for major subassemblies may be found

at the end of the Troubleshooting and Replacement section. Adetailed parts

list for each subassembly may be found at the end of the section describing

that particualr subassembly. Individual components may be ordered through

your local Radio Shack store using the Radio Shack Part Number or the

Manufacturer's Part Number if the Radio Shack Part Number is not

available.

We have included in this Manual —for reference only —the Shugart Diskette

Storage Drive Manual, 800/801 and the CDC Flexible Disk Drive Manual,

9404B. Data sheets on several of the Integrated Circuit chips used in this

system are also included to provide the user with additional data concerning

the operation of these devices.

To aid you in recognizing problem areas, you may purchase aSoftware

Diagnostics Diskette from your Computer Center or Radio Shack Store.

If you have any further problems with the TRS-80 Model II Microcomputer

System, contact your Radio Shack Store or Computer Center.

TABLE OF CONTENTS

Section Page

Number Number

TRS-80 Model II Microcomputer System

ISYSTEM DESCRIPTION 1

A. Introduction 3

Video Display Console 3

Keyboard Unit 4

Peripheral Interfaces 4

TROUBLESHOOTING/REPLACEMENT PROCEDURES 7

A. Troubleshooting Procedure 9

Synopsis of Power-On Diagnostics 9

Detailed Troubleshooting Instructions 9

B. Replacement Procedures ,11

System Disassembly 11

System Reassembly 12

Replacement Parts List -Subassemblies 15

III CPUMODULE 17

A. Functional Specifications 19

B. Theory of Operation 19

Decoding Logic 19

Bus Steering Logic 20

Wait State Generation Logic 20

Manual and Power-On Reset Logic 20

System Clock Generation Logic 21

Interrupt Priority Logic 21

El ABuffers 21

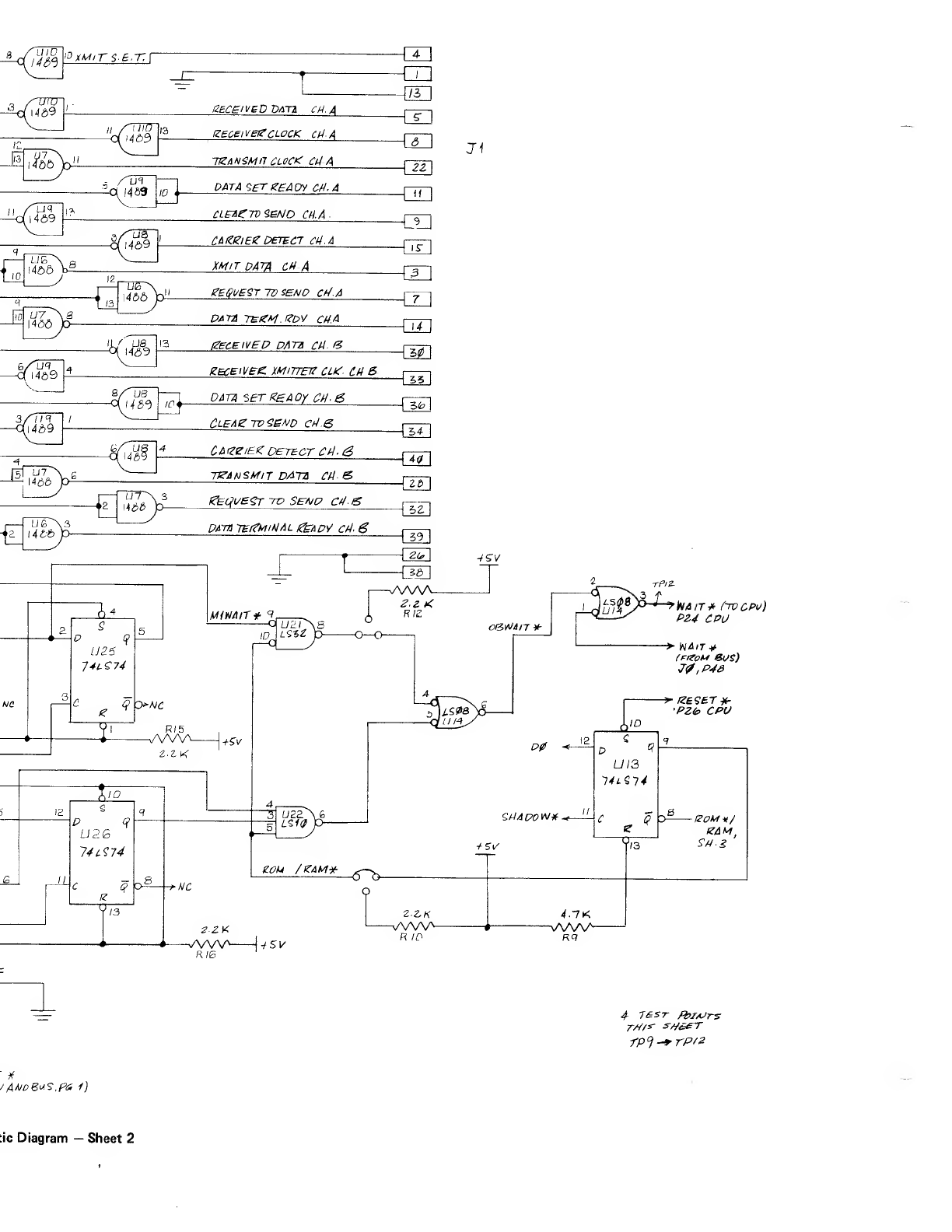

Connector Jl Signal Descriptions 22

Replacement Parts List -CPU Module ••25

IV FLOPPY DISK CONTROLLER BOARD 33

A. Functional Specifications 35

B. Theory of Operation 35

Decoding Logic 35

Bus Interface Logic 36

Z-80 -PIO Interface Logic 36

FD1791 -Floppy Disk Controller IC 36

FD1 791 Organization 37

Processor Interface 38

Floppy Disk Interface 38

Head Positioning 38

Disk Read Operations 39

Disk Write Operations 40

FDC and FDD Interface Logic 40

Recording Codes 40

Read Clock Recovery 41

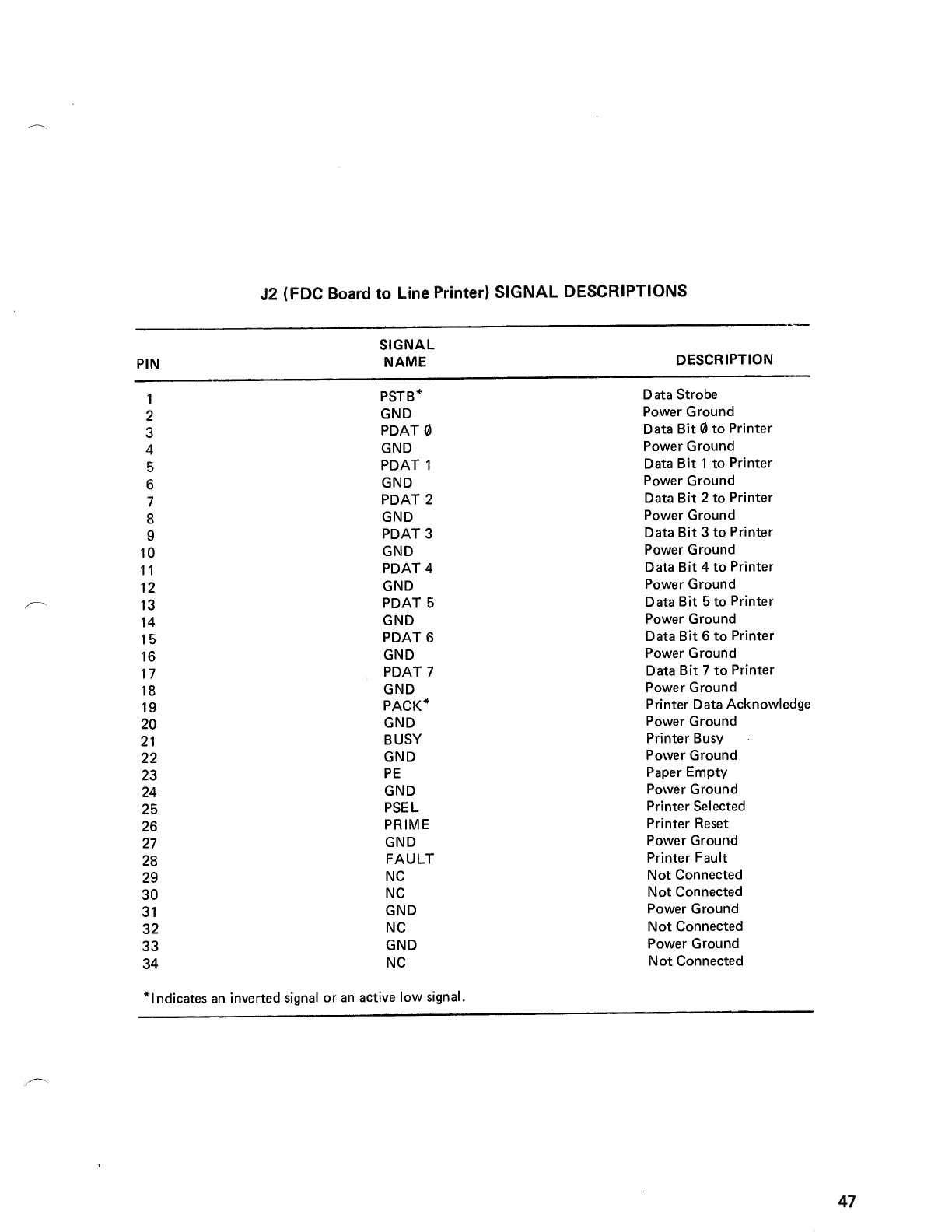

Write Compensation 42

Write Compensation Logic 43

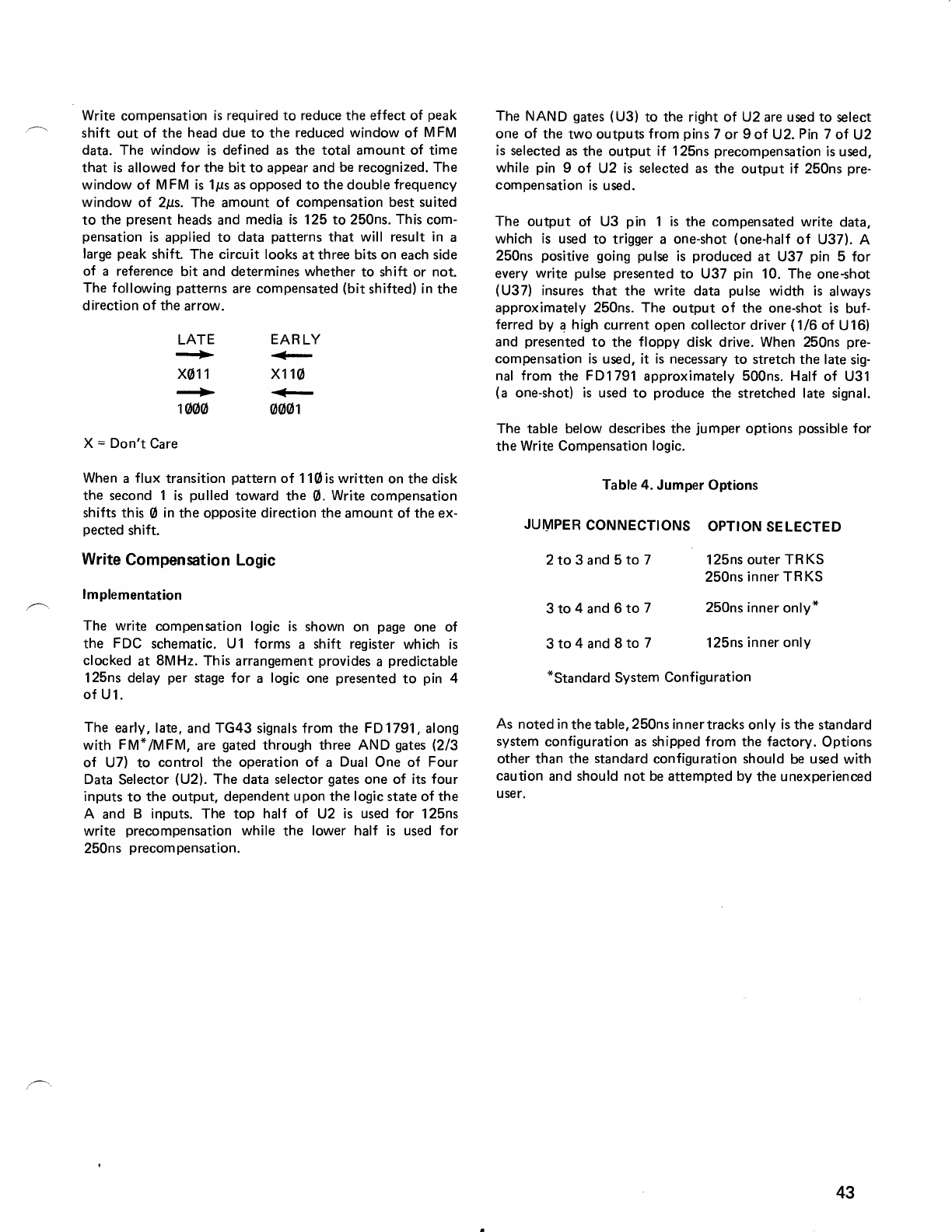

Port Allocation -Table 44

Bit Allocation, Port EFH -Table 44

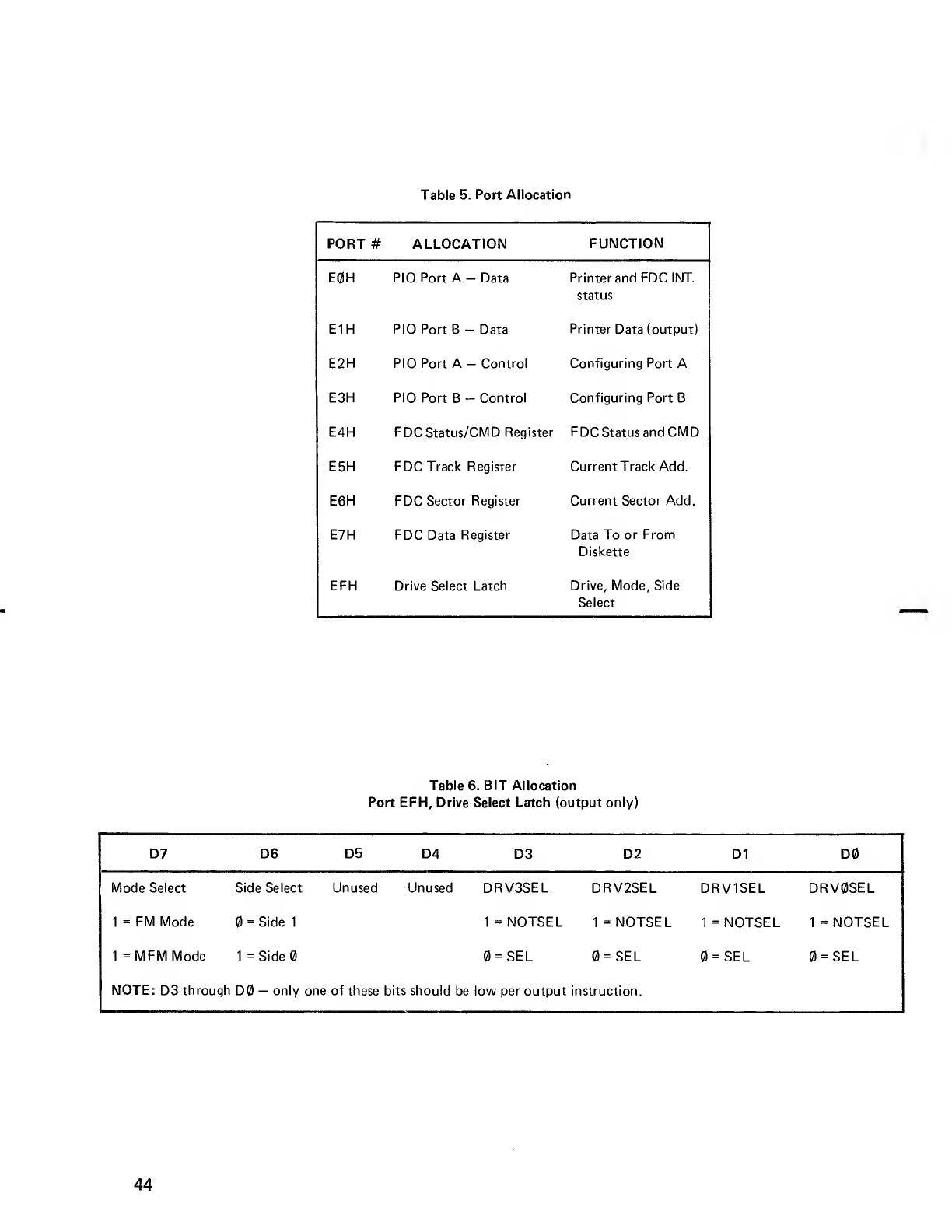

Bit Allocation, Port E0H -Table 45

J1 Signal Descriptions 46

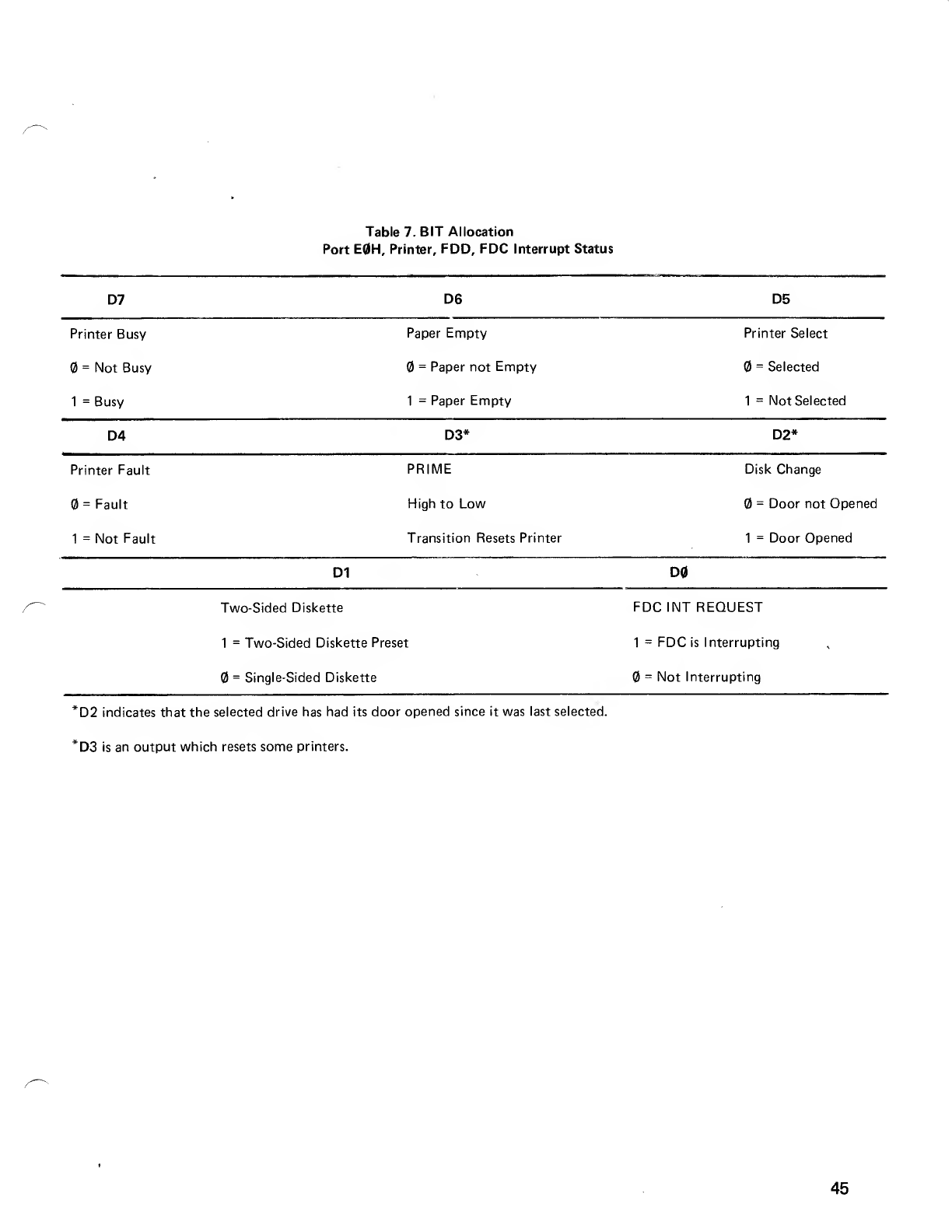

J2 Signal Descriptions 47

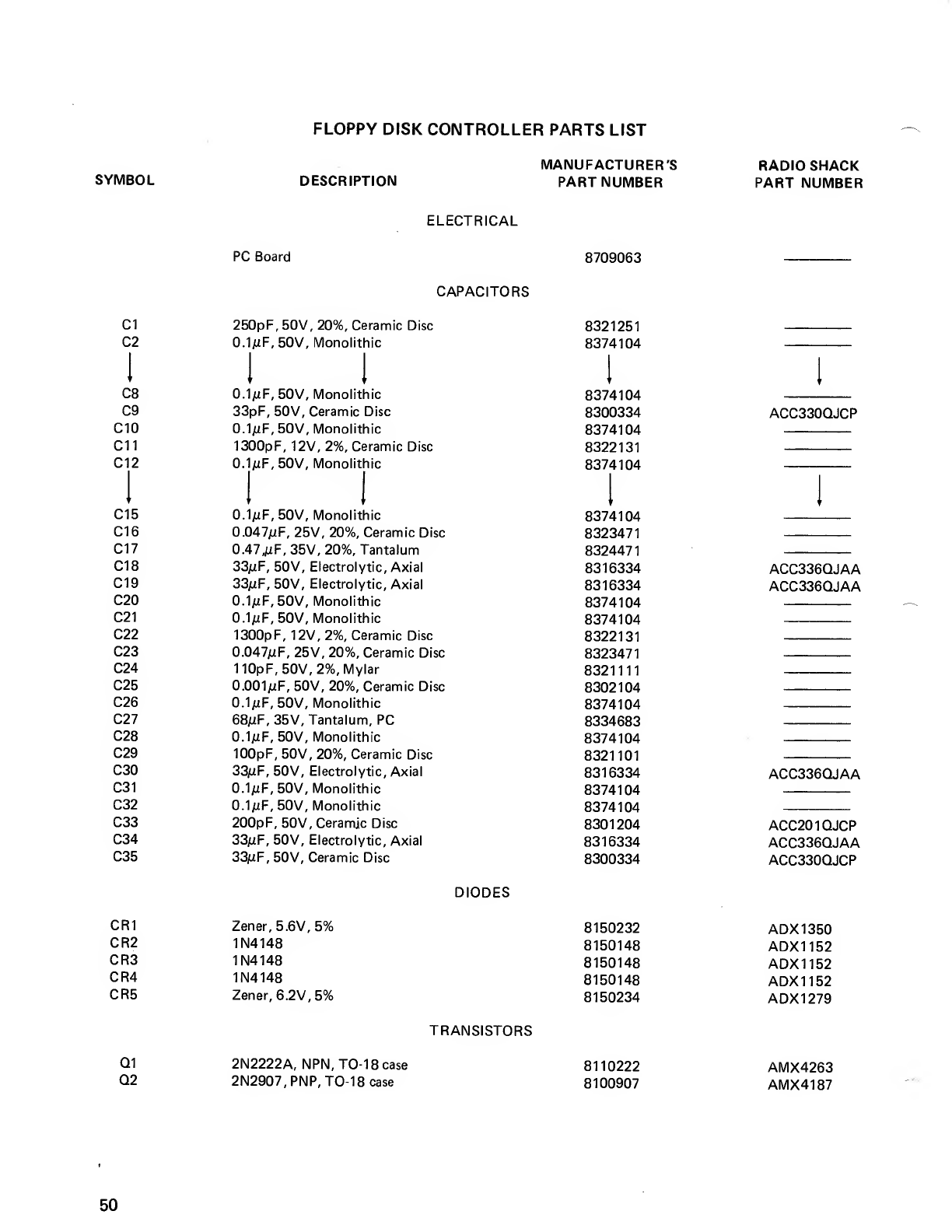

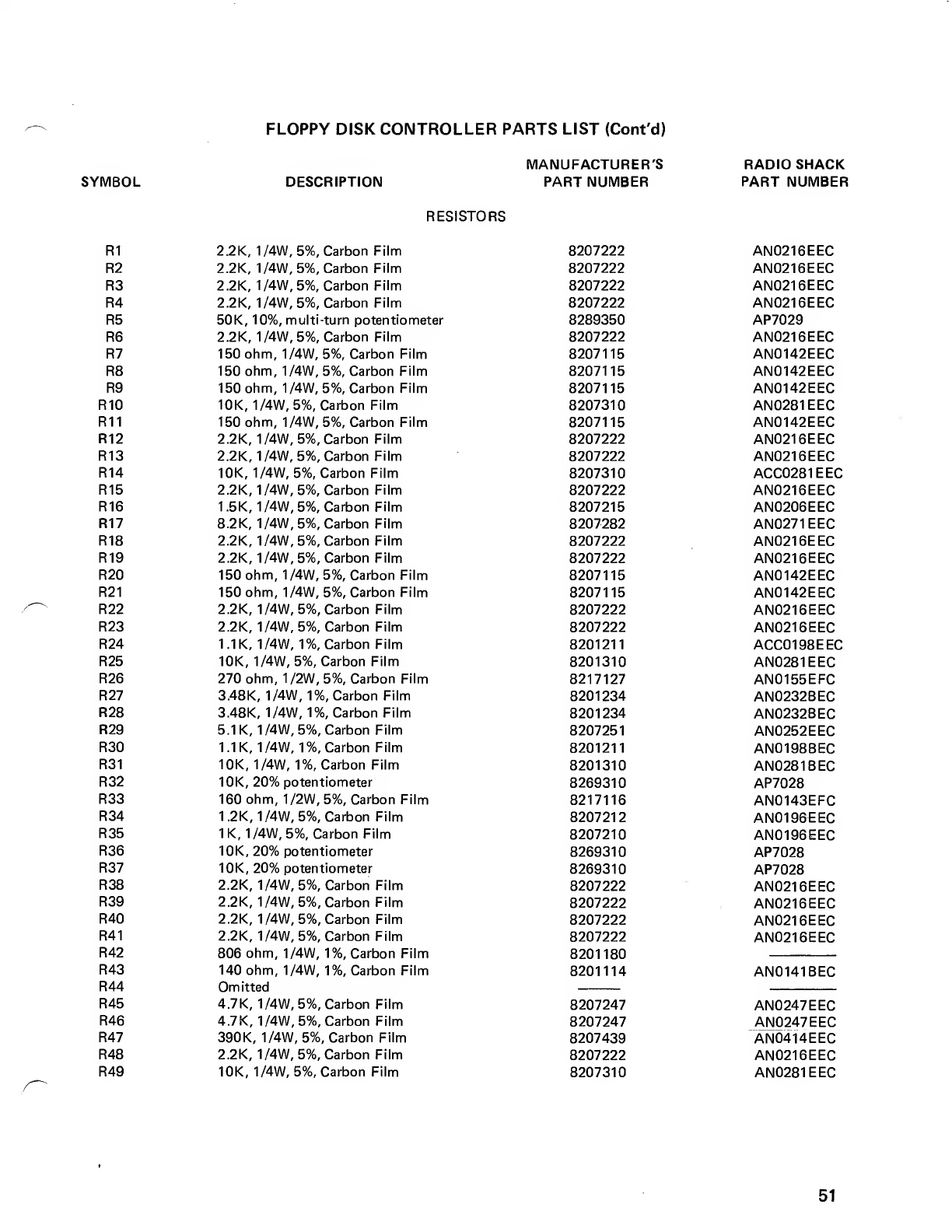

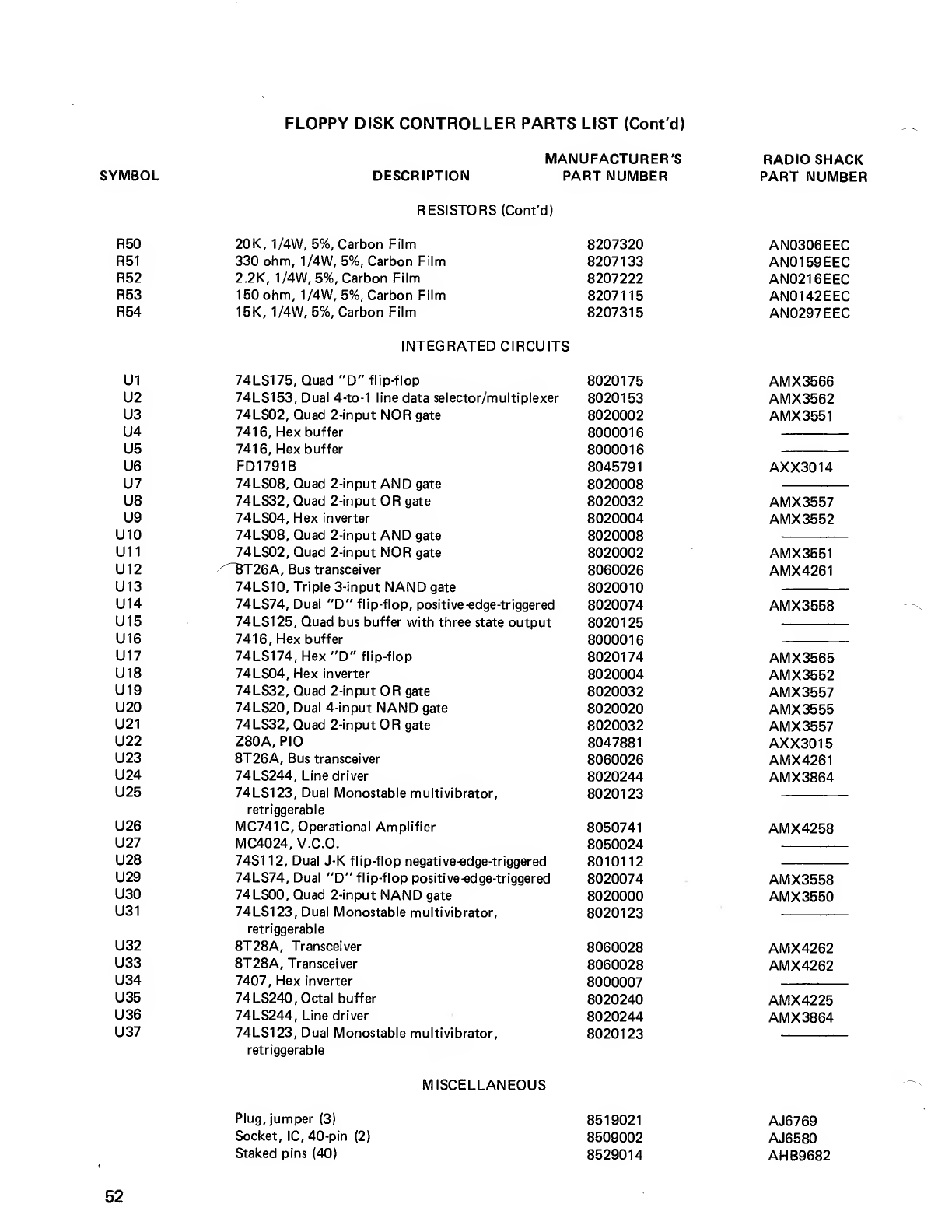

Replacement Parts List -FDC Board 50

TABLE OF CONTENTS (Cont'd)

Section

Number Number

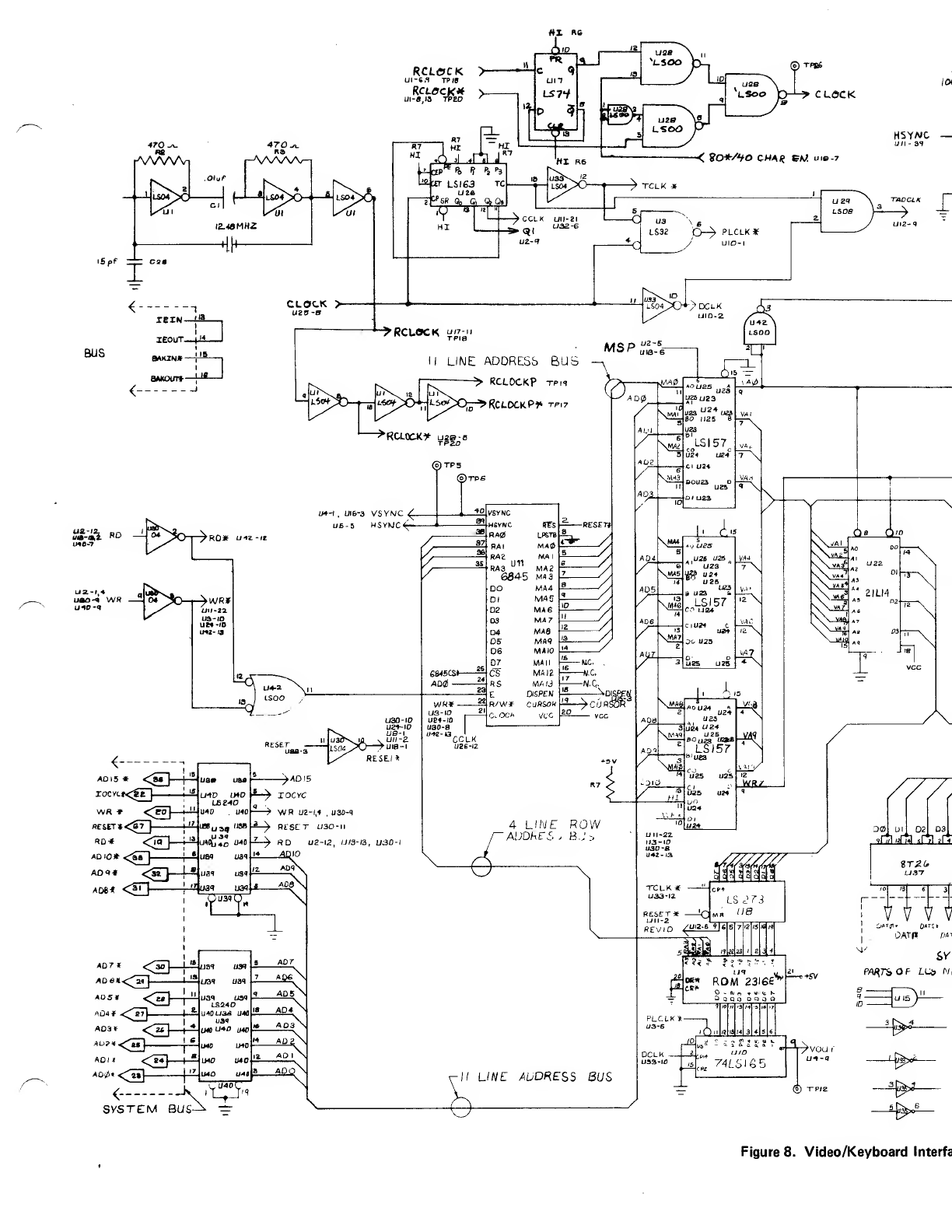

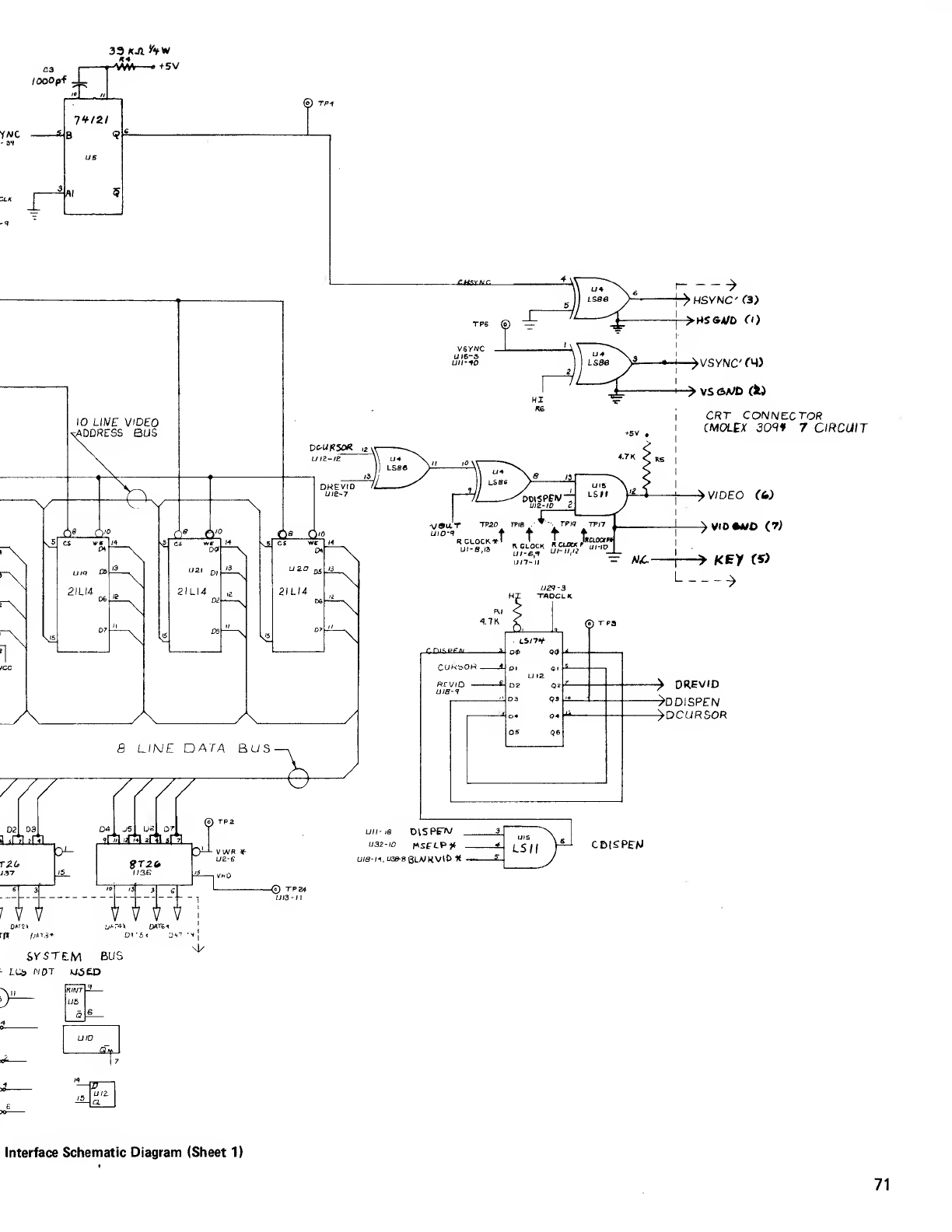

VVIDEO/KEYBOARD INTERFACE 55

A. Functional Specifications 57

B. Theory of Operation 58

High Speed Timing 58

Cathode Ray Tube Controller (CRTC) 58

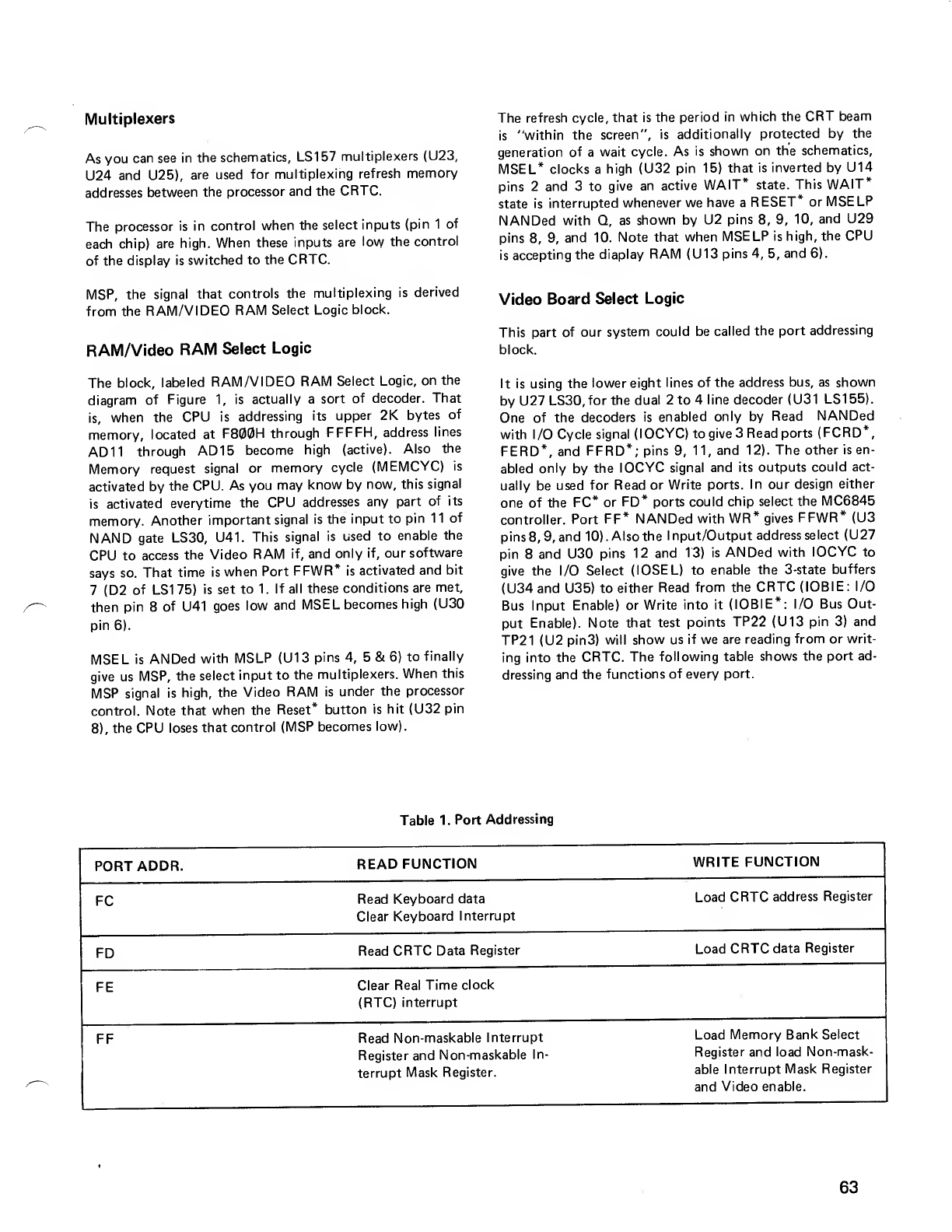

Multiplexers 63

RAM/Video RAM Select Logic 63

Video Board Select Logic 63

Other Logic Blocks 64

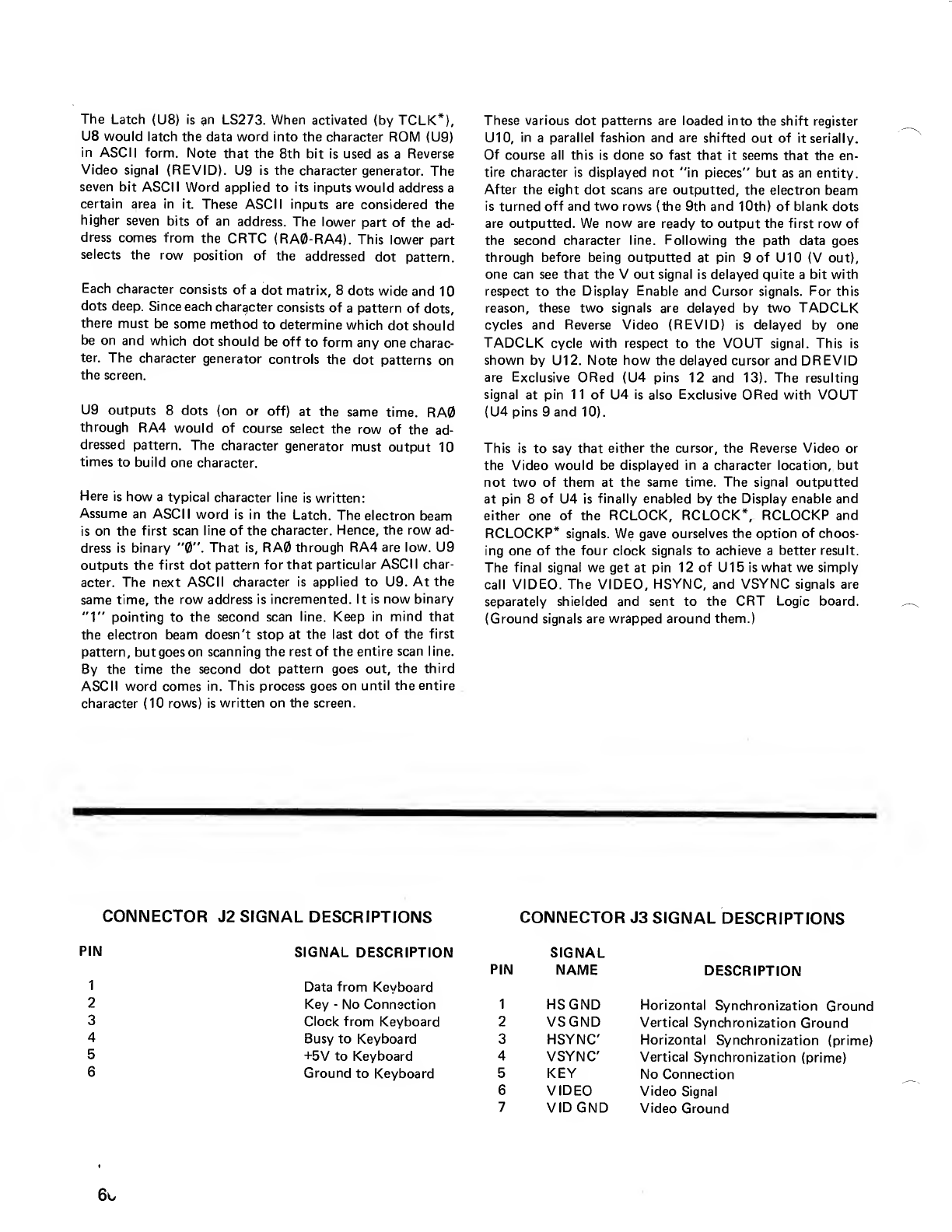

Connector J2 Signal Descriptions 66

Connector J3 Signal Descriptions 66

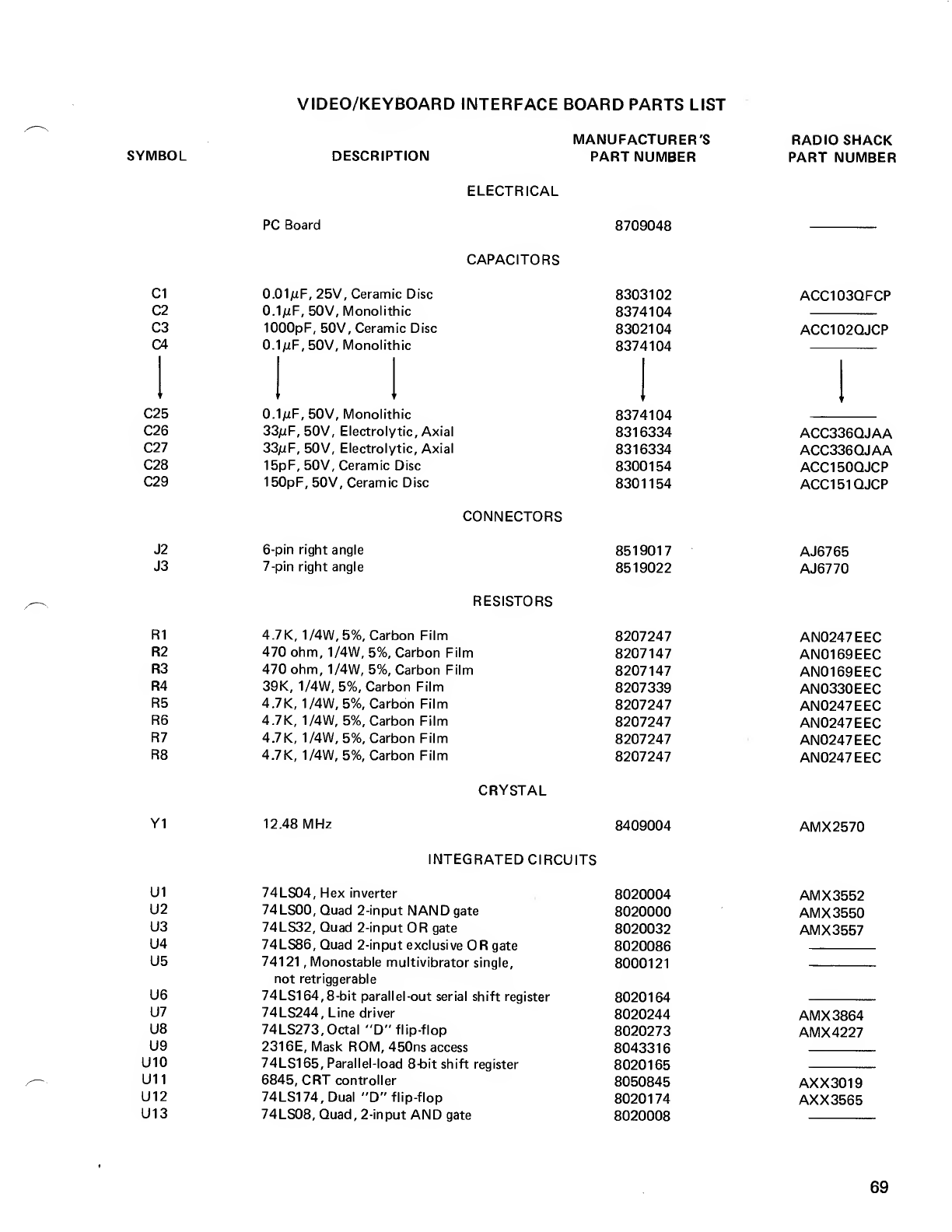

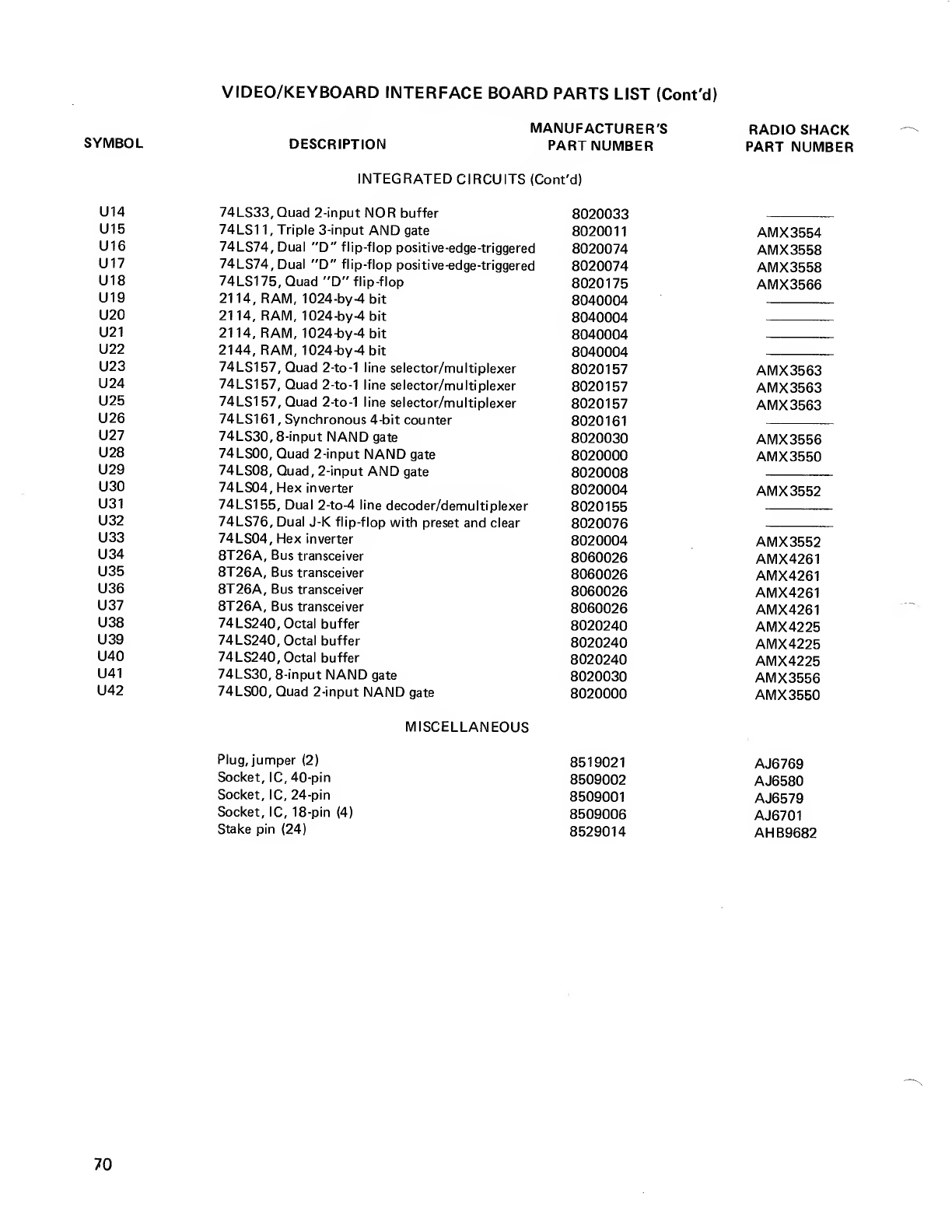

Replacement Parts List -Video/Keyboard Interface 69

VI MEMORY BOARD (32K RAM and 64K RAM) 73

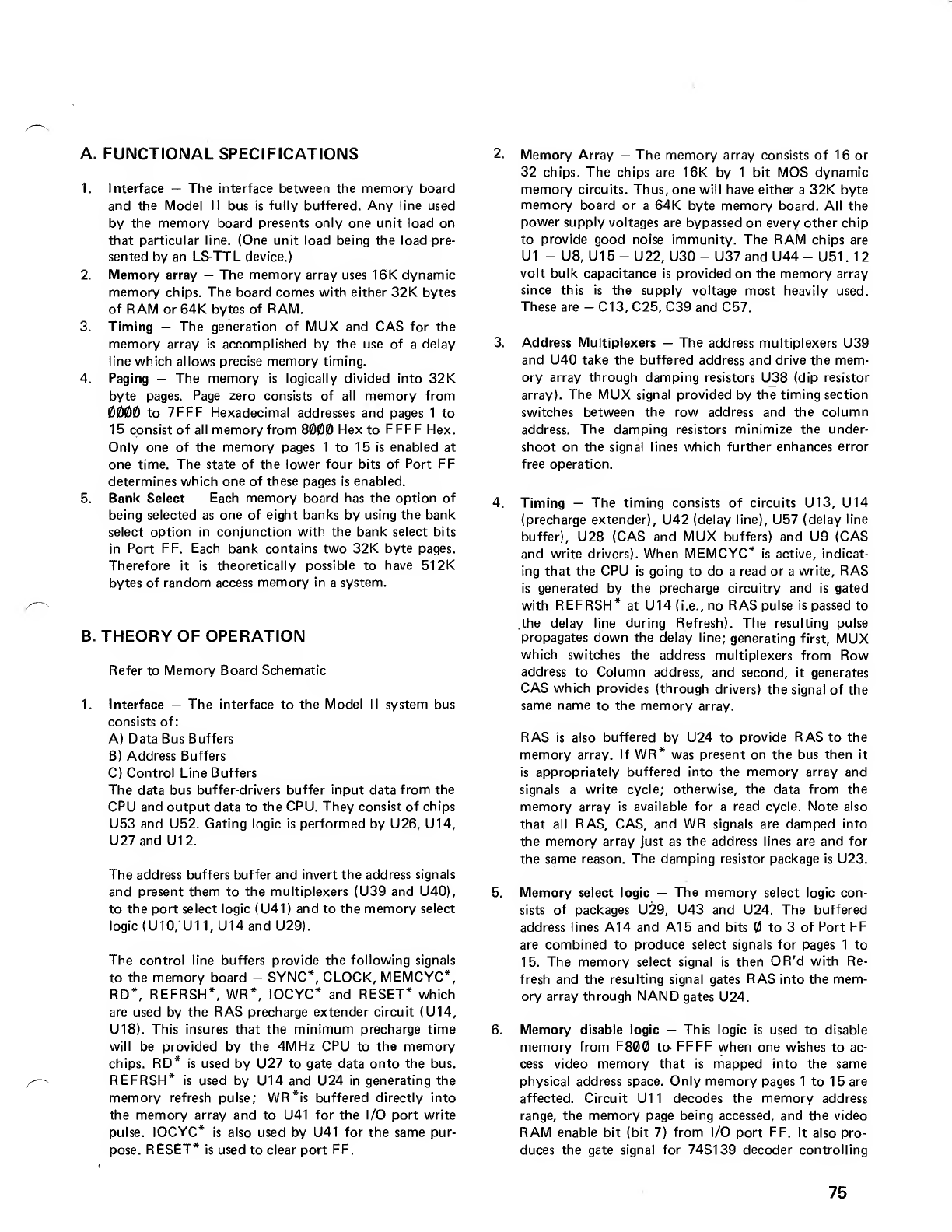

A. Functional Specifications 75

B. Theory of Operation 75

System Bus Interface 75

Memory Array 75

Address Multiplexers 75

Timing 75

Memory Select Logic 75

Memory Disable Logic 75

I/O Port FF and Select Logic 76

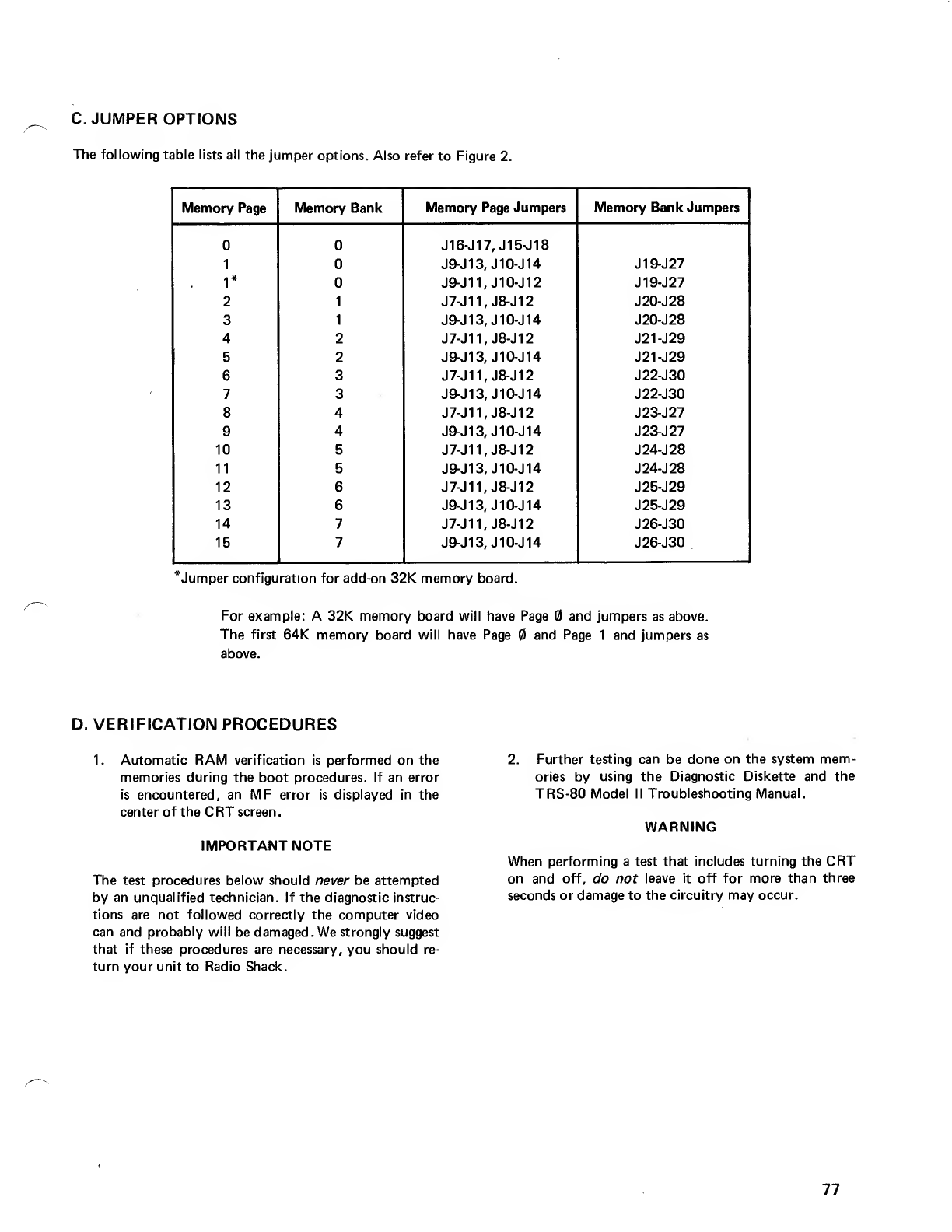

C. Jumper Options 77

D. Verification Procedures 77

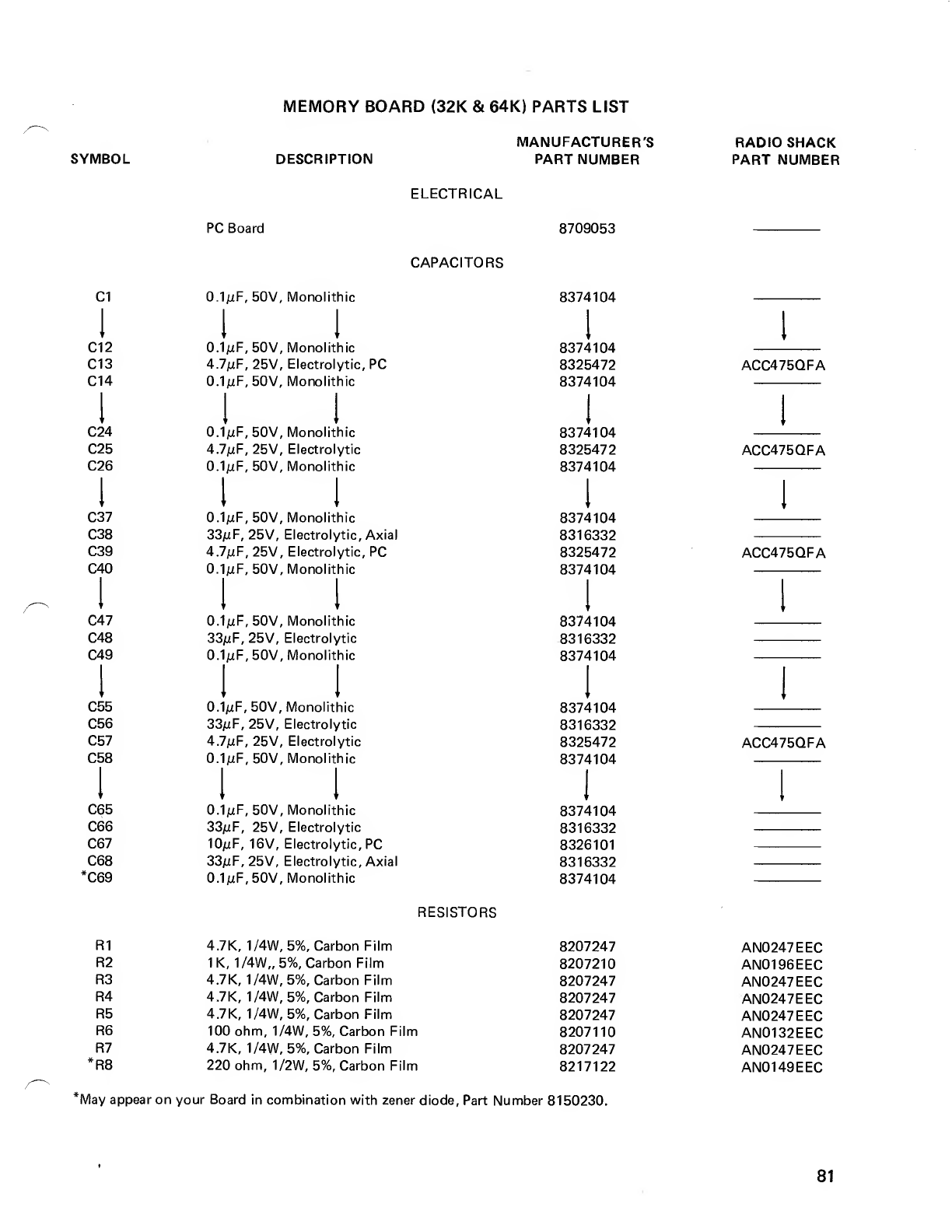

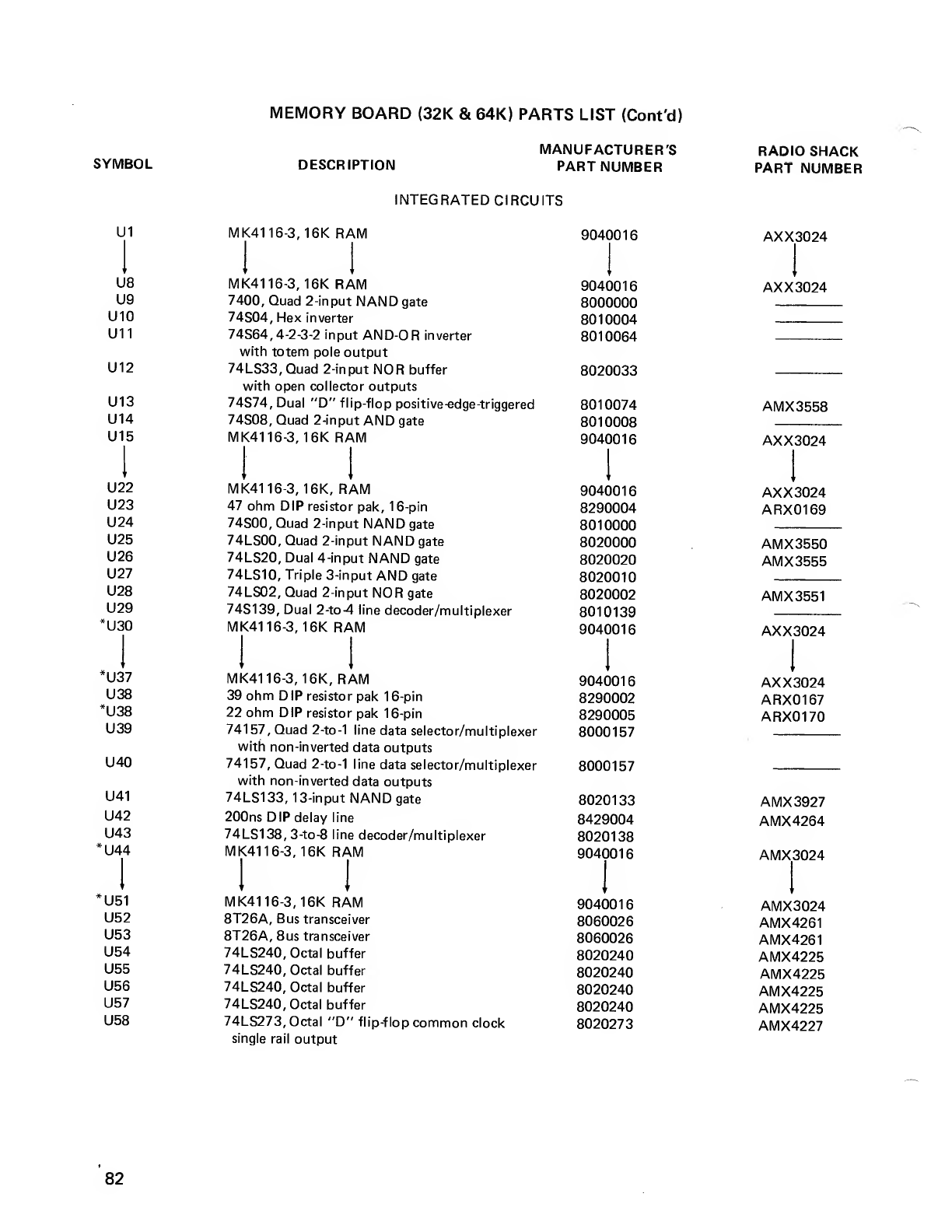

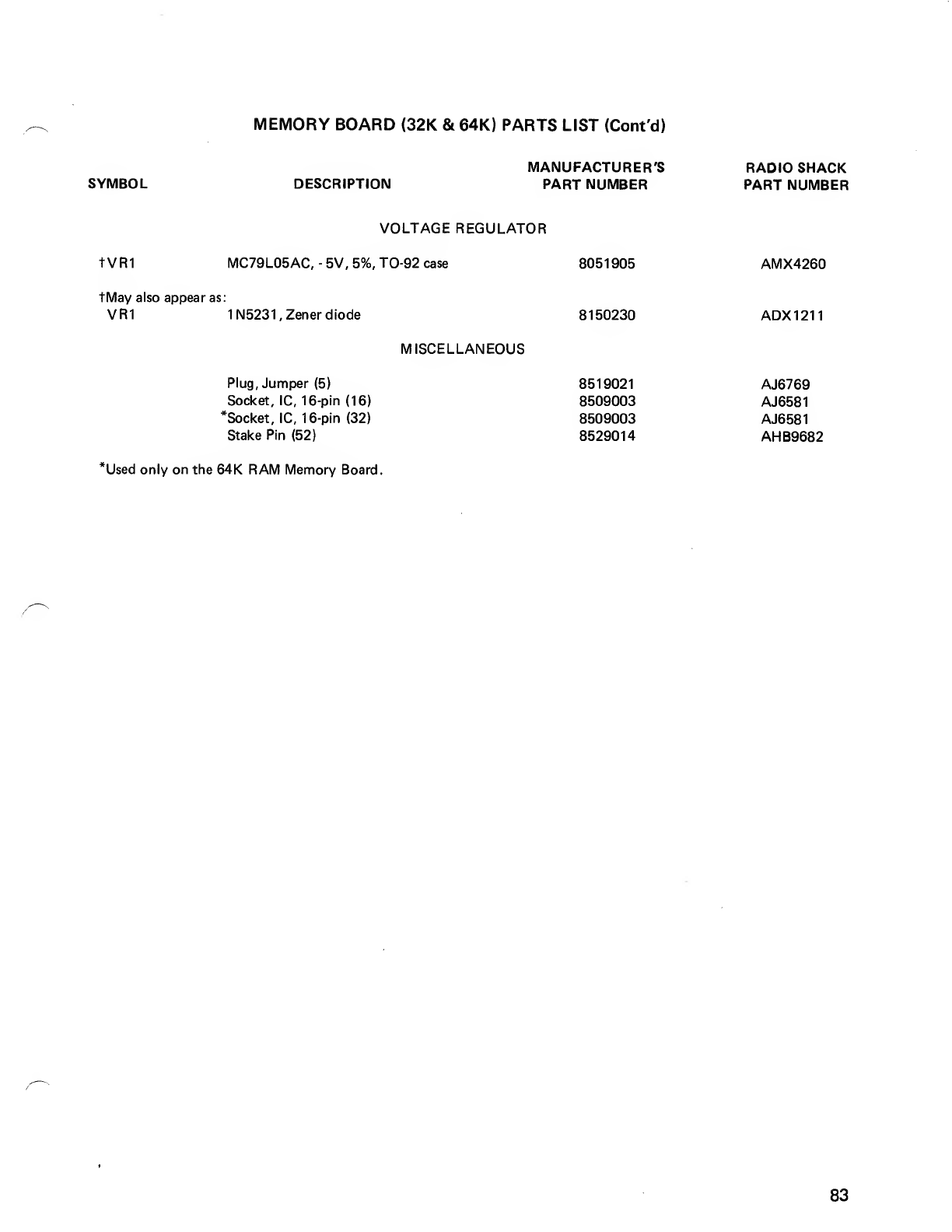

Replacement Parts List -Memory Board 81

VII VIDEO MONITOR (CRT) 87

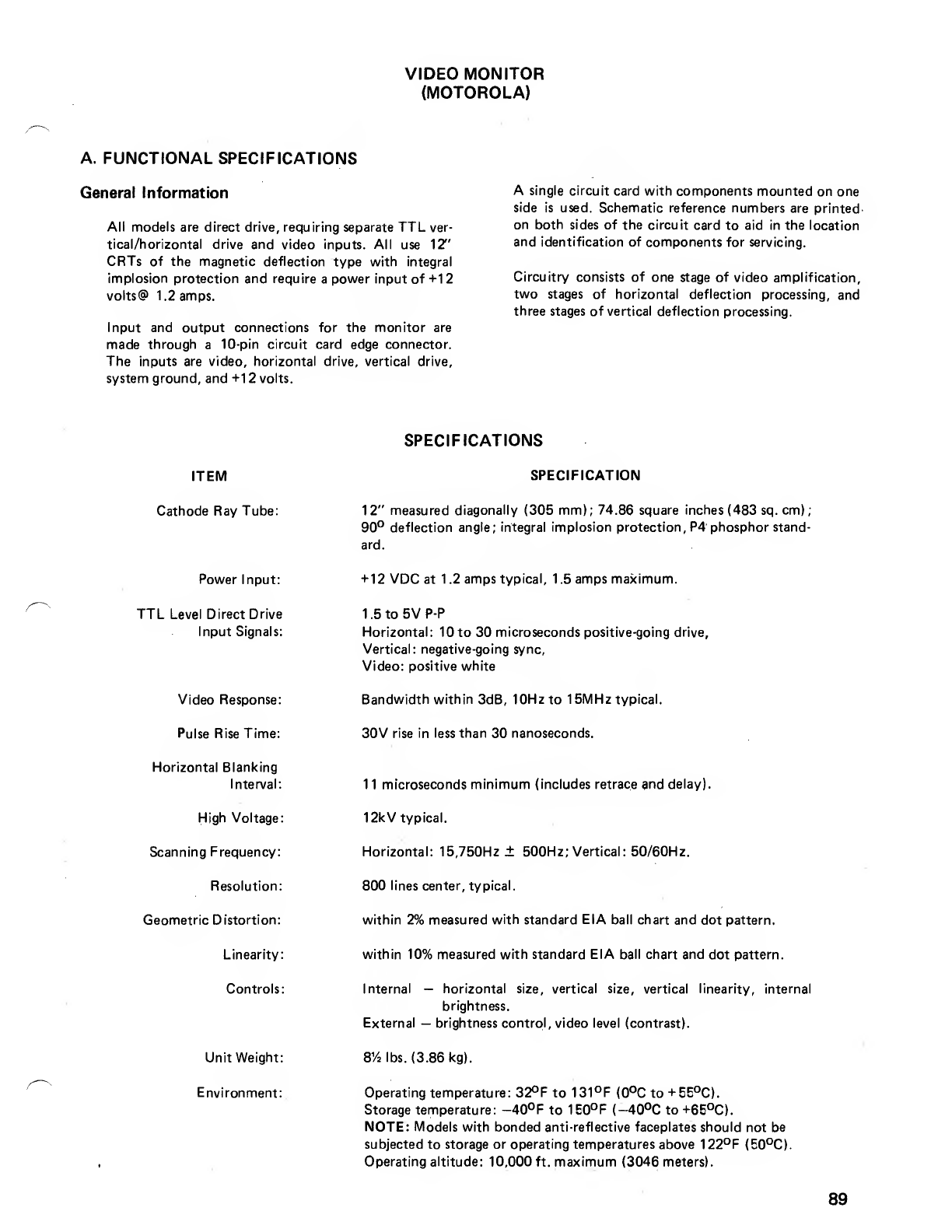

VIDEO MONITOR (MOTOROLA) 89

A. Functional Specifications 89

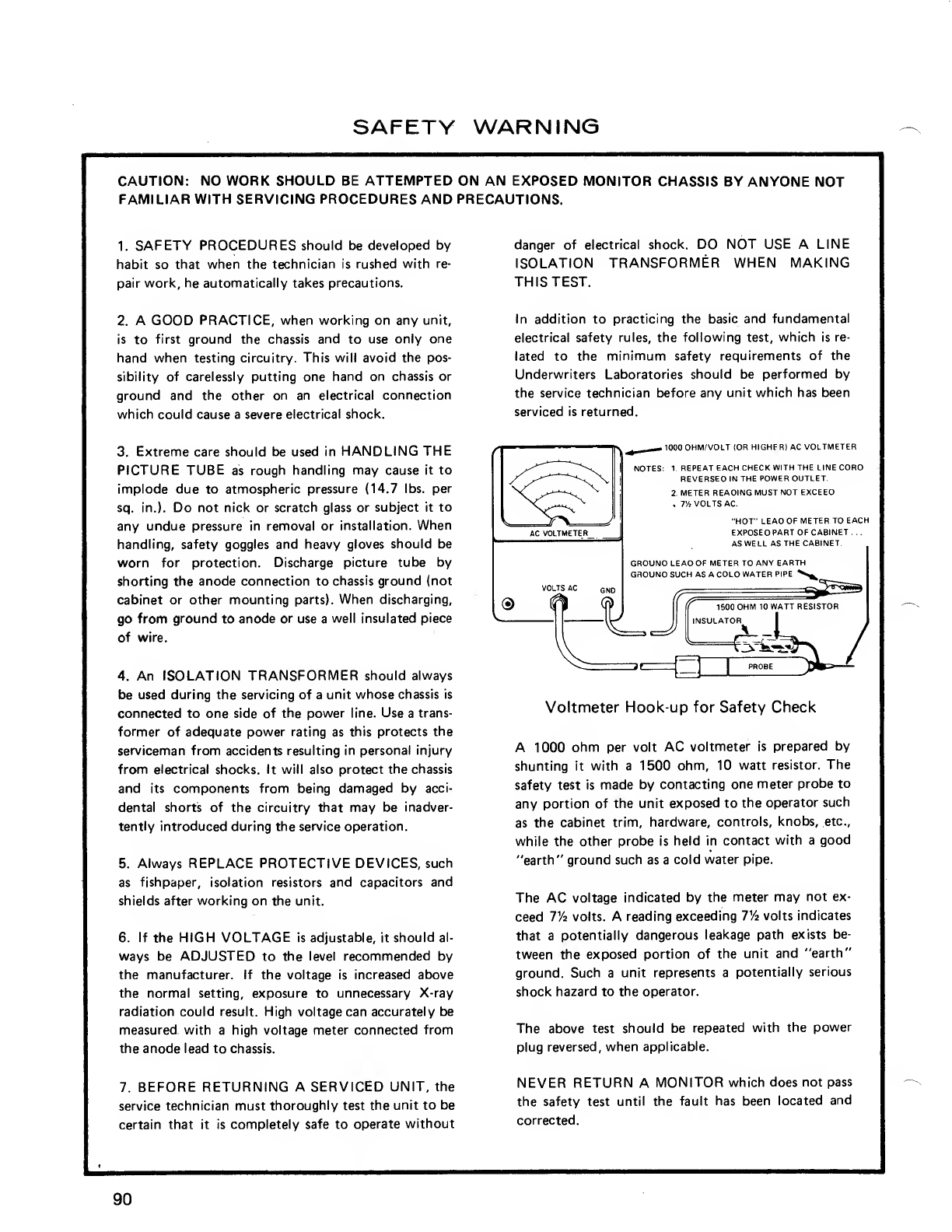

B. Service Notes 91

Circuit Tracing 91

CRT Replacement 91

C. Adjustments 91

D. Troubleshooting Guide 92

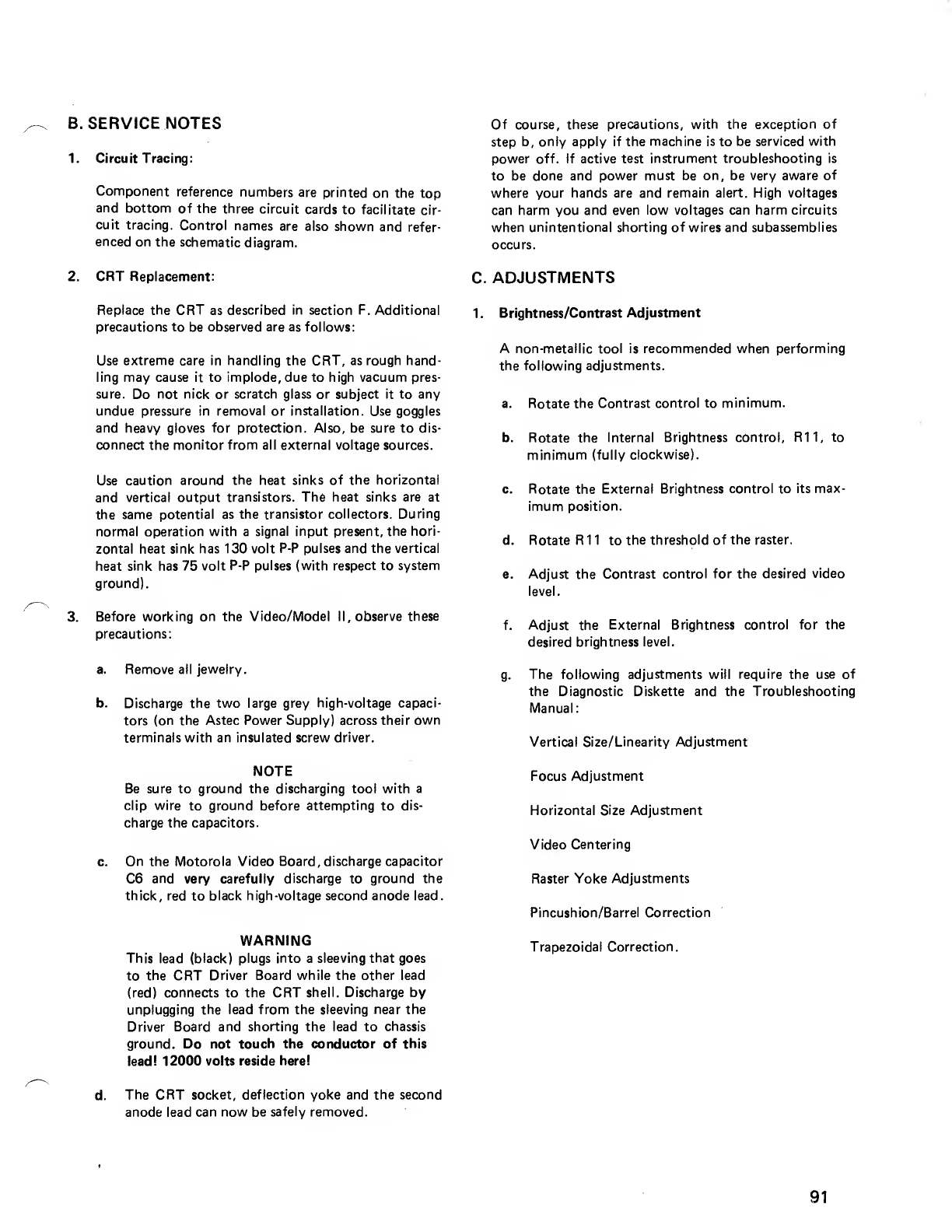

E. Theory of Operation 94

Video Amplifier 94

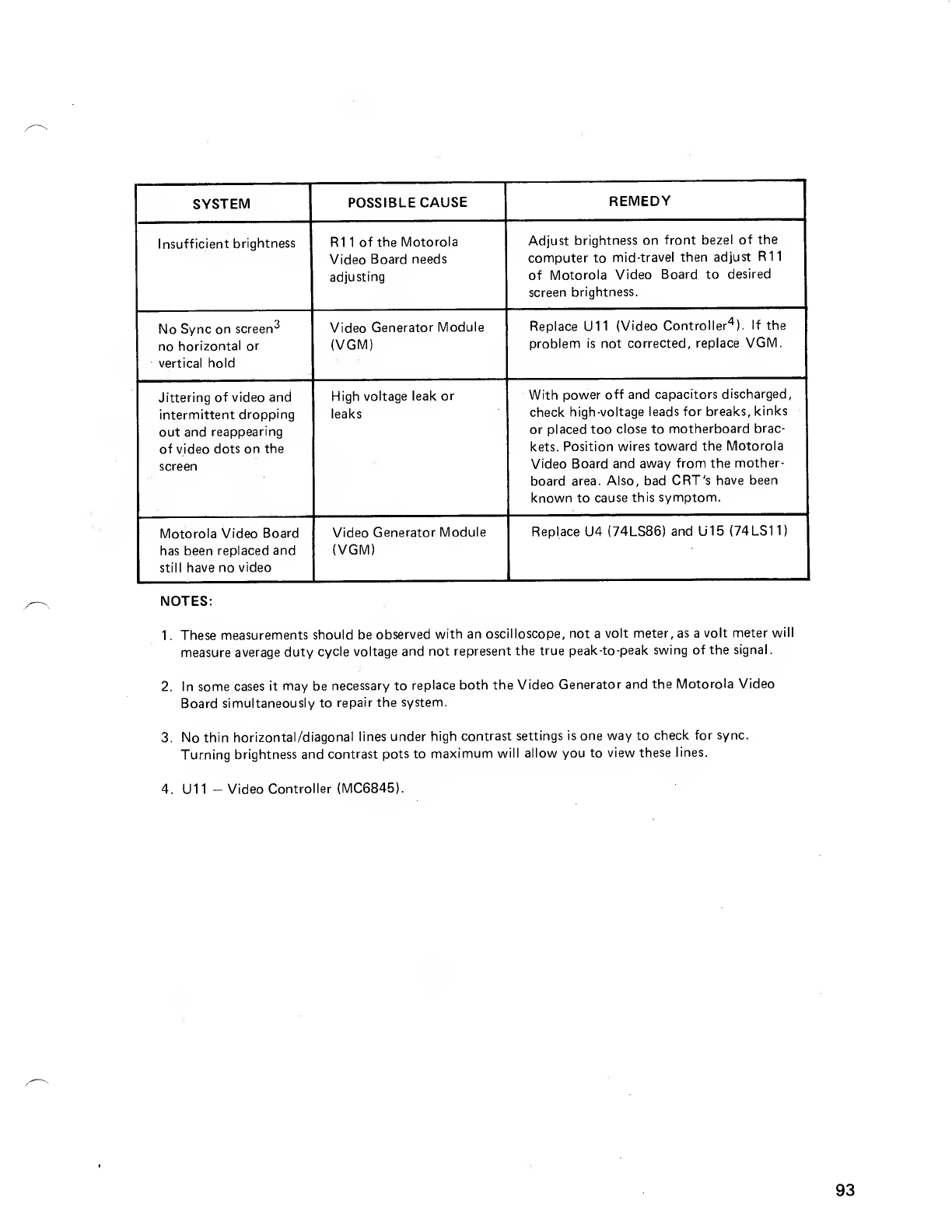

Horizontal Driver 94

Horizontal Output Transformer 95

Vertical Deflection 95

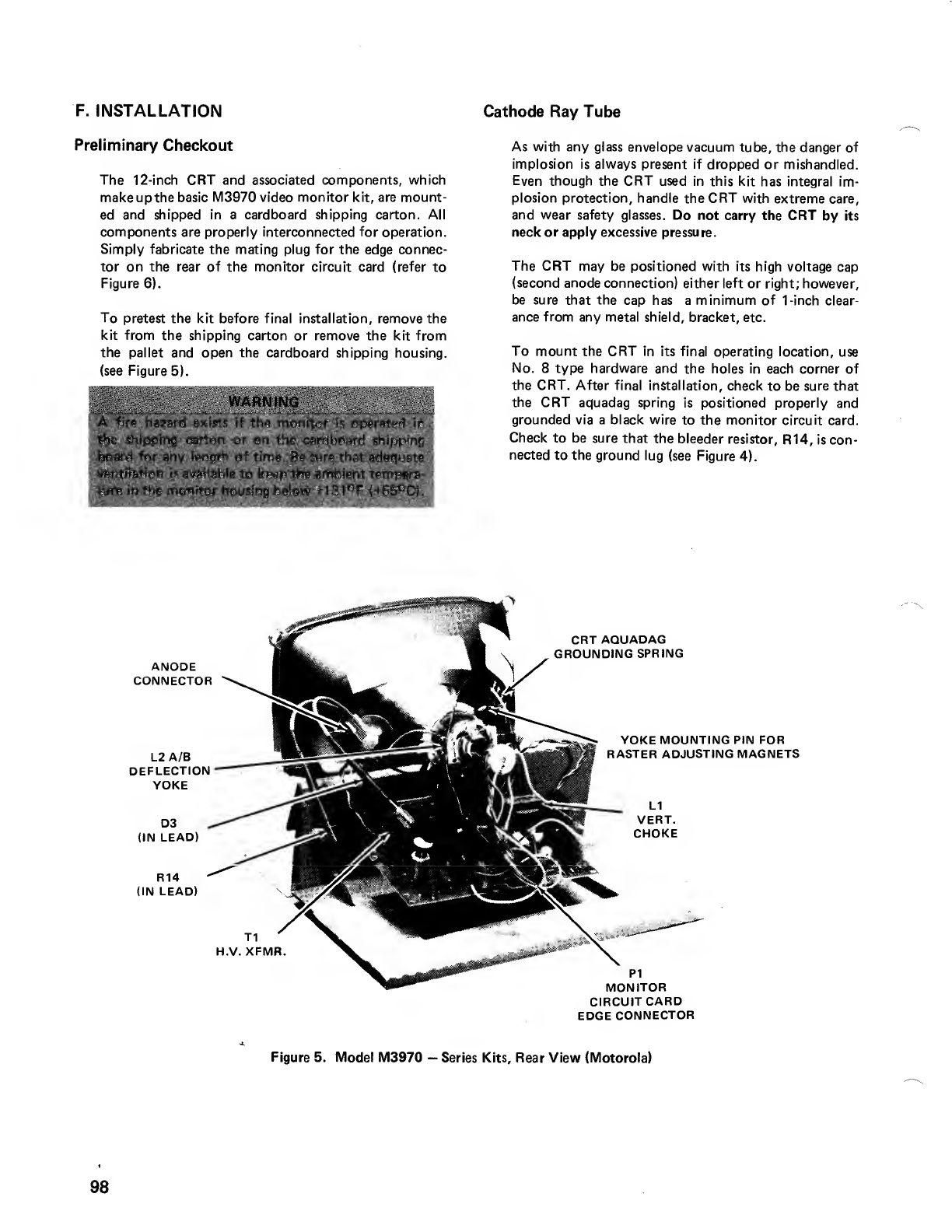

F. Installation 98

Preliminary Checkout 98

Cathode Ray Tube 98

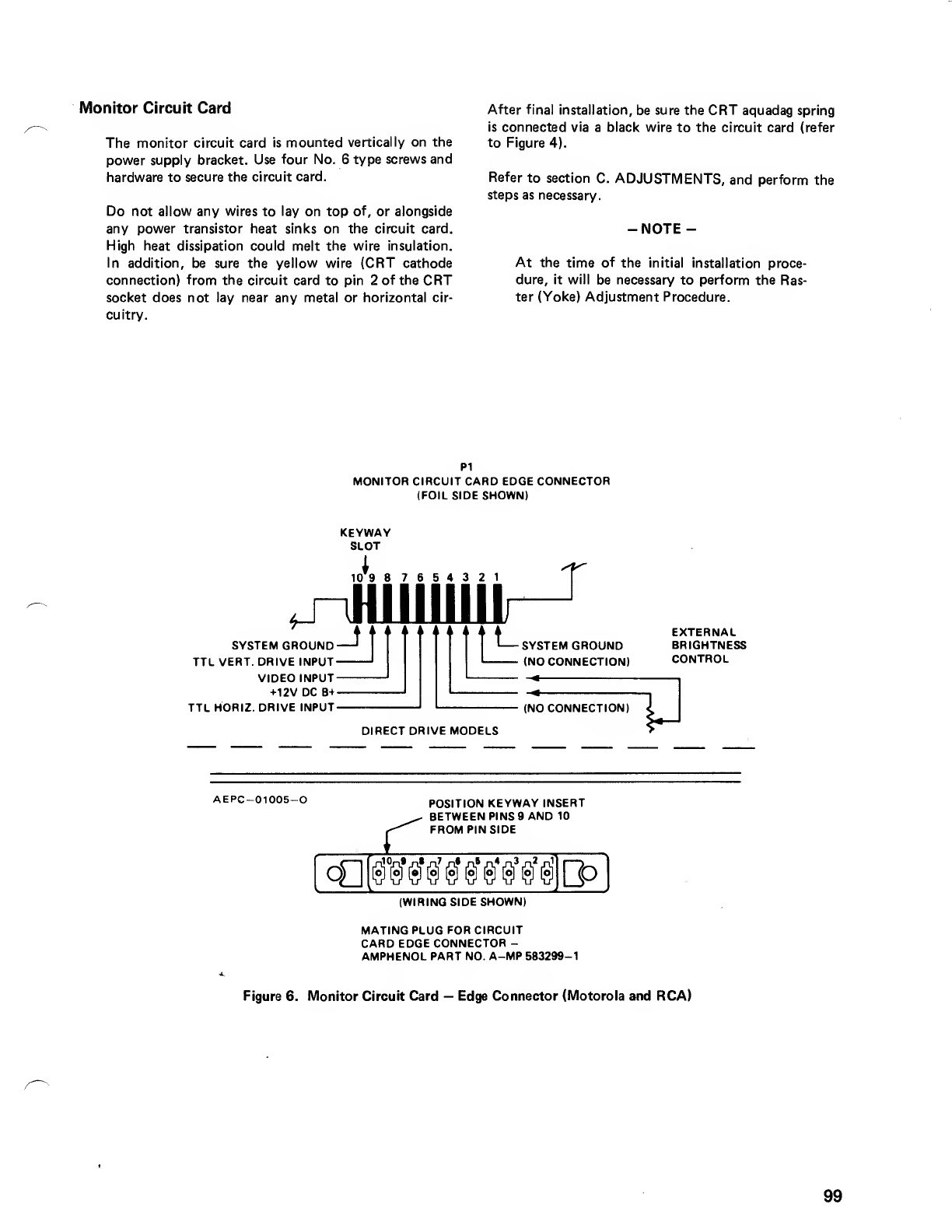

Monitor Circuit Card 99

G. General Servicing Precautions ...100

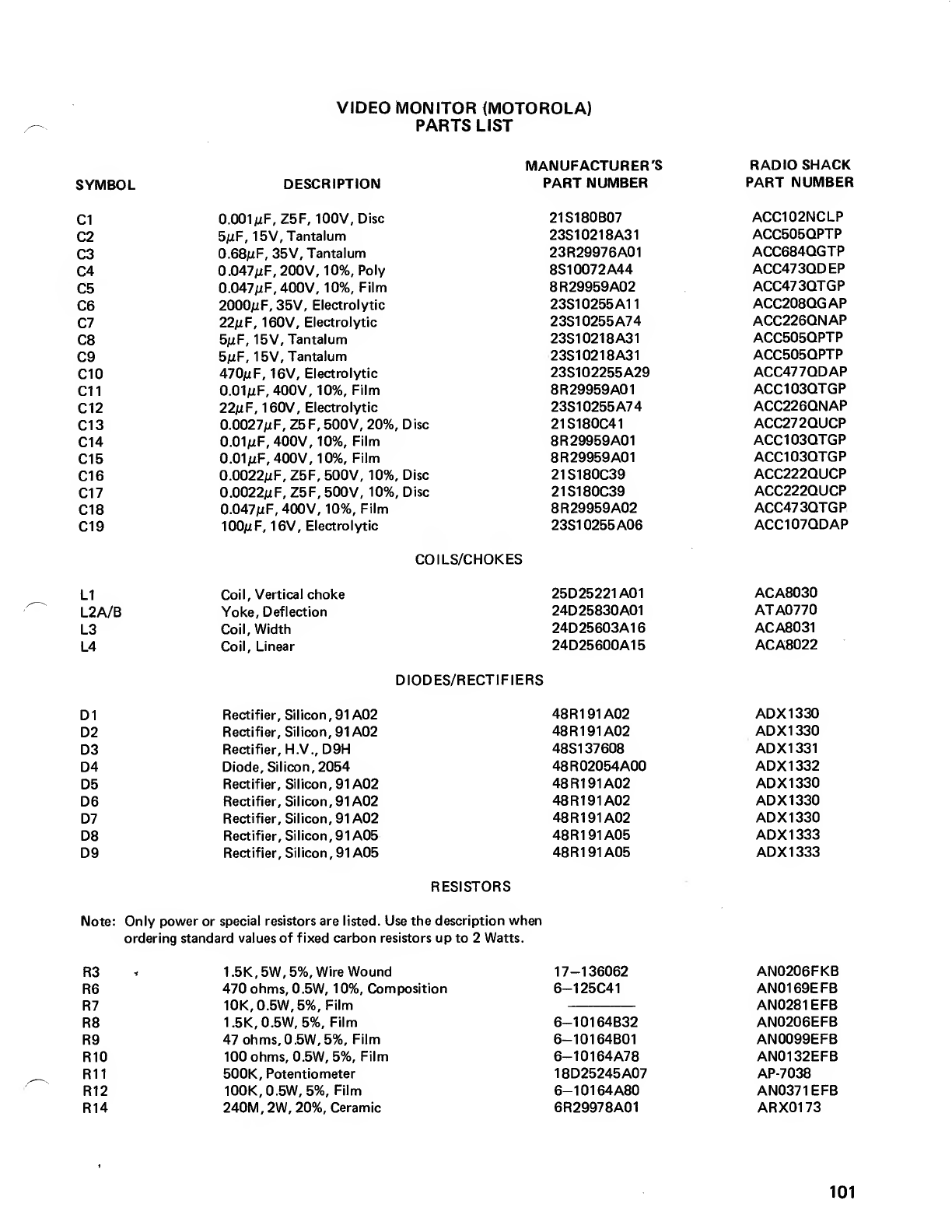

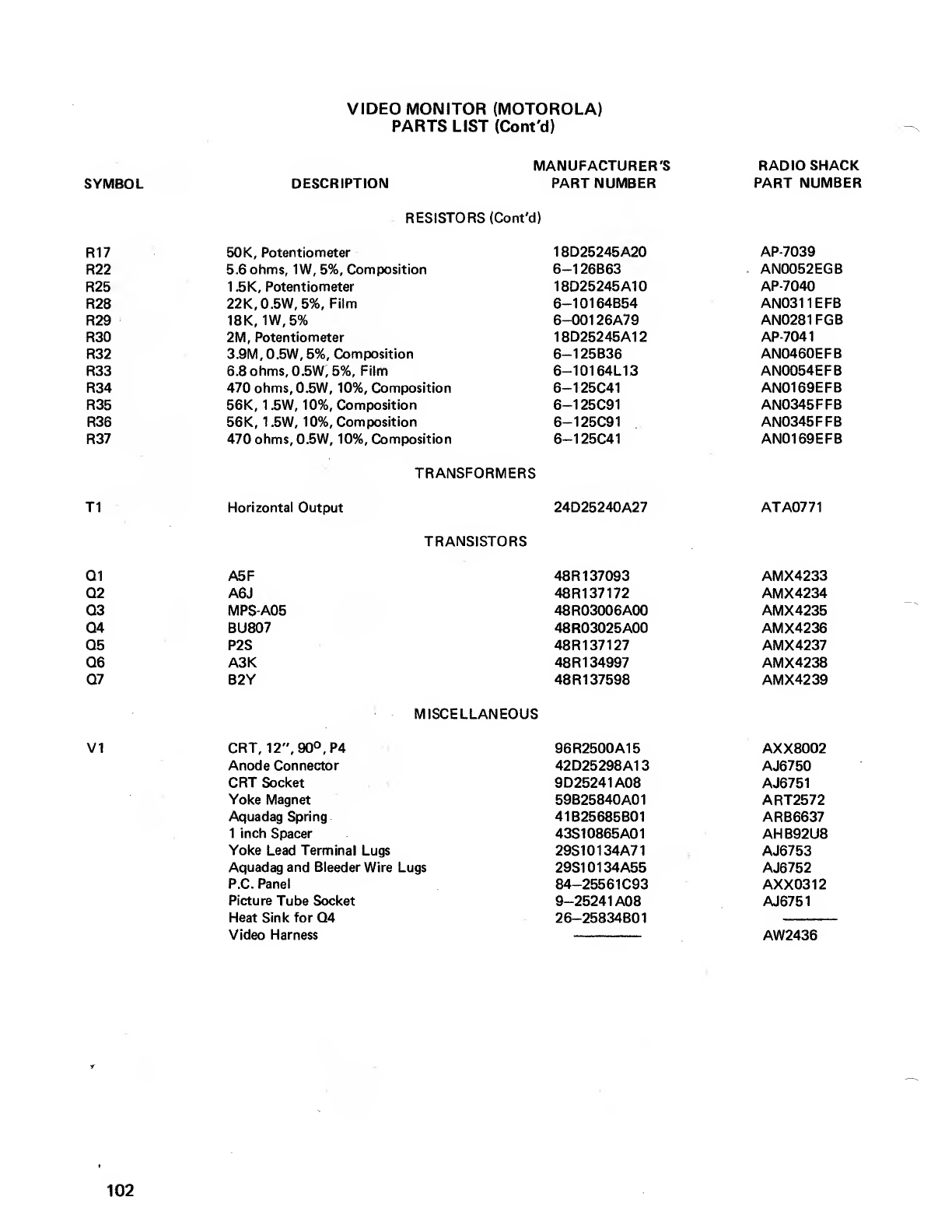

Video Monitor Parts List (Motorola) 101

VIDEO MONITOR (RCA) 105

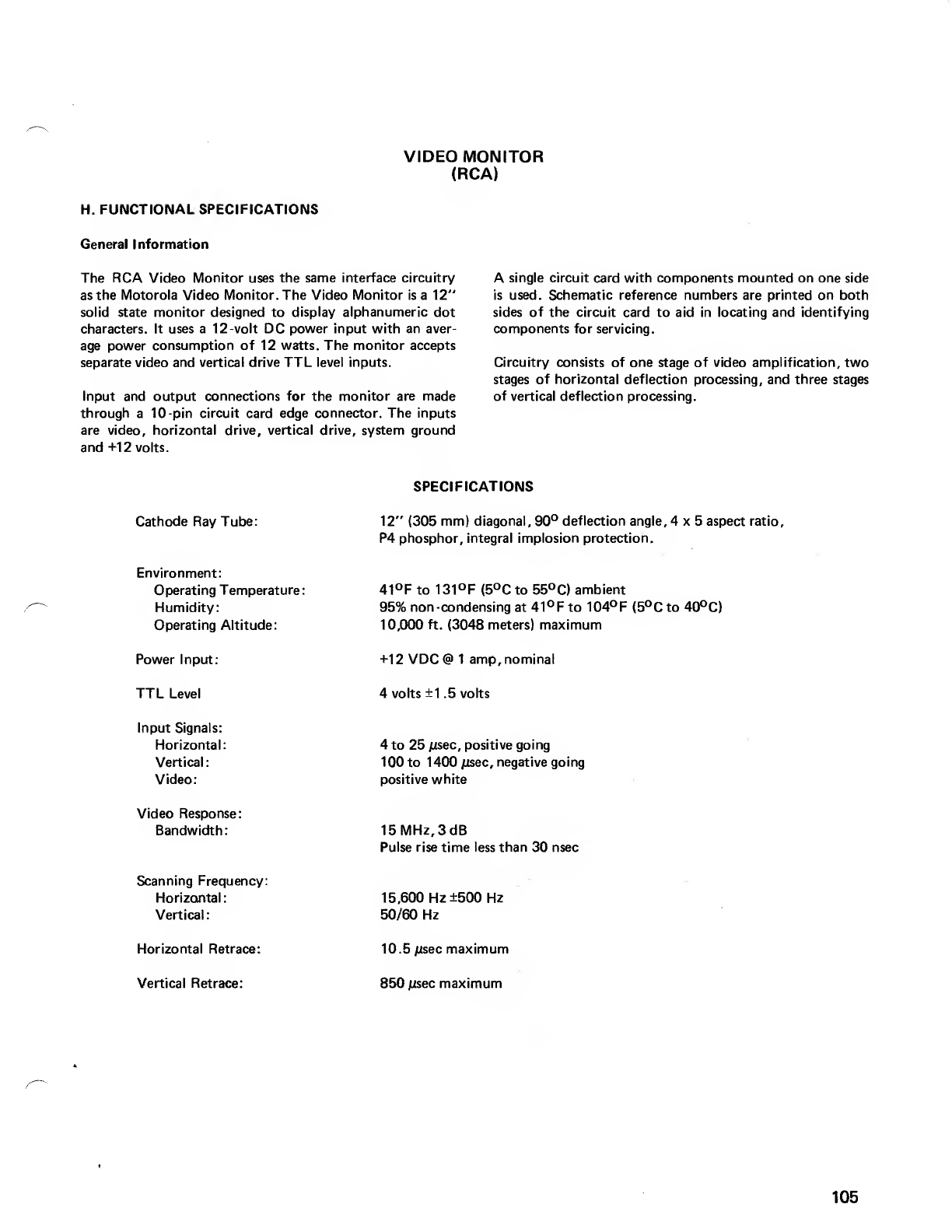

H. Functional Specifications 105

General Information 105

Specifications 105

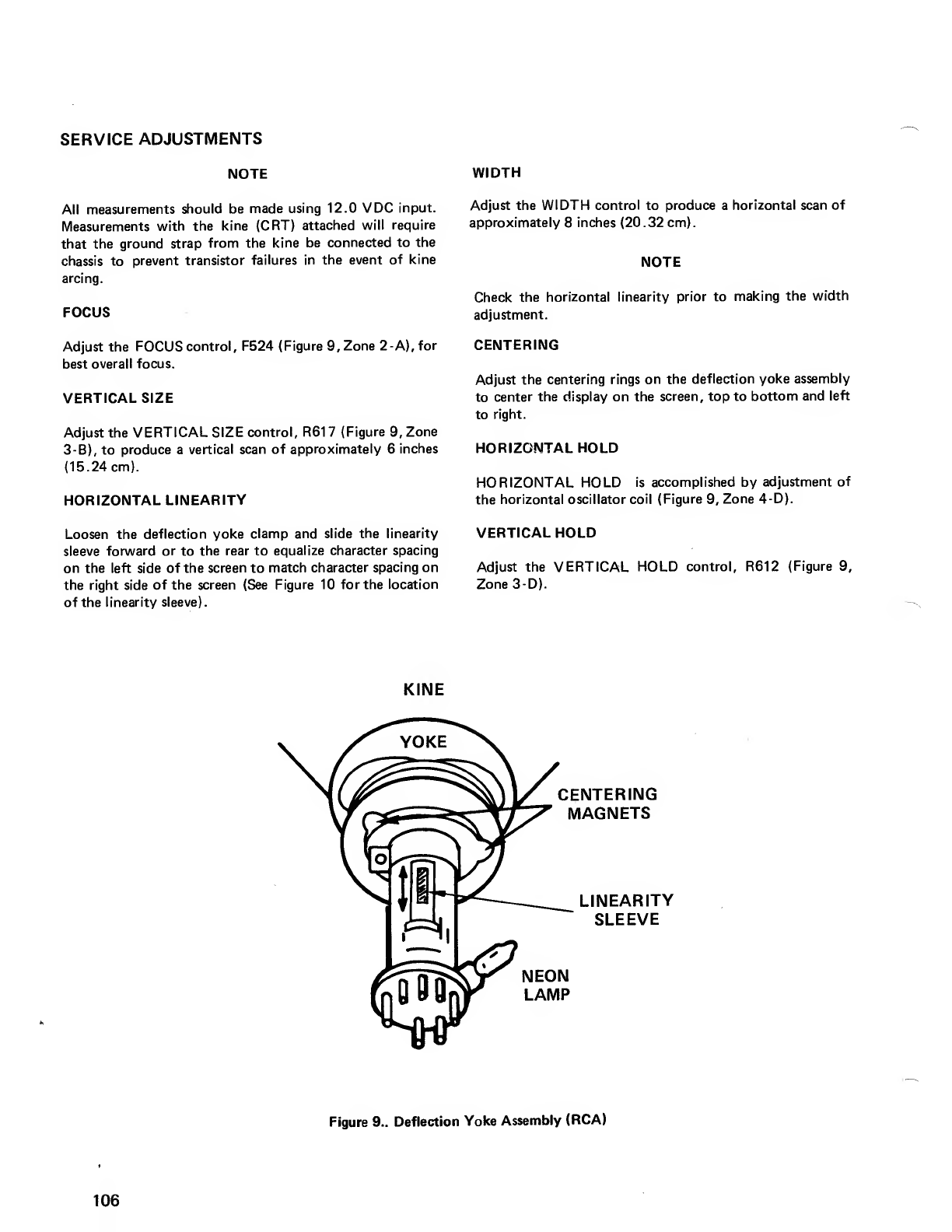

J. Service Adjustments 106

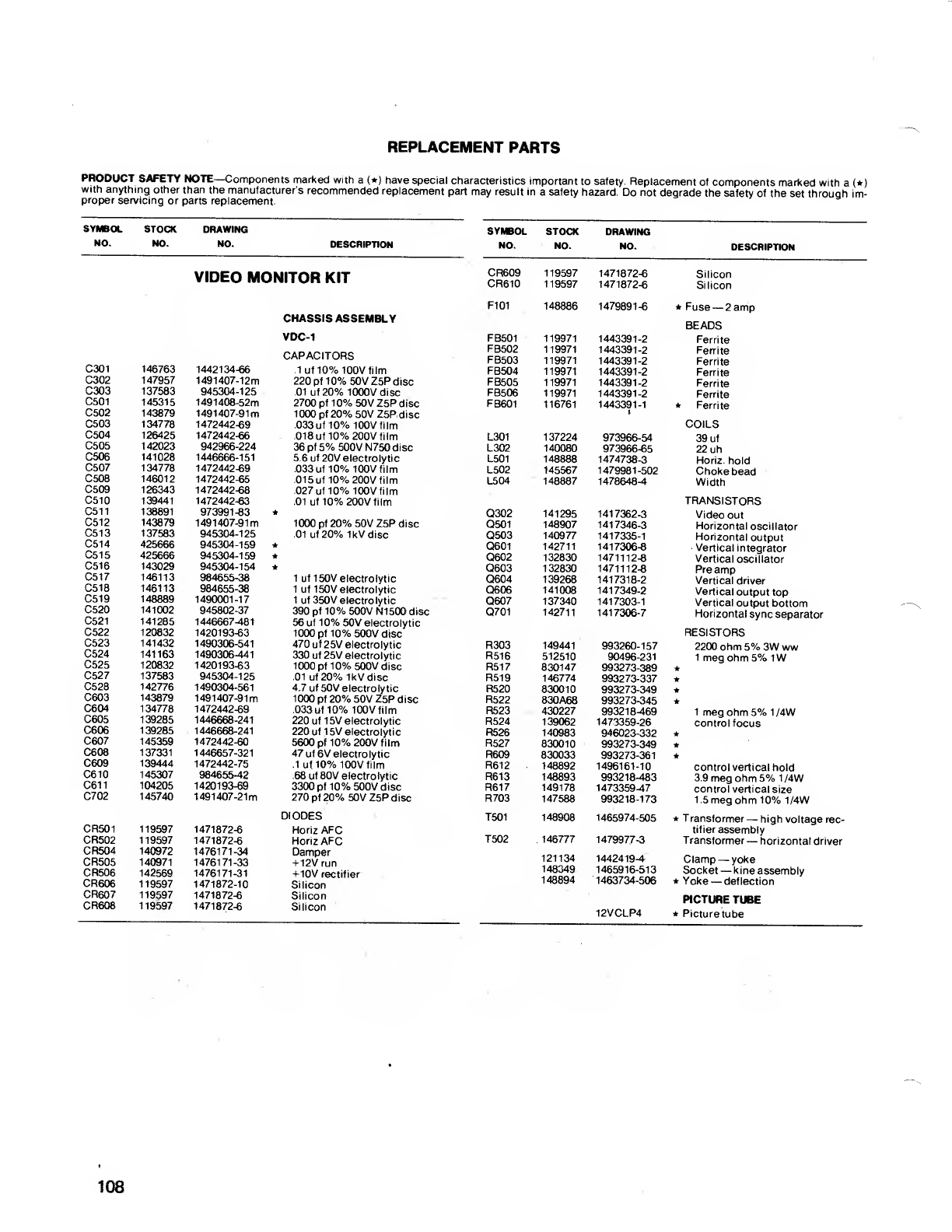

Replacement Parts (RCA) 108

TABLE OF CONTENTS (Cont'd)

Section Page

Number Number

VIII FLOPPY DISK DRIVE 111

A. Theory of Operation 113

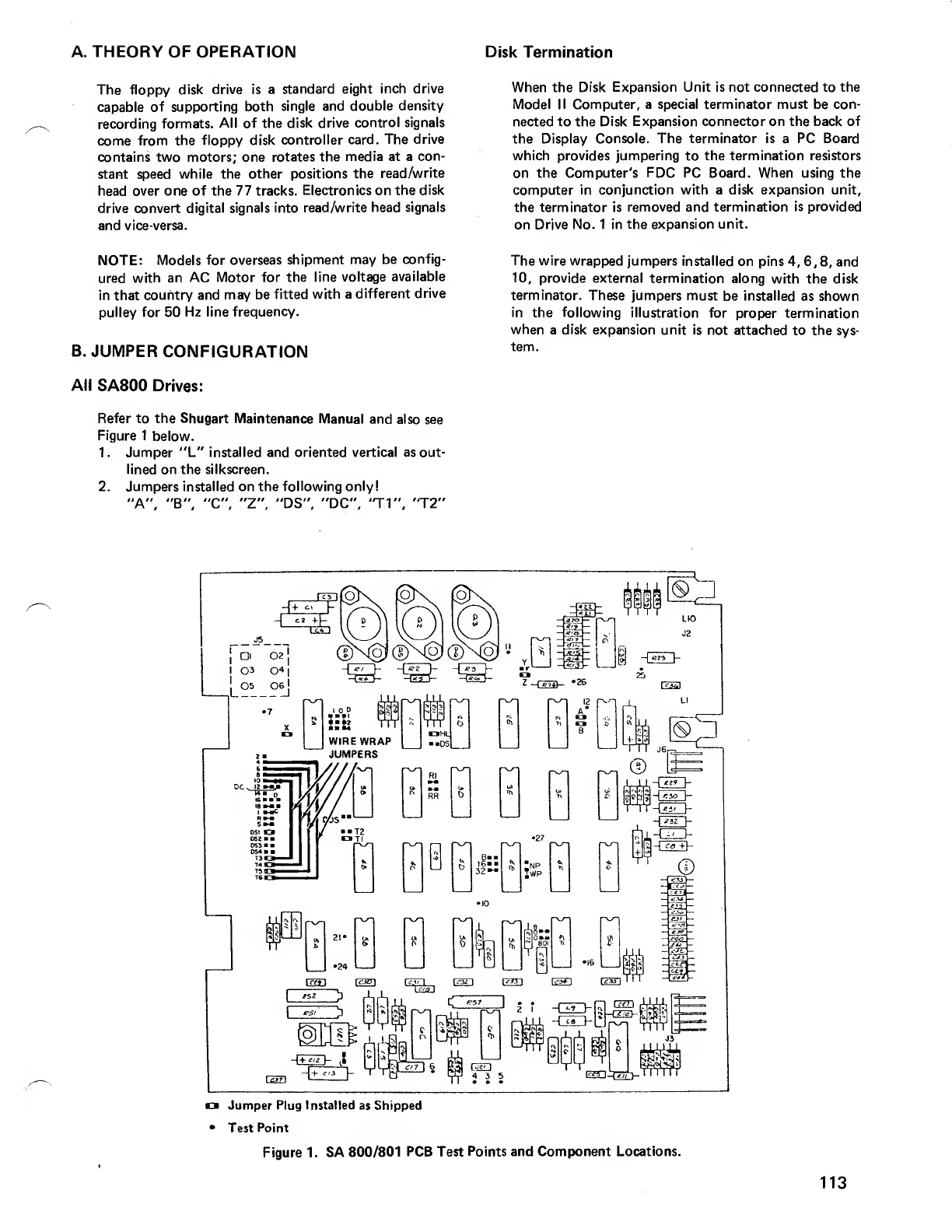

B. Jumper Configurations 113

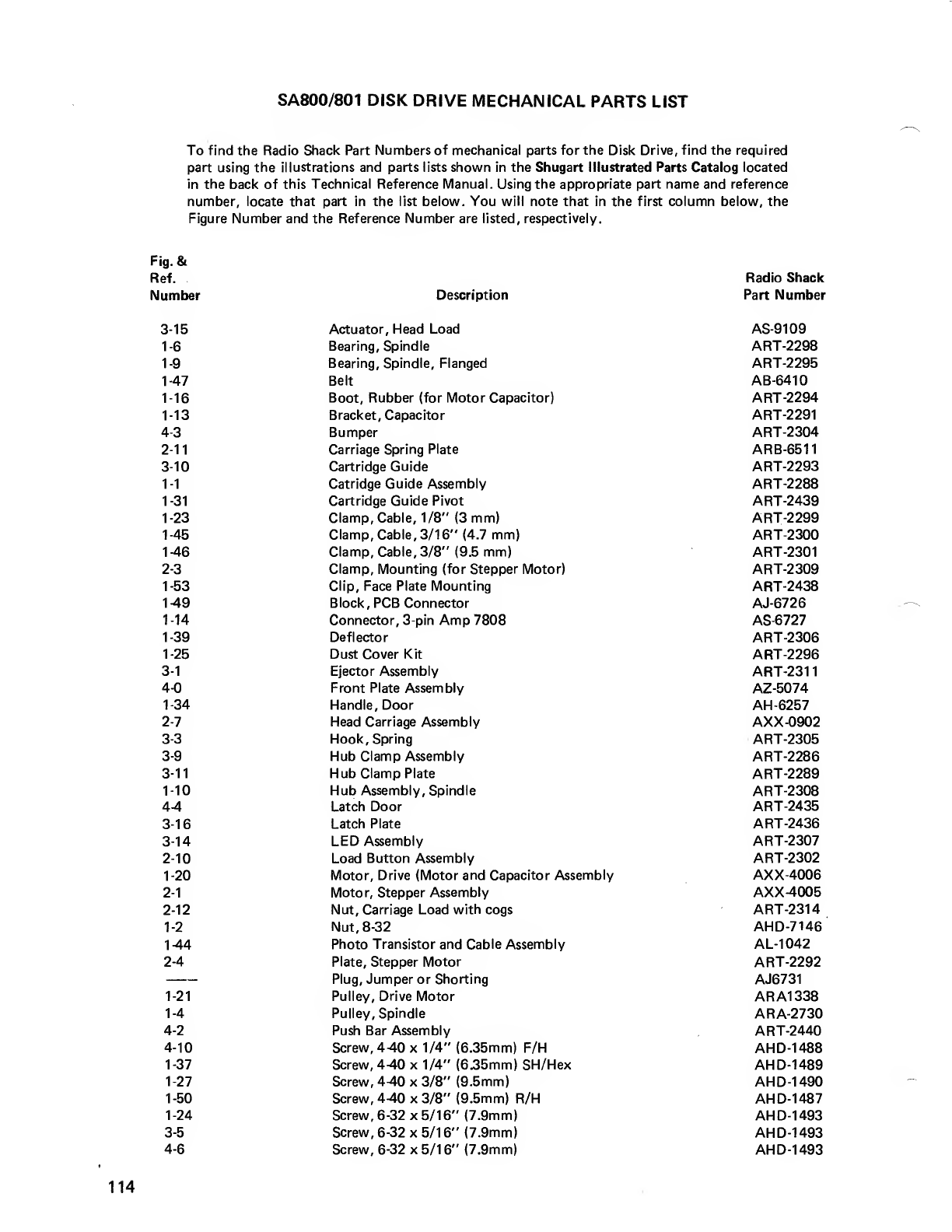

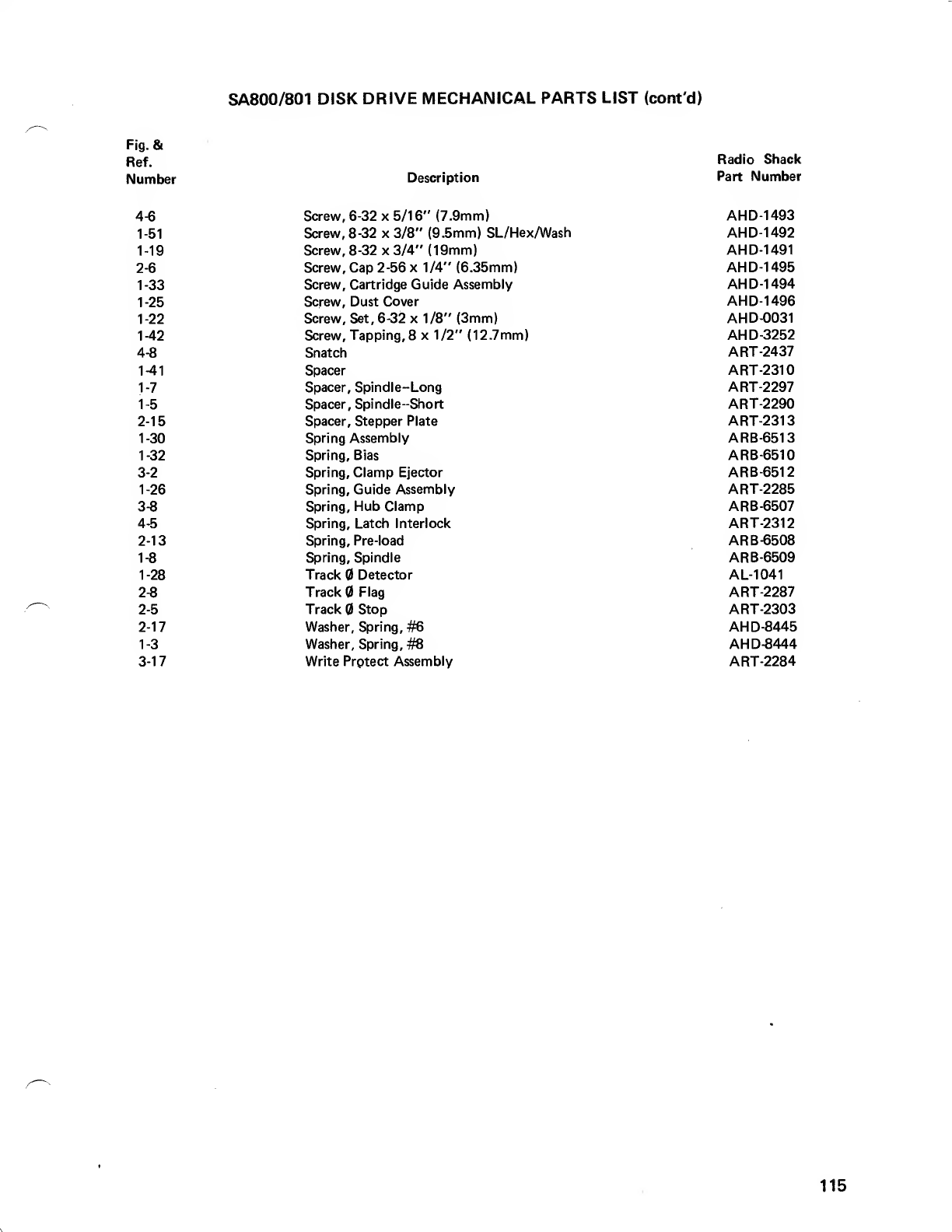

Replacement Parts List -Disk Drive 114

IX AA11080 POWER SUPPLY 117

A. Functional Specifications 119

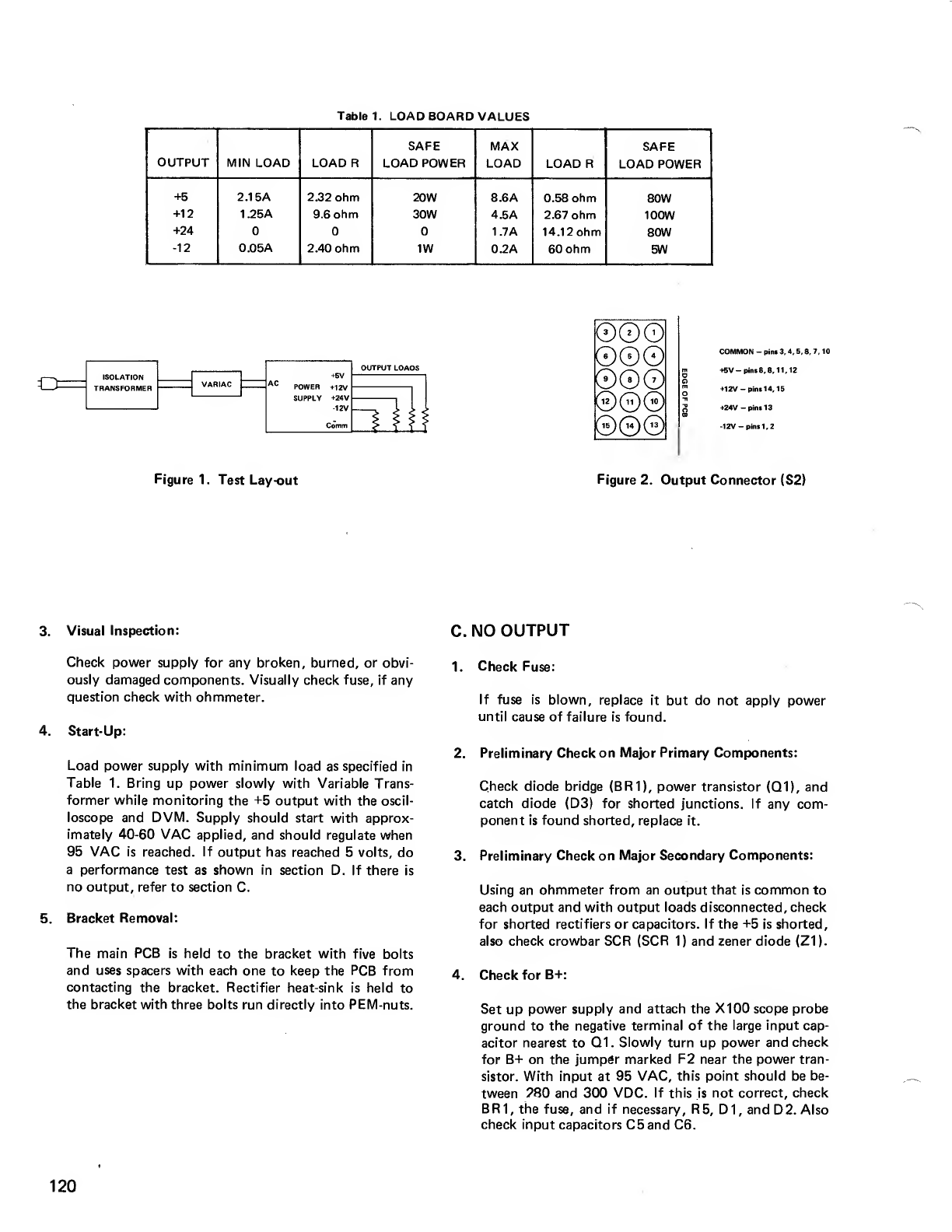

B. Troubleshooting 119

Equipment for Test Set-Up 119

Set -Up Procedure 119

Visual Inspection 120

Start-Up 120

Bracket Removal 120

C. No Output 120

D. Performance Test 121

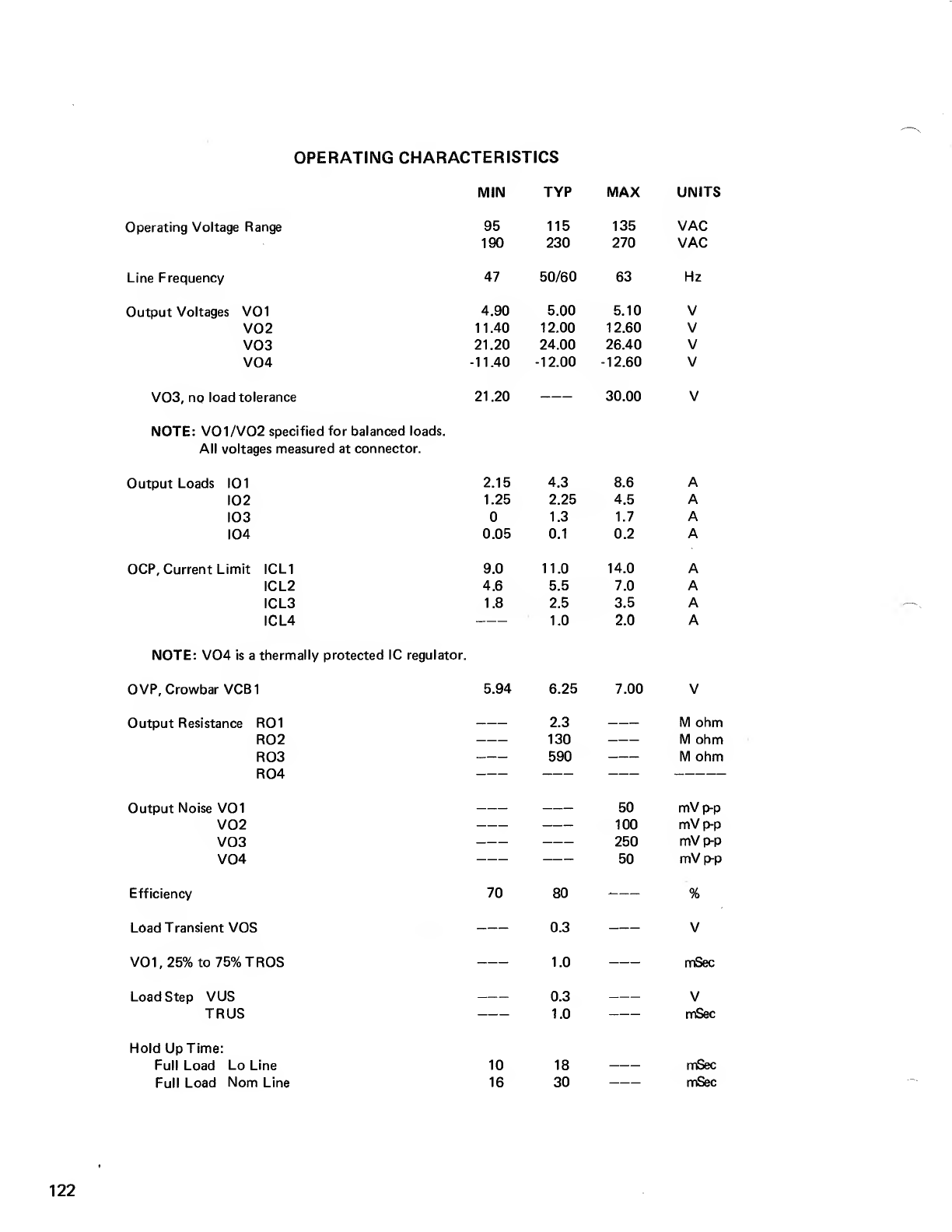

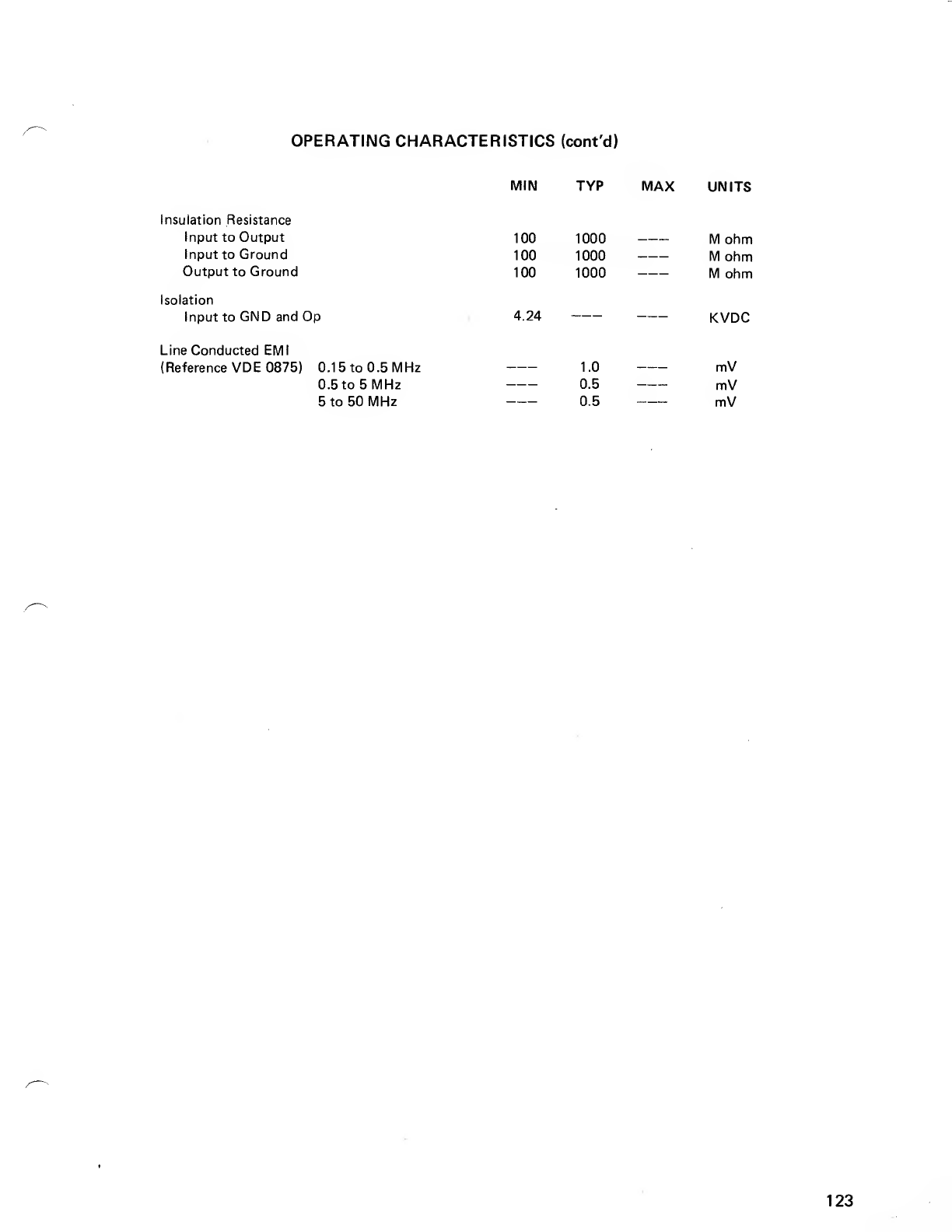

Operating Characteristics 122

XCARD CAGE AND MOTHERBOARD 125

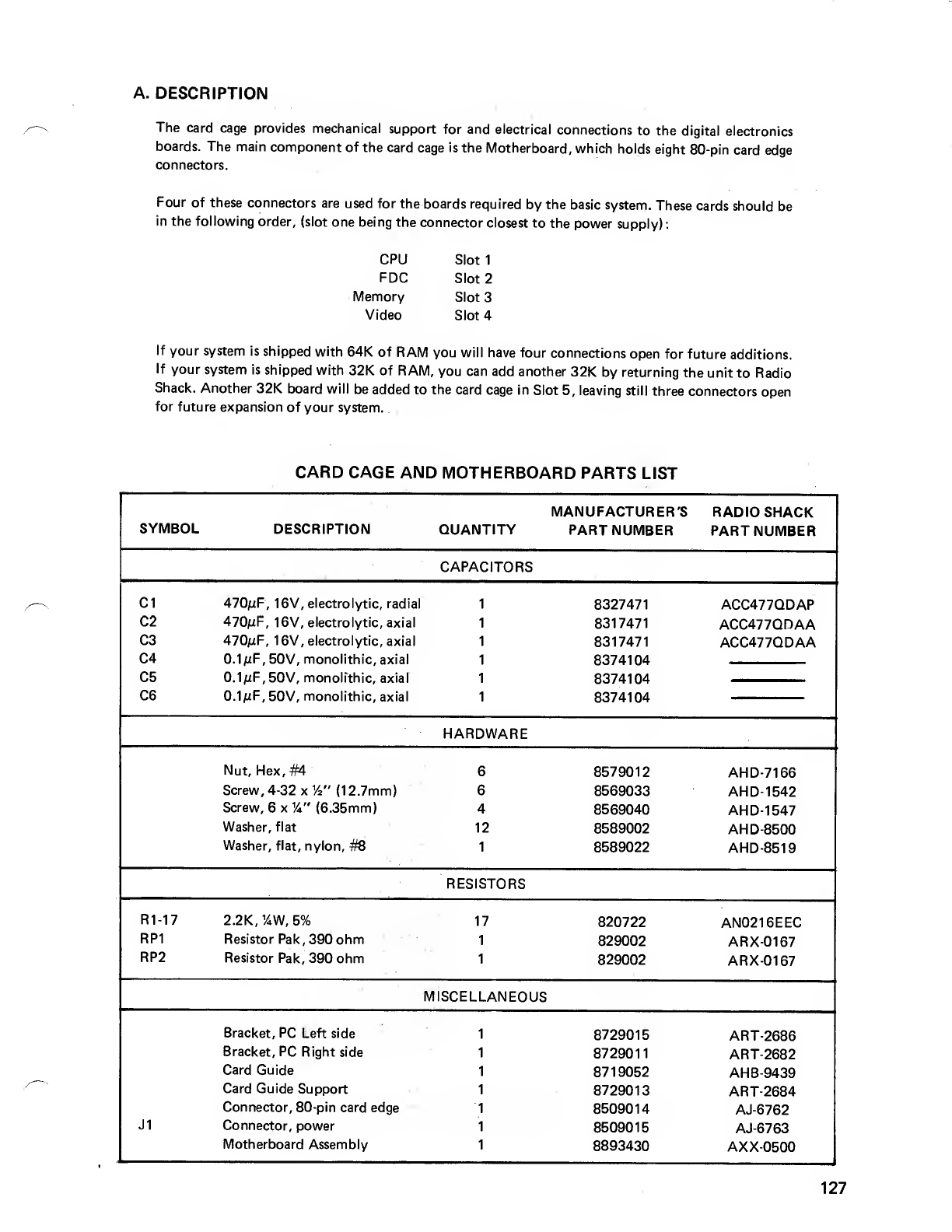

A. Description 127

Replacement Parts List -Card Cage and Motherboard 127

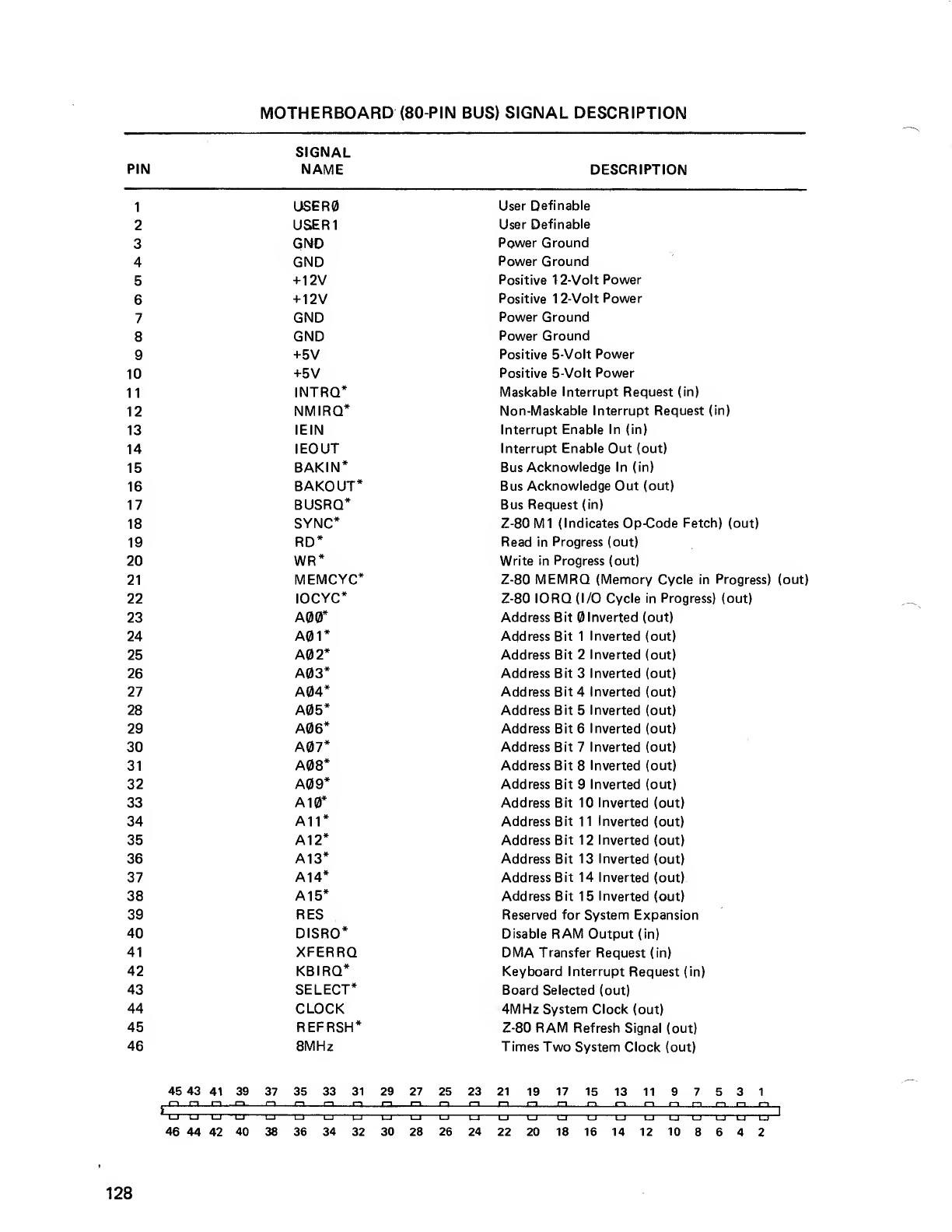

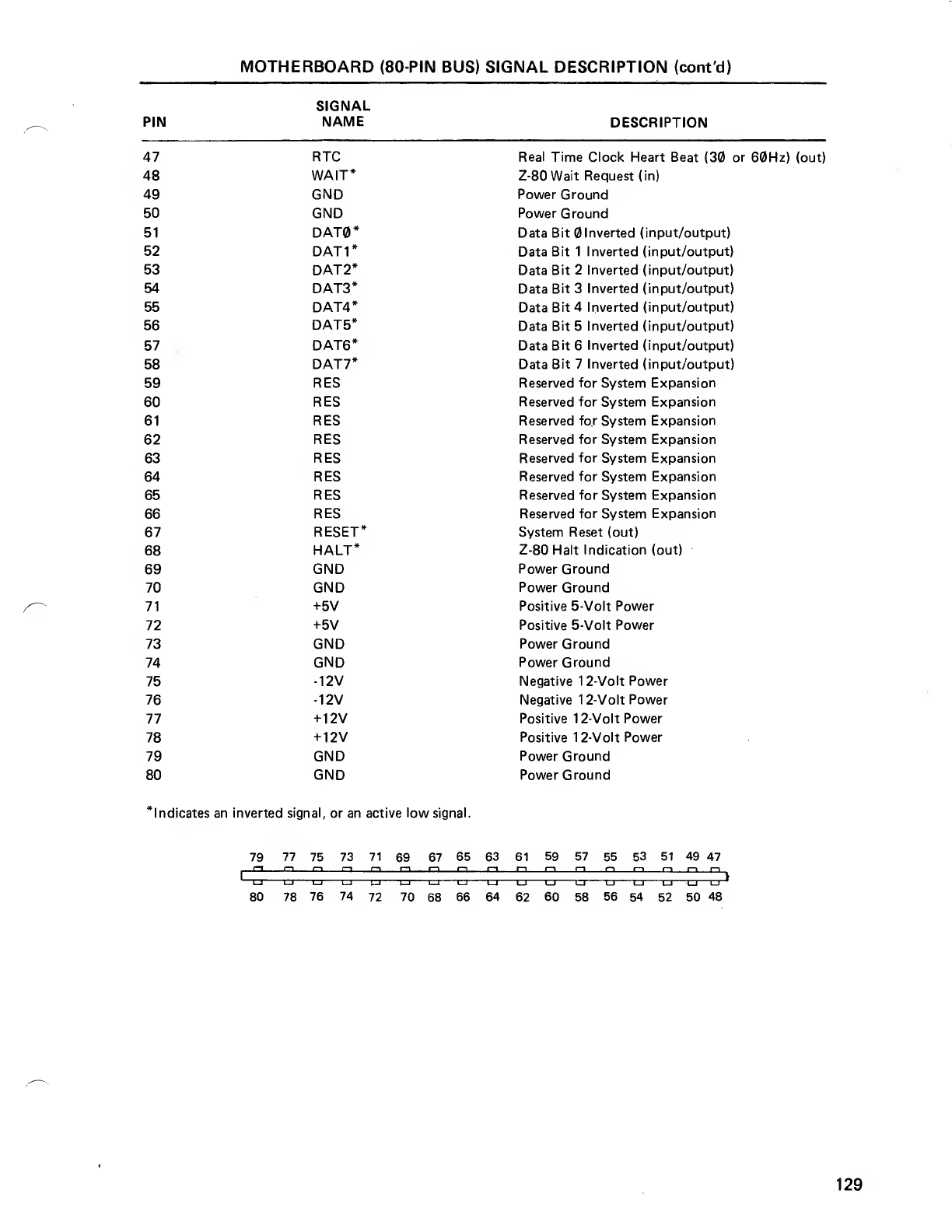

Motherboard Signal Descriptions 128

XI KEYBOARD UNIT 133

A. Introduction 135

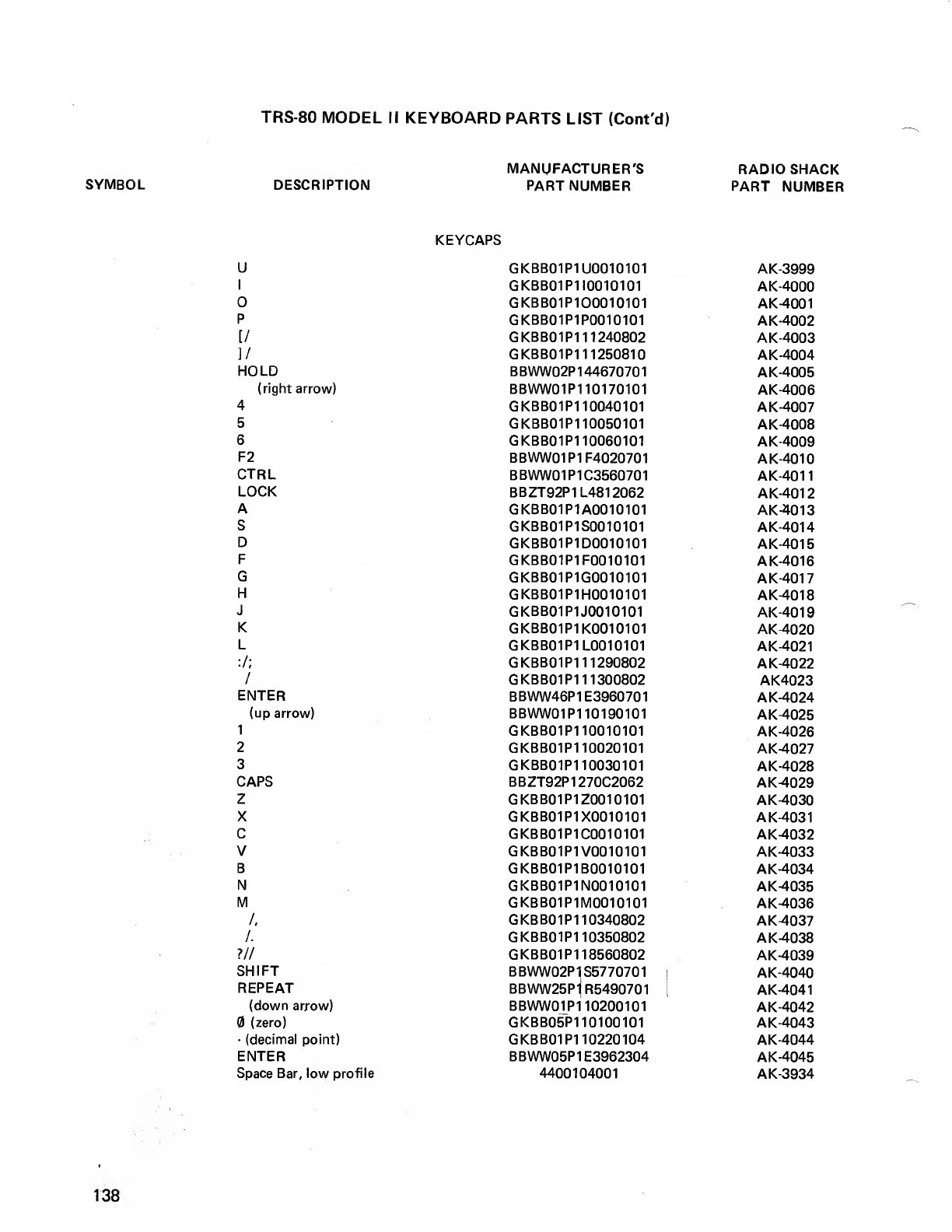

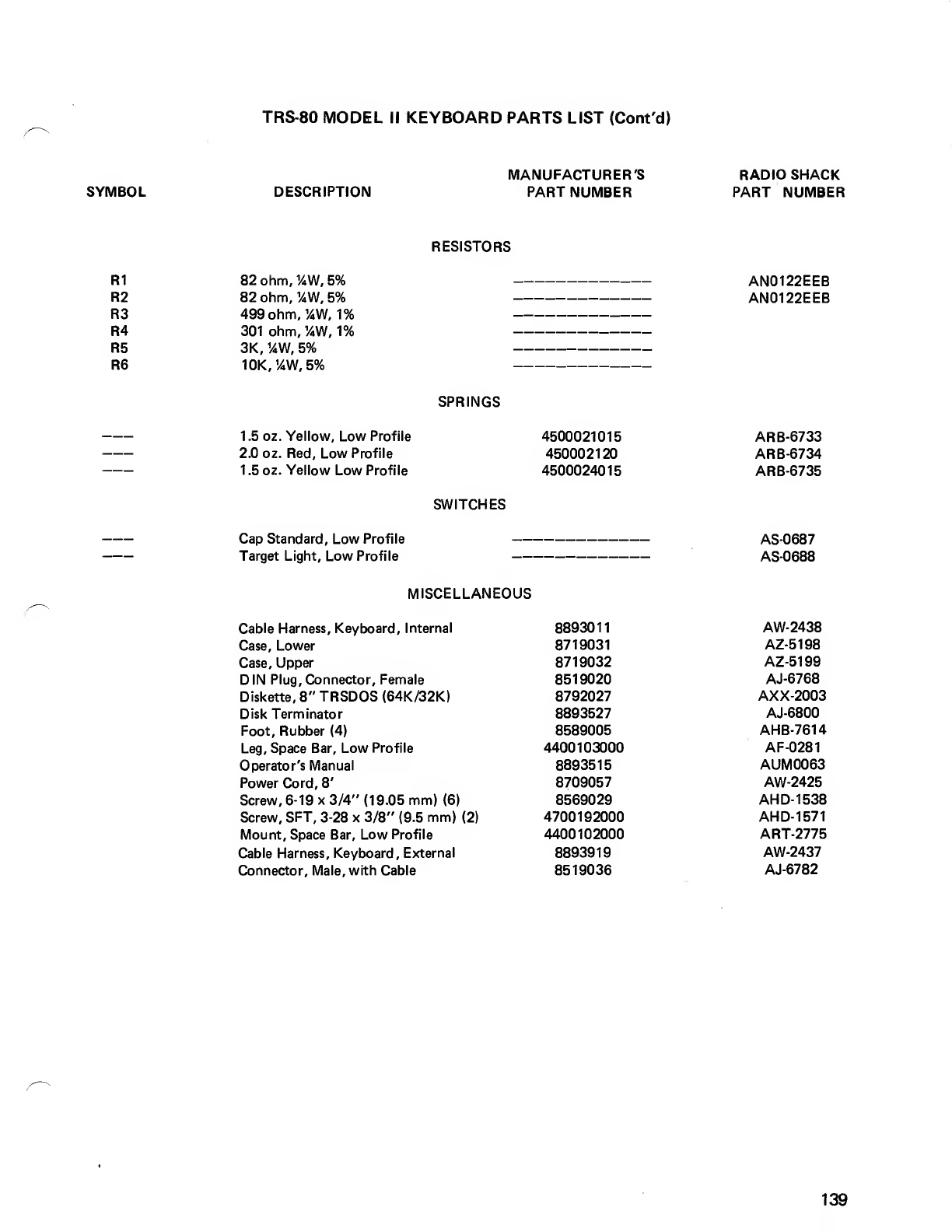

Replacement Parts List -Keyboard Unit 137

XII PERIPHERAL INTERFACES 141

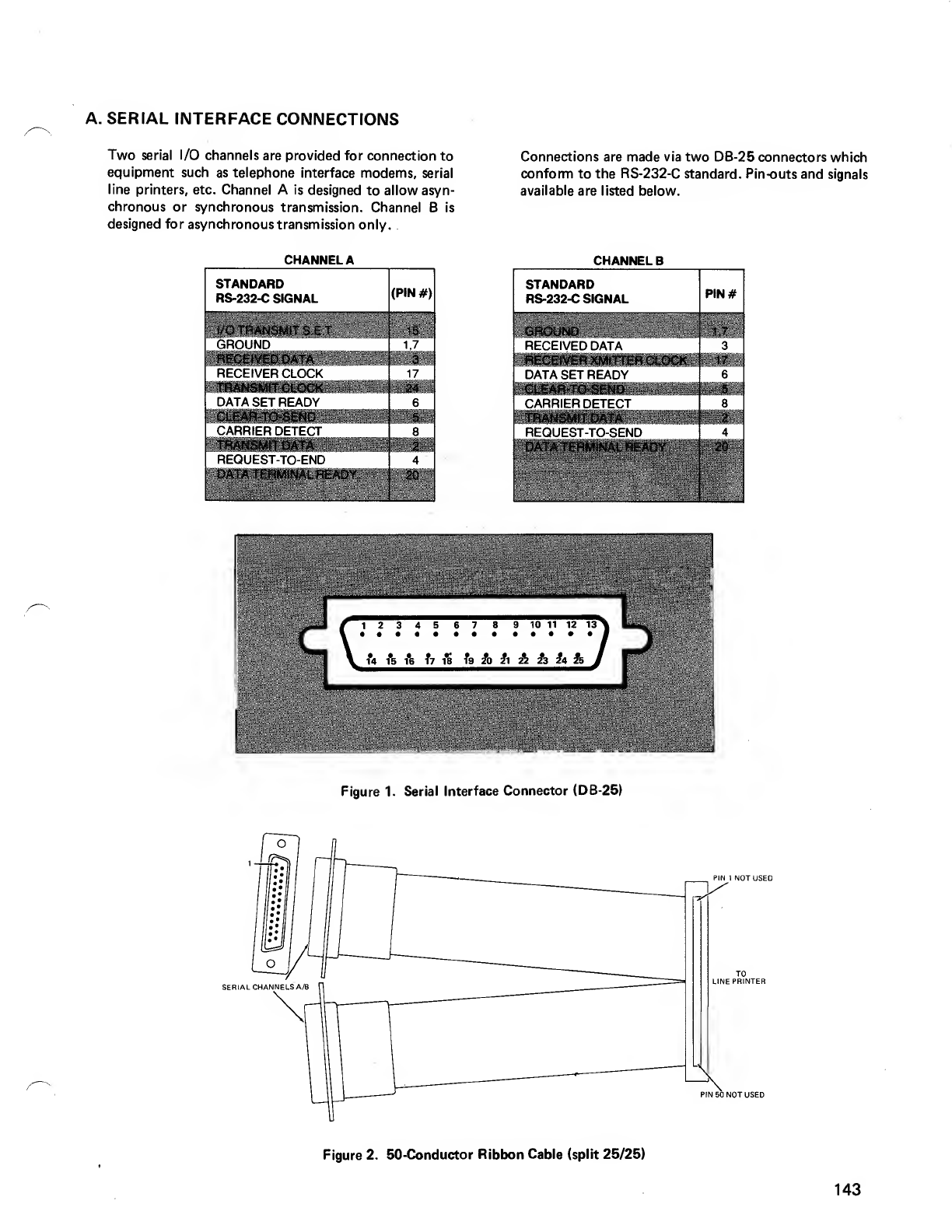

A. Serial Interface Connections 143

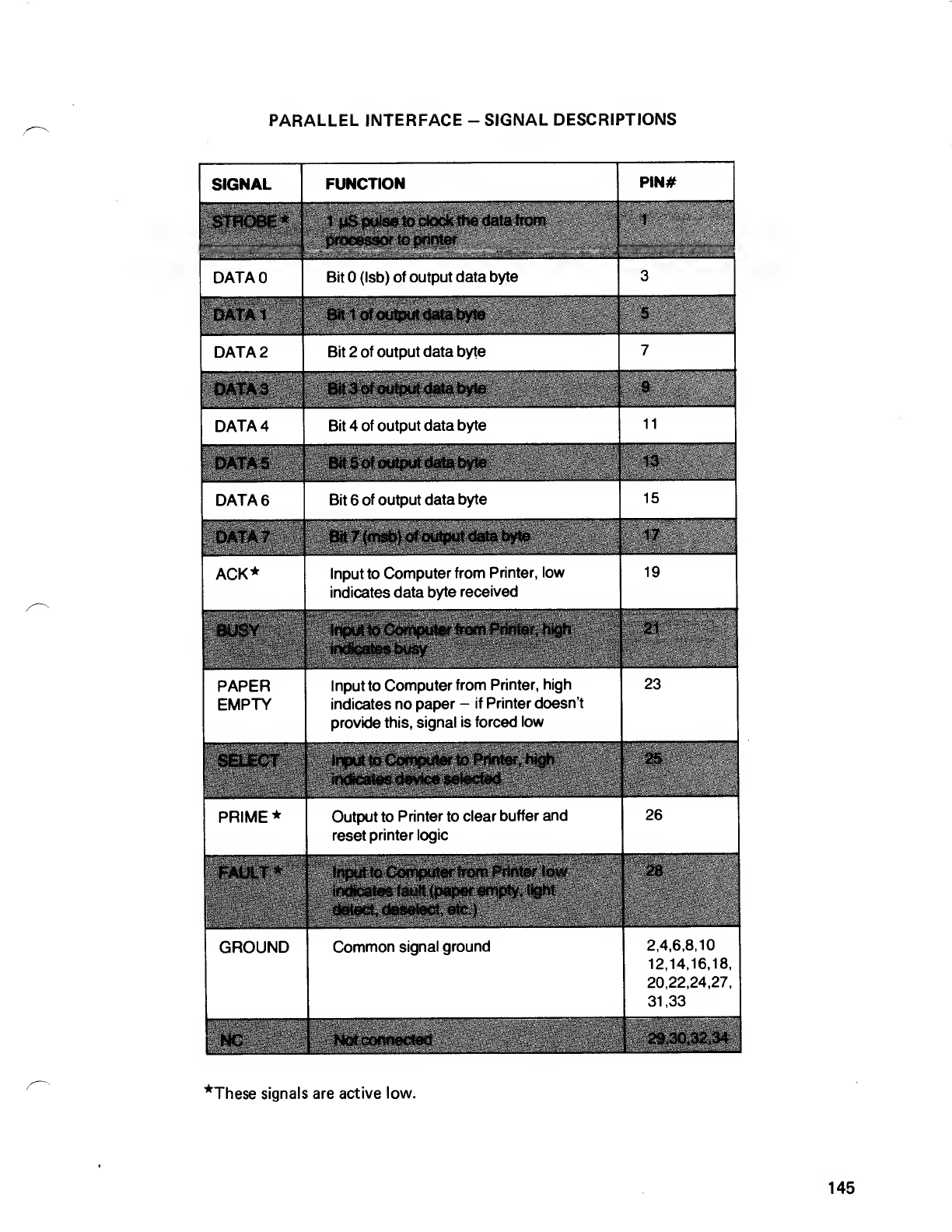

B. Parallel Interface 144

Parallel Interface Signal Descriptions 145

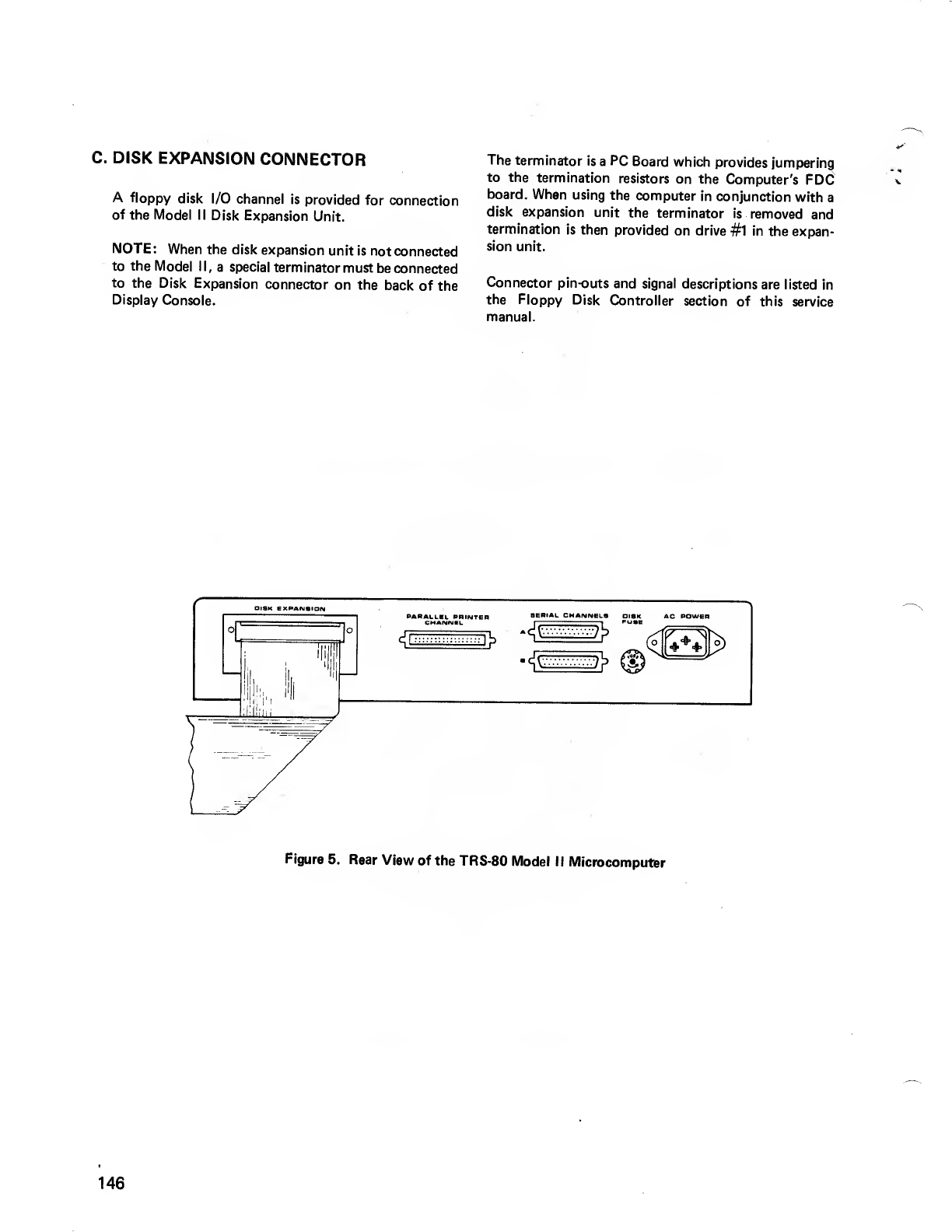

C. Disk Expansion Connector 146

TRS-80 Model II Disk Expansion System

XIII DISK EXPANSION UNIT 147

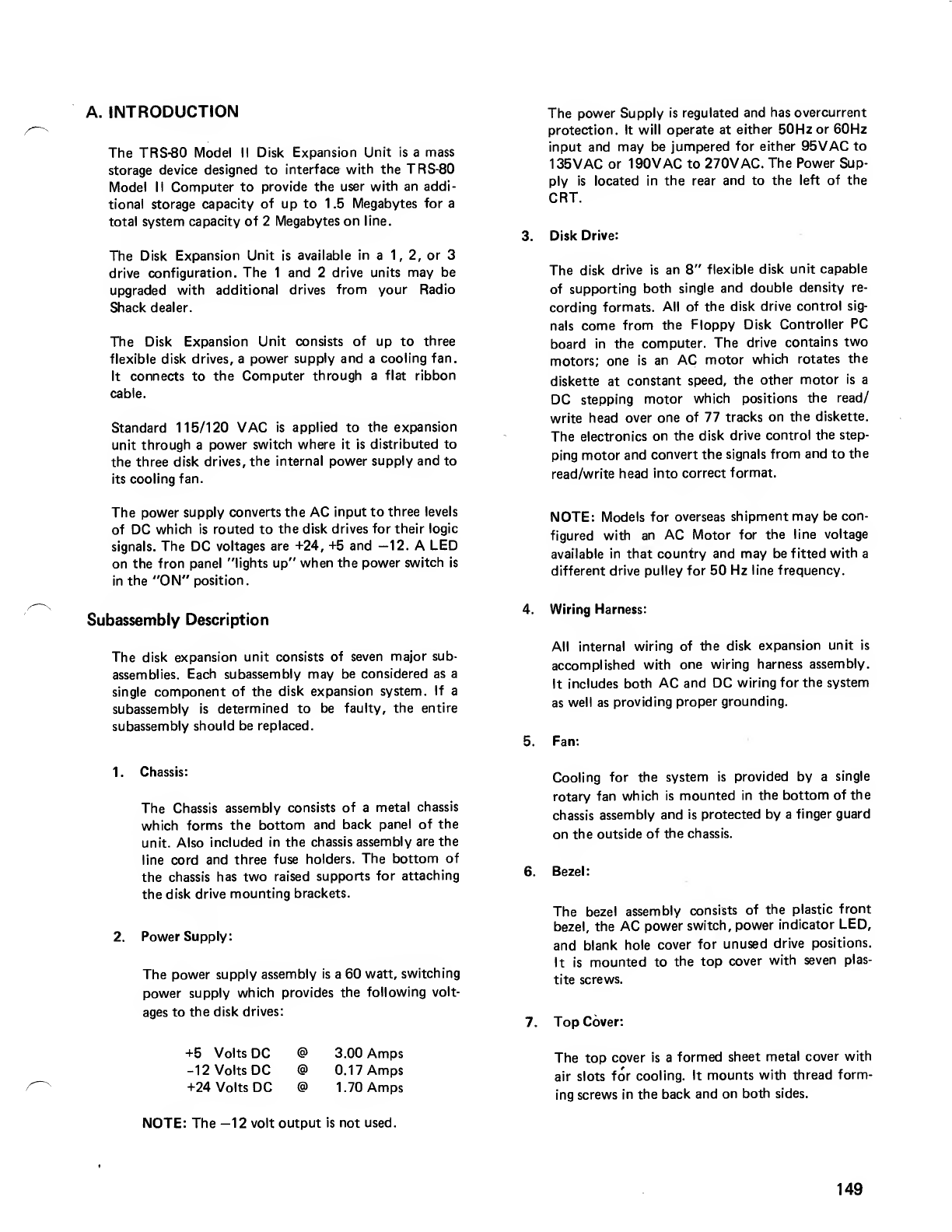

A. Introduction 149

Subassembly Description 149

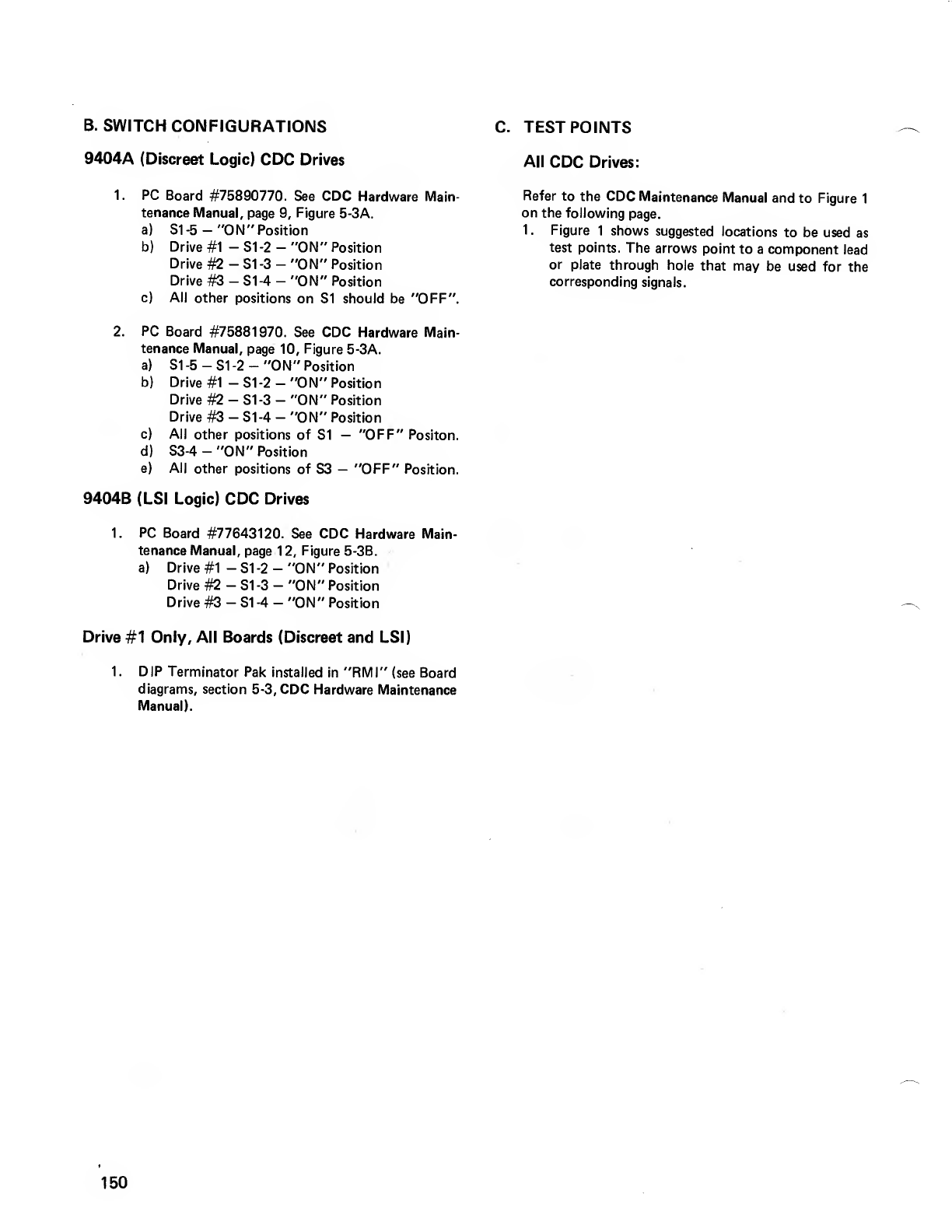

B. Switch Configurations 150

C. Test Points 150

XIV TROUBLESHOOTING -DISK SYSTEM 153

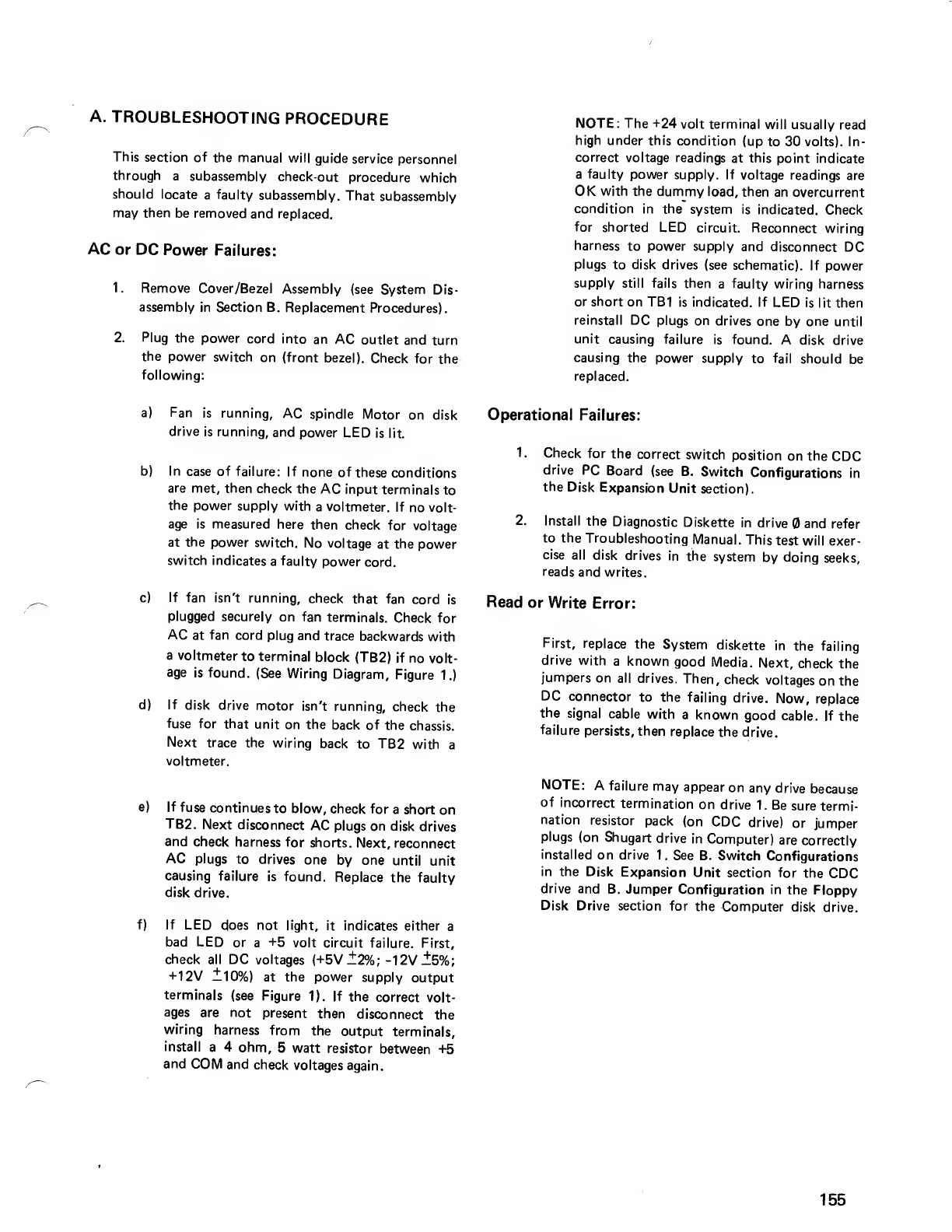

A. Troubleshooting Procedure 155

AC or DC Power Failures 155

Operational Failures '. ..155

Read or Write Error 155

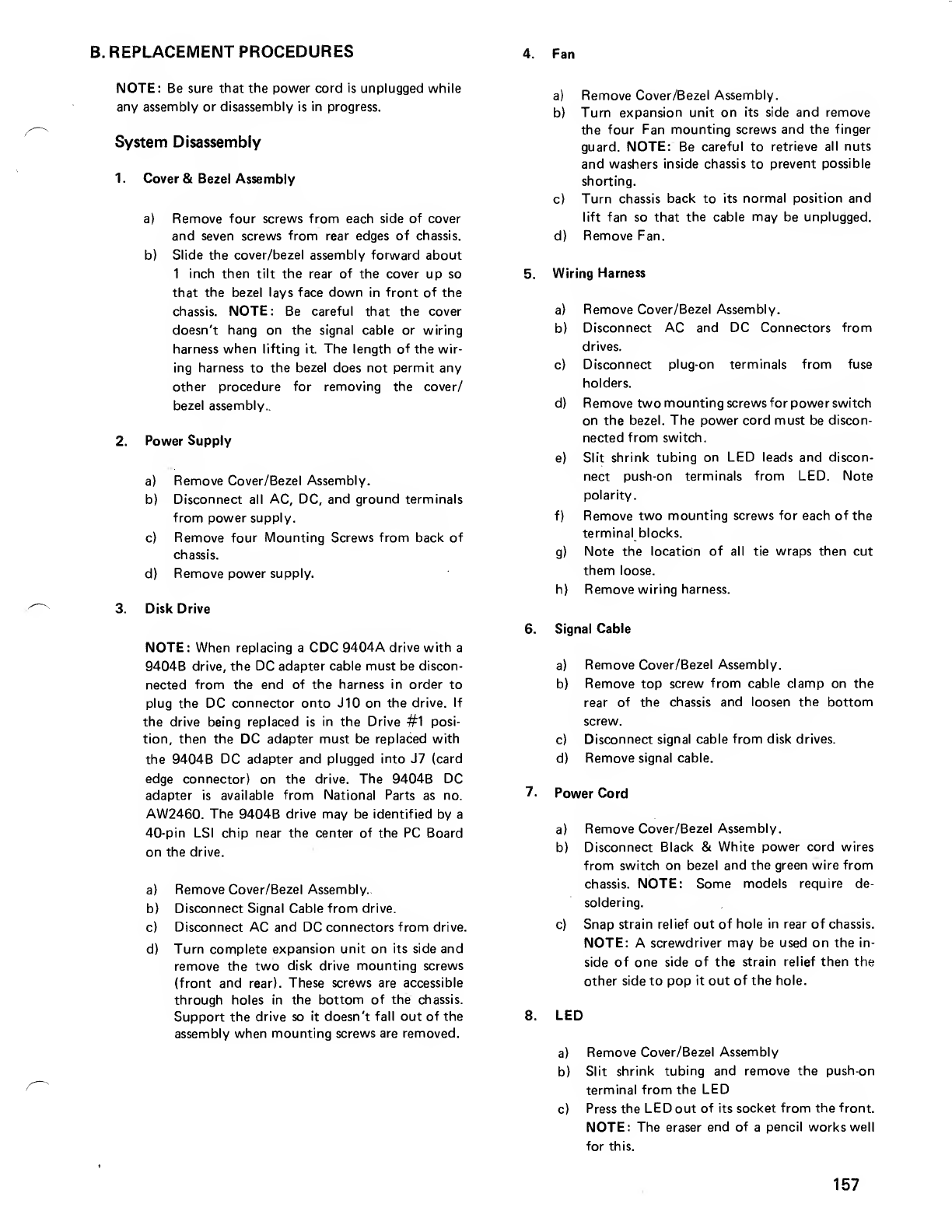

B. Replacement Procedures 157

System Disassembly 157

Subassembly Replacement 158

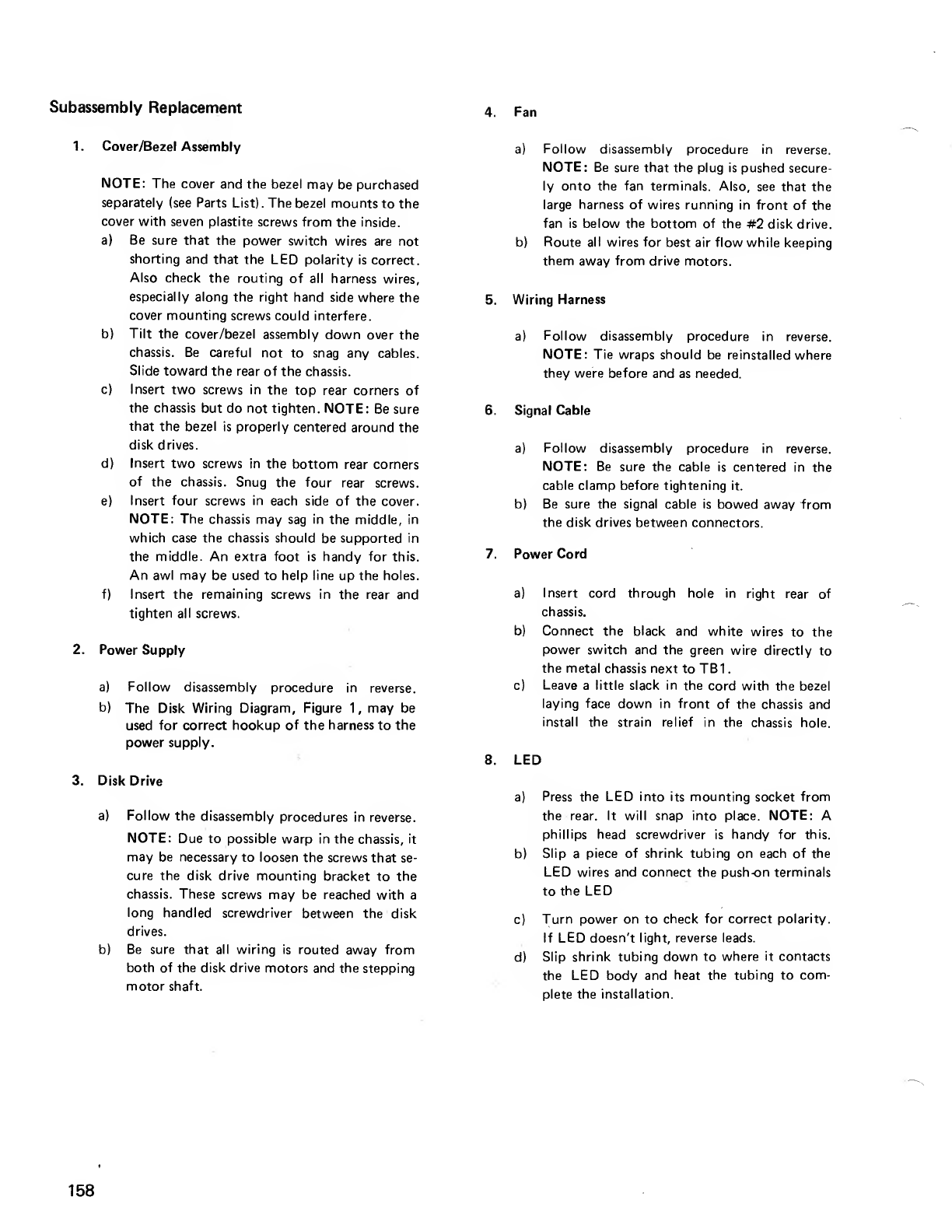

Replacement Parts List -Expansion Unit 159

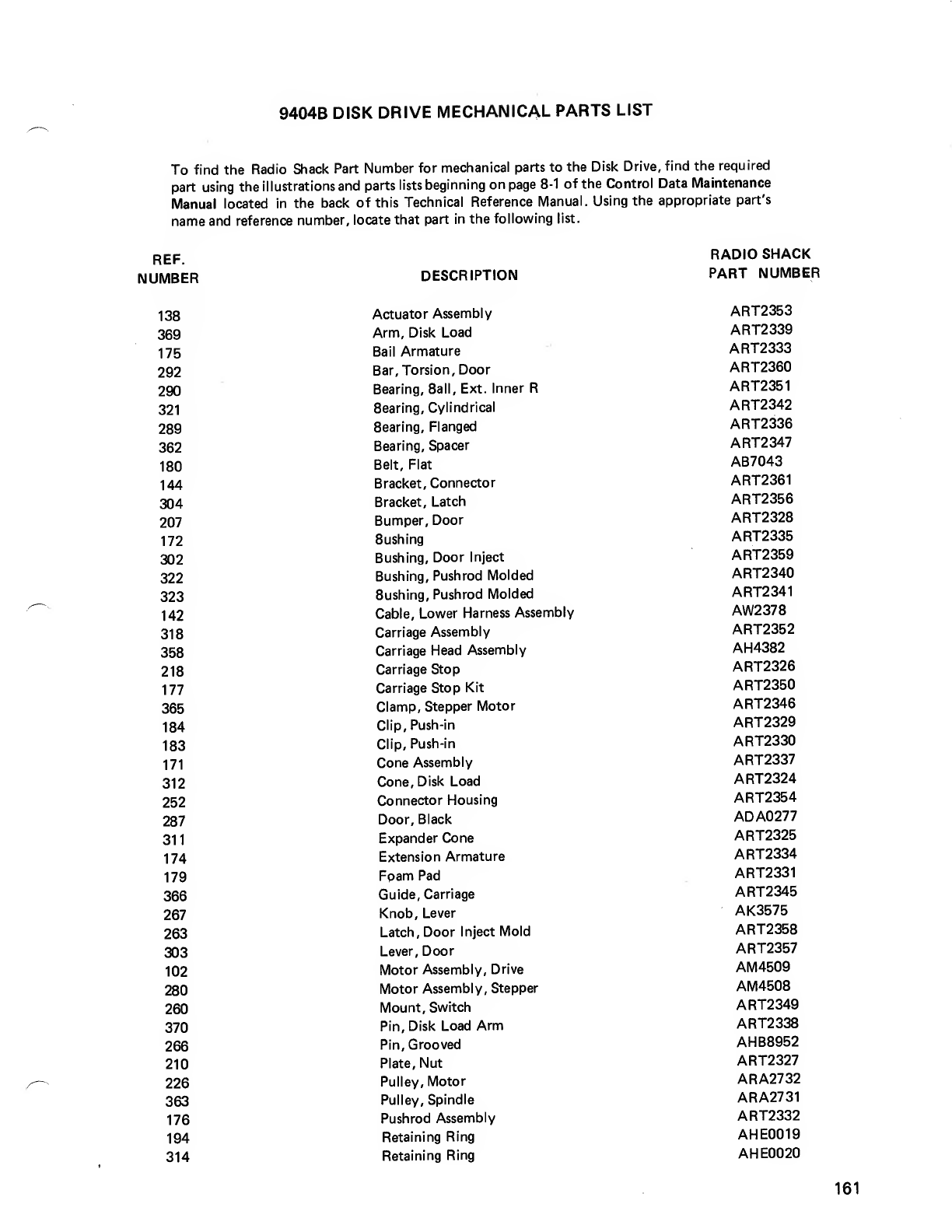

Replacement Parts List- 9404B Disk Drive, Mechanical 161

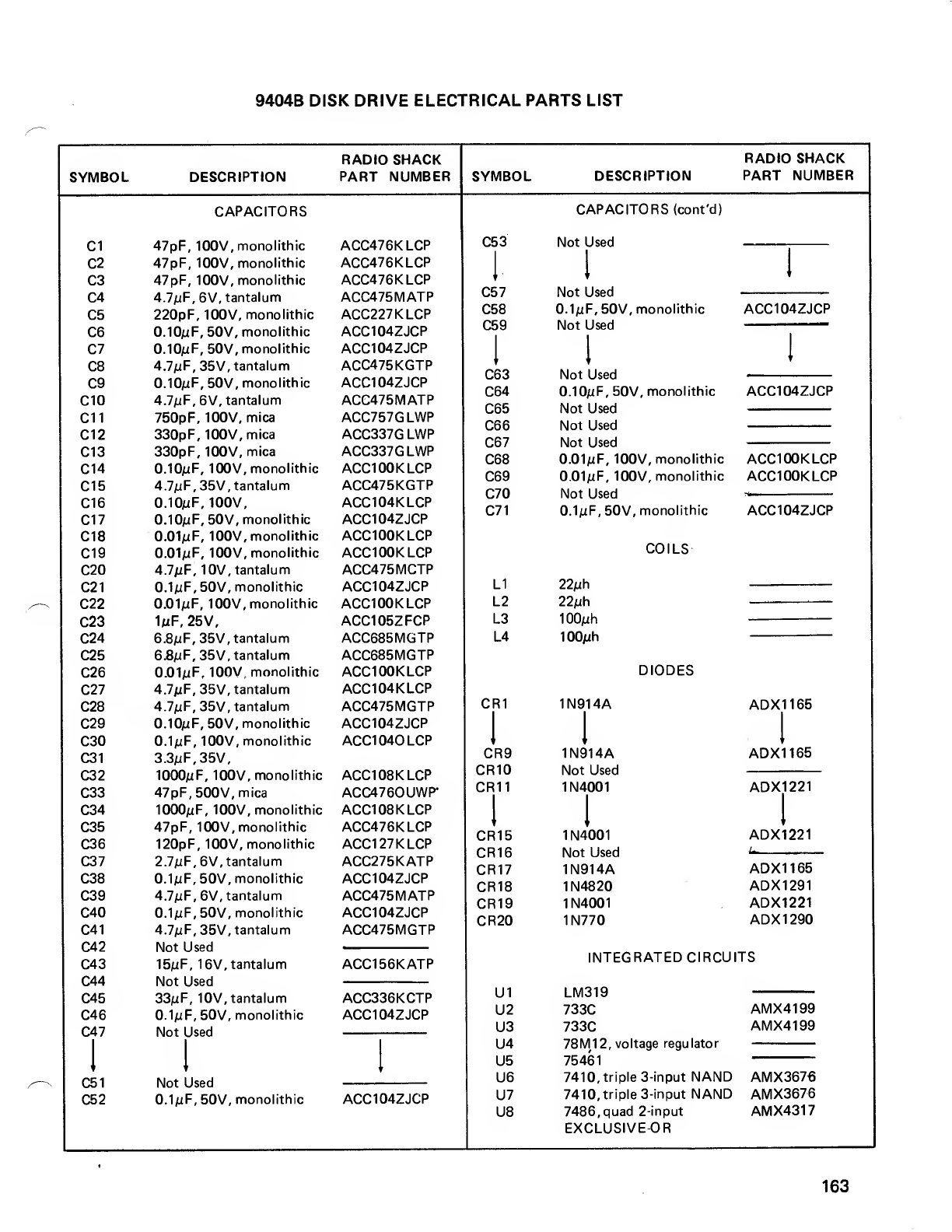

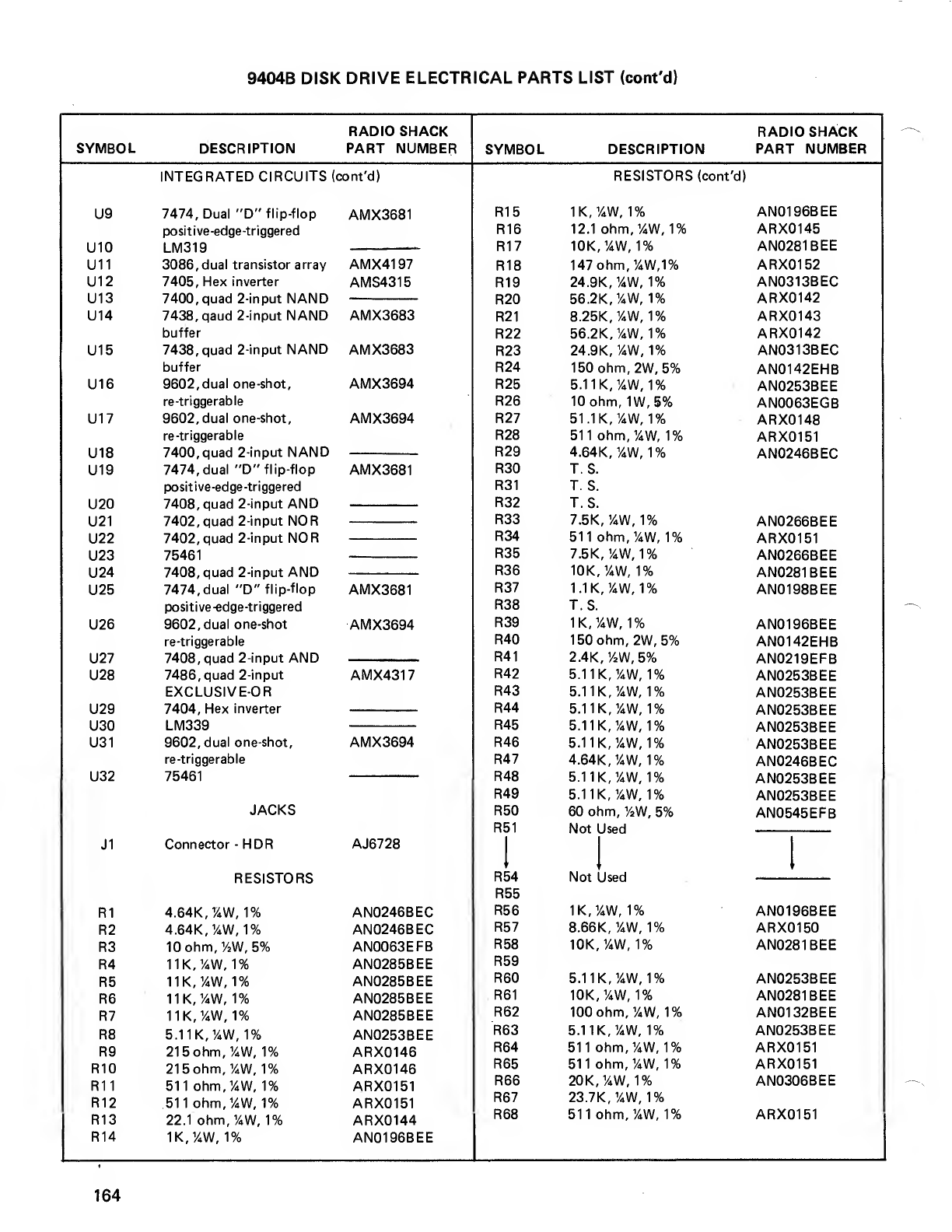

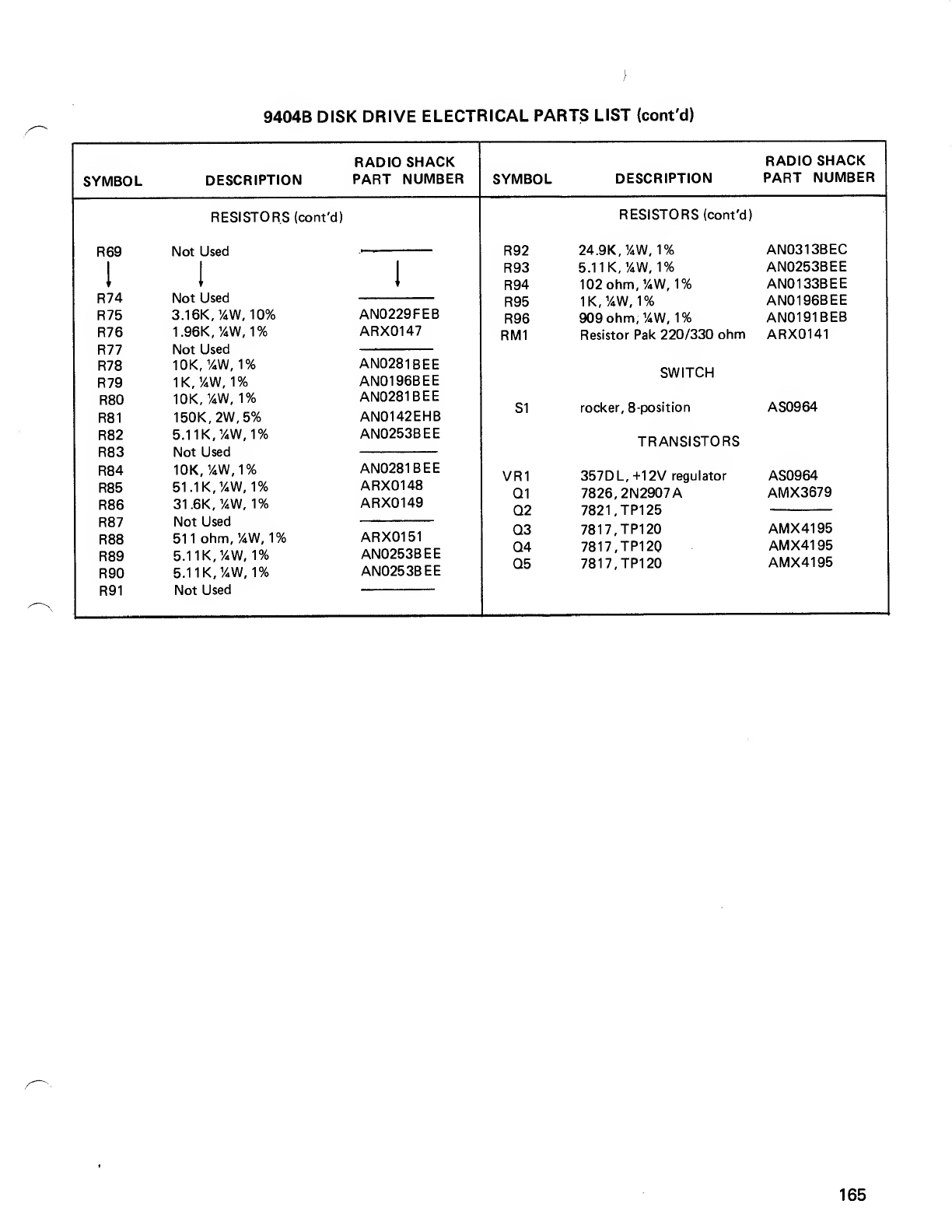

Replacement Parts List -9404B Disk Drive, Electrical 163

iii

TABLE OF CONTENTS (Cont'd)

Section

Number Number

XV AA11100 POWER SUPPLY 167

A. Functional Specifications 169

B. Troubleshooting 169

Equipment for Test Set -Up 169

Set-Up Procedure 169

Visual Inspection 169

Start-Up 169

Disassembly 170

C. No Output 170

D. Performance Test 171

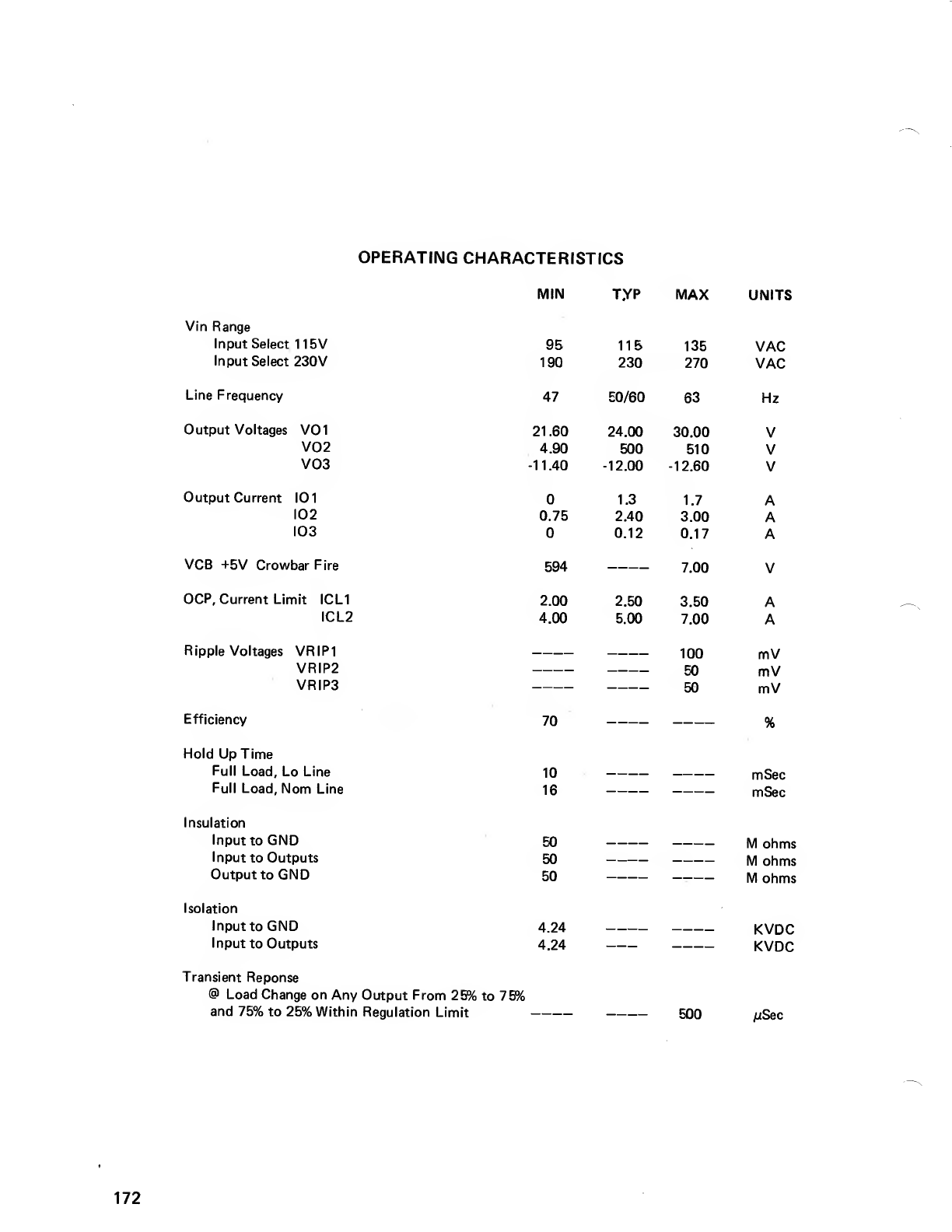

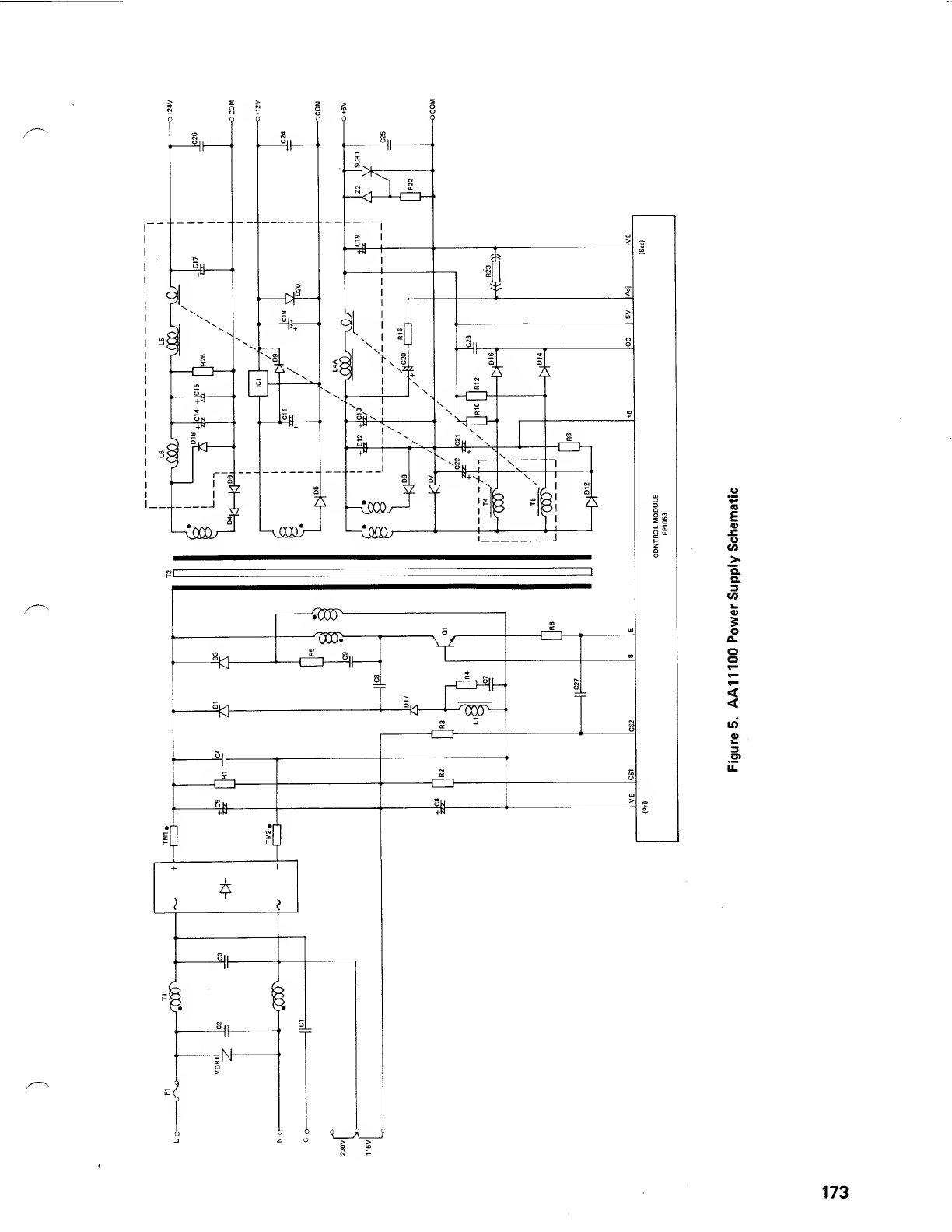

Operating Characteristics 172

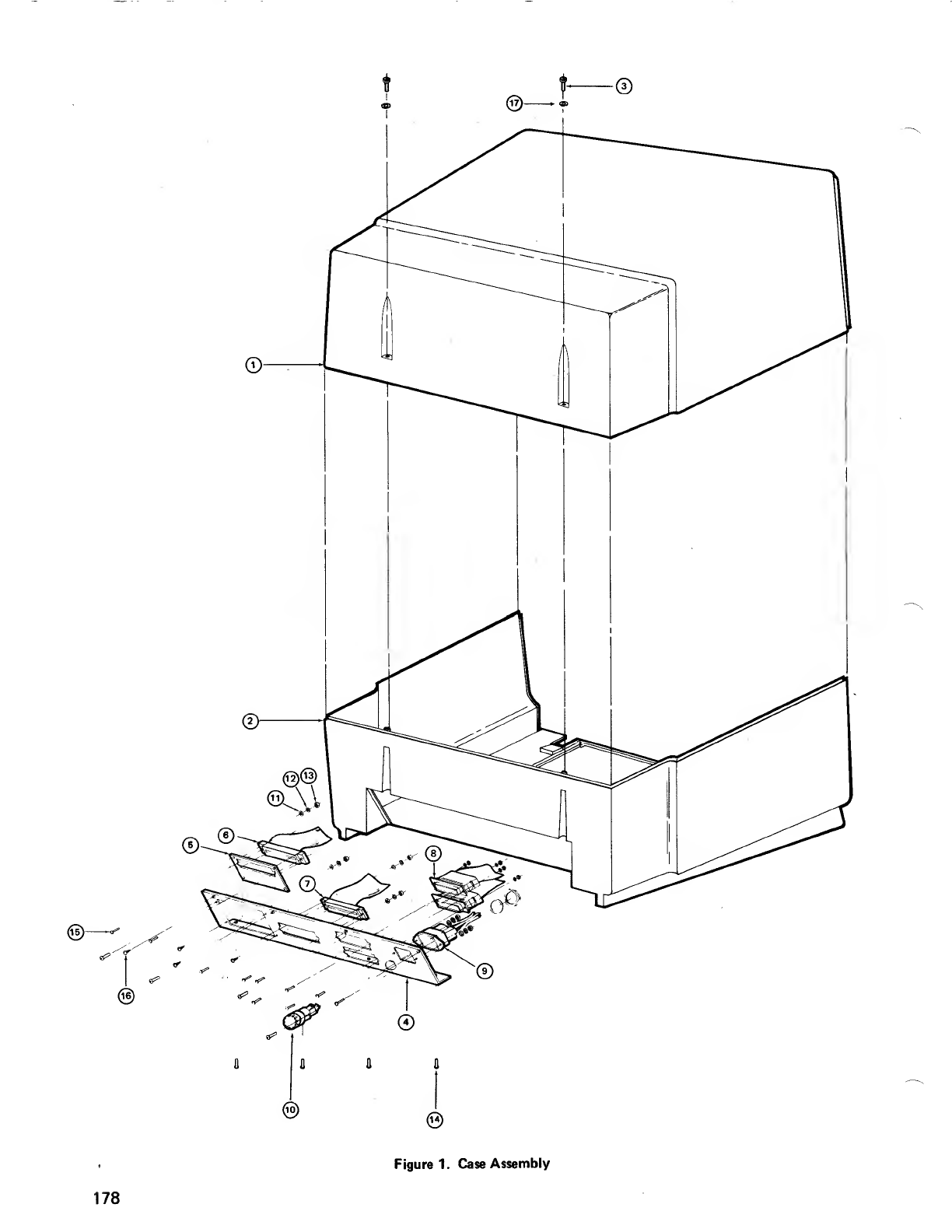

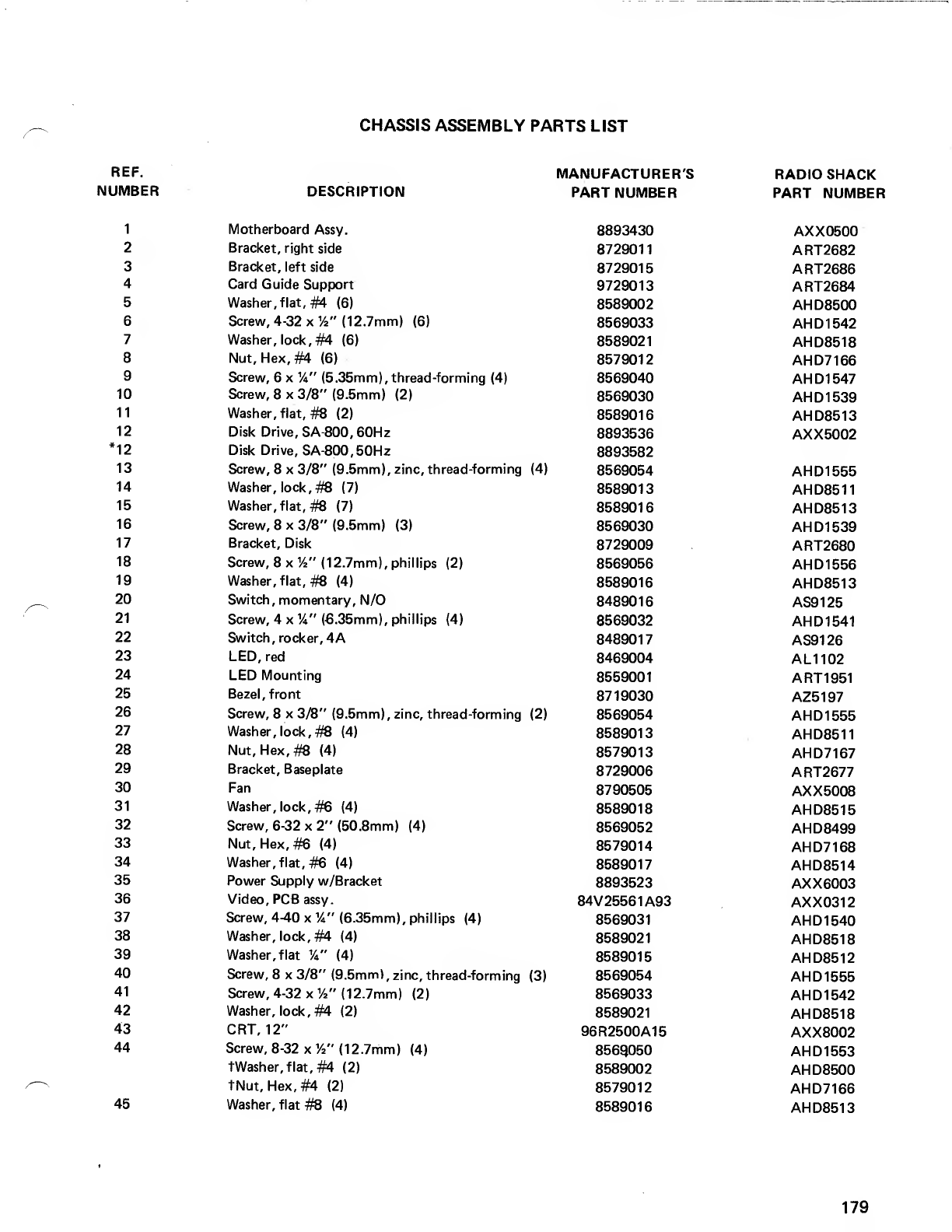

XVI ILLUSTRATED PARTS BREAKDOWN 175

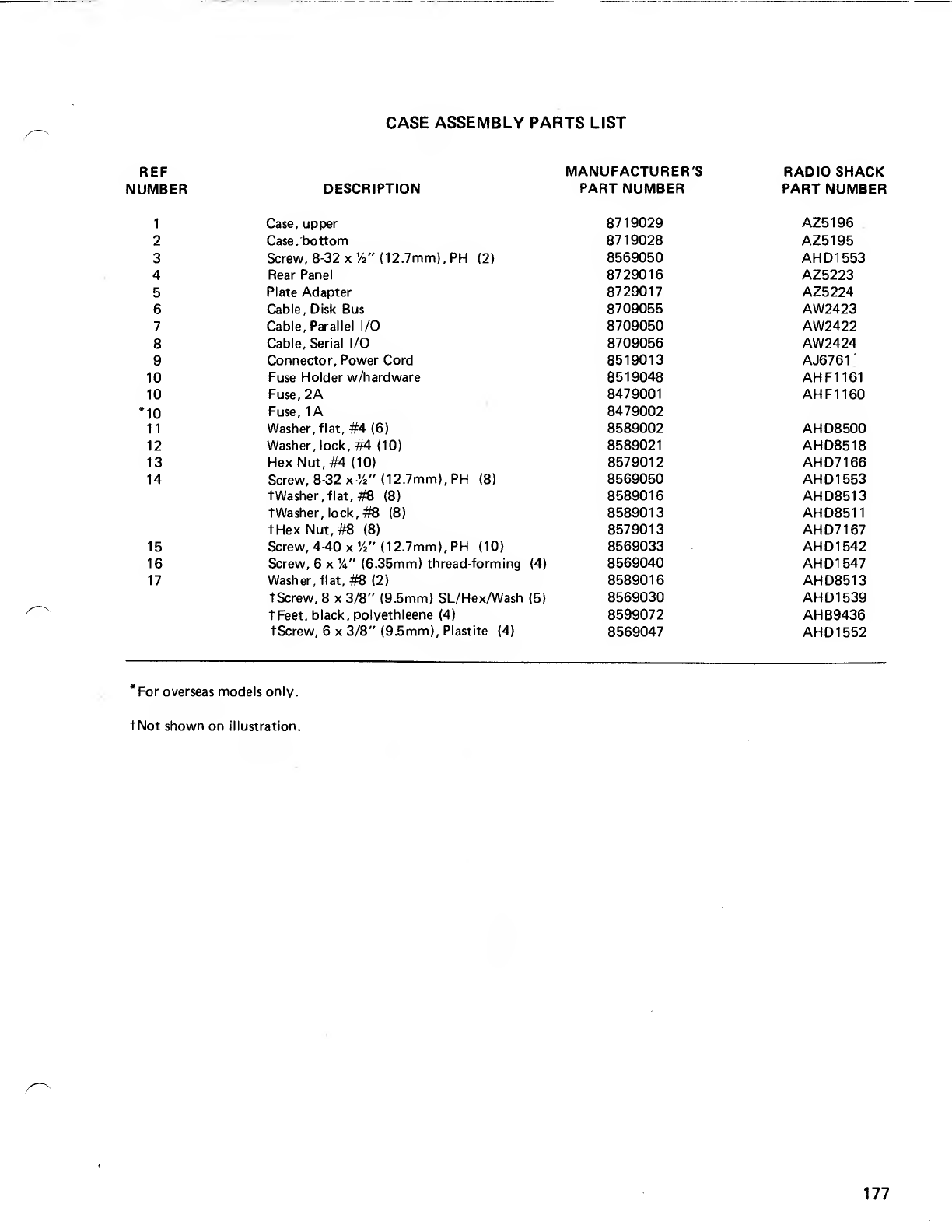

Case Assembly Parts List 177

Chassis Assembly Parts List 179

XVII APPENDIXES 183

Z80A-CPU -Zilog Product Specifications

Z80A-SIO -Zilog Product Specifications

Z80-CTC —Zilog Product Specifications

Z80-DMA -Zilog Product Specifications

Z80A-PIO -Zilog Product Specifications

FD1791 -Western Digital Product Specifications

MC6845, CRTC -Motorola Product Specifications

SA800/801 Disk Drive -Shugart Maintenance Manual

SA800/801 Illustrated Parts Catalog

9404B Disk Drive —Control Data Maintenance Manual

IV

LIST OF ILLUSTRATIONS

Figure Page

Number Number

SECTION I-SYSTEM DESCRIPTION

1Block Diagram 5

2Power Distribution 5

3Power Distribution Schematic 6

SECTION II -TROUBLESHOOTING AND REPLACEMENT

1Synchronization Signals 10

2Keyboard Disassembly 13

SECTION III -CPU MODULE

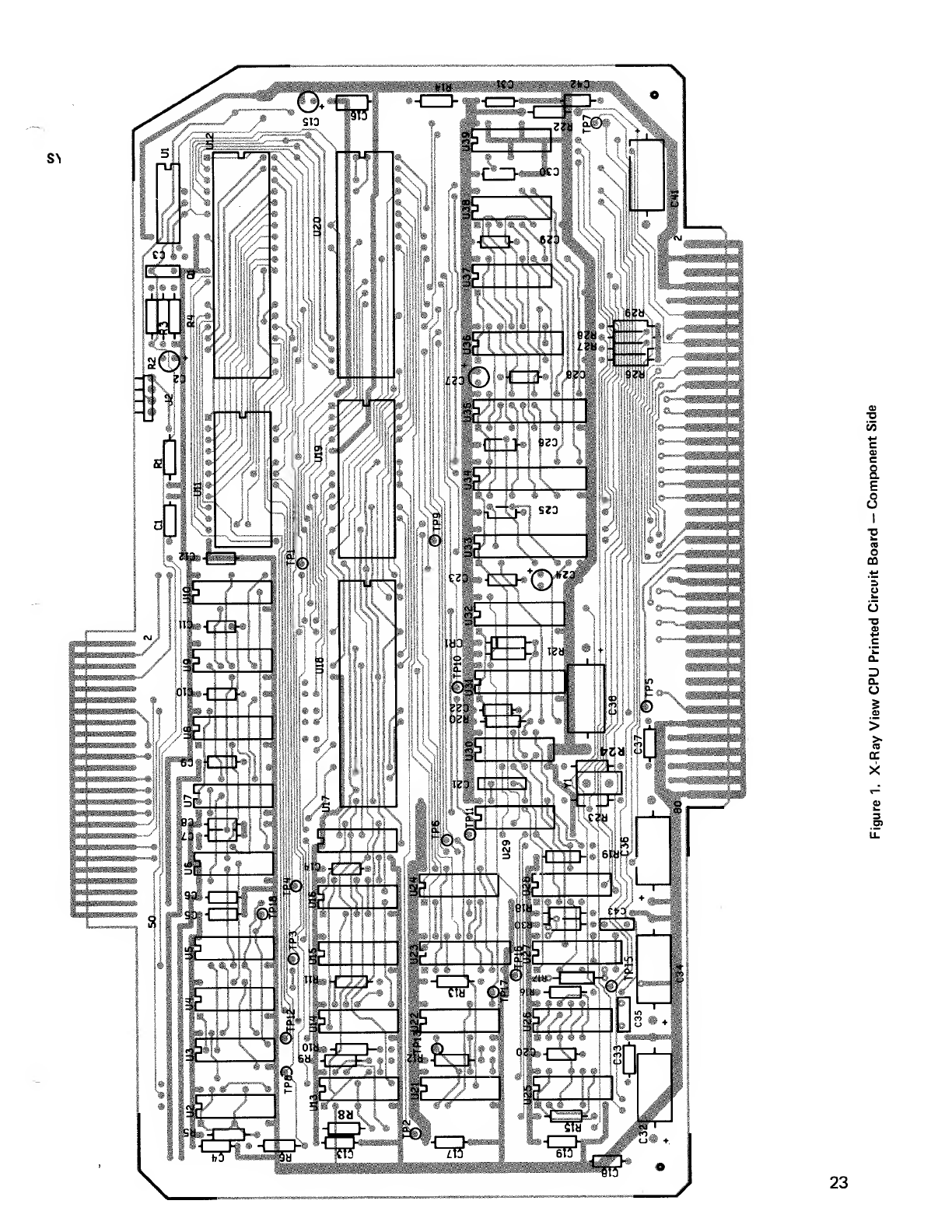

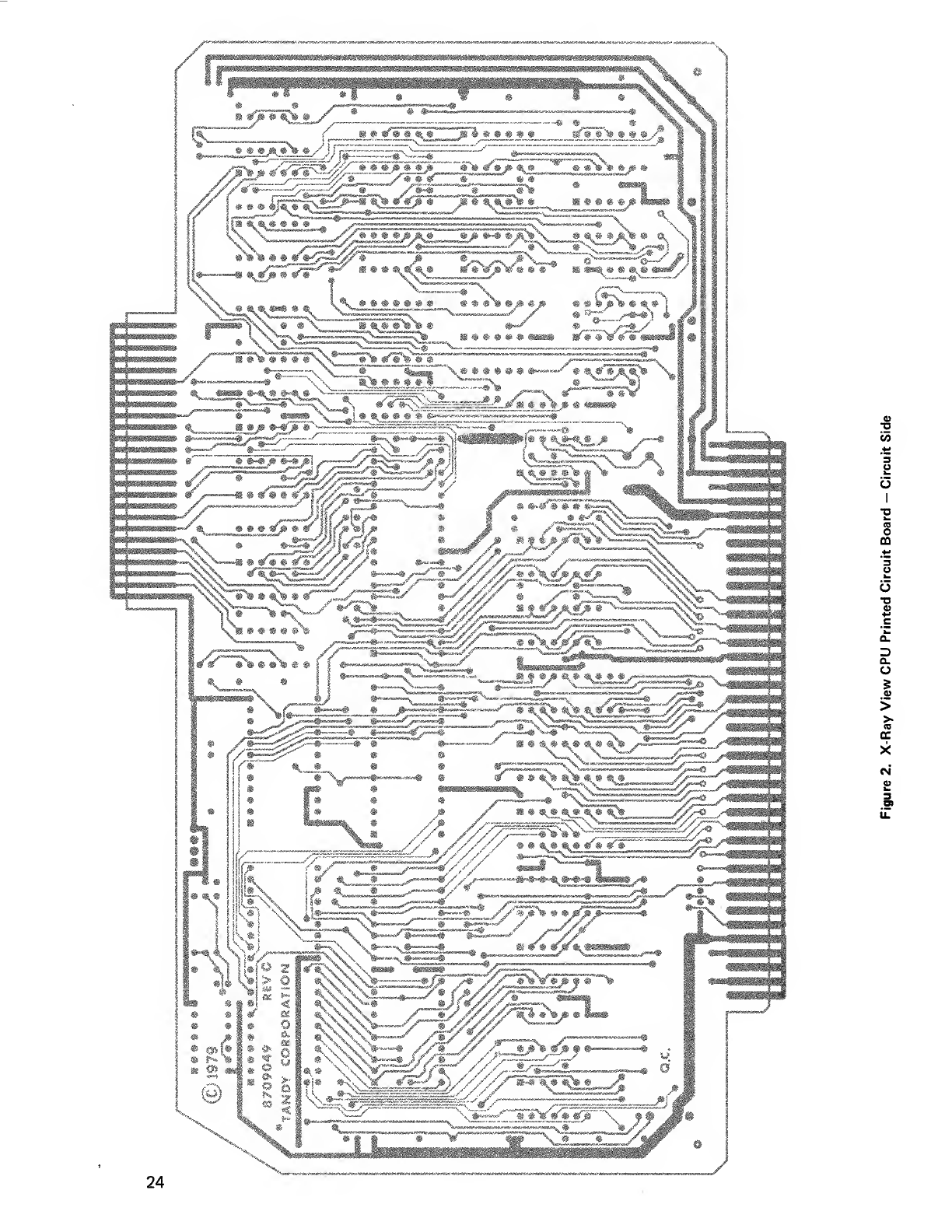

1X-Ray View of CPU Printed Circuit Board -Component Side 23

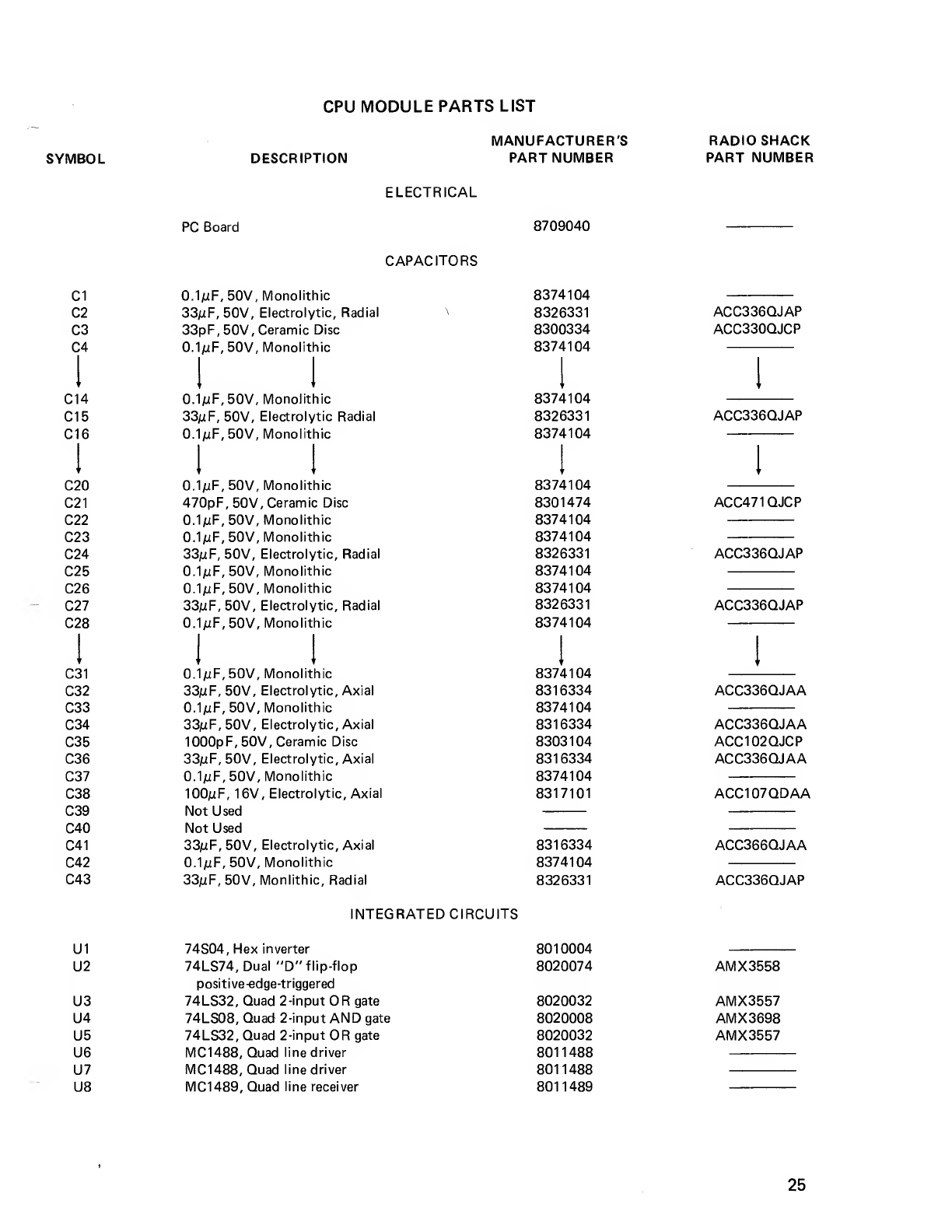

2X-Ray View of CPU Printed Circuit Board -Circuit Side 24

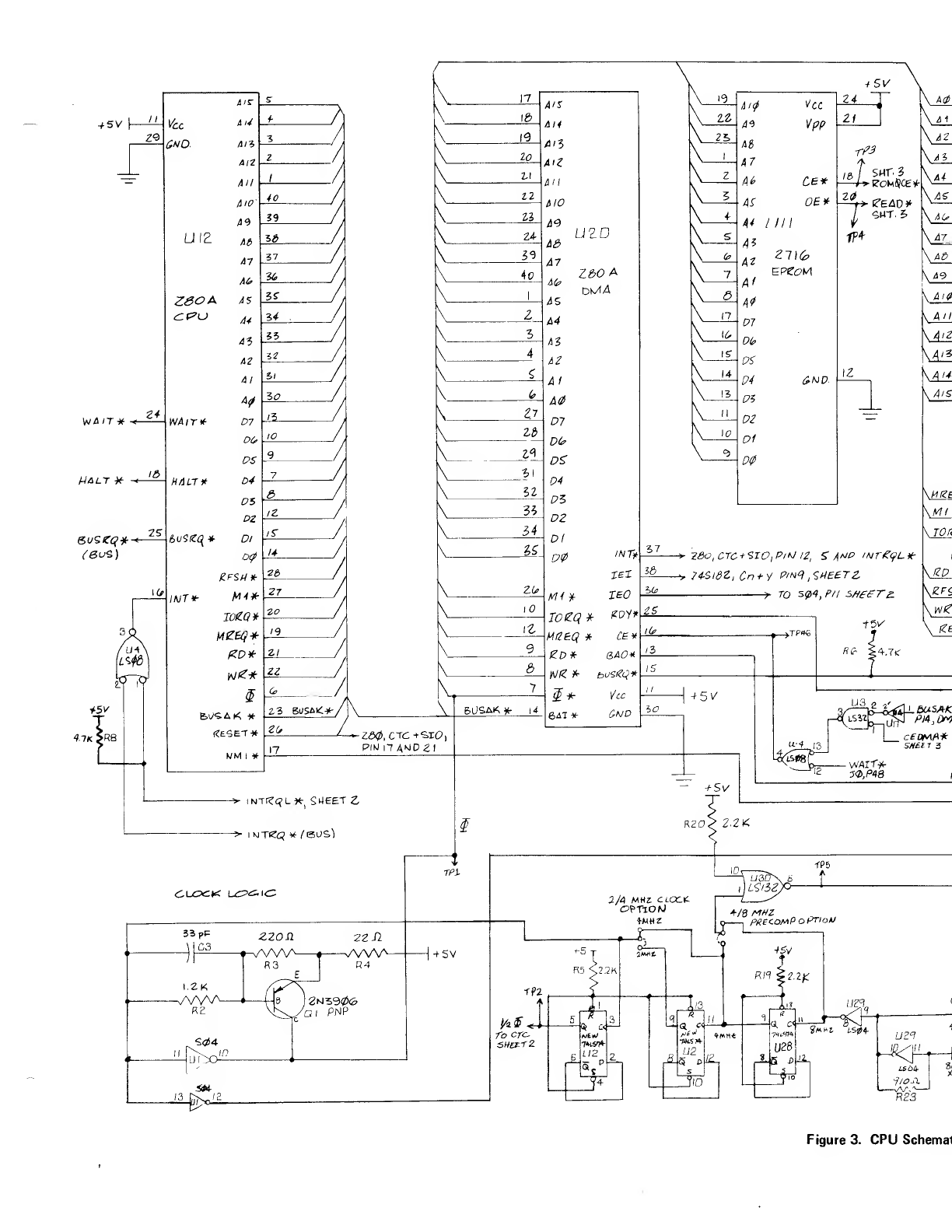

3CPU Schematic Diagram (Sheet 1) 29

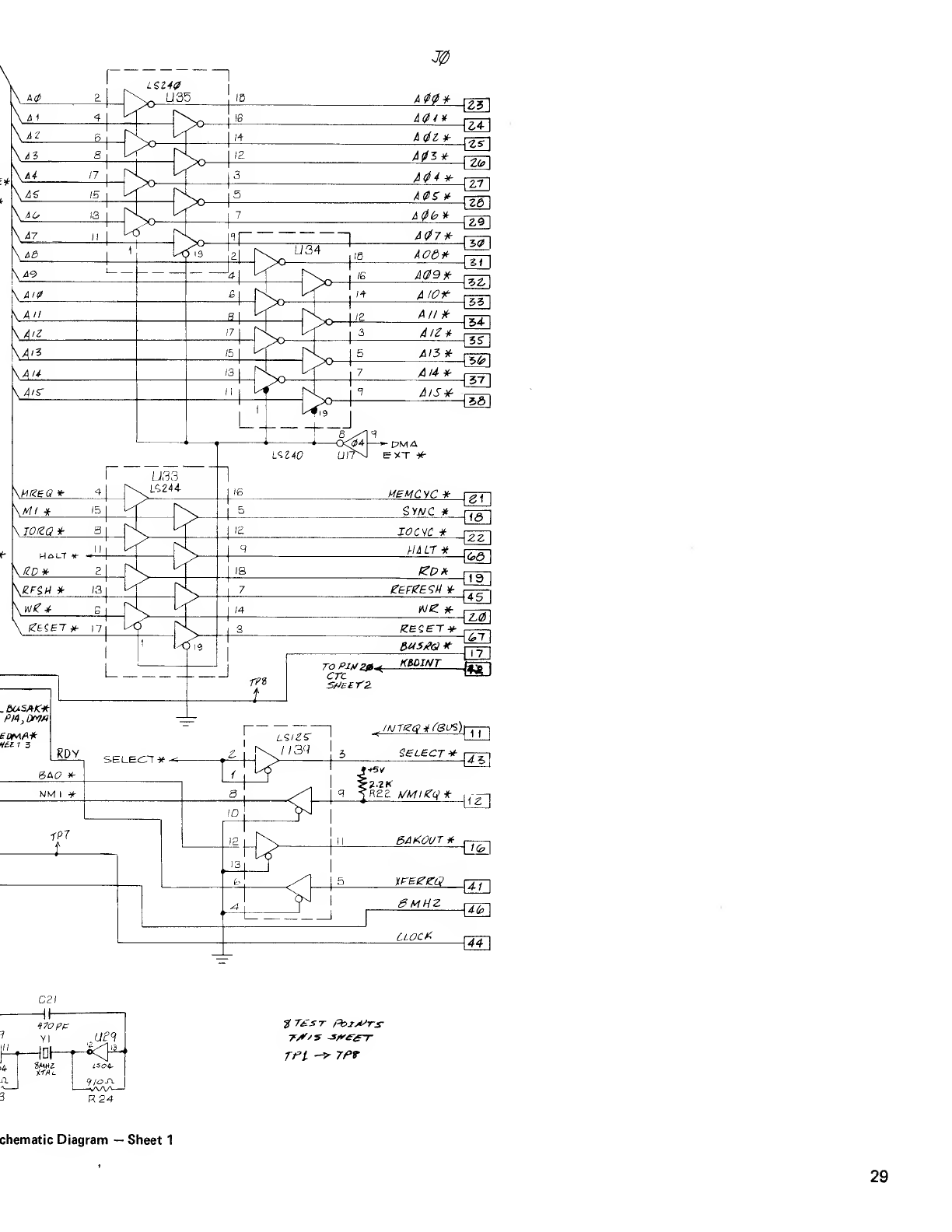

3CPU Schematic Diagram (Sheet 2) .30

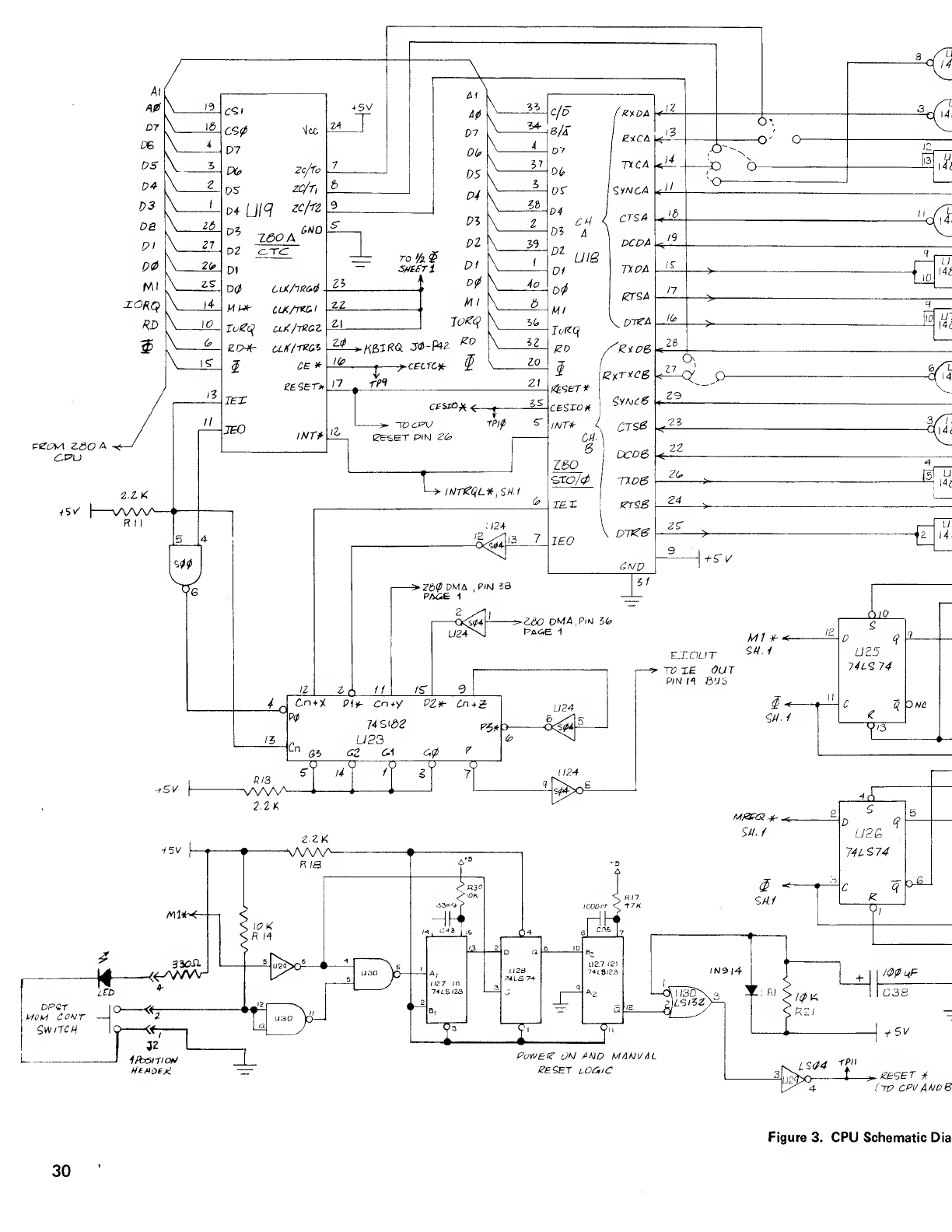

3CPU Schematic Diagram (Sheet 3) 31

SECTION IV -FLOPPY DISK CONTROLLER

1FD1791 Block Diagram 37

2Clock Recovery Block Diagram 41

3Interacting Clock/Data Pulses 42

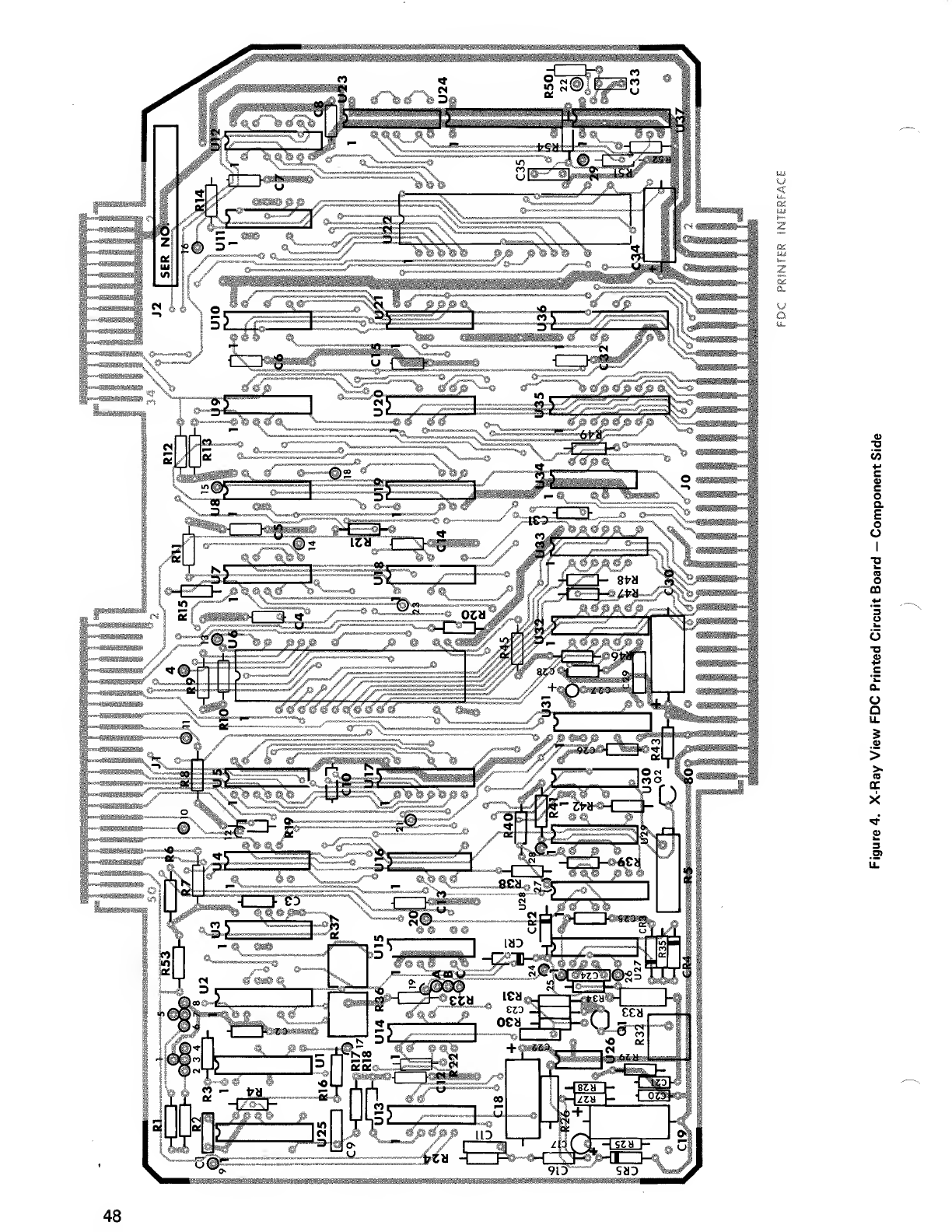

4FDC Printed Circuit Board -Component Side 48

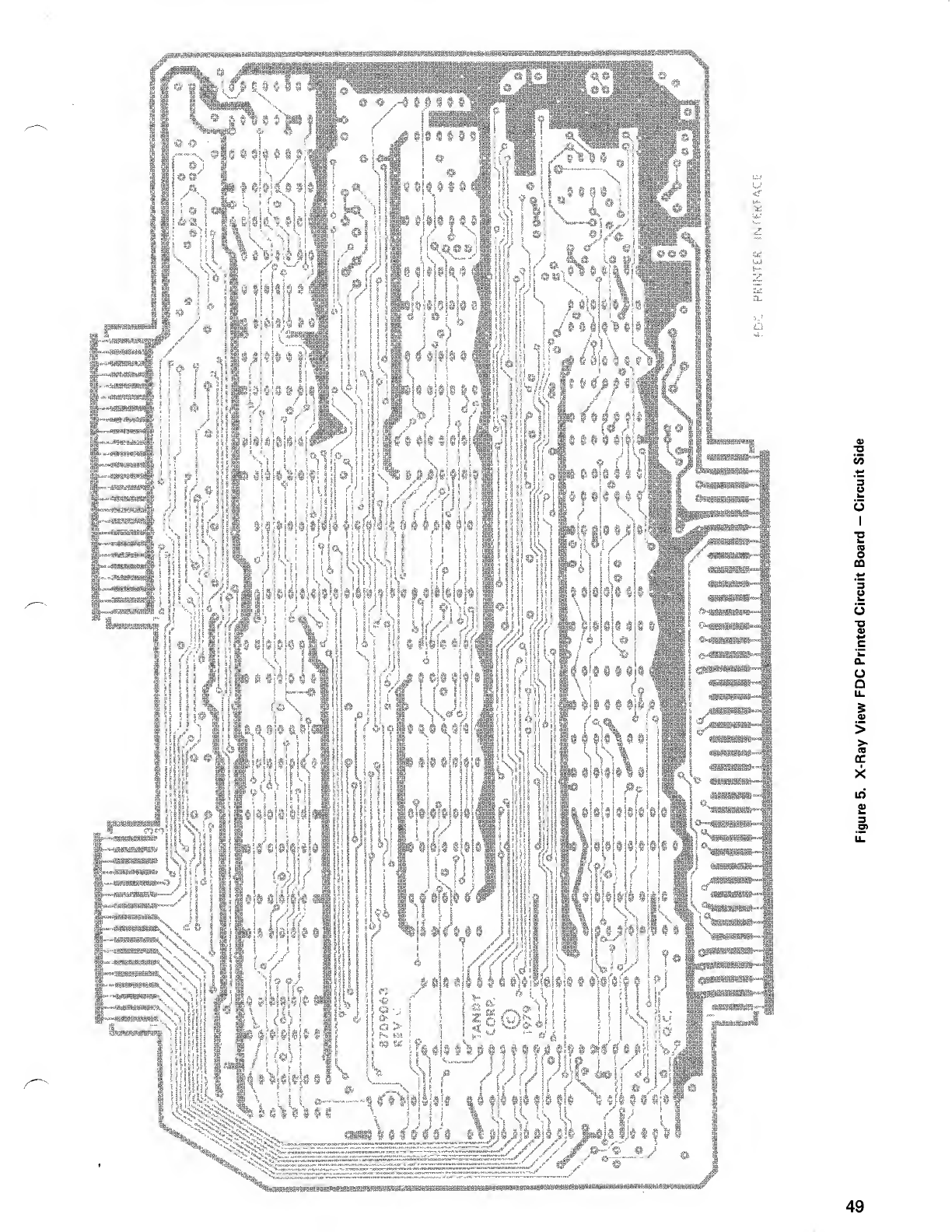

5FDC Printed Circuit Board -Circuit Side 49

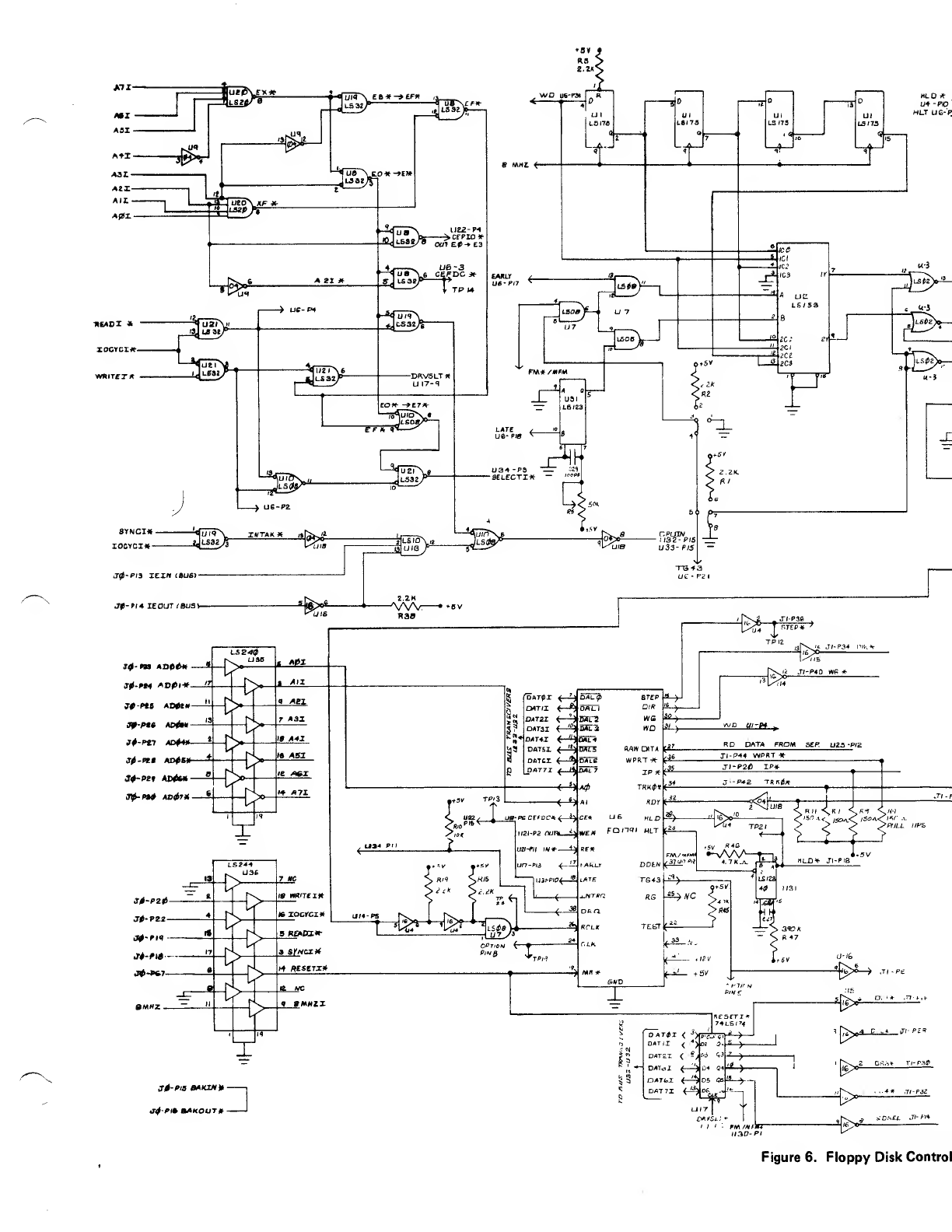

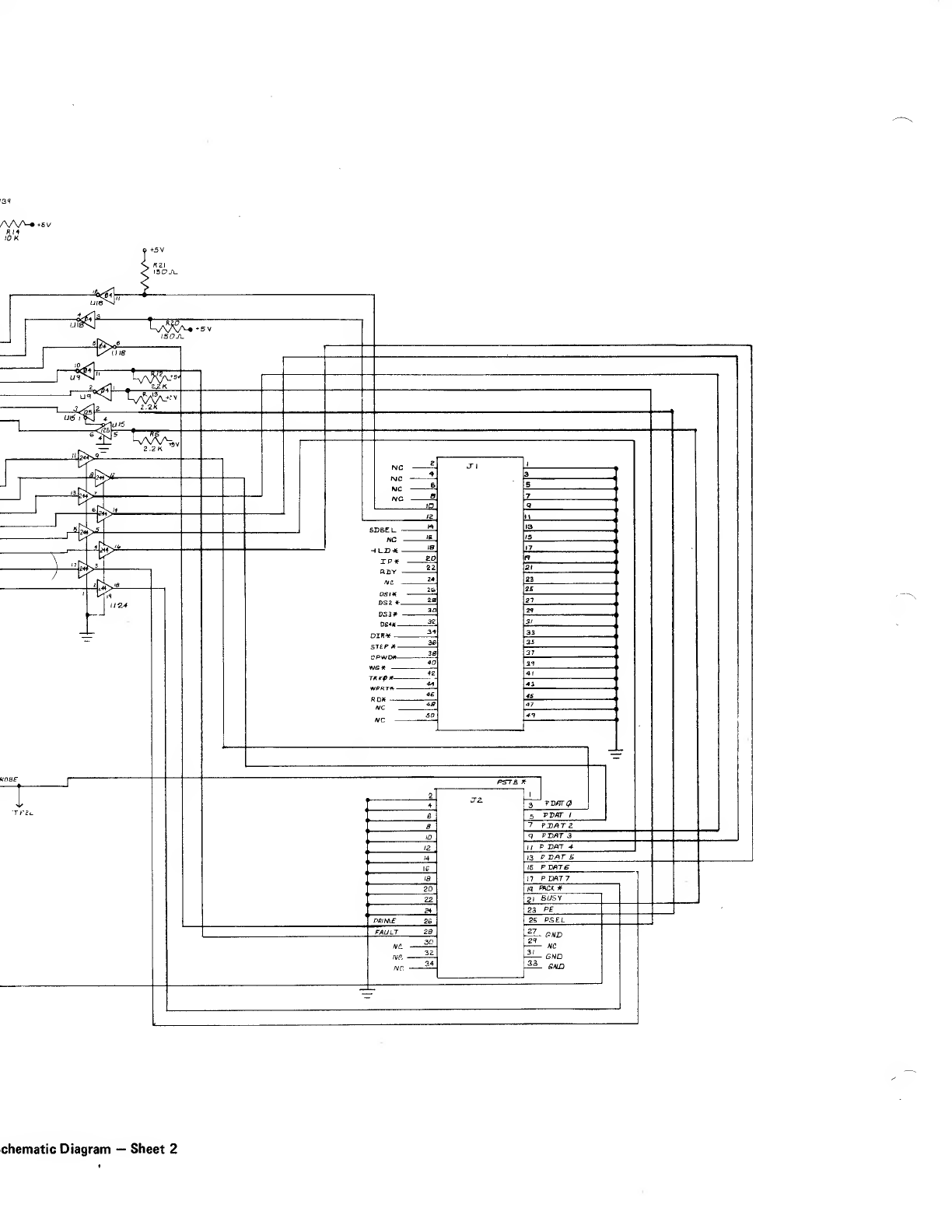

6Floppy Disk Controller Board Schematic Diagram (Sheet 1) 53

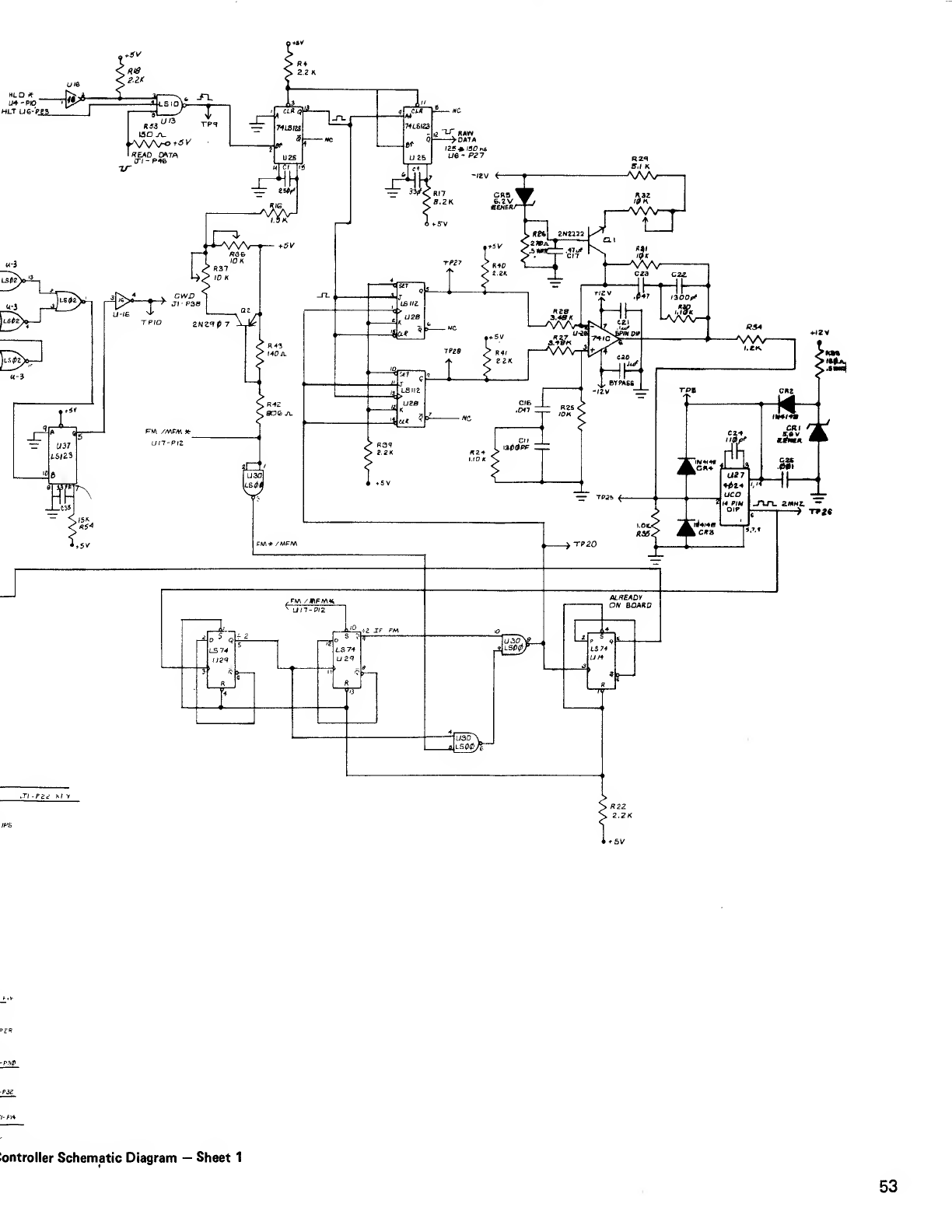

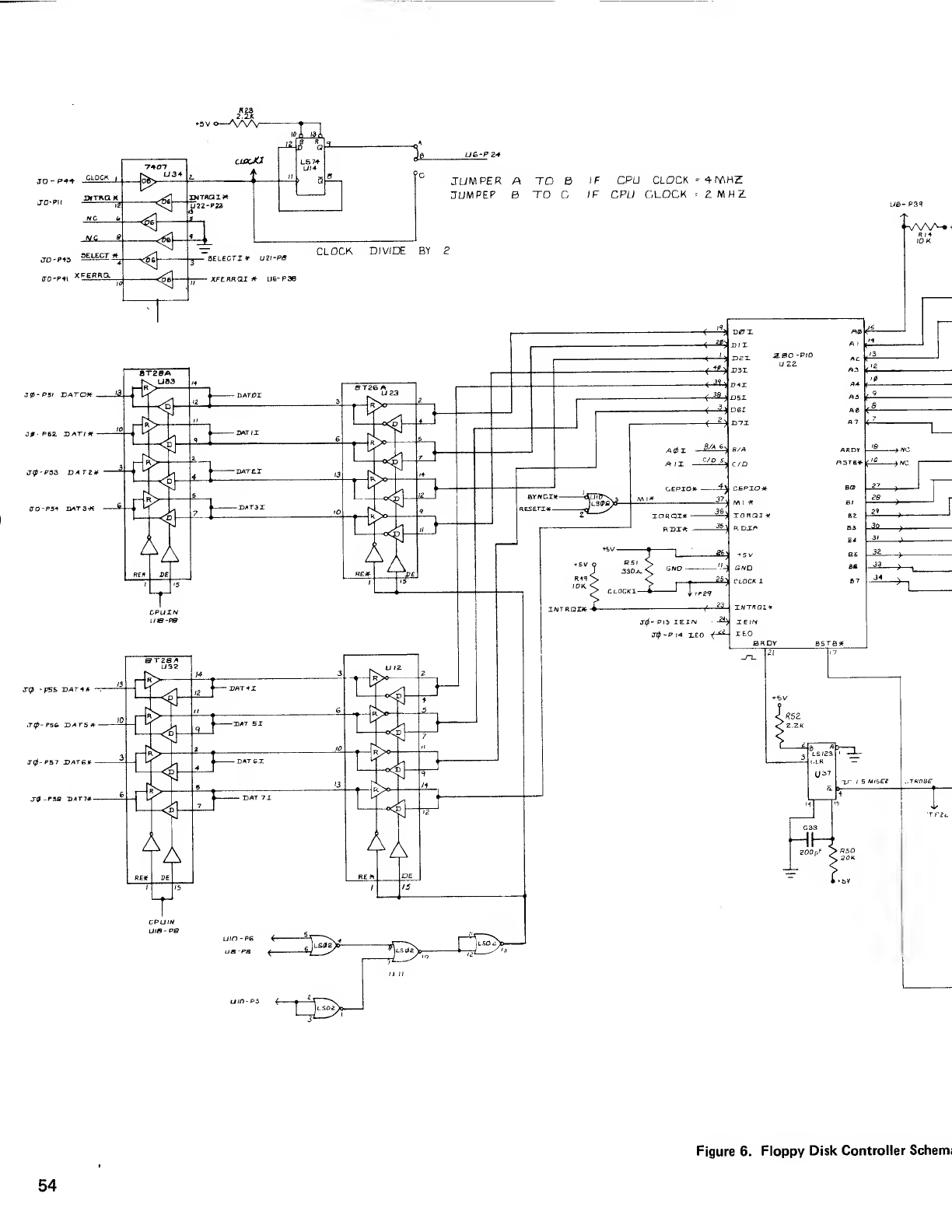

6Floppy Disk Controller Board Schematic Diagram (Sheet 2) 54

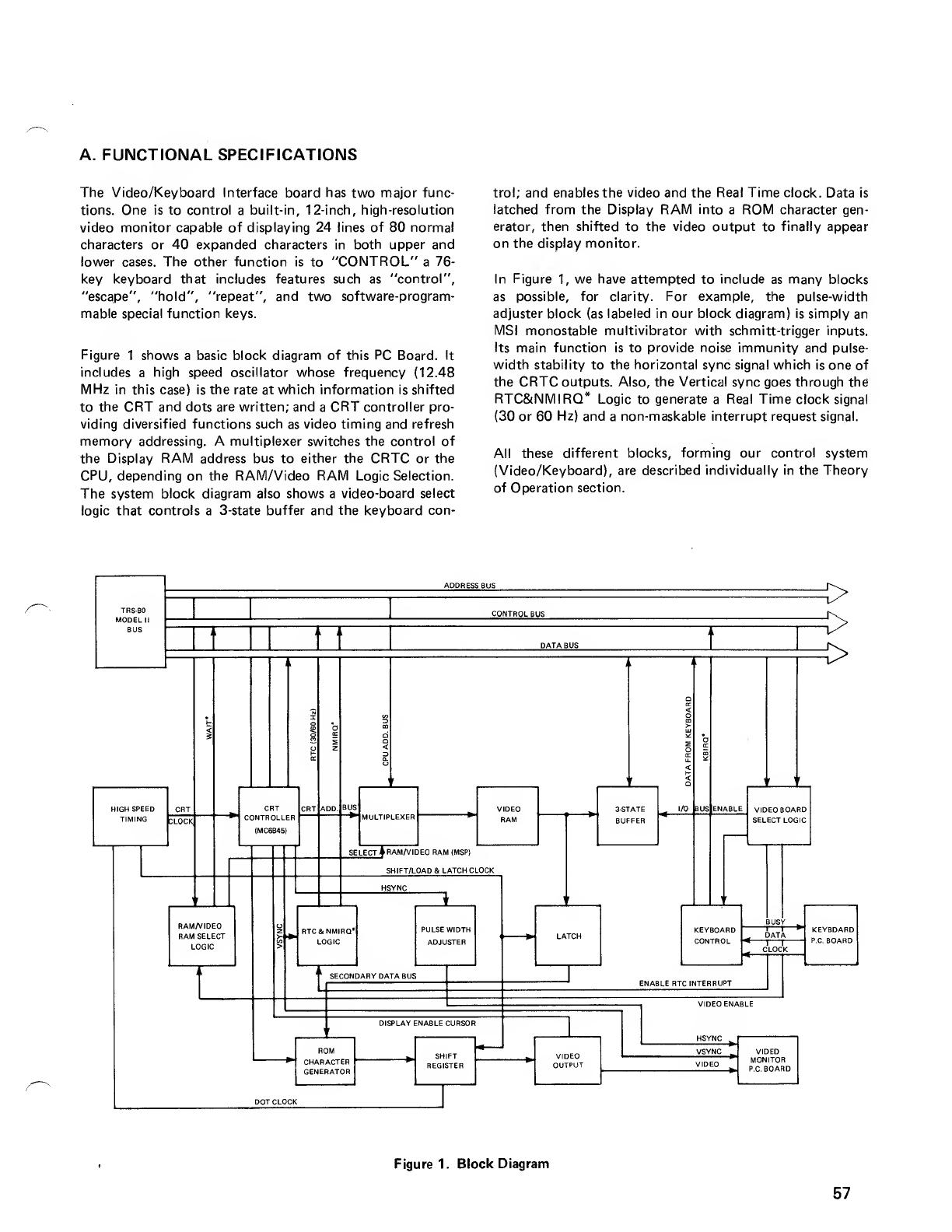

SECTION V-VIDEO/KEYBOARD INTERFACE

1Video/Keyboard Block Diagram 57

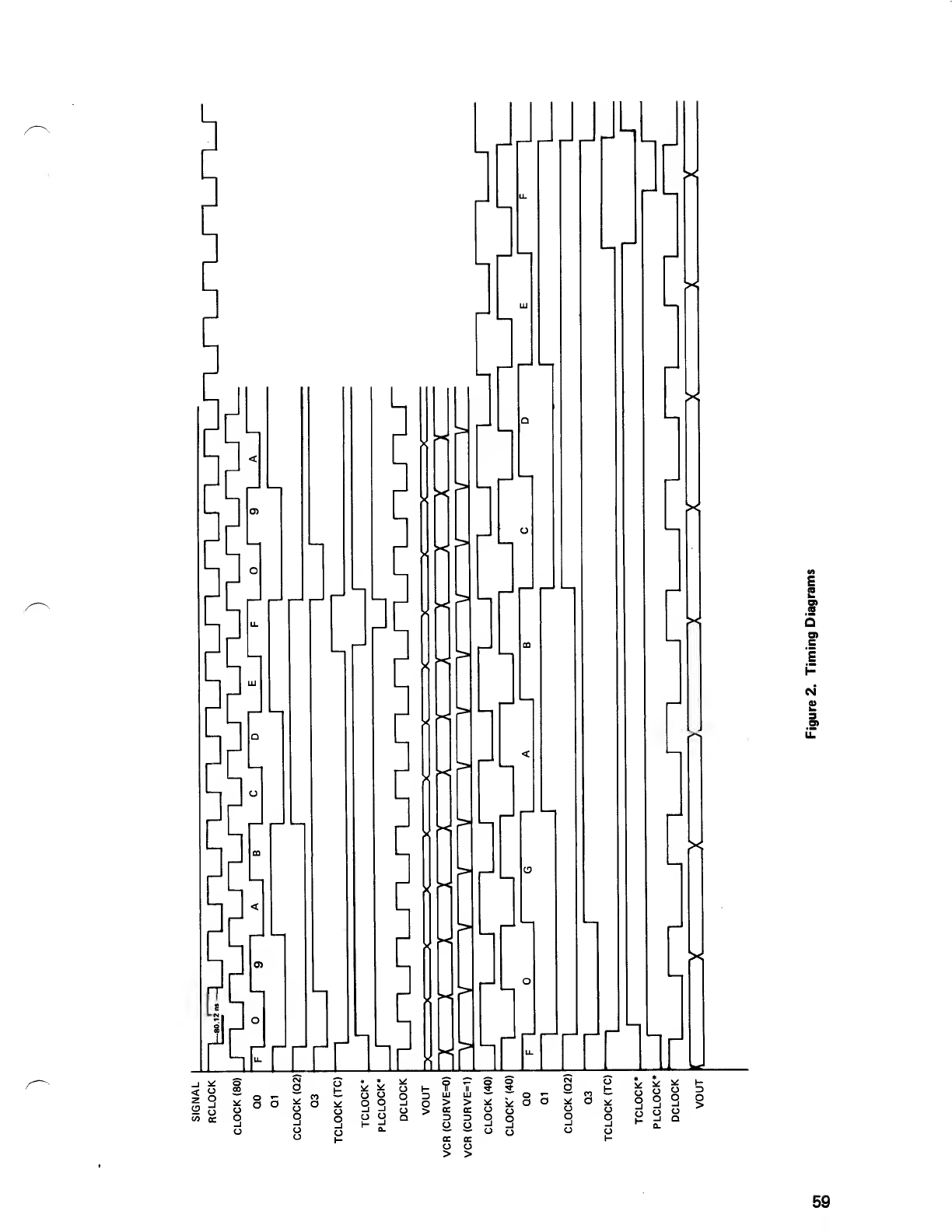

2Timing Diagram 59

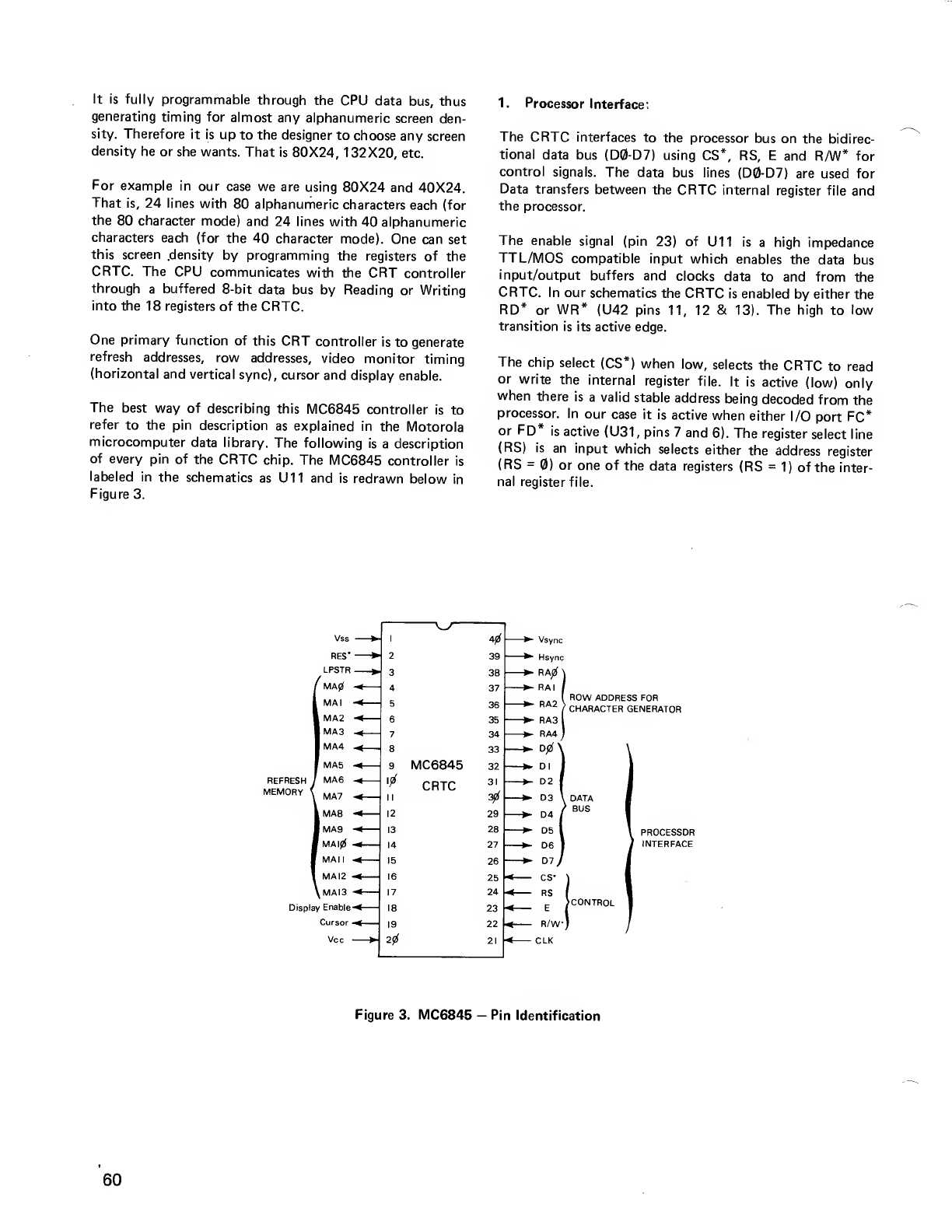

3MC6845 CRTC Pin Identification 60

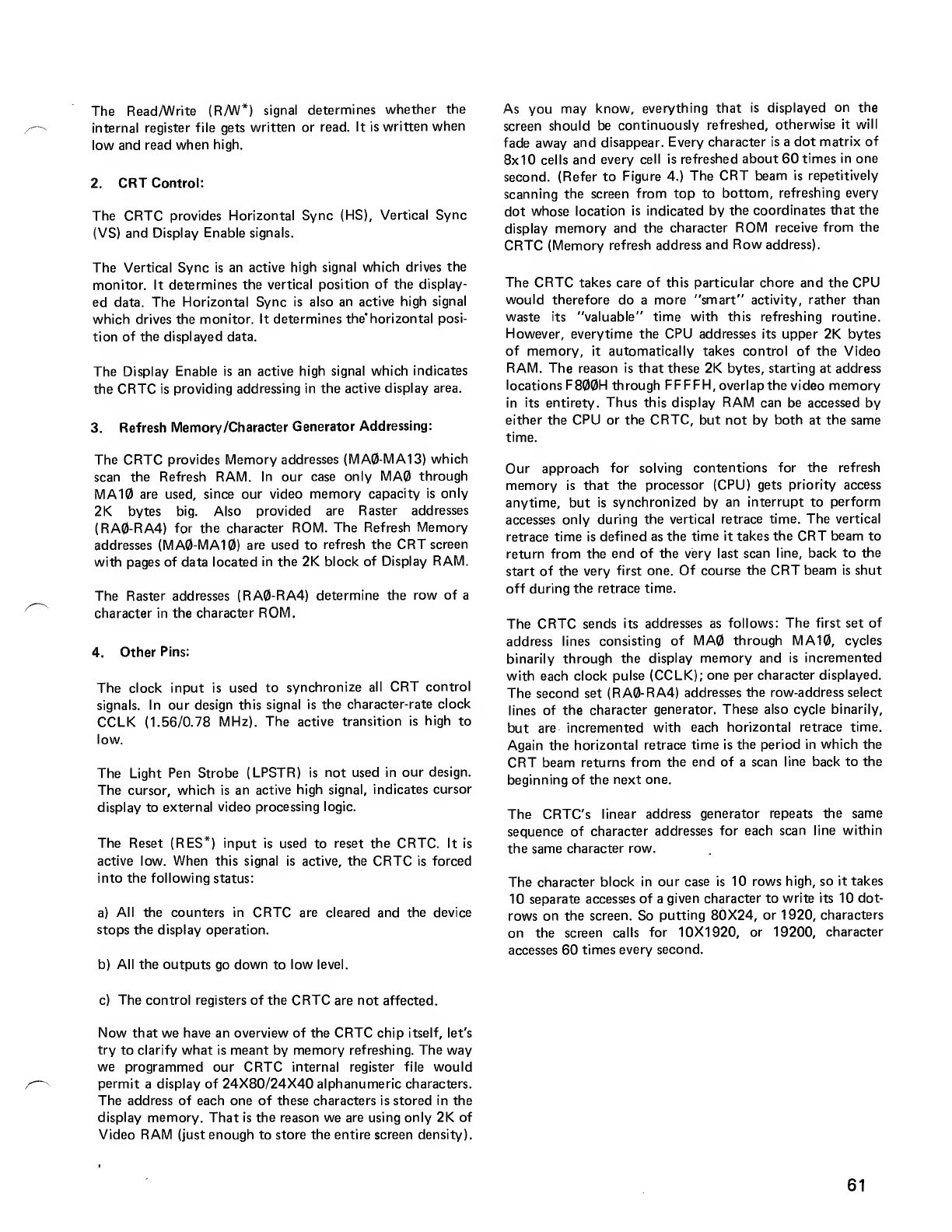

4Character Dot Pattern 62

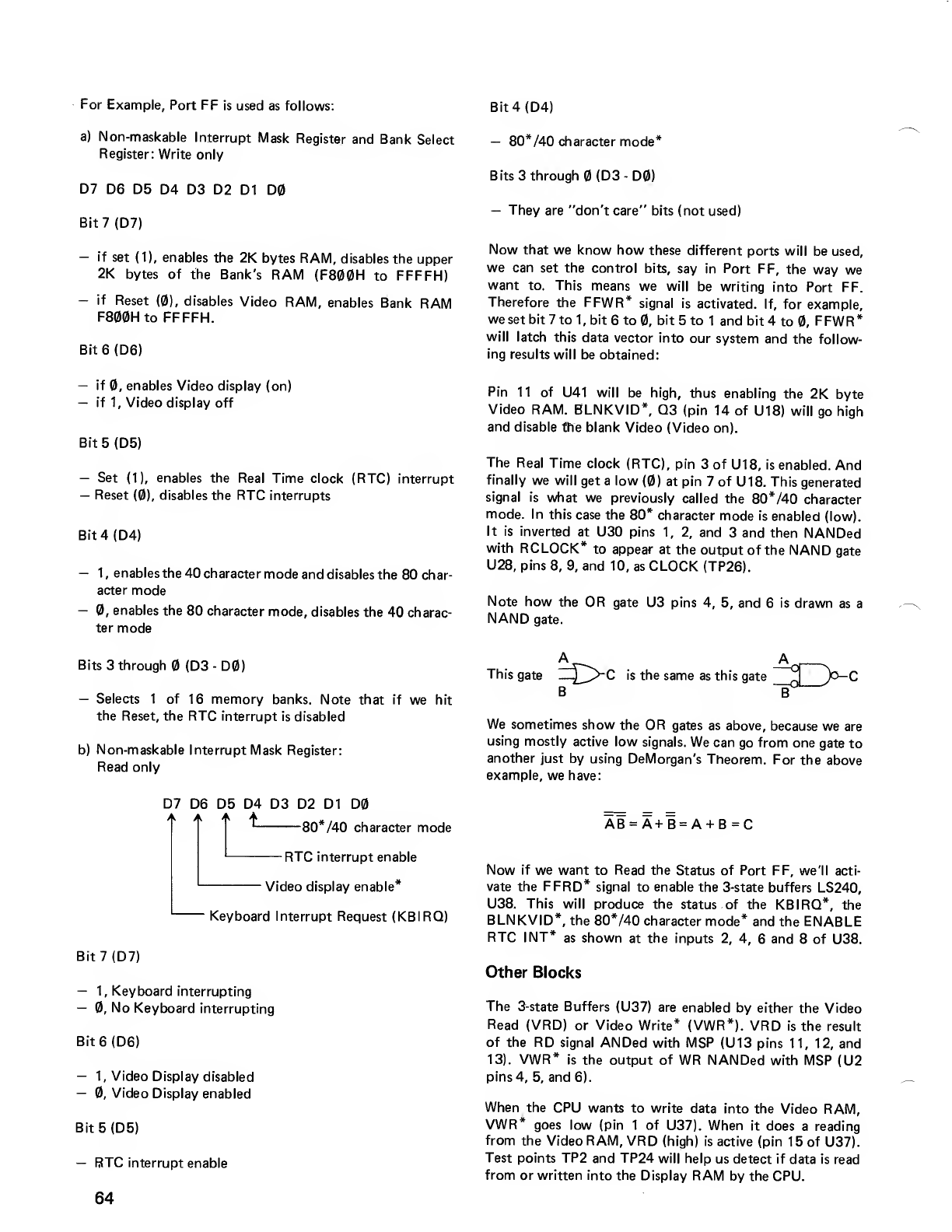

5Keyboard Timing Diagram 65

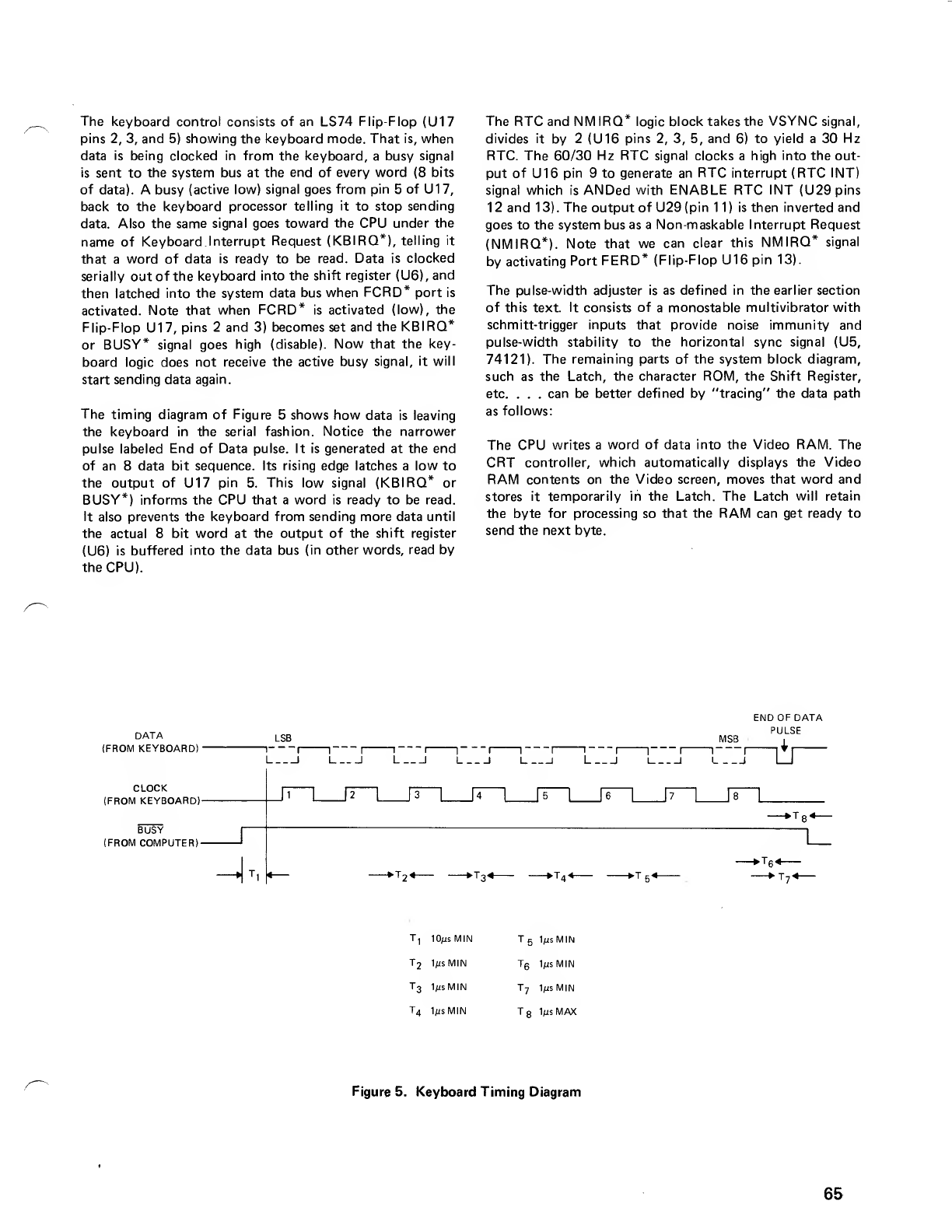

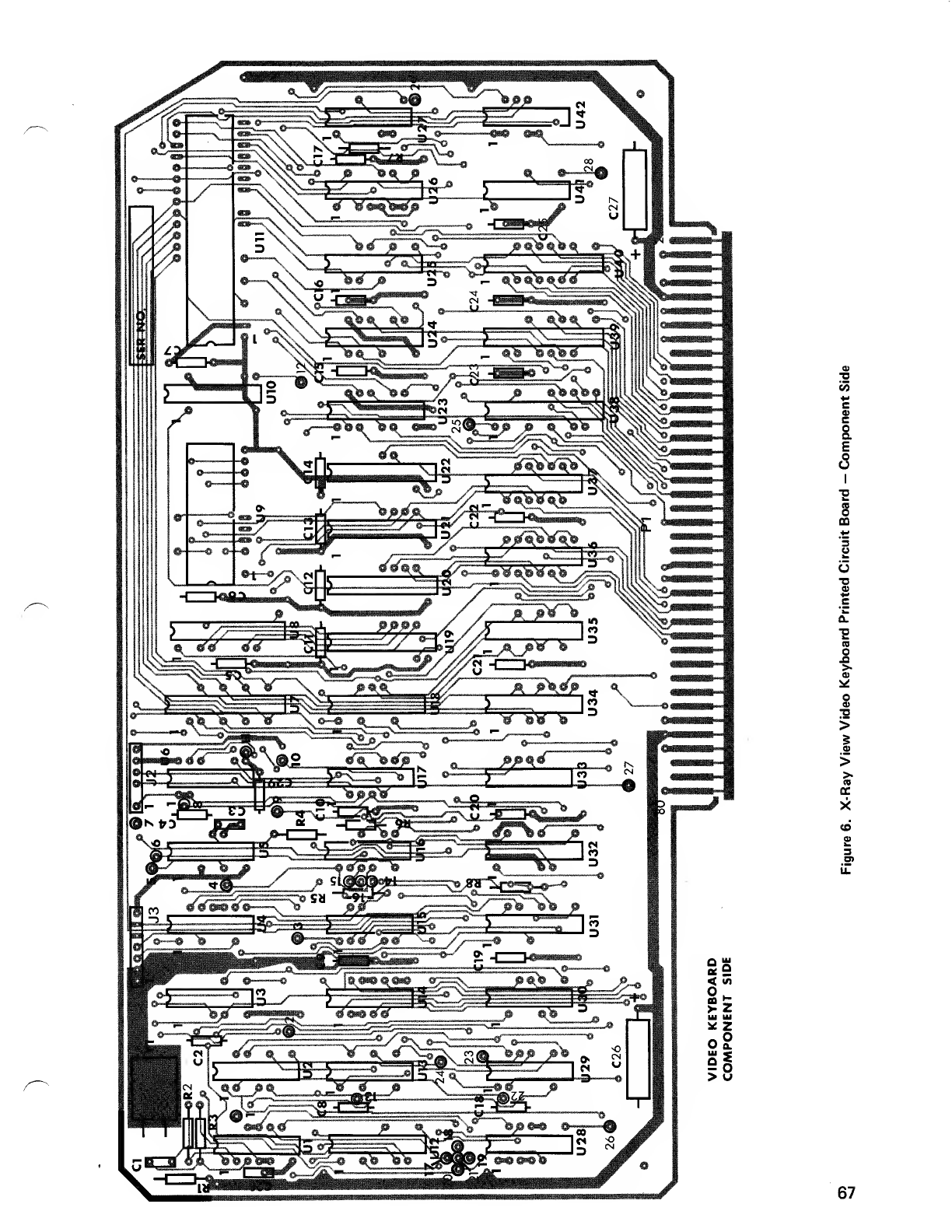

6X-Ray View of Video Keyboard Printed Circuit Board —Component Side .67

7X-Ray View of Video Keyboard Printed Circuit Board -Circuit Side 68

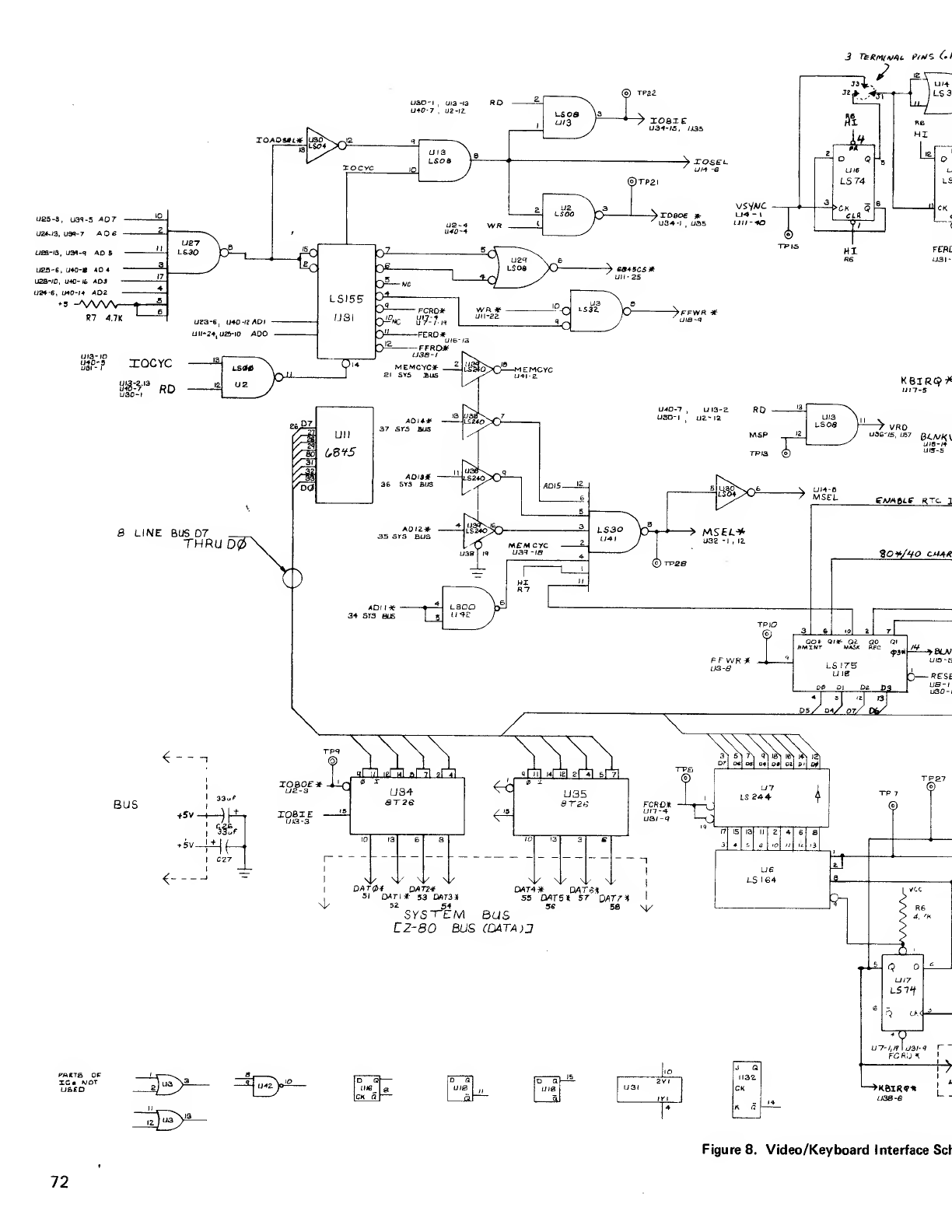

8Video/Keyboard Interface Schematic Diagram (Sheet 1) 71

8Video/Keyboard Interface Schematic Diagram (Sheet 2) 72

SECTION VI -MEMORY BOARD (64K and 32K RAM)

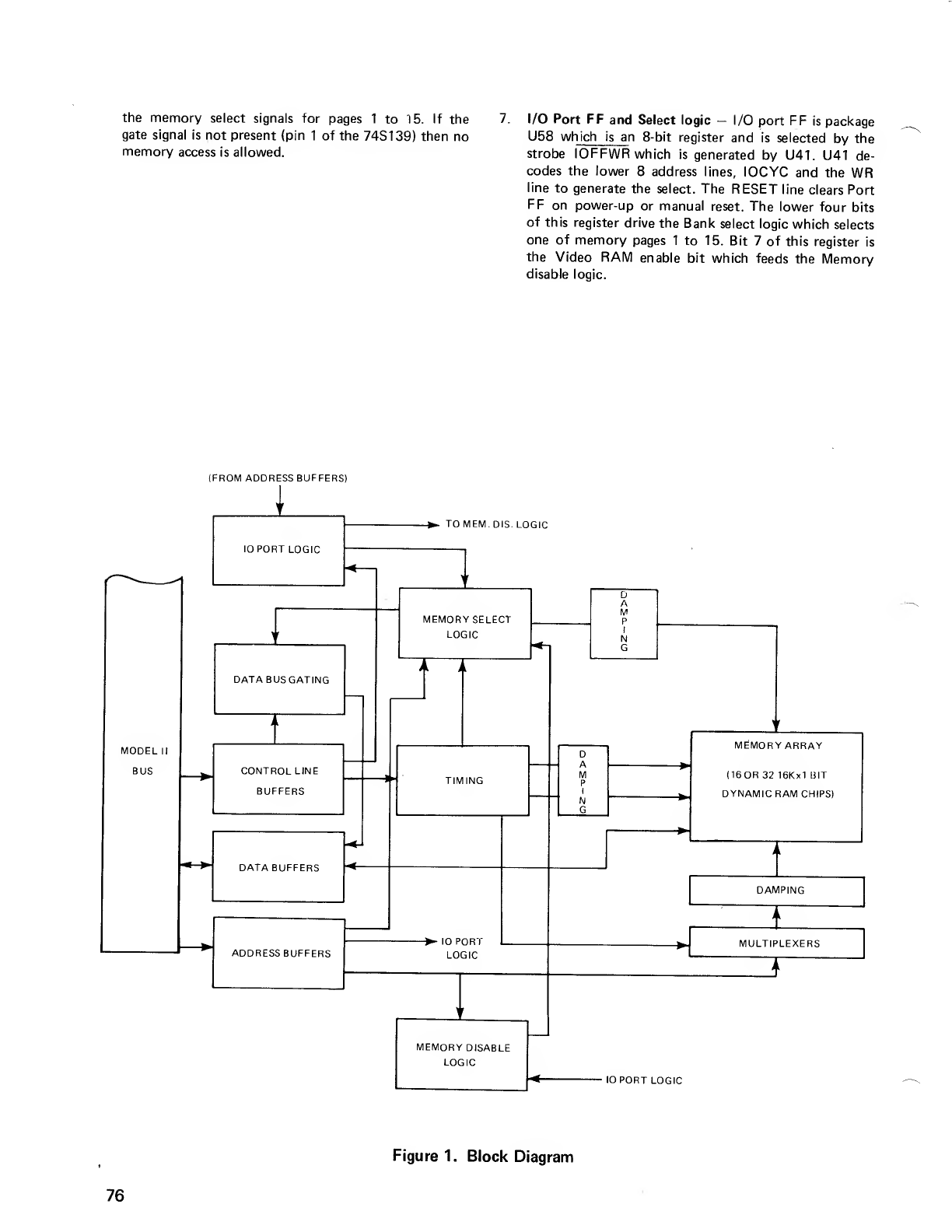

1Memory Board Block Diagram 76

2Jumper Locations and Address/Bit RAM Identification 78

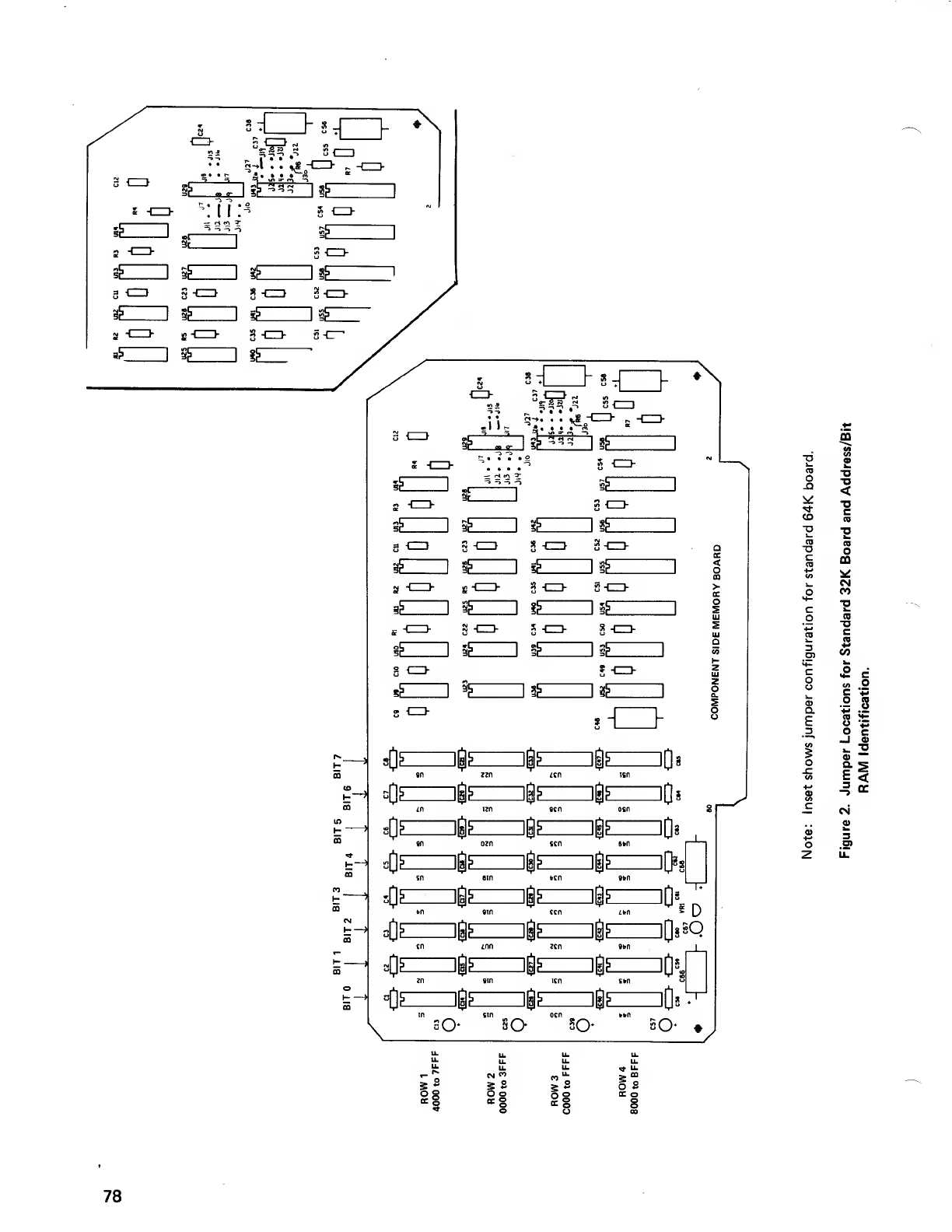

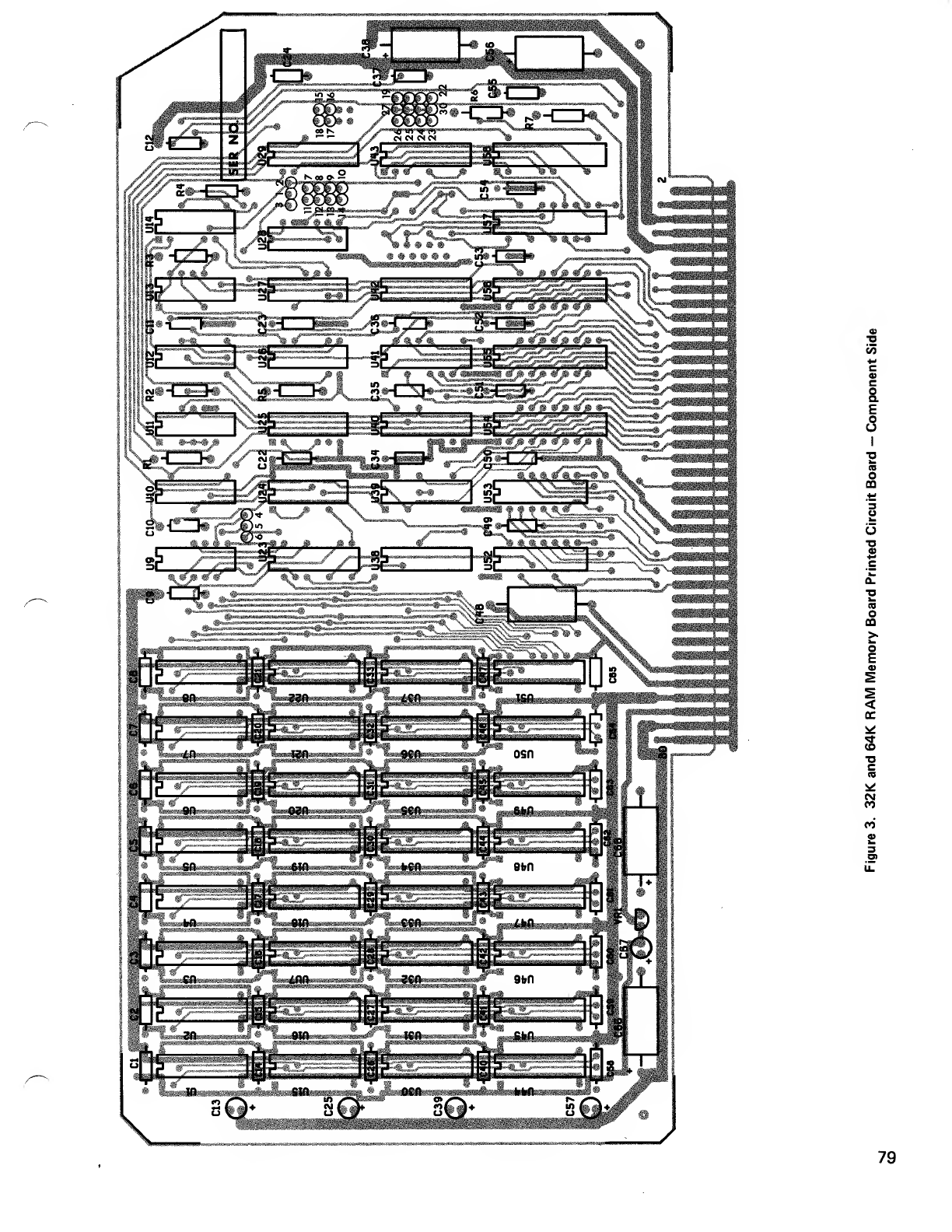

3X-Ray View of Memory Printed Circuit Board —Component Side 79

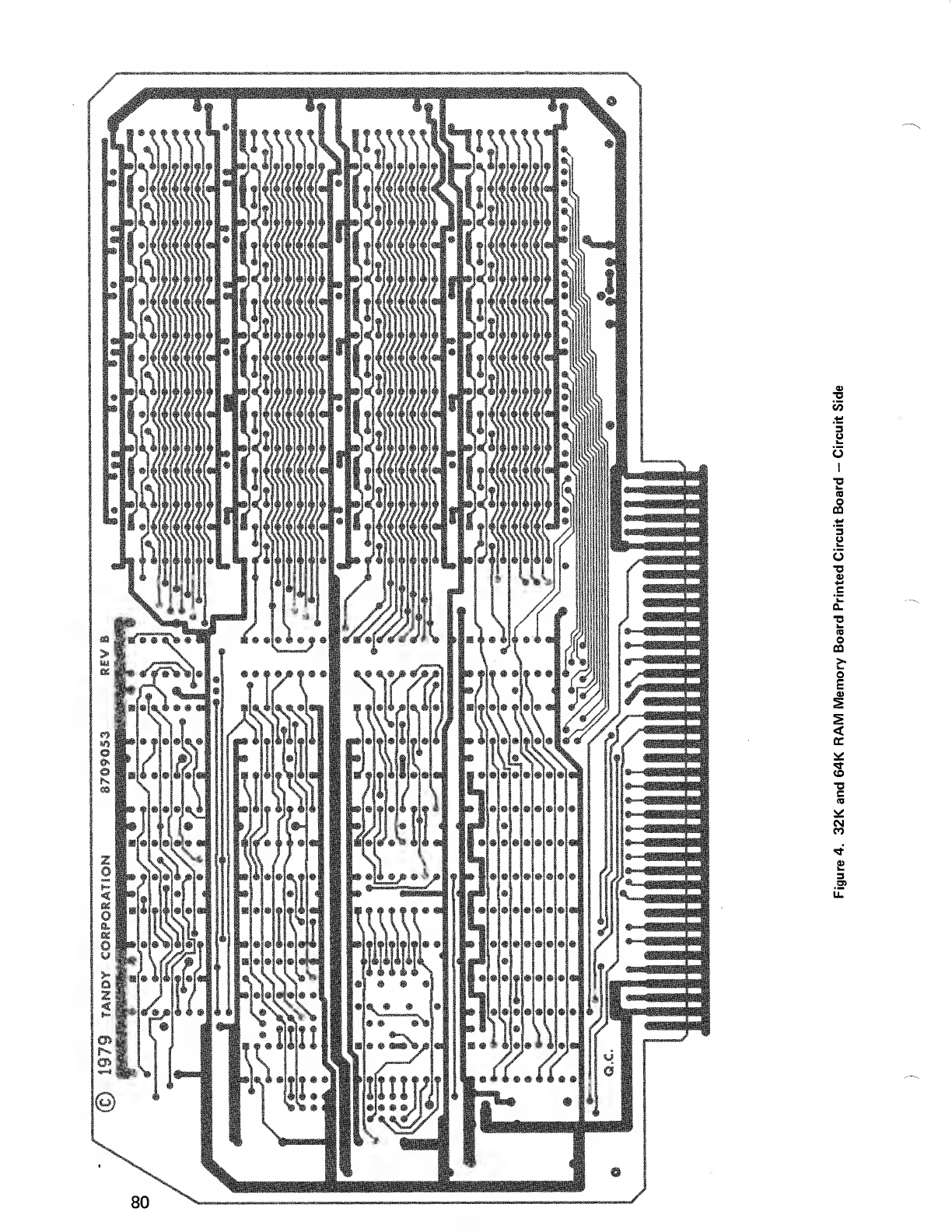

4X-Ray View of Memory Printed Circuit Board -Circuit Side 80

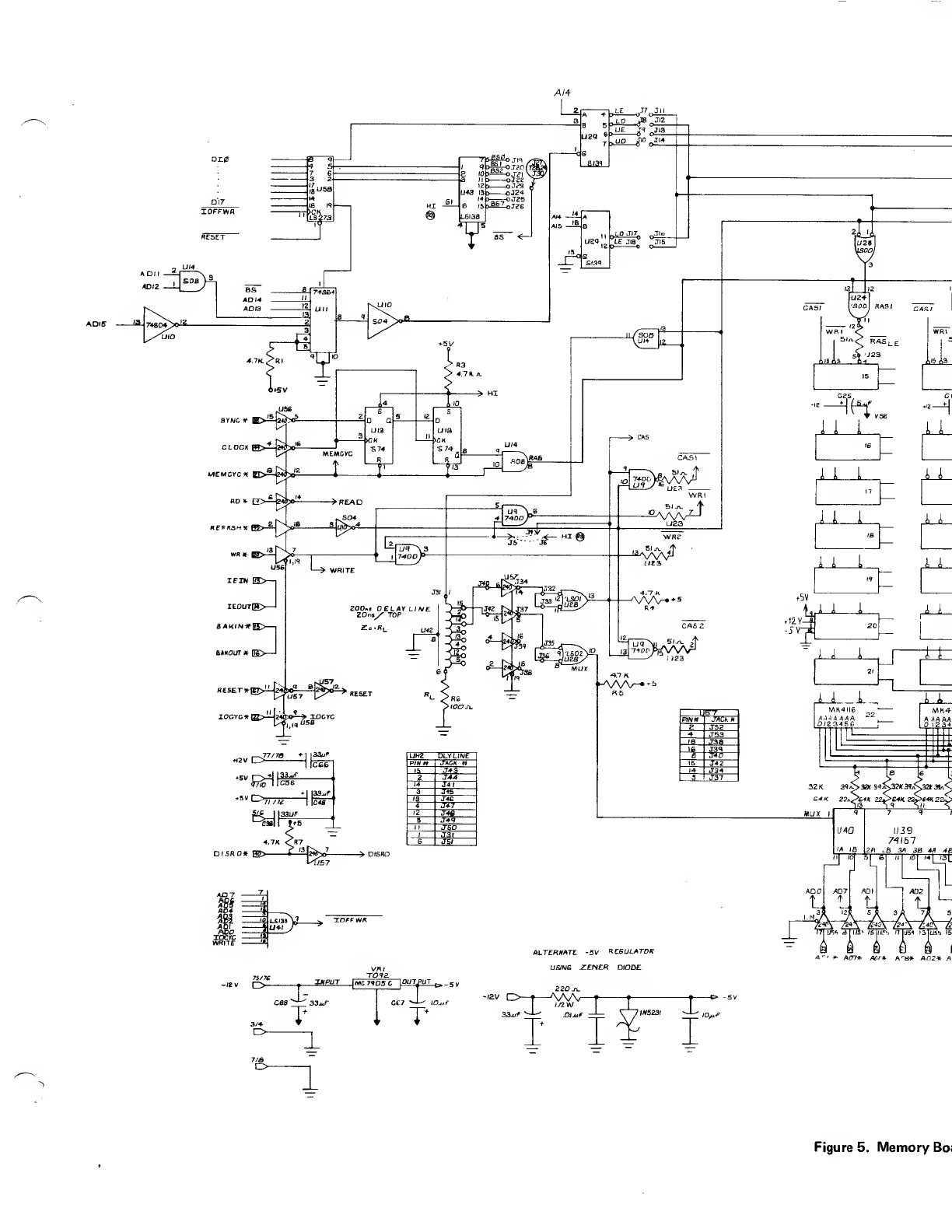

5Memory Board Schematic Diagram 85

LIST OF ILLUSTRATIONS (Cont'd)

Figure Page

Number Number

SECTION VII -VIDEO MONITOR (CRT)

1Block Diagram (Motorola and RCA) 94

2Horizontal Drive Signal (Motorola and RCA) 95

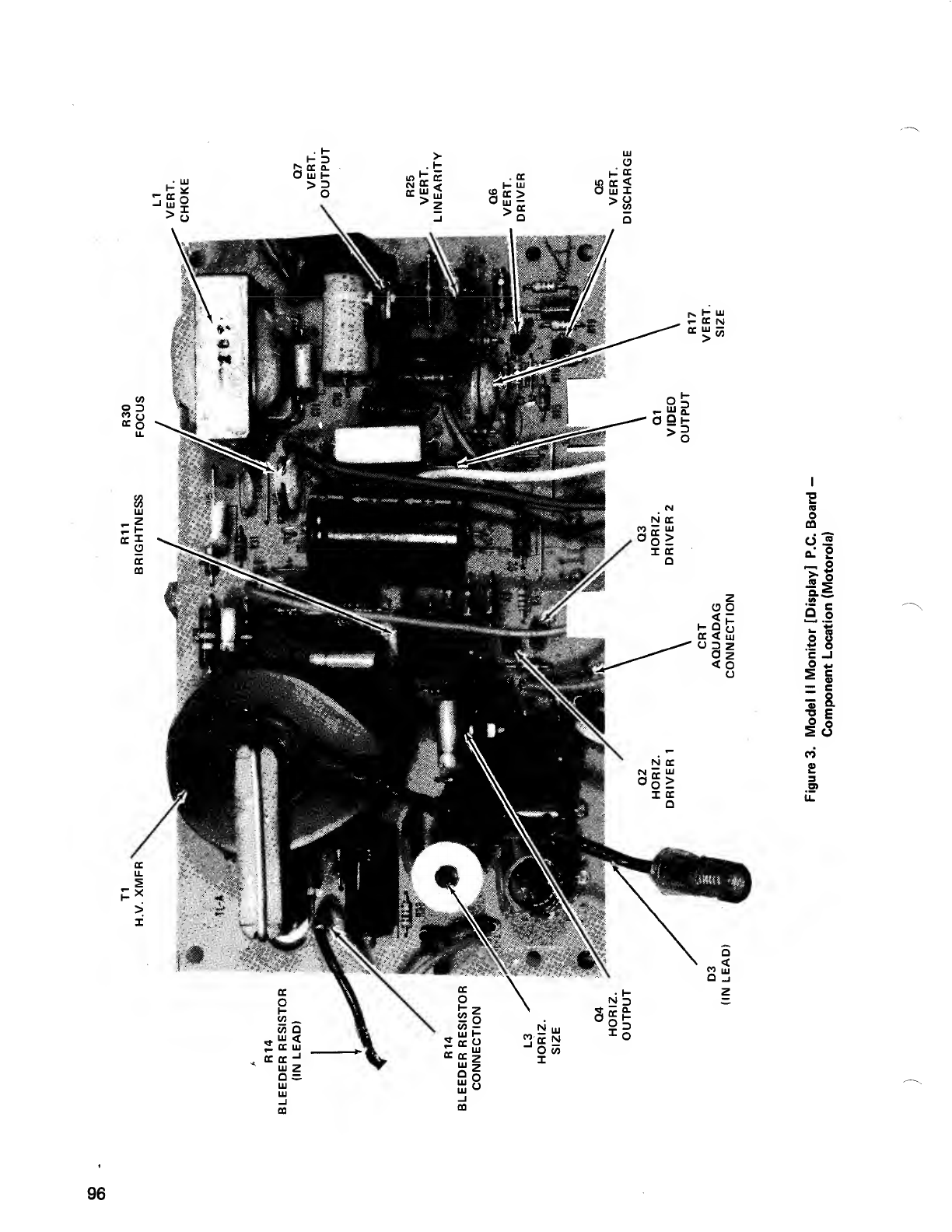

3Model II Monitor[Display] P.C. Board -Component Location (Motorola) .96

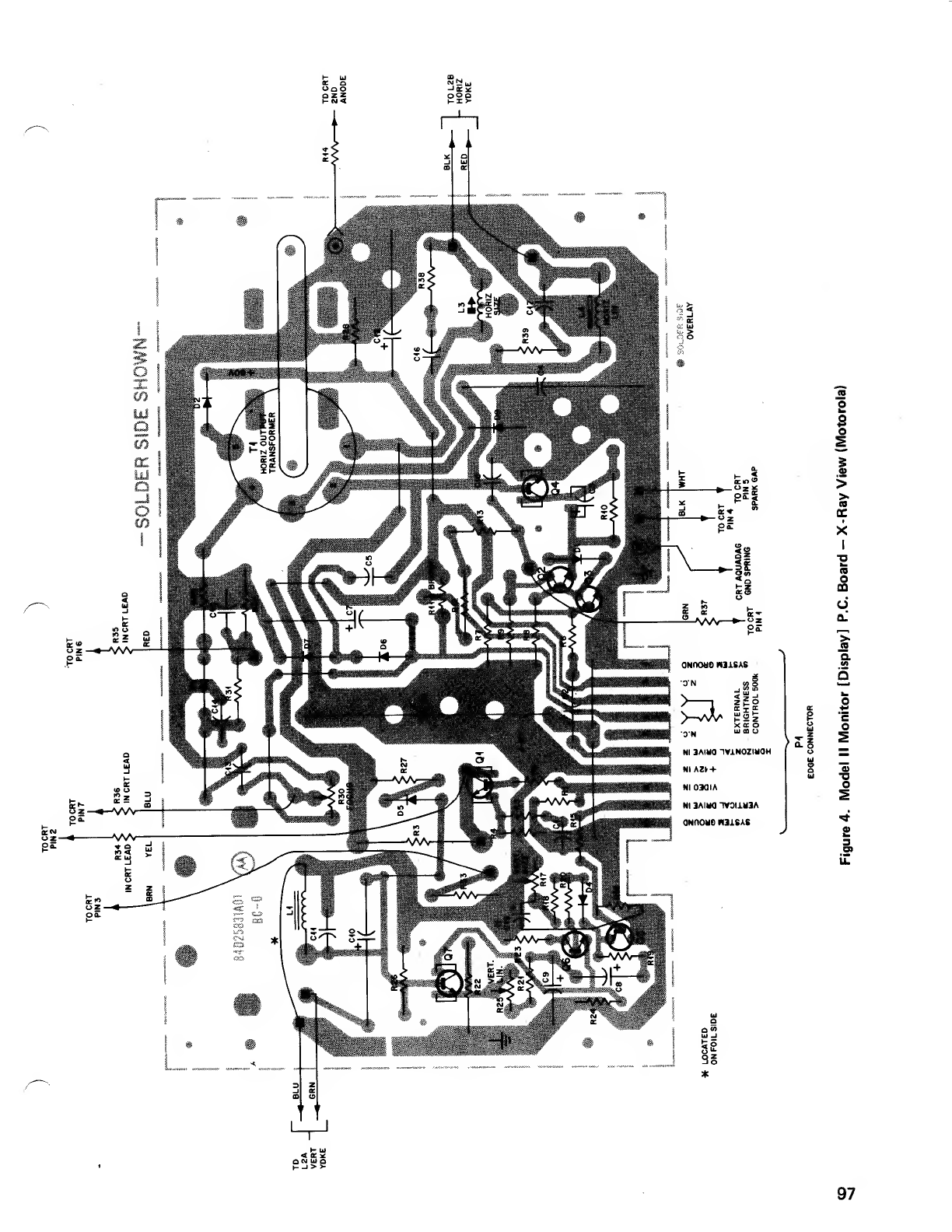

4Model II Monitor [Display] P.C. Board -X-Ray View (Motorola) 97

5Model M3970 -Series Kits, Rear View (Motorola) 98

6Monitor Circuit Card -Edge Connector (Motorola and RCA) 99

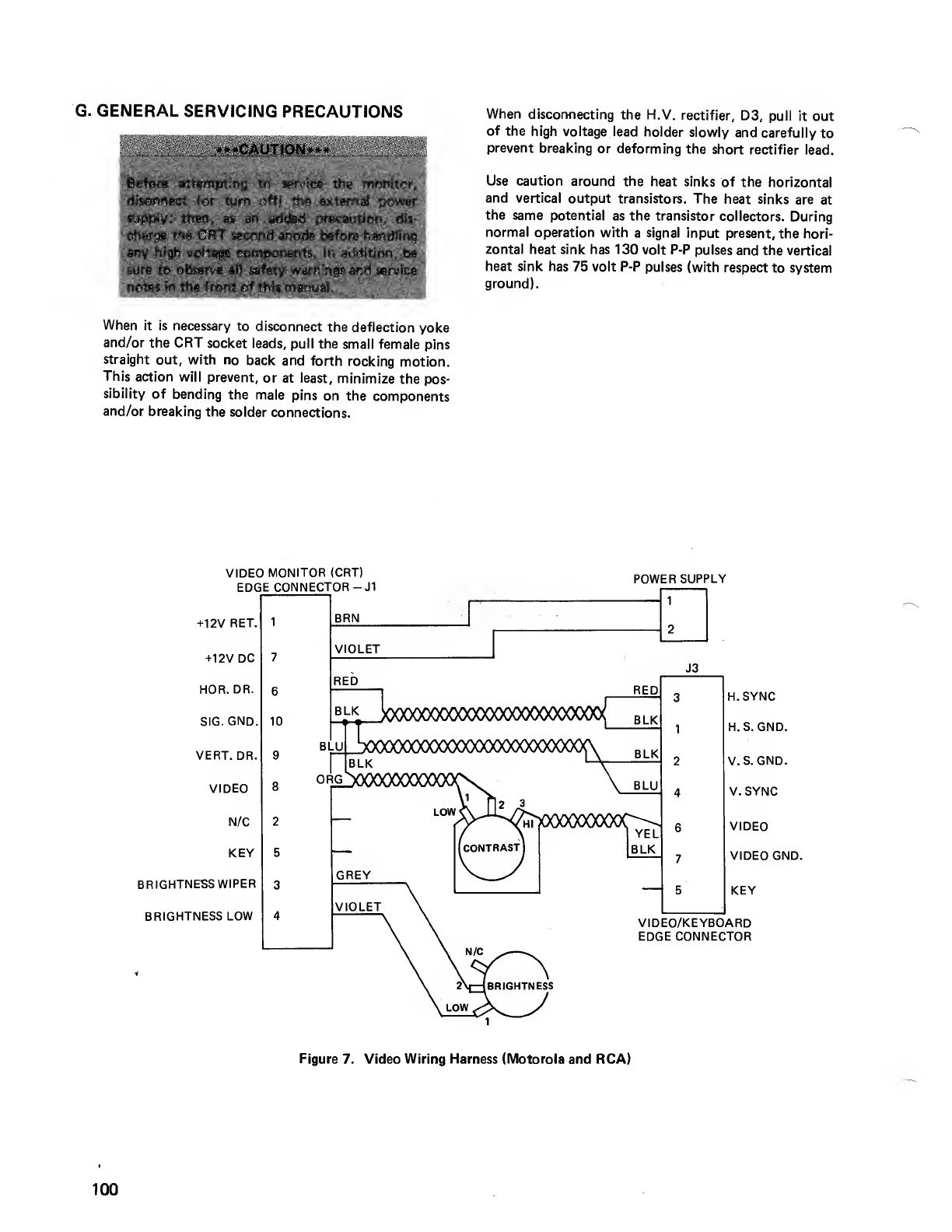

7Video Wiring Harness (Motorola and RCA) 100

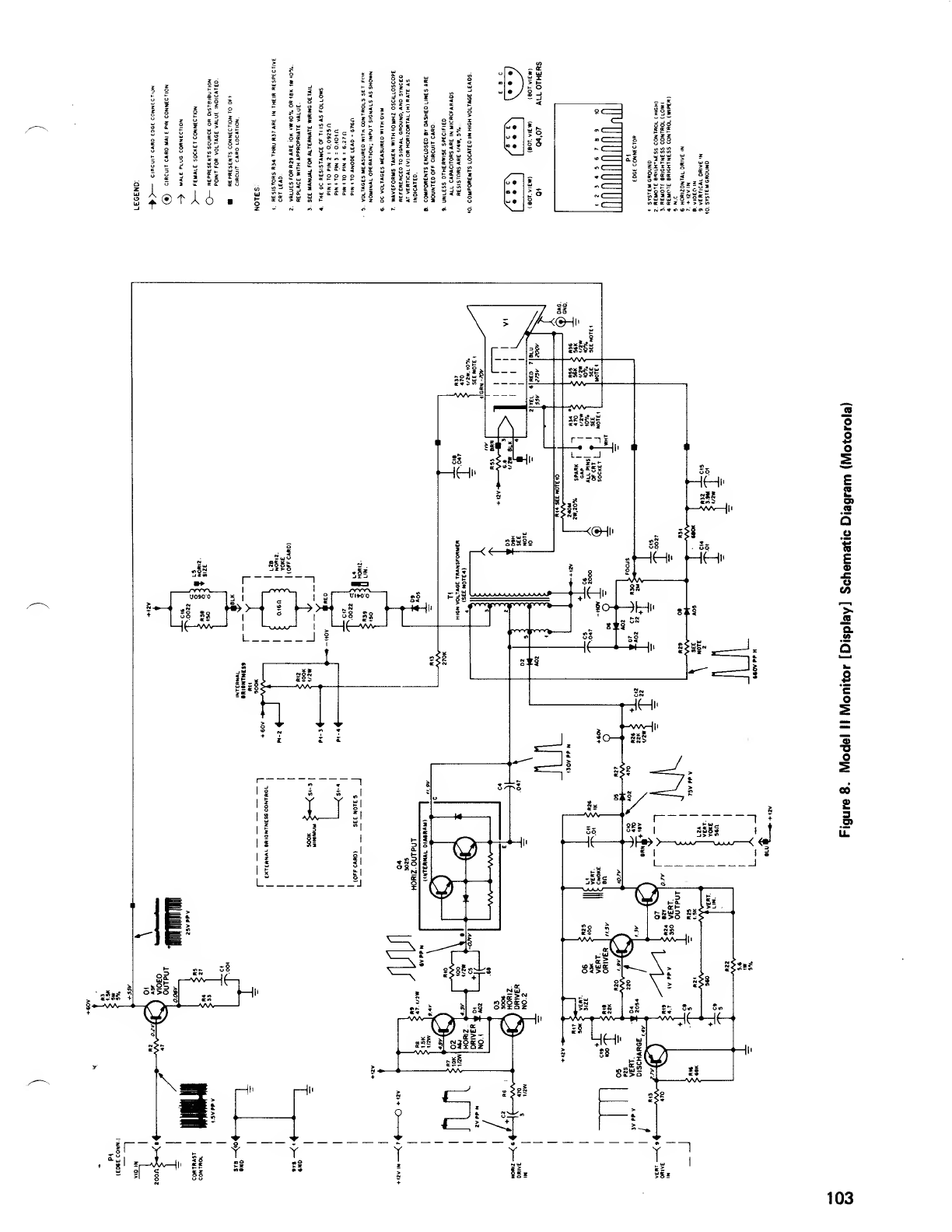

8Model II Monitor [Display] Schematic Diagram (Motorola) 103

9Deflection Yoke Assembly (RCA) 106

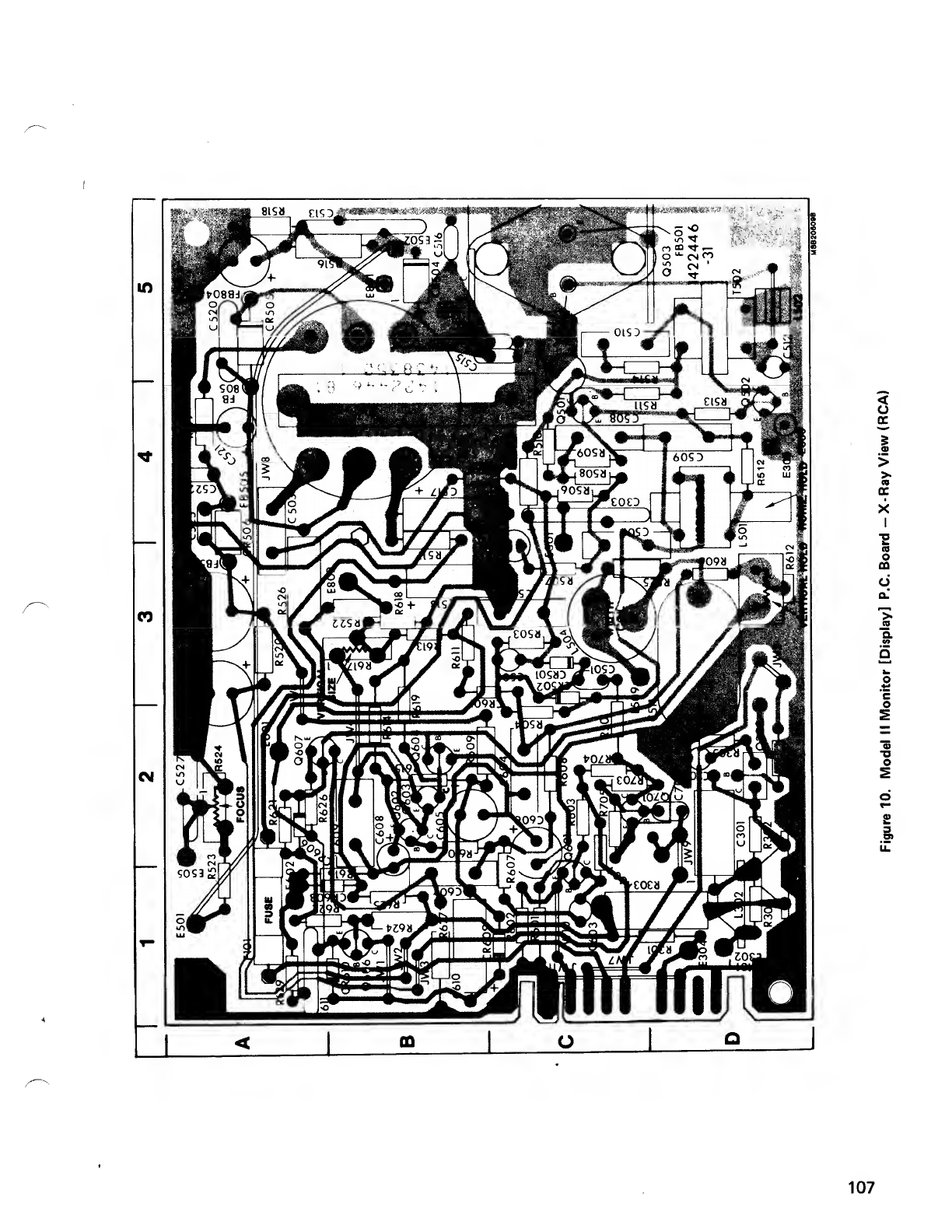

10 Model II Monitor [Display] P.C. Board -X-Ray View (RCA) 107

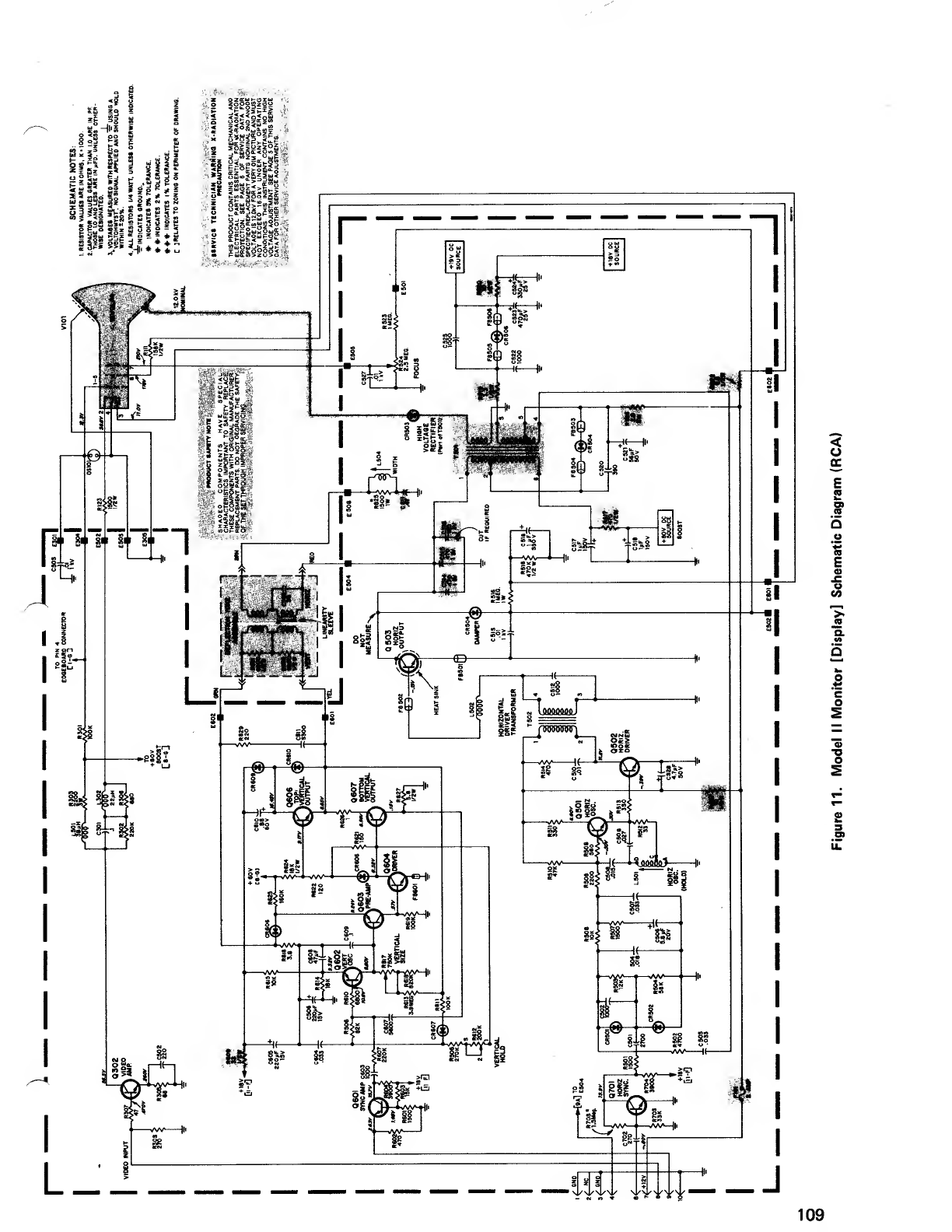

11 Model II Monitor [Display] Schematic Diagram (RCA) 109

SECTION VIII -FLOPPY DISK DRIVE

1SA 800/801 PCB Test Points and Component Locations 113

SECTION IX -AA11080 POWER SUPPLY

1Test Layout ,120

2Output Connector (S2) 120

3Q1 Collector Waveform 121

4Q1 Base Waveform 121

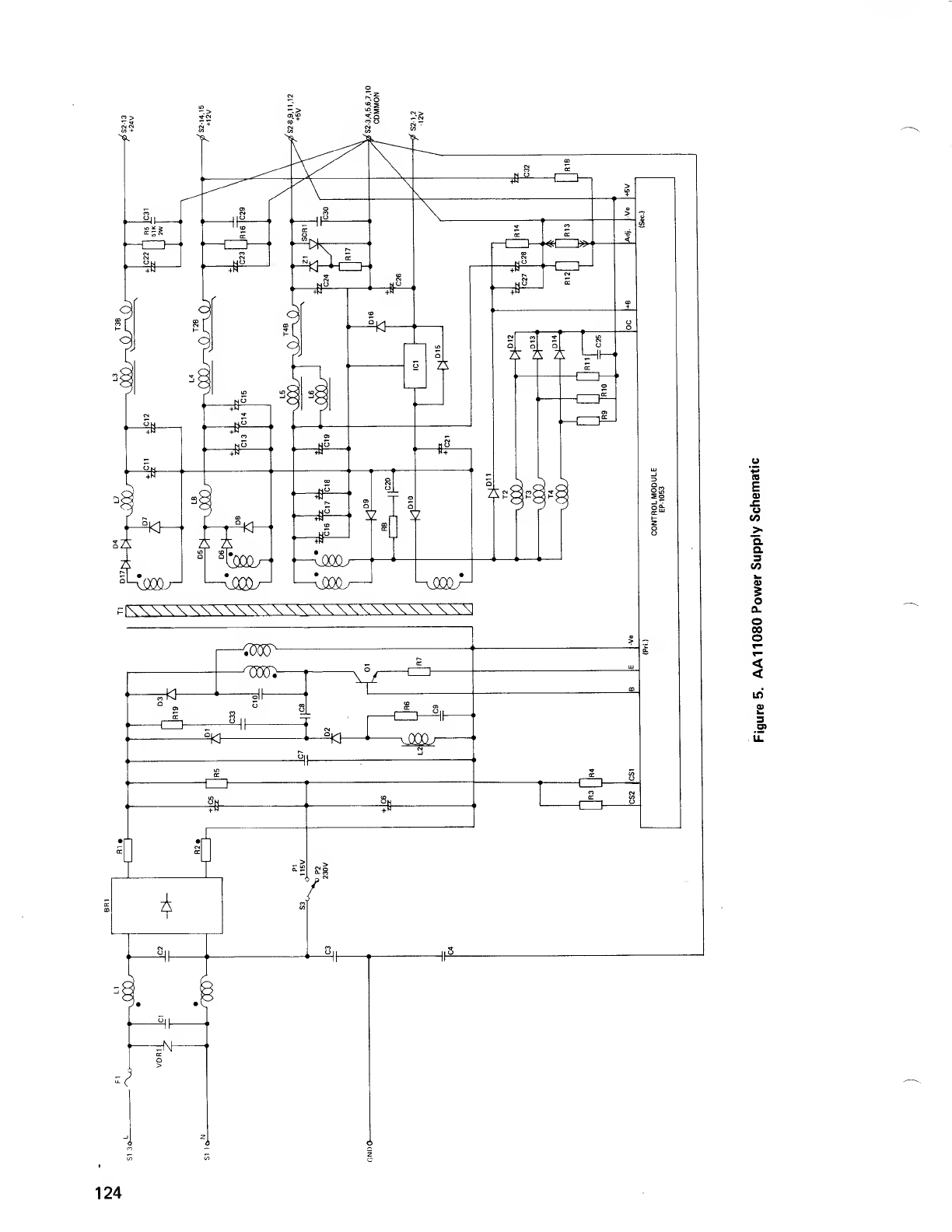

5AA11080 Power Supply Schematic Diagram 124

SECTION X-CARD CAGE and MOTHERBOARD

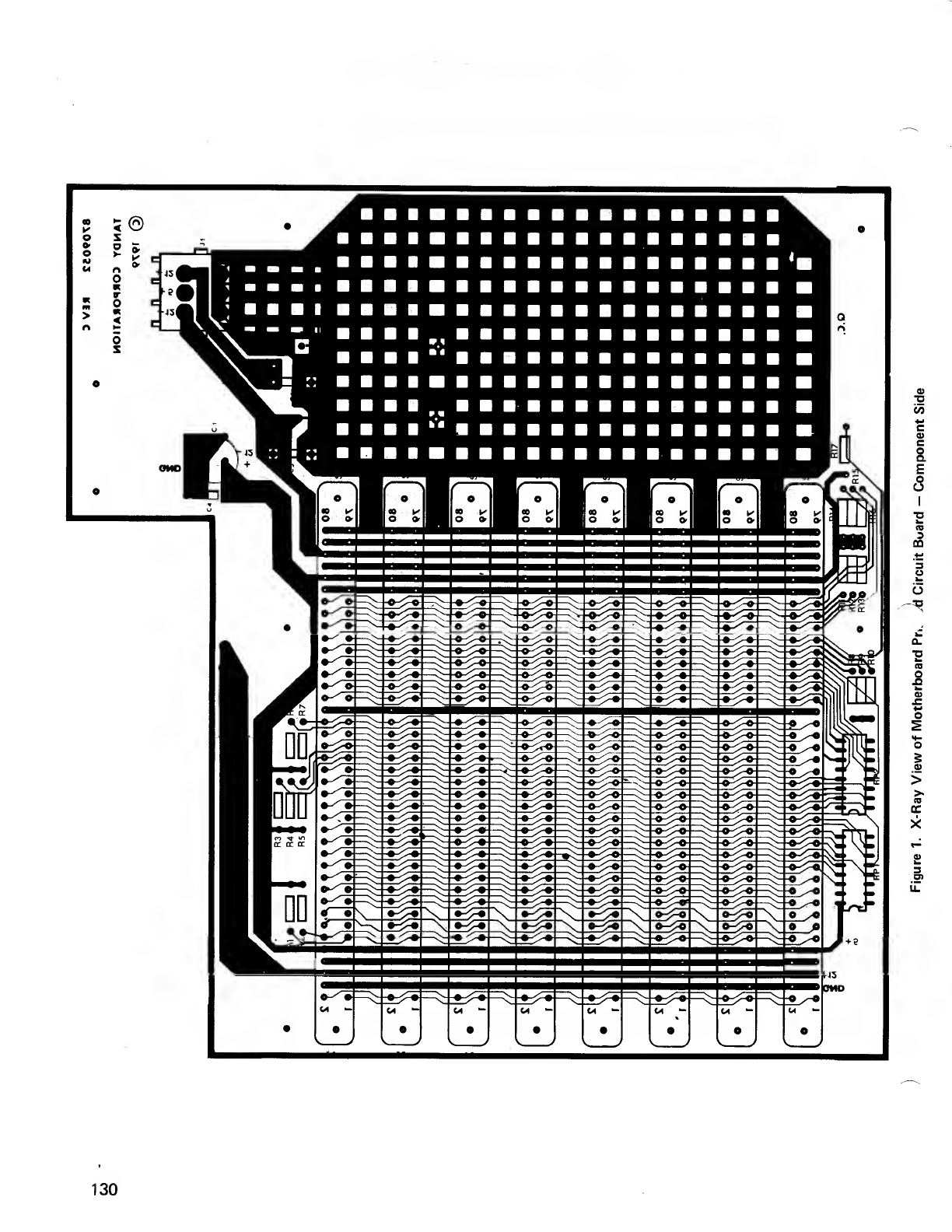

1Motherboard Printed Circuit Board -Component Side 130

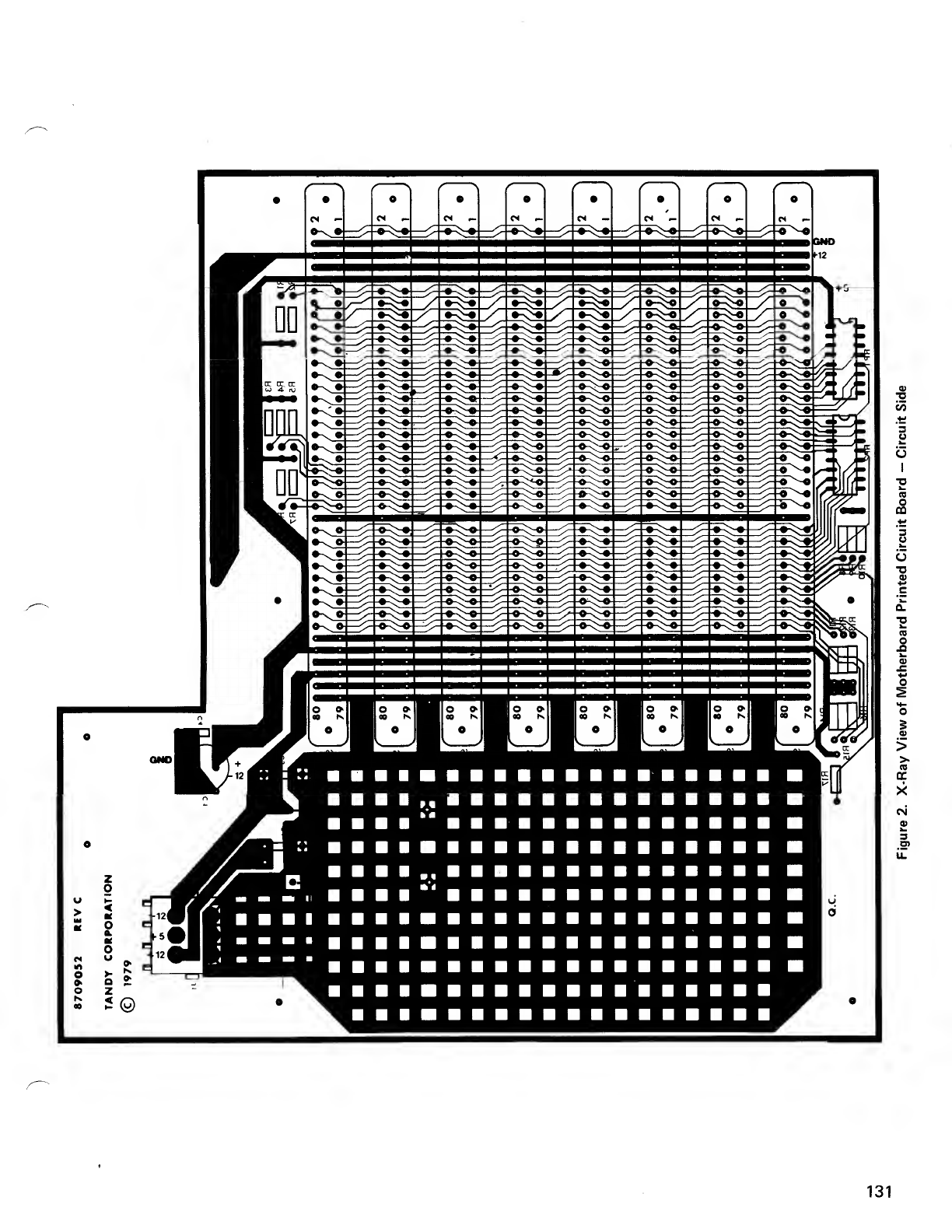

2Motherboard Printed Circuit Board -Circuit Side 131

SECTION XI -KEYBOARD UNIT

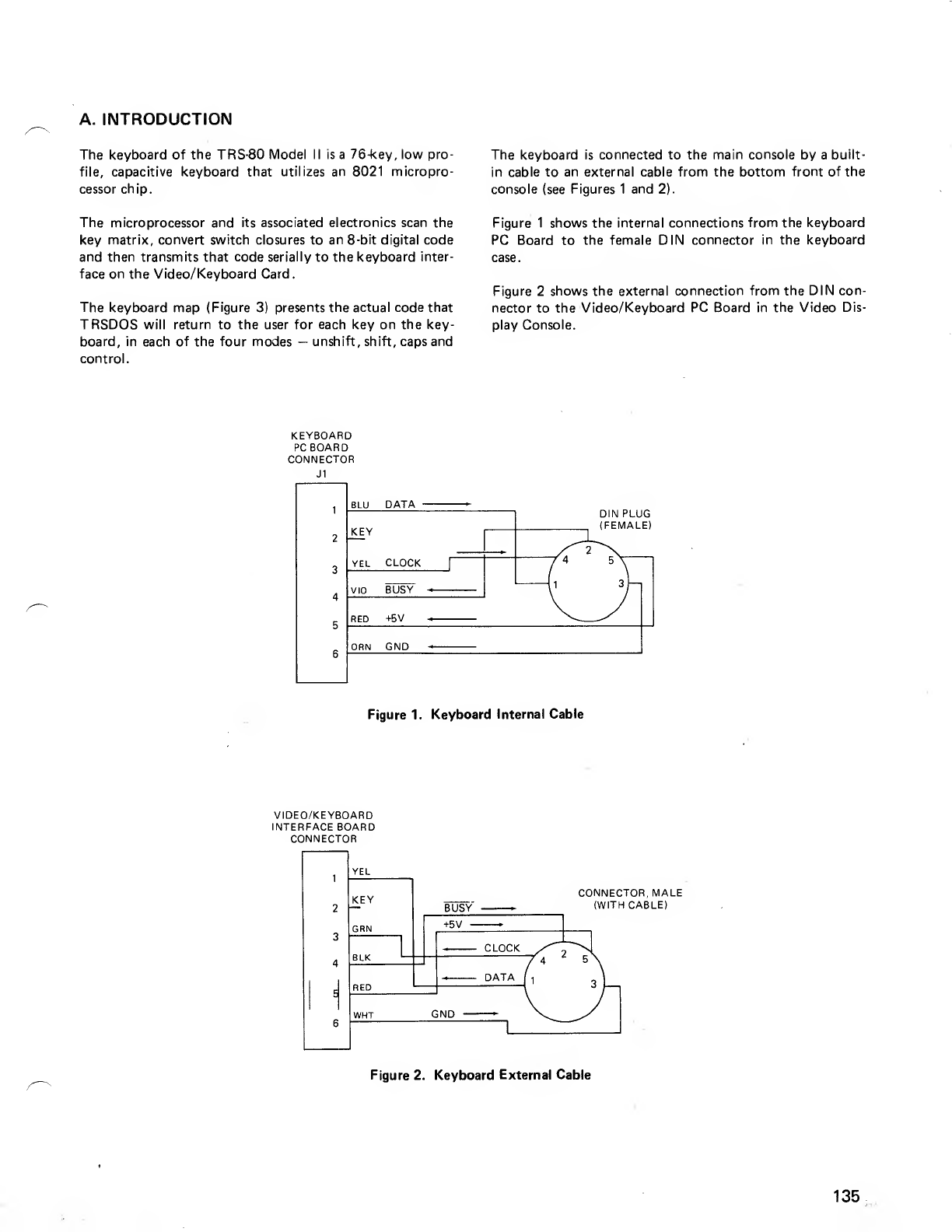

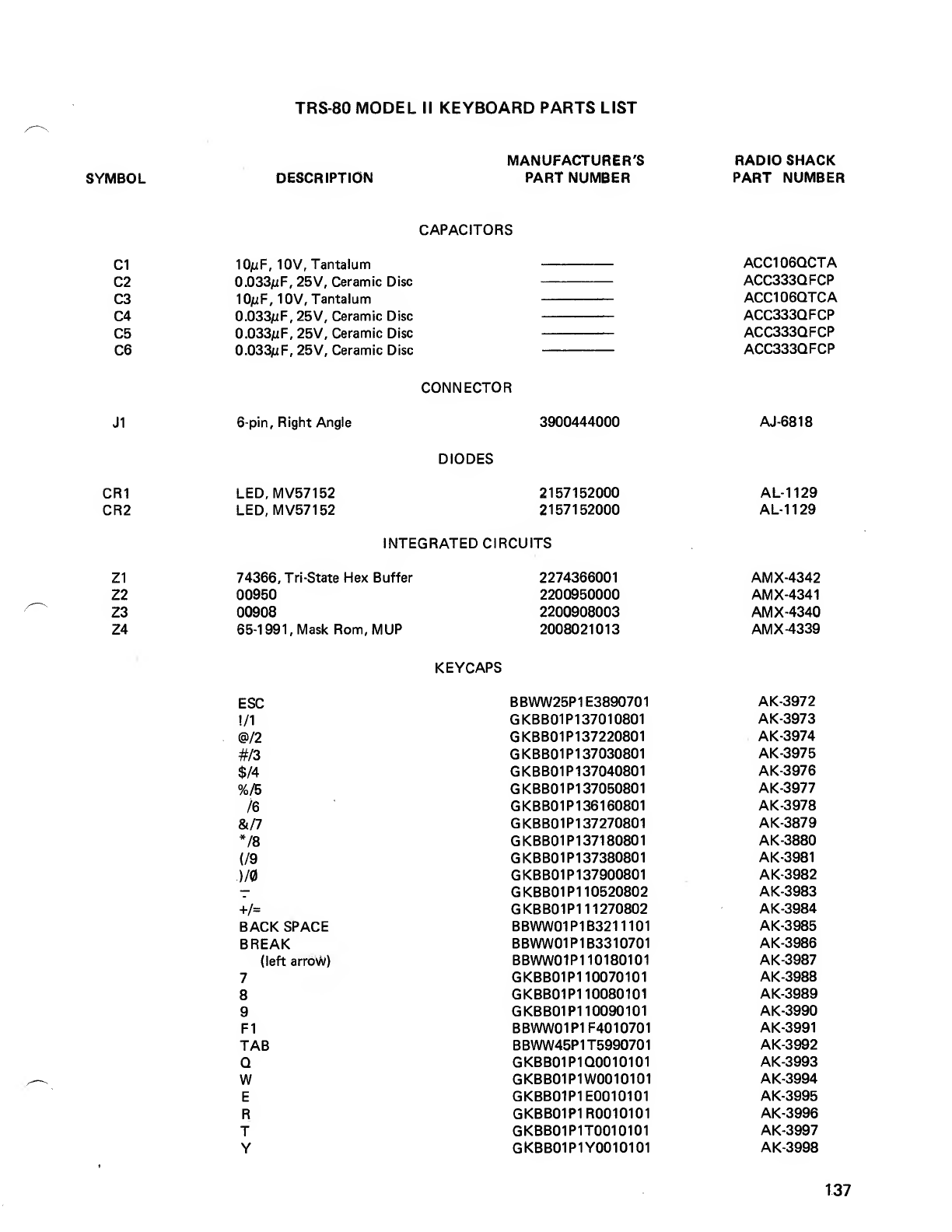

1Keyboard Internal Cable 135

2Keyboard External Cable 135

3Keyboard Code Map 136

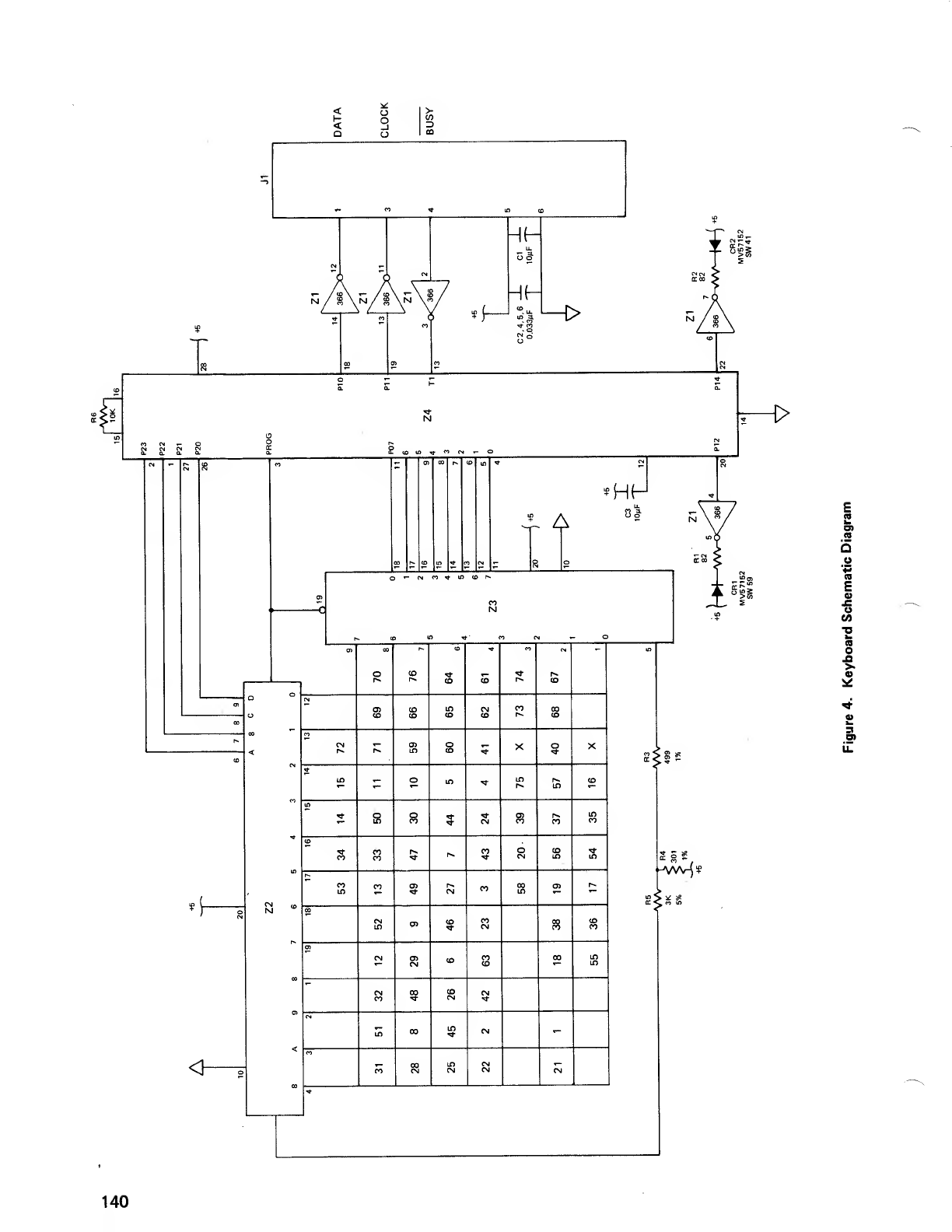

4Keyboard Schematic Diagram 140

SECTION XII -PERIPHERAL INTERFACES

1Serial Interface Connector 143

250-Conductor Ribbon Cable -Serial Cable 143

3Parallel Interface Connector 144

434-Conductor Ribbon Cable -Parallel Cable 144

5Rear View, TRS-80 Model II Computer 146

LIST OF ILLUSTRATIONS (Cont'd)

Figure pa9e

Number Number

SECTION XIII -DISK EXPANSION UNIT

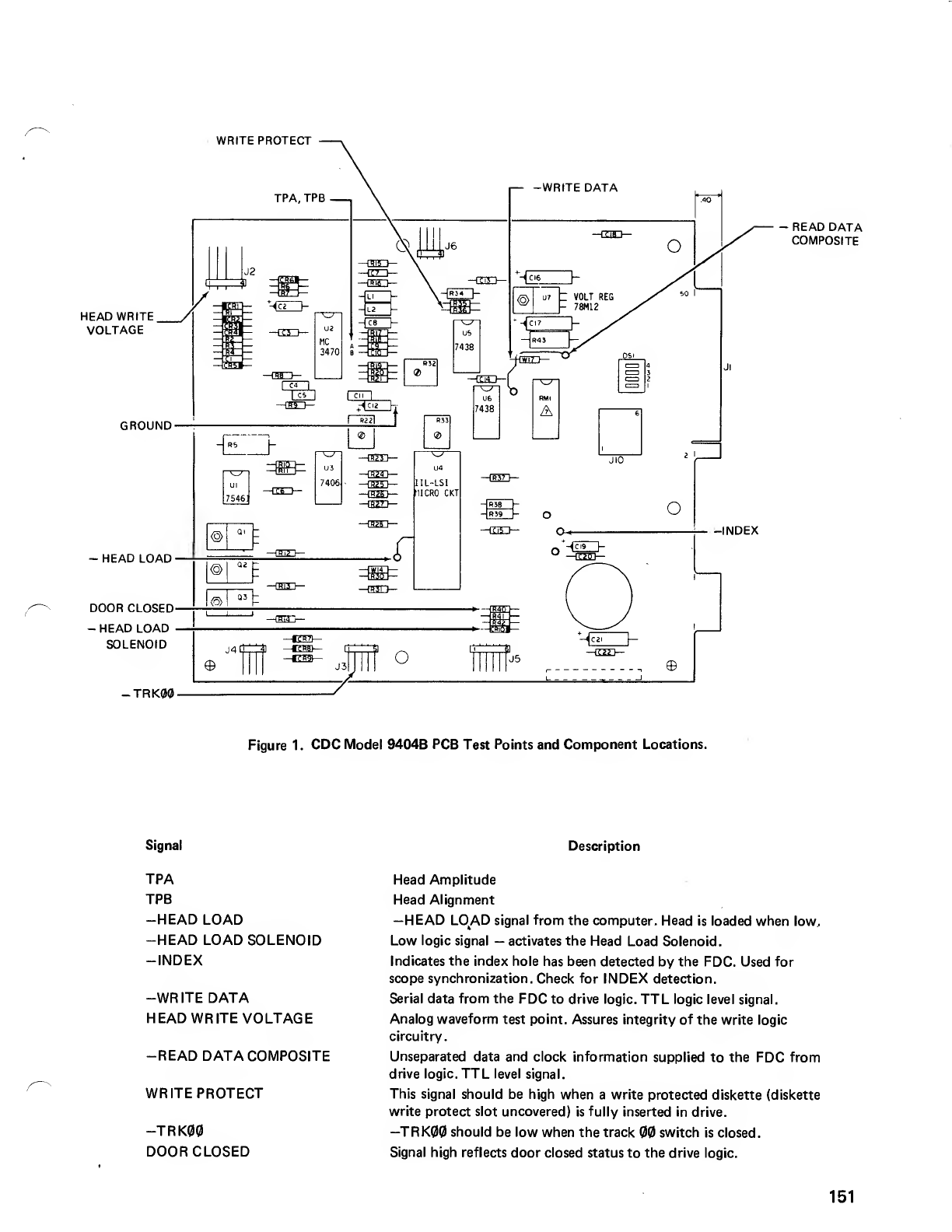

1CDC Model 9404B PCB Test Points and Component Locations 151

SECTION XIV -TROUBLESHOOTING -DISK SYSTEM

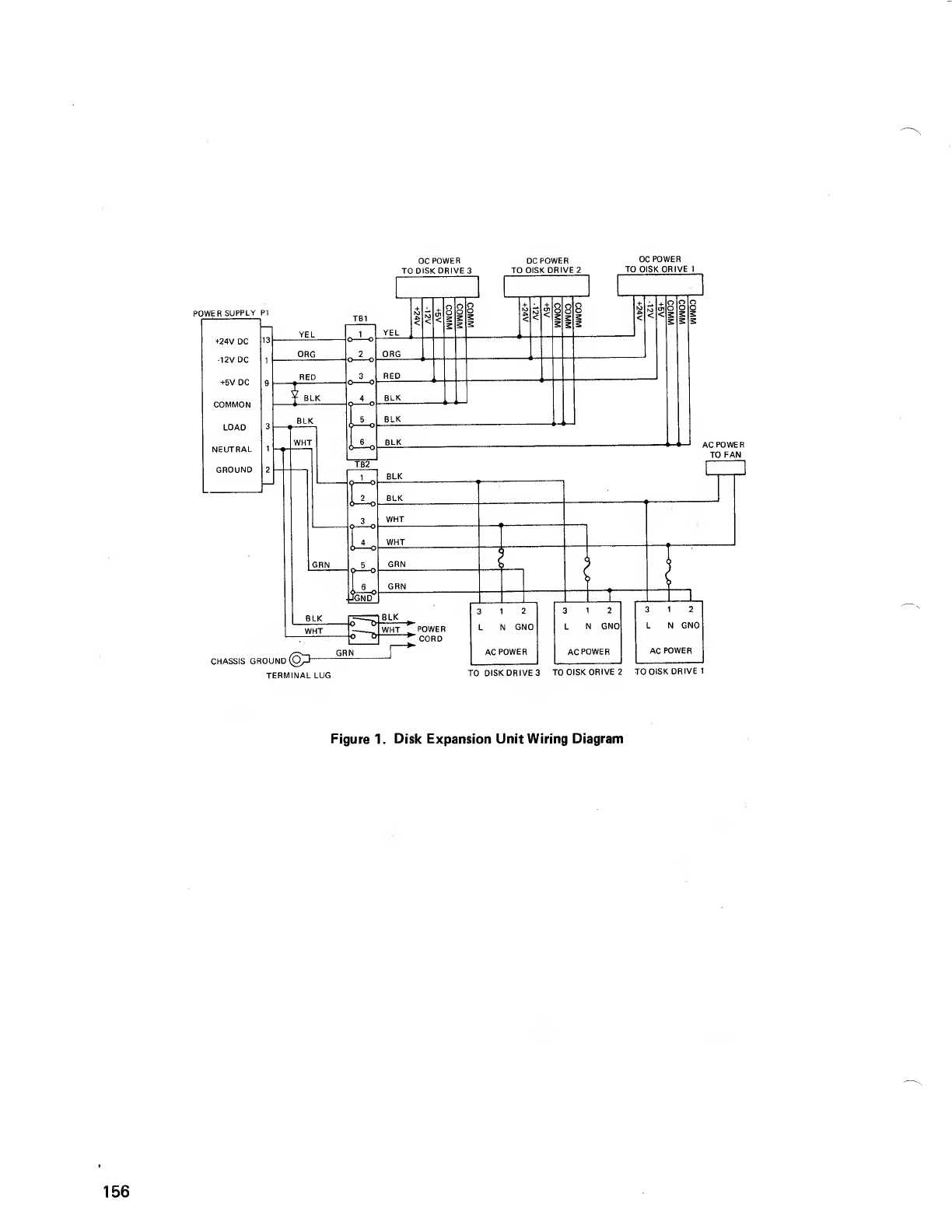

1Disk Expansion Unit Wiring Diagram 156

SECTION XV -AA1 11000 POWER SUPPLY

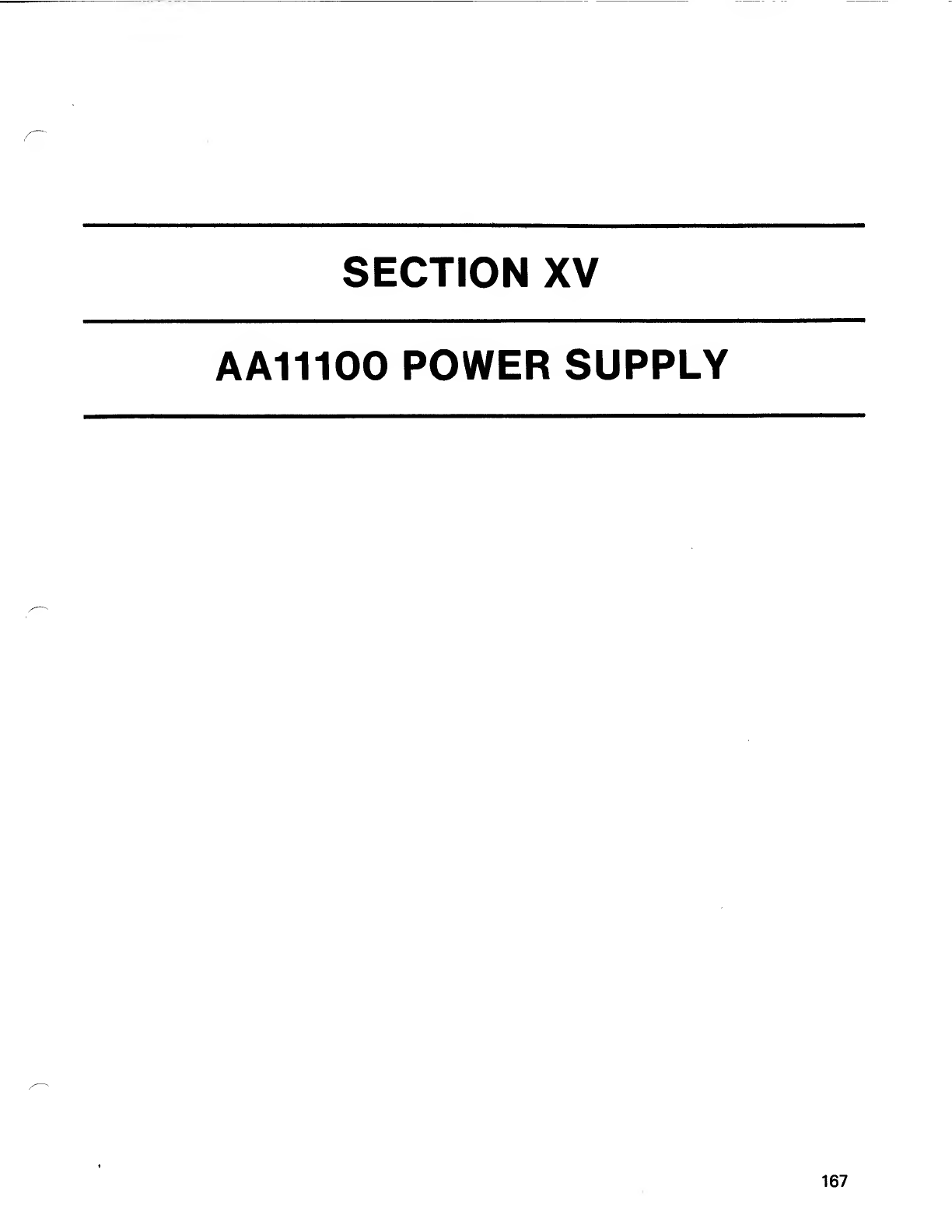

1Line Voltage Selection 169

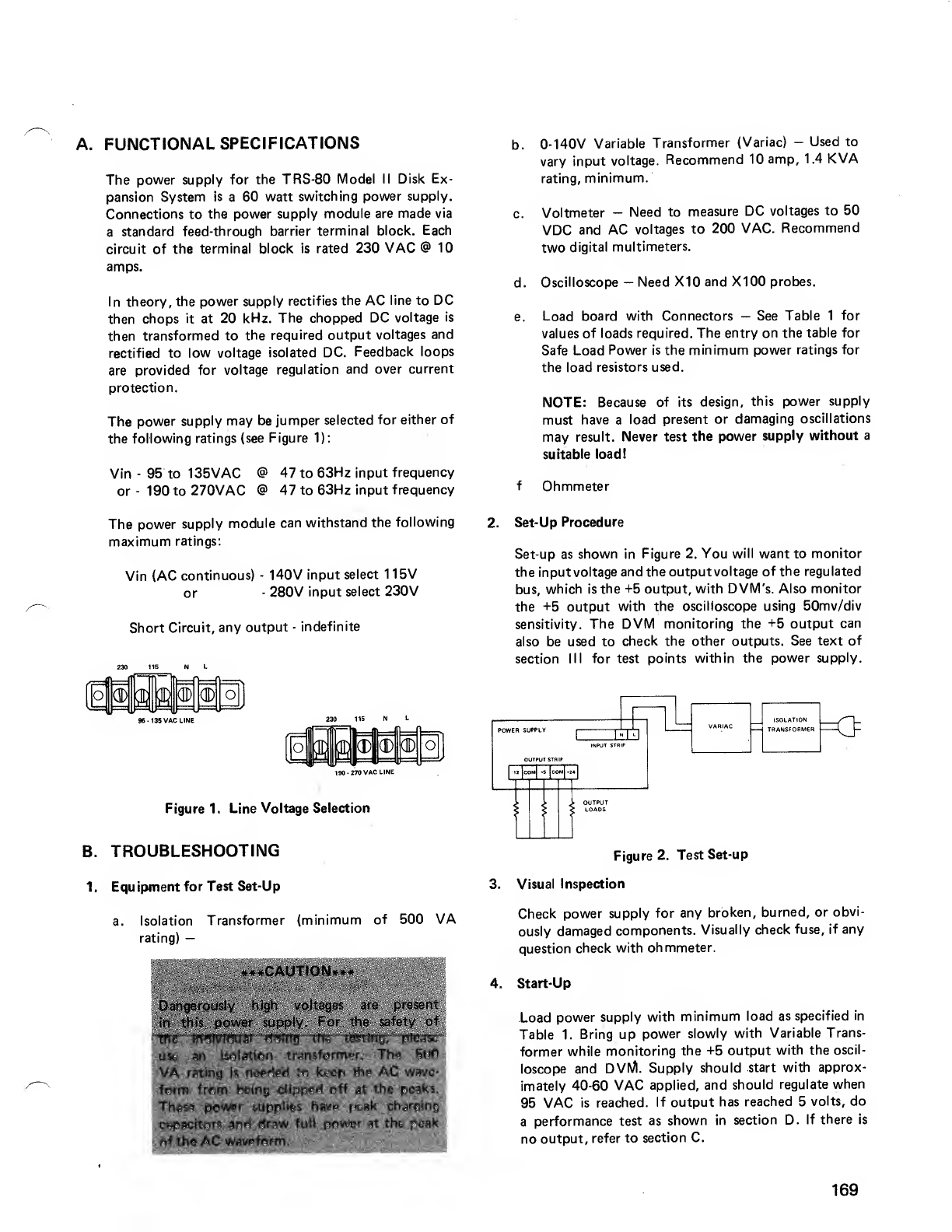

2Test Set-Up 169

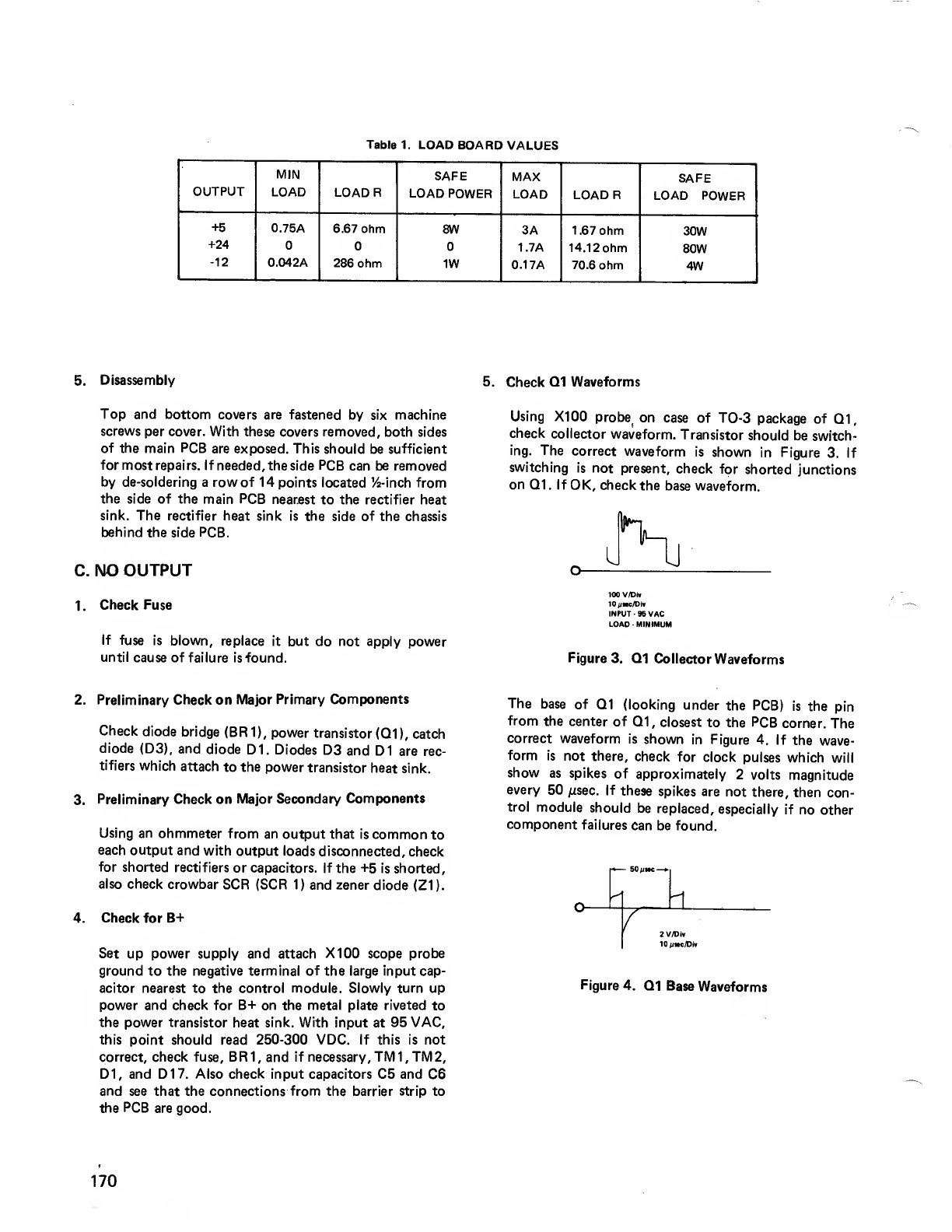

3Q1 Collector Waveforms 170

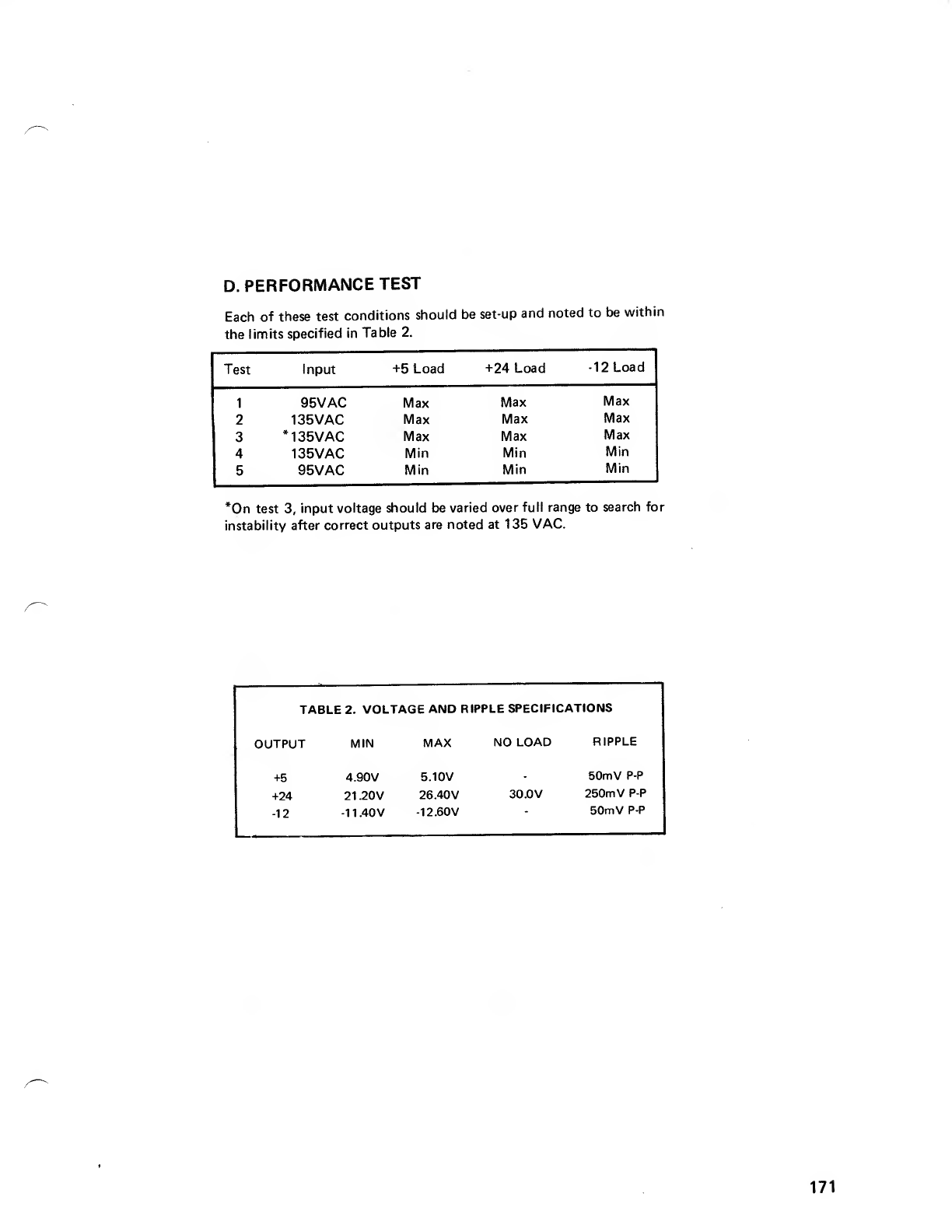

4Q1 Base Waveforms 170

5AA111000 Power Supply Schematic Diagram 173

SECTION XVI -ILLUSTRATED PARTS BREAKDOWN

1Case Assembly 178

2Chassis Assembly 181

VII

SECTION I

SYSTEM DESCRIPTION

A. INTRODUCTION

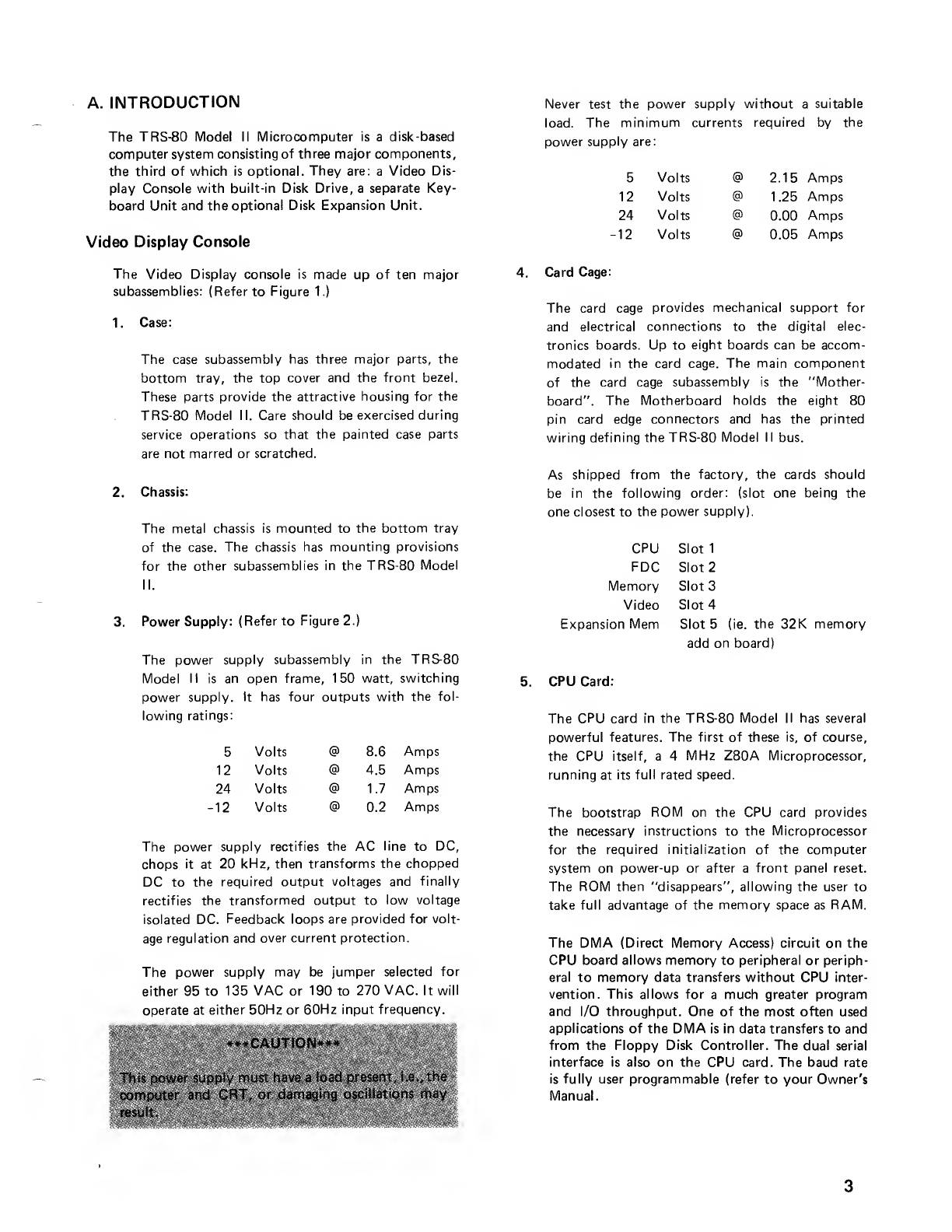

The TRS-80 Model II Microcomputer is adisk-based

computer system consisting of three major components,

the third of which is optional. They are: aVideo Dis-

play Console with built-in Disk Drive, aseparate Key-

board Unit and the optional Disk Expansion Unit.

Video Display Console

The Video Display console is made up of ten major

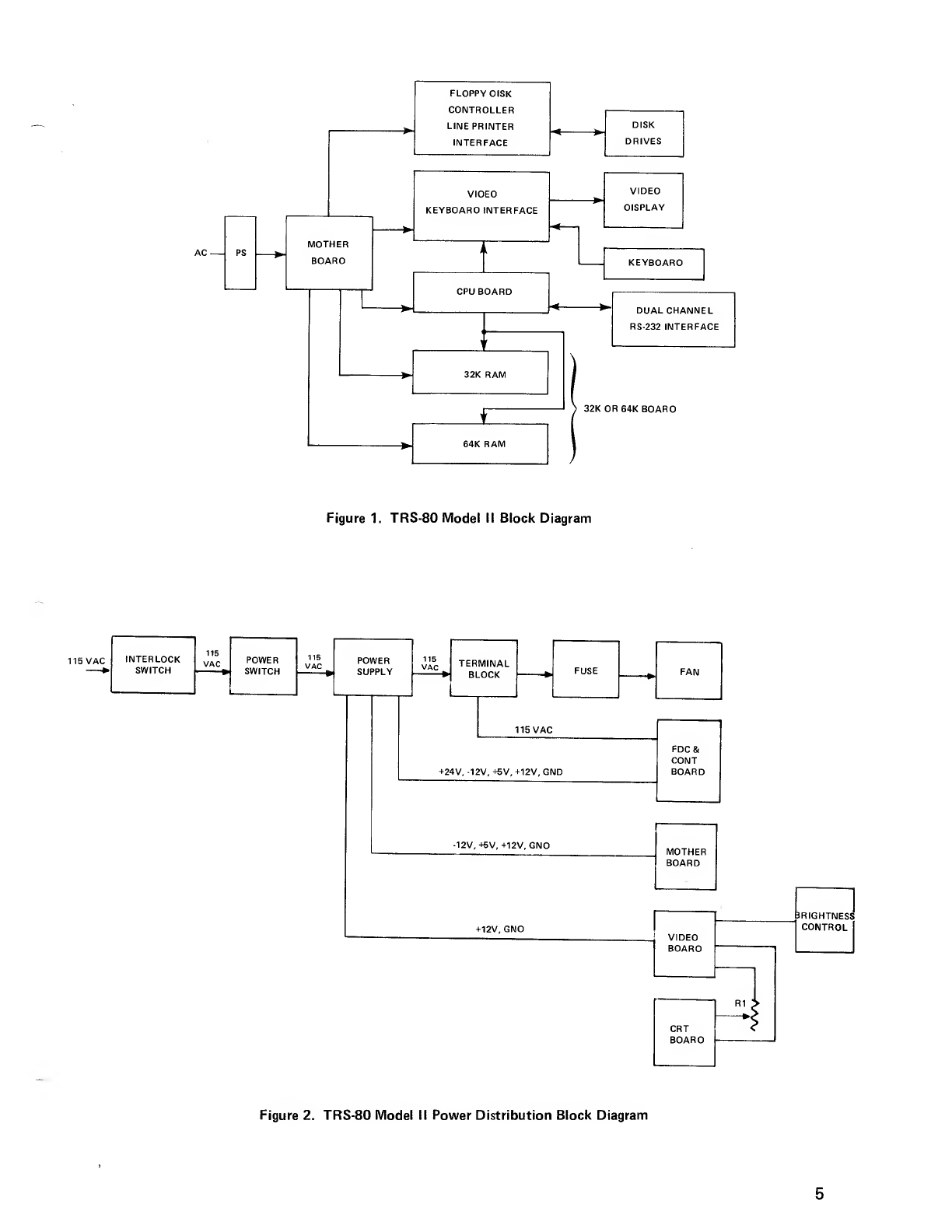

subassemblies: (Refer to Figure 1.)

1. Case:

The case subassembly has three major parts, the

bottom tray, the top cover and the front bezel.

These parts provide the attractive housing for the

TRS-80 Model II. Care should be exercised during

service operations so that the painted case parts

are not marred or scratched.

2. Chassis:

The metal chassis is mounted to the bottom tray

of the case. The chassis has mounting provisions

for the other subassemblies in the TRS-80 Model

II.

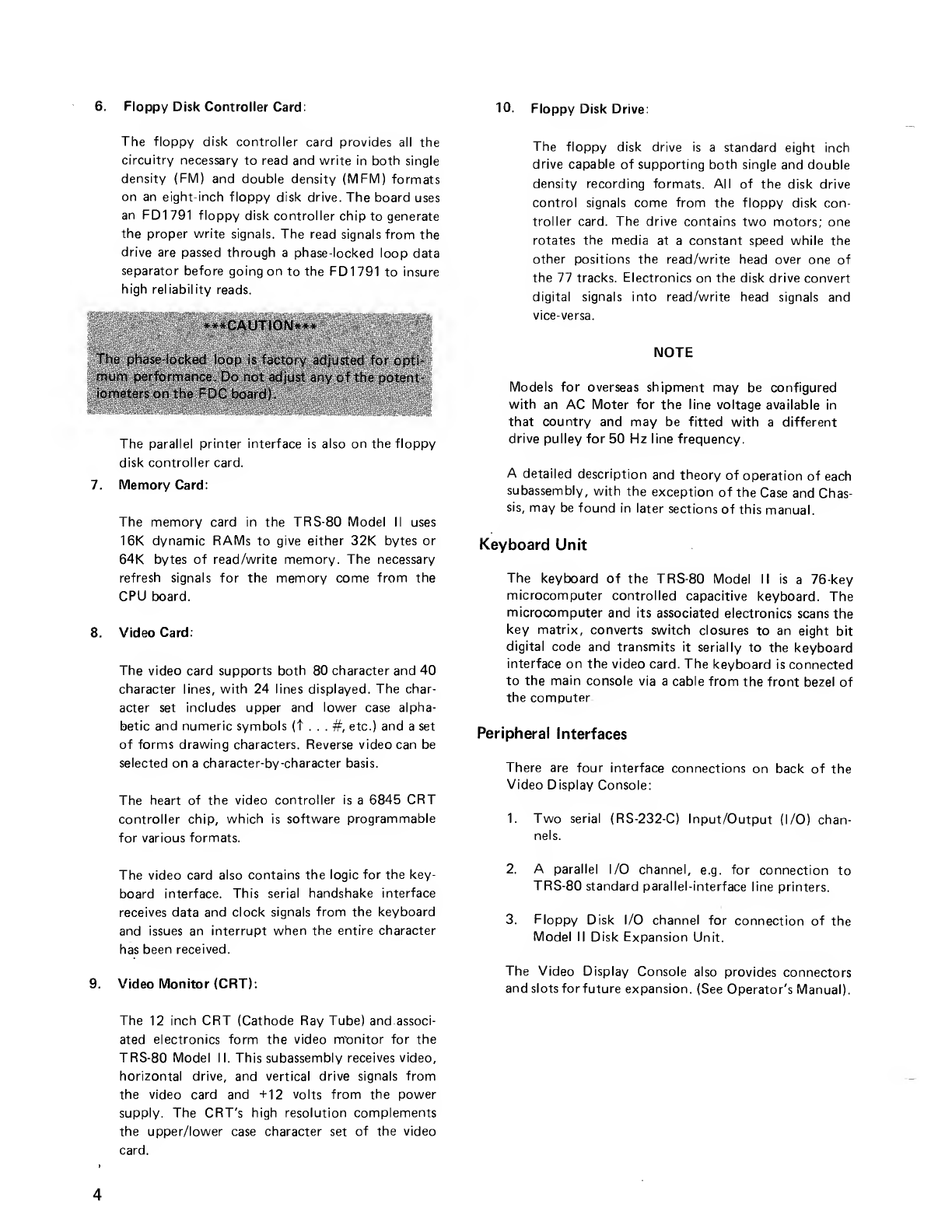

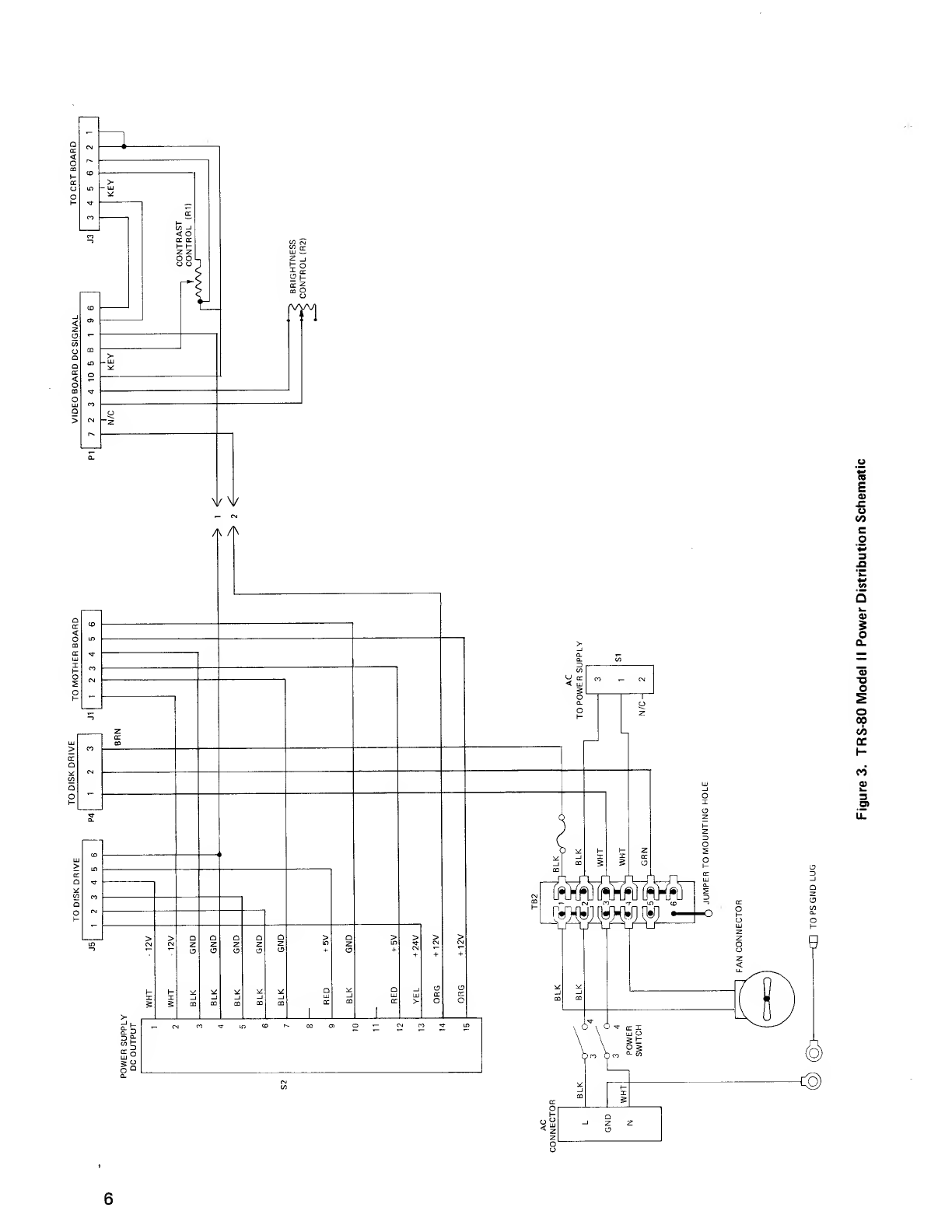

3. Power Supply: (Refer to Figure 2.)

The power supply subassembly in the TRS-80

Model II is an open frame, 150 watt, switching

power supply. It has four outputs with the fol-

lowing ratings:

Never test the power supply without asuitable

load. The minimum currents required by the

power supply are:

5 Volts

12 Volts

24 Volts

-12 Volts

@8.6 Amps

@4.5 Amps

@1.7 Amps

@0.2 Amps

The power supply rectifies the AC line to DC,

chops it at 20 kHz, then transforms the chopped

DC to the required output voltages and finally

rectifies the transformed output to low voltage

isolated DC. Feedback loops are provided for volt-

age regulation and over current protection.

The power supply may be jumper selected for

either 95 to 135 VAC or 190 to 270 VAC. It will

operate at either 50Hz or 60Hz input frequency.

**»CAUTION***

This power supply must have aload present, i.e., the

computer and CRT, or damaging oscillations may

5Volts @2.15 Amps

12 Volts @1.25 Amps

24 Volts @0.00 Amps

-12 Volts @0.05 Amps

Card Cage:

The card cage provides mechanical support for

and electrical connections to the digital elec-

tronics boards. Up to eight boards can be accom-

modated in the card cage. The main component

of the card cage subassembly is the "Mother-

board". The Motherboard holds the eight 80

pin card edge connectors and has the printed

wiring defining the TRS-80 Model II bus.

As shipped from the factory, the cards should

be in the following order: (slot one being the

one closest to the power supply).

CPU

FDC

Memory

Video

Expansion Mem

CPU Card:

Slot 1

Slot 2

Slot 3

Slot 4

Slot 5(ie. the 32K memory

add on board)

The CPU card in the TRS-80 Model II has several

powerful features. The first of these is, of course,

the CPU itself, a4MHz Z80A Microprocessor,

running at its full rated speed.

The bootstrap ROM on the CPU card provides

the necessary instructions to the Microprocessor

for the required initialization of the computer

system on power-up or after afront panel reset.

The ROM then "disappears", allowing the user to

take full advantage of the memory space as RAM.

The DMA (Direct Memory Access) circuit on the

CPU board allows memory to peripheral or periph-

eral to memory data transfers without CPU inter-

vention. This allows for amuch greater program

and I/O throughput. One of the most often used

applications of the DMA is in data transfers to and

from the Floppy Disk Controller. The dual serial

interface is also on the CPU card. The baud rate

is fully user programmable (refer to your Owner's

Manual.

6. Floppy Disk Controller Card: 10. Floppy Disk Drive:

The floppy disk controller card provides all the

circuitry necessary to read and write in both single

density (FM) and double density (MFM) formats

on an eight-inch floppy disk drive. The board uses

an FD1791 floppy disk controller chip to generate

the proper write signals. The read signals from the

drive are passed through aphase-locked loop data

separator before going on to the FD1791 to insure

high reliability reads.

***CAUTIOIM**»

The phase-locked loop is factory adjusted for opti-

mum performance. Do not adjust any of the potent-

iometers on the FDC board).

The parallel printer interface is also on the floppy

disk controller card.

7. Memory Card:

The memory card in the TRS-80 Model II uses

16K dynamic RAMs to give either 32K bytes or

64K bytes of read/write memory. The necessary

refresh signals for the memory come from the

CPU board.

8. Video Card:

The video card supports both 80 character and 40

character lines, with 24 lines displayed. The char-

acter set includes upper and lower case alpha-

betic and numeric symbols (t .. . #, etc.) and aset

of forms drawing characters. Reverse video can be

selected on acharacter-by-character basis.

The heart of the video controller is a6845 CRT

controller chip, which is software programmable

for various formats.

The floppy disk drive is astandard eight inch

drive capable of supporting both single and double

density recording formats. All of the disk drive

control signals come from the floppy disk con-

troller card. The drive contains two motors; one

rotates the media at aconstant speed while the

other positions the read/write head over one of

the 77 tracks. Electronics on the disk drive convert

digital signals into read/write head signals and

vice-versa.

NOTE

Models for overseas shipment may be configured

with an AC Moter for the line voltage available in

that country and may be fitted with adifferent

drive pulley for 50 Hz line frequency.

Adetailed description and theory of operation of each

subassembly, with the exception of the Case and Chas-

sis, may be found in later sections of this manual.

Keyboard Unit

The keyboard of the TRS-80 Model II is a76-key

microcomputer controlled capacitive keyboard. The

microcomputer and its associated electronics scans the

key matrix, converts switch closures to an eight bit

digital code and transmits it serially to the keyboard

interface on the video card. The keyboard is connected

to the main console via acable from the front bezel of

the computer

Peripheral Interfaces

There are four interface connections on back of the

Video Display Console:

1. Two serial (RS-232-C) Input/Output (I/O) chan-

nels.

The video card also contains the logic for the key-

board interface. This serial handshake interface

receives data and clock signals from the keyboard

and issues an interrupt when the entire character

has been received.

9. Video Monitor (CRT):

The 12 inch CRT (Cathode Ray Tube) and associ-

ated electronics form the video rrronitor for the

TRS-80 Model II. This subassembly receives video,

horizontal drive, and vertical drive signals from

the video card and +12 volts from the power

supply. The CRT's high resolution complements

the upper/lower case character set of the video

card.

2. Aparallel I/O channel, e.g. for connection to

TRS-80 standard parallel-interface line printers.

3. Floppy Disk I/O channel for connection of the

Model II Disk Expansion Unit.

The Video Display Console also provides connectors

and slots for future expansion. (See Operator's Manual).

MOTHER

BOARD

FLOPPY DISK

CONTROLLER

LINE PRINTER

INTERFACE

VIDEO

KEYBOARD INTERFACE

CPU BOARD

DISK

DRIVES

VIDEO

DISPLAY

DUAL CHANNEL

RS-232 INTERFACE

32K OR 64K BOARD

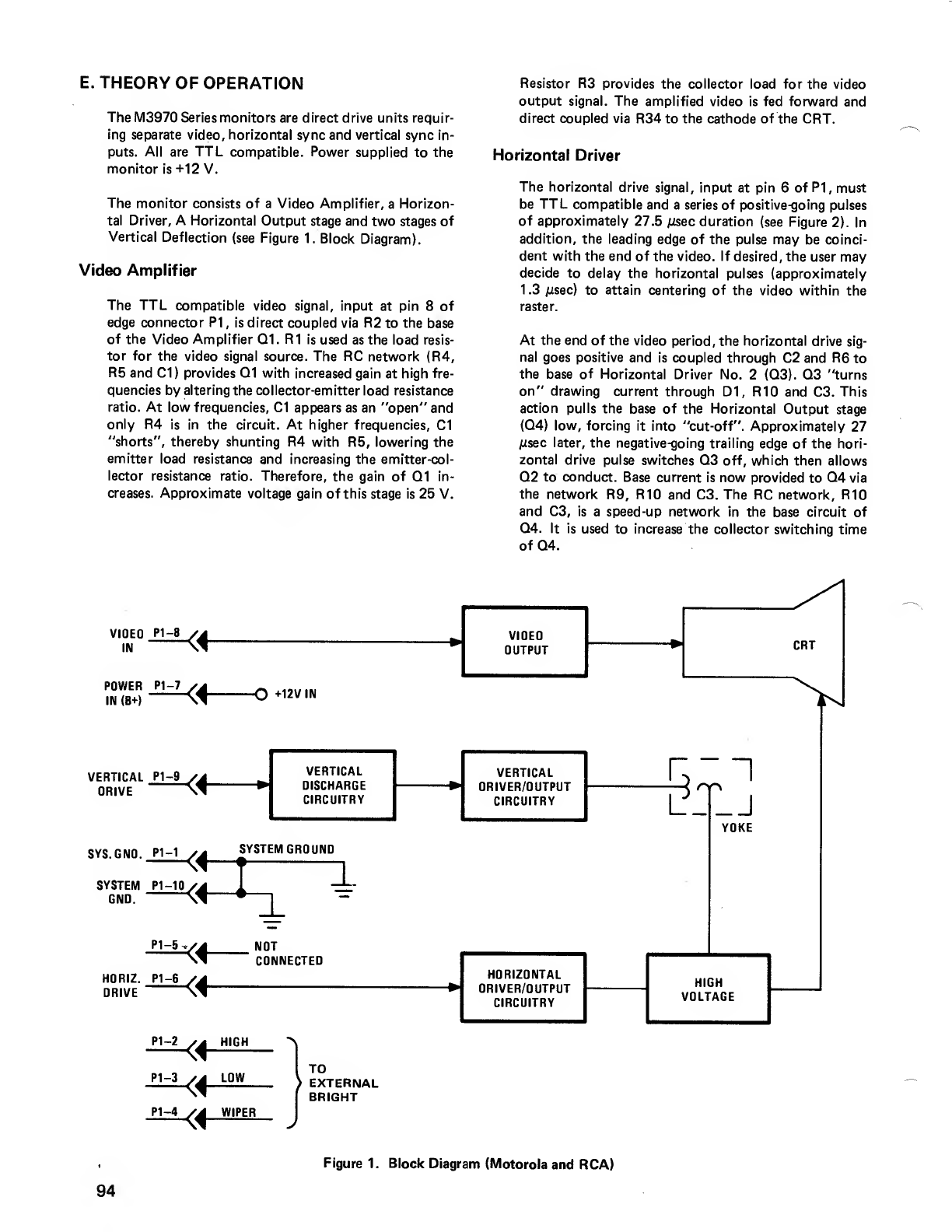

Figure 1. TRS-80 Model II Block Diagram

INTERLOCK

SWITCH

115

VAC POWER

SWITCH

115

VAC POWER

SUPPLY

115

VAC TERMINAL

BLOCK FUSE

+24V, -12V, +6V, +12V, GND

-12V, +6V, +12V, GND

+12V, GND

FDC&

CONT

BOARD

MOTHER

BOARD

VIDEO

BOARD

CRT

BOARD

ri ;

—».

TIGHTNESS

CONTROL

Figure 2. TRS-80 Model II Power Distribution Block Diagram

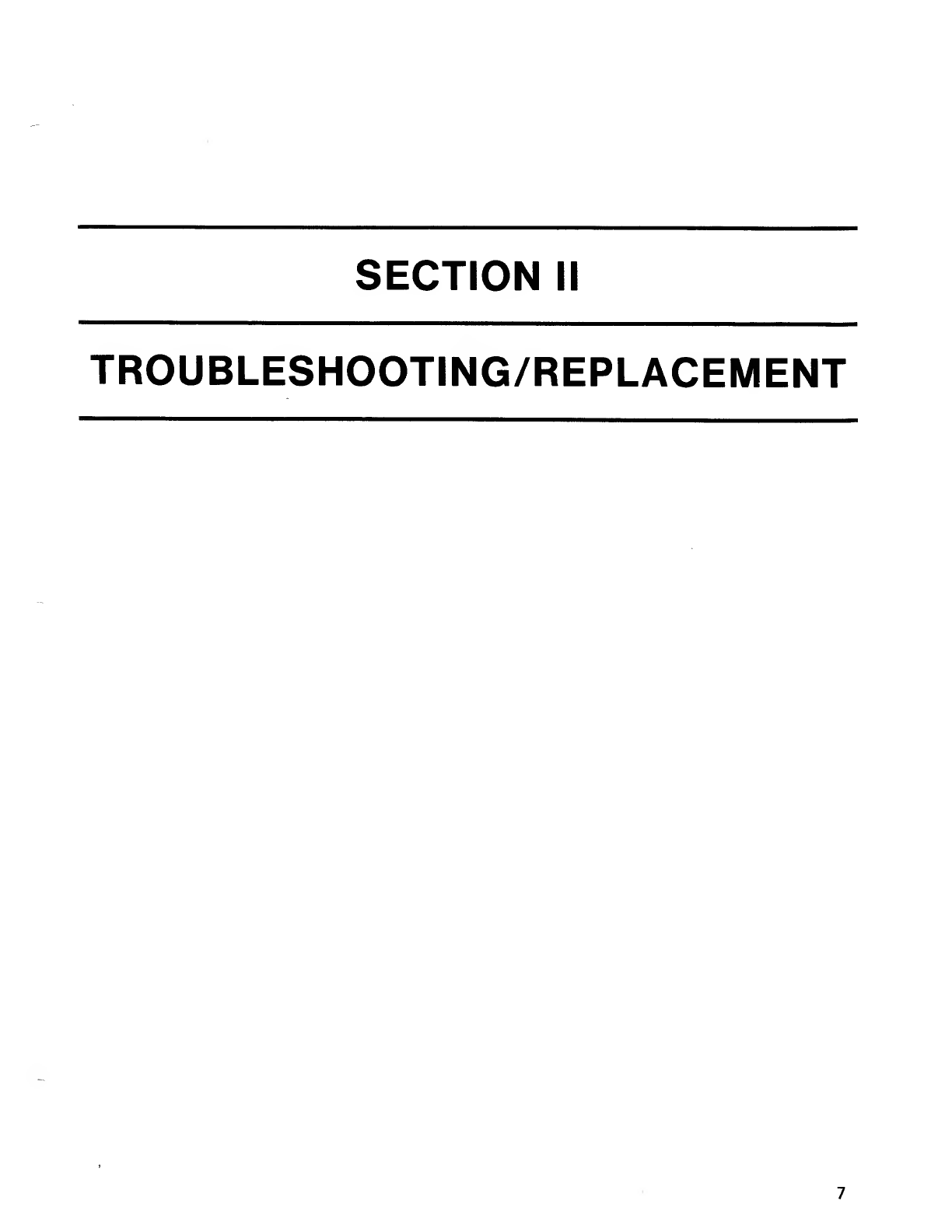

1

CN l

rr

<r*.

o

CU

rr >

O

l-

)=C

** ~

CO cc

V) -J

cc cc

oo egg

2_J

~< So

Vu

iO)

,

<

<£ r-

to

n

atn

cc O

o

on

a

>CM ~z

a.

^/\ /

*/N

<LU

(0

E

0)

jC

o

CO

3

.fl

S

o

T5

O

O

00

GO

DC

I-

co"

0)

SECTION II

TROUBLESHOOTING/REPLACEMENT

A. TROUBLESHOOTING PROCEDURE

General

This section of the manual will guide service personnel

through the system checkout procedure. The trouble-

shooting steps are organized in aflowchart manner.

Following these steps will guide you to the possible

failing board or boards.

Connect the power cord and keyboard as described in

the Operator's Manual.

Remove the top cover of the display console by remov-

ing the two screws at the rear of the unit. Carefully

set the top cover aside to prevent accidental scratch-

ing. If the unit has an interlock switch, enable the test

mode by pulling up on the interlock switch plunger.

At this point, there should be no diskette in the drive,

and the disk terminator should be installed as des-

cribed in the Operator's Manual.

Synopsis of Power-On Diagnostics

When the power switch on the TRS-80 Model II is

raised to the "ON" position, the Z80 microprocessor

automatically starts executing the program in the

bootstrap ROM on the CPU board. The program per-

forms the following functions in order:

1. The initialization parameters are sent to the CRT

controller and the screen memory is set to the

value 0A0H. This causes the CRT to come on

with asolid white screen.

2. The ROM checksum is verified to assure that the

ROM is present and functioning properly. If the

checksum indicates that the ROM data is bad,

"CK ERROR" will be outputted to the CRT and

the computer will halt.

3. ACPU test program is run to verify proper data

transfers between registers in the Z80 CPU. Any

failure of this test will cause "Z8 ERROR" to be

output to the CRT and the computer will halt.

4. The RAM memory from 1000H to 7FFFH is then

tested with asimple read-complement-write-com-

pare-complement-write routine. Any faulty mem-

ory locations in this 28K byte range will cause

"MF ERROR" to be output to the CRT and the

computer will halt.

5. The keyboard will be "flushed" of any characters

input up until this time.

6. The message "INSERT DISKETTE" is displayed

on the CRT.

Bootstrap Sequence

7. Wait until diskette is inserted and door is closed.

8. Screen is cleared to spaces (all black).

9. Track seek command is sent to floppy disk

controller.

10. Wait three seconds and check disk status.

11. "DC ERROR" if floppy disk controller is still

busy or seek error is indicated or drive not re-

stored to track 0.

12. "D0 ERROR" if drive indicates not ready.

13. "SC ERROR" if there is aCRC error in the

track ID field.

14. Read track into RAM.

15. "TK ERROR" if program not found on track 0.

16. "SC ERROR" if there is aCRC error in the

record ID.

17. "LD ERROR" if alost data error occurs.

18. "RS ERROR" if the data loaded in is not in Radio

Shack boot record format.

19. Call system diagnostic routine.

20. Jump to TRSDOS.

Detailed Troubleshooting Instructions

1. Turn on the Model II Computer by raising the

power switch to "ON". Wait afew seconds for

the CRT to warm up. Adjust brightness and con-

trast controls at the front of the console. If the

video display comes on, go to 10. If not, go to 2.

NOTE: For overseas models configured for 50 Hz

operation, the "HERZ50" programs on the TRS-

DOS diskette must be called to prevent "jittering"

of the video display and to provide accuracy of the

real time clock.

2. If the pilot light is on, go to 4. If the pilot light/

reset switch connector is seated correctly on the

CPU board, go to 3. If not, reposition the connec-

tor and go to 2.

3. Check for +5 volts on one of the P.C. boards. If

this is not in the range from 4.8 to 5.2 volts, go

to 5. If the voltage is incorrect, the LED must be

burned out. Replace and go to 1

.

4. Check the filament of the CRT. If it is lit, go to 7.

If it is not:

Check the +12 volt supply at the CRT electronics

board (pin 1is ground, pin 7is +12V).

If +12 volts is present, go to 6.

5. Switch off power. Check the power supply fuse

and replace if necessary. Check for shorts across

the power supplies. If shorts are found, remove

cards from card cage until the shorts disappear,

then replace the offending card. Reassemble and

go to 1

.

Otherwise, power supply may have malfunctioned.

Remove and replace the power supply. Go to 1.

6. CRT has burned out filament. Replace and go to

1. (Refer to Section VII for installation proced-

ures.)

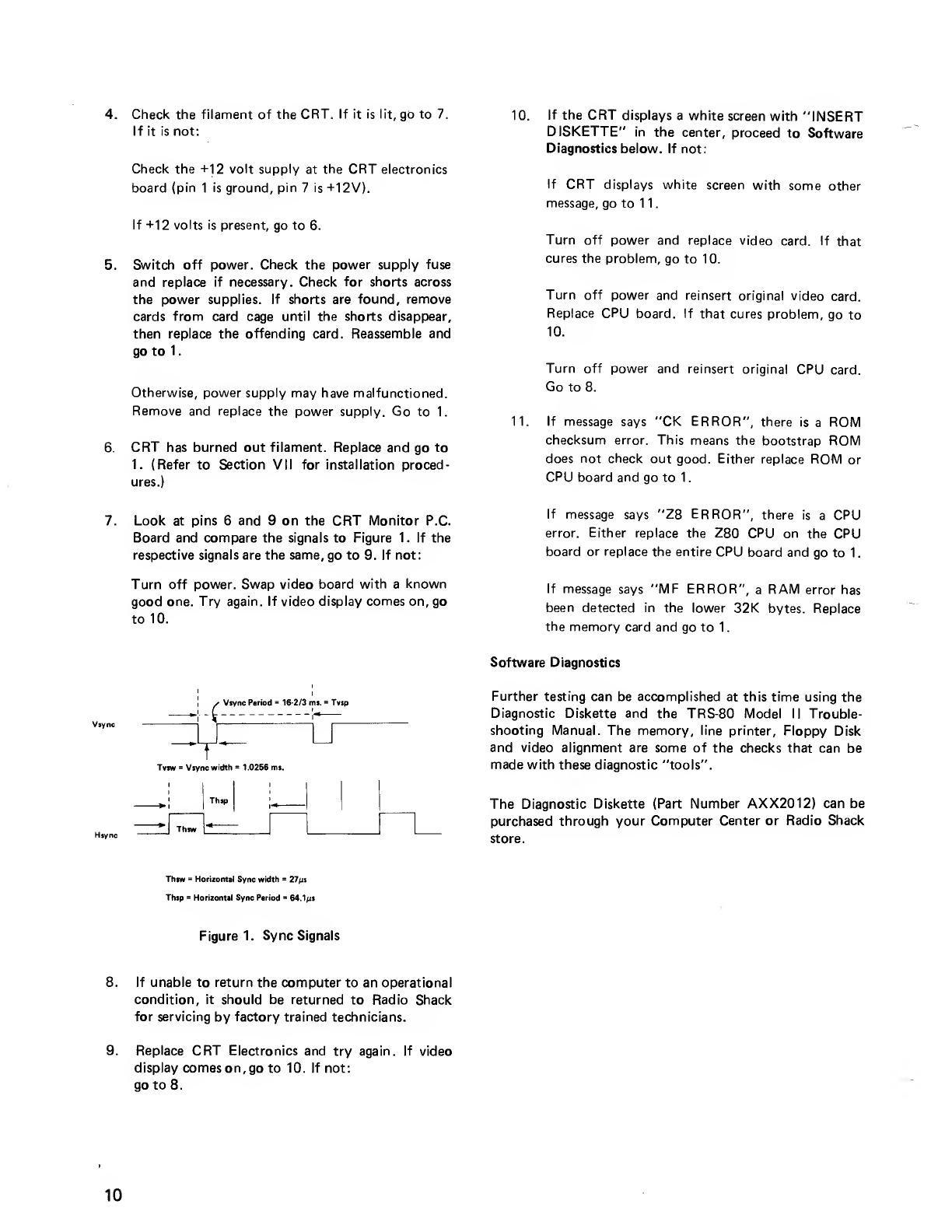

7. Look at pins 6 and 9on the CRT Monitor P.C.

Board and compare the signals to Figure 1. If the

respective signals are the same, go to 9. If not:

Turn off power. Swap video board with aknown

good one. Try again. If video display comes on, go

to 10.

10. If the CRT displays awhite screen with "INSERT

DISKETTE" in the center, proceed to Software

Diagnostics below. If not:

If CRT displays white screen with some other

message, go to 11

.

Turn off power and replace video card. If that

cures the problem, go to 10.

Turn off power and reinsert original video card.

Replace CPU board. If that cures problem, go to

10.

Turn off power and reinsert original CPU card.

Go to 8.

11. If message says "CK ERROR", there is aROM

checksum error. This means the bootstrap ROM

does not check out good. Either replace ROM or

CPU board and go to 1.

If message says "Z8 ERROR", there is aCPU

error. Either replace the Z80 CPU on the CPU

board or replace the entire CPU board and go to 1

.

If message says "MF ERROR", aRAM error has

been detected in the lower 32K bytes. Replace

the memory card and go to 1.

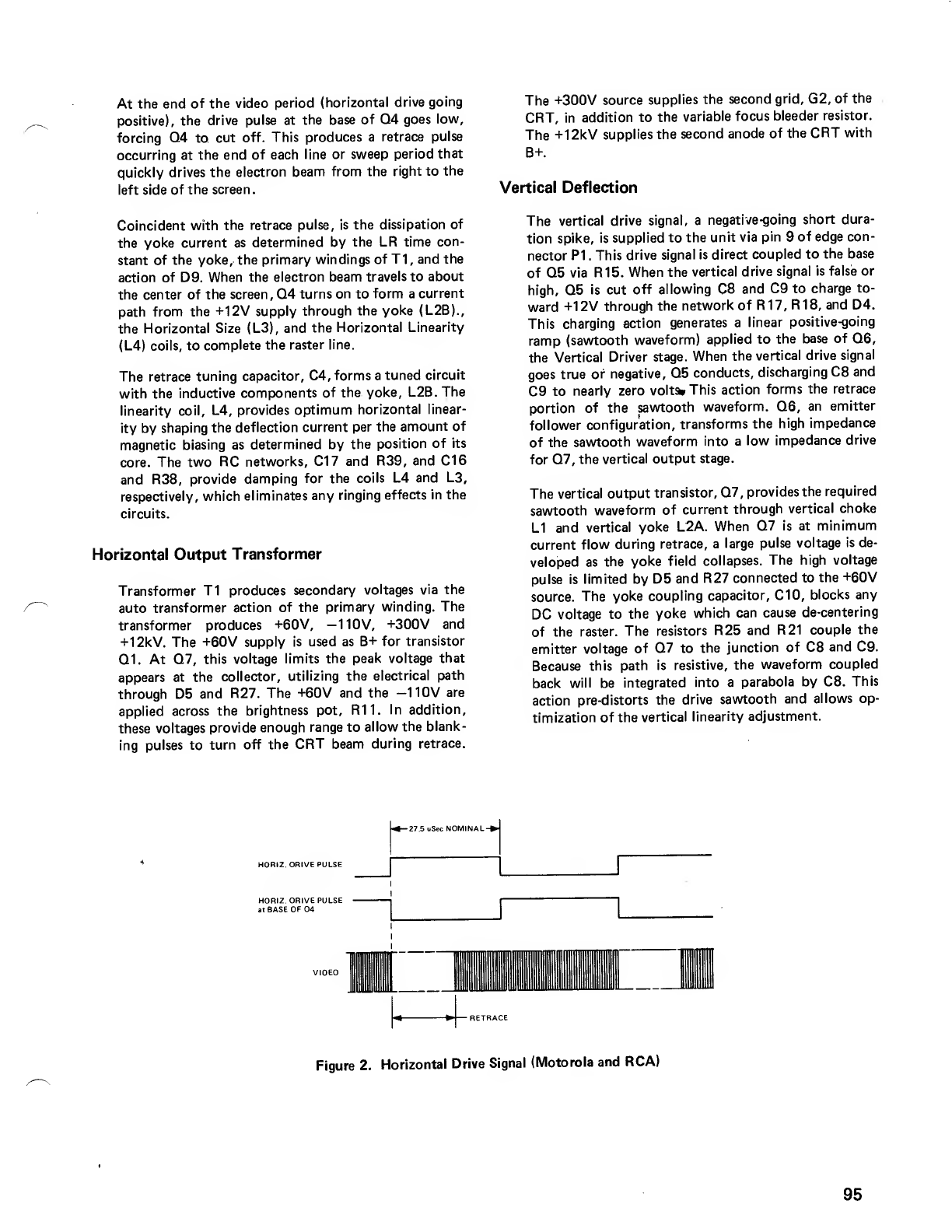

Vsync

Hjync

•Vsync Period =16-2/3 mi. =Tvsp

-T~

Tvsw =Vsync width =1.0256 ms.

Thip

*

Thsw I

* *

L

Software Diagnostics

Further testing can be accomplished at this time using the

Diagnostic Diskette and the TRS-80 Model II Trouble-

shooting Manual. The memory, line printer. Floppy Disk

and video alignment are some of the checks that can be

made with these diagnostic "tools".

The Diagnostic Diskette (Part Number AXX2012) can be

purchased through your Computer Center or Radio Shack

store.

Thtw =Horizontal Sync width =27/is

Thip =Horizontal Sync Period s64.1jus

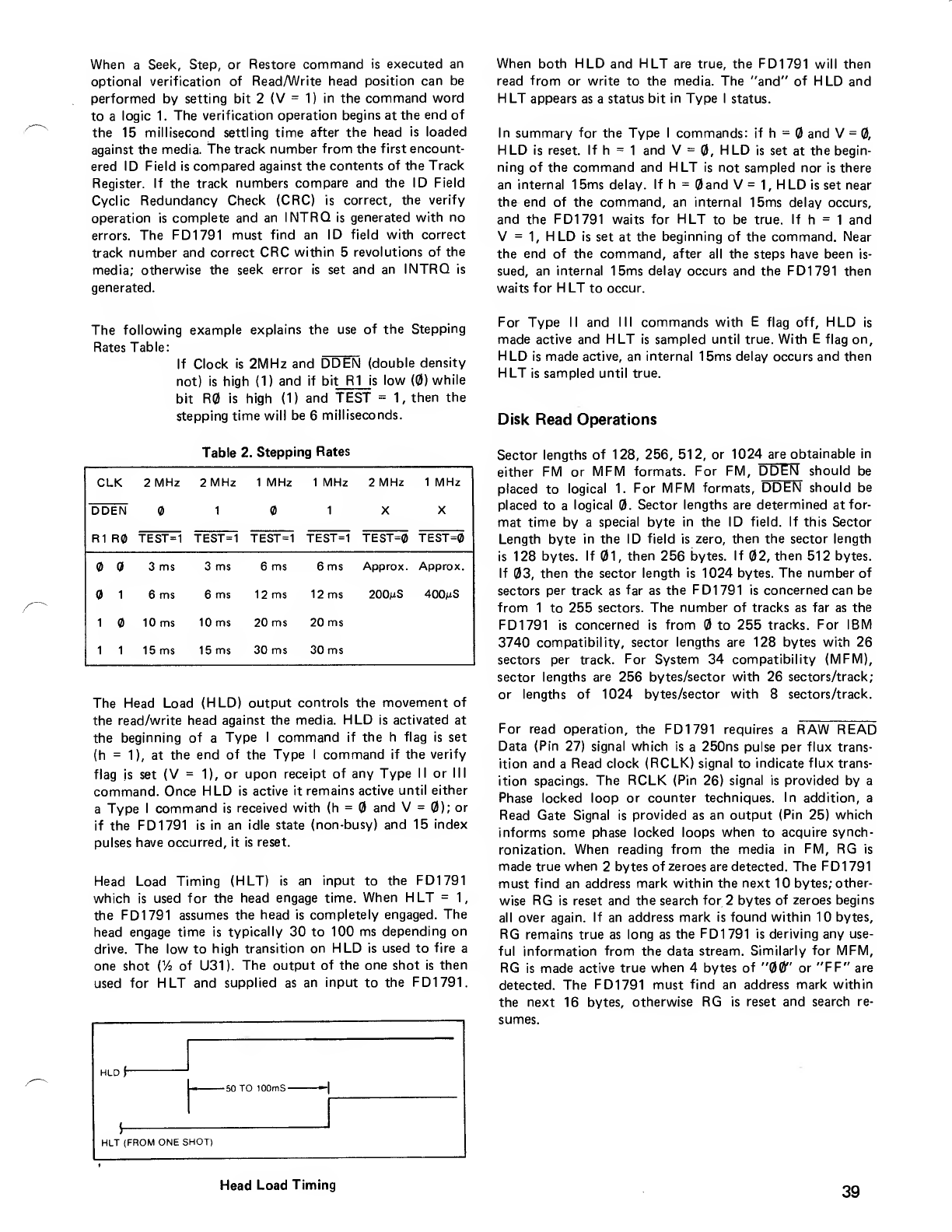

Figure 1. Sync Signals

8. If unable to return the computer to an operational

condition, it should be returned to Radio Shack

for servicing by factory trained technicians.

9. Replace CRT Electronics and try

display comes on, go to 10. If not:

goto 8.

sin. If video

10

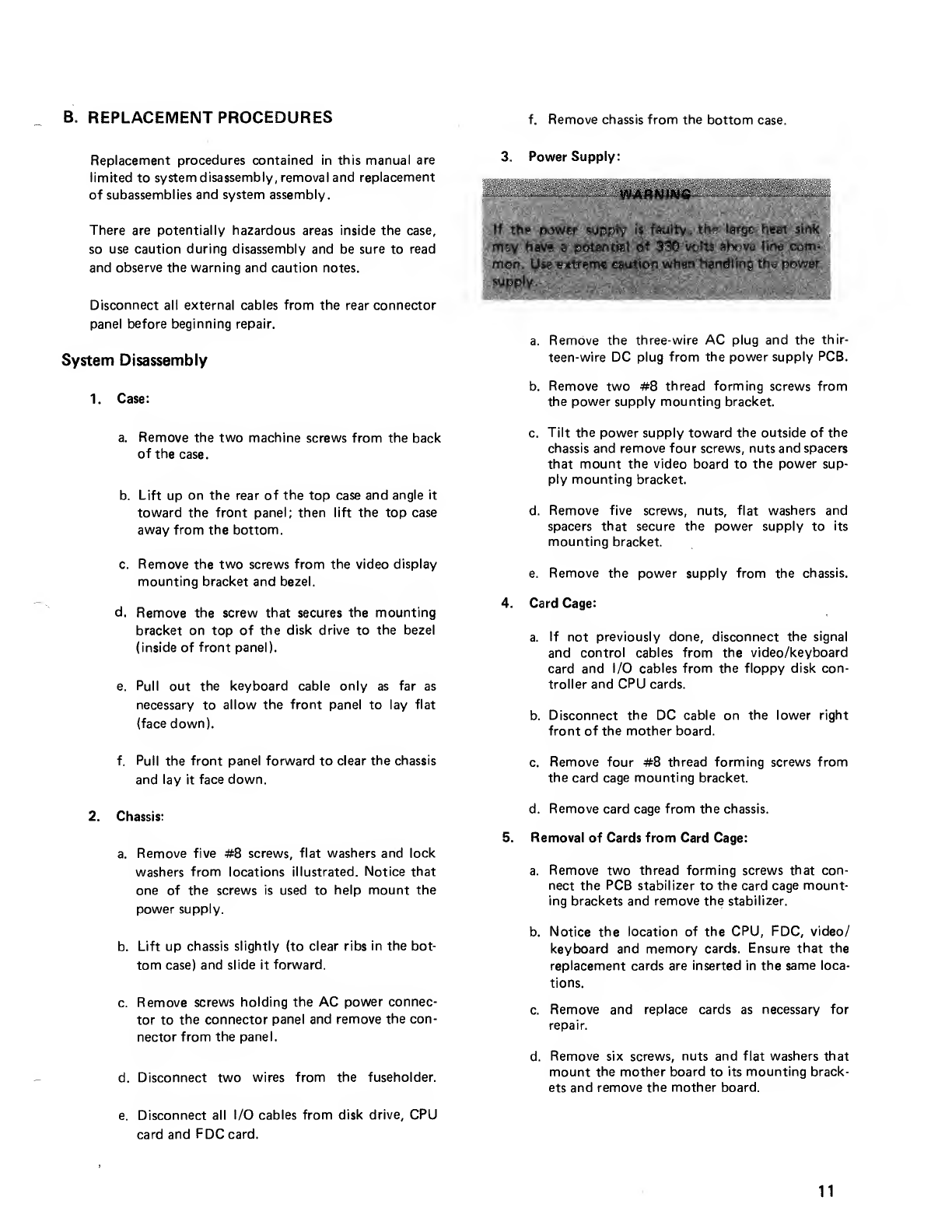

B. REPLACEMENT PROCEDURES f. Remove chassis from the bottom case.

Replacement procedures contained in this manual are

limited to system disassembly, removal and replacement

of subassemblies and system assembly.

There are potentially hazardous areas inside the case,

so use caution during disassembly and be sure to read

and observe the warning and caution notes.

Disconnect all external cables from the rear connector

panel before beginning repair.

System Disassembly

1. Case:

a. Remove the two machine screws from the back

of the case.

b. Lift up on the rear of the top case and angle it

toward the front panel; then lift the top case

away from the bottom.

c. Remove the two screws from the video display

mounting bracket and bezel.

d. Remove the screw that secures the mounting

bracket on top of the disk drive to the bezel

(inside of front panel).

e. Pull out the keyboard cable only as far as

necessary to allow the front panel to lay flat

(face down).

f. Pull the front panel forward to clear the chassis

and lay it face down.

2. Chassis:

a. Remove five #8 screws, flat washers and lock

washers from locations illustrated. Notice that

one of the screws is used to help mount the

power supply.

b. Lift up chassis slightly (to clear ribs in the bot-

tom case) and slide it forward.

c. Remove screws holding the AC power connec-

tor to the connector panel and remove the con-

nector from the panel.

d. Disconnect two wires from the fuseholder.

e. Disconnect all I/O cables from disk drive, CPU

card and FDC card.

3. Power Supply:

''" ;^"~-'^ A~'*-p&ijiM-'~'

""""" :-/^/v \.- >j

If the power supply is faulty, the large heat sink

may have apotential of 330 volts above line com-

mon. Use extreme caution when handling the power

a. Remove the three-wire AC plug and the thir-

teen-wire DC plug from the power supply PCB.

b. Remove two #8 thread forming screws from

the power supply mounting bracket.

c. Tilt the power supply toward the outside of the

chassis and remove four screws, nuts and spacers

that mount the video board to the power sup-

ply mounting bracket.

d. Remove five screws, nuts, flat washers and

spacers that secure the power supply to its

mounting bracket.

e. Remove the power supply from the chassis.

4. Card Cage:

a. If not previously done, disconnect the signal

and control cables from the video/keyboard

card and I/O cables from the floppy disk con-

troller and CPU cards.

b. Disconnect the DC cable on the lower right

front of the mother board.

c. Remove four #8 thread forming screws from

the card cage mounting bracket.

d. Remove card cage from the chassis.

5. Removal of Cards from Card Cage:

a. Remove two thread forming screws that con-

nect the PCB stabilizer to the card cage mount-

ing brackets and remove the stabilizer.

b. Notice the location of the CPU, FDC, video/

keyboard and memory cards. Ensure that the

replacement cards are inserted in the same loca-

tions.

c. Remove and replace cards as necessary for

repair.

d. Remove six screws, nuts and flat washers that

mount the mother board to its mounting brack-

ets and remove the mother board.

11

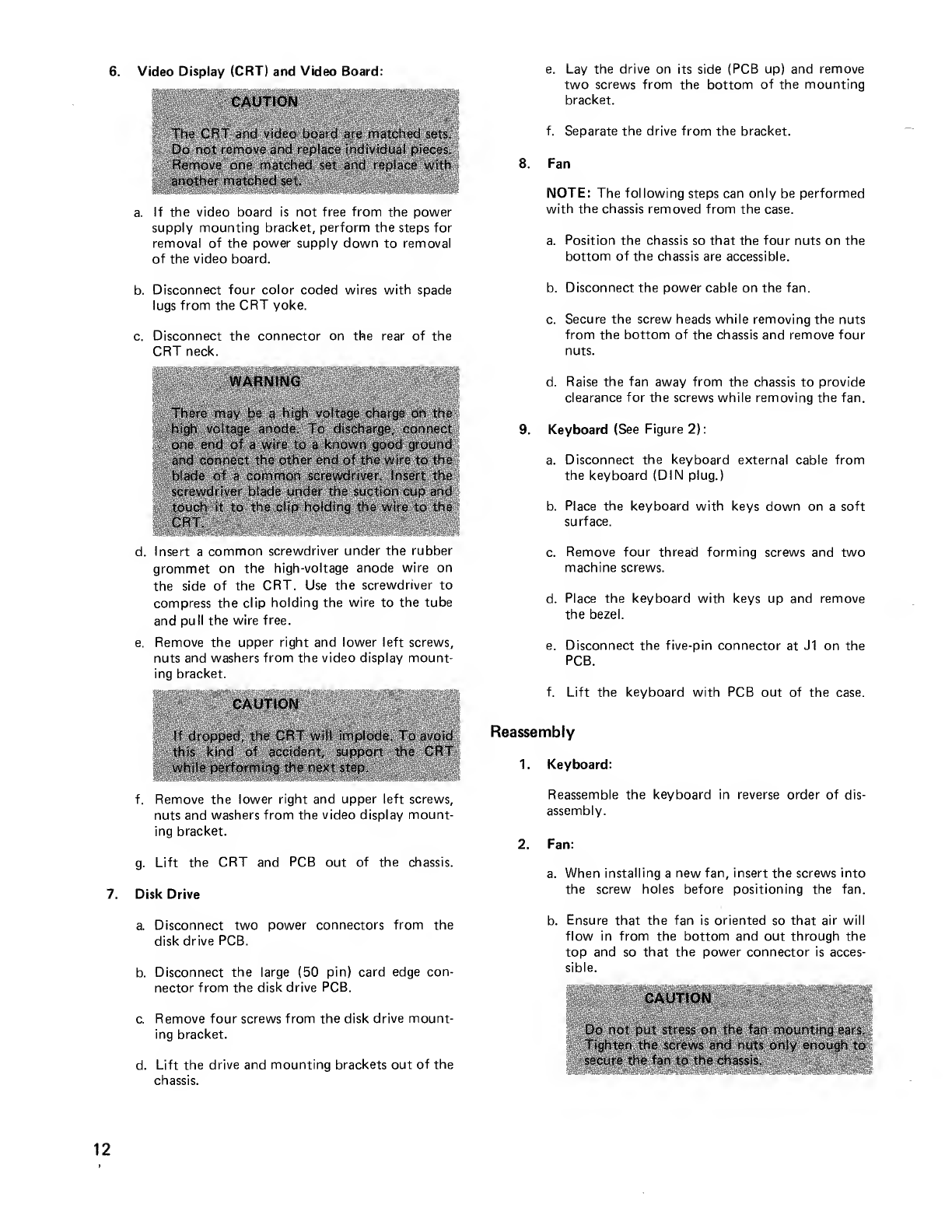

6. Video Display (CRT) and Video Board:

CAUTION

The CRT and video board are matched sets.

Do not remove and replace individual pieces.

Remove one matched set and replace with

another matched set.

a. If the video board is not free from the power

supply mounting bracket, perform the steps for

removal of the power supply down to removal

of the video board.

b. Disconnect four color coded wires with spade

lugs from the CRT yoke.

c. Disconnect the connector on the rear of the

CRT neck.

WARNING

There may be ahigh voltage charge on the

high voltage anode. To discharge, connect

one end of awire to aknown good ground

and connect the other end of the wire to the

blade of acommon screwdriver. Insert the

screwdriver blade under the suction cup and

touch it to the clip holding the wire to the

d. Insert acommon screwdriver under the rubber

grommet on the high-voltage anode wire on

the side of the CRT. Use the screwdriver to

compress the clip holding the wire to the tube

and pull the wire free.

e. Remove the upper right and lower left screws,

nuts and washers from the video display mount-

ing bracket.

CAUTION

If dropped, the CRT will implode. To avoid

this kind of accident, support the CRT

while performing the next step.

f. Remove the lower right and upper left screws,

nuts and washers from the video display mount-

ing bracket.

g. Lift the CRT and PCB out of the chassis.

7. Disk Drive

a. Disconnect two power connectors from the

disk drive PCB.

b. Disconnect the large (50 pin) card edge con-

nector from the disk drive PCB.

c. Remove four screws from the disk drive mount-

ing bracket.

d. Lift the drive and mounting brackets out of the

chassis.

e. Lay the drive on its side (PCB up) and remove

two screws from the bottom of the mounting

bracket.

f. Separate the drive from the bracket.

8. Fan

NOTE: The following steps can only be performed

with the chassis removed from the case.

a. Position the chassis so that the four nuts on the

bottom of the chassis are accessible.

b. Disconnect the power cable on the fan.

c. Secure the screw heads while removing the nuts

from the bottom of the chassis and remove four

nuts.

d. Raise the fan away from the chassis to provide

clearance for the screws while removing the fan.

9. Keyboard (See Figure 2):

a. Disconnect the keyboard external cable from

the keyboard (DIN plug.)

b. Place the keyboard with keys down on asoft

surface.

c. Remove four thread forming screws and two

machine screws.

d. Place the keyboard with keys up and remove

the bezel.

e. Disconnect the five-pin connector at J1 on the

PCB.

f. Lift the keyboard with PCB out of the case.

Reassembly

1. Keyboard:

Reassemble the keyboard in reverse order of dis-

assembly.

2. Fan:

a. When installing anew fan, insert the screws into

the screw holes before positioning the fan.

b. Ensure that the fan is oriented so that air will

flow in from the bottom and out through the

top and so that the power connector is acces-

sible.

CAUTION

Do not put stress on the fan mounting ears.

Tighten the screws and nuts only enough to

secure the fan to the chassis.

12

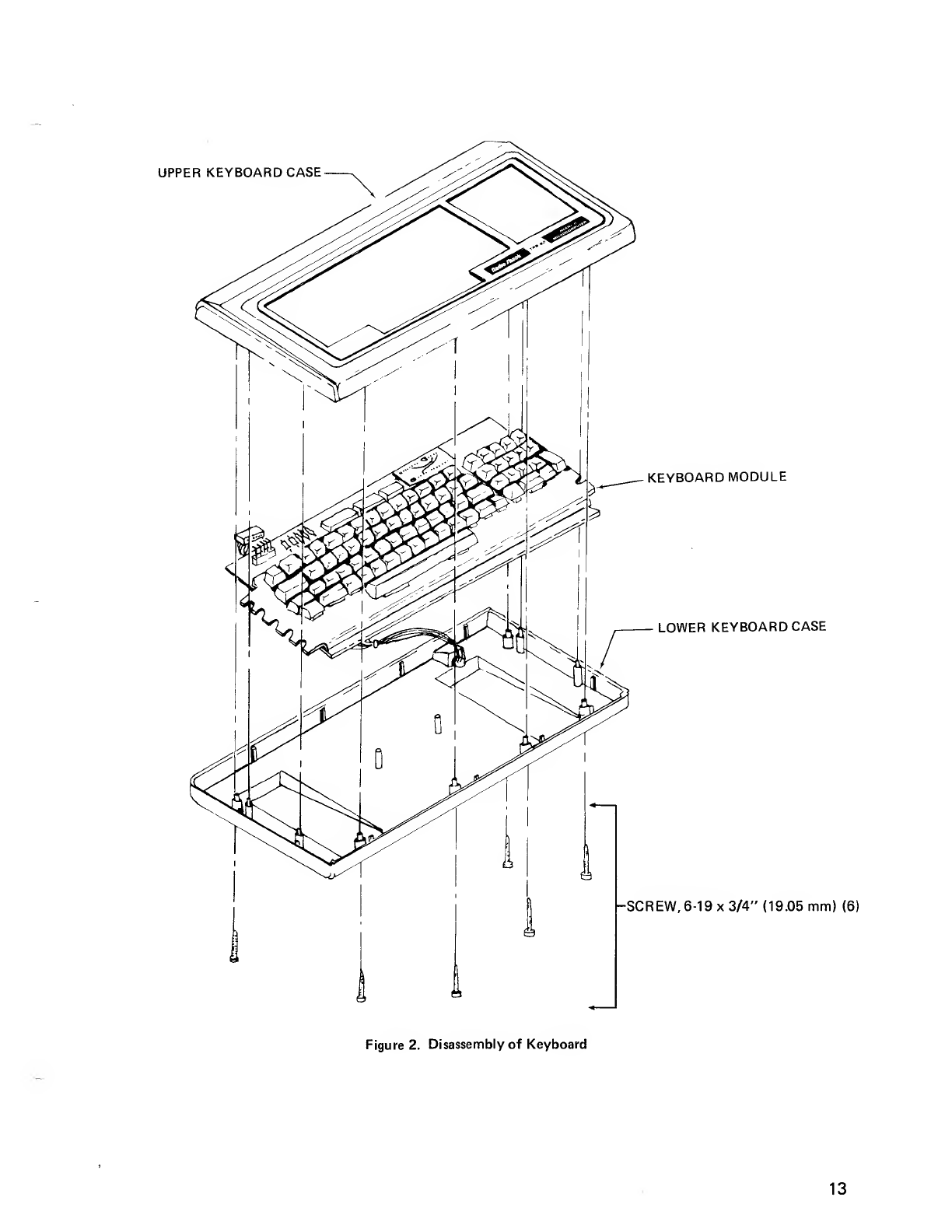

UPPER KEYBOARD CASE

KEYBOARD MODULE

-LOWER KEYBOARD CASE

-SCREW, 6-19 x3/4" (19.05 mm) (6)

Figure 2. Disassembly of Keyboard

13

c. Position the chassis so that the fan mounting

screws are accessible from the bottom of the

chassis.

d. Secure the screw heads while installing the nuts.

e. Tighten the nuts only enough to ensure that the

fan is secure.

3. Disk Drive:

a. Lay the disk drive on its side (PCB up) and

position its chassis mounting bracket (wide end

forward) to align holes in bracket with the

holes in the drive base plate.

b. Install two screws that secure the drive to the

mounting bracket.

c. Place the drive with mounting bracket into

the chassis and align the screw holes in the

bracket and in the chassis.

d. Install four screws loosely so that the drive's

position can be properly adjusted. Then tighten

the screws that secure the bracket to the chassis.

e. Install two power connectors and the card edge

connector on the drive.

4. Video Display (CRT) and Video Board

a. Position the CRT and align its mounting holes

with its mounting bracket.

b. Install the upper left and lower right screws and

mounting hardware.

c. Install the lower left and upper right screws and

mounting hardware.

d. Position the CRT matched video board inside

of the chassis.

e. Install the plug on the rear of the CRT neck.

f. Install the four color coded wires with spade

lugs to their associated terminals (as determined

by acolored dot on the yoke near each term-

inal).

g. The video board will be installed on the power

supply mounting bracket, (see the procedures

for installation of the power supply).

5. Card Cage:

a. Align the mother board mounting holes with

the holes in the left and right PCB mounting

brackets. (The left bracket has aleft 90° bend

at the rear and the right bracket has aright

90° bend at the rear).

b. Install six screws, nuts and flat washers that

secure the mother board to the brackets.

c. Install the CPU, FDC, video/keyboard and

memory cards to the mother board. Be sure of

proper orientation in the card cage.

d. Align the holes in the PCB stabilizer with the

holes in the left and right PCB bracket and in-

stall two thread forming screws.

e. Position the card cage inside of the chassis and

align the holes in the brackets with the holes

in the chassis.

f. Install four screws that secure the card cage to

the chassis.

g. Connect the DC cables to the connector on the

lower right front of the mother board.

h. Connect the I/O cables to the FDC and CPU

cards and connect the control cables to the

video/keyboard card.

6. Power Supply:

a. Align the power supply mounting holes with

the holes in its bracket mounting plate.

b. Individually, position five spacers to align with

the mounting holes between the power supply

board and its mounting plate.

c. Install five screws, nuts and flat washers that

secure the power supply to the bracket.

d. Position the power supply in the chassis and

tilt it toward the outside of the chassis.

e. Align the video board mounting holes with its

mounting holes on the power supply bracket

mounting plate.

f. Position four spacers to align with the mount-

ing holes.

g. Install four screws, nuts and flat washers that

secure the video board to the bracket.

h. Position the holes in the mounting bracket to

the holes in the chassis and install two thread

forming screws that secure the bracket to the

chassis.

7. Chassis:

a. Position the chassis inside the bottom case so

that the two wires can be connected to the

terminals on the fuse holder and the AC power

input connector can be installed on the connec-

tor panel.

b. Install the two wires to the fuse holder.

c. Install two screws that secure the AC power

input connector to the connector panel.

14

d. Lift up the chassis (to clear the ribs on the case

bottom) and position it so that its mounting

holes align with those in the case.

e. Install five screws, flat washers and lockwashers

that secure the chassis to the bottom case.

8. Case:

a. Position the front panel (bezel) on the chassis.

b. Install one screw that secures the bezel to the

top bracket on the disk drive.

c. Install the two screws that secure the bezel to

the video display mounting bracket.

d. Position the top case at the lip of the bottom

case and angle it downward (toward the back)

until the top case is properly seated.

e. Install two machine screws that secure the top

case to the bottom case.

REPLACEMENT PARTS LIST (Subassemblies)

Manufacturer's Radio Shack

Description Part Number Part Numbei

CPU Board 8893405 AXX0501

CRT (with Video Board) 8709043 AXX8000

Disk Drive, SA800 8709042 AXX5002

Disk Drive, SA800 PCB AXX0308

FDC Board 8893425 AXX0505

Keyboard Module 8790504 AXX0204

Memory Board, 32K 8893410 AXX0502

Memory Board, 64K 8893415 AXX0503

Mother Board Assembly 8893430 AXX0500

Power Supply, AA1 1080 8790010 AXX6003

Video Generator Board 8893420 AXX0504

15

SECTION

CPU MODULE

17

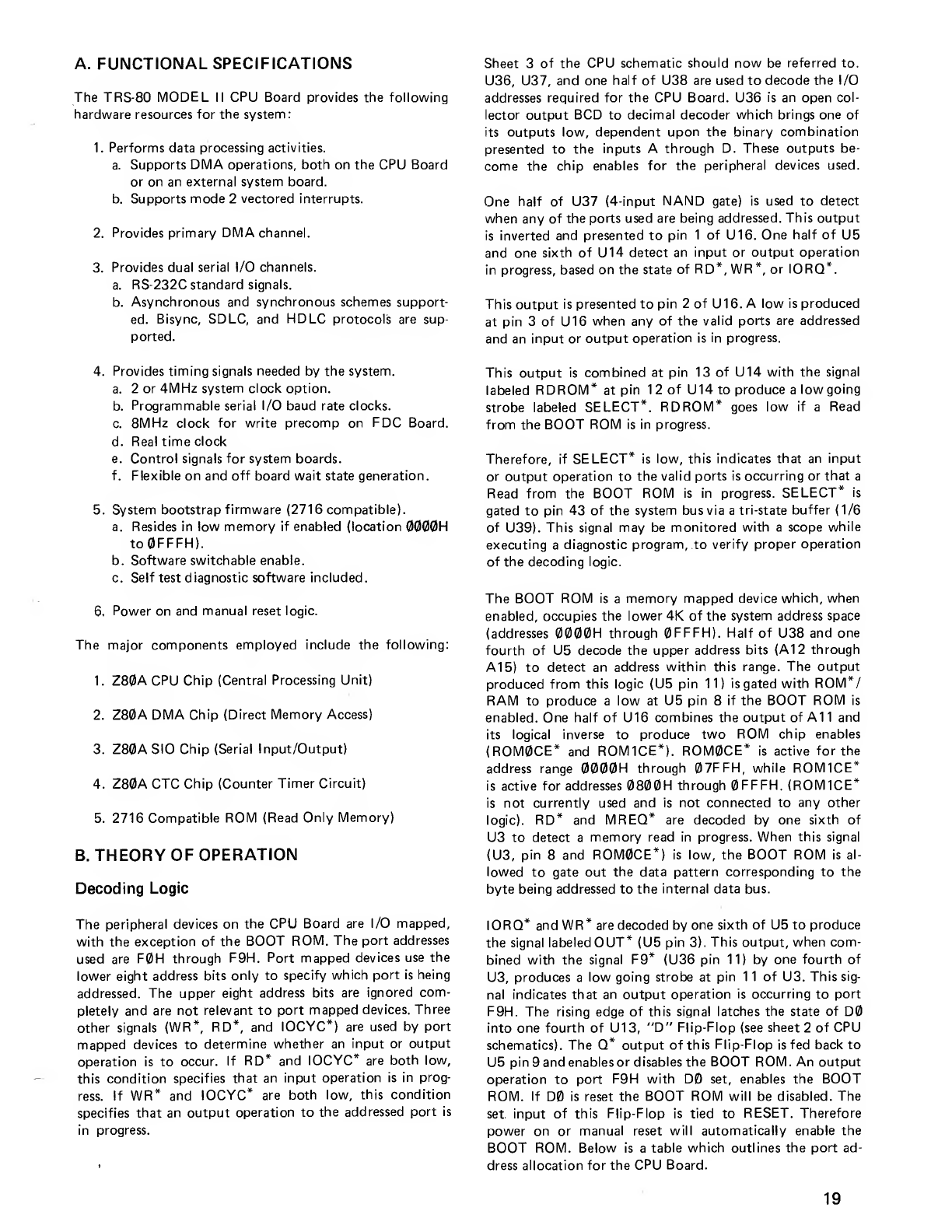

A. FUNCTIONAL SPECIFICATIONS

The TRS-80 MODEL II CPU Board provides the following

hardware resources for the system:

1. Performs data processing activities.

a. Supports DMA operations, both on the CPU Board

or on an external system board.

b. Supports mode 2vectored interrupts.

2. Provides primary DMA channel.

3. Provides dual serial I/O channels.

a. RS-232C standard signals.

b. Asynchronous and synchronous schemes support-

ed. Bisync, SDLC, and HDLC protocols are sup-

ported.

4. Provides timing signals needed by the system.

a. 2or 4M Hz system clock option.

b. Programmable serial I/O baud rate clocks.

c. 8MHz clock for write precomp on FDC Board.

d. Real time clock

e. Control signals for system boards.

f. Flexible on and off board wait state generation.

5. System bootstrap firmware (2716 compatible).

a. Resides in low memory if enabled (location 0000H

to0FFFH).

b. Software switchable enable.

c. Self test diagnostic software included.

6. Power on and manual reset logic.

The major components employed include the following:

1. Z80A CPU Chip (Central Processing Unit)

2. Z80A DMA Chip (Direct Memory Access)

3. Z80ASIO Chip (Serial Input/Output)

4. Z80A CTC Chip (Counter Timer Circuit)

5. 2716 Compatible ROM (Read Only Memory)

B. THEORY OF OPERATION

Decoding Logic

The peripheral devices on the CPU Board are I/O mapped,

with the exception of the BOOT ROM. The port addresses

used are F0H through F9H. Port mapped devices use the

lower eight address bits only to specify which port is being

addressed. The upper eight address bits are ignored com-

pletely and are not relevant to port mapped devices. Three

other signals (WR\ RD*, and IOCYC*) are used by port

mapped devices to determine whether an input or output

operation is to occur. If RD* and IOCYC* are both low,

this condition specifies that an input operation is in prog-

ress. If WR* and IOCYC* are both low, this condition

specifies that an output operation to the addressed port is

in progress.

Sheet 3of the CPU schematic should now be referred to.

U36, U37, and one half of U38 are used to decode the I/O

addresses required for the CPU Board. U36 is an open col-

lector output BCD to decimal decoder which brings one of

its outputs low, dependent upon the binary combination

presented to the inputs Athrough D. These outputs be-

come the chip enables for the peripheral devices used.

One half of U37 (4-input NAND gate) is used to detect

when any of the ports used are being addressed. This output

is inverted and presented to pin 1of U16. One half of U5

and one sixth of U14 detect an input or output operation

in progress, based on the state of RD*, WR *, or IORQ*.

This output is presented to pin 2of U16. Alow is produced

at pin 3of U16 when any of the valid ports are addressed

and an input or output operation is in progress.

This output is combined at pin 13 of U14 with the signal

labeled RDROM* at pin 12 of U14 to produce alow going

strobe labeled SELECT*. RDROM* goes low if aRead

from the BOOT ROM is in progress.

Therefore, if SELECT* is low, this indicates that an input

or output operation to the valid ports is occurring or that a

Read from the BOOT ROM is in progress. SELECT* is

gated to pin 43 of the system bus via atri-state buffer (1/6

of U39). This signal may be monitored with ascope while

executing adiagnostic program, to verify proper operation

of the decoding logic.

The BOOT ROM is amemory mapped device which, when

enabled, occupies the lower 4K of the system address space

(addresses 0000H through 0FFFH). Half of U38 and one

fourth of U5 decode the upper address bits (A12 through

A15) to detect an address within this range. The output

produced from this logic (U5 pin 11) is gated with ROM*/

RAM to produce alow at U5 pin 8if the BOOT ROM is

enabled. One half of U16 combines the output of A1 1and

its logical inverse to produce two ROM chip enables

(ROM0CE* and ROM1CE*). ROM0CE* is active for the

address range 0000H through 07FFH, while ROM1CE*

is active for addresses 0800H through 0FFFH. (ROM1CE*

is not currently used and is not connected to any other

logic). RD* and MREQ* are decoded by one sixth of

U3 to detect amemory read in progress. When this signal

(U3, pin 8and ROM0CE*) is low, the BOOT ROM is al-

lowed to gate out the data pattern corresponding to the

byte being addressed to the internal data bus.

IORQ* and WR* are decoded by one sixth of U5 to produce

the signal labeledOUT* (U5 pin 3). This output, when com-

bined with the signal F9* (U36 pin 11) by one fourth of

U3, produces alow going strobe at pin 11of U3. This sig-

nal indicates that an output operation is occurring to port

F9H. The rising edge of this signal latches the state of D0

into one fourth of U13, "D" FMp-Flop (see sheet 2of CPU

schematics). The Q* output of this Flip-Flop is fed back to

U5 pin 9and enablesor disables the BOOT ROM. An output

operation to port F9H with DD set, enables the BOOT

ROM. If D0 is reset the BOOT ROM will be disabled. The

set. input of this Flip-Flop is tied to RESET. Therefore

power on or manual reset will automatically enable the

BOOT ROM. Below is atable which outlines the port ad-

dress allocation for the CPU Board.

19

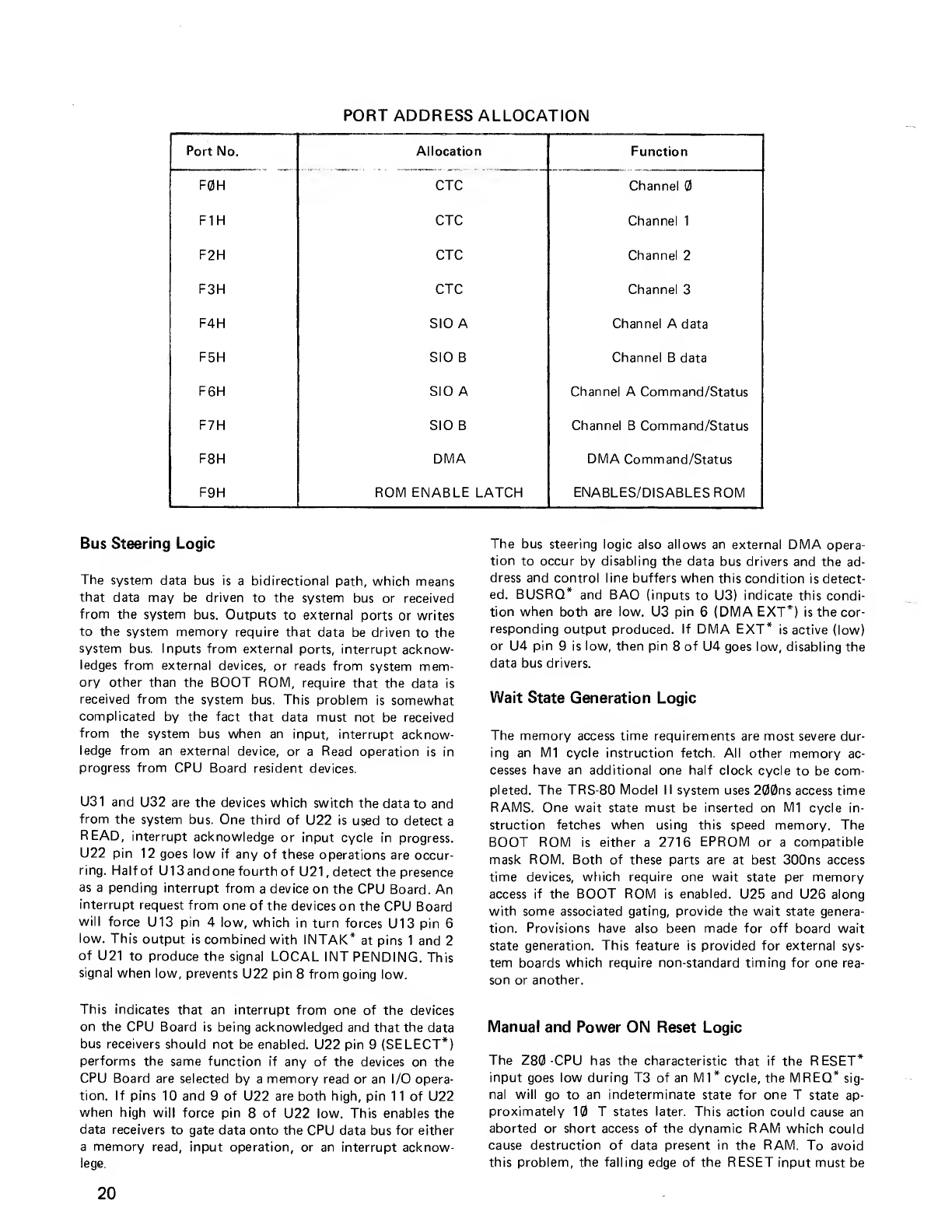

PORT ADDRESS ALLOCATION

Port No. Allocation Function

F0H CTC Channel

F1H CTC Channel 1

F2H CTC Channel 2

F3H CTC Channel 3

F4H SIO AChannel Adata

F5H SIO BChannel Bdata

F6H SIO AChannel ACommand/Status

F7H SIOB Channel BCommand/Status

F8H DMA DMA Command/Status

F9H ROM ENABLE LATCH ENABLES/DISABLES ROM

Bus Steering Logic

The system data bus is abidirectional path, which means

that data may be driven to the system bus or received

from the system bus. Outputs to external ports or writes

to the system memory require that data be driven to the

system bus. Inputs from external ports, interrupt acknow-

ledges from external devices, or reads from system mem-

ory other than the BOOT ROM, require that the data is

received from the system bus. This problem is somewhat

complicated by the fact that data must not be received

from the system bus when an input, interrupt acknow-

ledge from an external device, or aRead operation is in

progress from CPU Board resident devices.

U31 and U32 are the devices which switch the data to and

from the system bus. One third of U22 is used to detect a

READ, interrupt acknowledge or input cycle in progress.

U22 pin 12 goes low if any of these operations are occur-

ring. Half of U13 and one fourth of U21 ,detect the presence

as apending interrupt from adevice on the CPU Board. An

interrupt request from one of the devices on the CPU Board

will force U13 pin 4low, which in turn forces U13 pin 6

low. This output is combined with INTAK* at pins 1and 2

of U21 to produce the signal LOCAL INT PENDING. This

signal when low, prevents U22 pin 8from going low.

This indicates that an interrupt from one of the devices

on the CPU Board is being acknowledged and that the data

bus receivers should not be enabled. U22 pin 9(SELECT*)

performs the same function if any of the devices on the

CPU Board are selected by amemory read or an I/O opera-

tion. If pins 10 and 9of U22 are both high, pin 1 1 of U22

when high will force pin 8of U22 low. This enables the

data receivers to gate data onto the CPU data bus for either

amemory read, input operation, or an interrupt acknow-

lege.

The bus steering logic also allows an external DMA opera-

tion to occur by disabling the data bus drivers and the ad-

dress and control line buffers when this condition is detect-

ed. BUSRQ* and BAO (inputs to U3) indicate this condi-

tion when both are low. U3 pin 6(DMA EXT*) is the cor-

responding output produced. If DMA EXT* is active (low)

or U4 pin 9is low, then pin 8of U4 goes low, disabling the

data bus drivers.

Wait State Generation Logic

The memory access time requirements are most severe dur-

ing an M1 cycle instruction fetch. All other memory ac-

cesses have an additional one half clock cycle to be com-

pleted. The TRS-80 Model II system uses 200ns access time

RAMS. One wait state must be inserted on M1 cycle in-

struction fetches when using this speed memory. The

BOOT ROM is either a2716 EPROM or acompatible

mask ROM. Both of these parts are at best 300ns access

time devices, which require one wait state per memory

access if the BOOT ROM is enabled. U25 and U26 along

with some associated gating, provide the wait state genera-

tion. Provisions have also been made for off board wait

state generation. This feature is provided for external sys-

tem boards which require non-standard timing for one rea-

son or another.

Manual and Power ON Reset Logic

The Z80-CPU has the characteristic that if the RESET*

input goes low during T3 of an Ml* cycle, the MREQ* sig-

nal will go to an indeterminate state for one Tstate ap-

proximately 10 Tstates later. This action could cause an

aborted or short access of the dynamic RAM which could

cause destruction of data present in the RAM. To avoid

this problem, the falling edge of the RESET input must be

20

synchronized with the falling edge of M1 *. One half of U28

and U27 perform this sychronization as well as provide a

one-shot to limit the duration of the CPU RESET pulse.

The one-shot duration is approximately 70ns per switch de-

pression, and is required to avoid suspending CPU refresh of

dynamic memory for aperiod long enough to destroy

RAM contents. Without the one-shot this could occur if

the reset switch were held closed for along period. The

connector J2 connects the reset switch to this logic and also

provides the current limited +5 volts for the "Power-On"

indicator on the front panel.

System Clock Generation Logic

The heart of the clock generation logic is an 8MHz crystal

oscillator formed by Y1 ,C21 ,R23, R24, and three 74LS74

Flip-Flops (page 1of the CPU schematics). The output of

U29, pin 8should be an 8MHz square wave. The 8MHz

signal is divided down by one half of U28 and U2 to pro-

duce the 4MHz, 2MHz, and 1MHz clocks needed by the

system. The 8MHz signal is buffered by one fourth of U30

and fed directly to pin 46 of the system bus. This clock is

utilized by the write compensation circuitry of the FDC

Board. Ajumper option is provided to select either a4MHz

or 2MHz main system clock for the Z80 family parts. This

output is divided by 2, to provide the clock inputs for the

Z80-CTC when operating in the counter mode. Normal

system operation requires that the main system clock run

at 4MHz and should be used at 2MHz only under unusual

circumstances. The output of U28pin 9(main system clock)

is conditioned by the clock buffer circuitry implemented

with Q1, C3, R2, R3, R4, and a74S04 inverter. The clock

buffer circuitry insures fast rise and fall times and close to

5volts peak to peak amplitude transitions. These clock

characteristics are important to the Z80A family of com-

ponents when operating at maximum frequency (4 MHz).

terrupting by pulling low on its IEO line. The next device in

the chain, sensing alow at the IEI input, will pass this pri-

ority signal on to the next device by pulling low on its IEO

line.

This priority scheme works fine as long as no more than

four Z80 family devices are connected to the chain. If more

than four devices are used, the delays through each MOS

part get excessive and not enough time will be allowed to

resolve interrupt contention. The Model II system currently

uses four Z80 family parts in the daisy chain. To allow for

expansion of the system, acarry look ahead scheme was

employed using U23 (74S182) and four 74S04 inverters.

This scheme anticipates IEO low condition at any of the

three devices on the CPU Board and generates alook-ahead

signal to the propagate output (U23 pin 7). This signal is in-

verted and fed to IEO (pin 14) of the system bus. This sig-

nal when low, prevents downstream devices from generat-

ing an interrupt and results in a25ns maximum ripple time

for any IEO to propagate out for the devices on the CPU

Board. This allows up to four more family devices (eight

total) to be used in the system without additional logic.

El ABuffers

The logic internal to the CPU Board (SIO inputs and out-

puts in this discussion) operate with TTL logic levels (3.5V

or more =Logic 1, and 0.8V or less =Logic 0). The logic

convention used for interfacing two RS-232-C devices is

EIA levels (-3V or less =logic 1, +3V or more =Logic 0).

The logic levels must therefore be converted from one con-

vention to the other when interfacing to an external device.

U10, U9, and U8 provide the EIA to TTL conversion

while U7 and U6 provide the TTL to EIA conversion.

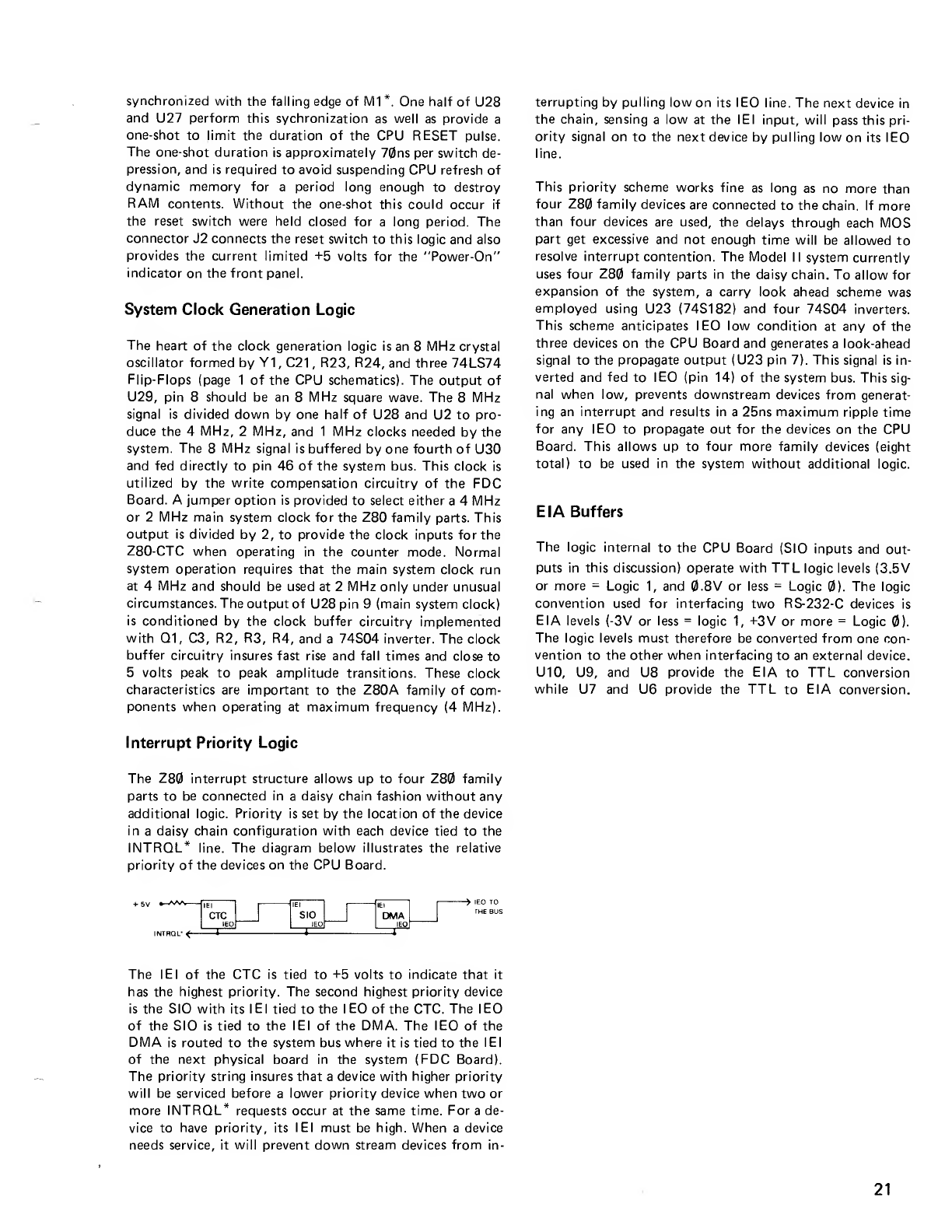

Interrupt Priority Logic

The Z80 interrupt structure allows up to four Z80 family

parts to be connected in adaisy chain fashion without any

additional logic. Priority is set by the location of the device

in adaisy chain configuration with each device tied to the

INTRQL* line. The diagram below illustrates the relative

priority of the devices on the CPU Board.

CTC SIO

INTRQL" ^-

DMA

IEO

-> IEO TO

THE BUS

The IEI of the CTC is tied to +5 volts to indicate that it

has the highest priority. The second highest priority device

is the SIO with its IEI tied to the IEO of the CTC. The IEO

of the SIO is tied to the IEI of the DMA. The IEO of the

DMA is routed to the system bus where it is tied to the IEI

of the next physical board in the system (FDC Board).

The priority string insures that adevice with higher priority

will be serviced before alower priority device when two or

more INTRQL* requests occur at the same time. For ade-

vice to have priority, its IEI must be high. When adevice

needs service, it will prevent down stream devices from in-

21

CONNECTOR J1 SIGNAL DESCRIPTIONS

PIN SIGNAL DESCRIPTION

1Power Ground

2Not Connected

3Transmit Data Channel A

4Transmit S.E.T.

5Received Data Channel A

6Not Connected

7Request to Send Channel A

8Receiver Clock Channel A

9Clear to Send Channel A

10 Not Connected

1

1

Data Set Ready Channel A

12 Not Connected

13 Power Ground

14 Data Terminal Ready Channel A

15 Carrier Detect Channel A

16-21 Not Connected

22 Transmit Clock Channel A

23 Not Connected

24 Not Connected

25 Not Connected

26 Power Ground

27 Not Connected

28 Transmit Data Channel B

29 Not Connected

30 Received Data Channel B

31 Not Connected

32 Request to Send Channel B

33 Receiver/Transmitter Clock Channel B

34 Clear to Send Channel B

35 Data Set Ready Channel B

36 Not Connected

37 Not Connected

38 Power Ground

39 Data Terminal Ready Channel B

40 Carrier Detect Channel B

22

s>

010

^iII

63 -CZJ-

L1Ji11

fer

ll"?P!

fill

-&

IJ-r~rif 2

m

W8:-tea --' z+o

i{2Z>«-*3

%6|H

£

s5^

m^i it-it in ii mi i«yjip

•tttl» PJ

~">L_

M' frkm sz3

nl jfe 4^\

v?B *sHO#ZJi

Fl

Jail |-

o

o

a

E

o

o

(0

o

CQ

+^

'5

o

a

a)

D

Q.

o

>

>-

CO

DC

x

23

a

3

o

re

O

O

D

Q.

D

Q.

o

91

>•

n

0)

3

24 'J

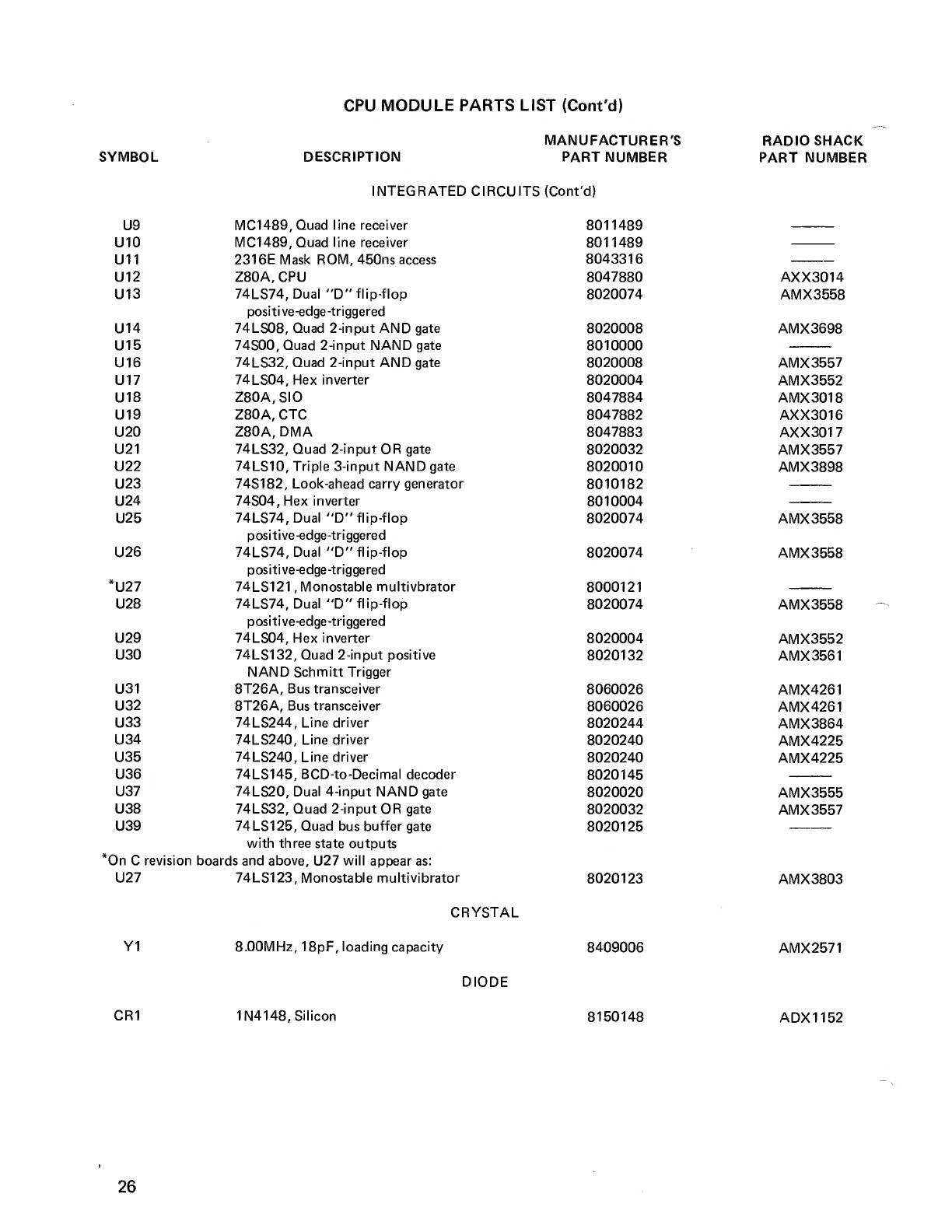

CPU MODULE PARTS LIST

SYMBOL DESCRIPTION

MANUFACTURER'S

PART NUMBER RADIO SHACK

PART NUMBER

ELECTRICAL

PC Board 8709040

CAPACITORS

C1

C2

C3

C4

C14

C15

C16

C20

C21

C22

C23

C24

C25

C26

C27

C28

C31

C32

C33

C34

C35

C36

C37

C38

C39

C40

C41

C42

C43

0.1/uF, 50V, Monolithic

33;uF, 50V, Electrolytic, Radial

33pF, 50V, Ceramic Disc

0.1juF, 50V, Monolithic

0.1;iiF, 50V, Monolithic

33/iF, 50V, Electrolytic Radial

0.1/iF, 50V, Monolithic

0.1juF, 50V, Monolithic

470pF, 50V, Ceramic Disc

O.ljuF, 50V, Monolithic

0.1/nF- 50V, Monolithic

33juF, 50V, Electrolytic, Radial

0.1/zF, 50V, Monolithic

0.1/xF, 50V, Monolithic

33/xF, 50V, Electrolytic, Radial

0.1/zF, 50V, Monolithic

0.1juF, 50V, Monolithic

33juF, 50V, Electrolytic, Axial

0.1//F, 50V, Monolithic

33/zF, 50V, Electrolytic, Axial

1000pF, 50V, Ceramic Disc

33;uF, 50V, Electrolytic, Axial

O.ljuF, 50V, Monolithic

100juF, 16V, Electrolytic, Axial

Not Used

Not Used

33jUF, 50V, Electrolytic, Axial

0.1#F, 50V, Monolithic

33/iF, 50V, Monlithic, Radial

8374104

8326331

8300334

8374104

8374104

8326331

8374104

8374104

8301474

8374104

8374104

8326331

8374104

8374104

8326331

8374104

8374104

8316334

8374104

8316334

8303104

8316334

8374104

8317101

8316334

8374104

8326331

ACC336QJAP

ACC330QJCP

ACC336QJAP

ACC471QJCP

ACC336QJAP

ACC336QJAP

ACC336QJAA

ACC336QJAA

ACC102QJCP

ACC336QJAA

ACC107QDAA

ACC366QJAA

ACC336QJAP

INTEGRATED CIRCUITS

U1

U2

U3

U4

U5

U6

U7

U8

74S04,Hex inverter

74LS74,Dual "D" flip-flop

positive-edge-triggered

74LS32, Quad 2-input OR gate

74LS08, Quad 2-input AND gate

74LS32, Quad 2-input OR gate

MC1488, Quad line driver

MC1488, Quad line driver

MC1489, Quad line receiver

8010004

8020074

8020032

8020008

8020032

8011488

8011488

8011489

AMX3558

AMX3557

AMX3698

AMX3557

25

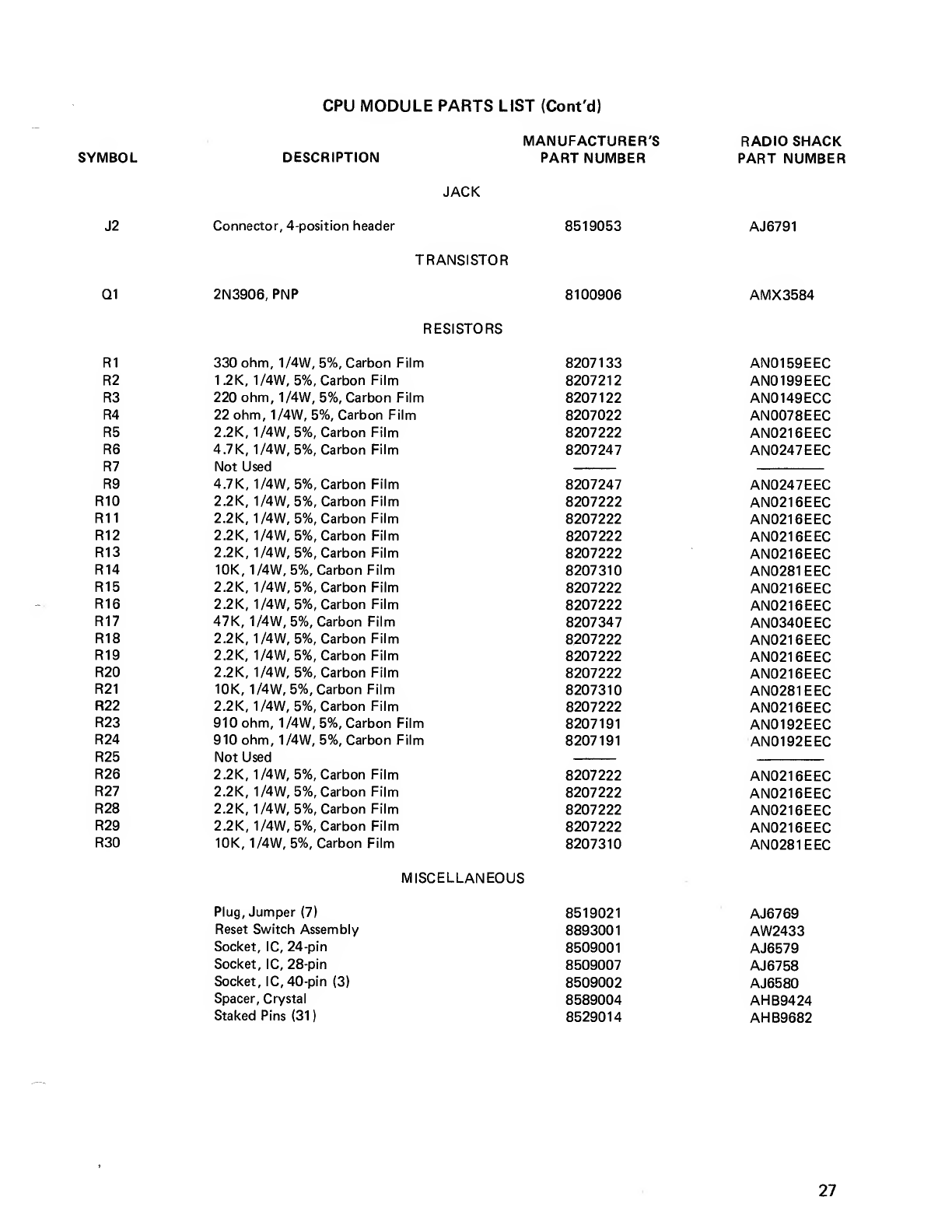

CPU MODULE PARTS LIST (Cont'd)

SYMBOL DESCRIPTION

MANUFACTURER'S

PART NUMBER RADIO SHACK

PART NUMBER

INTEGRATED CIRCUITS (Cont'd)

U9 MC1489, Quad line receiver

U10 MC1489, Quad line receiver

U11 231 6E Mask ROM, 450ns access

U12 Z80A, CPU

U13 74LS74,Dual "D" flip-flop

positive -edge-triggered

U14 74LS08, Quad 2-input AND gate

U15 74S00, Quad 2-input NAND gate

U16 74LS32, Quad 2-input AND gate

U17 74LS04, Hex inverter

U18 Z80A,SIO

U19 Z80A, CTC

U20 Z80A, DMA

U21 74LS32, Quad 2-input OR gate

U22 74LS10, Triple 3-input NAND gate

U23 74S182, Look-ahead carry generator

U24 74S04, Hex inverter

U25 74LS74,Dual "D" flip-flop

positive -edge-triggered

U26 74LS74,Dual "D" flip-flop

positive-edge-triggered

*U27 74LS121 ,Monostable multivbrator

U28 74LS74,Dual "D" flip-flop

positive-edge-triggered

U29 74LS04, Hex inverter

U30 74LS132, Quad 2-input positive

NAND Schmitt Trigger

U31 8T26A, Bus transceiver

U32 8T26A, Bus transceiver

U33 74LS244, Line driver

U34 74LS240, Line driver

U35 74LS240, Line driver

U36 74LS145, BCD-to-Decimal decoder

U37 74LS20, Dual 4-input NAND gate

U38 74LS32, Quad 2-input OR gate

U39 74LS125, Quad bus buffer gate

with three state outputs

On Crevision boards and above, U27 will appear as:

U27 74LS123, Monostable multivibrator

8011489

8011489

8043316

8047880

8020074

8020008

8010000

8020008

8020004

8047884

8047882

8047883

8020032

8020010

8010182

8010004

8020074

8020074

8000121

8020074

8020004

8020132

8060026

8060026

8020244

8020240

8020240

8020145

8020020

8020032

8020125

8020123

AXX3014

AMX3558

AMX3698

AMX3557

AMX3552

AMX3018

AXX3016

AXX301

7

AMX3557

AMX3898

AMX3558

AMX3558

AMX3558

AMX3552

AMX3561

AMX4261

AMX4261

AMX3864

AMX4225

AMX4225

AMX3555

AMX3557

AMX3803

CRYSTAL

Y1 8.00MHz, 18pF, loading capacity 8409006 AMX2571

DIODE

CR1 1N4148, Silicon 8150148 ADX1152

26

CPU MODULE PARTS LIST (Cont'd)

SYMBOL DESCRIPTION

MANUFACTURER'S

PART NUMBER RADIO SHACK

PART NUMBER

JACK

J2 Connector, 4-position header 8519053 AJ6791

TRANSISTOR

Q1 2N3906, PNP 8100906 AMX3584

RESISTORS

R1

R2

R3

R4

R5

R6

R7

R9

R10

R11

R12

R13

R14

R15

R16

R17

R18

R19

R20

R21

R22

R23

R24

R25

R26

R27

R28

R29

R30

330 ohm, 1/4W, 5%, Carbon Film

1.2K, 1/4W, 5%, Carbon Film

220 ohm, 1/4W, 5%, Carbon Film

22 ohm, 1/4W, 5%, Carbon Film

2.2K, 1/4W, 5%, Carbon Film

4.7K, 1/4W, 5%, Carbon Film

Not Used

4.7K, 1/4W, 5%, Carbon Film

2.2K, 1/4W, 5%, Carbon Film

2.2K, 1/4W, 5%, Carbon Film

2.2K, 1/4W, 5%, Carbon Film

2.2K, 1/4W, 5%, Carbon Film

10K, 1/4W, 5%, Carbon Film

2.2K, 1/4W, 5%, Carbon Film

2.2K, 1/4W, 5%, Carbon Film

47K, 1/4W, 5%, Carbon Film

2.2K, 1/4W, 5%, Carbon Film

2.2K, 1/4W, 5%, Carbon Film

2.2K, 1/4W, 5%, Carbon Film

10K, 1/4W, 5%, Carbon Film

2.2K, 1/4W, 5%, Carbon Film

910 ohm, 1/4W, 5%, Carbon Film

910 ohm, 1/4W, 5%, Carbon Film

Not Used

2.2K, 1/4W, 5%, Carbon Film

2.2K, 1/4W, 5%, Carbon Film

2.2K, 1/4W, 5%, Carbon Film

2.2K, 1/4W, 5%, Carbon Film

10K, 1/4W, 5%, Carbon Film

8207133

8207212

8207122

8207022

8207222

8207247

8207247

8207222

8207222

8207222

8207222

8207310

8207222

8207222

8207347

8207222

8207222

8207222

8207310

8207222

8207191

8207191

8207222

8207222

8207222

8207222

8207310

AN0159EEC

AN0199EEC

AN0149ECC

AN0078EEC

AN0216EEC

AN0247EEC

AN0247EEC

AN0216EEC

AN0216EEC

AN0216EEC

AN0216EEC

AN0281EEC

AN0216EEC

AN0216EEC

AN0340EEC

AN0216EEC

AN0216EEC

AN0216EEC

AN0281EEC

AN0216EEC

AN0192EEC

AN0192EEC

AN0216EEC

AN0216EEC

AN0216EEC

AN0216EEC

AN0281EEC

MISCELLANEOUS

Plug, Jumper (7)

Reset Switch Assembly

Socket, IC, 24-pin

Socket, IC, 28-pin

Socket, IC, 40-pin (3)

Spacer, Crystal

Staked Pins (31

)

8519021

8893001

8509001

8509007

8509002

8589004

8529014

AJ6769

AW2433

AJ6579

AJ6758

AJ6580

AHB9424

AHB9682

27

iSV

2<3

UIZ

zeoA

WAIT* -t-

I4ALT ¥-*

(ews.)

Z4 WAIT*

HALT*

6u$izq *

us

Ai4

Ali

Alt

All

AW

A°>

At

AT

A6>

45

A4

A2

Al

**

Dl

D(s

PS

D4

OS

DZ

PI

40

39

30

36

3?

S4

J5

5c?

Ii_

INT*

gFSH*

IO&Q*

fZD*

HZ*

\

V

V

\

V

V

IS

14

Z6 /

27

19

Zl

zz

z^ BusaK-*-

lo

11

11

24

l°>

4c

\

\

\

UZD

V

z&

l°i

Jk 1

3*

34

$£_

zo>

\0

\t

\

20

17

-Z60, CTC+S.I0,

-»- int^l.*-, SMEET ;

-> IMTI%? */BUSl

clock l£?<z-icz

33 pP

\|C3

I.ZK

RE

220-Q Z2i2

WW «-AAAA-

R3

2rJ590<&

aiPNP

5USAK y-

/'3

in

no

A9

A3

AT

lib

AS

A4

AS

AZ

Al

A0

Dl

Db

DS

04

PS

DZ

Dl

D0

M4 *

lozq*

Maaq *

tzo*

Niz *

$>*

en*

zb>oa

DK/IA

INT*

lex

IE0

C£*

&A0*

busizq*

Vic

&ND

37

Id

hU>

zs

lie

12

IS

io

-isv

\- i9

,\ ZZ

?.*>

\I

\z

\5

\4

s

Vb

\7

\&

\17

\\(,

\Iff

\14

\13

\II

\10

\<5

M<f

A?

AS

A7

Ai

AS

A*

Al

At

A'

At

Dl

Db

DS

94

DS

DZ

Dl

Vcc

Vpp

Ce*

OB*

till

£HD.

24

Z\

h<p

r?3

•A

zd

SAX. I

KOU$C£*

>1?EAD *

V

1?+

-* ZBo,CTC +SIOiP/*J 12, ZA\"P iNTZlfL*-

-y 74-ildt, Cn-hV PinI ^HEBTZ

^to sjz4, piisneerz.

+5V

i-Sv

-^TPxe

AH

All

\AI±

\AI±

A'S

,IZD

\ZFC,

\WI?

IZE

£LL bUSAK

$2.2K

H+SV

S&4

fP5

J-

2/A MHZ CLOC£

muz

-^s,—4/8 MHZ

O1PReCOfAPoPTloU

U23„

^-<p

iS^4-

as ^4-

-W."

—

R23

Figure 3. CPU Schemal

chematic Diagram —Sheet 1

29

V

V

19

lb

FdOVA Z.SO A

CPU

g.£K

yS/ I^AAAA-

RII

+5/

Ml*-<-

ice

330H

IDPCT

Switch

32

1fb5iTicW

iiL

CTC

WO

INT*

*5V

TA

-^cecrcpr

3+

5?

39

4o

56

52

lo

rfi 2\

EesET PIN Z&>

iS

IHT£QL*,SU.t

IZ

15

c/o fR*DA

B/S \

'gxcA

07

DC ™A

pr KywcA

04 CACTSA

Dl A\PCPA

DZ uie

Dl TtDA

o4 ersA

Ml VDm*

luizq

£0 /Z^OS.

3'

mg%TXCS

&<;eT*

CZZTO* <Zim6

CCD6

STO/<Z)

.12

.13

n

it*

28

o-

o- MJt

*o

27

Z9

-jT 14

+S"/

//

-^760 DMA ,P'NJ 3S

PA£6 1

pfi^e -l

Cn +X

Cn

74SI&2

U23

Gi GZ (5.1

it

~TT

1124

EX-OUT

TO I£ OUT

PIN 11 8'JS

M1 **r-

c.H.1

<SlQ

q

UE5

74CS 74

Hqohc

LIZ7 12)

74t8l23 IN9I4

POWEZ ON />AJO MANUAL

ZES.ET LOCiC

3L.RI

luF

IC3S

-tSv

IS<?4 T£"

Xo 1—^upset #

A- (to cpv A^c6

Figure 3. CPU Schematic Dia

30

ftAIT* flVCPo)

P24 CPU

(FiZoM SOS)

70, P43

RIB

4T£st fbi/urs

/AtJoS^s.pa 1)

:ic Diagram -Sheet 2

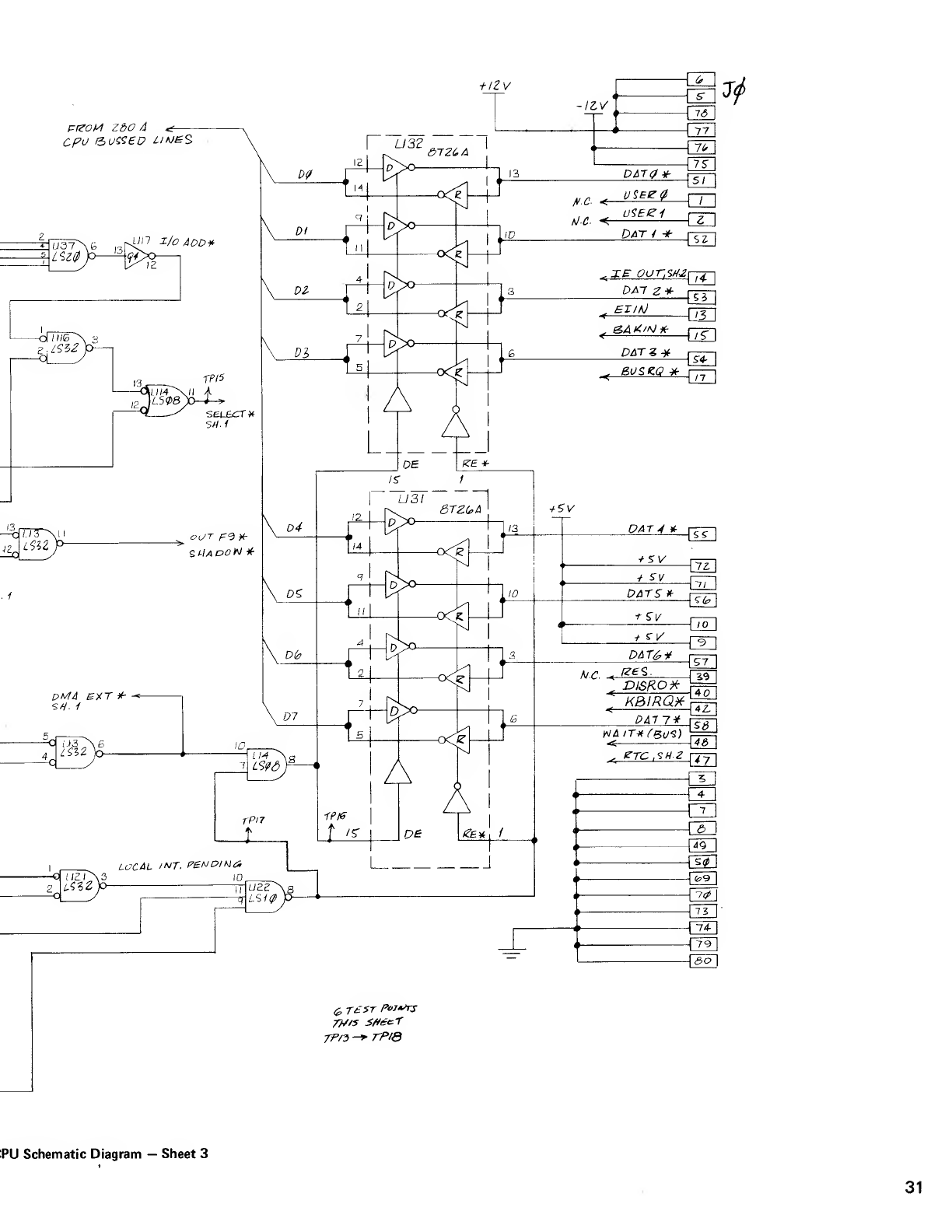

BUSSED DATA UKJES

-*

peoM Z&O A<Zf\J

Select* •*

Figure 3. CPU Schema

FIZOM ZdO A<=

CpO SUSSED LlhJBS

U37\£ 13

un x/o AoDi

our P3X-

St-IADON *

St/. /

4ZS?2)o- I0>

t>C

Di

D2.

Di

04

DZ

D(a

D7

114

J—

+iZv

Y~ U32

f^> 612CA

I•-

$r

f^r -4i

l

-

LOCAL INT. PENPINt*

TizT\3 io

dizp nL'HC

-IZV -un

-Q3

-T7*l

zf

DATtf'*\1S

5/

«.c < useei CO

-fsF|

Pat /-*-

El/fJ

S3

PI

P/iTg -*

gl^Sgt? *- -t^:

-DE]

•/SV

O/dTV *

/5^

Vs"y

P/3T5~*

•^S"/

/SV

DAT6*

~{5D

-cei

~9

*.C. -_£!£ 57

-|~ie~

14Z.

P477* \S3

NA IT* {BUS) ,

<[46

-m

4^n

-R5

-tia

-IfoQ

-[7£]

-|<9o

PU Schematic Diagram —Sheet 3

tp/3 -* rPie

31

SECTION IV

FLOPPY DISK CONTROLLER

33

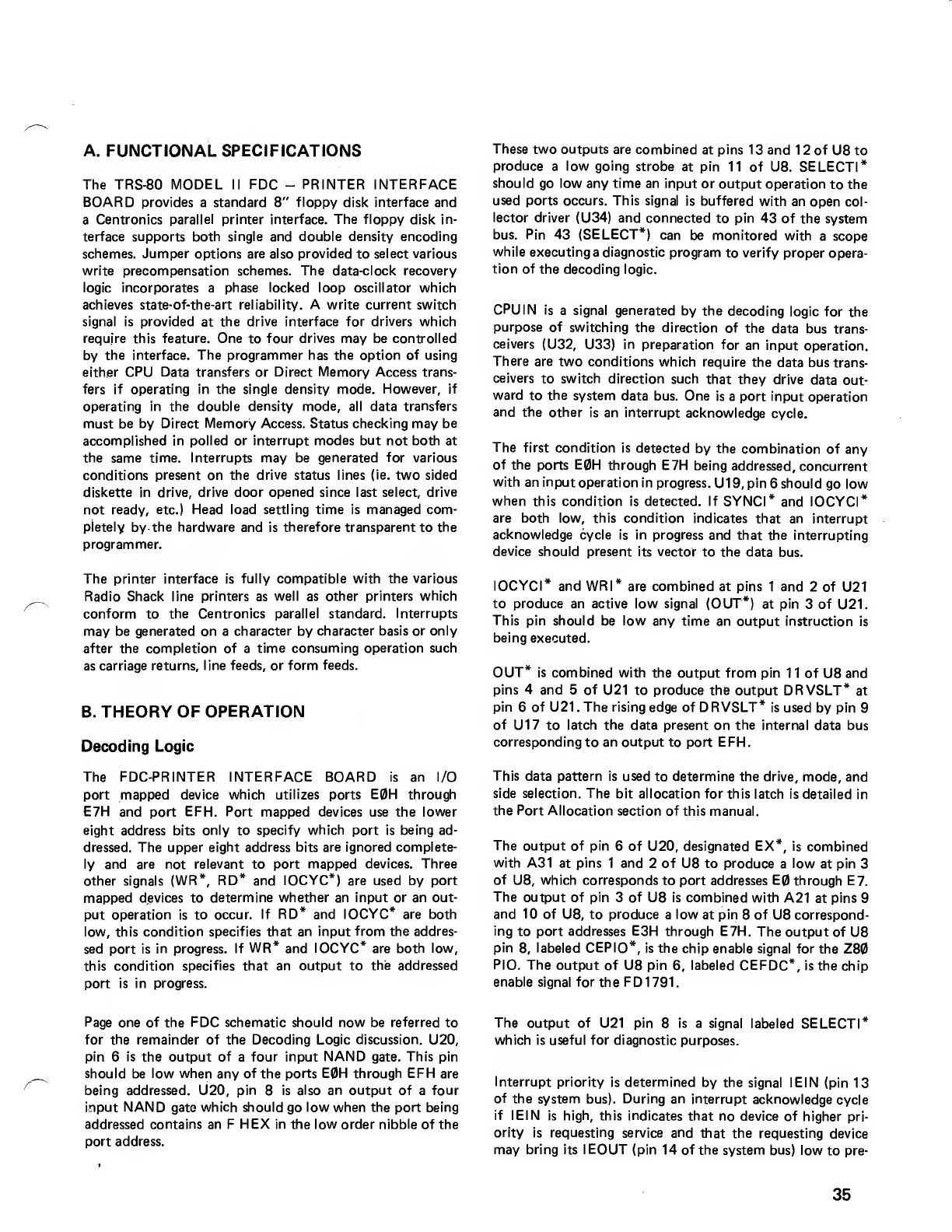

A. FUNCTIONAL SPECIFICATIONS

The TRS-80 MODEL II FDC -PRINTER INTERFACE

BOARD provides astandard 8" floppy disk interface and

aCentronics parallel printer interface. The floppy disk in-

terface supports both single and double density encoding

schemes. Jumper options are also provided to select various

write precompensation schemes. The data-clock recovery

logic incorporates aphase locked loop oscillator which

achieves state-of-the-art reliability. Awrite current switch

signal is provided at the drive interface for drivers which

require this feature. One to four drives may be controlled

by the interface. The programmer has the option of using

either CPU Data transfers or Direct Memory Access trans-

fers if operating in the single density mode. However, if

operating in the double density mode, all data transfers

must be by Direct Memory Access. Status checking may be

accomplished in polled or interrupt modes but not both at

the same time. Interrupts may be generated for various

conditions present on the drive status lines (ie. two sided

diskette in drive, drive door opened since last select, drive

not ready, etc.) Head load settling time is managed com-

pletely by the hardware and is therefore transparent to the

programmer.

The printer interface is fully compatible with the various

Radio Shack line printers as well as other printers which

conform to the Centronics parallel standard. Interrupts

may be generated on acharacter by character basis or only

after the completion of atime consuming operation such

as carriage returns, line feeds, or form feeds.

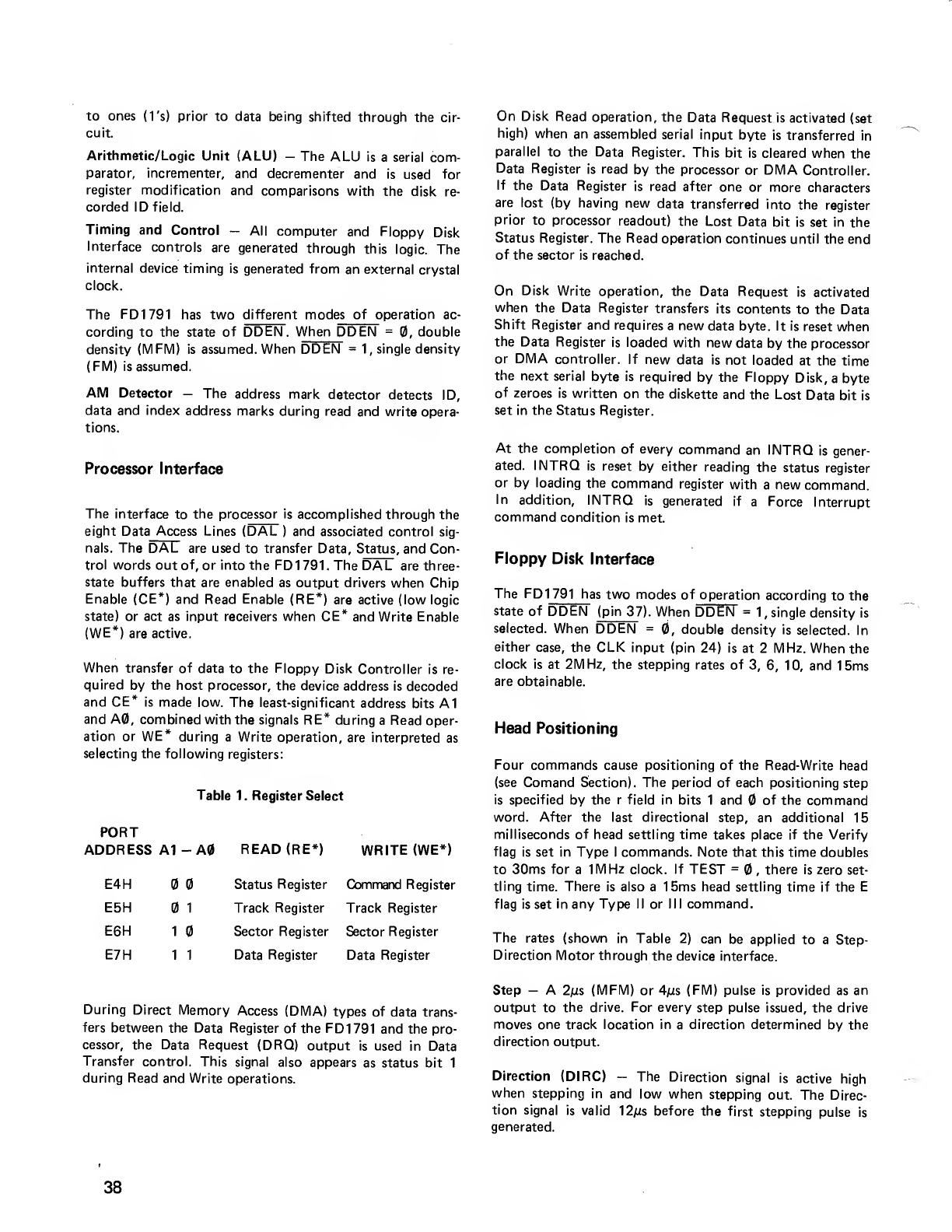

B. THEORY OF OPERATION

Decoding Logic

The FDC-PR INTER INTERFACE BOARD is an I/O

port mapped device which utilizes ports E0H through

E7H and port EFH. Port mapped devices use the lower

eight address bits only to specify which port is being ad-

dressed. The upper eight address bits are ignored complete-

ly and are not relevant to port mapped devices. Three

other signals (WR*, RD* and IOCYC*) are used by port

mapped devices to determine whether an input or an out-

put operation is to occur. If RD* and IOCYC* are both

low, this condition specifies that an input from the addres-

sed port is in progress. If WR* and IOCYC* are both low,

this condition specifies that an output to the addressed

port is in progress.

These two outputs are combined at pins 13 and 12 of U8 to

produce alow going strobe at pin 11 of U8. SELECTI*

should go low any time an input or output operation to the

used ports occurs. This signal is buffered with an open col-

lector driver (U34) and connected to pin 43 of the system

bus. Pin 43 (SELECT*) can be monitored with ascope

while executing adiagnostic program to verify proper opera-

tion of the decoding logic.

CPUIN is asignal generated by the decoding logic for the

purpose of switching the direction of the data bus trans-

ceivers (U32, U33) in preparation for an input operation.

There are two conditions which require the data bus trans-

ceivers to switch direction such that they drive data out-

ward to the system data bus. One is aport input operation

and the other is an interrupt acknowledge cycle.

The first condition is detected by the combination of any

of the ports E0H through E7H being addressed, concurrent

with an input operation in progress. U19, pin 6should go low

when this condition is detected. If SYNCI* and IOCYCI*

are both low, this condition indicates that an interrupt

acknowledge cycle is in progress and that the interrupting

device should present its vector to the data bus.

IOCYCI* and WRI* are combined at pins 1and 2of U21

to produce an active low signal (OUT*) at pin 3of U21.

This pin should be low any time an output instruction is

being executed.

OUT* is combined with the output from pin 11 of U8 and

pins 4and 5 of U21 to produce the output DRVSLT* at

pin 6of U21 .The rising edge of DRVSLT* is used by pin 9

of U17 to latch the data present on the internal data bus

corresponding to an output to port EFH.

This data pattern is used to determine the drive, mode, and

side selection. The bit allocation for this latch is detailed in

the Port Allocation section of this manual.

The output of pin 6of U20, designated EX*, is combined

with A31 at pins 1and 2of U8 to produce alow at pin 3