Rockchip Developer Guide Linux4.4 CPUFreq CN

Rockchip-Developer-Guide-Linux4.4-CPUFreq-CN

User Manual:

Open the PDF directly: View PDF ![]() .

.

Page Count: 21

2

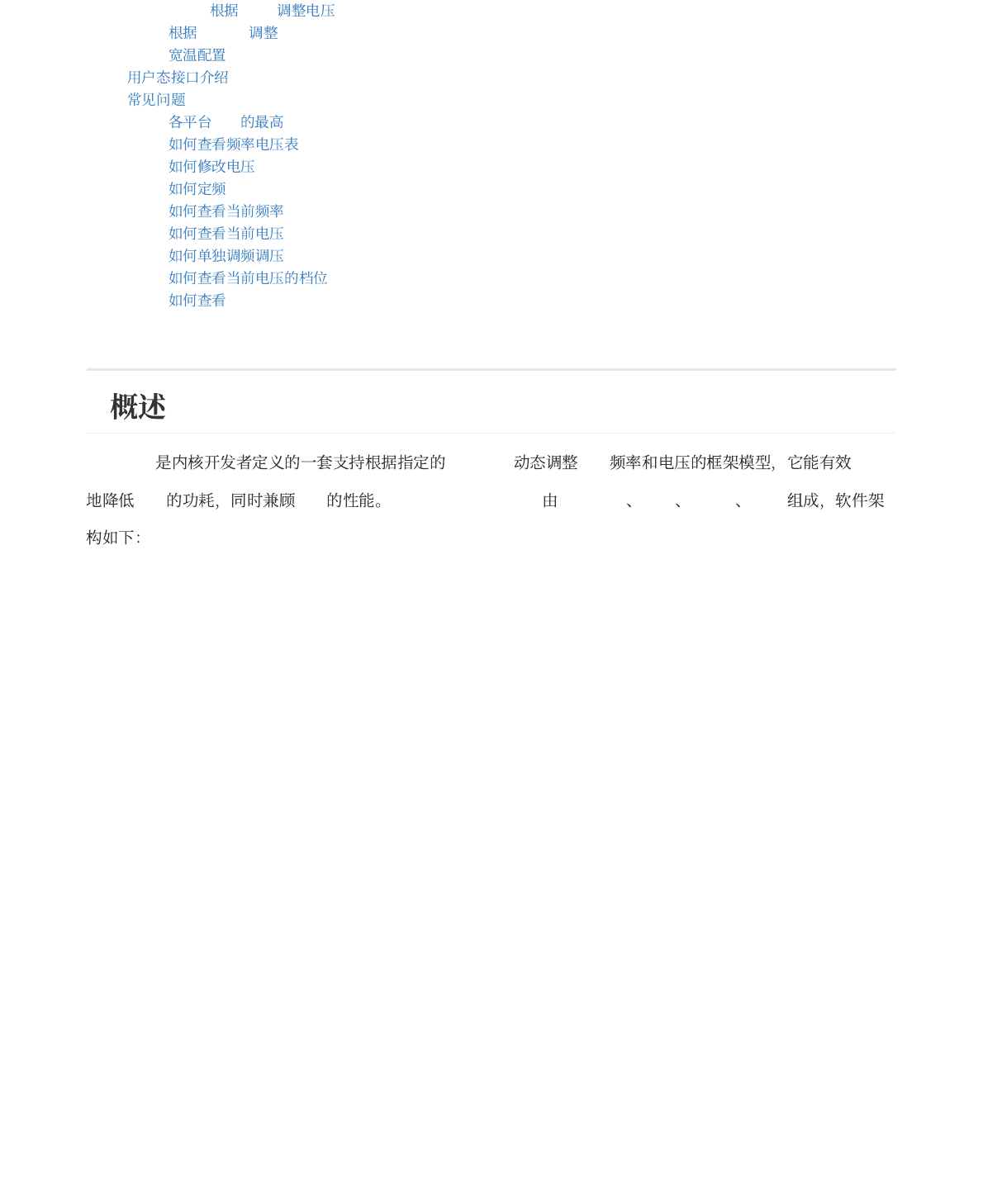

Governor

Stats

Core

Driver

3

3.1 Menuconfig

drivers/cpufreq/cpufreq_conservative.c /* conservative */

drivers/cpufreq/cpufreq_ondemand.c /* ondemand */

drivers/cpufreq/cpufreq_interactive.c /* interactive */

drivers/cpufreq/cpufreq_userspace.c /* userspace */

drivers/cpufreq/cpufreq_performance.c /* performance */

kernel/sched/cpufreq_schedutil.c /* schedutil */

drivers/cpufreq/cpufreq_stats.c

drivers/cpufreq/cpufreq.c

drivers/cpufreq/cpufreq-dt.c /* platform driver */

drivers/cpufreq/rockchip-cpufreq.c /* platform device */

drivers/soc/rockchip/rockchip_opp_select.c /* */

CPU Power Management --->

CPU Frequency scaling --->

[*] CPU Frequency scaling

<*> CPU frequency translation statistics /* cpufreq stats */

[ ] CPU frequency translation statistics details

[*] CPU frequency time-in-state statistics

Default CPUFreq governor (interactive) ---> /* cpufreq governor */

<*> 'performance' governor

<*> 'powersave' governor

<*> 'userspace' governor for userspace frequency scaling

<*> 'ondemand' cpufreq policy governor

-*- 'interactive' cpufreq policy governor

<*> 'conservative' cpufreq governor

[ ] 'schedutil' cpufreq policy governor

*** CPU frequency scaling drivers ***

<*> Generic DT based cpufreq driver /* platform driver */

< > Generic ARM big LITTLE CPUfreq driver

“Default CPUFreq governor”

3.2 Clock

CPU “clock” DTSI Clock

clock

RK3326 RK3328 CPU0 “clocks = <&cru ARMCLK>;”

RK3328

RK3368 RK3399 CPU “clocks = <&cru ARMCLKB>;”

CPU “clocks = <&cru ARMCLKL>;” RK3399

<*> Rockchip CPUfreq driver /* platform device */

cpu0: cpu@0 {

device_type = "cpu";

compatible = "arm,cortex-a53", "arm,armv8";

...

clocks = <&cru ARMCLK>;

};

cpu_l0: cpu@0 {

device_type = "cpu";

compatible = "arm,cortex-a53", "arm,armv8";

...

clocks = <&cru ARMCLKL>;

};

cpu_l1: cpu@1 {

device_type = "cpu";

compatible = "arm,cortex-a53", "arm,armv8";

...

clocks = <&cru ARMCLKL>;

};

cpu_l2: cpu@2 {

device_type = "cpu";

compatible = "arm,cortex-a53", "arm,armv8";

...

clocks = <&cru ARMCLKL>;

};

cpu_l3: cpu@3 {

device_type = "cpu";

compatible = "arm,cortex-a53", "arm,armv8";

...

clocks = <&cru ARMCLKL>;

};

clock CPUFreq

3.3 Regulator

CPU “cpu-supply” DTS

Regulator Regulator PMIC

CPU0 “cpu-supply” RK3328

cpu_b0: cpu@100 {

device_type = "cpu";

compatible = "arm,cortex-a72", "arm,armv8";

...

clocks = <&cru ARMCLKB>;

};

cpu_b1: cpu@101 {

device_type = "cpu";

compatible = "arm,cortex-a72", "arm,armv8";

...

clocks = <&cru ARMCLKB>;

};

cpu cpu0: failed to get clock: -2

cpufreq-dt: probe of cpufreq-dt failed with error -2

&i2c1 {

status = "okay";

rk805: rk805@18 {

compatible = "rockchip,rk805";

status = "okay";

...

regulators {

compatible = "rk805-regulator";

status = "okay";

...

vdd_arm: RK805_DCDC2 {

regulator-compatible = "RK805_DCDC2";

regulator-name = "vdd_arm";

regulator-init-microvolt = <1225000>;

regulator-min-microvolt = <712500>;

regulator-max-microvolt = <1450000>;

regulator-initial-mode = <0x1>;

regulator-ramp-delay = <12500>;

regulator-boot-on;

regulator-always-on;

regulator-state-mem {

regulator-mode = <0x2>;

regulator-on-in-suspend;

regulator-suspend-microvolt = <950000>;

CPU “cpu-supply” RK3399

regulator cpufreq

3.4 OPP Table

Linux4.4 devicetree

OPP Table OPP Table OPP leaakge PVTM

OPP

};

};

...

};

};

};

&cpu0 {

cpu-supply = <&vdd_arm>;

};

&cpu_l0 {

cpu-supply = <&vdd_cpu_l>;

};

&cpu_l1 {

cpu-supply = <&vdd_cpu_l>;

};

&cpu_l2 {

cpu-supply = <&vdd_cpu_l>;

};

&cpu_l3 {

cpu-supply = <&vdd_cpu_l>;

};

&cpu_b0 {

cpu-supply = <&vdd_cpu_b>;

};

&cpu_b1 {

cpu-supply = <&vdd_cpu_b>;

};

Documentation/devicetree/bindings/opp/opp.txt

Documentation/power/opp.txt

3.4.1 OPP Table

OPP Table CPU “operating-points-v2”

DTSI RK3328

cpu0: cpu@0 {

device_type = "cpu";

compatible = "arm,cortex-a53", "arm,armv8";

...

operating-points-v2 = <&cpu0_opp_table>;

};

cpu1: cpu@1 {

device_type = "cpu";

compatible = "arm,cortex-a53", "arm,armv8";

...

operating-points-v2 = <&cpu0_opp_table>;

};

cpu2: cpu@2 {

device_type = "cpu";

compatible = "arm,cortex-a53", "arm,armv8";

...

operating-points-v2 = <&cpu0_opp_table>;

};

cpu3: cpu@3 {

device_type = "cpu";

compatible = "arm,cortex-a53", "arm,armv8";

...

operating-points-v2 = <&cpu0_opp_table>;

};

cpu0_opp_table: opp_table0 {

compatible = "operating-points-v2";

opp-shared; /* OPP Table CPU */

/*

*

* 13 1296MHz OPP Table 1296MHz

*

*/

rockchip,avs-scale = <13>;

opp-408000000 {

opp-hz = /bits/ 64 <408000000>; /* Hz */

opp-microvolt = <950000 950000 1350000>;/* uV <target min max> */

clock-latency-ns = <40000>; /* ns */

/*

* CPU CPU CPU

* OPP OPP Table OPP

*/

opp-suspend;

};

...

operating-points-v2 cpufreq

3.4.2 OPP

OPP “status = "disabeld";”

DTS OPP Table OPP “status = "disabeld";”

3.5 leakage OPP Table

IDDQ(Integrated Circuit Quiescent Current) CMOS

opp-1296000000 {

opp-hz = /bits/ 64 <1296000000>;

opp-microvolt = <1350000 1350000 1350000>;

clock-latency-ns = <40000>;

};

}

cpu cpu0: OPP-v2 not supported

cpu cpu0: couldn't find opp table for cpu:0, -19

cpu0_opp_table: opp_table0 {

compatible = "operating-points-v2";

opp-shared;

opp-408000000 {

opp-hz = /bits/ 64 <408000000>;

opp-microvolt = <950000 950000 1350000>;

clock-latency-ns = <40000>;

};

...

opp-1296000000 {

opp-hz = /bits/ 64 <1296000000>;

opp-microvolt = <1350000 1350000 1350000>;

clock-latency-ns = <40000>;

status = "disabled";

};

}

&cpu0_opp_table {

opp-1296000000 {

status = "disabled";

}

};

leakage CPU leakage CPU

leakage eFuse OTP

3.5.1 leakage

Vmin leakage Vmin leakage Vmin

leakage leakage

eFuse OTP CPU leakage OPP

eFuse OTP eFuse OTP OPP

Table “rockchip,leakage-voltage-sel” “nvmem-cells” “nvmem-cell-names” OPP

“opp-microvolt-<name>” DTSI RK3328

cpu0_opp_table: cpu0-opp-table {

compatible = "operating-points-v2";

opp-shared;

/*

* eFuse OTP CPU leakage

*/

nvmem-cells = <&cpu_leakage>;

nvmem-cell-names = "cpu_leakage";

/*

* leakage 1mA-10mA opp-microvolt-L0

* leakage 11mA-254mA opp-microvolt-L1

*

* rockchip,leakage-voltage-sell leakage

* opp-microvolt

*/

rockchip,leakage-voltage-sel = <

1 10 0

11 254 1

>;

opp-408000000 {

opp-hz = /bits/ 64 <408000000>;

opp-microvolt = <950000 950000 1350000>;

opp-microvolt-L0 = <950000 950000 1350000>;

opp-microvolt-L1 = <950000 950000 1350000>;

clock-latency-ns = <40000>;

opp-suspend;

};

...

opp-1296000000 {

opp-hz = /bits/ 64 <1296000000>;

opp-microvolt = <1350000 1350000 1350000>;

opp-microvolt-L0 = <1350000 1350000 1350000>;

“rockchip,leakage-voltage-sel” opp-microvolt

3.6 PVTM OPP Table

CPU PVTM(Process-Voltage-Temperature Monitor) CPU

3.6.1 PVTM

Vmin PVTM Vmin PVTM

Vmin PVTM PVTM

PVTM PVTM

OPP

PVTM PVTM OPP Table

“rockchip,pvtm-voltage-sel” “rockchip,thermal-zone” “rockchip,pvtm-<name>”

“nvmem-cells” “nvmem-cell-names” OPP “opp-microvolt-<name>”

DTSI RK3288

opp-microvolt-L1 = <1300000 1300000 1350000>;

clock-latency-ns = <40000>;

};

};

cpu0_opp_table: opp_table0 {

compatible = "operating-points-v2";

opp-shared;

...

/*

* eFuse OTP CPU

* ;

*

*/

nvmem-cells = <&process_version>;

nvmem-cell-names = "process";

/*

* PVTM rockchip,pvtm-voltage-sel OPP

* opp-microvolt-L0 opp-microvolt-L1

*

* pvtm 0 1 2

* rockchip,p0-pvtm-voltage-sel rockchip,p1-pvtm-voltage-sel

* OPP opp-microvolt-P0-L0 opp-microvolt-P1-L0

* 2 rockchip,pvtm-voltage-sel

*

* PVTM 0-14300 opp-microvolt-L0

* PVTM 14301-15000 opp-microvolt-L1

“rockchip,pvtm-voltage-sel” opp-microvolt

3.7 IR-Drop OPP Table

IR-Drop

EVB

* PVTM 15001-16000 opp-microvolt-L2

* PVTM 16001-99999 opp-microvolt-L3

*

* rockchip,pvtm-voltage-sel PVTM

* opp-microvolt

*/

rockchip,pvtm-voltage-sel = <

0 14300 0

14301 15000 1

15001 16000 2

16001 99999 3

>;

rockchip,pvtm-freq = <408000>; /* PVTM CPU Khz */

rockchip,pvtm-volt = <1000000>; /* PVTM CPU uV */

rockchip,pvtm-ch = <0 0>; /* PVTM < sel > */

rockchip,pvtm-sample-time = <1000>; /* PVTM us */

rockchip,pvtm-number = <10>; /* PVTM */

rockchip,pvtm-error = <1000>; /* */

rockchip,pvtm-ref-temp = <35>; /* */

/* PVTM < > */

rockchip,pvtm-temp-prop = <(-18) (-18)>;

rockchip,thermal-zone = "soc-thermal"; /* thermal-zone */

opp-126000000 {

opp-hz = /bits/ 64 <126000000>;

opp-microvolt = <950000 950000 1350000>;

opp-microvolt-L0 = <950000 950000 1350000>;

opp-microvolt-L1 = <950000 950000 1350000>;

opp-microvolt-L2 = <950000 950000 1350000>;

opp-microvolt-L3 = <950000 950000 1350000>;

clock-latency-ns = <40000>;

};

...

opp-1608000000 {

opp-hz = /bits/ 64 <1608000000>;

opp-microvolt = <1350000 1350000 1350000>;

opp-microvolt-L0 = <1350000 1350000 1350000>;

opp-microvolt-L1 = <1350000 1350000 1350000>;

opp-microvolt-L2 = <1300000 1300000 1350000>;

opp-microvolt-L3 = <1250000 1250000 1350000>;

clock-latency-ns = <40000>;

};

};

IR-Drop OPP Table

EVB

OPP Table “rockchip,max-volt ” “rockchip,evb-irdrop”

“rockchip,board-irdrop” “rockchip,board-irdrop” DTS DTSI

RK3326 DTSI

DTS

“rockchip,board-irdrop”

3.8

-40~85

cpu0_opp_table: cpu0-opp-table {

compatible = "operating-points-v2";

opp-shared;

/* uV */

rockchip,max-volt = <1350000>;

rockchip,evb-irdrop = <25000>;/* EVB SDK */

}

&cpu0_opp_table {

/*

* max IR-drop values on different freq condition for this board!

*/

/*

* :

* 0Mhz-815MHz 37500uV 12500uV 37500-25000 evb

* 816Mhz-1119MHz 50000uV 25000uV 50000-25000 evb

* 1200Mhz-1512MHz 75000uV 50000uV 75000-25000 evb

*/

rockchip,board-irdrop = <

/*MHz MHz uV */

0 815 37500

816 1119 50000

1200 1512 75000

>;

};

OPP Table “rockchip,temp-hysteresis” “rockchip,low-temp“

”rockchip,low-temp-min-volt“ “rockchip,low-temp-adjust-volt” “rockchip,max-volt” OPP

Table “rockchip,temp-hysteresis” “rockchip,high-temp” “rockchip,high-temp-max-volt”

DTSI

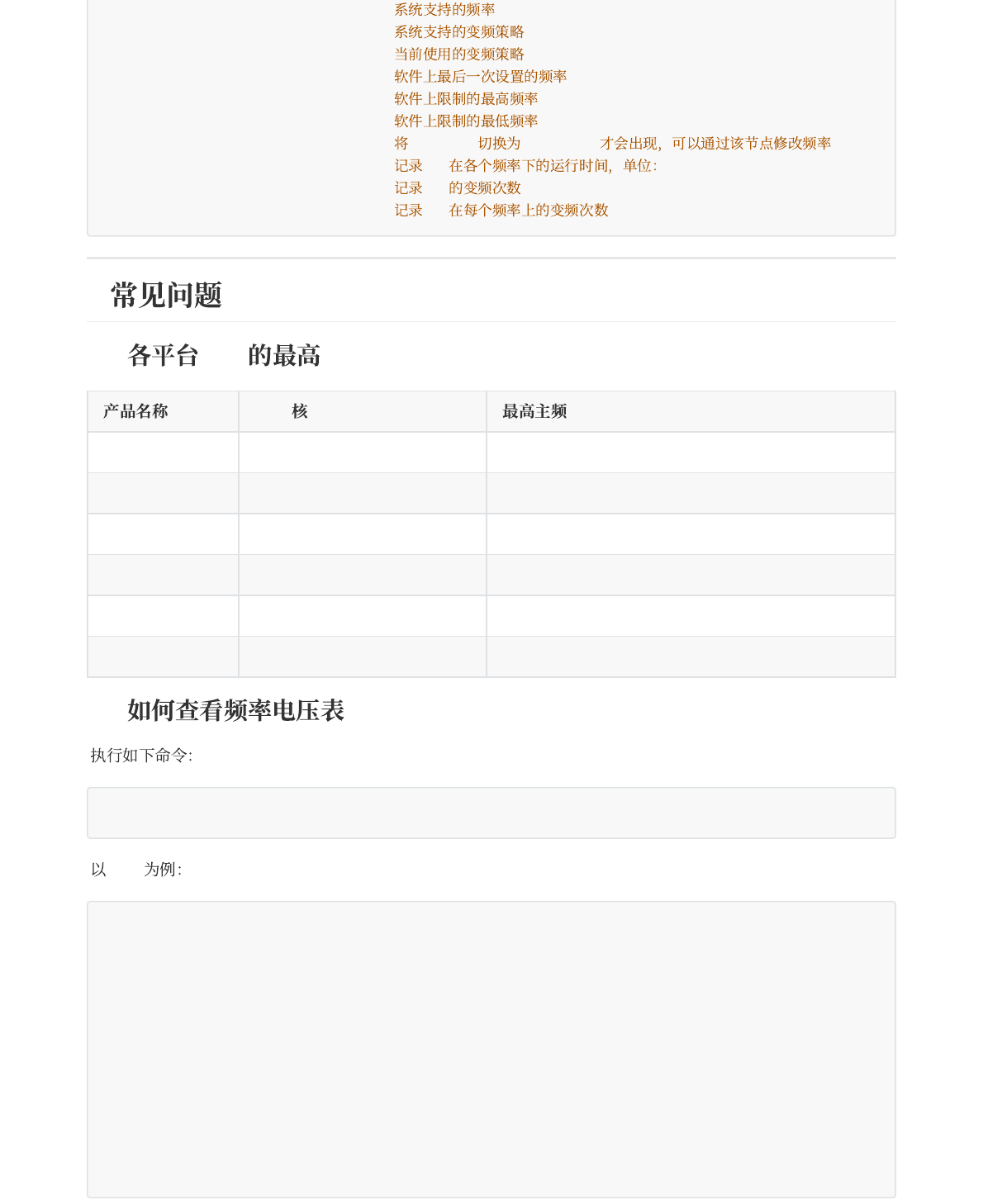

4

RK3288 RK3326 RK3328 CPU clock

/sys/devices/system/cpu/cpufreq/policy0/

RK3368 RK3399 cluster cluster clock

cluster0 /sys/devices/system/cpu/cpufreq/policy0/ cluster1

/sys/devices/system/cpu/cpufreq/policy4/

governor

cpu0_opp_table: opp_table0 {

compatible = "operating-points-v2";

opp-shared;

/*

* millicelsius

* 0 0+5 85 85-5

*/

rockchip,temp-hysteresis = <5000>;

rockchip,low-temp = <0>; /* millicelsius*/

rockchip,low-temp-min-volt = <900000>; /* uV */

rockchip,low-temp-adjust-volt = <

/* MHz MHz uV */

0 1800 25000 /* 0-1800MHz 25mV */

>;

/* uV */

rockchip,max-volt = <1250000>;

rockchip,high-temp = <85000>; /* millicelsius */

/* uV */

rockchip,high-temp-max-volt = <1200000>;

...

}

related_cpus /* cluster CPU */

affected_cpus /* cluster CPU */

cpuinfo_transition_latency /* ns */

cpuinfo_max_freq /* CPU */

cpuinfo_min_freq /* CPU */

cpuinfo_cur_freq /* CPU */

ARM

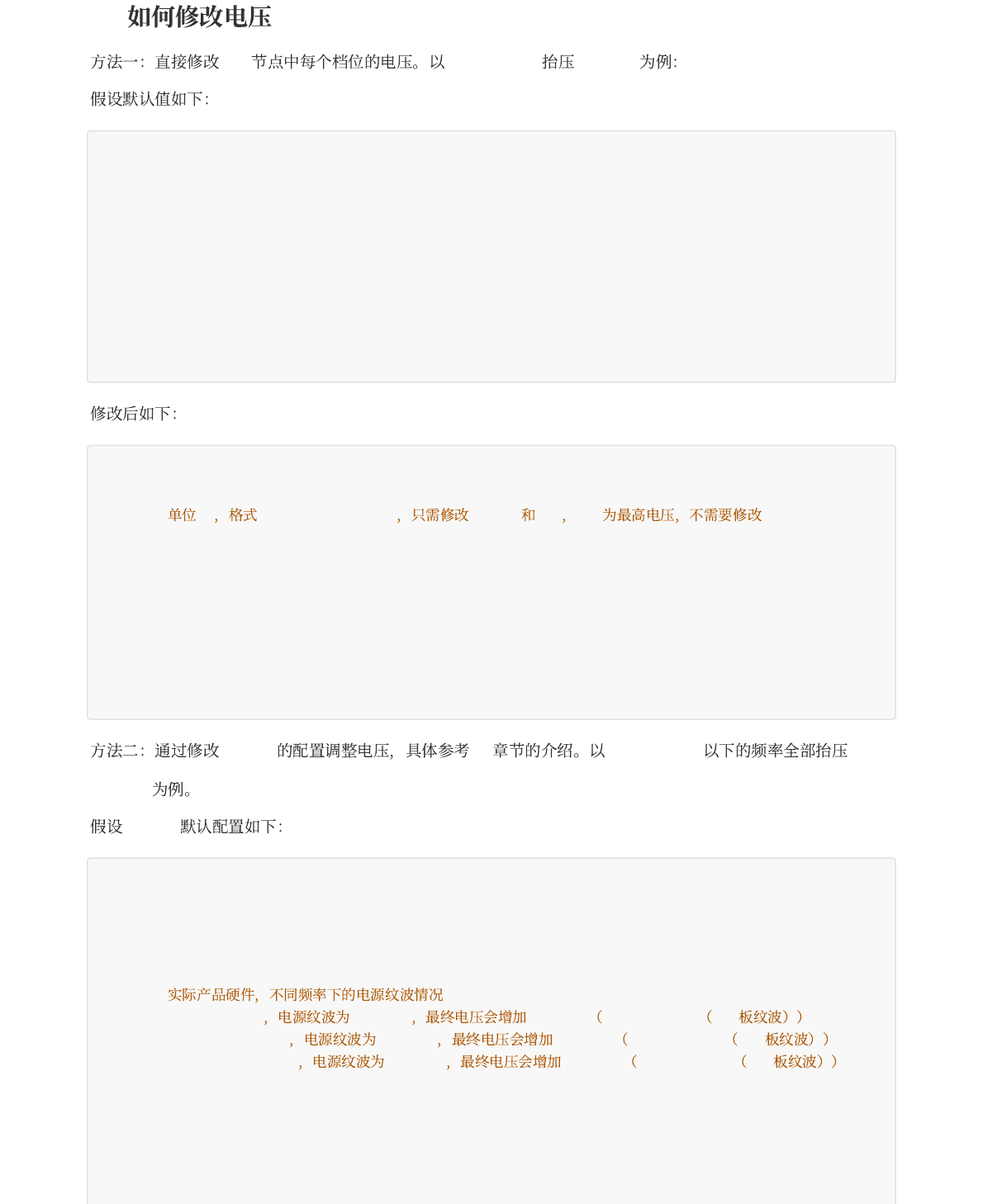

RK312x 4 * A7 1200MHz

RK322x 4 * A7 1464MHz

RK3288 4 * A17 1608MHz

RK3328 4 * A53 1296MHz

RK3368 4 * A53 + 4 * A53 1512MHz(big) + 1200MHz(little)

RK3399 2 * A72 + 4 * A53 1800MHz(big) + 1416MHz(little)

5

5.1 CPU

5.2

PX30

scaling_available_frequencies /* */

scaling_available_governors /* */

scaling_governor /* */

scaling_cur_freq /* */

scaling_max_freq /* */

scaling_min_freq /* */

scaling_setspeed /* governor userspace */

stats/time_in_state /* CPU 10ms */

stats/total_trans /* CPU */

stats/trans_table /* CPU */

cat /sys/kernel/debug/opp/opp_summary

device rate(Hz) target(uV) min(uV) max(uV)

-------------------------------------------------------------------

cpu0

408000000 950000 950000 1350000

600000000 950000 950000 1350000

816000000 1000000 1000000 1350000

1008000000 1125000 1125000 1350000

1200000000 1275000 1275000 1350000

1248000000 1300000 1300000 1350000

1296000000 1350000 1350000 1350000

1416000000 1350000 1350000 1350000

1512000000 1350000 1350000 1350000

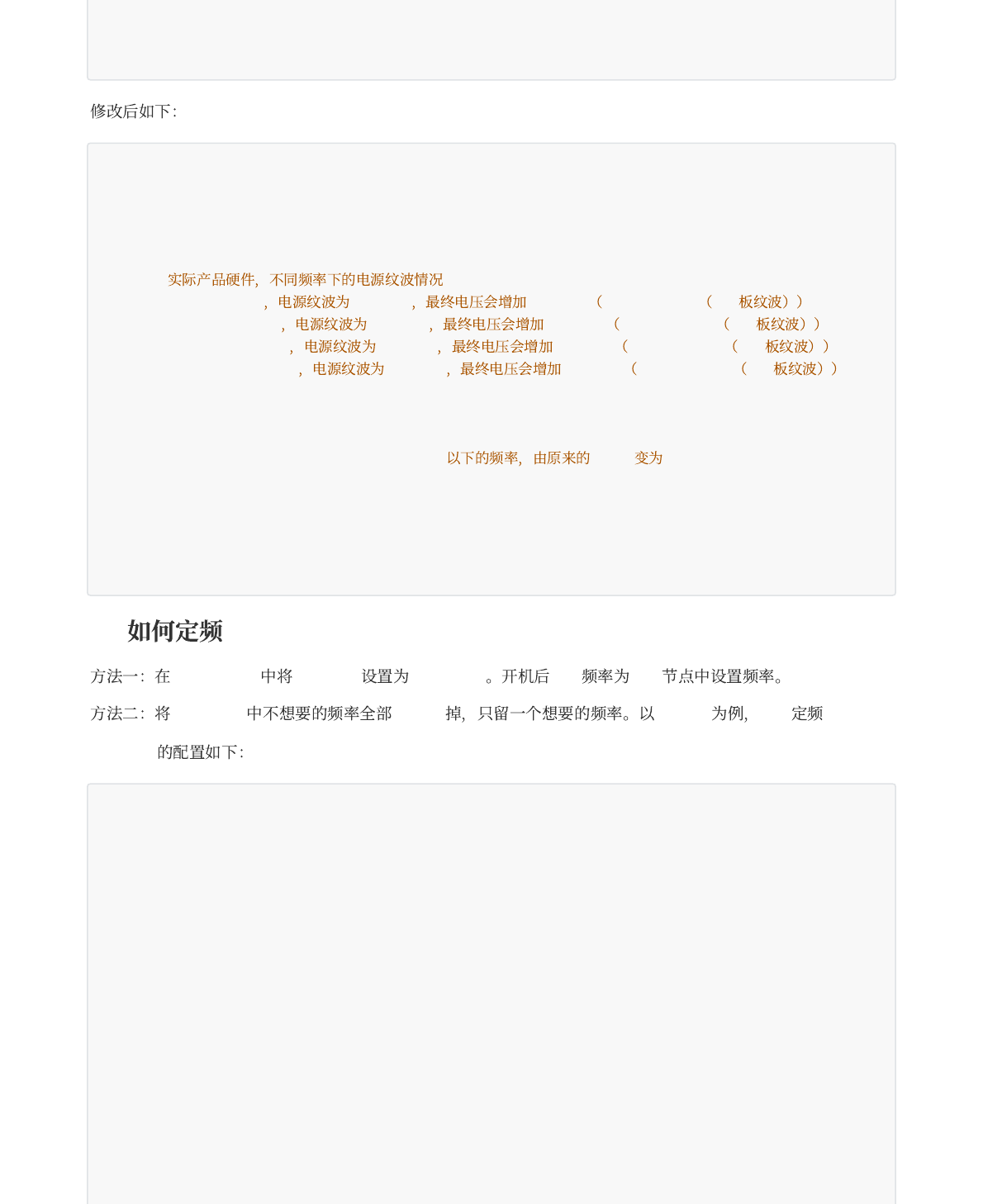

5.3

OPP CPU 816MHz 25000uV

IR-Drop 3.7 CPU 408MHz

25000uV

IR-Drop

opp-816000000 {

opp-hz = /bits/ 64 <816000000>;

opp-microvolt = <1075000 1075000 1350000>;

opp-microvolt-L0 = <1075000 1075000 1350000>;

opp-microvolt-L1 = <1050000 1050000 1350000>;

opp-microvolt-L2 = <1000000 1000000 1350000>;

opp-microvolt-L3 = <950000 950000 1350000>;

clock-latency-ns = <40000>;

opp-suspend;

};

opp-816000000 {

opp-hz = /bits/ 64 <816000000>;

/* uV <target min max> target min max */

opp-microvolt = <1100000 1100000 1350000>;

opp-microvolt-L0 = <1100000 1100000 1350000>;

opp-microvolt-L1 = <107500 1075000 1350000>;

opp-microvolt-L2 = <1025000 1025000 1350000>;

opp-microvolt-L3 = <975000 975000 1350000>;

clock-latency-ns = <40000>;

opp-suspend;

};

&cpu0_opp_table {

/*

* max IR-drop values on different freq condition for this board!

*/

/*

* :

* 0Mhz-815MHz 37500uV 12500uV 37500-25000 evb

* 816Mhz-1119MHz 50000uV 25000uV 50000-25000 evb

* 1200Mhz-1512MHz 75000uV 50000uV 75000-25000 evb

*/

rockchip,board-irdrop = <

/*MHz MHz uV */

0 815 37500

816 1119 50000

5.4

menuconfig governor userspace CPU CRU

OPP Table disable RK3308 CPU

1008MHz

1200 1512 75000

>;

};

&cpu0_opp_table {

/*

* max IR-drop values on different freq condition for this board!

*/

/*

* :

* 0Mhz-408MHz 62500uV 37500uV 62500-25000 evb

* 409Mhz-815MHz 37500uV 12500uV 37500-25000 evb

* 816Mhz-1119MHz 50000uV 25000uV 50000-25000 evb

* 1200Mhz-1512MHz 75000uV 50000uV 75000-25000 evb

*/

rockchip,board-irdrop = <

/*MHz MHz uV */

0 408 62500 /* 408MHz 37500 63500 */

409 815 37500

816 1119 50000

1200 1512 75000

>;

};

cpu0_opp_table: cpu0-opp-table {

compatible = "operating-points-v2";

opp-shared;

opp-408000000 {

opp-hz = /bits/ 64 <408000000>;

opp-microvolt = <950000 950000 1340000>;

clock-latency-ns = <40000>;

opp-suspend;

status = "disabled";

};

opp-600000000 {

opp-hz = /bits/ 64 <600000000>;

opp-microvolt = <950000 950000 1340000>;

clock-latency-ns = <40000>;

status = "disabled";

};

opp-816000000 {

RK3288

RK3399

cpufreq CPU

5.5

cpufreq clock debug

opp-hz = /bits/ 64 <816000000>;

opp-microvolt = <1025000 1025000 1340000>;

clock-latency-ns = <40000>;

status = "disabled";

};

opp-1008000000 {

opp-hz = /bits/ 64 <1008000000>;

opp-microvolt = <1125000 1125000 1340000>;

clock-latency-ns = <40000>;

};

opp-1200000000 {

opp-hz = /bits/ 64 <1200000000>;

opp-microvolt = <1250000 1250000 1340000>;

clock-latency-ns = <40000>;

status = "disabled";

};

opp-1296000000 {

opp-hz = /bits/ 64 <1296000000>;

opp-microvolt = <1300000 1300000 1340000>;

clock-latency-ns = <40000>;

status = "disabled";

};

};

/* governor userspace */

echo userspace > /sys/devices/system/cpu/cpufreq/policy0/scaling_governor

/* 216MHz */

echo 216000 > /sys/devices/system/cpu/cpufreq/policy0/scaling_setspeed

/* governor userspace */

echo userspace > /sys/devices/system/cpu/cpufreq/policy0/scaling_governor

/* 216MHz */

echo 216000 > /sys/devices/system/cpu/cpufreq/policy0/scaling_setspeed

/* governor userspace */

echo userspace > /sys/devices/system/cpu/cpufreq/policy4/scaling_governor

/* 408MHz */

echo 408000 > /sys/devices/system/cpu/cpufreq/policy4/scaling_setspeed

5.6

5.7

CPU 5.3

clock debug

regulator debug

/* cpufreq */

cat /sys/devices/system/cpu/cpufreq/policy0/scaling_cur_freq

/* clock debug */

cat /sys/kernel/debug/clk/armclk/clk_rate

/* cpufreq */

cat /sys/devices/system/cpu/cpufreq/policy0/scaling_cur_freq /* */

cat /sys/devices/system/cpu/cpufreq/policy4/scaling_cur_freq /* */

/* clock debug */

cat /sys/kernel/debug/clk/armclkl/clk_rate /* */

cat /sys/kernel/debug/clk/armclkb/clk_rate /* */

/* vdd_core regulator */

cat /sys/kernel/debug/regulator/vdd_core/voltage

/* vdd_core_l vdd_core_b regulator */

cat /sys/kernel/debug/regulator/vdd_core_l/voltage /* */

cat /sys/kernel/debug/regulator/vdd_core_b/voltage /* */

/* RK3288 216MHz */

echo 216000000 > /sys/kernel/debug/clk/armclk/clk_rate /* */

cat /sys/kernel/debug/clk/armclkl/clk_rate /* */

/* RK3399 216MHz 408Mhz */

echo 216000000 > /sys/kernel/debug/clk/armclkl/clk_rate /* */

cat /sys/kernel/debug/clk/armclkl/clk_rate /* */

echo 408000000 > /sys/kernel/debug/clk/armclkb/clk_rate /* */

cat /sys/kernel/debug/clk/armclkb/clk_rate /* */

5.8

PVTM

RK3399 CPU

leakage

5.9 leakage

RK3399 CPU

/*

* RK3288 950mV

* vdd_core regulator

*/

echo 950000 > /sys/kernel/debug/regulator/vdd_core/voltage /* */

cat /sys/kernel/debug/regulator/vdd_core/voltage /* */

/*

* RK3399 950mV 1000mV,

* vdd_core_l vdd_core_b regulator

*/

echo 950000 > /sys/kernel/debug/regulator/vdd_core_l/voltage /* */

cat /sys/kernel/debug/regulator/vdd_core_l/voltage /* */

echo 950000 > /sys/kernel/debug/regulator/vdd_core_b/voltage /* */

cat /sys/kernel/debug/regulator/vdd_core_b/voltage /* */

dmesg | grep pvtm

[ 0.669456] cpu cpu0: temp=22222, pvtm=138792 (140977 + -2185)

/* pvtm-volt-sel=0 opp-microvolt-L0 */

[ 0.670601] cpu cpu0: pvtm-volt-sel=0

[ 0.683008] cpu cpu4: temp=22222, pvtm=148761 (150110 + -1349)

/* pvtm-volt-sel=1 opp-microvolt-L1 */

[ 0.683109] cpu cpu4: pvtm-volt-sel=1

[ 1.495247] rockchip-dmc dmc: Failed to get pvtm

[ 3.366028] mali ff9a0000.gpu: temp=22777, pvtm=120824 (121698 + -874)

[ 3.366915] mali ff9a0000.gpu: pvtm-volt-sel=0

dmesg | grep leakage

dmesg | grep leakage

[ 0.656175] cpu cpu0: leakage=10 /* leakage=10 leakage 10mA */

[ 0.671092] cpu cpu4: leakage=20 /* leakage=20 leakage 20mA */

[ 1.492769] rockchip-dmc dmc: Failed to get leakage

[ 3.341084] mali ff9a0000.gpu: leakage=15