Saturn_V_LVDC_Vol2_Jan65 Saturn V LVDC Vol2 Jan65

Saturn_V_LVDC_Vol2_Jan65 Saturn_V_LVDC_Vol2_Jan65

User Manual: Saturn_V_LVDC_Vol2_Jan65

Open the PDF directly: View PDF ![]() .

.

Page Count: 240 [warning: Documents this large are best viewed by clicking the View PDF Link!]

LAUNCH

VEHICLE

ASA-CB-12^280)

i-

%>w M « v

«»*w

»

™,

_

~_

_

Laboratory

Maintenance

Instructions.

JJi'-LR

JUd

vu

La

t-v/«.

|

.»i»-...^.-...,„

(International

Business

Machines Corp.)

VOLUME

II OF II

Laboratory

Maintenance

Instructions

SATURN

V

LAUNCH

VEHICLE

DIGITAL

COMPUTER

Simplex

Models

NASA

Part

No.

50M35010

IBM

Part

No.

6109030

W

~L°fl'h

IDT

(International

Business Machines

CorpOTOfthgV1rH.:'

r^az

'

^

U°O»

^

Contract

MAS

8-11561

LATEST

CHANGED

PAGES SUPERSEDE

THE

SAME

PAGES

OF

PREVIOUS

DATE

Insert

changed

pages

into

basic

publication.

Destroy

superseded

pages.

VOLUME

II

MAINTENANCE

DATA

30

NOVEMBER

1964

CHANGED

4

JANUARY

1965

LIST

OF

EFFECTIVE PAGES

INSERT

LATEST

CHANGED

PAGES.

DESTROY SUPERSEDED PAGES.

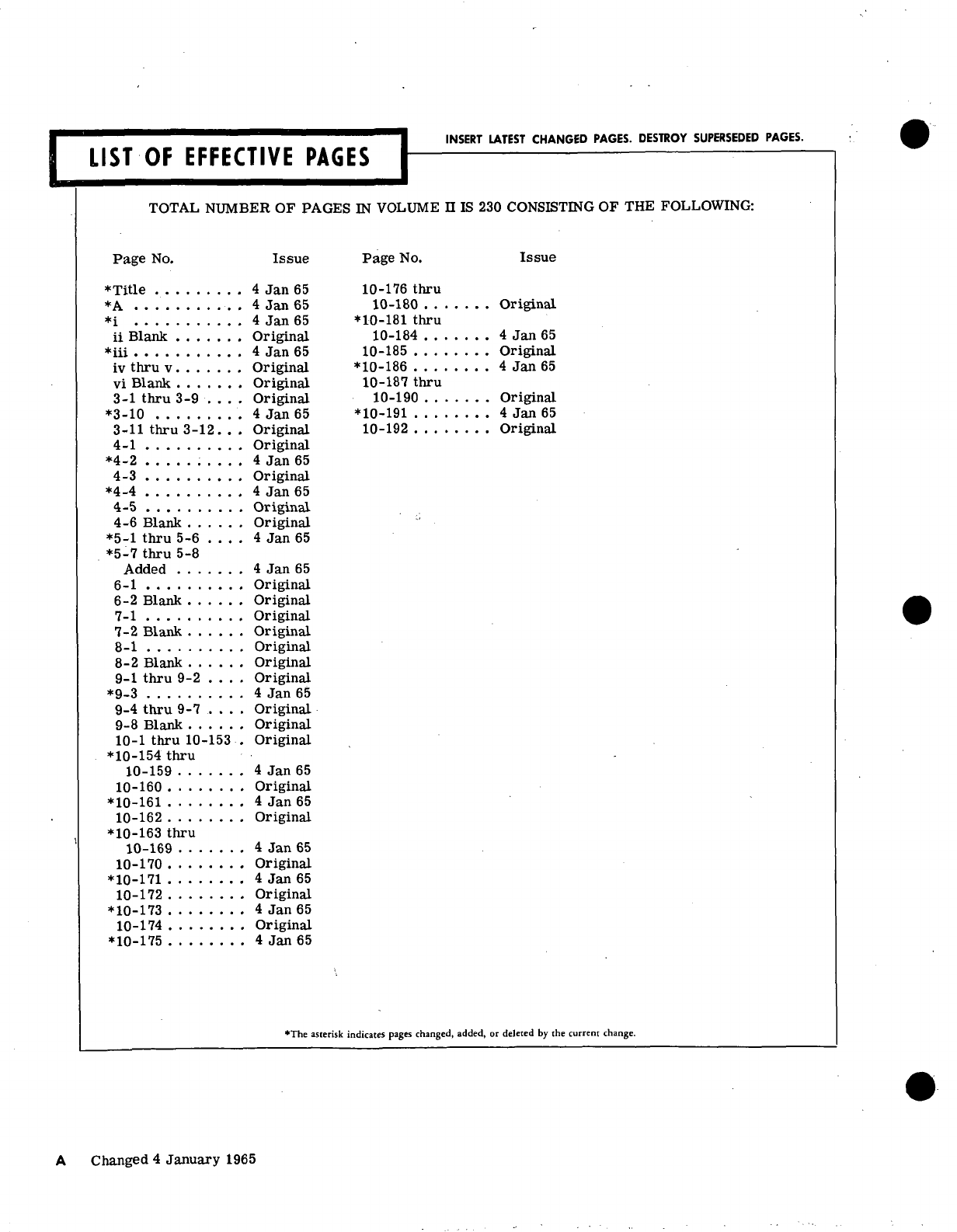

TOTAL

NUMBER

OF

PAGES

IN

VOLUME

H IS 230

CONSISTING

OF THE

FOLLOWING:

Page

No.

Issue

Page

No.

*Title

4 Jan 65

10-176

thru

*A

. . . 4 Jan 65

10-180

. . .

*i 4 Jan 65

*10-181

thru

ii

Blank Original 10-184

. . .

*iii

4 Jan 65

10-185

iv

thru

v

Original *10-186

. . . .

vi

Blank Original 10-187 thru

3-1

thru

3-9

.... Original 10-190

. . .

*3-10

4 Jan 65

*10-191

3-11 thru 3-12.

. .

Original 10-192

4-1

Original

*4-2

4 Jan 65

4-3

Original

*4-4

4 Jan 65

4-5

Original

4-6

Blank Original

;

*5-l thru

5-6

....

4 Jan 65

*5-7 thru

5-8

Added

4 Jan 65

6-1

Original

6-2

Blank Original

7-1

Original

7-2

Blank Original

8-1

Original

8-2

Blank Original

9-1

thru

9-2

.... Original

*9-3

4 Jan 65

9-4

thru

9-7

....

Original

9-8

Blank Original

10-1 thru 10-153

.

Original

*10-154 thru

10-159

4 Jan 65

10-160 Original

*10-161

4 Jan 65

10-162 Original

*10-163 thru

10-169

4 Jan 65

10-170 Original

*10-171

4 Jan 65

10-172

Original

*10-173

4 Jan 65

10-174 Original

*10-175

4 Jan 65

Issue

Original

4

Jan 65

Original

4

Jan 65

Original

4

Jan 65

Original

*The

asterisk indicates pages changed, added,

or

deleted

by the

current

change.

A

Changed

4

January 1965

MAY

9

\1966

*

)

VOLUME

II OF II

Laboratory

Maintenance

Instructions

SATURN

V

LAUNCH

VEHICLE

DIGITAL

COMPUTER

Simplex

Models

NASA

Part

No.

50M35010'

r

.-,&-

-

IBM

Part

No.

6109030

^^

f S^ '• \ - - ' J •- :',

'-K

- ' .* i •

'•'~

• i *

"l;.*r"

(International

Business

Machines

Corporation]

Contract

MAS

8-11561

VOLUME

II

MAINTENANCE

DATA

30

NOVEMBER

1964

Technical

Library,

Bellcomm,

!ncs

•r

LIST

OF

EFFECTIVE PAGES

INSERT

LATEST

CHANGED

PAGES.

DESTROY

SUPERSEDED

PAGES.

NOTE:

The

portion

of the

text

affected

by the

changes

is

indicated

by 3

vertical

line

in the

outer

margins

of the

page.

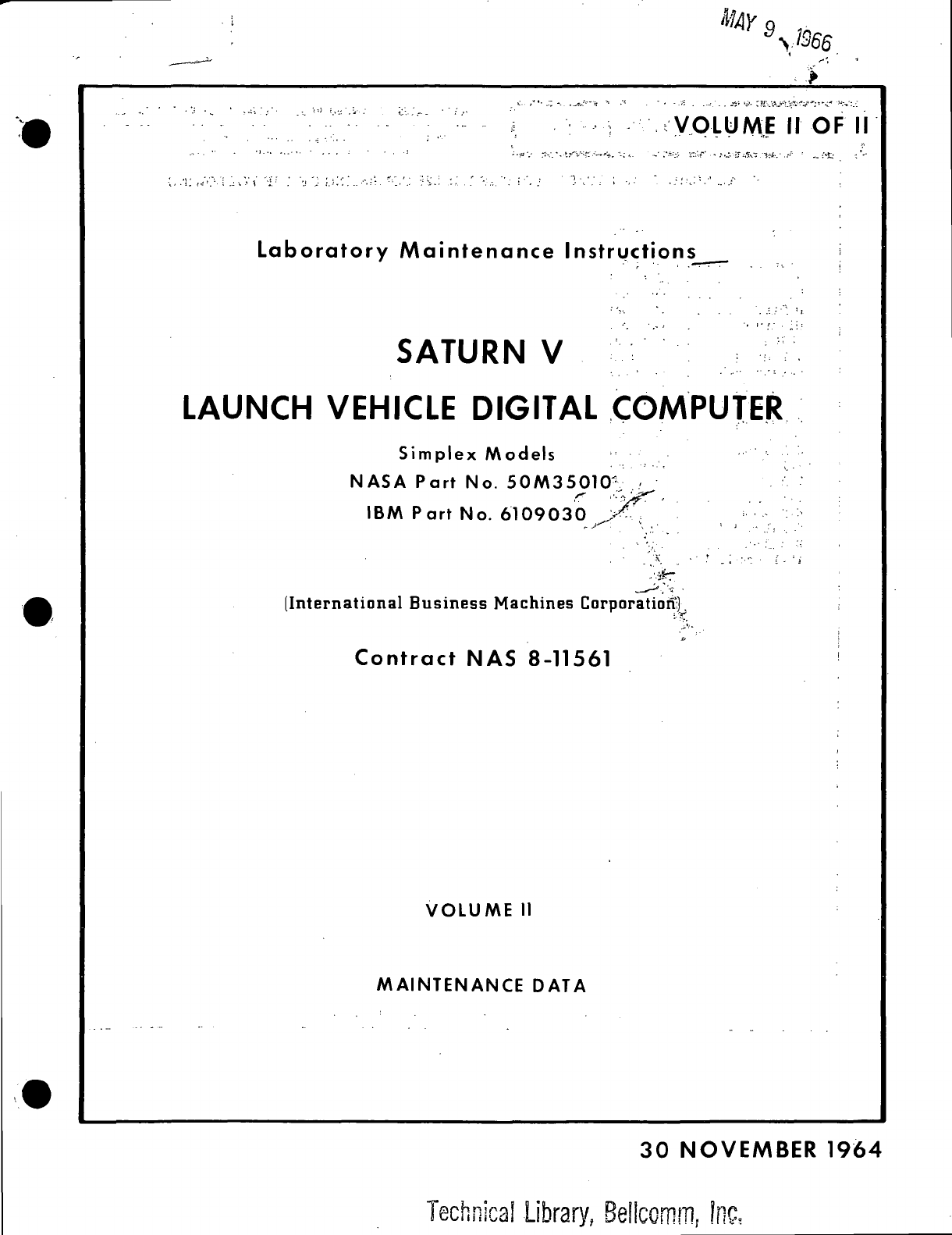

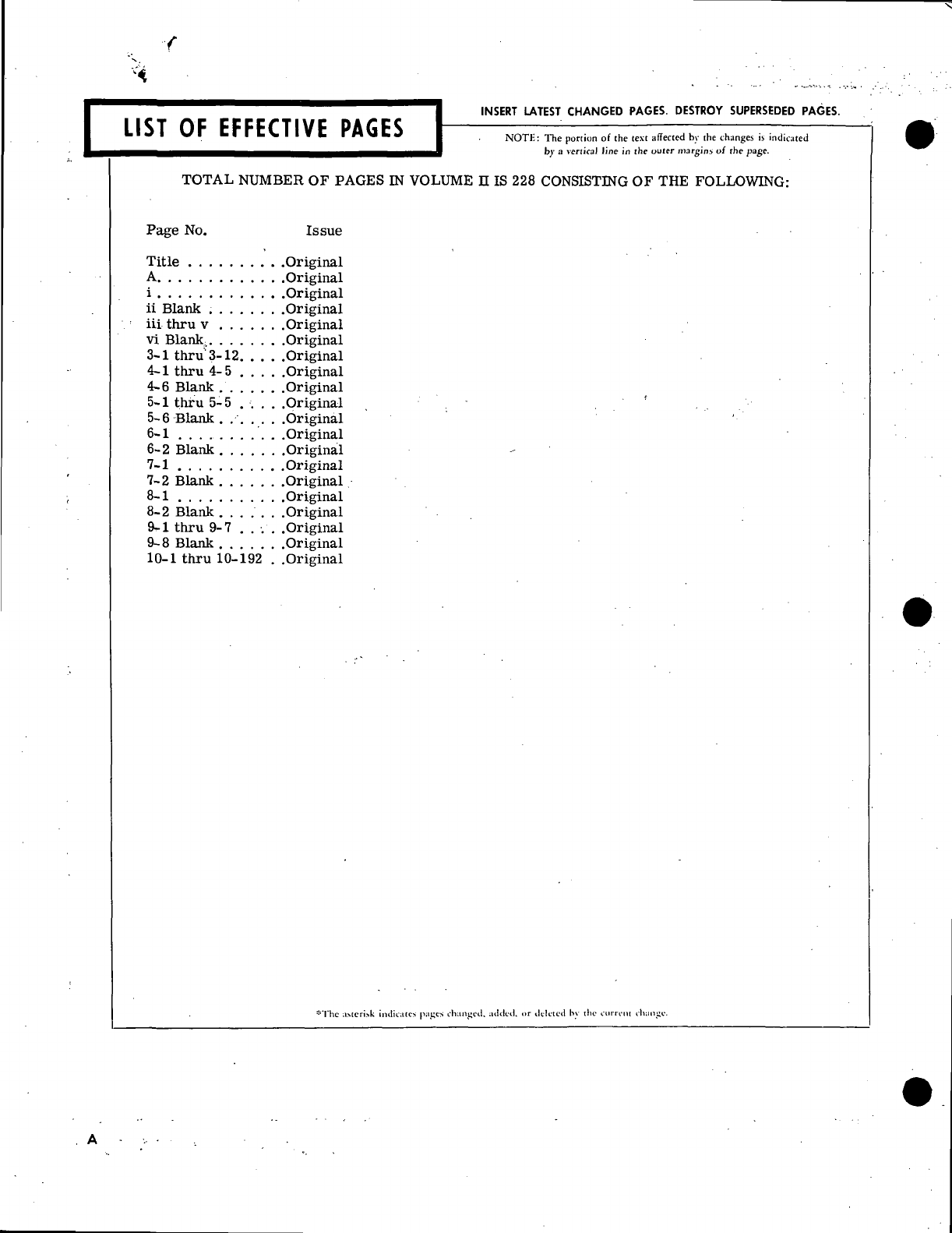

TOTAL

NUMBER

OF

PAGES

IN

VOLUME

H IS 228

CONSISTING

OF THE

FOLLOWING:

Page

No.

Issue

Title Original

A

Original

i

Original

ii

Blank Original

iii

thru

v

Original

vi

Blank,

Original

3-1

thru 3-12 Original

4-1

thru

4-5

Original

4-6

Blank

.

Original

5-1

thru

5-5

....

.Original

5-6

Blank

.

Original

6-1

..........

.Original

6-2

Blank Original

7-1

Original

7-2

Blank Original

8-1

Original

8-2

Blank

......

.Original

9-1

thru

9-7 . ...

.Original

9-8

Blank

Original

10-1 thru 10-192

.

.Original

^Thc

;istcri.sk

indicates

pai;es

chunked,

added,

or

deleted

bv the

current

clunije

Volume

II

TABLE

OF

CONTENTS

Section

Title

Page

m

INTERFACE

AND

ADJUSTMENTS.

. , . ...

....

.

.......

3-1

3-1.

Interface

. 3-1

3-3. Adjustments

. 3-1

IV

TEST

EQUIPMENT

AND

SPECIAL TOOLS

.............

4-1

4-1. Test Equipment

. . . 4-1

4-2. Standard Test Equipment.

........

.....

. .

....

4-1

4-4. Special Test Equipment.

4-1

4-6. Special Tools.

. . .

....

f 4-1

V

PREPARATION

FOR

USE,

STORAGE

AND

SHIPMENT.....

5-1

5-1. Preparation

for Use 5-1

5-2A.

Inspection

and

Test

......

'.'.

....

.".'

.........

5-4

5-3. Preparation

for

Storage

. .

'.'....'

5-4

5-5. Preparation

for

Shipment.

................

. .. . 5-5

5-7

General

Computer

Handling

..........

. 5-7

Vl"

PREVENTIVE MAINTENANCE.

....................

6-1

VH

CHECKOUT

7-1

7-1. Operating Test Procedures

7-1

VEQ

TROUBLE ISOLATION

8-1

IX

REPAIR

9-1

9-1. Repair

9-1

X

DIAGRAMS

10-1

10-1. Diagrams

10-1

10-3. Signal Tracing

10-2

Changed

4

January 1965

i/ii

Volume

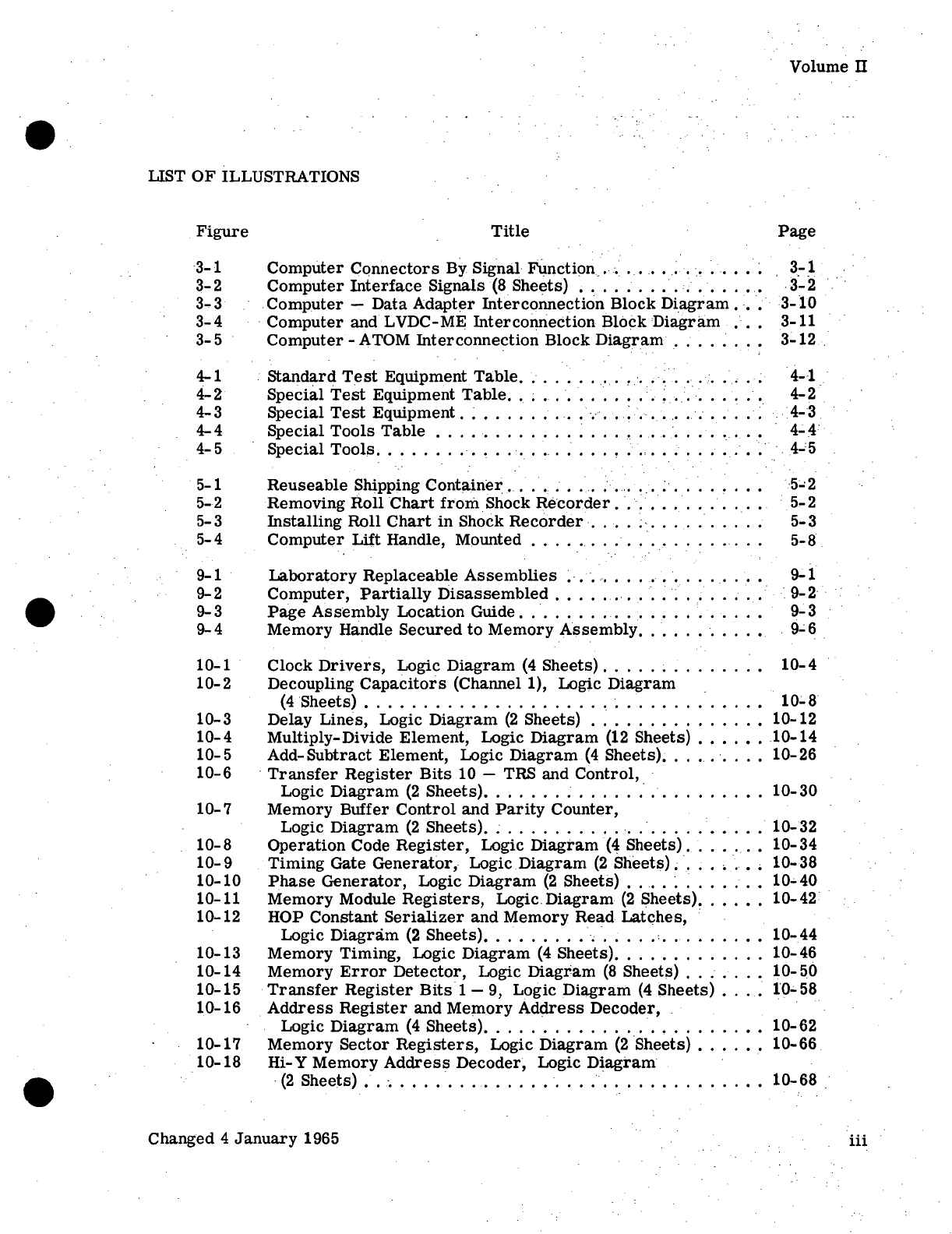

LIST

OF

ILLUSTRATIONS

Figure

Title

Page

3-1

Computer Connectors

By

Signal

Function^.

. ... . . . .

.....

, 3-1

3-2

Computer Interface Signals

(8

Sheets)

.......

...

......

3-2

3-3

Computer

—

Data Adapter Interconnection Block

Diagram..

.

3-10

3-4

Computer

and

LVDC-ME

Interconnection Block Diagram

. . .

3-11

3-5

Computer

-

ATOM

Interconnection Block Diagram

........ 3-12

4-1

Standard

Test

Equipment

Table.

......

... . . ... . . .

.'..-

. . 4-1

4-2

Special

Test

Equipment

Table.

..........

. .

;..;.'•.

.....

4-2

4-3

Special

Test

Equipment.

. • ... ...

......

. . . . . . . 4-3

4-4

Special Tools Table

. . .

........

4-4

4-5

Special Tools

........................

"." 4-5

5-1

Reuseable Shipping Container.

. . . . .

....

..... ......... 5-^2

5-2

Removing Roll Chart

from

Shock Recorder

....

. ,'.

......

5-2

5-3

Installing

Roll Chart

in

Shock Recorder

.

...;..........

5-3

5-4

Computer Lift Handle,

Mounted

5-8

9-1

Laboratory Replaceable Assemblies

...

..............

9-1

9-2

Computer,

Partially

Disassembled

9-2

9-3

Page

Assembly Location Guide.

9-3

9-4

Memory Handle Secured

to

Memory Assembly.

..........

9-6

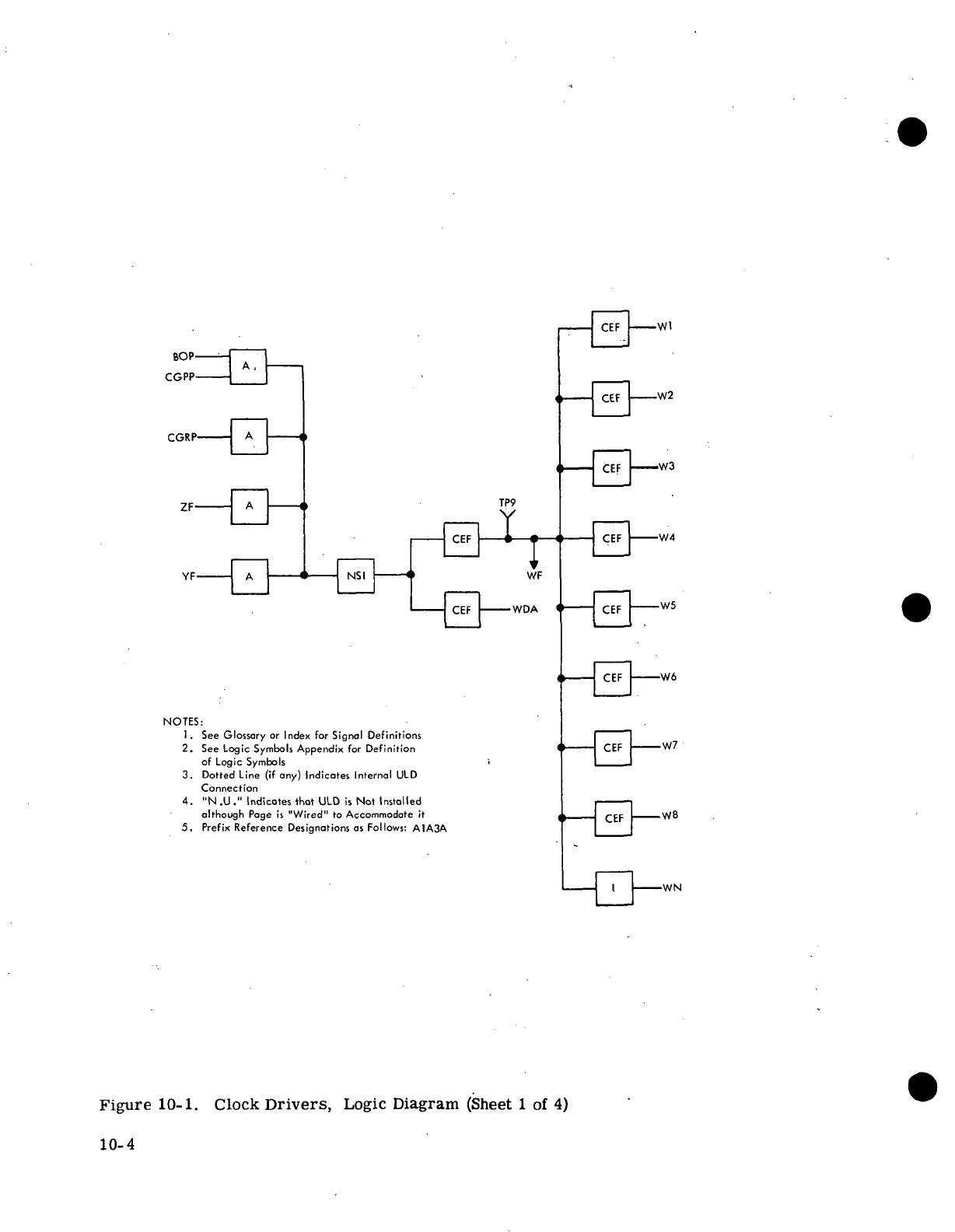

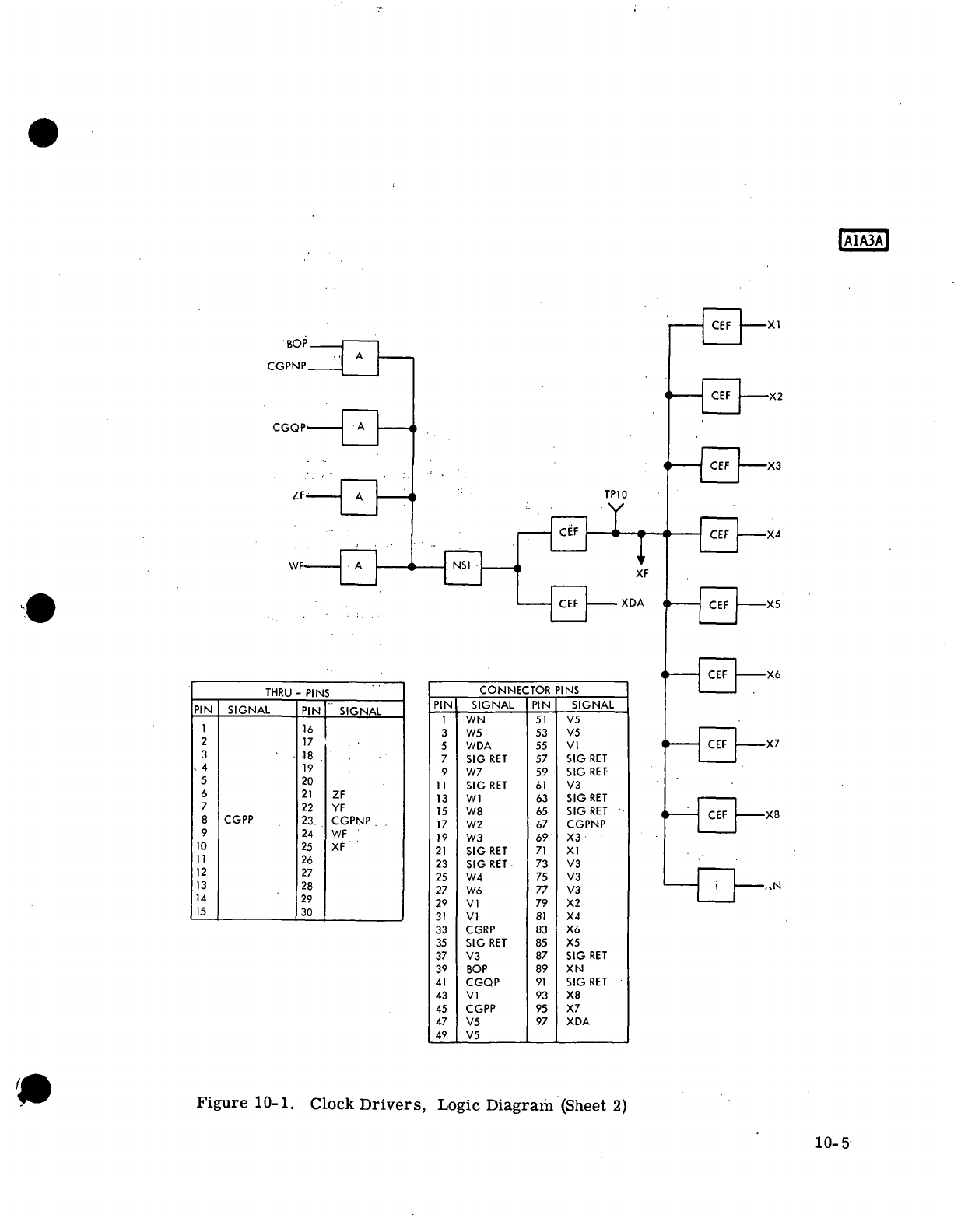

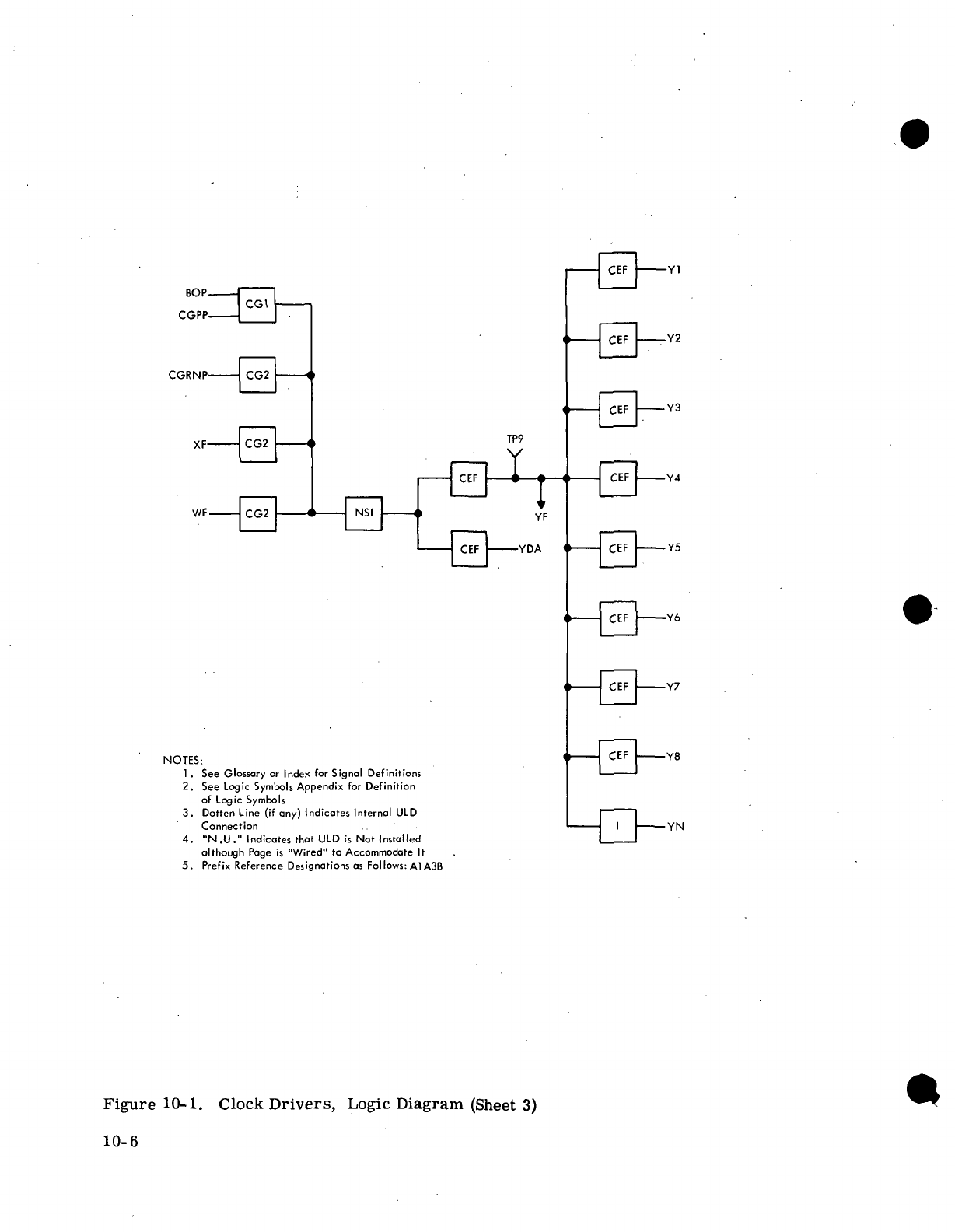

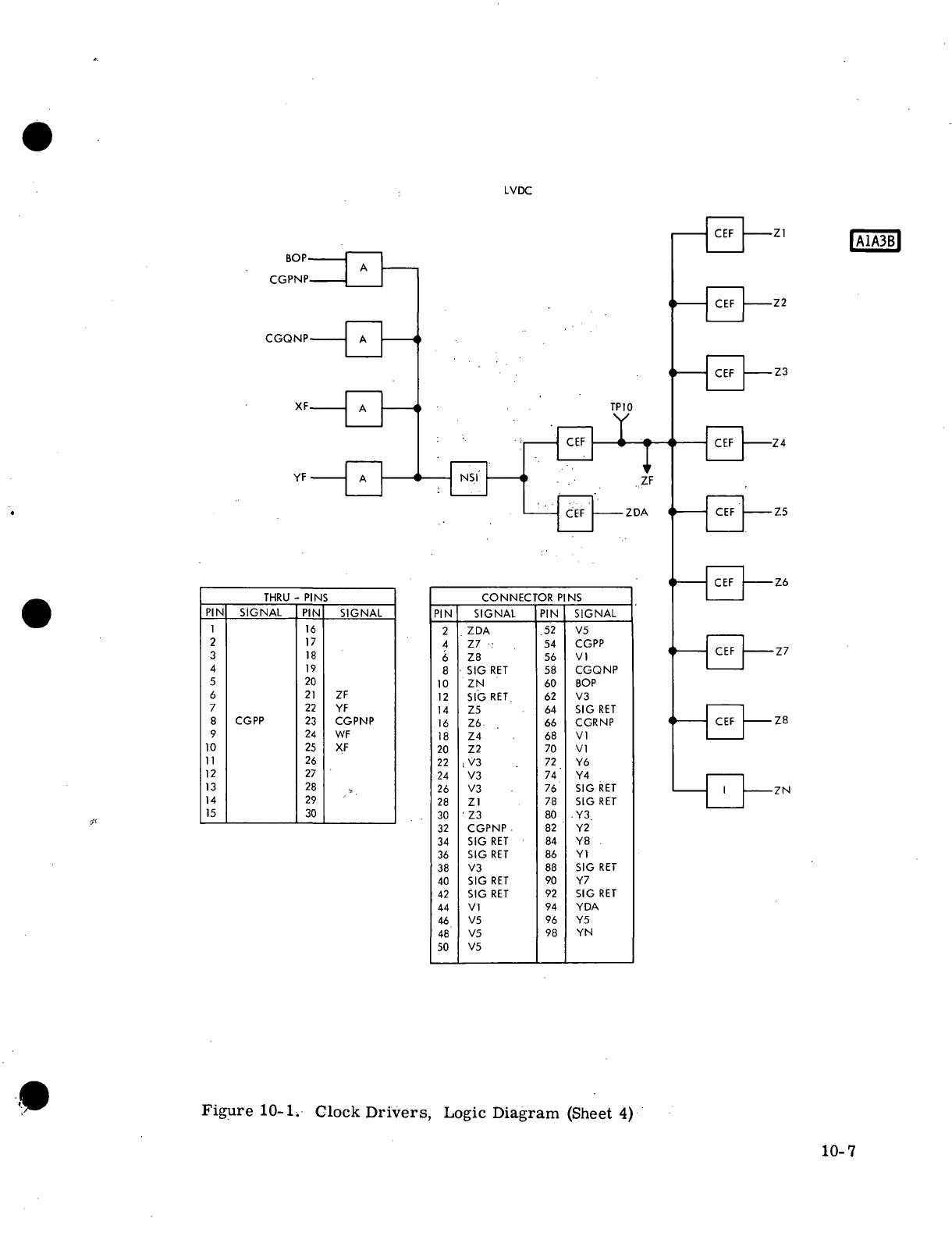

10-1 Clock

Drivers,

Logic Diagram

(4

Sheets)

10-4

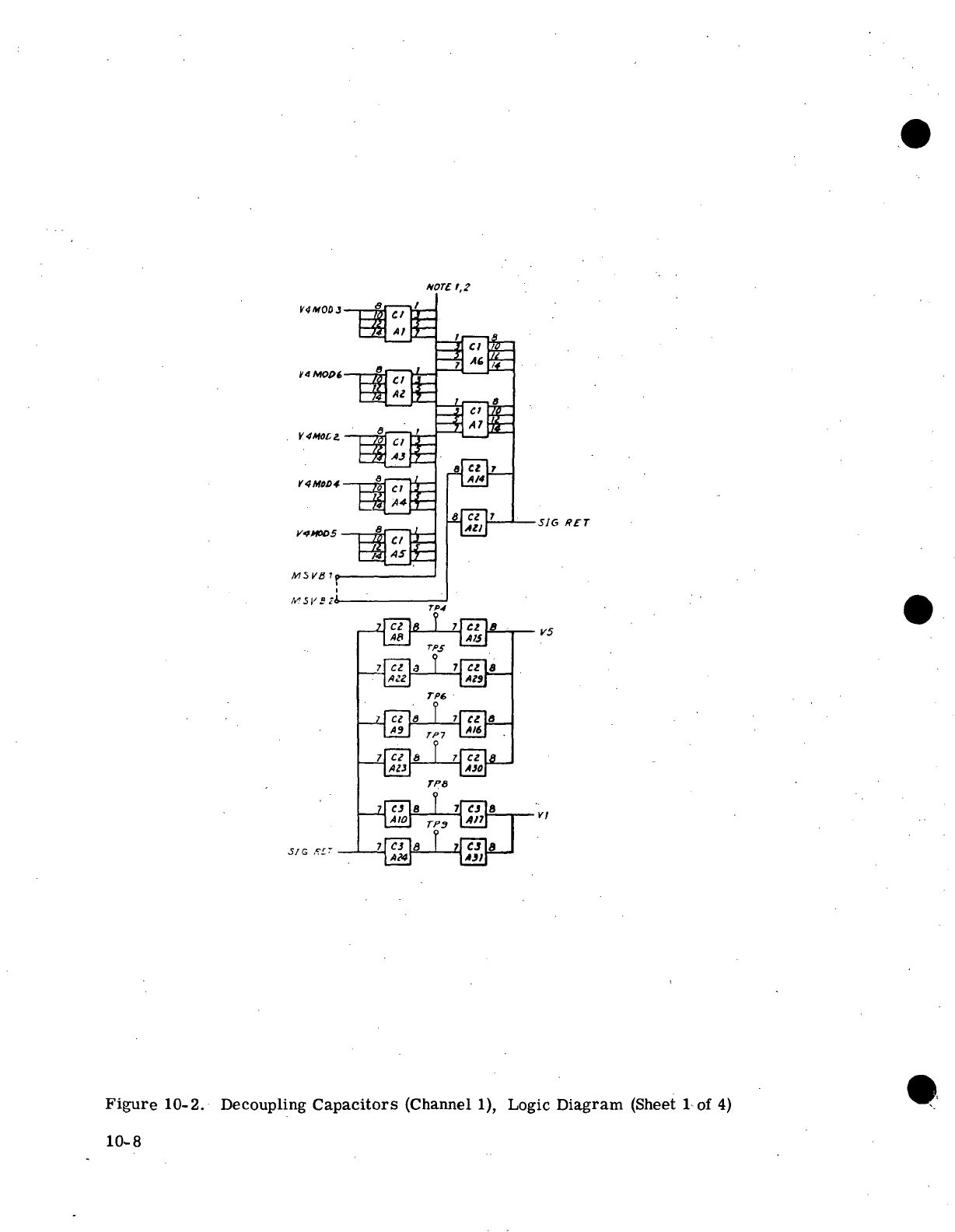

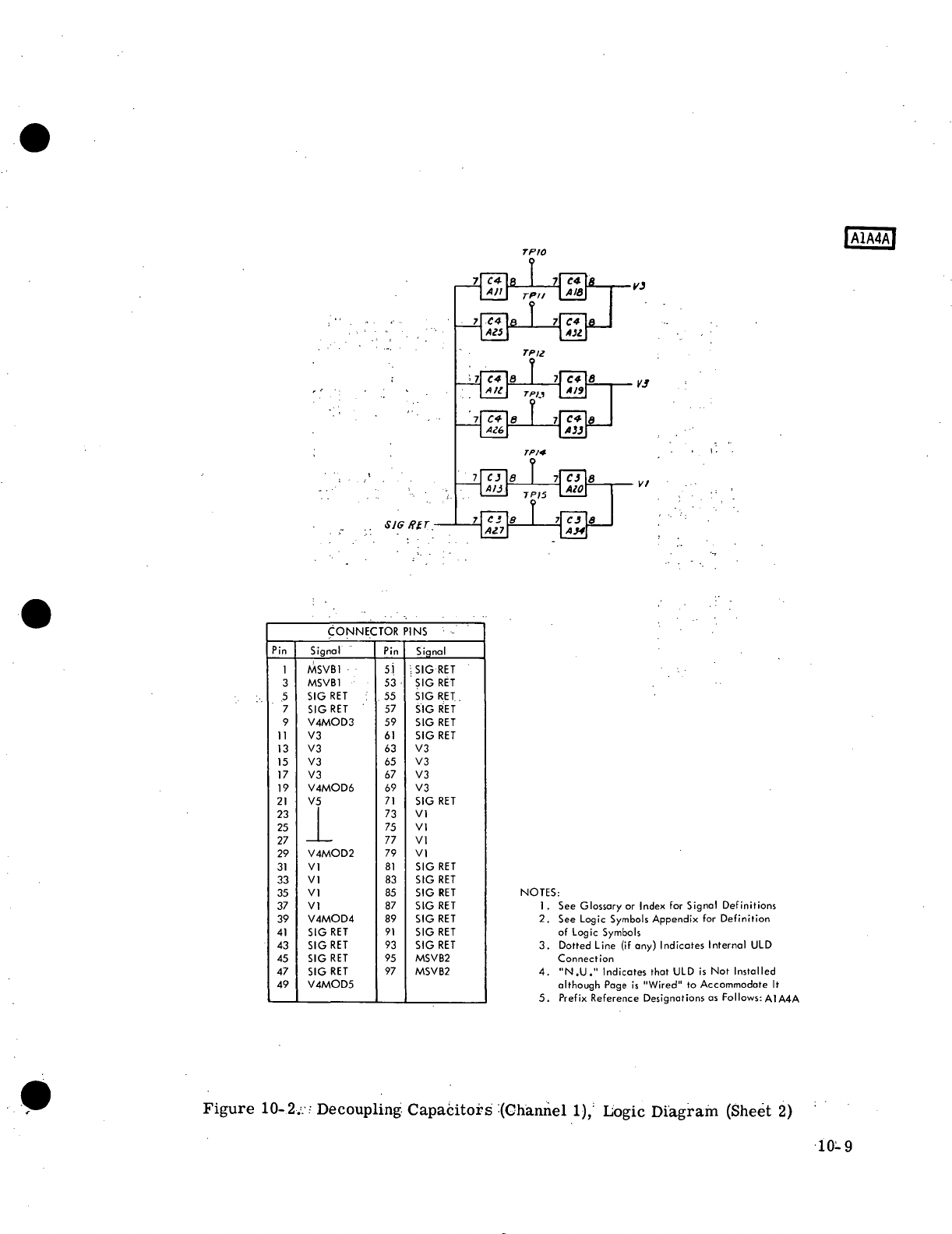

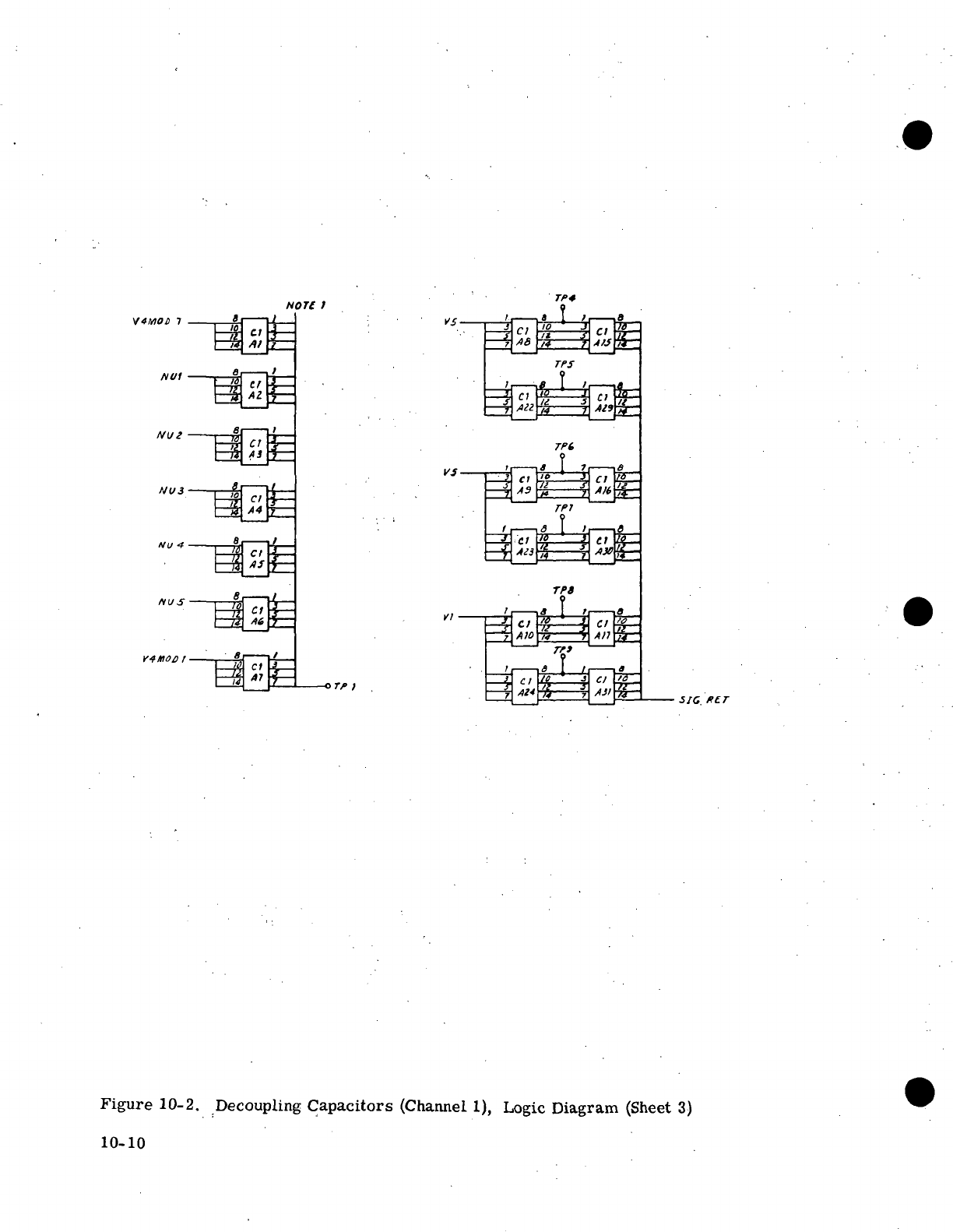

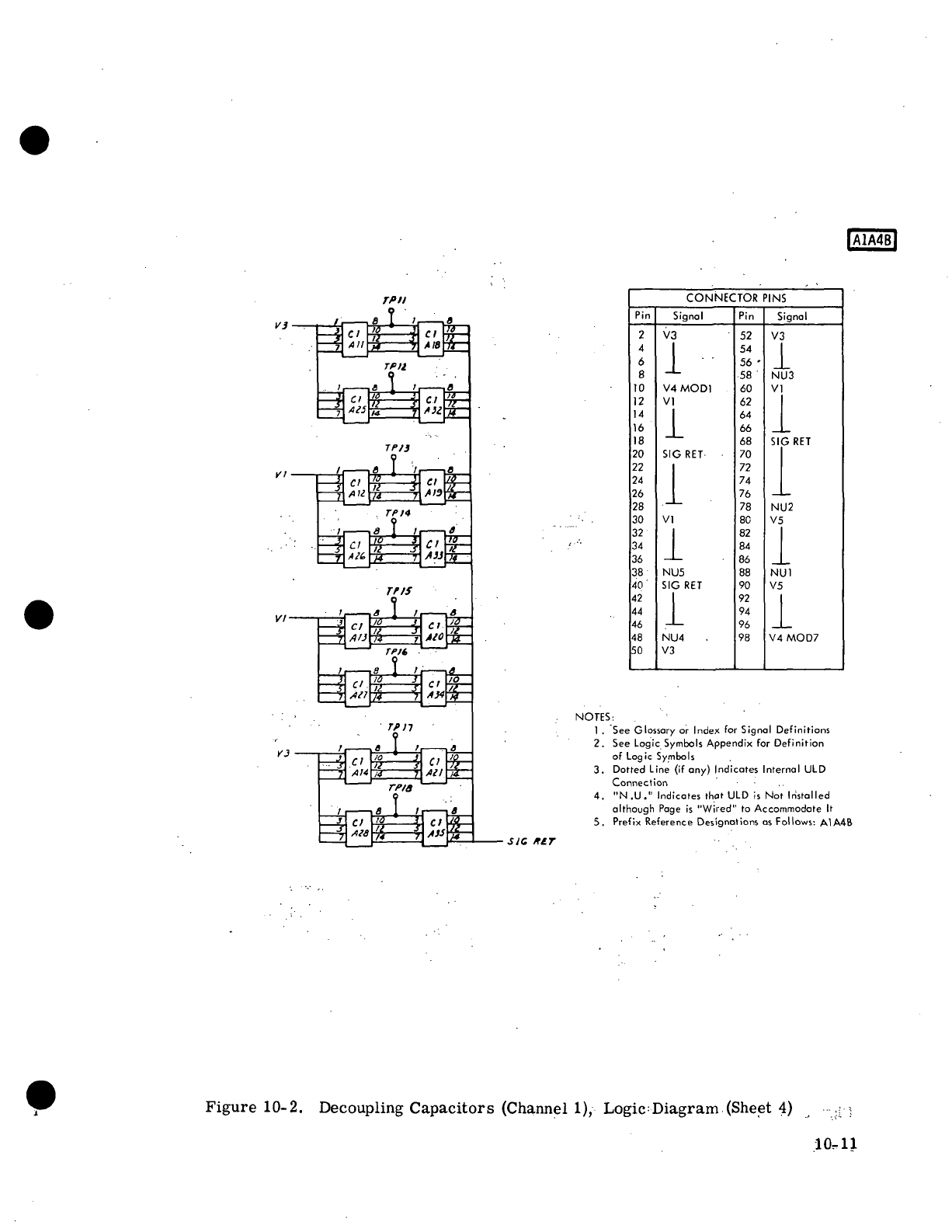

10-2 Decoupling Capacitors (Channel

1),

Logic Diagram

(4

Sheets)

.

10-8

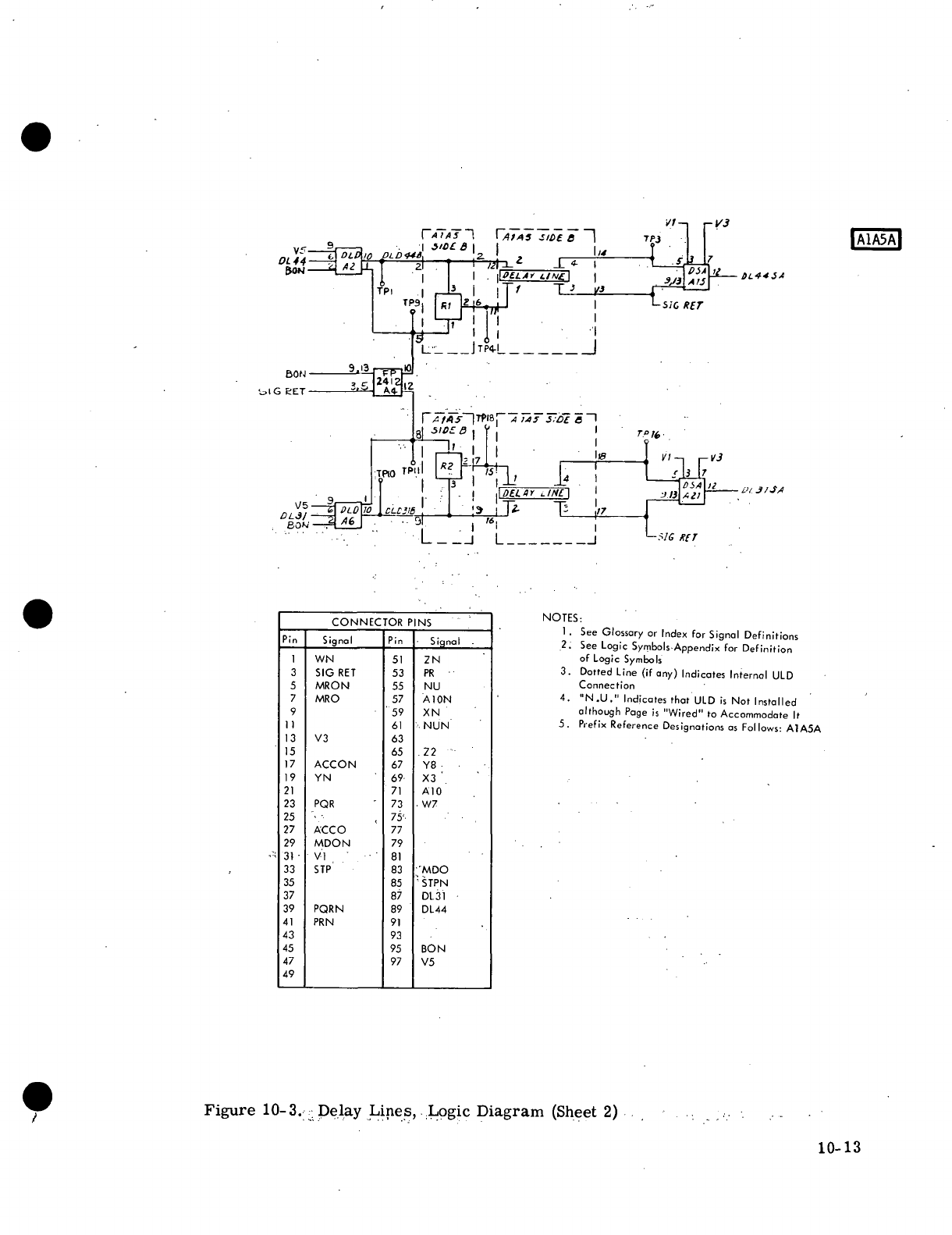

10-3 Delay Lines, Logic Diagram

(2

Sheets)

10-12

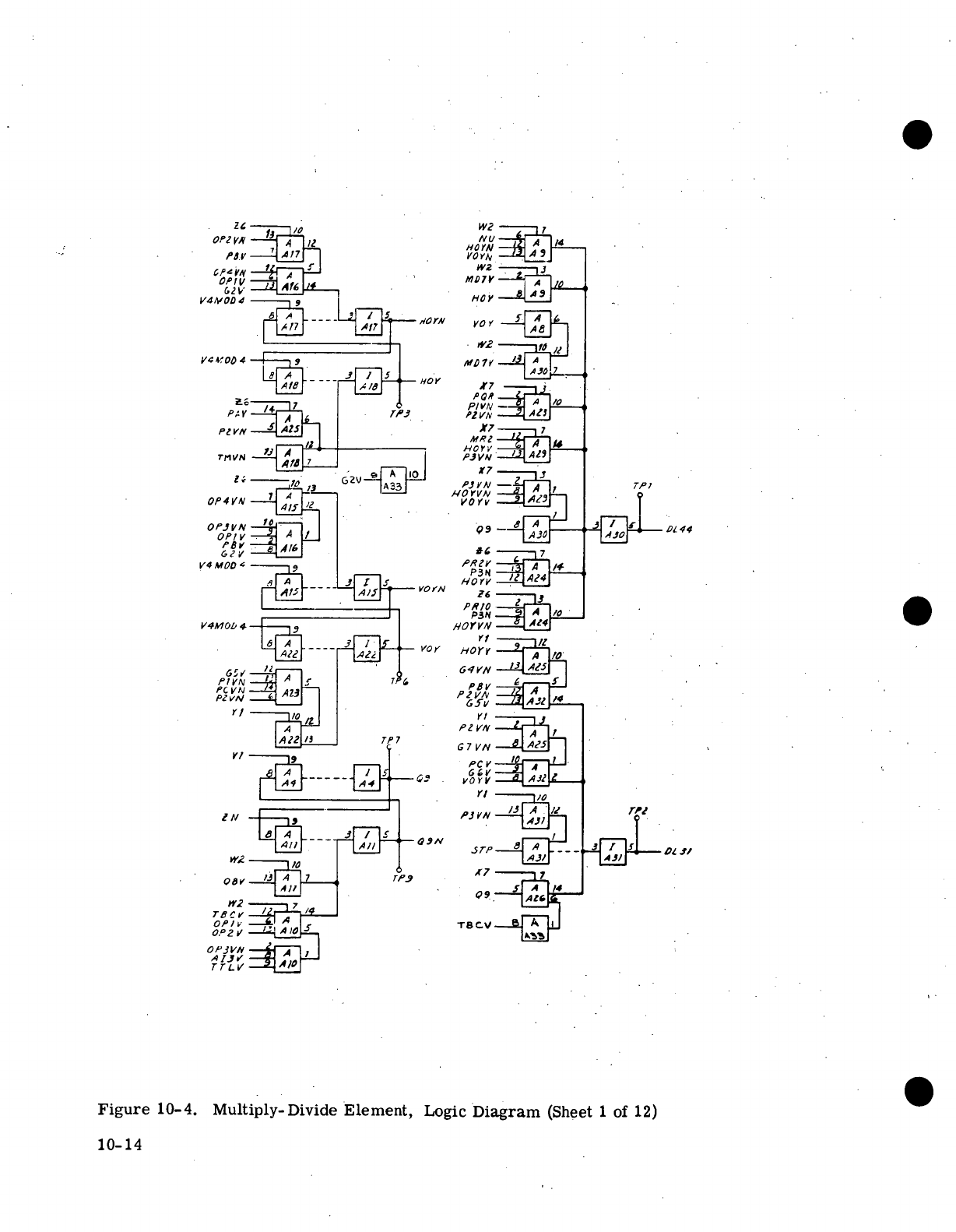

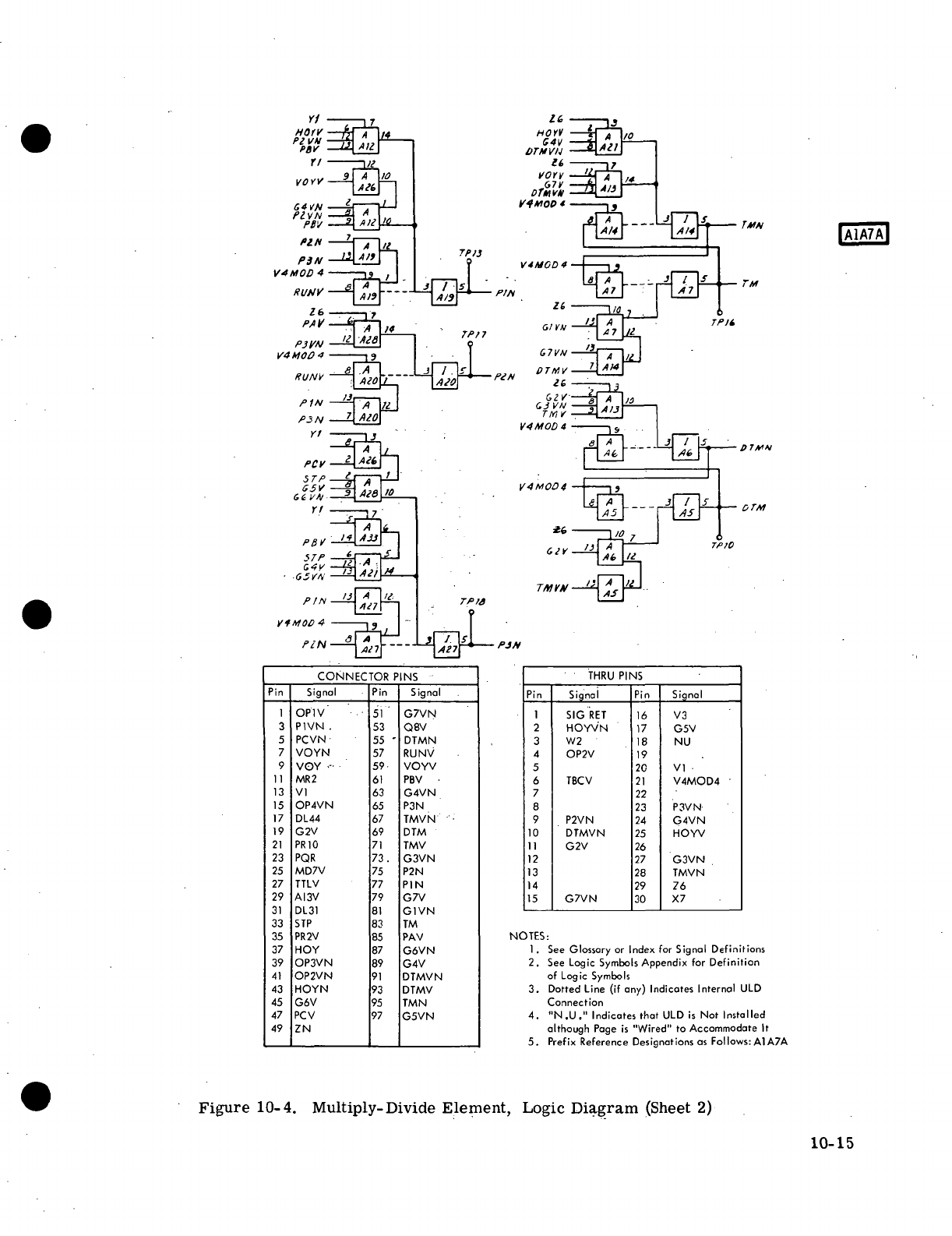

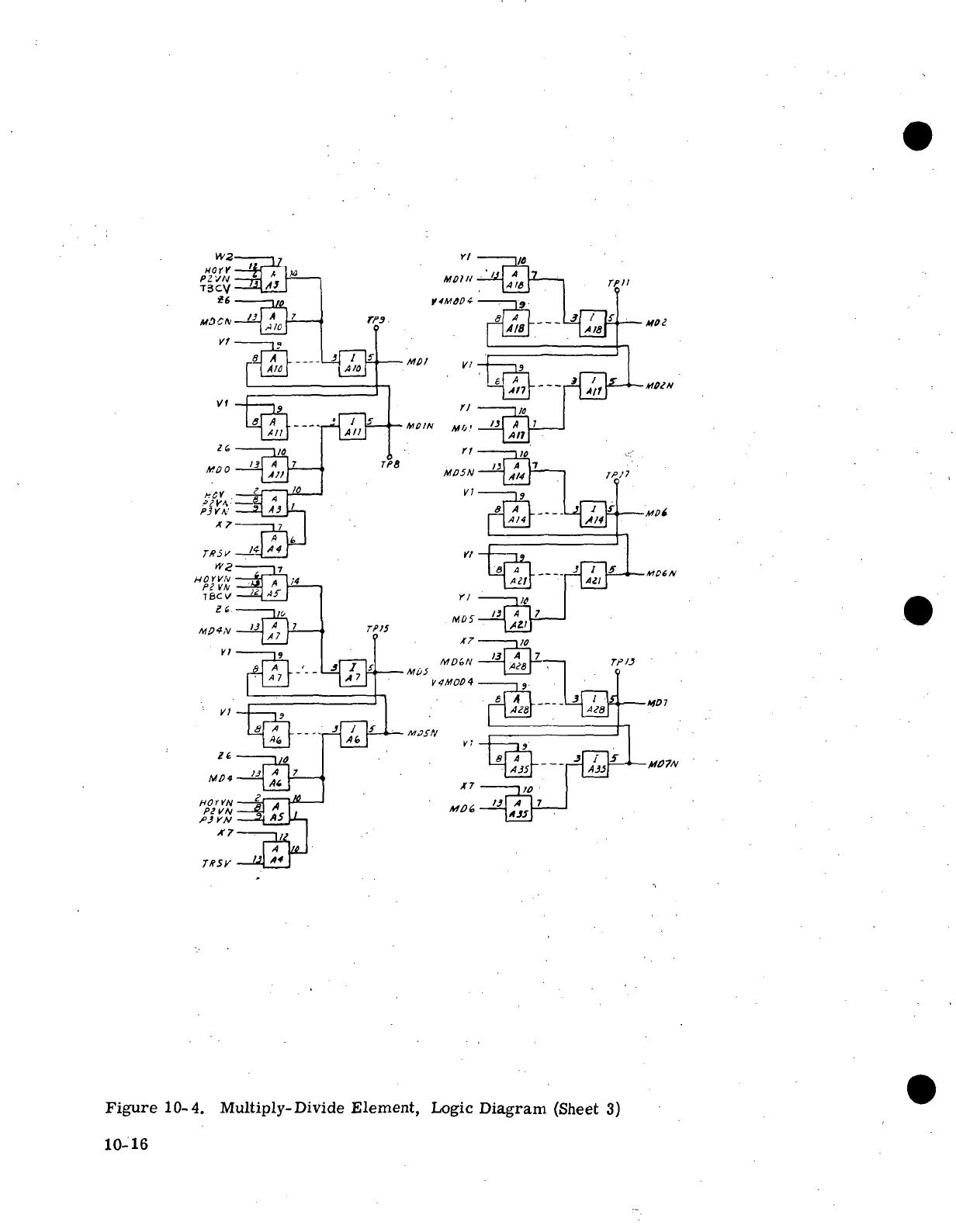

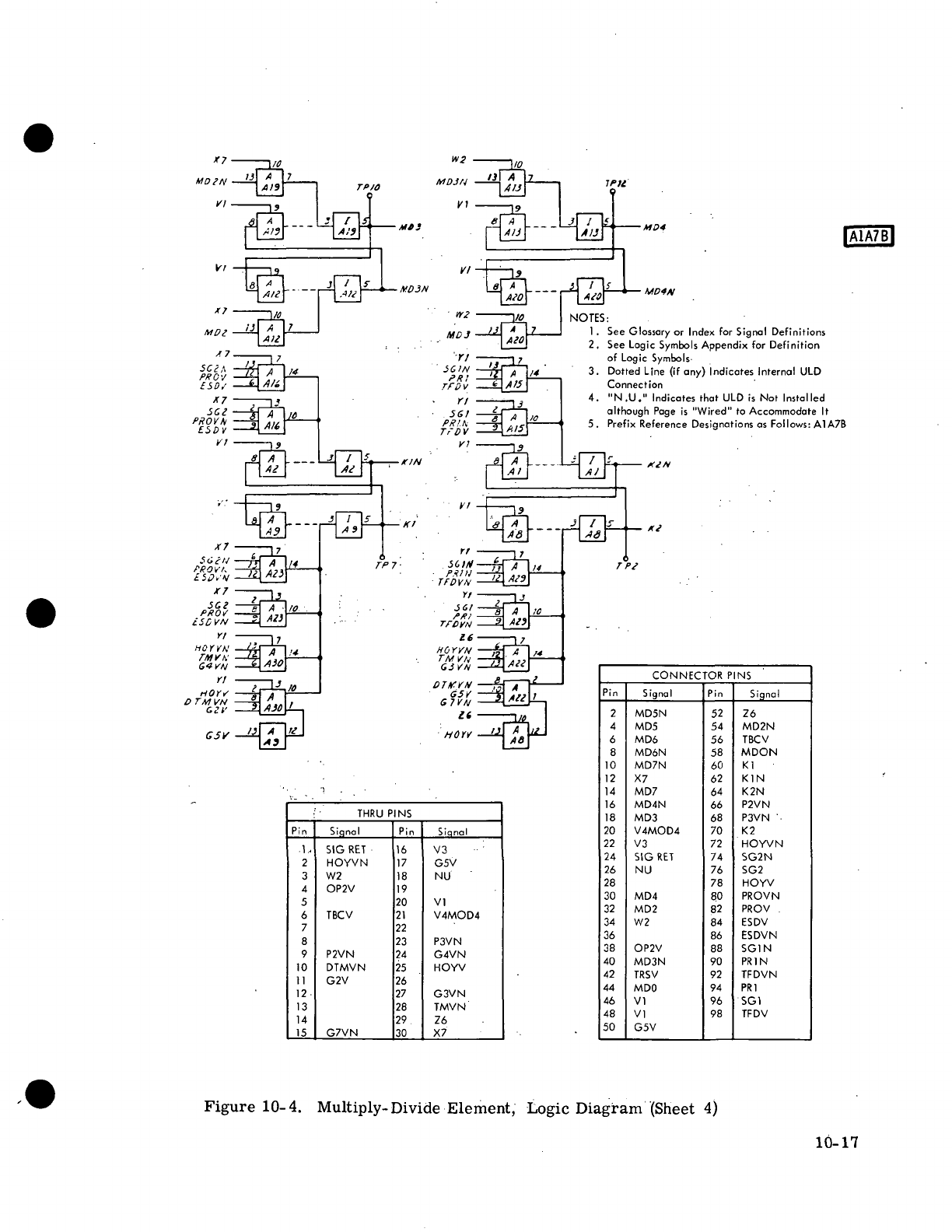

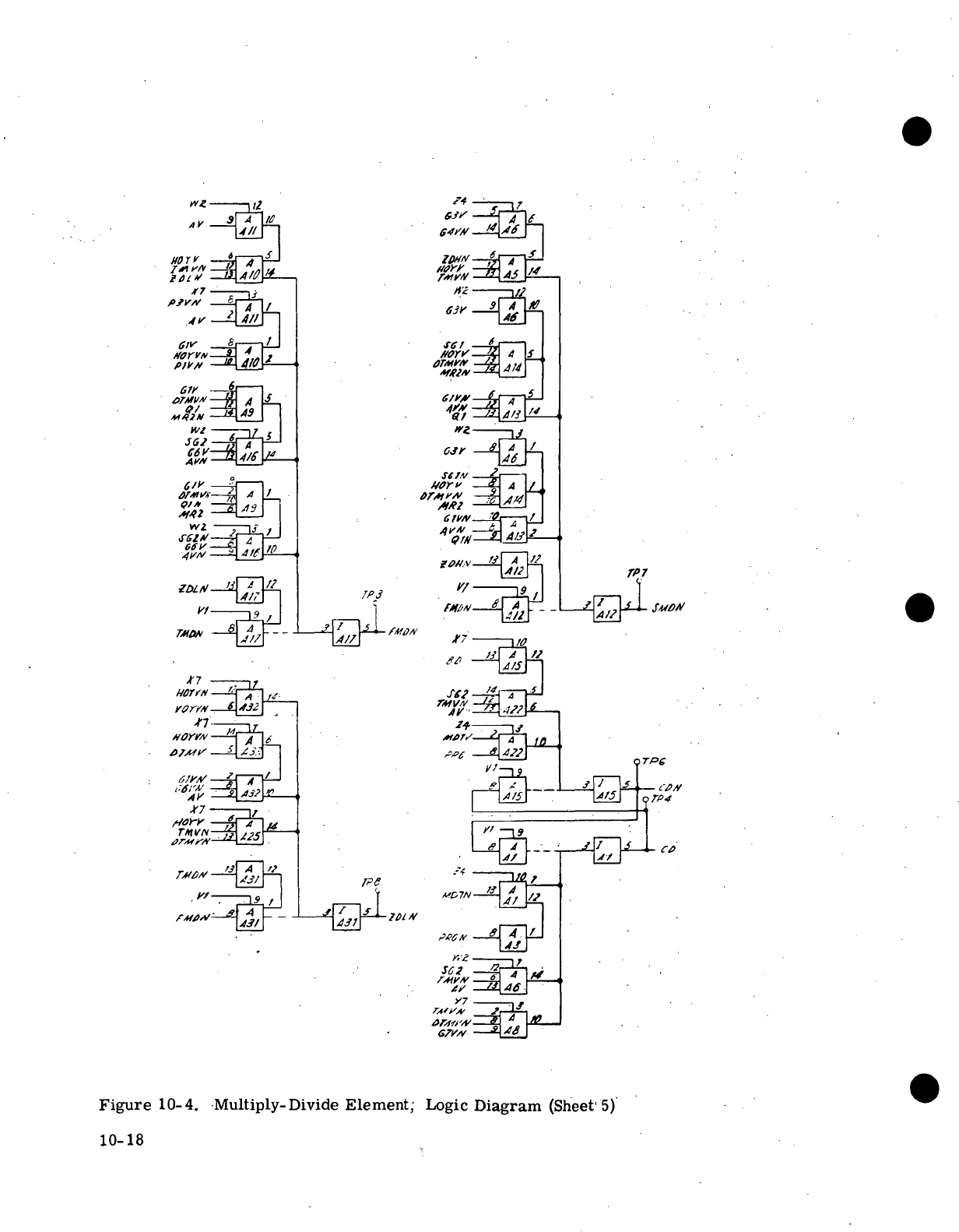

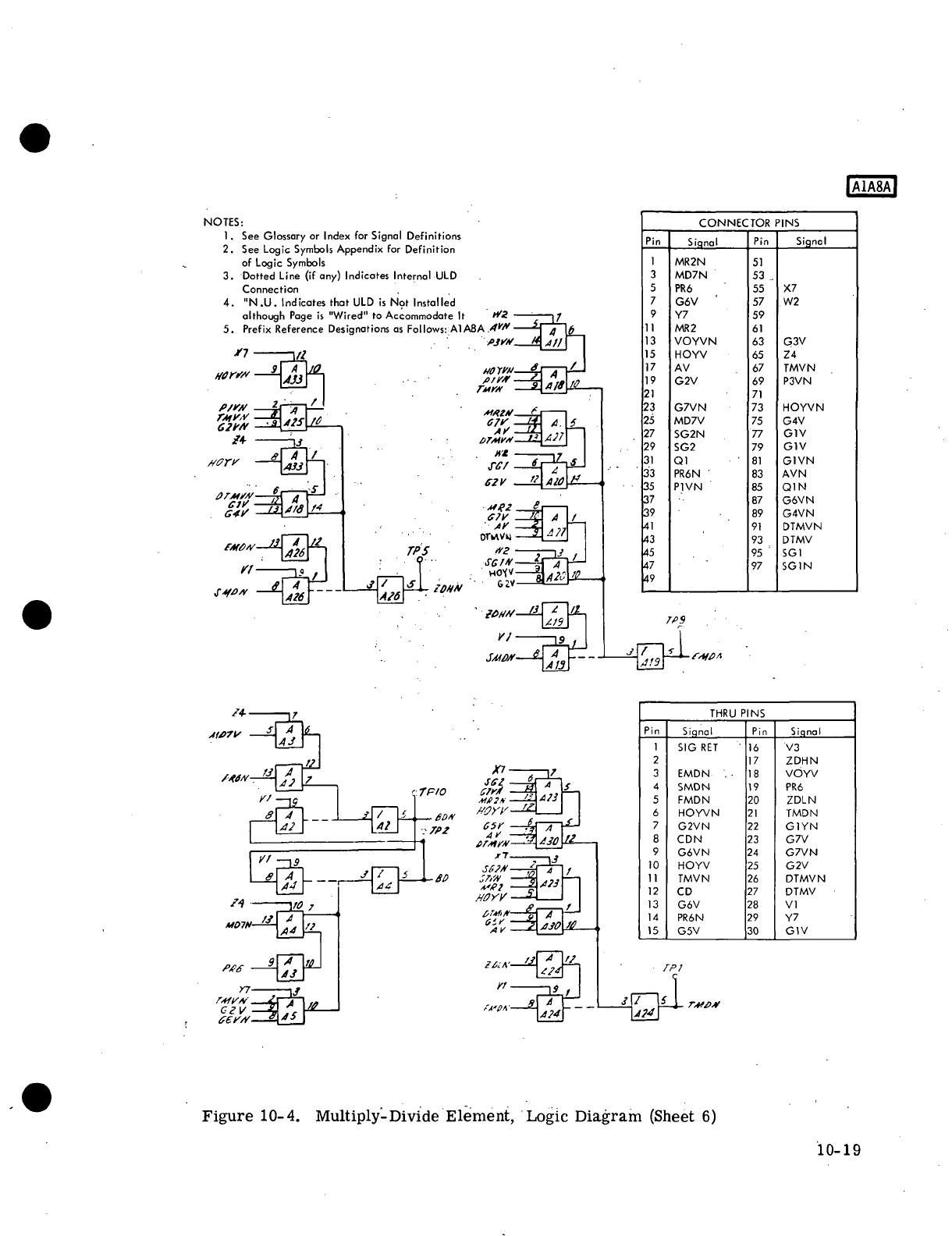

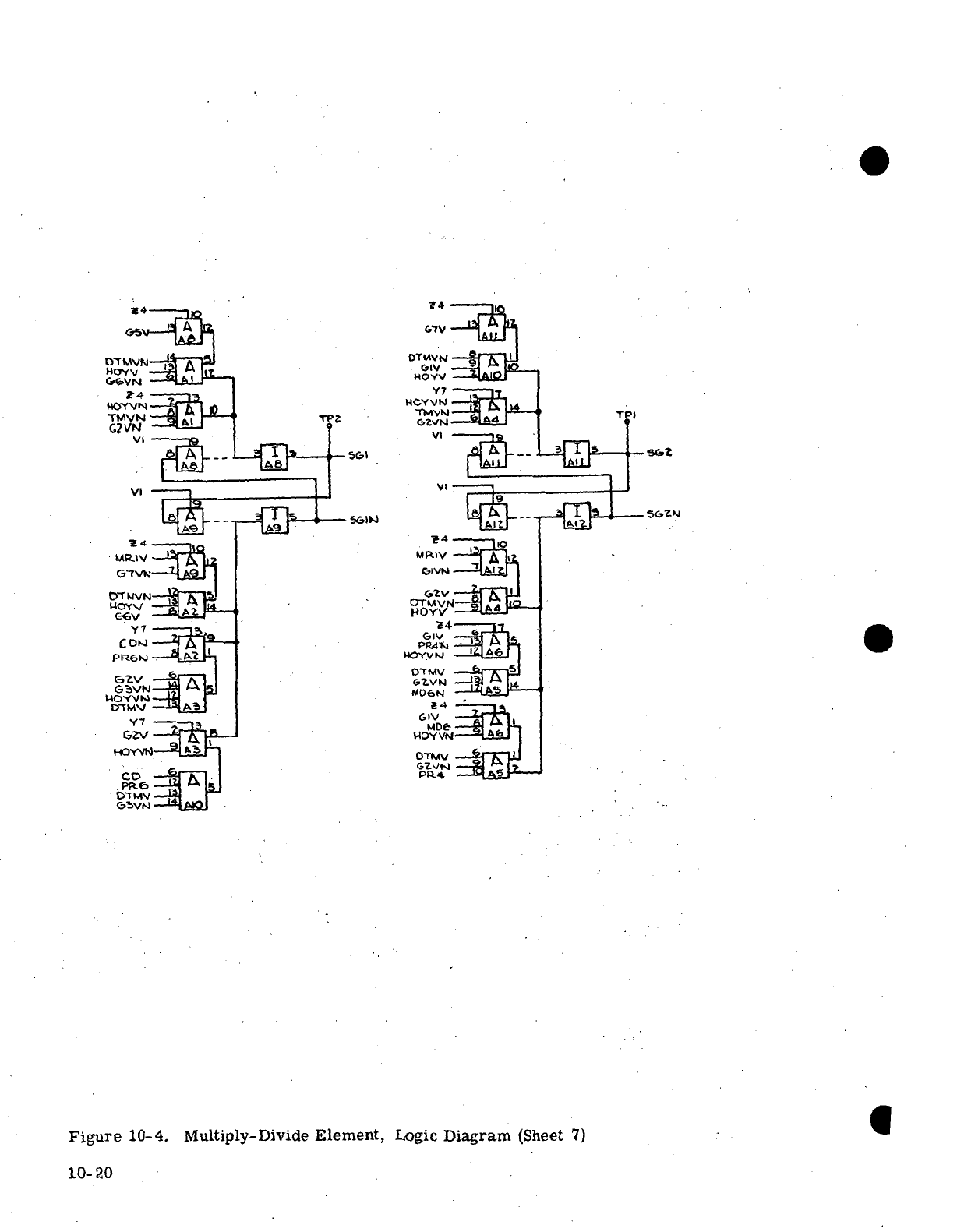

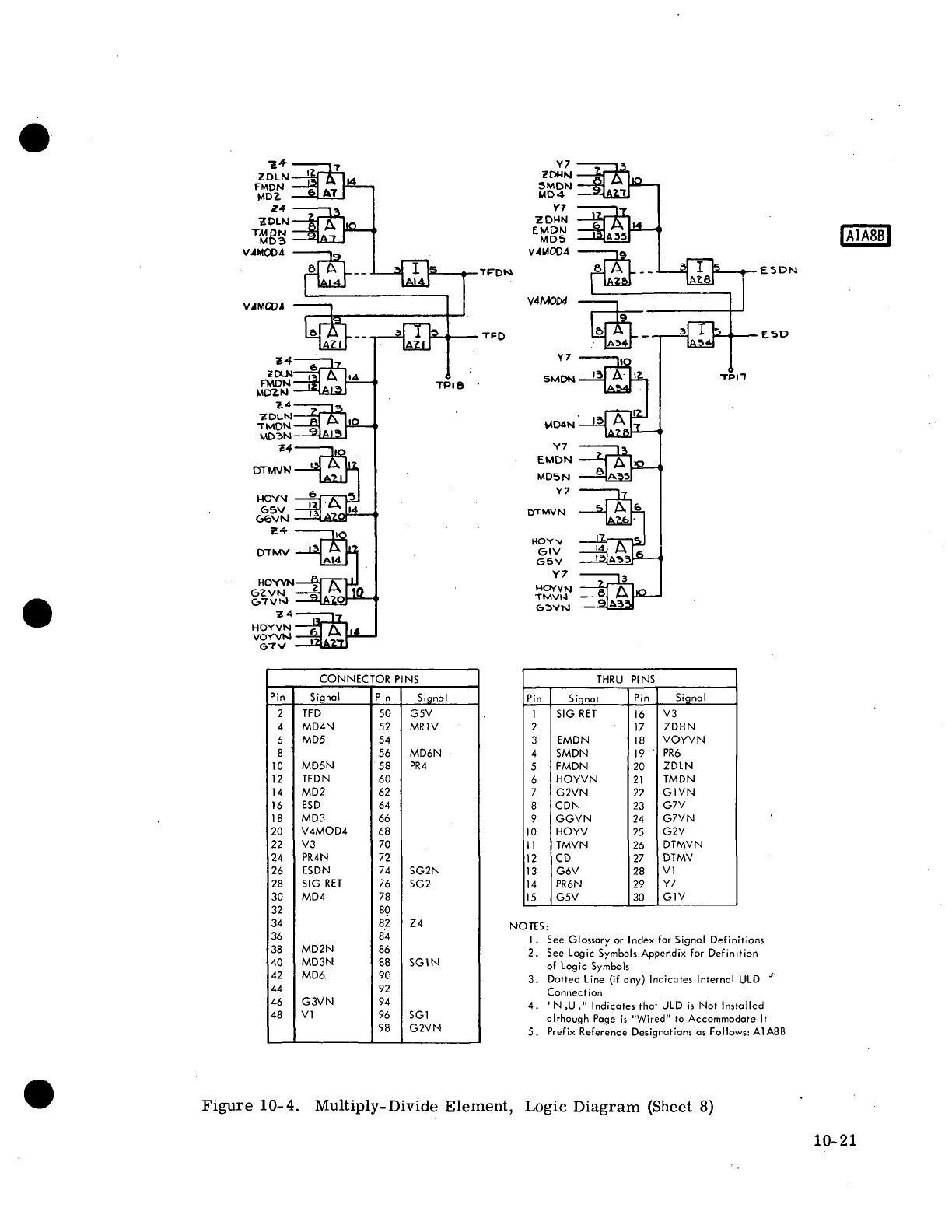

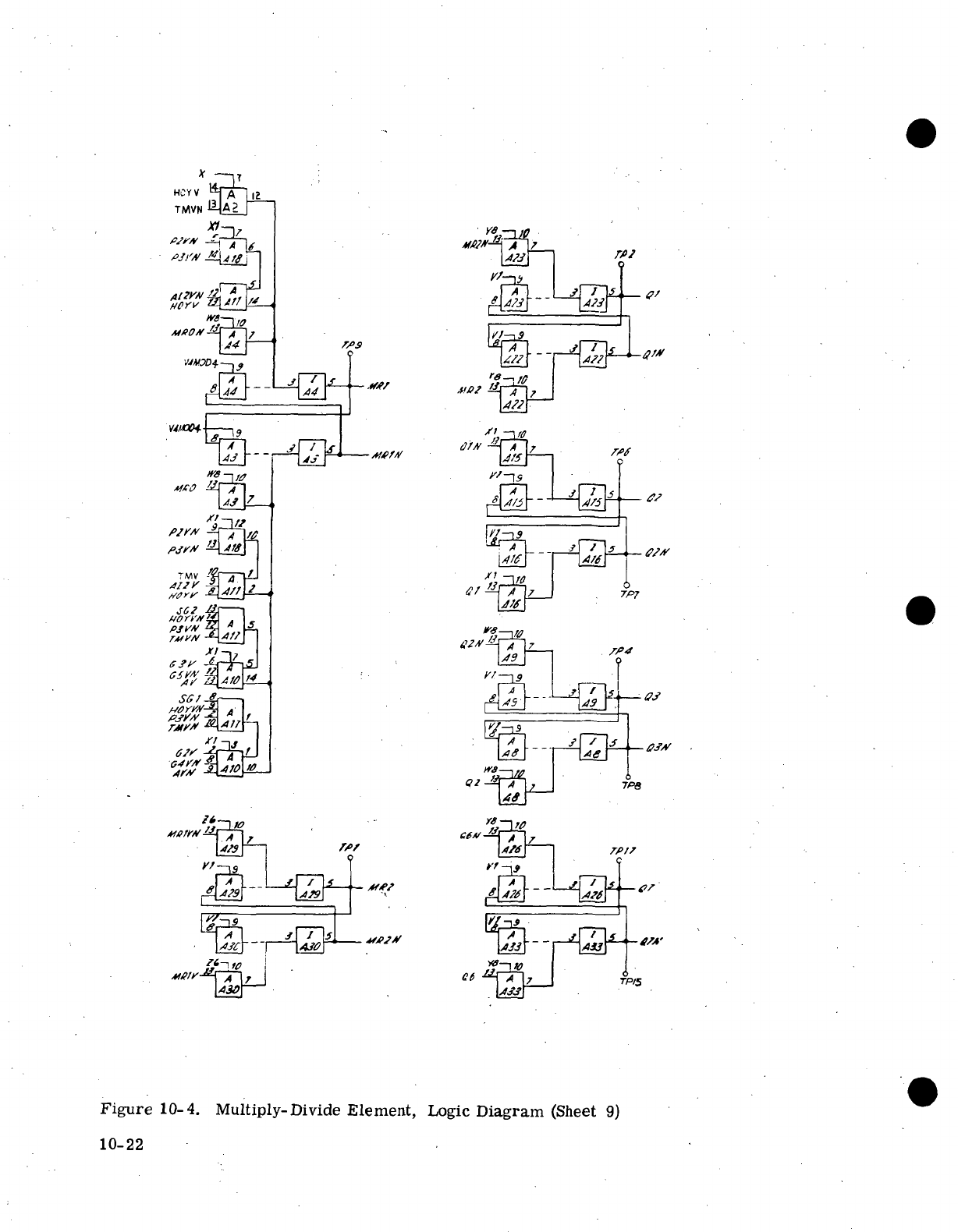

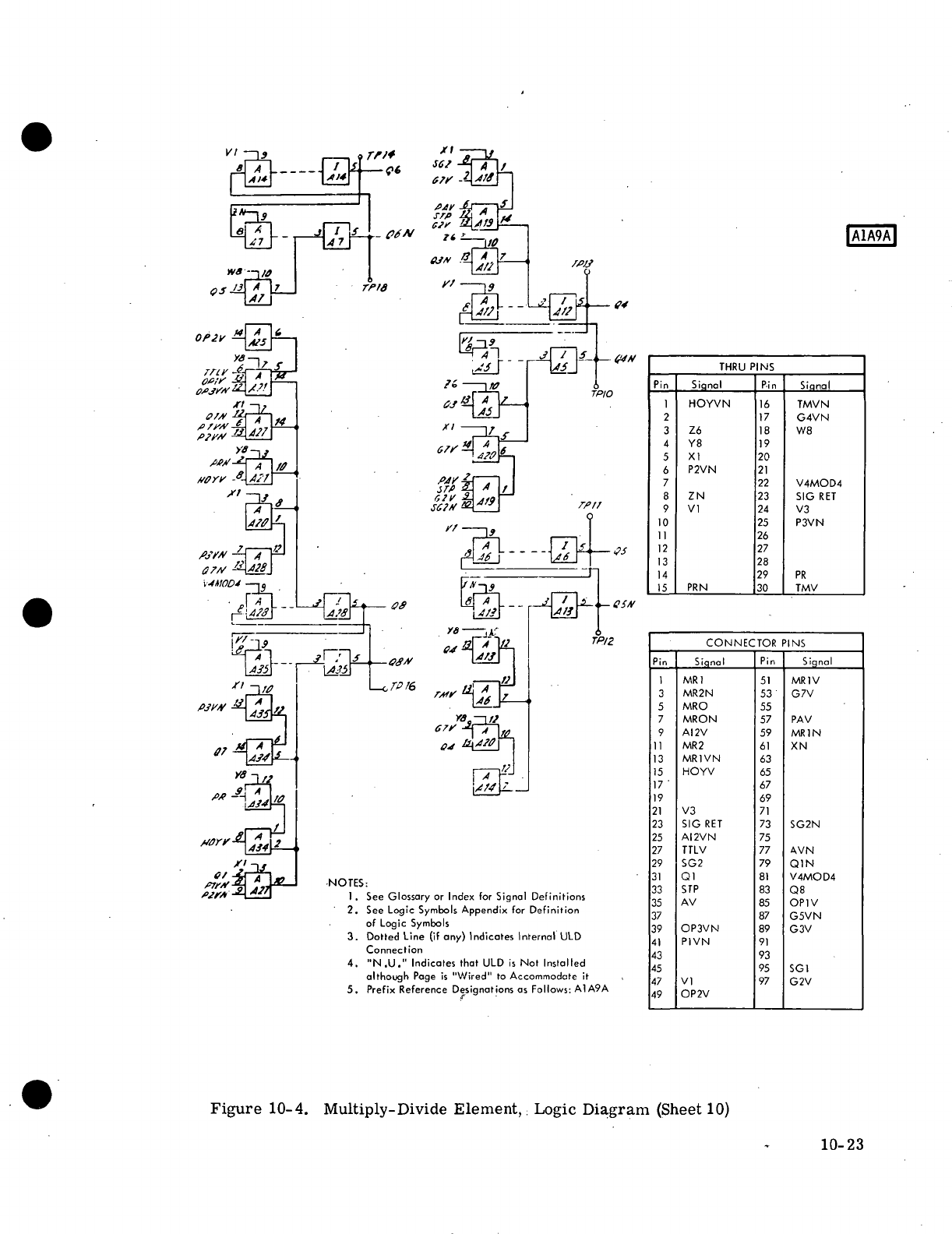

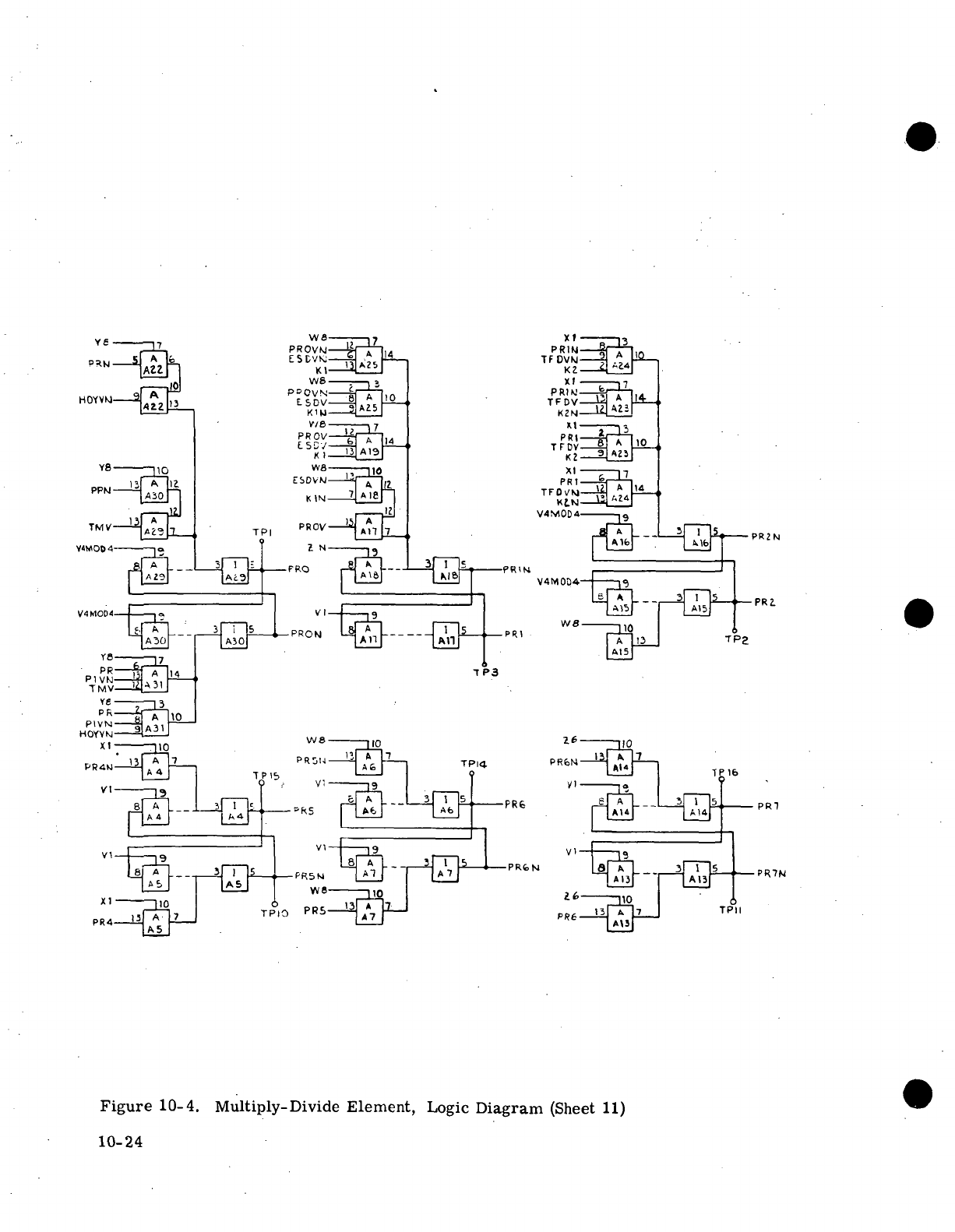

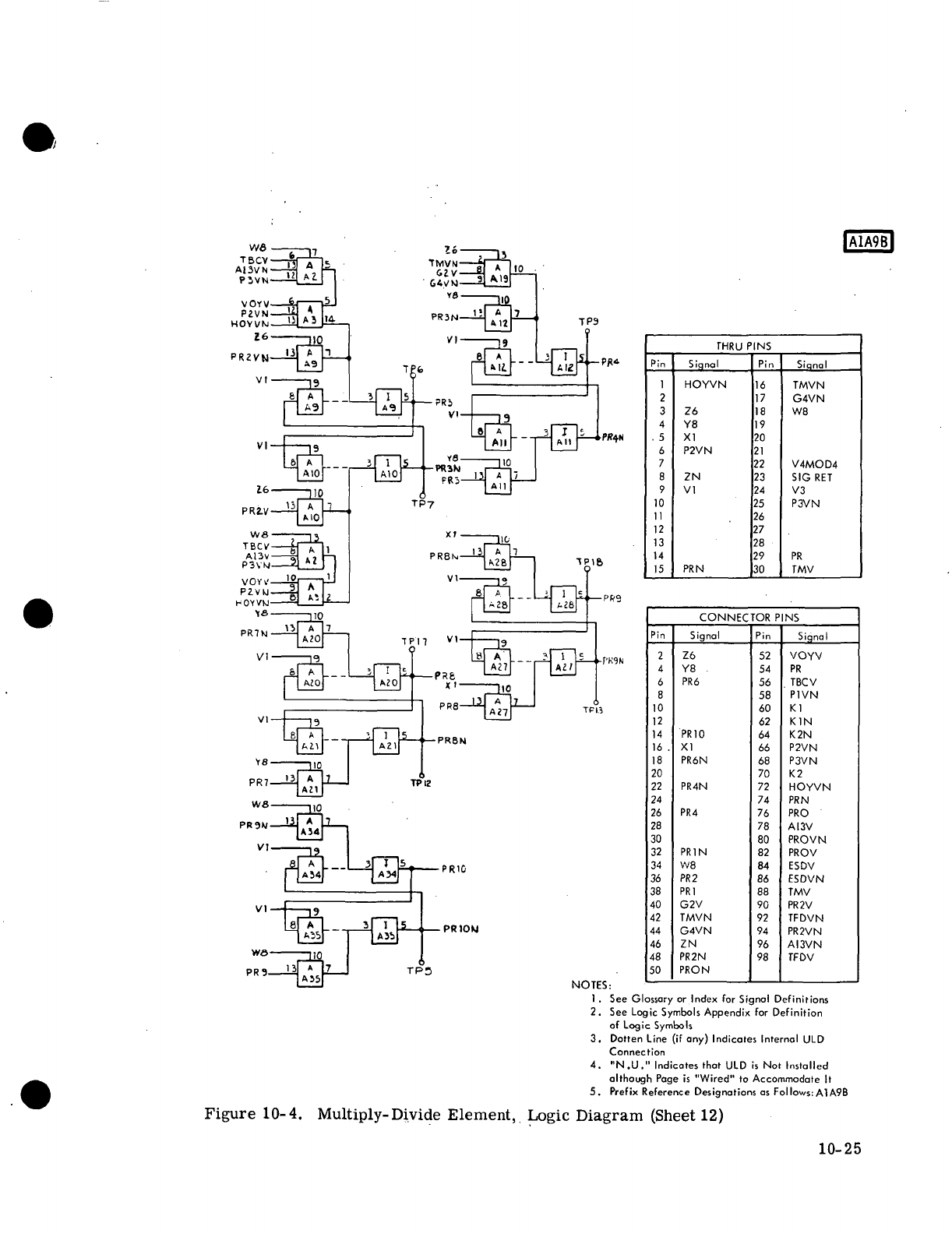

10-4 Multiply-Divide Element, Logic Diagram

(12

Sheets)

10-14

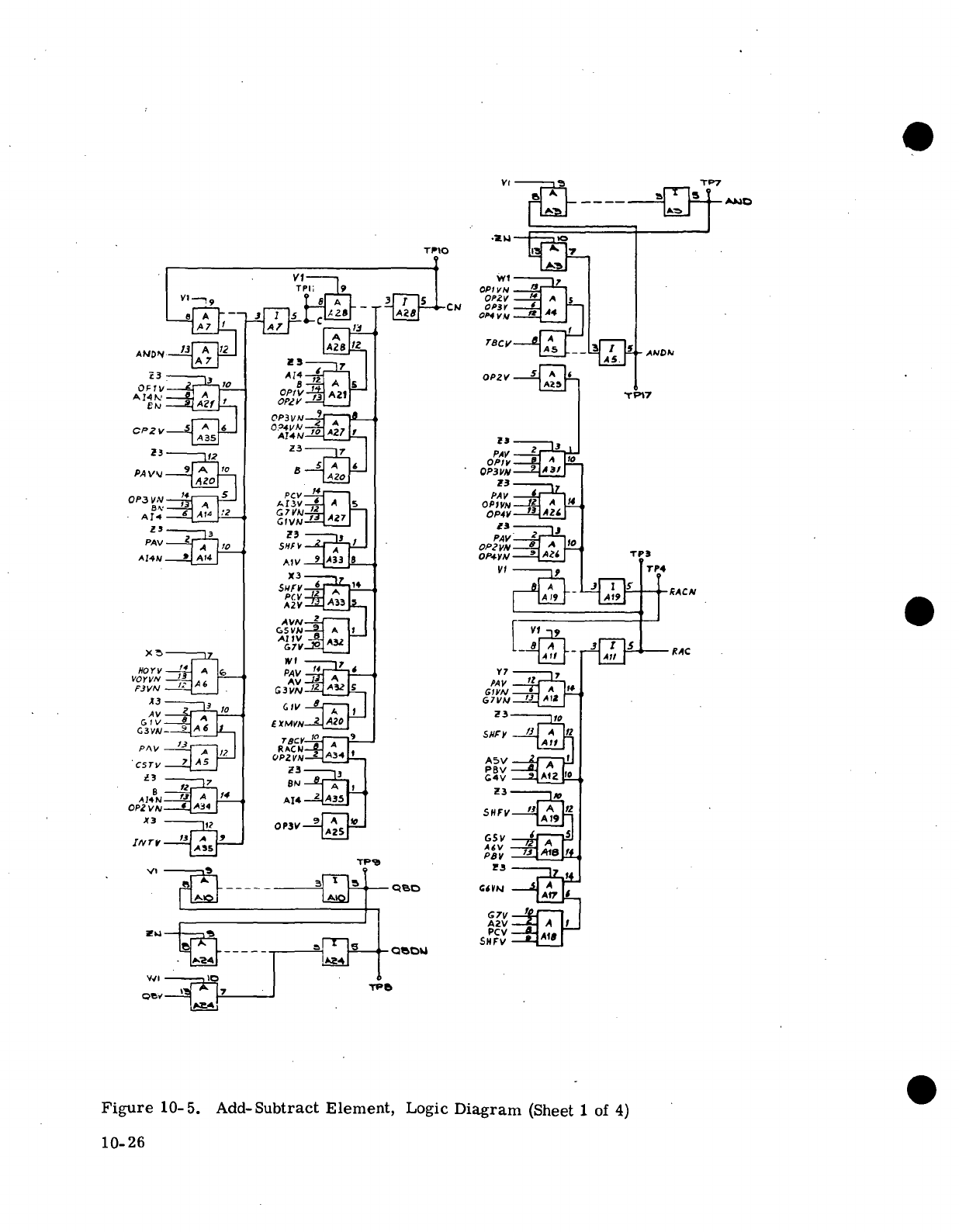

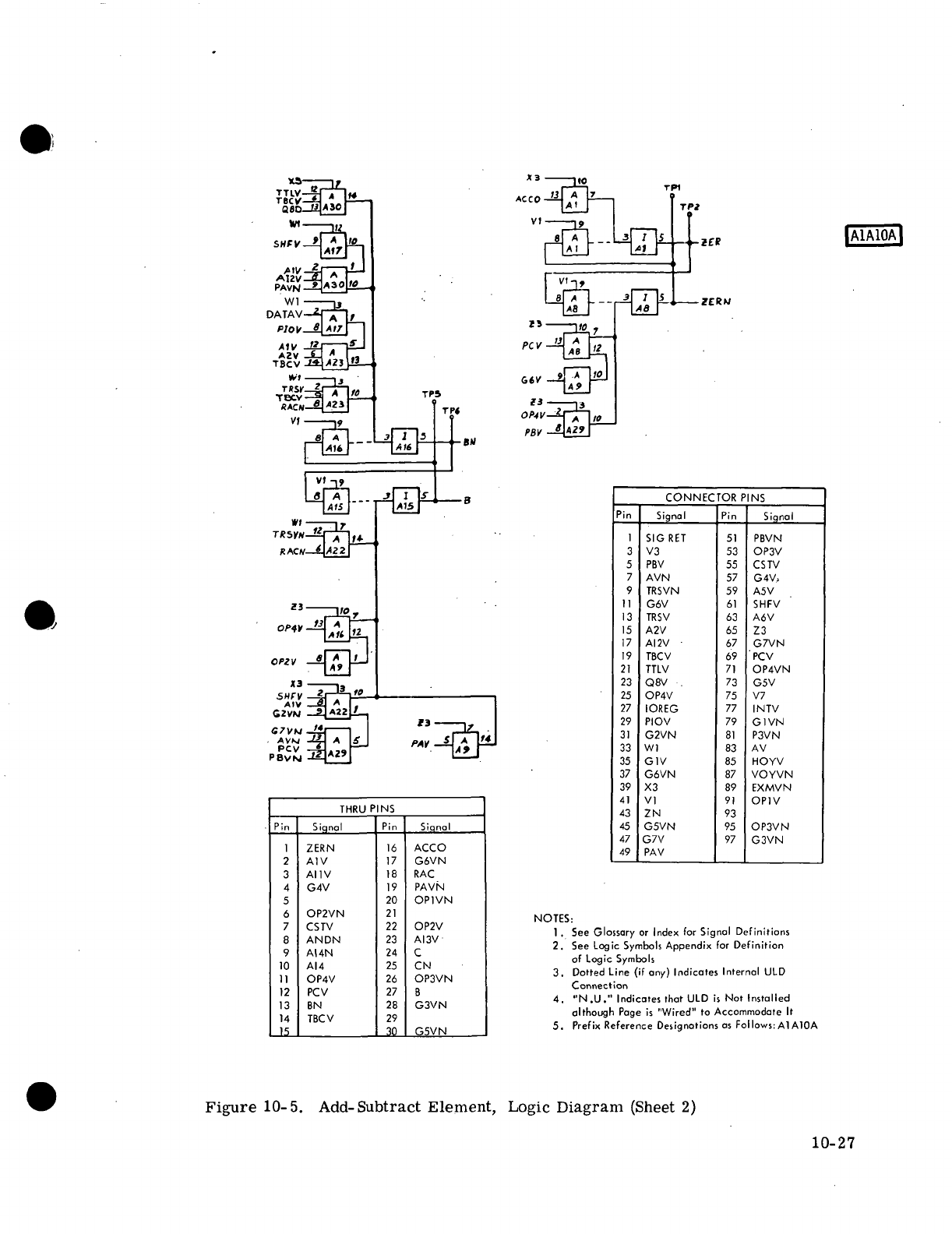

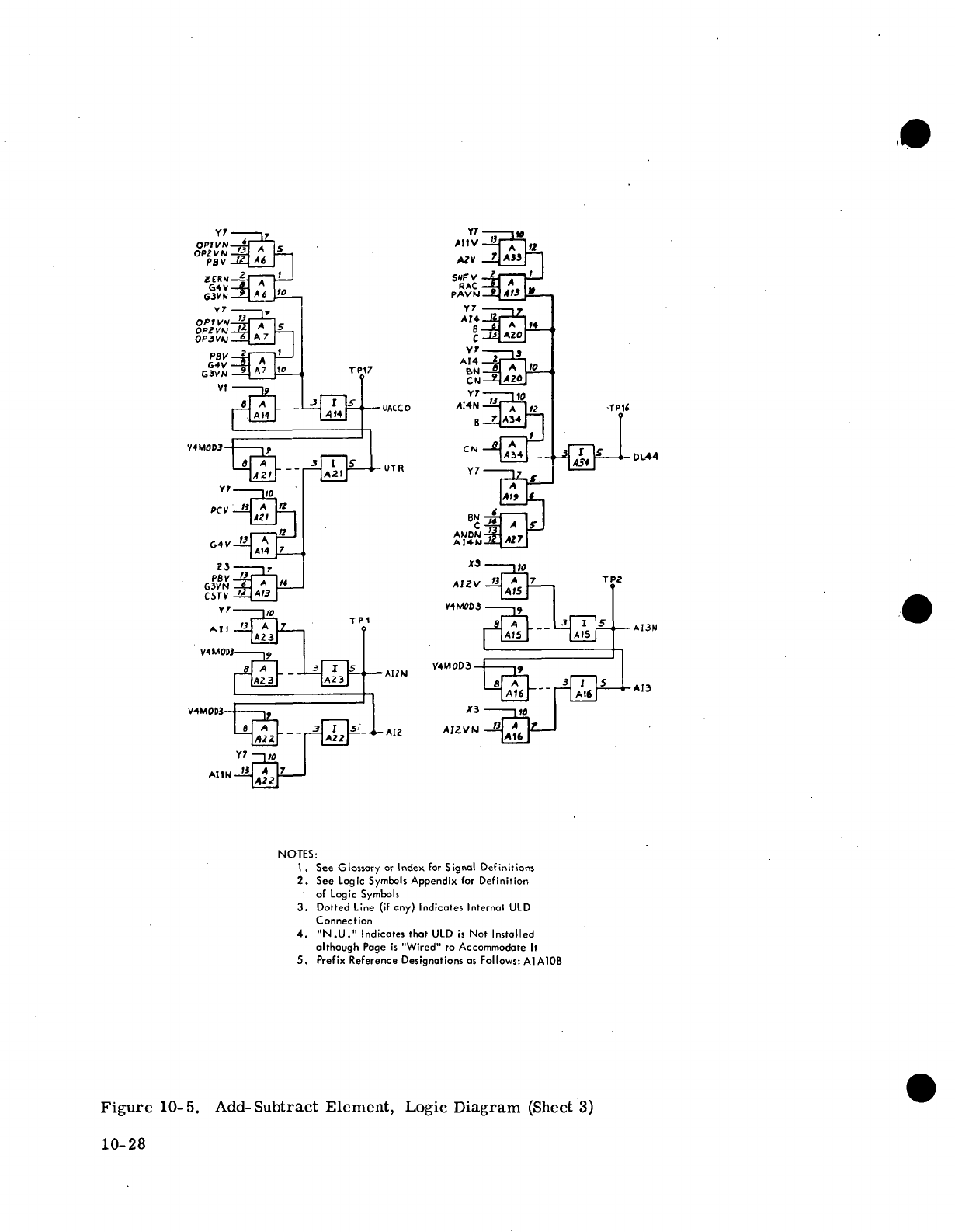

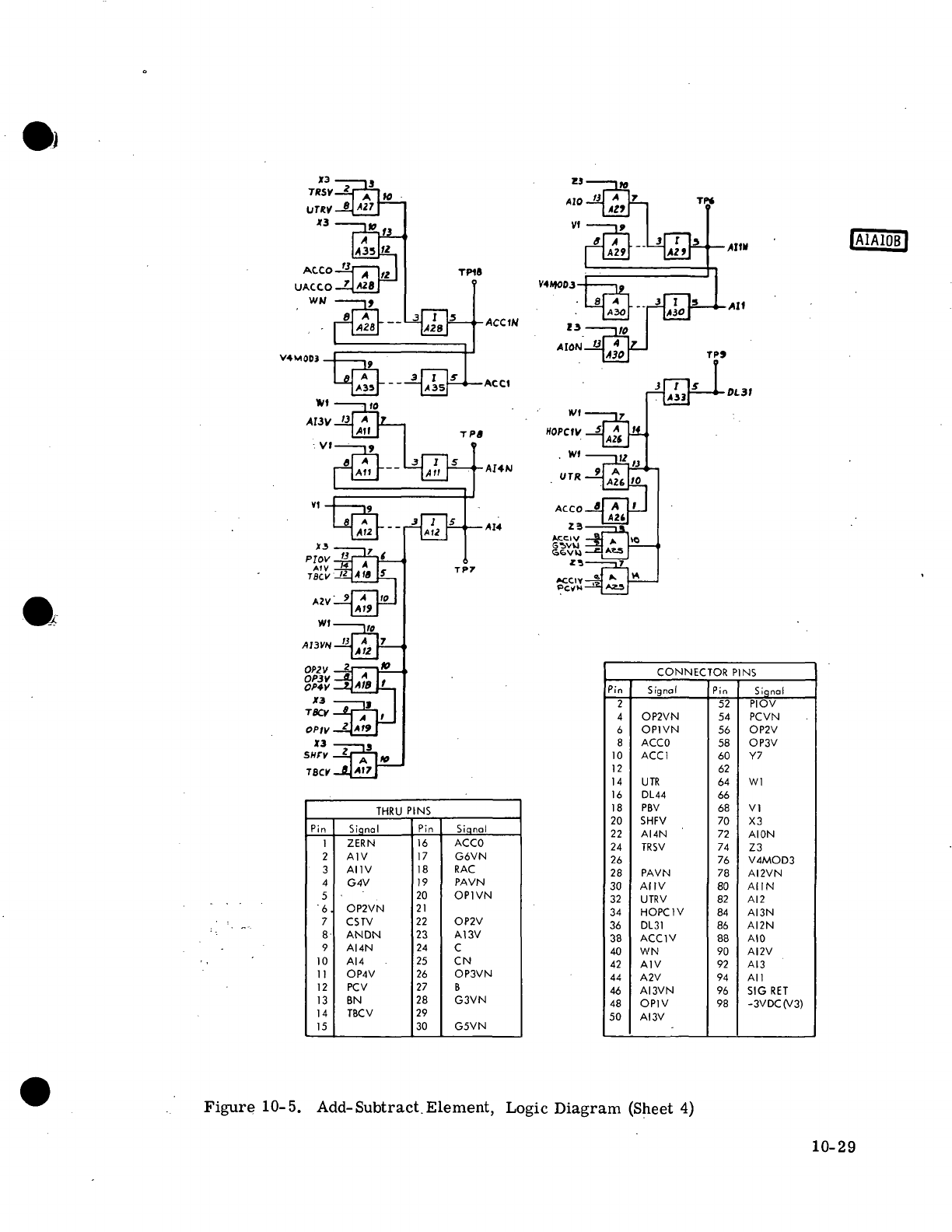

10-5 Add-Subtract Element, Logic Diagram

(4

Sheets).

........

10-26

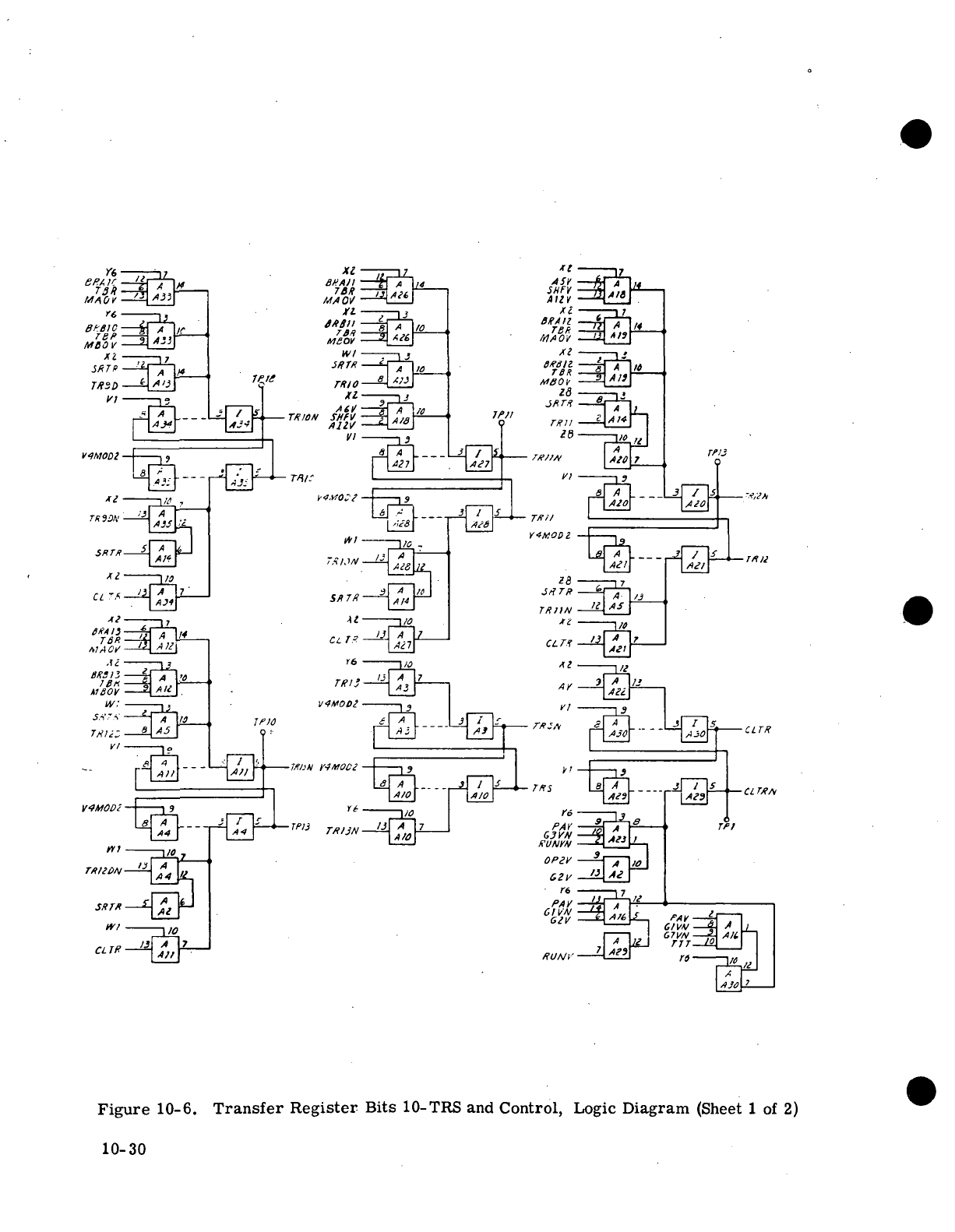

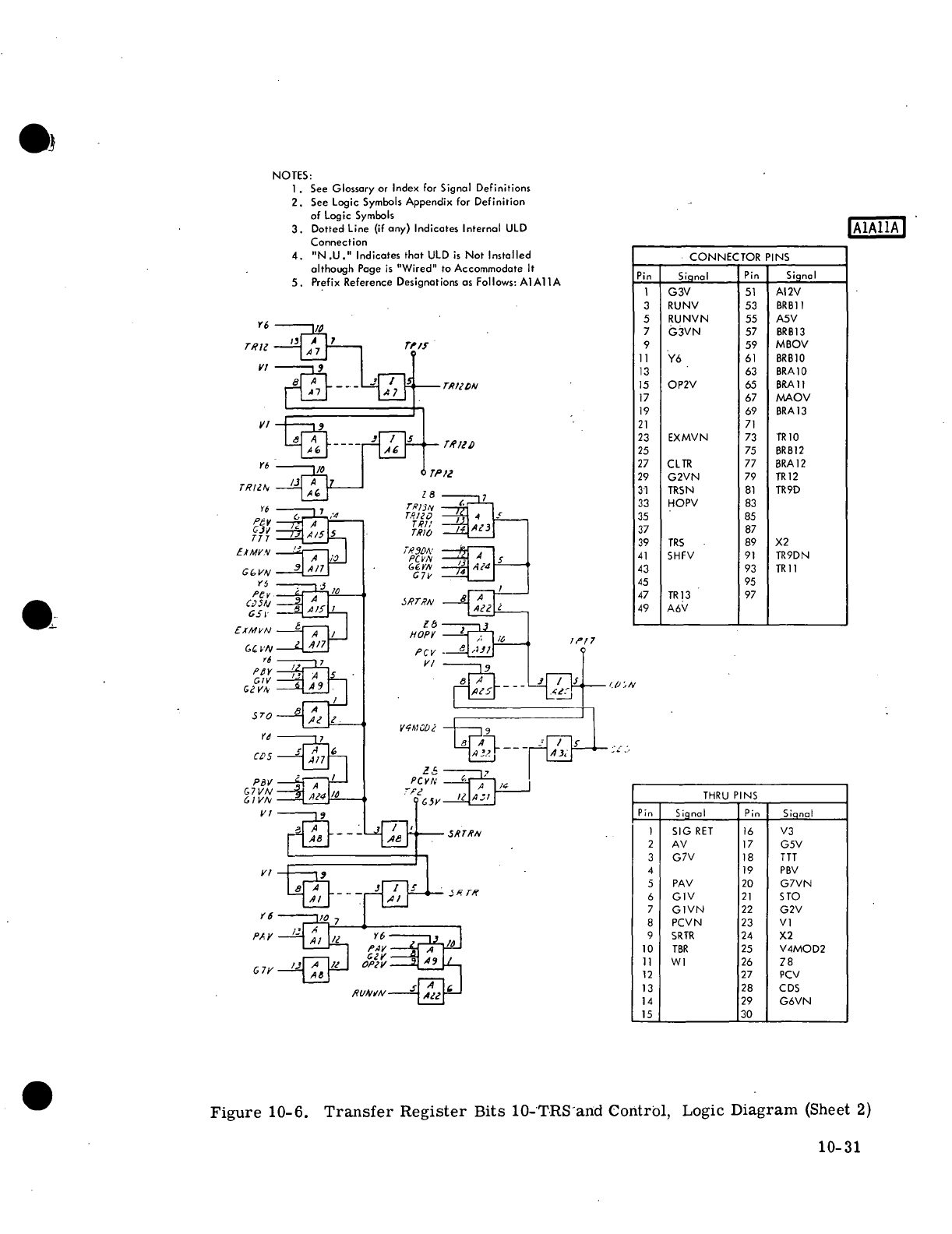

10-6 Transfer Register

Bits

10 — TRS and

Control,

Logic Diagram

(2

Sheets)

10-30

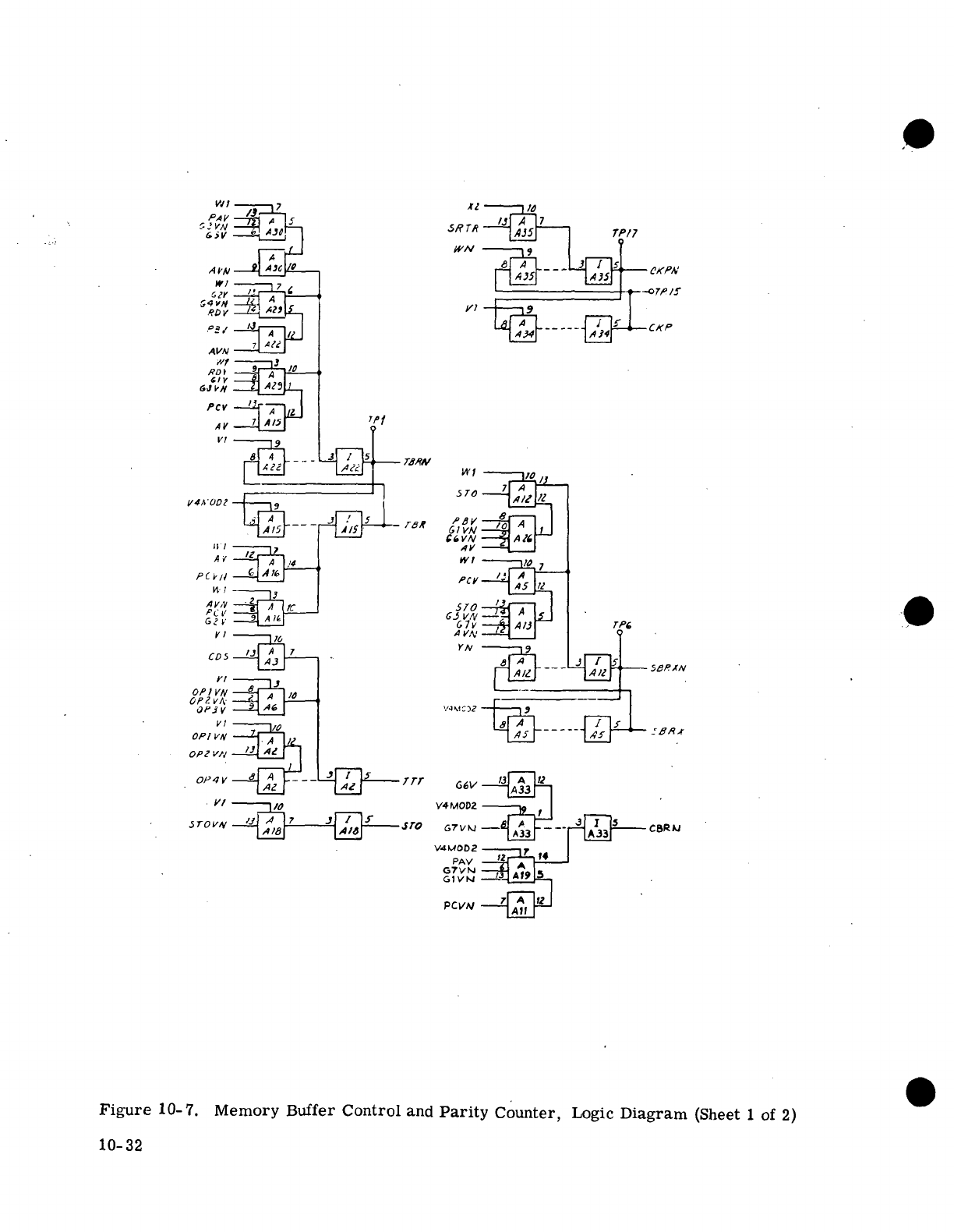

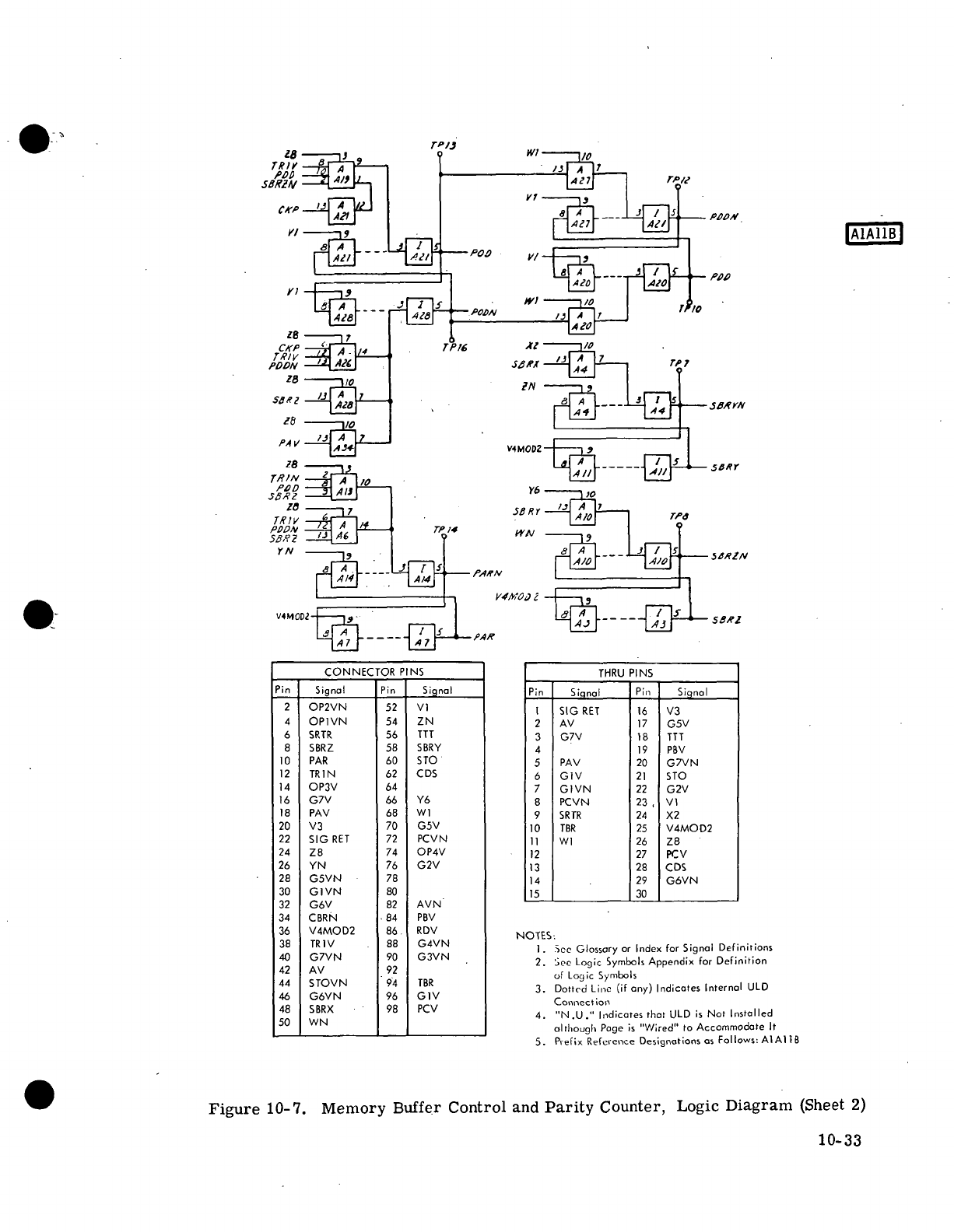

10-7 Memory

Buffer

Control

and

Parity

Counter,

Logic Diagram

(2

Sheets).

10-32

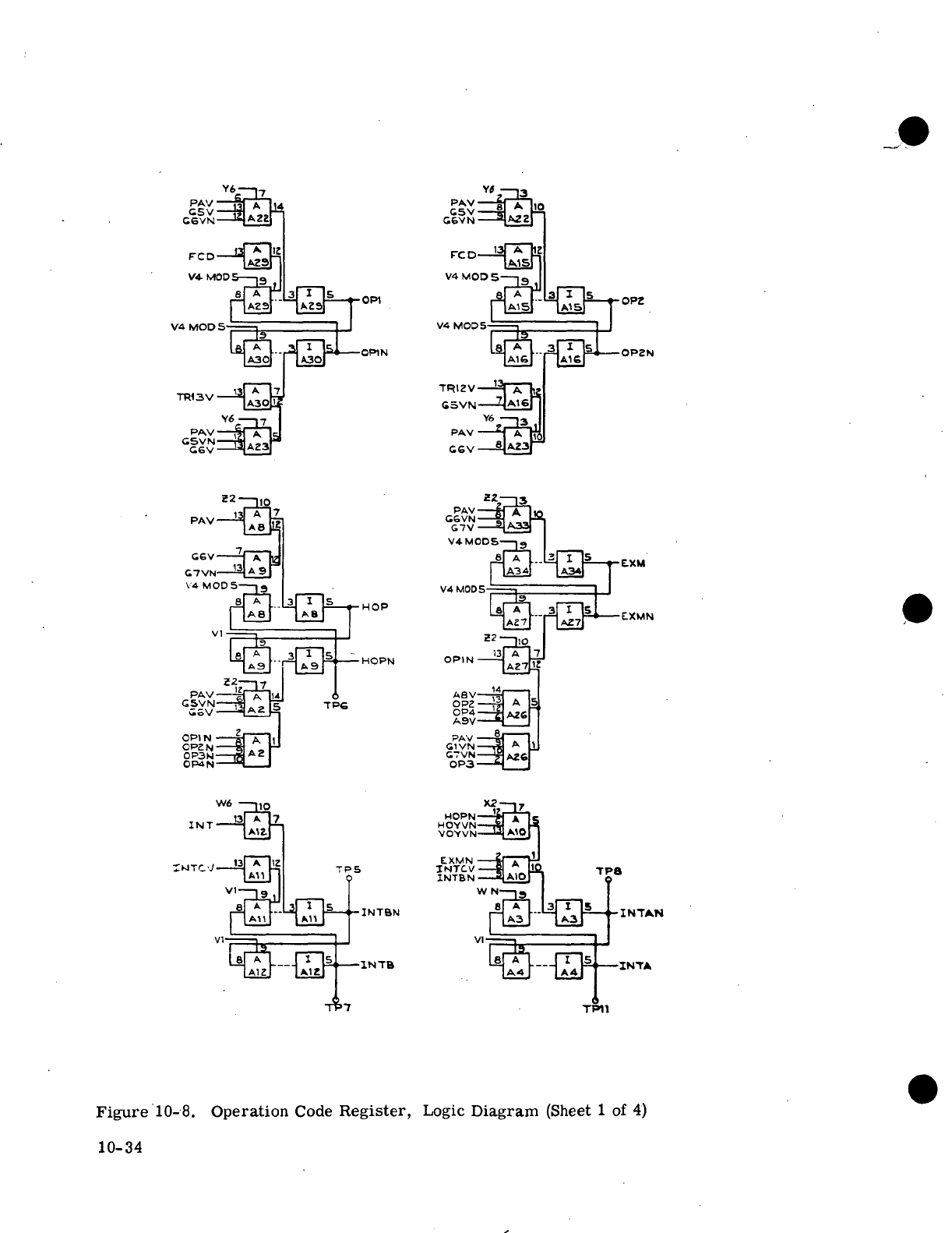

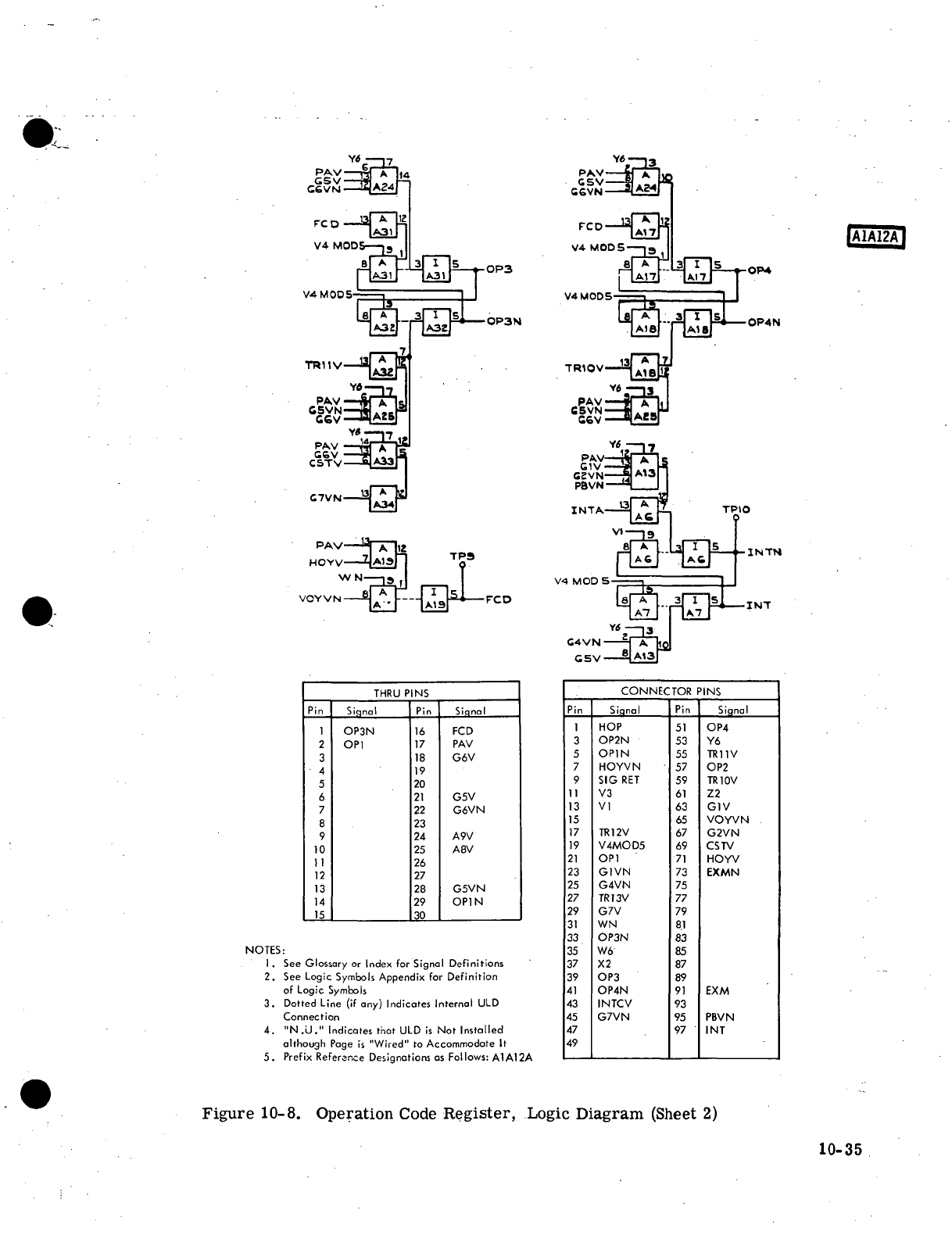

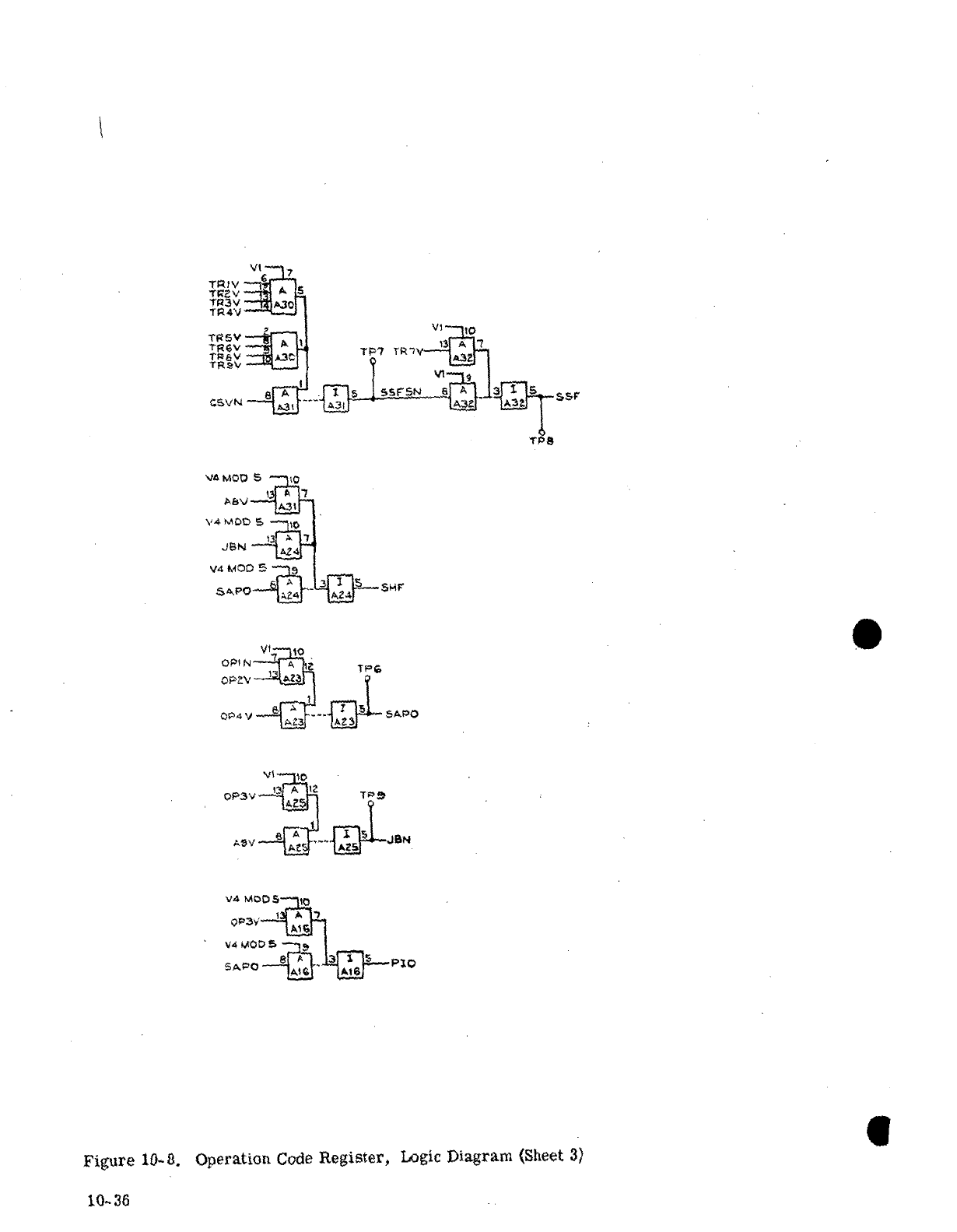

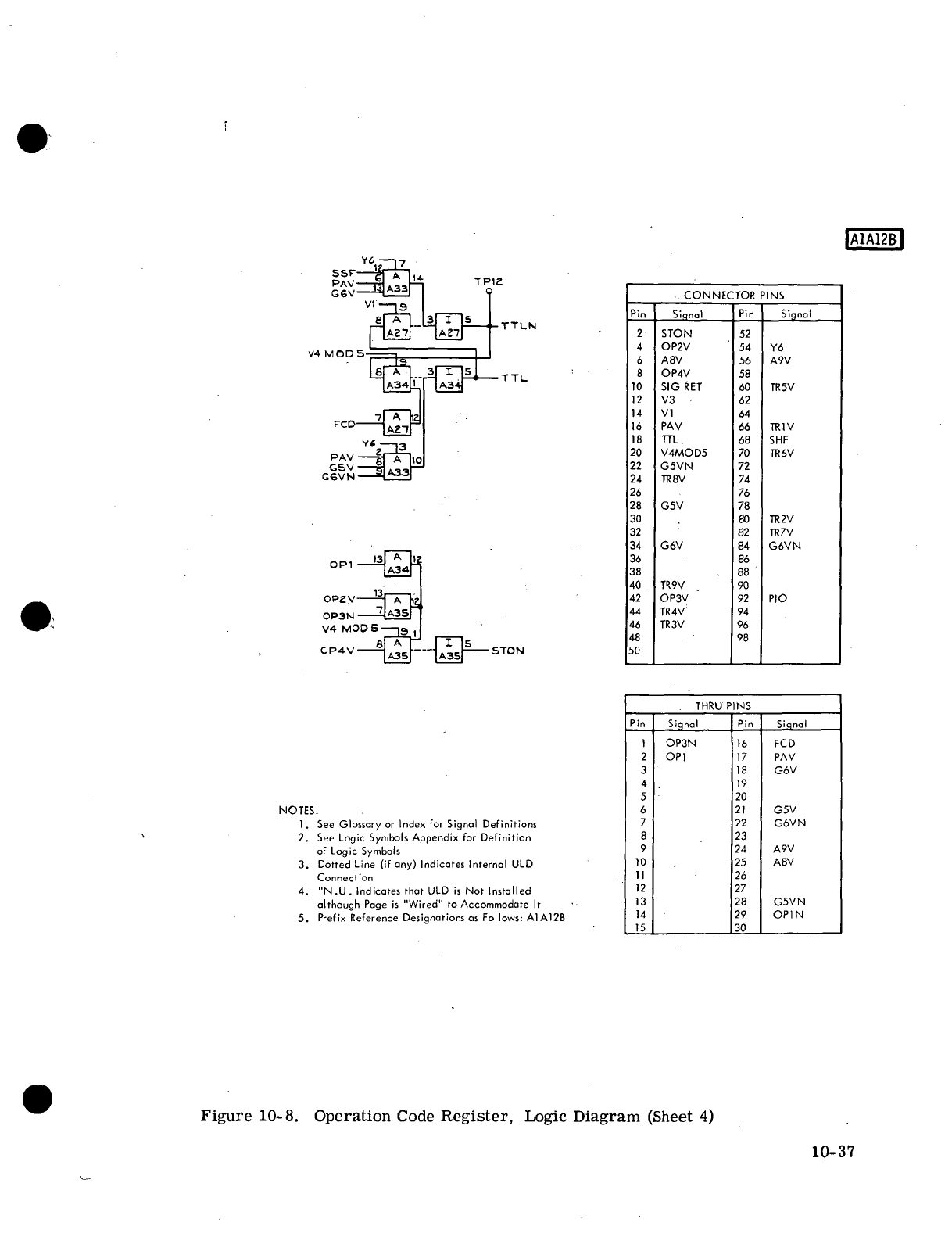

10-8 Operation

Code

Register,

Logic Diagram

(4

Sheets).

.

.....

10-34

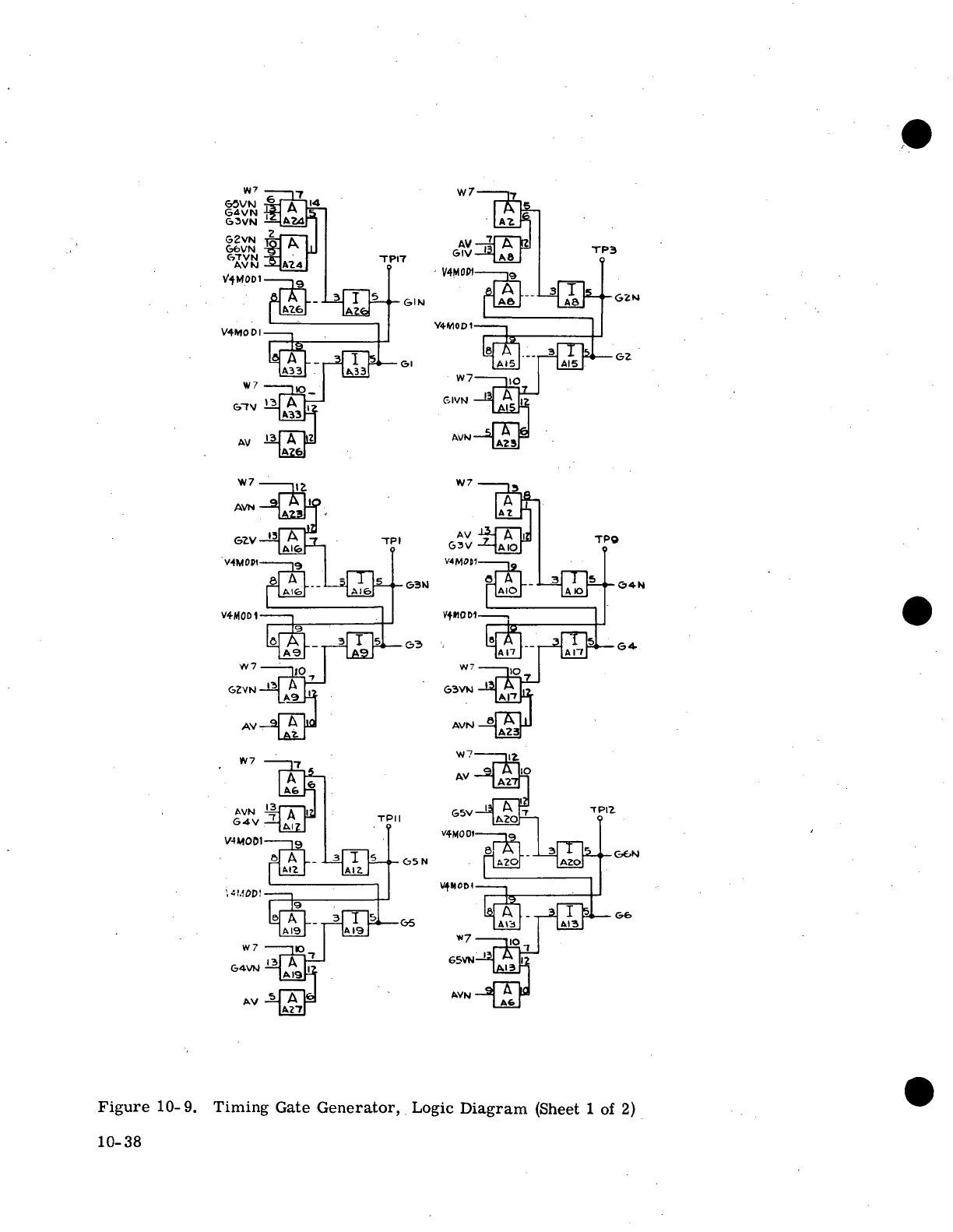

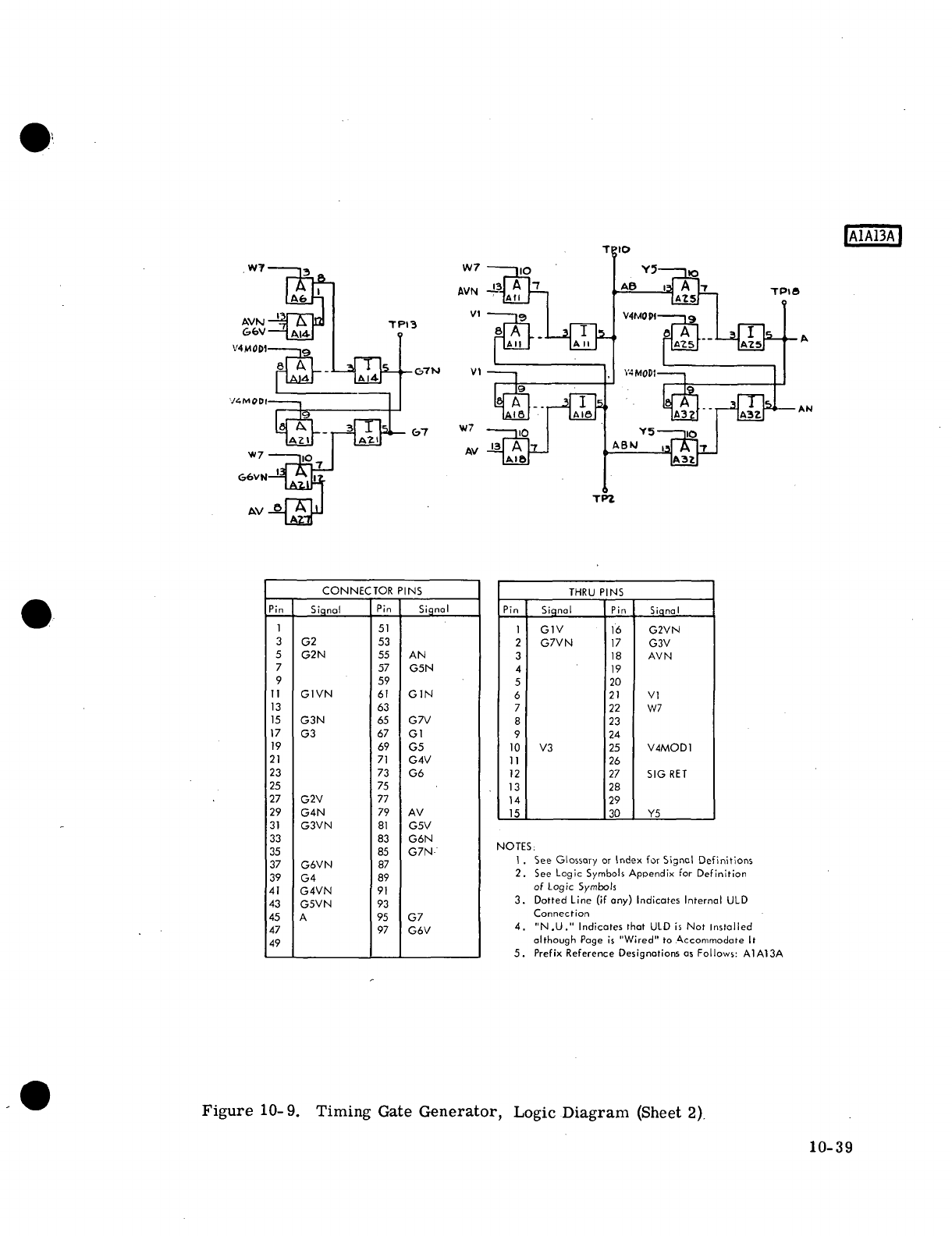

10-9 Timing Gate Generator, Logic Diagram

(2

Sheets).

. . .

•.'..

. .

10-38

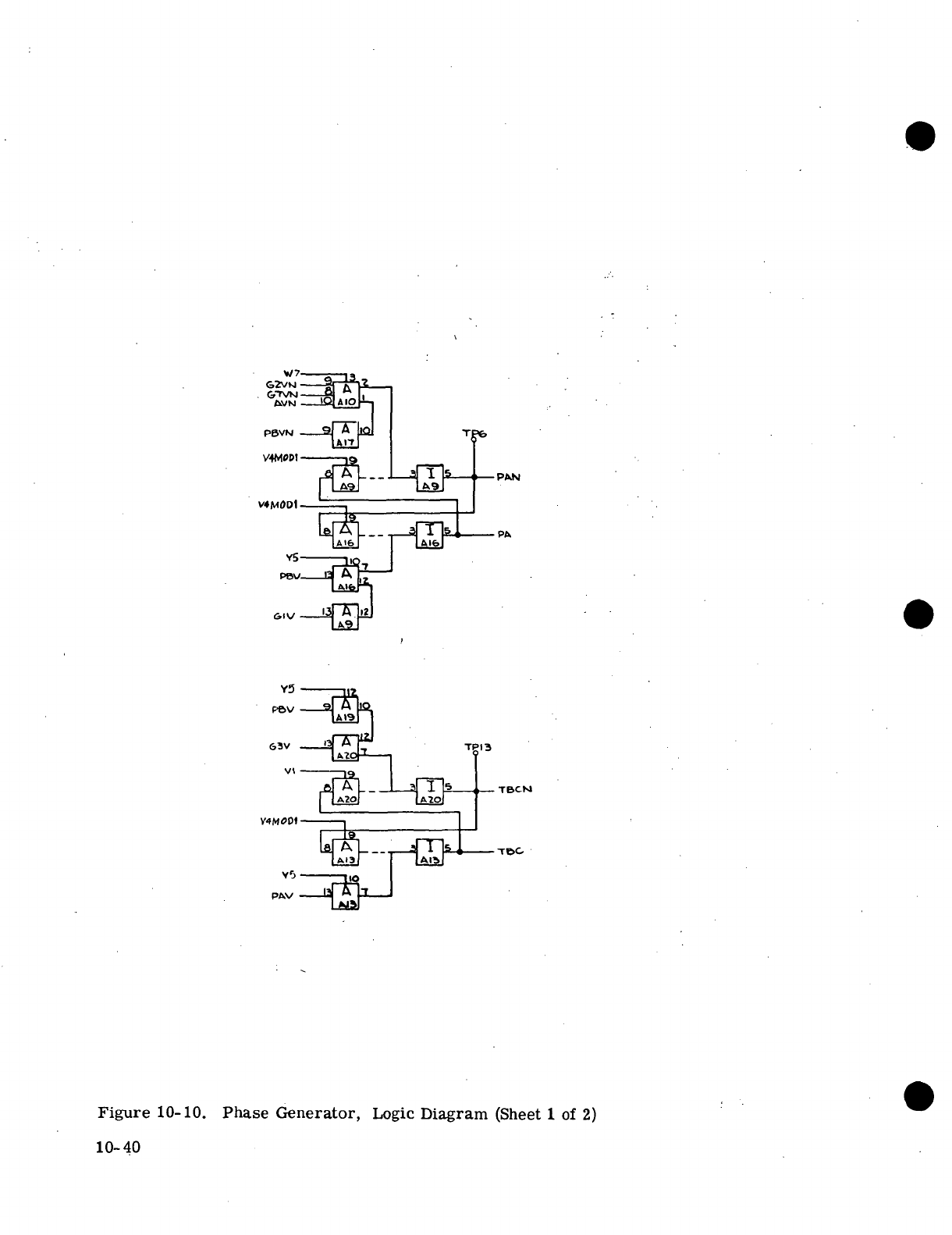

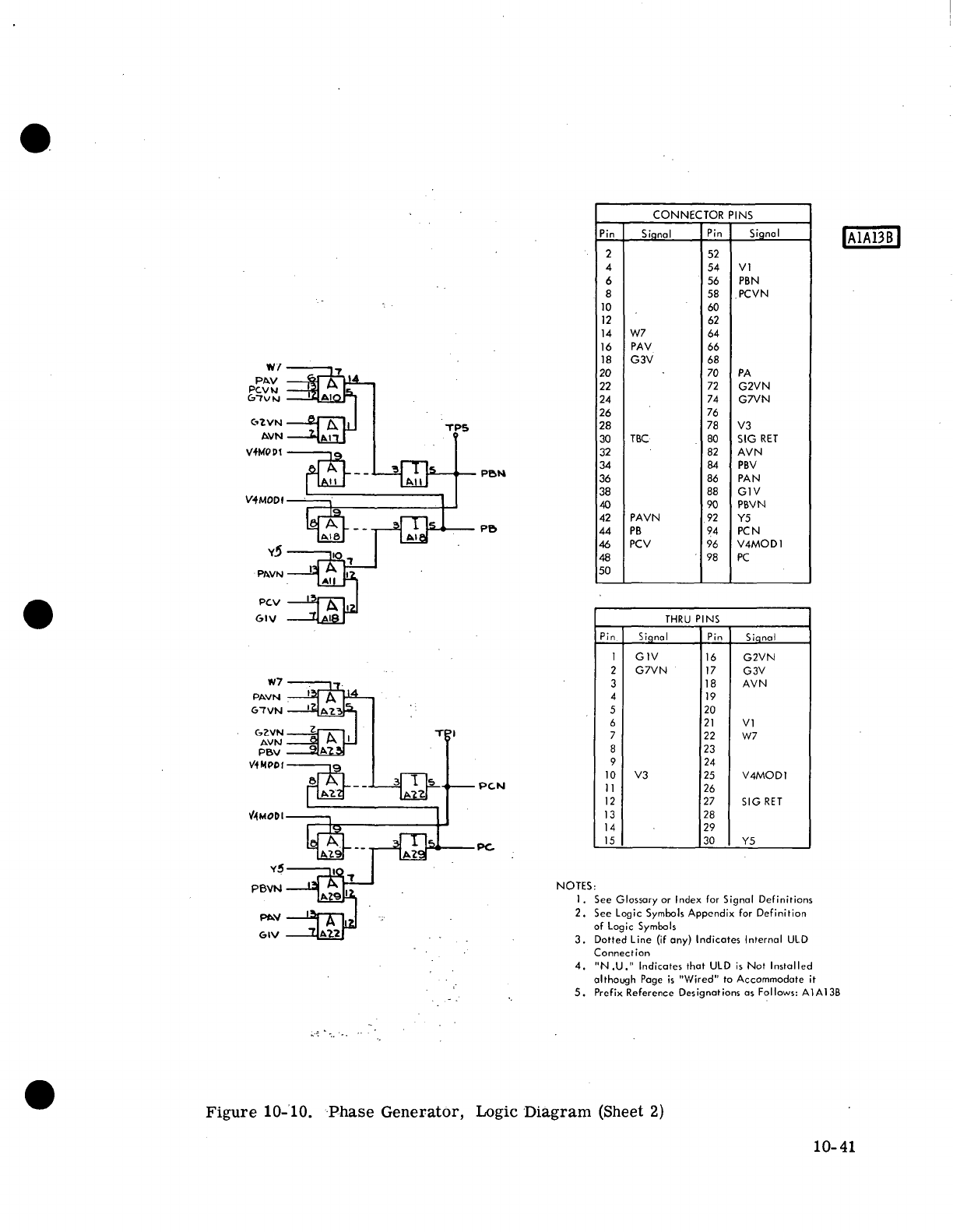

10-10

Phase

Generator, Logic Diagram

(2

Sheets)

............ 10-40

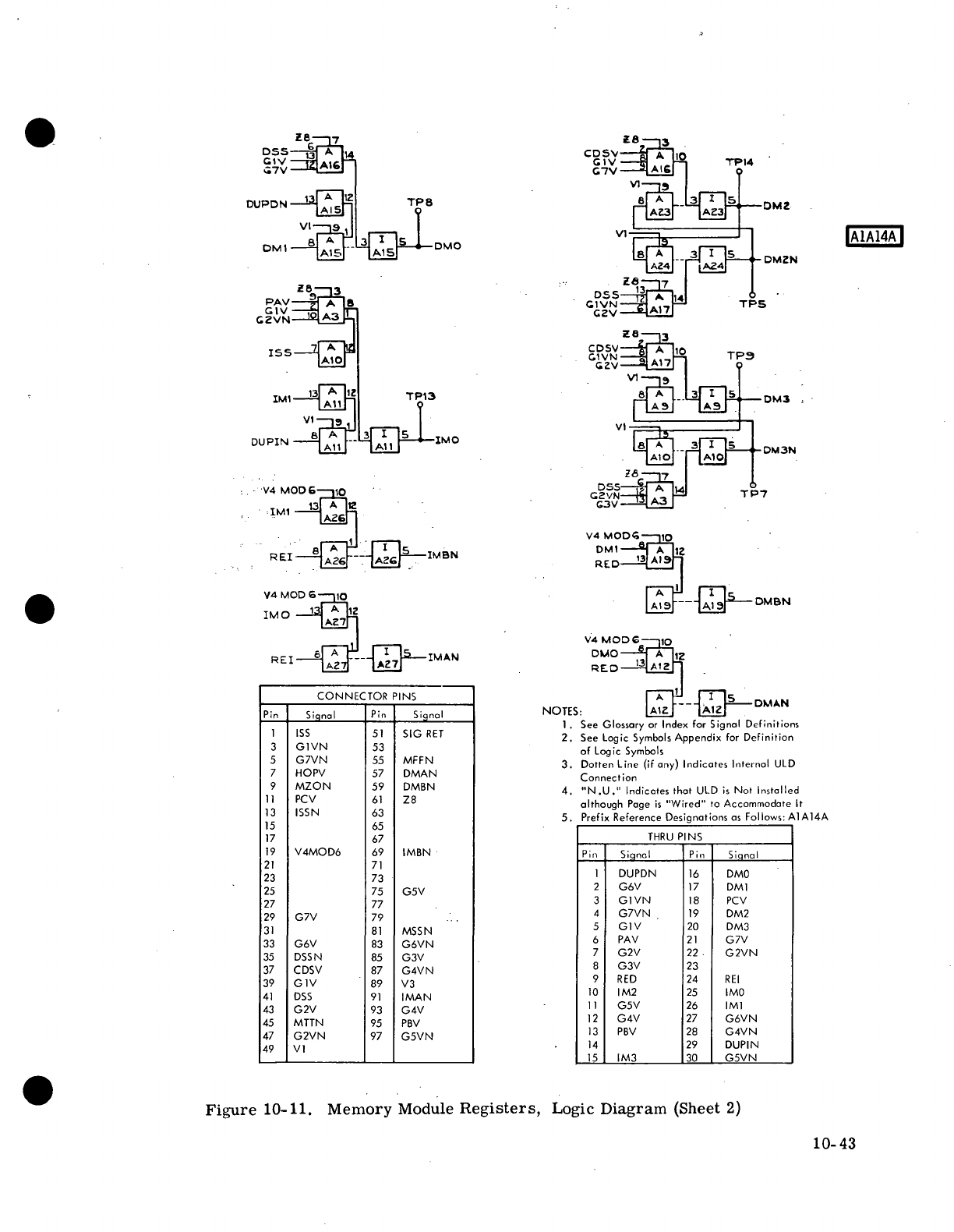

10-11 Memory Module

Registers,

Logic Diagram

(2

Sheets)

10-42

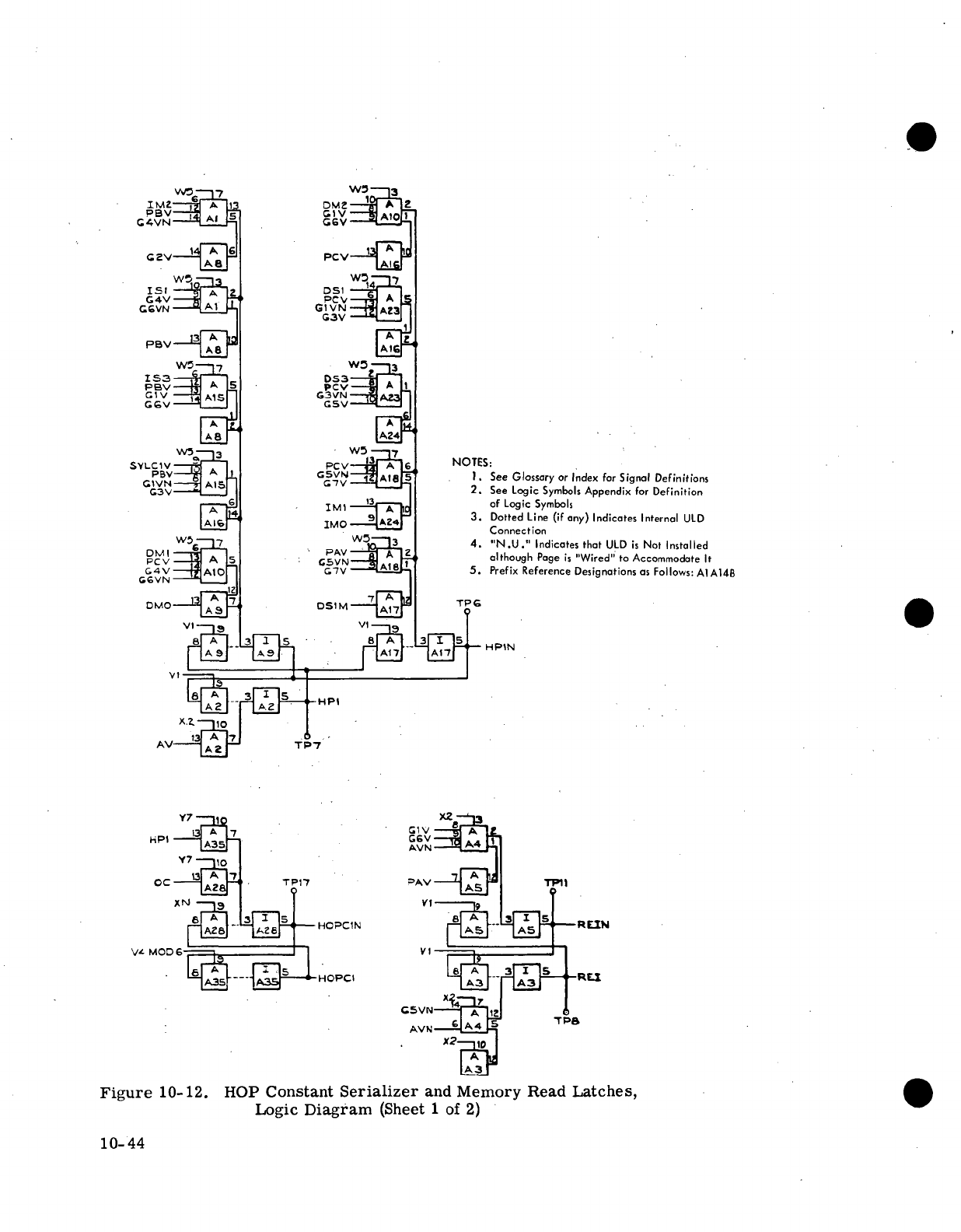

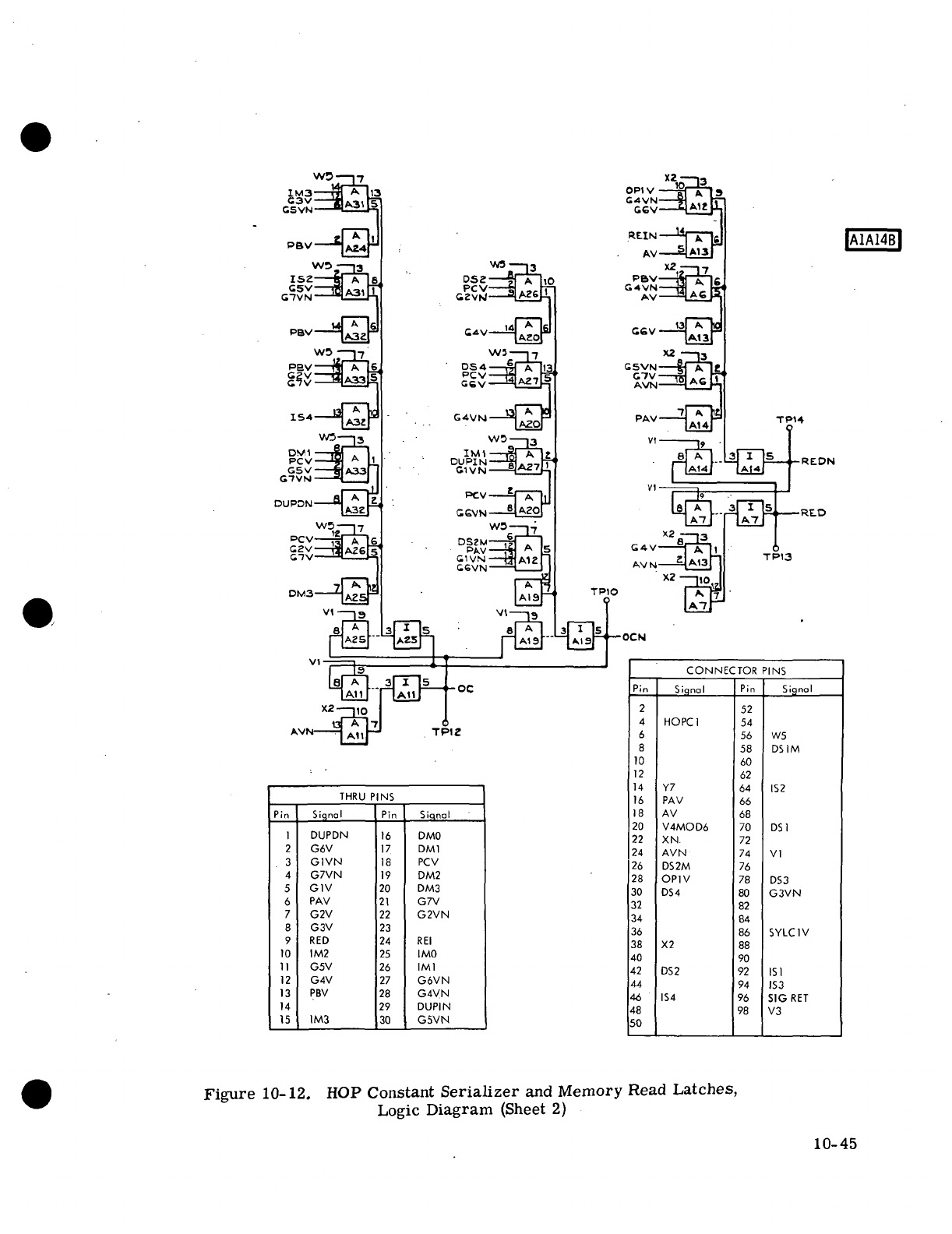

10-12

HOP

Constant

Serializer

and

Memory Read Latches,

Logic Diagram

(2

Sheets).

.

10-44

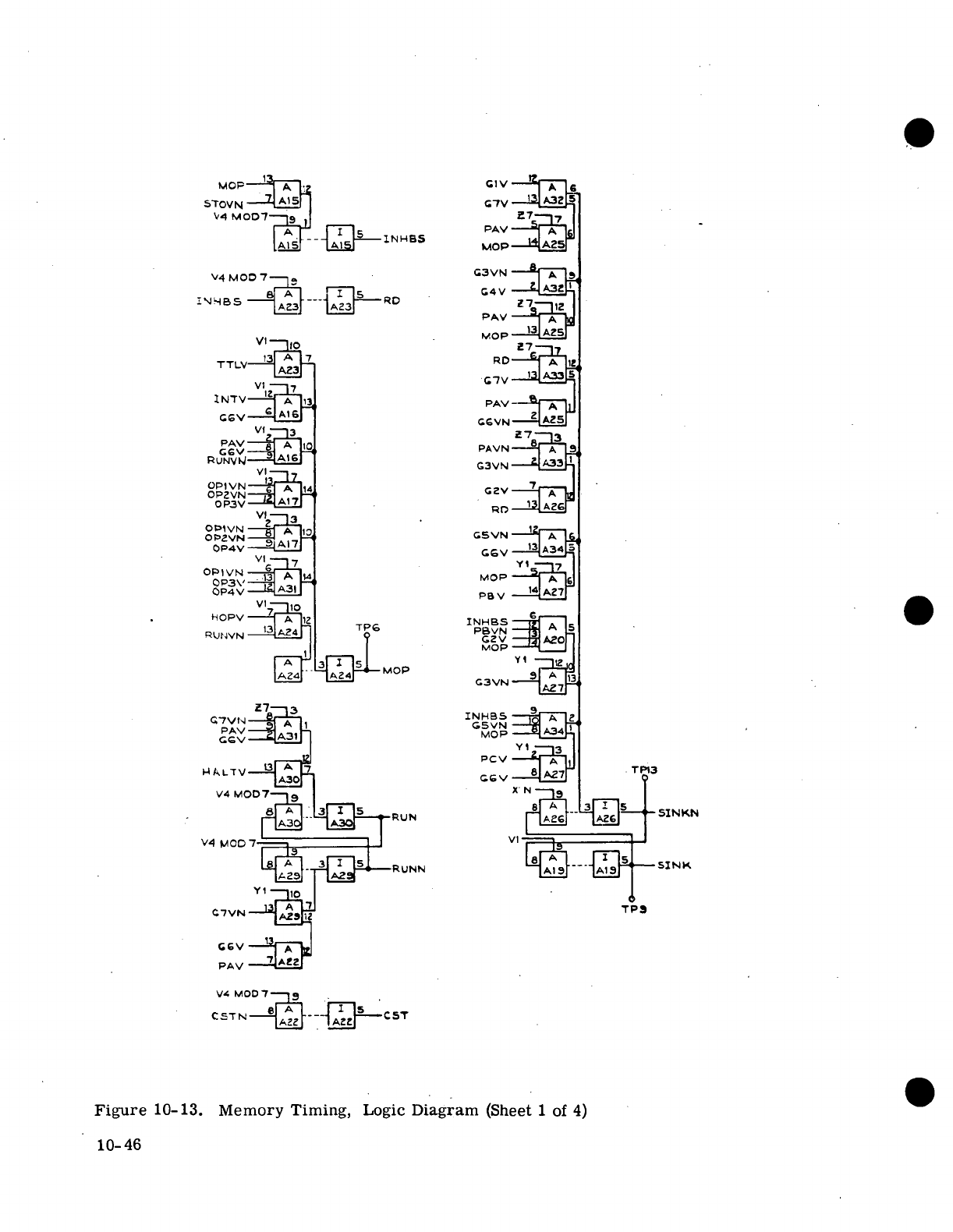

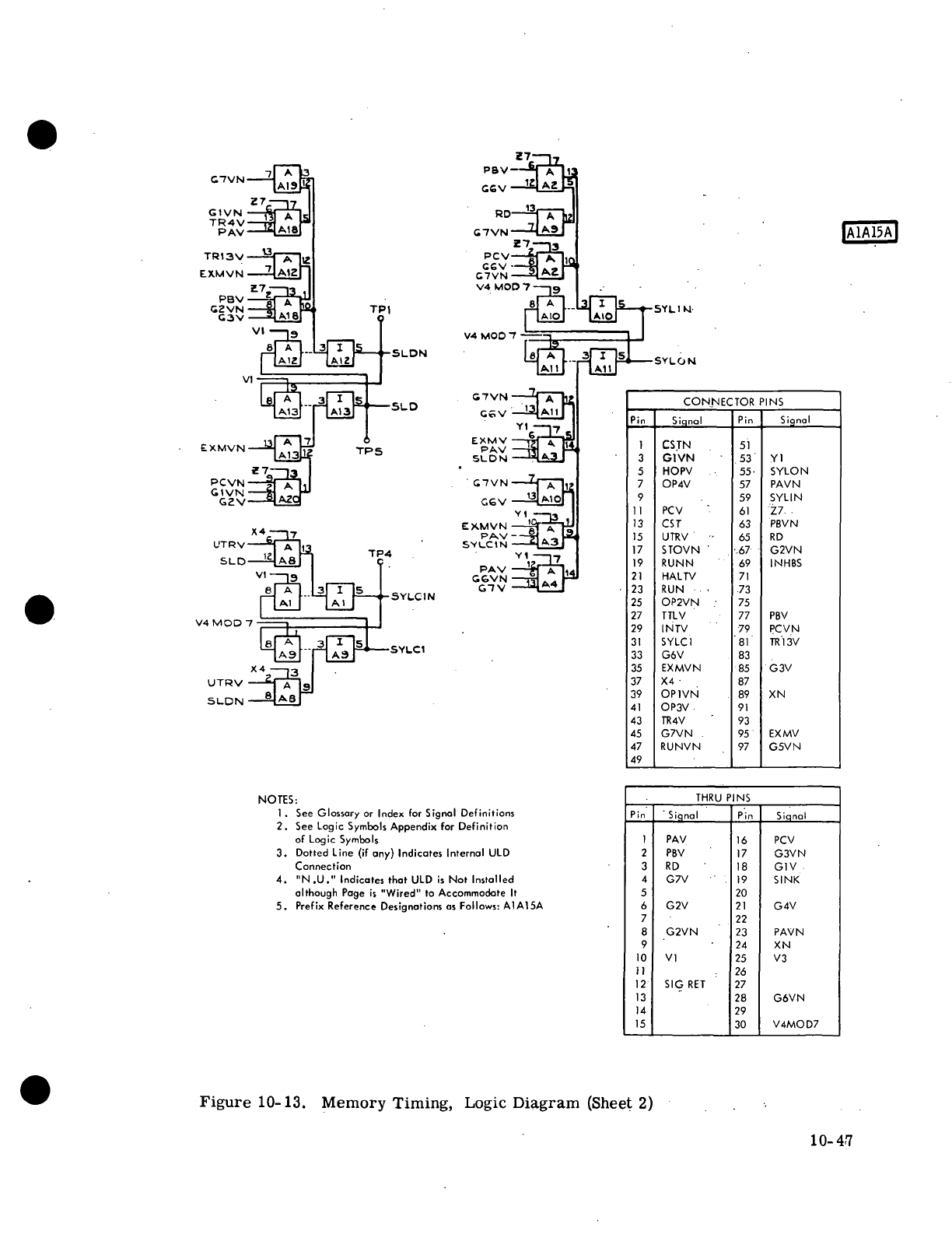

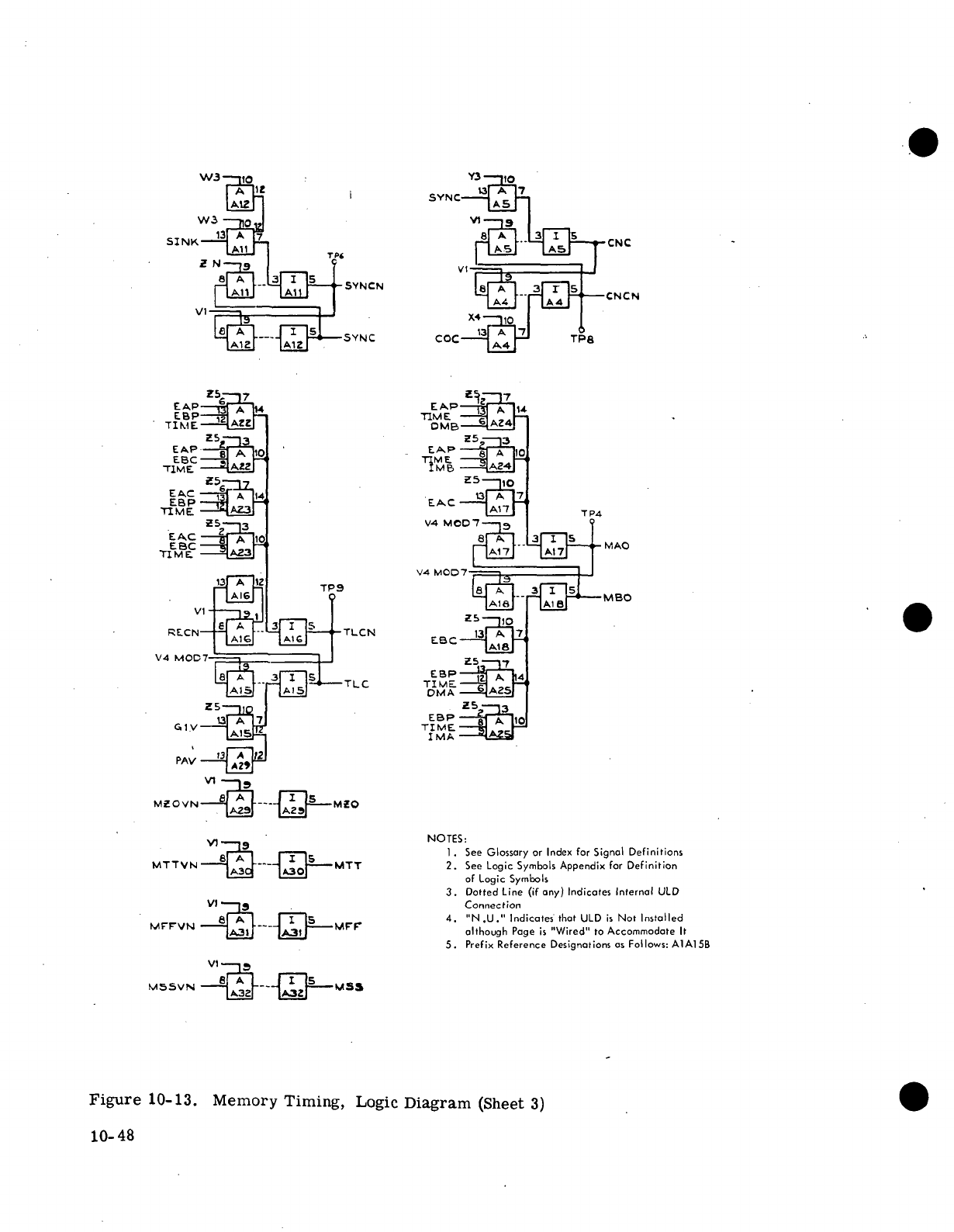

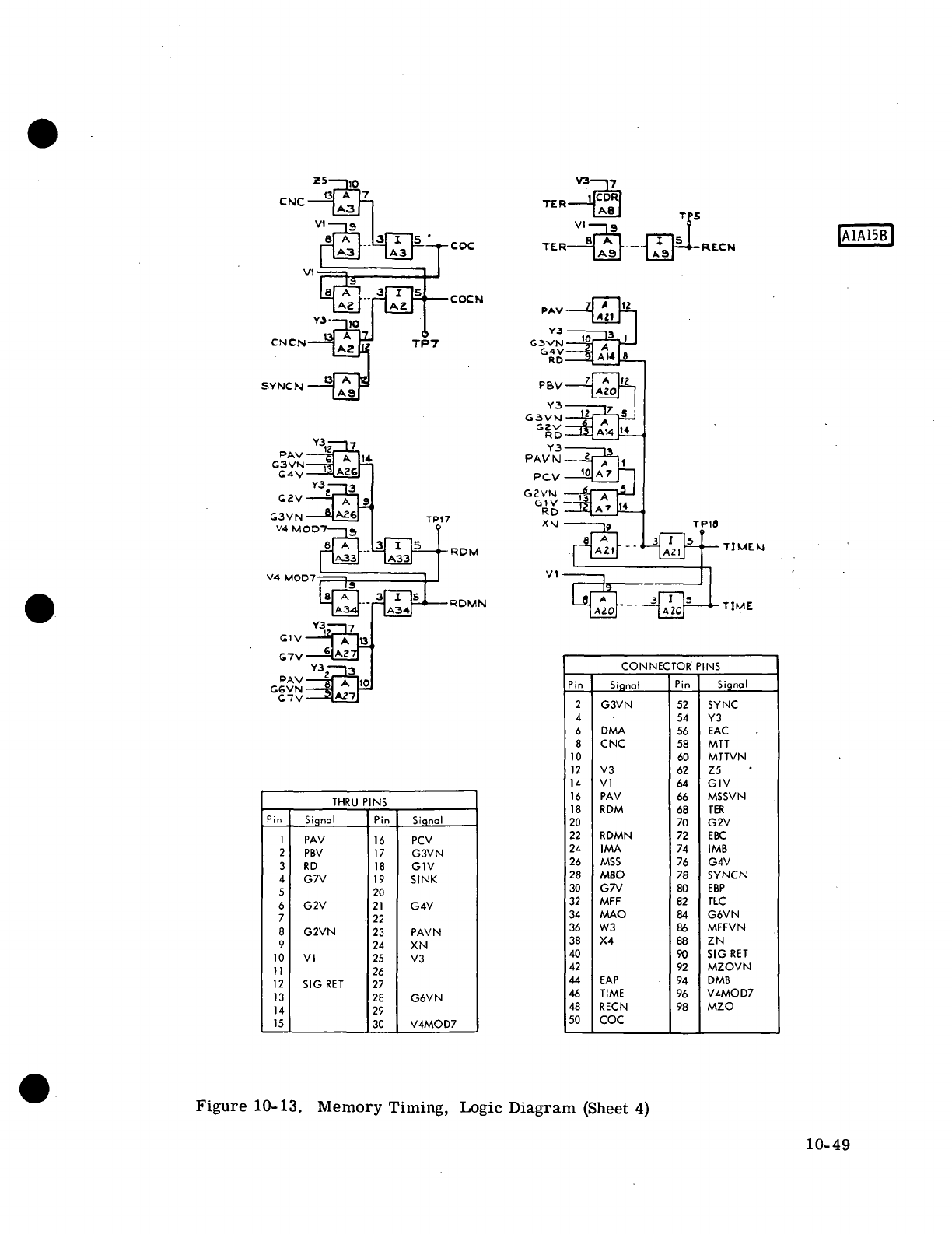

10-13 Memory Timing, Logic Diagram

(4

Sheets).

. . .

10-46

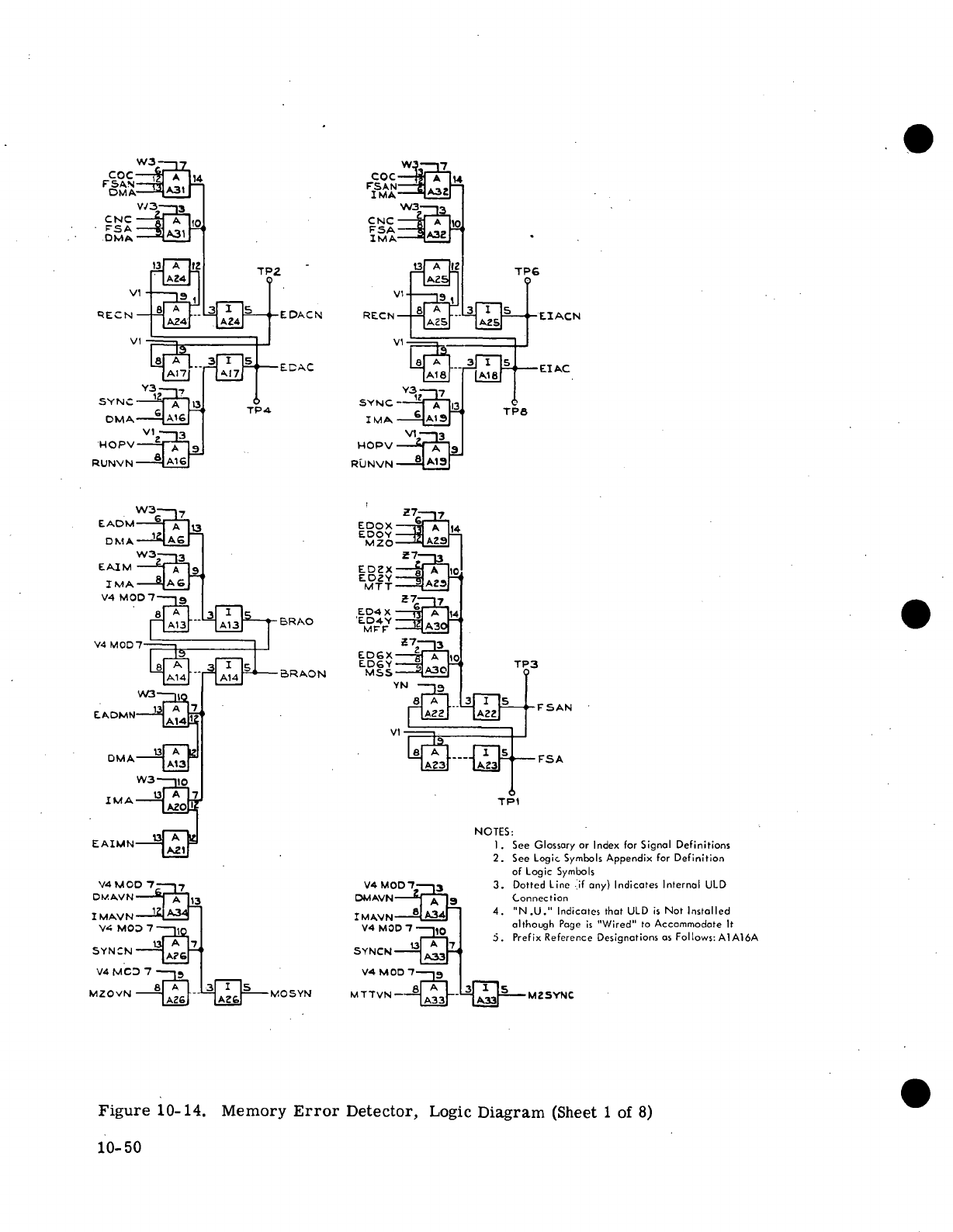

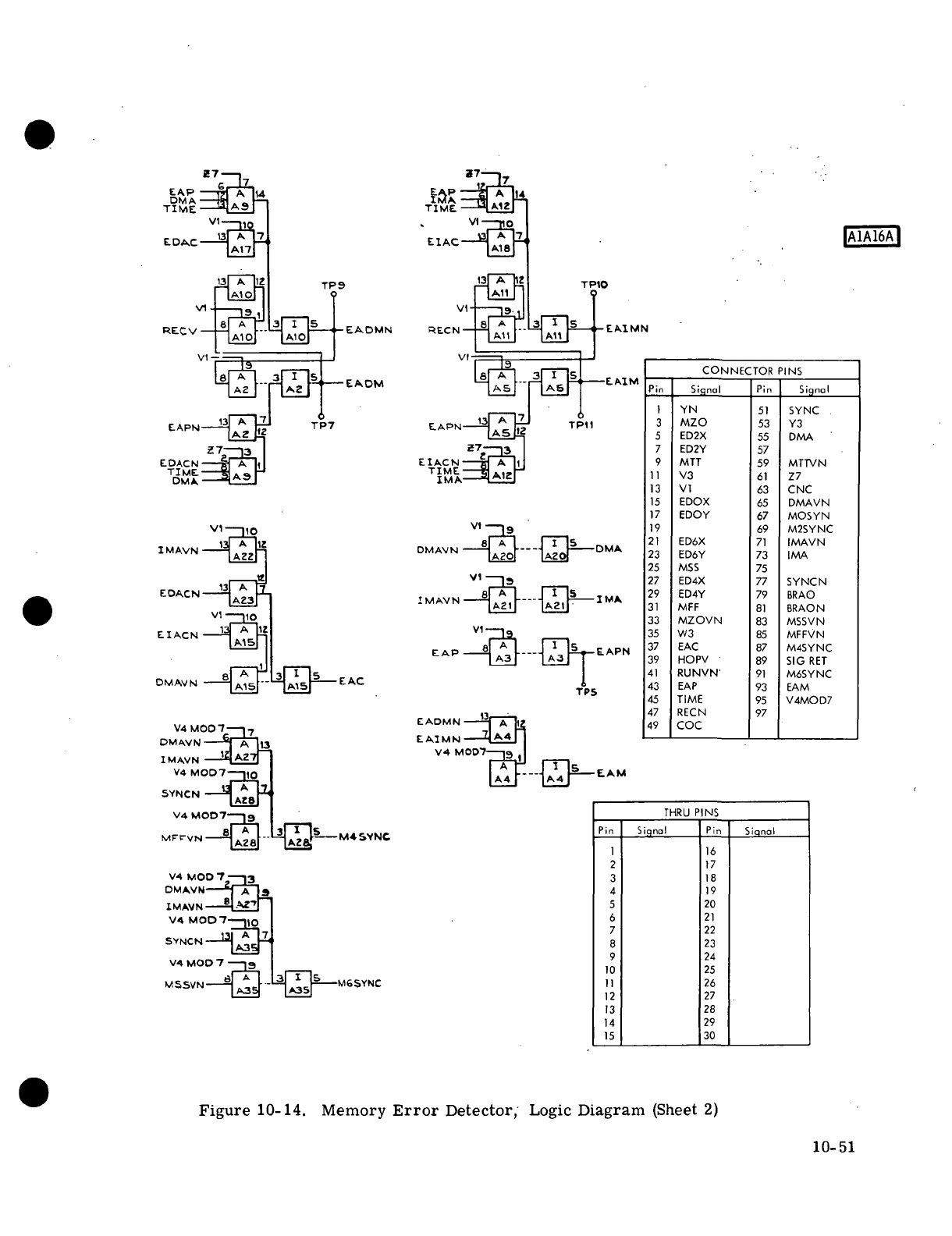

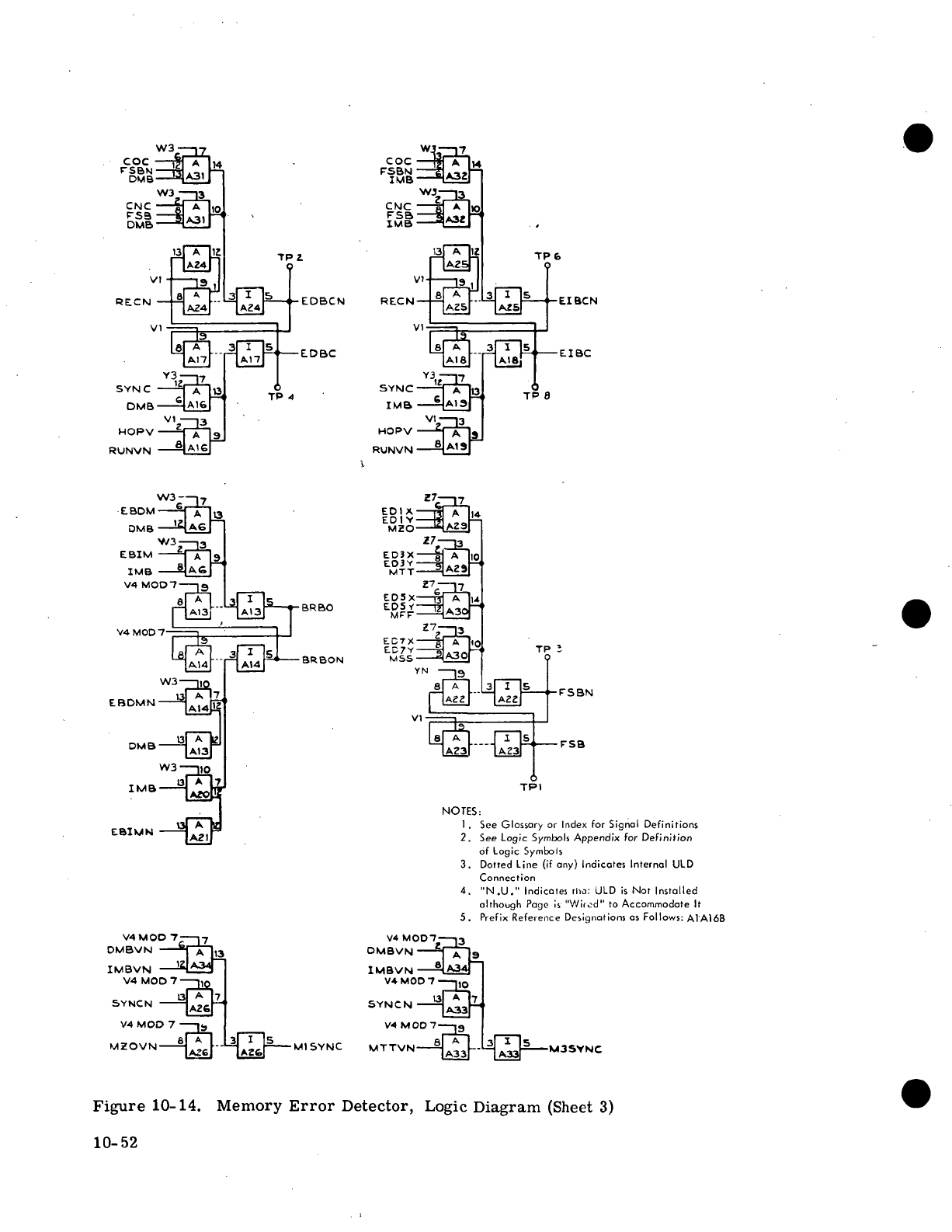

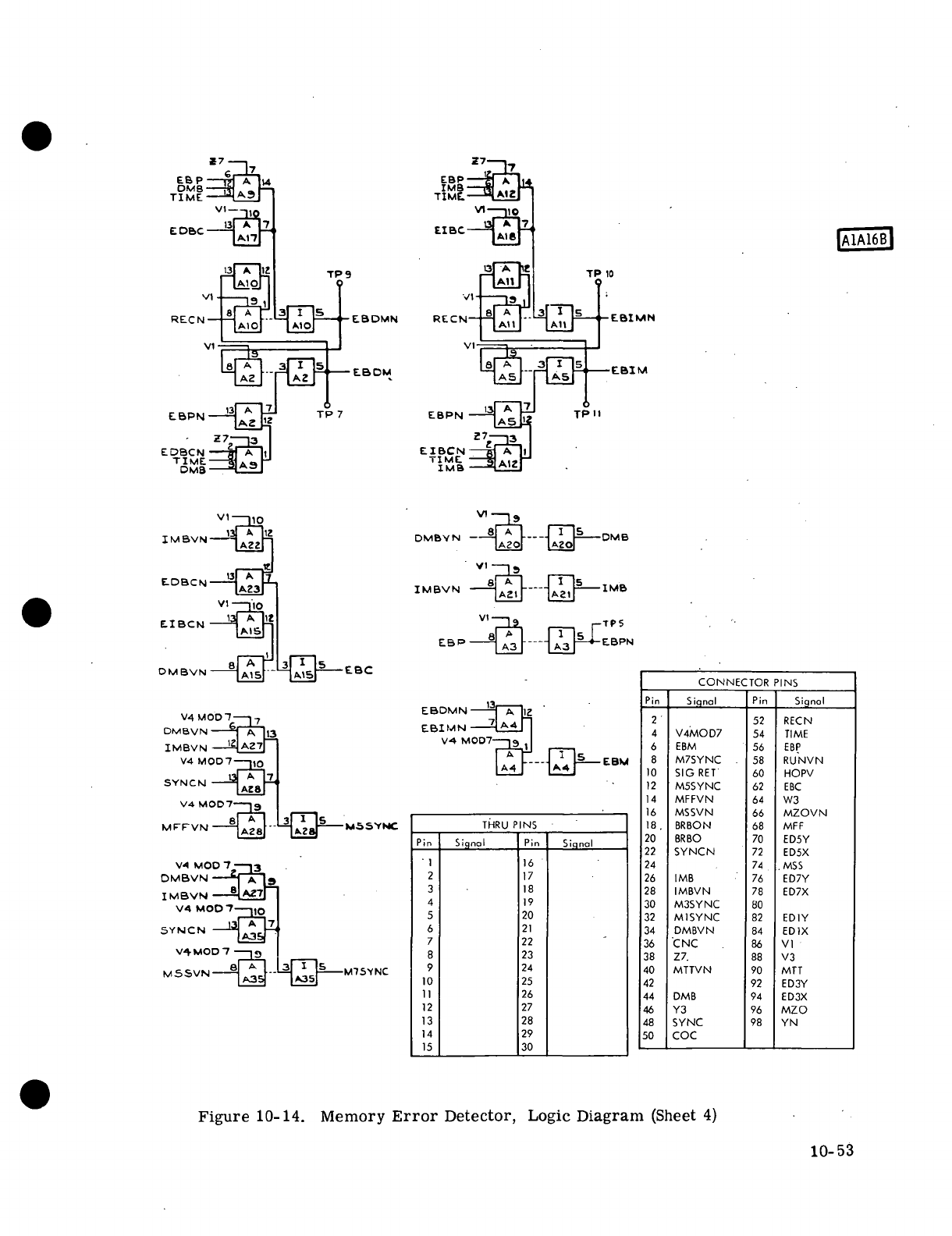

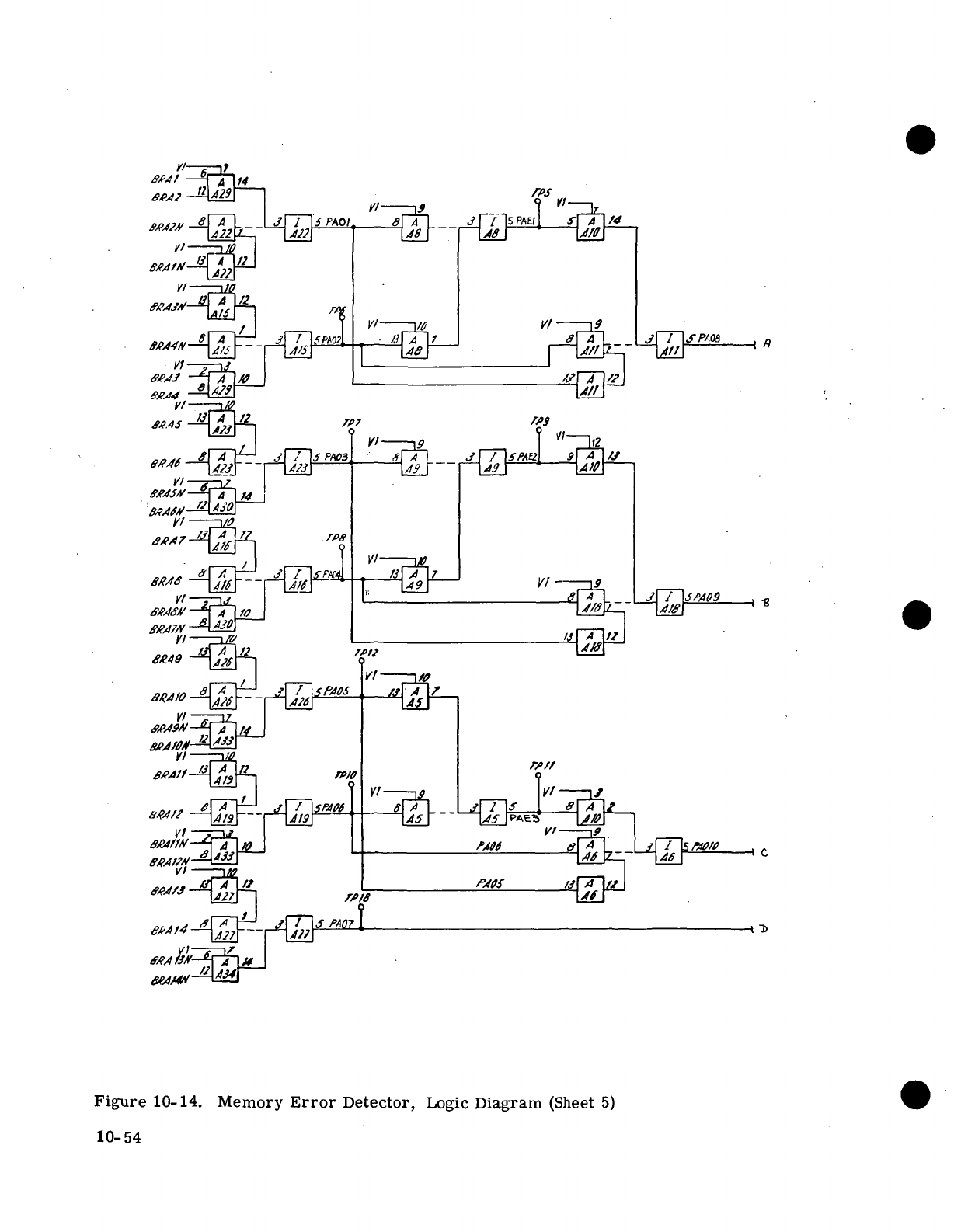

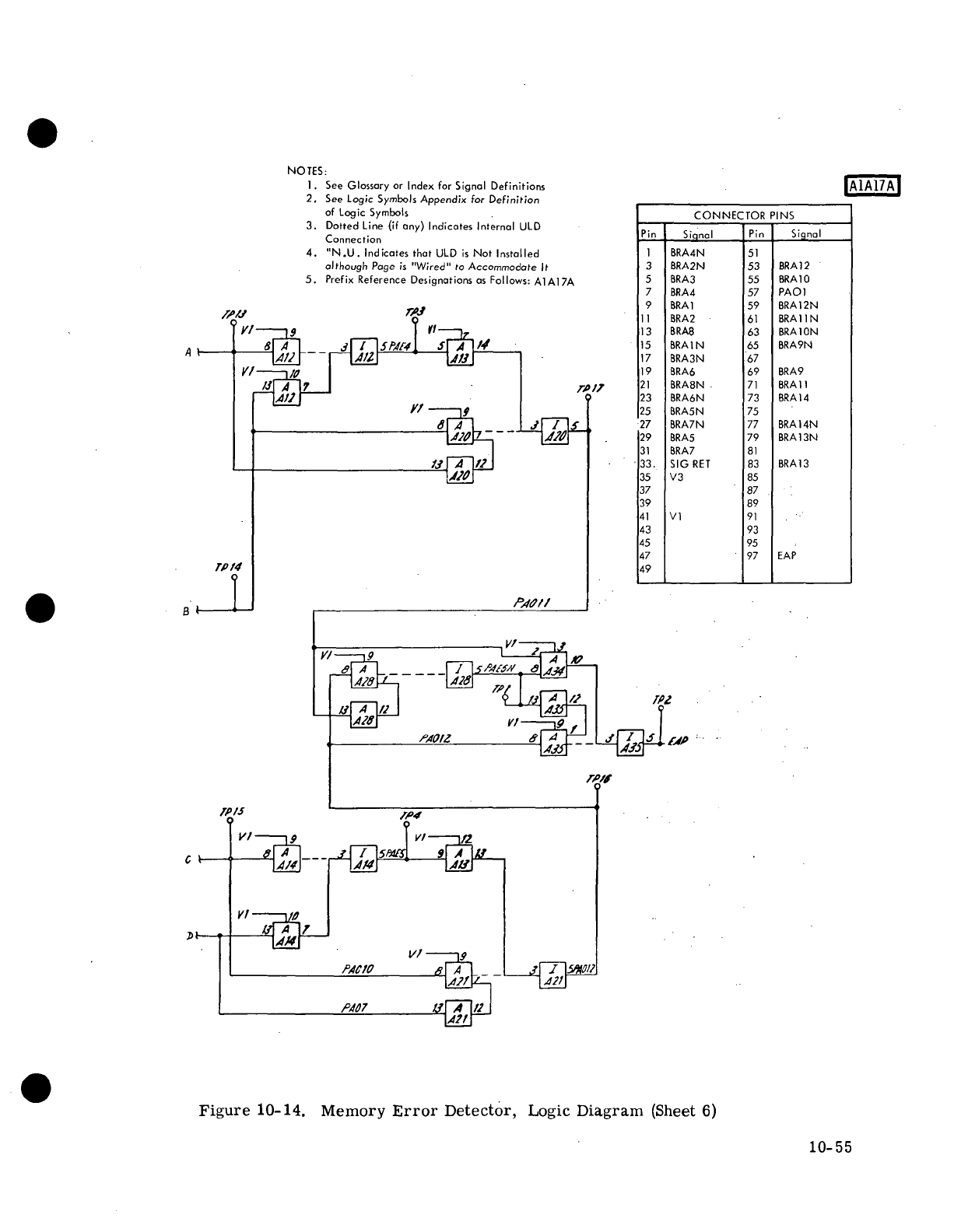

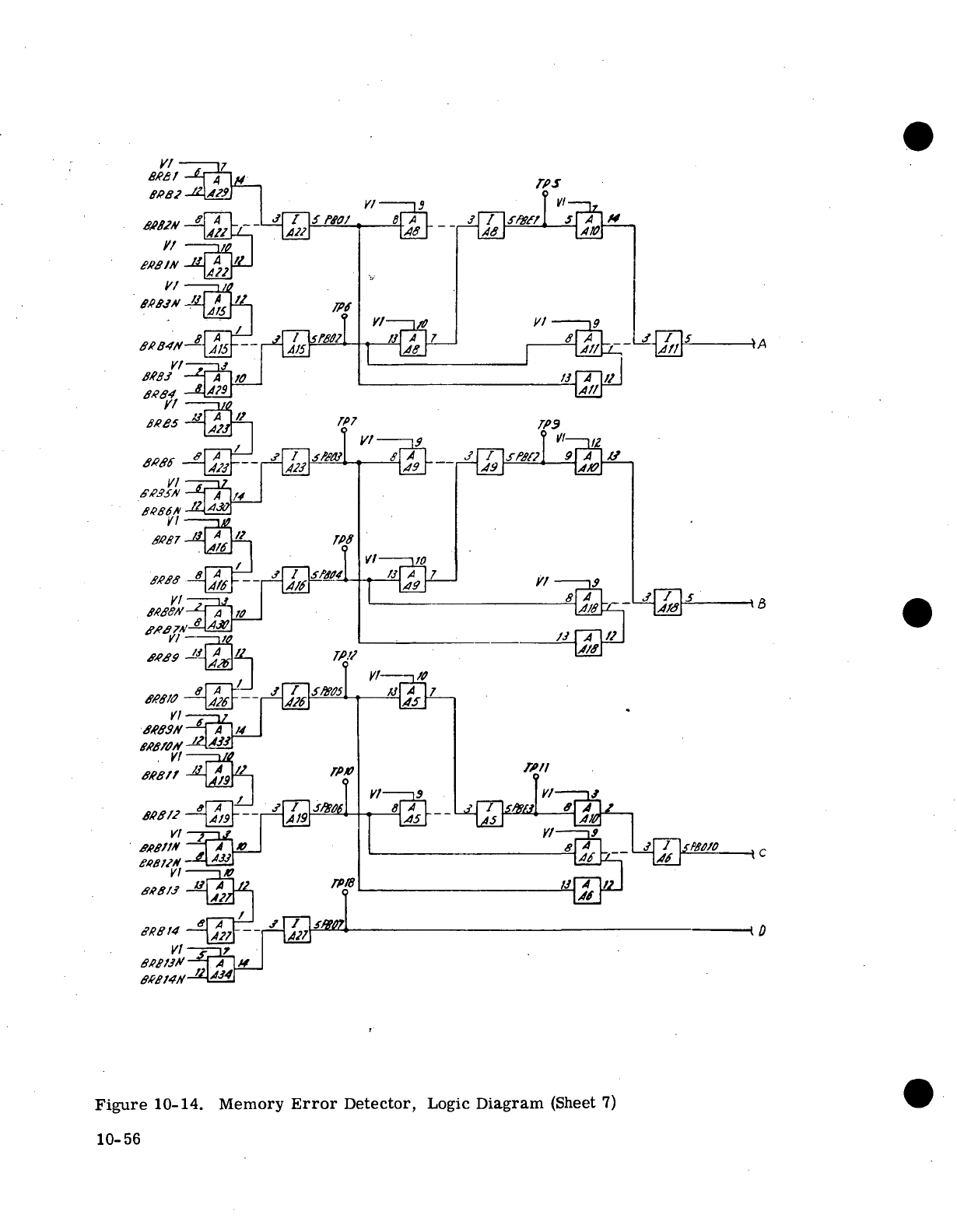

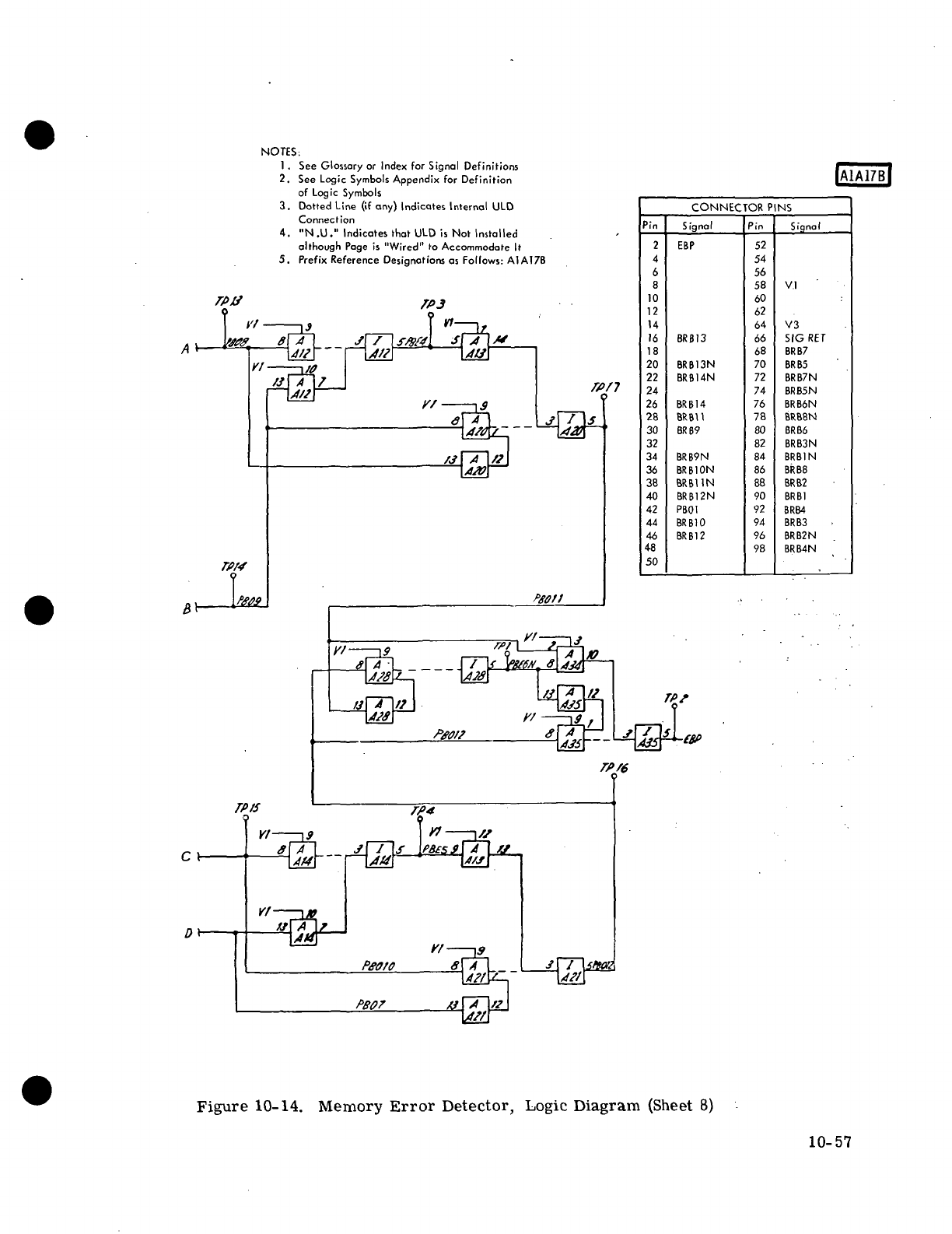

10-14 Memory

Error

Detector, Logic Diagram

(8

Sheets)

.......

10-50

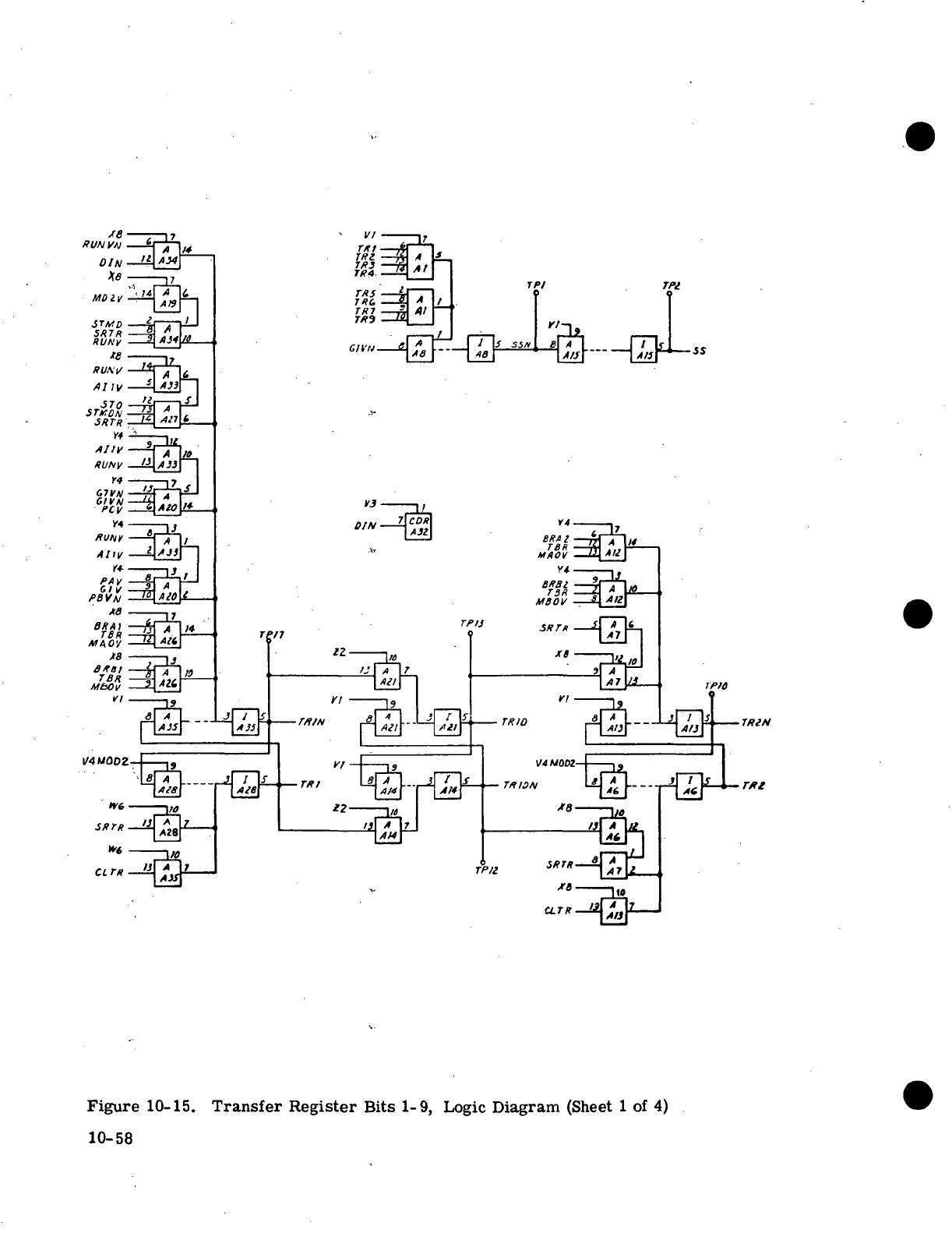

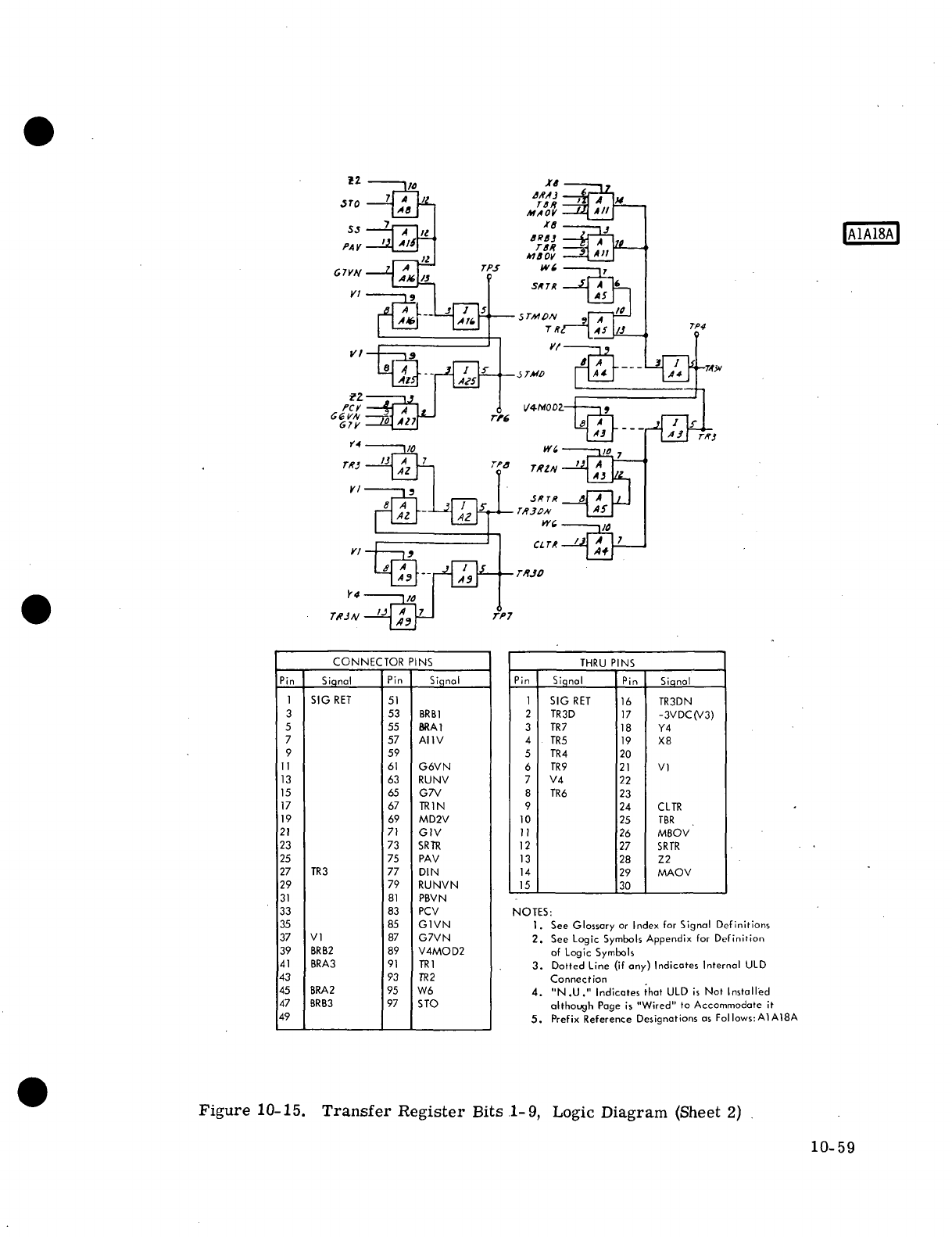

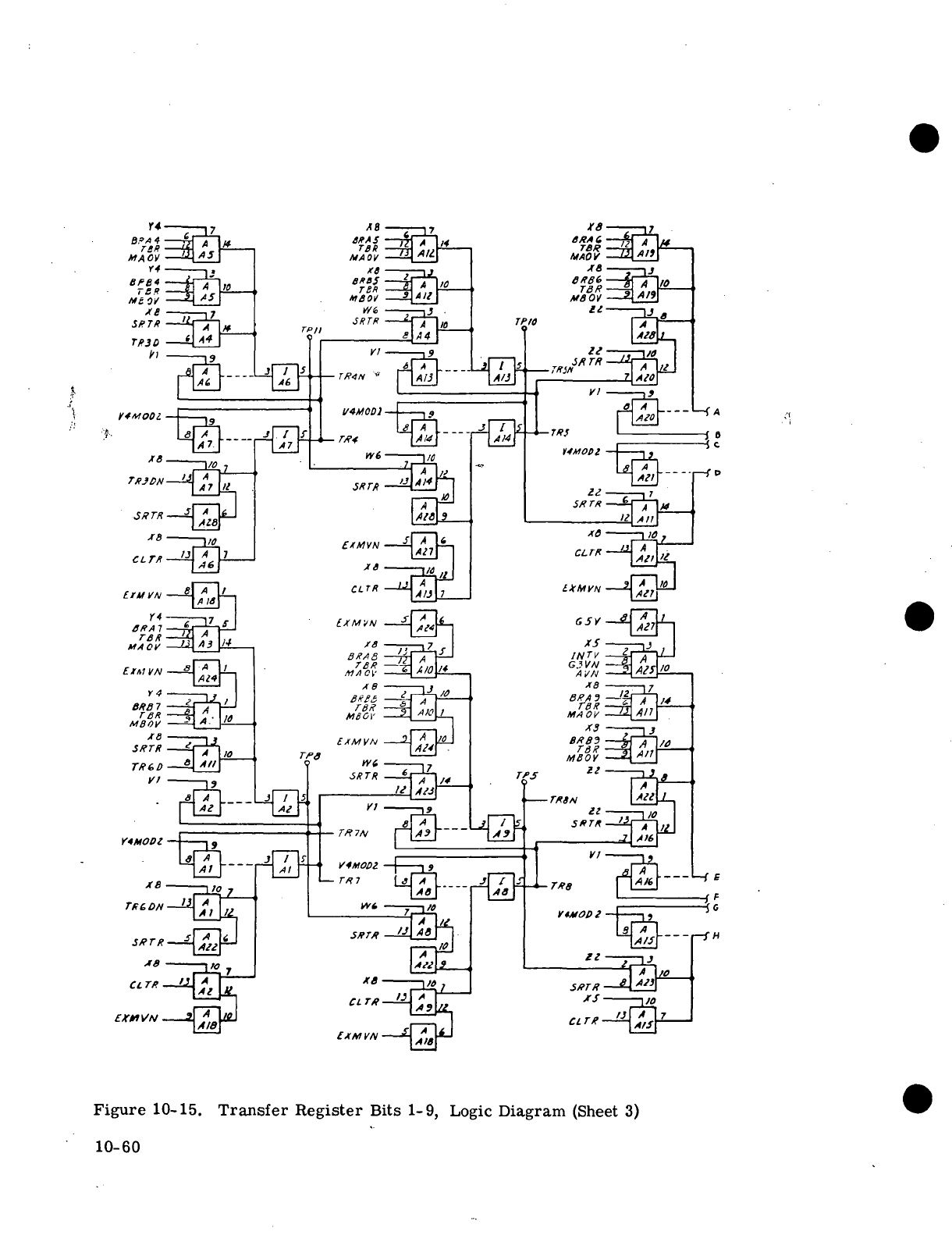

10-15 Transfer Register

Bits'1

- 9,

Logic Diagram

(4

Sheets)

. . ...

10-58

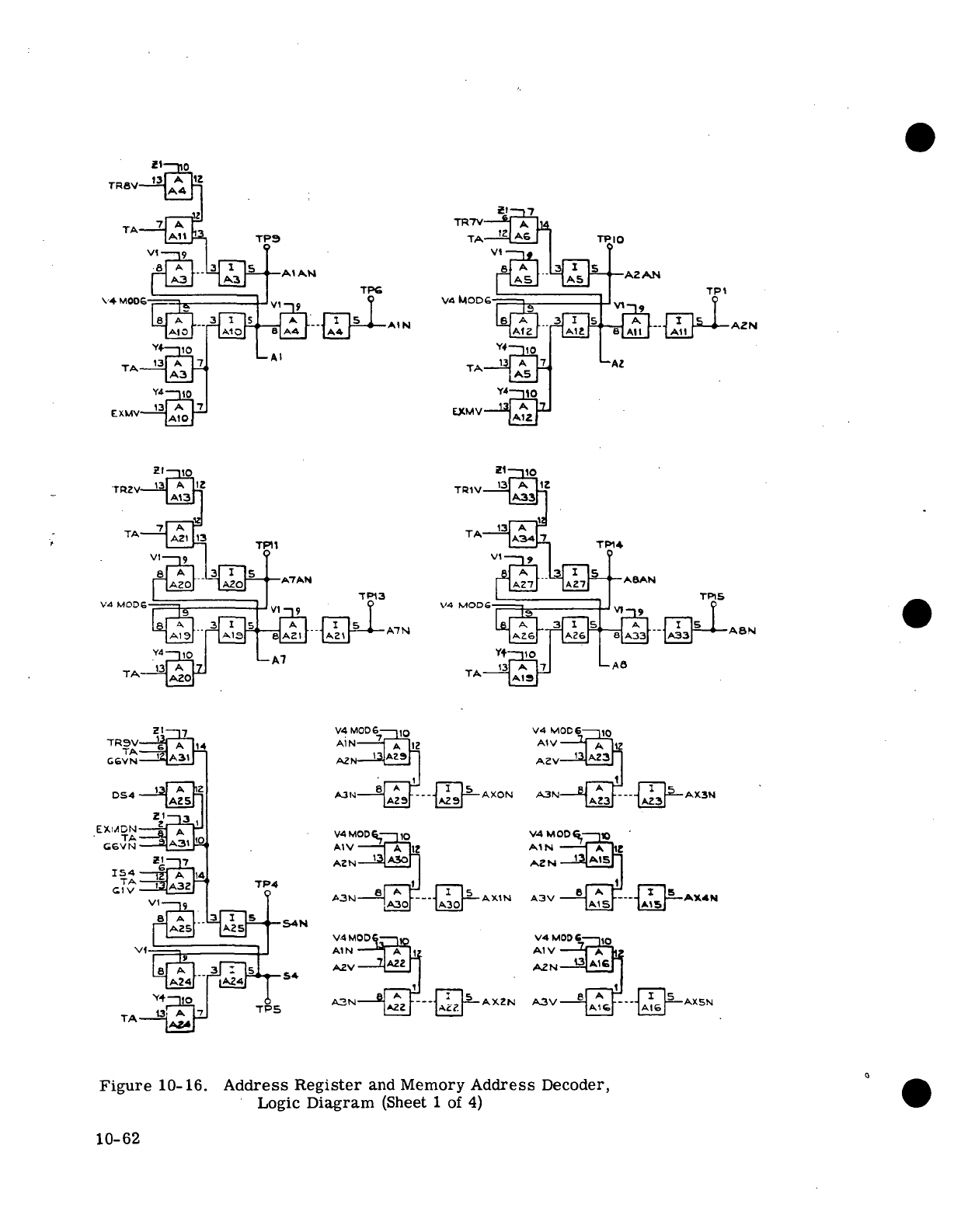

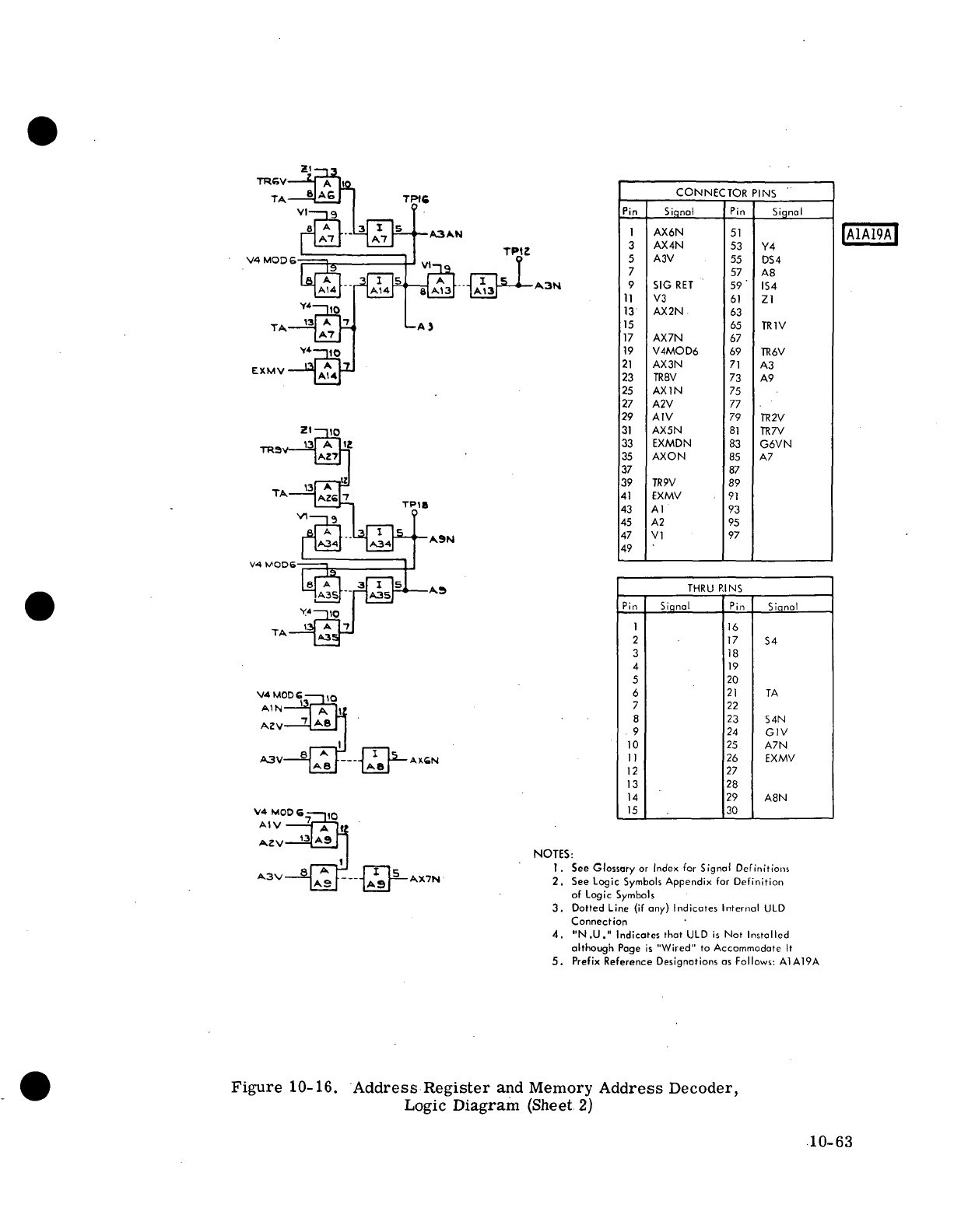

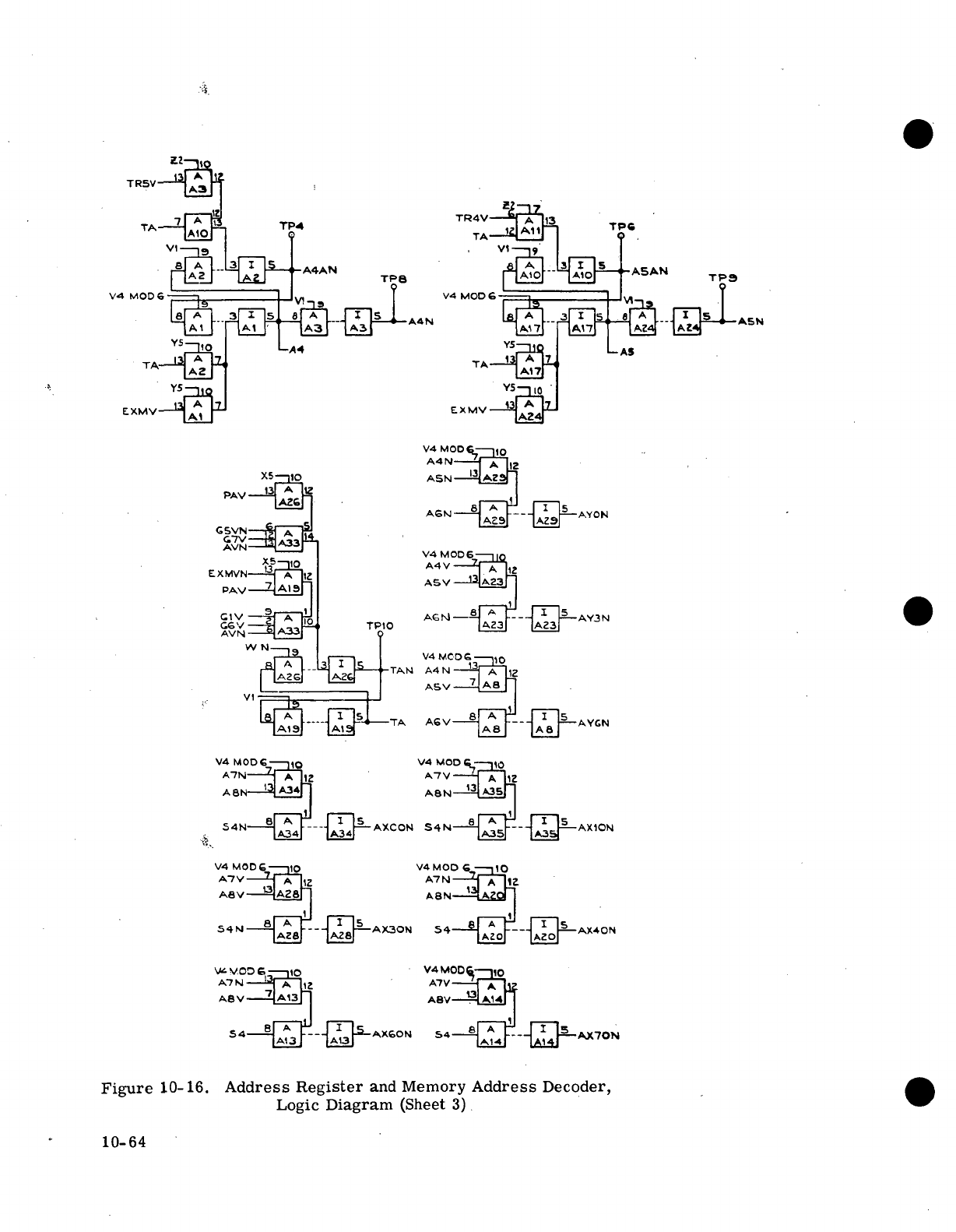

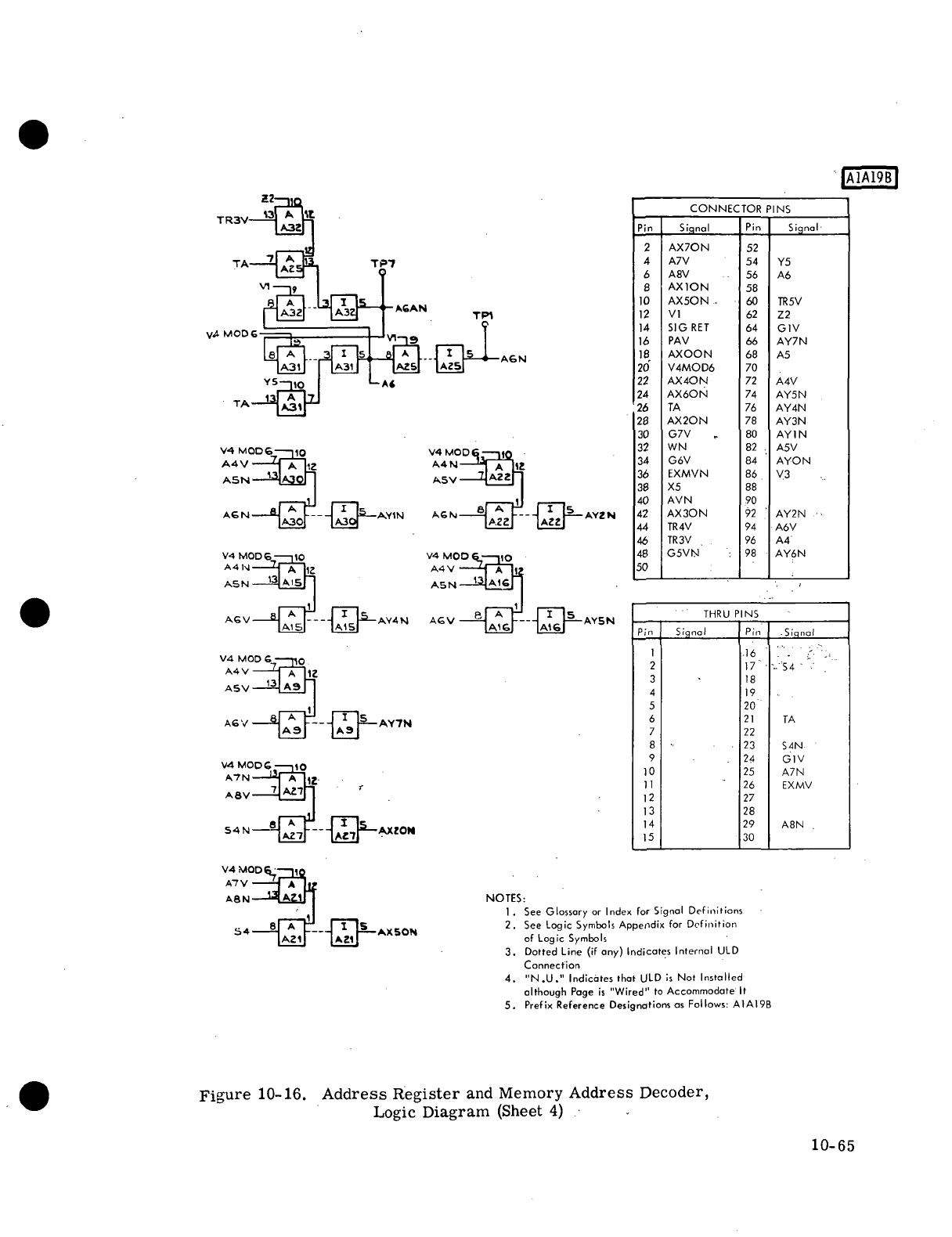

10-16 Address

Register

and

Memory

Address

Decoder,

Logic Diagram

(4

Sheets)

10-62

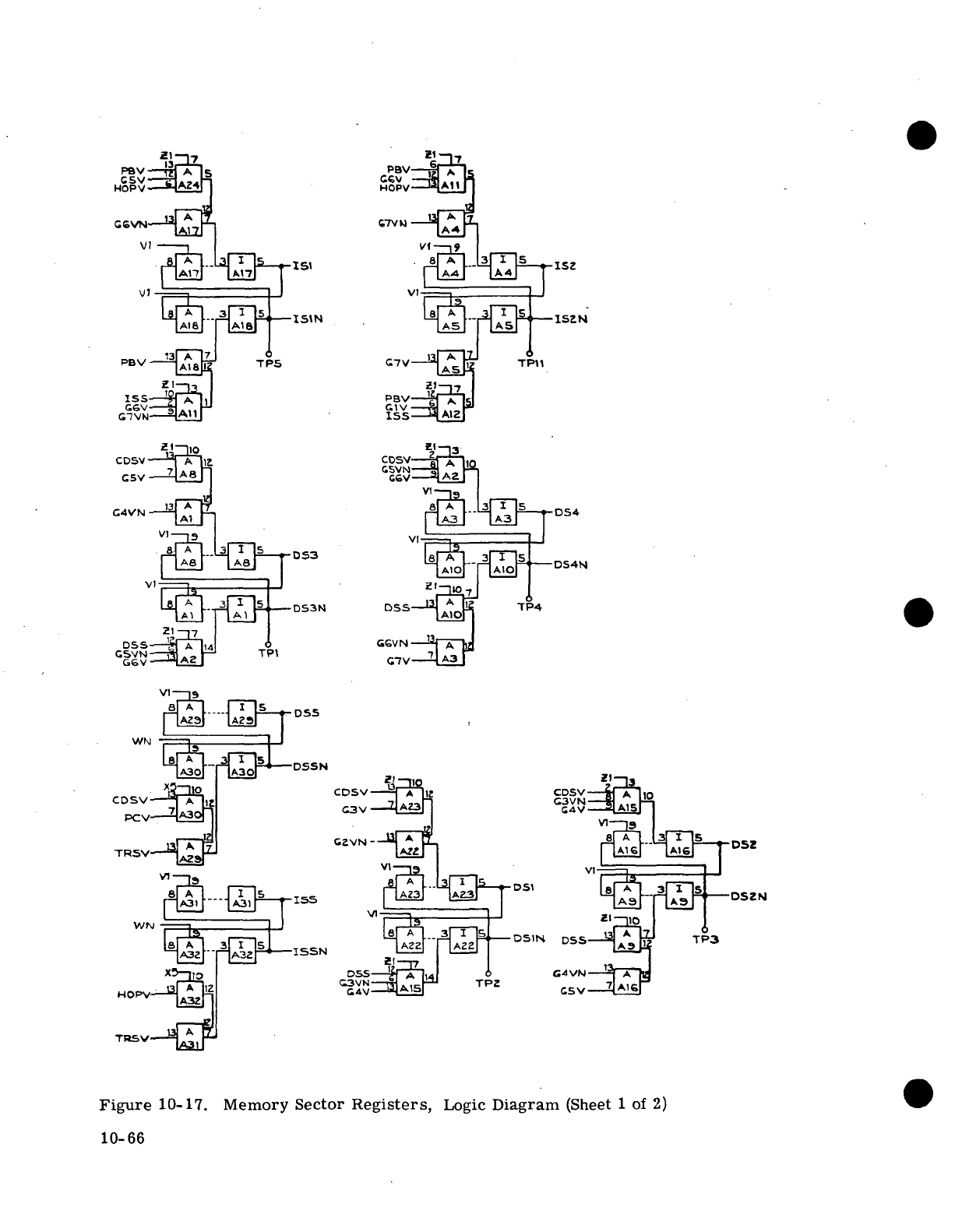

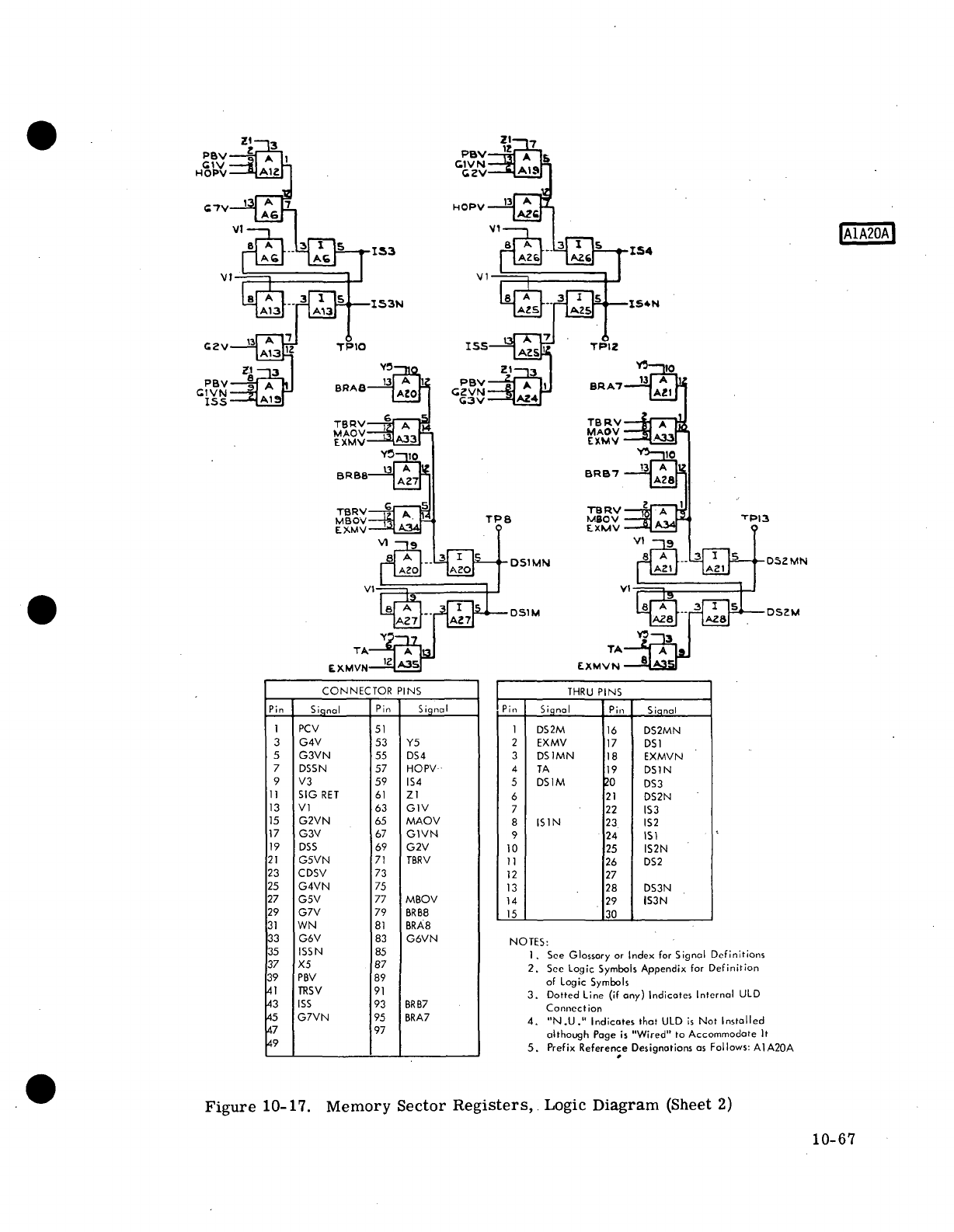

10-17 Memory Sector

Registers,

Logic Diagram

(2

Sheets)

10-66

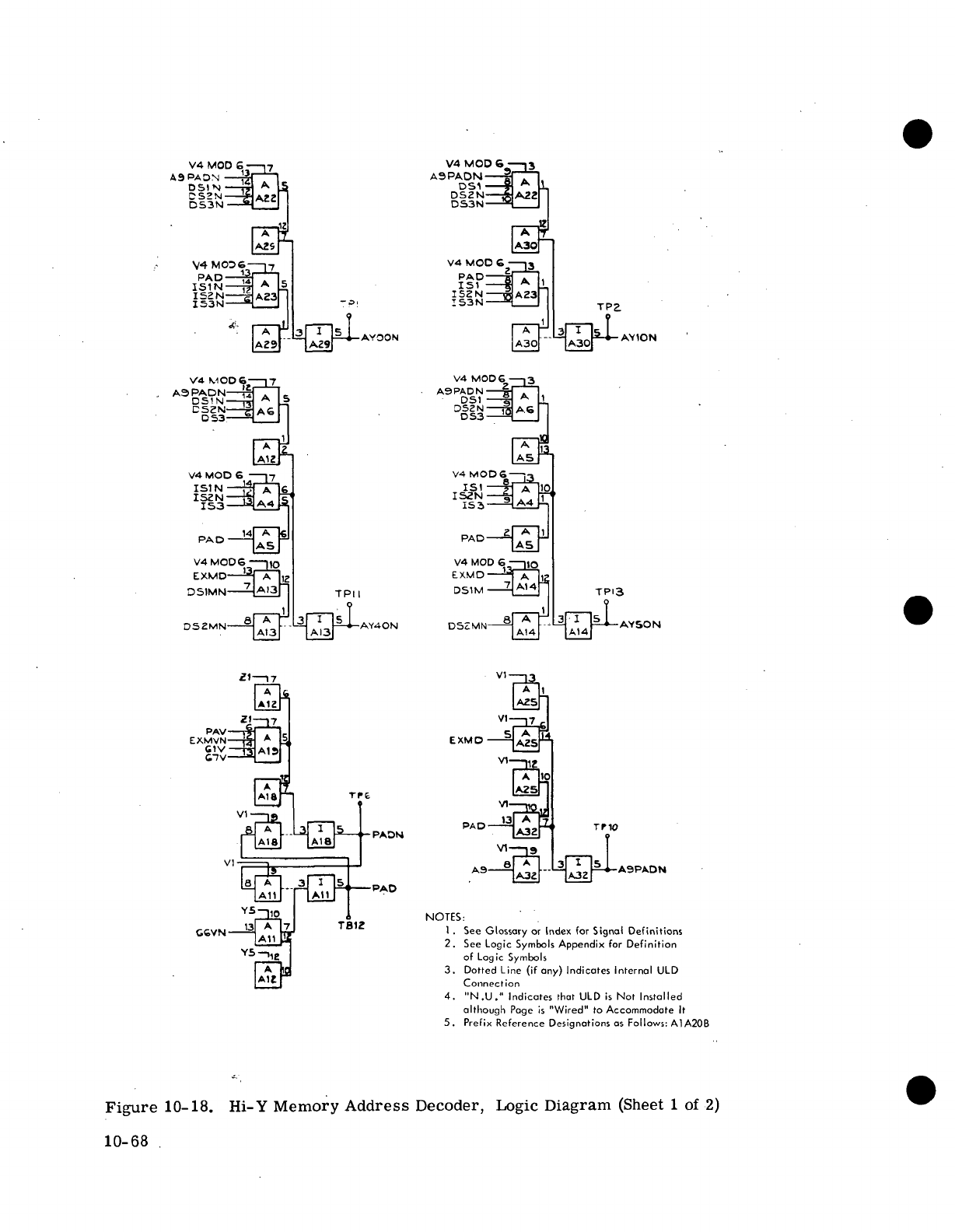

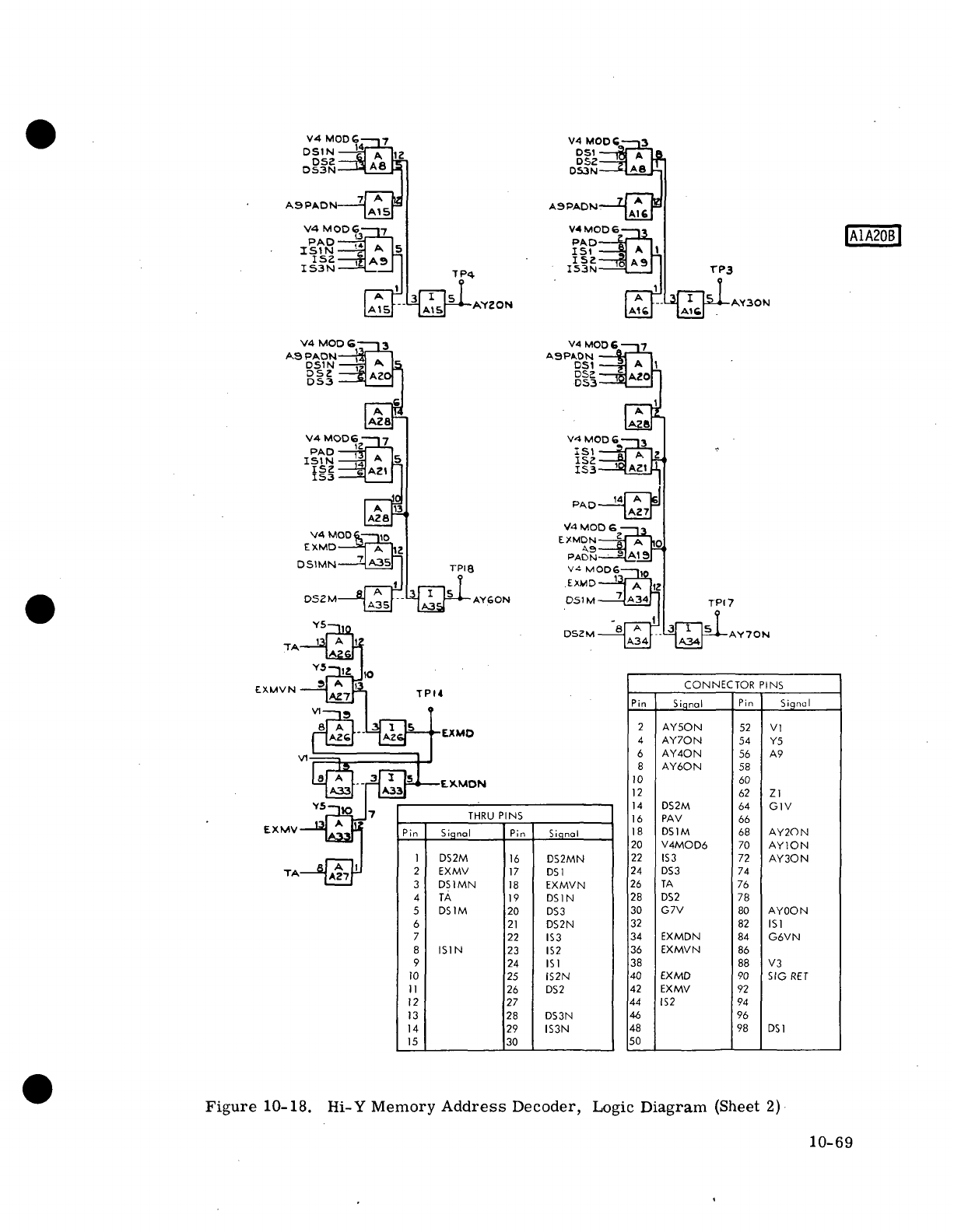

10-18 Hi-Y Memory Address Decoder, Logic Diagram

(2

Sheets)

10-68

Changed

4

January 1965

iii

Volume

II

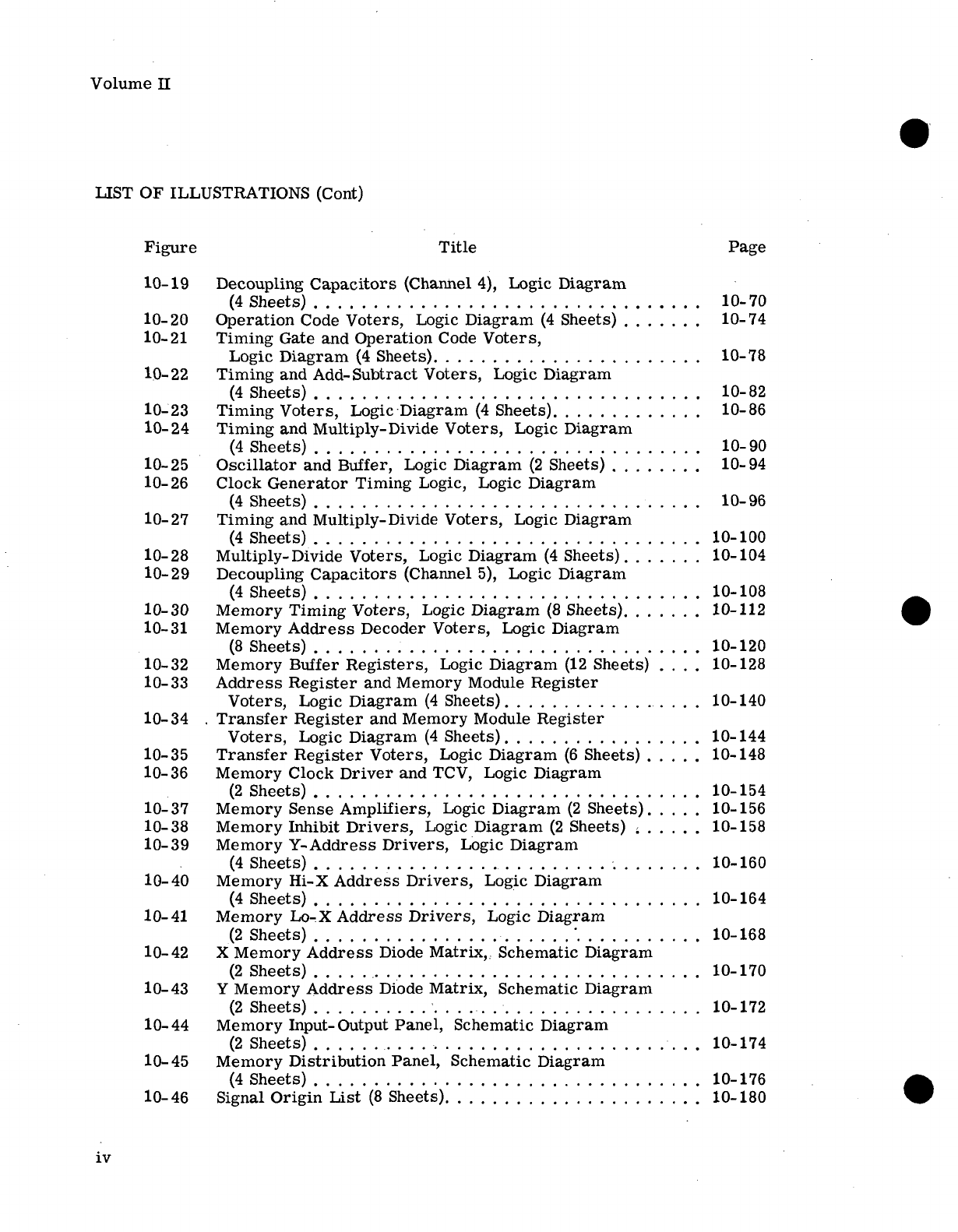

LIST

OF

ILLUSTRATIONS

(Cont)

Figure

Title

Page

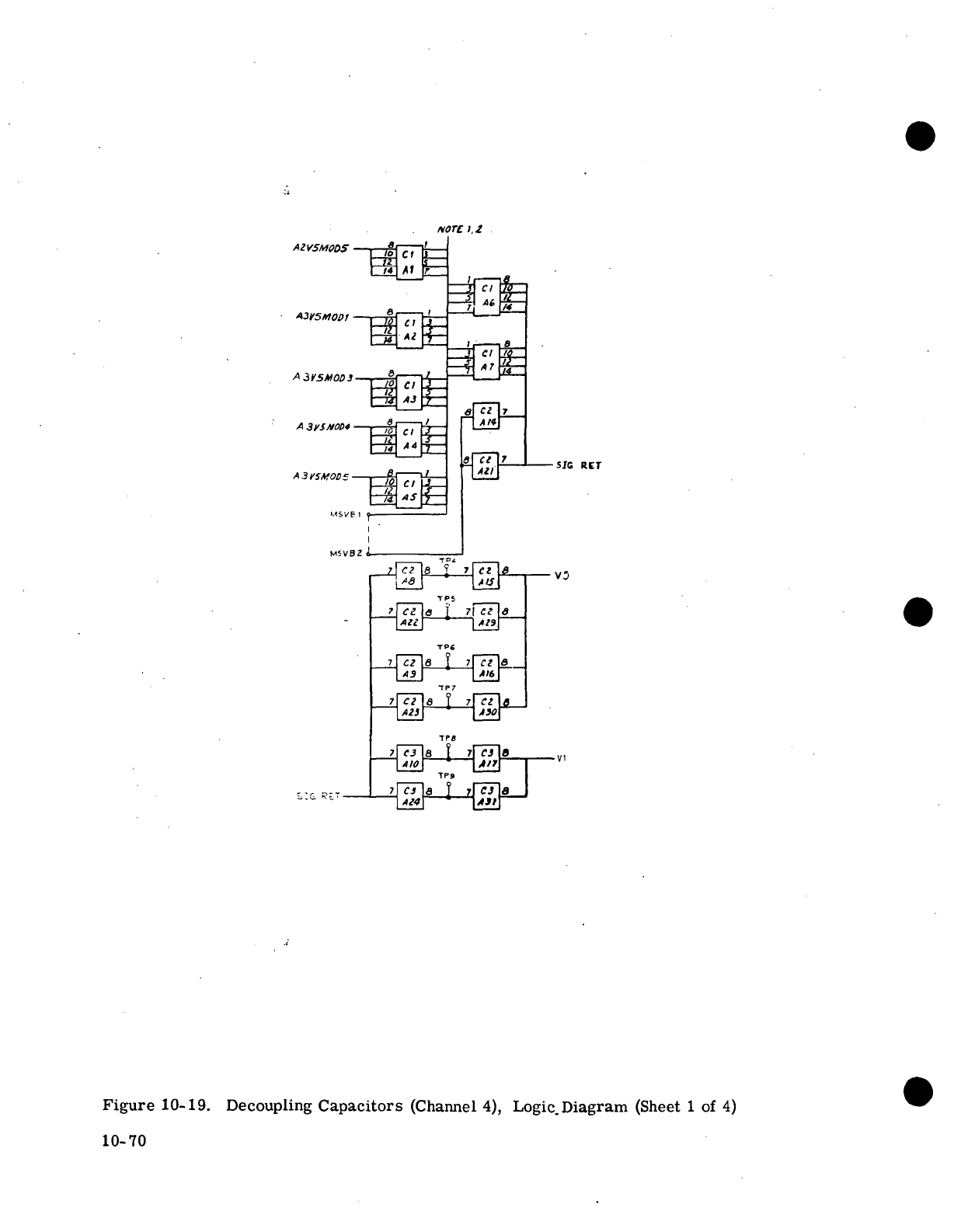

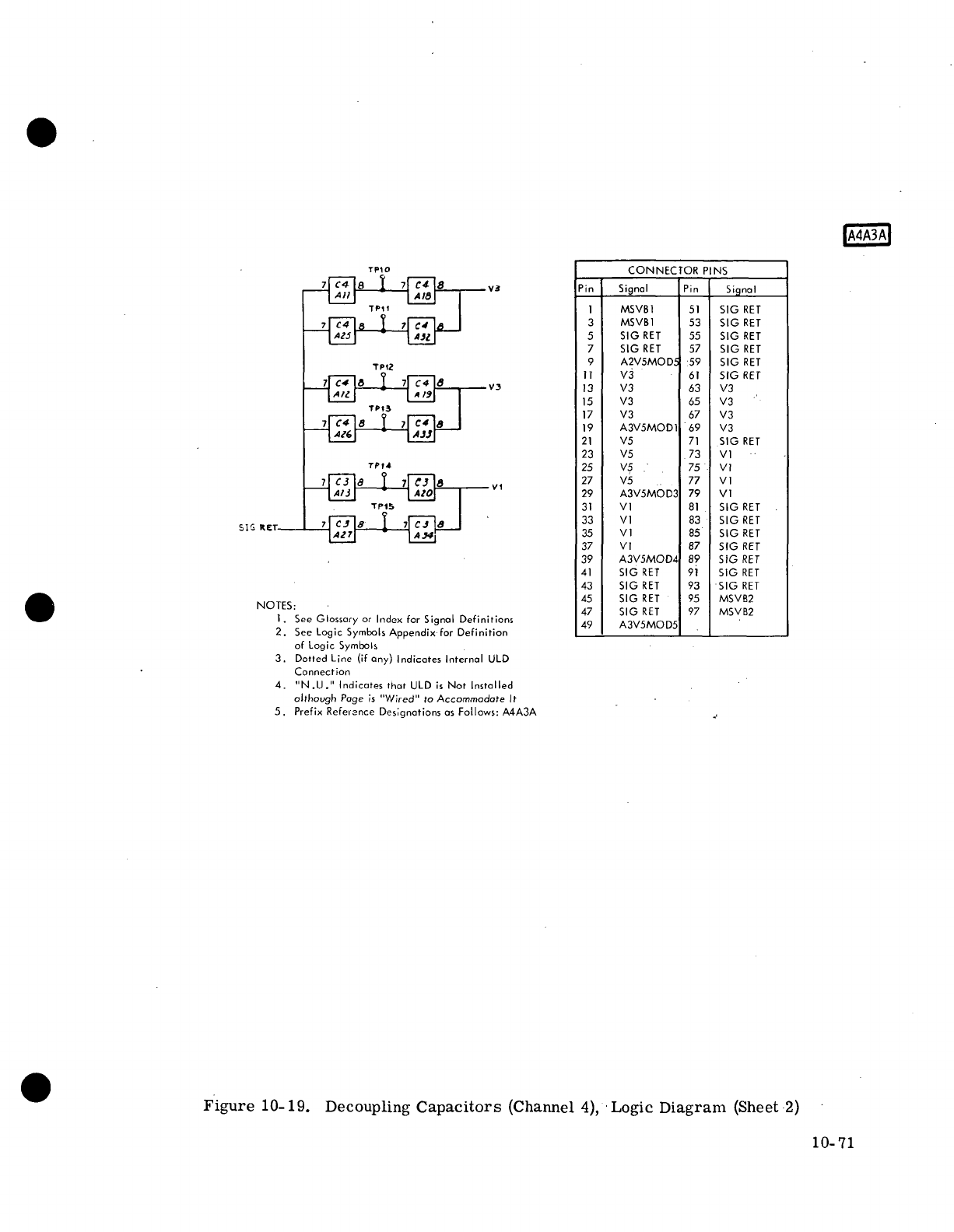

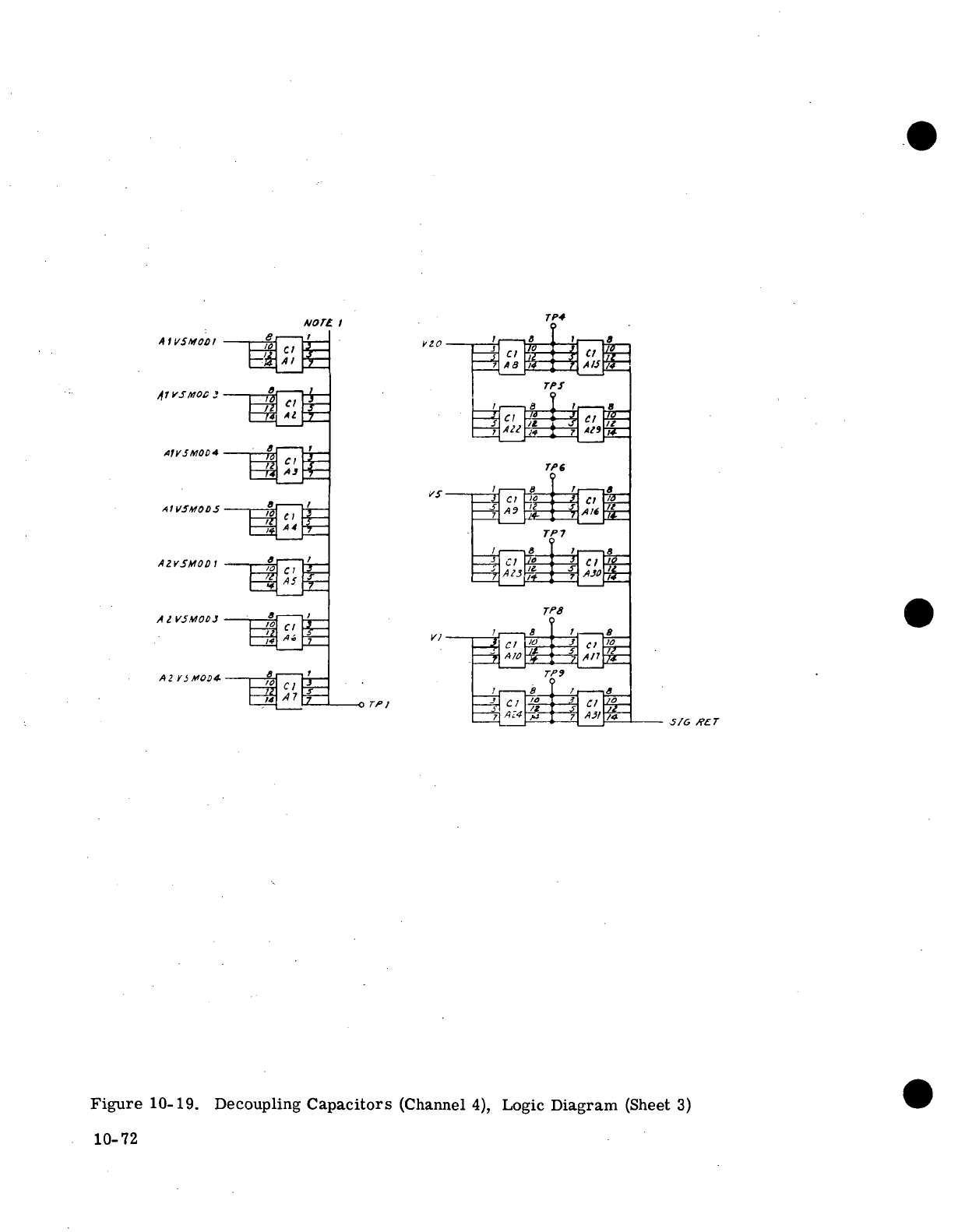

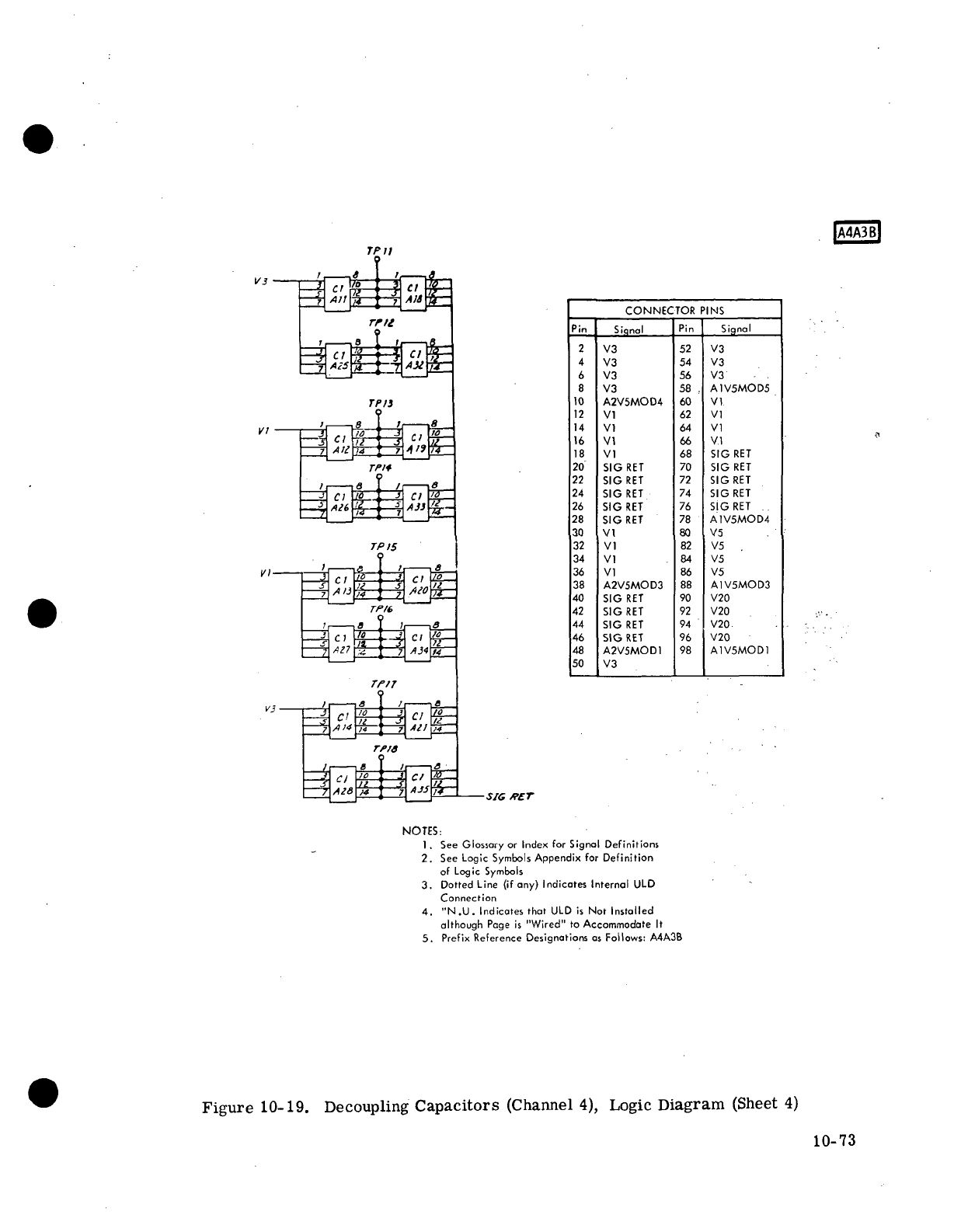

10-19 Decoupling

Capacitors

(Channel

4),

Logic Diagram

(4

Sheets) 10-70

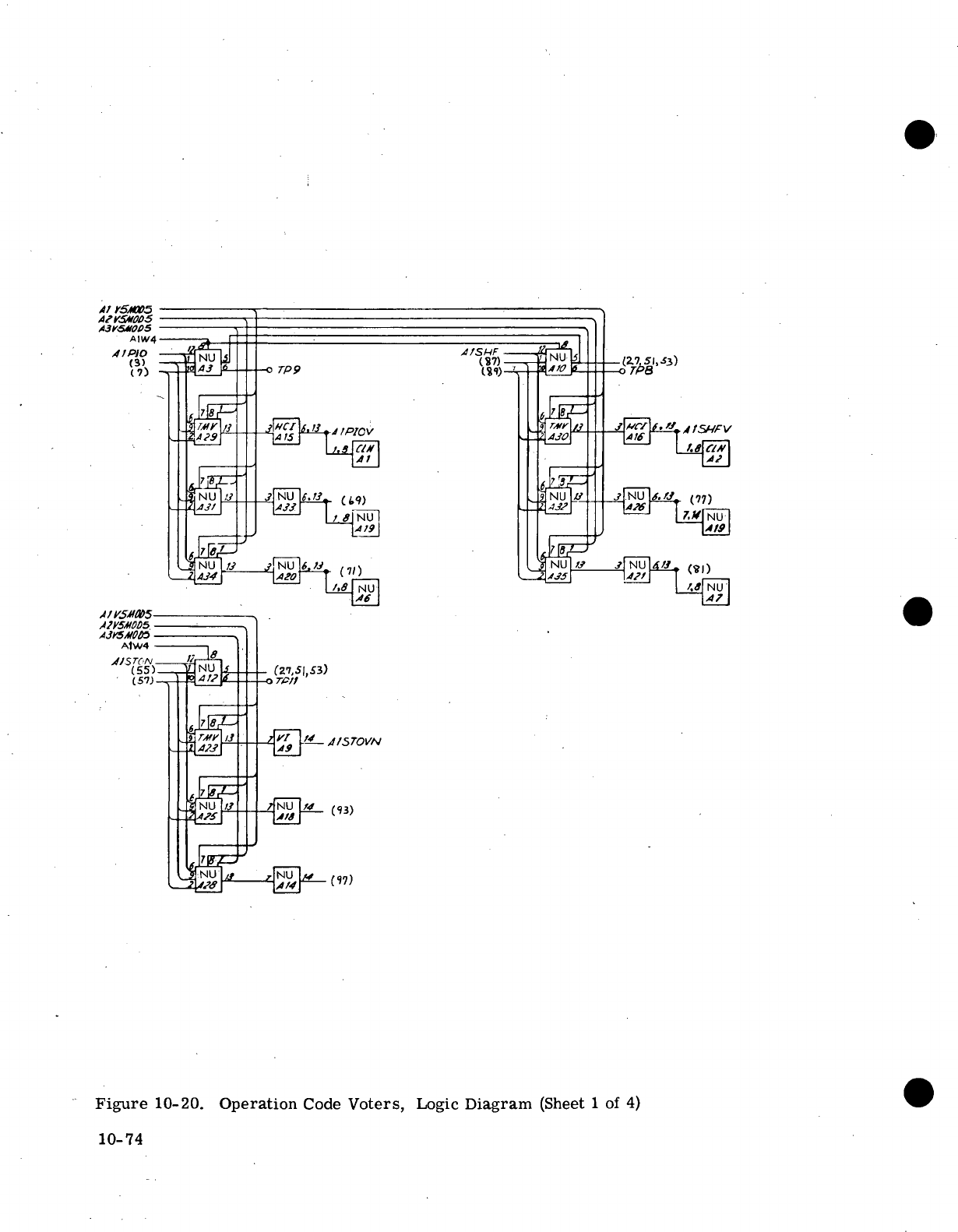

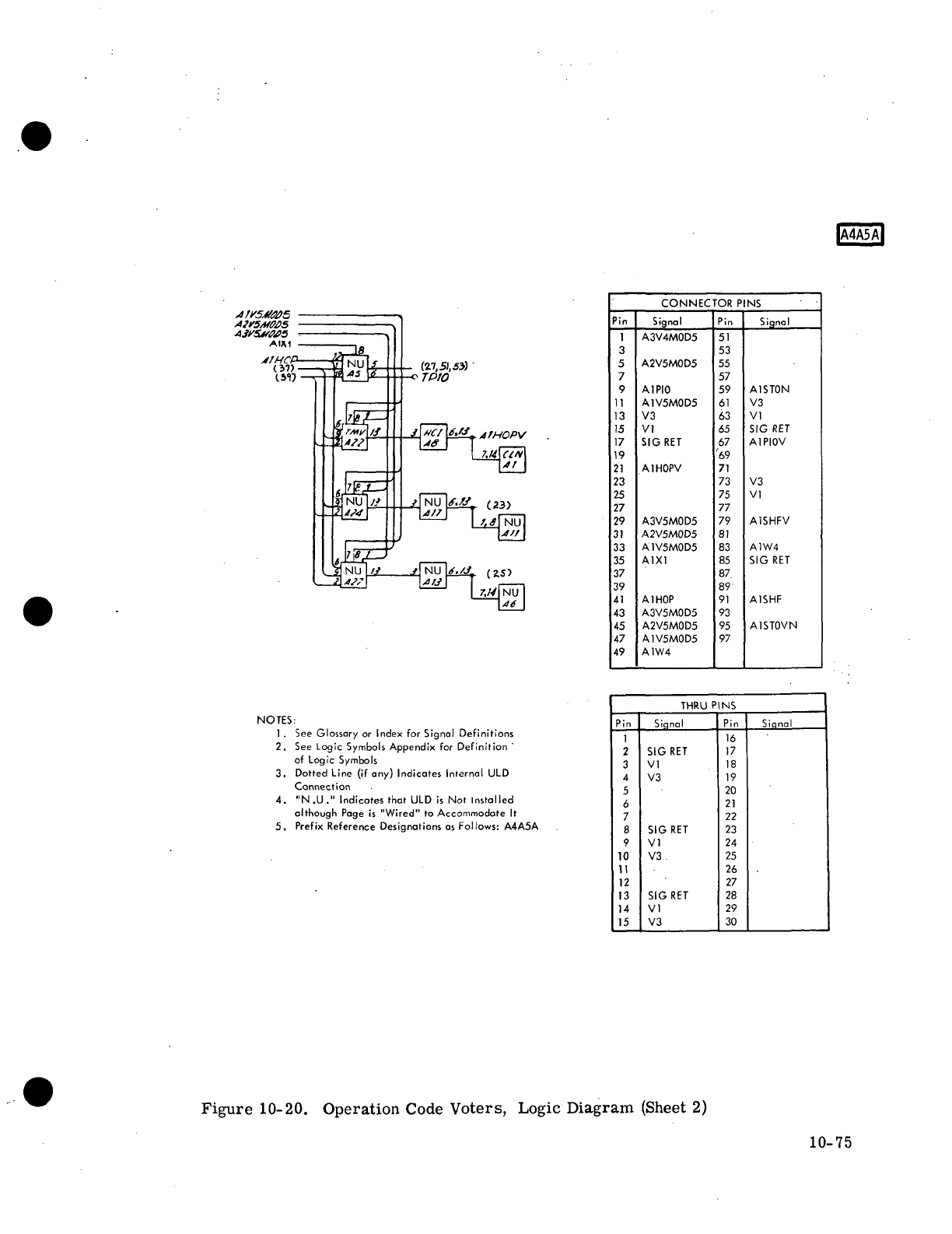

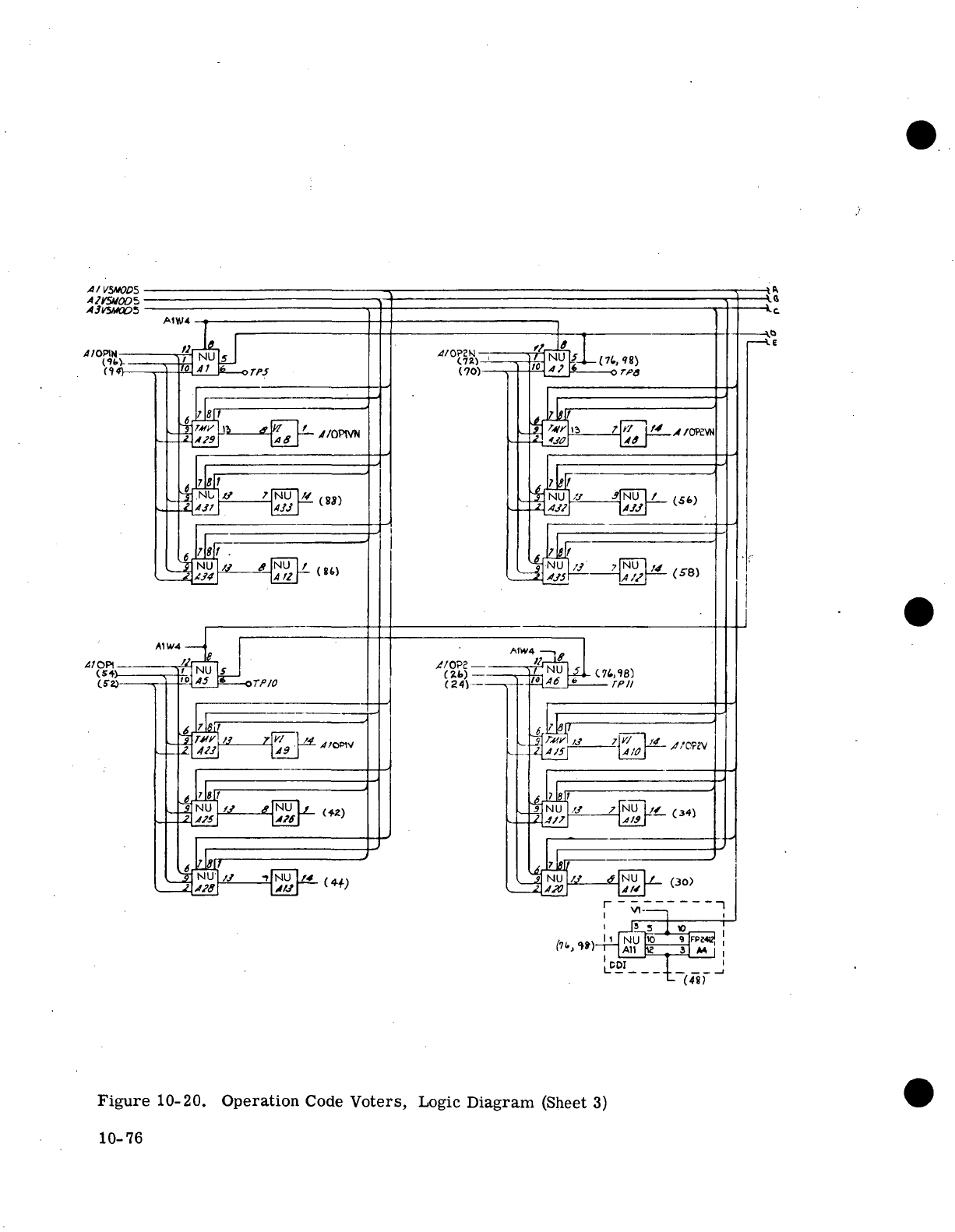

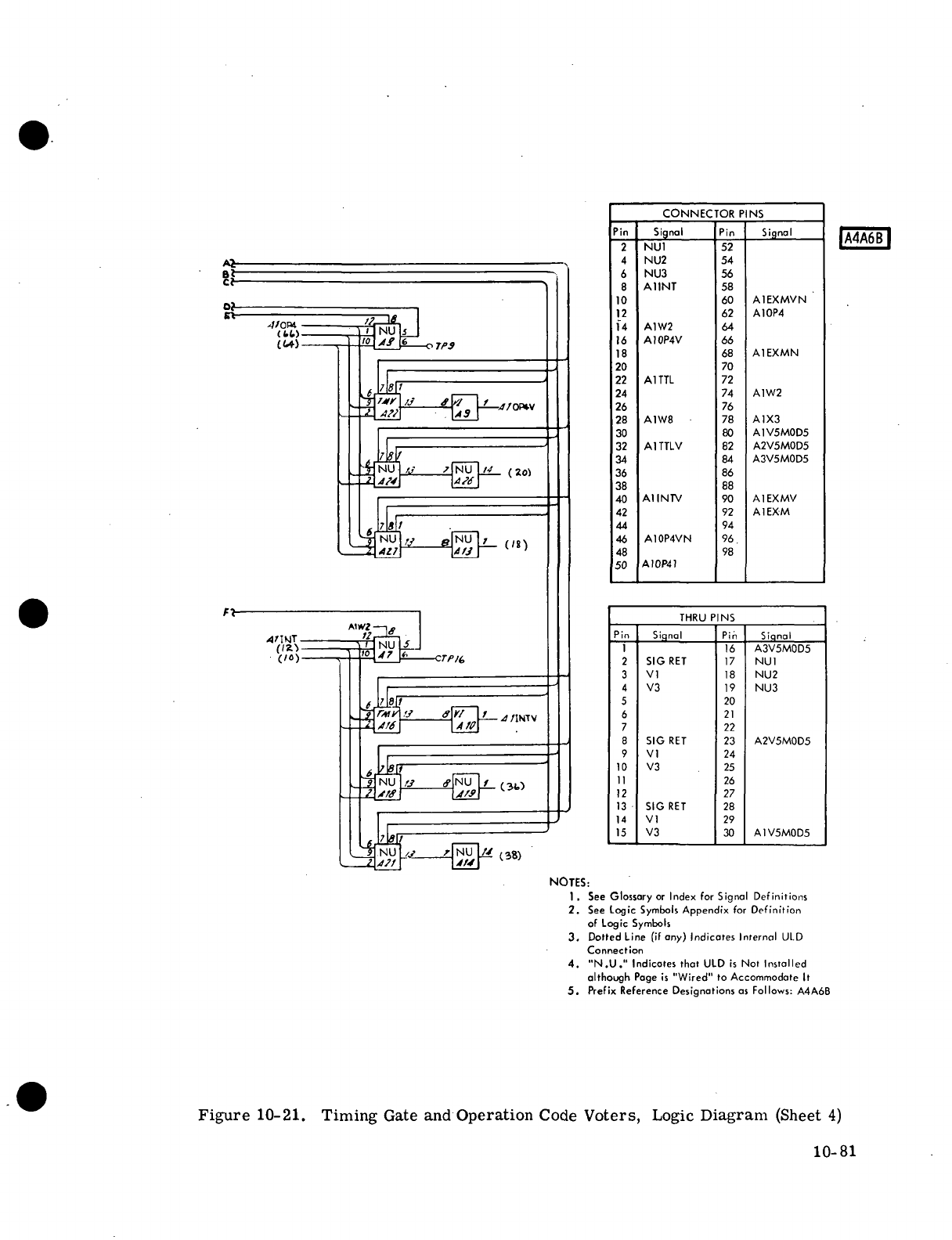

10-20

Operation

Code

Voters, Logic Diagram

(4

Sheets) 10-74

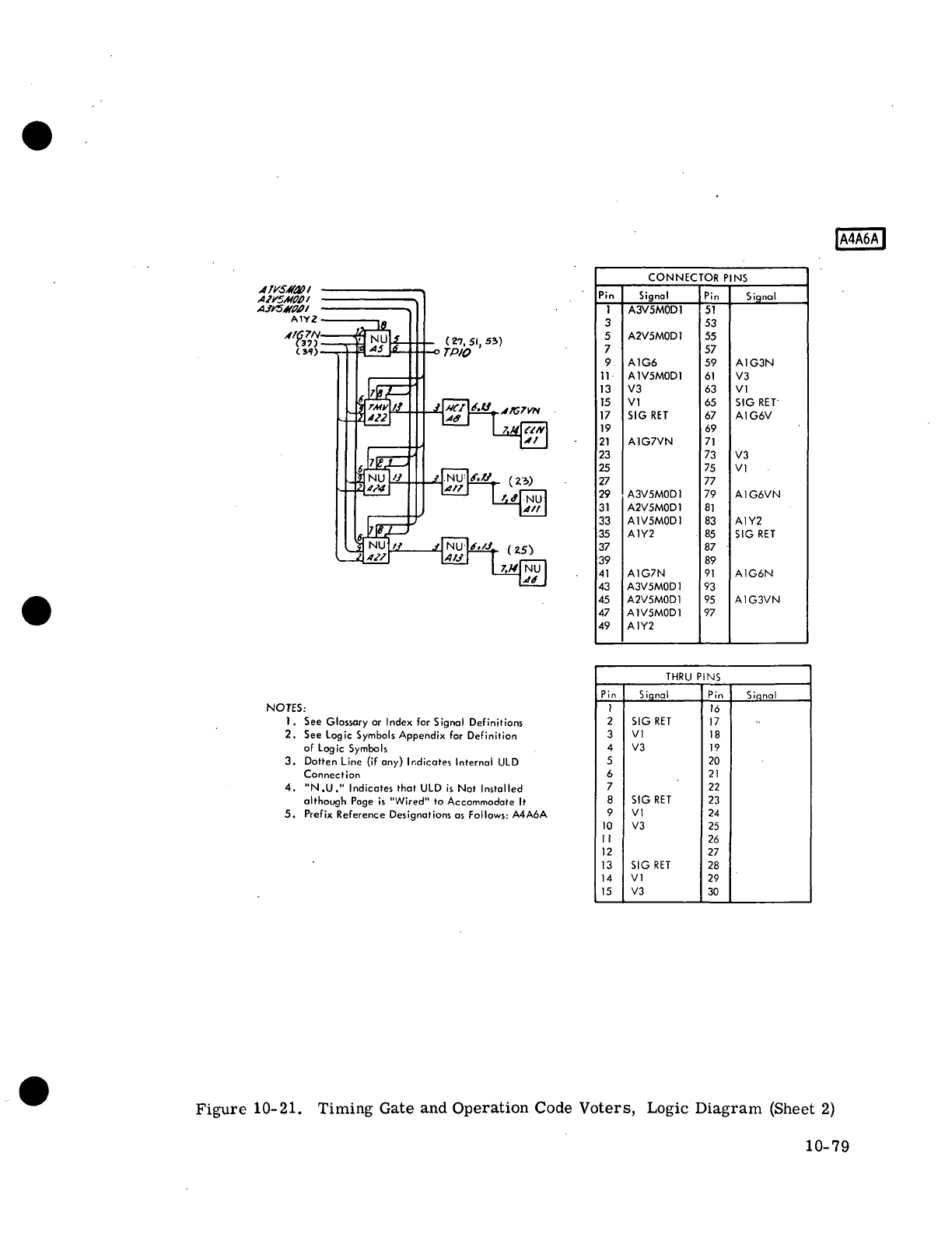

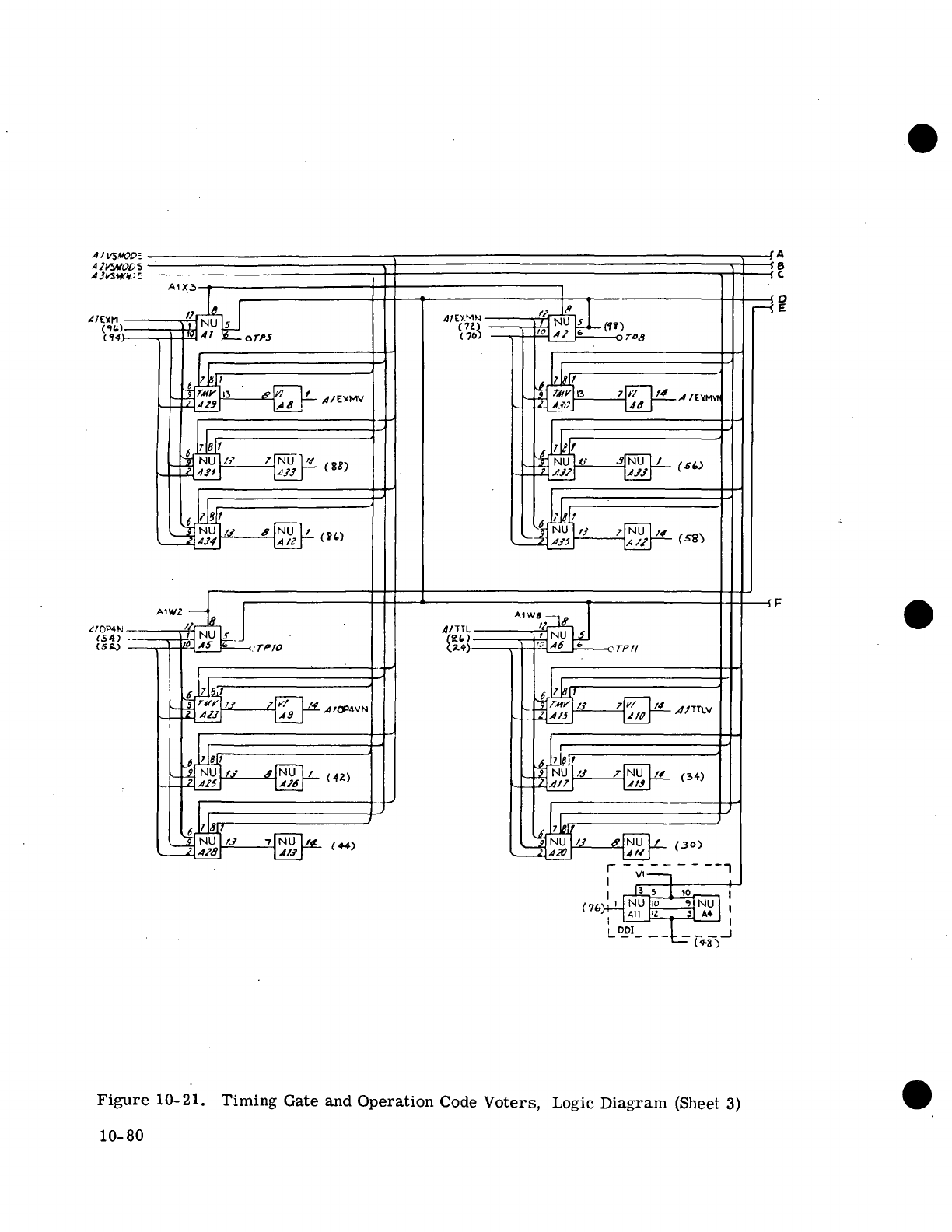

10-21 Timing Gate

and

Operation

Code

Voters,

Logic

Diagram

(4

Sheets) 10-78

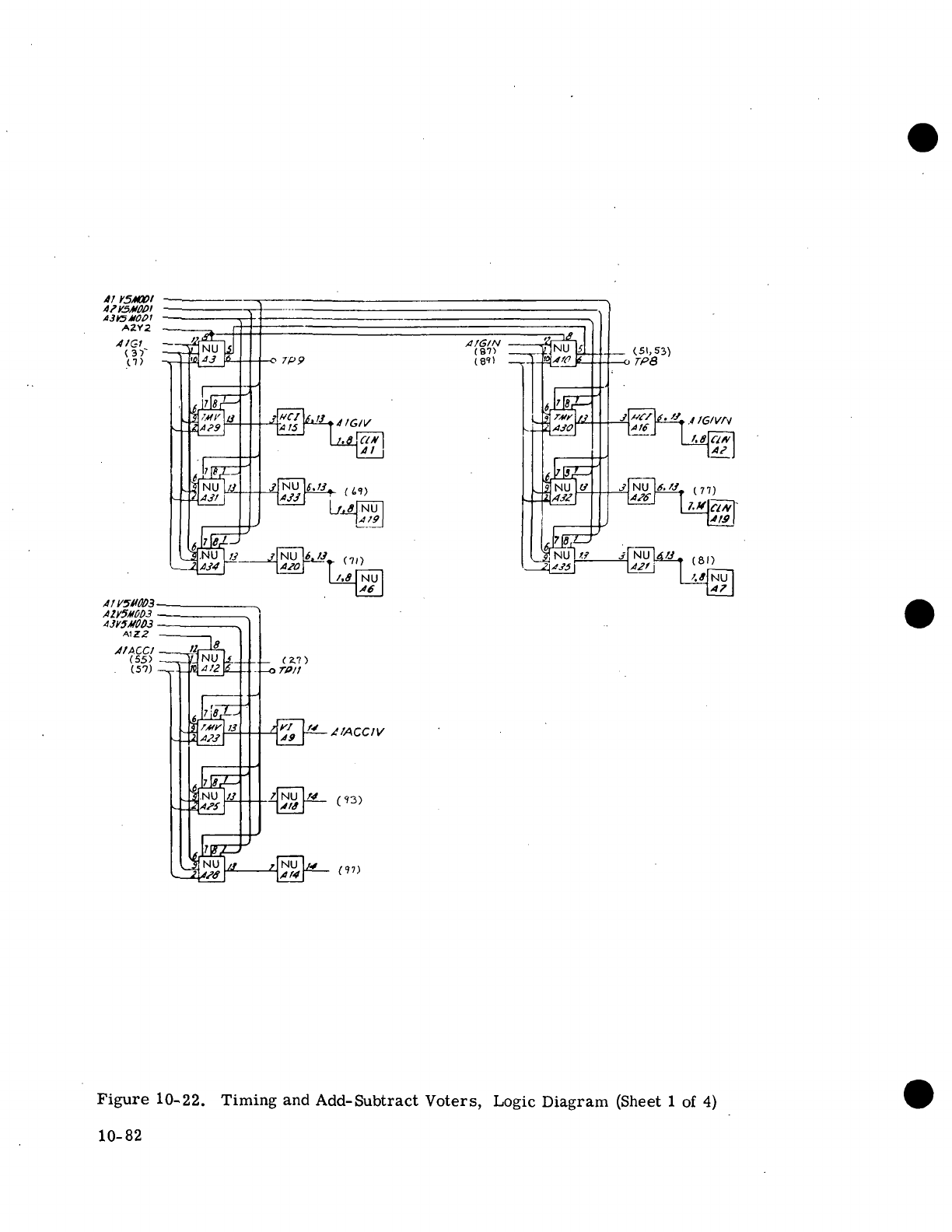

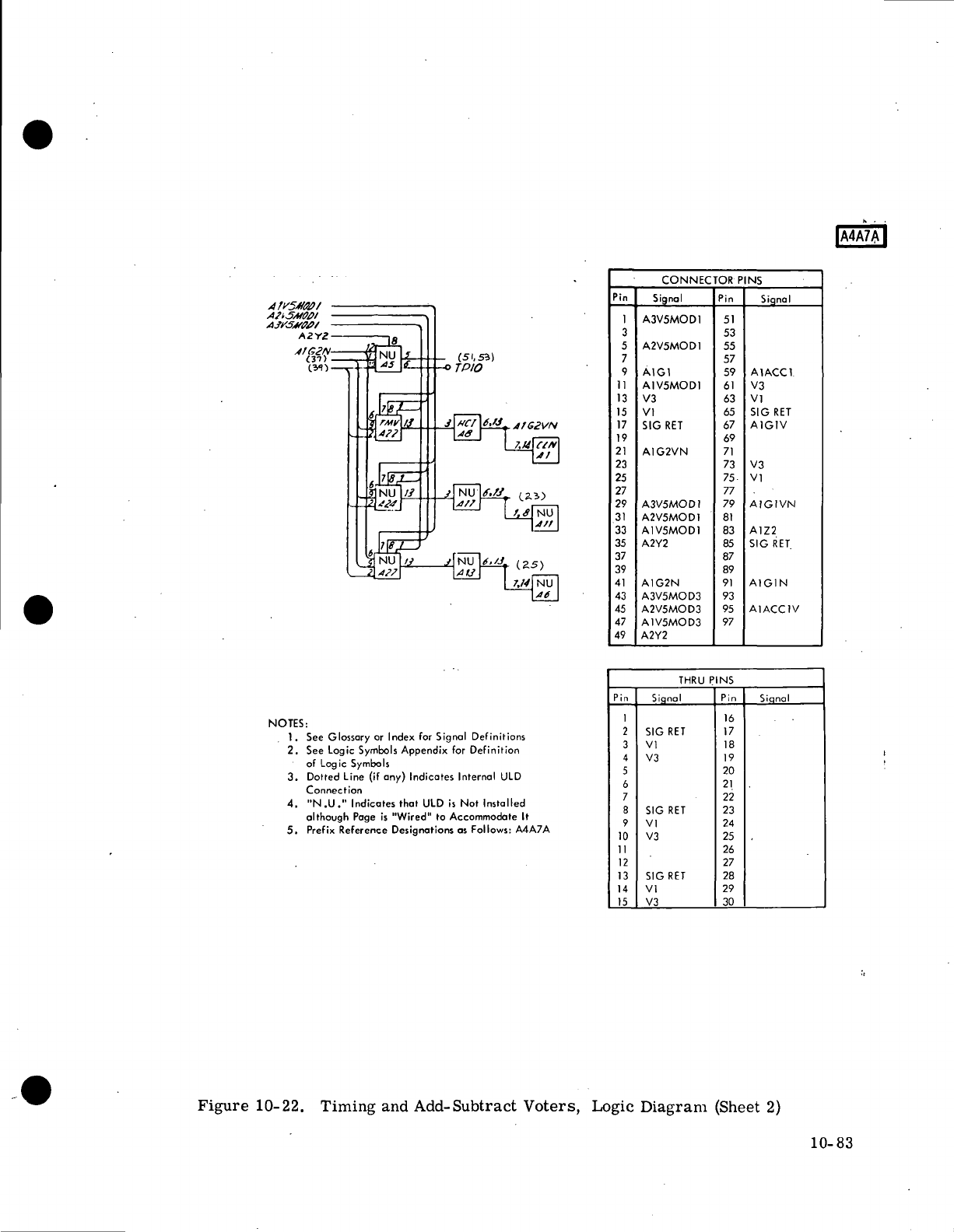

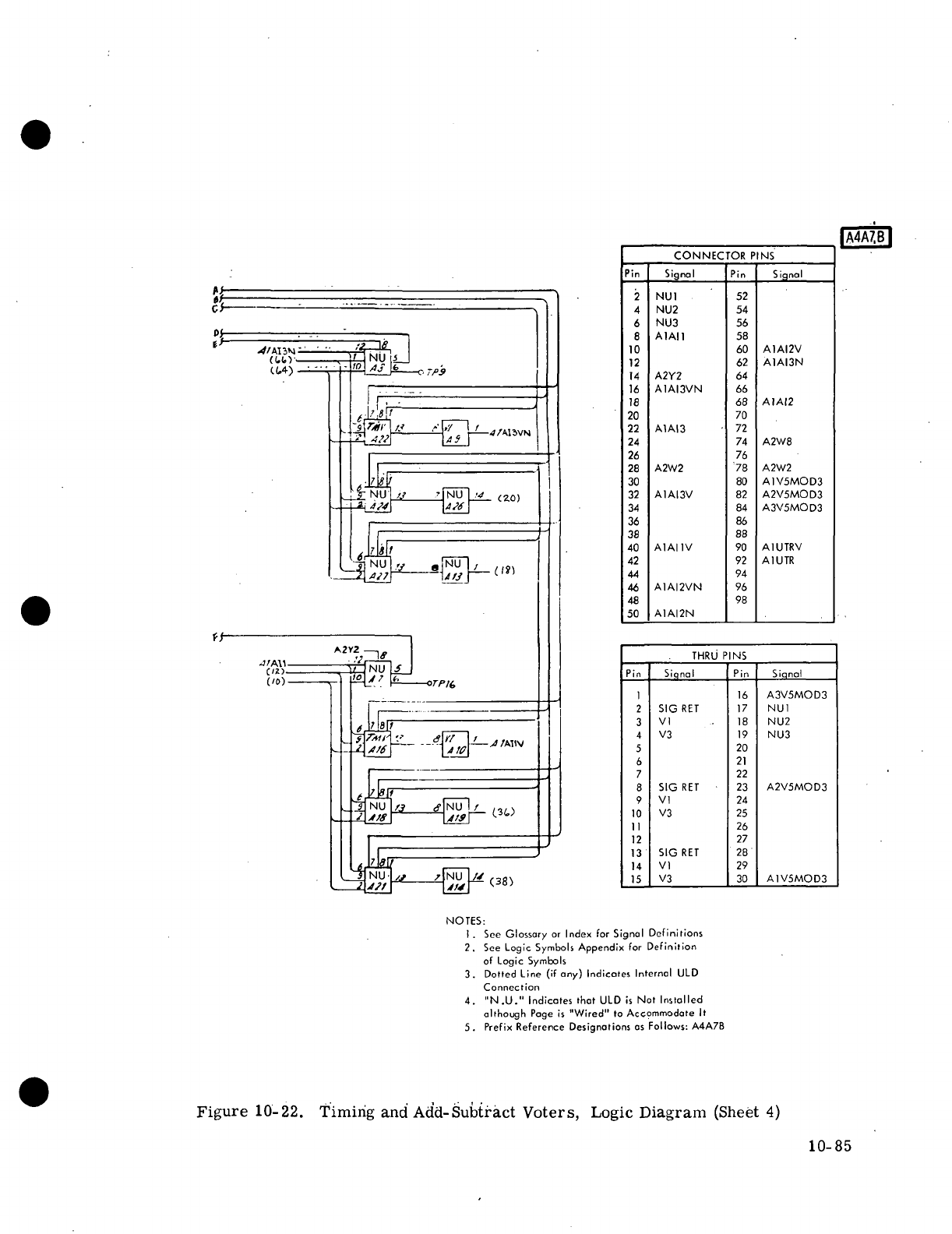

10-22

Timing

and

Add-Subtract Voters, Logic Diagram

(4

Sheets) 10-82

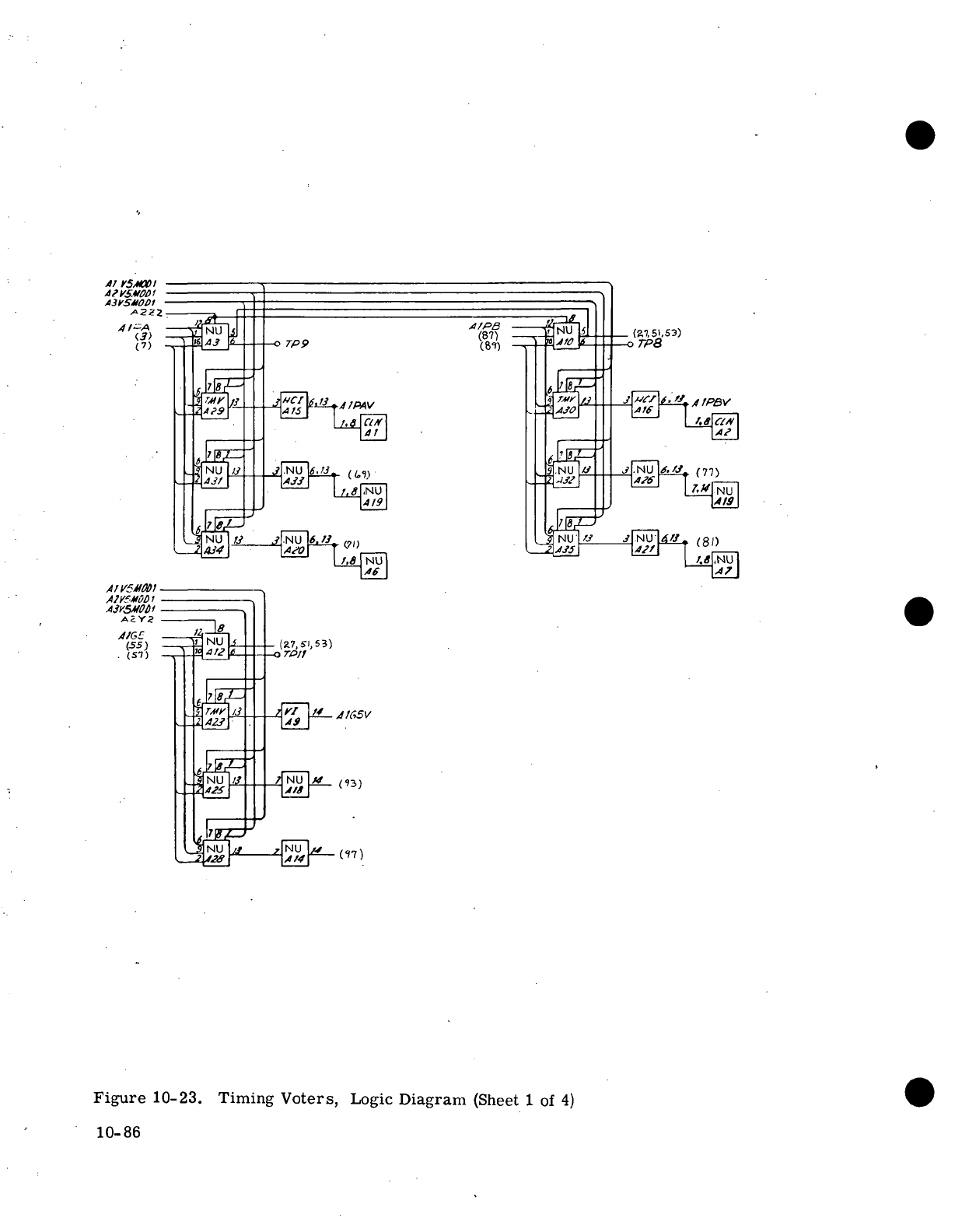

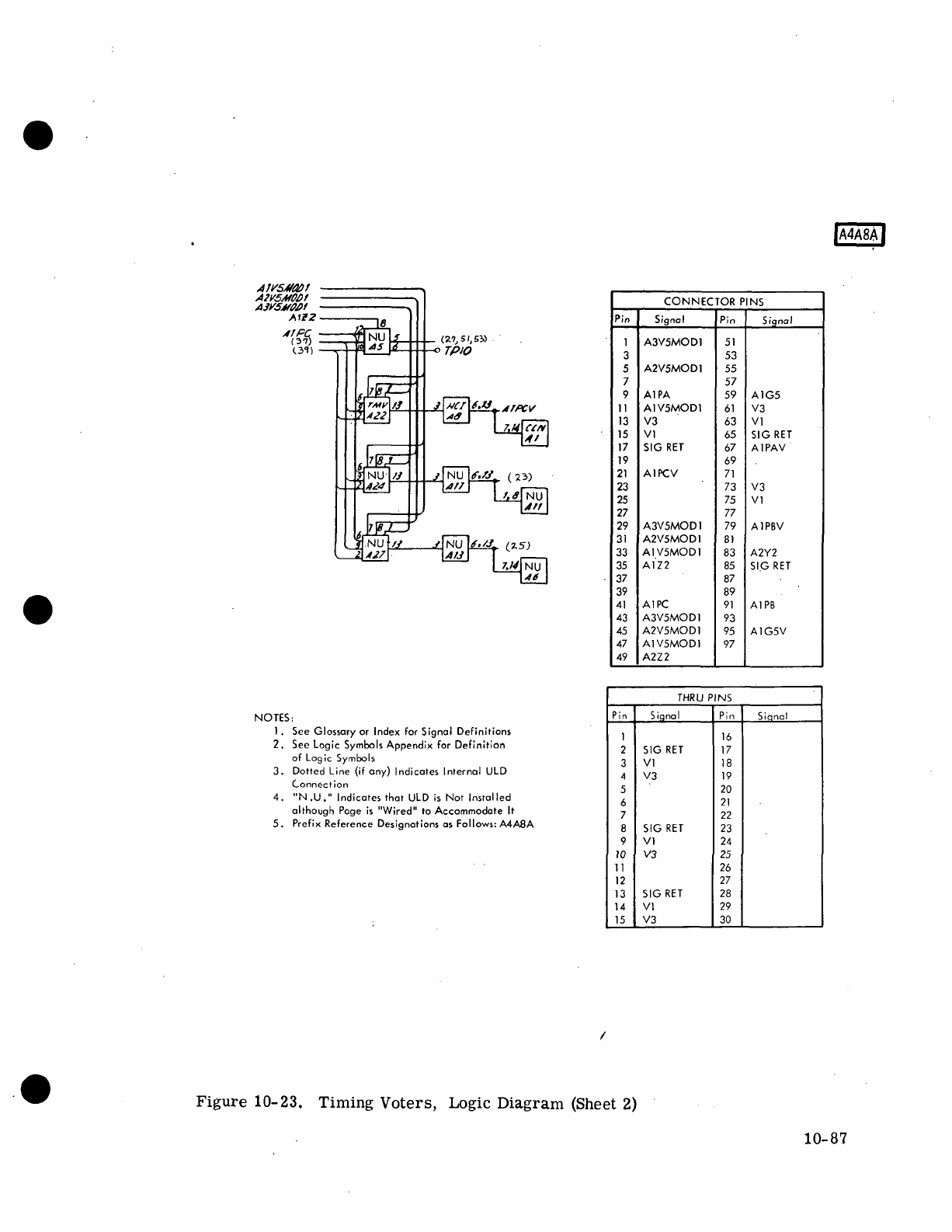

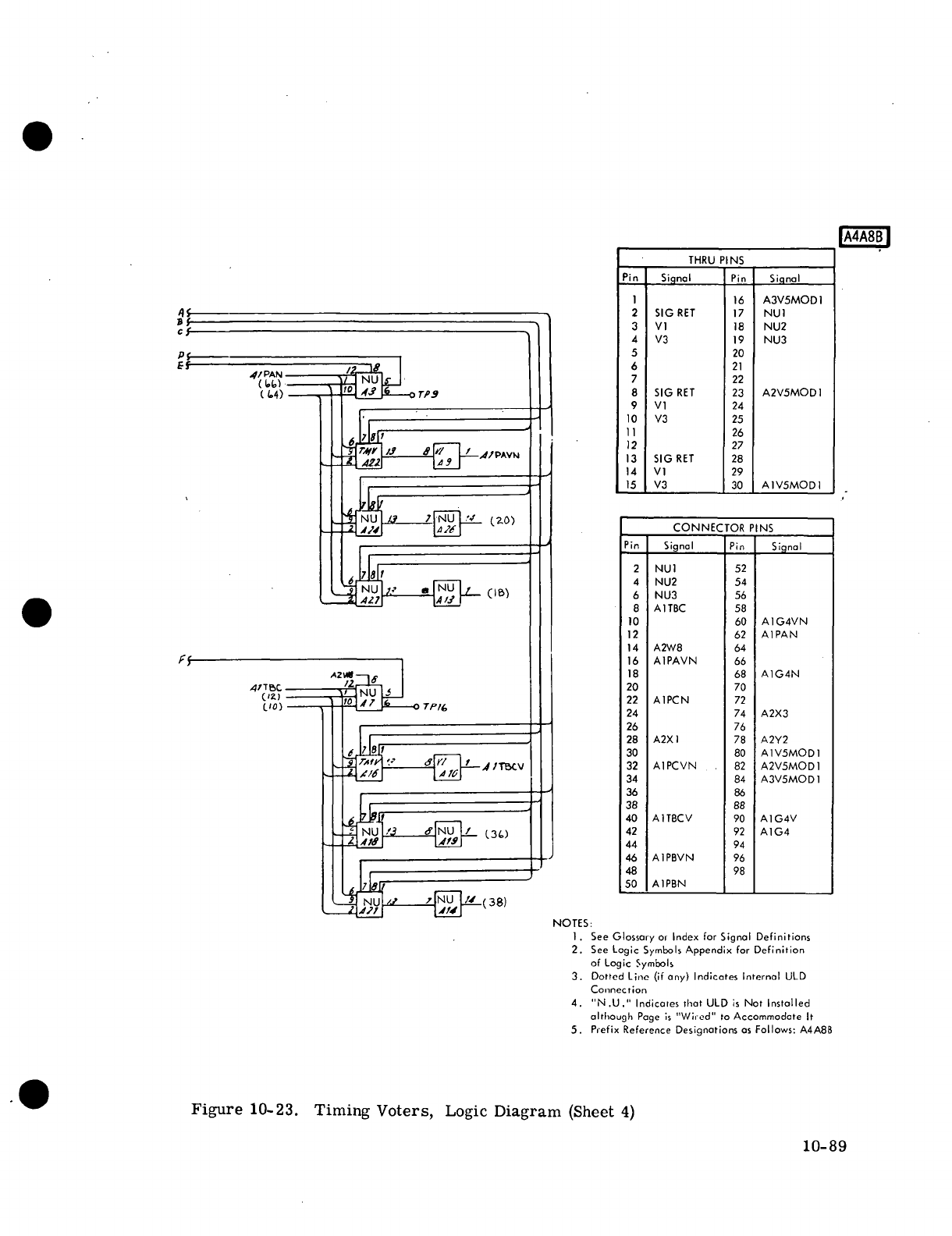

10-23 Timing Voters, Logic Diagram

(4

Sheets) 10-86

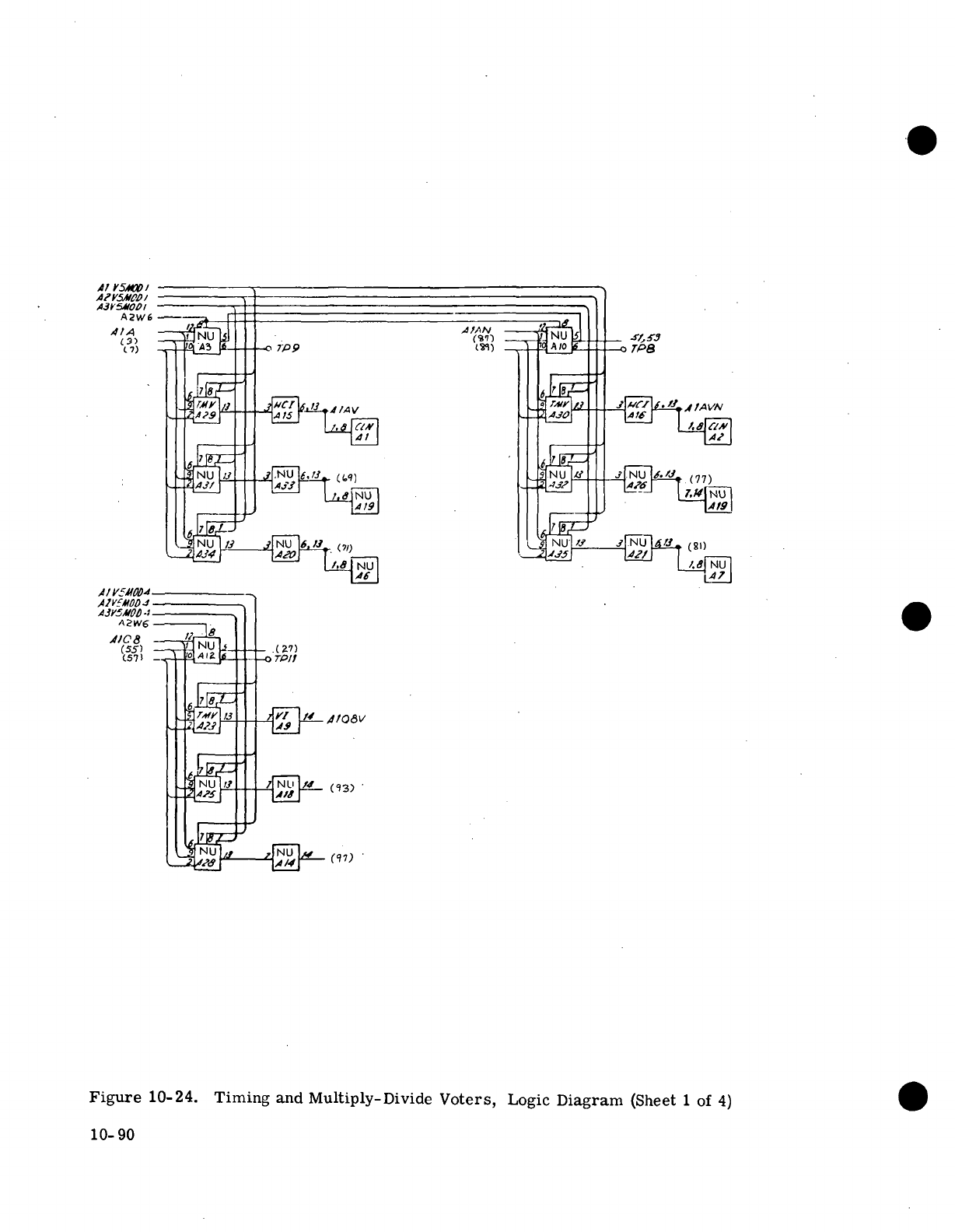

10-24

Timing

and

Multiply-Divide Voters, Logic Diagram

(4

Sheets) 10-90

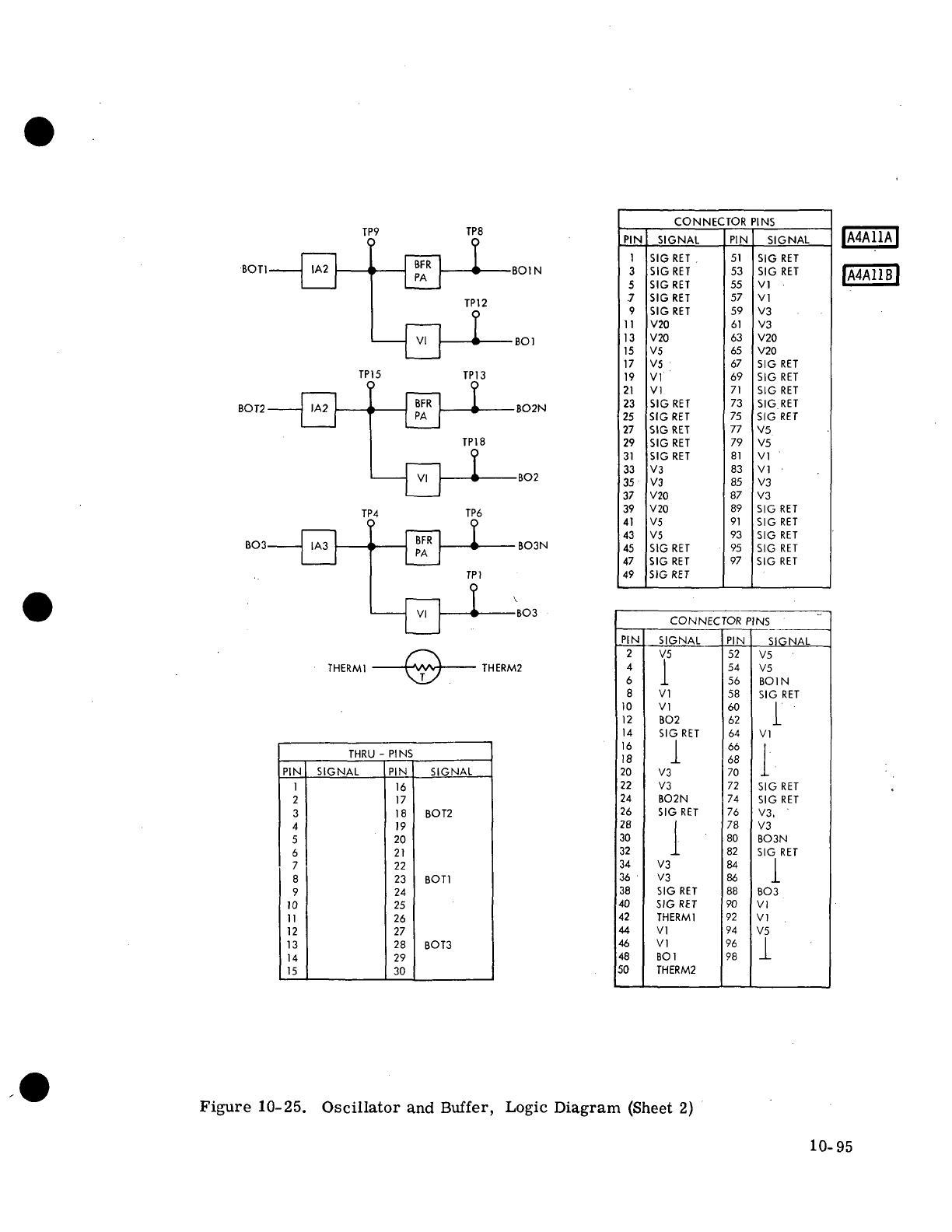

10-25

Oscillator

and

Buffer,

Logic Diagram

(2

Sheets) 10-94

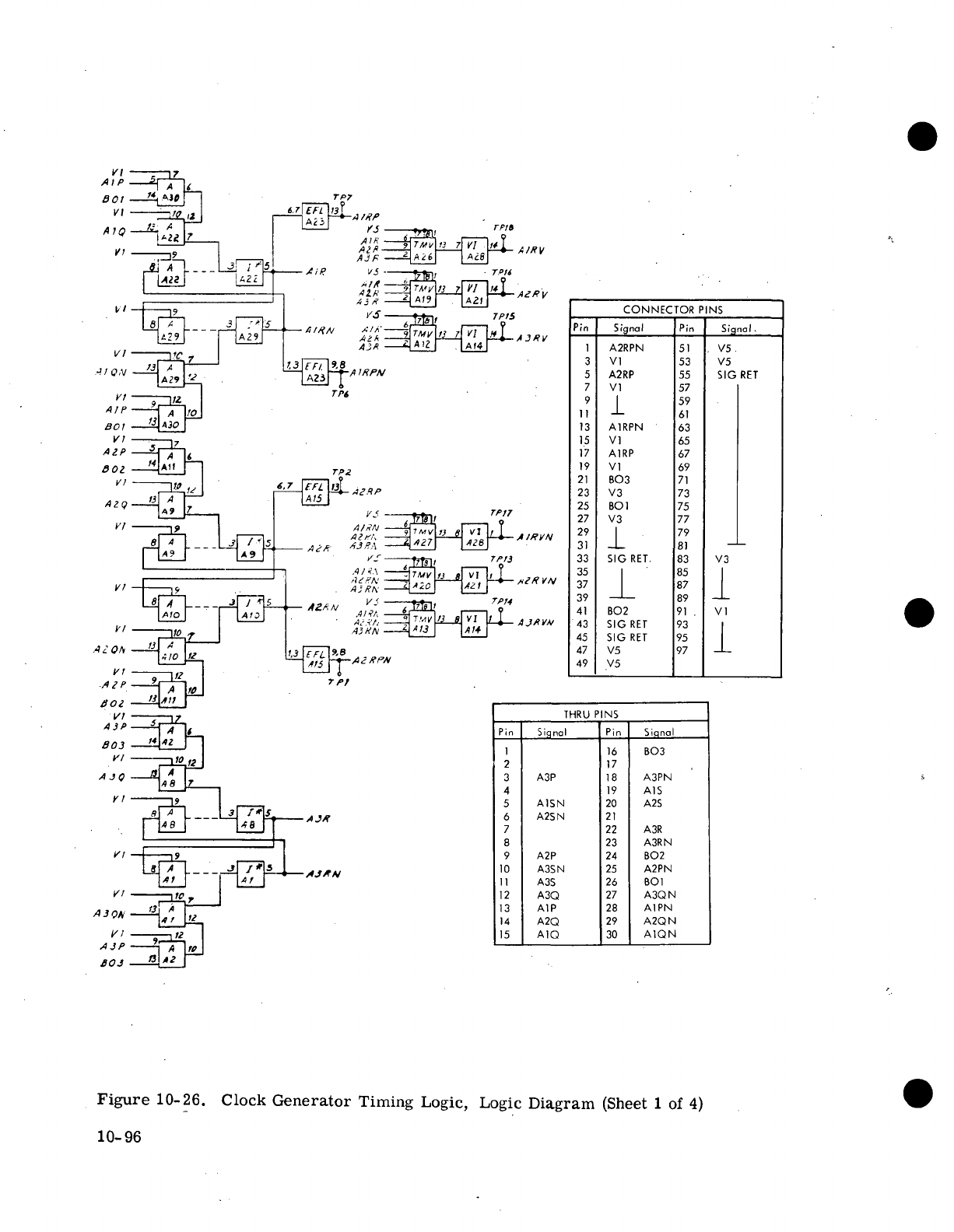

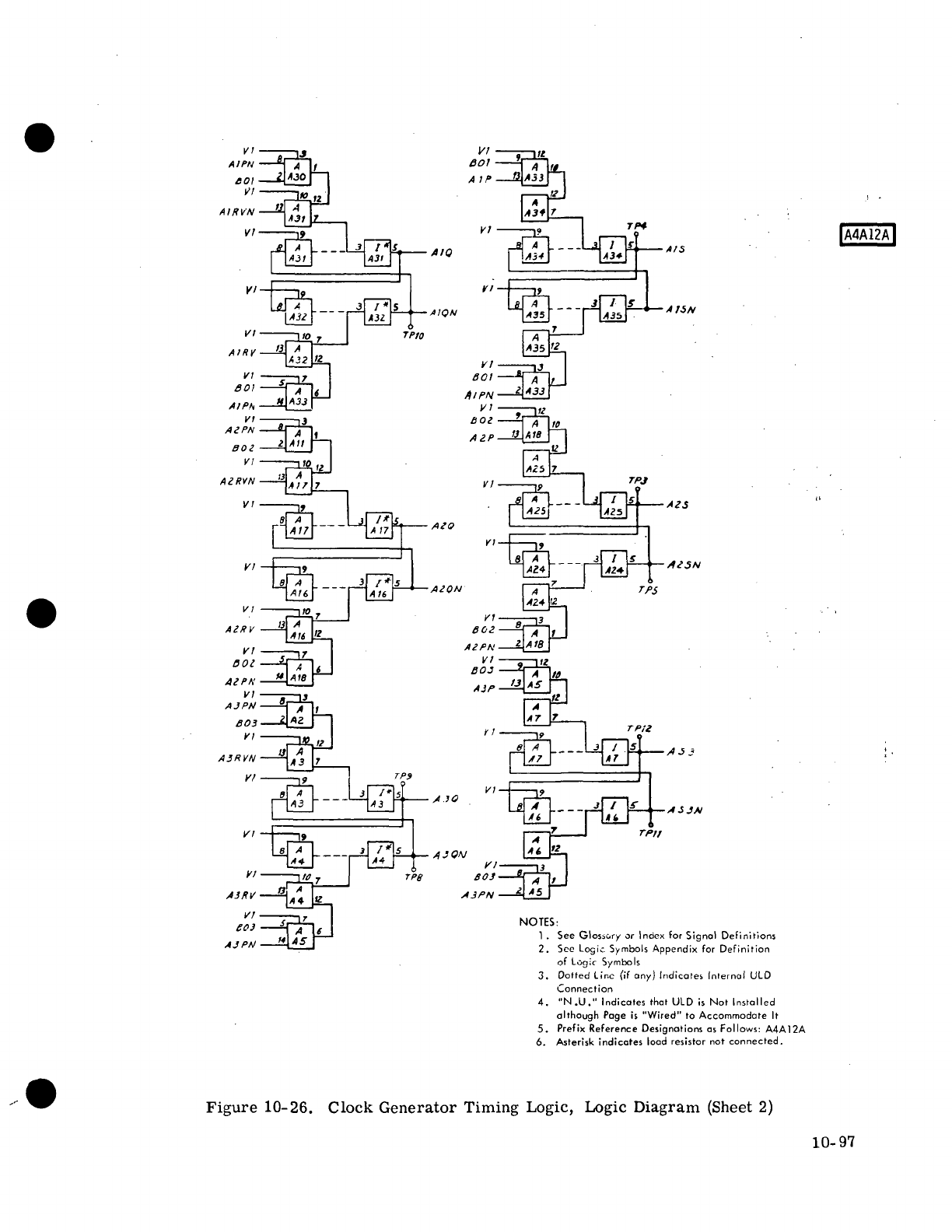

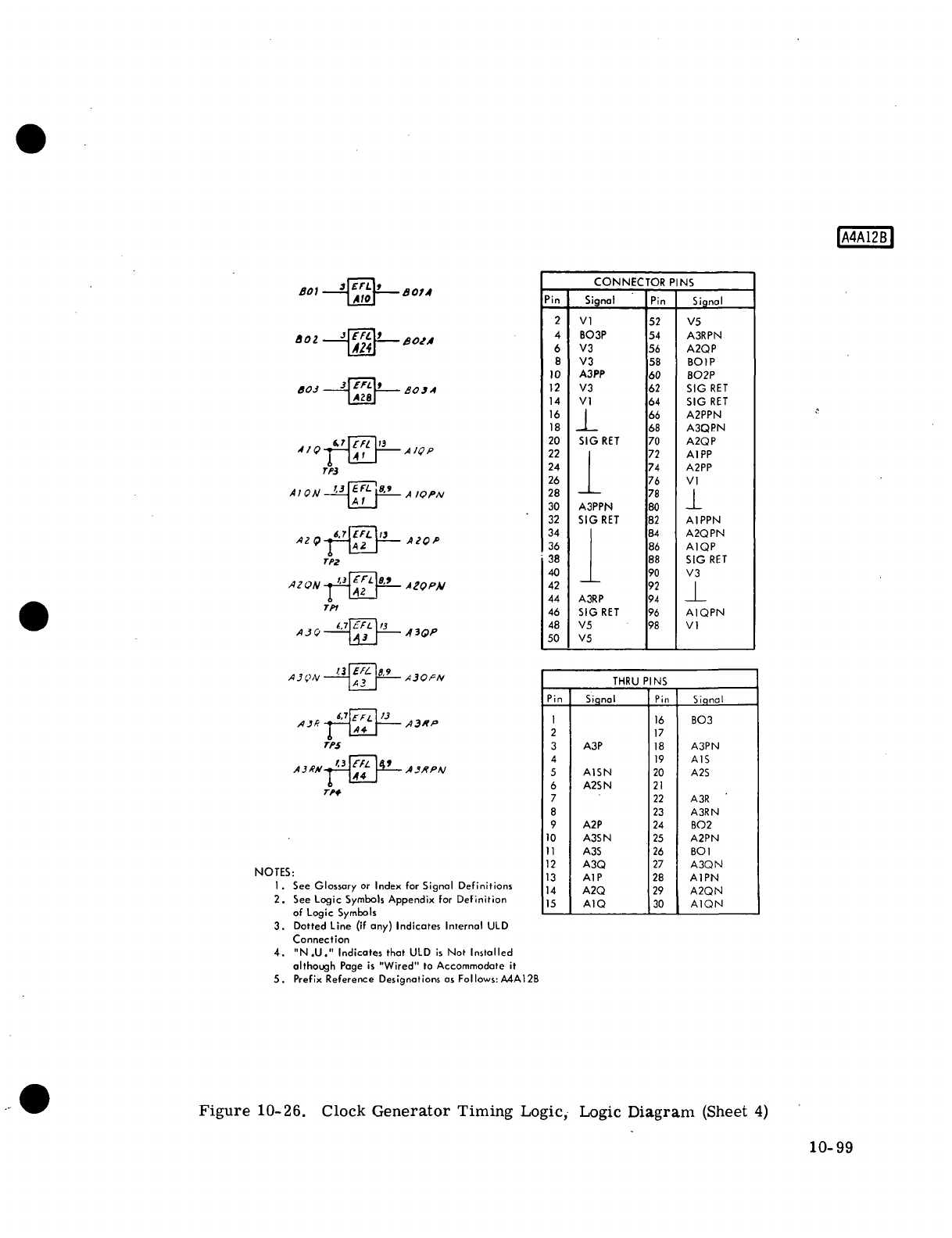

10-26

Clock Generator Timing Logic, Logic Diagram

(4

Sheets) 10-96

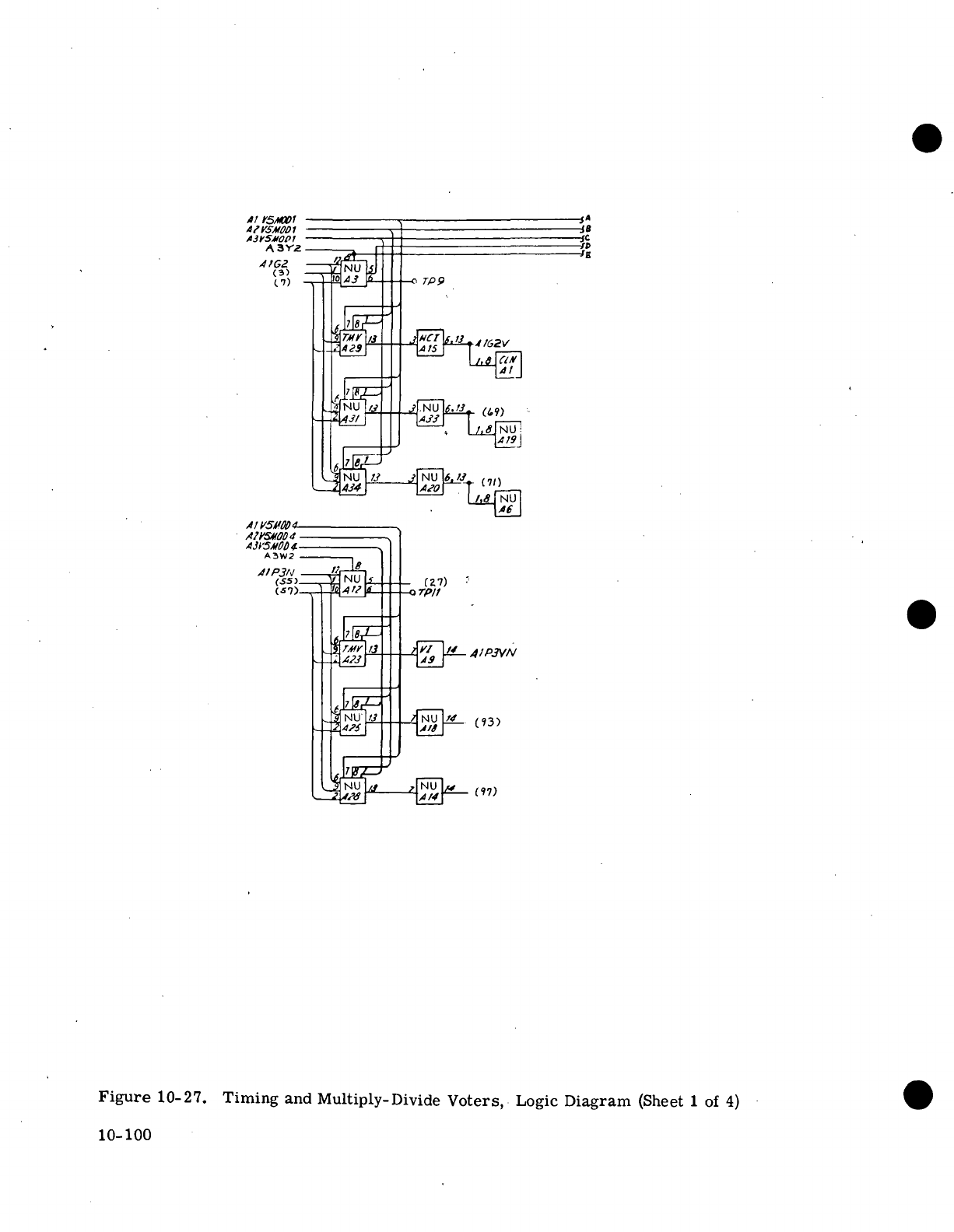

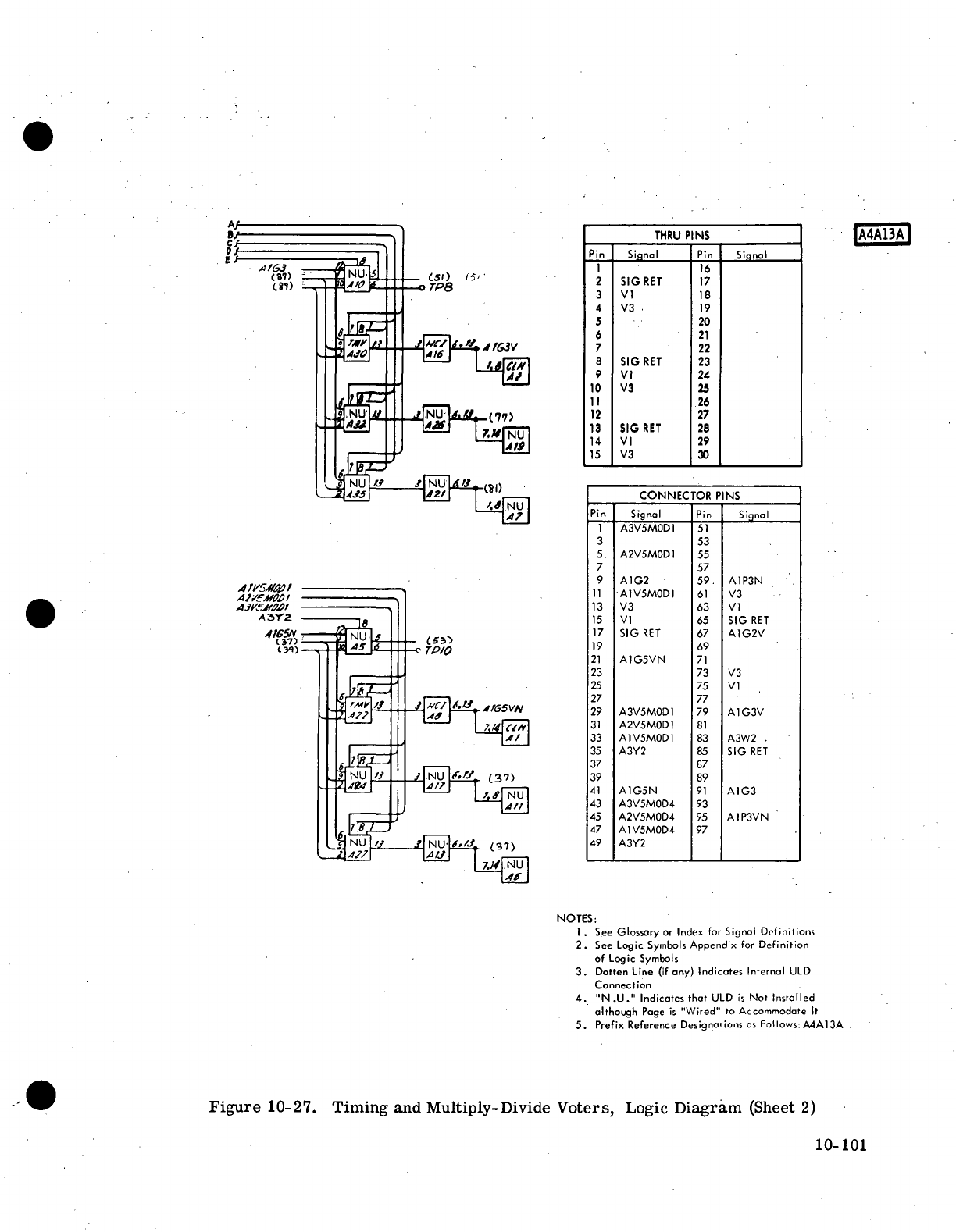

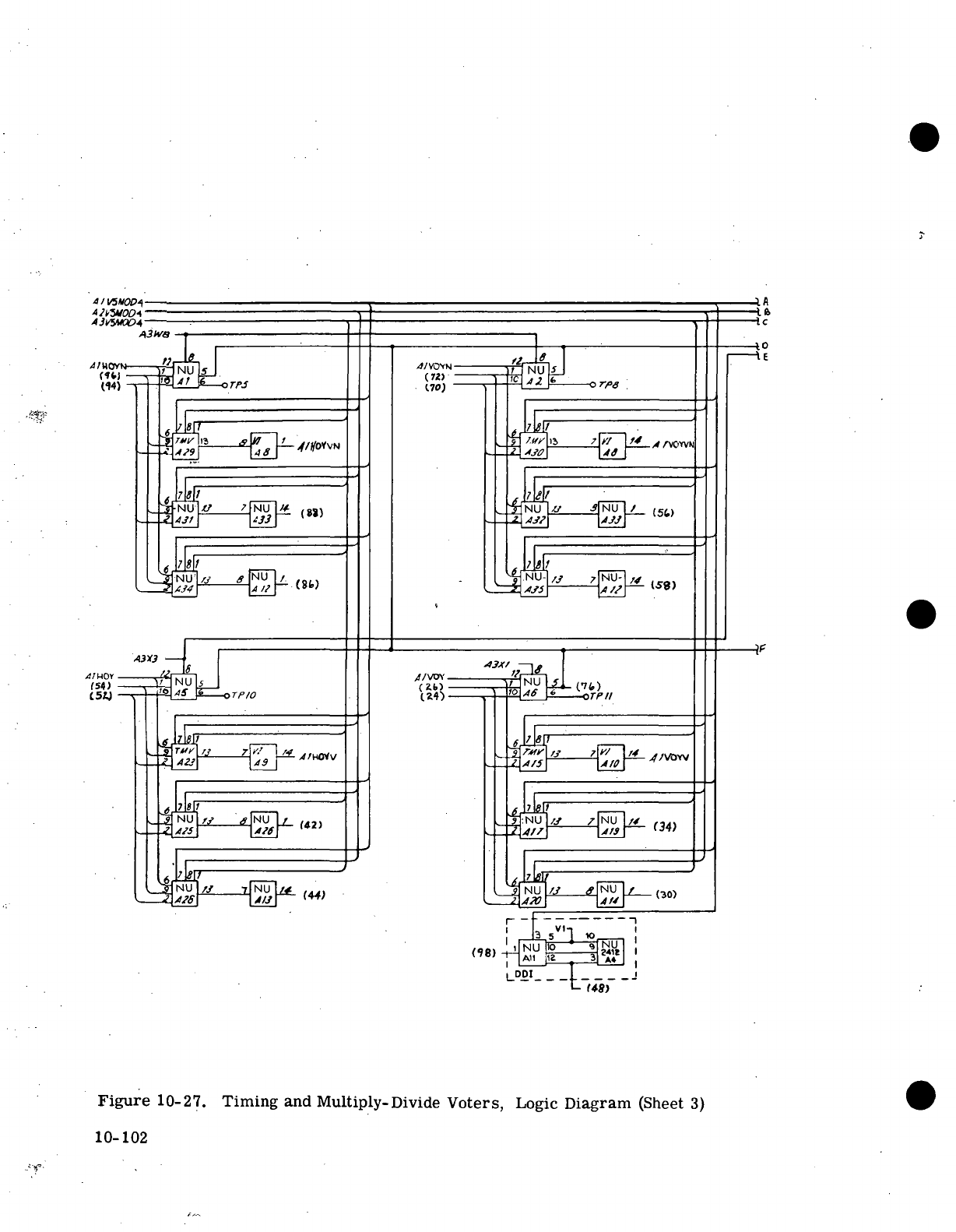

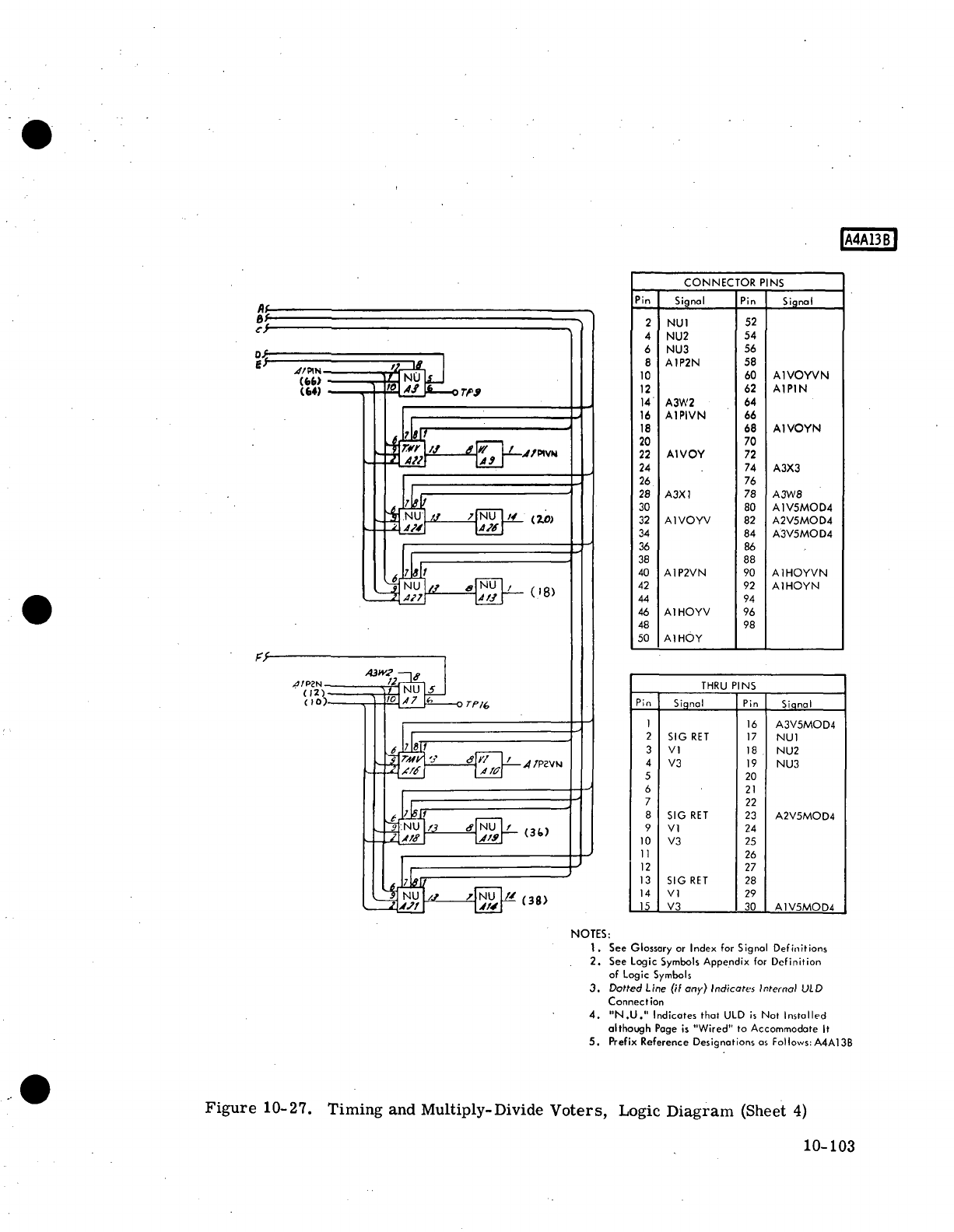

10-27

Timing

and

Multiply-Divide Voters, Logic Diagram

(4

Sheets) 10-100

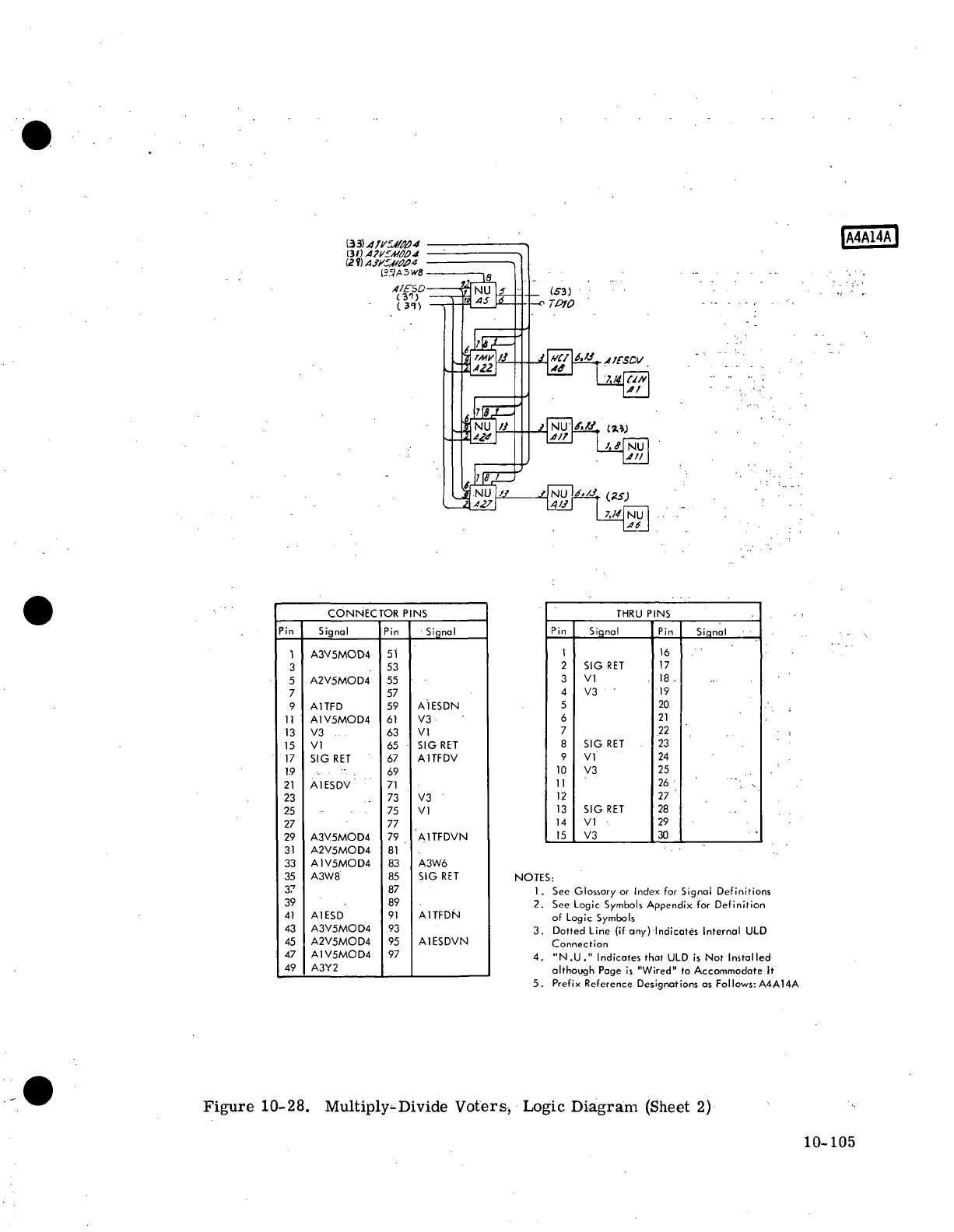

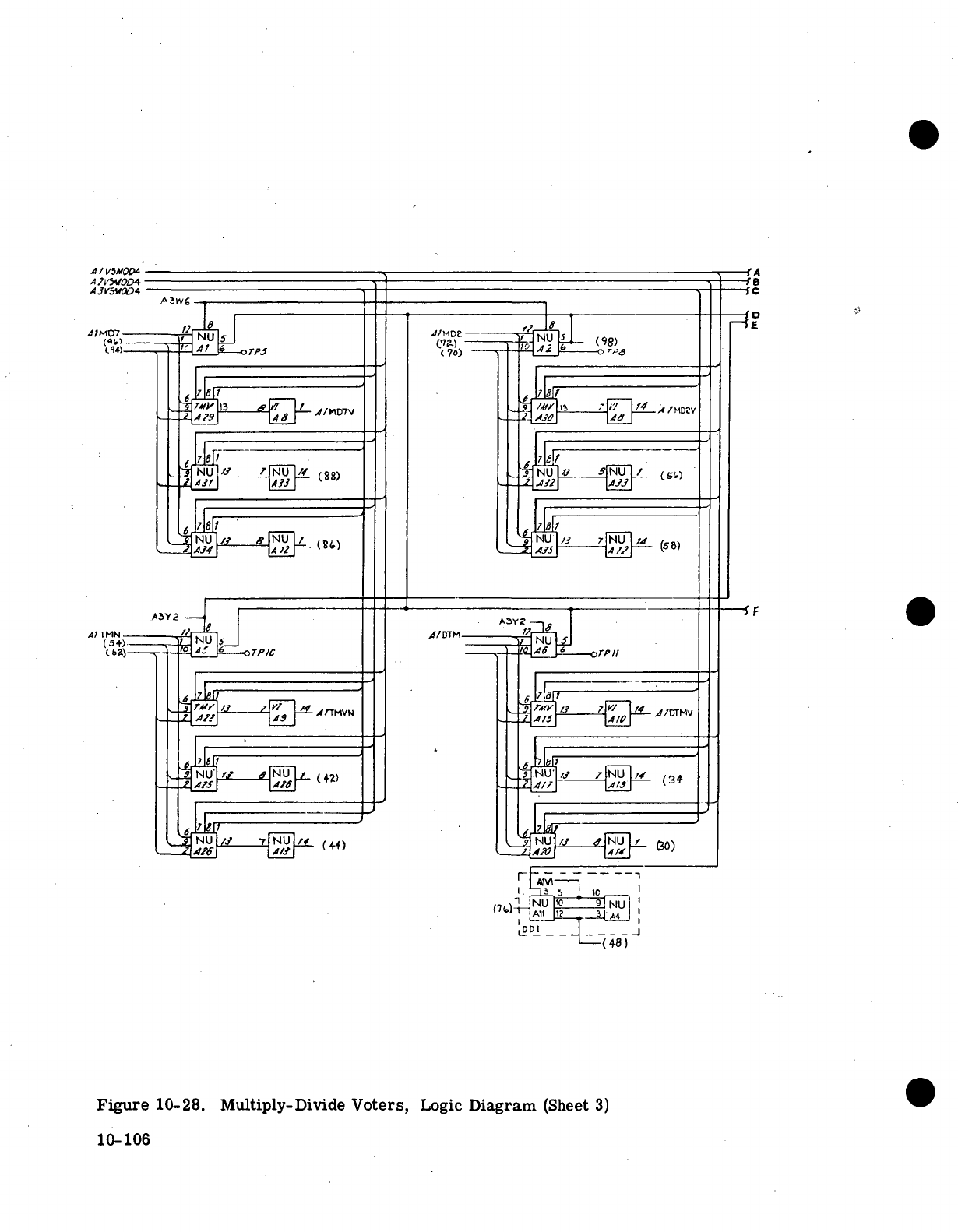

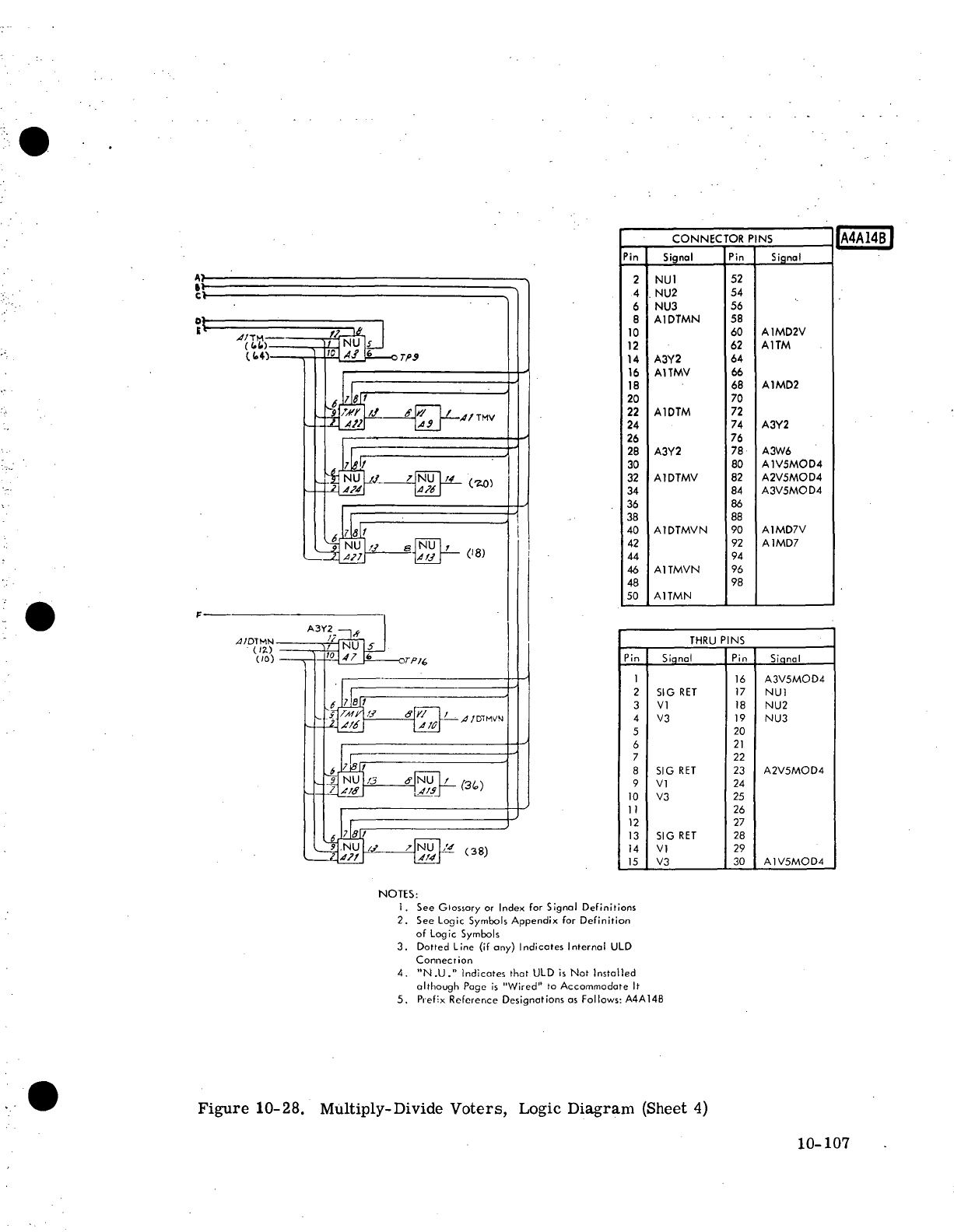

10-28 Multiply-Divide Voters, Logic Diagram

(4

Sheets) 10-104

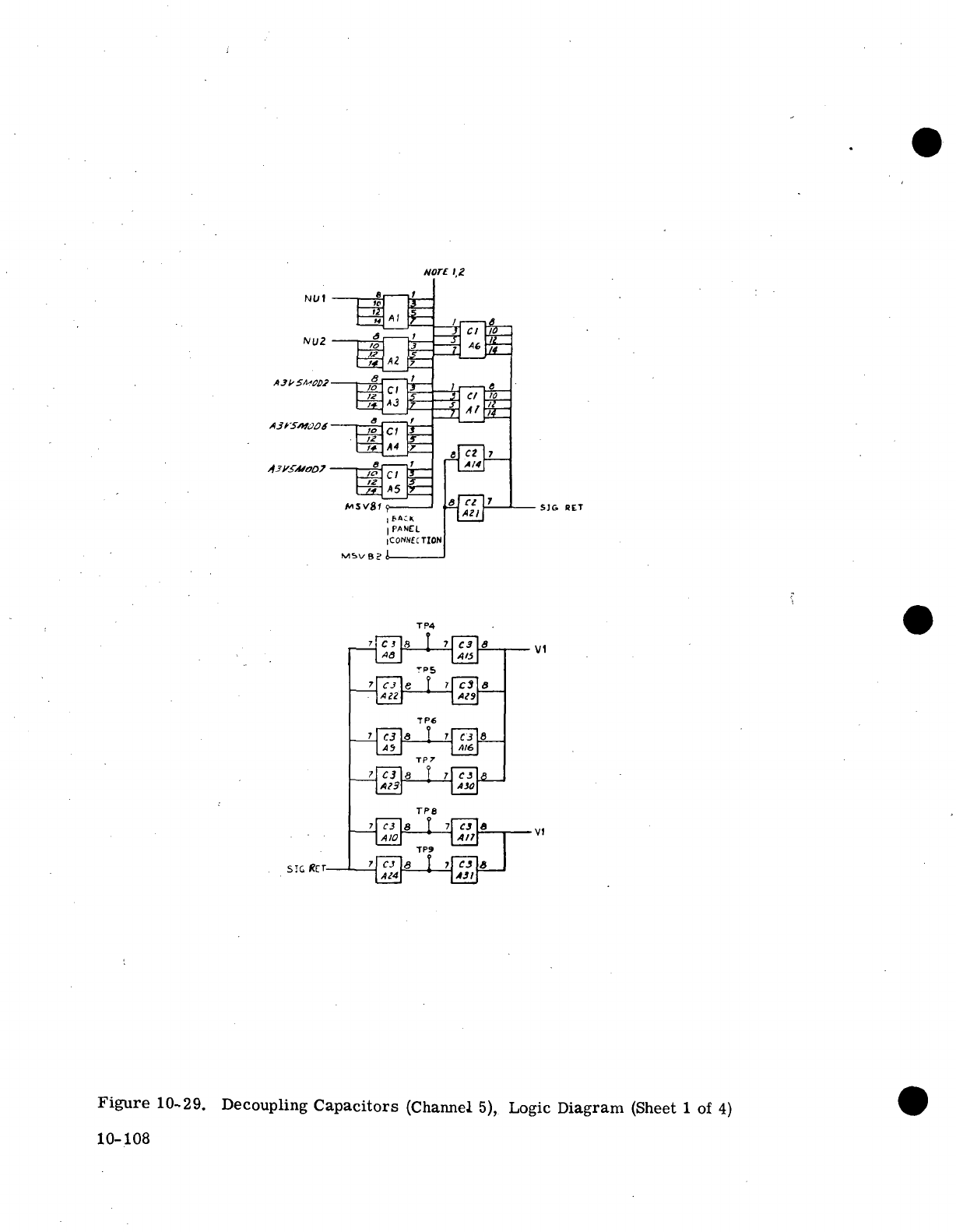

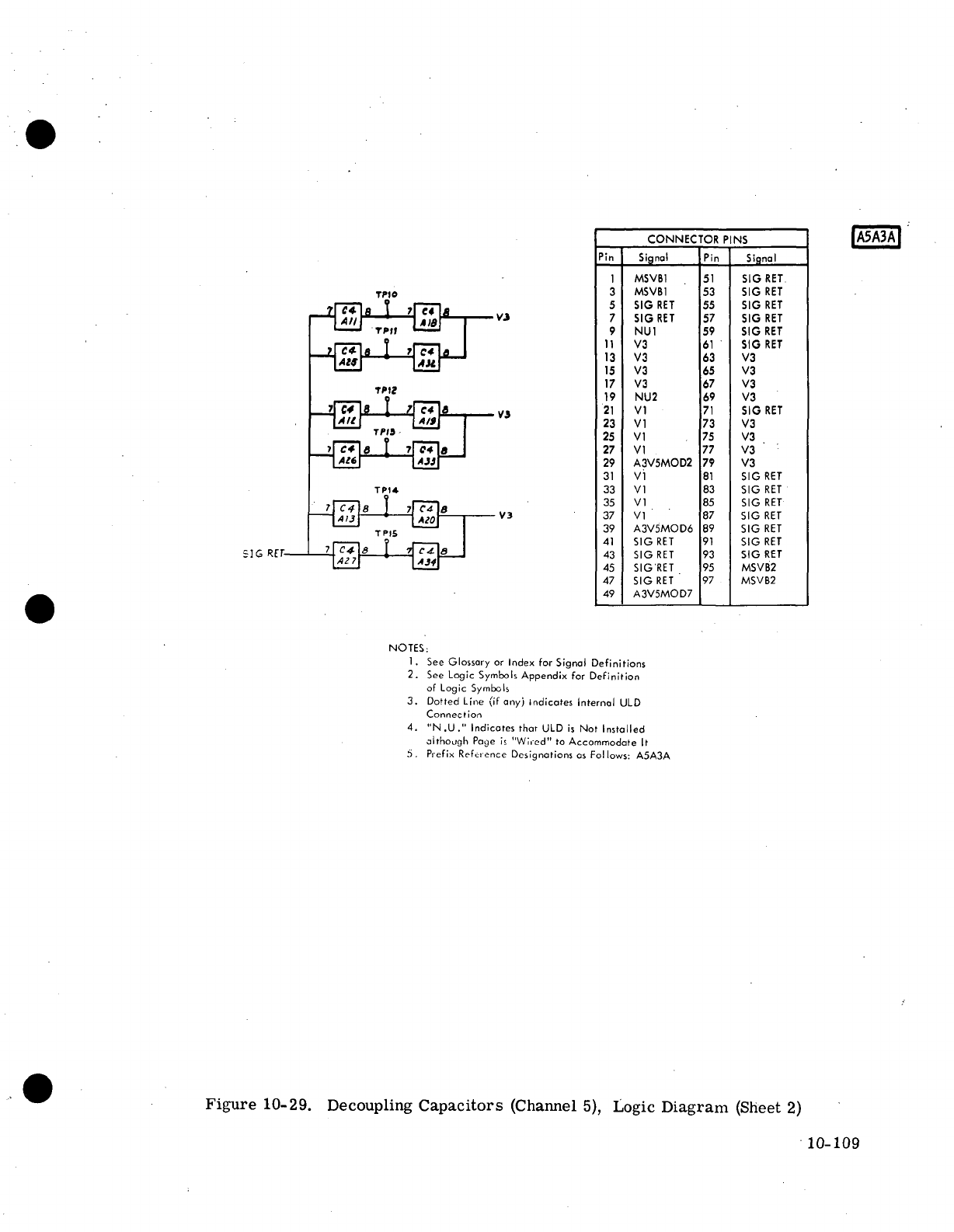

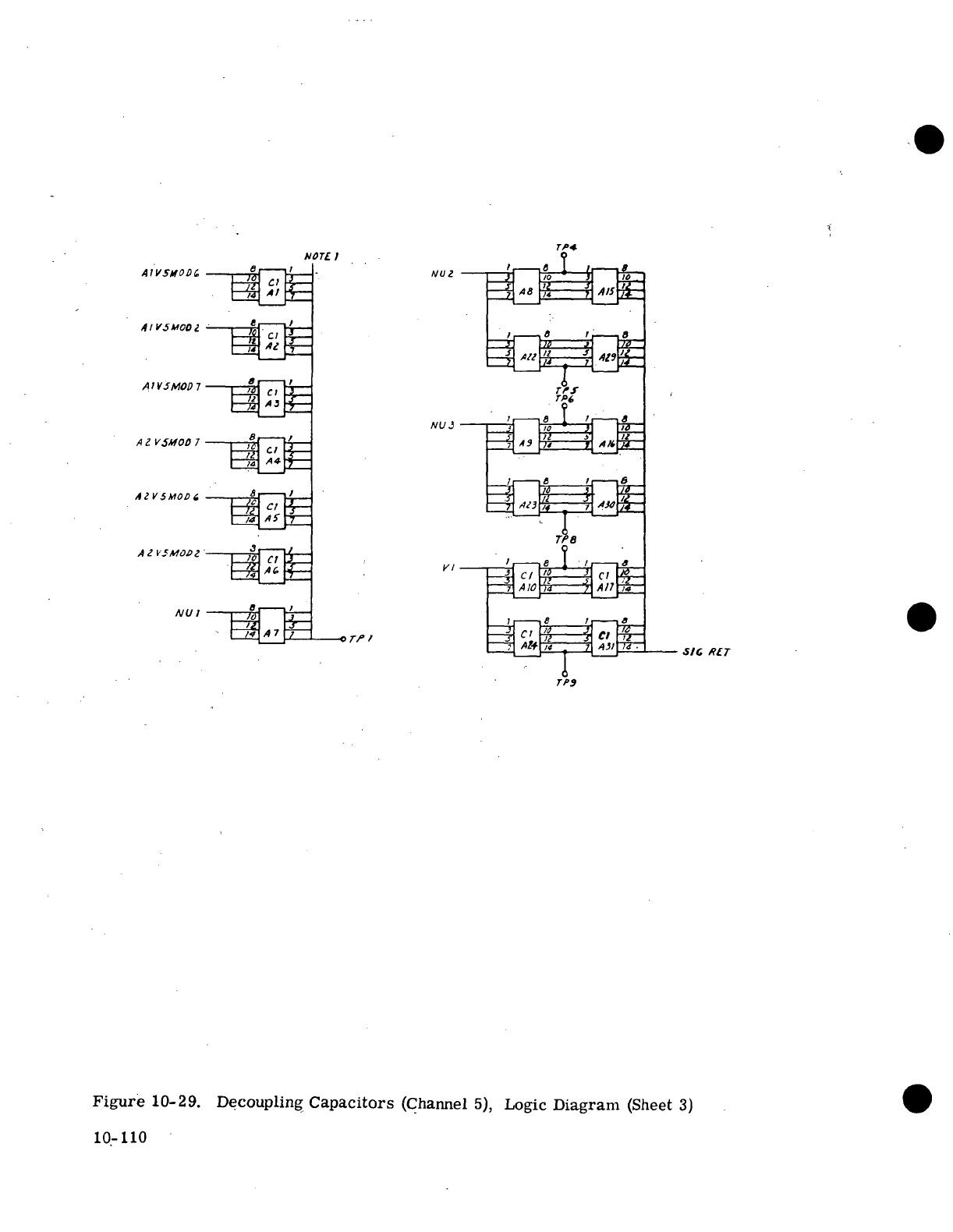

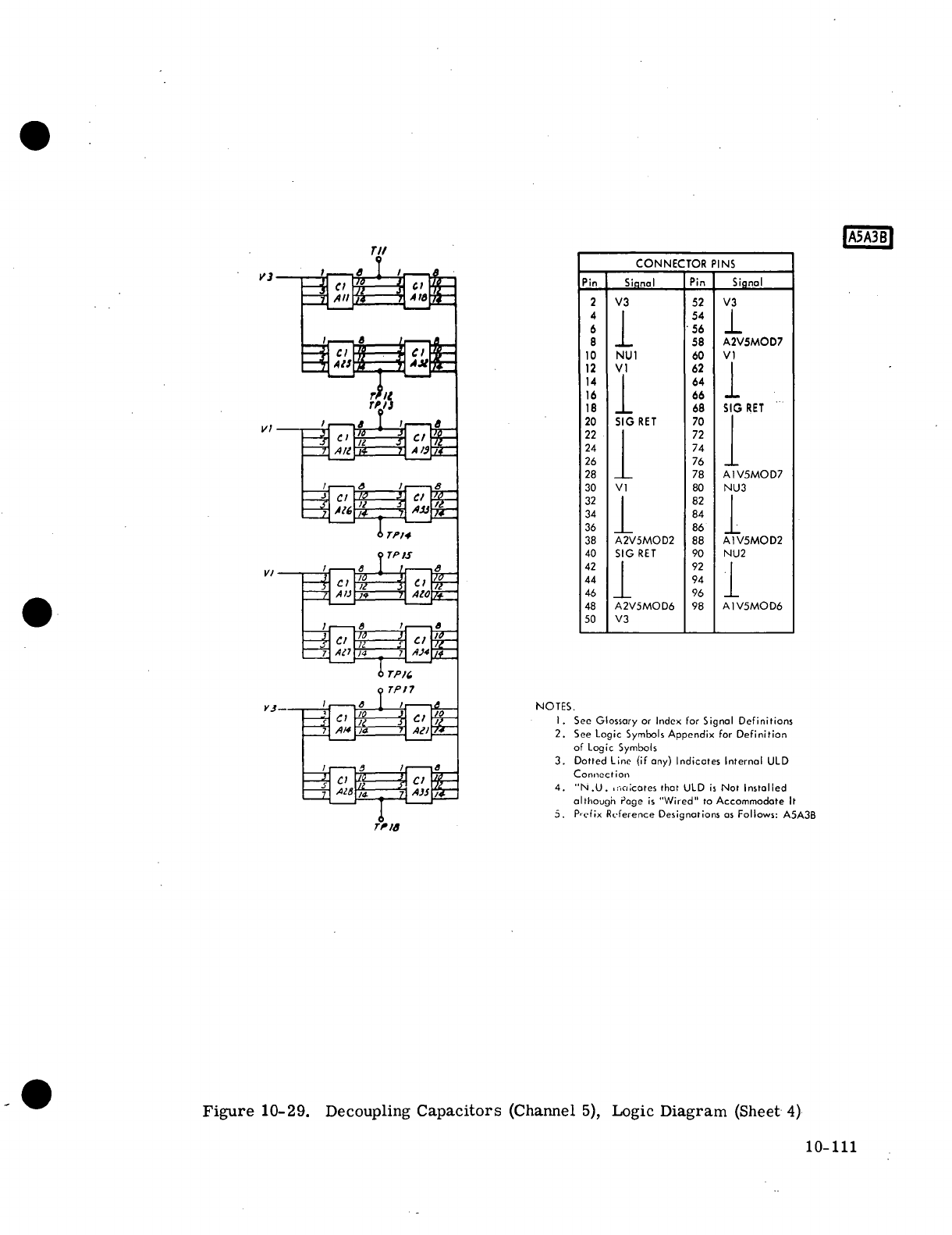

10-29 Decoupling Capacitors (Channel

5),

Logic Diagram

(4

Sheets) 10-108

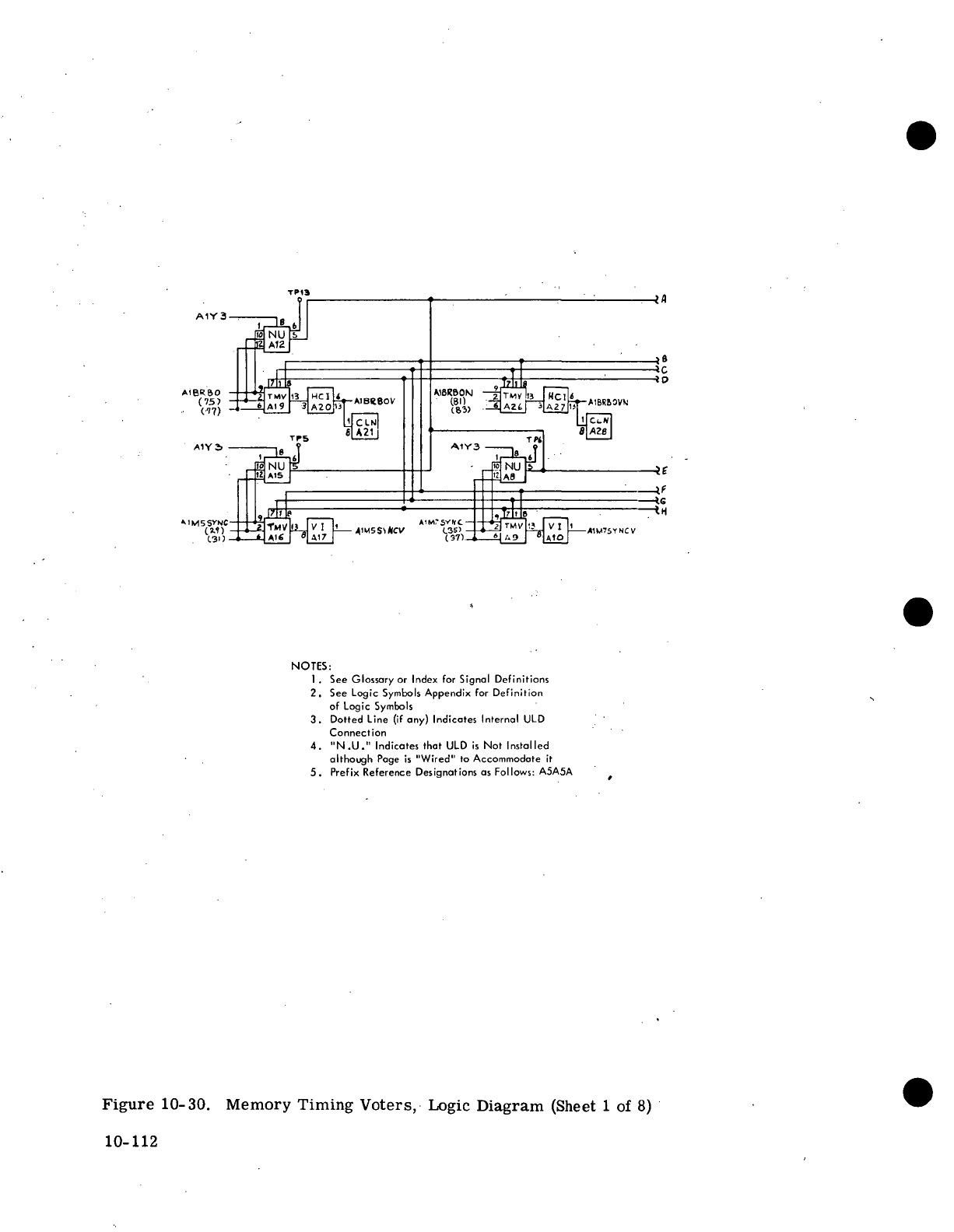

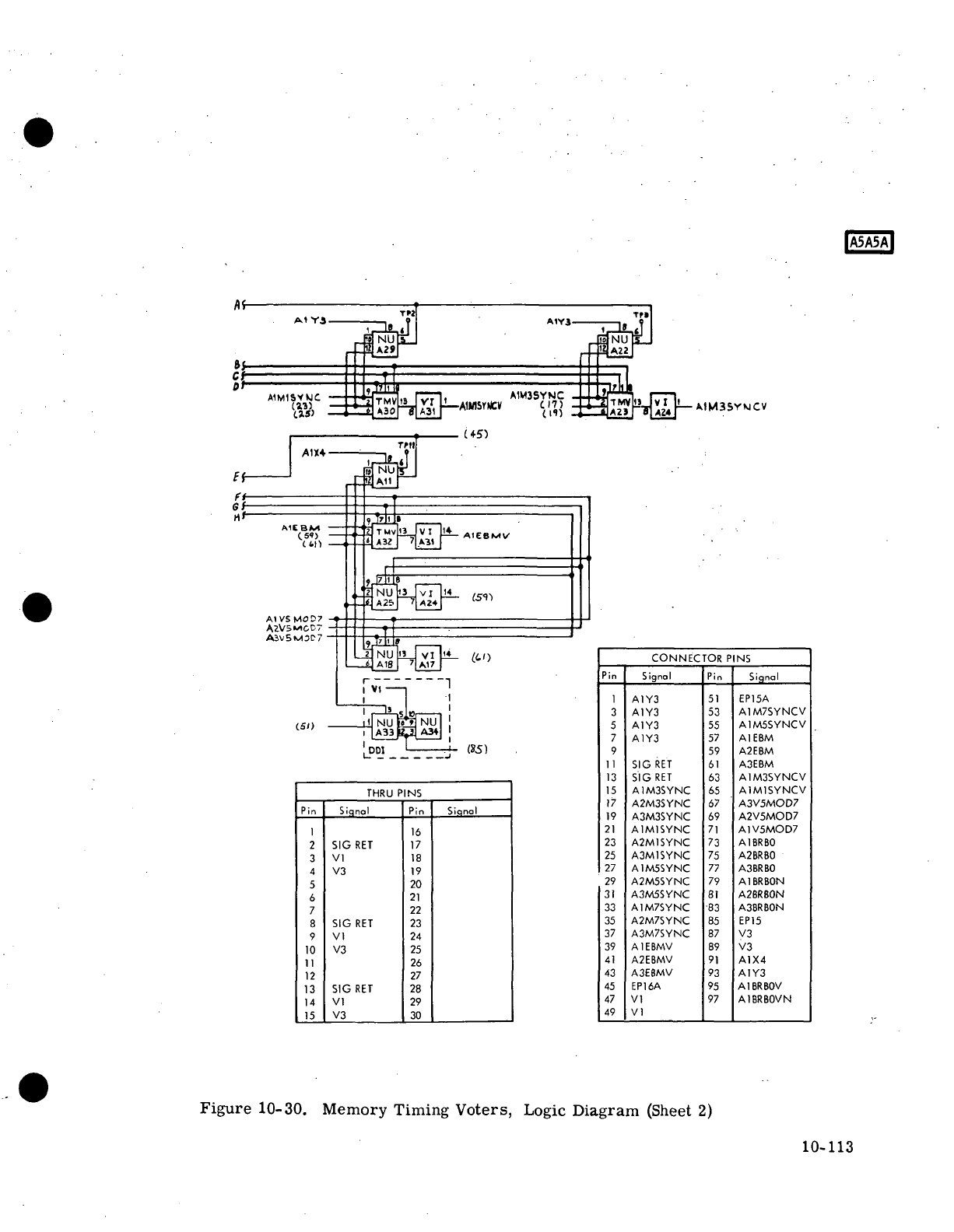

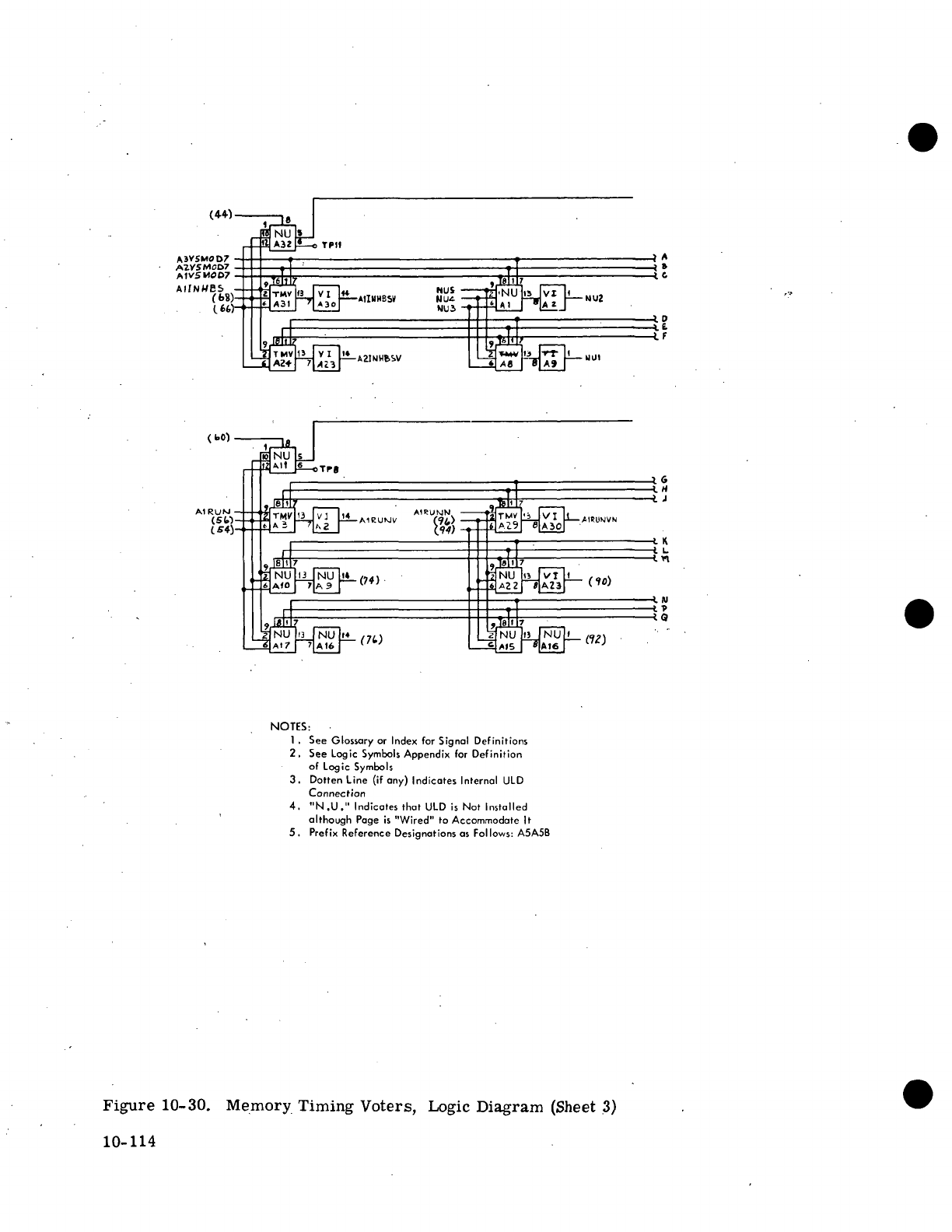

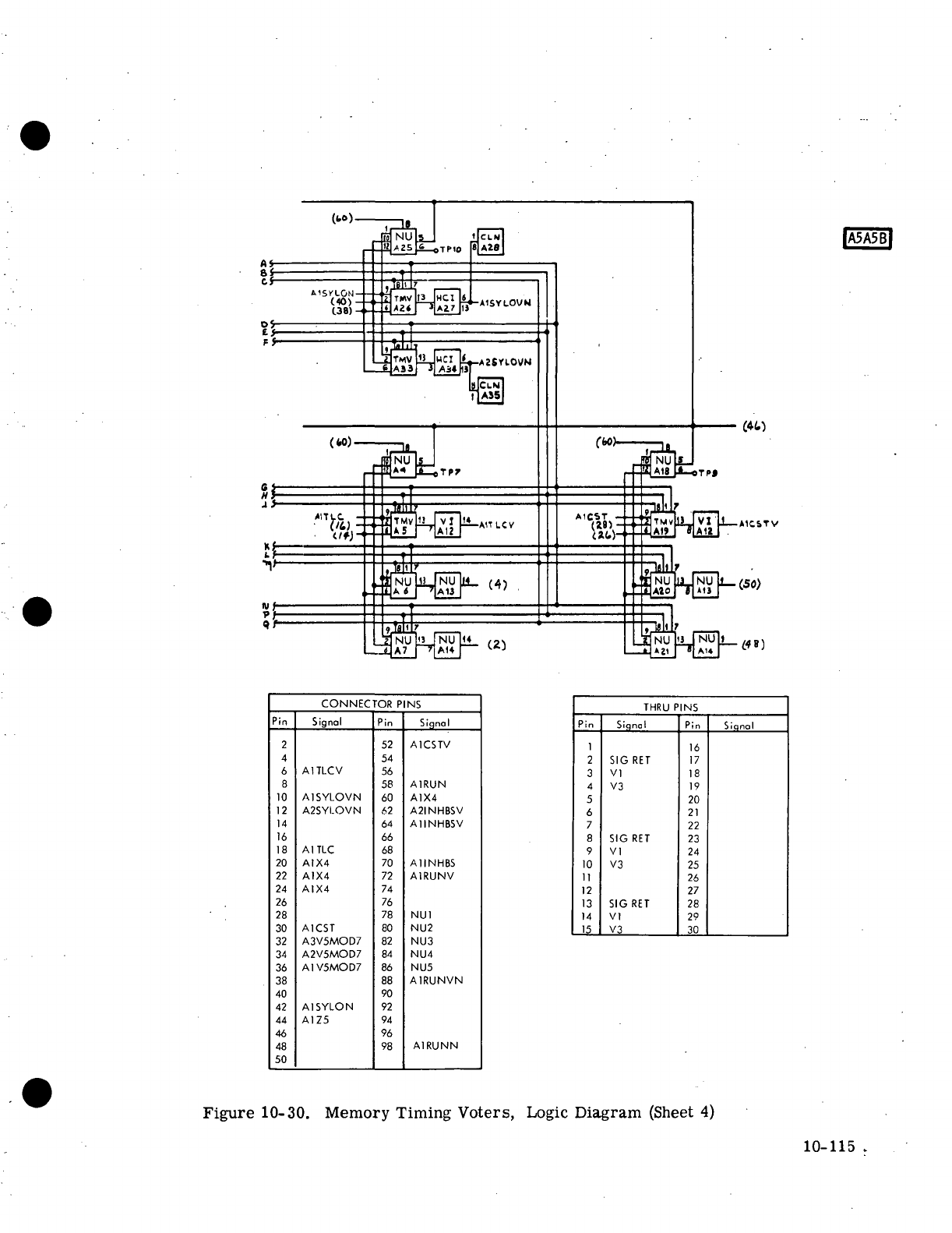

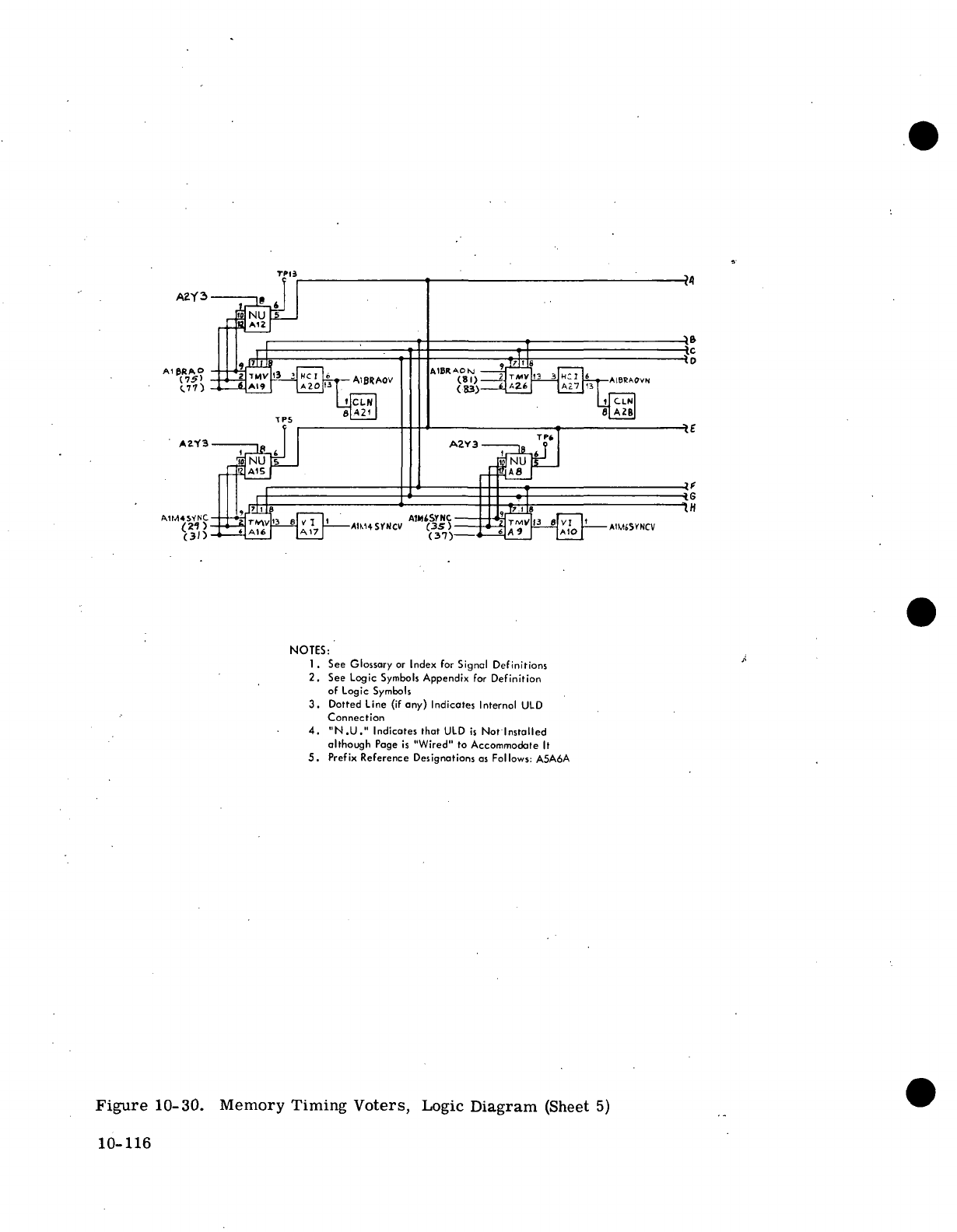

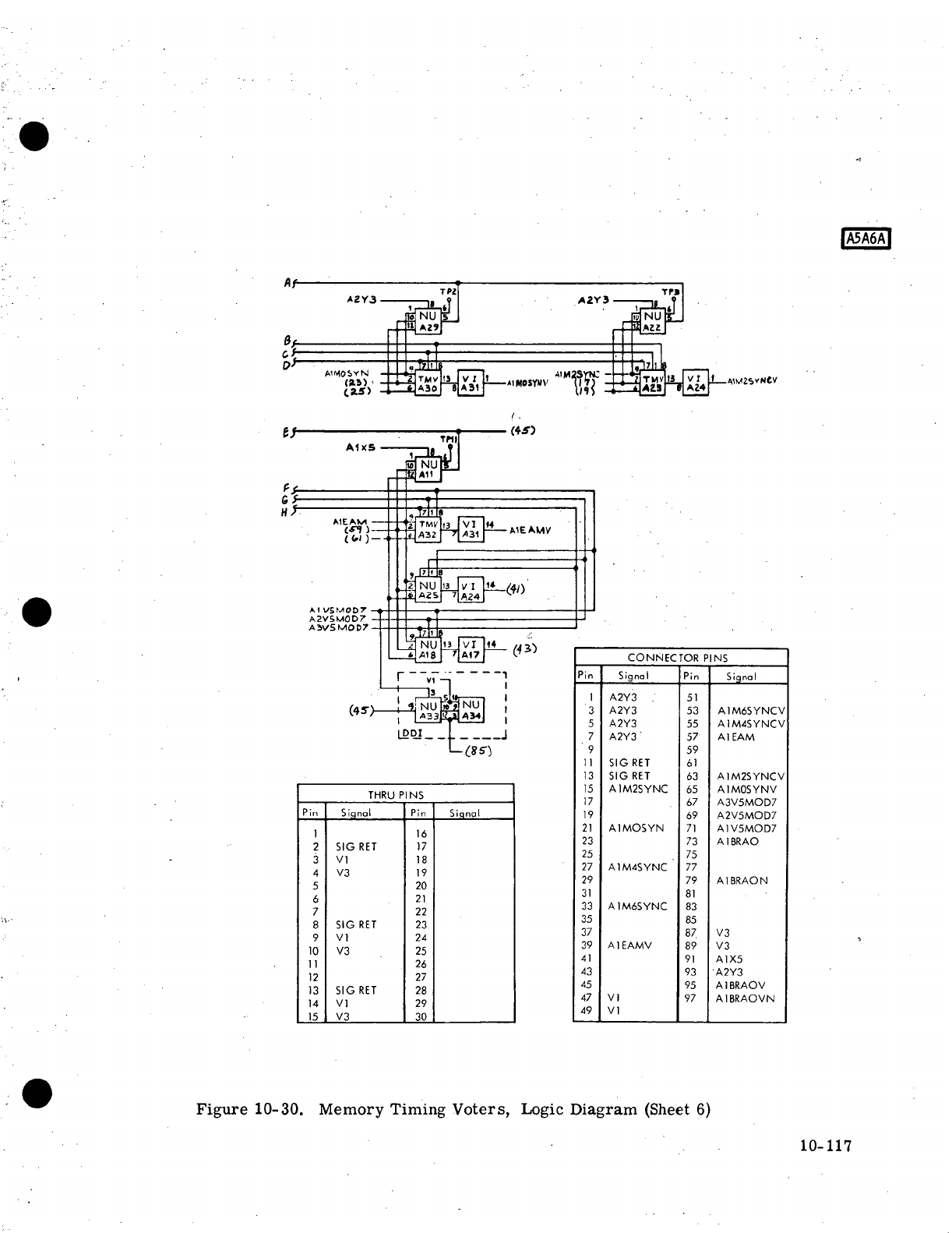

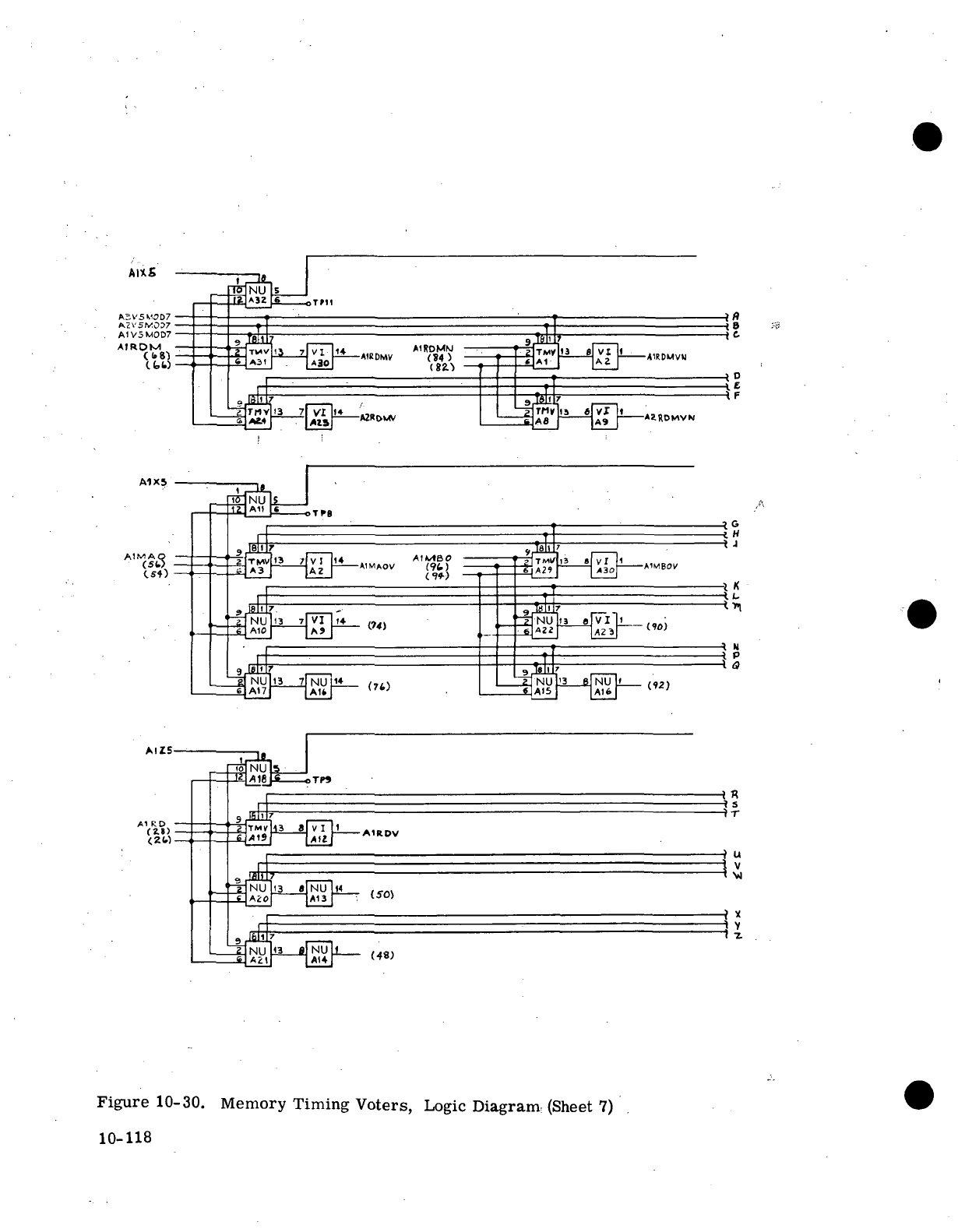

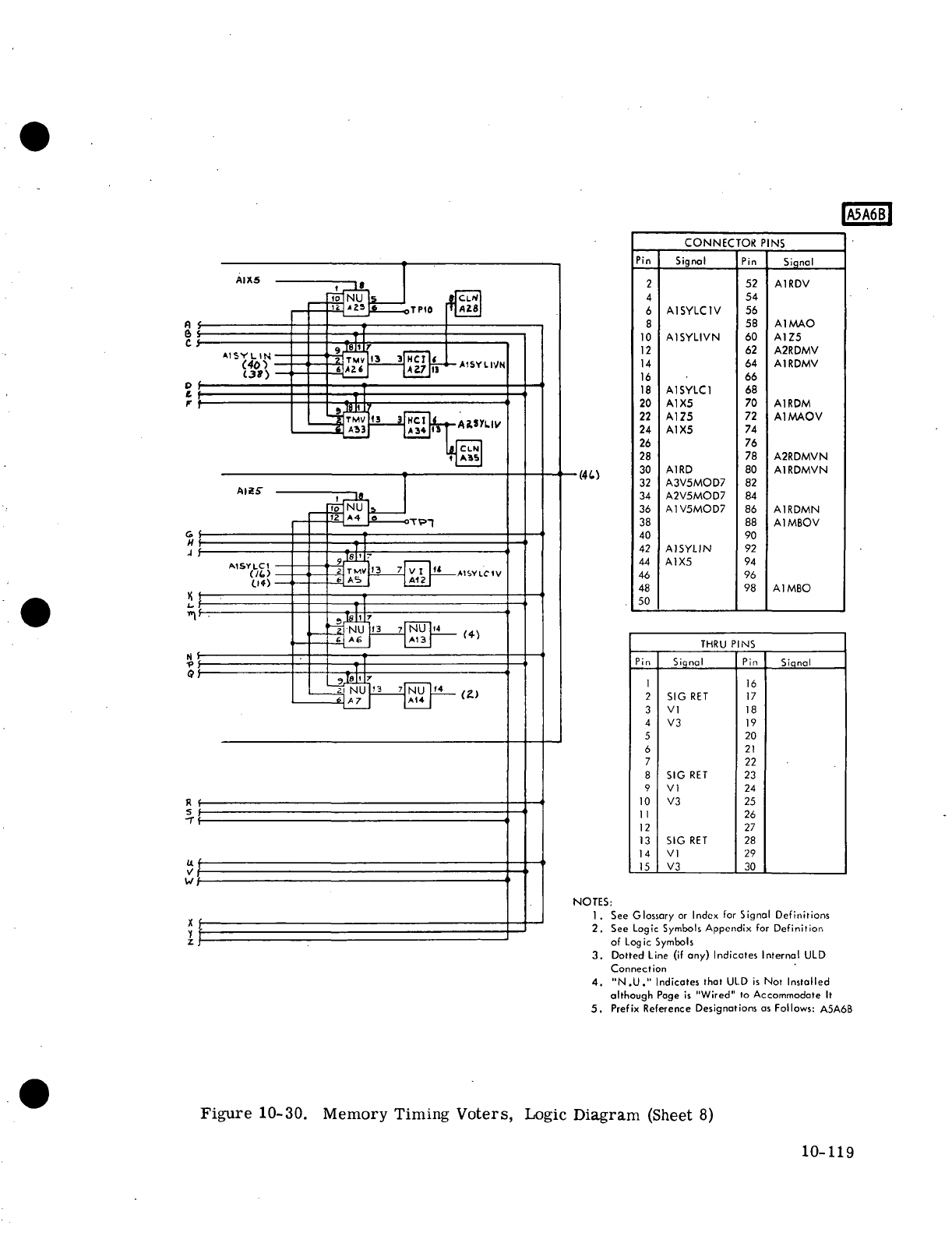

10-30 Memory Timing Voters, Logic Diagram

(8

Sheets) 10-112

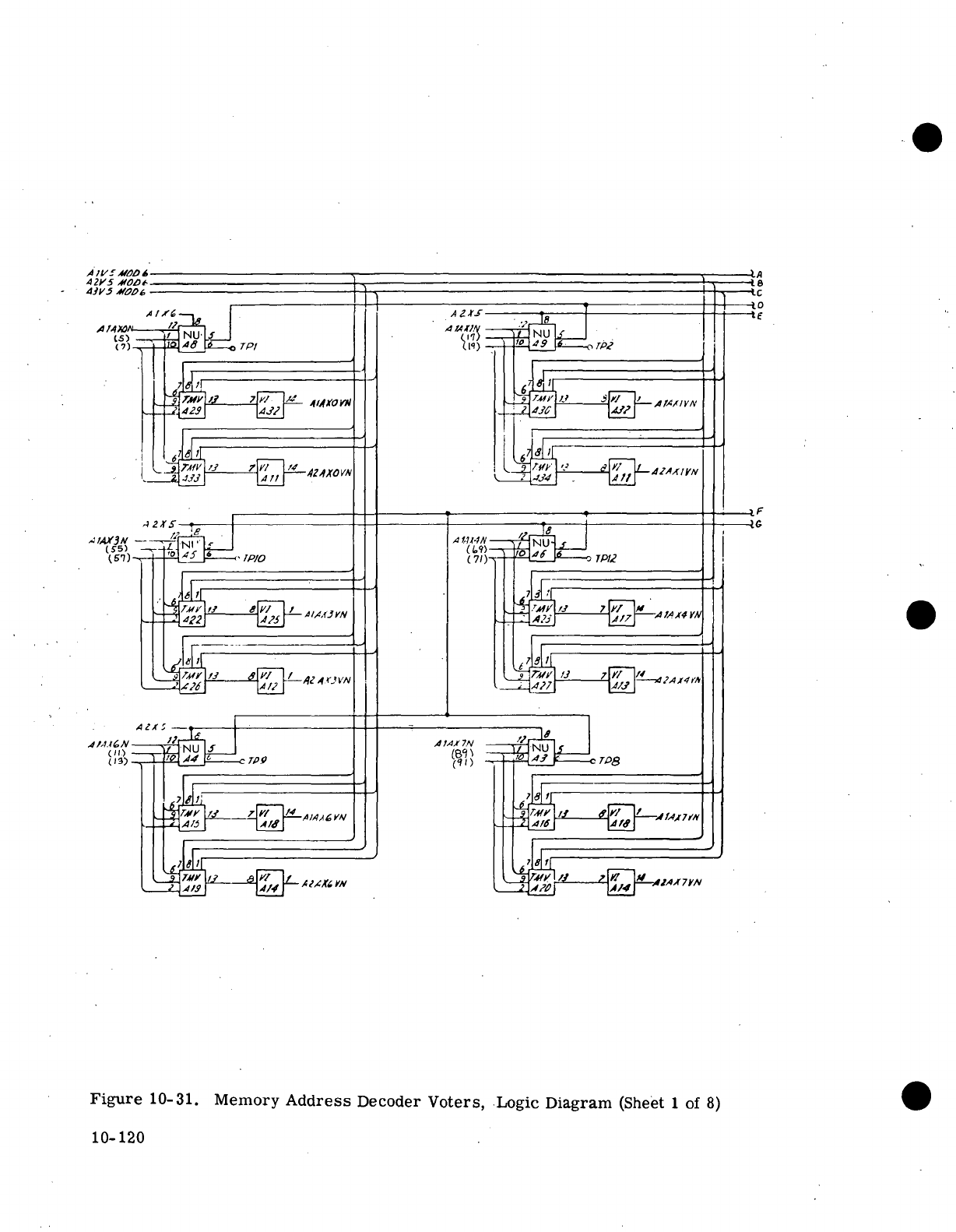

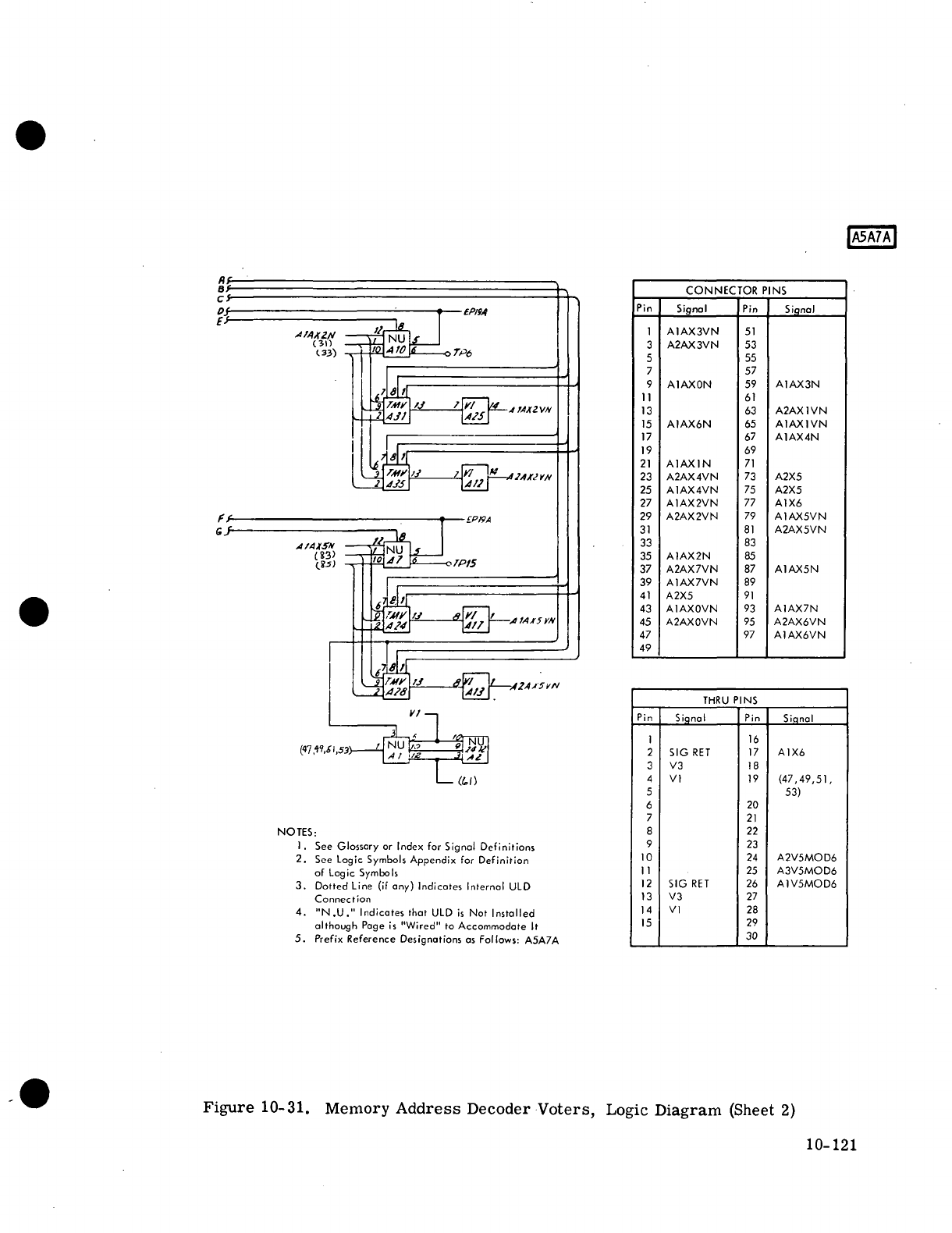

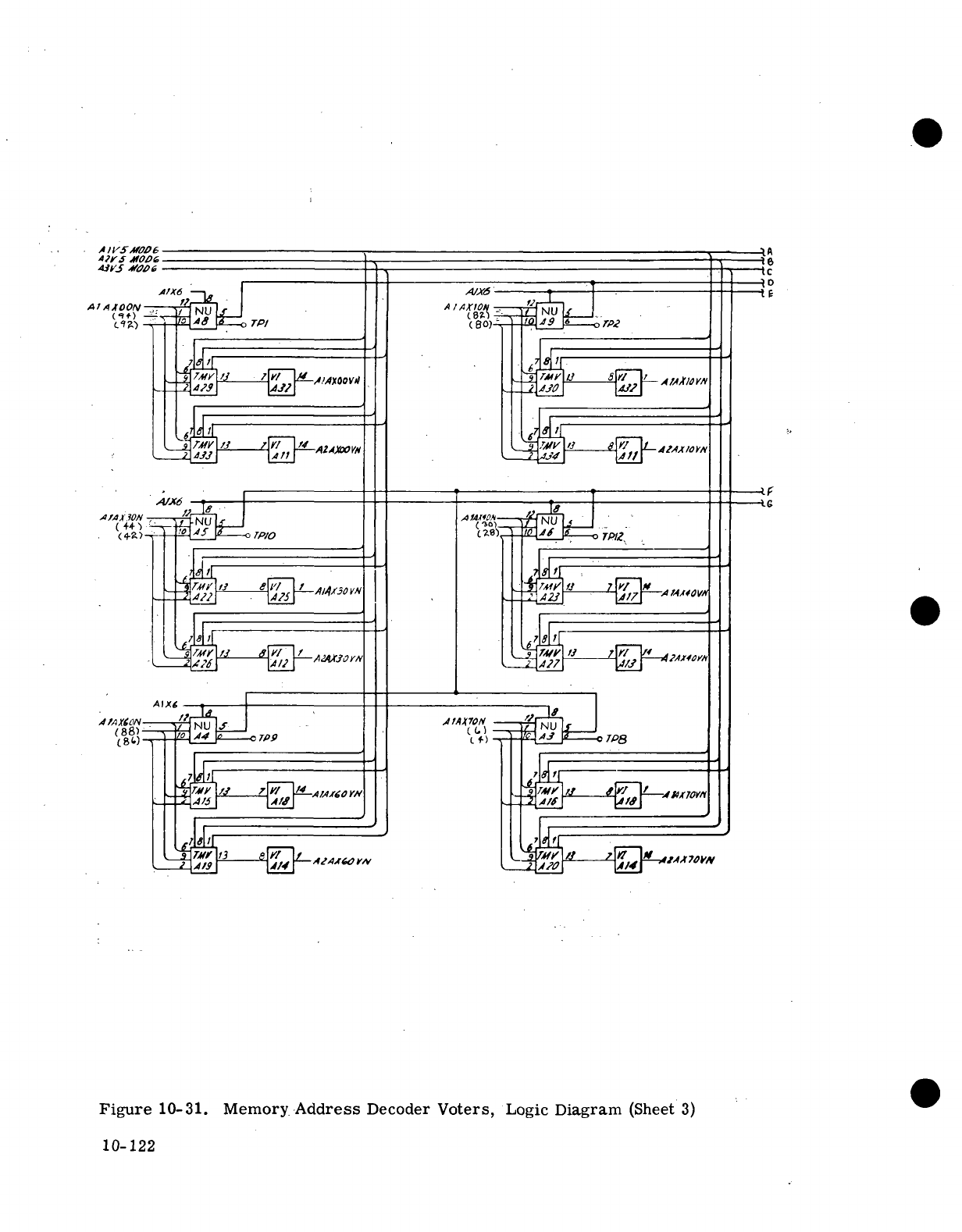

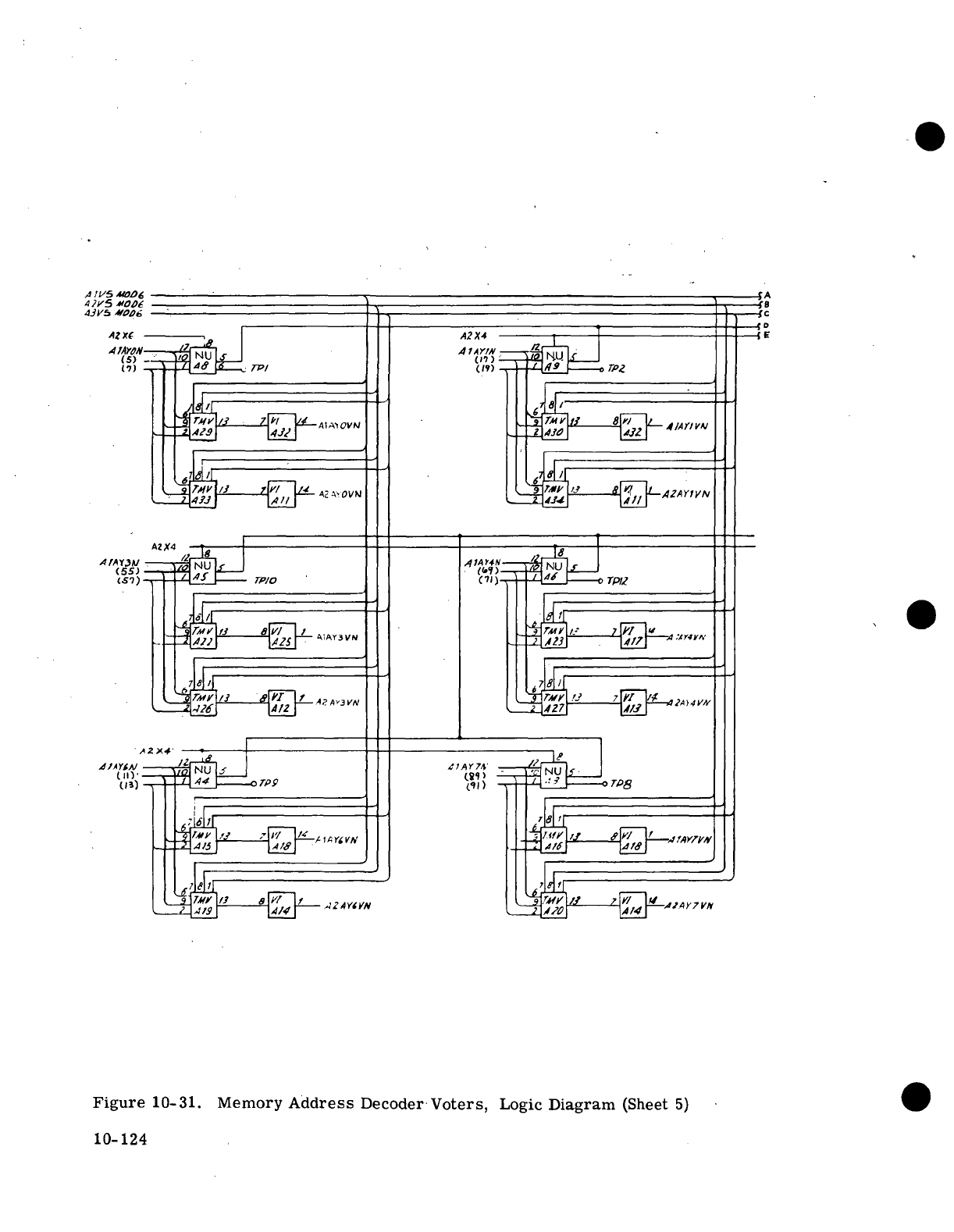

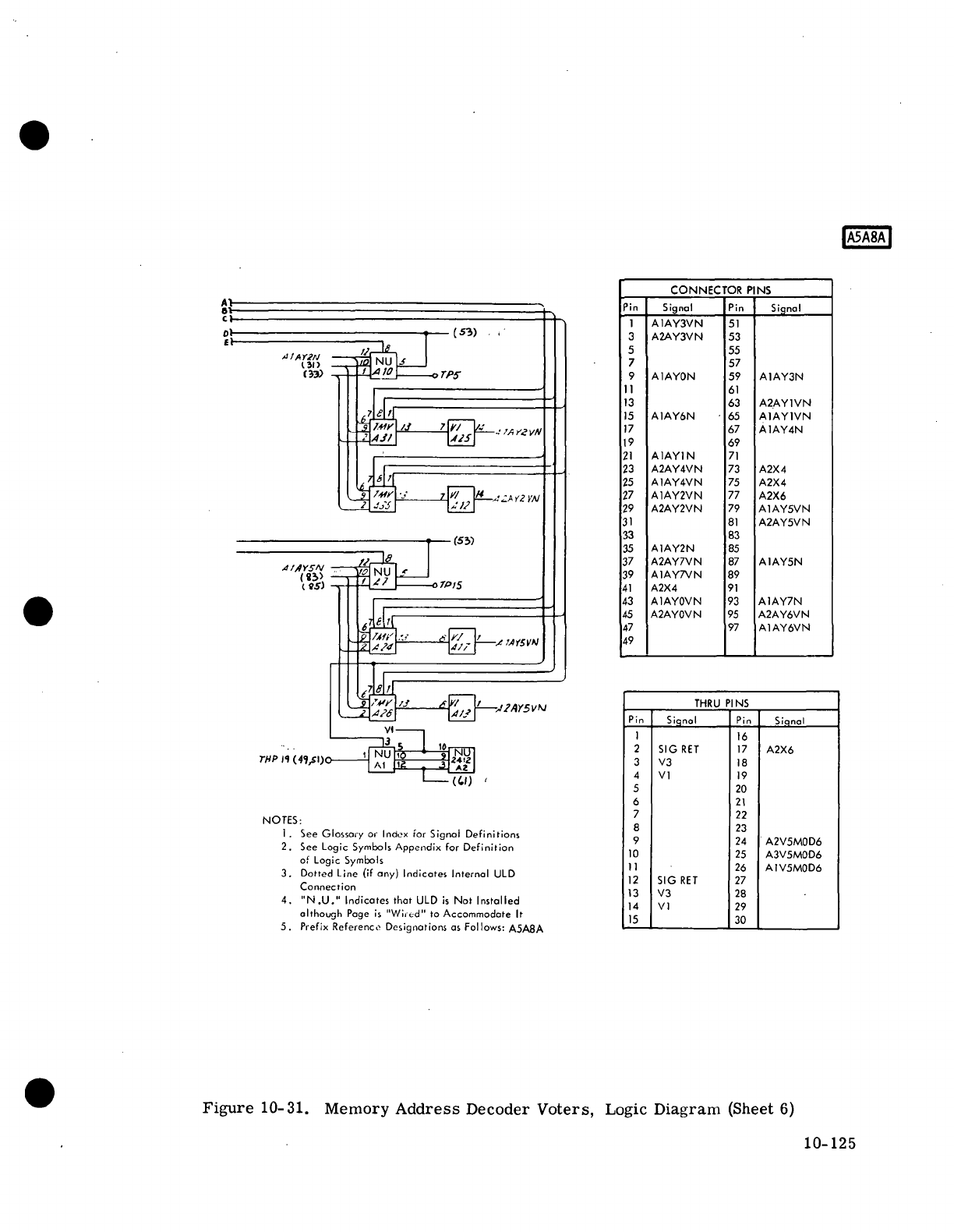

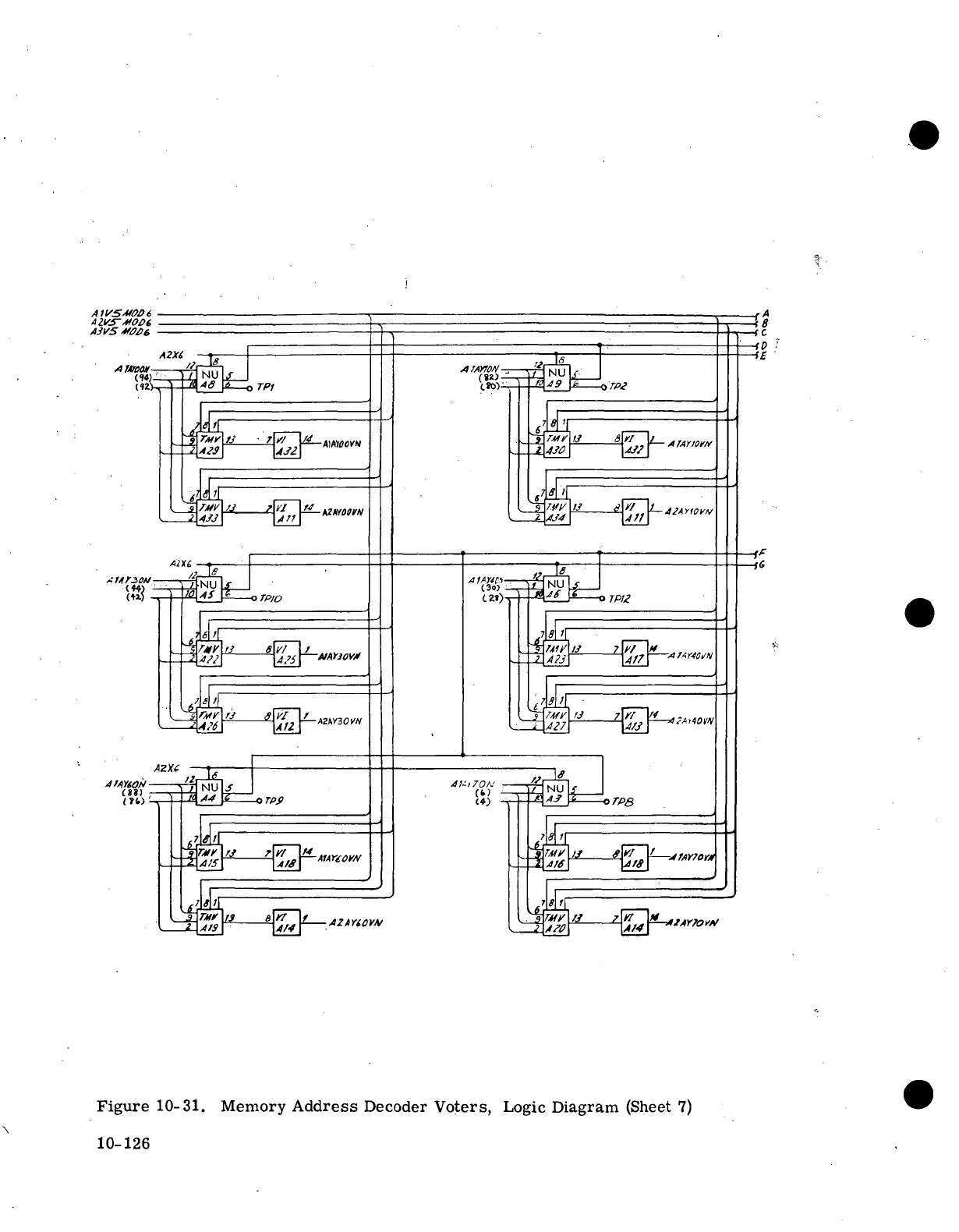

10-31 Memory Address Decoder Voters, Logic Diagram

(8

Sheets) 10-120

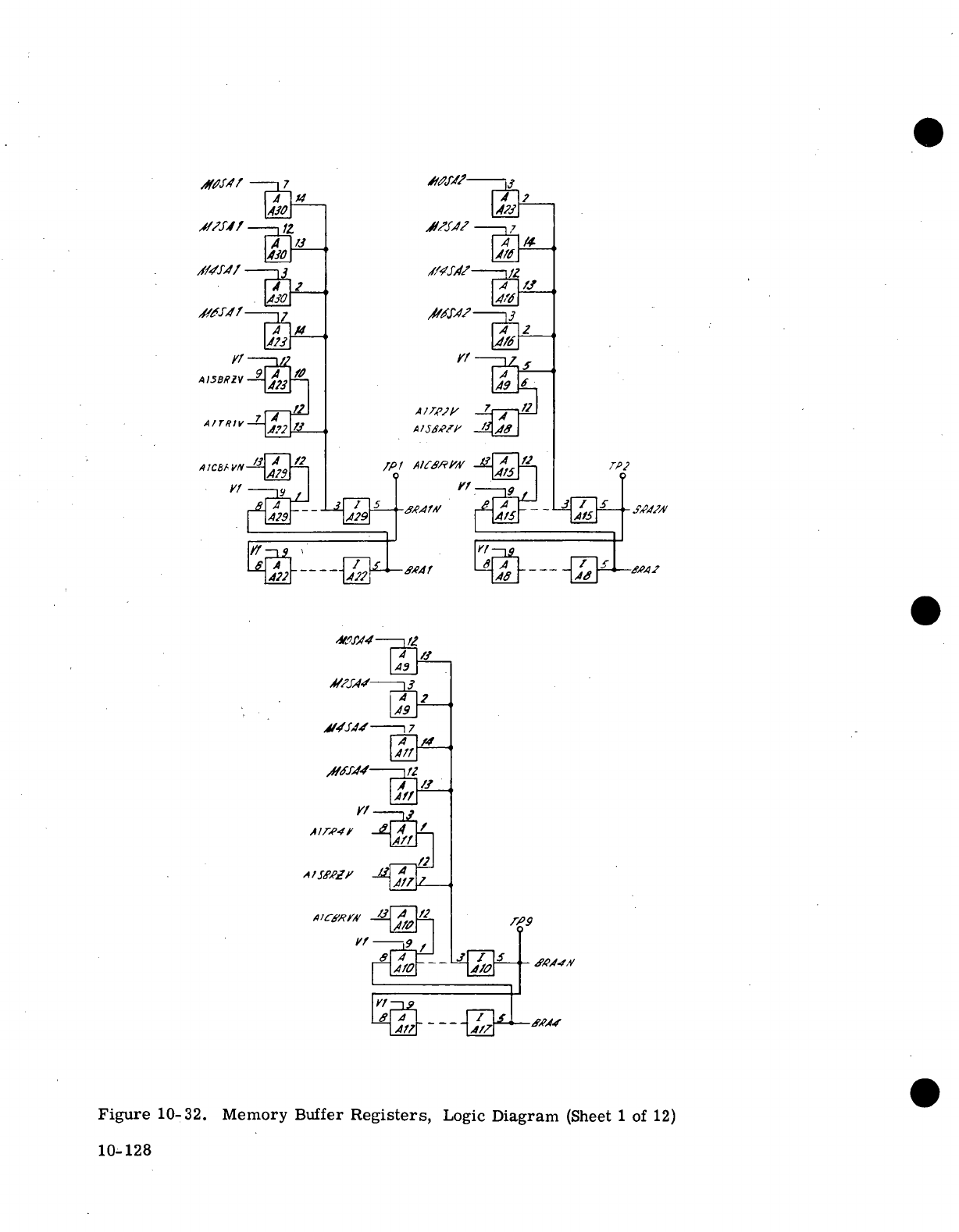

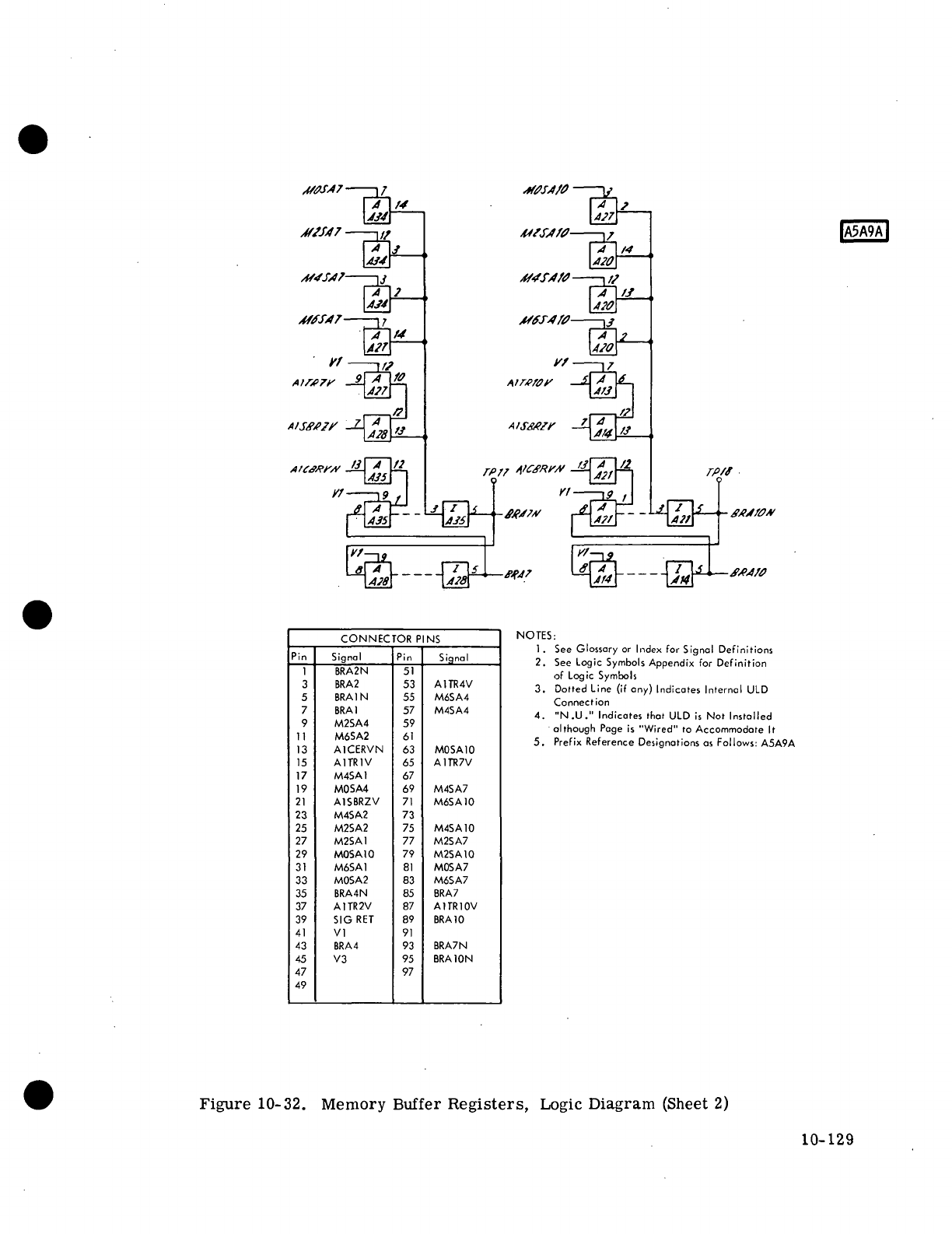

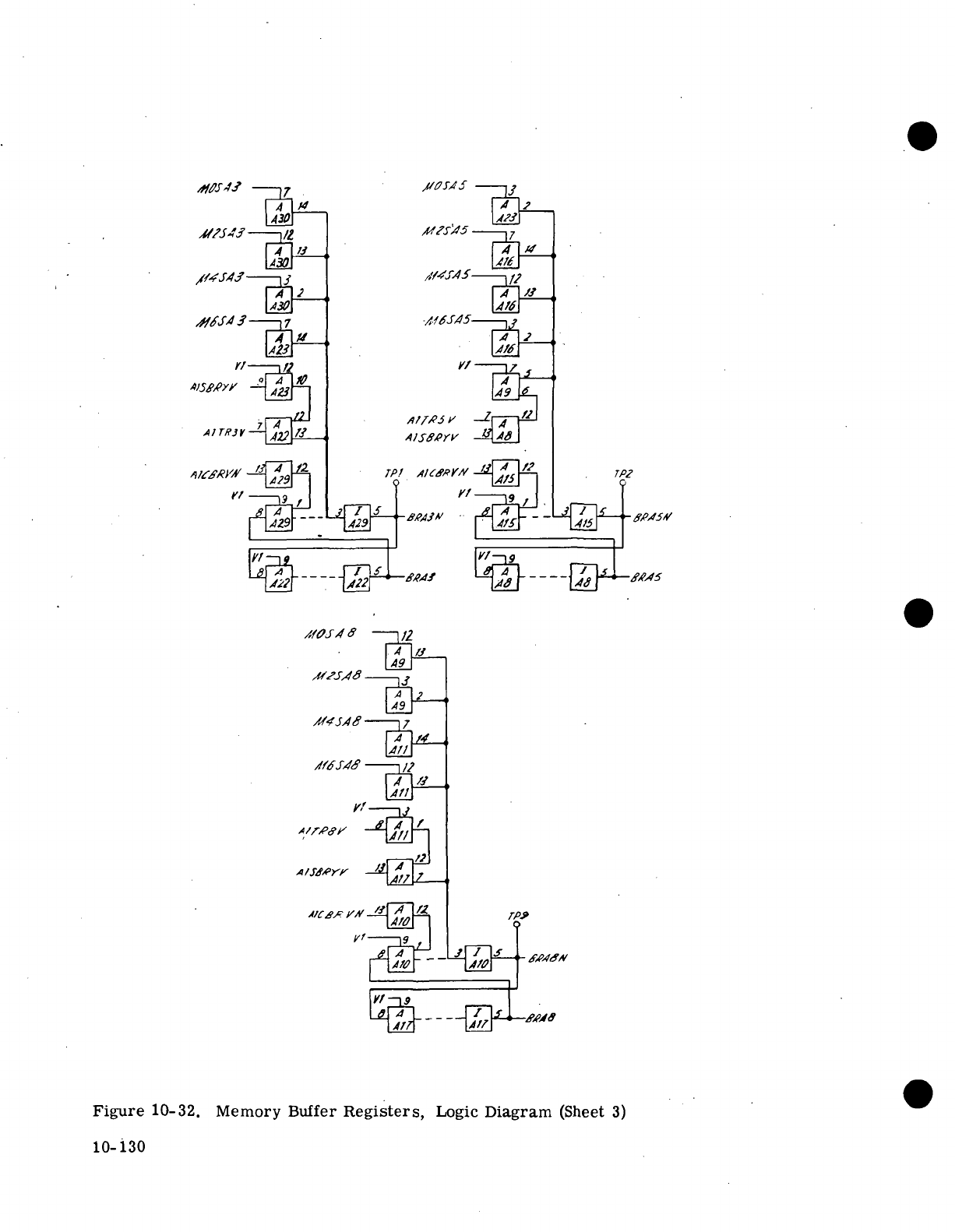

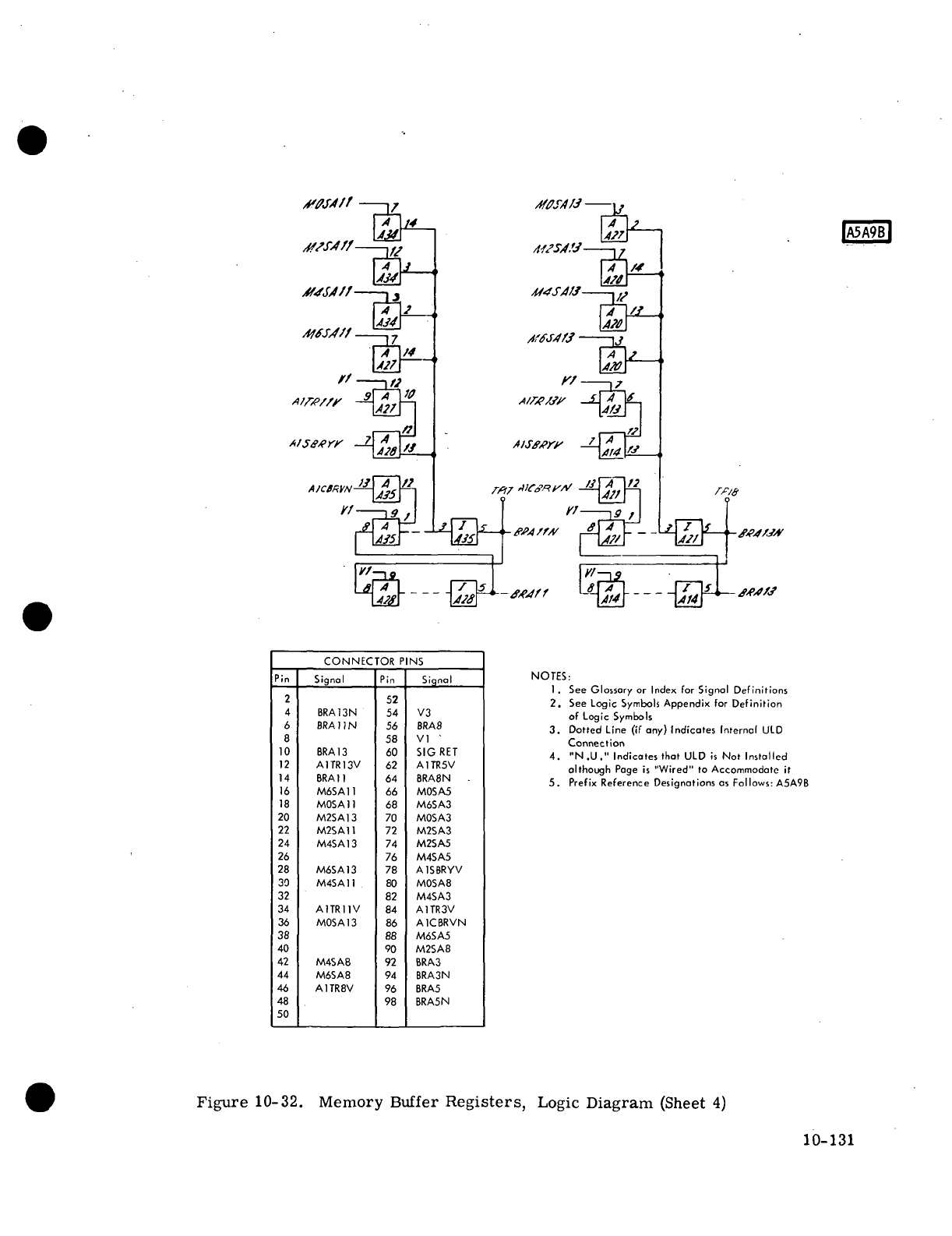

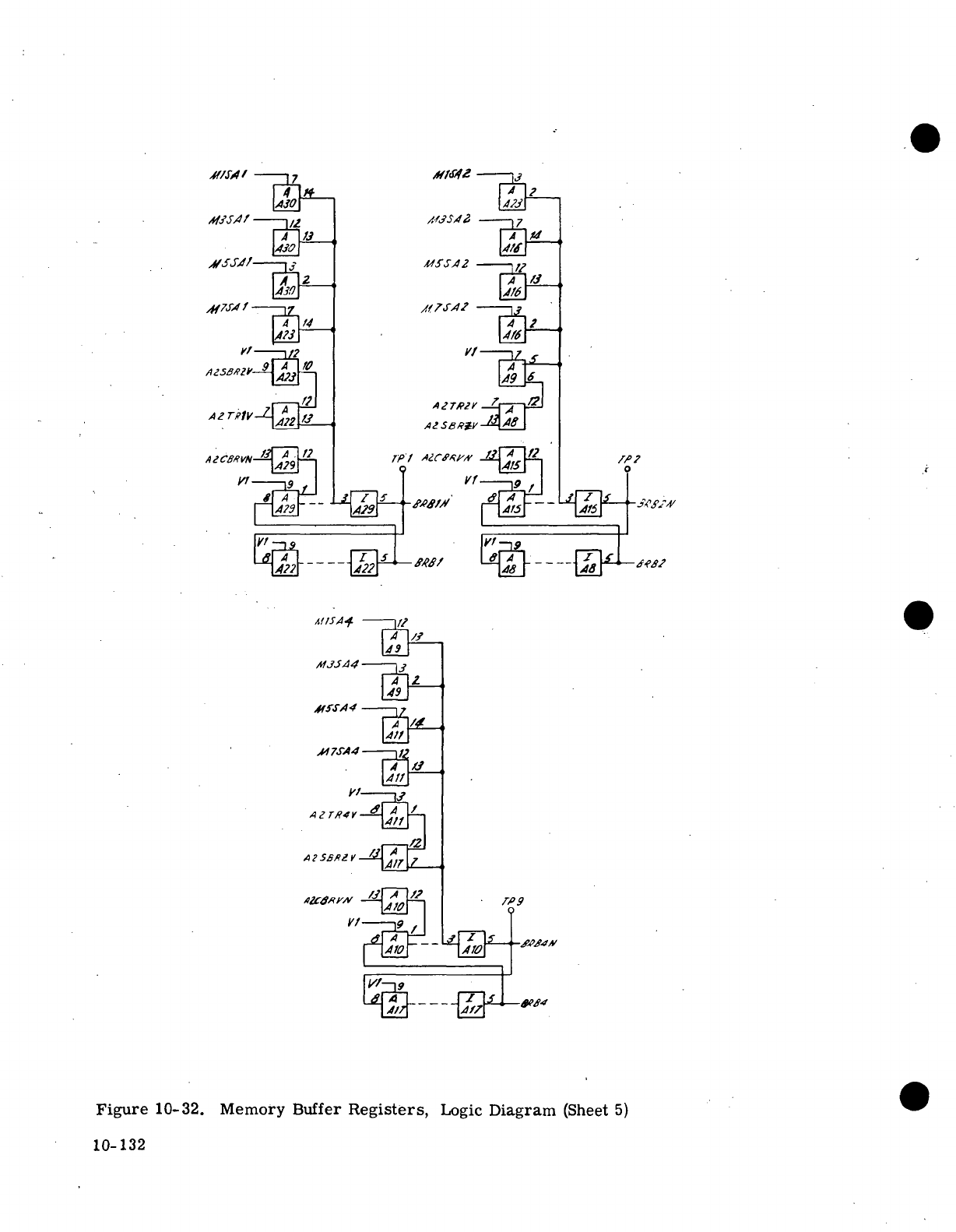

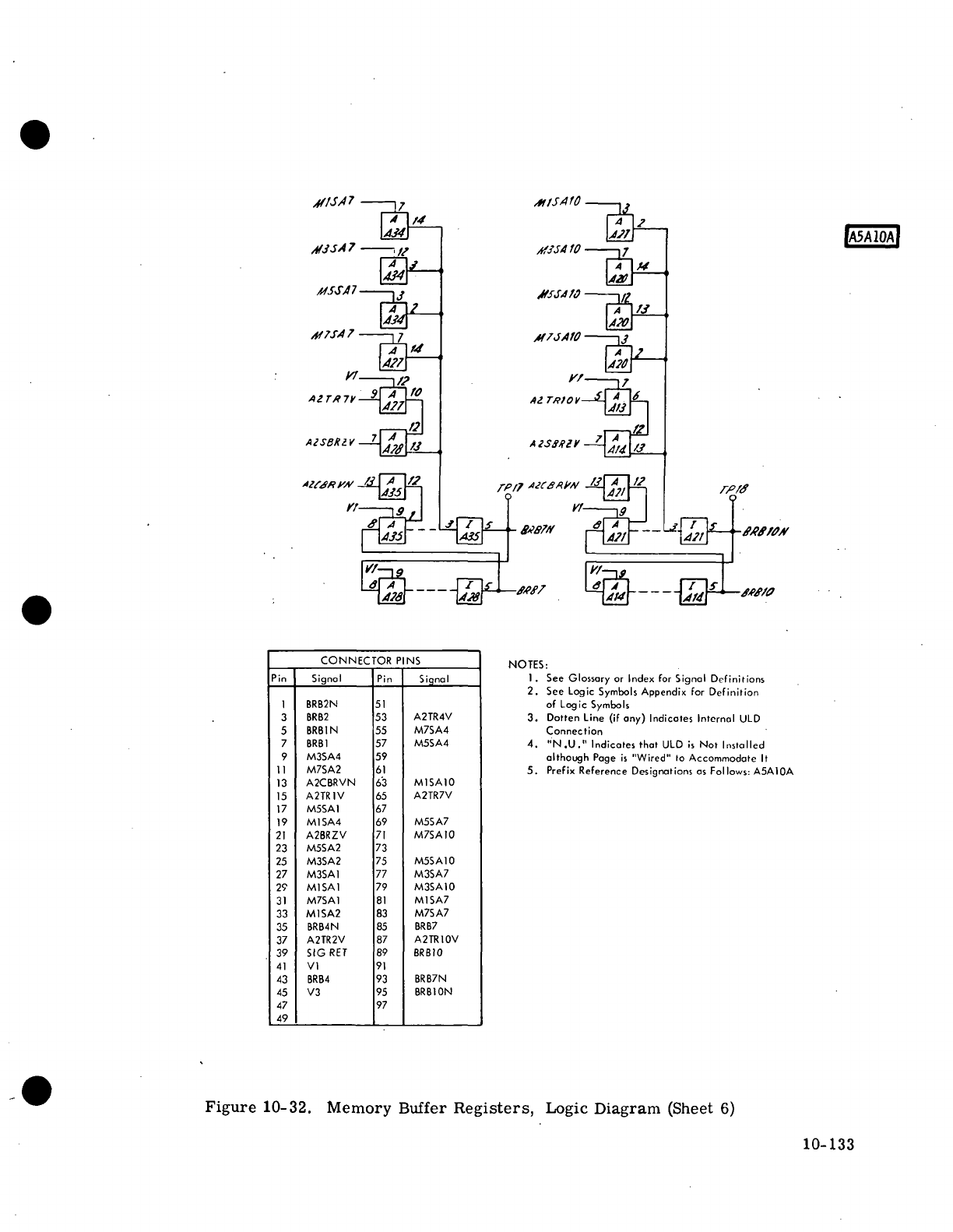

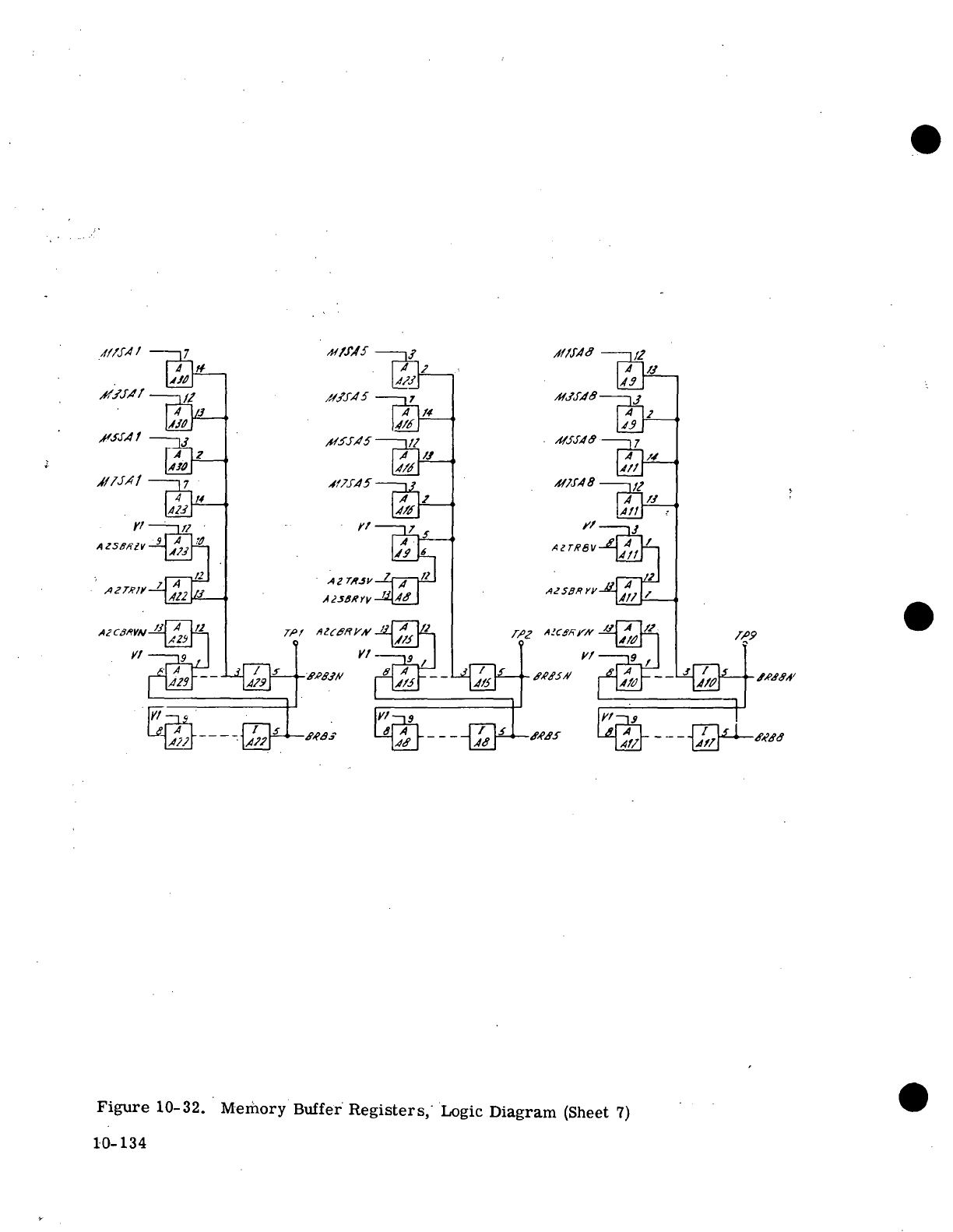

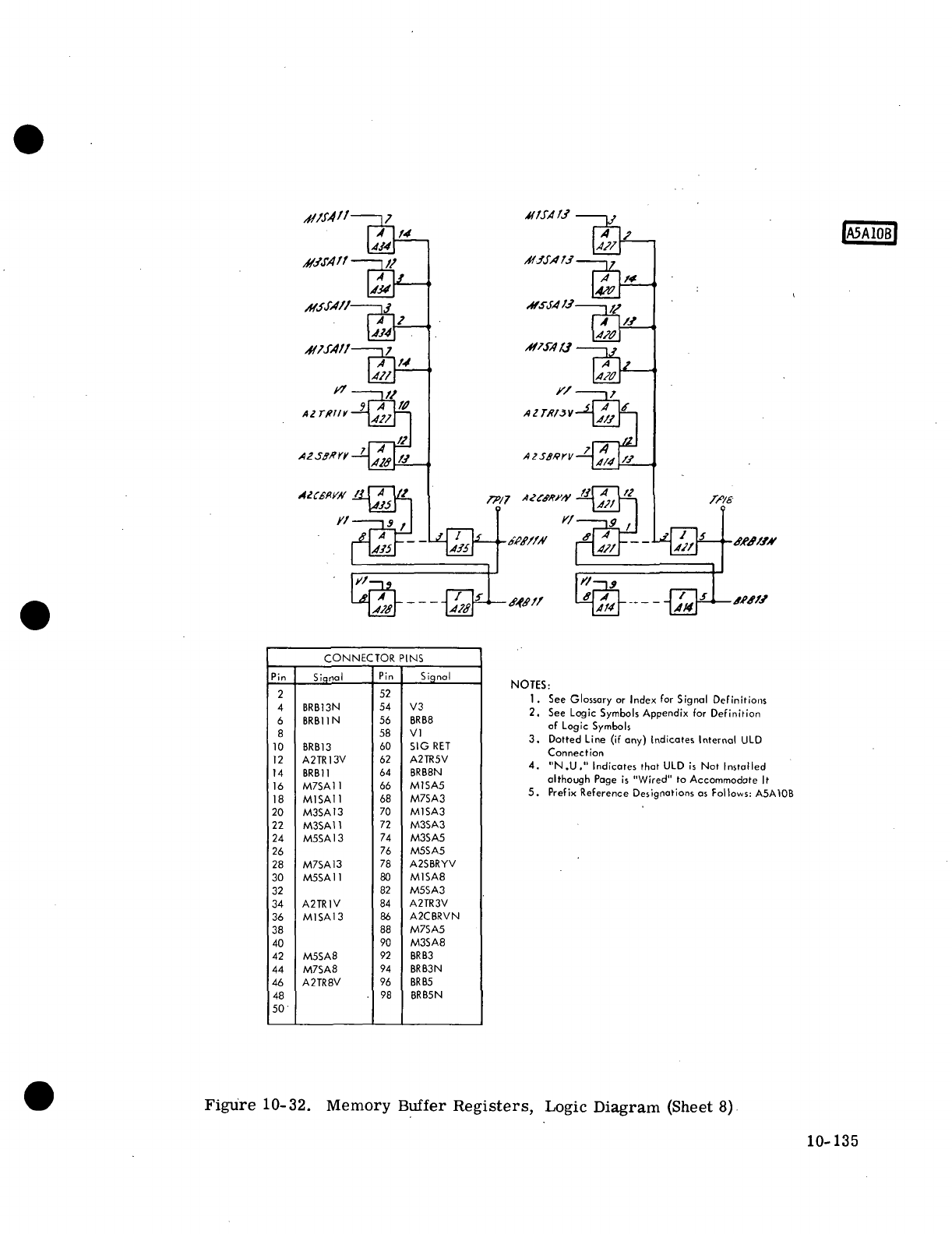

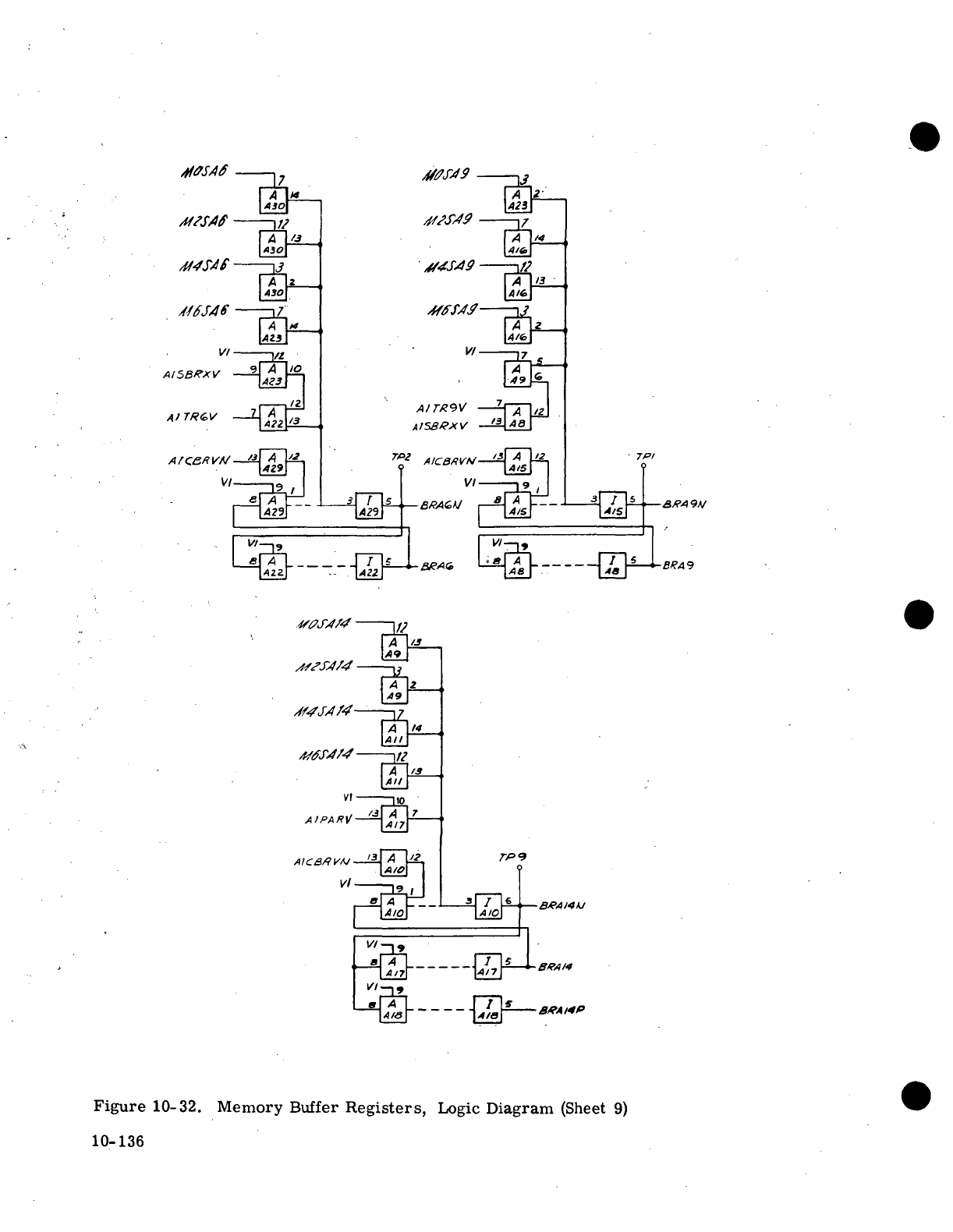

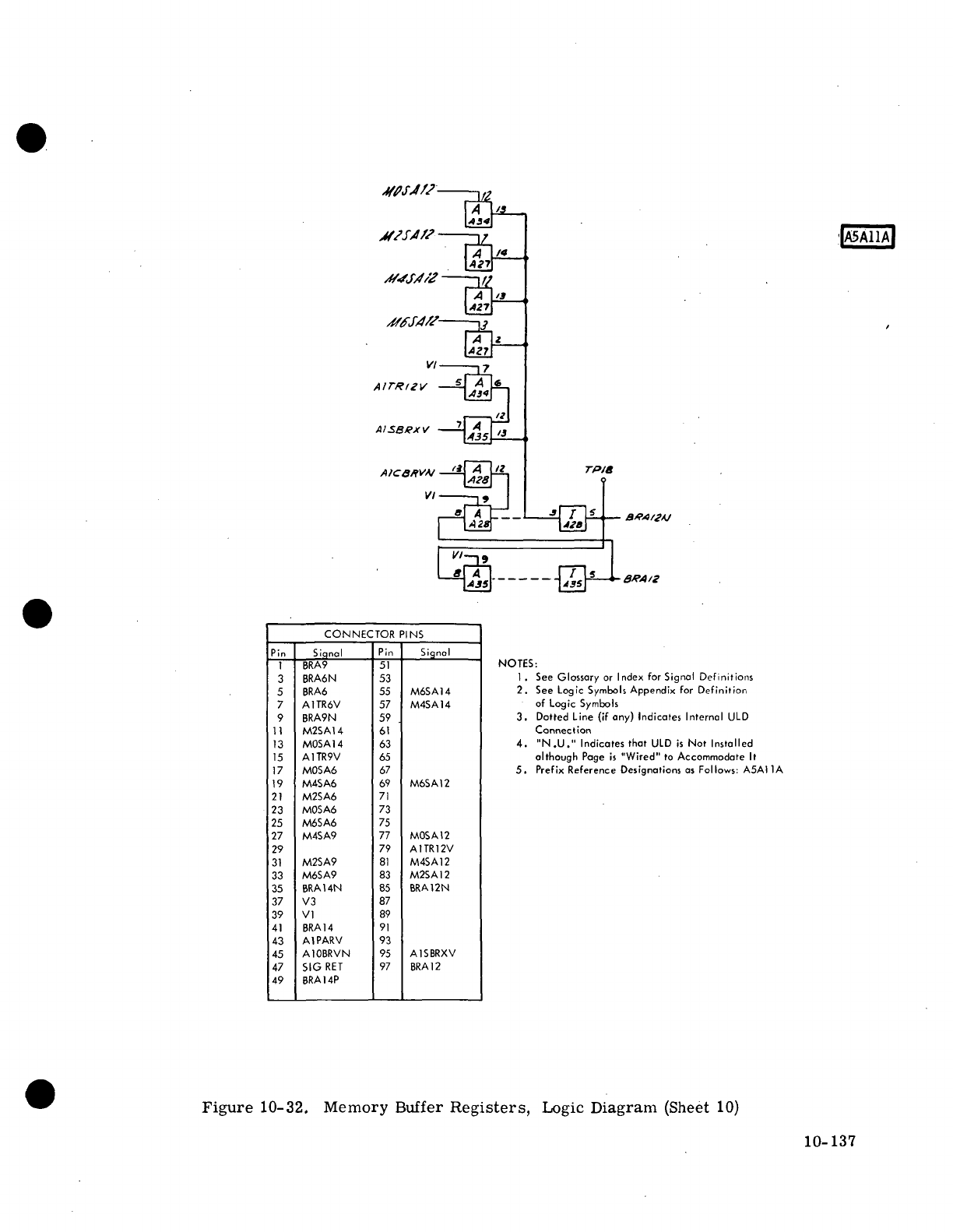

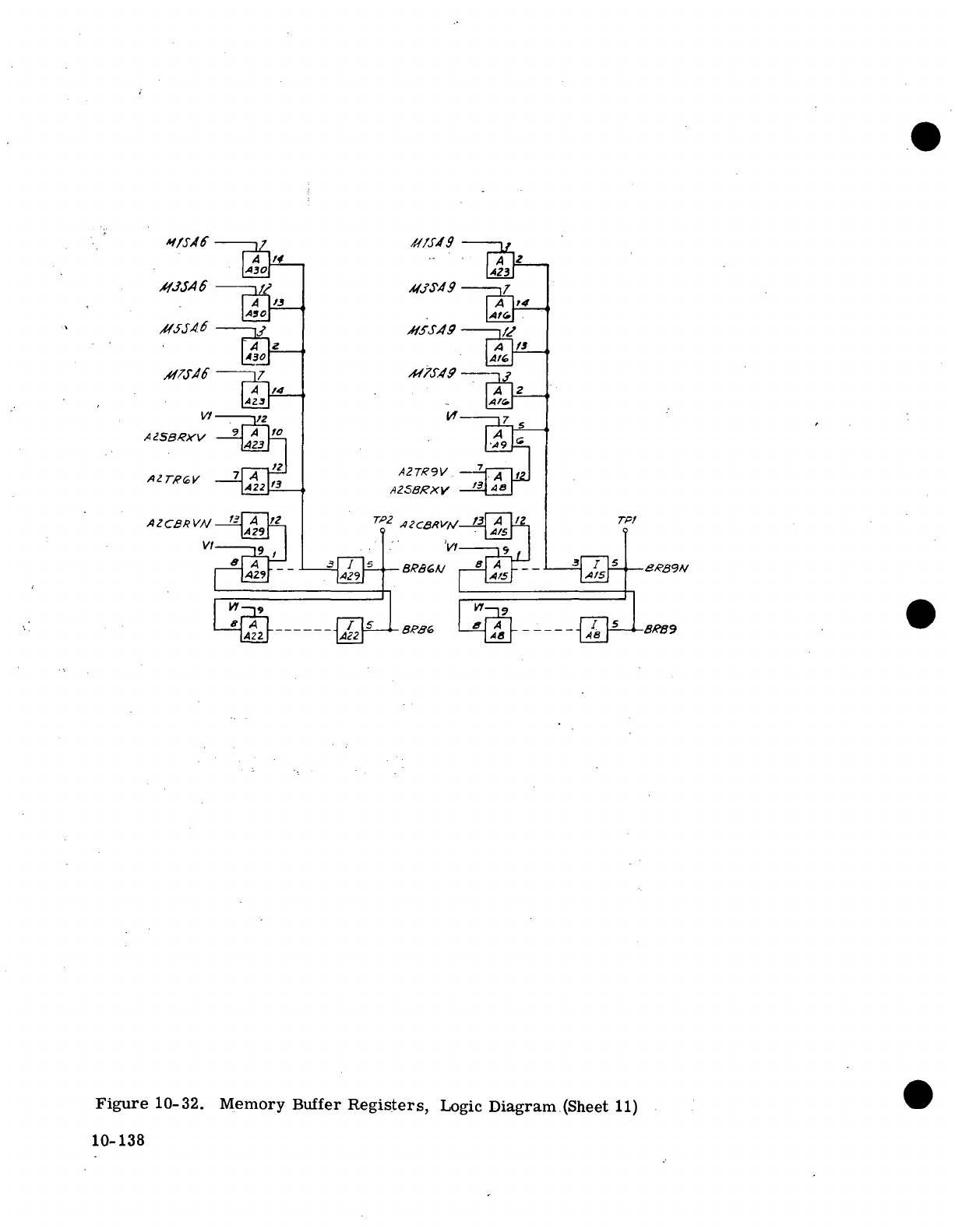

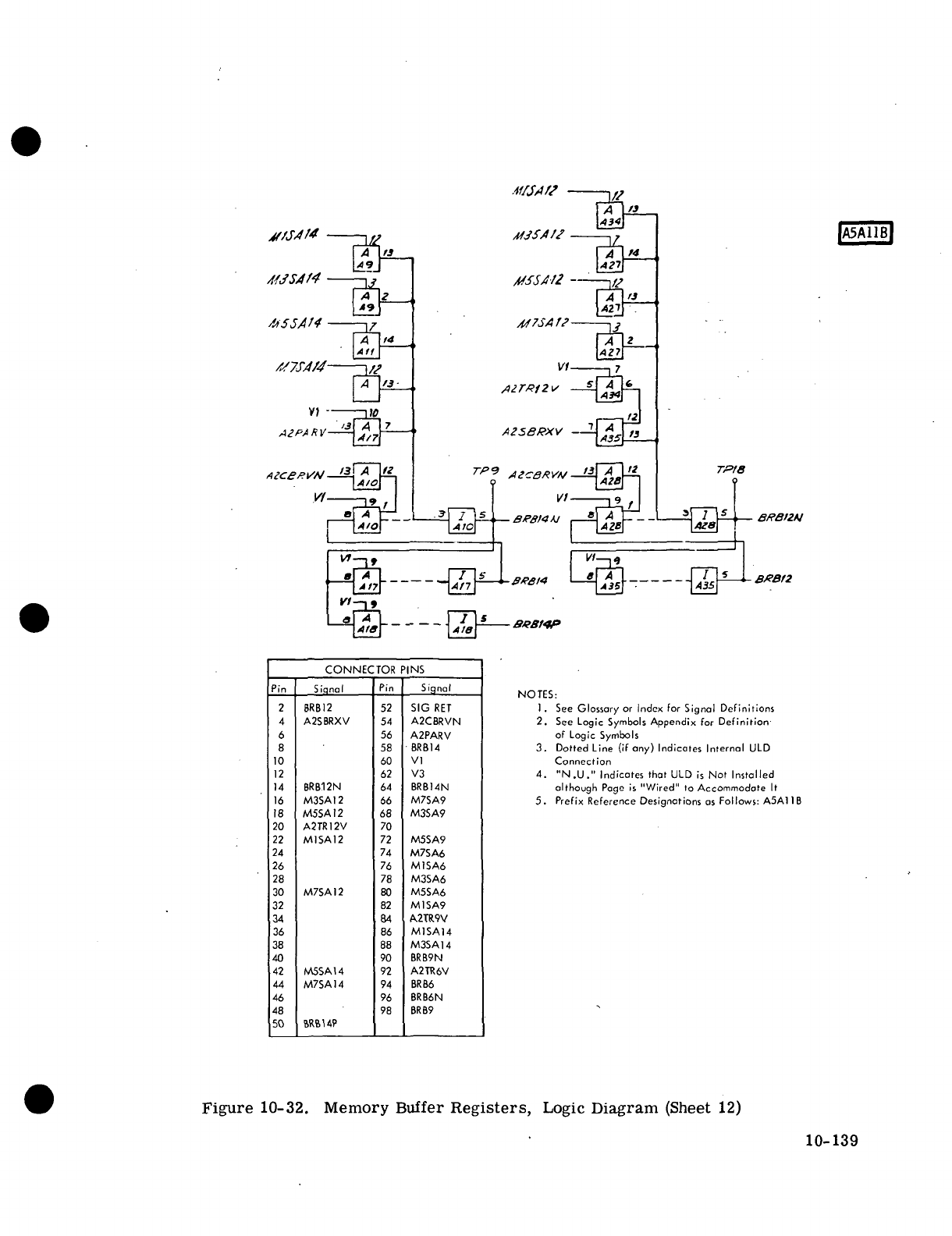

10-32

Memory

Buffer

Registers,

Logic Diagram

(12

Sheets) .... 10-128

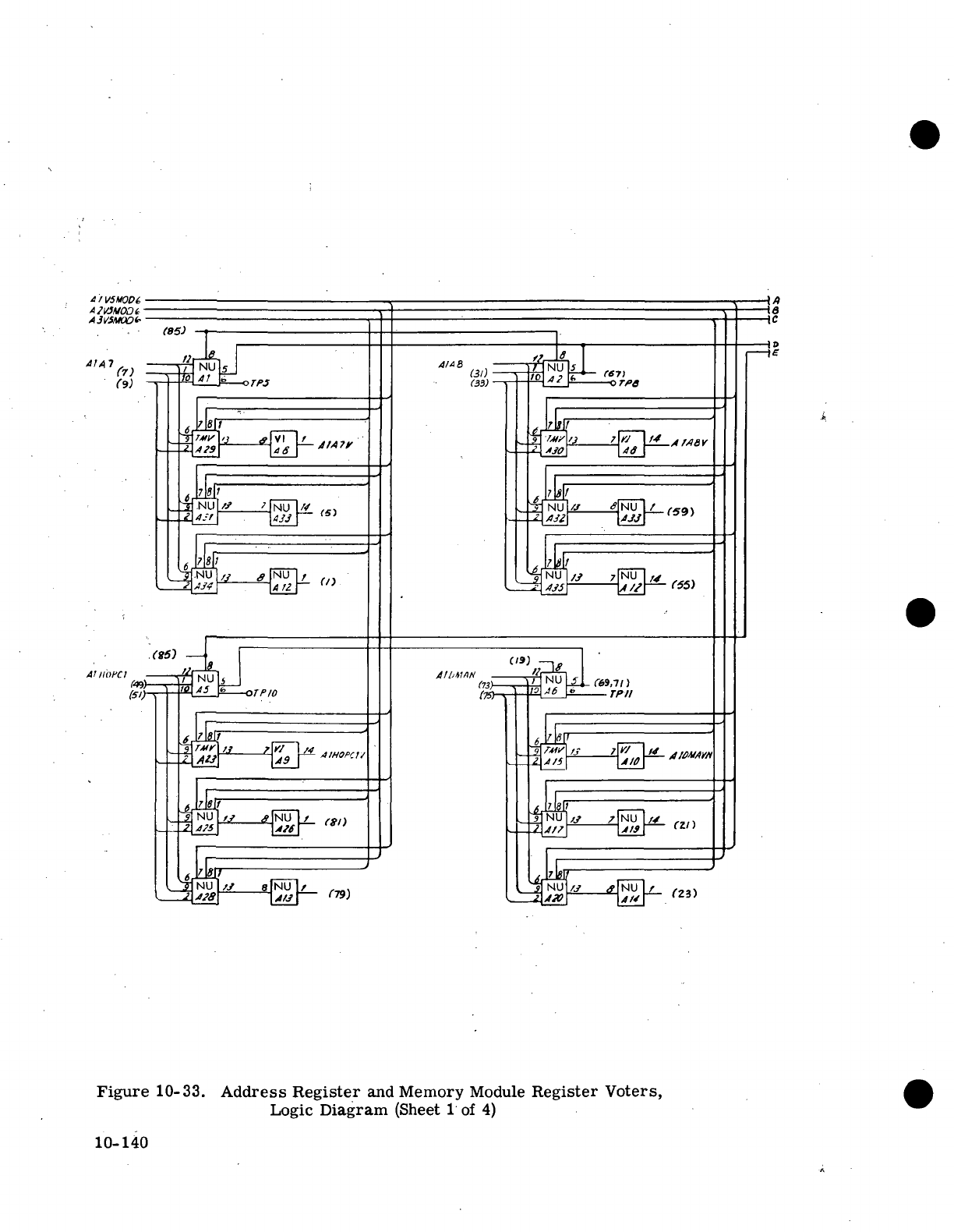

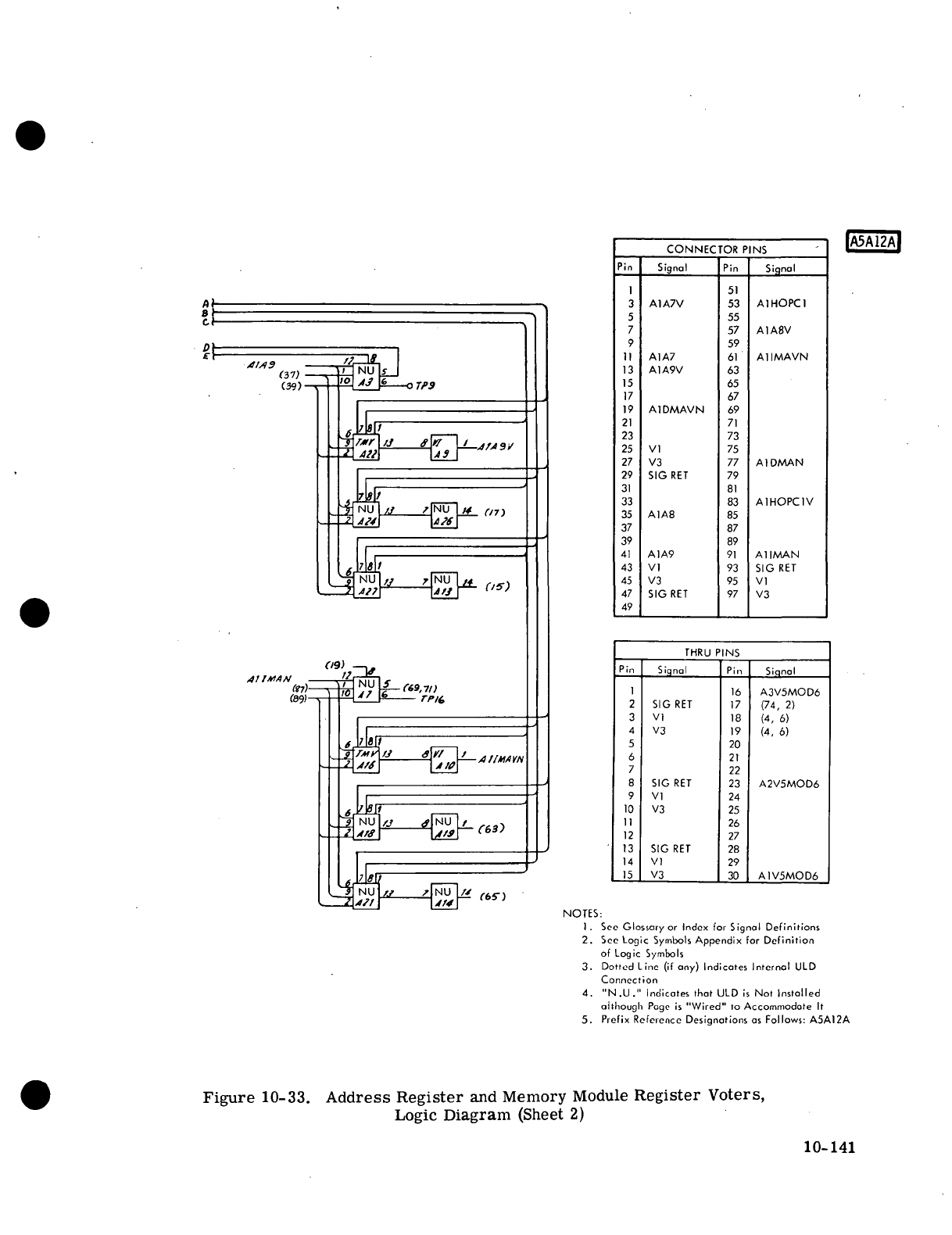

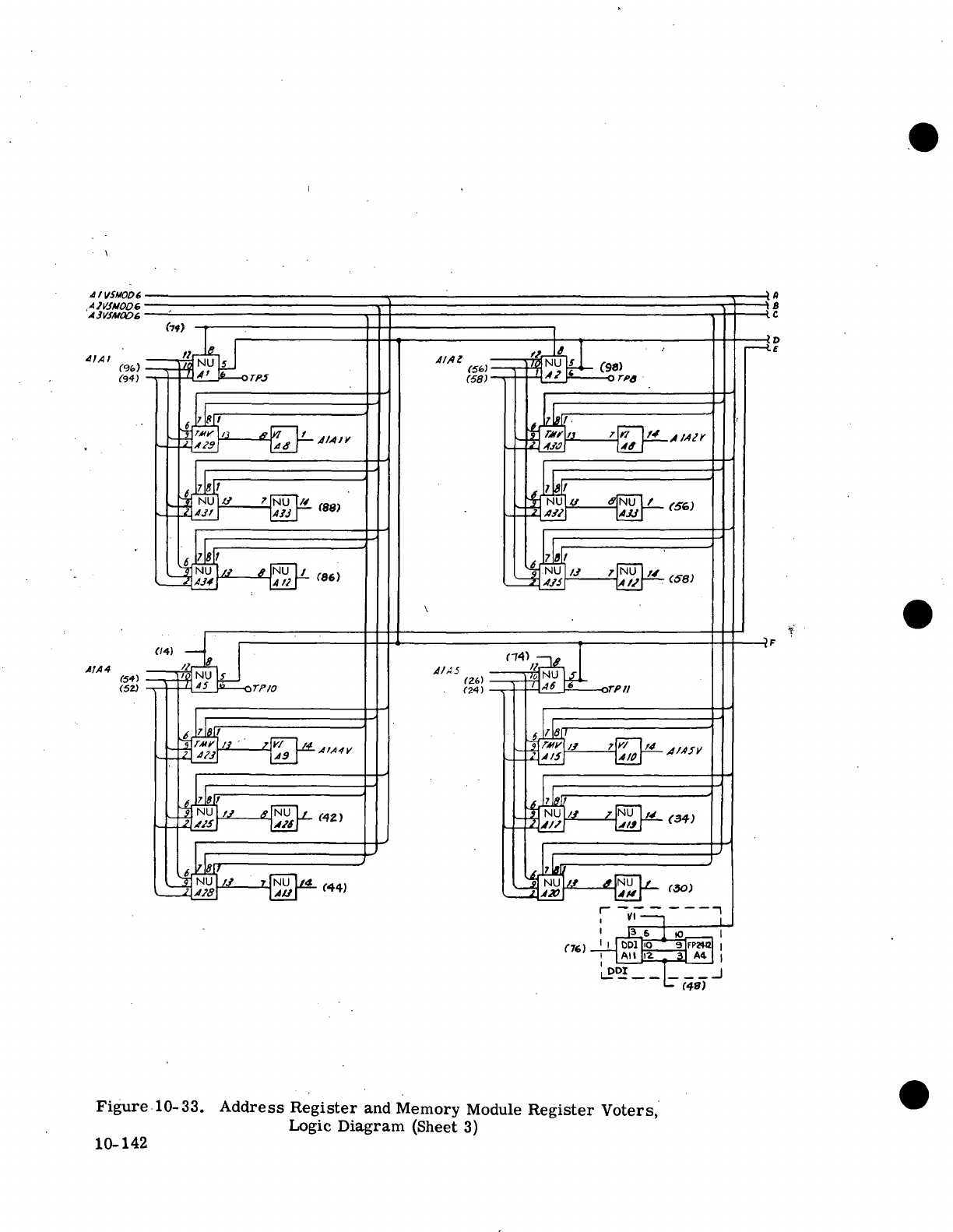

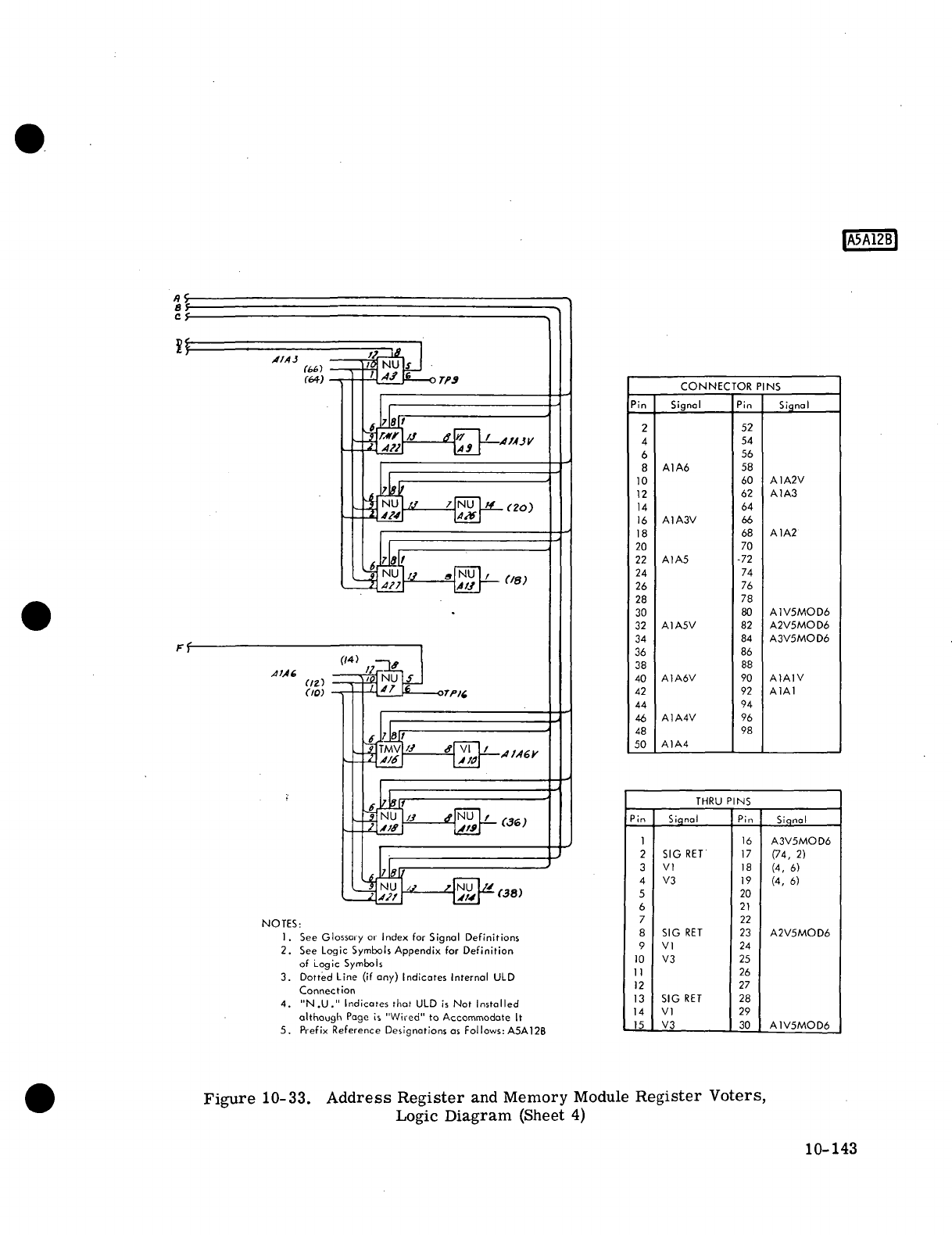

10-33 Address Register

and

Memory

Module

Register

Voters, Logic Diagram

(4

Sheets) 10-140

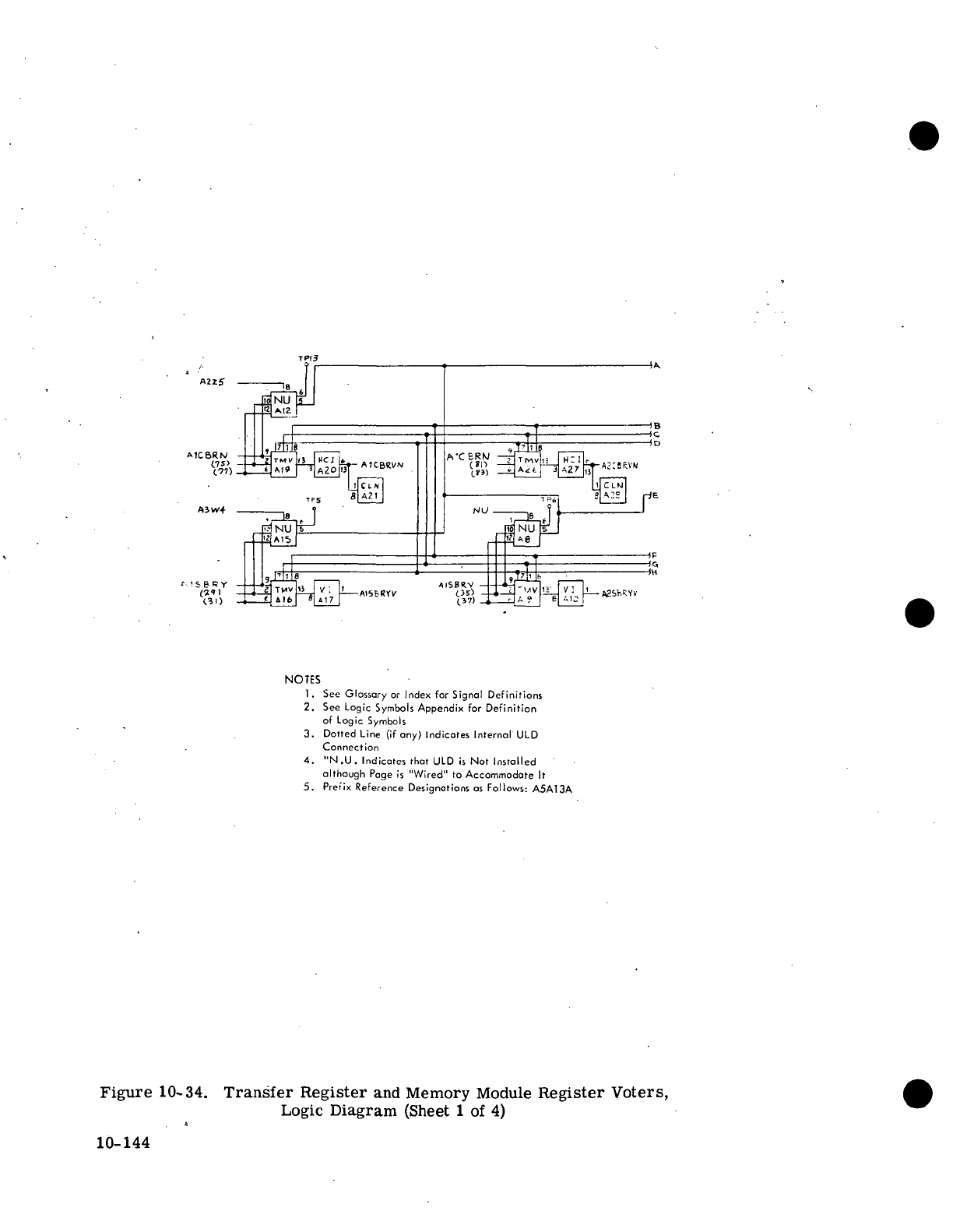

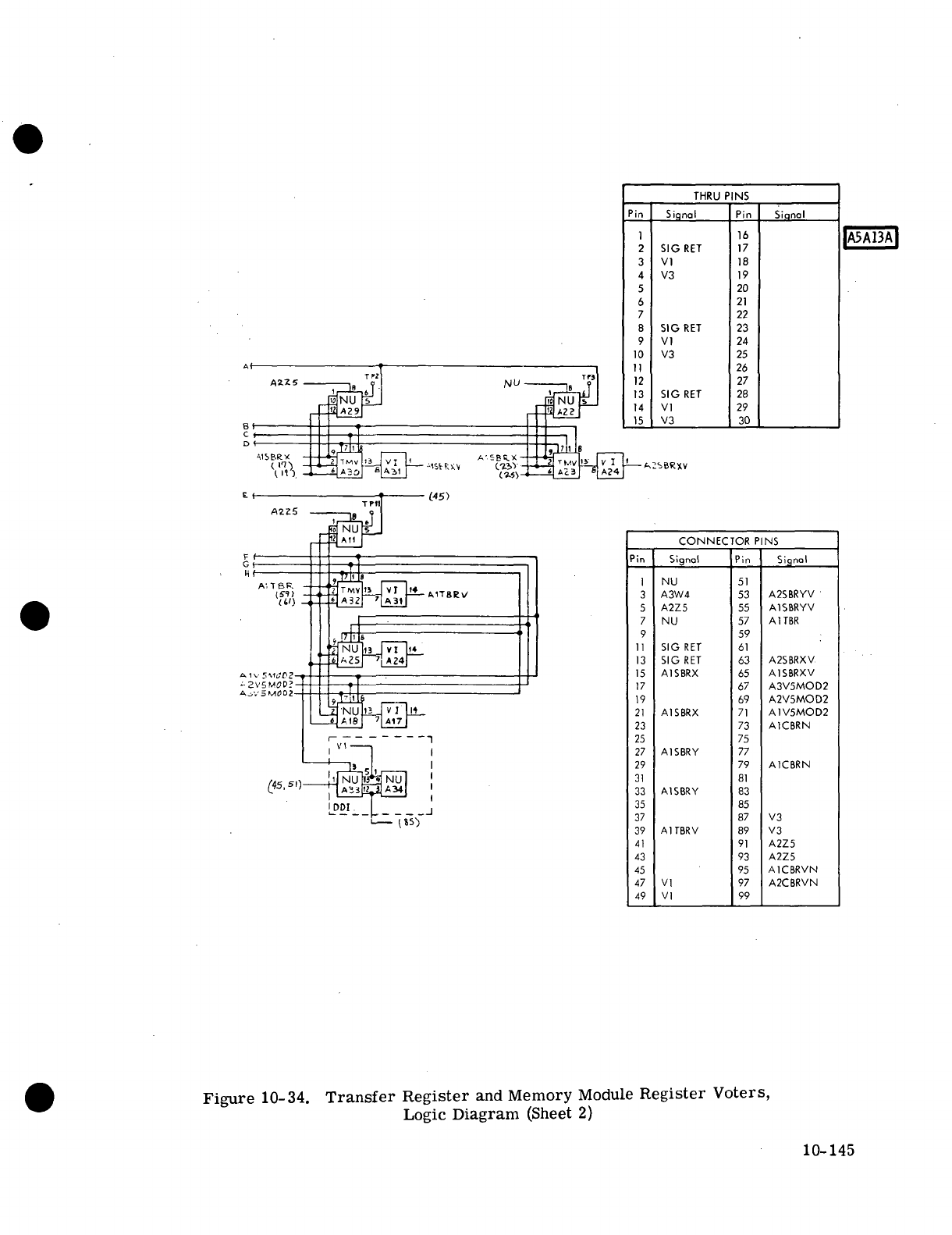

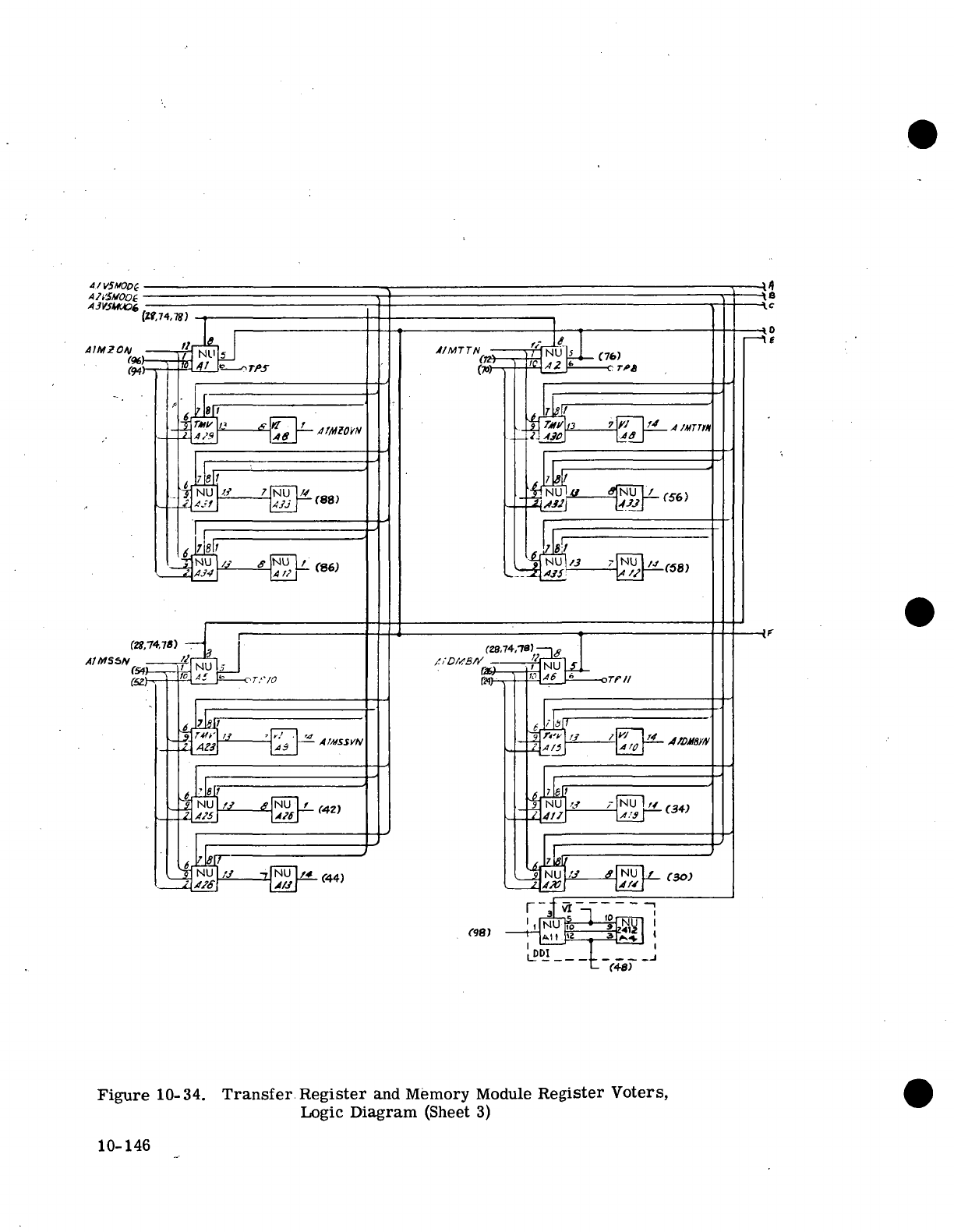

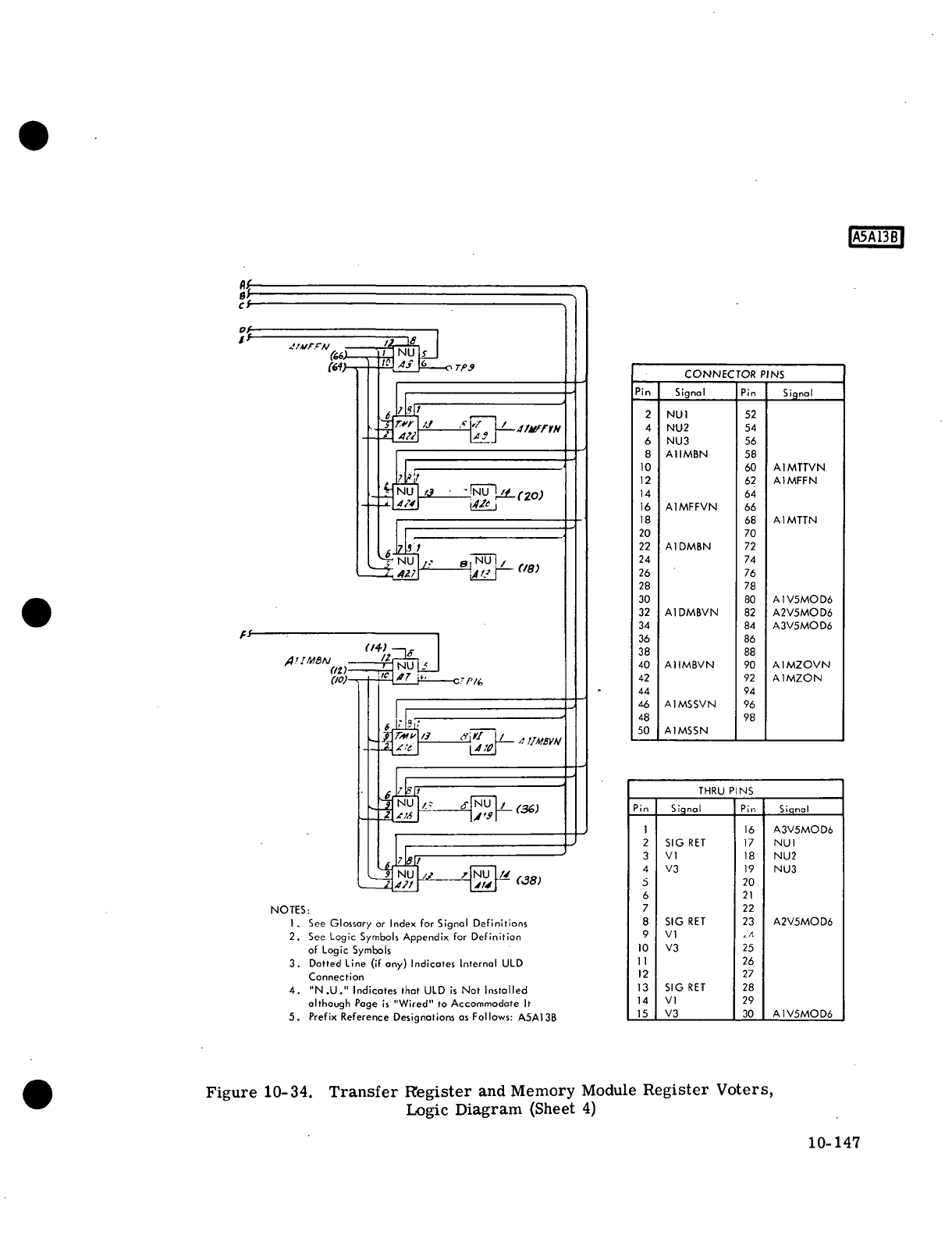

10-34

.

Transfer

Register

and

Memory

Module

Register

Voters, Logic Diagram

(4

Sheets) 10-144

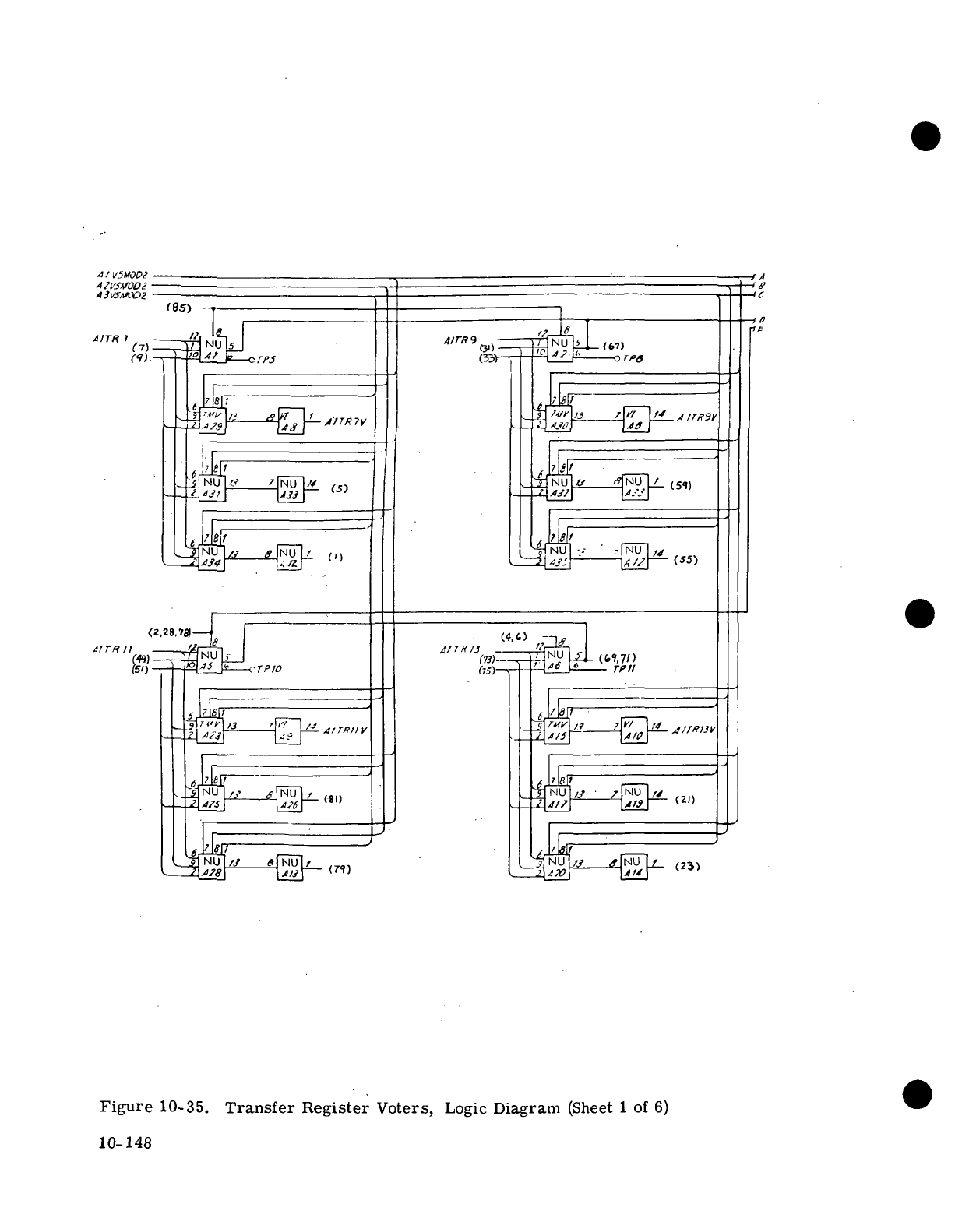

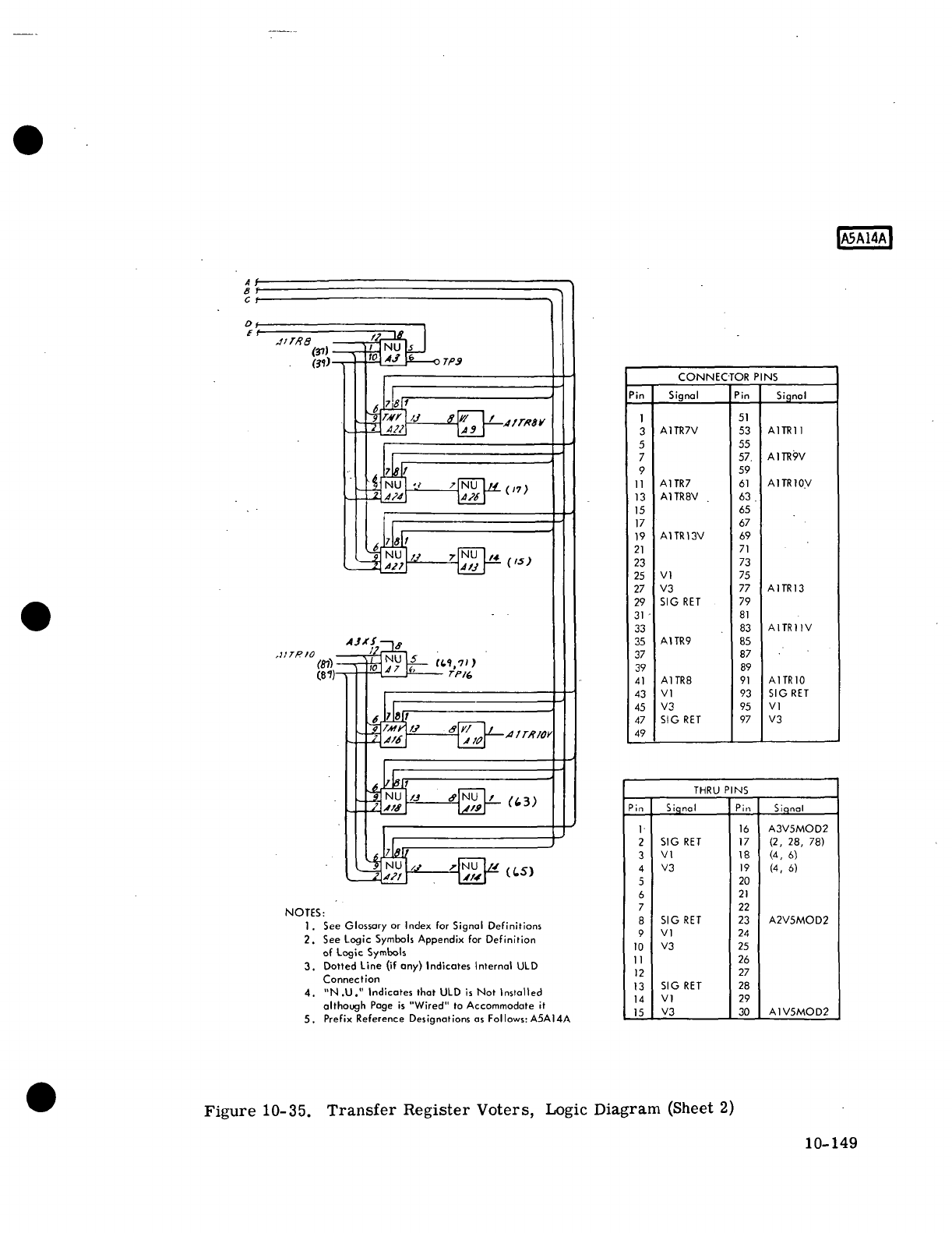

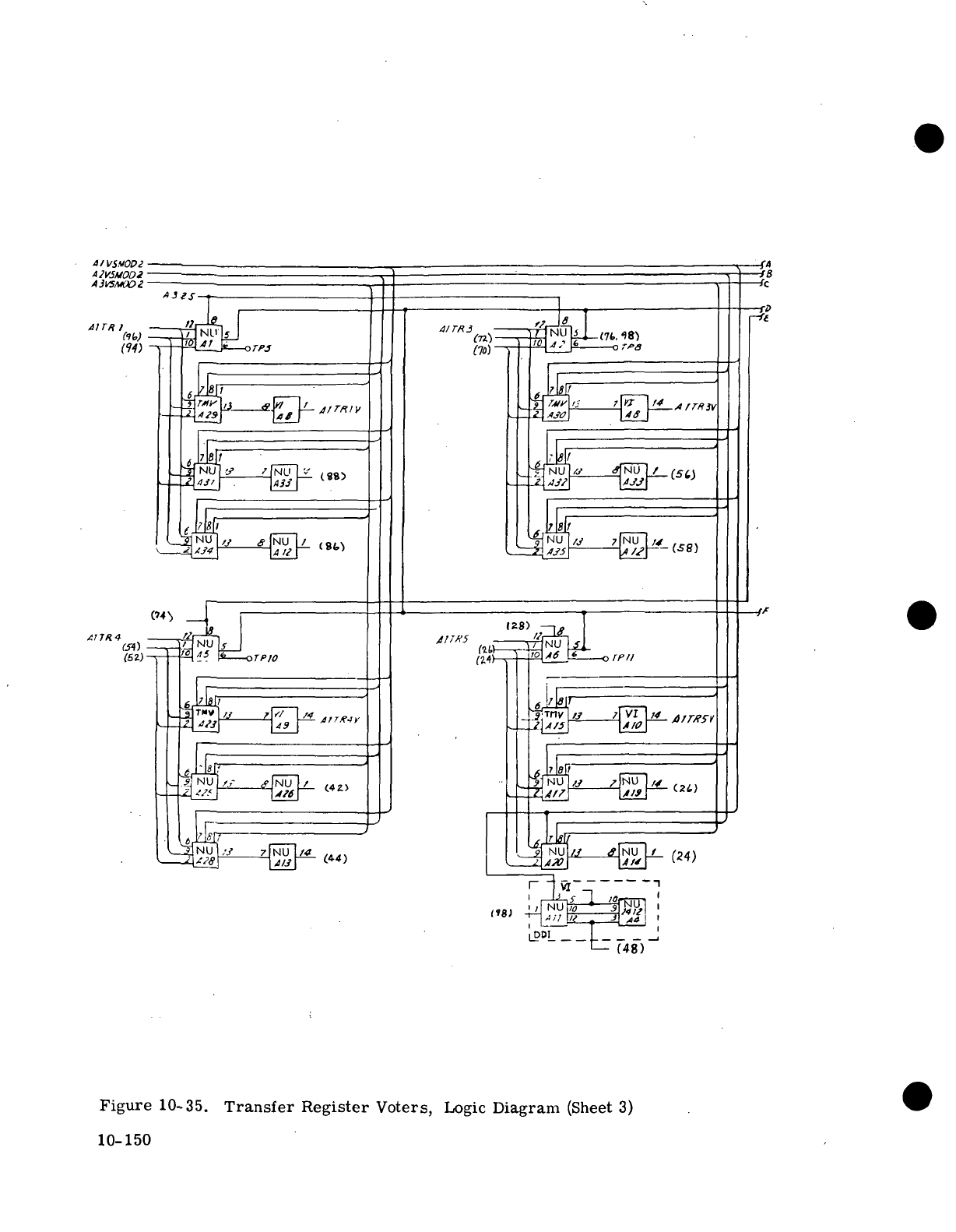

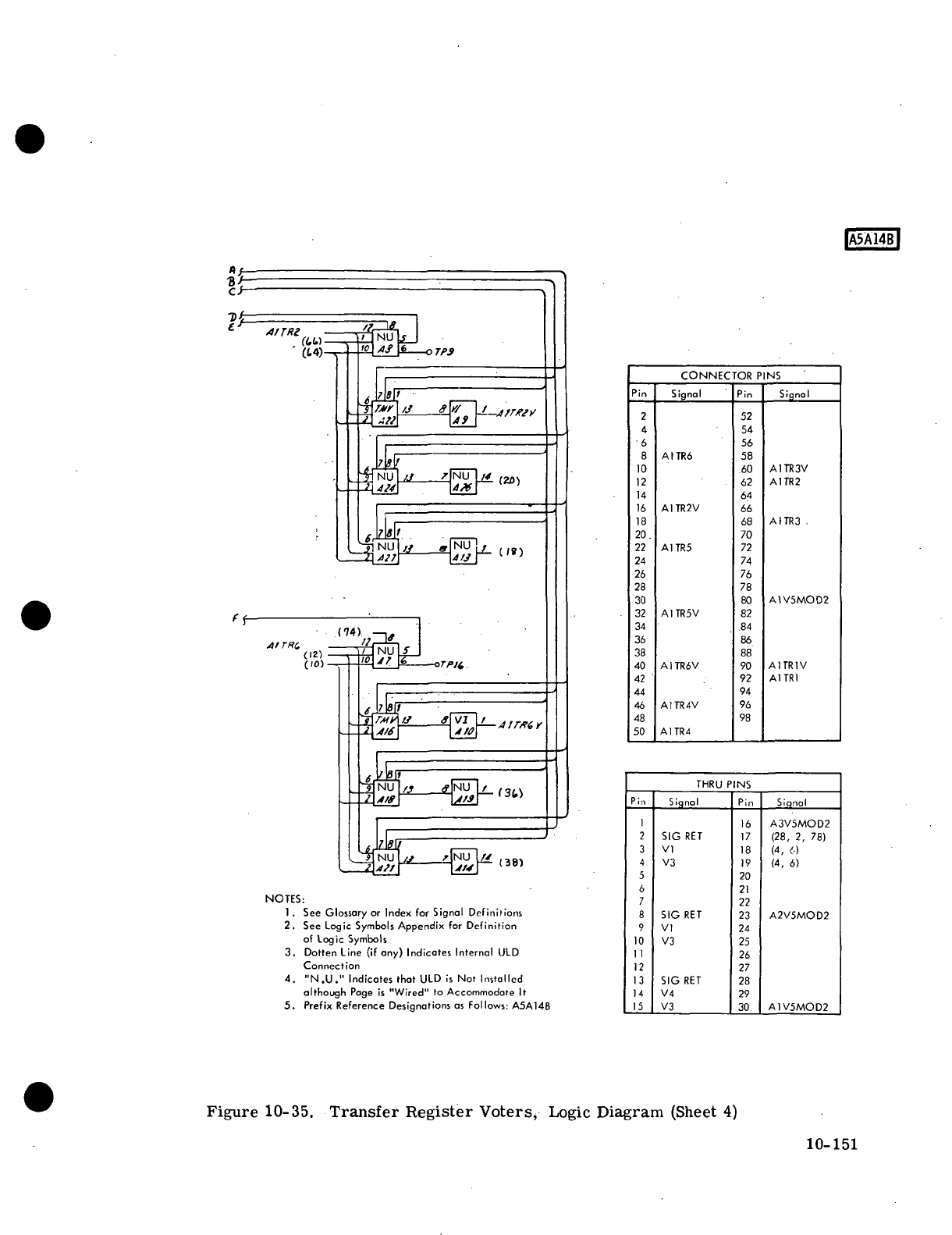

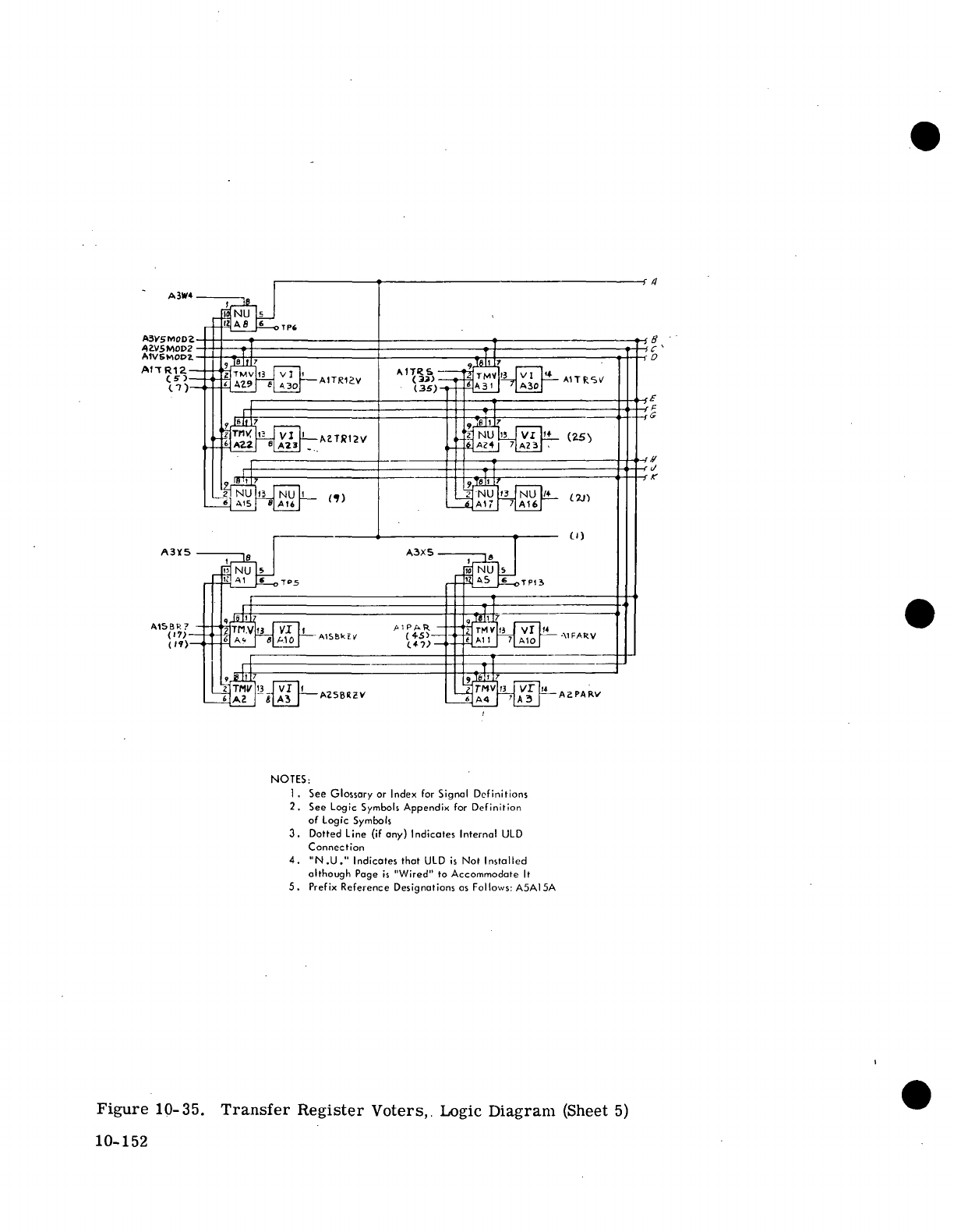

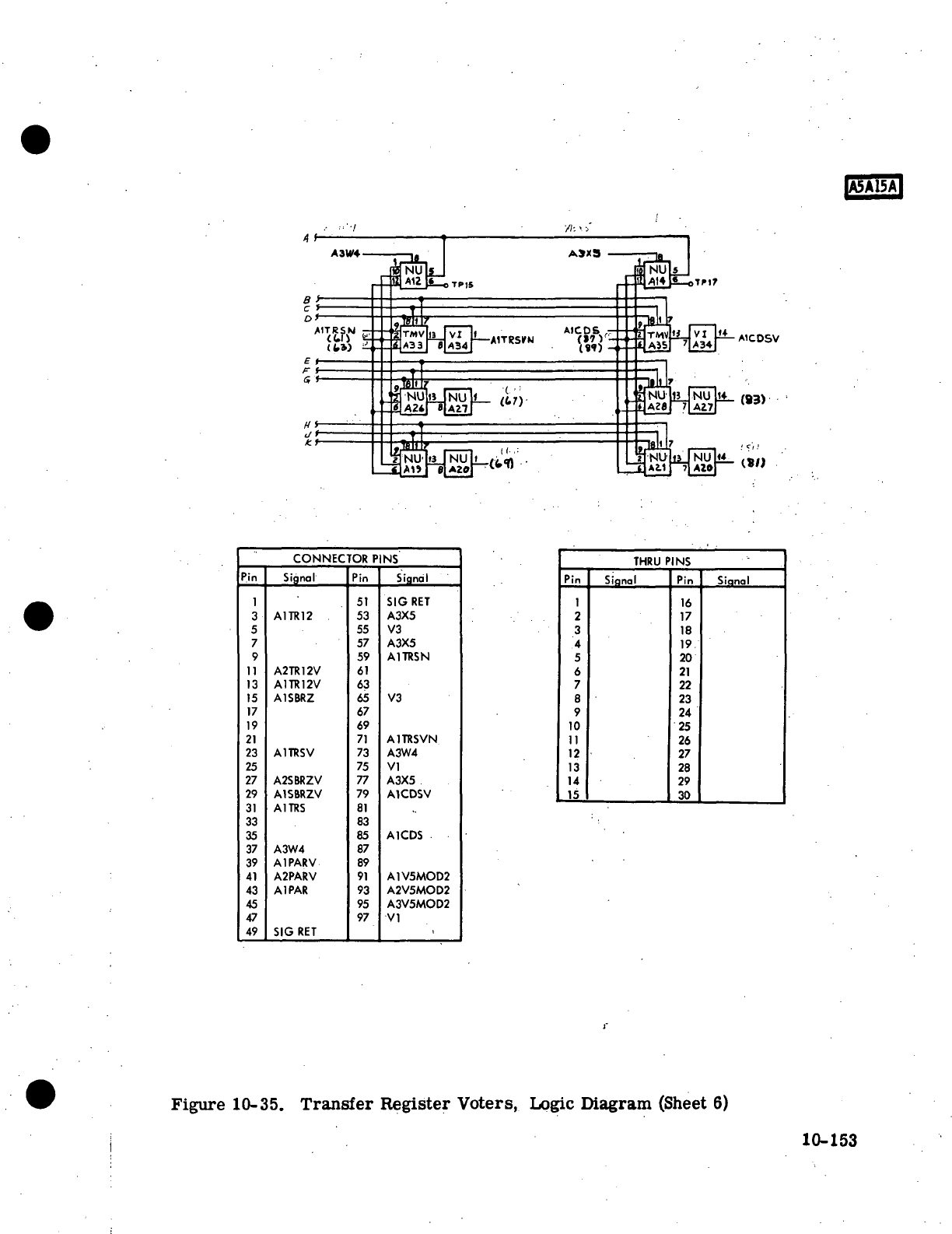

10-35 Transfer Register Voters, Logic Diagram

(6

Sheets) 10-148

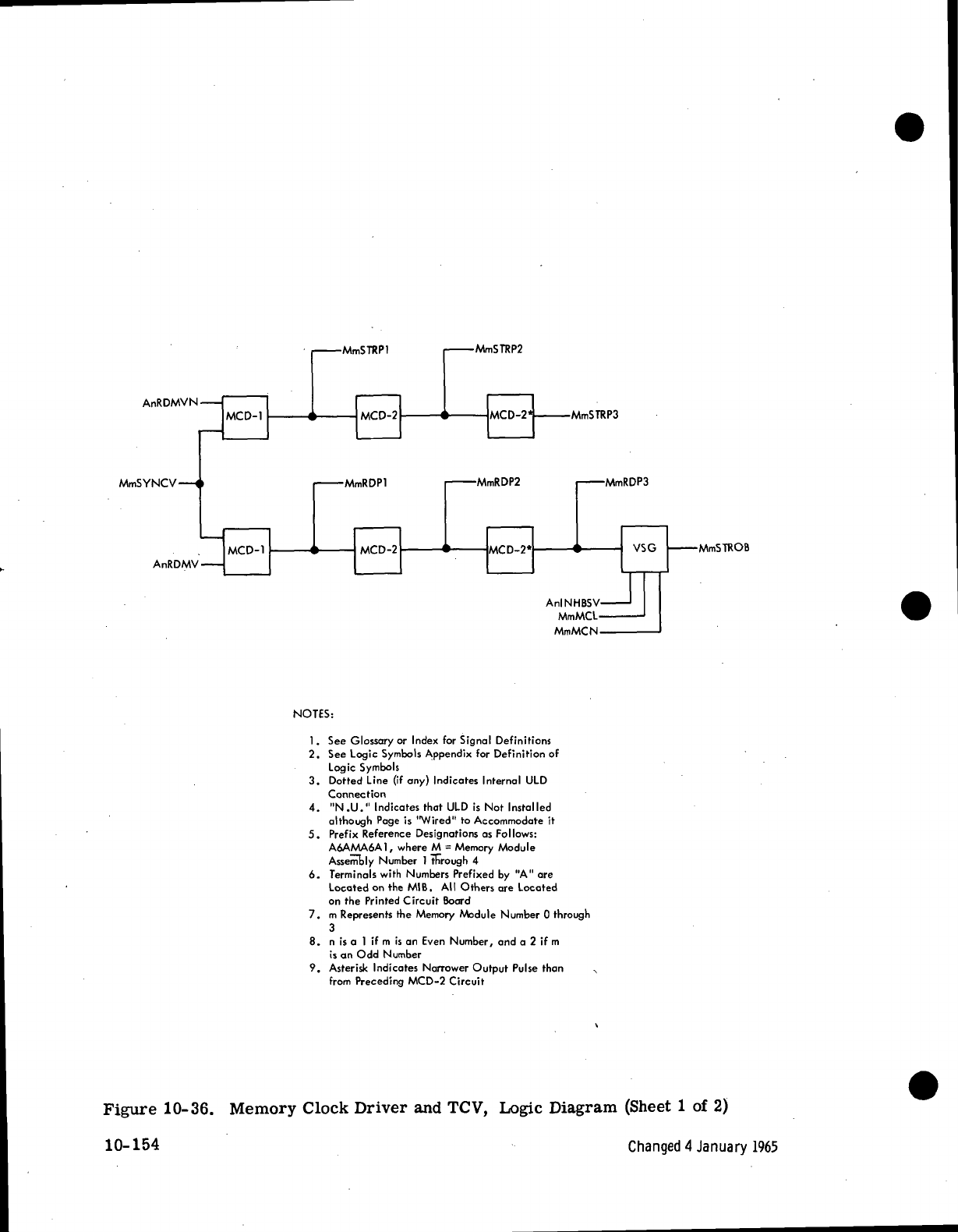

10-36 Memory Clock Driver

and

TCV, Logic Diagram

(2

Sheets) 10-154

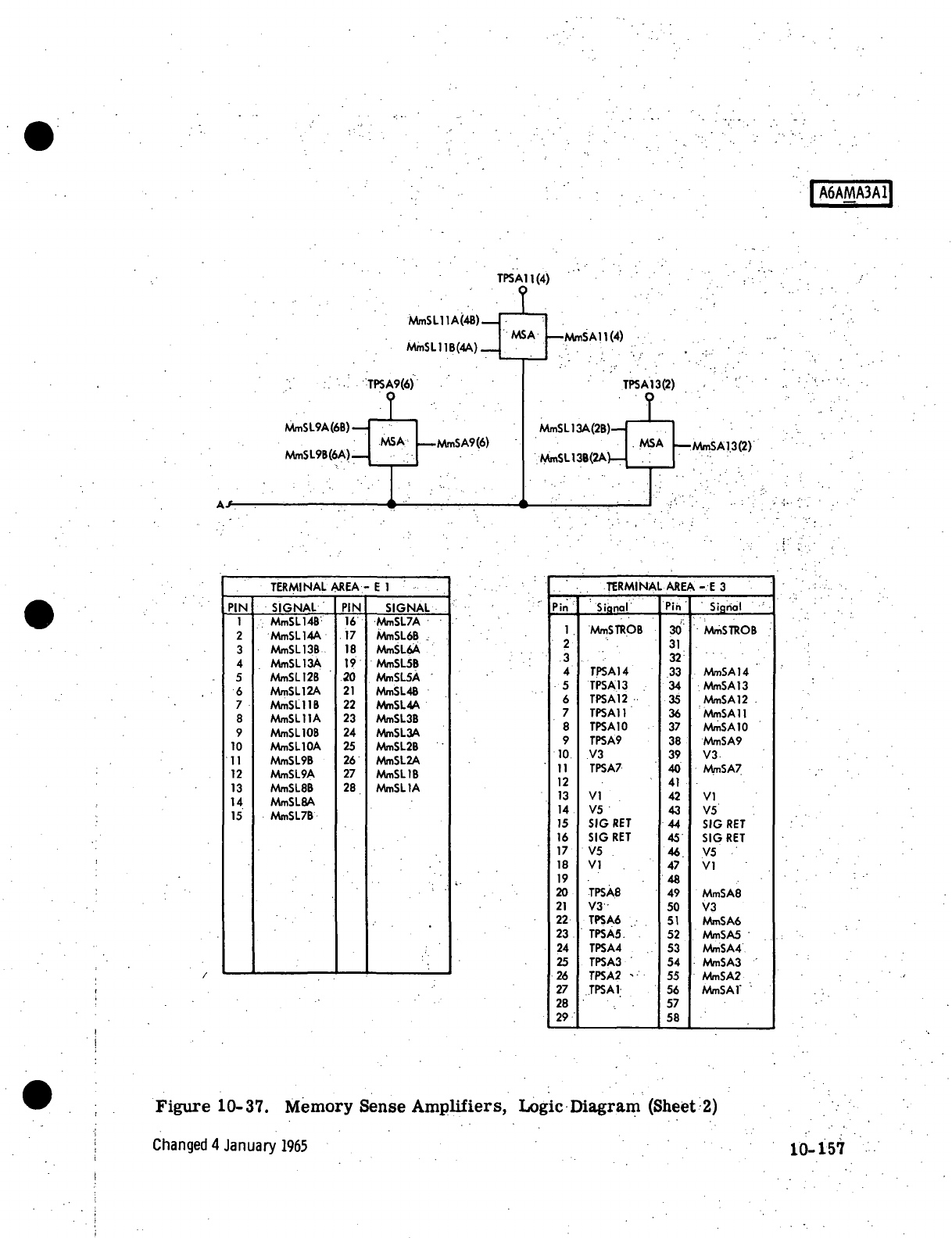

10-37 Memory Sense Amplifiers, Logic Diagram

(2

Sheets) 10-156

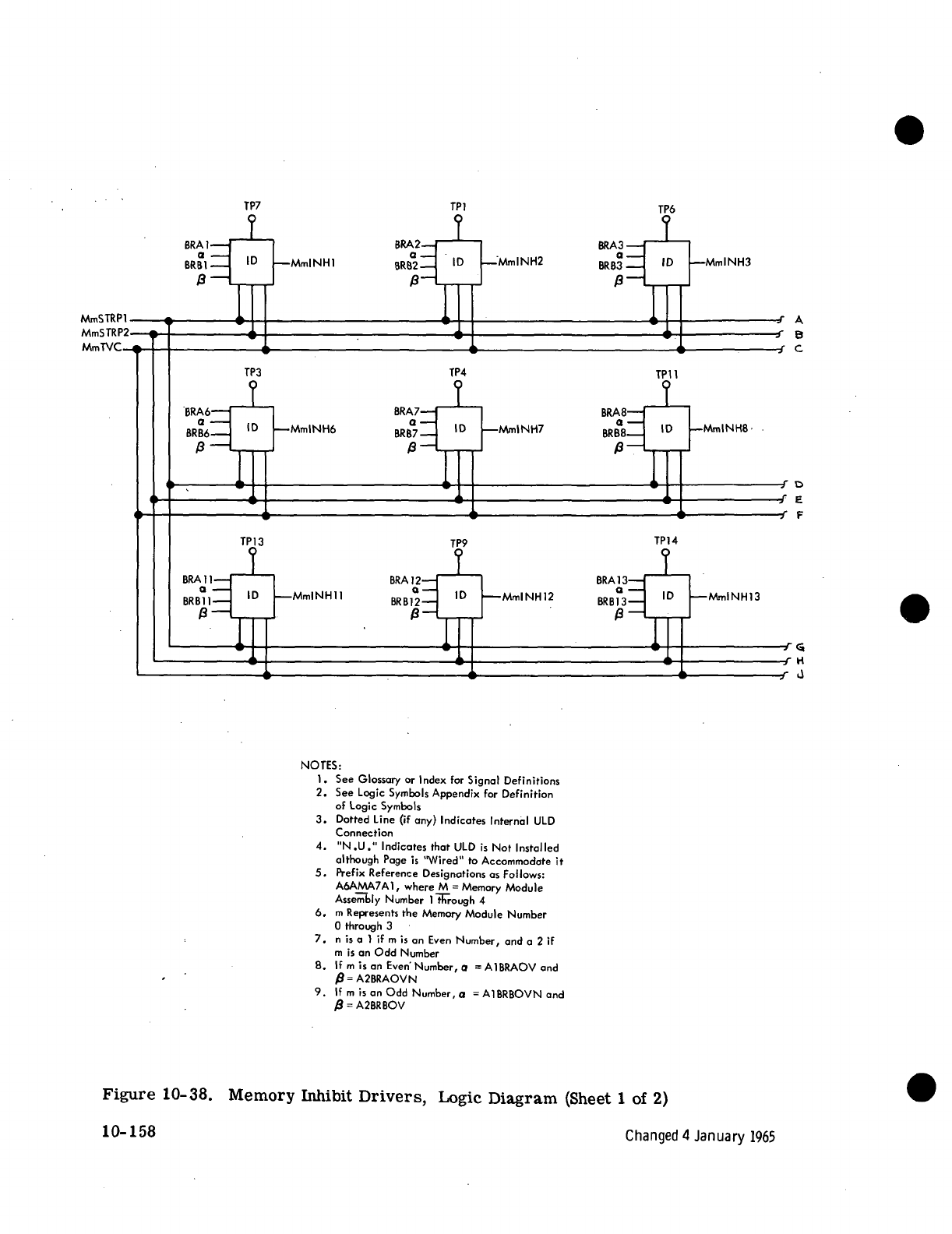

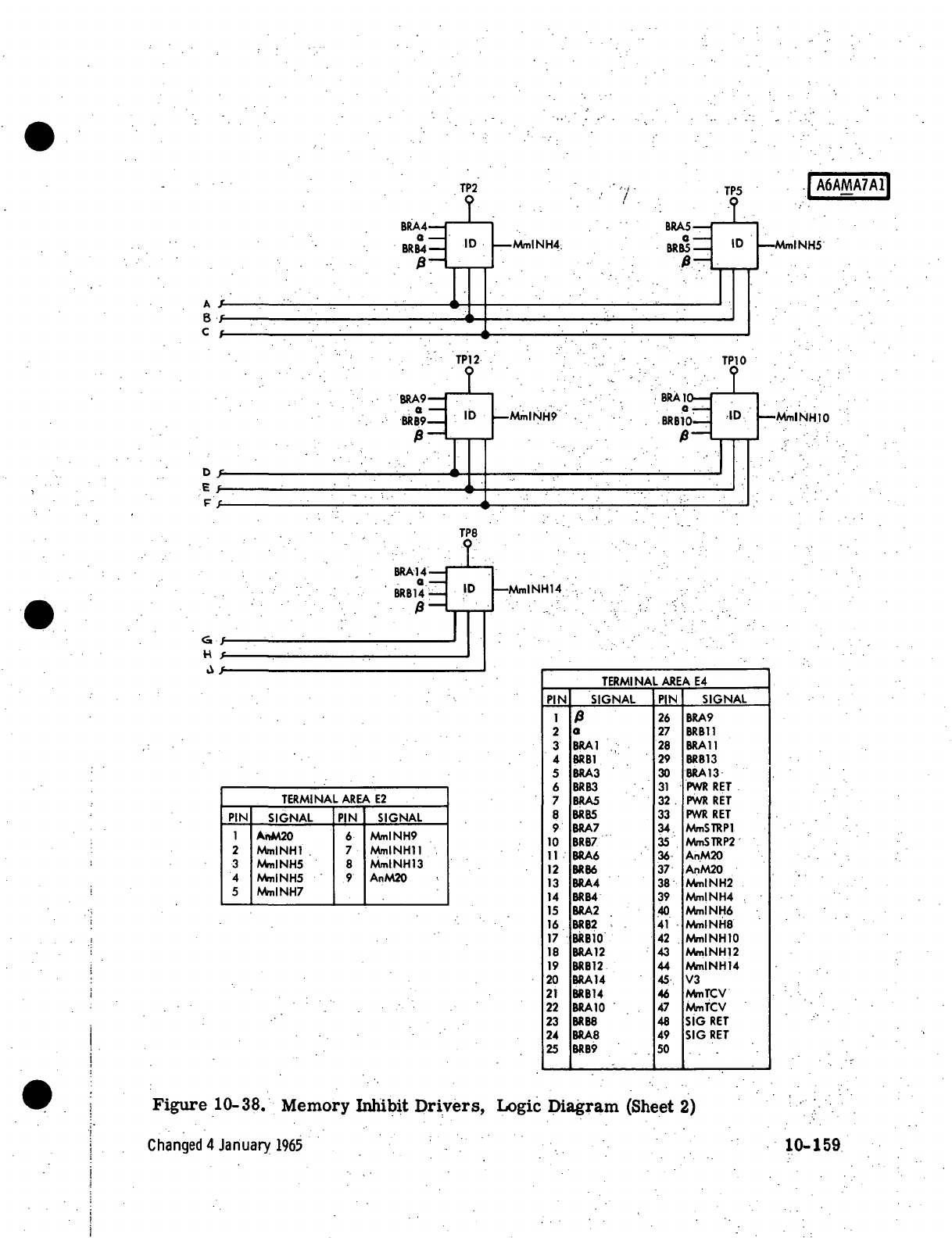

10-38 Memory Inhibit Drivers, Logic Diagram

(2

Sheets)

;

10-158

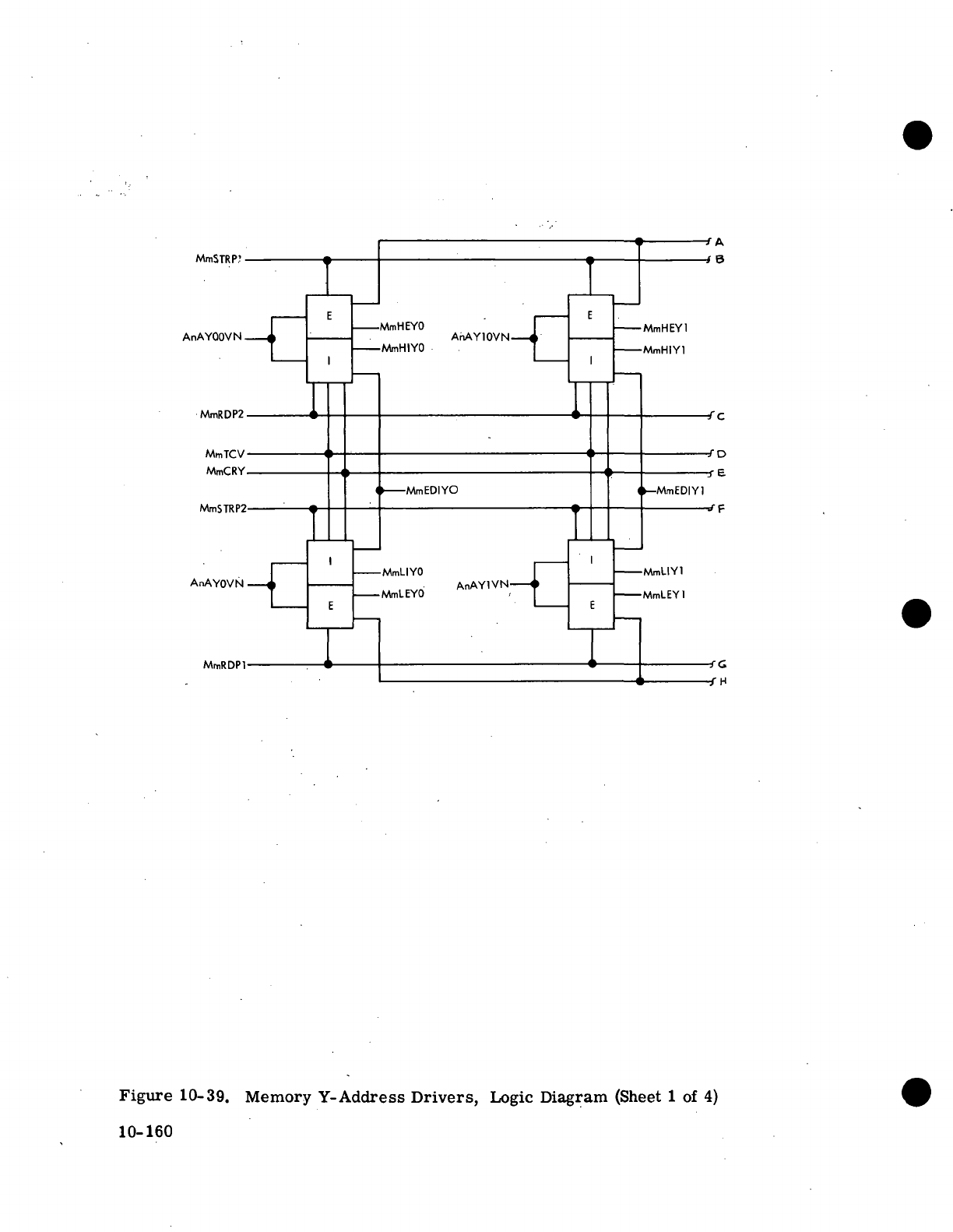

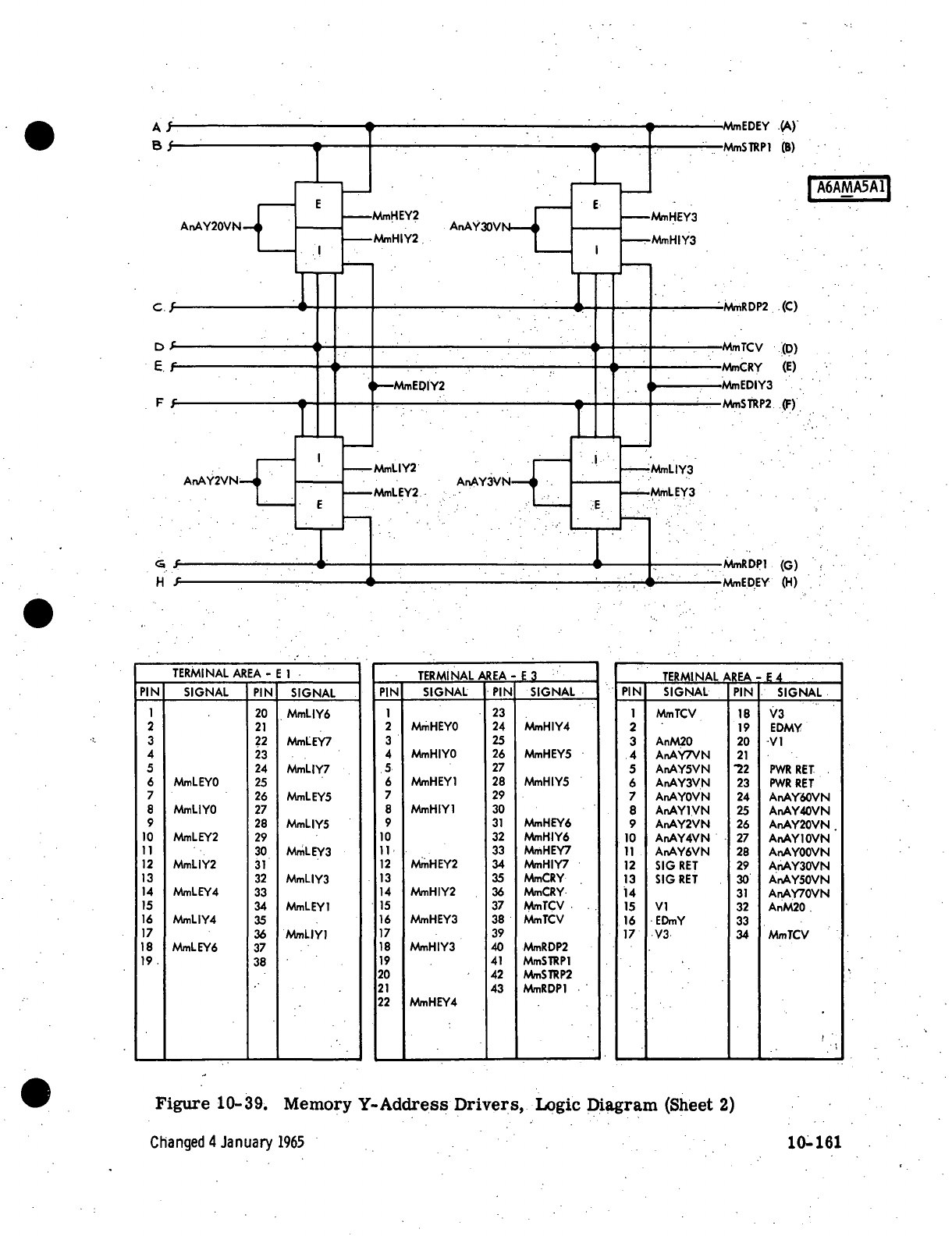

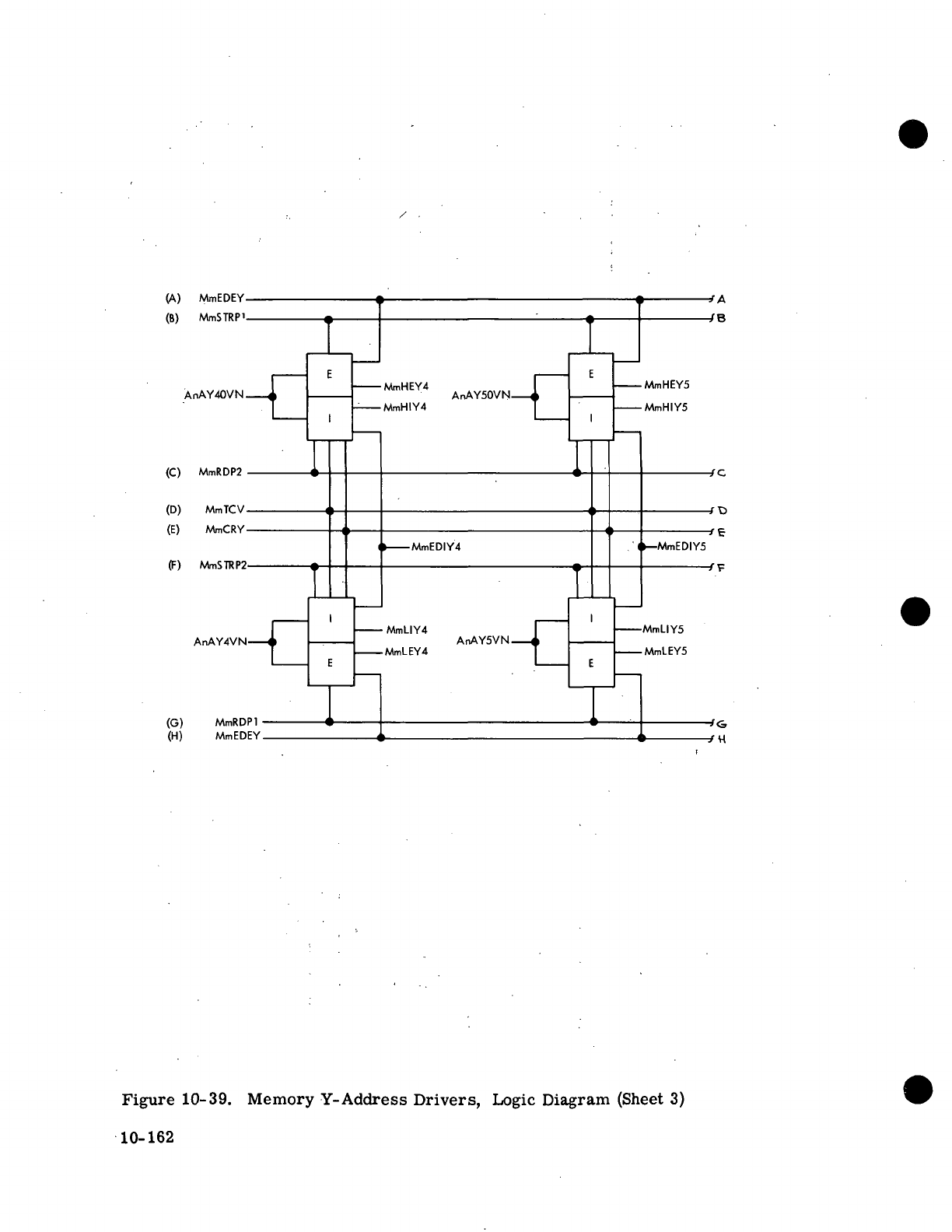

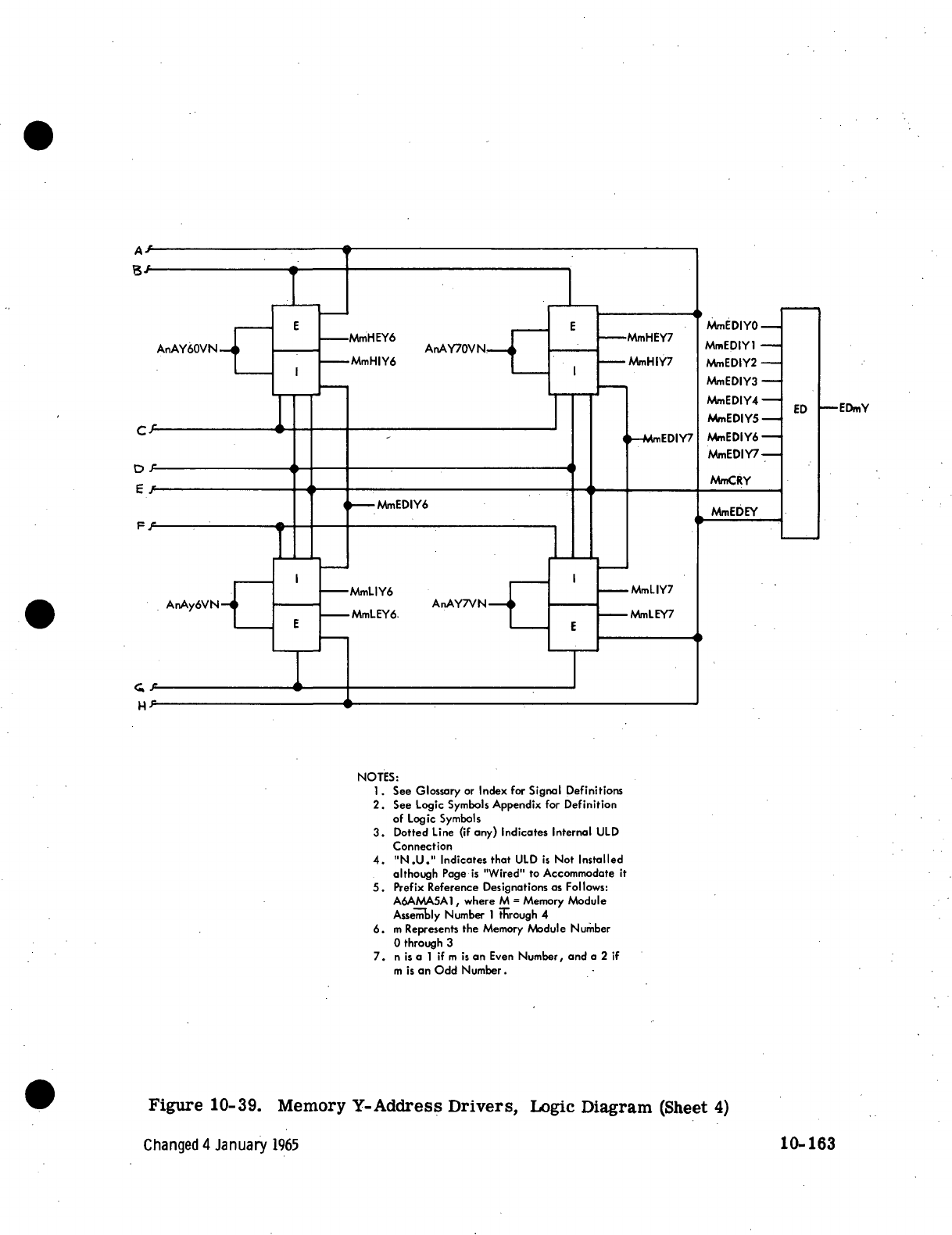

10-39 Memory Y-Address Drivers, Logic Diagram

(4

Sheets) 10-160

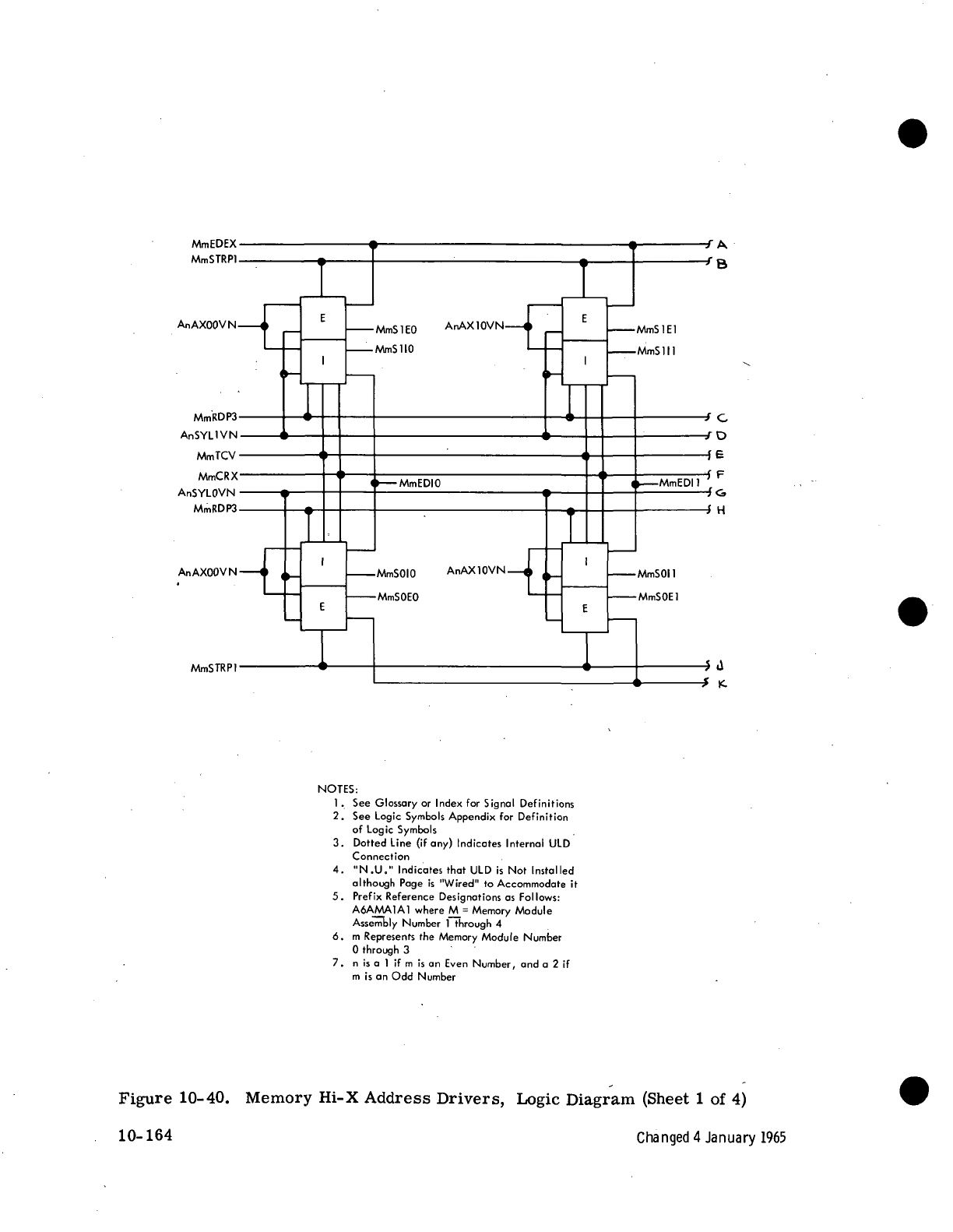

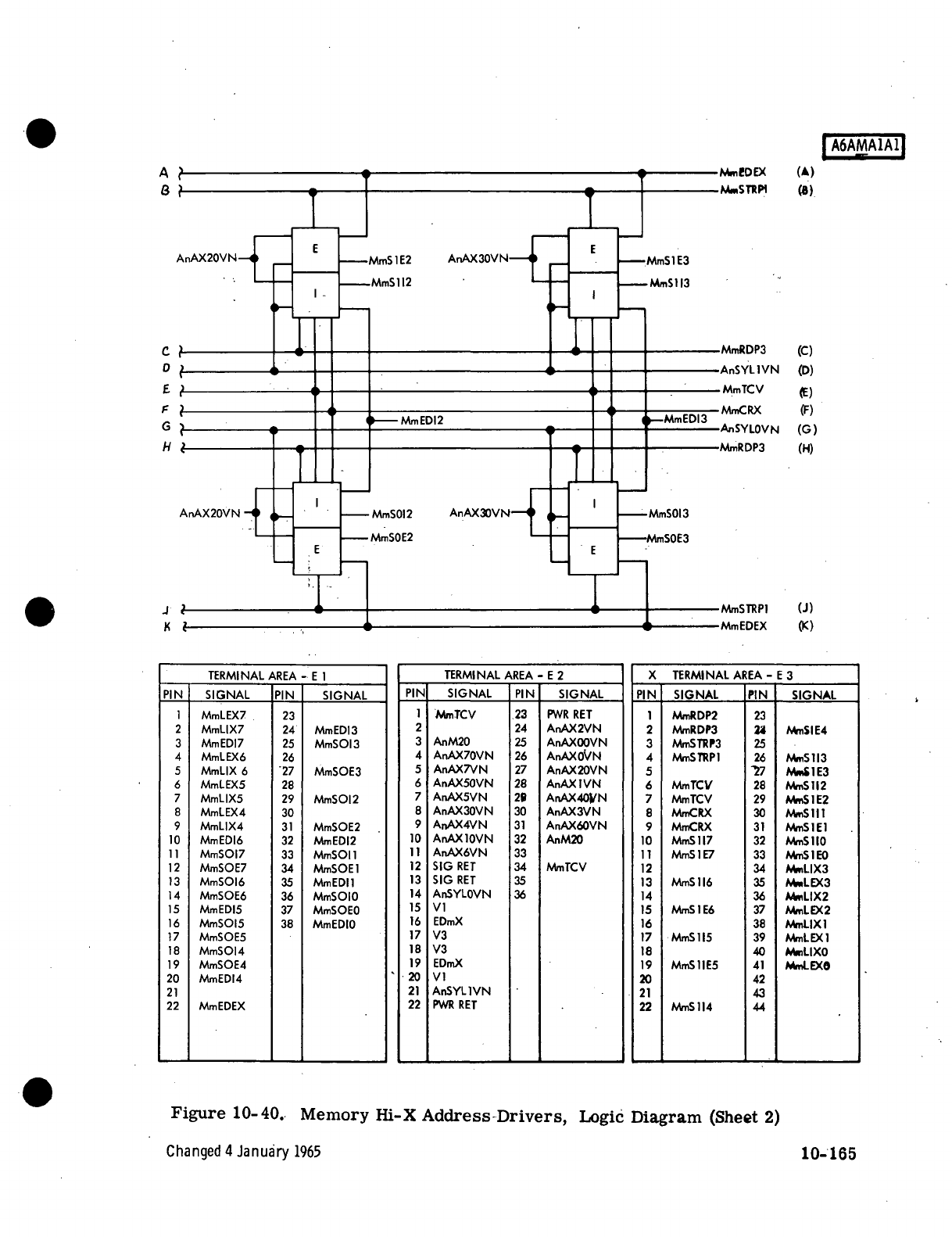

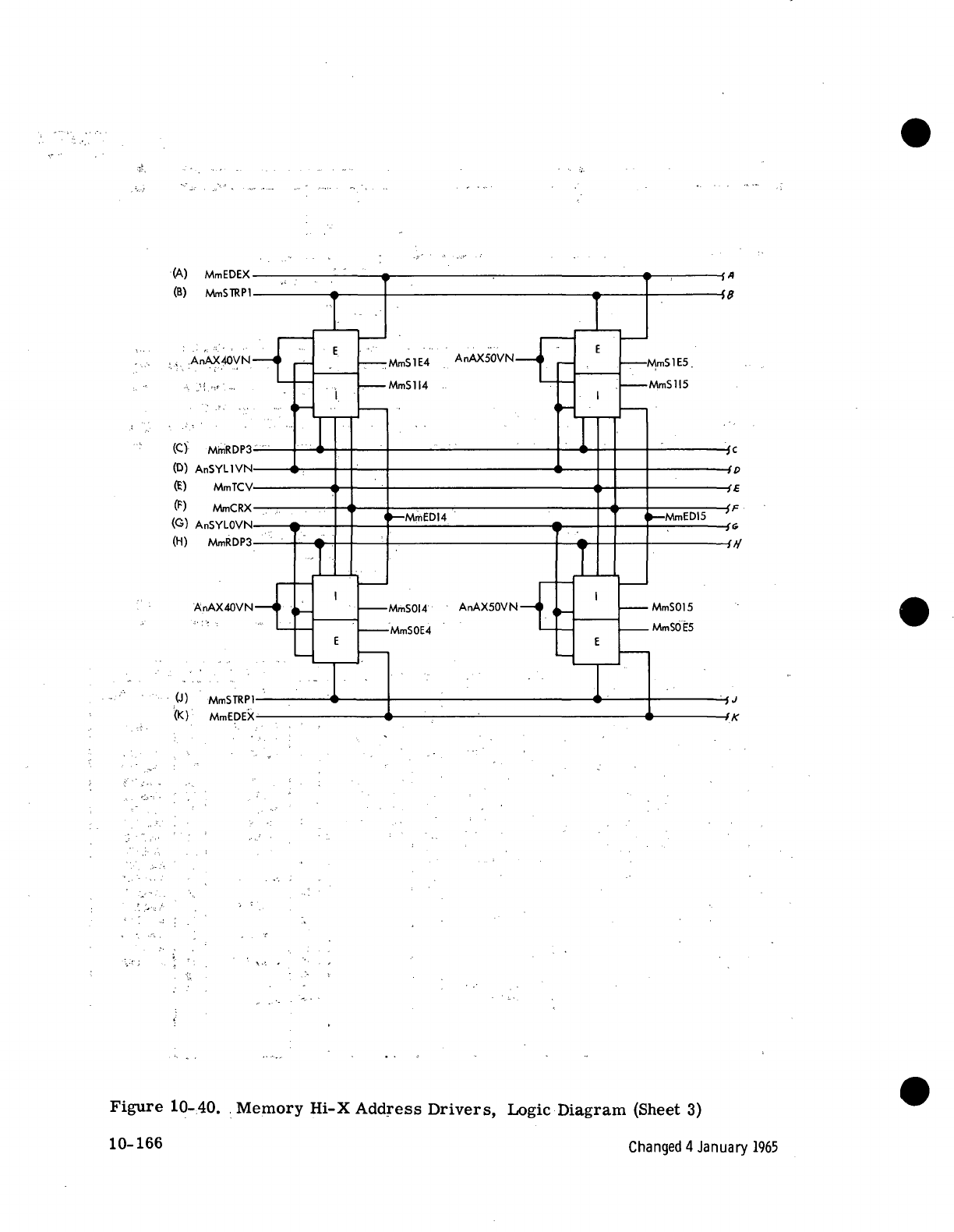

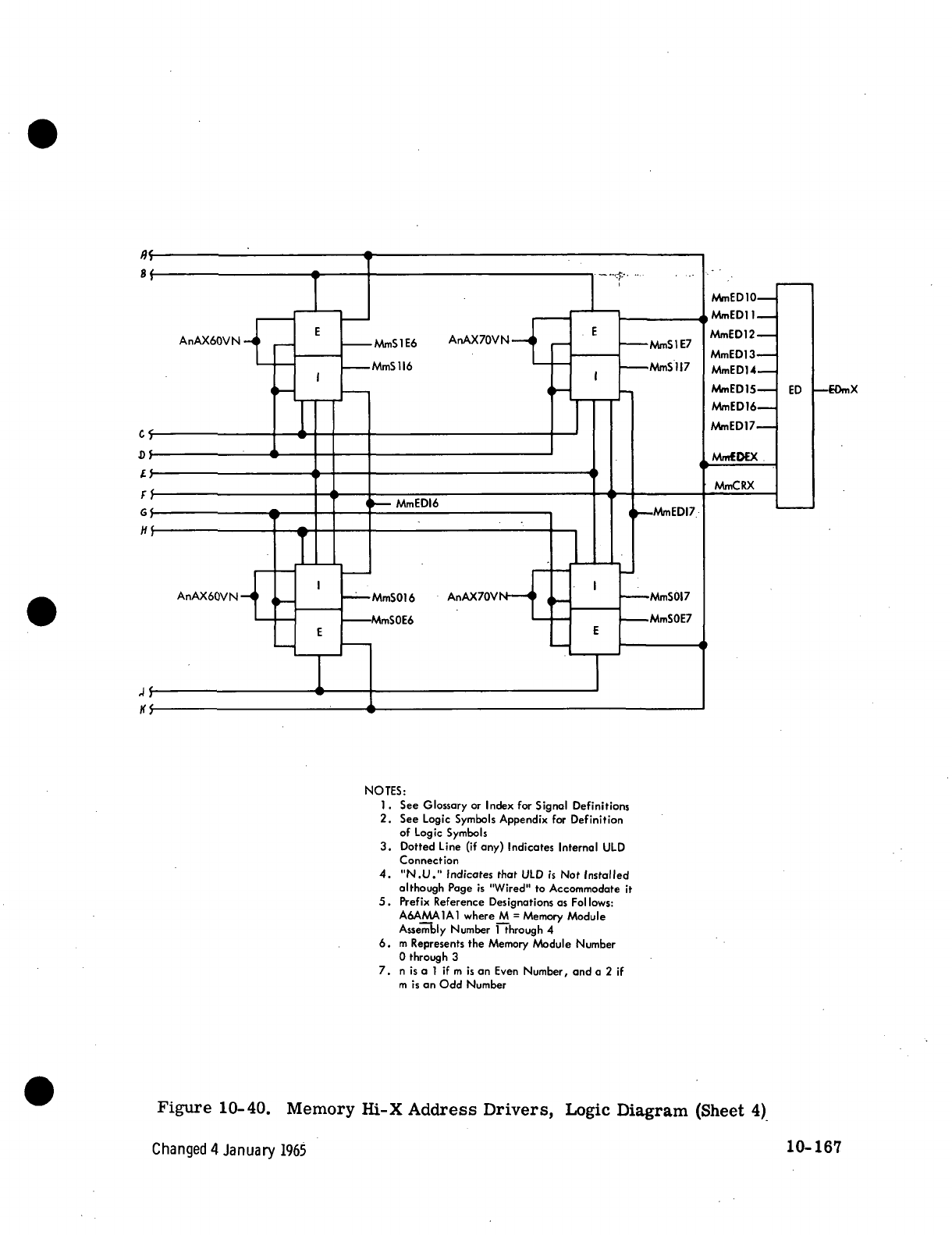

10-40

Memory Hi-X Address Drivers, Logic Diagram

(4

Sheets) 10-164

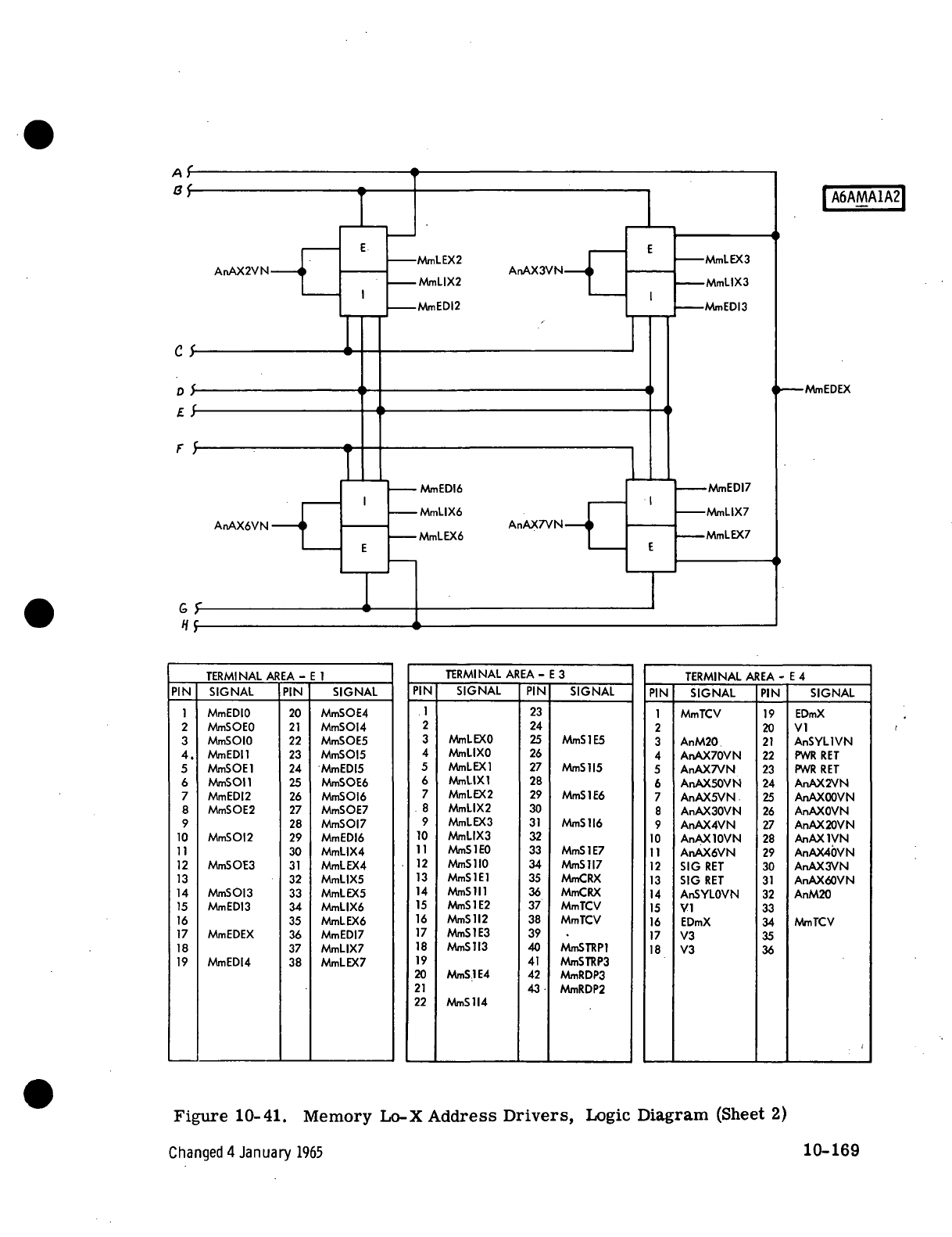

10-41 Memory Lo-X Address

Drivers,

Logic Diagram

(2

Sheets)

'

10-168

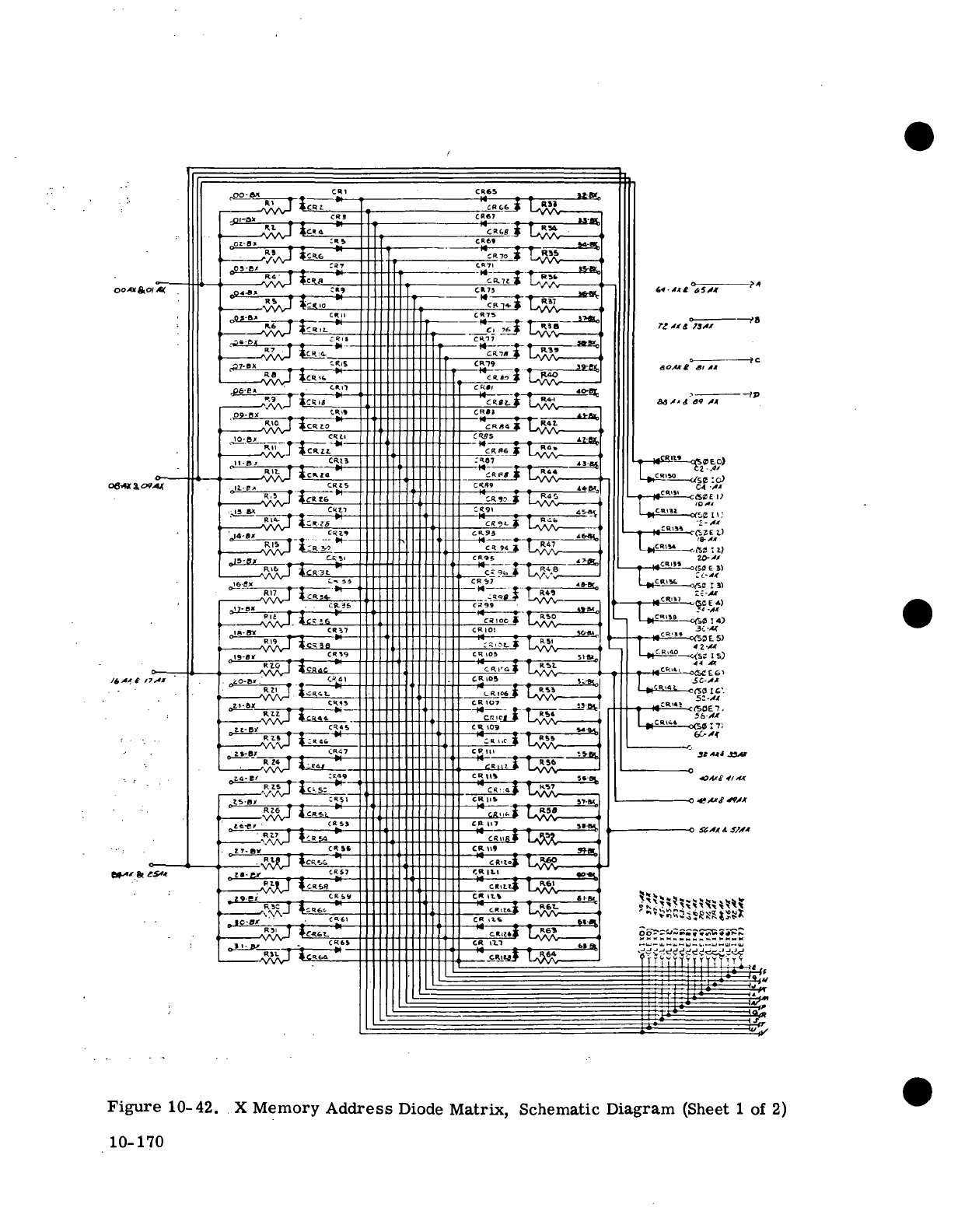

10-42

X

Memory Address

Diode

Matrix, Schematic Diagram

(2

Sheets) 10-170

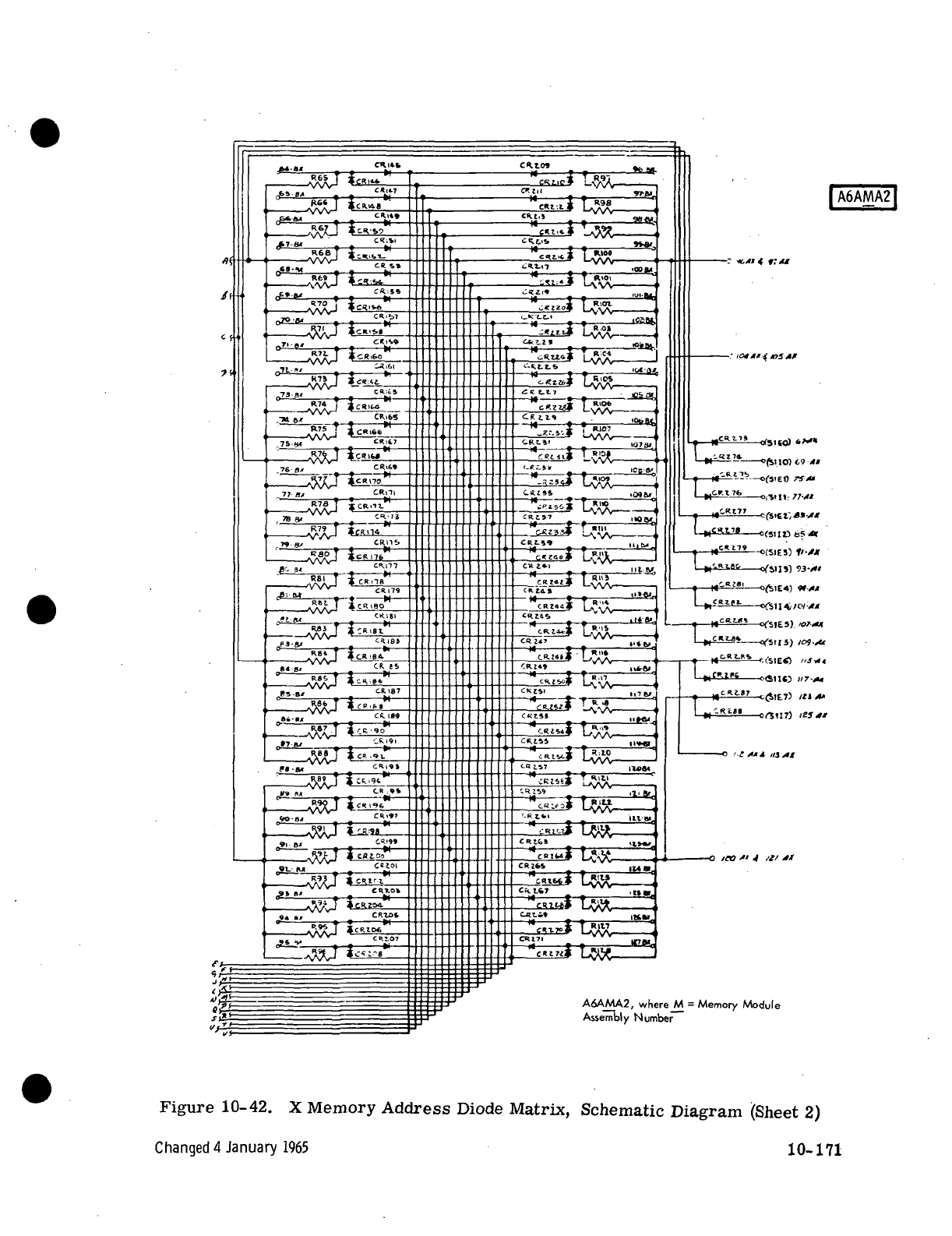

10-43

Y

Memory Address

Diode

Matrix, Schematic Diagram

(2

Sheets) 10-172

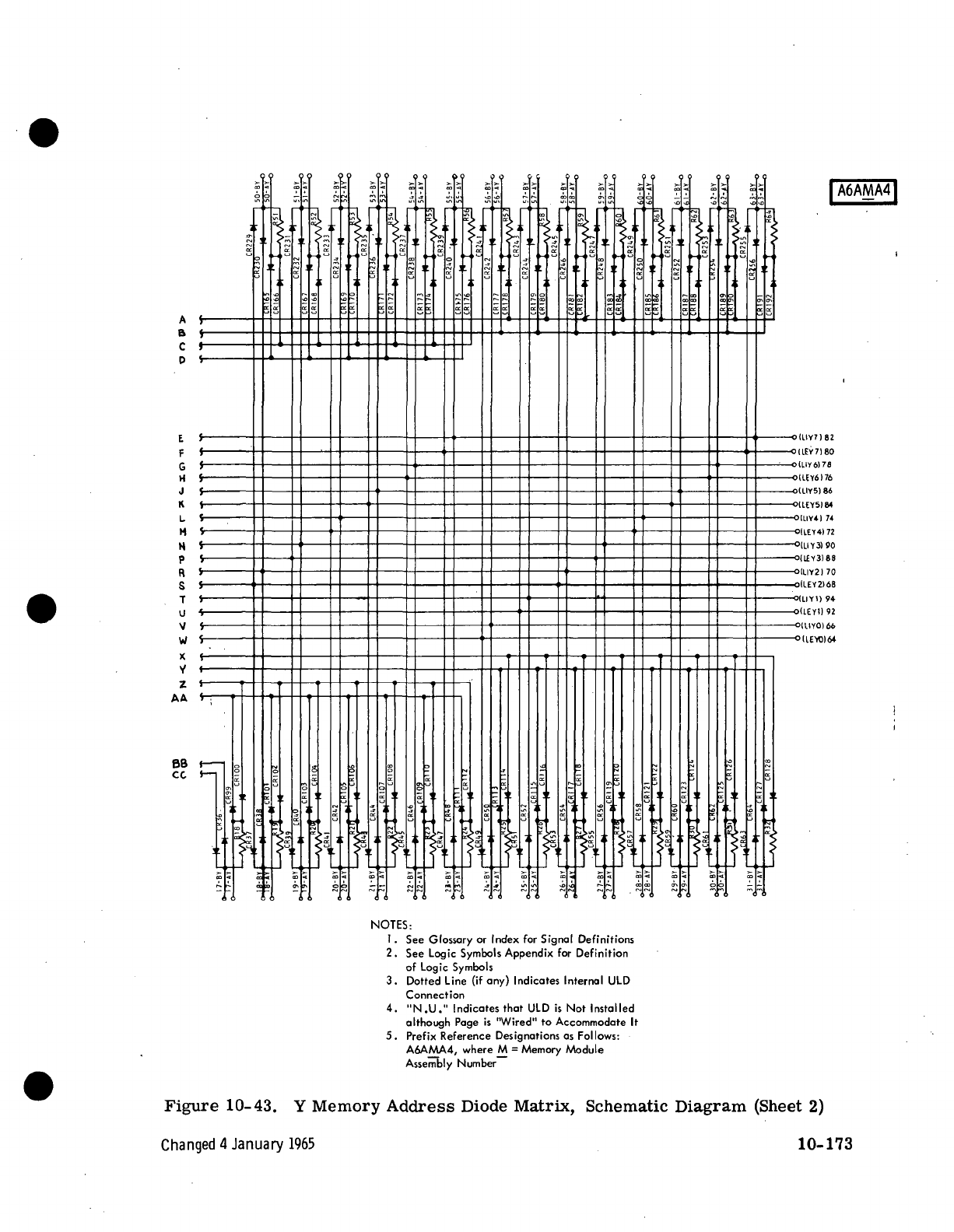

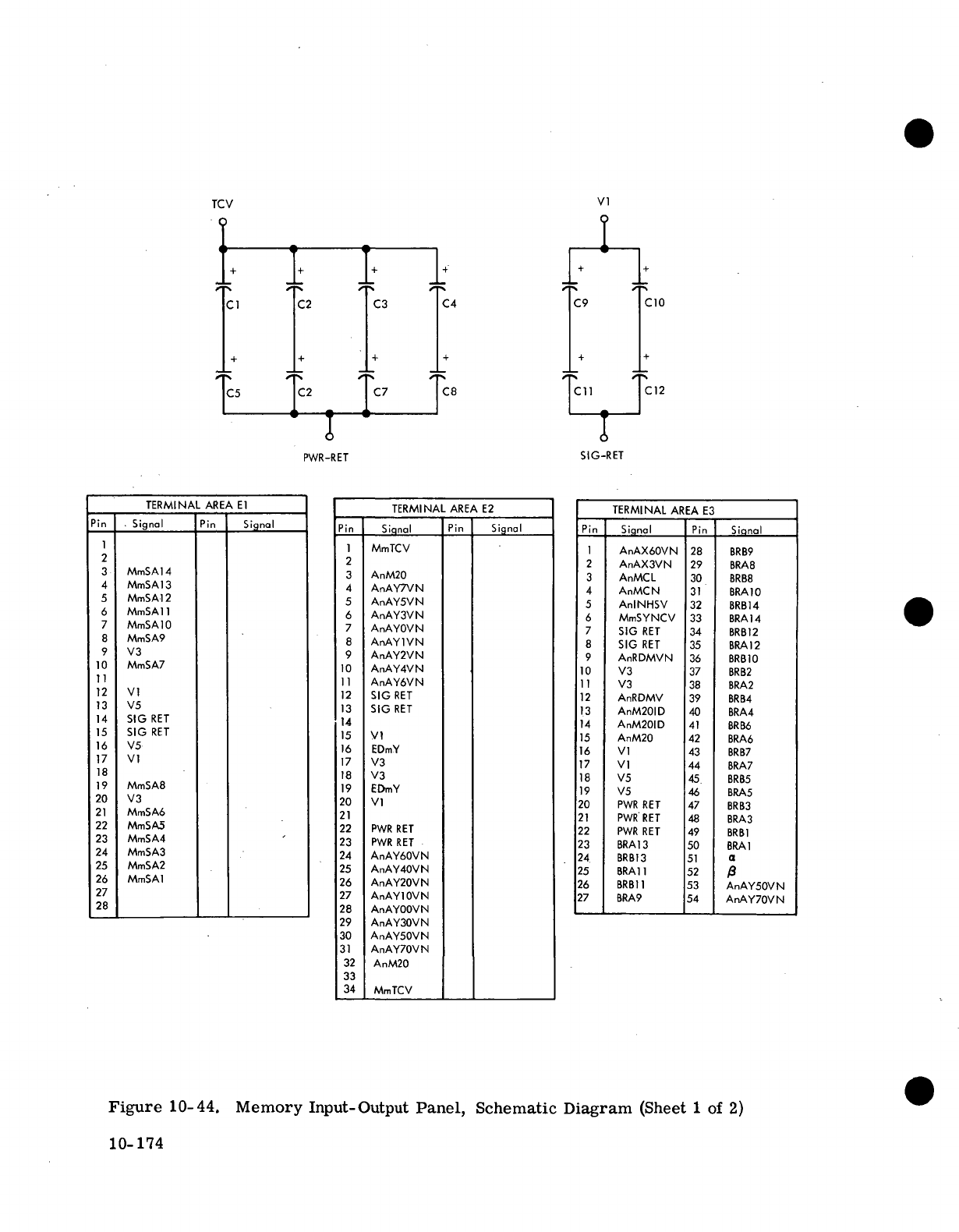

10-44

Memory

Input-Output Panel, Schematic Diagram

(2

Sheets) 10-174

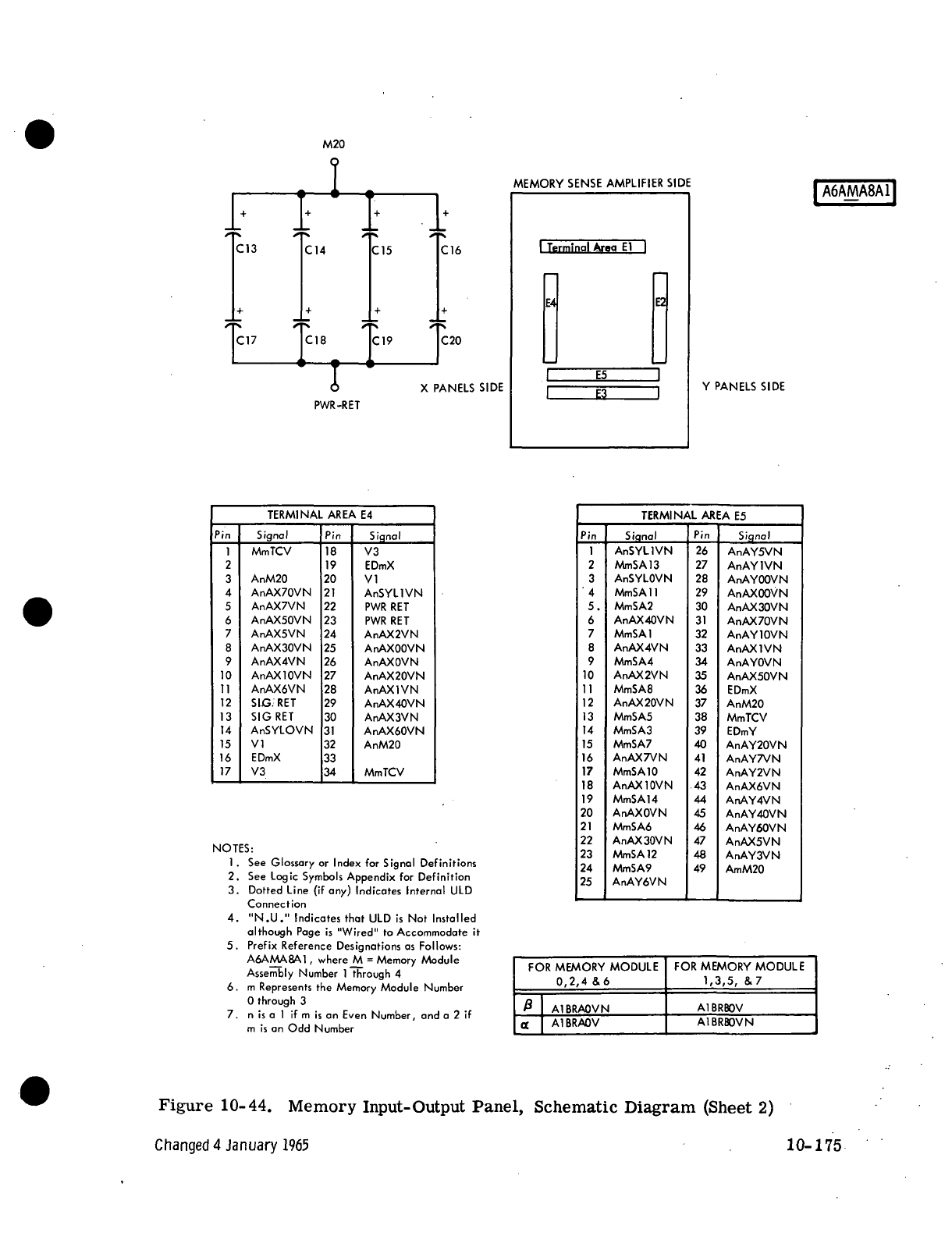

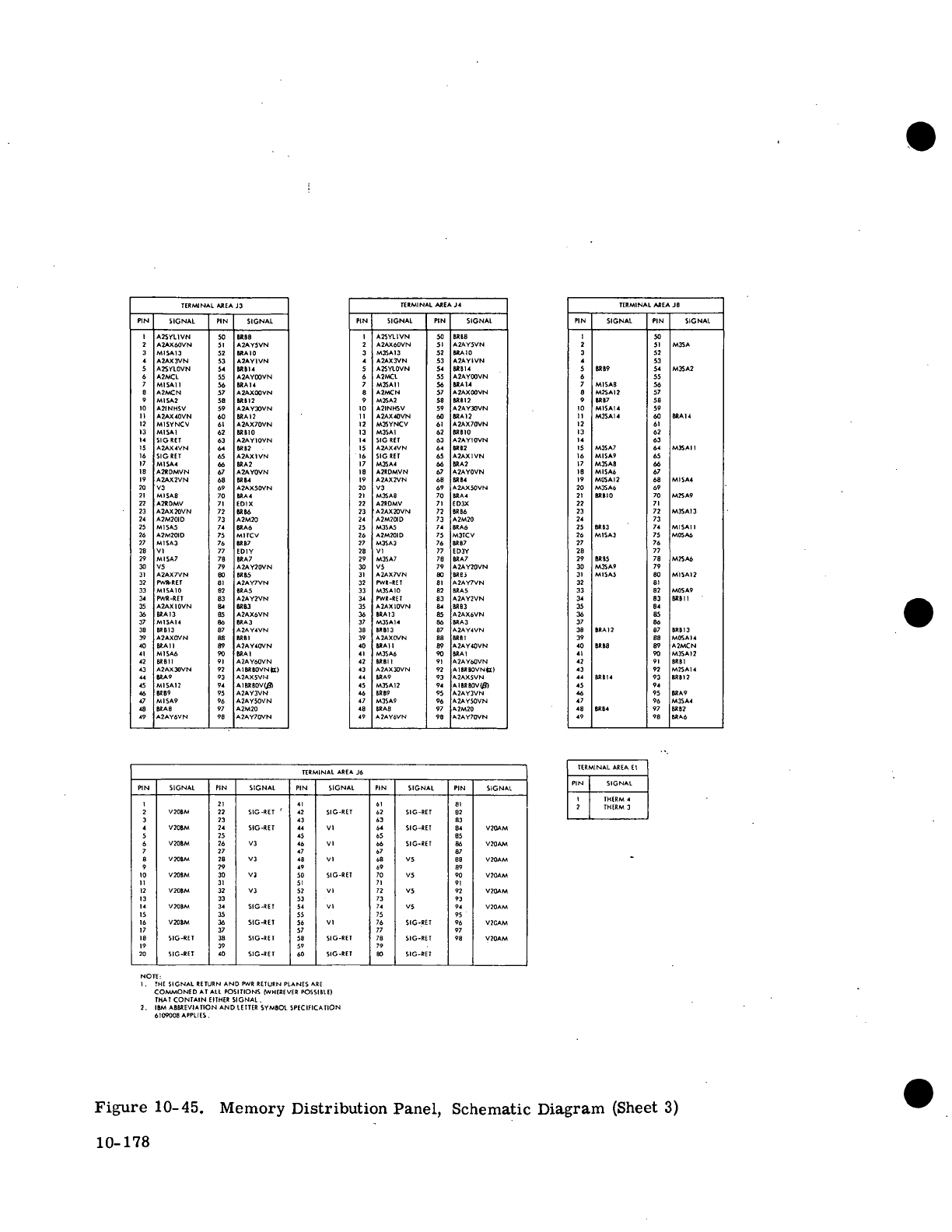

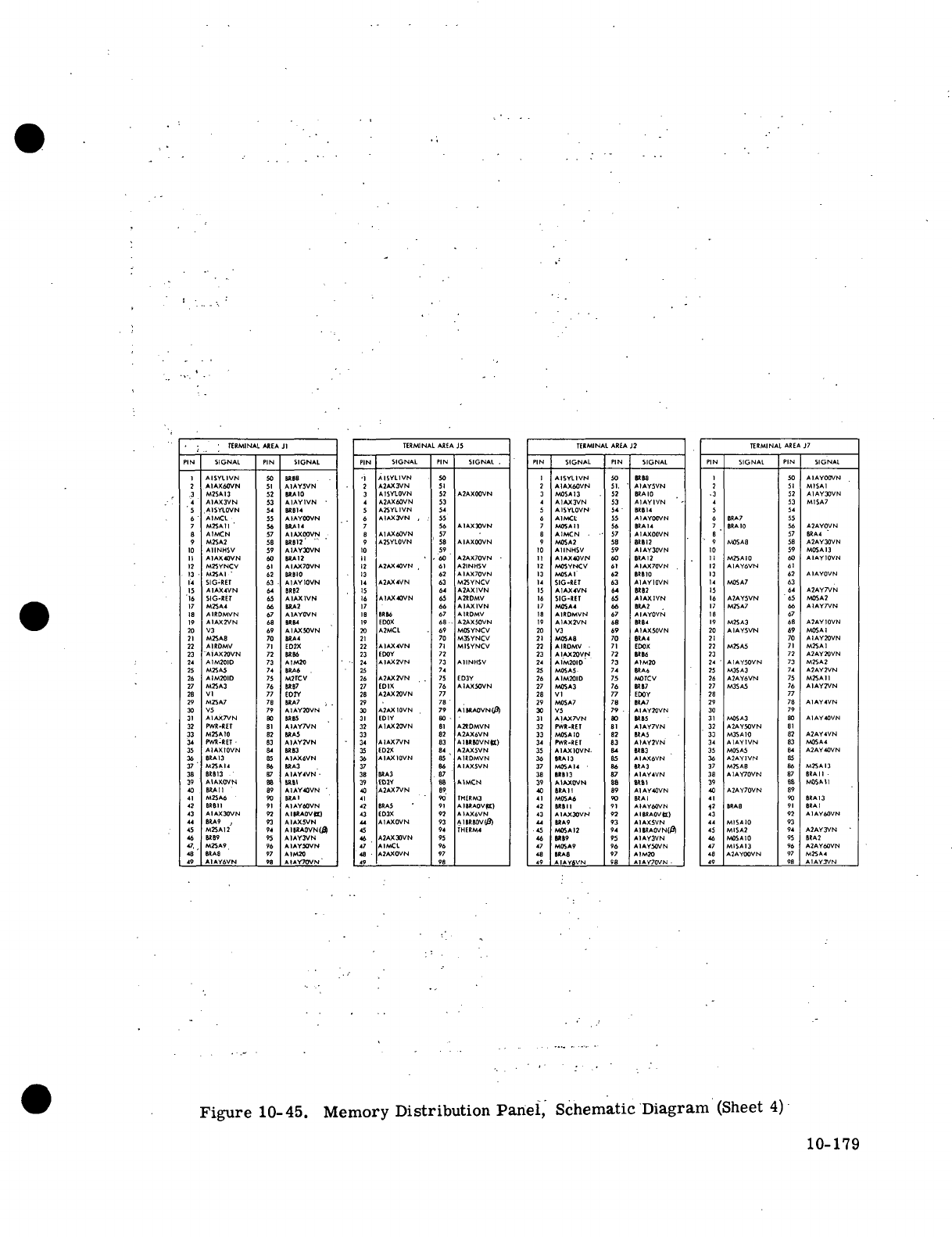

10-45 Memory Distribution Panel, Schematic Diagram

(4

Sheets) 10-176

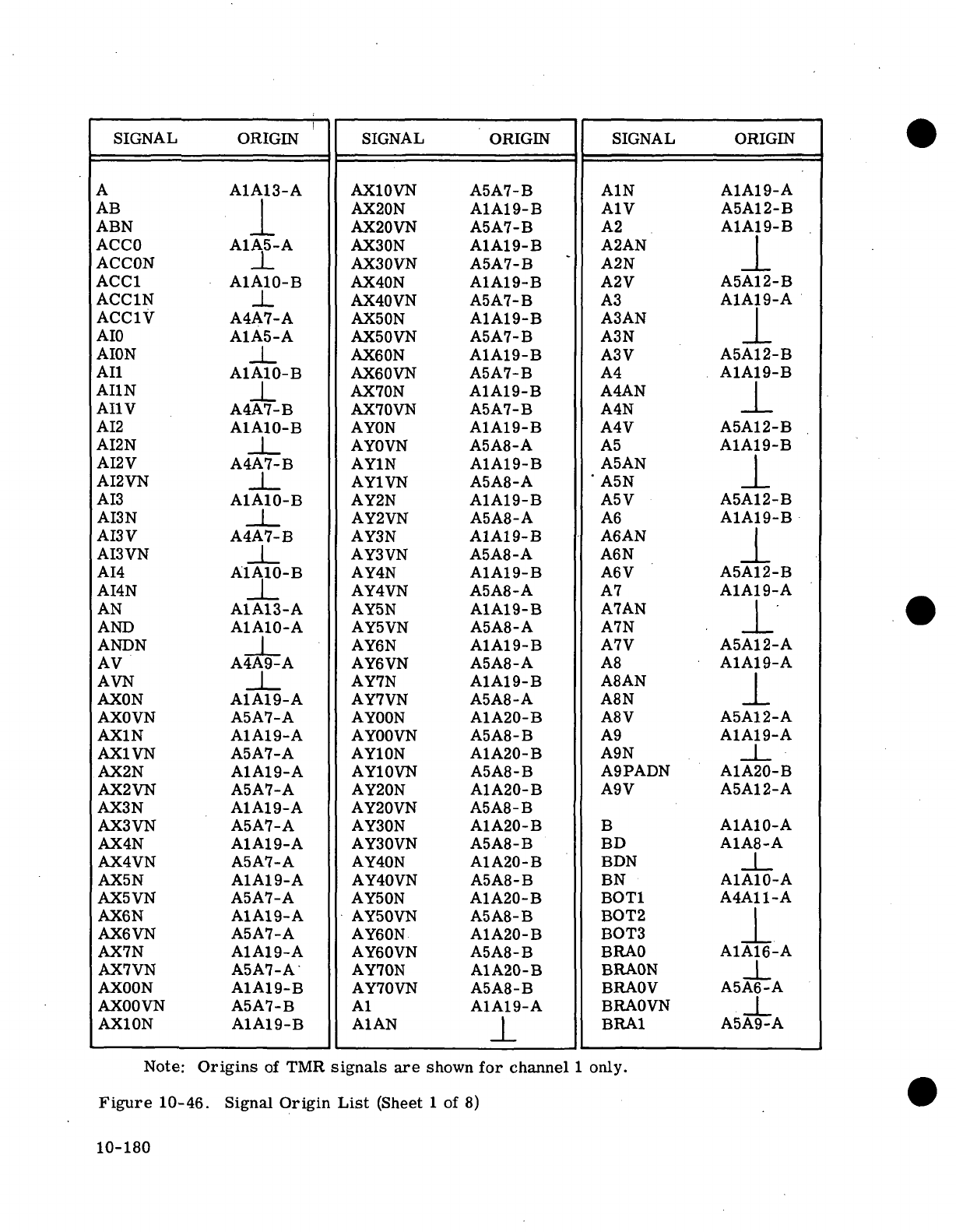

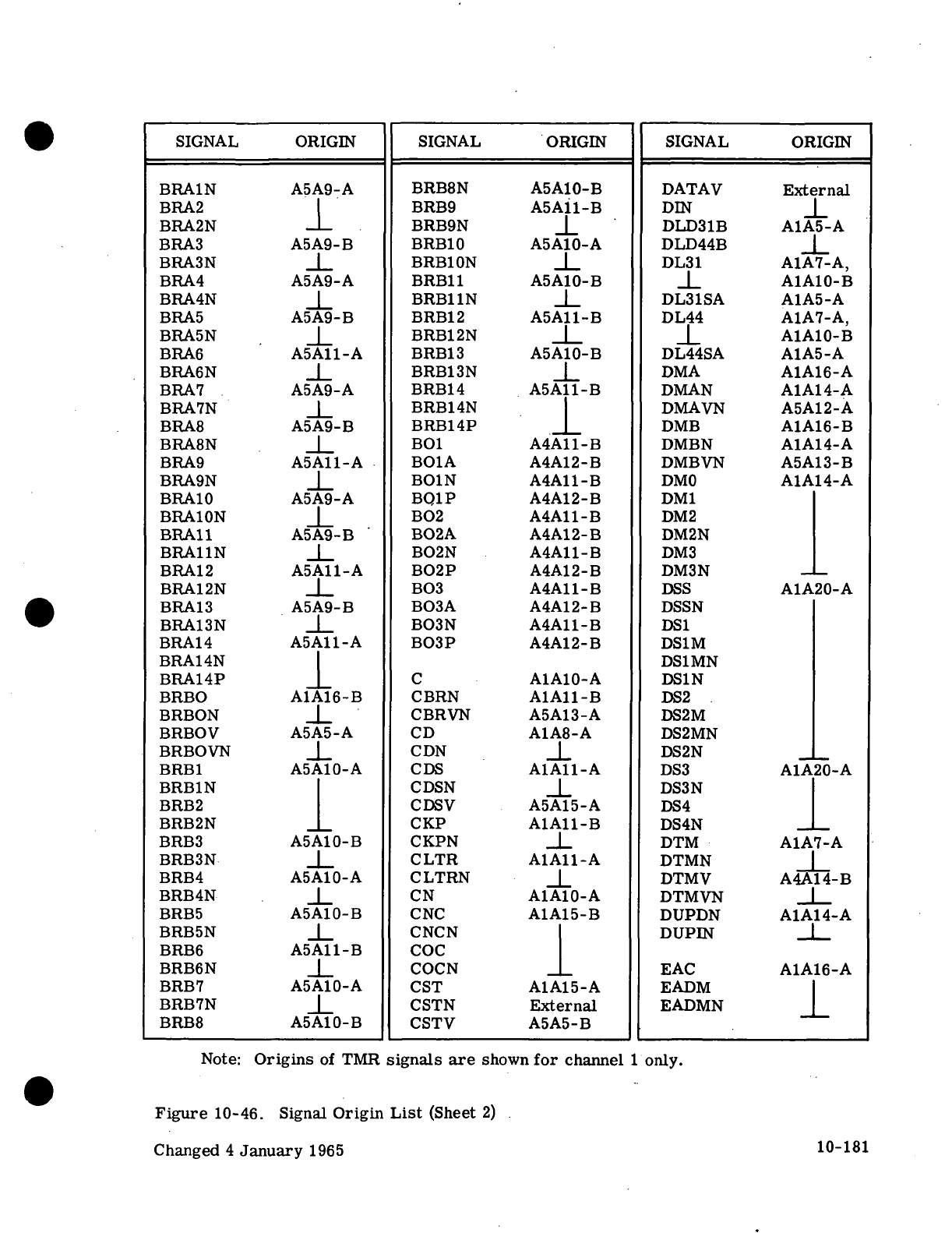

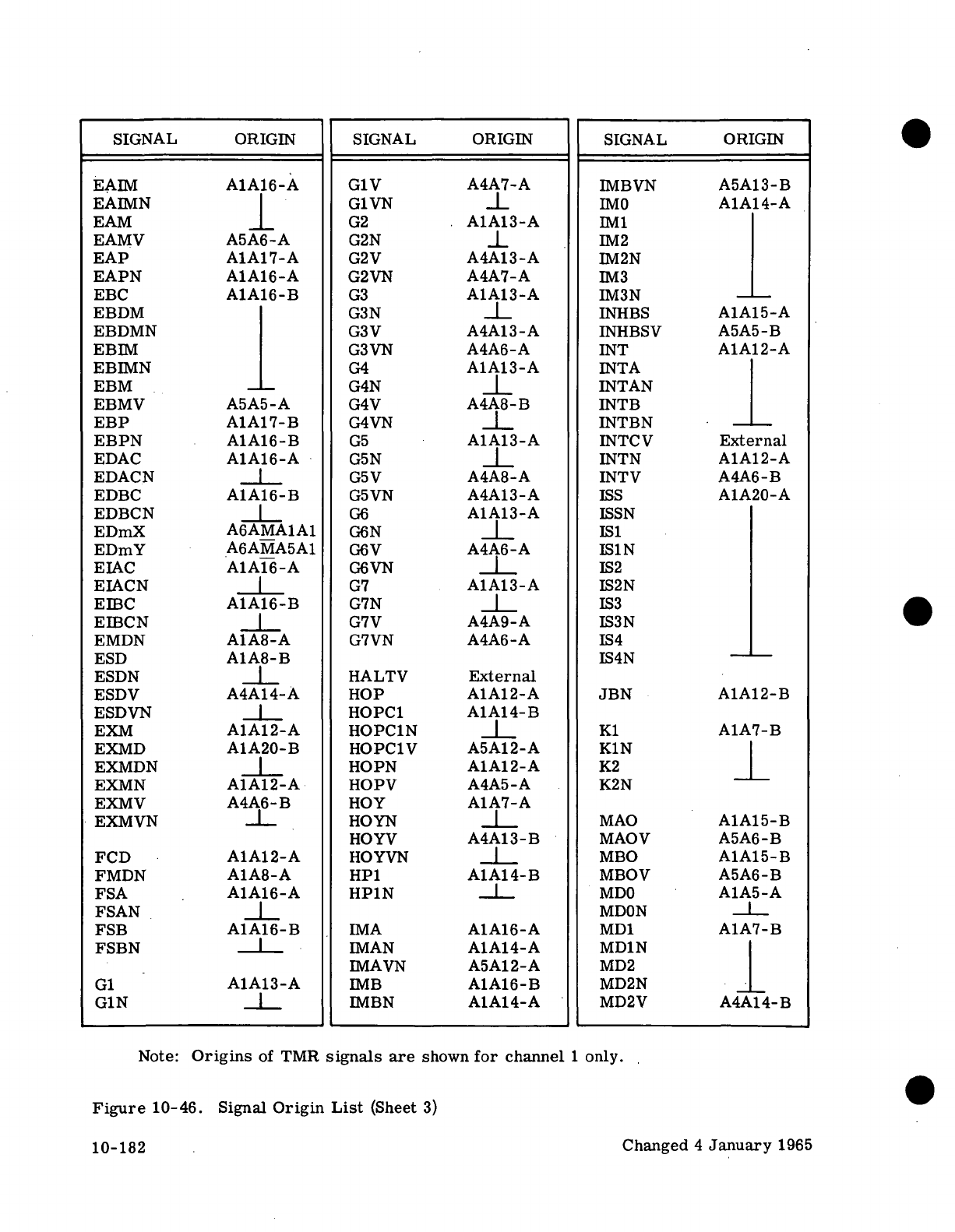

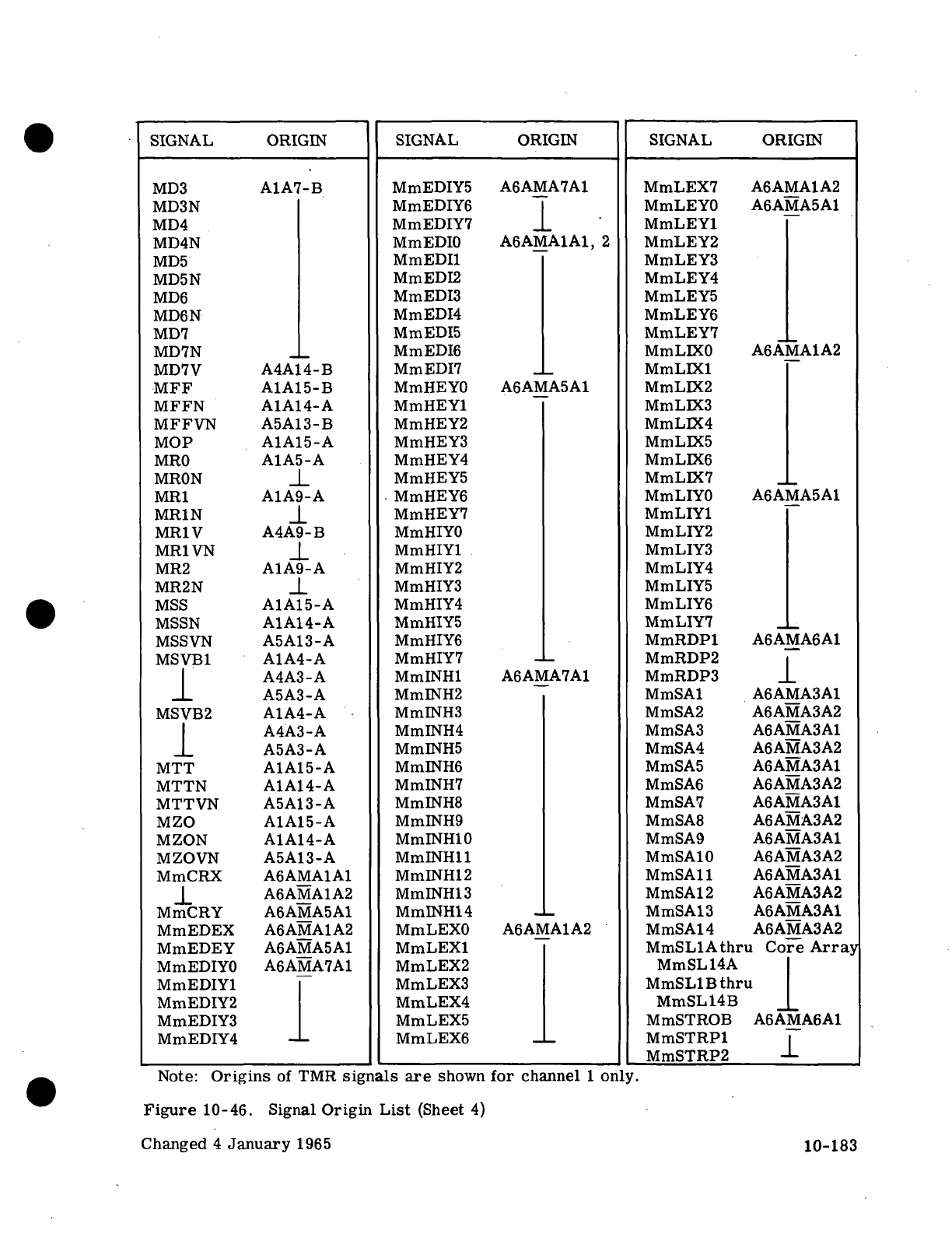

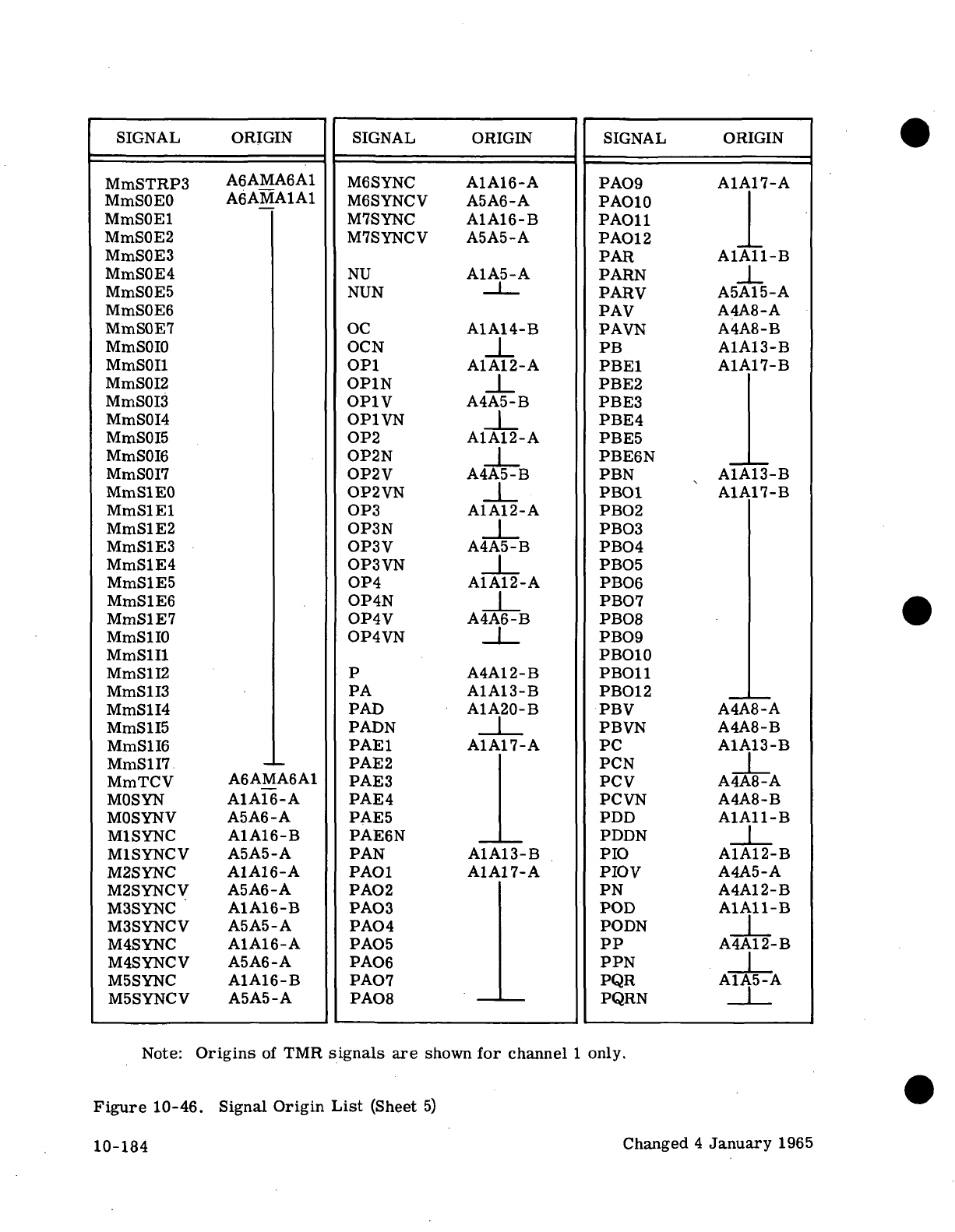

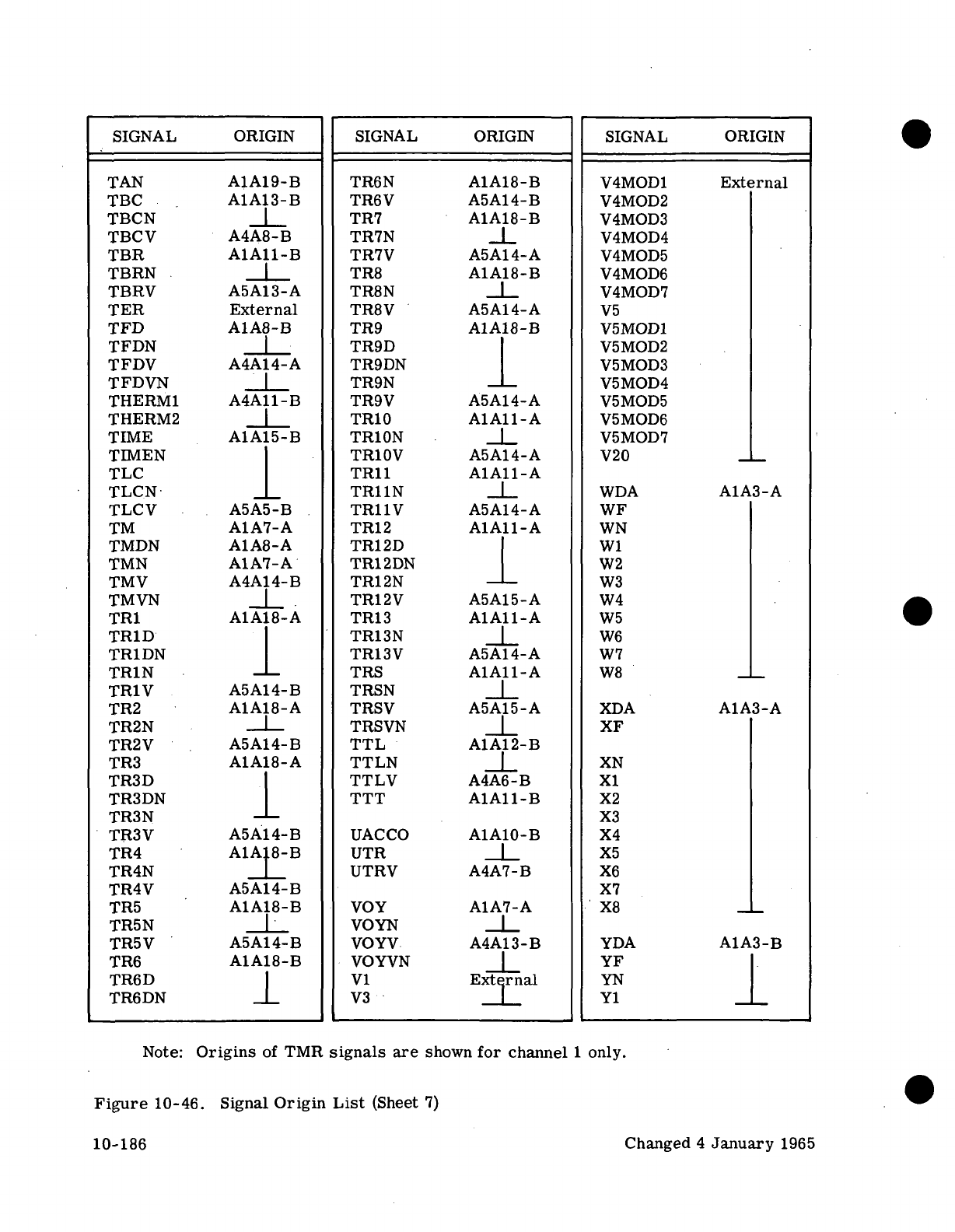

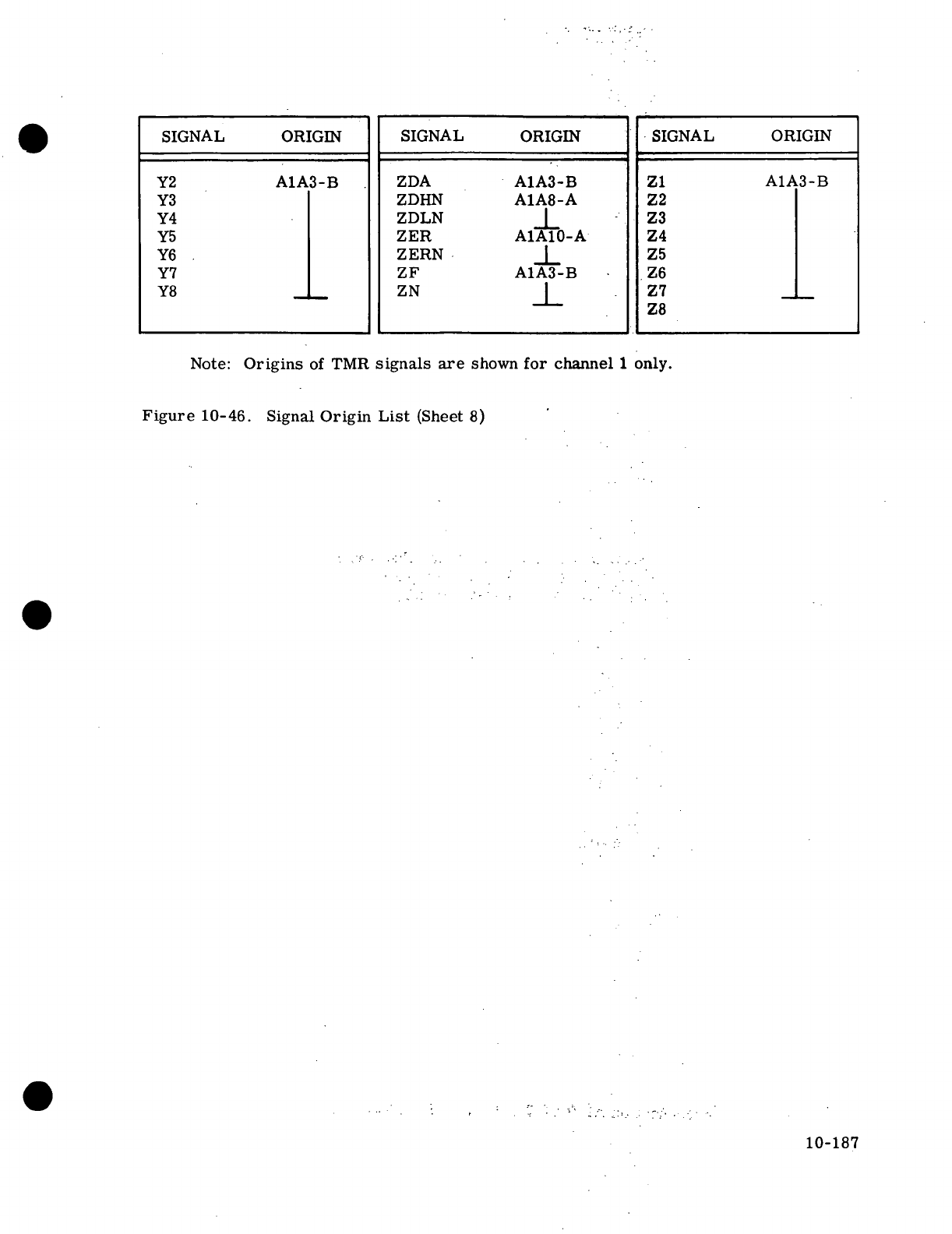

10-46 Signal Origin

List

(8

Sheets) 10-180

IV

Volume

H

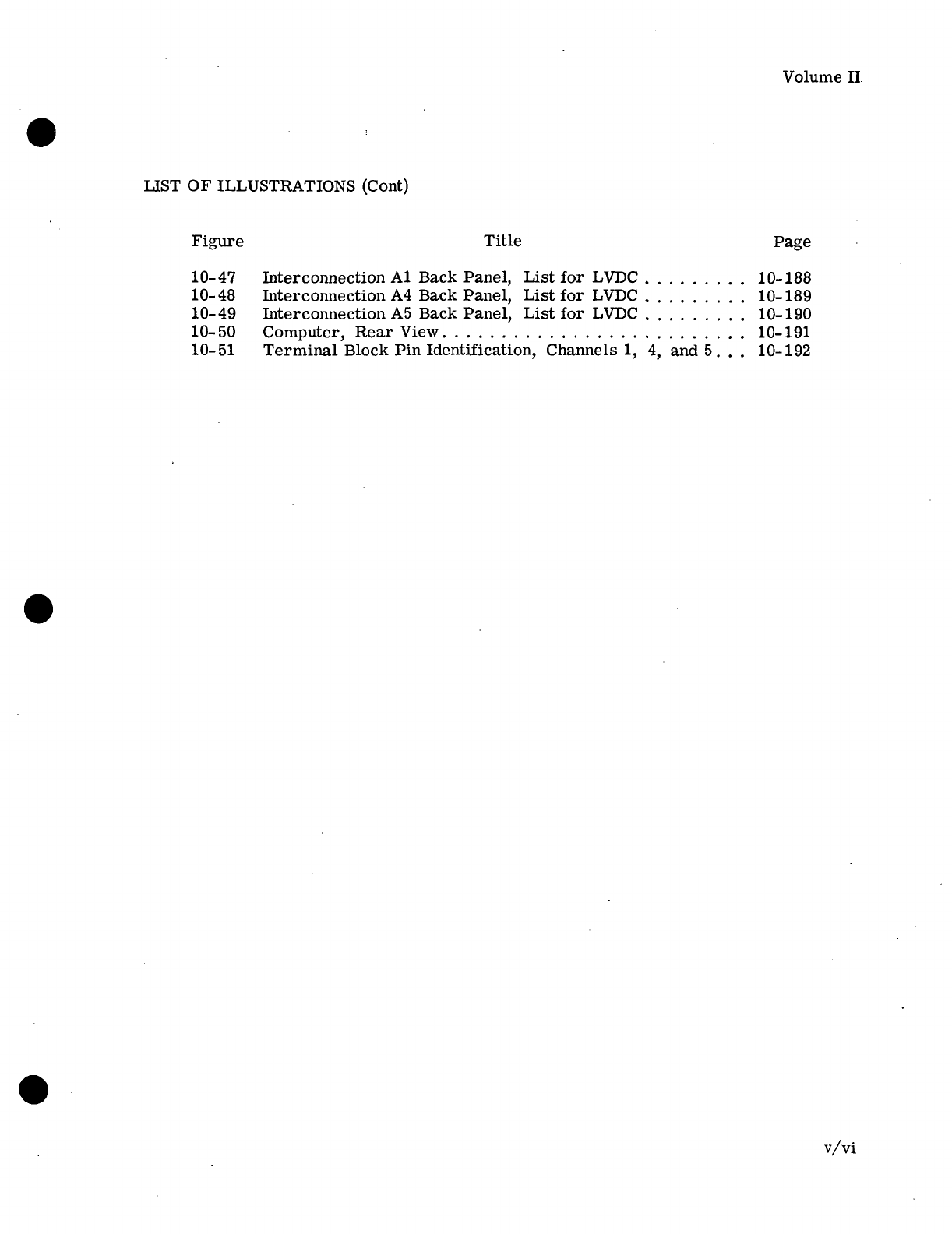

LIST

OF

ILLUSTRATIONS (Cont)

Figure

Title

Page

10-47 Interconnection

Al

Back

Panel,

List

for

LVDC

10-188

10-48 Interconnection

A4

Back Panel, List

for

LVDC

10-189

10-49 Interconnection

A5

Back

Panel,

List

for

LVDC

10-190

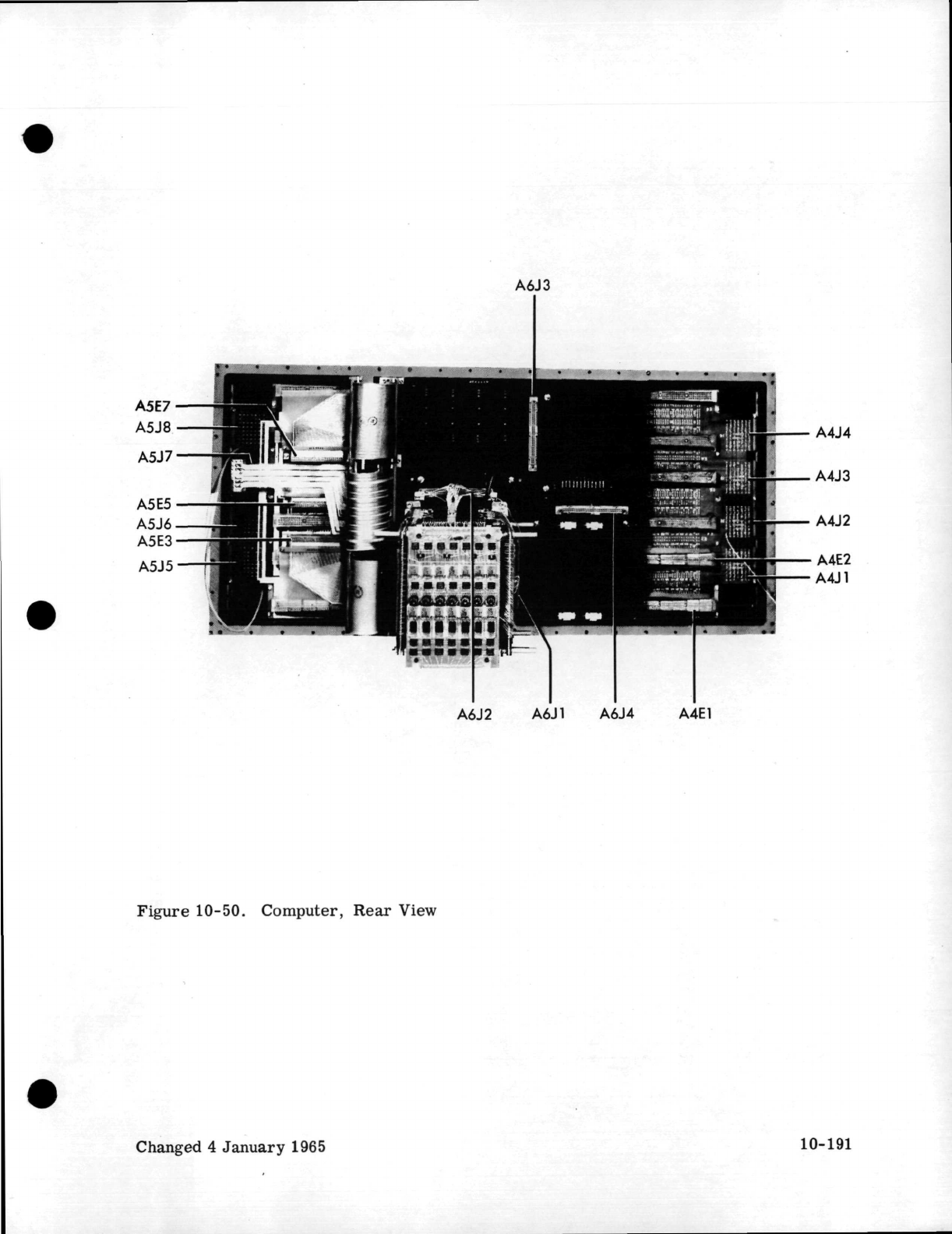

10-50 Computer, Rear

View

10-191

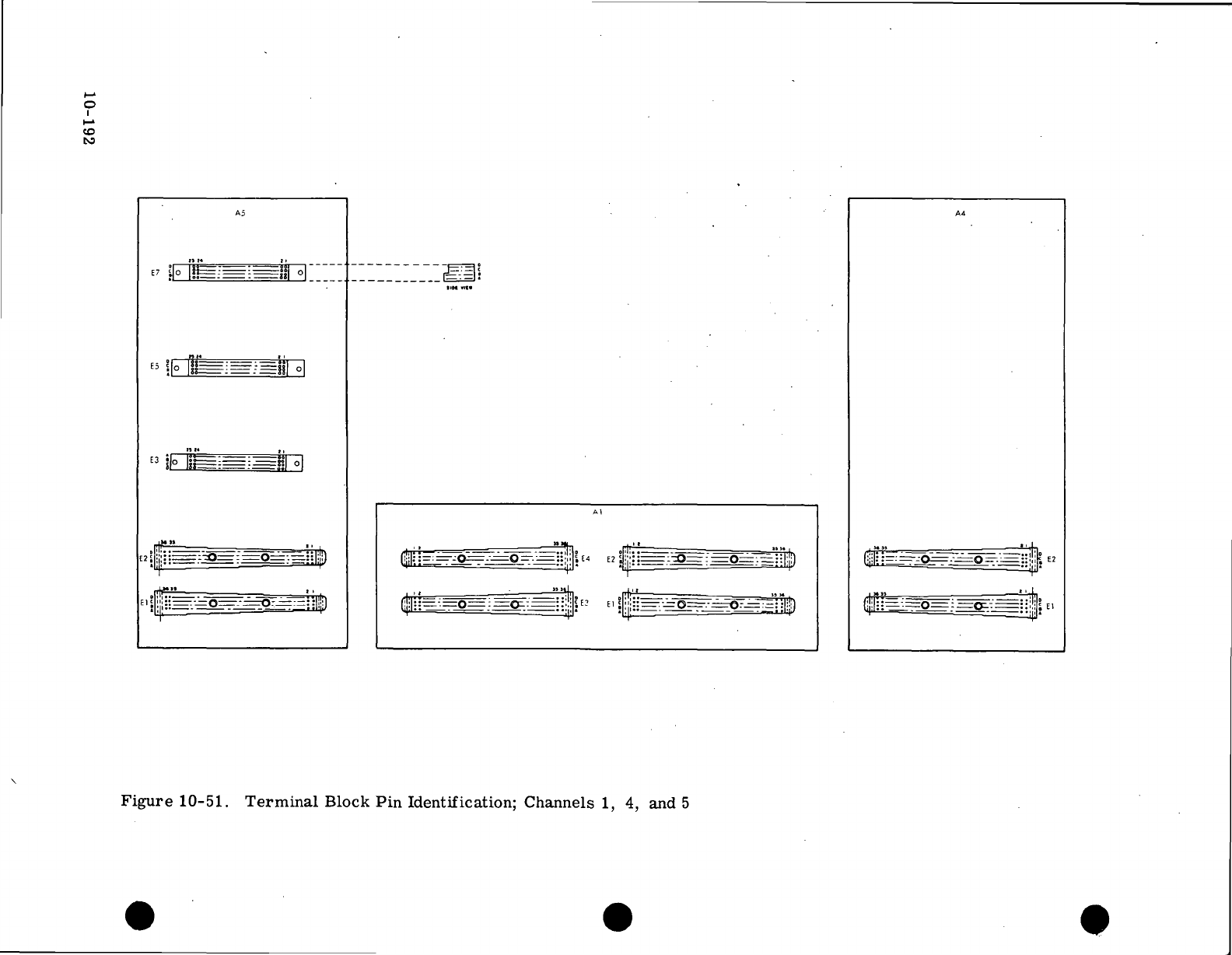

10-51 Terminal

Block

Pin

Identification, Channels

1, 4, and 5. . .

10-192

v/vi

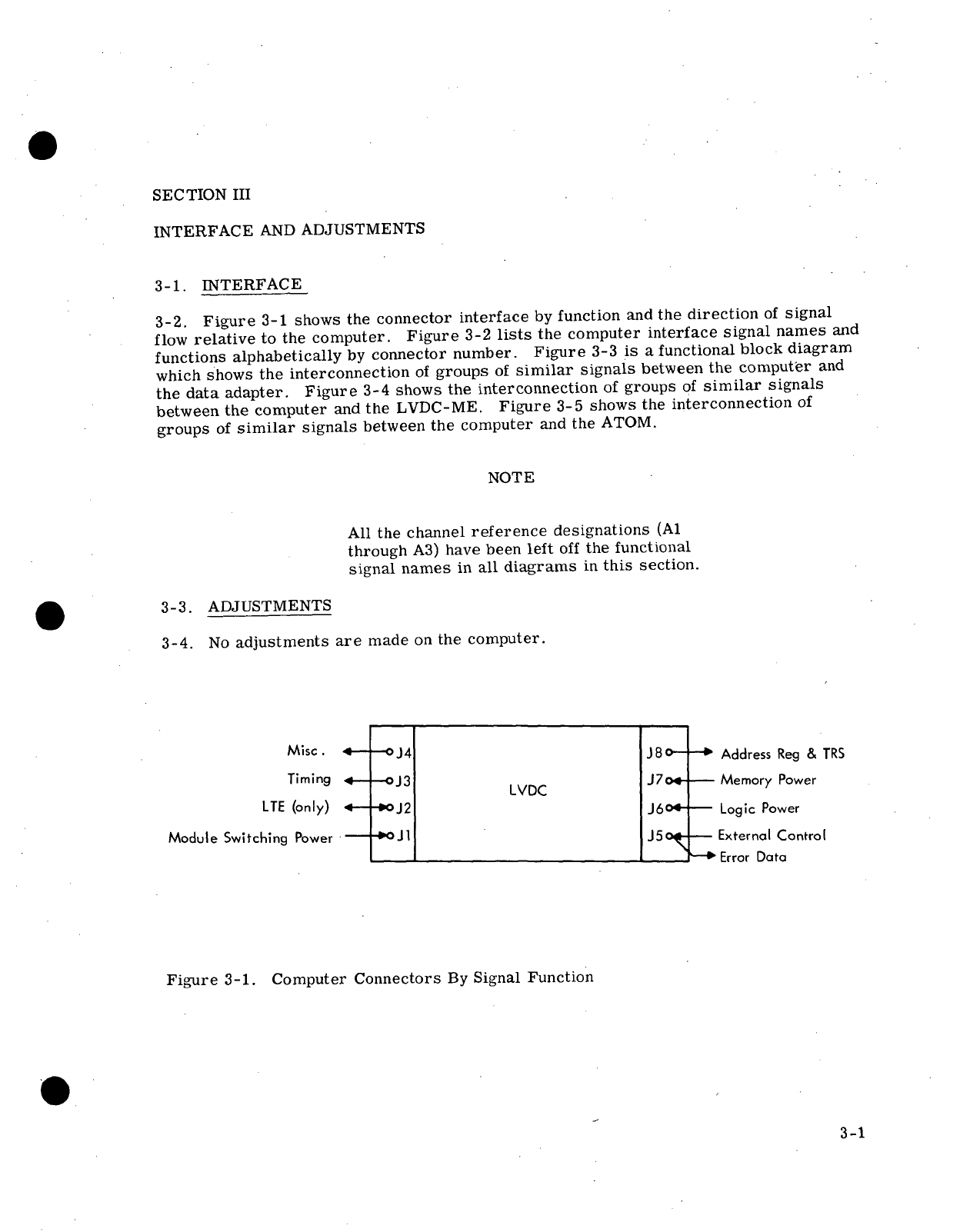

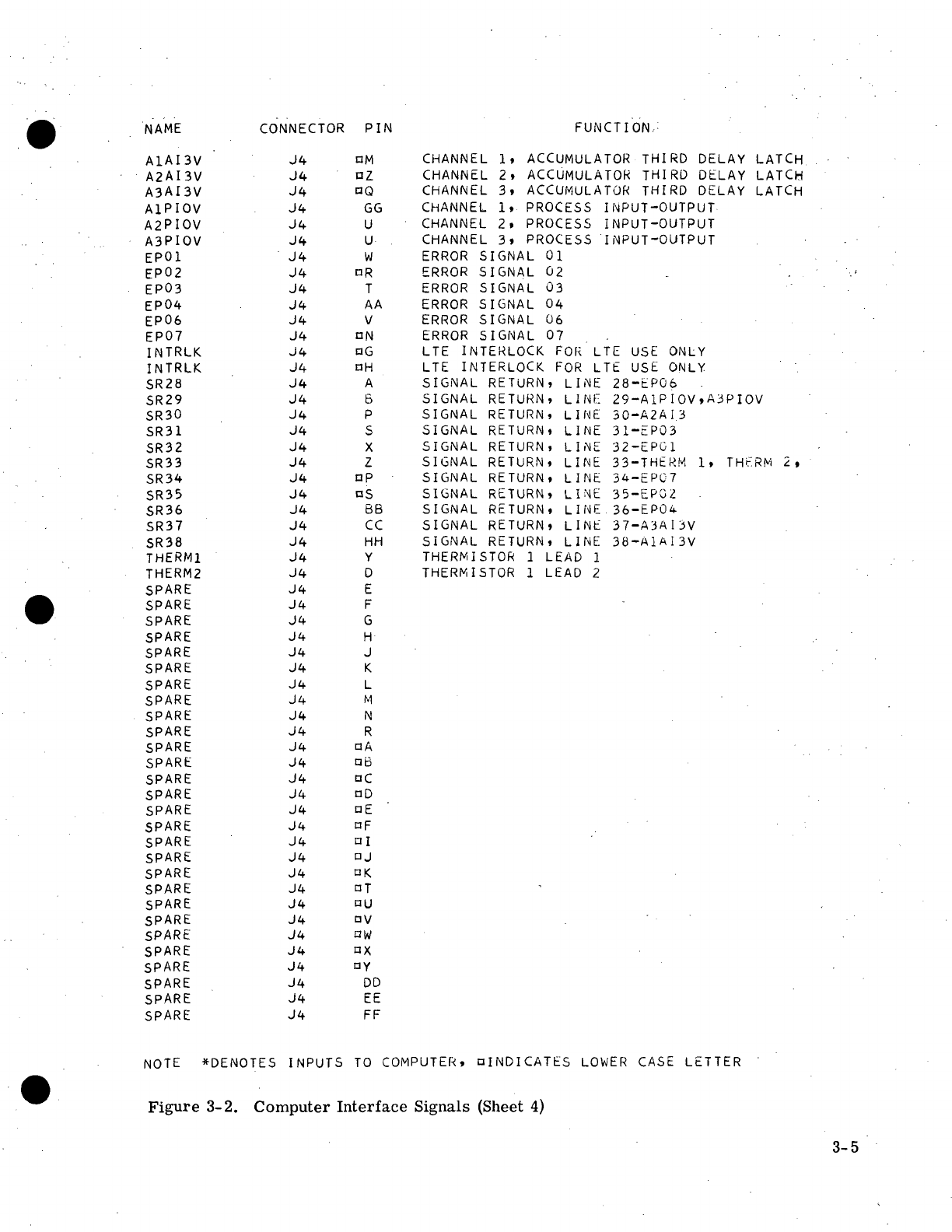

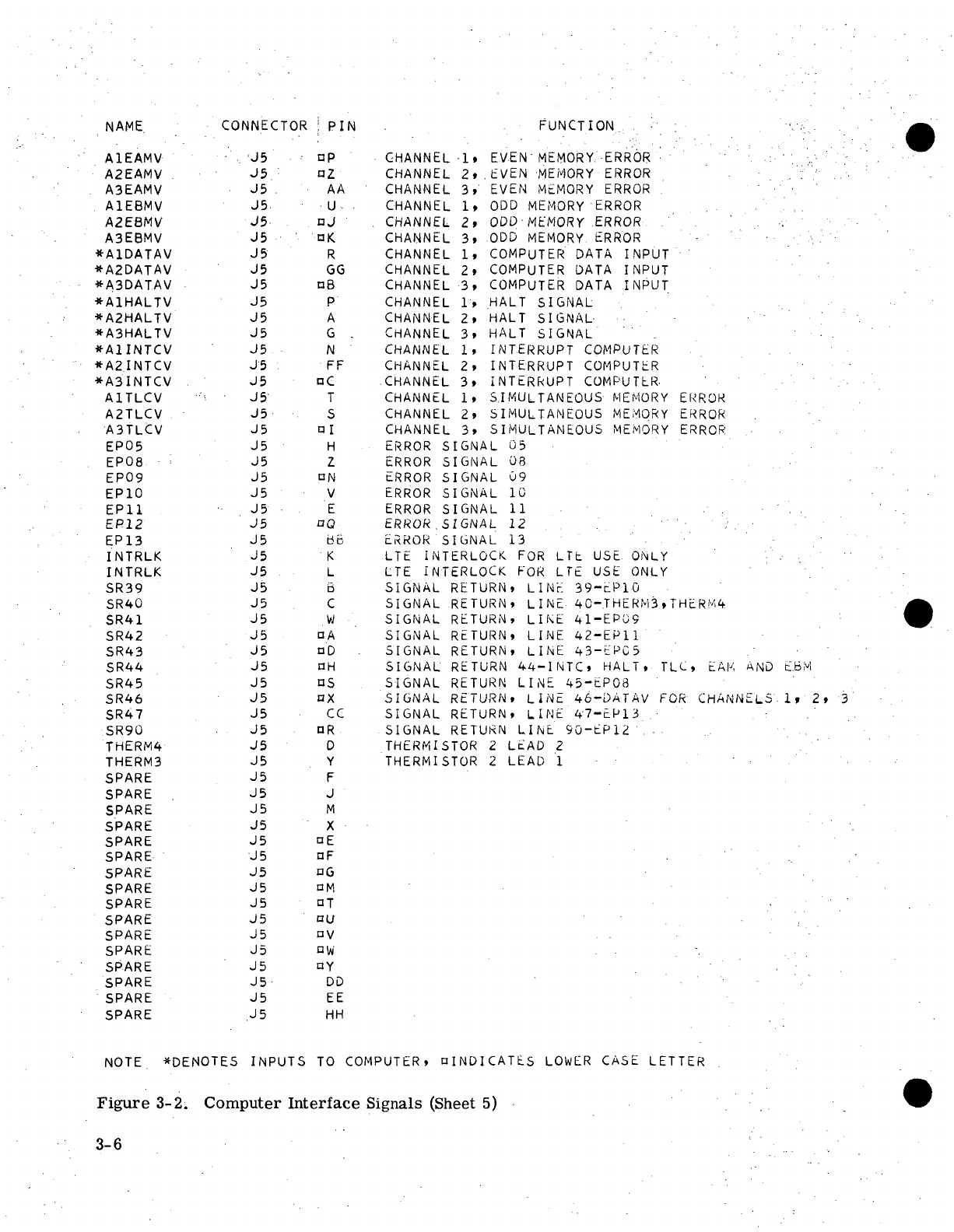

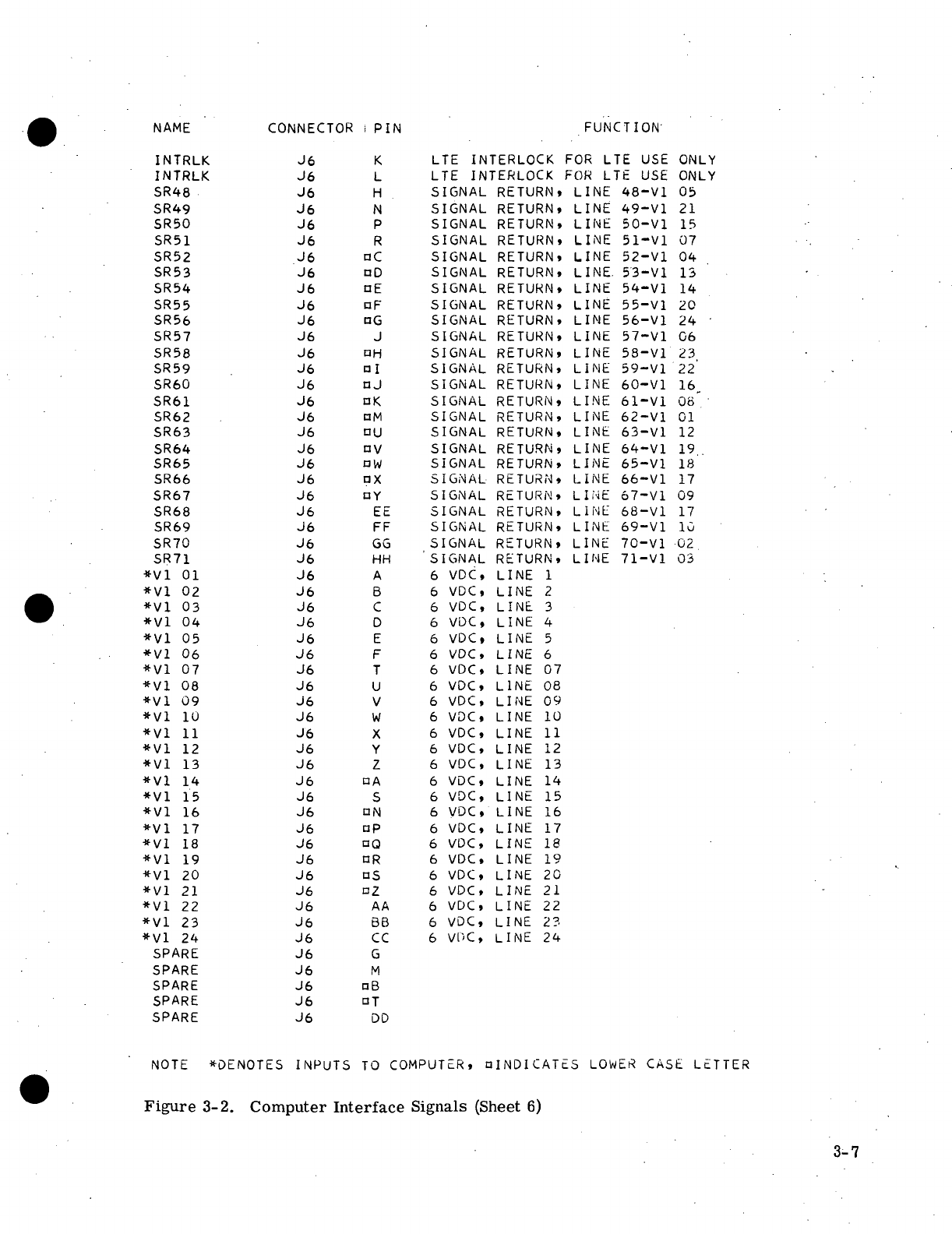

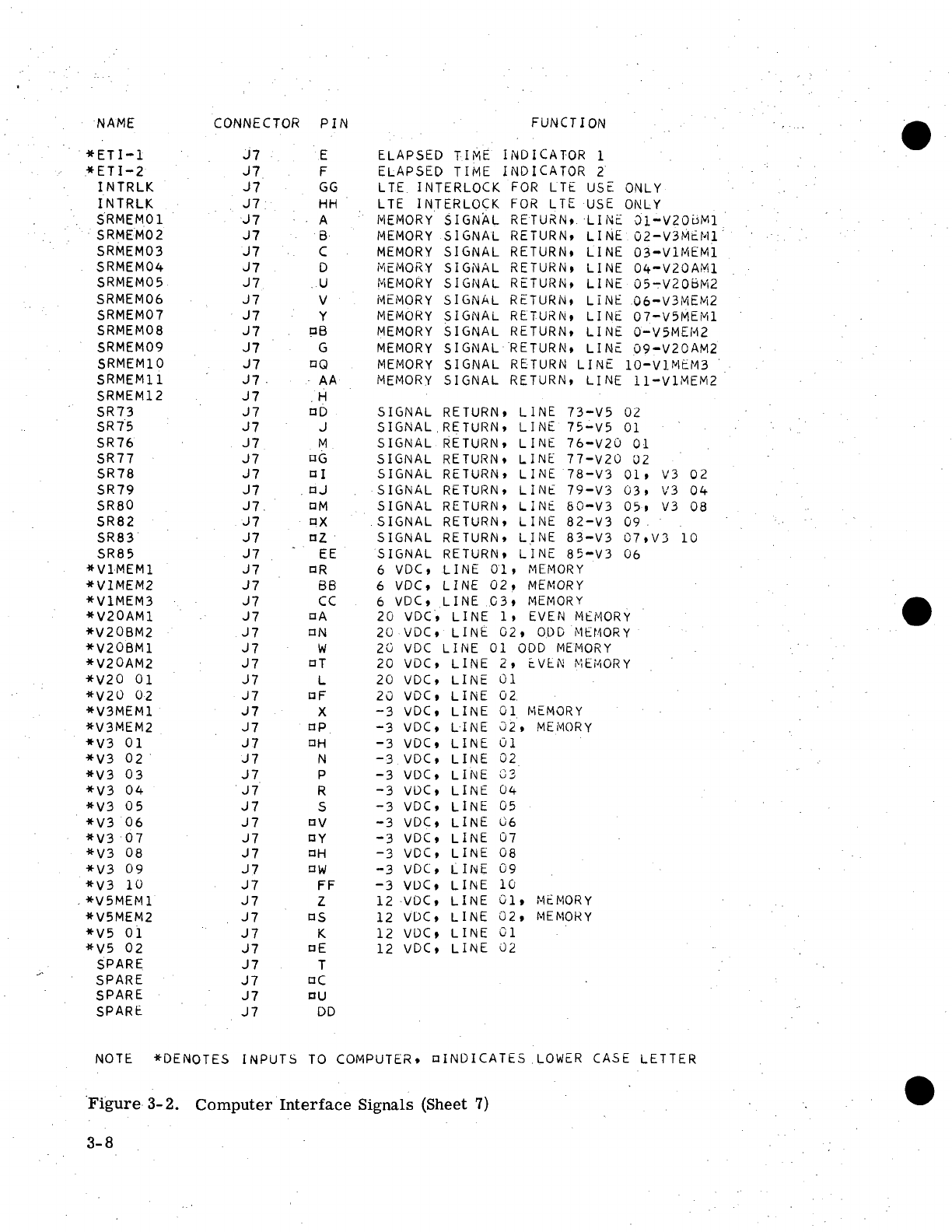

SECTION

III

INTERFACE

AND

ADJUSTMENTS

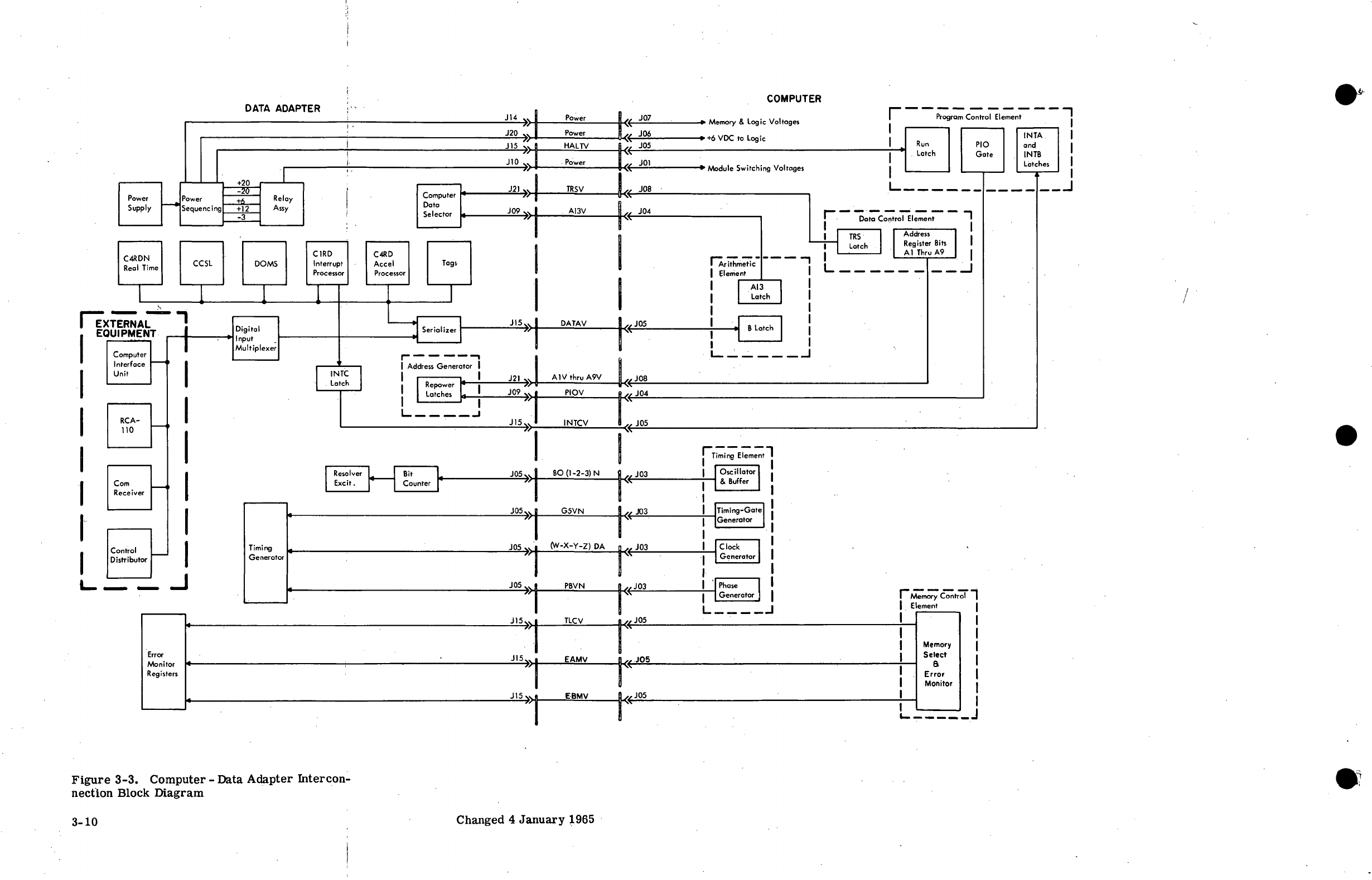

3-1.

INTERFACE

3-2

Figure

3-1

shows

the

connector interface

by

function

and the

direction

of

signal

flow

relative

to the

computer. Figure

3-2

lists

the

computer interface signal names

and

functions

alphabetically

by

connector number. Figure

3-3 is a

functional block

diagram

which

shows

the

interconnection

of

groups

of

similar

signals

between

the

computer

and

the

data

adapter

Figure

3-4

shows

the

interconnection

of

groups

of

similar

signals

between

the

computer

and the

LVDC-ME.

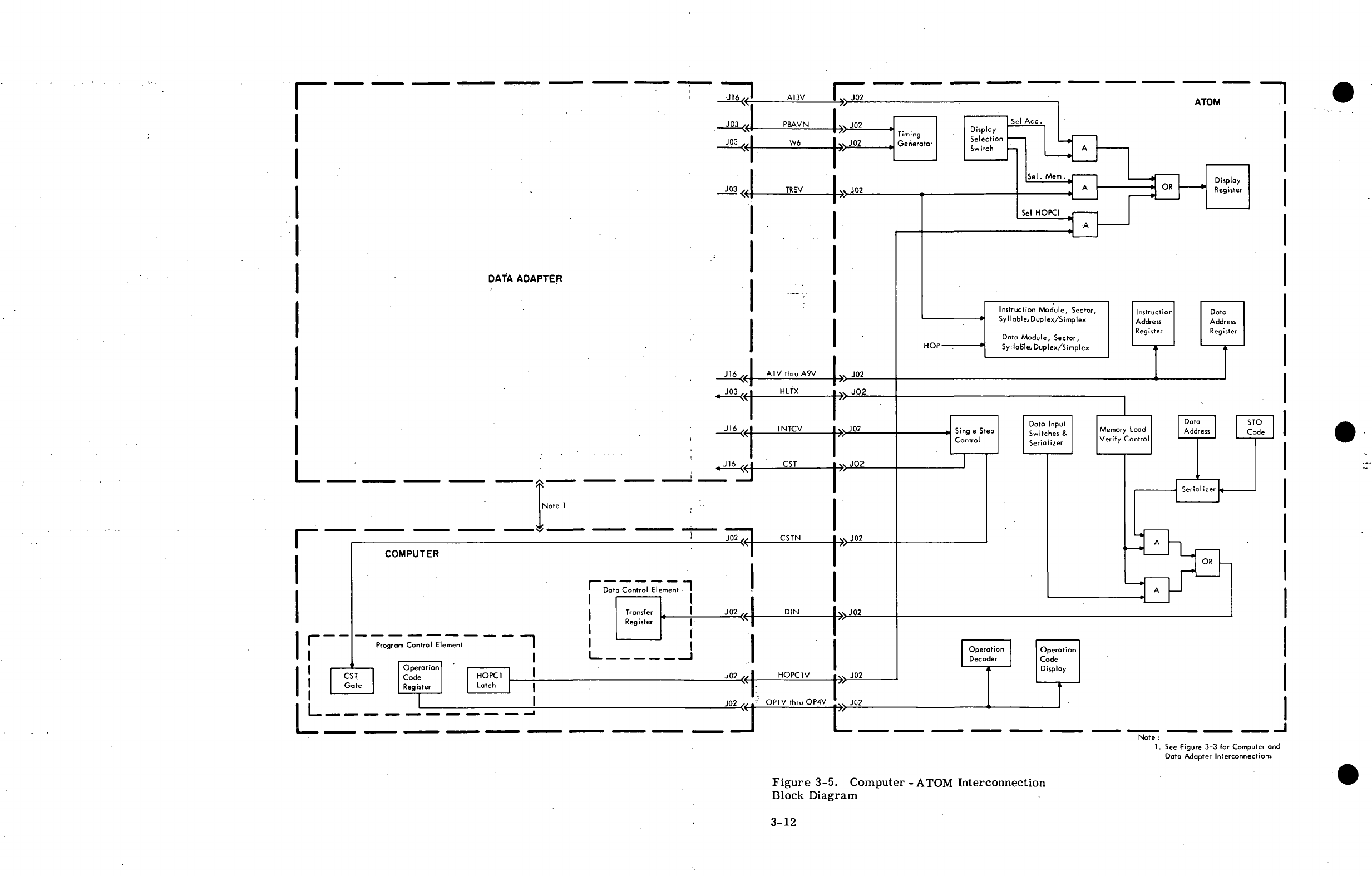

Figure

3-5

shows

the

interconnection

of

groups

of

similar

signals

between

the

computer

and the

ATOM.

NOTE

All

the

channel reference designations

(Al

through

A3)

have been left

off the

functional

signal

names

in all

diagrams

in

this

section.

3-3. ADJUSTMENTS

3-4.

No

adjustments

are

made

on the

computer.

Misc.

Timing

LTE

(only)

Module

Switching

Power

-OJ4

-OJ3

HOJ2

-»OJ1

LVDC

J80-

J7o«-

J604-

J5o^-

Address

Reg & TRS

•

Memory

Power

Logic

Power

External

Control

•

Error

Data

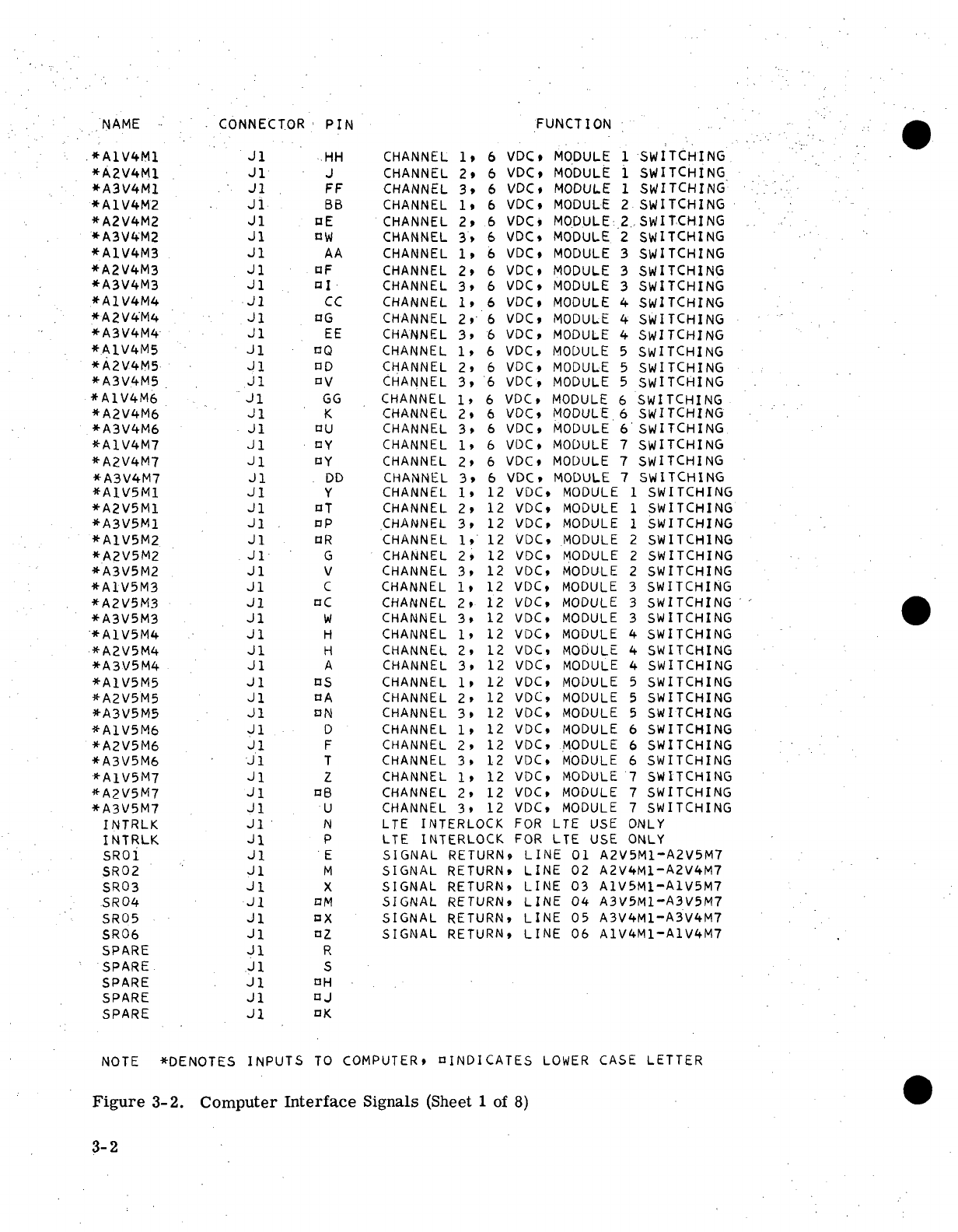

Figure

3-1. Computer Connectors

By

Signal Function

3-1

NAME

CONNECTOR

PIN

FUNCTION

.*A1V4M1

*A2V4M1

*A3V4M1

*A1V4M2

*A2V4M2

*A3V4M2

*A1V4M3

*A2V4M3

*A3V4M3

*A1V4M4

*A3V4M4

*A1V4M5

*A2V4M5

*A3V4M5

*A1V4M6

*A2V4M6

*A3V4M6

*A1V4M7

*A2V4M7

*A3V4M7

*A1V5M1

*A2V5M1

*A3V5M1

*A1V5M2

*A2V5M2

*A3V5M2

*A1V5M3

*A2V5M3

*A3V5M3

*A1V5M4

*A2V5M4

*A3V5M4

*A1V5M5

*A2V5M5

*A3V5M5

*A1V5M6

*A2V5M6

*A3V5M6

*A1V5M7

*A2V5M7

*A3V5M7

INTRLK

INTRLK

SR01

SR02

SR03

SR04

SR05

SR06

SPARE

SPARE

SPARE

SPARE

SPARE

Jl

Jl

Jl

Ji

Ji

Ji

Ji

Ji

Ji

Ji

Ji

Ji

Ji

Ji

.Ji

Ji

Ji

Ji

Ji

Ji

Ji

Ji

Ji

Ji .

Ji

Ji

Ji

Ji

Ji

Ji

Ji

Ji

Ji

Ji

Ji

Ji

Ji

Ji

Ji

Ji

Ji

Ji

Ji

Ji

Ji

Ji

Ji

Ji

Ji

Ji

Ji

Ji

Ji

Ji

Ji

HH

J

FF

BB

nE

nw

AA

nF

nl

CC

0G

EE

nQ

no

nv

GG

K

nu

ny

DY

DD

Y

nT

np

nR

G

V

c

nC

W

H

H

A

nS

nA

ON

D

F

T

Z

nB

u

N

P

E

M

X

nM

nx

nZ

R

S

BH

nj

n<

CHANNEL

1. 6

VDC» MODULE

1

CHANNEL

2» 6

VDC» MODULE

1

CHANNEL

3» 6 VDC »

MODULE

1

CHANNEL

1> 6

VDC» MODULE

2

CHANNEL

2, 6

VDC. MODULE

2

CHANNEL

3> 6

VDC»

MODULE

2

CHANNEL

1> 6 VDC »

MODULE

3

CHANNEL

2> 6

VDC»

MODULE

3

CHANNEL

3» 6 VDC »

MODULE

3

CHANNEL

1» 6 VDC f

MODULE

4

CHANNEL

2/6

VDC. MODULE

4

CHANNEL

3> 6 VDC ,

MODULE

4

CHANNEL

1> 6

VDC» MODULE

5

CHANNEL

2. 6

VDC» MODULE

5

CHANNEL

3. 6

VDC, MODULE

5

CHANNEL

1, 6

VDC» MODULE

6 ':

CHANNEL

2» 6

VDC»

MODULE

6

CHANNEL

3» 6 VDC »

MODULE

6'

CHANNEL

1» 6

VDC»

MODULE

7

CHANNEL

2> 6

VDC, MODULE

7

CHANNEL

3» 6

VDC,

MODULE

7

CHANNEL

1, 12

VDC, MODULE

1

CHANNEL

2, 12

VDC, MODULE

1

CHANNEL

3, 12

VDC, MODULE

1

CHANNEL

1, 12

VDC, MODULE

2

CHANNEL

2, 12

VDC, MODULE

2

CHANNEL

3, 12

VDC, MODULE

2

CHANNEL

1, 12

VDC, MODULE

3

CHANNEL

2, 12

VDC, MODULE

3

CHANNEL

3, 12

VDC, MODULE

3

CHANNEL

1, 12

VDC, MODULE

4

CHANNEL

2, 12

VDC,

MODULE

4

CHANNEL

3, 12

VDC, MODULE

4

CHANNEL

1, 12

VDC, MODULE

5

CHANNEL

2, 12

VDC, MODULE

5

CHANNEL

3, 12

VDC,

MODULE

5

CHANNEL

1, 12

VDC, MODULE

6

CHANNEL

2, 12

VDC, MODULE

6

CHANNEL

3, 12

VDC, MODULE

6

CHANNEL

1, 12

VDC, MODULE

7

CHANNEL

2, 12

VDC, MODULE

7

CHANNEL

3, 12

VDC, MODULE

7

LTE

INTERLOCK

FOR LTE USE 01

LTE

INTERLOCK

FOR LTE USE 01

SIGNAL RETURN, LINE

01

A2V5I

SIGNAL RETURN, LINE

02

A2V4I

SIGNAL RETURN, LINE

03

A1V5!

SIGNAL

RETURN,

LINE

04

A3V5I

SIGNAL

RETURN, LINE

05

A3V4I

SIGNAL

RETURN, LINE

06

A1V4I

SWITCHING

SWITCHING

SWITCHING

SWITCHING

SWITCHING

SWITCHING

SWITCHING

SWITCHING

SWITCHING

SWITCHING

SWITCHING

SWITCHING

SWITCHING

SWITCHING

SWITCHING

SWITCHING

SWITCHING

SWITCHING

SWITCHING

SWITCHING

SWITCHING

SWITCHING

SWITCHING

SWITCHING

SWITCHING

SWITCHING

SWITCHING

SWITCHING

SWITCHING

SWITCHING

SWITCHING

SWITCHING

SWITCHING

SWITCHING

SWITCHING

SWITCHING

SWITCHING

SWITCHING

SWITCHING

SWITCHING

SWITCHING

SWITCHING

NOTE

^DENOTES

INPUTS

TO

COMPUTER* niNDICATES LOWER

CASE

LETTER

Figure

3-2.

Computer

Interface

Signals

(Sheet

1 of 8)

3-2

NAME

CONNECTOR

PIN

FUNCTION

*A1CSTN

*A2CSTN

*A3CSTN

.

*A1DIN

*A2DIN

*A3DIN

A1HOPC1V

A2HOPC1V

A3HOPC1V

*A1MCL

#A2MCL

*A1MCN

*A2MCN

A1MD7V

A2MD7V

A3MD7V

A1MR1V

A2MR1V

A3MR1V

A10P1V

A20P1V

A30P1V

A10P2V

A20P2V

A30P2V

A10P3V

A20P3V

A30P3V

A10P4

A20P4V

A30P4V

A1PROV

A2PROV

A3PROV

*A1TER

*A2TER

*A3TER

BRA14P

BRB14P

INTRLK

INTRLK

SIGRET

SIGRET

SIGRET

SIGRET

SIGRET

SPARE

SPARE

SPARE

SPARE

SPARE.

SPARE

SPARE

SPARE

SPARE

J2

J2

J2

J2

J2

J2

J2

J2

J2

J2

J2

J2

J2

J2

J2

J2

J2

J2

J2

J2

J2

J2

J2

J2

J2

J2

J2

J2

J2

J2

J2

J2

J2

J2

J2

J2

J2

J2

J2

J2

J2

J2

J2

J2

J2

J2

J2

J2

J2

J2

J2

J2

J2

J2

J2

nK

E

K

DM

DA

L

R

HH

nC

D

U

CC

an

N

M

F

nu

J

H

G

B

C

A

np

Z

nx

S

ns

DG

nD

av

EE

W

aw

DD

nB

nY

az

P

X

Y

BB

FF

T

V

aF

aj

n(\|

no

PR

AA

GG

CHANNEL

1,

SINGLE

STEP

CONTROL

CHANNEL

2»

SINGLE

STEP

CONTROL

CHANNEL

3»

SINGLE

STEP

CONTROL

CHANNEL

1»

MEMORY

LOAD

CHANNEL

2»

MEMORY

LOAD

CHANNEL

3.

MEMORY

LOAD

CHANNEL

1. HOP

CONSTANT

CHANNEL

2» HOP

CONSTANT

CHANNEL

3»

CHANNEL

1»

CHANNEL

2»

CHANNEL

1,

CHANNEL

2»

CHANNEL

1.

CHANNEL

2.

CHANNEL

3,

CHANNEL

1»

CHANNEL

2.

CHANNEL

3»

CHANNEL

1.

CHANNEL

2.

OPERATION CODE REGISTER

CHANNEL

3,

OPERATION

CODE

REGISTER

CHANNEL

1»

OPERATION CODE REGISTER

CHANNEL

2»

OPERATION CODE REGISTER

CHANNEL

3,

OPERATION

CODE

REGISTER

CHANNEL

1>

OPERATION CODE REGISTER

CHANNEL

2»

OPERATION CODE REGISTER

CHANNEL

3.

OPERATION CODE REGISTER

CHANNEL

1.

OPERATION CODE REGISTER

CHANNEL

2.

OPERATION

CODE

REGISTER

CHANNEL

3.

OPERATION CODE REGISTER

CHANNEL

1.

PRODUCT

REMAINDER

LATCH

CHANNEL

2»

PRODUCT

REMAINDER

LATCH.

CHANNEL

3.

CHANNEL

1,

CHANNEL

2.

CHANNEL

3.

BUFFER REGISTER

BUFFER REGISTER

LTE

INTERLOCK

FOR

LTE

INTERLOCK

FOR

HOP

CONSTANT

MARGINAL

CHECK

MARGINAL

CHECK

MARGINAL

CHECK

MARGINAL

CHECK

MULTIPLICAND DIVISOR REGISTER

MULTIPLICAND DIVISOR REGISTER

MULTIPLICAND DIVISOR REGISTER

MULTIPLIER

REGISTER LATCH

MULTIPLIER REGISTER LATCH

MULTIPLIER

REGISTER LATCH

OPERATION

CODE

REGISTER LATCH

OPERATION CODE REGISTER LATCH

OPERATION

CODE

REGISTER LATCH

OPERATION

CODE REGISTER LATCH

OPERATION CODE REGISTER LATCH

OPERATION

CODE

REGISTER LATCH

LATCH

LATCH

LATCH

LATCH

LATCH

LATCH

LATE»

STROBE

CONTROL

STROBE

CONTROL

STROBE

CONTROL

STROBE

CONTROL

LATCH

7

LATCH

7

LATCH

7

SIGNAL

SIGNAL

SIGNAL

SIGNAL

SIGNAL

PRODUCT

REMAINDER

LATCH

RESET MEMORY tRROR

INDICATION

RESET MEMORY ERROR

INDICATION

RESETS MEMORY ERROR

INDI

CAT I ON

A,

PARITY

BIT

B

PARITY

SIT

LTE

USE

ONLY

LTE

USE

ONLY

RETURN.

DC

REGULATED

RETURN.

DC

REGULATED

RETURN.

DC

REGULATED

RETURN. REGULATED

DC

RETURN. REGULATED

i;C

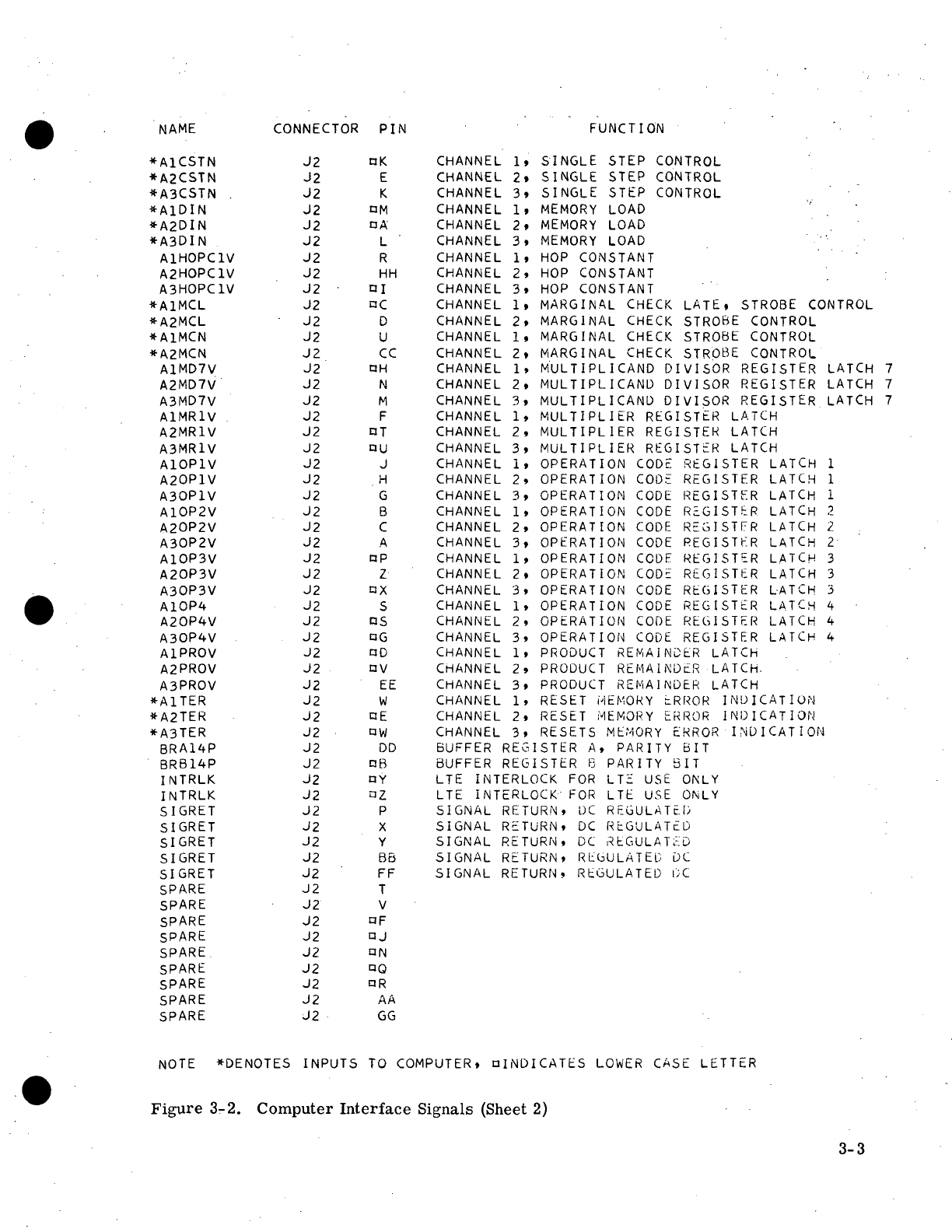

NOTE

*DENOTES

INPUTS

TO

COMPUTER.

nlNDICATES LOWER CASE LETTER

Figure

3-2.

Computer

Interface

Signals

(Sheet

2)

3-3

NAME

CONNECTOR

PIN

FUNCTION

A1G5VN

A2.G5VN

A3G5VN

A1PBVN

A2PBVN

A3PBVN

A1WDA

A2WDA

A3WDA

A1XDA

A2XDA

A3XDA

A1YDA

A2YDA

A3YDA

A1ZDA

A2ZDA

A3ZDA

B01N

B02N

B03N

INTRLK

INTRLK

SR07

SR08

SR09

SR1.0

SR11

SR12

SR13

SR14-

SRI

5

SRI

6

SR17

SR18

SR19

SR20

SR21

SR22

SR23

SR24

SR25

SR26

SR27

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

J3

J3

J3

J3

J3

J3

J3

J3

J3

J3

J3

J3

J3

J3

J3

J3

J3

J3

J3

J3

J3

J3

J3 •

J3

J3

J3

J3

J3

J3

J3

J3

J3

J3

J3

J3

J3

J3.

J3

J3

J3

J3

J3

J-3

J3

J3

J3

J3

J3

J3

J3

J3

J3

J3 .

J3

J3

C

n'Y

np

ns

nA

.

R

nB

K

N

F

J

HH

H

nH

QK

G

M

nj

DD

nF

a\f

W

X

E .

L

P . .

S

z

nC

Q

^

Q

E

nG

nl

nN

nR

nT

nu

nw .

nx

nz

CC

EE

FF

GG

A

B

D

T

U

V

Y

nM

nQ

AA

BB

CHANNEL

1,

TIMING

SYNC

FOR

DATA

CHANNEL

2,

TIMING SYNC

FOR

DATA

CHANNEL

3,

TIMING

SYNC

FOR

DATA

CHANNEL

1,

TIMING SYNC

FOR

DATA

CHANNEL

2,

TIMING

SYNC

FOR

DATA

CHANNEL

3,

TIMING SYNC

FOR

DATA

CHANNEL

1,

TIMING SYNC

FOR

DATA

CHANNEL

2,

TIMING SYNC

FOR

DATA

CHANNEL

3,

TIMING

SYNC

FOR

DATA

CHANNEL

1,

TIMING

SYNC

FOR

DATA

CHANNEL

2,

TIMING

SYNC

FOR

DATA

CHANNEL

3,

TIMING

SYNC

FOR

DATA

CHANNEL

1,

TIMING SYNC

FOR

DATA

CHANNEL

2,

TIMING

SYNC

FOR

DATA

CHANNEL

3,

TIMING SYNC

FOR

DATA

CHANNEL

1,

TIMING

SYNC

FOR

DATA

CHANNEL

2,

TIMING

SYNC

FOR

DATA

CHANNEL

3».

TIMING

SYNC

FOR

DATA

2.048

MC

TIMING

2.048

MC

TIMING

2.048

MC

TIMING

LTE

INTERLOCK

FOR LTE USE

ONLY

LTE

INTERLOCK

FOR LTE USE

ONLY

SIGNAL RETURN.. LINE 07-A1XDA

SIGNAL RETURN.. LINE

08-A2WUA

SIGNAL RETURN. LINE 09-A3PBVN

.

SIGNAL RETURN. LINE 10-A3YDA

SIGNAL RETURN, LINE 11-A2PBVN

.

SIGNAL RETURN, LINE

12-A1ZOA

.

SIGNAL R.ETURN, LINE 13-A1YDA

SIGNAL RETURN, LINE

14-A2XOA

.

SIGNAL RETURN, LINE

15-A2ZDA

SIGNAL RETURN, LINE 16-A3WDA

SIGNAL

RETURN, LINE 17-A3G5VN

SIGNAL RETURN, LINE 18-A1G5N

SIGNAL RETURN, LINE 19-A1WDA

SIGNAL RETURN, LINE

20-B01N

SIGNAL RETURN, LINE

21-B02N

SIGNAL RETURN, LINE 22-A2YJA

SIGNAL RETURN, LINE

23-A3ZDA

SIGNAL RETURN/LINE 24-A3XOA

SIGNAL RETURN, LINE

25-BC3N

SIGNAL RETURN, LIKE

26-A3XDA

SIGNAL RETURN, LINE 27-A2G5VN

ADAPTER

ADAPTER

ADAPTER,

ADAPTER

ADAPTER

ADAPTER

ADAPTER

ADAPTER

ADAPTER

ADAPTER

ADAPTER

ADAPTER

ADAPTER

ADAPTER

ADAPTER.

ADAPTER

ADAPTER

ADAPTER

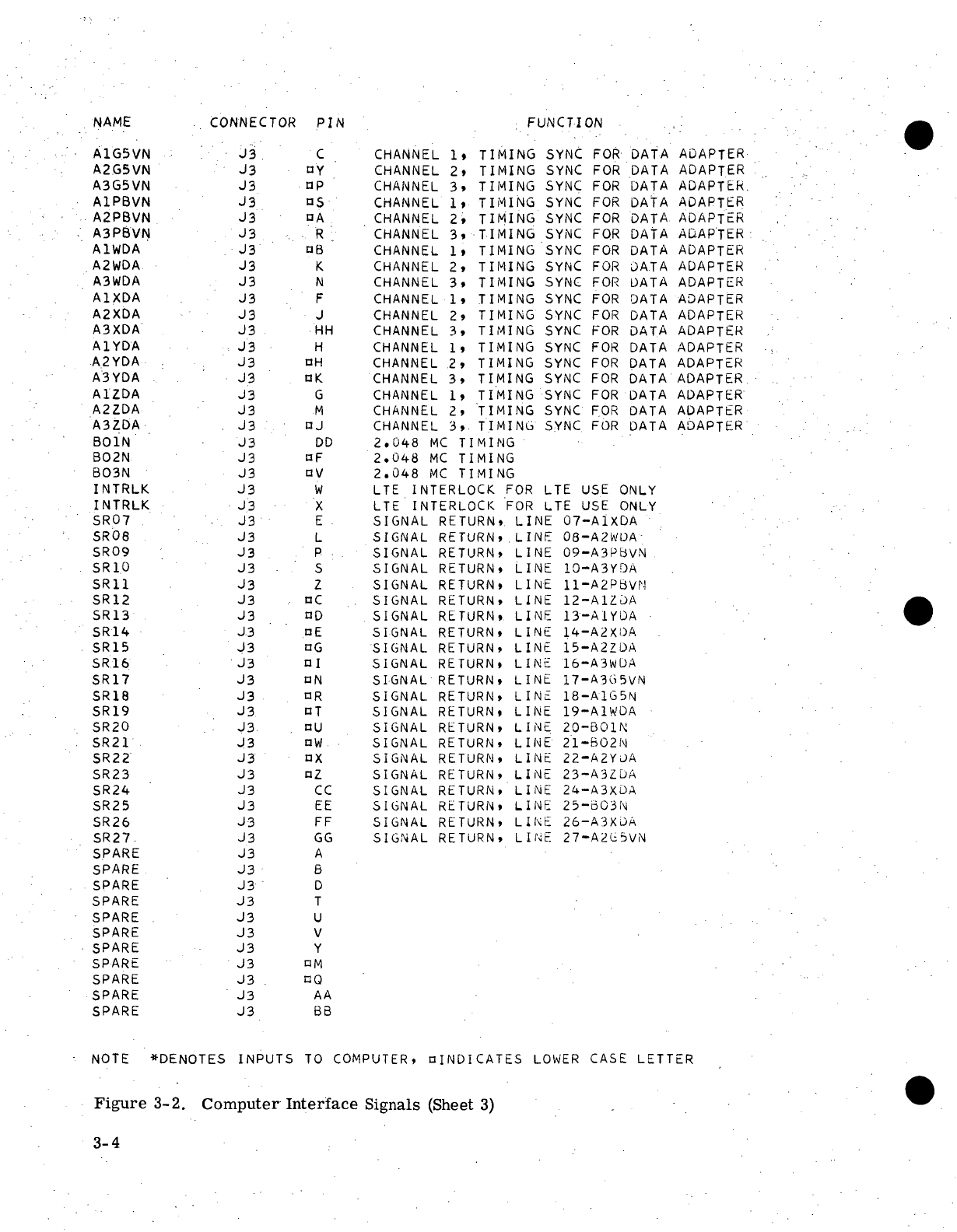

NOTE

#DENOTES

INPUTS

TO

COMPUTER, nlNDICATES LOWER CASE LETTER

Figure 3-2. Computer

Interface

Signals

(Sheet

3)

3-4

NAME

CONNECTOR

PIN

FUNCTION,

A1AI3V

A2AI3V

A3AI3V

A1PIOV

A2PIOV

A3PIOV

EP01

EP02

EP03

EP04

EP06

EP07

INTRLK

INTRLK

SR28

SR29

SR30

SR31

SR32

SR33

SR34

SR35

SR36

SR37

SR38

THERM1

THERM2

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

J4

J4

J4

J4

J4

J4

J4

J4

J4

J4

J4

J4

J4

J4

J4

J4

J4

J4

J4

J4

J4

J4

J4

J4

J4

J4

J4

J4

J4

J4

J4

J4

J4

J4

J4

J4

J4

J4

J4

J4

J4

J4

J4

J4

J4

J4

J4

J4

J4

J4

J4

J4

J4

J4

J4

nM

nz

nQ

GG

U

u

w

nR

T

AA

V

nN

nG

nH

A

B

P

S

X

z

np

as

BB

CC

HH

Y

D

E

F

G

H

J

K

L

M

N

R

aA

nB

aC

nD

a£

nF

nl

nj

nK

nT

PU

av

nw

nx

QY

DD

EE

FF

CHANNEL

1»

ACCUMULATOR THIRD DELAY LATCH

CHANNEL

2.

ACCUMULATOR THIRD DELAY LATCH

CHANNEL

3»

ACCUMULATOR THIRD DELAY LATCH

CHANNEL

1,

PROCESS INPUT-OUTPUT

CHANNEL

2»

PROCESS INPUT-OUTPUT

CHANNEL

3»

PROCESS

INPUT-OUTPUT

ERROR

SIGNAL

01

ERROR

SIGNAL

02 . .

ERROR

SIGNAL

03

ERROR

SIGNAL

04

ERROR

SIGNAL

06 ' • .

ERROR

SIGNAL

07

LTE

INTERLOCK

FOR LTE USE

ONLY

LTE

INTERLOCK

FOR LTE USE

ONLY

SIGNAL

SIGNAL

SIGNAL

SIGNAL

SIGNAL

SIGNAL

SIGNAL

SIGNAL

SIGNAL

SIGNAL

SIGNAL

THERMISTOR

THERMISTOR

RETURN*

RETURN*

RETURN*

RETURN.

RETURN.

RETURN.

RETURN.

RETURN.

RETURN.

RETURN.

RETURN,

1

1

LINE

LINE

LINE

LINE

LINE

LINE

LINE

LINE

LINE.

LINE

LINE

LEAD

1

LEAD

2

28-EP06

29-A1PIOV.A3PIOV

30-A2AI.3

31-EP03

32-EP01

33-THEKM

34-EPC7

35-EPC2

36-EP04

37-A3AI3V

38-A1AI3V

THERM

2,

NOTE

*DENOTES

INPUTS

TO

COMPUTER,

nINDICATES

LOWER

CASE

LETTER

Figure

3-2.

Computer

Interface

Signals

(Sheet

4)

3-5

NAME.

CONNECTOR

\ PIN

FUNCTION.

A1EAMV

A2EAMV

A3EAMV

A1EBMV

A2EBMV

A3EBMV

*A1DATAV

*A2DATAV

*A3DATAV

*A1HALTV

*A2HALTV

*A3HALTV

*A1INTCV

*A2INTCV

*A3INTCV

A1TLCV

A2TLCV

A3TLCV

EP05

EP08

;

EP09

EP10

EP11

EP12

EP13

INTRLK

INTRLK

SR39

SR40

SR41

SR42

SR43

SR44

SR45

SR46

SR47

SR90

THERM4

THERMS

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

J5

J5 :

J5

J5

J5

J5

J5

J5

J5

J5

J5

J5

J5

J5 .

J5

J5

J5

J5

J5

J5

J5

J5

J5

J5

J5

J5

J5

J5

J5

J5

J5

J5

J5

J5

J5

J5

J5

J5

J5

J5

J5

J5

J5

J5

J5

J5

J5

J5

J5

J5

J5

J5

J5

J5

J5

•

np

nz

AA

U

nj

'

n<

R

GG

nB

P

A

G

N

FF

nC

T

S

al

H

Z

EN

V

E

DQ

B5

'

K

L

6

C

.w

QA

a'D

nH

ns

nx

cc

nR

D

Y

F

J

M

X

aE

nF

nG

aw

nT

nu

nv

nw

ay

DD

EE

HH

CHANNEL

•!»

EVEN' MEMORY, ERROR

: ' „

CHANNEL

2..EVEN

MEMORY ERROR

- .;,

CHANNEL

3»

EVEN MEMORY ERROR

. ^ •

CHANNEL

1» ODD

MEMORY ERROR

..

....

CHANNEL

2»

ODD•MEMORY

.ERROR

. . . .

CHANNEL

3» ODD

MEMORY. ERROR

- •• ,.

CHANNEL

1,

COMPUTER DATA INPUT

CHANNEL

2»

COMPUTER

DATA INPUT

CHANNEL

3»

COMPUTER

DATA INPUT

CHANNEL

1>

HALT SIGNAL

-.' . ,

CHANNEL

2»

HALT

SIGNAL-

CHANNEL

3»

HALT SIGNAL

" . • .

CHANNEL

1»

INTERRUPT COMPUTER

CHANNEL

2»

INTERRUPT COMPUTER

-CHANNEL

3»

INTERRUPT COMPUTER-

CHANNEL

1»

SIMULTANEOUS

MEMORY ERROR

CHANNEL

2»

SIMULTANEOUS MEMORY ERROR

CHANNEL

3»

SIMULTANEOUS MEMORY ERROR

ERROR

SIGNAL

05

ERROR

SIGNAL

08

ERROR SIGNAL

09

ERROR

SIGNAL

1C

ERROR SIGNAL

11 . . . .

ERROR.SIGNAL

12 . . ; .

ERROR SIGNAL

13

LTE

INTERLOCK

FOR

LTfc

USE

ONLY

. ,

LTE

INTERLOCK

FOR LTE USE

ONLY

SIGNAL RETURN. LINE

39-EP10

SIGNAL RETURN* LINE 40-.THERM3»THERM4

SIGNAL RETURN. LINE

41-EP09

SIGNAL RETURN*

LINE

42-EP11

SIGNAL

RETURN, LINE

43-EPG5

.

SIGNAL RETURN 44-1

NTC»

HALT, TLC,

EAK AND

t.BM

SIGNAL RETURN

LINE

45-EP08

SIGNAL

RETURN,

LINE

46-DATAV

FOR

CHANNELS.

1, 2,

SIGNAL RETURN, LINE

47-EP13

. :

SIGNAL RETURN LINE

90-EP12

..

THERMISTOR

2

LEAD

2 .

THERMISTOR

2

LEAD

1 '

NOTE

^DENOTES

INPUTS

TO

COMPUTER, nlNDICATES LOWER

CASE

LETTER

Figure

3-2. Computer

Interface Signals (Sheet

5)

3-6

NAME

CONNECTOR

i PIN

FUNCTION'

INTRLK

INTRLK

SR48

SR49

SR50

SR51

SR52

SR53

SR54

SR55

SR56

SR57

SR58

SR59

SR60

SR61

SR62

SR63

SR64

SR65

SR66

SR67

SR68

SR69

SR70

SR71

*V1

01

*V1

02

*V1

03

*V1

04

*V1

05

*V1

06

*V1

07

*V1

08

*V1

09

*V1 10

*V1 11

*V1 12

*V1 13

*V1

14

*V1 15

*V1 16

*V1 17

*V1 18

*V1 19

*V1

20

*V1 21

*V1

22

*V1 23

*V1

24

SPARE

SPARE

SPARE

SPARE

SPARE

J6

J6

J6

J6

J6

J6

J6

J6

J6

J6

J6

J6

J6

J6

J6

J6

J6

J6

J6

J6

J6

J6

J6

J6

J6

J6

J6

J6

J6

J6

J6

J6

J6

J6

J6

J6

J6

J6

J6

J6

J6

J6

J6

J6

J6

J6

J6

J6

J6

J6

J6

J6

J6

J6

J6

K

L

H

N

P

R

nC

nD

n£

aF

QG

J

nH

Ql

nj

nK

nM

DU

nv

aw

ax

DY

EE

FF

GG

HH

A

B

C

D

E

F

T

U

V

w

X

Y

Z

nA

S

aN

ap

no

aR

nS

DZ

AA

BB

CC

G

M

aB

LTE

INTERLOCK

FOR LTE USE

LTE

INTERLOCK

FOR LTE USE

SIGNAL

SIGNAL

SIGNAL

SIGNAL

SIGNAL

SIGNAL

SIGNAL

SIGNAL

SIGNAL

SIGNAL

SIGNAL

SIGNAL

SIGNAL

SIGNAL

SIGNAL

SIGNAL

SIGNAL

SIGNAL

SIGNAL

SIGNAL

SIGNAL

SIGNAL

SIGNAL

'

SIGNAL

6

VDC,

6

VDC,

6

VDC,

6

VDC,

6

VDC,

6

VDC,

6

VDC,

6

VDC,

6

VDC,

6

VDC,

6

VDC,

6

VDC,

6

VDC,

6

VDC,

6

VDC,

6

VDC,

6

VDC,

6

VDC,

6

VDC,

6

VDC,

6

VDC,

6

VDC,

6

VDC,

6

VOC,

RETURN,

RETURN,

RETURN,

RETURN,

RETURN,

RETURN,

RETURN,

RETURN,

RETURN,

RETURN,

RETURN,

RETURN,

RETURN,

RETURN,

RETURN,

RETURN,

RETURN,

RETURN,

RETURN,

RETURN,

RETURN,

RETURN,

RETURN,

RETURN,

LINE

1

LINE

2

LINE

3

LINE

4

LINE

5

LINE

6

LINE

07

LINE

08

LINE

09

LINE

10

LINE

11

LINE

12

LINE

13

LINE

14

LINE

15

LINE

16

LINE

17

LINE

18

LINE

19

LINE

20

LINE

21

LINE

22

LINE

2?

LINE

24

LINE

LINE

LINE

LINE

LINE

LINE.

LINE

LINE

LINE

LINE

LINE

LINE-

LINE

LINE

LINE

LINE

LINE

LINE

LINE

LINE

LINE

LINE

LINE

LINE

48-V1

49-V1

50-V1

51-V1

52-V1

53-V1

54-V1

55-V1

56-V1

57-V1

58-V1

59-V1

60-V1

61-V1

62-V1

63-V1

64-V1

65-V1

66-V1

67-V1

68-V1

69-V1

70-V1

71-V1

ONLY

ONLY

05

21

15

07

04

13

14

20

24 •

06

23

22'

16

Oo" '

01

12

19 .

18

17

09

17

10

02 .

03

DO

NOTE

*OENOTES

INPUTS

TO

COMPUTER,

nINDICATtS

LOWER

CASE

LETTER

Figure

3-2. Computer Interface Signals

(Sheet

6)

3-7

NAME

CONNECTOR

PIN

FUNCTION

*ETI-1

*ETI-2

INTRLK

INTRLK

SRMEMOl

SRMEM02

SRMEM03

SRMEM04

SRMEM05

SRMEM06

SRMEM07

SRMEM08

SRMEM09

SRMEM10

SRMEM11

SRMEM12

SR73

SR75

SR76

SR77

SR78

SR79

SR80

SR82

SR83

SR85

*V1MEM1

*V1MEM2

*V1MEM3

*V20AM1

*V20BM2

*V20BM1

*V20AM2

*V20

01

*V20

02

*V3MEM1

»V3MEM2

*V3 01

*V3

02

*V3

03

*V3

04

*V3 05

*V3

06

*V3

07

*V3 08

*V3

09

*V3 10

*V5MEM1

#V5MEM2

*V5 01

*V5

02

SPARE

SPARE

SPARE

SPARE

J7

J7

J7

J7

J7

J7

J7

J7

J7

J7

J7

J7

J7

J7

J7

J7

J7

J7

J7

J7

J7

J7

J7.

J7

J7

J7

J7

J7

J7

J7

J7

J7

J7

J7

J7

J7

J7

J7

J7

J7

J7

J7

J7

J7

J7

J7

J7

J7

J7

J7

J7

J7

J7

J7

J7

E

F

GG

HH

: A

B

.

C

D

..U

V

Y

aB

G

no

AA

.

H

nD

J

M

nG

nl

.

nj

DM

nx

nZ

"

EE

nR

BB

CC

nA

nN

W

nT

L

nF

X

np

nH

N

P

R

S

nv

nY

nH

aw

FF

Z

ns

K

n£

T

aC

DU

DD

ELAPSED

TIME INDICATOR

1

ELAPSED

TIME INDICATOR

2

LTE.

INTERLOCK

FOR LTt USE

ONLY

LTE

INTERLOCK

FOR LTE USE

ONLY

MEMORY SIGNAL

RETURN*.

LINc

01-V20bMl

MEMORY SIGNAL RETURN. LINE

02-V3MEM1

MEMORY SIGNAL RETURN. LINE

03-V1MEM1

MEMORY SIGNAL RETURN. LINE

04-V20AM1

MEMORY SIGNAL RETURN. LINE

05-V20BM2

MEMORY SIGNAL RETURN. LINE

.06-V3MEM2

MEMORY SIGNAL RETURN, LINE

07-V5MEM1

MEMORY SIGNAL RETURN. LINE

0-V5MEM2

MEMORY SIGNAL RETURN, LINE

09-V20AM2

MEMORY SIGNAL RETURN LINE

10-V1MEM3

MEMORY SIGNAL RETURN, LINE 11-V1MEM2

SIGNAL RETURN. LINE

73-V5

02

SIGNAL,

RETURN. LINE

75-V5

01

SIGNAL

RETURN.

LINE

76-V20

01

SIGNAL RETURN. LINE

77-V20

02

SIGNAL

RETURN.

LINE

78-V3

01. V3 02

SIGNAL RETURN. LINE

79-V3

03, V3 04

SIGNAL RETURN. LINE

SO-V3

05, V3 08

.SIGNAL RETURN. LINE

82-V3

09. .

SIGNAL RETURN. LINE

83-V3

07. V3 10

SIGNAL RETURN, LINE

85-V3

06

6

VDC,

LINE

01,

MEMORY

6

VDC,

LINE

02,

MEMORY

6

VDC,

LINE

..03,

MEMORY

20

VDC,

LINE

1,

EVEN MEMORY

20

VDC,

LINE

02, ODD

MEMORY

20 VDC

LINE

01 ODD

MEMORY

20

VDC,

LINE

2,

EVEN MEMORY

20

VDC.

LINE

01

20

VDC.

LINE

02.

-3

VDC,

LINE

01

MEMORY

-3

VDC.

LINE

02,

MEMORY

-3

VDC,

LINE

01

-3

VDC.

LINE

02

-3

VDC,

LINE

03

-3

VDC,

LINE

04

-3

VDC,

LINE

05

-3

VDC,

LINE

06

-3

VDC.

LINE

07

-3

VDC,

LINE

08

-3

VDC,

LINE

09

-3

VDC,

LINE

10

12

-VDC, LINE

01,

MEMORY

12

VDC,

LINE

02,

MEMORY

12

VDC,

LINE

01

12

VDC,

LINE

02

NOTE

*DENOTES

INPUTS

TO

COMPUTER.

nINDICATtS LOWER

CASt

LETTER

Figure

3-2.

Computer

Interface Signals (Sheet

7)

3-8

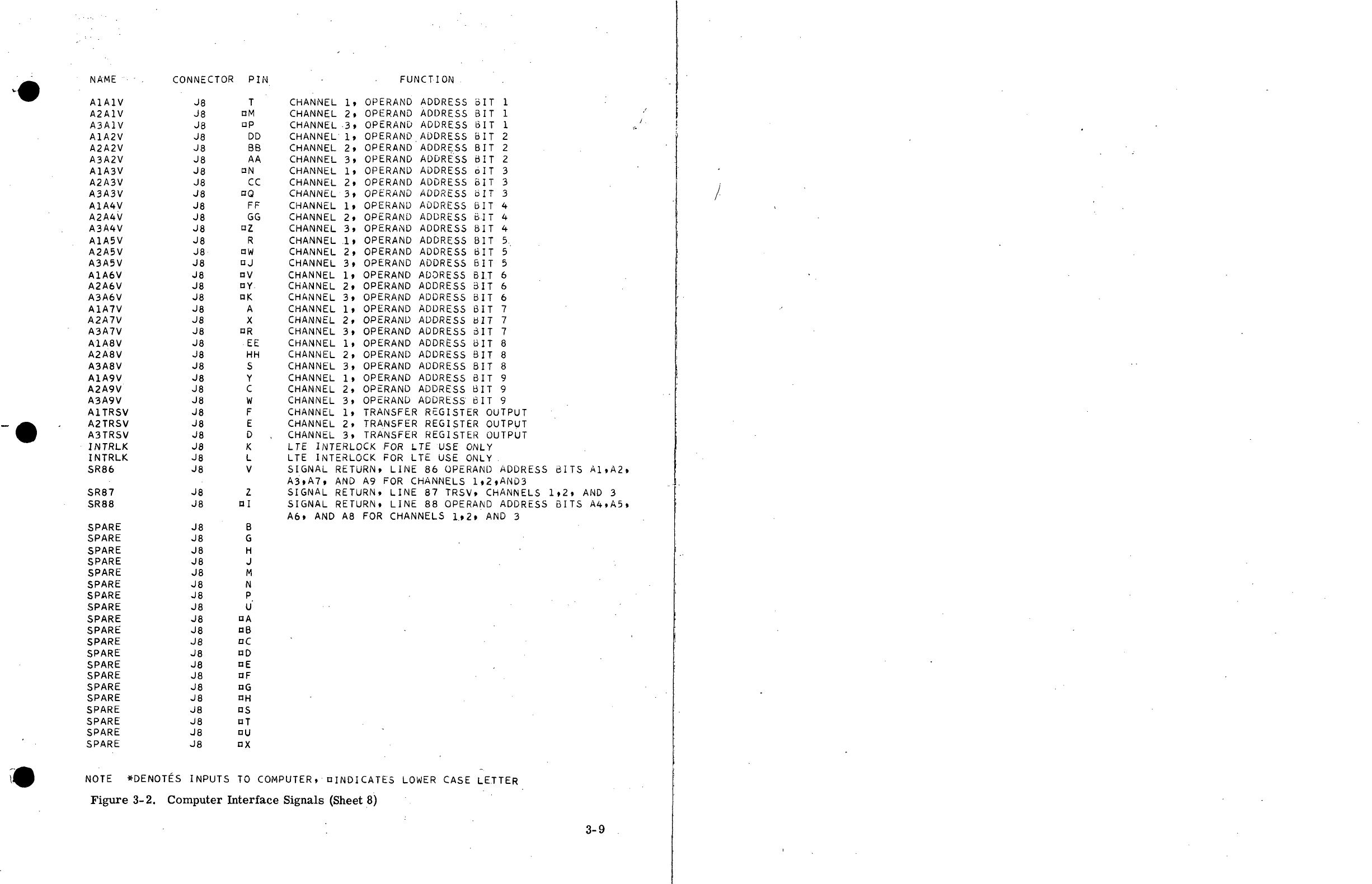

NAME

CONNECTOR

PIN

FUNCTION

A1A1V

A2A1V

A3A1V

A1A2V

A2A2V

A3A2V

A1A3V

A2A3V

A3A3V

A1A4V

A2A4V

A3A4V

A1A5V

A2A5V

A3A5V

A1A6V

A2A6V

A3A6V

A1A7V

A2A7V

A3A7V

A1A8V

A2A8V

A3A8V

A1A9V

A2A9V

A3A9V

A1TRSV

A2TRSV

A3TRSV

INTRLK

INTRLK

SR86

SR87

SR88

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

SPARE

J8

J8

J8

J8

J8

J8

J8

J8

J8

J8

J8

J8

J8

J8

J8

J8

J8

J8

J8

J8

J8

J8

J8

J8

J8

J8

J8

J8

J8

J8

J8

J8

J8

J8

J8

J8

J8

J8

J8

J8

J8

J8

J8

J8

J8

J8

J8

J8

J8

J8

J8

J8

J8

J8

J8

T

nM

np

DD

BB

AA

nN

CC

nQ

FF

GG

ol

R

aw

nj

nv

QY

nK

A

X

nR

EE

HH

S

Y

C

W

F

E

D

K

L

V

z

nl

B

G

H

J

M

N

P

u'

aA

nB

nC

nD

nE

nF

nG

nH

as

nT

nu

nx

CHANNEL

1,

OPERAND ADDRESS

3IT 1

CHANNEL

2»

OPERAND ADDRESS

BIT 1

CHANNEL

3.

OPERAND ADDRESS

BIT 1

CHANNEL

1»

OPERAND ADDRESS

BIT 2

CHANNEL

2»

OPERAND ADDRESS

BIT 2

CHANNEL

3»

OPERAND ADDRESS

BIT 2

CHANNEL

1»

OPERAND ADDRESS

oIT 3

CHANNEL

2.

OPERAND ADDRESS

BIT 3

CHANNEL

3»

OPERAND ADDRESS

oIT 3

CHANNEL

1»

OPERAND ADDRESS

BIT 4

CHANNEL

2»

OPERAND ADDRESS

BIT 4

CHANNEL

3»

OPERAND ADDRESS

BIT 4

CHANNEL

.1*

OPERAND ADDRESS

BIT 5

CHANNEL

2»

OPERAND ADDRESS

BIT 5

CHANNEL

3»

OPERAND ADDRESS

BIT 5

CHANNEL

1»

OPERAND ADDRESS

BIT 6

CHANNEL

2»

OPERAND ADDRESS

3IT 6

CHANNEL

3»

OPERAND ADDRESS

BIT 6

CHANNEL

1,

OPERAND ADDRESS

BIT 7

CHANNEL

2»

OPERAND

ADDRESS

BIT 7

CHANNEL

3»

OPERAND ADDRESS

BIT 7

CHANNEL

1,

OPERAND ADDRESS

BIT 8

CHANNEL

2.

OPERAND

ADDRESS

BIT 8

CHANNEL

3»

OPERAND ADDRESS

BIT 8

CHANNEL

1»

OPERAND

ADDRESS

BIT 9

CHANNEL

2»

OPERAND ADDRESS

BIT 9

CHANNEL

3»

OPERAND ADDRESS

BIT 9

CHANNEL

1.

TRANSFER REGISTER OUTPUT

CHANNEL

2.

TRANSFER

REGISTER OUTPUT

CHANNEL

3»

TRANSFER REGISTER OUTPUT

LTE

INTERLOCK

FOR LTE USE

ONLY

LTE

INTERLOCK

FOR LTE USE

ONLY

.

SIGNAL

RETURN*

LINE

86

OPERAND ADDRESS BITS

Al,A2»

A3»A7,

AND A9 FOR

CHANNELS

1.2.AND3

SIGNAL

RETURN.

LINE

87

TRSV»

CHANNELS 1»2»

AND 3

SIGNAL RETURN.

LINE

88

OPERAND ADDRESS BITS A4.A5»

A6. AND A8 FOR

CHANNELS 1..2.

AND 3

NOTE

*DENOTES

INPUTS

TO

COMPUTER.

^INDICATES

LOWER CASE LETTER

Figure

3-2.

Computer

Interface

Signals

(Sheet

8)

3-9

DATA

ADAPTERCOMPUTER

Power

Supply

i JN vv B

Power

I •

H +20

'ower

Sequencing

+6

+12

-3

C4RDN

Real

TimeCCSL

Relay

Assy

DOMS

i-

C1RD

Interrupt

Processor

C4RD

Accel

Processor

Computer

Data

Selector

Tags

J20

vv

|

Power

J15

y. B

HALTV

»'|

J10

vv \

Power

J21

w \

TB«v

^-»-

J°9»

AI3V

« J°5

„

JOS

„

J04

r

1

1

i

1

Arithmetic

i

Element

*-

AI3

Latch

1

1 1

1 Rur

i * Lot

1

'

Prog

ch

Data

Control

Element

TRS

Addres

~

Lotch

Re9'ste

— Al Thr

s

r

Bits

.. A9

Program

Control

Element

EXTERNAL

'

EQUIPMENT

Error

Monitor

Registers

DATAV

«J05

JlSvv

A1V

thru

A9V

PIOV

INTCV

tJOS

,

J04

„

JOS

Timing

Element

I

60(1-2-3)

N

G5VN

,

JOS

.

JOS

J05

(W-X-Y-Z)

DA

J03

PBVN

JlSvv

TLCV,J05

I I

EAMV

JOS

EBMV

J05

I

Memory

Control

|

Element

I

I

I

Memory

Select

Error

Monitor

Figure

3-3.

Computer

-

Data Adapter Intercon-

nection Block Diagram

3-10

Changed

4

January 1965

COMPUTER

Timing

Element

Timing

Gate

Generator

Phase

Generator

Clock

Generator

1

1

Module

Switching

Voltages*

.

Memory

&

Logic Voltages

*

+6

VDC to

Logic*

JOKvl

"\

J06V,

1

ff 1

J07vv

1

1

Power

Power

Power

„

J19

jj

J07

V.V

xx J06

\v

Power

j

Sequencing

&

Relay

Assy

ff J14 TO

Error

Checking

! '

Muitiply-Divide

Element

Figure

3-4.

Computer

and

LVDC-ME

Intercon-

nection

Block Diagram

3-11

DATA

ADAPTER

r

Note

1

r

COMPUTER

J'6«

J03«

J03<(

AI3V

1 ^x J02

:

PBAVN

W6

V>

J02

f

»J°2

»

Timing

Generator

Display

Selection

Switch

Sel

Ace.

ATOM

~1

TRSV

. J02

JI6

JI6

„

*^«

A1V

thru

A9V

h»

J02

HLTX

w J02

INTCV

CST

.J02

CSTN

Data

Control

Element

.J02

Program

Control

Element

"I

DIN

.J02

Operation

Code

Register

HOPC1V

HOP-

Instruction

Module,

Sector

Syllable,

Duplex/Simplex

Data

Module,

Sector,

Syllab1e,Duplex/Simpl

LL

OP1V thru OP4V

;xv JC2

JU/

ss |- ^^r iv

iniu

v^f

•*

T

j

Note:

1. See

Figure

3-3 for

Computer

and

Data

Adapter Interconnections

Figure

3-5.

Computer

-

ATOM

Interconnection

Block

Diagram

3-12

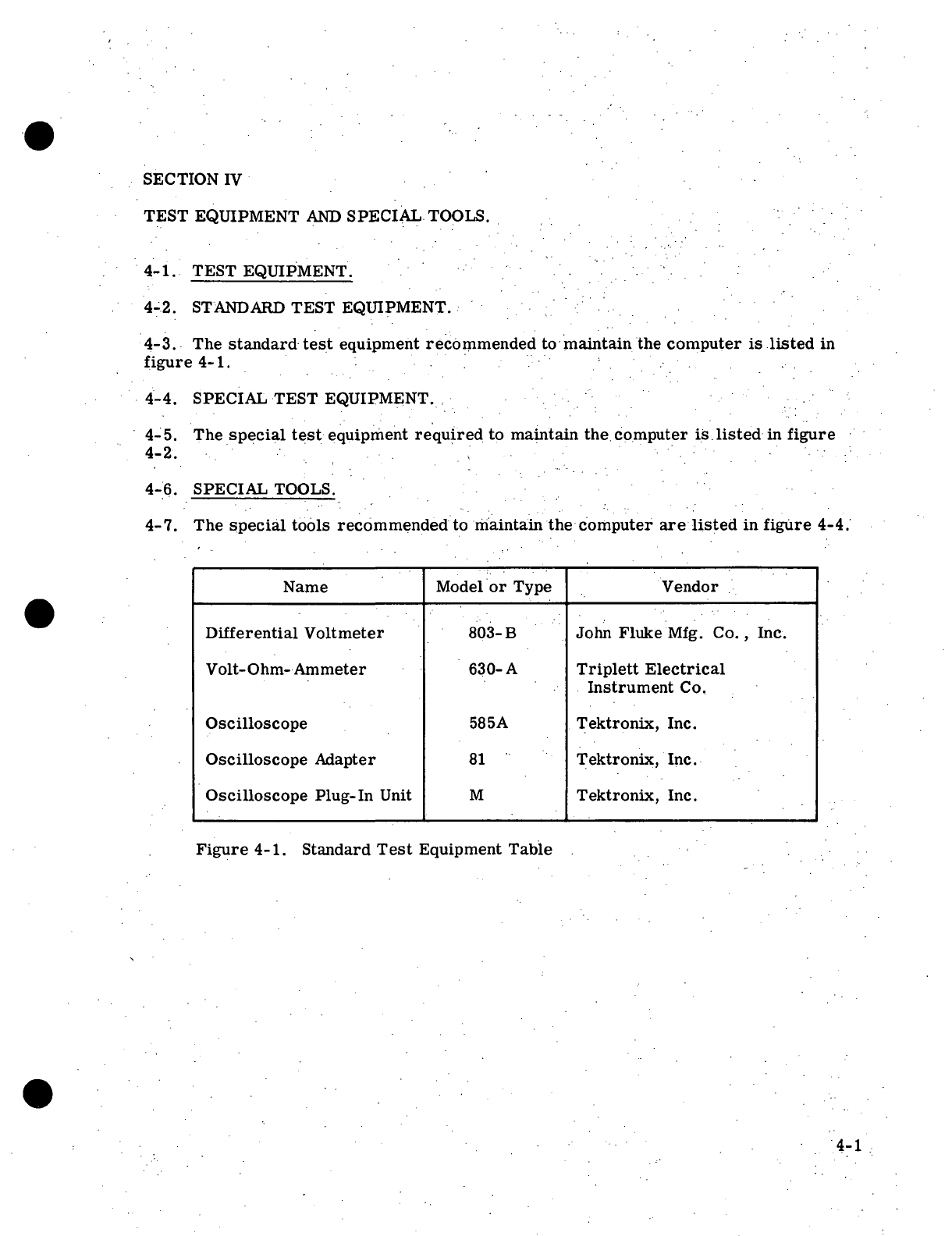

SECTION

IV

TEST EQUIPMENT

AND

SPECIAL TOOLS.

4-1. TEST EQUIPMENT.

4-2.

STANDARD

TEST EQUIPMENT.

4-3.

The

standard

test

equipment recommended

to

maintain

the

computer

is

listed

in

figure 4-1.

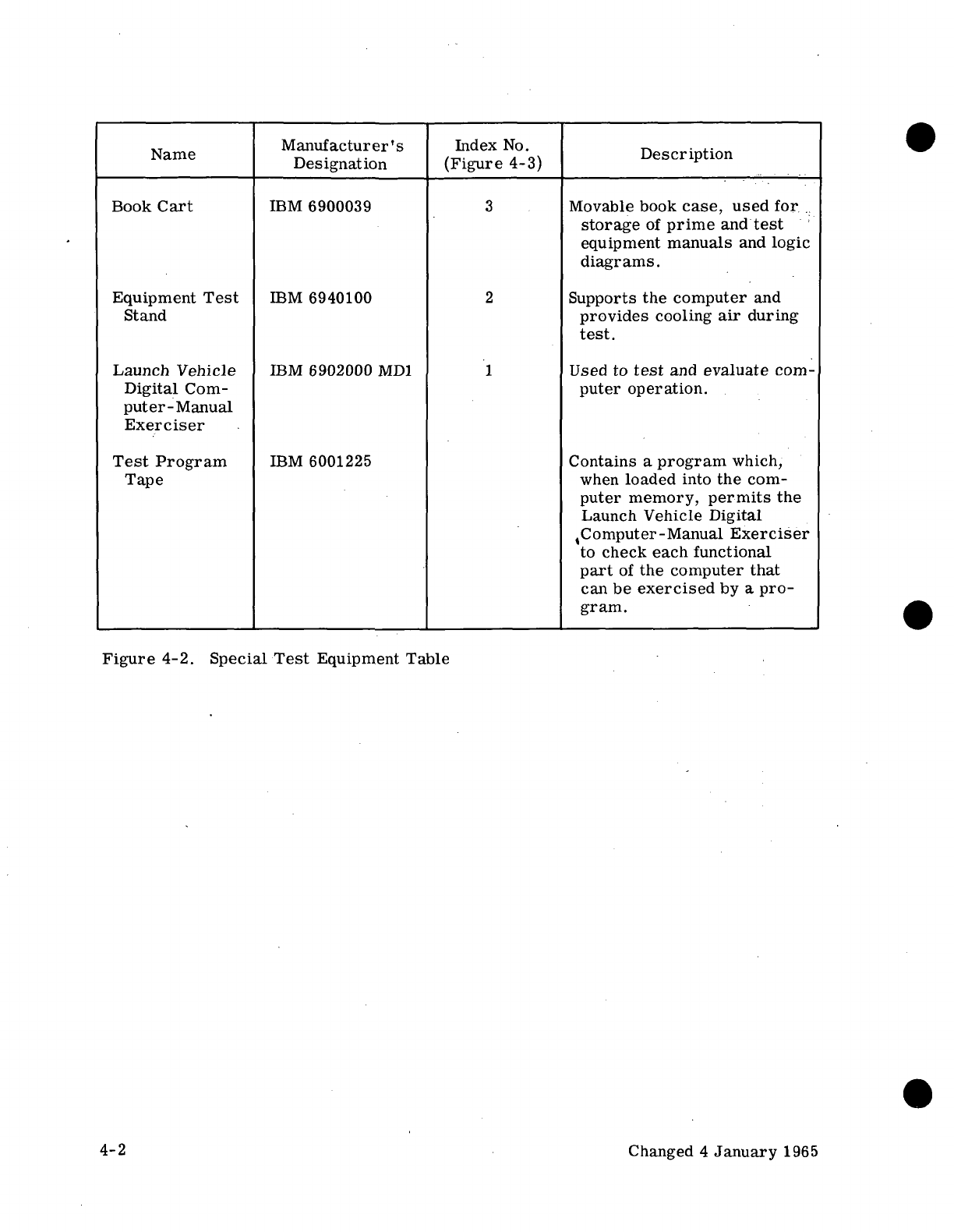

4-4. SPECIAL TEST EQUIPMENT.

4-5.

The

special

test

equipment

required

to

maintain

the

computer

is

listed

in

figure

4-2.

-.. ' ' .' . . '. ; '.-•'.-•

'''•''•.-'"..•' '•'••

:

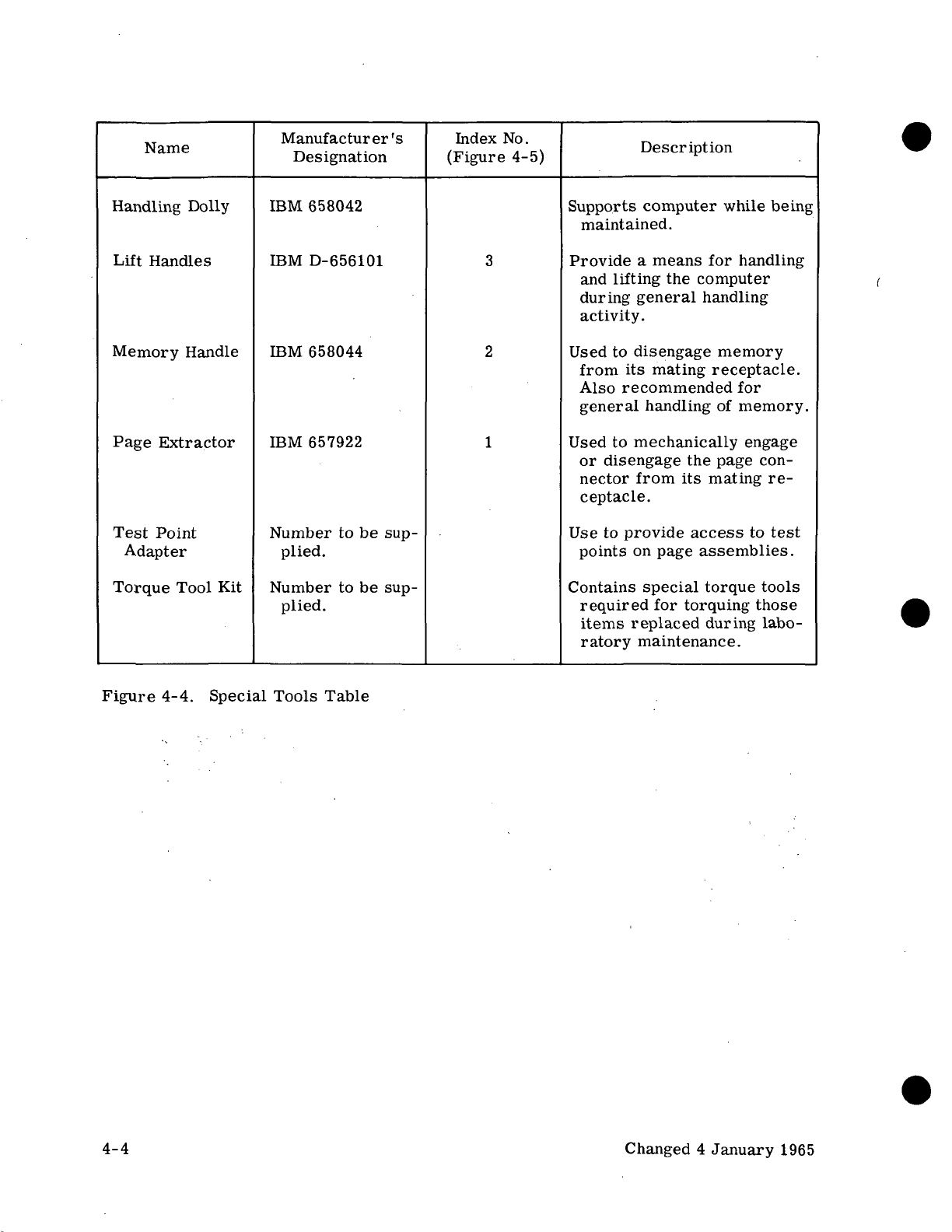

4-6. SPECIAL TOOLS.

4-7.

The

special

tools

recommended

to

maintain

the

computer

are

listed

in

figure 4-4.

Name

Differential Voltmeter

Volt- Ohm- Ammeter

Oscilloscope

Oscilloscope

Adapter

Oscilloscope

Plug-

In

Unit

Model

or

Type

803-

B

630-

A

58

5 A

81

M

Vendor

John Fluke Mfg.

Co. ,

Inc.

Triplett

Electrical

Instrument

Co,

Tektronix,

Inc.

Tektronix,

Inc.

Tektronix,

Inc.

Figure

4-1. Standard

Test

Equipment

Table

4-1

Name

Manufacturer's

Designation

Index

No.

(Figure 4-3)Description

Book

Cart

IBM

6900039

Equipment

Test

Stand

Launch

Vehicle

Digital Com-

puter-Manual

Exerciser

Test

Program

Tape

IBM

6940100

IBM

6902000

MD1

IBM

6001225

Movable

book

case,

used

for .

storage

of

prime

and

test

equipment

manuals

and

logic

diagrams.

Supports

the

computer

and

provides

cooling

air

during

test.

Used

to

test

and

evaluate

com-

puter operation.

Contains

a

program which,

when

loaded into

the

com-

puter memory,

permits

the

Launch

Vehicle Digital

^Computer-Manual

Exerciser

to

check each functional

part

of the

computer that

can

be

exercised

by a

pro-

gram.

Figure

4-2. Special

Test

Equipment Table

4-2

Changed

4

January 1965

.

...'.-ii^i-rt-'-vtr

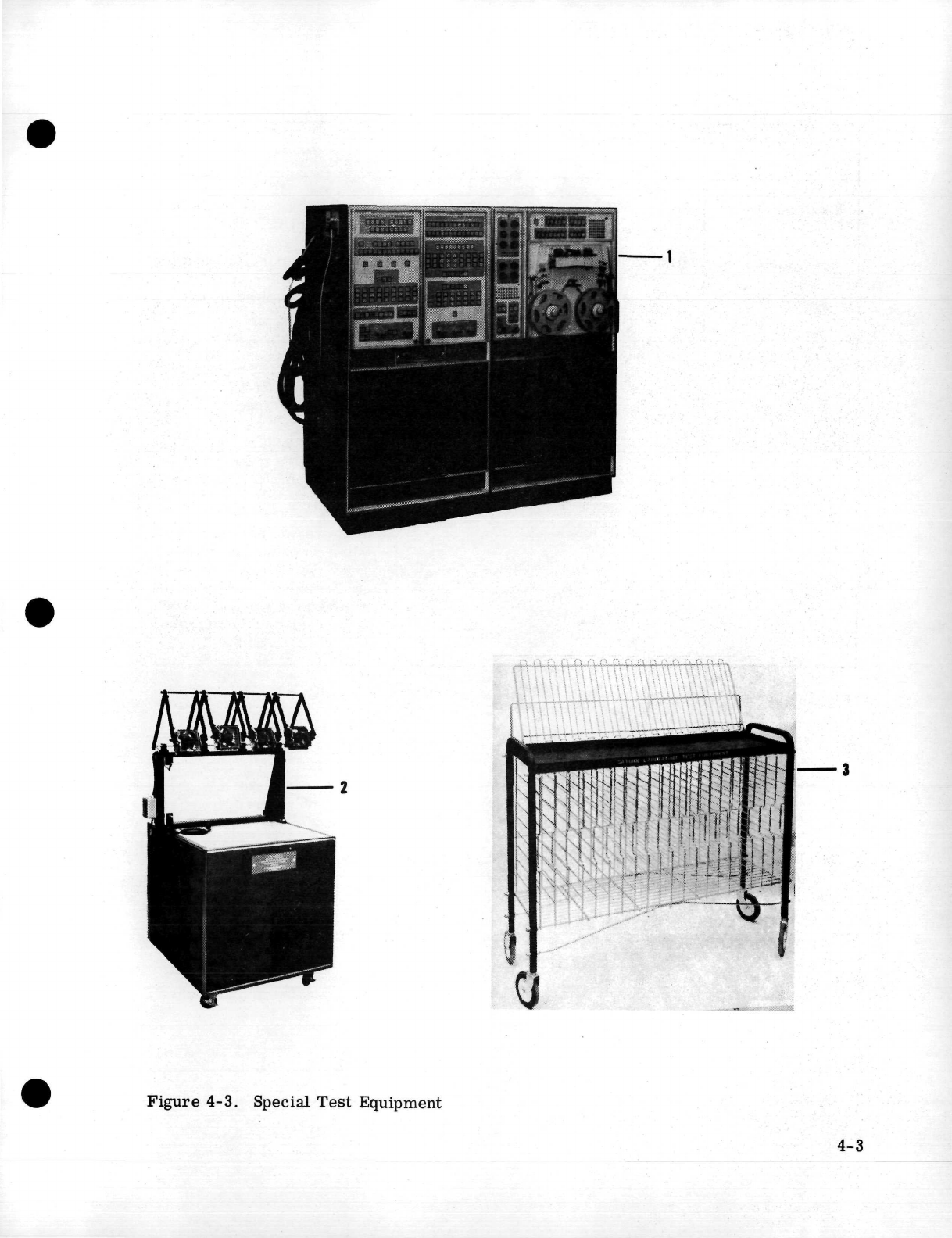

Figure

4-3. Special Test

Equipment

4-3

Name

Handling Dolly

Lift

Handles

Memory

Handle

Page

Extractor

Test

Point

Adapter

Torque Tool

Kit

Manufacturer's

Designation

IBM

658042

IBM

D-656101

IBM

658044

IBM

657922

Number

to be

sup-

plied.

Number

to be

sup-

plied.

Index

No.

(Figure 4-5)

3

2

1

Description

Supports computer while being

maintained.

Provide

a

means

for

handling

and

lifting

the

computer

during

general handling

activity.

Used

to

disengage memory

from

its

mating receptacle.

Also recommended

for

general handling

of

memory.

Used

to

mechanically engage

or

disengage

the

page con-

nector

from

its

mating

re-

ceptacle.

Use

to

provide

access

to

test

points

on

page

assemblies.

Contains

special torque tools

required

for

torquing those

items

replaced

during

labo-

ratory maintenance.

Figure

4-4. Special Tools Table

4-4

Changed

4

January 1965

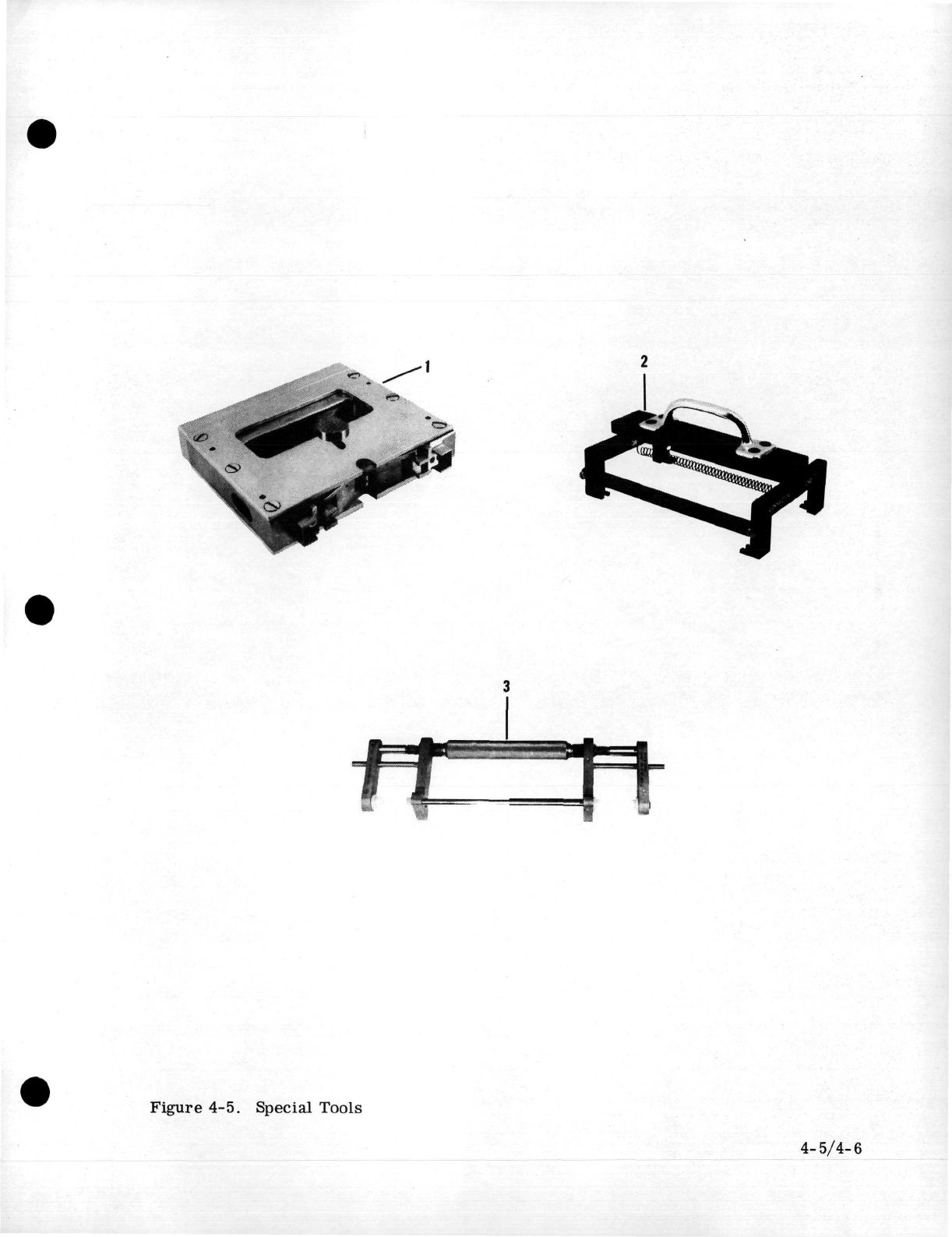

Figure 4-5. Special Tools

4-5/4-6

SECTION

V

PREPARATION

FOR

USE, STORAGE

AND

SHIPMENT

5-1. PREPARATION

FOR

USE.

.

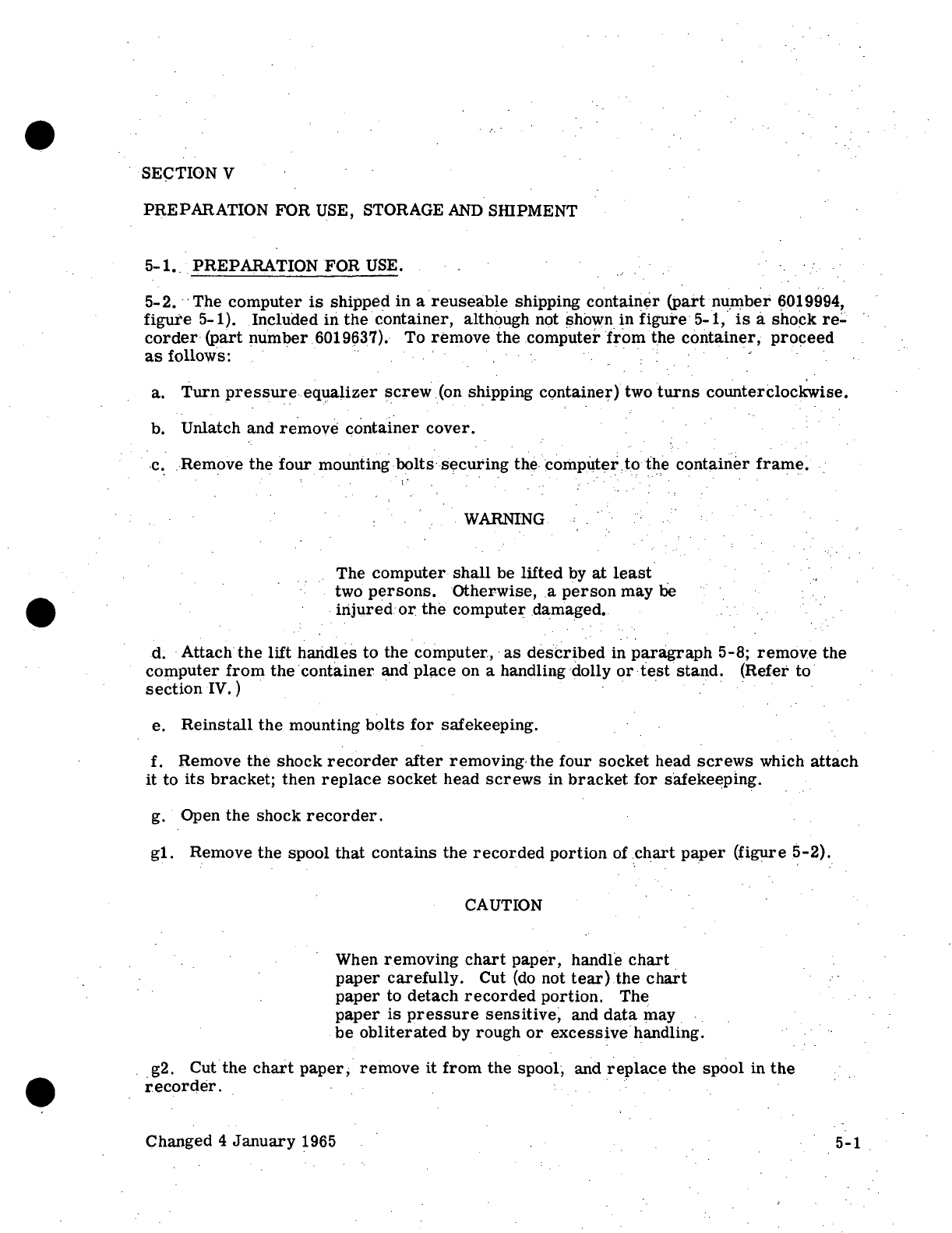

5-2.

The

computer

is

shipped

in a

reuseable

shipping container

(part

number 6019994,

figure

5-1). Included

in the

container, although

not

shown

in

figure 5-1,

is a

shock

re-

corder (part number 6019637).

To

remove

the

computer

from

the

container, proceed

as

follows:

, : J

a.

Turn

pressure

equalizer

screw

(on

shipping container)

two

turns

counterclockwise.

b.

Unlatch

and

remove container cover.

c.

Remove

the

four

mounting bolts securing

the

computer

to the

container frame.

,'•."..".

WARNING

••• . :

The

computer

shall

be

lifted

by at

least

two

persons.

Otherwise,

a

person

may be

injured

or the

computer damaged.

d.

Attach

the

lift

handles

to the

computer,

as

described

in

paragraph 5-8; remove

the

computer

from

the

container

and

place

on a

handling

dolly

or

test

stand.

(Refer

to

section IV.)

e.

Reinstall

the

mounting

bolts

for

safekeeping.

f.

Remove

the

shock recorder after removing

the

four

socket head screws

which

attach

it to its

bracket; then replace socket head

screws

in

bracket

for

safekeeping.

g.

Open

the

shock

recorder.

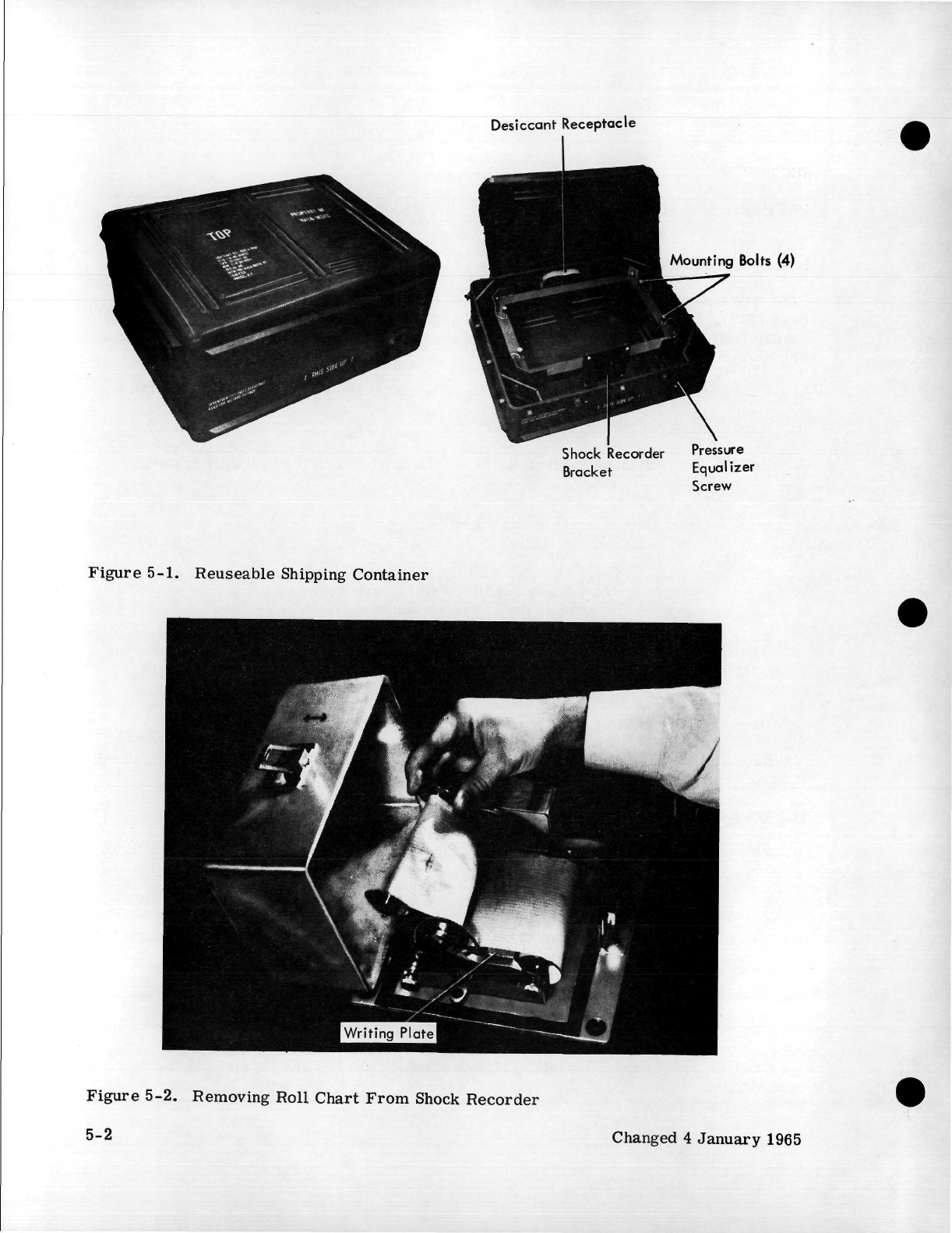

gl.

Remove

the

spool that contains

the

recorded portion

of

chart paper

(figure

5-2).

CAUTION

When

removing chart paper, handle chart

paper carefully.

Cut (do not

tear)

the

chart

paper

to

detach recorded portion.

The

paper

is

pressure

sensitive,

and

data

may

be

obliterated

by

rough

or

excessive

handling.

g2.

Cut the

chart paper, remove

it

from

the

spool,

and

replace

the

spool

in the

recorder.

Changed

4

January 1965

5-1

Desiccant

Receptacle

Mounting

Bolts

(4)

Shock Recorder Pressure

Bracket

Equalizer

Screw

Figure 5-1. Reuseable Shipping Container

Figure 5-2. Removing Roll Chart From Shock Recorder

5-2

Changed

4

January 1965

NOTE

The

recorder

clock mechanism will operate

until

its

spring mechanism

has

unwound.

If

the

recorder

is not to be

used immediately,

do

not

rethread

the

chart paper. Instead,

tape

the

loose

end of the

chart paper

to the

writing

plate. (See

figure

5-2.)

This procedure

saves paper

and

protects

the

styluses

which

would

otherwise

rest

on the

hard surface

of

the

plate.

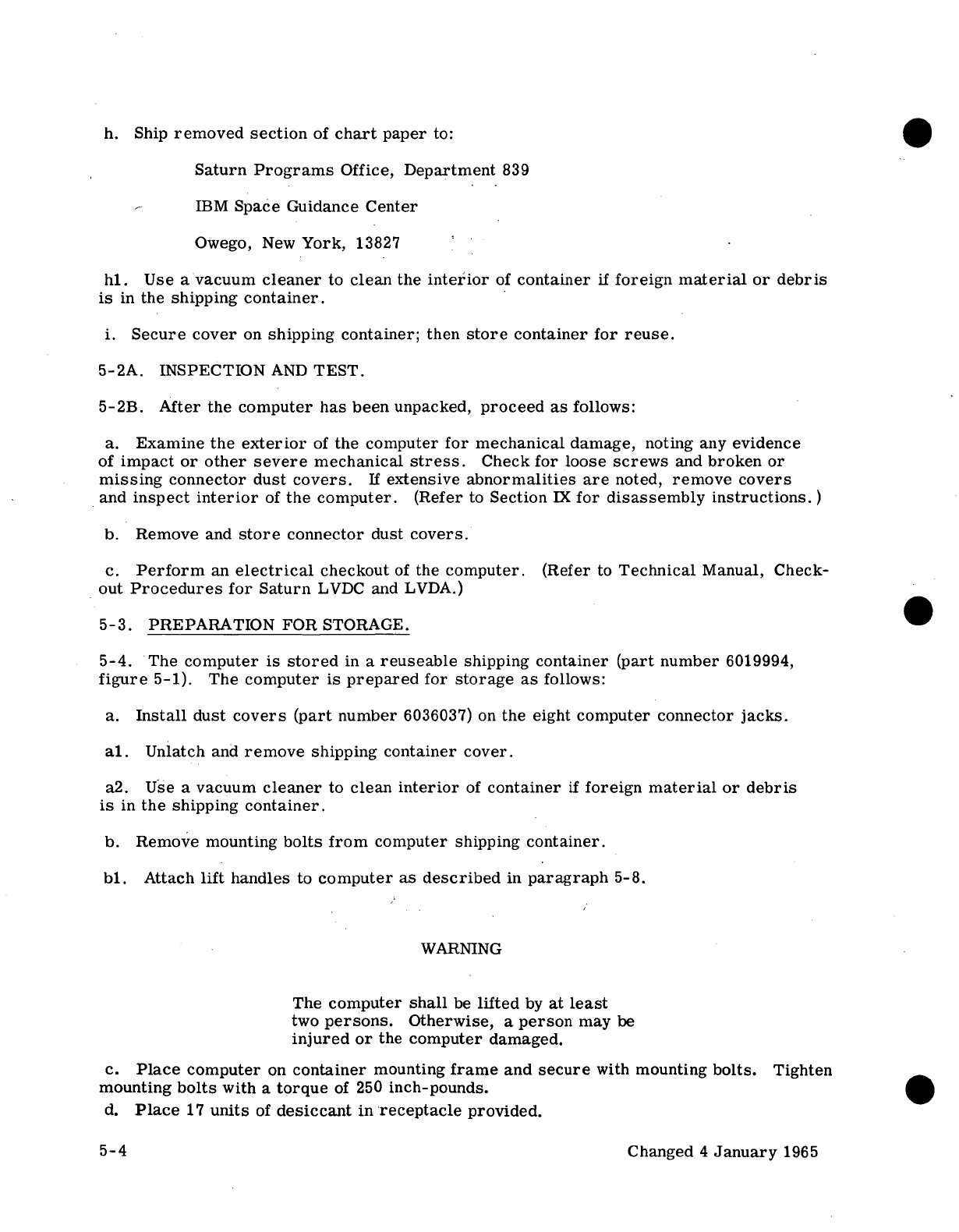

g3.

Rethread

the

chart paper onto

the

takeup spool

(figure

5-3),

or

tape

the

paper

to

the

writing

plate.

g4.

Close

and

latch

the

shock

recorder.

g5.

Reinstall

the

shock

recorder

(handle

side

up) in the

shipping container.

g6.

On a

blank portion

of the

removed section

of

chart paper, record

the

Government

Bill

of

Lading

Number

Receiving

Location

and

Receiving Individual's Signature

Unit

Name,

Part

Number,

and

Serial

Number

Container

Serial

Number

and

Recorder

Serial

Number

Data

and

Local Time recorder

was

opened.

TAKEUP

SUPPLY

( B )

FEED

DIAGRAM

(A)

ROLL

CHART

PARTIALLY

INSTALLED

(C)

ROLL

CHART

COMPLETELY

INSTALLED

Figure

5-3.

Installing

Roll

Chart

in

Shock

Recorder

Changed

4

January 1965

5-3

h.

Ship removed section

of

chart paper

to:

Saturn

Programs

Office,

Department

839

IBM

Space Guidance Center

Owego,

New

York,

13827

'

hi. Use a

vacuum cleaner

to

clean

the

interior

of

container

if

foreign material

or

debris

is in the

shipping container.

i.

Secure cover

on

shipping container; then

store

container

for

reuse.

5-2A. INSPECTION

AND

TEST.

5-2B. After

the

computer

has

been unpacked, proceed

as

follows:

a.

Examine

the

exterior

of the

computer

for

mechanical damage, noting

any

evidence

of

impact

or

other

severe

mechanical

stress.

Check

for

loose screws

and

broken

or

missing connector dust

covers.

If

extensive abnormalities

are

noted, remove covers

and

inspect interior

of the

computer.

(Refer

to

Section

K for

disassembly instructions.)

b.

Remove

and

store

connector dust covers.

c.

Perform

an

electrical

checkout

of the

computer.

(Refer

to

Technical Manual, Check-

out

Procedures

for

Saturn

LVDC

and

LVDA.)

5-3. PREPARATION

FOR

STORAGE.

5-4.

The

computer

is

stored

in a

reuseable shipping container (part number

6019994,

figure

5-1).

The

computer

is

prepared

for

storage

as

follows:

a.

Install dust covers (part number

6036037)

on the

eight computer connector jacks.

al.

Unlatch

and

remove shipping container cover.

a2. Use a

vacuum cleaner

to

clean interior

of

container

if

foreign

material

or

debris

is in the

shipping container.

b.

Remove mounting bolts

from

computer shipping container.

bl.

Attach

lift

handles

to

computer

as

described

in

paragraph 5-8.

WARNING

The

computer

shall

be

lifted

by at

least

two

persons.

Otherwise,

a

person

may be

injured

or the

computer damaged.

c.

Place

computer

on

container

mounting

frame

and

secure

with

mounting

bolts. Tighten

mounting

bolts

with

a

torque

of 250

inch-pounds.

d.

Place

17

units

of

desiccant

in

receptacle

provided.

5-4

Changed

4

January 1965

NOTE

The

17

units

of

desiccant

are

packaged

in

three

bags.

The

package

part

number,

units

of

desiccant

per

package,

and the

quantity

of

each

part

number used

are as

follows:

IBM

Part

Number

No. of

Units Quantity Used

6019623

8 2

6019653

1 1

e.

Secure cover

on

shipping

container.

f.

Turn

pressure

equalizer

screw

fully

clockwise.

NOTE

During

storage,

the

container humidity

indicator should

be

checked

at

least

once

a

week (more

often

if

high

humidity condi-

tions.prevail).

If the

"40"

sector

of the

humidity

indicator

turns

pink,

the

tainer

dessicant

should

be

replaced.

5-5. PREPARATION

FOR

SHIPMENT.

5-6.

The

computer

is

shipped

in a

reuseable

shipping container (part number 6019994,

figure

5-1). Included

in the

container

is a

shock

recorder

(part

number 6019637).

The

computer

is

prepared

for

shipment

as

follows:

a.

Install

dust covers (part number

6036037)

on the

eight computer connector jacks,

al.

Unlatch

and

remove container cover.

b.

Remove mounting

bolts

from

computer shipping container.

WARNING

The

computer

shall

be

lifted

by at

least

two

persons.

Otherwise,

a

person

may be

injured

or the

equipment damaged.

c.

Place

computer

on

container mounting frame

and

secure with mounting

bolts.

Tighten

mounting

bolts

with

a

torque

of 250

inch-pounds.

Changed

4

January

1965

5-5

CAUTION

Verify

that shock

recorder

styluses

are

marked

"100g".

Otherwise,

recorder

will

not be

capable

of

recording excessive

shock with accuracy.

cl.

Remove

the

shock

recorder

after removing

the

four

socket head screws

which

attach

the

recorder

to its

bracket.

Replace socket head screws

in

bracket

for

safe-

keeping.

c2.

Open

the

shock recorder

and

check

for

damage.

d.

Thread

roll

chart onto takeup spool

of

shock recorder. (See figure 5-3.)

dl.

Close cover

and

strike

recorder

sharply

against

floor. Open cover

and

verify that

all

three

styluses

have made

a

discernable impression

on the

chart

paper.

NOTE

A

full

roll

of

chart paper

is

long

enough

to

record

shock

for a

period

of 60

half

days

(30

days).

The

numbers

on the

left-

hand

margin indicate

the

number

of

half

days remaining

on the

roll.

The

mechanism

is

capable

of

running

for

eight days

(16

half

days).

Verify

that

the

number

on the

left-

hand

margin

is 16 or

greater

at the

point

where

recording

starts.

Reorder chart

paper

from

the

following

address:

-

Electrical Standards, Dept.

331

Attention:

Manager

IBM

Space Guidance Center

Owego,

New

York, 13827

d2.

On the

chart paper record

the

Government

Bill

of

Lading Number

Sending

Location

and

Sending Individual's Signature

Unit

Name,

Part

Number

and

Serial

Number

Container

Serial

Number

and

Recorder

Serial

Number

Date

and

Local Time recorder

was

started

5-6

Changed

4

January 1965

NOTE

The

chart paper

is

calibrated

in

A.M.

and

P.M. hours,

but it is not

necessary

to .

align

the

paper

with

the

local time.

Simply

write

the

local time

at the

point

where

the

recorder

was

started.

•:,.••

d3.

Wind

the

shock recorder,

and

verify

that

the

paper

is

moving

and

that

all

three

styluses

are

tracking.

d4.

Close

and

latch

the

shock recorder,,

but do not

lock

the

latch.

e.

Remove

socket head screws

from

shock recorder

mounting

bracket.

f.

Install shock recorder

on

bracket, using socket head screws previously removed.

g.

Place

17

units

of

desiccant

in

receptacle provided.

' . '-. '•'.'••"-. •'••-•;•

'•'•:••.':

'•;•-;•'..'

NOTE.-' '-^'''••v-:"':,.;.-:'v^--'v

'•',-.

• ••

;..'.

The 17

units

of

desiccant

are

packaged

in

<

three ;bags.

; The

package

part

number,

units

of

desiccant

per

package,

and the

quantity

of

each

part

number used

are as

follows:

IBM

Part

Number

No. of

Units Quantity Used

6019623

8 2

6019653

1 1

h.

Secure cover

on

shipping container.

i.

Turn

pressure

equalizer screw

fully

clockwise.

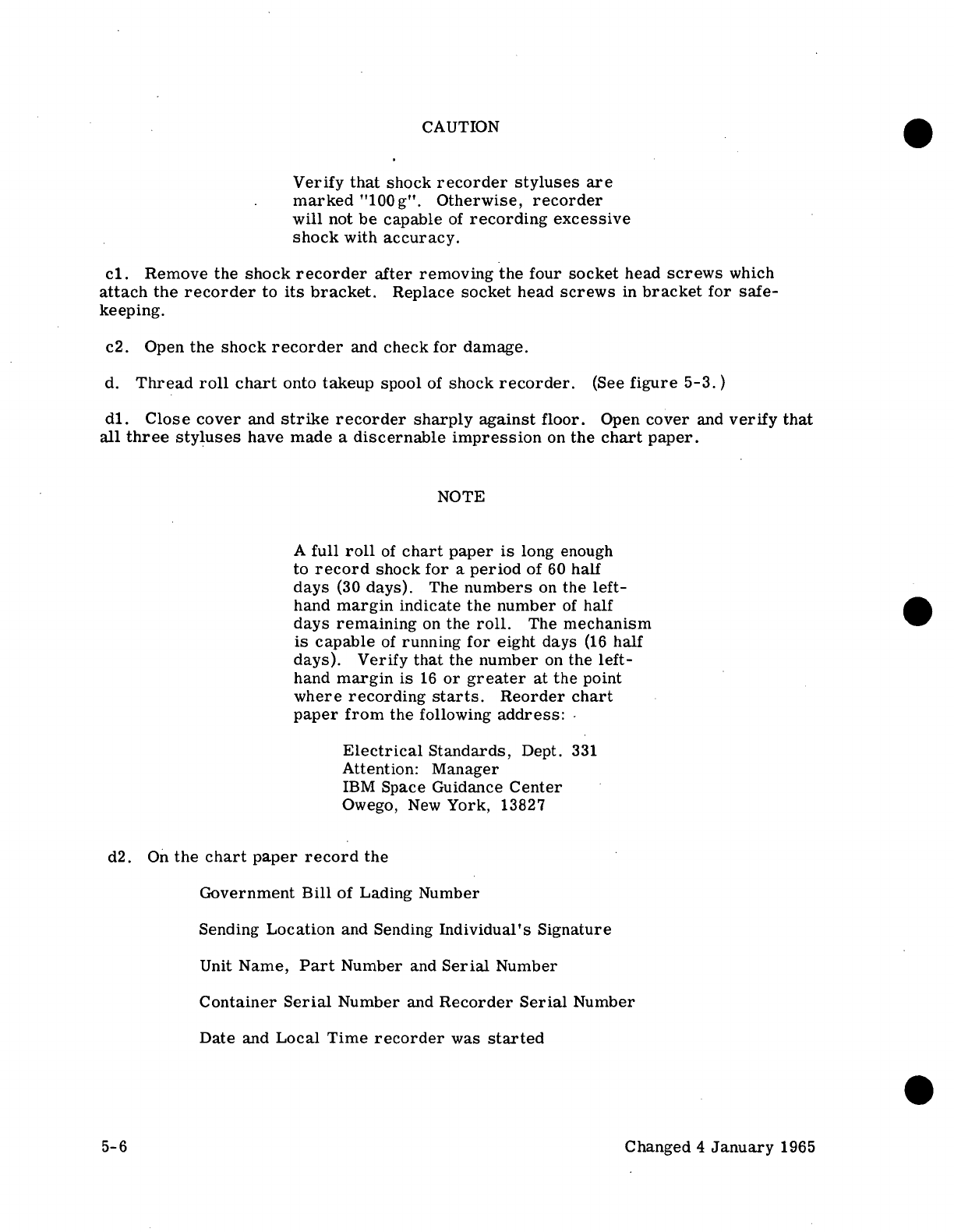

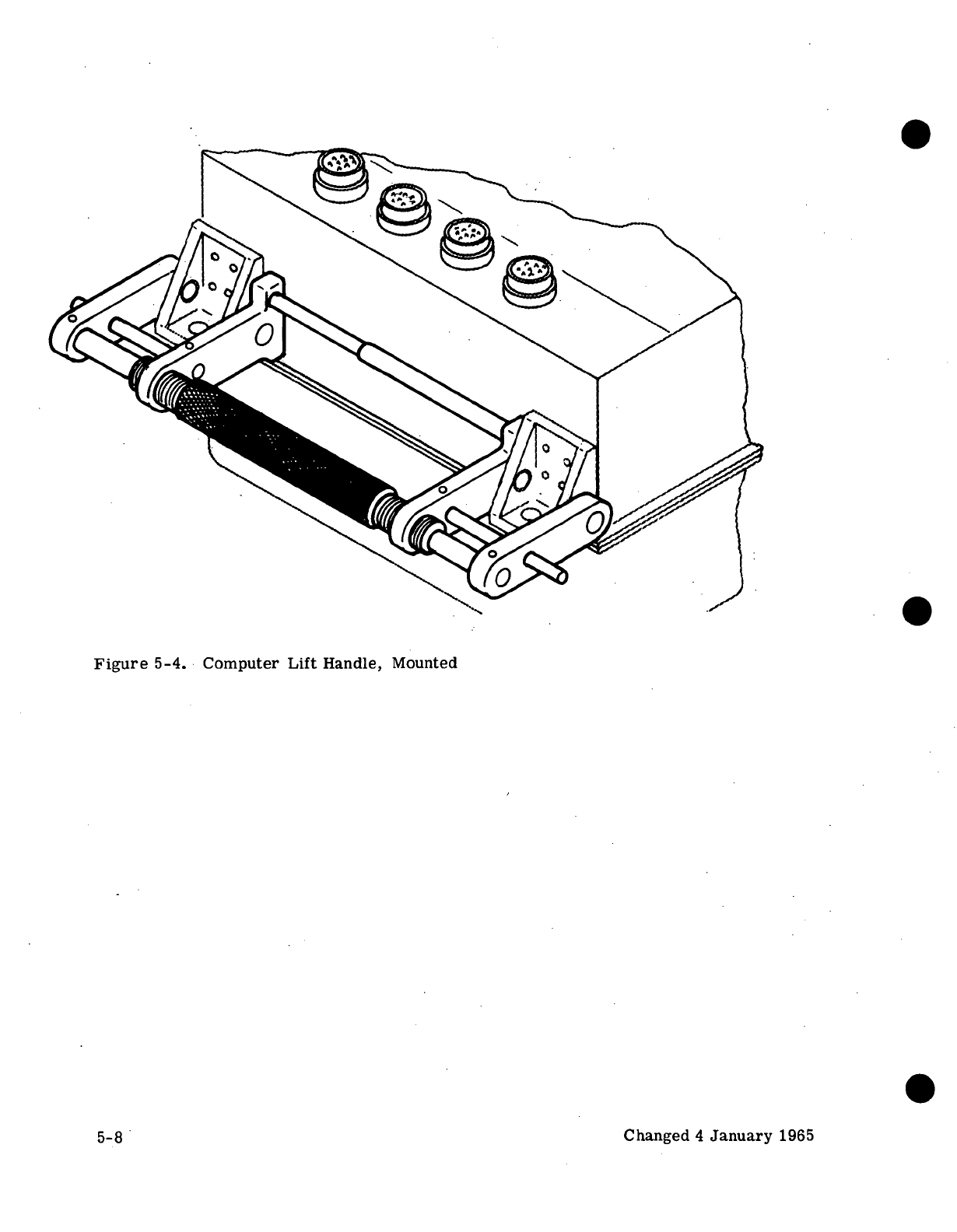

5-7.

GENERAL

COMPUTER

HANDLING.

5-8.

Computer

lift

handles (IBM Tool

Number

D-656101)

are

used

for

general

handling

of

the

computer.

Two

computer

lift

handles .are needed

for

computer handling;

one

handle

is

mounted

on the

left

side

of the

computer

and the

other handle

is

mounted

on the

right side

of the

computer.

Mount

the

computer

lift

handles

as

shown

in

figure

5-4.

Changed

4

January 1965

' 5-7

Figure

5-4.

Computer Lift Handle, Mounted

5-8

Changed

4

January 1965

SECTION

VI

PREVENTIVE

MAINTENANCE

No

preventive maintenance

is

performed

on

the

breadboard models.

6-1/6-2

SECTION

VH

CHECKOUT

7-1.

OPERATING TEST PROCEDURES.

7-2.

Instructions

for

testing

the

computer

are

located

in the

Saturn

V

Launch

Vehicle

Digital Computer

and

Data Adapter Checkout Procedures Laboratory Maintenance

Instructions.

7-1/7-2

SECTION

vm

TROUBLE

ISOLATION

This section

is not

applicable

for

breadboard equipments.

8-1/8-2

SECTION

DC

REPAIR

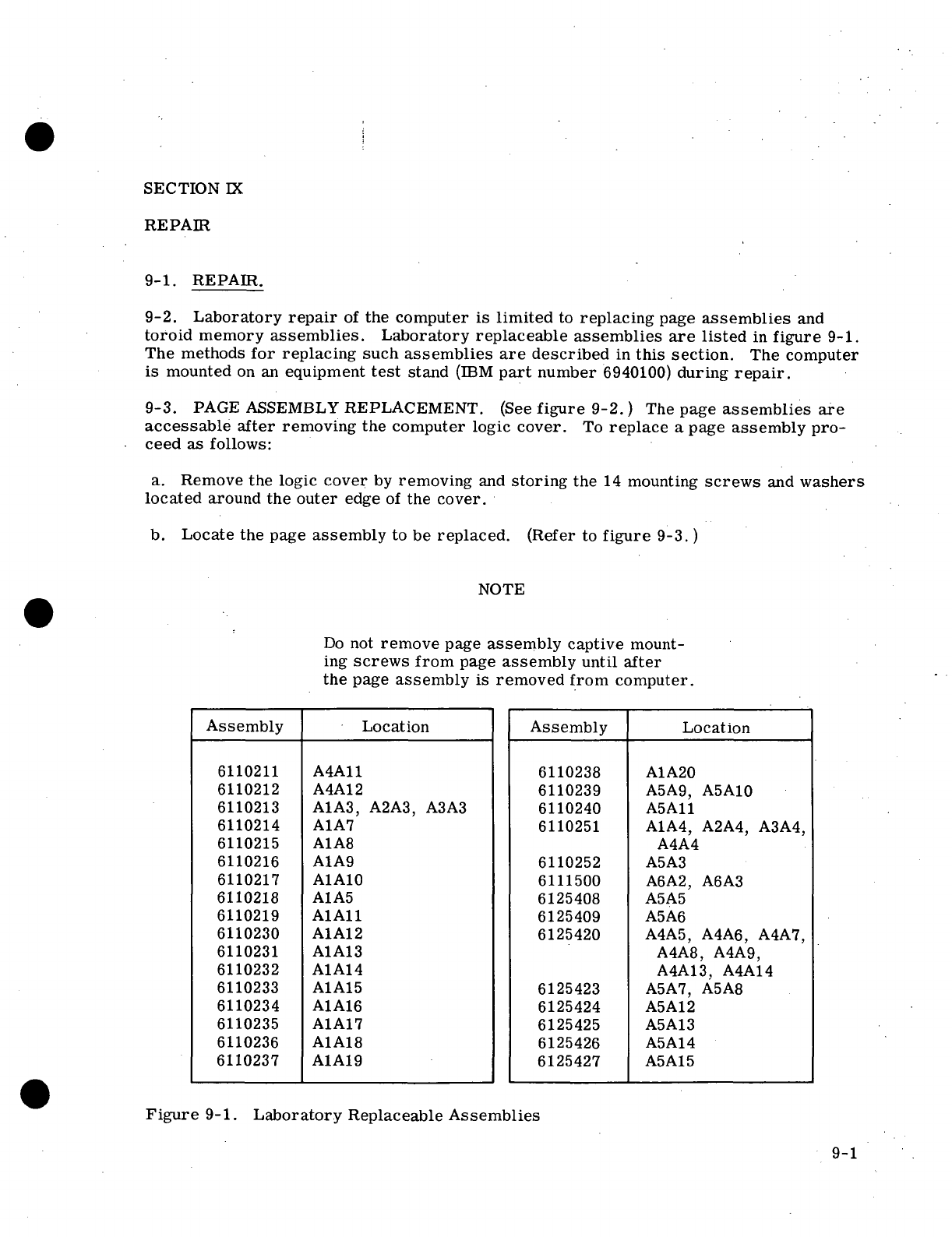

9-1. REPAIR.

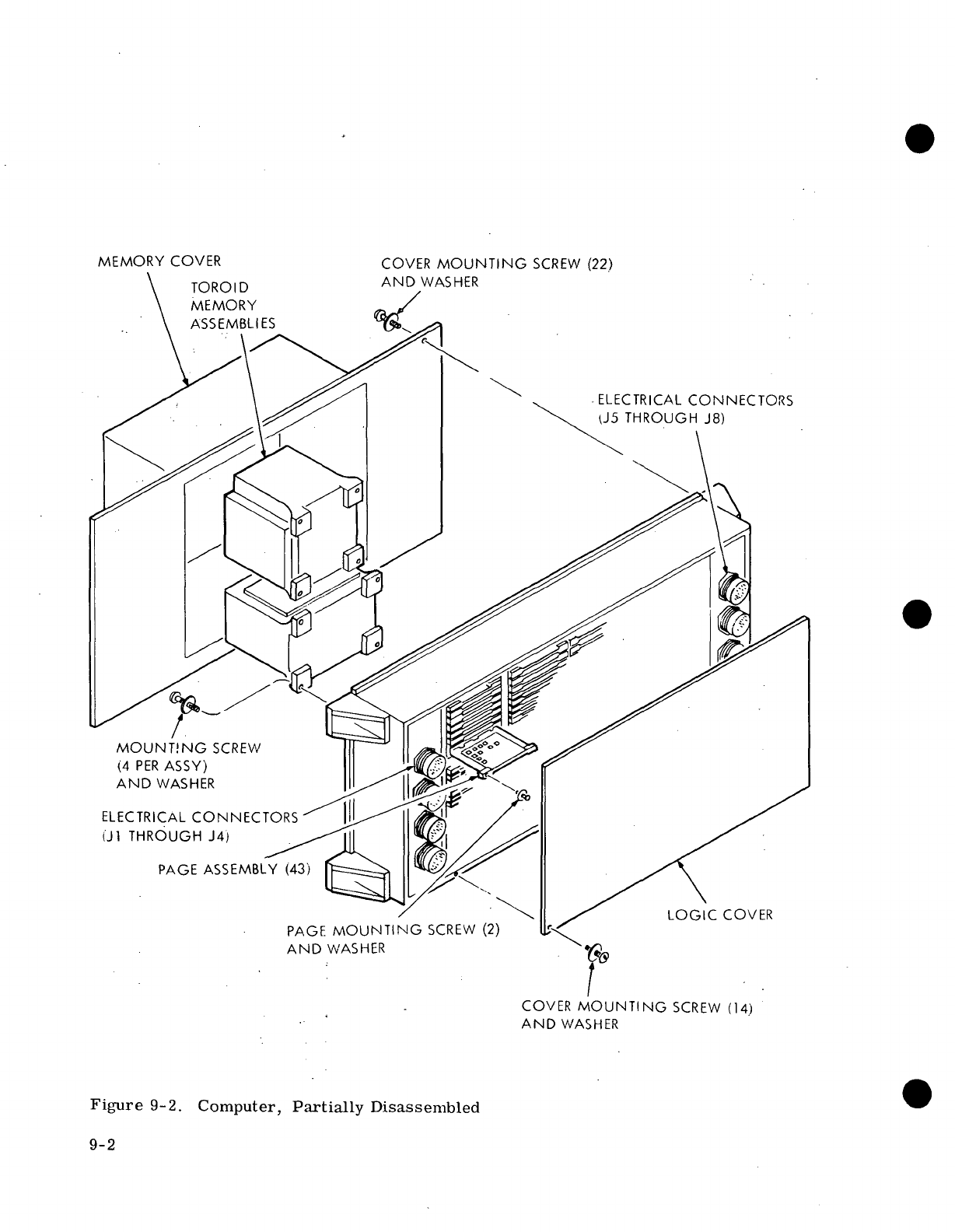

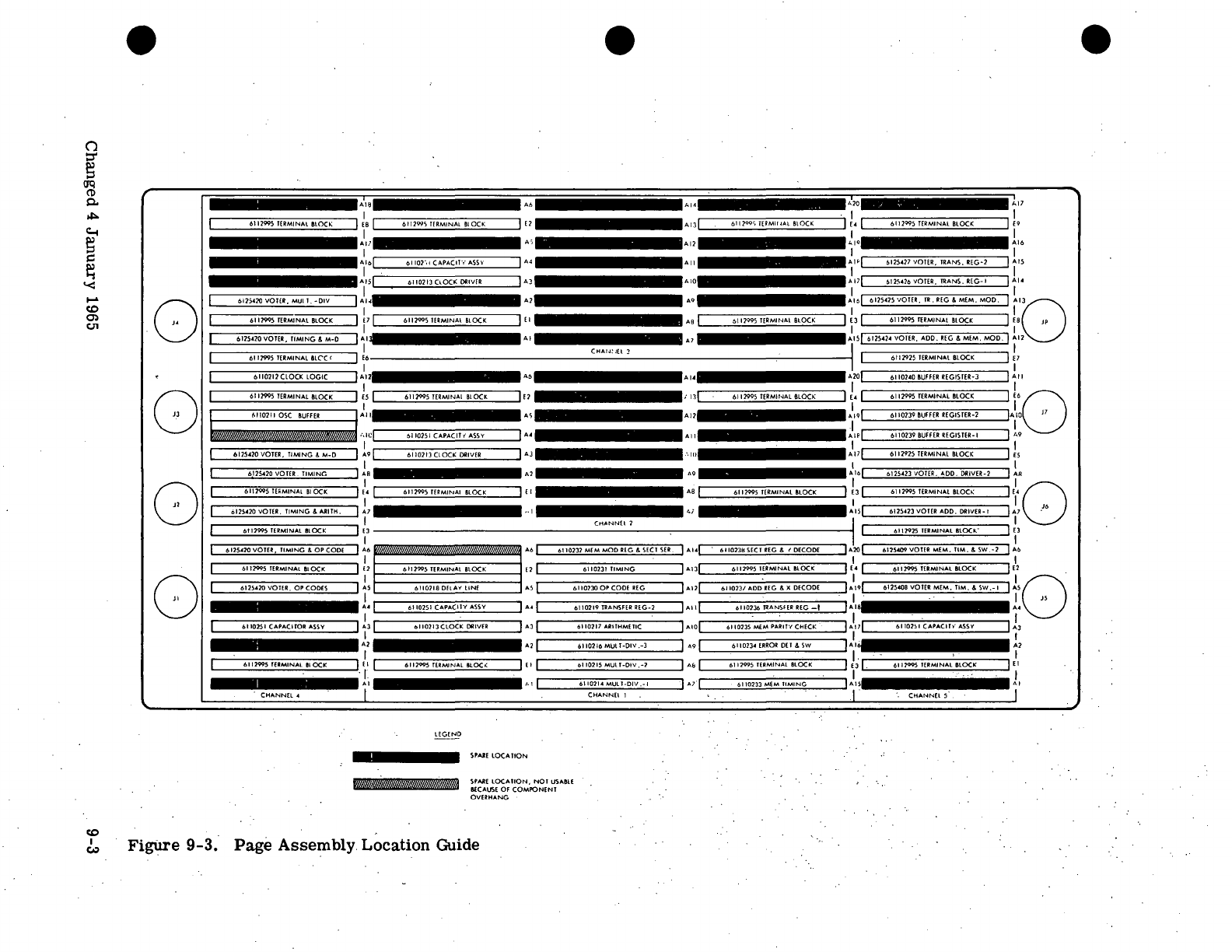

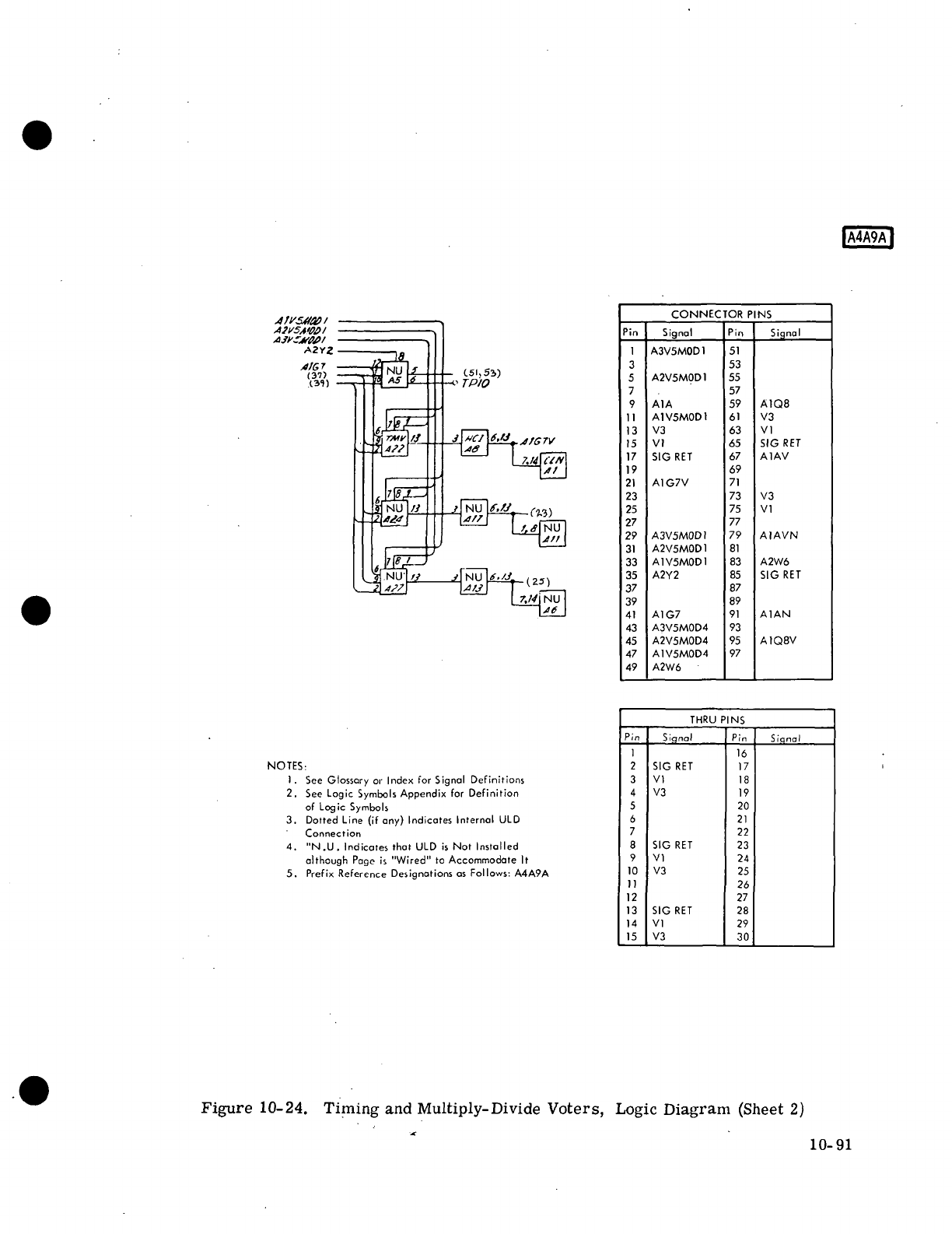

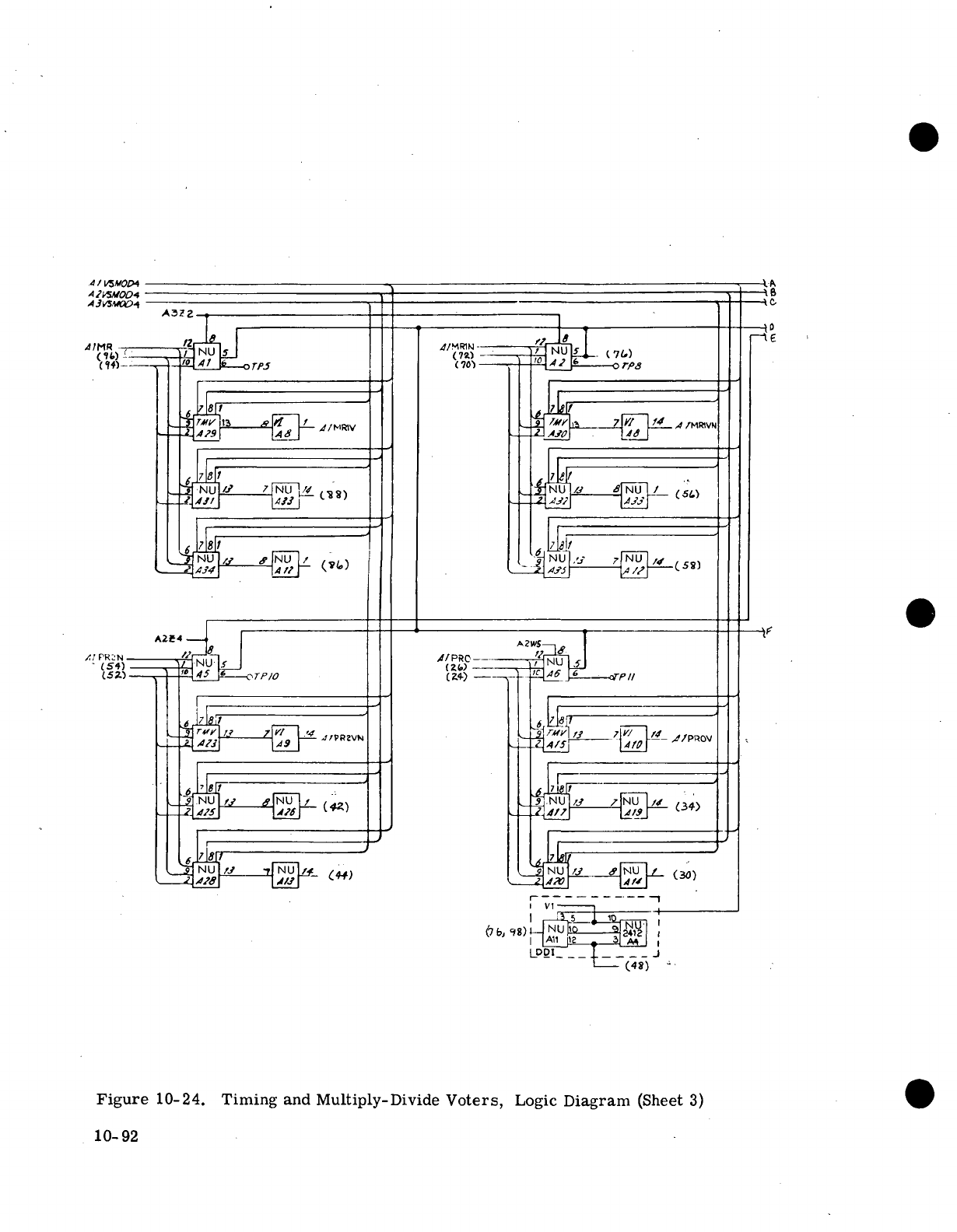

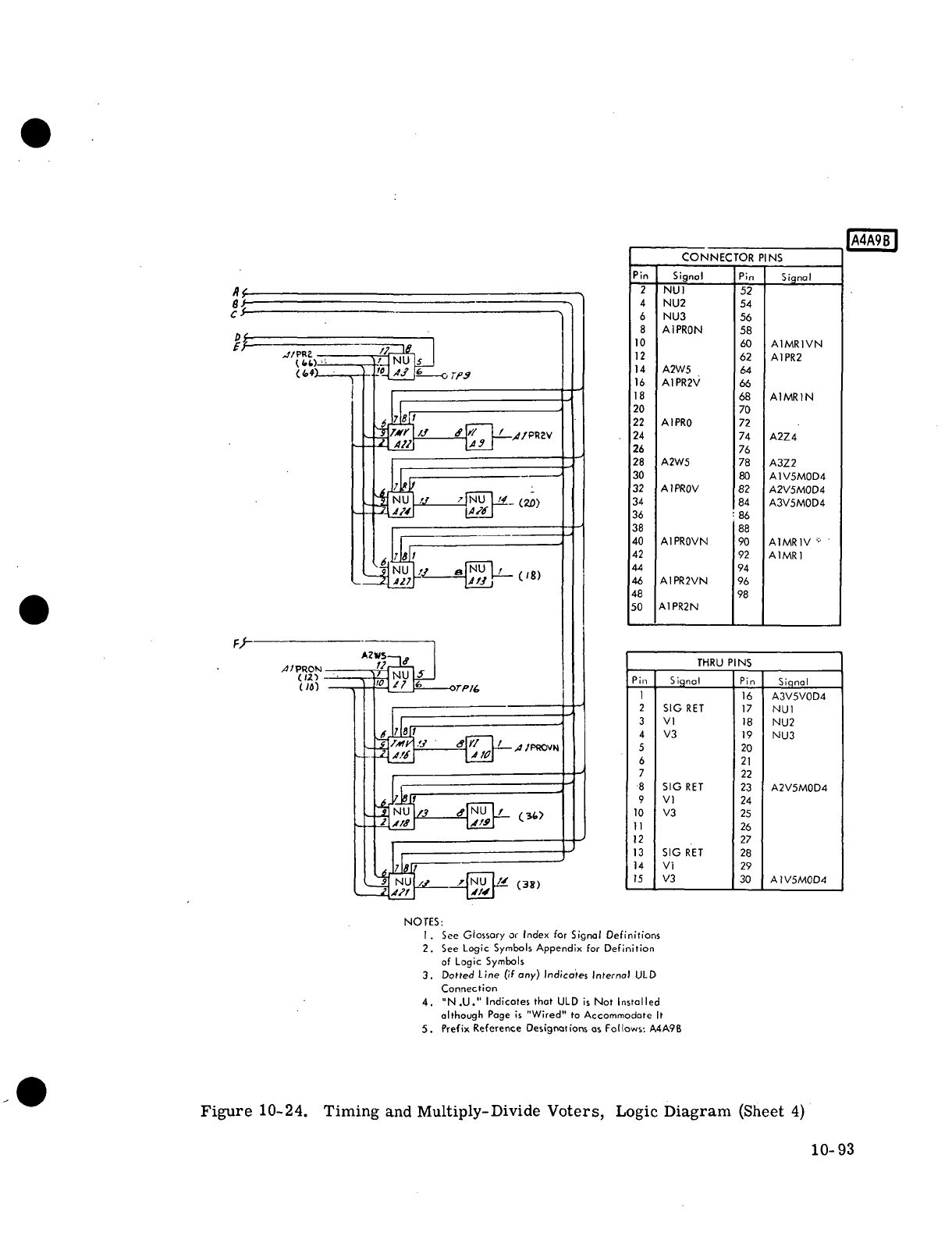

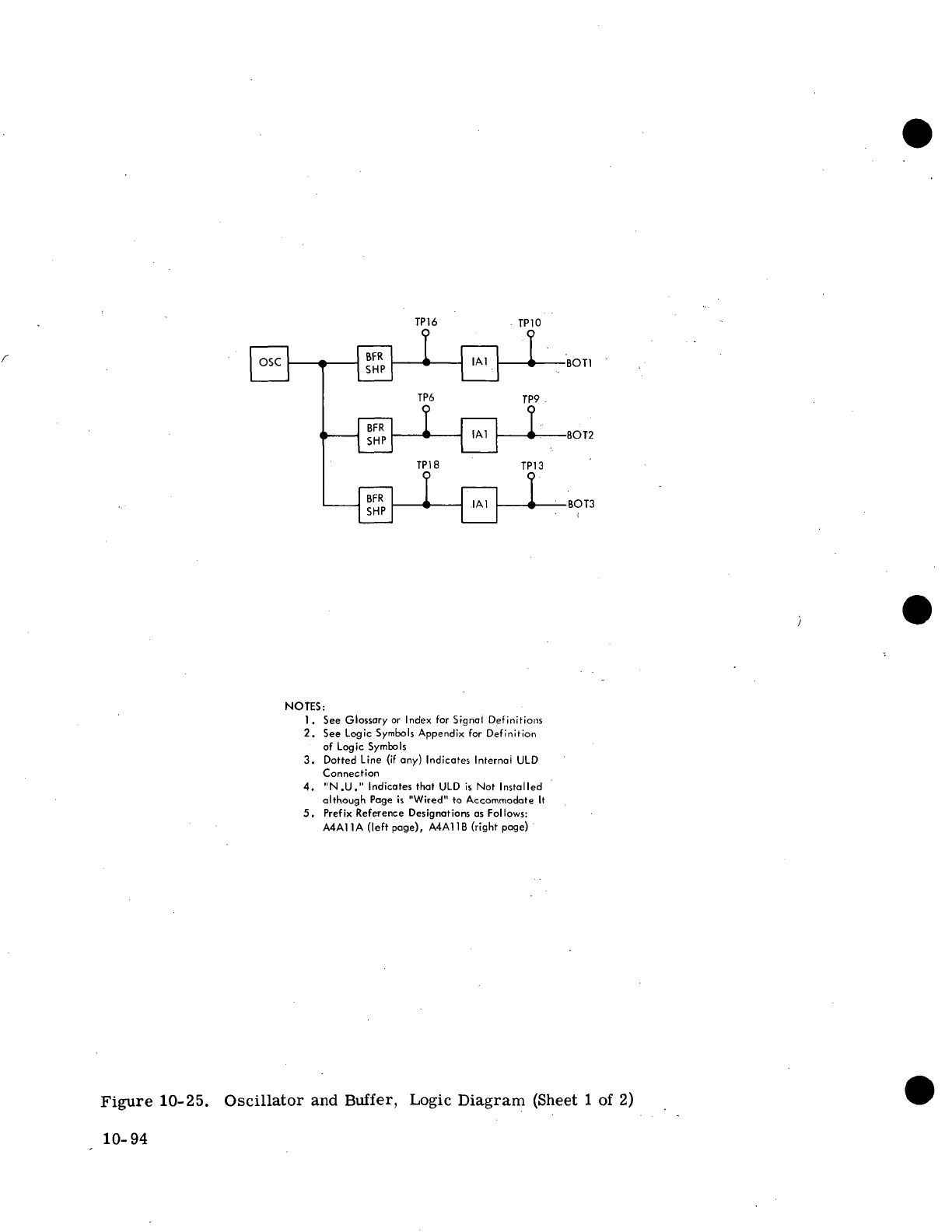

9-2. Laboratory