VHDL Tutorial

User Manual: VHDL-Tutorial

Open the PDF directly: View PDF ![]() .

.

Page Count: 224 [warning: Documents this large are best viewed by clicking the View PDF Link!]

- 1. VHDL – Genel Bakış ve Uygulama Alanı

- 1.1 HDL Uygulamaları (1)

- /1.1.1 HDL Uygulamaları (2)

- 1.1.2 Kullanımın Sıralanması

- 1.2 VHDL ‘e Kısaca Göz Atalım

- VHDL geliştirme ilk olarak Amerikan Savunma Departmanı tarafından başlatılmıştır. Onlar, donanımı tanımlamak için, bilgisayar ve insanlar tarafından aynı anda okunabilir olacak ve geliştiricileri yapısal ve anlaşılır kod yazmaya zorlayacak, yani kay...

- 1987 ‘de, VHDL Amerikan Elektrik ve Elektronik Mühendisleri Enstitüsü(IEEE) tarafından ilk resmi güncelleştirilmesi 1993 yılında yapılarak ilk kez standartlaştırıldı. Dosya işleme prosedürü dışında bu iki standart birbiriyle uyumludur.Dilin standardı...

- 1.2.1 VHDL – Tarihçesi

- 1.2.2 VHDL – Uygulama Alanı

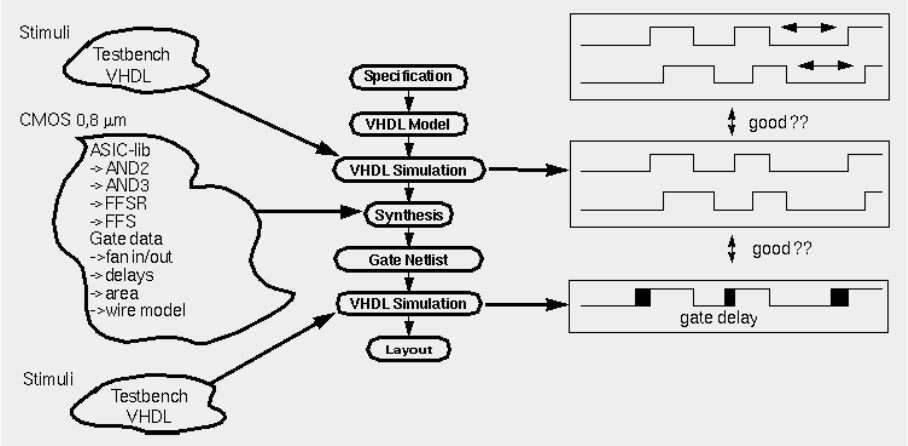

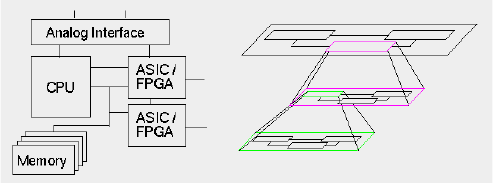

- 1.2.3 ASIC Geliştirme

- /

- 1.3 VHDL’in Kavramları

- 1.3.1 Soyutlama

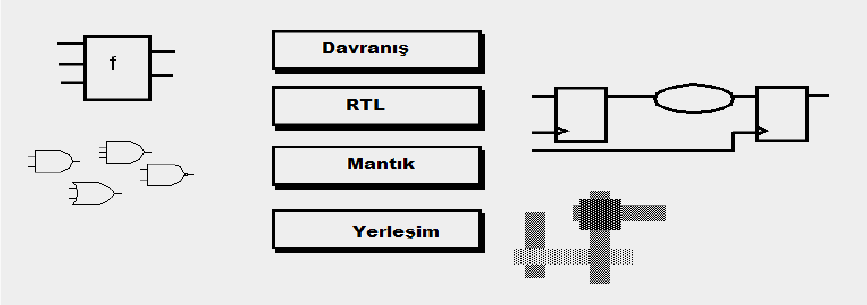

- 1.3.2 IC Tasarımında Soyutlama Seviyeleri

- /

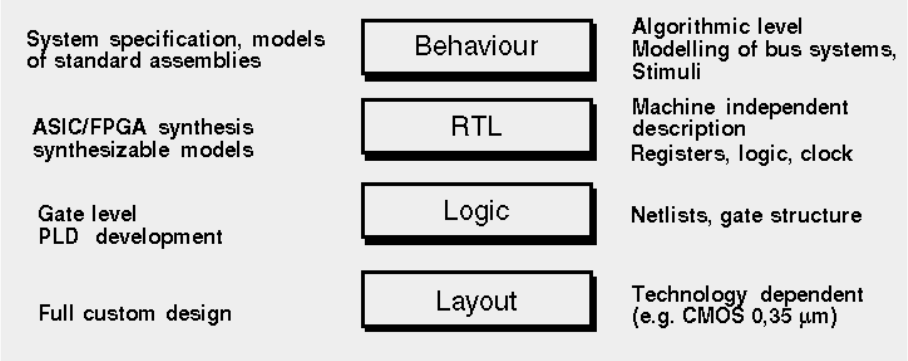

- Bir sayısal devre tasarımının dört soyutlama seviyesi şekilde gösterilmiştir. Modelin fonksiyonel tanımlaması davranışsal modelde özetlenir. Burada sistem saati yoktur ve sinyal geçişleri anahtarlama zamanına uyacak şekilde asenkrondur. Genellikl...

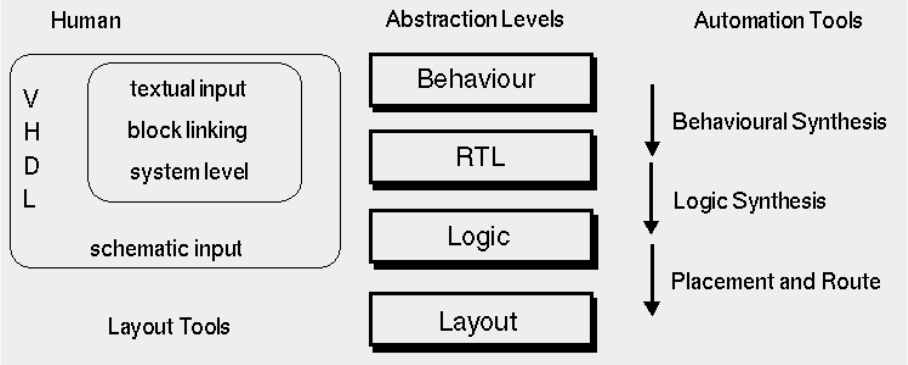

- 1.3.3 Soyutlama Seviyeleri ve VHDL

- /

- VHDL üstteki üç soyutlama seviyeleri için uygulanabilir. VHDL bir yerleşim tanımlamaya uygun değildir. Davranışsal ve RT seviyedeki tasarım girişi genellikle metin editörleri tarafından yapılır. Grafik araçları da mevcuttur ancak deneyimli kullanıcı...

- 1.3.4 Soyut Seviylerin Tanımlamaları

- /

- Davranış seviyesinde tüm sistem modellenebilir. Veri iletim yolu veya kompleks algoritmalar, sentezlenebilirliği göz önünde bulundurulmadan tanımlanmalıdır. RTL modellerin simülasyonu için tepki(stimuli) davranış seviyesinde tanımlanır. Tepki, model...

- 1.3.5 VHDL’de Davranışsal Tanımlama

- /

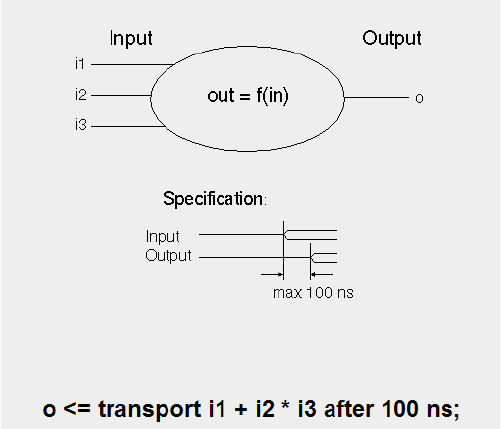

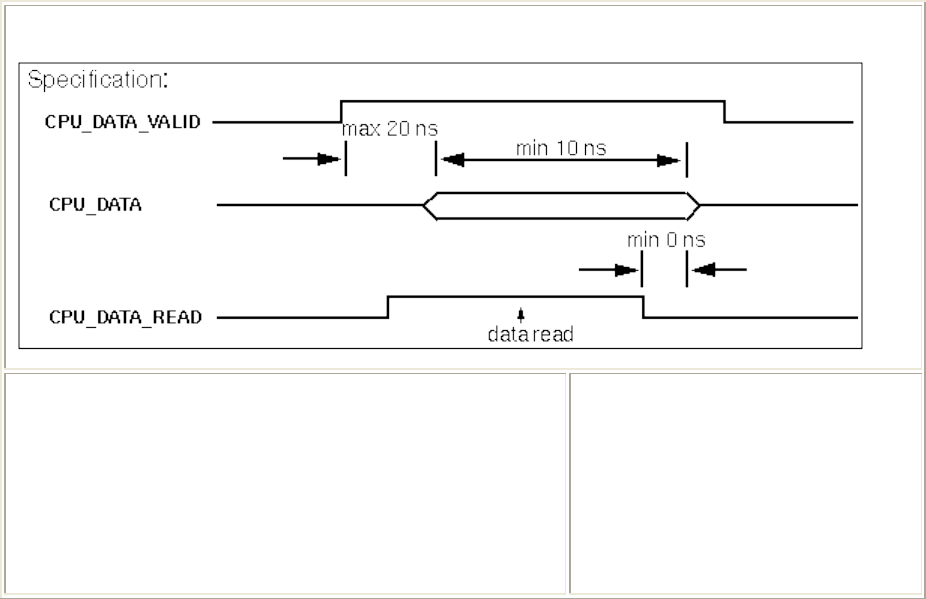

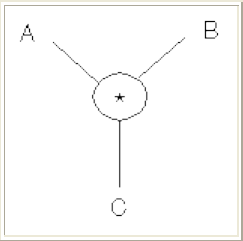

- Bir modelin basit bir belirtim(specification) fonksiyonu gösterilmiştir. Çıkış üç giriş değeri i1, i2 ve i3 ‘e bağlıdır.Ayrıca yeni çıkış değeri giriş değeri değiştirildikten sonra 100ns sonunda hazır olmalıdır. Bir davranışsal VHDL tanımlamada, f...

- 1.3.6 VHDL’de RT Seviyesi

- /

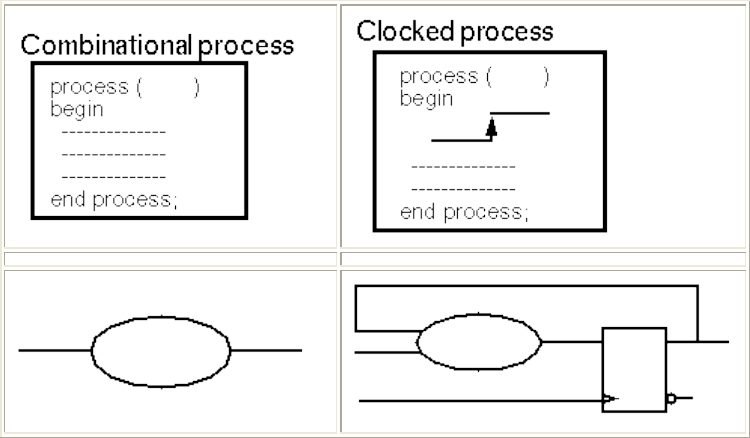

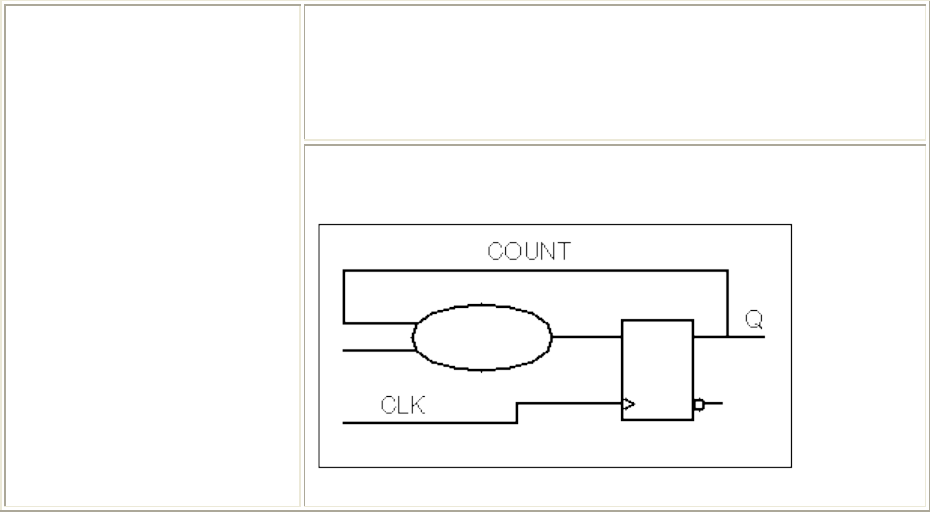

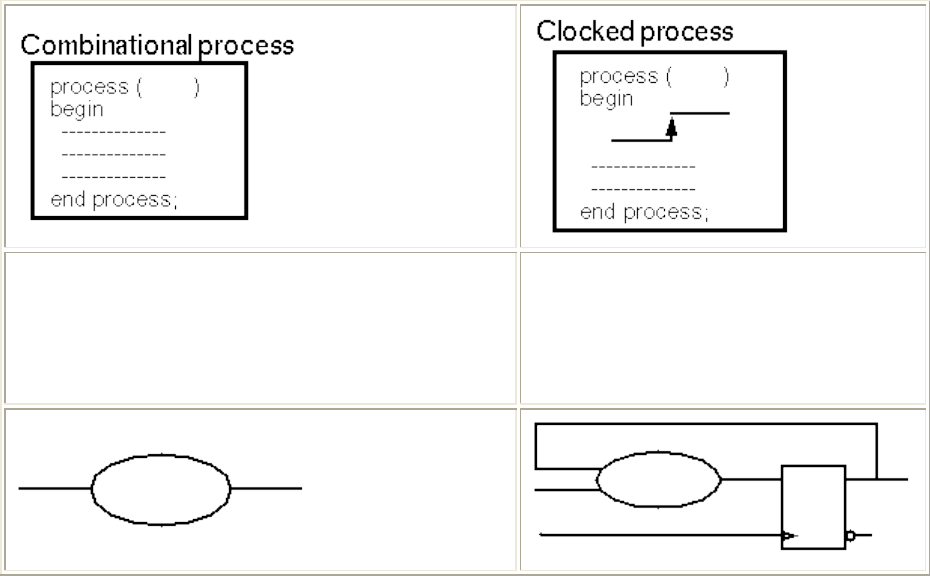

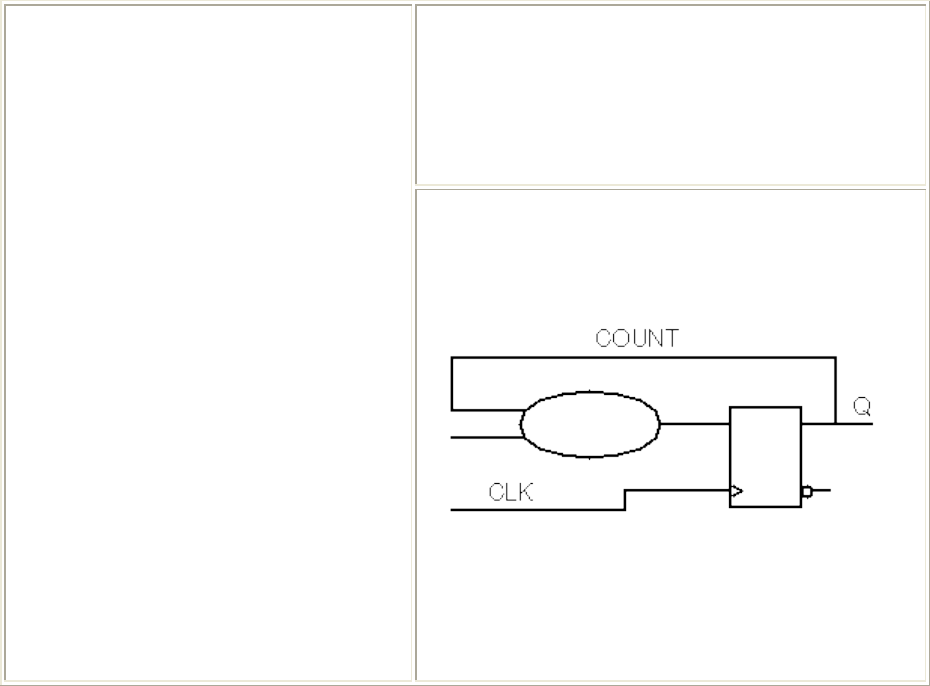

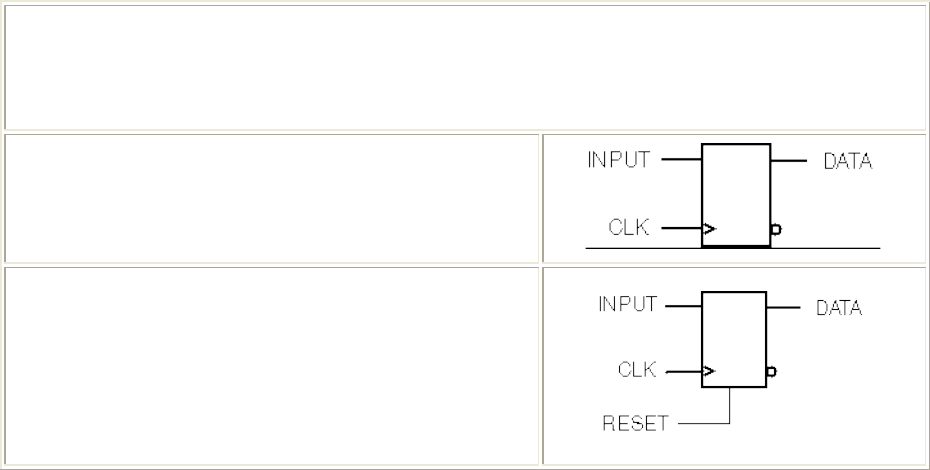

- VHDL’de fonksiyonel davranış sözde süreçler ile modellenir. RT seviyesi tanımlamalarında iki farklı tipte süreç bulunmaktadır: tamamen kombinasyonel süreç (combinational process) ve saatsel süreç(clocked process). Tüm saatsel süreçler Flip Floplar o...

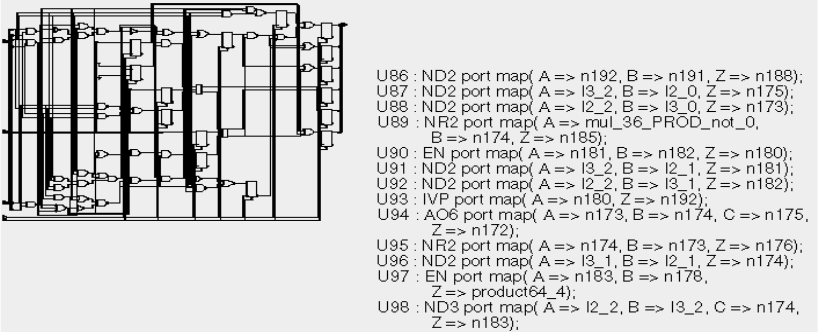

- 1.3.7 VHDL’de Kapı Seviyesi

- /

- Bir VHDL kapı seviyesi tanımlaması tasarımda kullanılan bir kapı(bileşenleri) listesi içermektedir.Diğer kısım bileşenlerin gerçek örneklemini ve onların karşılıklı bağlantılarının(interconnection) listesini tutmaktadır. Bir dijital devrenin ka...

- 1.3.8 Soyut Seviyenin Bilgi İçeriği (Information Content of Abstraction Levels)

- /

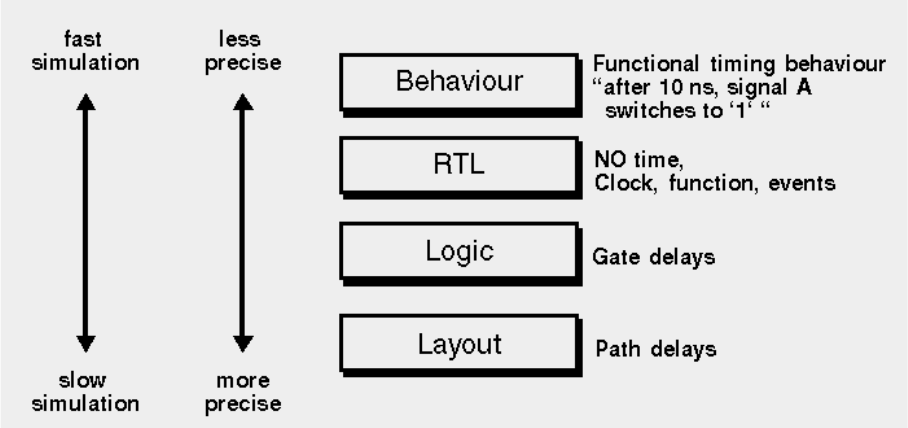

- Davranış model, bir devrenin davranışını tanımlamanın basit bir yoludur, alışılmış yazılım programlama dilleri PASCAL veya C ‘ye benzer şekilde. Bu tanımlamadan yola çıkarak sadece fonksiyonel davranış VHDL simülatörü ile simüle edilebilinir. Saat...

- 1.4 Modülarite ve Hiyerarşi

- 1.5 Özet

- 2. VHDL Dili ve Sözdizim(Syntax)

- 2.1 Genel Yapısı

- 2.1.1 Tanıtıcı(identifier)

- 2.1.2 İsimlendirme Kuralları

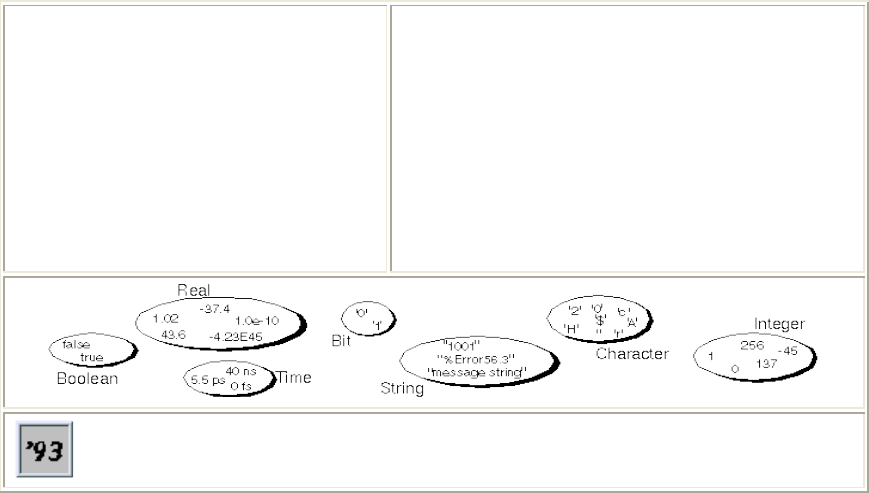

- İsimlendirme kuralları, anahtar sözcükler küçük harfle yazılır, kullanıcı tanımlı tanıtıcılar ise büyük harflerle yazılır. Eğer bir şeye dikkat çekmek isteniyorsa koyu harflerle yazılır. Burada birçok kendini açıklayan ikon vardır. Bunlar VHDL'93 ...

- 2.2 VHDL ‘in Yapısal Elemanları

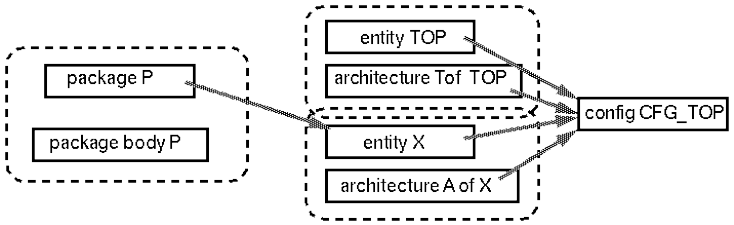

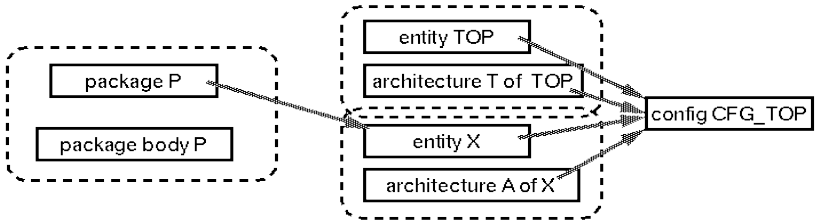

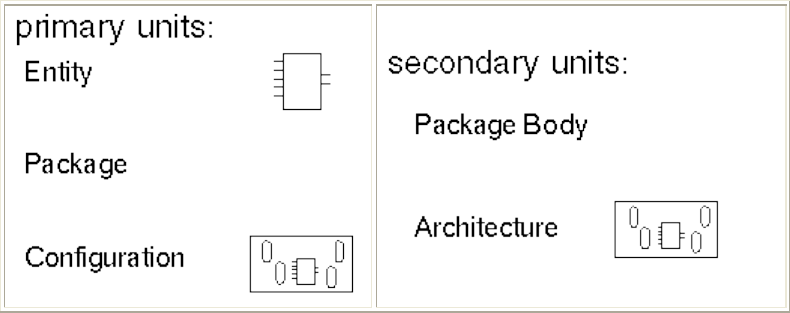

- VHDL deki temel birimler varlıklar, mimariler, konfigürasyon ve paketlerdir. Bir varlık genelde port listesini içeren bir arayüz tanımlarken,bir mimari ilgili modüllerin fonksiyonlarını tanımlar. Genelde bir konfigürasyon sadece simülasyon süreci ...

- 2.2.1 VHDL Objelerinin Bildirimi-Tanımlanması

- (Declaration of VHDL Objects)

- 2.2.2 Varlık(Entity)

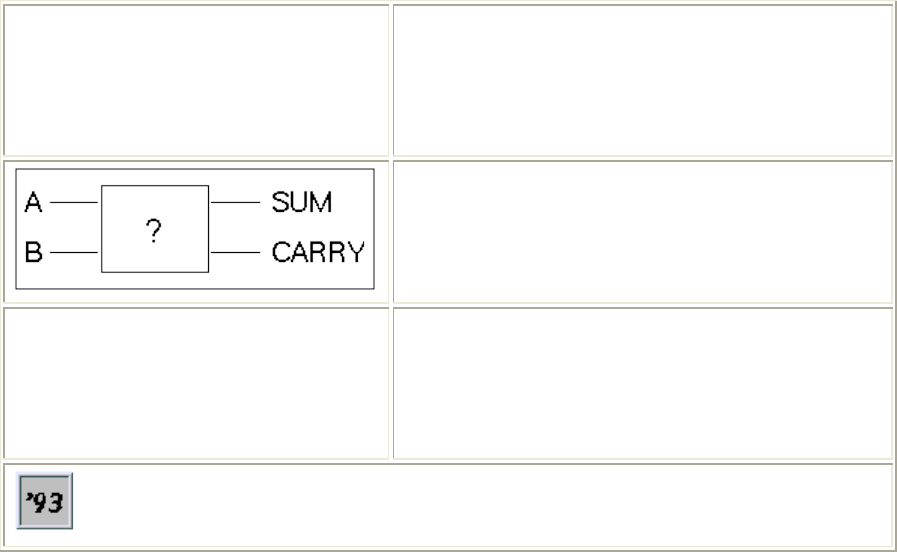

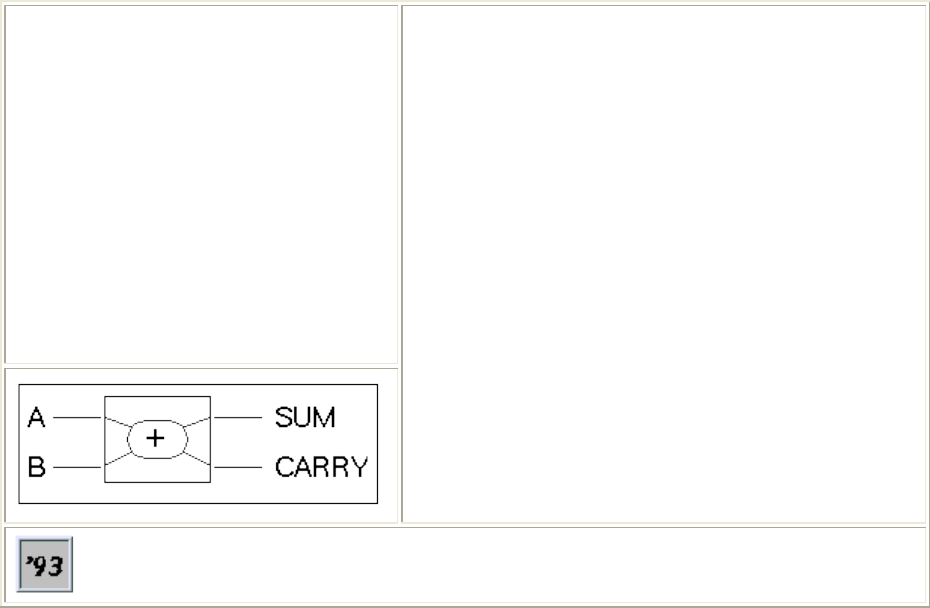

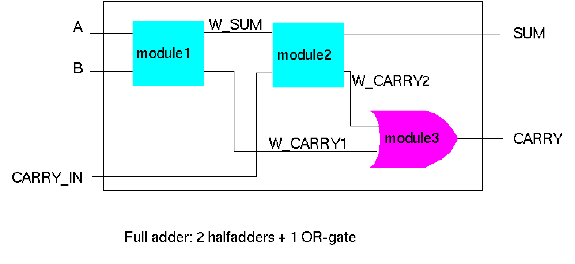

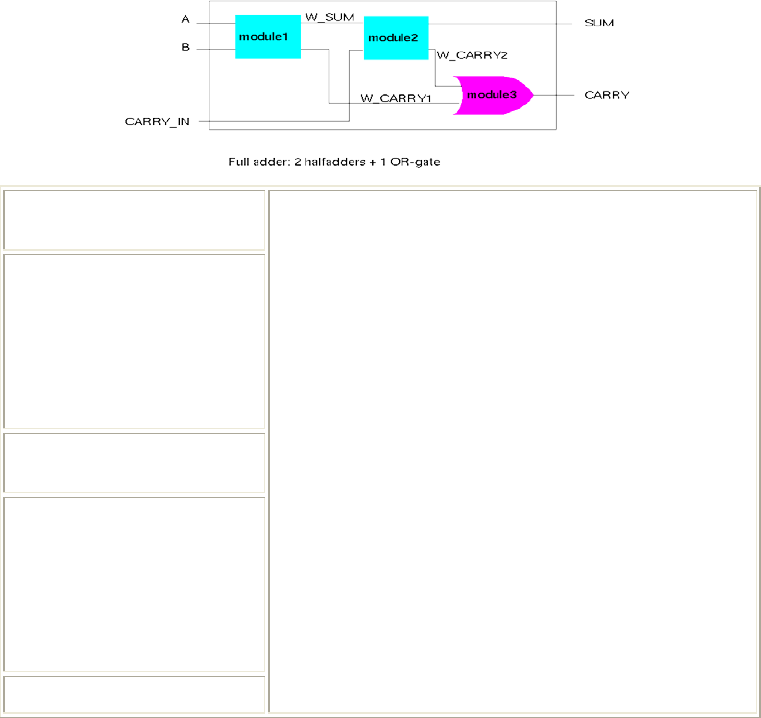

- Yukarıda, bir tam toplayıcı(full adder), iki yarım toplayıcıyı(half adder) ve bir VEYA(OR) kapısını içerecek şekilde adım adım oluşturulmuştur. Kendimizi tamamen yapısal bir tasarımla kısıtlamaktayız, örneğin kapı seviyesi tanımlama kullanıyoruz ve ...

- 2.2.3 Mimari(Architecture)

- Mimari bir davranışsal tanımlama(davranışsal seviye veya eğer sentezlenebiliyorsa RT seviyesi) veya bir yapısal netlist veya bir karışım alternatiflerinden birini bir varlık için gerçekler(implement). Bir mimari kesinlikle belirli bir varlığa bağl...

- 2.2.4 Mimari Yapısı(Architecture Structure)

- Herbir mimari opsiyonel olan bir bildirimsel bölüme ve tanımlama bölümüne ayrılır. Bildirimsel bölüm ' is ' ve ' begin ' anahtar sözcükleri arasında bulunmaktadır. Mimarideki sabitler,veritipleri,sinyaller, altprogramlar,vb. yeni objeler burada bi...

- 2.2.5 Varlık Port Modları

- Bir varlığın portunun modu verinin akış yönünü sınırlar. Port modu ' in ' kullanılan mimairideki bu sinyallerin sadece okunabilir olduğunu belirtir. Bunların değerlerini değiştirmek mümkün değildir. Benzer şekilde ‘out’ port modunda sinyallerin d...

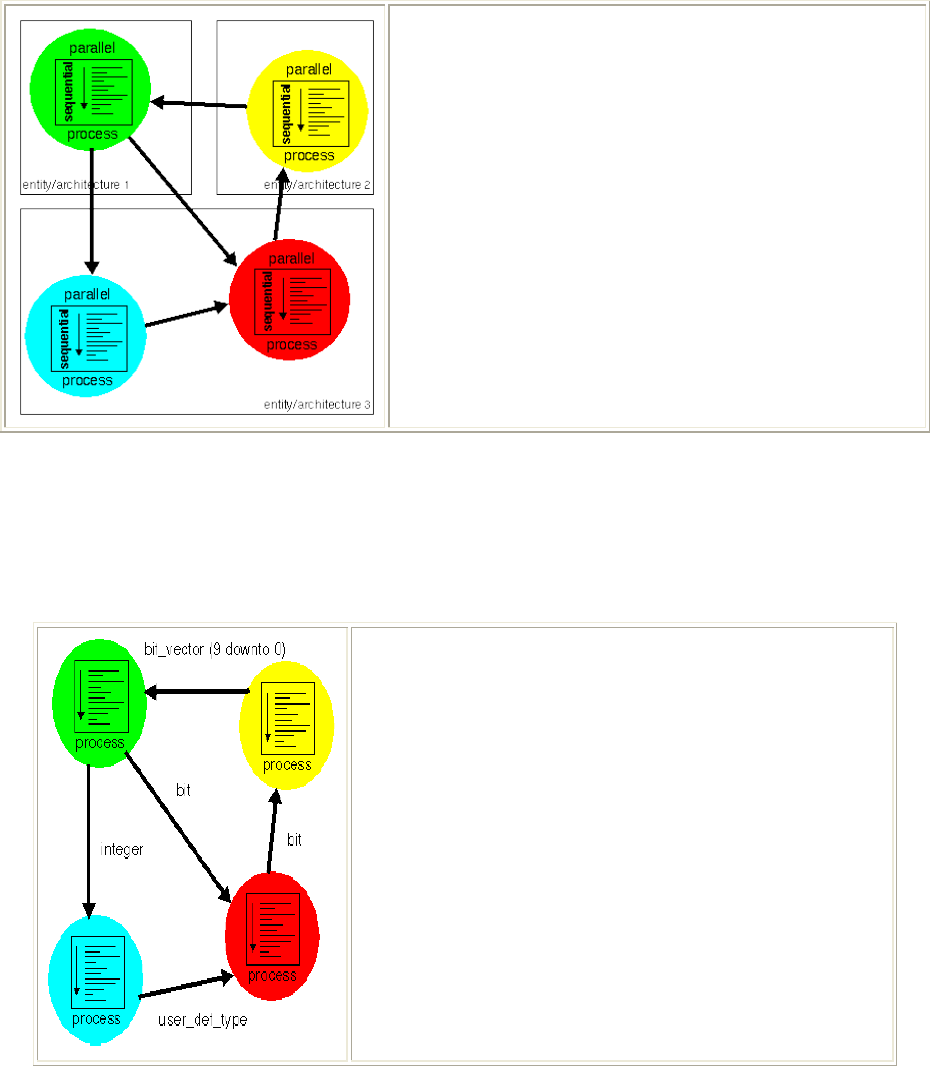

- 2.2.6 Hiyerarşik Model Yerleşimi

- VHDL hiyerarşik model yerleşimine izin vermektedir, bu da bir modül birden fazla altmodülün biraraya getirilmesinden oluşmaktadır anlamına gelmektedir. Alt modüllerin birbiriyle bağlantıları mimari içindeki üst modül tarafından tanımlanmaktadır. Şek...

- 2.2.7 Bileşen Bildirimi

- Tam toplayıcı varlığı blok diyagramdan doğrudan türetilebilir. Girişler A,B ve CARRY_IN gereklidir, bununla birlikte SUM ve CARRY sinyalleri ise çıkışları oluşturmaktadır. Tamtoplayıcı birçok altmodül içermektedir, önce bunlar tamıtılmalıdır. Bir ...

- 2.2.8 Bileşen Örnekleme

- Eğer bir bileşen tanımlandıysa ,bu artık soket tipi sabittir ve gerekli olan yerlerde kullanılabilir demektir. Gerçek soket üretildiğinde bu bileşen örneklemi ile yapılır. PCB(printed circuit board) deki soketlerin yerleşimi için karşılaştırılabilir...

- 2.2.9 Bileşen Örnekleme: İsimlendirilmiş Sinyal İlişkileri

- Bir önceki örnekte konumsal ilişki yerine, mimari sinyallerini doğrudan seçilen portlara bağlamak mümkündür. Bu isimlendirilmiş sinyal ilişkileri ile yapılmaktadır sinyallerin sırası önemli değildir. Bileşen tanımlamadan gelen port ismine “resmile...

- 2.2.10 Konfigürasyon(Configuration)

- Varlıkların tanımlanması ve örneklenmesi gerçekte kullanılan VHDL modellerinden bağımsızdır. VHDL konfigürasyon işinde bileşenlerin ,tam bir tasarım yapmak için, varlık/mimari çiftine bağlantı oluşturulur. Özet olarak,bir bileşen tanımlanması kesin b...

- 2.2.11 Konfigürasyon: İşlemleri ve Uygulaması

- Varlıkla mimari arasındaki ilişki konfigürasyonda kullanılan simülasyonla desteklenir, son tasarım hiyerarşisini oluşturur. Bu en üst seviye varlık mimarisinin seçimini içerir. Konfigürasyon VHDL deki sentezlenebilen ve simüle edilebilen tek objedir...

- Örnek, yapısal mimari için varsayılan konfigürasyonu göstermektedir. Bazı simülatörler bu tip en üst seviye varlıklar için kesin konfigürasyon tanımlamalarına ihtiyaç duymaktadır. Bir konfigürasyon özel bir varlığı tercih eder,burada FULLADDER(tamtopl...

- 2.2.12 Konfigürasyon: Örnek (1)

- Şekilden ve koddan anlaşıldığı üzere bir tamtoplayıcının kodu görülmektedir. Şekille kodu eşleştirmeye çalışın.

- Elemanların portları mimarinin sinyalleriyle, pozisyonları yardımıyla bağlantı kurulmuştur, ör. ilk sinyal ilk portla bağlantılıdır. HALFADDER(yarımtoplayıcı) varlığı kullanılamaz ancak bunun iki varlığı A ve B ‘nin RTL ve GATE diye farklı mimariler...

- 2.2.13 Konfigürasyon: Örnek(2)

- Tekrardan FULLADDER varlığı için STRUCT mimarisi seçilmiştir.Bu for döngüsü içerisinde, varlıklar ve mimariler alt bileşenler için seçilmiştir. Bunun için for ifadesi yeniden kullanılmıştır. ' for ' anahtar sözcüğünden sonra kullanılan ilk isim b...

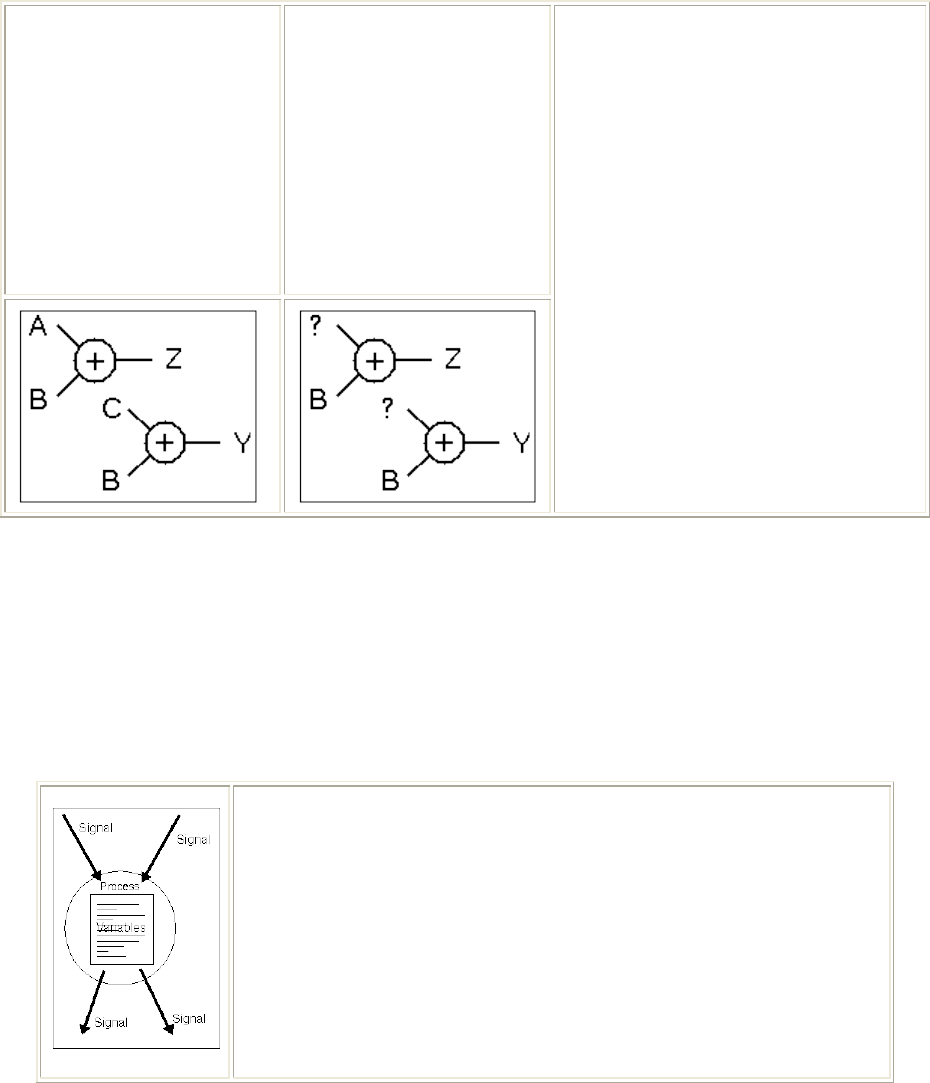

- 2.2.14 İşlem(Process)

- Bir mimari içindeki ifadeler aynı anda oluşan başka VHDL yapılarını yönetmek için sıralı davranışı gerçekleştirmek için gereklidir. Bir işlem, mimarideki diğer ifadeler gibi davranmaktadır ve geleneksel programlama dillerindeki gibi biri diğerinden...

- 2.2.15 VHDL İletişim Modeli

- 2.2.16 Signals

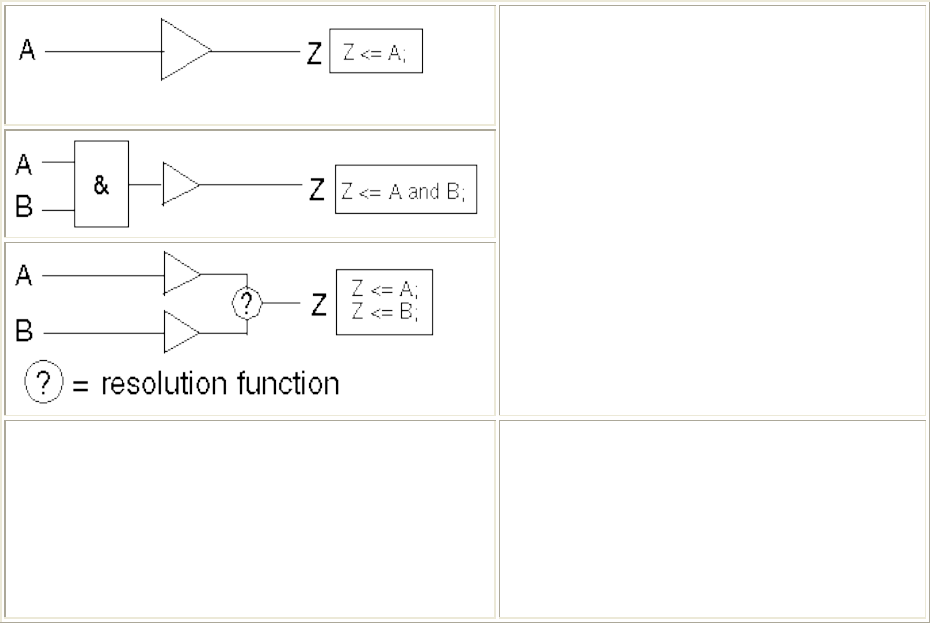

- Her bir sinyalin önceden tanımlı bir veri tipi vardır bu sinyalin alabileceği değerlerin sayısını kısıtlamaktadır. Sentezlenebilir veri tipleri sadece berlirli sayıda değere izin verir. Bu değerleri bir dizi kabloya atayabilir. Sadece temel veri tipl...

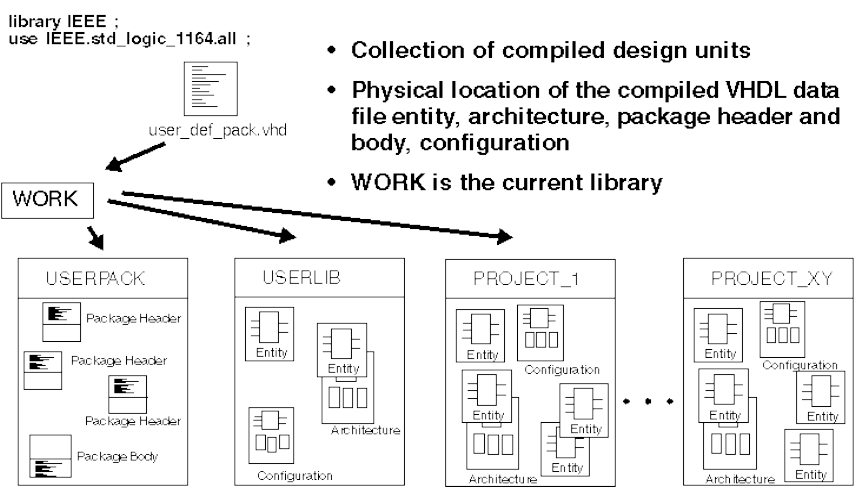

- 2.2.17 Paket(Package)

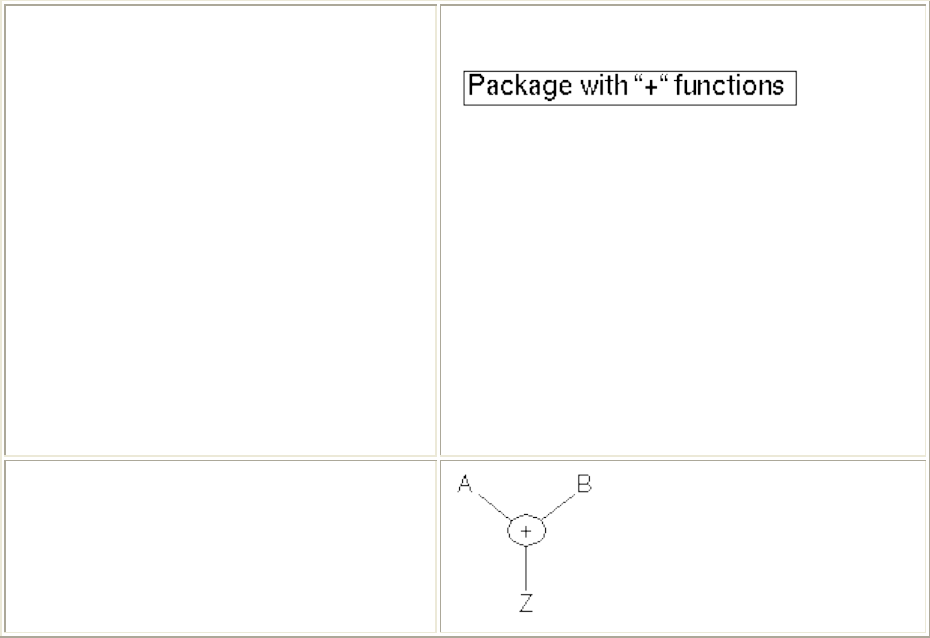

- Bir paket, veri tiplerinin, altprogramların, sabitlerin, vb tanımlamalardan oluşur. Bu takım çalışması için kullanışlıdır böylece herkes aynı veri tipleri,vb çalışacaktır. Bu farklı tasarımcıların modüllerinin bir araya getirilip VHDL model in oluştu...

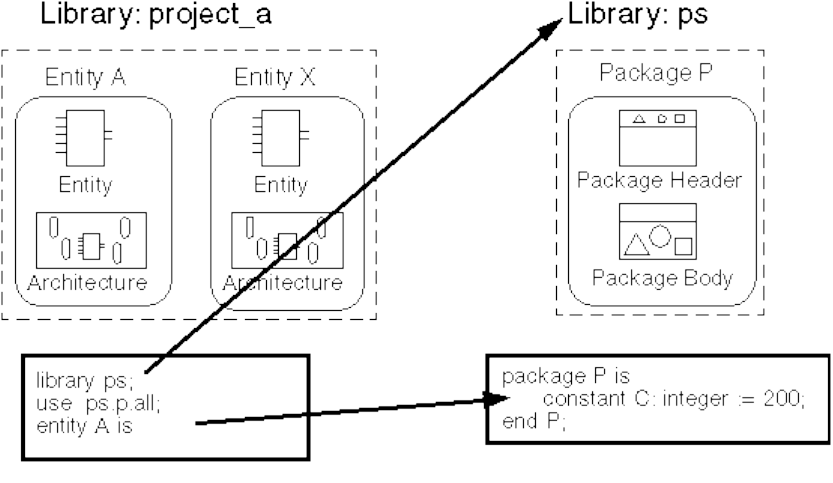

- 2.2.18 Kütüphane(Library)

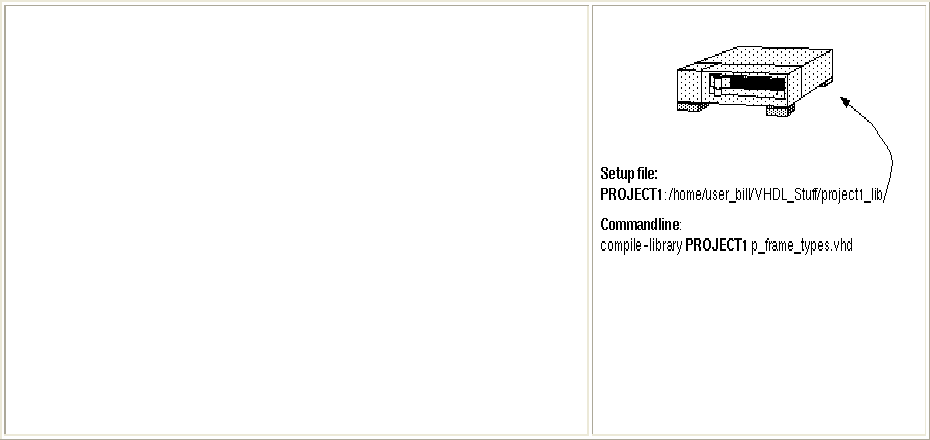

- Bir kütüphanede tüm incelenmiş objeler yani paketler, paket gövdeleri, varlıklar, mimariler ve konfigürasyonları bulabilirsiniz. VHDL ‘de kütüphane, derlenmiş objelerin grup halinde bulunduğu ve referans verilebildiği mantıksal isimdir. Varsayılan k...

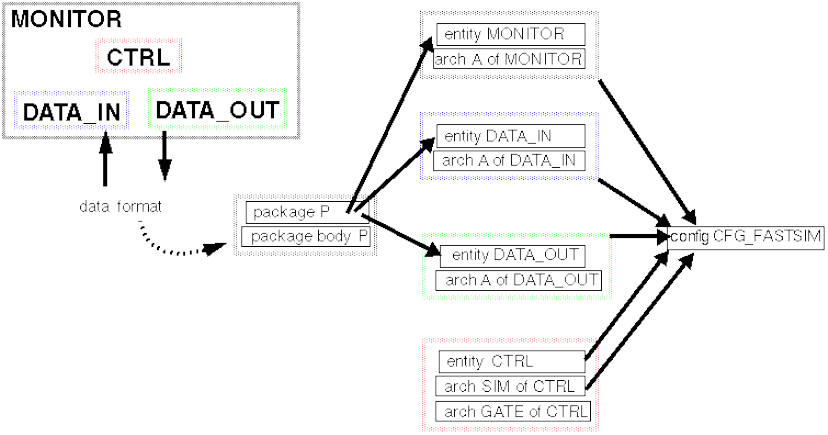

- 2.2.19 Tasarım Yapısı: Örnek

- Örnekte görüldüğü gibi tasarım dört modelden oluşmaktadır. En üstte MONITOR modülü bulunmaktadır, bu da üç alt modülü kullanmaktadır. Bunlar; CTRL, DATA_IN ve DATA_OUT alt modülleridir. Verinin formatı için olan veri tipleri package P de tanımlanmış...

- 2.2.20 Derleme Sırası

- Derleme sırası modelin bölümlerinin bağımlılıklarına bağlıdır.Eğer bir bağımlılık ağacı çıkarıldıysa, düşük seviyeden en üsttekine doğru derleme yapılır. İkinci birimler ilk birimlerdeki bilgiler açığa çıkıktan sonra açığa çıkar(arayüz sinyalleri ...

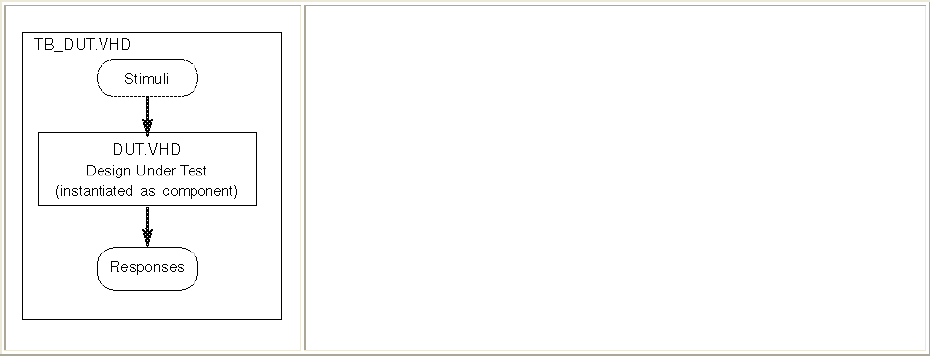

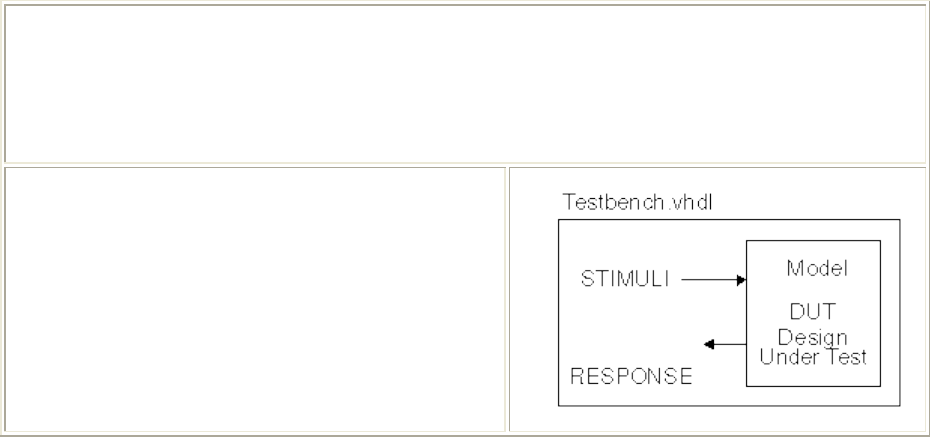

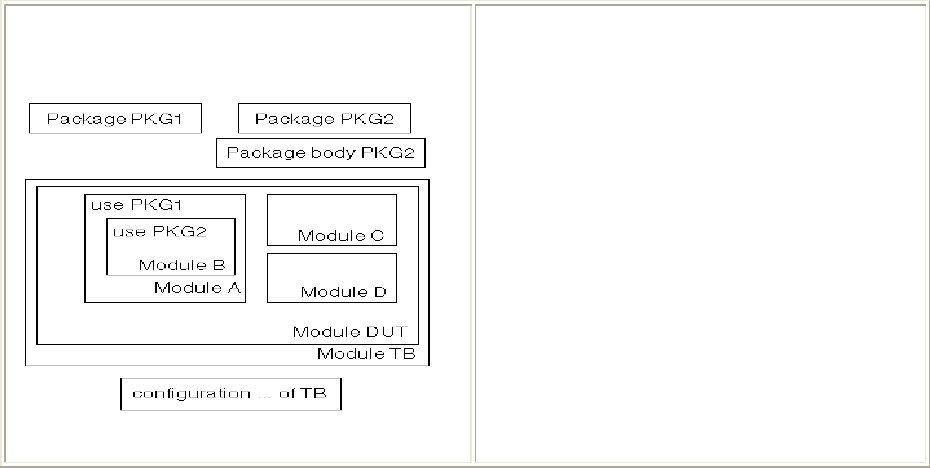

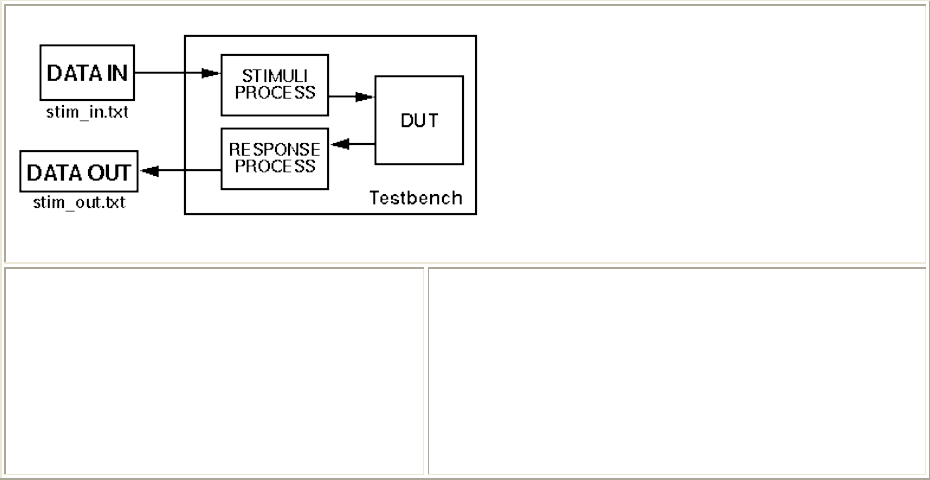

- 2.2.21 Görünüm: Testtezgahı-testbenç (Testbench)

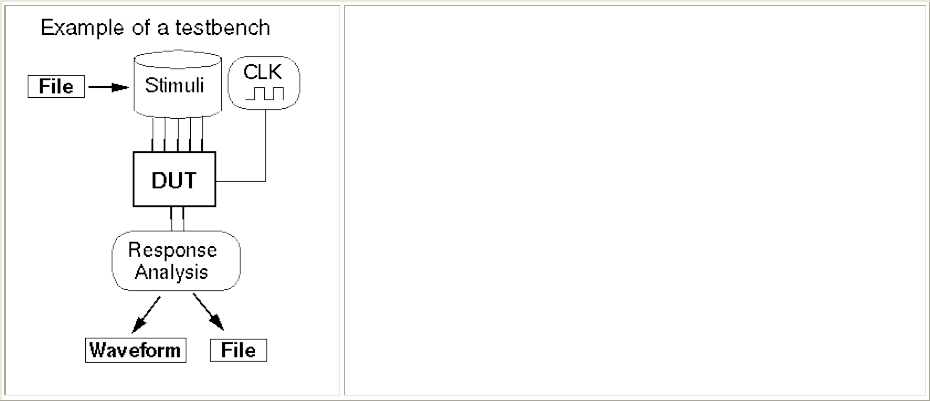

- Stimuli: uyarı Response: yanıt Bir tasarımı doğrulamak için en sık kullanılan metot simülasyondur. VHDL de ilk alanda dijital donanımda simülasyonu sağlamak için geliştirilmiştir, bu dil tarafından iyi bir şekilde desteklenmektedir. Yeni bir en üst...

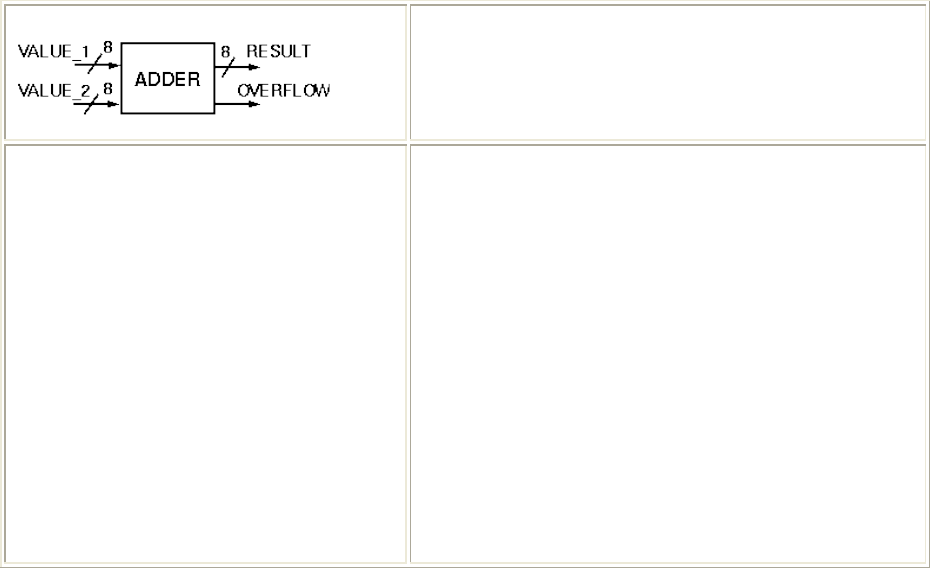

- 2.2.22 Basit Testbenç Örneği

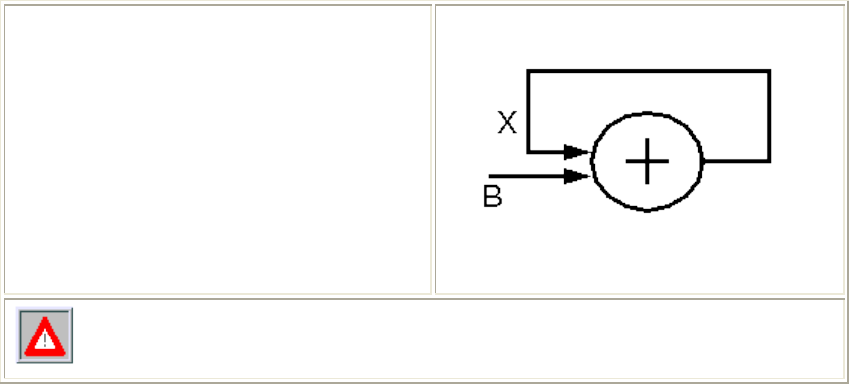

- Örnek basit bir tasarım için VHDL kodunu ve ona uygun testbenci içermektedir. Test edilecek tasarım bir ADDER(toplayıcı),bir yarım toplayıcıyı gerçekler. RTL mimarisi tam bir kombinasyonel süreci içerir, bu SUM ve CARRY sinyallerini, giriş sinyalleri...

- 2.2.23 Özet

- VHDL çok katı bir dildir. Her bir sinyal,örneğin, kesin bir veri tipi olması gerekmektedir, ve belirtilen yerde belirtilmesi gerekmektedir, sadece aynı veri tipindeki atamaları kabul etmektedir. Bir VHDL modele fonksiyonel bir test uygulamak için, ...

- 2.2.24 Sorular

- CEVAPLAR: 1.1 :HAYIR 1.2:EVET 1.3:EVET 2.1:HAYIR 2.2:EVET

- 2.2.25 Sorular

- 2.2.26 Sorular

- 2.3 Veri Tipleri

- 2.3.1 Standart Veri Tipleri

- 2.3.2 'time'(zaman) Veritipi

- 2.3.3 Dizilerin Tanımlanması

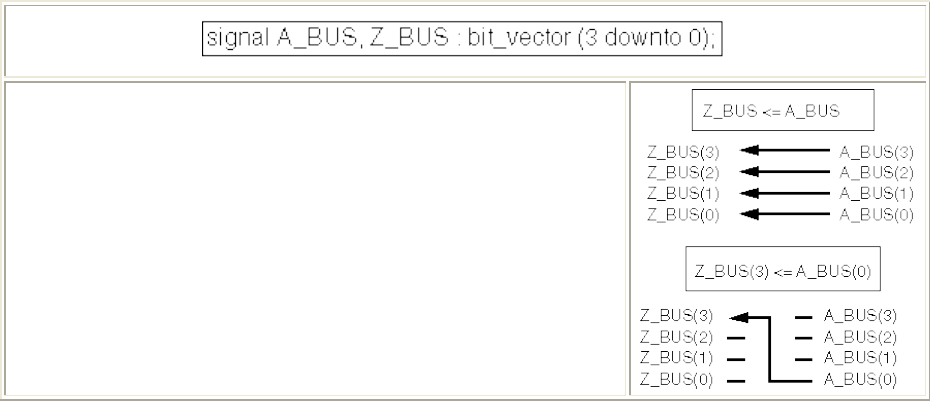

- Diziler(Arrays) aynı tip ve anlamdaki sinyalleri gruplamak için kullanışlıdır. VHDL de öntanımlı olarak bulunan ve sınırlandırılmamış yani boyutları belli olmayan iki dizi veri tipi vardır bunlar ;' bit_vector ' ve ' string ' dir ve bit ve character...

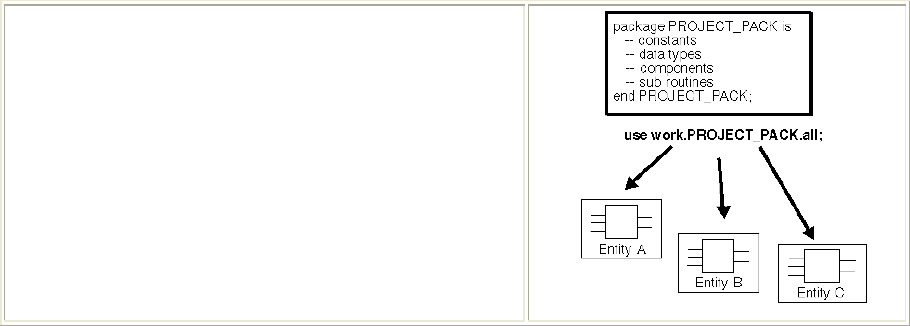

- 2.3.4 'integer' ve 'bit' Tipleri

- Integer(tam sayı) sinyaller sentez sırasında bir dizi kabloyla eşleştirilebilinir. Bu kablolar ' bit_vector ' ile modellenebilir, ' bit_vector ' sinyallerin önceden sayısal bir yorumlamaya gerek yoktur. Bu nedenle sentez iki örnek mimari için aynı şek...

- 2.3.5 Dizi Tipleriyle Atamalar

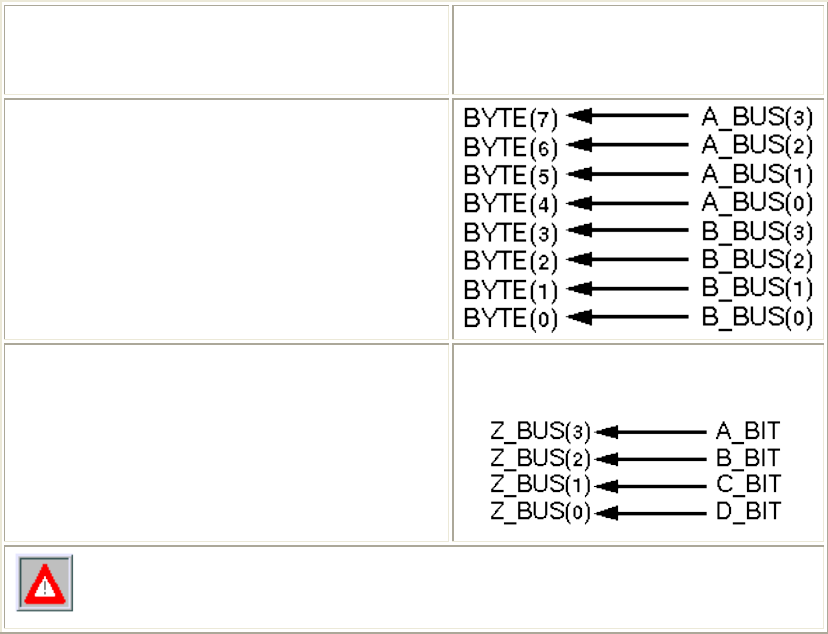

- Diziler için özellikle dikkat edilmesi gereken şey sinyal atamalarıdır. Bunun için veri tipi ve genişliği uyuşmalıdır, bu dizi elemanlarının sırası için geçerli değildir. Değerler birbirlerine dizideki pozisyonlarına göre atanmaktadır, dizine göre de...

- 2.3.6 'bit' Veri Tipi İçin Atama Şekilleri

- Sinyal değerlerinin belirtimi temel tiplerine göre farklılık göstermektedir, eğer temel tipi 'character' ve'bit' ise bunlara uygun dizi tipi 'string' ve 'bit_vector' ’dür. Tek değerler herzaman (') tek tırnakla verilir, dizi değerlerini girmek için...

- 2.3.7 Birleştirme-Bağlama(Concatenation)

- Sinyalleri atamak için operatörün her iki tarafındaki veri tiplerinin birbiriyle eşleşmesi gerekmektedir. Birleştirme operatörü ' & ' sağındaki ve solundaki aynı veri tipindeki elemanları gruplar. Yine sadece dizinin pozsiyonu önemlidir indisi öneml...

- 2.3.8 Kümeleme(Aggregates)

- Sinyalleri atamanın bir diğer sınırlama derdi olmayan acısız yolu yapıları kümelemektir. Son diziyi oluşturacak sinyalleri '(' ')' arasında belirtilir ve birbirinden ',' ile ayrılır. Basit birleştirme (concatenation) yerine, bunda dizi elemanlarına ...

- 2.3.9 Diziyi Bölümleme

- Birleştirme ve kümelemenin tersi olan bölümleme, bir dizinin bölümlerinin seçilmesi demektir, sadece dizinin bir kısmı kullanılabilinir. Kullanılan dizinin bölümleri parantezlerle belirlenir ve sinyalin belirtim tipine uymalı. Tabiki, bir dizinin te...

- 2.3.10 Sorular

- Sorulara sadece doğru yada yanlış şeklinde cevap verin.

- CEVAPLAR:

- 7.1:EVET 7.2:HAYIR 7.3:HAYIR 8.1:HAYIR 8.2:EVET

- CEVAPLAR: 9.1:EVET 9.2:EVET 9.3:HAYIR

- 9.4:EVET 9.5:HAYIR

- 2.4 Genişletilmiş Veri Tipleri

- 2.4.1 Tip Sınıflama

- 2.4.2 Numaralanmış(Enumeration)Tip

- 2.4.3 Numaralanmış Tip(Enumeration) -Örnek

- 2.4.4 BIT Tipi Sorunları

- 2.4.5 Çok-değerli Tipler

- 2.4.6 IEEE Standart Mantık Tipi (Standard Logic Type)

- 2.4.7 Kararlı ve Kararsız Tipler (Resolved and Unresolved)

- 2.4.8 Std_Logic_1164 Paketi

- 2.4.9 Karar Fonksiyonu

- 2.4.10 STD_LOGIC ile STD_ULOGIC Karşılaştırma

- 2.4.11 NUMERIC_STD Paketi

- 2.4.12 Diziler(Arrays)

- 2.4.13 Çokboyutlu Diziler

- 2.4.14 Kümeleme ve Çok Boyutlu Diziler

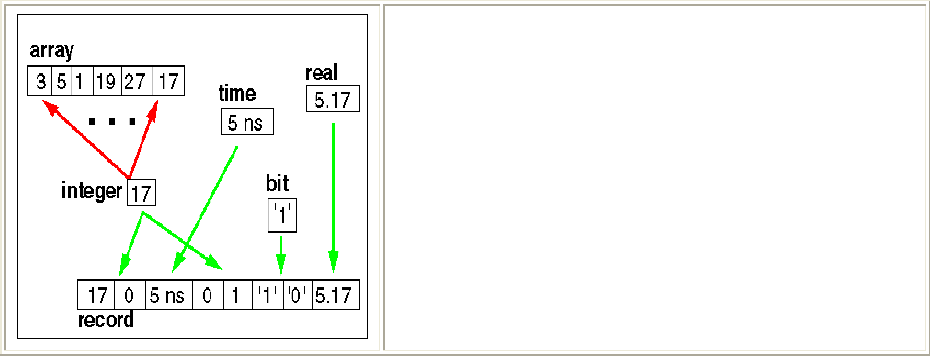

- 2.4.15 Kayıtlar(Records)

- 2.4.16 Tip Dönüşümü

- 2.4.17 Alttipler(Subtypes)

- 2.4.18 Takma Ad(Aliases)

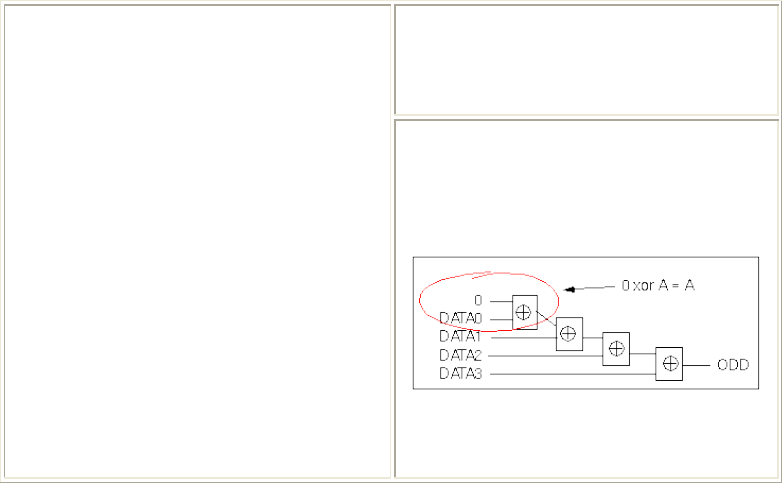

- 2.5 Operatörler-İşletmenler

- 2.5.1 Mantıksal Operatörler

- 2.5.2 Dizilerle Mantıksal Operasyonlar-İşlemlşer

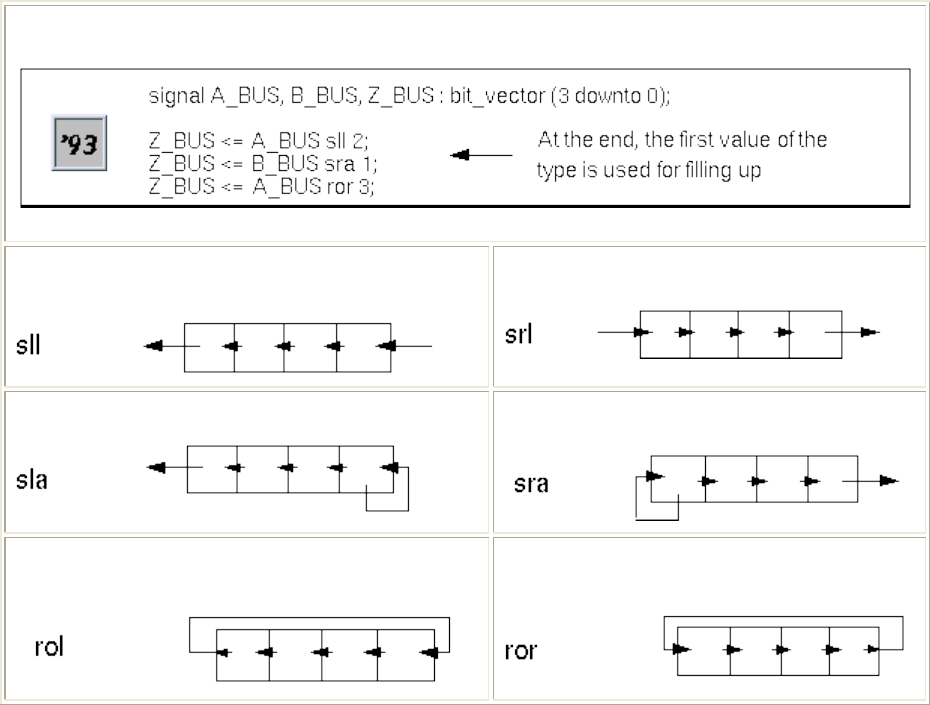

- 2.5.3 Kaydırma(Shift) Operatörleri: Örneklerle

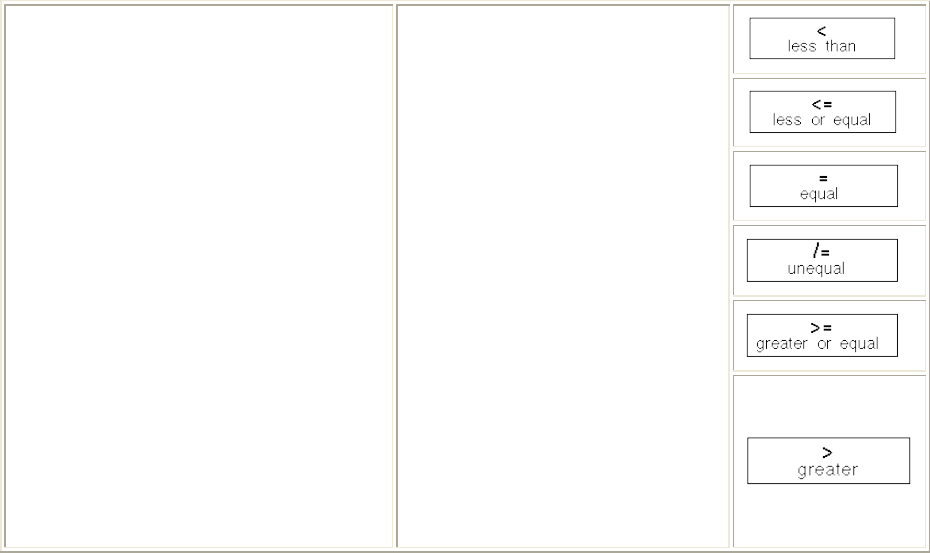

- 2.5.4 İlişkisel Operatörler

- 2.5.5 Dizilerle Karşılaştırma İşlemleri

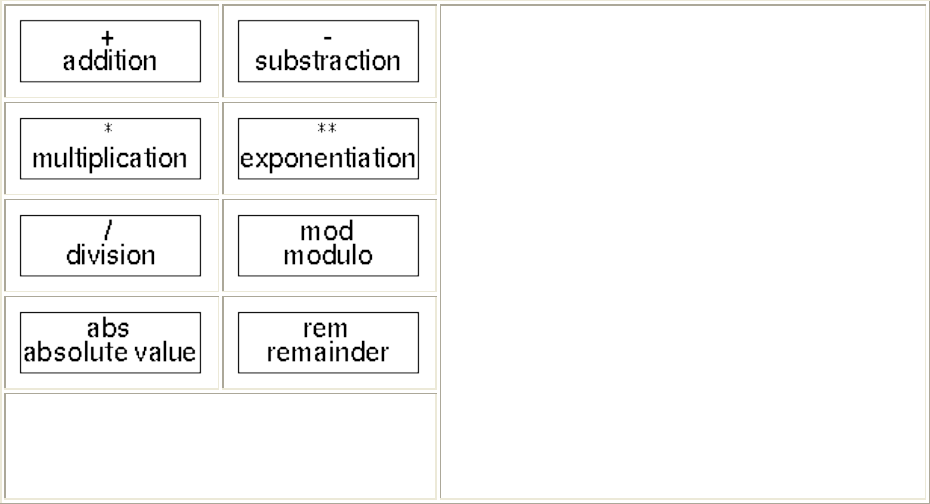

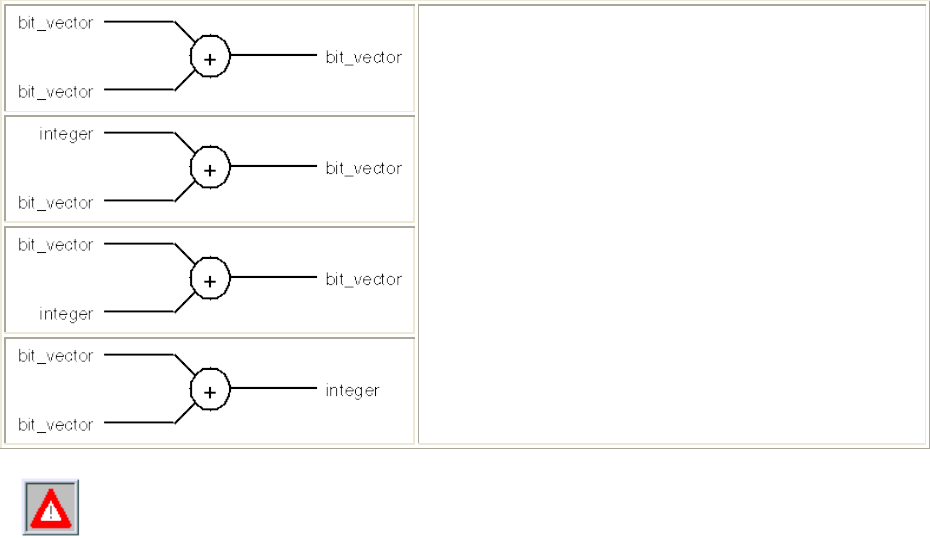

- 2.5.6 Aritmetik Operatörler

- 2.5.8 Sorular

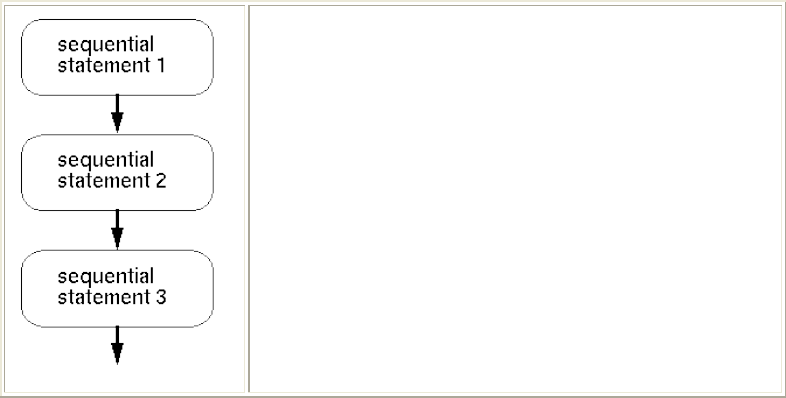

- 2.6 Sıralı-Ardışıl(Sequential) İfadeler

- 2.6.1 IF İfadesi

- 2.6.2 IF İfadesi: Örnek

- 2.6.3 CASE İfadesi

- 2.6.5 Değer Kümesinin(Range) Tanımı

- 2.6.6 FOR Döngüleri

- 2.6.7 Loop Sözdizimi(Syntax)

- 2.6.8 Döngü Örnekleri

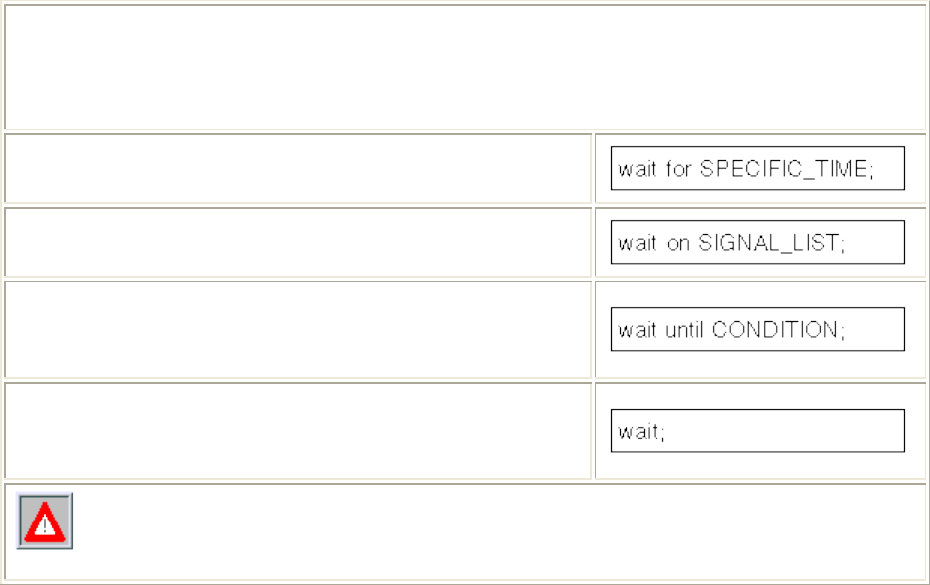

- 2.6.9 Bekleme(WAIT) İfadesi

- 2.6.10 WAIT İfadesi: Örnek

- 2.6.11 WAIT İfadeleri ve Davranışsal Modelleme

- 2.6.12 Değişkenler(Variables)

- 2.6.13 Değişkenler (Variables) / Sinyaller (Signals)

- 2.6.14 Değişkenlerin Kullanımı

- 2.6.15 Değişkenler: Örnek

- 2.6.16 Global Değişkenler (VHDL'93)

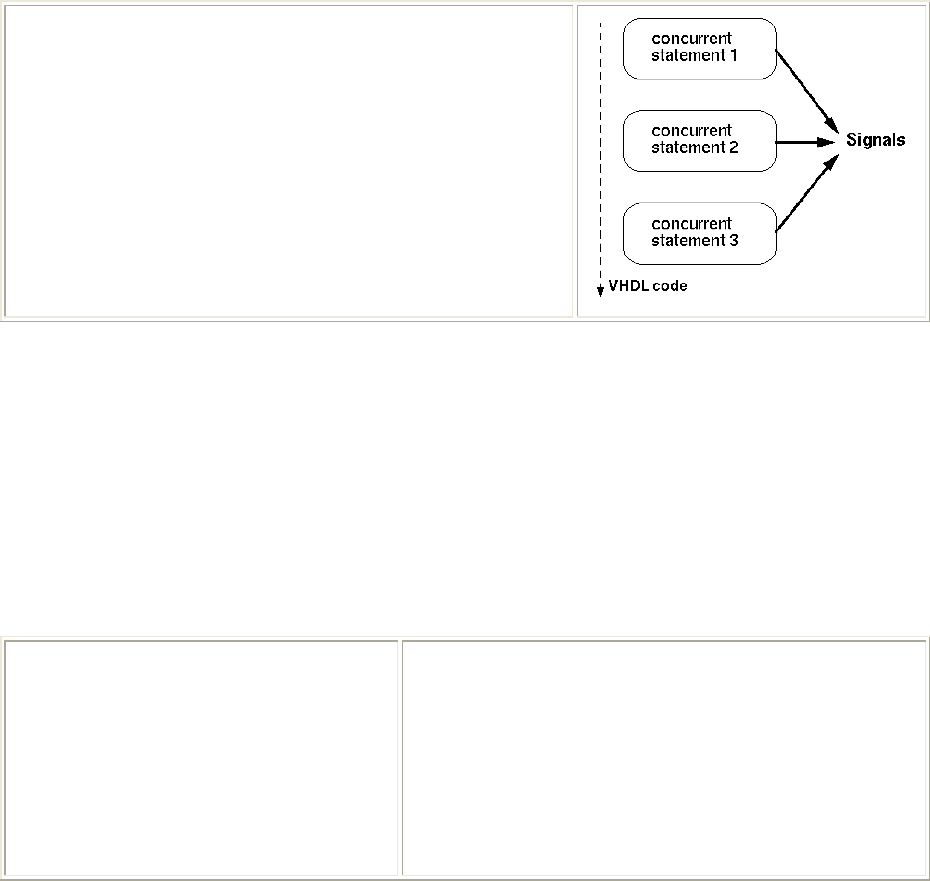

- 2.7 Koşutzamanlı(Concurrent) İfadeler

- 2.7.1 Koşullu Sinyal Atama

- 2.7.2 Koşullu Sinyal Atama: Örnek

- 2.7.3 Seçilmiş Sinyal Ataması

- 2.7.4 Seçilmiş Sinyal Ataması: Örnek

- 2.7.5 Koşutzamanlı İfadeler: Özet

- 2.8 RTL-Stili

- 2.8.1 Kombinasyonel İşlemler: Hassasiyet Listesi

- 2.8.2 Bekleme WAIT İfadesi <-> Hassasiyet Listesi

- 2.8.3 Kombinasyonel İşlemler: Eksik Atamalar

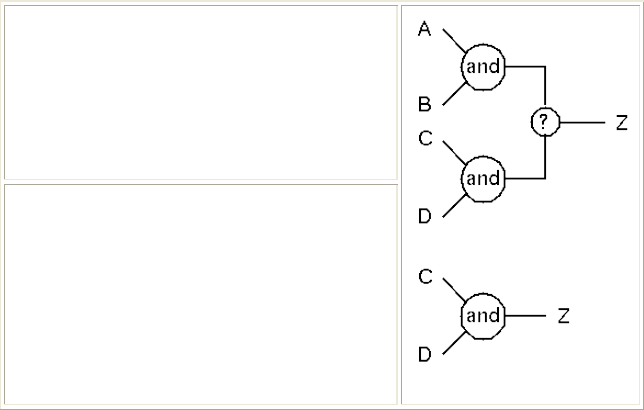

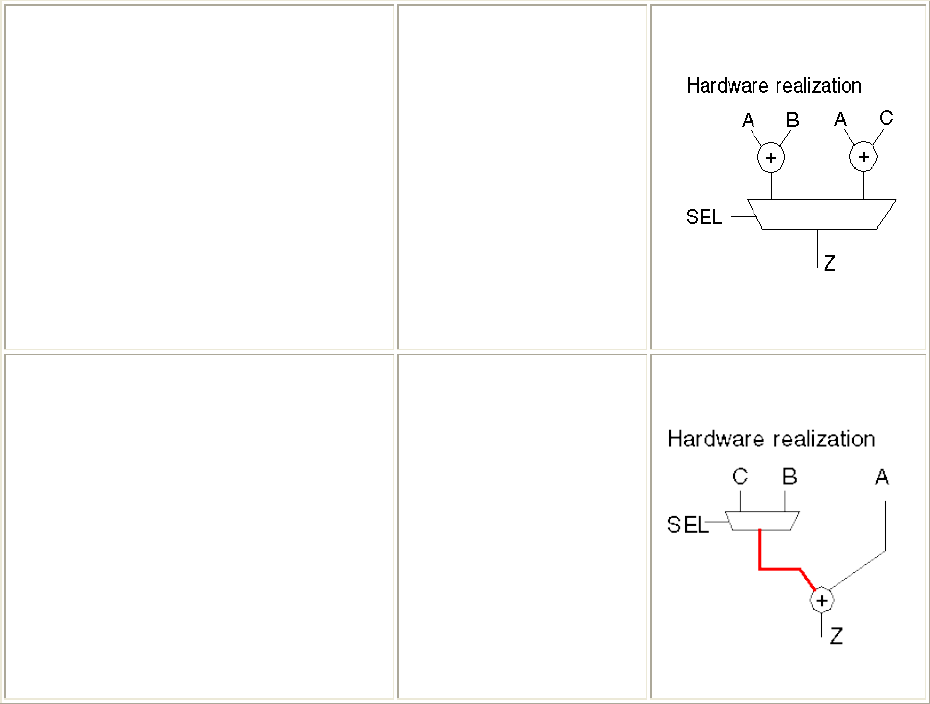

- Kombinasyonel donanım modellenirken tutucuların üretilmesini engellemek için özel durumlar gereklidir. En soldaki kod örneğinde koşulsuz else dallanması eksiktir. Bu nedenle SEL='0' olduğu durumda giriş sinyali değişsede Z eski değerini korumuş olur....

- 2.8.4 Kombinasyonel İşlem: Kuralları

- 2.8.5 Saat İşlemleri: Saat Kenar Bulma(Clock Edge Detection)

- 2.8.6 Artan Kenarın Fonksiyon Kullanarak Tesbiti

- 2.8.7 Yazmaç Çıkarımı(Register Inference)

- 2.8.8 Asenkron Atama/Yeniden Başlatma (Set/Reset)

- 2.8.9 Saatli İşlemler: Kuralları

- 2.8.10 Sorular

- 2.9 Altprogramlar(Subprogram)

- 2.9.1 Parametreler ve Modlar

- 2.9.2 Fonksiyonlar

- 2.9.3 Prosedürler

- 2.10 Altprogramın Bildirimi ve Aşırı Yüklenmesi(Overloading)

- 2.10.1 Aşırı Yükleme(Overloading) Örneği

- 2.10.2 Aşırı Yükleme(Overloading) – Geçersiz Yeniden Bildirim

- 2.10.3 Aşırı Yüklemede(Overloading) – Muğlaklık(Ambiguity)

- 2.10.4 Operatör Aşırı Yükleme (Overloading)

- 2.10.5 Operatör Aşırı Yükleme - Örneği

- 2.10.6 Sorular

- 3. Simülasyon(Simulation)

- 3.1 Derleme Sırası (Sequence of Compilation)

- Örnek

- 3.2 Simülasyonun Akışı

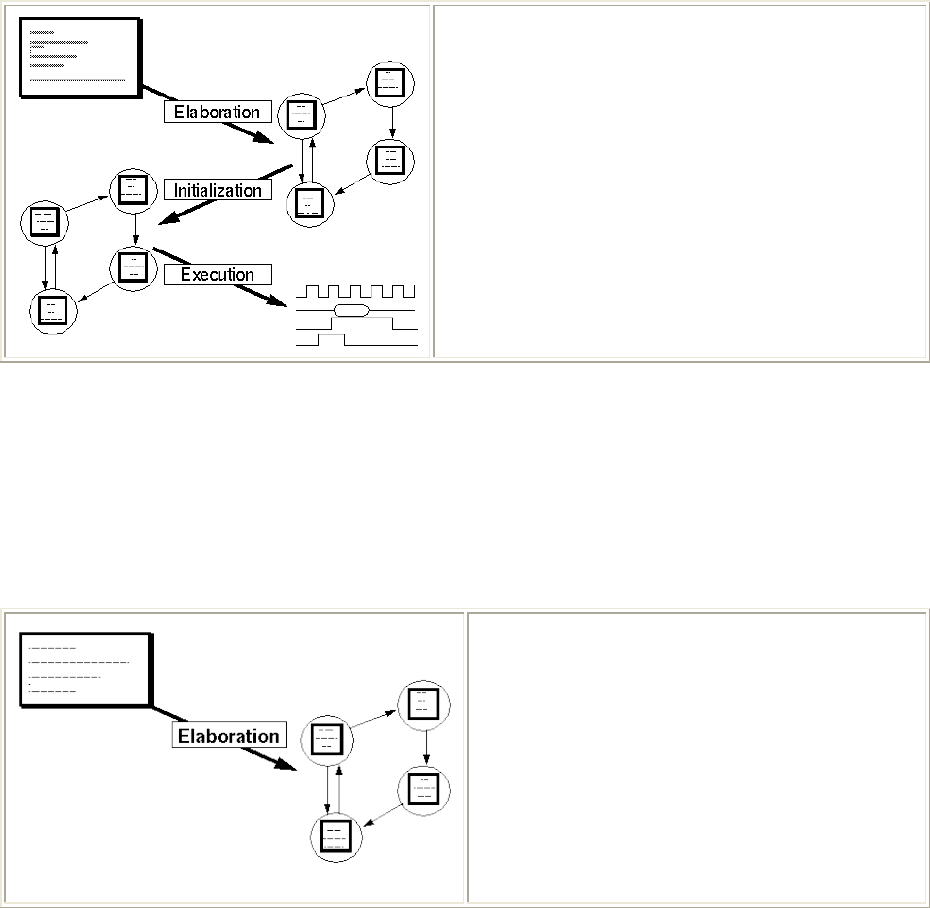

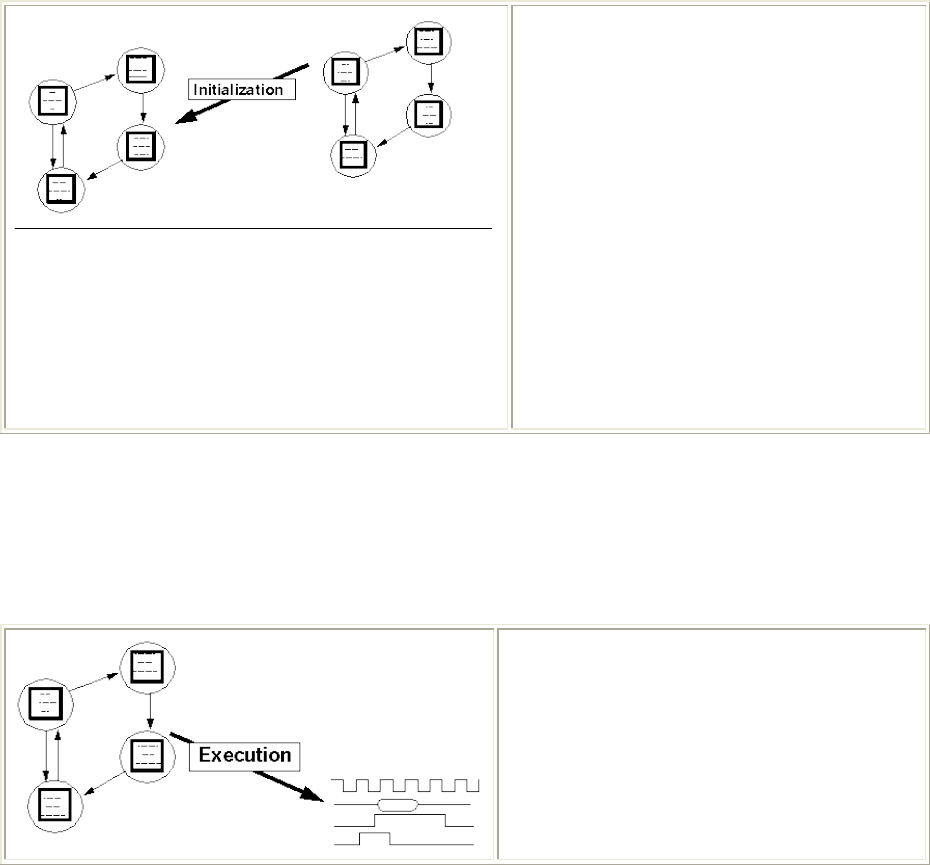

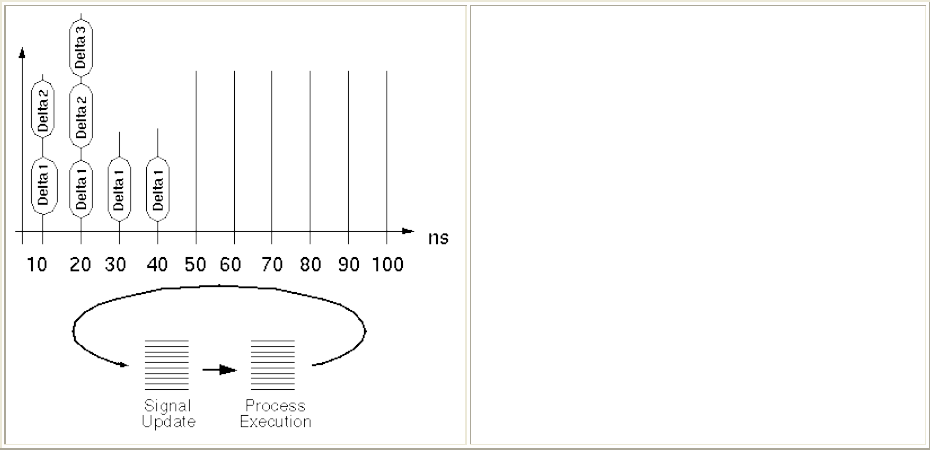

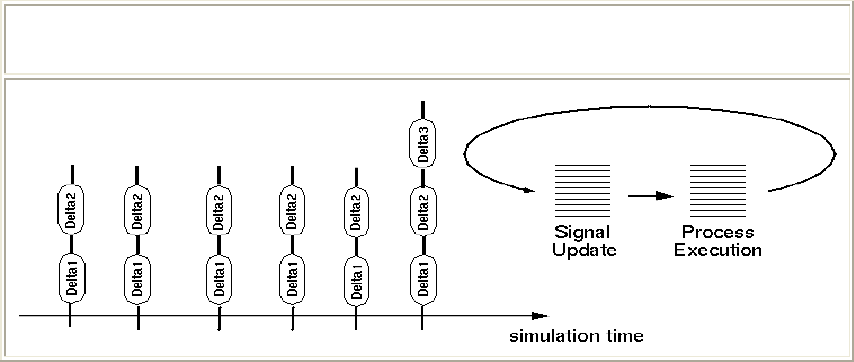

- Bir VHDL modelinin simülasyonu üç adımda yürütülür. Önce, ayrıntılandırma fazında(elaboration) simülasyon modeli yaratılır. İlklendirme (initialisation) fazında tüm sinyallere bir başlangıç değeri atanır. Gerçekleştirme fazında modelin kendisi gerçe...

- 3.2.1 Ayrıntılandırma (Elaboration)

- 3.2.2 İlklendirme (Initialization)

- 3.2.3 Yürütme(Execution)

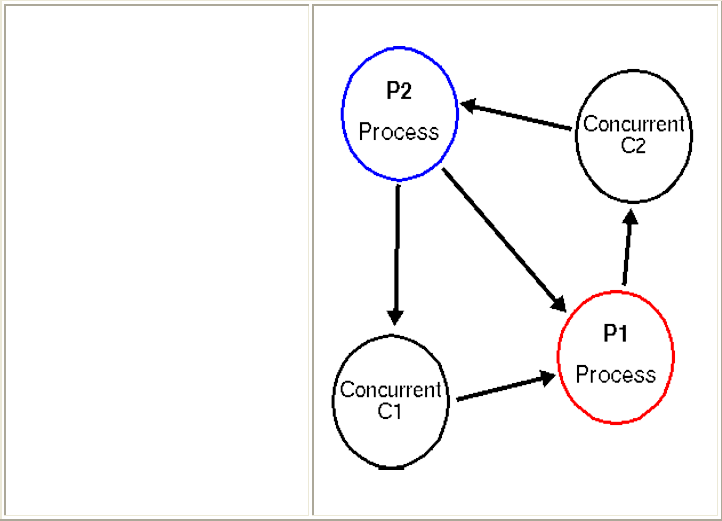

- 3.3 İşlem Yürütme(Process Execution)

- 3.3.1 Koşutzamanlı ve Sıralı Yürütmenin Karşılaştırılması

- 3.3.2 Sinyal Güncelleme

- 3.3.3 Delta Dönüşü-Çevrimi (1)

- 3.3.4 Delta Çevrimi(2)

- 3.3.5 Delta Çevrim - Örneği

- 3.3.6 İşlem Davranışı

- 3.3.7 Ertelenmiş İşlemler (Postponed Processes)

- 3.4 Gecikme Modelleri

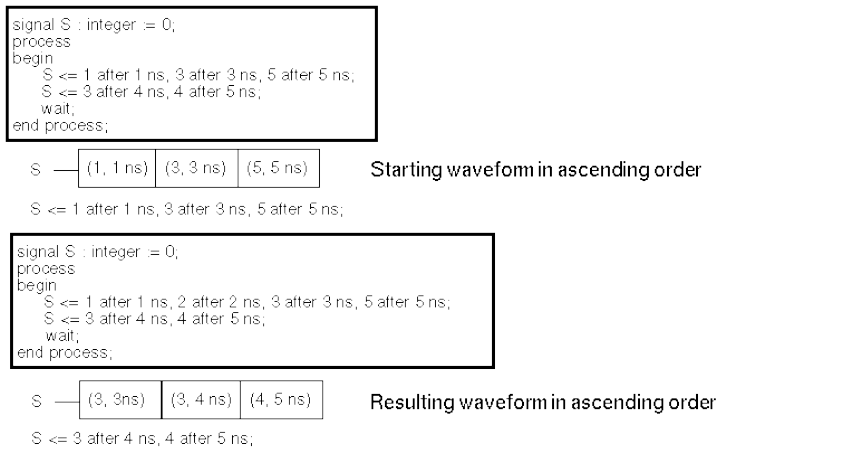

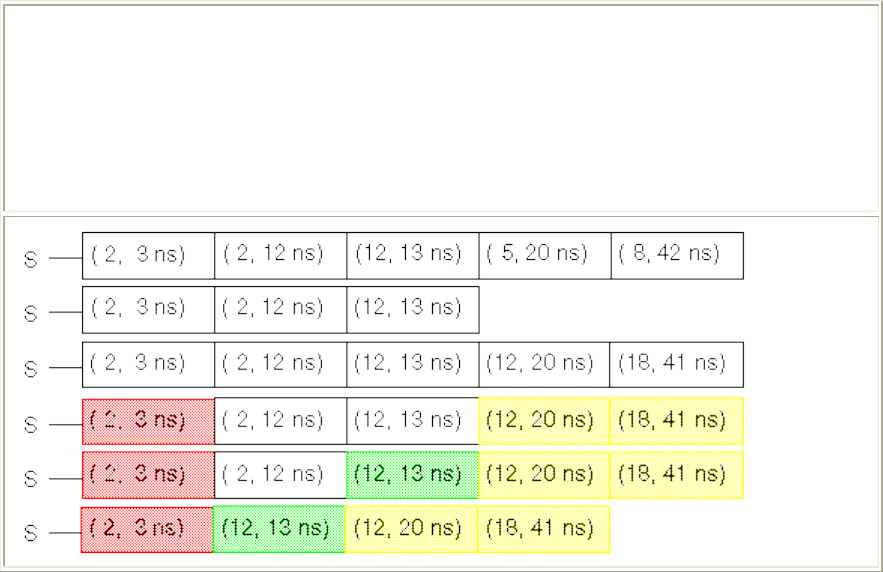

- 3.4.1 Projelendirilmiş Çıkış DalgaFormları(Projected Output Waveforms (LRM))

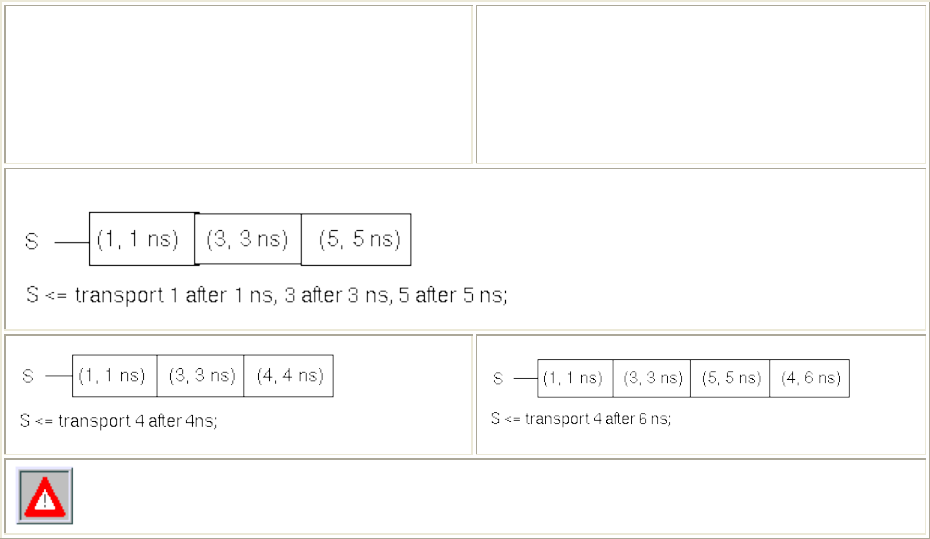

- 3.4.2 Taşıma Gecikmesi (Transport Delay) (1)

- 3.4.3 Taşıma Gecikmesi (Transport Delay) (2)

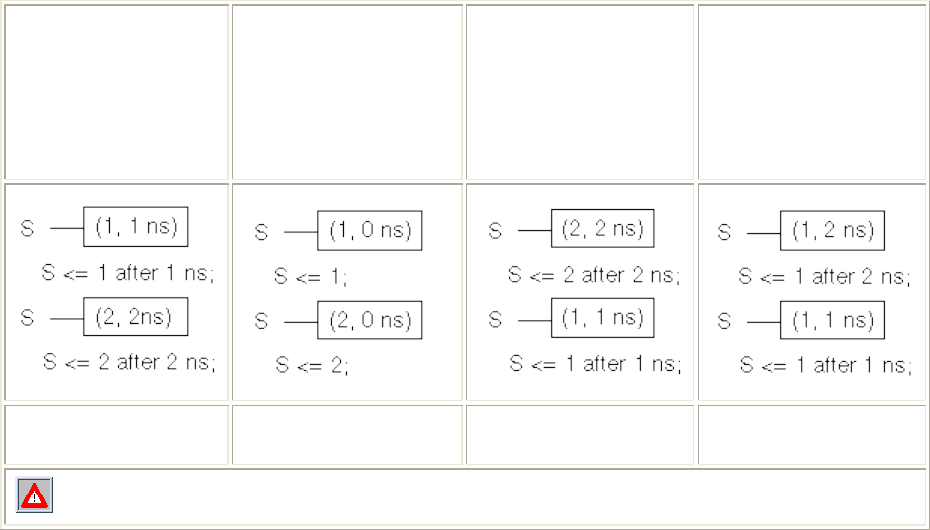

- 3.4.4 Eylemsiz Gecikme(Inertial Delay) (1)

- 3.4.5 Eylemsiz Gecikme(Inertial Delay) (2)

- 3.4.6 Eylemsiz Gecikme(Inertial Delay) (3)

- 3.5 Testbenç(Testbenches)

- 3.5.1 VHDL Testbenç’in Yapısı

- 3.5.2 Örnek

- Saat(Clock) ve YenidenBaşlatma(Reset) Üretimi

- Yanıt-Tepki Analizi(Response Analysis)

- 3.6 Dosya Giriş/Çıkışı(File I/O)

- 3.6.1 Dosya (File)I/O Örnek(1/4)

- Örnek(2/4)

- Örnek(3/4)

- Örnek (4/4)

- 4. Sentez (Synthesis)

- 4.1 • Sentez nedir?

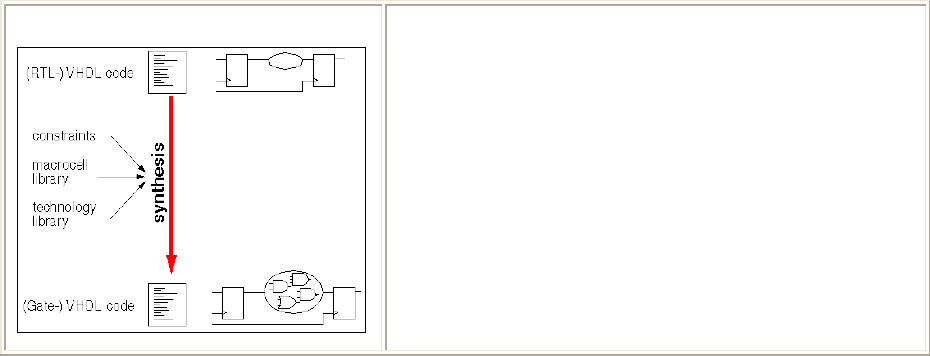

- 4.1.1 Sentezlenebilirlik(Synthesizability)

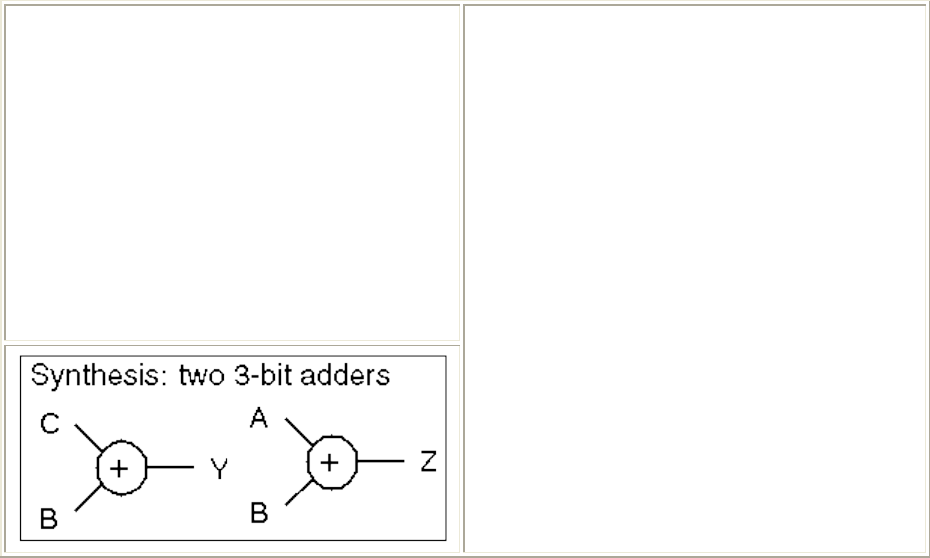

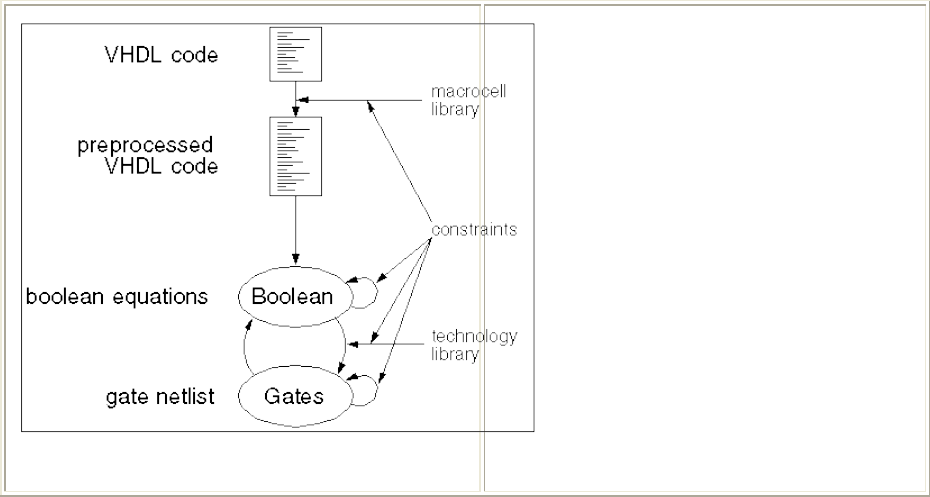

- 4.1.2 Sentez İçin Farklı Dil Destekleri /

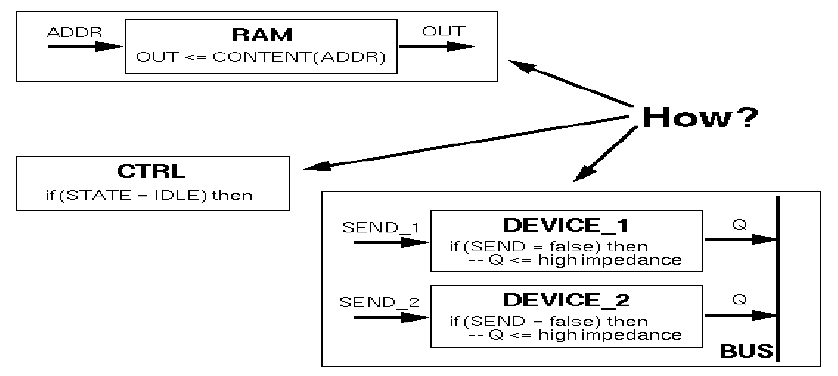

- 4.1.3 Nasıl Yapılır ?

- 4.1.4 Sentez İçin Gerekli Bilgiler

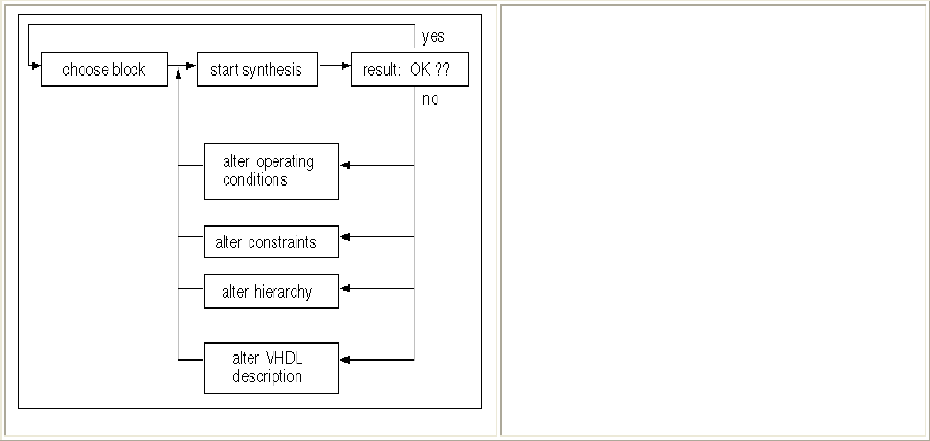

- 4.1.5 Pratikte Sentez Süreci

- 4.1.6 Sentez Araçlarıyla İlgili Problemler

- 4.1.7 Sentez Stratejisi

- 4.2 RTL-stili

- 4.2.1 Objelerin Kombinasyonları (Combinatorics)

- 4.2.2 Tam hassasiyet listesi

- 4.2.3 WAIT ifadesi < - > Hassasiyet Listesi

- 4.2.4 Eksik atamalar

- 4.2.5Kombinasyonel Lojiği Sentezlemek İçin Kurallar

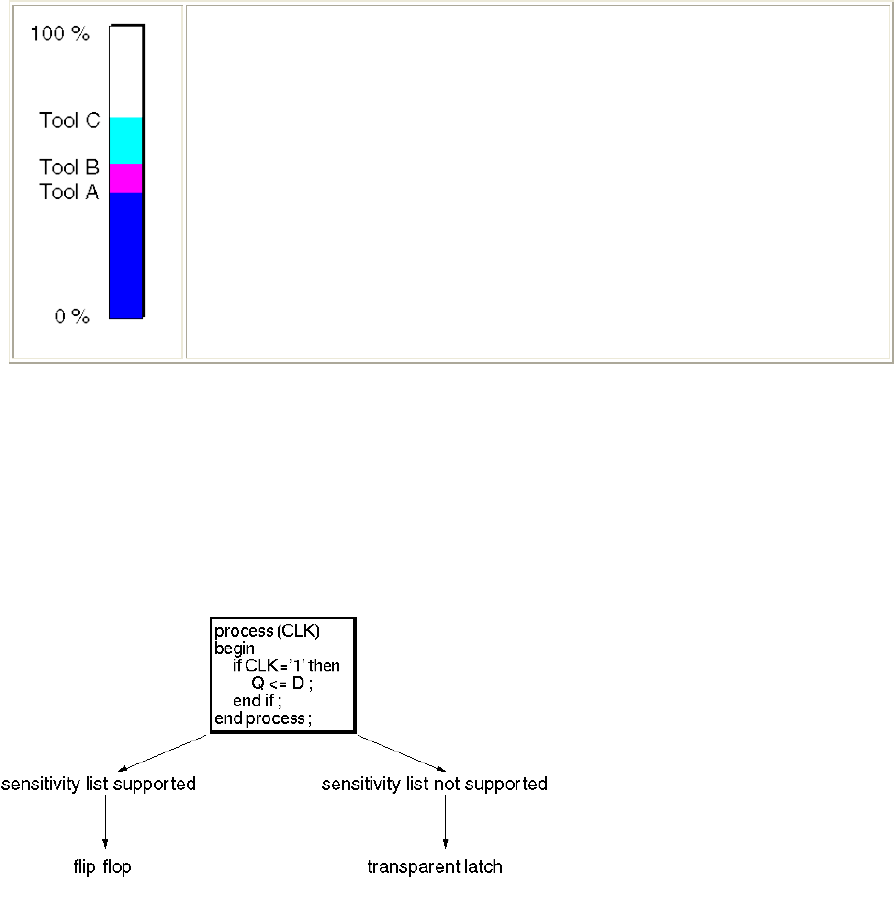

- 4.2.6 Flip Flopların Modellenmesi

- 4.2.7 Sentez İçin Artan Saat Kenarının Tanımı

- 4.2.8 Artan Saat Kenarının Fonksiyon Çağrımı ile Tanımlanması

- 4.2.9 Sayıcı Sentezi

- 4.2.10 FF İle Asenkron Reset(Yeniden Başlatma)

- 4.2.11 Zamanlı İşlemler İçin Kurallar

- 4.2.12 Sorular

- 4.3 Kombinasyonel Lojik(Combinational Logic)

- 4.3.1 Akıcı Kodlama Stili

- 4.3.2 Kaynak Kod Optimizasyonu

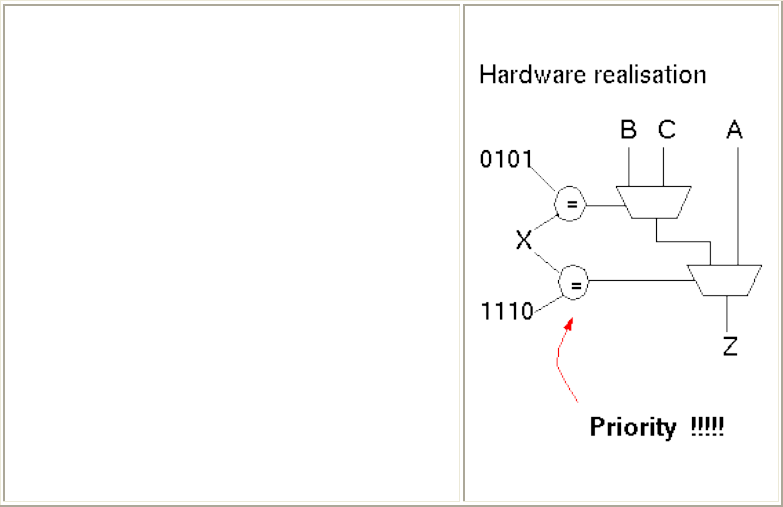

- 4.3.3 IF yapısı < - > CASE yapısı

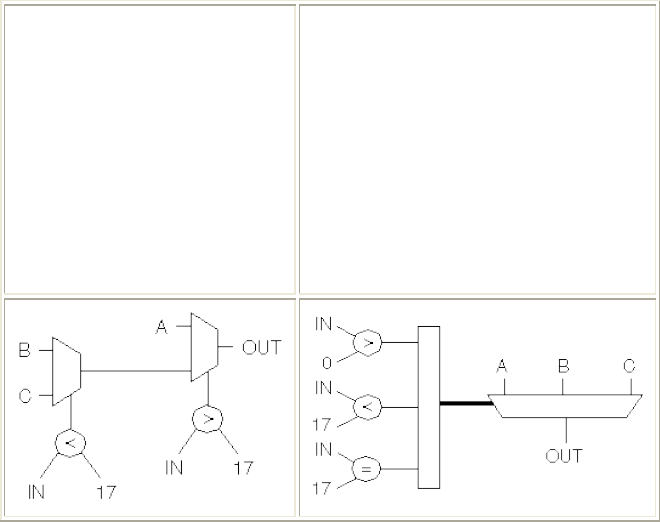

- 4.3.4 Veri Yolunun Gerçekleştirilmesi

- İç Veri Yolu Yapısı Sorunları

- Taşınabilir ve Güvenli Yol Yapısı

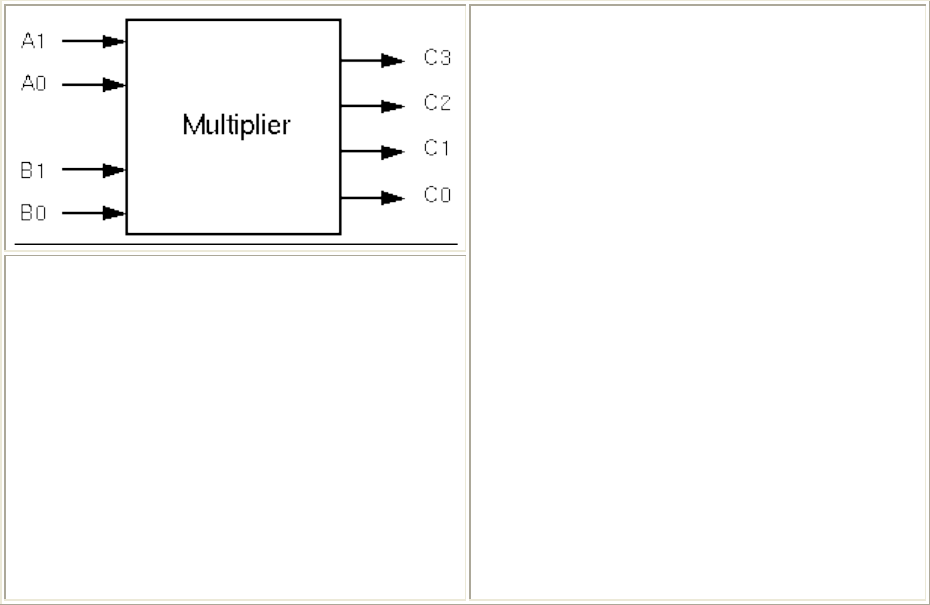

- 4.3.5 Bir Çarpan(Multiplier) Örneği

- Çarpan(Multiplier) Fonksiyon Tablosu

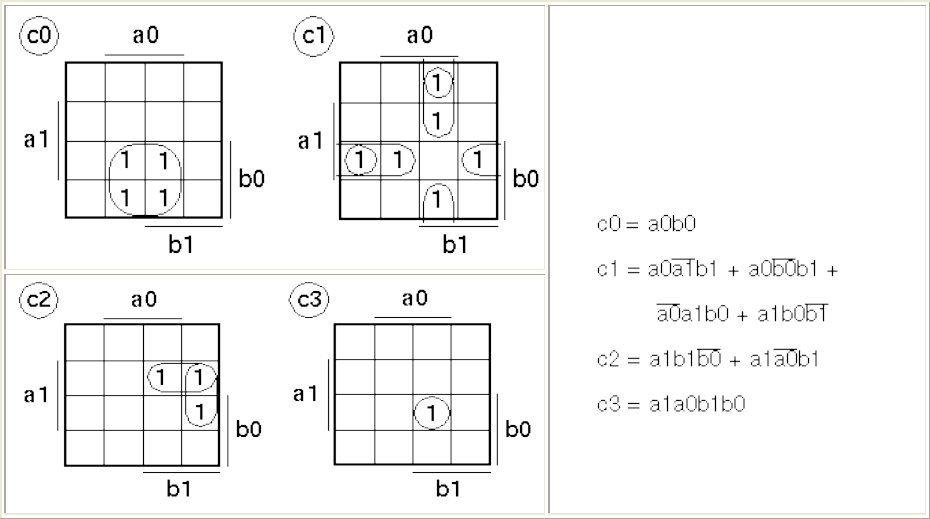

- Çarpanların Minterm’leri -- Karnaugh Diyagramı

- Çarpan(Multiplier): Fonksiyon Tablosuyla Oluşturulmuş VHDL Kodu

- Çarpan(Multiplier): Minterm Dönüşümü

- Çarpan : Tamsayı(Integer) Gerçekleştirme

- 4.3.6 Operatörlerin Sentezi

- Sentez Sonuçları

- 4.3.7 Toplama Örneği

- 4.4 Sıralı Mantık(Sequential Logic)

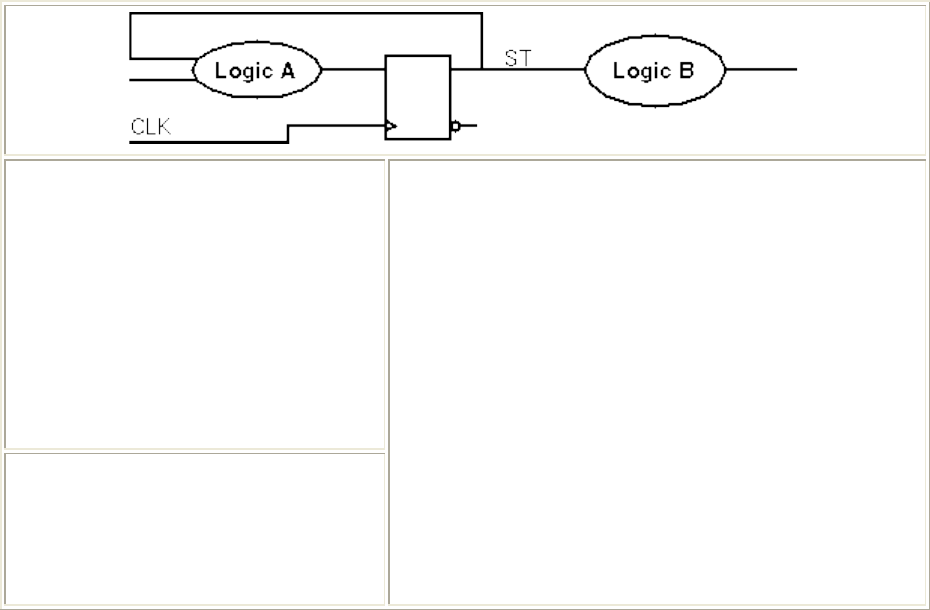

- 4.4.1 RTL – Kombinasyonel Mantık ve Yazmaçlar

- 4.4.2 Zamanlı İşlemlerde Değişkenler

- Örnek

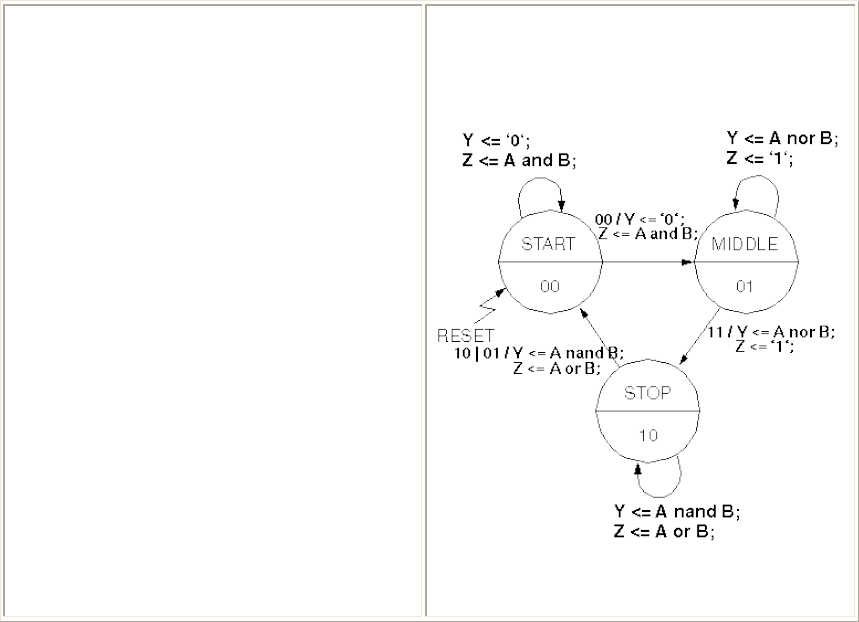

- 4.5 Sonlu Durum Makineleri ve VHDL ( FSM-Finite State Machines)

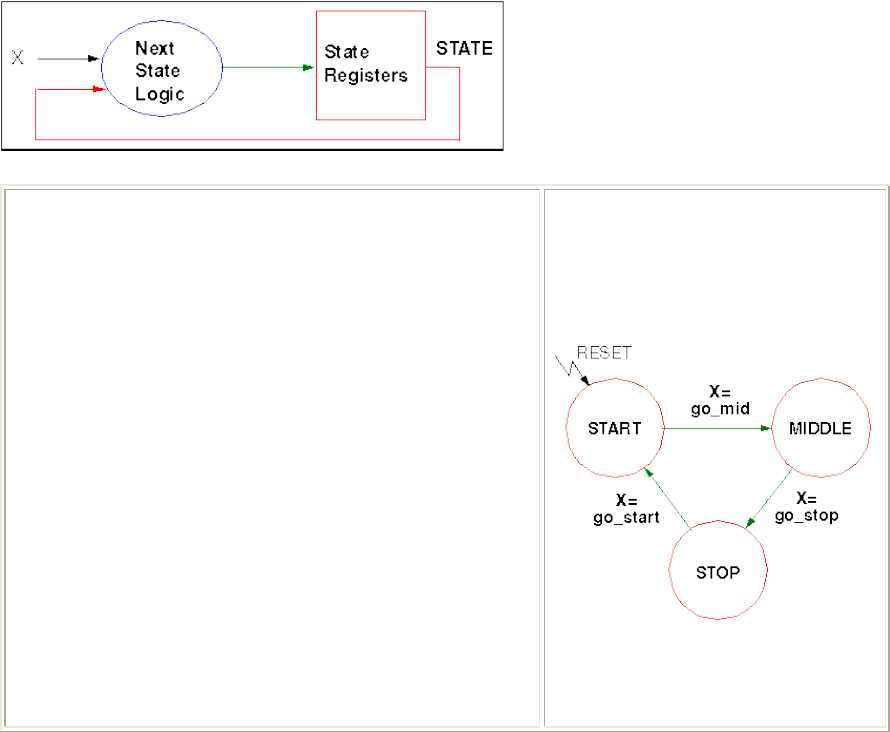

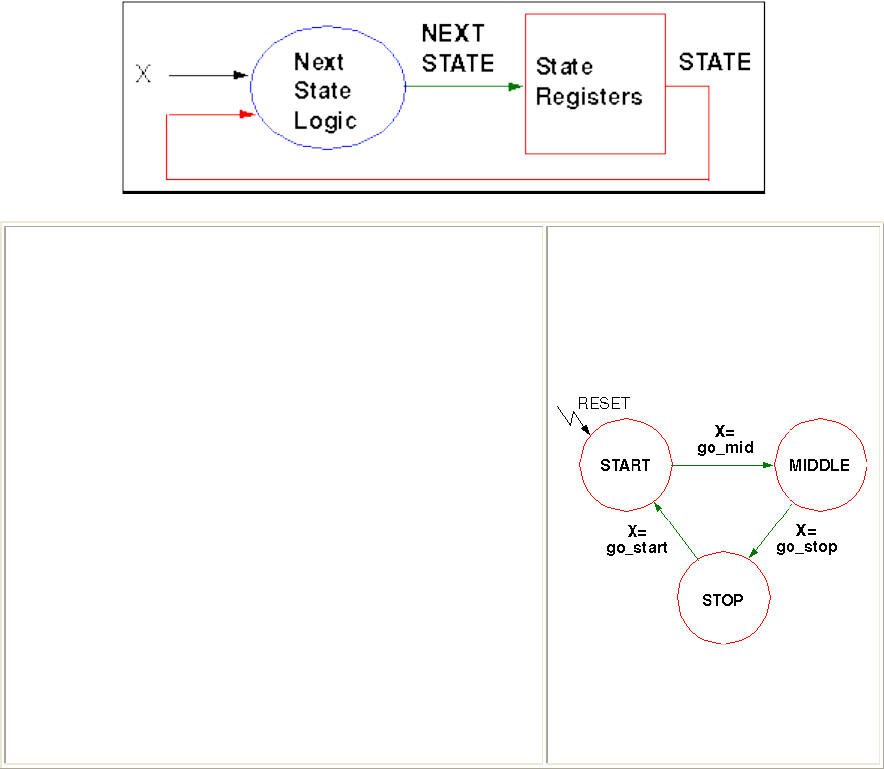

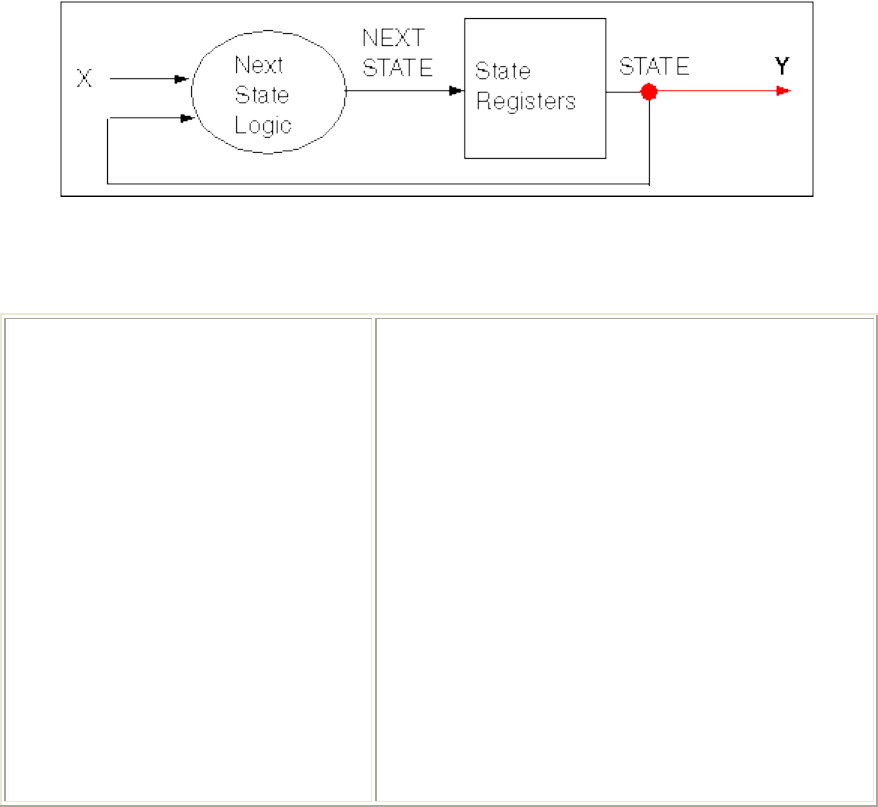

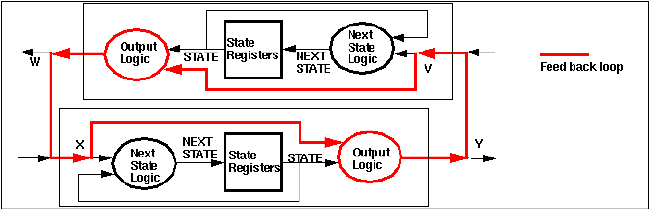

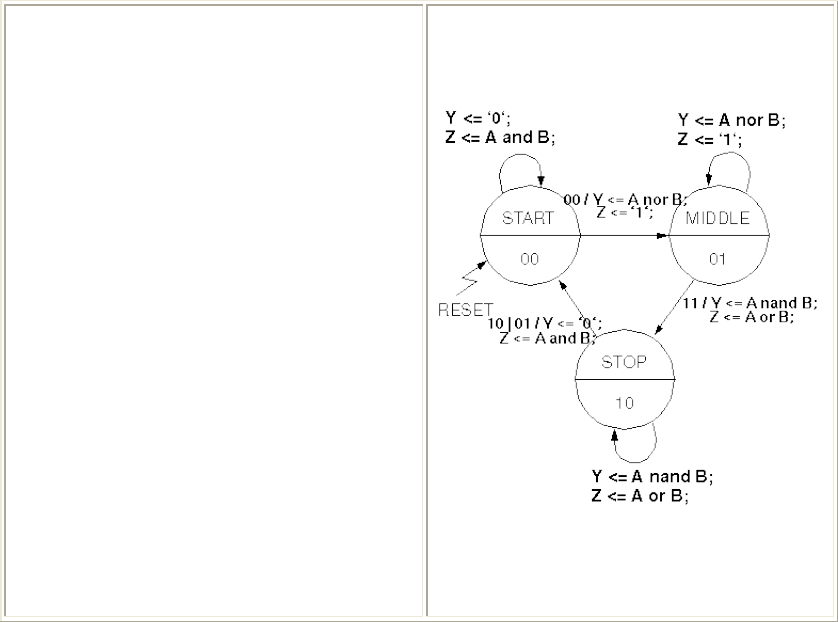

- 4.5.1 Bir "State"Durum İşlemi /

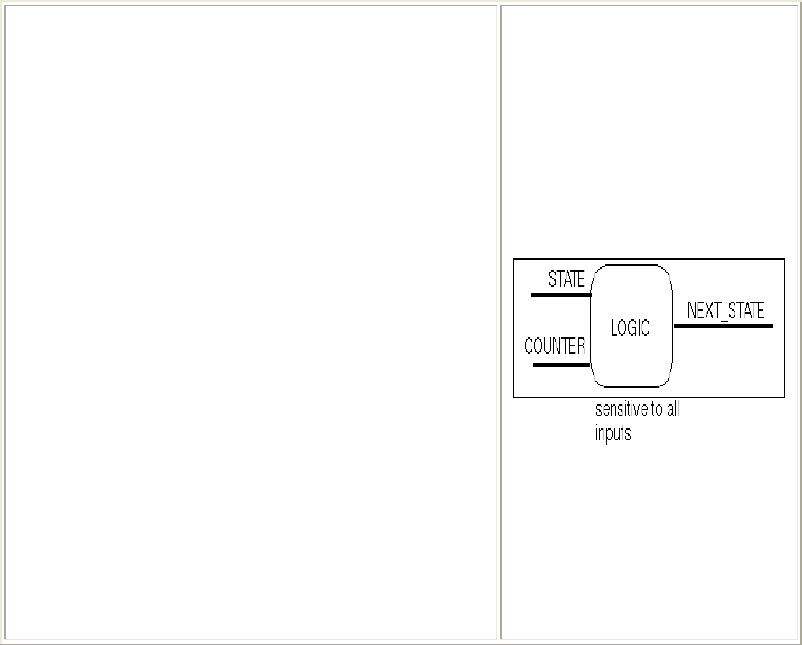

- 4.5.2 İki "State"Durumlu İşlemler

- 4.5.3 Kaç tane İşlem?

- 4.5.4 Durum Şifreleme-Kodlama (State Encoding)

- 4.5.5 Case İfadesinin Eki

- 4.5.6 Tip Bildirimini Eki

- 4.5.7 Elle Kodlama

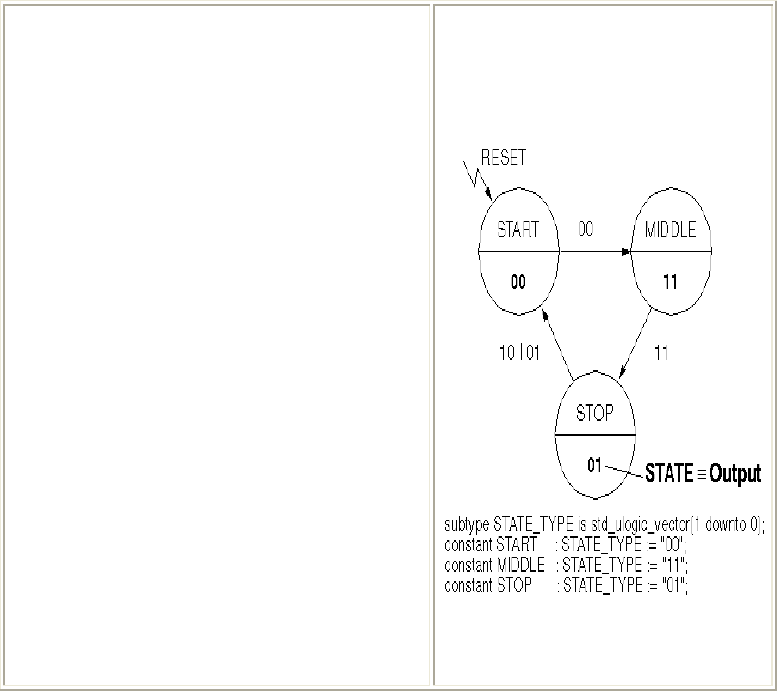

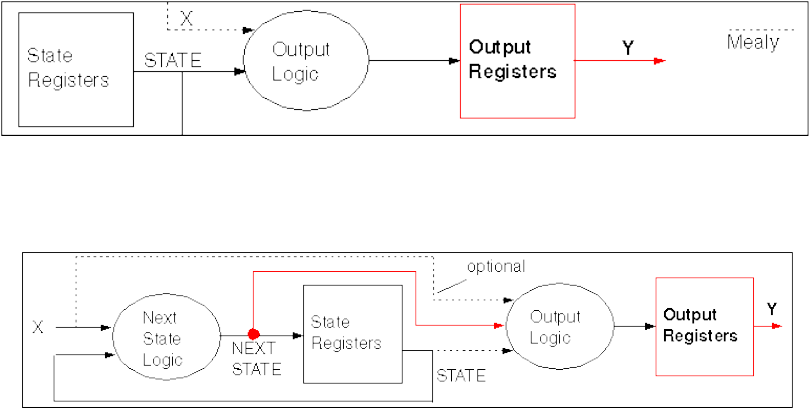

- 4.5.8 FSM: Medvedev

- 4.5.9 Medvedev Örneği

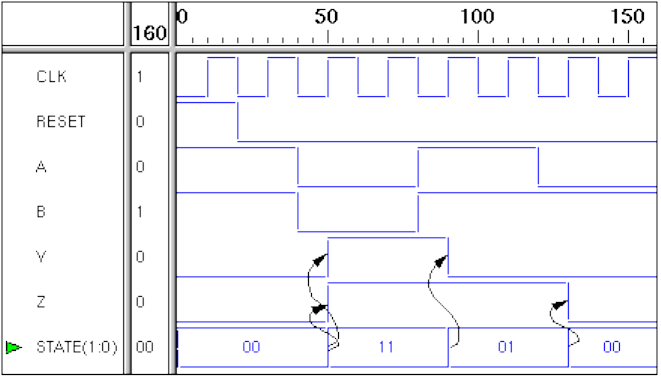

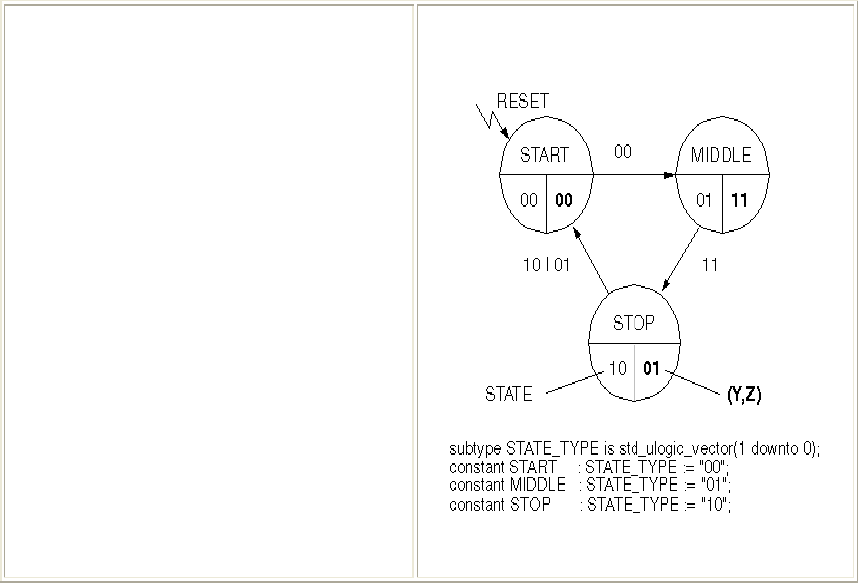

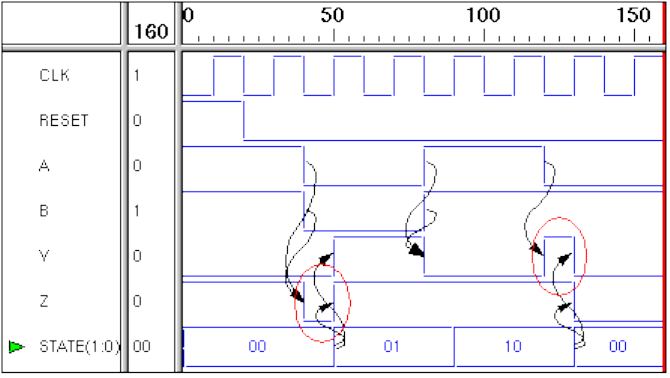

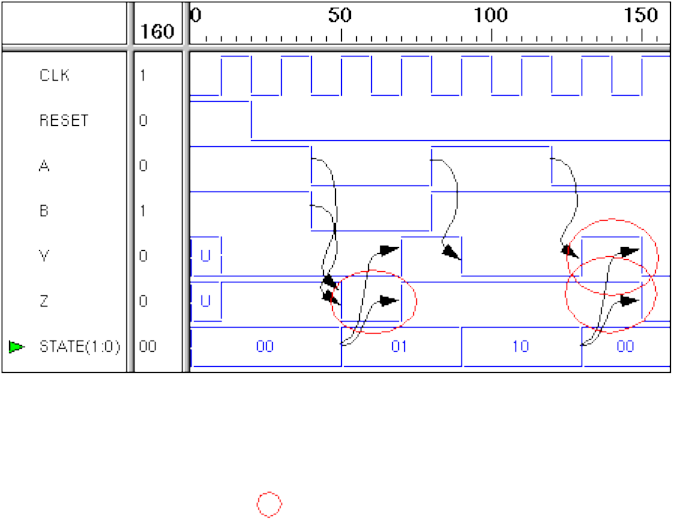

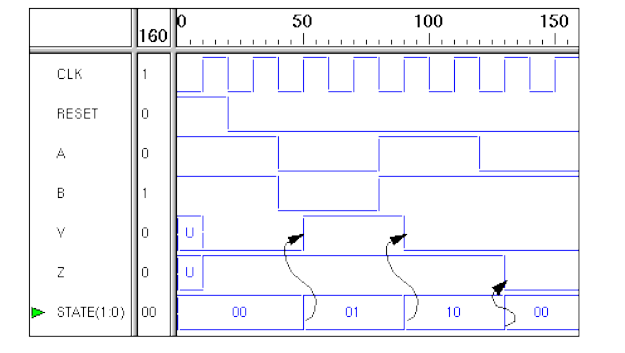

- 4.5.10 Medvedev Örneğinin Dalgaformu (Waveform)

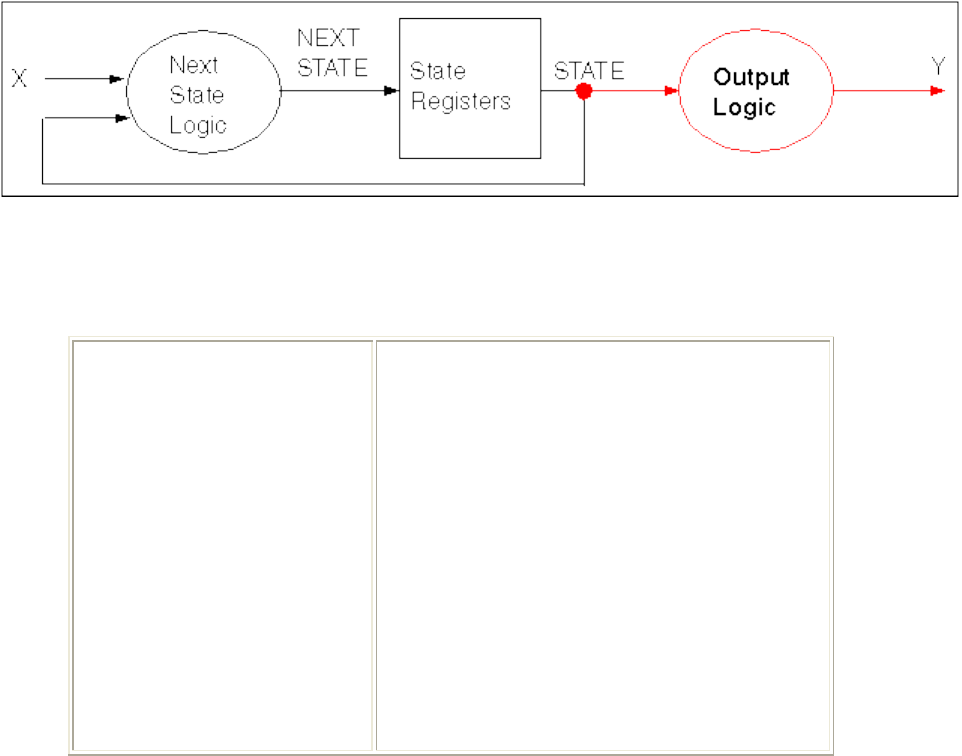

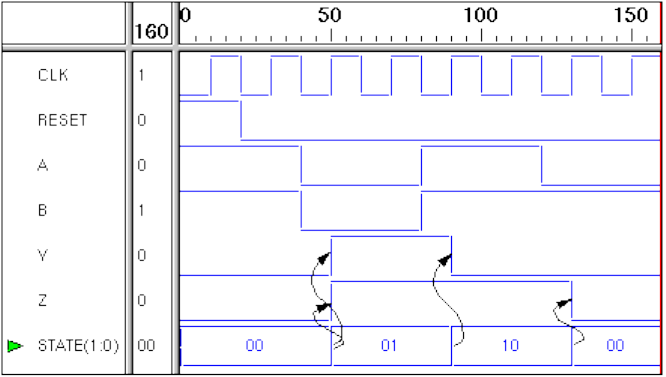

- 4.5.11 FSM: Moore

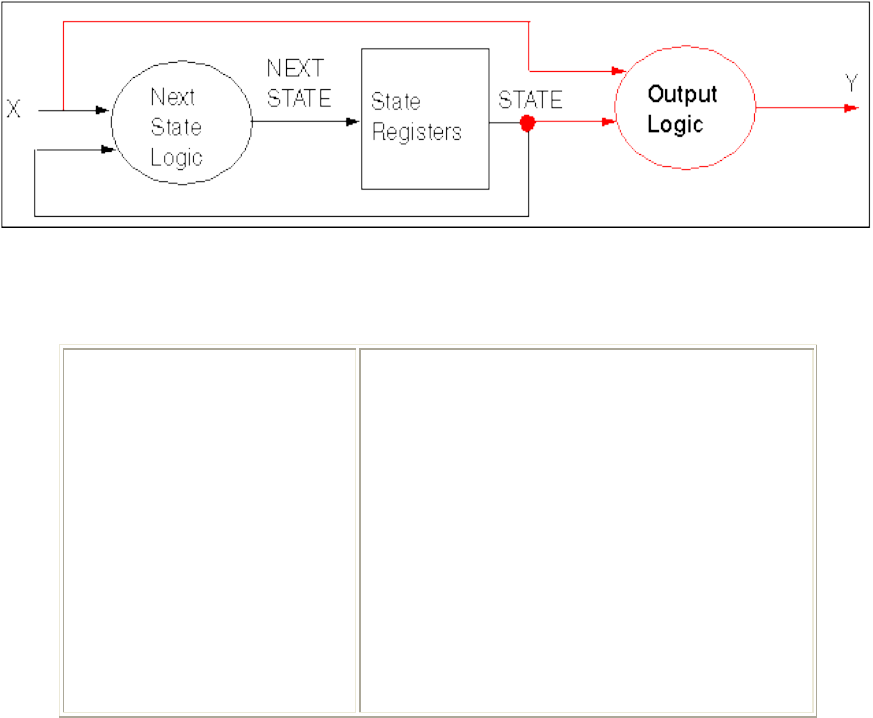

- 4.5.12 Moore Örneği

- 4.5.13 Moore Örneğinin Dalgaformu (Waveform)

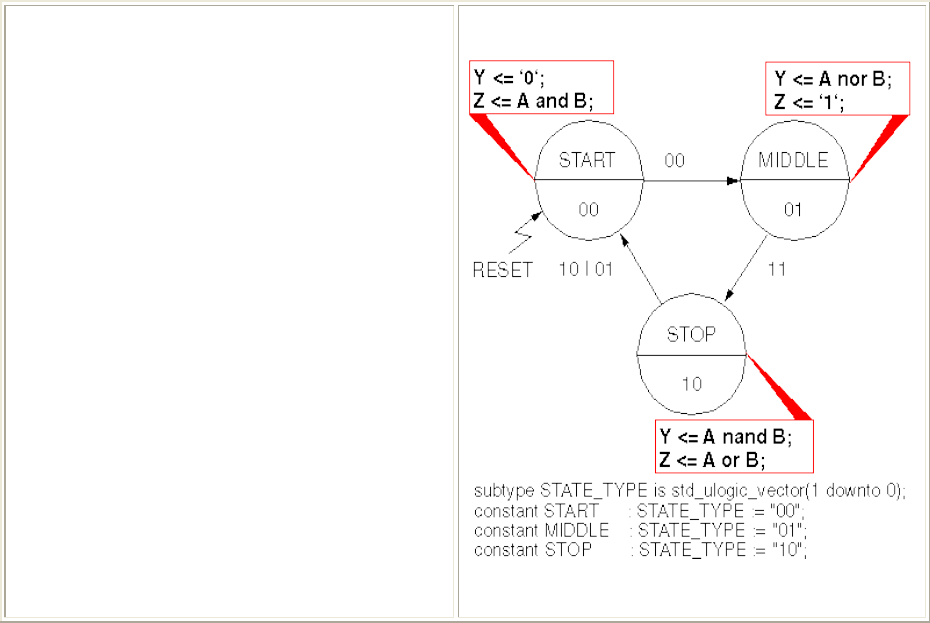

- 4.5.14 FSM: Mealy

- 4.5.15 Mealy Örneği

- 4.5.16 Mealy Örneği Dalgaformu (Waveform)

- 4.5.17 Modellemeye Bakış

- 4.5.18 Yazmaçlı Çıkış(Registered Output)

- 4.5.19 Yazmaçlı Çıkış Örneği (1)

- 4.5.20 Yazmaçlı Çıkış Örneği Dalgaformu (1)

- 4.5.21 Yazmaçlı Çıkış Örneği (2)

- 4.5.22 Yazmaçlı Çıkış Örneği Dalgaformu (2)

- 4.6 İleri Düzey Sentezleme

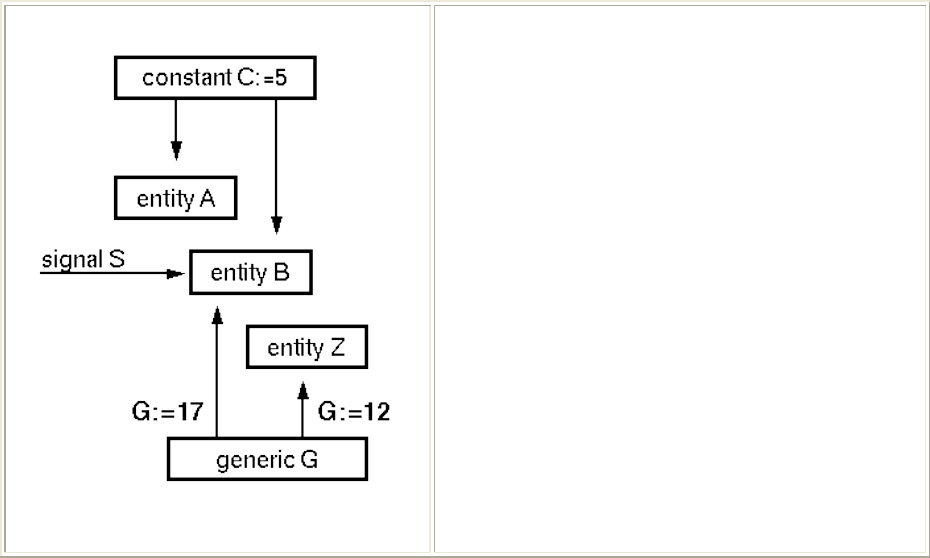

- 4.6.1 Sabitlerle Parametreleştirme

- 4.6.2 Jeneriklerle Parametreleştirme (1) (Generics)

- 4.6.3 Jenerikle Parametreleştirme(2)

- 4.6.4 Üretme(GENERATE)

- 4.6.5 Koşullu Üretme İfadesi (Conditional GENERATE)

- 4.6.6 Parametreleştirme ve Sinyaller

- 5. Proje Yönetimi(Project Management)

- 5.1 Tasarım Bileşenleri

- 5.1.1 Kütüphaneler(Libraries)

- 5.1.2 LIBRARY (Kütüphane) İfadesi

- 5.1.3 USE(Kullanma) İfadesi

- 5.2 Ad Uzayları(Name Spaces)

- 5.3 Dosya Yapısı (File Organisation)

- 5.3.1 Paketler(Packages)

- 5.3.2 Paket Sözdizimi(Package Syntax)

- 5.3.3 Paket Örneği

- 5.3.4 Paketlerin Kullanımı

- 5.3.5 Paket İçeriğinin Görülebilirliği

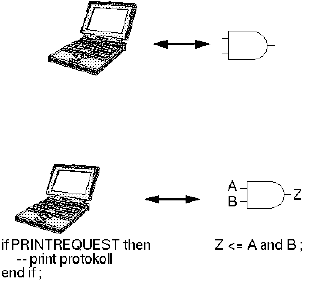

1. VHDL – Genel Bakış ve Uygulama Alanı

• Donanım nedir ?

• Ne tür tanımlamalar yapılır ?

Donanım Tanımlama Dili [Hardware Description Language (HDL)] = Donanım modelleme

için programlama dilidir.

VHDL bir donanım tanımlama dilidir. Donanım kelimesi,bir taraftan kişisel bilgisayarlar gibi geniş

bir içeriği tanımlamak için kullanılsada diğer bir taraftan küçük mantık kapıları ve onların içindeki

entegre devreleri tanımlamak için de kullanılır.

Bu nedenle donanımın işlevselliğinin farklı tanımları bulunmaktadır. Kompleks sistemler genellikle

dışarıdan gözlemlenebilir davranışlarla tanımlanmaktadır. Soyut davranışsal modeller(abstract

behavioural models) implementasyon detaylarını gizlemek için kullanılır.Bu örneğimizde, yazdırma

protokolü yazdırma isteği(PRINTREQUEST) geldiğinde gerçekleşir. Bu istek bir buton yada bir

yazılım komutu,vb. olabilir.Diğer taraftan temel bir mantık kapısı sadece bir ikili sistem(boolean)

eşitliğiyle tanımlanabilir.Bu çok kısa ve kesin bir tanımlamadır.

VHDL dili,tam bir uygulama dizisinden ve genel olarak bir donanımsal(sayısal) modellemeden

ibarettir.

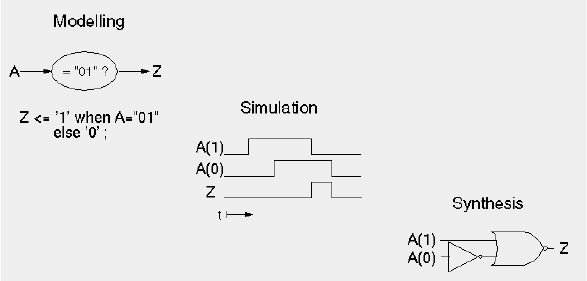

1.1 HDL Uygulamaları (1)

Donanım tanımlama dilinin uygulama alanına bir göz atalım:

Uygulamaya en iyi kanıt belkide bir sistemin davranışal gelişiminin biçimsel modellemesidir.

Sistematik olarak yanlış anlaşılmalar ve yorumlamalar ortadan kaldırılmış olmaktadır. VHDL in kendi

kendine dokümantasyon(selfdocumenting) özelliği ile VHDL modeli sistem dokümanının standart bir

biçimde hazırlanmasını sağlar.

Donanım tanımlama dilinin büyük avantajlarından biride kodunuzu adım adım çalıştırabilmenizdir.

Prensipte, özelleşmiş bir programlama dilinden başka bir şey değildir.Biçimsel bir modeldeki kodlama

hataları yada sistemdeki kavramsal hatalar simülasyon çalıştırılarak bulunabilmektedir.

Oluşturduğunuz modeldeki farklı giriş değerlerine göre sisteminizin verdiği yanıt simülasyonla

gözlemlenebilir ve analiz edilebilmektedir.

Geliştirme sürecinde, tanımlama biz ürünü üretene kadar bize gittikçe daha kesin sonuçlar

vermektedir. Genel tanımlamalardan ayrıntılı tanımlara (otomatik)dönüştürme işlemine

sentez(synthesis) denir. Mevcut sentez araçları donanım tanımlama dilindeki spesifik elemanları

tümleşik devrelerdeki standart elemanlarla eşleştirmektedir.Bu açıdan, donanım sisteminin genel

yapısı önceki çalışmalar kullanılarak oluşturulabilinir. Yazılımdesteği, bu iyileştirme adımlarını

desteklemektedir.

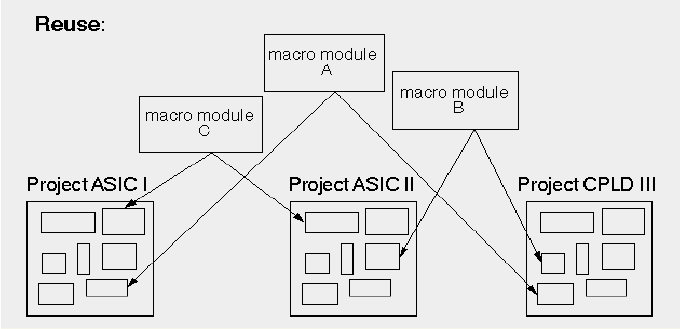

1.1.1 HDL Uygulamaları (2)

Ek olarak, donanım tanımlama dilleri tasarımın yeniden kullanılabilmesini sağlamaktadır. Basit

elektronik elemanlara benzer şekilde, dirençler gibi, uygun HDL modeli birçok tasarım/projede

yeniden kullanılabilinir. Bunun sık olarak kullanım şekli gereken fonksiyon bloklarının(makroların)

model kütüphanesi altında toplanması şeklindedir. Tasarım mühendisi için tek kısıt varolan modüllerin

seçimi değildir ayrıca bazen sentez araçları da kısıt olabilir.

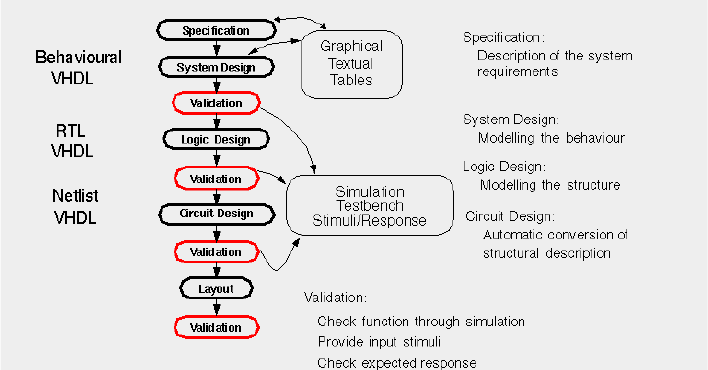

1.1.2 Kullanımın Sıralanması

Tasarım(design) süreci herzaman belirtim(specification) fazı ile başlar: Tasarlanacak eleman işlevine,

boyutuna ve arayüzüne uygun şekilde tanımlanmalıdır. Son ürün ne kadar karmaşık olsa da tasarım

genelde, basit metotlarla, kağıt kalem kullanılarak yapılır.

Daha sonra, sistem seviyesindeki iç içe modüller tanımlanmalıdır. Kendi içindeki etkileşimleri tam

olarak tanımlanmalıdır ve arayüzler( giriş, çıkış,veri biçimi), saat hızı ve sıfırlama(reset)

mekanizması belirlenmelidir. Bu bilgiler elimizde bulunduğu zaman tam bir devre simülasyon modeli

geliştirilebilinir. Standart bileşenlerin davranış modelleri sisteme ticari model geliştiricilerin

kütüphaneleri ile entegre ediliebilinir . Böylece tüm sistem hali hazırda simule edilmiştir.

Mantık seviyesinde(logic level), tasarlanan modellerin tüm sentezleri tanımlanır. VHDL yapısının

tutarlı bir altkümesi kullanıldığı sürece, ticari sentez programları soyut model tanımlamalarından boole

fonksiyonlarını türetebilir ve onları ASIC kapı kütüphanelerinin elemanları veya FPGA’in

ayarlanabilen mantık blokları ile eşleştirebilir.

Son olarak, spesifik ASIC teknolojisi için devrenin yerleşimi netlist tanımlamalarından gelen diğer

araçlarla oluşturulmuş olunur.

Herbir düşük soyutlama seviyesi için geçiş, fonksiyonel doğrulama ile kanıtlanmalıdır. Bu maksatla,

tanımlama simülasyonun alabileceği herbir giriş değeri için modülün verdiği yanıtlar ile

karşılaştırılarak simule edilir.

Bu açıdan VHDL, sistem seviyesinden(system level) kapı seviyesine(gate level) dizayn fazı için

uygundur.

1.2 VHDL ‘e Kısaca Göz Atalım

Çok Yüksek Hızda Tümleşik Devre Donanım Tanımlama Dili

(Very High Speed Integrated Circuit Hardware Description Language )

• Dijital sistem modelleme

• Koşutzamanlı(concurrent) and ardışık(sequential) deyimler

• Bilgisayarca okunur (machine-readable) belirtim

• Tasarım süresi(design lifetime) > Tasarımcı süresi (designer lifetime)

• Kişi ve makine okunur dokümantasyon

Uluslararası Standartlar

• IEEE Standart 1076-1987

• IEEE Standart 1076-1993

Analog ve karma sinyal uzantısı (Analogue- and mixed-signal): VHDL-AMS

• IEEE Standart 1076.1-1999

LRM(Language Reference Manual) Dil Referans Elkitabındaki dilin salt tanımlanması

• Uygulama veya metodoloji için standart yoktur

VHDL geliştirme ilk olarak Amerikan Savunma Departmanı tarafından başlatılmıştır. Onlar,

donanımı tanımlamak için, bilgisayar ve insanlar tarafından aynı anda okunabilir olacak ve

geliştiricileri yapısal ve anlaşılır kod yazmaya zorlayacak, yani kaynak kodun kendisi bir tür belirtim

dokümanı (specification document) olarak sunulabilinecek bir dil istemekteydiler. Ayrıca kompakt

yapıdaki kompleks fonksiyonları modelleyecek ardışık deyimleri desteklemelidir.

1987 ‘de, VHDL Amerikan Elektrik ve Elektronik Mühendisleri Enstitüsü(IEEE) tarafından ilk resmi

güncelleştirilmesi 1993 yılında yapılarak ilk kez standartlaştırıldı. Dosya işleme prosedürü dışında bu

iki standart birbiriyle uyumludur.Dilin standardı(Language Reference Manual (LRM)) Dil Referans

Elkitabı ile tanımlanmıştır.

VHDL‘i analog ve karma sinyal dili elemanları için yükseltme çabaları ile yeni ve zor bir döneme

girilmiştir. Bu yükseltmeye VHDL-AMS ( a nalogue- m ixed- s ignal) denir ve VHDL onun bir üst

kümesidir. Sayısal mekanizma ve metotlar bu eklenti ile değişikliğe uğratılmamıştır.

Şu ana kadar,sadece analog kısmı için simülasyon yapılabilmiştir çünkü analog sentez birçok sınırlı

şartlardan etkilenen çok kompleks bir problemdir. Karma sinyal simulasyonu, şu ana kadar henüz tam

olarak çözülememiş dijital ve analog simulatörlerin senkronizasyon sorununun üstesinden

gelebilmelidir.

1.2.1 VHDL – Tarihçesi

70’lerin ilk dönemi: İlk görüşmeler

70’lerin sonları: İhtiyaçların tanımlanması

82’nin ortaları: IBM Intermetrics ve TI ile geliştirme anlaşması

84’ün ortaları: Versiyon 7.2

86’nın ortaları: IEEE Standardı

1987: DoD IEEE.1076 standardına adapte oldu

88’in ortaları: CAE üreticileri desteklerini arttırdı

91’in sonları: Revizyon

1993:Yeni standart

1999: VHDL-AMS eklentisi

VHDL sürekli gelişen ve değişen bir dildir. Orijinal standarttan resmi IEEE standardına gelmesi 16 yıl

sürmüştür. Dokümanlar komiteden geçtiğinde standardın her 5 yılda bir güncelleneceğine dair karar

alınmıştı. İlk gözden geçirmenin sonucu 1993‘deki güncellenmiş standarttı.

Bu standart gelişim kararı dışında eklentiler için ek çaba harcanmıştır. Bu eklentiler, geniş çapta

ihtiyaç duyulan veri tipleri ve alt programlara ait örnek paketler ( std_logic_1164, , numeric_bit,

numeric_std, ...), veya özel VHDL altkümelerinin örneğin sentez altküme IEEE 1076.6 tanımını

içermektedir.

Son eklenti ise VHDL-AMS adı verilen analog tanımlama mekanizmasını standartlaştıran eklenti idi.

1.2.2 VHDL – Uygulama Alanı

Donanım tasarımı

• ASIC: teknoloji eşleştirme(mapping)

• FPGA: CLB eşleştirme

• PLD: daha küçük yapılar, hemen hemen tüm VHDL kullanımı

• Standart çözümler, modeller, davranışsal tanımlamalar, ...

Yazılım tasarımı

• VHDL - C arayüzü (araç-spesifik)

• Temel araştırma odakları (donanım/yazılım etkileşimli tasarımı)

VHDL temelde Entegre Devrelerde Spesifik Uygulamaların(Application Specific Integrated Cicuits

(ASICs)) geliştirilmesinde kullanılır. VHDL koddan kapı seviyesi netlist’e(gate-level netlist) otomatik

dönüştürme araçları ilk zamanlarda geliştirilmeye başlanmıştı. Bu dönüşüm sentez olarak adlandırılır

ve şuanki tasarım sürecinin ayrılmaz bir parçasıdır.

Programlanabilir aygıtların(Field Programmable Gate Arrays (FPGAs)) kullanımında birçok sorun

mevcuttur. İlk adımda, boole denklemleri VHDL tanımlamalarından türetilmektedir,hedef teknolojinin

ASIC mi yoksa FPGA mi olduğunun bir önemi yoktu.Fakat şimdi, bu boole kodu FPGA‘in

ayarlanabilir mantık bloğunun(configurable logic blocks (CLB)) bir parçası olmak zorundadır. Bu,

ASIC kütüpanesine eşleştirmekten daha zordur. Bir diğer büyük problem FPGA in darboğazı olan

CLB’nin iç içe bağlı mevcut kaynaklarının yönlendirilmesidir.

Sentez araçları kompleks tasarımların üstesinden oldukça iyi bir şekilde gelirken, genellikle sadece

vasat(suboptimal) sonuçlar elde ederler. Bu nedenle VHDL neredeyse tamamen fazla karmaşık

olmayan programlanabilir mantık araçlarının(Programmable Logic Devices (PLDs)) tasarımında

kullanılır.

VHDL hedef teknolojilerden bağımsız olarak model sistem davranışlarına uygulanabilir. Standart

çözümler için bu kullanışlıdır, örneğin; mikrodenetleyiciler(micro controllers), kodlayıcı/kodçözücüler

için hata düzeltimi ve hedef ortamında yeni bir aygıt(RAM aygıtlarında) benzetimi yapabilmek

(simulate) için.

Araştırmanın şu an gelişen alanlarından biri de donanım/yazılım co-design’dır. En ilginç soru ise

sistemin hangi bölümü yazılımda gerçekleştirilecek hangi bölümü donanımda gerçekleştirilecektir.

Kesin kısıtlar ise maliyetleri ve gösterdiği performansıdır.

1.2.3 ASIC Geliştirme

VHDL model geliştirme fonksiyonel sınırlarıyla zamanlama davranışının belirtimleriyle başlar. Bazen

davranışsal VHDL modeli buradan türetilir, çünkü sentezlenebilir koda genelde buradan itibaren

ihtiyaç duyulur. VHDL kodun fonksiyonaliteye uygunluğu simüle ve kontrol edilebilinir.

Eğer model beklenen davranışı gösteriyorsa, VHDL tanımlaması sentezlenebilecektir. Bir sentez

aracı belirlenmiş ASIC kütüpanesinden uygun kapı ve ikidurumluyu(flip-flop) fonksiyonel

tanımlamaya uyacak şekilde yeniden üretir.Sentez prosedürü için olmazsa olmaz şey en uzun yol

boyunca bulunan ( herbir flip-flop‘un çıkışıyla diğerinin girişi arasındaki) kapı bekleme sürelerinin

saat periyodundan daha kısa olması gerekliliğidir.

ASIC kütüpanesinin elemanlarıyla oluşturulmuş bir model var olduğu sürece, kapı seviyesinde bir

simülasyon gerçeklenebilir. Şimdi kapılar ve yayılma süreleri(propogation delay) hesaba katılmak

zorundadır. Bekleme sürelerinin değerleri herbir VHDL model tanımlamasına eklenmelidir, örneğin

tasarımcının aldığı ilk ipuçları maksimum saat frekansı ve sentez sonrası kritik yollardır.

Önce sinyal kablolarının gecikme süresi tahmini olarak hesaplanmalıdır çünkü gerçek değerler ancak

tüm yerleşim bittikten sonra bulunabilir. VHDL modeline bu değerlerin atanması işlemine tersine ek

açıklama(back annotation) denir. Bu yapıldıktan sonra, devrenin belirlenmiş zaman kısıtlarına tam

olarak uyup uymadığı kontrol edilmelidir.

1.3 VHDL’in Kavramları

Atamaların yürütülmesi(Execution of assignments)

Sıralı (Sequential)

Koşutzamanlı (Concurrent)

Metodolojiler:

Soyutlama (Abstraction)

Modülerlik (Modularity)

Hiyerarşi-Sıradüzen (Hierarchy)

VHDL kendini atamalar yönünden diğer dillerden ayırır çünkü bilinen iki temel atama vardır. Bunlar:

Sıralı ifadeler yazılım programlama dillerindeki gibi biri diğerinden sonra gelecek şekilde yürütülür.

Son gelen ifade bir önceki ifadenin etkilerini geçersiz kılabilir. Sıralı ifadeler kullanıldığında

atamaların sırası göz önünde bulundurulmalıdır.

Koşutzamanlı ifadeler sürekli aktif durumdadır. Bu yüzden ifadelerin sırası önemli değildir.

Koşutzamanlı ifadeler özellikle paralel donanımlı modeller için uygundur.

Aynı zamanda VHDL‘in üç önemli modelleme tekniği vardır:

Soyutlama, sistemin farklı bölümleri için farklı miktarda ayrıntıda tanımlama yapılmasına izin verir.

Modüllere sadece simülasyon için ihtiyaç duyulur, modüllerin sentezlemedeki gibi ayrıntılı şekilde

tanımlanmasına gerek yoktur.

Modülerlik, tasarımcıların büyük fonksiyonel blokların bölünmesine ve herbir bölüm için ayrı bir

model yazılmasına olanak sağlar.

Hiyerarşide ise tasarımcılar birçok alt modül içerebilecek altmodüller tasarlarlar. Her bir seviyedeki

hiyerarşi farklı soyutlama seviyelerinde modüller içerebilirler. Bir modülün alt modülleri bir düşük

seviyedeki hiyerarşik seviyede bulunurlar.

1.3.1 Soyutlama

• Soyutlama ayrıntıları gizler: Zorunlu ve gereksiz bilgi arasındaki ayrım.

• Soyut seviyelerin oluşturulması: Her bir soyut seviyede sadece zorunlu bilgiler göz

önünde bulundurulur, gereksiz bilgiler atılır.

• Soyutlamanın dengeliliği(equability): Bir soyutlama seviyesinde bulunan bir

modeldeki tüm bilgiler aynı derecede soyutlama içerir.

Soyutlama çok ayrıntılı bilgilerin gizlenmesi olarak tanımlanır. Bu nedenle gerekli ve gereksiz

bilgilerin ayrılması gerekmektedir. Problemin şu anki durumunda önemsiz olan bilgiler

tanımlamadan çıkarılabilinir. Soyutlama seviyeleri, aynı seviyedeki tüm modellerdeki ortak bilginin

türüne göre tanımlanır.

Eğer, bir modelin, her bir modül aynı derecede soyutlamaya sahipse o modele kesin soyutlama

seviyesi denir. Eğer sahip değilse bu model farklı soyutlama seviyelerinin karışımı olarak

nitelendirilir.

1.3.2 IC Tasarımında Soyutlama Seviyeleri

Bir sayısal devre tasarımının dört soyutlama seviyesi şekilde gösterilmiştir. Modelin fonksiyonel

tanımlaması davranışsal modelde özetlenir. Burada sistem saati yoktur ve sinyal geçişleri anahtarlama

zamanına uyacak şekilde asenkrondur. Genellikle bu tanımlamalar simüle edilebilir fakat

sentezlenemezler.

Bir sonraki adımda, tasarım kombinasyonel mantık ve depolama elemanları olarak bölünür. Buna

Yazmaç Transfer Seviyesi(Register Transfer Level (RTL)) denir. Depolama elemanları (flip floplar

FFs, mandallar(latches) ) sistem saati tarafından kontrol edilir. Senkron tasarımlarda, sadece FF ‘lar

kullanılabilinirler, çünkü açık mandallar(transparent latches)(kontrol sinyaliyle sürülen) spike-proof

değildir. RT seviyedeki tanımlamalar için sadece yüzde 10-20 arasında VHDL dil yapısı gereklidir ve

katı bir metodoloji izlenmektedir. RT seviyedeki tanımlamaya sentezlenebilir tanımlama denir.

Mantık seviyesinde , tasarım lojik kapılarla ve saklama elemanlarıyla bir netlist olarak ifade edilir. Son

yerleşim hiyerarşinin en altındadır.Hedef teknolojideki farklı hücreler yongaya yerleştirilir ve

bağlantılar yönlendirilir(routed). Yerleşimin doğruluğu sağlandığında(verified), devre üretim sürecine

hazırdır.

1.3.3 Soyutlama Seviyeleri ve VHDL

VHDL üstteki üç soyutlama seviyeleri için uygulanabilir. VHDL bir yerleşim tanımlamaya uygun

değildir. Davranışsal ve RT seviyedeki tasarım girişi genellikle metin editörleri tarafından yapılır.

Grafik araçları da mevcuttur ancak deneyimli kullanıcılar genellikle kodu elleriyle yazmayı daha kolay

bulmaktadır. Kapı seviyesinde, VHDL netlist tanımlamalar olarak değiştirilen bir şematik çok yakında

oldukça karmaşık olmaya meğillidir.

Bir üst soyutlama seviyesinden daha düşük bir seviyeye geçiş daha çok veya az verimli yazılımlarla

desteklenir.

Davranışsal sentez birçok araştırmacıya göre hala bir rüyadan ibaret yalnızca çok basit davranışsal

modeller sentezlenebilir. Hedef teknoloji için RAM tasarımı yaygın bir uygulamadır, sadece genel

parametrelerin (genişlik,derinlik,port sayısı,senkronluğu,…) kesinlikle belirtilmesi gerekmektedir.

Buan rağmen, mantık sentezi, son yıllarda mükemmelleşmiştir. Tasarımcılar kendilerini RT

seviyesinde tanımlamalar için yeterli olan basit VHDL sınırları içinde tuttuğu sürece , sentez araçları

mantık seviyesindeki davranışı üretebilecektir.

Devam eden araştırmalarım bir sonucu olarak,mantık seviyesinden son yerleşime kadarki adımlar

verimli alan ve yönlendirme(route) algoritmaları ile dijital standart hücre tasarımı için geniş ölçüde

otomatikleştirilmiştir.

1.3.4 Soyut Seviylerin Tanımlamaları

Davranış seviyesinde tüm sistem modellenebilir. Veri iletim yolu veya kompleks algoritmalar,

sentezlenebilirliği göz önünde bulundurulmadan tanımlanmalıdır. RTL modellerin simülasyonu için

tepki(stimuli) davranış seviyesinde tanımlanır. Tepki, modeldeki giriş portlarının sinyal değerleridir ve

testbençte(testbench) (bazen onaylama bençi de denir) tanımlanır.

Tasarımcı belirtime(specification) ters düşmeyecek şekilde tutarlı bir giriş tepki kümesi bulma

konusunda çok fazla dikkat etmeli.Modelden alınan sonuçlar beklenen değerlerle,en basit durumlar

için,simüle edilmiş sinyal değerlerinin dalga formunun yardımıyla karşılaştırılmalıdır.

RT seviyesinde, sistem yazmaçlar(registers) ve bellek elemanlarının bir sonraki değerini hesaplayan

mantık(logic) ile tanımlanır. Kodu iki blok halinde ayırmak mümkündür, tamamen kombinasyonel

mantıkdan oluşan veya yazmaçlardan oluşan. Yazmaçlar saat sinyalleriyle bağlantılıdır ve

ardışıl(synchronous) davranışı sağlar. Pratikte, Flip Flopların kombinasyonel mantıktan kesin ayrımı

genellikle yazmaçları ve uygun güncelleme fonksiyonlarını tanımlayan döngülü ve zamanlı

işlemlerdir.

Kapı netlisti RT tnaımlarından sentez araçlarının yardımıyla üretilmiştir. Bu işlem için, hedef teknoloji

için mevcut kapıları ve onların parametre bilgilerini tutan bir hücre kütüphanesine ihtiyaç vardır.

Kapı netlistine dayanarak devrenin yerleşimi üretilmiştir(generated). Sonuçta oluşan kablo uzunlukları

kapı seviyesi modeldeki karşılığı- yayılma süresine(propagation delay) dönüştürülmelidir. Bu zaman

simülasyonunun herhangi ek simülatör yazılıma ihtiyaç olmadan gerçekleştirilmesini sağlar.

1.3.5 VHDL’de Davranışsal Tanımlama

Bir modelin basit bir belirtim(specification) fonksiyonu gösterilmiştir. Çıkış üç giriş değeri i1, i2 ve i3

‘e bağlıdır.Ayrıca yeni çıkış değeri giriş değeri değiştirildikten sonra 100ns sonunda hazır olmalıdır.

Bir davranışsal VHDL tanımlamada, fonksiyon basit bir denklem(ör. i1 + i2 * i3)artı bekleme süresi

100ns olarak modellenir. En kötü durumda, örneğin 100ns’ye yeni çıkış değerinin hesaplanması için

ihtiyaç vardır, burada varsayılan.

1.3.6 VHDL’de RT Seviyesi

VHDL’de fonksiyonel davranış sözde süreçler ile modellenir. RT seviyesi tanımlamalarında iki farklı

tipte süreç bulunmaktadır: tamamen kombinasyonel süreç (combinational process) ve saatsel

süreç(clocked process). Tüm saatsel süreçler Flip Floplar olarak ifade edilir ve durum makinesi

sözdizimi(state machine syntax) kurallarına göre tanımlanır.

RT seviyesi modellemede, veri girş ve çıkış sinyaline ek olarak, kontrol sinyali-modül saati

gibi(CLOCK) ve asenkron sıfırlanabilir FF için sıfırlama (RESET) dikkate alınmalıdır. Senkron

sıfırlama stratejisi kullanıldığında, sıfırlama girişi sıradan bir veri girişi olarak işleme alınır.

Buna takiben, RT seviyesi VHDL kodu, depolayabilir ve depolayamayan elemanlar olarak bölünmüş

fonksiyonel davranışa ek olarak bazı yapısal bilgiler içermektedir. Sinyal değerleri güncellendiğinde

zamanlama konusu ayrıca göz önünde bulundurulmalıdır.

1.3.7 VHDL’de Kapı Seviyesi

Bir VHDL kapı seviyesi tanımlaması tasarımda kullanılan bir kapı(bileşenleri) listesi

içermektedir.Diğer kısım bileşenlerin gerçek örneklemini ve onların karşılıklı

bağlantılarının(interconnection) listesini tutmaktadır.

Bir dijital devrenin kapı yapısının şematiği resmin sol kısmında görülmektedir.Sağ kısım ise uygun

VHDL tanımlarının bir bölümünü göstermektedir.Devredeki her bir tek eleman(ör: ND2), bağlı

olduğu uygun sinyallerle(n192, n191, n188) desteklenmektedir. Kullanılan tüm kapılar seçilen

teknolojinin kütüphanesinin bir parçasıdır ve burada alan(area), yayılma süresi(propagation delay),

kapasite(capacity), vb. bilgiler kaydedilmiştir.

1.3.8 Soyut Seviyenin Bilgi İçeriği

(Information Content of Abstraction Levels)

Davranış model, bir devrenin davranışını tanımlamanın basit bir yoludur, alışılmış yazılım

programlama dilleri PASCAL veya C ‘ye benzer şekilde. Bu tanımlamadan yola çıkarak sadece

fonksiyonel davranış VHDL simülatörü ile simüle edilebilinir.

Saat darbesi, RT seviyesi tanımlaması için ayırt edici özelliktir. Tüm işlemler saat sinyaliyle

ilişkilendirilmiştir. RT seviyesi simülasyon gerçek zamanlı davranış hakkında herhangi bir bilgi

vermez, tüm sinyallere bir saat periyodunda sabit değerler atanmıştır yada atanmamıştır demek

imkansızdır.

Model, mantık seviyesinde tanımlandığında, kullanılan kapılara göre bekleme süreleri simülasyon için

uygulanmıştır. Zamanlama bilgisi sentez kütüpanesinin bir parçasıdır.Bu zamansal davranışın

onaylanmasını hızlı bir şekilde yapılmasına olanak sağlar. Sinyal kablolarının gecikme sürelerinden

kaynaklanan kararsız sistemler henüz göz önüne alınmamıştır. Büyük tasarımlardaki tüm beklemeler

çok iyi makyajlanmıştır.

Yerleşim tamamlandığında, kablo uzunlukları ve bunlardan kaynaklanan gecikme süreleri bilinmiş

olmaktadır. Tasarım, tüm devrenin zamanlama davranışı ve gecikme süreleri ile kapı seviyesinde

simüle edilebilmektedir. Ancak devre hakkında bilgi arttıkça simülasyon süresi gözle görülür şekilde

artmaktadır bu da kompleks tasarımlardaki küçük parçaların zamanlama simülasyonu için kısıt

oluşturmaktadır.

1.4 Modülarite ve Hiyerarşi

Tasarımın bölümlere ayrılması

Karmaşıklığı sınırlama

Takımçalışmasına imkan vermesi

Alternatif gerçekleştirmeleri

çalıştırabilmesi

Yazılımsal makrolar

Simülasyon modelleri

Modülarite, büyük fonksiyonel blokların küçük birimler şeklinde parçalara ayrılmasına ve birbiriyle

yakın ilişki içerisinde olan birbirini içeren parçaları gruplamaya izin verir,bunlara modül denir. Bu

yönden, karmaşık bir sistem yönetilebilinir alt parçalara bölünebilir. Parçalara ayırmanın metodu

tasarımdan tasarıma değişebilmektedir. Genelde fonksiyonel durum parçalamadaki kısıt olarak göz

önünde bulundurulur.İyi tanımlanmış altsistemlerin varlığı aynı proje üzerinde çalışan birçok

tasarımcıya paralel çalışma imkanı sunar, her bir tasarımcı kendi bölümünü tam bir sistem olarak ele

alabilir.

Hiyerarşi, modüllerden oluşmuş bir tasarımın yapılmasını sağlar, bu modeüller de (alt)modüllerden

oluşmuş olabilir. Bir seviyedeki hiyerarşik tanımlama bir veya birden fazla modül içerebilir, herbir

modül farklı derecelerde soyutlamaya sahiptir. Bu modüller kendisinden bir alt seviyedeki hiyerarşik

seviyedeki alt modülleri içermektedir.

Modülarite ve hiyerarşi bir projenin tasarımının basitleştirilmesinde ve düzenlenmesine yardımcı

olmaktadır. Bir başka avantajı ise modüller için farklı gerçekleme alternatiflerinin incelenmesini

sağlamaktadır. Tüm model için sadece belirtilen parçanın örnekleminin değiştirilmesine ihtiyaç

duyulabilir. Aynı zamanda analog arayüzler VHDL de modellenebilir ve simülasyon için sistem

modeline eklenebilir. Bazen, araçların simülasyon modelleri , yeni tasarıma bağlanmış olabilir ve test

aşamasında bir simülasyonun gerçek çalışma ortamı altında testi kullanılabilinir.

1.5 Özet

Donanım ve yazılım kavramları

Sistem tasarımının parçası olarak donanım

Davranışsal ve RTL sitili

Yapısı

Eş zamanlılık (simultaneity)

Sıralı ifadeler

Zamanlama davranışının tanımlanması mümkündür

Model tasarımı ve doğrulanması için bir dildir.

VHDL’de dijital bir sistemi modellemek için donanım ve yazılım kavramları mevcuttur. Sentez için

RT seviyesi modelleme ve salt davranışsal model arasında bariz bir fark vardır.

VHDL dijital bir sistemin yapısal(modüler) ve hiyerarşik tanımlanmasına izin vermektedir.

VHDL için uyumluluk önemli bir kavramdır: Birbiriyle uyumlu ifadeler sanal olarak paralel olarak

yürütülürler. Simülasyon olayların peşpeşe işlemesidir. Eğer kaçınılmaz bir olay gerçekleştiyse , bu

olayla ilgili işlemler hemen tetiklenir(triggered). Bu işlemler birbiri ardına gerçekleştirilen sıralı

ifadeleri içerir. Her bir işlem başlı başına koşutzamanlı(concurrent) ifadeler olarak görülebilinir.Bu

yönden, sinyal değerlerinin değişimine, simülasyonda birçok işlemin aynı zamanda gerçekleştirilmesi

neden olmaktadır.

Bununla birlikte, VHDL de zaman davranışını tanımlamak mümkündür. Bu diğer dillerdeki gibi test

amaçlı uyarıların oluşturulmasını veya son tasarımdaki zamanın doğrulamayı ortadan kaldırmıştır.

2. VHDL Dili ve Sözdizim(Syntax)

Genel Yapısı

Tanıtıcılar(Identifiers)

İsimlendirme Kuralları(Naming Convention)

2.1 Genel Yapısı

----------------------------------

-- VHDL Kodu Örneği --

----------------------------------

signal mySignal: bit; -- örnek sinyal

MYsignal <= '0', -- '0' dan başlar

'1' AFTER 10 ns, -- ve diğer duruma geçer

'0' after 10 ns, -- her 10 ns de bir

'1' afTer 10 ns;

• Büyük küçük harf duyarlı

değildir.

• Açıklamalar: '--' den başlar satır

sonuna kadar devam eder

• İfadeler(statement) ';' ile

sonlandırılır

(birden fazla satıra yayılabilir)

• Liste sınırlandırıcısı: ','

• Sinyal ataması: '<='

• Kullanıcı tanımlı isimler:

o harfler, sayılar, altçizgi

o bir harfle başlanır

VHDL büyük küçük harf duyarlı değildir.Bu da VHDL kaynak kodu için kendi kurallar belirlememiz

gerekliliğini ortaya koyar.Örneğin, VHDL anahtar sözcükleri(keyword) küçük harflerle, kendi

tanımladığımız tanıtıcılara(identifier) büyük harfler kullanabiliriz. Bu kural bundan sonraki sayfalar

için geçerli olacaktır. Böylece anahtar sözcüklerle kendi tanıtıcılarımız arasındaki fark kolaylıkla

anlaşılacaktır kodu okumak daha kolay olacaktır.

VHDL‘de ifadeler(statements) noktalı virgül(‘;’) ile sonlandırılırlar. Bu istediğiniz şekilde satır arası

veya boşluk oluşturabileceğiniz yada silebileceğiniz anlamına gelmektedir. VHDL

derleyicisi(compiler) sadece noktalıvirgülü(‘;’) göz önünde bulundurur.

Liste normalde virgül(‘,’) ile birbirinden ayrılır. Sinyal atamaları kompozit atama operatörü '<=' ile

gösterilir.

VHDL 87 standardında kendi tanımlamalarımız harfleri, sayıları ve altçizgi içerebilir ancak muhakkak

bir harfle başlamak zorundadır. Hiçbir VHDL anahtar sözcüğü kendi tanımlamamız olarak

kullanılamaz. VHDL 93 standardı daha esnek tanımlama yapabilmemize olanak sağlamıştır.

2.1.1 Tanıtıcı(identifier)

mySignal_23 -- normal tanıtıcı

rdy, RDY, Rdy -- özdeş(aynı) tanıtıcılar

vector_&_vector -- X : özel karakter ’&’

last of Zout -- X : boşluklu(white spaces)

idle__state -- X : ardarda altçizgili

24th_signal -- X : r a k a ml a başlayan

open, register -- X : VHDL anahtar sözcükler

X:kullanılamayan yapılardır.

* (Normal) Tanıtıcı

o Harfler, rakam, altçizgiler

o Büyük küçük harf duyarsızdır.

o Ardarda iki altçizgi kullanılamaz

o Bir harfle başlamak zorundadır

o VHDL anahtar sözcükler kullanılamaz

VHDL 87 standardıyla tanımlanmış basit tanıtıcılar harf, rakam ve altçizgi içerebilir.Bu nedenle

'mySignal_23' geçerli bir tanıtıcıdır. Bununla birlikte VHDL büyük küçük harf duyarsızcır bu nedenle

'rdy', 'RDY' ve 'Rdy' birbirinin aynıdır. '24th_signal' geçersiz bir tanıtıcıdır çünkü ilk harfi bir rakamla

başlamış, ilk harf muhakkak bir harf olmak zorundadır. Ayrıca grafiksel karakterler, boşluk, ardarda

altçizgiler ve VHDL anahtar sözcüklere izin verilmez.

VHDL 93 standardında yeni bir tipte tanıtıcılar tanımlanmıştır. Bunlara genişletilmiş(extended)

tanıtıcılar denmektedir ve bunlar ters kesme işareti’/ ’ arasına alınmıştır. Bu ters kesme işaretleri ile

herbir karakter, rakam, boşluk ve altçizgi kombinasyonuna izin verilmektedir. Burada önemli olan şey

ise artık tanıtıcılar büyük küçük harfe duyarlıdır. Böylece'/rdy/', ' / R D Y / ' ve ' / R d y / ' üç farklı tanıtıcı

haline gelmiştir.

2.1.2 İsimlendirme Kuralları

architecture CONVENTION of NOTATION is

end architecture CONVENTION ;

• VHDL anahtar sözcükler küçük harfle

yazılır

• Önemli yerler koyu harflerle yazılır.

Anahtar sözcük 'architecture' 'end' anahtar

sözcüğünden sonra gelebilir

• VHDL'93 standardırnı açıklayan sözdizimi

Çıkış(output) portu modları birbirine uymak

zorundadır

• Özel konulara yada sorunlara dikkat çekmek

için kullanılır

Genellikle sentezlenemez

• Sentezle ilgili kısıtlara dikkat çekmek için

kullanılır

Dizilerin yönü herzaman aynı yönde

tanımlanmalıdır.

• Dili etkili bir biçimde kullanmak için ipucu

verir

İsimlendirme kuralları, anahtar sözcükler küçük harfle yazılır, kullanıcı tanımlı tanıtıcılar ise büyük

harflerle yazılır. Eğer bir şeye dikkat çekmek isteniyorsa koyu harflerle yazılır.

Burada birçok kendini açıklayan ikon vardır. Bunlar VHDL'93 sözdizimi(syntax) (VHDL'87 ile

karşılaştırma) hakkında özel konuları gösterirler.

2.2 VHDL ‘in Yapısal Elemanları

• Varlık(Entity) : Arayüz(Interface)

• Mimari(Architecture) : Gerçekleştirim(Implementation), davranış(behaviour),

fonksiyon

• Konfigürasyon(Configuration) : Model zincirleme(model chaining), yapı(structure),

hiyerarşi(hierarchy)

• İşlem(Process) : Uyumluluk(Concurrency), olay denetimi(event controlled)

• Paket(Package) : Modüler tasarım, standart çözüm, veri tipleri, sabitler

• Kütüphane: Derleme(Compilation), obje(nesne) kodu

VHDL deki temel birimler varlıklar, mimariler, konfigürasyon ve paketlerdir.

Bir varlık genelde port listesini içeren bir arayüz tanımlarken,bir mimari ilgili modüllerin

fonksiyonlarını tanımlar. Genelde bir konfigürasyon sadece simülasyon süreci için kullanılır. Aslında

konfigürasyon, varlık/mimari çiftini tam bir model için seçen VHDL deki tek simüle edilebilir

objelerdir. Paketler sık kullanılan veri tipleri, sabitler ve altprogramlar için tanımlamaları tutar.

Bir diğer önemli yapı ise işlemlerdir. VHDL deki ifadeler doğal olarak kendi içinde uyumludur, bu

yapı atamaların sıralı olarak gerçekleştirilmesine izin verir . İşin kendi,bir obje olarak incelendiğinde

eşzamanlıdır(uyumludur). Gerçekte, işlem kodu her zaman yürütülemez. Bunun yerine, beklenen olay

gerçekleşene kadar işlem askıya alınır.

VHDL deki bir kütüphane bir dizi derlenmiş VHDL birimlerinin(obje kodunun) mantıksal adıdır. Bu

mantıksal isim kullanılan simülasyon veya sentez aracı tarafından bilgisayarın dosya sistemindeki bir

fiziksel yola eşleştirilmelidir(mapped).

2.2.1 VHDL Objelerinin Bildirimi-

Tanımlanması

(Declaration of VHDL Objects)

Entity

Architecture

Process/Subprogram

Package

Subprogram

x

x

x

x

Component

x

x

Configuration

x

Constant

x

x

x

x

Datatype

x

x

x

x

Port

x

Signal

x

x1(Process)

x

Variable

x2(Subprogram)

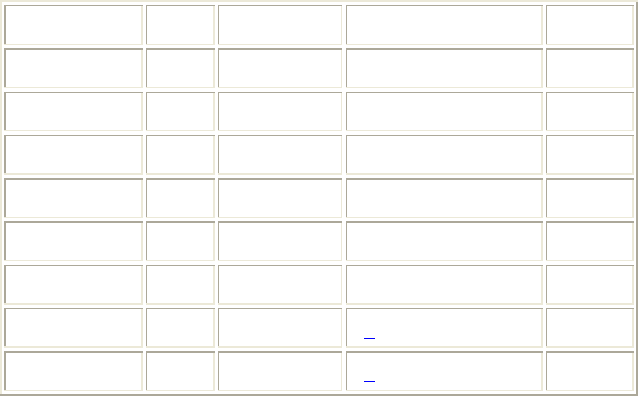

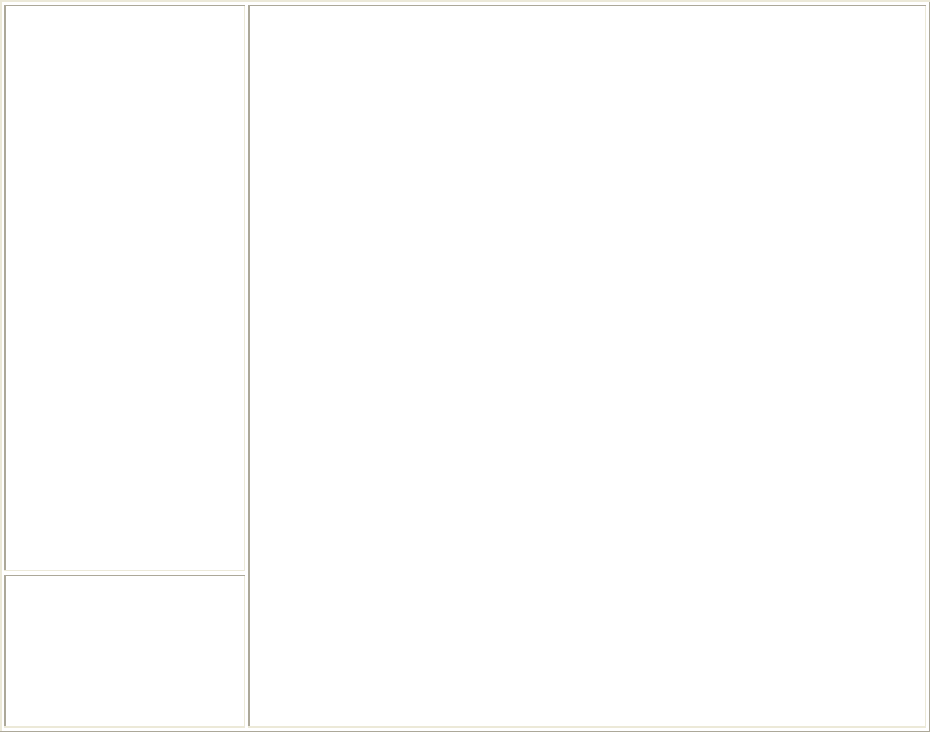

Yukarıdaki tablo farklı objelerin bildirimi için geçerli alanları göstermektedir:

Bir altprogram(subprogram) C deki bir fonksiyona benzer ve VHDL de tasarım yapılırken birçok kez

çağırılabilinir. Altprogram, bir varlık(entity), m i ma r i , işlemin bildirim kısmında veya başka bir

altprogram ve paketin içinde tanımlanabilir. Bir altprogram genelde bir pakette tanımlanır ve birçok

yerde(mimarilerde) kullanılabilinir.

Bileşenler(Components) bir üst seviyedeki hiyerarşi seviyesindeki mimariye varlık/mimari çiftine

eklemek için gereklidir. Bu bileşenler sadece bir mimaride veya bir pakette tanımlanabilirler. Bu

faydalıdır çünkü eğer bir varlık/mimari çifti birçok mimaride kullanılacaksa bir tek tanımlama

yapılması yeterlidir.

Konfigürasyonların(Configurations), kendileri eksiksiz bir VHDL tasarım birimidir. Fakat

konfigürasyon ifadelerini mimarinin bildirilebilir bölümünde tanımlamak mümkündür. Bu olanak çok

nadir kullanılır, fakat genel modelden bağımsız bir model yaratmak daha iyidir.

Sabitler ve veri tipleri tüm kullanılan objeler için tanımlanabilir.

Port bildirimleri sadece varlıkların içinde izin verilir. Bunlar arayüzde diğer modüllerde kullanılan

mimari sinyallerini listeler. Ek iç sinyaller mimarilerde,işlemlerde, altprogramlarda ve paketlerde

tanımlanabilirler. Lütfen dikkat edin, bu sinyaller fonksiyonlarda yani özel bir tip olan altprogramlarda

tanımlanamazlar.

Genellikle, değişkenler sadece işlemlerde ve altprogramlarda tanımlanabilirler. VHDL'93’de , global

değişkenler varlıkların, mimarilerin ve paketlerin içinde belirtilmiş şekilde tanımlanmıştır.

1. Sinyaller fonksiyonların içinde tanımlanamazlar.

2. Global değişkenler (VHDL '93) varlıkların, mimarilerin ve paketlerin içinde tanımlanabilirler.

2.2.2 Varlık(Entity)

entity HALFADDER is

port(

A, B: in bit;

SUM, CARRY: out bit);

end HALFADDER;

-- VHDL'93: end entity HALFADDER ;

• Arayüz tanımlama

• Davranışsal tanımlama yoktur

entity ADDER is

port(

A, B: in integer range 0 to 3;

SUM: out integer range 0 to 3;

CARRY: out bit );

end ADDER;

• Port sinyallerini birbirine bağlama

o Veri tipleri(integer,bit)

o Sinyal genişliği(range 0 to 3)

o Sinyal yönü(in,out)

‘entity’ anahtar sözcüğü ‘end ’anahtar sözcüğü ile sonlandırıldıktan sonra başka yerlerde de

kullanılabilinir.

Yukarıda, bir tam toplayıcı(full adder), iki yarım toplayıcıyı(half adder) ve bir VEYA(OR) kapısını

içerecek şekilde adım adım oluşturulmuştur. Kendimizi tamamen yapısal bir tasarımla kısıtlamaktayız,

örneğin kapı seviyesi tanımlama kullanıyoruz ve herhangi bir sentez aracına ihtiyaç duymuyoruz.

Temel fikir farklı VHDL objeleri arasındaki ilişkiyi hiçbirşey açıkta kalmayacak şekilde tanıtmak.

Bir modülle onun çevresi arasındaki arayüz varlık bildirimi ' entity ' anahtar sözcüğü ile tanımlanır.

Bunu kullanıcı tanımlı bir (tanıtıcı)tanımlayıcı isim takip eder, burada: HALFADDER kullanılmıştır .

Arayüz tanımlama ‘is’ anahtar sözcüğü aralarına yerleştirilir ve varlık ifadesinin sonlandırılması ‘end’

anahtar sözcüğü ve varlığın ismiyle sağlanır. VHDL’93 standardında ‘entity’ gerekirse ‘end’ den

sonra yeniden kullanılabilir.

Giriş ve çıkış sinyalleri ve onların tipleri port ifadelerinde ' port ' anahtar sözcüğü ile tanımlanır.

Portların listesi '(' ')' içerisinde bulunur.Listedeki her bir eleman için önce portun adı daha sonra da‘:’

kullanılır. Listenin içinde ';' sembolü elemanları bölmek için kullanılır, bir ifadeyi sonlandırmak için

değil. Bu nedenle listenin son elemanından sonra ';' ge l m e z !

Aynı moddaki birçok port ve veri tipi port adları ',' ile ayrılarak tek bir port ifadesiyle tanımlanabilir.

Port modu veri akışını tanımlar(in:input(giriş),sinyal modülün davranışını etkiler; out:output(çıkış),

sinyal değeri modül tarafından üretilir), veri tipleri ise sinyalin simülasyonda kullanılırken alacağı

değerlerin aralıklarını tanımlar.

2.2.3 Mimari(Architecture)

entity HALFADDER is

port(

A, B: in bit;

SUM, CARRY: out bit);

end HALFADDER;

architecture RTL of HALFADDER is

begin

SUM <= A xor B;

CARRY <= A and B;

end RTL;

-- VHDL'93: end architecture RTL ;

• Tasarımın gerçekleştirilmesi

• Herzaman belirli bir varlık ile bağlıdır

o Bir varlık birçok mimariye sahip olabilir

o Varlık portları mimarideki sinyaller olarak

kullanılabilinirler.

• Koşutzamanlı(aynı zamanda olan) ifadeler içerirler

'architecture' anahtar sözcüğü 'end' ile sonlandırıldıktan sonra tekrar edebilir.

Mimari bir davranışsal tanımlama(davranışsal seviye veya eğer sentezlenebiliyorsa RT seviyesi) veya

bir yapısal netlist veya bir karışım alternatiflerinden birini bir varlık için gerçekler(implement).

Bir mimari kesinlikle belirli bir varlığa bağlanmalıdır. Bir varlık, içerisinde birden fazla mimari

barındırabilir, örneğin aynı algoritmanın farklı gerçekleştirmeleri veya farklı soyutlama seviyesi. Aynı

varlığın farklı mimarileri farklı şekilde isimlendirilmelidir ki ayırt edilebilir olsun. İsim 'architecture'

anahtar sözcüğünden sonra gelmelidir. 'RTL' bu açıdan seçilmiştir.

Bunu takiben ' of ' anahtar sözcüğü kullanılır ve varlığın ismi arayüz('HALFADDER') olarak

kullanılır. Mimarinin başlığı ' is ' ile sonlandırılır, varlık ifadelerindeki gibi. Bu açıdan ' begin '

anahtar sözcüğü ifade sonlandırılmadan önce biryerlere koyulmalıdır. Buvarlık ifadelerindeki gibi

yapılır: ' end ' anahtar sözcüğü mimari isminden sonra kullanılır. Bir kez daha VHDL'93 ‘de '

architecture ' anahtar sözcüğü ‘end’ kullanıldıktan sınra gerektiğinde tekrarlanabilir.

VHDL kodu sentezlenebildiği zaman, RTL bir mimari ismi olarak seçilmiştir.Bu basit fonksiyon

olduğu takdirde,davranışsal(algoritmik) tanımlama ile arasında bir fark yoktur. Biz 'BEHAVE', 'RTL',

'GATE', 'STRUCT' ve 'TEST' ‘i sırayla soyutlama seviyesini ve gerçeklenmiş davranışını belirtmek

için kullanacağız. 'EXAMPLE' ismi, mimari özel bir varlıkla ilişkisi olmayan yeni VHDL elemanı

gösterdiği zaman kullanılacaktır.

2.2.4 Mimari Yapısı(Architecture Structure)

architecture EXAMPLE of STRUCTURE is

subtype DIGIT is integer range 0 to 9;

constant BASE: integer := 10;

signal DIGIT_A, DIGIT_B: DIGIT;

signal CARRY: DIGIT;

begin

DIGIT_A <= 3;

SUM <= DIGIT_A + DIGIT_B;

DIGIT_B <= 7;

CARRY <= 0 when SUM < BASE else

1;

end EXAMPLE ;

• Bildirimsel(Declarative) bölüm:

o Veri tipleri(data types)

o Sabitler(constants)

o Ek sinyaller(additional signals)

("actual" signals)

o Bileşenler(components)

o ...

• Tanımlama(Definition) bölümü ('begin' den sonraki):

o Sinyal atamaları(signal assignments)

o İşlemler(processes)

o Bileşen örnekleme(component

instantiations)

o Koşutzamanlı ifadeler(concurrent

statements): sıranın önemli olmadığı

Herbir mimari opsiyonel olan bir bildirimsel bölüme ve tanımlama bölümüne ayrılır.

Bildirimsel bölüm ' is ' ve ' begin ' anahtar sözcükleri arasında bulunmaktadır. Mimarideki

sabitler,veritipleri,sinyaller, altprogramlar,vb. yeni objeler burada bildirilir.

Tanımlama kısmı ' begin ' anahtar sözcüğü ile başlar ve koşutzamanlı(concurrent) ifadeleri

bulundurur. Bunlar basit sinyal atamaları, işlem durumları, grup olarak birleştirilmiş sıralı ifadeler, ve

bileşen örneklemleridir. Koşutzamanlılık(aynı anda kullanım-concurrency) demek VHDL kodundaki

görünme sırası önemli değil demektir. Örneğin SUM sinyali, DIGIT_A ve DIGIT_B nin

atamalarından bağımsız olarak herzaman (3+7) sonucunu almaktadır.

Sinyal atamaları ' <= ' operatörü ile sağlanır. Bu sembol veri akış yönünü gösterir, sol taraftaki değeri

değişecek olan sinyal, sağ taraftaki ise yeni sinyal değerini gösterir.Sağ taraftaki ve sol taraftaki veri

tipleri birbirinin aynı olmalıdır. Şunu unutmayın ki örnekte kullanılan sinyaller tamamen varlığın port

bildiriminde tanımlanmıştır.

2.2.5 Varlık Port Modları

• in: (giriş)

o sinyal değerleri yalnızca okunabilir

• out: (çıkış)

o sinyal değerleri sadece yazılabilir

o çoklu sürücüler

• buffer: (arabellek)

o çıkış için karşılaştırılabilinir

o sinyal değerleri okunabilir

o sadece 1 sürücü

• inout: (girişçıkış)

o çiftyönlü(bidirectional) port

Çıkış portlarının modları birbiriyle eşleşmek zorundadır

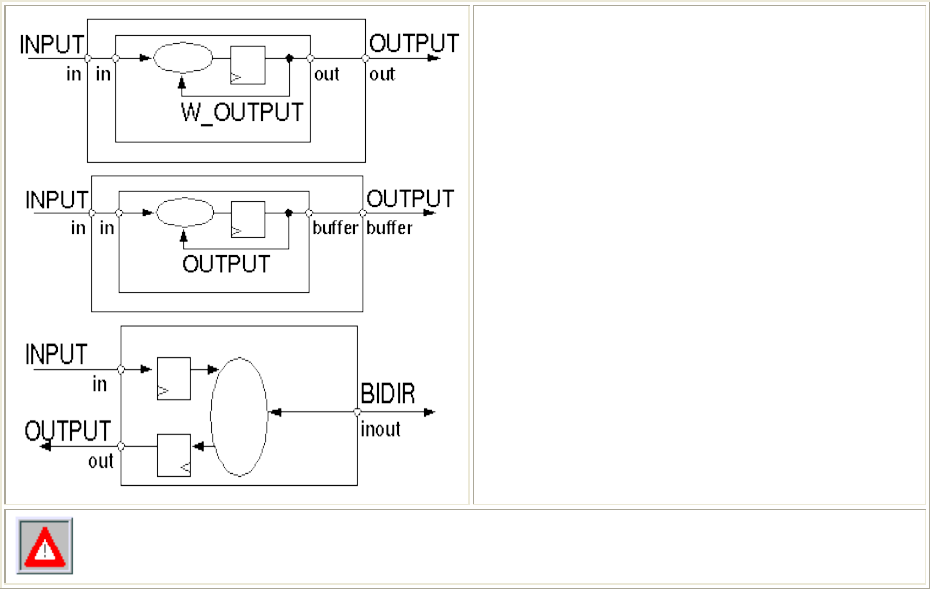

Bir varlığın portunun modu verinin akış yönünü sınırlar. Port modu ' in ' kullanılan mimairideki bu

sinyallerin sadece okunabilir olduğunu belirtir. Bunların değerlerini değiştirmek mümkün değildir.

Benzer şekilde ‘out’ port modunda sinyallerin değerleri mimari tarafından üretilir. Portun değerleri

herhangi bir şekilde davranışı etkileyecek biçimde kullanılmaz. Eğer o anki çıkış değeri bir sonraki

sinyalin değerini hesaplamak için kullanılacaksa, örneğin bir sayıcı modülü, bir geçiş sinyali

tanımlanmalıdır. İç sinyallerin onlarla ilgili bir veri akış yönü yoktur.

Buna alternatif olarak, port modu olarak ' buffer ' kullanılabilinir. Bu ek bir sinyalin tnaımlanma

gerekliliğini ortadan kaldırır. Ancak, bu sinyaller için sadece bir kaynak kullanılabilir.

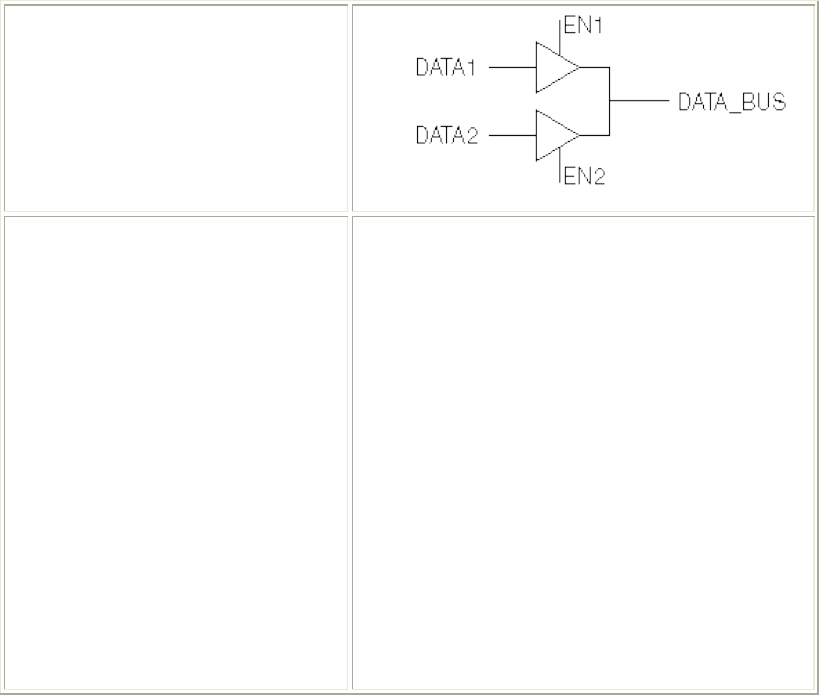

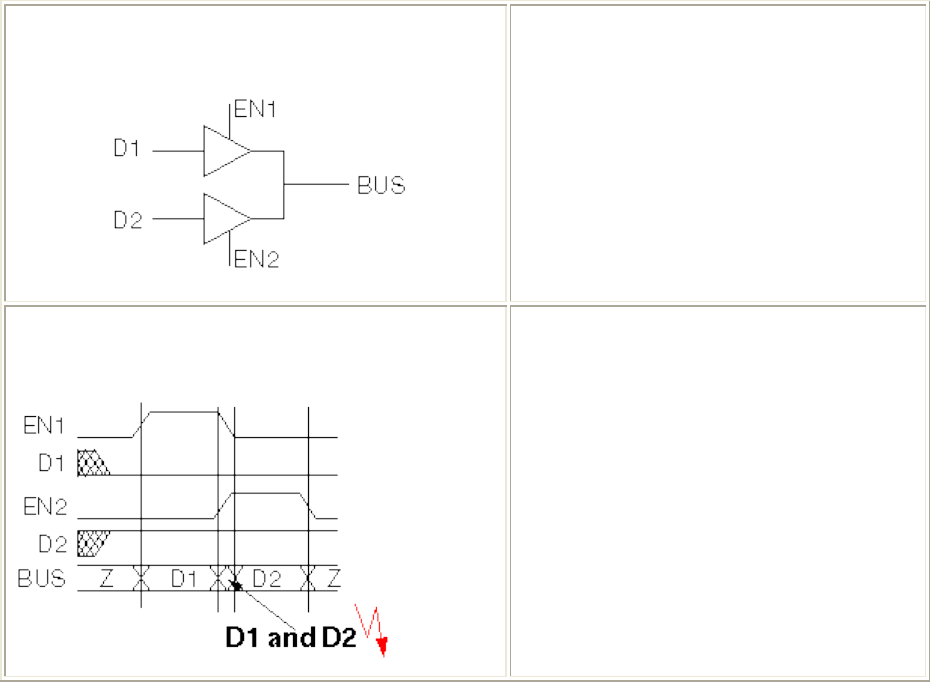

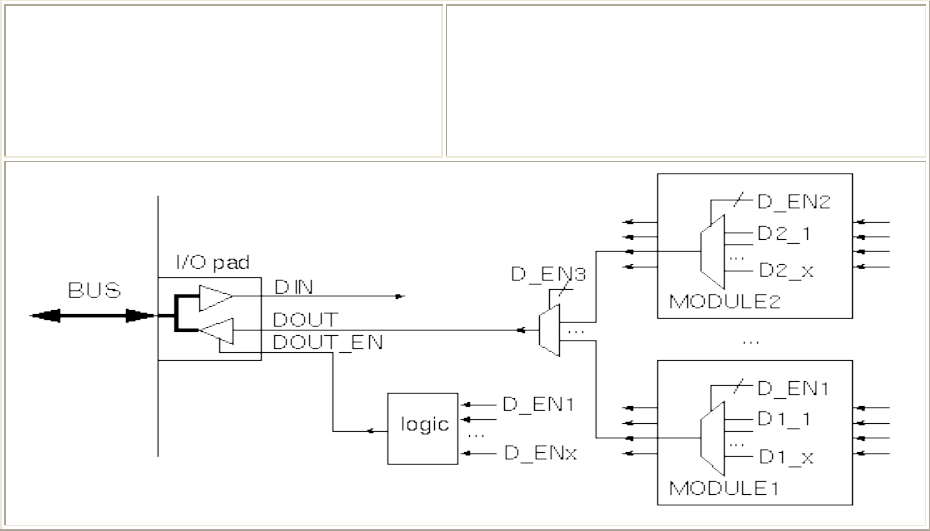

Model yolu için ,çoklu birimler aynı veri hattına ulaşacaksa,’out’ port modu kullanılmalıdır, eğer

herbir birim sadece bu veri yoluna yazacaksa, port modu ' inout ' çok yönlü veri akışına izin verir.

Lütfen unutmayın ki port modları birbiriyle uyuşmalıdır, bir altmodülün çıkış portu doğrudan bir üst

seviyedeki varlığın çıkış portuna bağlanmış olmalıdır. En kötü olasılıkta, ara sinyaller derleme

hatalarını önlemek için tanımlanmalıdır.

2.2.6 Hiyerarşik Model Yerleşimi

VHDL hiyerarşik model yerleşimine izin vermektedir, bu da bir modül birden fazla altmodülün

biraraya getirilmesinden oluşmaktadır anlamına gelmektedir. Alt modüllerin birbiriyle bağlantıları

mimari içindeki üst modül tarafından tanımlanmaktadır. Şekilde görüldüğü gibi ,bir tamtoplayıcı iki

yarım toplayıcı(module1,module2) ve bir VEYA(OR) kapısının(module3) yardımıyla

oluşturulmaktadır.

Yalnızca bir yapısal mimari hiçbir fonksiyonaliteyi tanımlamaz, ve sadece bileşenlerin listesini verir,

onların örneklemleri ve içbağlantılarının tanımlarını verir.

2.2.7 Bileşen Bildirimi

entity FULLADDER is

port (A,B, CARRY_IN: in bit;

SUM, CARRY: out bit);

end FULLADDER;

architecture STRUCT of FULLADDER is

signal W_SUM, W_CARRY1, W_CARRY2 : bit;

component HALFADDER

port (A, B : in bit;

SUM, CARRY : out bit);

end component;

component ORGATE

port (A, B : in bit;

RES : out bit);

end component;

begin

. . .

• Mimarinin bildirimsel bölümündedir

• `socket`-tipi için karşılaşılaştırılabilir

Bileşen port listesi bağlantı sinyallerinin bildirimi ile değiştirilemez

Tam toplayıcı varlığı blok diyagramdan doğrudan türetilebilir. Girişler A,B ve CARRY_IN gereklidir,

bununla birlikte SUM ve CARRY sinyalleri ise çıkışları oluşturmaktadır.

Tamtoplayıcı birçok altmodül içermektedir, önce bunlar tamıtılmalıdır. Bir bileşen bildiriminde tüm

modül tipleri kullanılacaktır,kullanılmıştır. Bu bildirim mimari ifadesinin ‘begin’ anahtar sözcüğünden

önce olmak zorundadır. Şuna dikkat edin ki burada sadece modüllerin arayüzleri verilmektedir,

onların nasıl kullanıldığı henüz belirtilmemiştir. Bu açıdan bileşen tanımlanması soket

tanımlanmasıyla karşılaştırılabilinir, eğer uygun varlık daha önce eklendiyse bir yada birden fazla kez

kullanılabilinir. Bileşenlerin port listesi elemanları lokal elemanlar olarak adladırılırlar, bu onların

sinyal olmadığı anlamına gelmektedir.

Bu durumda şunu söyleyebiliriz ki, sadece iki farklı sokete, HALFADDER(yarımtoplayıcı) ve

ORGATE(VEYAKAPISI) ihtiyacımız vardır. Bileşenlerin isimlerini istediğimiz gibi seçebiliriz ama

size önerim varlığın adını kullanmanız olacaktır. Buna ek olarak, port tanımlanması birbiriyle aynı

olmalı. Tasarım birleştirildiğinde , yazılım VHDL konfigürasyonlarını reddedecek ve varsayılan

kuralları uygulayacaktır bu açıdan kesinlikle gereklidir.

2.2.8 Bileşen Örnekleme

architecture STRUCT of FULLADDER is

component HALFADDER

port (A, B : in b it;

SUM, CARRY : out bit);

end component;

component ORGATE

port (A, B : in bit;

RES : out bit);

end component;

signal W_SUM, W_CARRY1, W_CARRY2: bit;

begin

MODULE1: HALFADDER

port m a p ( A, B, W_SUM, W_CARRY1 );

MODULE2: HALFADDER

port m a p ( W_SUM, CARRY_IN,

SUM, W_CARRY2 );

MODULE3: ORGATE

port m a p (

W_CARRY2, W_CARRY1, CARRY );

end STRUCT;

• Soketleri üret

• Kaç tane ihtiyacı m v a r ?

• Mimarinin tanımlama bölümünün örneklemi

('begin' den sonra)

• PCB’de soketleri yerleştir

• Kablo sinyalleri:

o Varsayılan:konumsal ilişki

Eğer bir bileşen tanımlandıysa ,bu artık soket tipi sabittir ve gerekli olan yerlerde kullanılabilir

demektir. Gerçek soket üretildiğinde bu bileşen örneklemi ile yapılır. PCB(printed circuit board) deki

soketlerin yerleşimi için karşılaştırılabilir. Varlık/mimari çifti VHDL tasarımı gerçekleştirilirken

bileşenler sokete yerleştirildiğinde fonksiyonaliteyi sağlar.

Herbir bileşen örneğine tasarımcı tarafından bileşenin kendi ismiyle birlikte benzersiz bir isim(etiket )

daha verilir. Bileşen örnekleme mimarinin tanımlama bölümünde gerçekleşir(‘begin’ den sonra).

Bileşenlerin seçimi belirtimsel bölümde veya paketteke daha önce tanımlanmış bileşenlerle sınırlıdır.

Bileşenlerin portları veya soket pinleri devreye bağlanması için bir port harita ifadesi gereklidir.

Kullanılacak mimari sinyallerinin isimlerini listelemelidir. Varsayılan olarak, konumsal ilişki kuralları

uygulanır, örneğin port haritasının ilk sinyali bileşen tanımlamadaki ilk porta bağlanır .

2.2.9 Bileşen Örnekleme: İsimlendirilmiş

Sinyal İlişkileri

entity FULLADDER is

port (A,B, CARRY_IN: in bit;

SUM, CARRY: out bit);

end FULLADDER;

architecture STRUCT of FULLADDER is

component HALFADDER

port (A, B : in bit;

SUM, CARRY : out bit);

end component;

. . .

signal W_SUM, W_CARRY1, W_CARRY2 : bit;

begin

MODULE1: HALFADDER

port m a p ( A => A,

SUM => W_SUM,

B => B,

CARRY => W_CARRY1

);

. . .

end STRUCT;

• İsimsel ilişki:

o Sol taraf: "resmi" (bileşen tanımlamadan

gelen port isimleri)

o Sağ taraf: "şuanki"

(mimari sinyalleri)

• Bileşen tanımlama sıralamadan bağımsızdır.

Bir önceki örnekte konumsal ilişki yerine, mimari sinyallerini doğrudan seçilen portlara bağlamak

mümkündür. Bu isimlendirilmiş sinyal ilişkileri ile yapılmaktadır sinyallerin sırası önemli değildir.

Bileşen tanımlamadan gelen port ismine “resmiler”(“formals”) ' => ' ile varlığın sinyalleriyle

”şuankiler” ("actuals") ilişkilendirilirler.

Örnekte görüldüğü üzere , SUM’ın çıkış portu bileşen tamımlamasında üçüncü sırada yer almaktadır.

Fakat port haritası ifadesinde, port W_SUM sinyaliyle bağlantısı ikinci sırada yapılmıştır. Unutmayın

ki port tanımlamasındaki liste elemanları ‘,’ sembolü ile birbirinden ayrılır.

2.2.10 Konfigürasyon(Configuration)

entity HALFADDER is

port(A, B: in bit;

SUM, CARRY: out bit);

end HALFADDER;

. . .

component HALFADDER

port(A, B: in bit;

SUM, CARRY: out bit);

end HALFADDER;

signal W_SUM, W_CARRY1, W_CARRY2: bit;

· · ·

MODULE1 : HALFADDER

port map(A, B, W_SUM, W_CARRY1);

Varlıklar daha önce belirtilmiş bir bileşen belirtimi olmadan doğrudan

örneklenebilir.

Varlıkların tanımlanması ve örneklenmesi gerçekte kullanılan VHDL modellerinden bağımsızdır.

VHDL konfigürasyon işinde bileşenlerin ,tam bir tasarım yapmak için, varlık/mimari çiftine bağlantı

oluşturulur. Özet olarak,bir bileşen tanımlanması kesin bir soket tipinin bileşen örneklenmesi ile

belirlenmesi demektir. Bir aygıtın örneklenmiş sokete gerçekten eklenmesi konfigürasyon ile

yapılmaktadır.

VHDL'93 de varlıklar daha önce belirtilmiş bir bileşen belirtimi olmadan doğrudan

örneklenebilir.

2.2.11 Konfigürasyon: İşlemleri ve

Uygulaması

entity FULLADDER is

. . .

end FULLADDER;

architecture STRUCT of FULLADDER is

. . .

end STRUCT;

configuration CFG_FULLADDER of

FULLADDER is

for STRUCT -- select architecture STRUCT

-- use default configuration rules

end for;

end configuration CFG_FULLADDER ;

• En üst seviyedeki, varlık için mimariyi seç

• Örneklenmiş bileşenler için varlık/mimari

çiftini seç

• Hiyerarşiyi oluştur

• Simüle edilebilir objeler yarat

• Varsayılan bağlama kuralları:

o Bileşenle aynı isimdeki varlığı seç

o Sinyaller isimleriyle ilişkilendirilir

o Son derlenmiş mimari kullanılır

'configuration' (konfigürasyon) anahtar sözcüğü 'end' kullanıldıktan sonra tekrarlanabilir.

Varlıkla mimari arasındaki ilişki konfigürasyonda kullanılan simülasyonla desteklenir, son tasarım

hiyerarşisini oluşturur. Bu en üst seviye varlık mimarisinin seçimini içerir. Konfigürasyon VHDL deki

sentezlenebilen ve simüle edilebilen tek objedir. Konfigürasyon sürecinin simülasyon amaçlı elle

kontrolü mümkün olduğunda, sentez araçları herzaman varsayılan kural kümesini uygular.

Bunu başarılı bir şekilde gerçekleştirmek için bileşen isimleri ile varolan varlık isimleri birbiriyle

uyuşmalıdır. Buna ek olarak, port isimleri, modlar ve veri tipleri birbiriyle uyumlu olmalıdır-bileşen

tanımlamadaki portların sırası önemli değildir.

Örnek, yapısal mimari için varsayılan konfigürasyonu göstermektedir. Bazı simülatörler bu tip en üst

seviye varlıklar için kesin konfigürasyon tanımlamalarına ihtiyaç duymaktadır. Bir konfigürasyon özel

bir varlığı tercih eder,burada FULLADDER(tamtoplayıcı). Mimari STRUCT(yapı) ilk 'for' ifadesiyle

seçilmiştir. Bundan başka herhangi bir konfigürasyon komutu verilemediği için, diğer bileşenler için

varsayılan kurallar uygulanacaktır.

2.2.12 Konfigürasyon: Örnek (1)

entity FULLADDER is

port(A, B, CARRY_IN: in bit;

SUM, CARRY: out bit);

end FULLADDER;

architecture STRUCT of FULLADDER is

component HALFADDER

port(A, B: in bit;

SUM, CARRY: out bit);

. . .

signal W_SUM, W_CARRY1, W_CARRY2: bit;

begin

MODULE1: HALFADDER

port map (A, B, W_SUM, W_CARRY1);

MODULE2: HALFADDER

port map(W_SUM, CARRY_IN, SUM, W_CARRY2);

. . .

end STRUCT;

entity A is

port(A, B: in bit;

SUM, CARRY: out bit);

end A;

architecture RTL of A is

· · ·

entity B is

port(U,V: in bit;

X,Y: out bit);

end B;

architecture GATE of B is

· · ·

Şekilden ve koddan anlaşıldığı üzere bir tamtoplayıcının kodu görülmektedir. Şekille kodu

eşleştirmeye çalışın.

Elemanların portları mimarinin sinyalleriyle, pozisyonları yardımıyla bağlantı kurulmuştur, ör. ilk

sinyal ilk portla bağlantılıdır.

HALFADDER(yarımtoplayıcı) varlığı kullanılamaz ancak bunun iki varlığı A ve B ‘nin RTL ve

GATE diye farklı mimarileri vardır ve bunlar kullanılabilinir.Her iki varlık da eleman tanımlamasıyla

uyuşmaktadır.

2.2.13 Konfigürasyon: Örnek(2)

configuration CFG_FULLADDER of

FULLADDER is

for STRUCT

for MODULE2: HALFADDER

use entity work.B(GATE);

port map ( U => A,

V => B,

X => SUM,

Y => CARRY );

end for;

for others : HALFADDER

use entity work.A(RTL);

end for;

end for;

end CFG_FULLADDER;

• Varlık/mimari çifti aşağıdakiler kullanılarak seçilir:

o Örnek isimleri

o 'all':kullanılan eleman için tüm örneklemler

o 'others': tam olarak bahsedilmemiş tüm

örneklemler

• Eğer port isimleri farklıysa

=> port harita ifadesi

• Varolan bir altmodülün konfigürasyonuna referans

gösterebilme

Tekrardan FULLADDER varlığı için STRUCT mimarisi seçilmiştir.Bu for döngüsü içerisinde,

varlıklar ve mimariler alt bileşenler için seçilmiştir.

Bunun için for ifadesi yeniden kullanılmıştır. ' for ' anahtar sözcüğünden sonra kullanılan ilk isim

bileşen örnekleminin adıdır,bunu takiben ‘: ’ kullanılır ve bileşenin adı kullanılır.’all’ anahtar sözcüğü

eğer bir bileşenin tüm örnekleri adreslenmişse kullanılabilir. For döngüsü içinde use ifadesi belirtilen

objeye kadar olan yoldan varlığı seçer. Açıkça değiştirilmediği sürece, tüm VHDL objeleri kütüphane

işi üzerinde derlenir.Seçilen varlık için mimari, '(' ')' çifti içine alınır.

B varlığının port isimleri bileşen tanımlamasına uymadığı için port haritası ifadesine gerek vardır.

Haritayı sırayla yapmak mümkündür ancak okunabilirlik açısından resmi parametrelerle kullanılan

isimler eşleştirilmelidir.

Ayrıca henüz konfigüre edilmemiş diğer bileşenler ‘others’ anahtar sözcüğüyle tanımlanabilir.

MODULE2 için RTL mimarisi kullanılmıştır bunun için port haritasına gerek yoktur çünkü others

kullanılmıştır.

Diğer tüm bileşenler varsayılan konfigürasyon kurallarıyla ele alınırlar.

Büyük tasarımlarım hiyerarşi tanımlamasını kolaylaştırmak için, altmodüllerin konfiügrasyonlarını

tanımlamak ve en üst seviyedeki bu konfigürasyonlara referans vermek gerekir.

2.2.14 İşlem(Process)

entity AND_OR_XOR is

port (A,B : in bit;

Z_OR, Z_AND, Z_XOR : out bit);

end AND_OR_XOR;

architecture RTL of AND_OR_XOR is

begin

A_O_X: process (A, B)

begin

Z_OR <= A or B;

Z_AND <= A and B;

Z_XOR <= A xor B;

end process A_O_X ;

end RTL;

• Sıralı olarak yürütülen ifadeler içerir

• Sadece bir mimarinin içinde bulunur

• Birçok iş aynı zamanda yürütülebilir

• Yürütüm (Execution) şunlarla kontrol edilir:

o Hassaslık listesi(sensitivity list)

(tetikleyici sinyallerini içerir), veya

o Bekleme ifadeleri

• İşlem etiketi isteğe bağlıdır

Bir mimari içindeki ifadeler aynı anda oluşan başka VHDL yapılarını yönetmek için sıralı davranışı

gerçekleştirmek için gereklidir. Bir işlem, mimarideki diğer ifadeler gibi davranmaktadır ve geleneksel

programlama dillerindeki gibi biri diğerinden sonra gelen ifadeler içerirler. Aslında işlem ifadelerini

VHDL ifadelerindeki koşutzamanlı tek ifade olarak kullanmak mümkündür.

Bir işlemin gerçekleştirilmesi olayların tetiklenmesiyle ilgilidir. Olası olay kaynakları hassasiyet

listesinde veya kesin bekleme ifadelerinde listelenmiştir ve gerçekleştirmenin akışını kontrol etmek

için kullanılır. Bu iki seçenek birbiriyle karşılıklı ilişkilidir birinden biri olabilir yalnızca,hassaslık

listesinde bekleme ifadesi olamaz. Hassasiyet listesi sentez araçları tarafında yok sayılır, bir VHDL

simülatörü listelenmiş sinyallerden biri değiştiğinde işlem kodunu çağırır. Tüm sinyaller

kombinasyonel süreç içerisinde okunmuştur, bu davranışı etkiler,hassasiyet listesinde bahsedilmiş

olmalıdır ki sentezlenmiş donanım simülasyonla aynı sonucu üretsin. Elbette aynısı zamanlı işlemler

içinde geçerlidir, yeni girilmiş değerler herbir aktif saat darbesinde hesaplanırlar. Bu nedenle

hassasiyet listesi saat sinyallerini ve asenkron kontrol sinyallerini de içerir(reset-sıfırlama).

Bir işlem ifadesi isteğe bağlı bir etiketle başlar ve ‘:’ sembolünden sonra ' process ' anahtar sözcüğü

takip eder. Hassasiyet listesi isteğe bağlıdır ve '(' ')' çifti arasında tanımlanır. Mimari ifadesine benzer

olarak , tanıtılan bölüm başlık kodu ile ‘begin’ anahtar sözcüğü arasında bulunmaktadır. Sıralı ifadeler

' begin ' ve ' end process ' arasında bulunmaktadır. Anahtar sözcük ' process ' tekrarlanmalıdır. Eğer

bir etiket bir işlem için seçildiyse son ifadede tekrarlanmalıdır.

2.2.15 VHDL İletişim Modeli

• İşlemler koşutzamanlı(aynı zamanda olan-

concurrent) ifadelerdir

• Birçok işlem

o Paralel çalışır

o Hassasiyet listesindeki sinyallerle

birbirine bağlıdır

o İfadeler sıralı olarak gerçekleştirilirler

• Diğer bir varlık/mimari çiftinin işlemine

bağlantı varlık arayüzü ile sağlanır

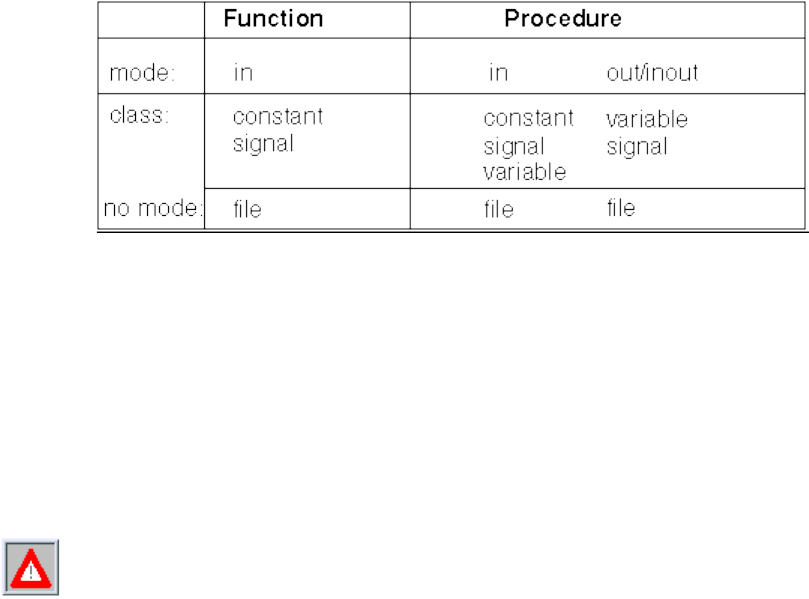

2.2.16 Signals