FAN6749 — Highly Integrated Ultra Green Mode PWM Controller Fairchild

User Manual: Marking of electronic components, SMD Codes 67, 67**, 6721, 6741, 6741A, 6742HL, 6742HR, 6742ML, 6742MR, 6747, 6749ML. Datasheets BAS40-07V, FAN6747, FAN6749MLM, IRF6721SPbF, NUP4302MR6, SG6741A, SG6741SY, SG6742HL, SG6742HR, SG6742ML, SG6742MR, STP3467.

Open the PDF directly: View PDF ![]() .

.

Page Count: 16

October 2012

© 2012 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN6749 • Rev. 1.0.3

FAN6749 — Highly Integrated Ultra Green-Mode PWM Controller

FAN6749

Highly Integrated Ultra Green-Mode PWM Controller

Features

High-Voltage Startup

Low Operating Current: 1.8 mA

Linearly Decreasing PWM Frequency to 24 kHz

Proprietary Frequency Hopping to Reduce EMI

Two-Level Over-Current Protection (OCP),

1400 ms Delay for Normal Peak Load

Two-Level OCP, 56 ms Delay for Super Peak Load

Output Short-Circuit Protection (SCP)

Peak-Current Mode Operation with Cycle-by-Cycle

Current Limiting

HV Pin Brown-in/out Protection with Hysteresis

Constant Power Limit by HV Sampling

Internal FB Open-Loop Protection (OLP)

GATE Output Maximum Voltage Clamp: 14.5V

VDD Over-Voltage Protection (OVP)

Programmable Over-Temperature Protection (OTP)

Integrated 6ms Soft-Start Function

Internal Latch Circuit (OVP, OTP, OCP, OLP, SCP)

Internal OTP Sensor with Hysteresis

Applications

General-Purpose Switched-Mode Power Supplies and

Flyback Power Converters, including:

Power Adapters

Open-Frame SMPS; Specifically for SMPS with

Surge-Current Output, such as for Printer, Scanner,

Motor Drivers

Description

The FAN6749 highly integrated PWM controller

enhances the performance of flyback converters. To

minimize standby power consumption, a proprietary

Green-Mode function continuously decreases the

switching frequency under light-load conditions. Under

zero-load conditions, the power supply enters Burst

Mode and completely shuts off PWM output. Green

Mode helps power supplies meet international power

conservation requirements.

The FAN6749 is designed for SMPS with surge-current

output and incorporates a two-level Over-Current

Protection (OCP) function. Besides the cycle-by-cycle

current limiting, two-level OCP can handle peak loading

within a specified delay time.

FAN6749 also integrates a frequency-hopping function

that helps reduce EMI emission of a power supply with

minimum line filters. Built-in synchronized slope

compensation helps achieve stable peak-current control.

To keep constant output power limit over universal AC

input range, the current limit and OCP threshold voltage

are adjusted according to AC line voltage detected by

the HV pin. Gate output is clamped at 14.5 V to protect

the external MOSFET from over-voltage damage.

Other protection functions include: AC input brownout

protection with hysteresis, Short-Circuit Protection

(SCP) for output-short condition, and VDD Over-Voltage

Protection (OVP). For over-temperature protection, an

external NTC thermistor can be applied to sense the

ambient temperature. When OLP, OCP, SCP, VDD OVP,

or OTP is activated, an internal latch circuit latches off

the controller. The latch resets when VDD is removed.

OVP OCP OLP OTP SCP

Latch Latch Latch Latch Latch

There are three differences from FAN6748 to FAN6749:

Over-current protection debounce time is extended

to 1400 ms.

Brown-out debounce time is extended to 100 ms.

No SENSE short-circuit protection function.

Ordering Information

Part Number Operating Temperature Range Package Packing

Method

FAN6749MLM -40 to +105°C 8-Pin Small Outline Package (SOP) Reel & Tape

© 2012 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN6749 • Rev. 1.0.3 2

FAN6749 — Highly Integrated Ultra Green-Mode PWM Controller

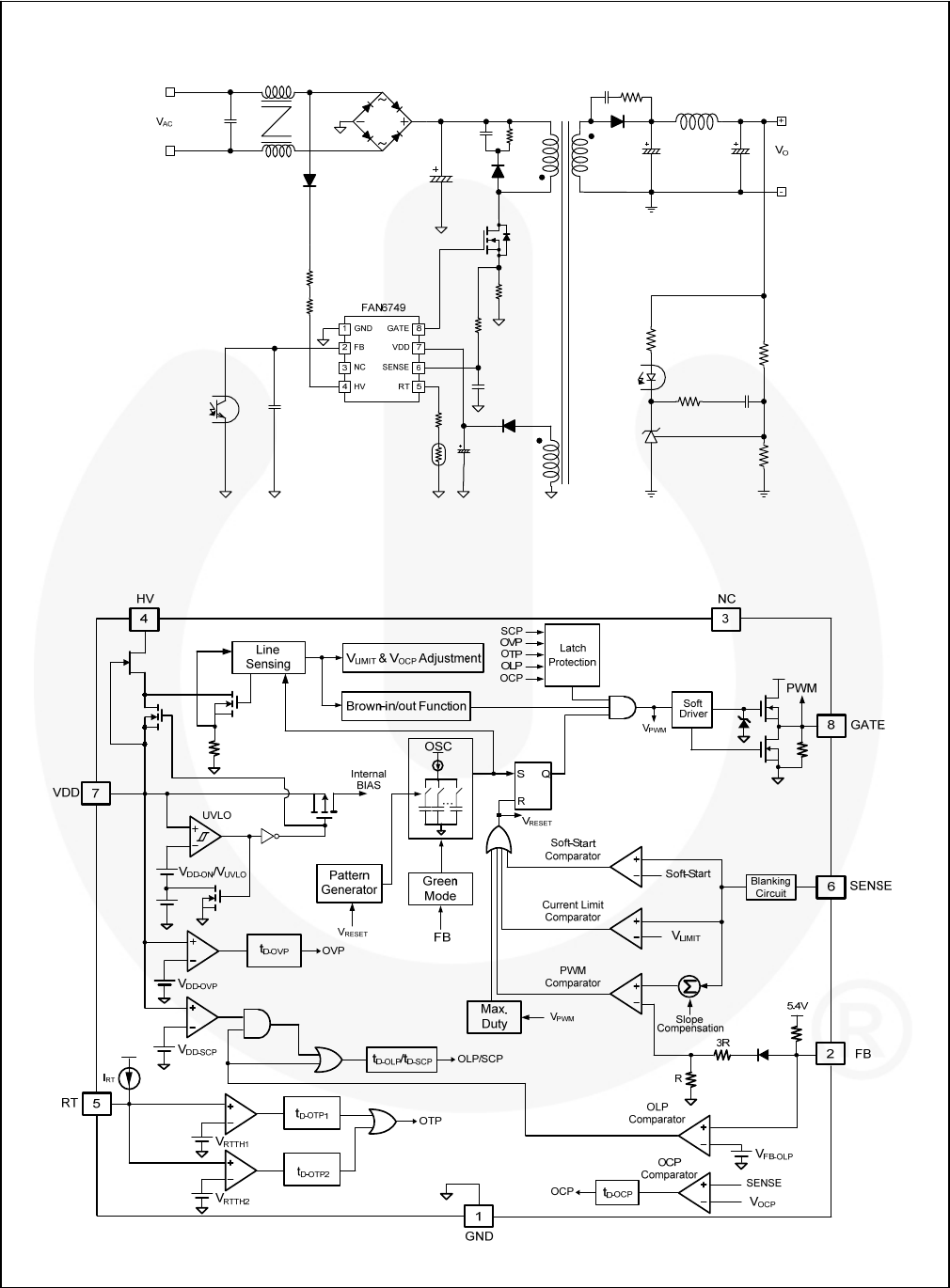

Application Diagram

Figure 1. Typical Application

Internal Block Diagram

Figure 2. Functional Block Diagram

© 2012 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN6749 • Rev. 1.0.3 3

FAN6749 — Highly Integrated Ultra Green-Mode PWM Controller

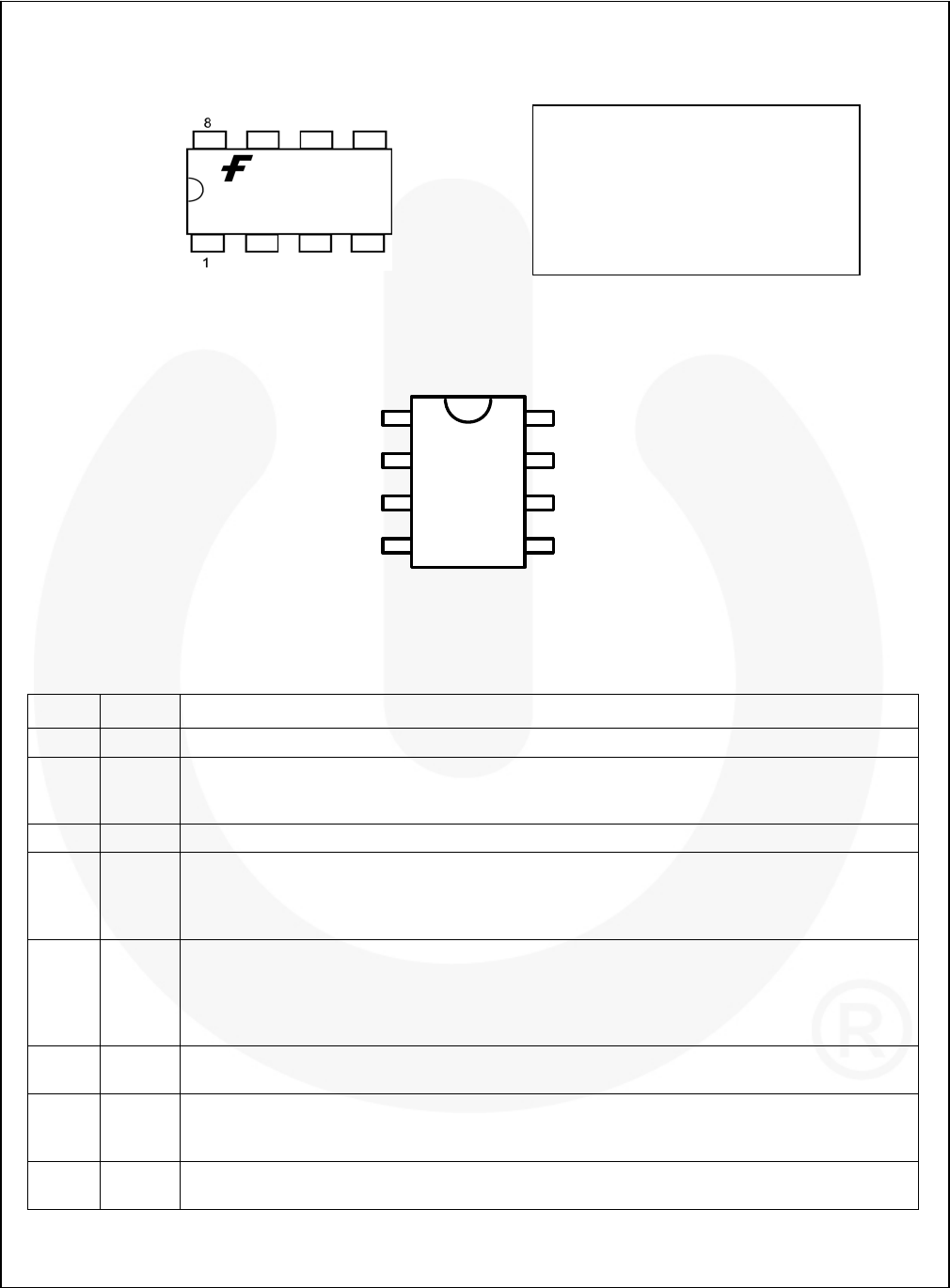

F - Fairchild Logo

Z - Plant Code

X - 1-Digit Year Code

Y - 1-Digit Week Code

TT - 2-Digit Die Run Code

T - Package Type (M=SOP)

M - Manufacture Flow Code

Marking Information

Figure 3. Top Mark

Pin Configuration

GND

SENSE

VDD

RT

GATE

HV

NC

FB

18

7

6

54

2

3

Figure 4. Pin Configuration (Top View)

Pin Definitions

Pin # Name Description

1 GND

Ground Pin. A 0.1 µF decoupling capacitor between VDD and GND is recommended.

2 FB

Feedback Pin. The output voltage feedback information from the external compensation circuit is

fed into this pin. The PWM duty cycle is determined by comparing the FB signal with current-

sense signal from the SENSE pin.

3 NC No Connection

4 HV

High-Voltage Startup. The HV pin is typically connected to the AC line input through an external

diode and a resistor (RHV). This pin is used not only to charge VDD capacitor during startup, but

also to sense the line voltage. The line voltage information is used for brown-out protection and

power limit line compensation.

5 RT

Over-Temperature Protection. An external NTC thermistor is connected from this pin to the

GND pin. Once the voltage of the RT pin drops below the threshold voltage, the controller latches

off the PWM. The RT pin also provides external latch protection. If the RT pin is not connected to

an NTC resistor for over-temperature protection, place a 100 k resistor to ground to prevent

noise interference.

6 SENSE

Current Sense. The sensed voltage is used for peak-current-mode control, over-current

protection, short-circuit protection, and cycle-by-cycle current limiting.

7 VDD

Power Supply of IC. A holdup capacitor typically connects from this pin to ground. A rectifier

diode in series with the transformer auxiliary winding connects to this pin to supply bias during

normal operation.

8 GATE

Gate Drive Output. The totem-pole output driver for the power MOSFET; internally limited to

VGATE-CLAMP.

ZXYTT

6749ML

TM

© 2012 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN6749 • Rev. 1.0.3 4

FAN6749 — Highly Integrated Ultra Green-Mode PWM Controller

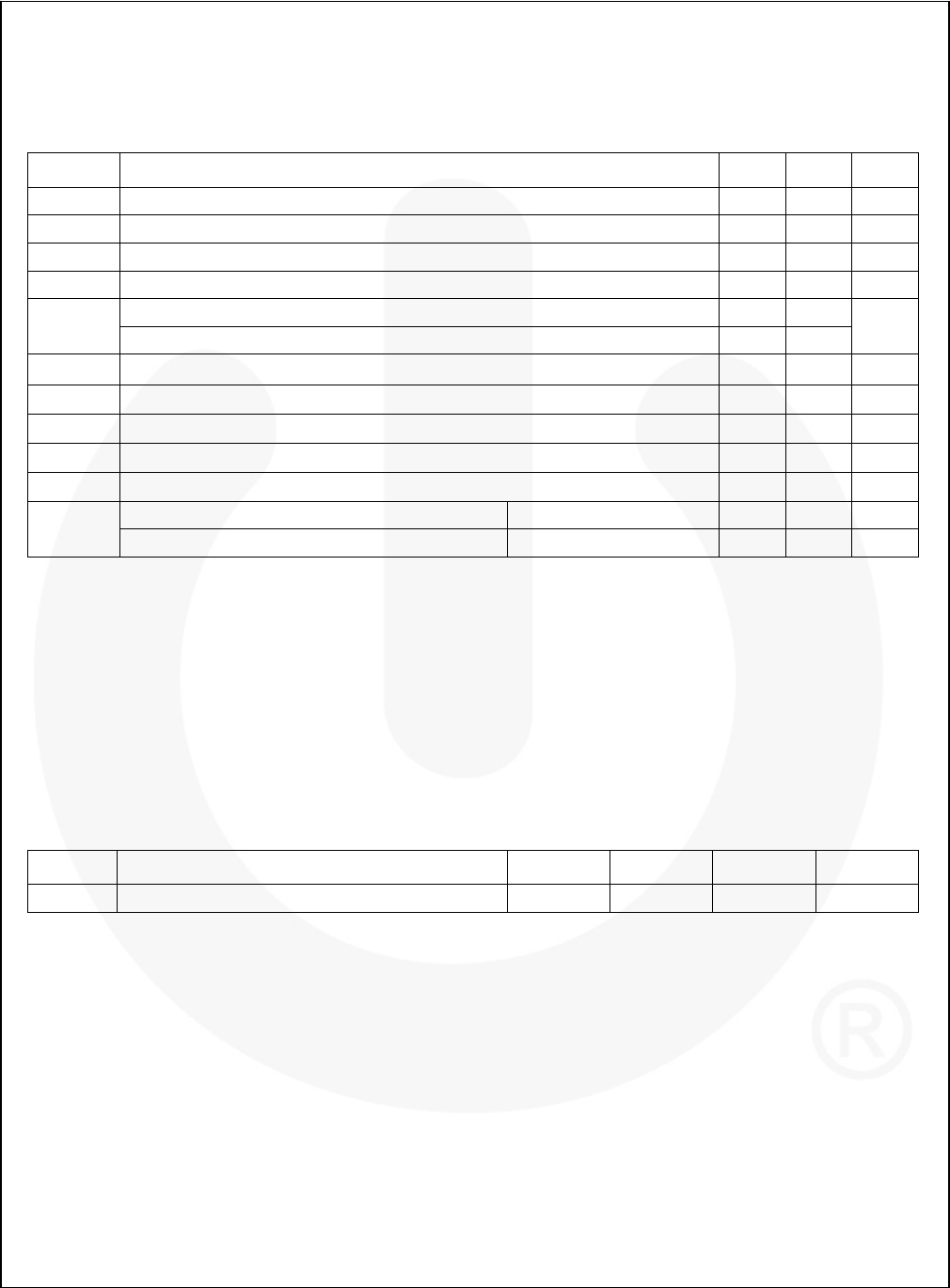

Absolute Maximum Ratings

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be

operable above the recommended operating conditions and stressing the parts to these levels is not recommended.

In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability.

The absolute maximum ratings are stress ratings only.

Symbol Parameter Min. Max. Unit

VDD DC Supply Voltage(1,2) 30 V

VFB FB Pin Input Voltage -0.3 7.0 V

VSENSE SENSE Pin Input Voltage -0.3 7.0 V

VRT RT Pin Input Voltage -0.3 7.0 V

VHV Continuous Input Voltage 500 V

Pulse Input Voltage(3) 640

PD Power Dissipation (TA<50°C) 400 mW

JA Thermal Resistance (Junction-to-Air) 150 C/W

TJ Operating Junction Temperature -40 +125

C

TSTG Storage Temperature Range -55 +150 C

TL Lead Temperature (Wave Soldering or IR, 10 Seconds) +260 C

ESD Human Body Model(4), JEDEC:JESD22-A114 All Pins Except HV Pin 6 kV

Charged Device Model(4), JEDEC:JESD22-C101 All Pins Except HV Pin 2 kV

Notes:

1. All voltage values, except differential voltages, are given with respect to the network ground terminal.

2. Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device.

3. Duration of pulse input voltage is less than or equal to 1 second.

4. ESD with the HV pin CDM=1000 V and HBM=500 V.

Recommended Operating Conditions

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended

operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not

recommend exceeding them or designing to Absolute Maximum Ratings.

Symbol Parameter Min. Typ. Max. Unit

RHV HV Startup Resistor 150 200 250 k

© 2012 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN6749 • Rev. 1.0.3 5

FAN6749 — Highly Integrated Ultra Green-Mode PWM Controller

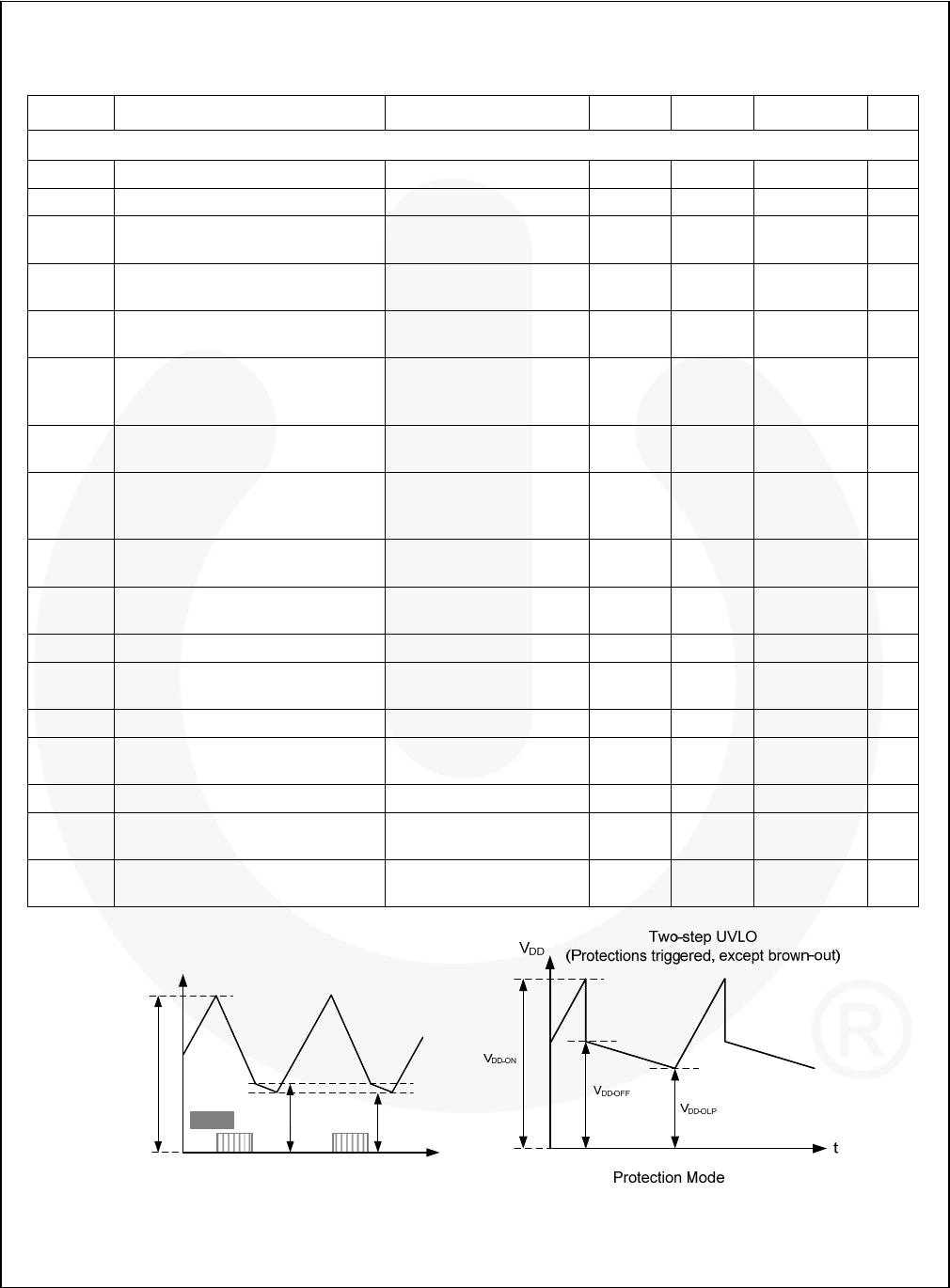

Electrical Characteristics

VDD=15 V and TA=25C unless otherwise noted.

Symbol Parameter Conditions Min. Typ. Max. Unit

VDD Section

VOP Continuously Operating Voltage Limited by VDD OVP 25 V

VDD-ON Threshold Voltage to Startup VDD Rising 16 17 18 V

VDD-OFF Threshold Voltage to Stop

Switching in Protection Mode VDD Falling 10 11 12 V

VDD-OLP Threshold Voltage to Turn On HV

Startup in Protection Mode VDD Falling 6.5 7.5 8.5 V

VUVLO Threshold Voltage to Stop

Switching in Normal Mode VDD Falling 6.0 6.5 7.0 V

VRESTART

Threshold Voltage to Enable HV

Startup to Charge VDD in Normal

Mode

VDD Falling 4.5 5.0 5.5 V

VDD-LH Threshold Voltage to Release

Latch Mode VDD Falling 3.5 4.0 4.5 V

VDD-AC

Threshold Voltage on VDD Pin for

Disable Brown-in to Avoid Startup

Failure

VUVLO

+2.5 VUVLO +3 VUVLO +3.5 V

VDD-SCP Threshold Voltage on VDD Pin for

Short-Circuit Protection (SCP) VFB > VFB-OLP VDD-OFF

+1.0

VDD-OFF

+1.5

VDD-OFF +2.0 V

tD-SCP Debounce Time for SCP VFB>VFB-OLP

& VDD< VDD-SCP 12 17 22 ms

IDD-ST Startup Current VDD-ON – 0.16 V 30 µA

IDD-OP1 Supply Current in PWM Operation VDD=20 V, VFB = 3 V

Gate Open 1.8 2.4 mA

IDD-OP2 Supply Current when PWM Stops VDD=15 V, VFB < 1.4 V 1.0 1.9 mA

ILH Operating Current when VDD<VDD-

OFF in Protection Mode VDD = 5 V 100 120 140 µA

IDD-OLP Internal Sink Current VDD-OLP+0.1 V 265 325 385 µA

VDD-OVP Threshold Voltage for VDD Over-

Voltage Protection 28.5 29.0 29.9 V

tD-VDDOVP VDD Over-Voltage Protection

Debounce Time 160 200 240 µs

VDD-ON

VDD

VUVLO

t

Normal Mode

GATE VRESTART

Figure 5. VDD Behavior

Continued on the following page…

© 2012 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN6749 • Rev. 1.0.3 6

FAN6749 — Highly Integrated Ultra Green-Mode PWM Controller

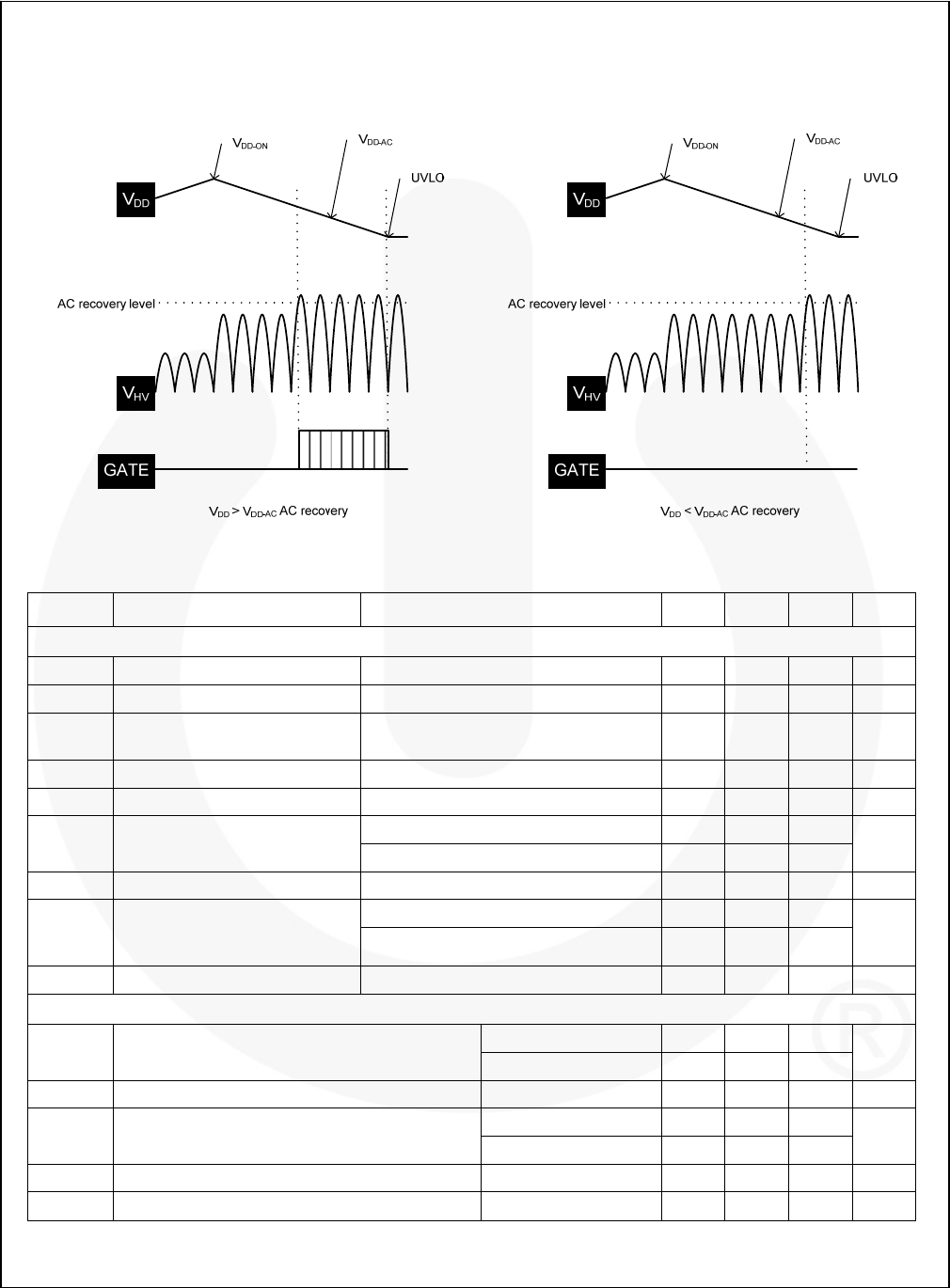

Electrical Characteristics (Continued)

VDD=15 V and TA=25C unless otherwise noted.

Figure 6. VDD-AC & AC Recovery

Symbol Parameter Conditions Min. Typ. Max. Unit

HV Section

IHV Supply Current from HV Pin VDC=120 V, VDD=0 V 2.0 3.5 5.0 mA

IHV-LC Leakage Current after Startup HV=500 V, VDD=VDD-OFF+1 V 1 20 µA

VAC-OFF Threshold Voltage for

Brownout DC Source Series R=200 k to HV Pin 90 100 110 V

VAC-ON Threshold Voltage for Brown-In DC Source Series R=200 k to HV Pin 100 110 120 V

△VAC V

AC-ON - VAC-OFF DC Source Series R=200 k to HV Pin 8 10 17 V

tS-CYCLE Line Voltage Sample Cycle(7) VFB > VFB-N 170 200 230 µs

VFB < VFB-G 400 520 640

tH-TIME Line Voltage Hold Period(7) 18 23 28 µs

tUPDATE

Peak Line Voltage Data

Update Cycle for High / Low

Line Compensation(7)

VFB > VFB-N 20 24 28

ms

VFB = VFB-G 64 72 80

tD-AC-OFF Debounce Time for Brownout 70 100 130

ms

Oscillator Section

fOSC Switching Frequency when VFB>VFB-N Center Frequency 62 65 68

kHz

Hopping Range ±3.5 ±4.0 ±4.5

tHOP Hopping Period 16 20 24 ms

fOSC-G Switching Frequency When VFB<VFB-G Center Frequency 20 24 28 kHz

Hopping Range ±1.25 ±1.55 ±1.85

fDV Frequency Variation vs. VDD Deviation VDD=11 V to 22 V 5 %

fDT Frequency Variation vs. Temperature Deviation TA=-40 to 105C 5 %

Continued on the following page…

© 2012 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN6749 • Rev. 1.0.3 7

FAN6749 — Highly Integrated Ultra Green-Mode PWM Controller

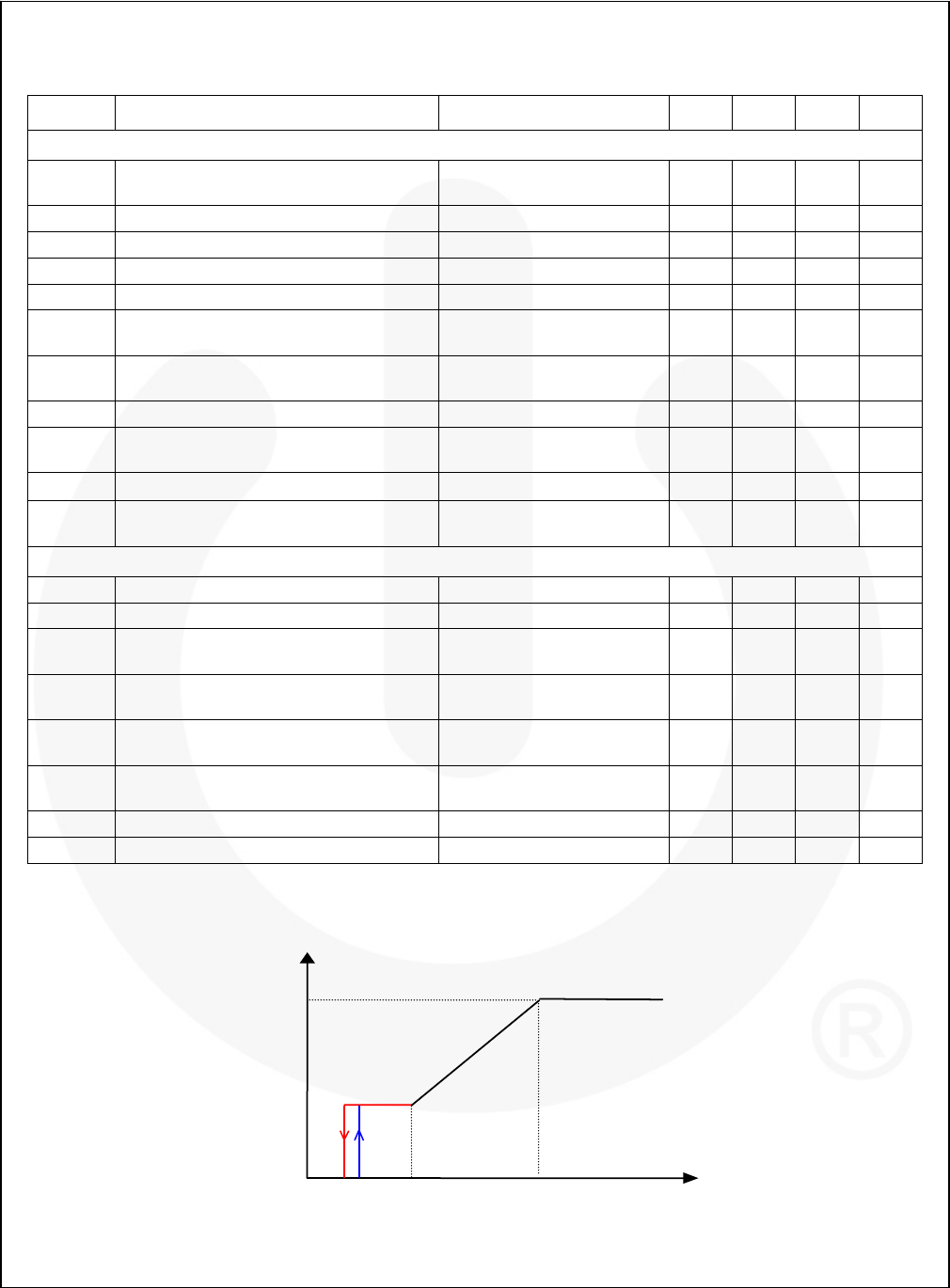

Electrical Characteristics (Continued)

VDD=15 V and TA=25C unless otherwise noted.

Symbol Parameter Conditions Min. Typ. Max. Unit

Feedback Input Section

AV Input Voltage to Current-Sense

Attenuation 1/4.5 1/4.0 1/3.5 V/V

ZFB FB Internal Pull-High Impedance 15 17 19 k

VFB-OPEN FB internal Biased Voltage FB Pin Open 5.2 5.4 5.6 V

VFB-OLP Threshold Voltage for OLP 4.3 4.6 4.9 V

tD-OLP Debounce Time for OLP 40 56 72 ms

VFB-N Threshold Voltage for Maximum

Switching Frequency Pin, FB Voltage(VFB=VFB-N) 2.5 2.7 2.9 V

VFB-G Threshold Voltage for Minimum Switching

Frequency Pin, FB Voltage(VFB=VFB-G) 2.05 2.25 2.45 V

SG Slope for Green-Mode Modulation 85 Hz/mV

VFB-ZDCR Threshold Voltage for Zero Duty Cycle

Recovery 1.9 2.1 2.3 V

VFB-ZDC Threshold Voltage for Zero Duty Cycle 1.8 2.0 2.2 V

VFB-ZDCR -

VFB-ZDC Zero Duty Cycle Hysteresis 0.05 0.10 0.15 V

Current-Sense Section

tPD Delay to Output 65 200 ns

tLEB Leading-Edge Blanking 230 270 310 ns

VLIMIT-L Current Limit Level at Low Line

(VAC-RMS=86 V)

VDC=122 V,

Series R=200 k to HV 0.790 0.825 0.860 V

VLIMIT-H Current Limit Level at High Line

(VAC-RMS=259 V)

VDC=366 V,

Series R=200 k to HV 0.690 0.725 0.760 V

VOCP-L OCP Trigger Level at Low Line

(VAC-RMS=86 V)

VDC=122 V,

eries R=200 k to HV 0.45 0.48 0.51 V

VOCP-H OCP Trigger Level at High Line

(VAC-RMS=259 V)

VDC=366 V,

Series R=200 k to HV 0.39 0.42 0.45 V

tSS Soft-start time Startup Time 4.5 6.0 7.5 ms

tD-OCP Debounce Time for OCP VSENSE>VOCP 1000 1400 1800 ms

Continued on the following page…

Figure 7. VFB vs. PWM Frequency

PWM Frequency

fOSC

fOSC-G

VFB-N

VFB-G

VFB-ZDC VFB

VFB-ZDCR

© 2012 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN6749 • Rev. 1.0.3 8

FAN6749 — Highly Integrated Ultra Green-Mode PWM Controller

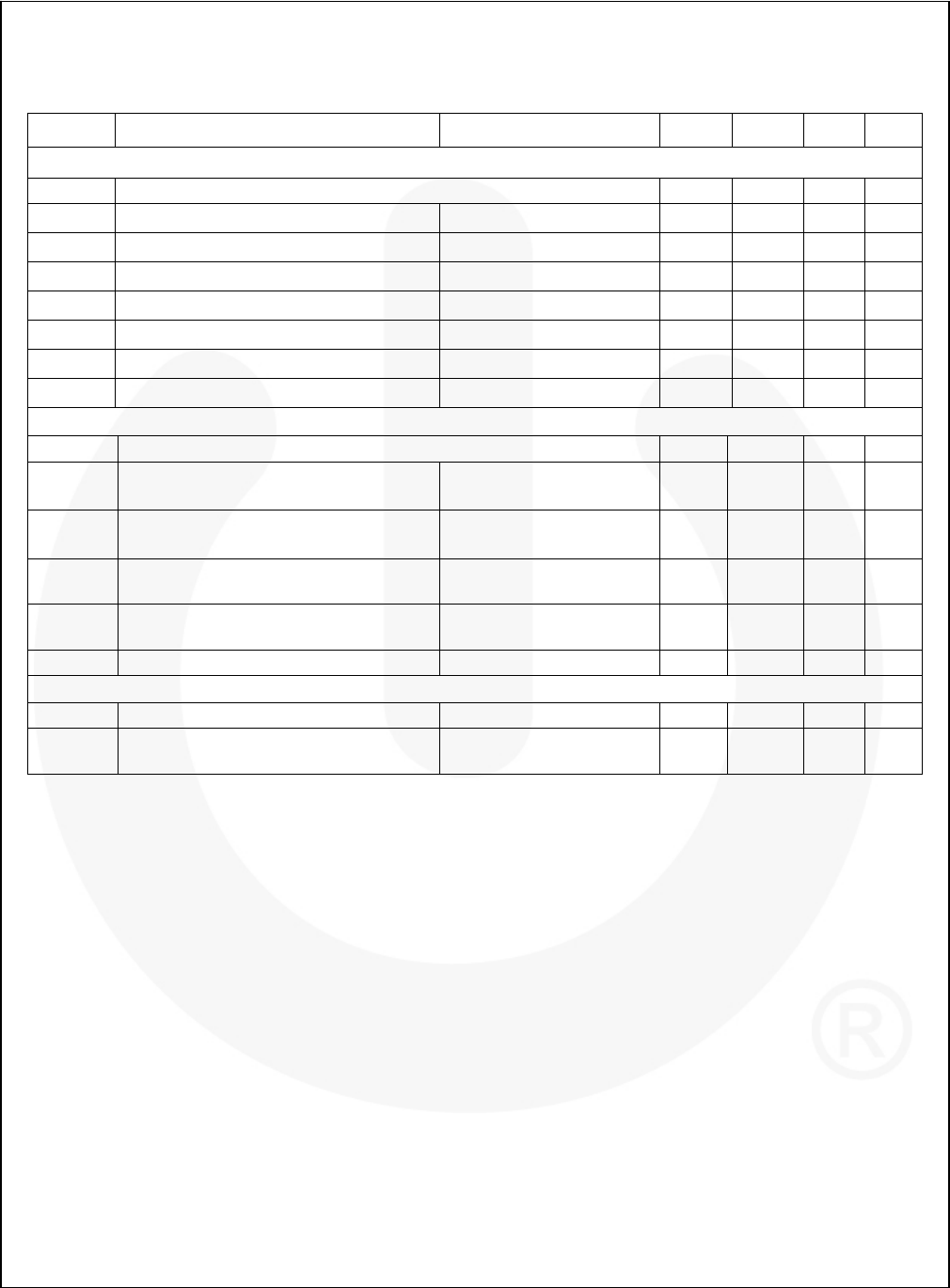

Electrical Characteristics (Continued)

VDD=15 V and TA=25C unless otherwise noted.

Symbol Parameter Conditions Min. Typ. Max. Unit

GATE Section

DMAX Maximum Duty Cycle 80 85 90 %

VGATE-L Gate Low Voltage VDD=15 V, IO=50 mA 1.5 V

VGATE-H Gate High Voltage VDD=12 V, IO=50 mA 8 V

tr Gate Rising Time (20-80%) VDD=15 V, CL=1 nF 60 75 90

ns

tf Gate Falling Time (80-20%) VDD=15 V, CL=1 nF 15 25 35

ns

IGATE-SINK Gate Sink Current(7) V

DD=15 V 300

mA

IGATE-SOURCE Gate Sourcing Current(7) V

DD=15 V, GATE=6 V 250

mA

VGATE-CLAMP Gate Output Clamping Voltage VDD=22 V 11.0 14.5 18.0

V

RT Section

IRT Output Current of RT Pin 90 100 110 µA

VRTTH1 Threshold Voltage for Over-Temperature

Protection

0.7 V < VRT < 1.05 V,

After 14 ms Latch Off 1.015 1.050 1.085 V

VRTTH2 Threshold Voltage for Latch Triggering VRT < 0.7 V, After 165 µs

Latch Off 0.65 0.70 0.75 V

ROTP Maximum External Resistance of RT Pin

to Trigger Latch Protection 9.66 10.50 11.34 k

tD-OTP1 Debounce Time for Over-Temperature

Protection Triggering VRTTH2 < VRT < VRTTH1 11 14 18 ms

tD-OTP2 Debounce Time for Latch Triggering VRT < VRTTH2 90 165 240 µs

Over-Temperature Protection Section (OTP)

TOTP Protection Junction Temperature(5,7) +135 °C

TRestart Restart Junction Temperature(6,7) TOTP-

25 °C

Notes:

5. When activated, the output is disabled and the latch is turned off.

6. The threshold temperature for enabling the output again and resetting the latch after OTP has been activated.

7. Guaranteed by design.

© 2012 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN6749 • Rev. 1.0.3 9

FAN6749 — Highly Integrated Ultra Green-Mode PWM Controller

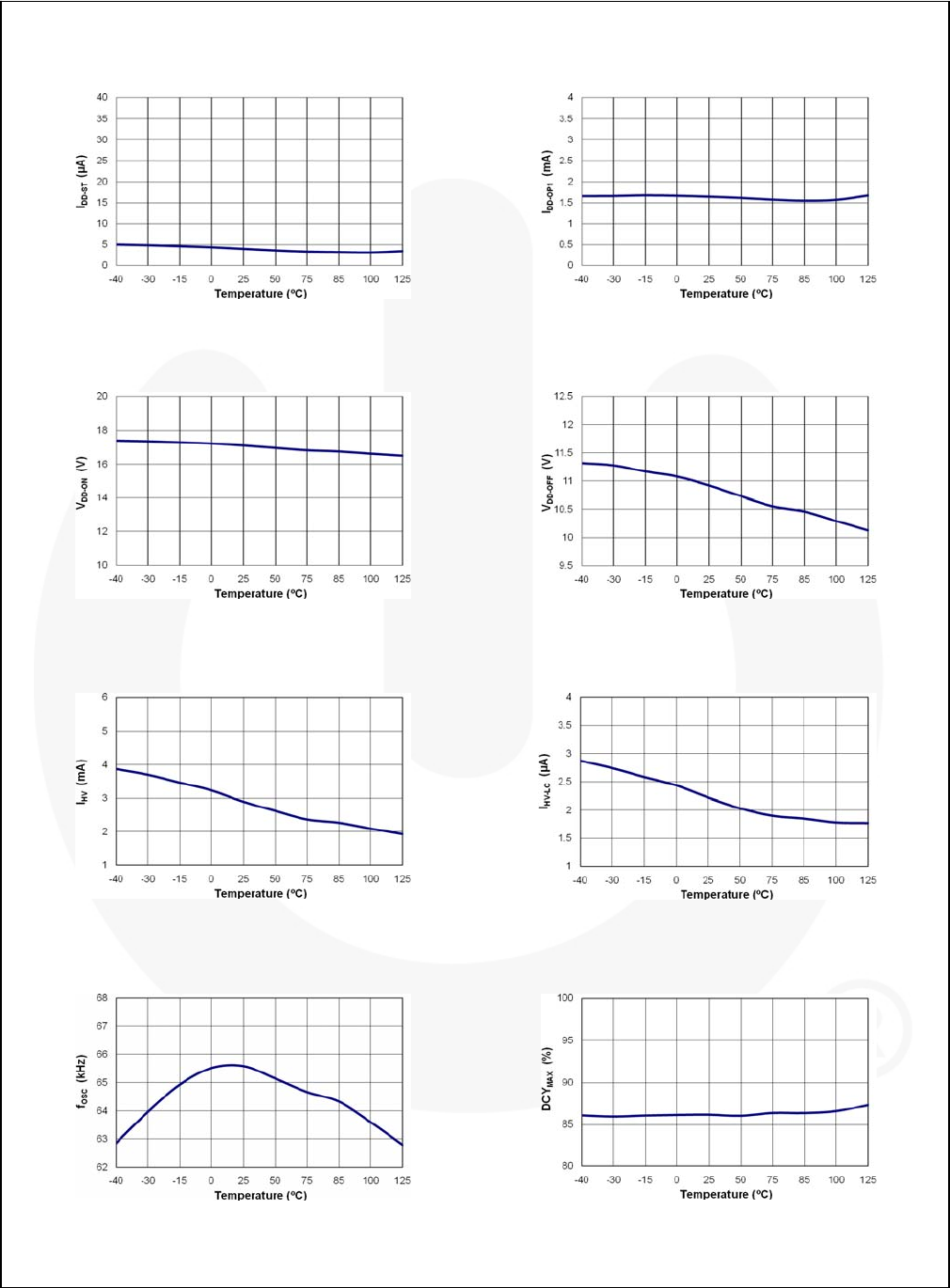

Typical Performance Characteristics

Figure 8. Startup Current (IDD-ST) vs. Temperature Figure 9. Operation Supply Current (IDD-OP1)

vs. Temperature

Figure 10. Start Threshold Voltage (VDD-ON)

vs. Temperature Figure 11. Minimum Operating Voltage (VDD-OFF)

vs. Temperature

Figure 12. Supply Current Drawn from HV Pin (IHV)

vs. Temperature Figure 13. HV Pin Leakage Current After Startup (IHV-LC)

vs. Temperature

Figure 14. Frequency in Normal Mode (fOSC) vs.

Temperature Figure 15. Maximum Duty Cycle (DCYMAX) vs.

Temperature

© 2012 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN6749 • Rev. 1.0.3 10

FAN6749 — Highly Integrated Ultra Green-Mode PWM Controller

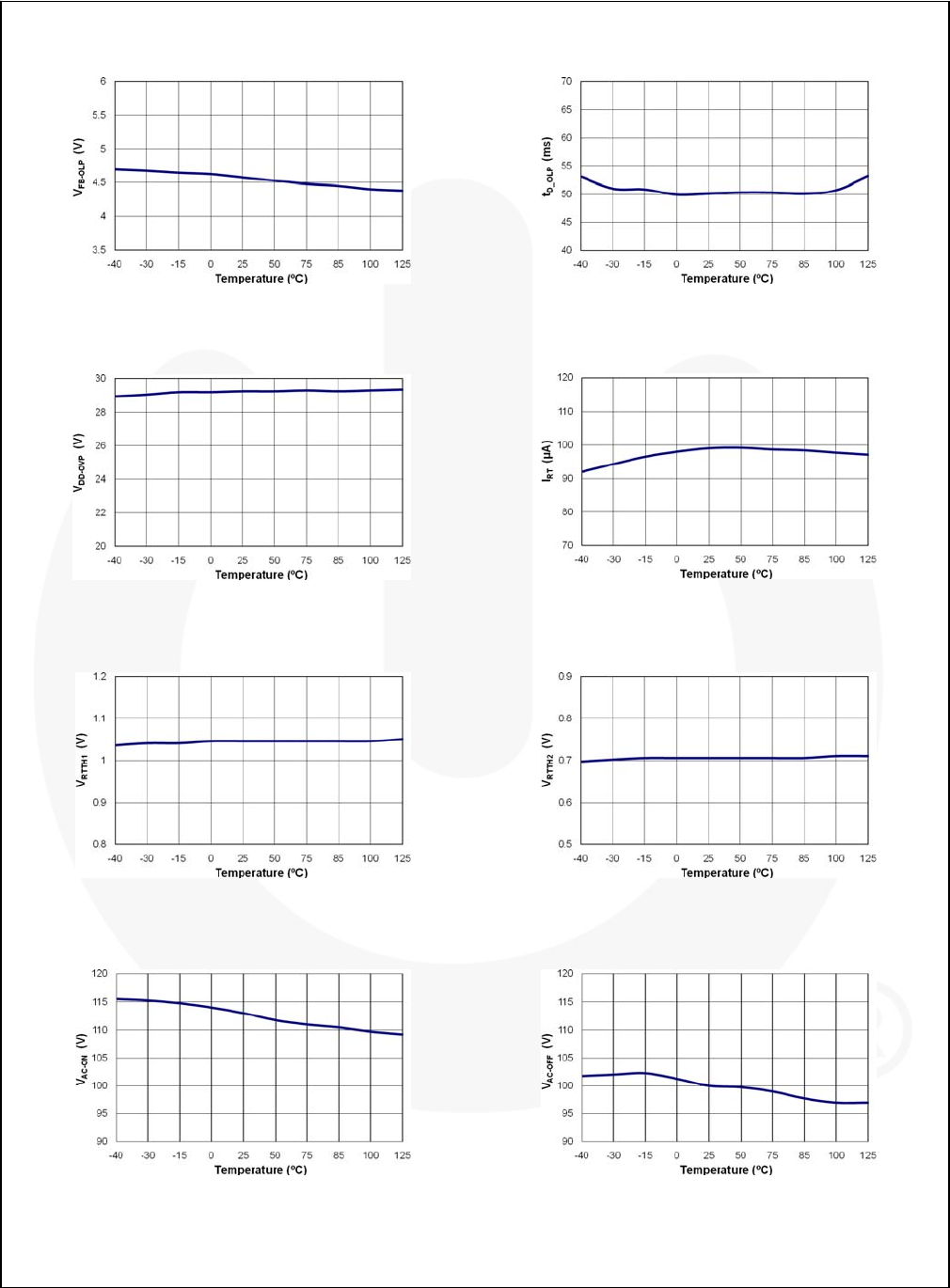

Typical Performance Characteristics

Figure 16. FB Open-Loop Trigger Level (VFB-OLP) vs.

Temperature Figure 17. Delay of FB Pin Open-Loop Protection (tD-OLP)

vs. Temperature

Figure 18. VDD Over-Voltage Protection (VDD-OVP)

vs. Temperature Figure 19. Output Current from RT Pin (IRT)

vs. Temperature

Figure 20. Over-Temperature Protection Threshold

Voltage (VRTTH1) vs. Temperature Figure 21. Over-Temperature Protection Threshold

Voltage (VRTTH2) vs. Temperature

Figure 22. Brown-in (VAC-ON) vs. Temperature Figure 23. Brown-out (VAC-OFF) vs. Temperature

© 2012 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN6749 • Rev. 1.0.3 11

FAN6749 — Highly Integrated Ultra Green-Mode PWM Controller

Functional Description

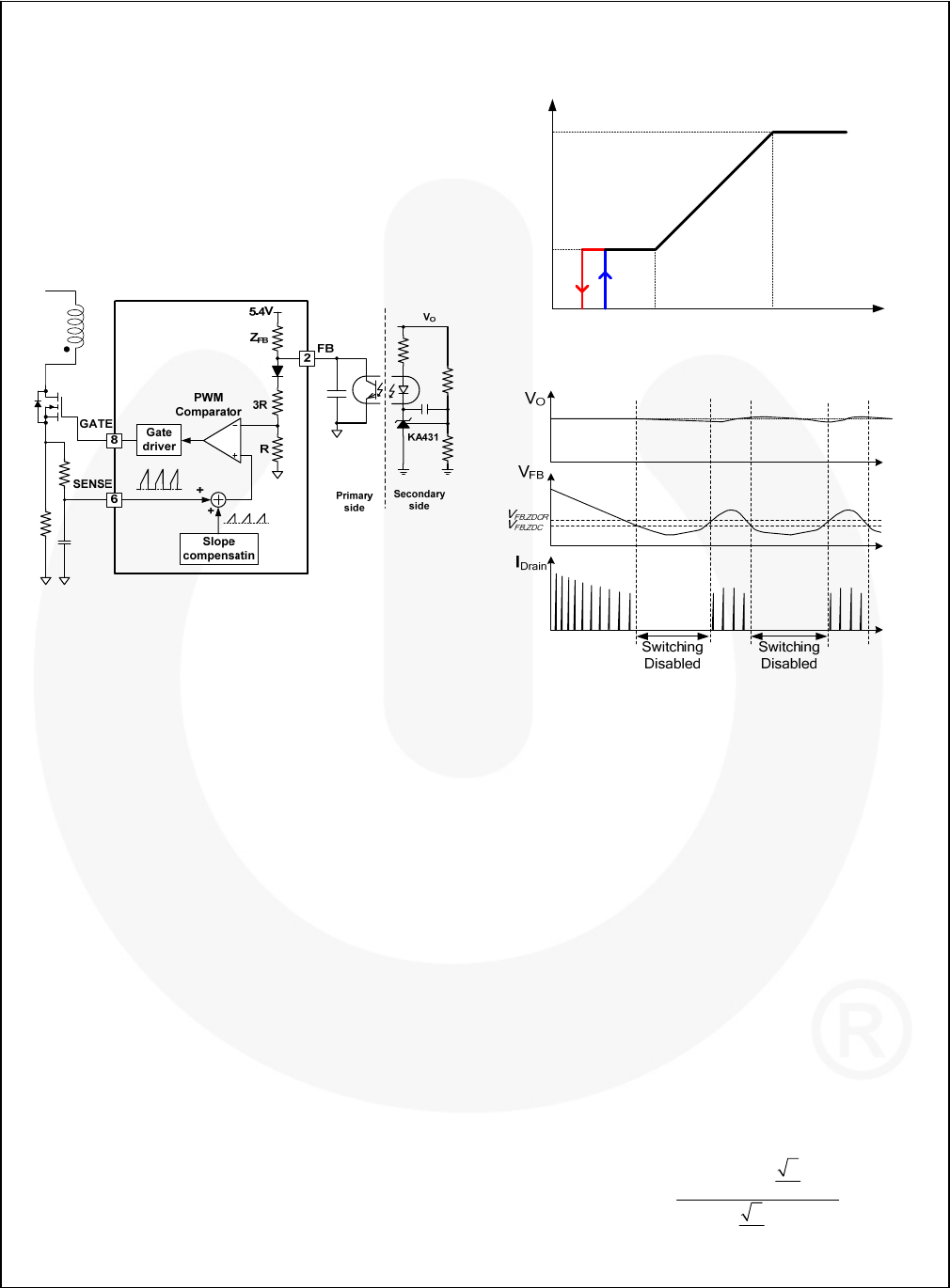

Current Mode Control

FAN6749 employs peak current mode control, as shown

in Figure 24. An opto-coupler (such as the H11A817A)

and a shunt regulator (such as the KA431) are typically

used to implement the feedback network. Comparing the

feedback voltage with the voltage across the Rsense

resistor makes it possible to control the switching duty

cycle. The built-in slope compensation stabilizes the

current loop and prevents sub-harmonic oscillation.

Figure 24. Current Mode Control Circuit Diagram

Green-Mode Operation

FAN6749 modulates the PWM frequency as a function

of the FB voltage to improve the medium- and light-load

efficiency, as shown in Figure 25. Since the output

power is proportional to the FB voltage in current mode

control, the switching frequency decreases as load

decreases. In heavy-load conditions, the switching

frequency is fixed at 65 kHz. Once VFB decreases below

VFB-N (2.7 V), the PWM frequency starts linearly

decreasing from 65 kHz to 24 kHz to reduce switching

losses. As VFB drops to VFB-G (2.25 V), where switching

frequency is decreased to 24 kHz, the switching

frequency is fixed to avoid acoustic noise.

When VFB falls below VFB-ZDC (2.0 V) as load decreases

further, FAN6749 enters Burst Mode, where PWM

switching is disabled. Then the output voltage starts to

drop, causing the feedback voltage to rise. Once VFB

rises above VFB-ZDCR (2.1 V), switching resumes. Burst

Mode alternately enables and disables switching,

thereby reducing switching loss for lower power

consumption, as shown in Figure 26

fOSC

fOSC-G

VFB-ZDC VFB-ZDCR VFB-G VFB-N VFB

fS

Figure 25. VFB vs. PWM Frequency

Figure 26. Burst Switching in Green Mode

Operating Current

In normal condition, operating current is around 1.8 mA

(IDD-OP1); when VFB<1.4 V, operating current is further

reduced to 1 mA (IDD-OP2) by disabling several blocks of

FAN6749. The low operating current improves light-load

efficiency and reduces the requirement of VDD hold-up

capacitance.

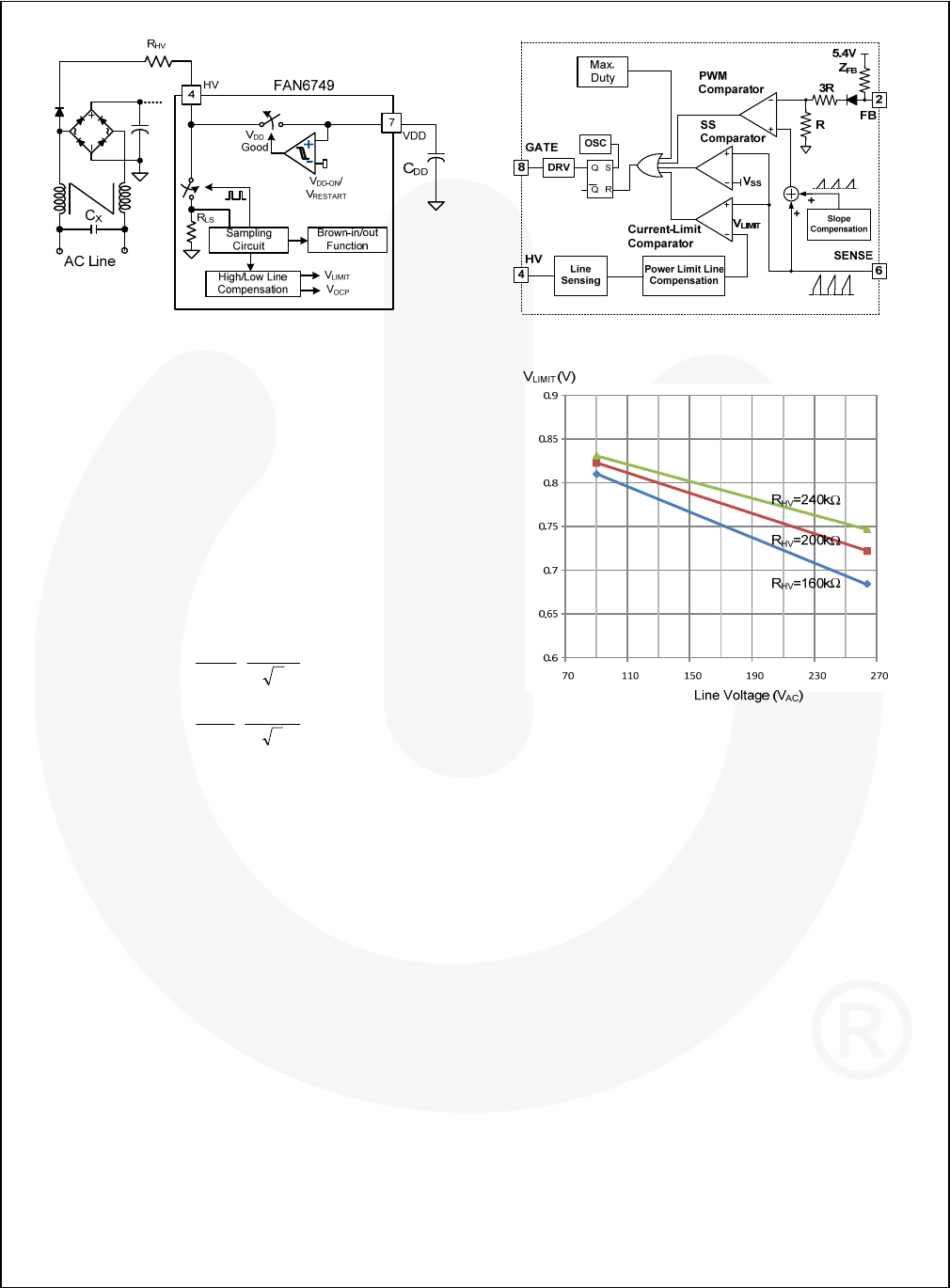

High-Voltage Startup and Line Sensing

The HV pin is typically connected to the AC line input

through an external diode and a resistor (RHV), as shown

in Figure 27. When AC line voltage is applied, the VDD

hold-up capacitor is charged by the line voltage through

the diodes and resistor. After VDD voltage reaches the

turn-on threshold voltage (VDD-ON), the startup circuit

charging VDD capacitor is switched off and VDD is

supplied by the auxiliary winding of the transformer.

Once FAN6749 starts up, it continues operation until

VDD drops below 6.5 V (VUVLO). The IC startup time with

a given AC line input voltage is given as:

2

ln 2

AC IN

STARTUP HV DD

A

CIN DDON

V

tRC

VV

(1)

© 2012 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN6749 • Rev. 1.0.3 12

FAN6749 — Highly Integrated Ultra Green-Mode PWM Controller

Figure 27. Startup Circuit

The HV pin detects the AC line voltage using a switched

voltage divider that consists of external resistor (RHV)

and internal resistor (RLS), as shown in Figure 27. The

internal line-sensing circuit detects line voltage using a

sampling circuit and a peak-detection circuit. Since the

voltage divider causes power consumption when it is

switched on, the switching is driven by a signal with a

very narrow pulse width to minimize power loss. The

sampling frequency is adaptively changed according to

the load condition to minimize the power consumption in

the light-load condition.

Based on the detected line voltage, brown-in and brown-

out thresholds are determined as:

2

200k

(RMS)

ONAC

HV

IN-BROWN

V

R

V

(2)

2

200k

(RMS)

OFFAC

HV

OUT-BROWN

V

R

V

(3)

Since the internal resistor (RLS=1.62 k) of the voltage

divider is much smaller than RHV, the thresholds are

given as s function of RHV.

Note that VDD must be larger than VDD-AC to start up,

even though sensed line voltage satisfies Equation 2.

High/Low Line Compensation for Constant

Power Limit

FAN6749 has cycle-by-cycle current limit, as shown in

Figure 28, which limits the maximum input power with a

given input voltage. If the output consumes beyond this

maximum power, the dropping output voltage triggers

the overload protection.

As shown in Figure 28, the high/low line compensation

block adjusts the current limit level, VLIMIT, based on the

line voltage. Figure 29 shows how the cycle-by-cycle

current-limit level changes with the line voltage for

different RHV resistors. To maintain the constant output

power limit regardless of line voltage, the cycle-by-cycle

current limit level, VLIMIT, decreases as line voltage

increases. The current-limit level is also proportional to

the RHV resistor value and power limit level can be tuned

using different RHV resistors.

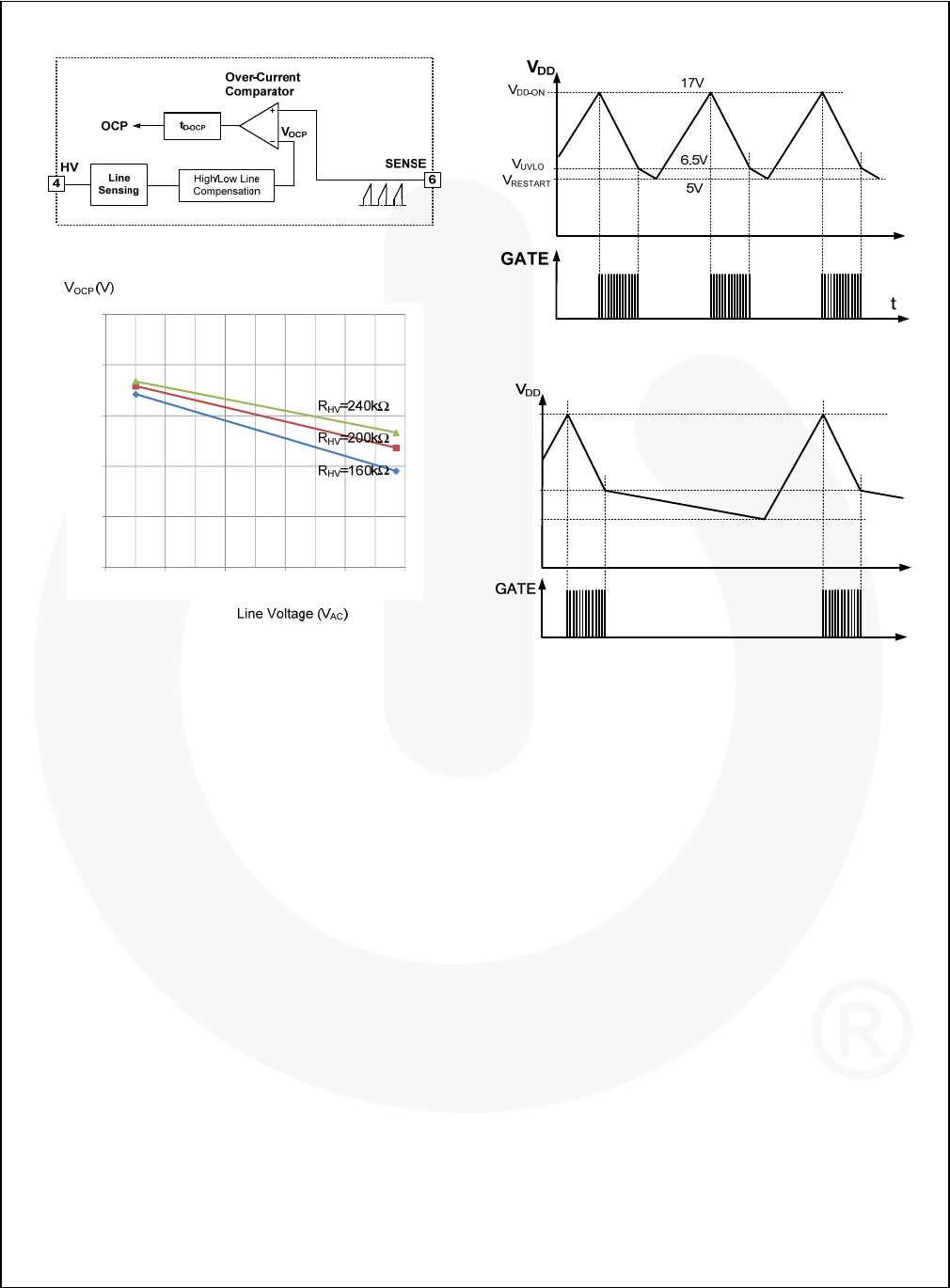

Figure 28. Cycle-by-Cycle Current-Limit Circuit

Figure 29. Current Limit vs. Line Voltage

Two-Level Over-Current Protection (OCP)

Other than cycle-by-cycle current limiting, FAN6749

applies another threshold voltage, VOCP, for current

sense. As shown in Figure 28, when peak of VSENSE

exceeds VOCP at each pulse for a period of time, tD-OCP;

over-current protection (OCP) is triggered. This

protection is designed for applications with surge-current

outputs. If a peak load is present for less than tD-OCP, the

controller operates as usual. If the peak load continues

longer than tD-OCP, GATE output is stopped to protect the

converter from overload condition.

Like VLIMIT, the VOCP is adjusted by high/low line

compensation block to maintain a constant over-current

protection level, regardless of line voltage. Figure 31

shows how VOCP changes with the line voltage with

different RHV resistors.

When OCP is triggered, it is recommended to have

VFB>VFB-N for whole AC input range. VFB>VFB-N ensures

switching frequency is fixed at 65 kHz. If OCP is

triggered in the frequency-reduction region (VFB<VFB-N),

output current is reduced due to lower switching

frequency. It causes the difference of OCP-triggering

point between high and low AC input voltages.

© 2012 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN6749 • Rev. 1.0.3 13

FAN6749 — Highly Integrated Ultra Green-Mode PWM Controller

Figure 30. Over-Current Protection Circuit

0.3

0.35

0.4

0.45

0.5

0.55

70 110 150 190 230 270

Figure 31. VOCP vs. Line Voltage

Short Circuit Protection (SCP)

The VDD voltage decreases every time the output of the

power supply is shorted because the impedance at

secondary windings becomes far lower than at auxiliary

winding and currents choose the low-impedance path.

When VFB is larger than VFB-OLP over a debounce time of

tD-SCP; if VDD is lower than VDD-SCP, PWM output is

latched off.

Under-Voltage Lockout (UVLO)

As shown in Figure 32, as long as protection is not

triggered, the turn-off threshold of VDD is fixed internally

at VUVLO (6.5 V). When a protection is triggered, the VDD

level to terminate PWM gate switching is changed to

VDD-OFF (11 V), as shown in Figure 33. When VDD drops

below VDD-OFF, the switching is terminated and the

operating current from VDD is reduced to IDD-OLP, to slow

down the discharge of VDD until VDD reaches VDD-OLP.

This delays restart after shutdown by protection to

minimize the input power and voltage/current stress of

switching devices during fault condition.

Figure 32. VDD UVLO in Normal Mode

VDD-ON

t

VDD-OLP

VDD-OFF

17V

11V

7.5V

Figure 33. VDD UVLO in Protection Mode

Leading-Edge Blanking (LEB)

Each time the power MOSFET is switched on, a turn-on

spike occurs on the sense resistor. To avoid premature

termination of the switching pulse, a leading-edge

blanking time, tLEB, is introduced. During this blanking

period, the current-limit comparator is disabled and

cannot switch off the gate driver.

Gate Output / Soft Driving

The BiCMOS output stage has a fast totem-pole gate

driver. The output driver is clamped by an internal

14.5 V Zener diode to protect power MOSFET gate from

over voltage. A soft driving is implemented to minimize

electromagnetic interference (EMI) by reducing the

switching noise.

VDD Over-voltage Protection (OVP)

VDD over-voltage protection prevents IC damage from

over-voltage exceeding the IC voltage rating. When the

VDD voltage exceeds 29 V, the protection is triggered.

This protection is typically caused by an open circuit in

the secondary-side feedback network.

© 2012 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN6749 • Rev. 1.0.3 14

FAN6749 — Highly Integrated Ultra Green-Mode PWM Controller

Soft-Start

FAN6749 has an internal soft-start circuit that

progressively increases the cycle-by-cycle current limit

level of the MOSFET for 6 ms during startup to establish

the correct working conditions for transformers and

capacitors to operate.

Over-Temperature Protection (OTP)

The RT pin provides adjustable Over-Temperature

Protection (OTP) and an external latch-triggering

function. For OTP application, an NTC thermistor, RNTC,

usually in series with a resistor, RA, is connected

between the RT pin and ground. The internal current

source, IRT, (100 µA) introduces voltage on RT as:

)(

ANTCRTRT

R

R

I

V

(4)

At high ambient temperature, RNTC decreases, which

reduces VRT. When VRT is lower than VRTTH1 (1.050 V)

for longer than tD-OTP1 (14 ms), the protection is triggered

and FAN6749 enters Latch Mode protection.

The OTP can be also trigged by pulling down the RT pin

voltage using an opto-coupler or transistor. Once VRT is

less than VRTTH2 (0.7 V) for longer than tD-OTP2 (165 µs),

the protection is triggered and FAN6749 enters Latch

Mode protection.

When VFB falls below 1.9 V, the RT pin function is

disabled for lower power consumption. If OTP is not

used, place a 100 k resistor between this pin and

ground to prevent noise interference.

Noise Immunity

Noise on the current sense or control signal may cause

significant pulse-width jitter, particularly in continuous-

conduction mode. Slope compensation helps alleviate

this problem. Good placement and layout practices

should be followed. Avoiding long PCB traces and

component leads, locating compensation and filter

components near the FAN6749, and increasing the

power MOS gate resistance improve performance.

© 2012 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN6749 • Rev. 1.0.3 15

FAN6749 — Highly Integrated Ultra Green-Mode PWM Controller

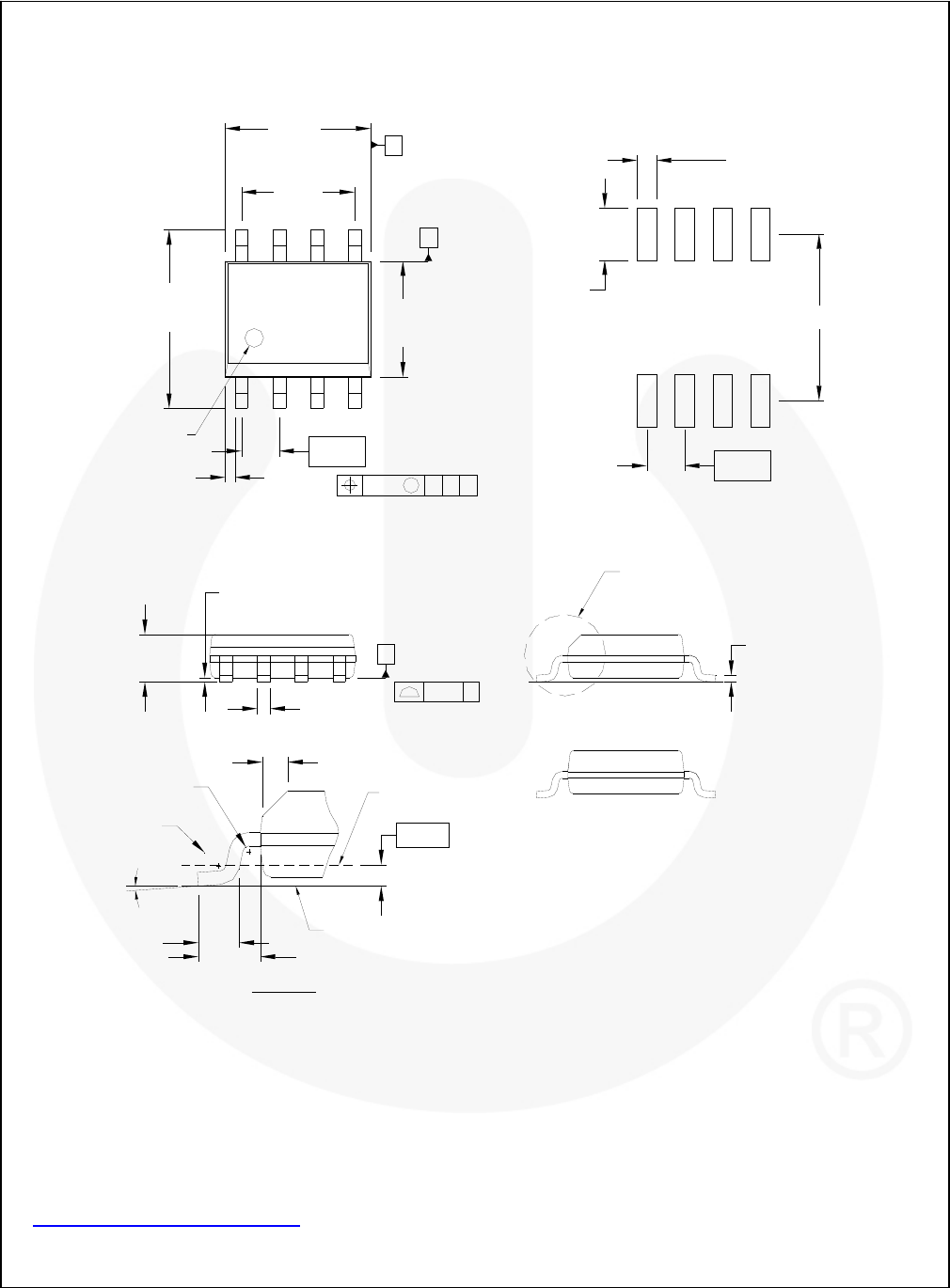

Physical Dimensions

8°

0°

SEE DETAIL A

NOTES: UNLESS OTHERWISE SPECIFIED

A) THIS PACKAGE CONFORMS TO JEDEC

MS-012, VARIATION AA, ISSUE C,

B) ALL DIMENSIONS ARE IN MILLIMETERS.

C) DIMENSIONS DO NOT INCLUDE MOLD

FLASH OR BURRS.

D) LANDPATTERN STANDARD: SOIC127P600X175-8M.

E) DRAWING FILENAME: M08AREV13

LAND PATTERN RECOMMENDATION

SEATING PLANE

0.10 C

C

GAGE PLANE

x 45°

DETAIL A

SCALE: 2:1

PIN ONE

INDICATOR

4

8

1

C

MBA0.25

B

5

A

5.60

0.65

1.75

1.27

6.20

5.80

3.81

4.00

3.80

5.00

4.80

(0.33)

1.27

0.51

0.33

0.25

0.10

1.75 MAX

0.25

0.19

0.36

0.50

0.25

R0.10

R0.10

0.90

0.406 (1.04)

OPTION A - BEVEL EDGE

OPTION B - NO BEVEL EDGE

Figure 34. 8-Pin SOP-8 Package

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner

without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or

obtain the most recent revision. Package specifications do not expand the terms of Fairchild’s worldwide terms and conditions,

specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor’s online packaging area for the most recent package drawings:

http://www.fairchildsemi.com/packaging/.

© 2012 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN6749 • Rev. 1.0.3 16

FAN6749 — Highly Integrated Ultra Green-Mode PWM Controller