MT6235 Datasheet. Www.s Manuals.com. R1.02 Mediatek

User Manual: Datasheets MT6235.

Open the PDF directly: View PDF ![]() .

.

Page Count: 600 [warning: Documents this large are best viewed by clicking the View PDF Link!]

MT6235 GSM/GPRS Baseband

Processor Data Sheet

Revision 1.02

Apr 07, 2008

MT6235 GSM/GPRS Baseband Processor Data Sheet Revision 1.02

2/599 MediaTek Inc. Confidential

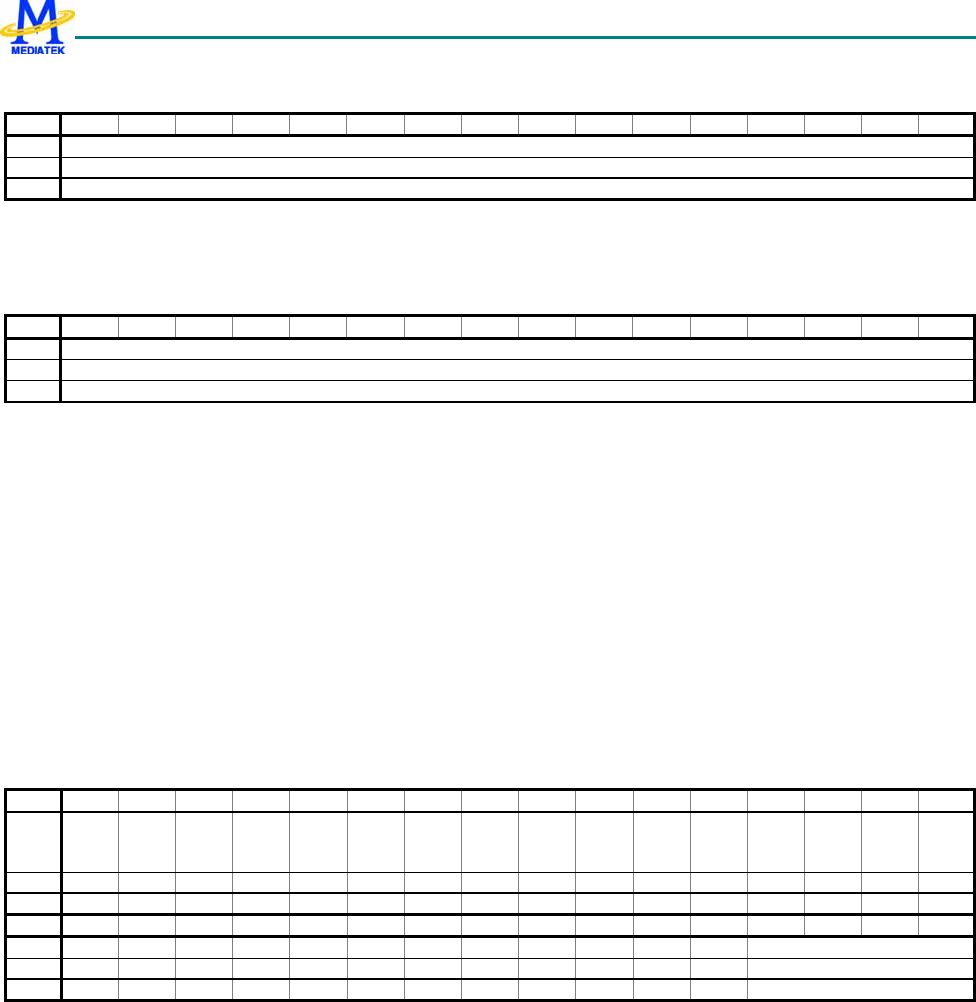

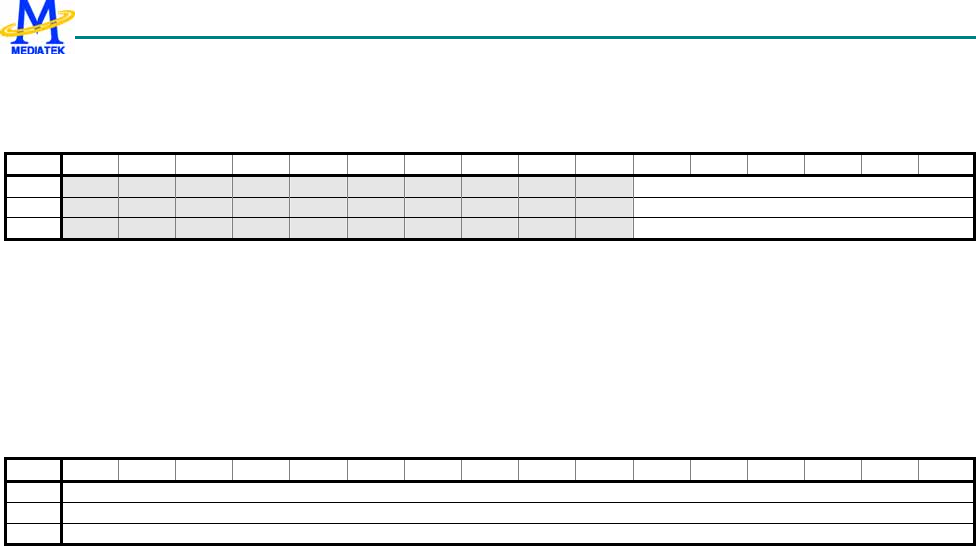

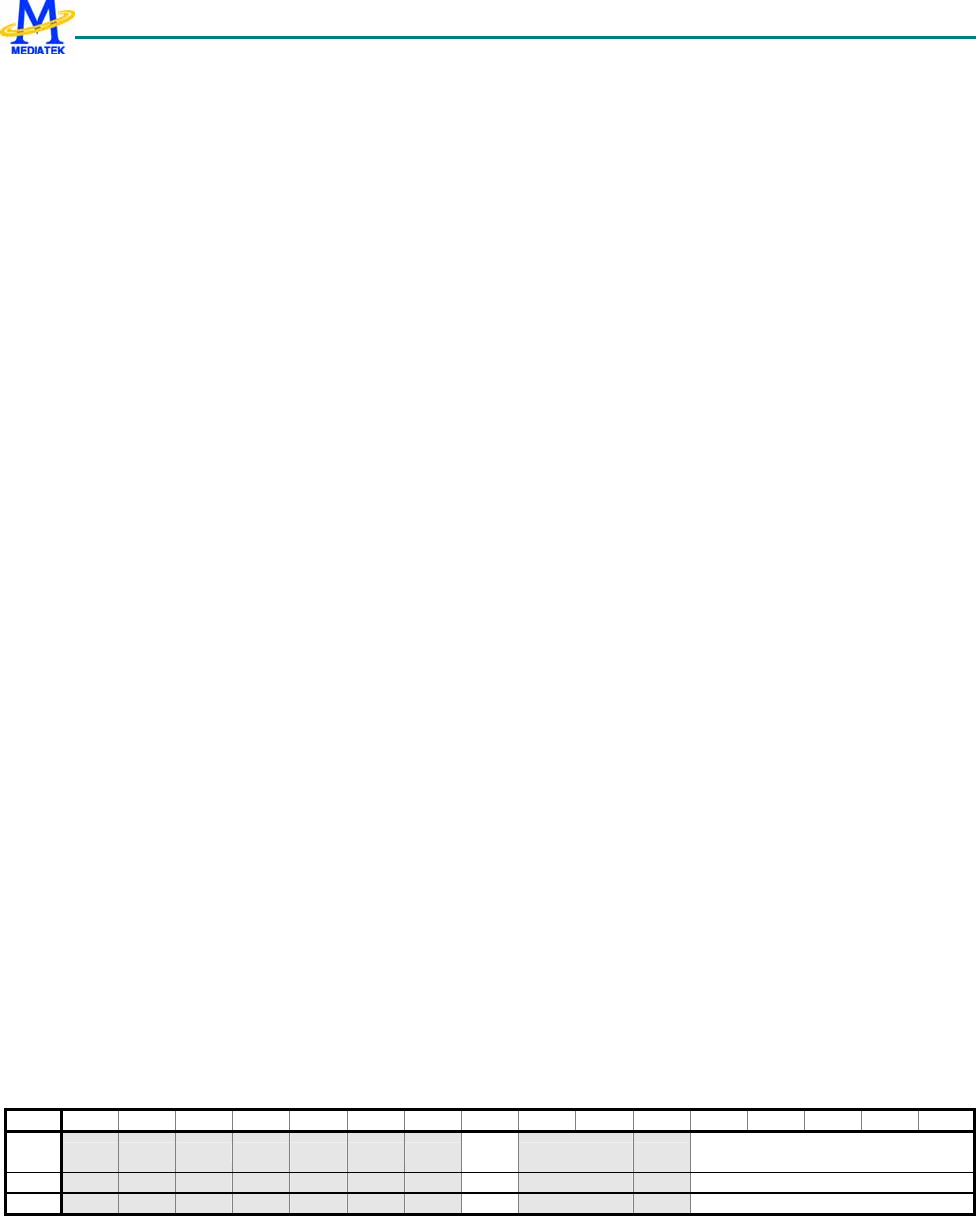

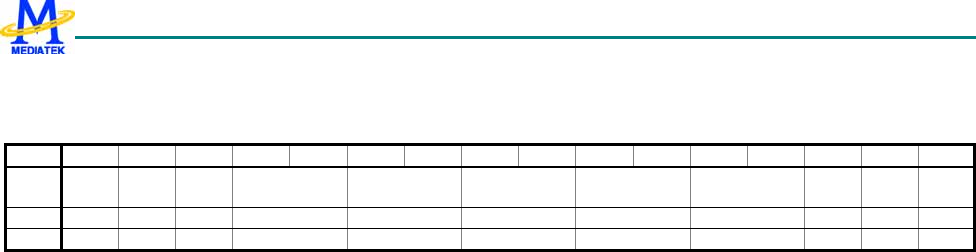

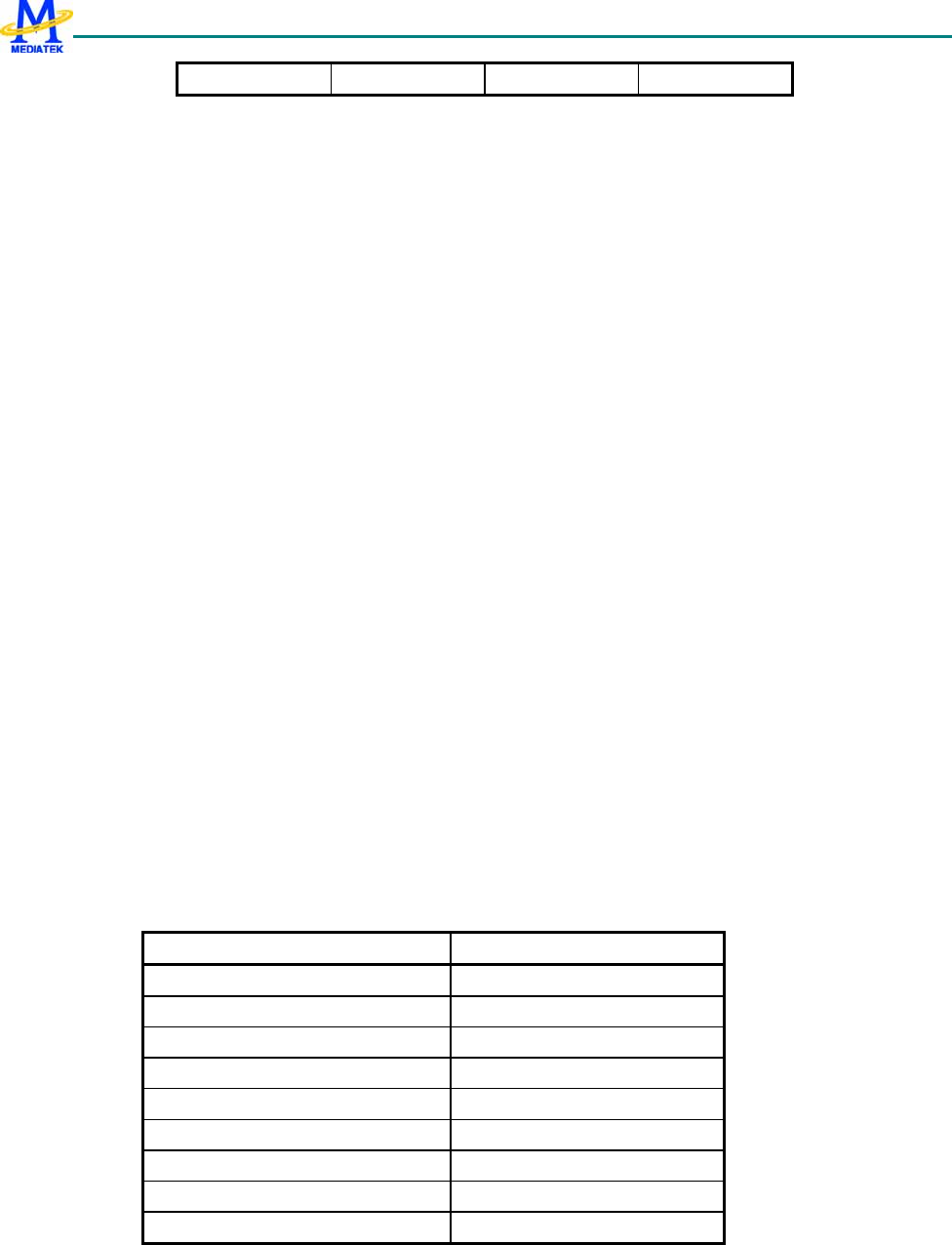

Revision History

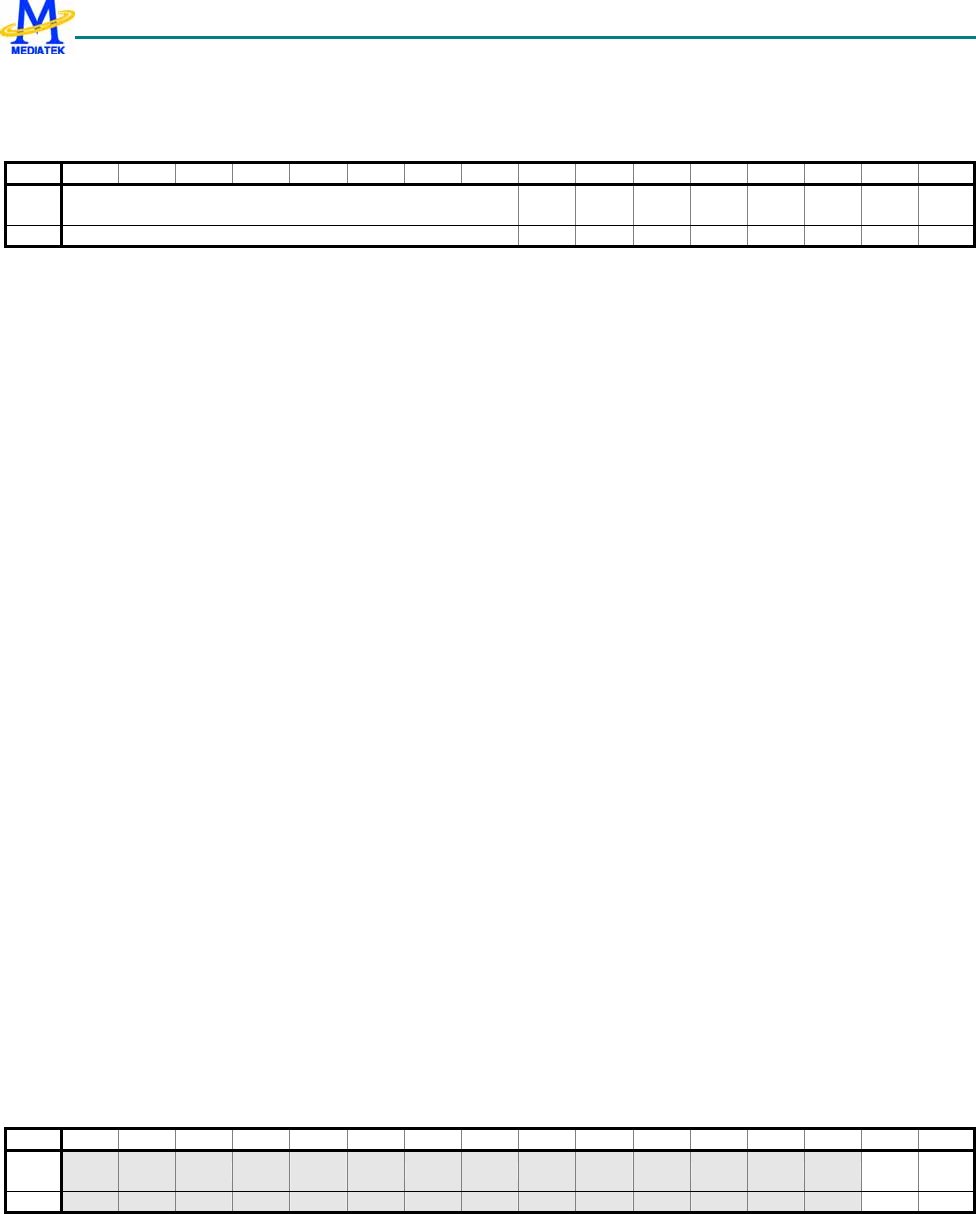

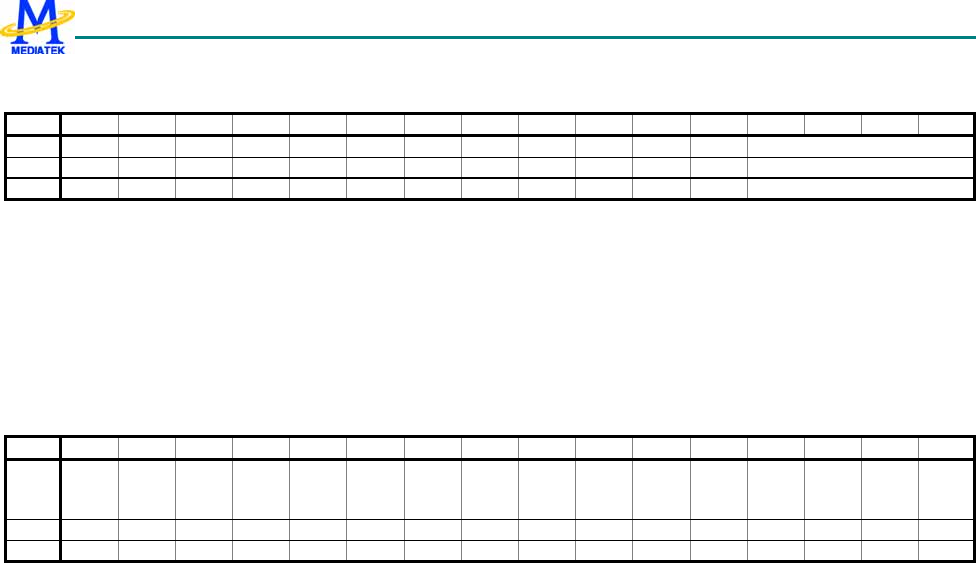

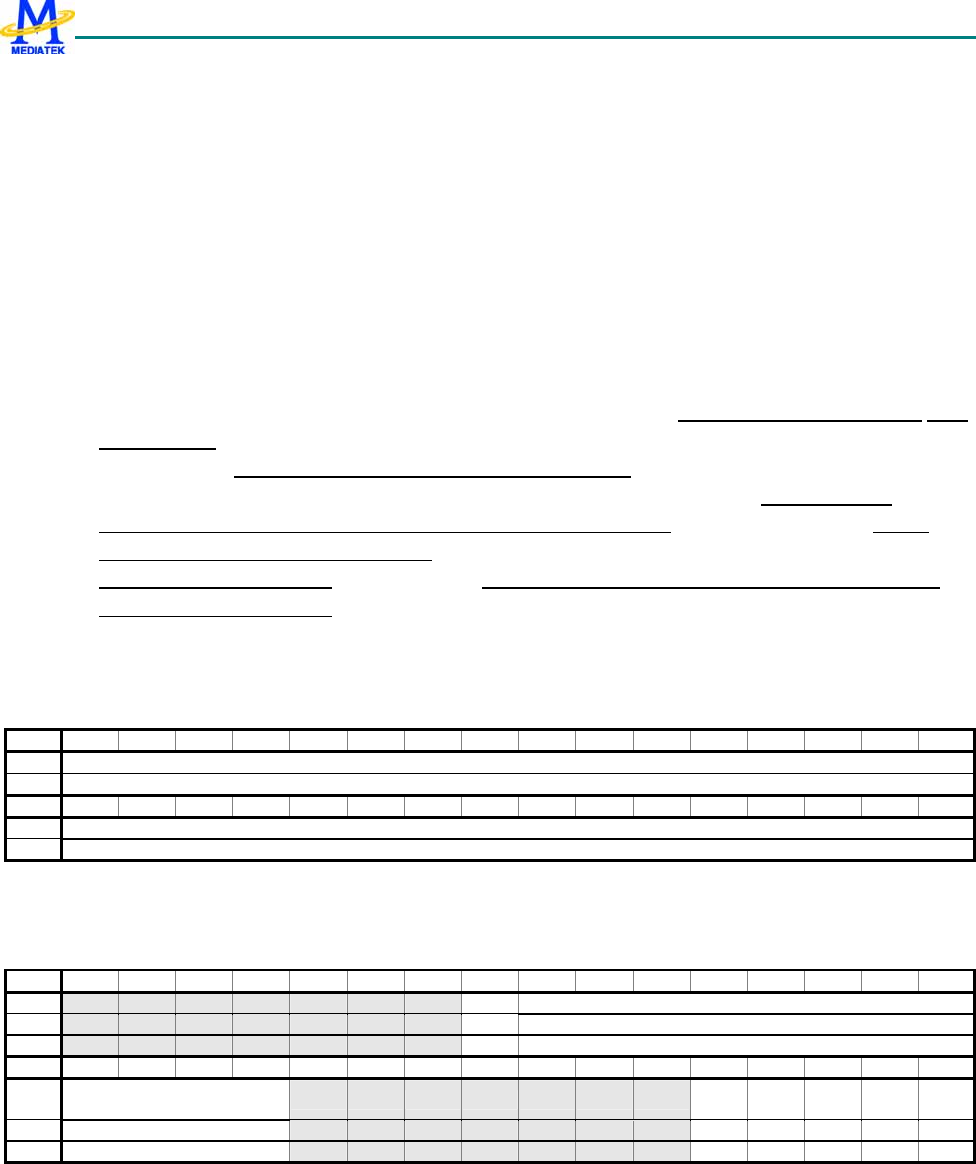

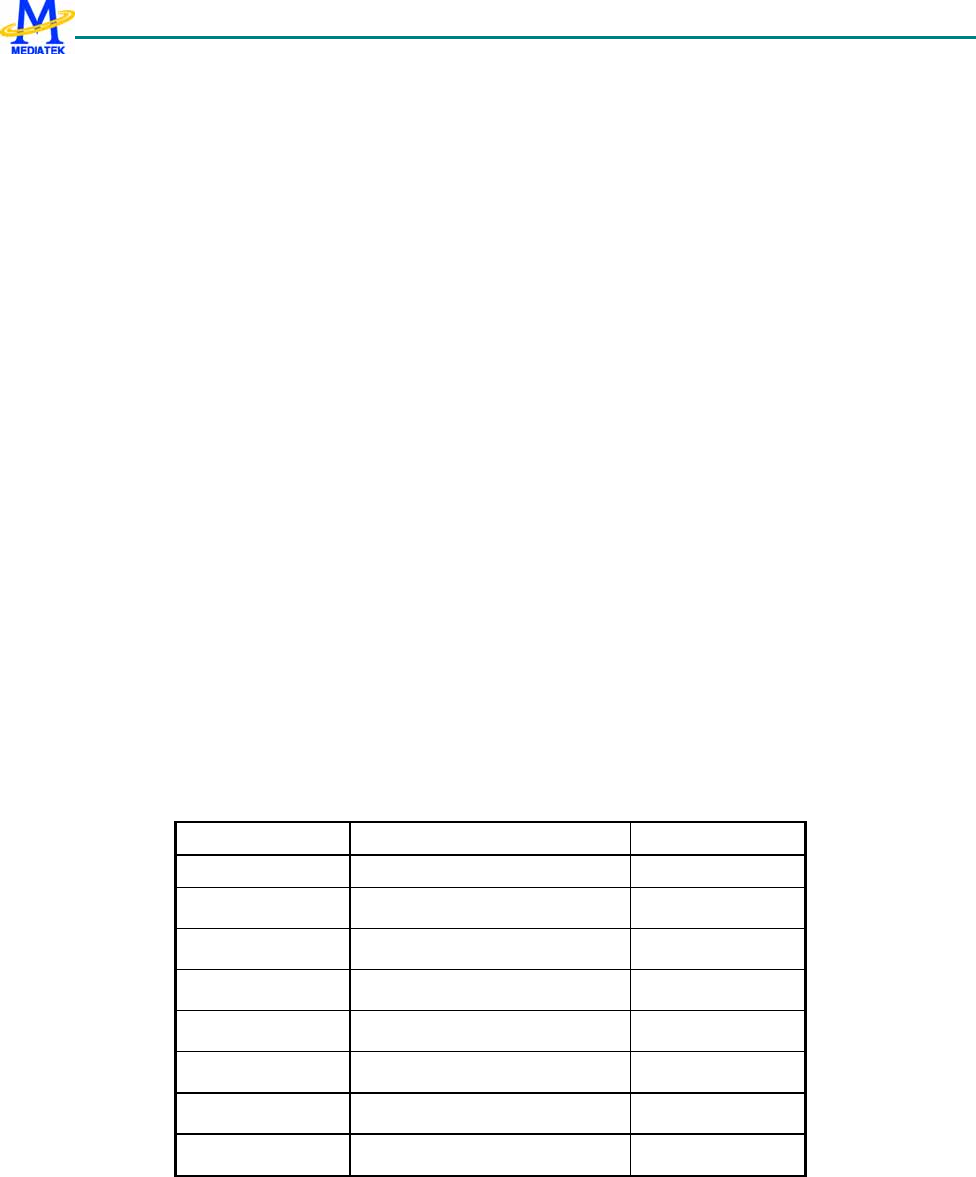

Revision Date Comments

1.00 Sept 18, 2007 First Release

1.01

Dec 13, 2007 1. Update GPIO10 GPIO11 mode definition

2. Update ch8 audio front end and ch13 analog front end & analog blocks for PMU ball name

change (VMC,VSW_A, VCAMERA) > (VBT, VCAM_A, VCAM_D)

1.02 Apr 07, 2008

1. Update RGU, MCU, RTC, SIM, EMI, GLCON, TG, System Overview, and Product

Description

MT6235 GSM/GPRS Baseband Processor Data Sheet Revision 1.02

3/599 MediaTek Inc. Confidential

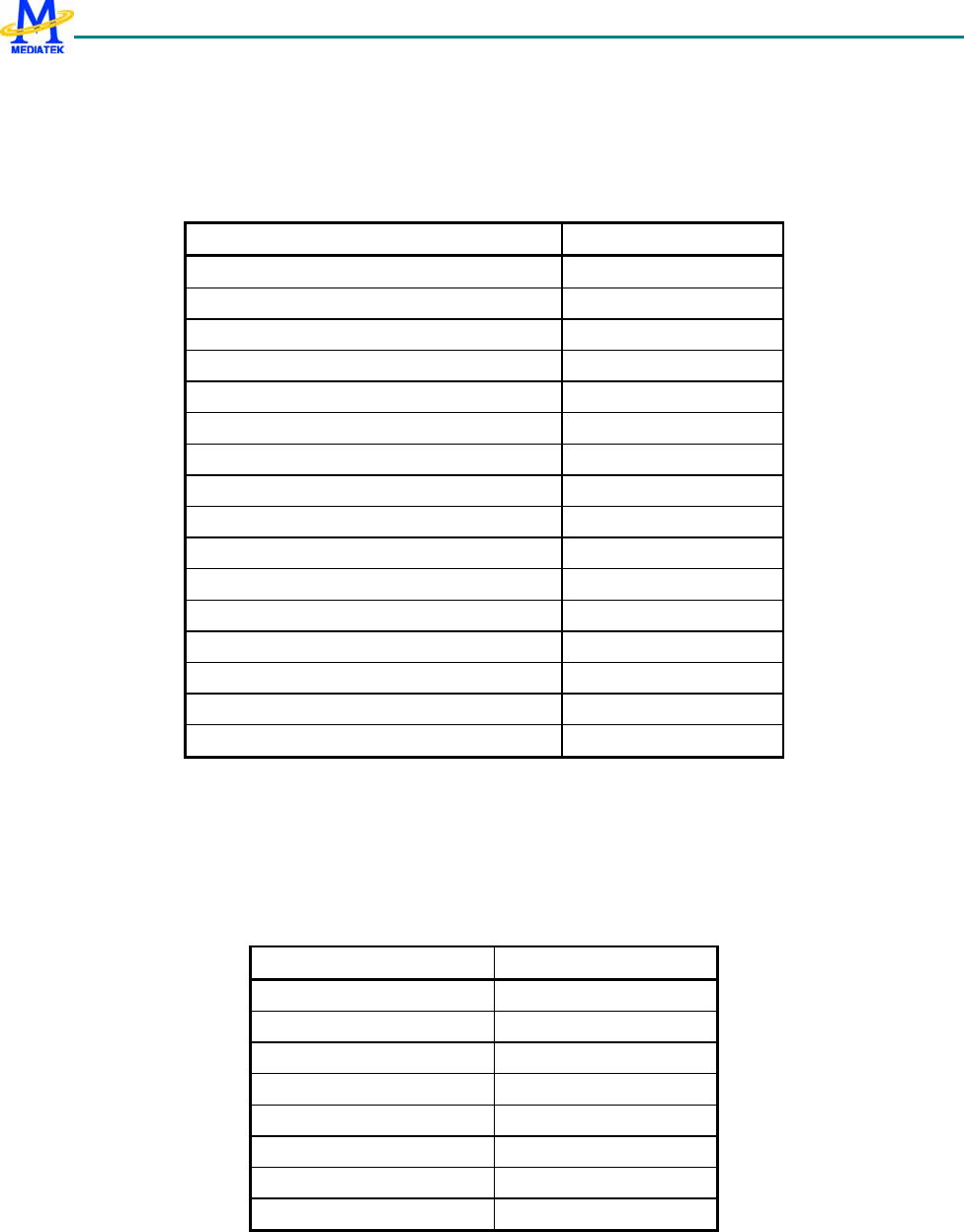

TABLE OF CONTENTS

Revision History......................................................................................................................................2

Preface......................................................................................................................................................5

1. System Overview...............................................................................................................................6

Platform Features................................................................................................................................................................. 9

1.1 MODEM Features.....................................................................................................................................................11

1.2 Multi-Media Features............................................................................................................................................... 12

1.3 General Description ................................................................................................................................................. 13

2 Product Description........................................................................................................................15

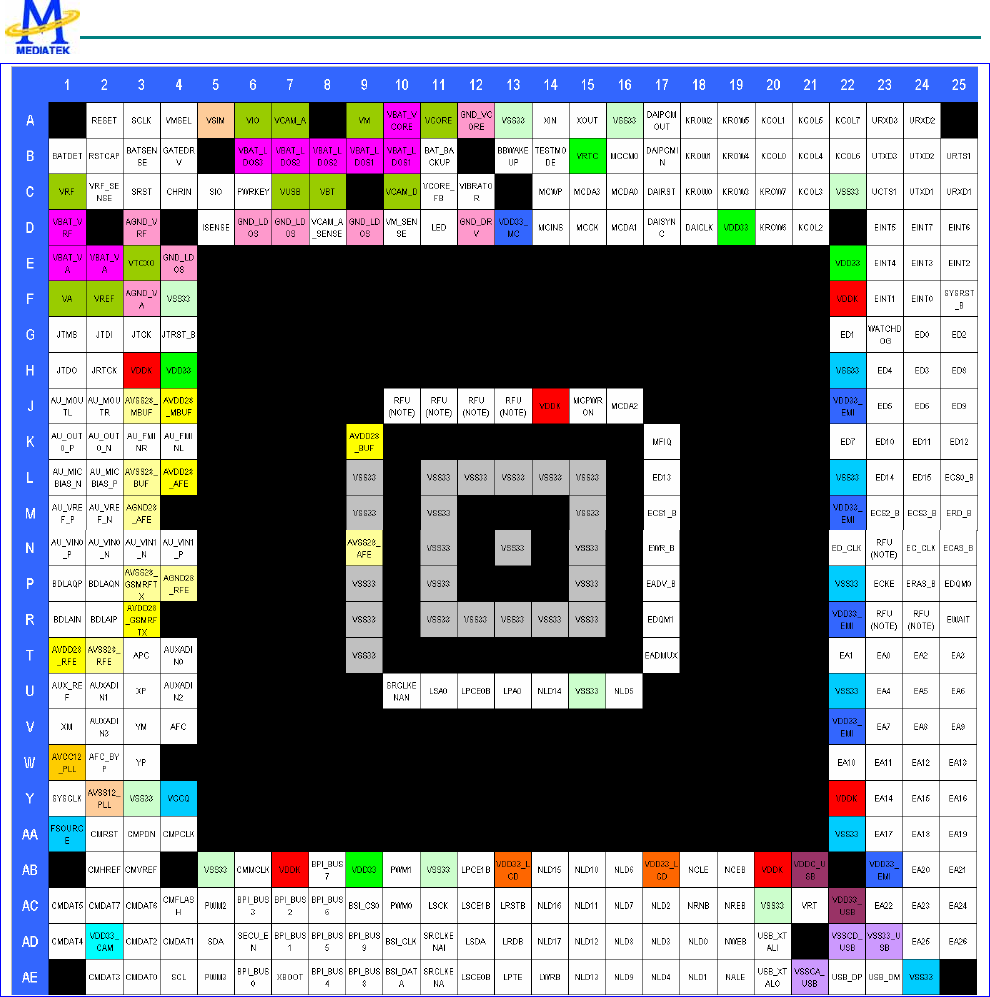

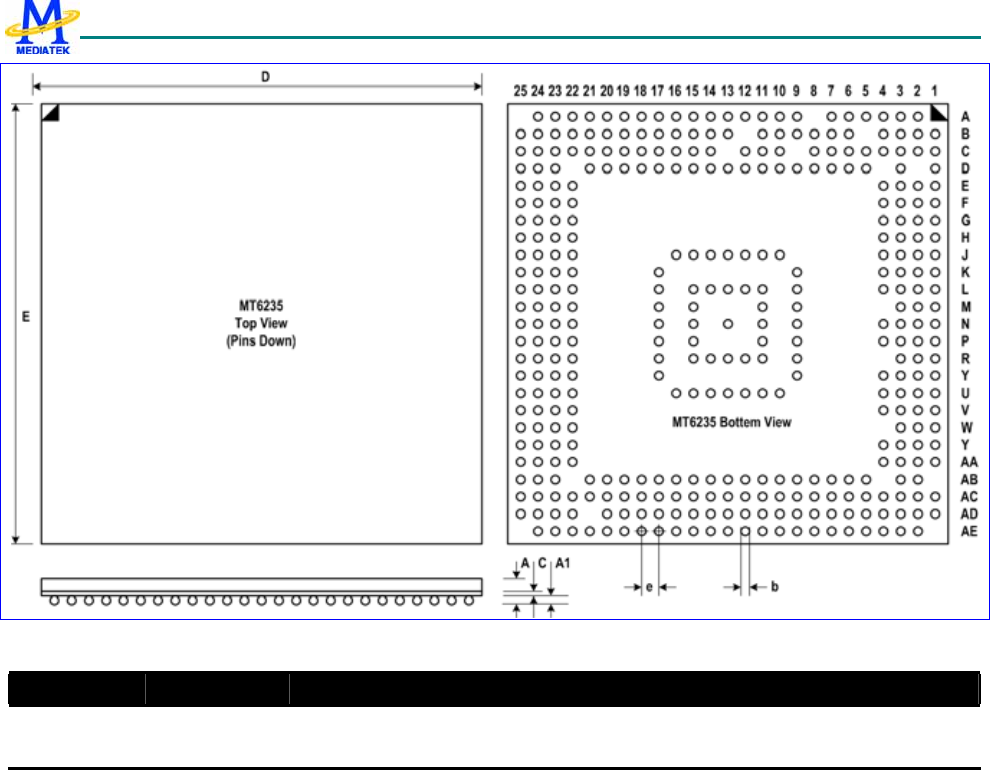

2.1 Pin Outs.................................................................................................................................................................... 15

2.2 Top Marking Definition ........................................................................................................................................... 18

2.3 DC Characteristics ................................................................................................................................................... 19

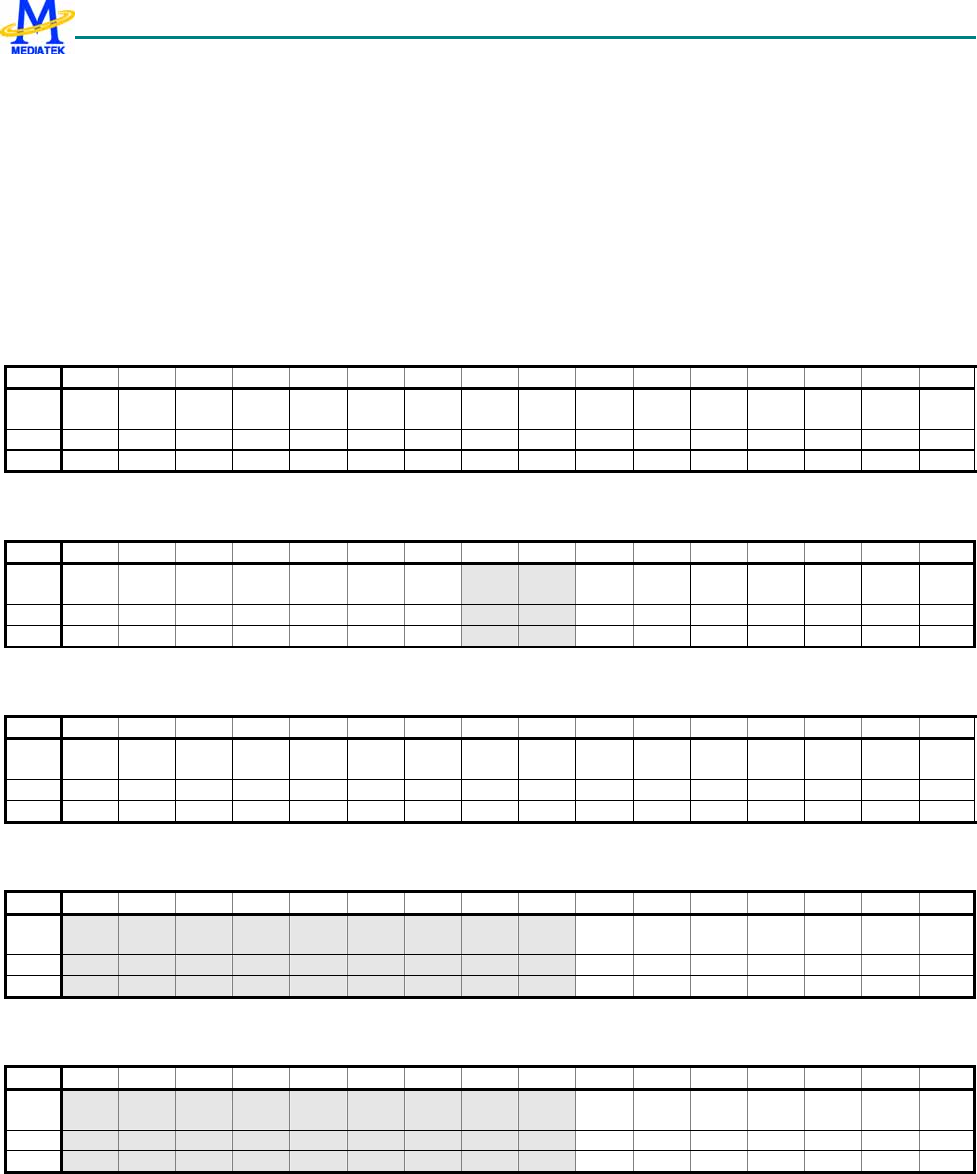

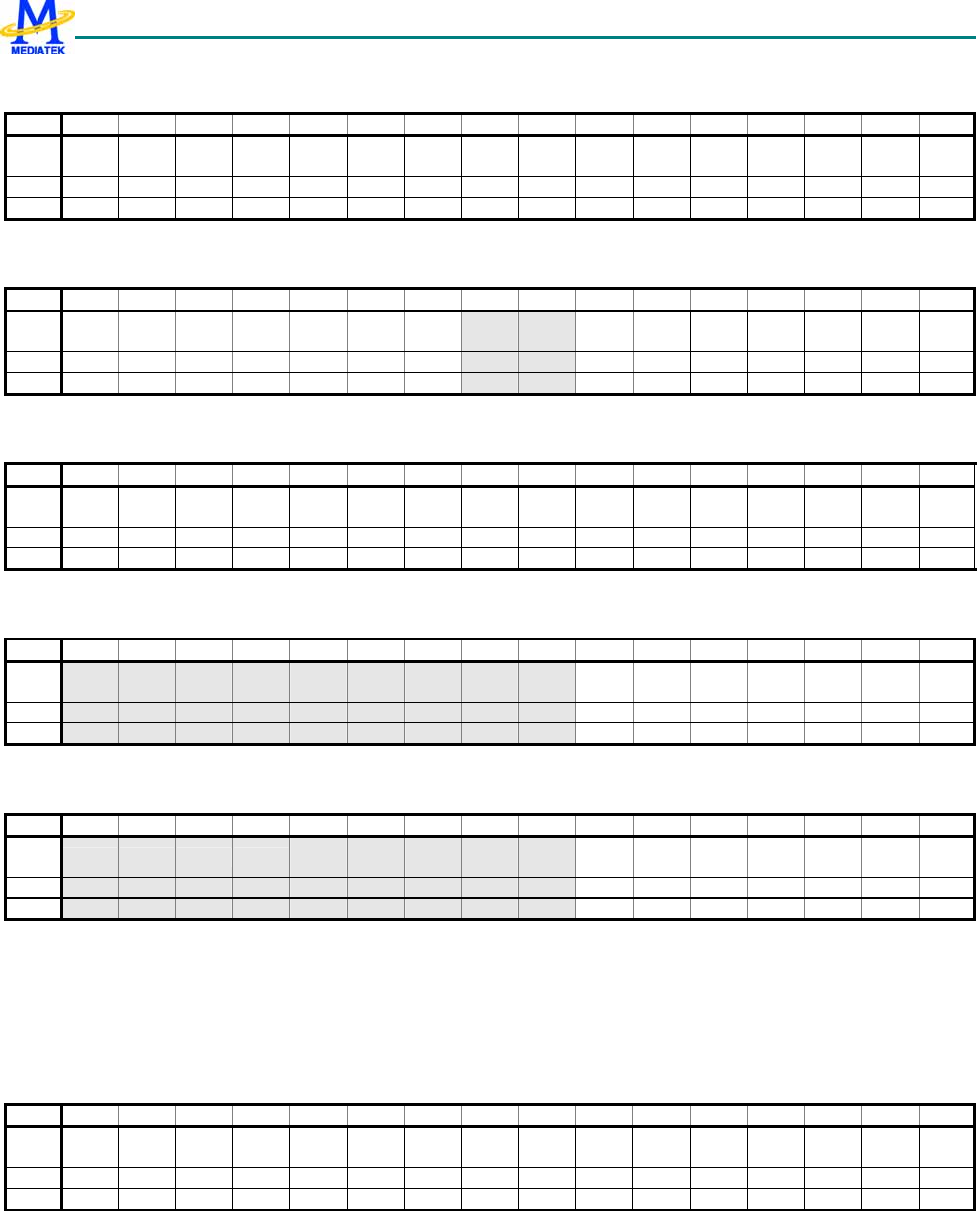

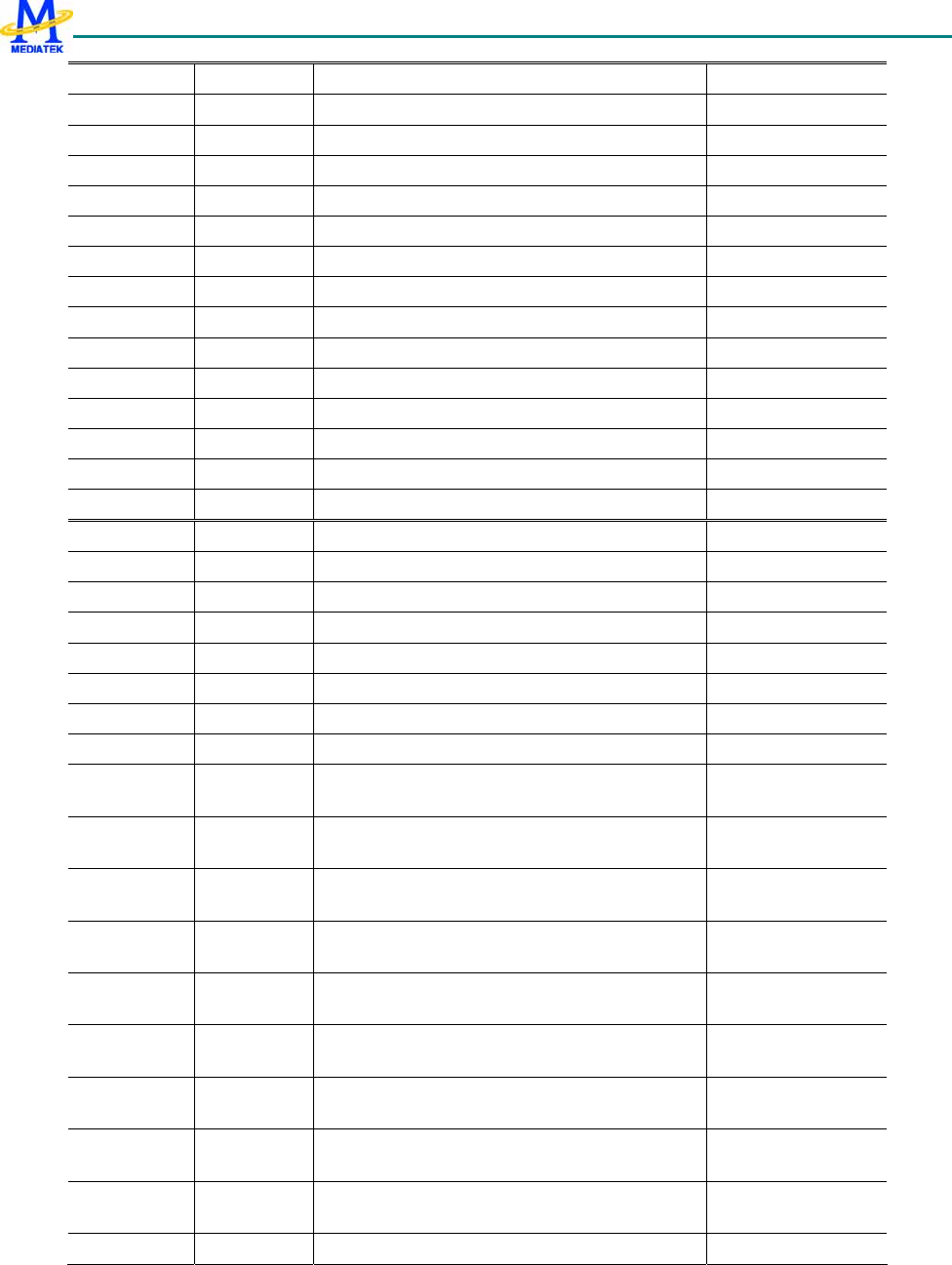

2.4 Pin Description......................................................................................................................................................... 20

2.5 Power Description.................................................................................................................................................... 32

3 Micro-Controller Unit Subsystem.................................................................................................40

3.1 Processor Core ......................................................................................................................................................... 41

3.2 Memory Management.............................................................................................................................................. 41

3.3 Bus System............................................................................................................................................................... 44

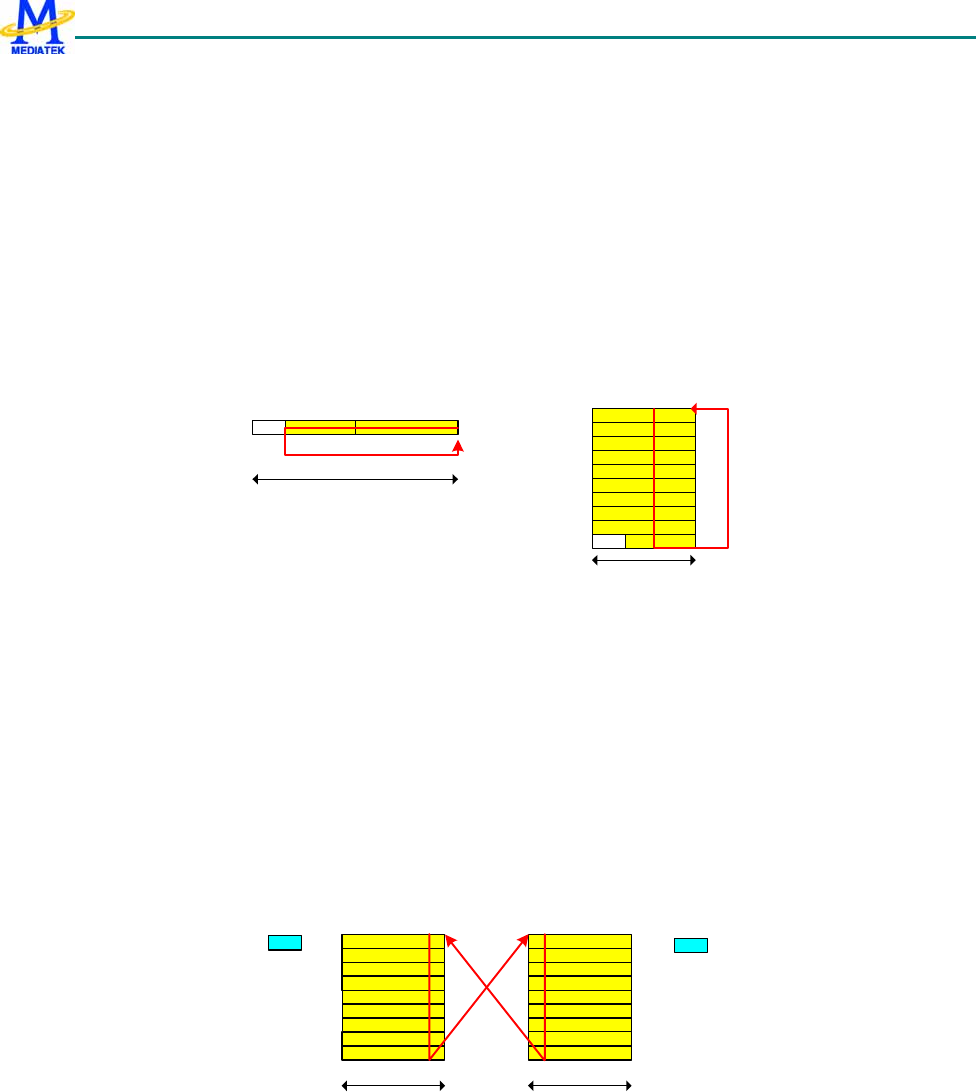

3.4 Direct Memory Access............................................................................................................................................. 48

3.5 Interrupt Controller .................................................................................................................................................. 66

3.6 BUS Monitor (BM).................................................................................................................................................. 82

3.7 External Memory Interface (6235)........................................................................................................................... 93

4 Microcontroller Peripherals ........................................................................................................104

4.1 Security Engine with JTAG control ....................................................................................................................... 104

4.2 EFUSE Controller (efusec) .................................................................................................................................... 107

4.3 Pulse-Width Modulation Outputs............................................................................................................................111

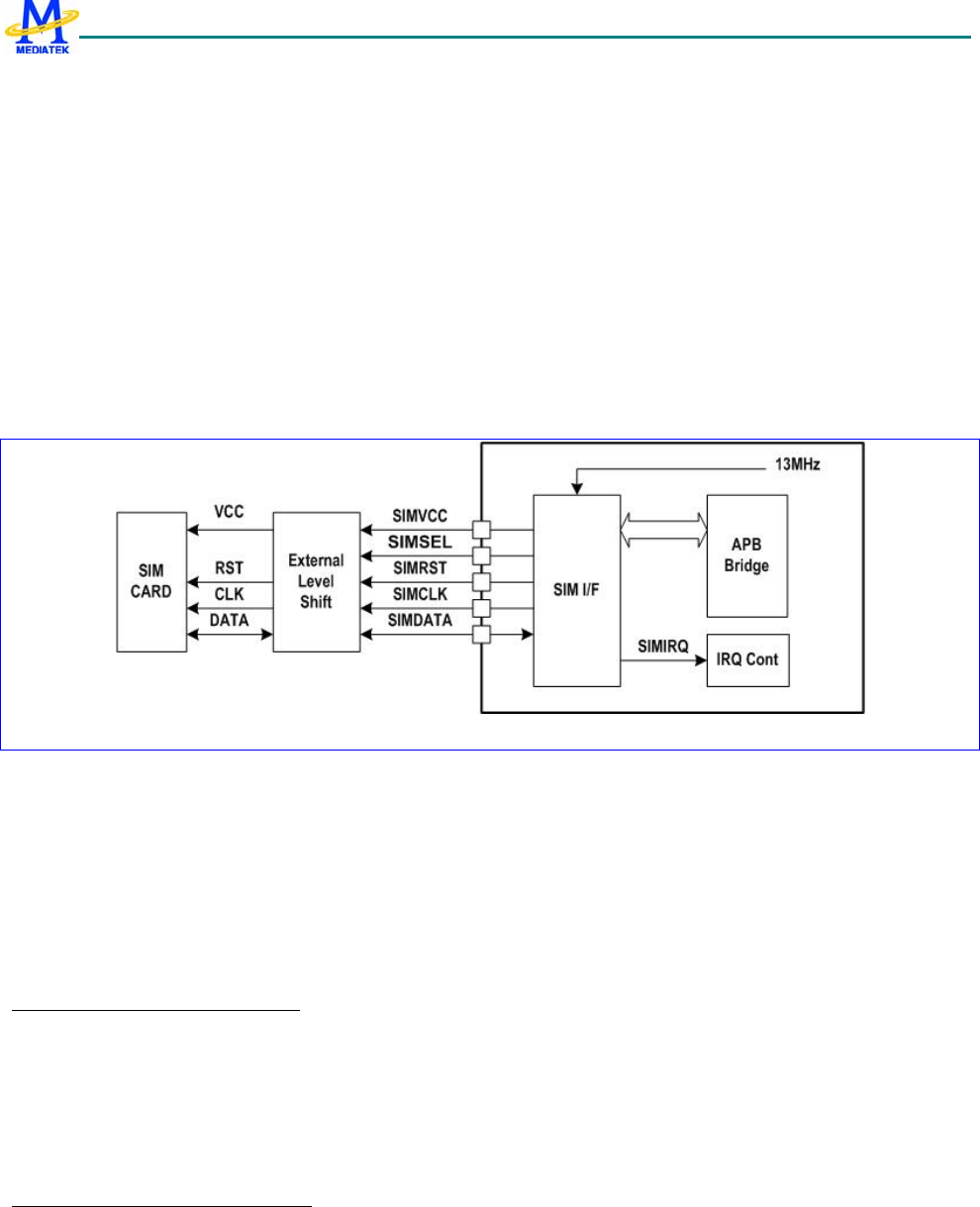

4.4 SIM Interface ......................................................................................................................................................... 150

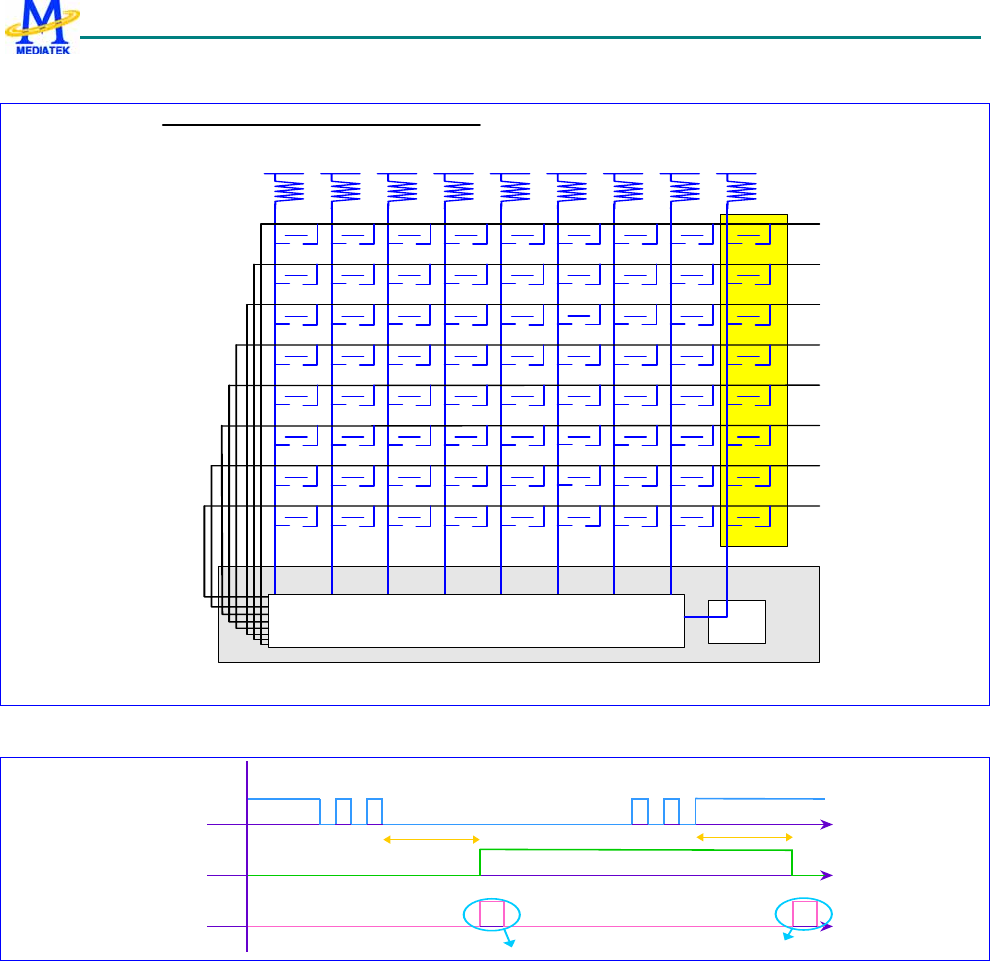

4.5 Keypad Scanner ..................................................................................................................................................... 159

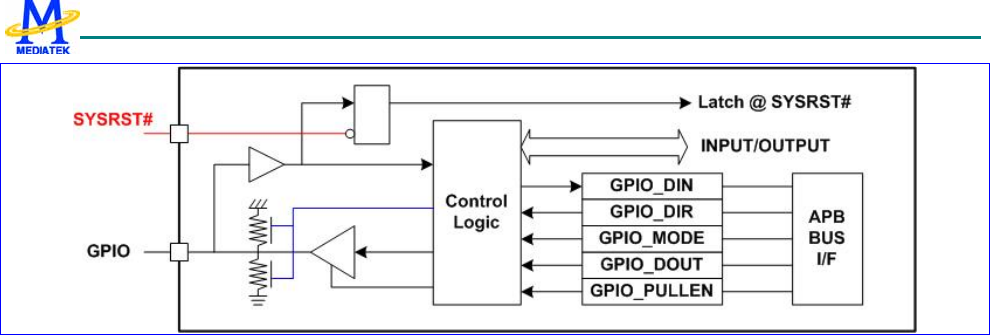

4.6 General Purpose Inputs/Outputs ............................................................................................................................ 162

4.7 General Purpose Timer........................................................................................................................................... 181

4.8 UART..................................................................................................................................................................... 184

4.9 IrDA Framer........................................................................................................................................................... 199

4.10 Real Time Clock..................................................................................................................................................... 208

4.11 Auxiliary ADC Unit ............................................................................................................................................... 216

4.12 I2C / SCCB Controller........................................................................................................................................... 220

5 Microcontroller Coprocessors .....................................................................................................232

5.1 Divider ................................................................................................................................................................... 232

5.2 CSD Accelerator .................................................................................................................................................... 234

5.3 FCS Codec ............................................................................................................................................................. 246

5.4 GPRS Cipher Unit.................................................................................................................................................. 248

6 MCU/DSP Interface......................................................................................................................252

6.1 MCU/DSP Shared Registers .................................................................................................................................. 254

6.2 MCU/DSP Shared RAM ........................................................................................................................................ 261

6.3 AHB-to-DDMA Bridge.......................................................................................................................................... 263

7 Multi-Media Subsystem ...............................................................................................................268

7.1 LCD Interface ........................................................................................................................................................ 268

7.2 Capture Resize ....................................................................................................................................................... 292

MT6235 GSM/GPRS Baseband Processor Data Sheet Revision 1.02

4/599 MediaTek Inc. Confidential

7.3 NAND FLASH interface ....................................................................................................................................... 300

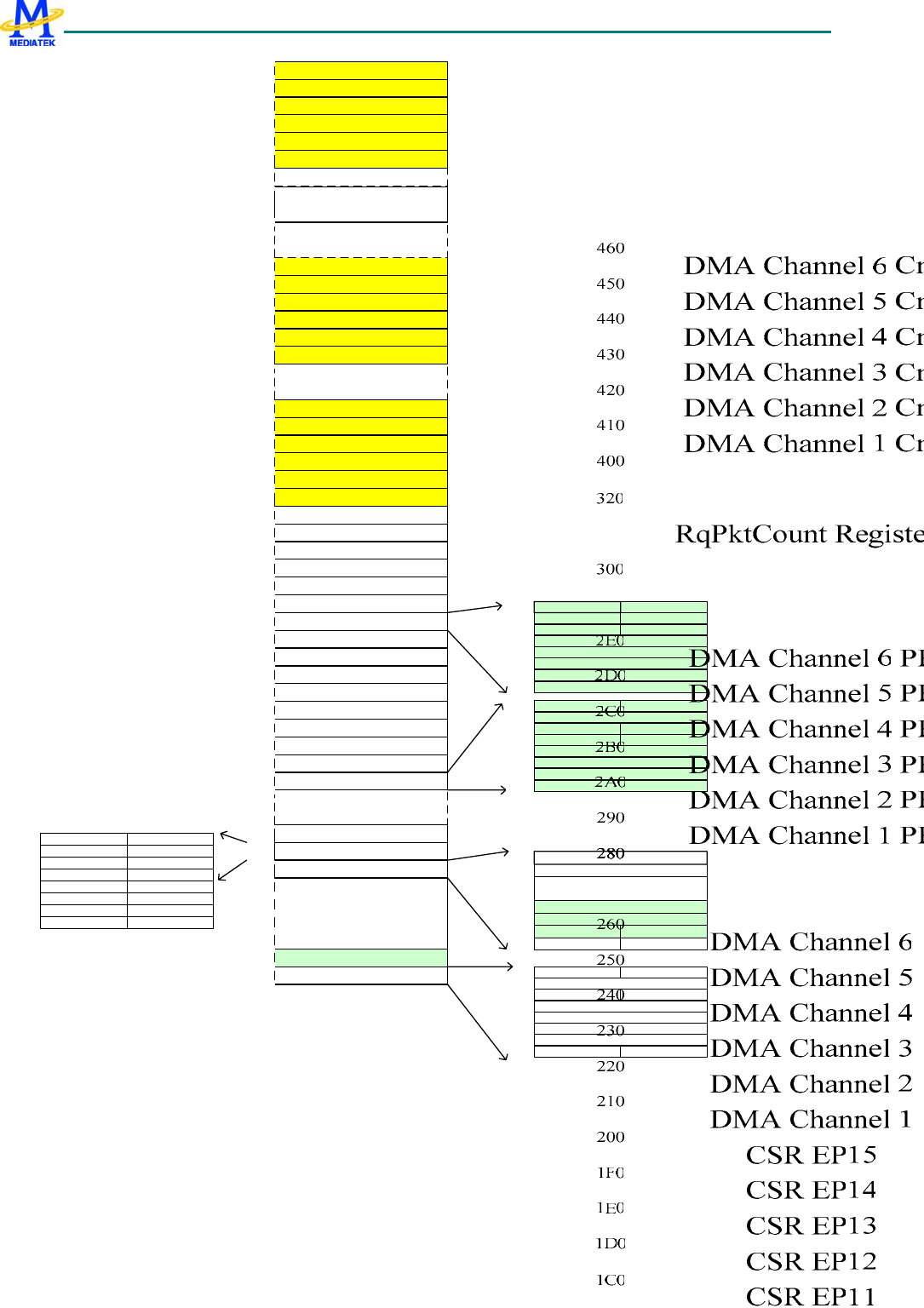

7.4 USB 2.0 High-Speed Dual-Role Controller........................................................................................................... 320

7.5 Memory Stick and SD Memory Card Controller ................................................................................................... 358

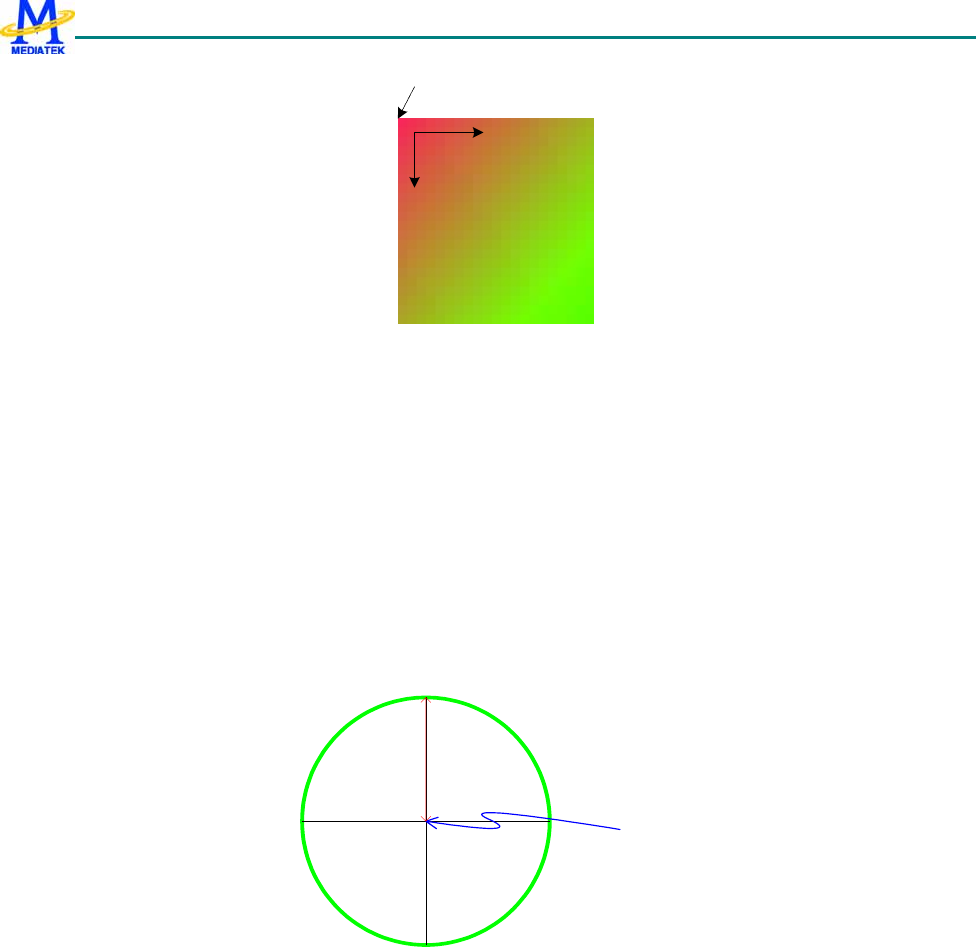

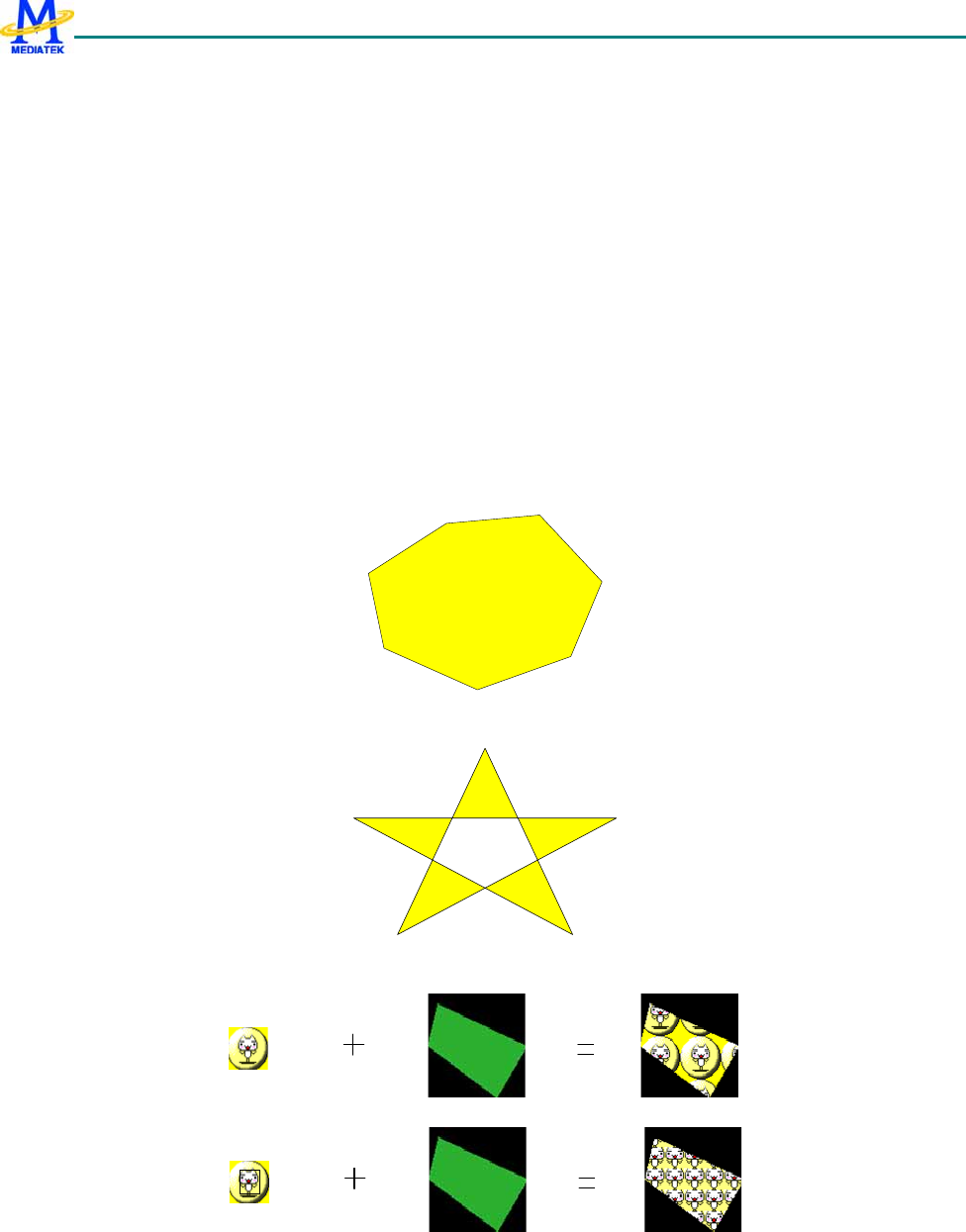

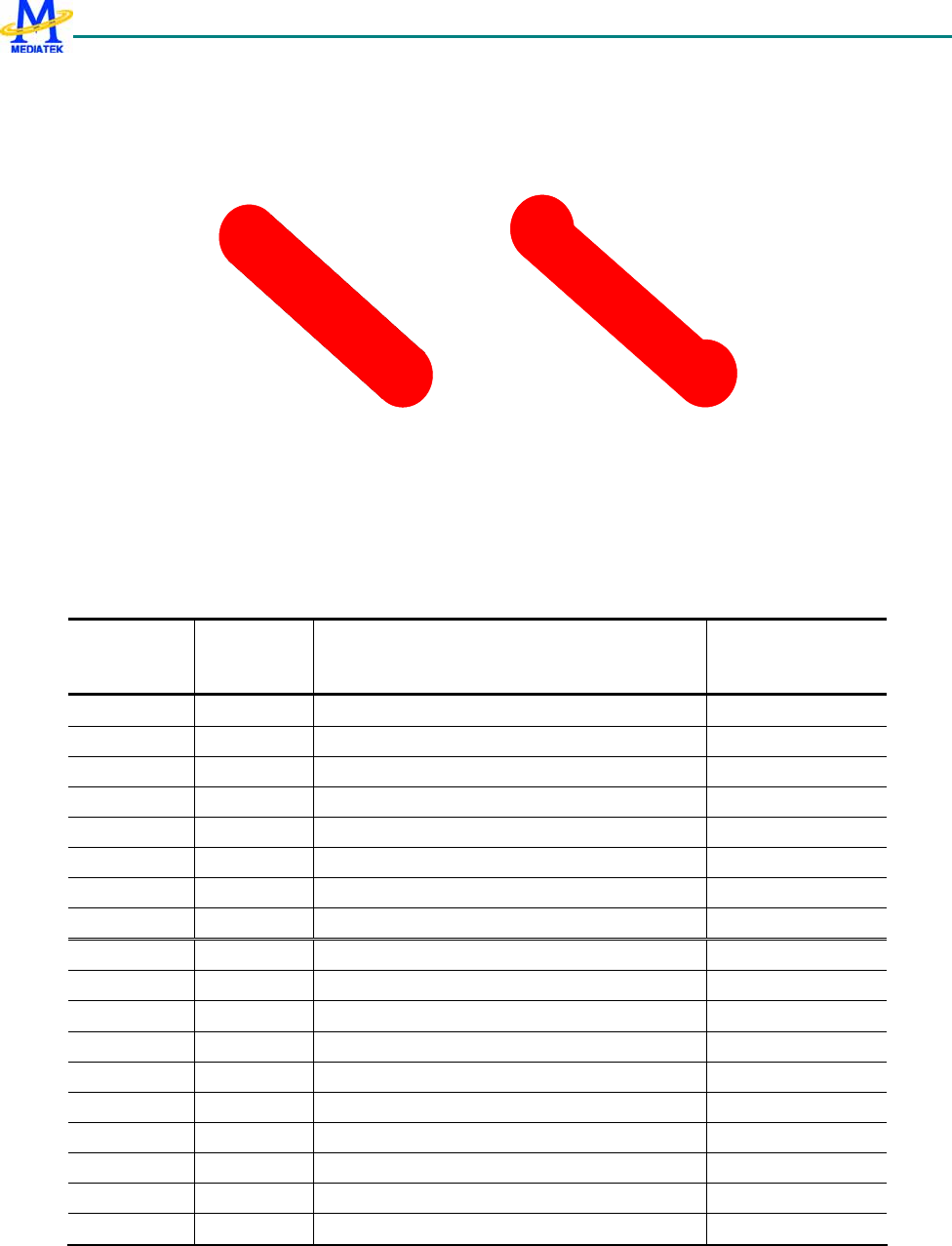

7.6 2D acceleration ...................................................................................................................................................... 383

7.7 Camera Interface.................................................................................................................................................... 410

8 Audio Front-End...........................................................................................................................422

8.1 General Description ............................................................................................................................................... 422

8.2 Register Definitions ............................................................................................................................................... 425

8.3 DSP Register Definitions ....................................................................................................................................... 439

8.4 Programming Guide............................................................................................................................................... 444

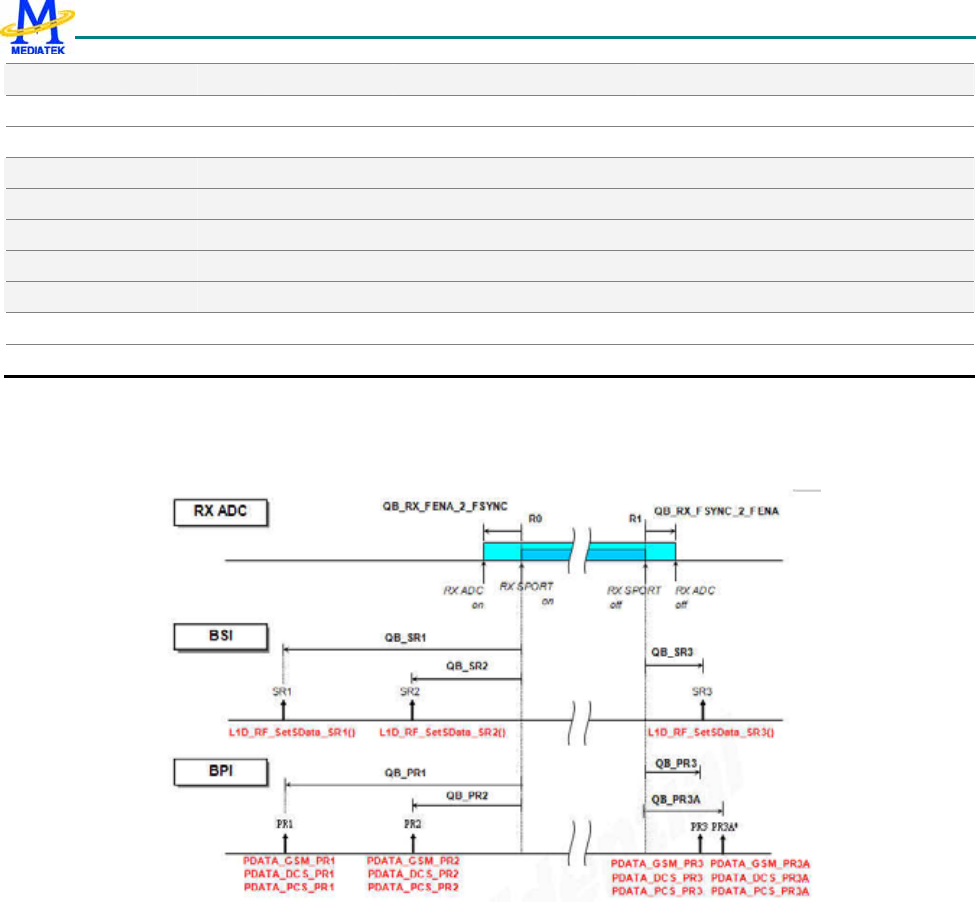

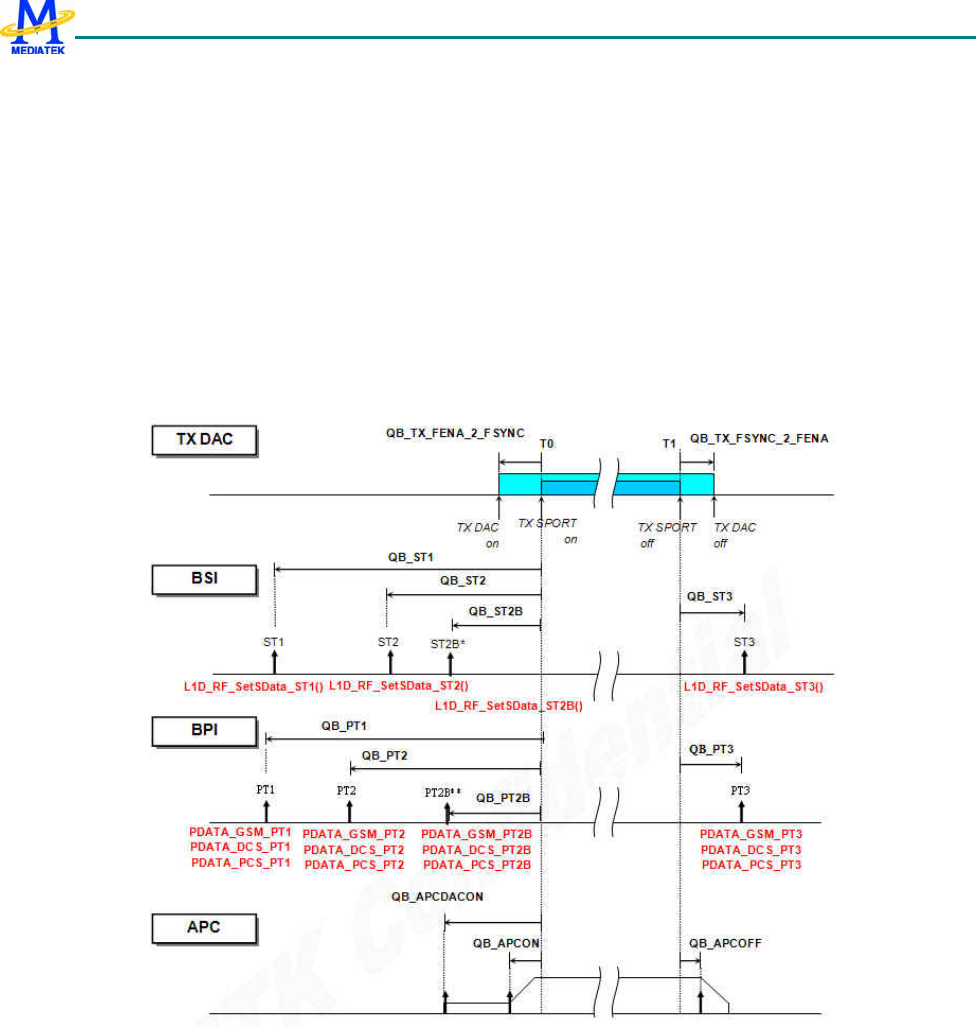

9 Radio Interface Control ...............................................................................................................446

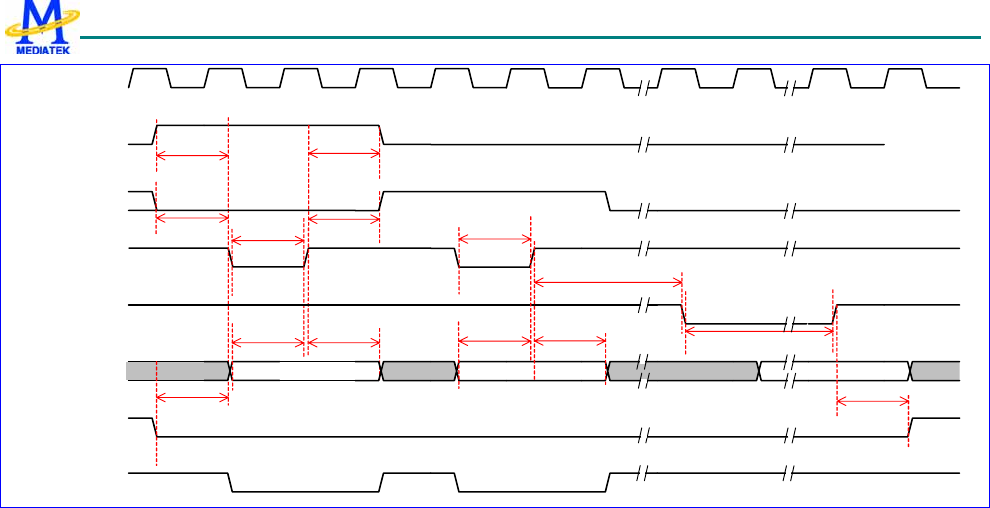

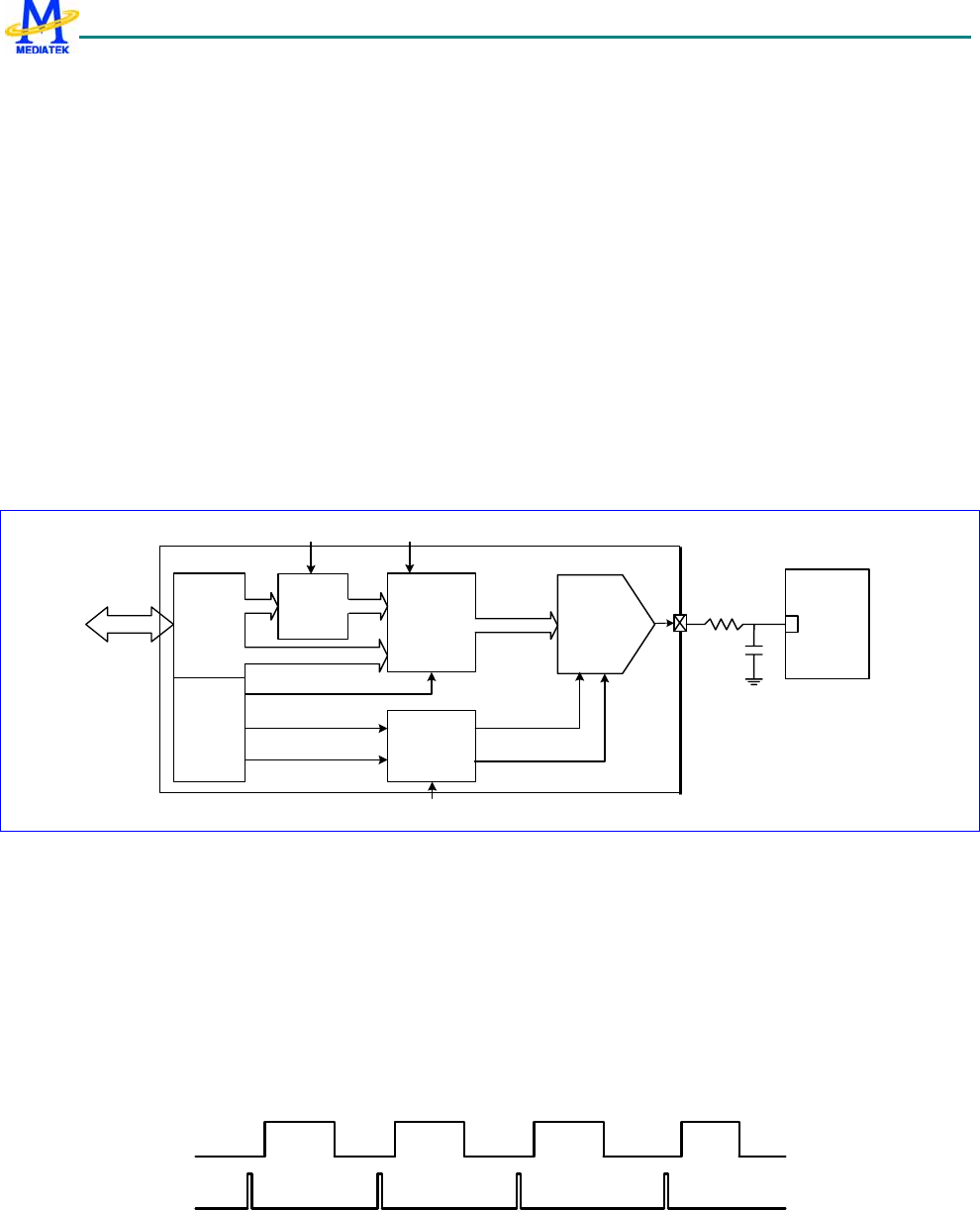

9.1 Baseband Serial Interface....................................................................................................................................... 446

9.2 Baseband Parallel Interface.................................................................................................................................... 454

9.3 Automatic Power Control (APC) Unit ................................................................................................................... 457

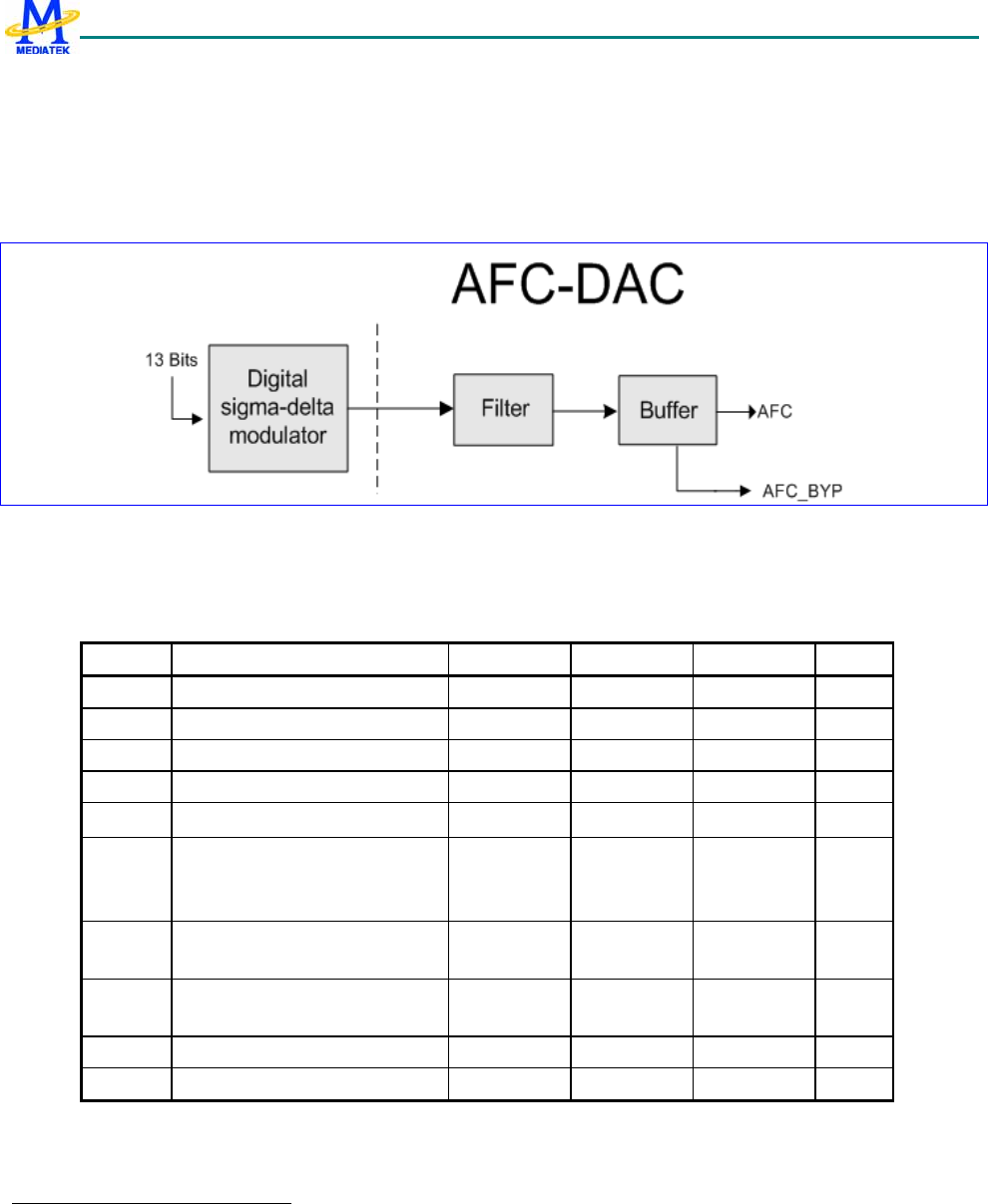

9.4 Automatic Frequency Control (AFC) Unit ............................................................................................................ 464

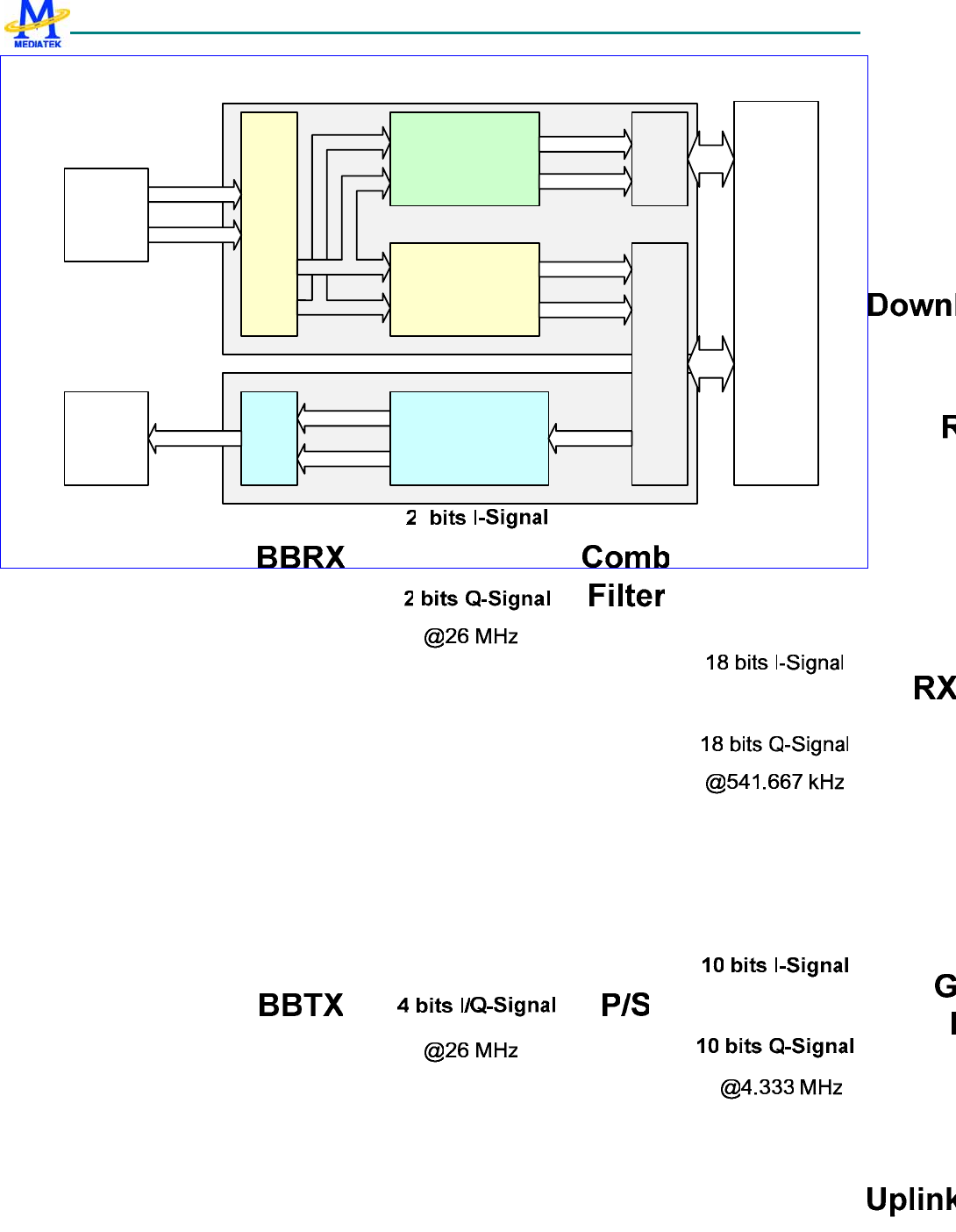

10 Baseband Front End.....................................................................................................................467

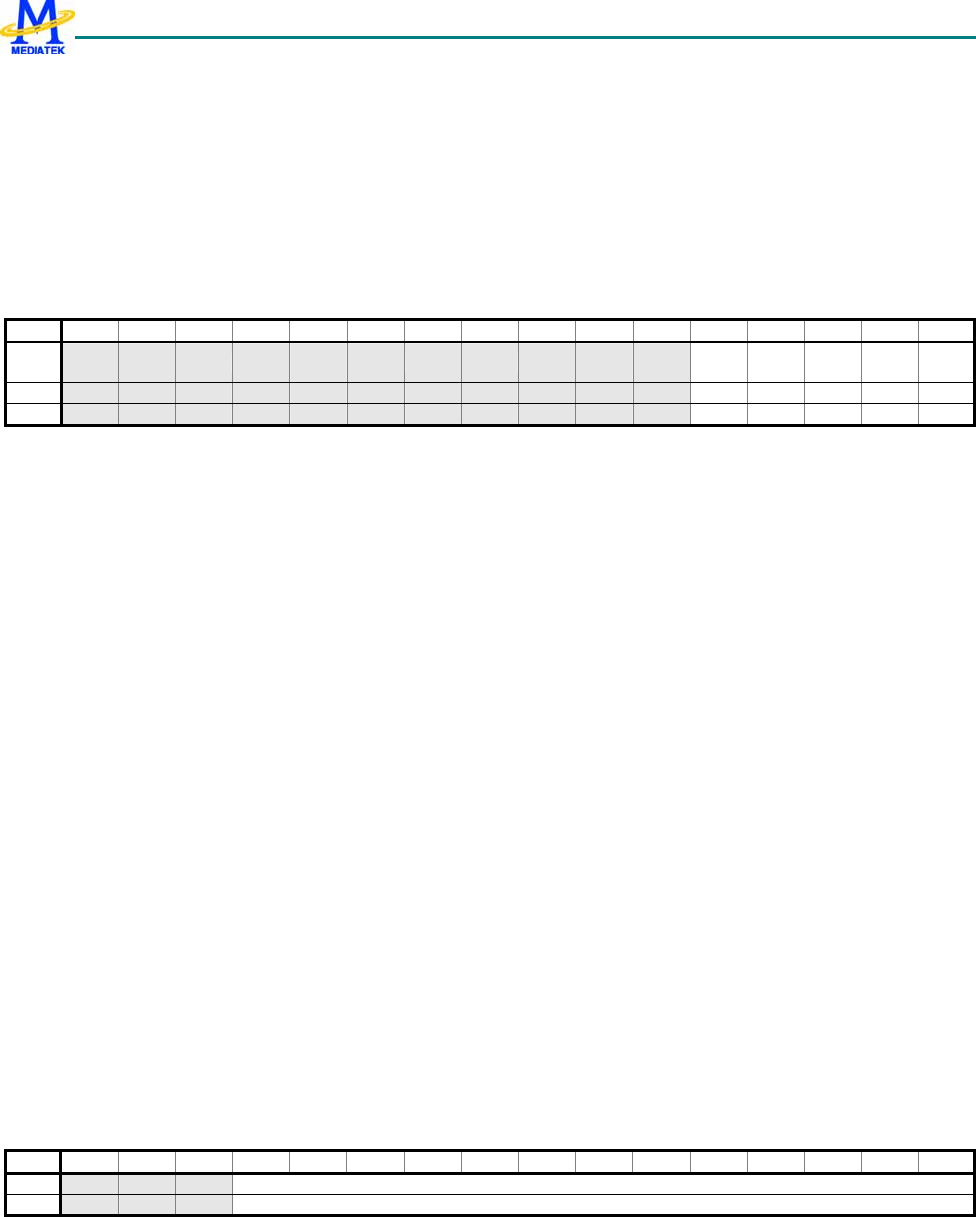

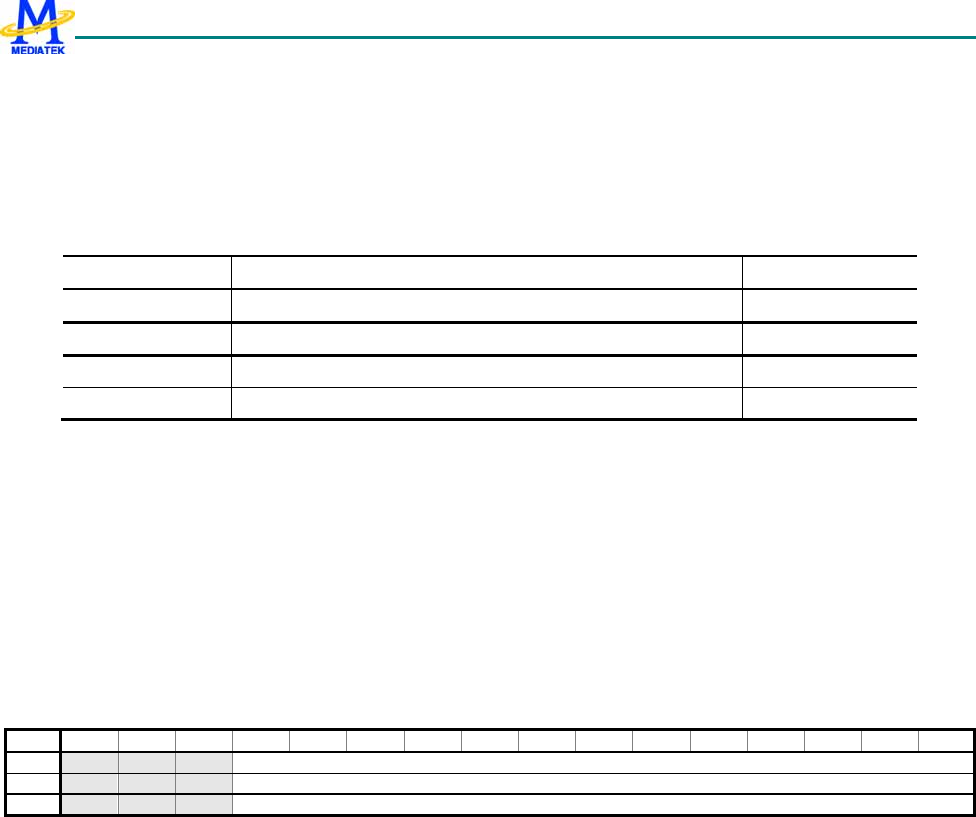

10.1 Baseband Serial Ports............................................................................................................................................. 468

10.2 Downlink Path (RX Path) ...................................................................................................................................... 472

10.3 Uplink Path (TX Path) ........................................................................................................................................... 480

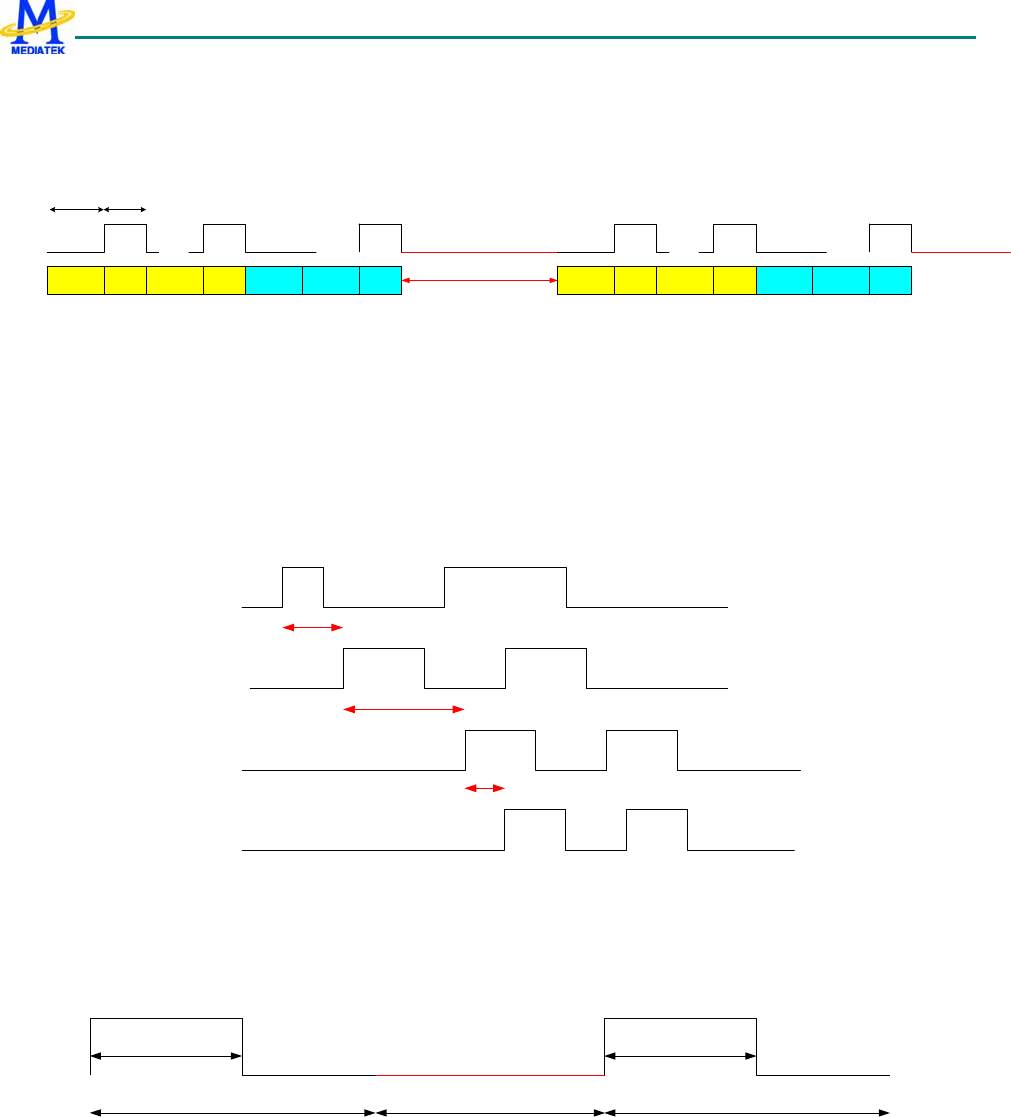

11 Timing Generator.........................................................................................................................487

11.1 TDMA timer........................................................................................................................................................... 487

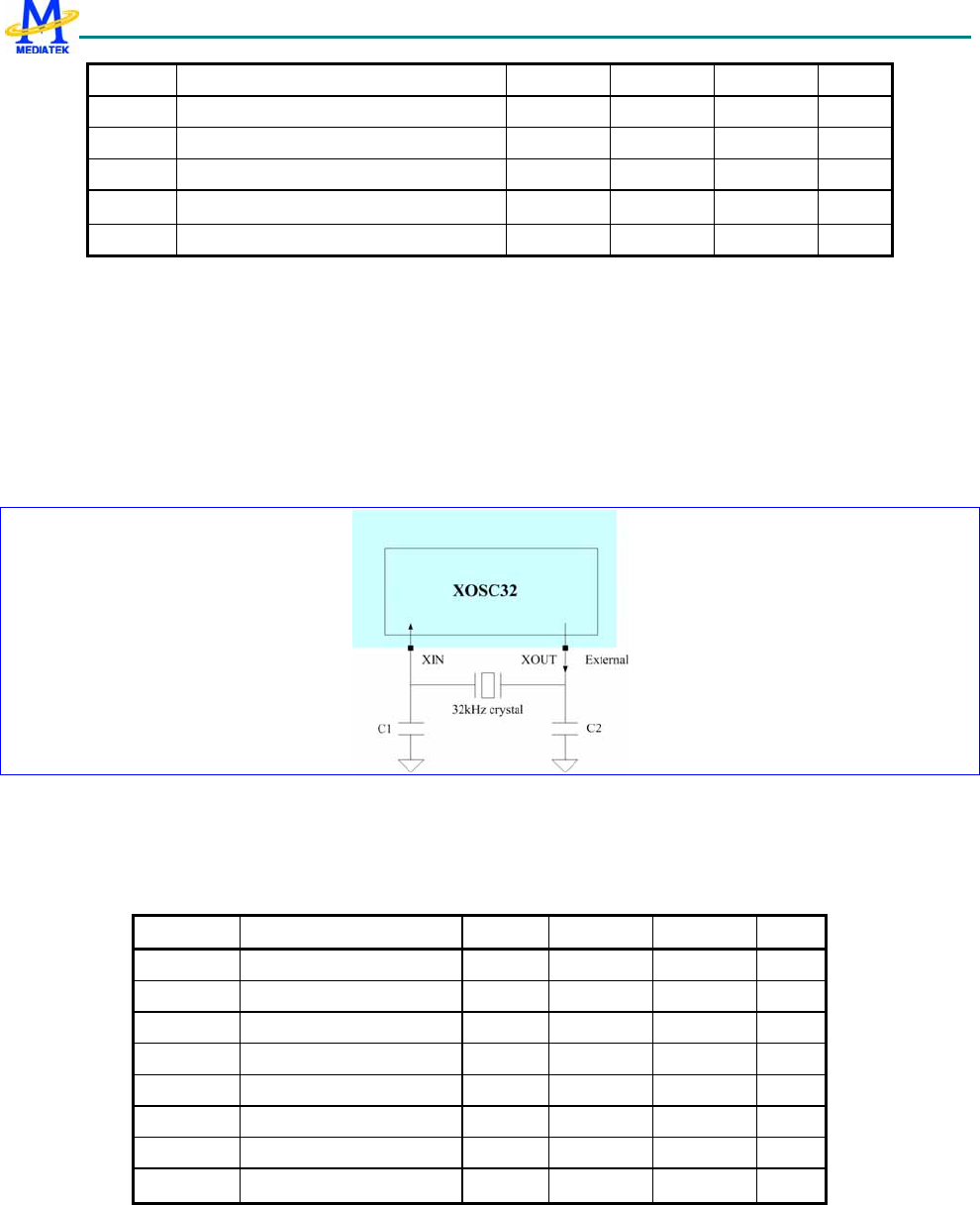

11.2 Slow Clocking Unit................................................................................................................................................ 499

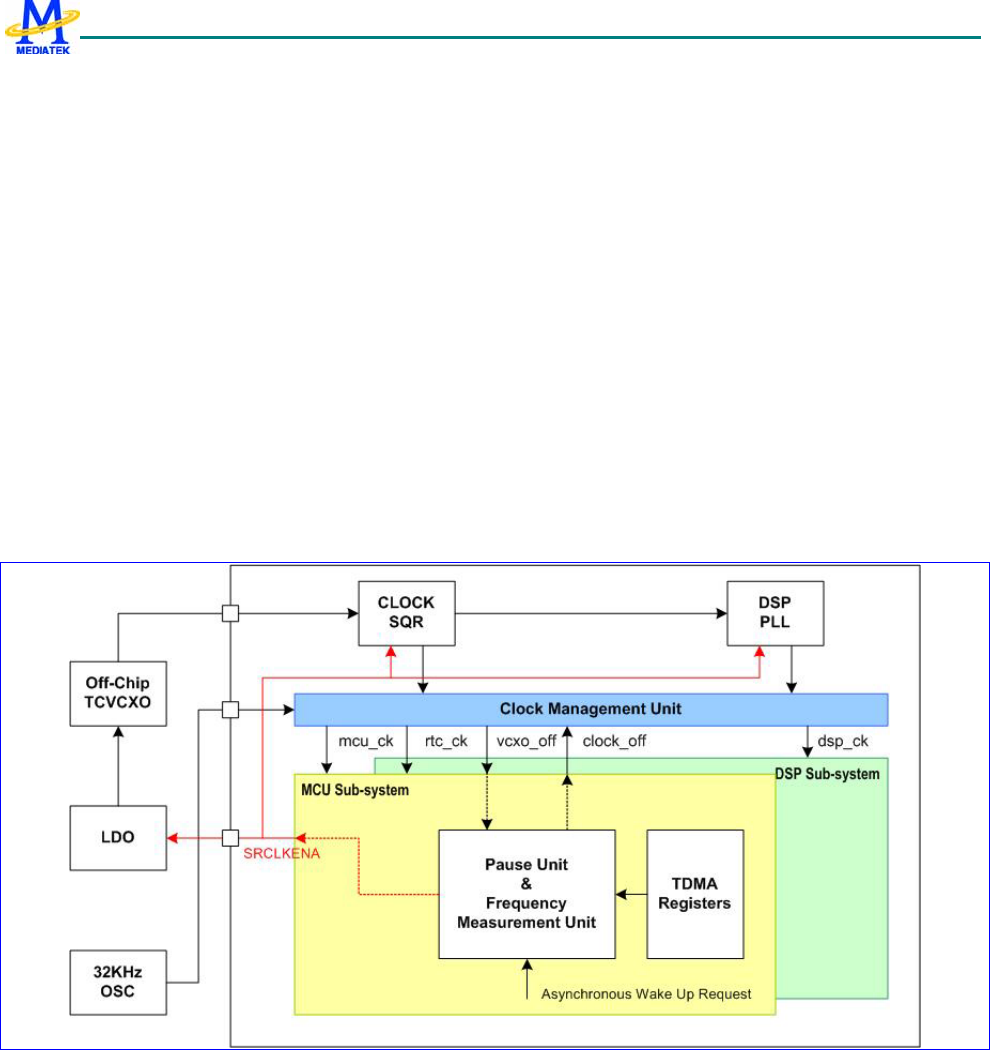

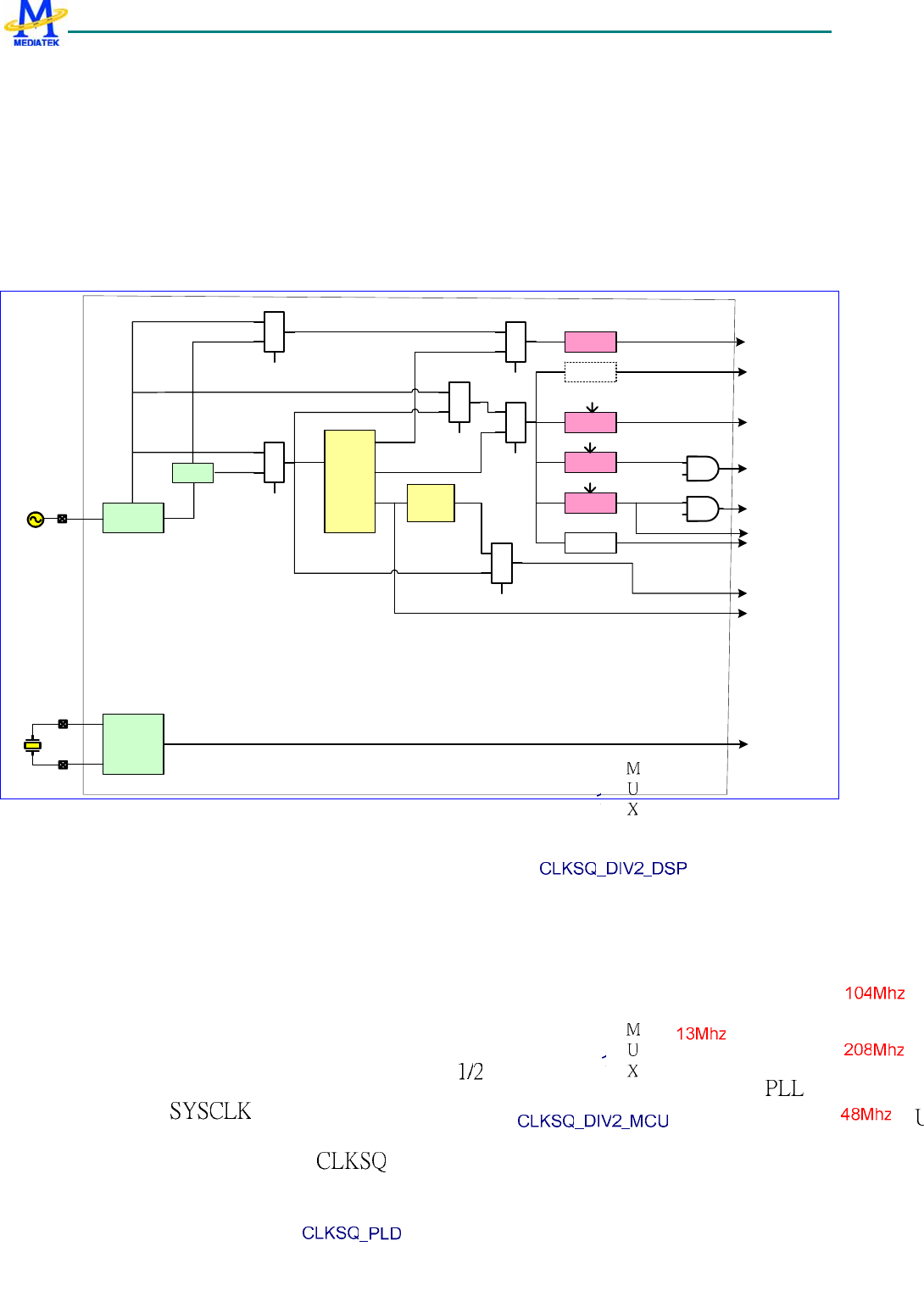

12 Power, Clocks and Reset ..............................................................................................................503

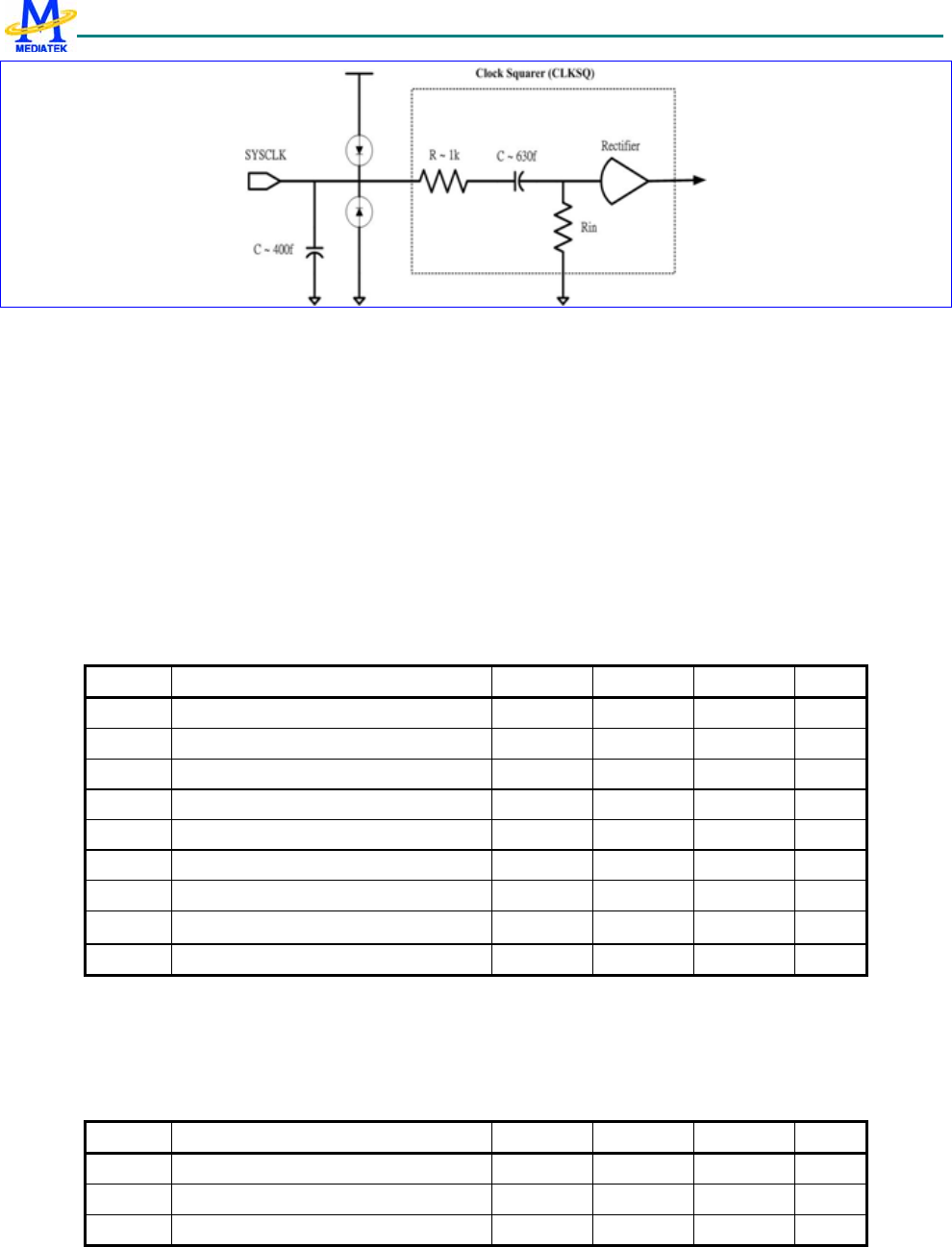

12.1 Clocks .................................................................................................................................................................... 503

12.2 Reset Generation Unit (RGU)................................................................................................................................ 507

12.3 Global Configuration Registers...............................................................................................................................511

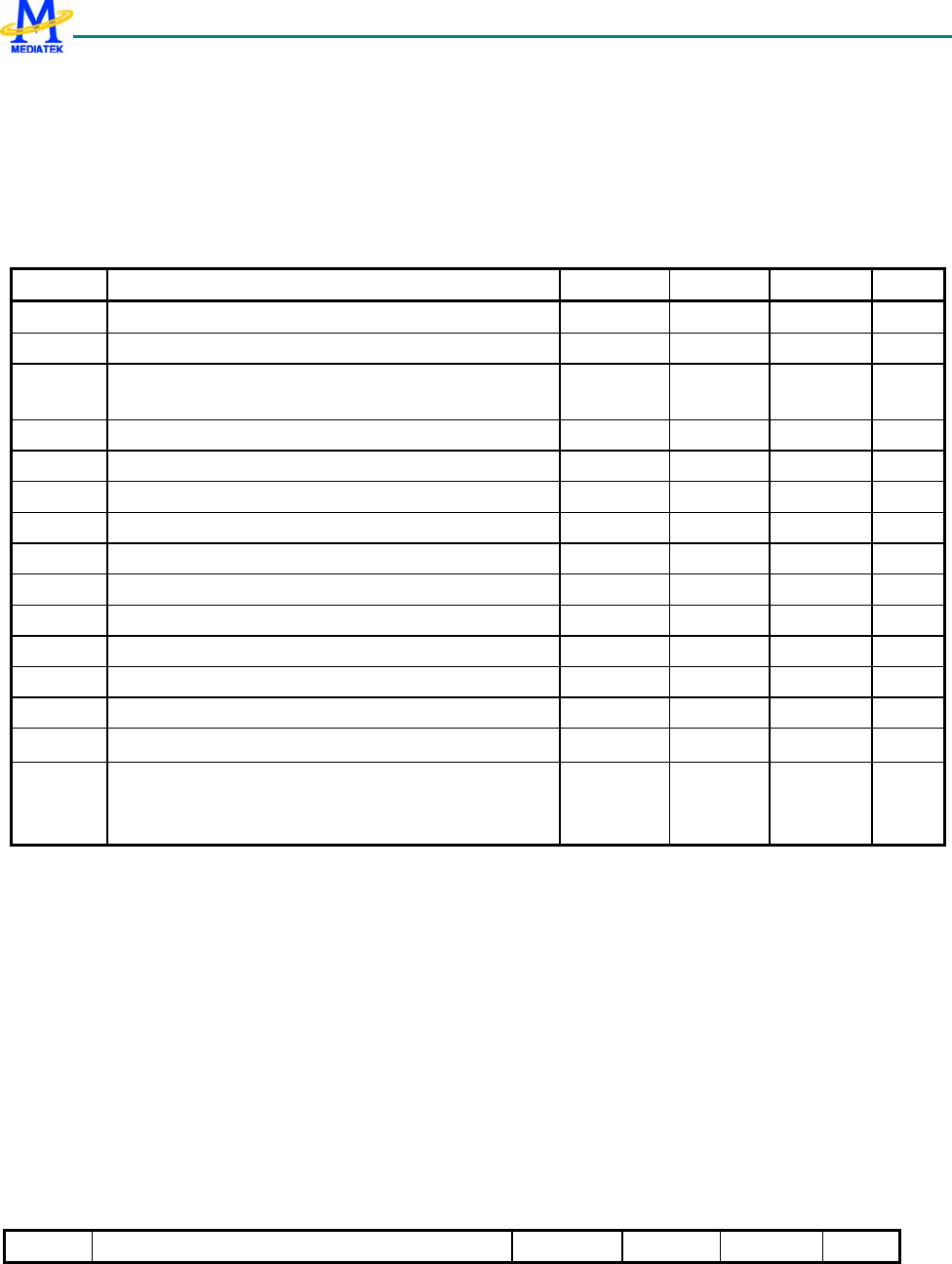

13 Analog Front-end & Analog Blocks............................................................................................526

13.1 General Description ............................................................................................................................................... 526

13.2 MCU Register Definitions ..................................................................................................................................... 537

13.3 Programming Guide............................................................................................................................................... 579

14 Digital Pin Electrical Characteristics..........................................................................................593

MT6235 GSM/GPRS Baseband Processor Data Sheet Revision 1.02

5/599 MediaTek Inc. Confidential

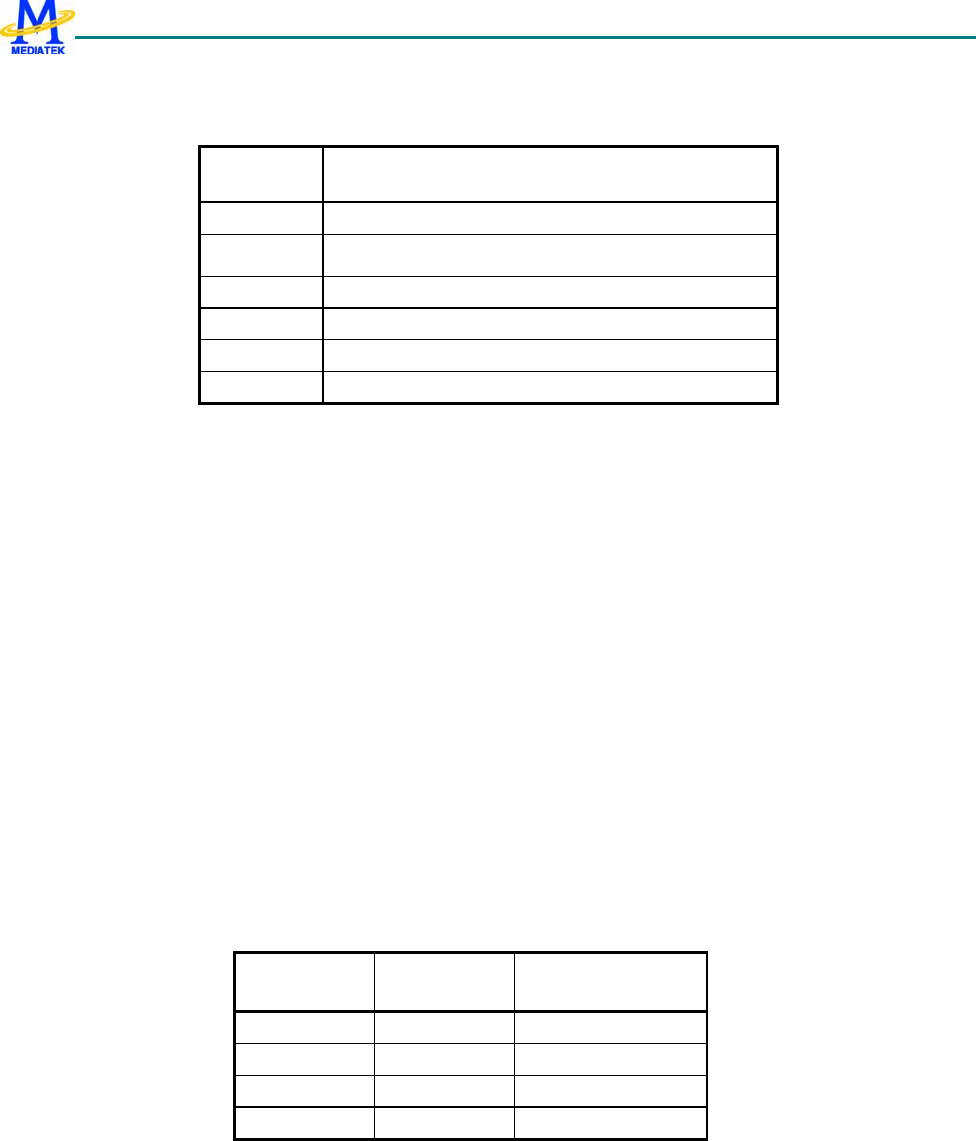

Preface

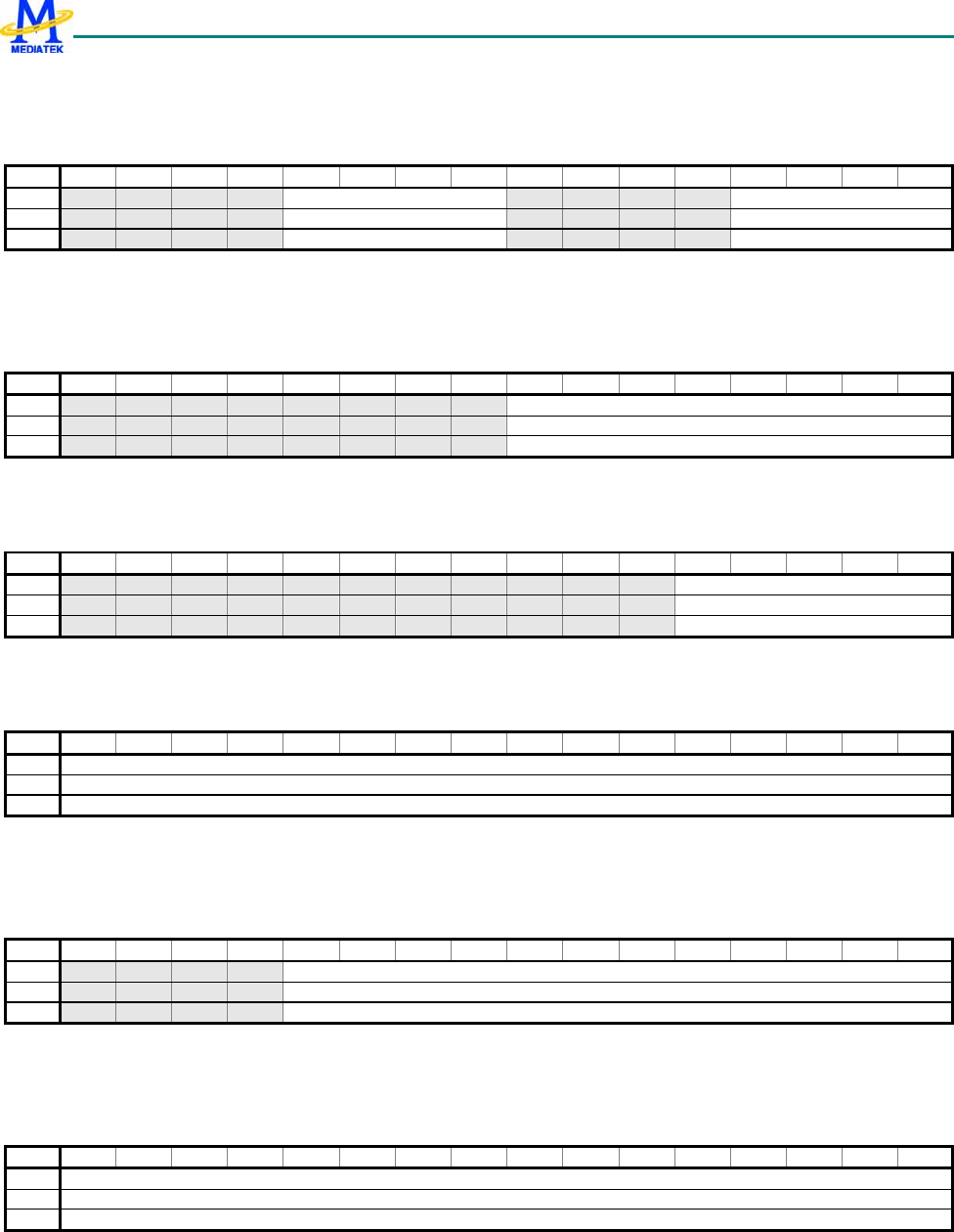

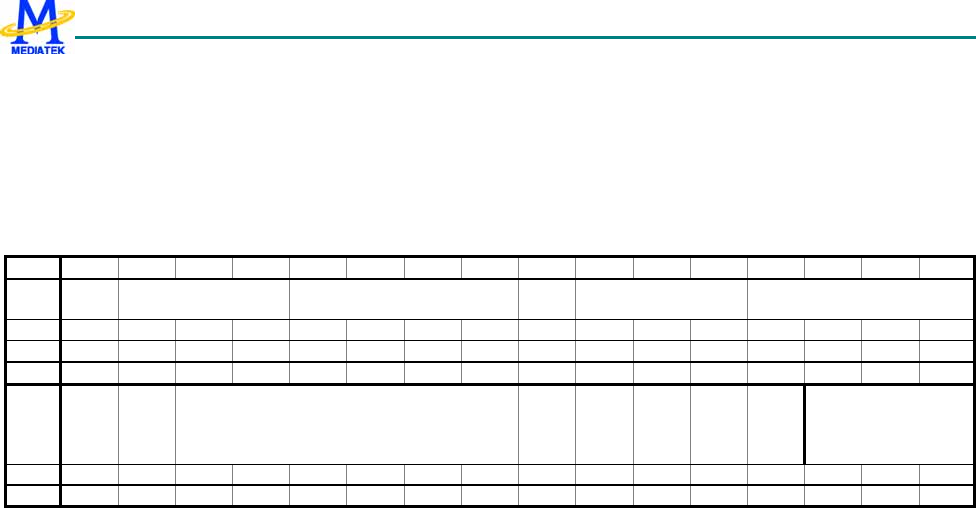

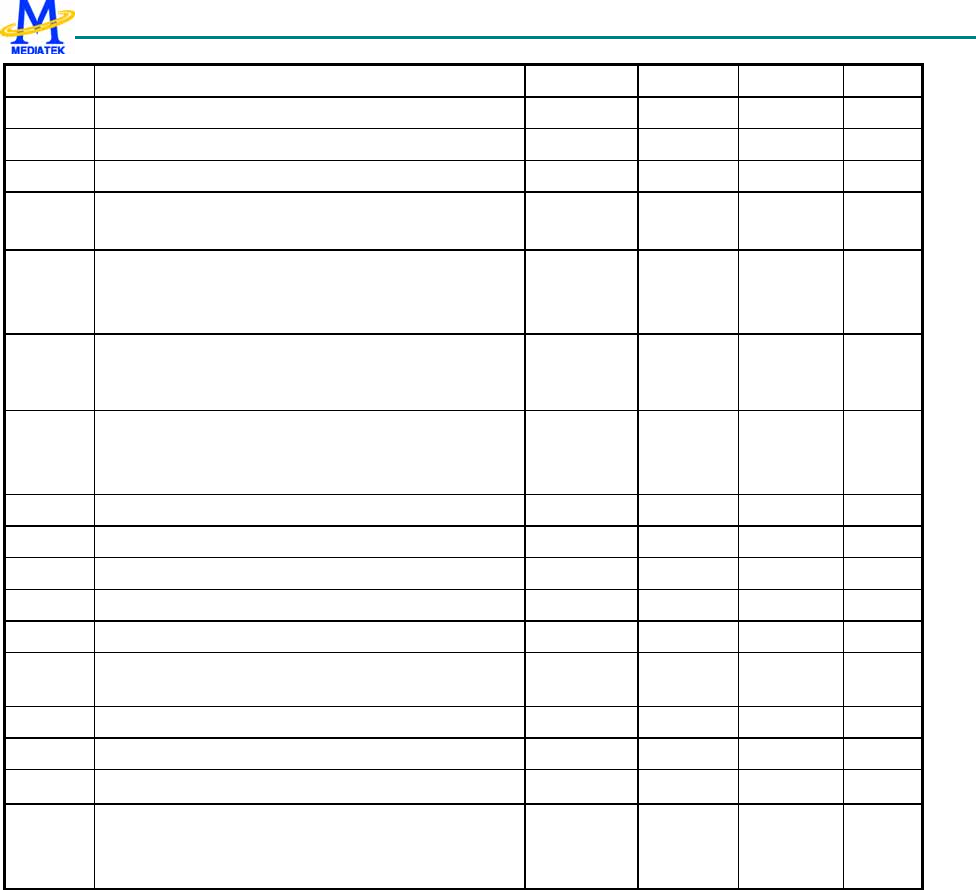

Acronym for Register Type

R/W Capable of both read and write access

RO Read only

RC Read only. After reading the register bank, each bit which is HIGH(1) will be cleared to LOW(0 )

automatically.

WO Write only

W1S Write only. When writing data bits to register bank, each bit which is HIGH(1) will cause the

corresponding bit to be set to 1. Data bits which are LOW(0) has no effect on the corresponding bit.

W1C Write only. When writing data bits to register bank, each bit which is HIGH(1) will cause the

corresponding bit to be cleared to 0. Data bits which are LOW(0) has no effect on the corresponding bit.

MT6235 GSM/GPRS Baseband Processor Data Sheet Revision 1.02

6/599 MediaTek Inc. Confidential

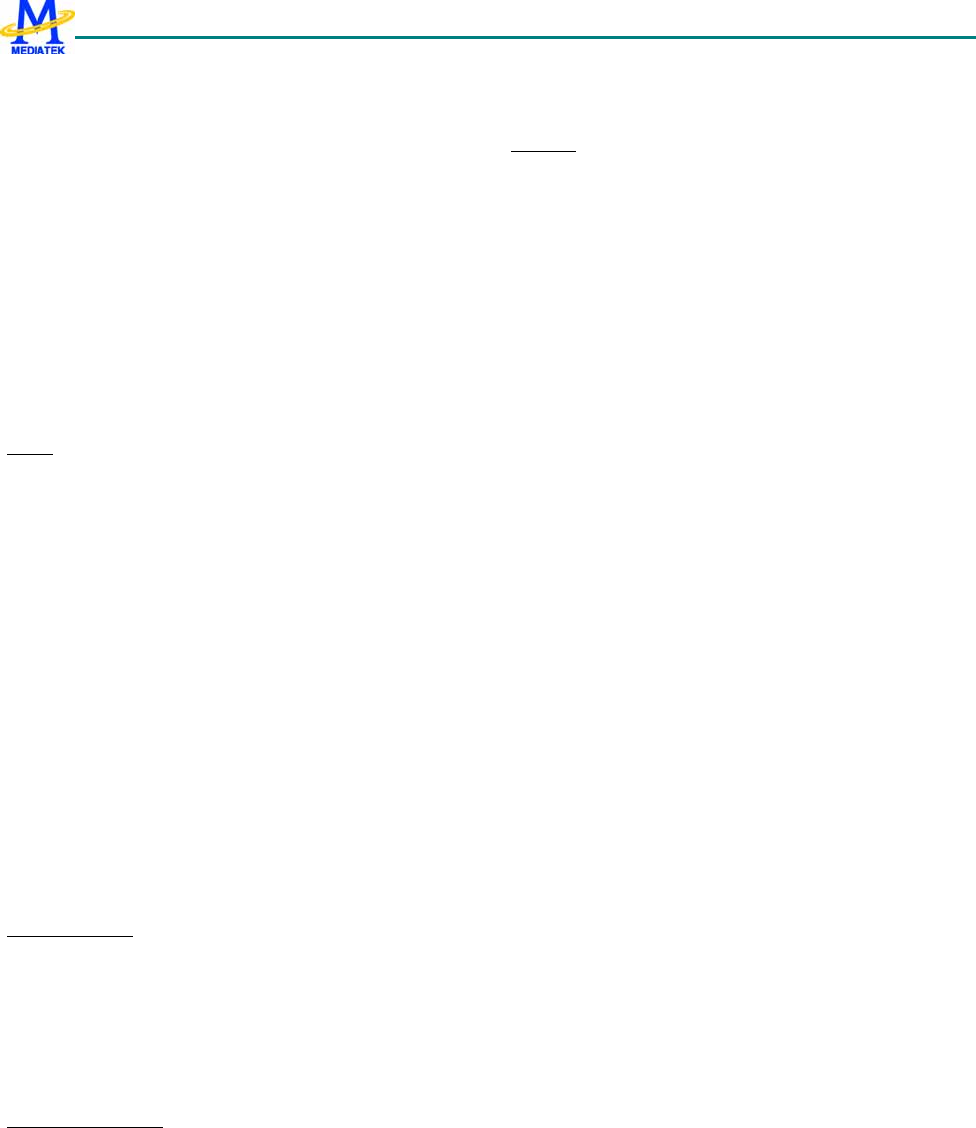

1. System Overview

MT6235 is a highly-integrated and extremely powerful

single-chip solution for GSM/GPRS/EDGE mobile phones.

Based on the 32-bit ARM926EJ-STM RISC processor,

MT6235’s superb processing power, along with high

bandwidth architecture and dedicated hardware support,

provides an unprecedented platform for high performance

GPRS/EDGE Class 12 MODEM application. Overall,

MT6235 presents a revolutionary platform for mobile

devices.

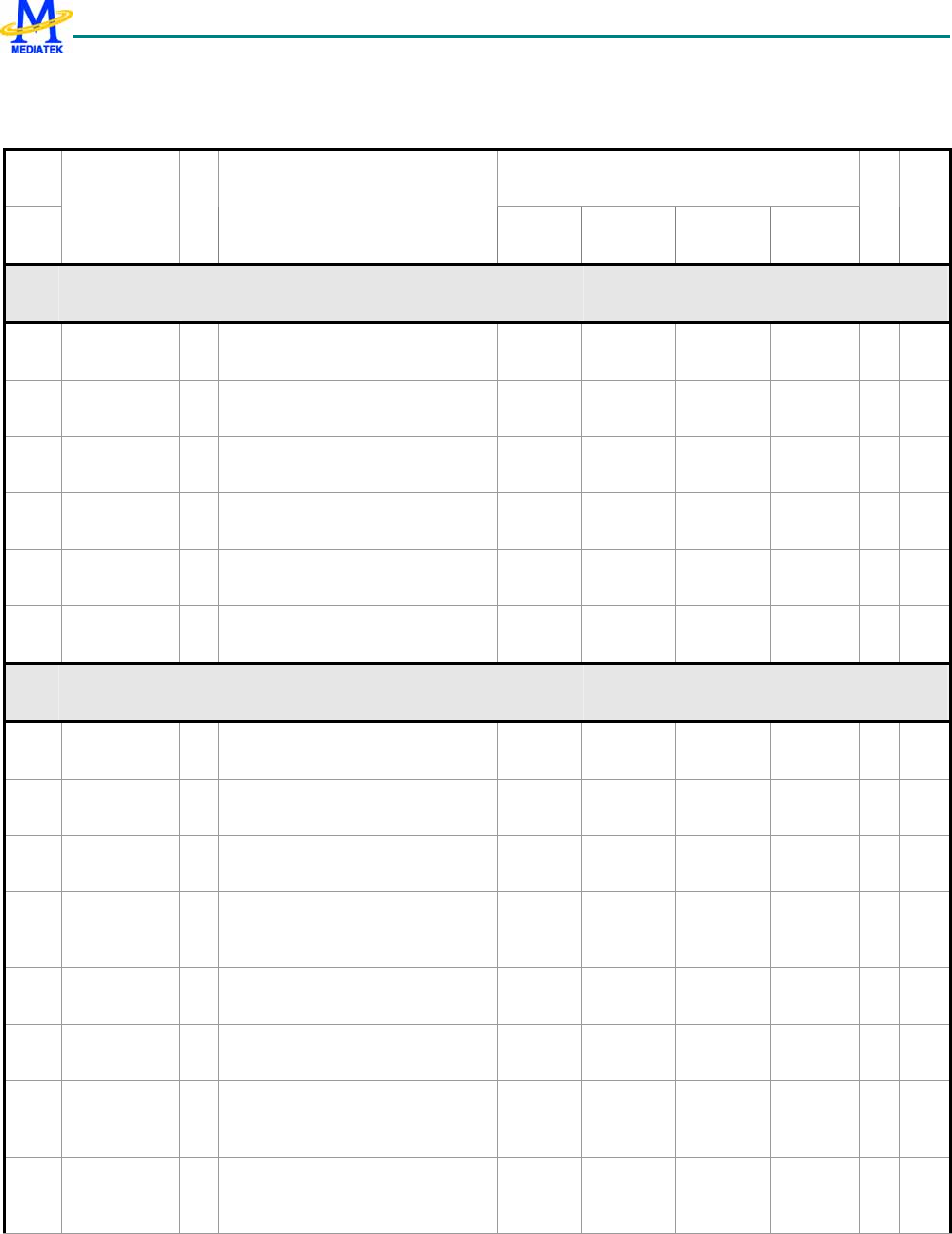

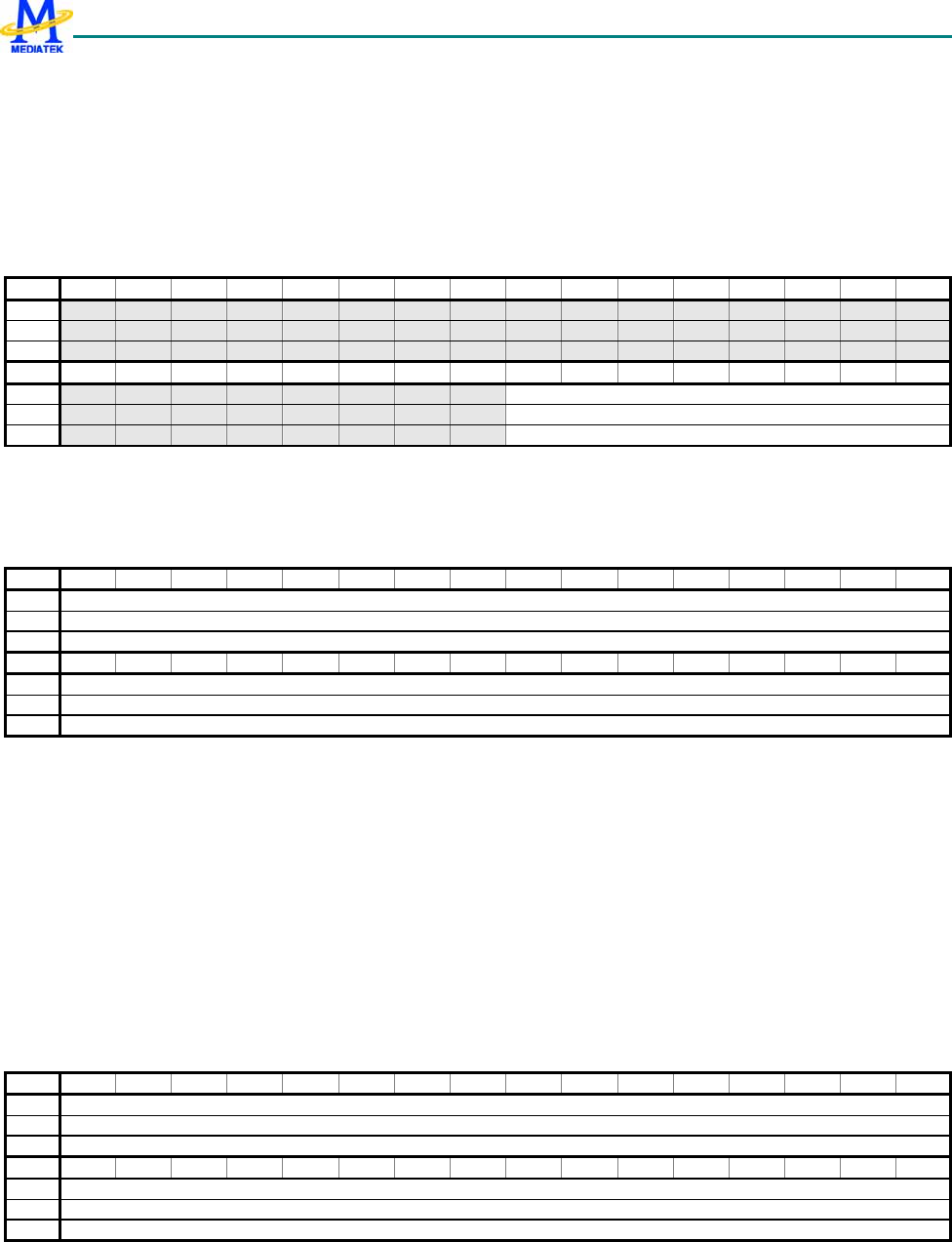

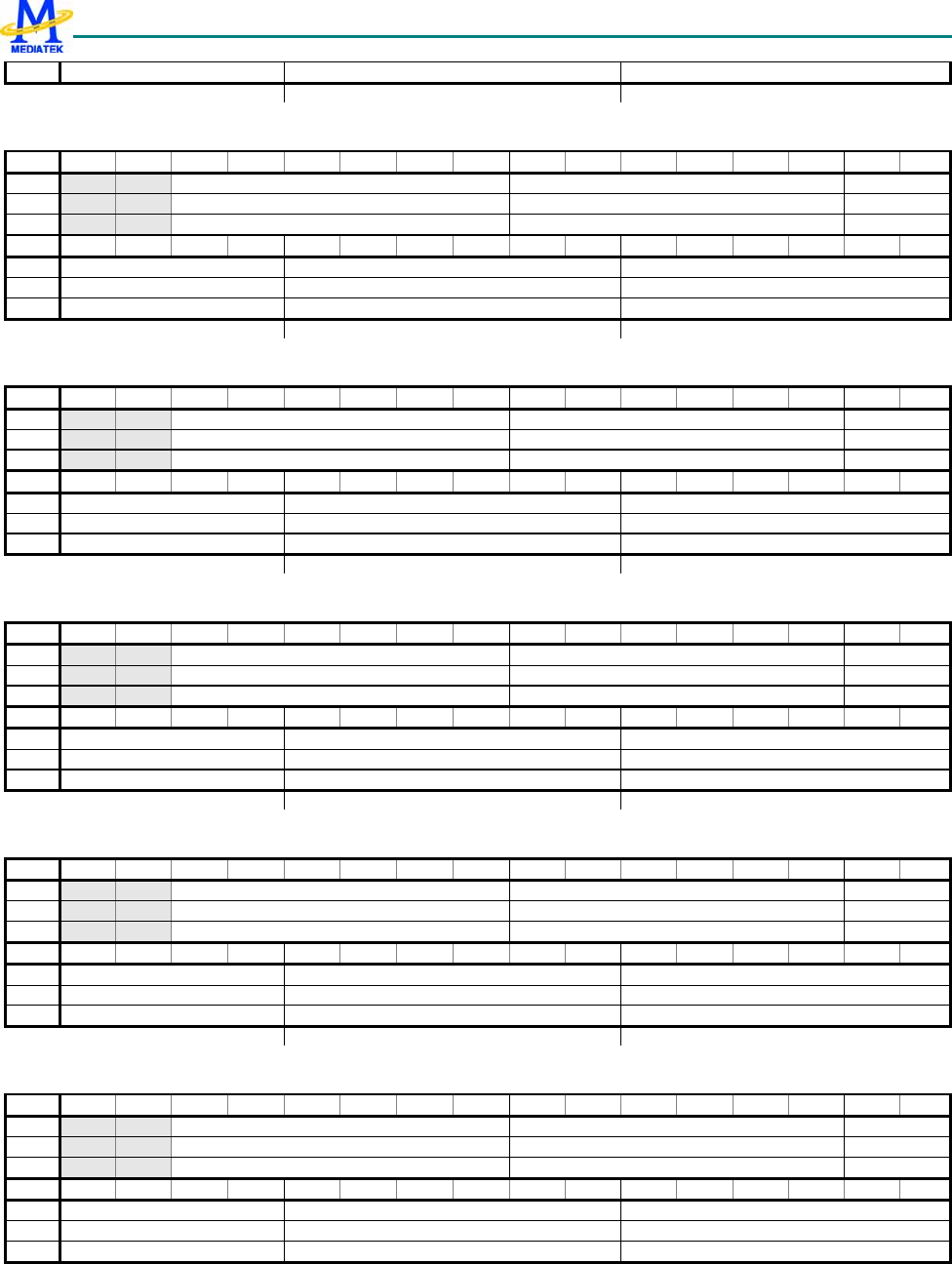

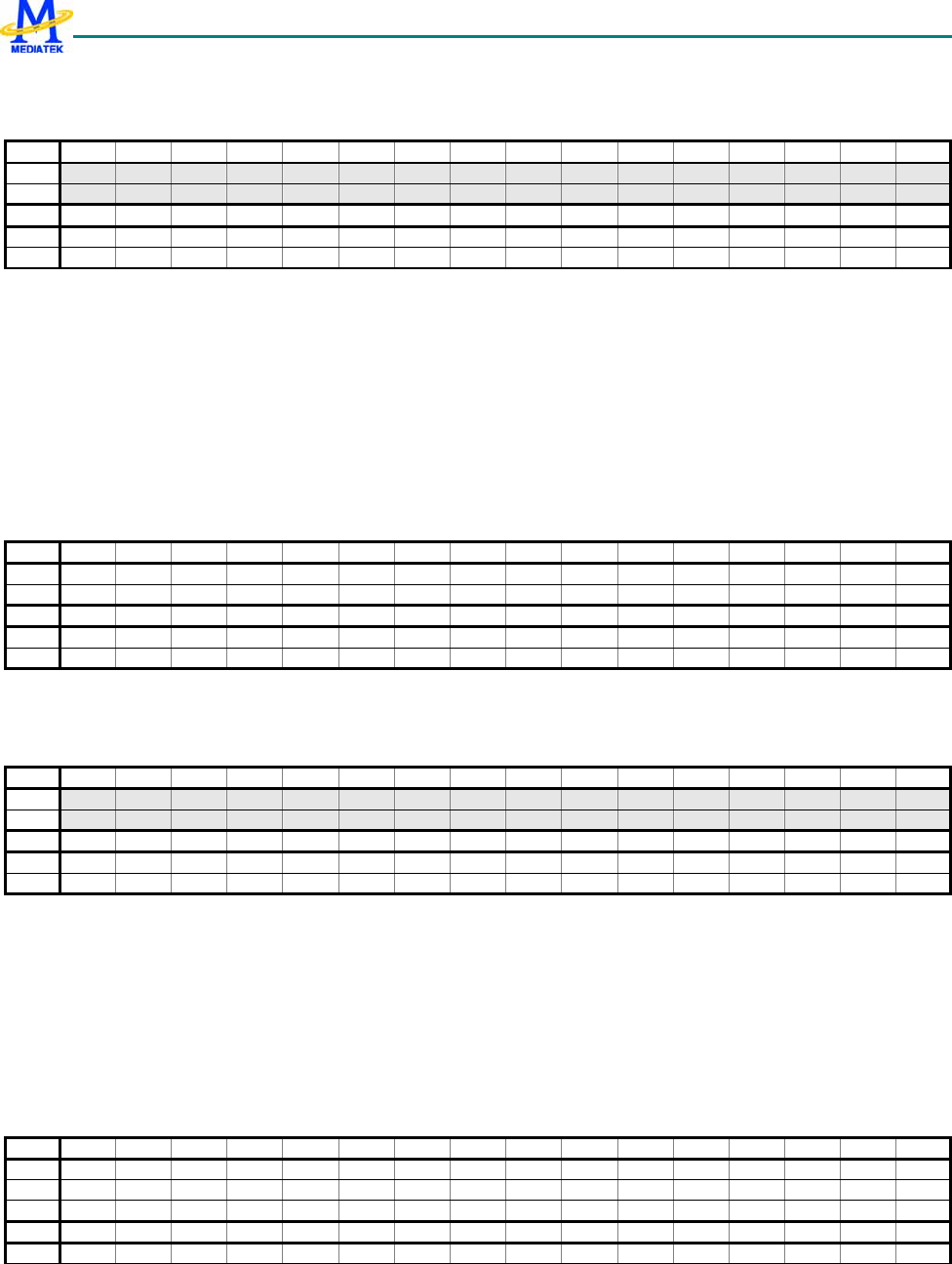

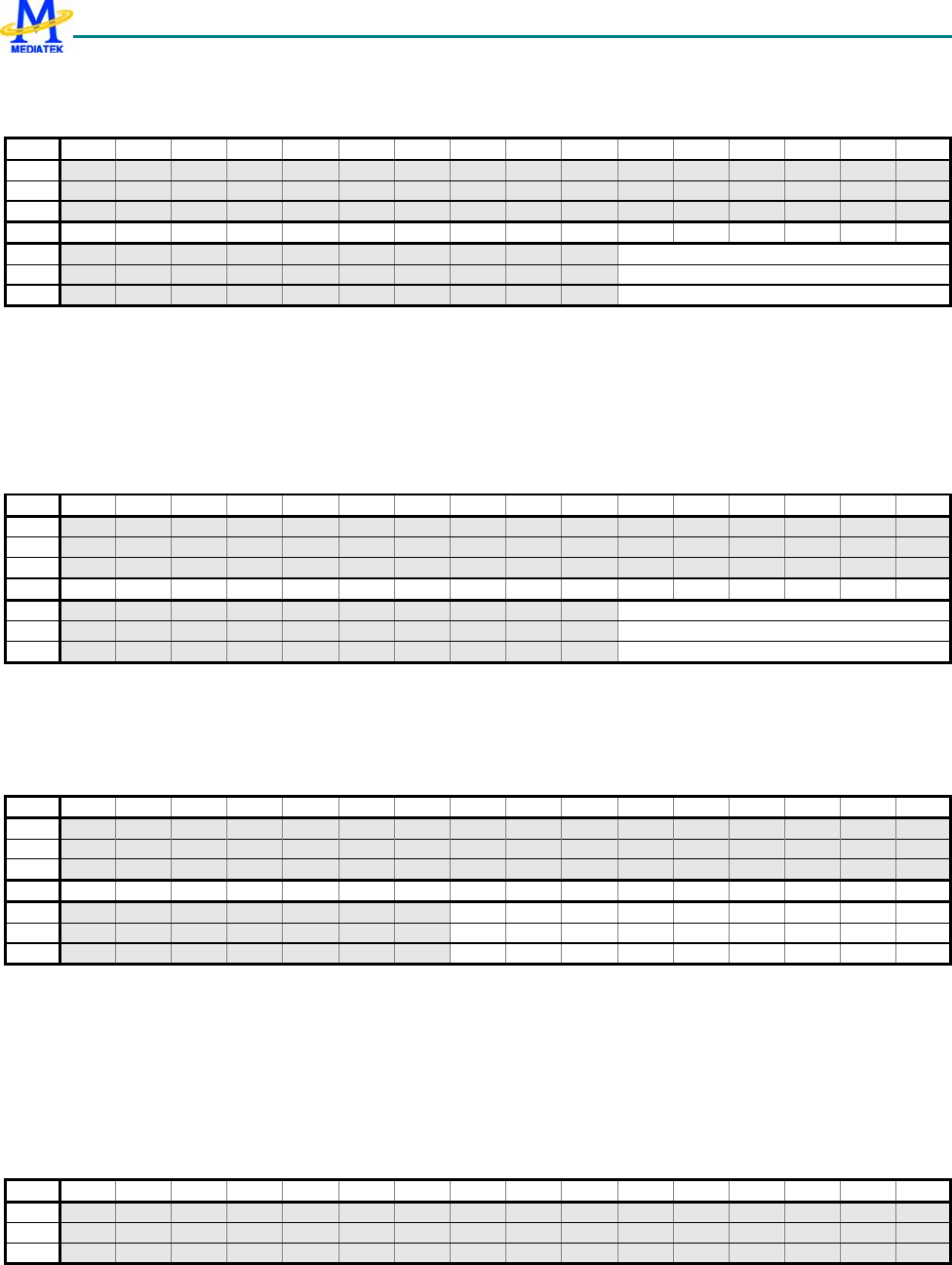

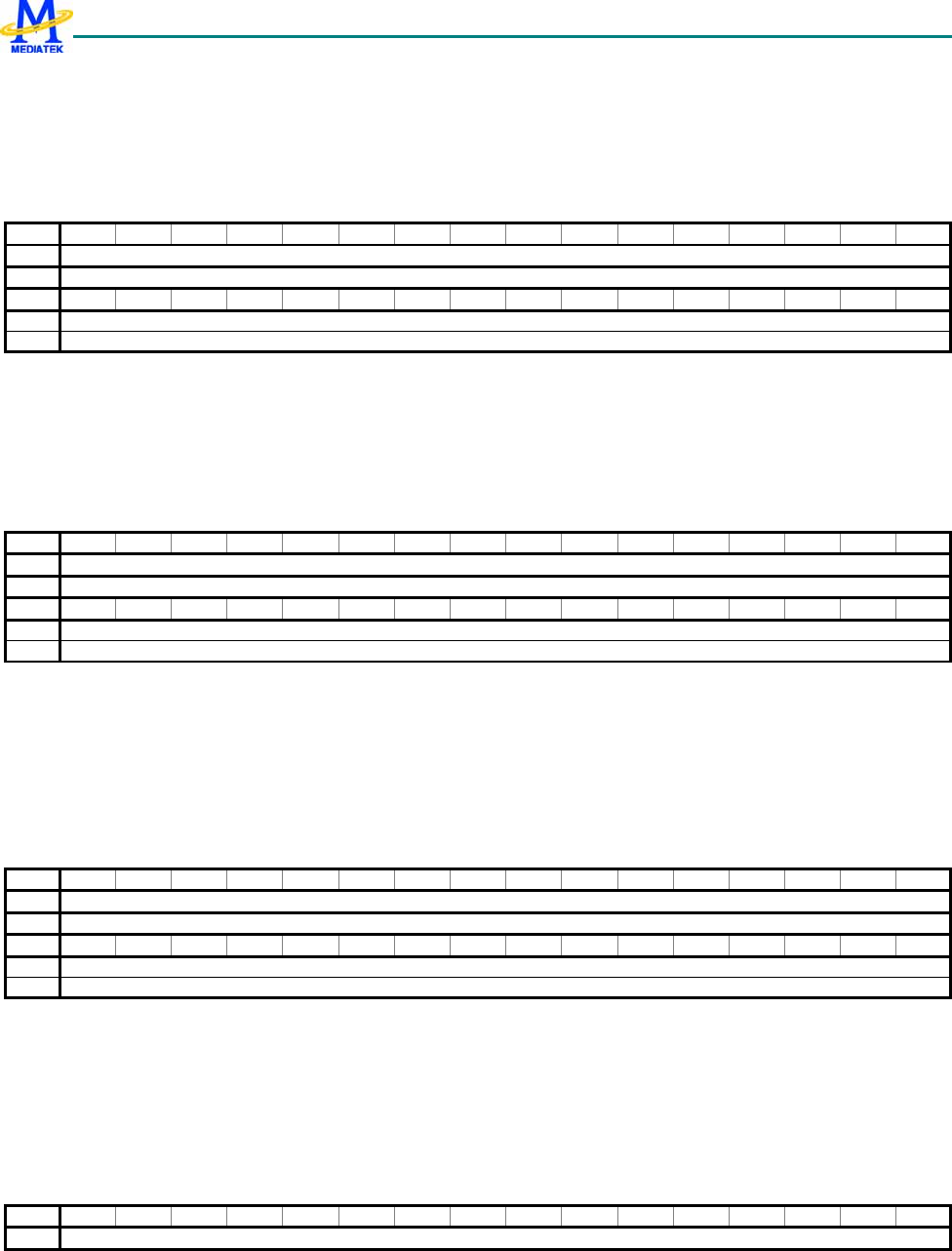

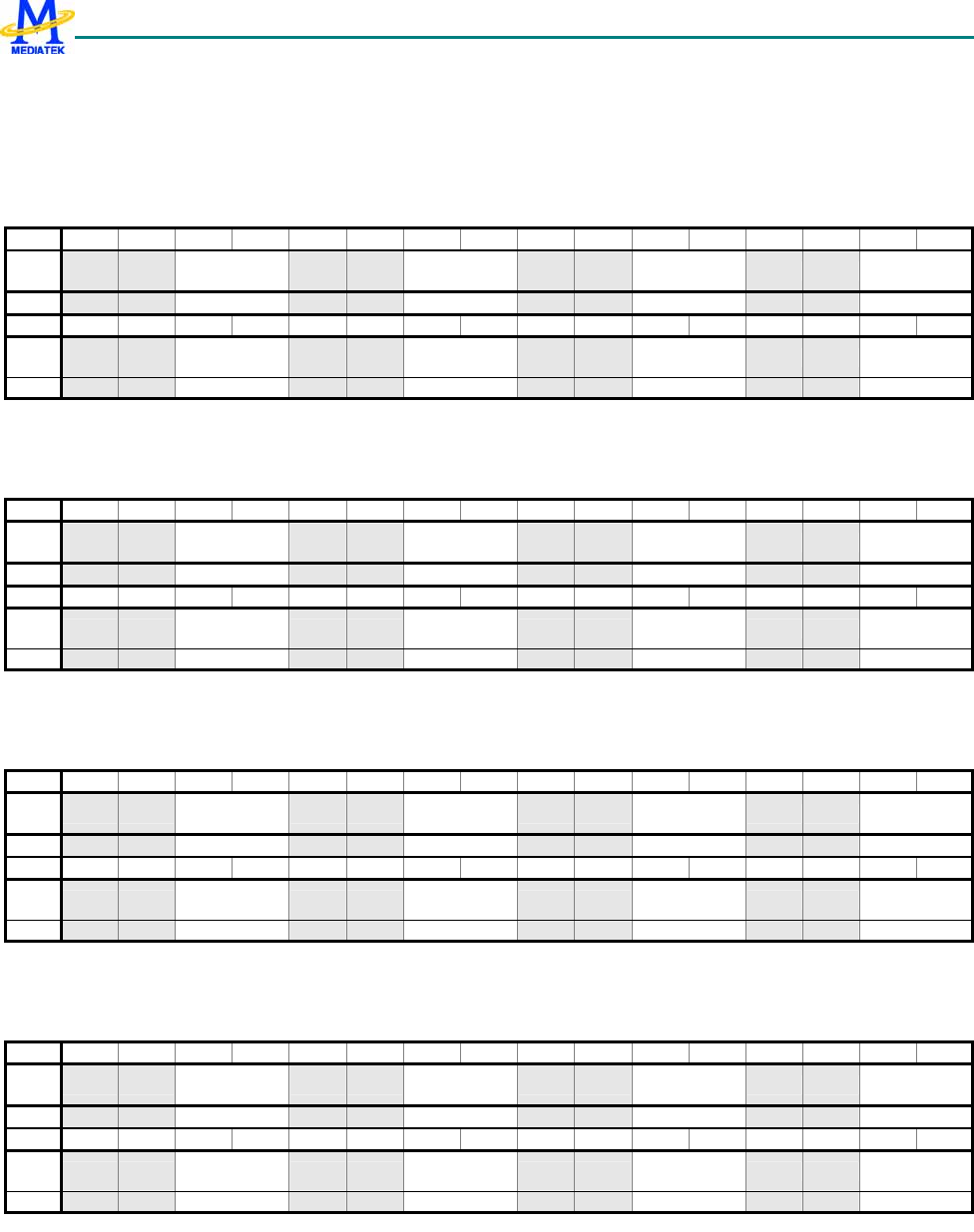

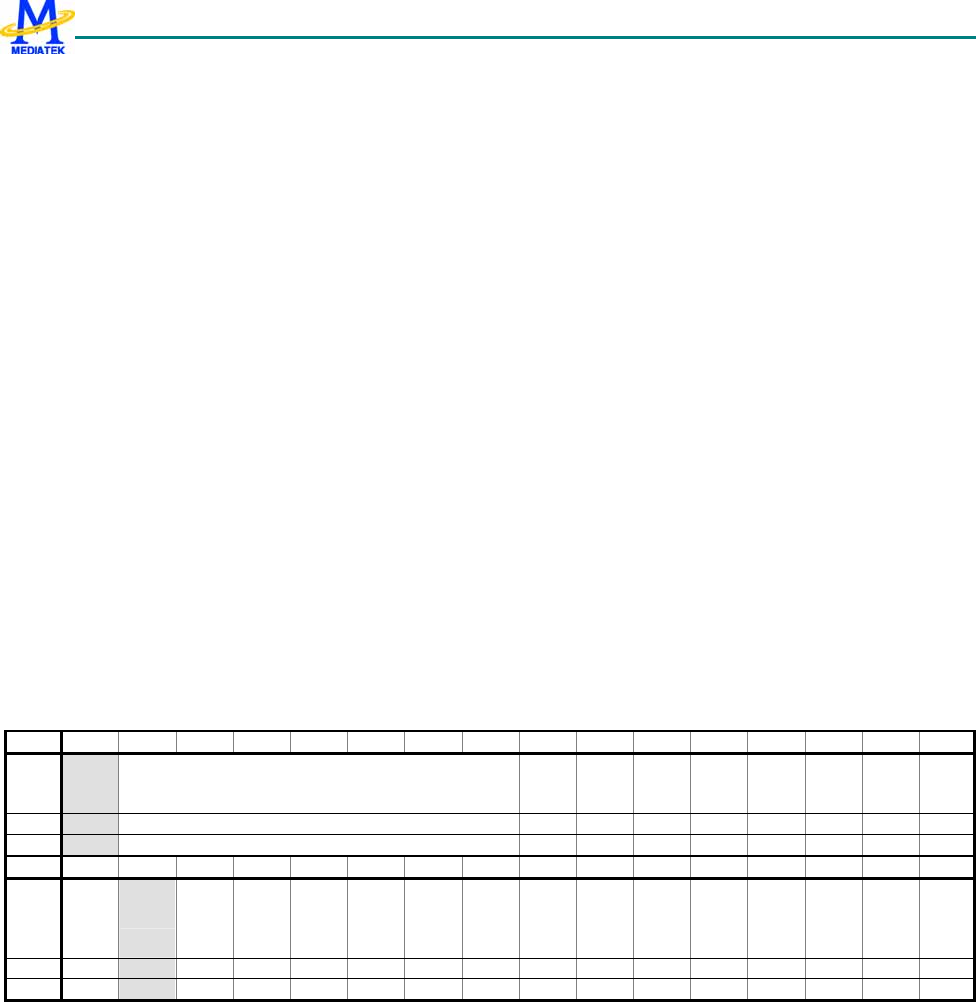

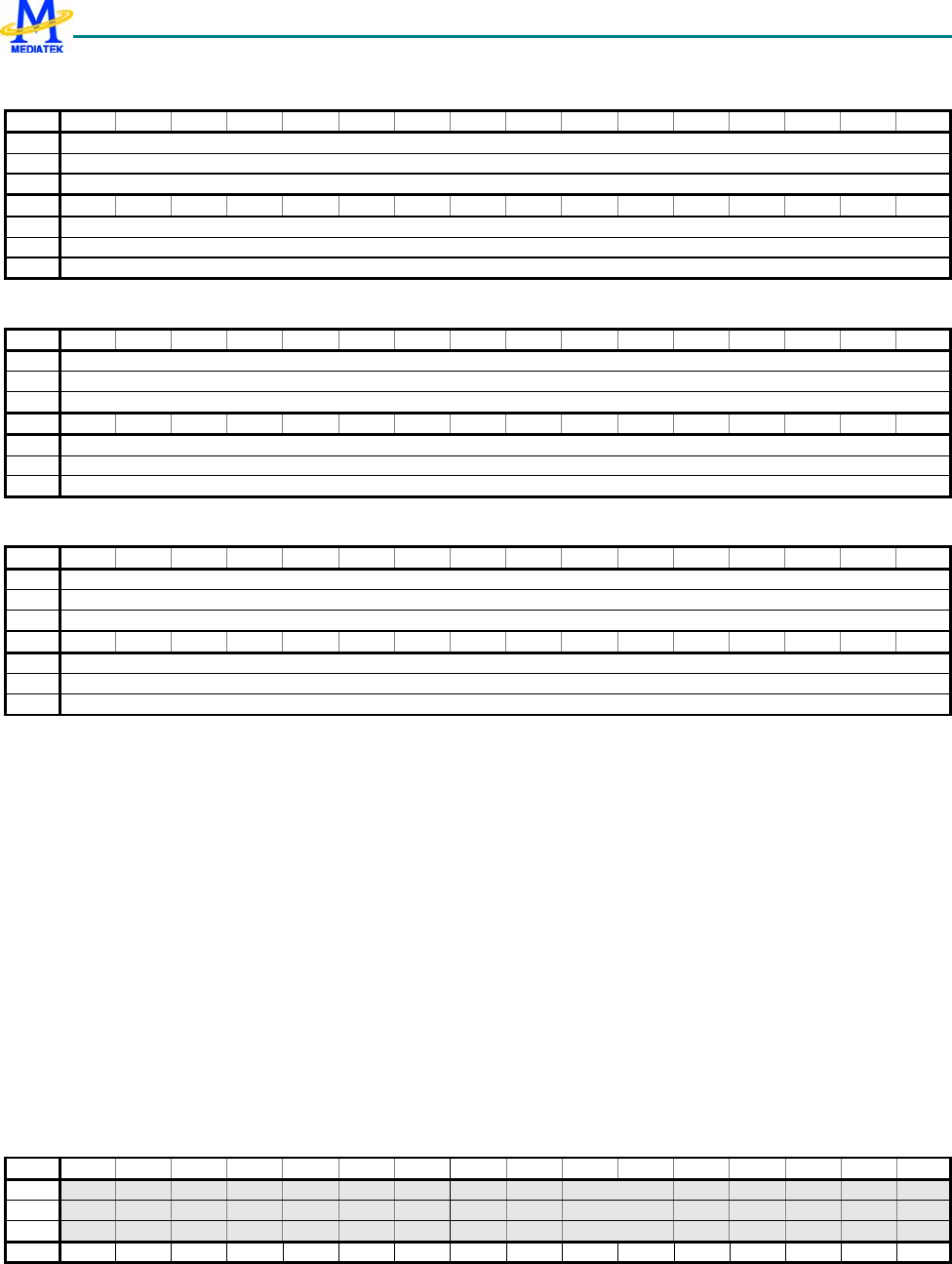

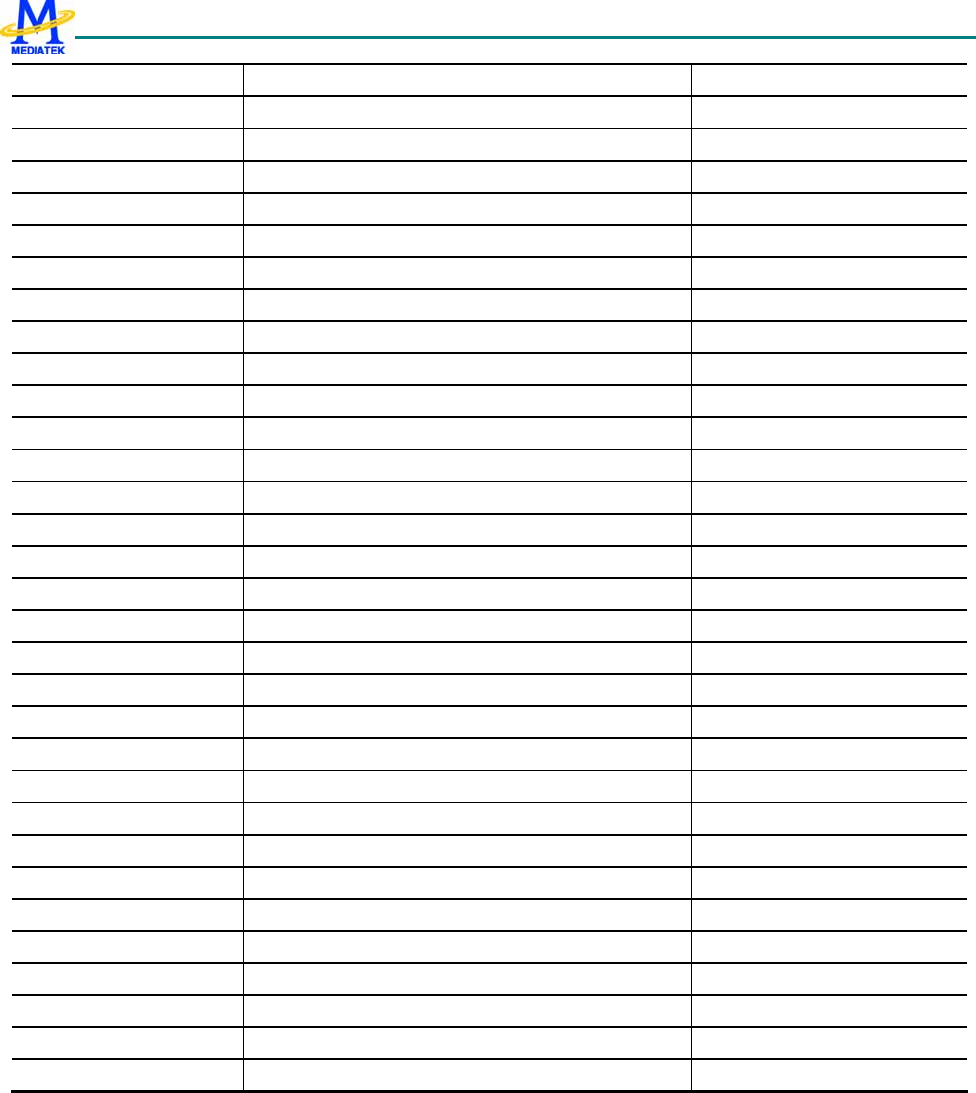

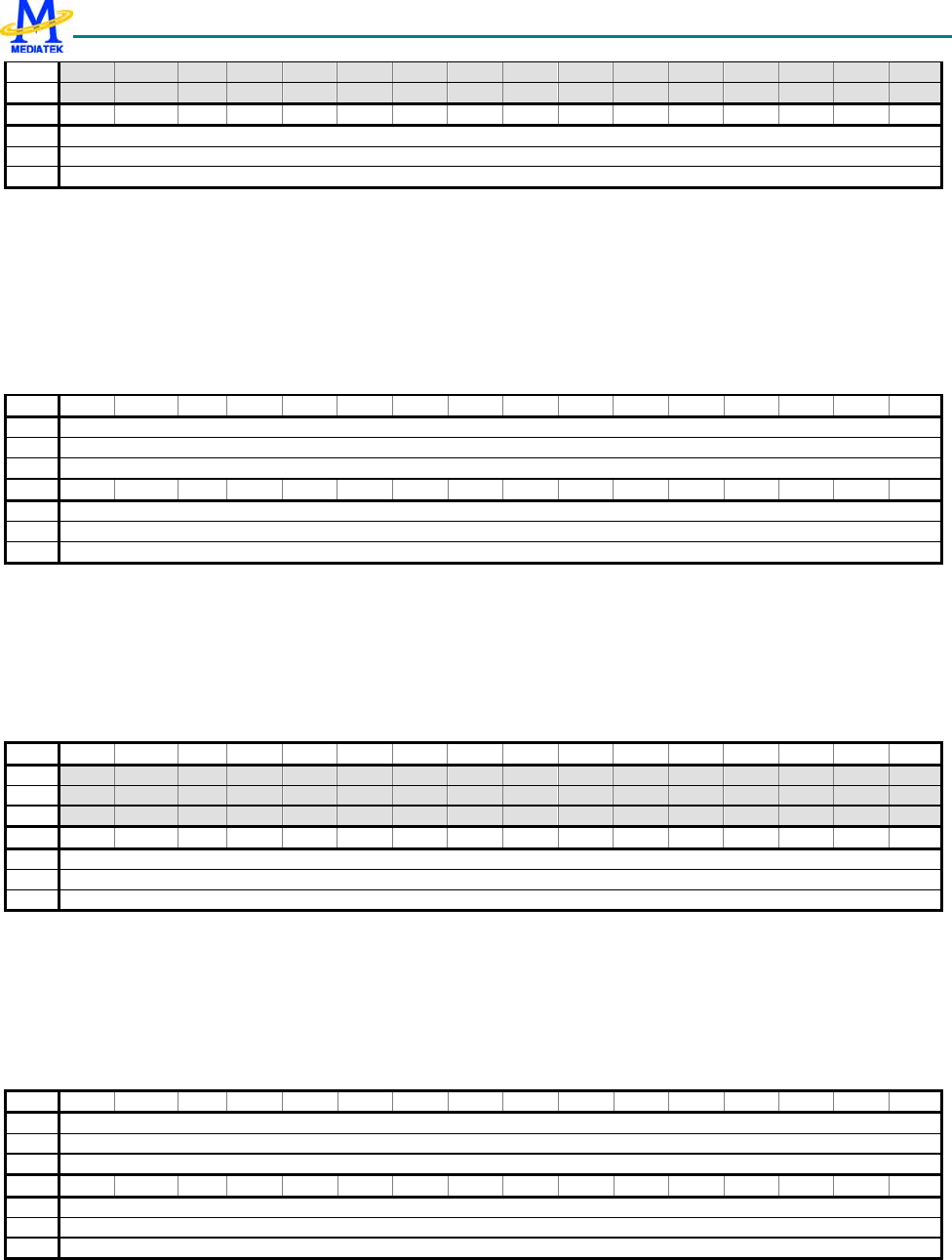

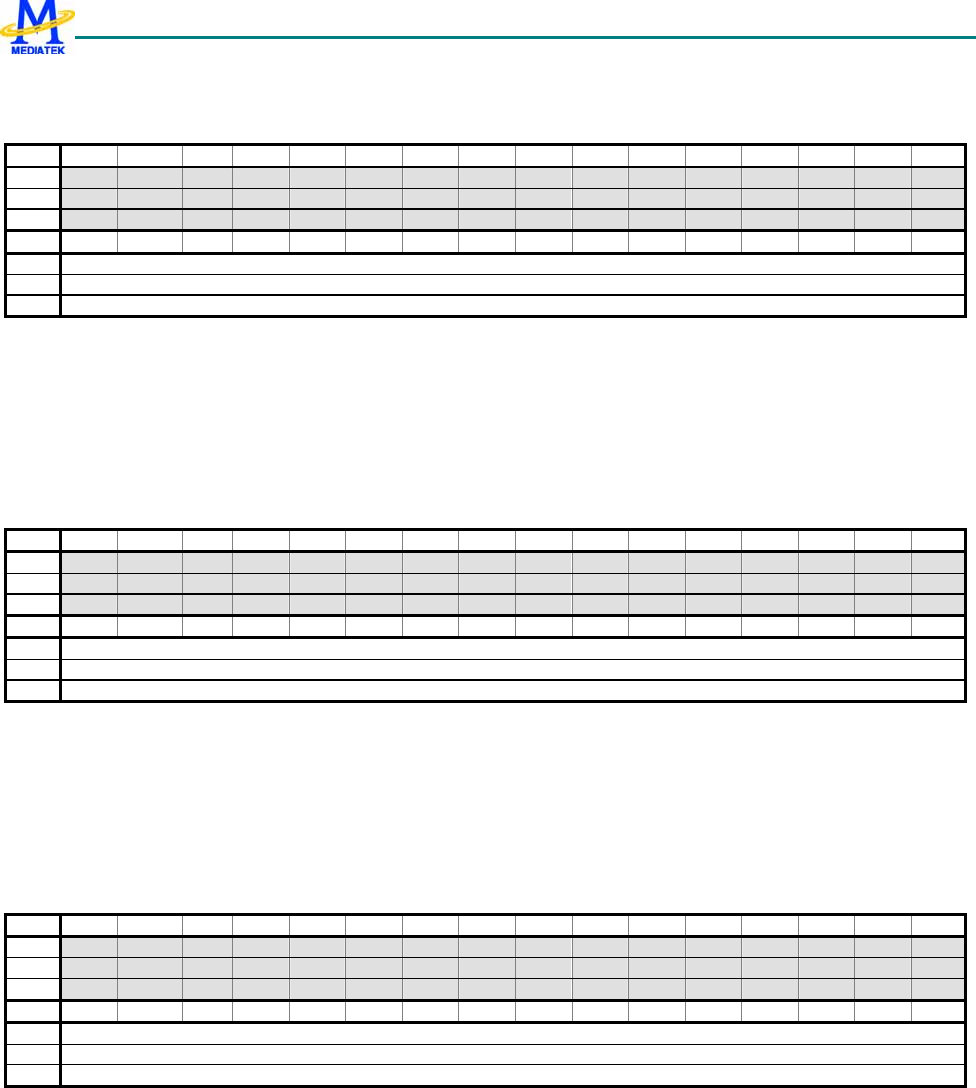

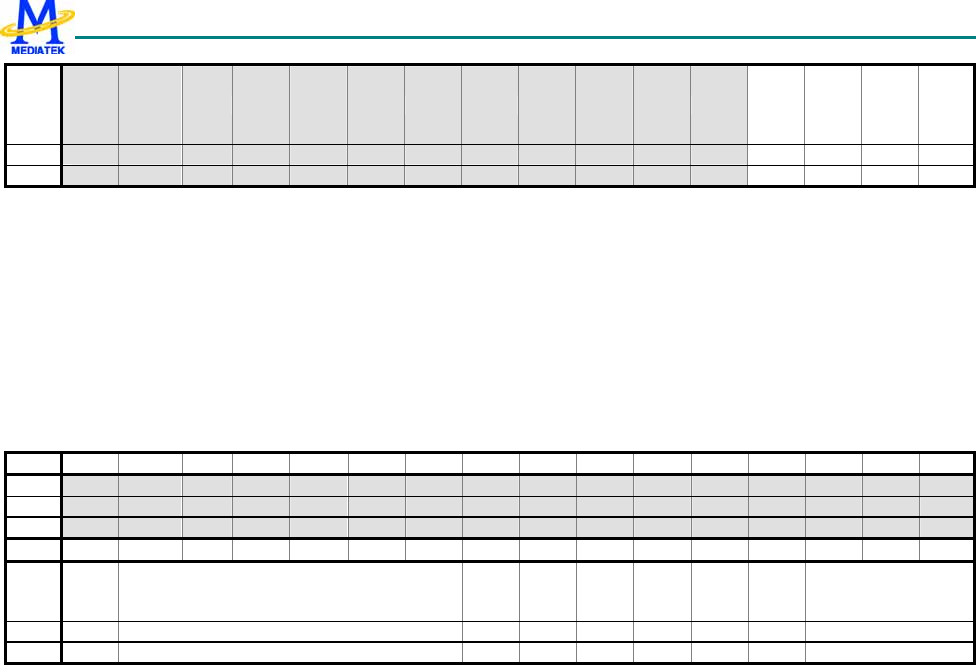

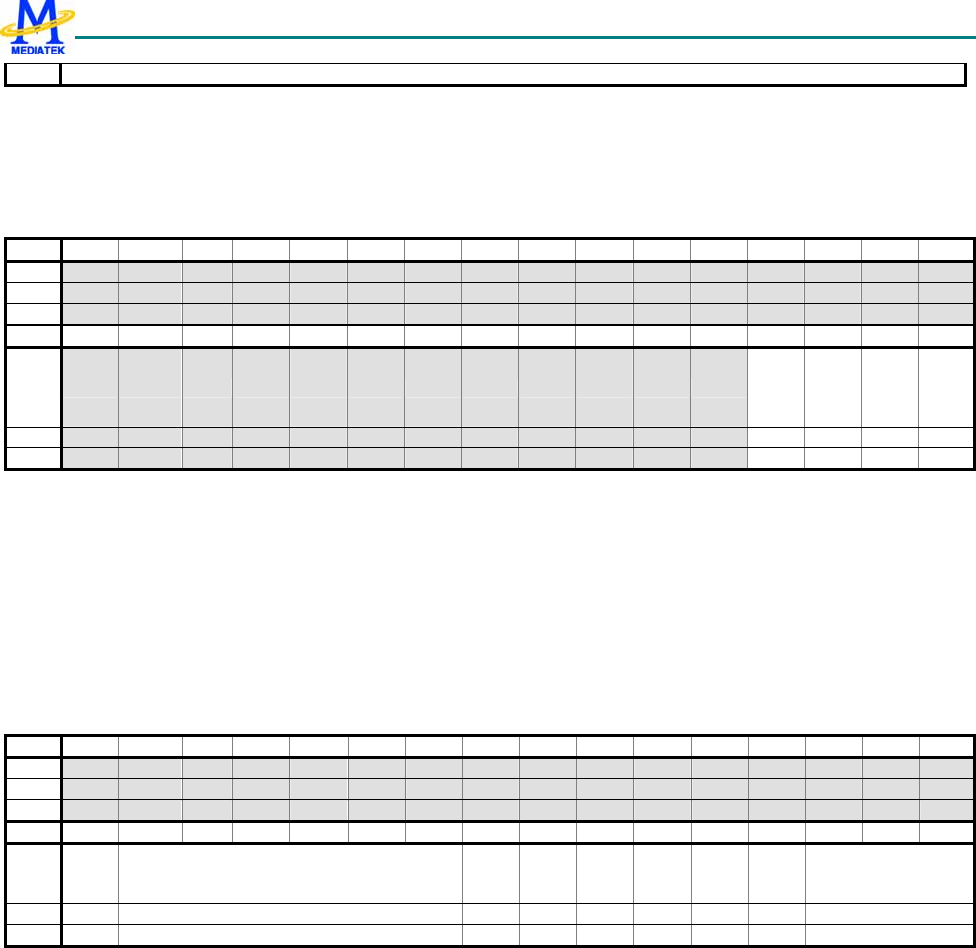

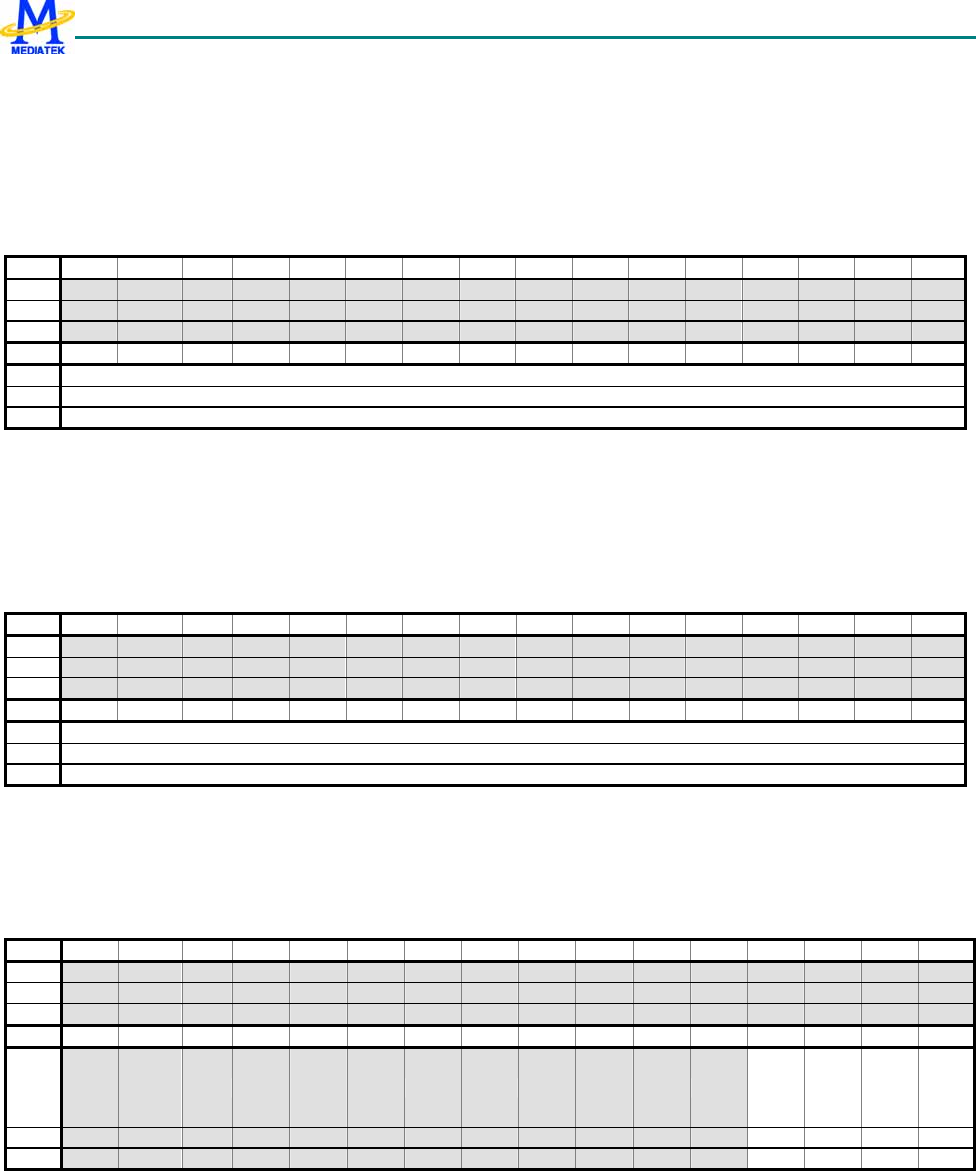

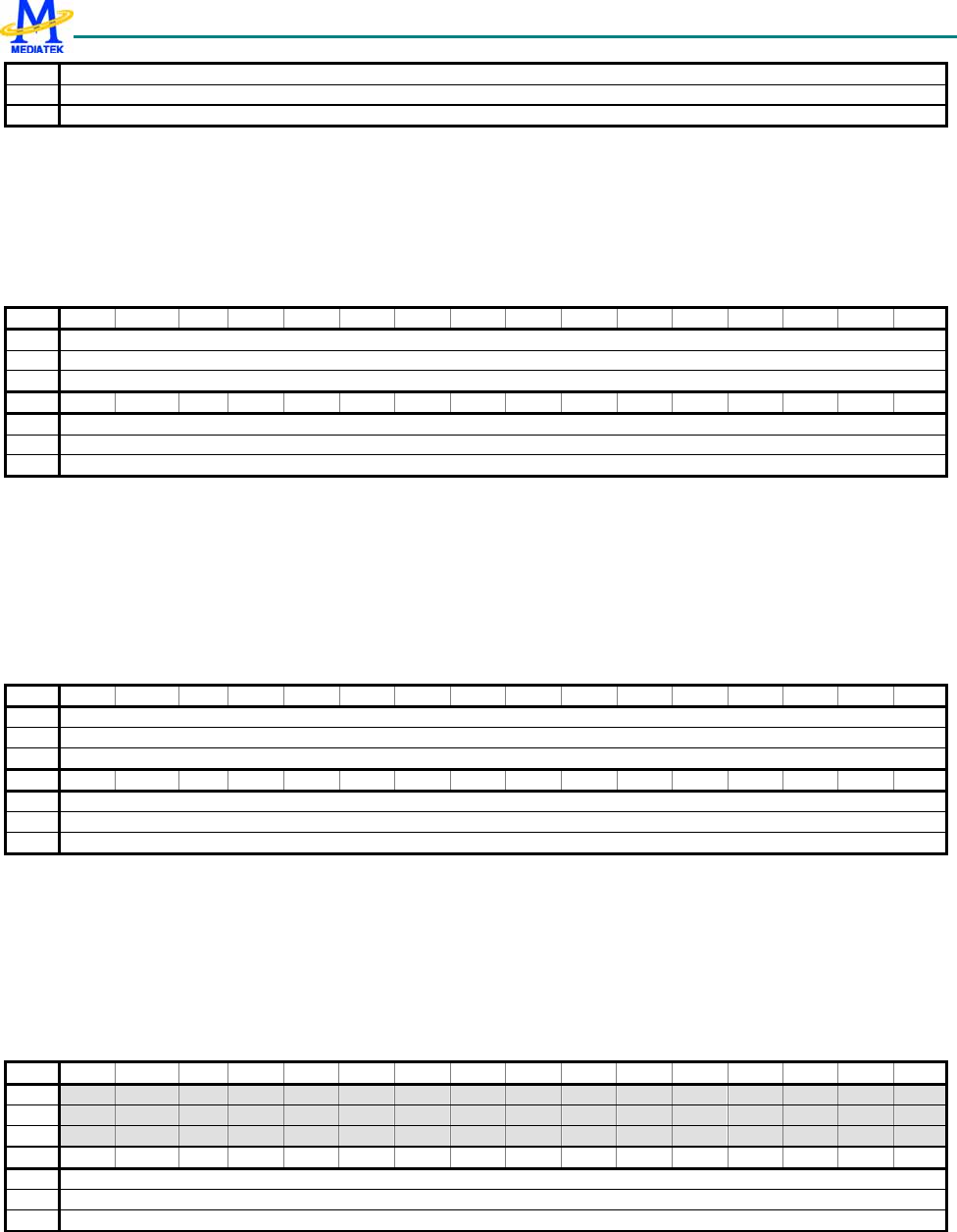

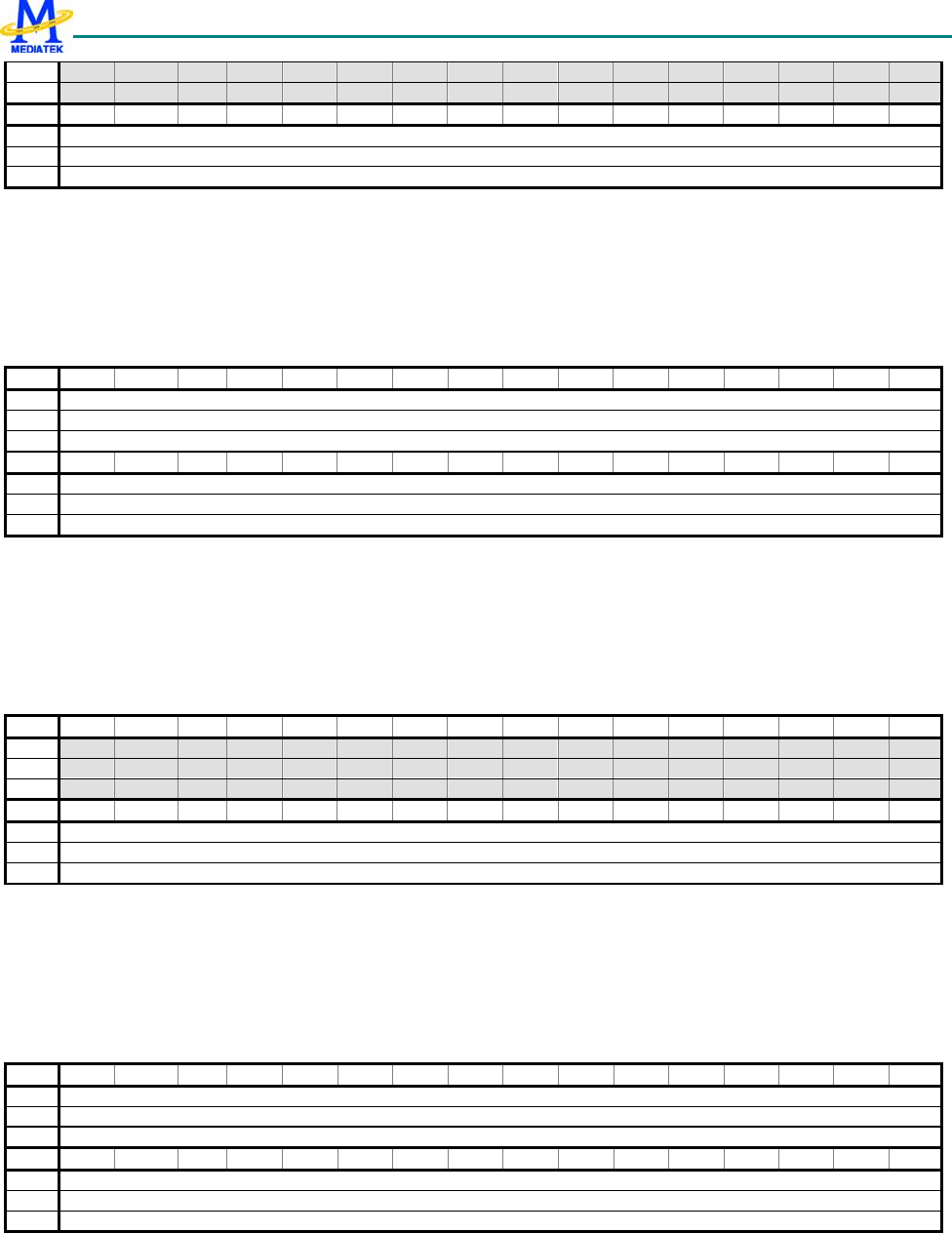

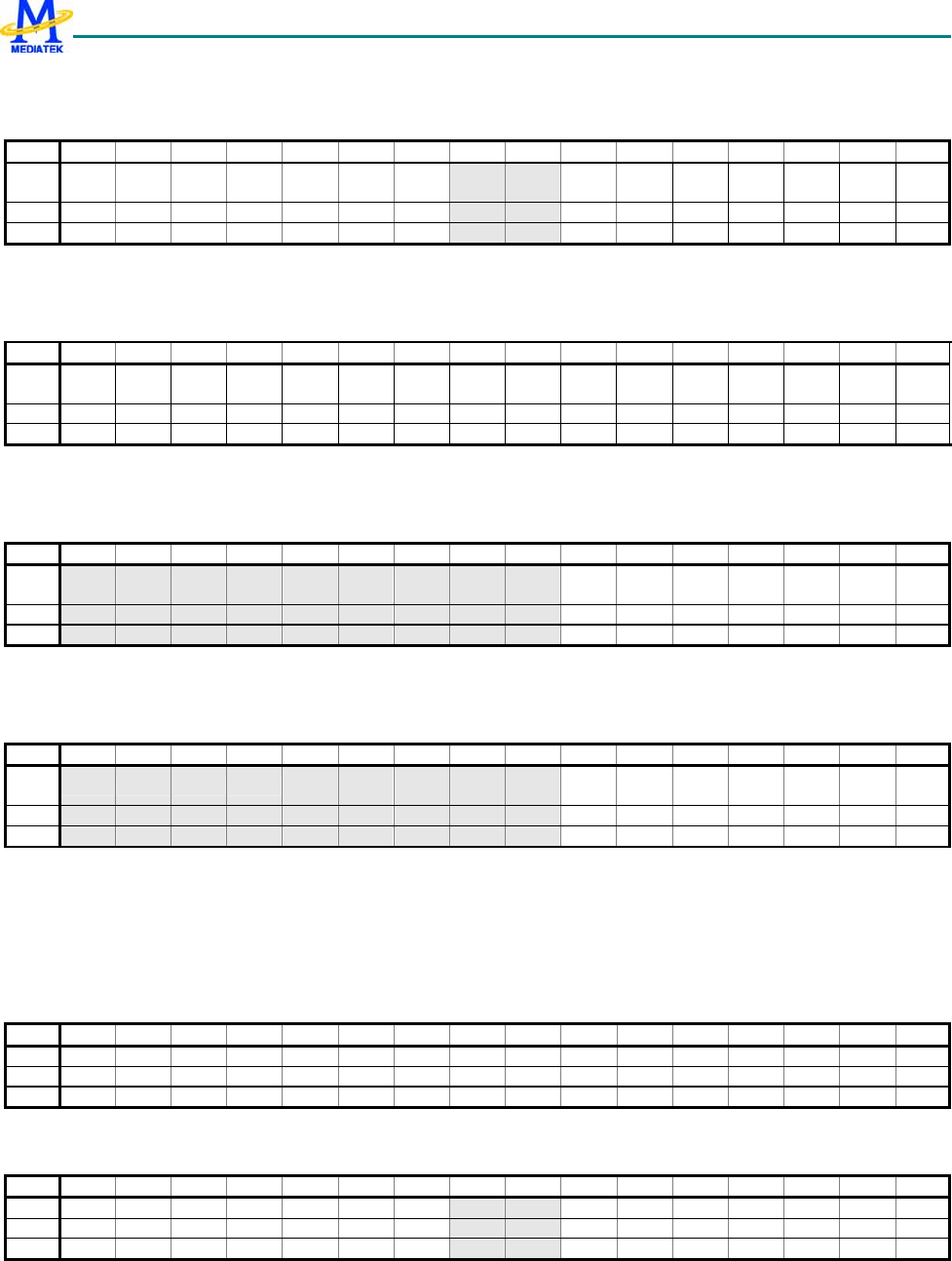

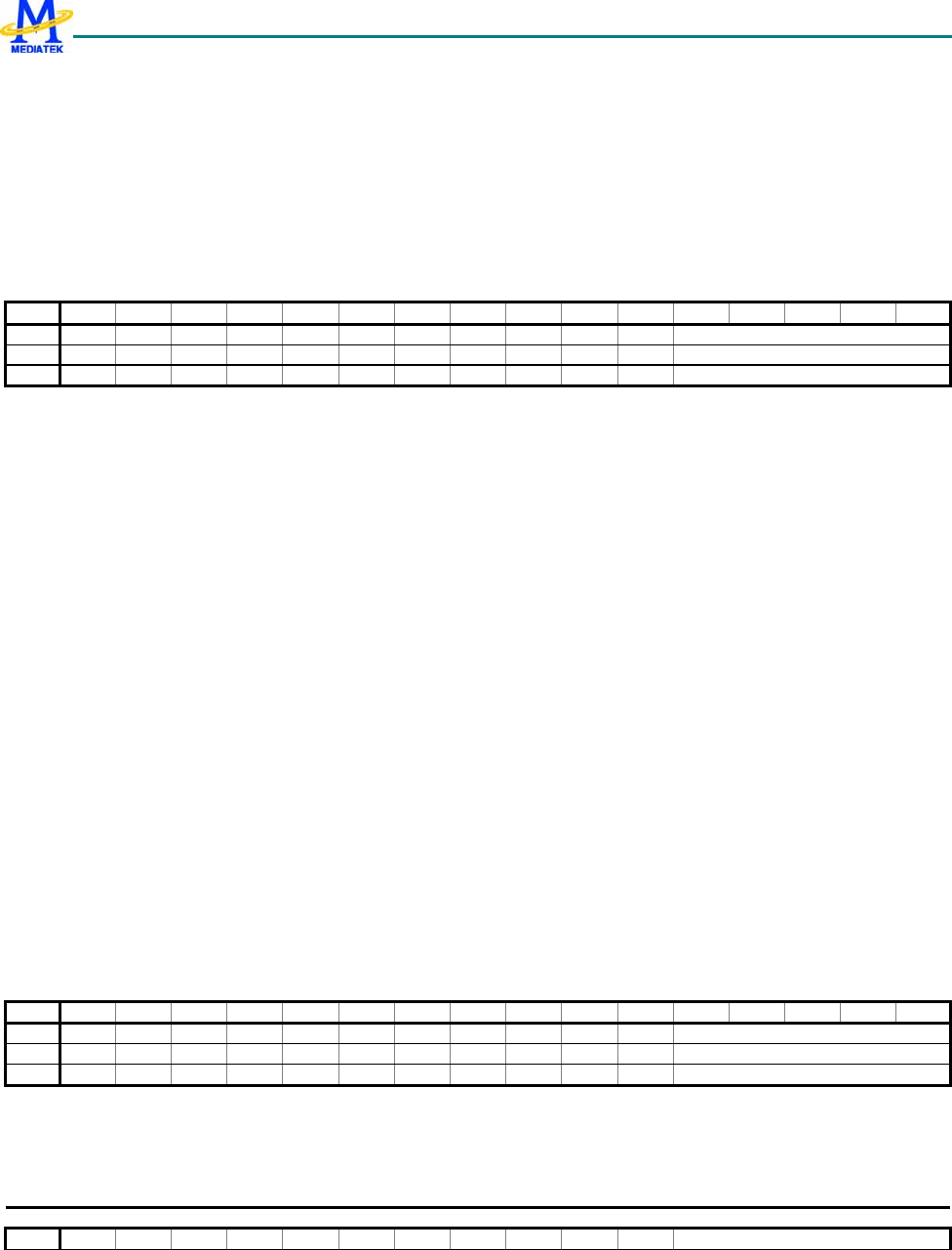

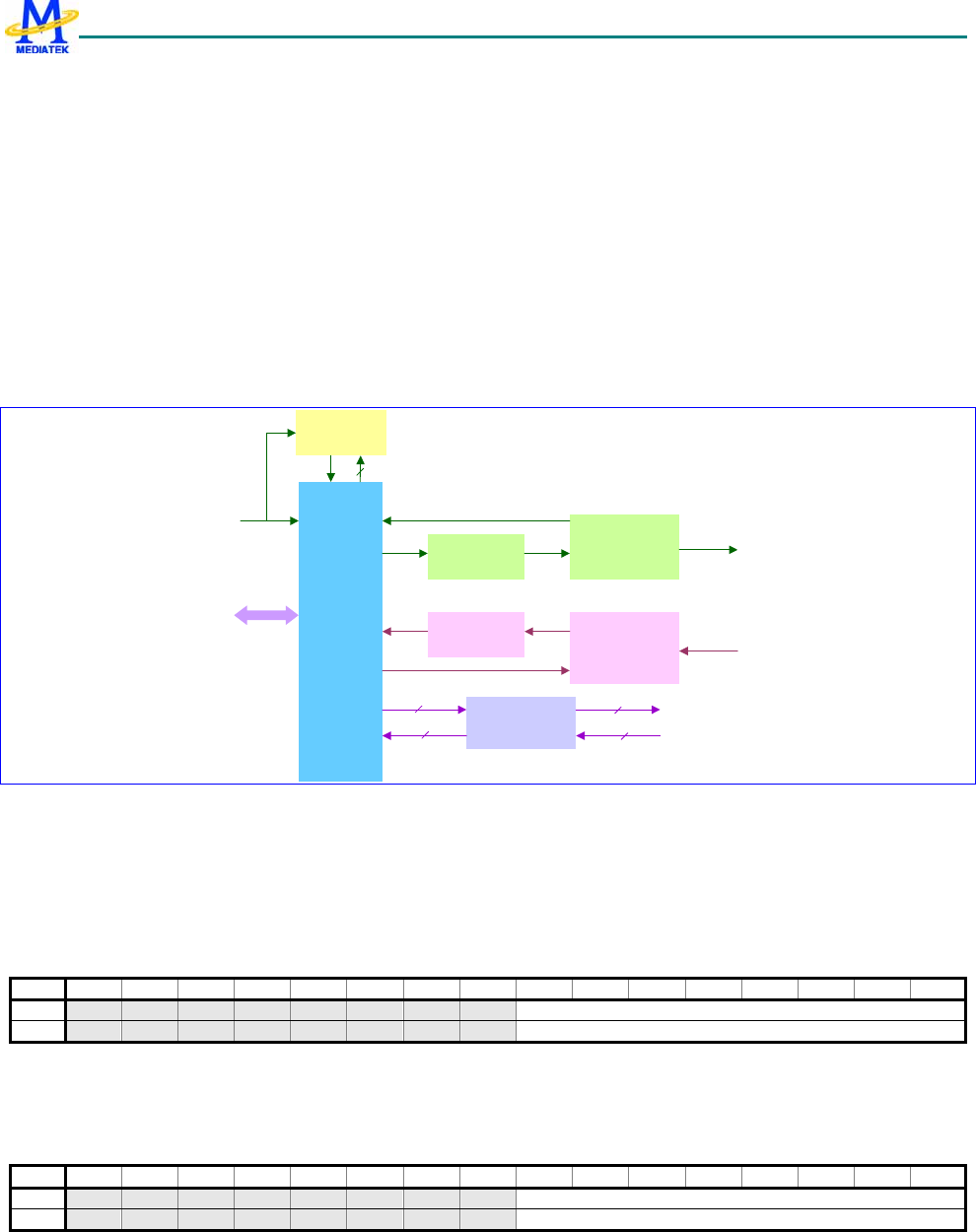

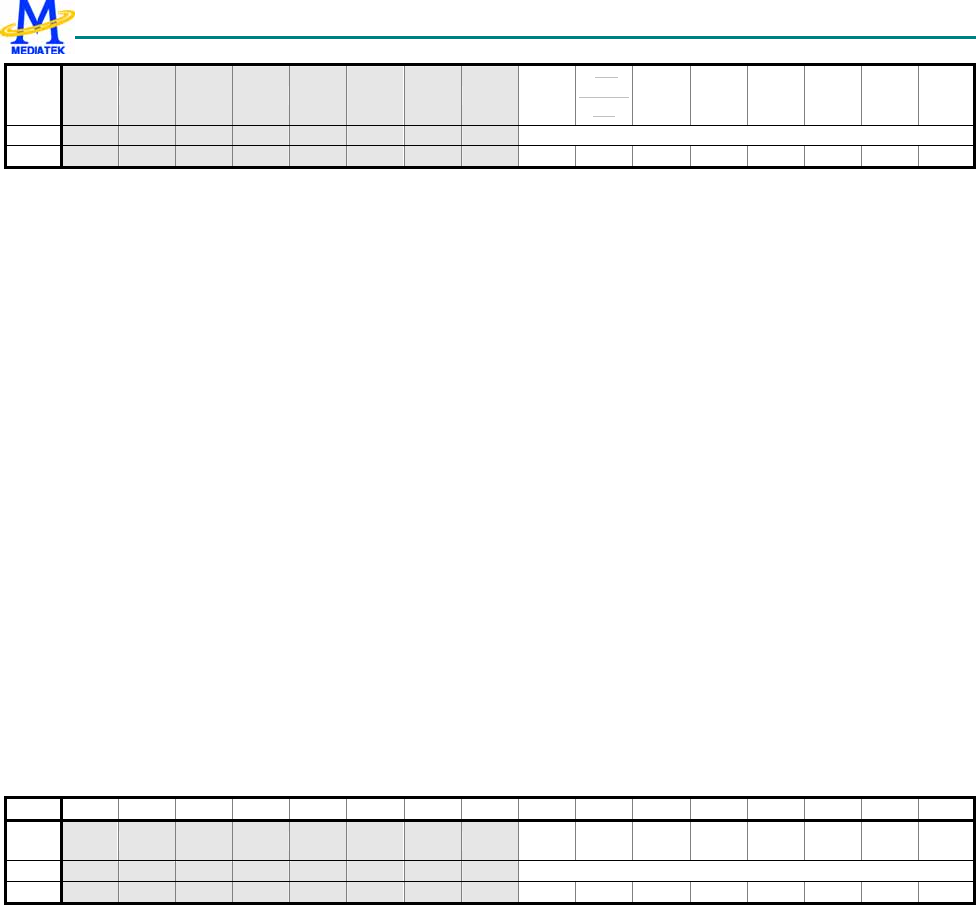

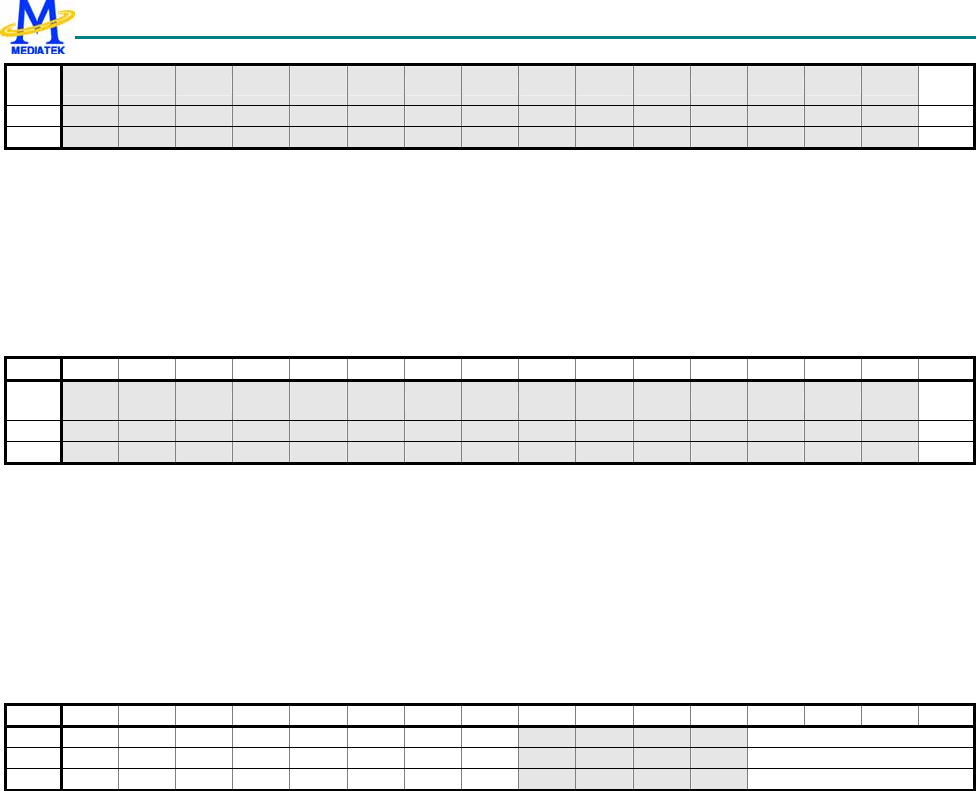

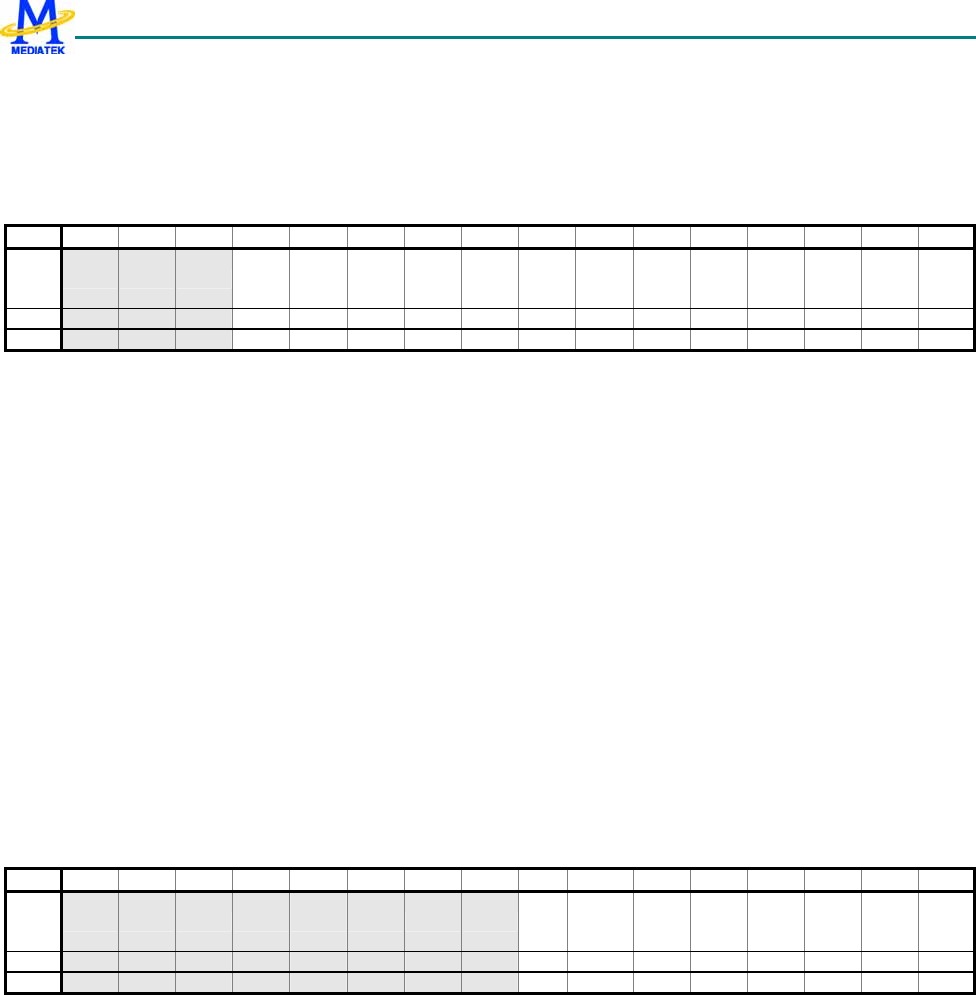

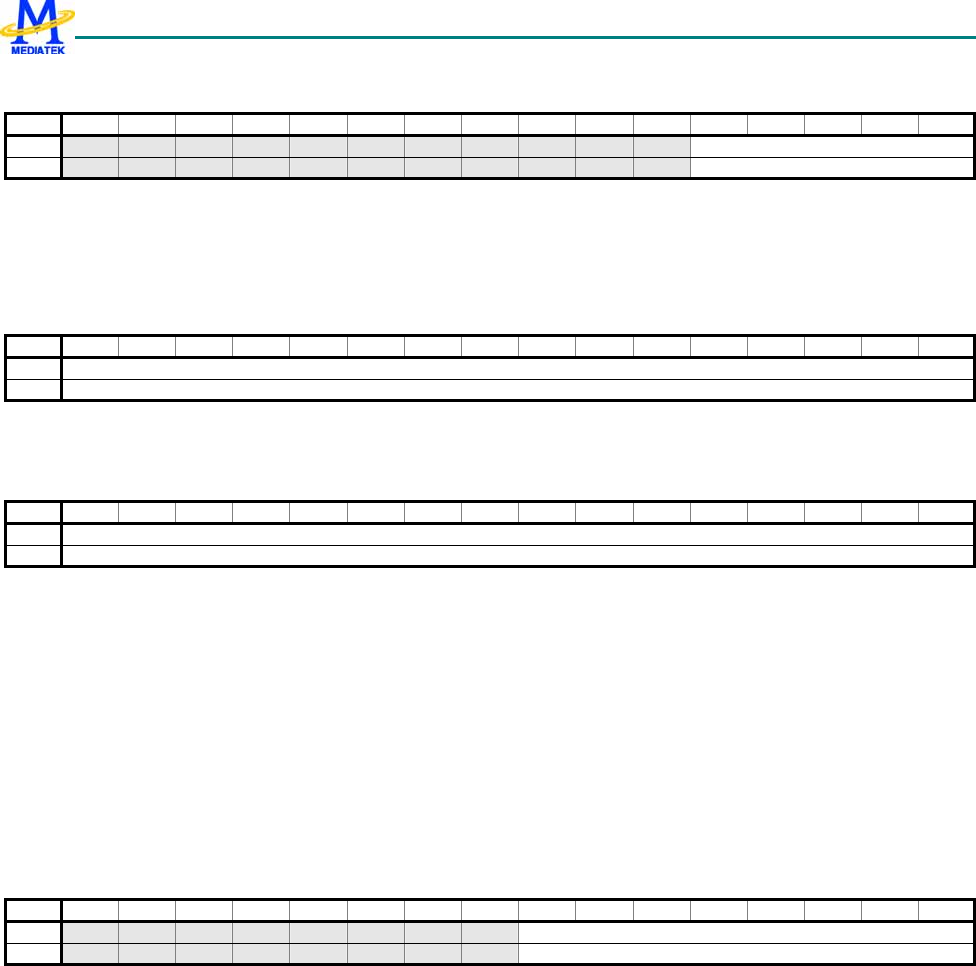

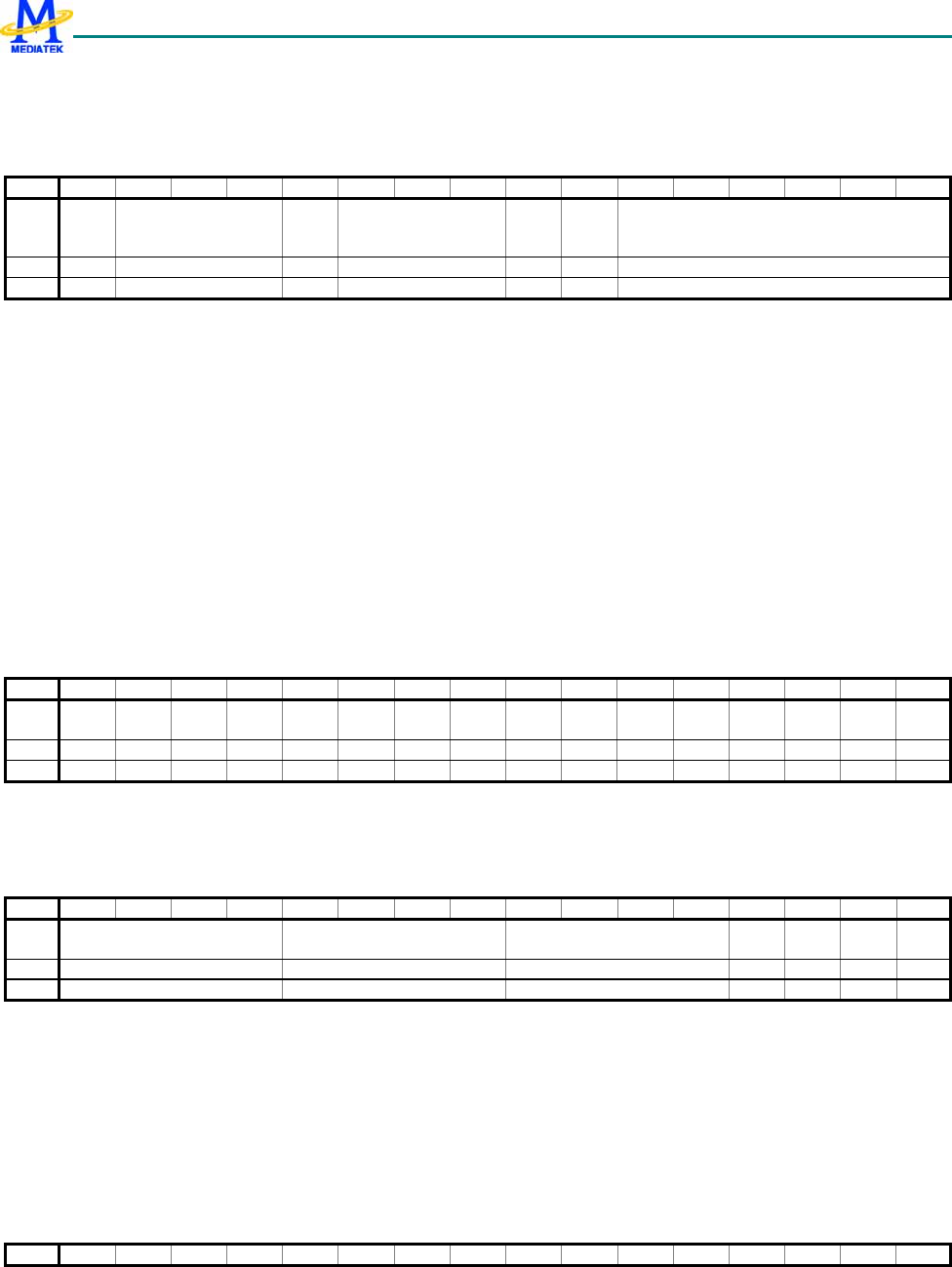

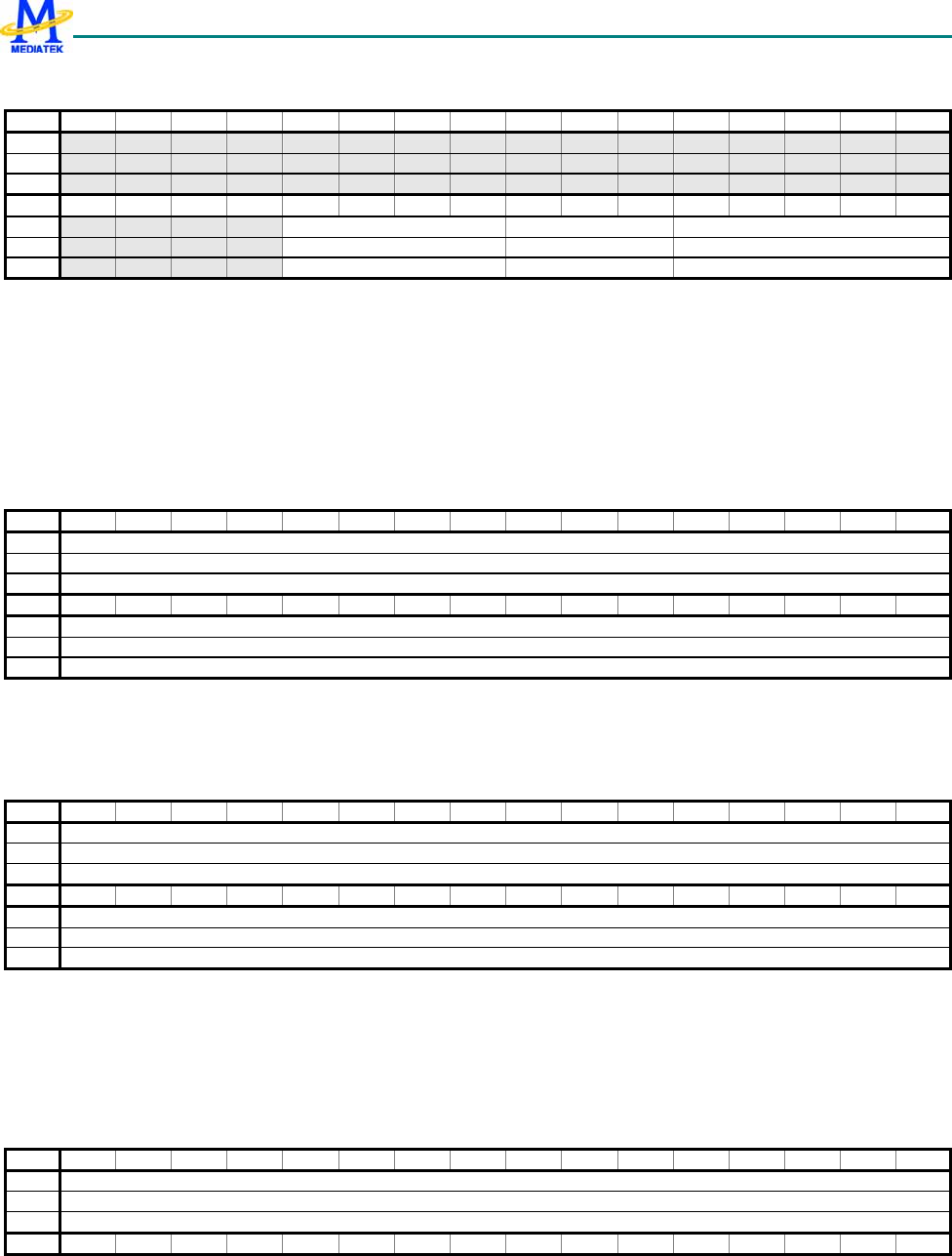

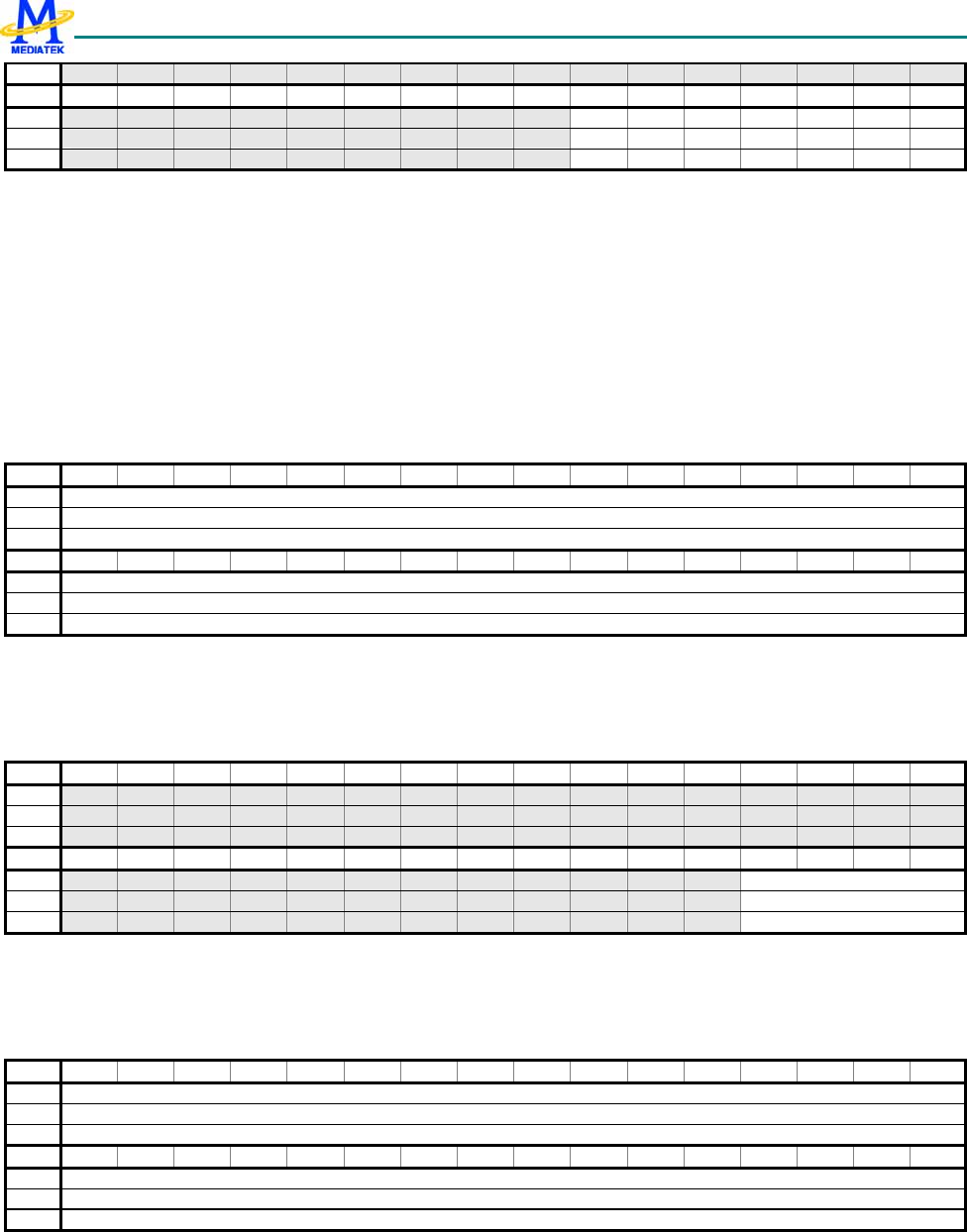

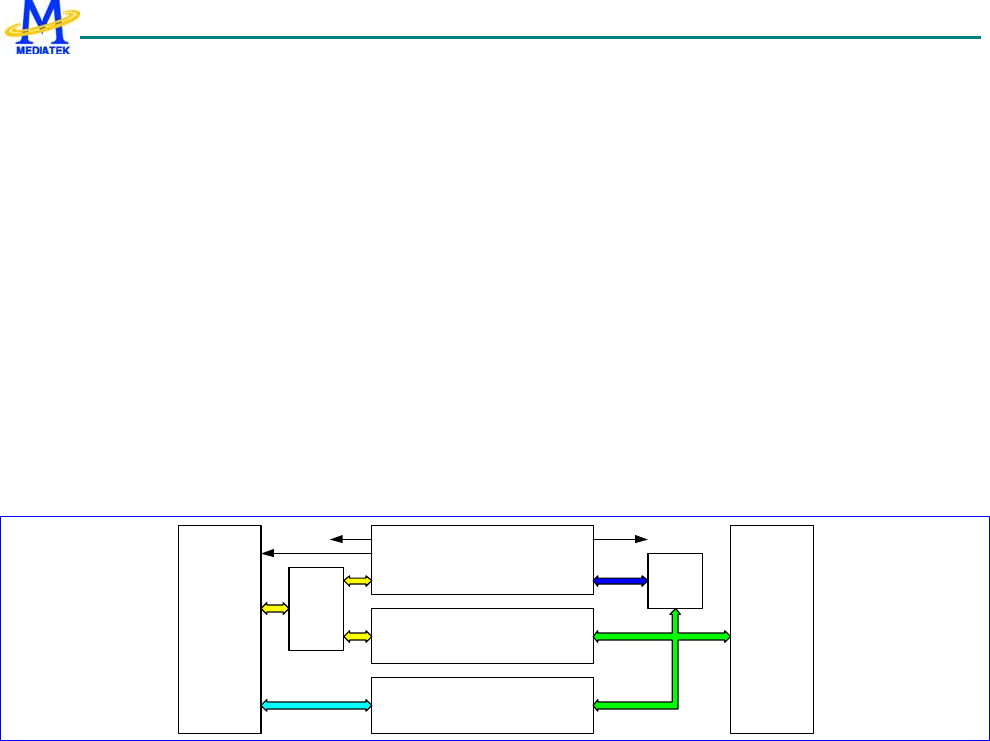

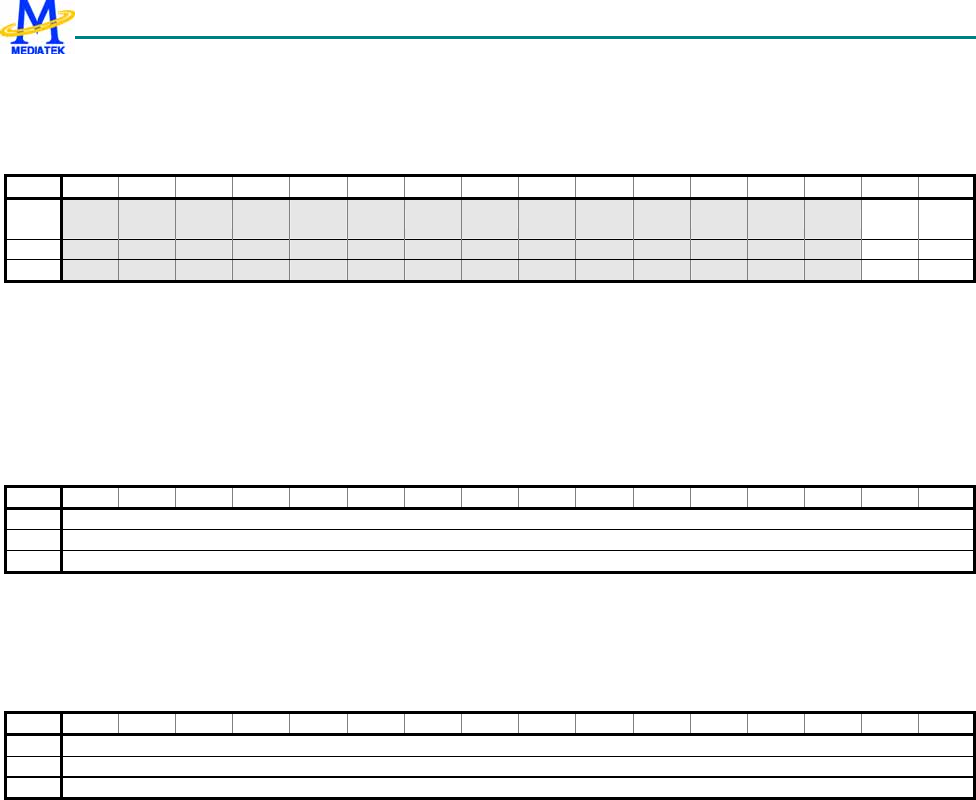

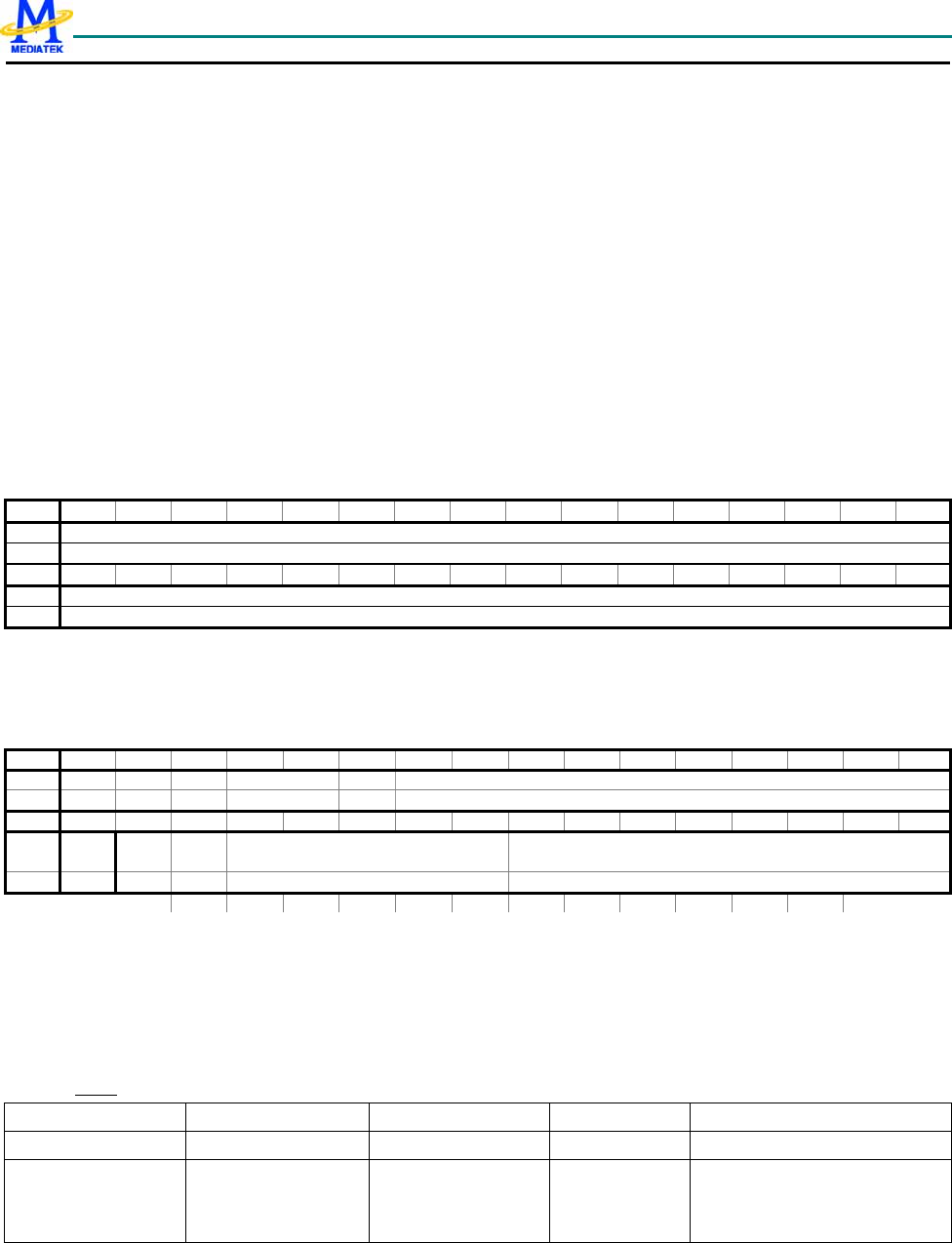

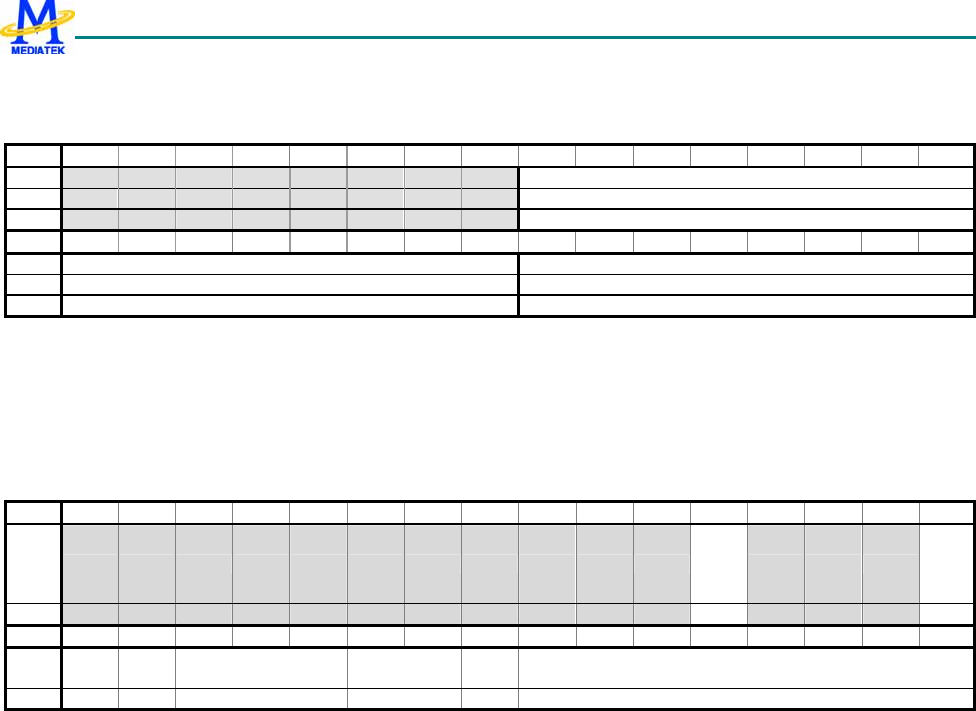

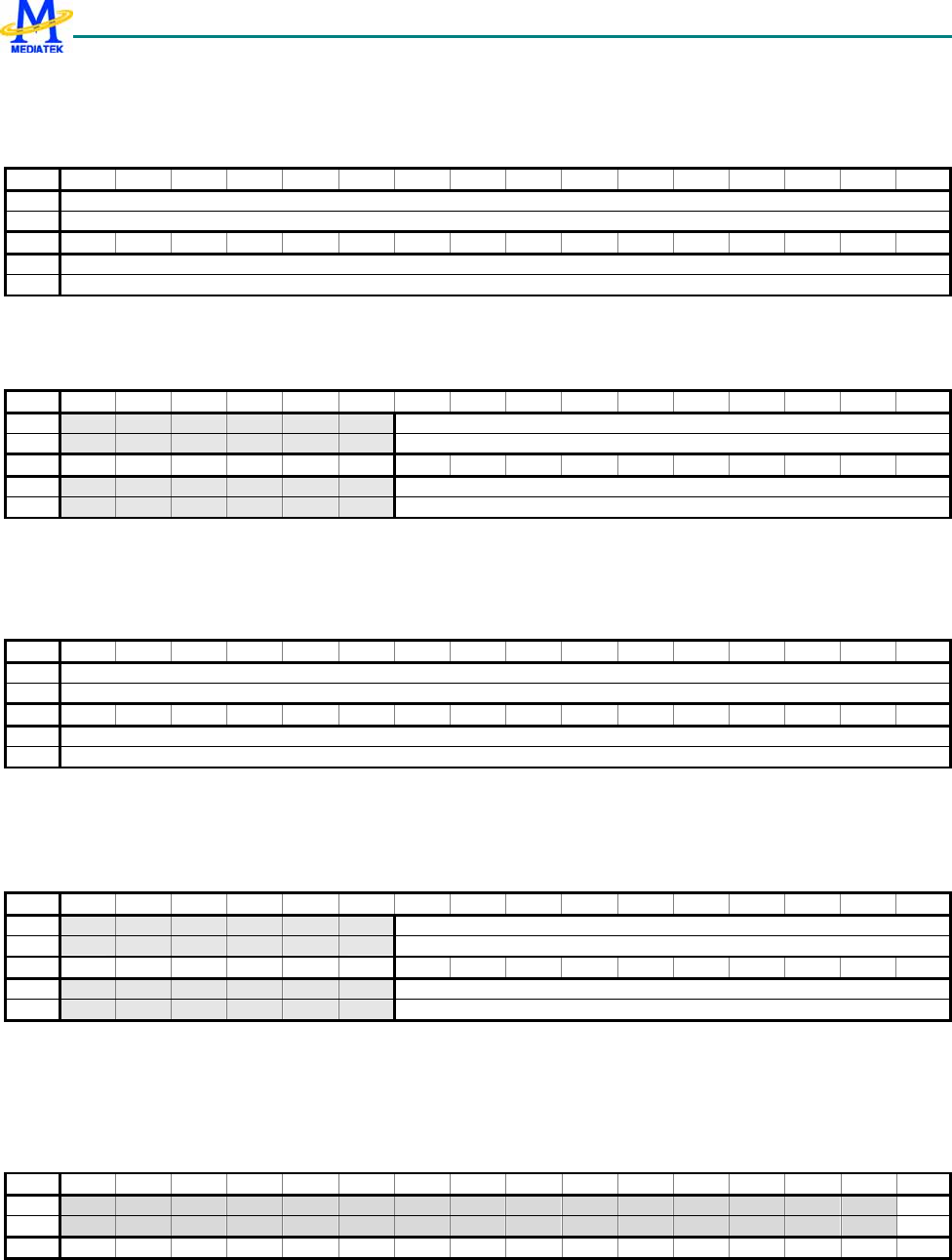

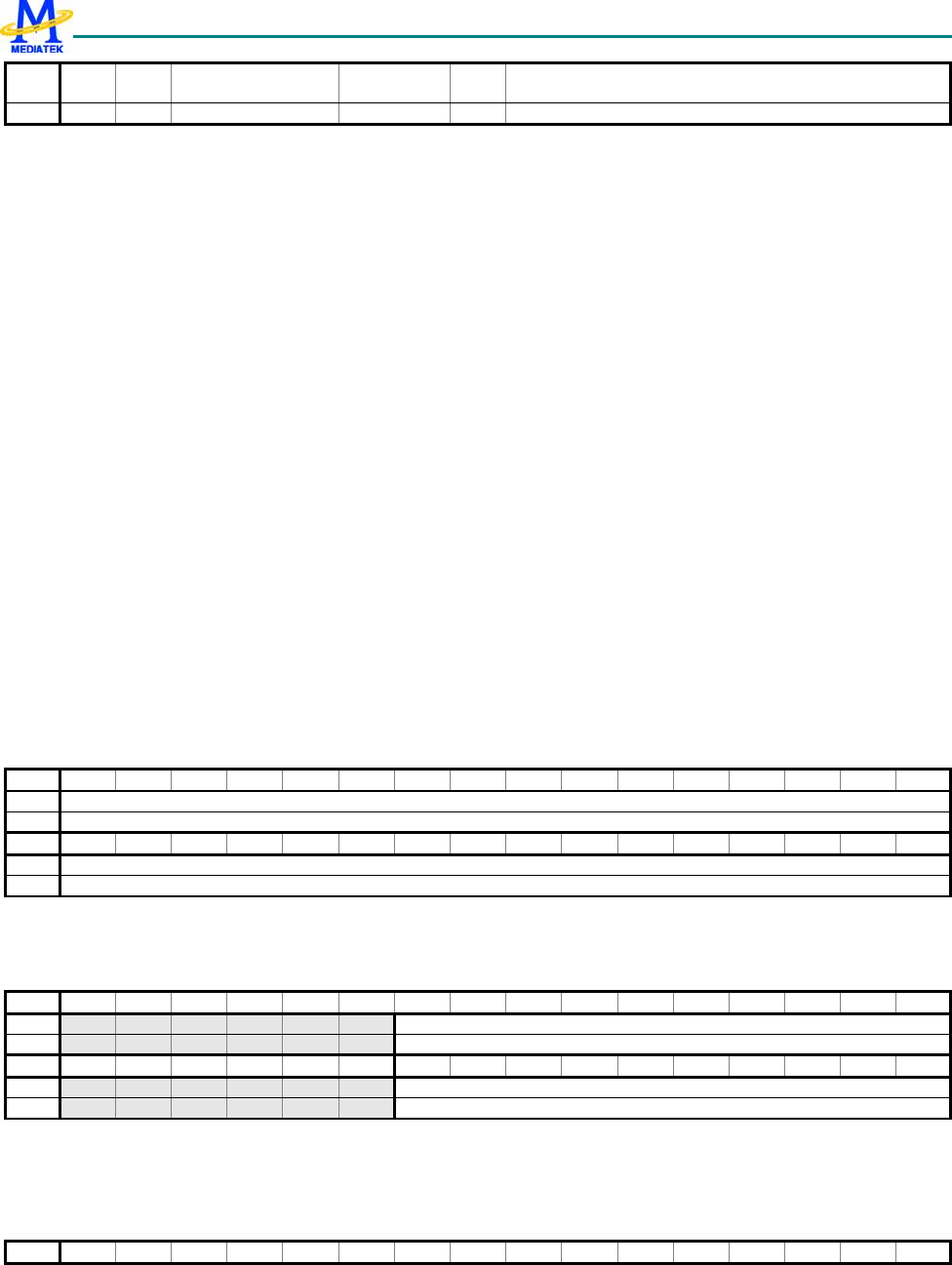

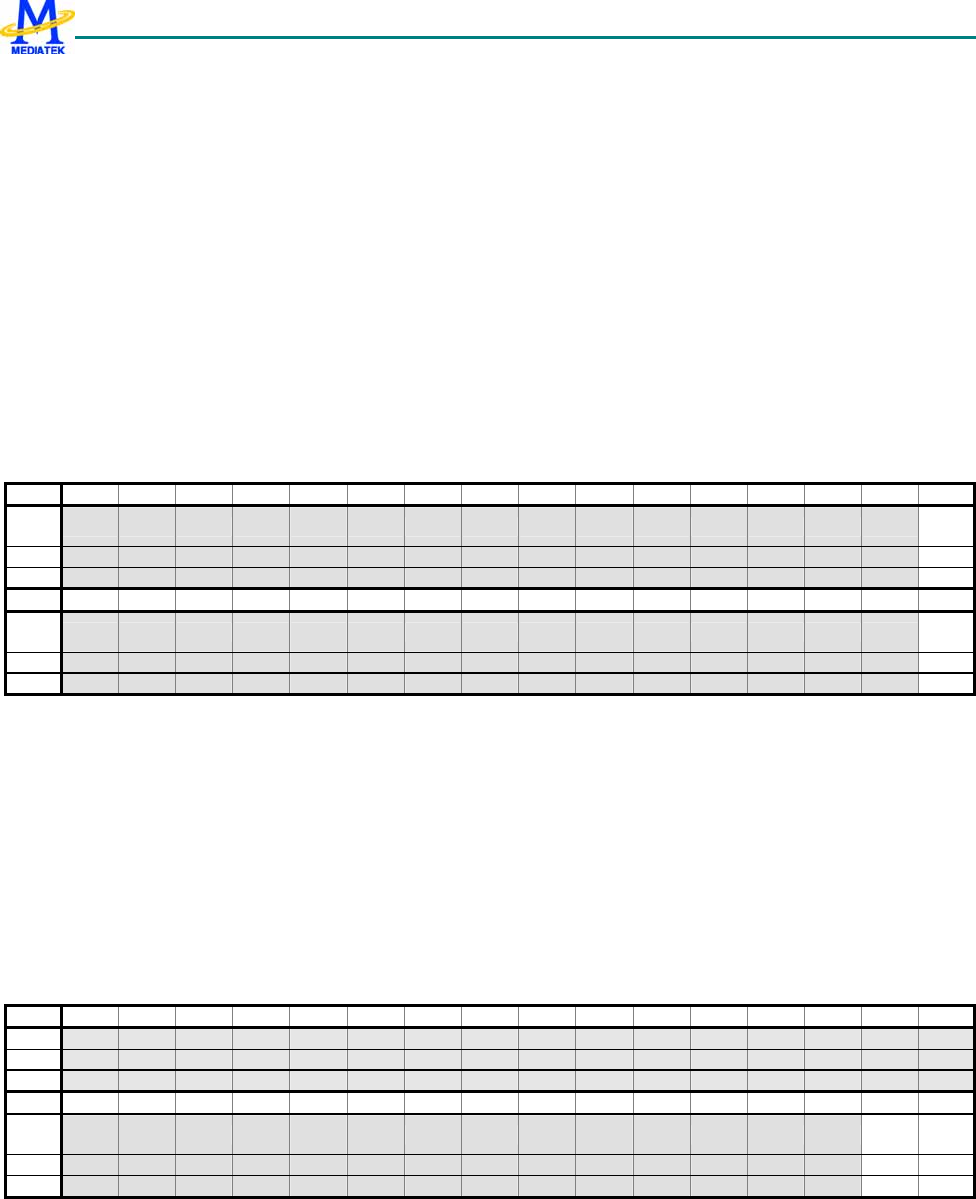

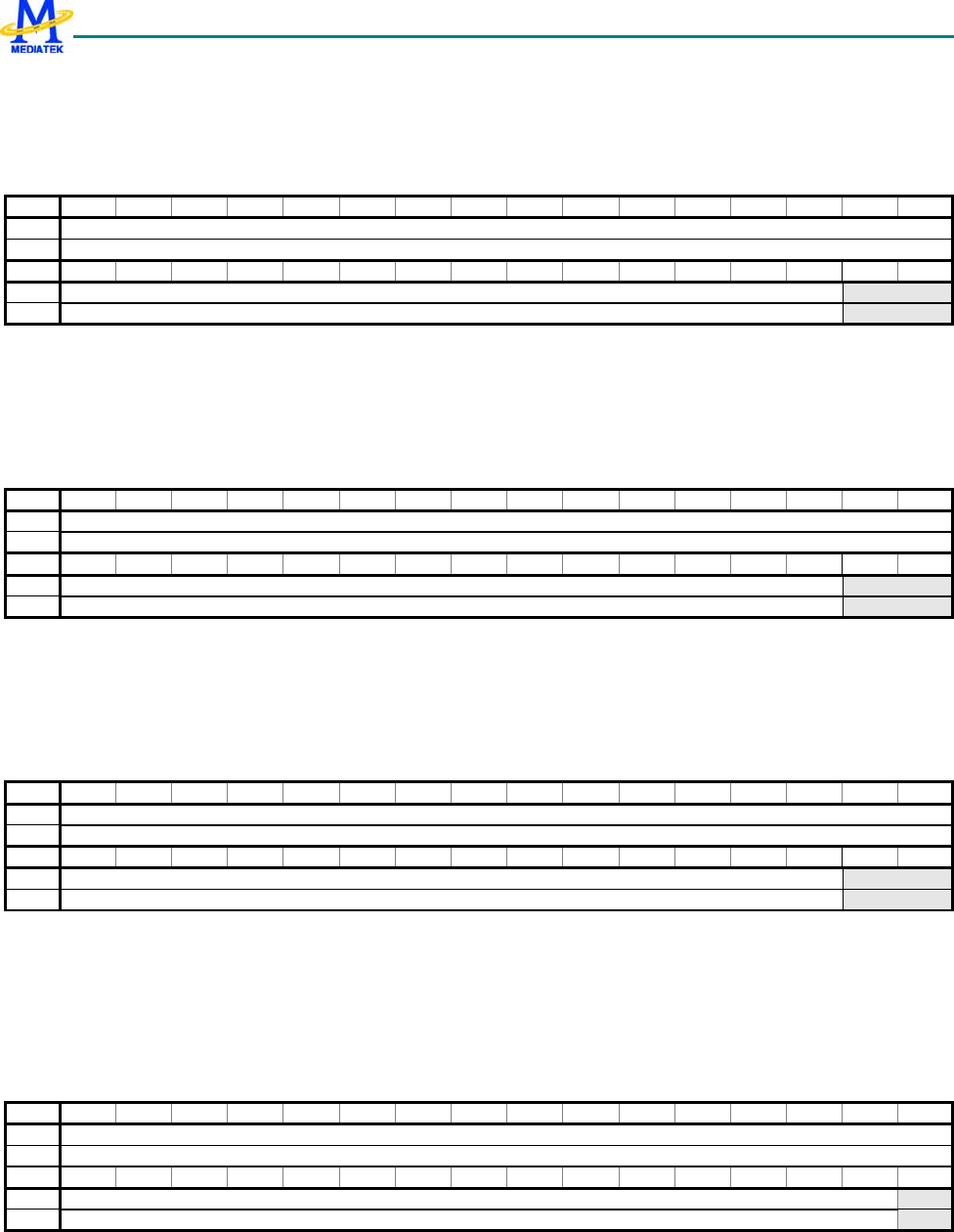

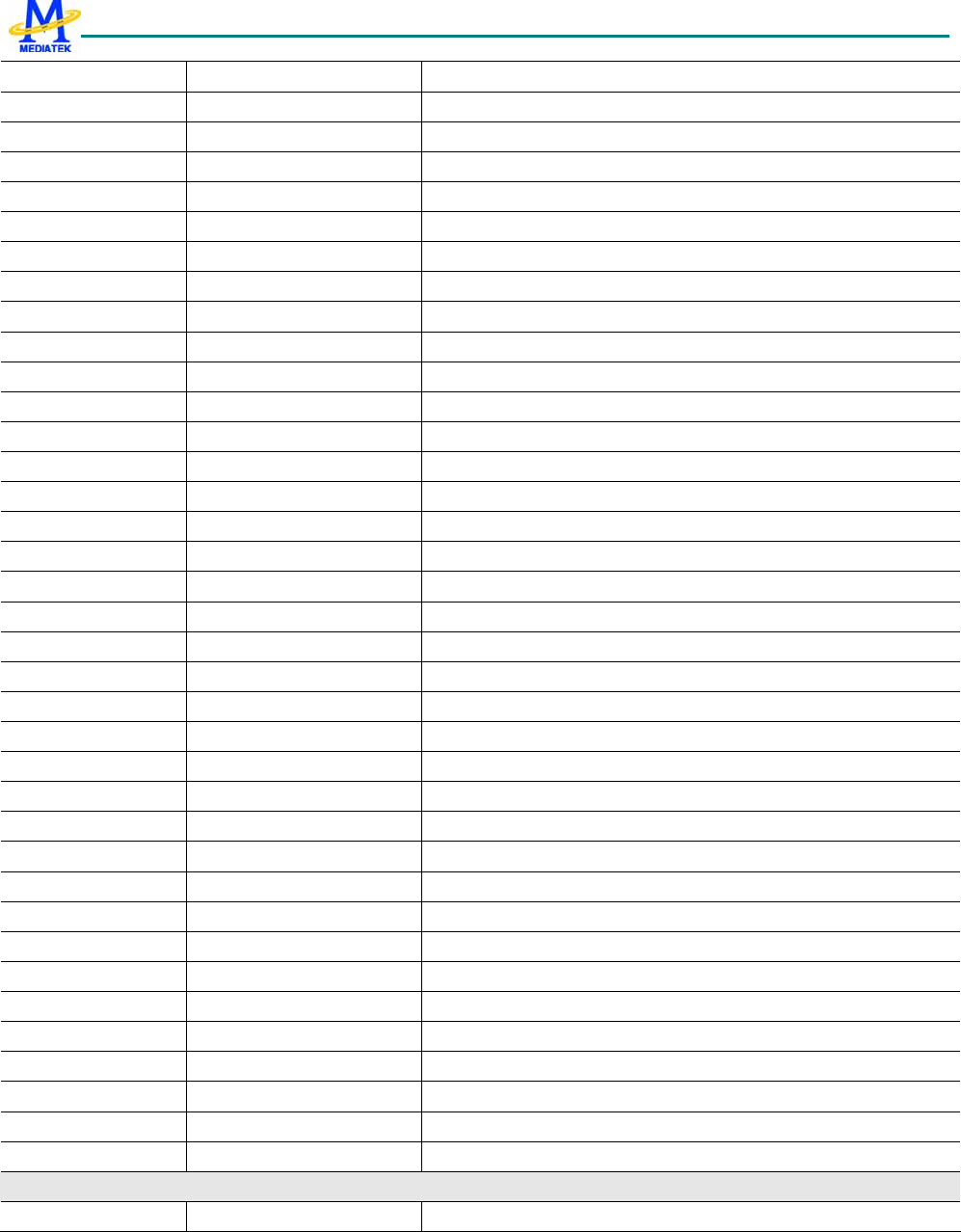

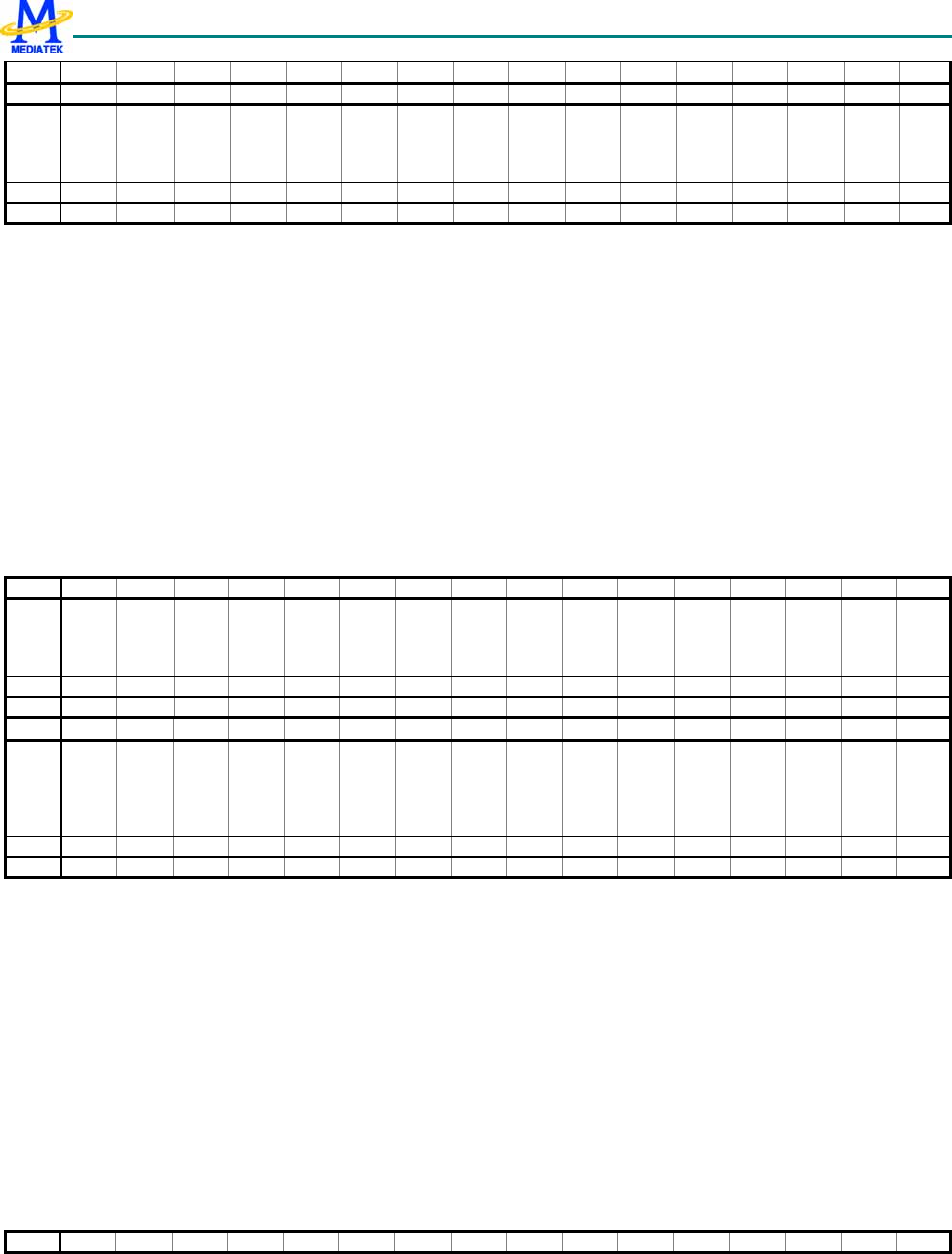

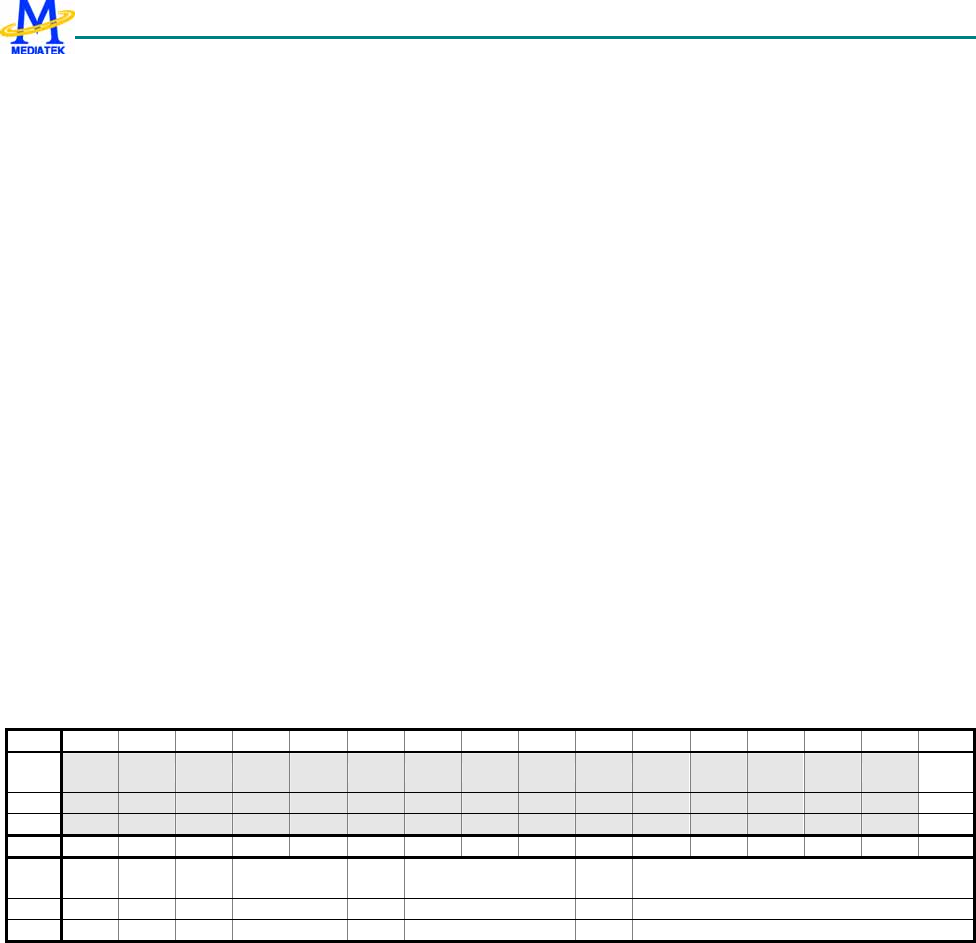

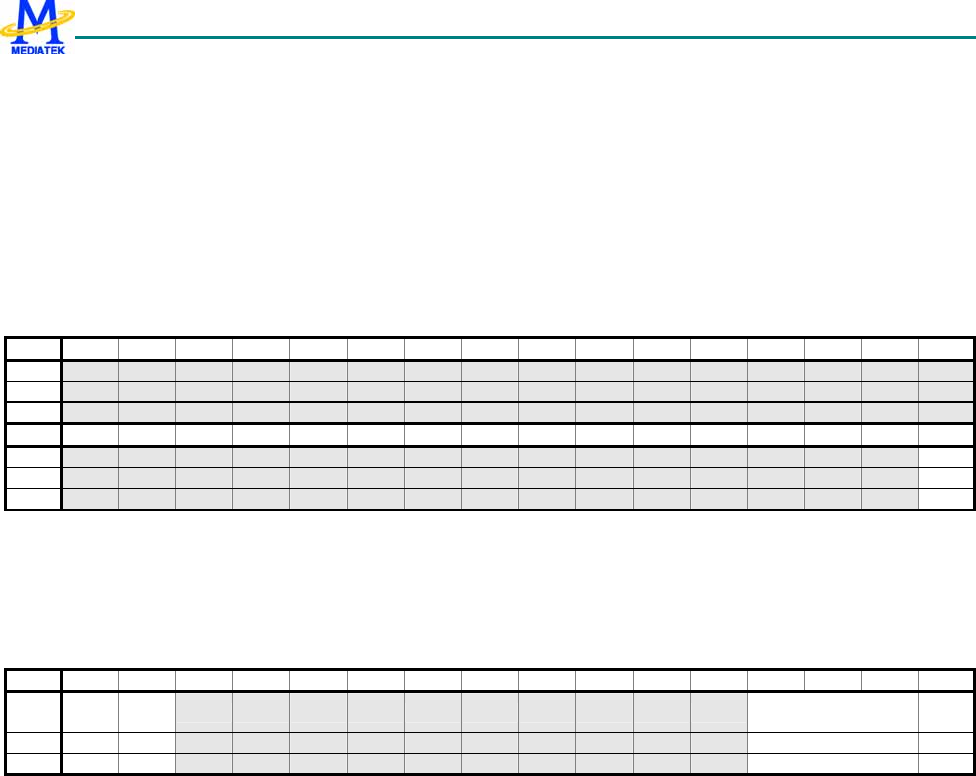

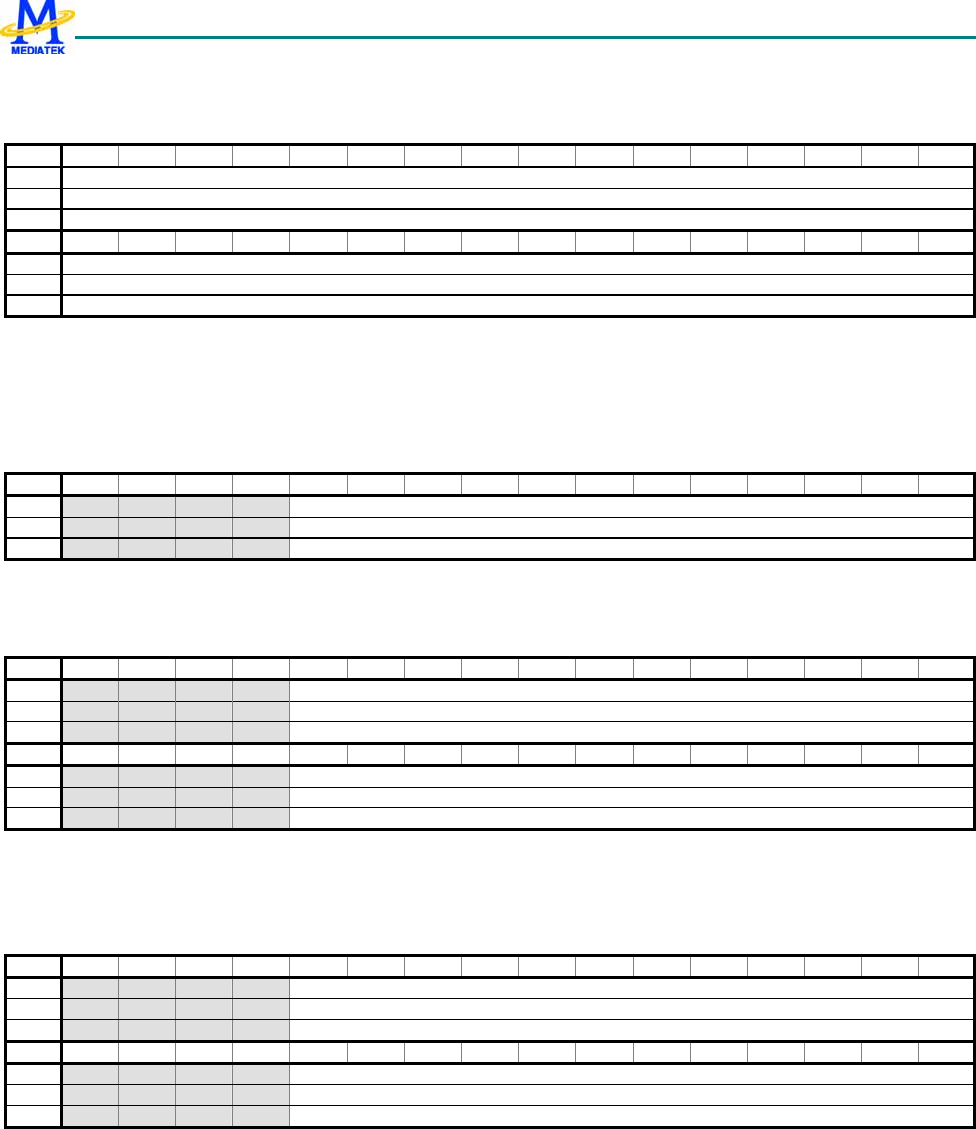

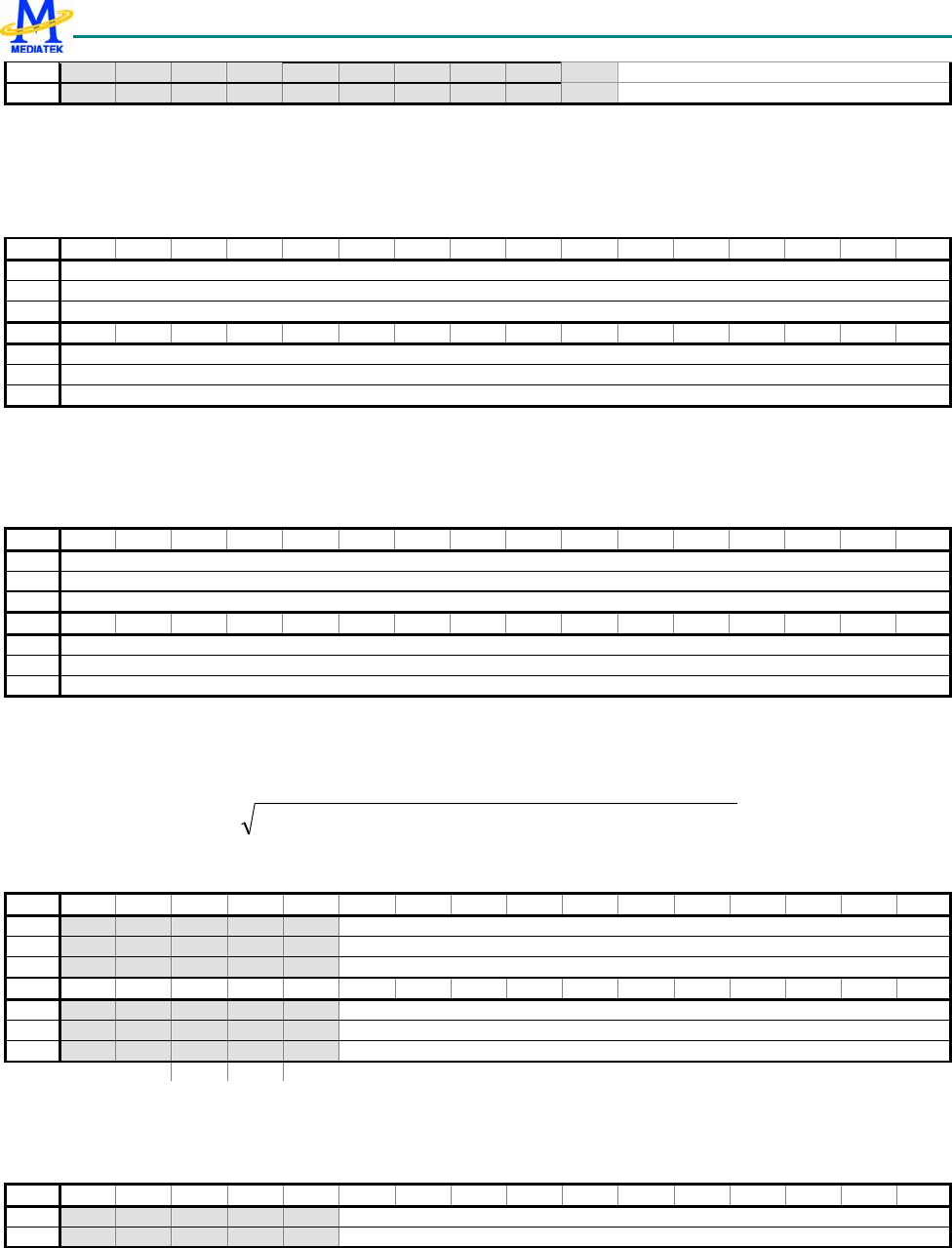

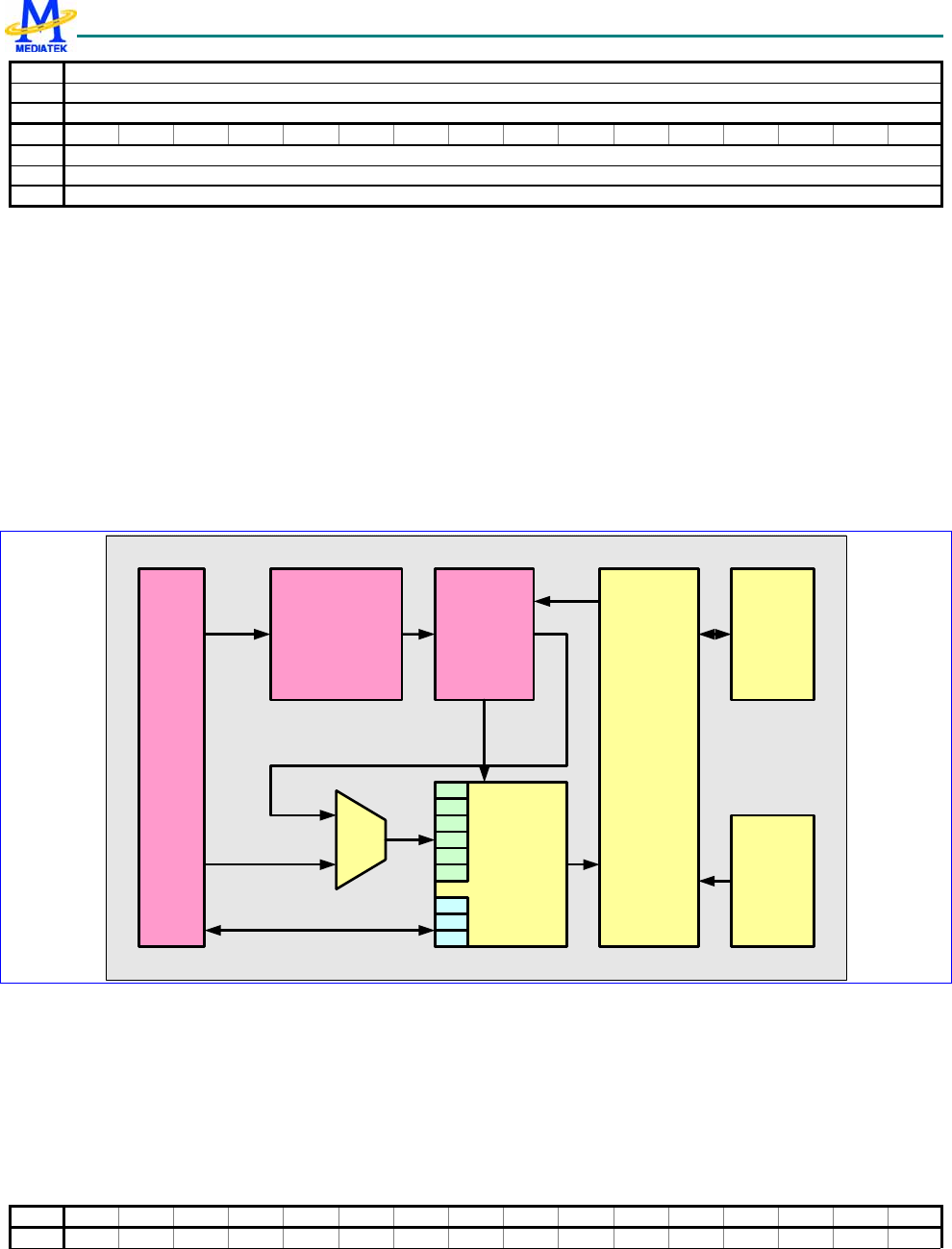

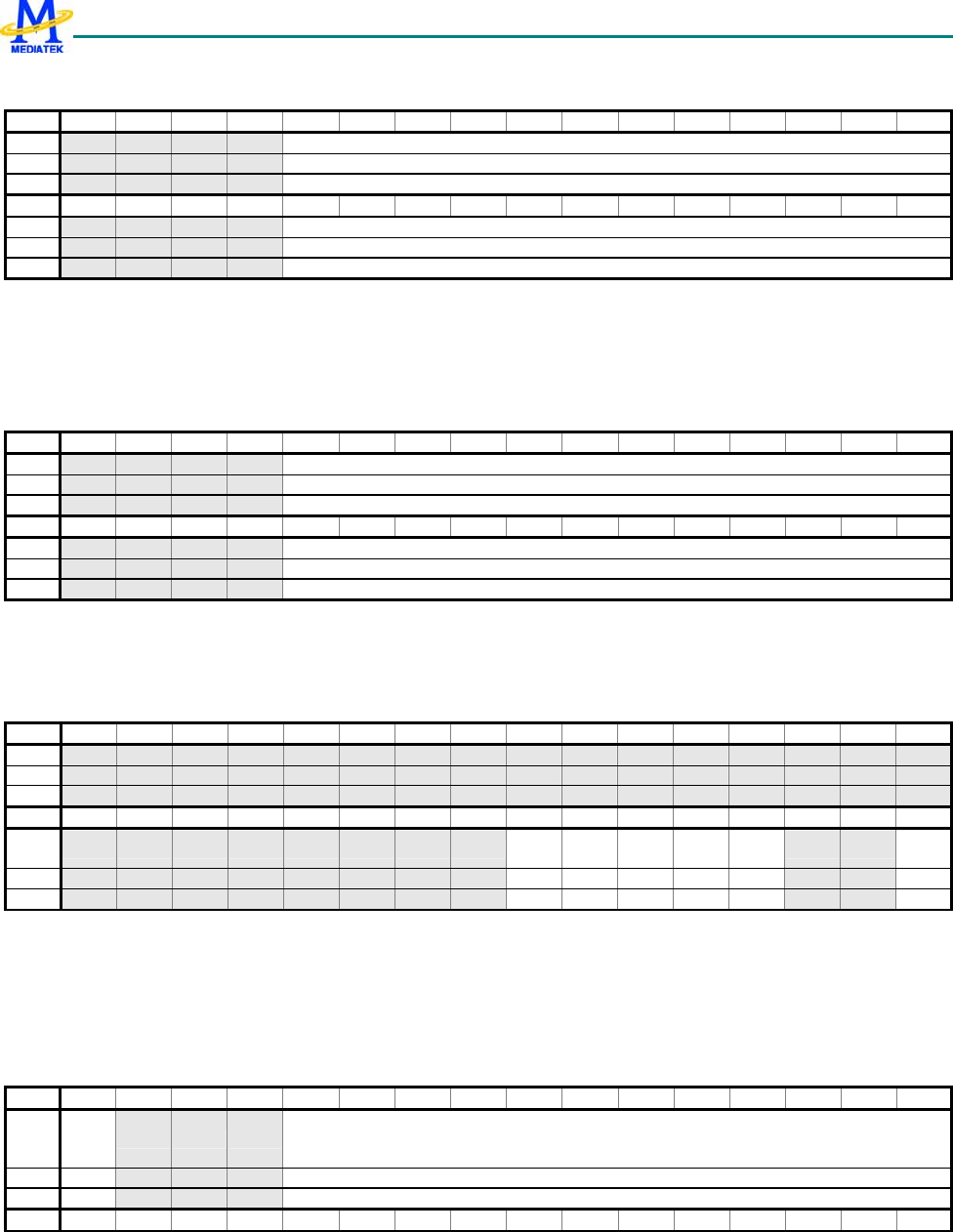

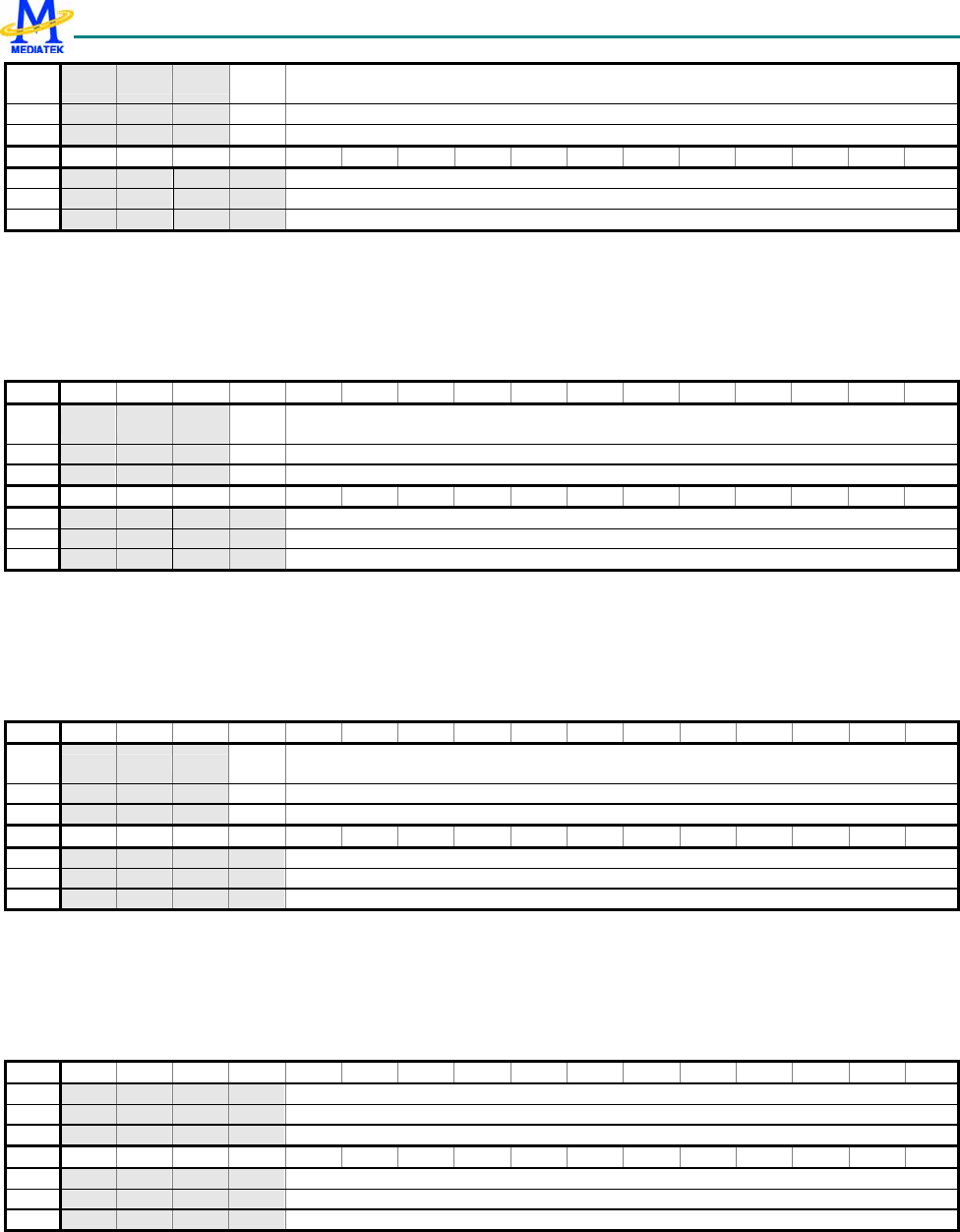

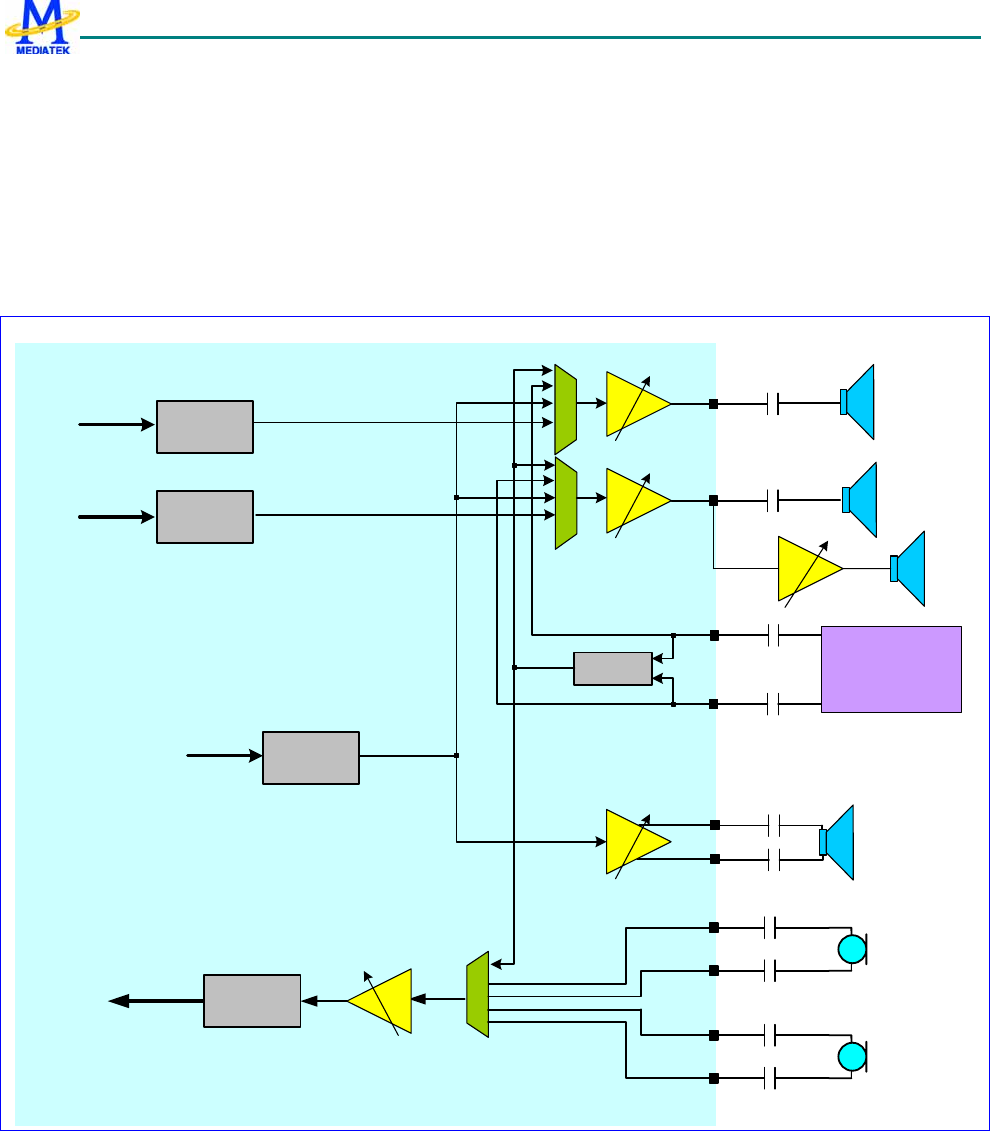

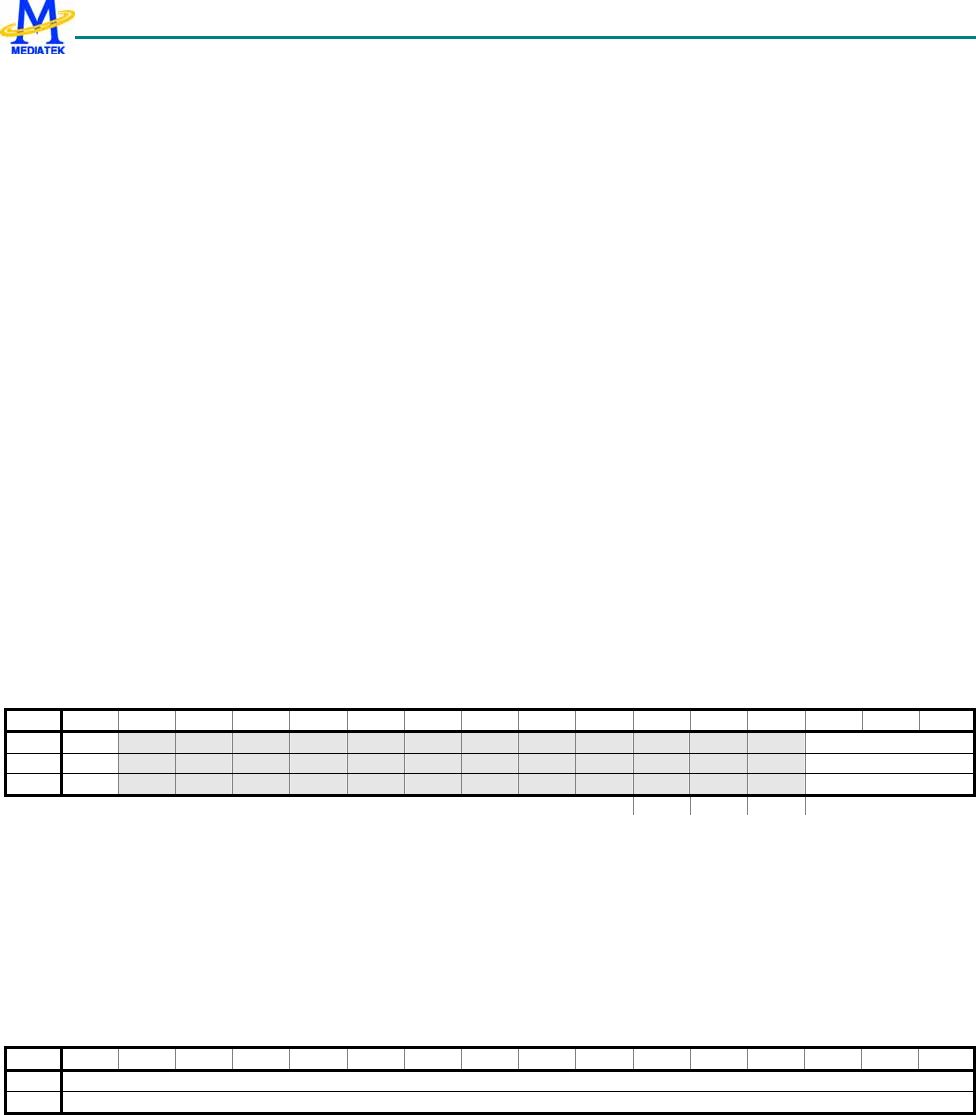

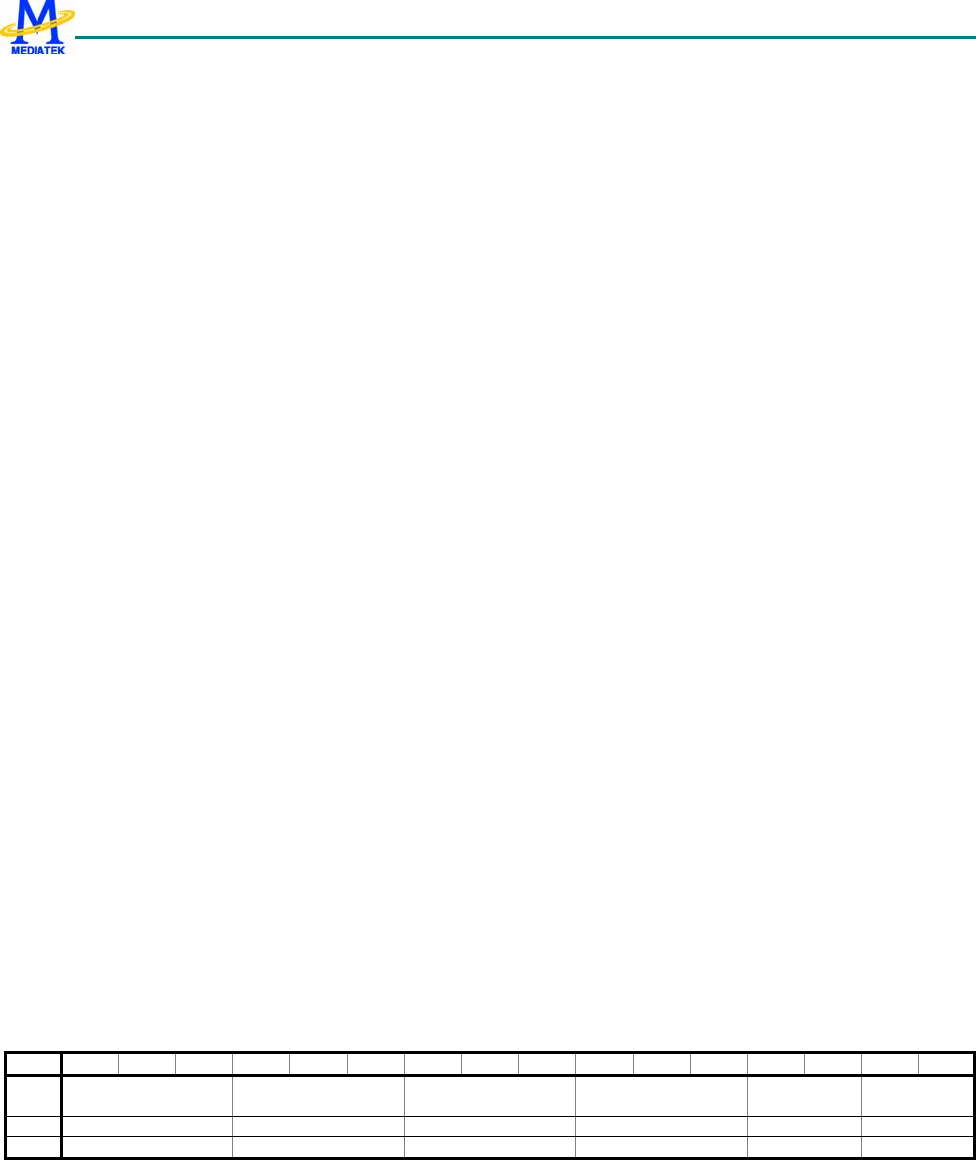

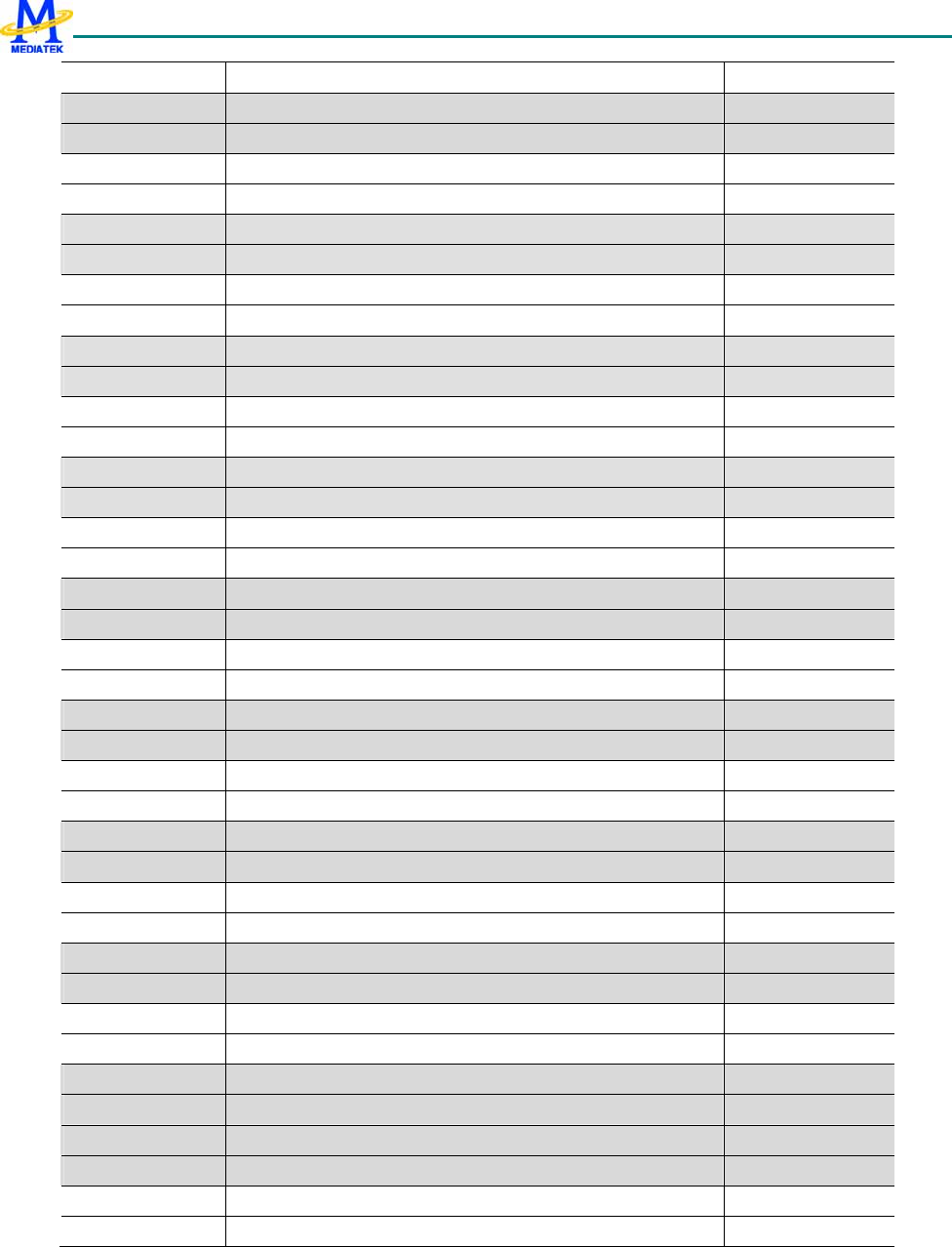

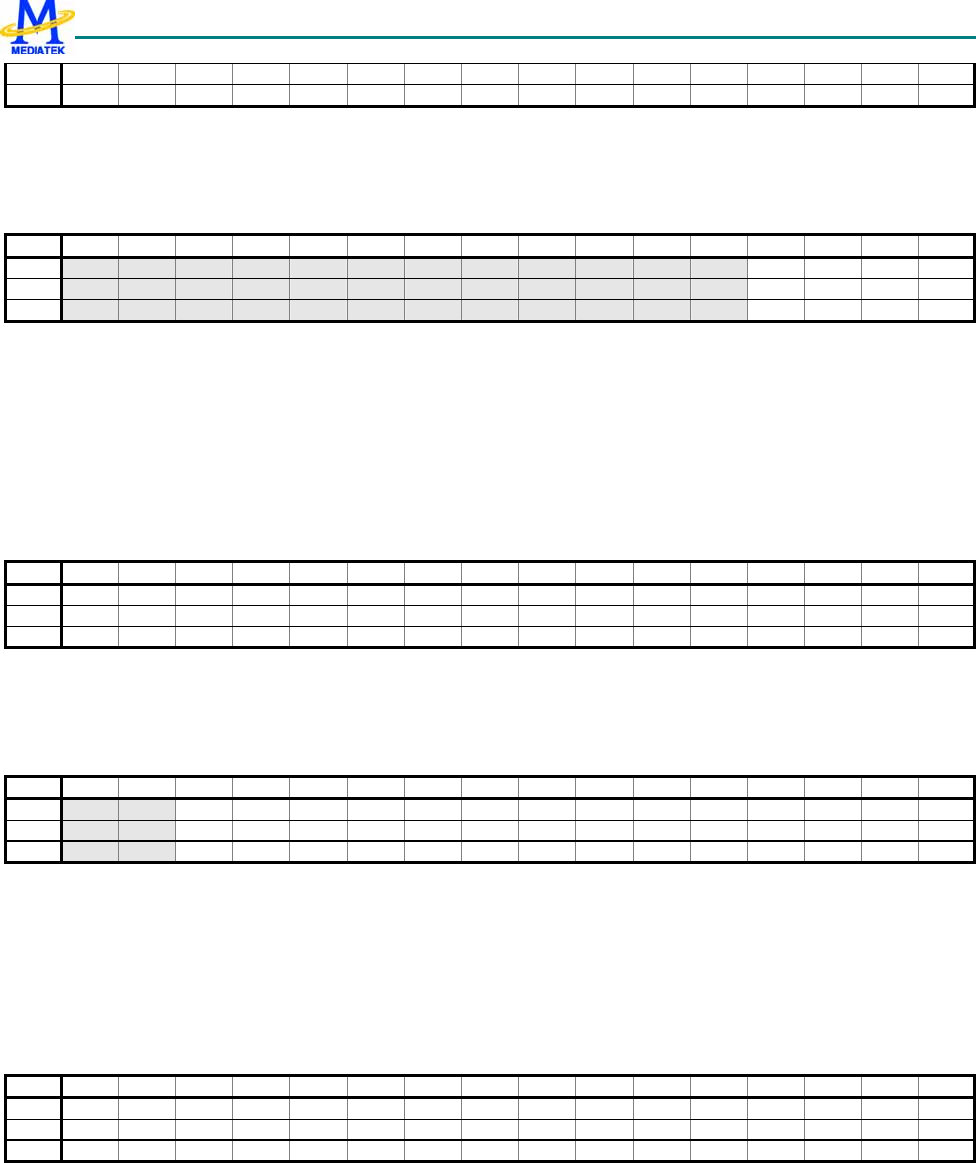

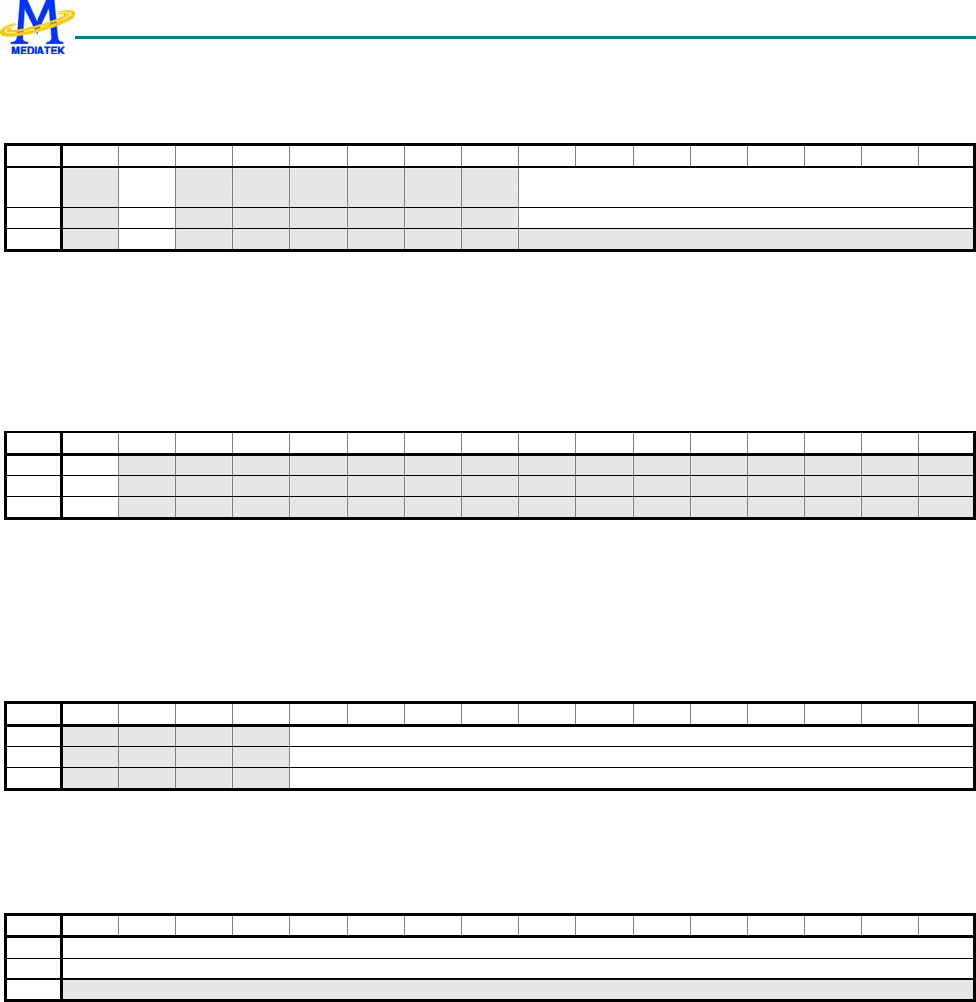

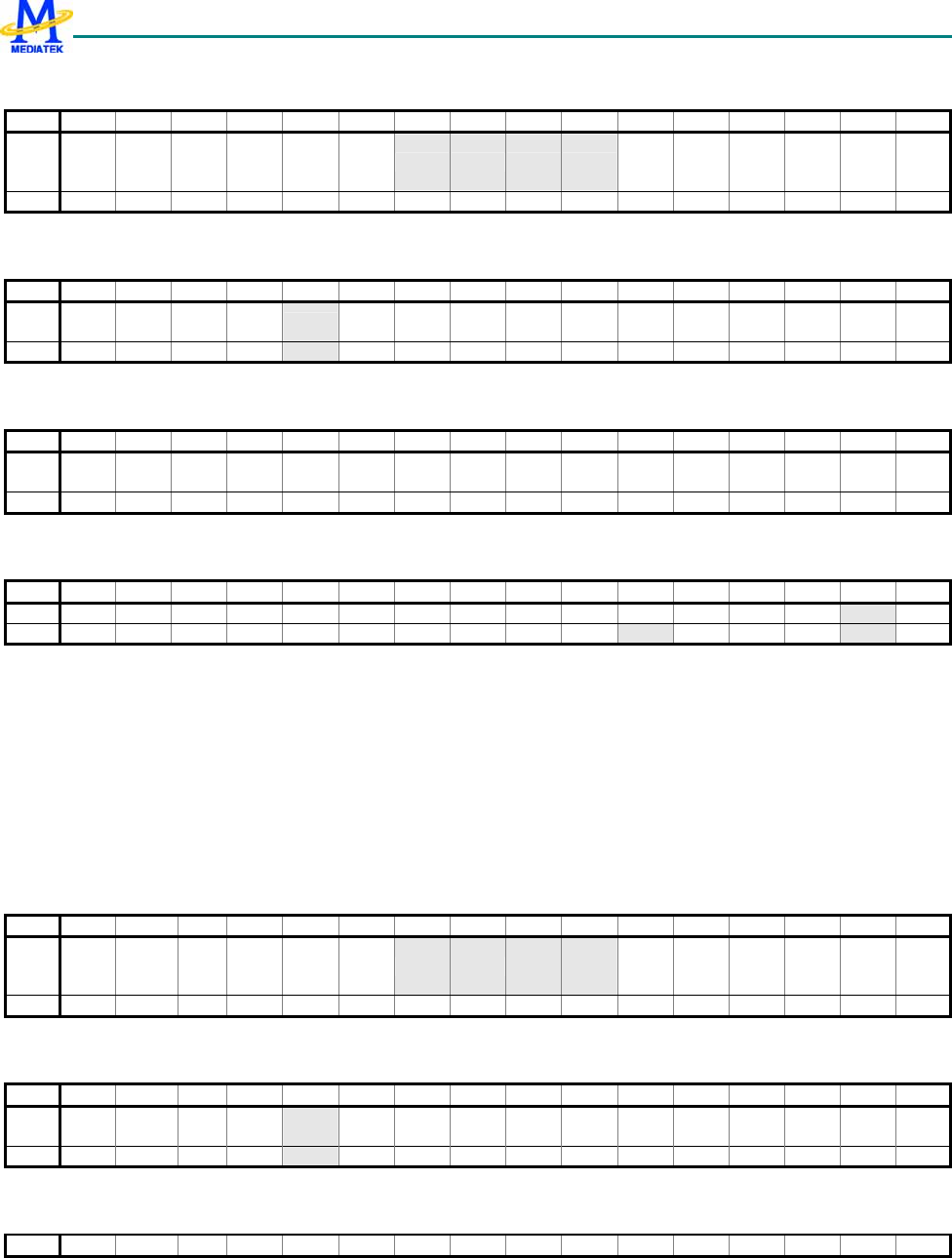

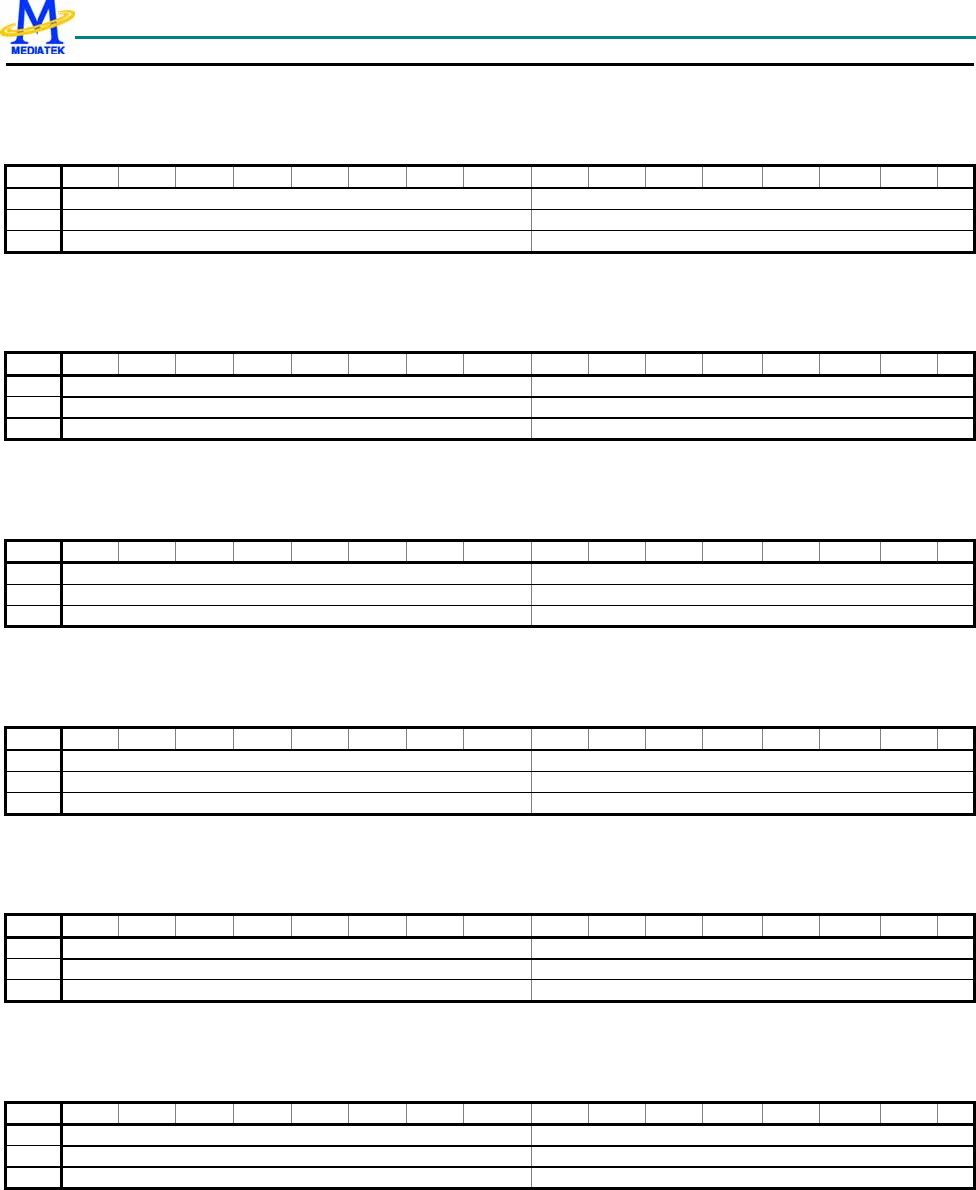

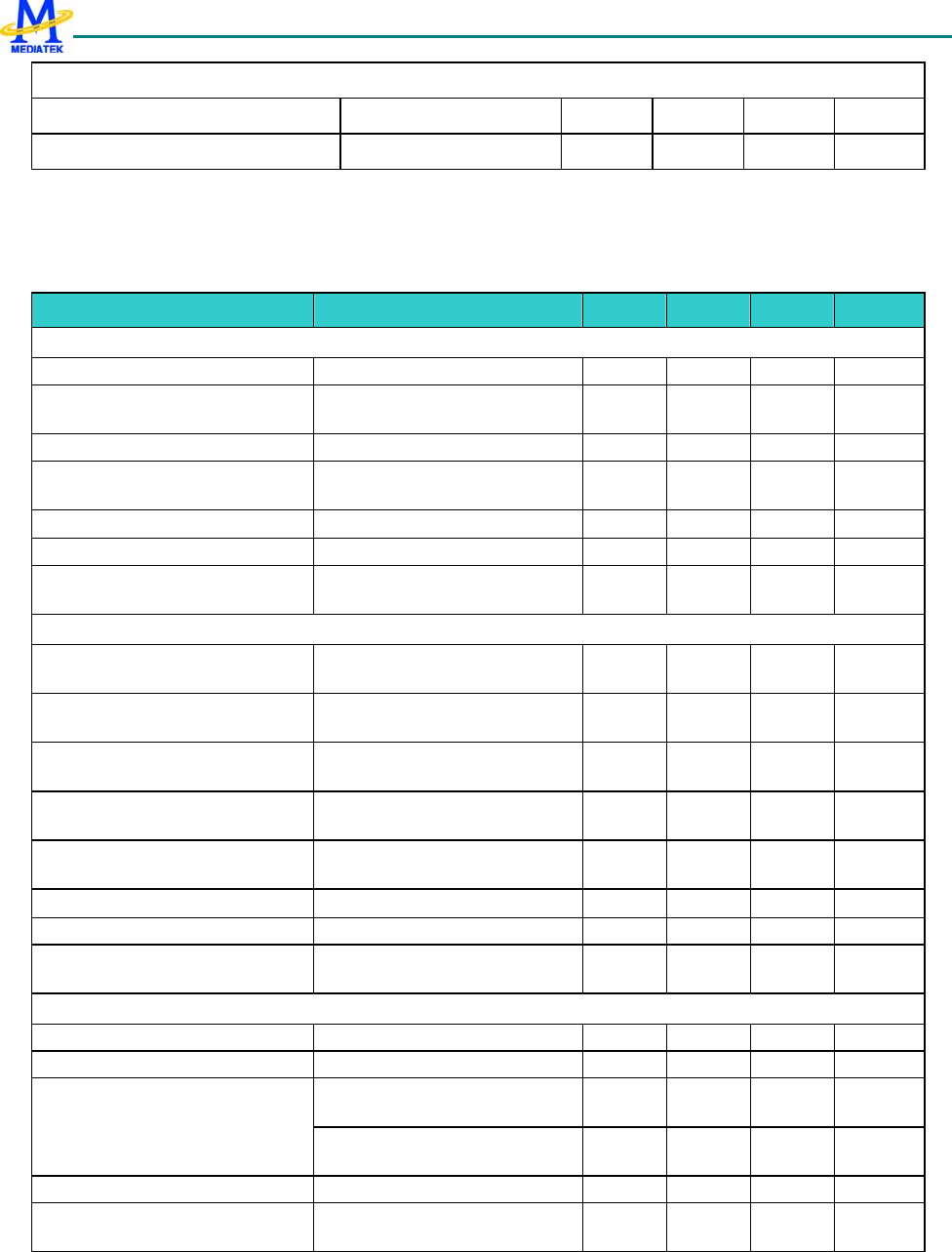

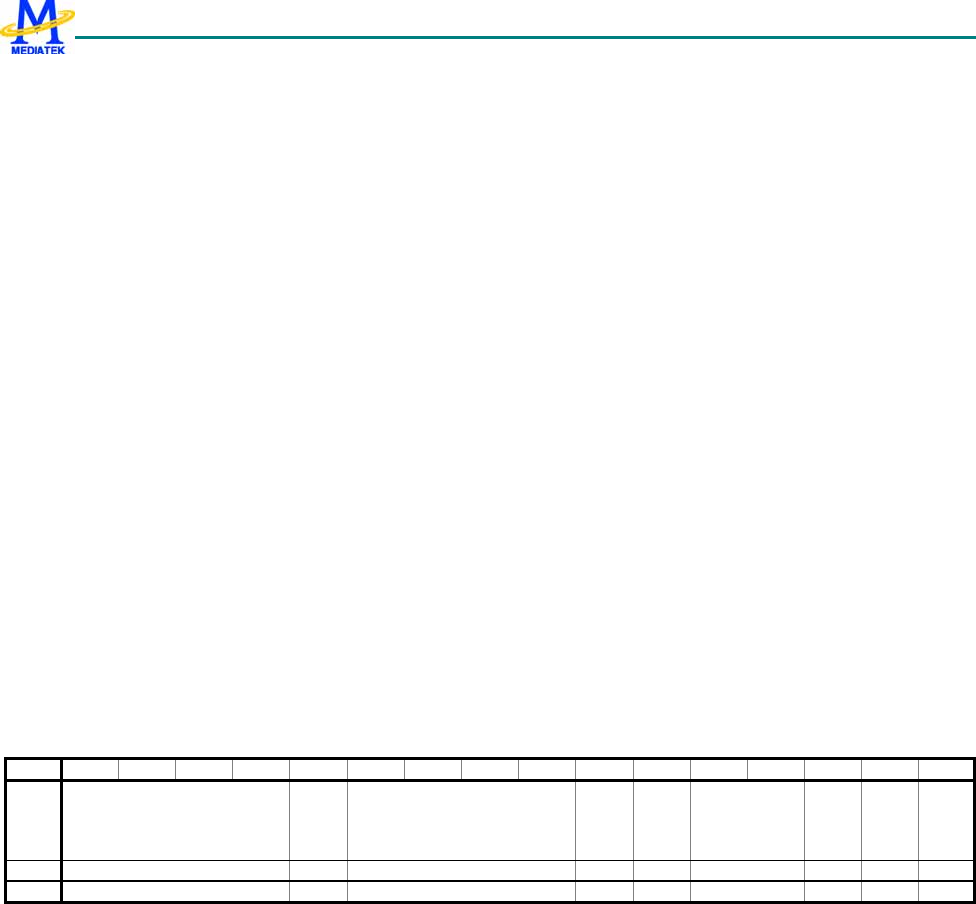

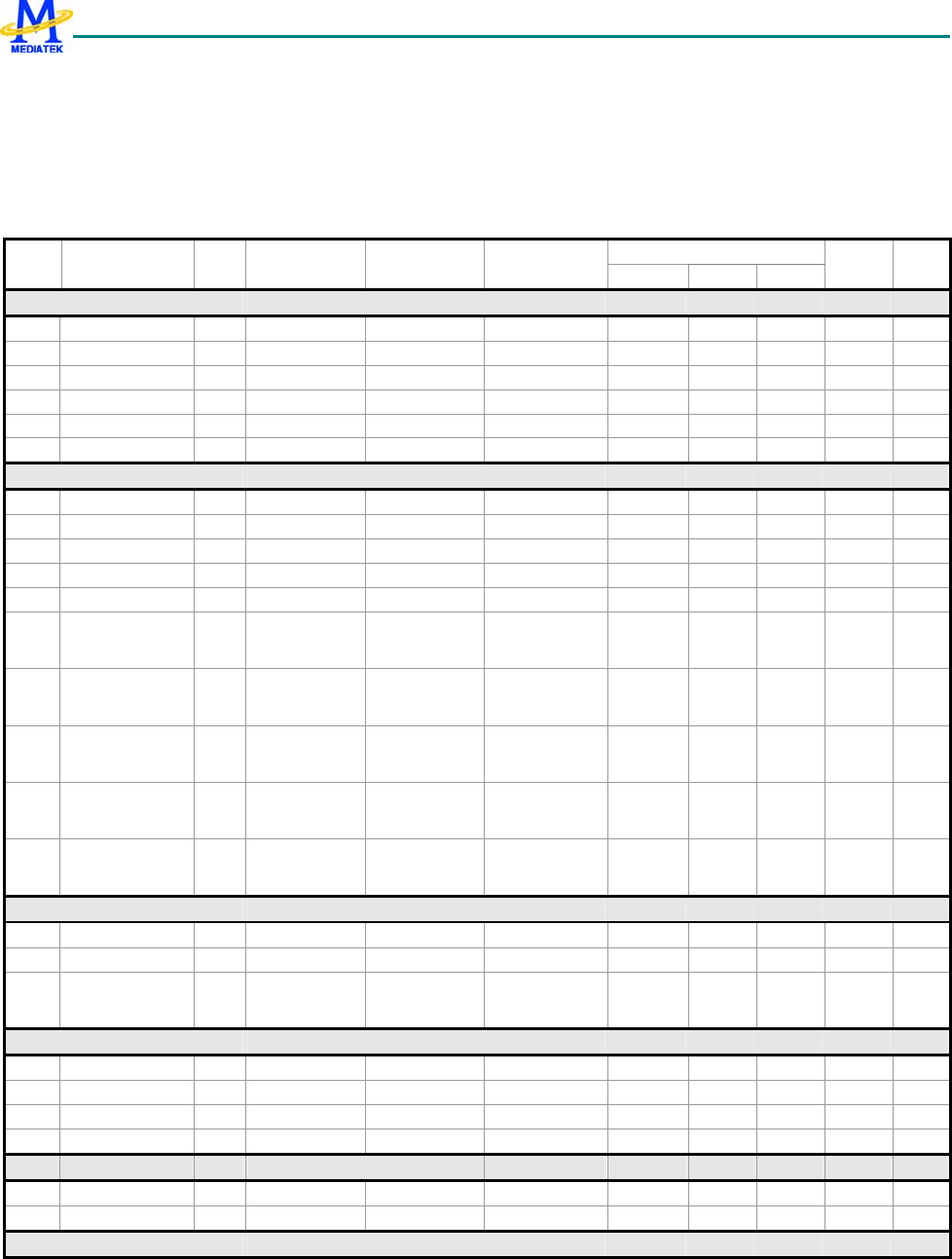

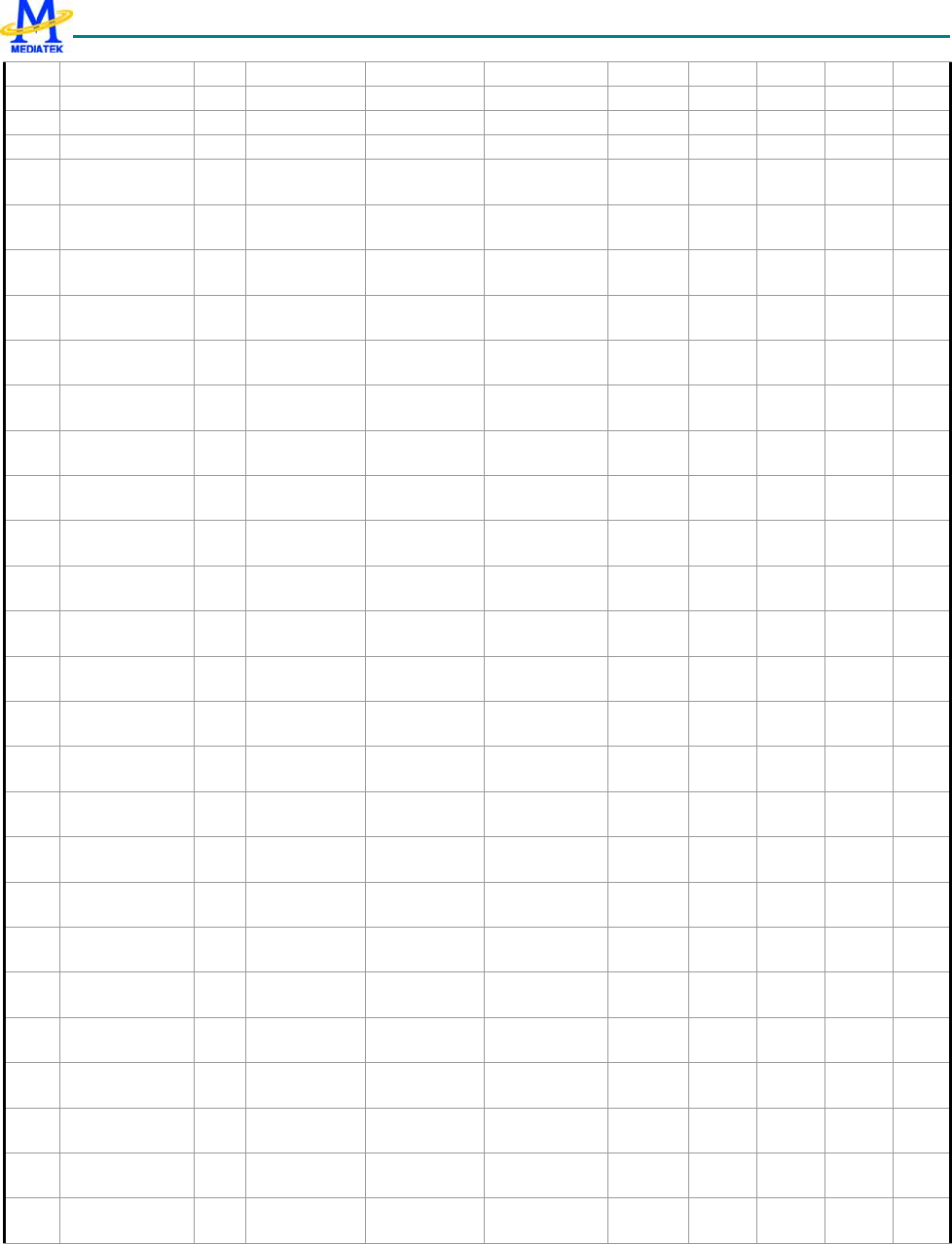

Typical application diagram is shown in Figure 1.

Platform

MT6235 is capable of running the ARM926EJ-STM RISC

processor at up to 208 MHz, thus providing fast data

processing capabilities. In addition to the high clock

frequency, separate CODE and DATA caches are also

included to further improve the overall system efficiency.

For large amounts of data transfer, high performance DMA

(Direct Memory Access) with hardware flow control is

implemented, which greatly enhances the data movement

speed while reducing MCU processing load.

Targeted as a high performance platform for mobile

applications, hardware flash content protection is also

provided to prevent unauthorized porting of the software

load to protect the manufacturer’s development

investment.

Memory

To provide the greatest capacity for expansion and

maximum bandwidth for data intensive applications such

as multimedia features, MT6235 supports up to 4 external

state-of-the-art devices through its 8/16-bit host interface.

High performance devices such as Mobile SDRAM and

Cellular RAM are supported for maximum bandwidth.

Traditional devices such as burst/page mode flash, page

mode SRAM, and Pseudo SRAM are also supported. For

greatest compatibility, the memory interface can also be

used to connect to legacy devices such as Color/Parallel

LCD, and multi-media companion chips are all supported

through this interface. To minimize power consumption

and ensure low noise, this interface is designed for flexible

I/O voltage and allows lowering of the supply voltage

down to 1.8V. The driving strength is configurable for

signal integrity adjustment.

Multi-media

The MT6235 multi-media subsystem provides a

connection to a CMOS image sensor and supports a

resolution up to 2.0 Mpixels. With its high performance

application platform, MT6235 allows efficient processing

of image and video data.

In addition to image and video features, MT6235 utilizes

high resolution DAC, digital audio, and audio synthesis

technology to provide superior audio features for all future

multi-media needs.

Connectivity and Storage

To take advantage of its incredible multimedia strengths,

MT6235 incorporates myriads of advanced connectivity

and storage options for data storage and communication.

MT6235 supports UART, Fast IrDA, USB 2.0, SDIO,

Bluetooth, Touch Screen Controller, WIFI Interface, and

MMC/SD/MS/MS Pro storage systems. These interfaces

provide MT6235 users with the highest degree of

flexibility in implementing solutions suitable for the

targeted application.

To achieve a complete user interface, MT6235 also brings

together all the necessary peripheral blocks for a

multi-media GSM/GPRS/EDGE phone. The peripheral

blocks include the Keypad Scanner with the capability to

detect multiple key presses, SIM Controller, Alerter, Real

Time Clock, PWM, Serial LCD Controller, and General

Purpose Programmable I/Os.

Furthermore, to provide much better configurability and

bandwidth for multi-media products, an additional 18-bit

parallel interface is incorporated. This interface enables

connection to LCD panels as well as NAND flash devices

for additional multi-media data storage.

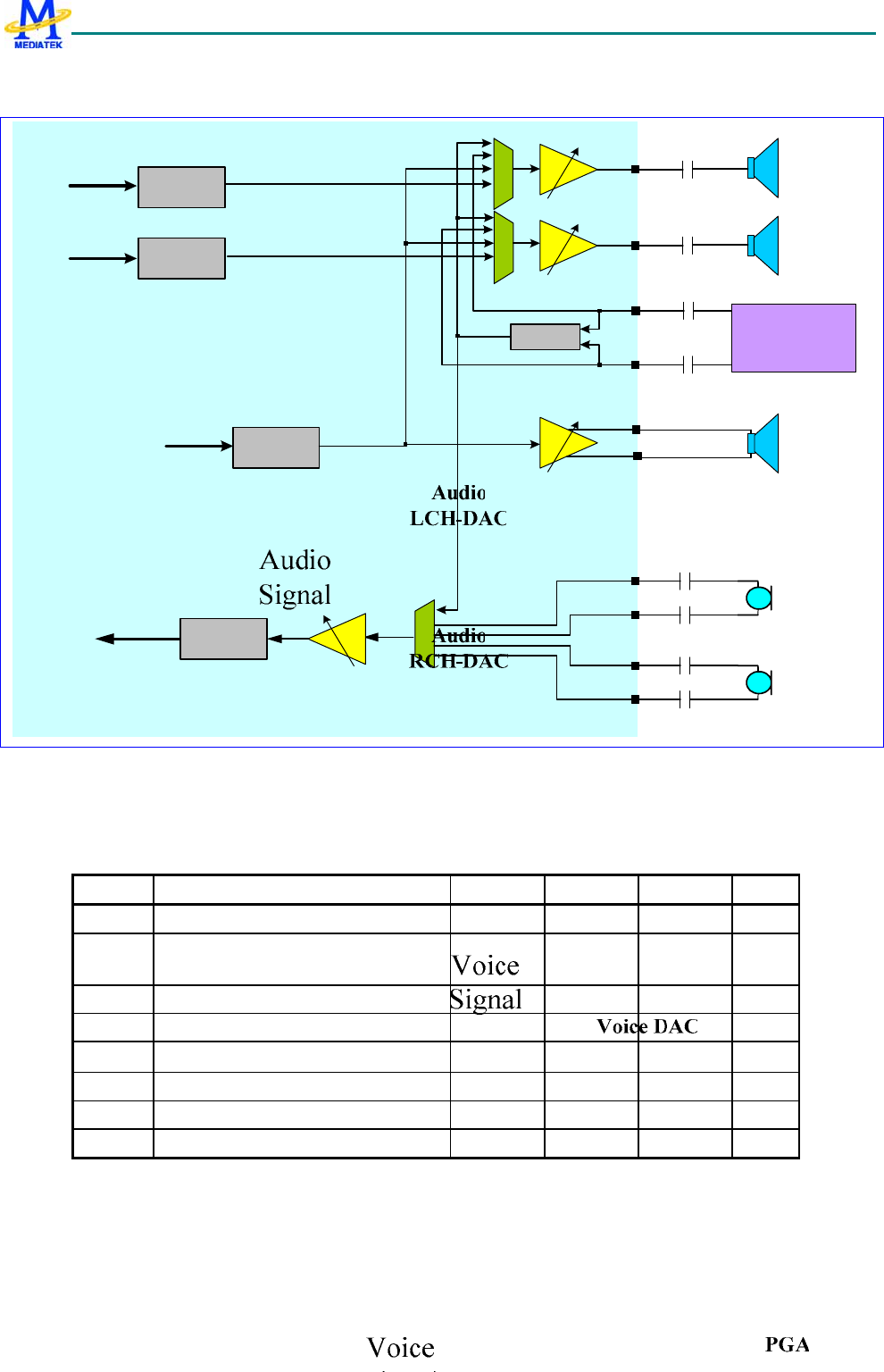

Audio

MT6235 GSM/GPRS Baseband Processor Data Sheet Revision 1.02

7/599 MediaTek Inc. Confidential

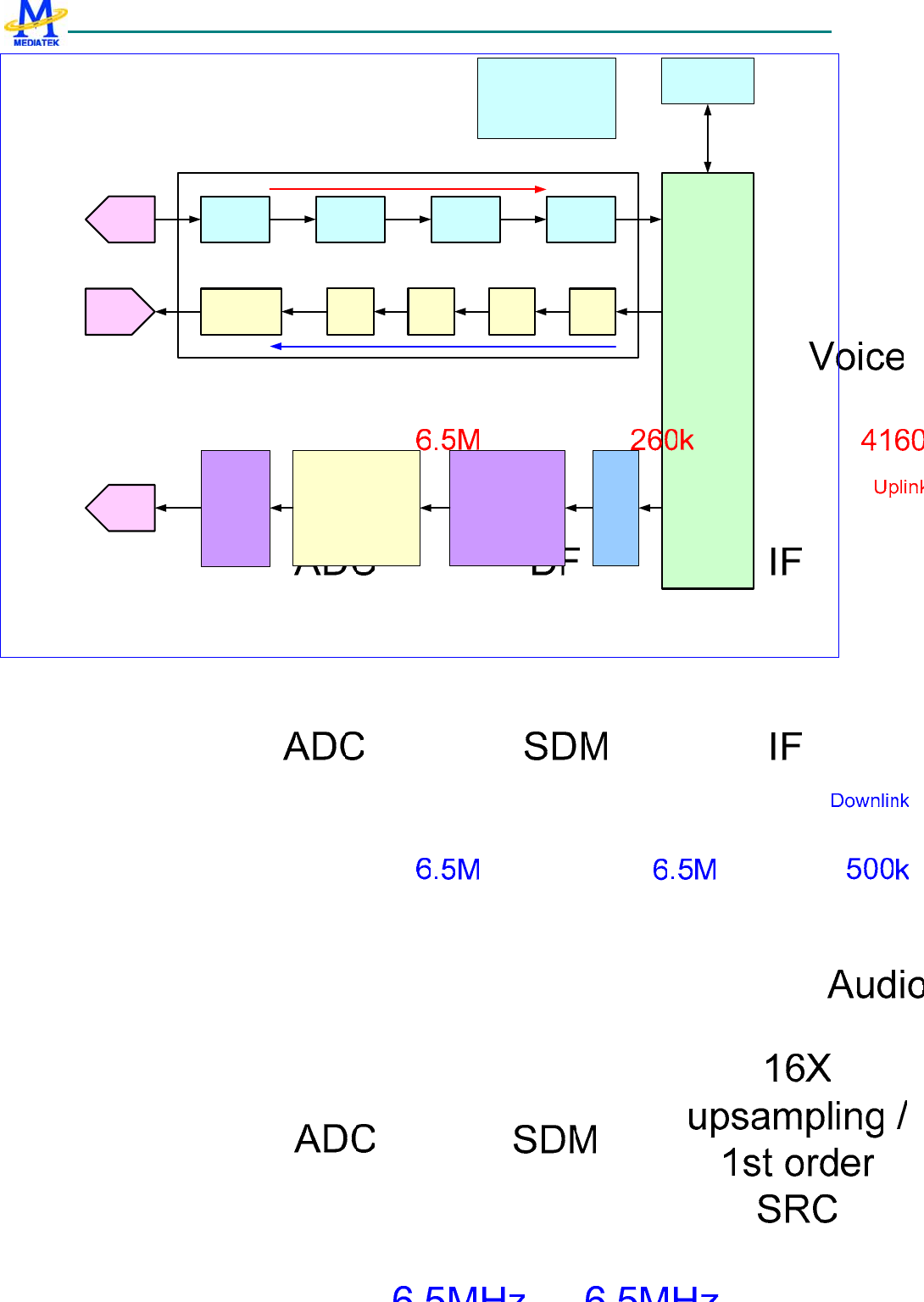

Using a highly integrated mixed-signal Audio Front-End,

the MT6235 architecture allows for easy audio interfacing

with direct connection to the audio transducers. The

audio interface integrates D/A and A/D Converters for

Voice band, as well as high resolution Stereo D/A

Converters for Audio band. In addition, MT6235 also

provides Stereo Input and Analog MUX.

MT6235 supports AMR codec to adaptively optimize

speech and audio quality. Moreover, HE-AAC codec is

implemented to deliver CD-quality audio at low bit rates.

On the whole, MT6235’s audio features provide a rich

solution for multi-media applications.

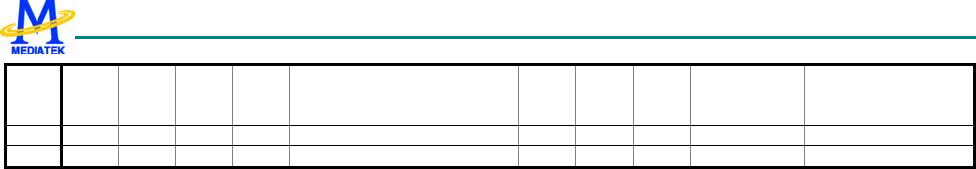

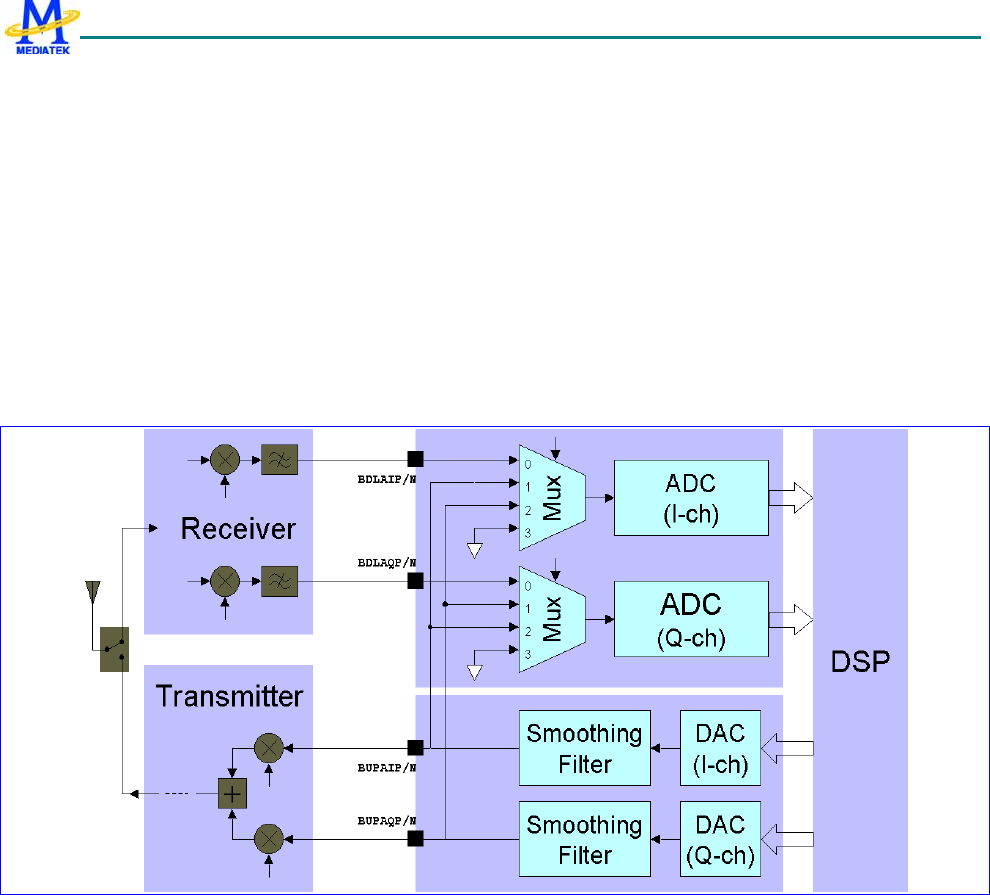

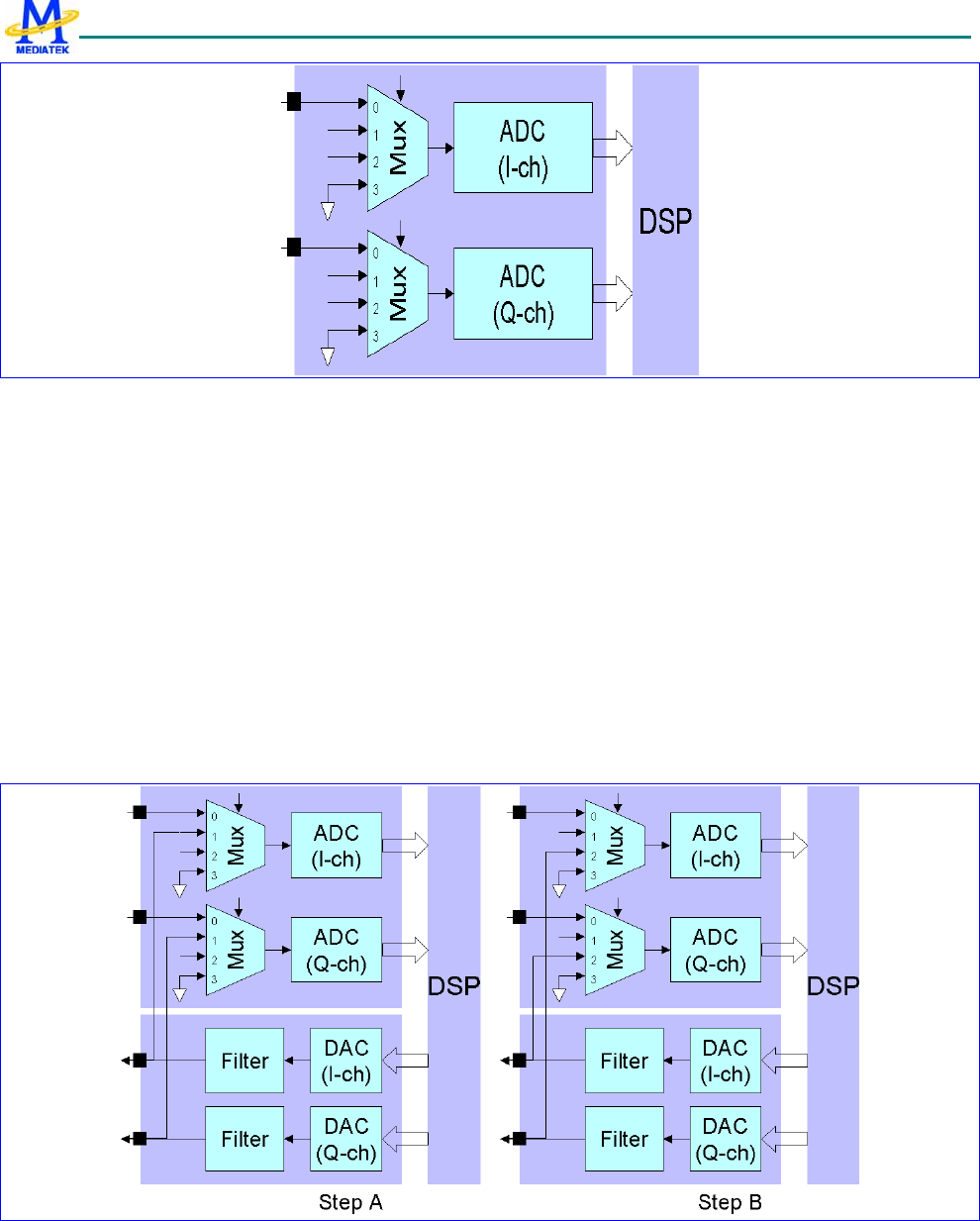

Radio

MT6235 integrates a mixed-signal baseband front-end in

order to provide a well-organized radio interface with

flexibility for efficient customization. The front-end

contains gain and offset calibration mechanisms, and filters

with programmable coefficients for comprehensive

compatibility control on RF modules. This approach

allows the usage of a high resolution D/A Converter for

controlling VCXO or crystal, reducing the need for an

expensive TCVCXO. MT6235 achieves great MODEM

performance by utilizing a 14-bit high resolution A/D

Converter in the RF downlink path. Furthermore, to

reduce the need for extra external current-driving

component, the driving strength of some BPI outputs is

designed to be configurable.

Debug Function

The JTAG interface enables in-circuit debugging of the

software program with the ARM926EJ-S core. With this

standardized debugging interface, MT6235 provides

developers with a wide set of options in choosing ARM

development kits from different third party vendors.

Power Management

The MT6235 offers various low-power features to help

reduce system power consumption. These features

include a Pause Mode of 32 KHz clocking in Standby State,

Power Down Mode for individual peripherals, and

Processor Sleep Mode. MT6235 is also fabricated in an

advanced low leakage CMOS process, hence providing an

overall ultra low leakage solution.

Package

The MT6235 device is offered in a 13mm×13mm, 362-ball,

0.5 mm pitch, TFBGA package.

MT6235 GSM/GPRS Baseband Processor Data Sheet Revision 1.02

8/599 MediaTek Inc. Confidential

Figure 1 Typical application of MT6235

MT6235 GSM/GPRS Baseband Processor Data Sheet Revision 1.02

9/599 MediaTek Inc. Confidential

Platform Features

General

z Integrated voice-band, audio-band and base-band

analog front ends

z TFBGA 13mm×13mm, 362-ball, 0.5 mm pitch

package

MCU Subsystem

z ARM926EJ-S 32-bit RISC processor

z High performance multi-layer AMBA bus

z Java hardware acceleration for fast Java-based

games and applets

z Operating frequency: 26/52/104/208 MHz

z Dedicated DMA bus

z 14 DMA channels

z 512K bits on-chip SRAM

z 384K bits Instruction-TCM

z 640K bits Data-TCM

z 128K bits Instruction-Cache

z 128K bits Data-Cache

z On-chip boot ROM for Factory Flash

Programming

z Watchdog timer for system crash recovery

z 3 sets of General Purpose Timer

z Circuit Switch Data coprocessor

z Division coprocessor

z PPP Framer coprocessor

External Memory Interface

z Supports up to 4 external memory devices

z Supports 8-bit or 16-bit memory components with

maximum size of up to 128M Bytes each

z Supports Mobile SDRAM and Cellular RAM

z Supports Flash and SRAM/PSRAM with page

mode or burst mode

z Industry standard Parallel LCD interface

z Supports multi-media companion chips with 8/16

bits data width

z Flexible I/O voltage of 1.8V ~ 2.8V for memory

interface

z Configurable driving strength for memory

interface

User Interfaces

z 8-row × 8-column keypad controller with

hardware scanner

z Supports multiple key presses for gaming

z SIM/USIM controller with hardware T=0/T=1

protocol control

z Real Time Clock (RTC) operating with a separate

power supply

z General Purpose I/Os (GPIOs)

z 4 sets of Pulse Width Modulation (PWM) output

z Alerter output with Enhanced PWM or PDM

z 8 external interrupt lines

Security

z Supports security key and 126 bit chip unique ID

Connectivity

z 3 UARTs with hardware flow control and speeds

up to 921600 bps

z IrDA modulator/demodulator with hardware

framer. Supports SIR/MIR/FIR operating speeds.

z USB 2.0 capability

z Multi Media Card, Secure Digital Memory Card,

Memory Stick, Memory Stick Pro host controller

with flexible I/O voltage power

MT6235 GSM/GPRS Baseband Processor Data Sheet Revision 1.02

10/599 MediaTek Inc. Confidential

z Supports SDIO interface for SDIO peripherals as

well as WIFI connectivity

z DAI/PCM and I2S interface for Audio application

Power Management

z Power Down Mode for analog and digital circuits

z Processor Sleep Mode

z Pause Mode of 32 KHz clocking in Standby State

z 4-channel Auxiliary 10-bit A/D Converter for

charger and battery monitoring and photo sensing

Test and Debug

z Built-in digital and analog loop back modes for

both Audio and Baseband Front-End

z DAI port complying with GSM Rec.11.10

z JTAG port for debugging embedded MCU

MT6235 GSM/GPRS Baseband Processor Data Sheet Revision 1.02

11/599 MediaTek Inc. Confidential

1.1 MODEM Features

Radio Interface and Baseband Front End

z GMSK modulator with analog I and Q channel

outputs

z 10-bit D/A Converter for uplink baseband I and Q

signals

z 14-bit high resolution A/D Converter for downlink

baseband I and Q signals

z Calibration mechanism of offset and gain

mismatch for baseband A/D Converter and D/A

Converter

z 10-bit D/A Converter for Automatic Power

Control

z 13-bit high resolution D/A Converter for

Automatic Frequency Control

z Programmable Radio RX filter

z 2 channels Baseband Serial Interface (BSI) with

3-wire control

z Bi-directional BSI interface. RF chip register

read access with 3-wire or 4-wire interface.

z 10-Pin Baseband Parallel Interface (BPI) with

programmable driving strength

z Multi-band support

Voice and Modem CODEC

z Dial tone generation

z Voice memo

z Noise reduction

z Echo suppression

z Advanced sidetone Oscillation Reduction

z Digital sidetone generator with programmable

gain

z Two programmable acoustic compensation filters

z GSM/GPRS quad vocoders for adaptive multirate

(AMR), enhanced full rate (EFR), full rate (FR)

and half rate (HR)

z GSM channel coding, equalization and A5/1, A5/2

and A5/3 ciphering

z GPRS GEA1, GEA2 and GEA3 ciphering

z Programmable GSM/GPRS/EDGE modem

z Packet Switched Data with CS1/CS2/CS3/CS4

coding schemes

z GSM Circuit Switch Data

z GPRS/EDGE Class 12

Voice Interface and Voice Front End

z Two microphone inputs sharing one low noise

amplifier with programmable gain and automatic

gain control (AGC) mechanisms

z Voice power amplifier with programmable gain

z 2nd order Sigma-Delta A/D Converter for voice

uplink path

z D/A Converter for voice downlink path

z Supports half-duplex hands-free operation

z Compliant with GSM 03.50

MT6235 GSM/GPRS Baseband Processor Data Sheet Revision 1.02

12/599 MediaTek Inc. Confidential

1.2 Multi-Media Features

LCD/NAND Flash Interface

z Dedicated Parallel Interface supports 3 external

devices with 8-/16-bit NAND flash interface,

8-/9-/16-/18-bit Parallel interface, and Serial

interface for LCM

z Built-in NAND Flash Controller with 1-bit ECC

for mass storage

LCD Controller

z Supports simultaneous connection to up to 3

parallel LCD and 2 serial LCD modules

z Supports LCM format: RGB332, RGB444,

RGB565, RGB666, RGB888

z Supports LCD module with maximum resolution

up to 800x600 at 24bpp

z Per pixel alpha channel

z True color engine

z Supports hardware display rotation

z Capable of combining display memories with up to

6 blending layers

Image Signal Processor

z 8 bit YUV format image input

z Capable of processing image of size up to 2.0 M

pixels

z IEEE Std 1180-1990 IDCT standards compliance

z Supports progressive image processing to

minimize storage space requirement

z Supports reload-able DMA for VLD stream

Image Data Processing

z Supports Digital Zoom

z Supports RGB888/565, YUV444 image

processing

z High throughput hardware scaler. Capable of

tailoring an image to an arbitrary size.

z Horizontal scaling in averaging method

z Vertical scaling in bilinear method

z YUV and RGB color space conversion

z Boundary padding

2D Accelerator

z Supports 32-bpp ARGB8888, 24-bpp RGB888,

16-bpp RGB565, and 8-bpp index color modes

z Supports SVG Tiny

z Rectangle gradient fill

z BitBlt: multi-BitBlt with 7 rotation, 16 binary ROP

z Alpha blending with 7 rotation

z Line drawing: normal line, dotted line,

anti-aliasing

z Circle drawing

z Bezier curve drawing

z Triangle flat fill

z Font caching: normal font, italic font

z Command queue with max depth of 2047

Audio CODEC

z Supports HE-AAC codec decode

z Supports AAC codec decode

z Wavetable synthesis with up to 64 tones

z Advanced wavetable synthesizer capable of

generating simulated stereo

z Wavetable including GM full set of 128

instruments and 47 sets of percussions

z PCM Playback and Record

z Digital Audio Playback

Audio Interface and Audio Front End

z Supports I2S interface

MT6235 GSM/GPRS Baseband Processor Data Sheet Revision 1.02

13/599 MediaTek Inc. Confidential

z High resolution D/A Converters for Stereo Audio

playback

z Stereo analog input for stereo audio source

z Analog multiplexer for stereo audio

z Stereo to mono conversion

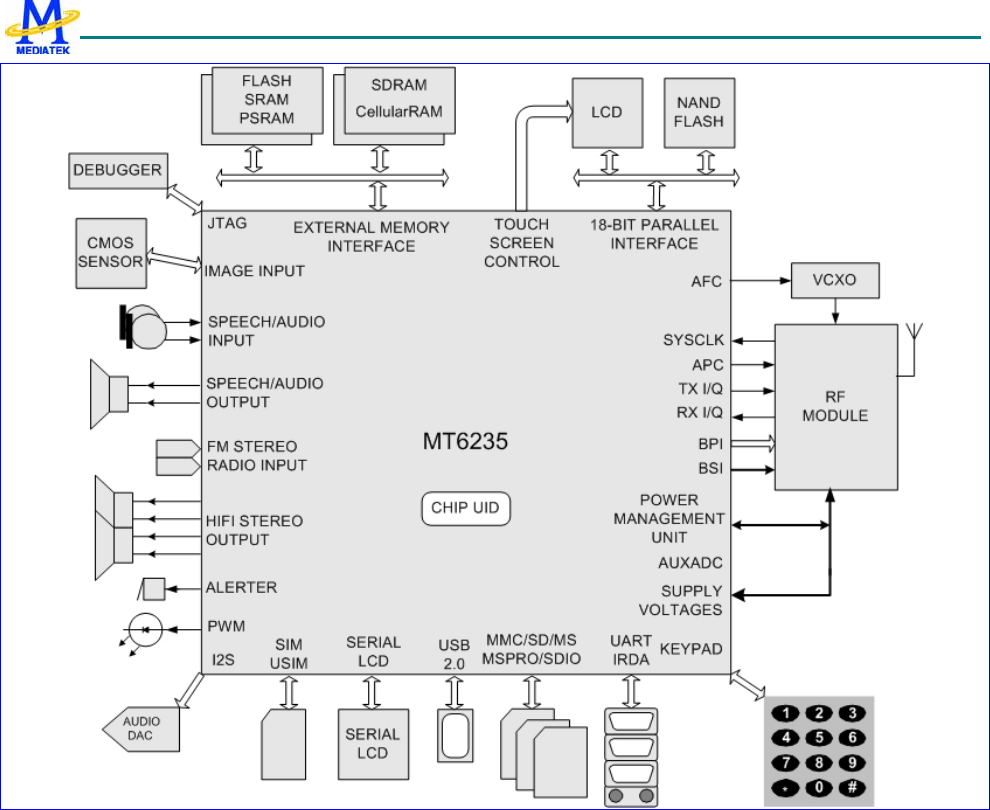

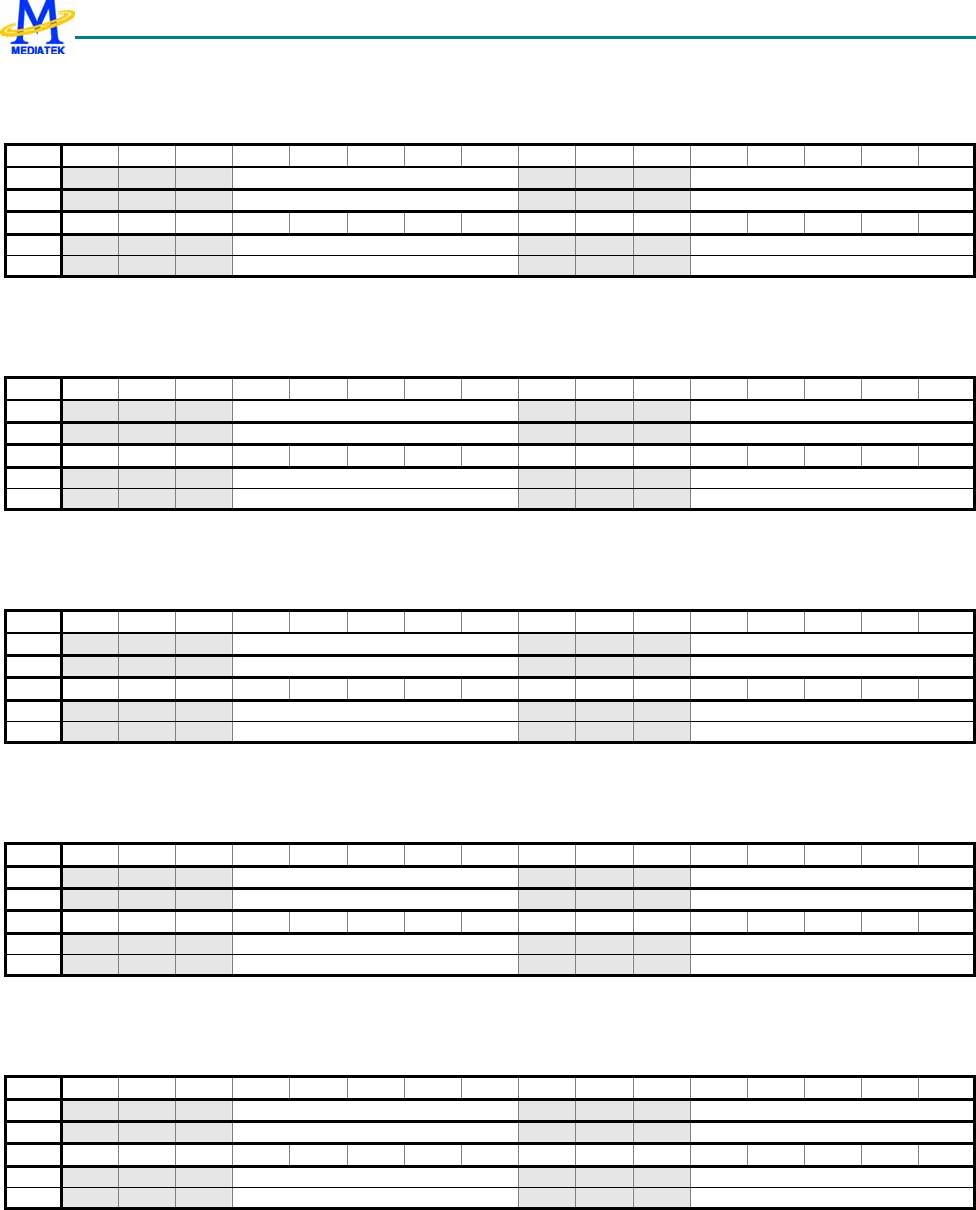

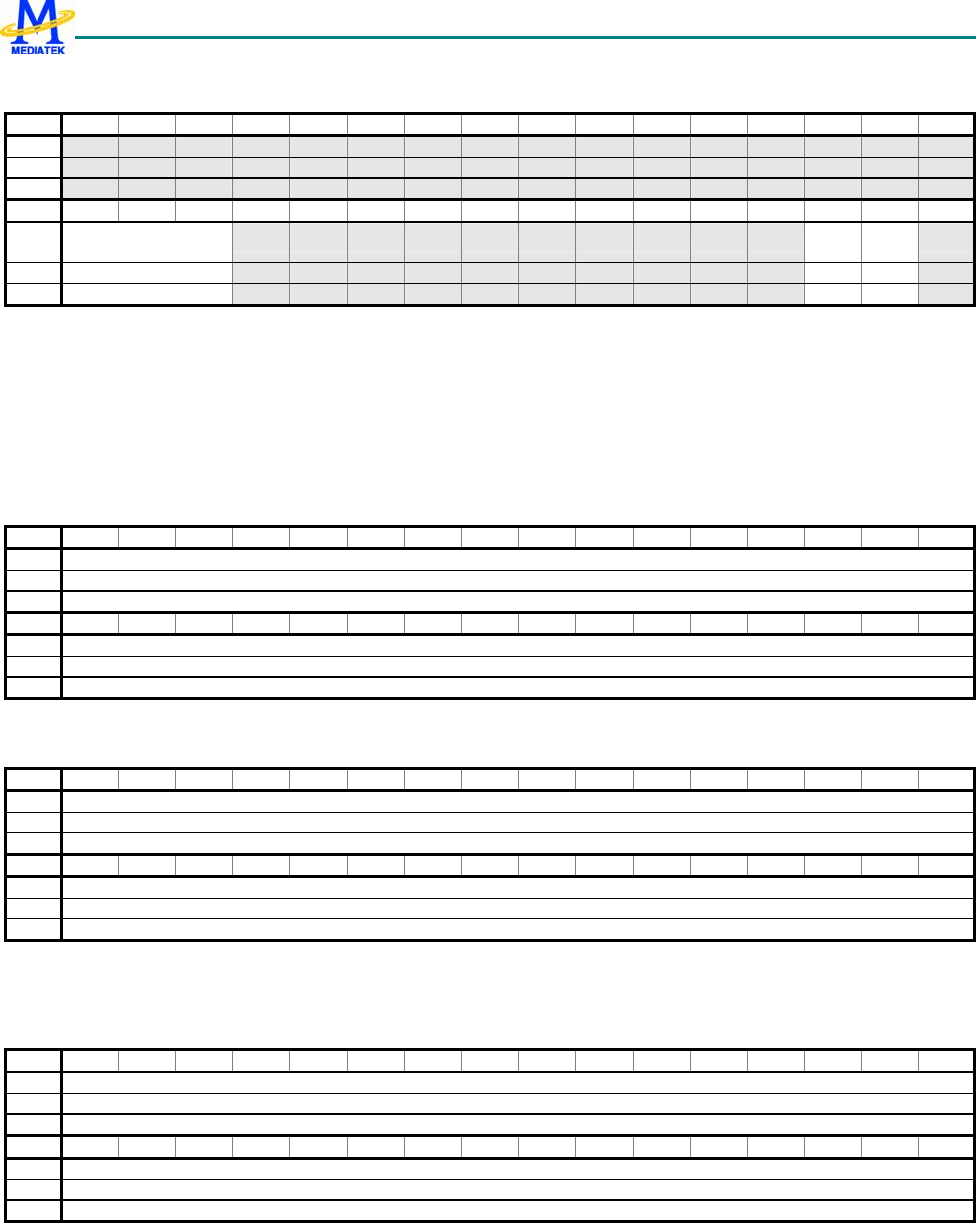

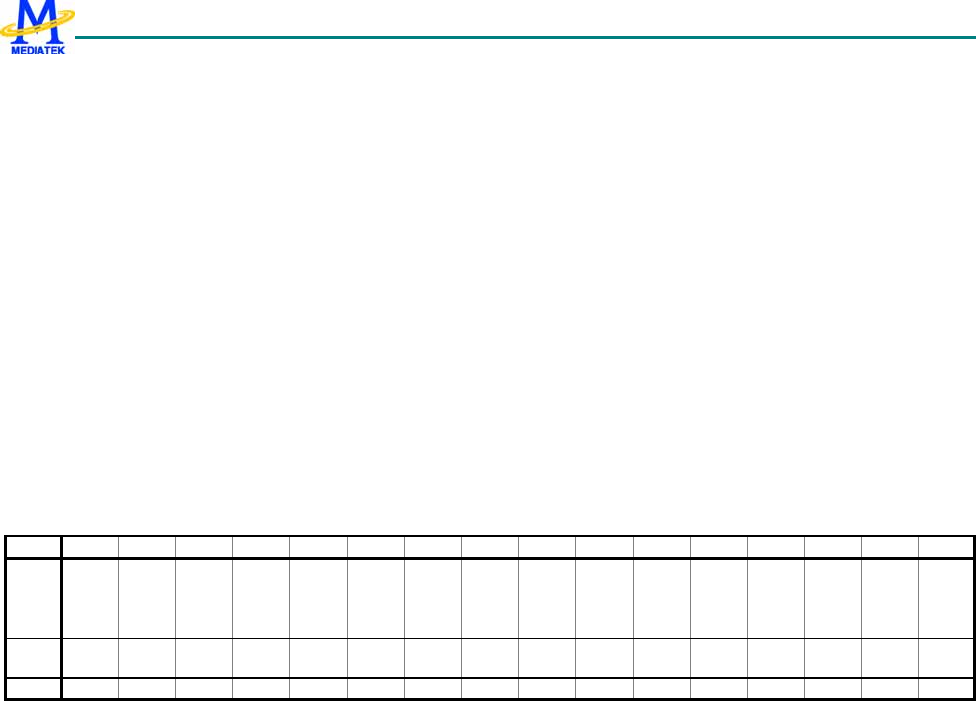

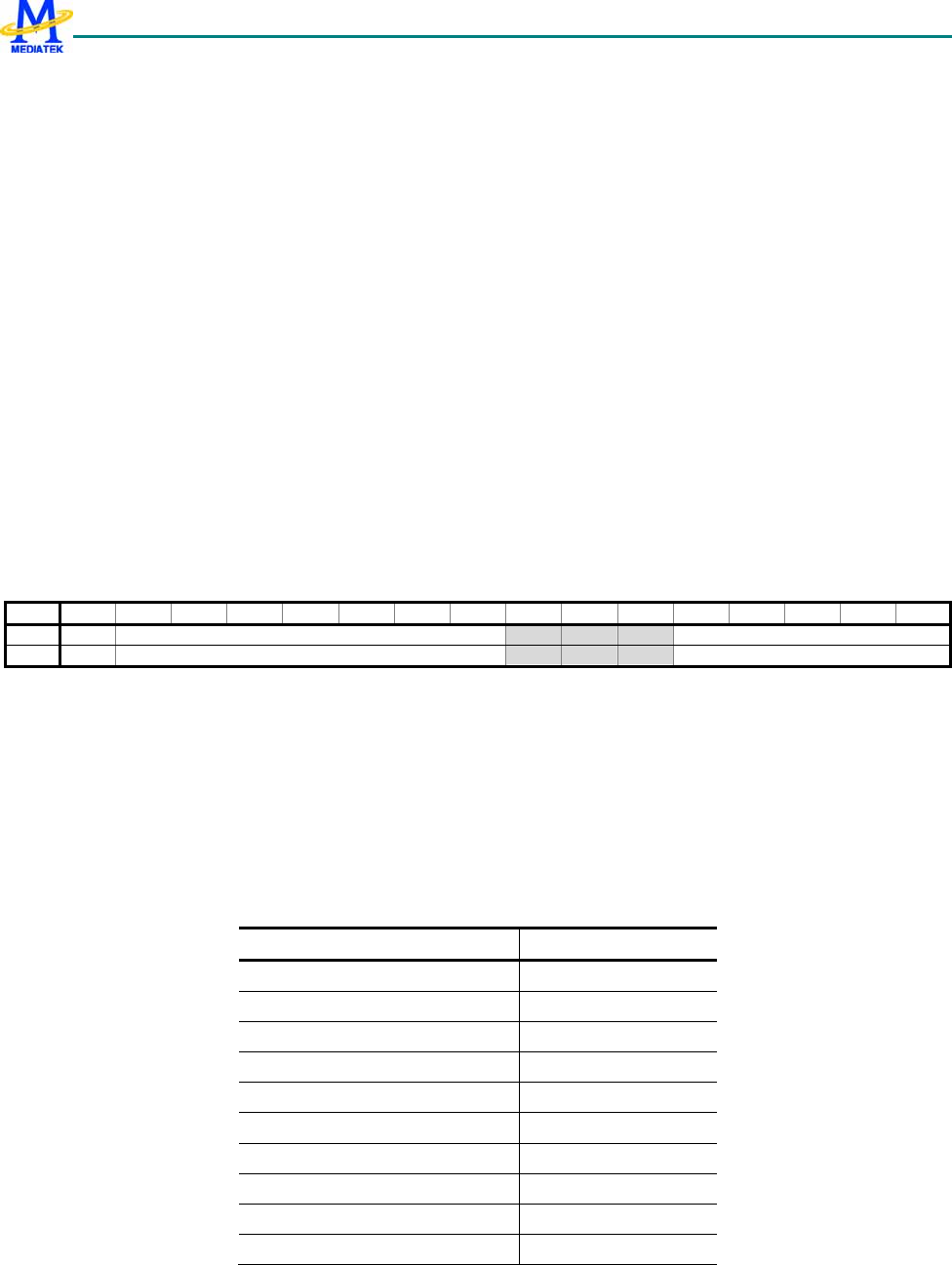

1.3 General Description

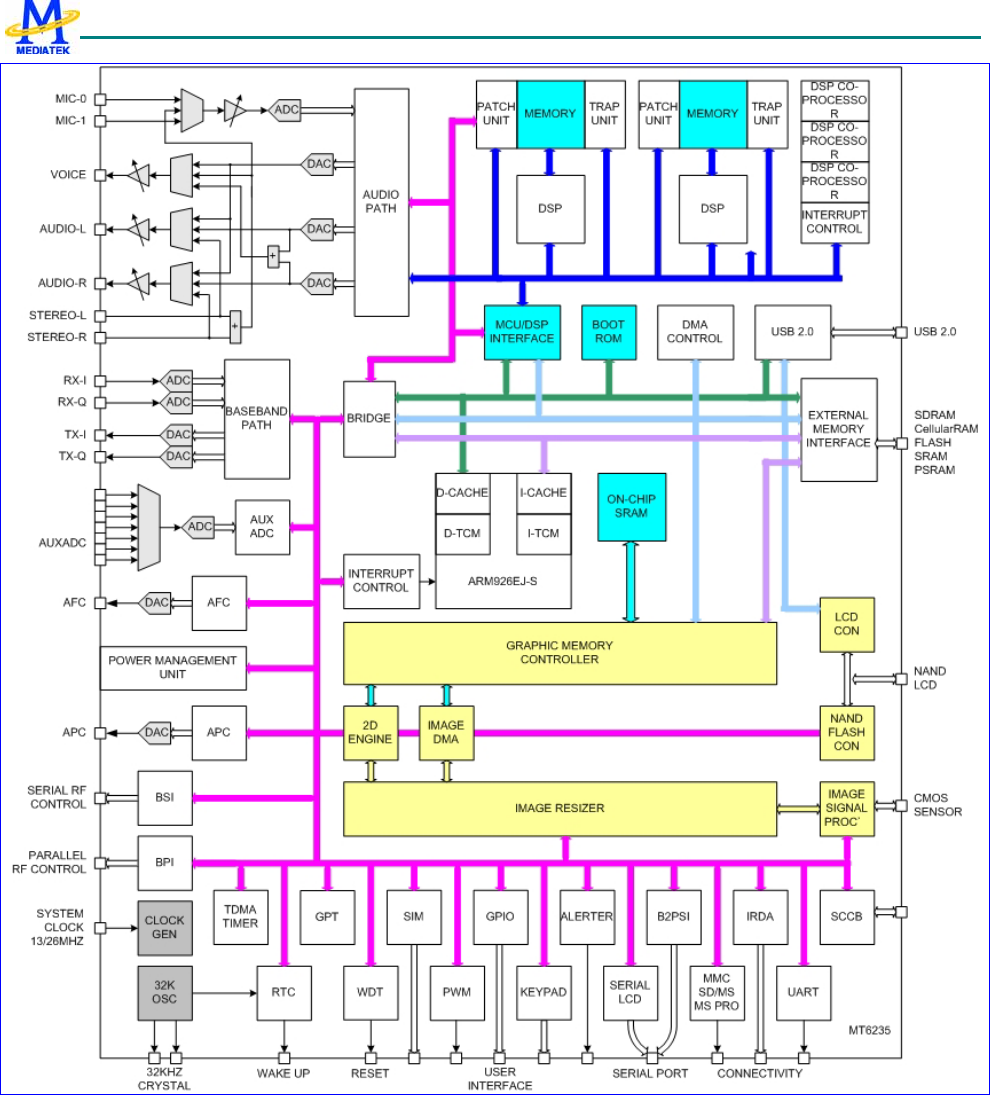

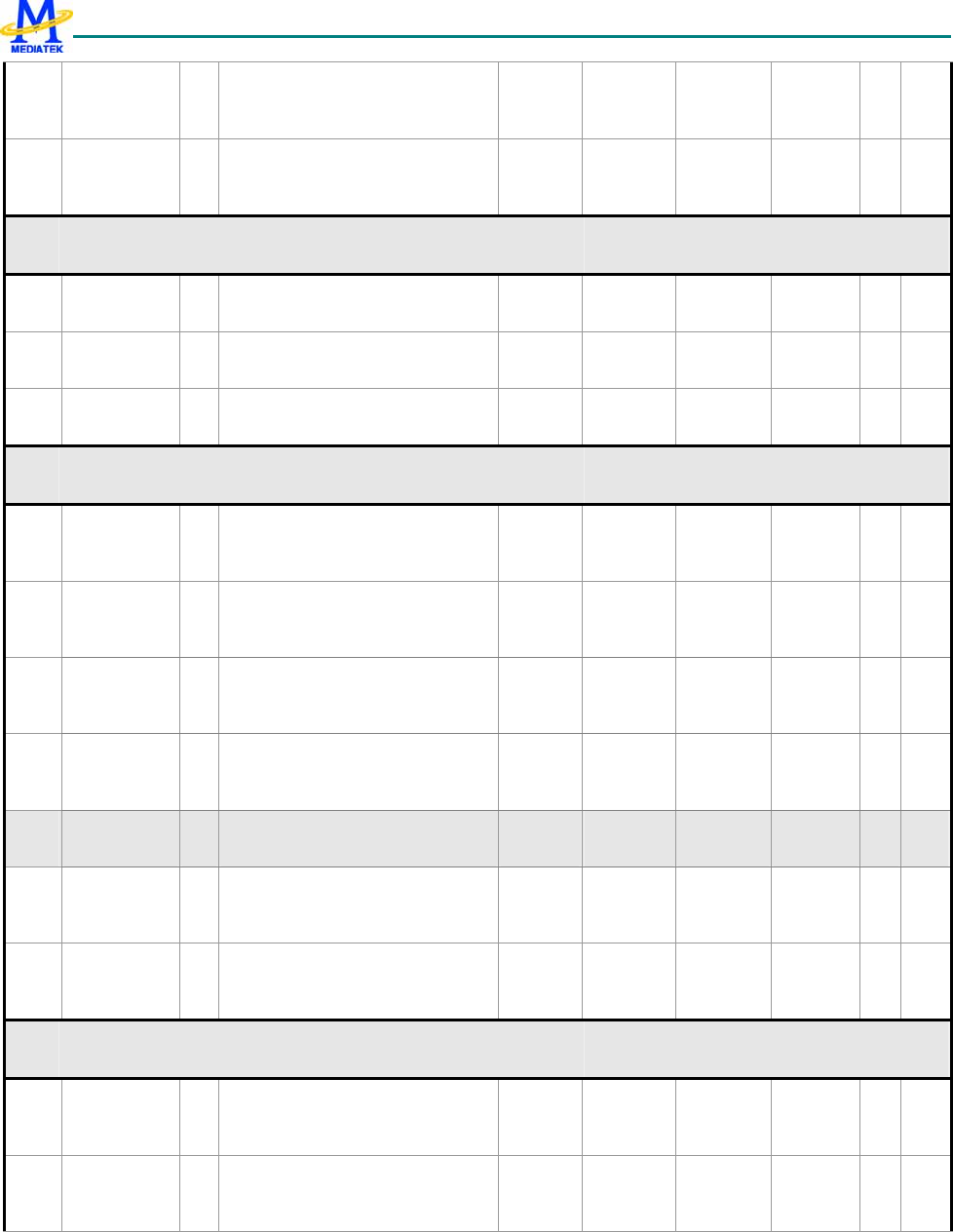

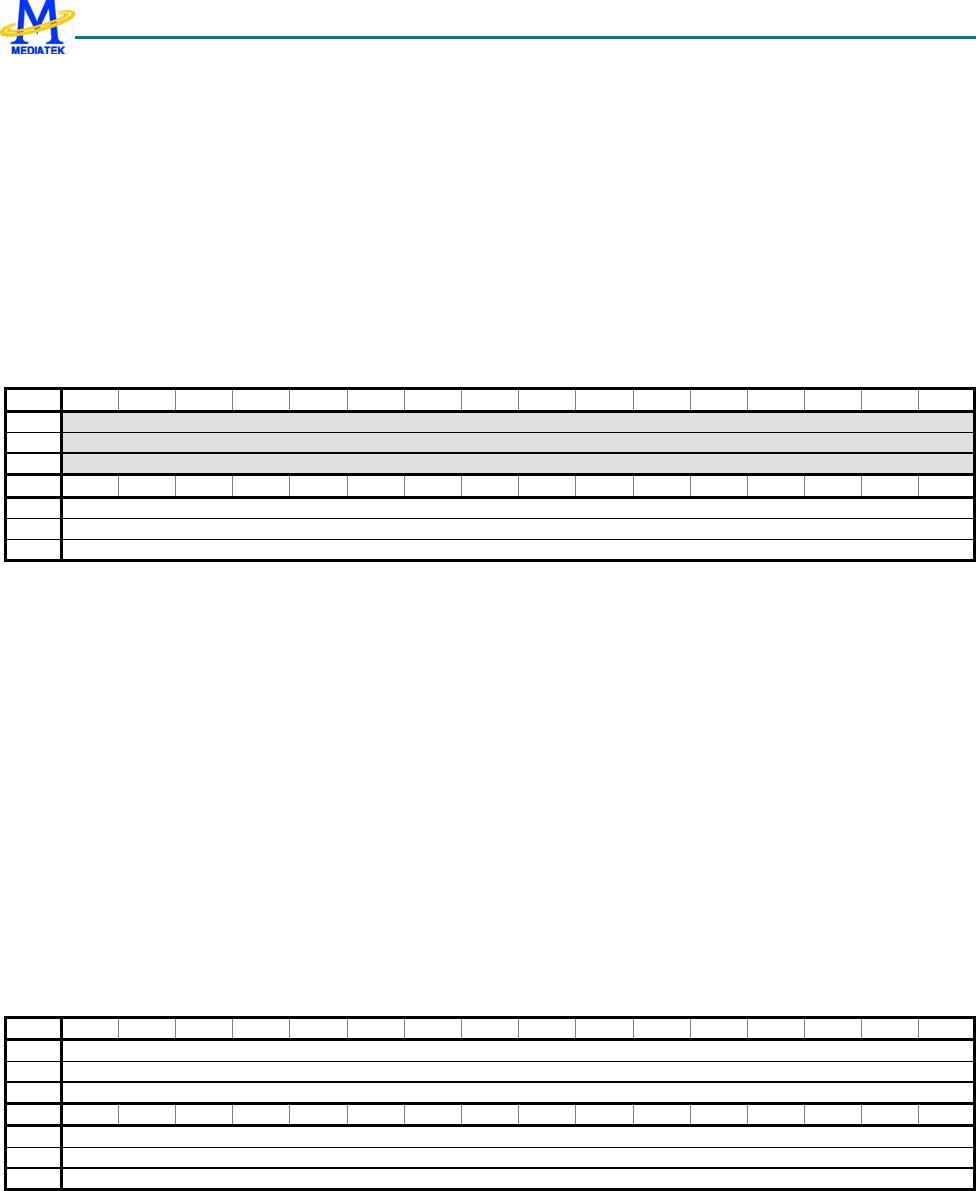

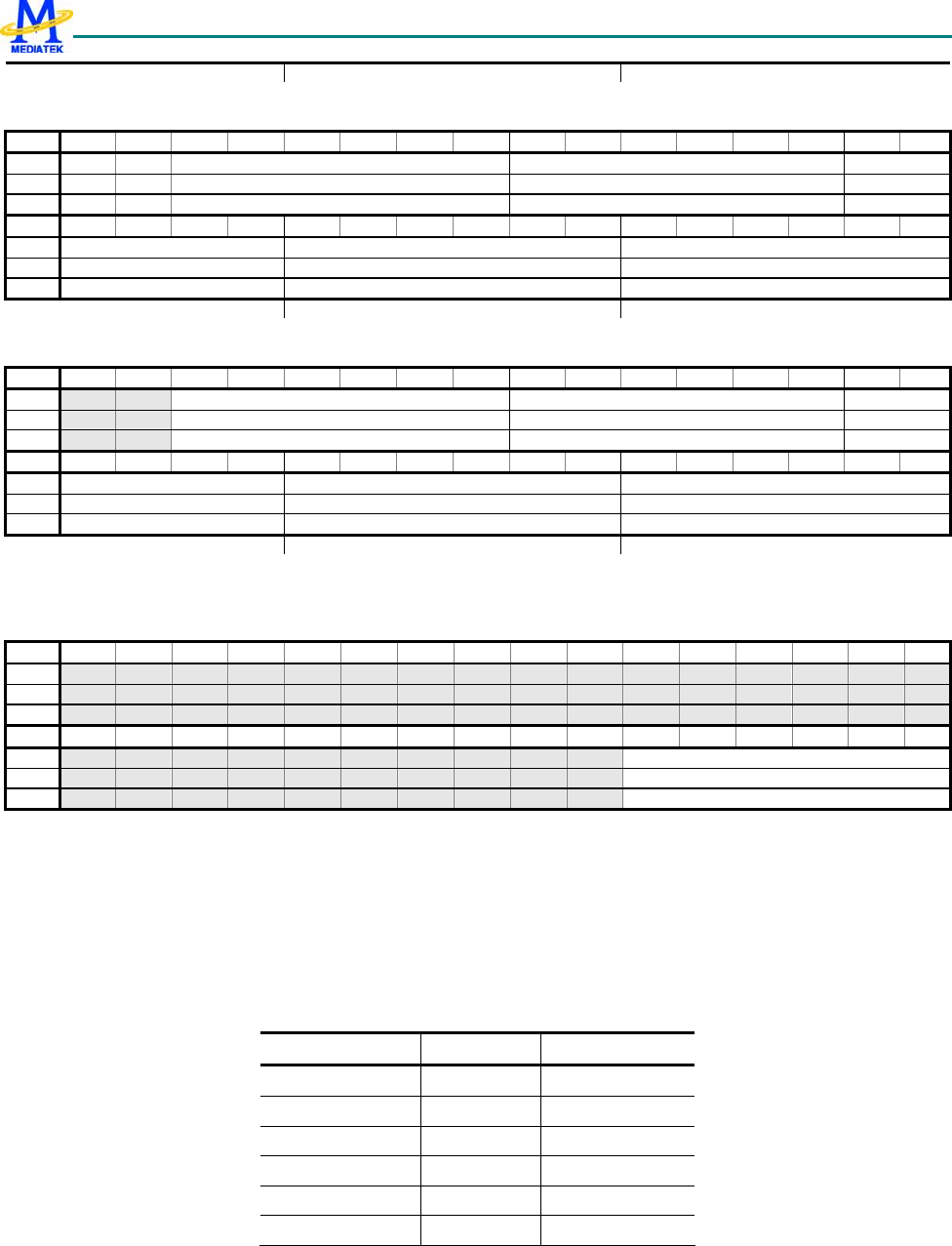

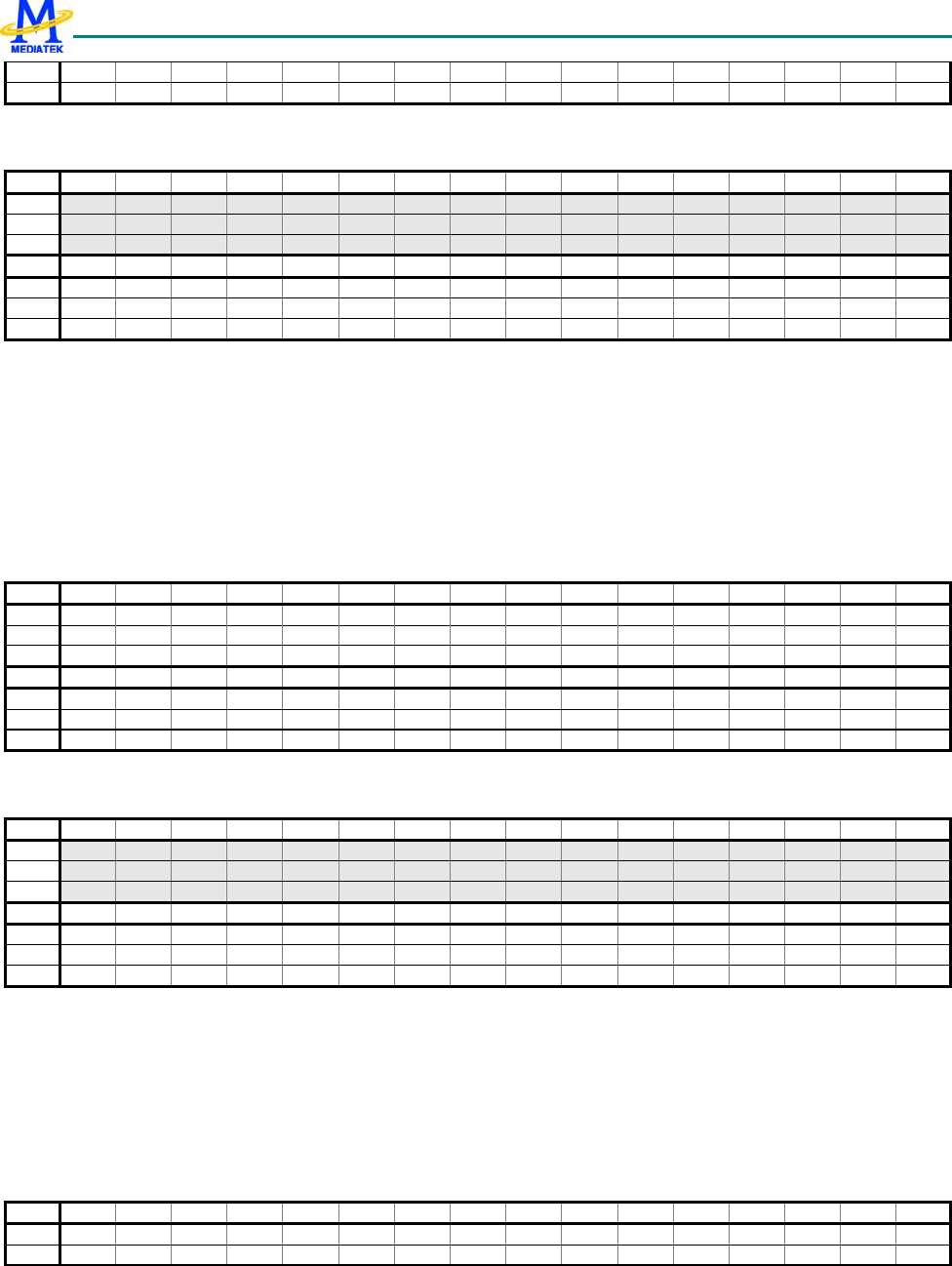

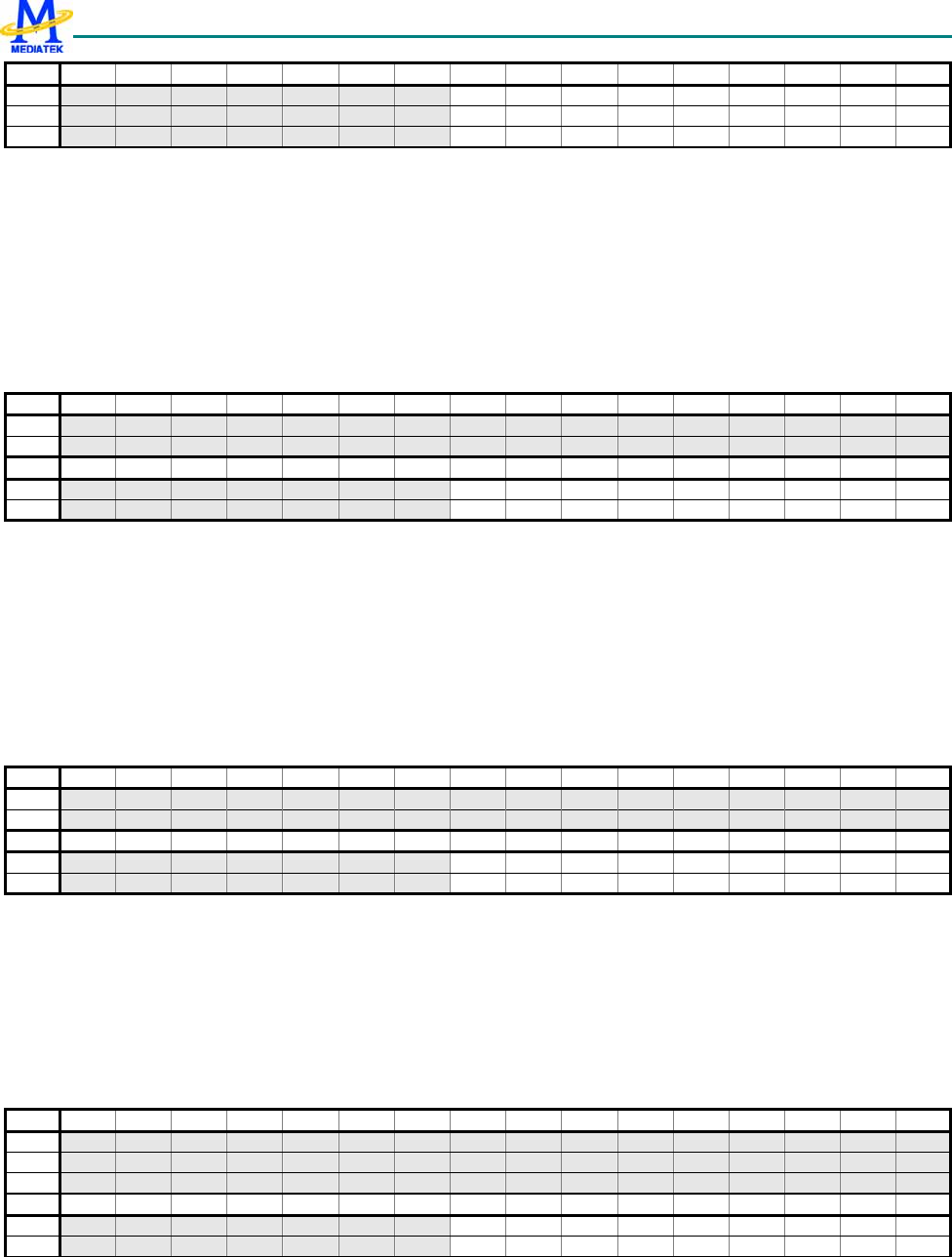

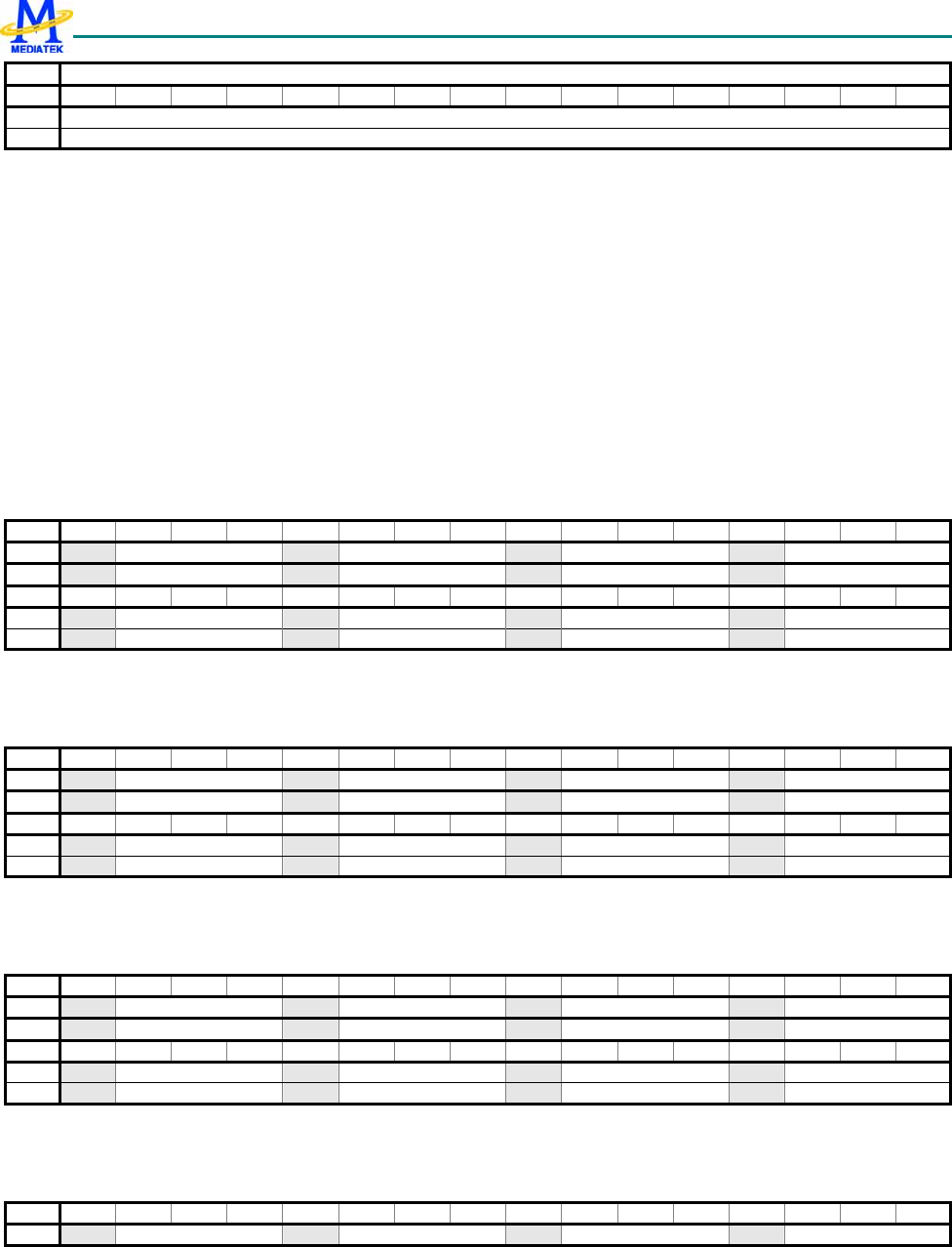

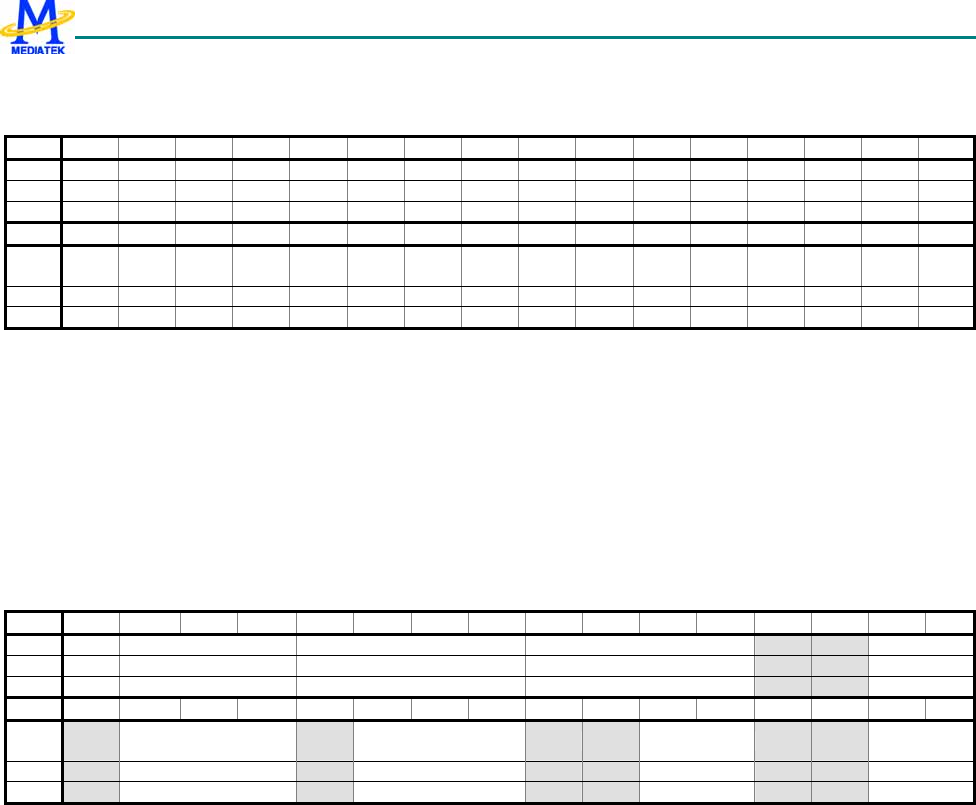

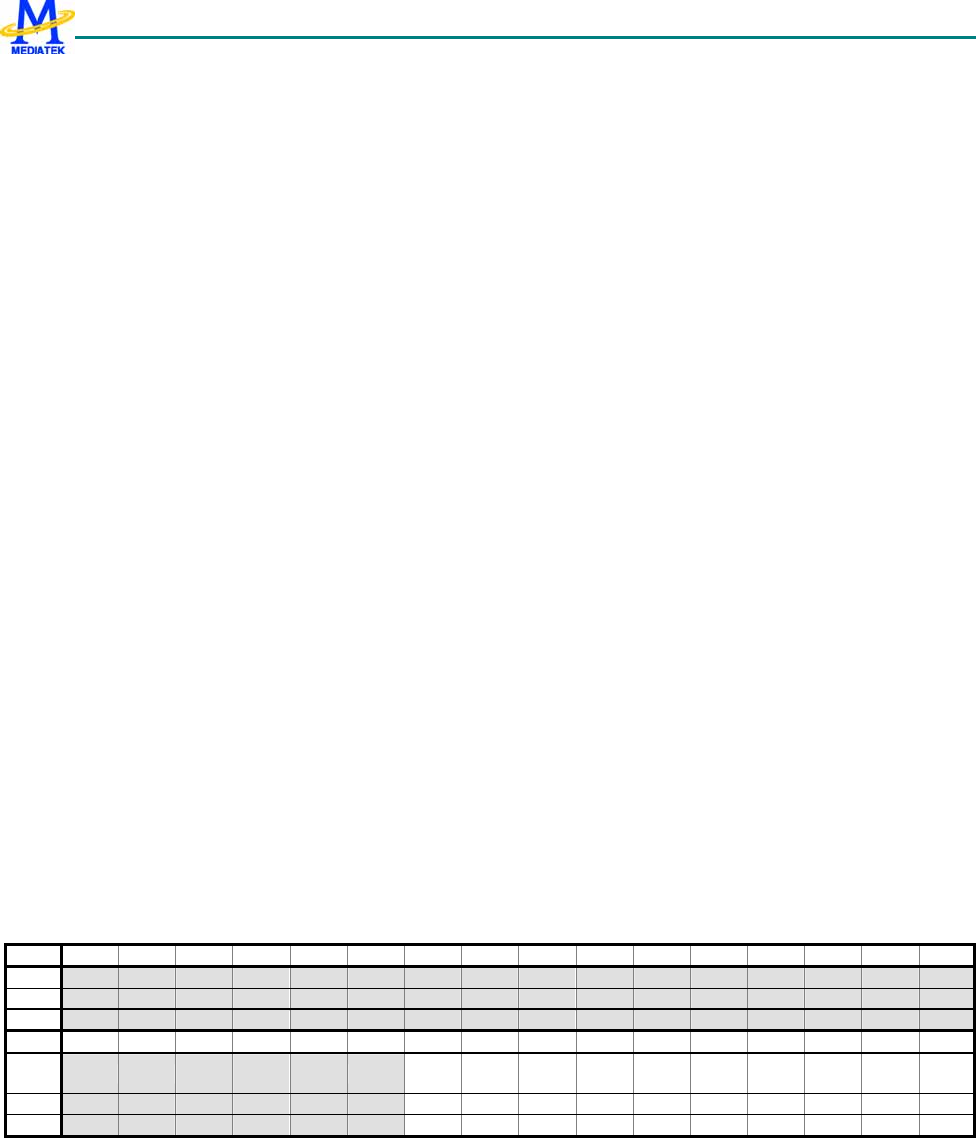

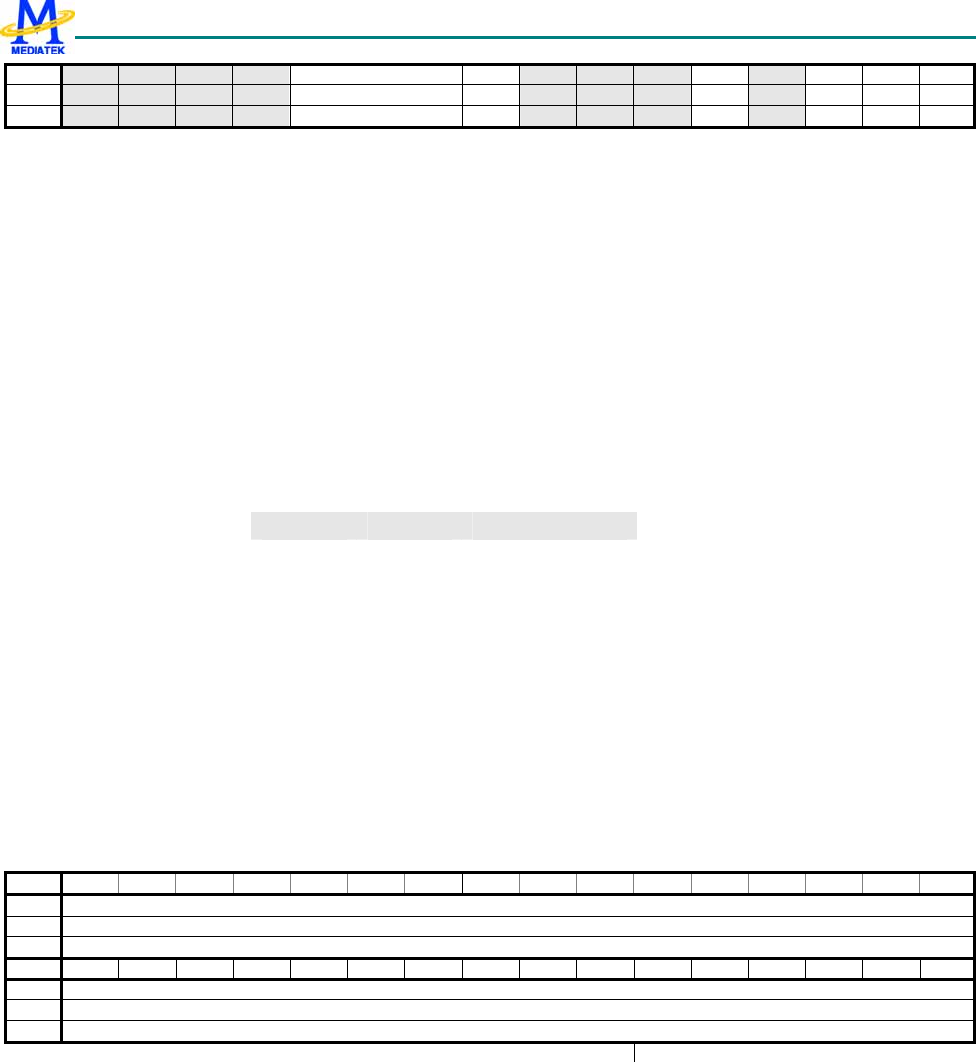

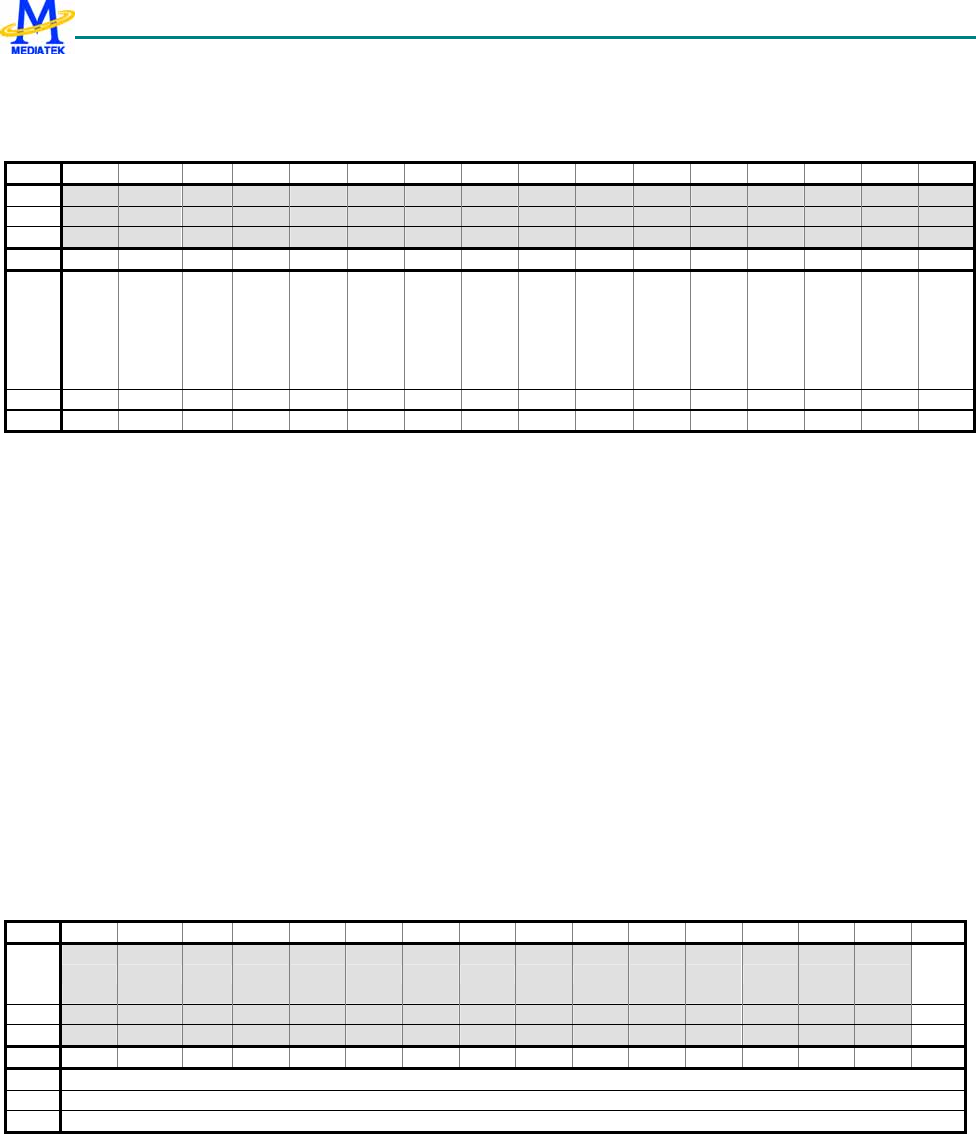

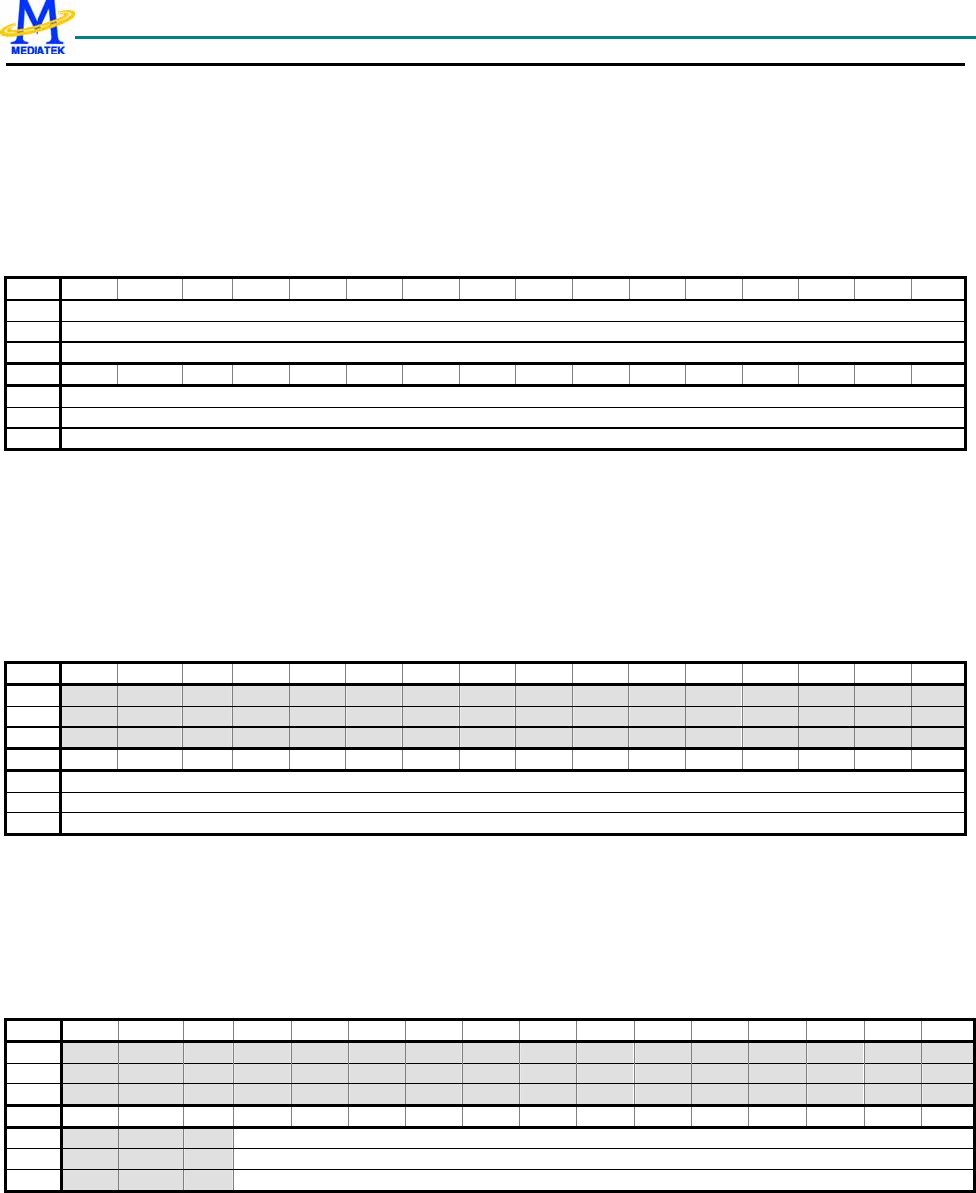

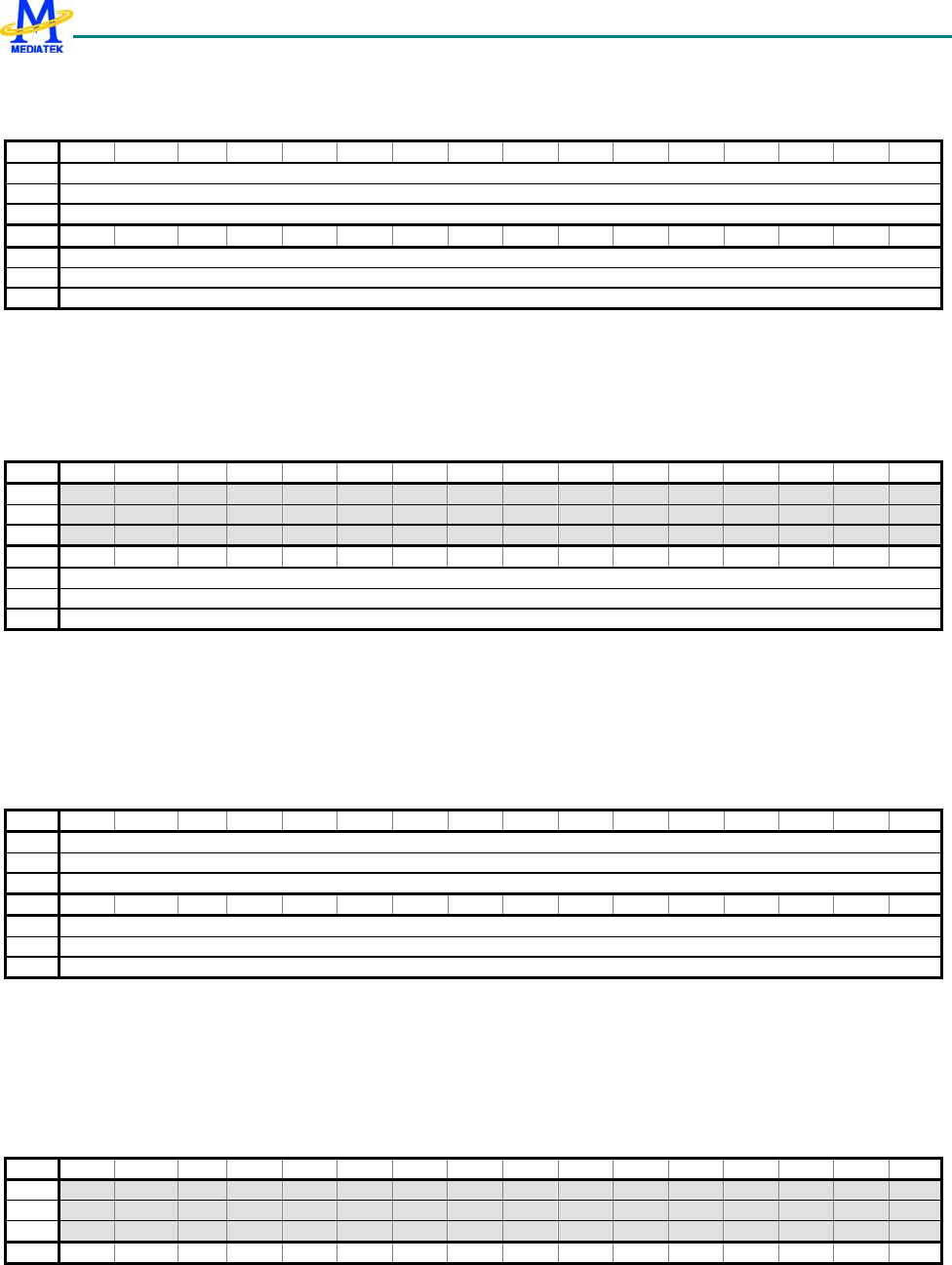

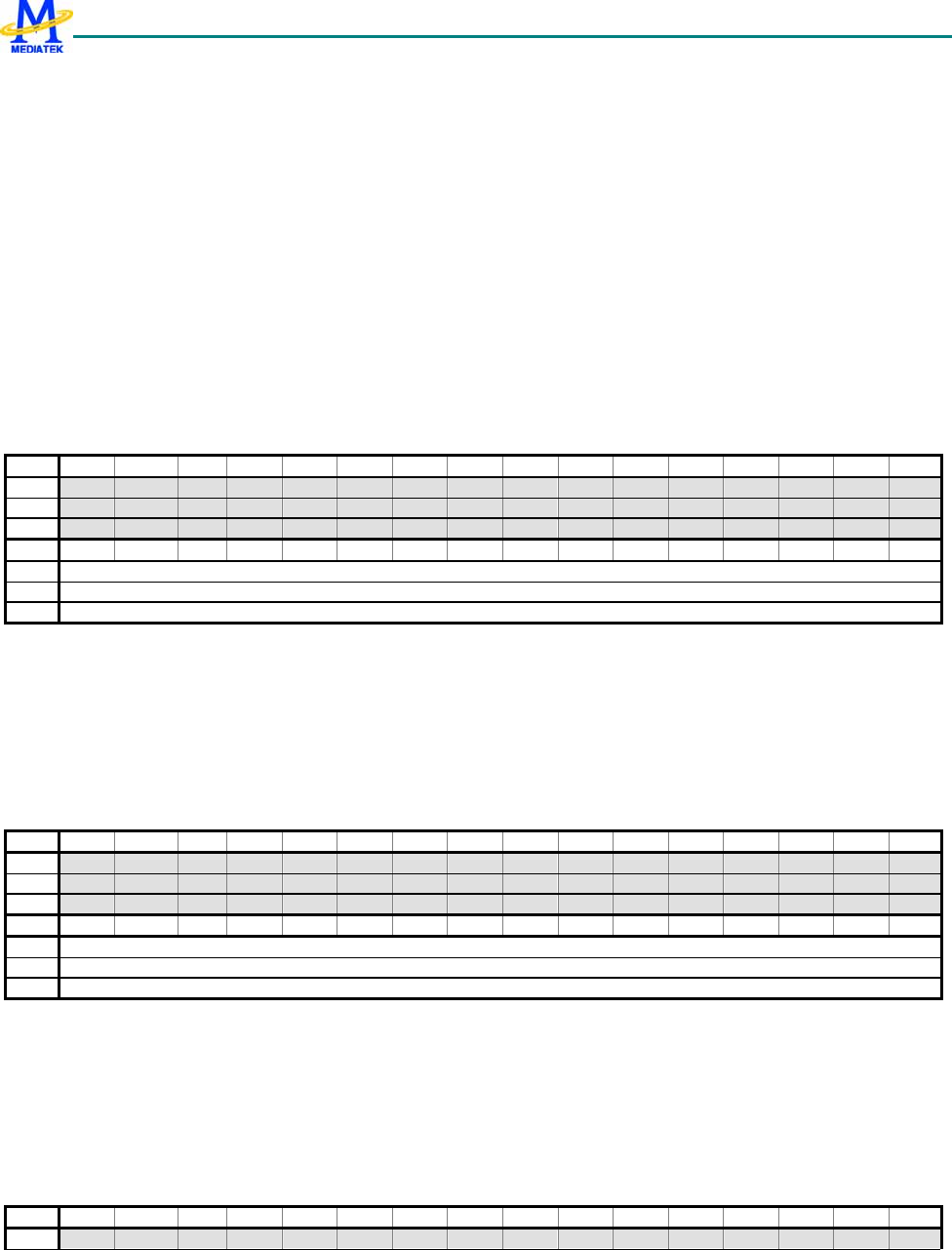

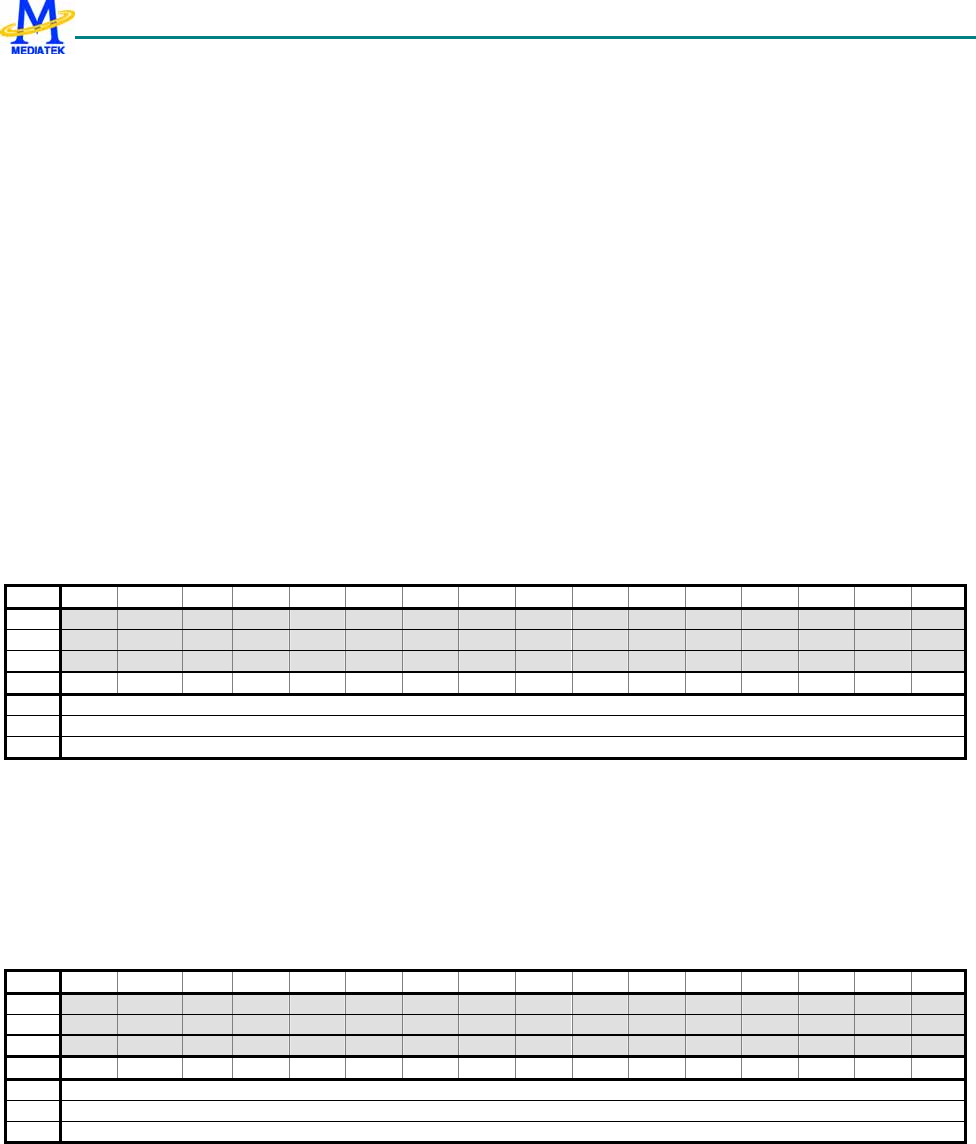

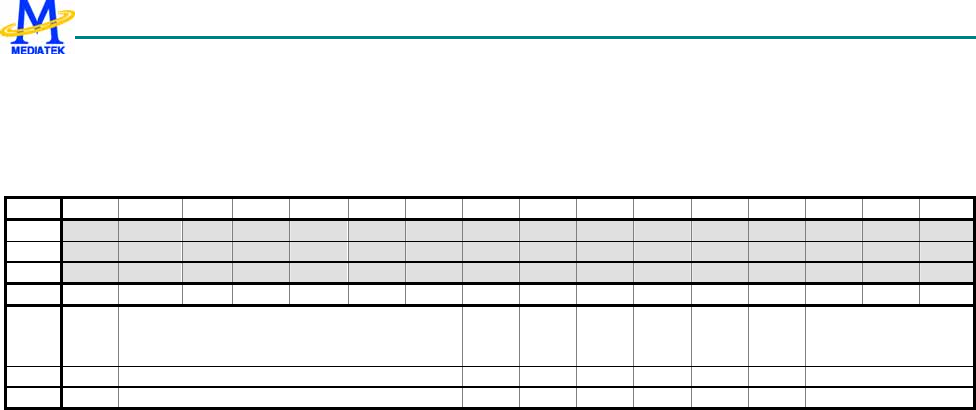

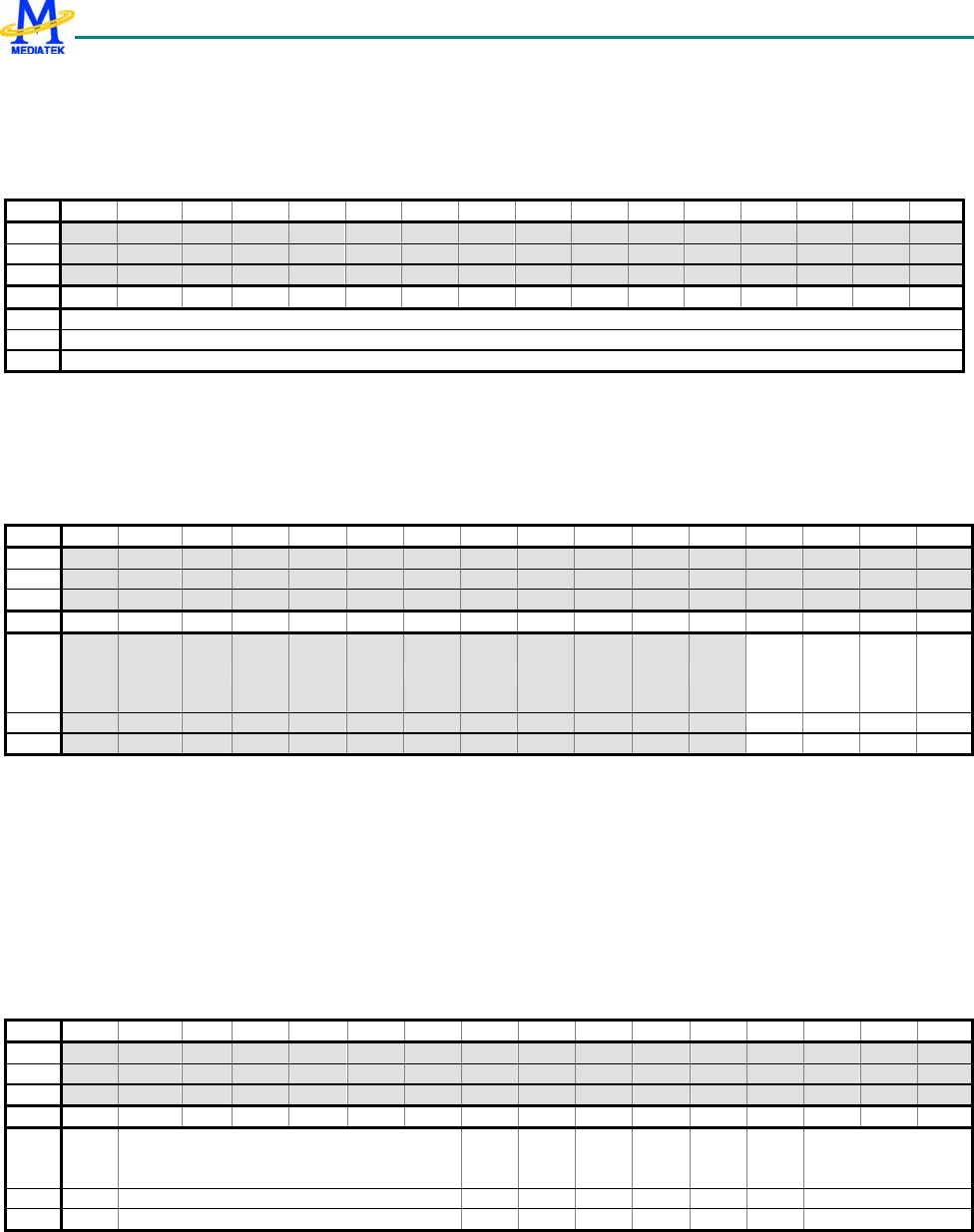

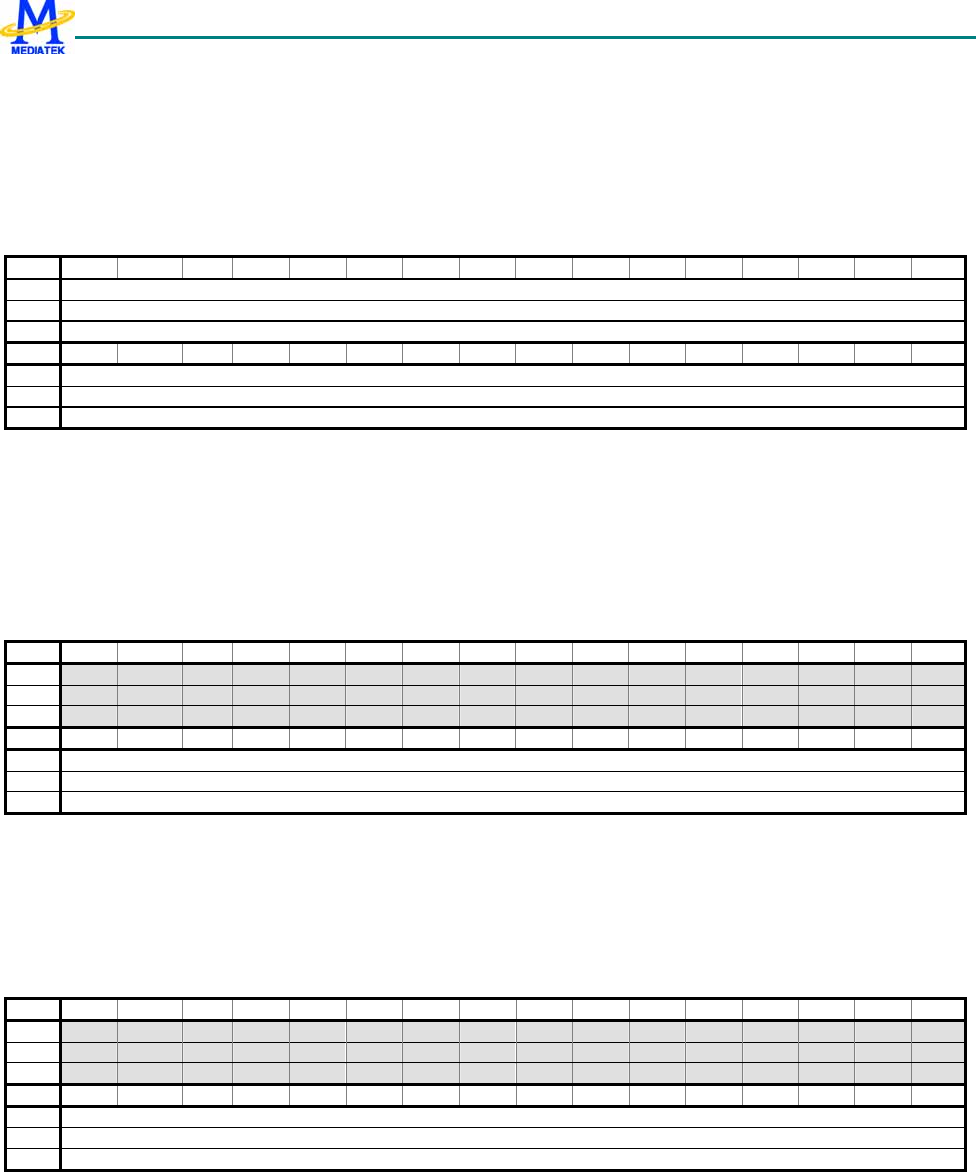

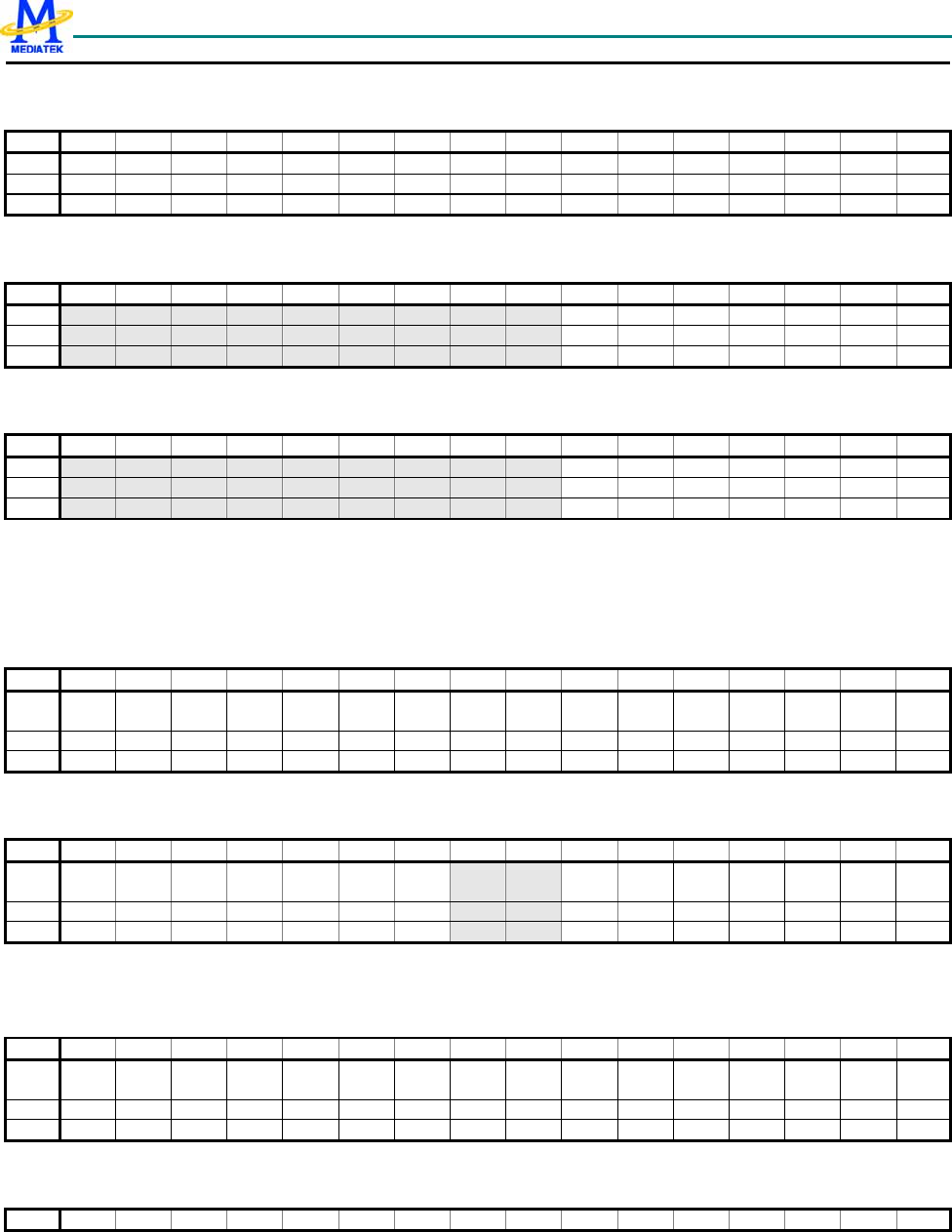

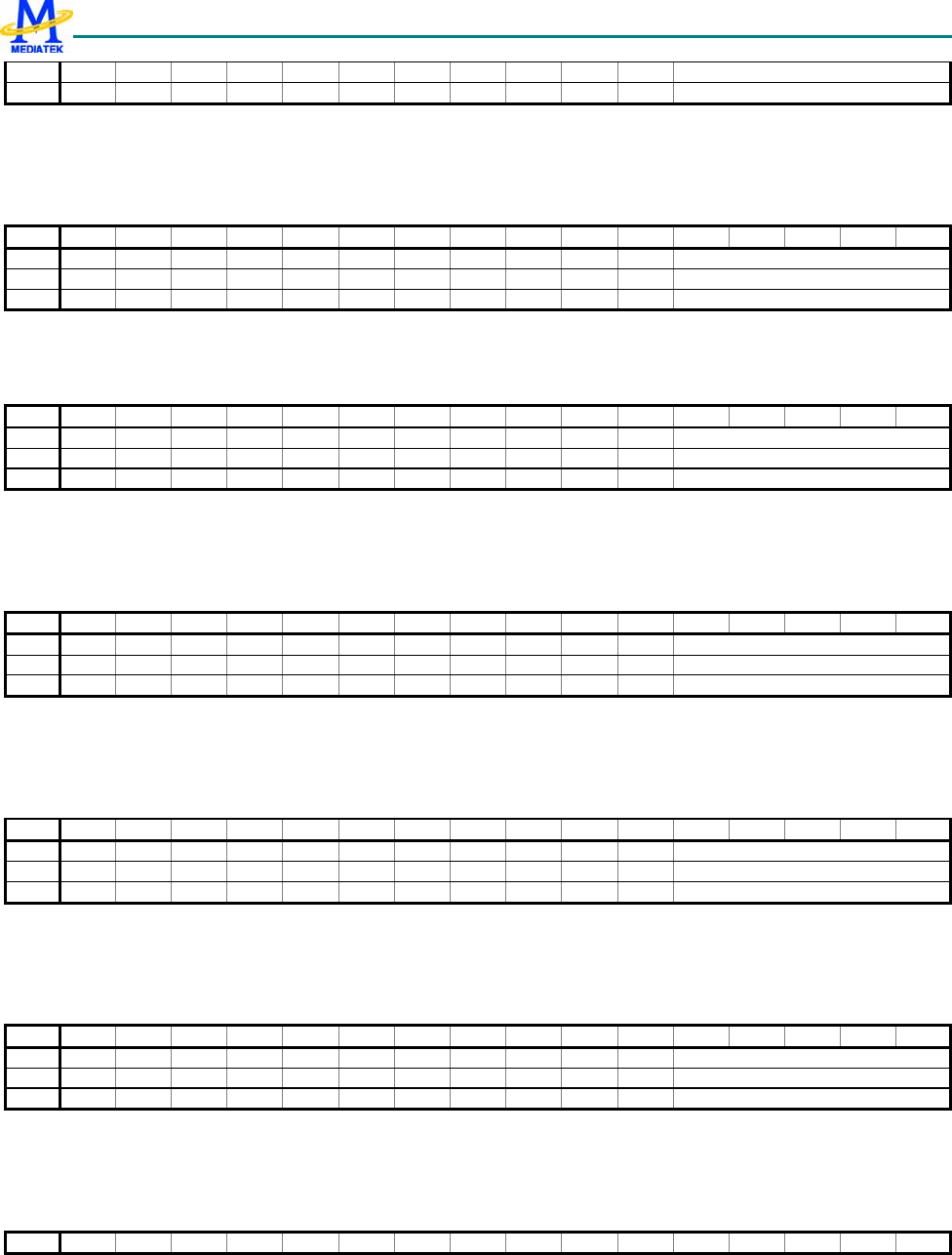

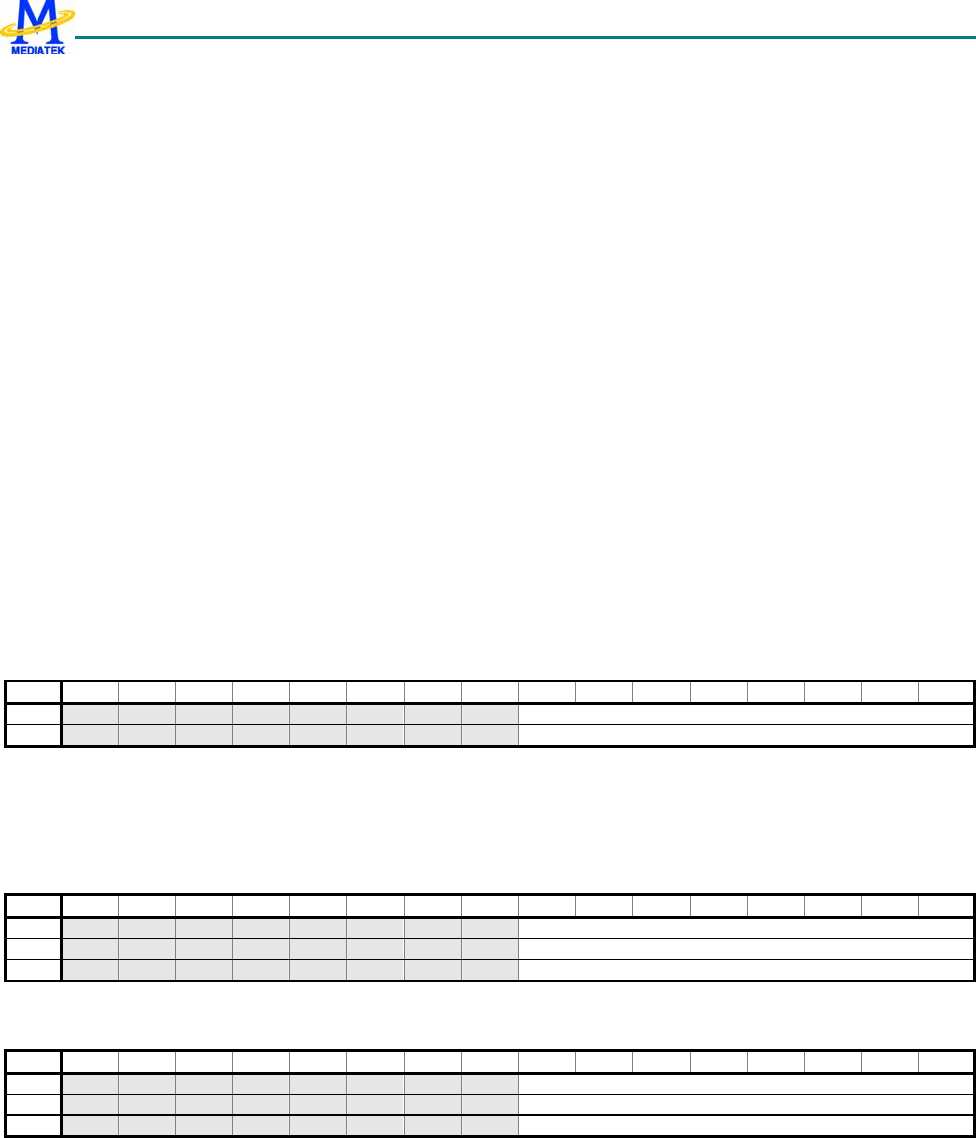

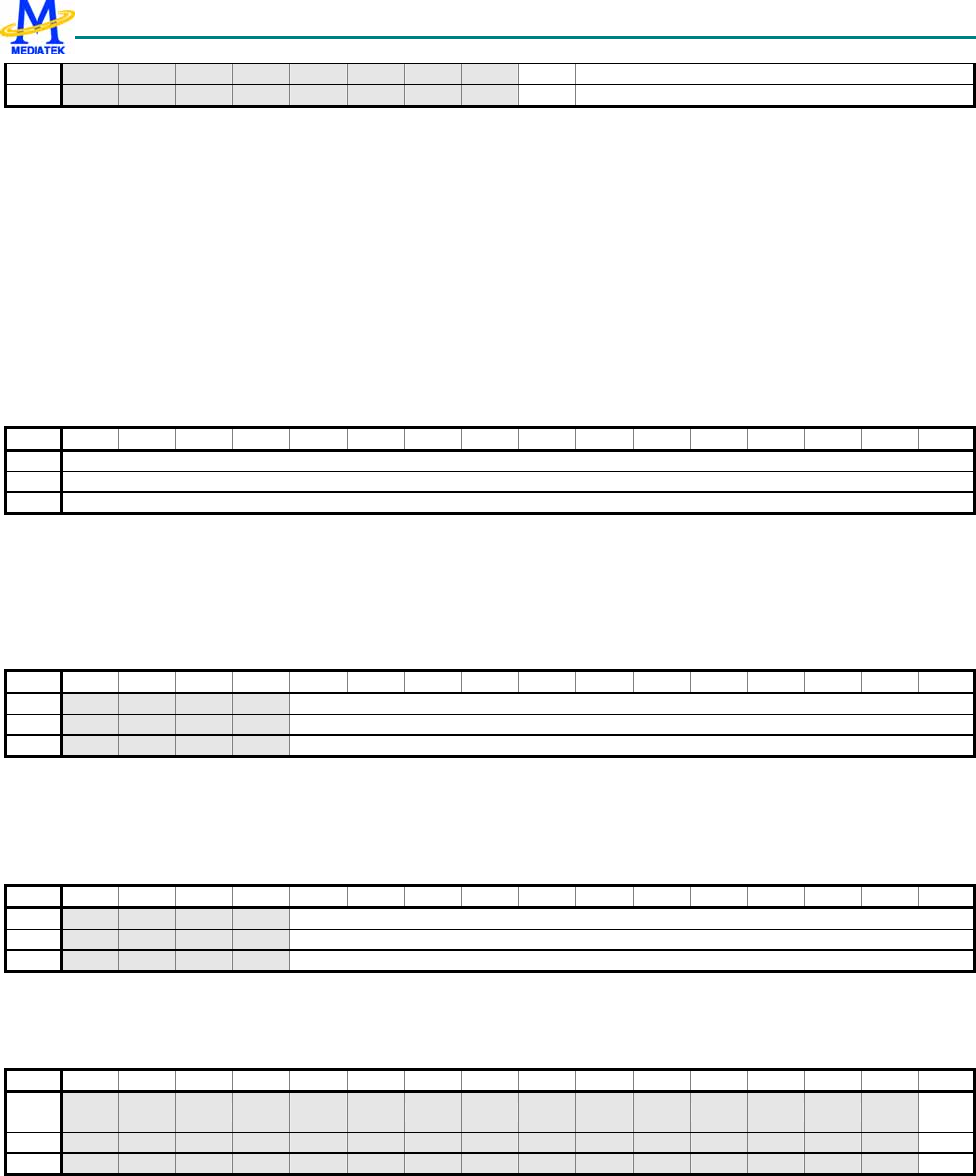

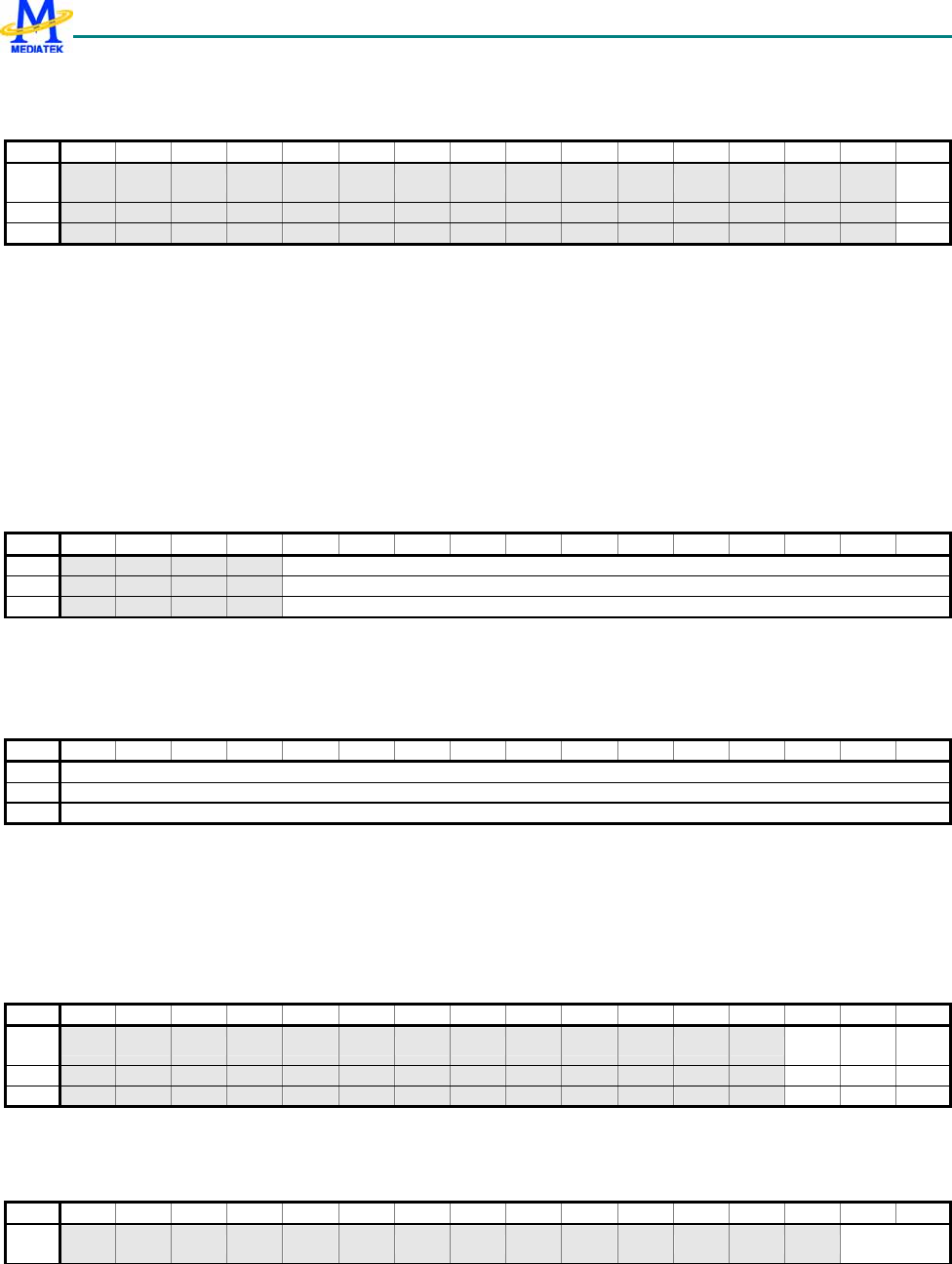

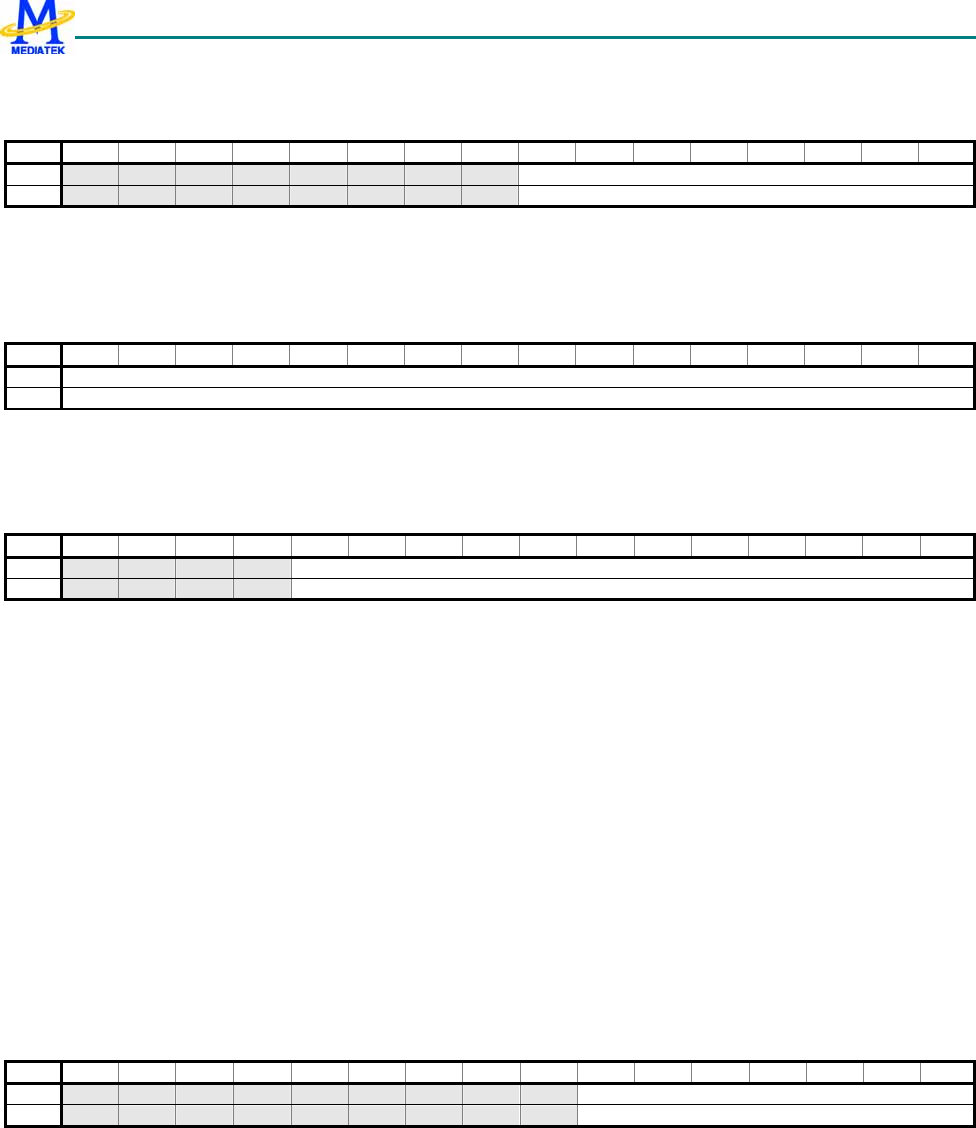

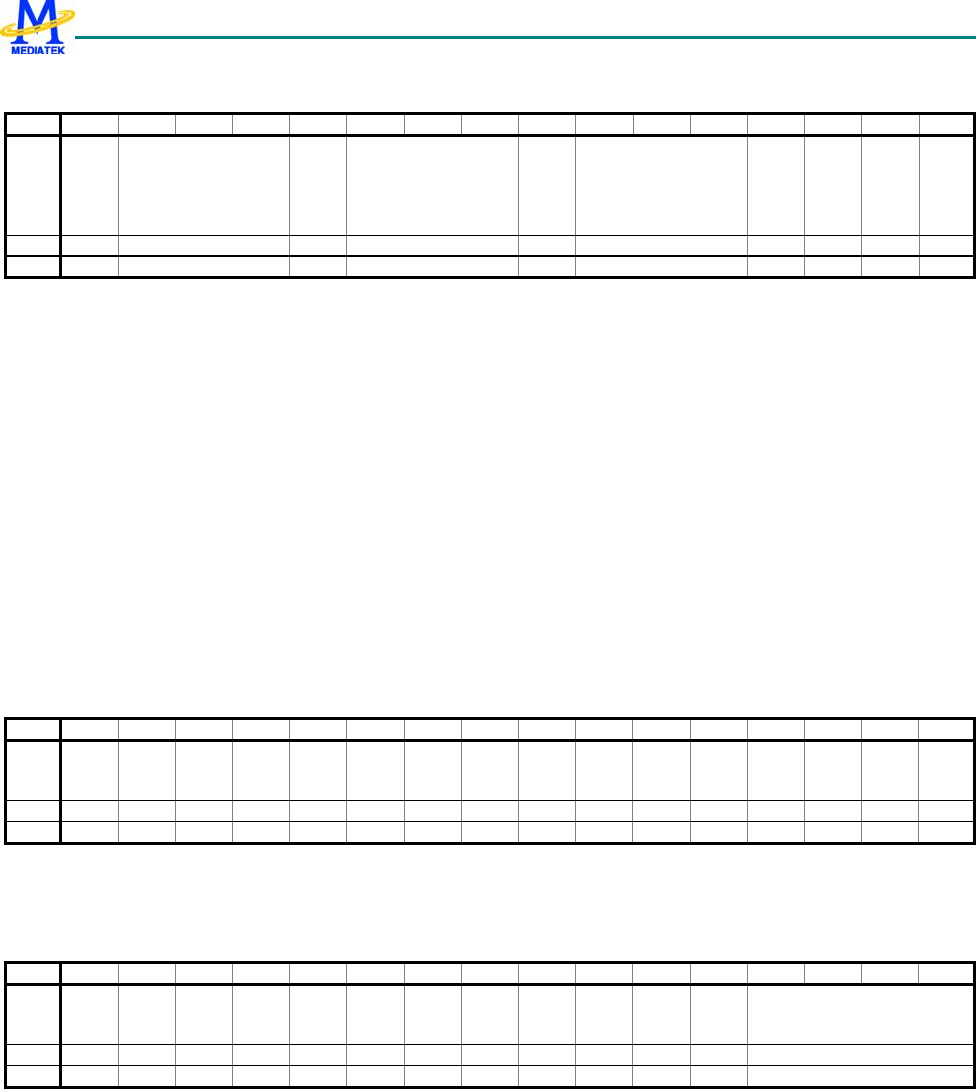

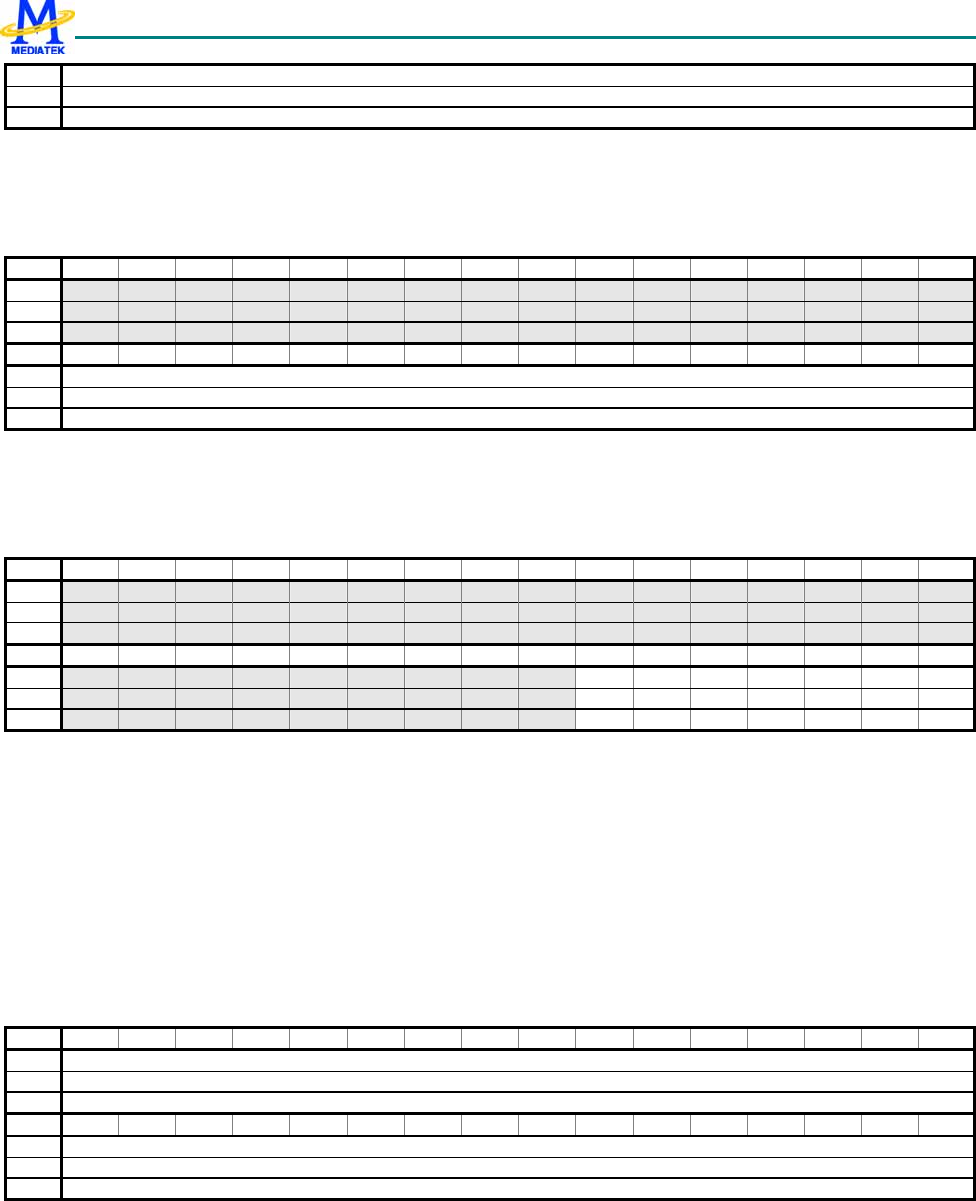

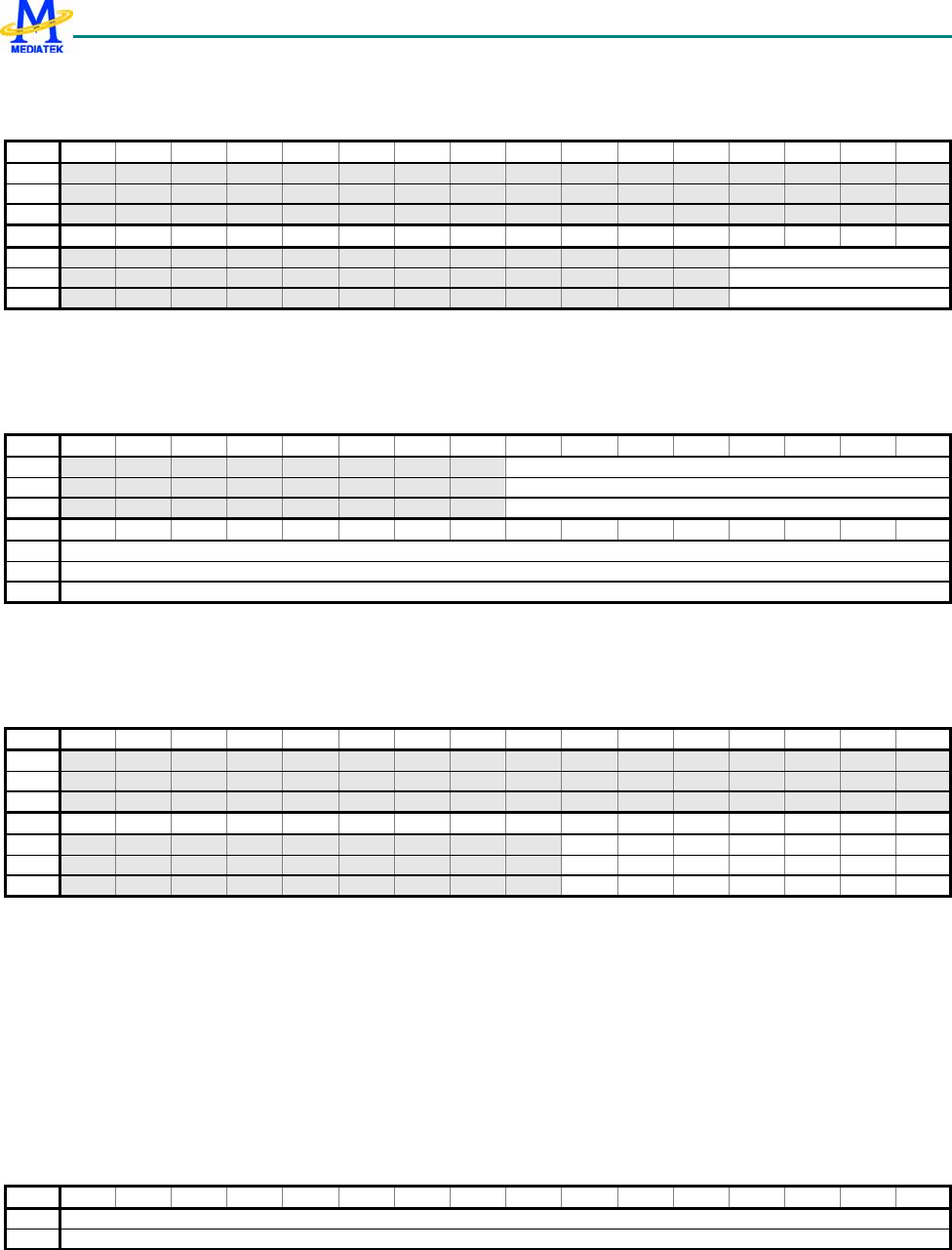

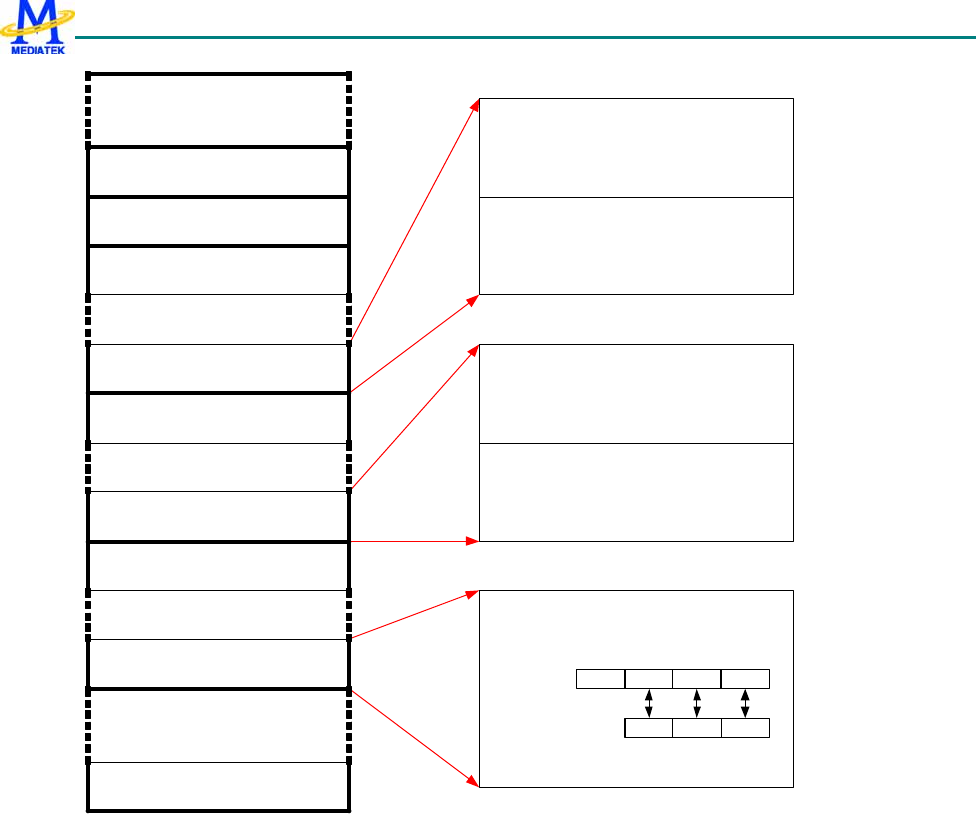

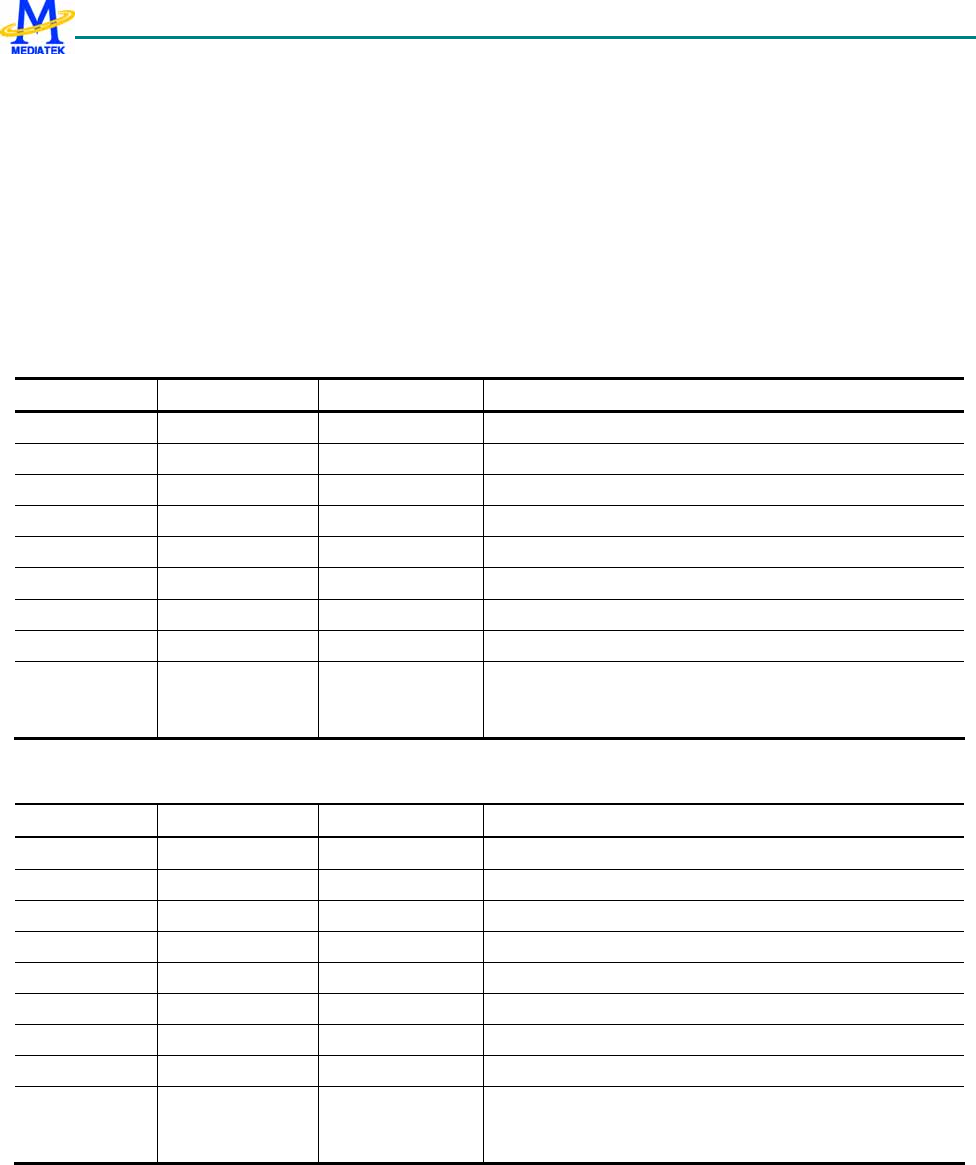

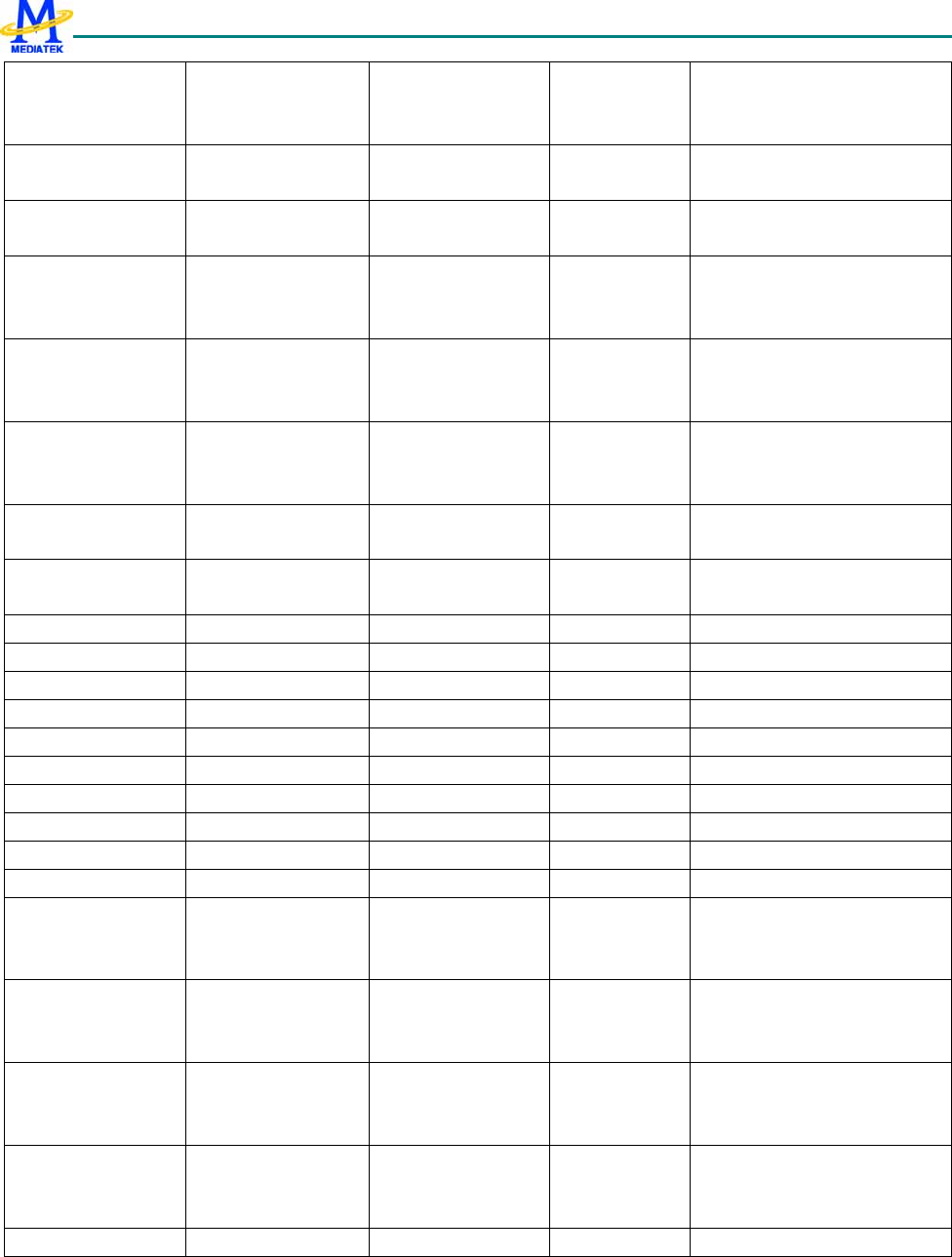

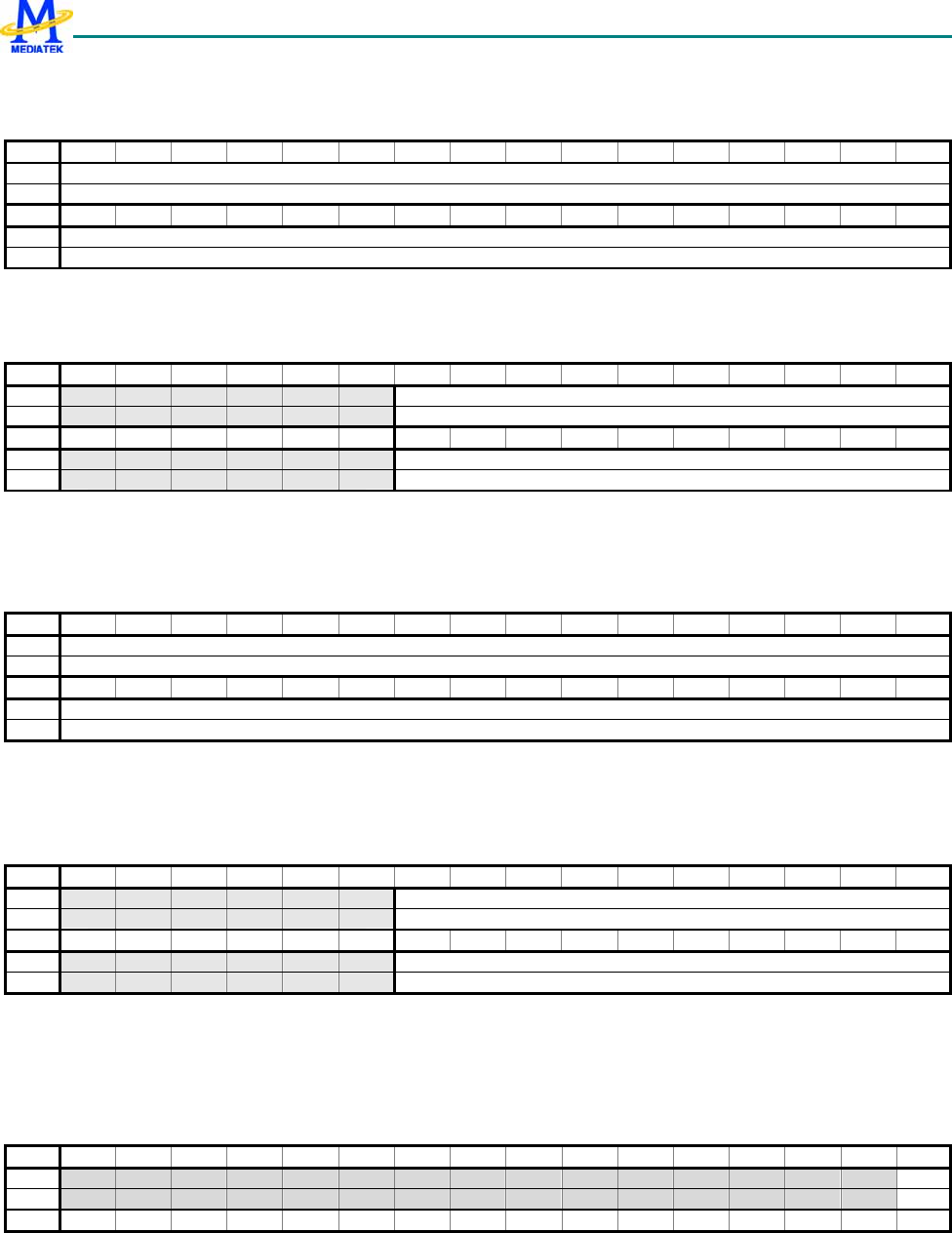

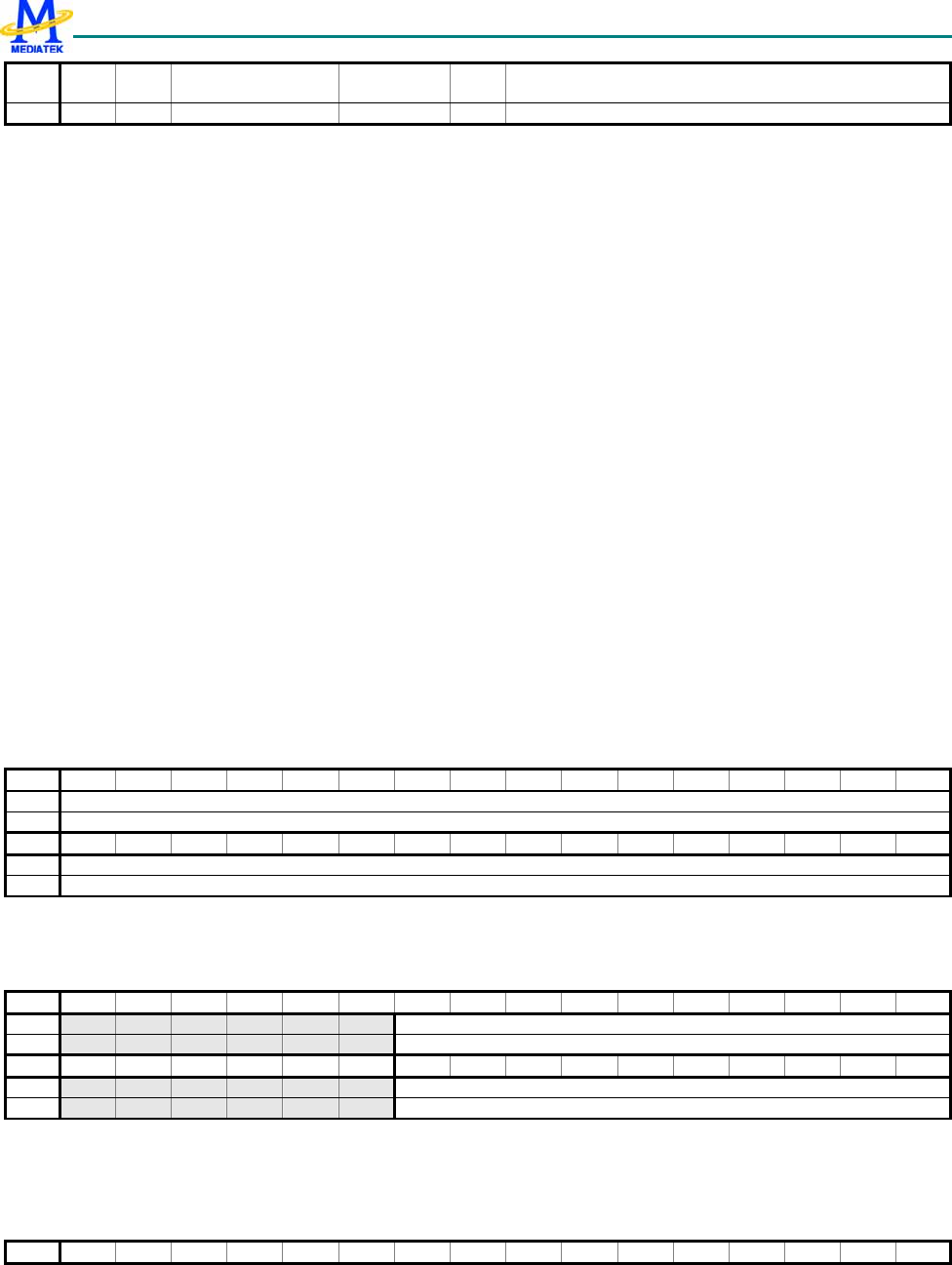

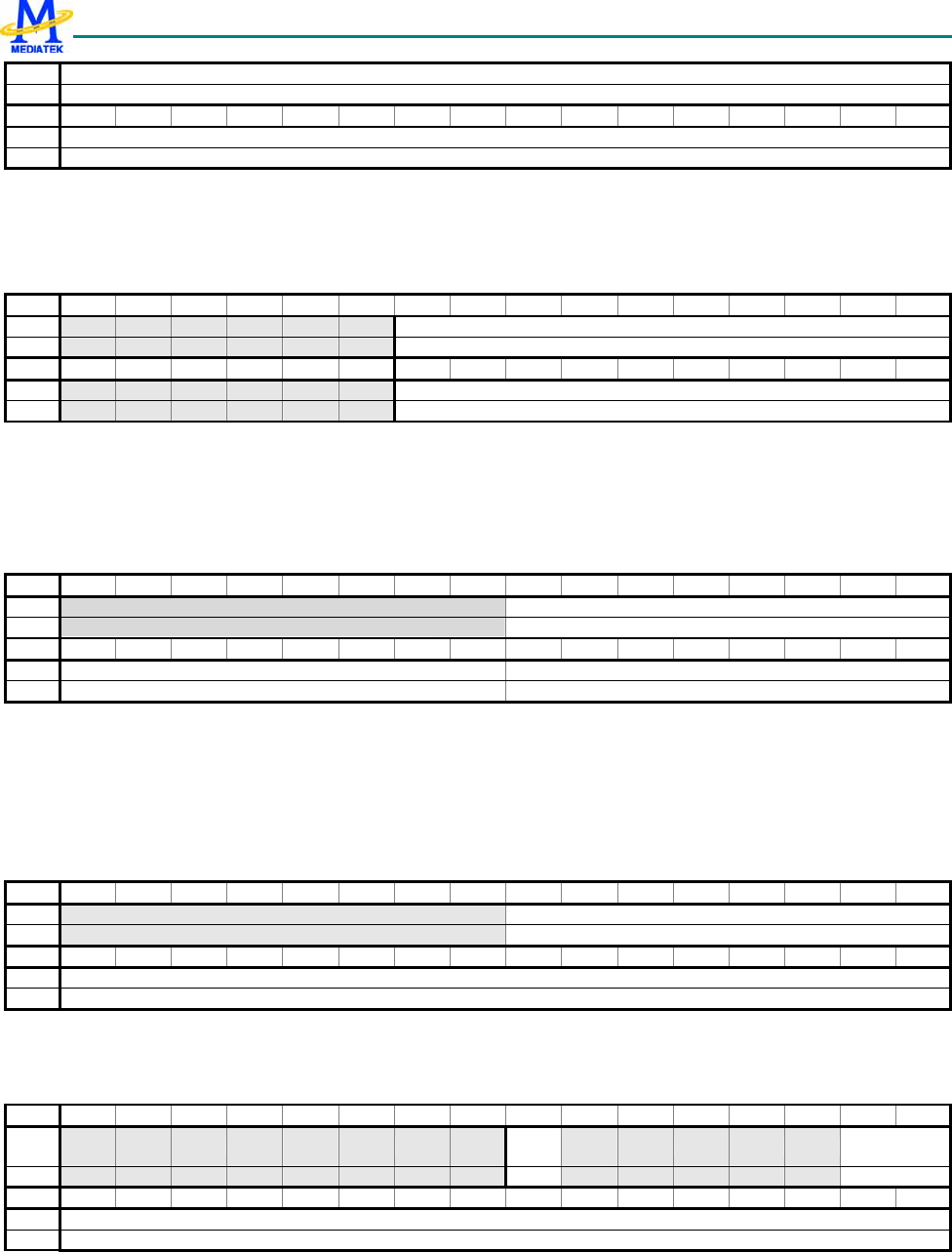

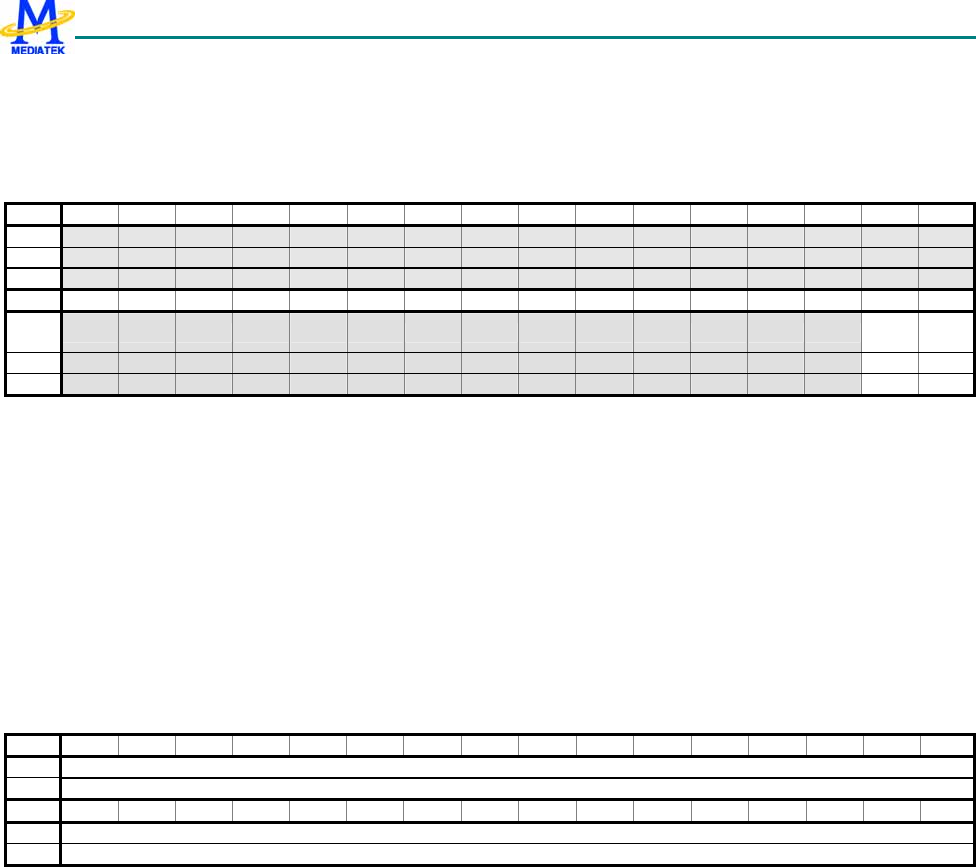

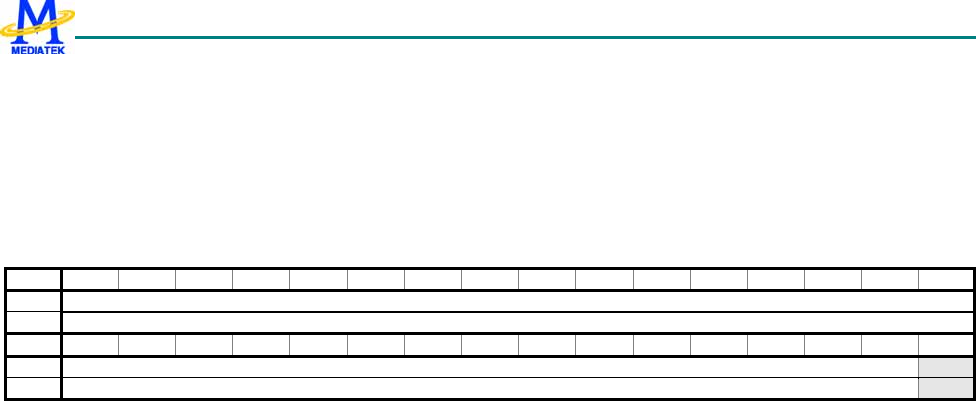

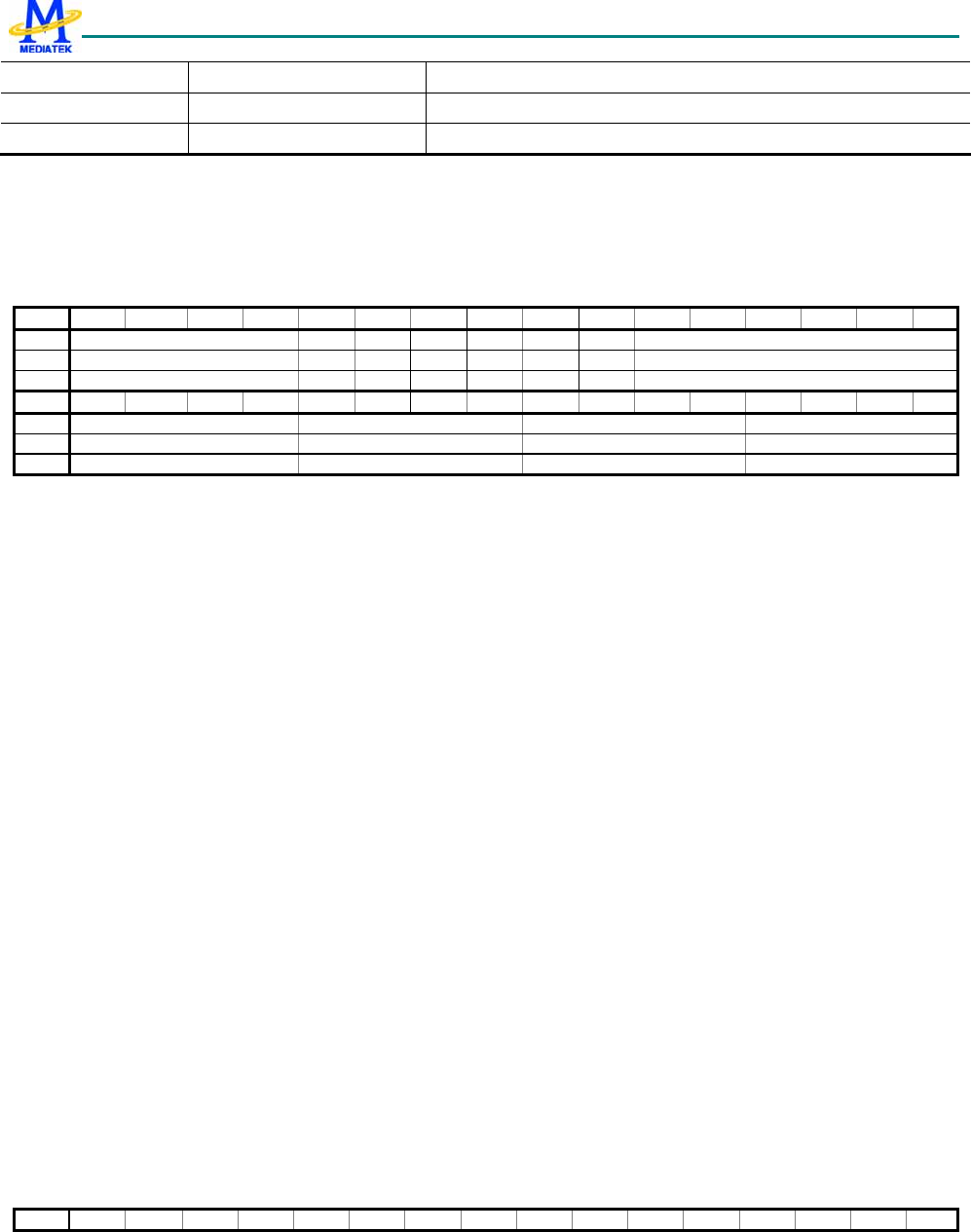

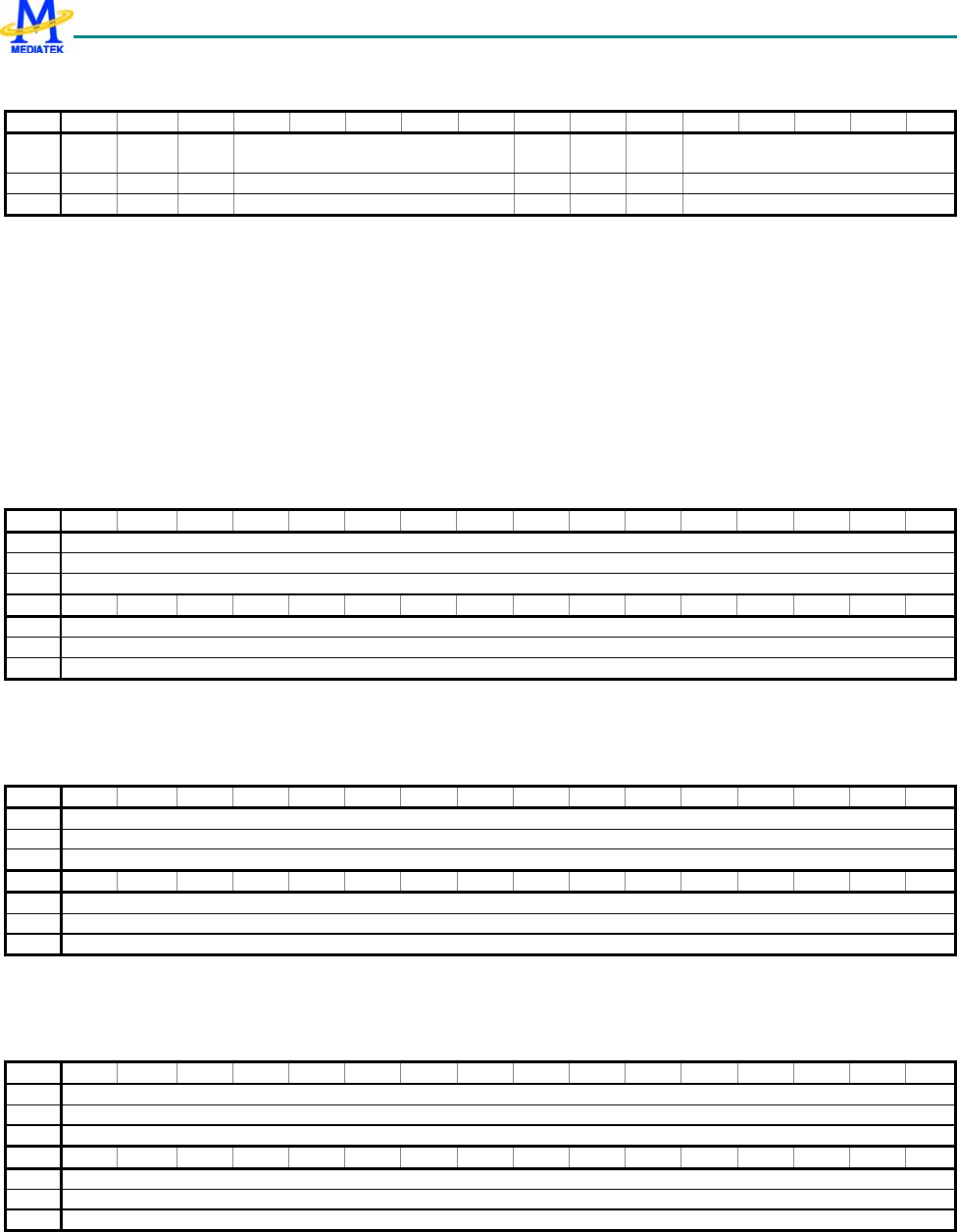

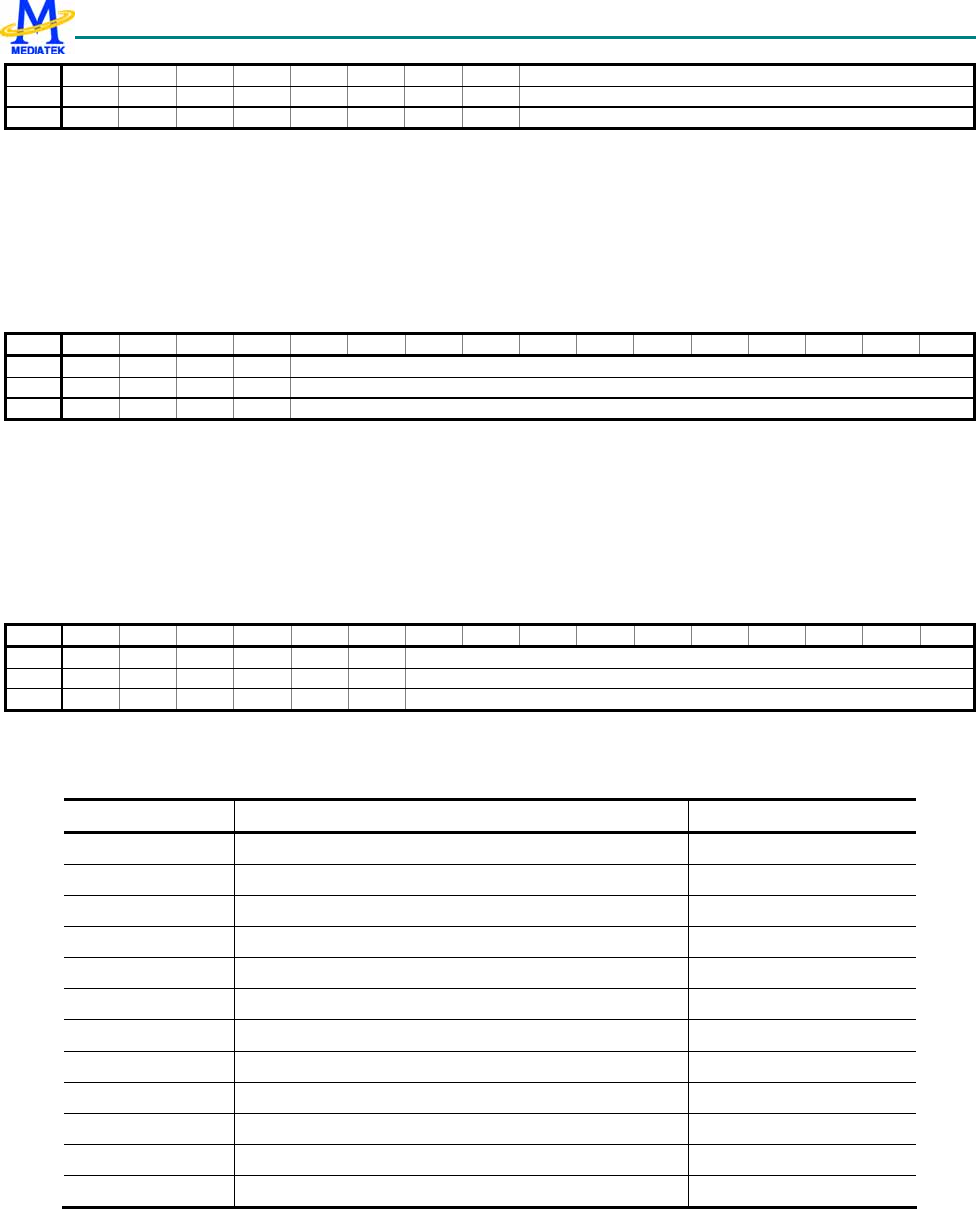

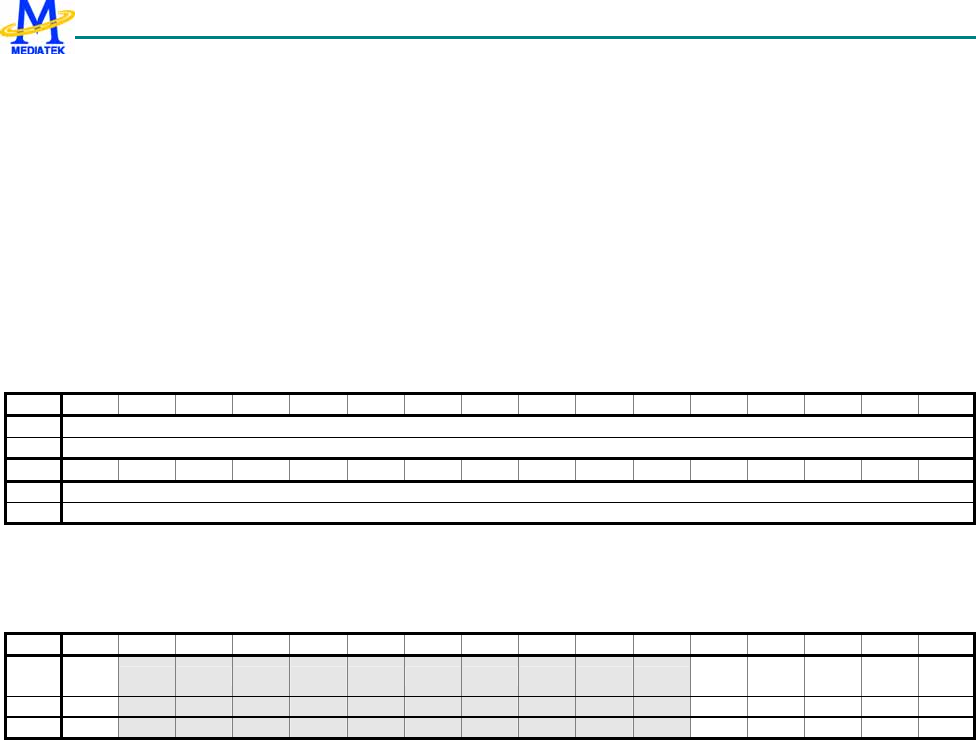

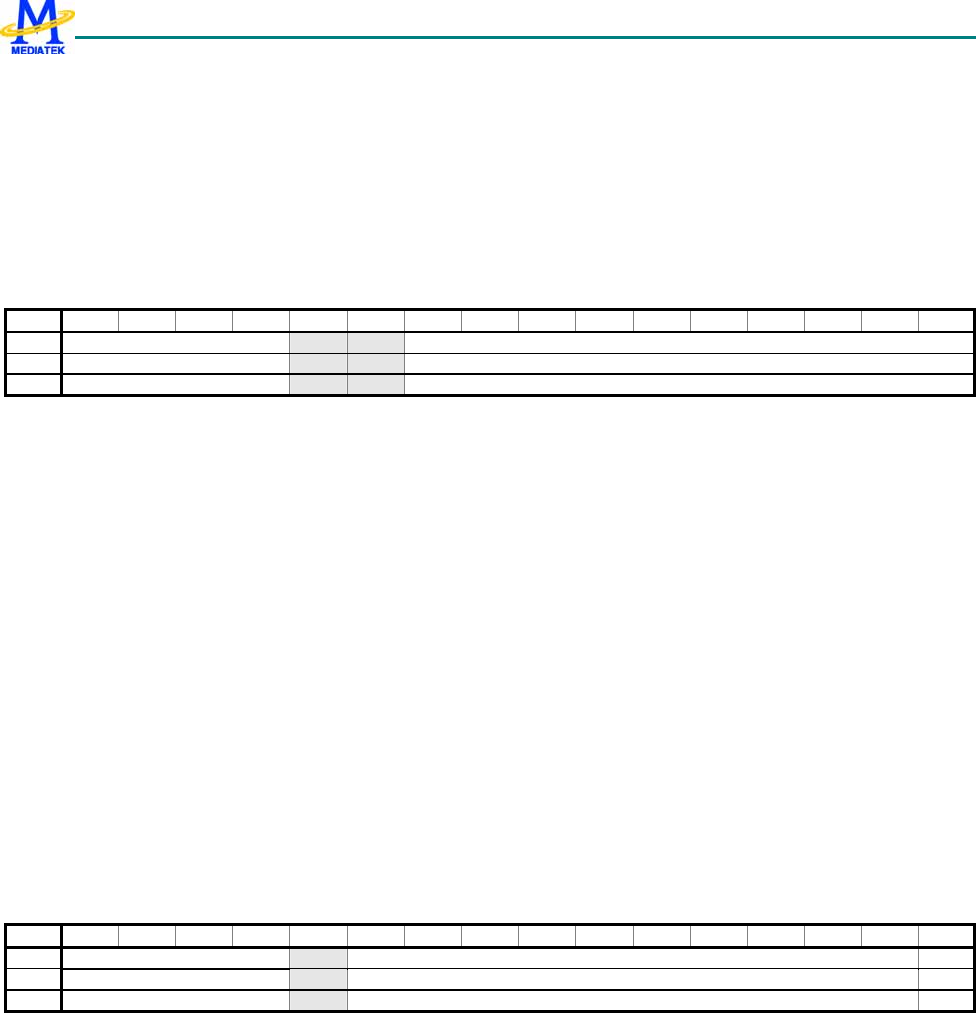

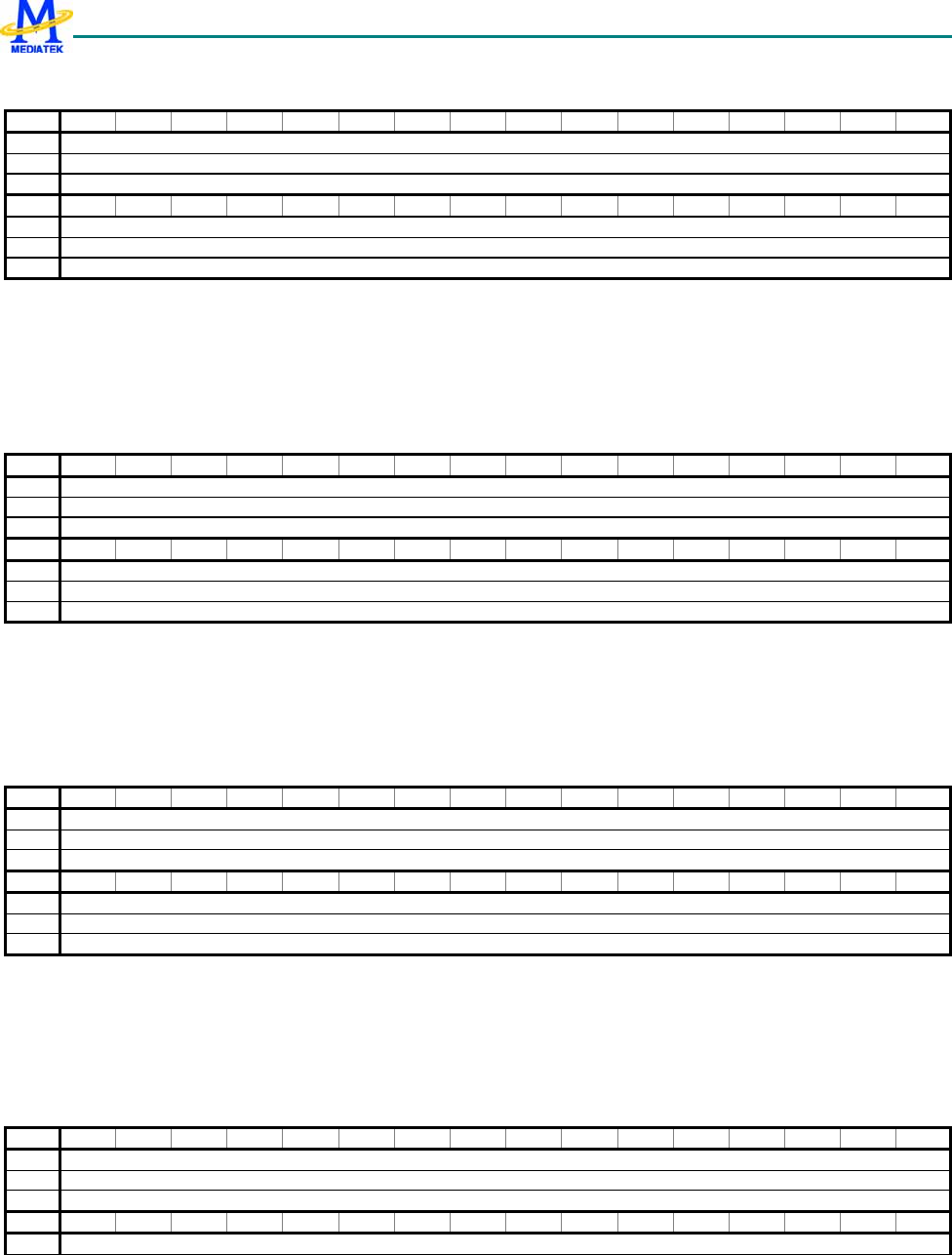

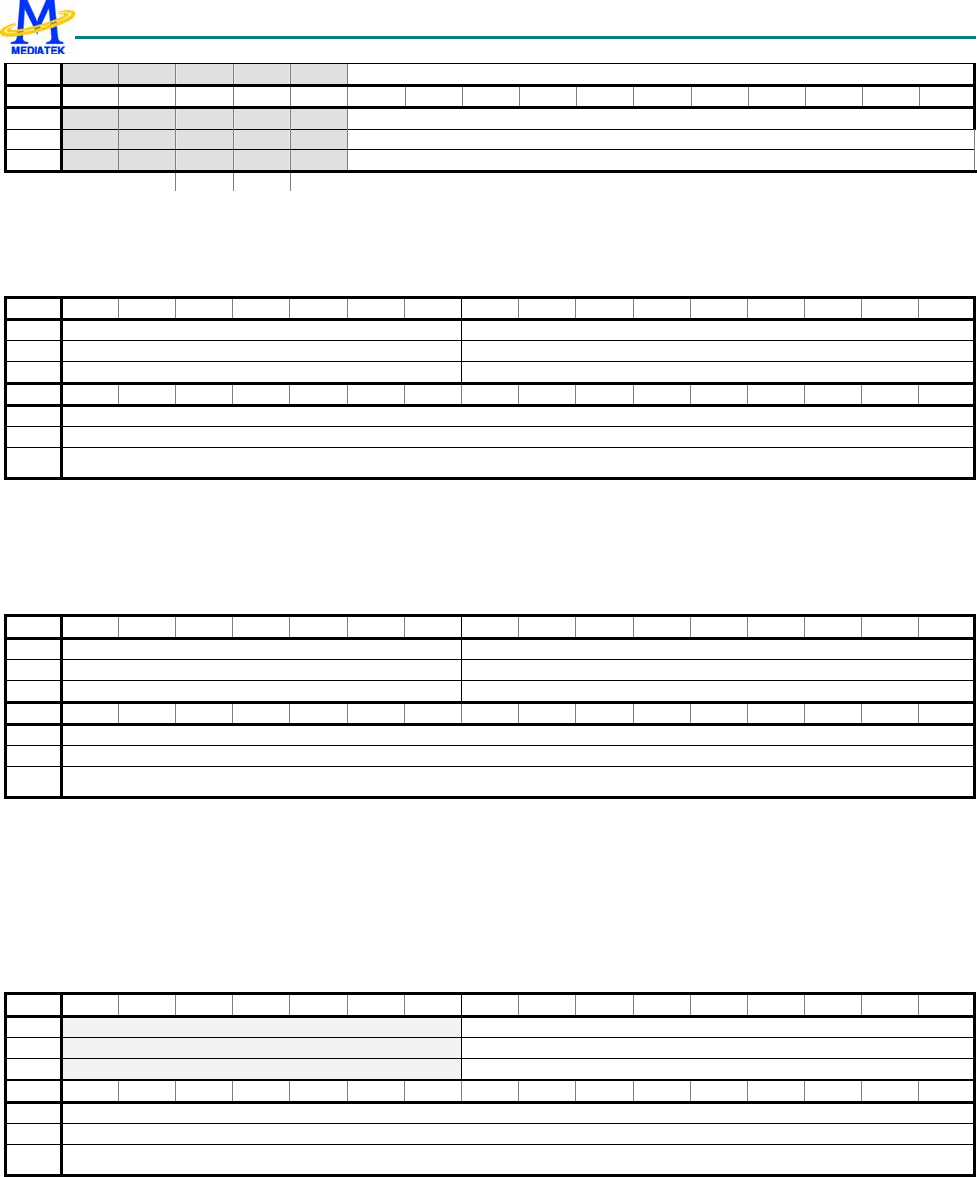

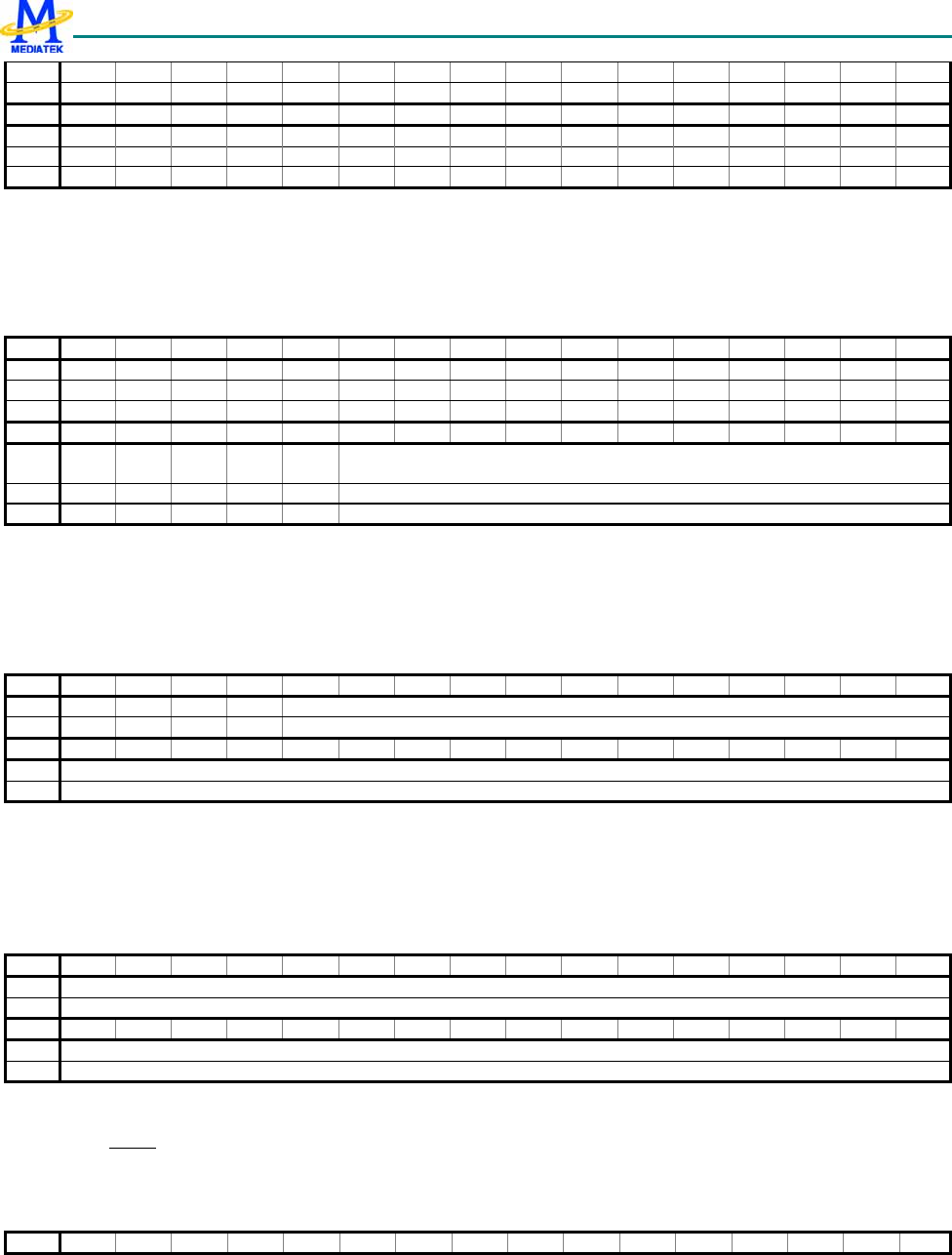

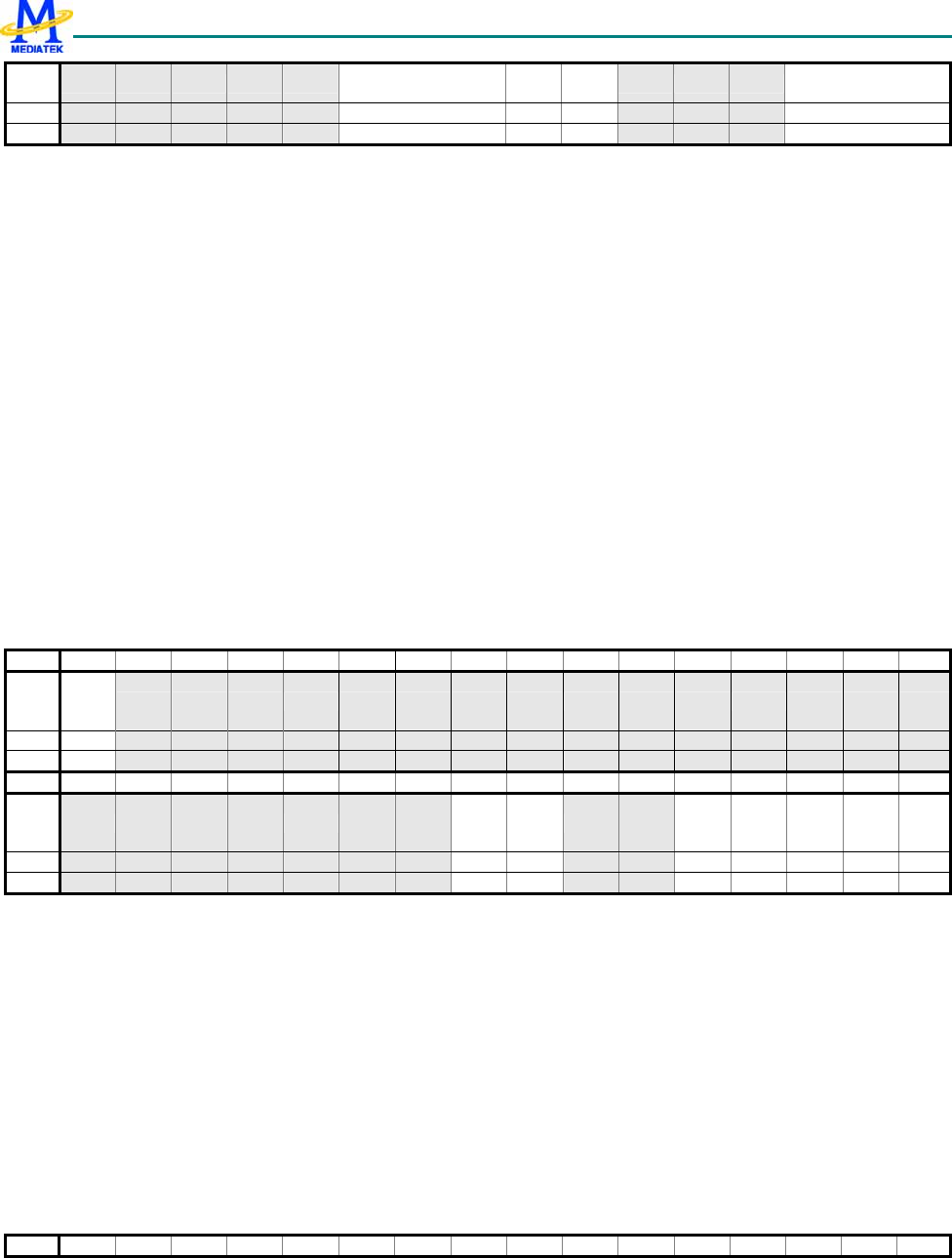

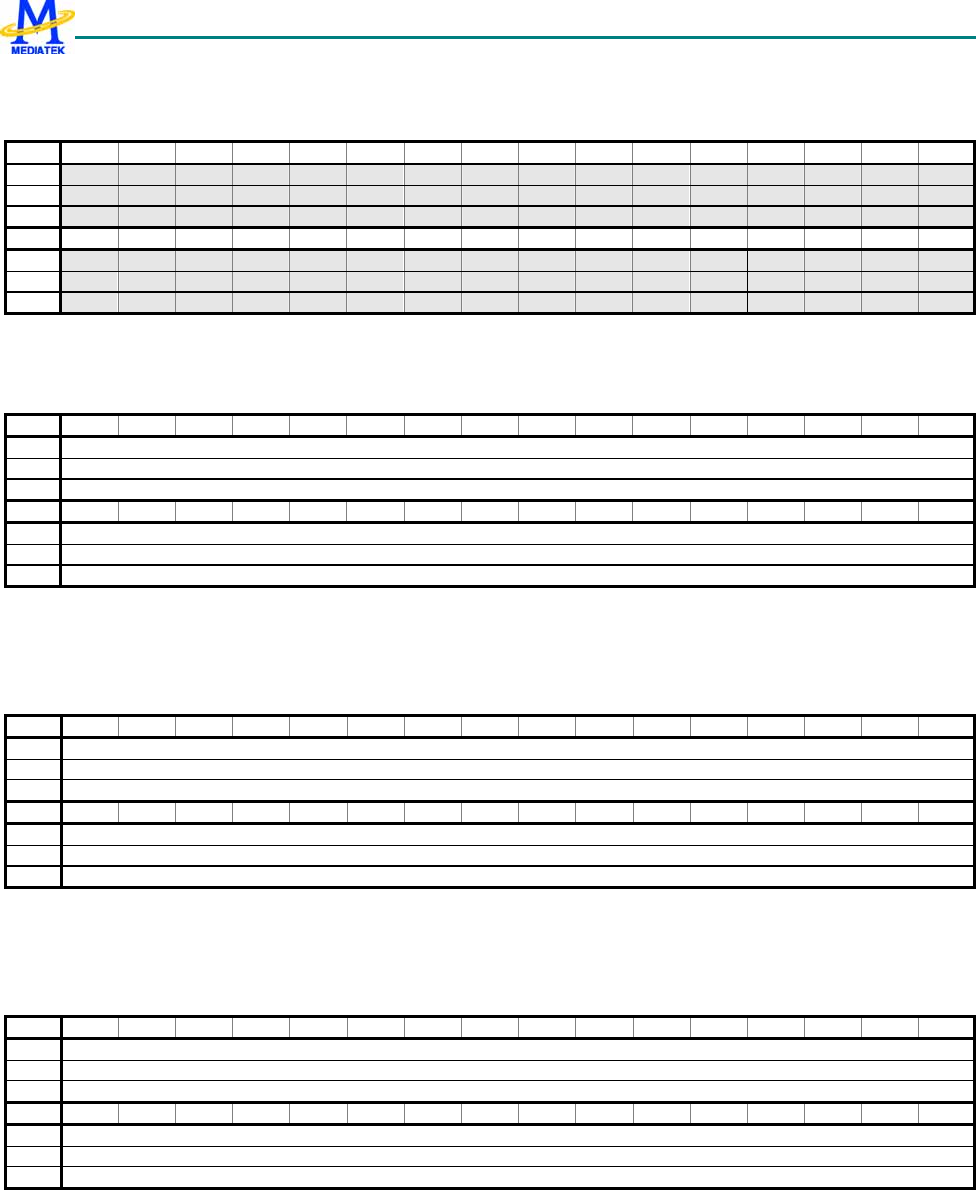

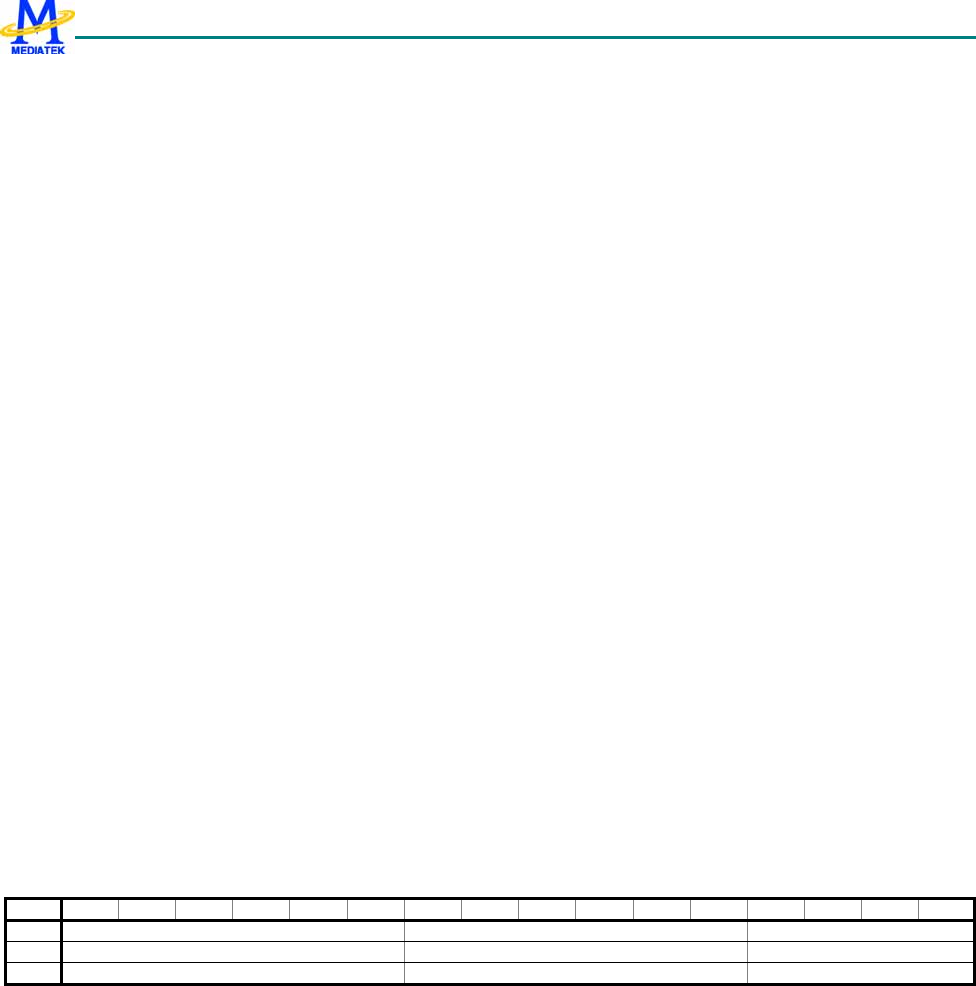

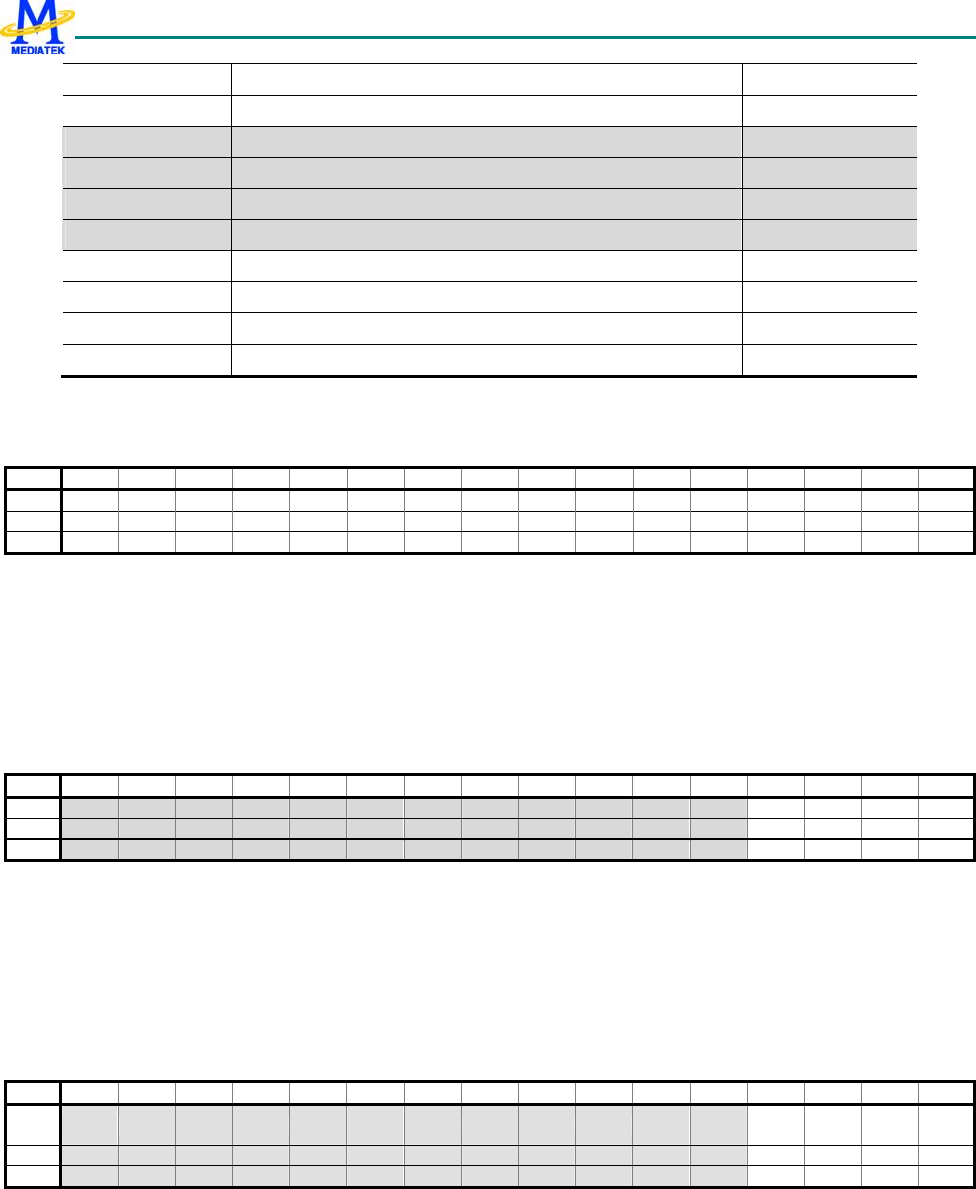

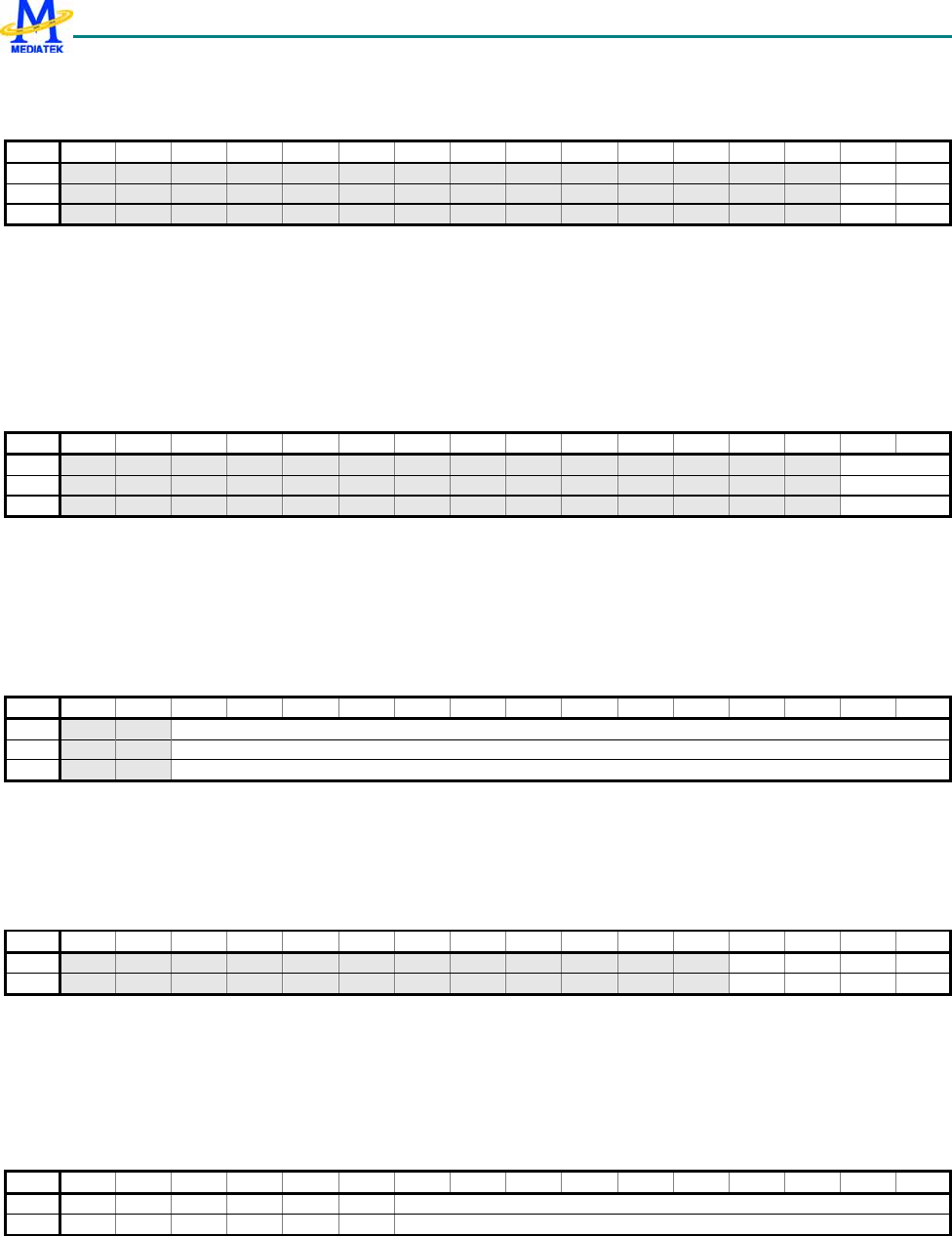

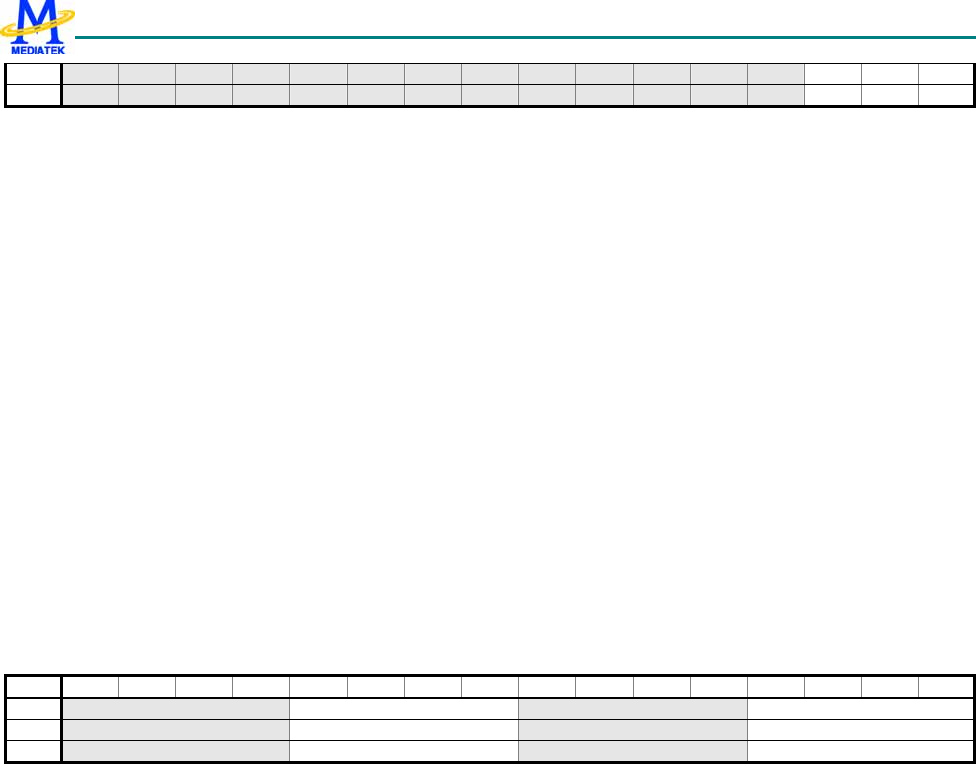

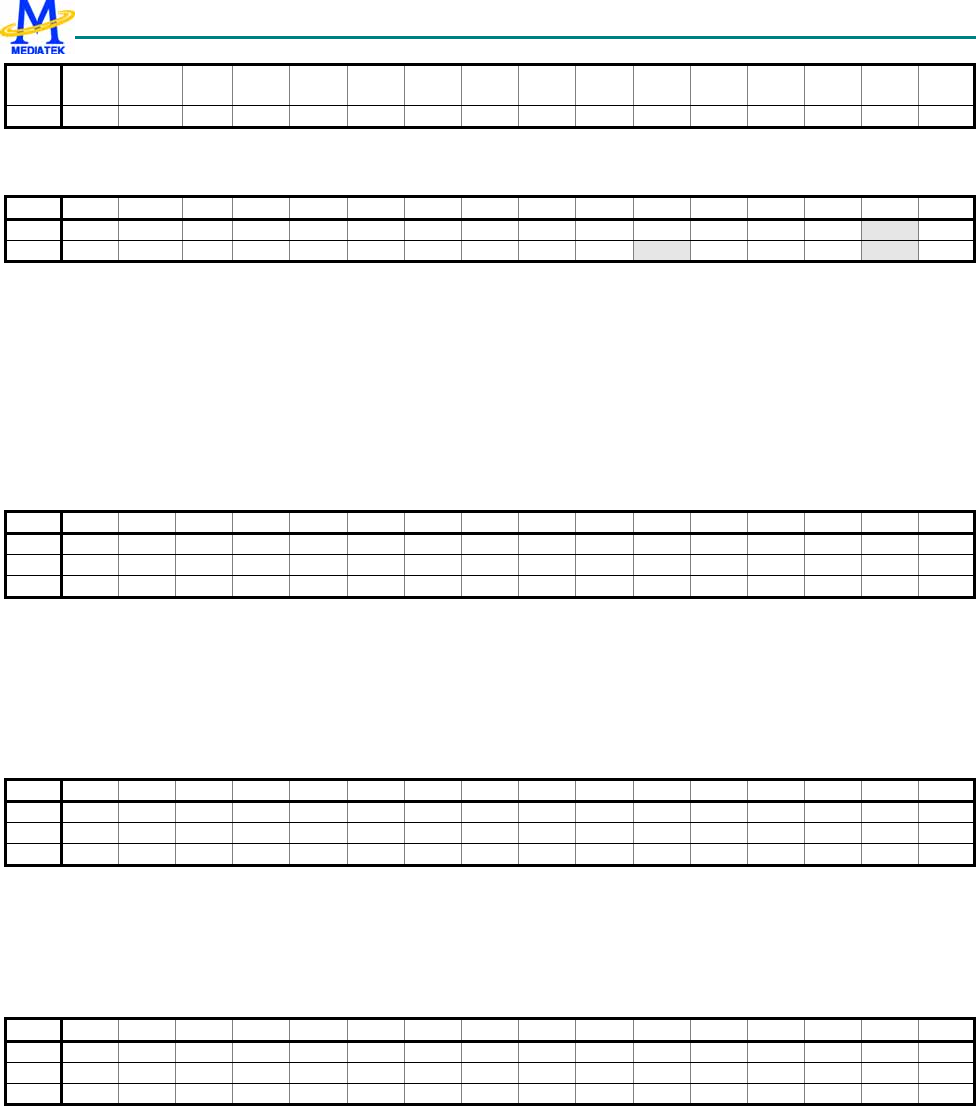

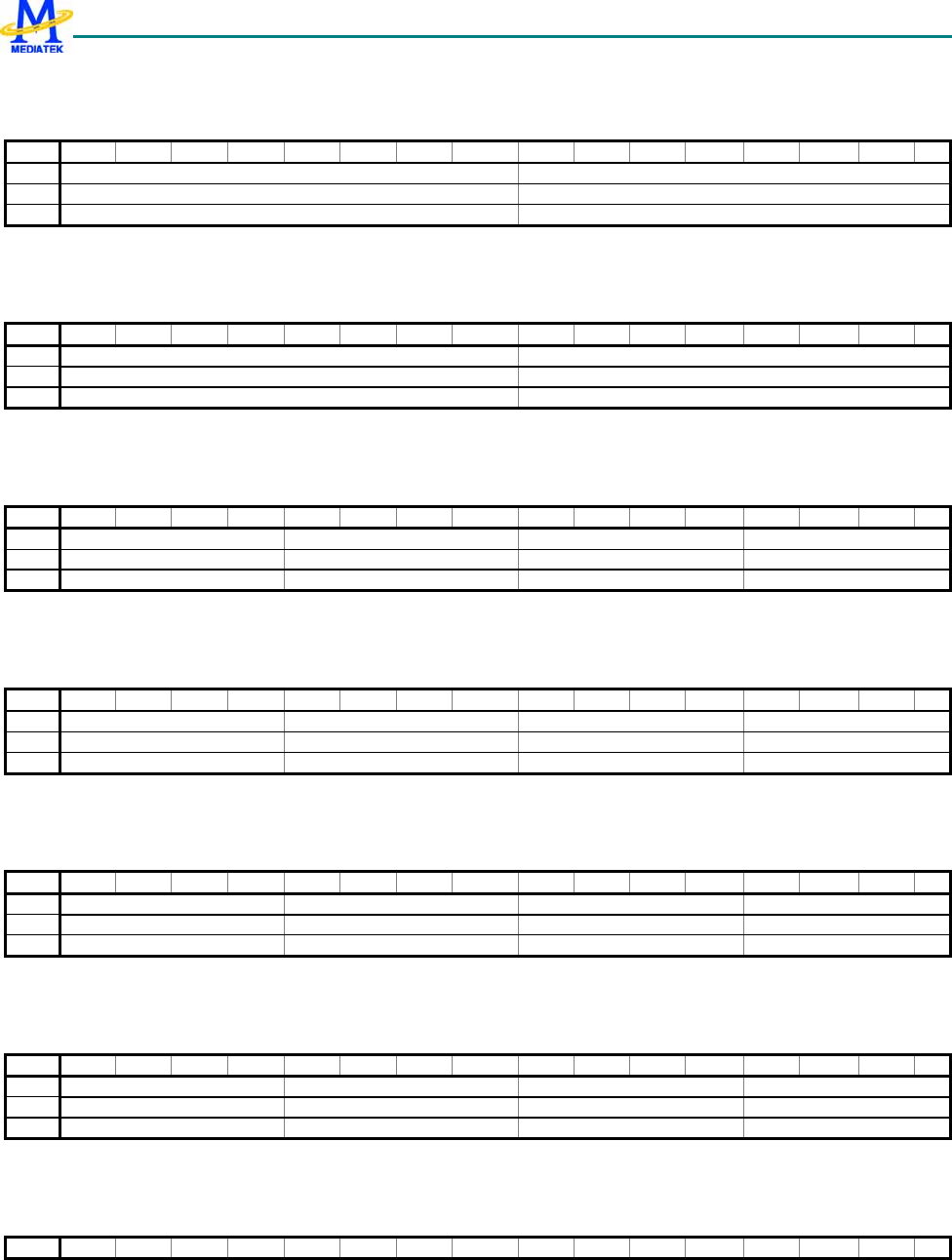

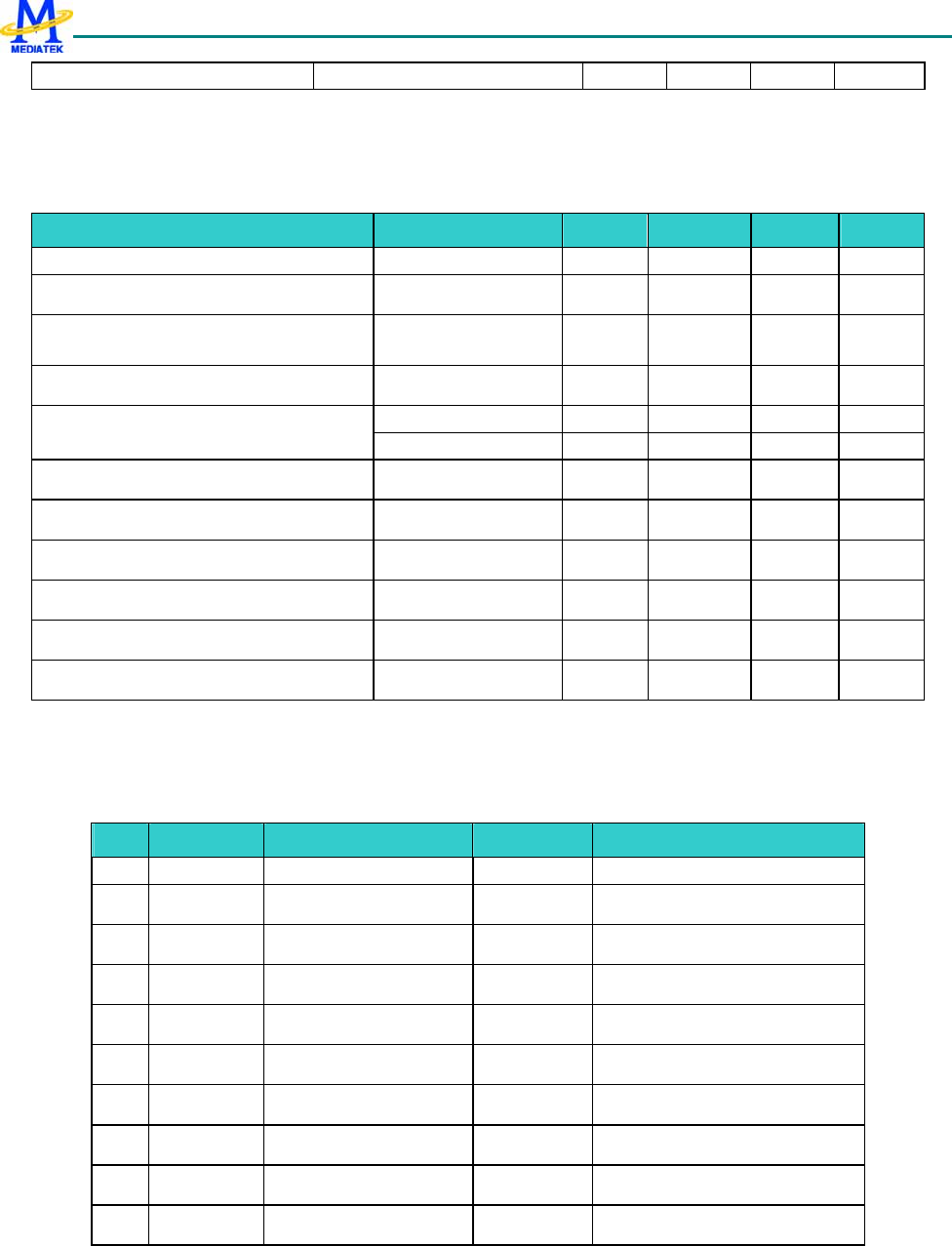

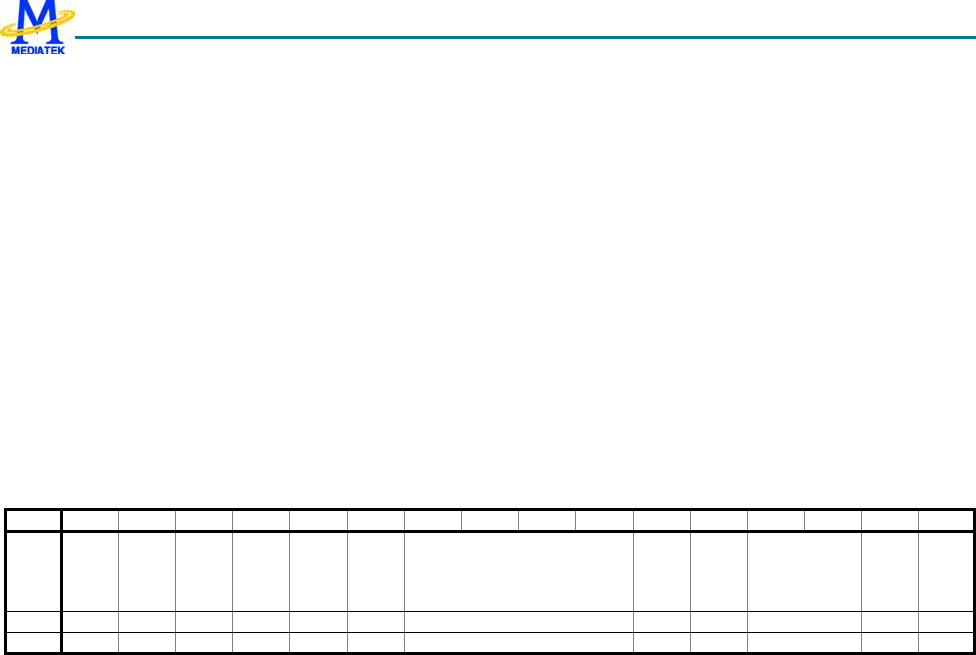

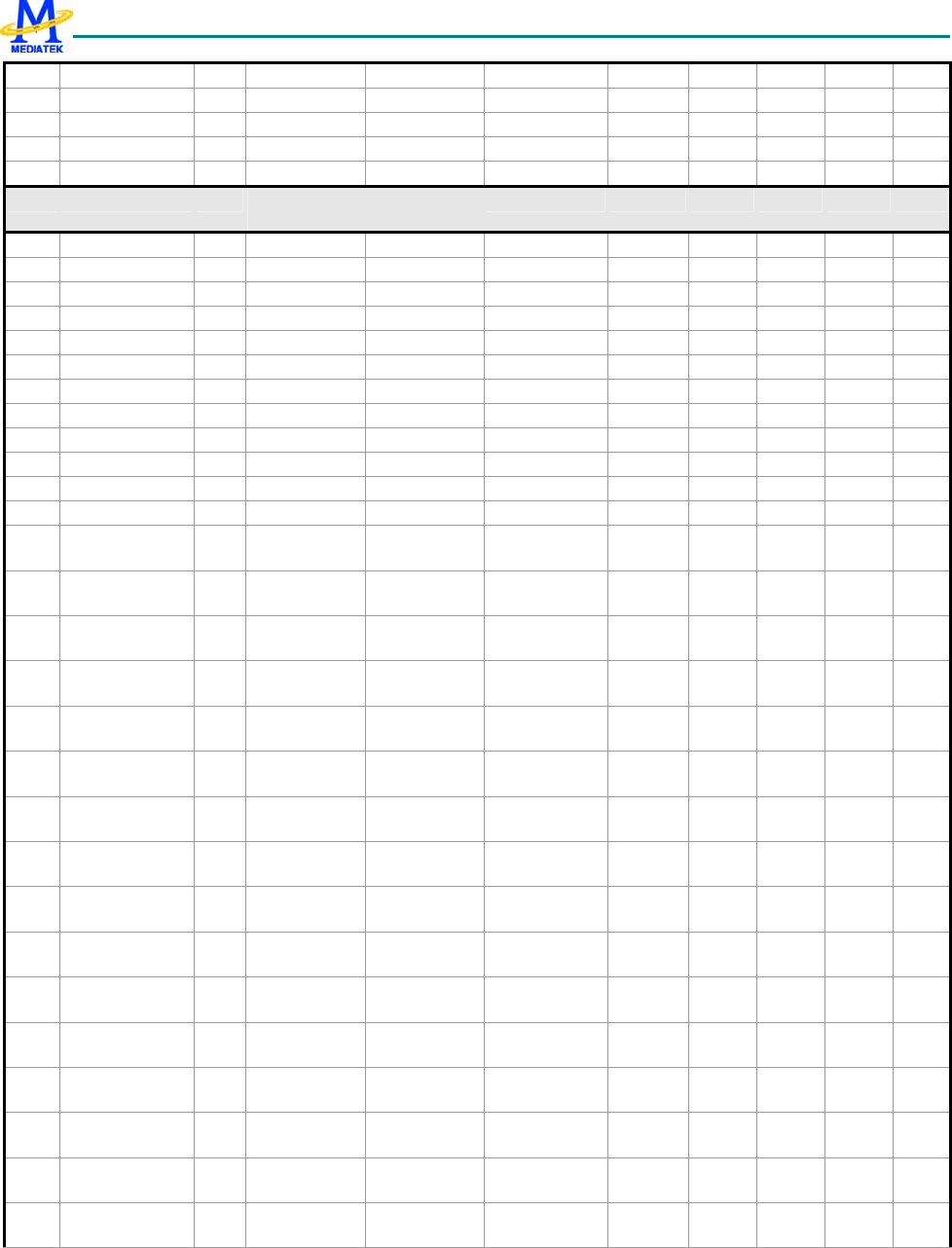

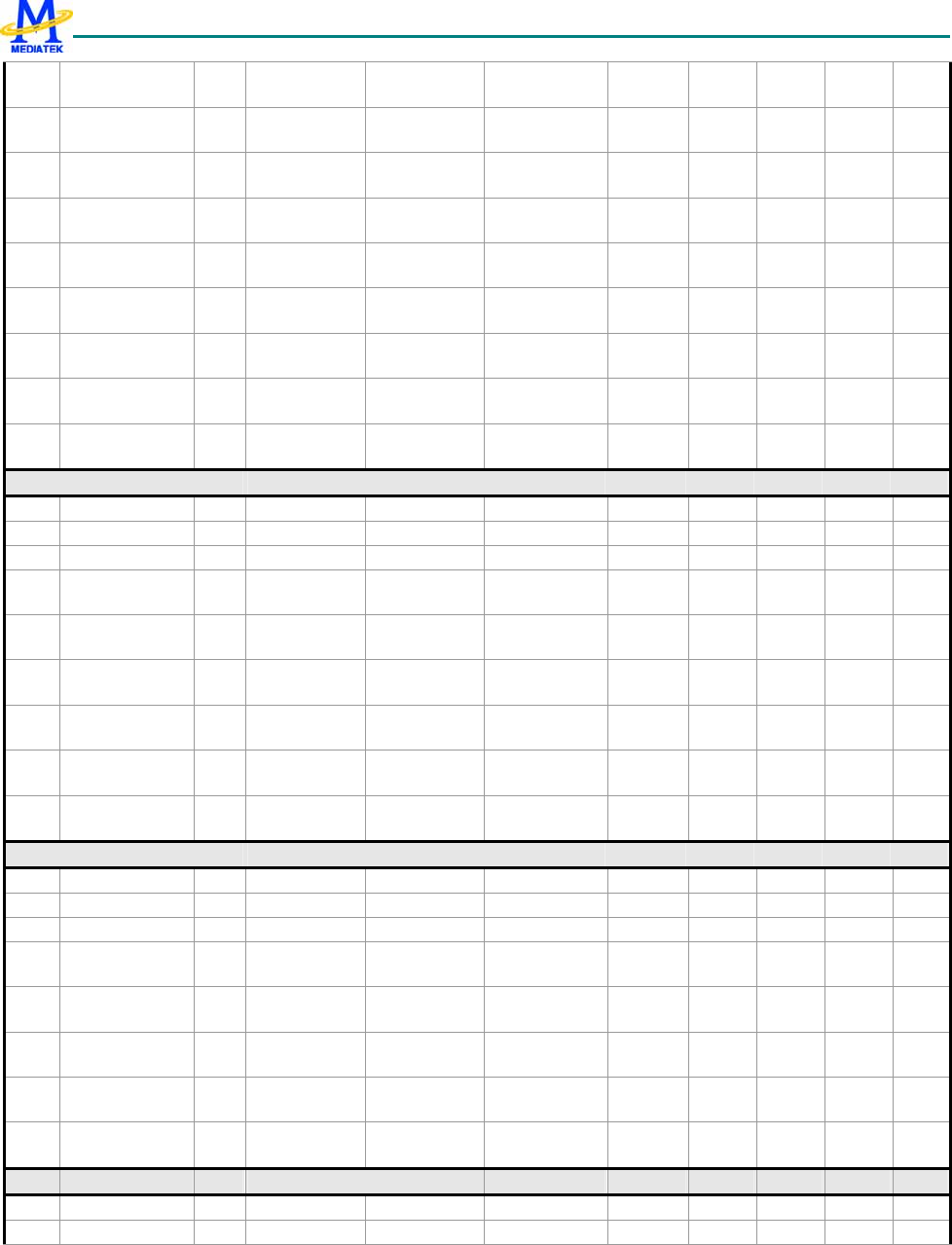

Figure 2 depicts the block diagram of MT6235. Based on a dual-processor architecture, MT6235 integrates both an

ARM926EJ-S core and a digital signal processor core. ARM926EJ-S is the main processor responsible for running

high-level GSM/GPRS protocol software as well as multi-media applications. The digital signal processor manages the

low-level MODEM as well as advanced audio functions. Except for a few mixed-signal circuitries, the other building

blocks in MT6235 are connected to either the microcontroller or the digital signal processor.

MT6235consists of the following subsystems:

z Microcontroller Unit (MCU) Subsystem: includes an ARM926EJ-S RISC processor and its accompanying

memory management and interrupt handling logics;

z Digital Signal Processor (DSP) Subsystem: includes a DSP and its accompanying memory, memory controller, and

interrupt controller;

z MCU/DSP Interface: the junction at which the MCU and the DSP exchange hardware and software information;

z Microcontroller Peripherals: includes all user interface modules and RF control interface modules;

z Microcontroller Coprocessors: runs computing-intensive processes in place of the Microcontroller;

z DSP Peripherals: hardware accelerators for GSM/GPRS/EDGE channel codec;

z Multi-media Subsystem: integrates several advanced accelerators to support multi-media applications;

z Voice Front End: the data path for converting analog speech to and from digital speech;

z Audio Front End: the data path for converting stereo audio from an audio source;

z Baseband Front End: the data path for converting a digital signal to and from an analog signal from the RF

modules;

z Timing Generator: generates the control signals related to the TDMA frame timing; and,

z Power, Reset and Clock Subsystem: manages the power, reset, and clock distribution inside MT6235.

Details of the individual subsystems and blocks are described in the following chapters.

MT6235 GSM/GPRS Baseband Processor Data Sheet Revision 1.02

14/599 MediaTek Inc. Confidential

Figure 2 MT6235 block diagram.

MT6235 GSM/GPRS Baseband Processor Data Sheet Revision 1.02

15/599 MediaTek Inc. Confidential

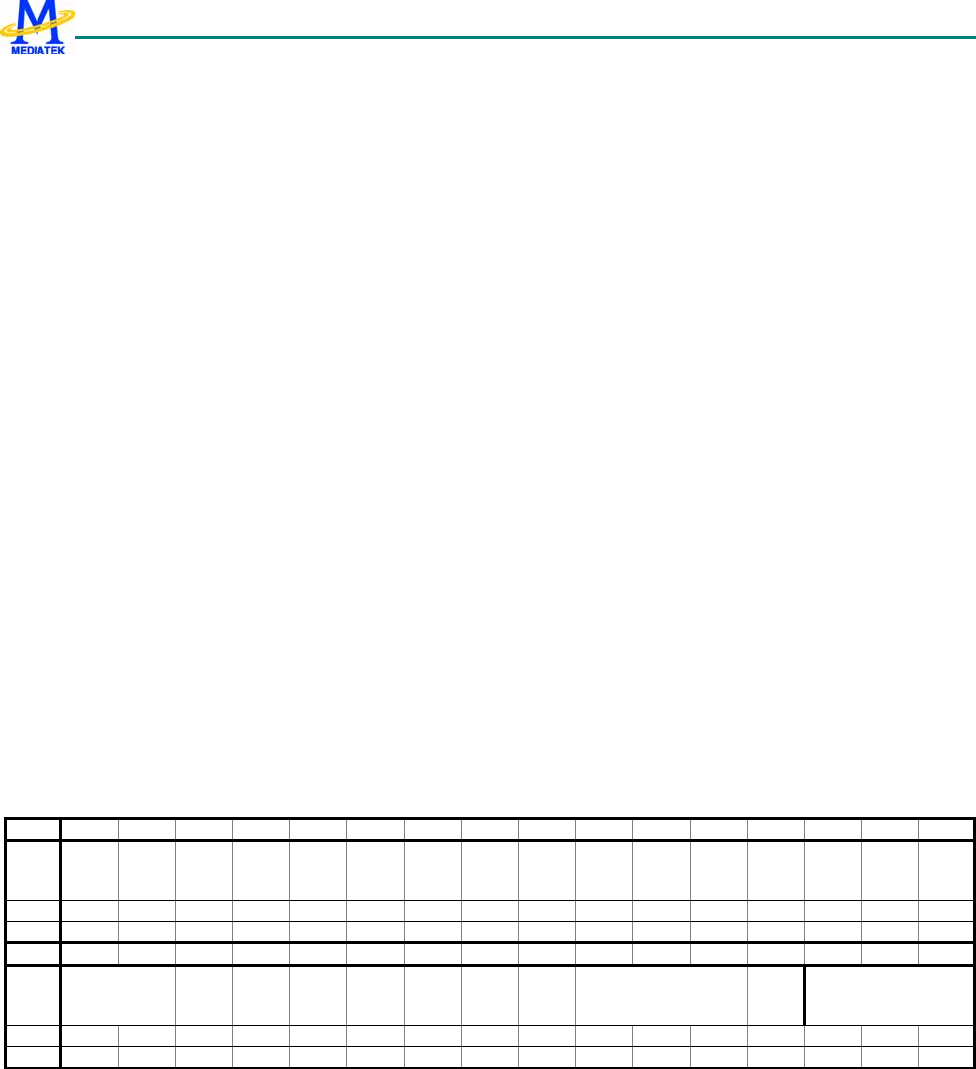

2 Product Description

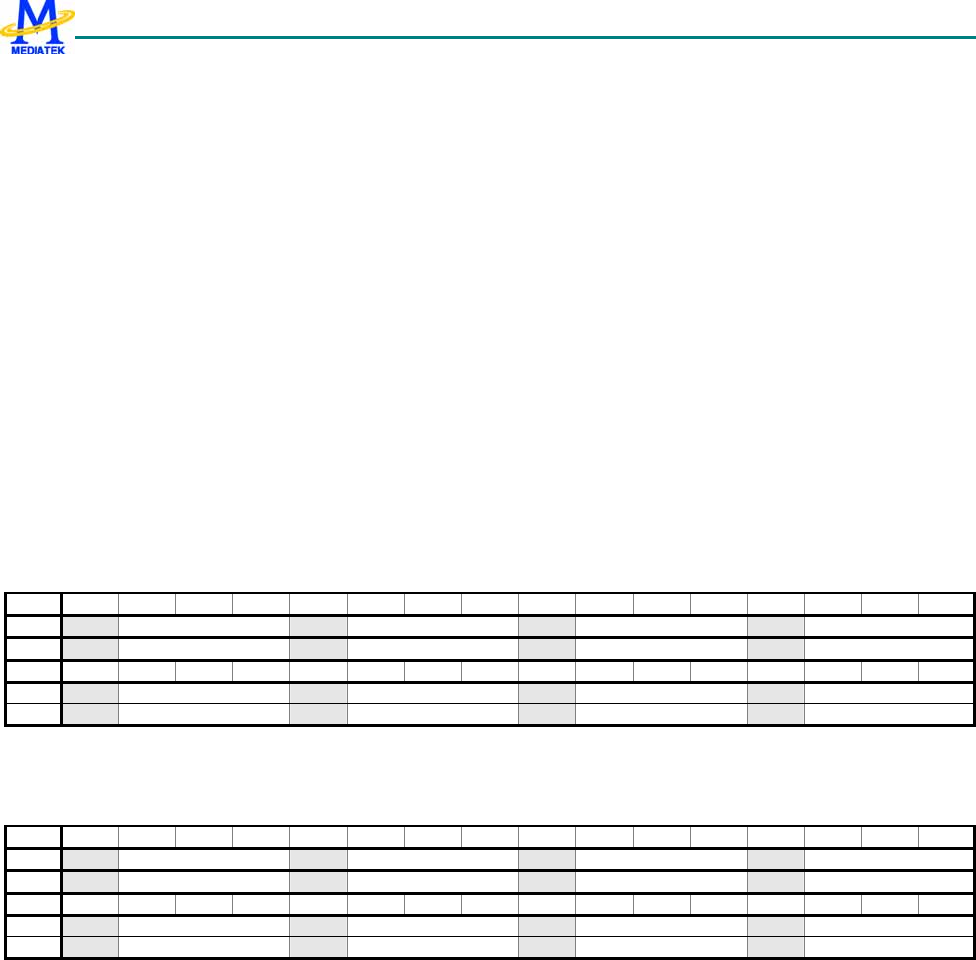

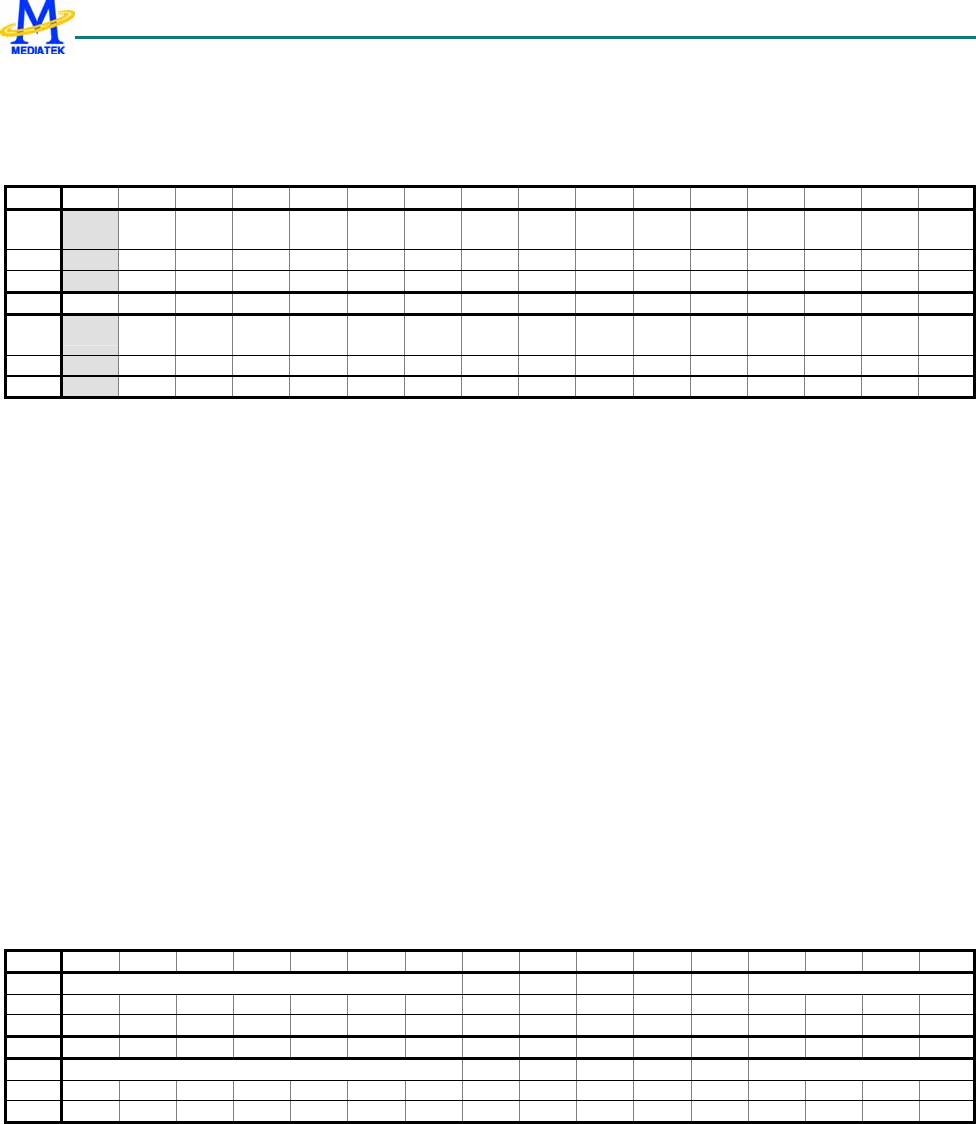

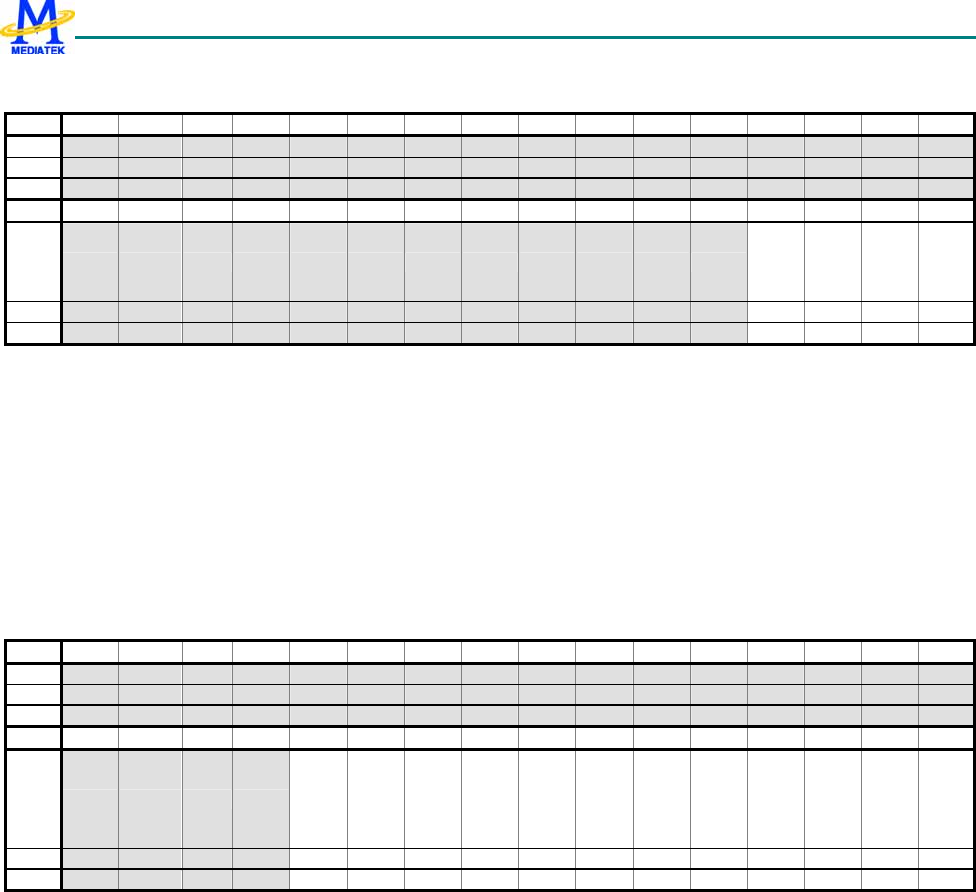

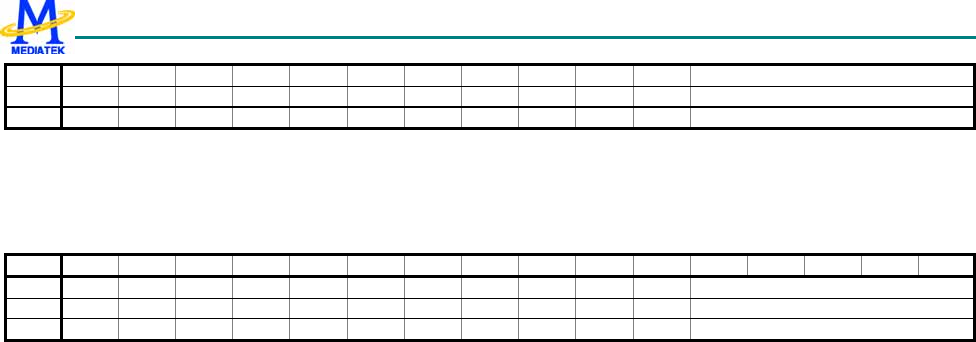

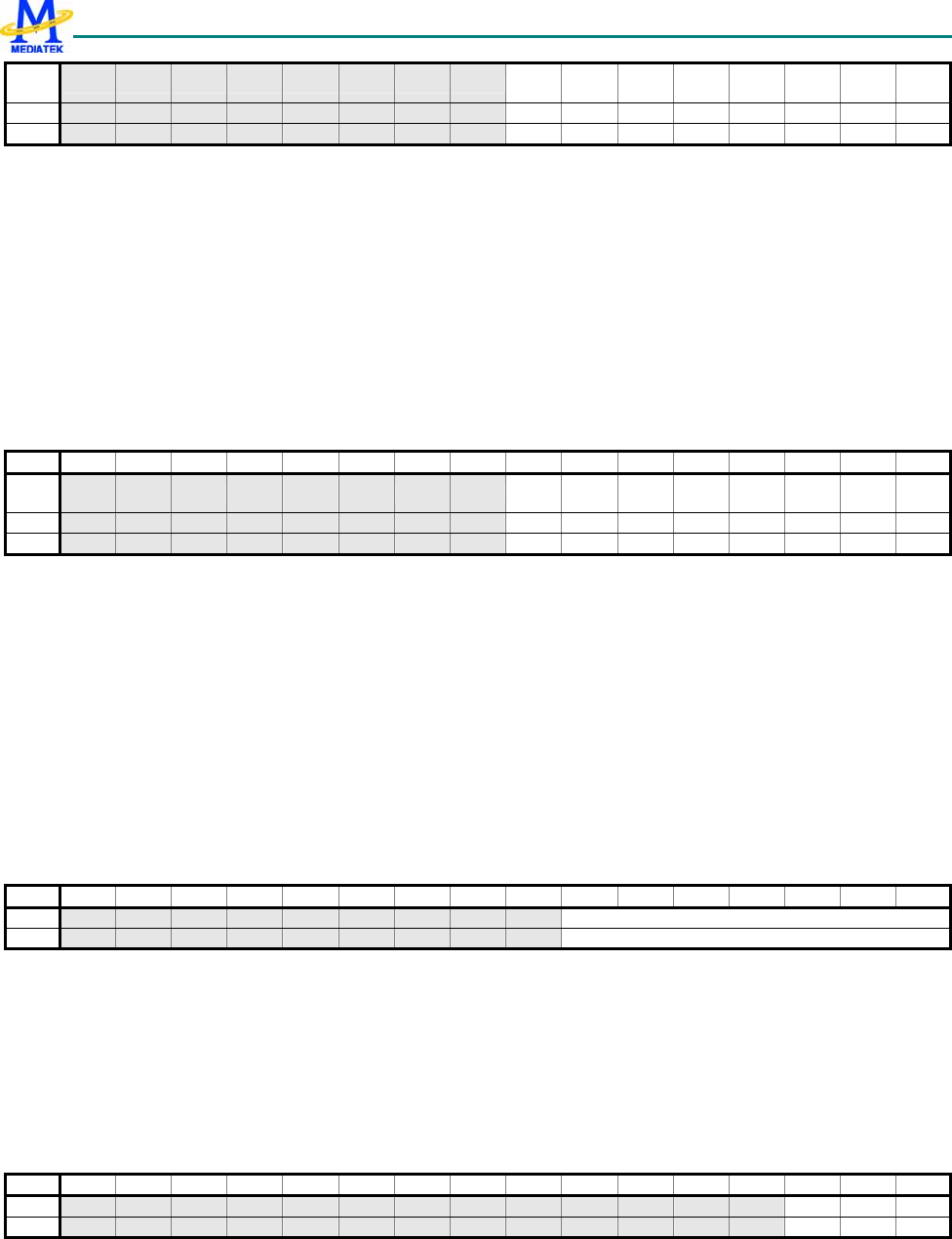

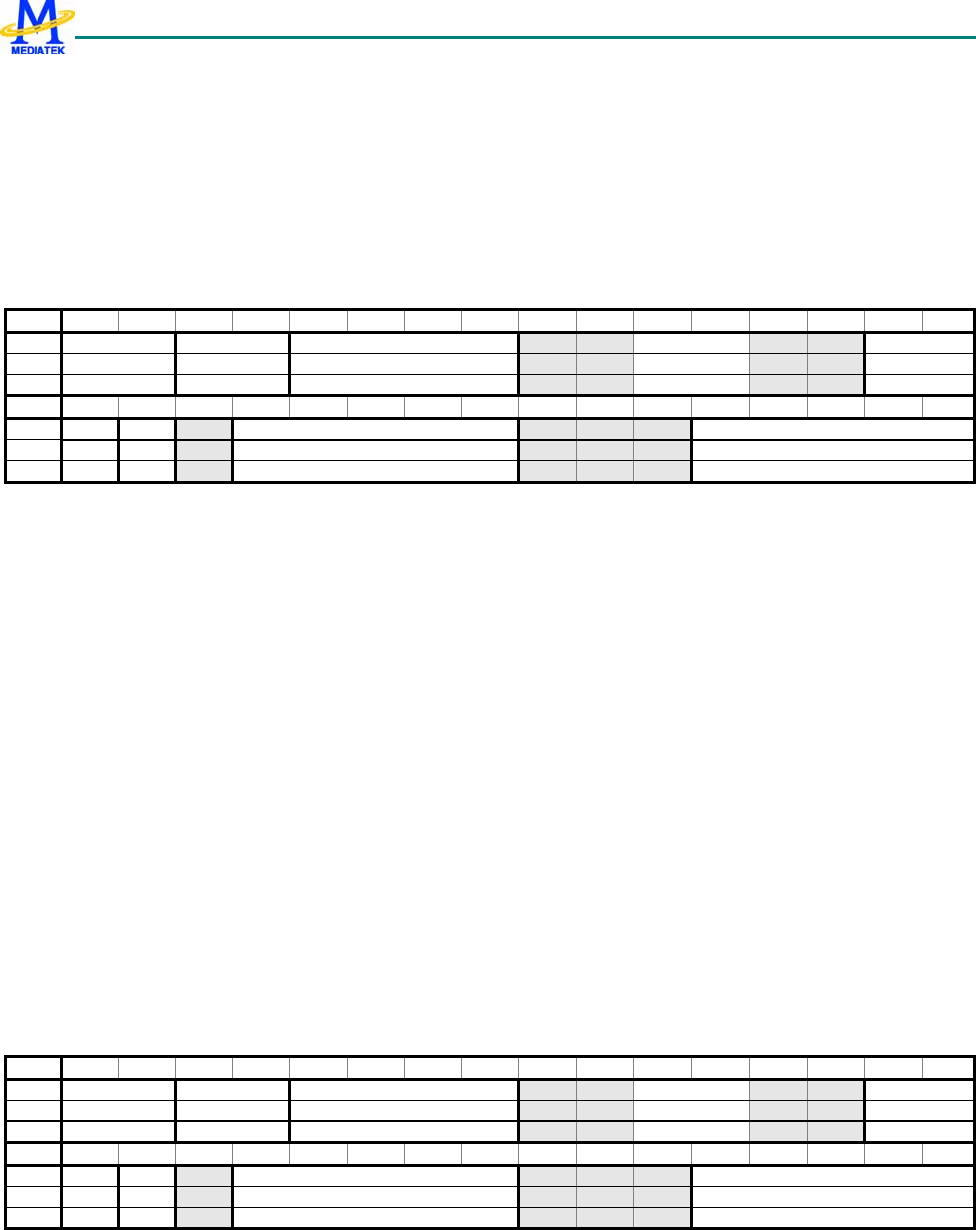

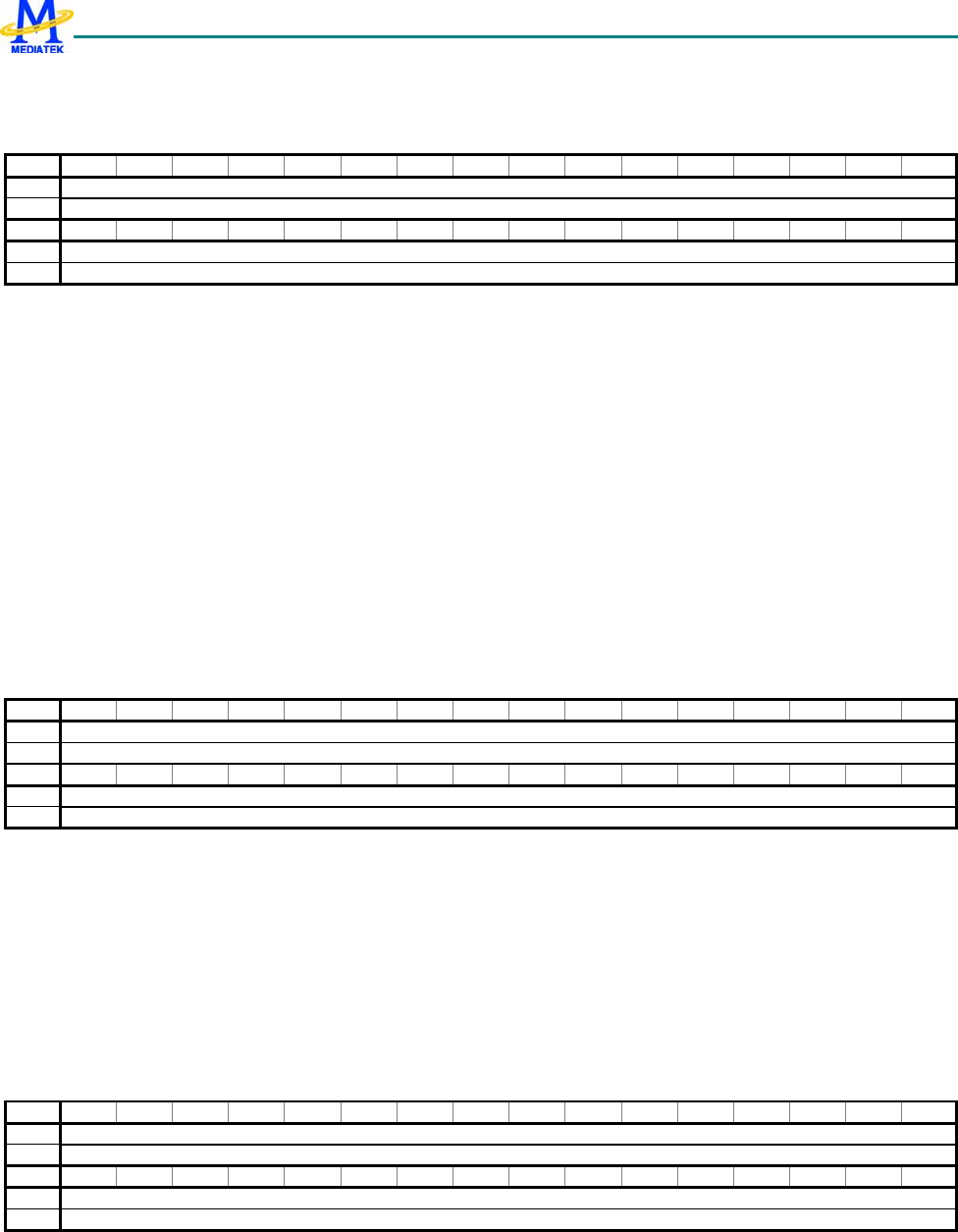

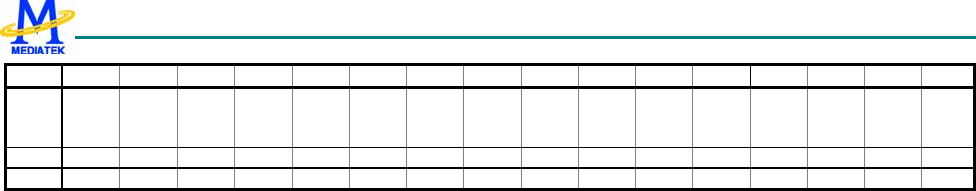

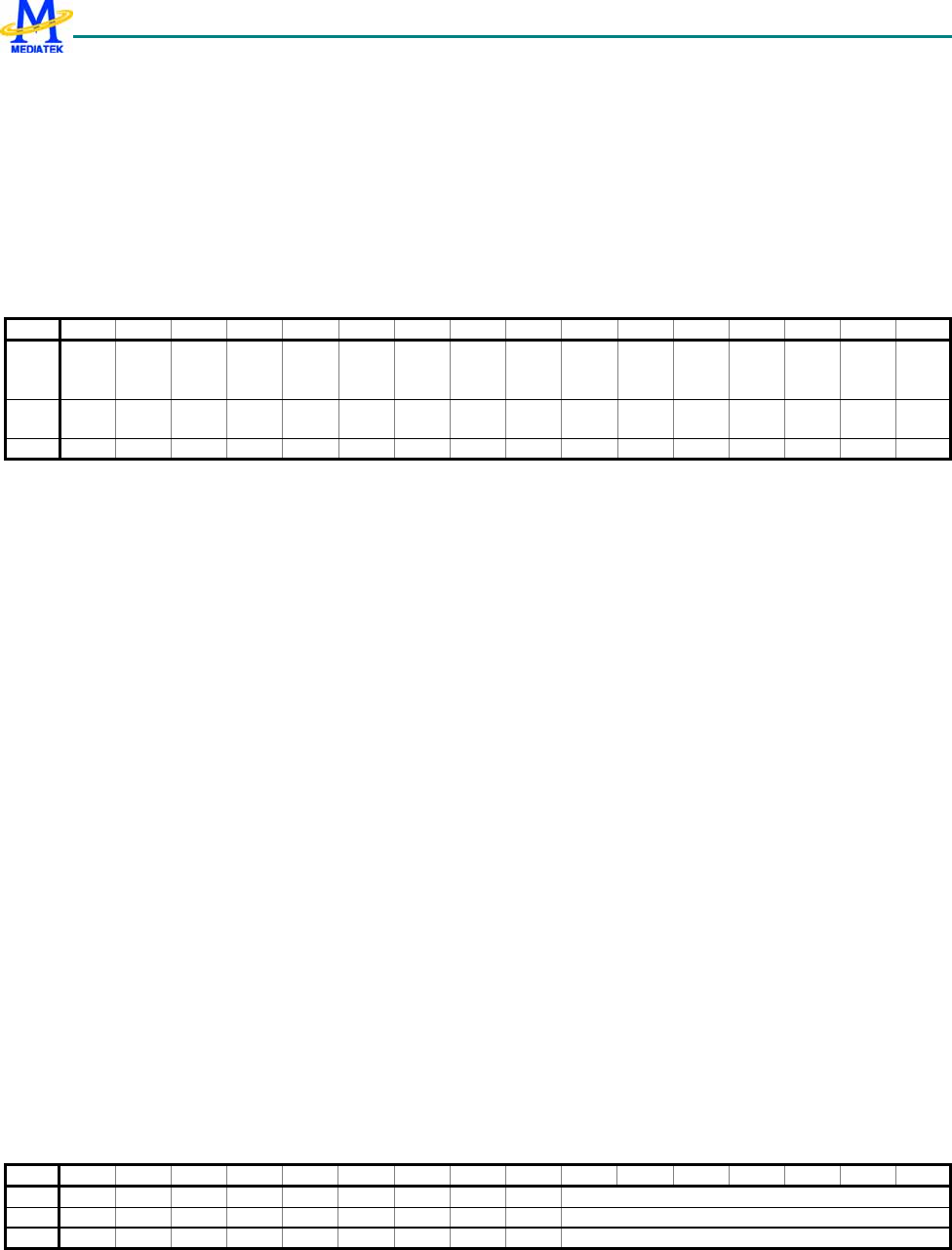

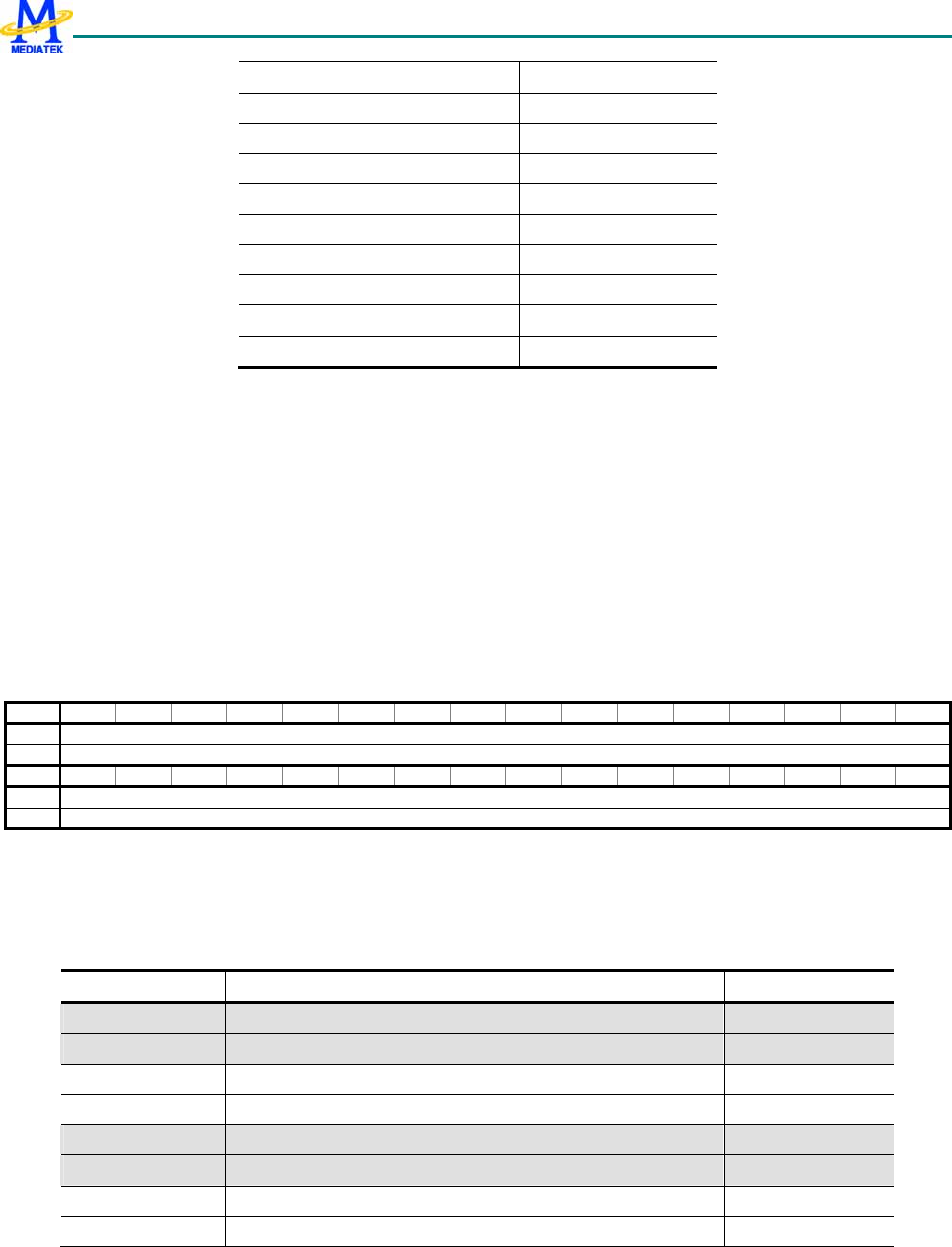

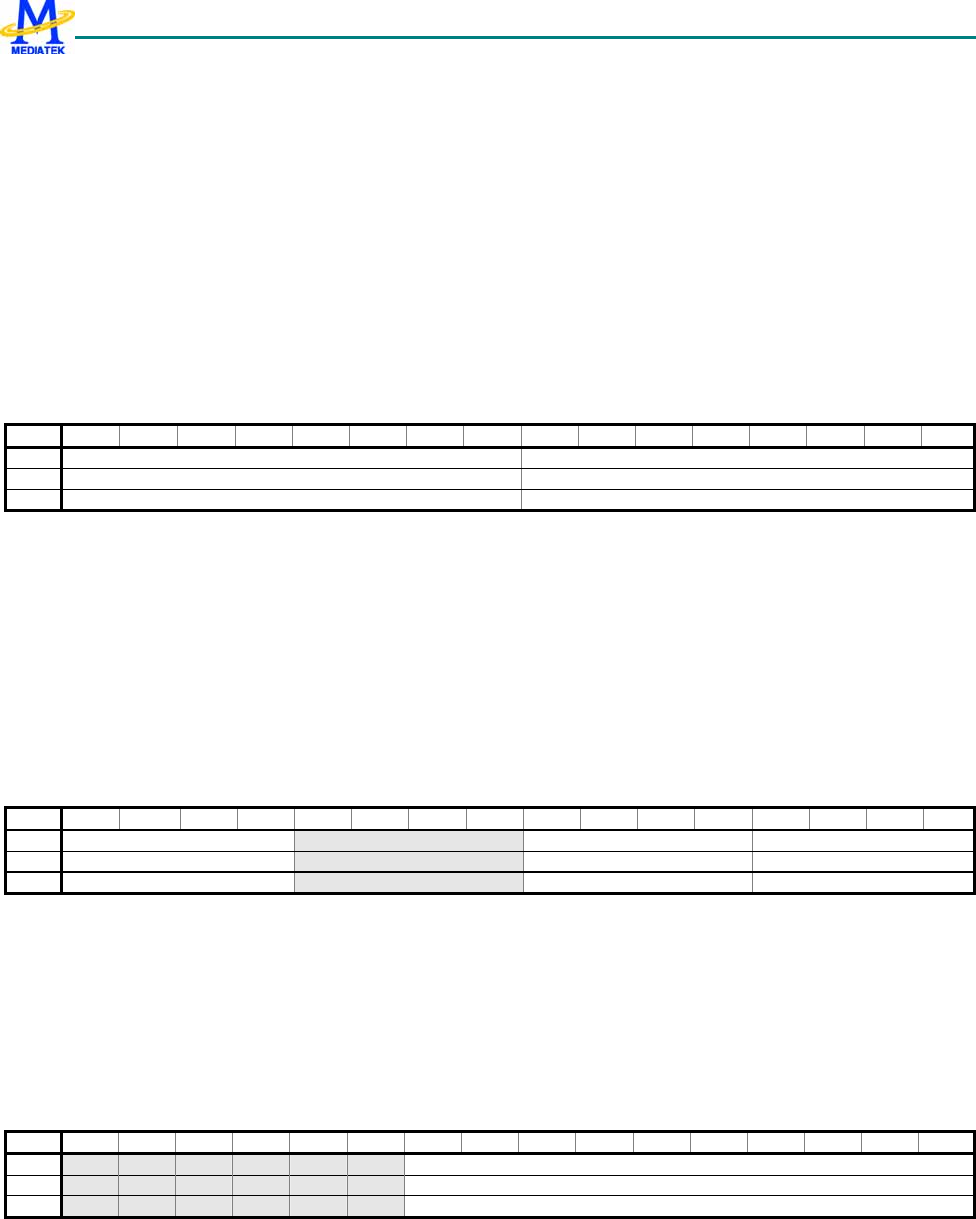

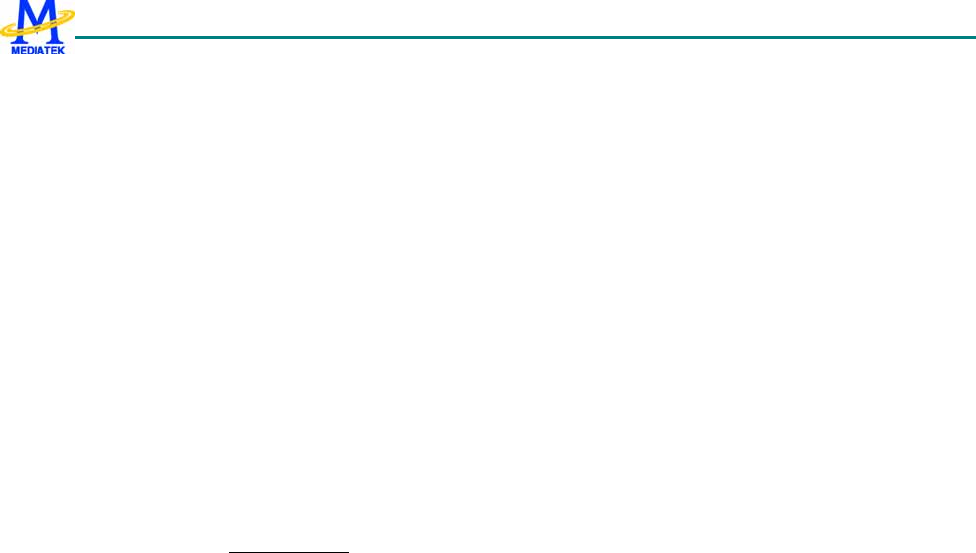

2.1 Pin Outs

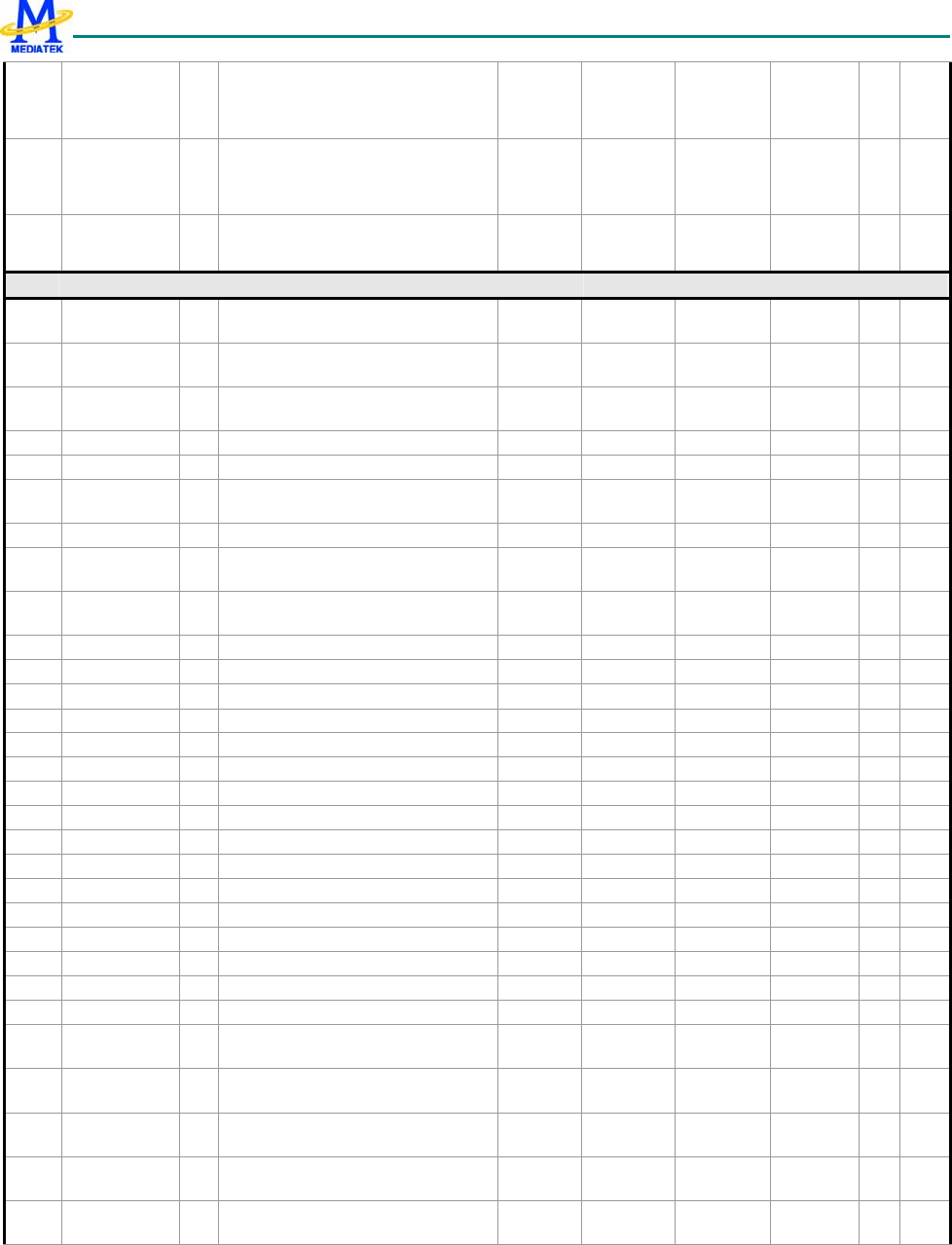

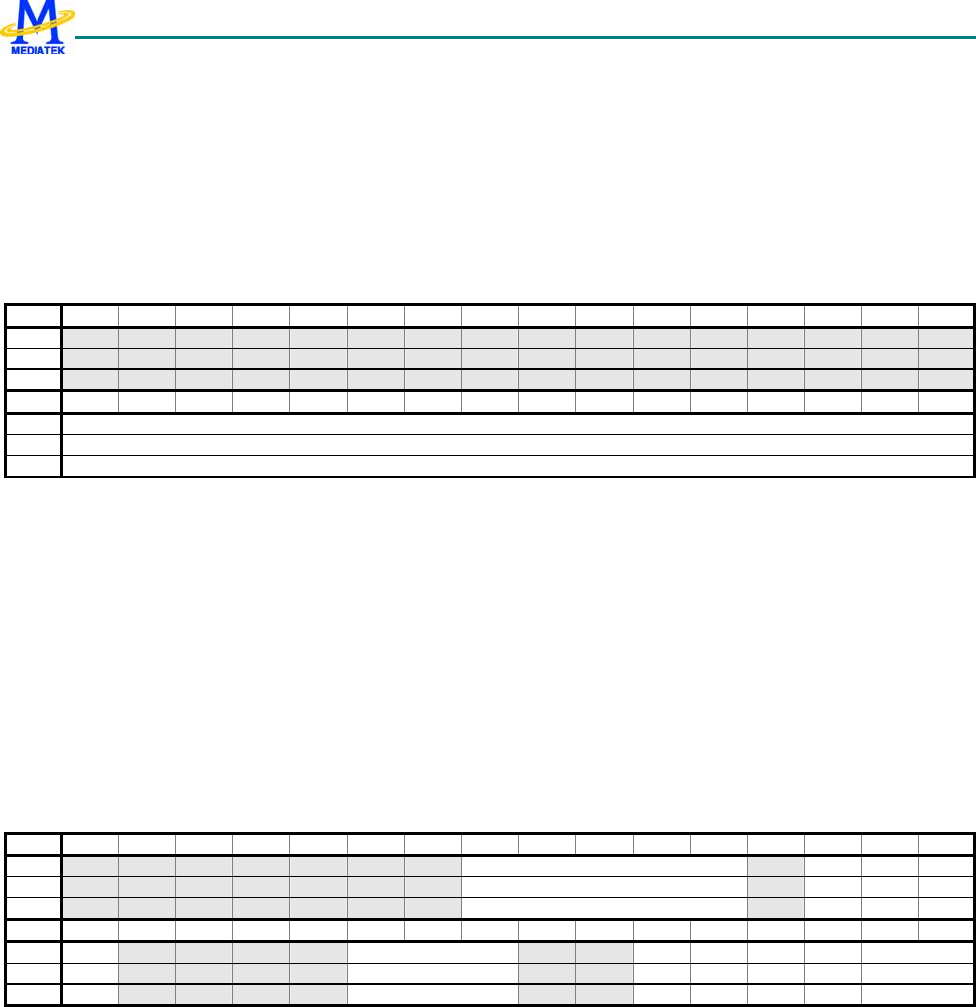

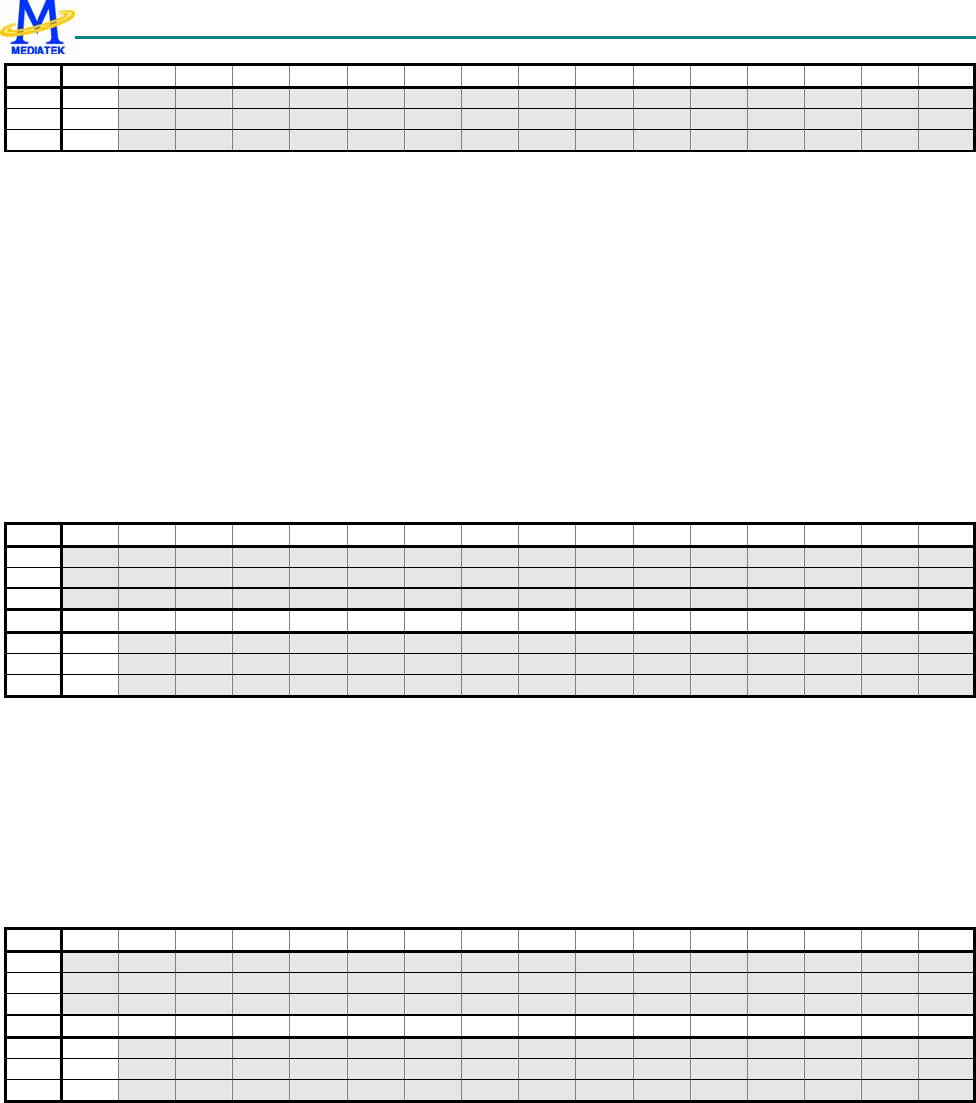

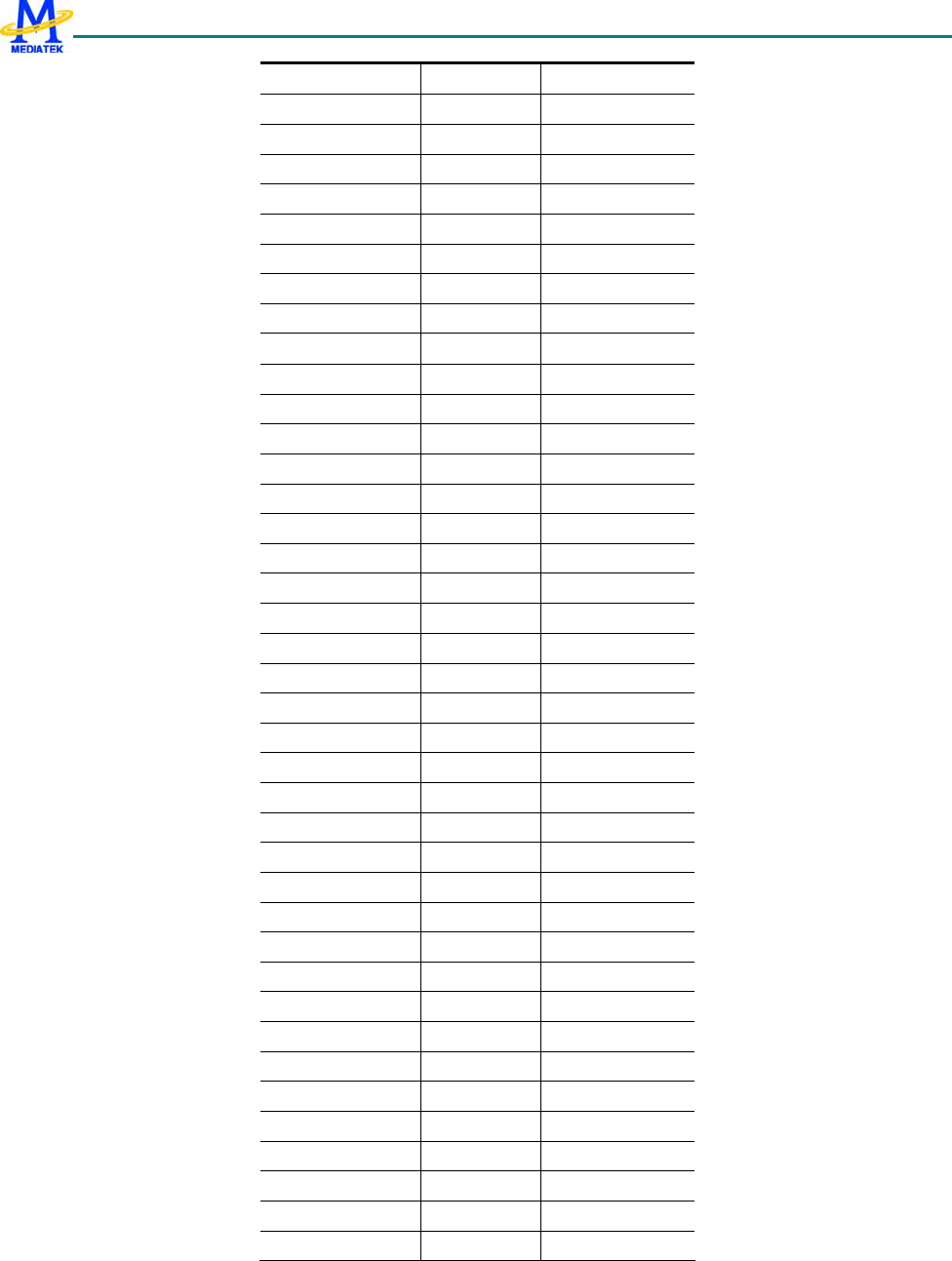

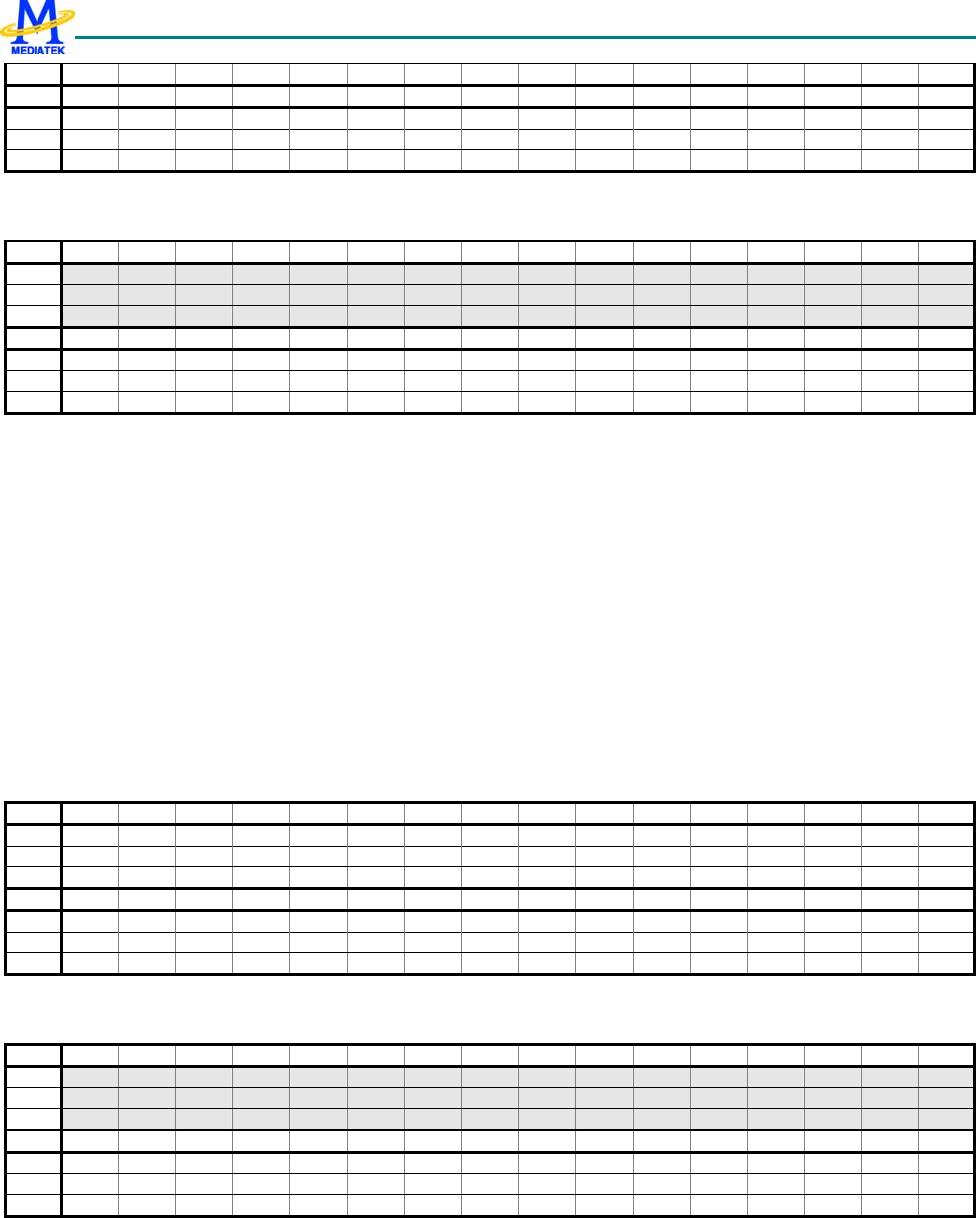

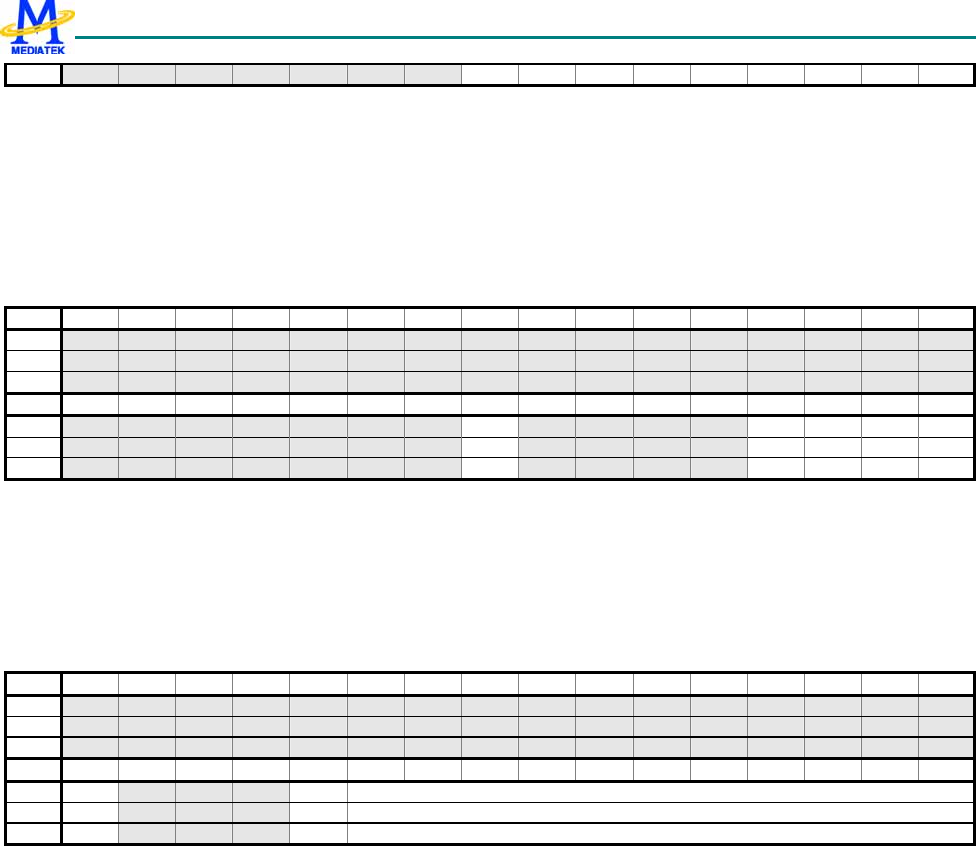

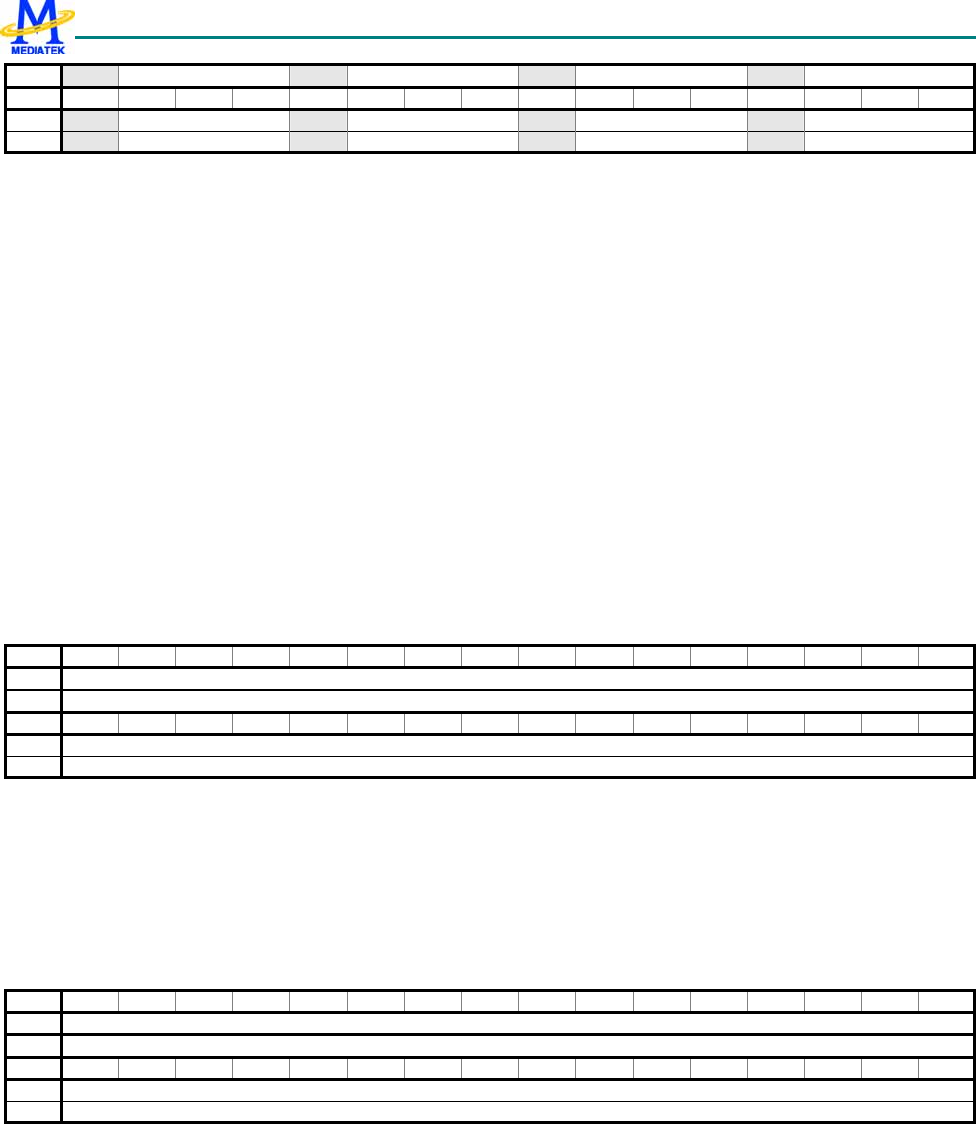

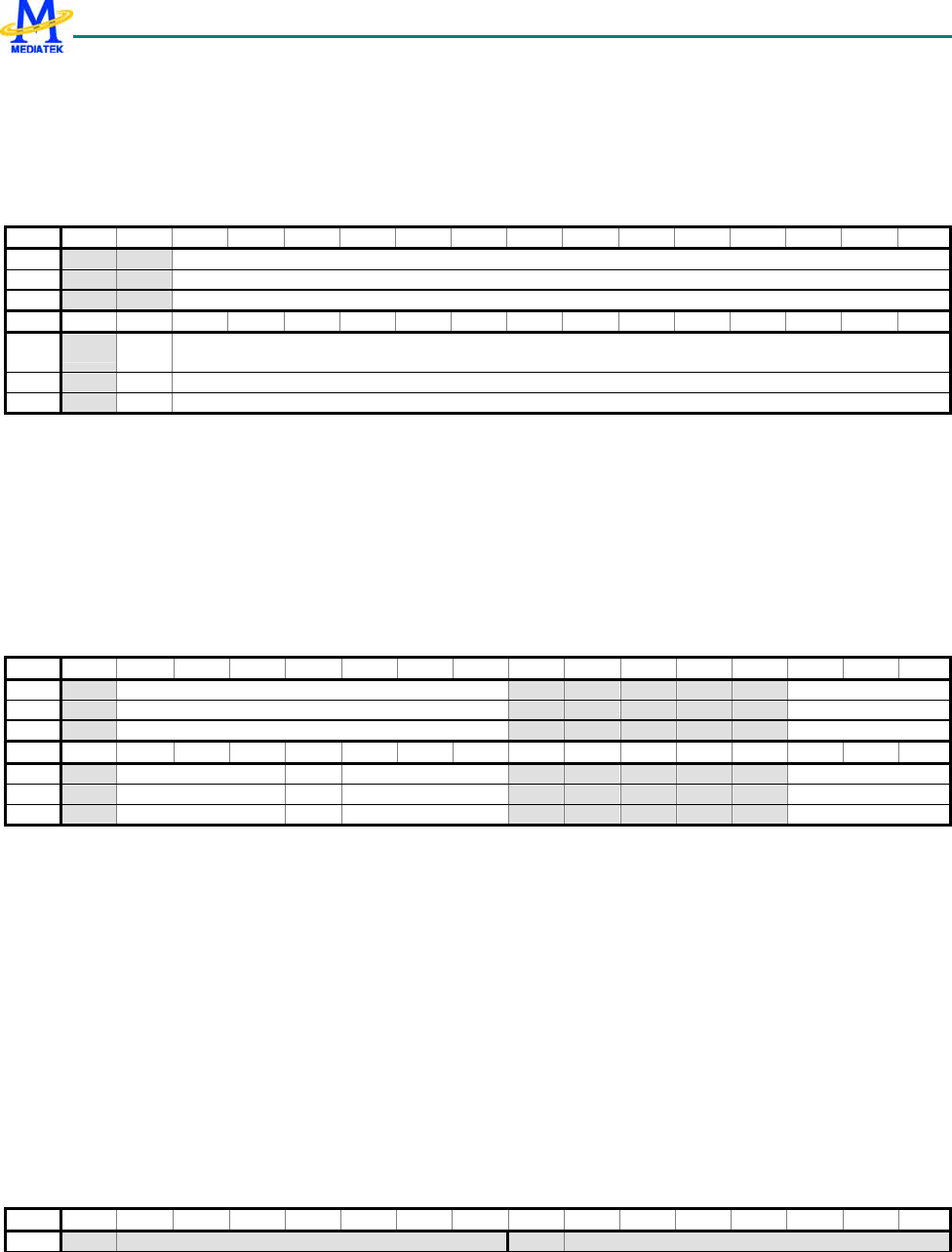

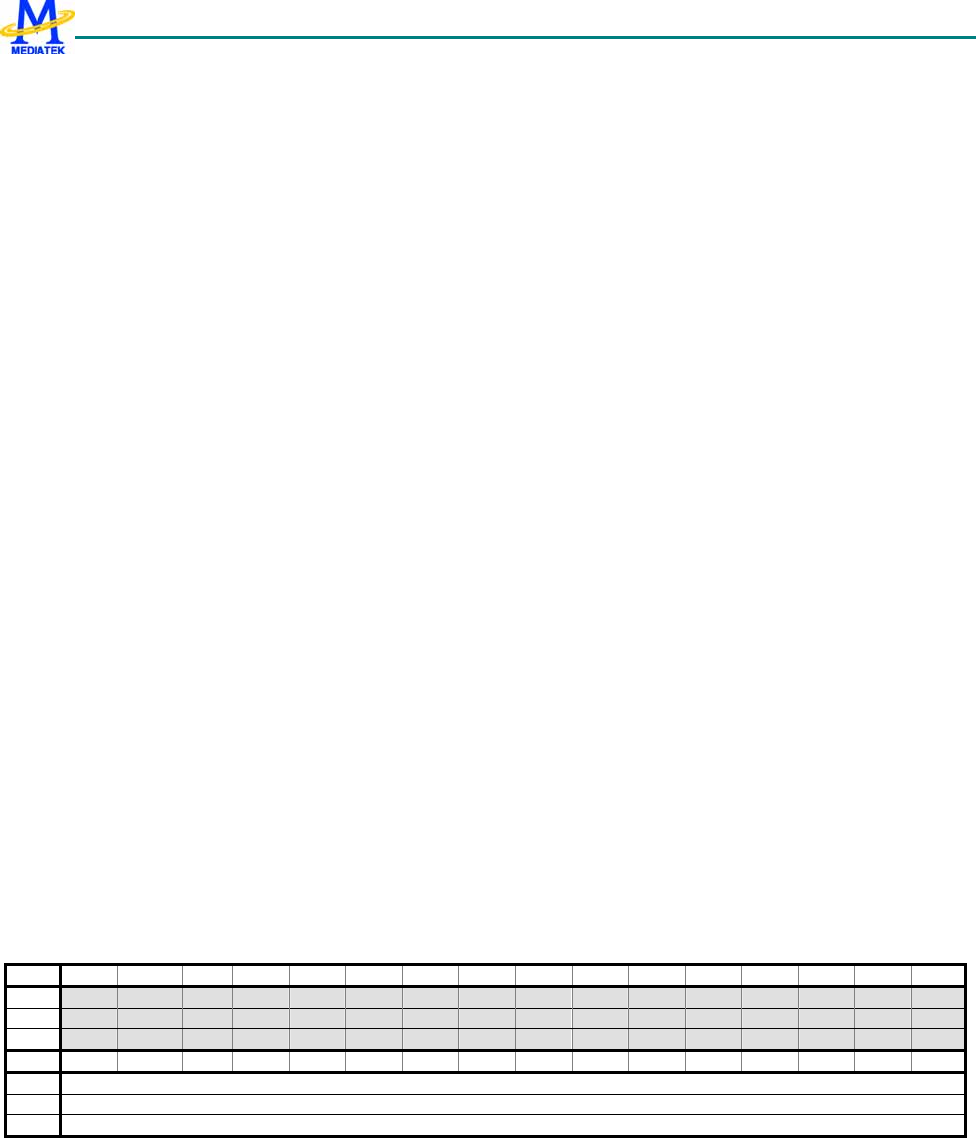

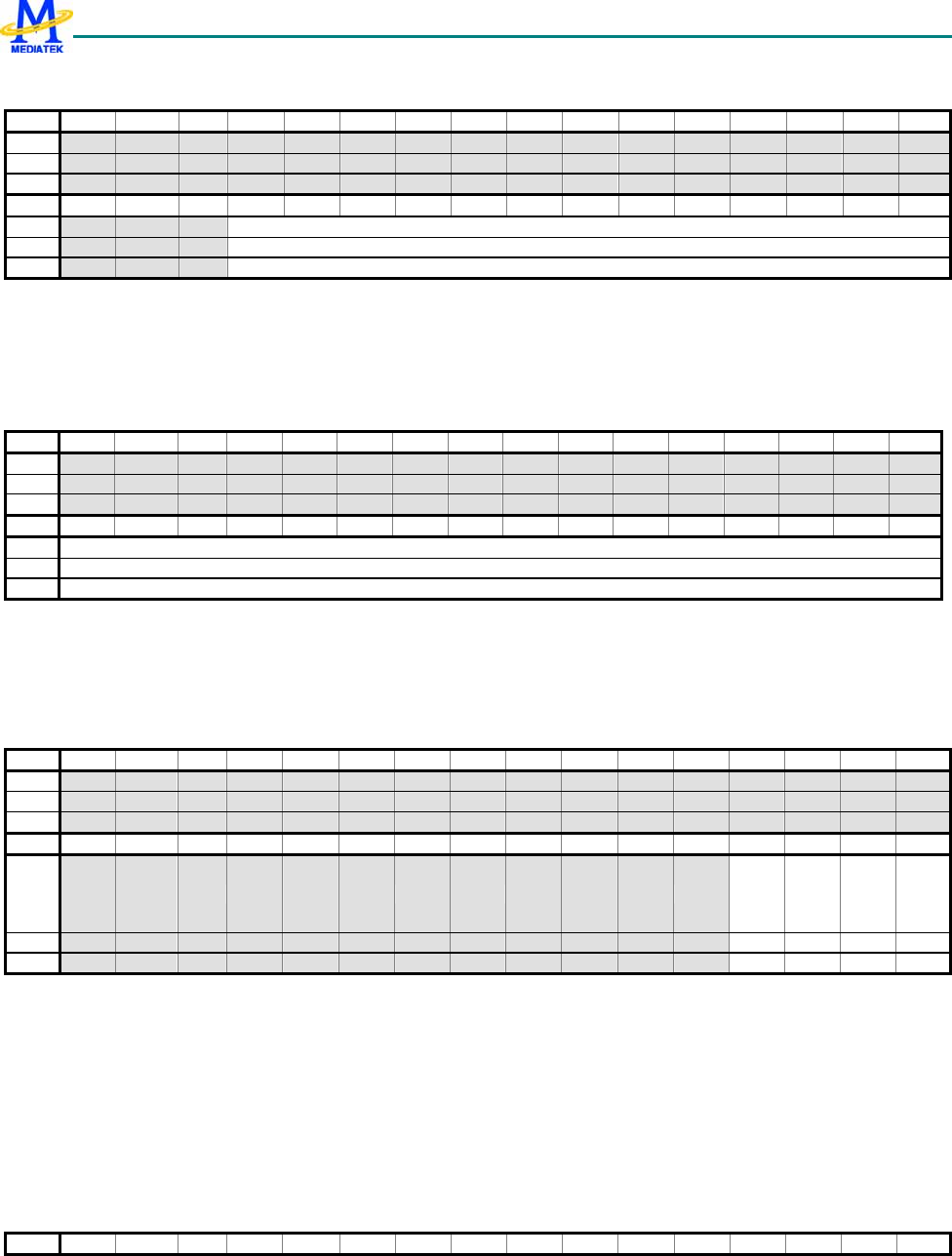

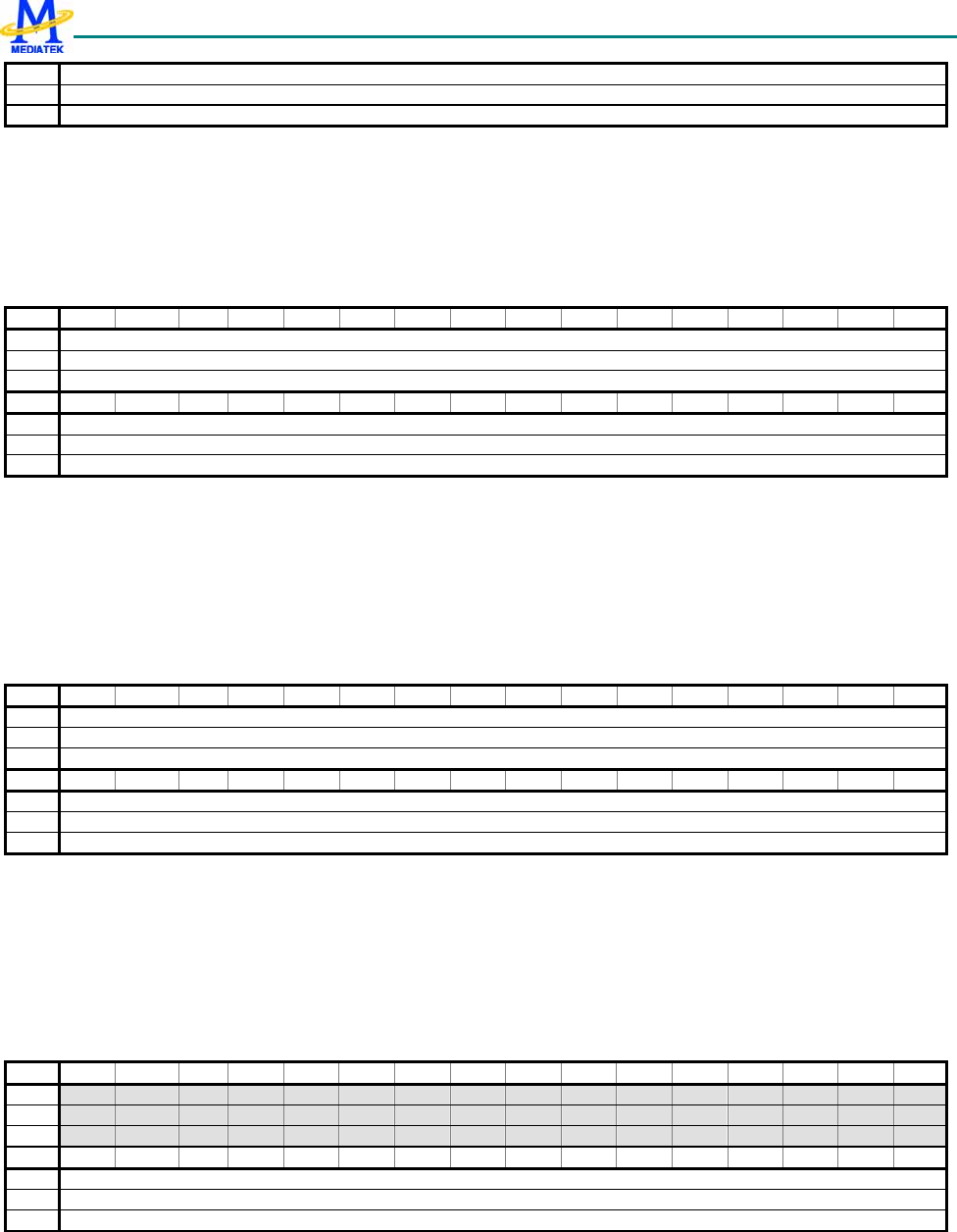

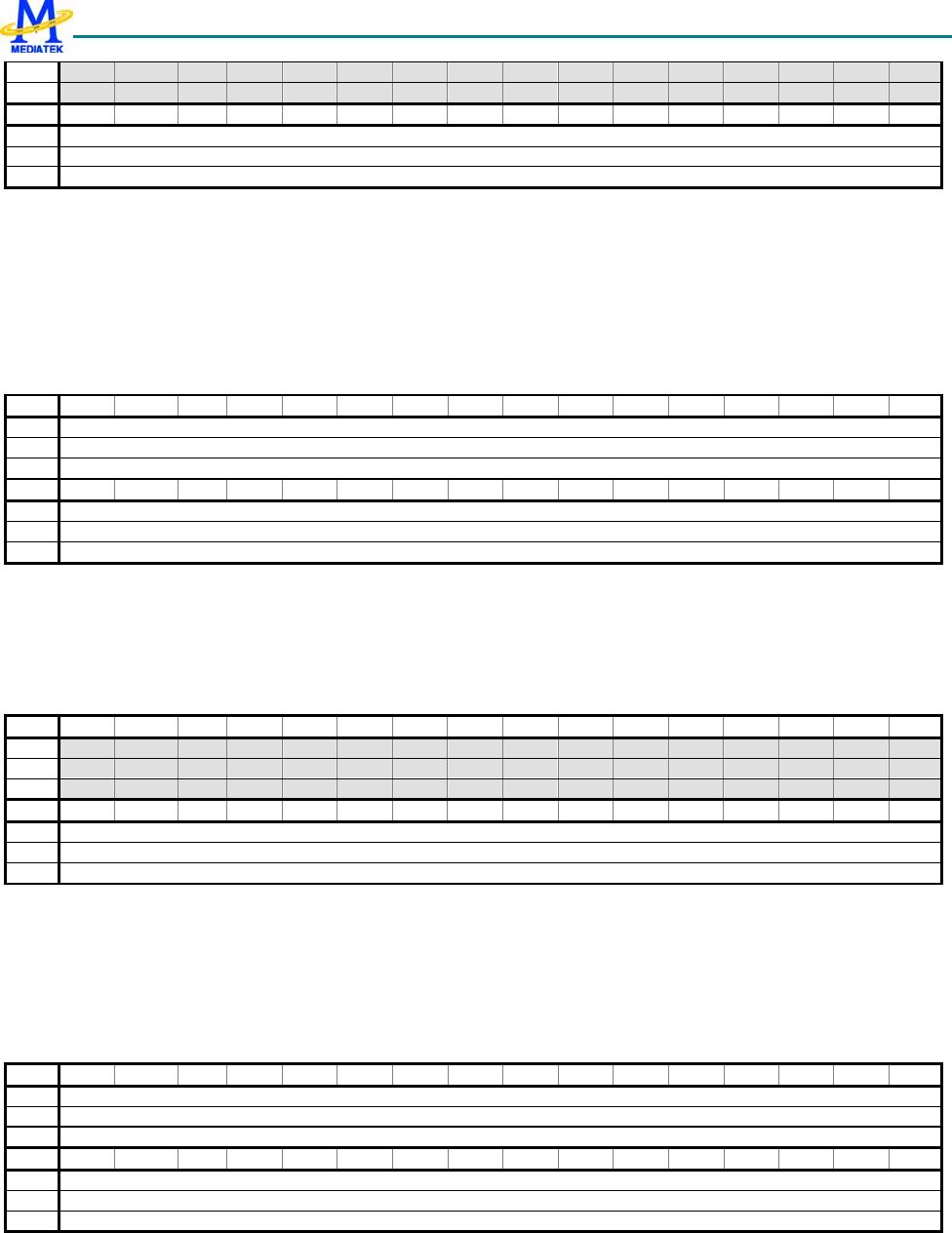

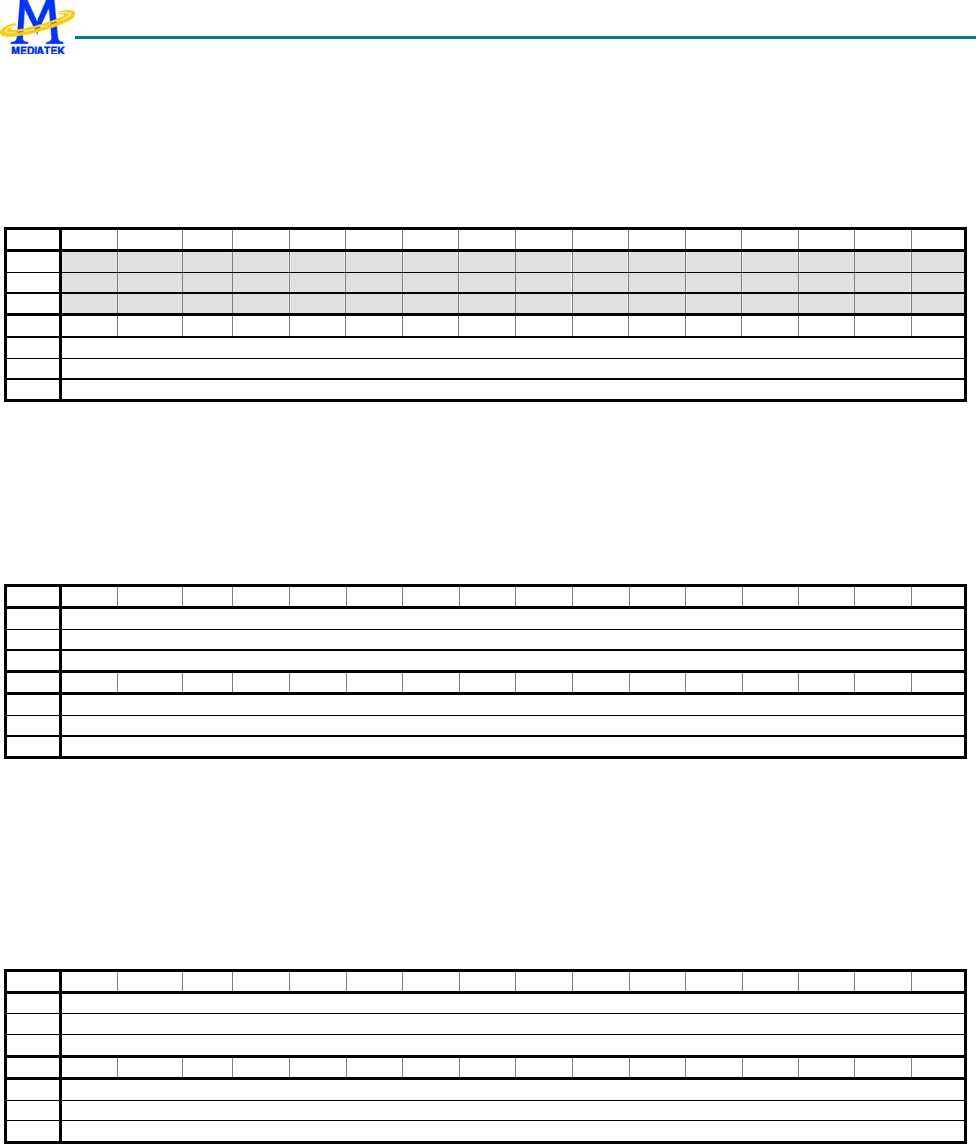

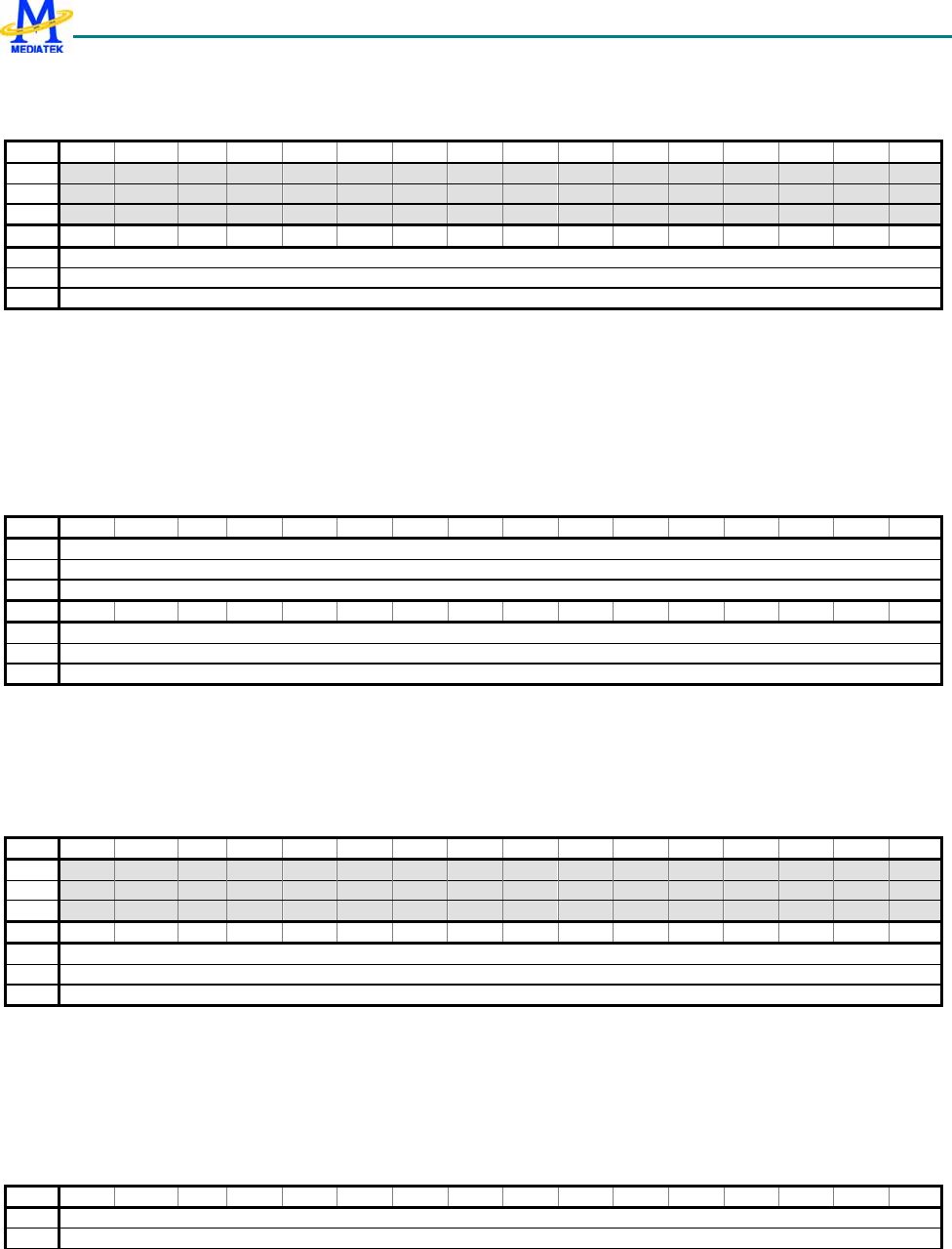

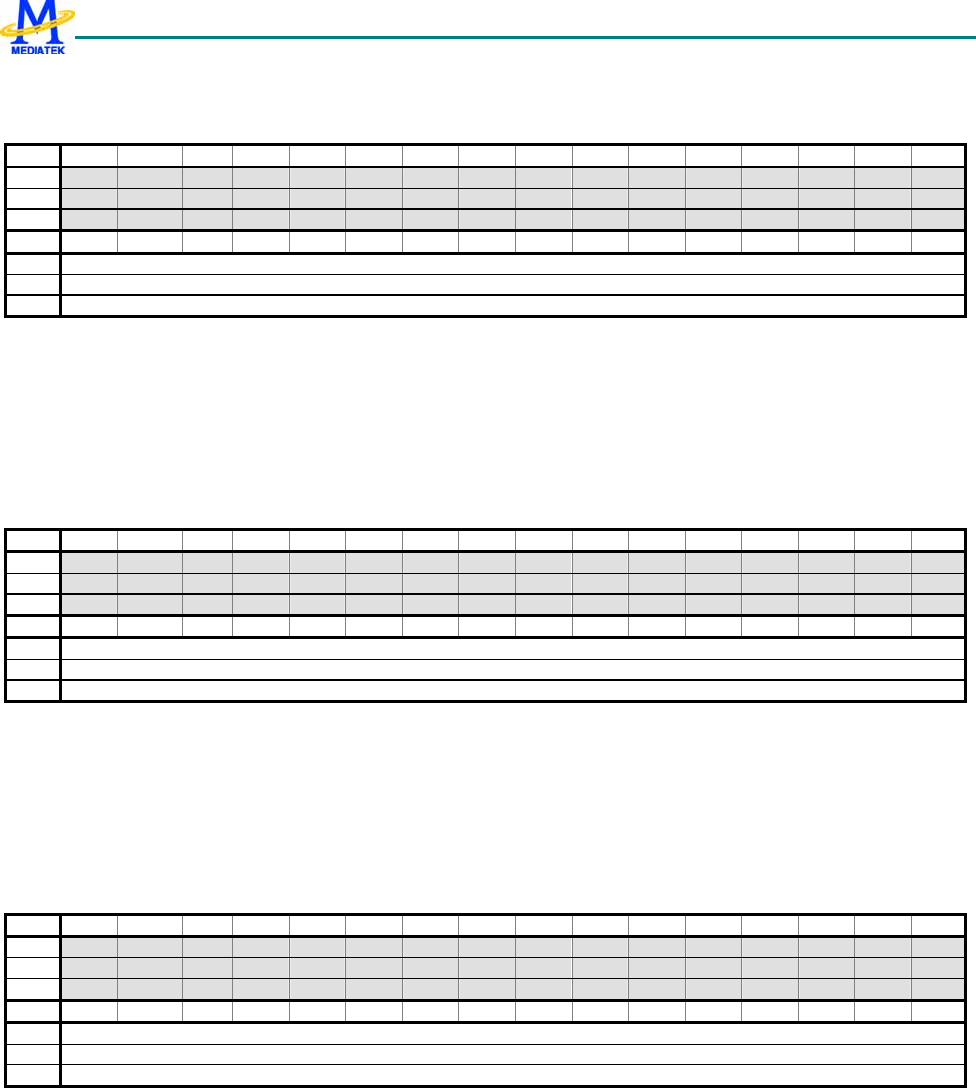

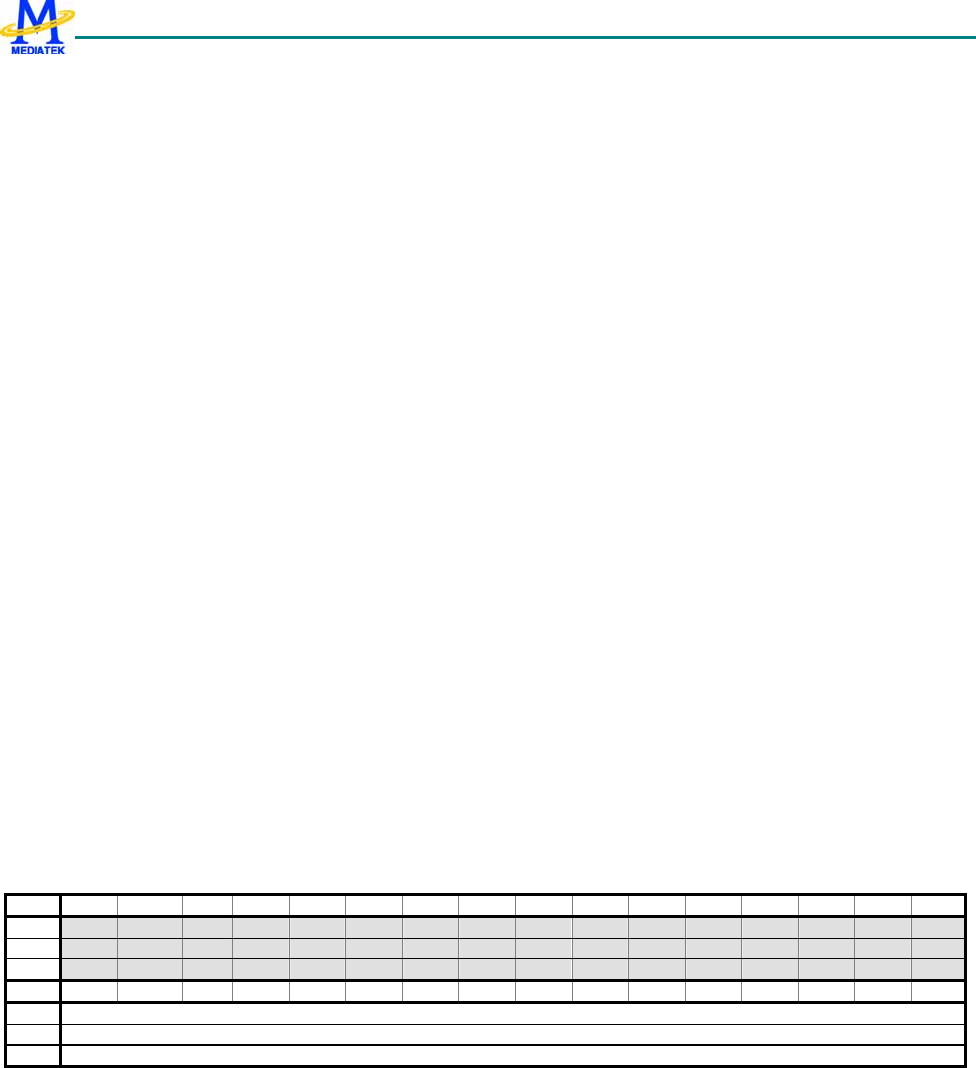

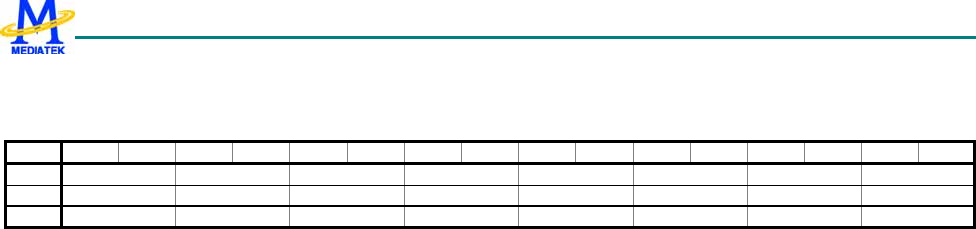

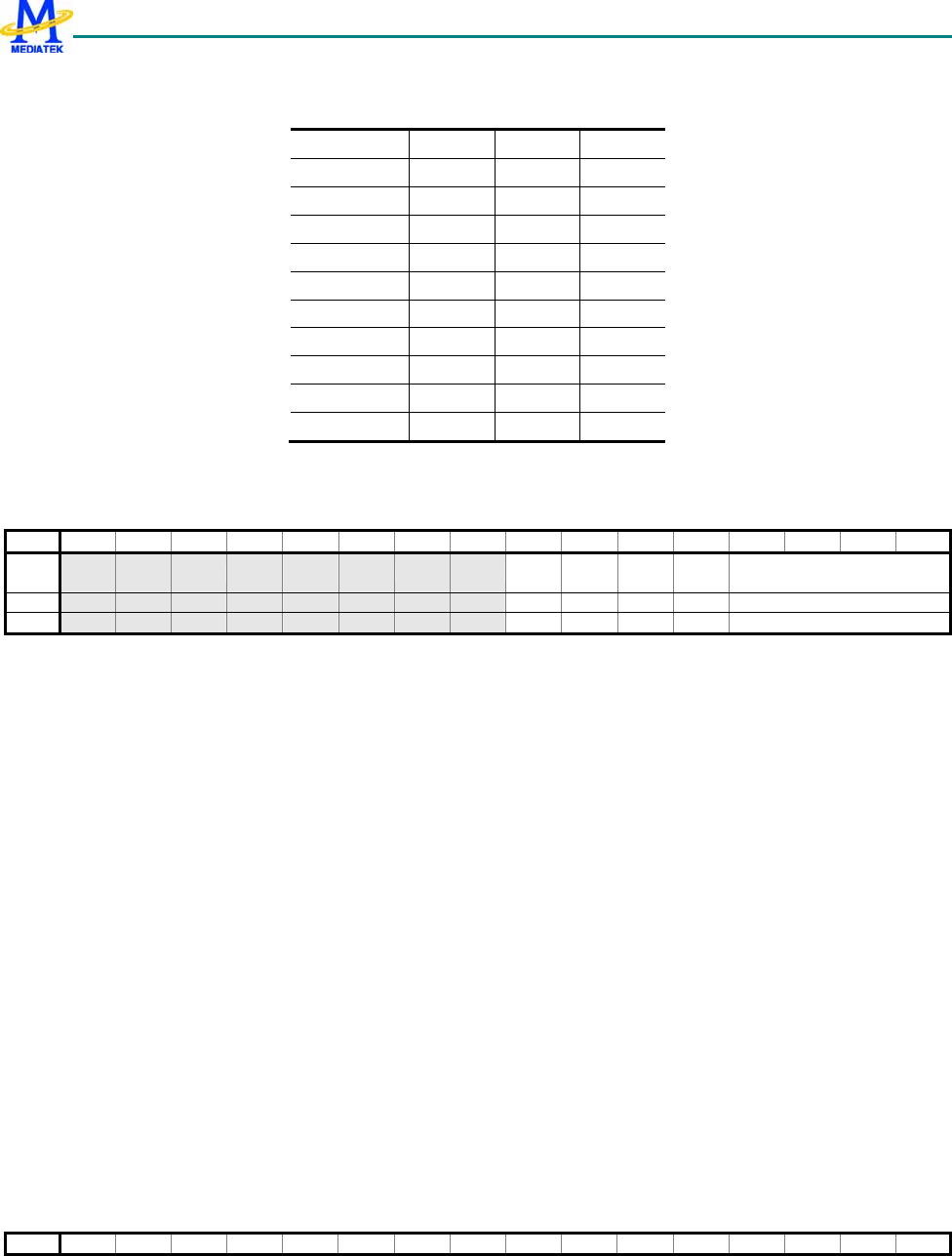

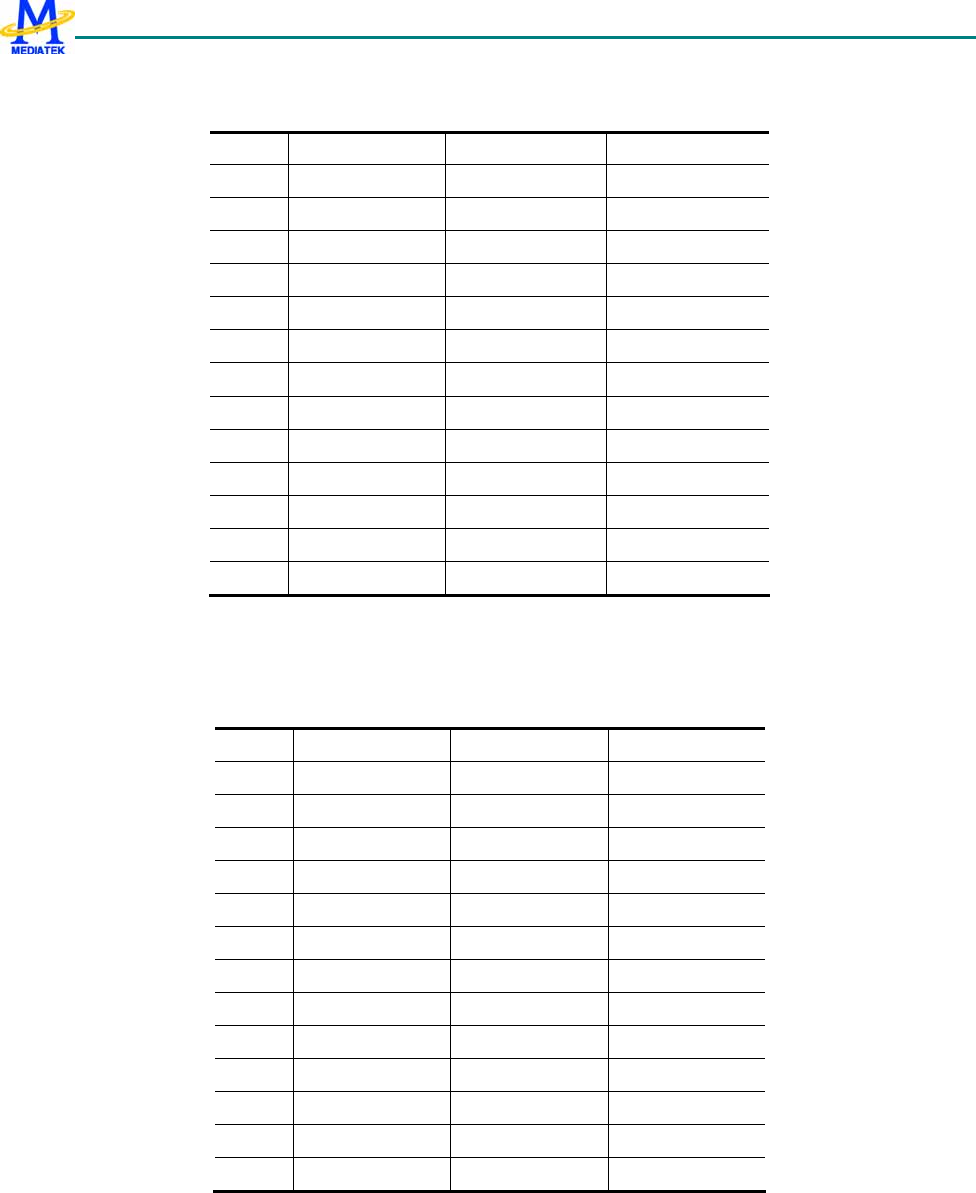

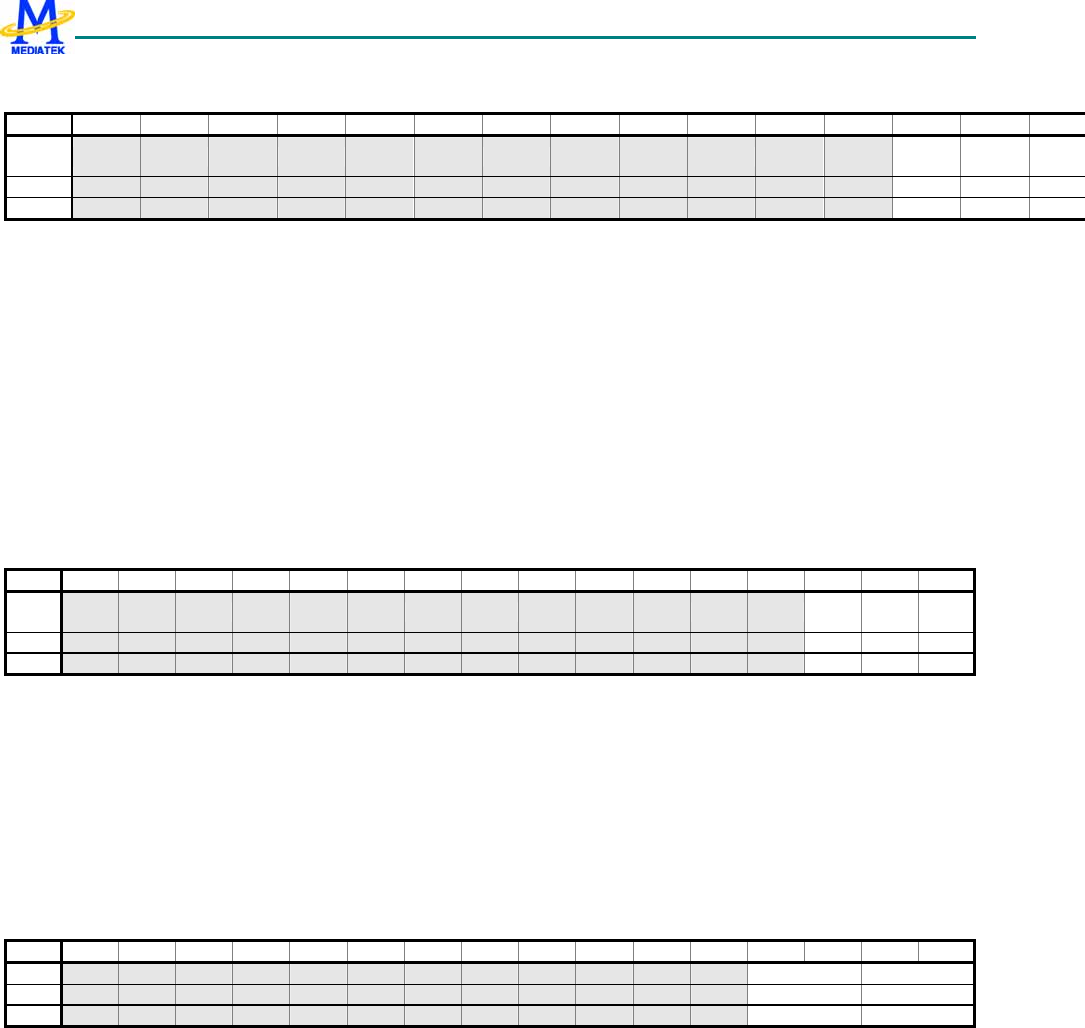

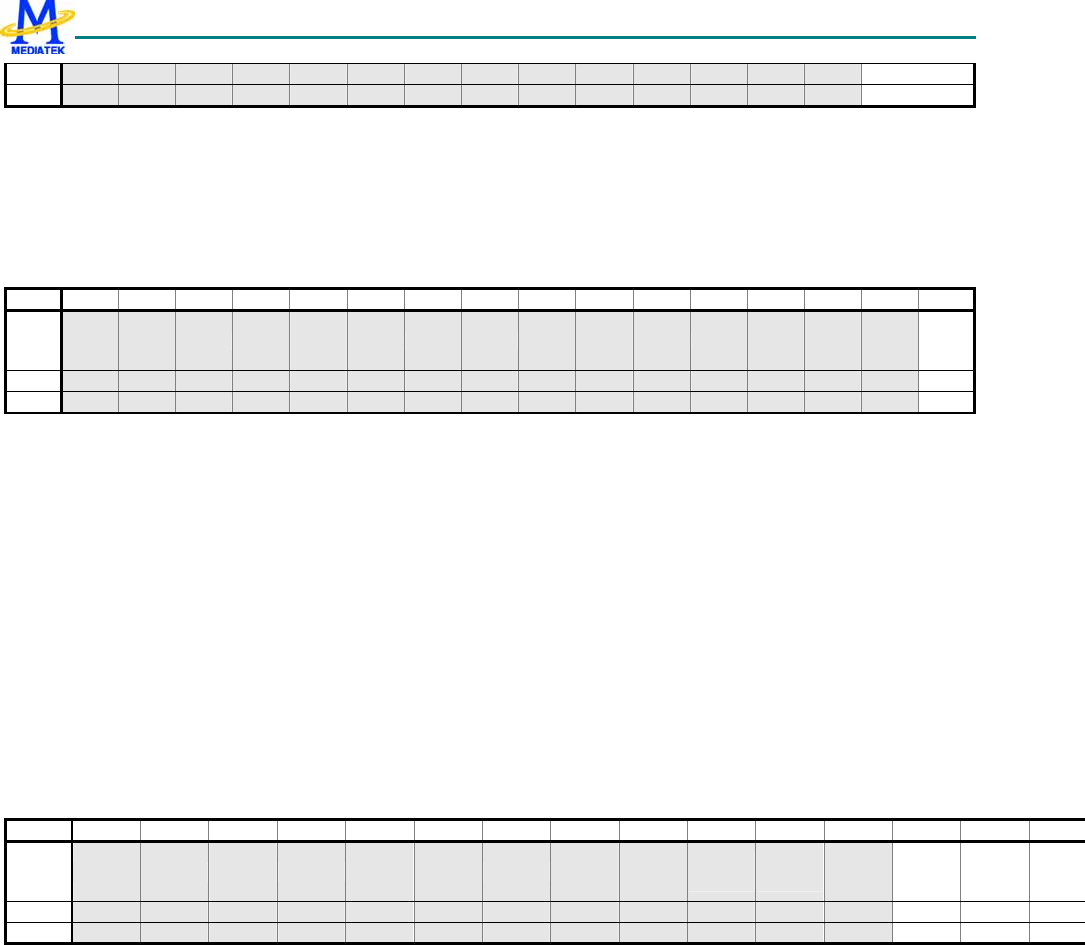

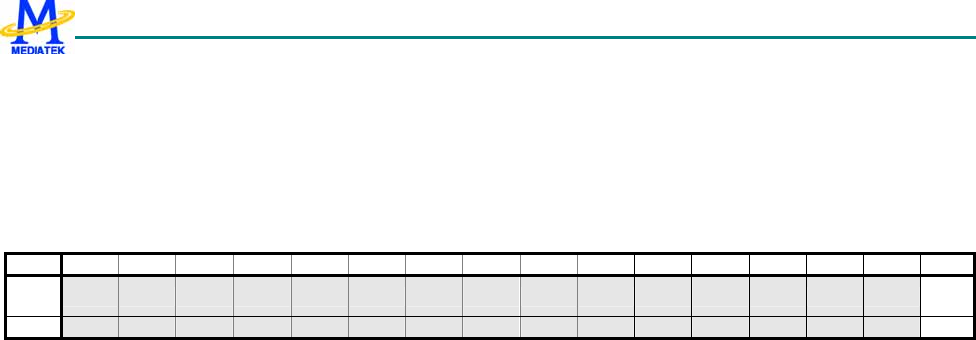

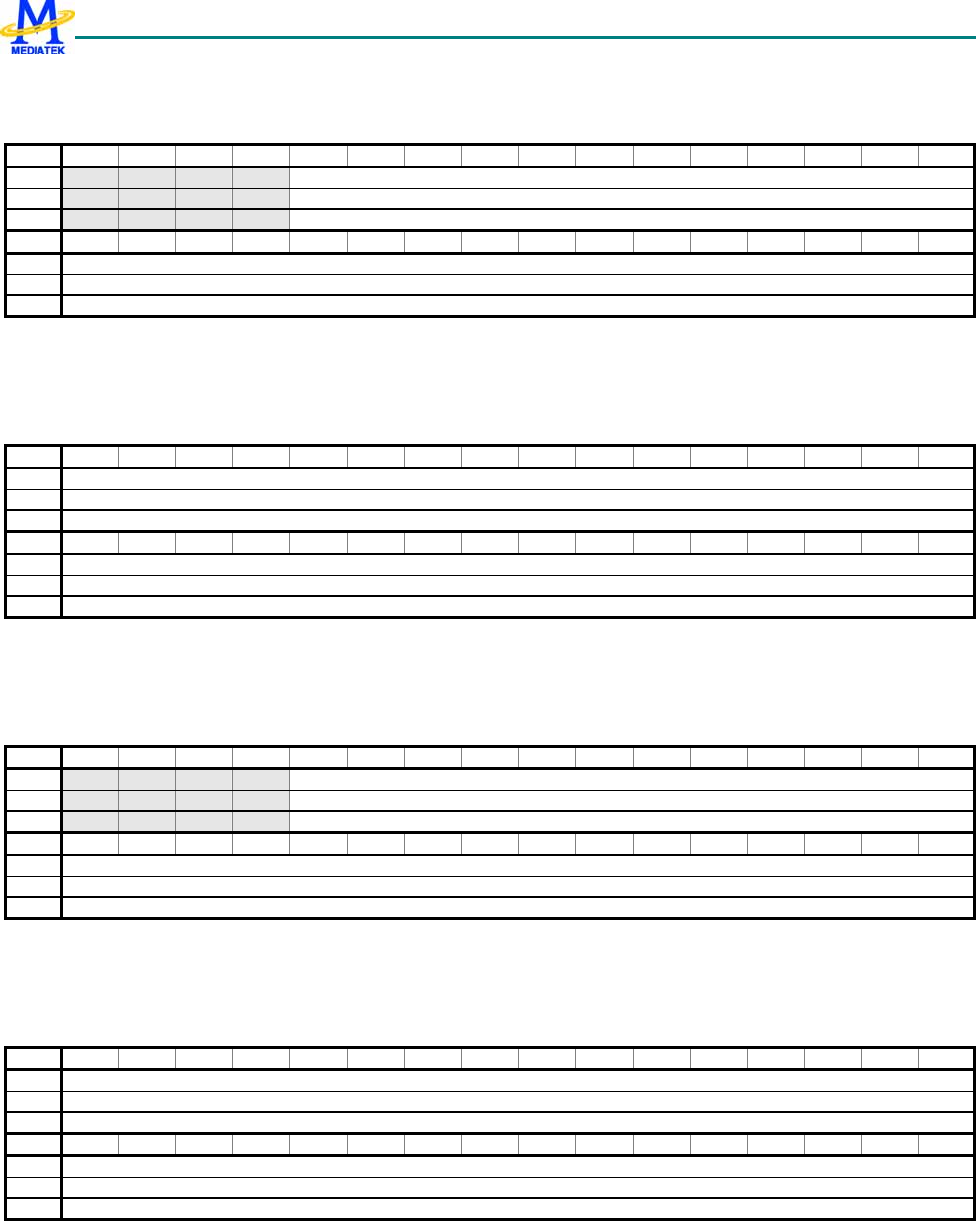

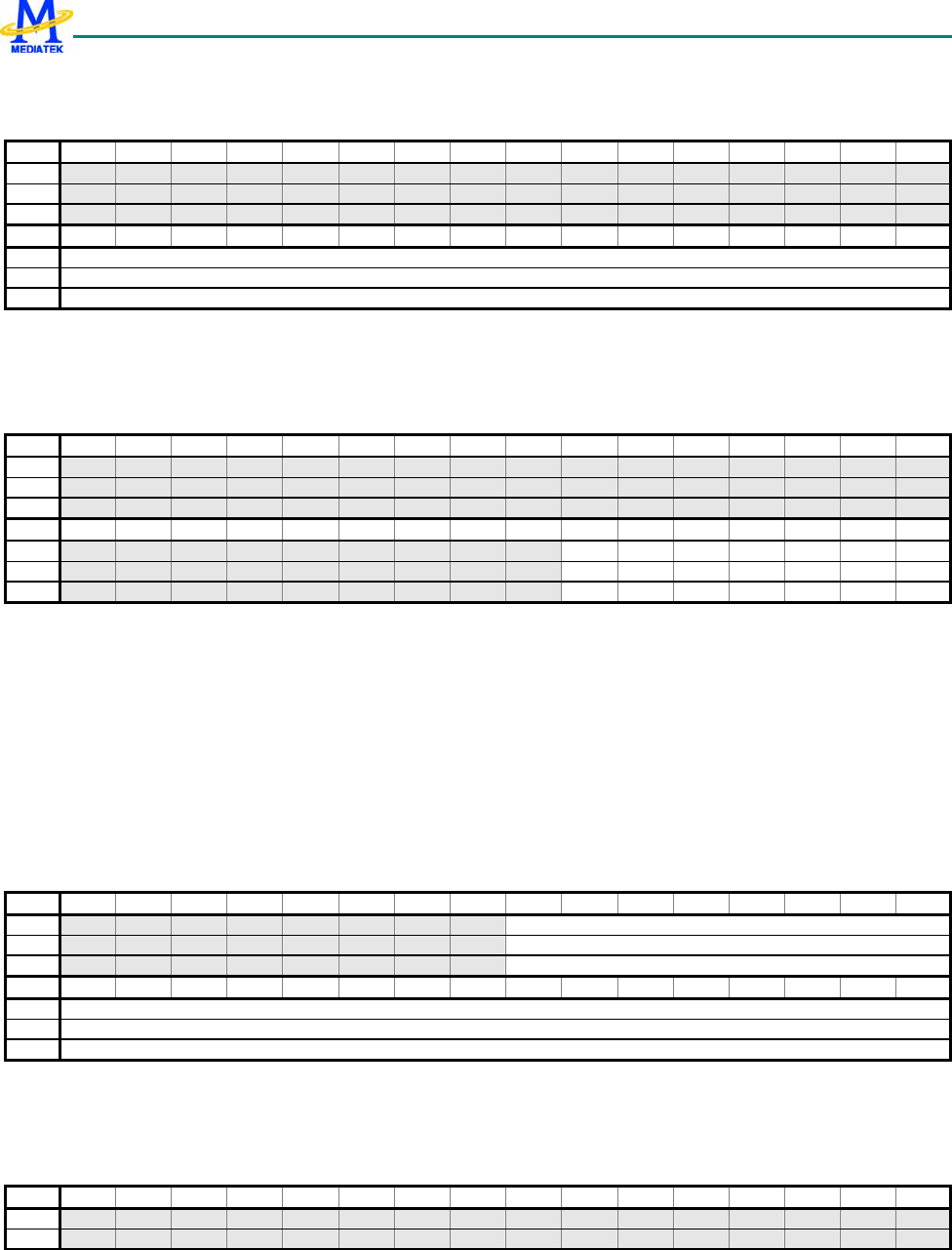

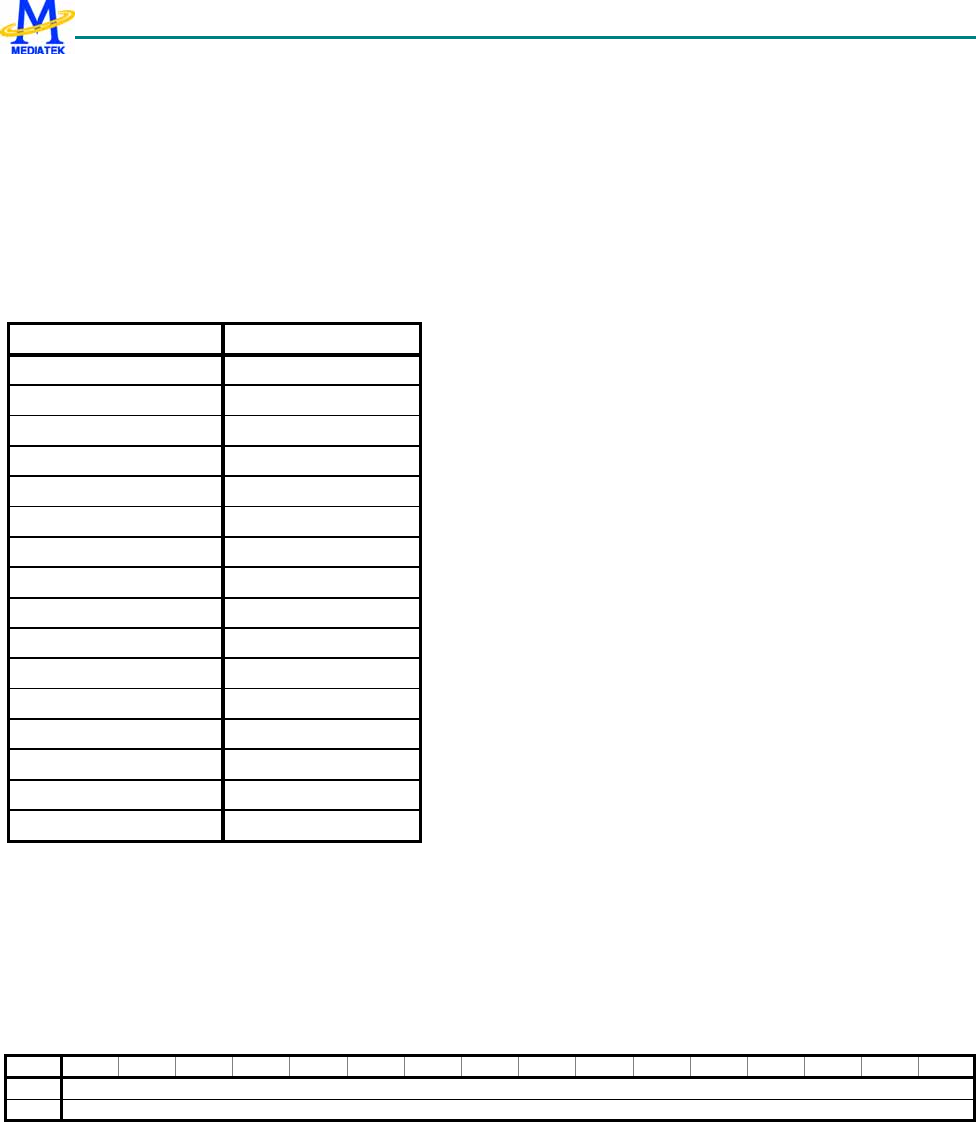

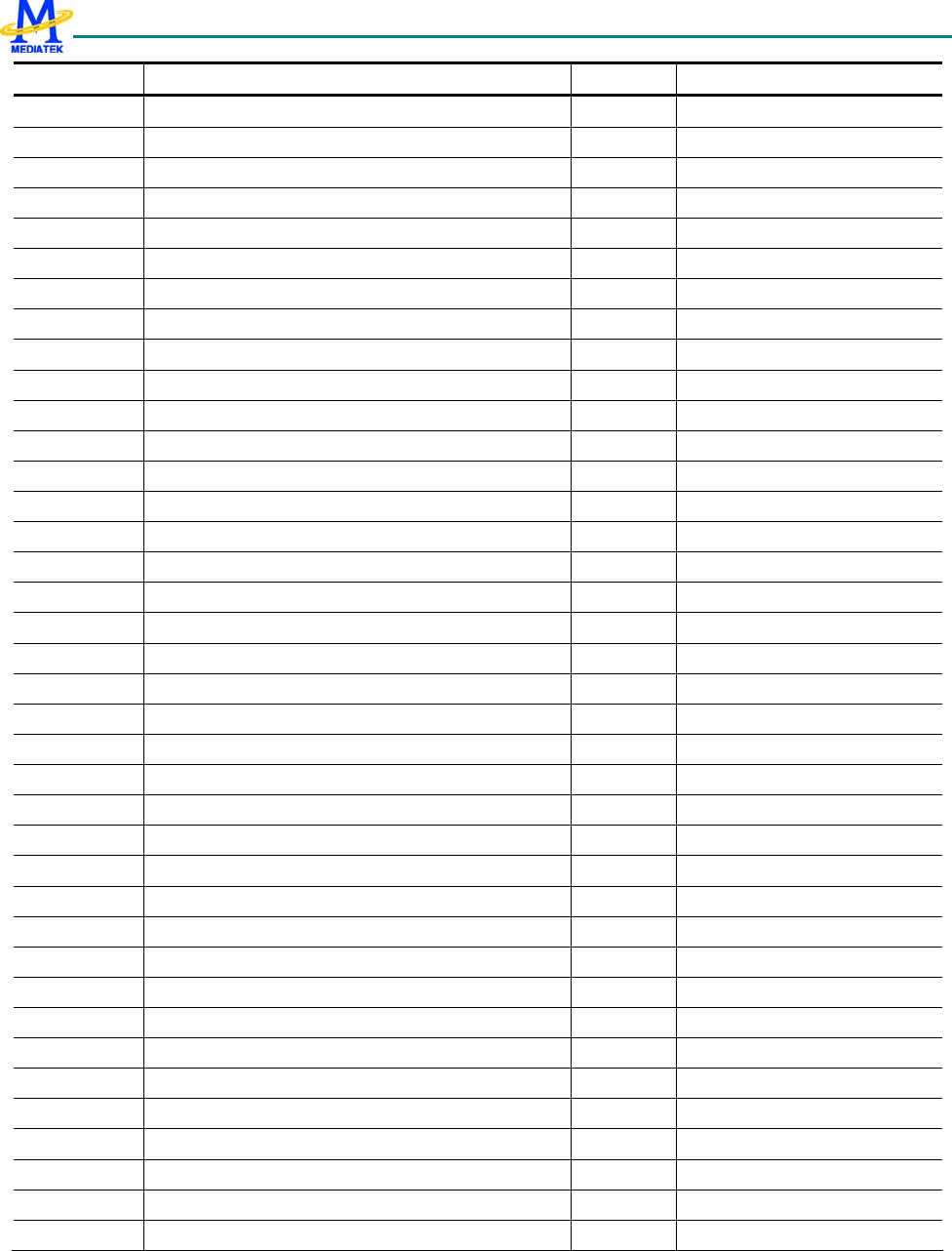

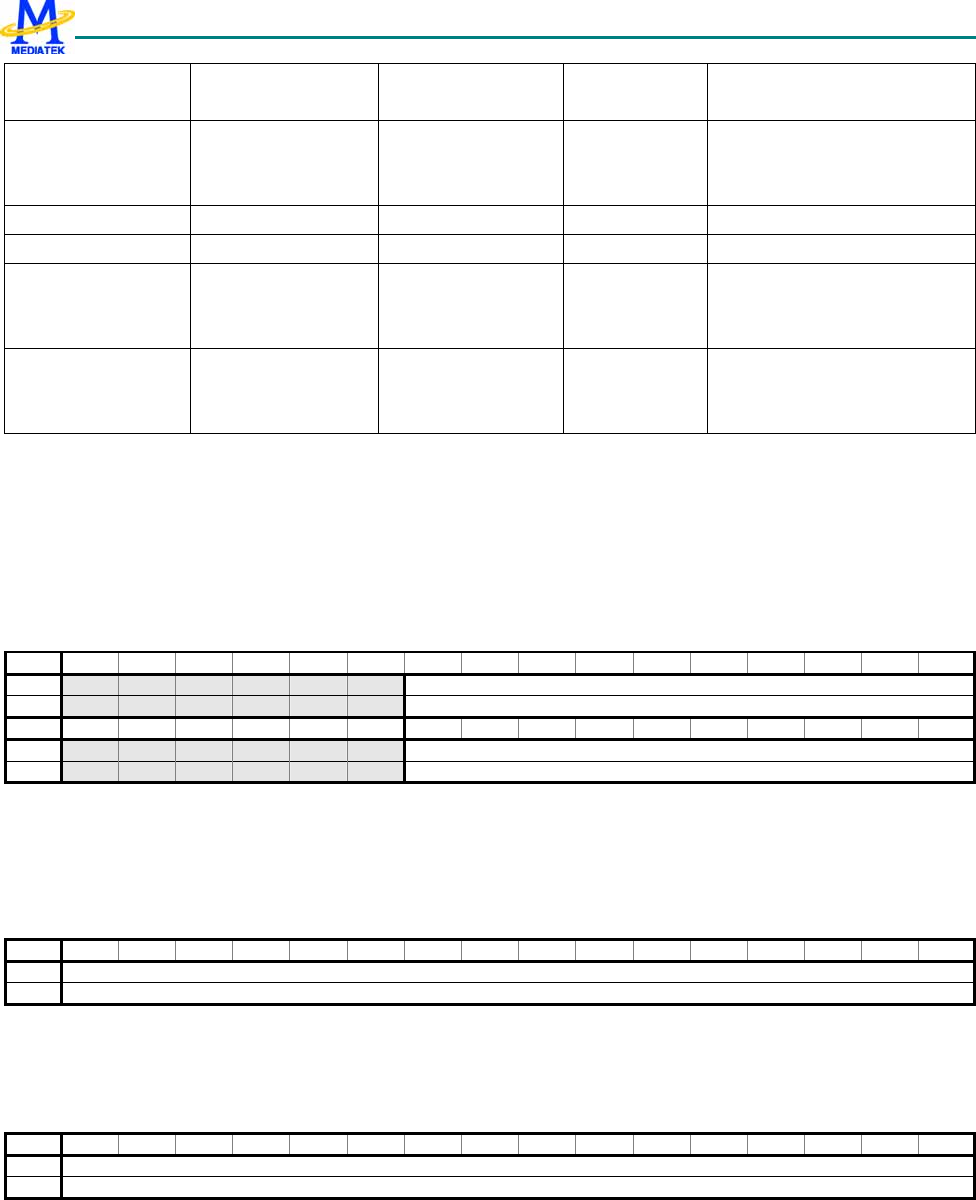

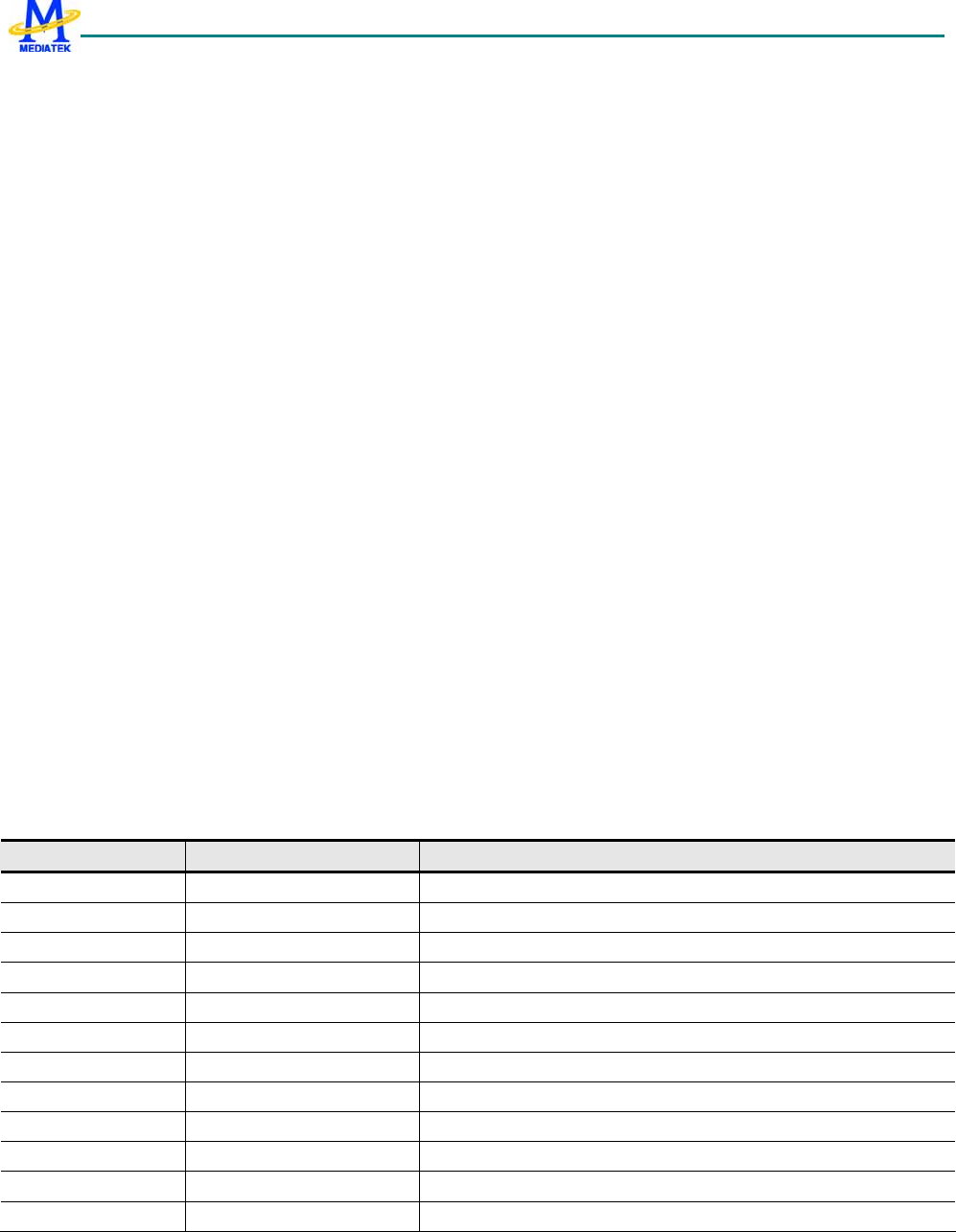

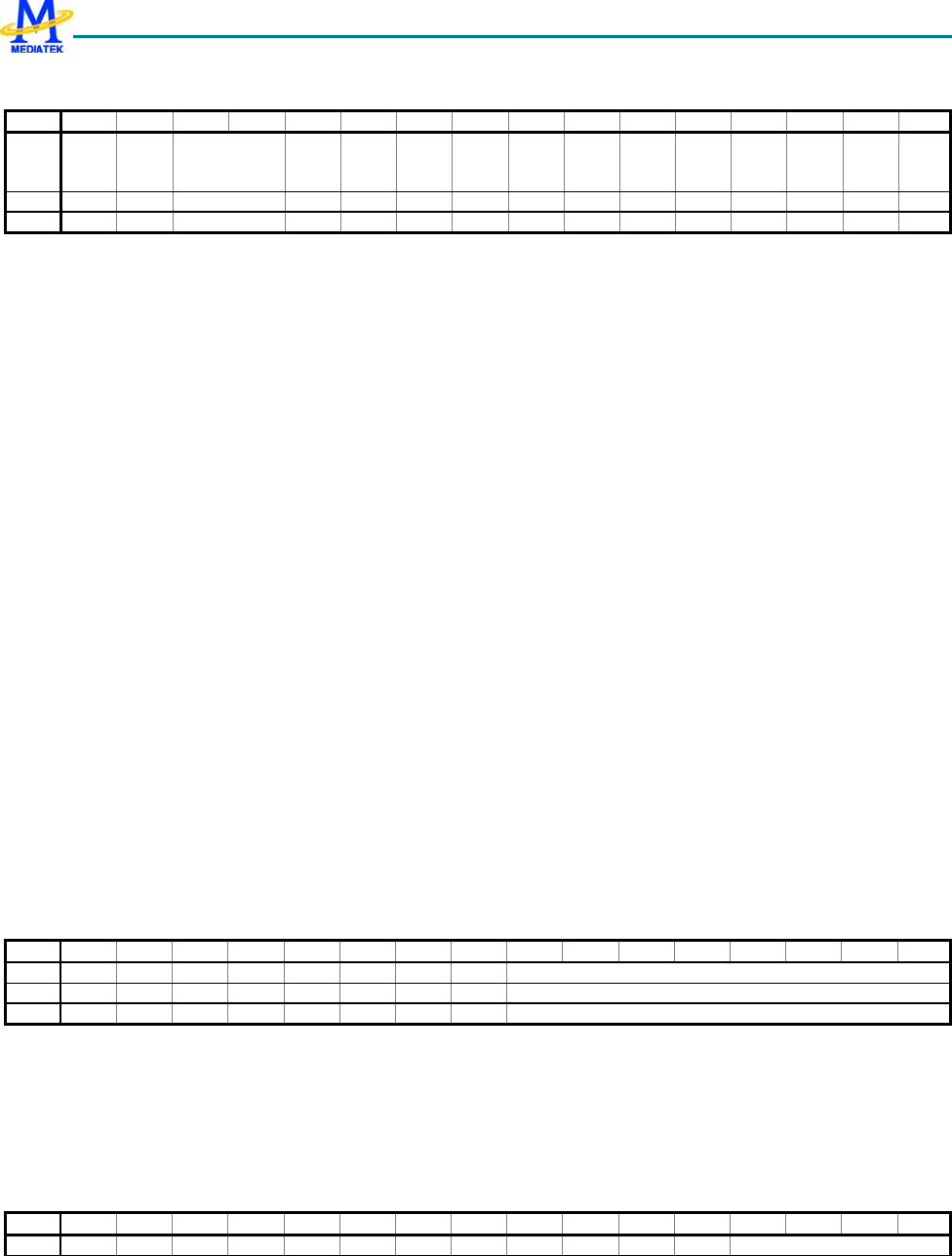

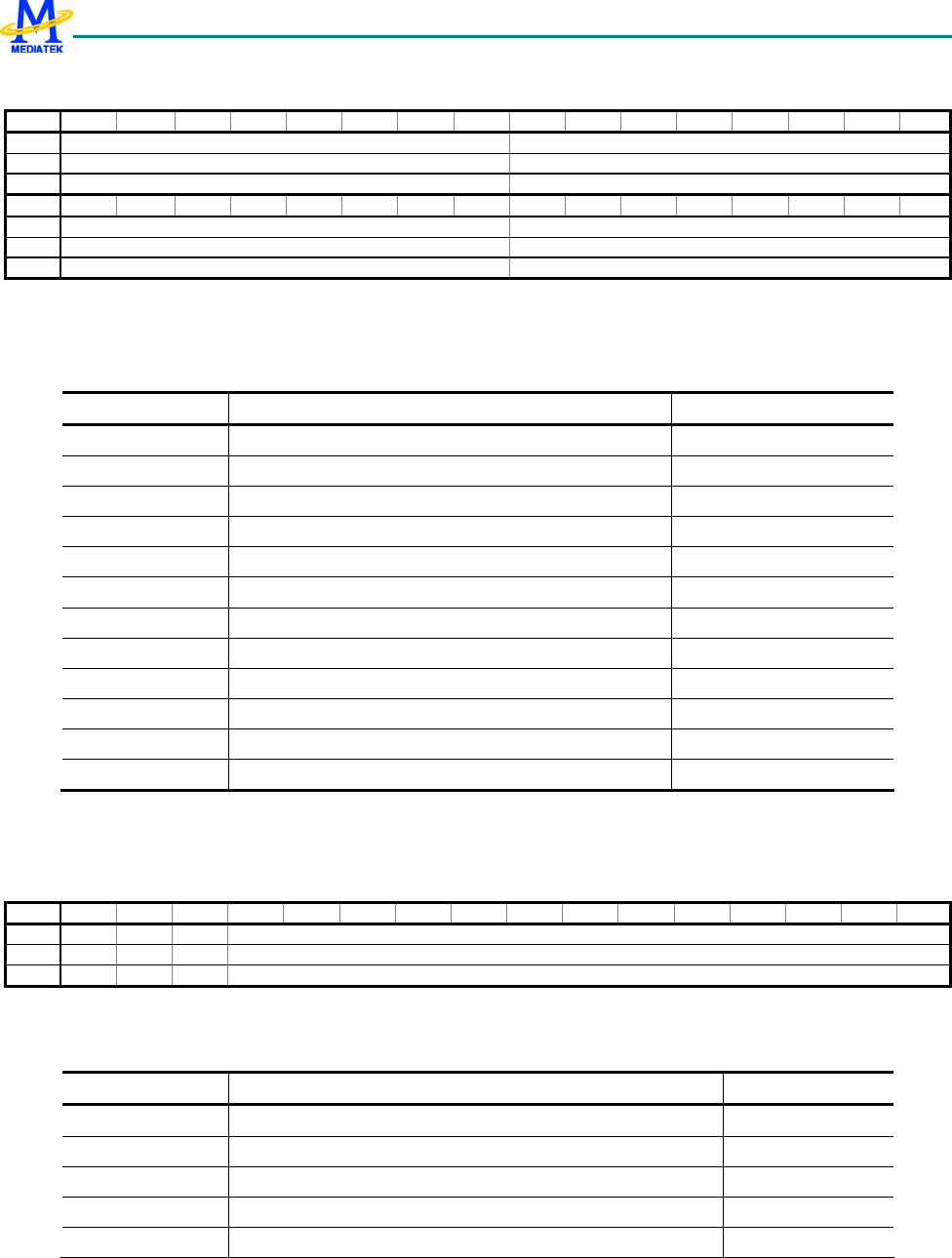

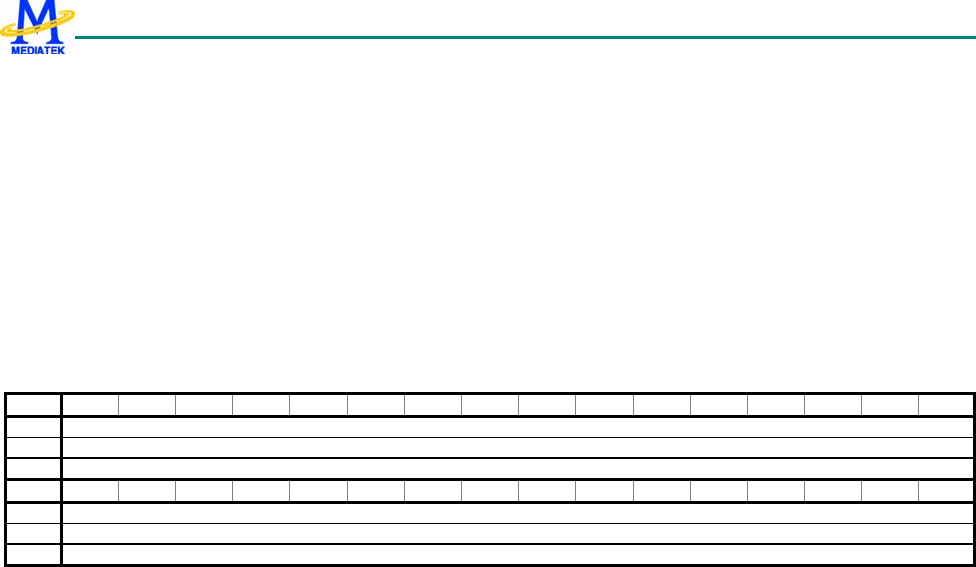

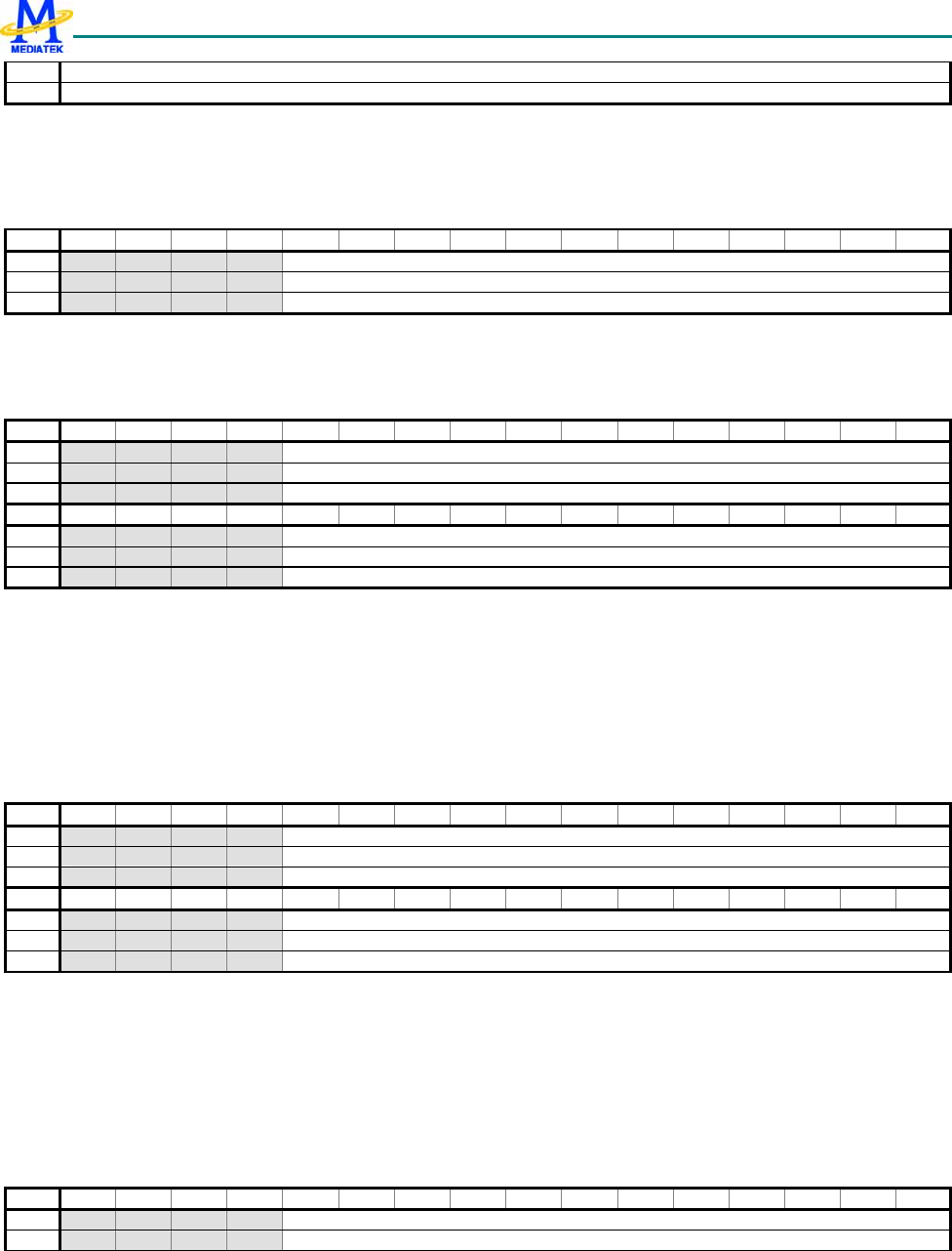

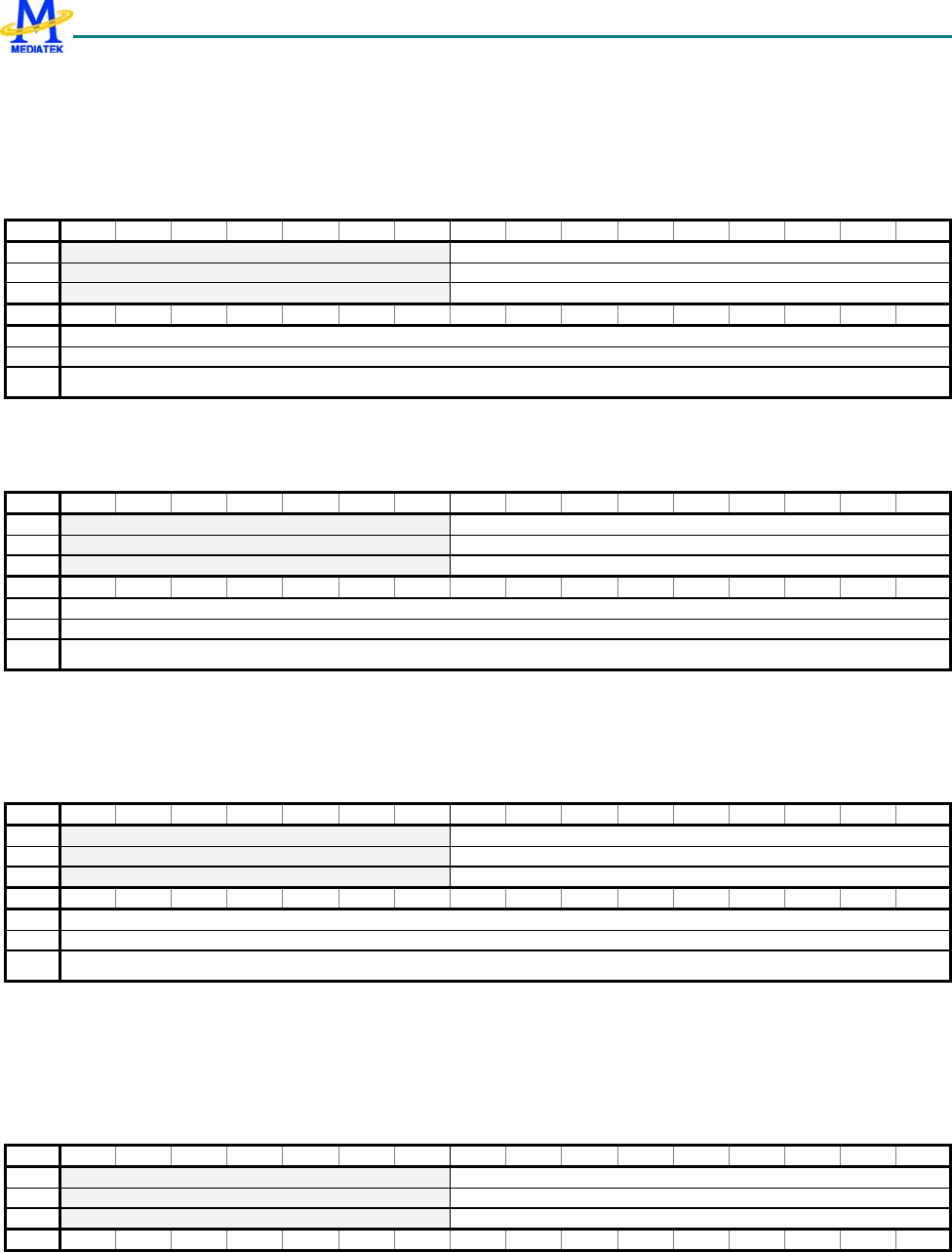

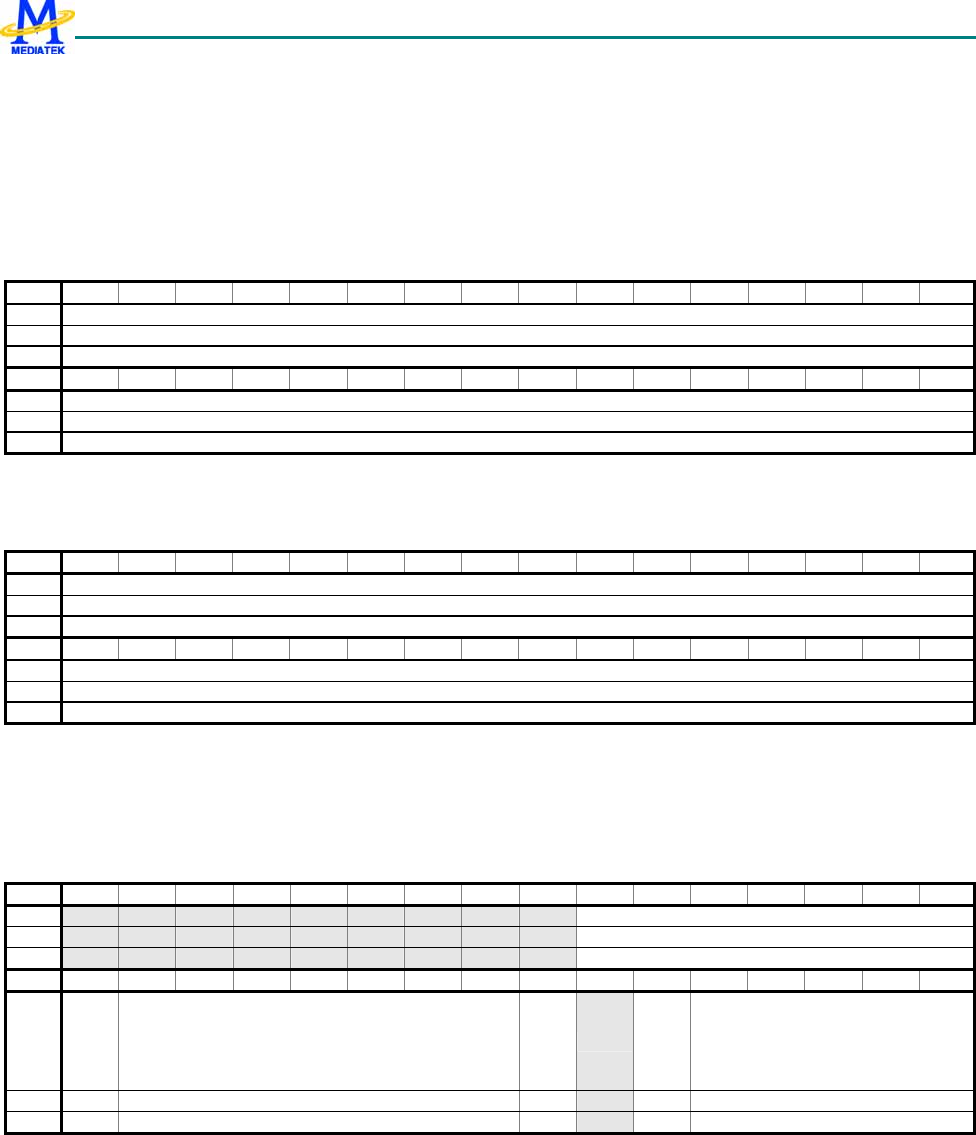

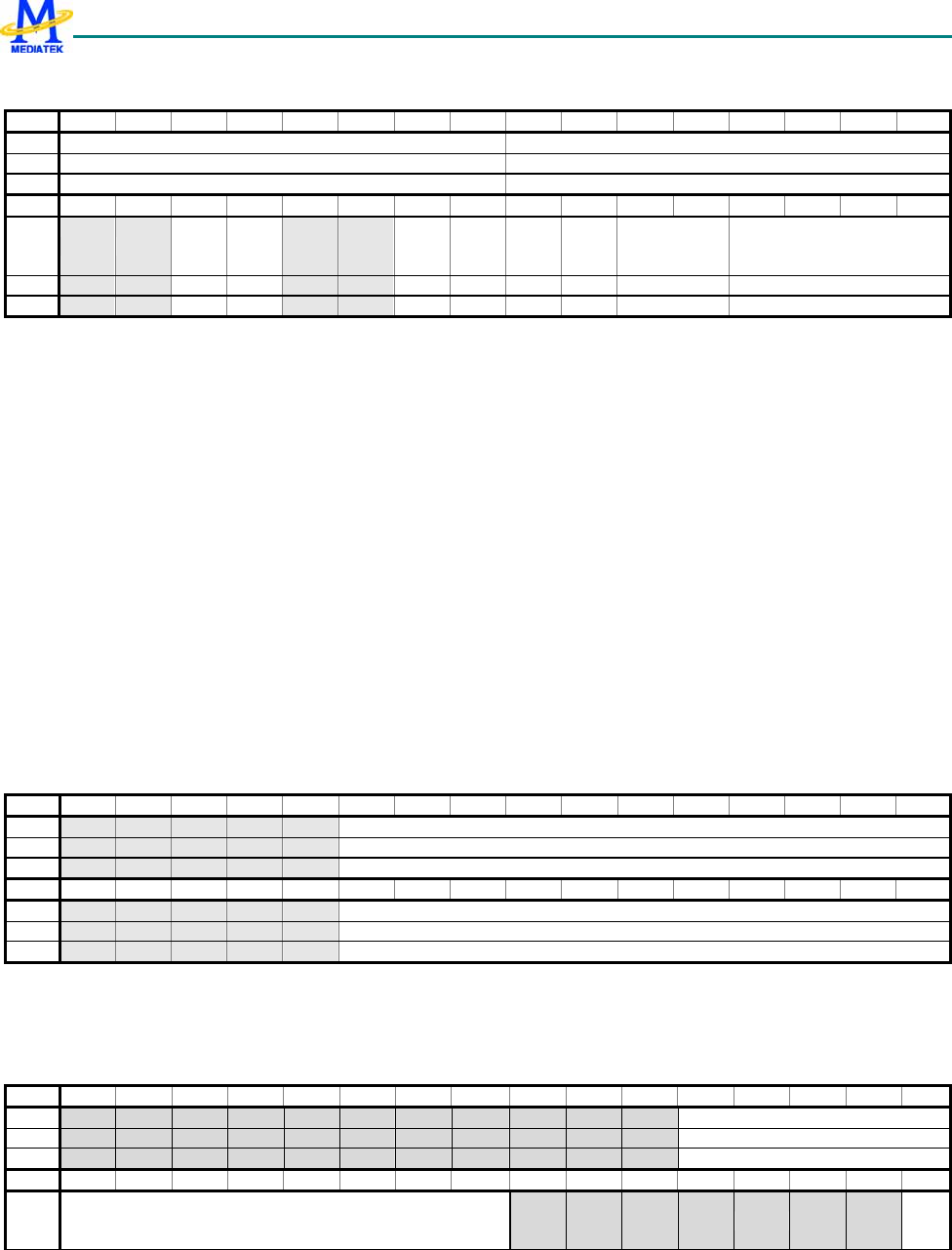

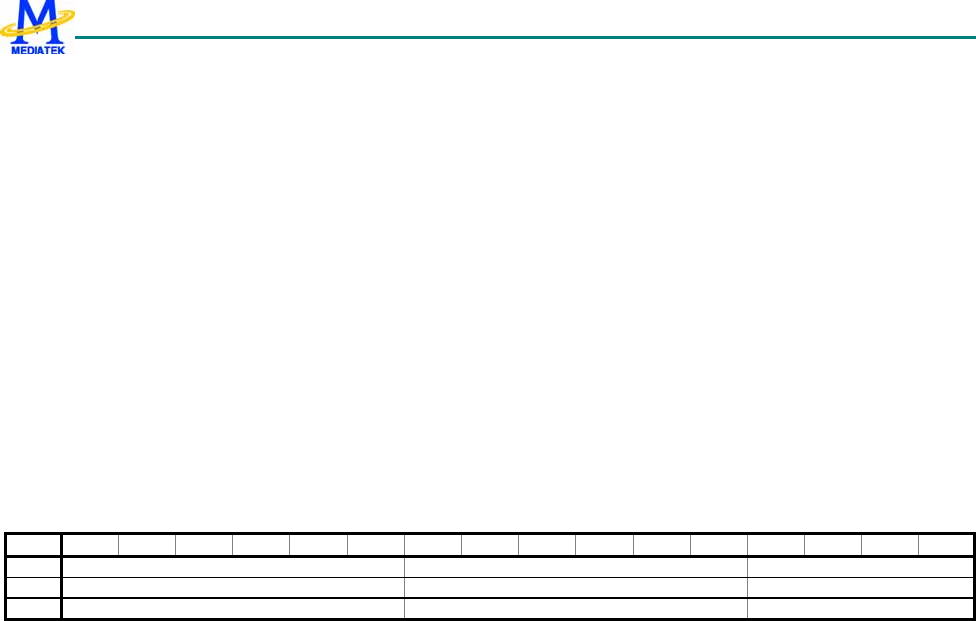

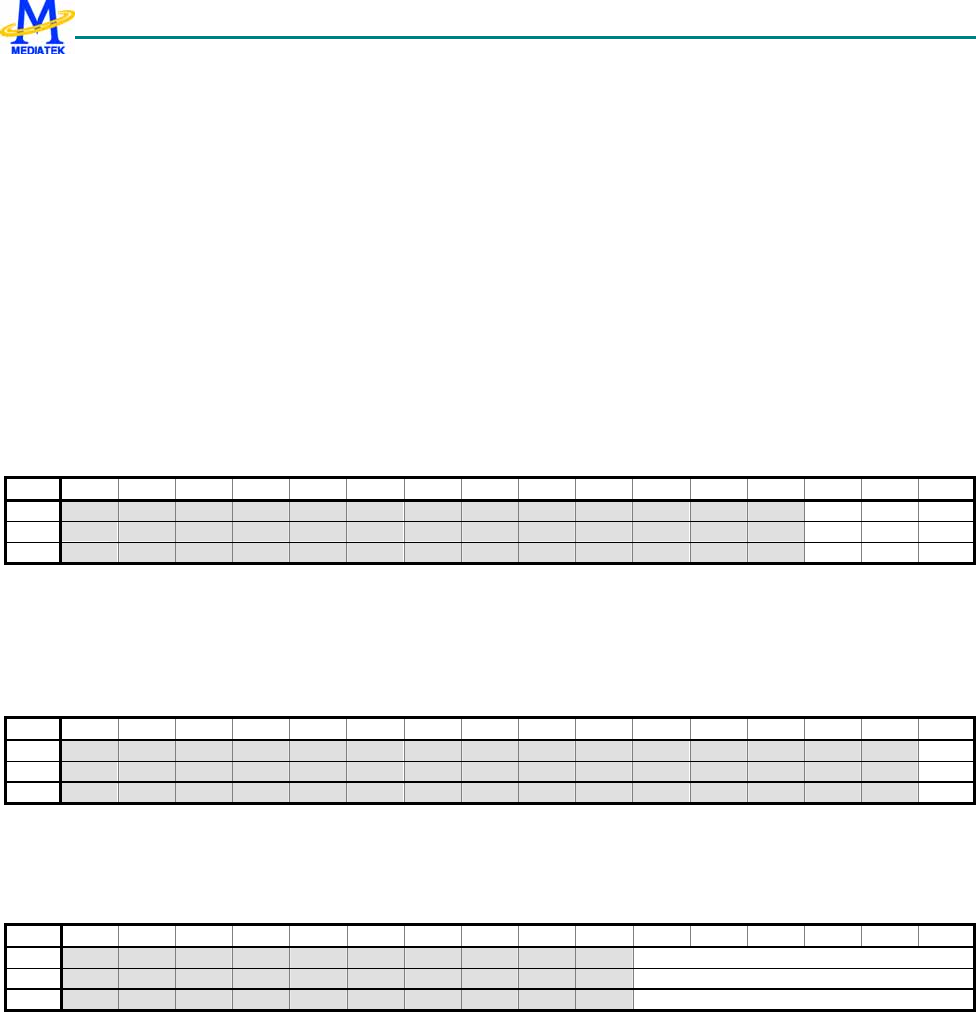

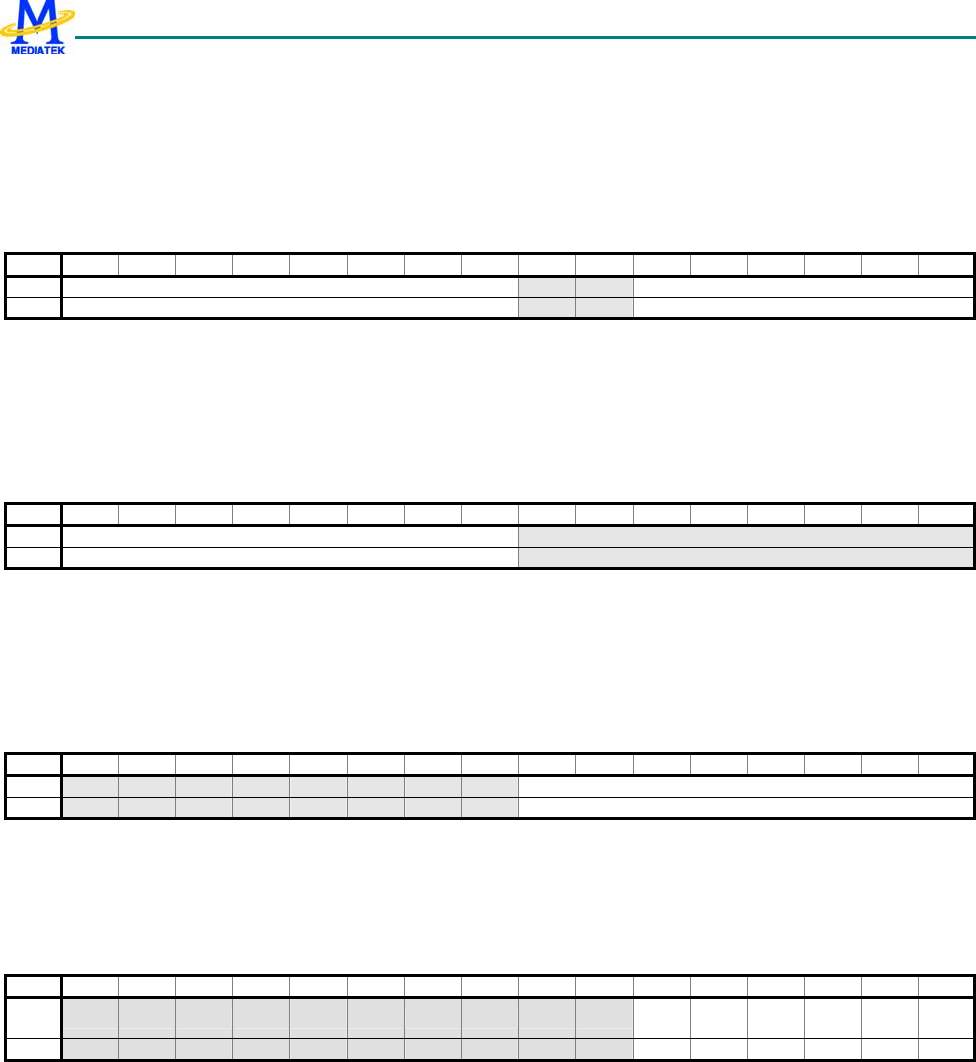

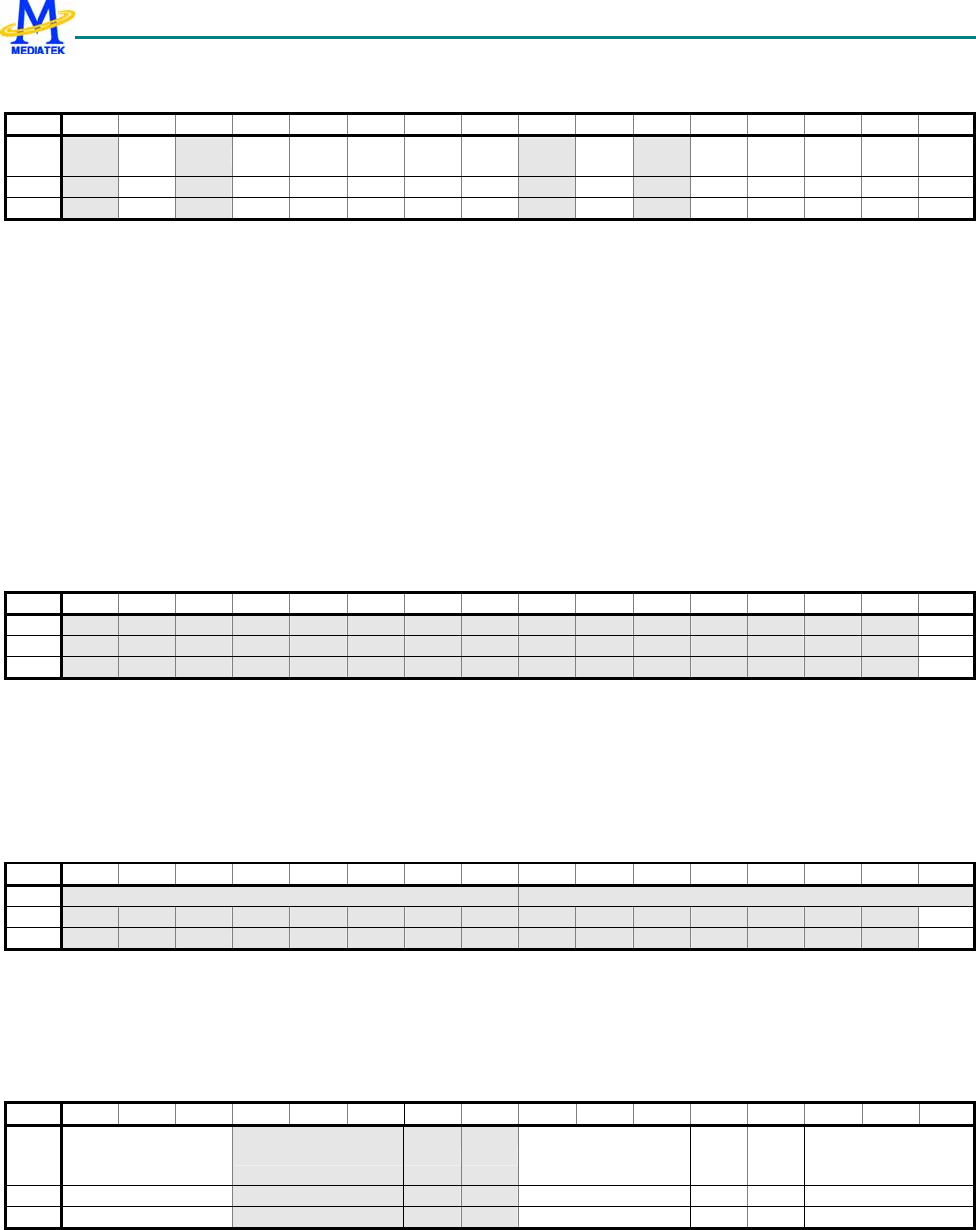

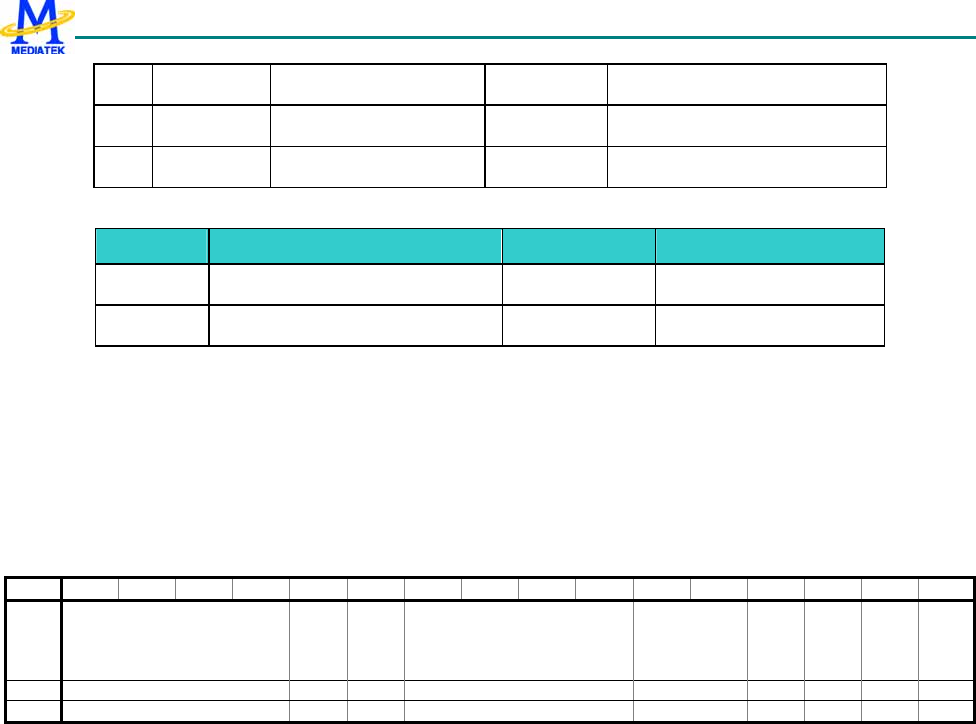

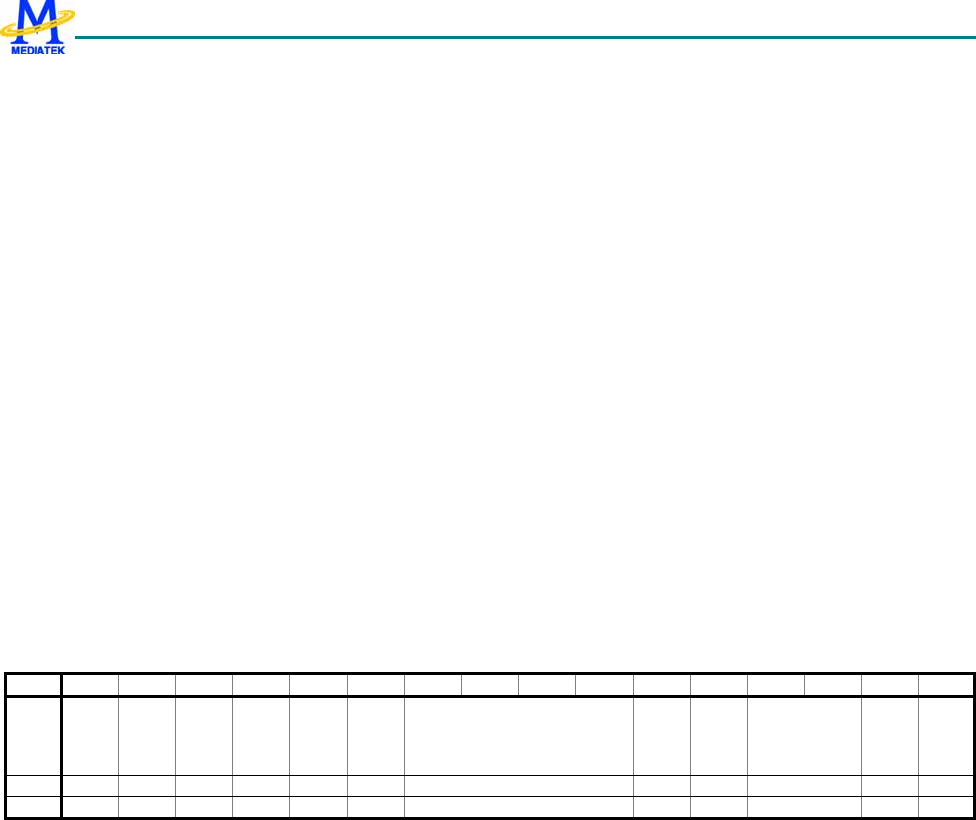

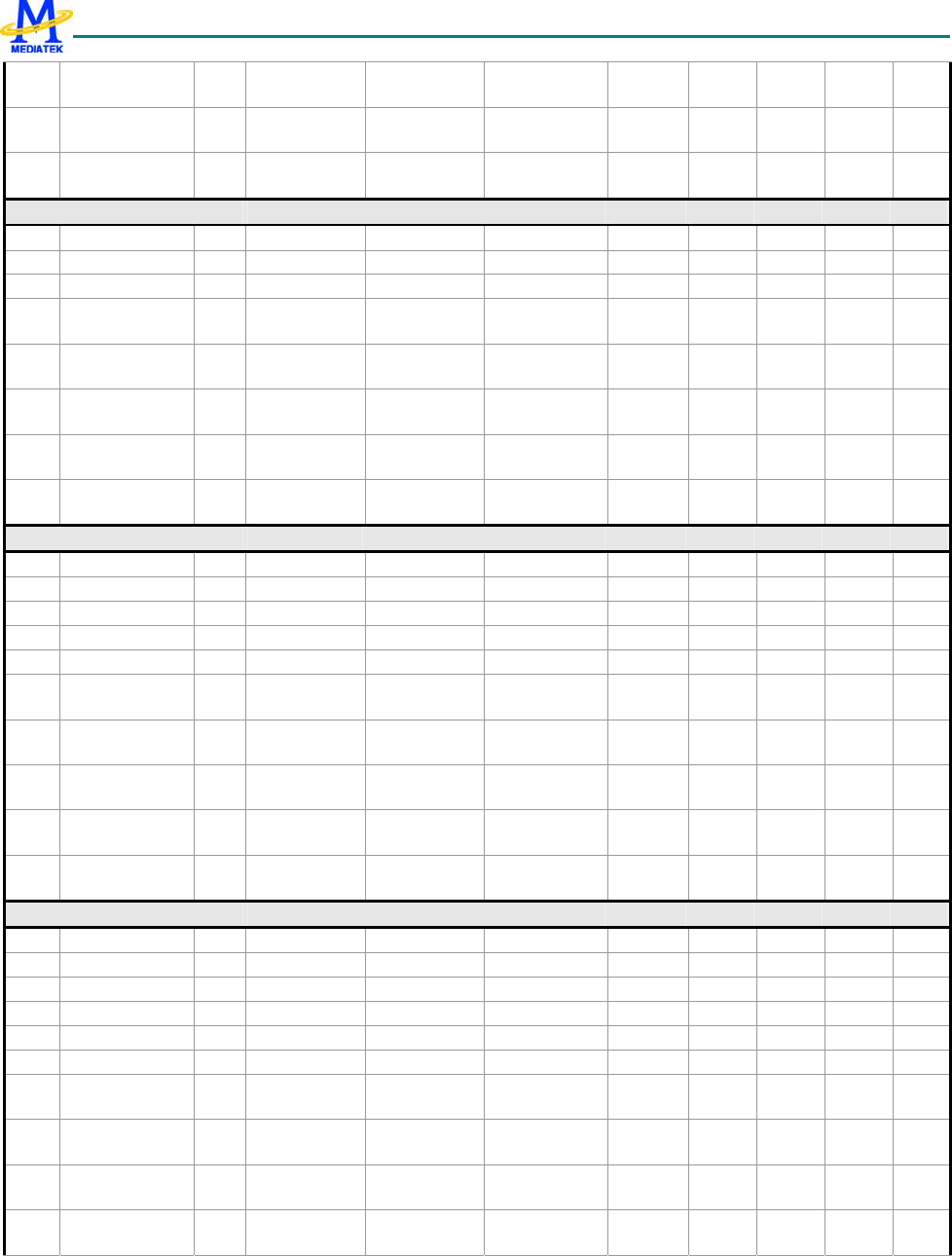

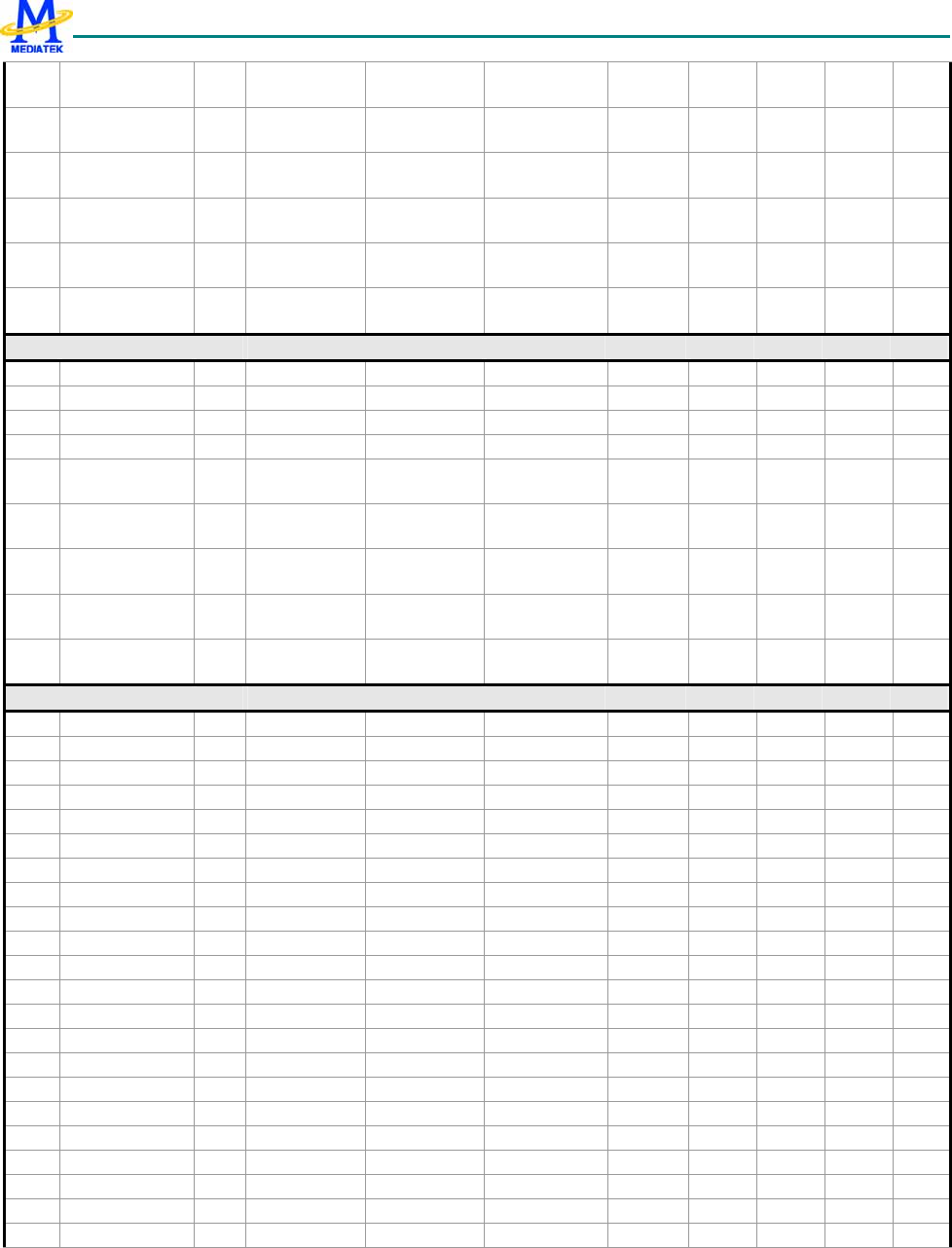

One type of package for this product, TFBGA 13mm*13mm, 362-ball, 0.5 mm pitch package, is offered.

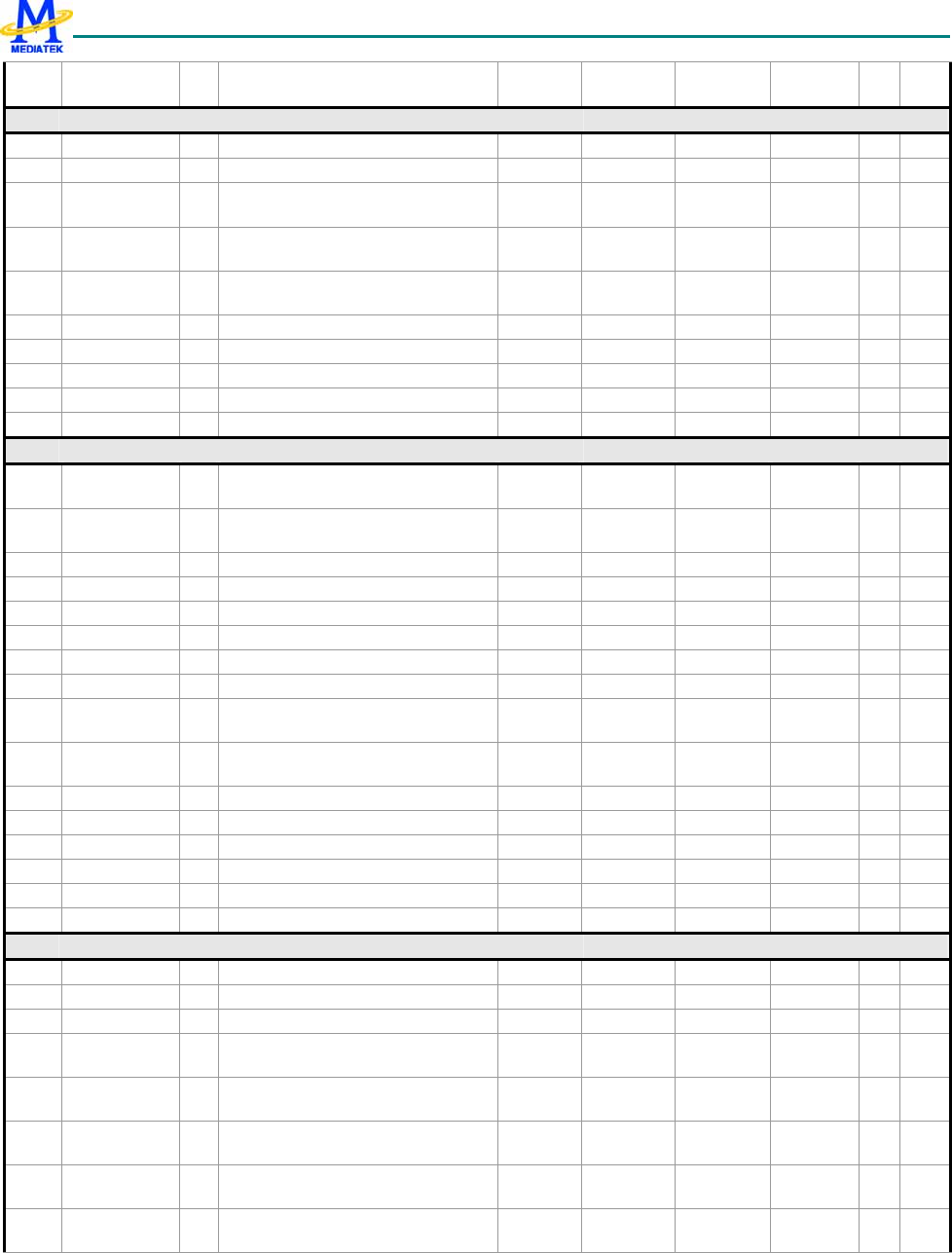

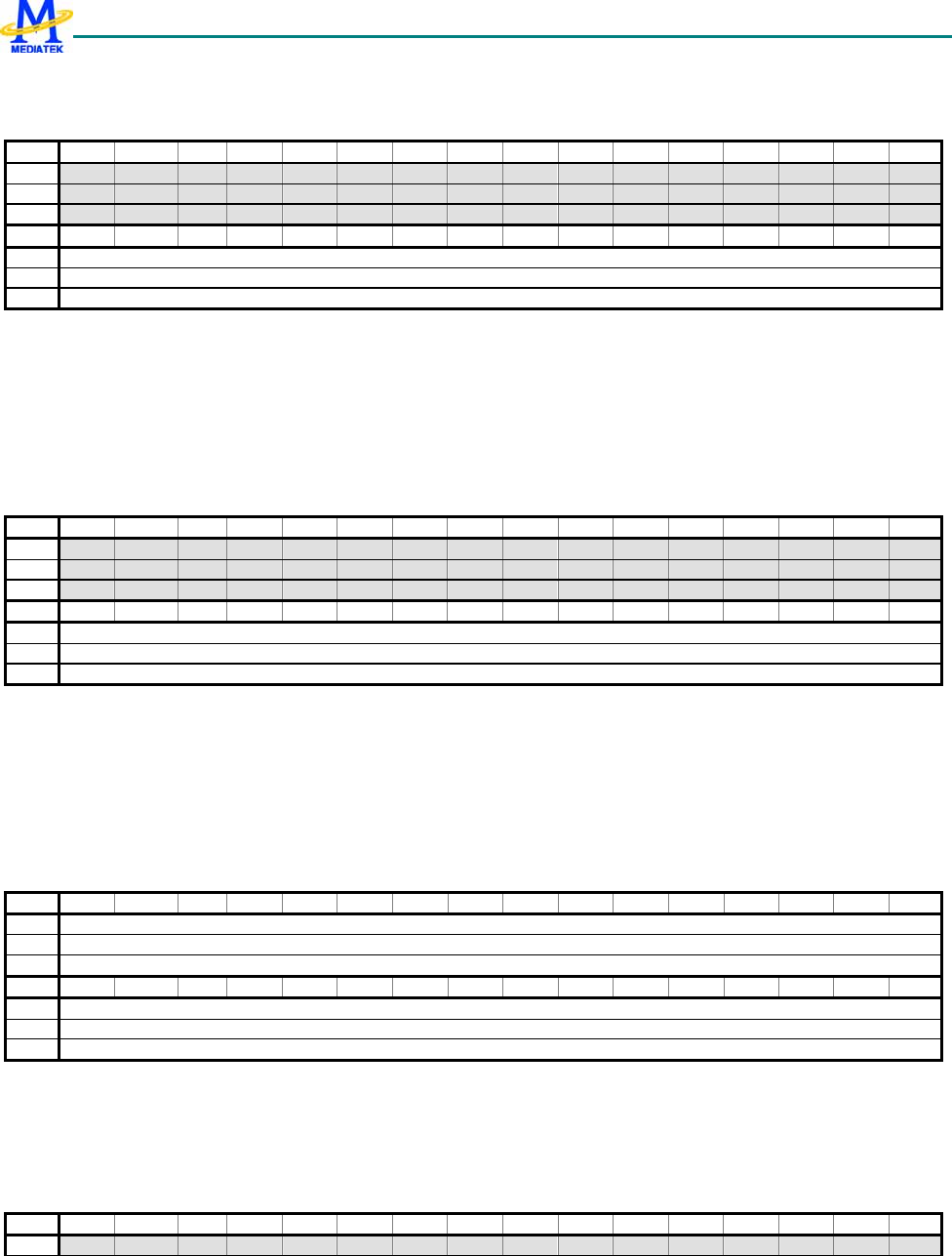

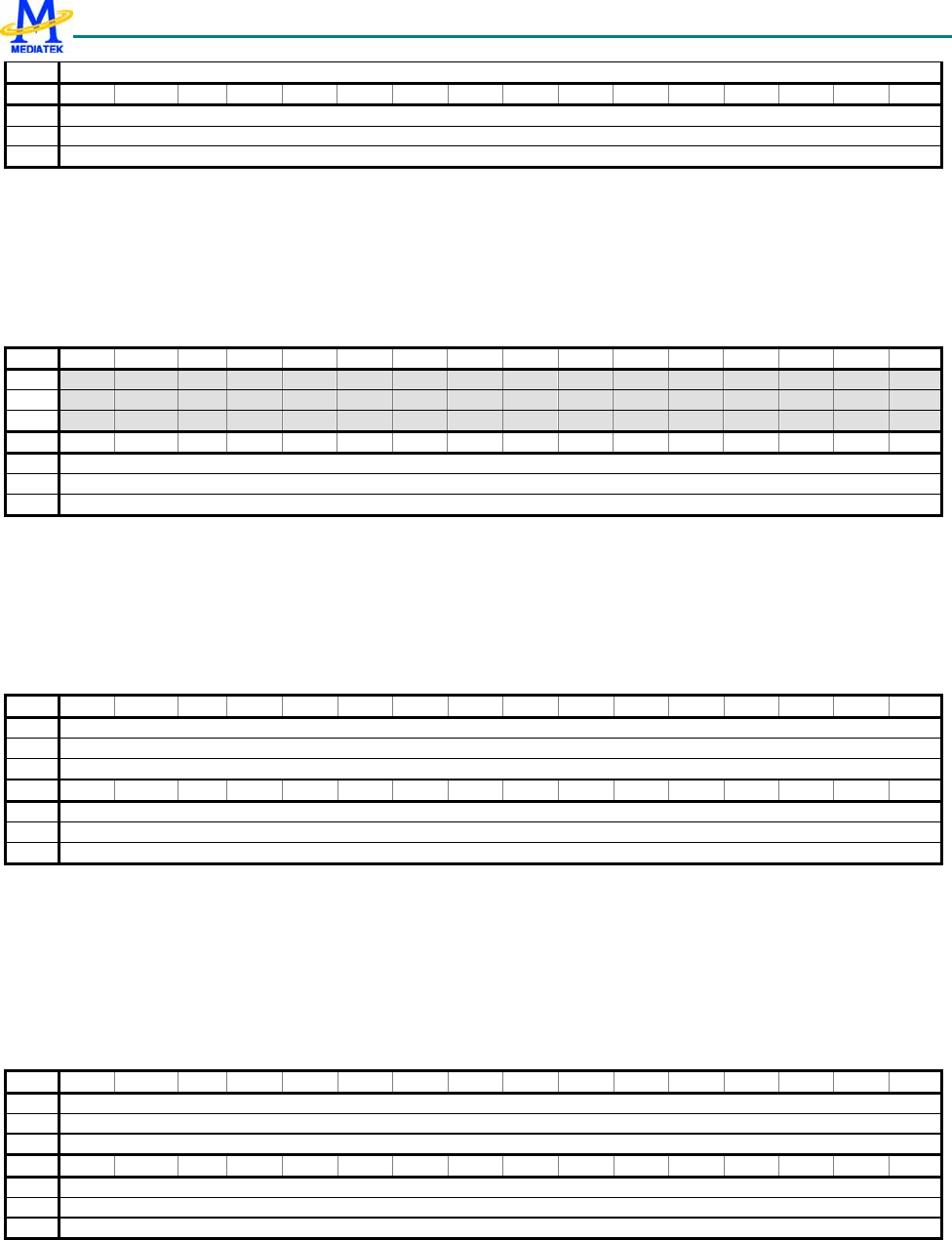

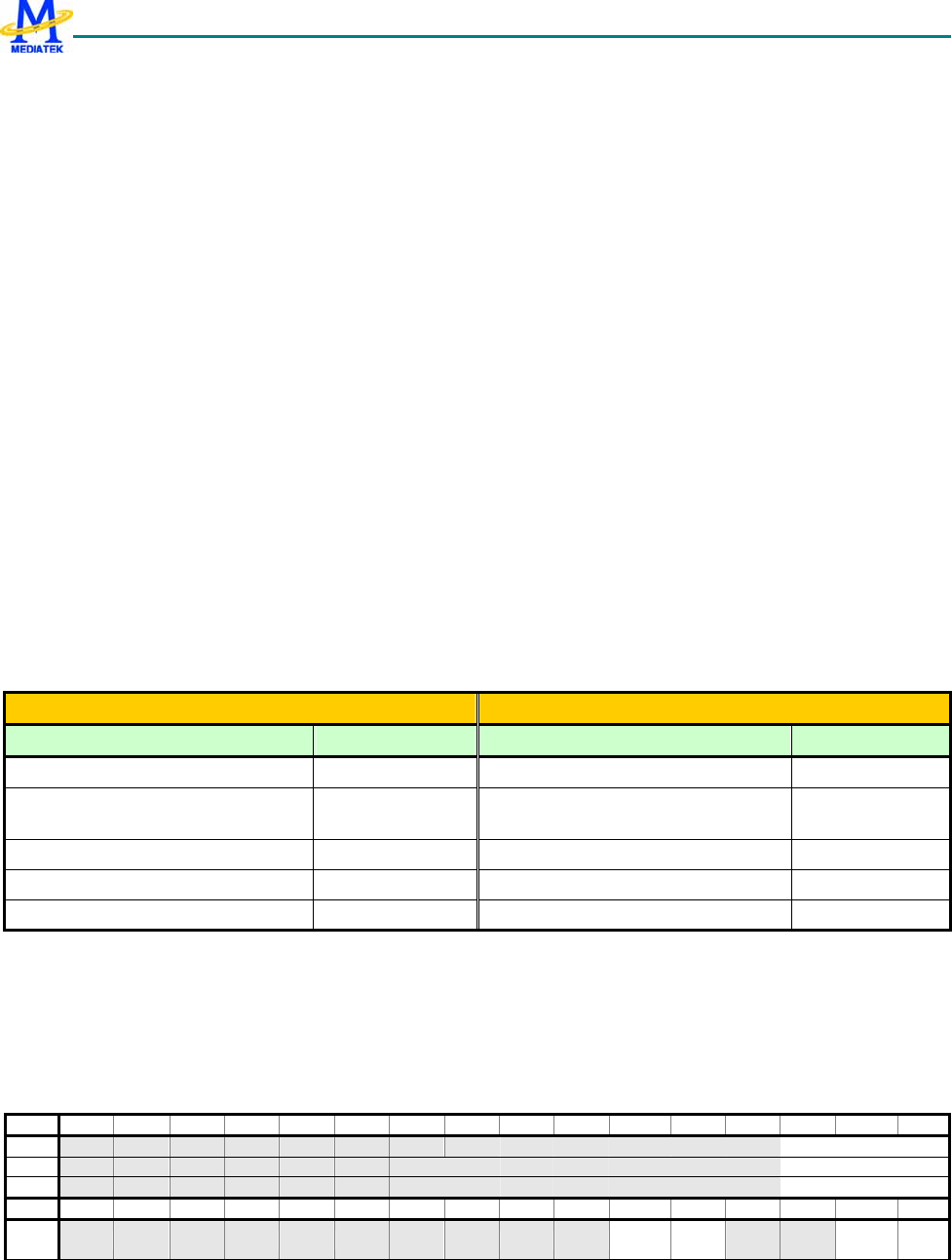

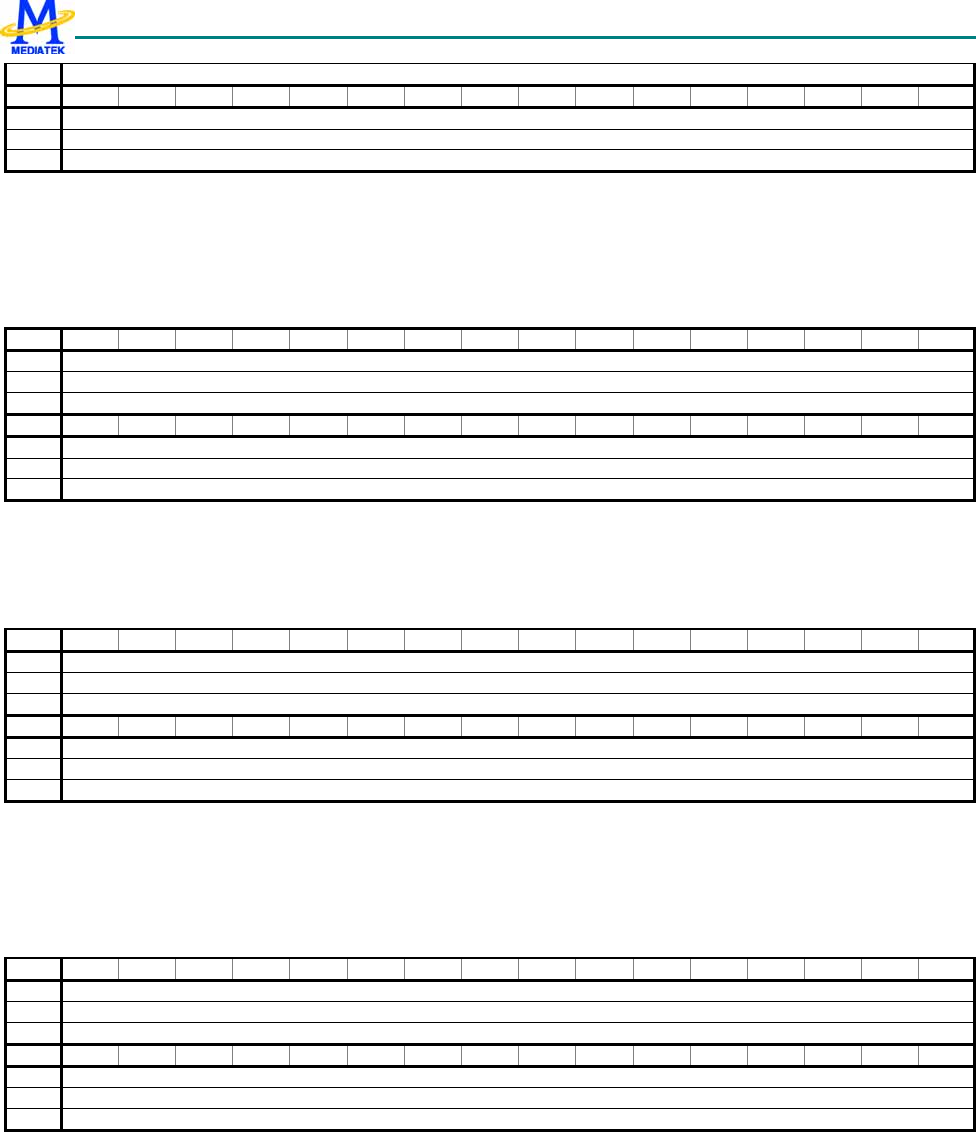

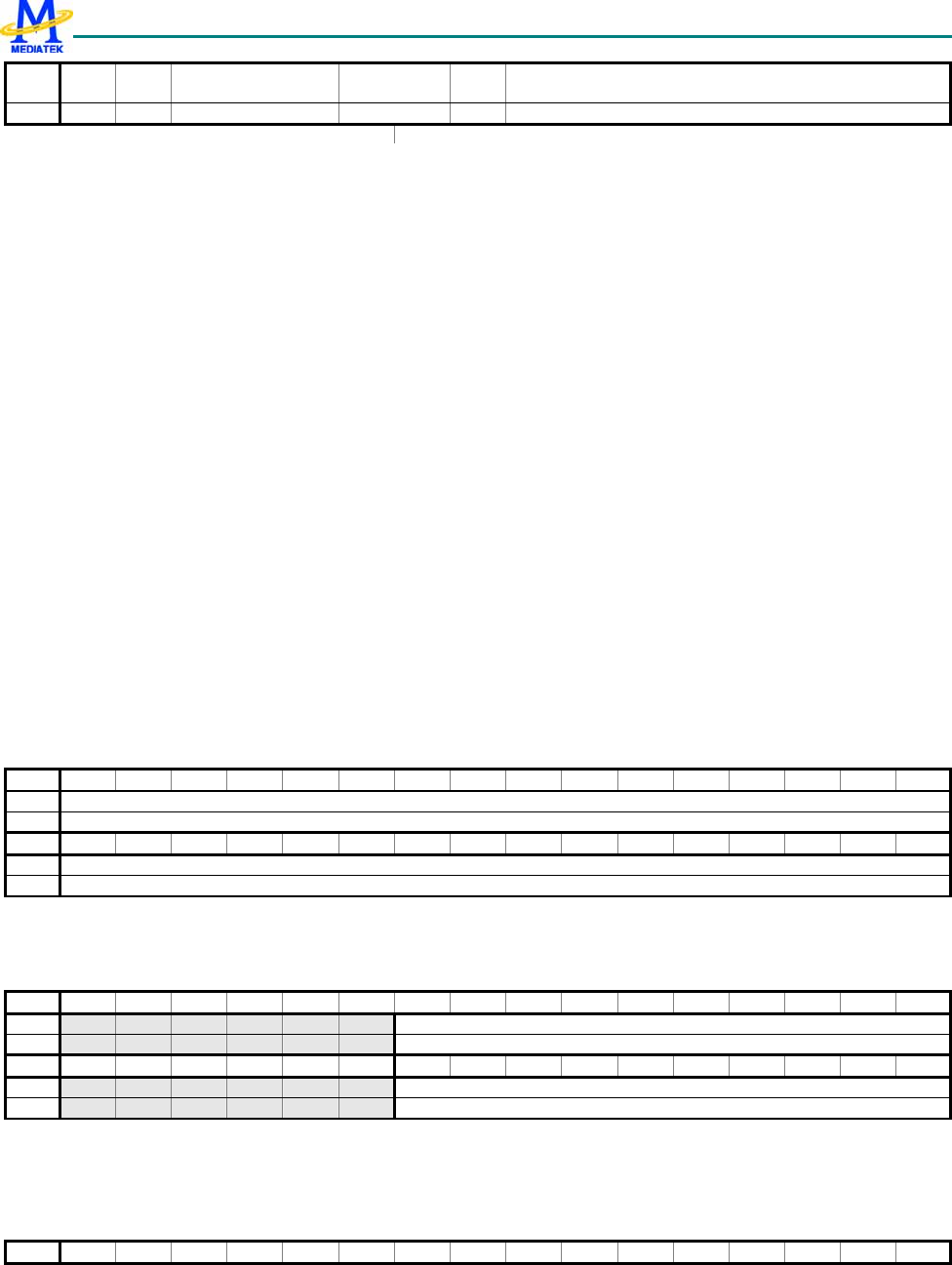

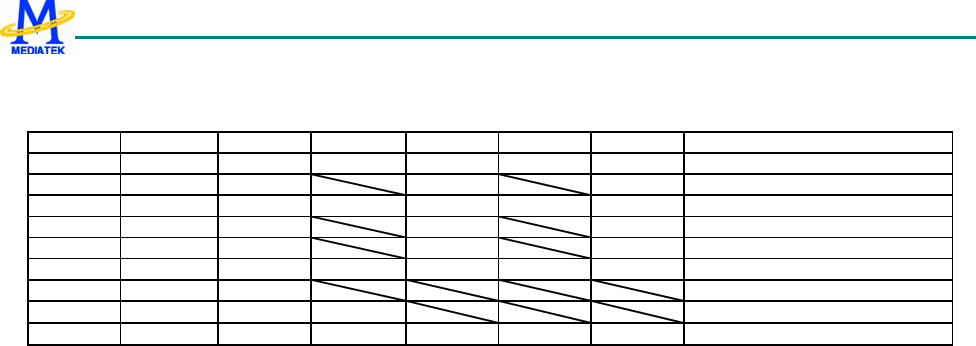

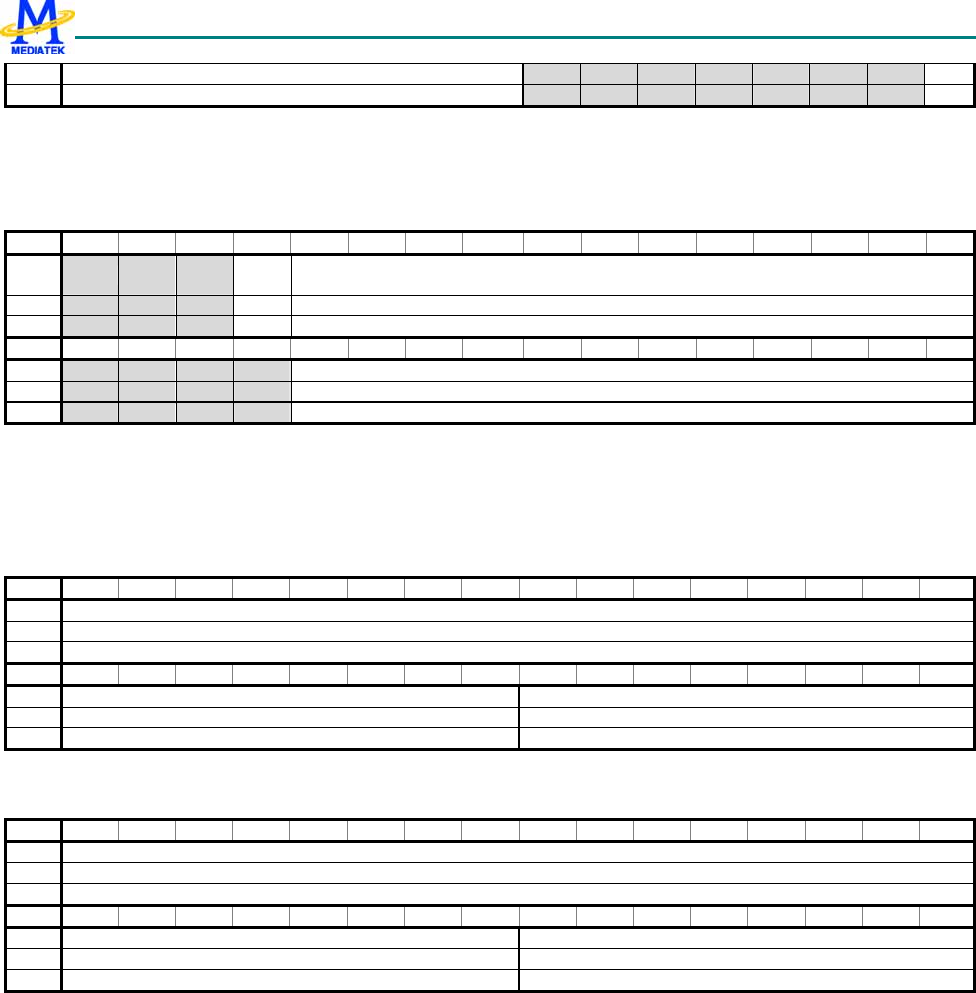

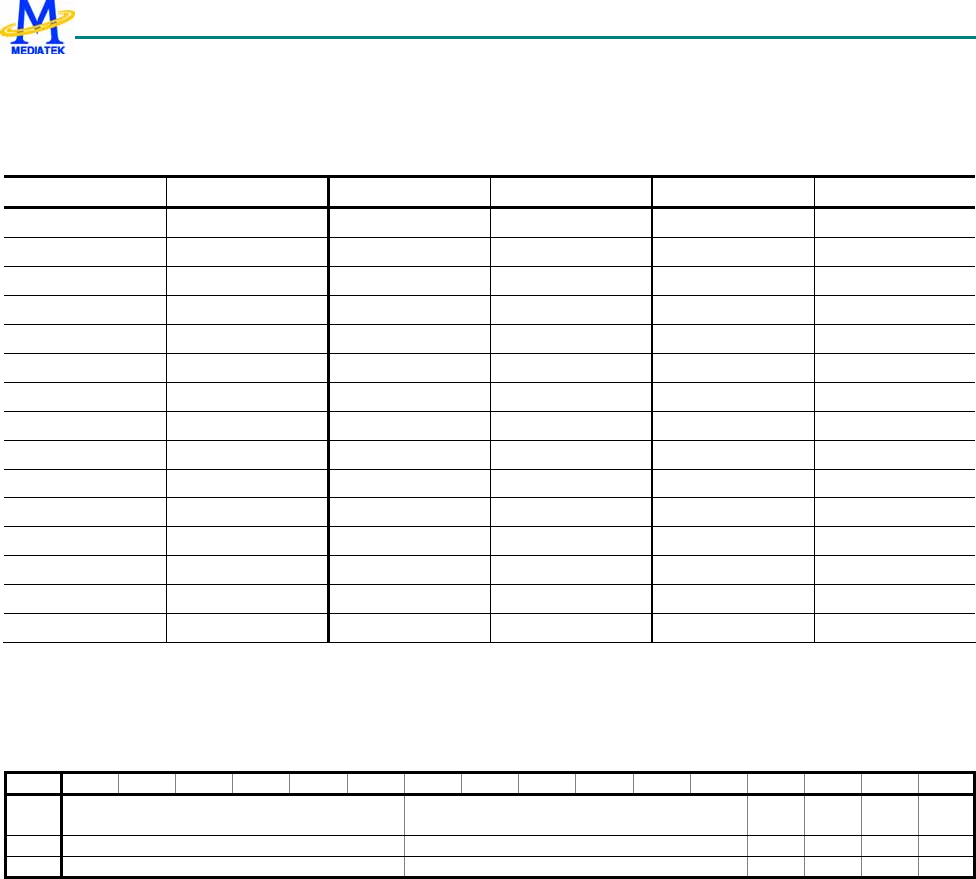

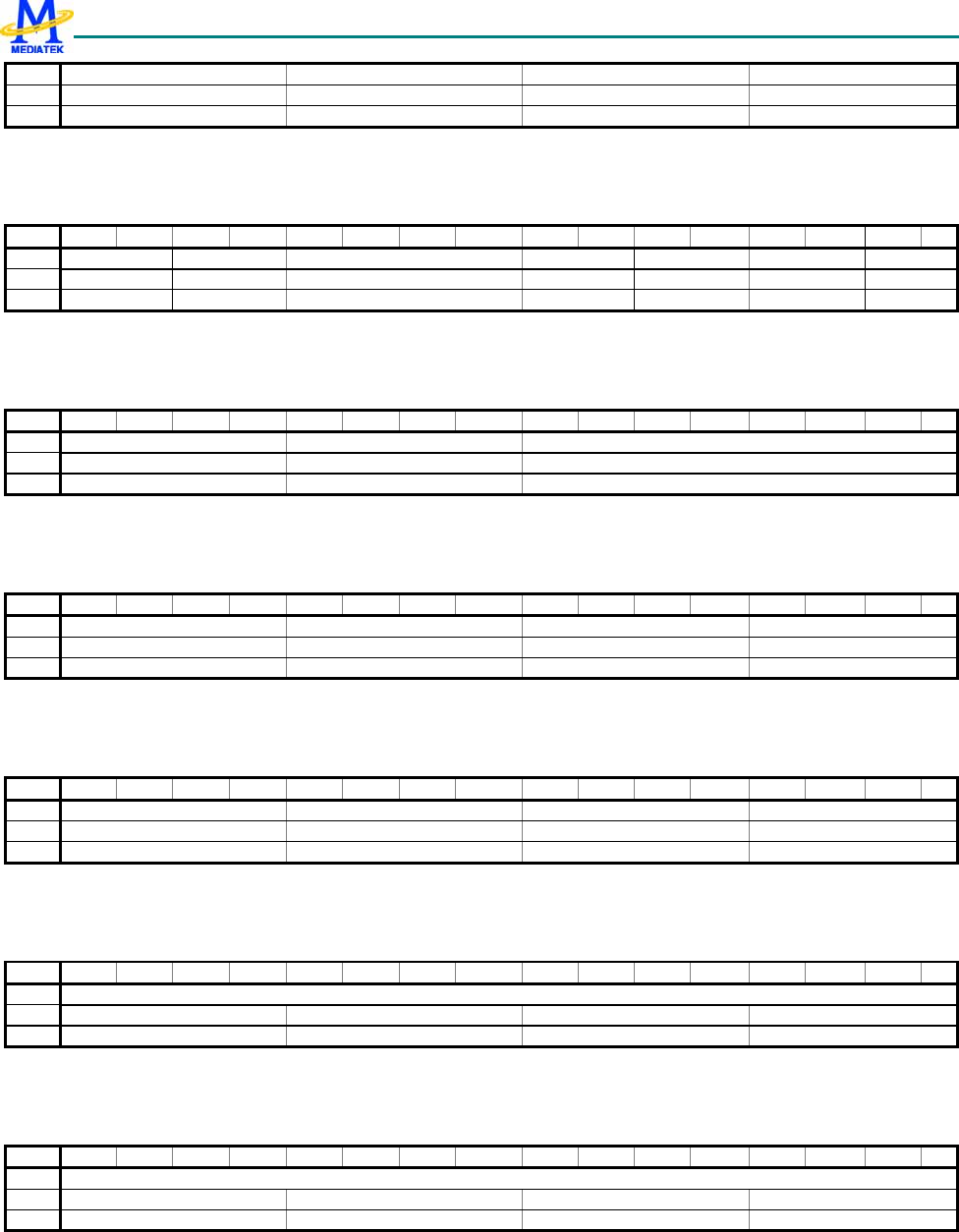

Pin-outs and the top view are illustrated in Figure 3 for this package. Outline and dimension of package is illustrated in

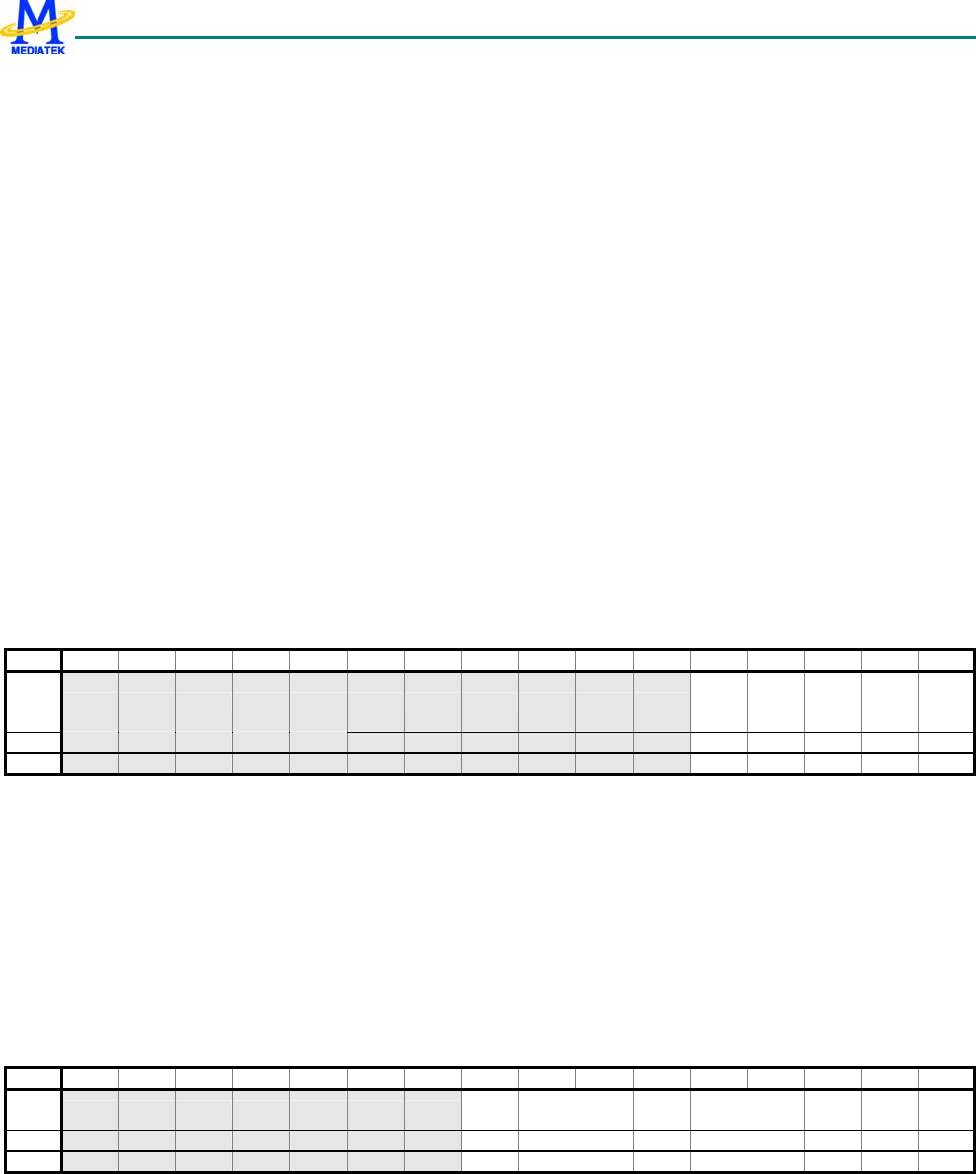

Figure 4, while the definition of package is shown in Table 1.

MT6235 GSM/GPRS Baseband Processor Data Sheet Revision 1.02

16/599 MediaTek Inc. Confidential

Figure 3 Top view of MT6235 TFBGA 13mm*13mm, 362-ball, 0.5 mm pitch package

Notes: RFU is reserved for future use and leave as NC in normal operation.

MT6235 GSM/GPRS Baseband Processor Data Sheet Revision 1.02

17/599 MediaTek Inc. Confidential

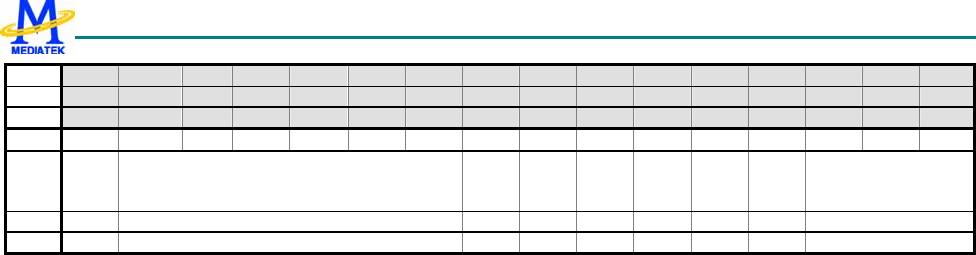

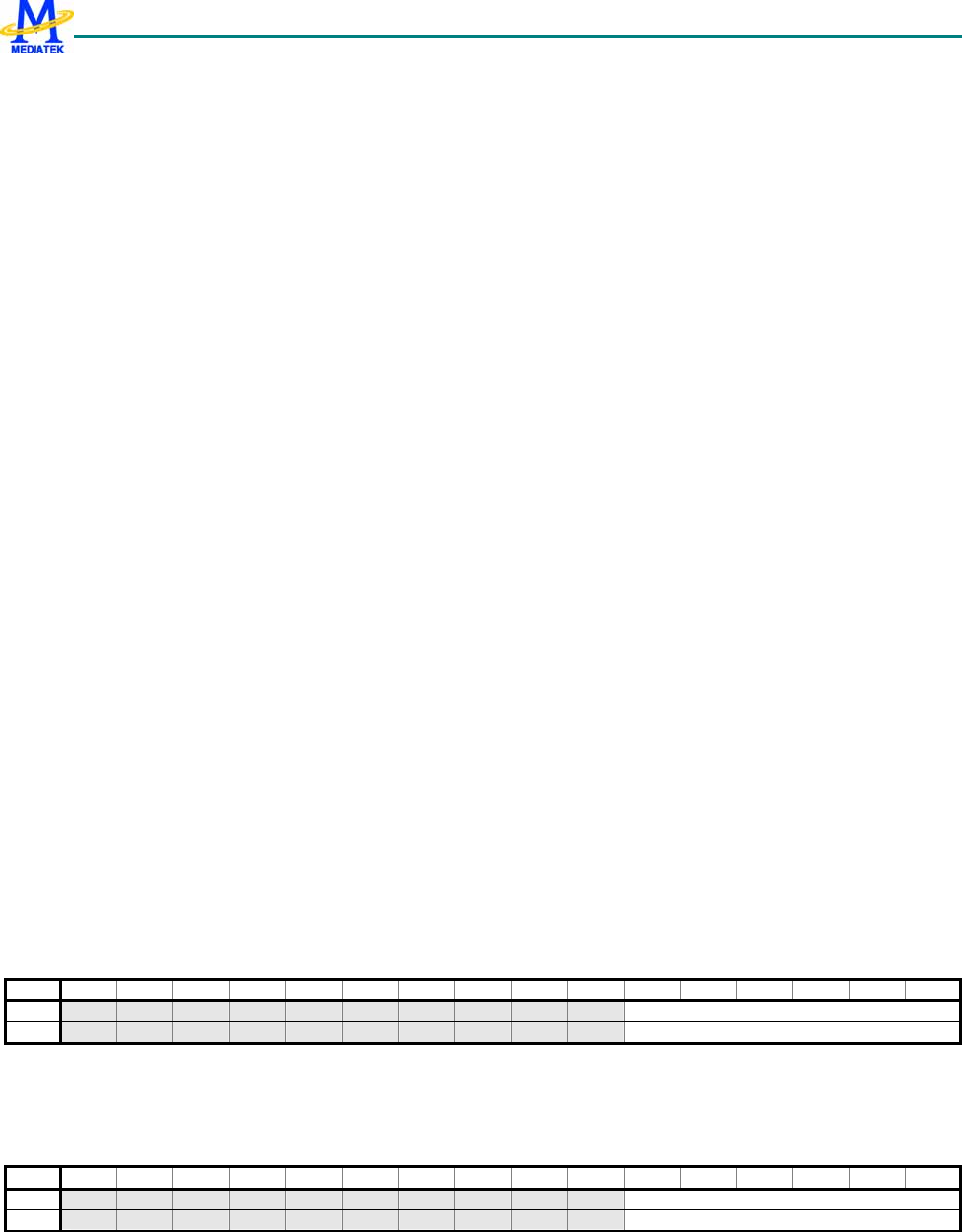

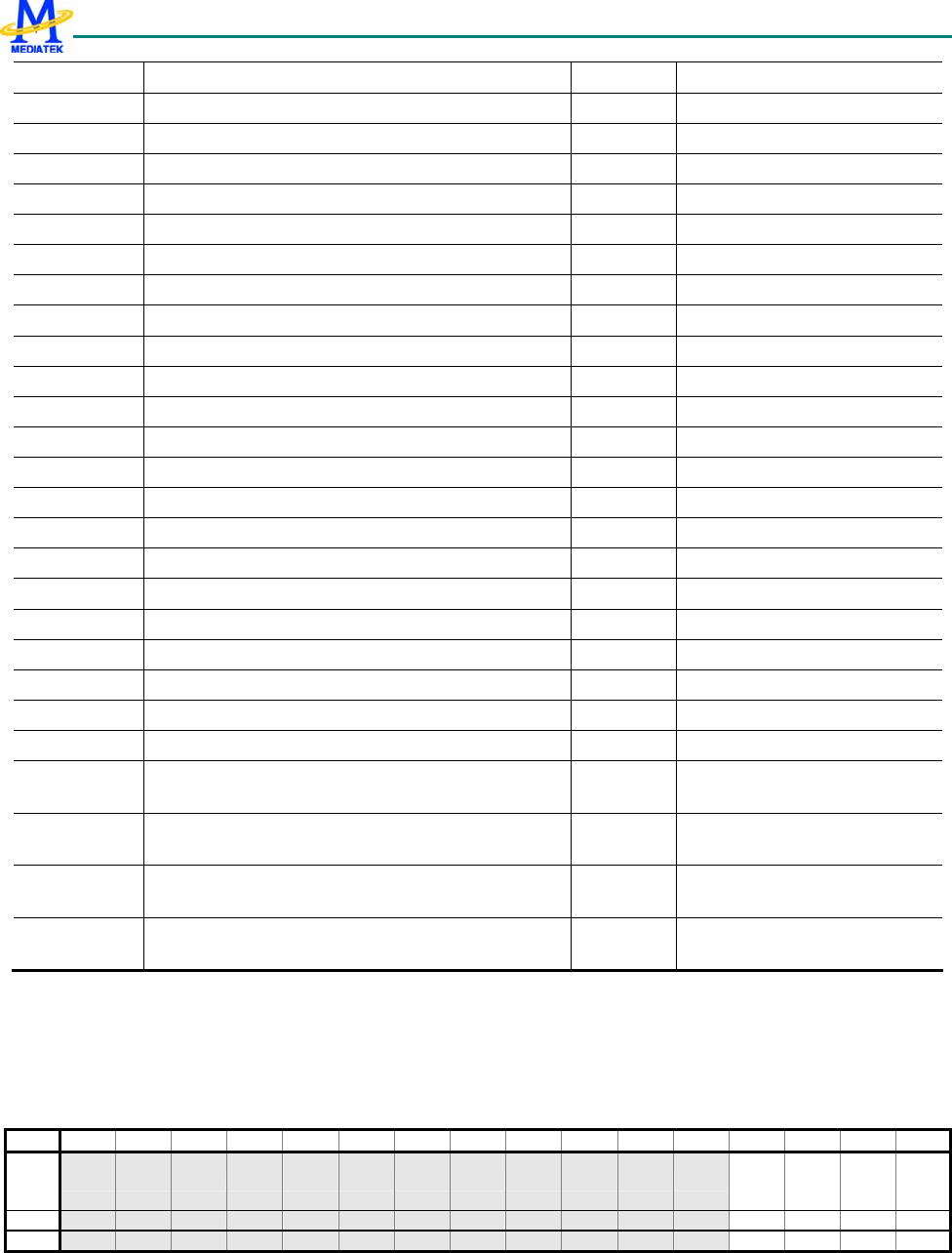

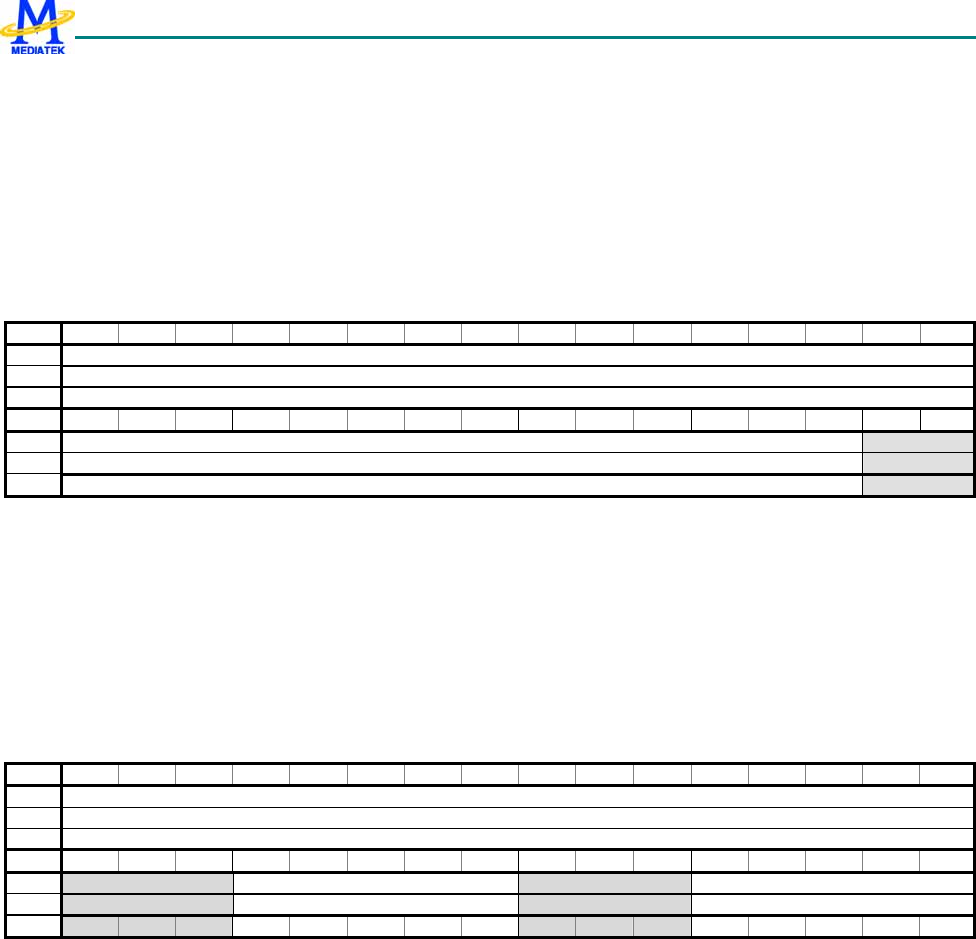

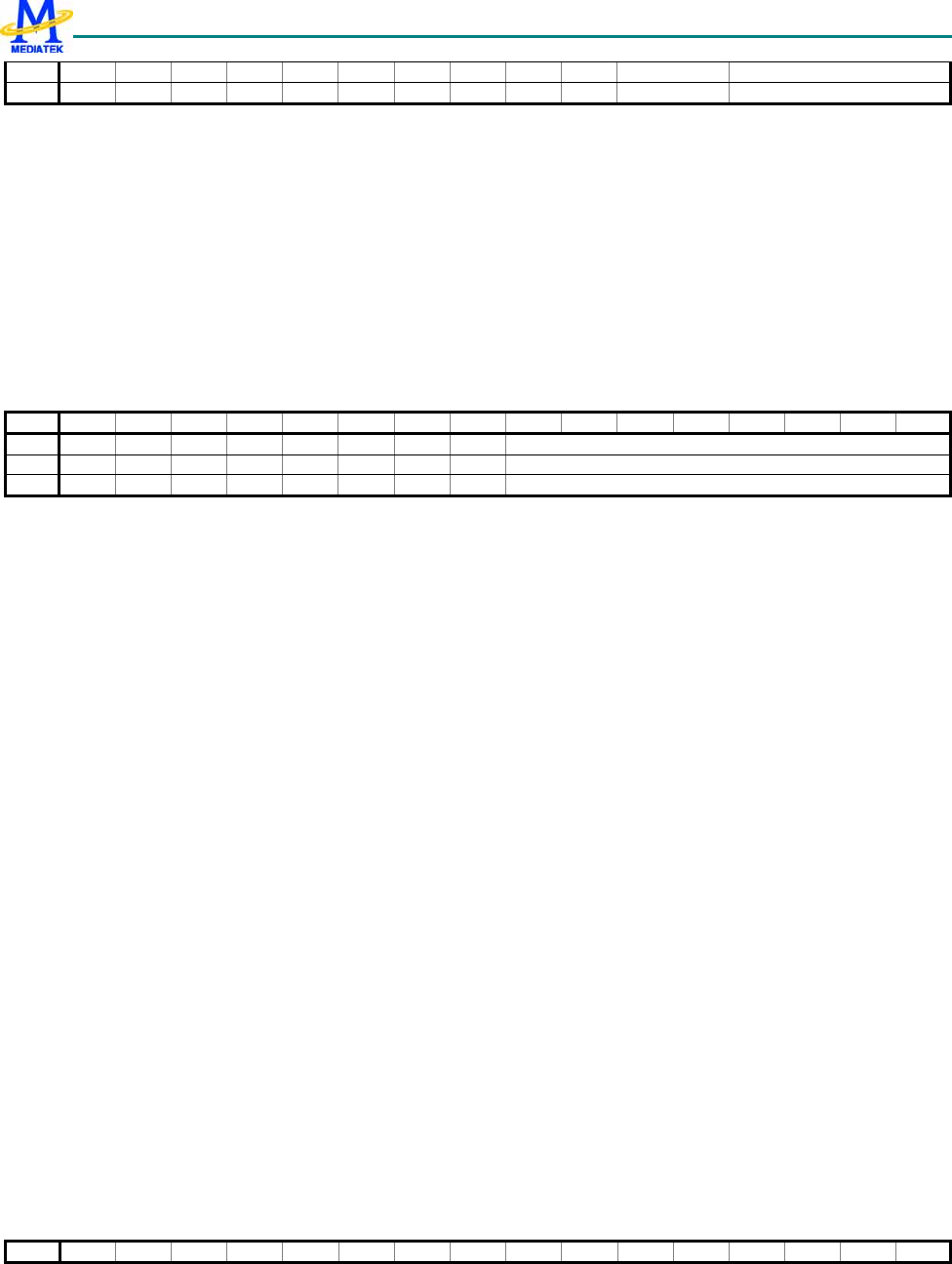

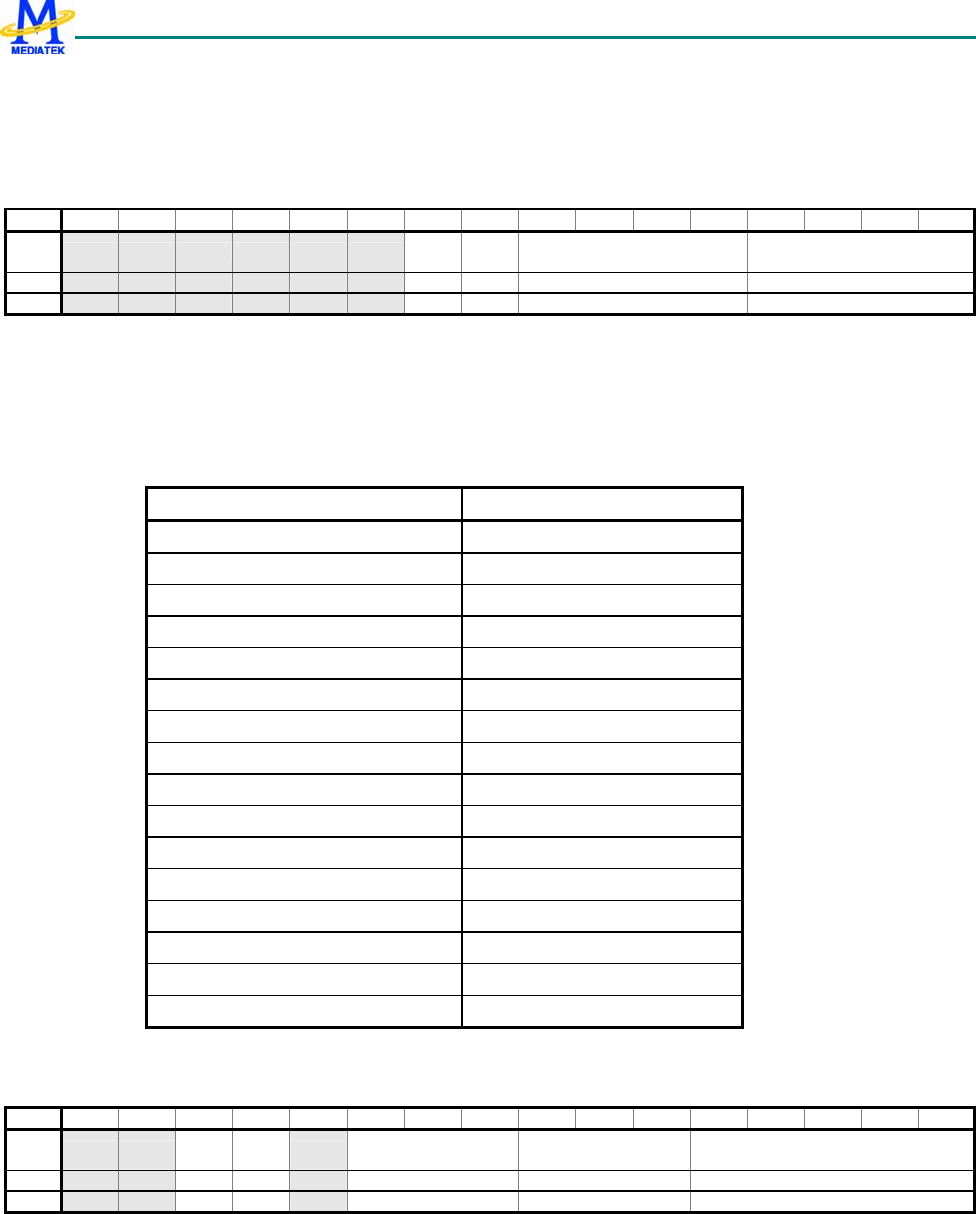

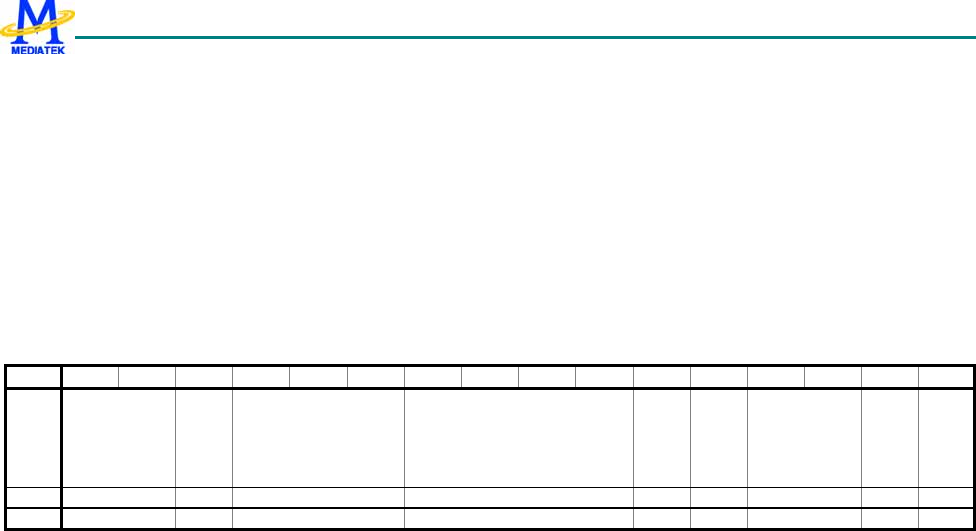

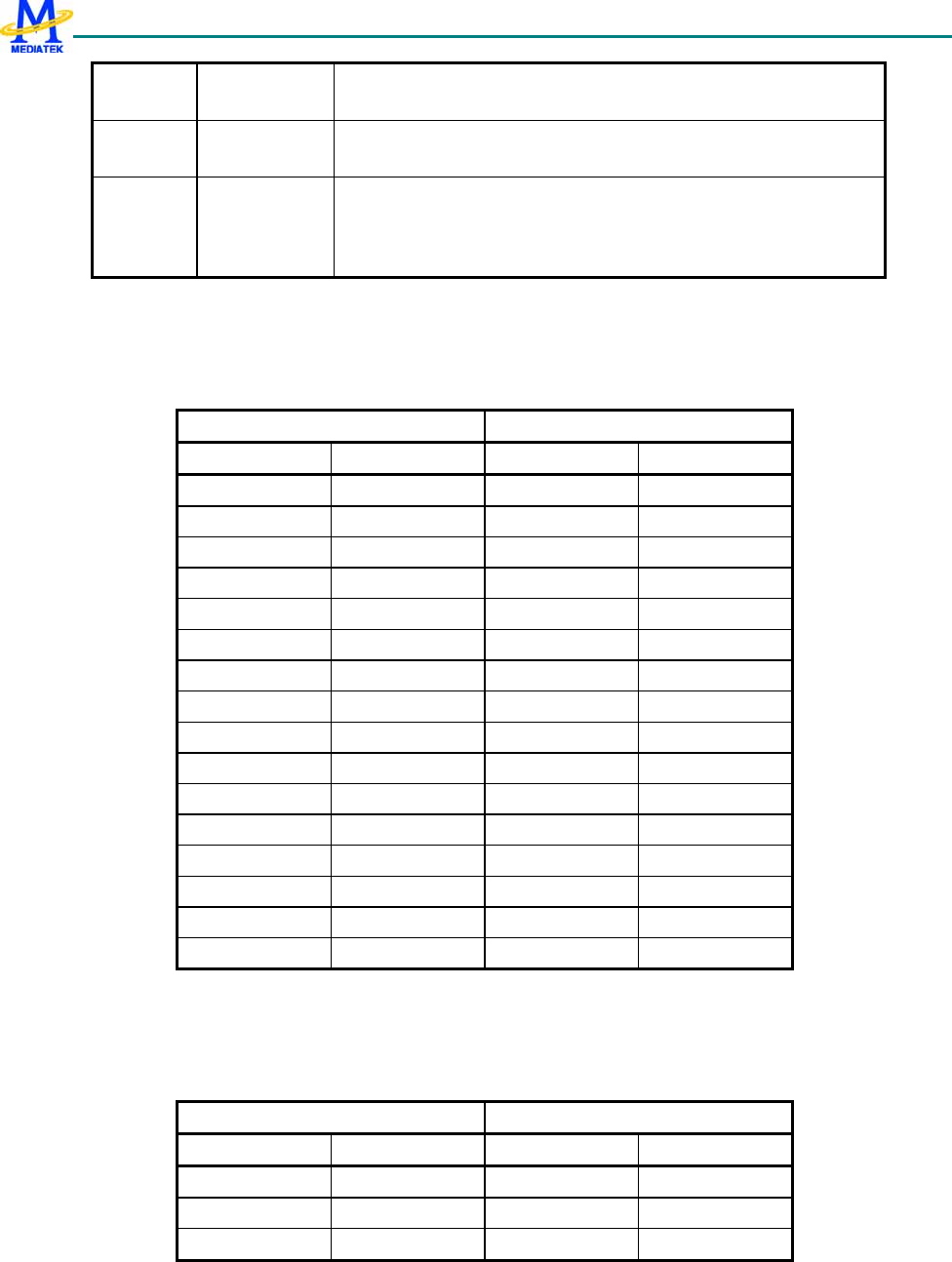

Figure 4 Outlines and dimension of TFBGA 13mm*13mm, 362-ball, 0.5 mm pitch package

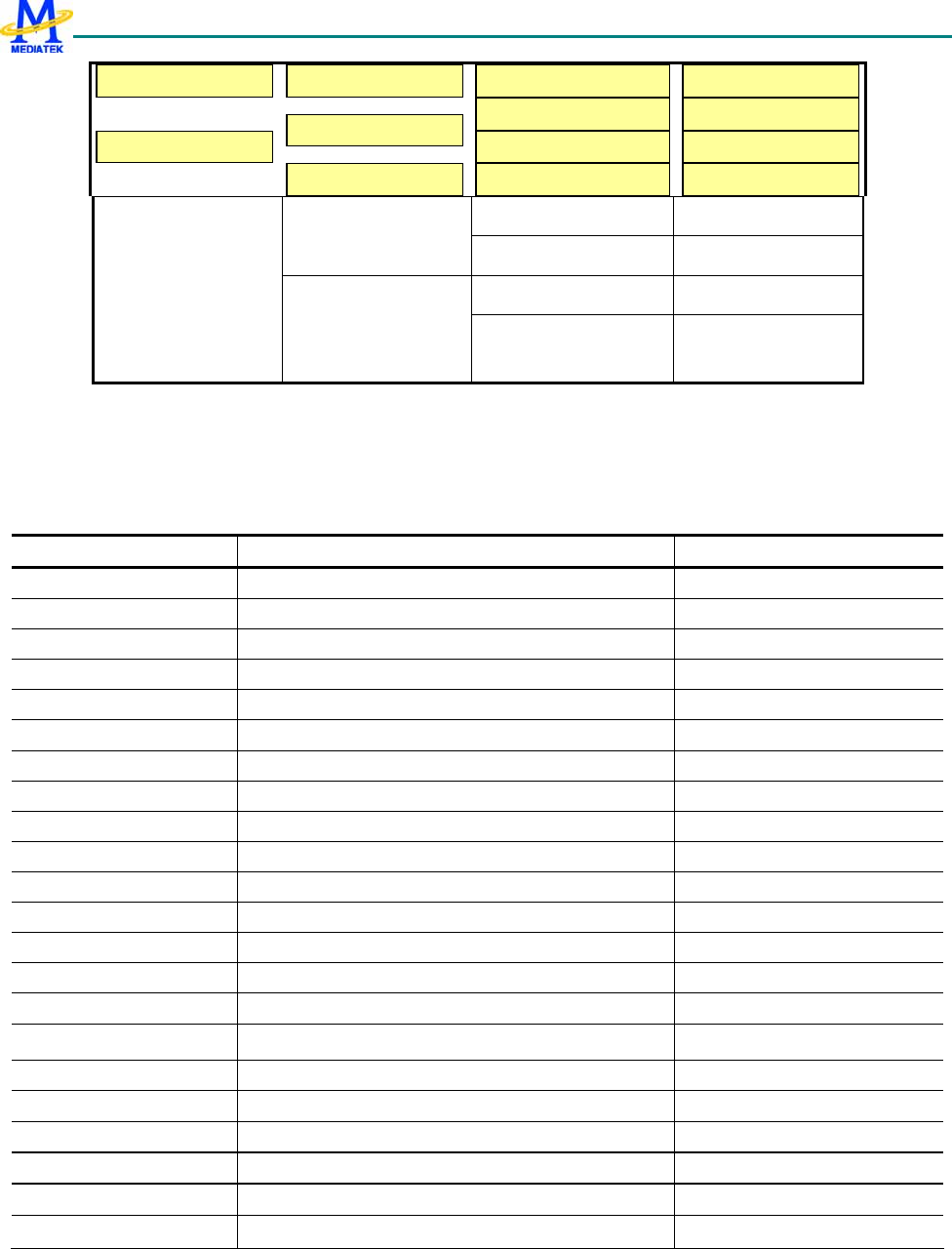

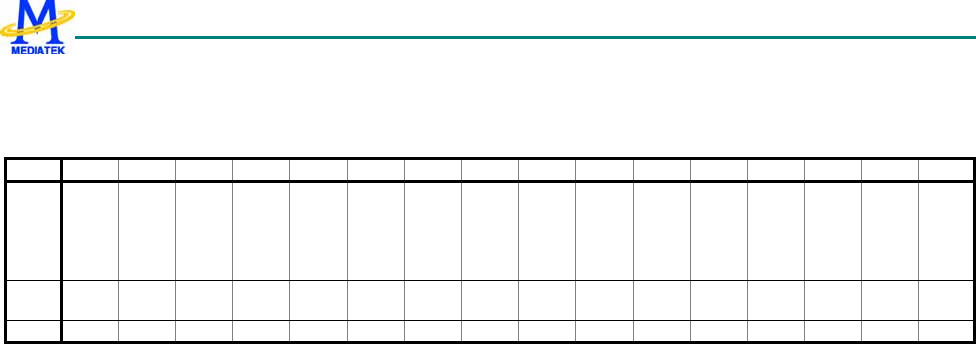

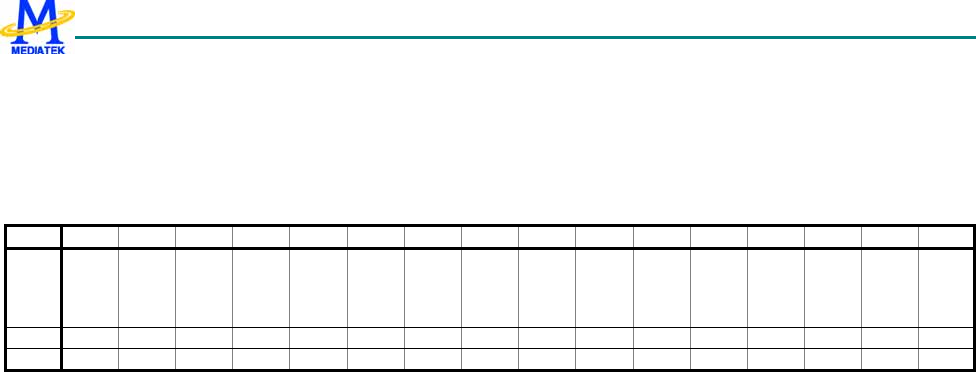

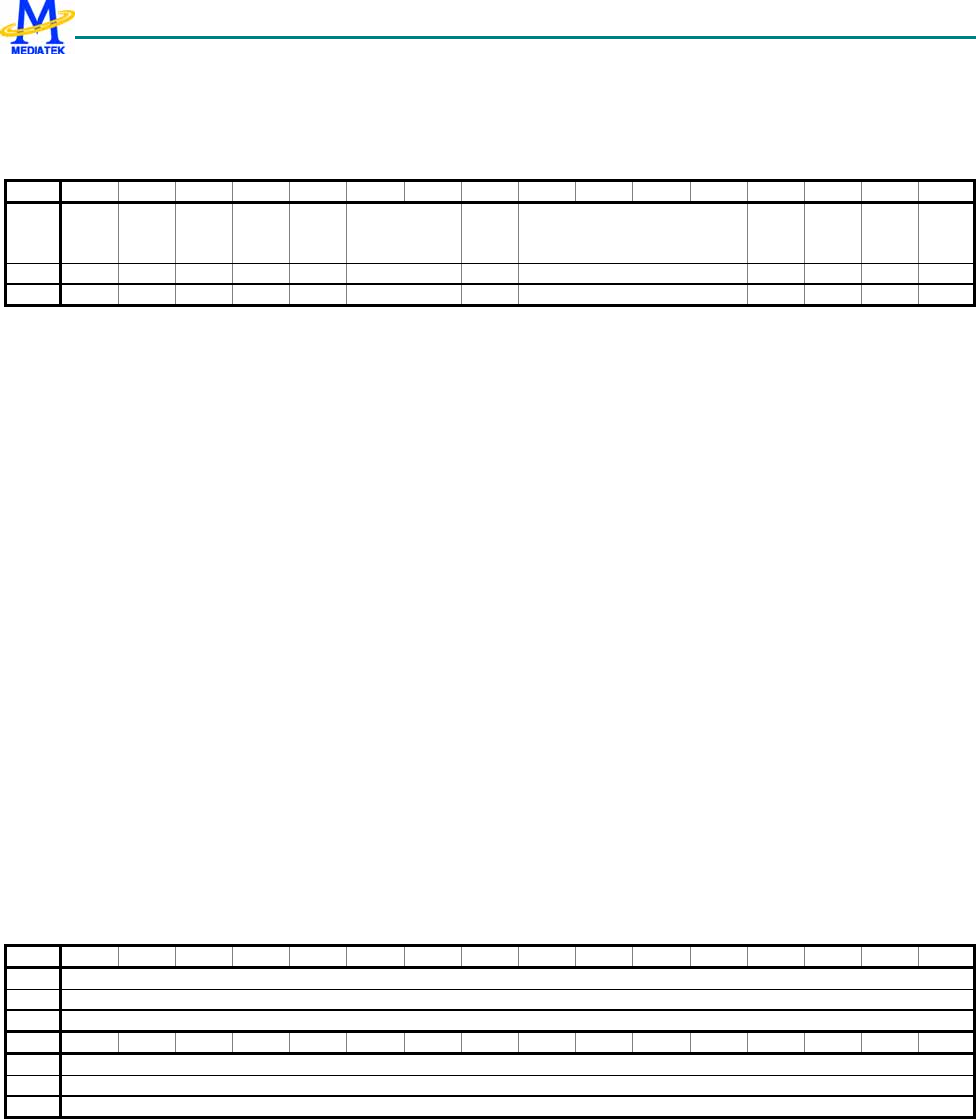

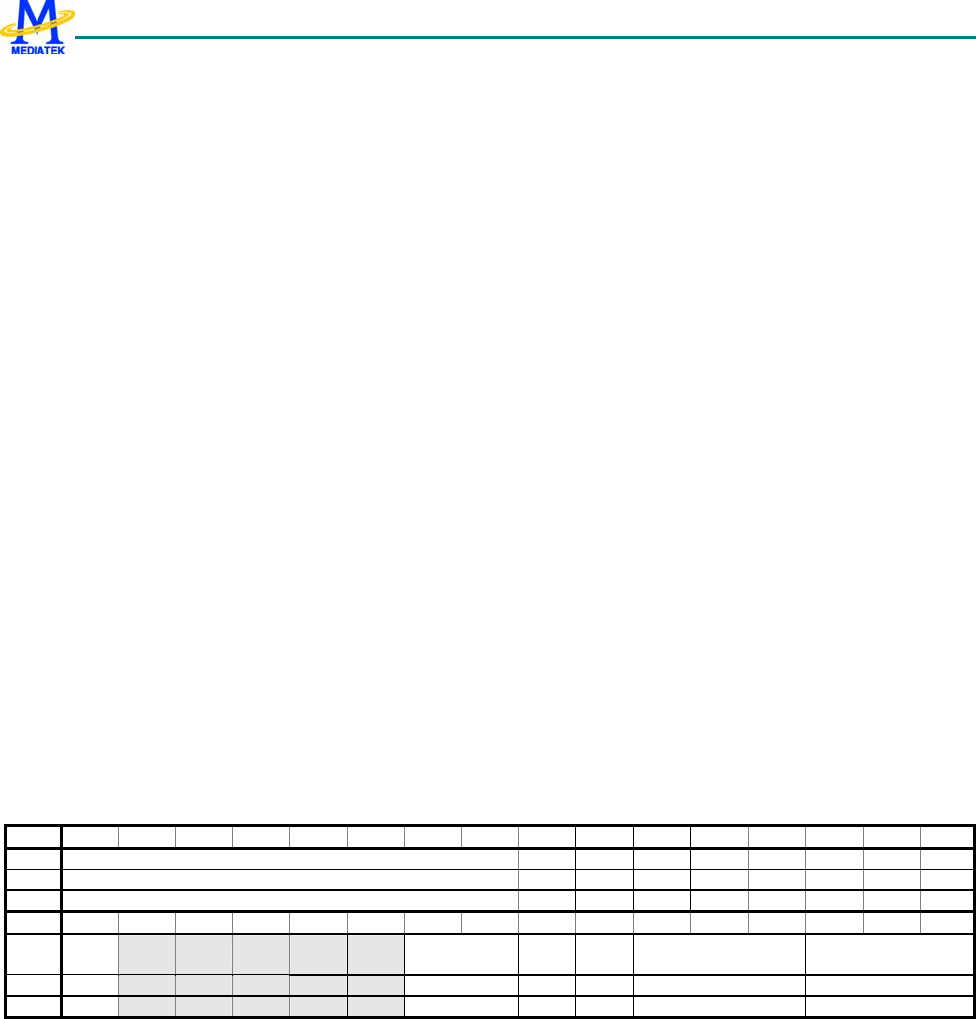

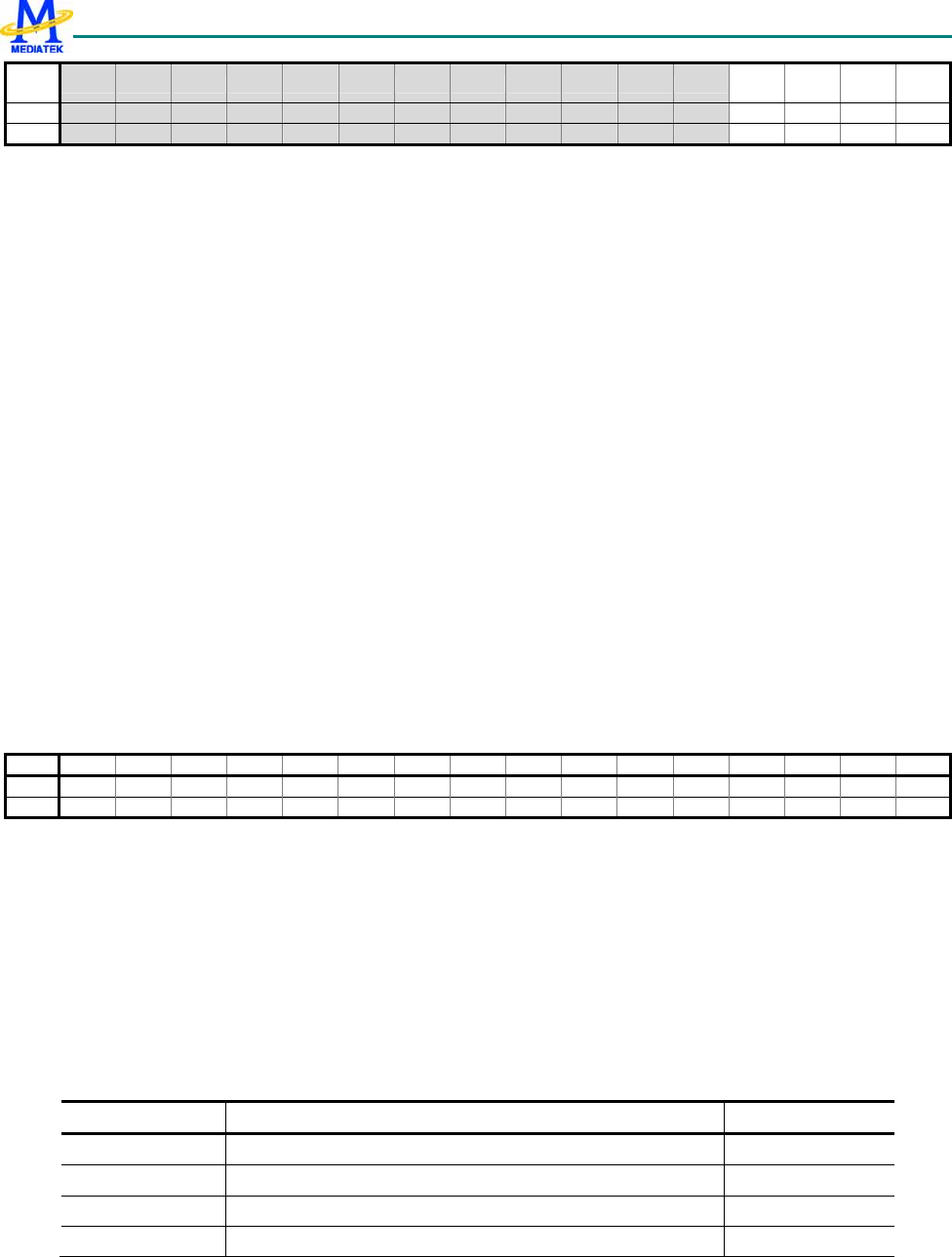

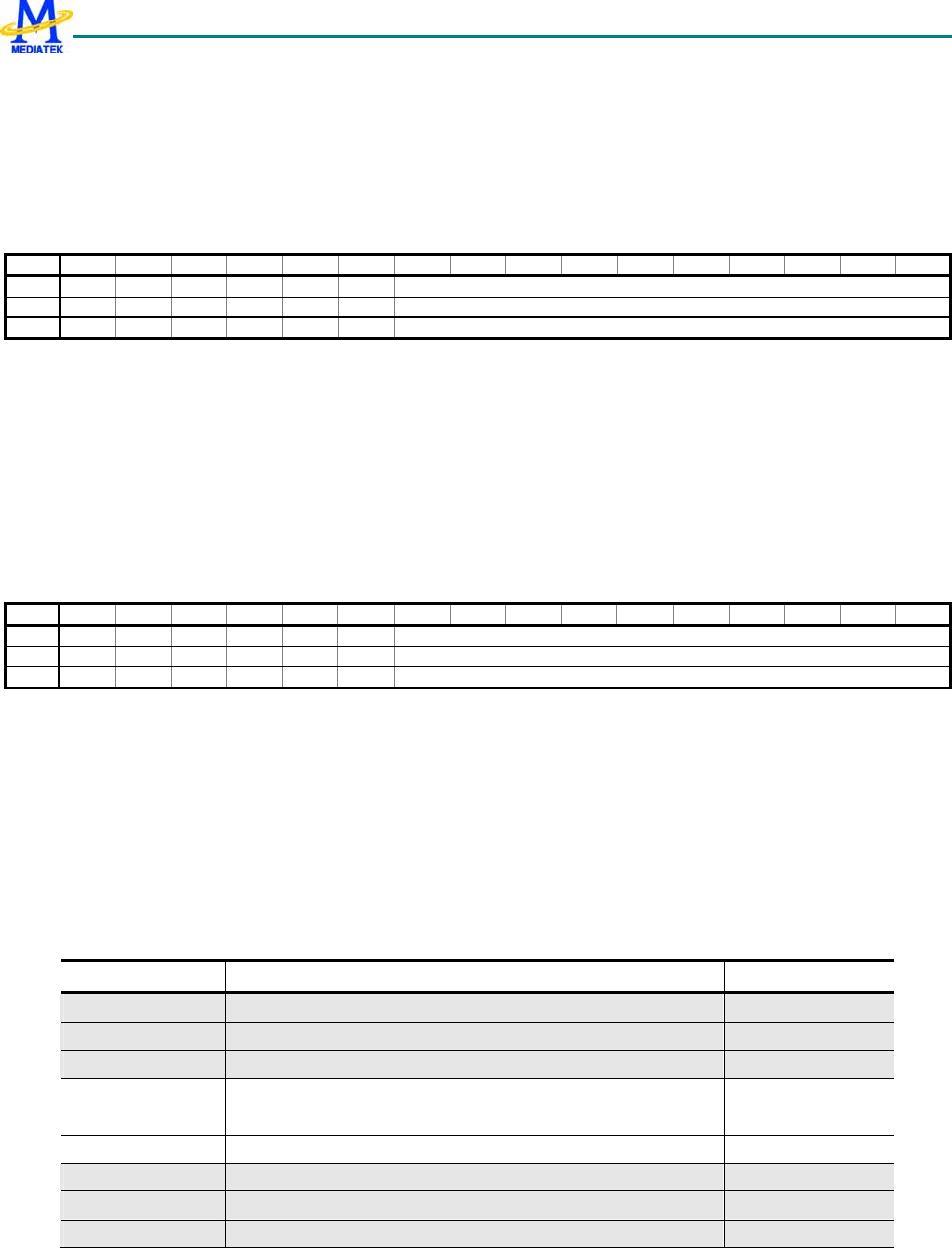

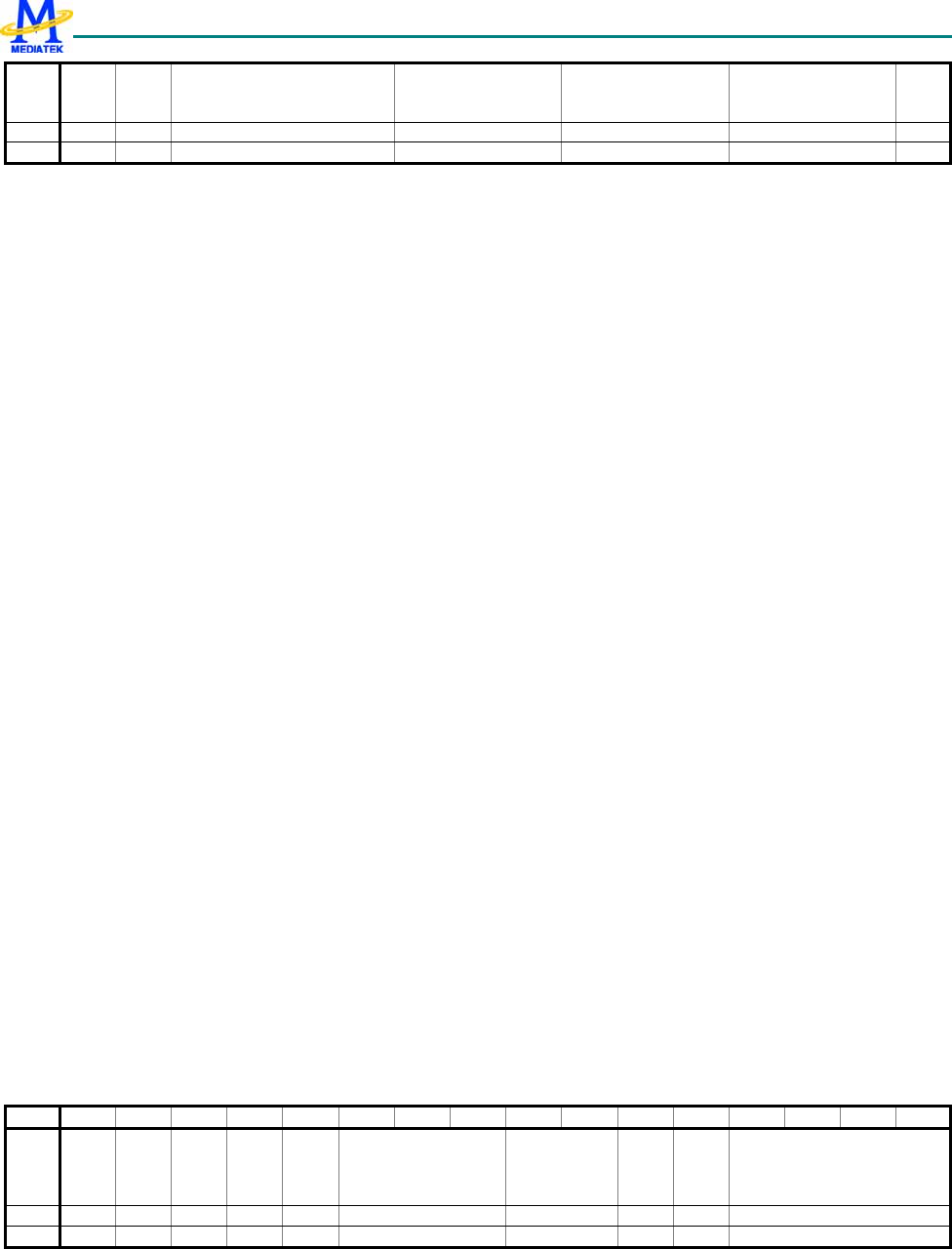

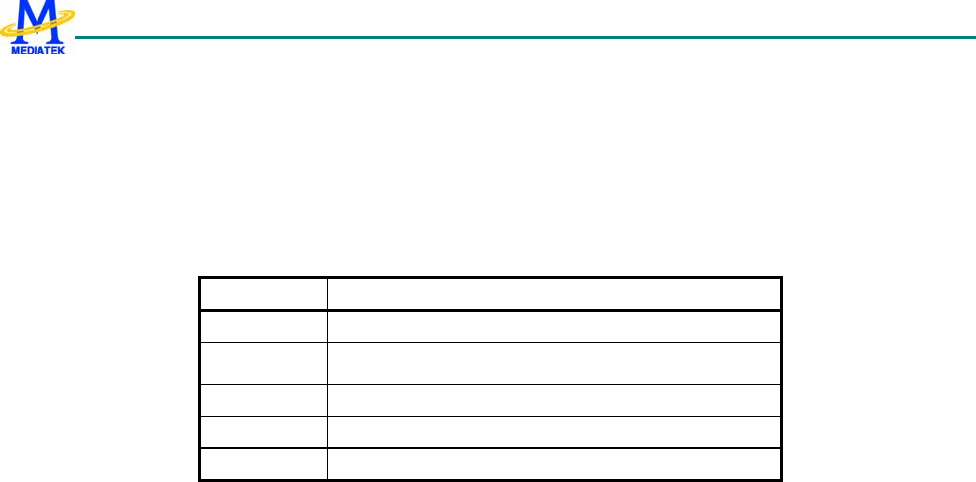

Body Size Ball Count Ball Pitch Ball Dia. Package Thk. Stand Off Substrate Thk.

D E N e b A (MAX) A1(NOM) C

13 13 362 0.5 0.3 1.2 0.21 0.36

Table 1 Definition of TFBGA 13mm*13mm, 362-ball, 0.5 mm pitch package (Unit: mm)

MT6235 GSM/GPRS Baseband Processor Data Sheet Revision 1.02

18/599 MediaTek Inc. Confidential

2.2 Top Marking Definition

S

MT6235A: Part No.

DDDD: Date Code

###: Subcontractor Code

LLLLL: U1 Die Lot No.

S: Special Code

MT6235A

DDDD-###

LLLLL

MT6235 GSM/GPRS Baseband Processor Data Sheet Revision 1.02

19/599 MediaTek Inc. Confidential

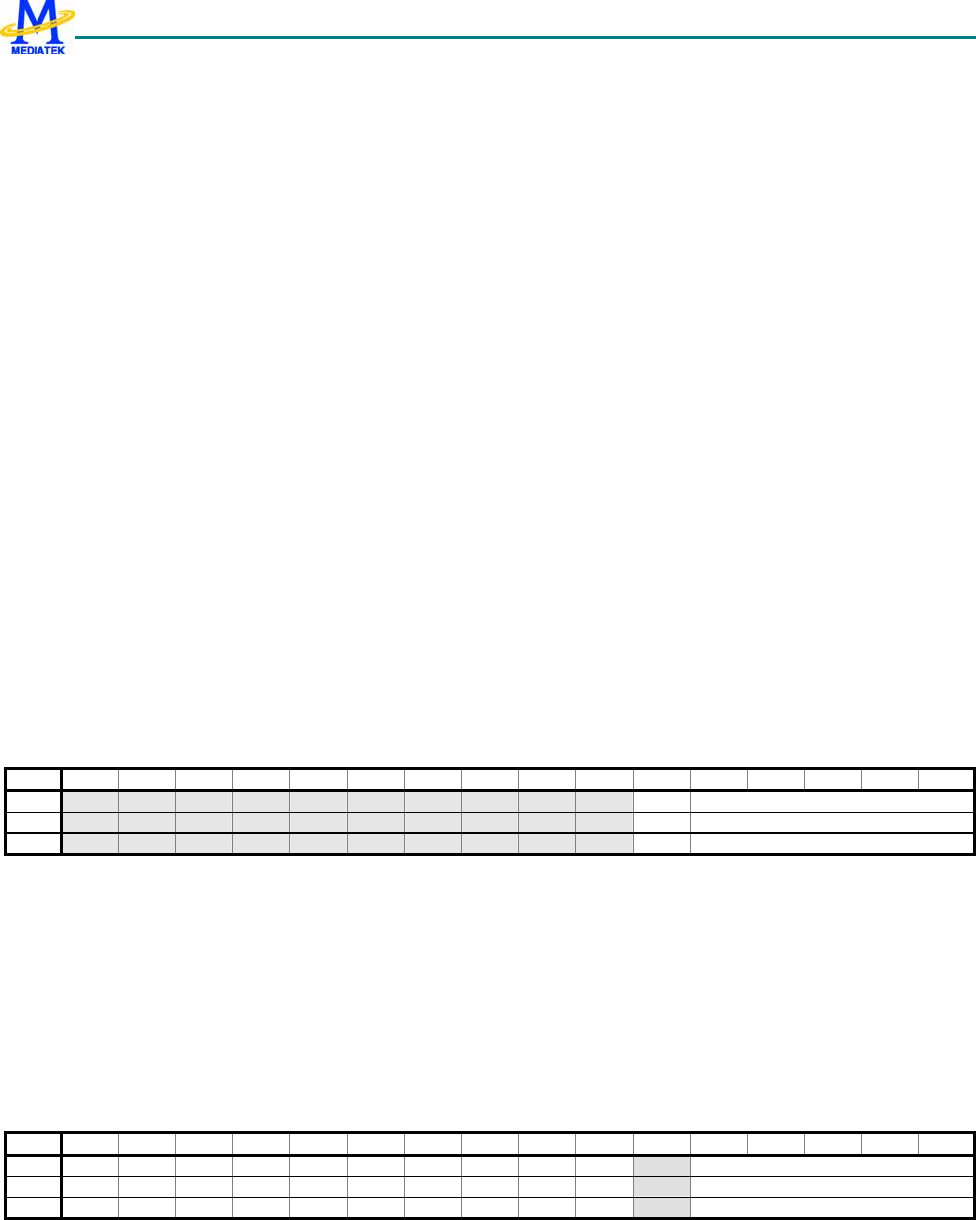

2.3 DC Characteristics

2.3.1 Absolute Maximum Ratings

Prolonged exposure to absolute maximum ratings may reduce device reliability. Functional operation at these maximum

ratings is not implied.

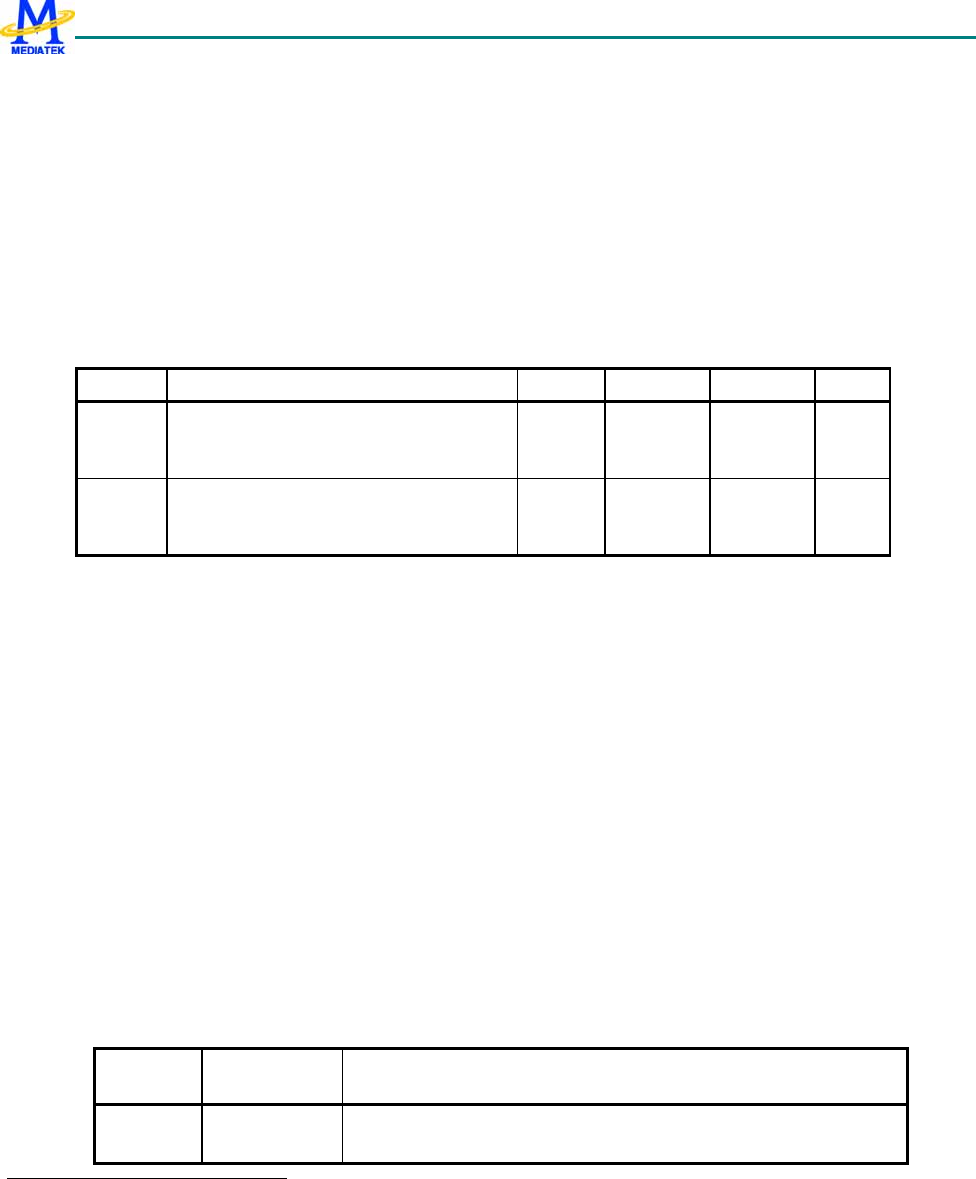

Item Symbol Min Max Unit

IO power supply VDD33 -0.3 VDD33+0.3 V

I/O input voltage VDD33 -0.3 VDD33+0.3 V

Operating temperature Topr -20 80 Celsius

Storage temperature Tstg -55 125 Celsius

MT6235 GSM/GPRS Baseband Processor Data Sheet Revision 1.02

20/599 MediaTek Inc. Confidential

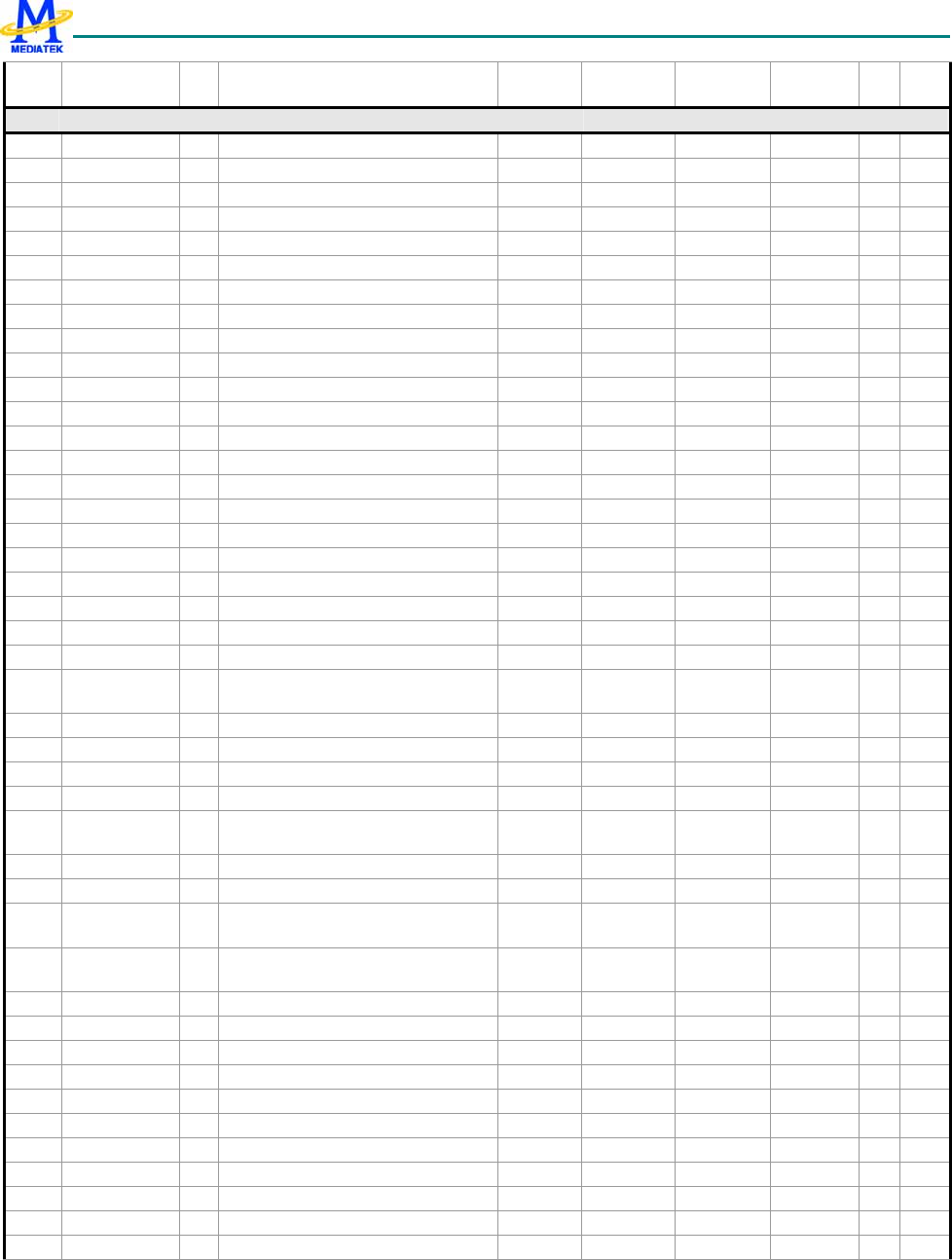

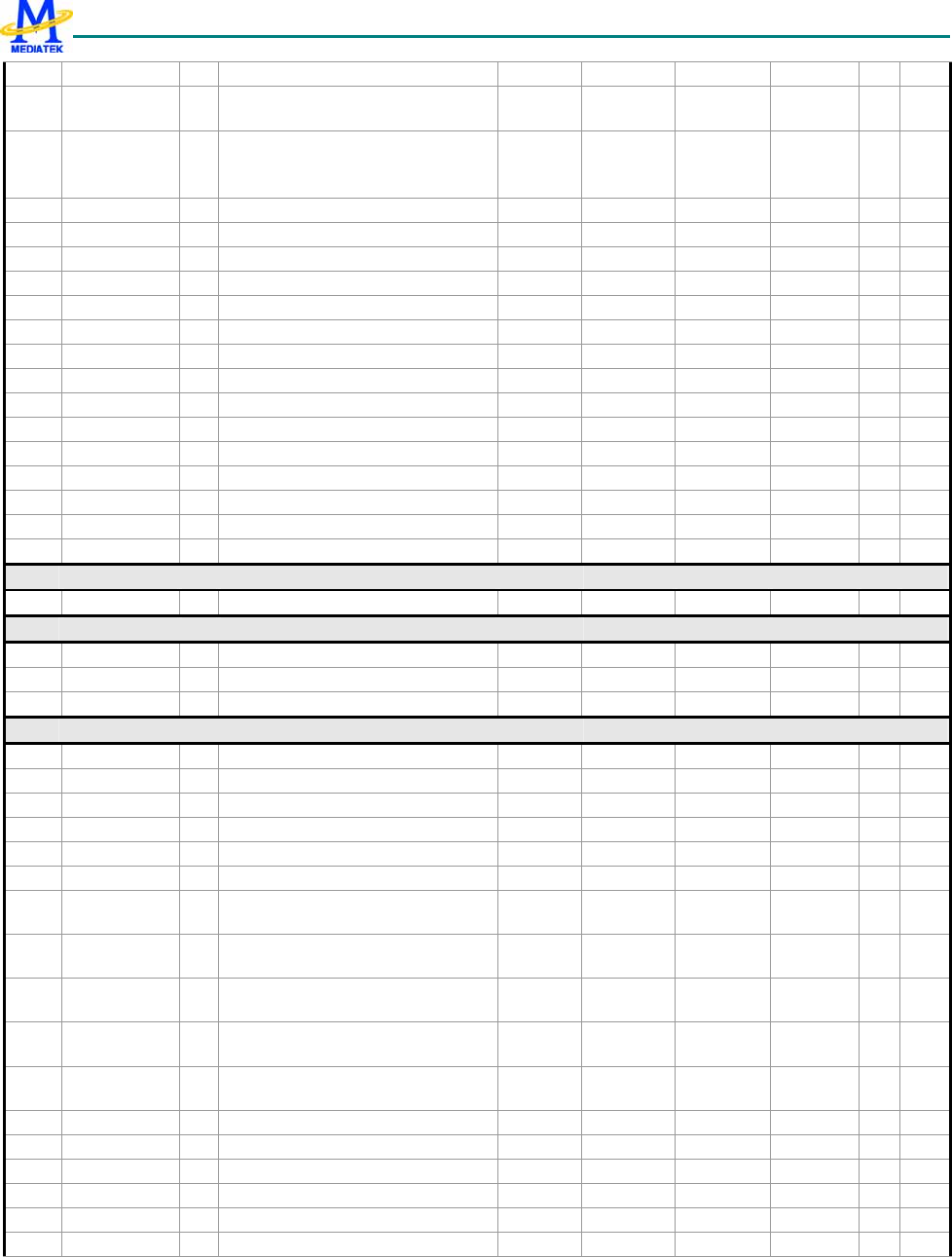

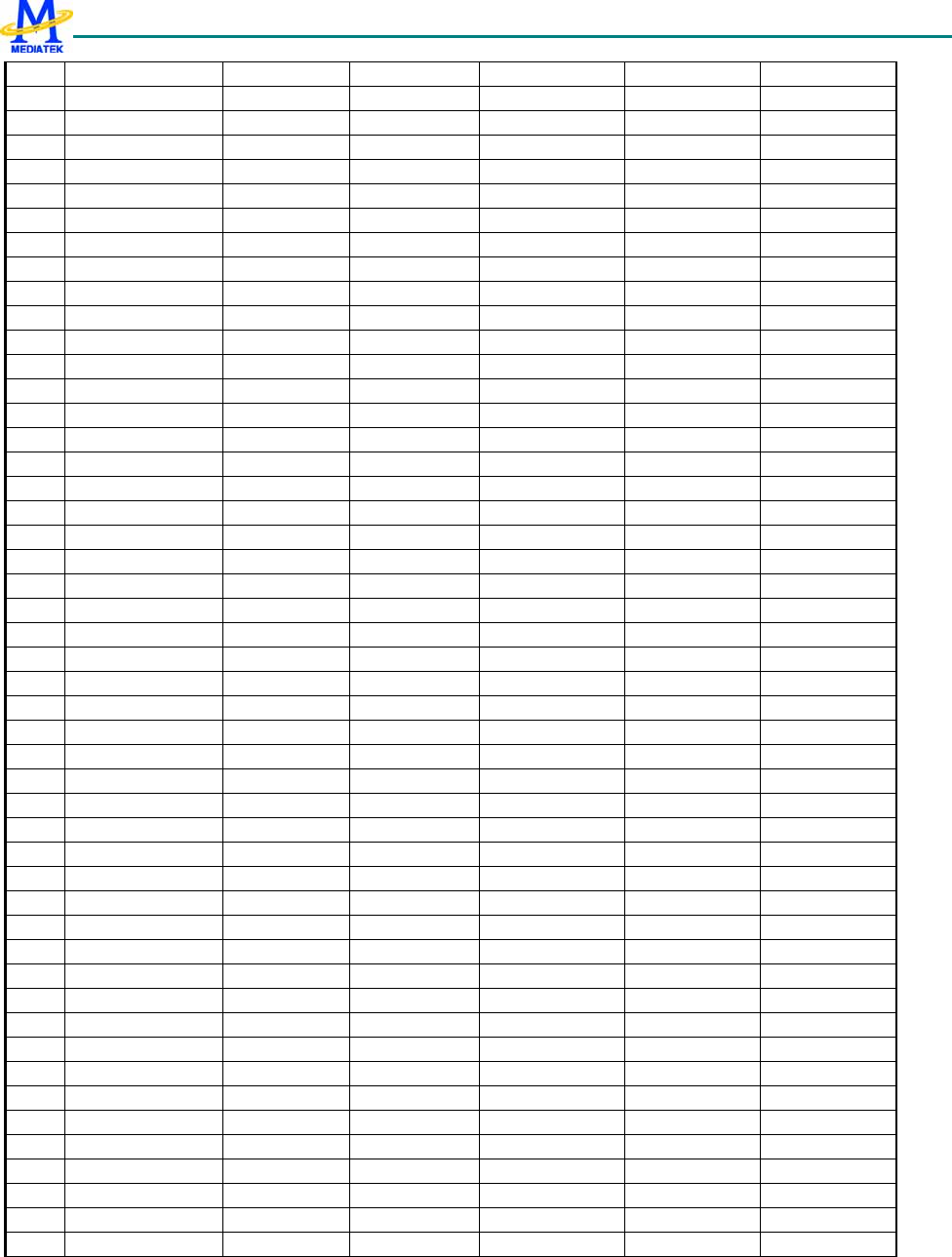

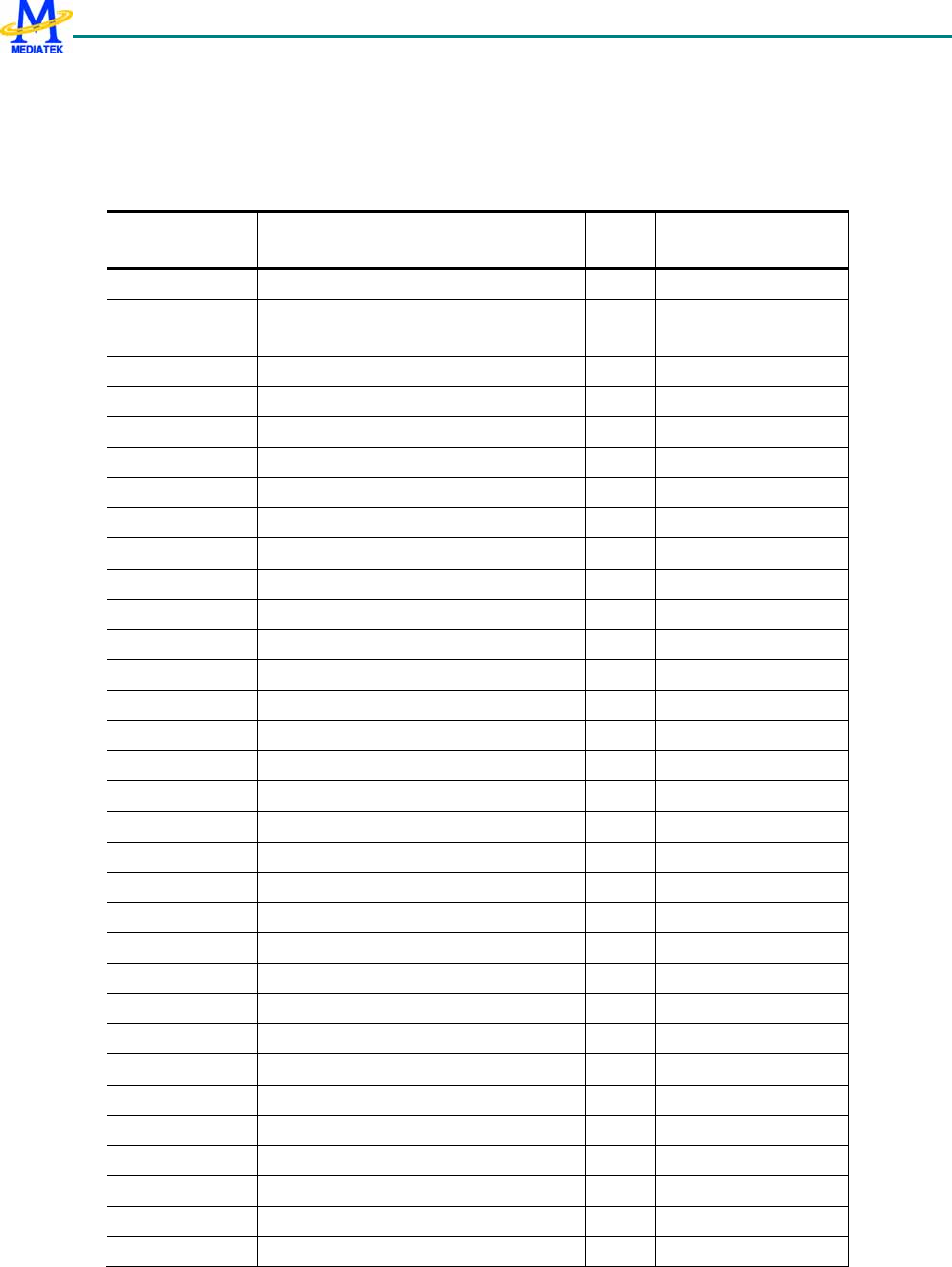

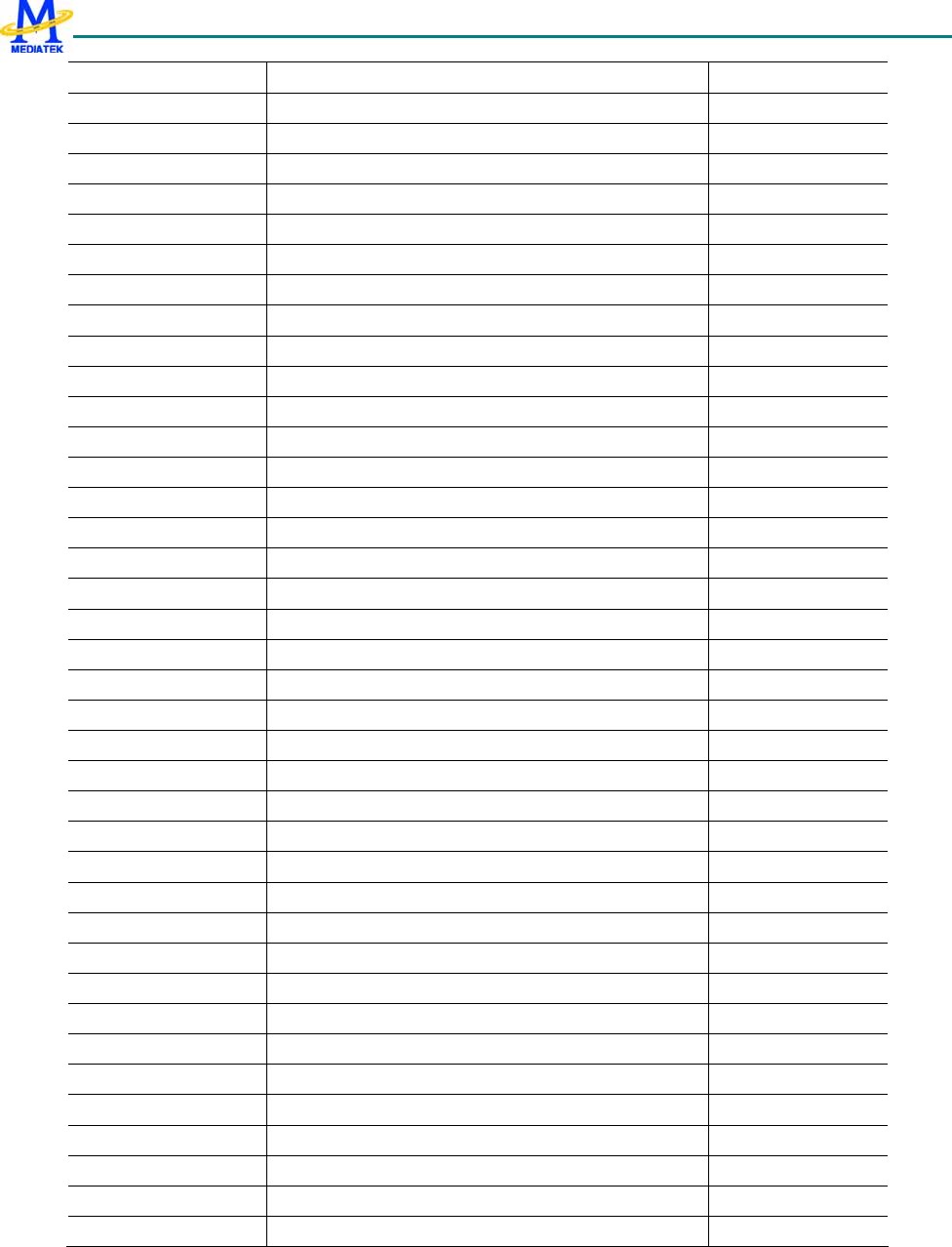

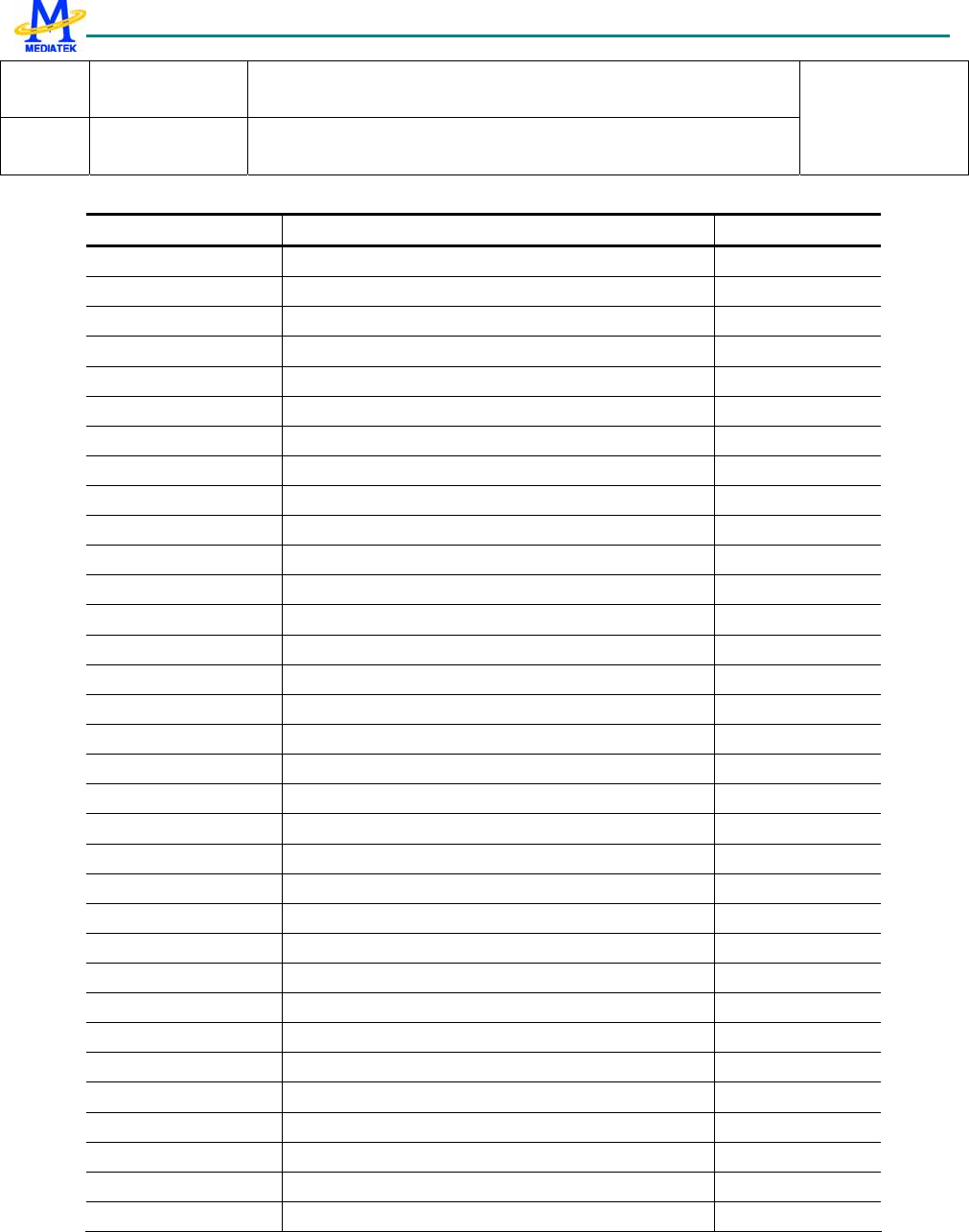

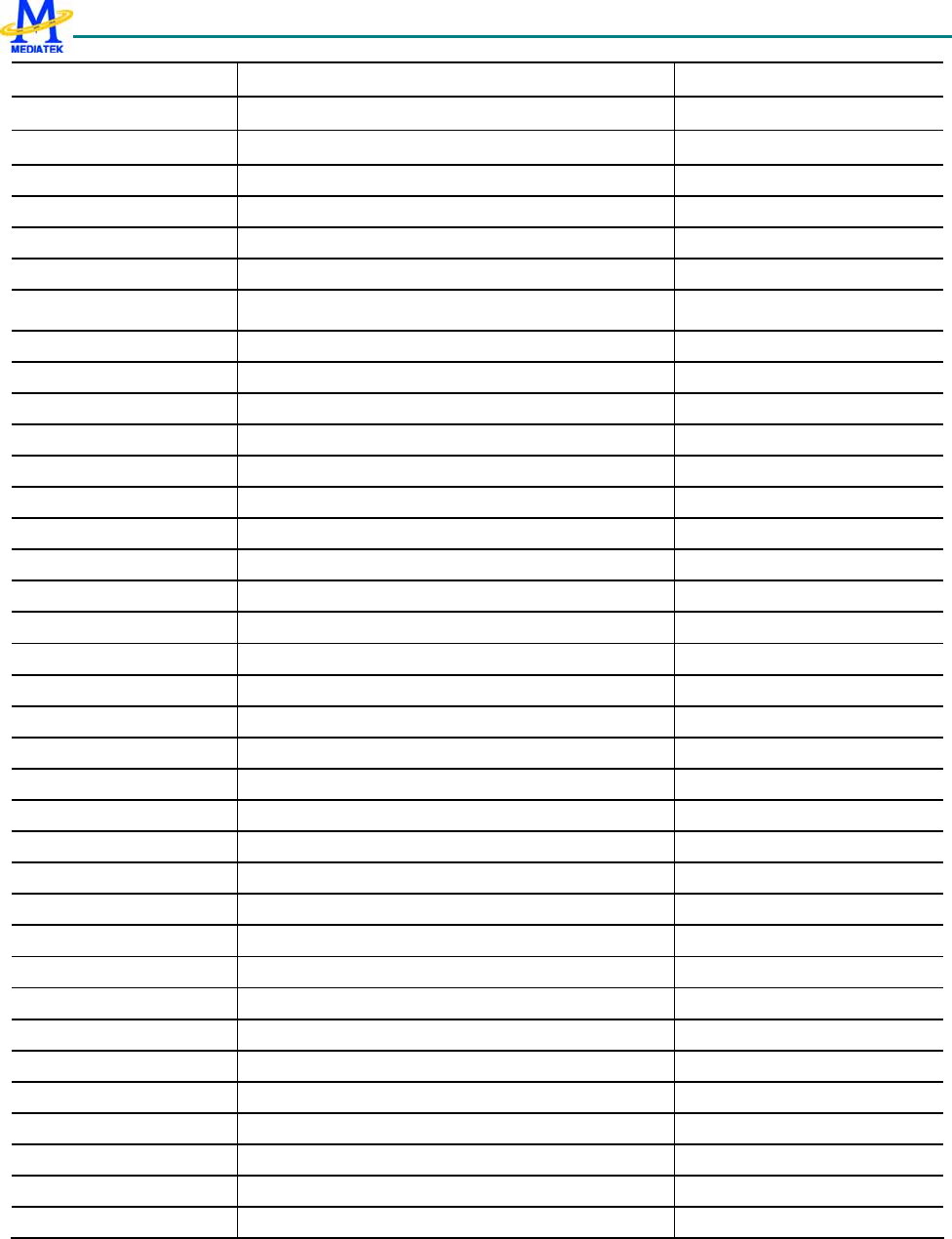

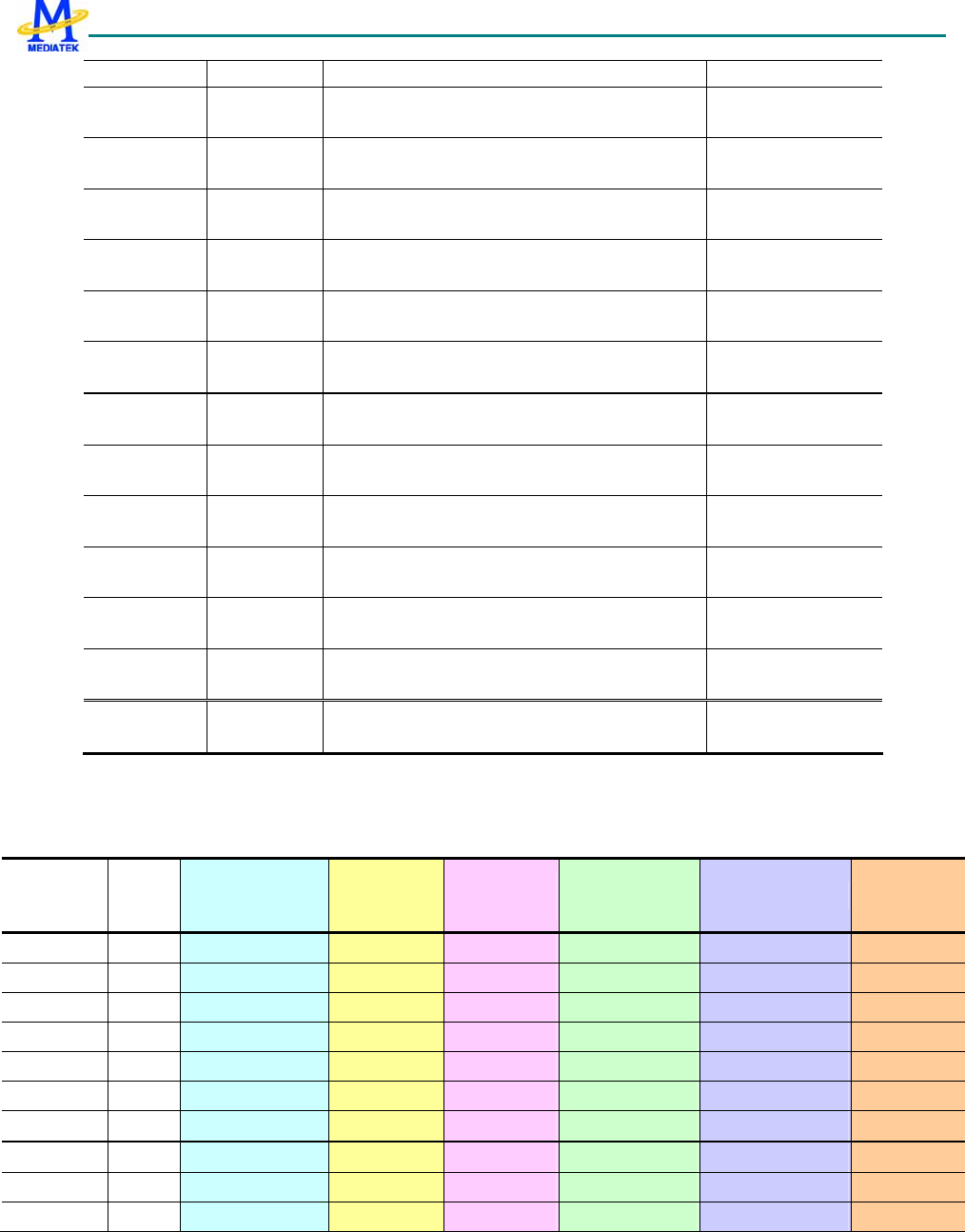

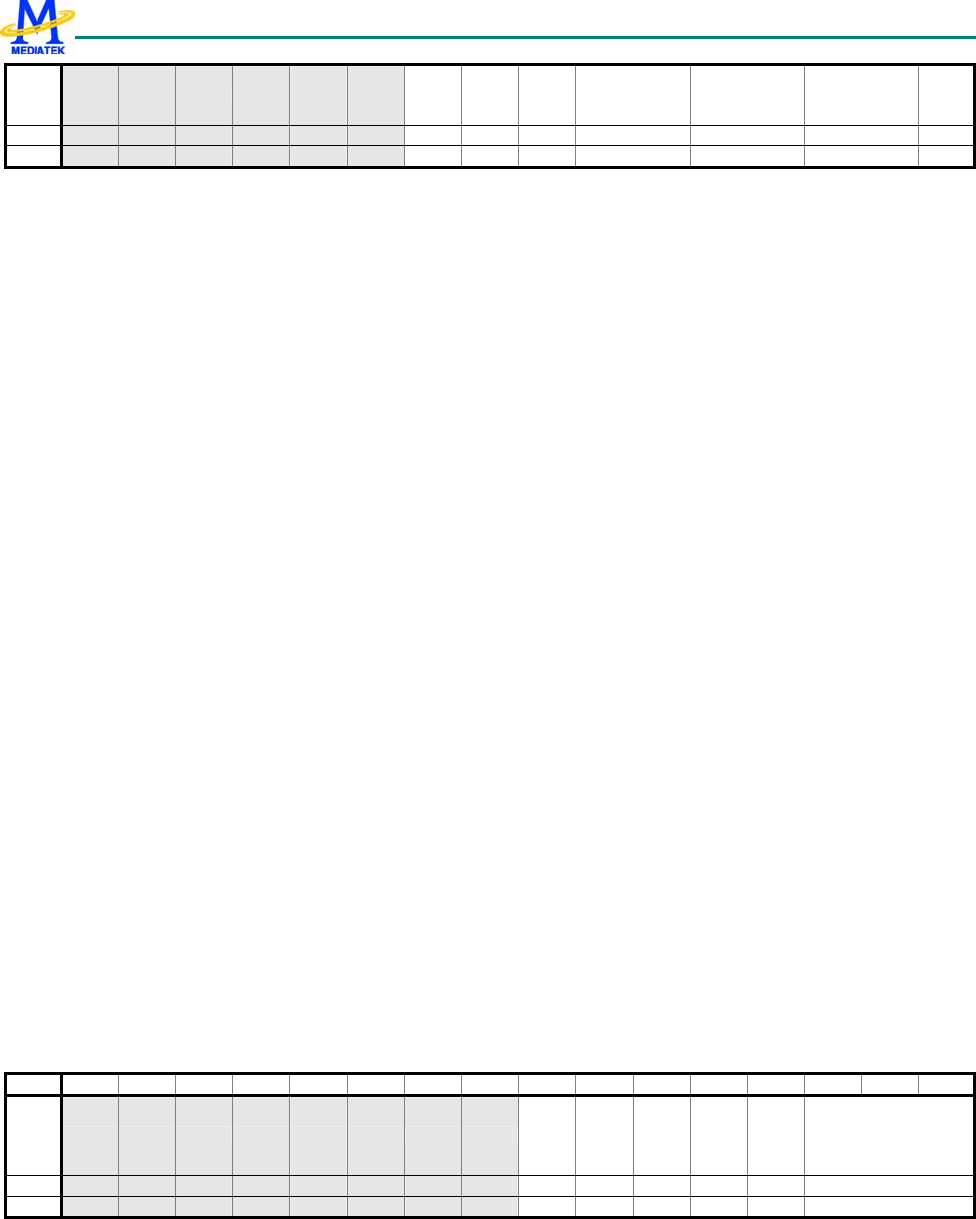

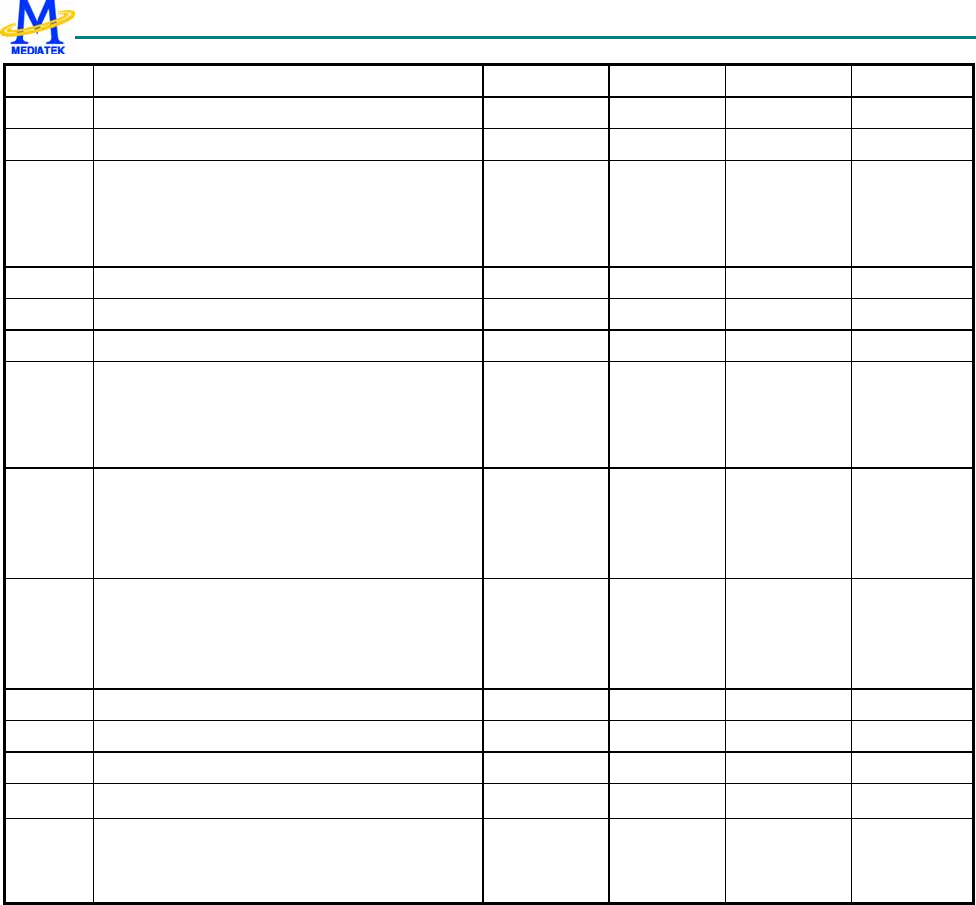

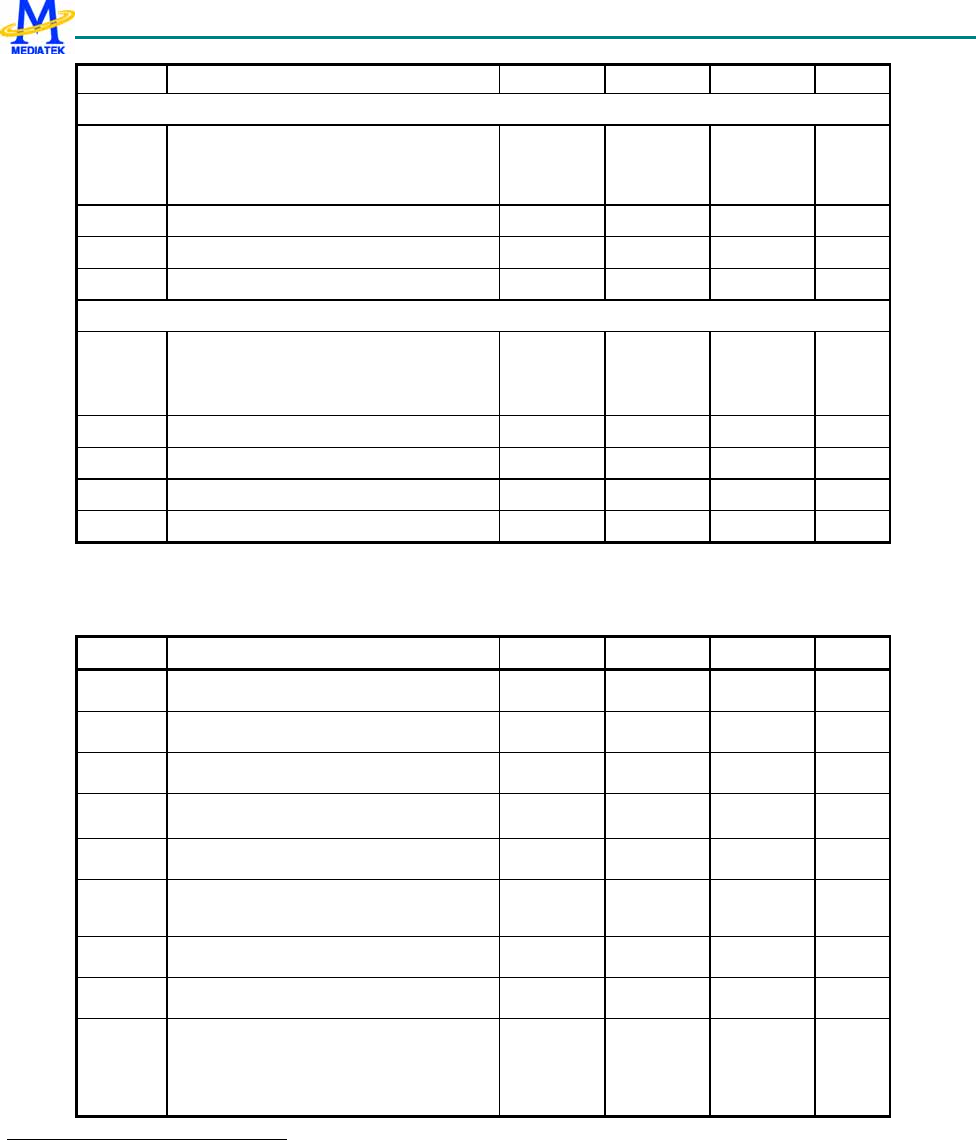

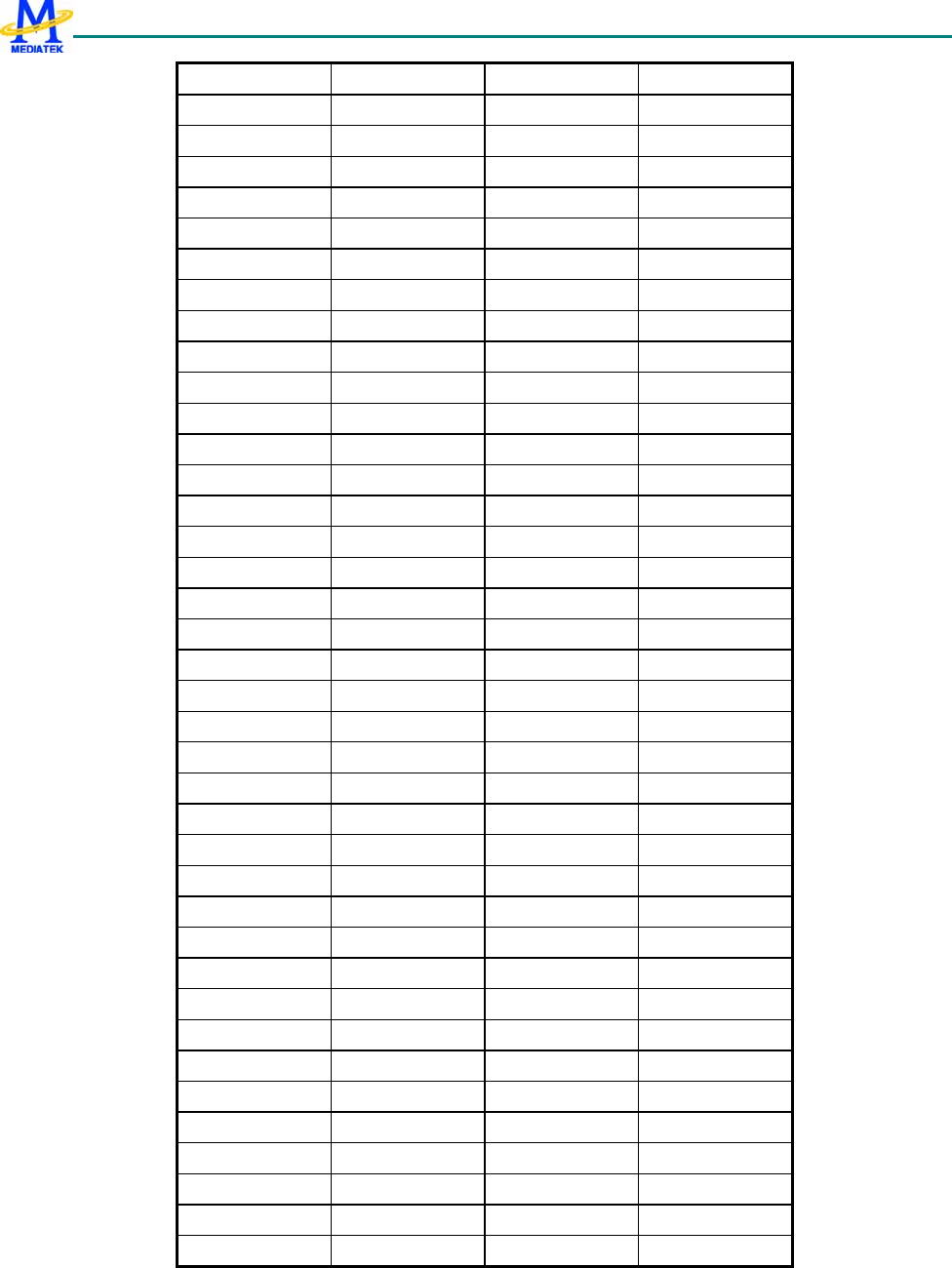

2.4 Pin Description

Ball

13X13 Name Dir

Description

Mode0 Mode1 Mode2 Mode3

PU/

PD Rese

t

JTAG Port

G4 JTRST_B I JTAG test port reset input PD PD

G3 JTCK I JTAG test port clock input PU PU

G2 JTDI I JTAG test port data input PU PU

G1 JTMS I JTAG test port mode switch PU PU

H1 JTDO IO JTAG test port data output

H2 JRTCK IO JTAG test port returned clock output

RF Parallel Control Unit

AE6 BPI_BUS0 IO RF hard-wire control bus 0

AD7 BPI_BUS1 IO RF hard-wire control bus 1

AC7 BPI_BUS2 IO RF hard-wire control bus 2

AC6 BPI_BUS3 IO RF hard-wire control bus 3 GPIO19 BPI_BUS3 PU/

PD

PD

AE8 BPI_BUS4 IO RF hard-wire control bus 4

AD8 BPI_BUS5 IO RF hard-wire control bus 5

AC8 BPI_BUS6 IO RF hard-wire control bus 6 GPIO20 BPI_BUS6 PU/

PD

PD

AB8 BPI_BUS7 IO RF hard-wire control bus 7 GPIO21 BPI_BUS7 PU/

PD

PD

MT6235 GSM/GPRS Baseband Processor Data Sheet Revision 1.02

21/599 MediaTek Inc. Confidential

AE9 BPI_BUS8 IO RF hard-wire control bus 8 GPIO22 BPI_BUS8 PU/

PD

PD

AD9 BPI_BUS9 IO RF hard-wire control bus 9 GPIO23 BPI_BUS9 BSI_CS1 PU/

PD

PD

RF Serial Control Unit

AC9 BSI_CS0 IO RF 3-wire interface chip select 0

AE10 BSI_DATA IO RF 3-wire interface data output

AD10 BSI_CLK IO RF 3-wire interface clock output

PWM Interface

AC10 PWM0 IO Pulse width modulated signal 0 GPIO39 PWM0 PU/

PD

PD

AB10 PWM1 IO Pulse width modulated signal 1 GPIO40 PWM1 BSI_RFIN PU/

PD

PD

AC5 PWM2 IO Pulse width modulated signal 2 GPIO17 PWM2 D2_TID5 PU/

PD

PD

AE5 PWM3 IO Pulse width modulated signal 3 GPIO18 PWM3 D2_TID6 PU/

PD

PD

Camera Control Interface

AE4 SCL IO GPIO15 SCL D2_TID3 PU/

PD

PU

AD5 SDA IO GPIO16 SDA D2_TID4 PU/

PD

PU

Serial LCD/PM IC Interface

AC11 LSCK IO Serial display interface data output GPIO24 LSCK DSP_GPO2 IRQ0 PU/

PD

PD

U11 LSA0 IO Serial display interface address output GPIO25 LSA0 DSP_GPO3 IRQ1 PU/

PD

PD

MT6235 GSM/GPRS Baseband Processor Data Sheet Revision 1.02

22/599 MediaTek Inc. Confidential

AD12 LSDA IO Serial display interface clock output GPIO26 LSDA CLKM1 TDTIRQ PU/

PD

PD

AE12 LSCE0B IO Serial display interface chip select 0

output

GPIO27 LSCE0B CLKM2 TCTIRQ2 PU/

PD

PU

AC12 LSCE1B IO

Serial display interface chip select 1

output

GPIO28 LSCE1B LPCE2B TCTIRQ1

PU/

PD

PU

Parallel LCD/NAND-Flash Interface

AB12 LPCE1B IO Parallel display interface chip select 1

output

GPIO29 LPCE1B NCE1B TEVTVAL

PU/

PD

PU

U12 LPCE0B IO

Parallel display interface chip select 0

output

AE13 LPTE IO GPIO30 LPTE PU/

PD

PD

AC13 LRSTB IO Parallel display interface Reset Signal

AD13 LRDB IO Parallel display interface Read Strobe

U13 LPA0 IO

Parallel display interface address

output

AE14 LWRB IO Parallel display interface Write Strobe

AD14 NLD17 IO Parallel LCD/NAND-Flash Data 17 GPIO31 NLD17 PU/

PD

PD

AC14 NLD16 IO Parallel LCD/NAND-Flash Data 16 GPIO32 NLD16 PU/

PD

PD

AB14 NLD15 IO Parallel LCD/NAND-Flash Data 15 PD

U14 NLD14 IO Parallel LCD/NAND-Flash Data 14 PD

AE15 NDL13 IO Parallel LCD/NAND-Flash Data 13 PD

AD15 NLD12 IO Parallel LCD/NAND-Flash Data 12 PD

AC15 NLD11 IO Parallel LCD/NAND-Flash Data 11 PD

AB15 NLD10 IO Parallel LCD/NAND-Flash Data 10 PD

AE16 NLD9 IO Parallel LCD/NAND-Flash Data 9 PD

AD16 NLD8 IO Parallel LCD/NAND-Flash Data 8 PD

AC16 NLD7 IO Parallel LCD/NAND-Flash Data 7 PD

AB16 NLD6 IO Parallel LCD/NAND-Flash Data 6 PD

U16 NLD5 IO Parallel LCD/NAND-Flash Data 5 PD

AE17 NLD4 IO Parallel LCD/NAND-Flash Data 4 PD

AD17 NLD3 IO Parallel LCD/NAND-Flash Data 3 PD

AC17 NLD2 IO Parallel LCD/NAND-Flash Data 2 PD

AE18 NLD1 IO Parallel LCD/NAND-Flash Data 1 PD

AD18 NLD0 IO Parallel LCD/NAND-Flash Data 0 PD

AC18 NRNB IO NAND-Flash Read/Busy Flag GPIO33 NRNB PU/

PD

PU

AB18 NCLE IO NAND-Flash Command Latch Signal GPIO34 NCLE

PU/

PD

AE19 NALE IO NAND-Flash Address Latch Signal GPIO35 NALE

PU/

PD

AD19 NWEB IO NAND-Flash Write Strobe GPIO36 NWEB

PU/

PD

AC19 NREB IO NAND-Flash Read Strobe GPIO37 NREB

PU/

PD

MT6235 GSM/GPRS Baseband Processor Data Sheet Revision 1.02

23/599 MediaTek Inc. Confidential

AB19 NCEB IO NAND-Flash Chip select output GPIO38 NCE0B

PU/

PD

Miscellaneous

F25 SYSRST_B I System reset input active low PU PU

G23 WATCHDOG IO Watchdog reset output

U10 SRCLKENAN IO

External TCXO enable output active

low

GPIO42 SRCLKEN

AN

PU/

PD

AE11 SRCLKENA IO External TCXO enable output active

high

GPIO41 SRCLKEN

A

PU/

PD

AD11 SRCLKENAI IO External TCXO enable input GPIO43 SRCLKEN

AI

PU/

PD

PD

B14 TESTMODE I TESTMODE enable input PD PD

Y4 VCCQ I

AA1 FSOURCE I

AD6 SECU_EN I

AE7 XBOOT I PD PD

Keypad Interface

A22 KCOL7 IO Keypad column 7 GPIO55 KCOL7 IRDA_PDN PU/

PD

PU

B22 KCOL6 IO Keypad column 6 GPIO56 KCOL6 PU/

PD

PU

A21 KCOL5 IO Keypad column 5 PU PU

B21 KCOL4 IO Keypad column 4 PU PU

C21 KCOL3 IO Keypad column 3 PU PU

D21 KCOL2 IO Keypad column 2 PU PU

A20 KCOL1 IO Keypad column 1 PU PU

B20 KCOL0 IO Keypad column 0 PU PU

C20 KROW7 IO Keypad row 7 GPIO57 KROW7 CLKM4 PU/

PD

PD

D20 KROW6 IO Keypad row 6 GPIO58 KROW6 PU/

PD

PD

A19 KROW5 IO Keypad row 5

B19 KROW4 IO Keypad row 4

C19 KROW3 IO Keypad row 3

A18 KROW2 IO Keypad row 2

B18 KROW1 IO Keypad row 1

C18 KROW0 IO Keypad row 0

External Interrupt Interface

F24 EINT0 IO External interrupt 0 PU PU

F23 EINT1 IO External interrupt 1 PU PU

E25 EINT2 IO External interrupt 2 PU PU

E24 EINT3 IO External interrupt 3 GPIO44 EINT3 DRF_DAT

A

IRQ2 PU/

PD

PU

E23 EINT4 IO External interrupt 4 GPIO45 EINT4 DRF_EN CLKM3

PU/

PD

PU

D23 EINT5 IO External interrupt 5 GPIO46 EINT5 EDICK PU/

PD

PU

D25 EINT6 IO External interrupt 6 GPIO47 EINT6 EDIWS PU/

PD

PU

D24 EINT7 IO External interrupt 7 GPIO48 EINT7 EDIDAT PU/

PD

PU

MT6235 GSM/GPRS Baseband Processor Data Sheet Revision 1.02

24/599 MediaTek Inc. Confidential

K17 MFIQ IO Interrupt to MCU GPIO66 :nFIQ CLKM7 PU/

PD

PU

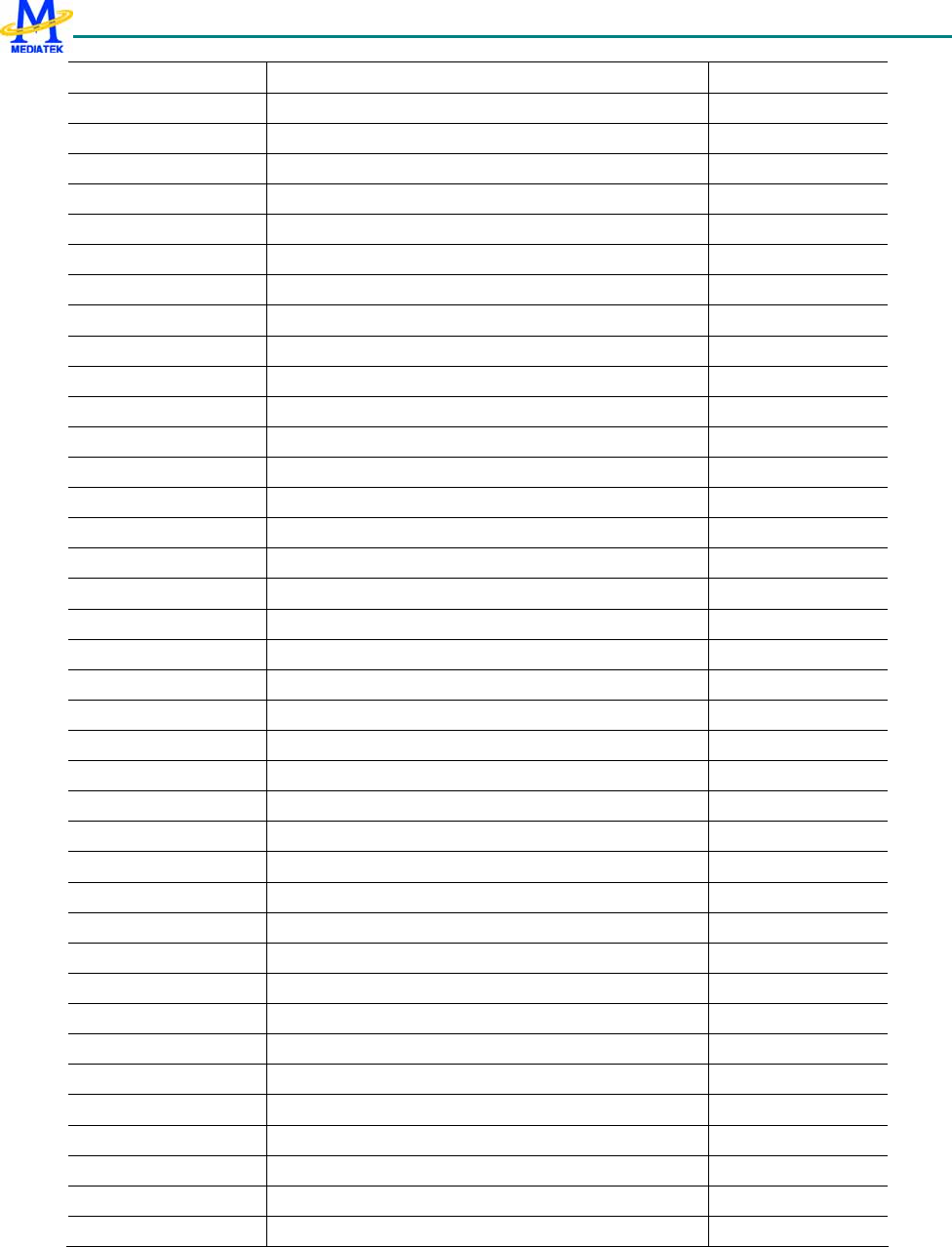

External Memory Interface

G24 ED0 IO External memory data bus 0

G22 ED1 IO External memory data bus 1

G25 ED2 IO External memory data bus 2

H24 ED3 IO External memory data bus 3

H23 ED4 IO External memory data bus 4

J23 ED5 IO External memory data bus 5

J24 ED6 IO External memory data bus 6

K22 ED7 IO External memory data bus 7

H25 ED8 IO External memory data bus 8

J25 ED9 IO External memory data bus 9

K23 ED10 IO External memory data bus 10

K24 ED11 IO External memory data bus 11

K25 ED12 IO External memory data bus 12

L17 ED13 IO External memory data bus 13

L23 ED14 IO External memory data bus 14

L24 ED15 IO External memory data bus 15

M25 ERD_B IO External memory read strobe

N17 EWR_B IO External memory write strobe

L25 ECS0_B IO External memory chip select 0

M17 ECS1_B IO External memory chip select 1

M23 ECS2_B IO External memory chip select 2

M24 ECS3_B IO External memory chip select 3

R25 EWAIT IO

Flash, PSRAM and CellularRAM data

ready

PD

N25 ECAS_B IO MobileRAM column address

P24 ERAS_B IO MobileRAM row address

P23 ECKE IO MobileRAM clock enable

N22 ED_CLK O MobileRAM clock

T17 EADMUX IO GPIO65

EADMUX CLKM6 PU/

PD

R17 EDQM1 IO

P25 EDQM0 IO

P17 EADV_B O

Flash, PSRAM and CellularRAM

address valid

N24 EC_CLK O Flash, PSRAM and CellularRAM

clock

T23 EA0 IO External memory address bus 0

T22 EA1 IO External memory address bus 1

T24 EA2 IO External memory address bus 2

T25 EA3 IO External memory address bus 3

U23 EA4 IO External memory address bus 4

U24 EA5 IO External memory address bus 5

U25 EA6 IO External memory address bus 6

V23 EA7 IO External memory address bus 7

V24 EA8 IO External memory address bus 8

V25 EA9 IO External memory address bus 9

W22 EA10 IO External memory address bus 10

MT6235 GSM/GPRS Baseband Processor Data Sheet Revision 1.02

25/599 MediaTek Inc. Confidential

W23 EA11 IO External memory address bus 11

W24 EA12 IO External memory address bus 12

W25 EA13 IO External memory address bus 13

Y23 EA14 IO External memory address bus 14

Y24 EA15 IO External memory address bus 15

Y25 EA16 IO External memory address bus 16

AA23 EA17 IO External memory address bus 17

AA24 EA18 IO External memory address bus 18

AA25 EA19 IO External memory address bus 19

AB24 EA20 IO External memory address bus 20

AB25 EA21 IO External memory address bus 21

AC23 EA22 IO External memory address bus 22

AC24 EA23 IO External memory address bus 23

AC25 EA24 IO External memory address bus 24

AD24 EA25 IO External memory address bus 25

AD25 EA26 IO External memory address bus 26 GPIO64 EA26 CLKM5 PU/

PD

USB Interface

AD20 USB_XTALI IO

AE20 USB_XTALO IO

AE21 VSSCA_USB IO

AD22 VSSCD_USB IO

AC21 VRT IO

AD23 VSS33_USB IO

AE22 USB_DP IO USB D+ Input/Output

AE23 USB_DM IO USB D- Input/Output

Memory Card Interface

B16 MCCM0 IO SD Command/MS Bus State Output GPIO67 MC0CM0 TDMA_C

K

PU/

PD

PU

C16 MCDA0 IO

SD Serial Data IO 0/MS Serial Data

IO

GPIO68 MC0DA0 TDMA_D

1

PU/

PD

PU

D16 MCDA1 IO SD Serial Data IO 1 GPIO69 MC0DA1 TDMA_D

0

PU/

PD

PU

J16 MCDA2 IO SD Serial Data IO 2 GPIO70 MC0DA2 TDMA_FS

PU/

PD

PU

C15 MCDA3 IO SD Serial Data IO 3 GPIO71 MC0DA3 PU/

PD

PU

D15 MCCK IO

SD Serial Clock/MS Serial Clock

Output

GPIO72 MC0CK PU/

PD

PU

J15 MCPWRON IO SD Power On Control Output GPIO73 MC0PWR

ON

CLKM8 PU/

PD

PU

C14 MCWP IO SD Write Protect Input GPIO74 MC0WP CLKM9 PU/

PD

PU

D14 MCINS IO SD Card Detect Input GPIO75 MC0INS PU/

PD

PU

UART/IrDA Interface

C25 URXD1 IO UART 1 receive data PU

C24 UTXD1 IO UART 1 transmit data

C23 UCTS1 IO UART 1 clear to send GPIO49 UCTS1 UCTS2 PU/

PD

PU

B25 URTS1 IO UART 1 request to send GPIO50 URTS1 URTS2 PU/

MT6235 GSM/GPRS Baseband Processor Data Sheet Revision 1.02

26/599 MediaTek Inc. Confidential

PD

A24 URXD2 IO UART 2 receive data GPIO51 URXD2 UCTS3 PU/

PD

PU

B24 UTXD2 IO UART 2 transmit data GPIO52 UTXD2 URTS3 PU/

PD

PU

A23 URXD3 IO UART 3 receive data GPIO53 URXD3 IRDA_RX

D

PU/

PD

PU

B23 UTXD3 IO UART 3 transmit data GPIO54 UTXD3 IRDA_TX

D

PU/

PD

PU

Digital Audio Interface

D18 DAICLK IO DAI clock output GPIO59 DAICLK PU/

PD

PD

A17 DAIPCMOUT IO DAI pcm data out GPIO60 DAIPCMO

UT

PU/

PD

PD

B17 DAIPCMIN IO DAI pcm data input GPIO61 DAIPCMI

N

PU/

PD

PD

C17 DAIRST IO DAI reset signal input GPIO62 DAIRST PU/

PD

PD

D17 DAISYNC IO

DAI frame synchronization signal

output

GPIO63 DAISYNC

PU/

PD

PD

CMOS Sensor Interface

AA2 CMRST IO CMOS sensor reset signal output GPIO0 CMRST CLKM0 DSP_GPO

0

PU/

PD

PD

AA3 CMPDN IO CMOS sensor power down control GPIO1 CMPDN DSP_GPO

1

PU/

PD

PD

AB3 CMVREF IO Sensor vertical reference signal input GPIO2 CMVREF TBTXEN D1_TID0 PU/

PD

PD

AB2 CMHREF IO

Sensor horizontal reference signal

input

GPIO3 CMHREF TBTXFS PU/

PD

PD

AA4 CMPCLK IO CMOS sensor pixel clock input GPIO4 CMPCLK TBRXEN D1_TID1 PU/

PD

PD

AB6 CMMCLK IO CMOS sensor master clock output GPIO5 CMMCLK TBRXFS PU/

PD

PD

AC2 CMDAT7 IO CMOS sensor data input 7 GPIO6 CMDAT7 D1ICK PU/

PD

PD

AC3 CMDAT6 IO CMOS sensor data input 6 GPIO7 CMDAT6 D1ID

PU/

PD

PD

AC1 CMDAT5 IO CMOS sensor data input 5 GPIO8 CMDAT5 D1IMS PU/

PD

PD

AD1 CMDAT4 IO CMOS sensor data input 4 GPIO9 CMDAT4 D2ICK PU/

PD

PD

AE2 CMDAT3 IO CMOS sensor data input 3 GPIO10 CMDAT3 D2ID PU/

PD

PD

AD3 CMDAT2 IO CMOS sensor data input 2 GPIO11 CMDAT2 D2IMS PU/

PD

PD

AD4 CMDAT1 IO CMOS sensor data input 1 GPIO12 CMDAT1 D2_TID0

PU/

PD

PD

AE3 CMDAT0 IO CMOS sensor data input 0 GPIO13 CMDAT0 D2_TID1

PU/

PD

PD

AC4 CMFLASH IO GPIO14 CMFLASH D2_TID2

PU/

PD

PD

Analog Interface

J1 AU_MOUTL O Audio analog output left channel

MT6235 GSM/GPRS Baseband Processor Data Sheet Revision 1.02

27/599 MediaTek Inc. Confidential

J2 AU_MOUTR O Audio analog output right channel

K4 AU_FMINL I FM radio analog input left channel

K3 AU_FMINR I FM radio analog input right channel

K2 AU_OUT0_N O Earphone 0 amplifier output (-)

K1 AU_OUT0_P O Earphone 0 amplifier output (+)

L2 AU_MICBIAS

_P

O Microphone bias supply (+)

L1 AU_MICBIAS

_N

O Microphone bias supply (-)

M2 AU_VREF_N O Audio reference voltage (-)

M1 AU_VREF_P O Audio reference voltage (+)

N1 AU_VIN0_P I Microphone 0 amplifier input (+)

N2 AU_VIN0_N I Microphone 0 amplifier input (-)

N3 AU_VIN1_N I Microphone 1 amplifier input (-)

N4 AU_VIN1_P I Microphone 1 amplifier input (+)

P1 BDLAQP I

Quadrature input (Q+) baseband codec

downlink

P2 BDLAQN I

Quadrature input (Q-) baseband codec

downlink

R1 BDLAIN I

In-phase input (I+) baseband codec

downlink

R2 BDLAIP I

In-phase input (I-) baseband codec

downlink

T3 APC I Automatic power control DAC output

T4 AUXADIN0 I Auxiliary ADC input 0

U2 AUXADIN1 I Auxiliary ADC input 1

U4 AUXADIN2 I Auxiliary ADC input 2

V2 AUXADIN3 I Auxiliary ADC input 3

U1 AUX_REF I Auxiliary ADC reference voltage input

U3 XP I

V1 XM I

W3 YP I

V3 YM I

V4 AFC O

Automatic frequency control DAC

output

W2 AFC_BYP O Automatic frequency control DAC

bypass capacitance

B1 BATDET I

C2 VRF_SENSE I

C1 VRF I

E3 VTCXO I

F2 VREF I

C12 VIBRATOR O

D11 LED O

A11 VCORE I

C11 VCORE_FB I

B11 BAT_BACKU

P

I

F1 VA

A9 VM I

D10 VM_SENSE I

MT6235 GSM/GPRS Baseband Processor Data Sheet Revision 1.02

28/599 MediaTek Inc. Confidential

C10 VCAM_D II

D8 VCAM_A_SE

NSE

I

A7 VCAM_A

I

C8 VBT I

A6 VIO I

C7 VUSB I

A5 VSIM I

C5 SIO IO

C6 PWRKEY I

D5 ISENSE I

A4 VMSEL I

B4 GATEDRV I

C4 CHRIN I

A3 SCLK I

B3 BATSENSE I

C3 SRST O

A2 RESET I

B2 RSTCAP IO

VCXO Interface

Y1 SYSCLK I 13MHz or 26MHz system clock input

RTC Interface

A14 XIN I 32.768 KHz crystal input

A15 XOUT O 32.768 KHz crystal output

B13 BBWAKEUP IO Baseband power on/off control

Supply Voltages

H3 VDDK Supply voltage of internal logic

AB7 VDDK Supply voltage of internal logic

AB20 VDDK Supply voltage of internal logic

Y22 VDDK Supply voltage of internal logic

F22 VDDK Supply voltage of internal logic

J14 VDDK Supply voltage of internal logic

AB23 VDD33_EMI Supply voltage of memory interface

driver

V22 VDD33_EMI Supply voltage of memory interface

driver

R22 VDD33_EMI Supply voltage of memory interface

driver

M22 VDD33_EMI Supply voltage of memory interface

driver

J22 VDD33_EMI Supply voltage of memory interface

driver

AD2 VDD33_CAM

AB13 VDD33_LCD

AB17 VDD33_LCD

AC22 VDD33_USB

AB21 VDDC_USB

D13 VDD33_MC

MT6235 GSM/GPRS Baseband Processor Data Sheet Revision 1.02

29/599 MediaTek Inc. Confidential

H4 VDD33 Supply voltage of drivers except

memory interface, USB and

MS/MMC/SD

AB9 VDD33 Supply voltage of drivers except

memory interface, USB and

MS/MMC/SD

E22 VDD33 Supply voltage of drivers except

memory interface, USB and

MS/MMC/SD

D19 VDD33 Supply voltage of drivers except

memory interface, USB and

MS/MMC/SD

F4 VSS33 Ground of drivers except memory

interface, USB and MS/MMC/SD

Y3 VSS33 Ground of drivers except memory

interface, USB and MS/MMC/SD

AB5 VSS33 Ground of drivers except memory

interface, USB and MS/MMC/SD

AB11 VSS33 Ground of drivers except memory

interface, USB and MS/MMC/SD

U15 VSS33 Ground of drivers except memory

interface, USB and MS/MMC/SD

AC20 VSS33 Ground of drivers except memory

interface, USB and MS/MMC/SD

AE24 VSS33 Ground of drivers except memory

interface, USB and MS/MMC/SD

AA22 VSS33 Ground of drivers except memory

interface, USB and MS/MMC/SD

U22 VSS33 Ground of drivers except memory

interface, USB and MS/MMC/SD

P22 VSS33 Ground of drivers except memory

interface, USB and MS/MMC/SD

L22 VSS33 Ground of drivers except memory

interface, USB and MS/MMC/SD

H22 VSS33 Ground of drivers except memory

interface, USB and MS/MMC/SD

C22 VSS33 Ground of drivers except memory

interface, USB and MS/MMC/SD

A16 VSS33 Ground of drivers except memory

interface, USB and MS/MMC/SD

A13 VSS33 Ground of drivers except memory

interface, USB and MS/MMC/SD

L9 VSS33 Ground of drivers except memory

interface, USB and MS/MMC/SD

L11 VSS33 Ground of drivers except memory

interface, USB and MS/MMC/SD

L12 VSS33 Ground of drivers except memory

interface, USB and MS/MMC/SD

L13 VSS33 Ground of drivers except memory

interface, USB and MS/MMC/SD

L14 VSS33 Ground of drivers except memory

interface, USB and MS/MMC/SD

L15 VSS33 Ground of drivers except memory

interface, USB and MS/MMC/SD

MT6235 GSM/GPRS Baseband Processor Data Sheet Revision 1.02

30/599 MediaTek Inc. Confidential

M9 VSS33 Ground of drivers except memory

interface, USB and MS/MMC/SD

M11 VSS33 Ground of drivers except memory

interface, USB and MS/MMC/SD

M15 VSS33 Ground of drivers except memory

interface, USB and MS/MMC/SD

N11 VSS33 Ground of drivers except memory

interface, USB and MS/MMC/SD

N13 VSS33 Ground of drivers except memory

interface, USB and MS/MMC/SD

N15 VSS33 Ground of drivers except memory

interface, USB and MS/MMC/SD

P9 VSS33 Ground of drivers except memory

interface, USB and MS/MMC/SD

P11 VSS33 Ground of drivers except memory

interface, USB and MS/MMC/SD

P15 VSS33 Ground of drivers except memory

interface, USB and MS/MMC/SD

R9 VSS33 Ground of drivers except memory

interface, USB and MS/MMC/SD

R11 VSS33 Ground of drivers except memory

interface, USB and MS/MMC/SD

R12 VSS33 Ground of drivers except memory

interface, USB and MS/MMC/SD

R13 VSS33 Ground of drivers except memory

interface, USB and MS/MMC/SD

R14 VSS33 Ground of drivers except memory

interface, USB and MS/MMC/SD

R15 VSS33 Ground of drivers except memory

interface, USB and MS/MMC/SD

T9 VSS33 Ground of drivers except memory

interface, USB and MS/MMC/SD

W1 AVCC12_PLL

Y2 AVSS12_PLL

B15 VRTC Supply voltage for Real Time Clock

Analog Supplies

J4 AVDD28_MB

UF

Supply Voltage for Audio band section

J3 AVSS28_MBU

F

GND for Audio band section

K9 AVDD28_BUF Supply voltage for voice band transmit

section

L3 AVSS28_BUF GND for voice band transmit section

L4 AVDD28_AFE Supply voltage for voice band receive

section

M3 AGND28_AFE GND reference voltage for voice band

section

N9 AVSS28_AFE GND for voice band receive section

P4 AGND28_RFE GND reference voltage for baseband

section, APC, AFC and AUXADC

P3 AVSS28_GSM

RFTX

GND for baseband transmit section

MT6235 GSM/GPRS Baseband Processor Data Sheet Revision 1.02

31/599 MediaTek Inc. Confidential

R3 AVDD28_GS

MRFTX

Supply voltage for baseband transmit

section

T2 AVSS28_RFE GND for baseband receive section,

APC, AFC and AUXADC

T1 AVDD28_RFE Supply voltage for baseband receive

section, APC, AFC and AUXADC

D1 VBAT_VRF

D3 AGND_VRF

E4 GND_LDOS

E2 VBAT_VA

E1 VBAT_VA

F3 AGND_VA

D12 GND_DRV

A12 GND_VCORE

A10 VBAT_VCOR

E

B10 VBAT_LDOS1

B9 VBAT_LDOS1

B8 VBAT_LDOS2

D7 GND_LDOS

B7 VBAT_LDOS2

B6 VBAT_LDOS3

D6 GND_LDOS

D9 GND_LDOS

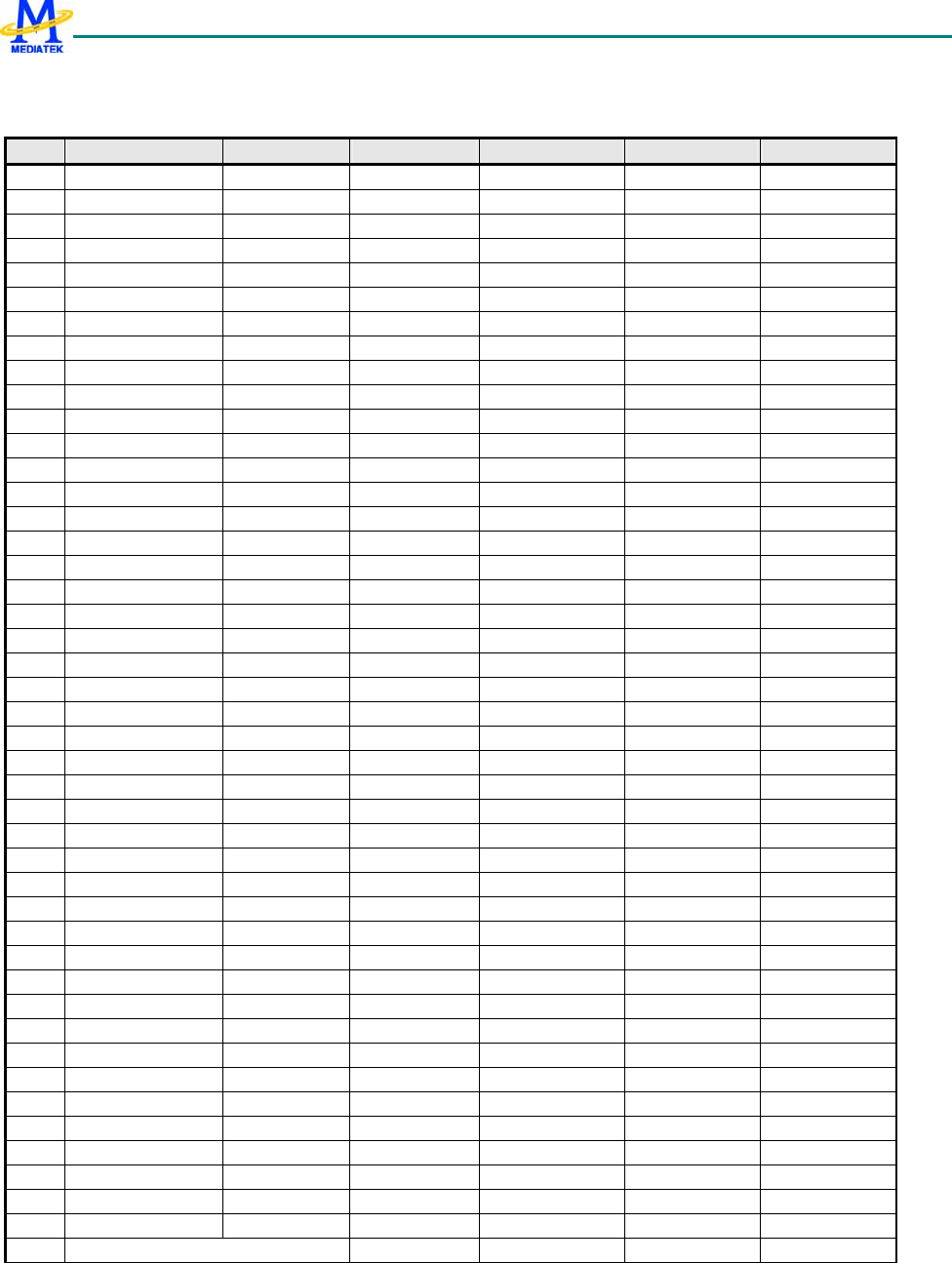

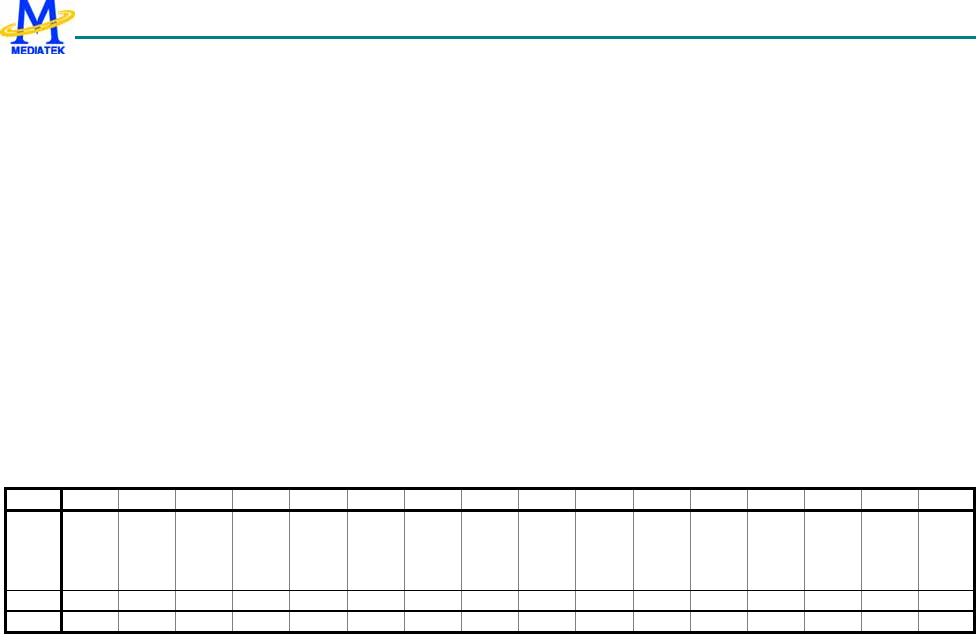

Table 2 Pin Descriptions (Bolded types are functions at reset)

MT6235 GSM/GPRS Baseband Processor Data Sheet Revision 1.02

32/599 MediaTek Inc. Confidential

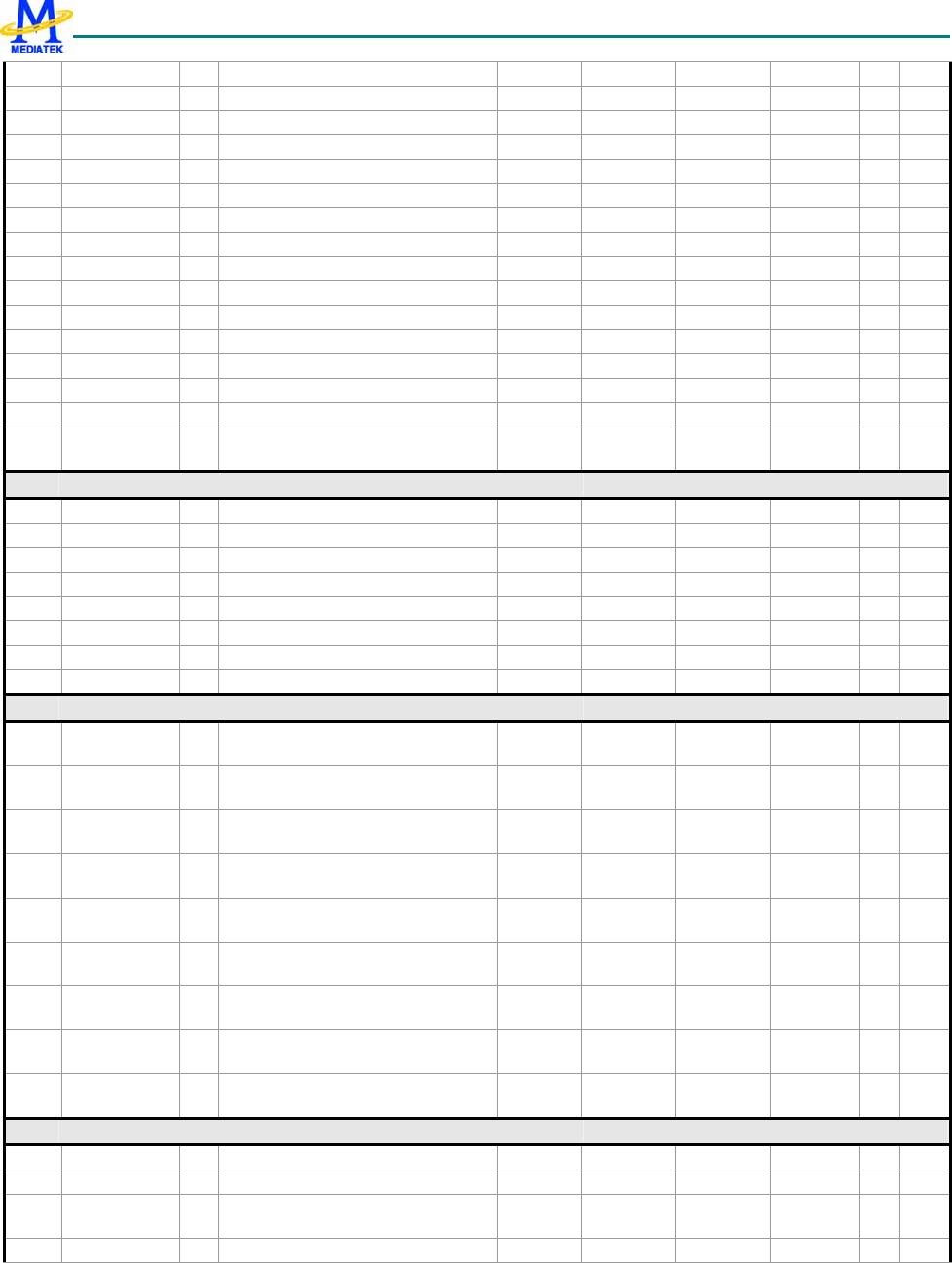

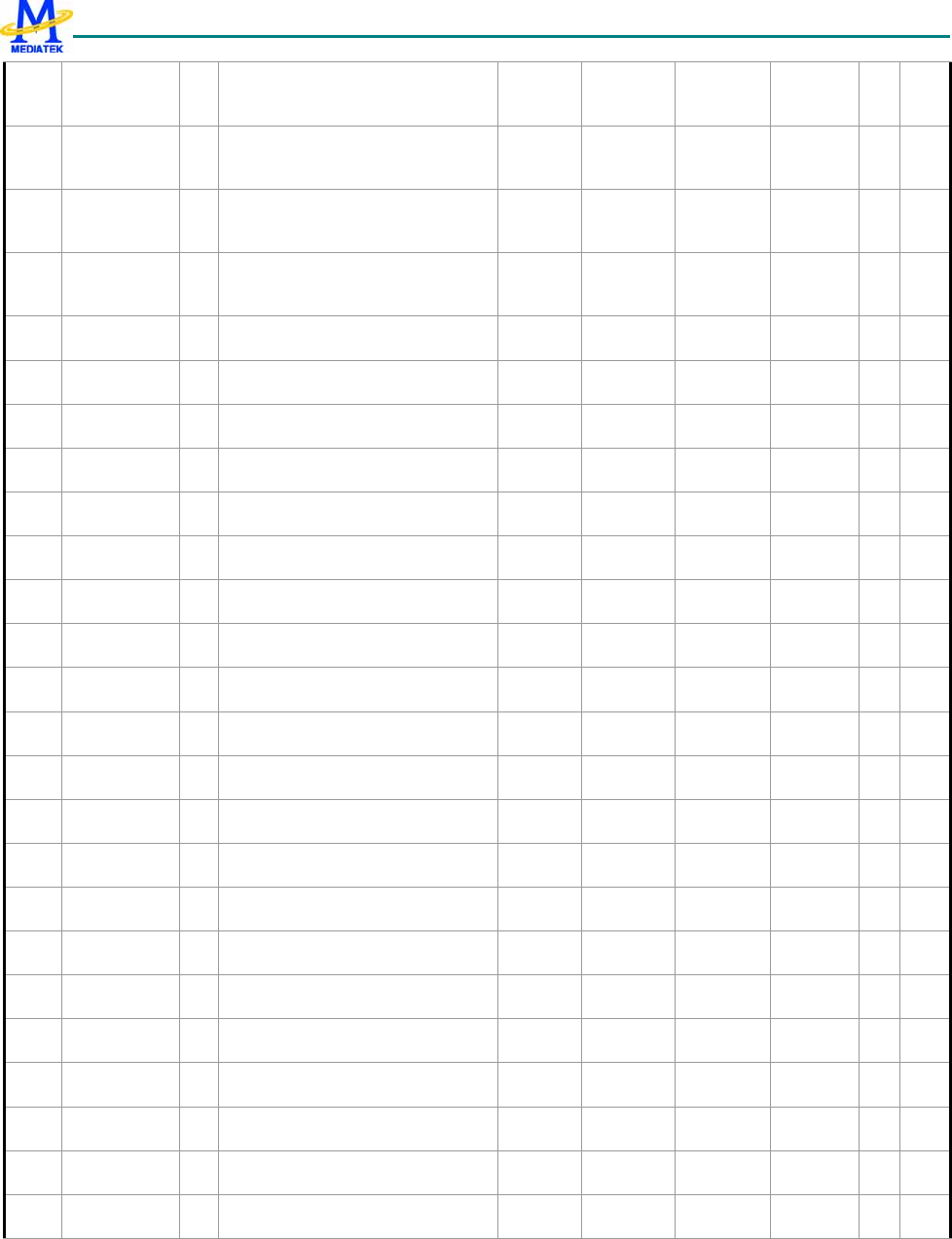

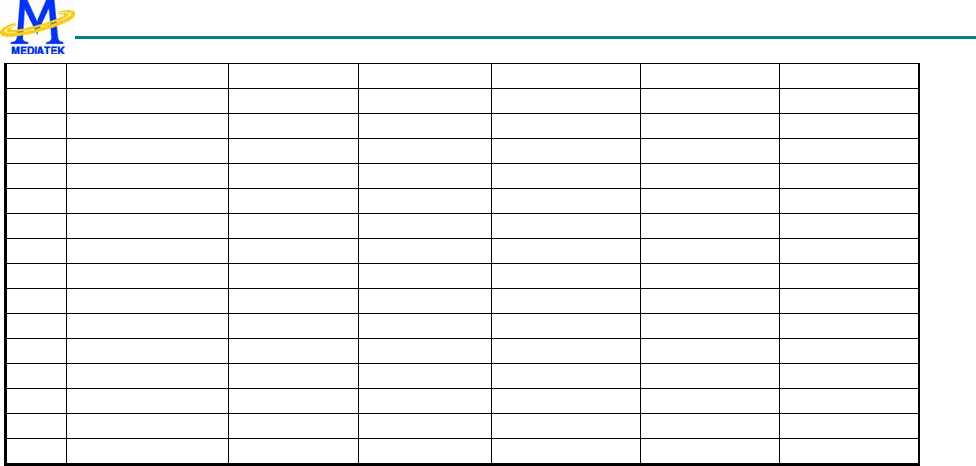

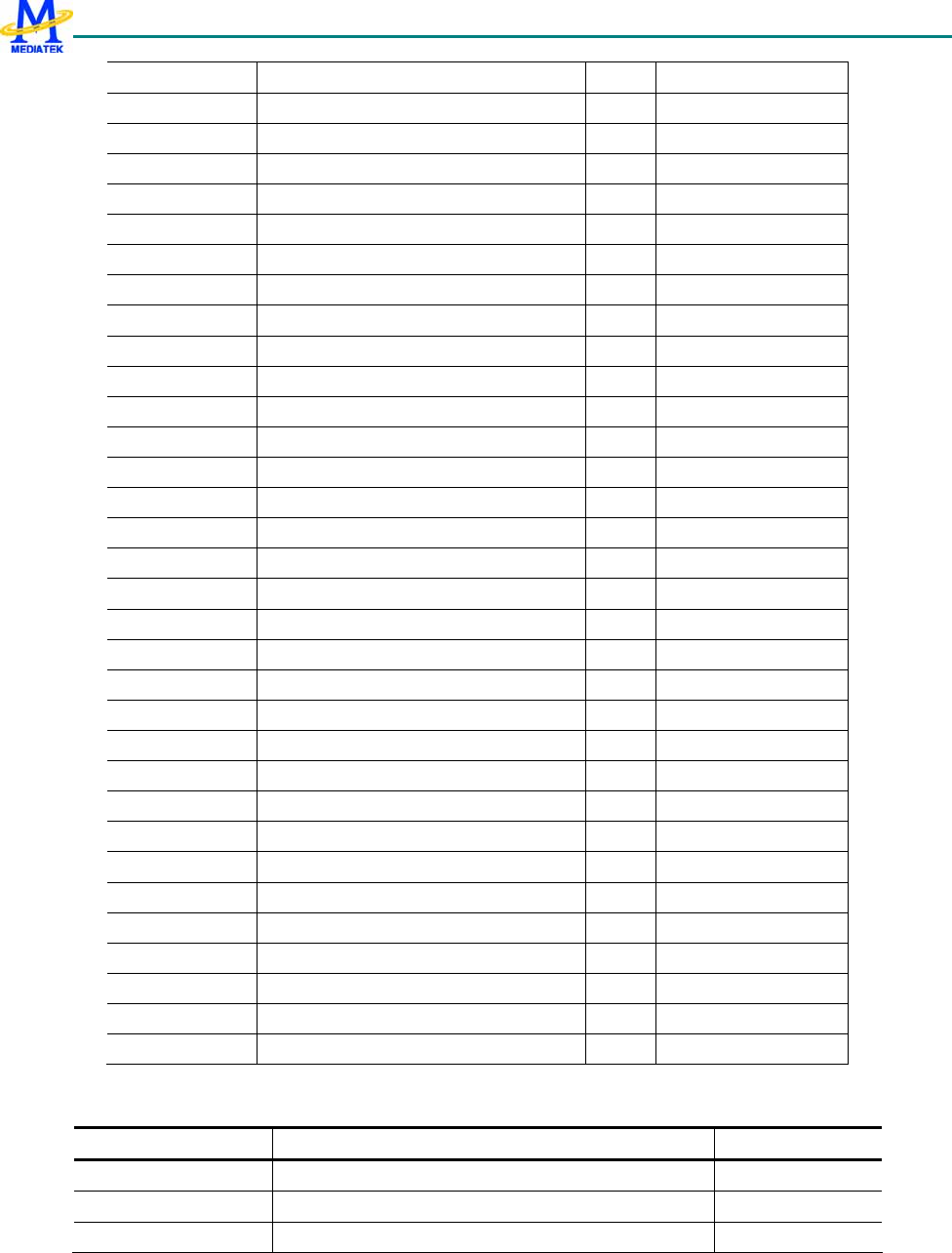

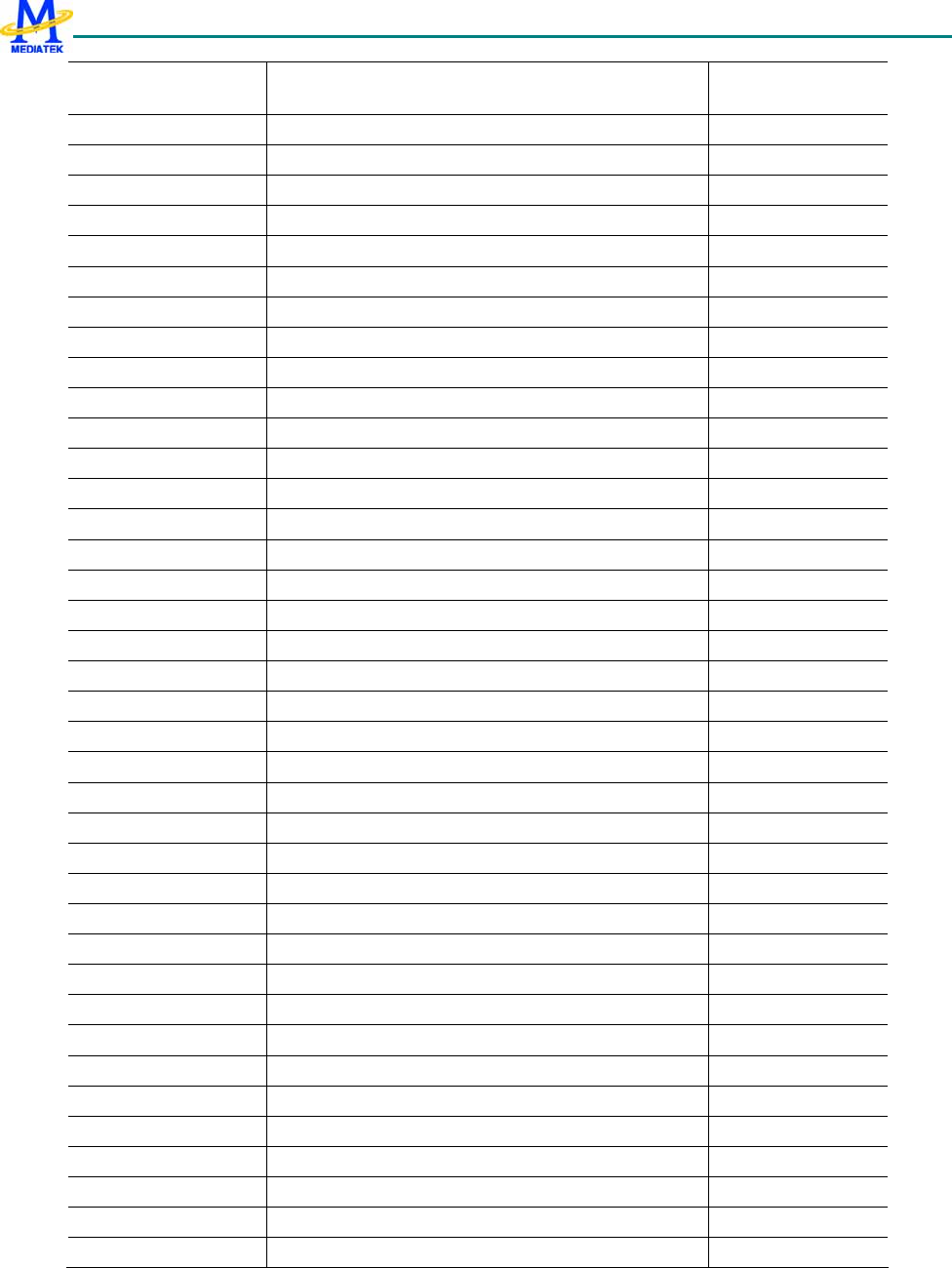

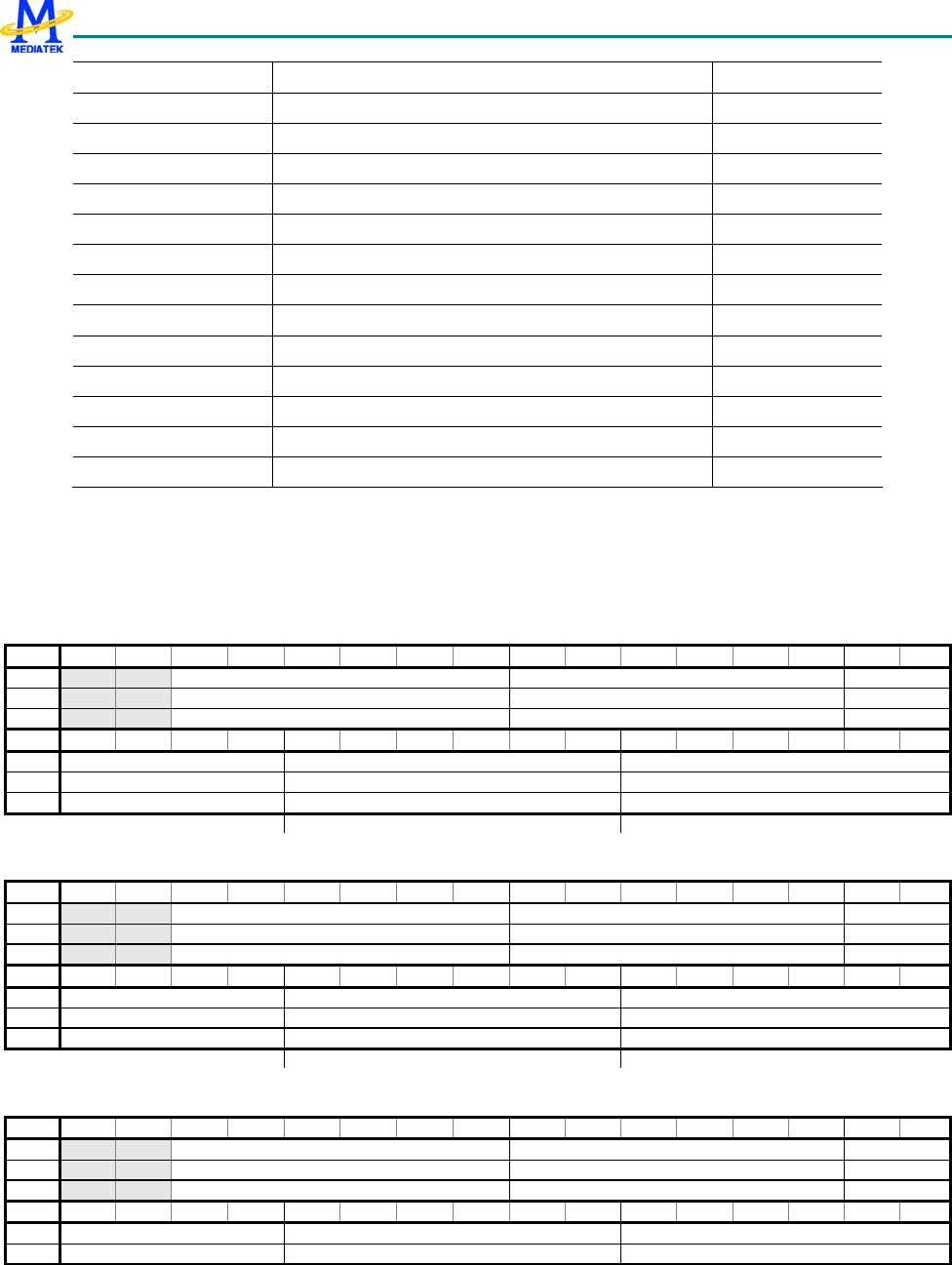

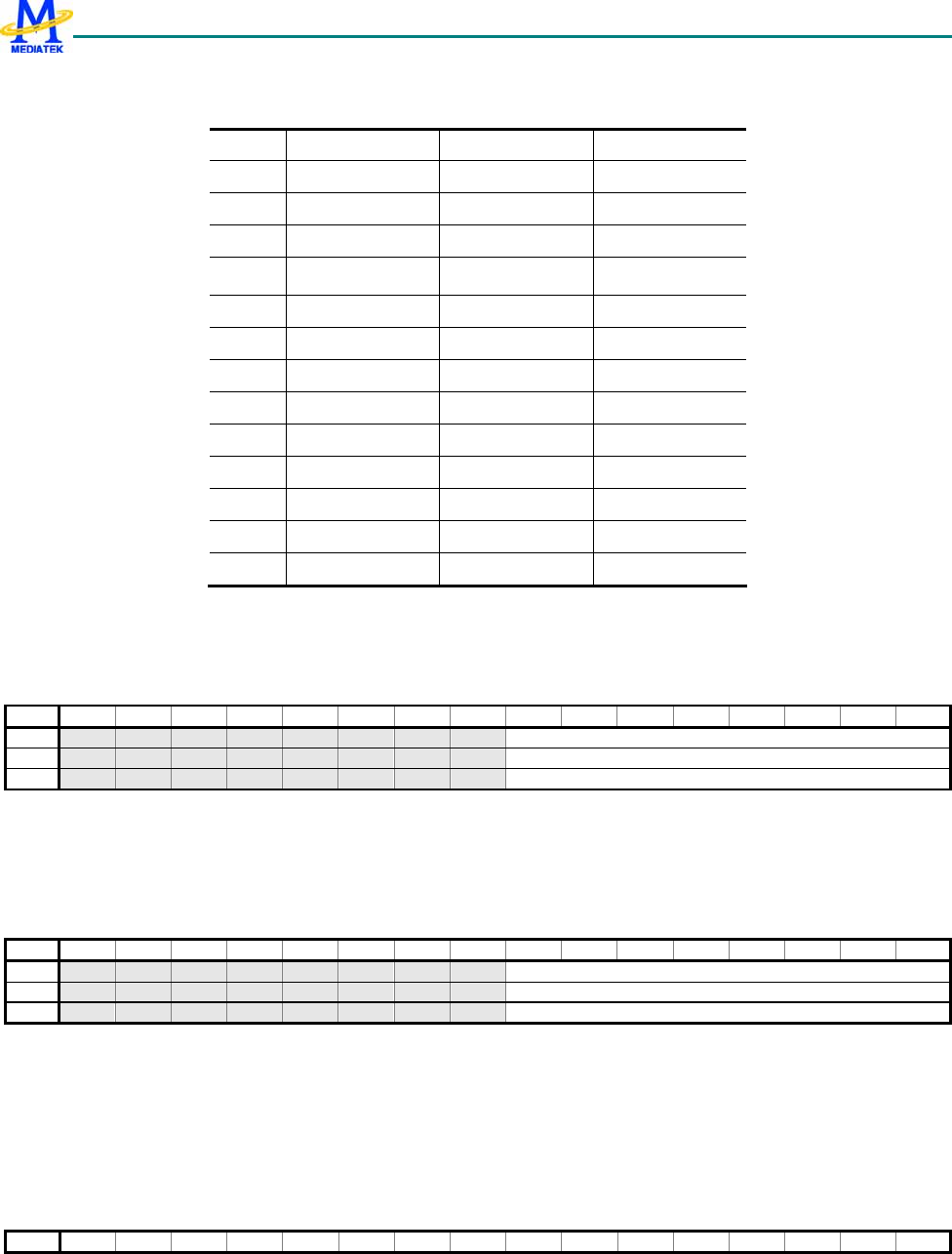

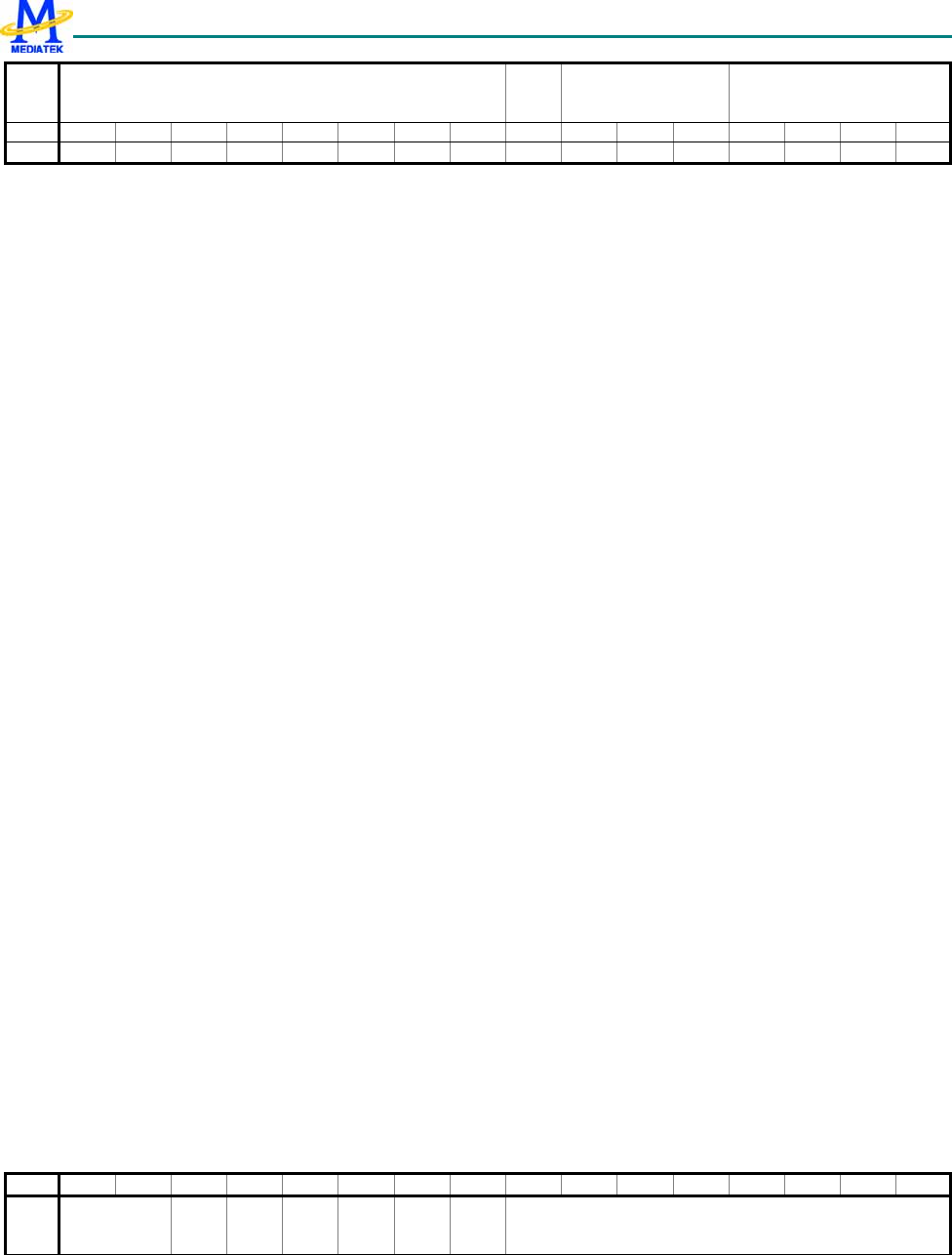

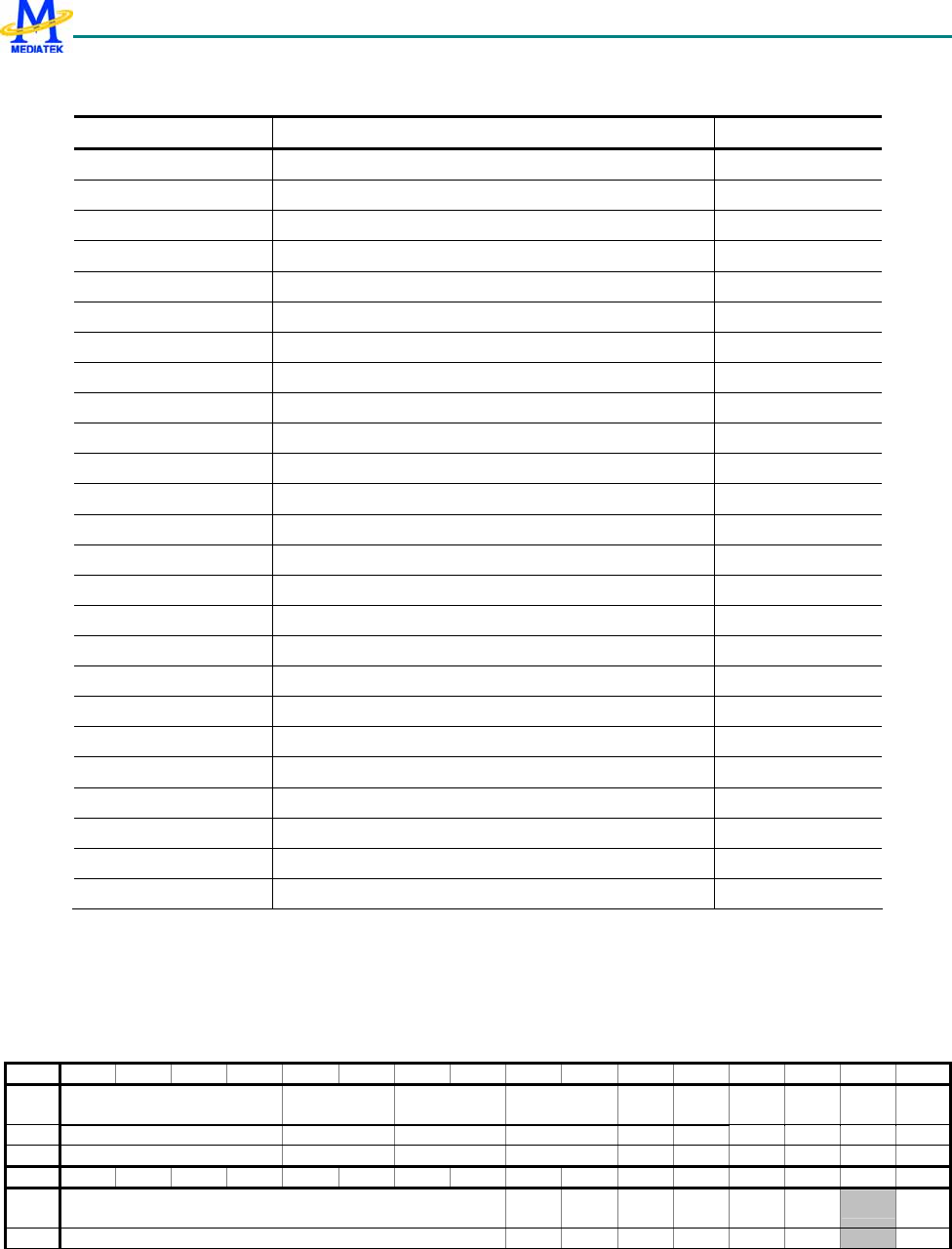

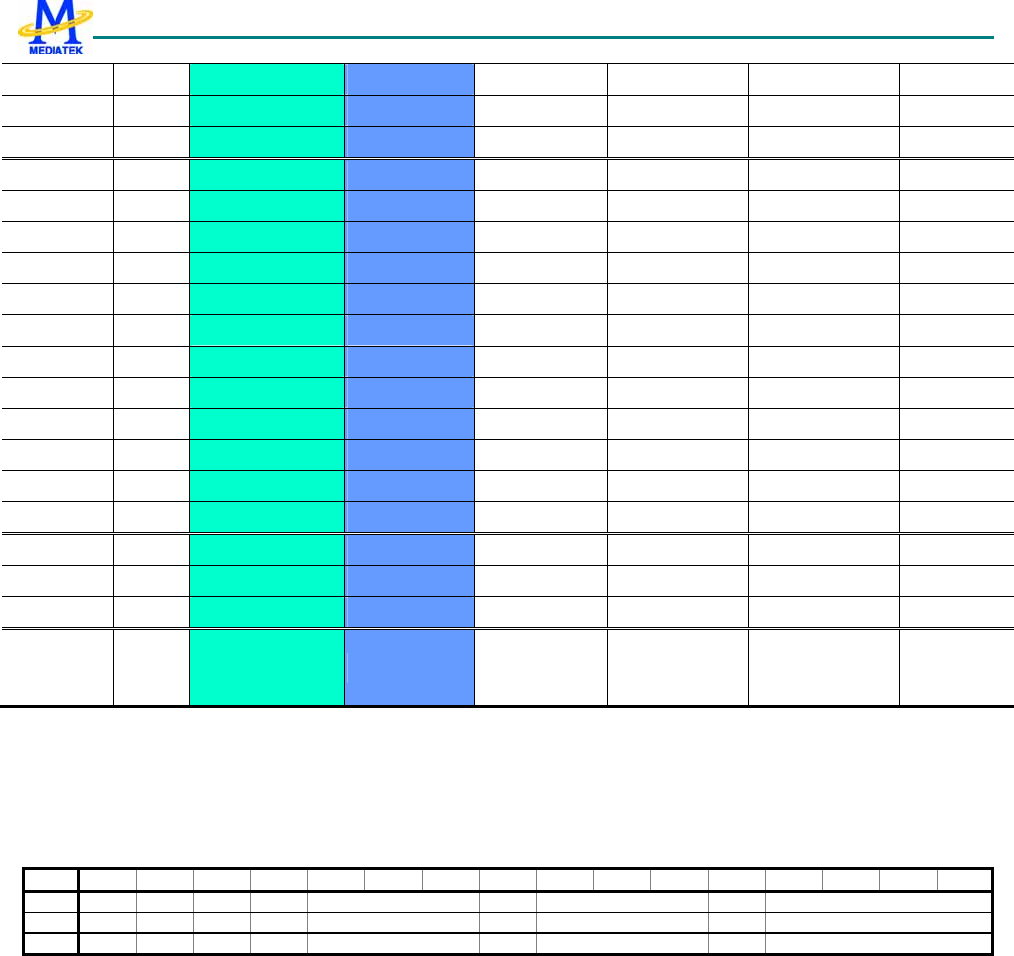

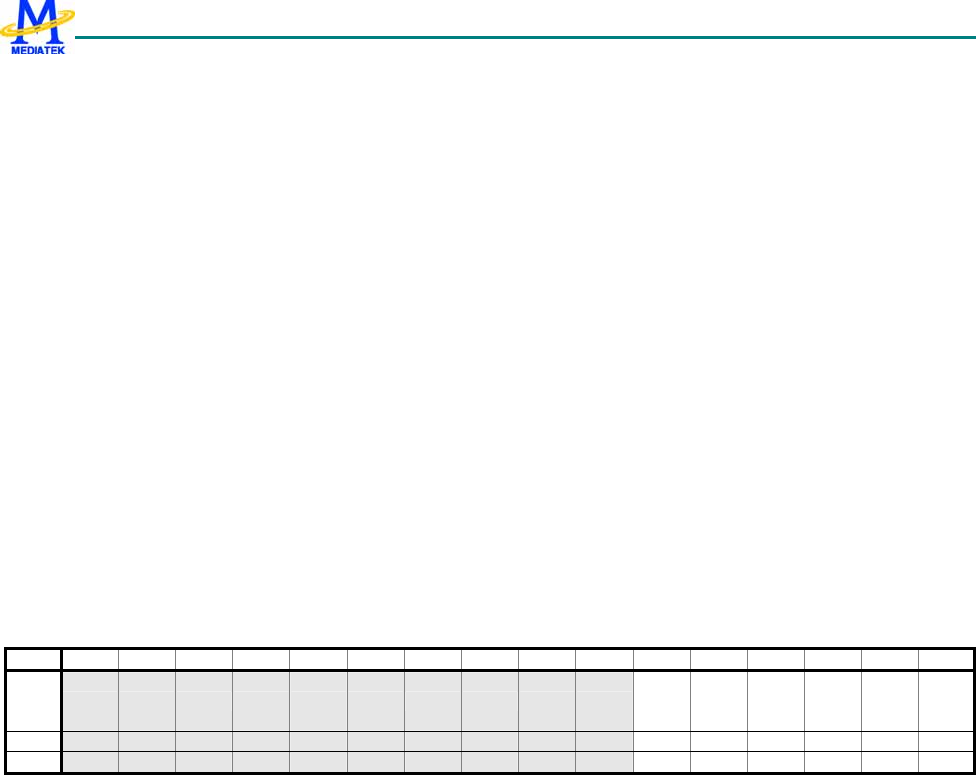

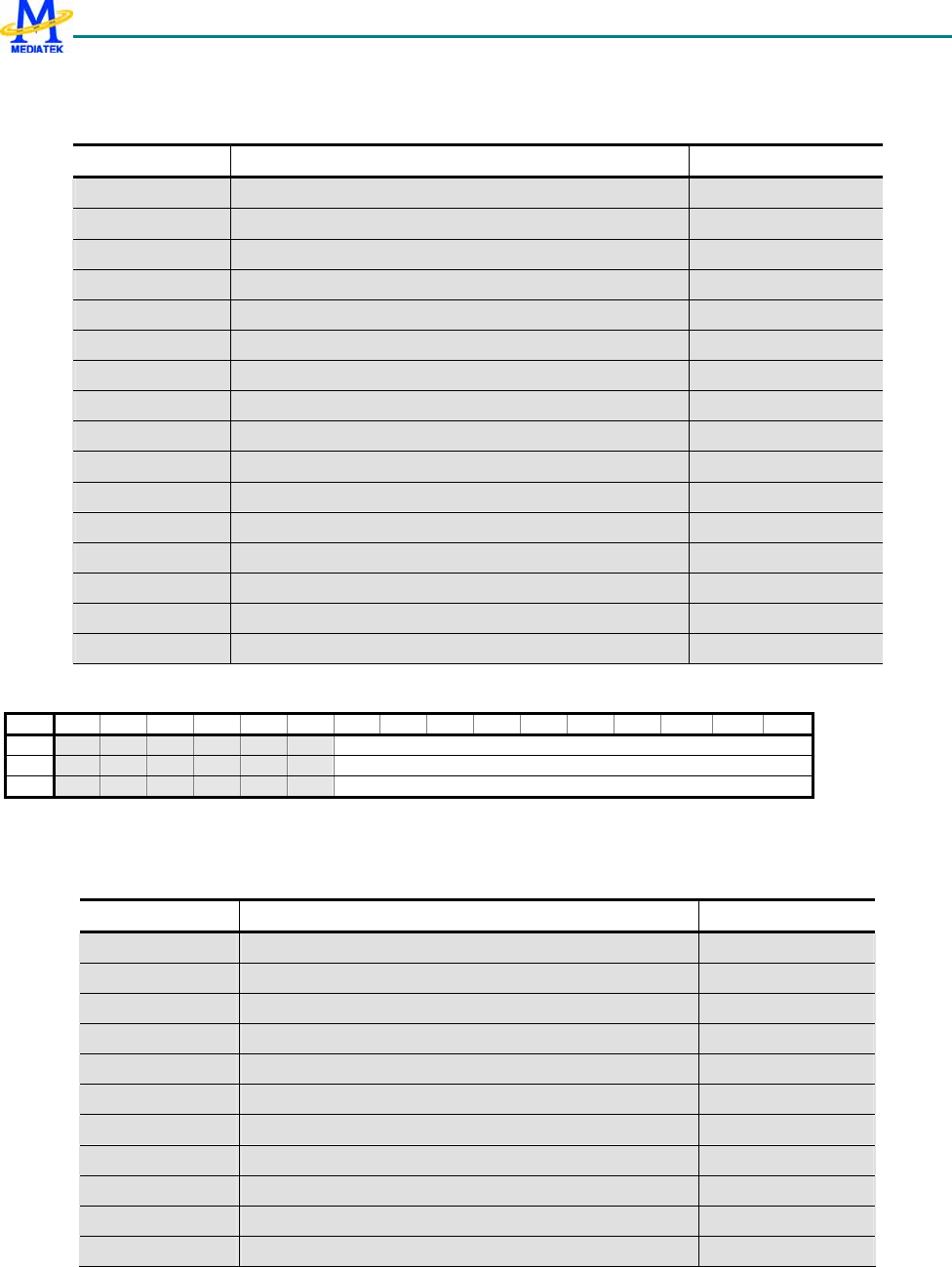

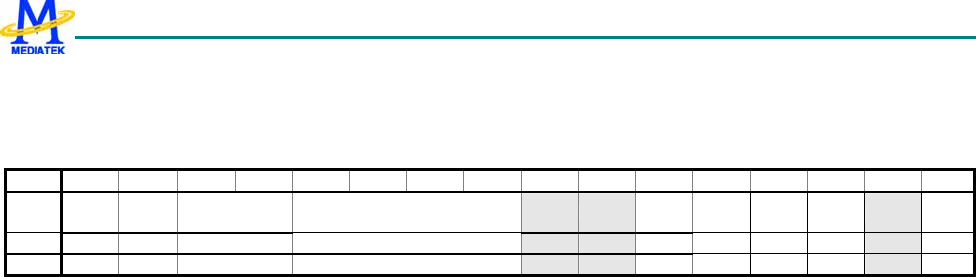

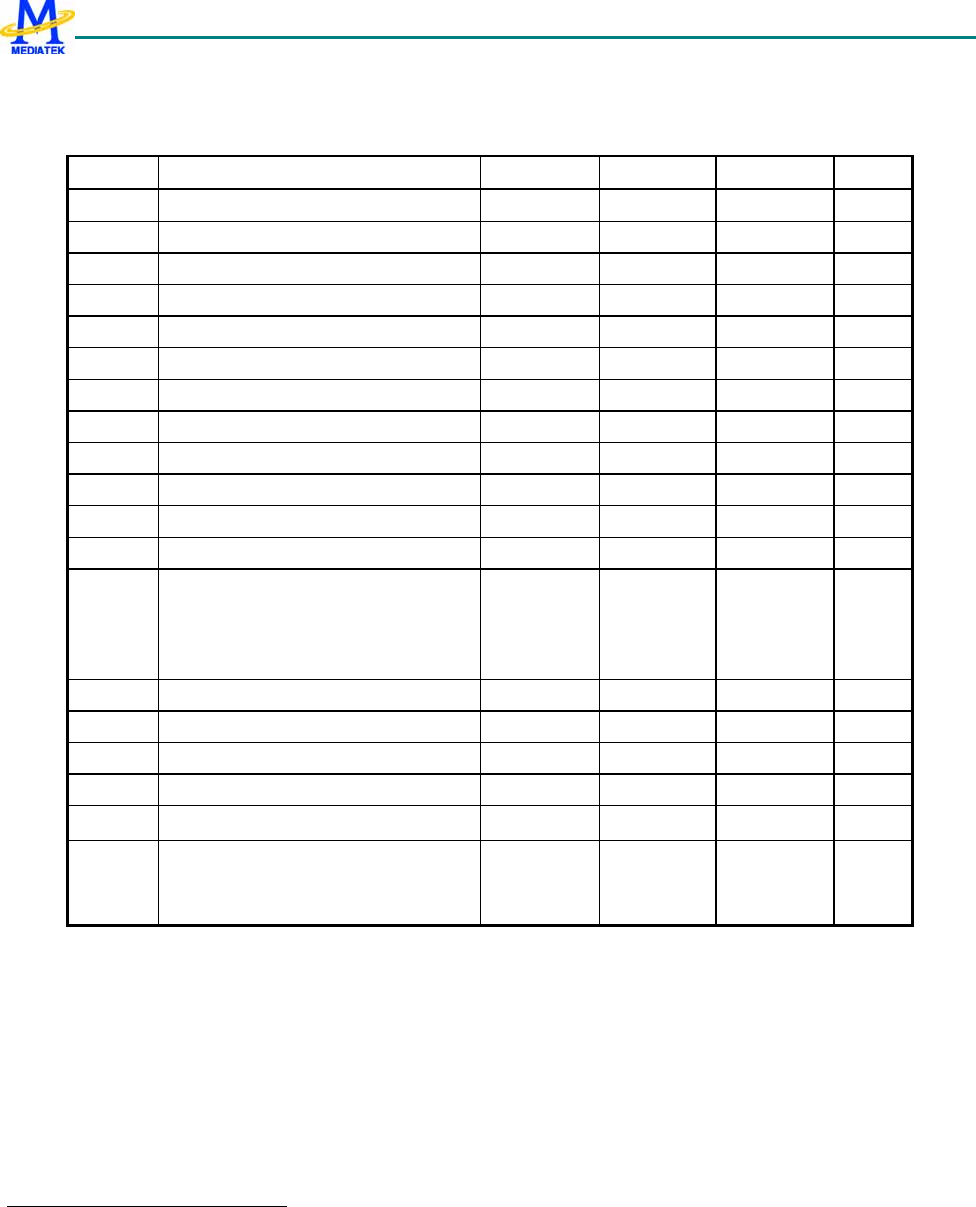

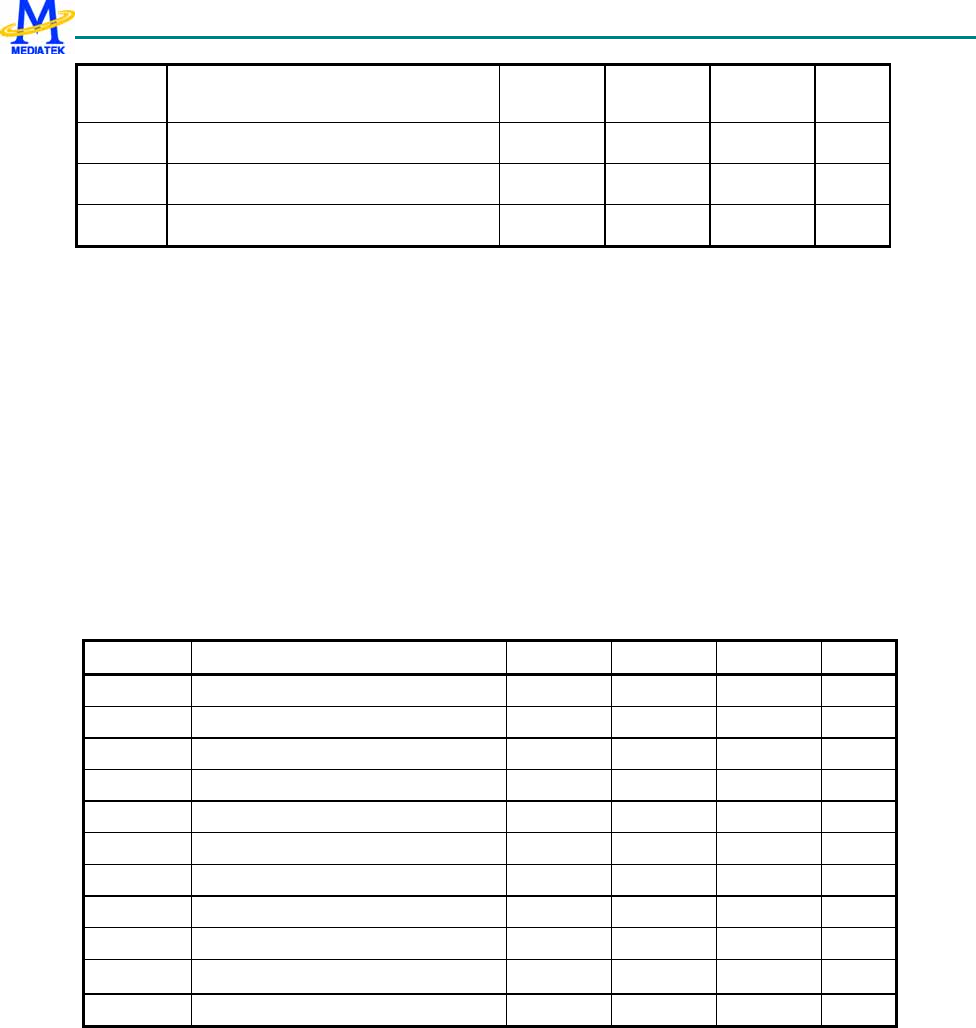

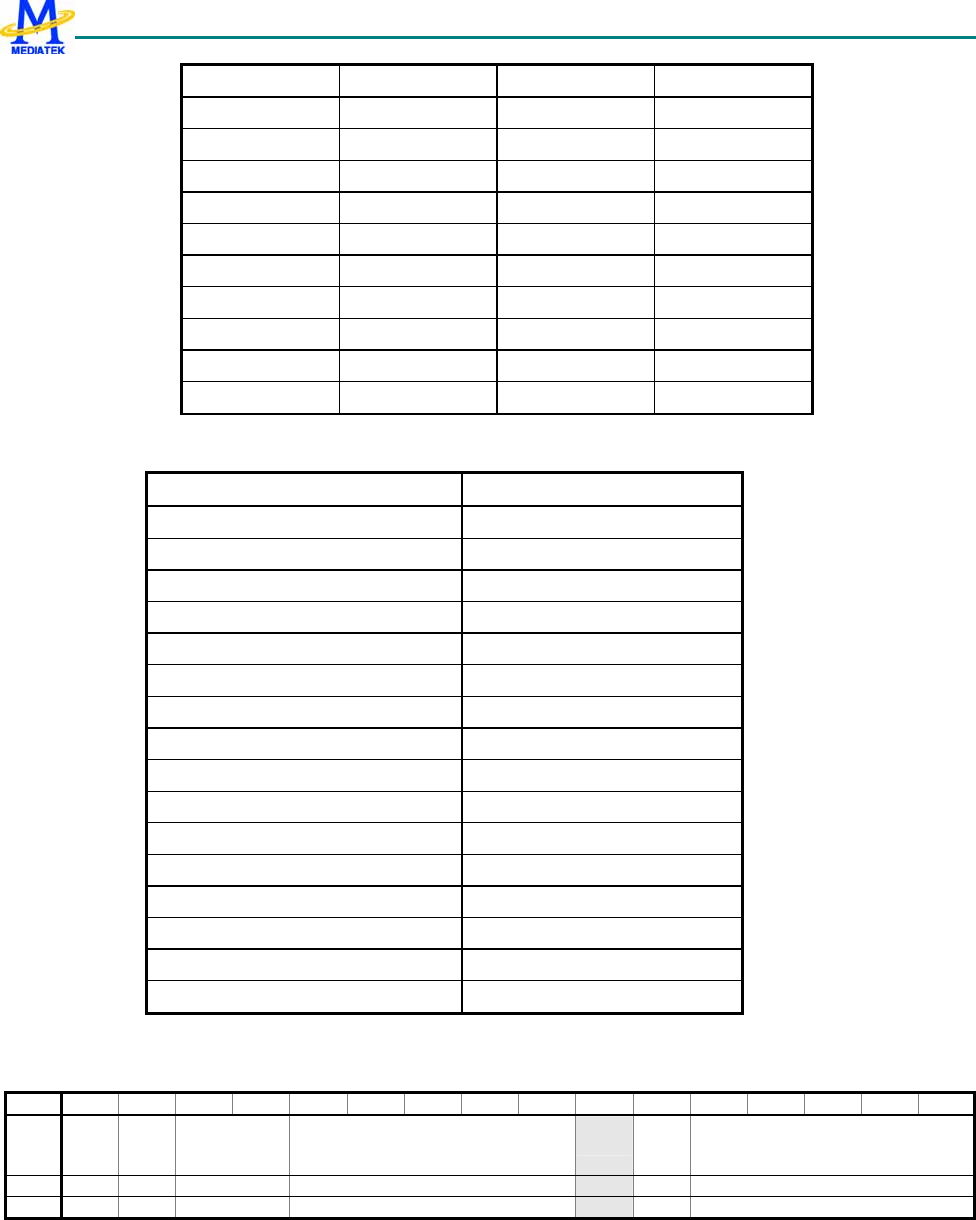

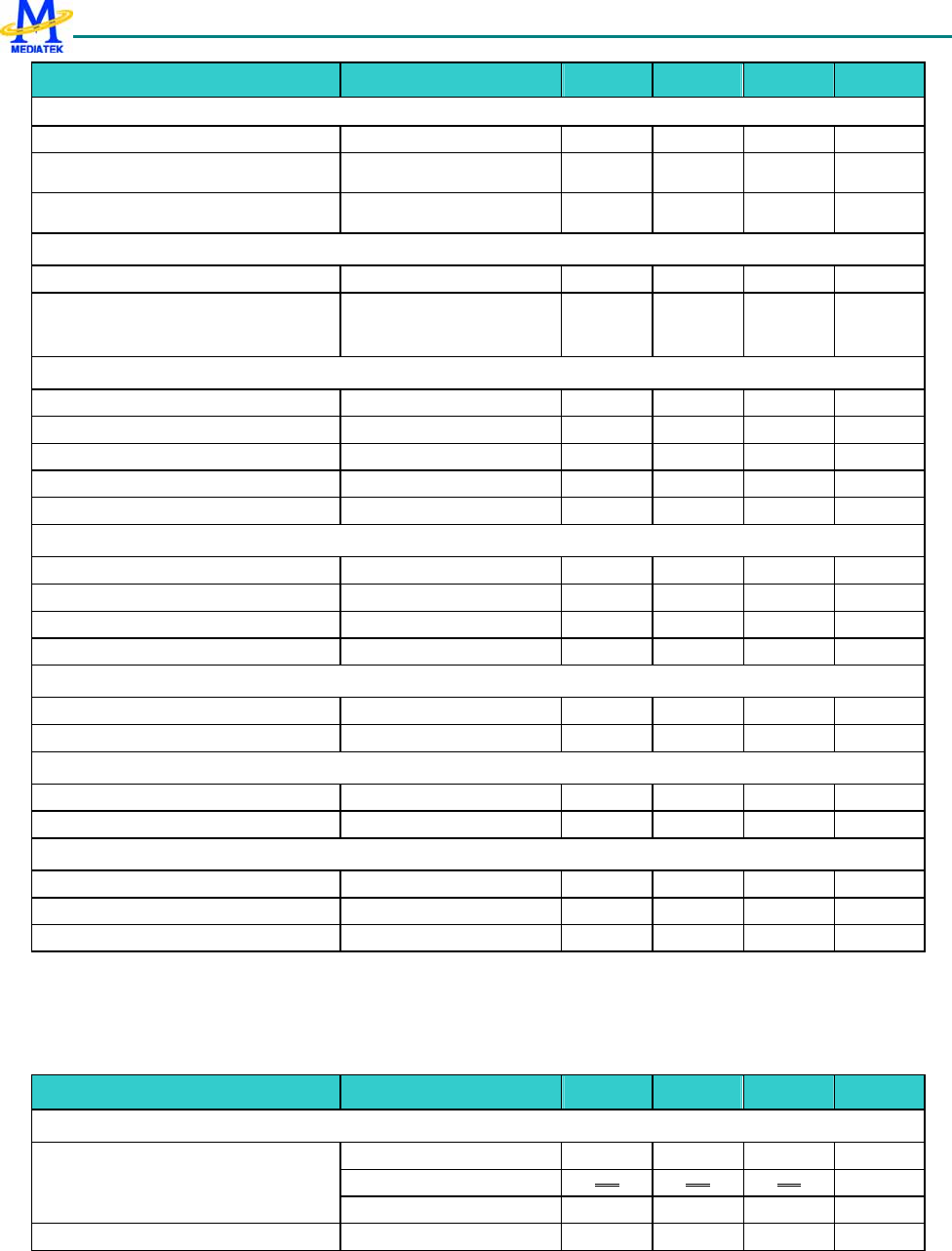

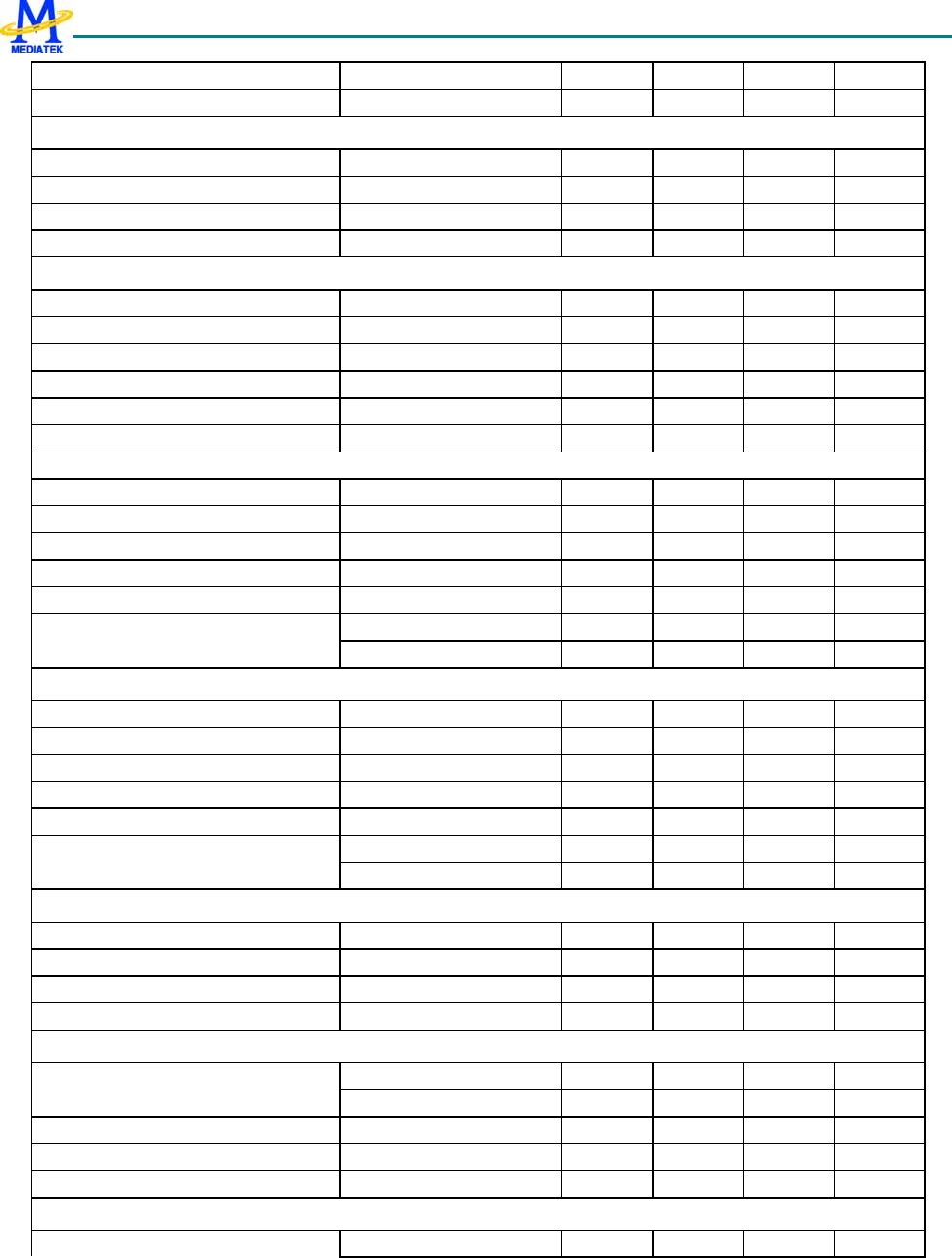

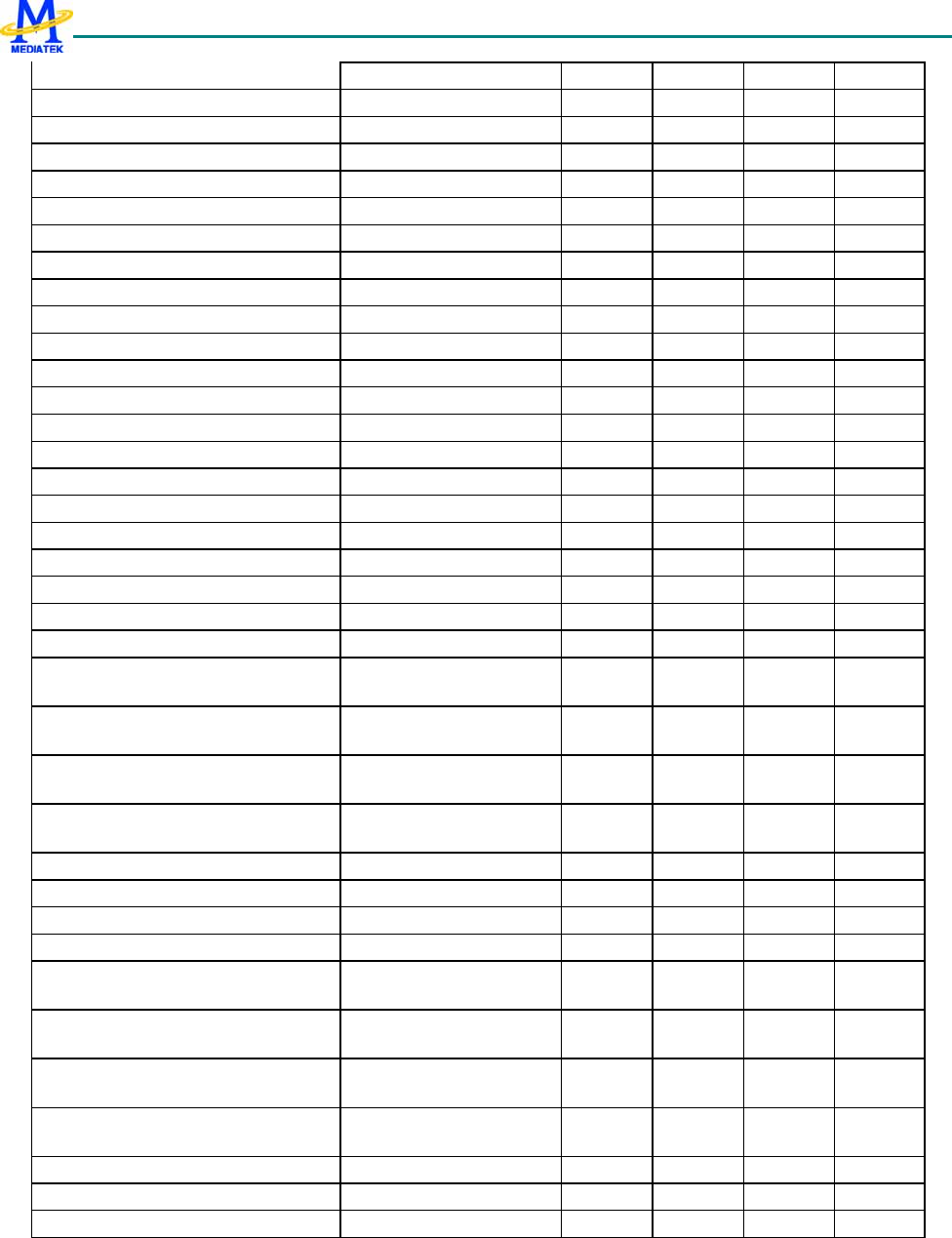

2.5 Power Description

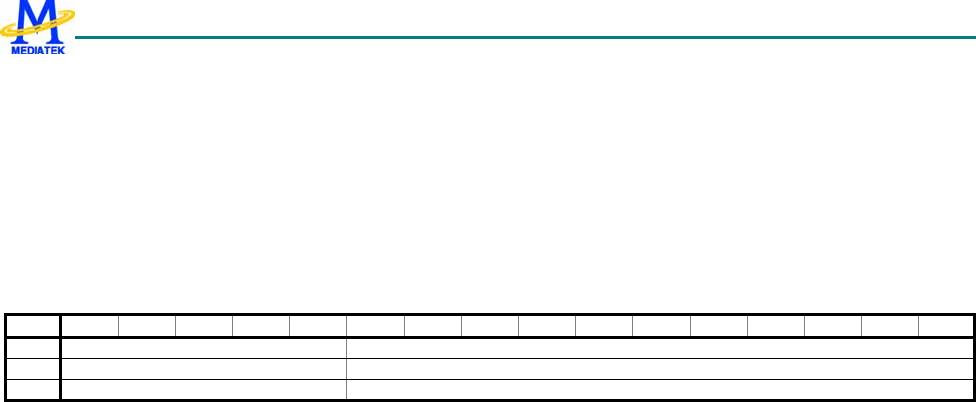

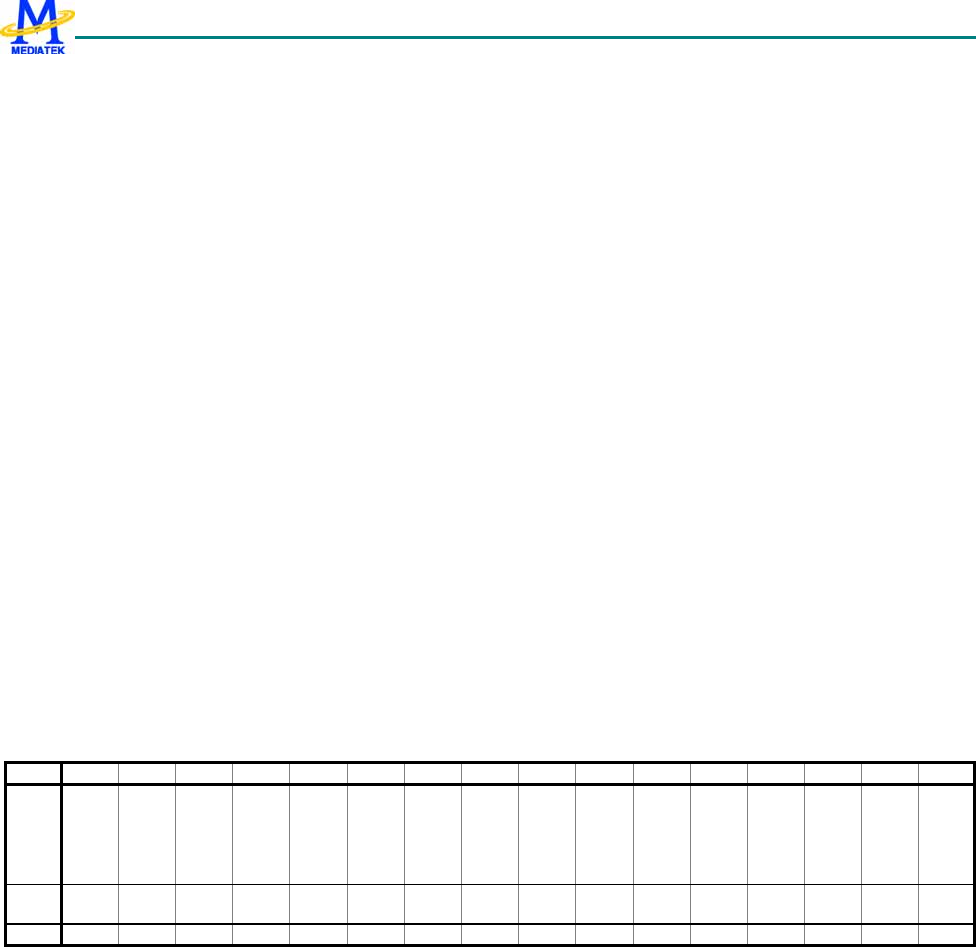

BALL NAME IO SUPPLY IO GND CORE SUPPLY CORE GND REMARK

B1 BATDET

C2 VRF_SENSE

C1 VRF

D1 VBAT_VRF

D3 AGND_VRF

E4 GND_LDOS

E3 VTCXO

E2 VBAT_VA

F1 VA

E1 VBAT_VA

F2 VREF

F3 AGND_VA

G4 JTRST_B VDD33 VSS33 VDDK VSS33

F4 VSS33

G3 JTCK VDD33 VSS33 VDDK VSS33

G2 JTDI VDD33 VSS33 VDDK VSS33

G1 JTMS VDD33 VSS33 VDDK VSS33

H1 JTDO VDD33 VSS33 VDDK VSS33

H3 VDDK

H2 JRTCK VDD33 VSS33 VDDK VSS33

H4 VDD33

J4 AVDD28_MBUF

J2 AU_MOUTR

J3 AVSS28_MBUF

J1 AU_MOUTL

K3 AU_FMINR

K4 AU_FMINL

K9 AVDD28_BUF

K2 AU_OUT0_N

K1 AU_OUT0_P

L3 AVSS28_BUF

L2 AU_MICBIAS_P

L1 AU_MICBIAS_N

L4 AVDD28_AFE

M2 AU_VREF_N

M1 AU_VREF_P

M3 AGND28_AFE

N1 AU_VIN0_P

N2 AU_VIN0_N

N3 AU_VIN1_N

N4 AU_VIN1_P

N9 AVSS28_AFE

P3 AVSS28_GSMRFTX

P4 AGND28_RFE

R3 AVDD28_GSMRFTX

MT6235 GSM/GPRS Baseband Processor Data Sheet Revision 1.02

33/599 MediaTek Inc. Confidential

P1 BDLAQP

P2 BDLAQN

R1 BDLAIN

R2 BDLAIP

T3 APC

T1 AVDD28_RFE

U1 AUX_REF

T4 AUXADIN0

U2 AUXADIN1

T2 AVSS28_RFE

U3 XP

U4 AUXADIN2

V1 XM

V2 AUXADIN3

V3 YM

V4 AFC

W3 YP

W2 AFC_BYP

W1 AVCC12_PLL

Y1 SYSCLK AVCC12_PLL AVSS12_PLL AVCC12_PLL AVSS12_PLL

Y2 AVSS12_PLL

Y3 VSS33

Y4 VCCQ

AA1 FSOURCE

AA2 CMRST VDD33_CAM VSS33 VDDK VSS33

AA3 CMPDN VDD33_CAM VSS33 VDDK VSS33

AB3 CMVREF VDD33_CAM VSS33 VDDK VSS33

AB2 CMHREF VDD33_CAM VSS33 VDDK VSS33

AA4 CMPCLK VDD33_CAM VSS33 VDDK VSS33

AB6 CMMCLK VDD33_CAM VSS33 VDDK VSS33

AC2 CMDAT7 VDD33_CAM VSS33 VDDK VSS33

AC3 CMDAT6 VDD33_CAM VSS33 VDDK VSS33

AC1 CMDAT5 VDD33_CAM VSS33 VDDK VSS33

AD2 VDD33_CAM

AD1 CMDAT4 VDD33_CAM VSS33 VDDK VSS33

AE2 CMDAT3 VDD33_CAM VSS33 VDDK VSS33

AD3 CMDAT2 VDD33_CAM VSS33 VDDK VSS33

AD4 CMDAT1 VDD33_CAM VSS33 VDDK VSS33

AE3 CMDAT0 VDD33_CAM VSS33 VDDK VSS33

AC4 CMFLASH VDD33_CAM VSS33 VDDK VSS33

AB7 VDDK

AE4 SCL VDD33_CAM VSS33 VDDK VSS33

AD5 SDA VDD33_CAM VSS33 VDDK VSS33

AC5 PWM2 VDD33_CAM VSS33 VDDK VSS33

AE5 PWM3 VDD33_CAM VSS33 VDDK VSS33

AB5 VSS33

AD6 SECU_EN VDD33 VSS33 VDDK VSS33

AE7 XBOOT VDD33 VSS33 VDDK VSS33

AE6 BPI_BUS0 VDD33 VSS33 VDDK VSS33

MT6235 GSM/GPRS Baseband Processor Data Sheet Revision 1.02

34/599 MediaTek Inc. Confidential

AD7 BPI_BUS1 VDD33 VSS33 VDDK VSS33

AC7 BPI_BUS2 VDD33 VSS33 VDDK VSS33

AC6 BPI_BUS3 VDD33 VSS33 VDDK VSS33

AE8 BPI_BUS4 VDD33 VSS33 VDDK VSS33

AD8 BPI_BUS5 VDD33 VSS33 VDDK VSS33

AC8 BPI_BUS6 VDD33 VSS33 VDDK VSS33

AB8 BPI_BUS7 VDD33 VSS33 VDDK VSS33

AE9 BPI_BUS8 VDD33 VSS33 VDDK VSS33

AB9 VDD33

AD9 BPI_BUS9 VDD33 VSS33 VDDK VSS33

AC9 BSI_CS0 VDD33 VSS33 VDDK VSS33

AE10 BSI_DATA VDD33 VSS33 VDDK VSS33

AD10 BSI_CLK VDD33 VSS33 VDDK VSS33

AC10 PWM0 VDD33 VSS33 VDDK VSS33

AB10 PWM1 VDD33 VSS33 VDDK VSS33

U10 SRCLKENAN VDD33 VSS33 VDDK VSS33

AE11 SRCLKENA VDD33 VSS33 VDDK VSS33

AD11 SRCLKENAI VDD33 VSS33 VDDK VSS33

AB11 VSS33

AC11 LSCK VDD33_LCD VSS33 VDDK VSS33

U11 LSA0 VDD33_LCD VSS33 VDDK VSS33

AD12 LSDA VDD33_LCD VSS33 VDDK VSS33

AE12 LSCE0B VDD33_LCD VSS33 VDDK VSS33

AC12 LSCE1B VDD33_LCD VSS33 VDDK VSS33

AB12 LPCE1B VDD33_LCD VSS33 VDDK VSS33

U12 LPCE0B VDD33_LCD VSS33 VDDK VSS33

AE13 LPTE VDD33_LCD VSS33 VDDK VSS33

AC13 LRSTB VDD33_LCD VSS33 VDDK VSS33

AD13 LRDB VDD33_LCD VSS33 VDDK VSS33

AB13 VDD33_LCD

U13 LPA0 VDD33_LCD VSS33 VDDK VSS33

AE14 LWRB VDD33_LCD VSS33 VDDK VSS33

AD14 NLD17 VDD33_LCD VSS33 VDDK VSS33

AC14 NLD16 VDD33_LCD VSS33 VDDK VSS33

AB14 NLD15 VDD33_LCD VSS33 VDDK VSS33

U14 NLD14 VDD33_LCD VSS33 VDDK VSS33

AE15 NLD13 VDD33_LCD VSS33 VDDK VSS33

AD15 NLD12 VDD33_LCD VSS33 VDDK VSS33

AC15 NLD11 VDD33_LCD VSS33 VDDK VSS33

U15 VSS33

AB15 NLD10 VDD33_LCD VSS33 VDDK VSS33

AE16 NLD9 VDD33_LCD VSS33 VDDK VSS33

AD16 NLD8 VDD33_LCD VSS33 VDDK VSS33

AC16 NLD7 VDD33_LCD VSS33 VDDK VSS33

AB16 NLD6 VDD33_LCD VSS33 VDDK VSS33

U16 NLD5 VDD33_LCD VSS33 VDDK VSS33

AE17 NLD4 VDD33_LCD VSS33 VDDK VSS33

AD17 NLD3 VDD33_LCD VSS33 VDDK VSS33

AC17 NLD2 VDD33_LCD VSS33 VDDK VSS33

MT6235 GSM/GPRS Baseband Processor Data Sheet Revision 1.02

35/599 MediaTek Inc. Confidential

AB17 VDD33_LCD

AE18 NLD1 VDD33_LCD VSS33 VDDK VSS33

AD18 NLD0 VDD33_LCD VSS33 VDDK VSS33

AC18 NRNB VDD33_LCD VSS33 VDDK VSS33

AB18 NCLE VDD33_LCD VSS33 VDDK VSS33

AE19 NALE VDD33_LCD VSS33 VDDK VSS33

AD19 NWEB VDD33_LCD VSS33 VDDK VSS33

AC19 NREB VDD33_LCD VSS33 VDDK VSS33

AB19 NCEB VDD33_LCD VSS33 VDDK VSS33

AB20 VDDK

AC20 VSS33

AD20 USB_XTALI

AE20 USB_XTALO

AE21 VSSCA_USB

AD22 VSSCD_USB

AB21 VDDC_USB

AC21 VRT

AD23 VSS33_USB

AC22 VDD33_USB

AE22 USB_DP

AE23 USB_DM

AE24 VSS33

AD25 EA26 VDD33_EMI VSS33 VDDK VSS33

AD24 EA25 VDD33_EMI VSS33 VDDK VSS33

AC25 EA24 VDD33_EMI VSS33 VDDK VSS33

AC24 EA23 VDD33_EMI VSS33 VDDK VSS33

AC23 EA22 VDD33_EMI VSS33 VDDK VSS33

AB25 EA21 VDD33_EMI VSS33 VDDK VSS33

AA22 VSS33

AB24 EA20 VDD33_EMI VSS33 VDDK VSS33

AA25 EA19 VDD33_EMI VSS33 VDDK VSS33

AA24 EA18 VDD33_EMI VSS33 VDDK VSS33

AB23 VDD33_EMI

AA23 EA17 VDD33_EMI VSS33 VDDK VSS33

Y25 EA16 VDD33_EMI VSS33 VDDK VSS33

Y22 VDDK

Y24 EA15 VDD33_EMI VSS33 VDDK VSS33

Y23 EA14 VDD33_EMI VSS33 VDDK VSS33

W25 EA13 VDD33_EMI VSS33 VDDK VSS33

W24 EA12 VDD33_EMI VSS33 VDDK VSS33

V22 VDD33_EMI

W23 EA11 VDD33_EMI VSS33 VDDK VSS33

W22 EA10 VDD33_EMI VSS33 VDDK VSS33

V25 EA9 VDD33_EMI VSS33 VDDK VSS33

V24 EA8 VDD33_EMI VSS33 VDDK VSS33

V23 EA7 VDD33_EMI VSS33 VDDK VSS33

U25 EA6 VDD33_EMI VSS33 VDDK VSS33

U24 EA5 VDD33_EMI VSS33 VDDK VSS33

U23 EA4 VDD33_EMI VSS33 VDDK VSS33

MT6235 GSM/GPRS Baseband Processor Data Sheet Revision 1.02

36/599 MediaTek Inc. Confidential

T25 EA3 VDD33_EMI VSS33 VDDK VSS33

U22 VSS33

T24 EA2 VDD33_EMI VSS33 VDDK VSS33

T22 EA1 VDD33_EMI VSS33 VDDK VSS33

T23 EA0 VDD33_EMI VSS33 VDDK VSS33

T17 EADMUX VDD33_EMI VSS33 VDDK VSS33

R25 EWAIT VDD33_EMI VSS33 VDDK VSS33

R17 EDQM1 VDD33_EMI VSS33 VDDK VSS33

P25 EDQM0 VDD33_EMI VSS33 VDDK VSS33

P24 ERAS_B VDD33_EMI VSS33 VDDK VSS33

N25 ECAS_B VDD33_EMI VSS33 VDDK VSS33

R22 VDD33_EMI

P17 EADV_B VDD33_EMI VSS33 VDDK VSS33

N22 ED_CLK VDD33_EMI VSS33 VDDK VSS33

P22 VSS33

N24 EC_CLK VDD33_EMI VSS33 VDDK VSS33

P23 ECKE VDD33_EMI VSS33 VDDK VSS33

N17 EWR_B VDD33_EMI VSS33 VDDK VSS33

M25 ERD_B VDD33_EMI VSS33 VDDK VSS33

M24 ECS3_B VDD33_EMI VSS33 VDDK VSS33

M23 ECS2_B VDD33_EMI VSS33 VDDK VSS33

M17 ECS1_B VDD33_EMI VSS33 VDDK VSS33

L25 ECS0_B VDD33_EMI VSS33 VDDK VSS33

L24 ED15 VDD33_EMI VSS33 VDDK VSS33

M22 VDD33_EMI

L23 ED14 VDD33_EMI VSS33 VDDK VSS33

L17 ED13 VDD33_EMI VSS33 VDDK VSS33

K25 ED12 VDD33_EMI VSS33 VDDK VSS33

L22 VSS33

K24 ED11 VDD33_EMI VSS33 VDDK VSS33

K23 ED10 VDD33_EMI VSS33 VDDK VSS33

J25 ED9 VDD33_EMI VSS33 VDDK VSS33

H25 ED8 VDD33_EMI VSS33 VDDK VSS33

K22 ED7 VDD33_EMI VSS33 VDDK VSS33

J24 ED6 VDD33_EMI VSS33 VDDK VSS33

J23 ED5 VDD33_EMI VSS33 VDDK VSS33

H23 ED4 VDD33_EMI VSS33 VDDK VSS33

H24 ED3 VDD33_EMI VSS33 VDDK VSS33

J22 VDD33_EMI

G25 ED2 VDD33_EMI VSS33 VDDK VSS33

G22 ED1 VDD33_EMI VSS33 VDDK VSS33

G24 ED0 VDD33_EMI VSS33 VDDK VSS33

K17 MFIQ VDD33_EMI VSS33 VDDK VSS33

G23 WATCHDOG VDD33_EMI VSS33 VDDK VSS33

H22 VSS33

F22 VDDK

F25 SYSRST_B VDD33 VSS33 VDDK VSS33

F24 EINT0 VDD33 VSS33 VDDK VSS33

F23 EINT1 VDD33 VSS33 VDDK VSS33

MT6235 GSM/GPRS Baseband Processor Data Sheet Revision 1.02

37/599 MediaTek Inc. Confidential

E25 EINT2 VDD33 VSS33 VDDK VSS33

E24 EINT3 VDD33 VSS33 VDDK VSS33

E23 EINT4 VDD33 VSS33 VDDK VSS33

D23 EINT5 VDD33 VSS33 VDDK VSS33

D25 EINT6 VDD33 VSS33 VDDK VSS33

D24 EINT7 VDD33 VSS33 VDDK VSS33

E22 VDD33

C25 URXD1 VDD33 VSS33 VDDK VSS33

C24 UTXD1 VDD33 VSS33 VDDK VSS33

C23 UCTS1 VDD33 VSS33 VDDK VSS33

B25 URTS1 VDD33 VSS33 VDDK VSS33

A24 URXD2 VDD33 VSS33 VDDK VSS33

B24 UTXD2 VDD33 VSS33 VDDK VSS33

A23 URXD3 VDD33 VSS33 VDDK VSS33

B23 UTXD3 VDD33 VSS33 VDDK VSS33

C22 VSS33

A22 KCOL7 VDD33 VSS33 VDDK VSS33

B22 KCOL6 VDD33 VSS33 VDDK VSS33

A21 KCOL5 VDD33 VSS33 VDDK VSS33

B21 KCOL4 VDD33 VSS33 VDDK VSS33

C21 KCOL3 VDD33 VSS33 VDDK VSS33

D21 KCOL2 VDD33 VSS33 VDDK VSS33

A20 KCOL1 VDD33 VSS33 VDDK VSS33

B20 KCOL0 VDD33 VSS33 VDDK VSS33

C20 KROW7 VDD33 VSS33 VDDK VSS33

D20 KROW6 VDD33 VSS33 VDDK VSS33

A19 KROW5 VDD33 VSS33 VDDK VSS33

D19 VDD33

B19 KROW4 VDD33 VSS33 VDDK VSS33

C19 KROW3 VDD33 VSS33 VDDK VSS33

A18 KROW2 VDD33 VSS33 VDDK VSS33

B18 KROW1 VDD33 VSS33 VDDK VSS33

C18 KROW0 VDD33 VSS33 VDDK VSS33

D18 DAICLK VDD33 VSS33 VDDK VSS33

A17 DAIPCMOUT VDD33 VSS33 VDDK VSS33

B17 DAIPCMIN VDD33 VSS33 VDDK VSS33

C17 DAIRST VDD33 VSS33 VDDK VSS33

A16 VSS33

D17 DAISYNC VDD33 VSS33 VDDK VSS33

B16 MCCM0 VDD33_MC VSS33 VDDK VSS33

C16 MCDA0 VDD33_MC VSS33 VDDK VSS33

D16 MCDA1 VDD33_MC VSS33 VDDK VSS33

J16 MCDA2 VDD33_MC VSS33 VDDK VSS33

C15 MCDA3 VDD33_MC VSS33 VDDK VSS33

D15 MCCK VDD33_MC VSS33 VDDK VSS33

J15 MCPWRON VDD33_MC VSS33 VDDK VSS33

C14 MCWP VDD33_MC VSS33 VDDK VSS33

J14 VDDK

D14 MCINS VDD33_MC VSS33 VDDK VSS33

MT6235 GSM/GPRS Baseband Processor Data Sheet Revision 1.02

38/599 MediaTek Inc. Confidential

D13 VDD33_MC

B15 VRTC

A15 XOUT VRTC VSS33 VDDK VSS33

A14 XIN VRTC VSS33 VDDK VSS33

B13 BBWAKEUP VRTC VSS33 VDDK VSS33

B14 TESTMODE VRTC VSS33 VDDK VSS33

A13 VSS33

C12 VIBRATOR

D12 GND_DRV

D11 LED

A12 GND_VCORE

A11 VCORE

C11 VCORE_FB

A10 VBAT_VCORE

B11 BAT_BACKUP

A9 VM

D10 VM_SENSE

B10 VBAT_LDOS1

C10 VCAM_D

B9 VBAT_LDOS1

D9 GND_LDOS

D8 VCAM_A_SENSE

A7 VCAM_A

C8 VBT

B8 VBAT_LDOS2

A6 VIO

D7 GND_LDOS

C7 VUSB

B7 VBAT_LDOS2

A5 VSIM

C5 SIO

C6 PWRKEY

B6 VBAT_LDOS3

D6 GND_LDOS

D5 ISENSE

A4 VMSEL

B4 GATEDRV

C4 CHRIN

A3 SCLK

B3 \BATSENSE

C3 SRST

A2 RESET

B2 RSTCAP

L9 VSS33

L11 VSS33

L12 VSS33

L13 VSS33

L14 VSS33

L15 VSS33

MT6235 GSM/GPRS Baseband Processor Data Sheet Revision 1.02

39/599 MediaTek Inc. Confidential

M9 VSS33

M11 VSS33

M15 VSS33

N11 VSS33

N13 VSS33

N15 VSS33

P9 VSS33

P11 VSS33

P15 VSS33

R9 VSS33

R11 VSS33

R12 VSS33

R13 VSS33

R14 VSS33

R15 VSS33

T9 VSS33

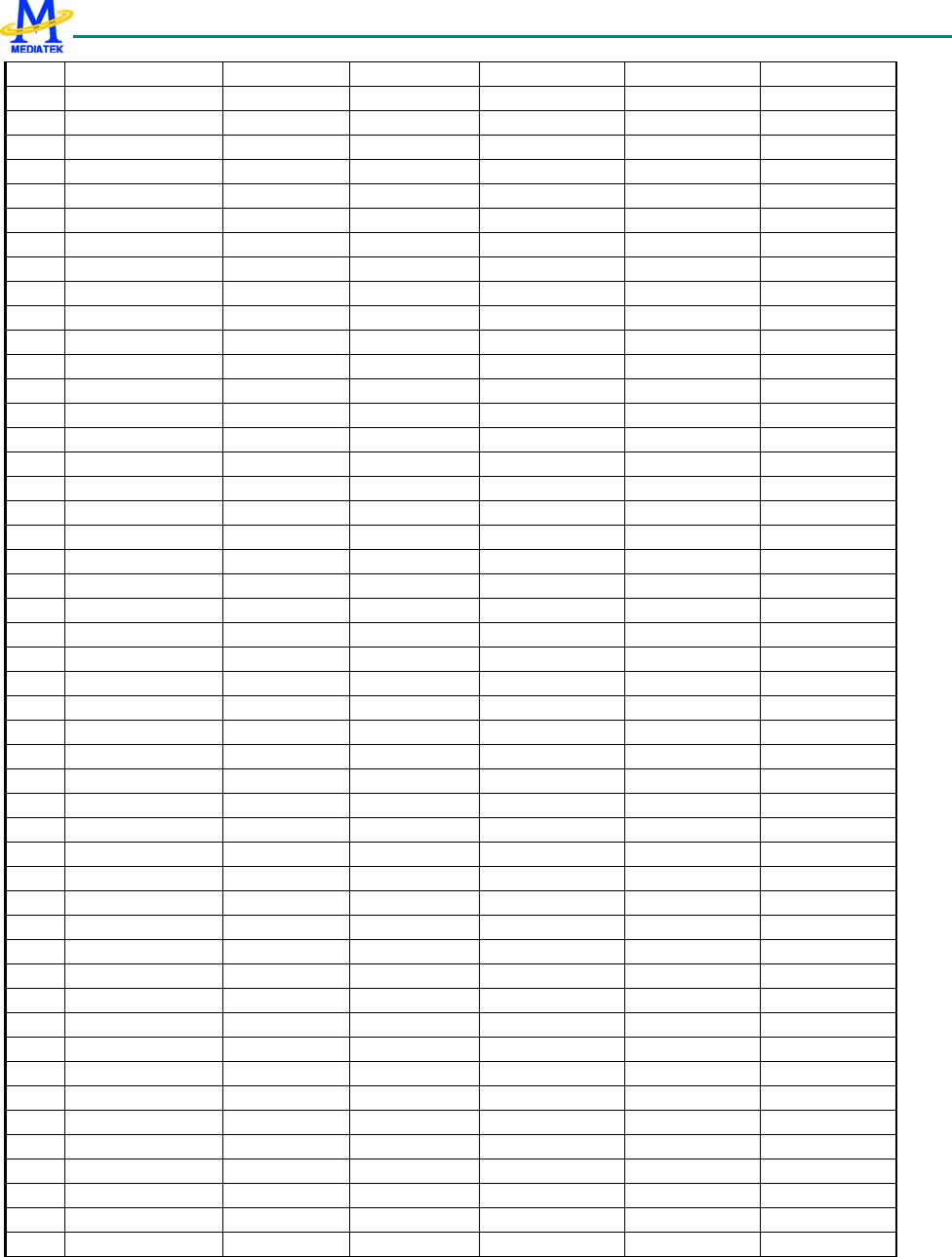

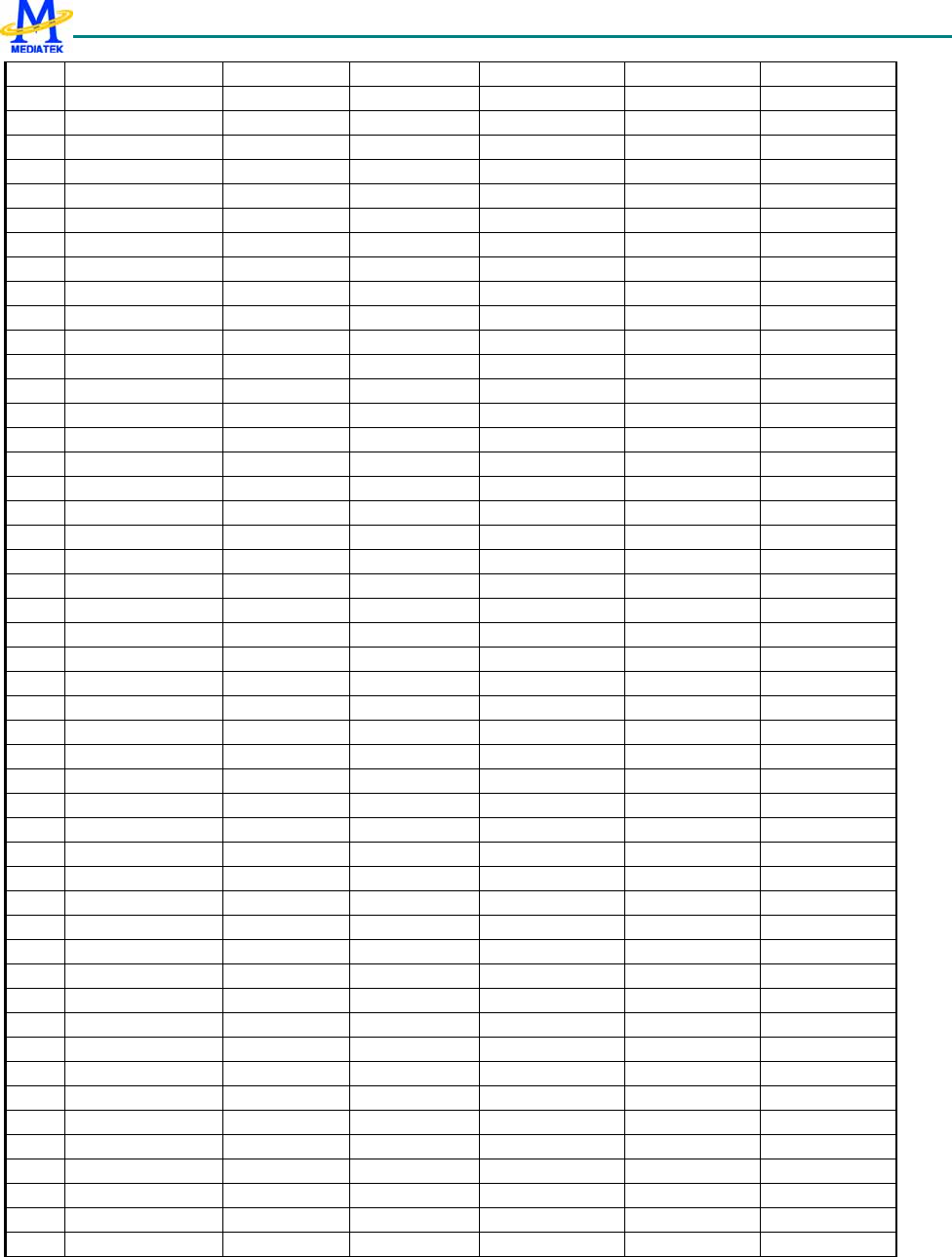

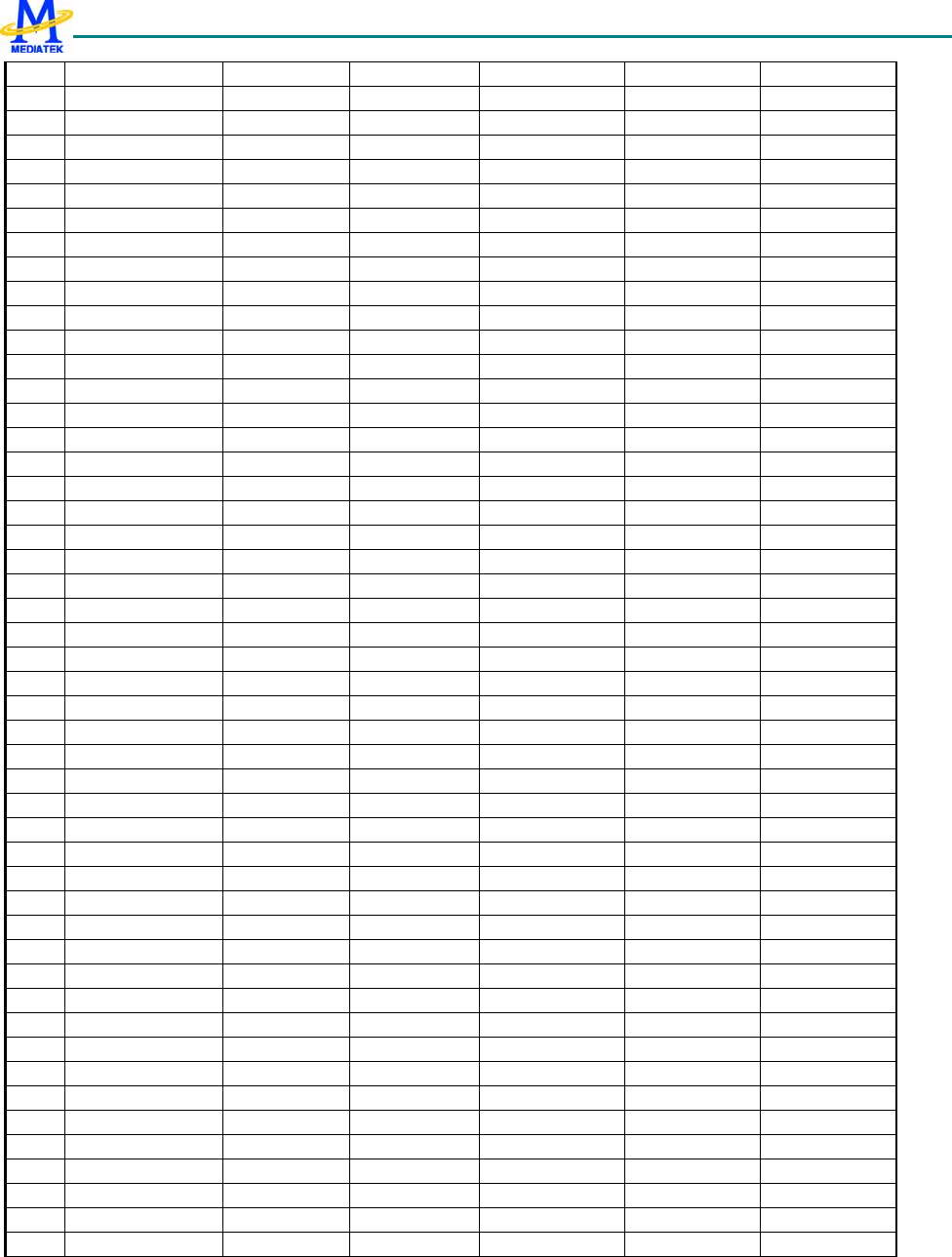

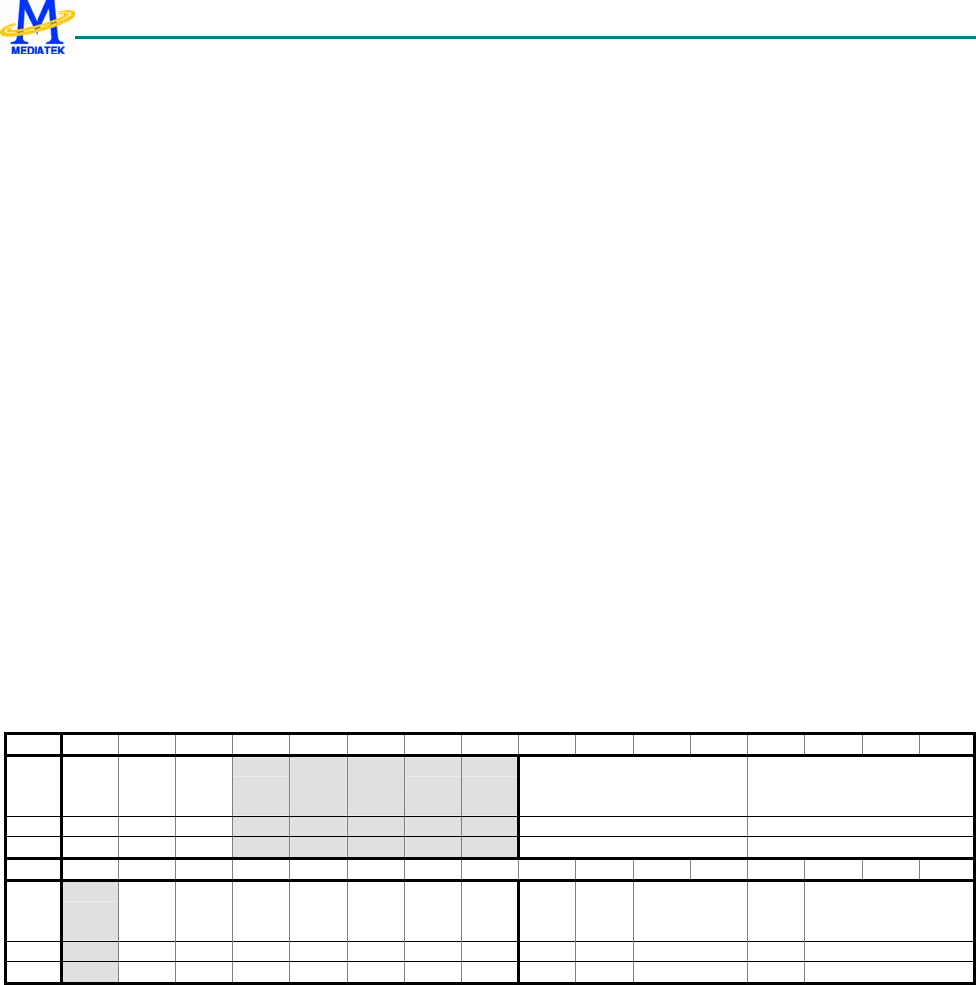

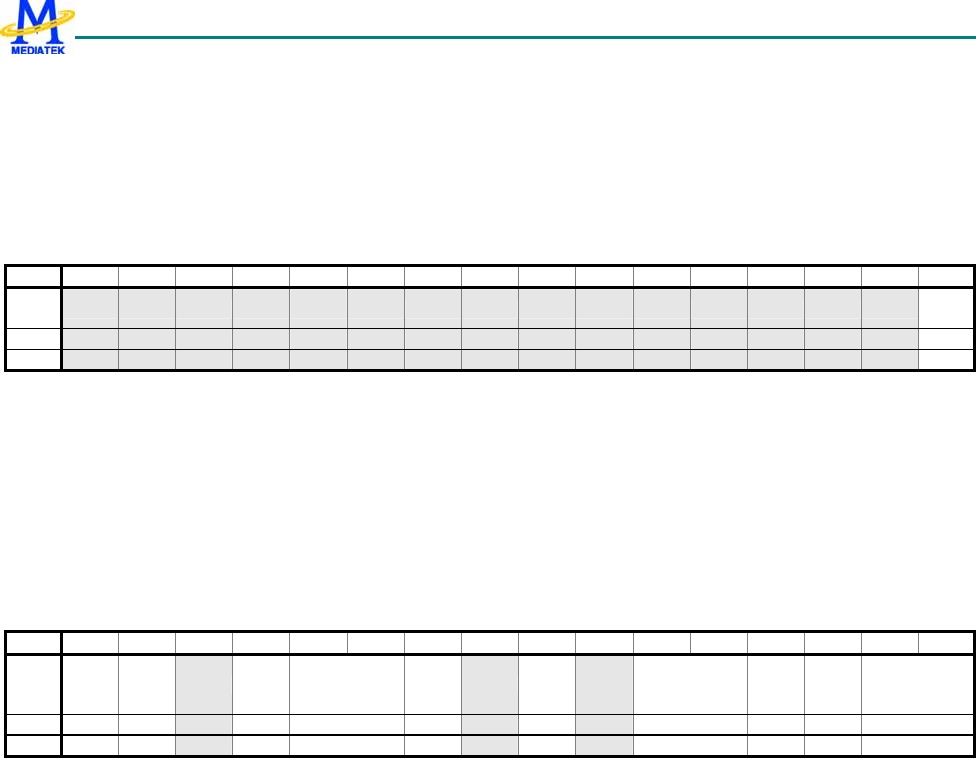

Table 3 Power Descriptions

MT6235 GSM/GPRS Baseband Processor Data Sheet Revision 1.02

40/599 MediaTek Inc. Confidential

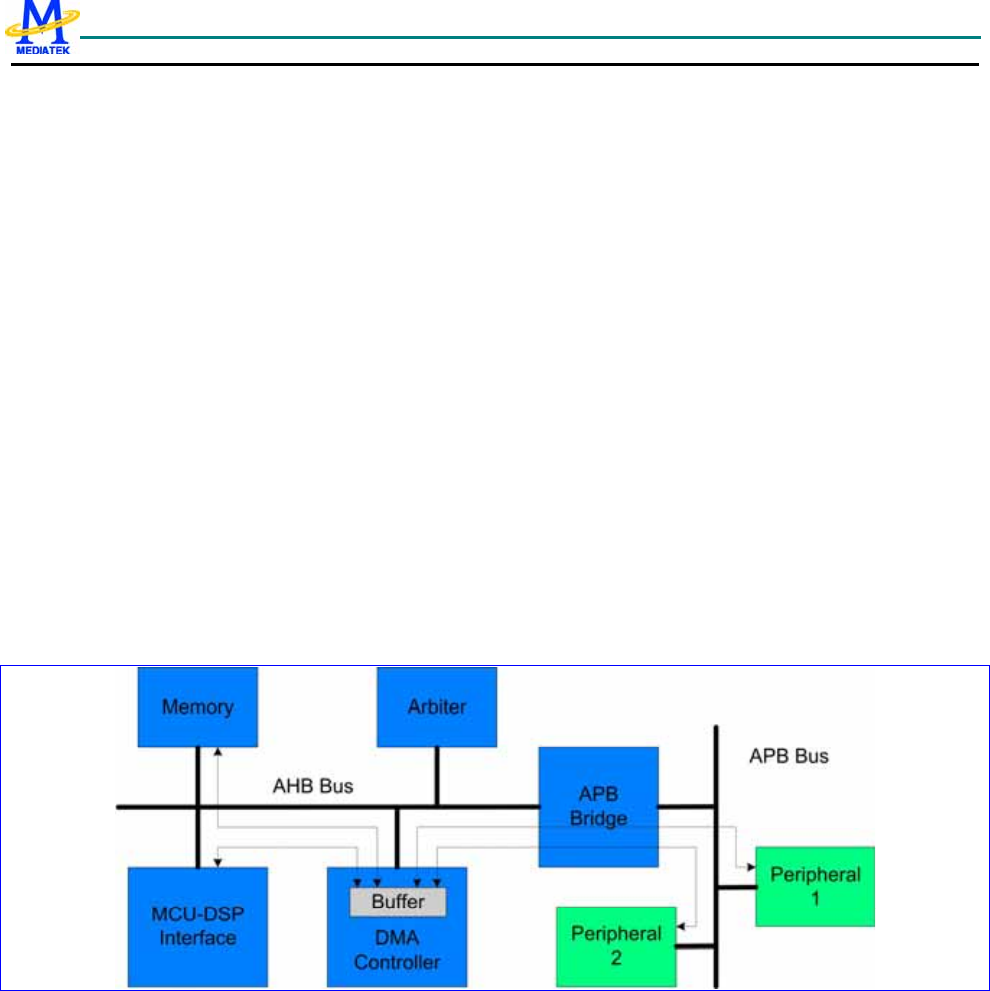

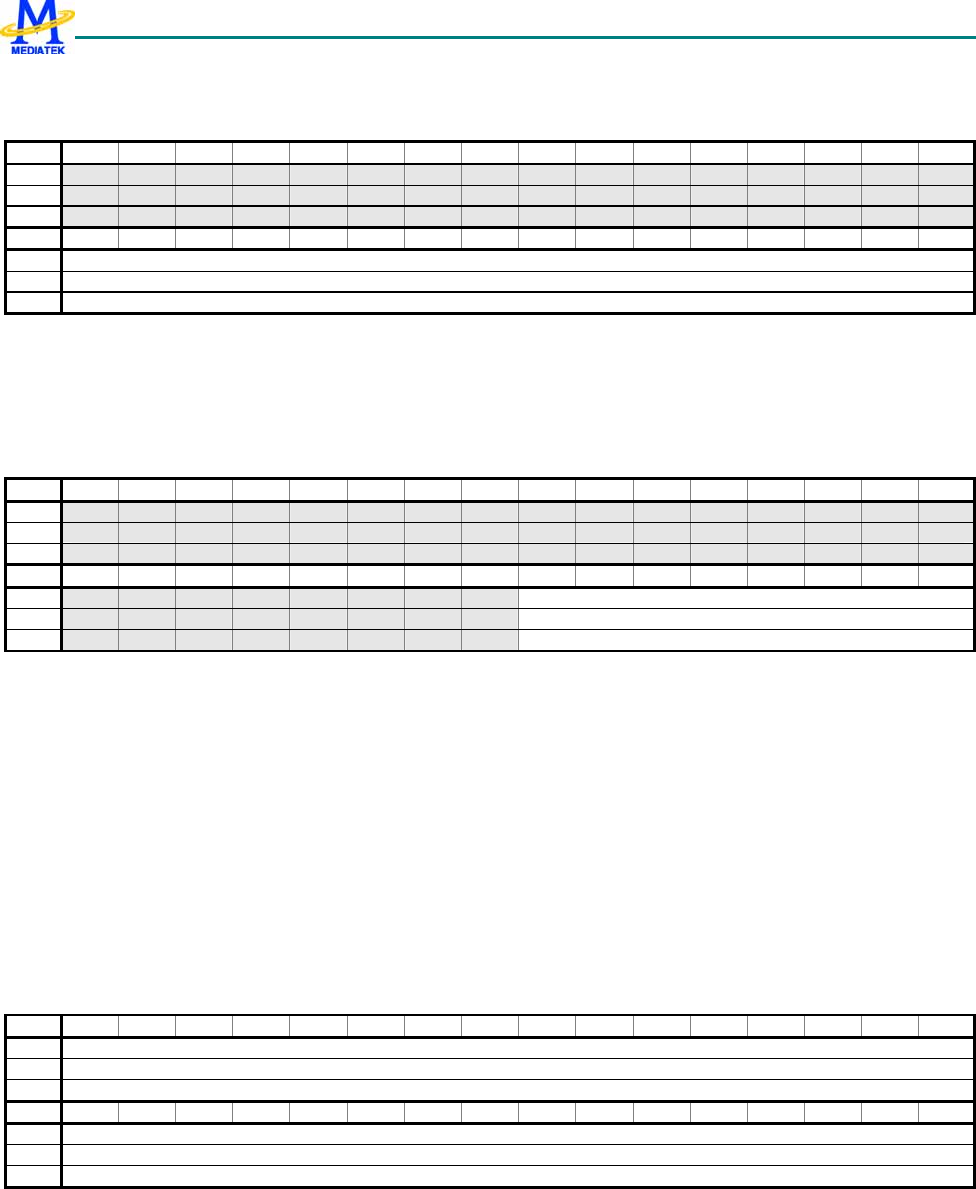

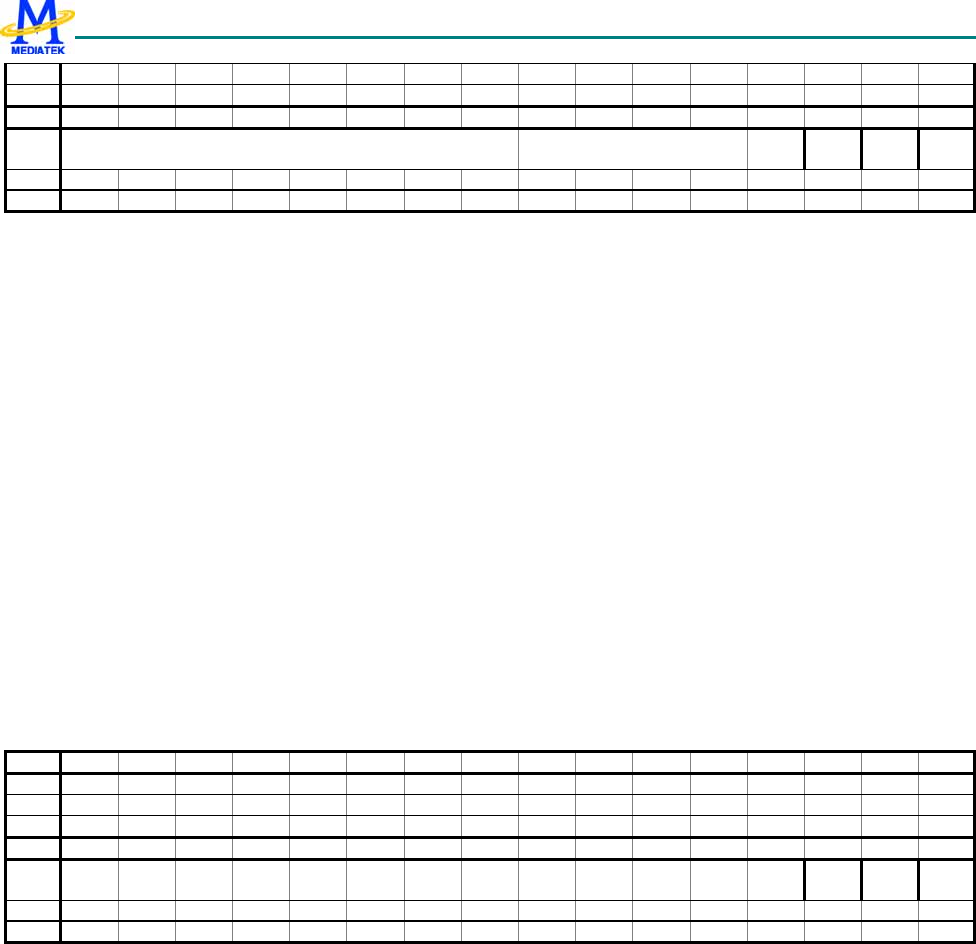

3 Micro-Controller Unit Subsystem

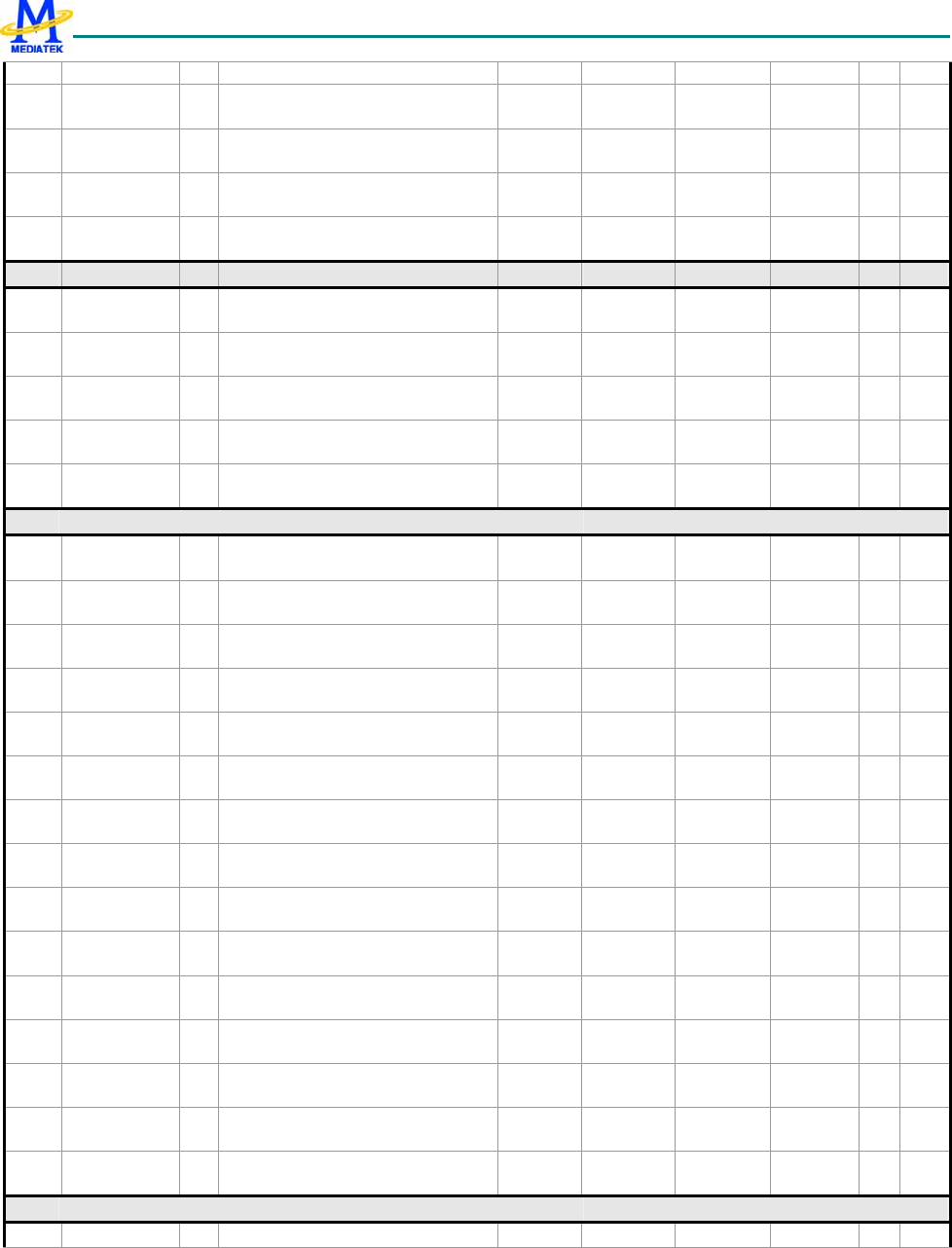

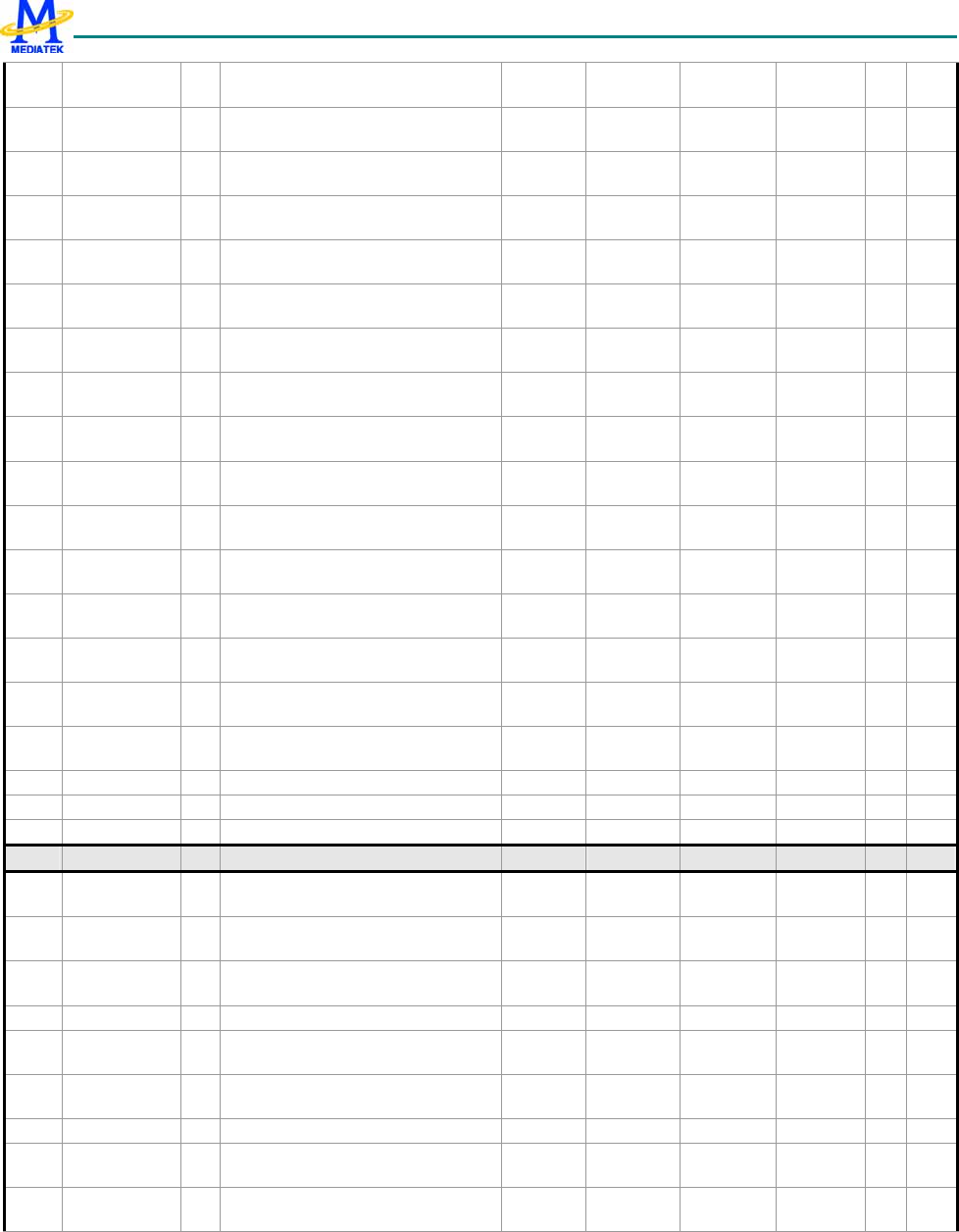

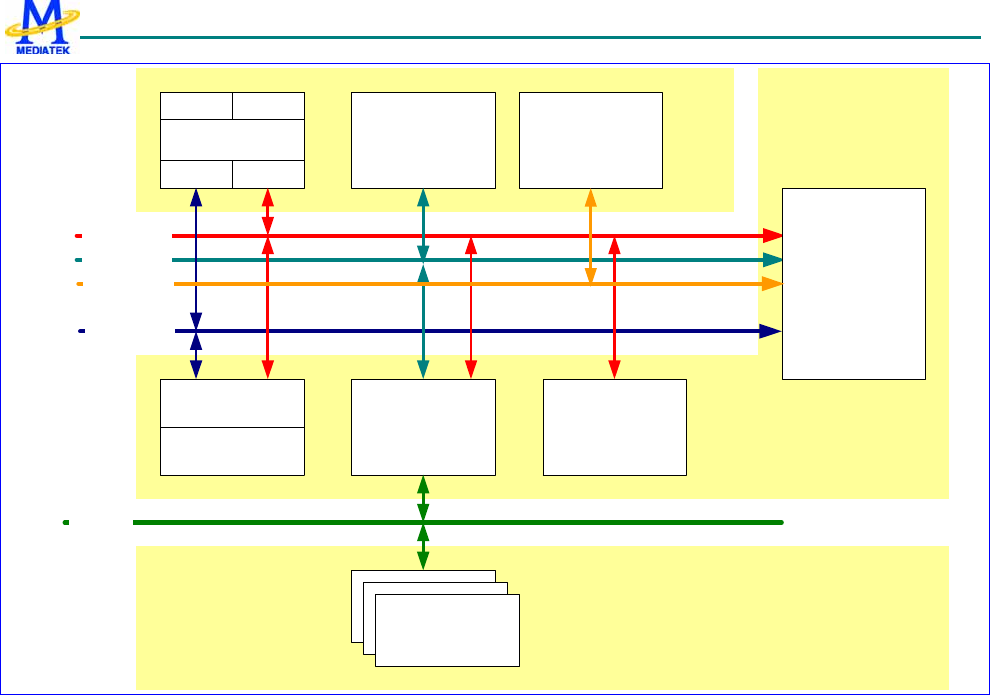

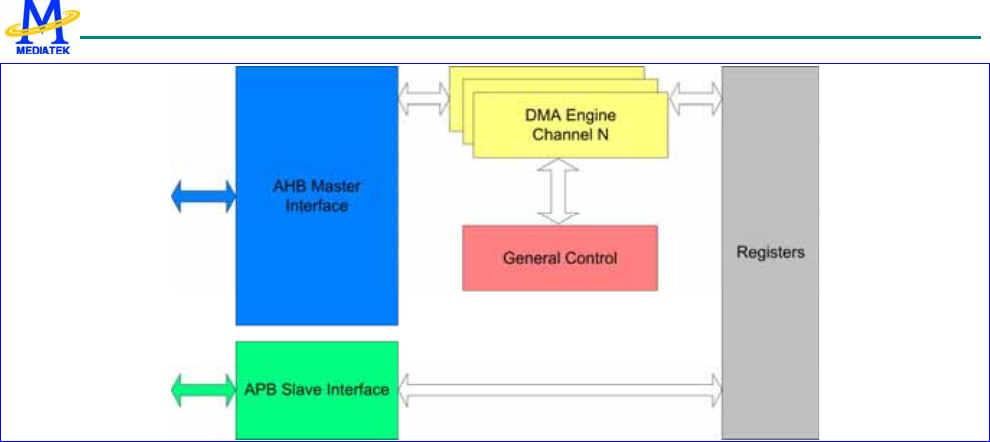

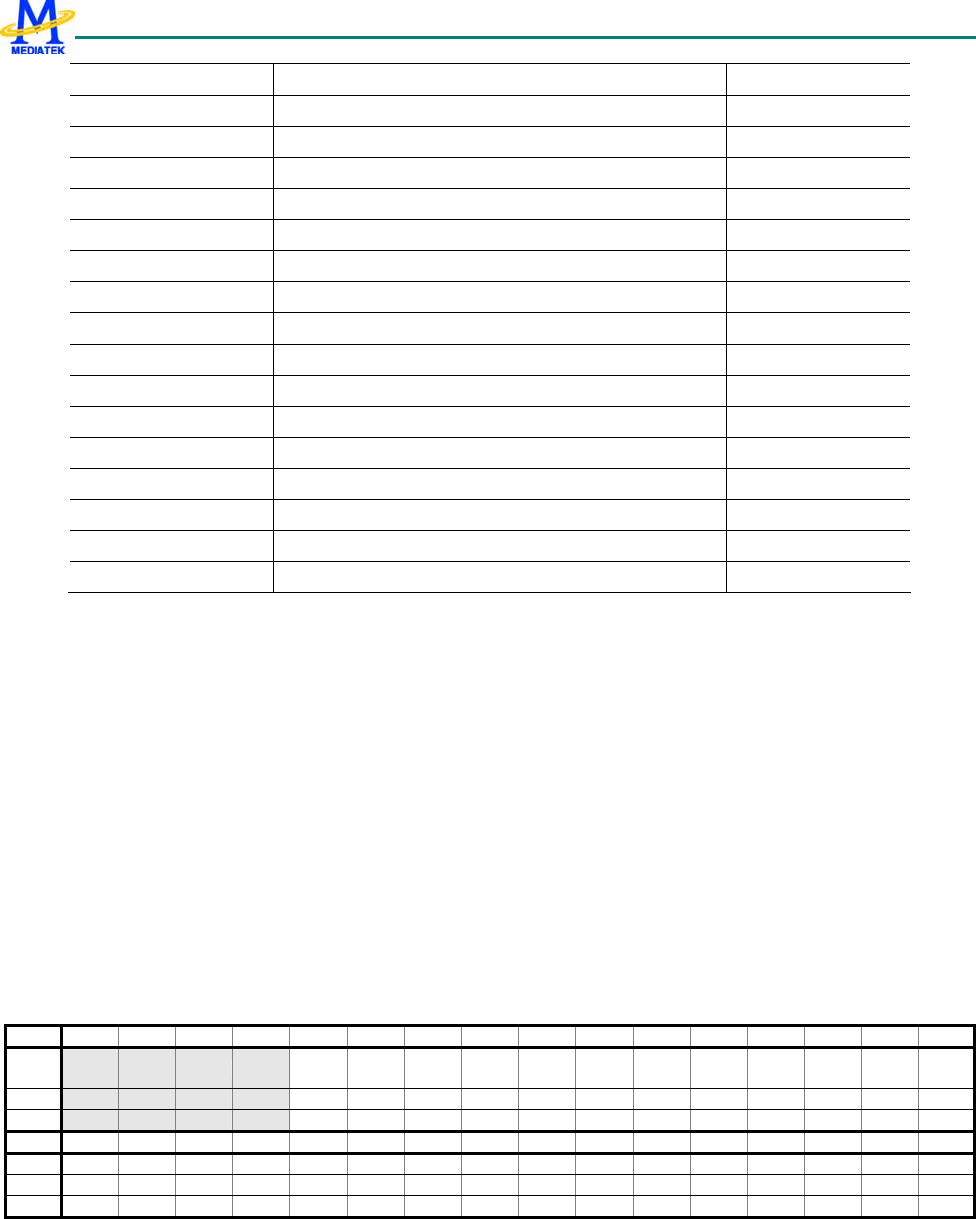

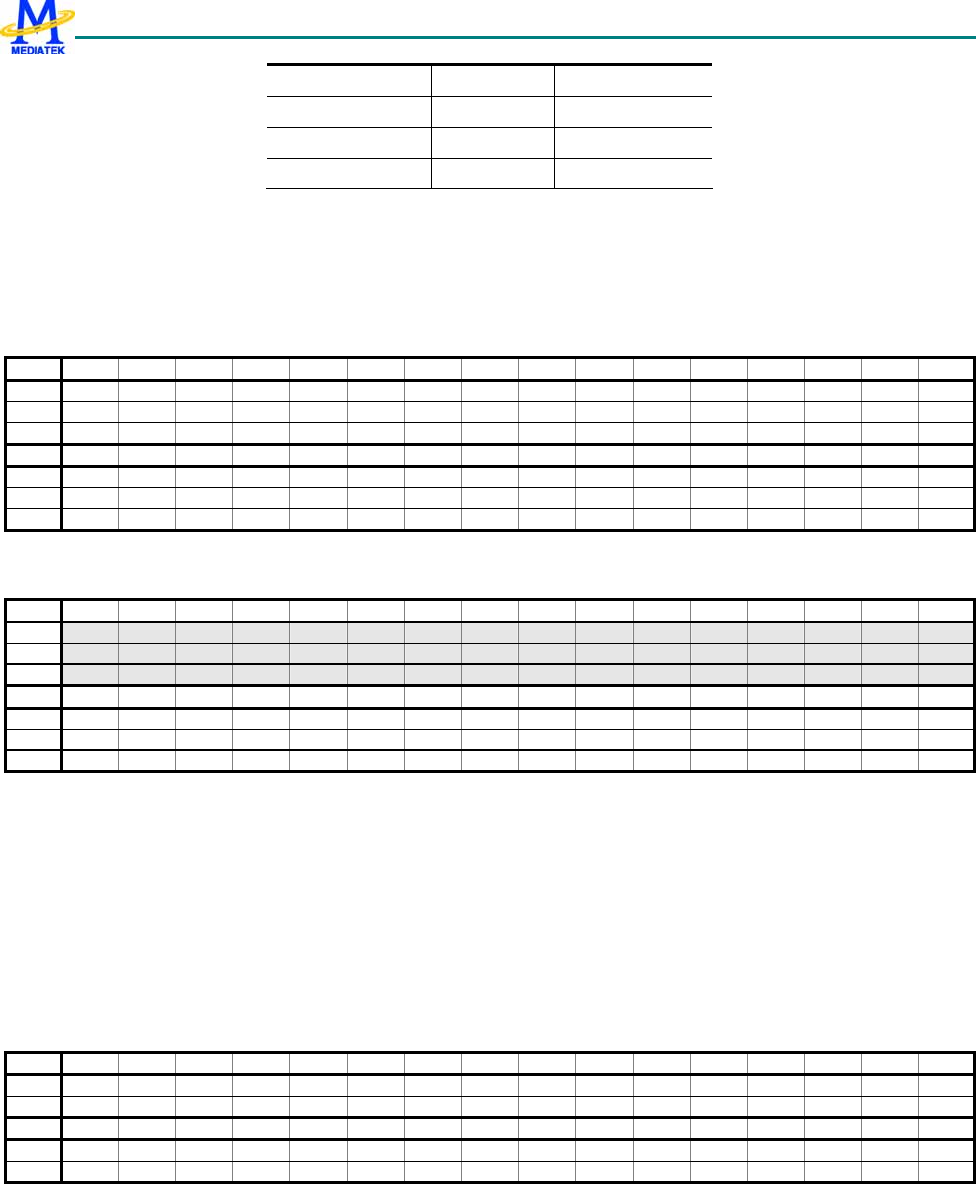

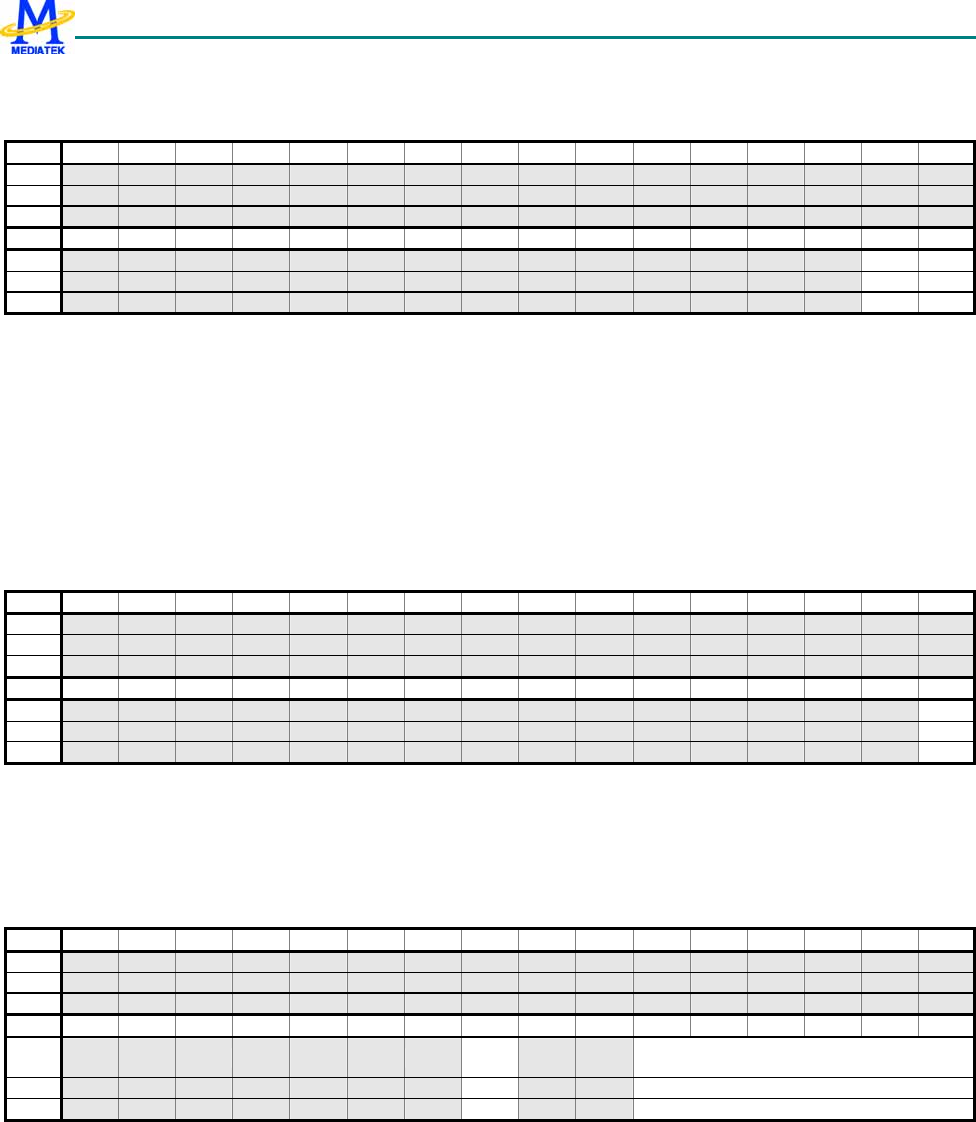

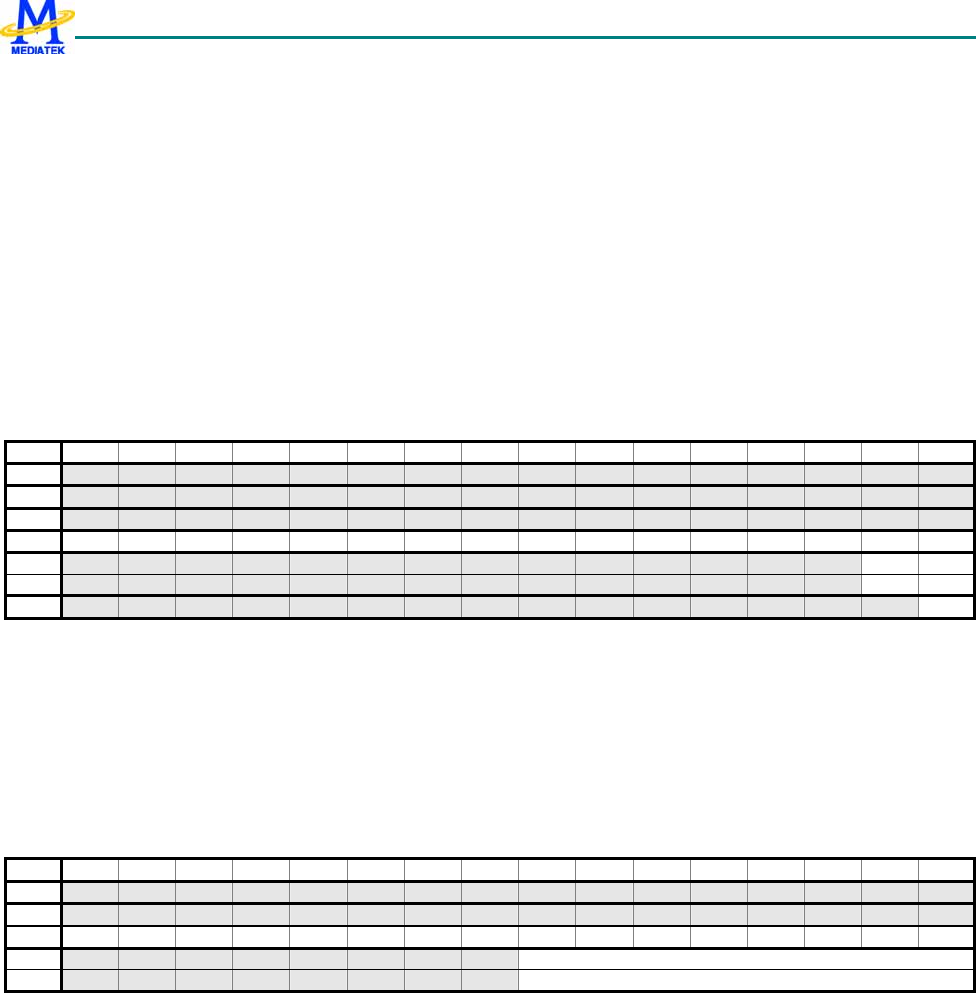

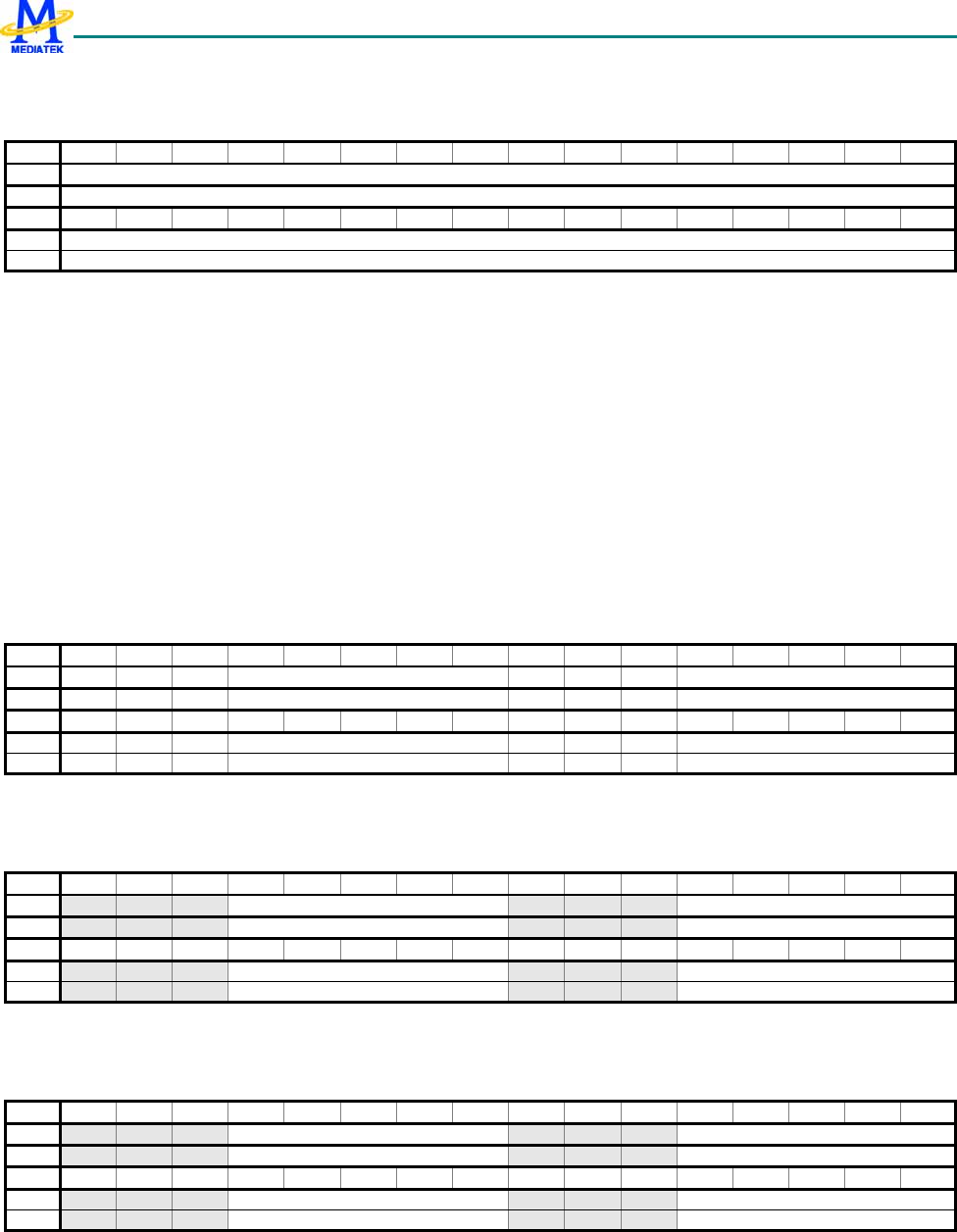

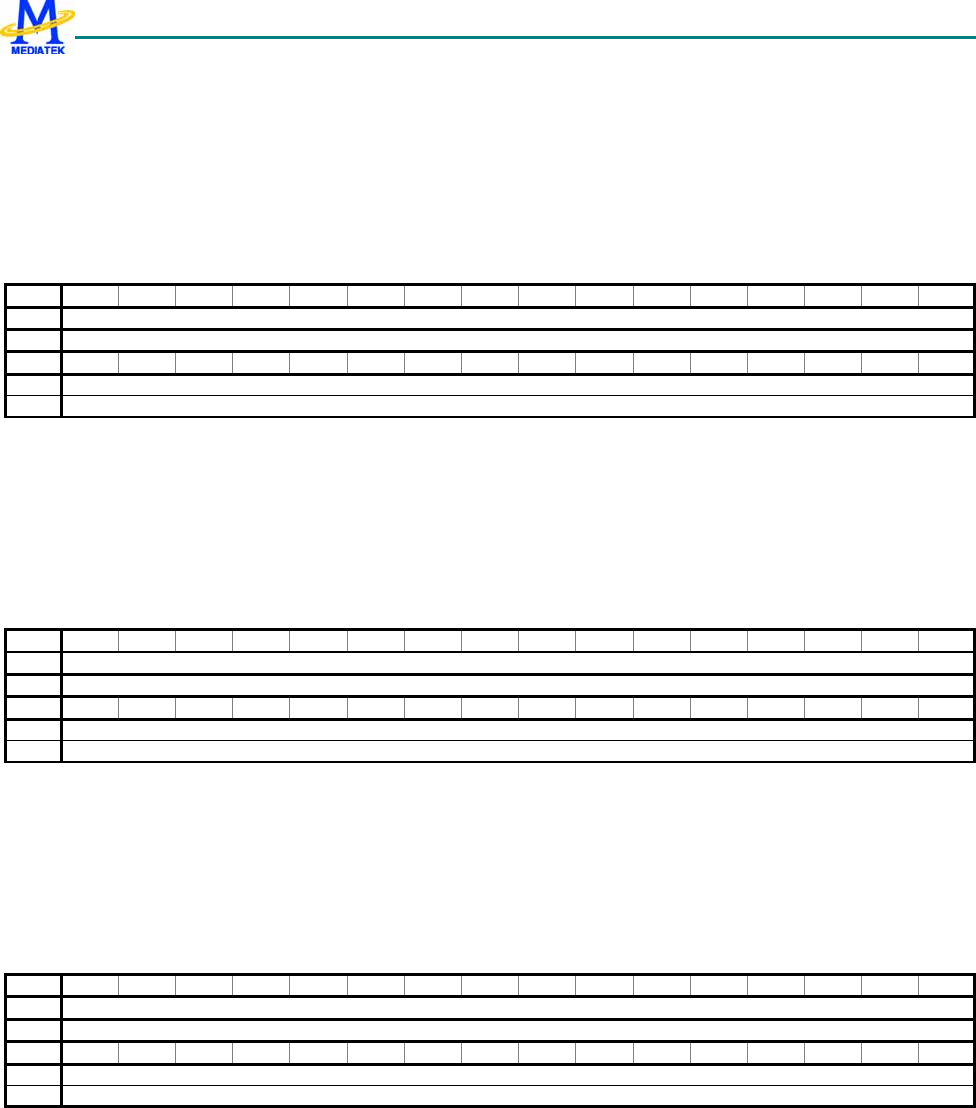

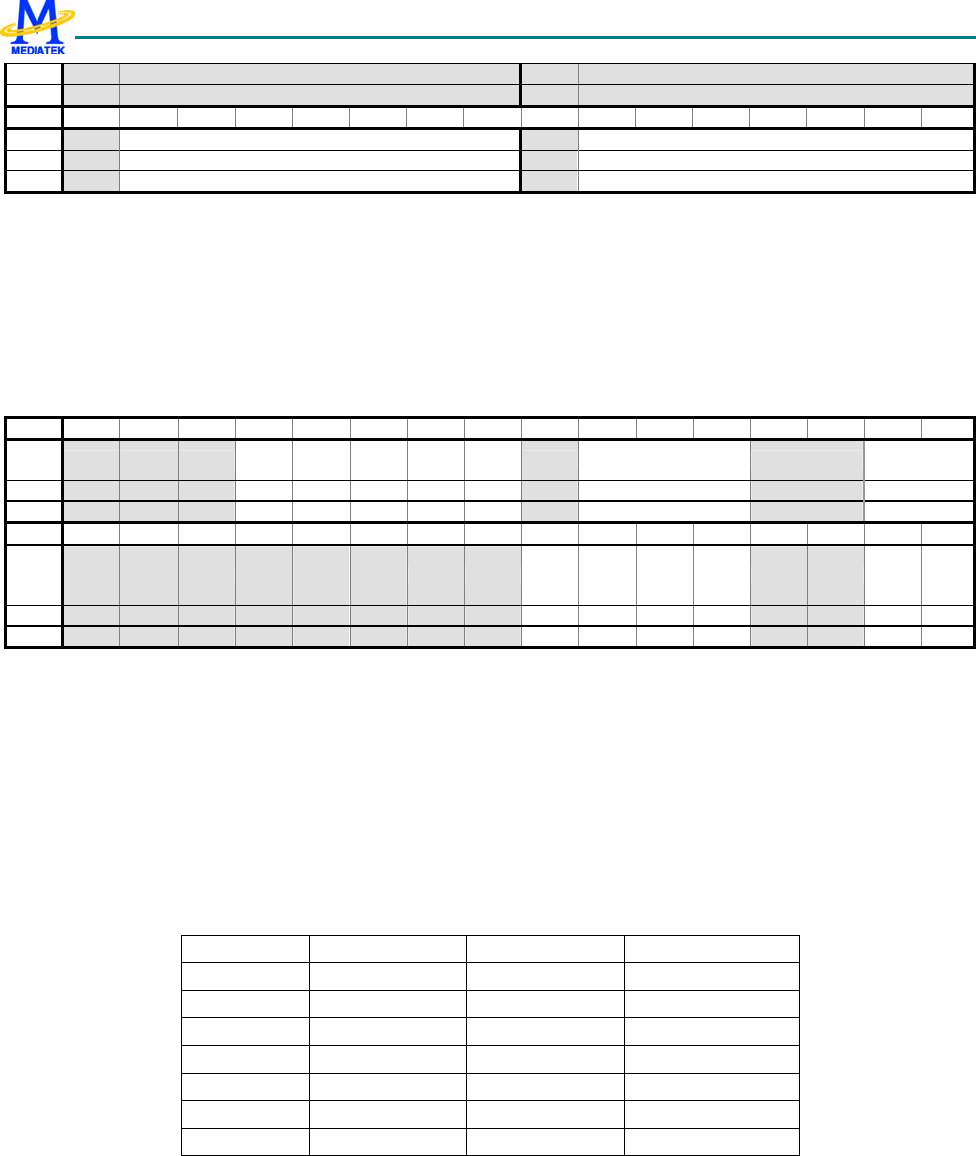

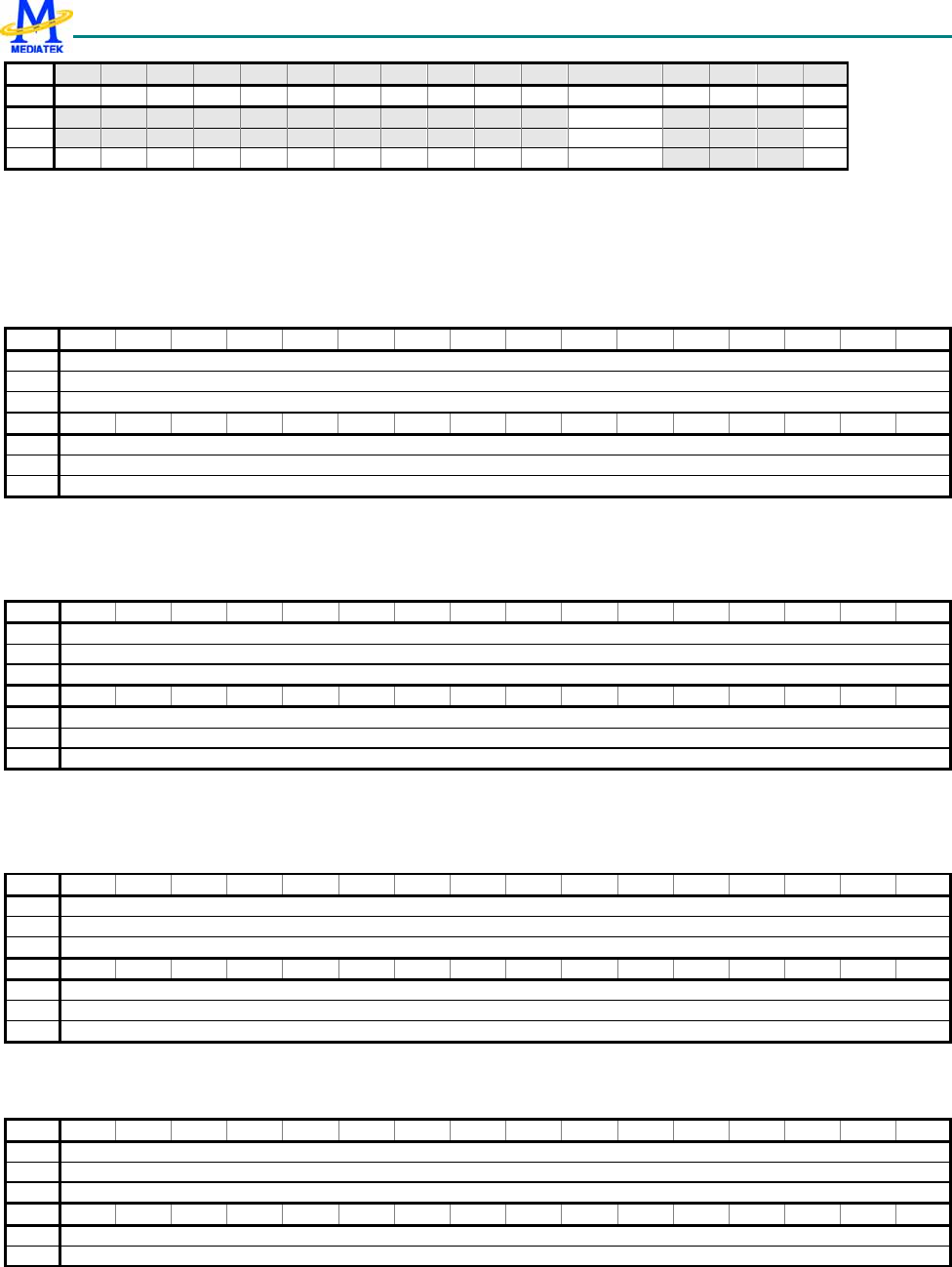

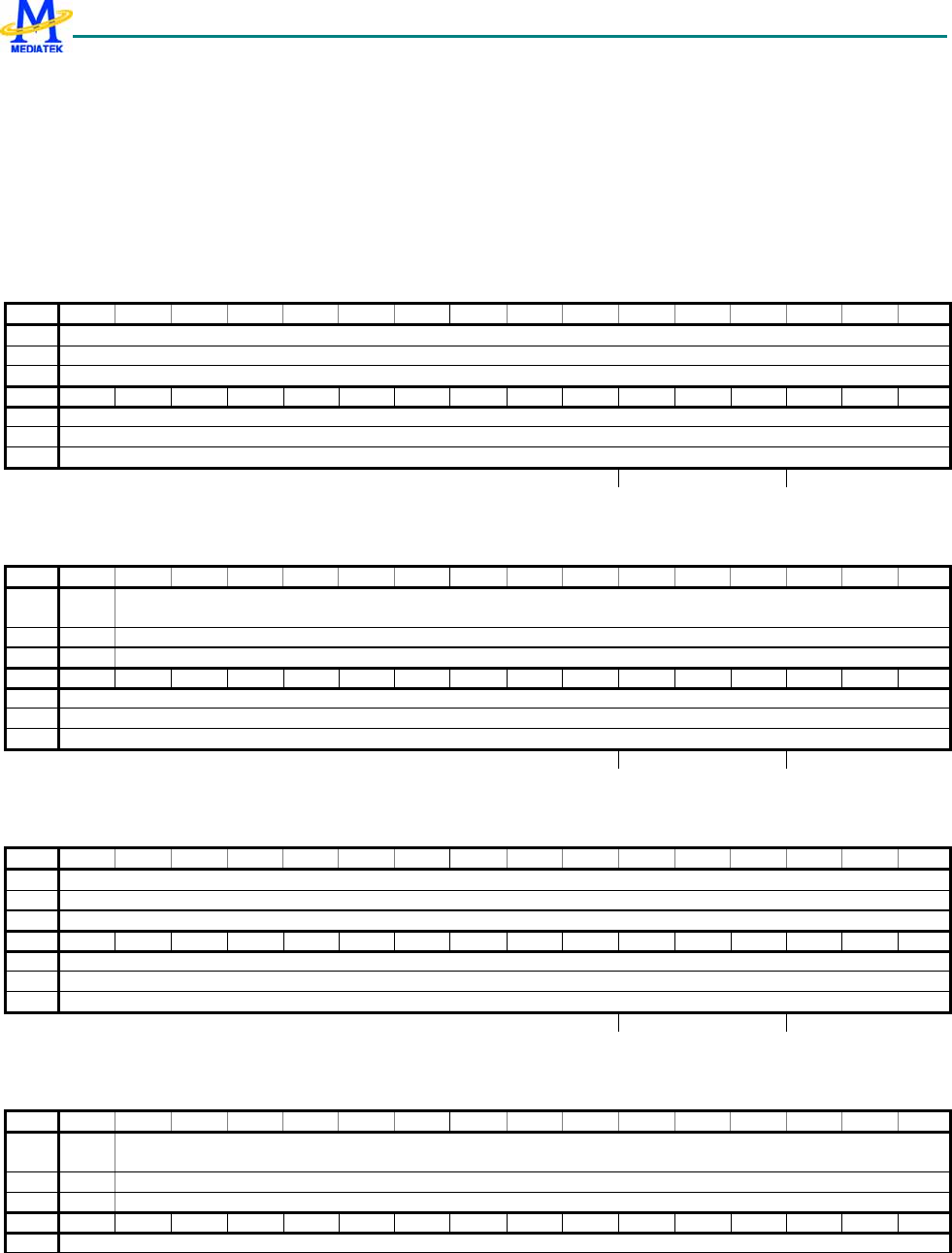

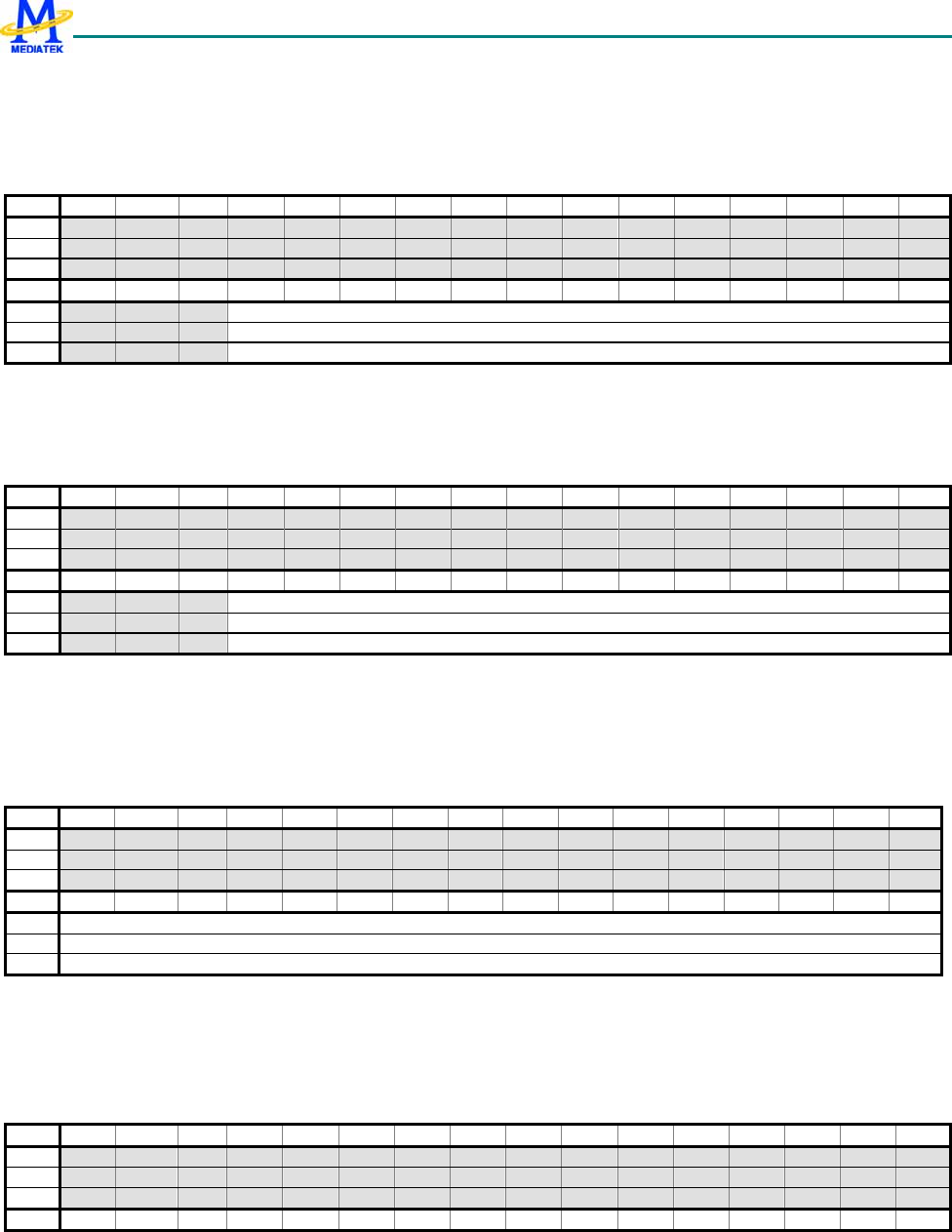

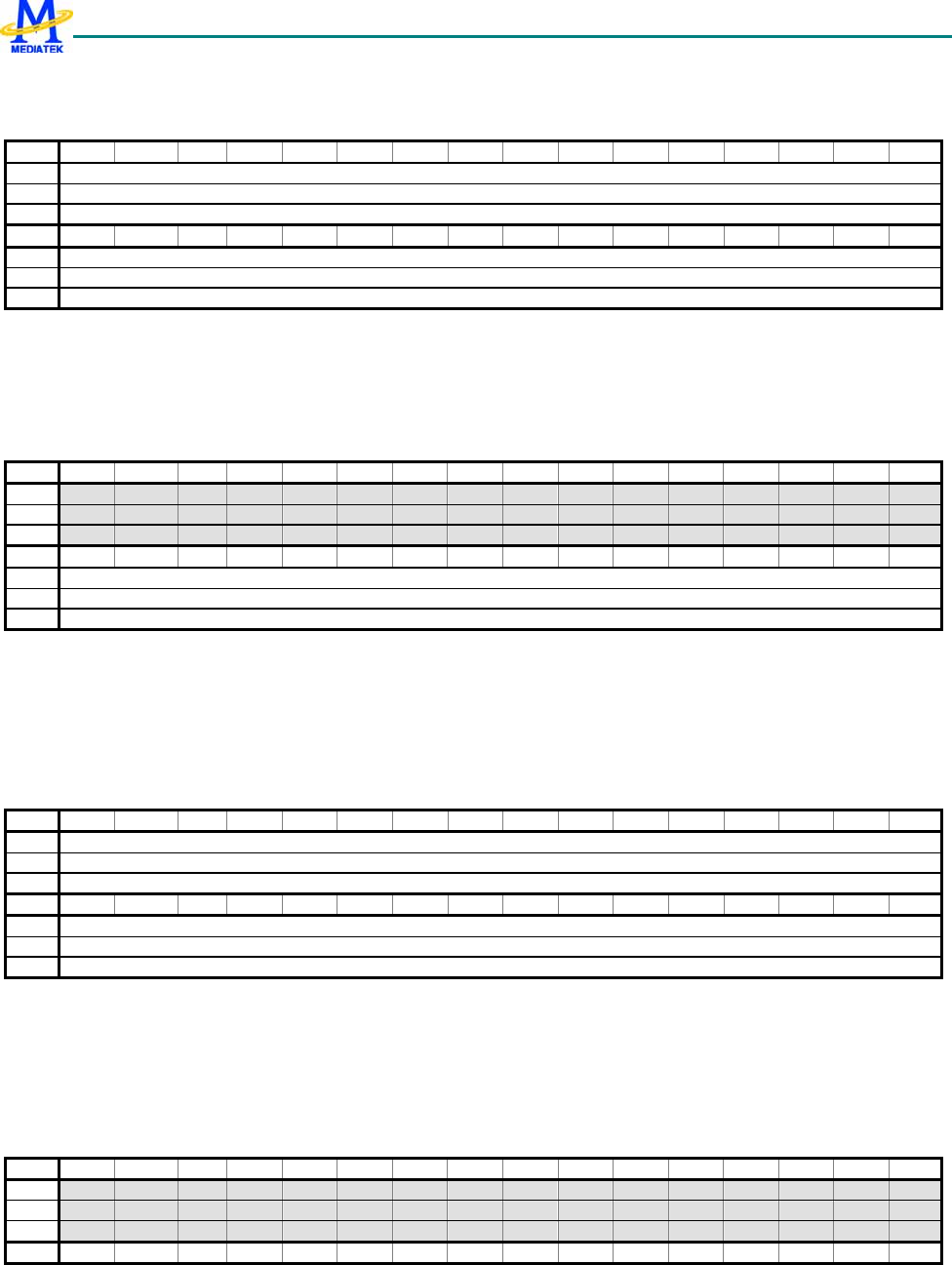

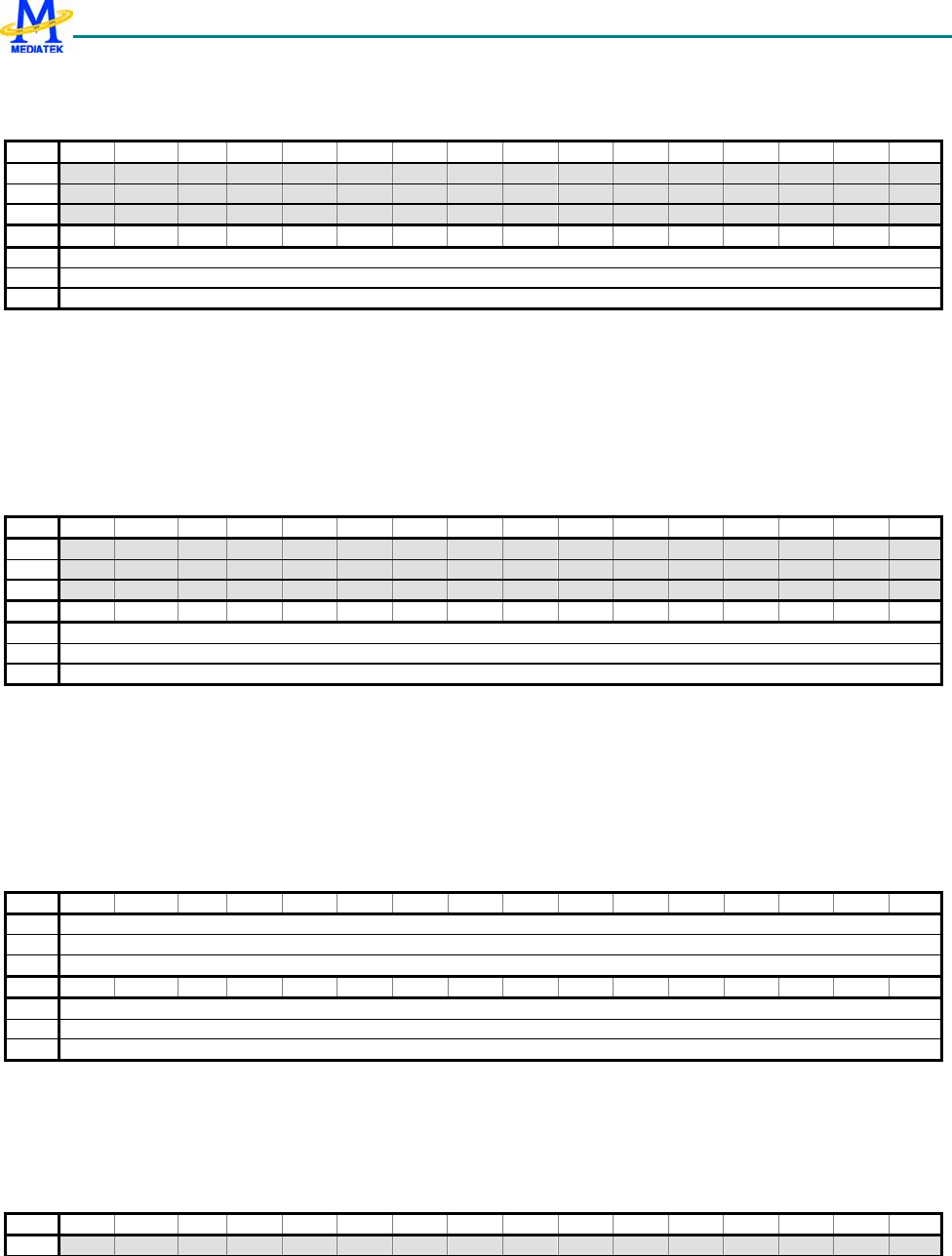

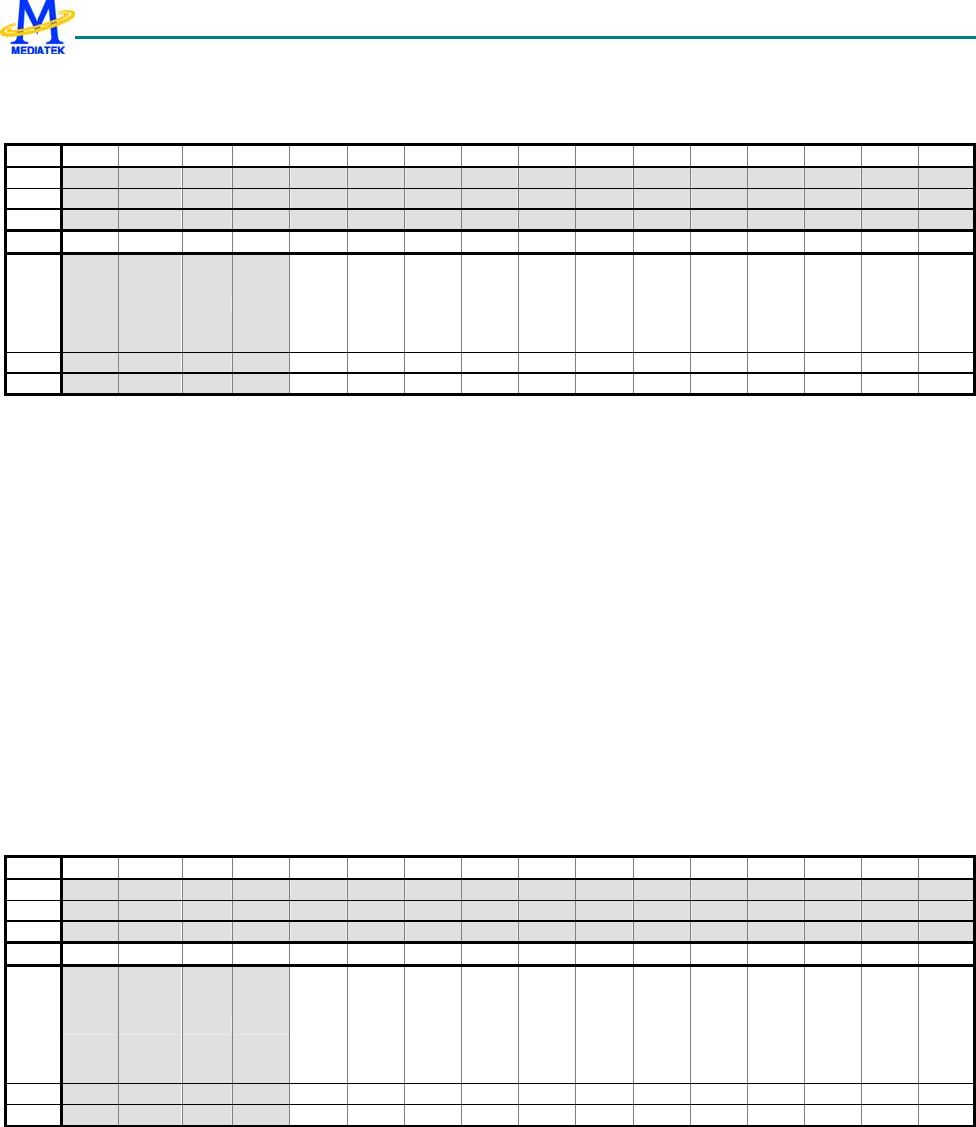

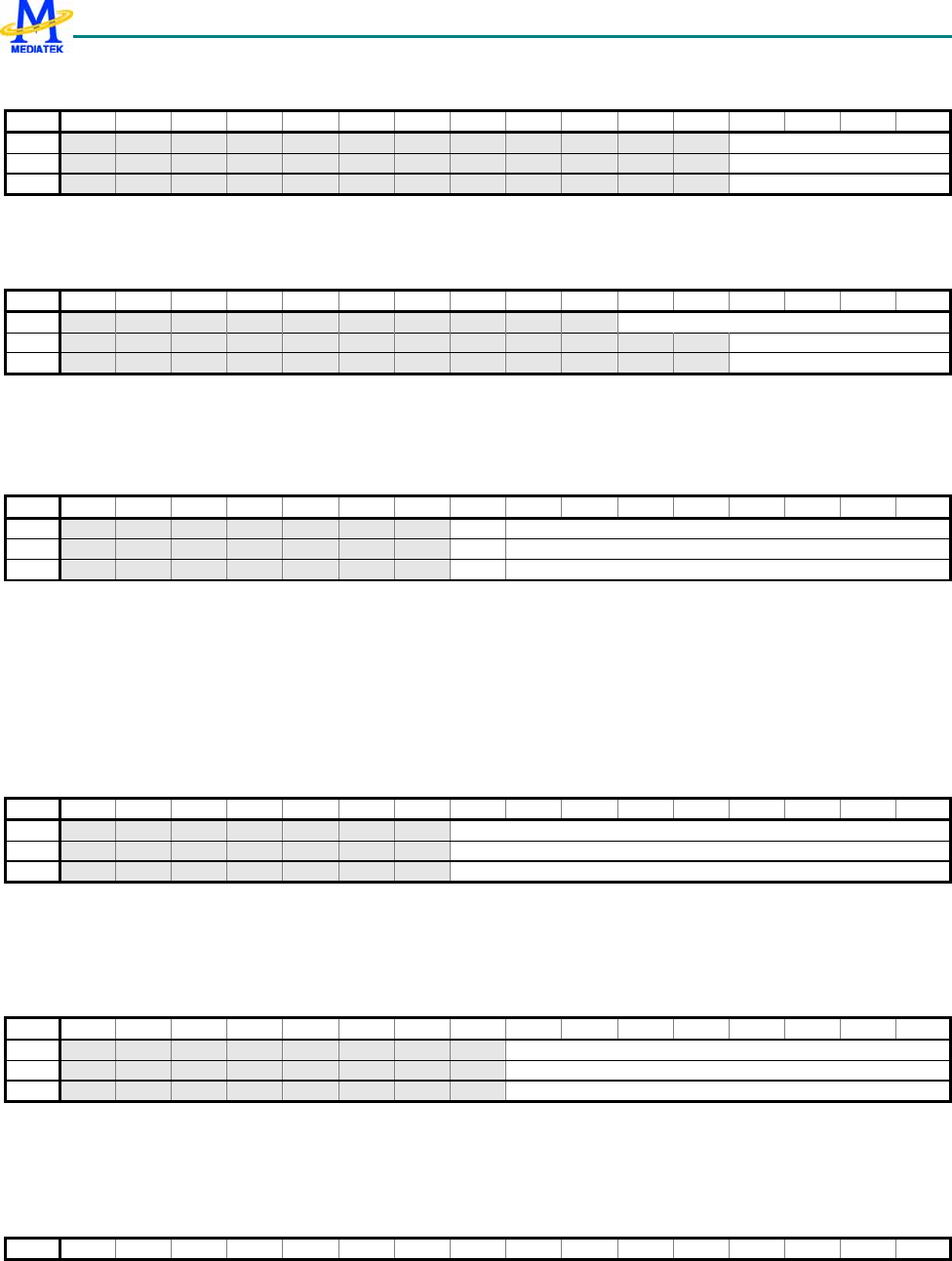

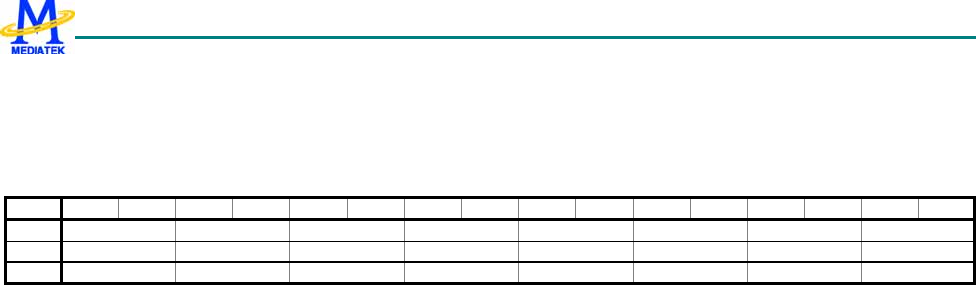

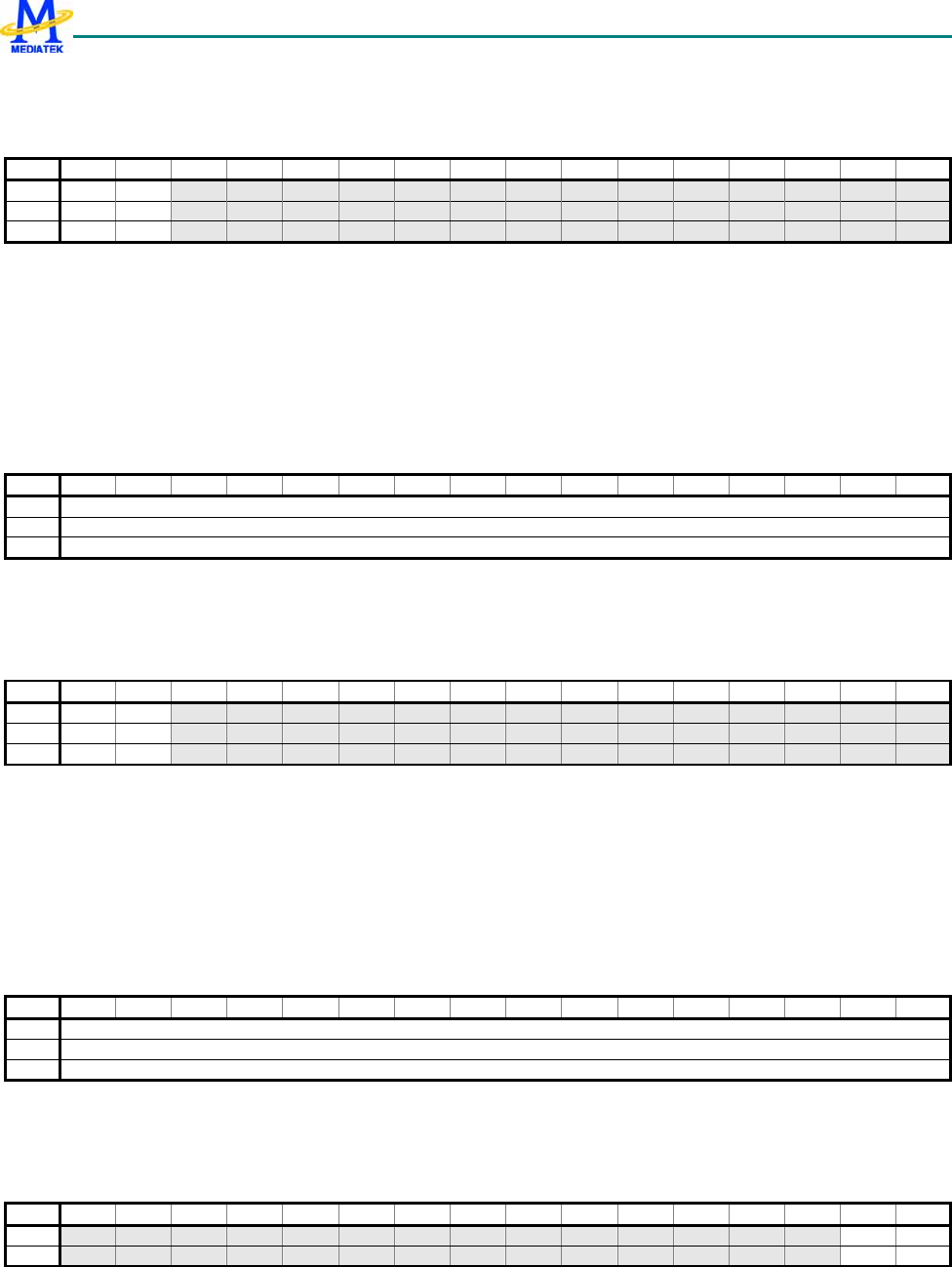

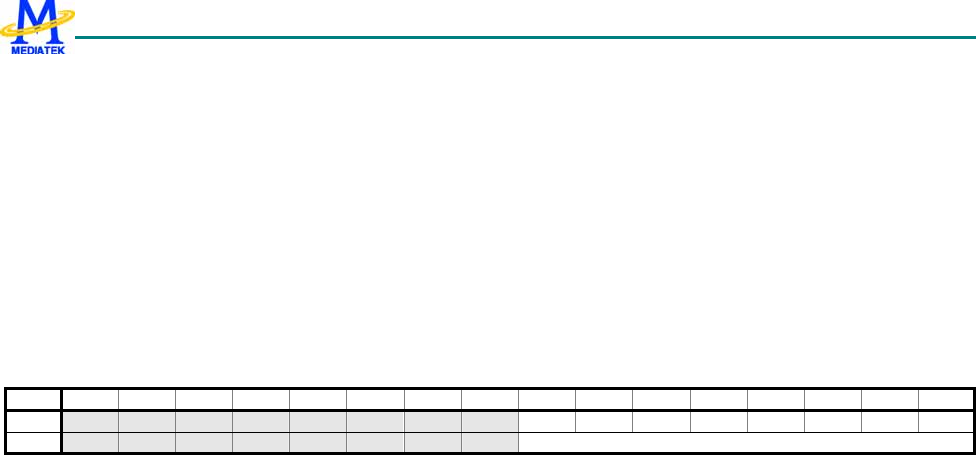

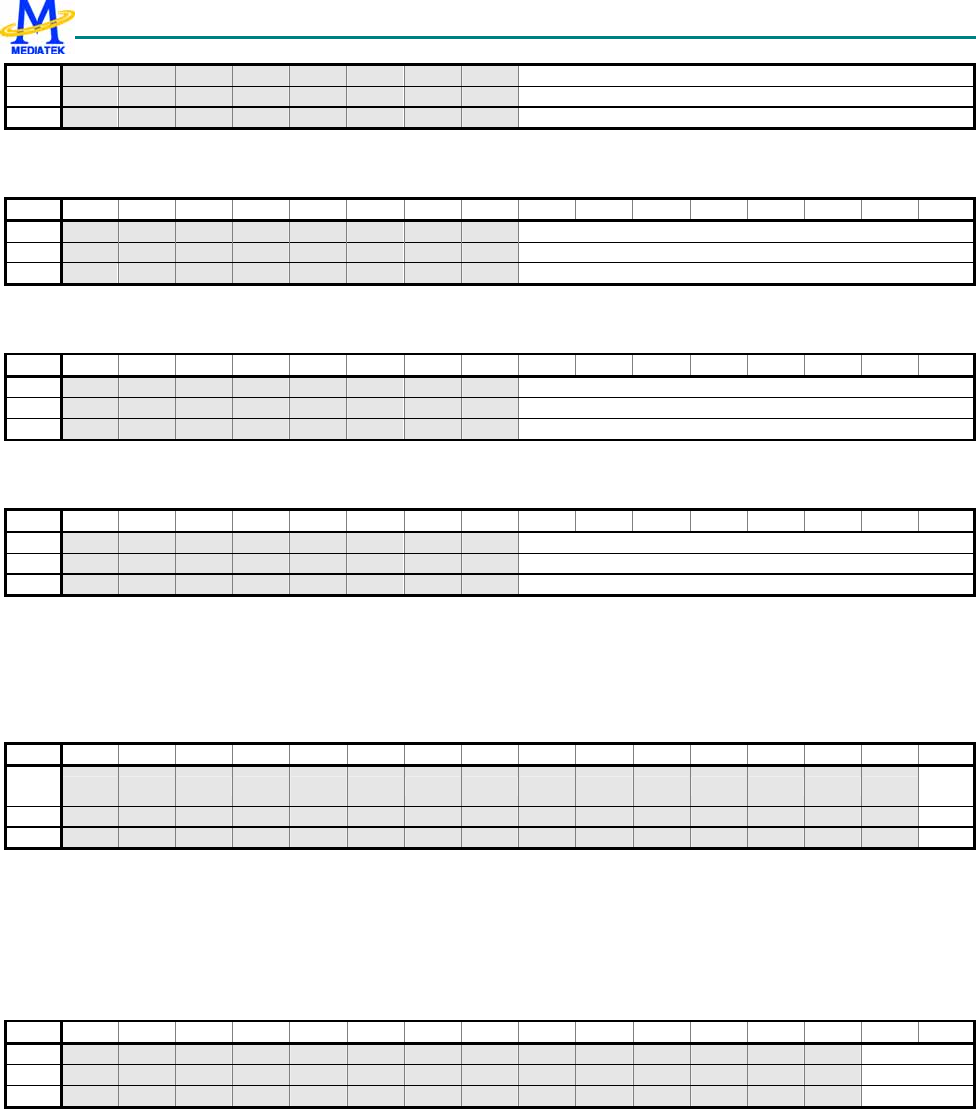

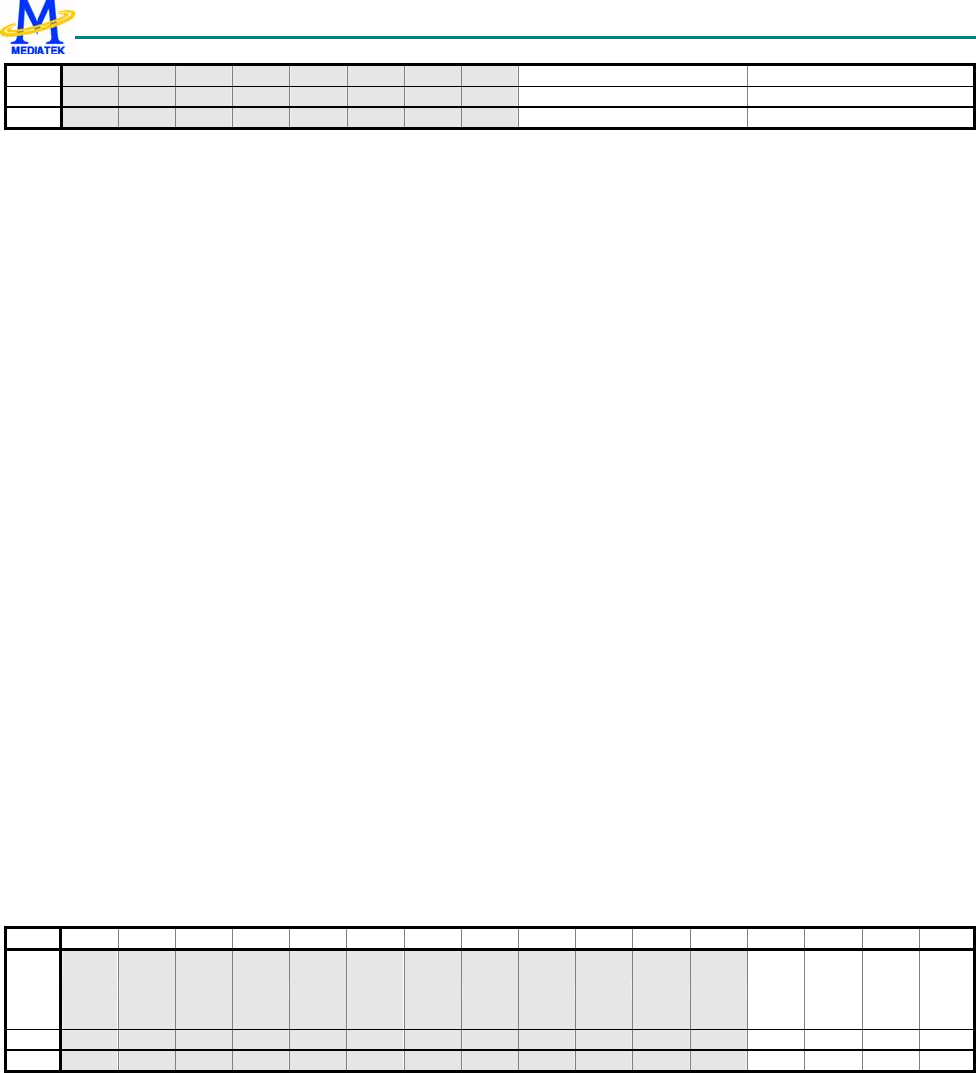

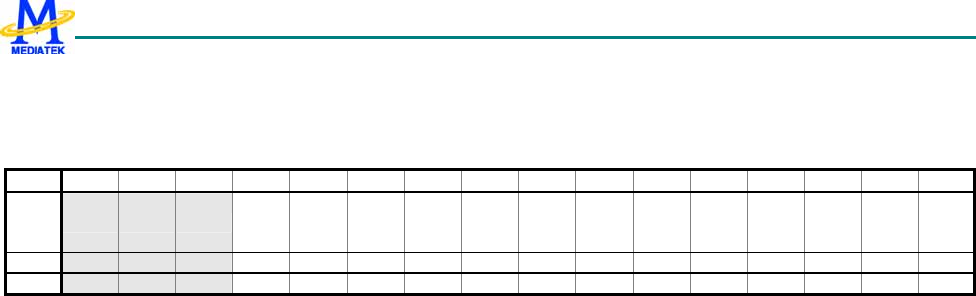

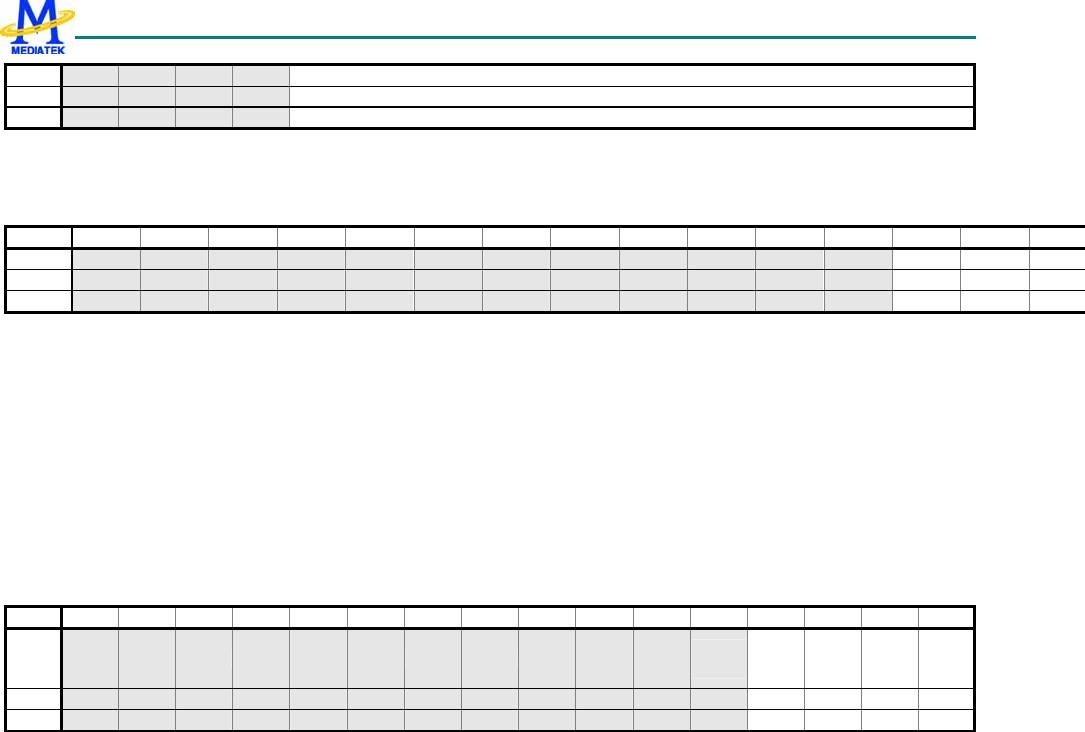

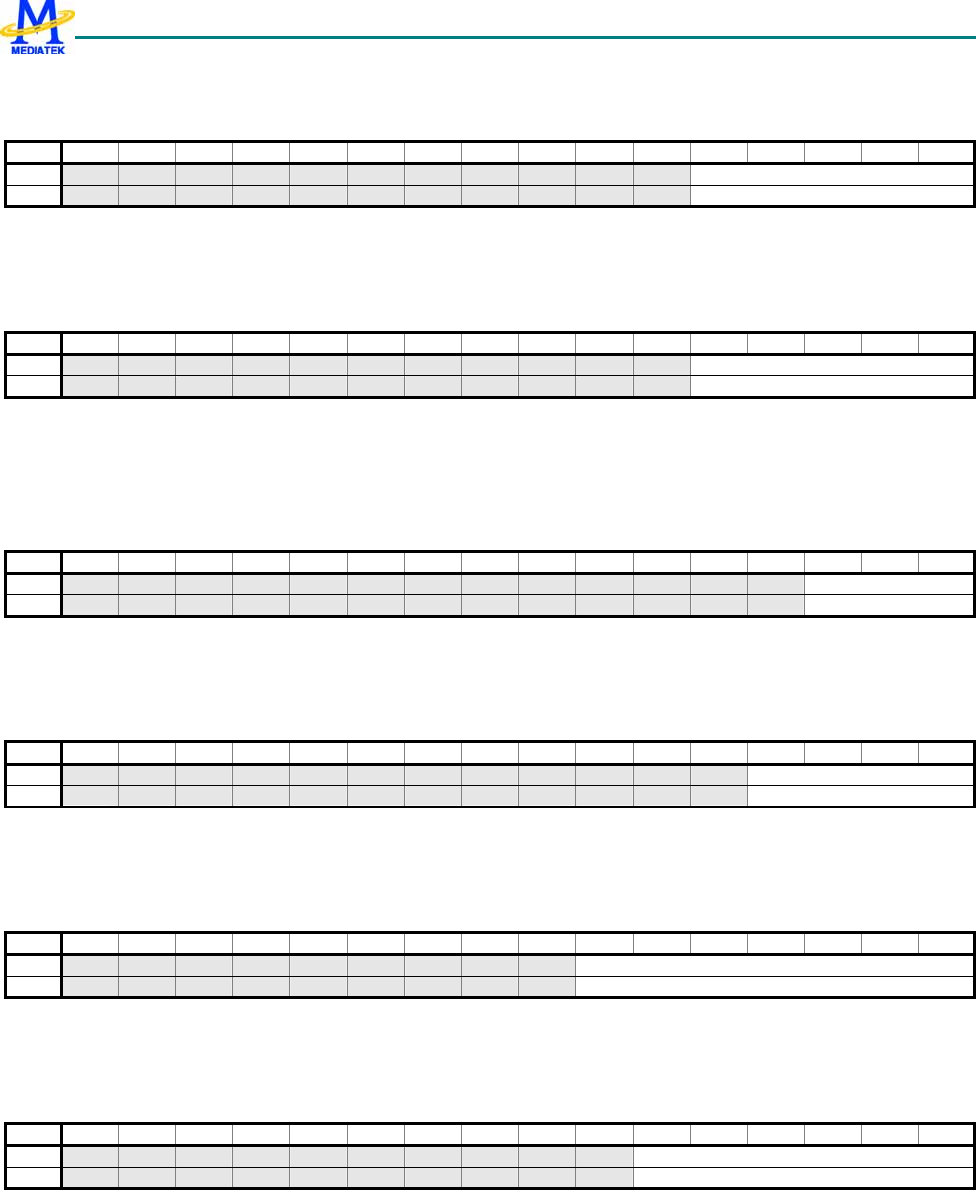

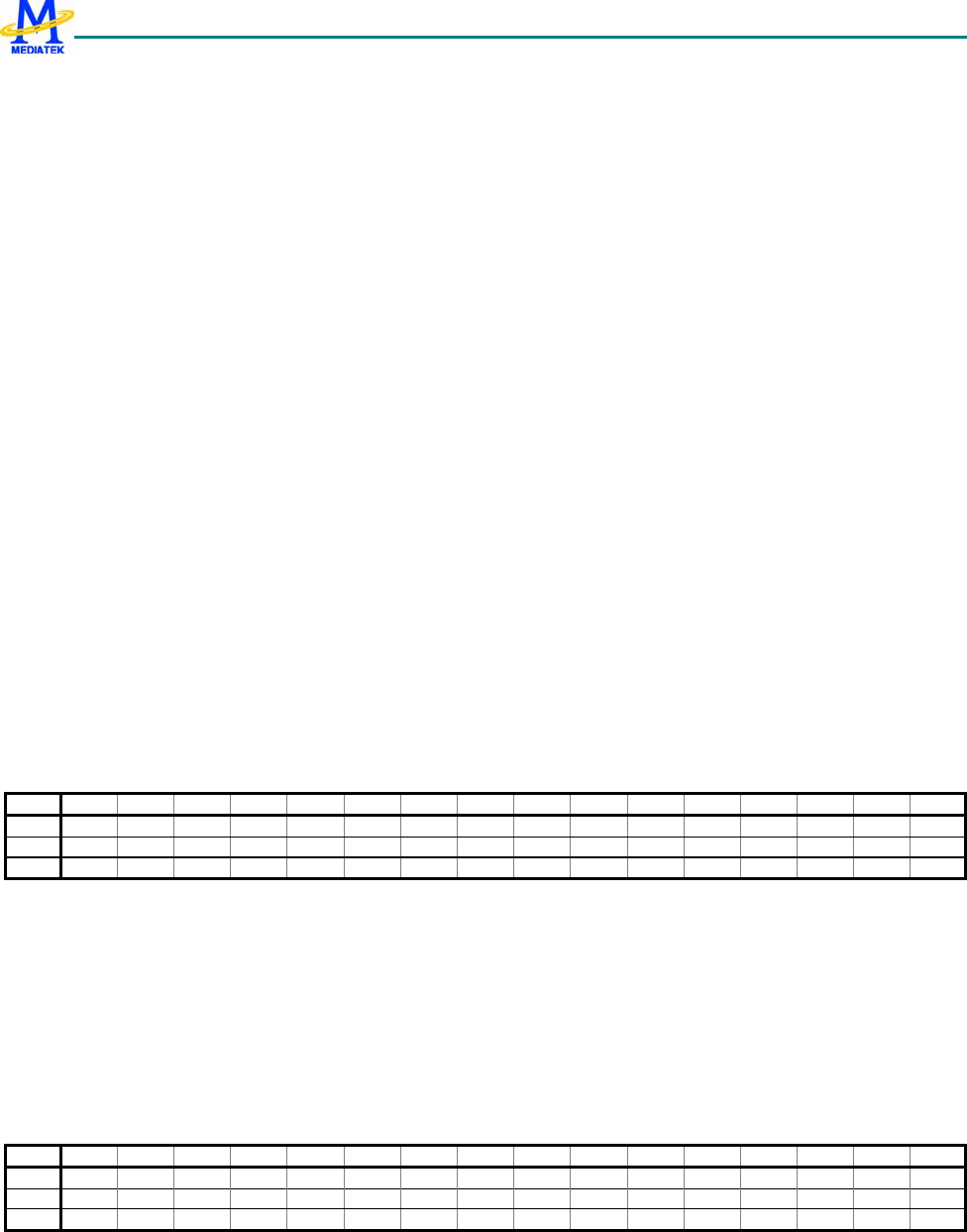

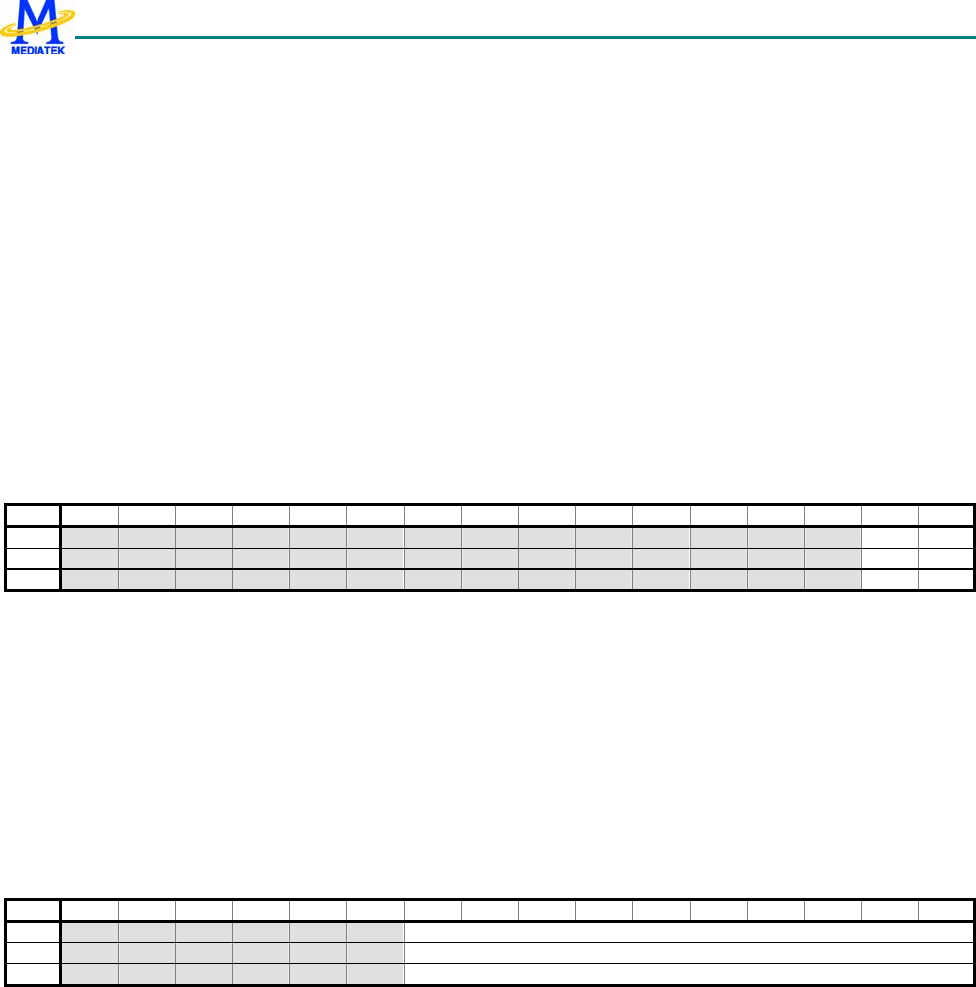

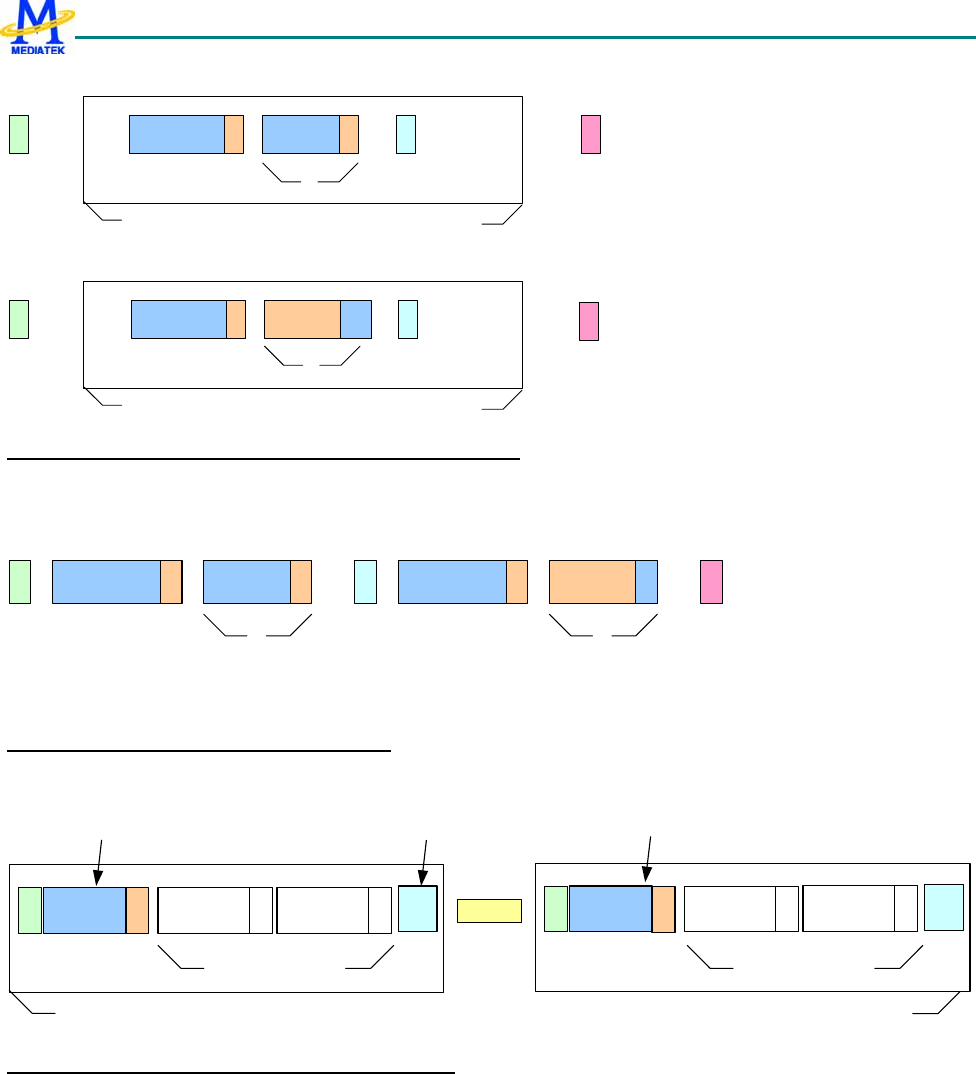

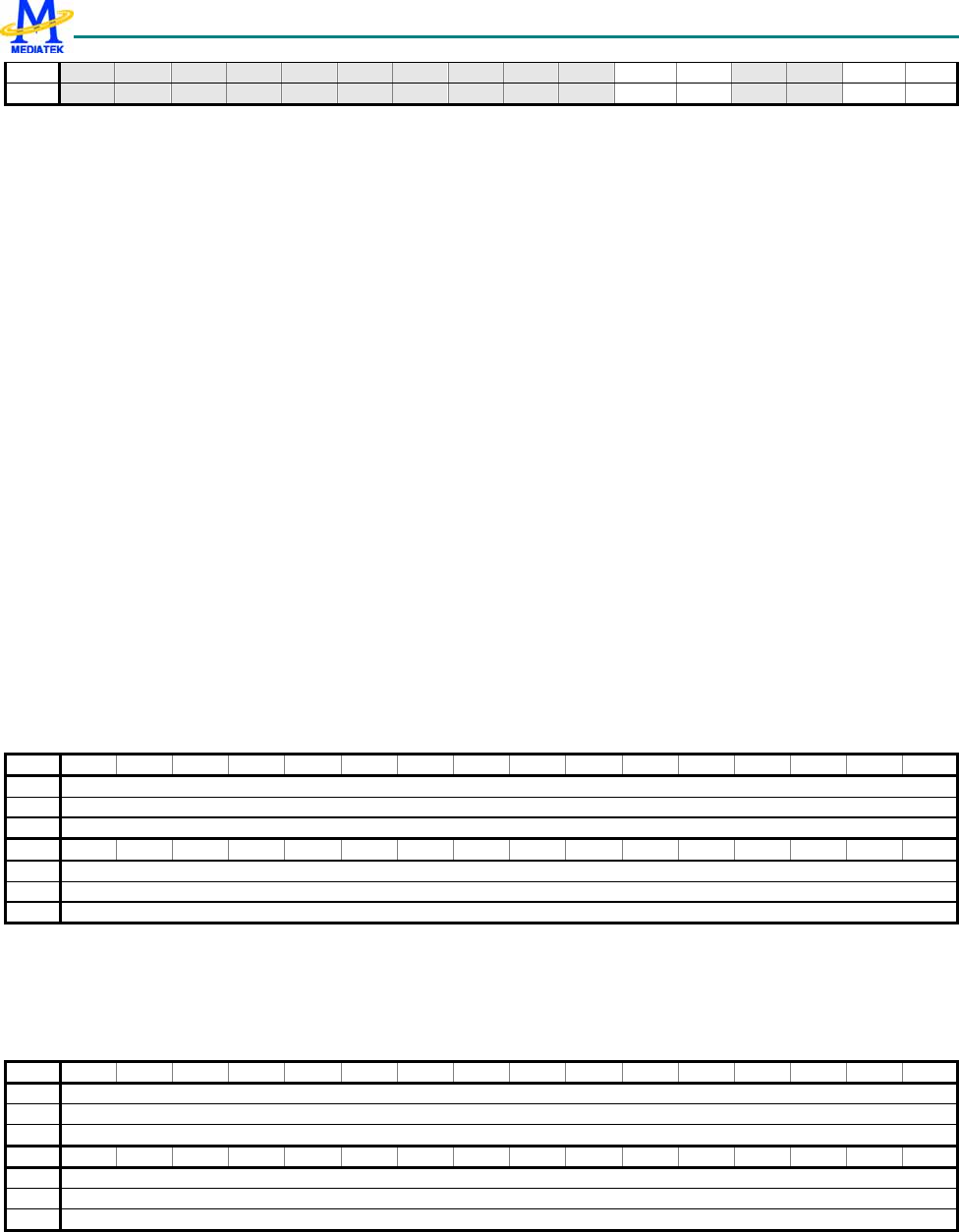

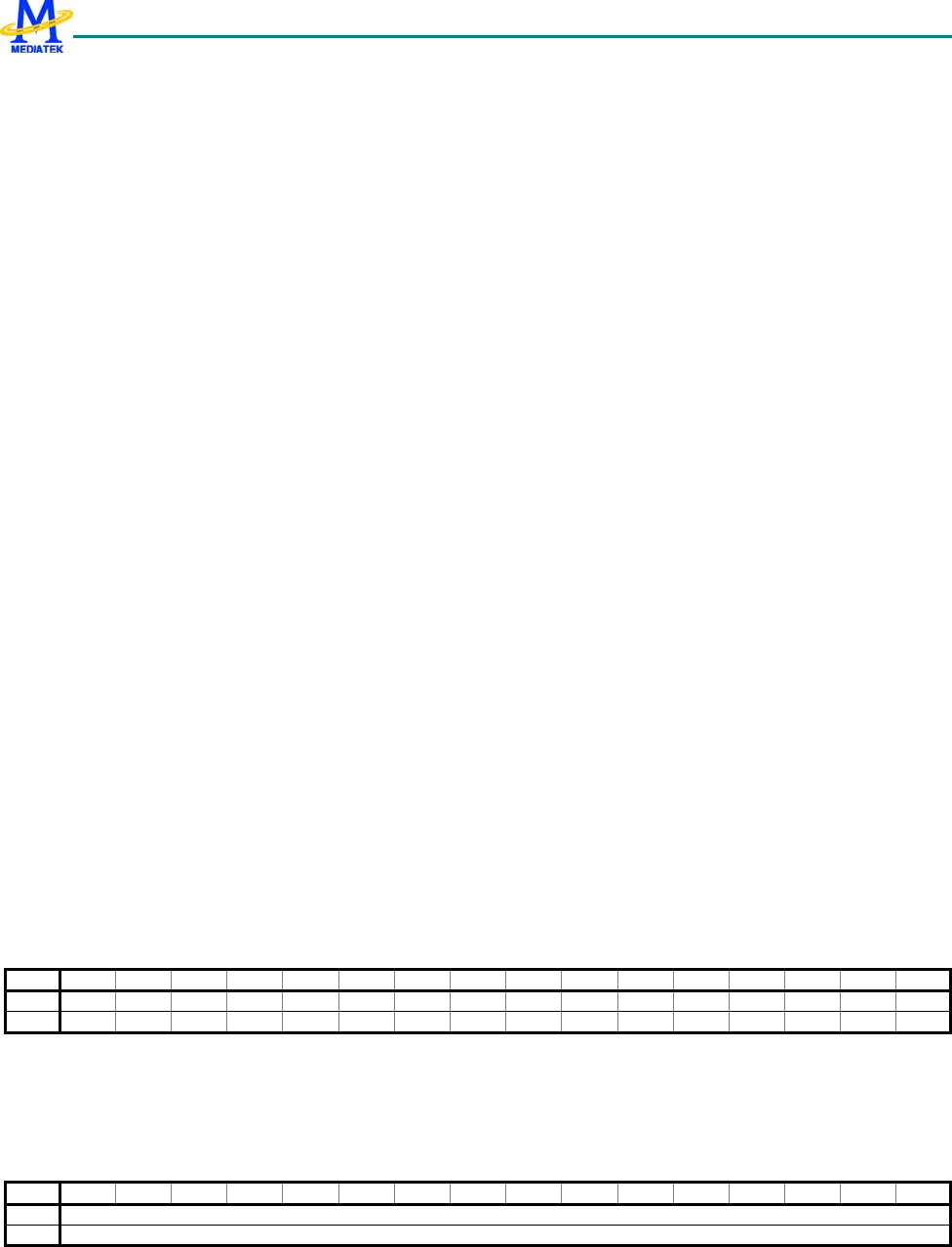

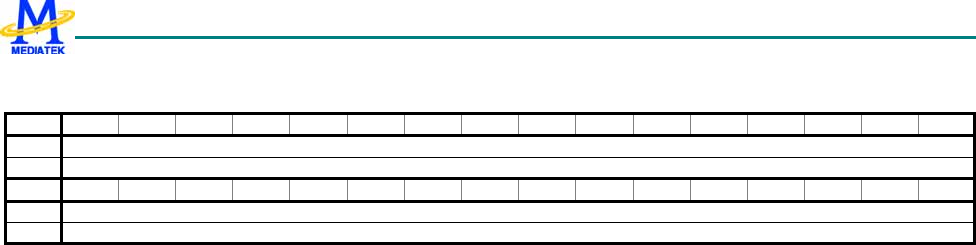

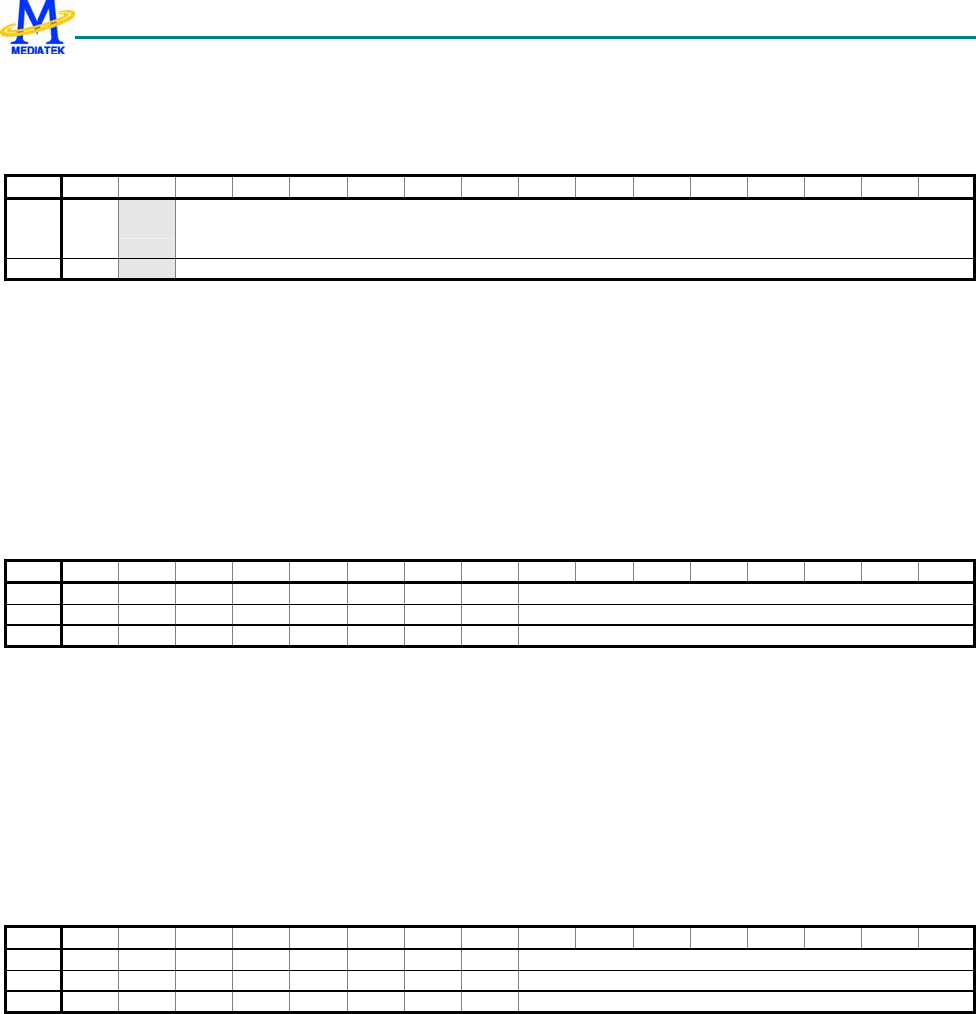

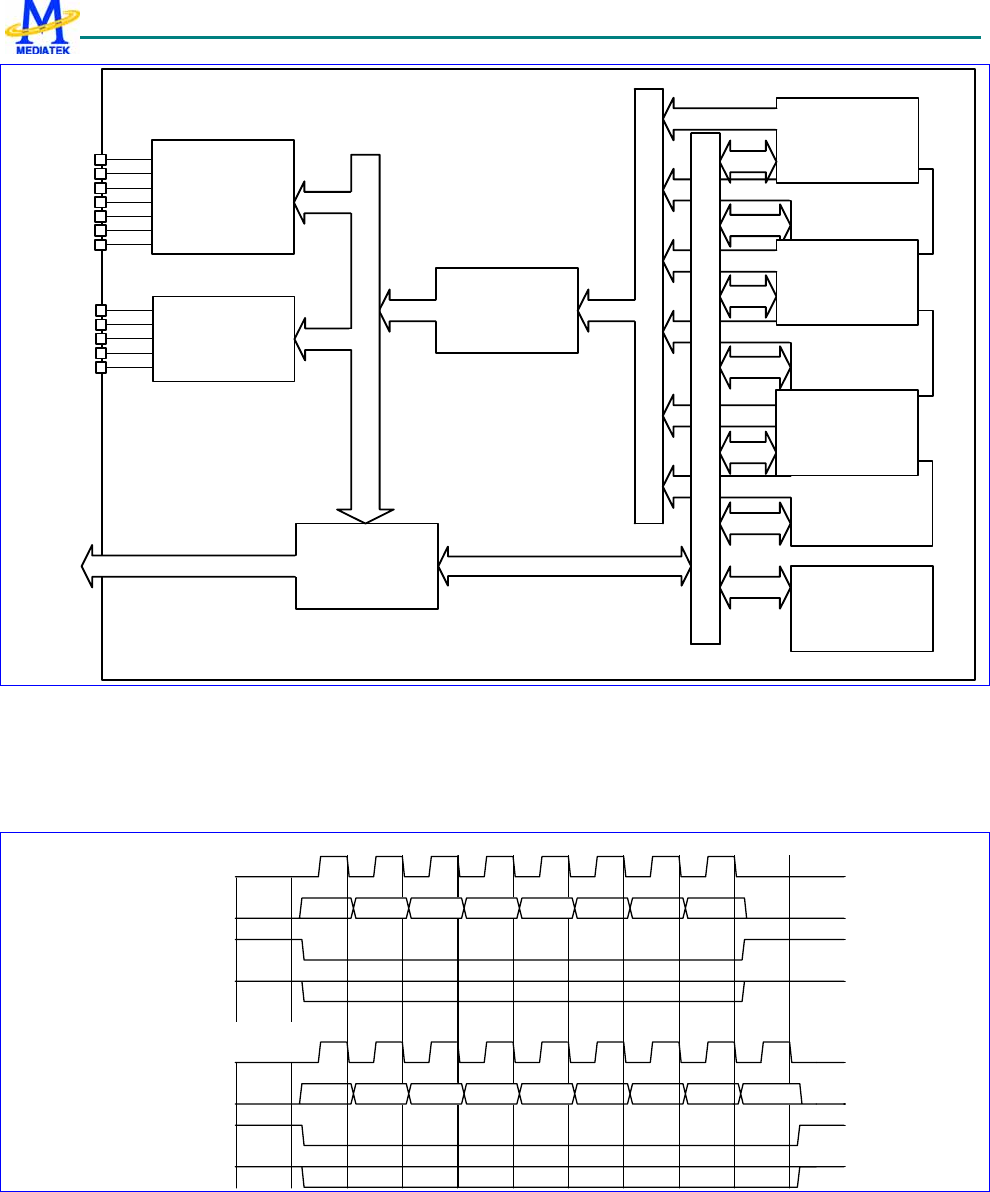

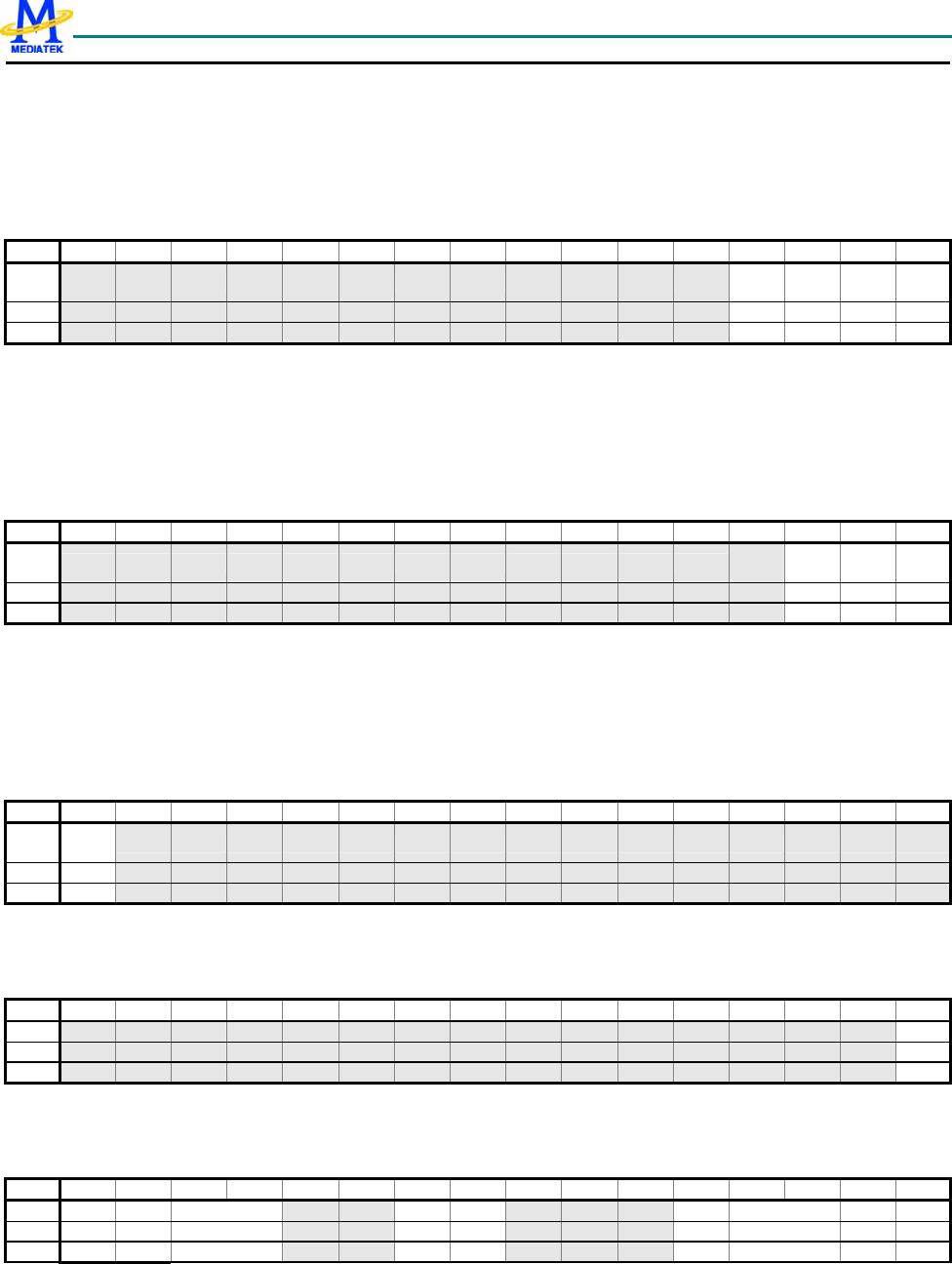

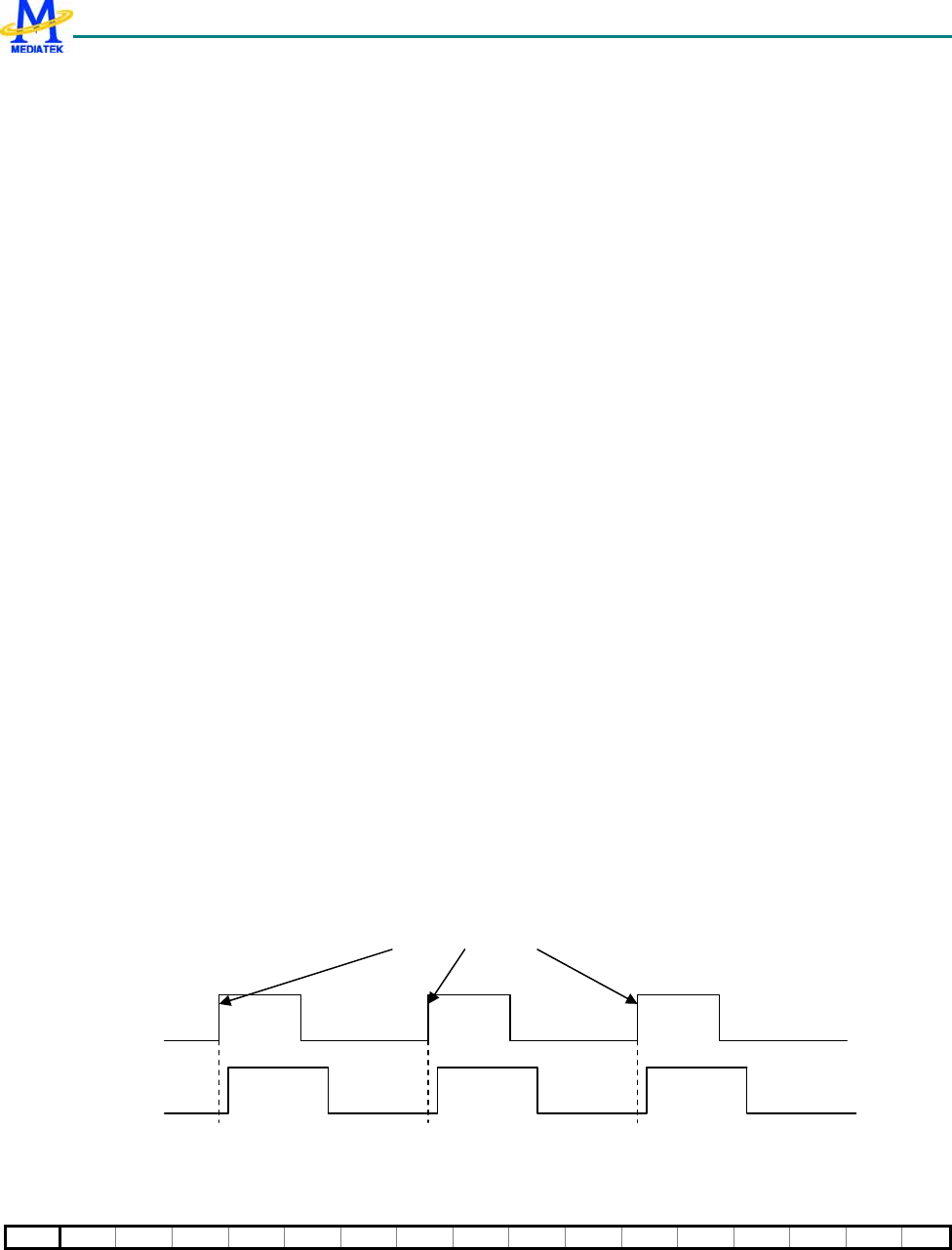

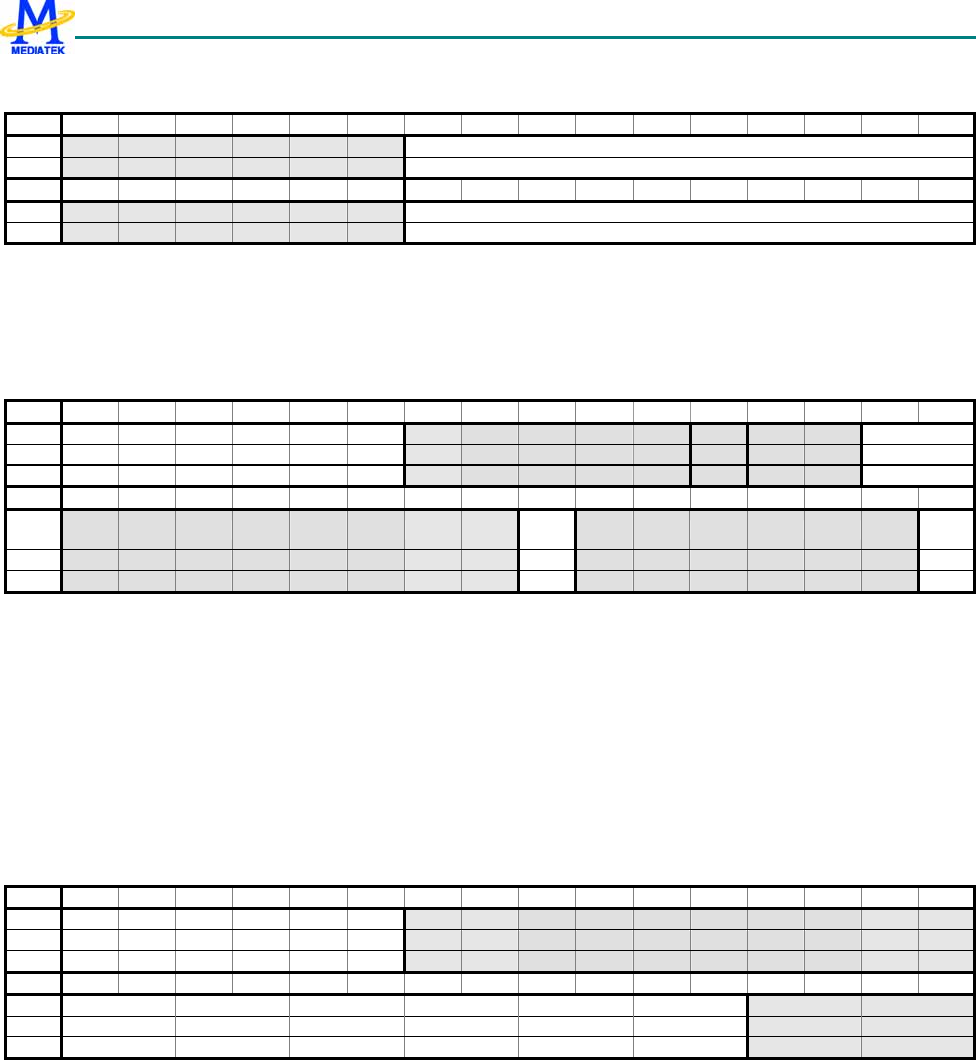

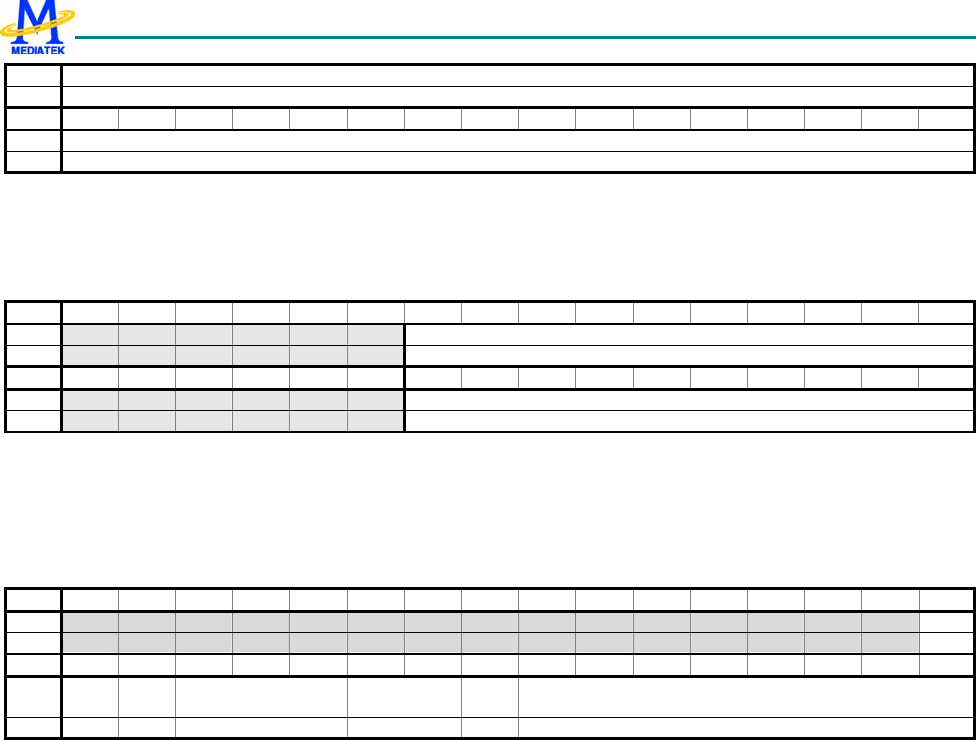

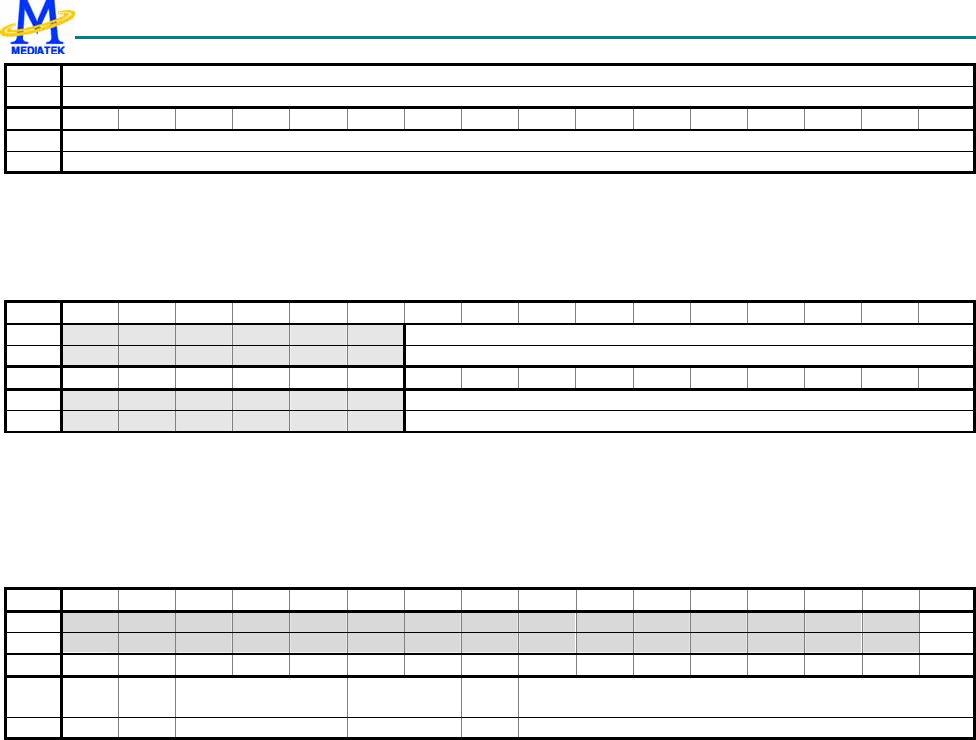

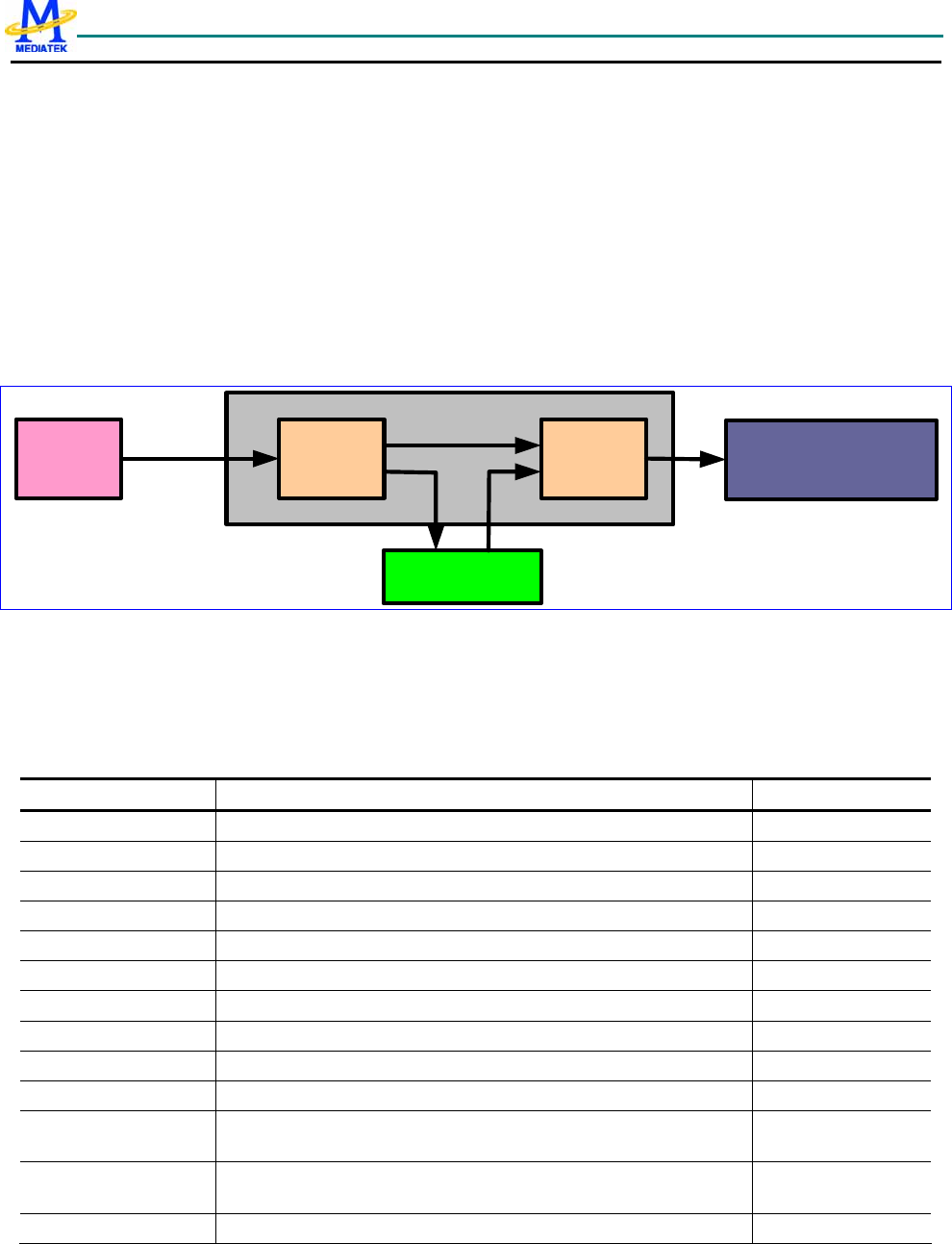

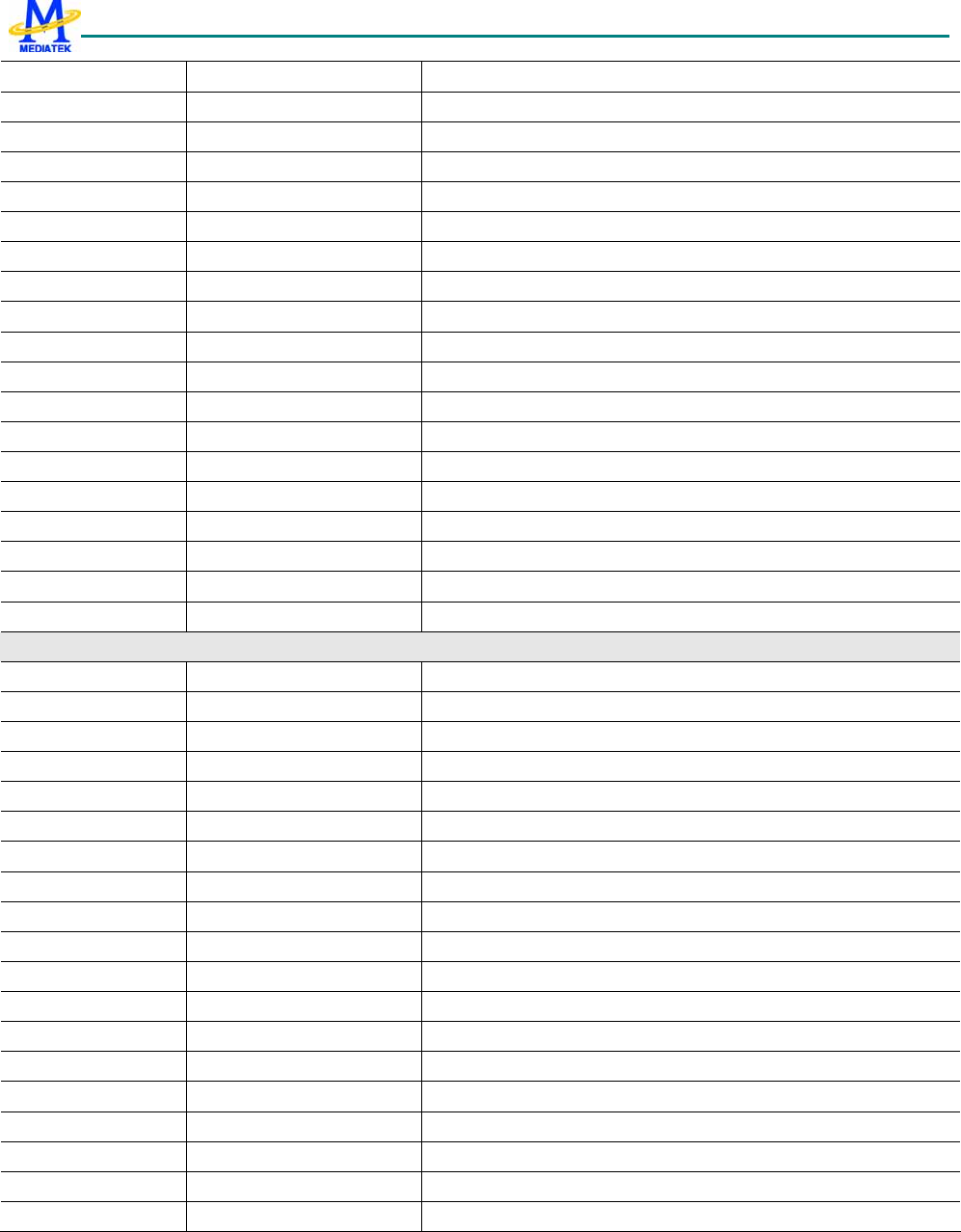

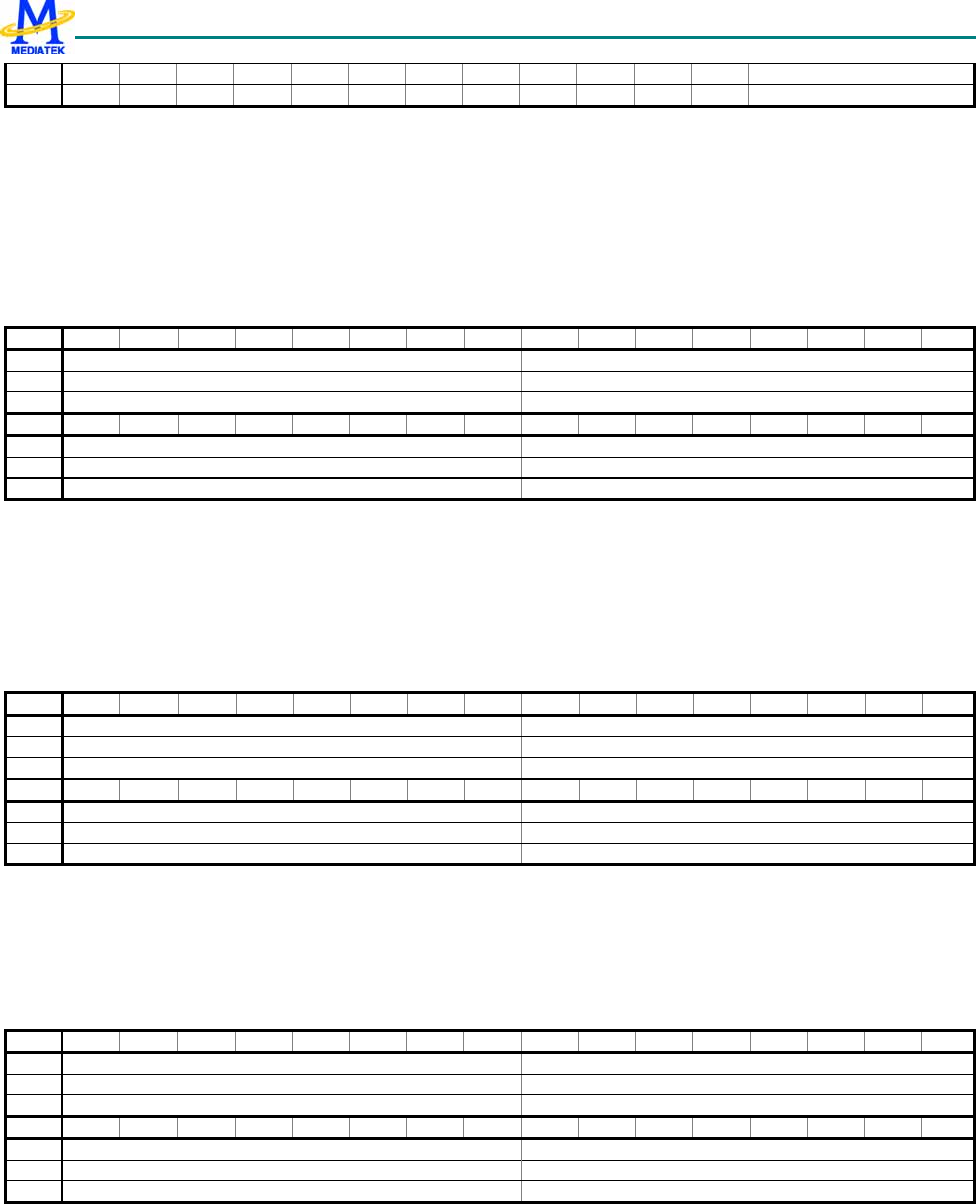

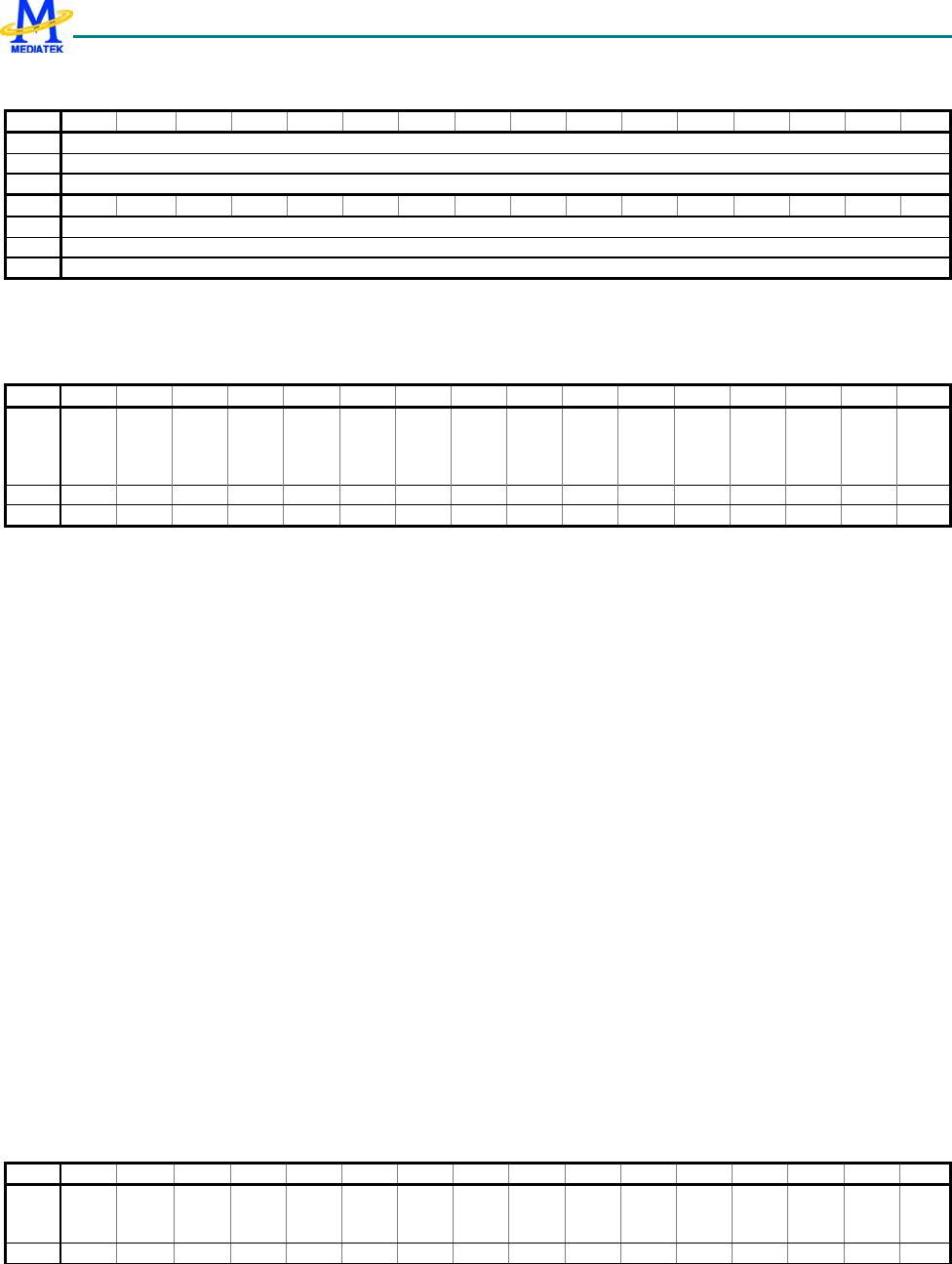

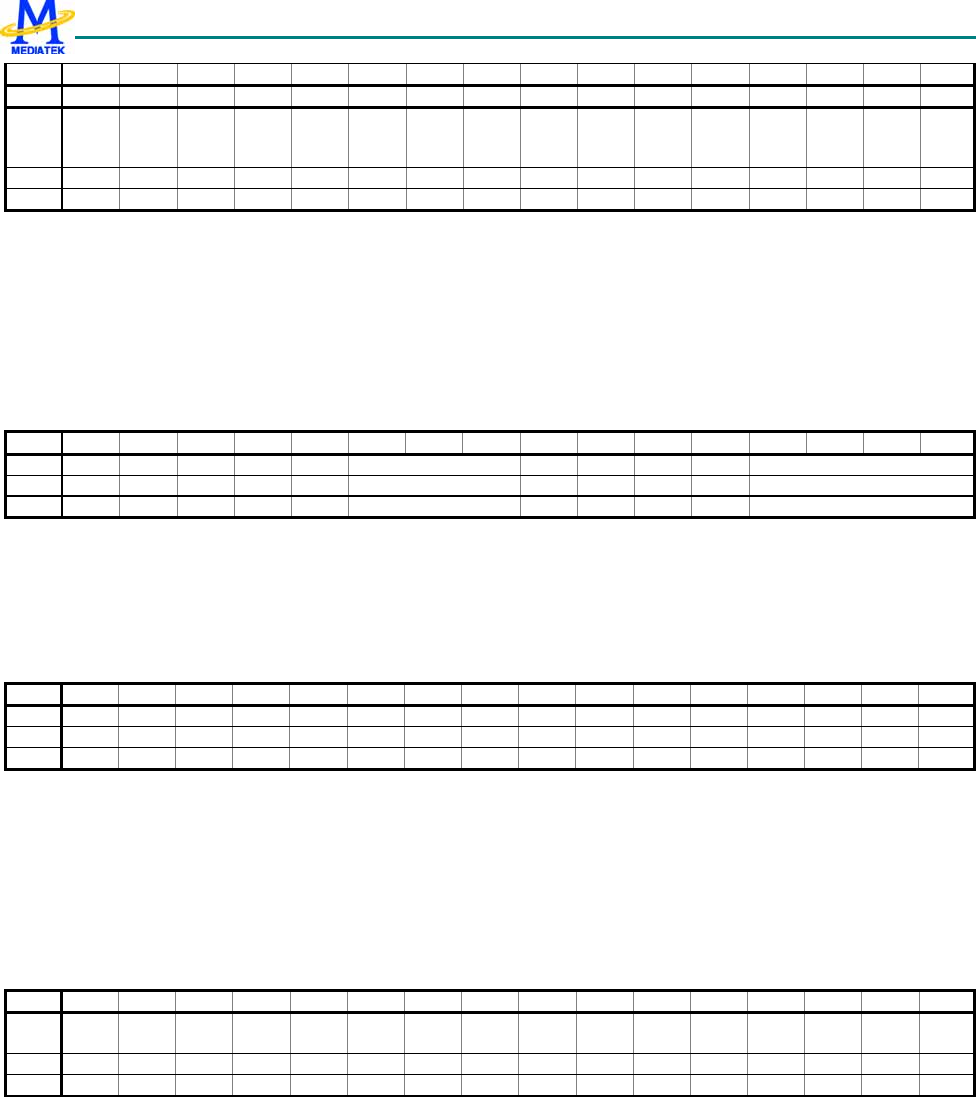

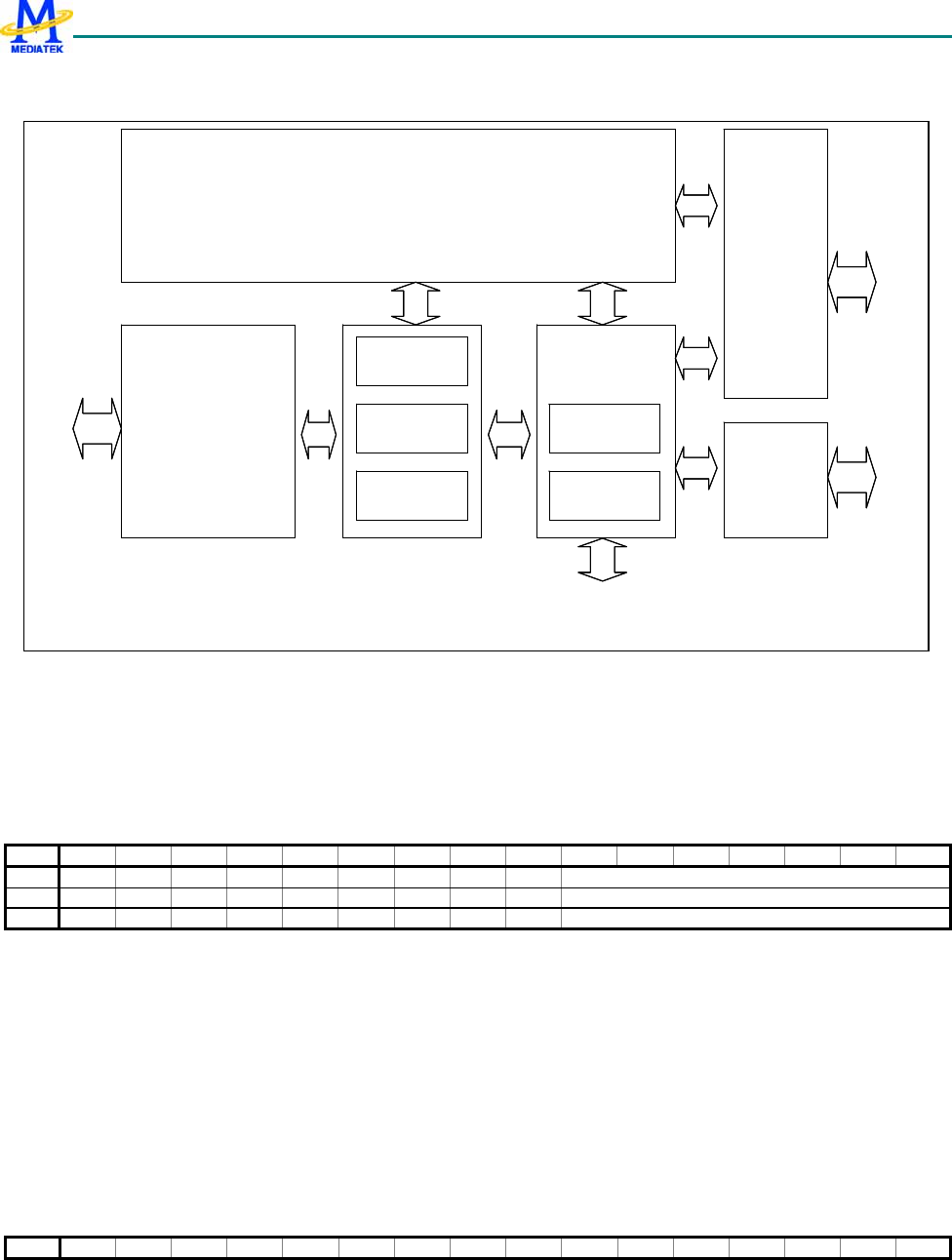

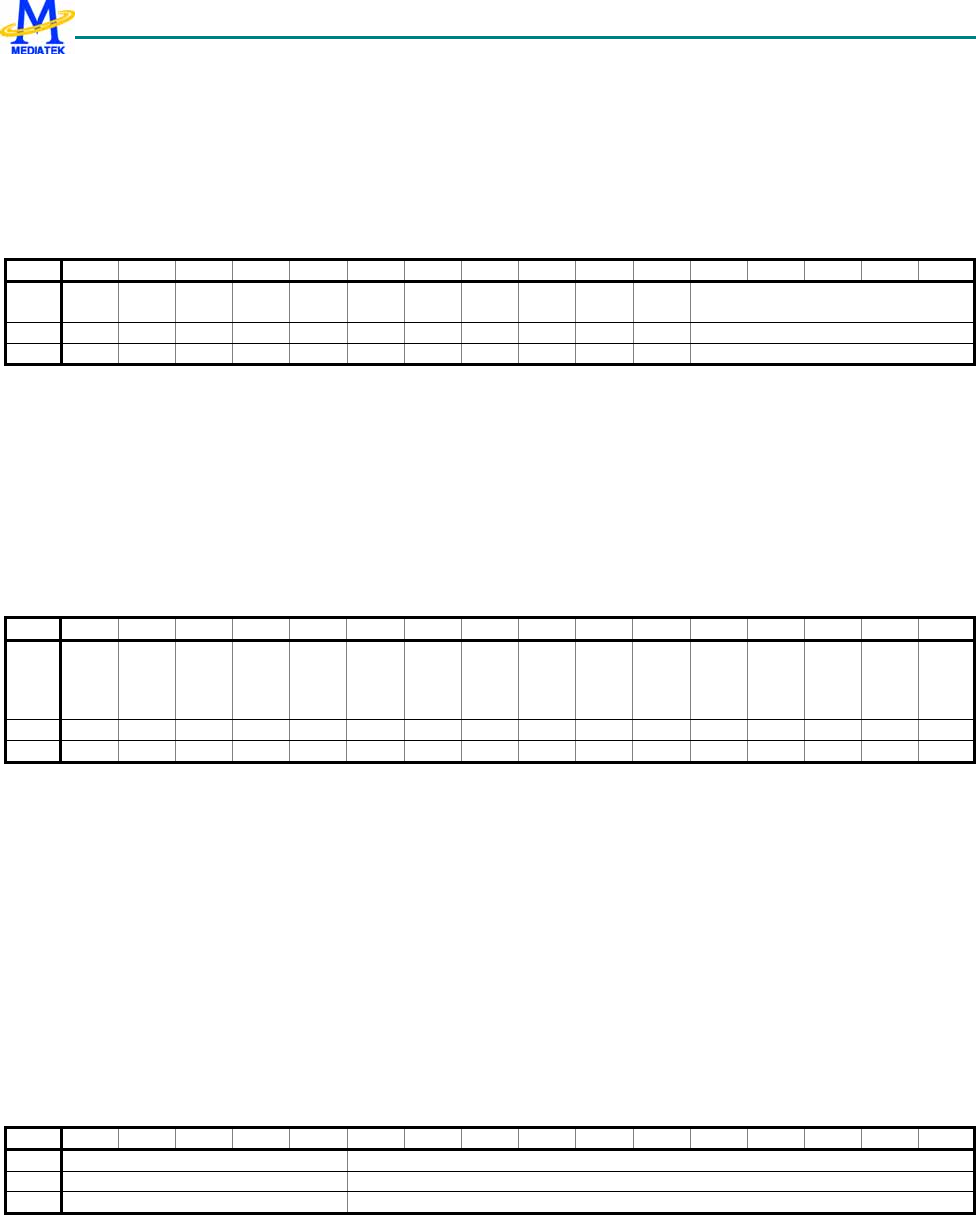

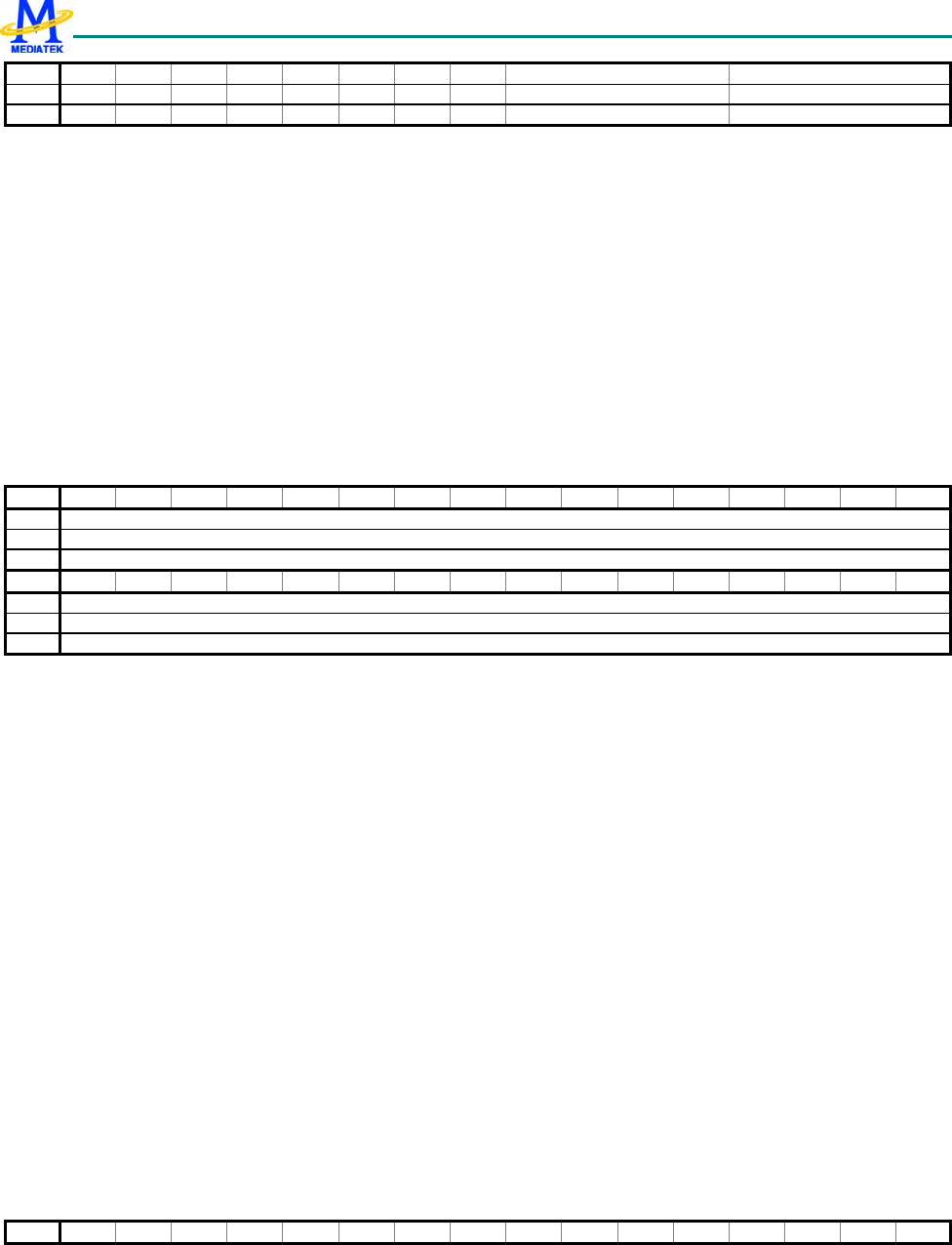

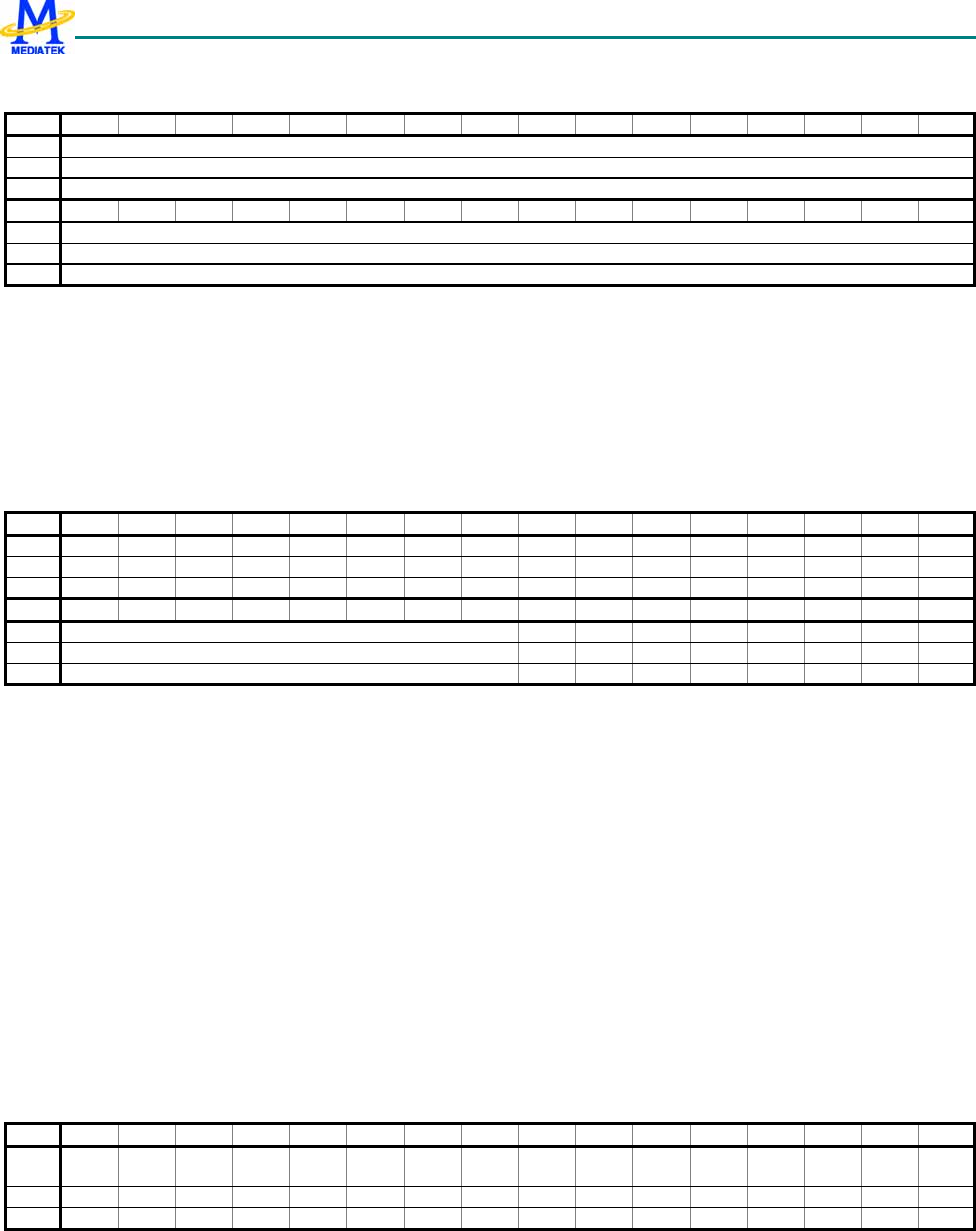

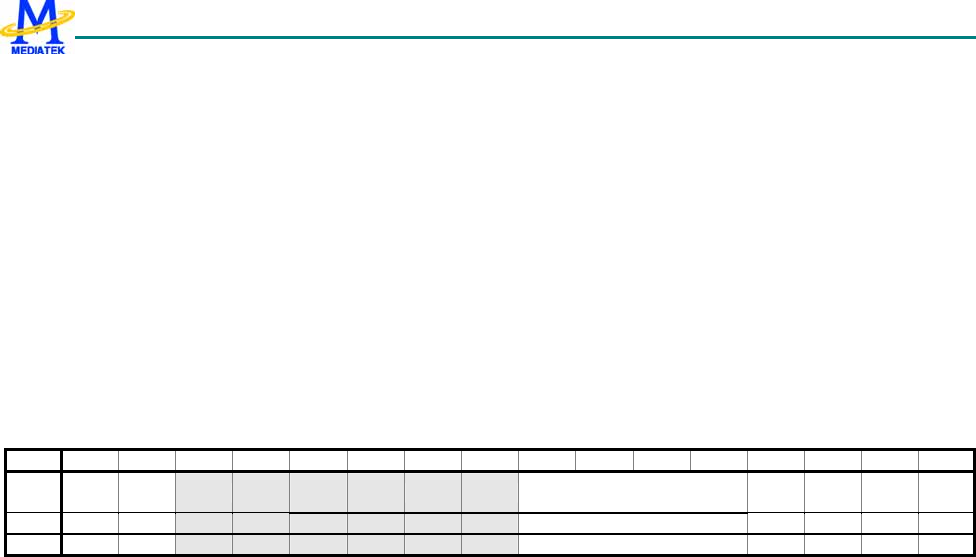

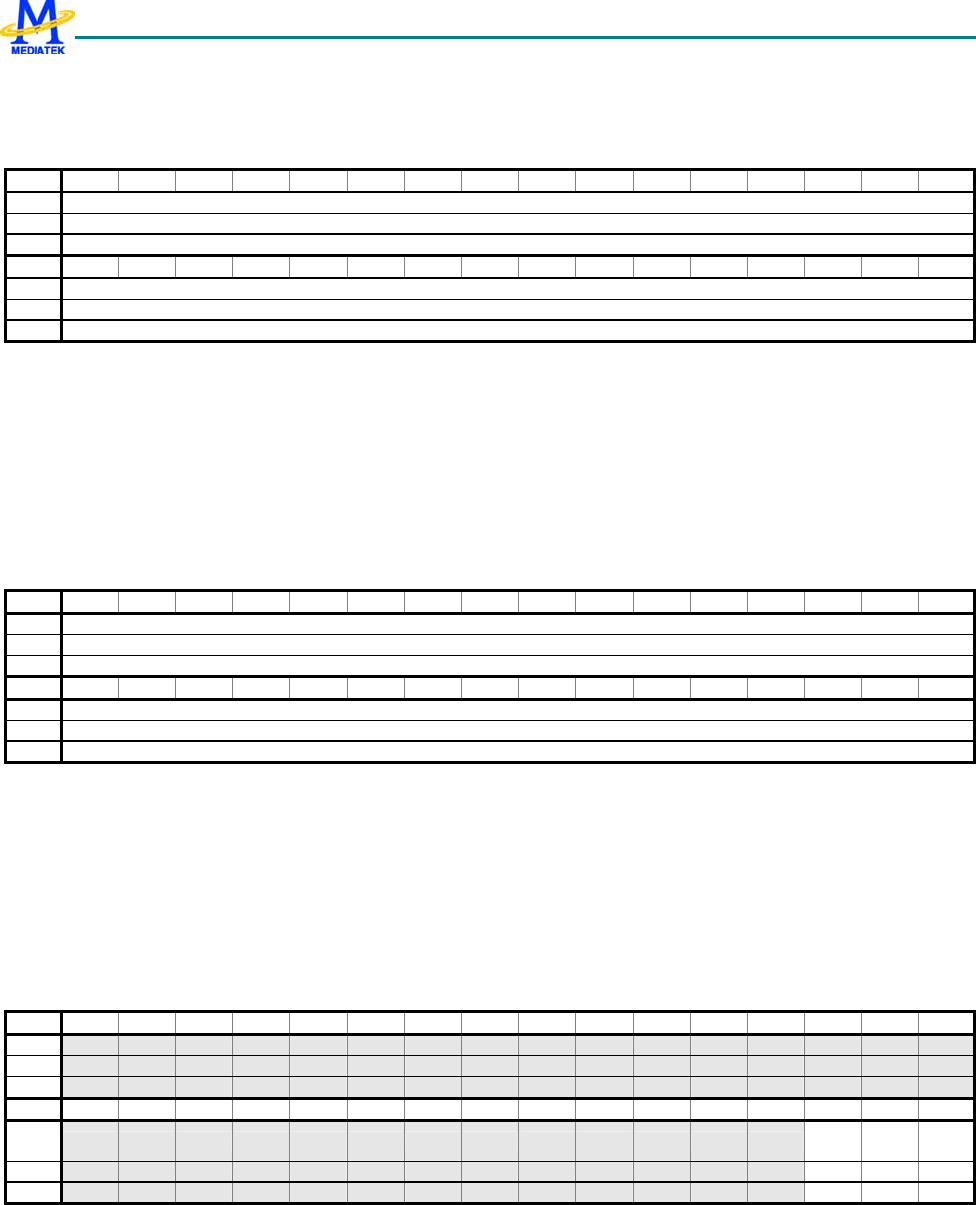

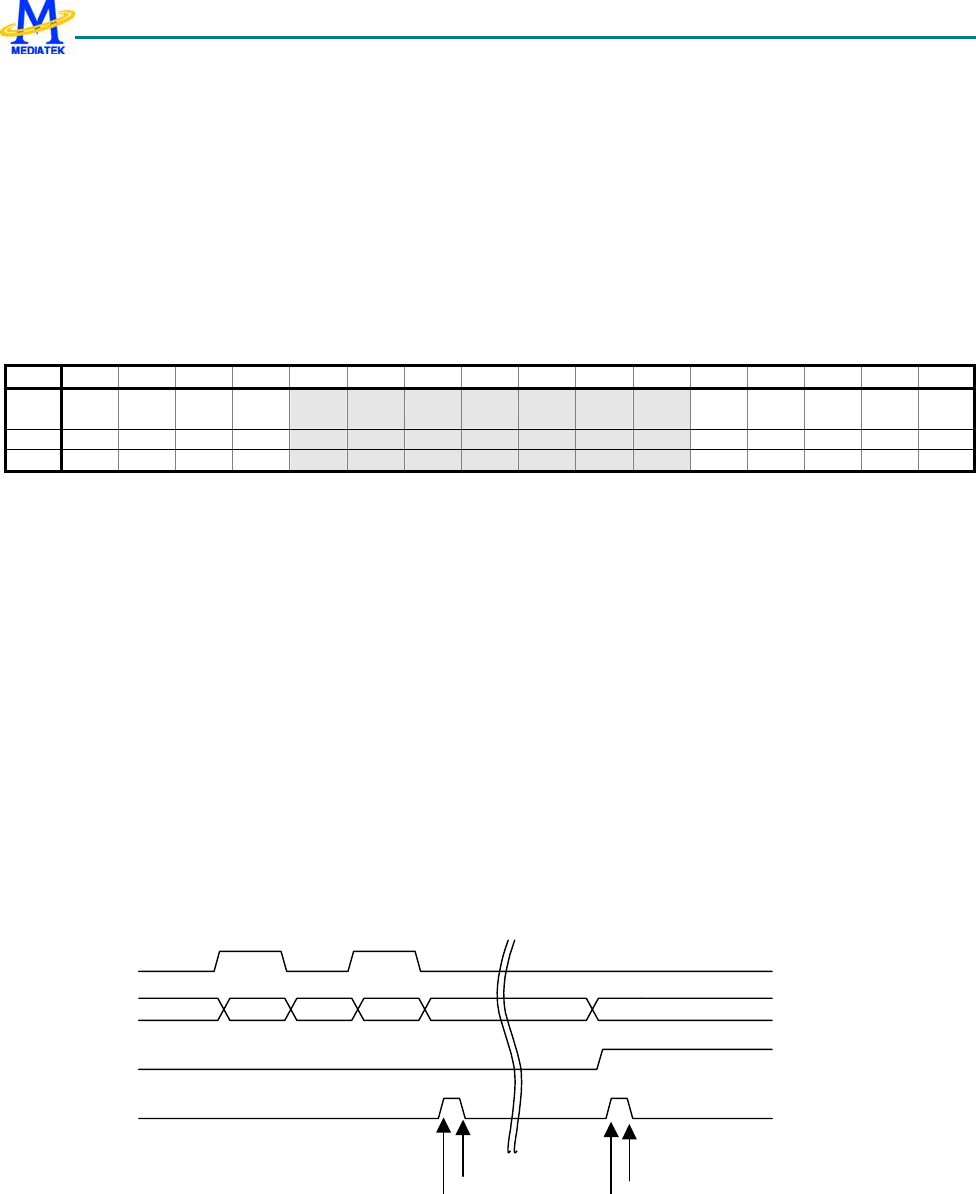

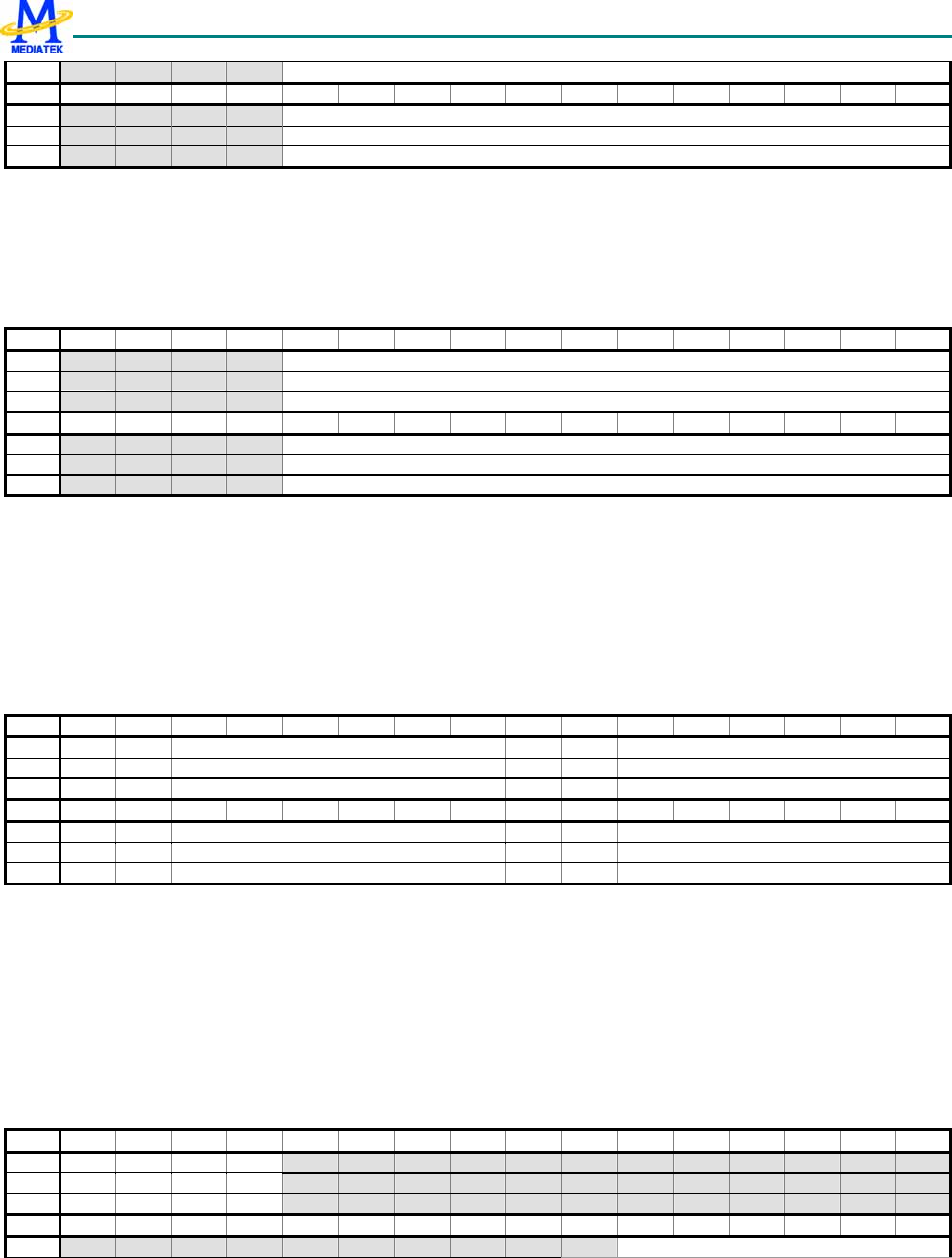

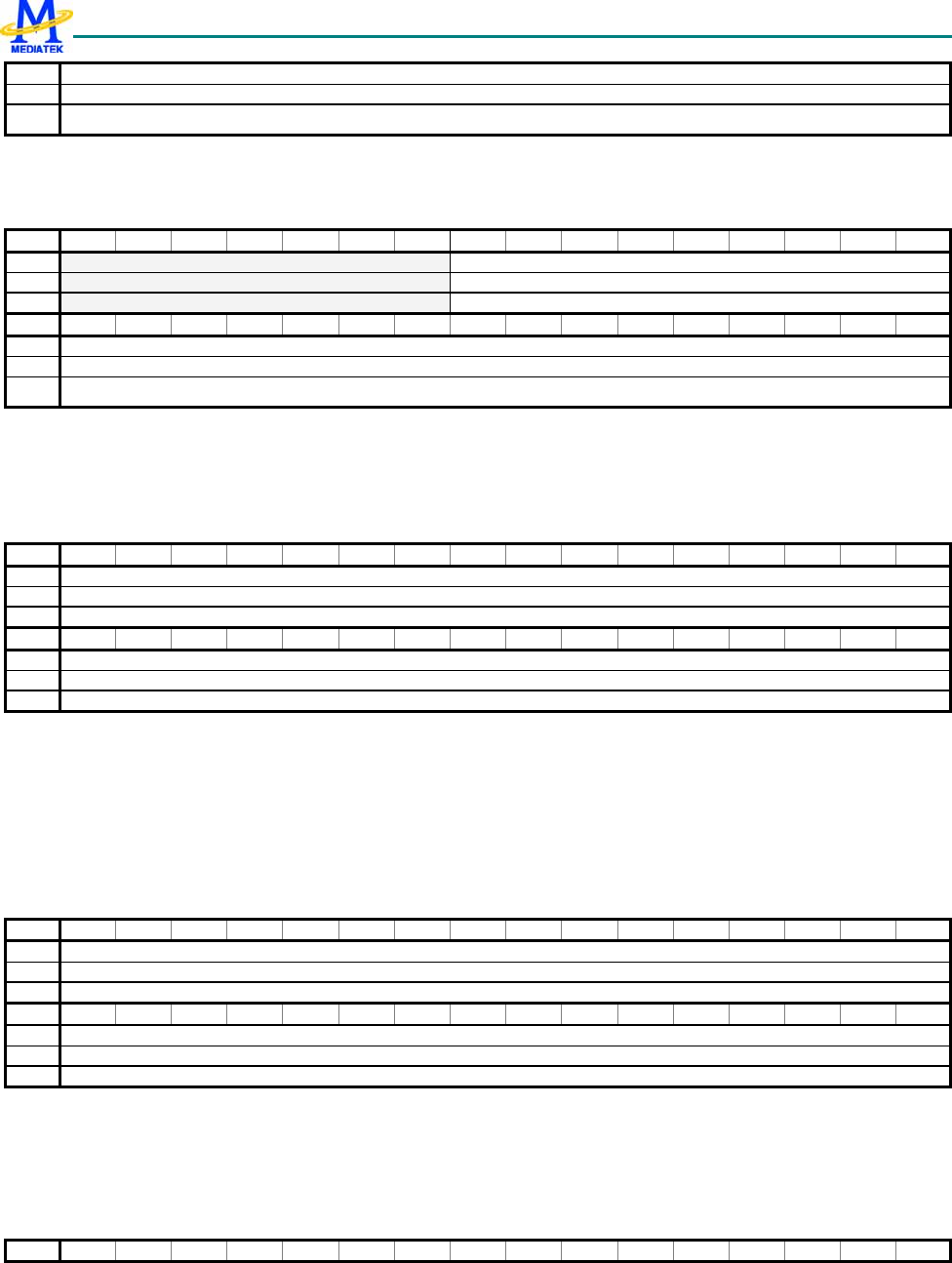

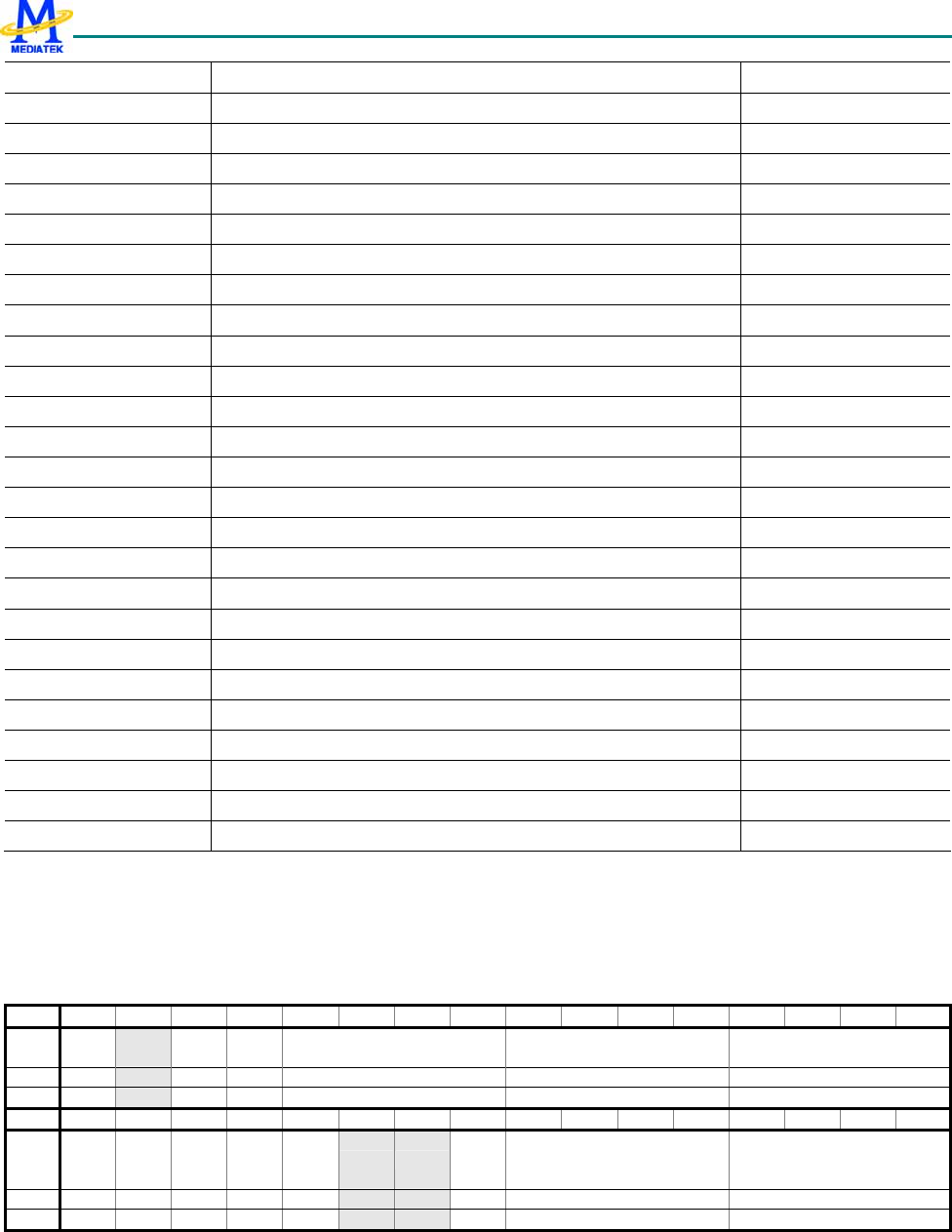

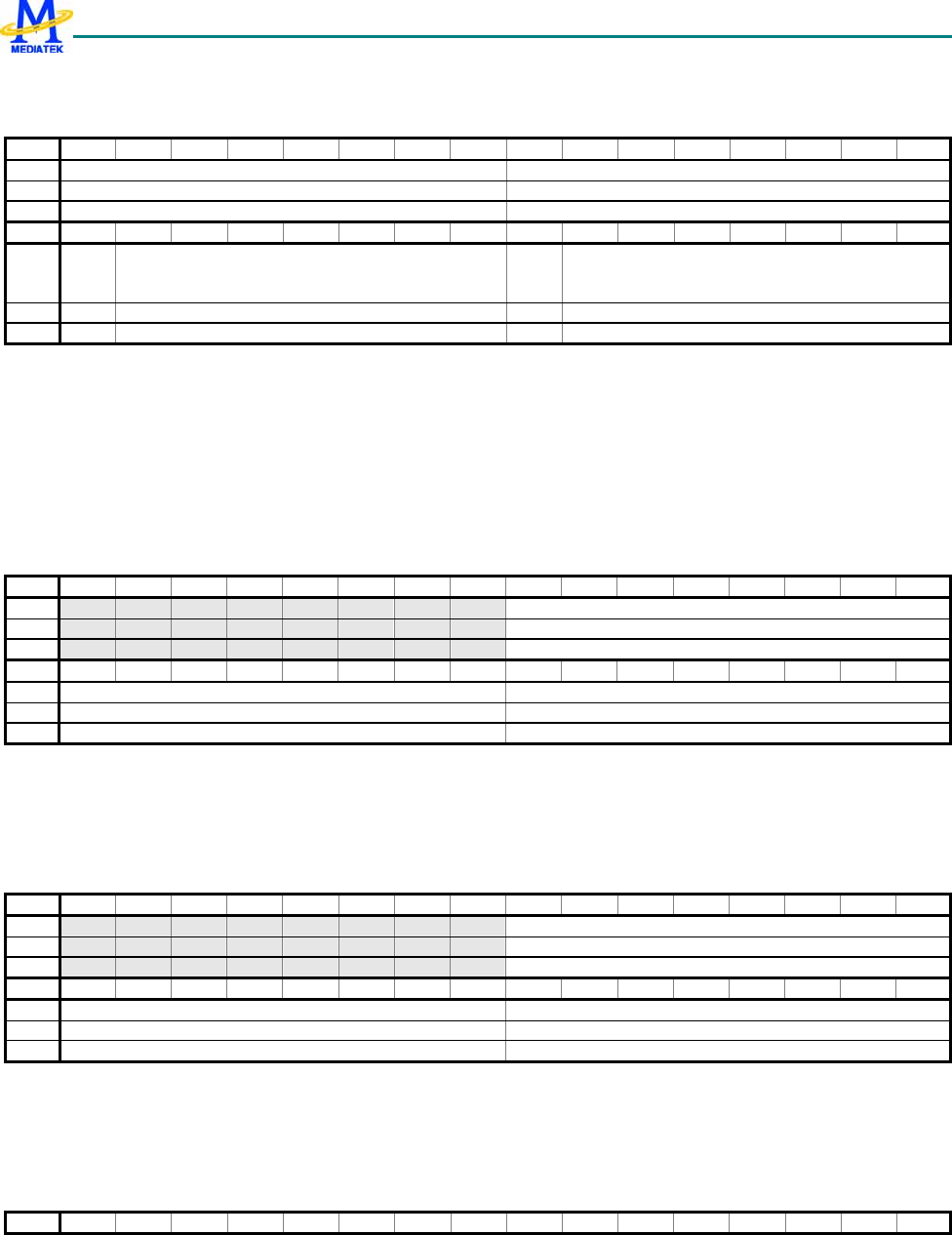

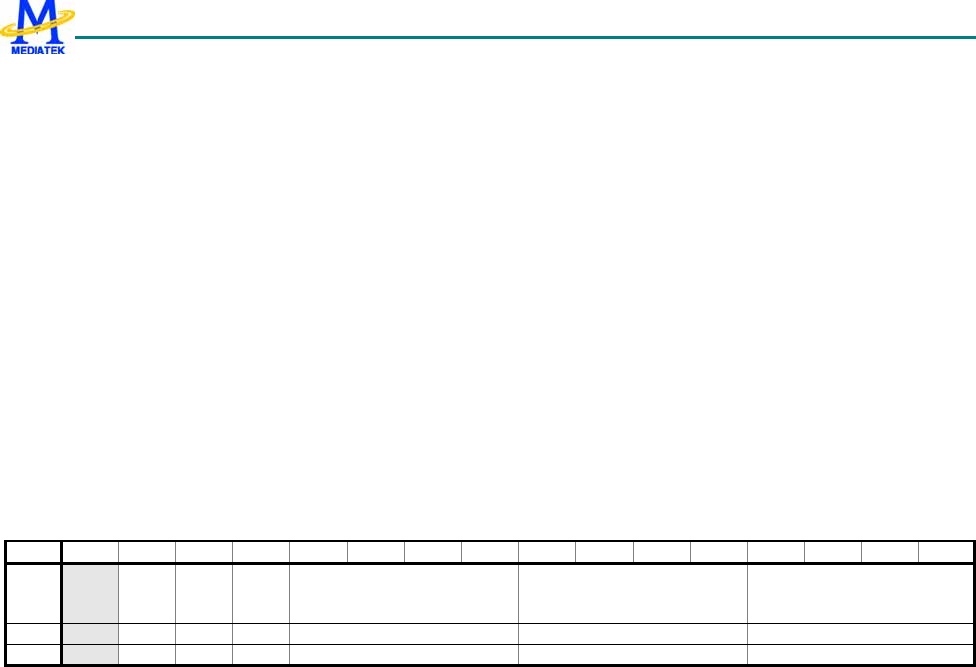

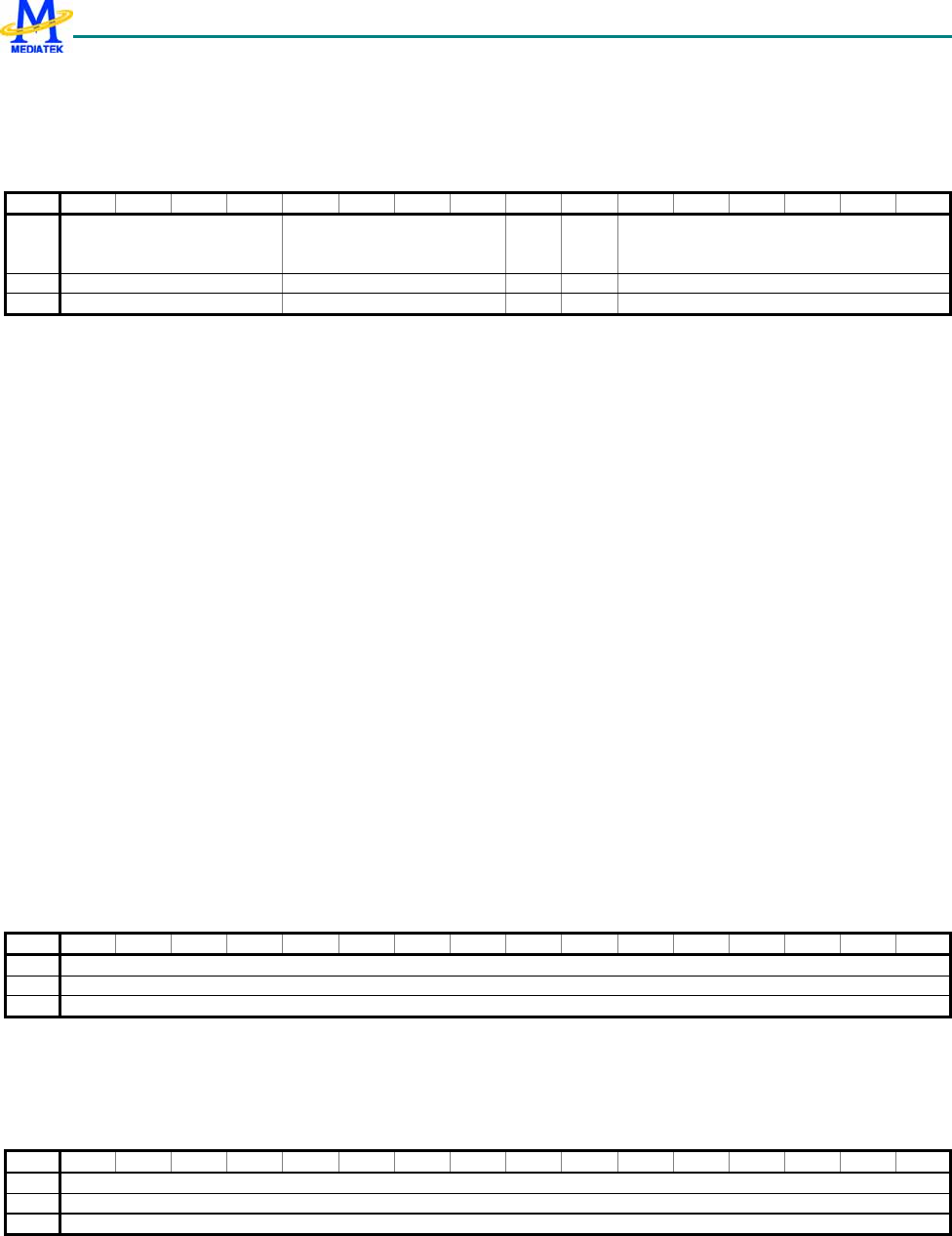

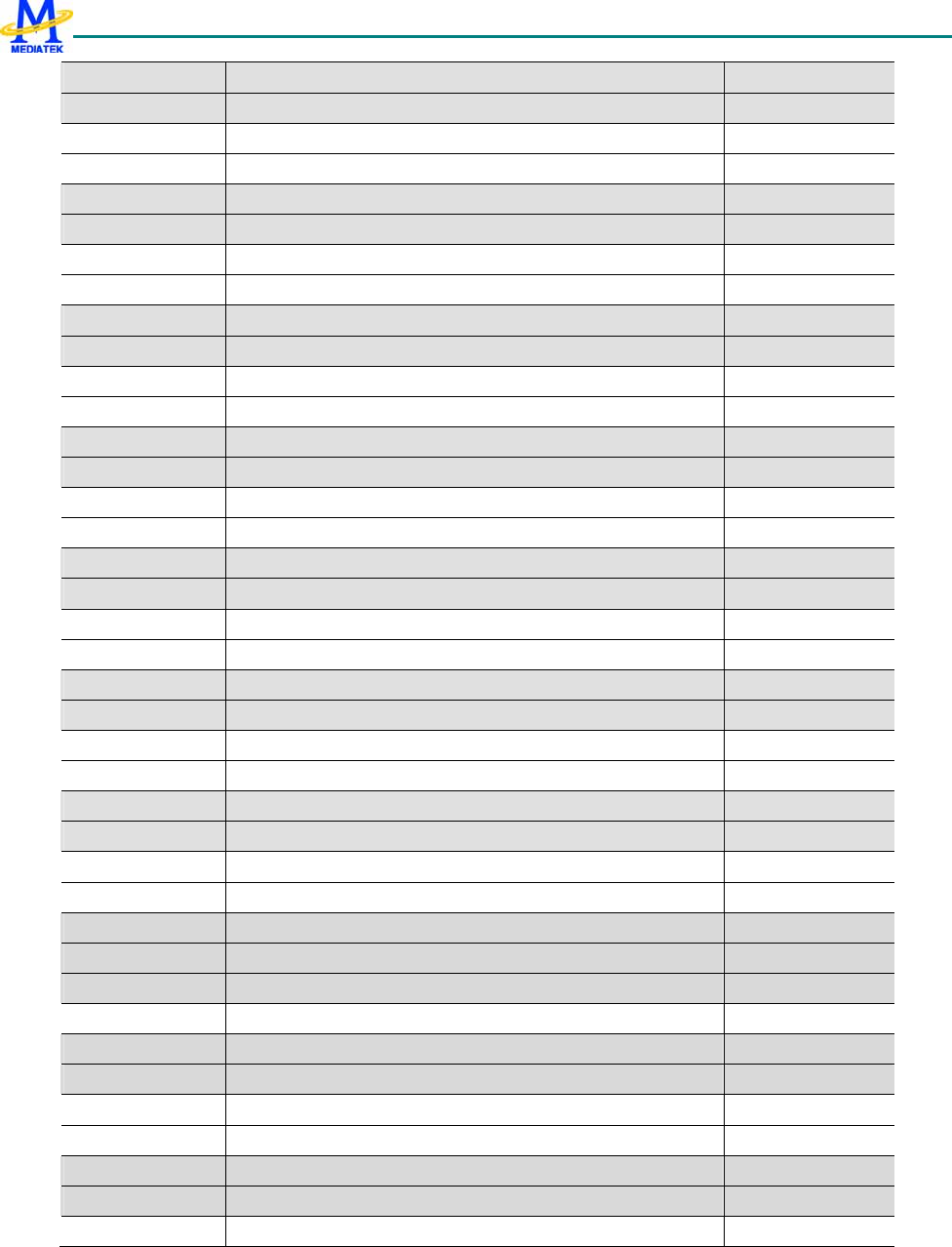

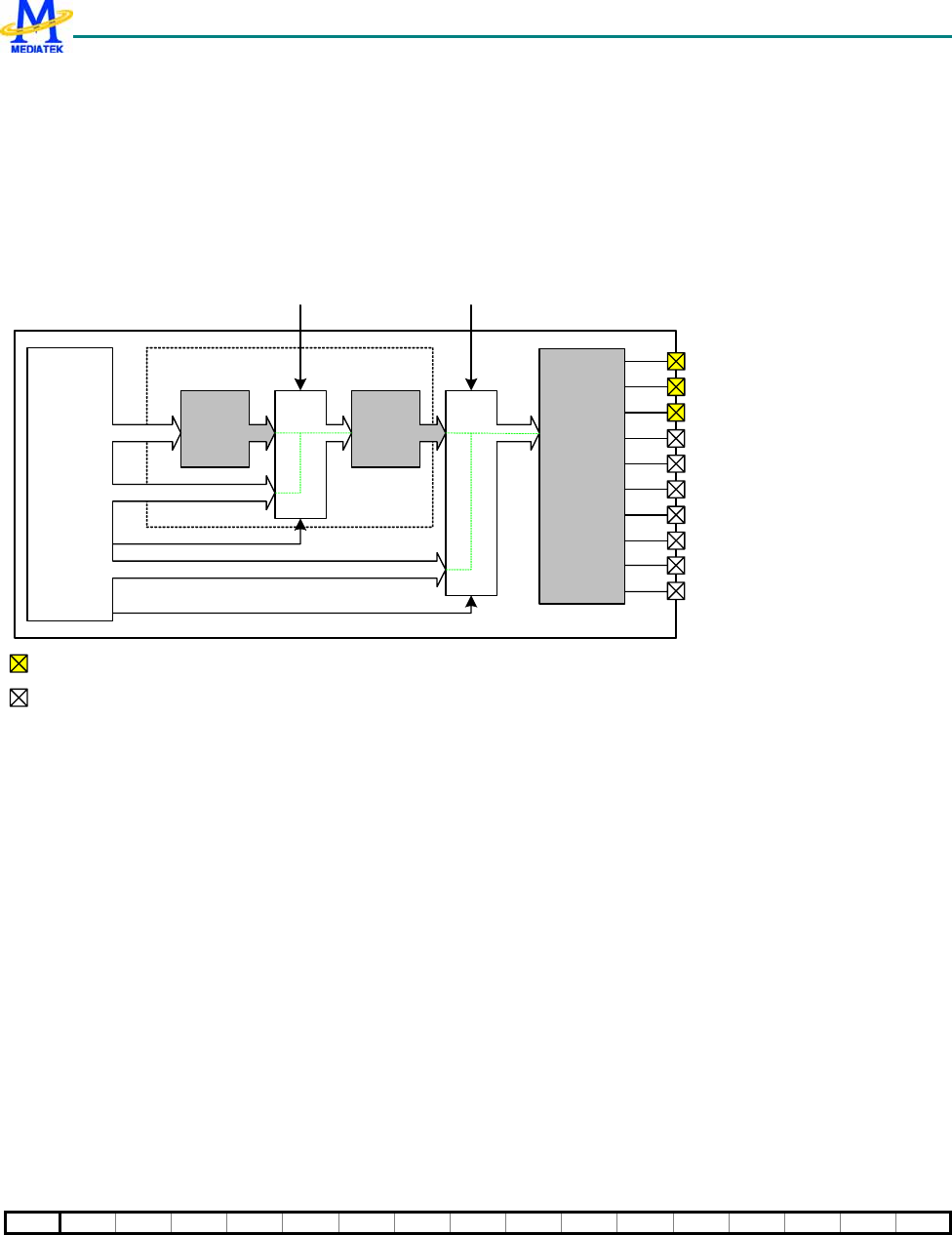

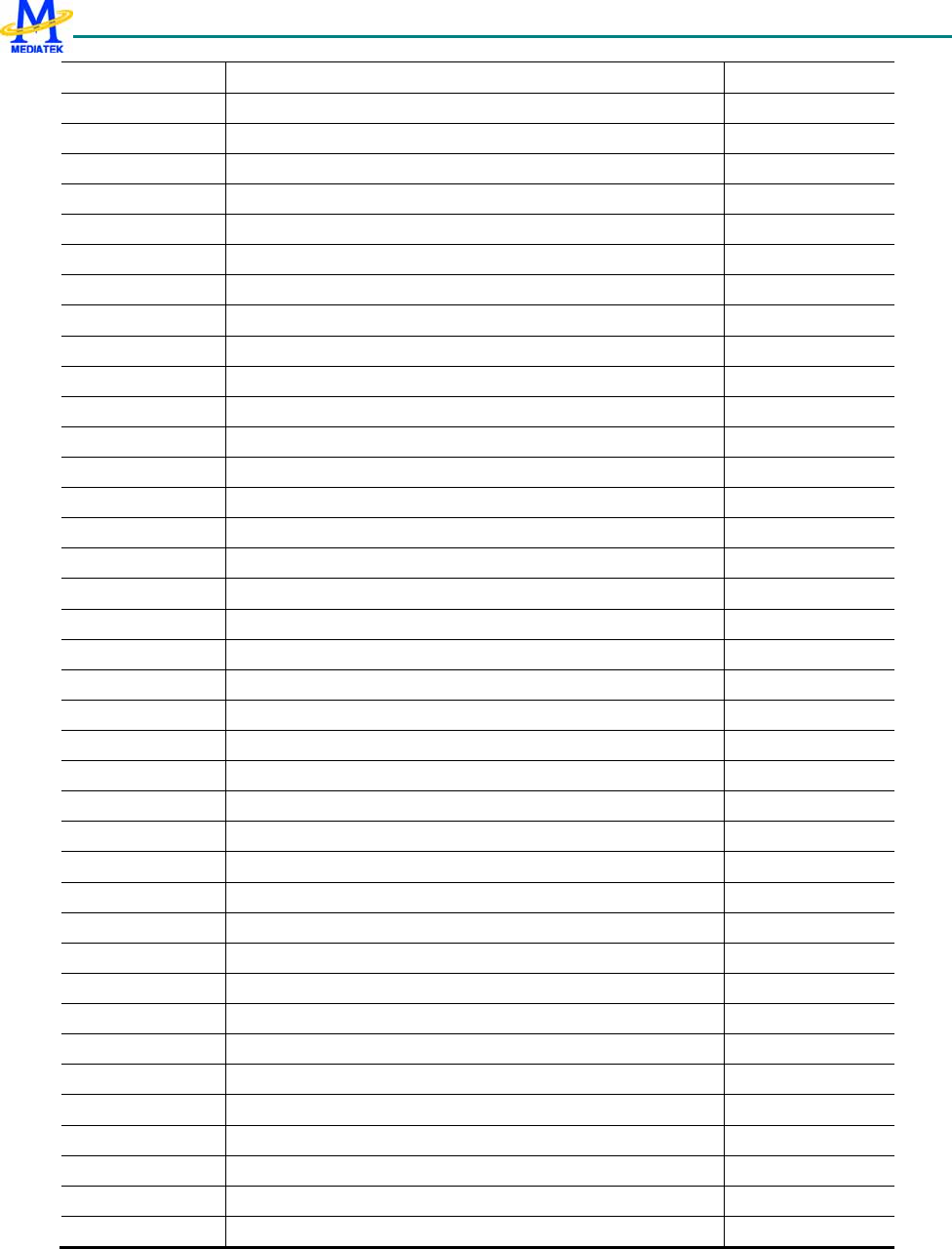

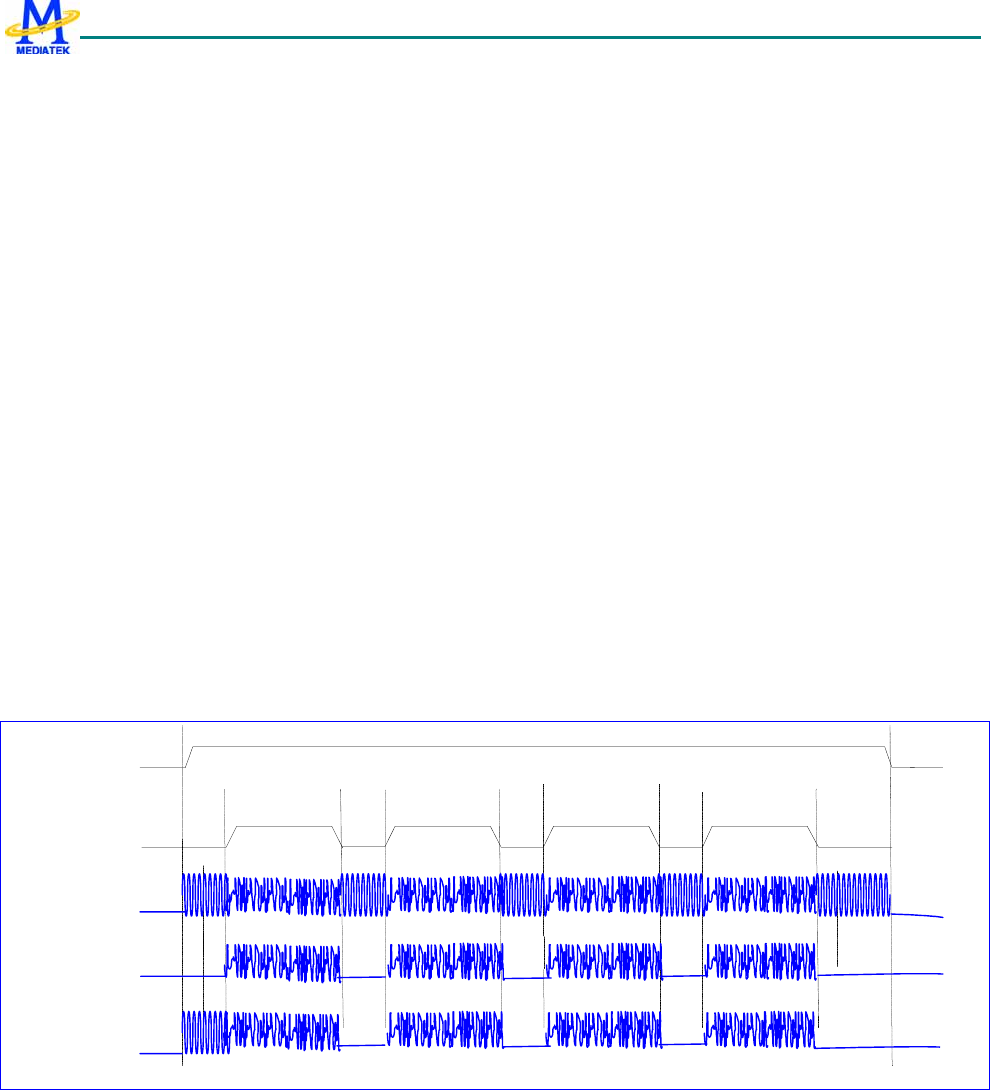

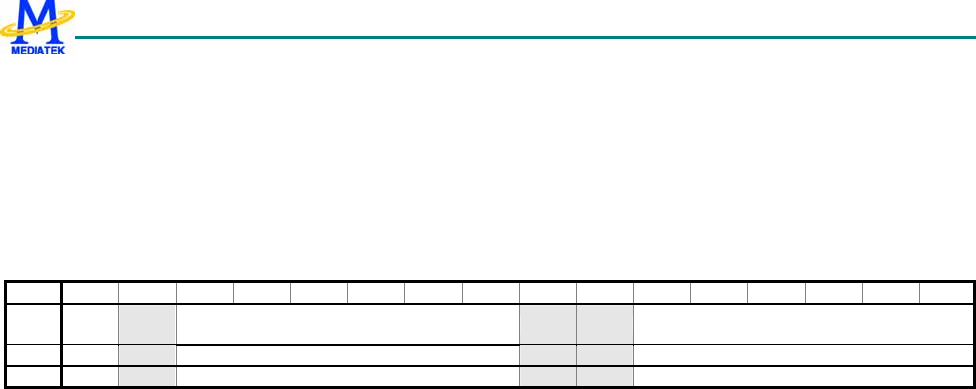

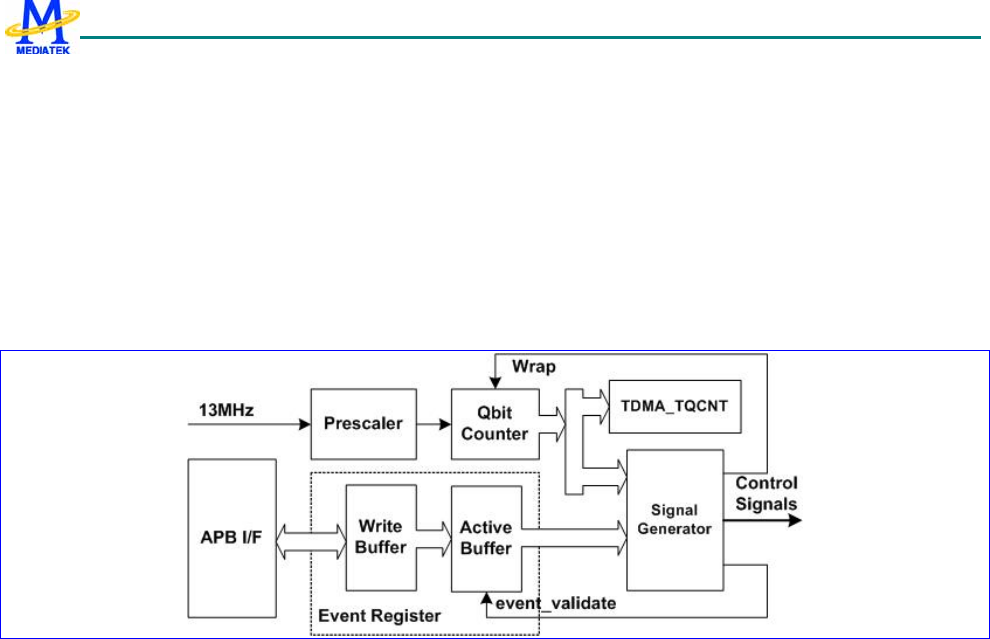

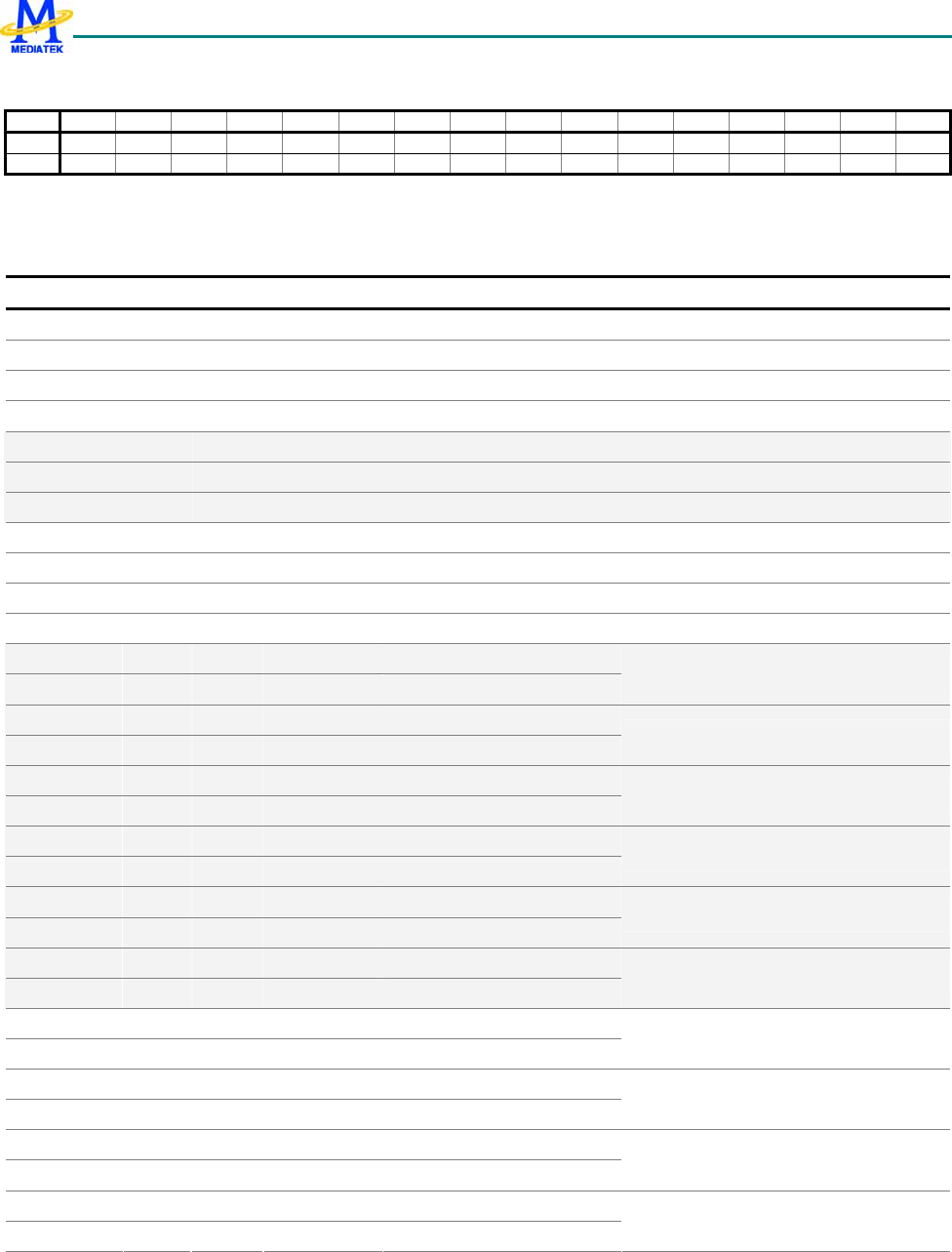

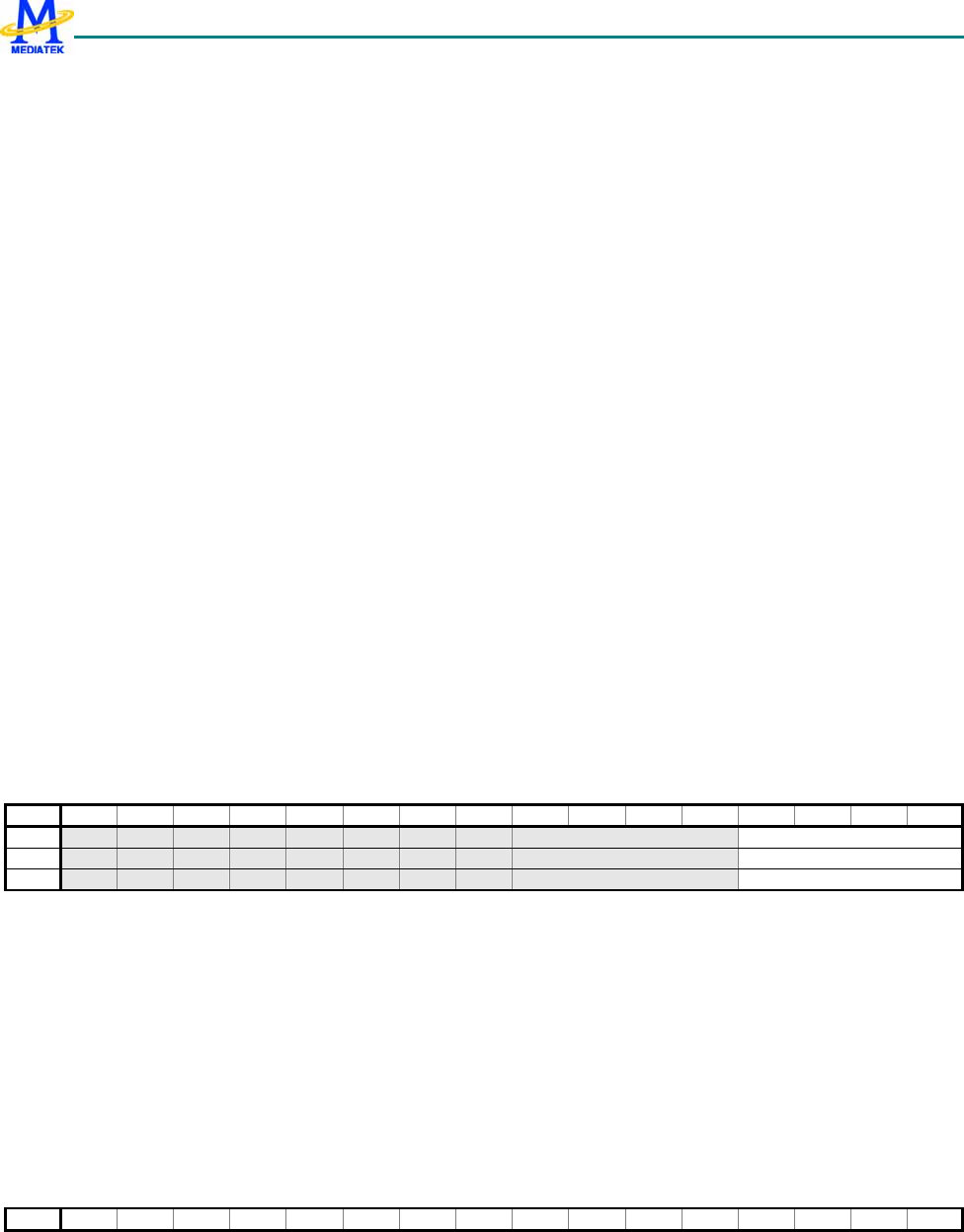

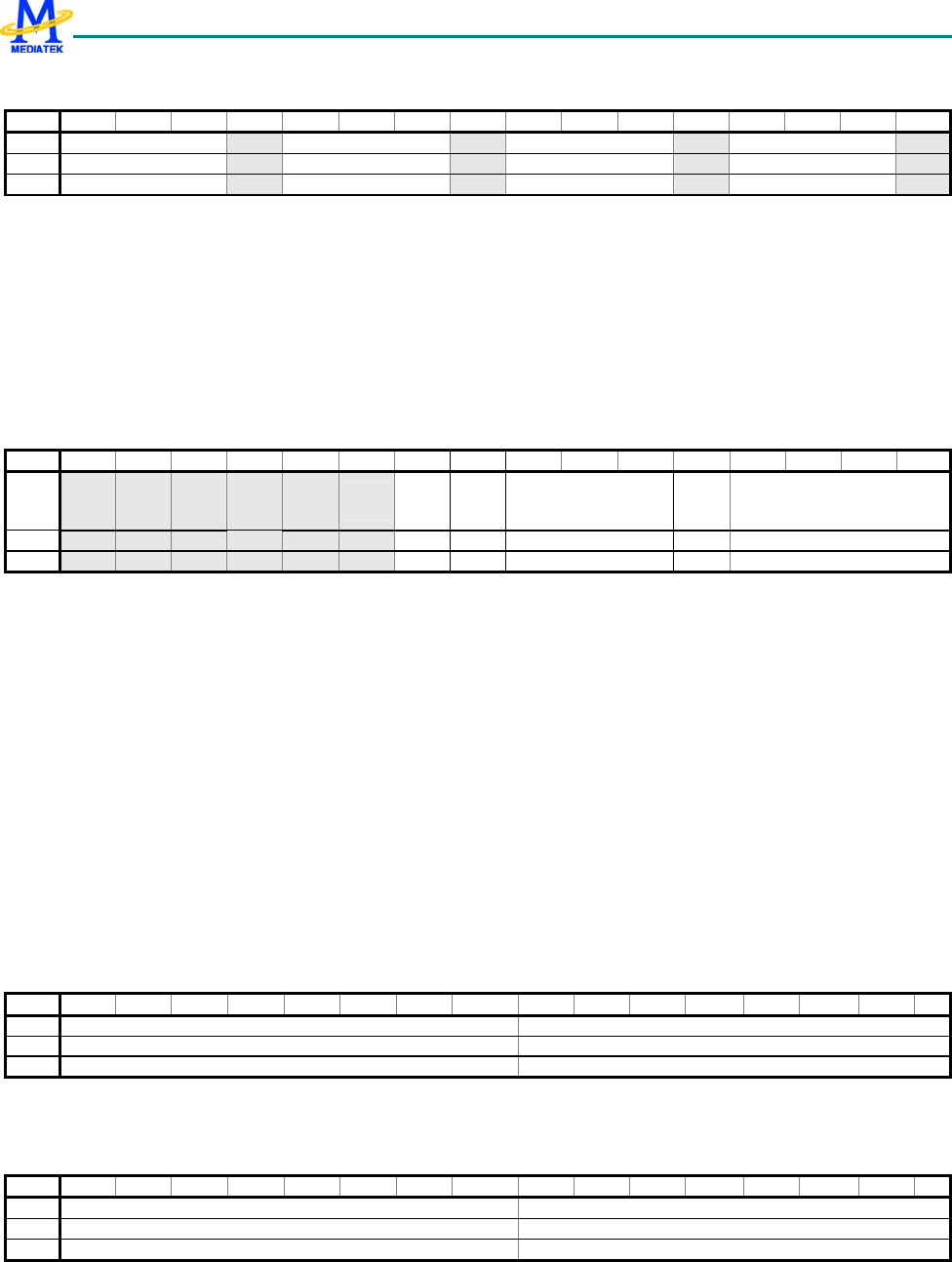

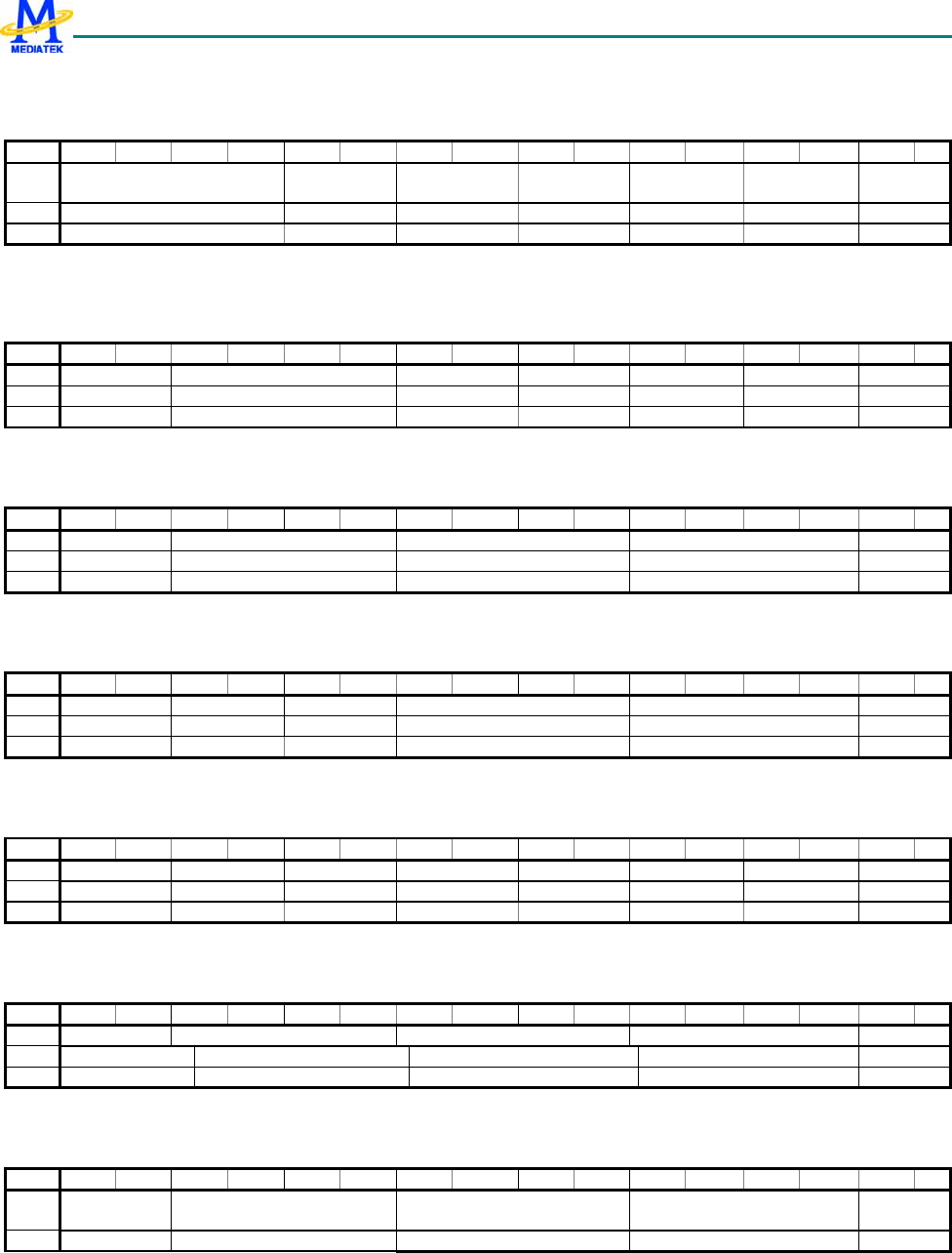

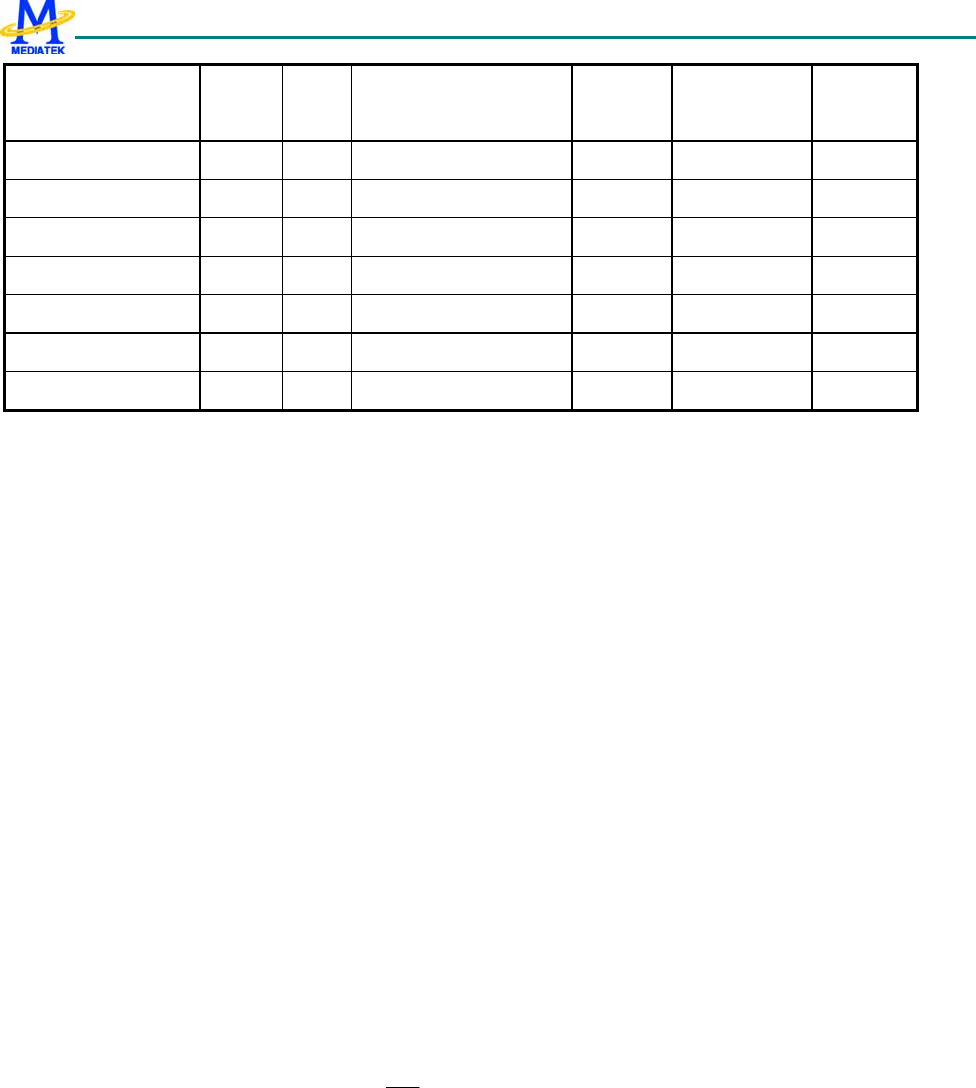

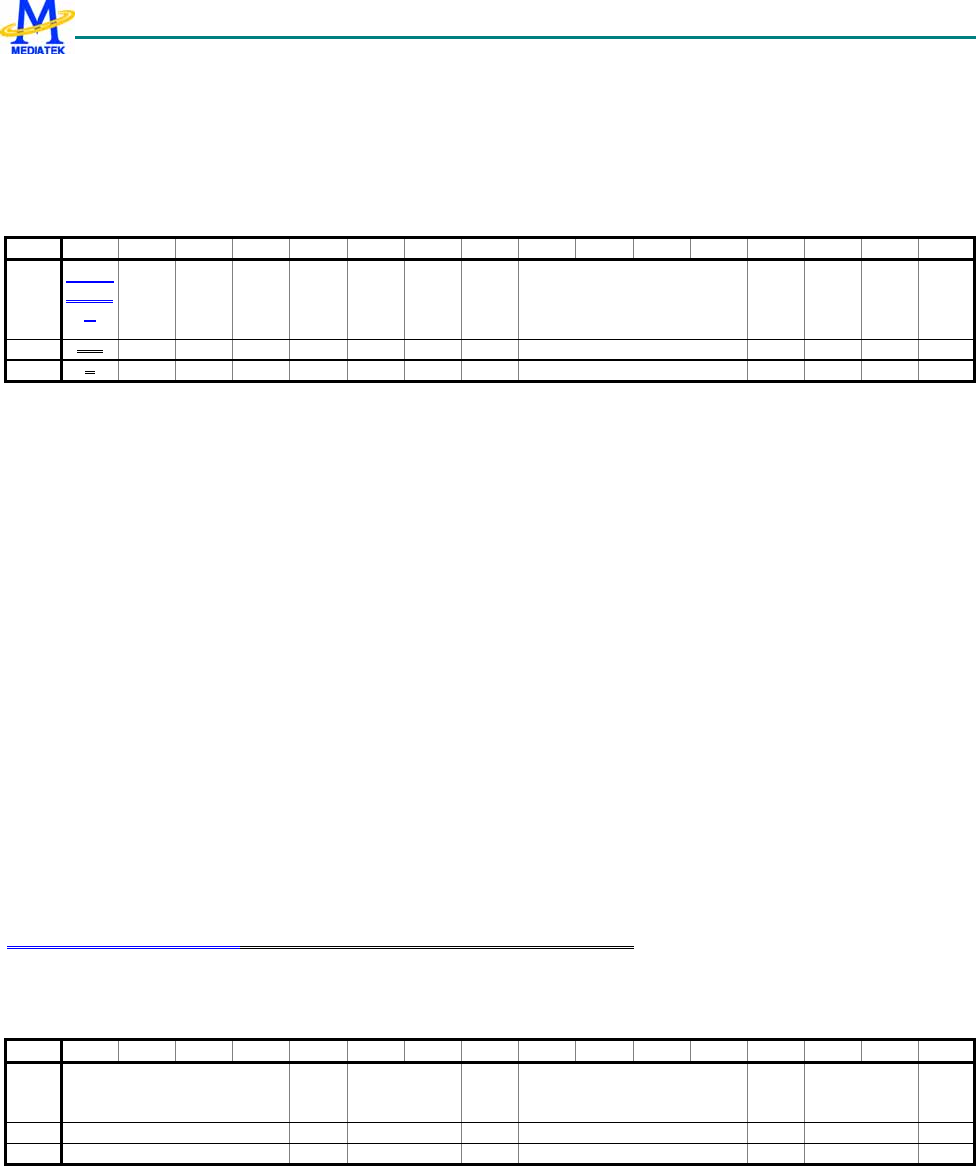

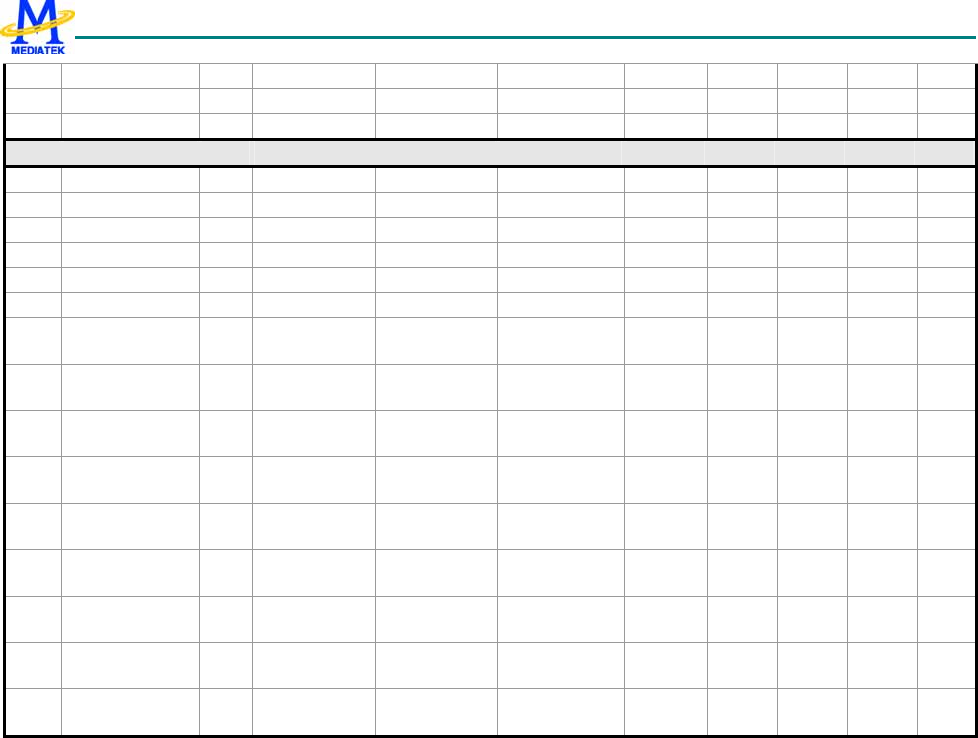

Figure 5 illustrates the block diagram of the Micro-Controller Unit Subsystem in MT6235.The subsystem utilizes a main

32-bit ARM926EJ-S RISC processor, which plays the role of the main bus master controlling the whole subsystem. The

ARM926EJ-S RISC is equipped with instruction cache, instruction TCM, data cache, and data TCM. The size of instruction

cache and data cache are both 16KB. The size of instruction TCM is 48KB. The size of data TCM is 80KB. If the requested

content is found in TCM or in cache, no bus transaction is required. If the code cache hit rate is high enough, bus traffic can

be effectively reduced and processor core performance maximized.

The bus comprises of two-level system buses: Advanced High-Performance Bus (AHB) and Advanced Peripheral Bus

(APB). All bus transactions originate from bus masters, while slaves can only respond to requests from bus masters.

Before data transfer can be established, the bus master must ask for bus ownership, accomplished by request-grant

handshaking protocol between masters and arbiters.

Two levels of bus hierarchy are designed to provide optimum usage for different performance requirements. Specifically,

AHB Bus, the main system bus, is tailored toward high-speed requirements and provides 32-bit data path with multiplex

scheme for bus interconnections. The APB Bus, on the other hand, is designed to reduce interface complexity for lower

data transfer rate, and so it is isolated from high bandwidth AHB Bus by APB Bridge. APB Bus supports 16-bit

addressing and both 16-bit and 32-bit data paths. APB Bus is also optimized for minimal power consumption by turning

off the clock when there is no APB bus activity.

During operation, if the target slave is located on AHB Bus, the transaction is conducted directly on AHB Bus. However,

if the target slave is a peripheral and is attached to the APB bus, then the transaction is conducted between AHB and APB

bus through the use of APB Bridge.

The MT6235 MCU subsystem supports only memory addressing method. Therefore all components are mapped onto the

MCU 32-bit address space. A Memory Management Unit is employed to allow for a central decode scheme. The MMU

generates appropriate selection signals for each memory-addressed module on the AHB Bus.

In order to off-load the processor core, a DMA Controller is designated to act as a master and share the bus resources on

AHB Bus to perform fast data movement between modules. This controller provides fourteen DMA channels.

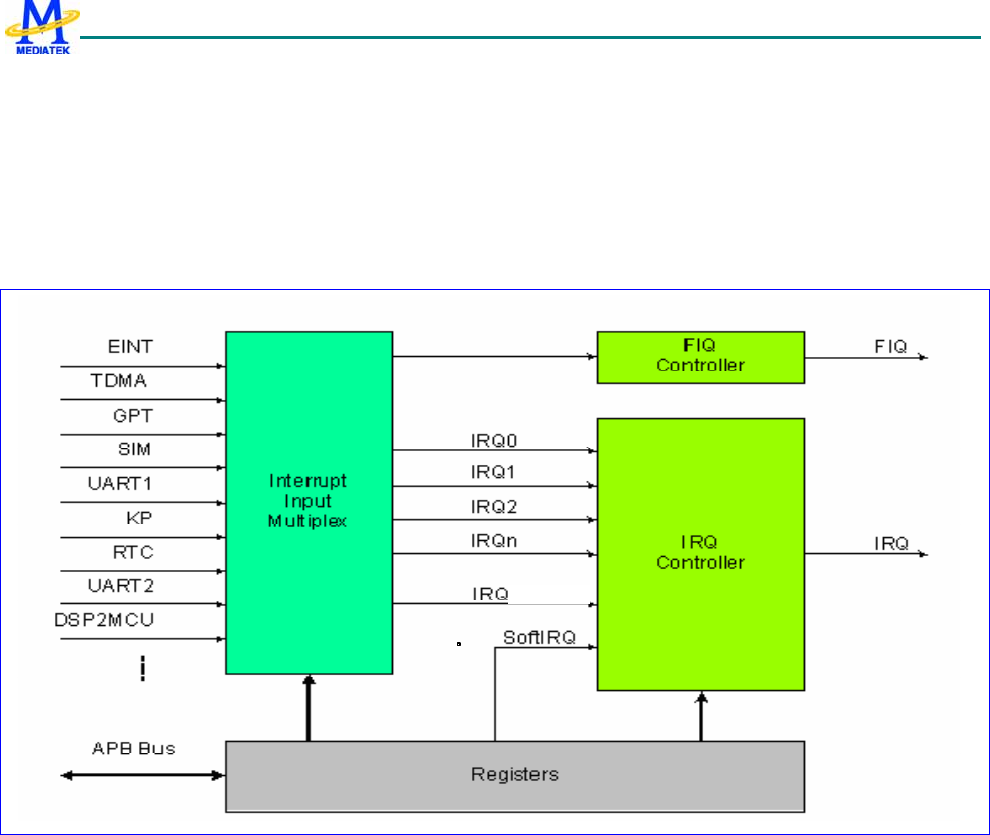

The Interrupt Controller provides a software interface to manipulate interrupt events; it can handle up to 50 interrupt

sources asserted at the same time. In general, the controller generates 2 levels of interrupt requests, FIQ and IRQ, to the

processor.

A 64K Byte SRAM is provided as system memory for high-speed data access. For factory programming purposes, a Boot

ROM module is also integrated. These two modules use the same Internal Memory Controller to connect to AHB Bus.

External Memory Interface supports both 8-bit and 16-bit devices. This interface supports both synchronous and

asynchronous components, such as Flash, SRAM, SDRAM and parallel LCD. This interface supports page and burst

mode type of Flash, Cellular RAM, as well as high performance MobileRAM. Since AHB Bus is 32-bit wide, all data

transfers are converted into several 8-bit or 16-bit cycles depending on the data width of the target device.

MT6235 GSM/GPRS Baseband Processor Data Sheet Revision 1.02

41/599 MediaTek Inc. Confidential

APB Slaves

AHB Slaves

AHB Masters

ARM926EJ-S

16KB

ICACHE 16KB

DCACHE

48KB ITCM 80KB DTCM

AHB Layer 1

AHB Layer 2

AHB Layer 4

Other AHB

Masters (DMA ,

USB, ...)

EMI Controller

System RAM

(64KB)

System ROM

AHB/APB

Bridge

APB Bus

APB

Peripherals

APB

Peripherals

APB

Peripherals

LCD Controller

Graphic

AHB Layer 3

Figure 5 Block Diagram of the Micro-Controller Unit Subsystem in MT6235

3.1 Processor Core

3.1.1 General Description

The Micro-Controller Unit Subsystem in MT6235 uses the 32-bit ARM926EJ-S RISC processor that is based on the Von

Neumann architecture with a single 32-bit data bus carrying both instructions and data. The memory interface of

ARM926EJ-S is totally compliant with the AMBA based bus system, which allows direct connection to the AHB Bus.

3.2 Memory Management

3.2.1 General Description

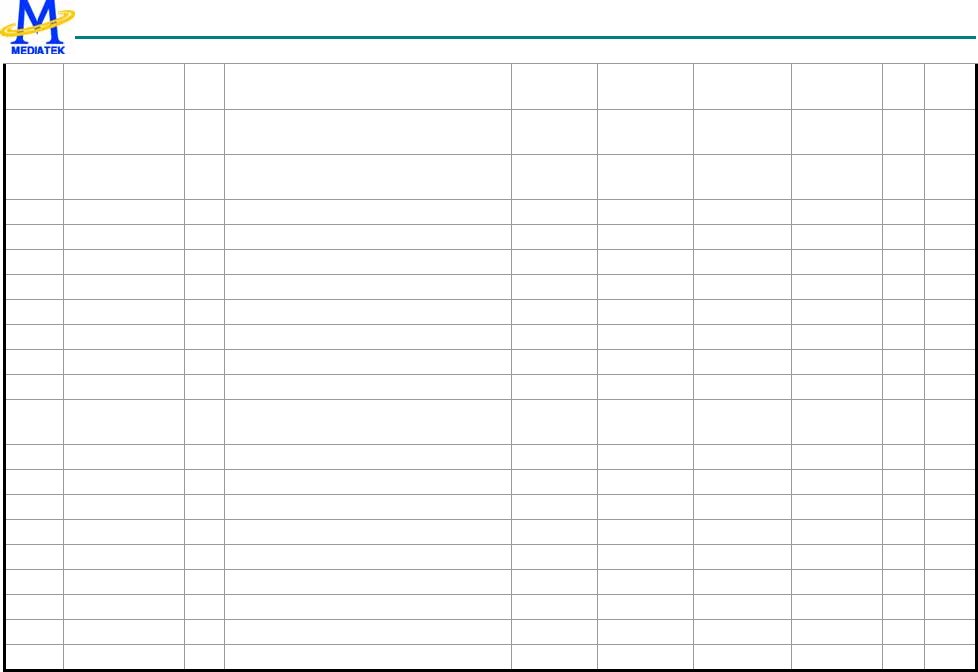

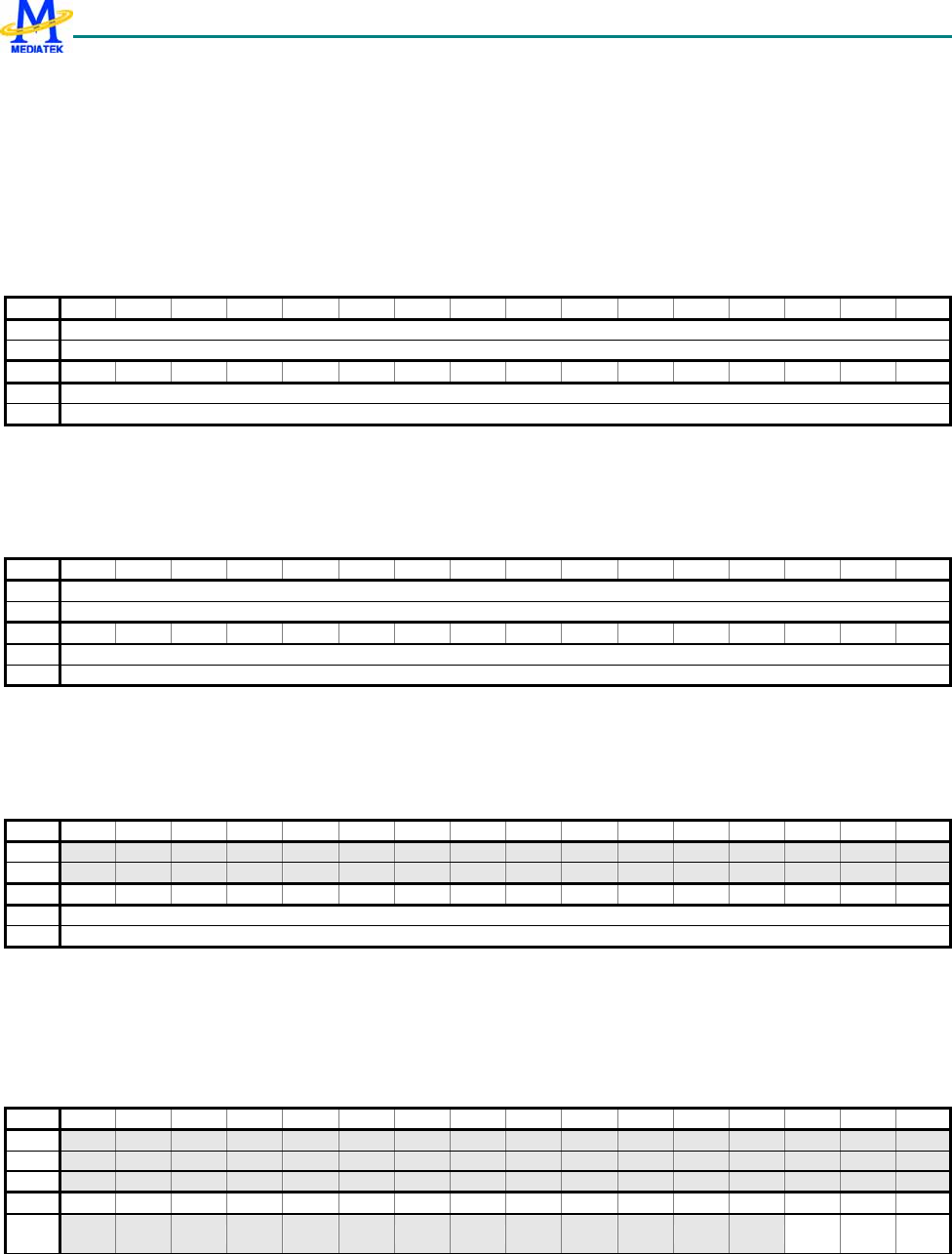

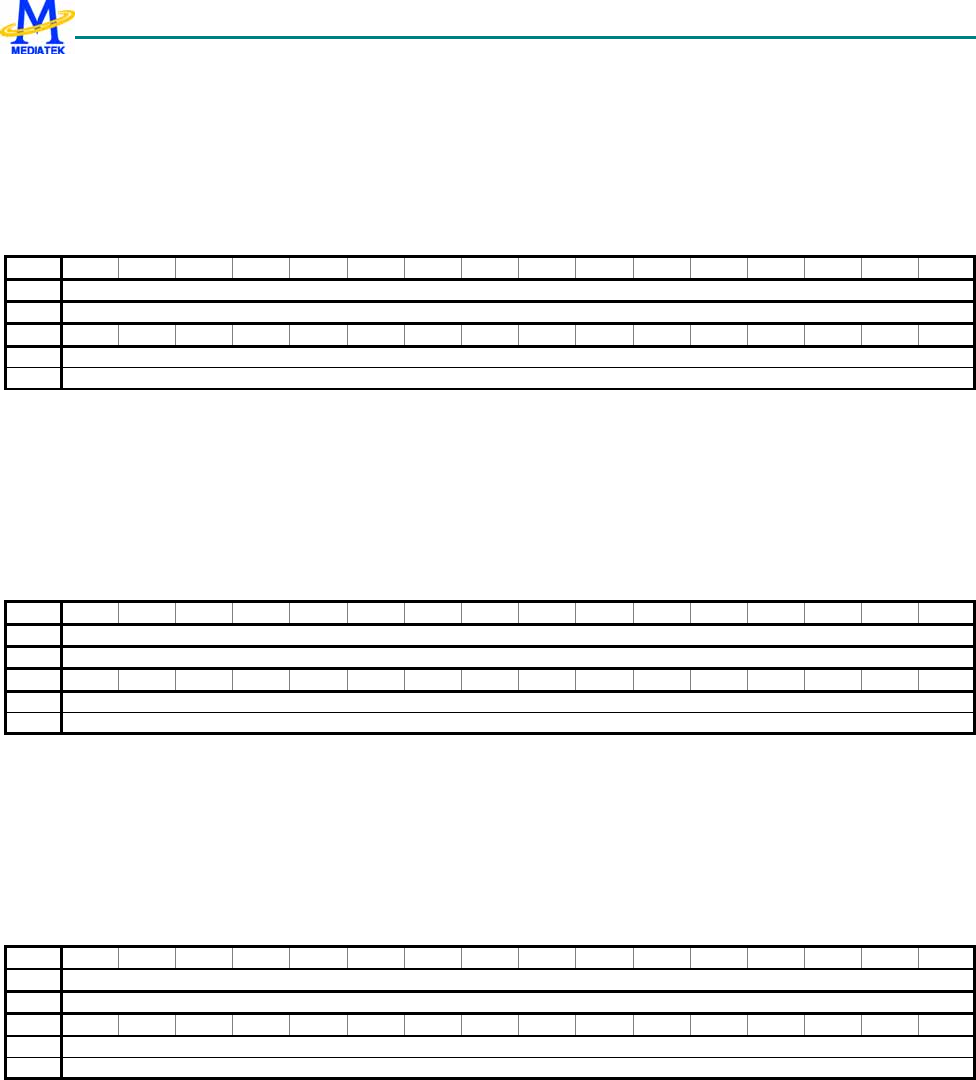

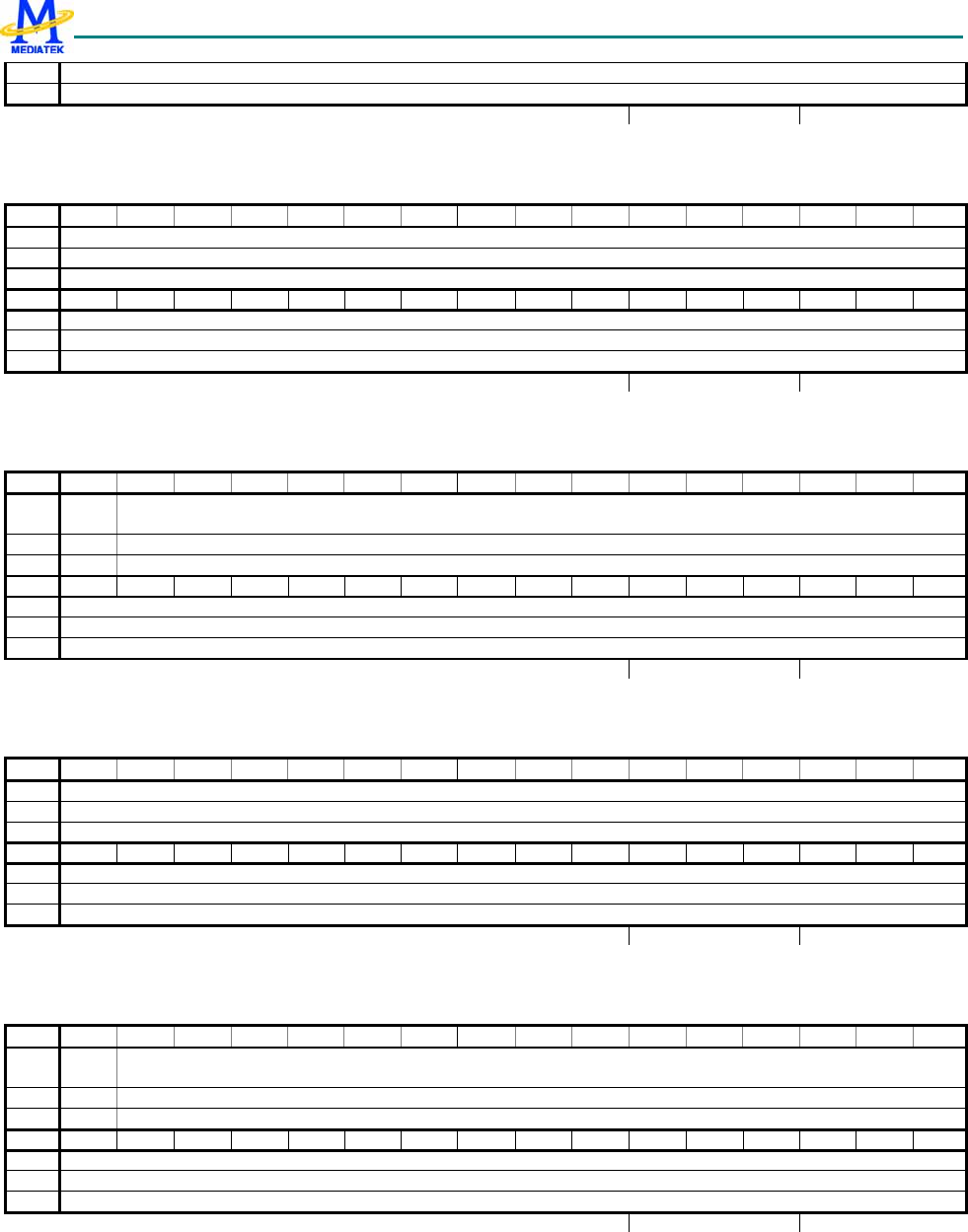

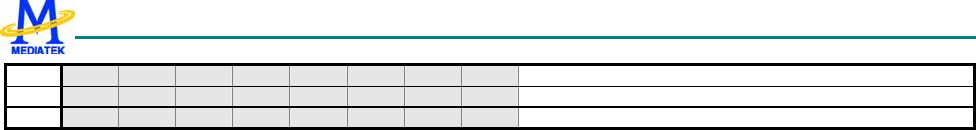

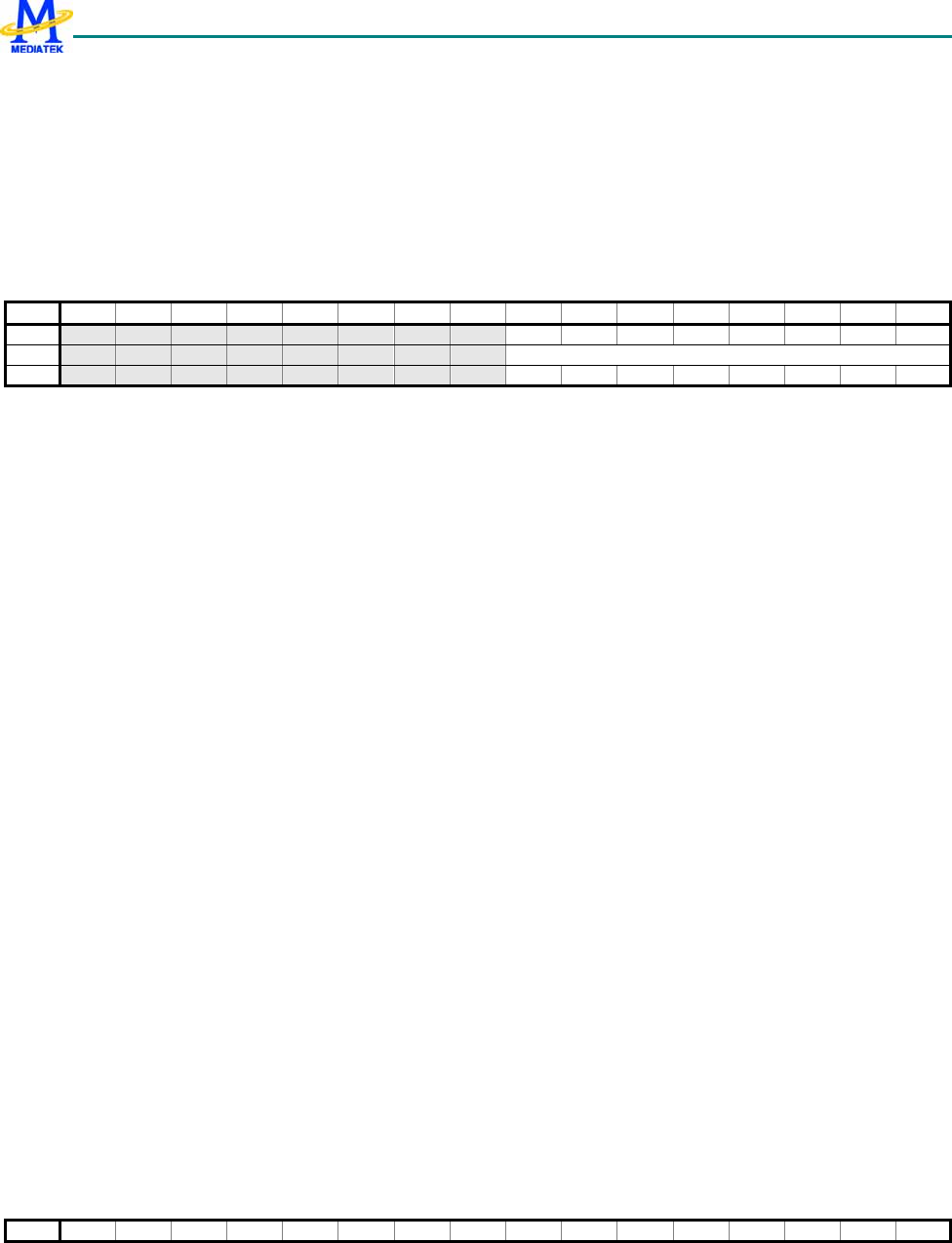

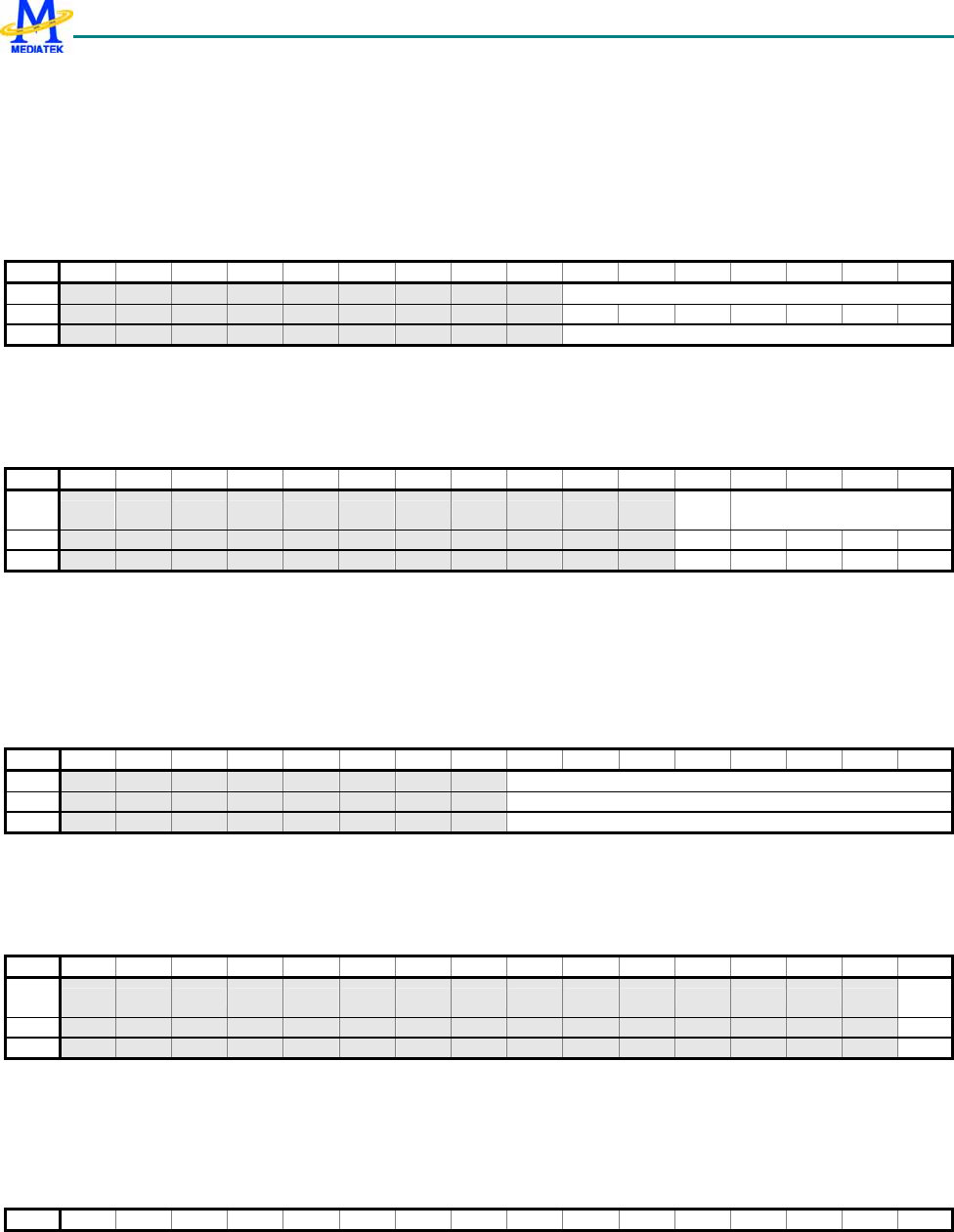

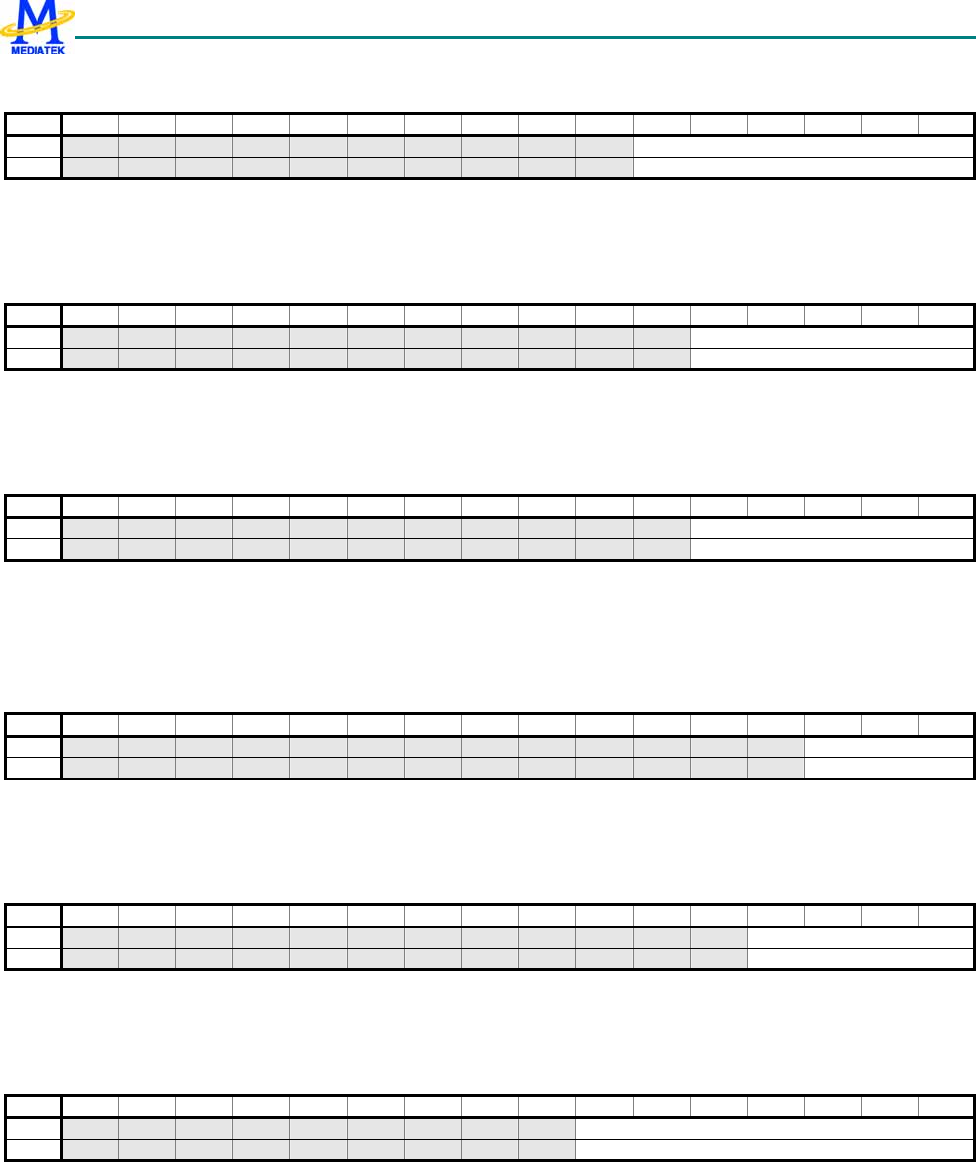

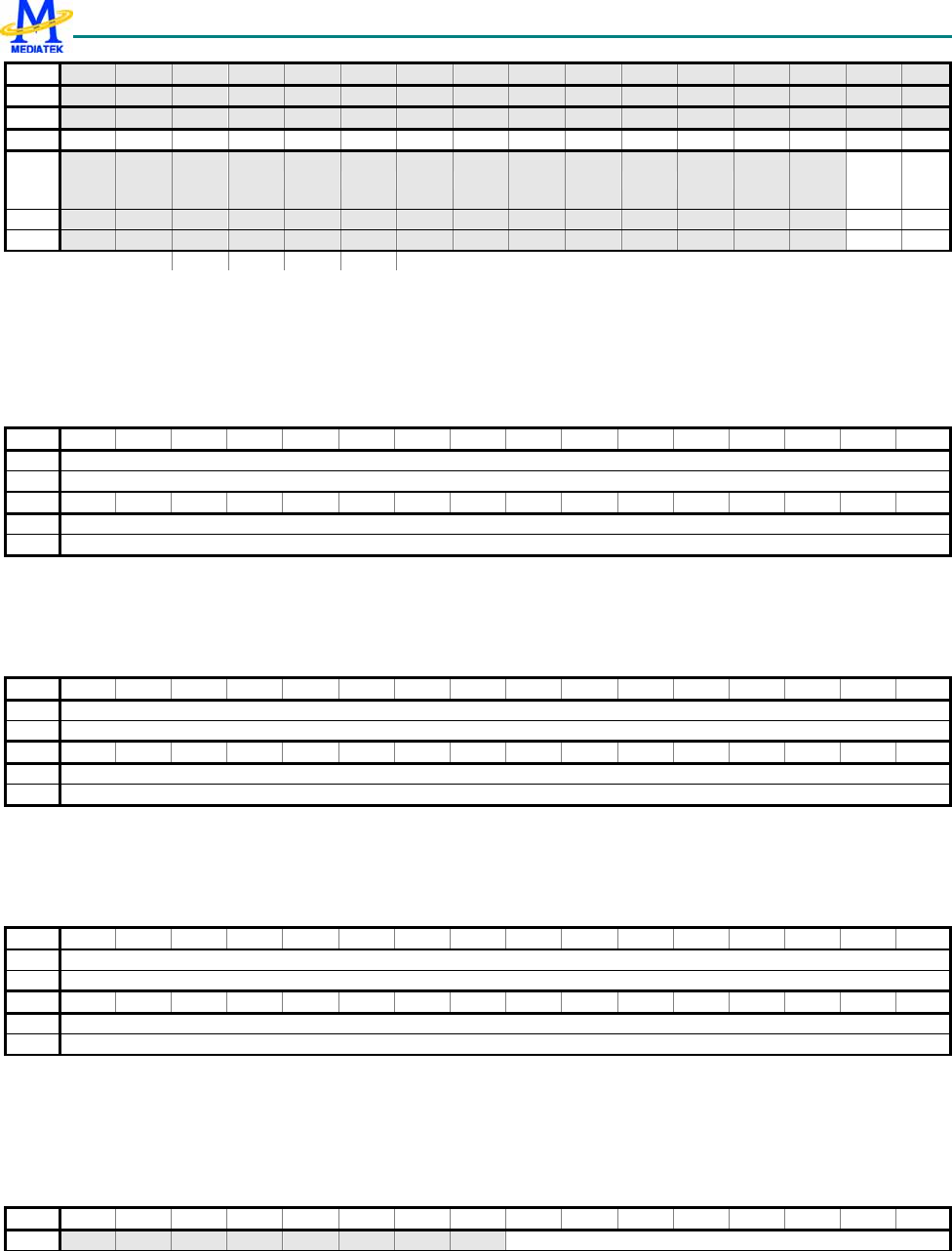

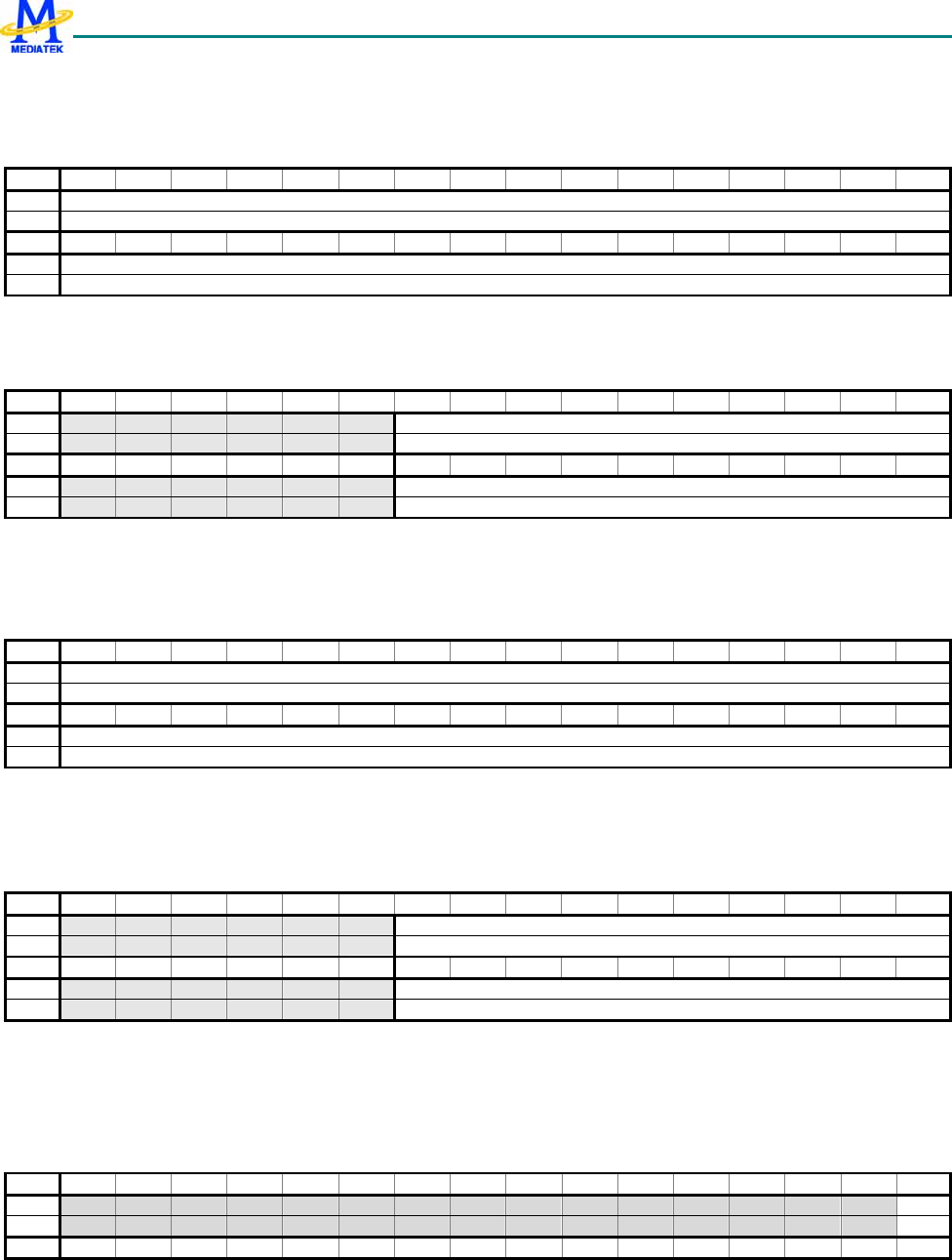

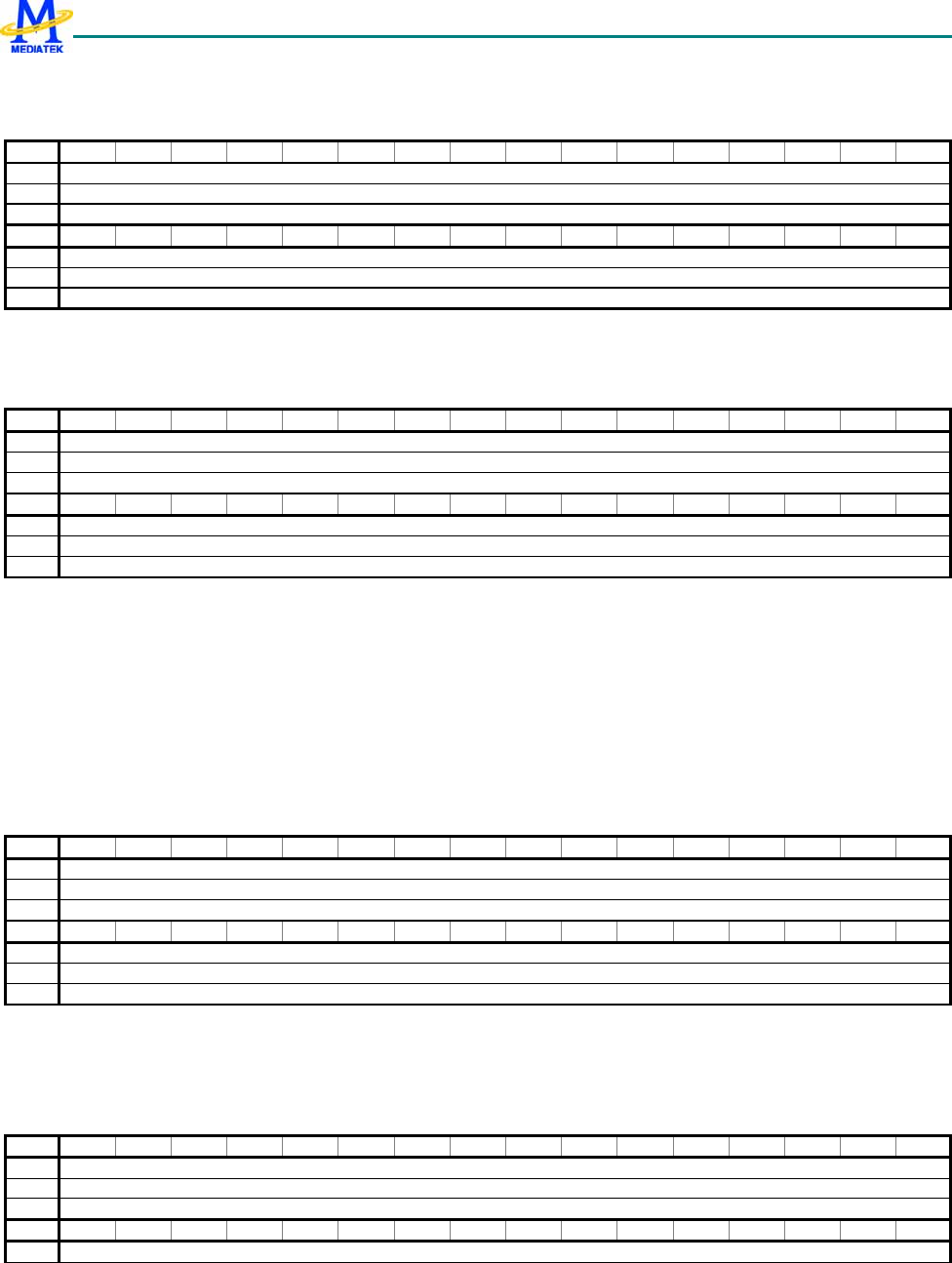

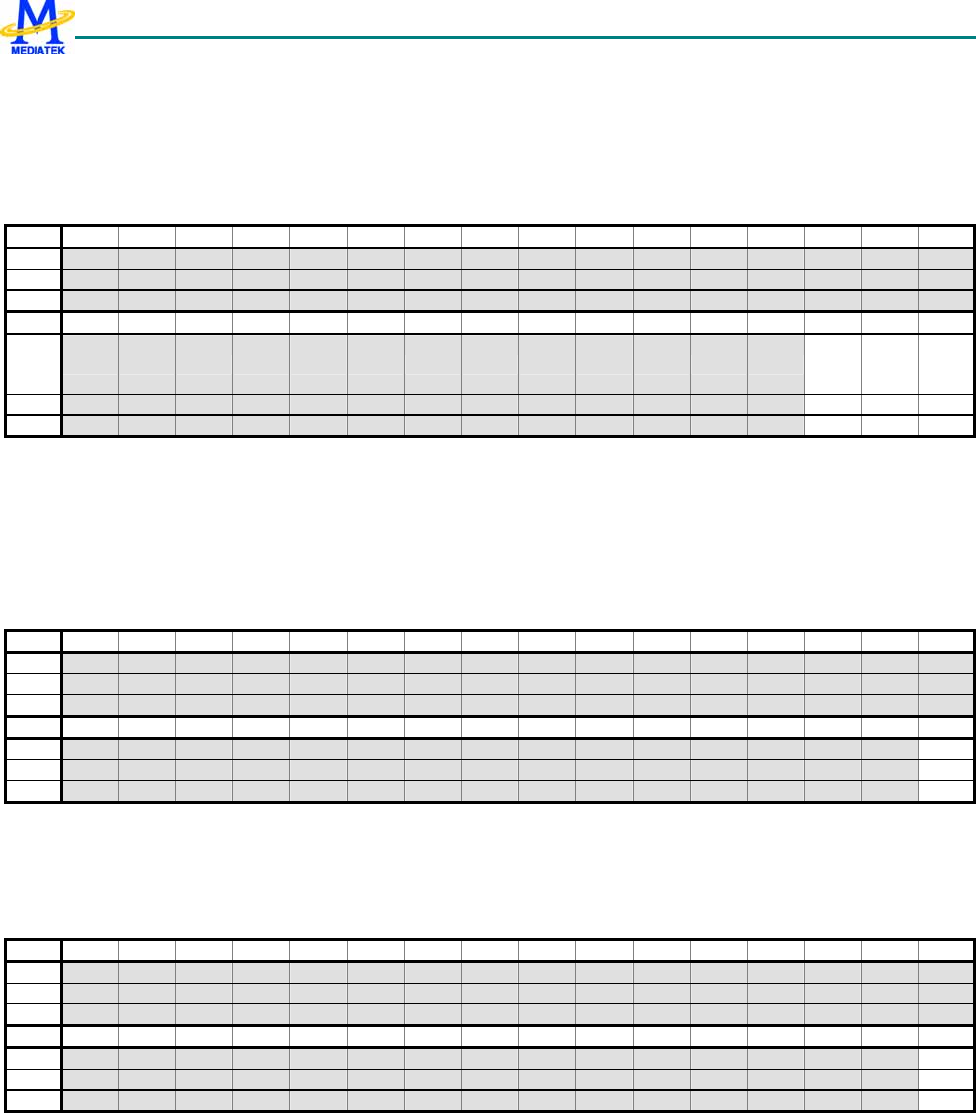

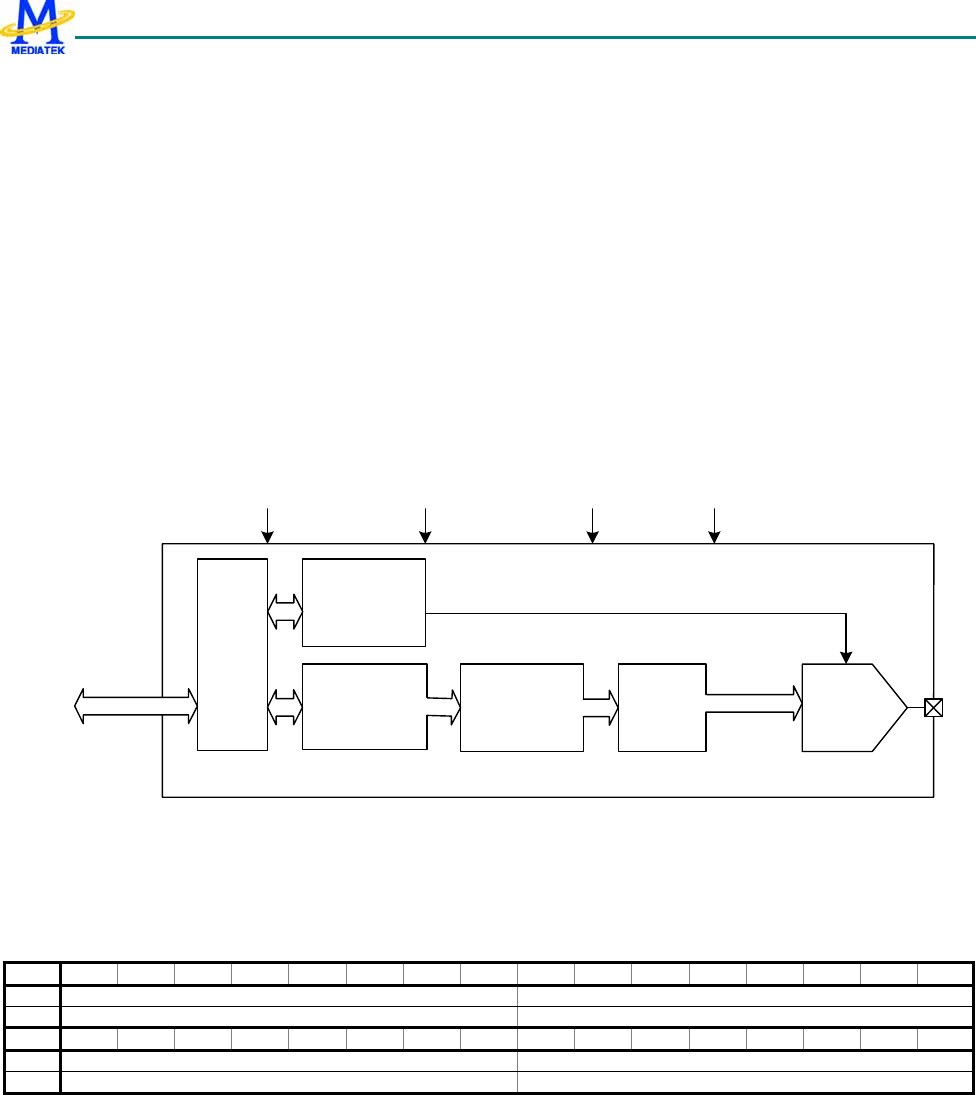

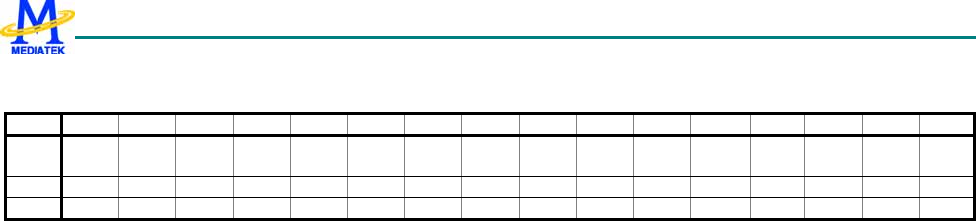

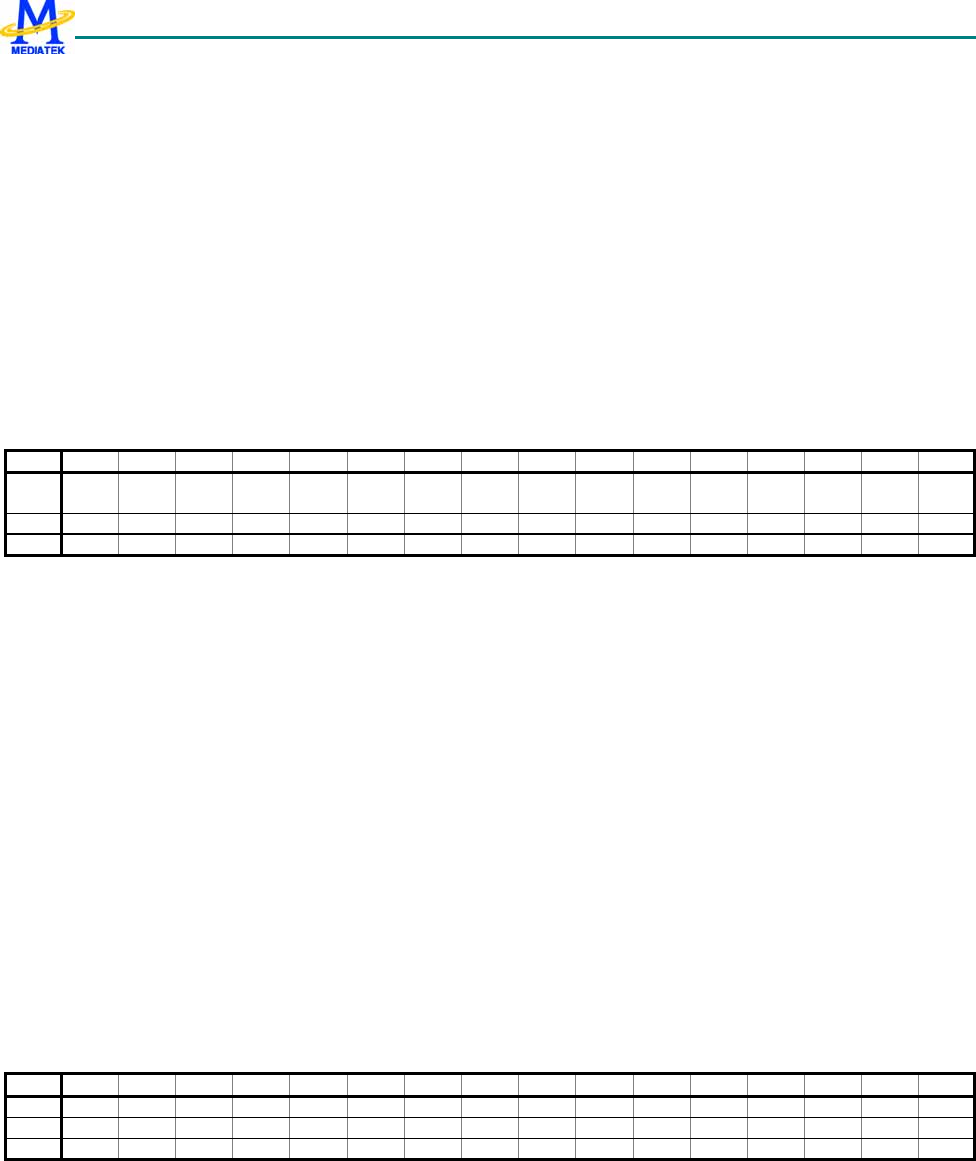

The processor core of MT6235 supports only a memory addressing method for instruction fetch and data access. The core

manages a 32-bit address space that has addressing capability of up to 4 GB. System RAM, System ROM, Registers,

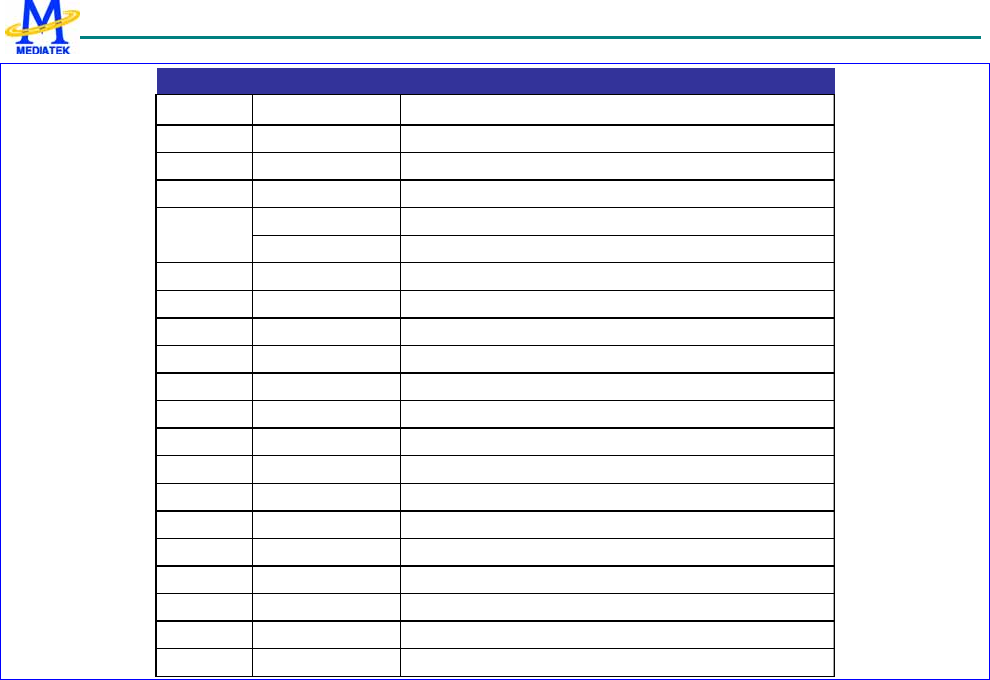

MCU Peripherals and external components are all mapped onto such 32-bit address space, as depicted in Figure 6.

MT6235 GSM/GPRS Baseband Processor Data Sheet Revision 1.02

42/599 MediaTek Inc. Confidential

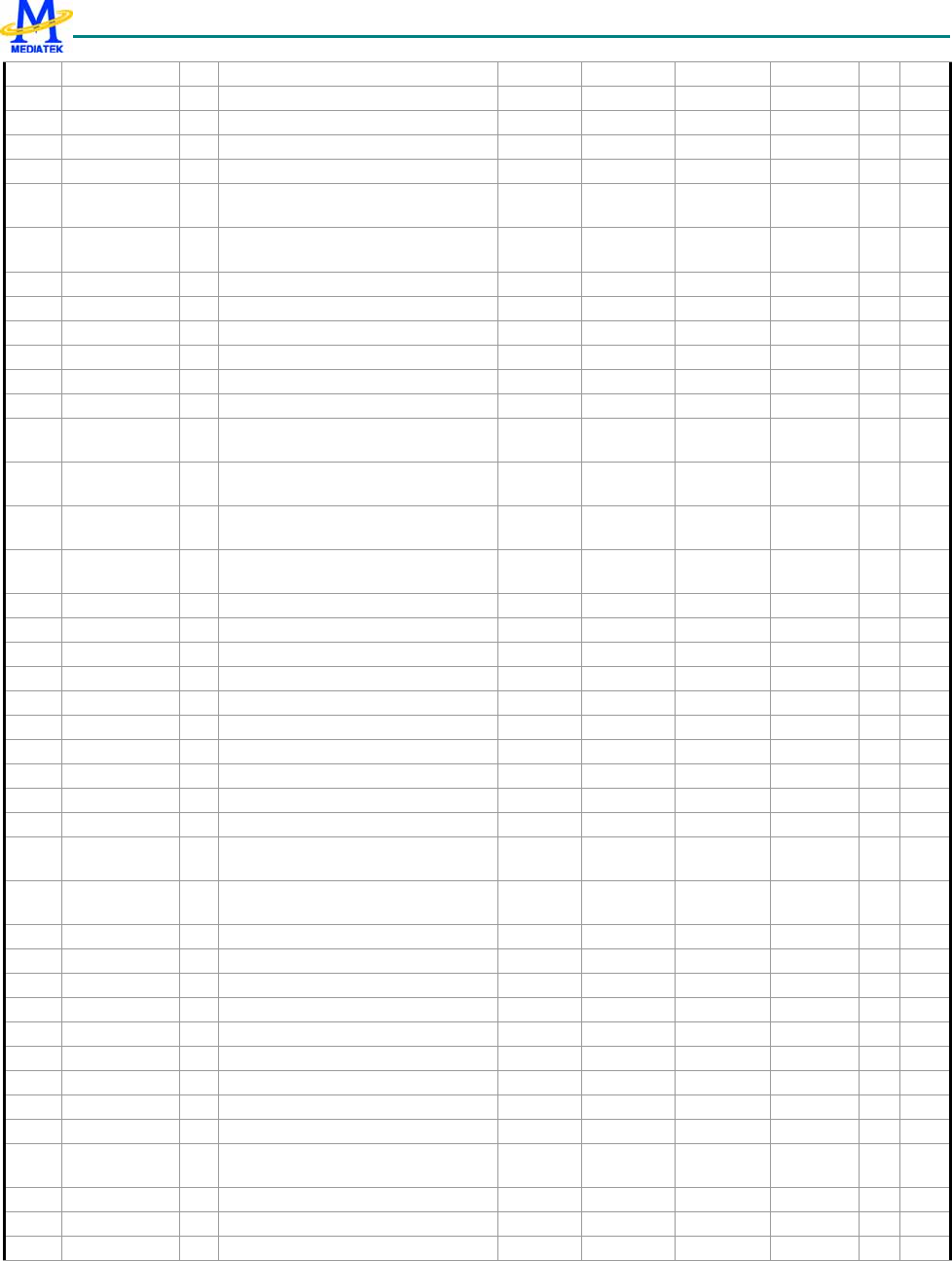

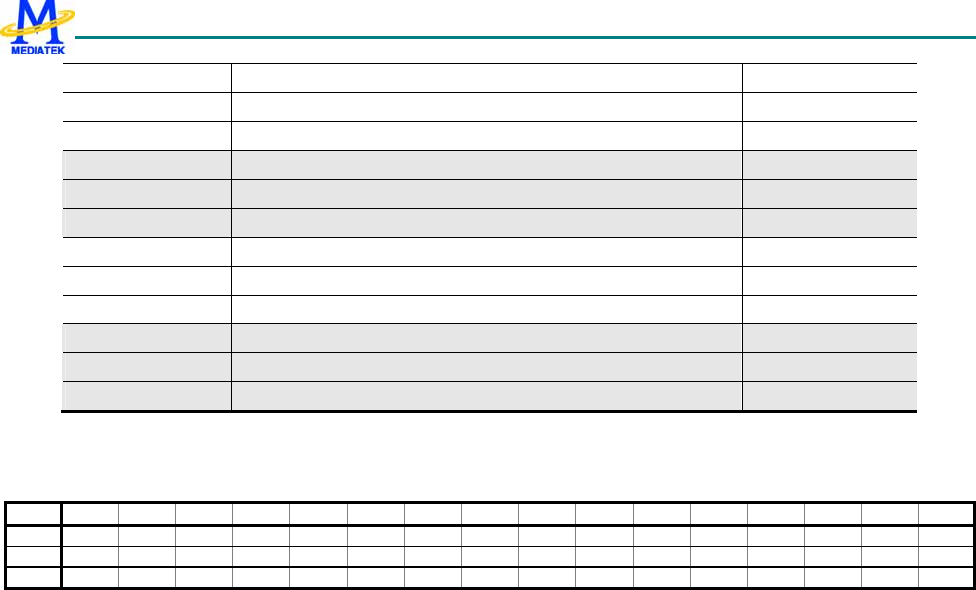

BANK Base Address Description

BANK0 0000_0000h EMI Band 0 / Boot Code

BANK1 1000_0000h EMI Bank 1

BANK2 2000_0000h EMI Bank 2

BANK3 3000_0000h EMI Bank 3

4000_0000h System RAM

4800_0000h System ROM

BANK5 5000_0000h TCM

BANK6 6000_0000h USB

6100_0000h Virtual FIFO Slave

BANK7 7000_0000h Reserved

BANK8 8000_0000h APB Peripheral

BANK9 9000_0000h LCD

BANK10 A000_0000h CPU-DSP Share RAM1

A100_0000h CPU-DSP Share RAM2

A200_0000h DSP IDMA Port 1

A300_0000h DSP IDMA Port 2

BANK11 B000_0000h Reserved

BANK12 C000_0000h Reserved

BANK13 D000_0000h Reserved

BANK14 E000_0000h Reserved

BANK15 F000_0000h Reserved

BANK4

Figure 6 The Memory Layout of MT6235

The address space is organized into blocks of 256 MB each. The block number is uniquely selected by address line

A31-A28 of the internal system bus.

3.2.1.1 External Access

To allow external access, the MT6235 can output 27bits (A26-A0) of address lines along with 4 selection signals that

correspond to the associated memory blocks. That is, MT6235 can support up to 4 MCU addressable external components.

The data width of internal system bus is fixed at 32-bit wide, while the data width of the external components is either 16–

bit or 8-bit.

Since devices are usually available with varied operating grades, adaptive configurations for different applications are

needed. MT6235 provides software programmable registers to configure their wait-states to adapt to different operating

conditions.

3.2.1.2 Memory Re-mapping Mechanism

To permit more flexible system configuration, a memory re-mapping mechanism is provided. The mechanism allows

software program to swap BANK0 (ECS0#) and BANK1 (ECS1#) dynamically. Whenever the bit value of RM0 in

register EMI_REMAP is changed, these two banks are swapped accordingly. Furthermore, it allows system to boot from

System ROM as detailed in 3.2.1.3 Boot Sequence.

MT6235 GSM/GPRS Baseband Processor Data Sheet Revision 1.02

43/599 MediaTek Inc. Confidential

3.2.1.3 Boot Sequence

Since the ARM926EJ-S core always starts to fetch instructions from the lowest memory address at 00000000h after system

has been reset, the system is designed to have a dynamic mapping architecture capable of associating Boot Code, external

Flash or external SRAM with the memory block 0000_0000h – 0fff_ffffh.

By default, the Boot Code is mapped onto 0000_0000h – 0fff_ffffh after a system reset. In this special boot mode,

External Memory Controller does not access external memory; instead, the EMI Controller send predefined Boot Code

back to the ARM926EJ-S core, which instructs the processor to execute the program in System ROM. This configuration

can be changed by programming bit value of RM1 in register EMI_REMAP directly.

MT6235 system provides one boot up scheme:

z Start up system of running codes from Boot Code for factory programming or NAND flash boot.

3.2.1.3.1 Boot Code

The Boot Code is placed together with Memory Re-Mapping Mechanism in External Memory Controller, and comprises of

just two words of instructions as shown below. A jump instruction leads the processor to run the code starting at address

48000000h where the System ROM is placed.

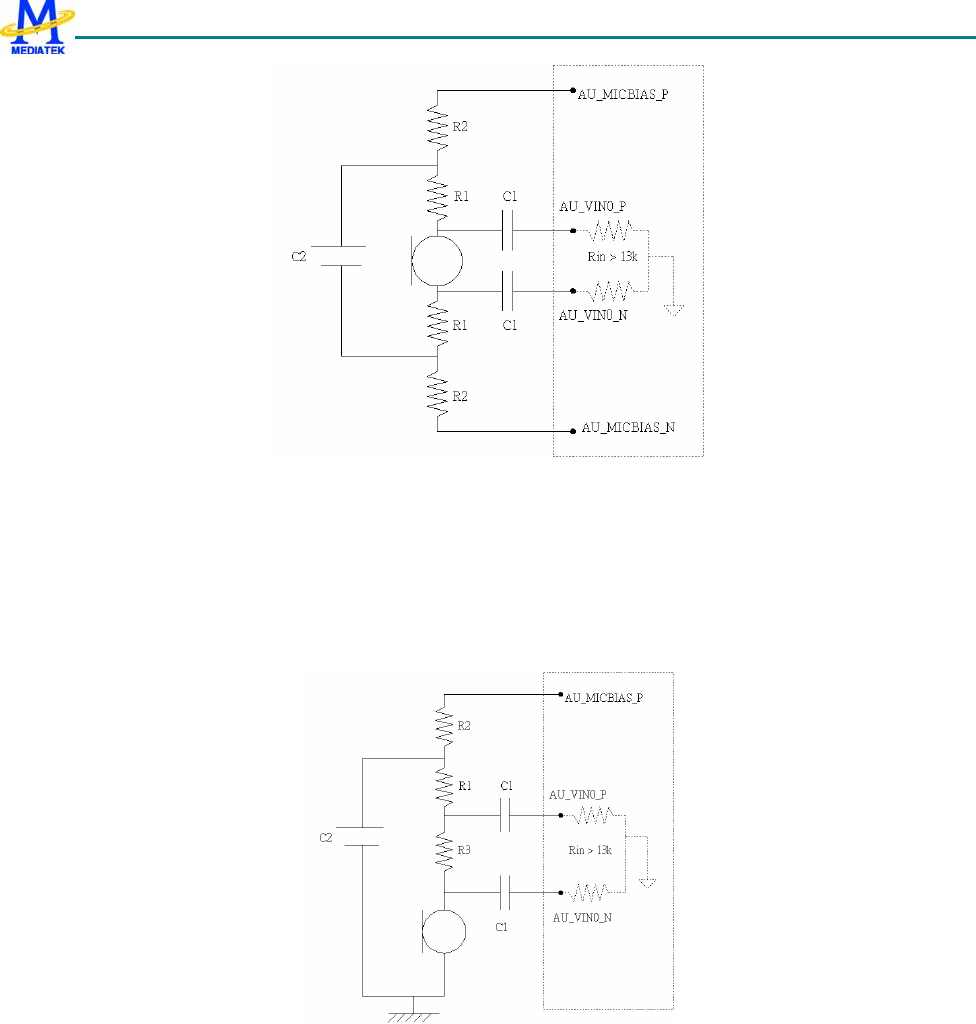

ADDRESS BINARY CODE ASSEMBLY

00000000h E51FF004h LDR PC, 0x4

00000004h 48000000h (DATA)

3.2.1.3.2 Factory Programming

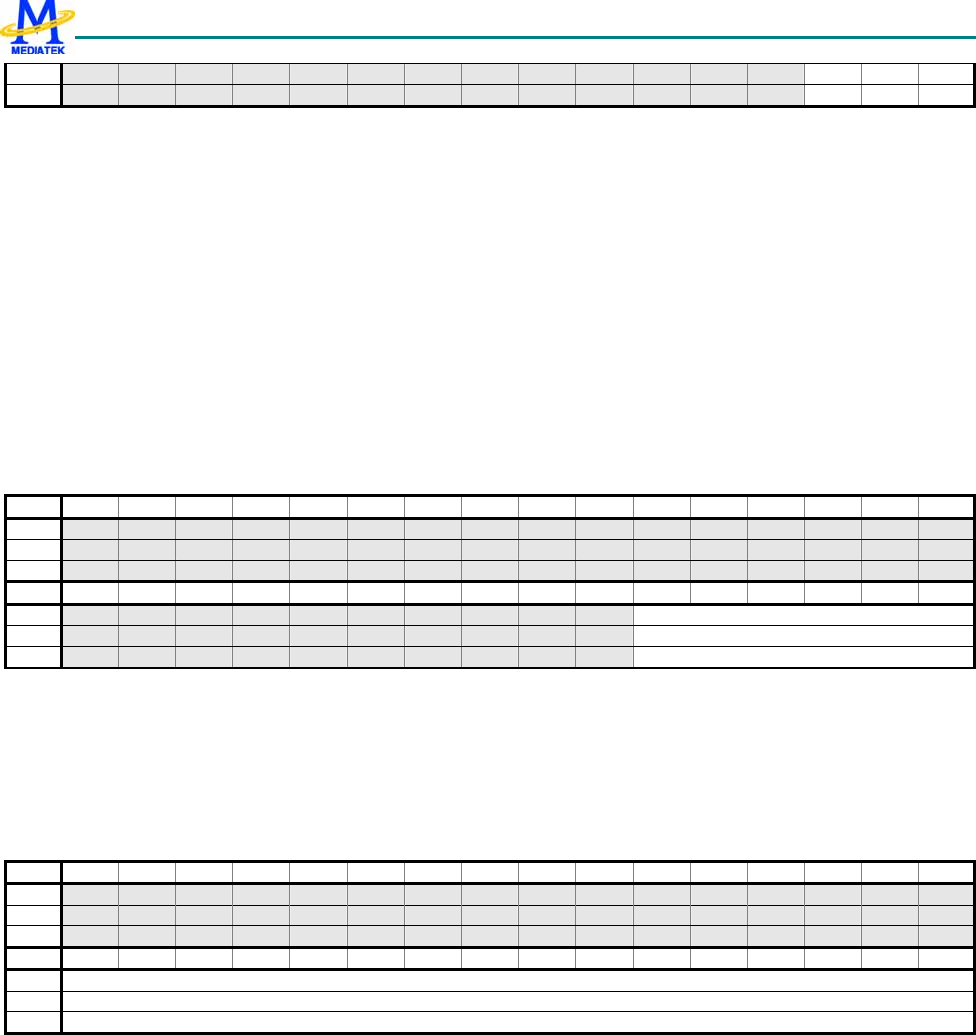

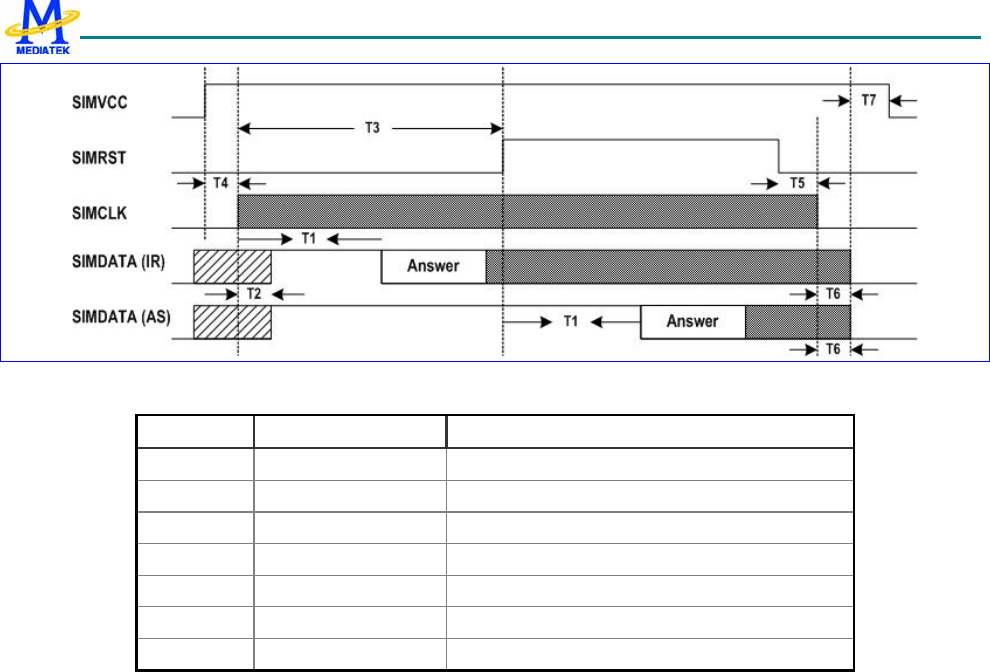

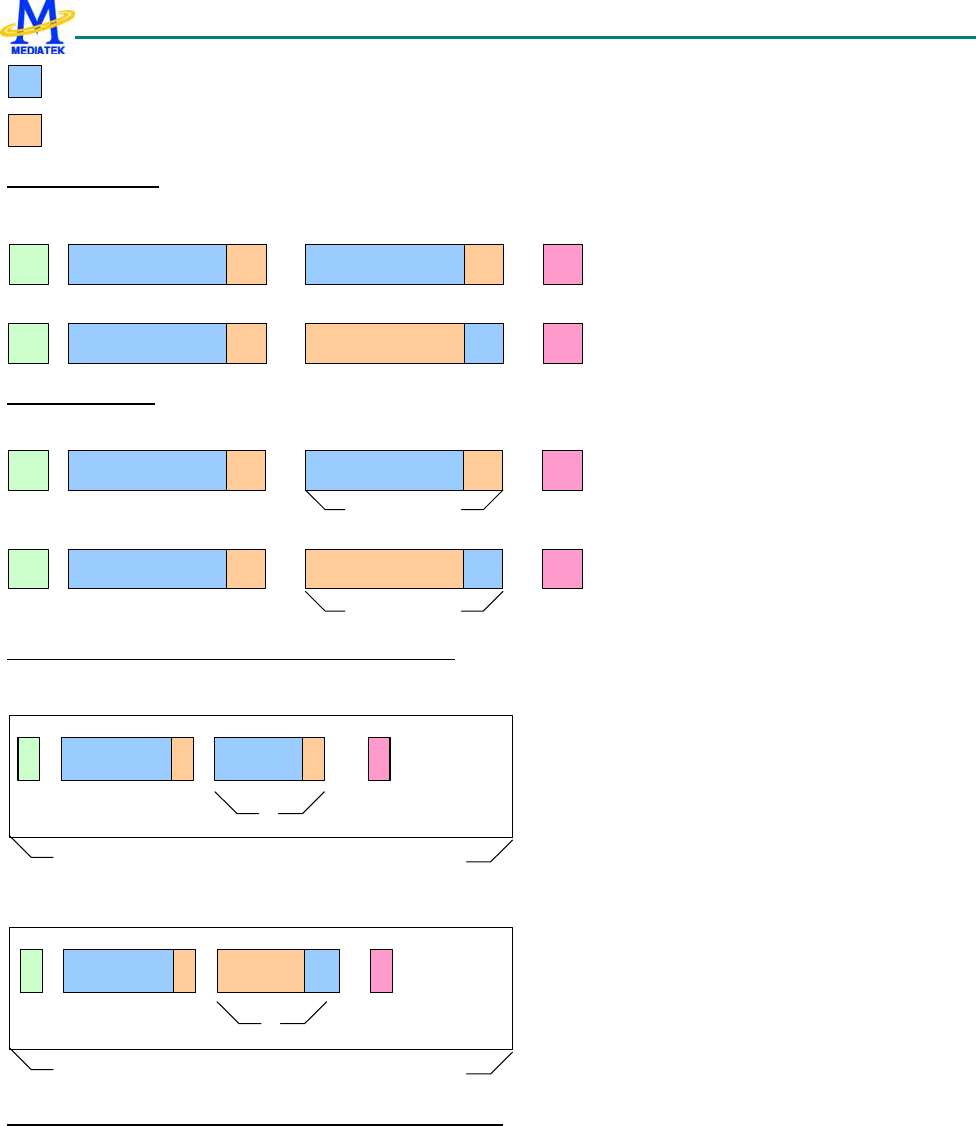

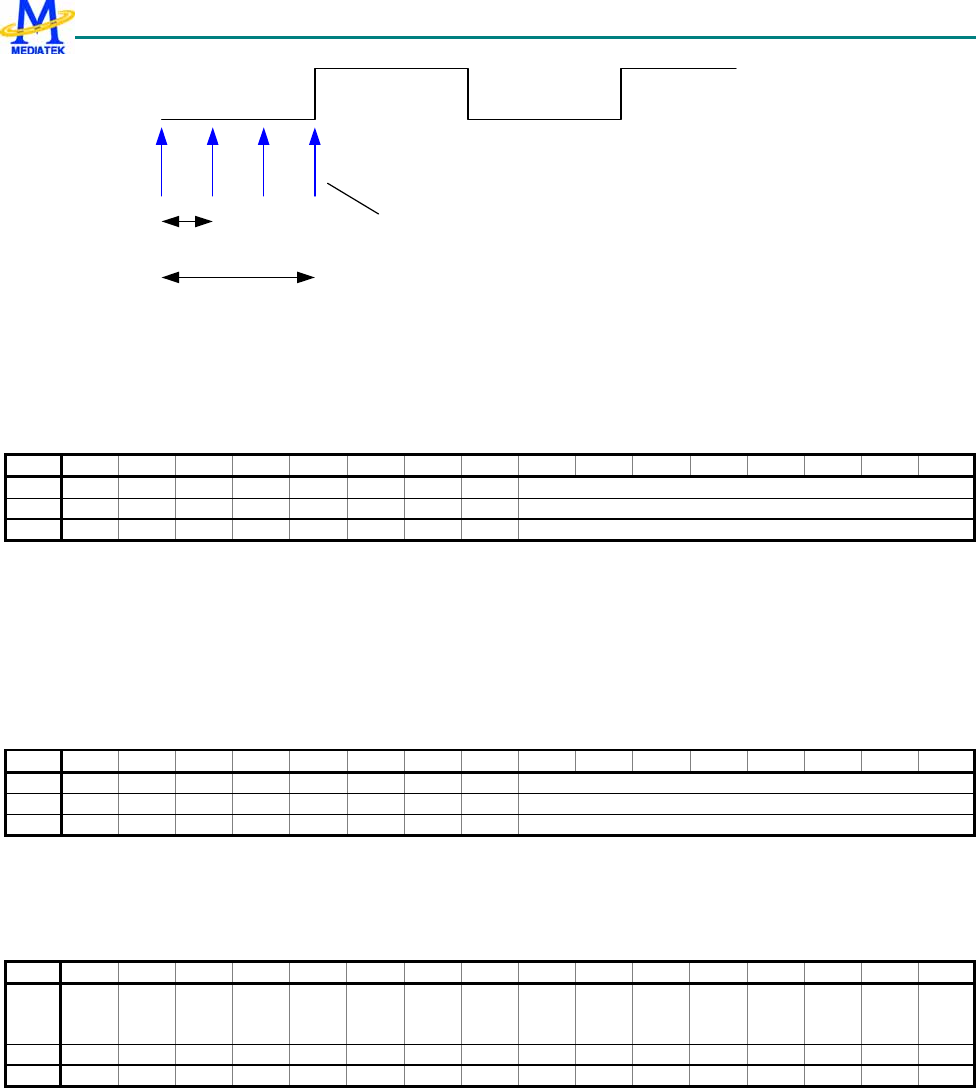

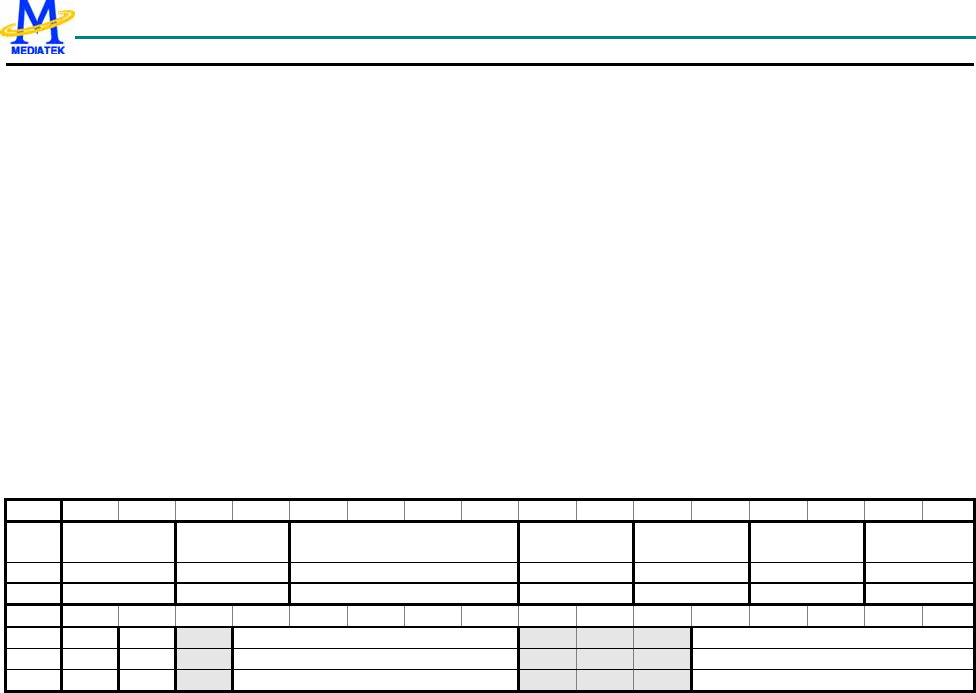

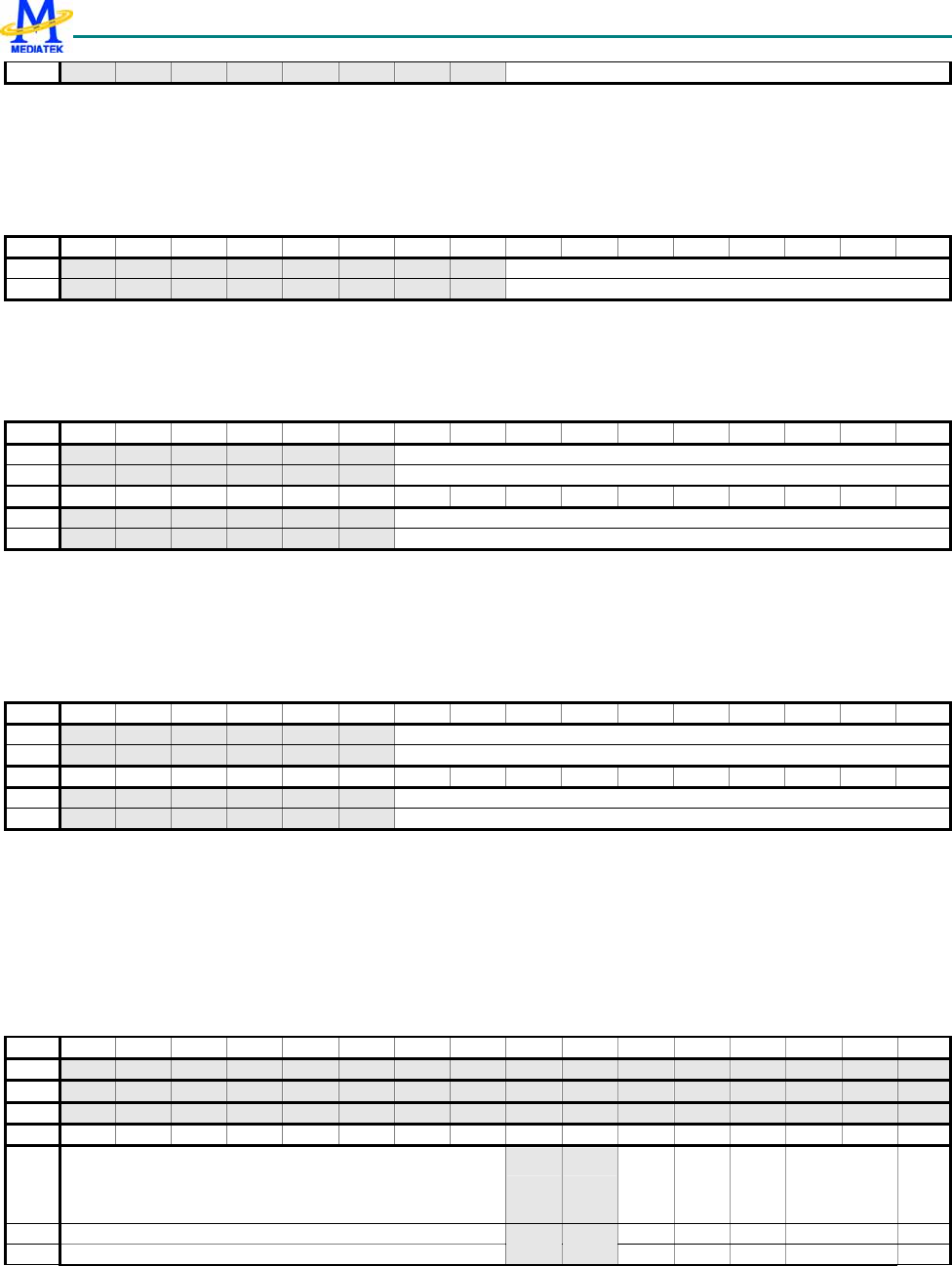

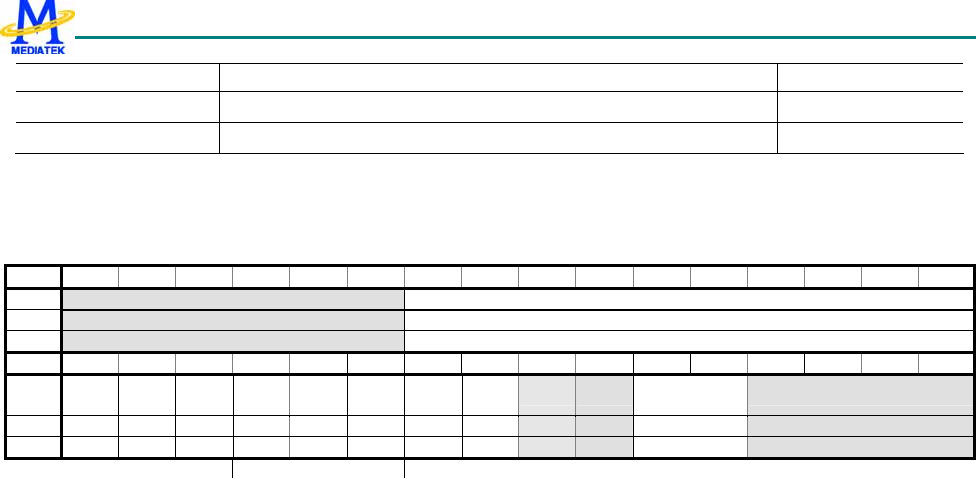

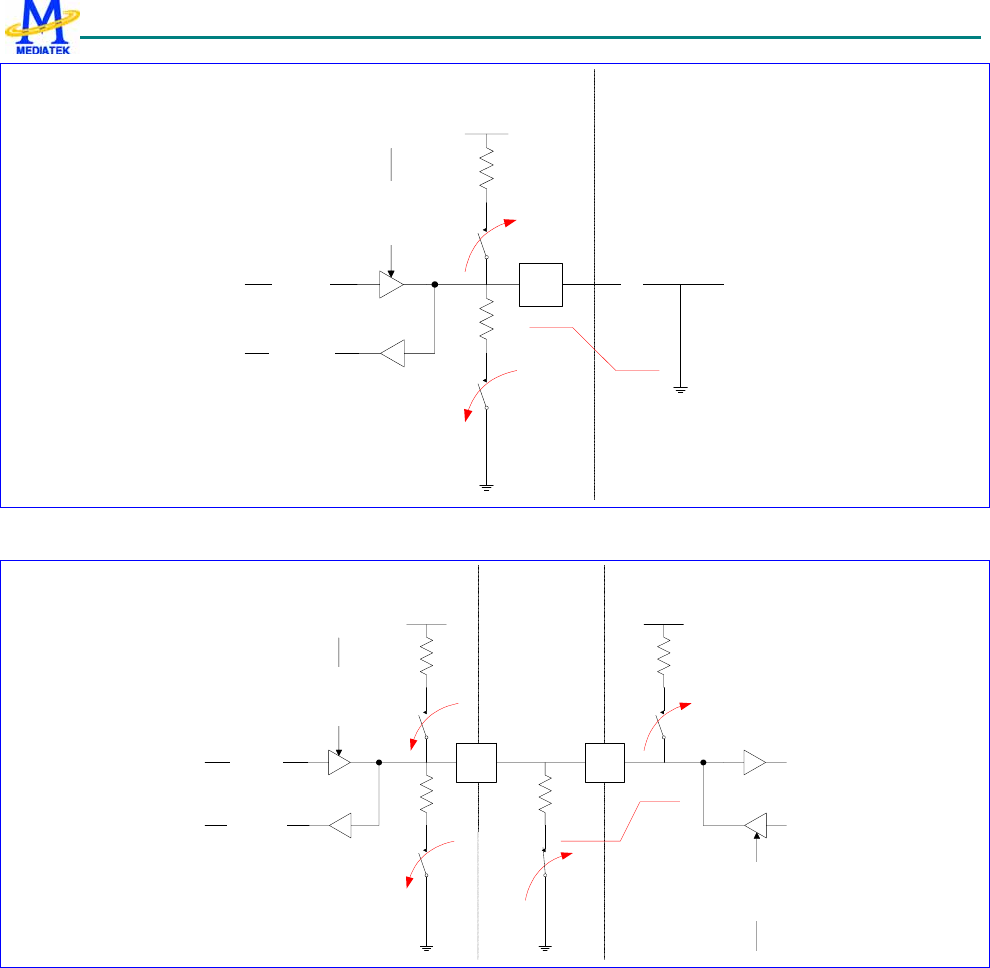

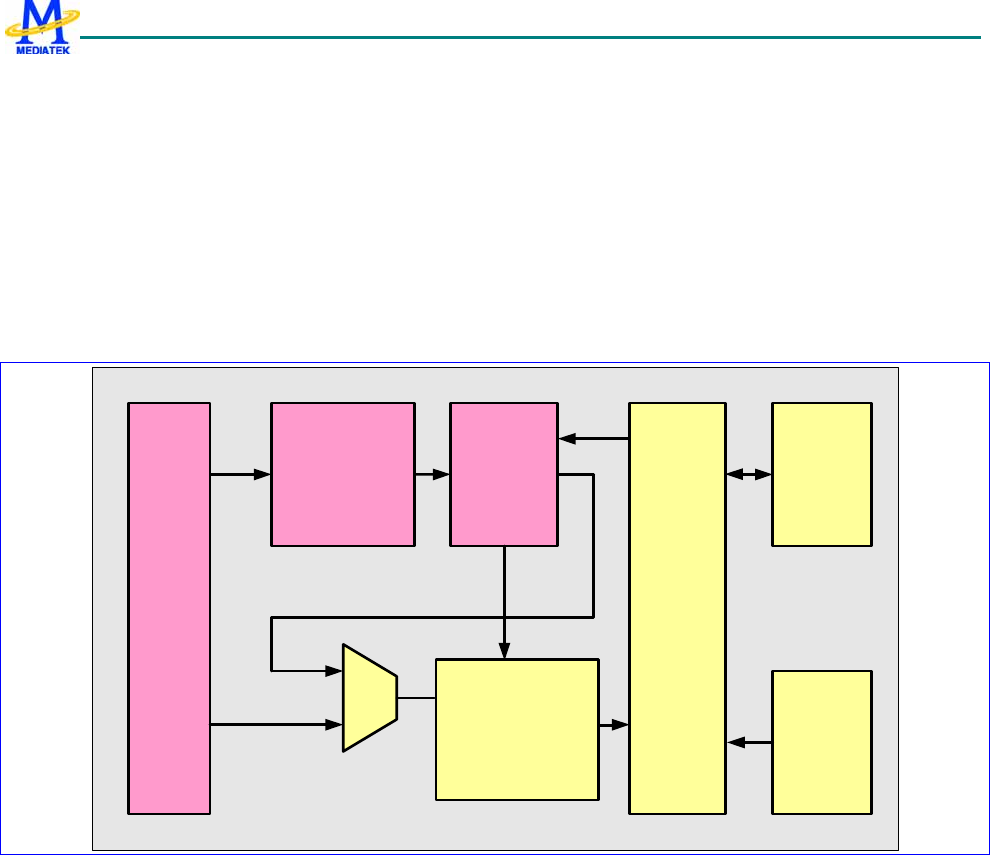

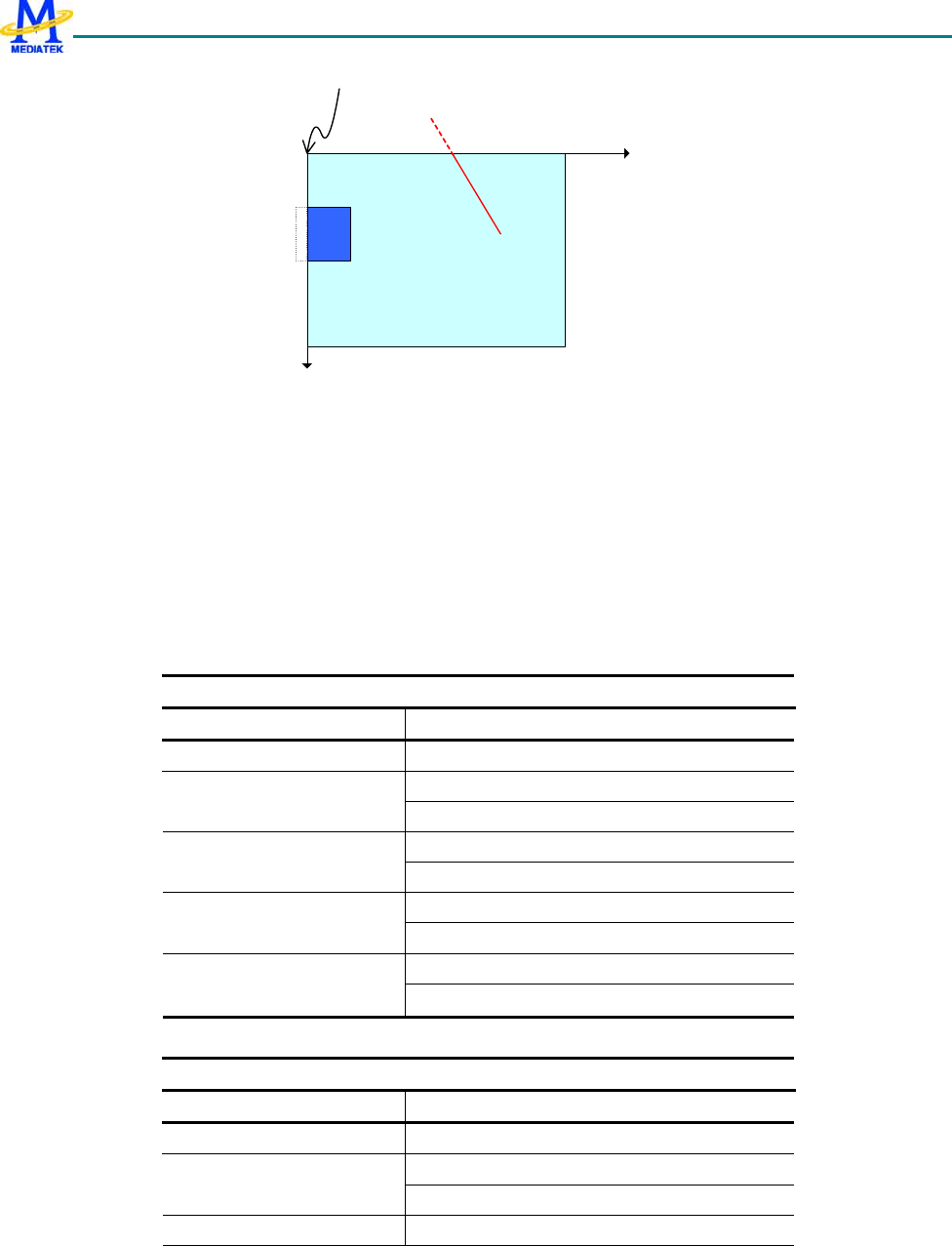

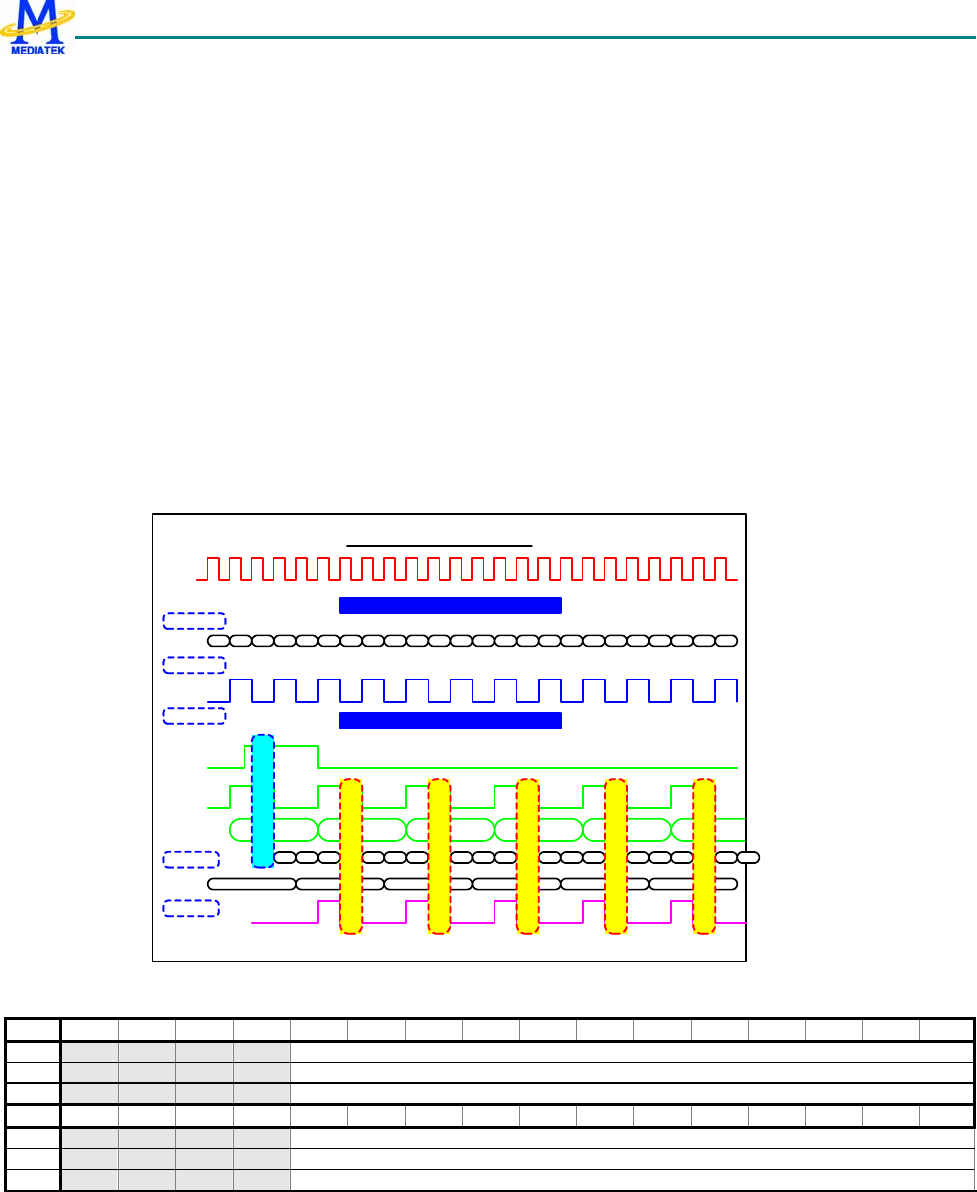

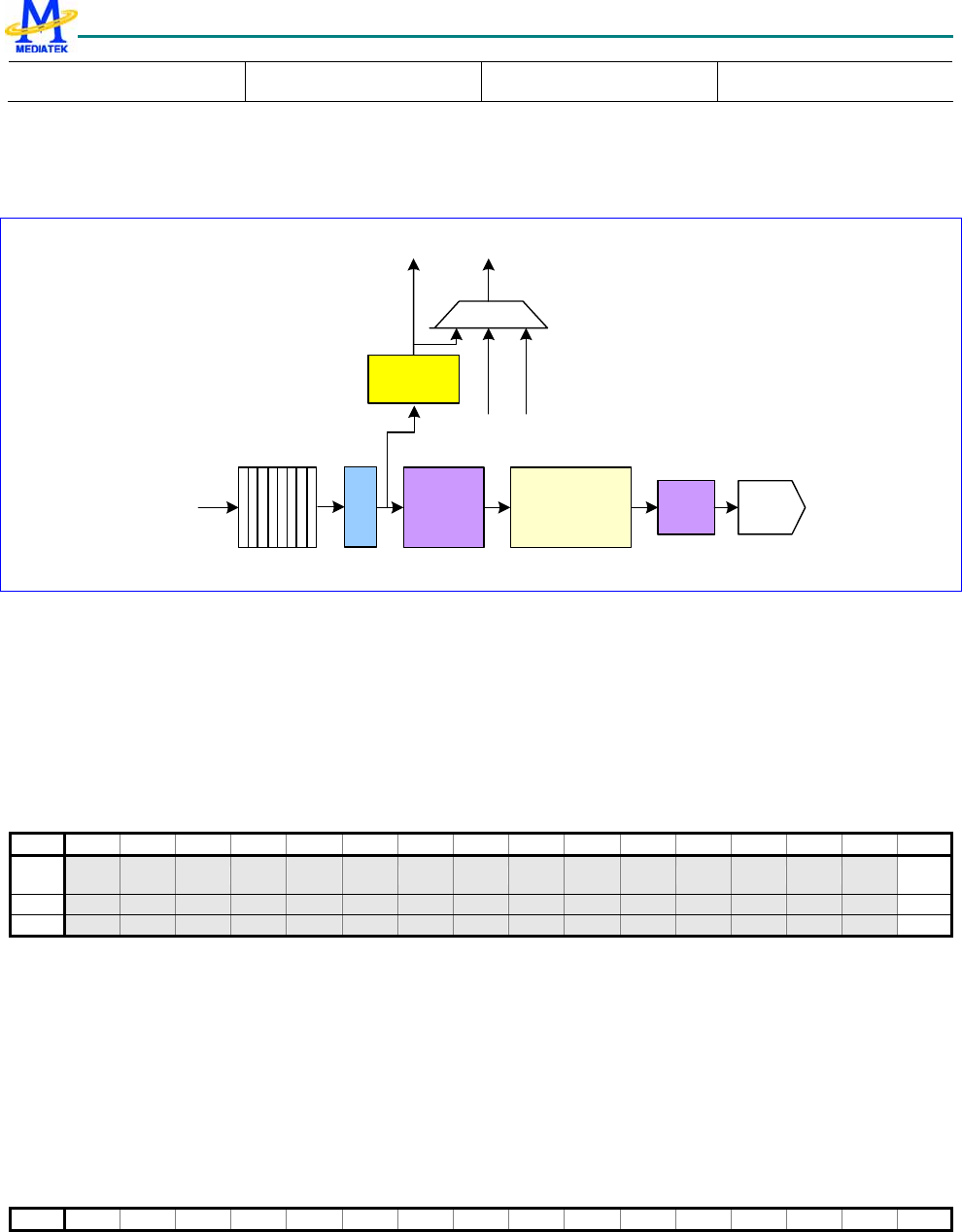

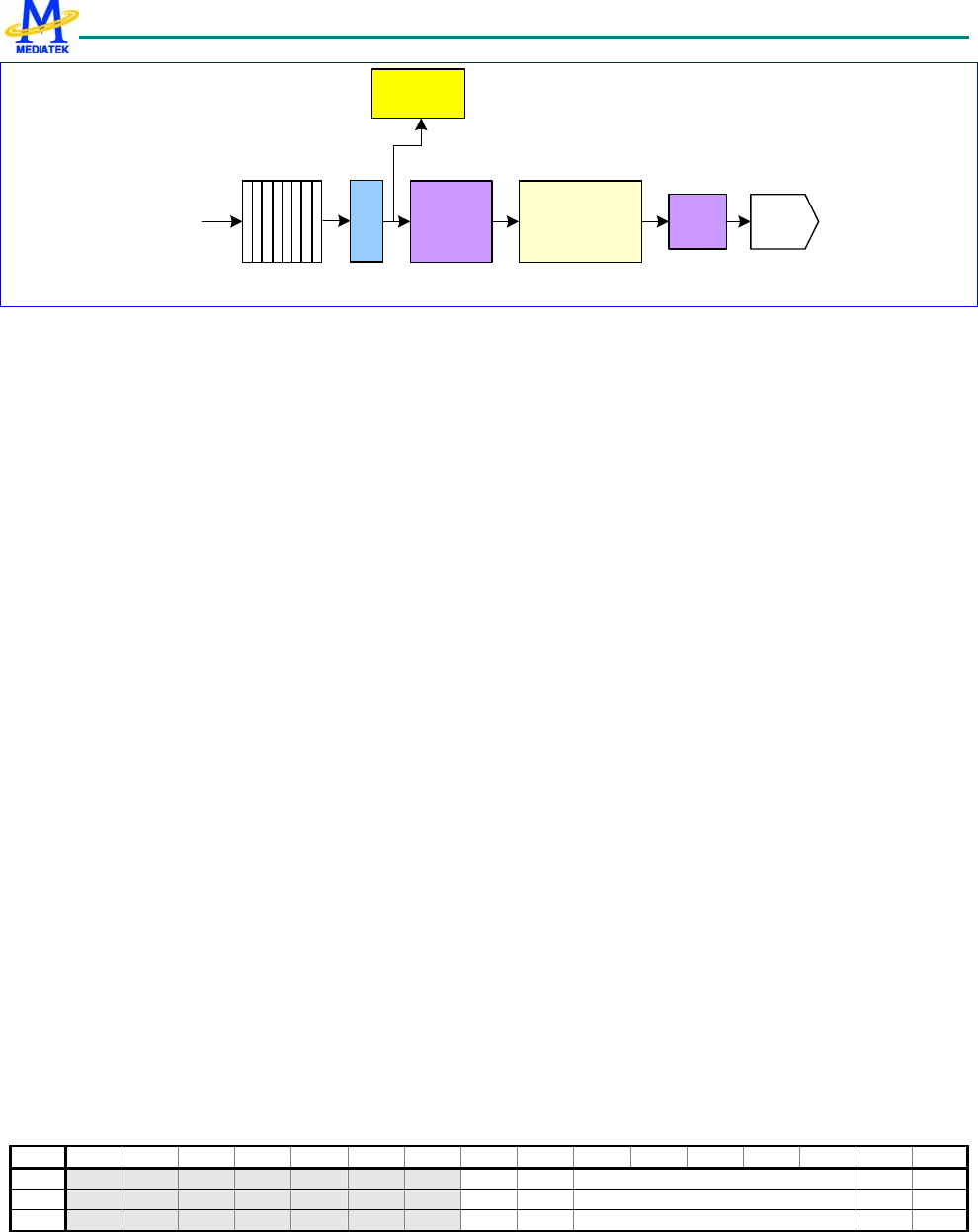

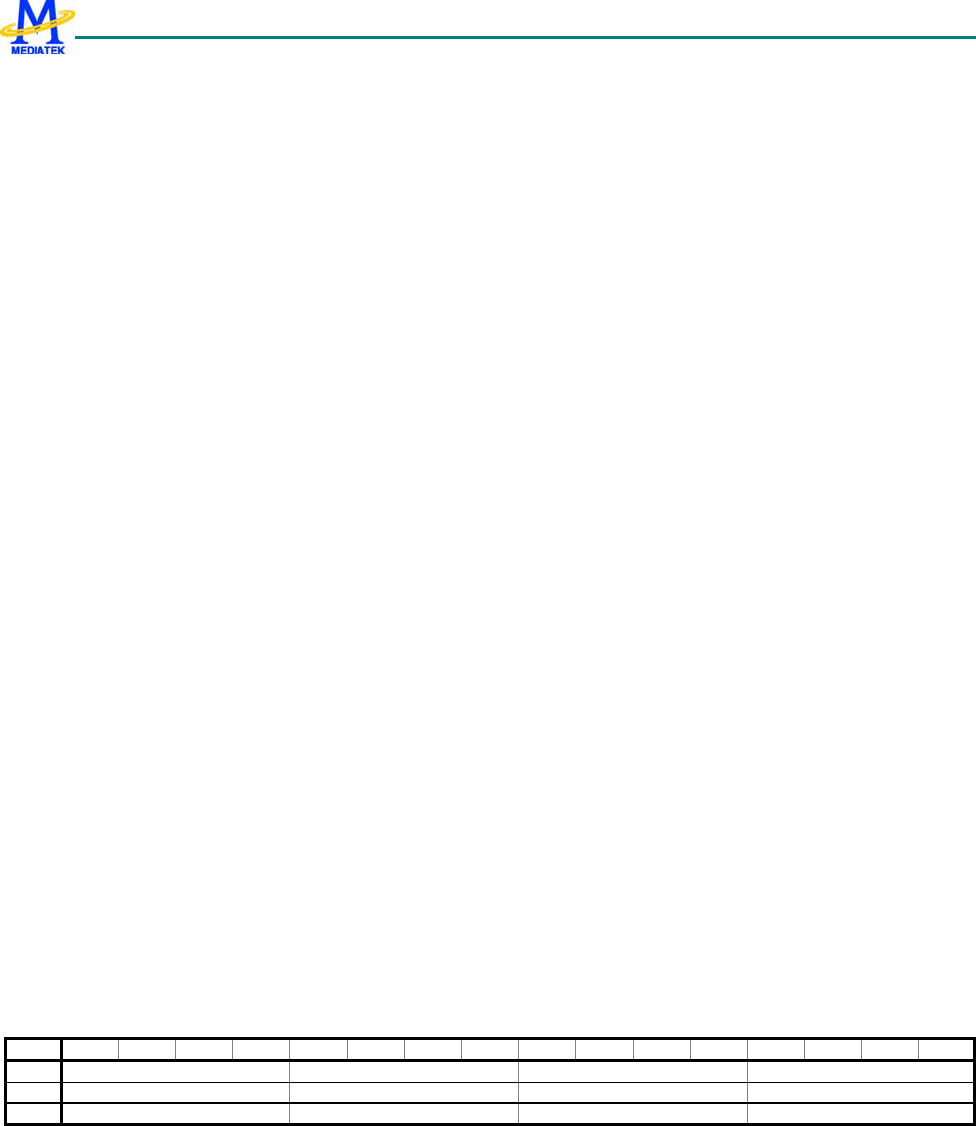

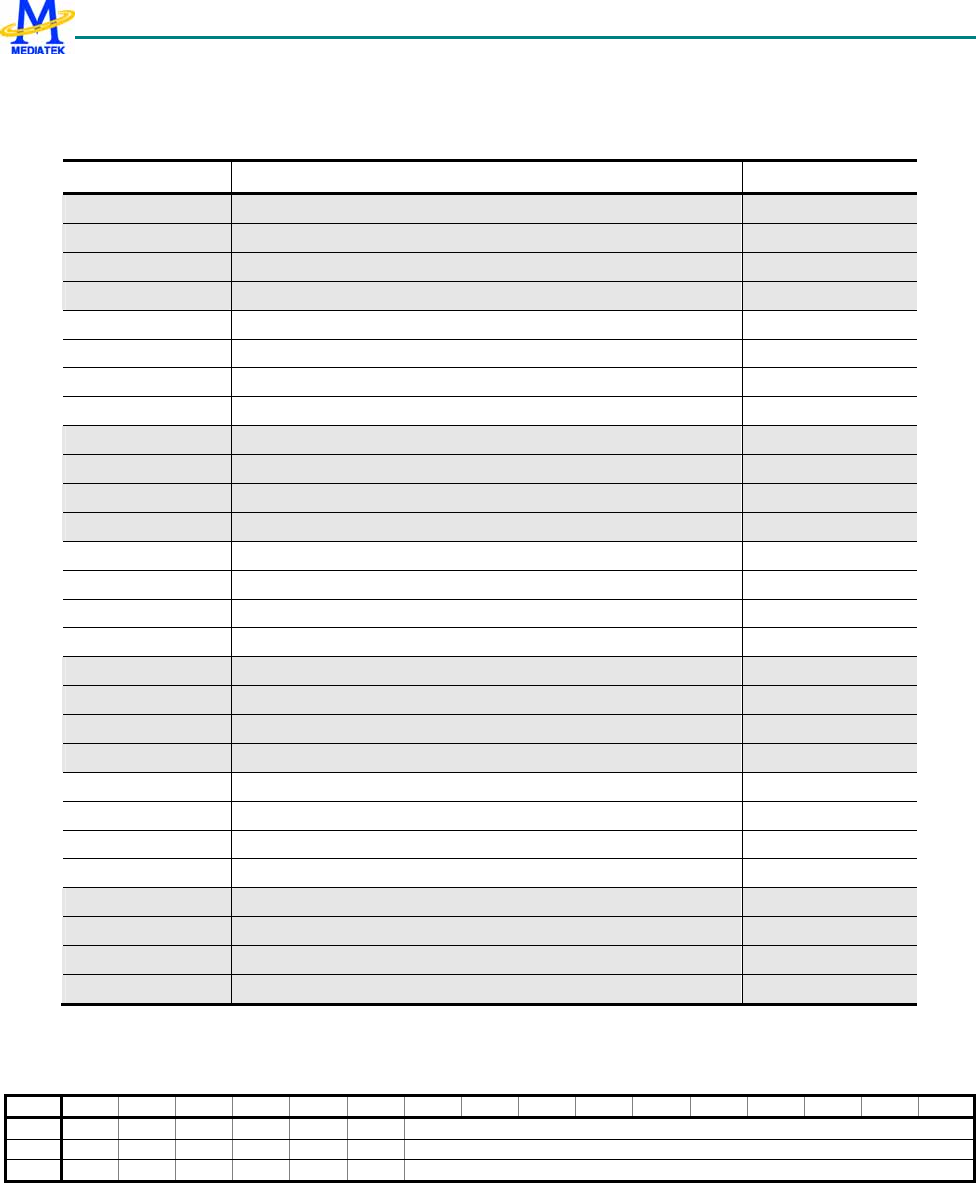

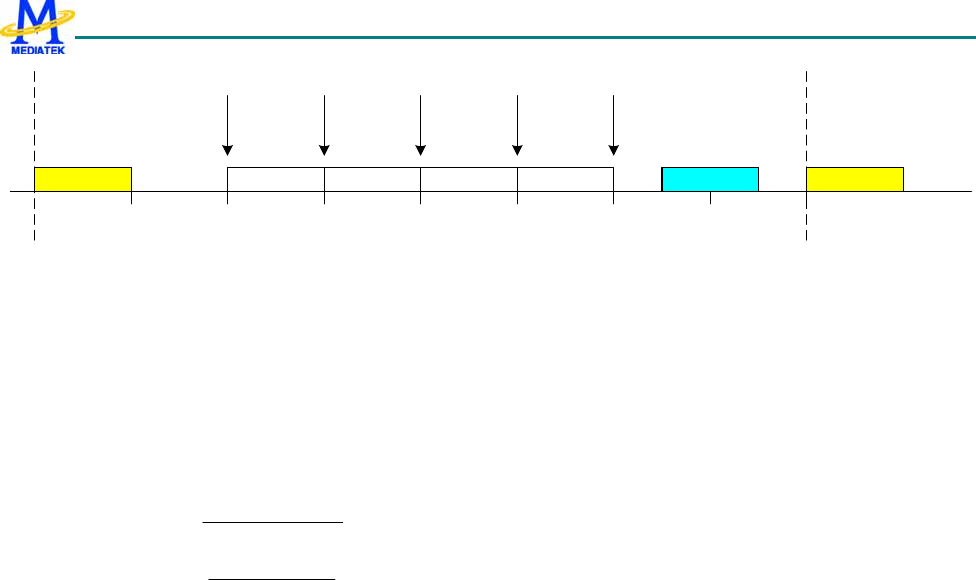

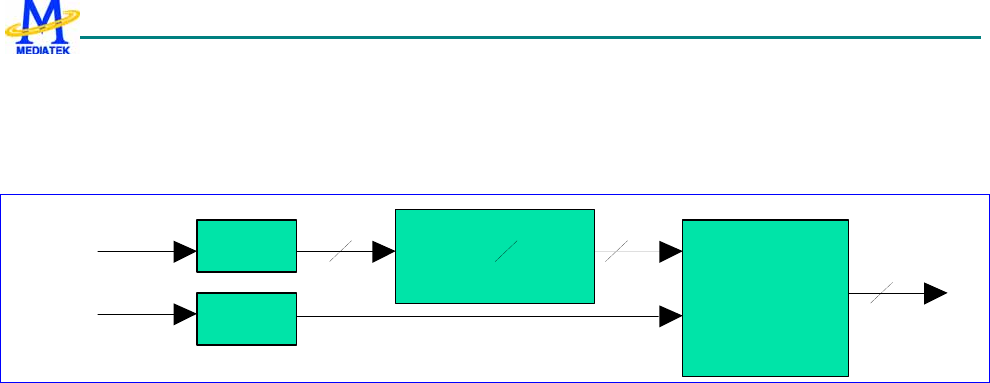

The configuration for factory programming is shown in Figure 7. Usually the Factory Programming Host connects with

MT6235 via the UART interface. The download speed can be up to 921K bps while MCU is running at 26MHz.

After the system has reset, the Boot Code guides the processor to run the Factory Programming software placed in System

ROM. Then, MT6235 starts and polls the UART1 port until valid information is detected. The first information received

on the UART1 is used to configure the chip for factory programming. The Flash downloader program is then transferred

into System RAM or external SRAM.

Further information is detailed in the MT6235 Software Programming Specification.

MT6235 Factory

Programming

Host

FLASH

UART

External

Memory

Interface

Figure 7 System configuration required for factory programming

MT6235 GSM/GPRS Baseband Processor Data Sheet Revision 1.02

44/599 MediaTek Inc. Confidential

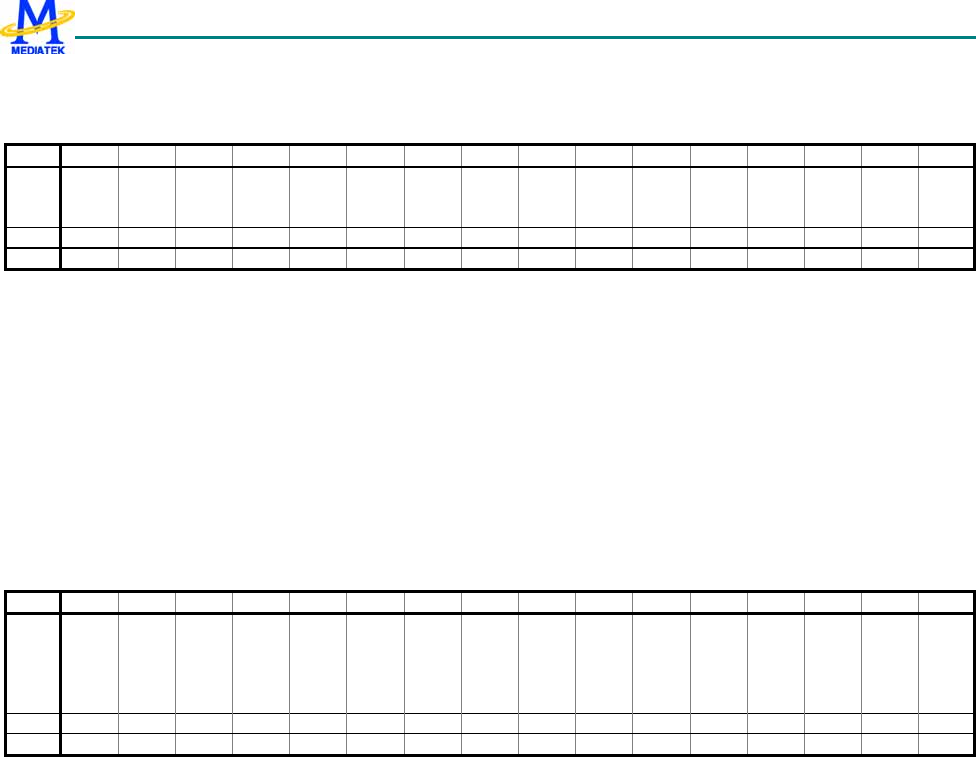

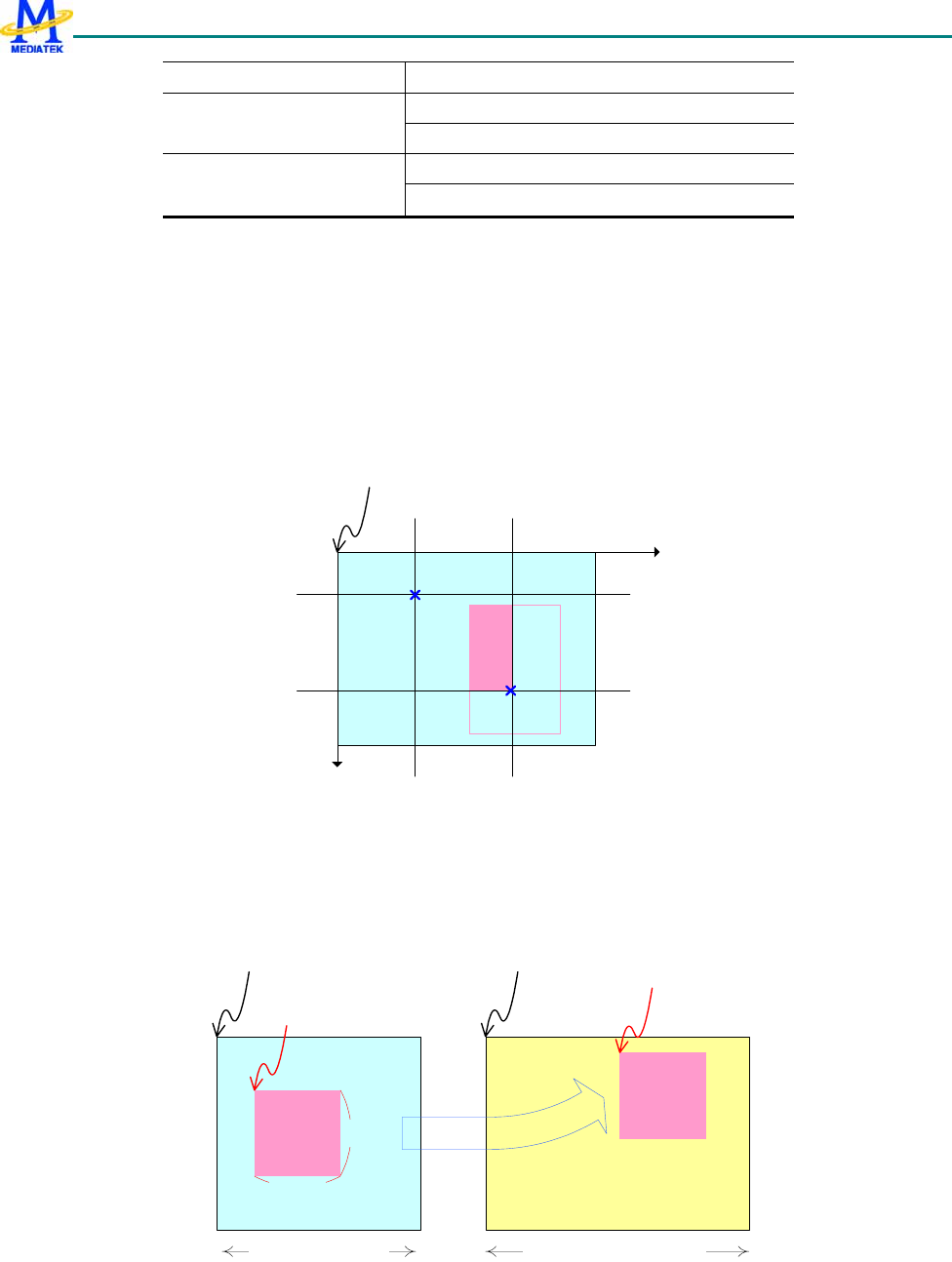

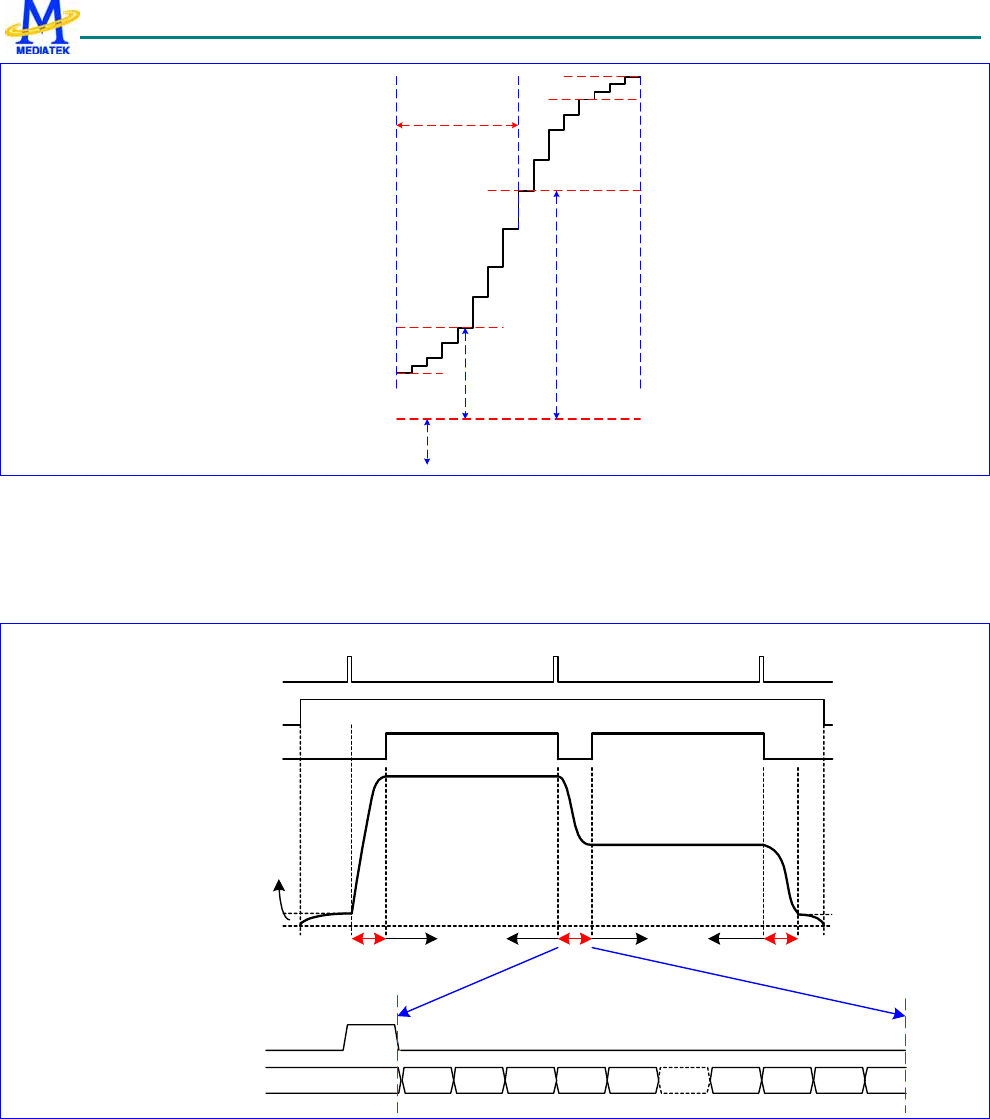

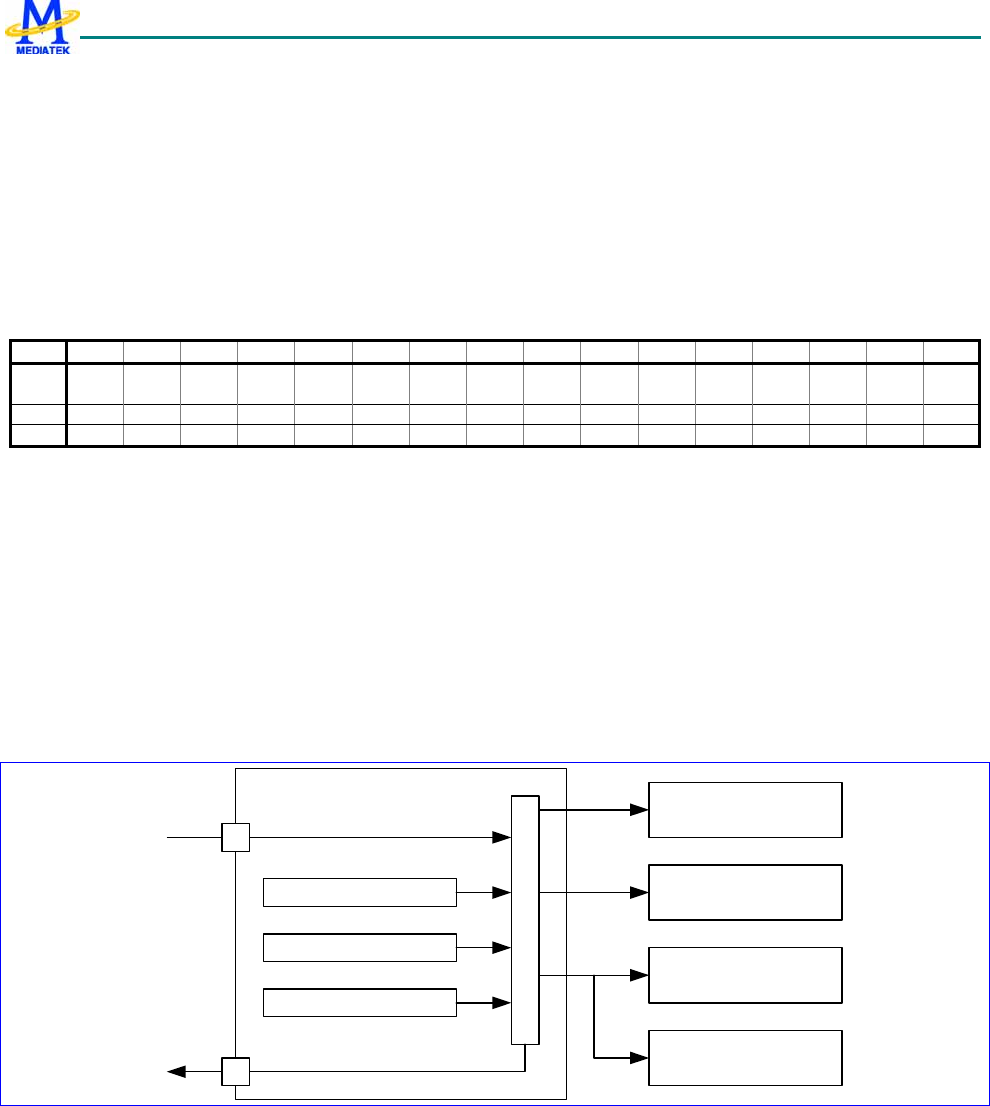

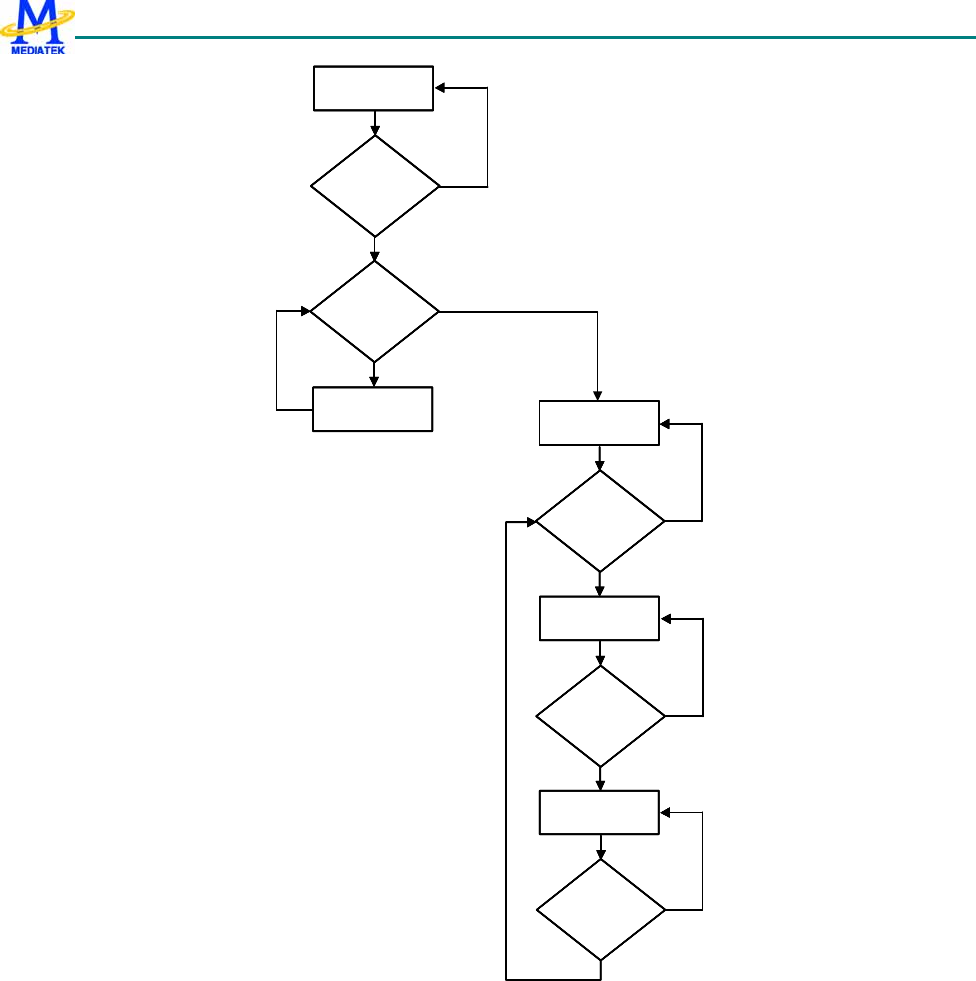

3.2.1.3.3 NAND Flash Booting

If MT6235 cannot receive data from UART1 for a certain amount of time, the program in System ROM checks if any valid

boot loader exists in NAND flash. If found, the boot loader code is copied from NAND flash to RAM (internal or external)

and executed to start the real application software. If no valid boot loader can be found in NAND flash, MT6235 starts

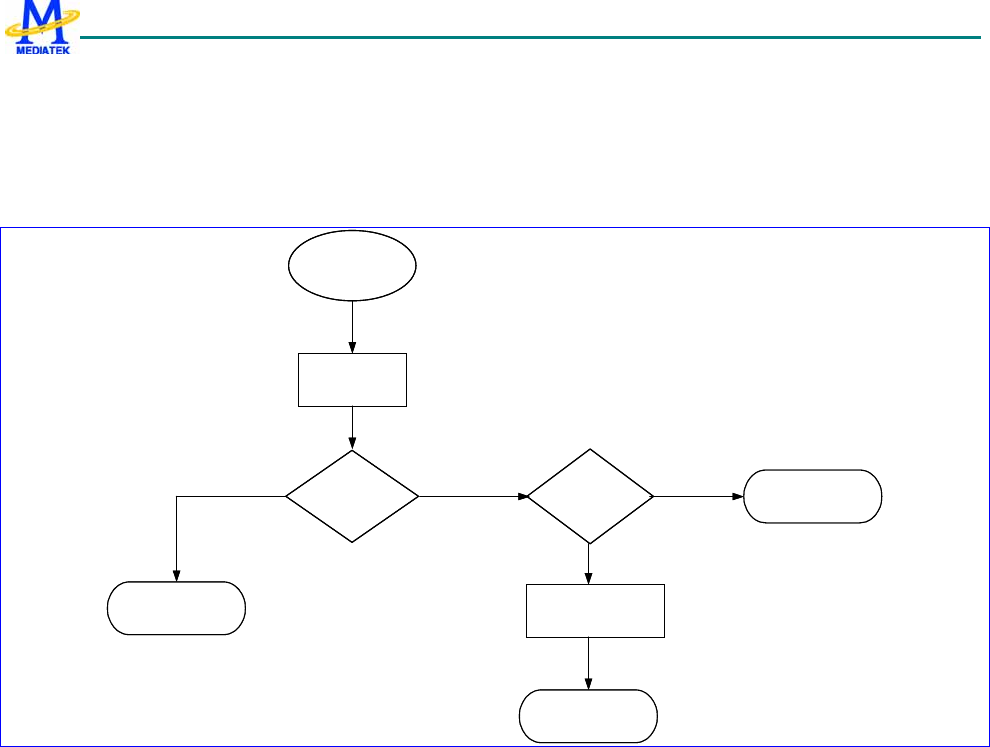

executing code in EMI bank0 memory. The whole boot sequence is shown in the following figure.

Boot from

System ROM

Check UART

input

Receive

from UART

Copy loader from

NAND to RAM

Valid loader

on NAND

YN

Y

N

Factory

programming

Boot from

loader in RAM

Boot from

EMI bank 0