P1403EVG Datasheet. Www.s Manuals.com. R1.3 Niko

User Manual: Datasheets P1403EVG.

Open the PDF directly: View PDF ![]() .

.

Page Count: 6

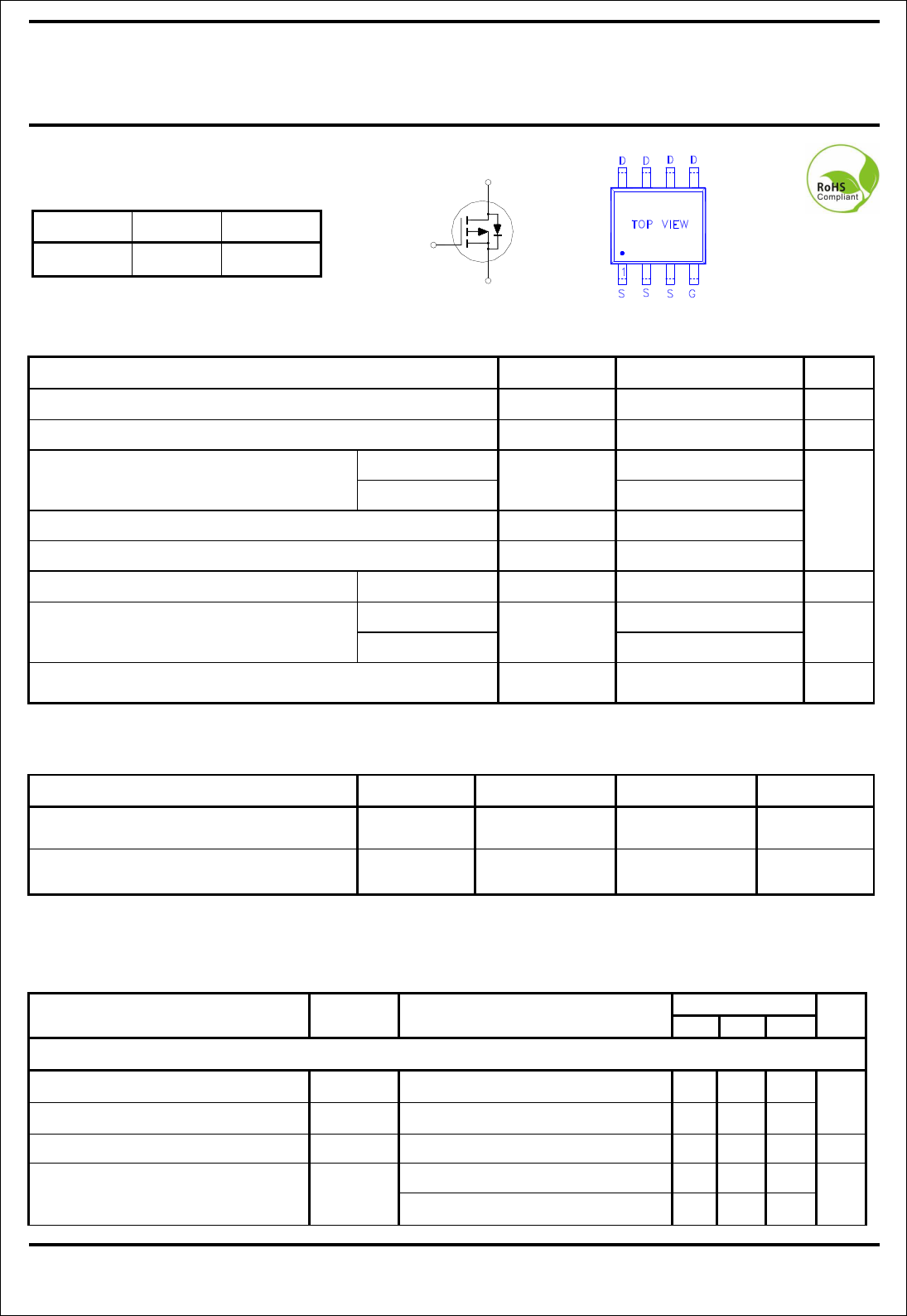

P-Channel Logic Level Enhancement

Mode

Field Effect Transistor

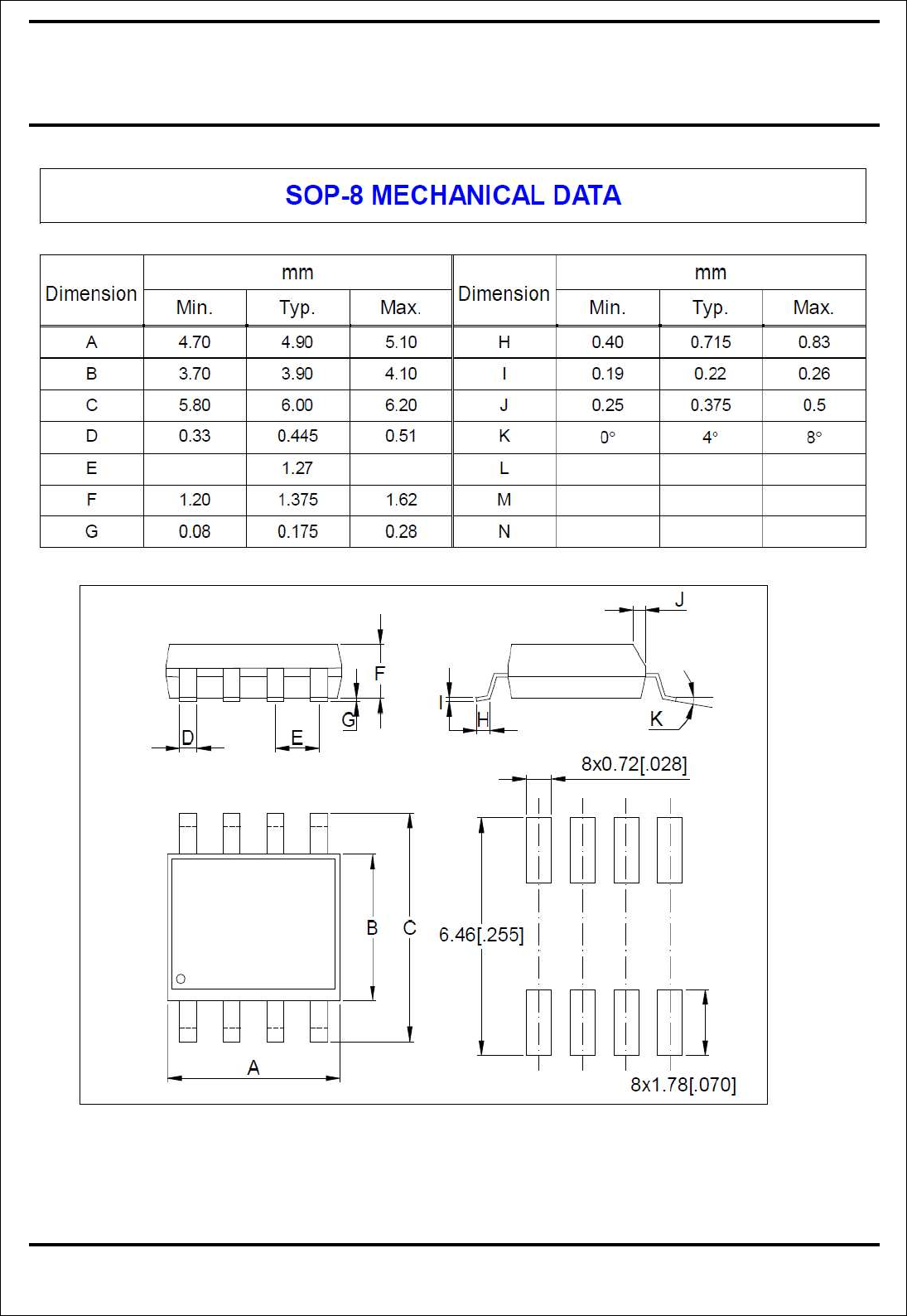

P1403EVG

SOP-8

Halogen-Free & Lead-Free

NIKO

-

SEM

1

Jun-22-2010

REV 1.3

ABSOLUTE MAXIMUM RATINGS (T

A

= 25 °C Unless O therwise Noted)

PARAMETERS/TEST CONDITIONS SYMBOL LIMITS UNITS

Drain-Source Voltage V

DS

-30 V

Gate-Source Voltage V

GS

±25 V

T

A

= 25 °C -11

Continuous Drain Current T

A

= 70 °C I

D

-9

Pulsed Drain Current

1

I

DM

-50

Avalanche Current I

AS

-43

A

Avalanche Energy L = 0.1mH E

AS

90 mJ

T

A

= 25 °C 2.5

Power Dissipation T

A

= 70 °C P

D

1.6 W

Operating Junction & Storage Temperature Range T

j

, T

stg

-55 to 150 °C

THERMAL RESISTANCE RATINGS

THERMAL RESISTANCE SYMBOL TYPICAL MAXIMUM UNITS

Junction-to-Case R

θJc

25 °C / W

Junction-to-Ambient R

θJA

50 °C / W

1

Pulse width limited by maximum junction temperature.

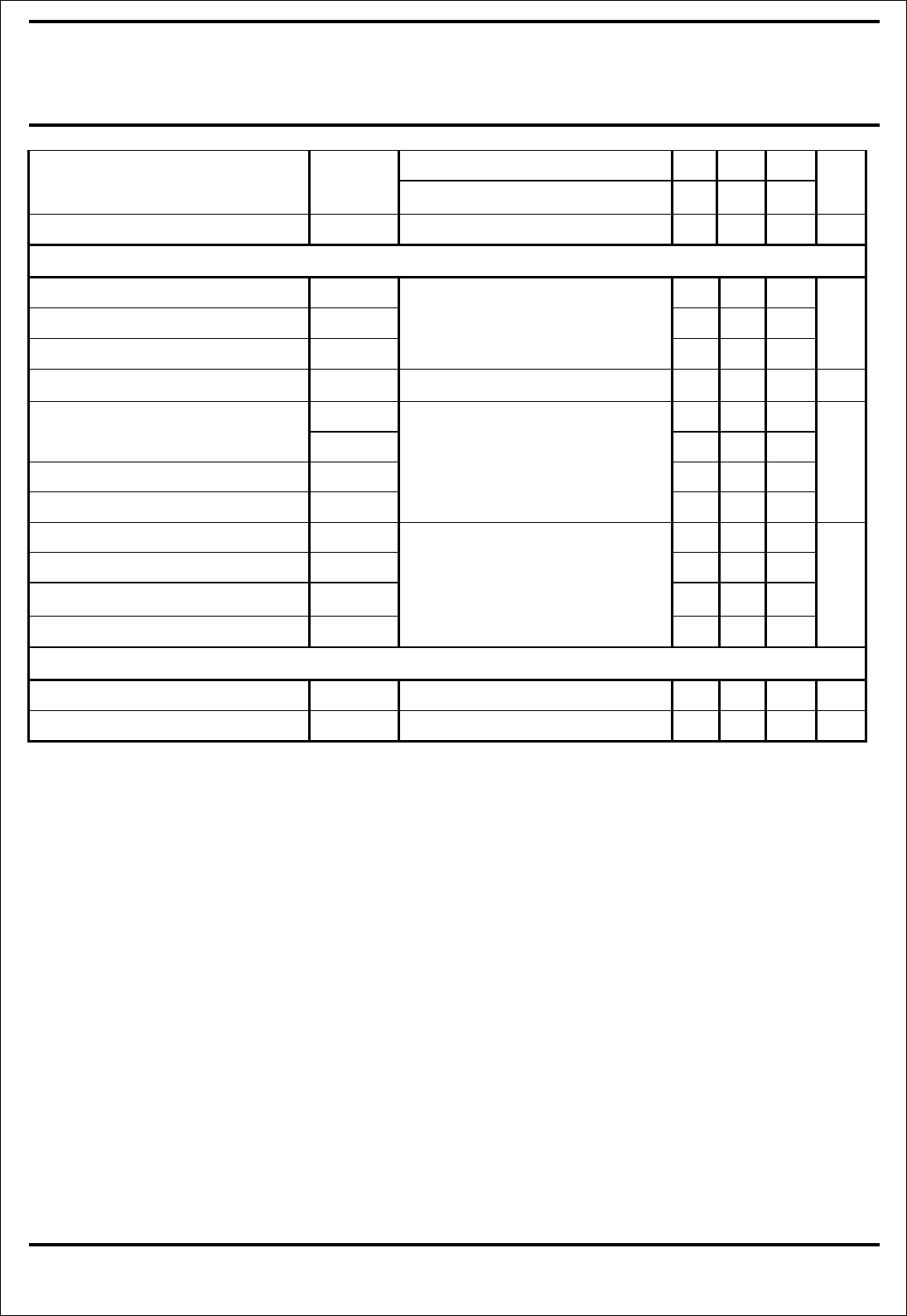

ELECTRICAL CHARACTERISTICS (T

A

= 25 °C, Unless Otherwise Noted)

LIMITS

PARAMETER SYMBOL

TEST CONDITIONS MIN

TYP

MAX

UNIT

STATIC

Drain-Source Breakdown Voltage V

(BR)DSS

V

GS

= 0V, I

D

= -250µA -30

Gate Threshold Voltage V

GS(th)

V

DS

= V

GS

, I

D

= -250µA -1

-1.7

-3

V

Gate-Body Leakage I

GSS

V

DS

= 0V, V

GS

= ±25V ±100

nA

V

DS

= -24V, V

GS

= 0V -1

Zero Gate Voltage Drain Current I

DSS

V

DS

= -20V, V

GS

= 0V, T

J

= 125 °C

-10

µA

4 :GATE

5,6,7,8 :DRAIN

1,2,3 :SOURCE

PRODUCT SUMMARY

V

(BR)DSS

R

DS(ON)

I

D

-30 14mΩ

-11

G

S

D

100% UIS tested

www.DataSheet.co.kr

Datasheet pdf - http://www.DataSheet4U.net/

P-Channel Logic Level Enhancement

Mode

Field Effect Transistor

P1403EVG

SOP-8

Halogen-Free & Lead-Free

NIKO

-

SEM

2

Jun-22-2010

REV 1.3

V

GS

= -4.5V, I

D

= -9A 14

22

Drain-Source On-State

Resistance

1

R

DS(ON)

V

GS

= -10V, I

D

= -12A 9 14

mΩ

Forward Transconductance

1

g

fs

V

DS

= -10V, I

D

= -12A 28

S

DYNAMIC

Input Capacitance C

iss

2510

Output Capacitance C

oss

449

Reverse Transfer Capacitance C

rss

V

GS

= 0V, V

DS

= -15V, f = 1MHz

349

pF

Gate Resistance Rg V

GS

= 0V, V

DS

= 0V, f = 1MHz 7.3

Ω

Q

g(VGS=10V)

48

Total Gate Charge

2

Q

g(VGS=4.5V)

26

Gate-Source Charge

2

Q

gs

7

Gate-Drain Charge

2

Q

gd

V

DS

= 0.5V

(BR)DSS

, V

GS

= -10V,

I

D

= -12A

9

nC

Turn-On Delay Time

2

t

d(on)

12

Rise Time

2

t

r

V

DS

= -15V, 16

Turn-Off Delay Time

2

t

d(off)

I

D

≅ -1A, V

GS

= -10V, R

GS

= 6Ω 50

Fall Time

2

t

f

100

nS

SOURCE-DRAIN DIODE RATINGS AND CHARACTERISTICS (T

A

= 25 °C)

Continuous Current I

S

-2.1

A

Forward Voltage

1

V

SD

I

F

= I

S

, V

GS

= 0V -1.2

V

1

Pulse test : Pulse Width ≤ 300 µsec, Duty Cycle ≤ 2%.

2

Independent of operating temperature.

REMARK: THE PRODUCT MARKED WITH “P1403EVG”, DATE CODE or LOT #

www.DataSheet.co.kr

Datasheet pdf - http://www.DataSheet4U.net/

P-Channel Logic Level Enhancement

Mode

Field Effect Transistor

P1403EVG

SOP-8

Halogen-Free & Lead-Free

NIKO

-

SEM

3

Jun-22-2010

REV 1.3

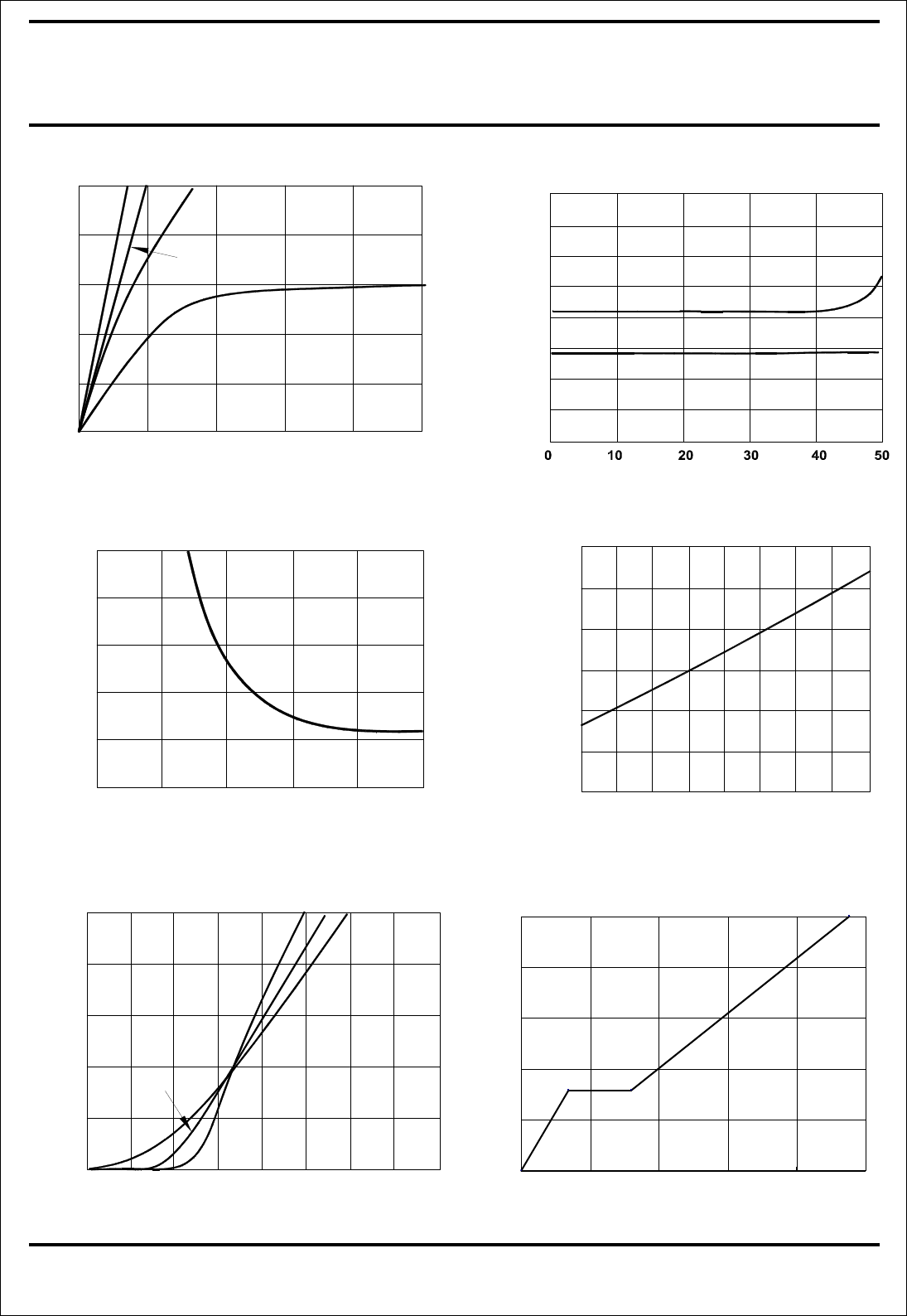

0

2

4

6

8

10

0 10 20 30 40 50

I

D

= 12A

V

DS

= 15V

0 1 2 3 4 5

10

20

30

40

50

V

GS

= 3V

V

GS

= 4.5V

V

GS

= 7V

V

GS

= 10V

0

0.005

0.010

0.015

0.020

0.025

0.030

0.035

0.040

V

GS

= 4.5V

V

GS

= 10V

0 2 4 6 8 10

0

0.01

0.02

0.03

0.04

0.05

I

D

= -12A

- 50 - 25 0 25 50 75 100 125 150

RDS(ON) x 0.6

I

D

= -12A

V

GS

= 10V

RDS(ON) x 0.8

RDS(ON) x 1.0

RDS(ON) x 1.2

RDS(ON) x 1.4

RDS(ON) x 1.6

RDS(ON) x 0.4

T

j

=125° C

0

10

20

30

40

50

T

j

=-20° C

5.02.0 2.5 3.0 3.5 4.0 4.5

T

j

=25° C

V

DS

= -10V

1.5

1.0

Output

Characteristics

-I

D

, Drain-To-Source Current(A)

-V

DS

, Drain-To-Source Voltage(V)

On

-

Resistance

VS Drain Current

R

DS(ON)

ON-Resistance(OHM)

-

I

D

, Drain

-

To

-

Source Current

On

-

Resistance

VS Gate

-

To

-

Source

R

DS(ON)

ON-Resistance(OHM)

-V

GS

, Gate-To-Source Voltage(V)

On

-

Resistance VS Temperature

R

DS(ON)

ON-Resistance(OHM)

T

J

, Junction Temperature(˚C)

Transfer

Characteristics

-I

D

, Drain-To-Source Current(A)

-V

GS

, Gate-To-Source Voltage(V)

Gate charge Characteristics

Characteristics

-V

GS

, Gate-To-Source Voltage(V)

Qg , Total Gate Charge(nC)

www.DataSheet.co.kr

Datasheet pdf - http://www.DataSheet4U.net/

P-Channel Logic Level Enhancement

Mode

Field Effect Transistor

P1403EVG

SOP-8

Halogen-Free & Lead-Free

NIKO

-

SEM

4

Jun-22-2010

REV 1.3

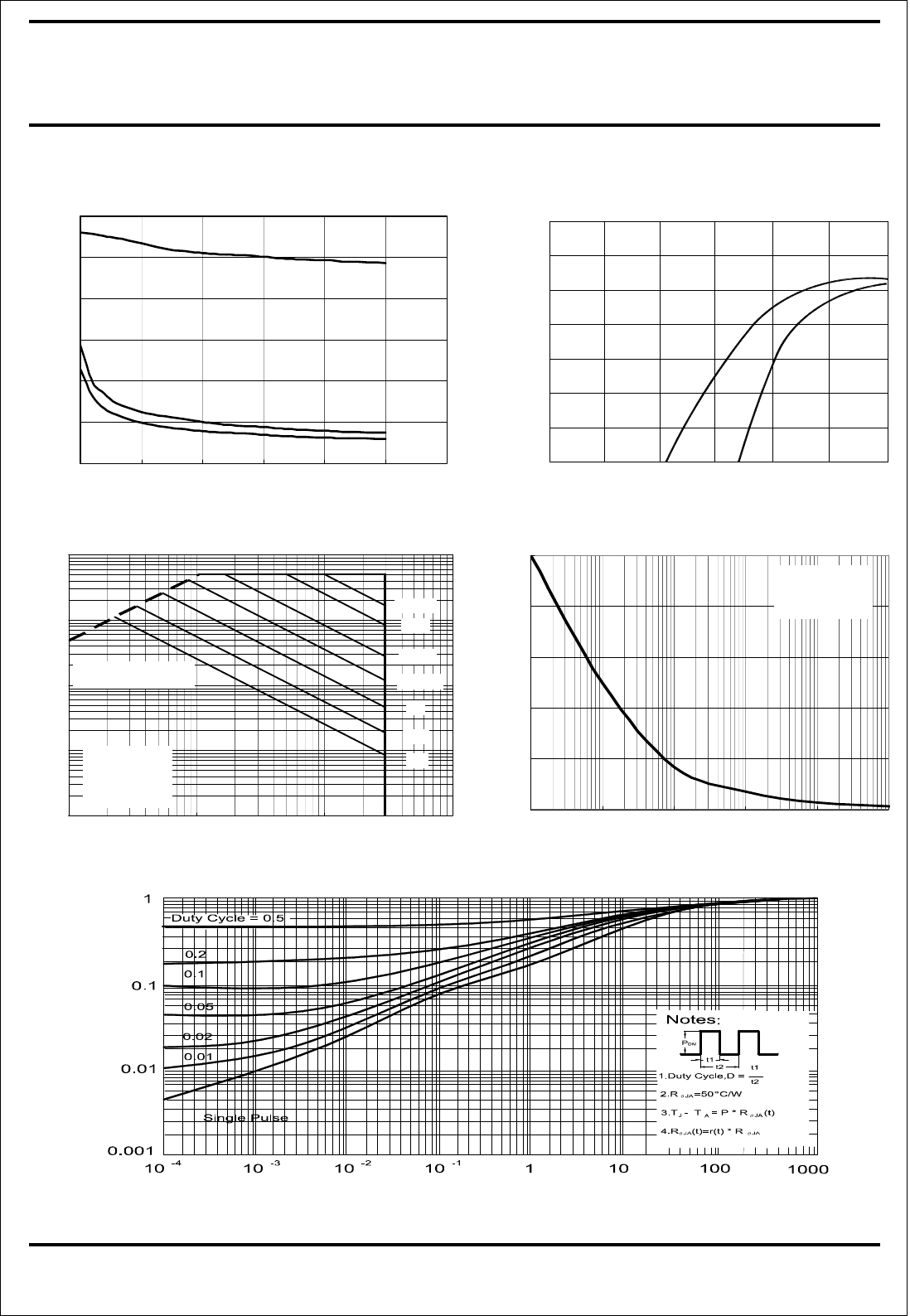

CISS

COSS

CRSS

0.00E+00

5.00E-10

1.00E-09

1.50E-09

2.00E-09

2.50E-09

3.00E-09

0 5 10 15 20 25 30

f = 1MHz

V

GS

= 0V

0

100

200

300

400

500

0.0001 0.001 0.01 0.1 1 10

SINGLE PULSE

R

θJA

= 50˚

˚˚

˚C/W

T

A

=25˚

˚˚

˚C

100us

10S

1S

DC

100ms

10ms

1ms

0.01

0.1

1

10

100

0.1 1 10 100

NOTE :

1.V

GS

= 10V

2.T

A

=25˚

˚˚

˚C

3.R

θJA

= 50˚

˚˚

˚C/W

4.Single Pulse

Operation in This Ar ea

is Lim ited by R

DS(ON)

↓

↓↓

↓

0 .0 0 .2 0 .4 0 .6 0 .8 1 .0 1 .2

1 .0 E + 0 1

T

J

= 1 5 0 ° C

T

J

= 2 5 ° C

1 .0 E + 0 0

1 .0 E - 0 1

1 .0 E - 0 2

1 .0 E -0 3

1 .0 E - 0 4

1 .0 E - 0 5

1 .0 E + 0 2

Capacitance Characteristic

C , Capacitance(pF)

-V

DS

, Drain-To-Source Voltage(V)

Body Diode Forward Voltage VS Source current

-I

S

, Source Current(A)

-V

SD

, Source-To-Drain Voltage(V)

T

1

, Square Wave Pulse Duration[sec]

r(t) , Normalized Effective

Transient Thermal Resistance

-I

D

, Drain Current(A)

Transient Thermal Response Curve

Safe Operating Area

-V

DS

, Drain-To-Source Voltage(V)

Power(W)

Single Pulse Maximum Power Dissipation

www.DataSheet.co.kr

Datasheet pdf - http://www.DataSheet4U.net/

P-Channel Logic Level Enhancement

Mode

Field Effect Transistor

P1403EVG

SOP-8

Halogen-Free & Lead-Free

NIKO

-

SEM

5

Jun-22-2010

REV 1.3

www.DataSheet.co.kr

Datasheet pdf - http://www.DataSheet4U.net/