Xilinx PG047 LogiCORE IP Ethernet 1000BASE X PCS/PMA Or SGMII V11.4, Product Guide Gig Eth Pcs Pma

User Manual: 1000BASE-X

Open the PDF directly: View PDF ![]() .

.

Page Count: 474 [warning: Documents this large are best viewed by clicking the View PDF Link!]

- LogiCORE IP Ethernet 1000BASE-X PCS/PMA or SGMII v11.4

- Table of Contents

- Section I: Summary

- IP Facts

- Overview

- Product Specification

- Designing with the Core

- The Ten-Bit Interface

- 1000BASE-X with Transceivers

- Transceiver Logic

- Clock Sharing Across Multiple Cores with Transceivers

- Example Design for 1000BASE-X with Transceivers

- Top-Level Example Design HDL

- Block Level HDL

- Transceiver Files for Zynq-7000, Virtex-7, Kintex-7, Artix-7 and Devices

- Transceiver Files for Spartan-6 Devices

- Transceiver Files for Virtex-6 Devices

- RocketIO Transceiver Files for Virtex-5 Devices

- Virtex-5 FPGA RocketIO GTX Transceiver Specific Files

- RocketIO Transceiver Files for Virtex-4 FX Devices

- Transmitter Elastic Buffer

- Demonstration Test Bench

- Customizing the Test Bench

- SGMII / Dynamic Standards Switching with Transceivers

- Receiver Elastic Buffer Implementations

- Logic Using the Transceiver Rx Elastic Buffer

- Transceiver Logic with the FPGA Logic Rx Elastic Buffer

- Virtex-4 Devices for SGMII or Dynamic Standards Switching

- Virtex-5 LXT or SXT Devices for SGMII or Dynamic Standards Switching

- Virtex-5 FXT and TXT Devices for SGMII or Dynamic Standards Switching

- Virtex-6 Devices for SGMII or Dynamic Standards Switching

- Spartan-6 LXT Devices for SGMII or Dynamic Standards Switching

- Virtex-7 Devices for SGMII or Dynamic Standards Switching

- Kintex-7 and Zynq-7000 Devices for SGMII or Dynamic Standards Switching

- Artix-7 Devices for SGMII or Dynamic Standards Switching

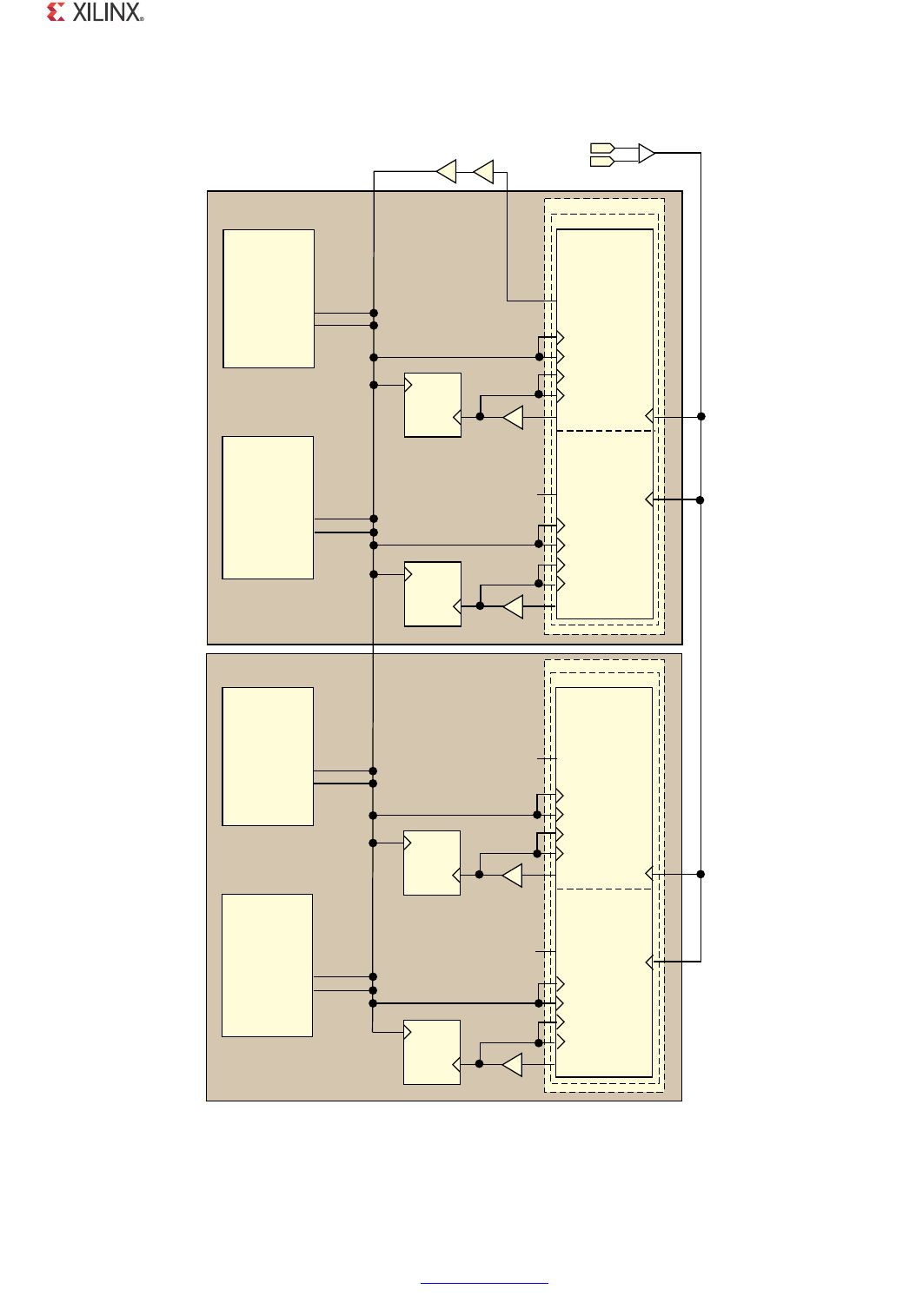

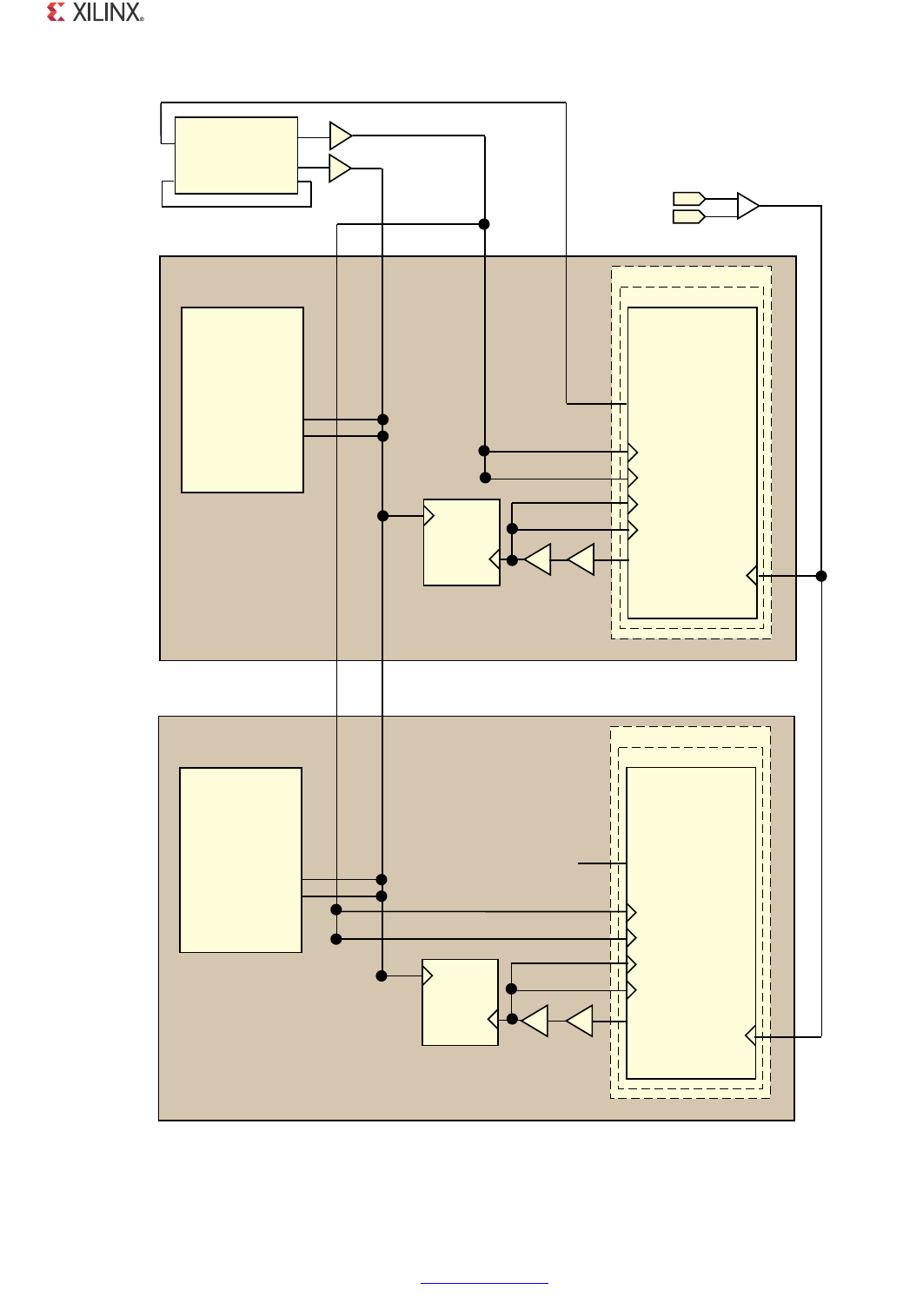

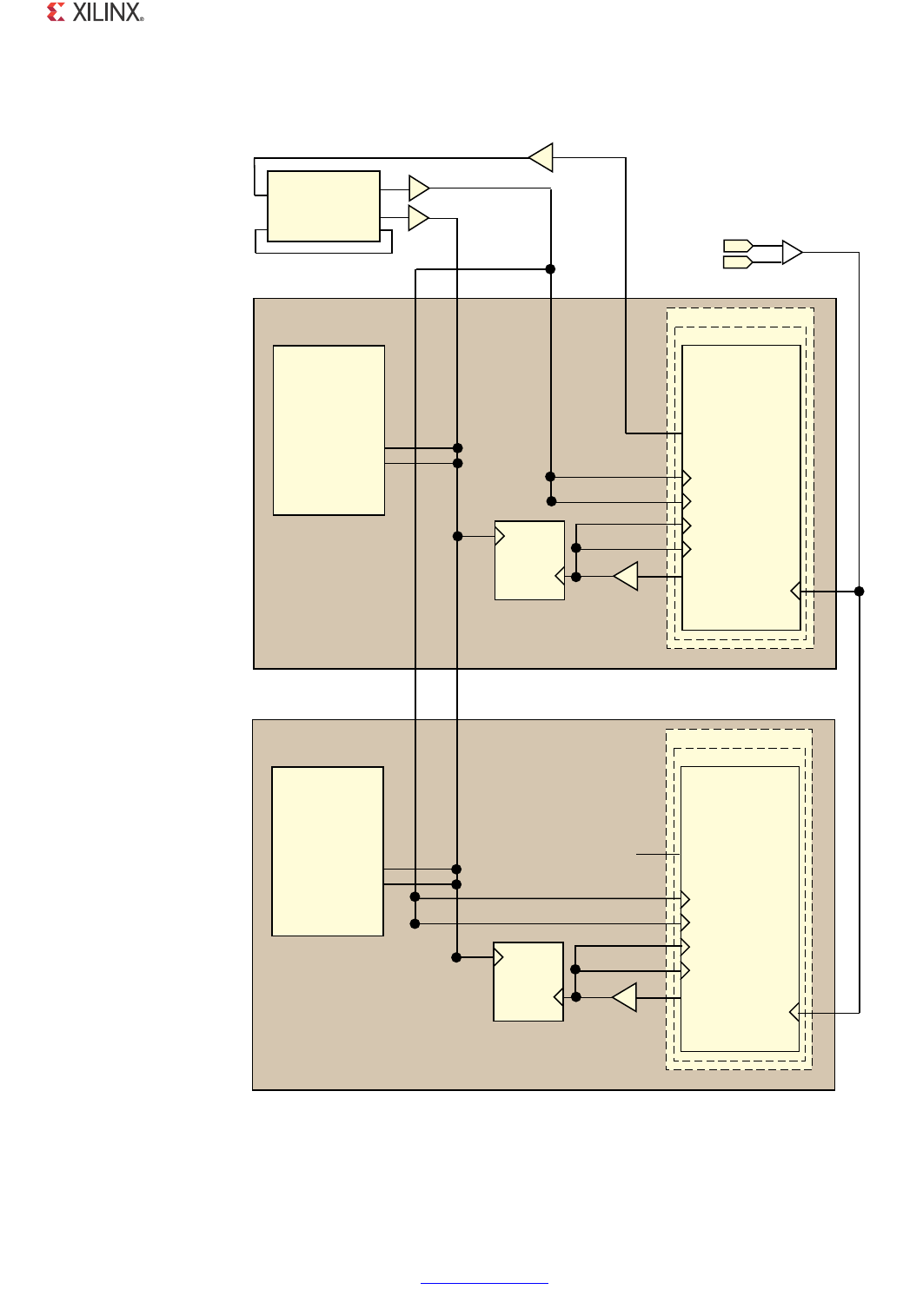

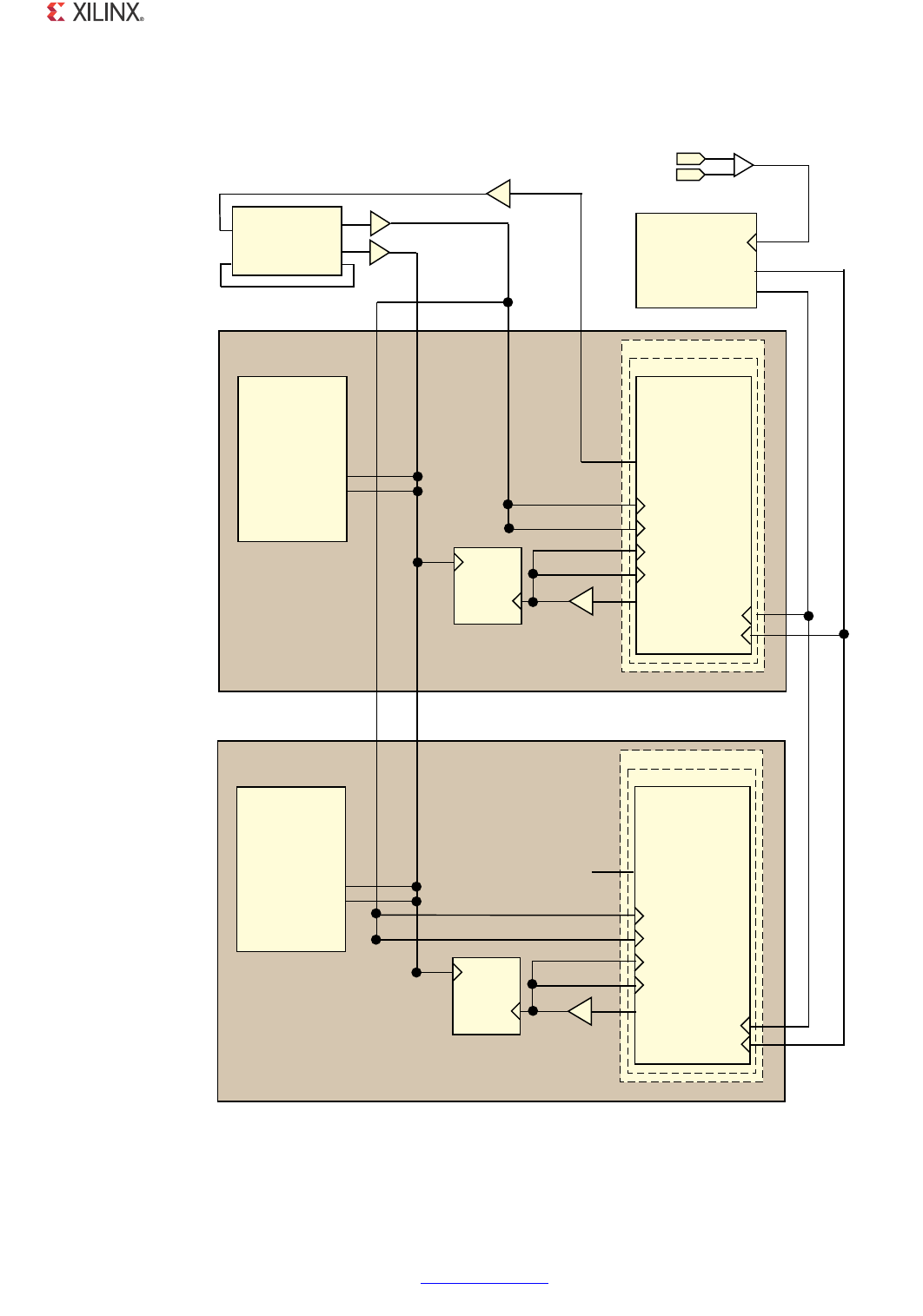

- Clock Sharing - Multiple Cores with Transceivers, FPGA Logic Elastic Buffer

- SGMII Example Design / Dynamic Switching Example Design Using a Transceiver

- Top-Level Example Design HDL

- Block Level HDL

- Transceiver Files for Zynq-7000, Virtex-7 Kintex-7, and Artix-7 Devices

- Transceiver Files for Spartan-6 Devices

- Transceiver Files for Virtex-6 Devices

- RocketIO Transceiver Files for Virtex-5 Devices

- RocketIO Transceiver Files for Virtex-4 FX Devices

- Receiver Elastic Buffer

- SGMII Adaptation Module

- Demonstration Test Bench

- Customizing the Test Bench

- SGMII over LVDS

- Using the Client-Side GMII Datapath

- Auto-Negotiation

- Dynamic Switching of 1000BASE-X and SGMII Standards

- GMII to PHY EDK Application for Zynq-7000 Device Processor Subsystem

- Interfacing to Other Cores

- Integration of the Tri-Mode Ethernet MAC for 1000BASE-X Operation

- Integration of the Tri-Mode Ethernet MAC for Tri-speed SGMII Operation

- Integration of the Tri-Mode Ethernet MAC to Provide SGMII (or Dynamic Switching) Functionality with TBI

- Integration of the Tri-Mode Ethernet MAC Using Device Specific Transceivers

- Integration of the Tri-Mode Ethernet MAC Using Asynchronous Oversampling over Virtex-6 LVDS

- Integration of the Tri-Mode Ethernet MAC Using Sync SGMII over Kintex-7/Virtex-7 LVDS

- Special Design Considerations

- Section II: Vivado Design Suite

- Section III: ISE Design Suite

- Customizing and Generating the Core

- Constraining the Core

- Device, Package, and Speed Grade Selection

- I/O Location Constraints

- Placement Constraints

- Virtex-4 FPGA MGT Transceivers for 1000BASE-X Constraints

- Virtex-4 FPGA RocketIO MGT Transceivers for SGMII or Dynamic Standards Switching Constraints

- Virtex-5 FPGA RocketIO GTP Transceivers for 1000BASE-X Constraints

- Virtex-5 FPGA RocketIO GTP Transceivers for SGMII or Dynamic Standards Switching Constraints

- Virtex-5 FPGA RocketIO GTX Transceivers for SGMII or Dynamic Standards Switching Constraints

- Virtex-6 FPGA GTX Transceivers for 1000BASE-X Constraints

- Virtex-6 FPGA GTX Transceivers for SGMII or Dynamic Standards Switching Constraints

- Spartan-6 FPGA GTP Transceivers for 1000BASE-X Constraints

- Spartan-6 FPGA GTP Transceivers for SGMII or Dynamic Standards Switching Constraints

- 7 Series and Zynq-7000 Device Transceivers for 1000BASE-X Constraints

- 7 Series and Zynq-7000 Device Transceivers for SGMII or Dynamic Standards Switching Constraints

- SGMII over LVDS Constraints

- Ten-Bit Interface Constraints

- Constraints When Implementing an External GMII

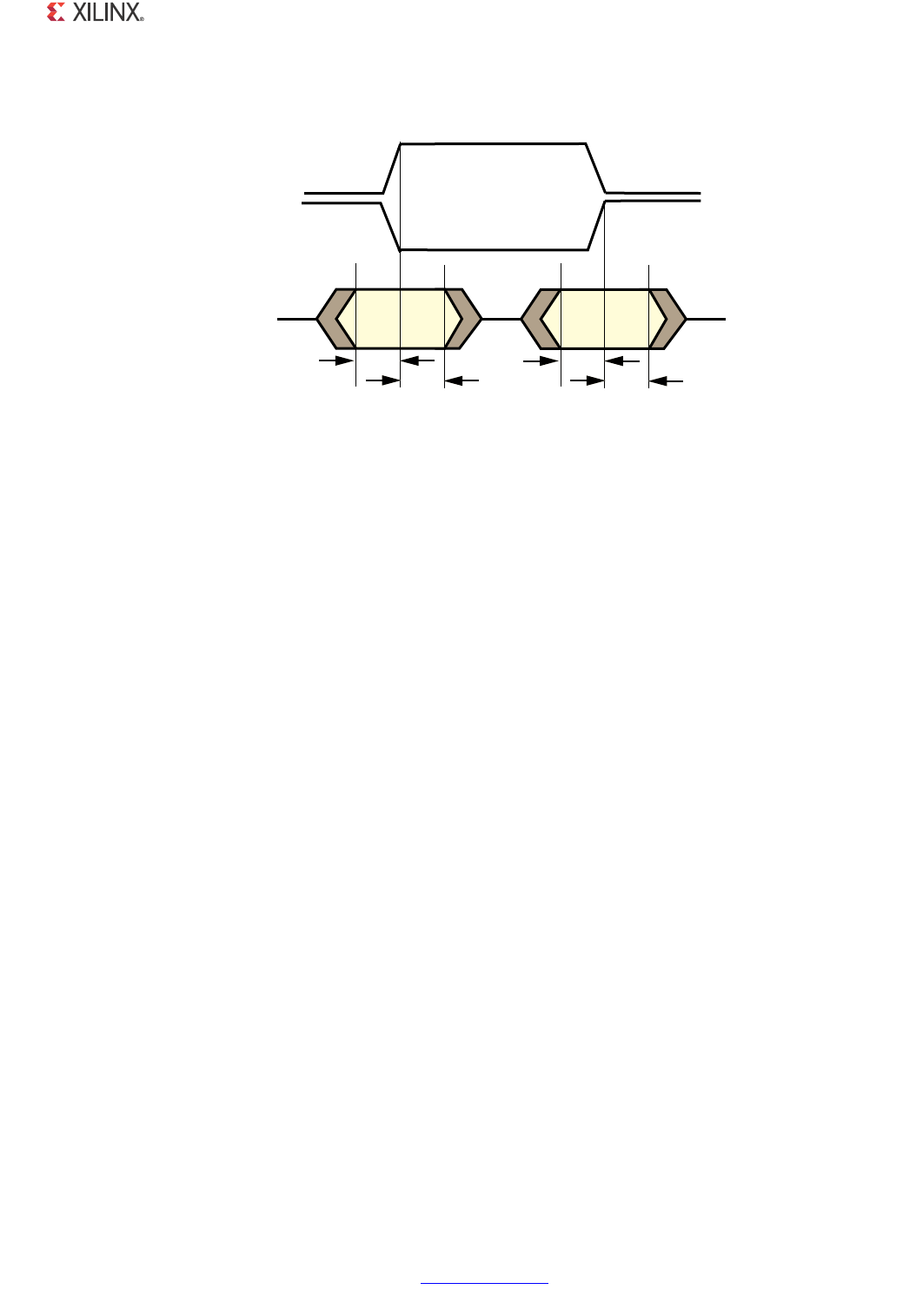

- Understanding Timing Reports for Setup/Hold Timing

- Implementing the Design

- Detailed Example Design

- Section IV: Appendices

LogiCORE IP Ethernet

1000BASE-X PCS/PMA or

SGMII v11.4

Product Guide

PG047 October 16, 2012

1000BASE-X PCS/PMA or SGMII v11.4 www.xilinx.com 2

PG047 October 16, 2012

Table of Contents

SECTION I: SUMMARY

IP Facts

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Chapter 1: Overview

Core Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Recommended Design Experience . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

System Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Verification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Licensing and Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Chapter 2: Product Specification

Overview of Ethernet Architecture. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Standards . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Performance. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Voltage Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Speed Grades . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Resource Utilization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Port Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Register Space . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Chapter 3: Designing with the Core

General Design Guidelines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

Clocking. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

Chapter 4: The Ten-Bit Interface

Ten-Bit-Interface Logic. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

Clock Sharing across Multiple Cores with TBI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

Example Designs for the Ten-Bit Interface (TBI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

1000BASE-X PCS/PMA or SGMII v11.4 www.xilinx.com 3

PG047 October 16, 2012

Chapter 5: 1000BASE-X with Transceivers

Transceiver Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

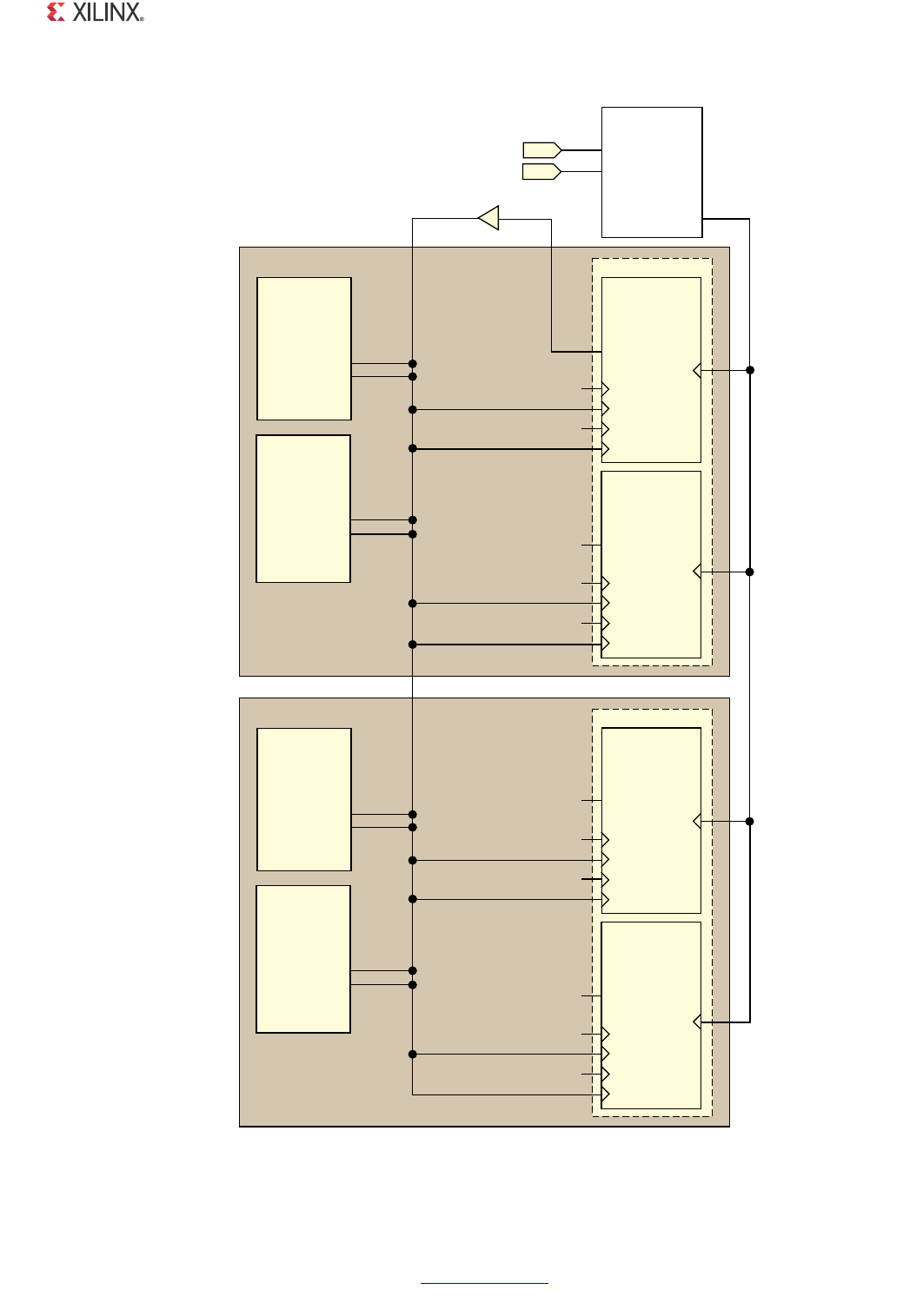

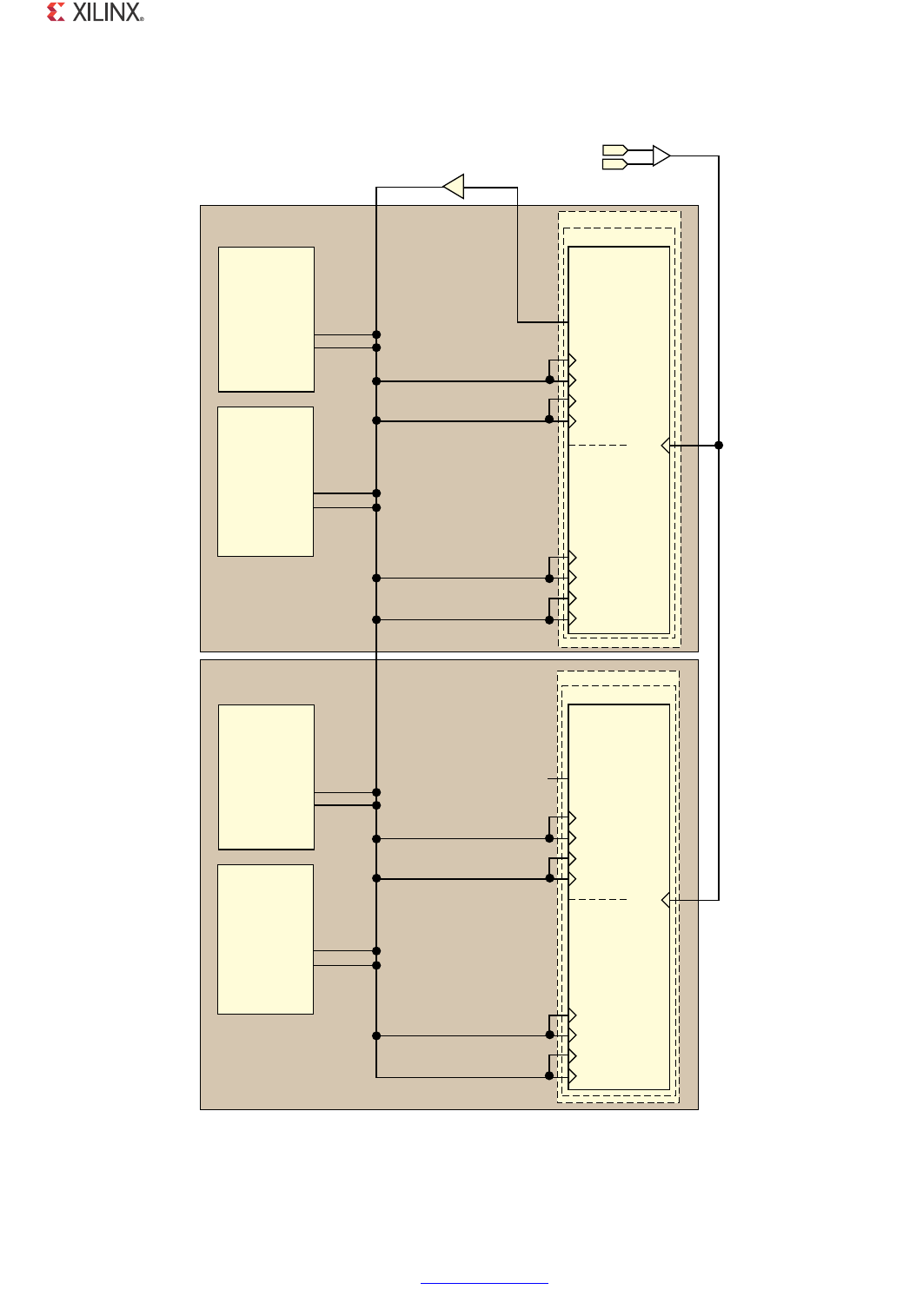

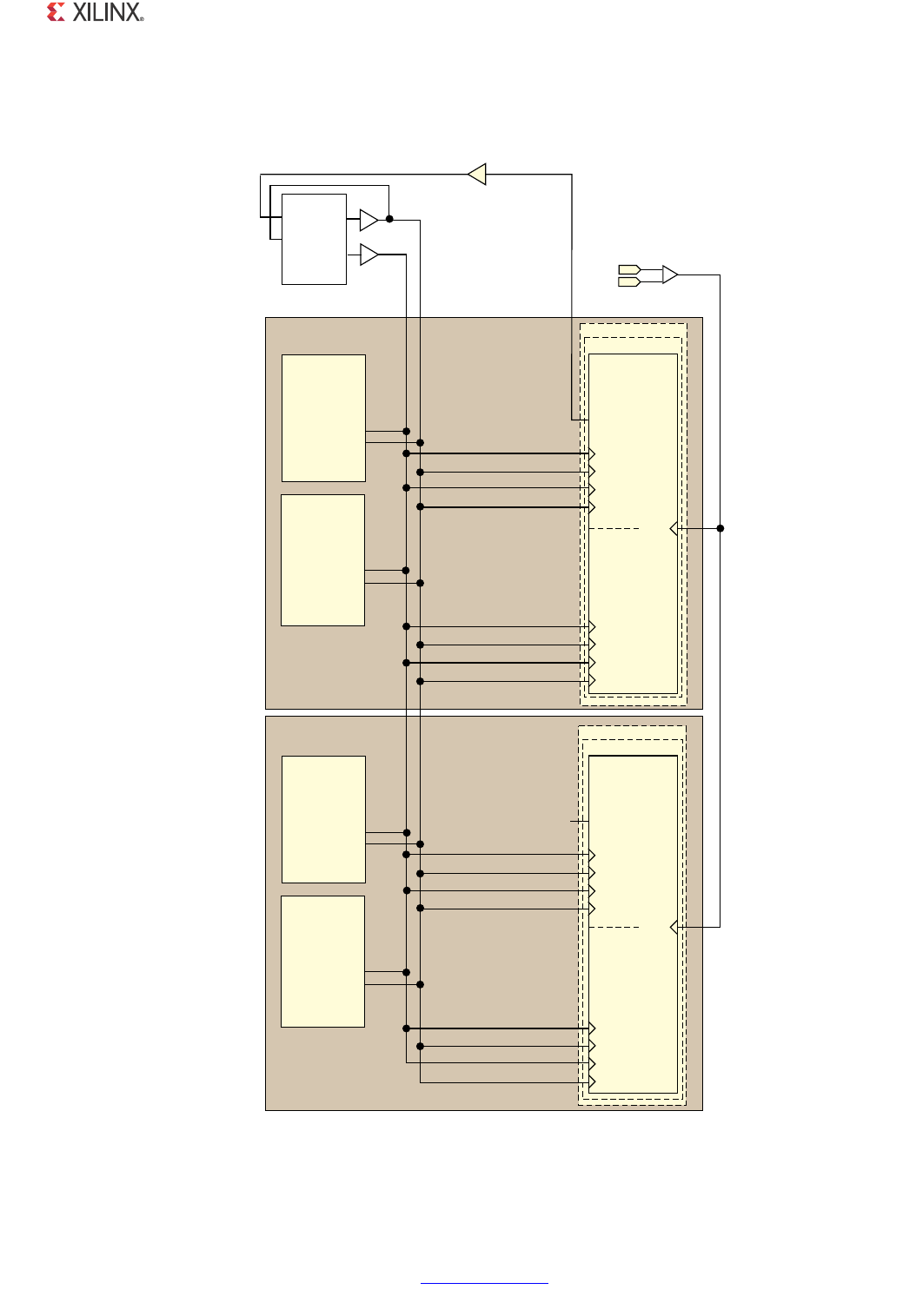

Clock Sharing Across Multiple Cores with Transceivers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

Example Design for 1000BASE-X with Transceivers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164

Chapter 6: SGMII / Dynamic Standards Switching with Transceivers

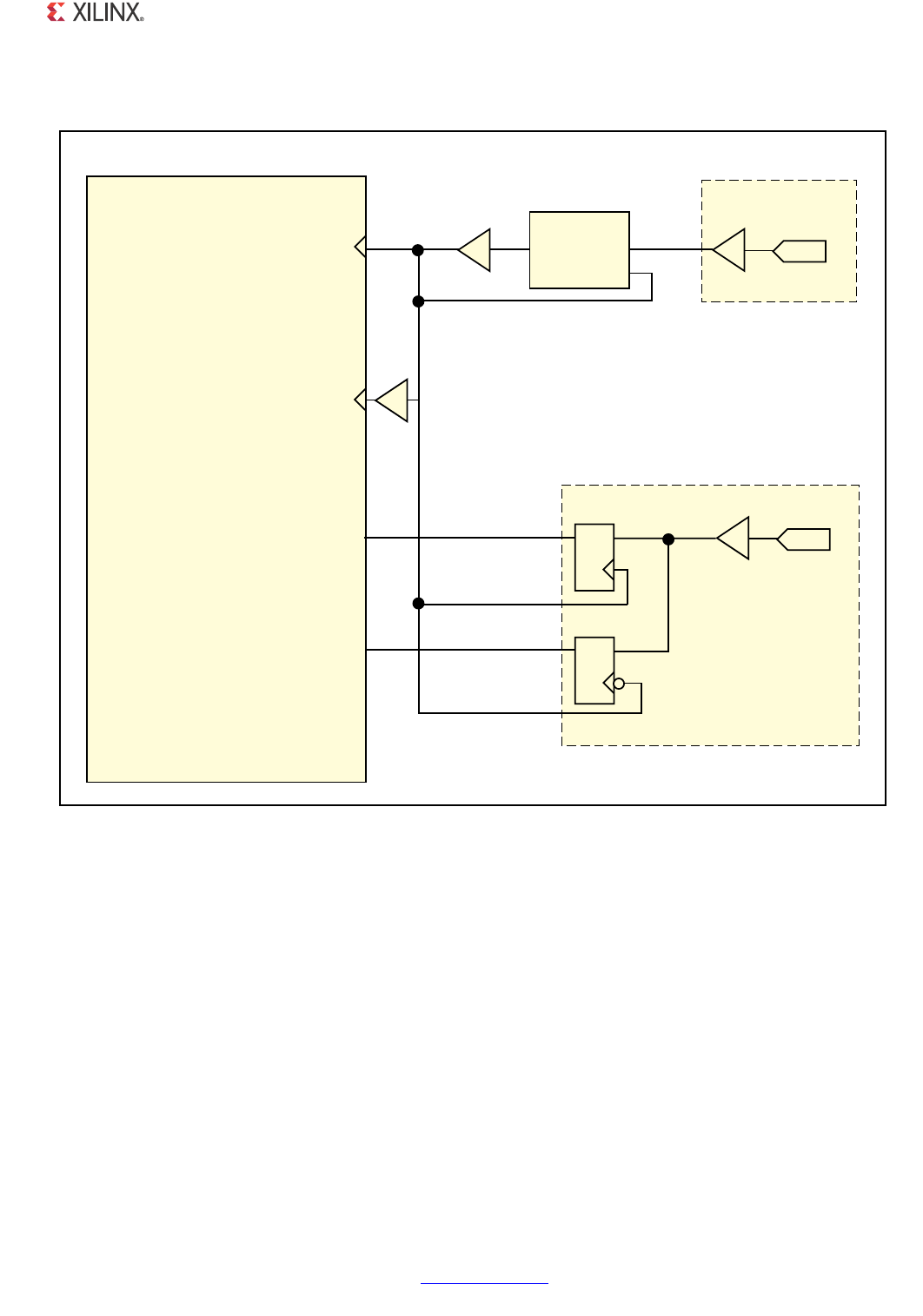

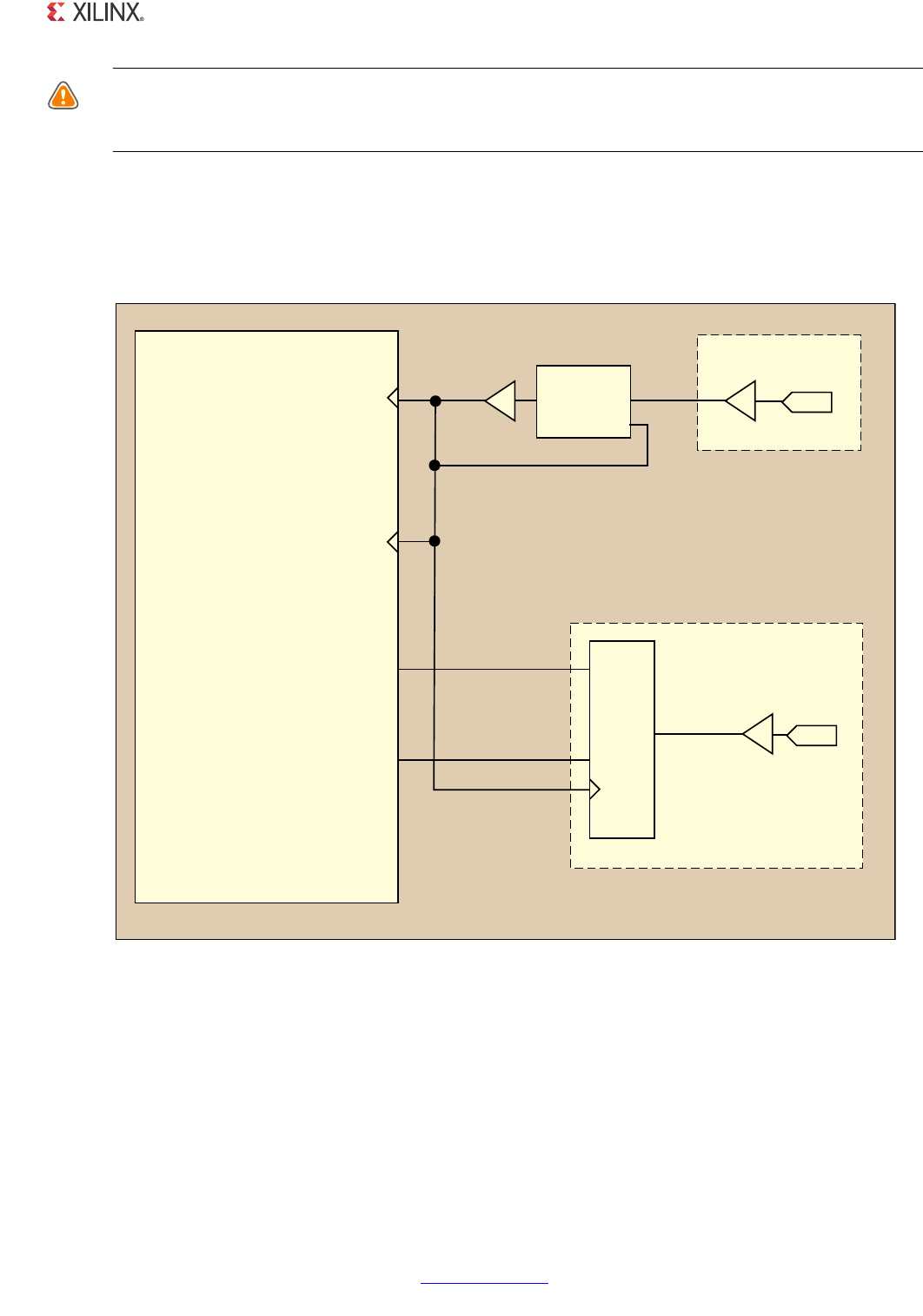

Receiver Elastic Buffer Implementations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 181

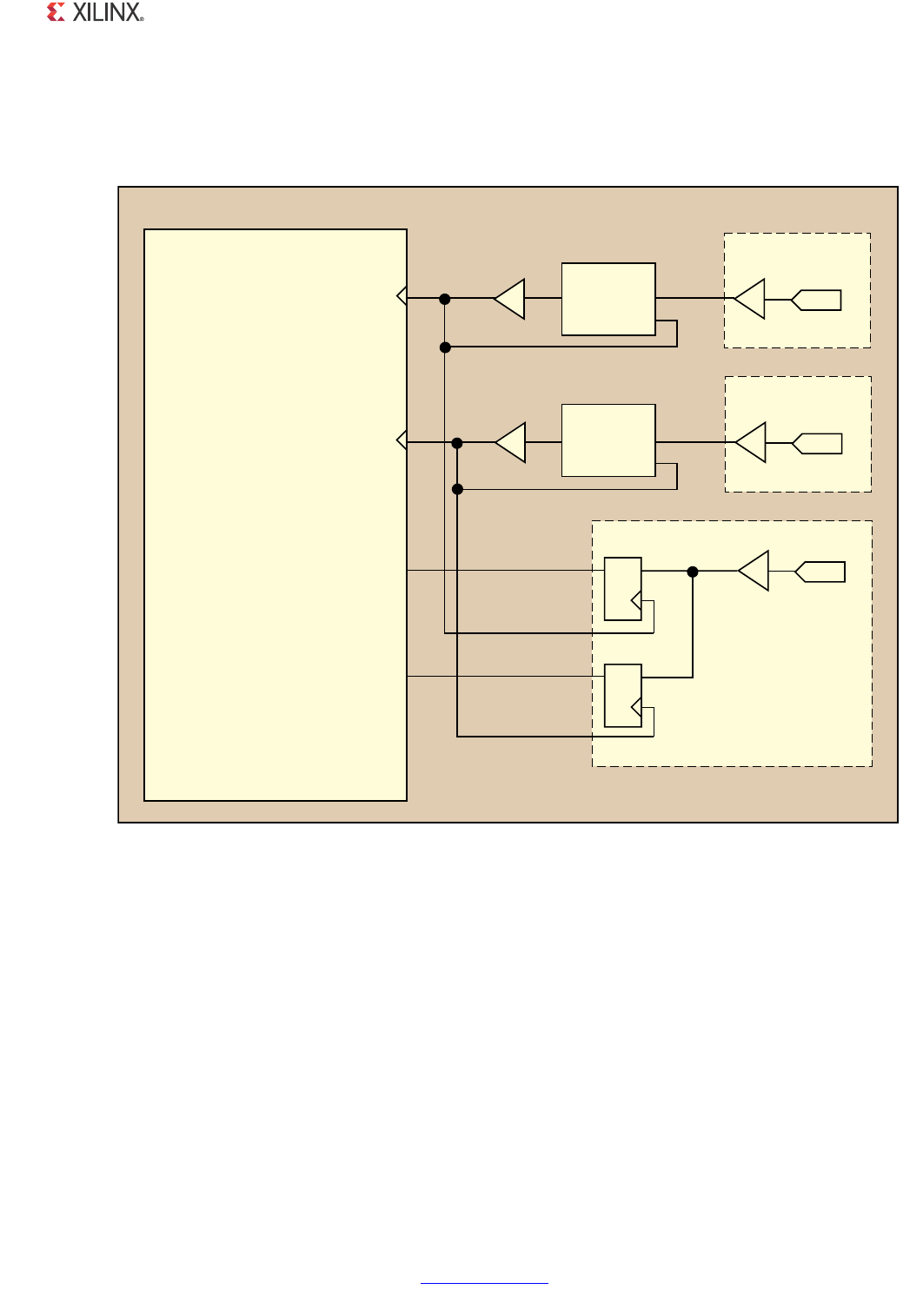

Logic Using the Transceiver Rx Elastic Buffer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 184

Transceiver Logic with the FPGA Logic Rx Elastic Buffer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 184

Clock Sharing - Multiple Cores with Transceivers, FPGA Logic Elastic Buffer . . . . . . . . . . . . . . . . 206

SGMII Example Design / Dynamic Switching Example Design Using a Transceiver . . . . . . . . . . . 222

Chapter 7: SGMII over LVDS

Synchronous SGMII over Virtex7/Kintex 7 FPGA LVDS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 239

SGMII Support Using Asynchronous Oversampling over Virtex-6 FPGA LVDS . . . . . . . . . . . . . . . 260

Chapter 8: Using the Client-Side GMII Datapath

Using the Core Netlist Client-side GMII for the 1000BASE-X Standard . . . . . . . . . . . . . . . . . . . . . 290

Using the Core Netlist Client-Side GMII for the SGMII Standard . . . . . . . . . . . . . . . . . . . . . . . . . . 296

Additional Client-Side SGMII Logic Provided in the Example Design . . . . . . . . . . . . . . . . . . . . . . . 299

Chapter 9: Auto-Negotiation

Overview of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 306

Setting the Configurable Link Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 311

Using the Auto-Negotiation Interrupt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 312

Use of Clock Correction Sequences in Device Specific Transceivers (1000BASE-X Standard). . . . 312

Conclusion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 313

Chapter 10: Dynamic Switching of 1000BASE-X and SGMII Standards

Typical Application. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 314

Operation of the Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 315

Chapter 11: GMII to PHY EDK Application for Zynq-7000 Device Processor

Subsystem

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 317

GMII to 1000BASEX . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 318

GMII to SGMII Using Zynq-7000 Device Gigabit Transceiver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 320

GMII to SGMII Using Zynq-7000 Device LVDS Transceiver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 322

1000BASE-X PCS/PMA or SGMII v11.4 www.xilinx.com 4

PG047 October 16, 2012

Chapter 12: Interfacing to Other Cores

Integration of the Tri-Mode Ethernet MAC for 1000BASE-X Operation . . . . . . . . . . . . . . . . . . . . 325

Integration of the Tri-Mode Ethernet MAC for Tri-speed SGMII Operation . . . . . . . . . . . . . . . . . 344

Chapter 13: Special Design Considerations

Power Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 369

Start-up Sequencing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 369

Loopback. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 370

SECTION II: VIVADO DESIGN SUITE

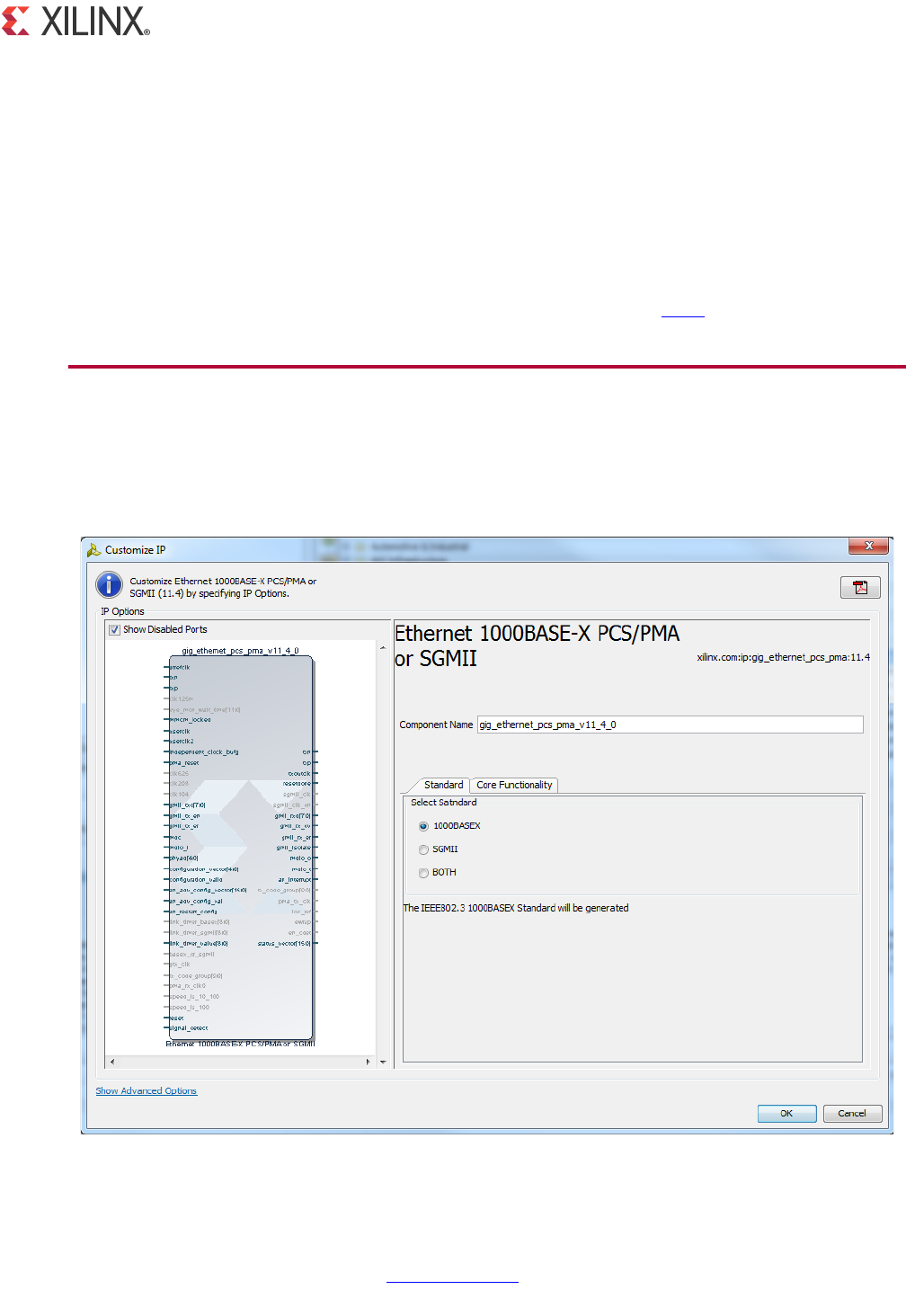

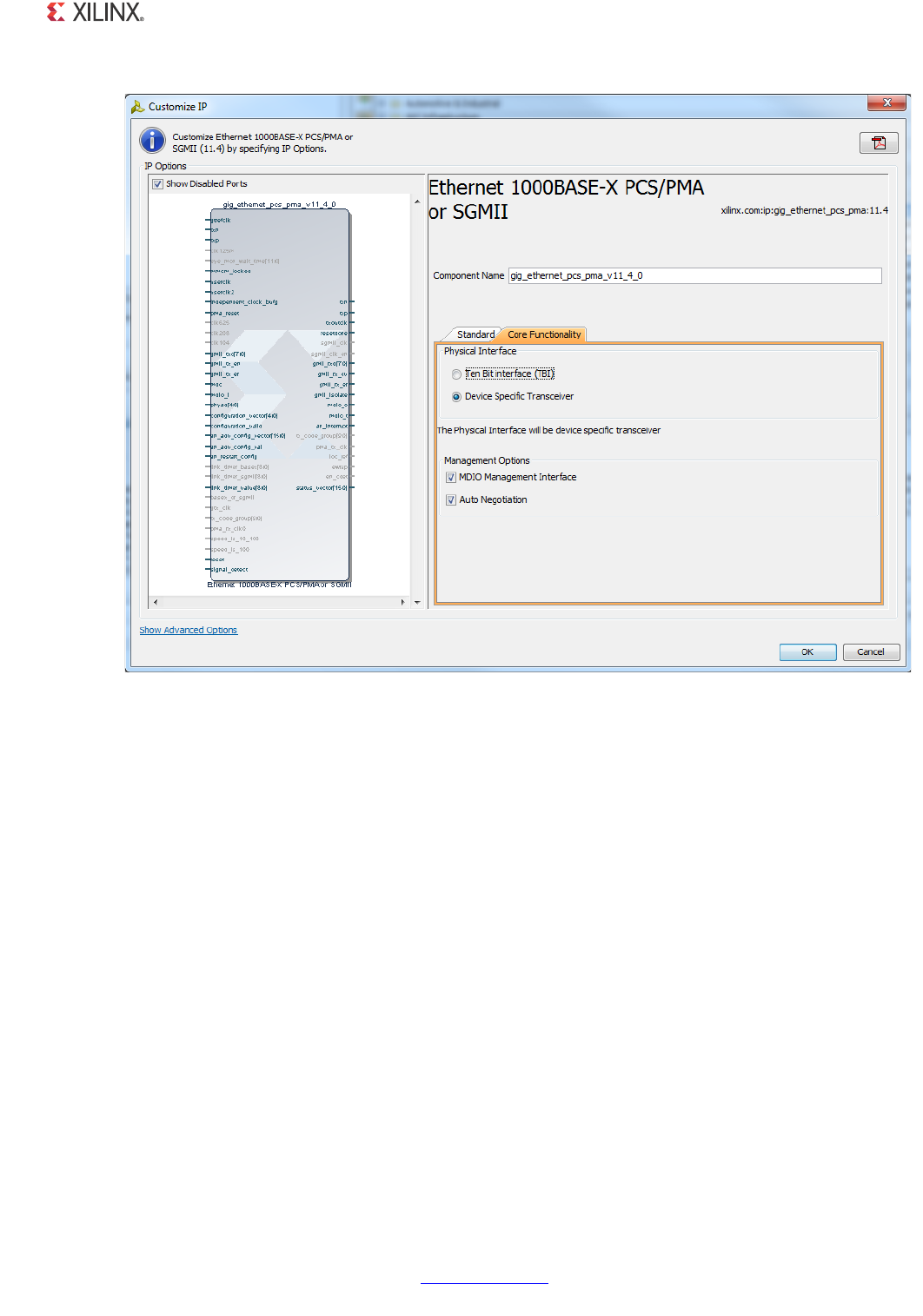

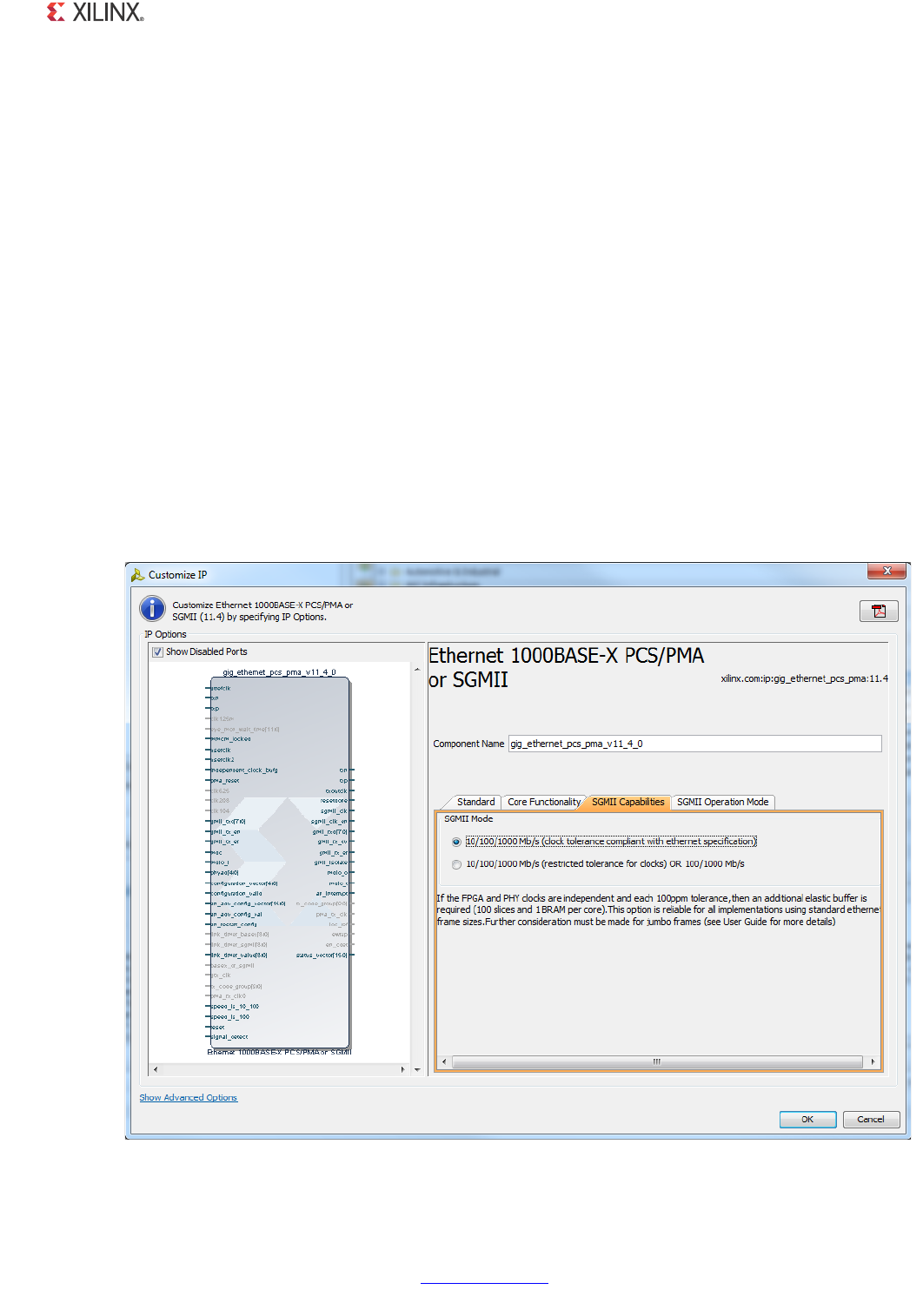

Chapter 14: Customizing and Generating the Core

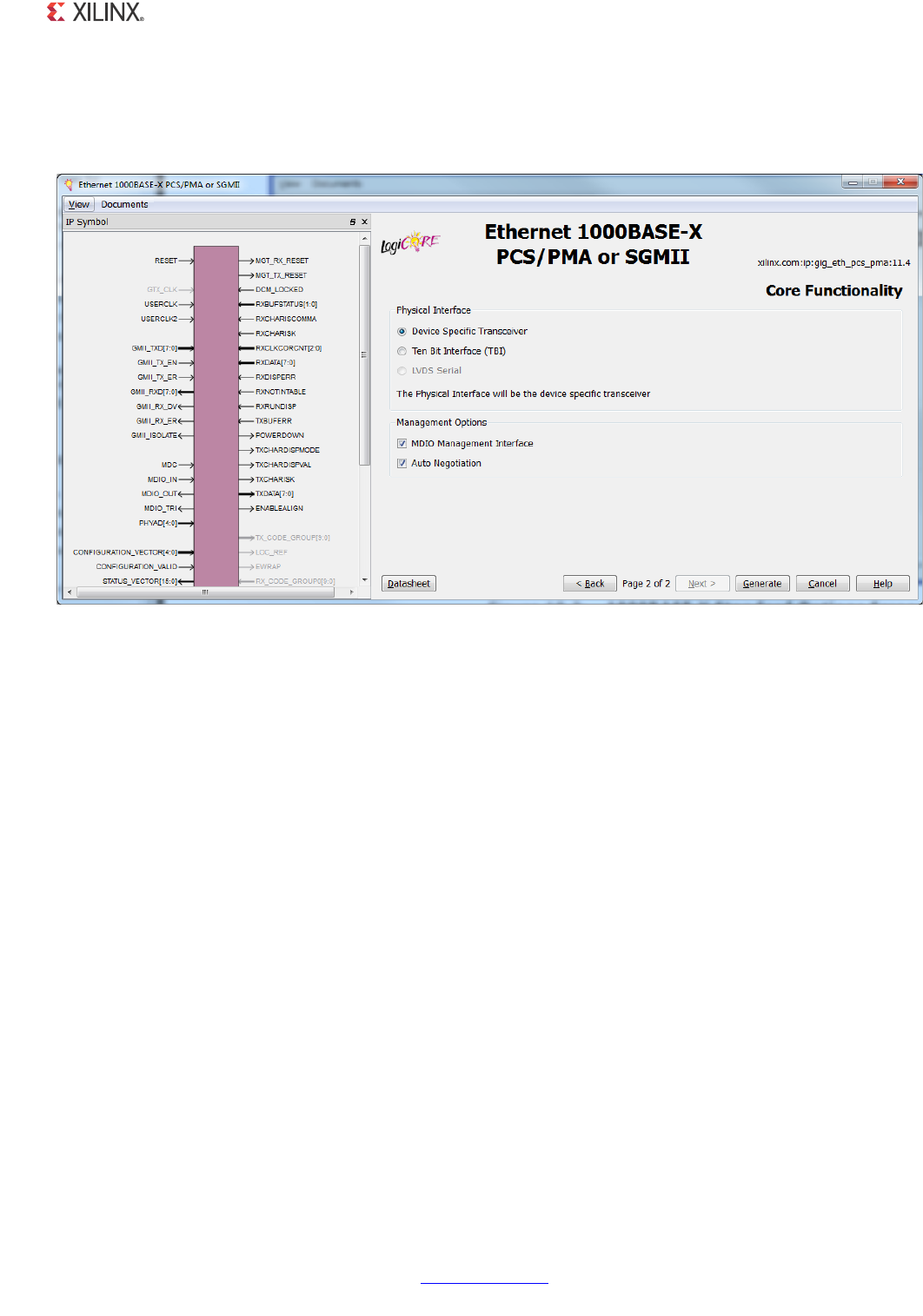

GUI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 373

Output Generation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 378

Chapter 15: Constraining the Core

Required Constraints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 379

Device, Package, and Speed Grade Selections. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 379

Clock Frequencies . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 380

I/O Standard and Placement. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 381

Chapter 16: Detailed Example Design

Example Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 382

Demonstration Test Bench . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 382

SECTION III: ISE DESIGN SUITE

Chapter 17: Customizing and Generating the Core

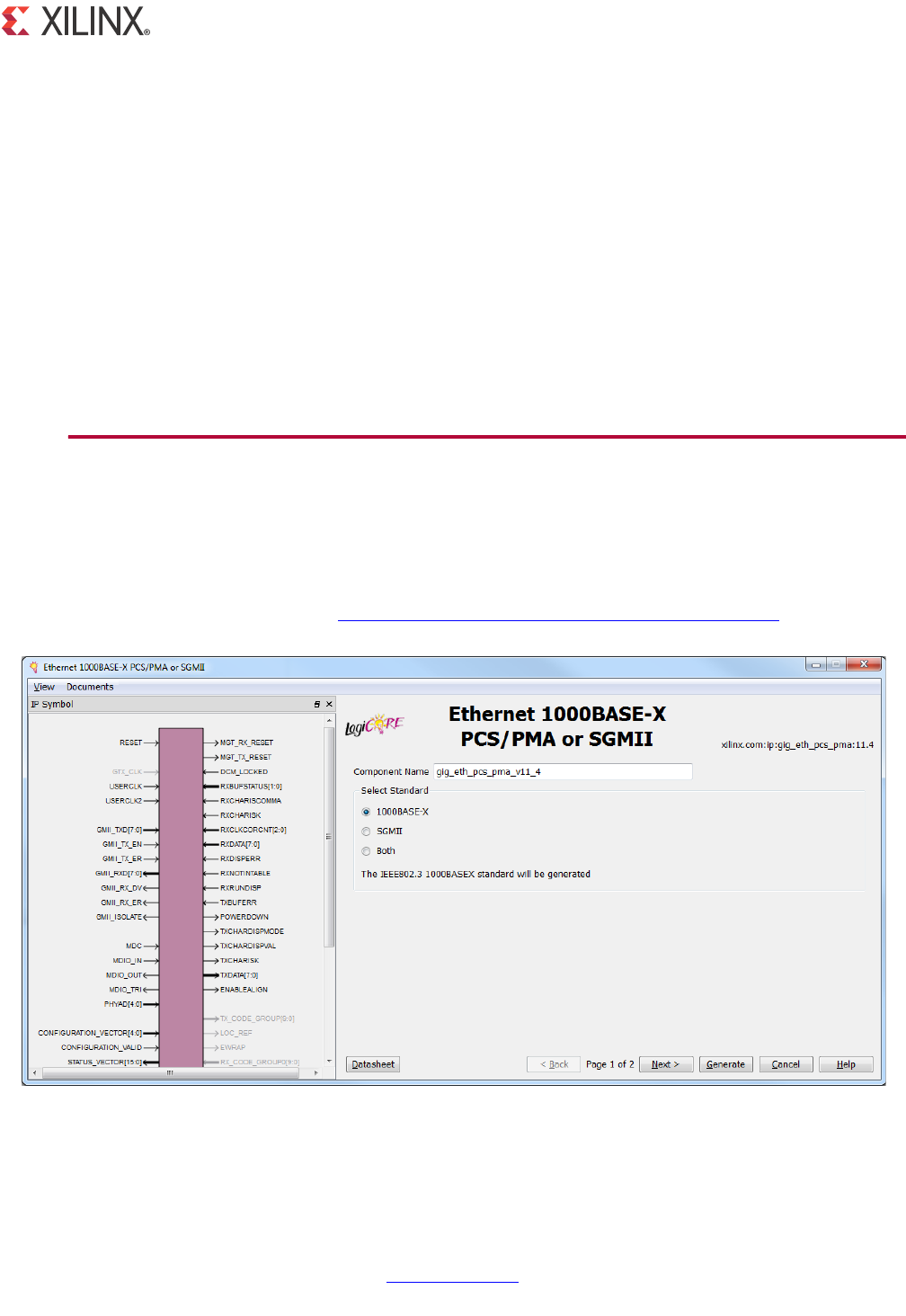

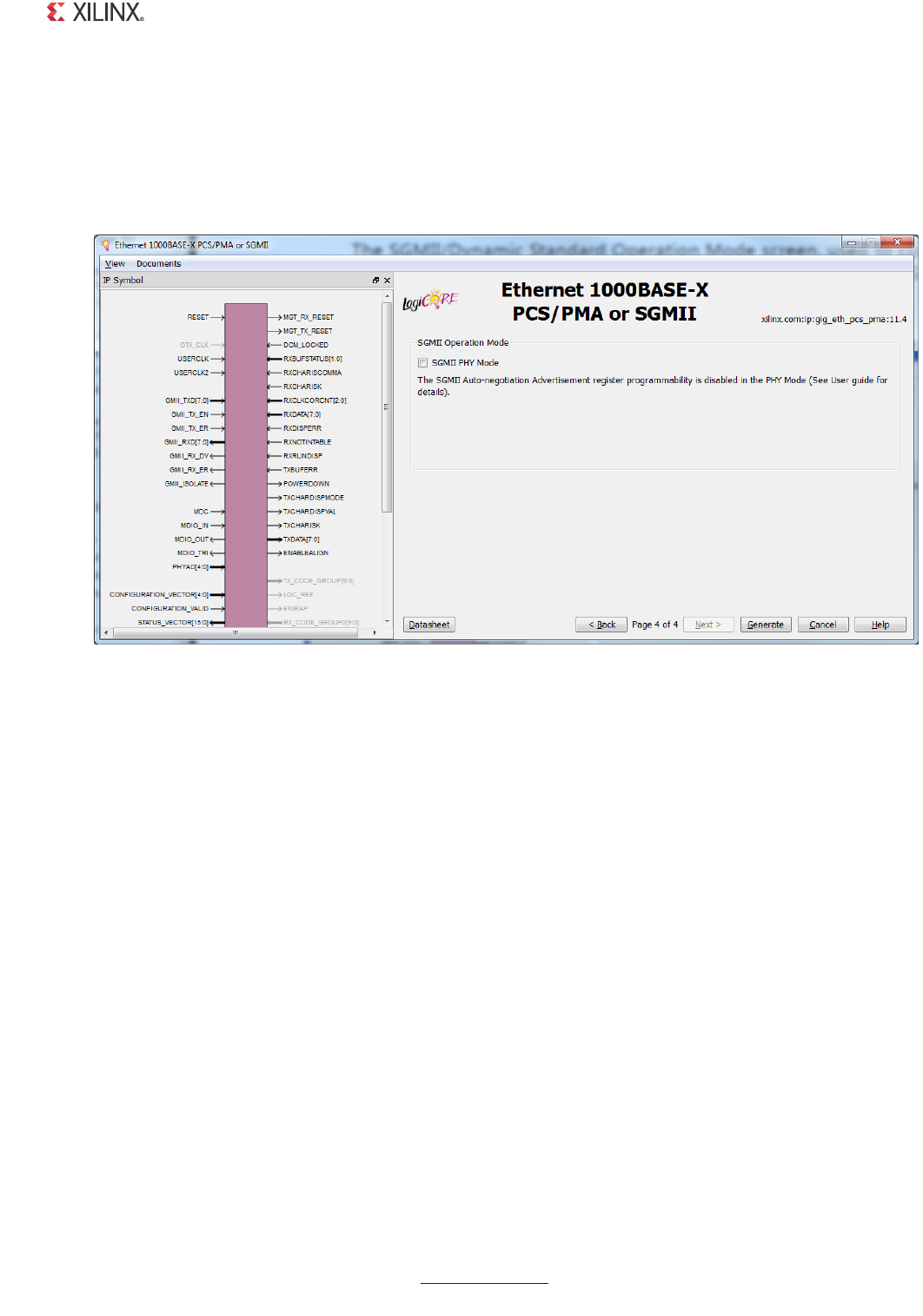

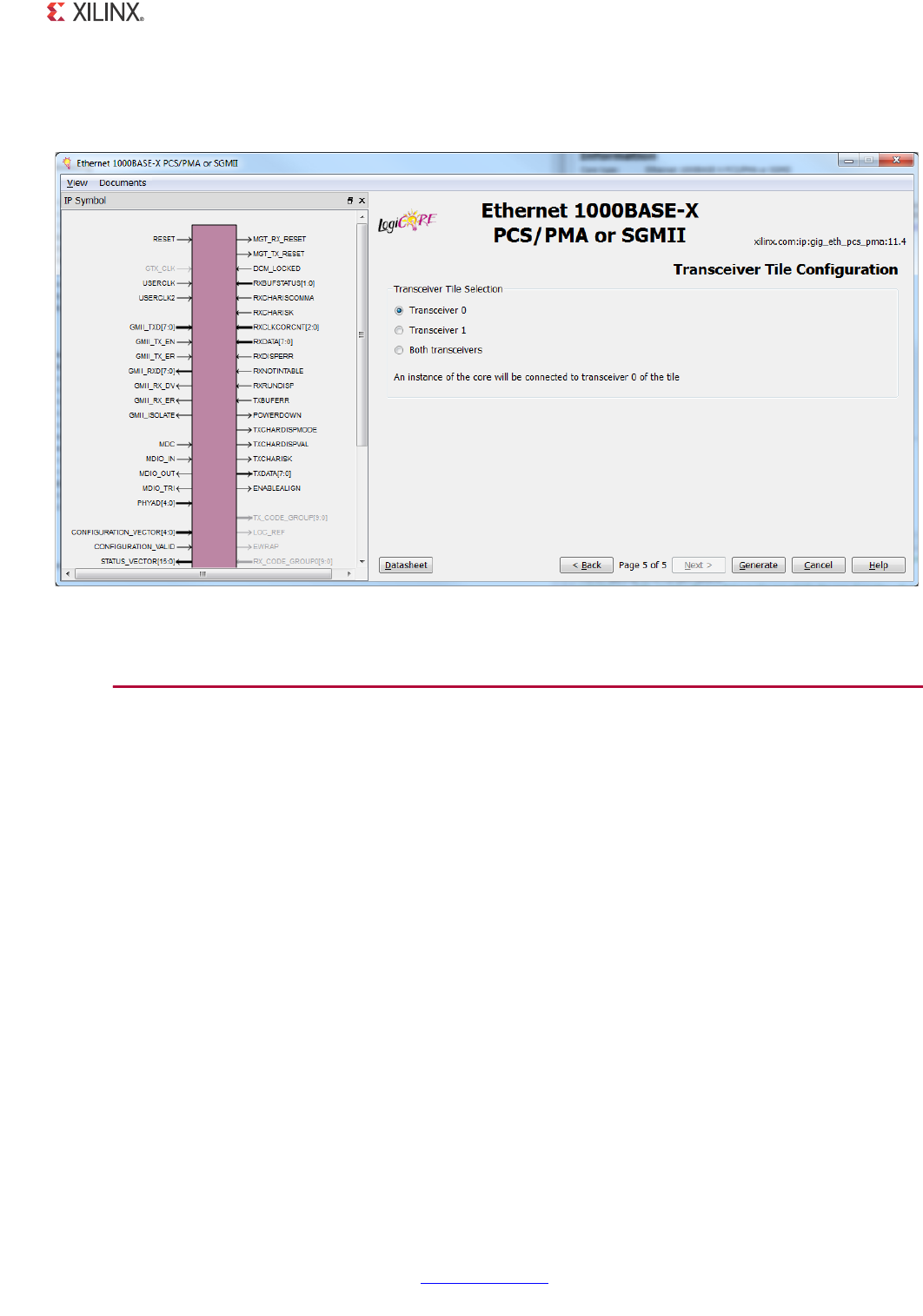

GUI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 384

Parameter Values in the XCO File . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 389

Output Generation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 390

Chapter 18: Constraining the Core

Device, Package, and Speed Grade Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 391

I/O Location Constraints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 392

Placement Constraints. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 392

Virtex-4 FPGA MGT Transceivers for 1000BASE-X Constraints . . . . . . . . . . . . . . . . . . . . . . . . . . . . 392

Virtex-4 FPGA RocketIO MGT Transceivers for SGMII or Dynamic Standards

Switching Constraints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 394

1000BASE-X PCS/PMA or SGMII v11.4 www.xilinx.com 5

PG047 October 16, 2012

Virtex-5 FPGA RocketIO GTP Transceivers for 1000BASE-X Constraints . . . . . . . . . . . . . . . . . . . . 394

Virtex-5 FPGA RocketIO GTP Transceivers for SGMII or Dynamic Standards

Switching Constraints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 395

Virtex-5 FPGA RocketIO GTX Transceivers for SGMII or Dynamic Standards

Switching Constraints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 397

Virtex-6 FPGA GTX Transceivers for 1000BASE-X Constraints . . . . . . . . . . . . . . . . . . . . . . . . . . . . 398

Virtex-6 FPGA GTX Transceivers for SGMII or Dynamic Standards Switching Constraints . . . . . . 399

Spartan-6 FPGA GTP Transceivers for 1000BASE-X Constraints . . . . . . . . . . . . . . . . . . . . . . . . . . . 400

Spartan-6 FPGA GTP Transceivers for SGMII or Dynamic Standards Switching Constraints . . . . 401

7 Series and Zynq-7000 Device Transceivers for 1000BASE-X Constraints . . . . . . . . . . . . . . . . . . 402

7 Series and Zynq-7000 Device Transceivers for SGMII or Dynamic Standards

Switching Constraints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 403

SGMII over LVDS Constraints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 404

Ten-Bit Interface Constraints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 404

Constraints When Implementing an External GMII. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 411

Understanding Timing Reports for Setup/Hold Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 418

Chapter 19: Implementing the Design

Pre-implementation Simulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 419

Using the Simulation Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 419

Synthesis. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 420

Implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 421

Post-Implementation Simulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 422

Other Implementation Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 423

Chapter 20: Detailed Example Design

Directory Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 425

Directory and File Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 426

Example Designs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 430

Demonstration Test Bench . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 430

Implementation Scripts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 430

Simulation Scripts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 431

SECTION IV: APPENDICES

Appendix A: Verification, Compliance, and Interoperability

Simulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 433

Hardware Testing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 433

Verification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 434

1000BASE-X PCS/PMA or SGMII v11.4 www.xilinx.com 6

PG047 October 16, 2012

Appendix B: Migrating

Appendix C: 1000BASE-X State Machines

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 436

Start of Frame Encoding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 437

End of Frame Encoding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 440

Appendix D: Rx Elastic Buffer Specifications

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 444

Rx Elastic Buffers: Depths and Maximum Frame Sizes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 444

Clock Correction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 450

Maximum Frame Sizes for Sustained Frame Reception . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 451

Jumbo Frame Reception . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 452

Appendix E: Implementing External GMII

GMII Transmitter Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 453

GMII Receiver Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 460

Appendix F: Calculating the DCM Fixed Phase Shift or IODelay Tap Setting

DCM Usage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 462

IODelay Usage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 464

Appendix G: Debugging

Solution Centers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 466

General Checks. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 466

Problems with the MDIO. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 466

Problems with Data Reception or Transmission . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 467

Problems with Auto-Negotiation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 467

Problems in Obtaining a Link (Auto-Negotiation Disabled) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 468

Problems with a High Bit Error Rate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 469

Appendix H: Additional Resources

Xilinx Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 471

References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 471

Additional Core Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 472

Technical Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 472

Feedback. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 473

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 474

Notice of Disclaimer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 474

1000BASE-X PCS/PMA or SGMII v11.4 www.xilinx.com 7

PG047 October 16, 2012

SECTION I: SUMMARY

IP Facts

Overview

Product Specification

Designing with the Core

The Ten-Bit Interface

1000BASE-X with Transceivers

SGMII / Dynamic Standards Switching with

Transceivers

SGMII over LVDS

Using the Client-Side GMII Datapath

Auto-Negotiation

GMII to PHY EDK Application for Zynq-7000

Device Processor Subsystem

1000BASE-X PCS/PMA or SGMII v11.4 www.xilinx.com 9

PG047 October 16, 2012 Product Specification

Introduction

The LogiCORE™ Ethernet 1000BASE-X

PCS/PMA or Serial Gigabit Media Independent

Interface (SGMII) core provides a flexible

solution for connection to an Ethernet Media

Access Controller (MAC) or other custom logic.

It supports two standards of operation that can

be dynamically selected:

• 1000BASE-X Physical Coding Sublayer (PCS)

and Physical Medium Attachment (PMA)

operation, as defined in the IEEE

802.3-2008 standard

• Gigabit Media Independent Interface (GMII)

to Serial-GMII (SGMII) bridge or SGMII to

GMII bridge, as defined in the Serial-GMII

specification (ENG-46158)

Features

• Supported physical interfaces for

1000BASE-X and SGMII standards:

• Integrated transceiver interface using one

of the following:

°Zynq™-7000 device GTX Transceiver

°Virtex®-7 FPGA GTH Transceiver

°Virtex-7 and Kintex™-7 FPGA GTX

Transceiver

°Artix ™-7 FPGA GTP Transceiver

°Virtex-6 FPGA GTX Transceiver

°Virtex-5 FPGA RocketIO™ GTP or GTX

Transceiver

°Virtex-4 FPGA RocketIO Multi-Gigabit

Transceiver (MGT)

°Spartan®-6 FPGA GTP Transceiver

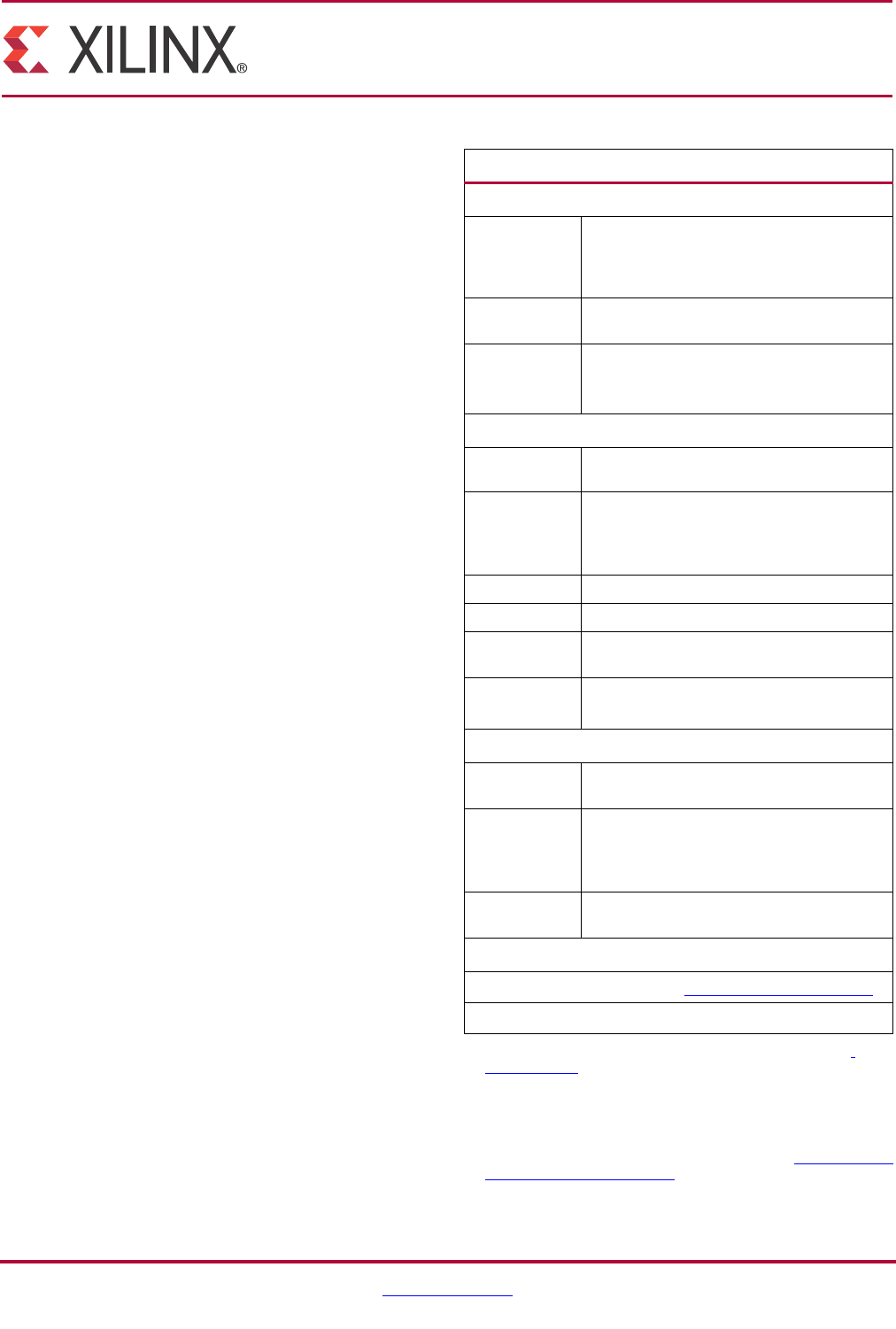

IP Facts

LogiCORE IP Facts Table

Core Specifics

Supported

Device

Family(1)

1. For a complete listing of supported devices, see the

release notes for this core. For supported family

configurations see Table 2-1. For supported speed grades

see Speed Grades.

Zynq-7000(2), Virtex-7, Kintex-7, Artix-7

Virtex-6, Virtex-5, Virtex-4,

Spartan-6, Spartan-3, Spartan-3E,

Spartan-3A/3A DSP

2. Supported in ISE Design Suite implementations only.

Supported

User Interfaces GMII

Resources

See Table 2-2, Tab l e 2 - 3 , Ta b l e 2 -4,

Table 2-5, Table 2-7, Table 2-8, and

Table 2-9

Provided with Core

Design Files ISE®: VHDL and Verilog, NGC Netlist

Vivado™: Encrypted RTL

Example

Designs

1000BASE-X PCS/PMA using a transceiver

1000BASE-X PCS with Ten -Bi t Inter face (3)

GMII to SGMII Bridge for all supported

interfaces(3)

3. See Licensing and Ordering Information.

Test Bench Demonstration Test Bench

Constraints File User Constraints File (.ucf)

Simulation

Model Verilog and VHDL

Supported

S/W Driver NA

Tested Design Flows(4)

4. For the supported versions of the tools, see the Xilinx Design

Tools: Release Notes Guide. Also see Simulation for more

information.

Design Entry ISE® Design Suite 14.3

Vivado Design Suite 2012.3(5)

5. Supports only 7 series devices.

Simulation

Mentor Graphics ModelSim

Cadence Incisive Enterprise Simulator

Synopsys Verilog Compiled Simulator (VCS) and

VCS MX

Synthesis Xilinx Synthesis Technology (XST)

Vivado Synthesis

Support

Provided by Xilinx, Inc.@ www.xilinx.com/support

Voltage Requirements

1000BASE-X PCS/PMA or SGMII v11.4 www.xilinx.com 10

PG047 October 16, 2012 Product Specification

Features

Features

• Support for SGMII over Select Input/Output (I/O) Low Voltage Differential Signaling (LVDS) in

Virtex-7, Kintex-7 and Virtex-6 FPGA -2 and faster devices

• Configured and monitored through the serial Management Data Input/Output (MDIO)

Interface (MII Management), which can optionally be omitted from the core

• Supports 1000BASE-X Auto-Negotiation for information exchange with a link partner, which

can optionally be omitted from the core

• Supports SGMII Auto-Negotiation for communication with the external Physical-Side Interface

(PHY) device

1000BASE-X PCS/PMA or SGMII v11.4 www.xilinx.com 11

PG047 October 16, 2012

Chapter 1

Overview

This product guide provides information for generating a Xilinx Ethernet 1000BASE-X

Physical Coding Sublayer/Physical Medium Attachment (PCS/PMA) or Serial Gigabit Media

Independent Interface (SGMII) core, customizing and simulating the core using the

provided example design, and running the design files through implementation using the

Xilinx tools.

The Ethernet 1000BASE-X PCS/PMA or SGMII IP core is a fully-verified solution that

supports Verilog Hardware Description Language (HDL) and VHSIC Hardware Description

Language (VHDL.) In addition, the example design provided with the core supports both

Verilog and VHDL.

For detailed information about the core, see the Ethernet 100BASE-X PCS/PMA product

page.

Transceivers are defined by device family in the following way:

• Zynq™-7000 devices, GTX Transceivers

• For Virtex®-7 devices, GTX and GTH transceivers

• For Artix™-7 devices, GTP transceivers

• Kintex™-7 devices, GTX transceivers

• For Virtex-6 devices, GTX transceivers

• For Virtex-5 LXT and SXT devices, RocketIO™ GTP transceivers; Virtex-5 FXT and TXT

devices, RocketIO GTX transceivers

• For Virtex-4 devices, RocketIO Multi-Gigabit transceivers (MGT)

• For Spartan®-6 devices, GTP transceivers

1000BASE-X PCS/PMA or SGMII v11.4 www.xilinx.com 12

PG047 October 16, 2012

Chapter 1: Overview

Core Overview

This section contains the following subsections:

•Ethernet 1000BASE-X PCS/PMA or SGMII Support Using a Device Specific Transceiver

•Ethernet 1000BASE-X PCS/PMA or SGMII Support with Ten-Bit Interface

•SGMII over LVDS

Ethernet 1000BASE-X PCS/PMA or SGMII Support Using a

Device Specific Transceiver

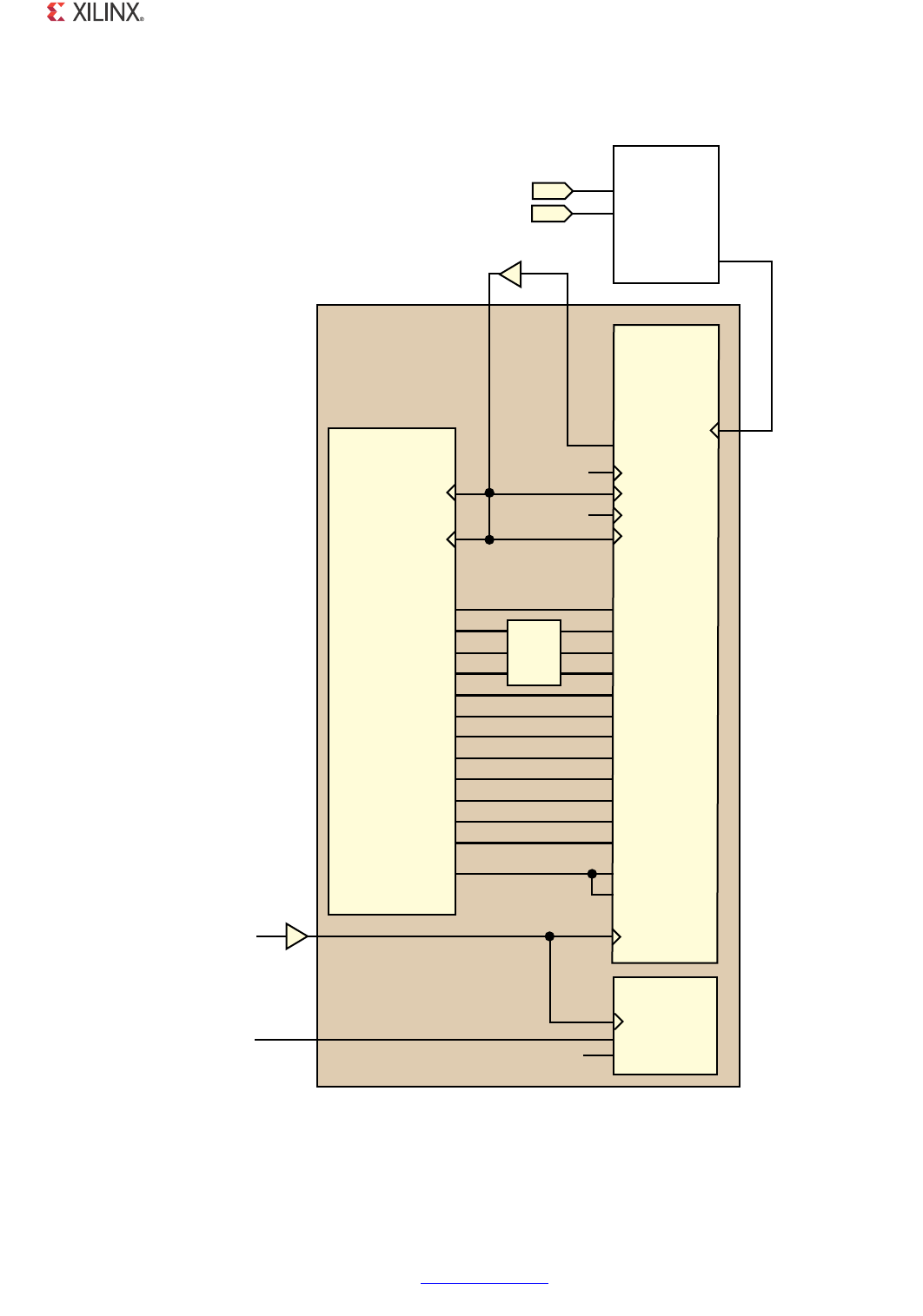

Using the Ethernet 1000BASE-X PCS/PMA or SGMII core with the device-specific transceiver

provides the functionality to implement the 1000BASE-X PCS and PMA sublayers.

Alternatively, it can be used to provide a GMII to SGMII bridge.

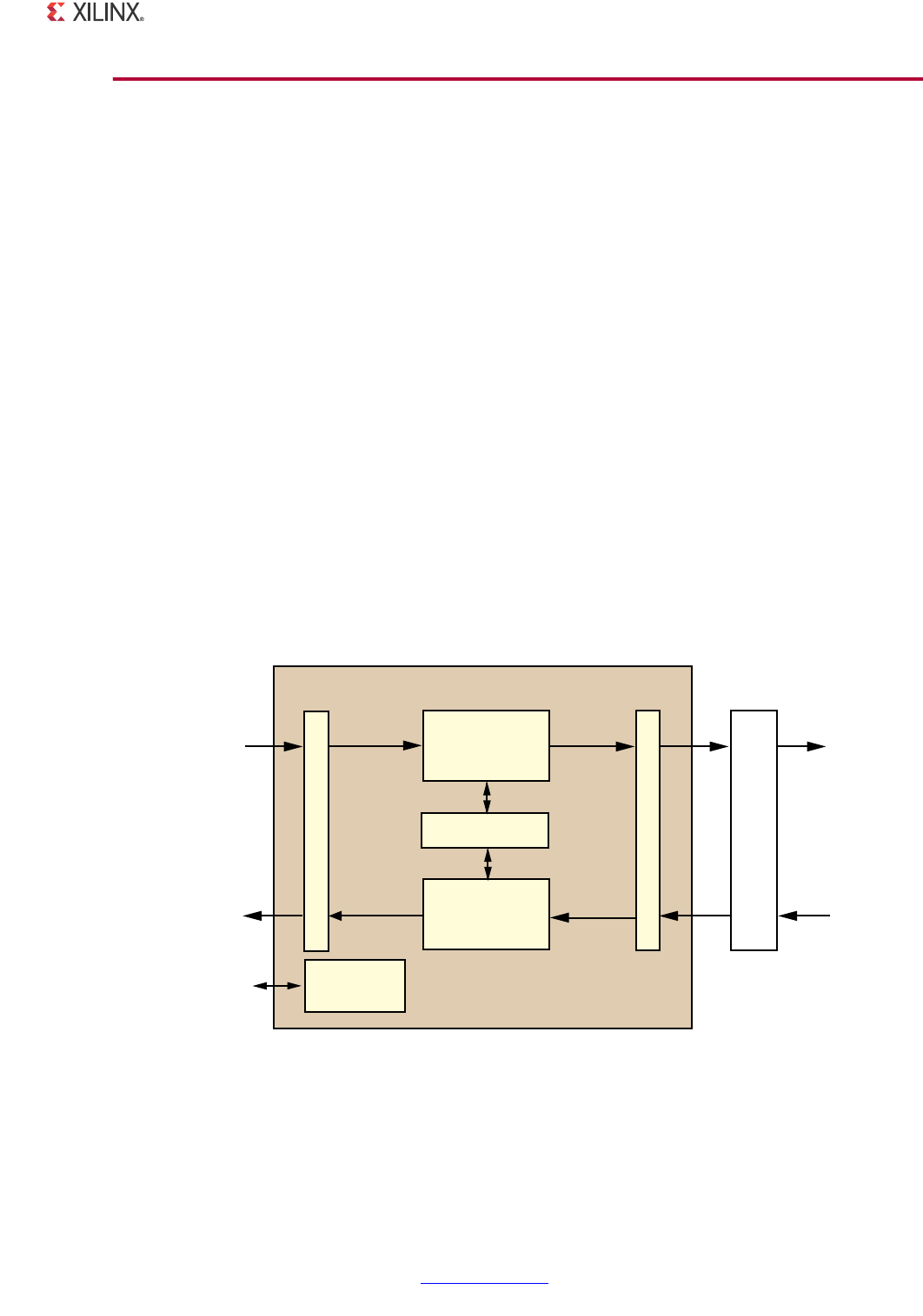

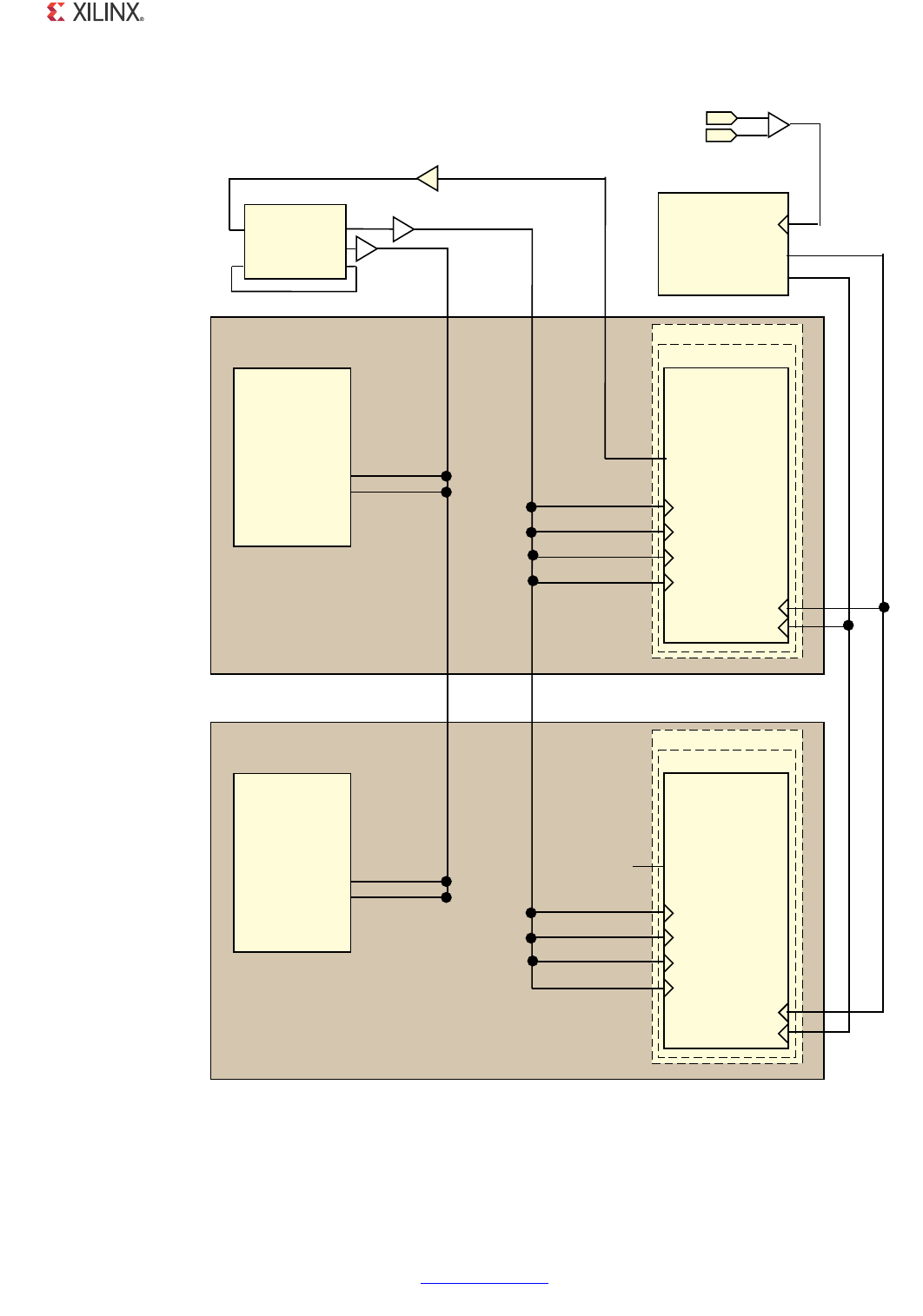

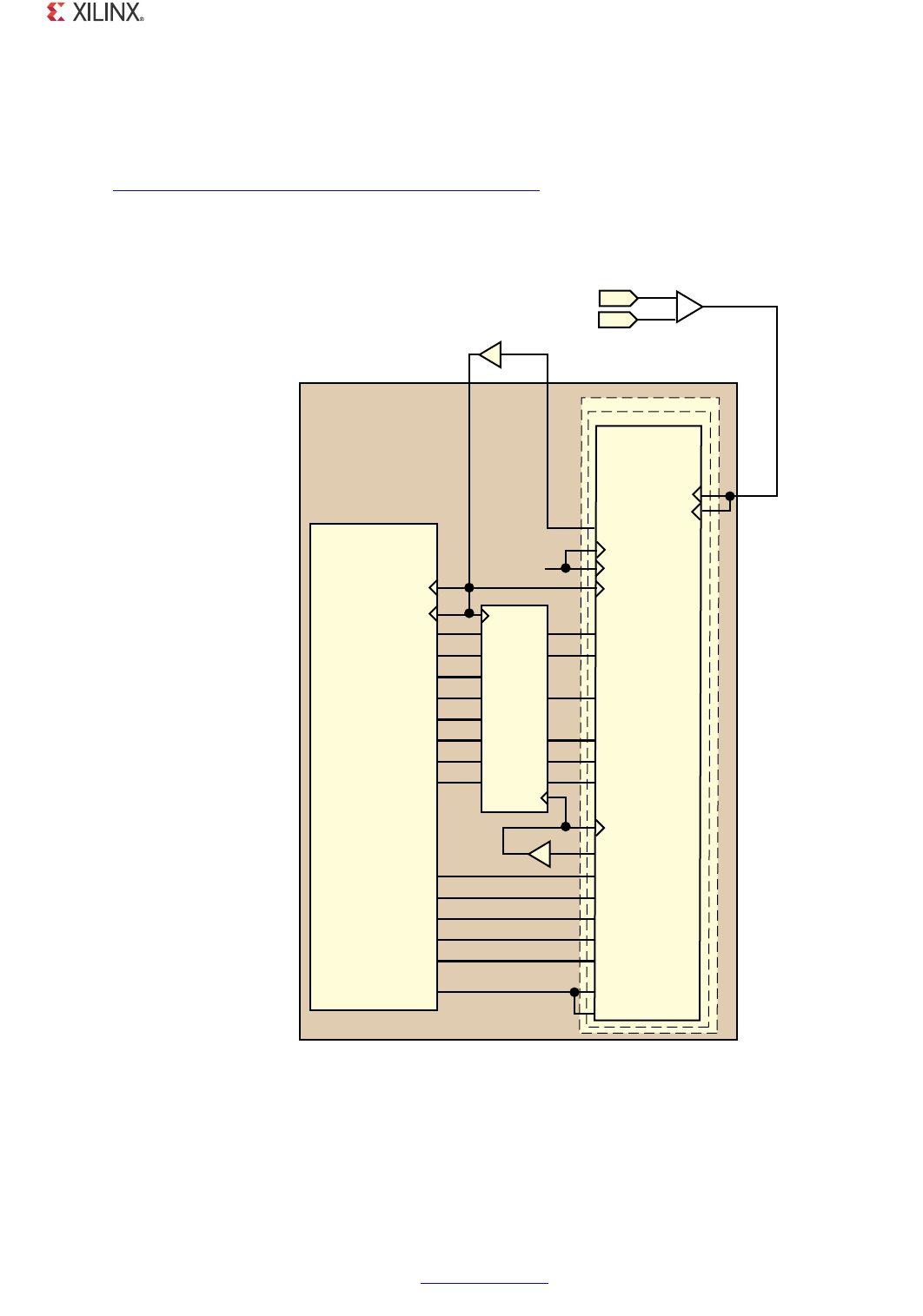

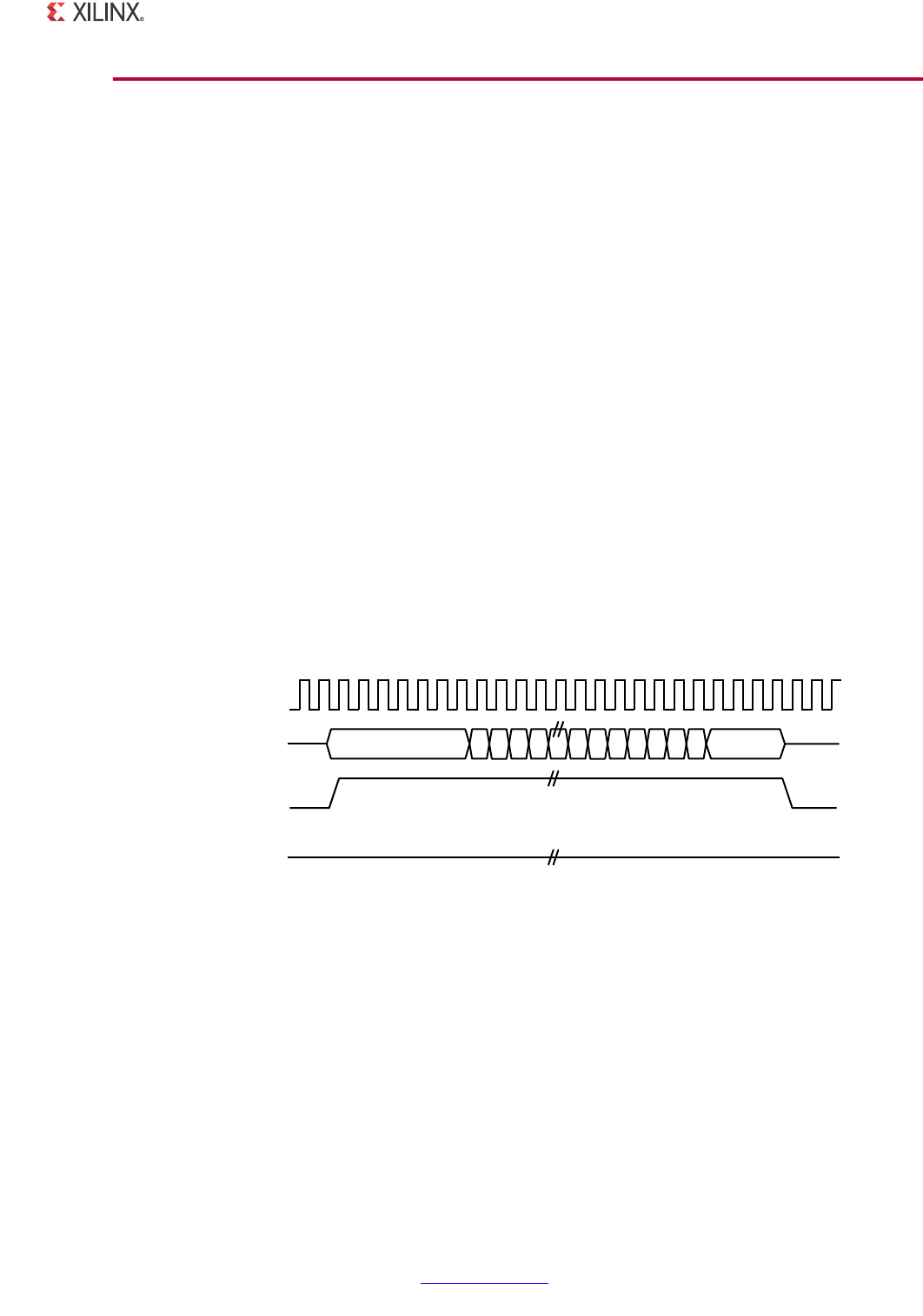

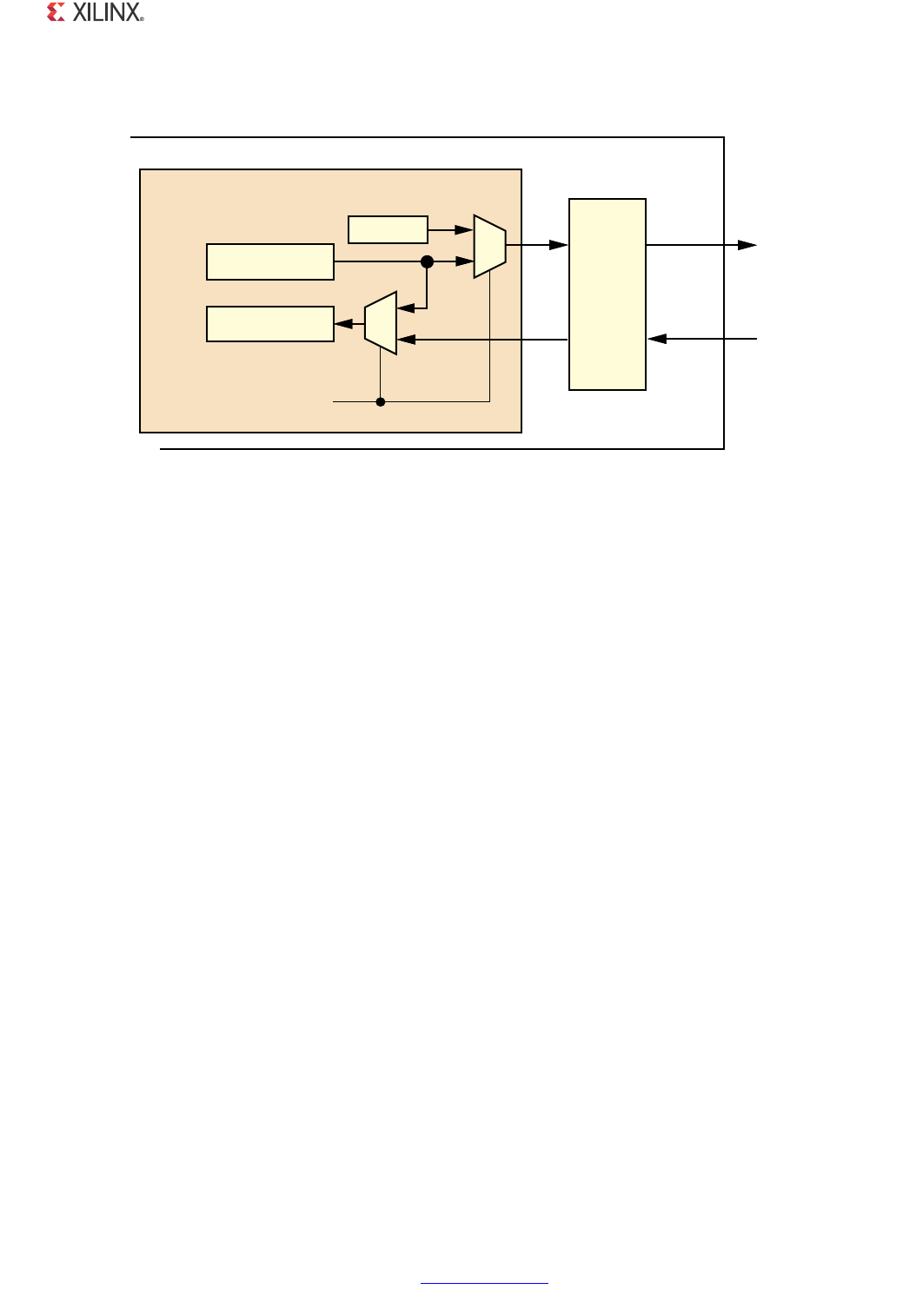

The core interfaces to a device-specific transceiver, which provides some of the PCS layer

functionality such as 8B/10B encoding/decoding, the PMA Serializer/Deserializer (SerDes),

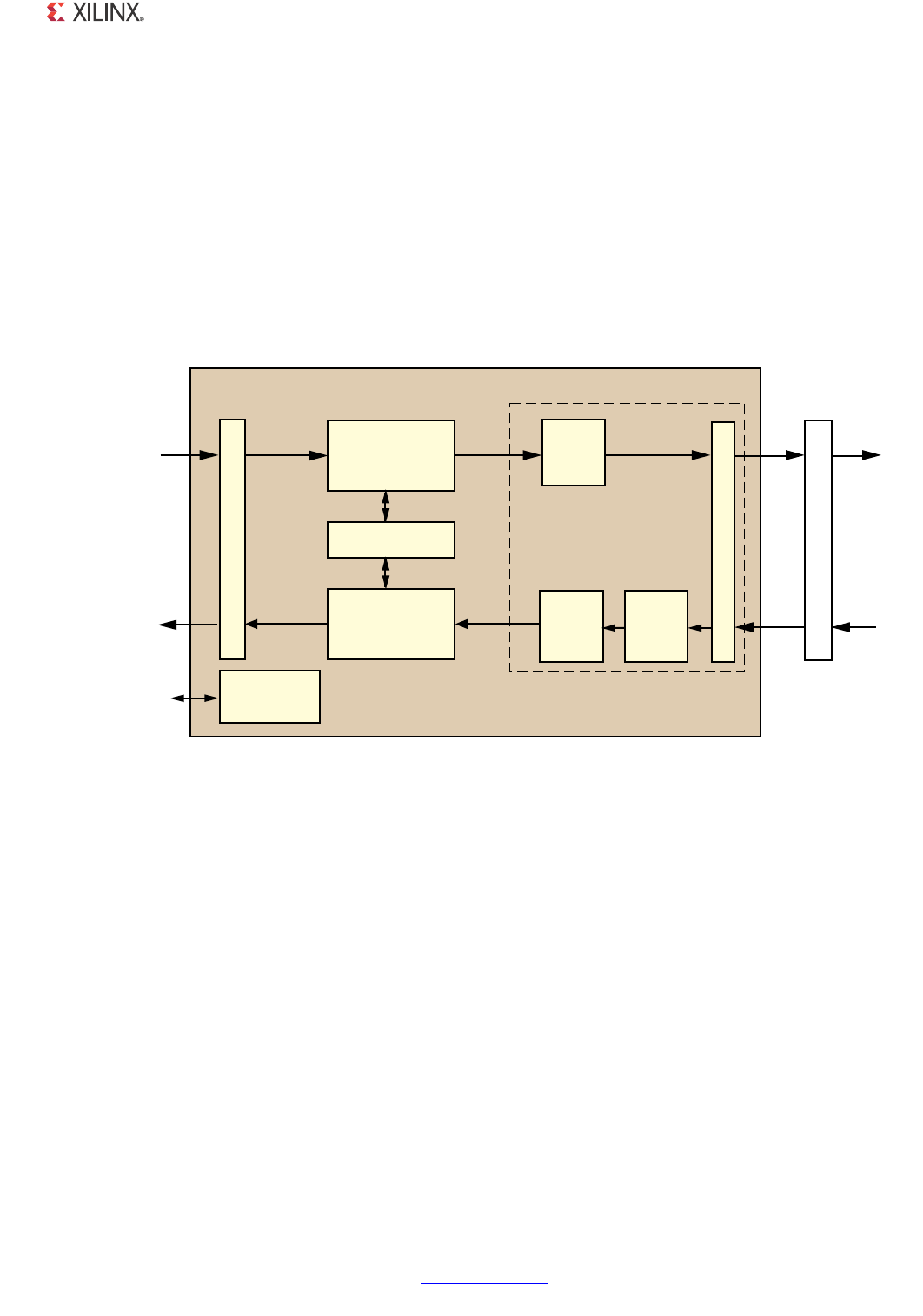

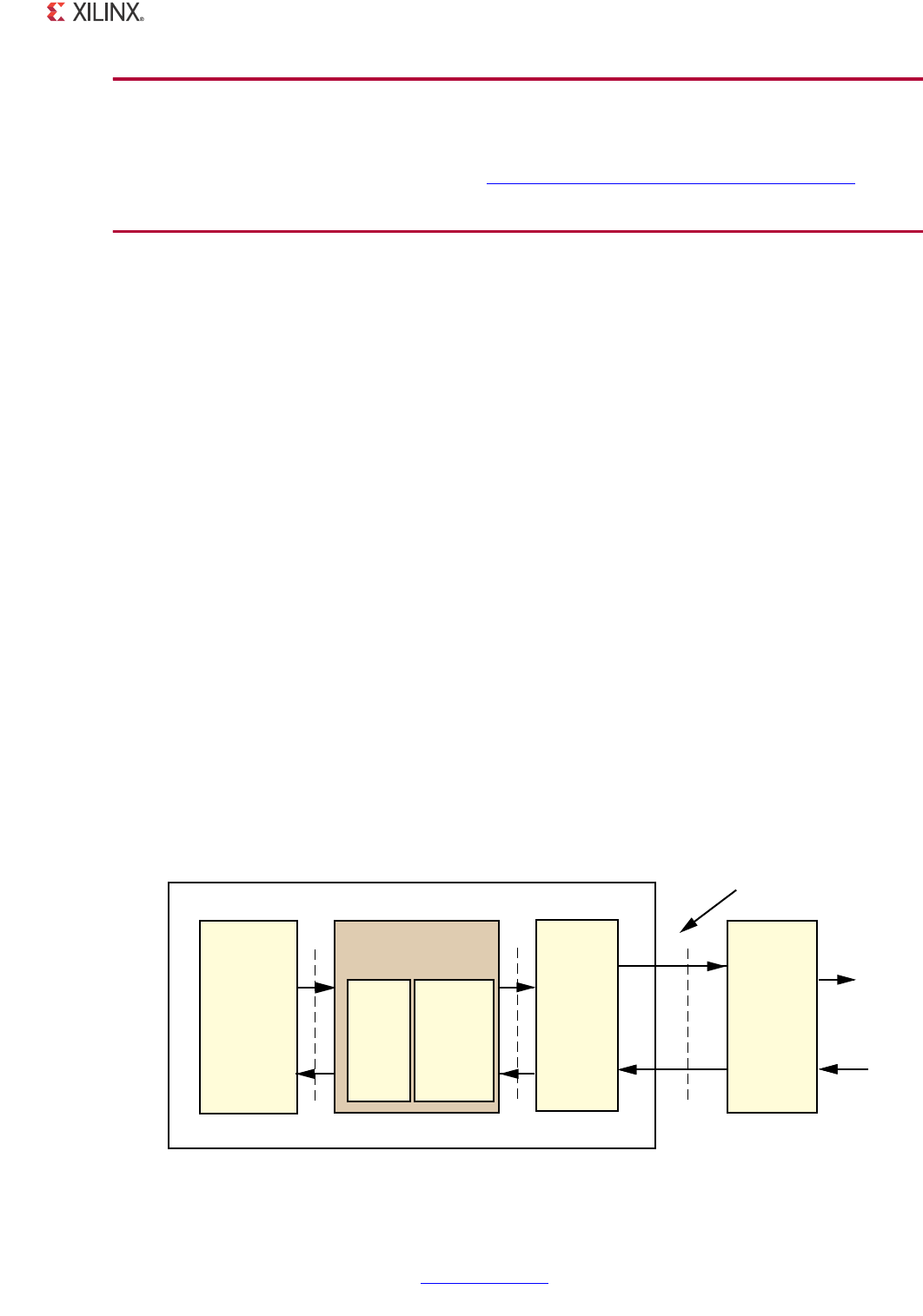

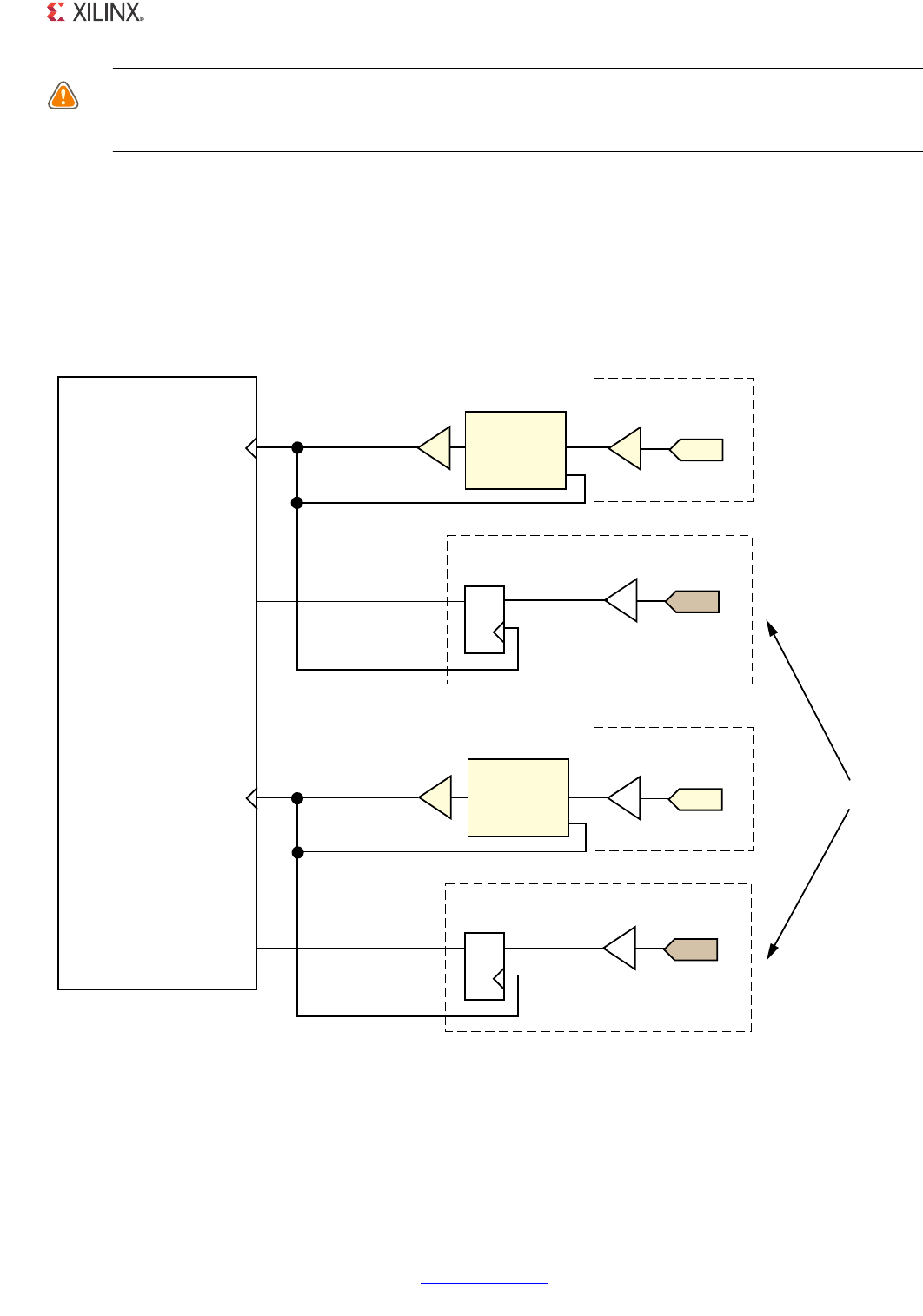

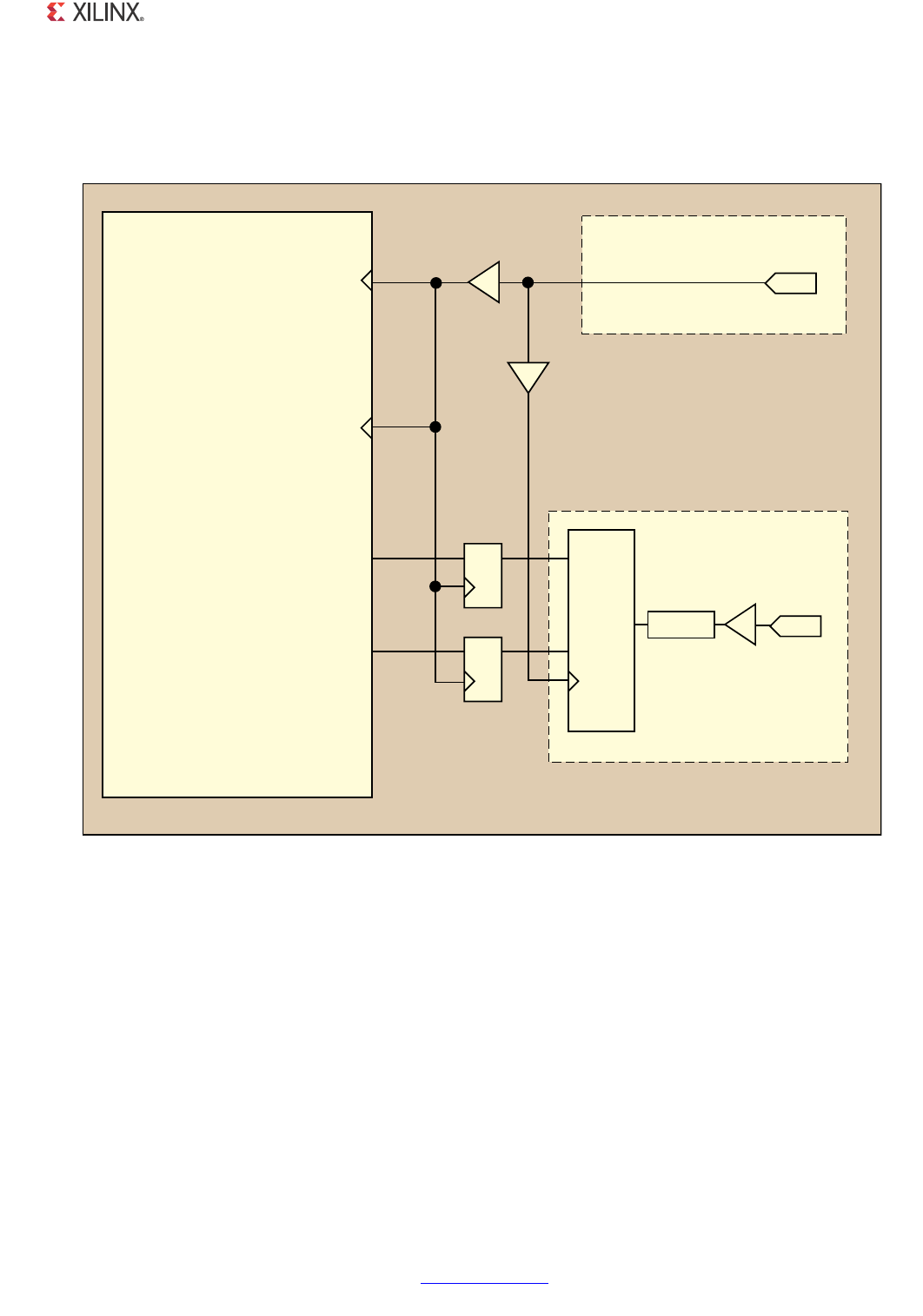

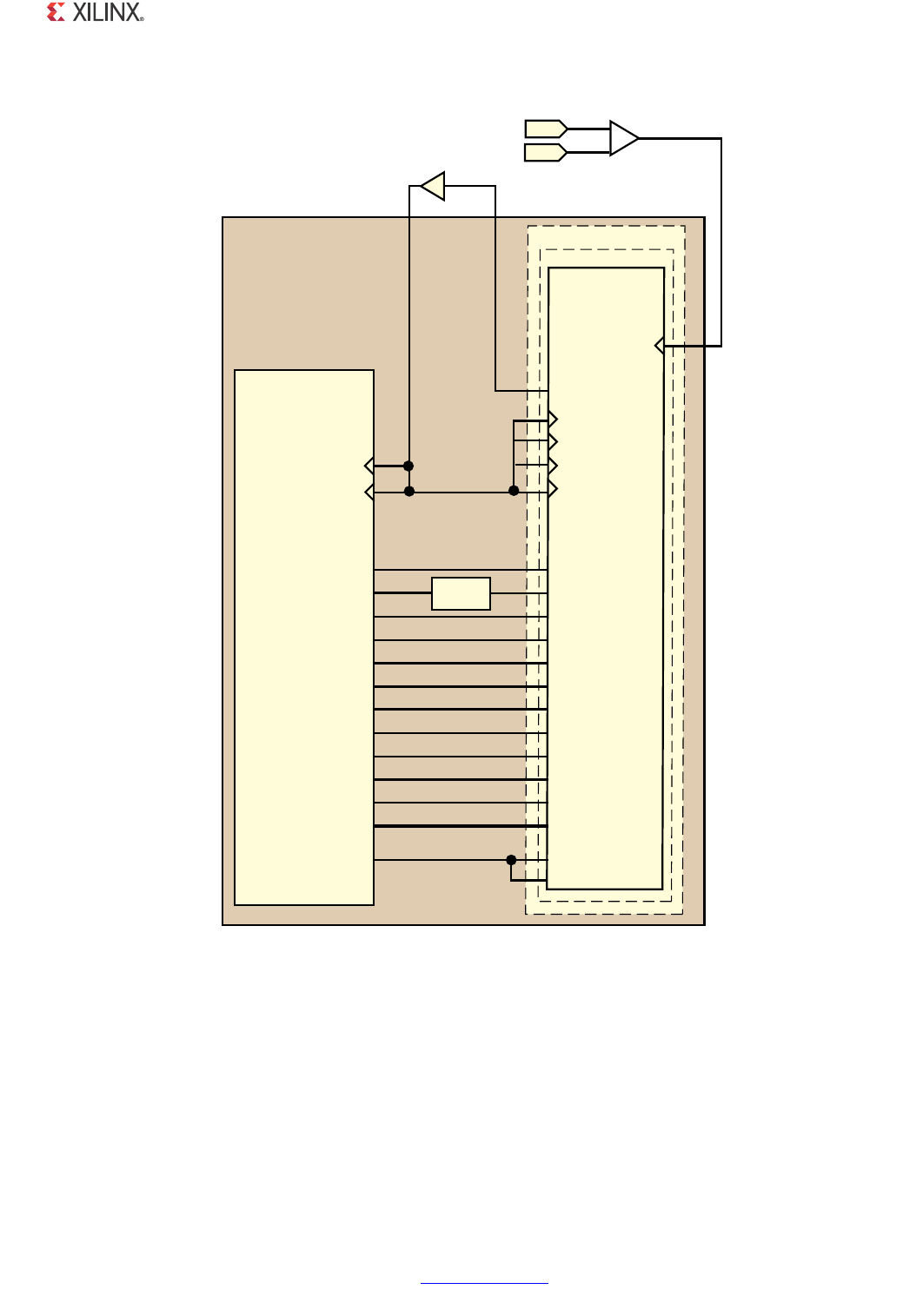

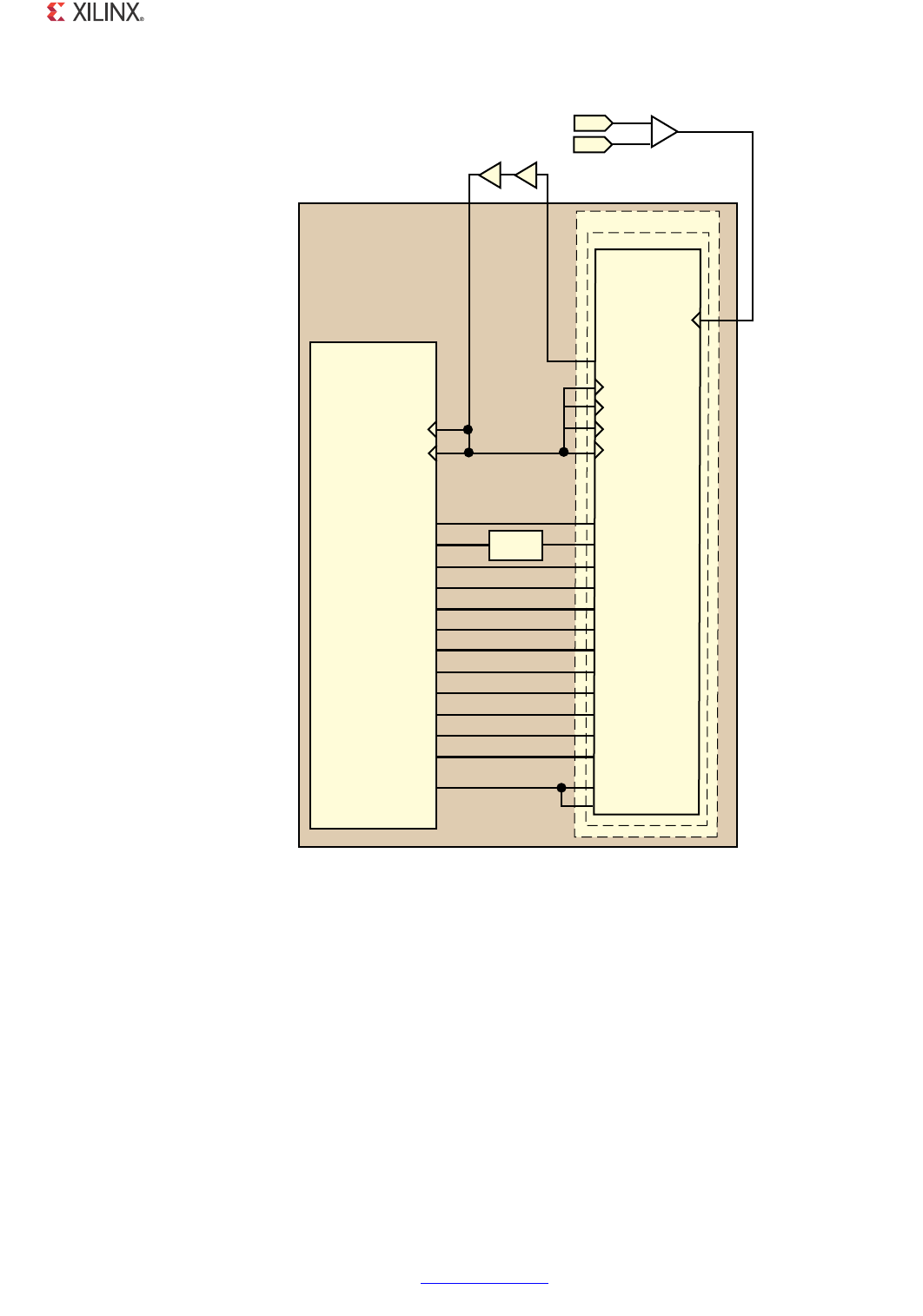

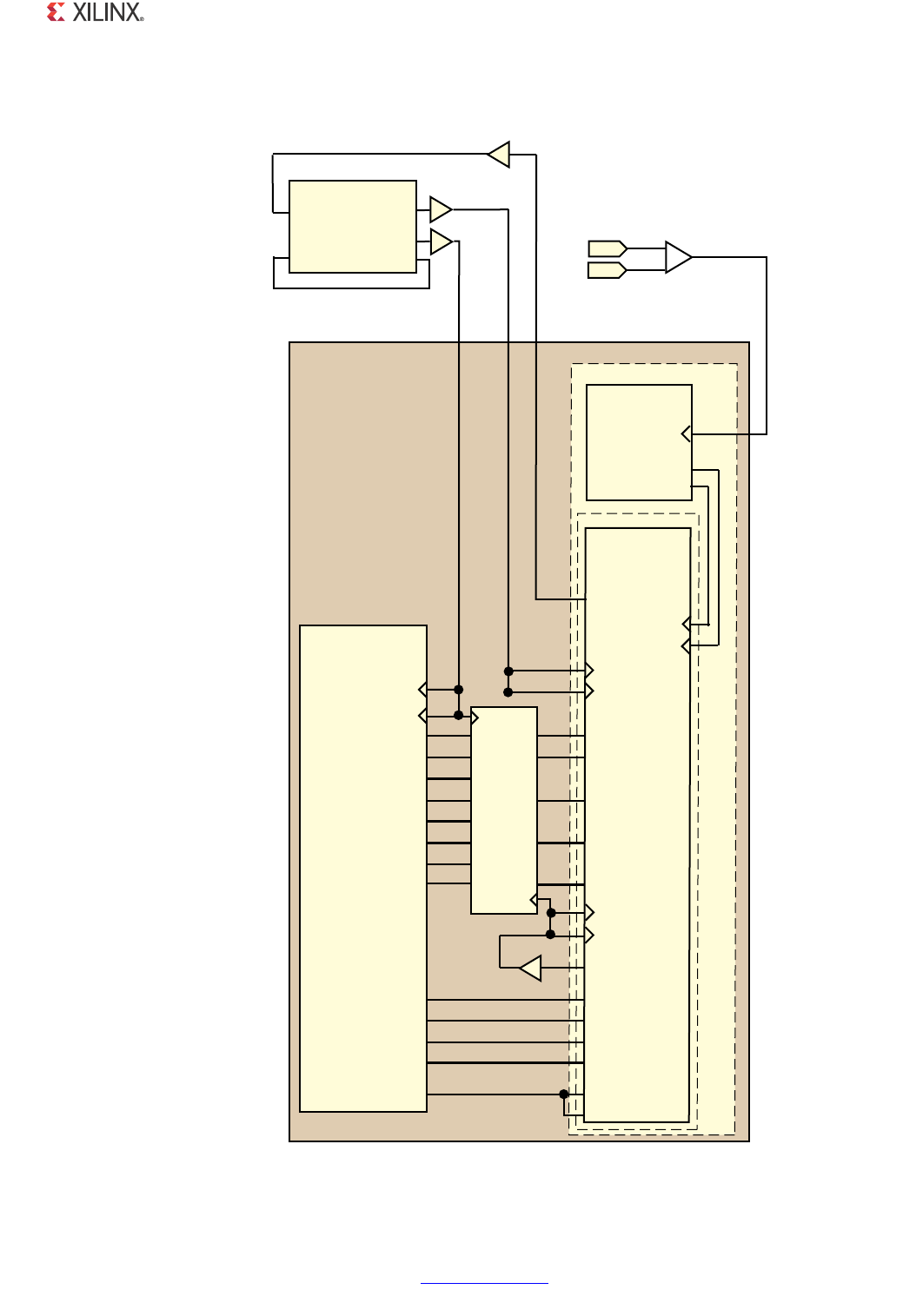

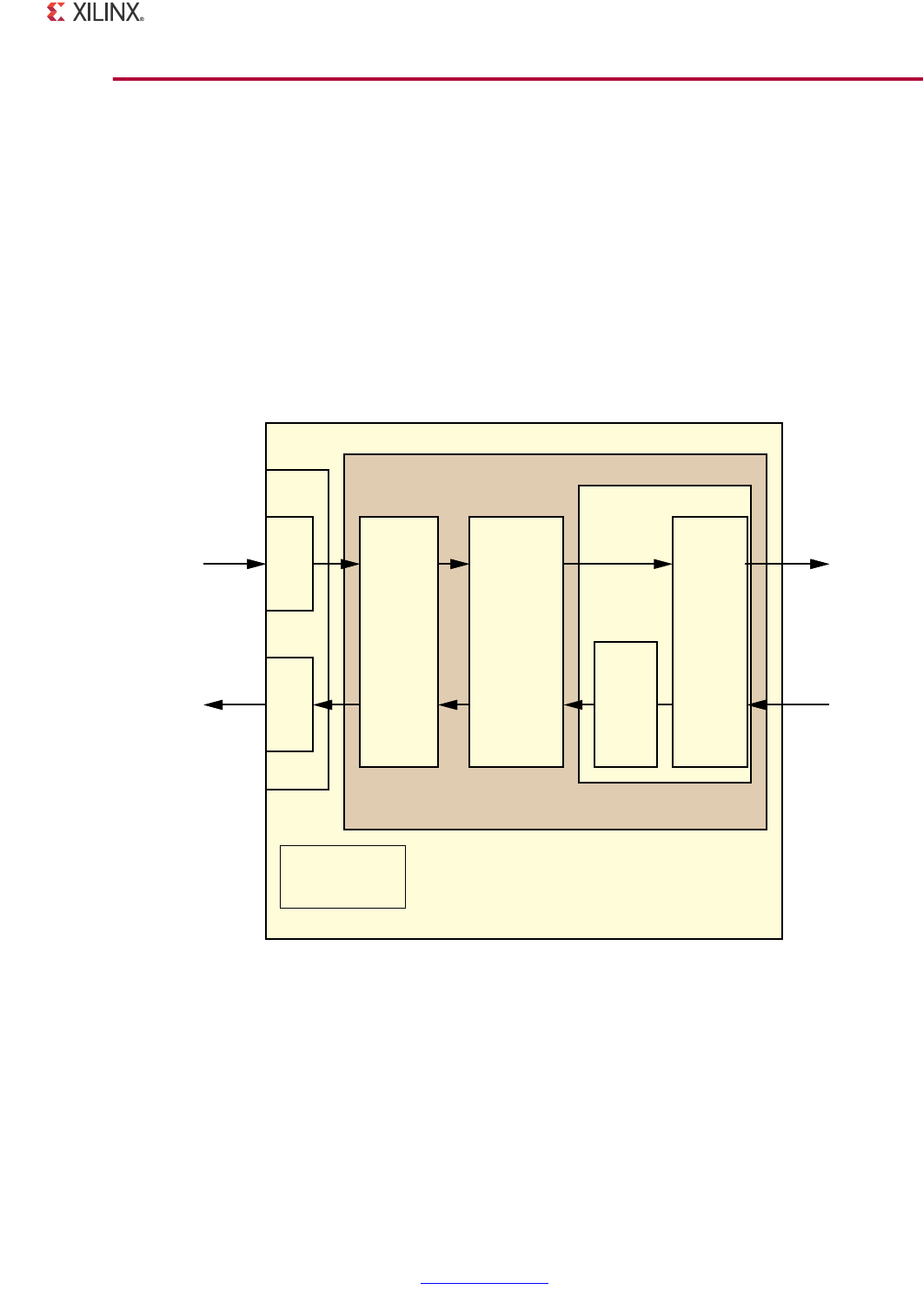

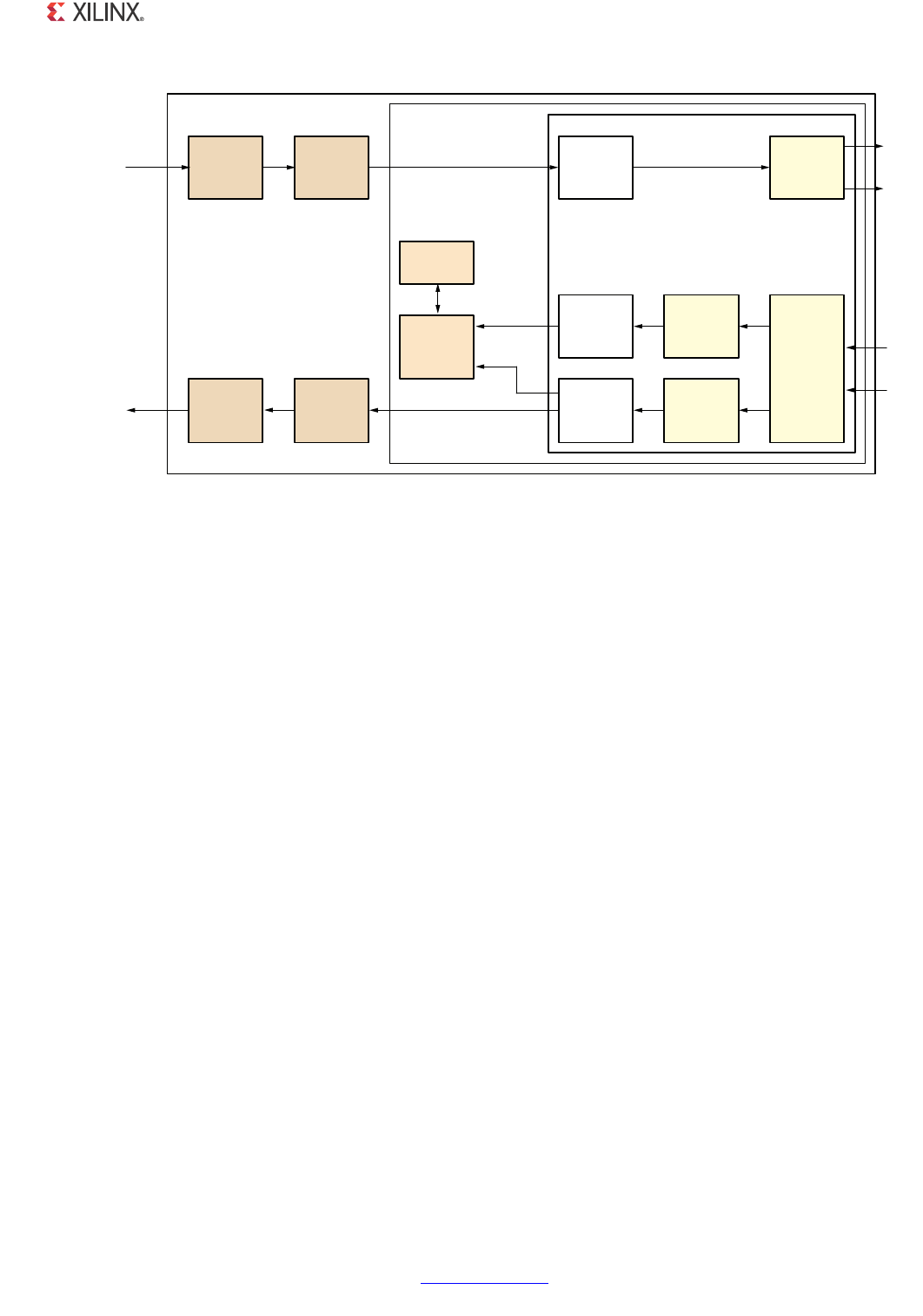

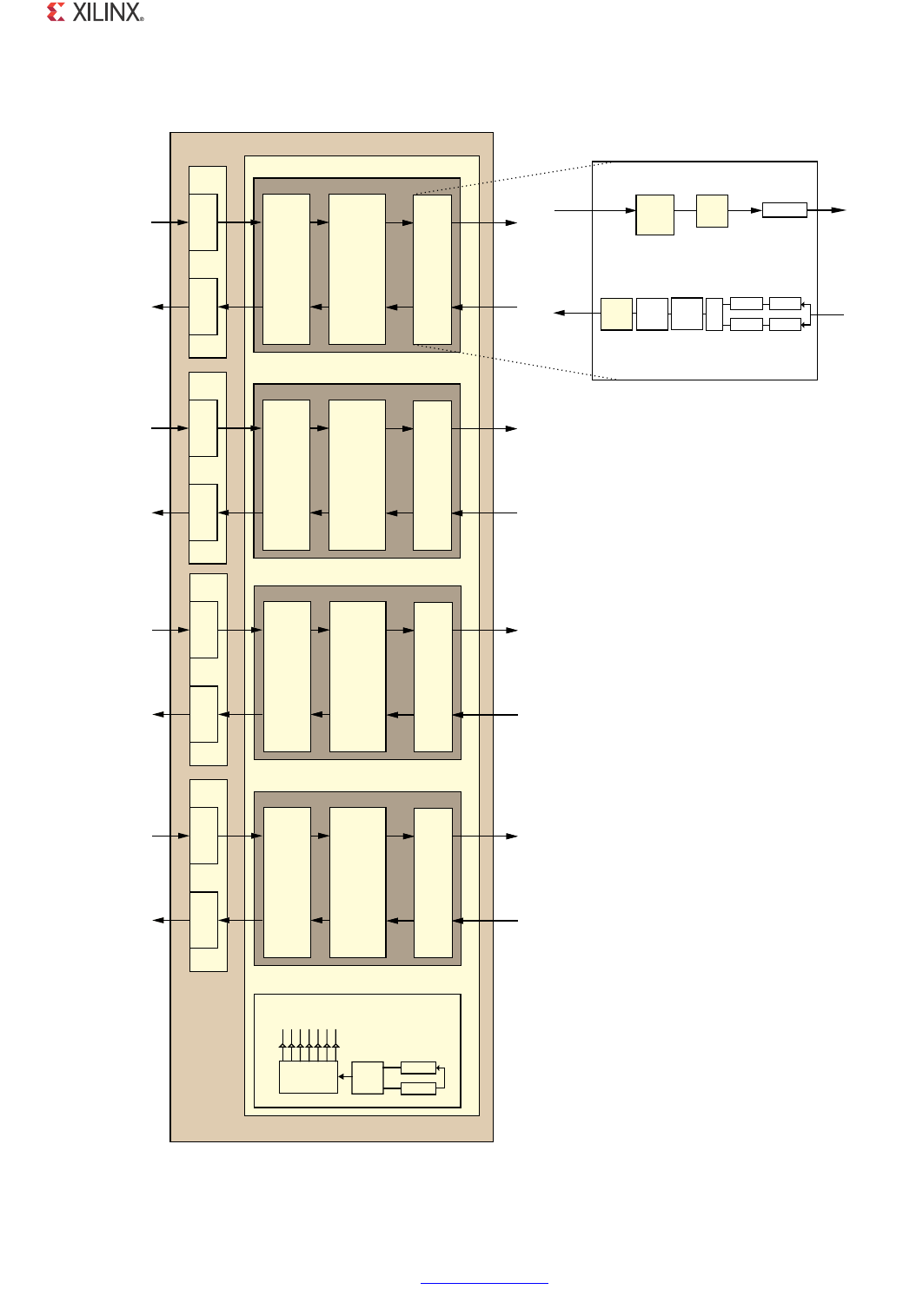

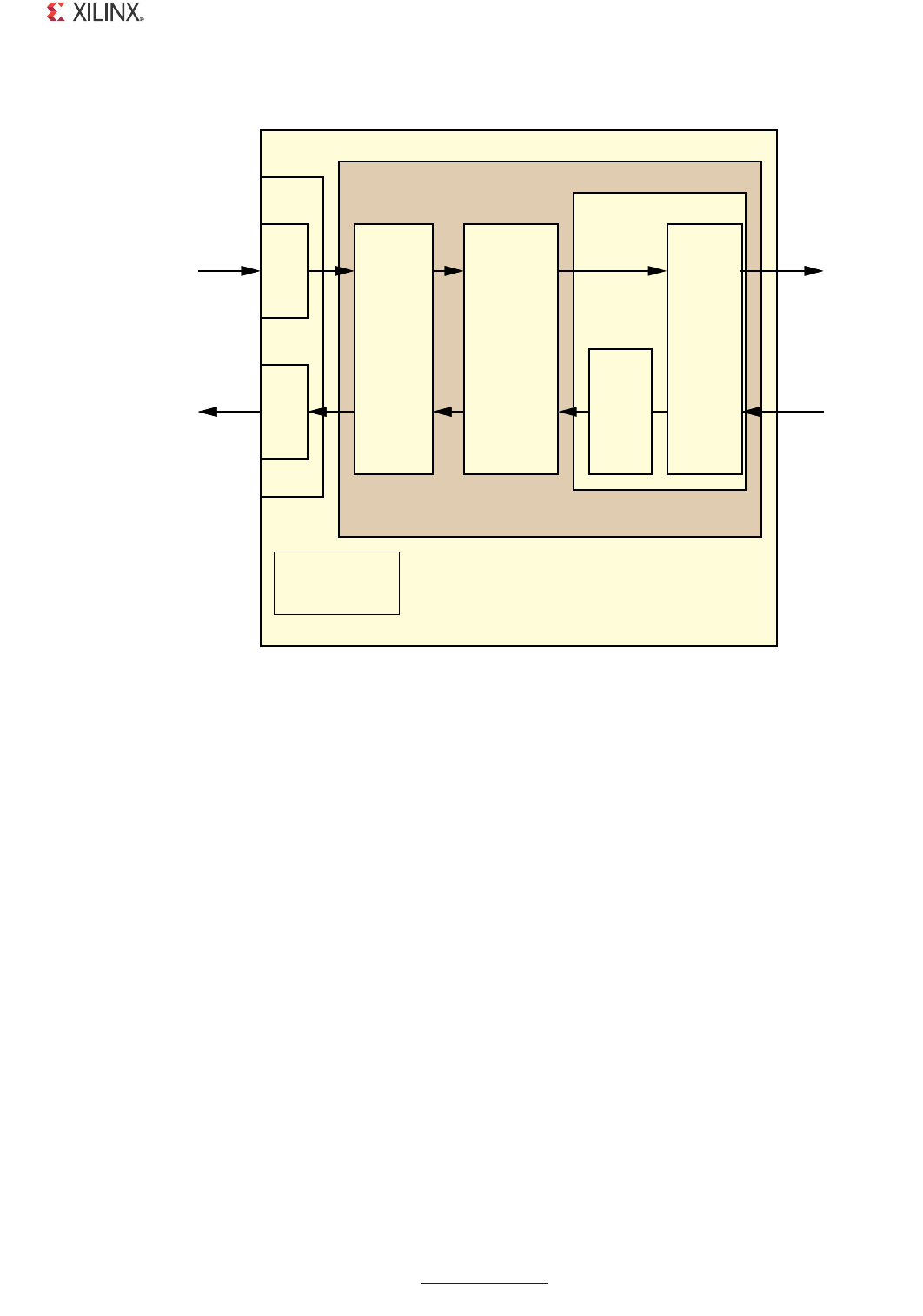

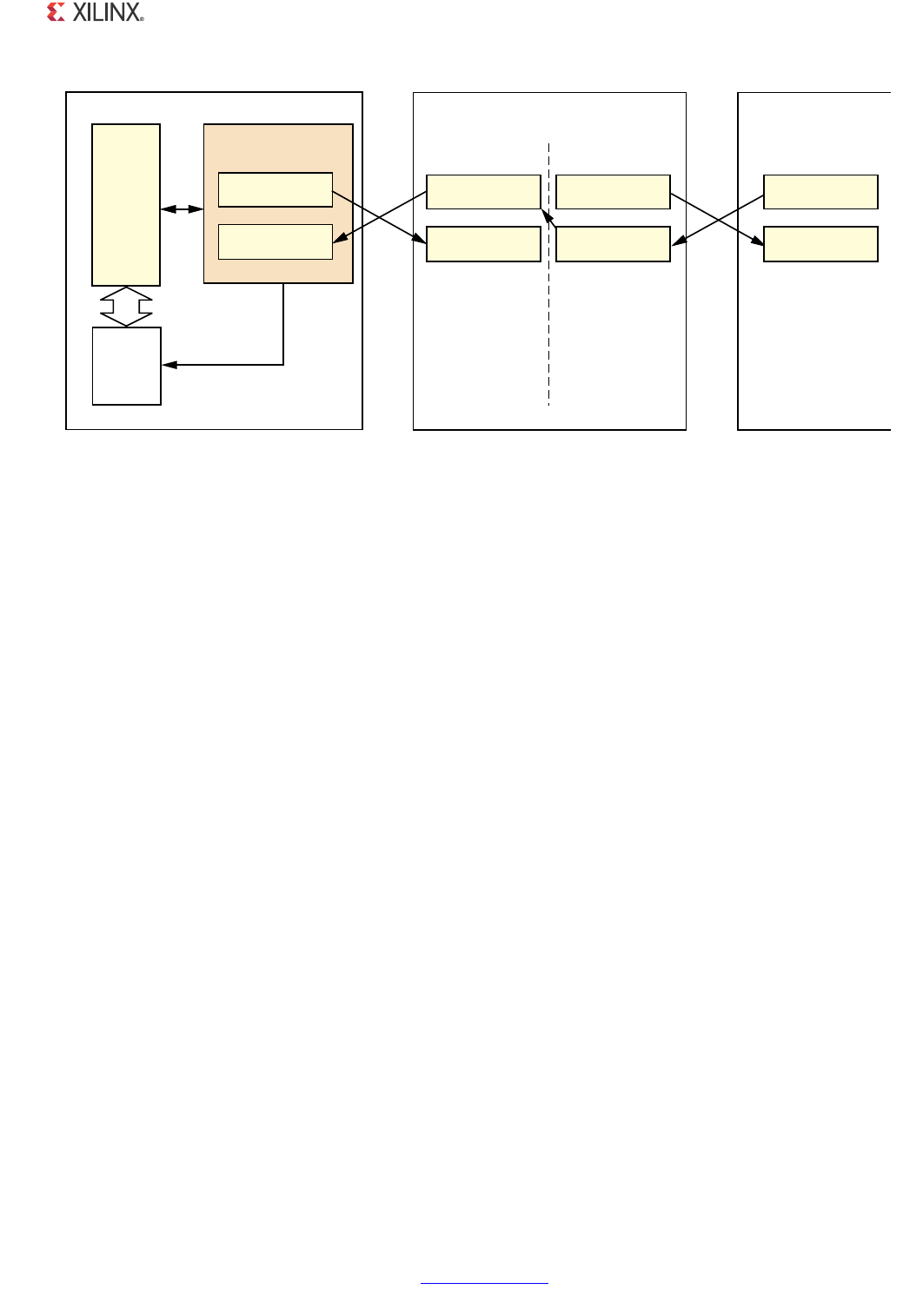

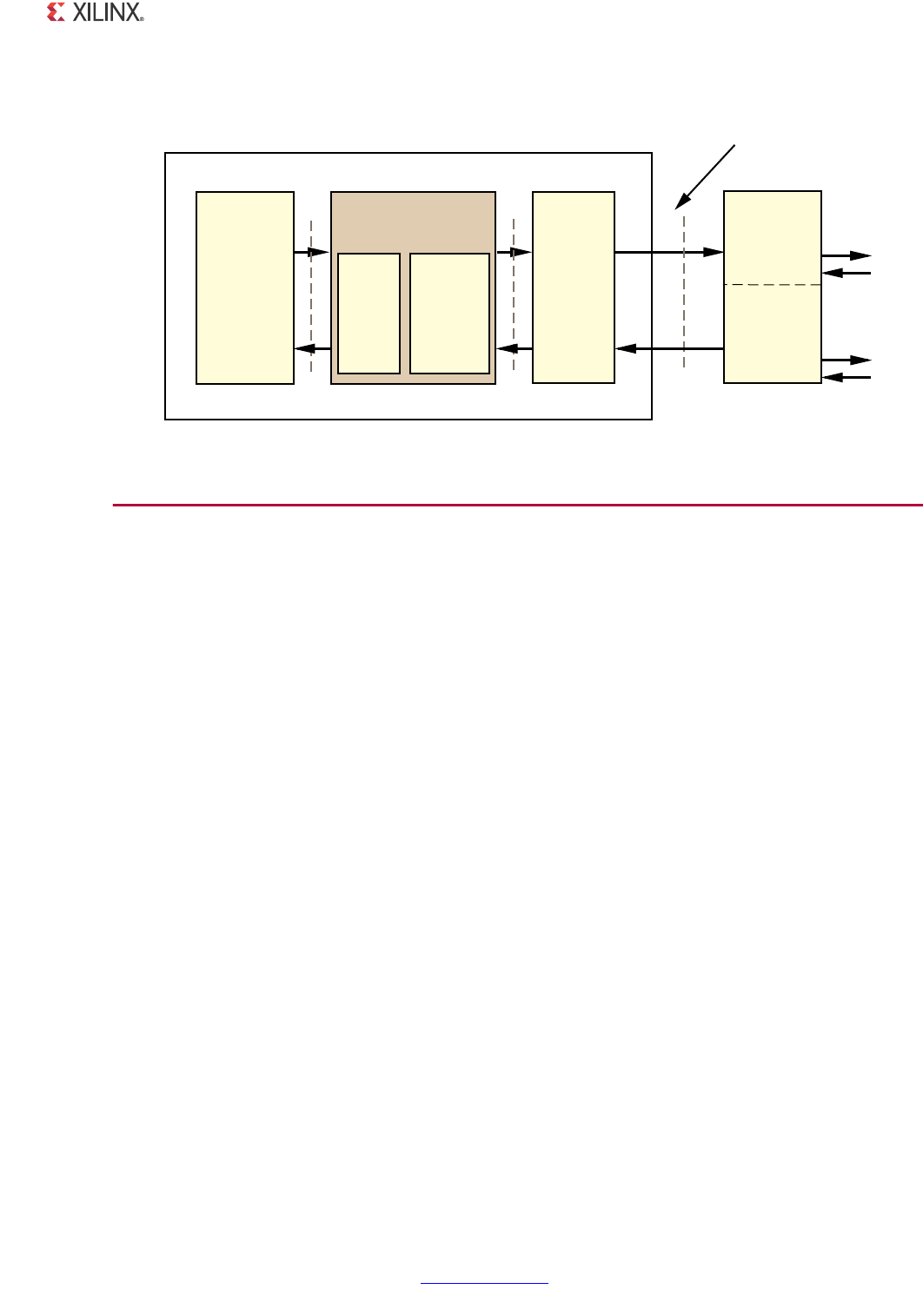

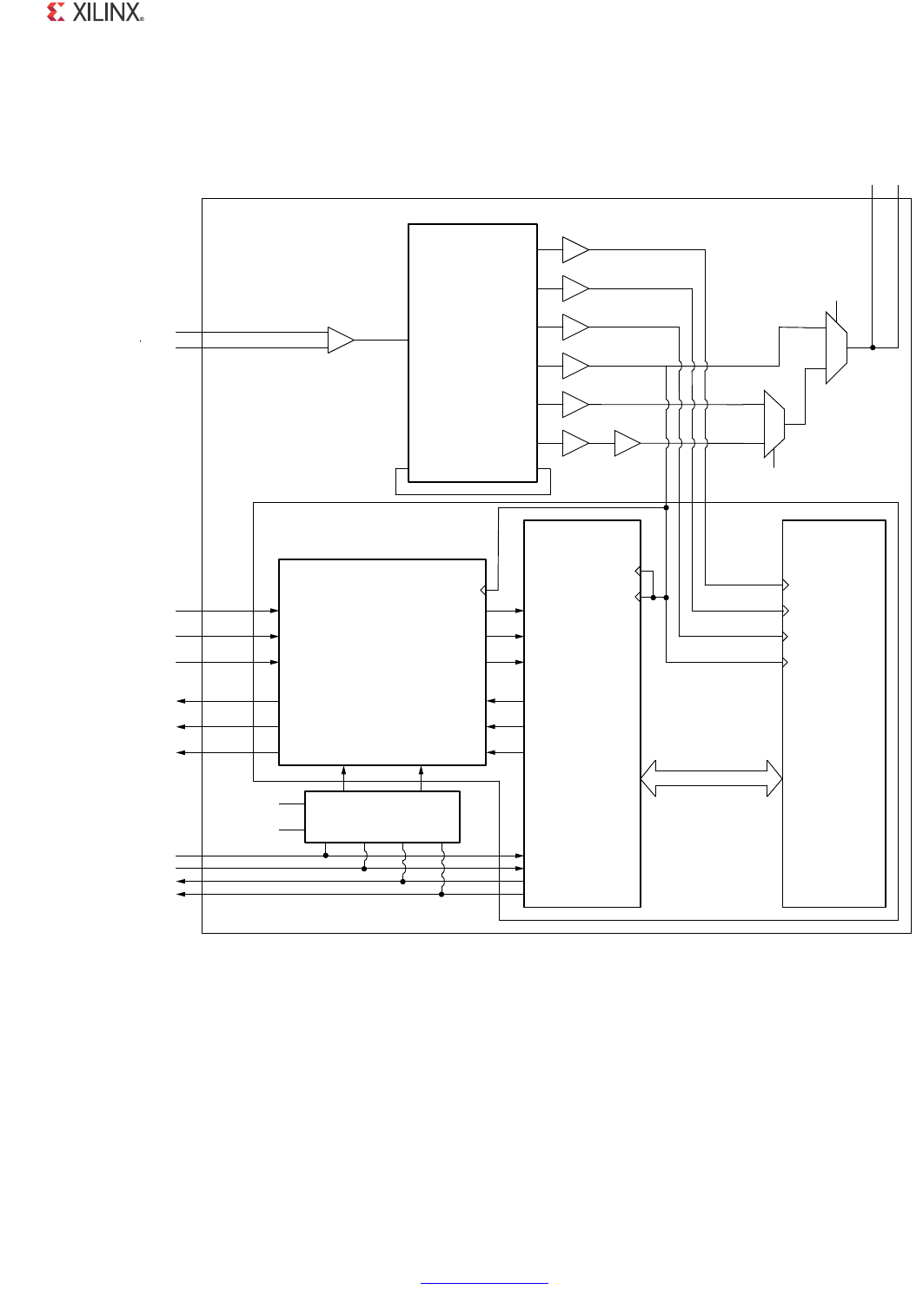

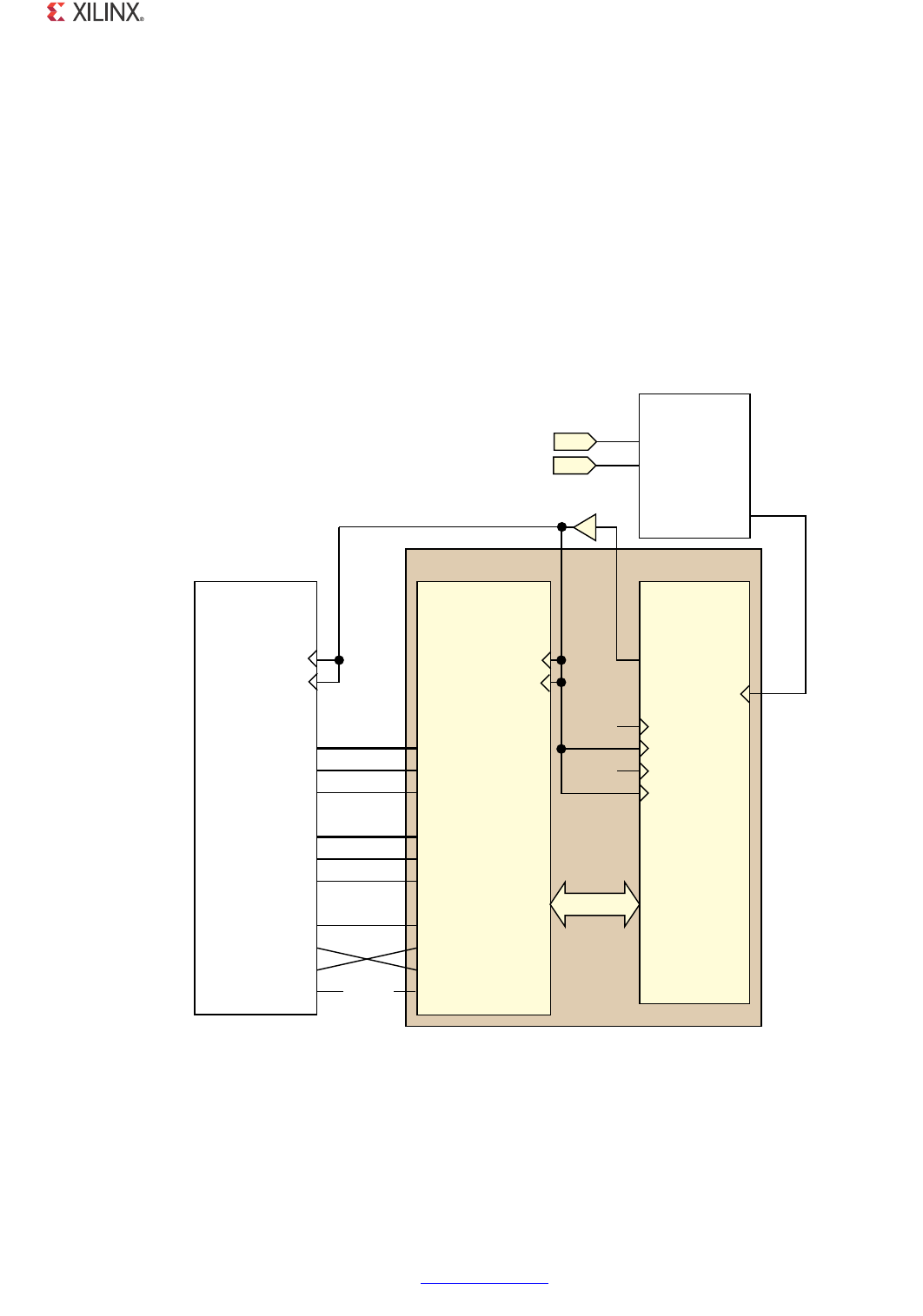

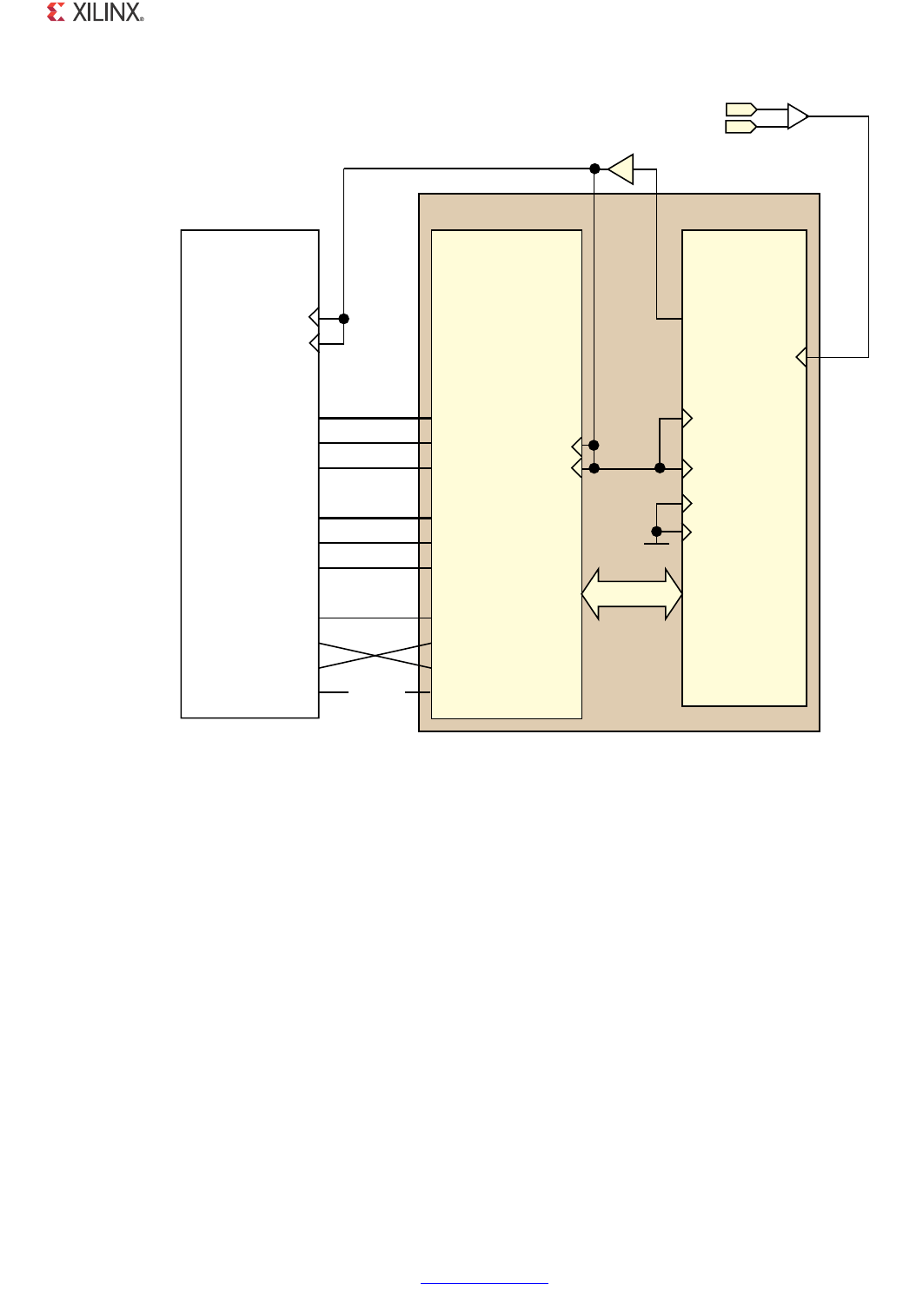

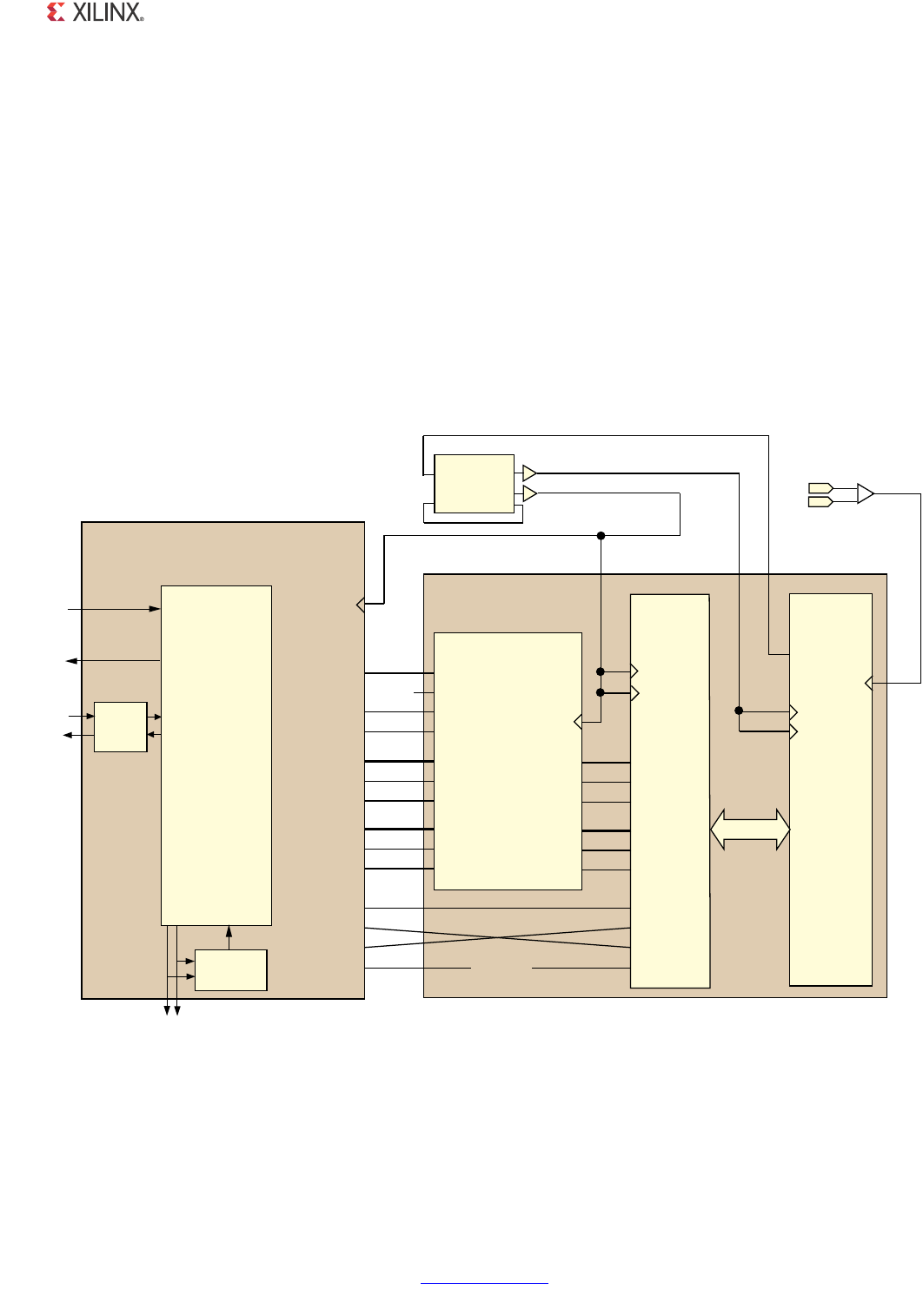

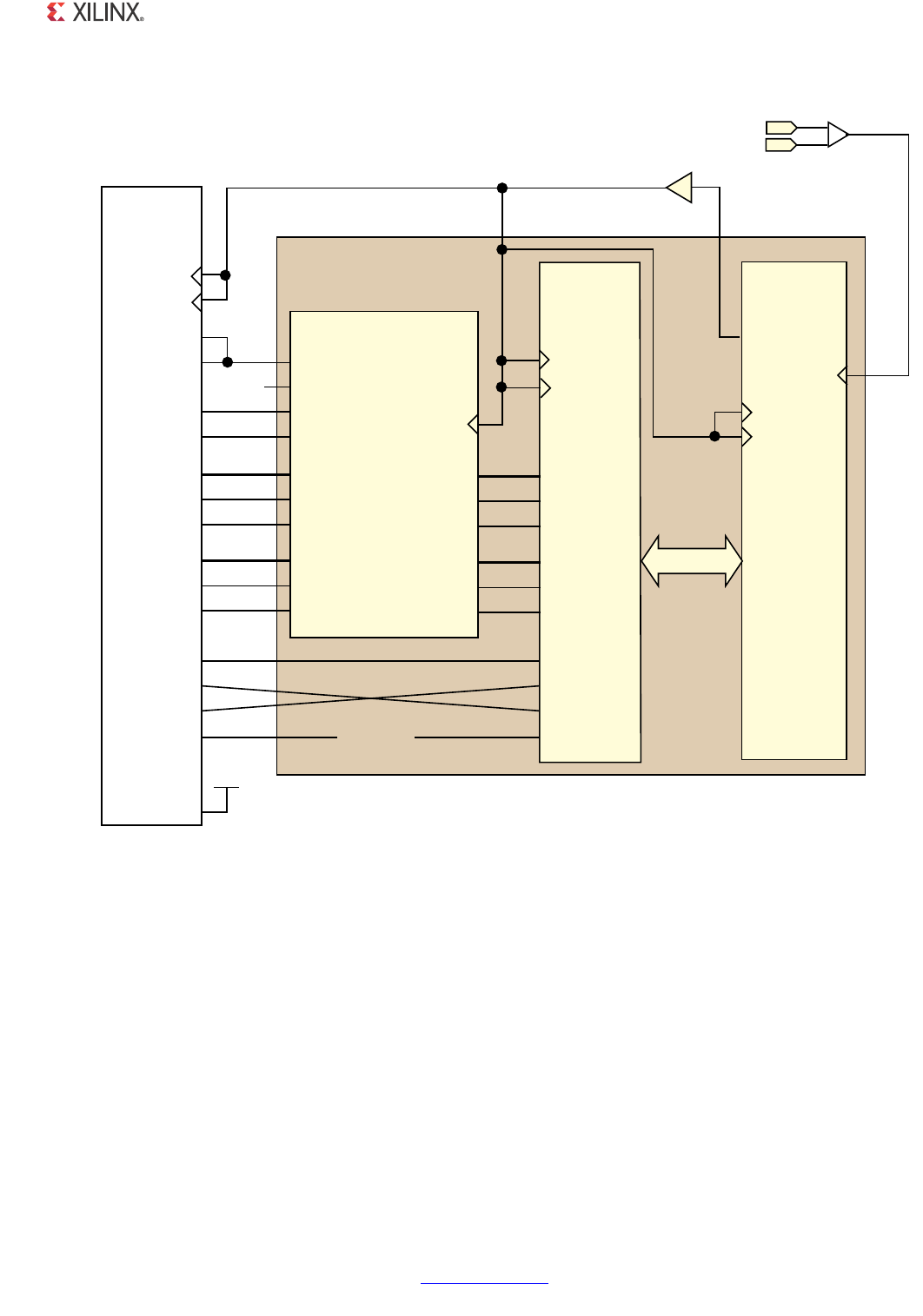

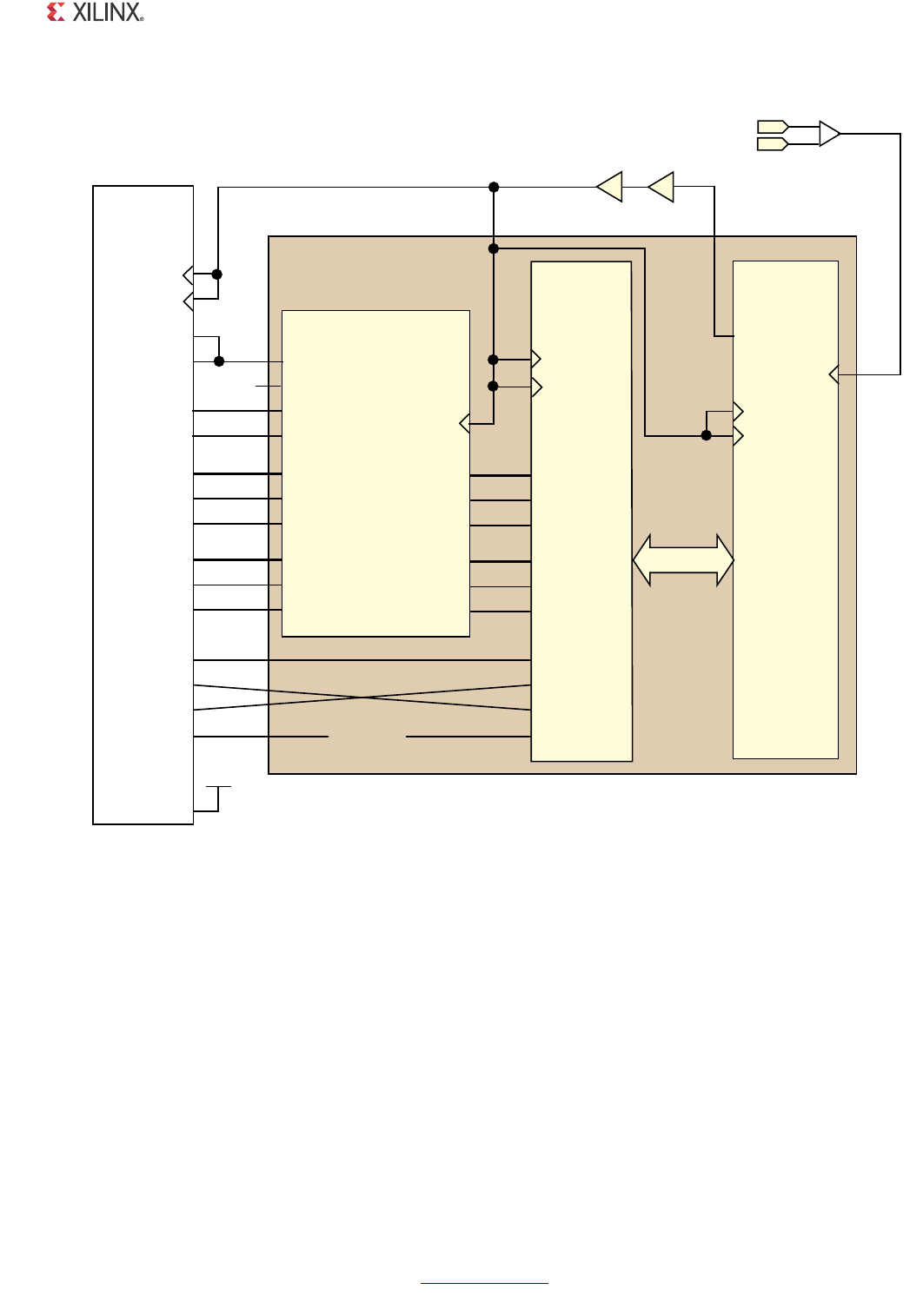

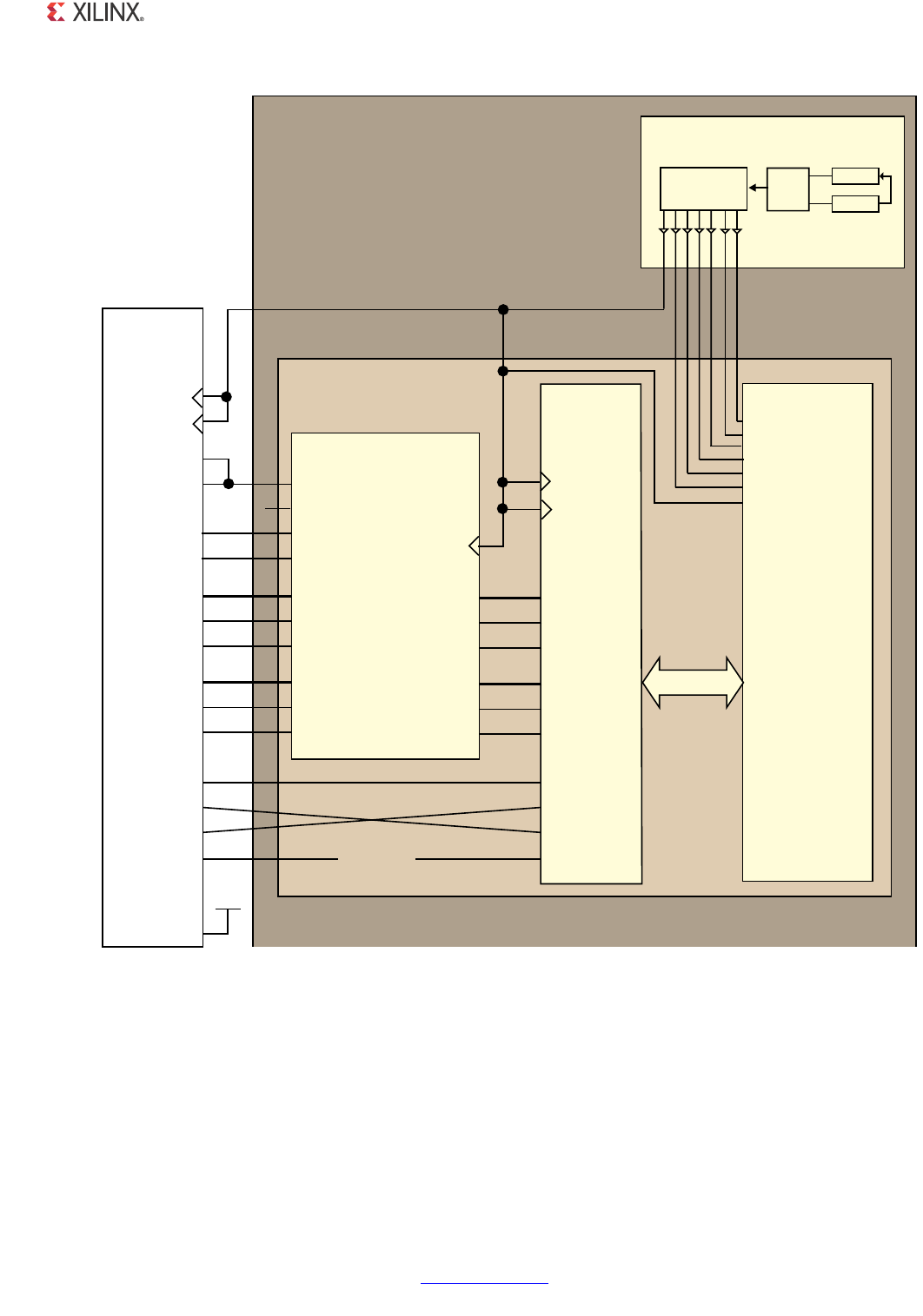

and clock recovery. Figure 1-1 illustrates the remaining PCS sublayer functionality and the

major functional blocks of the core. A description of the functional blocks and signals is

provided in subsequent sections.

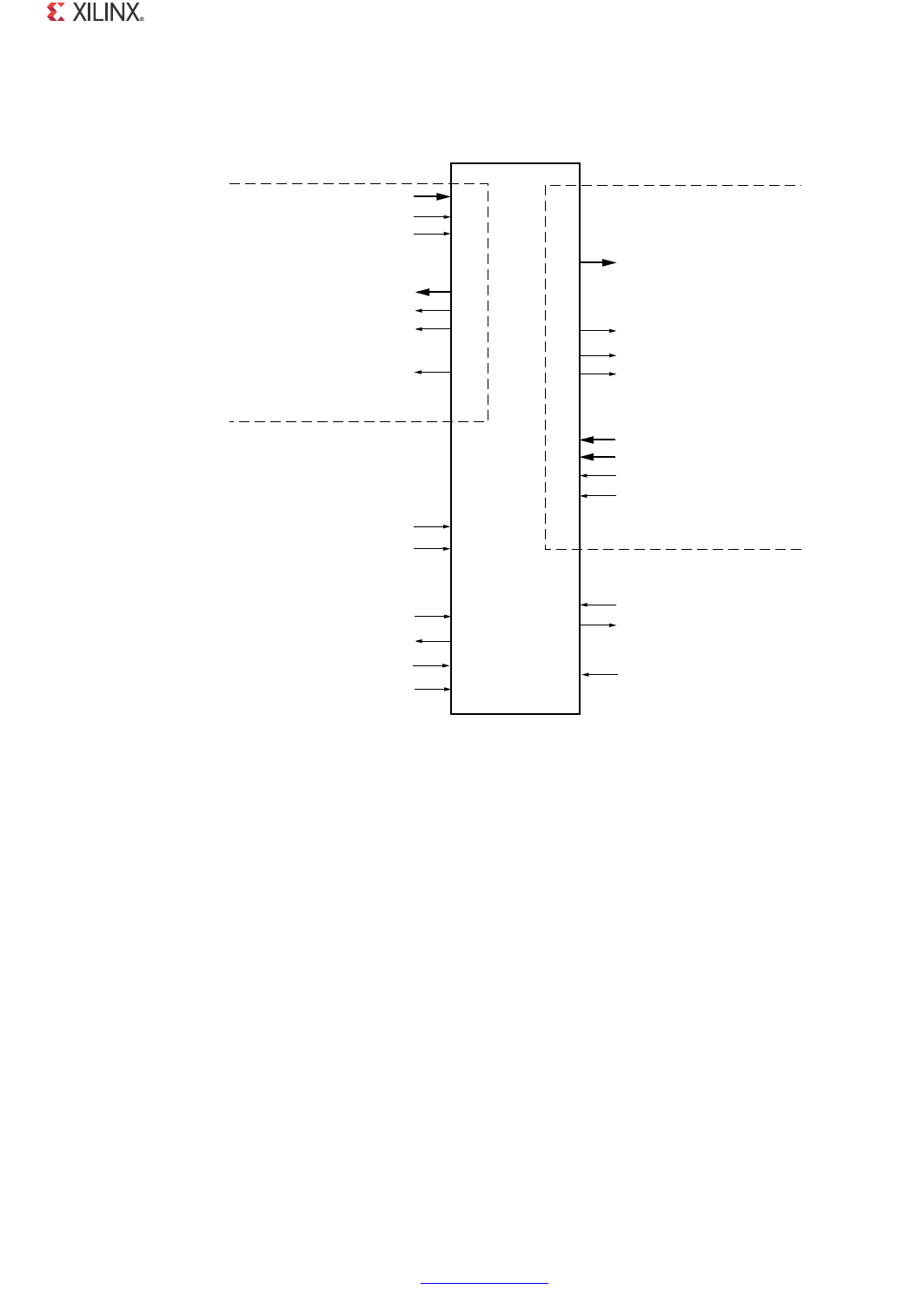

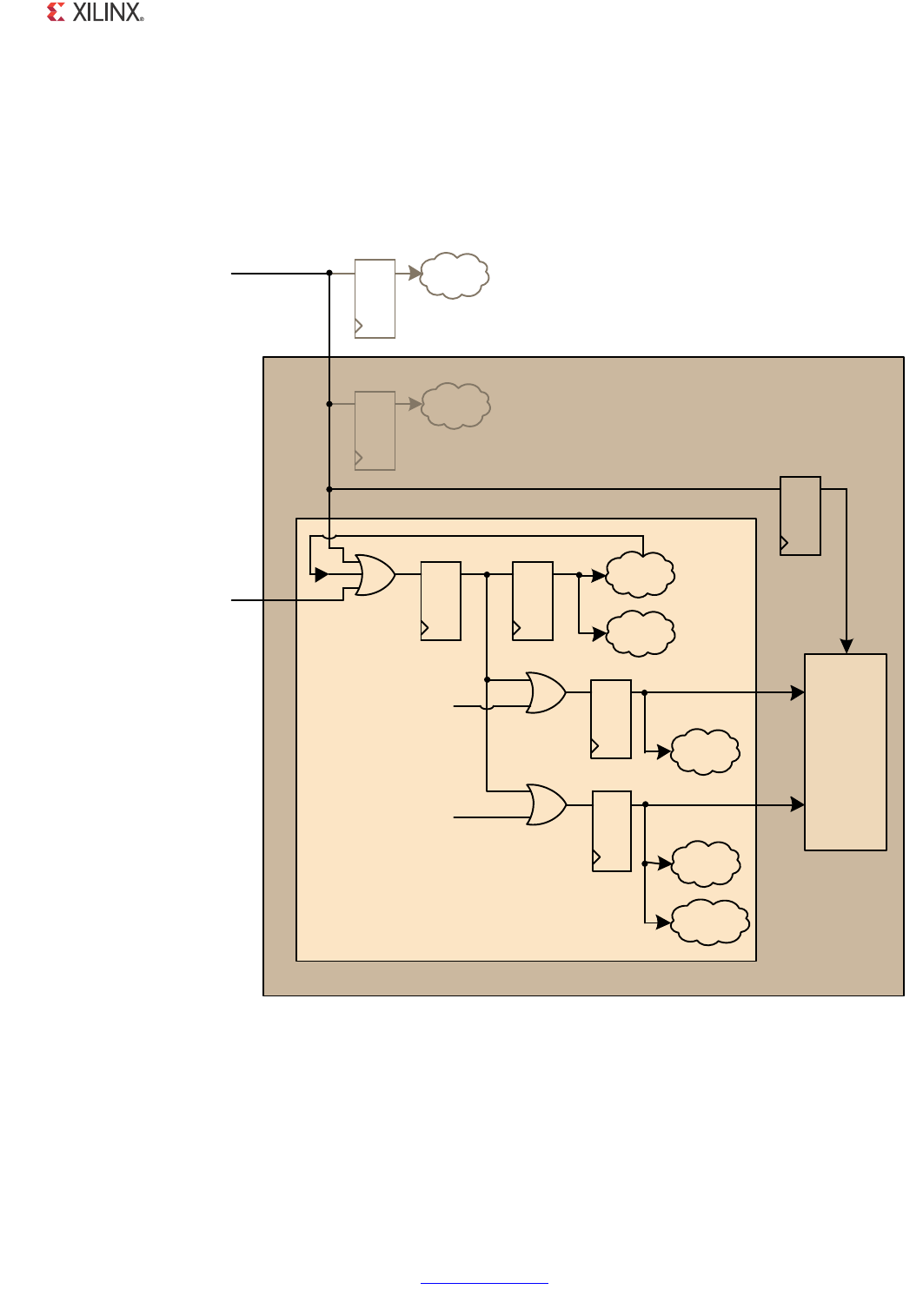

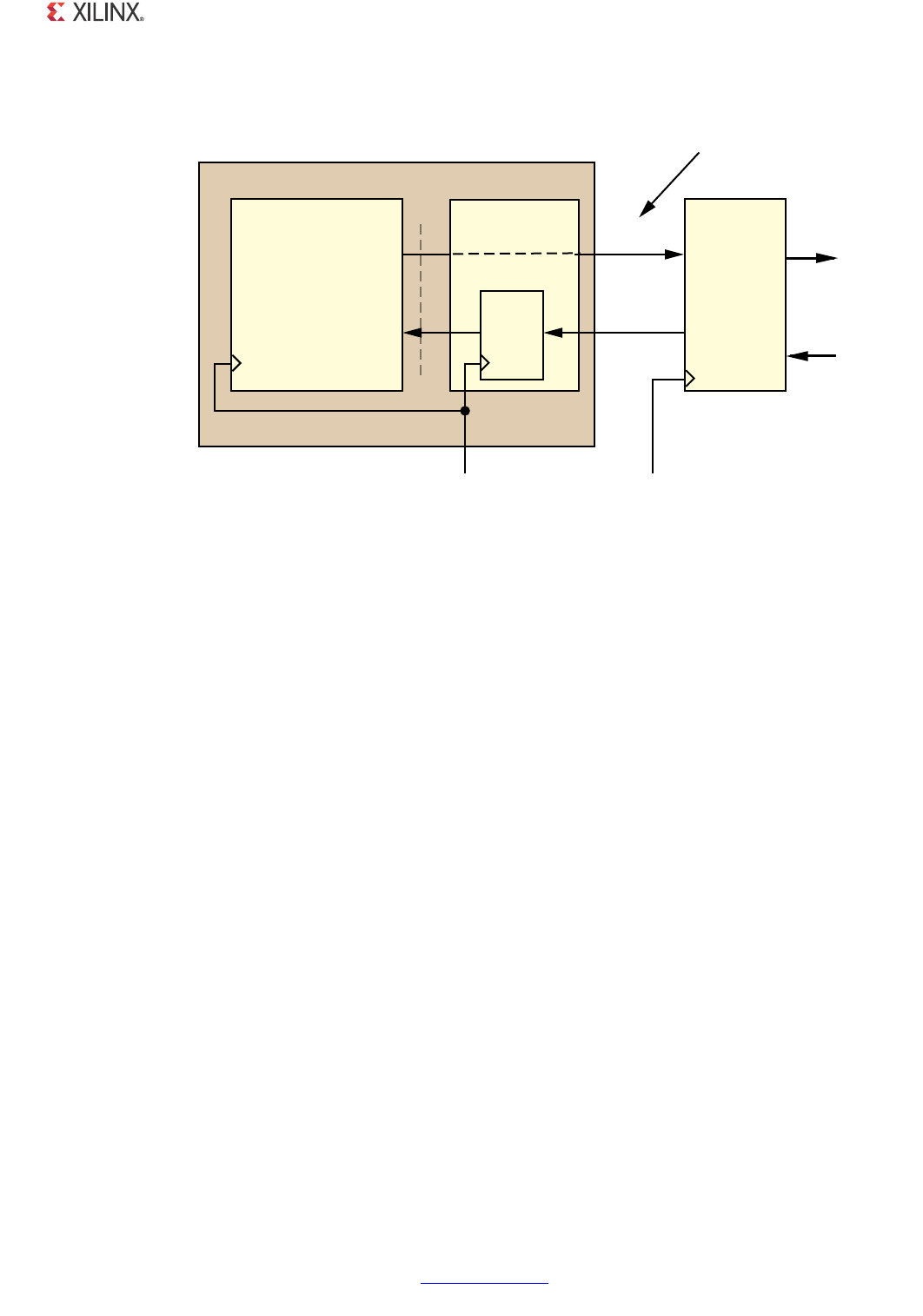

X-Ref Target - Figure 1-1

Figure 1-1: Ethernet 1000BASE-X PCS/PMA or SGMII Core Using a Device-Specific Transceiver

3&6 7UDQVPLW(QJLQH

3&65HFHLYH(QJLQH

DQG6\QFKURQL]DWLRQ

7UDQVFHLYHU

2SWLRQDO3&6

0DQDJHPHQW

*0,,

WR0$&

0',2

,QWHUIDFH

2SWLRQDO

$XWR1HJRWLDWLRQ 7R30'

6XEOD\HU

*0,,%ORFN

/RJL&25((WKHUQHW%$6(;3&630$RU6*0,,&RUH

7UDQVFHLYHU,)%ORFN

8

1000BASE-X PCS/PMA or SGMII v11.4 www.xilinx.com 13

PG047 October 16, 2012

Chapter 1: Overview

GMII Block

The core provides a client-side GMII. This can be used as an internal interface for

connection to an embedded Ethernet MAC or other custom logic. Alternatively, the core

GMII can be routed to device Input/Output Blocks (IOBs) to provide an off-chip GMII.

Virtex-7 devices support GMII at 3.3 V or lower only in certain parts and packages; see the

7 Series FPGAs SelectIO Resources User Guide. Virtex-6 devices support GMII at 2.5 V only;

see the Virtex-6 FPGA Data Sheet: DC and Switching Characteristics. Kintex-7, Artix-7,

Spartan-6, Virtex-5, Virtex-4 and Spartan-3 devices support GMII at 3.3 V or lower.

PCS Transmit Engine

The PCS transmit engine converts the GMII data octets into a sequence of ordered sets by

implementing the state diagrams of IEEE 802.3-2008 (Figures 36-5 and 36-6).

PCS Receive Engine and Synchronization

The synchronization process implements the state diagram of IEEE 802.3-2008 (Figure

36-9). The PCS receive engine converts the sequence of ordered sets to GMII data octets by

implementing the state diagrams of IEEE 802.3-2008 (Figures 36-7a and 36-7b).

Optional Auto-Negotiation Block

IEEE 802.3-2008 clause 37 describes the 1000BASE-X Auto-Negotiation function that allows

a device to advertise the supported modes of operation to a device at the remote end of a

link segment (link partner), and to detect corresponding operational modes that the link

partner might be advertising. Auto-Negotiation is controlled and monitored through the

PCS Management registers.

Optional PCS Management Registers

Configuration and status of the core, including access to and from the optional

Auto-Negotiation function, is performed with the 1000BASE-X PCS Management registers

as defined in IEEE 802.3-2008 clause 37. These registers are accessed through the serial

Management Data Input/Output Interface (MDIO), defined in IEEE 802.3-2008 clause 22, as

if it were an externally connected PHY.

An additional configuration interface is provided to program Control register (Register 0)

and Auto-Negotiation advertisement (Register 4) independent of the MDIO interface.

The PCS Management registers can be omitted from the core when the core is performing

the 1000BASE-X standard. In this situation, configuration and status is made possible by

using additional configuration vector and status signals. When the core is performing the

SGMII standard, PCS Management registers become mandatory and information in the

registers takes on a different interpretation.

1000BASE-X PCS/PMA or SGMII v11.4 www.xilinx.com 14

PG047 October 16, 2012

Chapter 1: Overview

Transceiver Interface Block

The interface block enables the core to connect to a device-specific transceiver.

Ethernet 1000BASE-X PCS/PMA or SGMII Support with Ten-Bit

Interface

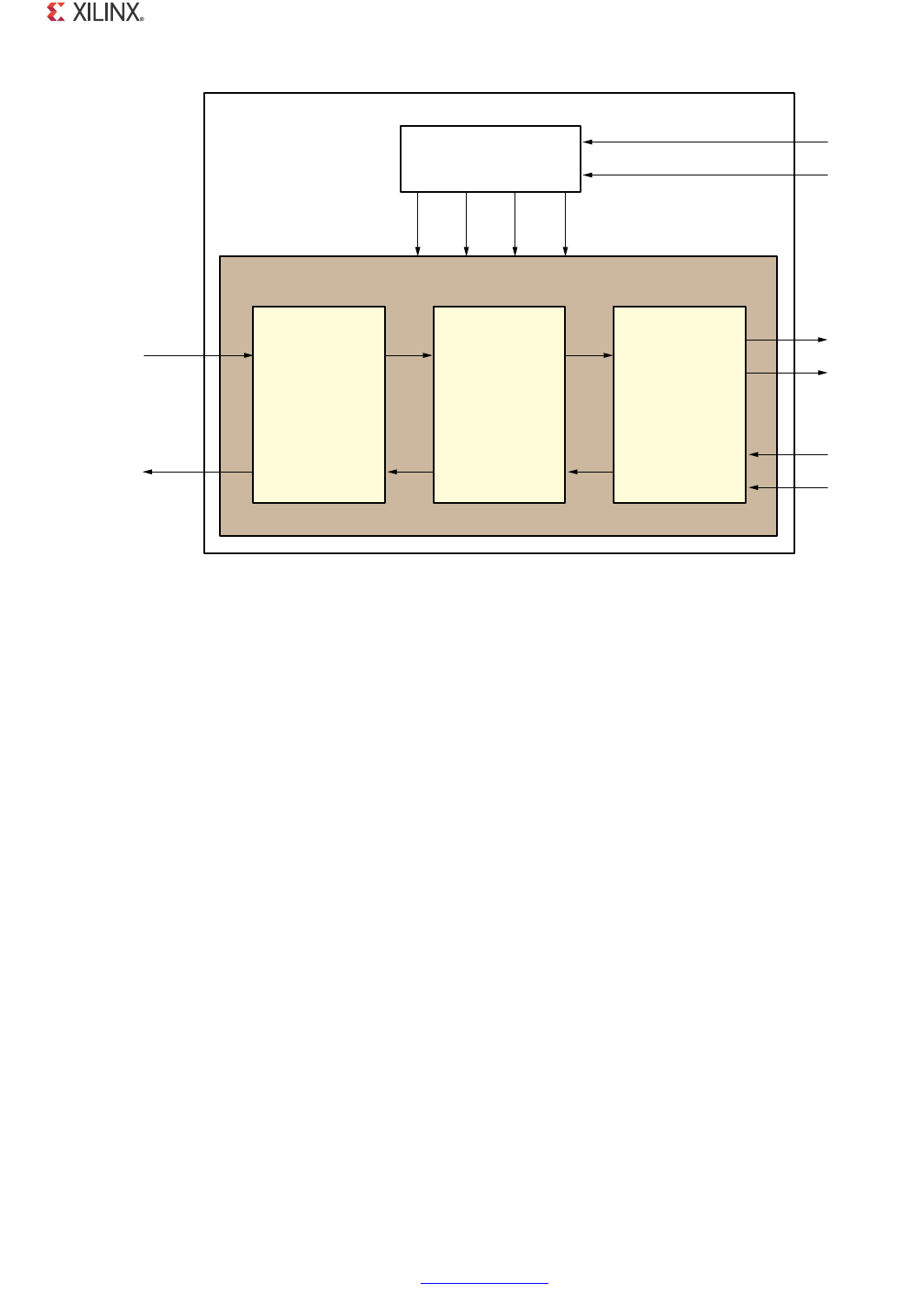

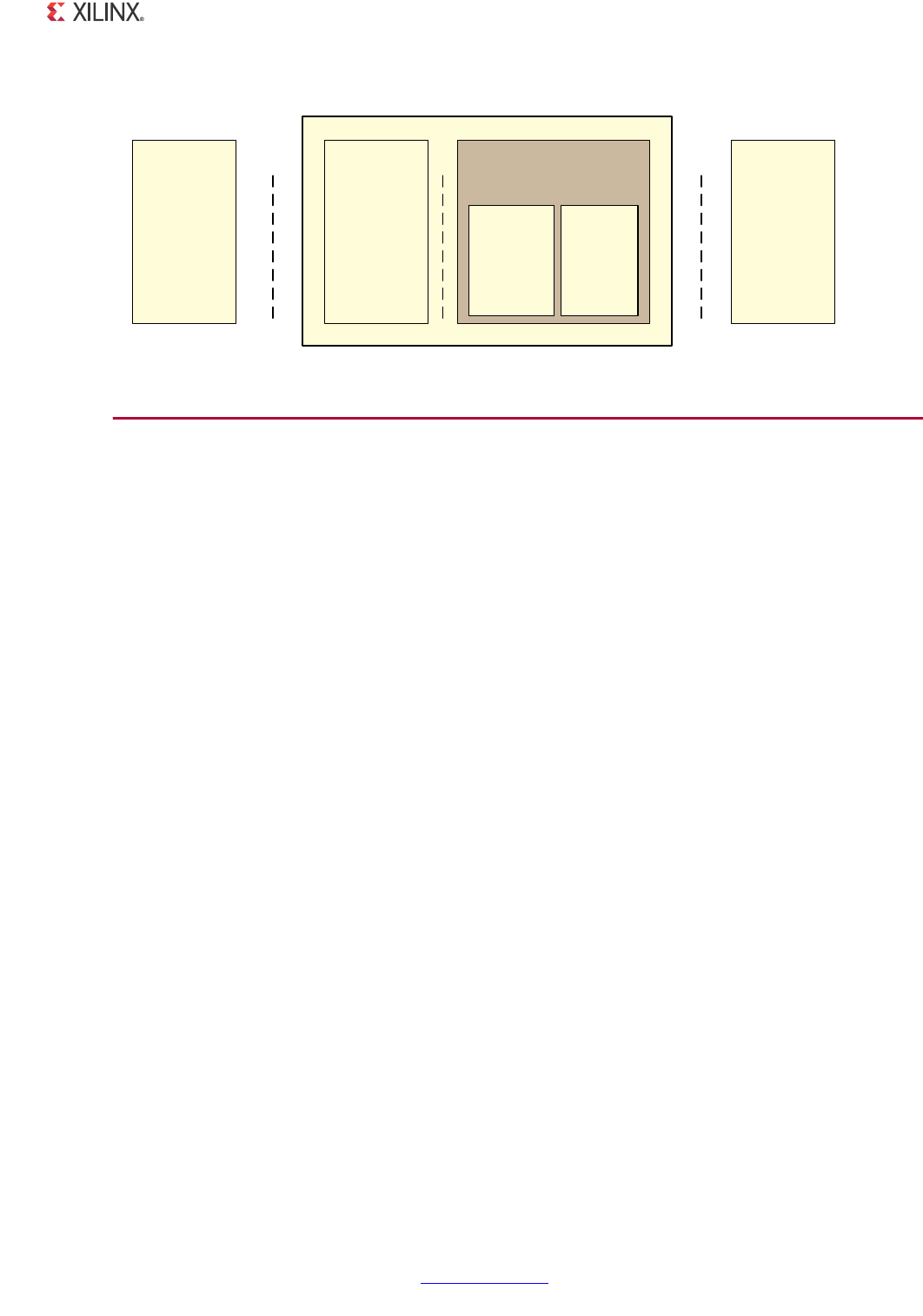

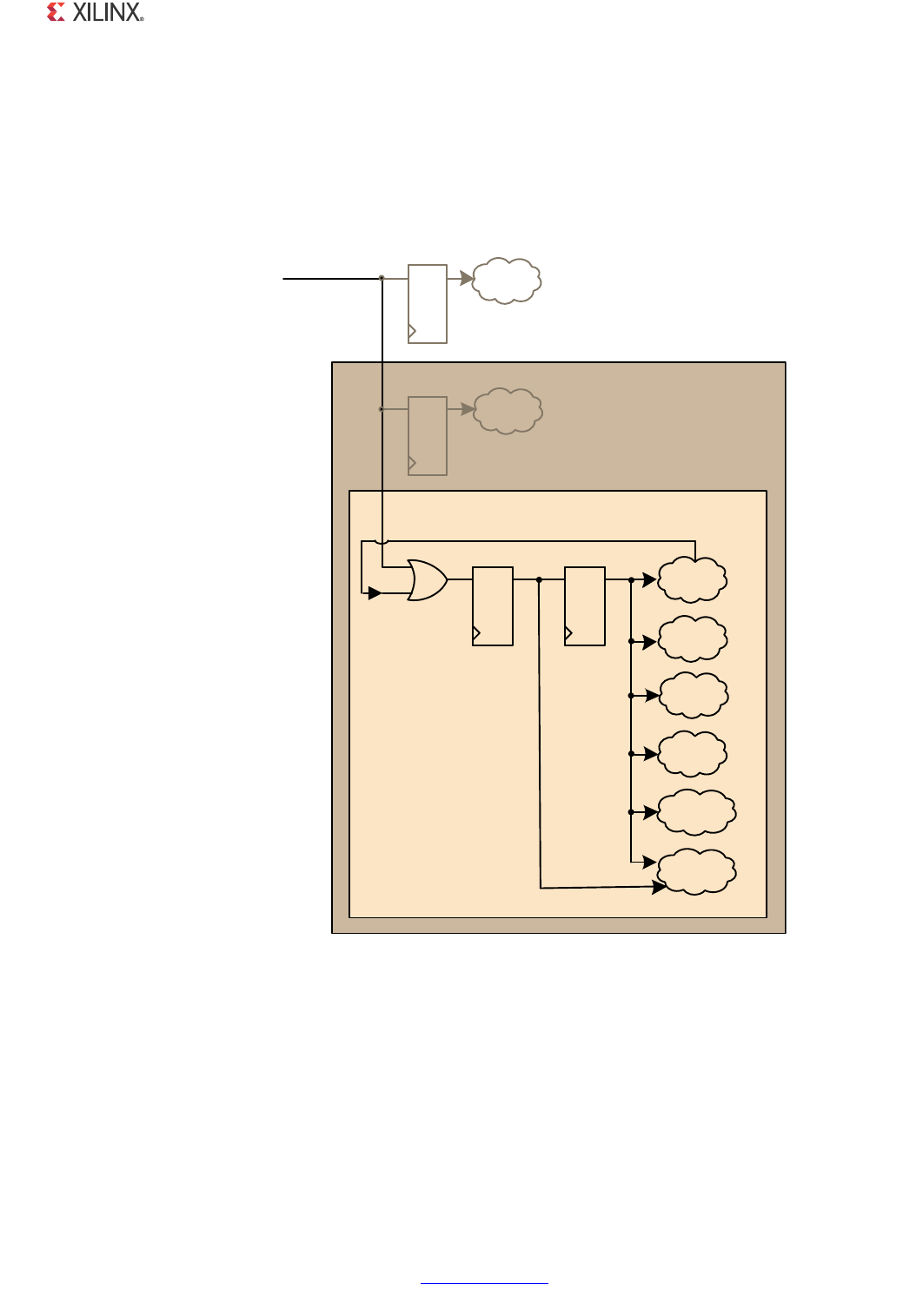

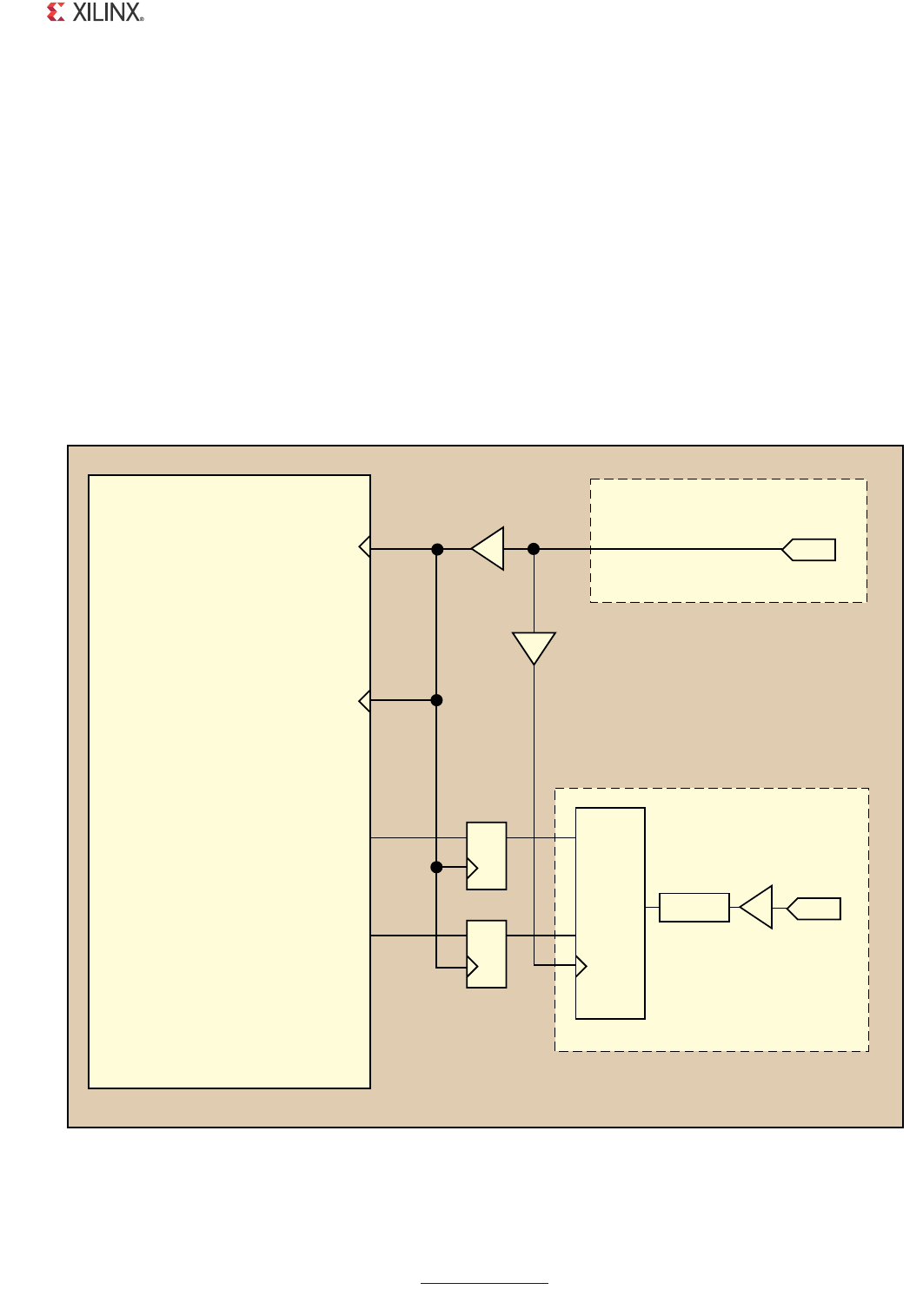

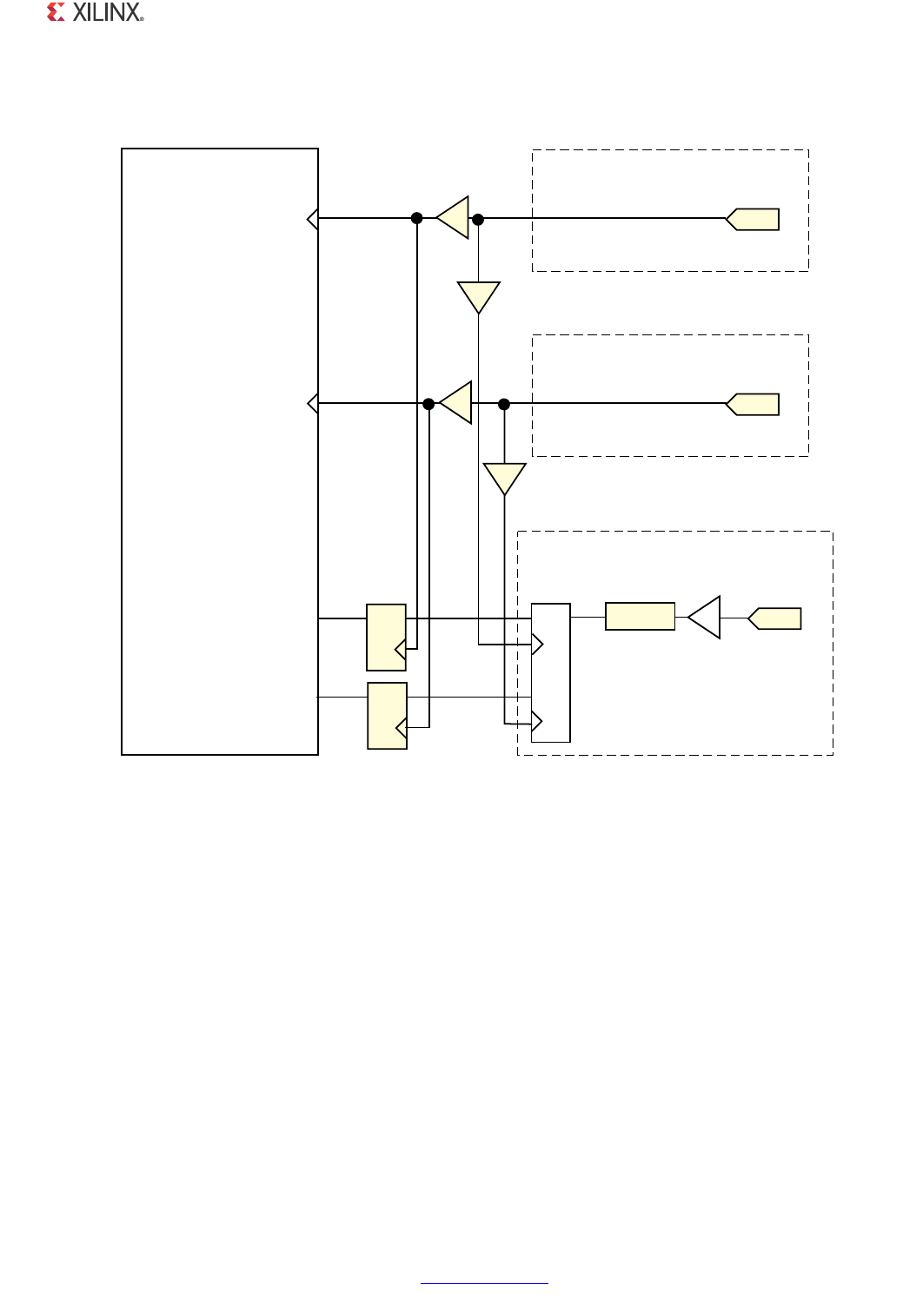

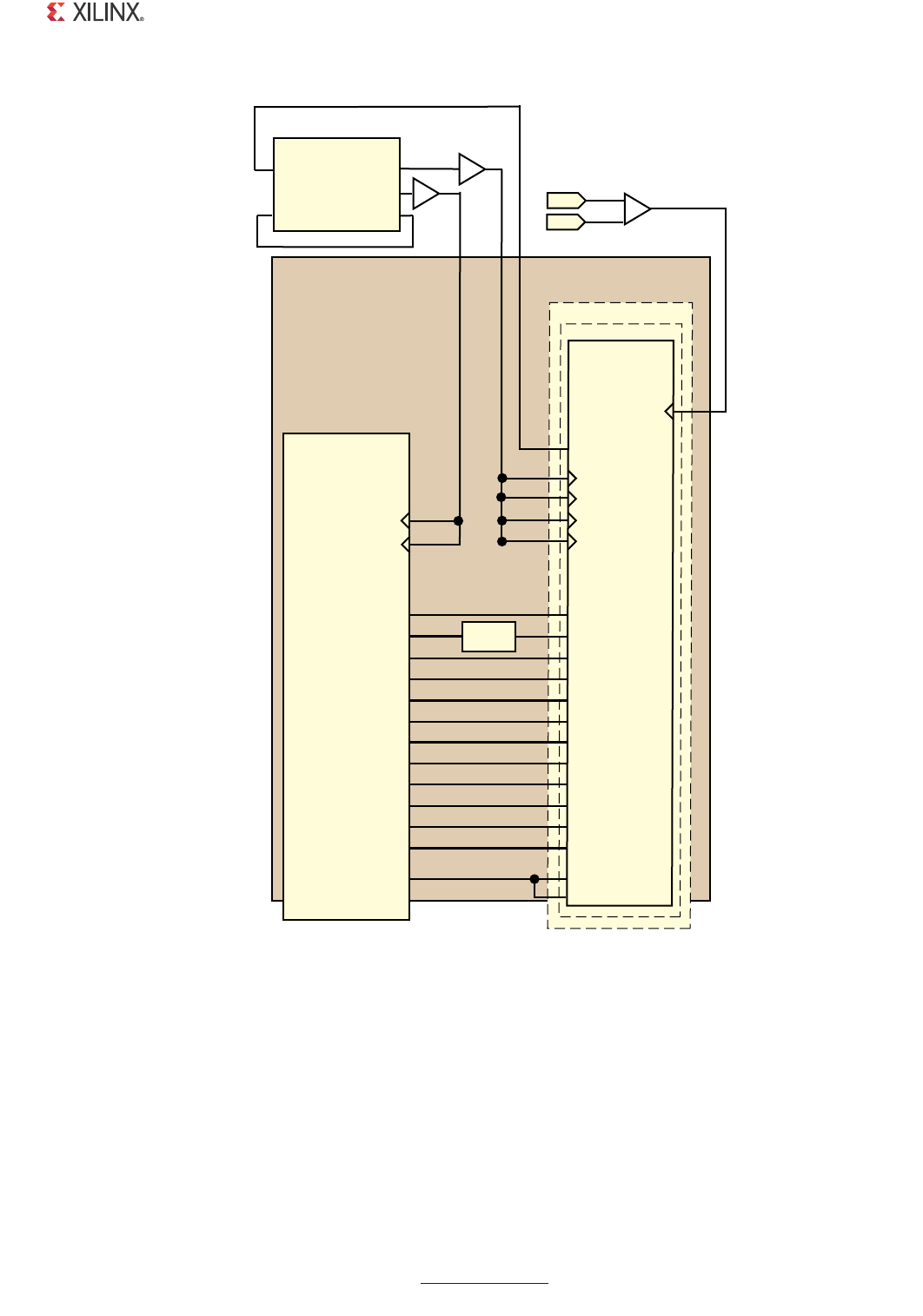

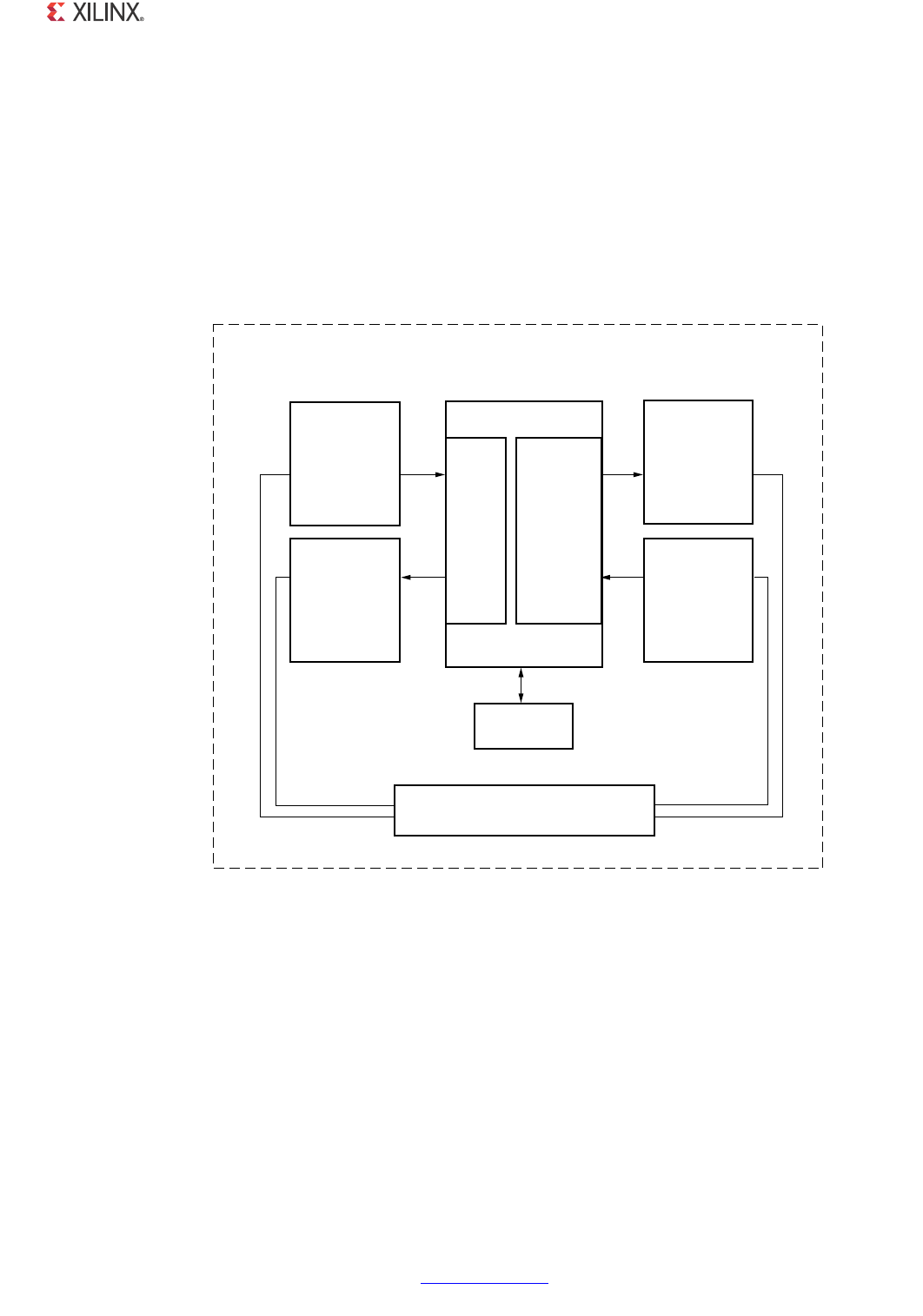

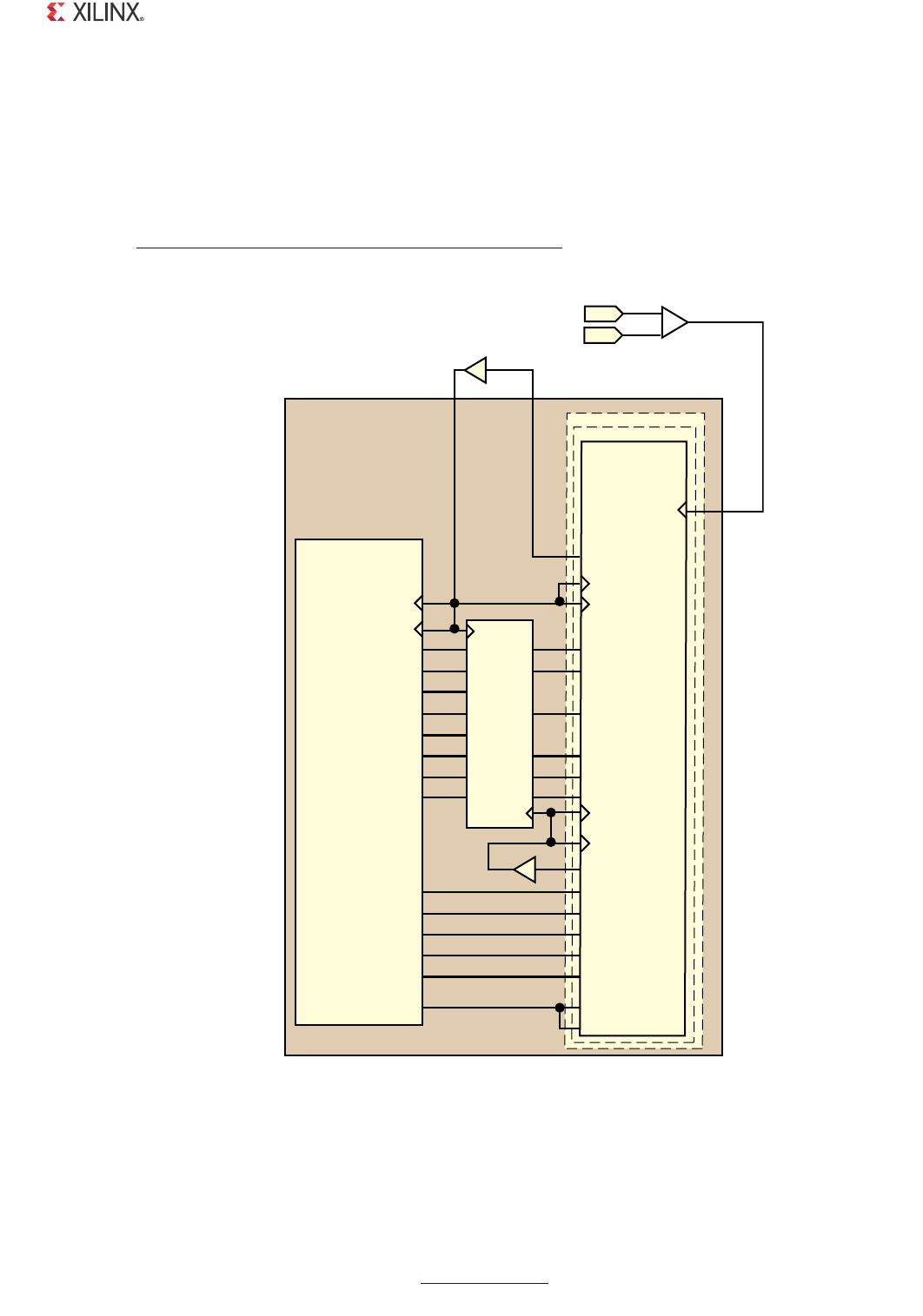

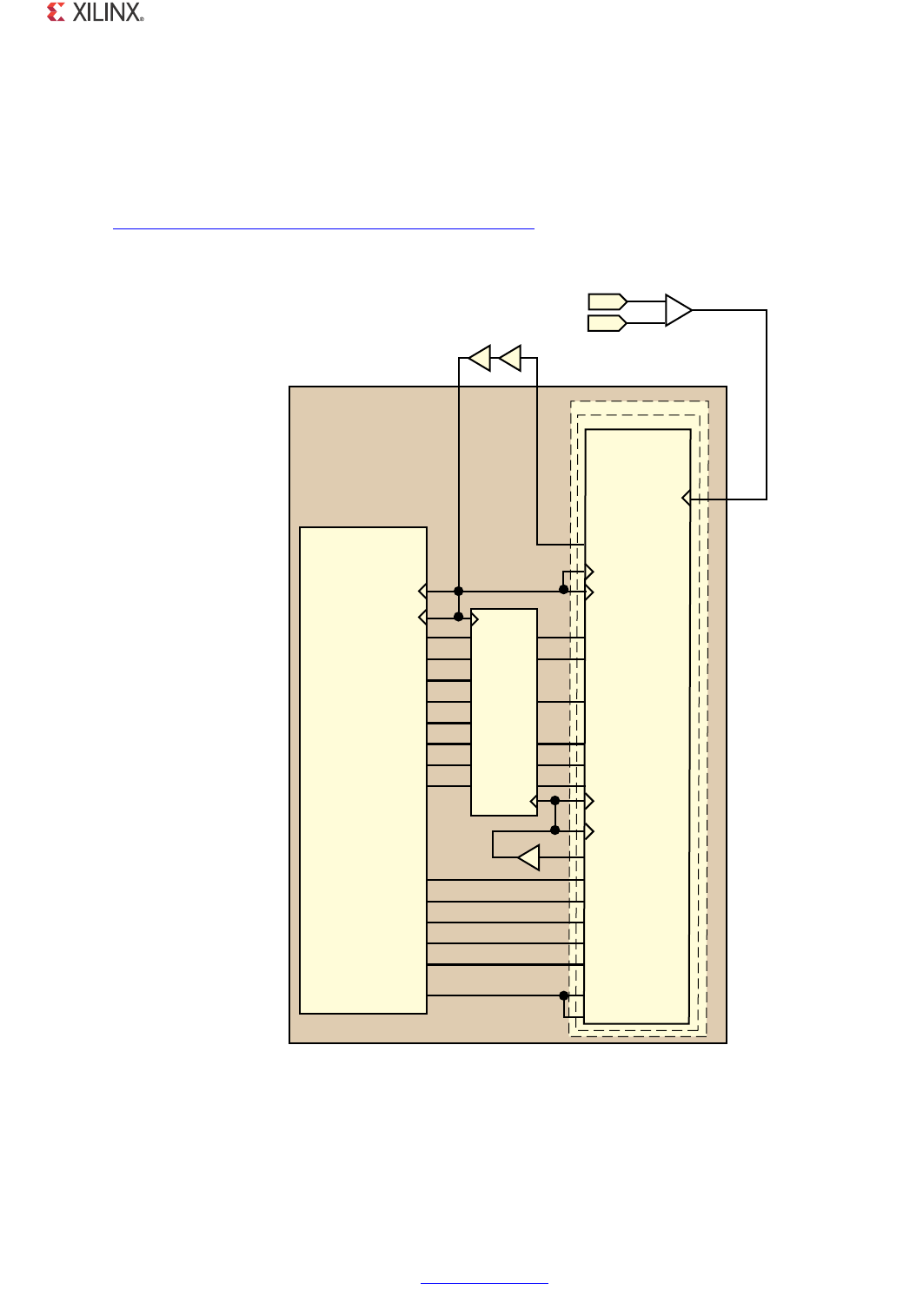

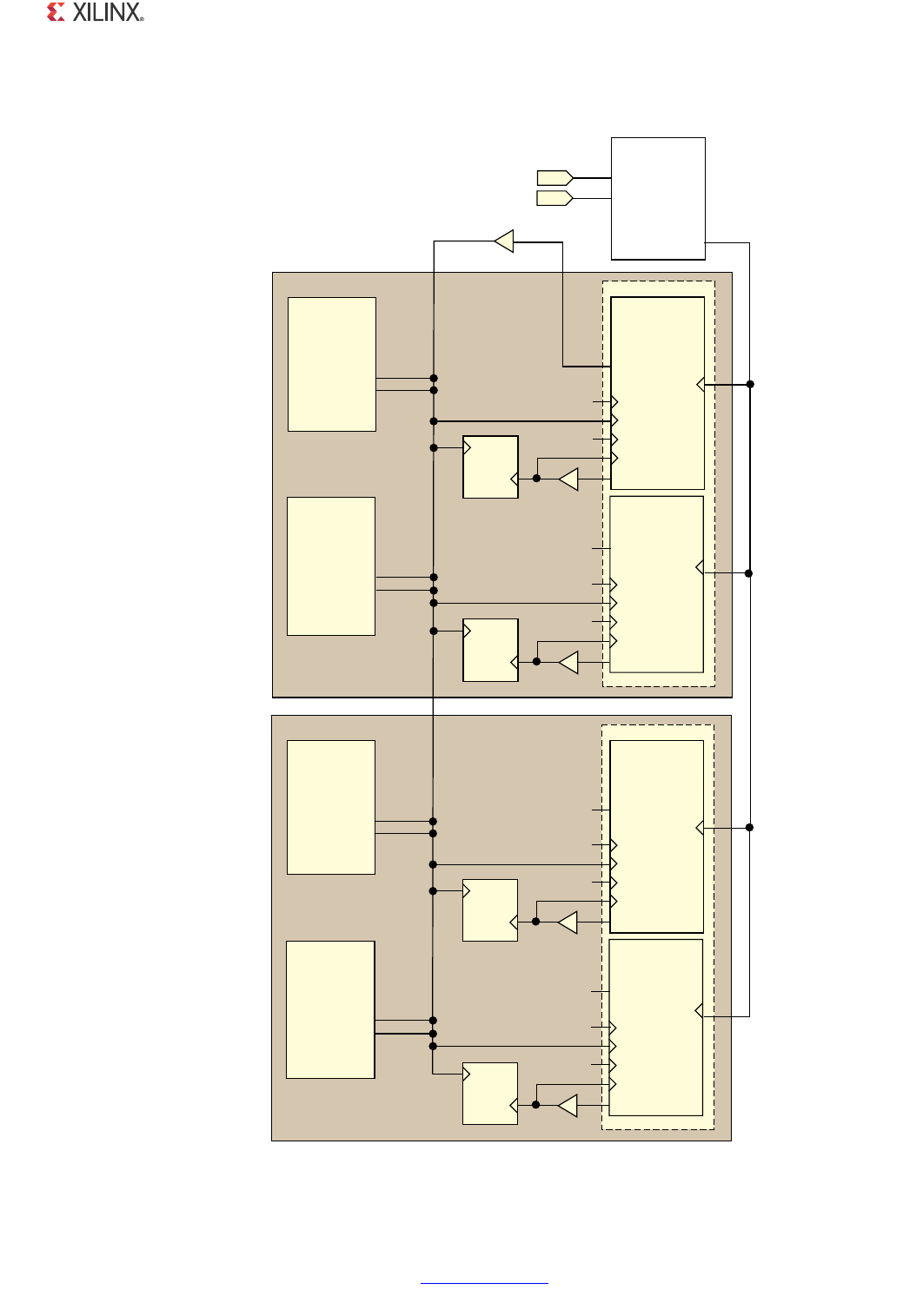

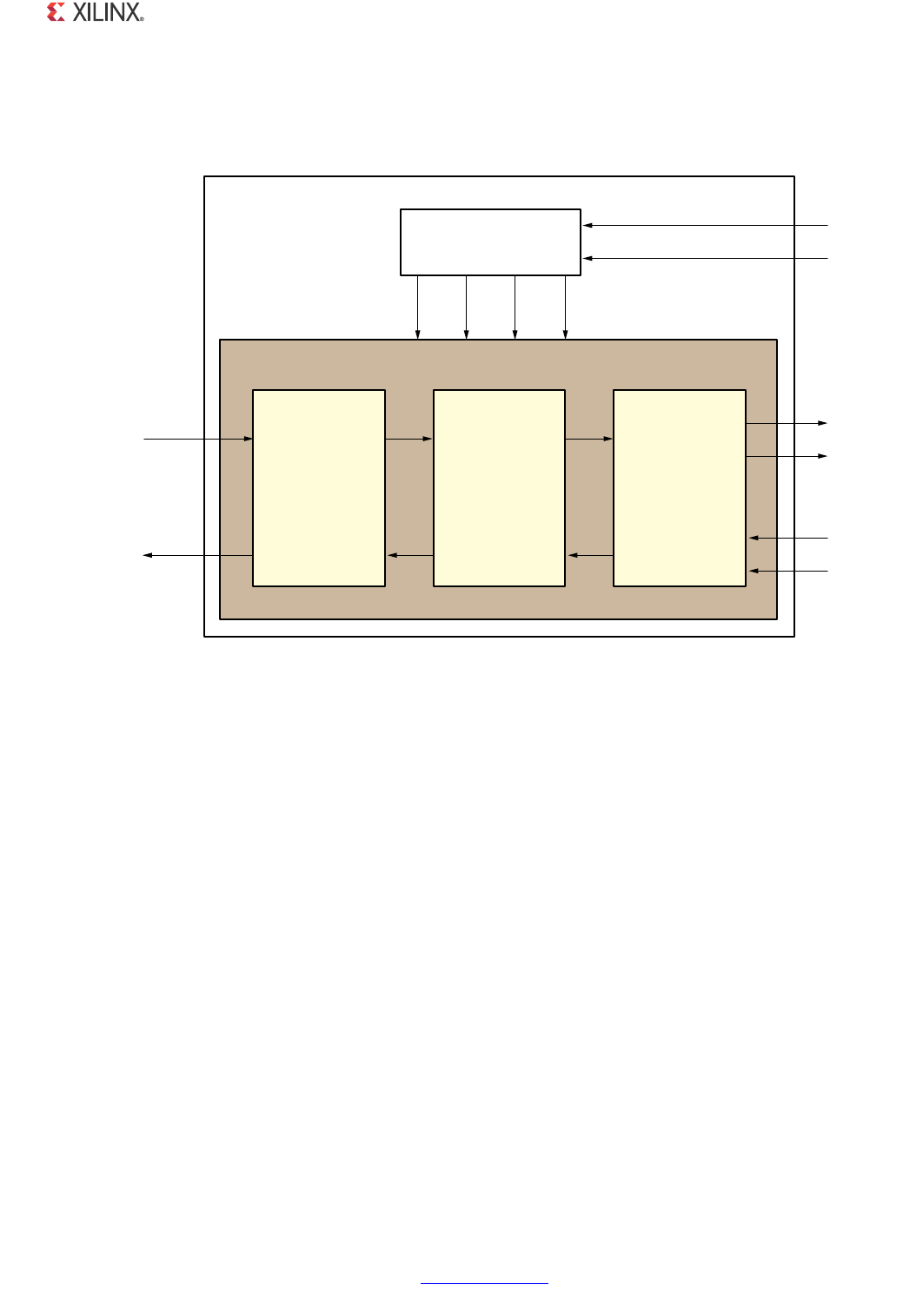

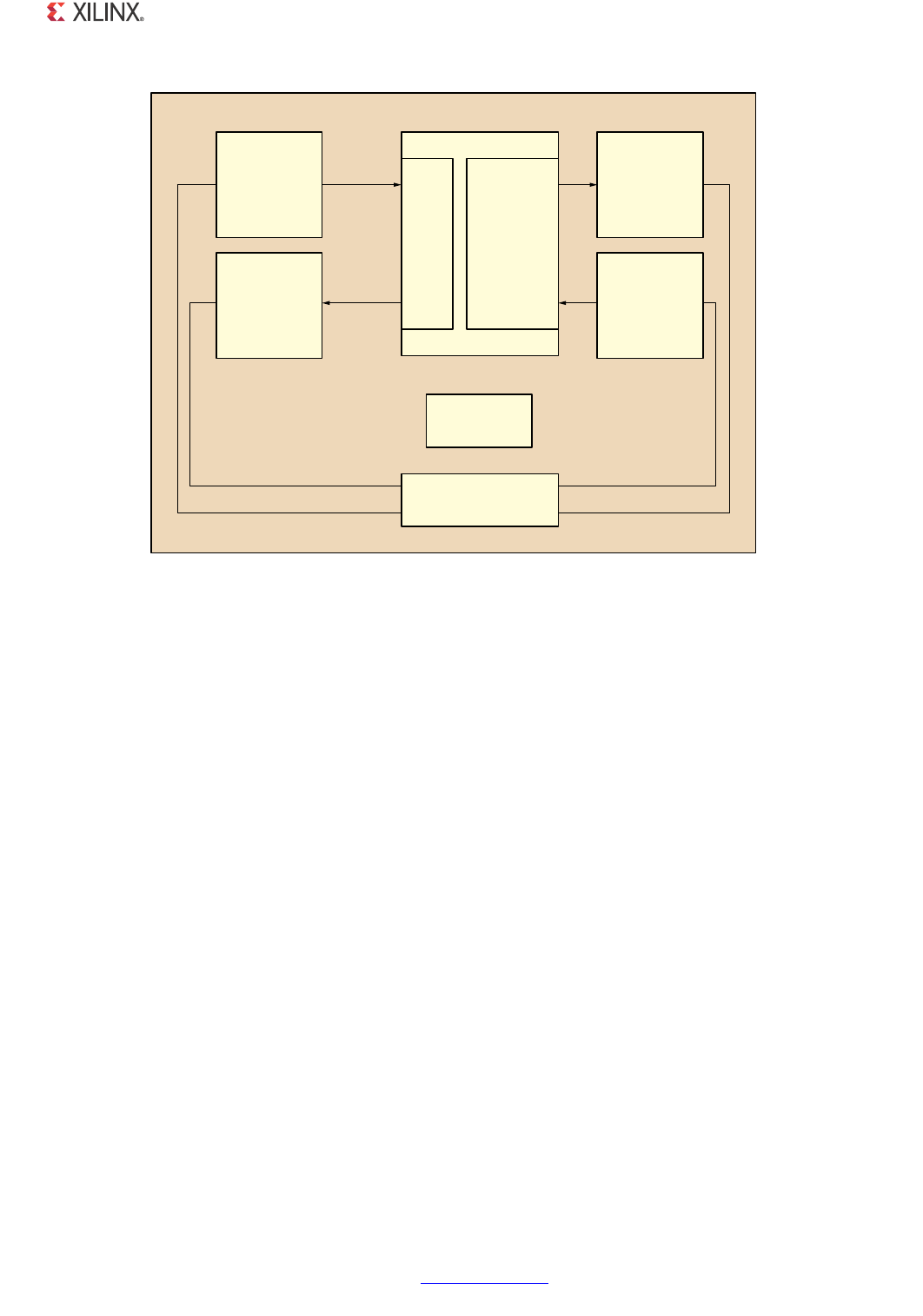

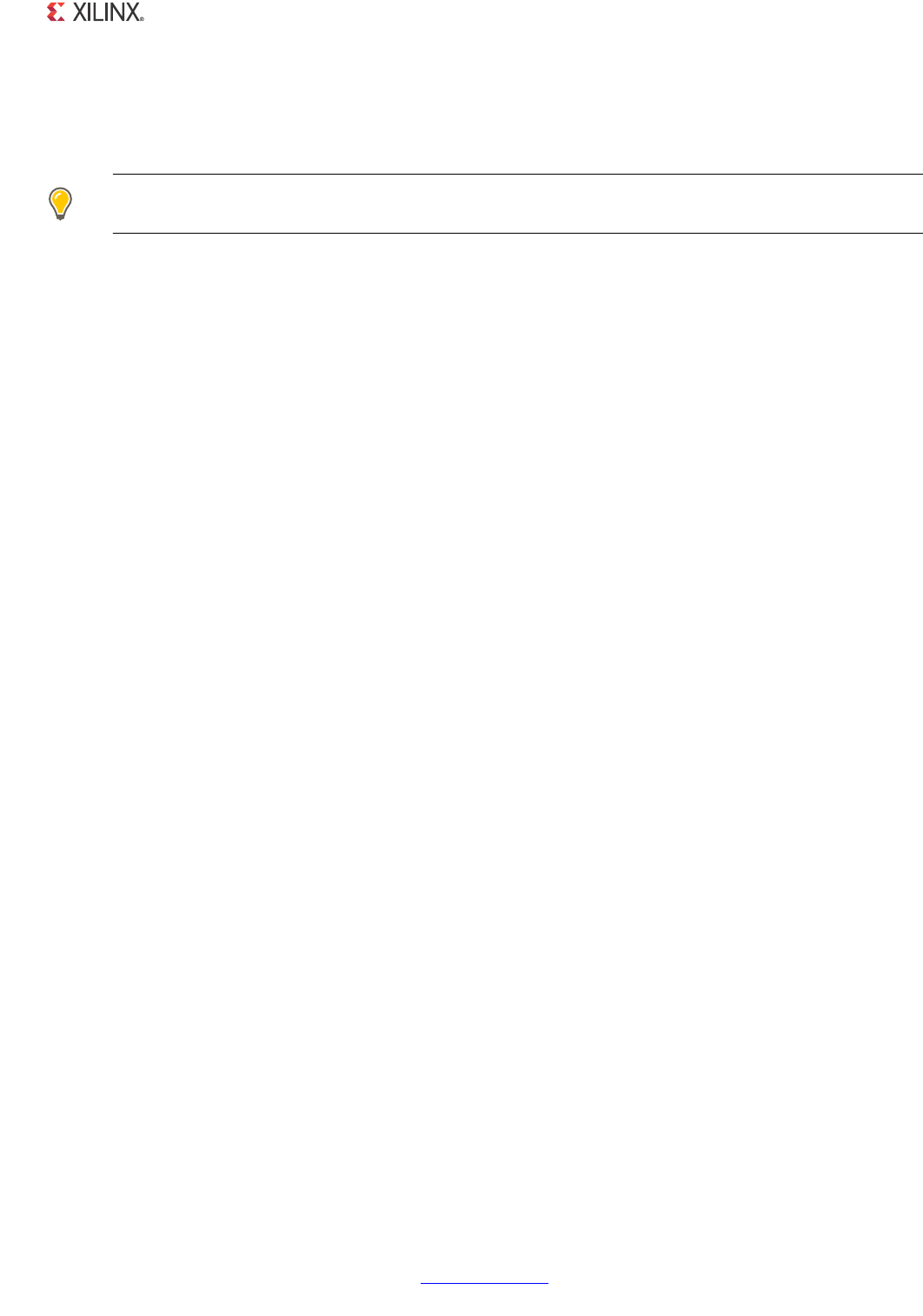

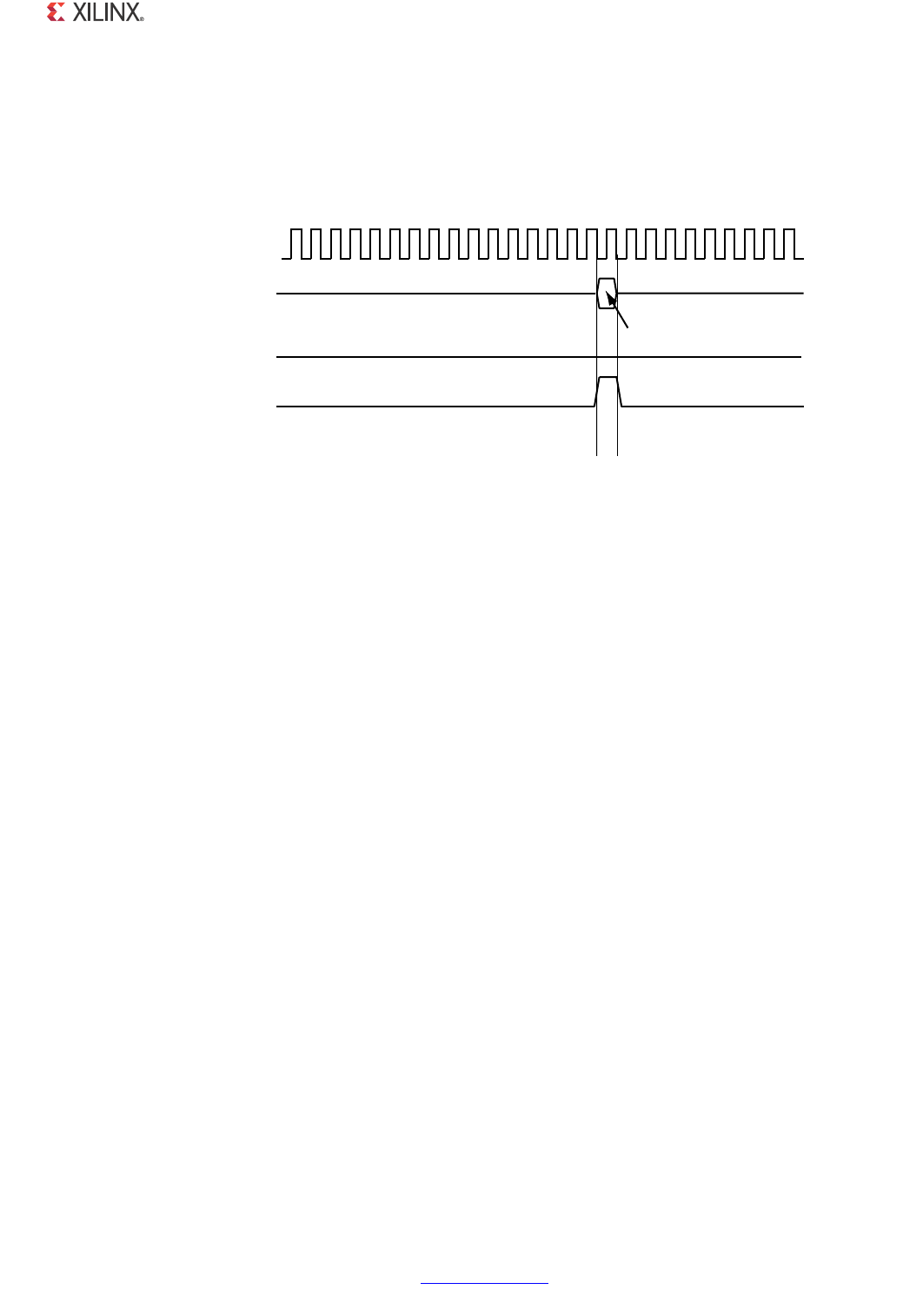

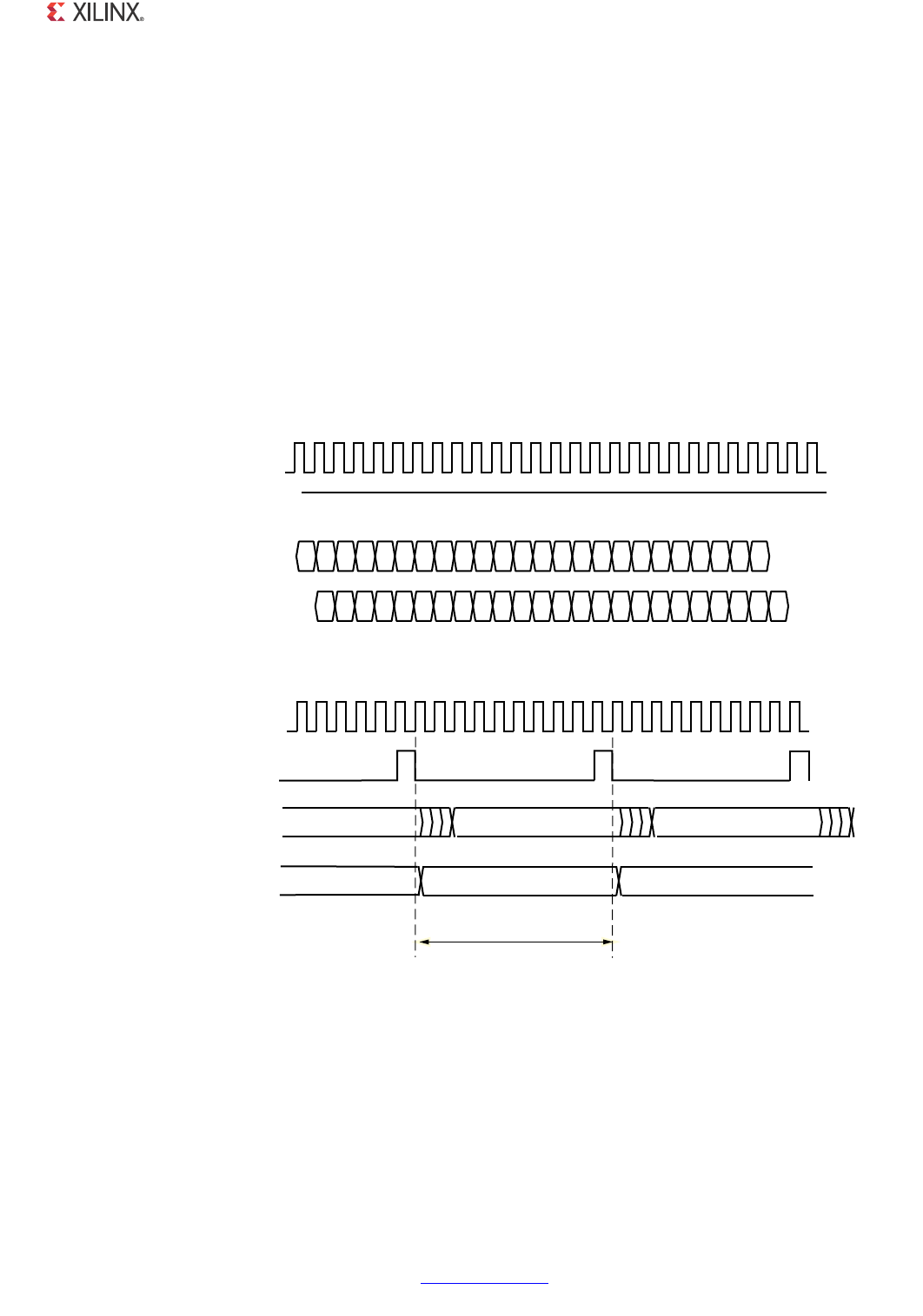

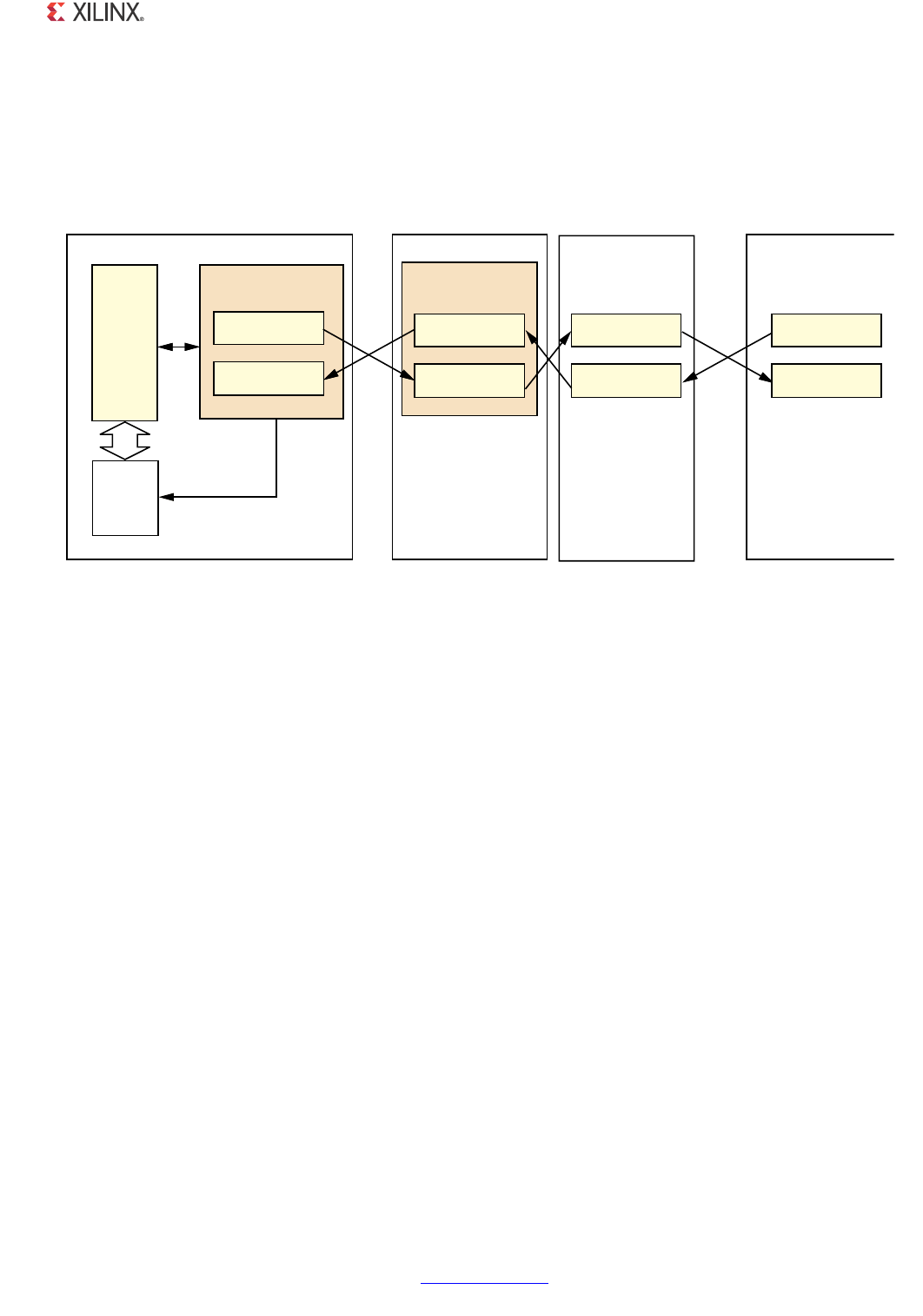

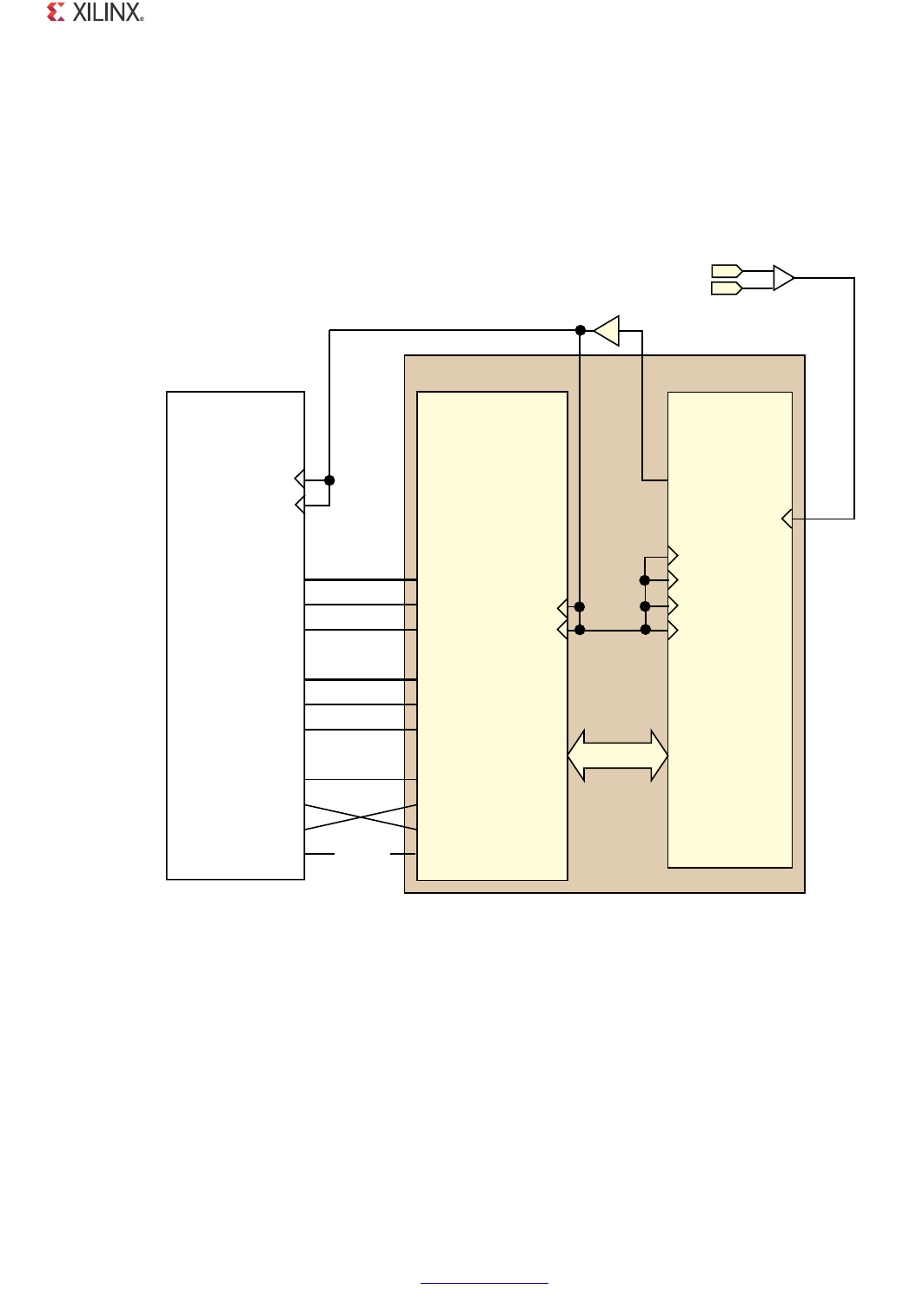

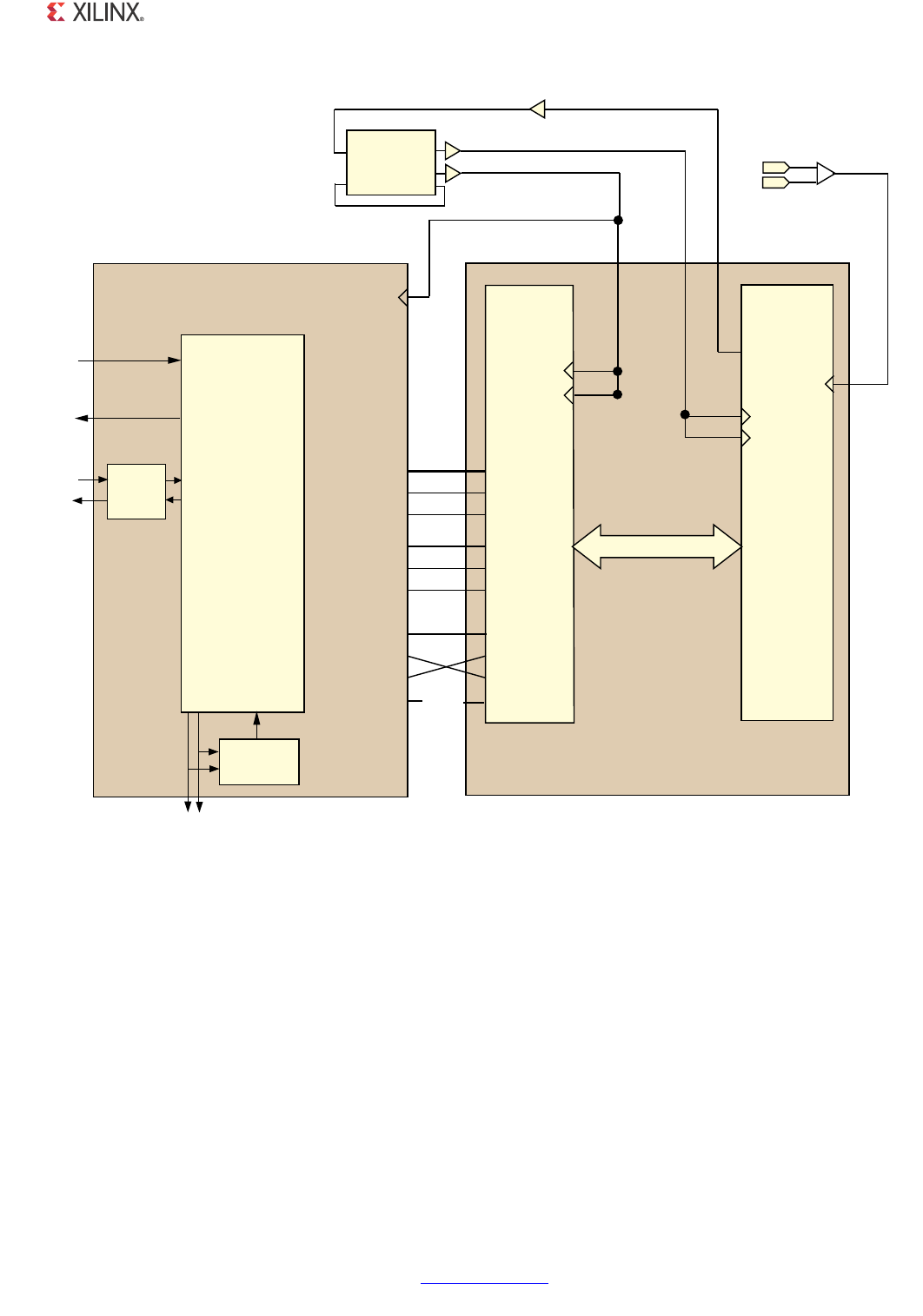

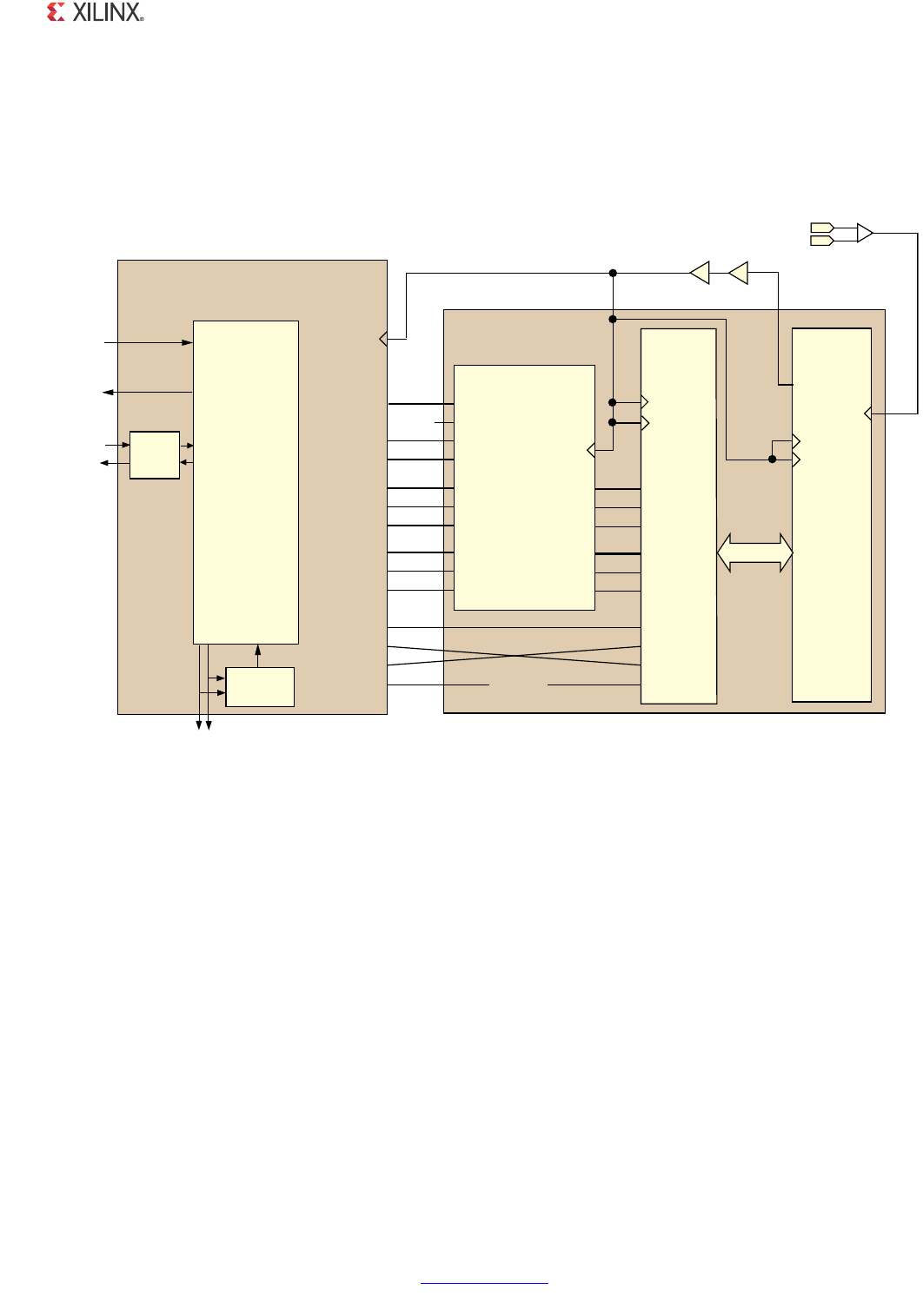

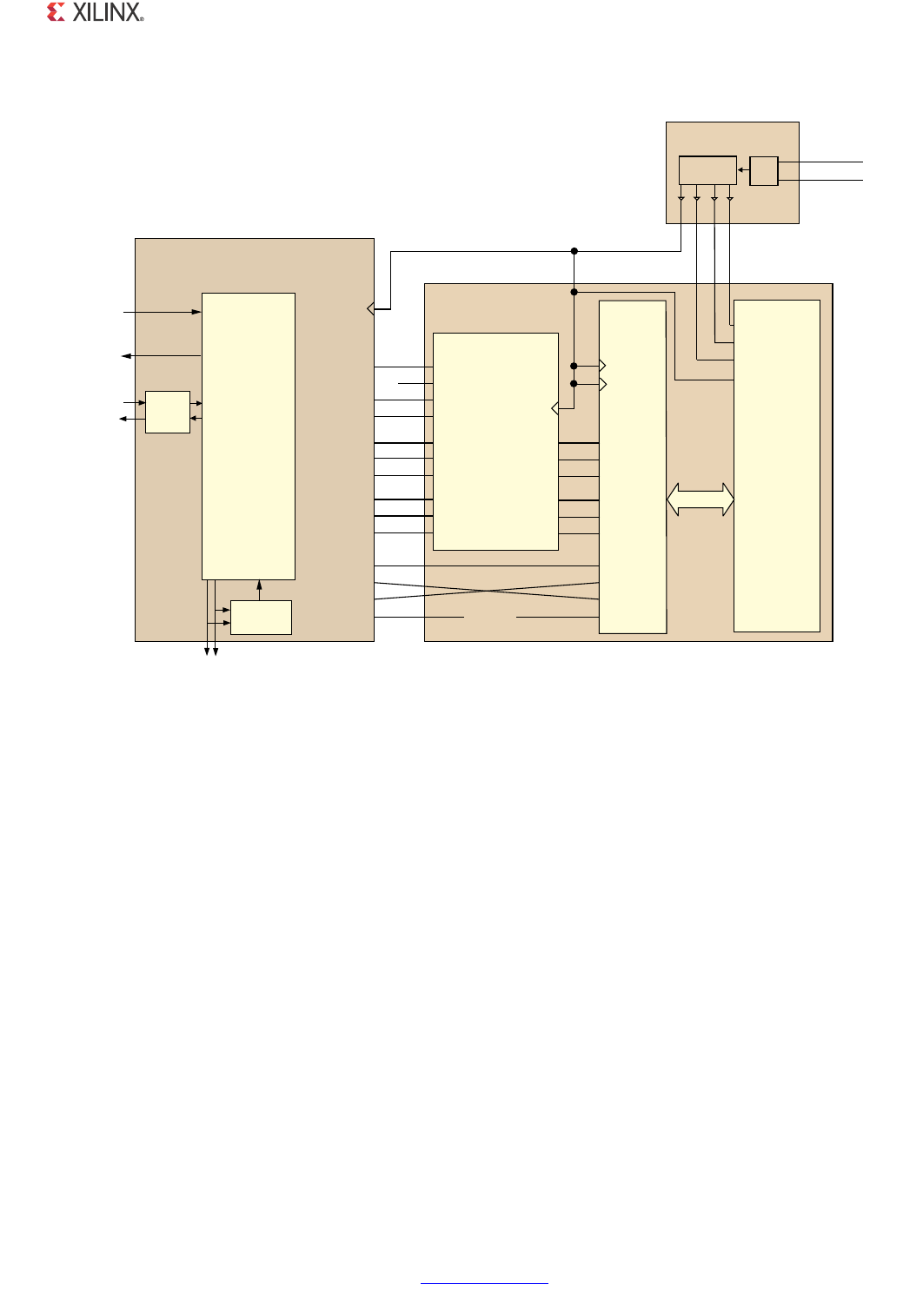

When used with the TBI, the Ethernet 1000BASE-X PCS/PMA or SGMII core provides the

functionality to implement the 1000BASE-X PCS sublayer (or to provide SGMII support) with

use of an external SerDes.

The optional TBI is used in place of the device-specific transceiver to provide a parallel

interface for connection to an external PMA SerDes device, allowing an alternative

implementation for families without device-specific transceivers. In this implementation,

additional logic blocks are required in the core to replace some of the device-specific

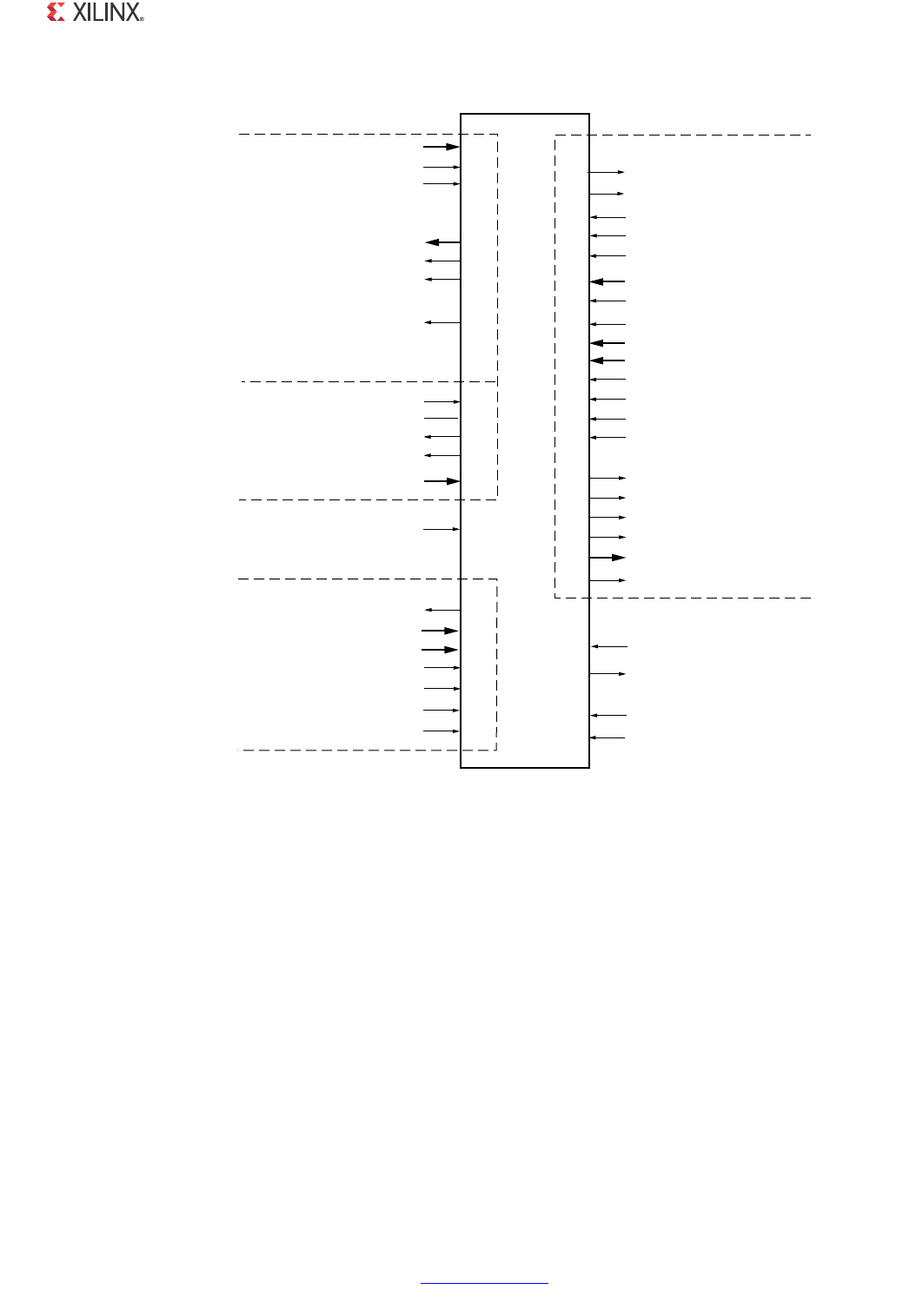

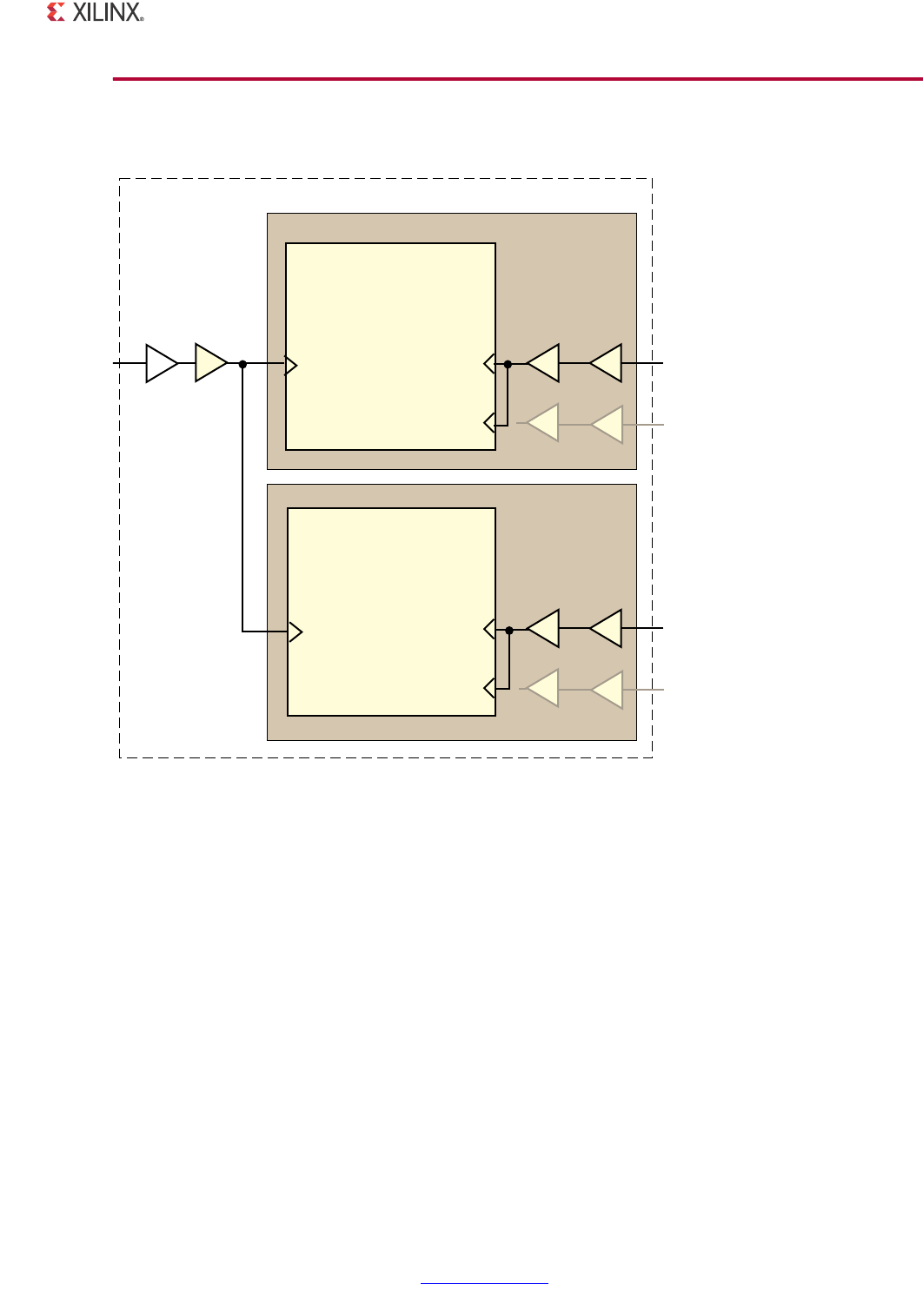

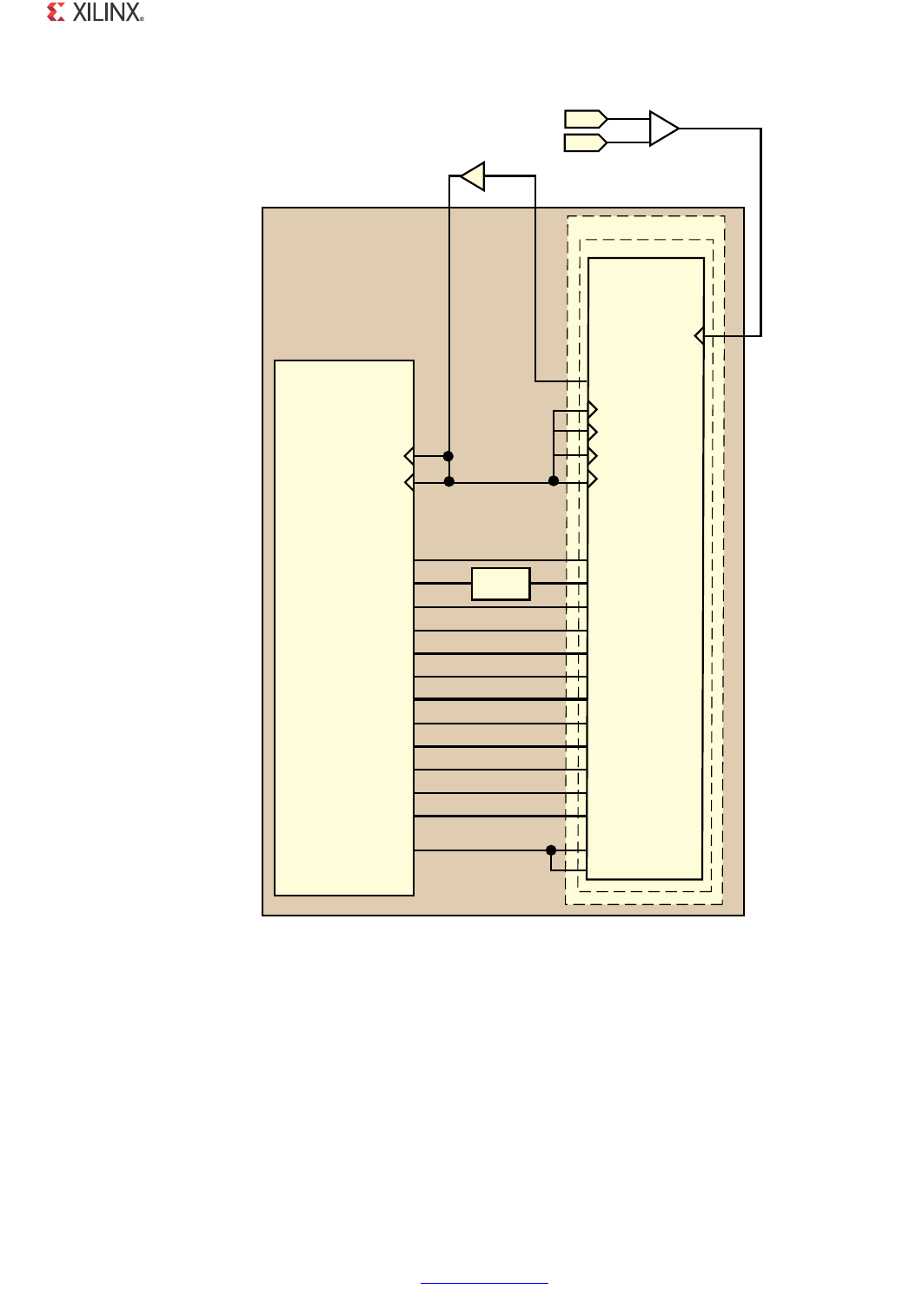

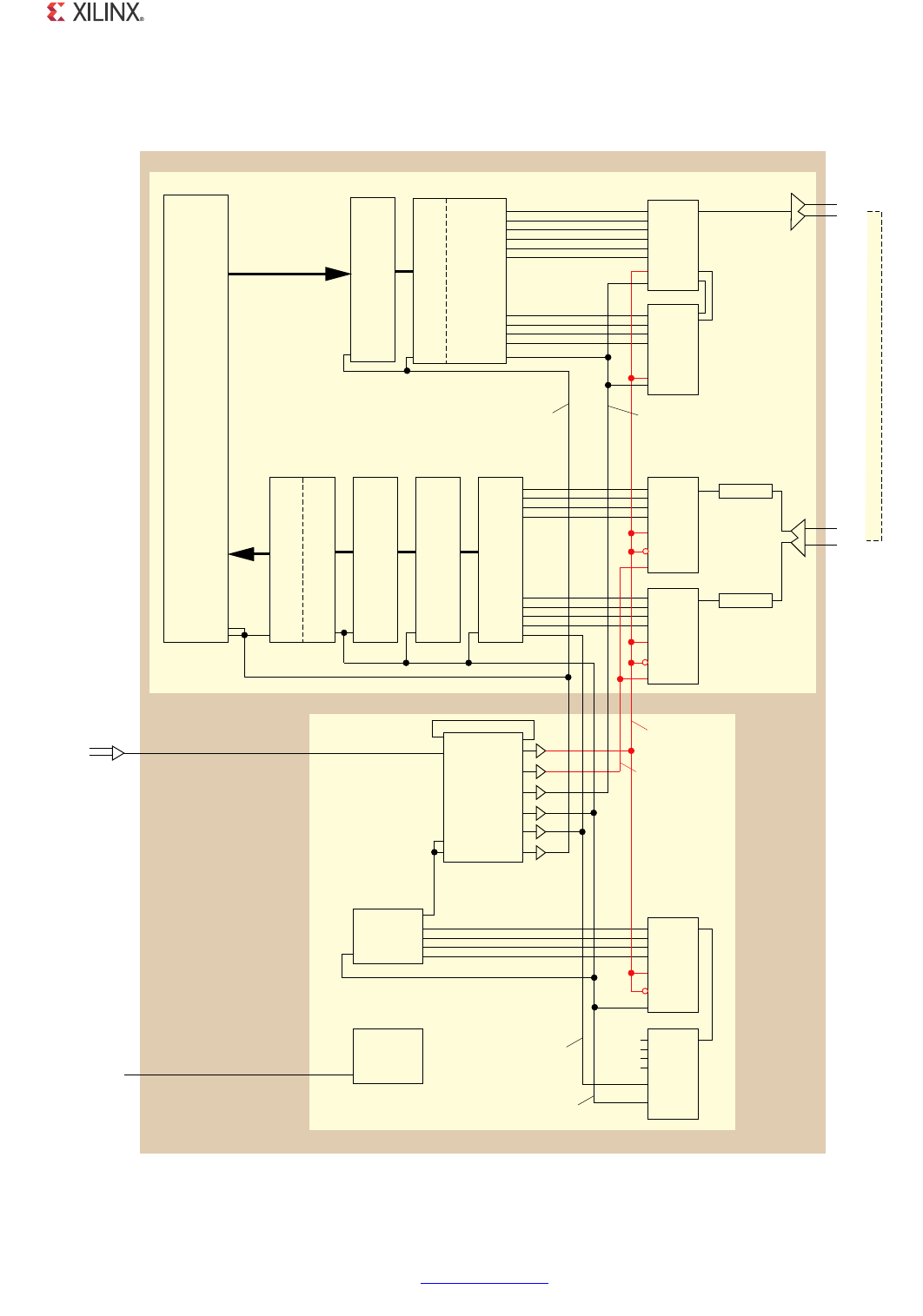

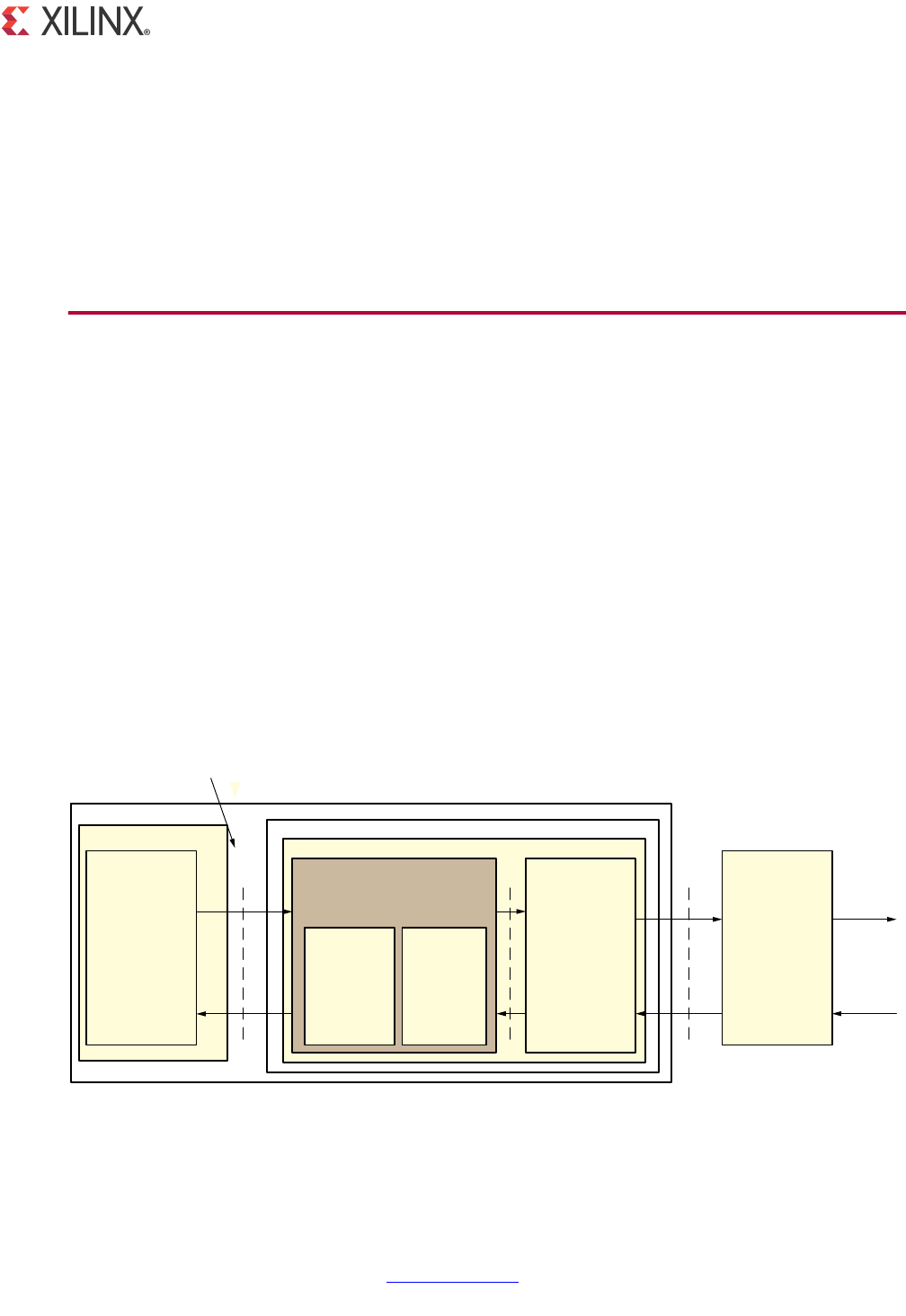

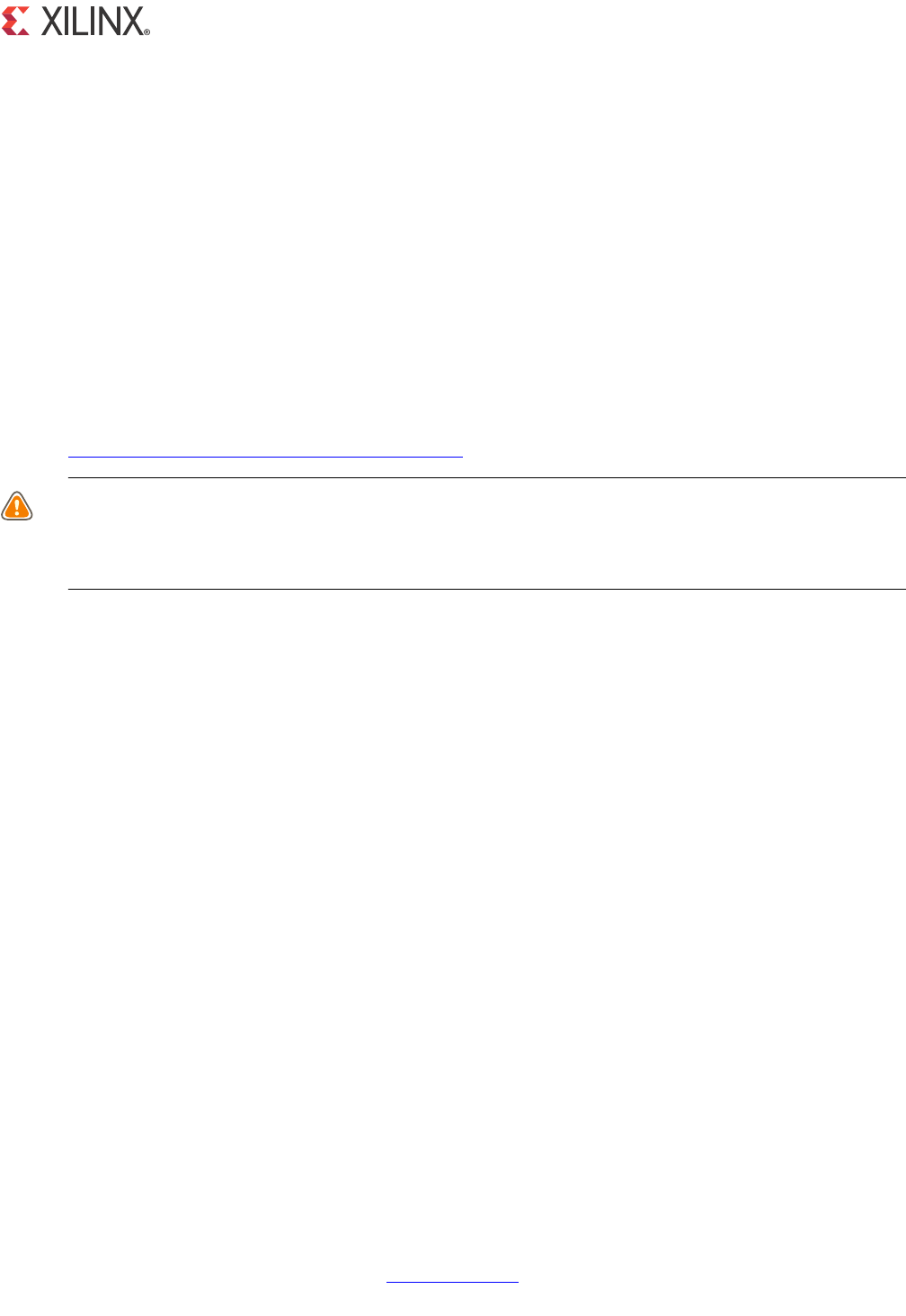

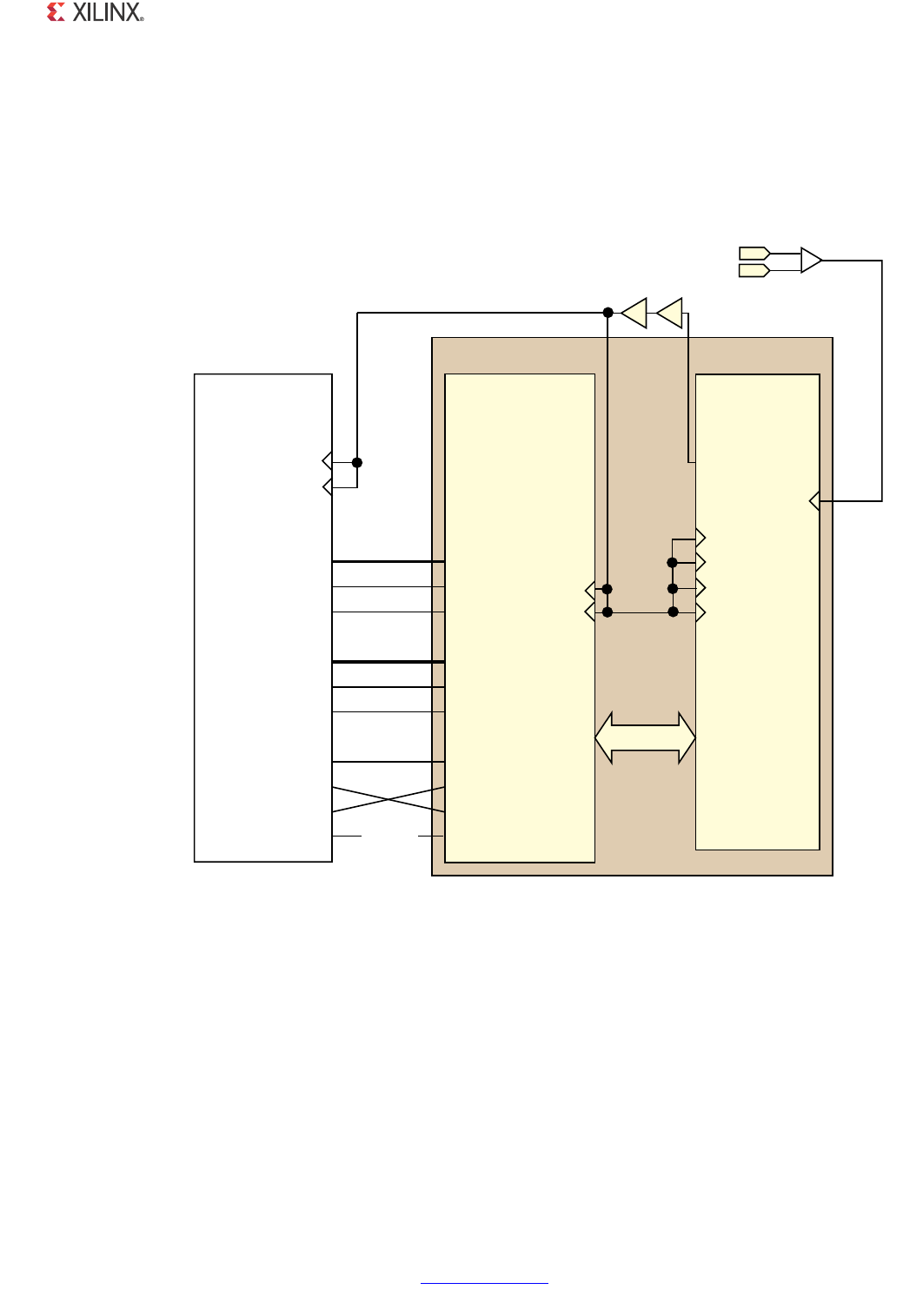

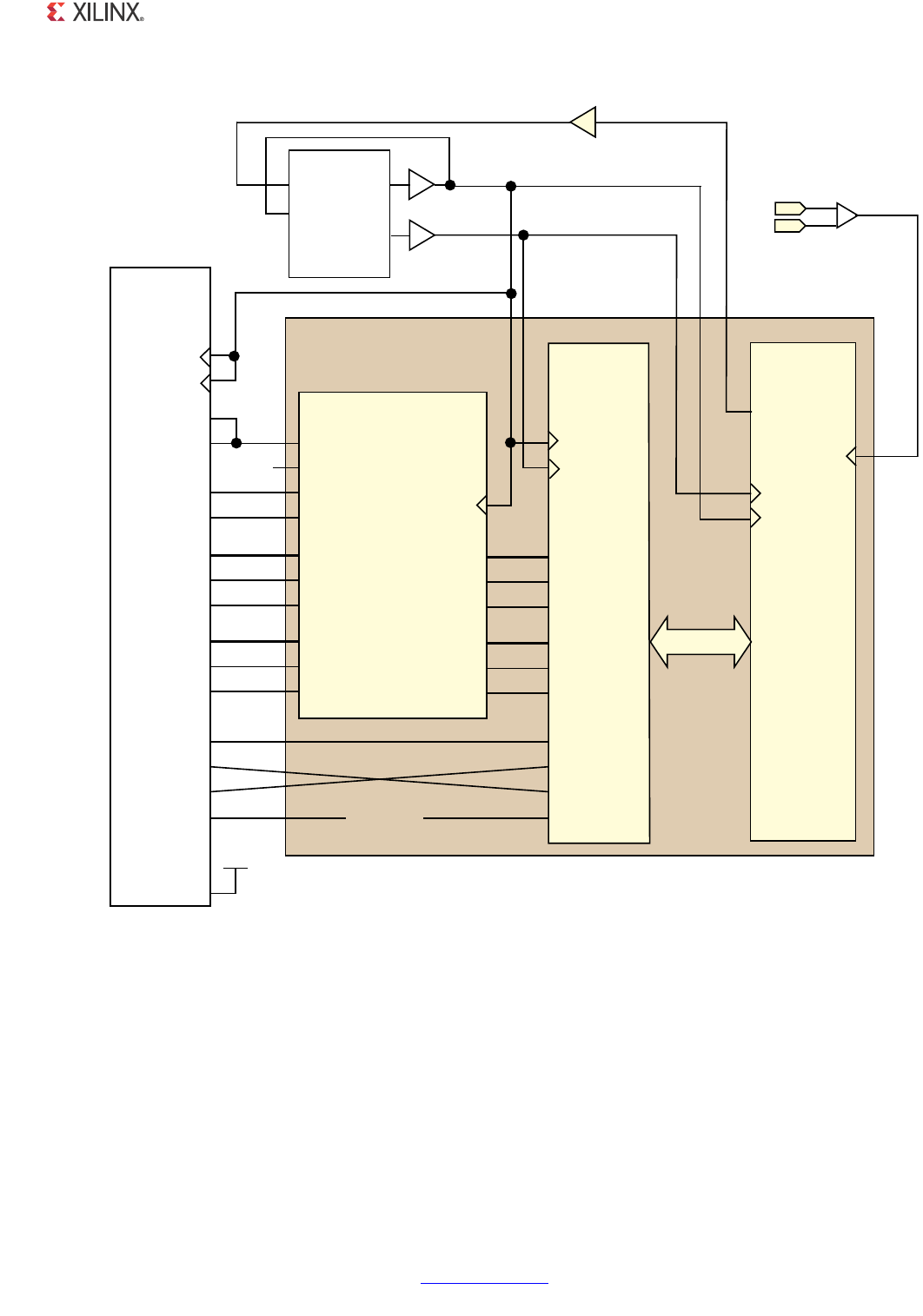

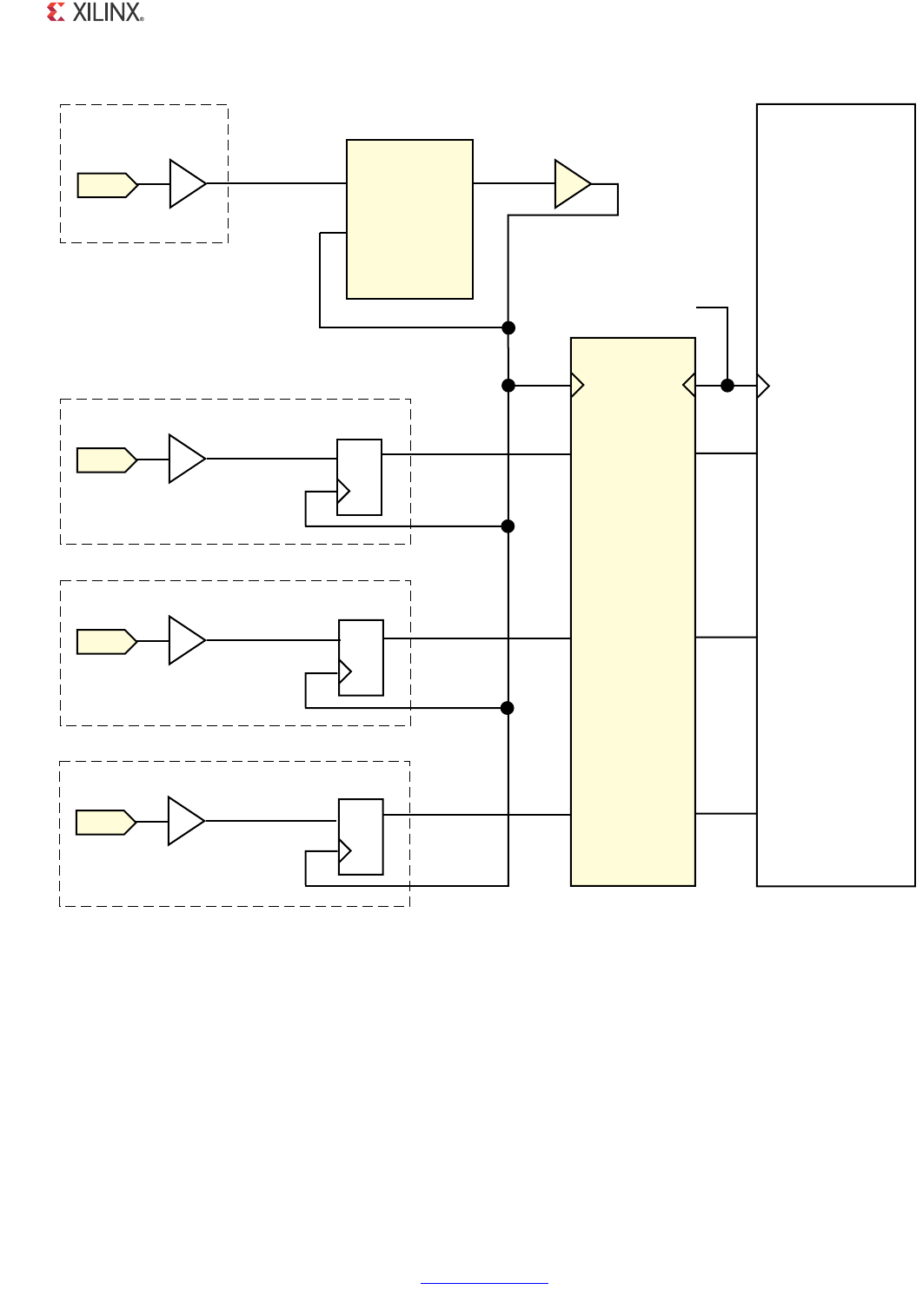

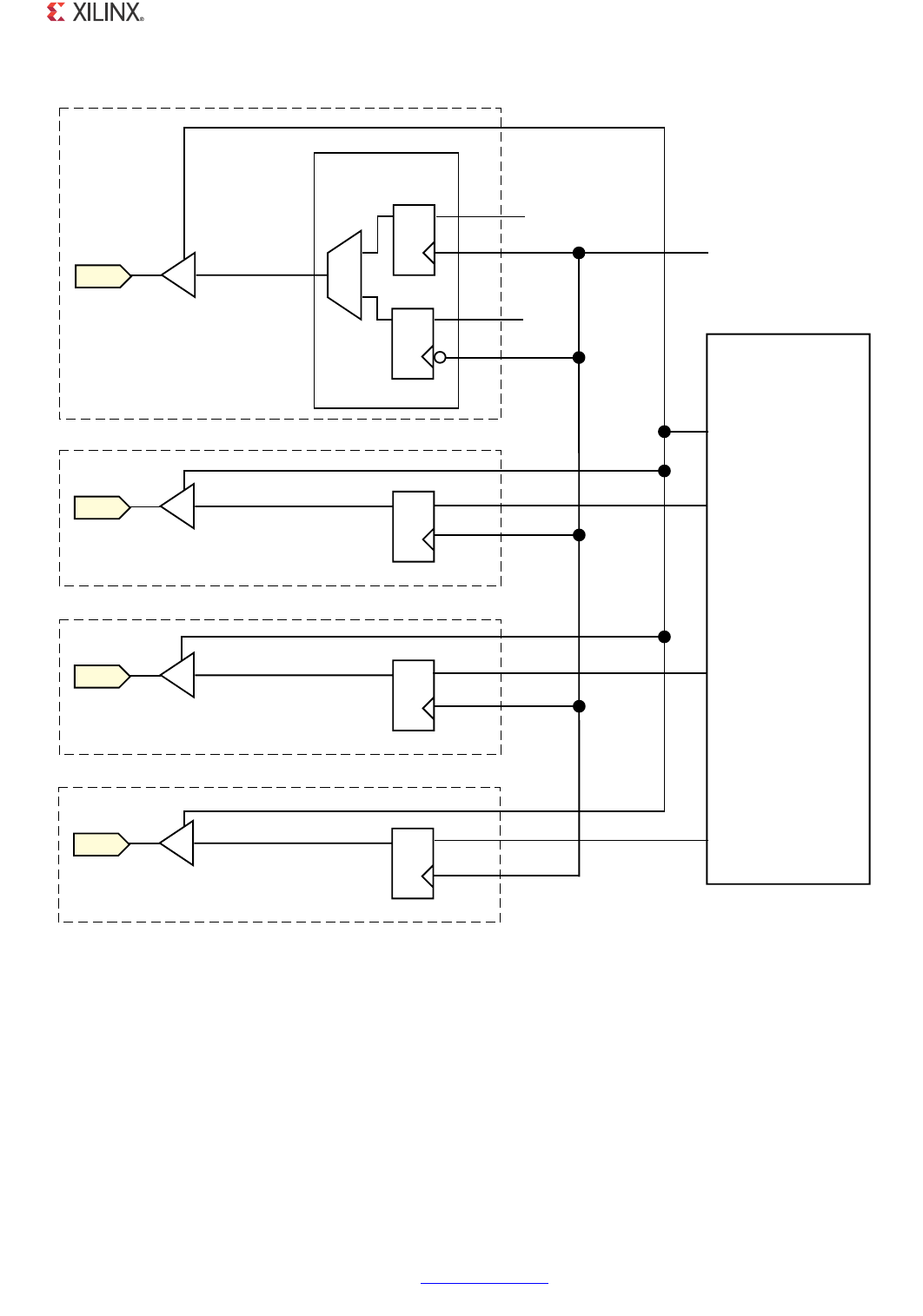

transceiver functionality. These blocks are surrounded by a dashed line (see Figure 1-2).

Other blocks are identical to those previously defined.

Zynq-7000, Artix-7 and Virtex-7 devices do not support TBI. Virtex-6 devices support TBI at

2.5 V only; see the Virtex-6 FPGA Data Sheet: DC and Switching Characteristics. Kintex-7,

Spartan-6, Virtex-5, Virtex-4 and Spartan-3 devices support TBI at 3.3 V or lower.

8B/10B Encoder

8B/10B encoding, as defined in IEEE 802.3-2008 specification (Tables 36-1a to 36-1e and

Table 36-2), is implemented in a block SelectRAM™ memory, configured as ROM, and used

as a large look-up table.

X-Ref Target - Figure 1-2

Figure 1-2: Functional Block Diagram of the Ethernet 1000BASE-X PCS/PMA or

SGMII Core with TBI

3&6 7UDQVPLW(QJLQH

3&65HFHLYH(QJLQH

DQG6\QFKURQL]DWLRQ

2SWLRQDO3&6

0DQDJHPHQW

*0,,

WR0$&

0',2

,QWHUIDFH

2SWLRQDO

$WXRQHJRWLDWLRQ

*0,,%ORFN

%%

(QFRGHU

%%

'HFRGHU

5;

(ODVWLF

%XIIHU

7%,%ORFN

/RJL&25((WKHUQHW%$6(;3&630$RU6*0,,&RUH

,2%V

4")

TOEXTERNAL

3%2$%3

8

1000BASE-X PCS/PMA or SGMII v11.4 www.xilinx.com 15

PG047 October 16, 2012

Chapter 1: Overview

8B/10B Decoder

8B/10B decoding, as defined in IEEE 802.3-2008 specification (Tables 36-1a to 36-1e and

Table 36-2), is implemented in a block SelectRAM memory, configured as ROM, and used as

a large look-up table.

Receiver Elastic Buffer

The Receiver Elastic Buffer enables the 10-bit parallel TBI data, received from the PMA

sublayer synchronously to the TBI receiver clocks, to be transferred onto the core internal

125 MHz clock domain.

The Receiver Elastic Buffer is an asynchronous First In First Out (FIFO) implemented in

internal RAM. The operation of the Receiver Elastic Buffer attempts to maintain a constant

occupancy by inserting or removing Idle sequences as necessary. This causes no corruption

to the frames of data.

TBI Block

The core provides a TBI interface, which should be routed to device IOBs to provide an

off-chip TBI.

SGMII over LVDS

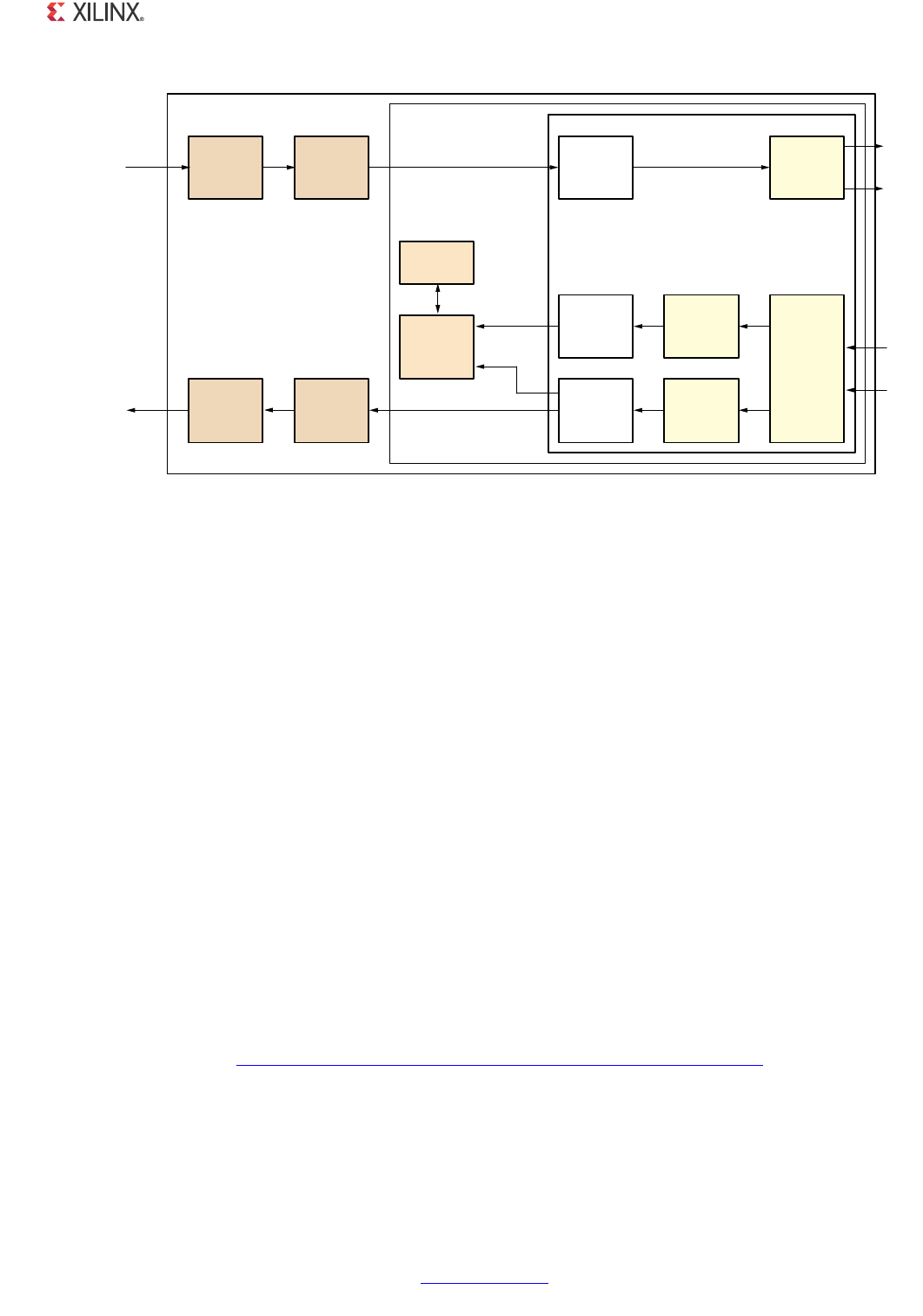

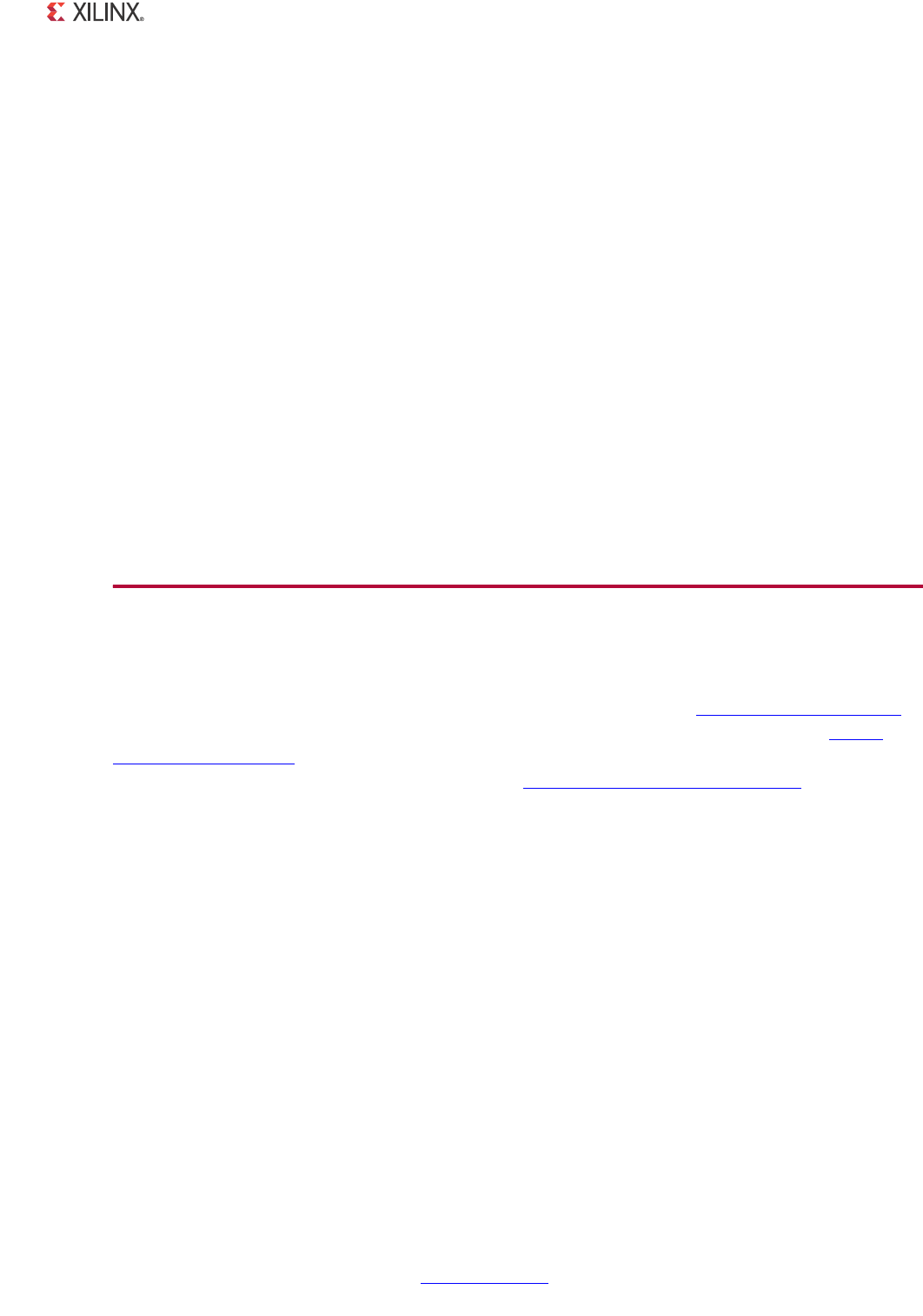

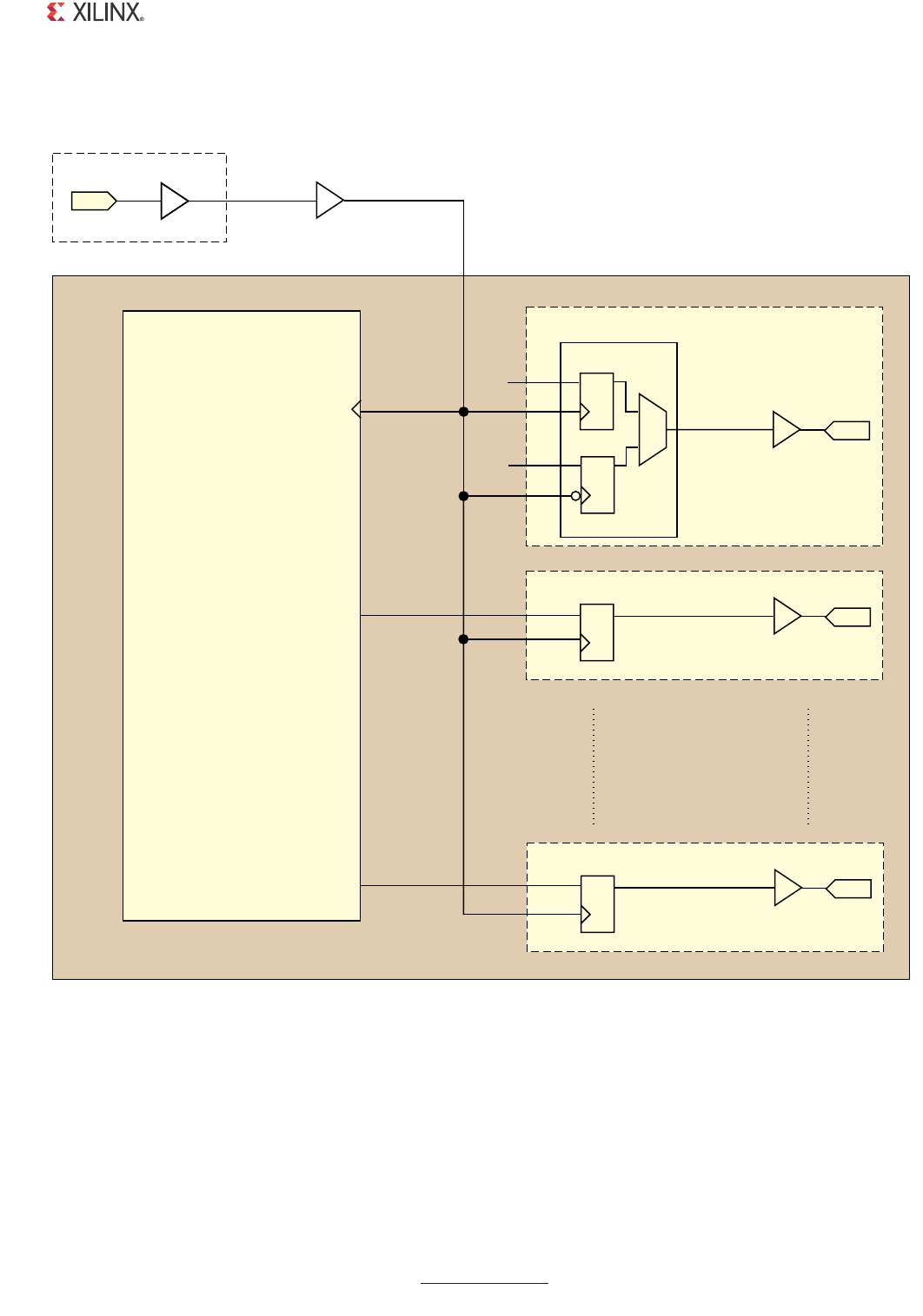

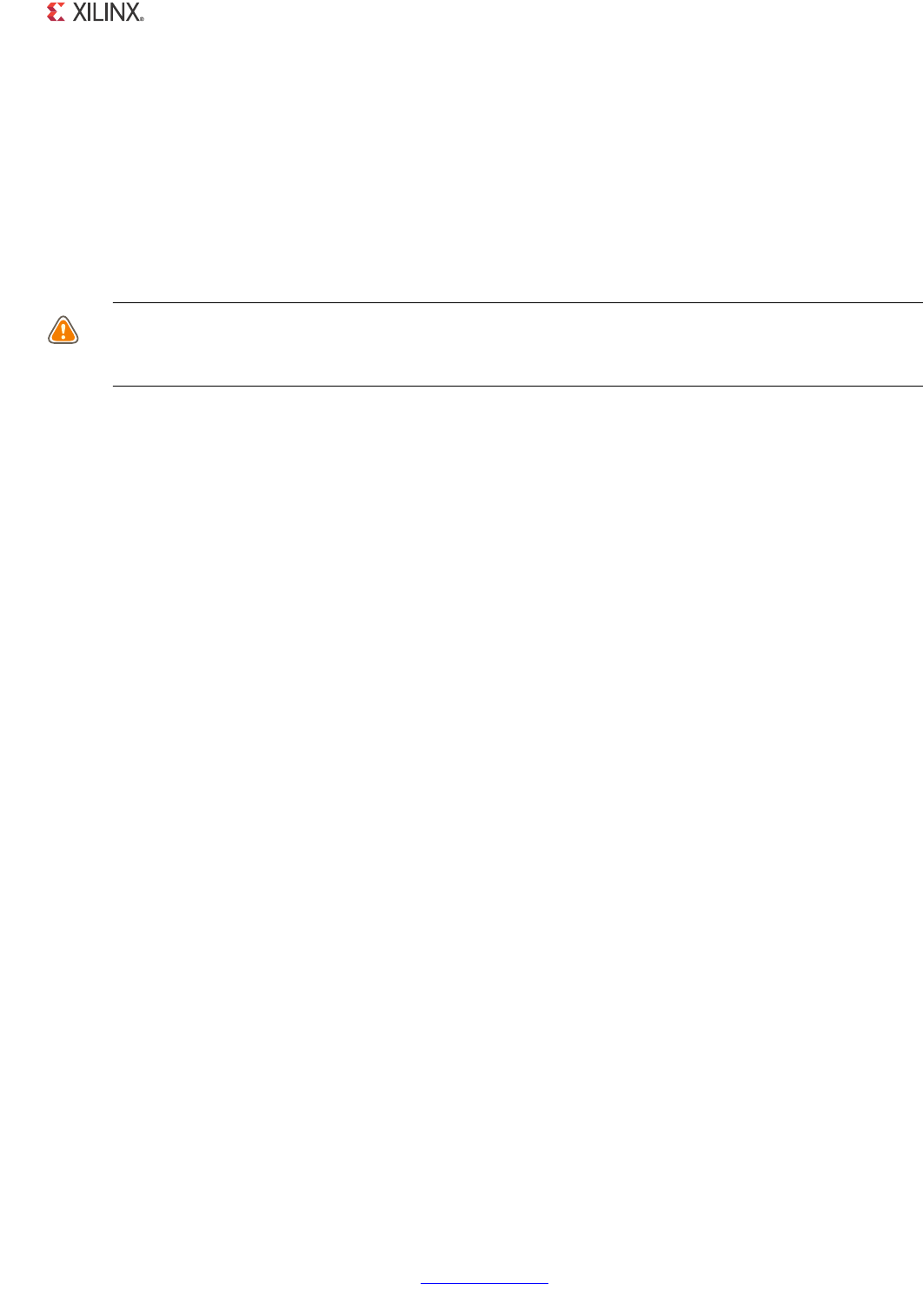

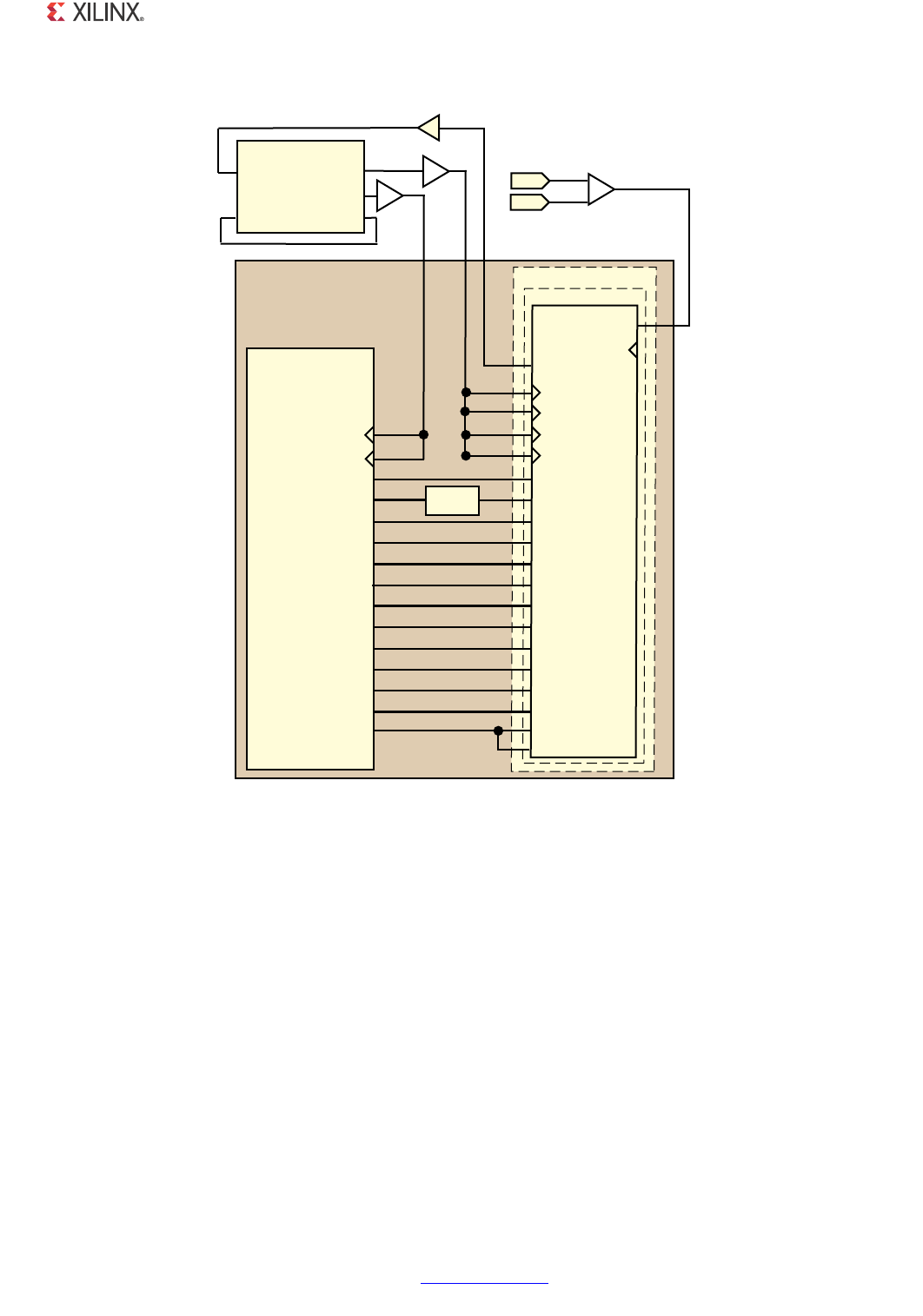

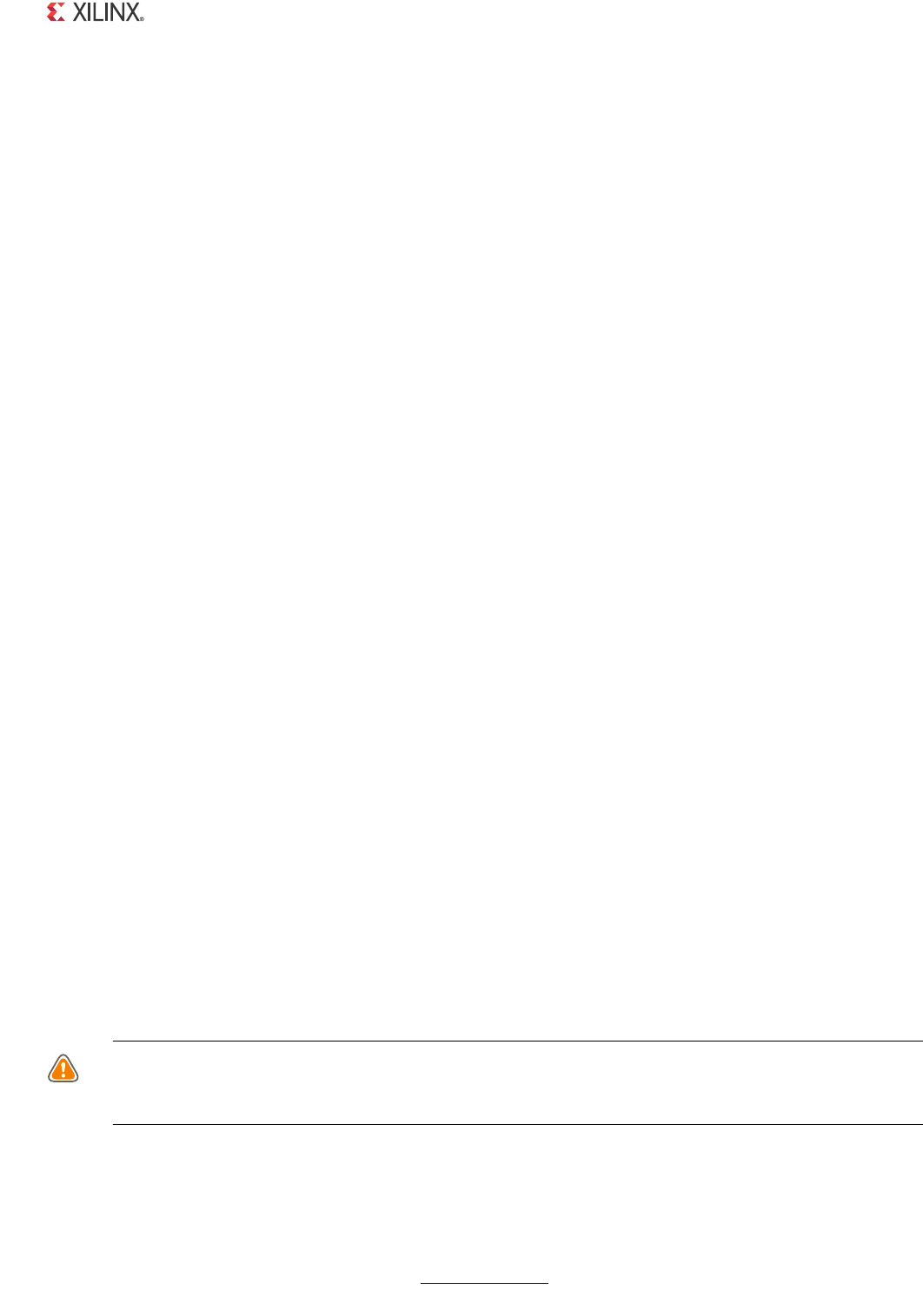

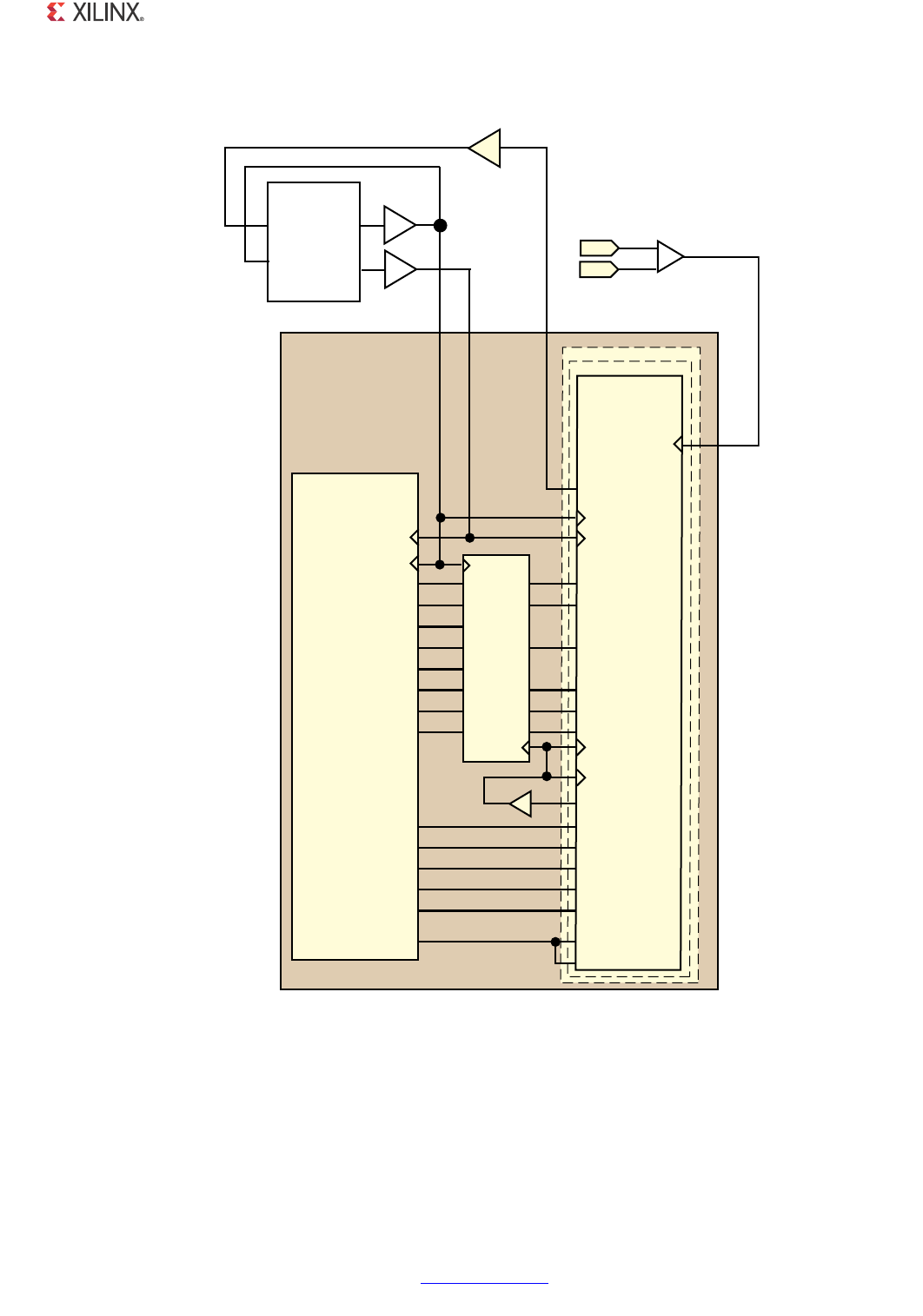

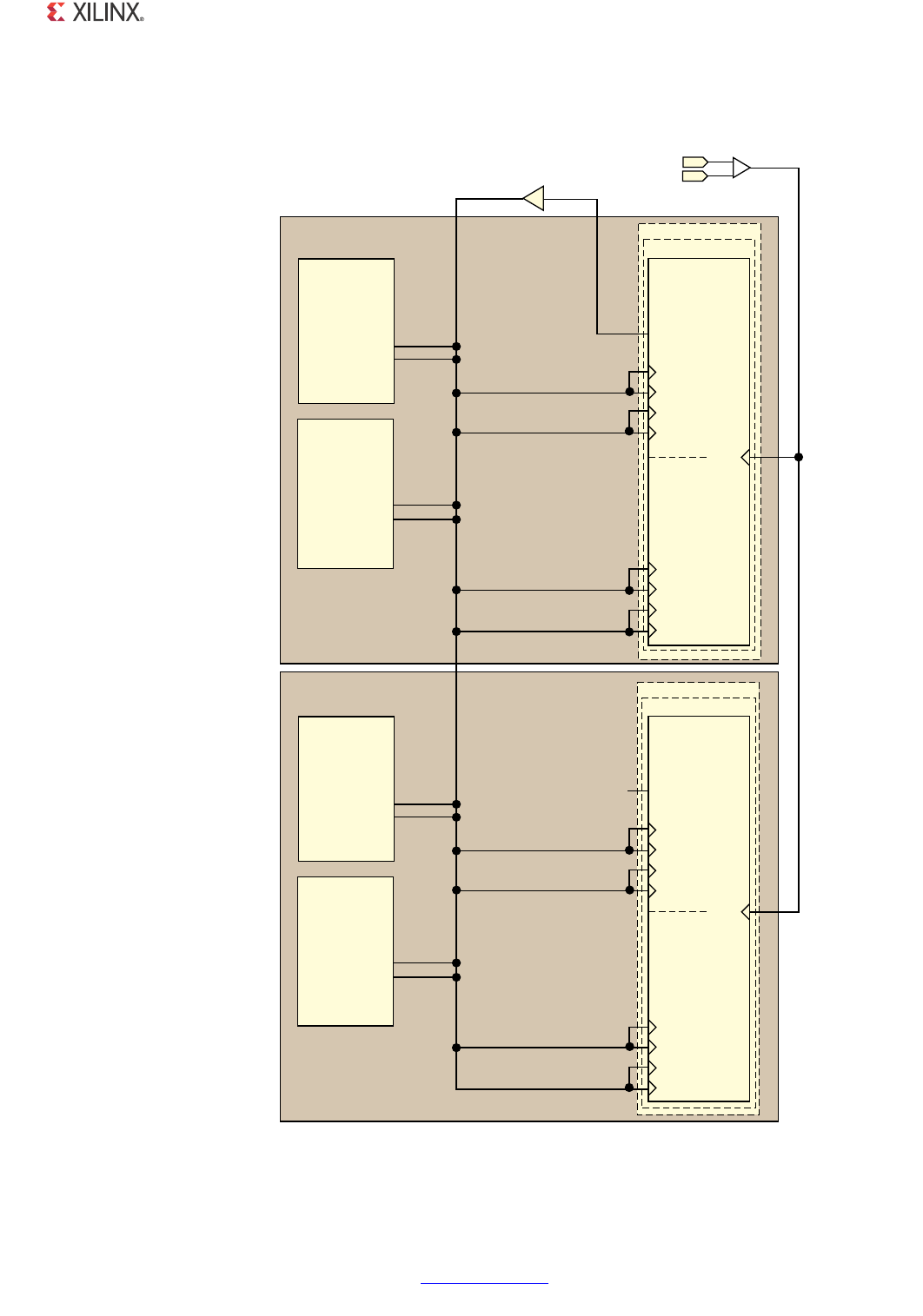

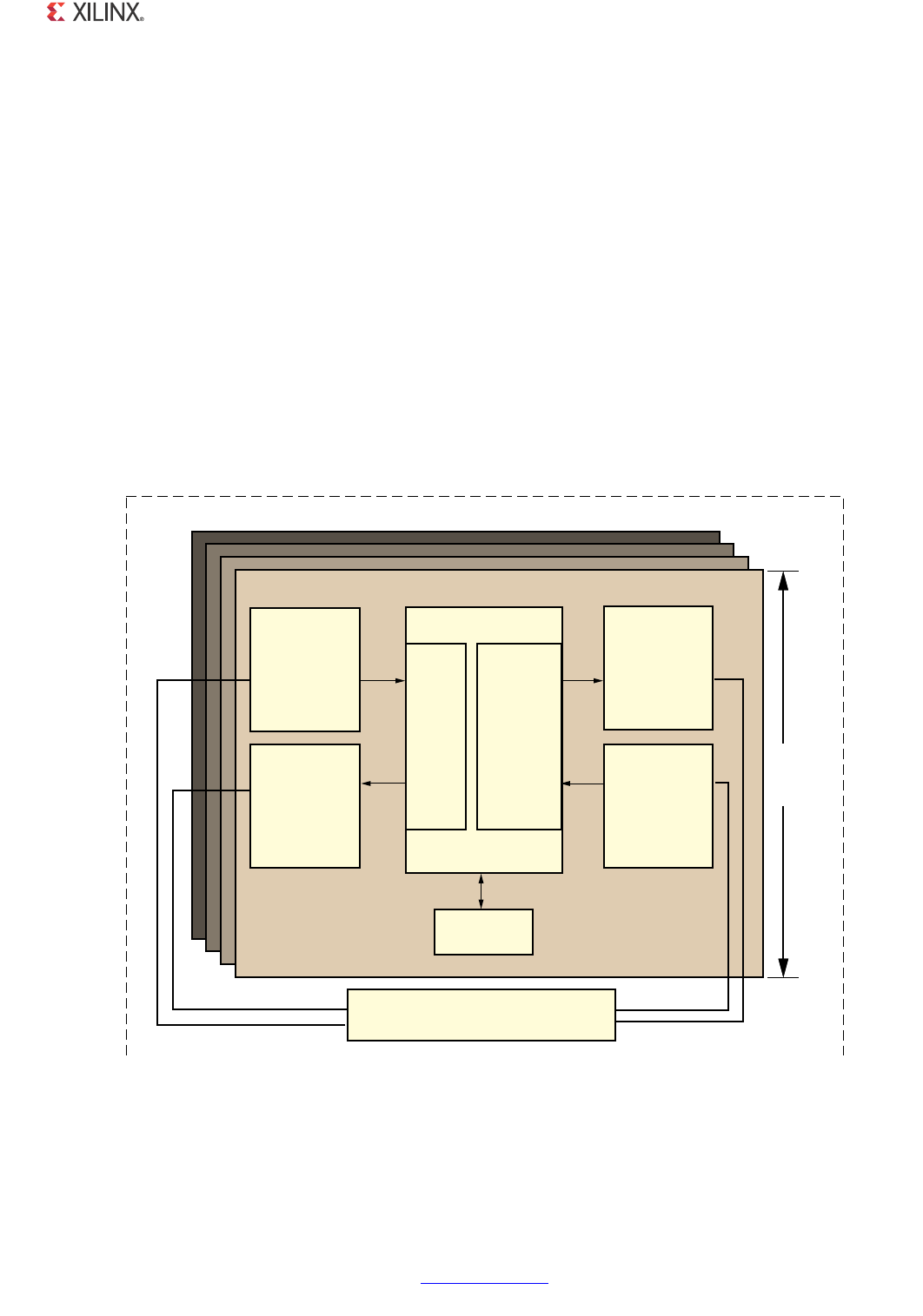

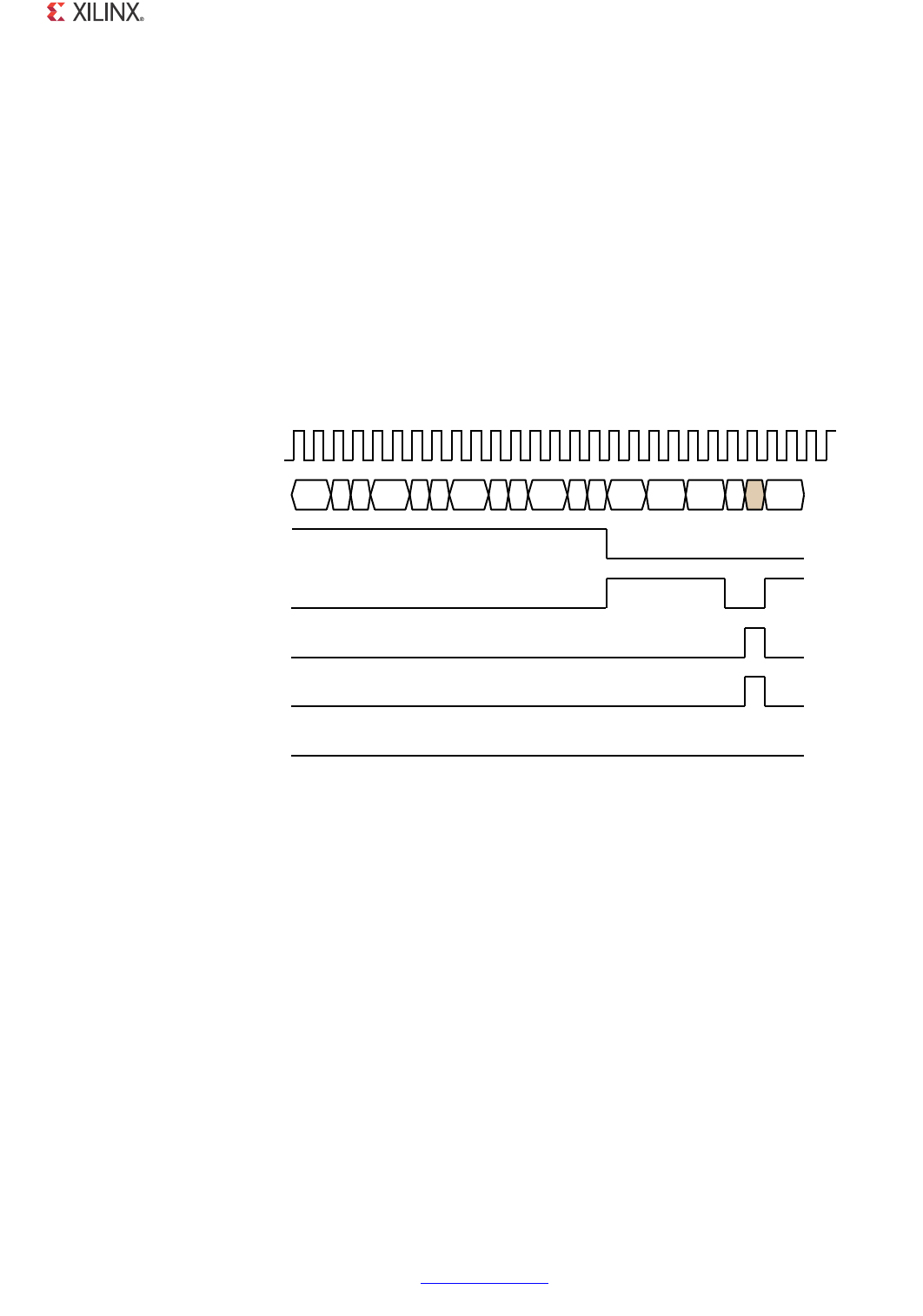

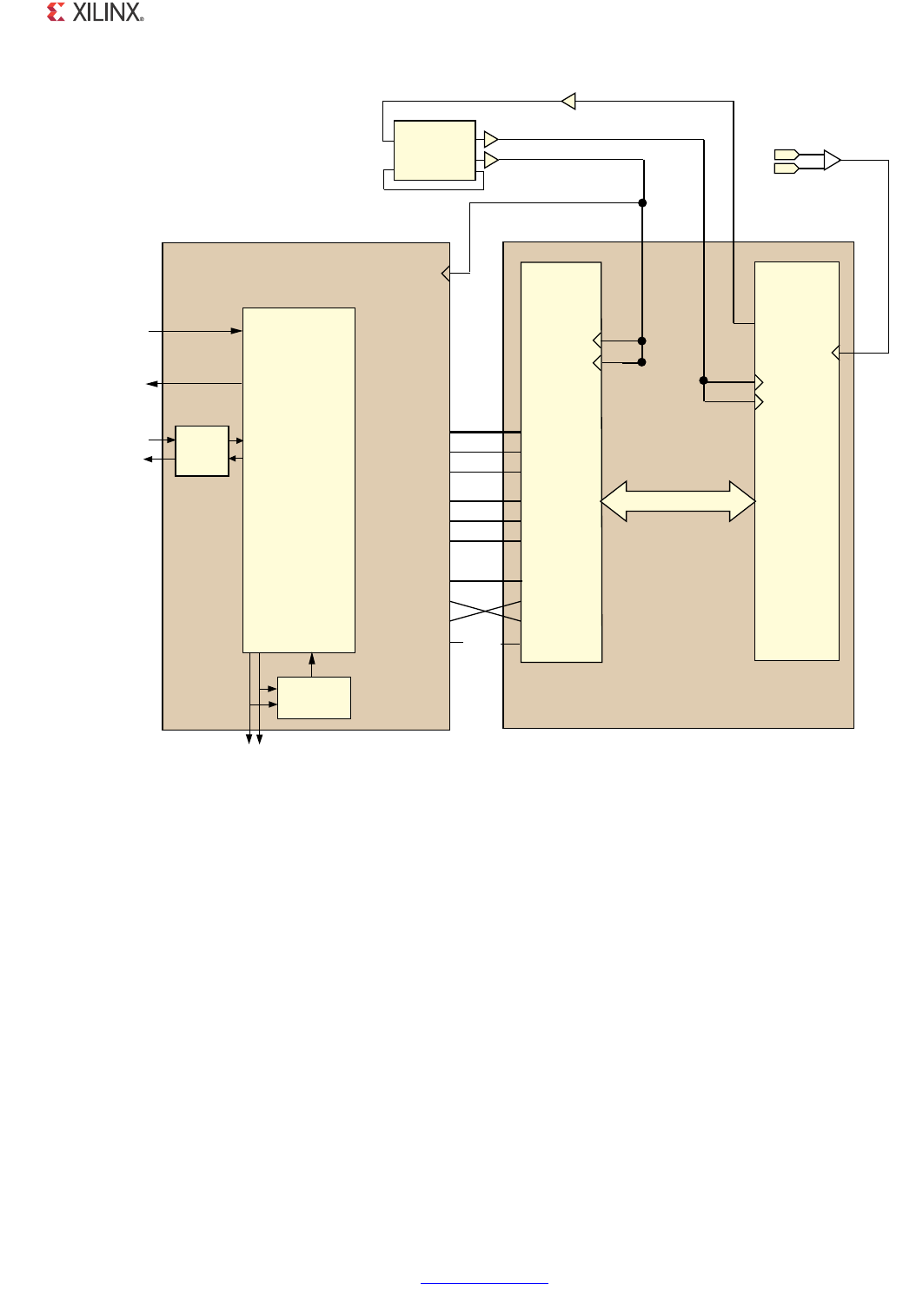

Synchronous SGMII over Virtex7/Kintex7 LVDS

Kintex-7/Virtex-7 devices, -2 speed grade or higher on HR Banks and -1 or higher for HP

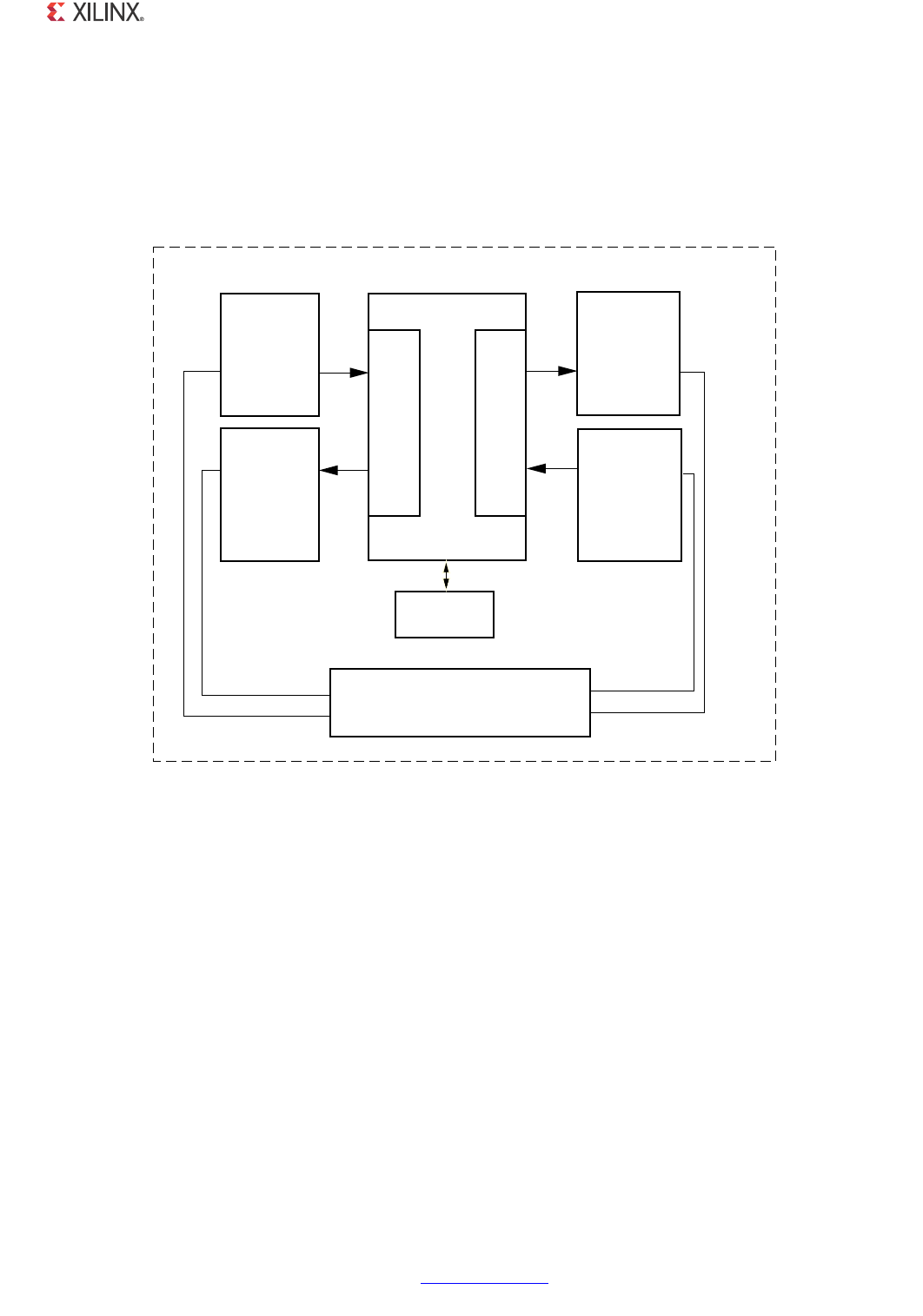

Banks, can fully support SGMII using standard LVDS SelectIO™ technology logic resources.

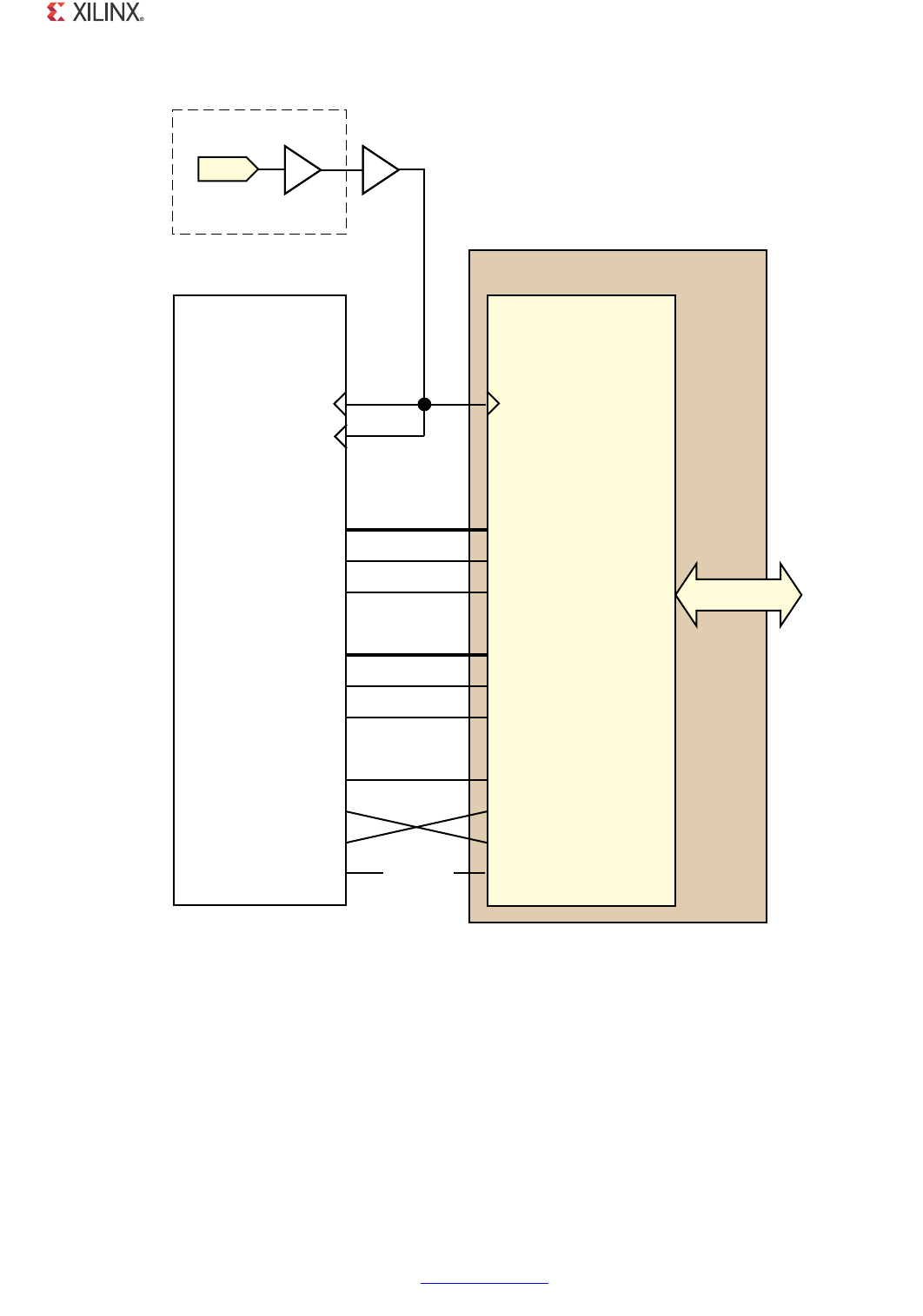

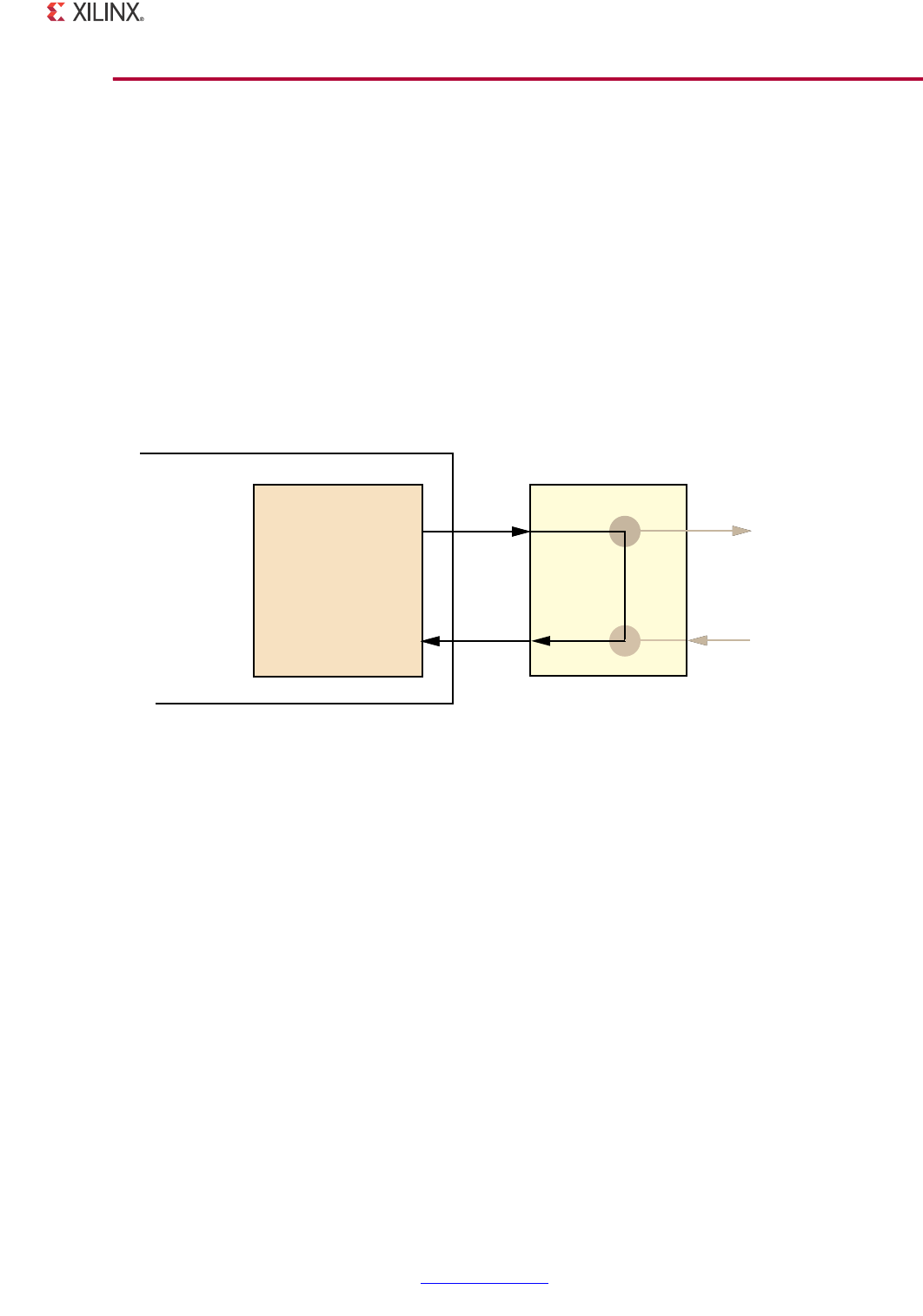

This enables direct connection to external PHY devices without the use of an FPGA

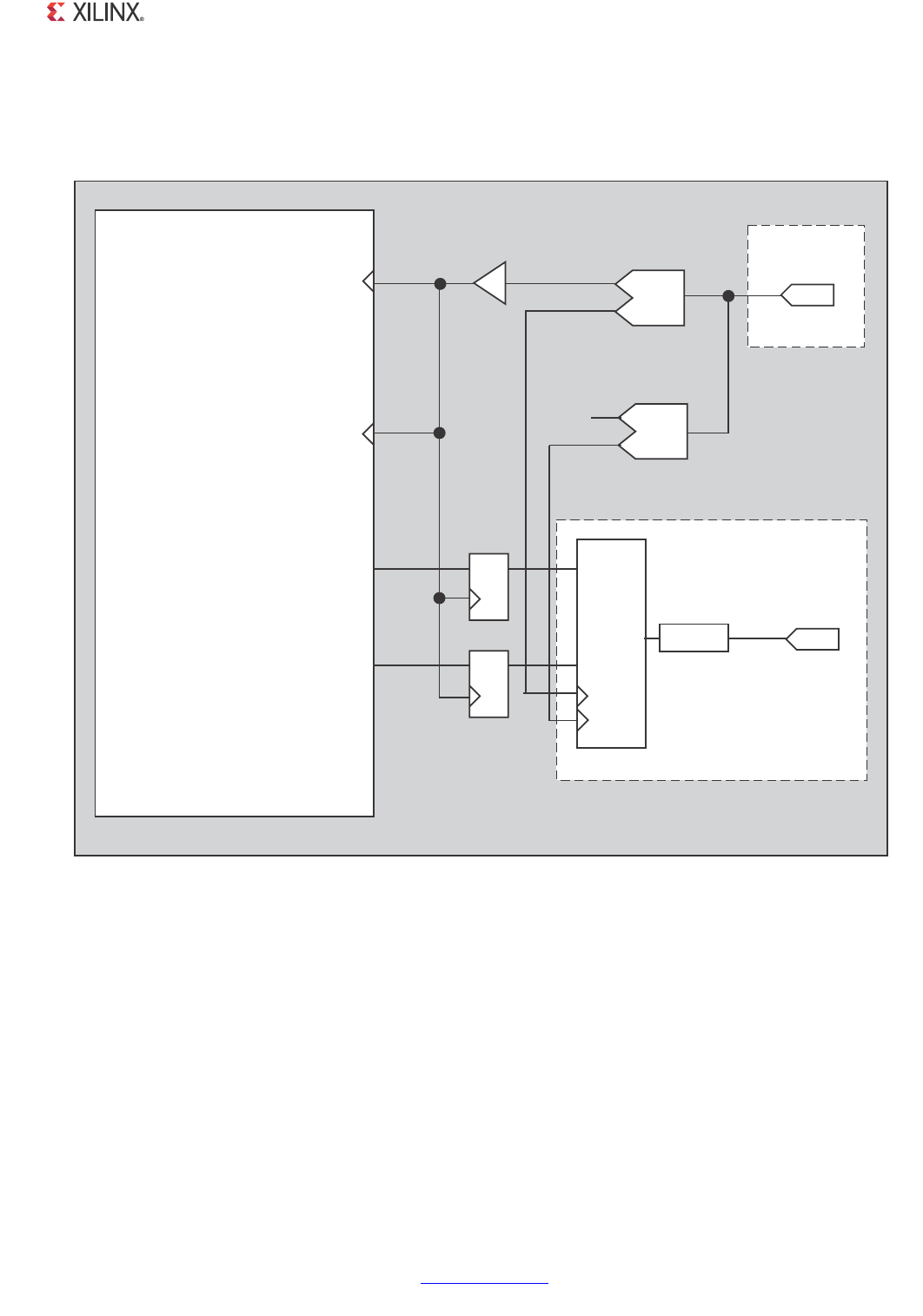

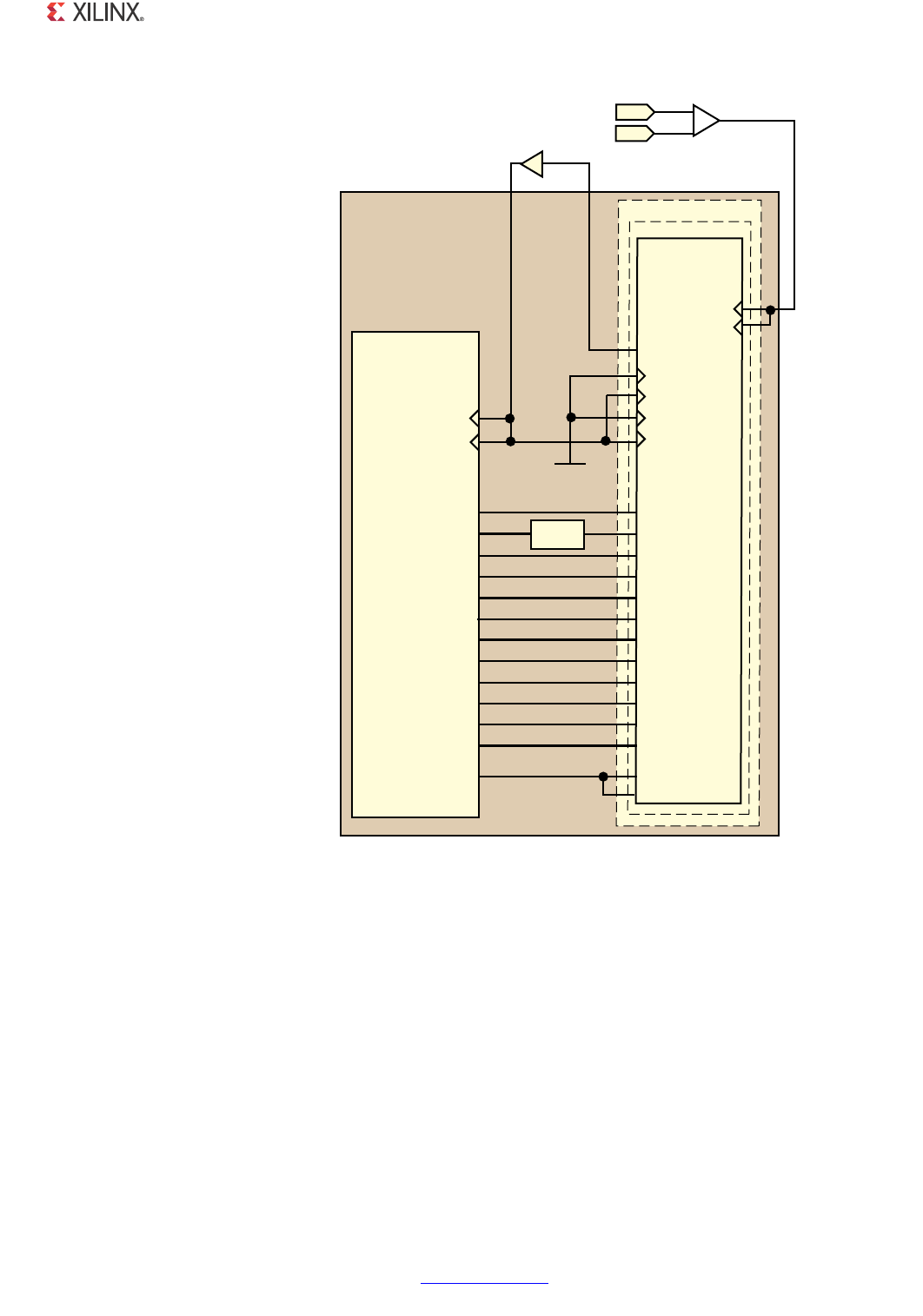

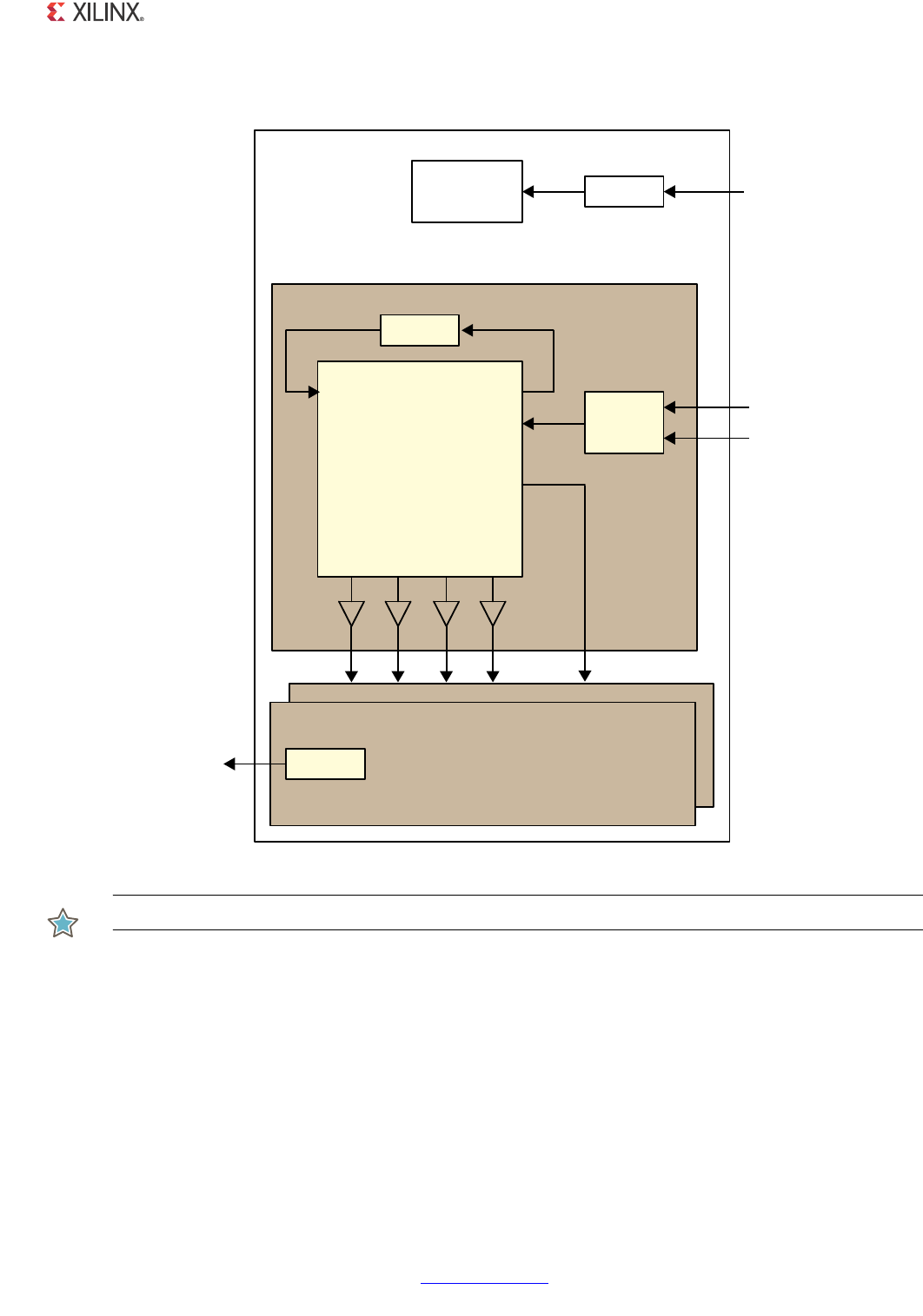

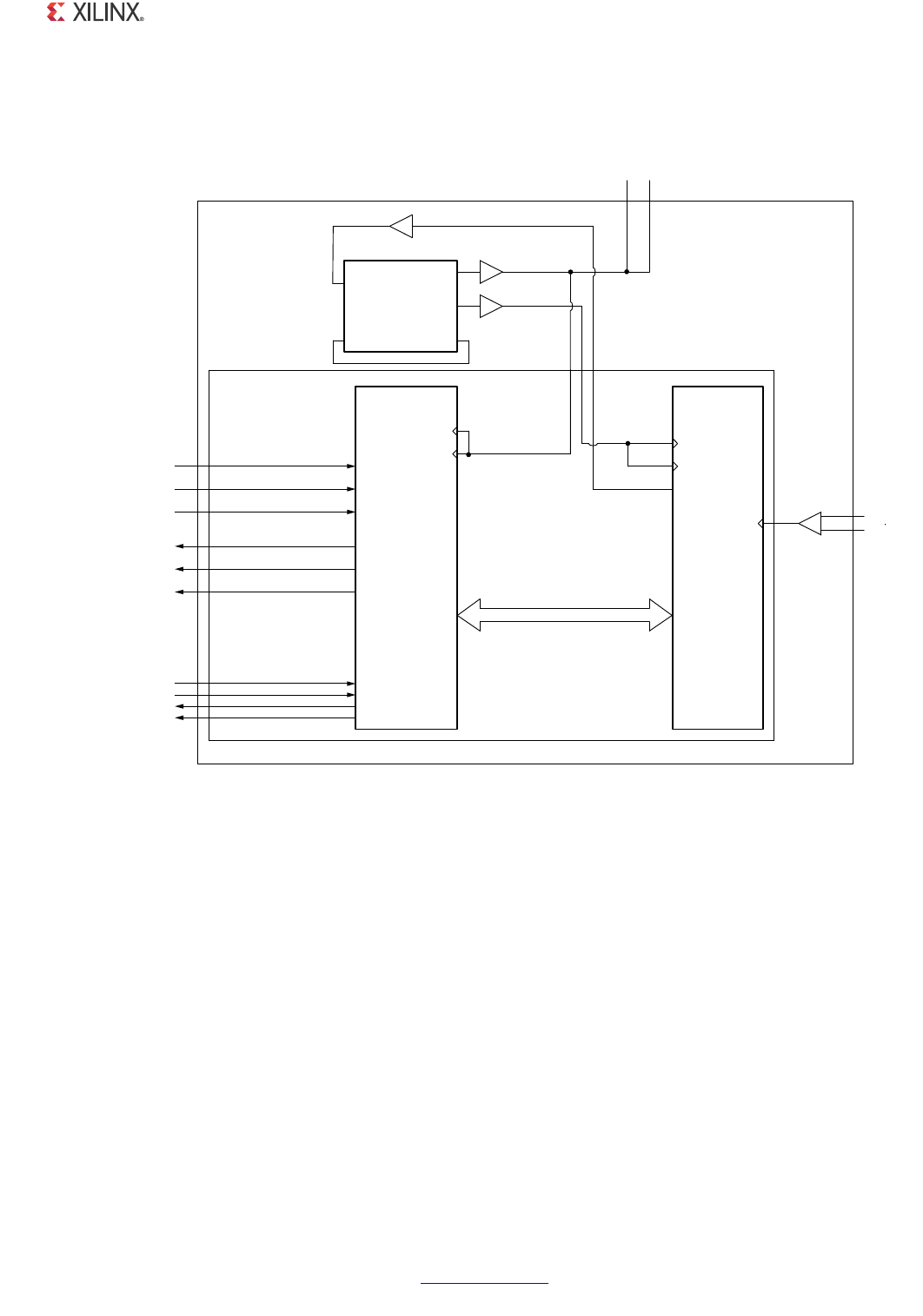

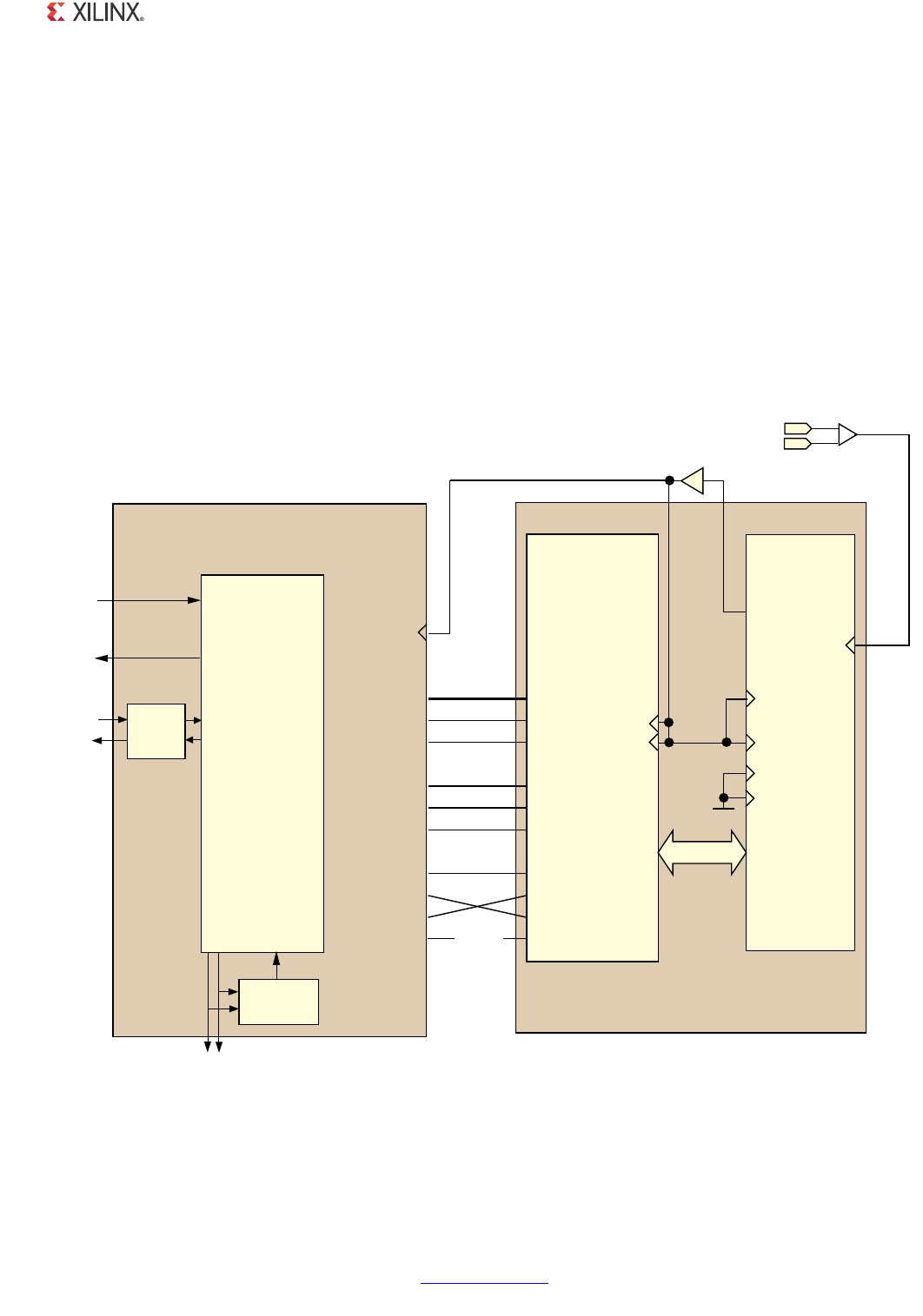

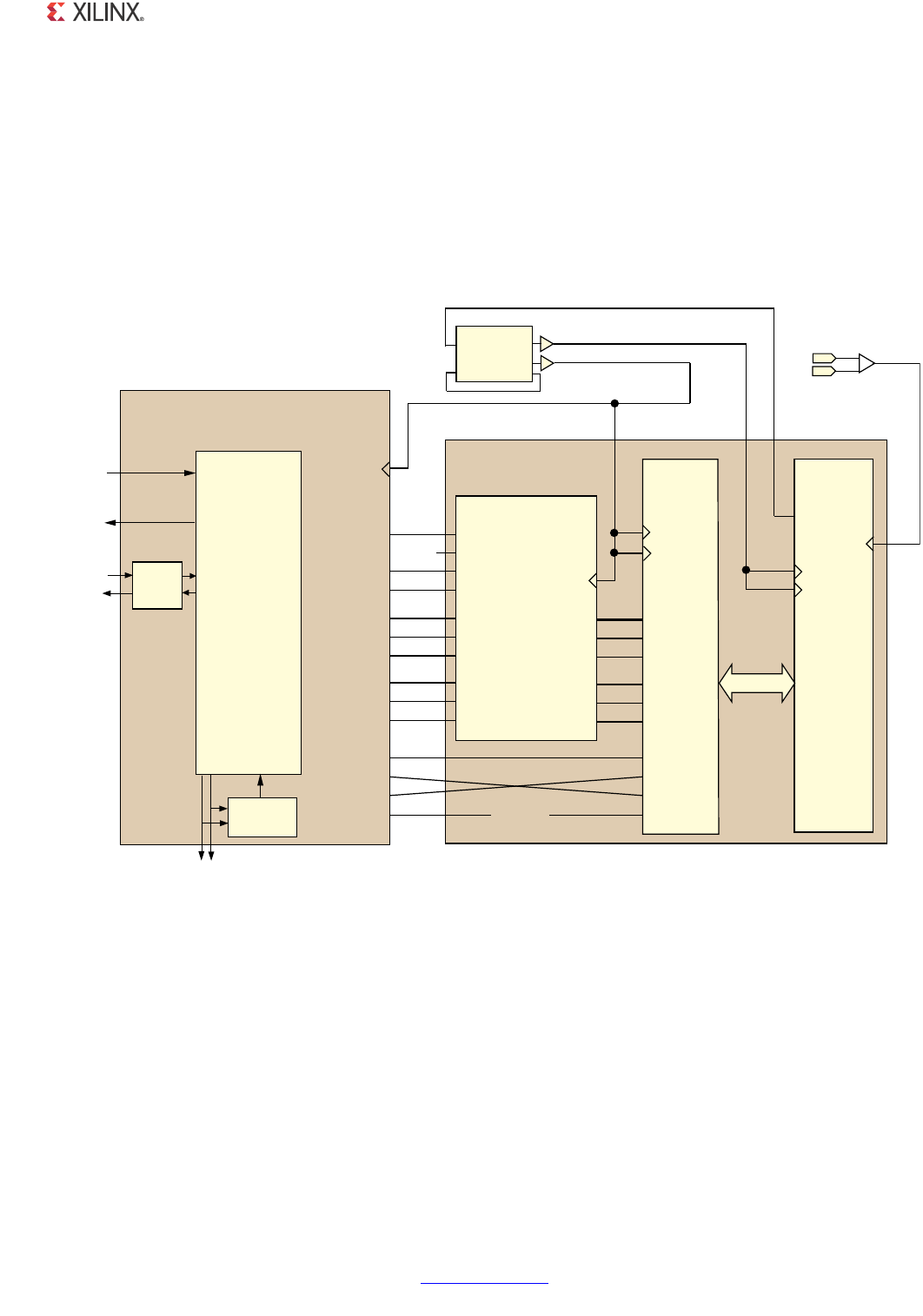

Transceiver. This implementation is illustrated in Figure 1-3.

1000BASE-X PCS/PMA or SGMII v11.4 www.xilinx.com 16

PG047 October 16, 2012

Chapter 1: Overview

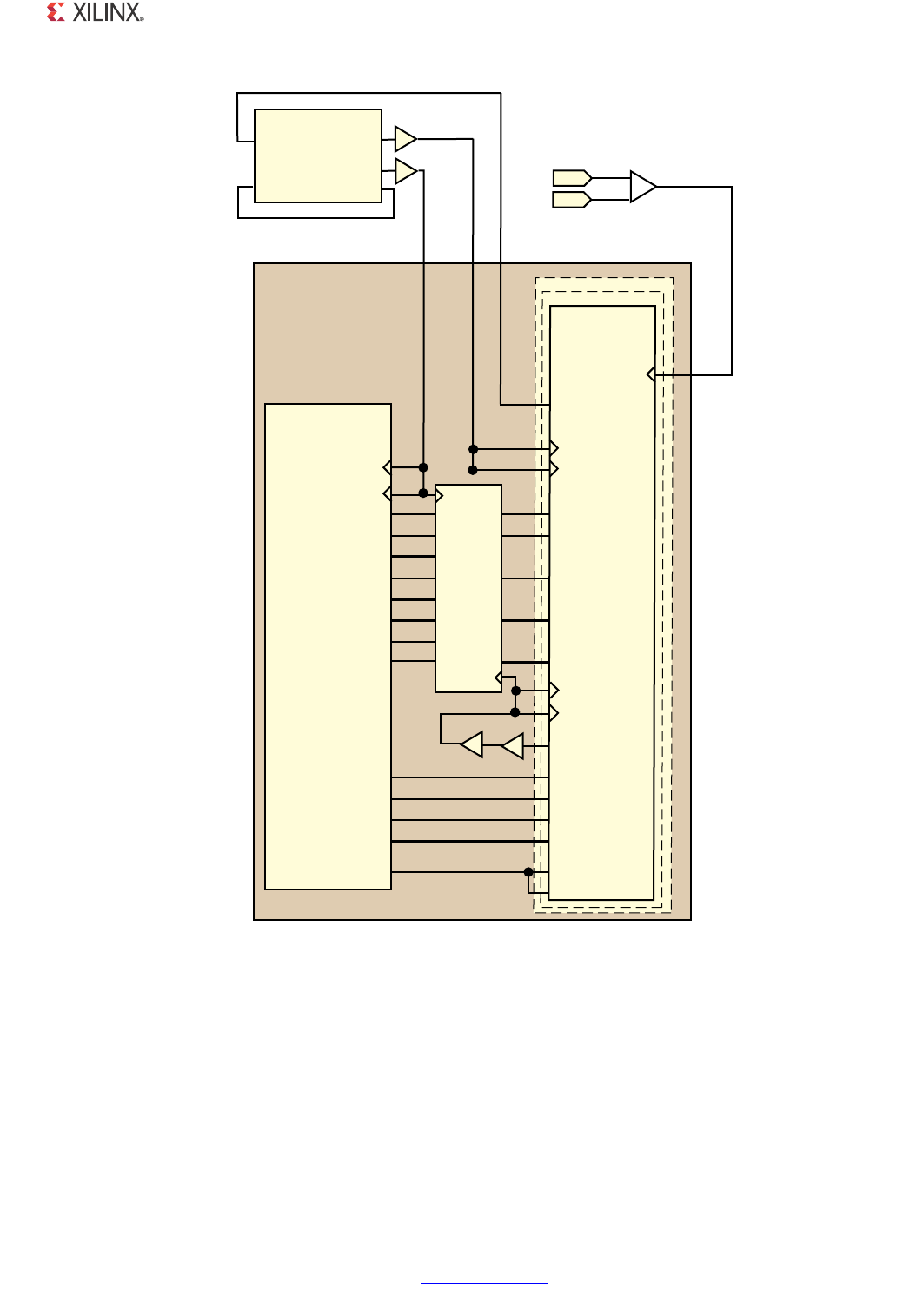

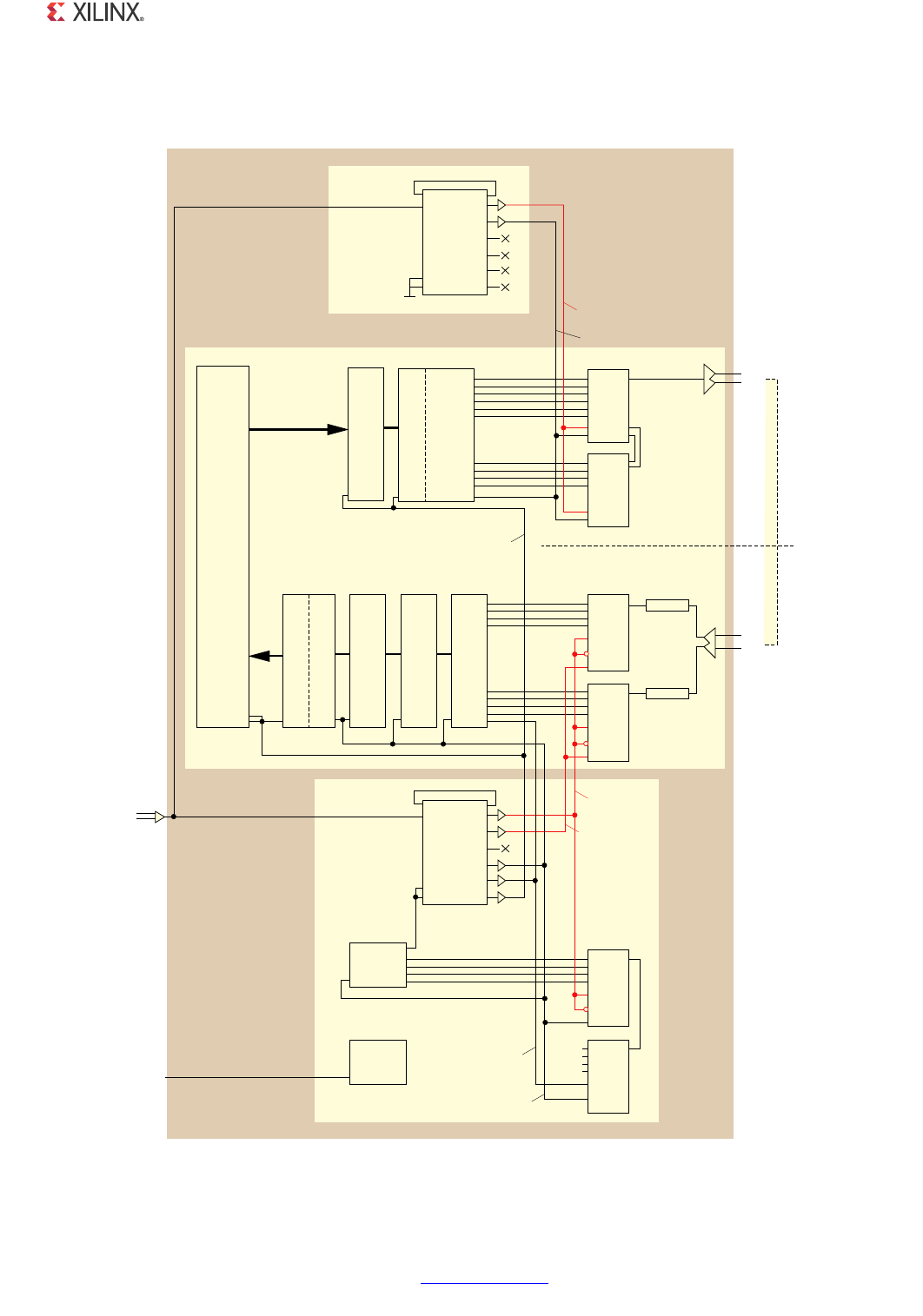

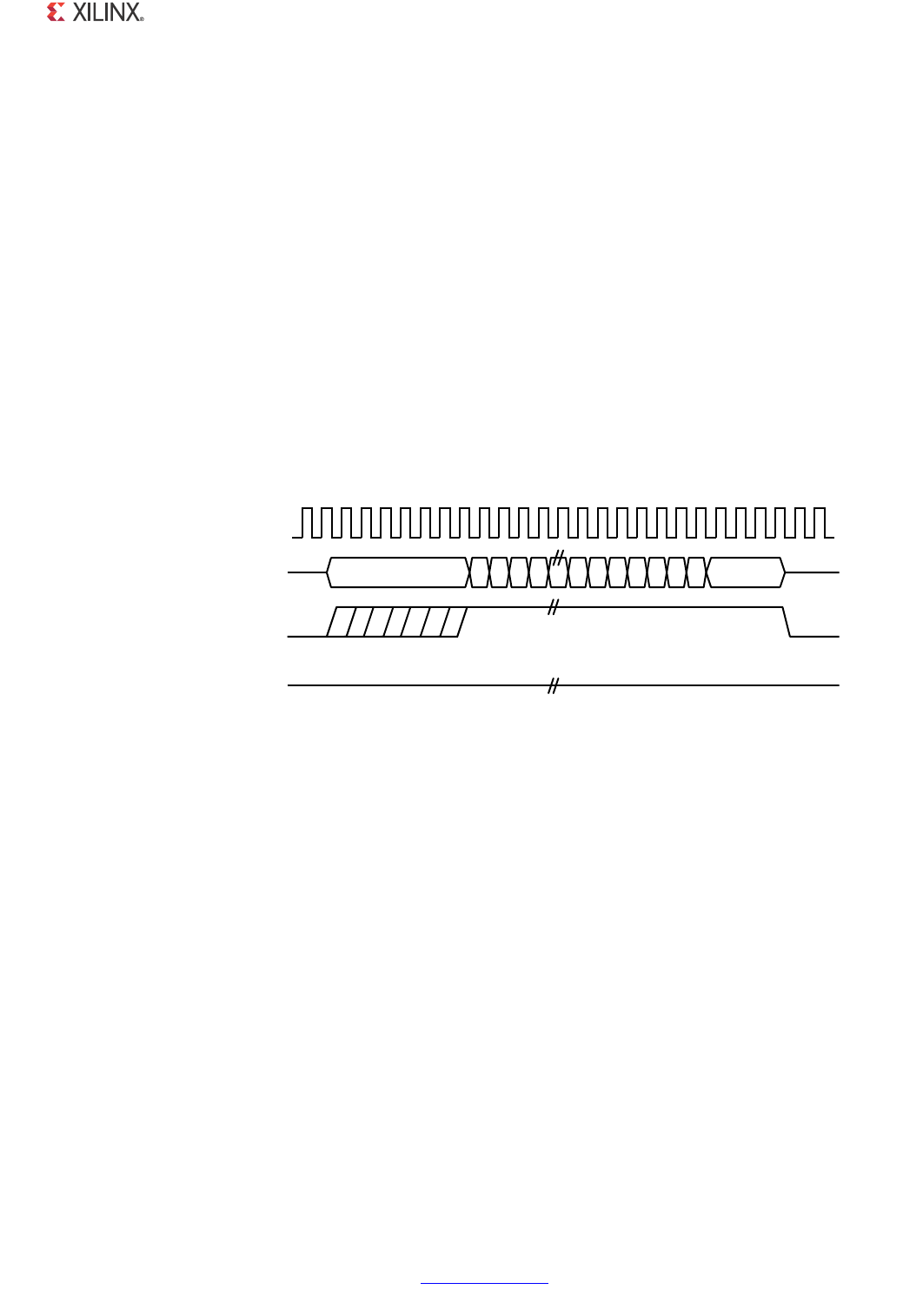

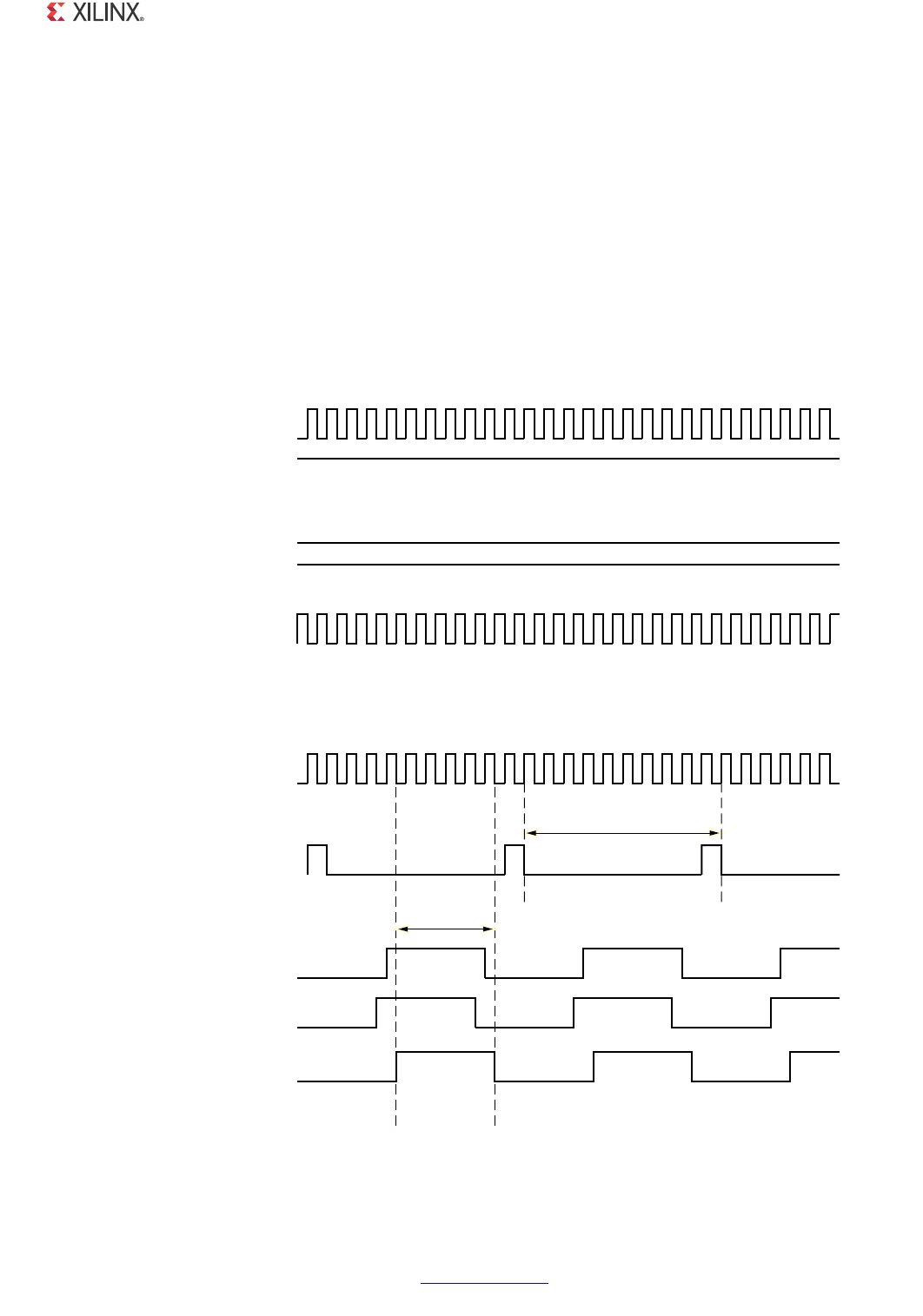

The core netlist in this implementation remains identical to that of Figure 1-1 and all core

netlist blocks are identical to those described in Ethernet 1000BASE-X PCS/PMA or SGMII

Support Using a Device Specific Transceiver.

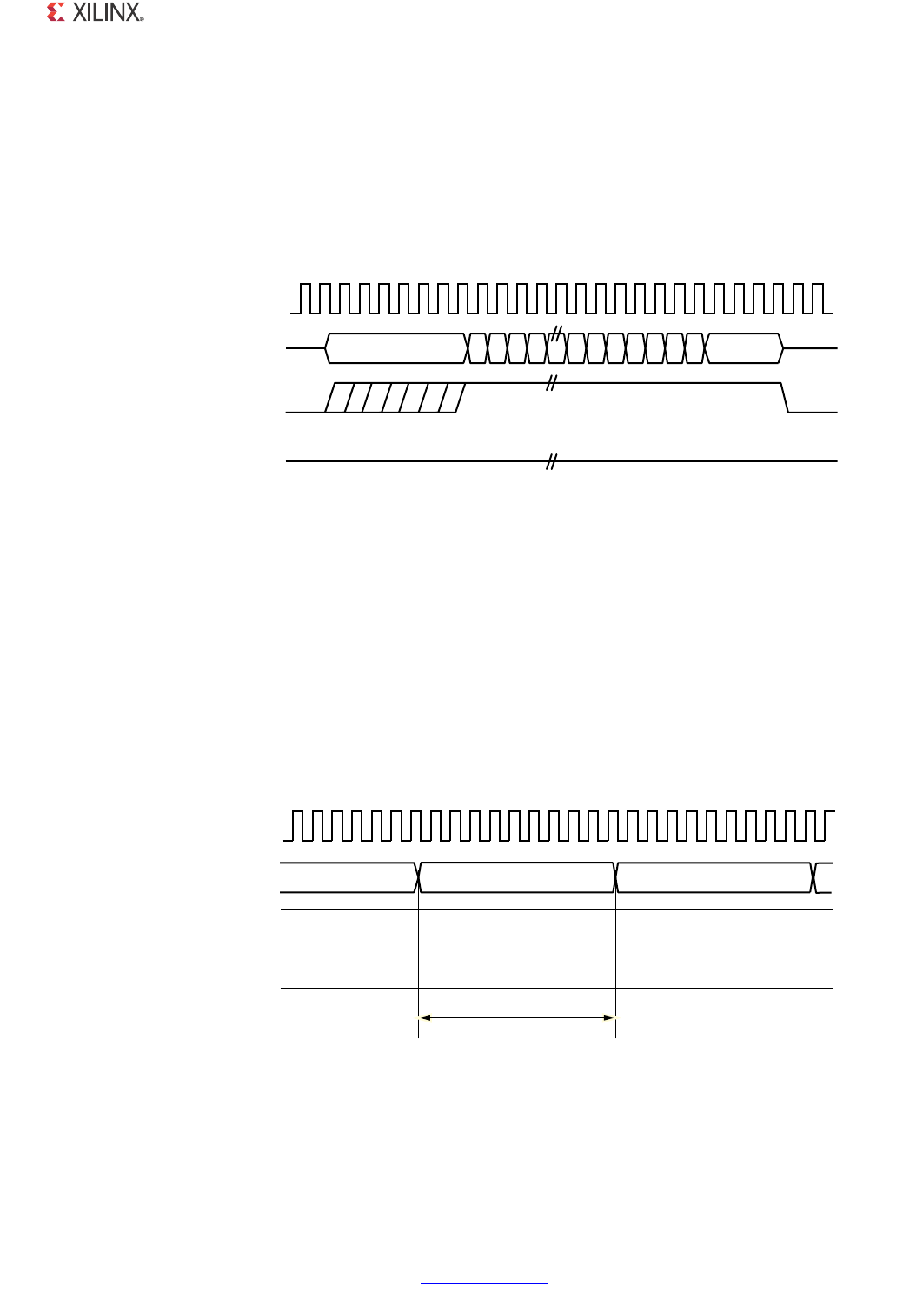

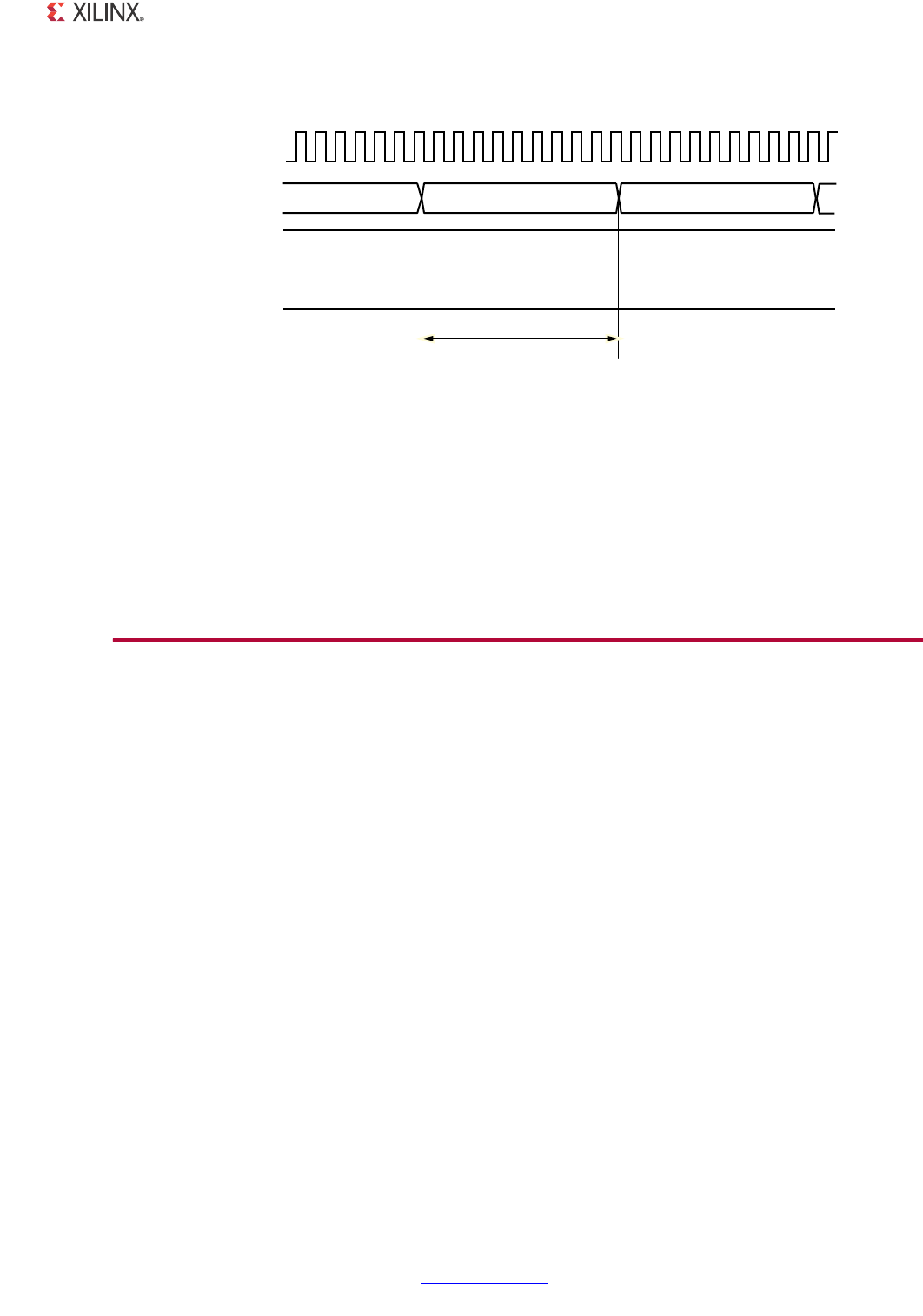

As illustrated in Figure 1-3, the Hardware Description Language (HDL) example design for

this implementation provides additional logic to form the "LVDS transceiver." The LVDS

transceiver block fully replaces the functionality otherwise provided by a 7 series FPGA

GTX/GTH transceiver. This is only possible at a serial line rate of 1.25 Gb/s. See Figure 1-4

for a block diagram of the LVDS transceiver.

X-Ref Target - Figure 1-3

Figure 1-3: Functional Block Diagram of the Core with Standard SelectIO Technology Support

for SGMII

#LOCKING,OGIC

REFCLK?P

REFCLK?N

CLKCLK CLK CLK

,6$34RANSCEIVER

RXN

RXP

TXN

TXP

COMPONENT?NAME?BLOCK

COMPONENT?NAME?EXAMPLE?DESIGN

%THERNET

3'-))

0#30-!#ORE

3'-))!DAPTATION

-ODULE

'-))3TYLE

BIT)&

8

1000BASE-X PCS/PMA or SGMII v11.4 www.xilinx.com 17

PG047 October 16, 2012

Chapter 1: Overview

The following subsections describe design requirements.

SGMII Only

The interface implemented using this method supports SGMII between the FPGA and an

external PHY device; the interface cannot directly support 1000BASE-X.

Supported Devices

• Kintex-7 devices, -2 speed grade or faster for devices with HR Banks or -1 speed grade

or faster for devices with HP banks.

• Virtex-7 devices, -2 speed grade or faster for devices with HR Banks or -1 speed grade

or faster for devices with HP banks.

Recommended for Chip-to-Chip Copper Implementations Only

This interface supports an SGMII link between the FPGA and an external PHY device across

a single PCB; keep the SGMII copper signal lengths to a minimum.

SGMII Support Using Asynchronous Oversampling over 7 Series FPGAs LVDS

See XAPP523 LVDS 4x Asynchronous Oversampling Using 7 Series FPGAs for information

about 7 series devices using asynchronous oversampling.

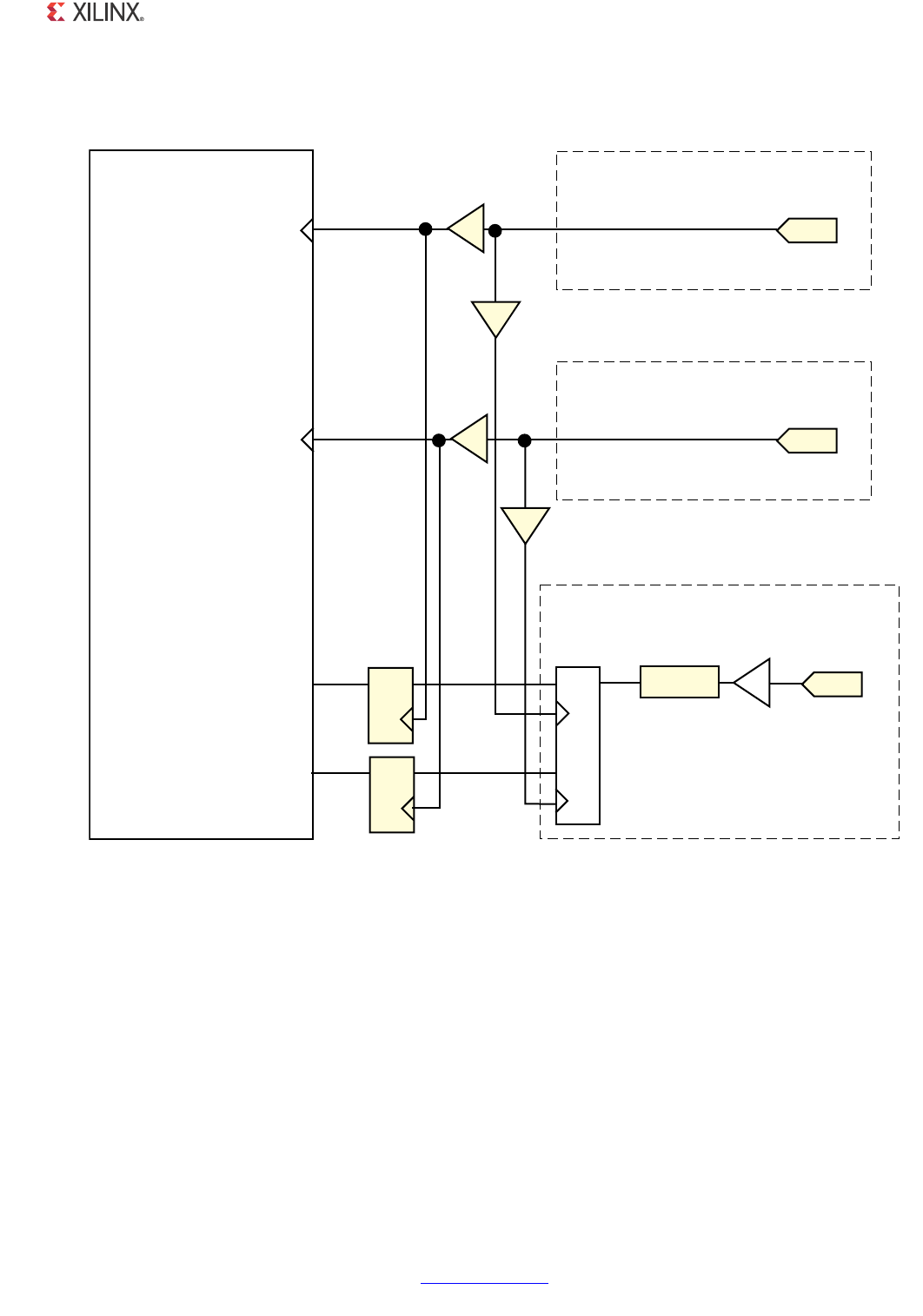

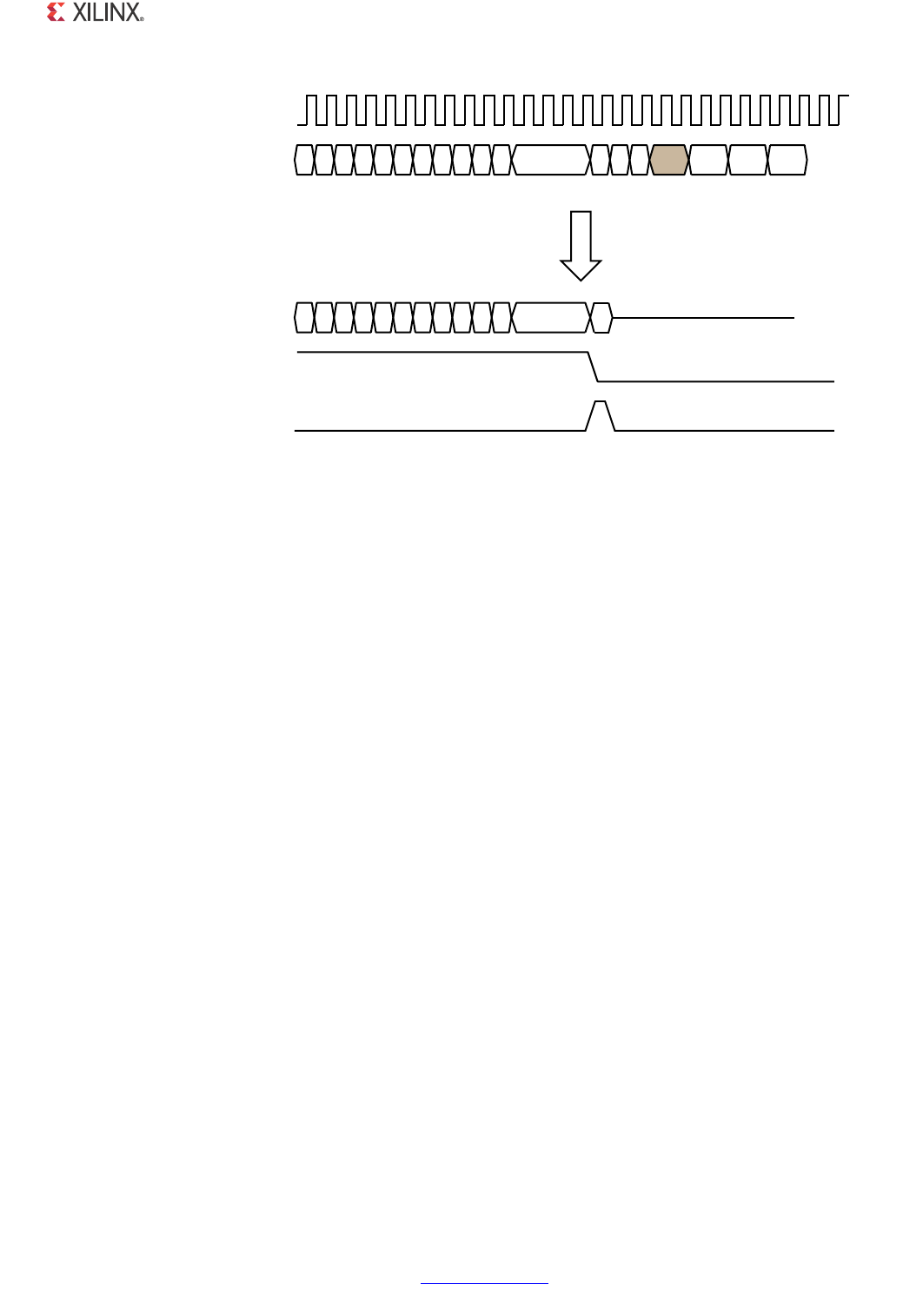

X-Ref Target - Figure 1-4

Figure 1-4: LVDS Transceiver Block Level Representation

""

%NCODER

""

'EARBOX

""

$ECODER

""

'EARBOX

)3%2$%3%

-ONITOR

3ERIALBITS

)3%2$%3%

$ATA

3ERIALBITS

%YE-ONITOR

O?RX?MON

O?RX?DATA?B

0HY

#ALLIBRATION

/3%2$%3%

BITS3ERIAL

)$%,!9%

)$%,!9%

/"5&$3

)"5&$3?$)&&

?/54

RXN

RXP

TXN

TXP

)"

)

/"

/

/"

/

)

COMPONENT?NAME?SGMII?PHY?IOB

COMPONENT?NAME?GPIO?SGMII?TOP

COMPONENT?NAME?LVDS?TRANSCEIVER

&ROM#ORE

4O#ORE

BITDATA

BITDATA

8

1000BASE-X PCS/PMA or SGMII v11.4 www.xilinx.com 18

PG047 October 16, 2012

Chapter 1: Overview

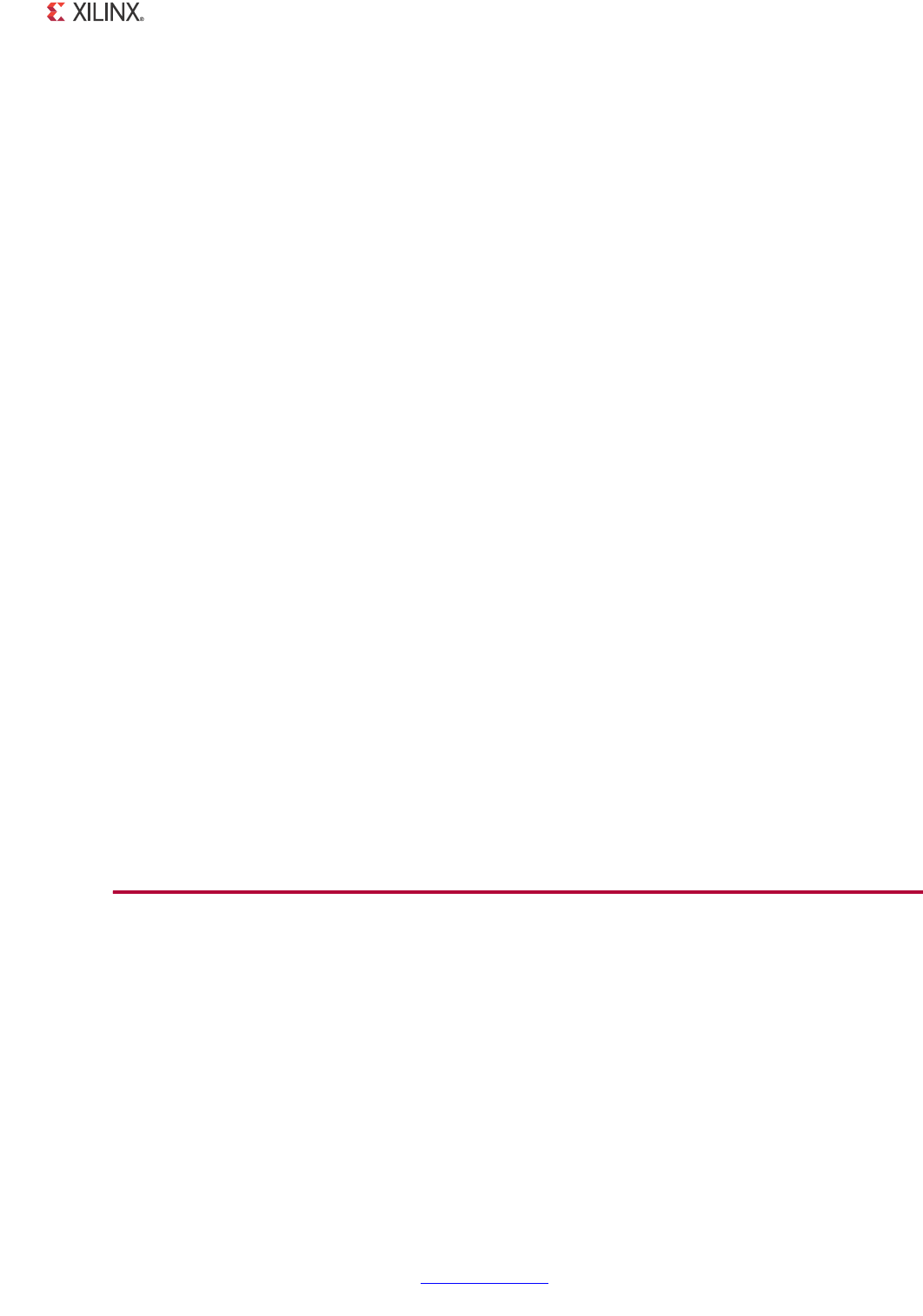

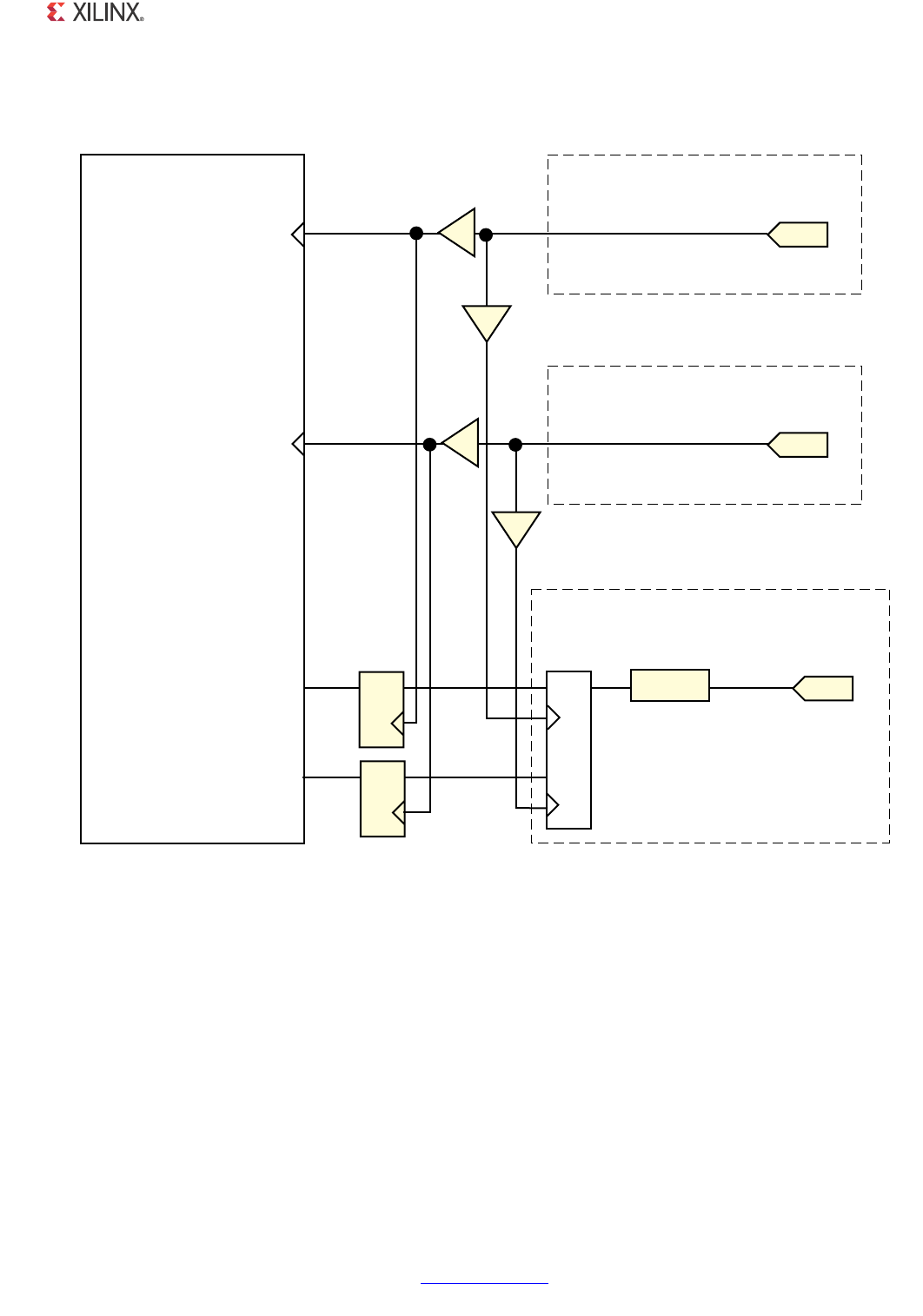

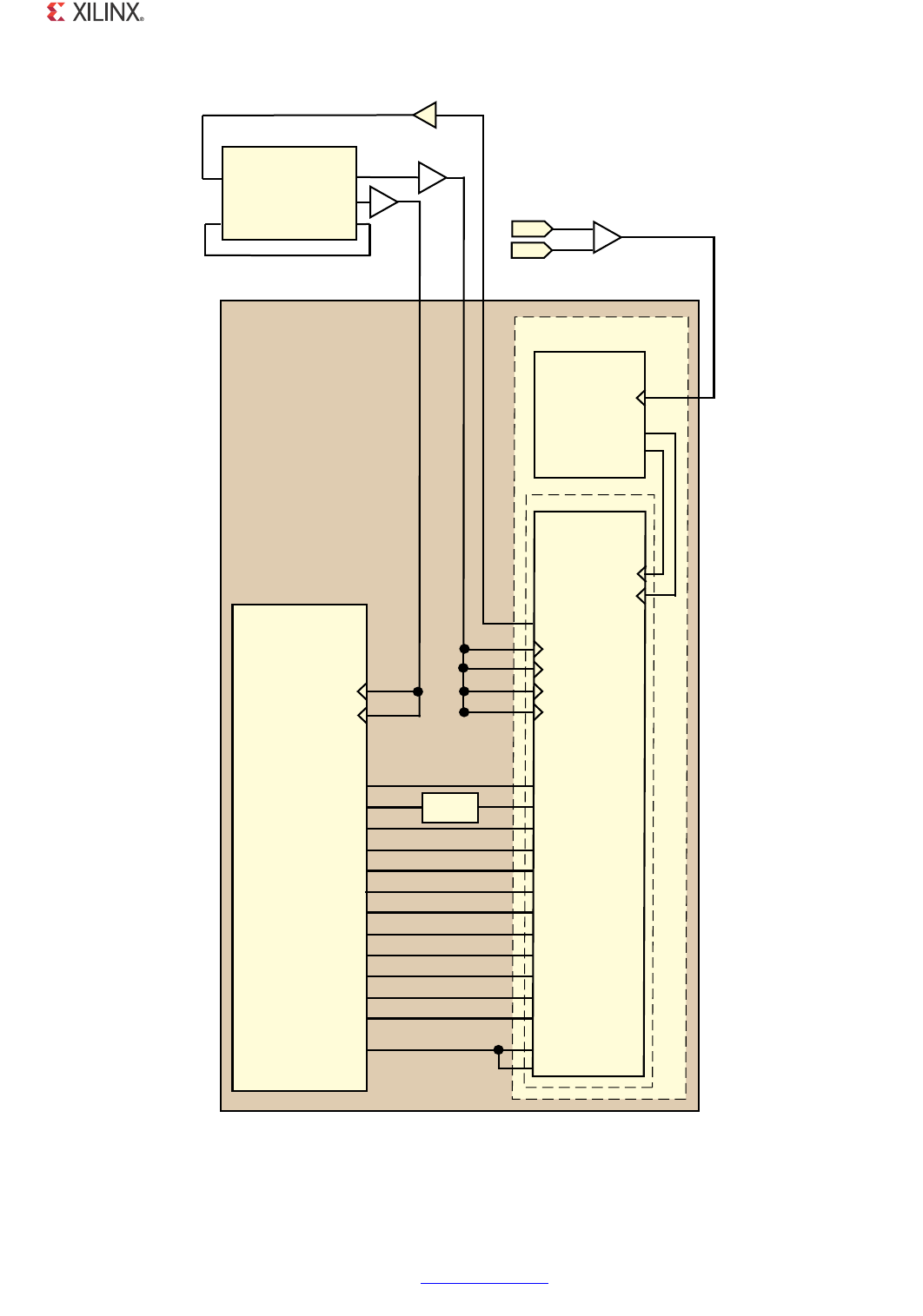

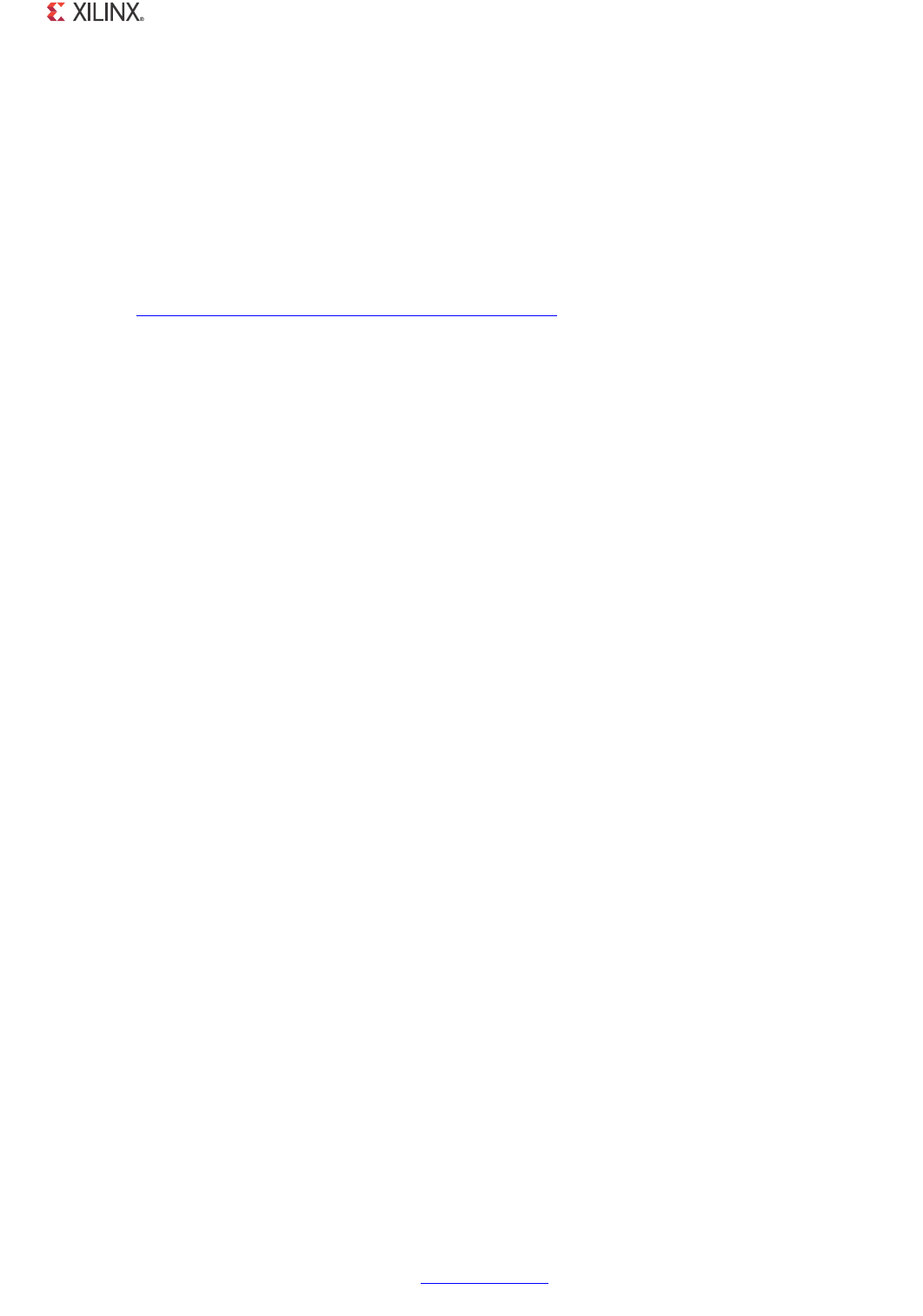

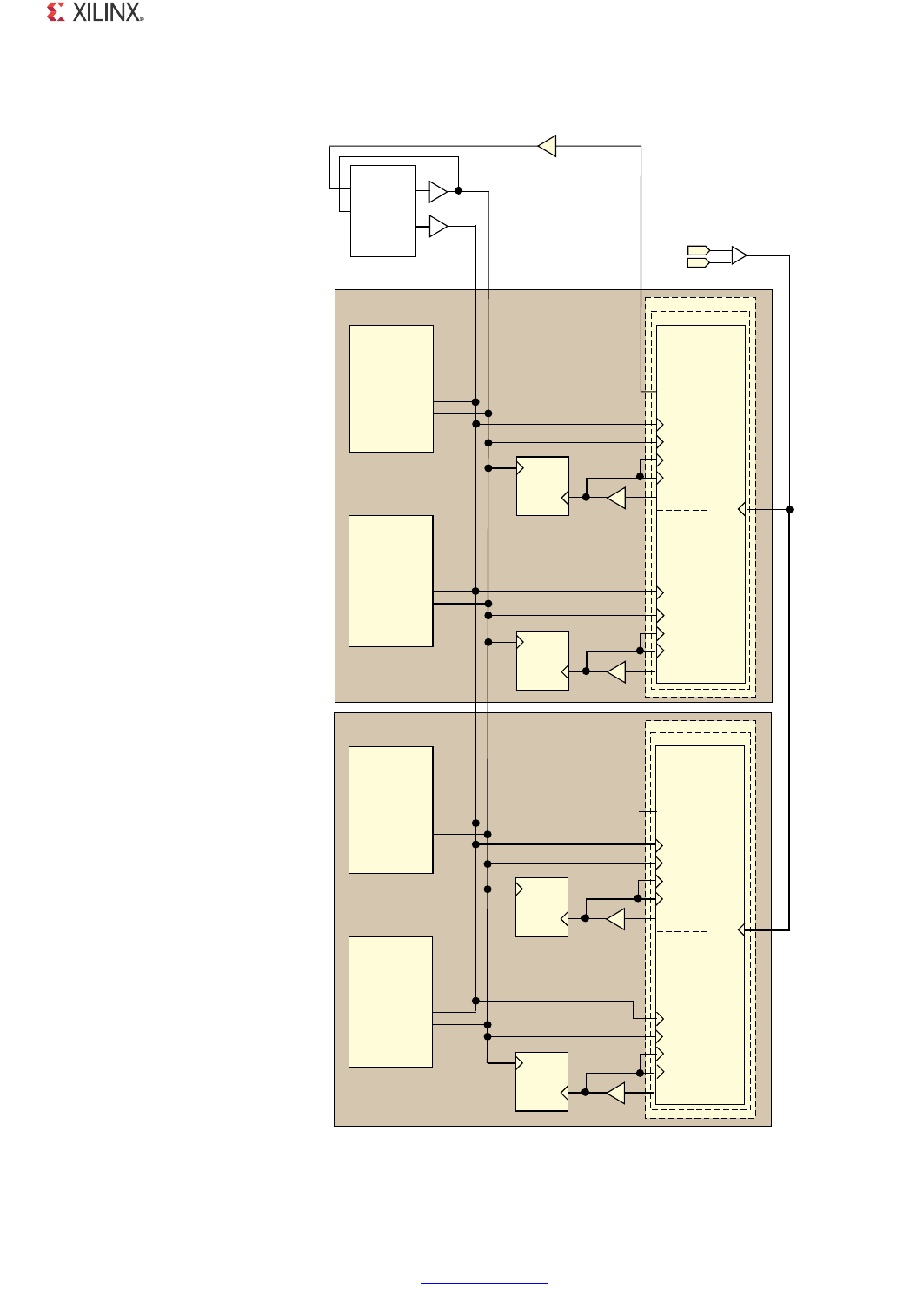

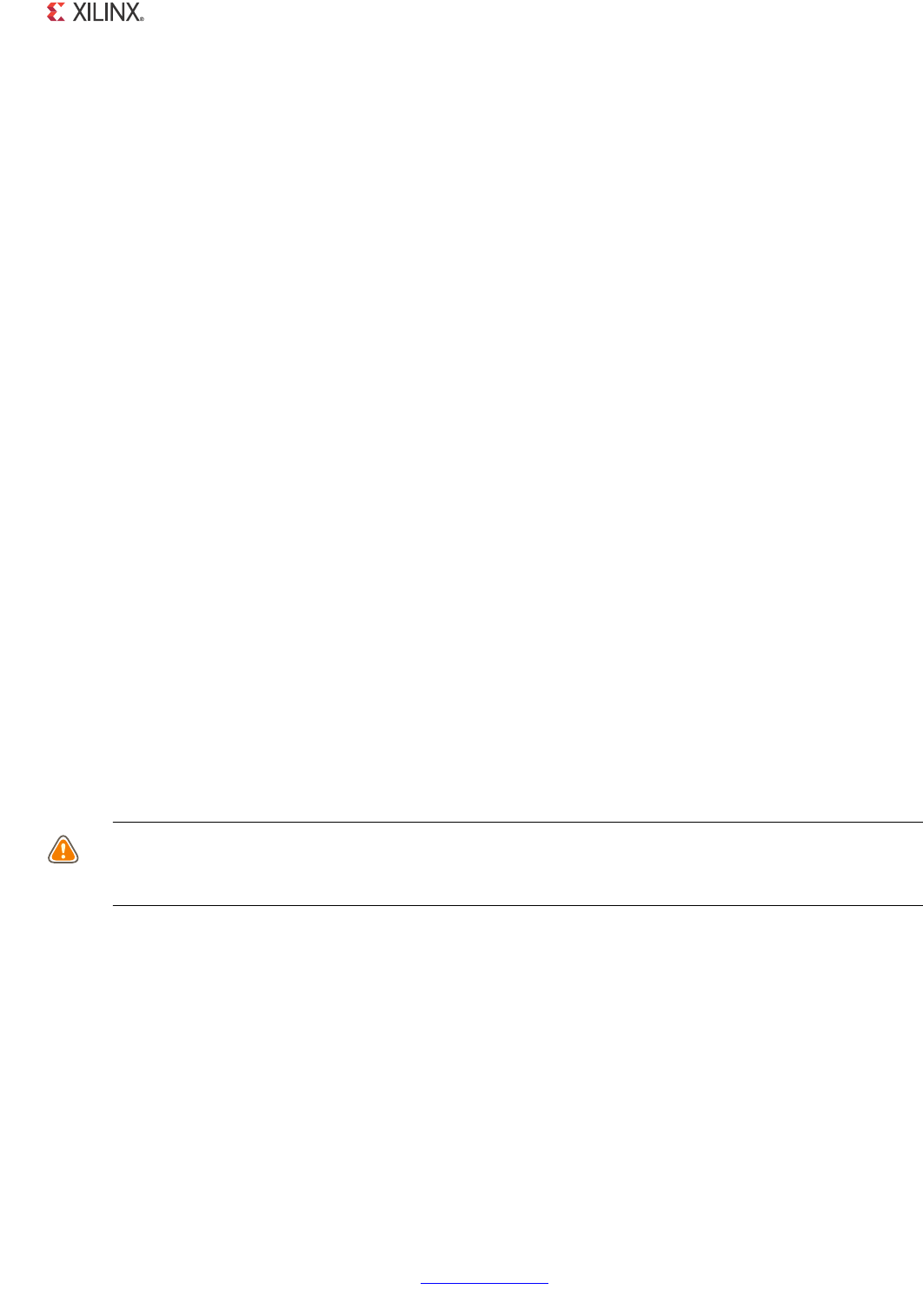

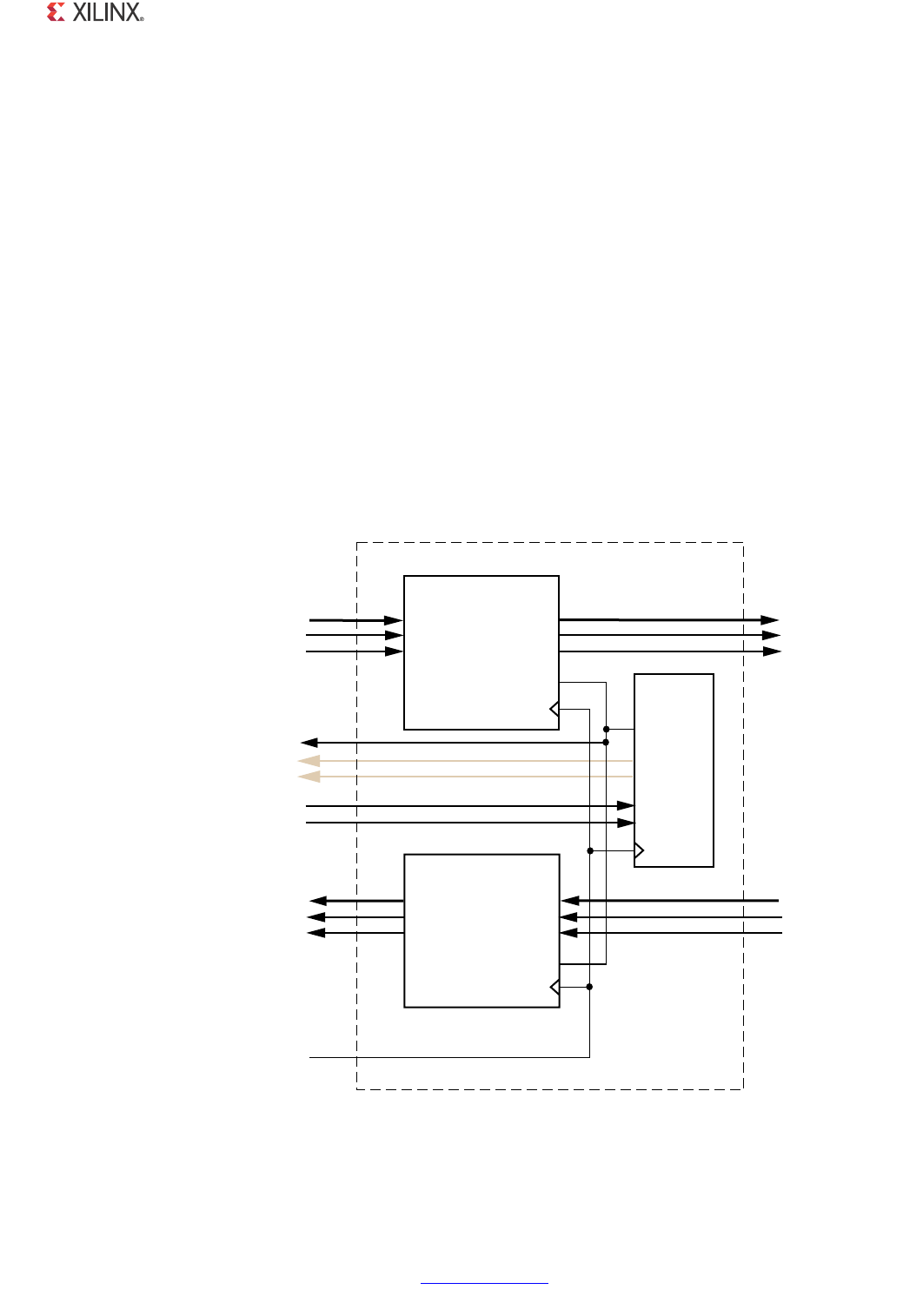

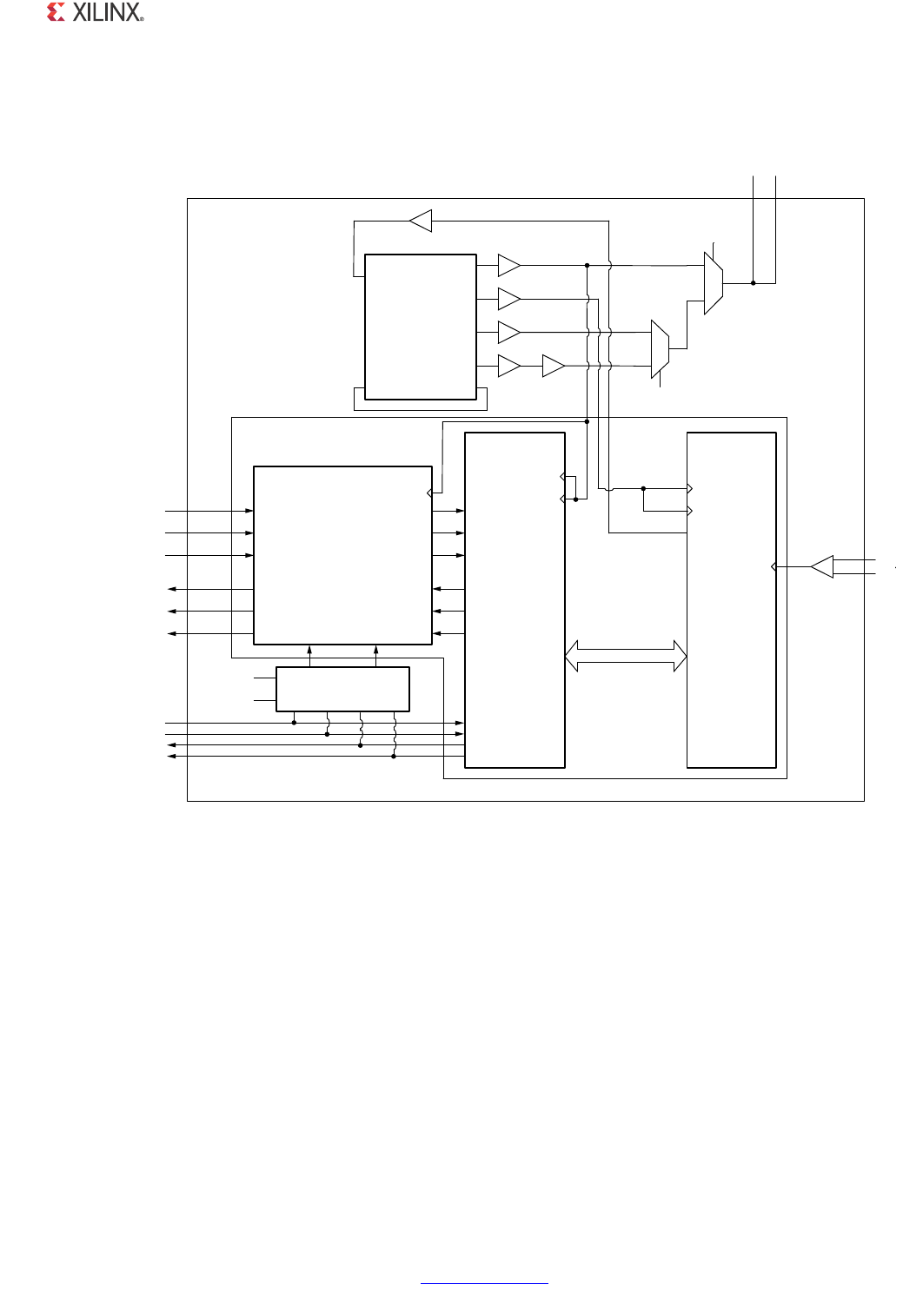

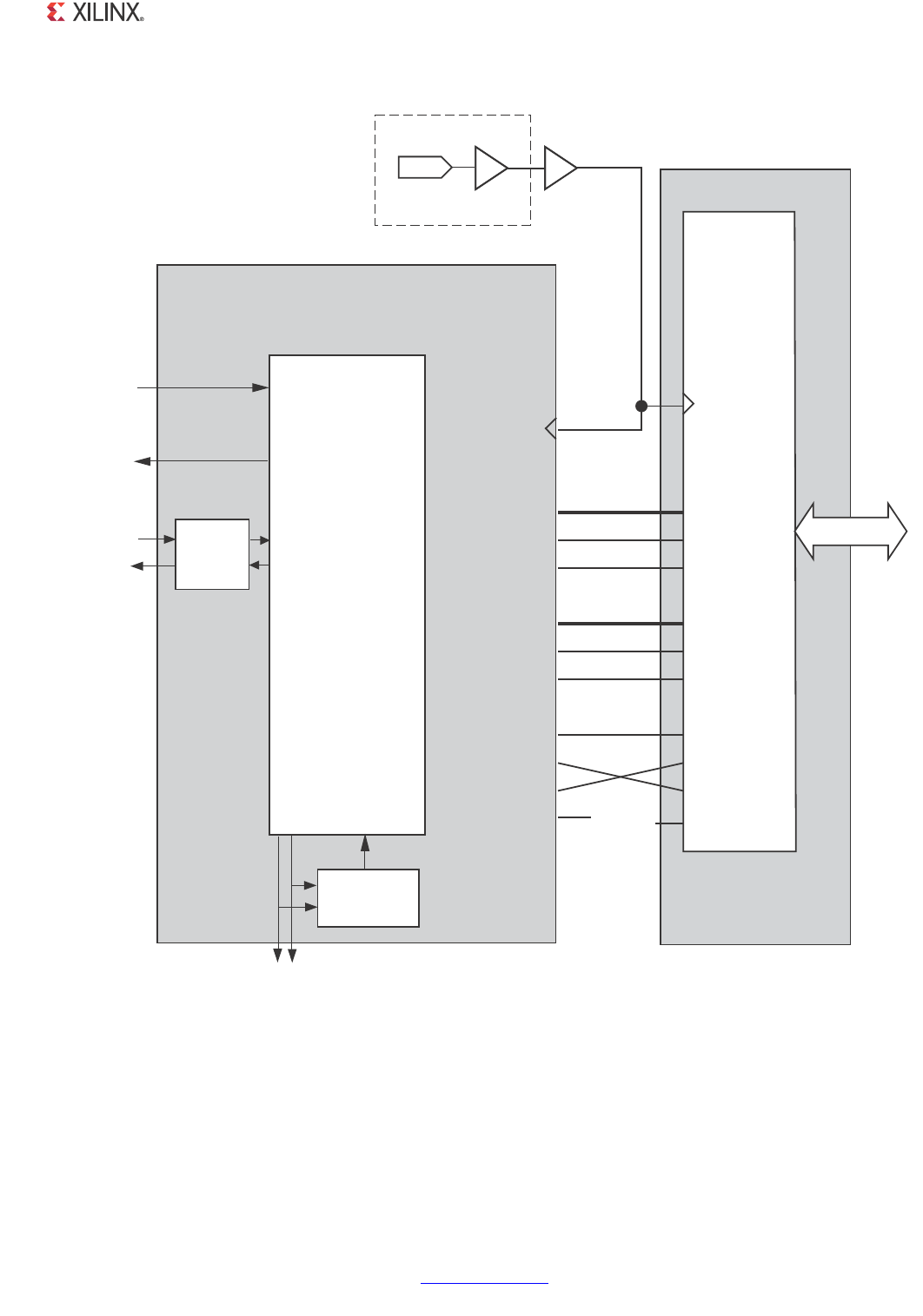

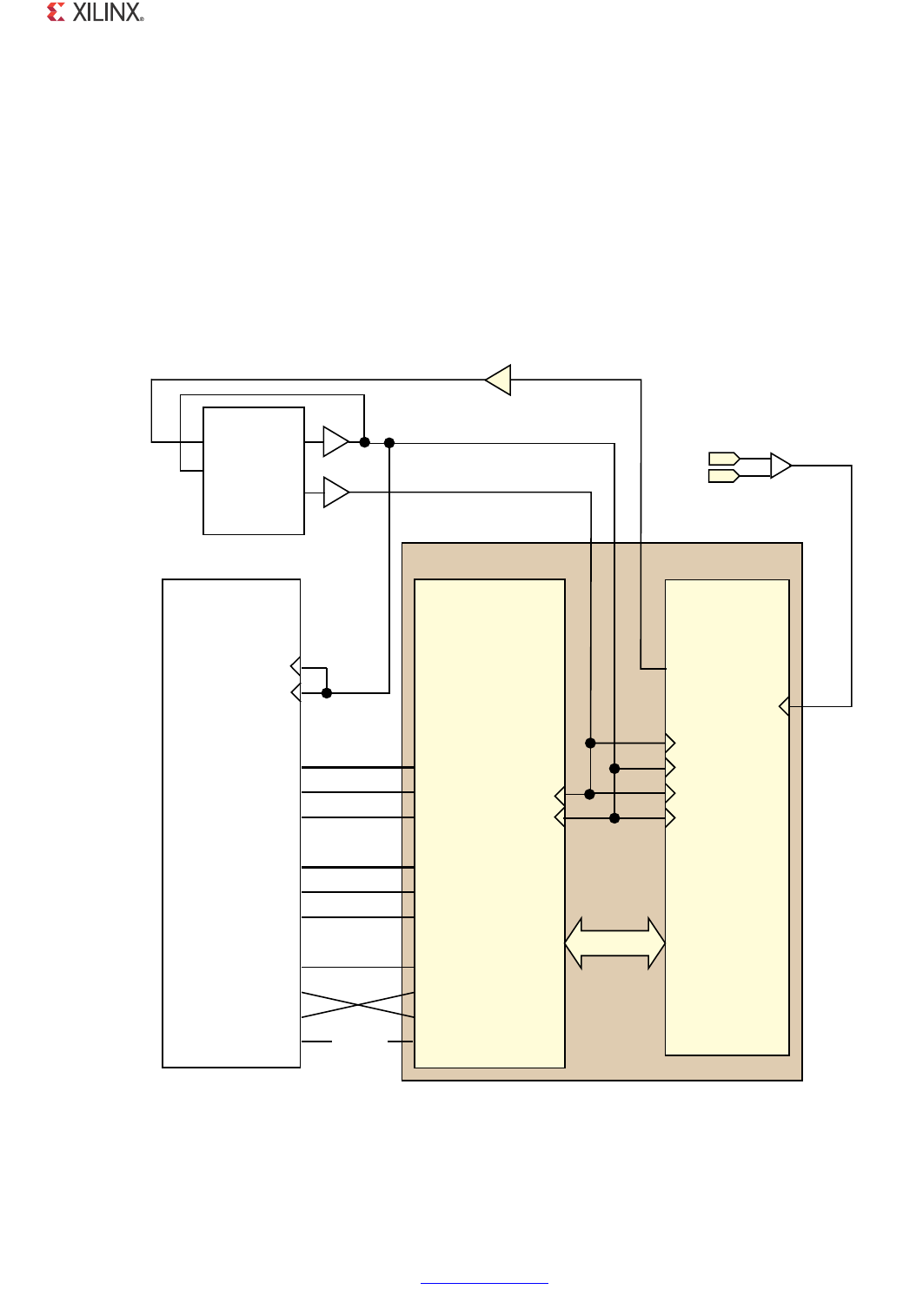

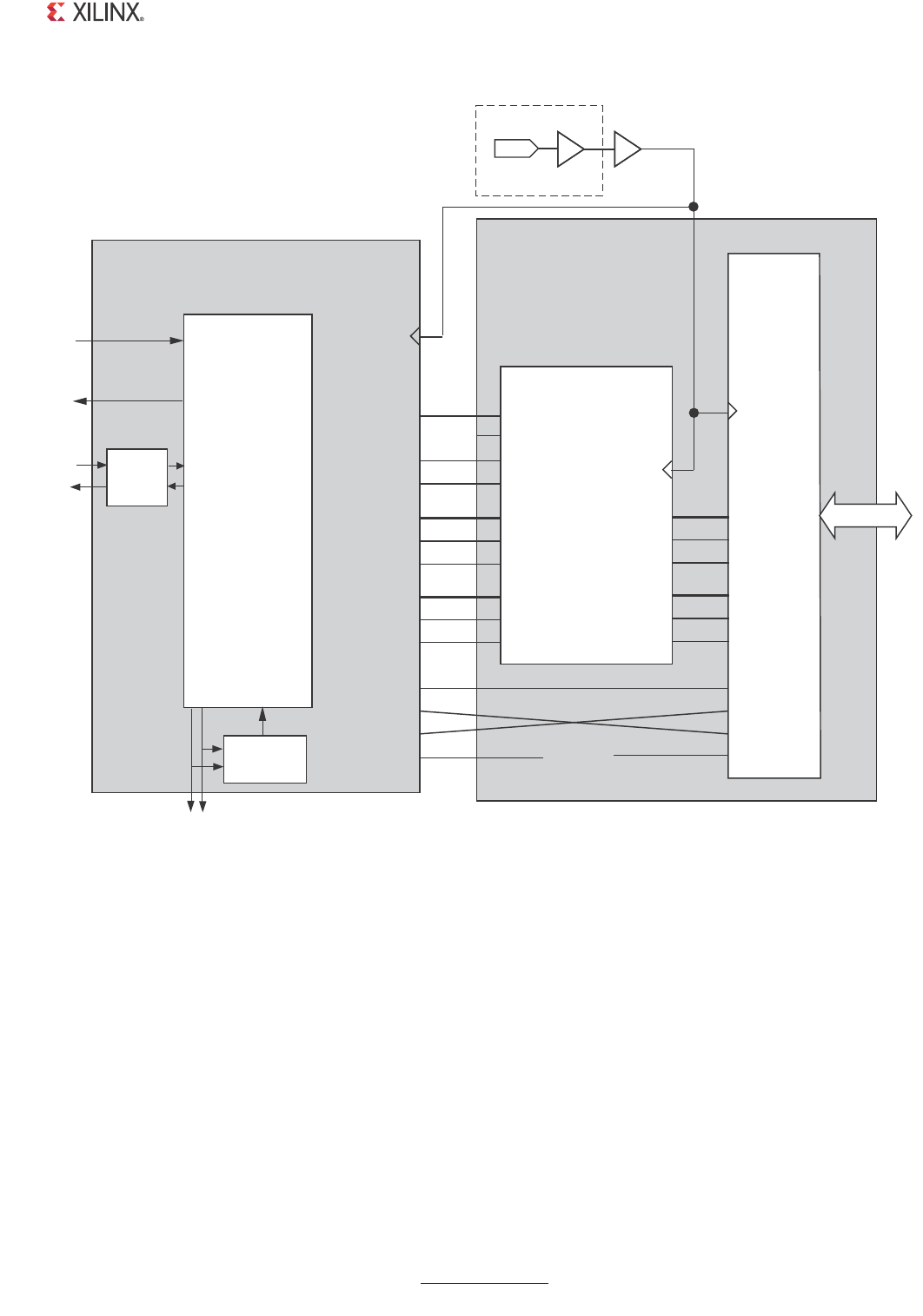

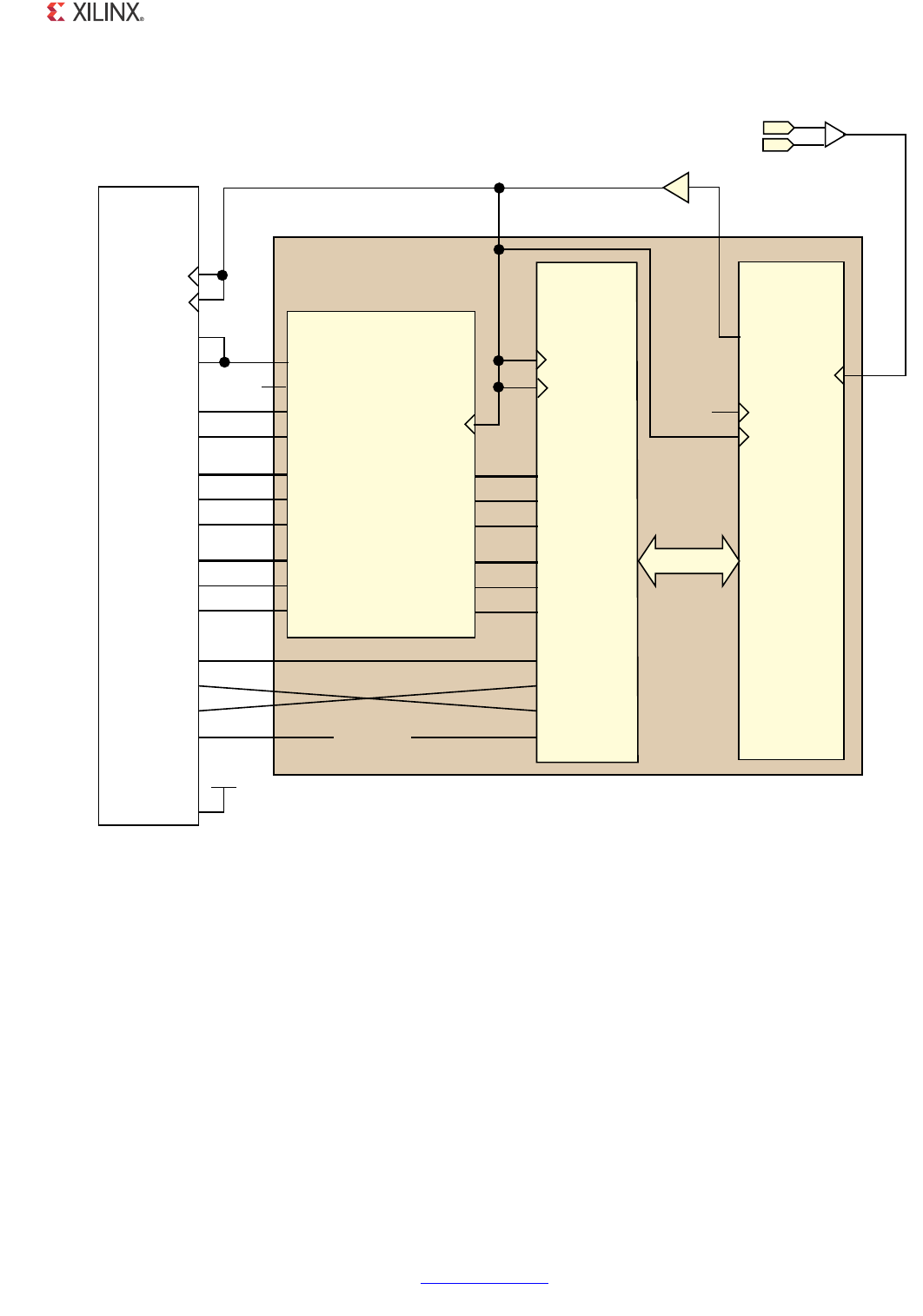

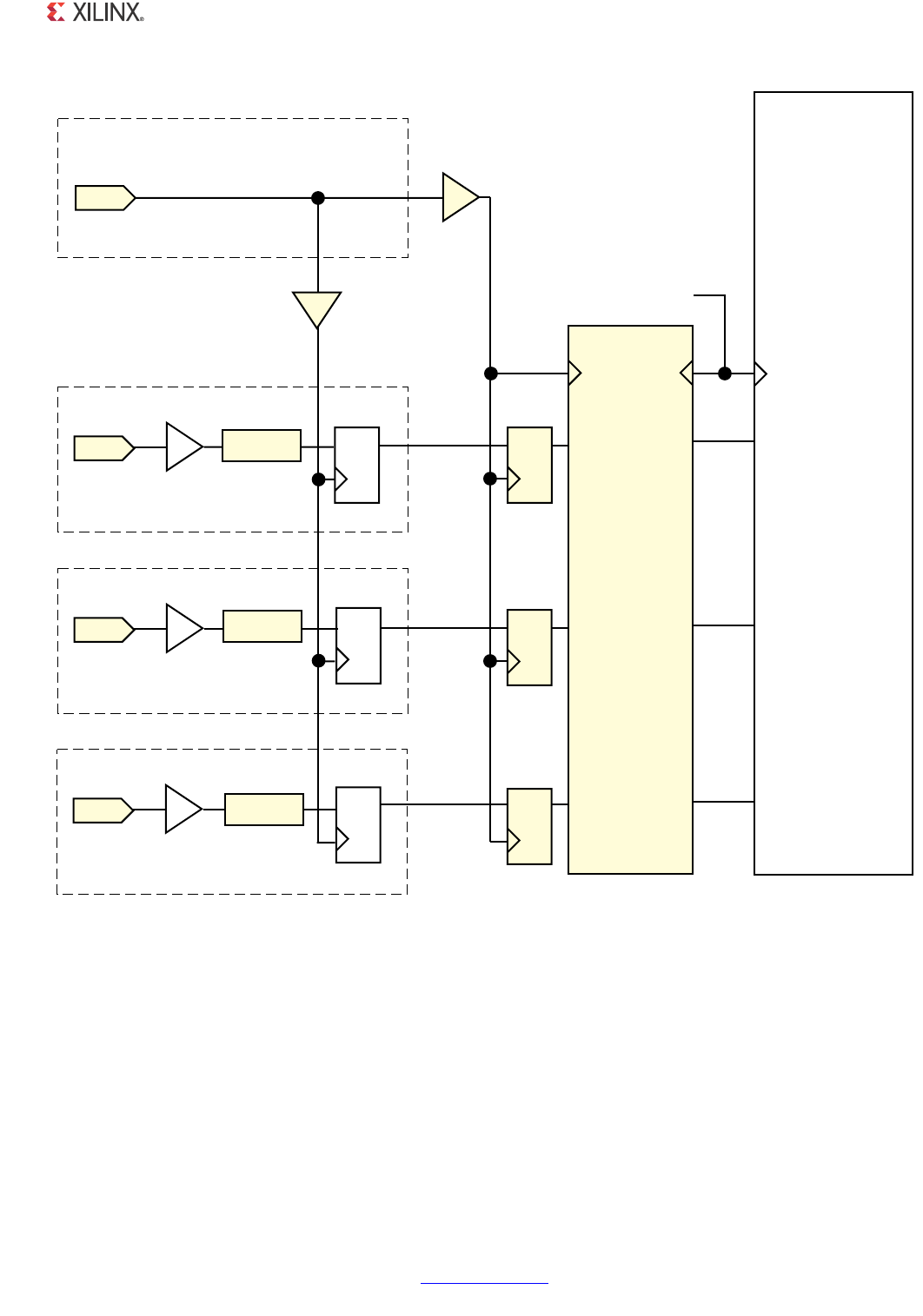

SGMII Support Using Asynchronous Oversampling over Virtex-6 FPGA LVDS

Virtex-6 devices, -2 speed grade or higher, can fully support SGMII using standard LVDS

SelectIO™ technology logic resources. This enables direct connection to external PHY

devices without the use of a Virtex-6 FPGA GTX transceiver.

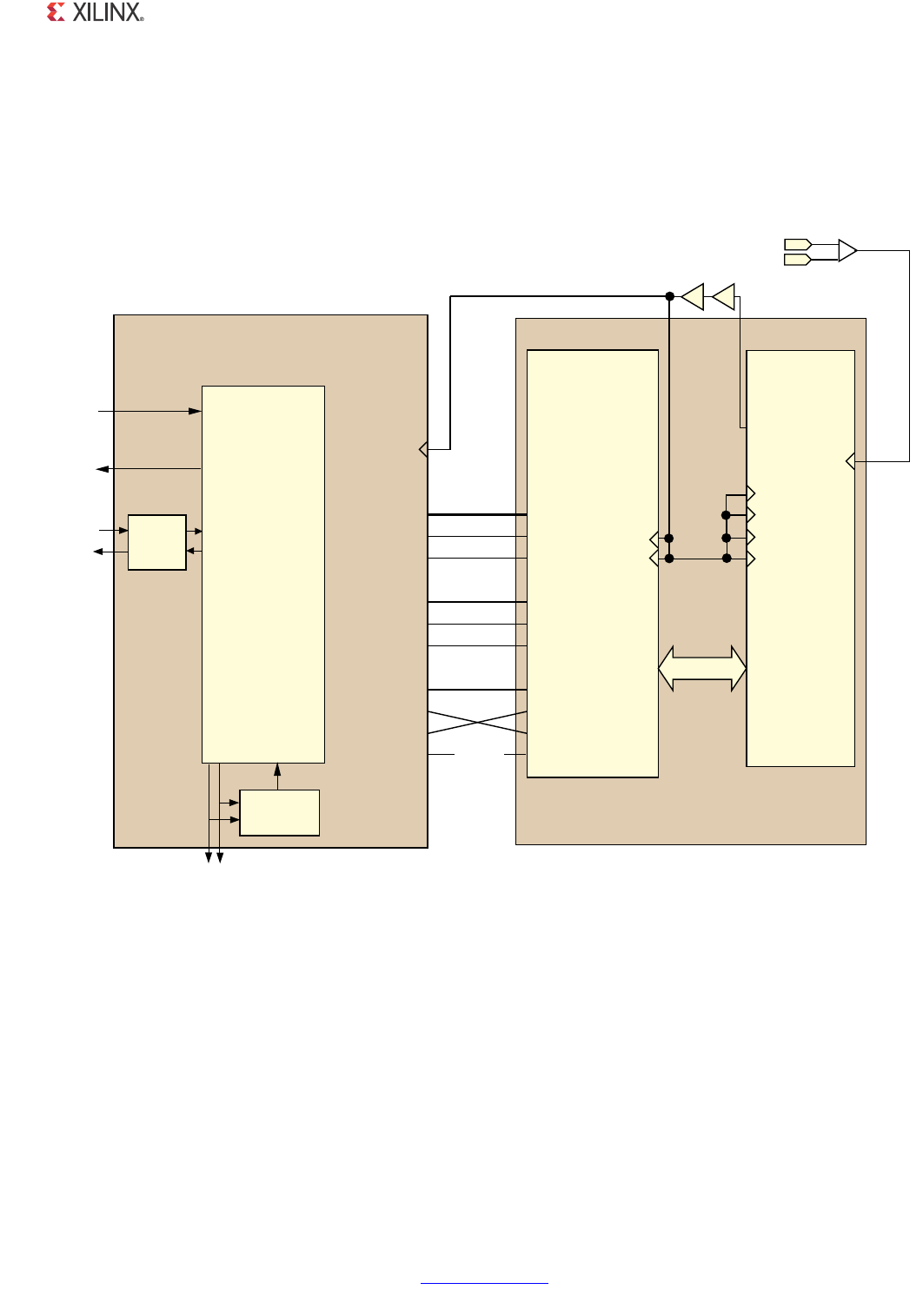

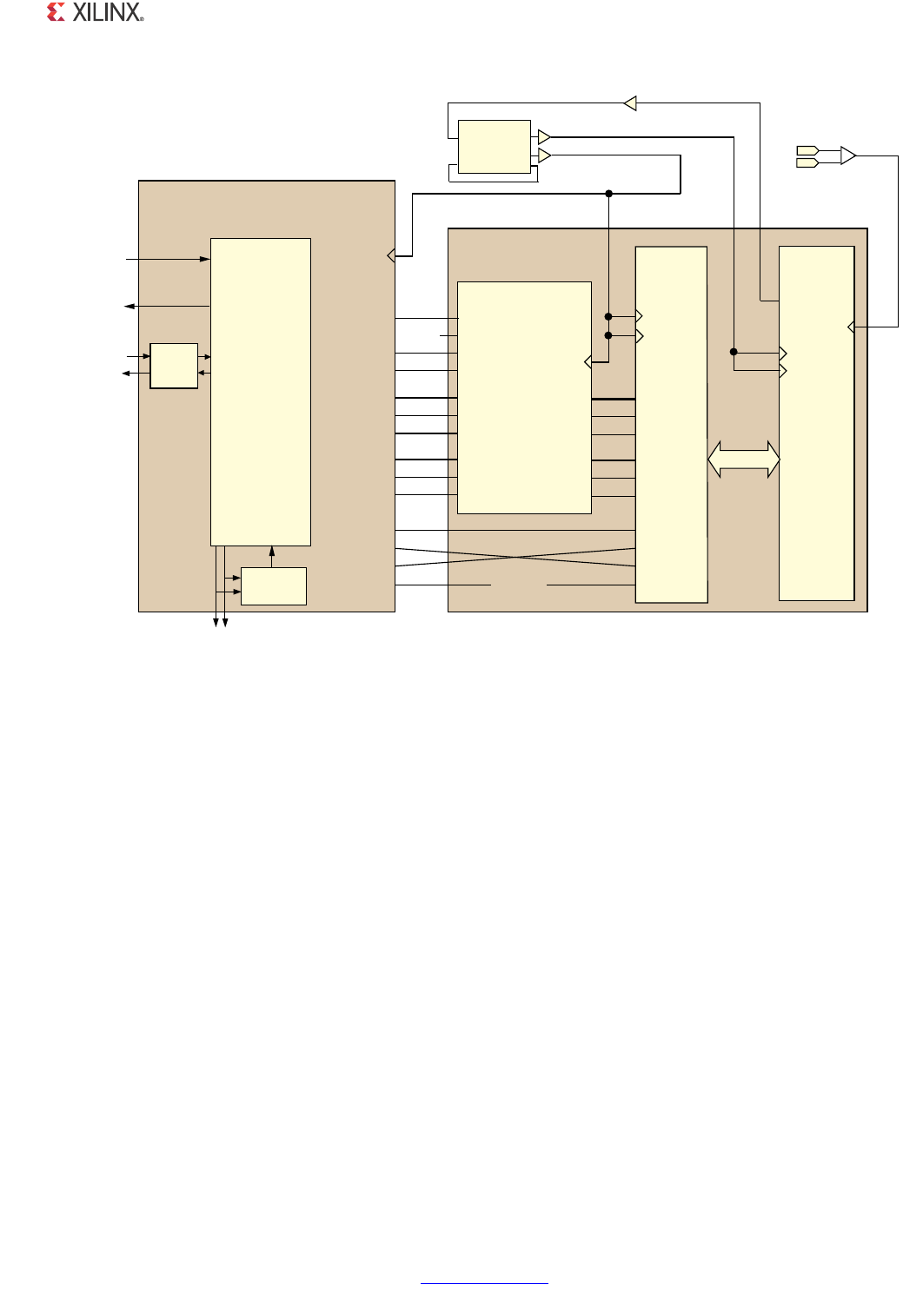

This implementation is illustrated in Figure 1-5.

The core netlist in this implementation remains identical to that of Figure 1-1 and all core

netlist blocks are identical to those described in Ethernet 1000BASE-X PCS/PMA or SGMII

Support Using a Device Specific Transceiver.

As illustrated in Figure 1-5, the Hardware Description Language (HDL) example design for

this implementation provides additional logic to form the “LVDS transceiver” block which

fully replaces the functionality otherwise provided by a Virtex-6 FPGA GTX transceiver. The

LVDS transceiver block contains IODELAY and ISERDES elements along with a Data Recovery

Unit (DRU). This block uses the Virtex-6 FPGA ISERDES elements in a new asynchronous

oversampling mode as described in XAPP881 1.25Gbs 4x Asynchronous Oversampling over

Virtex-6 LVDS. The full transceiver functionality is then completed with Comma Alignment,

8B/10B Decoder and Rx Elastic buffer blocks.

X-Ref Target - Figure 1-5

Figure 1-5: Functional Block Diagram of the Core with Standard SelectIO Technology Support

for SGMII

0#3 4RANSMIT%NGINE

0#32ECEIVE%NGINE

AND3YNCHRONIZATION

/PTIONAL0#3

-ANAGEMENT

'-))

TO-!#

-$)/

)NTERFACE

/PTIONAL

!UTO.EGOTIATION 3ERIAL3'-))

TO

EXTERNAL0(9

'-))"LOCK

,OGI#ORENETLIST

4RANSCEIVER)&"LOCK

%%

(QFRGHU /3%2$%3

)/$%,!9

)3%2$%3

$25

#OMMA

!LIGNMENT

4X

0HASE

"UFFER

""

$ECODER

)/$%,!9

)3%2$%3

,6$3TRANSCEIVER

--#-

CLOCK

ALIGNMENT

STATE

MACHINE

CLOCKBUFFERS

VARIOUSCLOCK

FREQUENCIES

ANDPHASES

/3%2$%3

)3%2$%3

)/"ANK#LOCKING

2X

%LASTIC

"UFFER

8

1000BASE-X PCS/PMA or SGMII v11.4 www.xilinx.com 19

PG047 October 16, 2012

Chapter 1: Overview

Figure 1-5 also illustrates the inclusion of the “I/O Bank Clocking.” This block creates all of

the clock frequencies and clock phases that are required by the LVDS transceiver block. As

the name of the block suggests, this logic can be shared across a single Virtex-6 FPGA I/O

bank. This I/O bank can be used for multiple instances of the core with LVDS I/O to create

several independent SGMII ports.

The following four subsections describe design requirements.

SGMII Only

The interface implemented using this asynchronous oversampling method supports SGMII

between the FPGA and an external PHY device; the interface cannot directly support

1000BASE-X.

Supported in Virtex-6 Devices, -2 Speed Grade or Faster

The SGMII LVDS implementation has only been characterized in the -2 speed grade and

faster Virtex-6 devices.

Timing closure of this interface is challenging; perform the layout and placement steps

described in Layout and Placement in Chapter 7.

Receiver UI Specification

The DRU must have at least two valid sampling points per data bit, requiring 0.5 UI of

opening. The settings of the FPGA add 0.125 UI of requirement making a total opening

requirement at the receiver of 0.625 UI.

Recommended for Chip-to-Chip Copper Implementations Only

This interface supports an SGMII link between the FPGA and an external PHY device across

a single PCB; keep the SGMII copper signal lengths to a minimum.

Recommended Design Experience

Although the Ethernet 1000BASE-X PCS/PMA or SGMII core is a fully-verified solution, the

challenge associated with implementing a complete design varies depending on the

configuration and functionality of the application. For best results, previous experience

building high-performance, pipelined Field Programmable Gate Array (FPGA) designs using

Xilinx implementation software and the User Constraint Files (UCF) is recommended.

Contact your local Xilinx representative for a closer review and estimation for your specific

requirements.

1000BASE-X PCS/PMA or SGMII v11.4 www.xilinx.com 20

PG047 October 16, 2012

Chapter 1: Overview

System Requirements

For a list of System Requirements, see the Xilinx Design Tools: Release Notes Guide.

Applications

Typical applications for the Ethernet 1000BASE-X PCS/PMA or SGMII core include the

following:

•Ethernet 1000BASE-X

•Serial-GMII

EDK specific applications targeting Gigabit Ethernet MAC (GEM) embedded in Zynq™-7000

devices is shown in Chapter 11, GMII to PHY EDK Application for Zynq-7000 Device

Processor Subsystem.

Ethernet 1000BASE-X

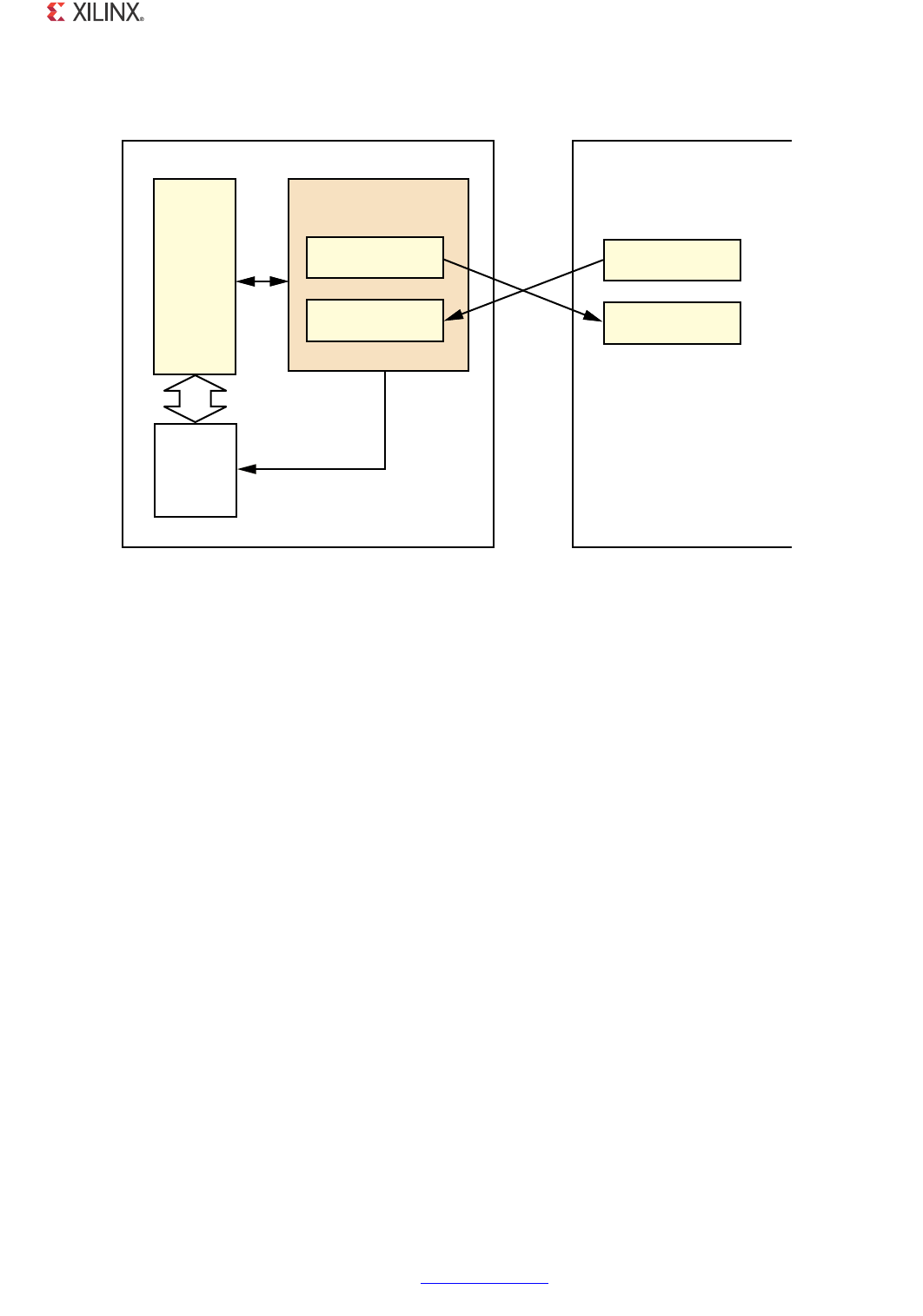

Figure 1-6 illustrates a typical application for the Ethernet 1000BASE-X PCS/PMA or SGMII

core with the core operating to the 1000BASE-X standard using a device-specific

transceiver to provide the Physical Coding Sublayer (PCS) and Physical Medium Attachment

(PMA) sublayers for 1-Gigabit Ethernet.

• The PMA is connected to an external off-the-shelf Gigabit Interface Converter (GBIC) or

Small Form-Factor Pluggable (SFP) optical transceiver to complete the Ethernet port.

• The GMII of the Ethernet 1000BASE-X PCS/PMA is connected to an embedded Ethernet

Media Access Controller (MAC), for example, the Xilinx Tri-Mode Ethernet MAC core.

X-Ref Target - Figure 1-6

Figure 1-6: Typical 1000BASE-X Application

(WKHUQHW%$6(;

3&630$RU6*0,,

&RUH

8VHU/RJLF

(WKHUQHW

0HGLD

$FFHVV

&RQWUROOHU

,QWHUQDO

*0,,

7UDQVFHLYHU

,QWHUIDFH

7;37;1

5;35;1

*%,&

RU

6)3

2SWLFDO

7UDQVFHLYHU

2SWLFDO

)LEHU

30$

7UDQVFHLYHU

8ILINX&0'!

8

1000BASE-X PCS/PMA or SGMII v11.4 www.xilinx.com 21

PG047 October 16, 2012

Chapter 1: Overview

Serial-GMII

Ethernet 1000BASE-X PCS/PMA or SGMII core can operate in two modes as shown in the

following subsections.

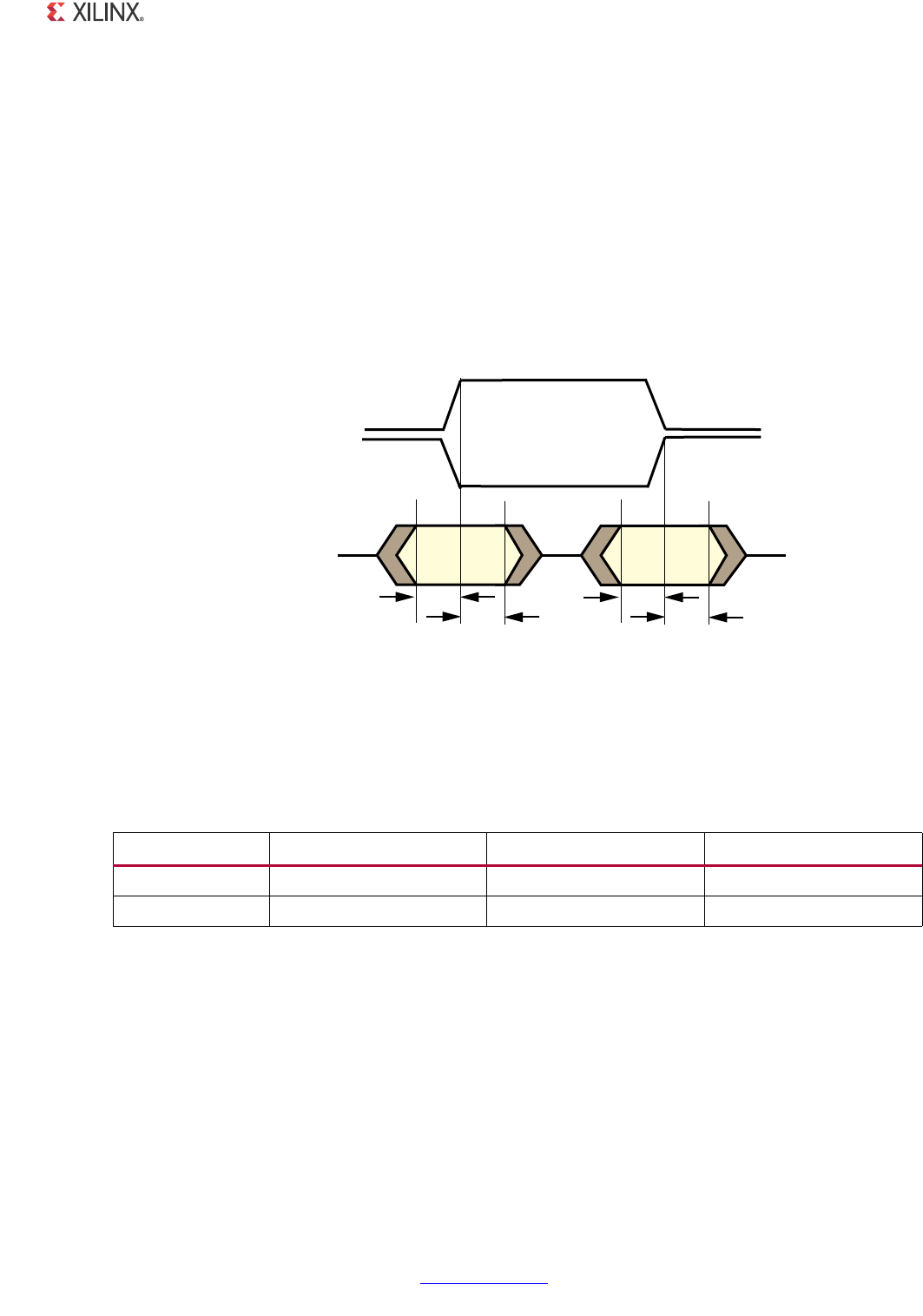

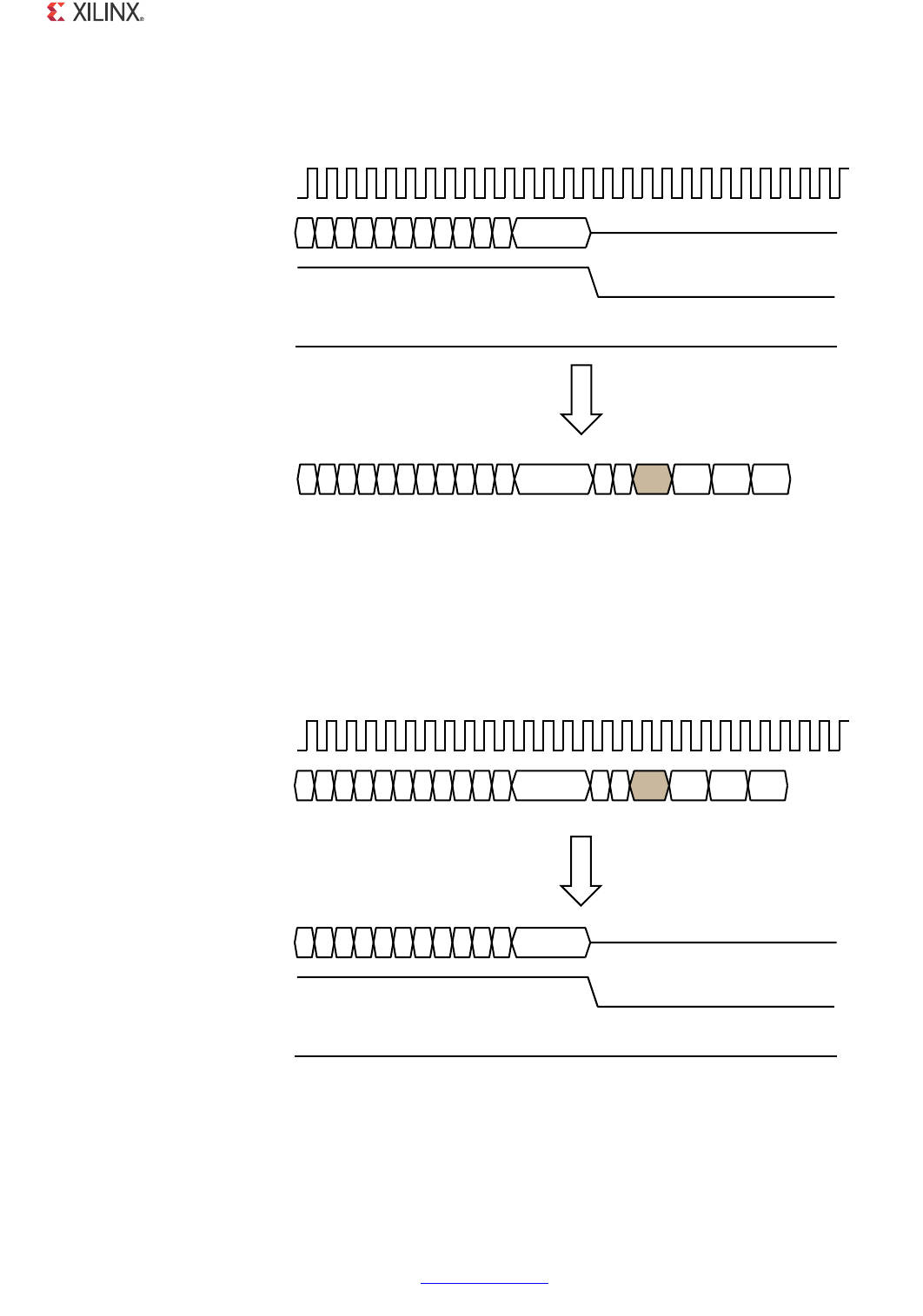

GMII to SGMII Bridge

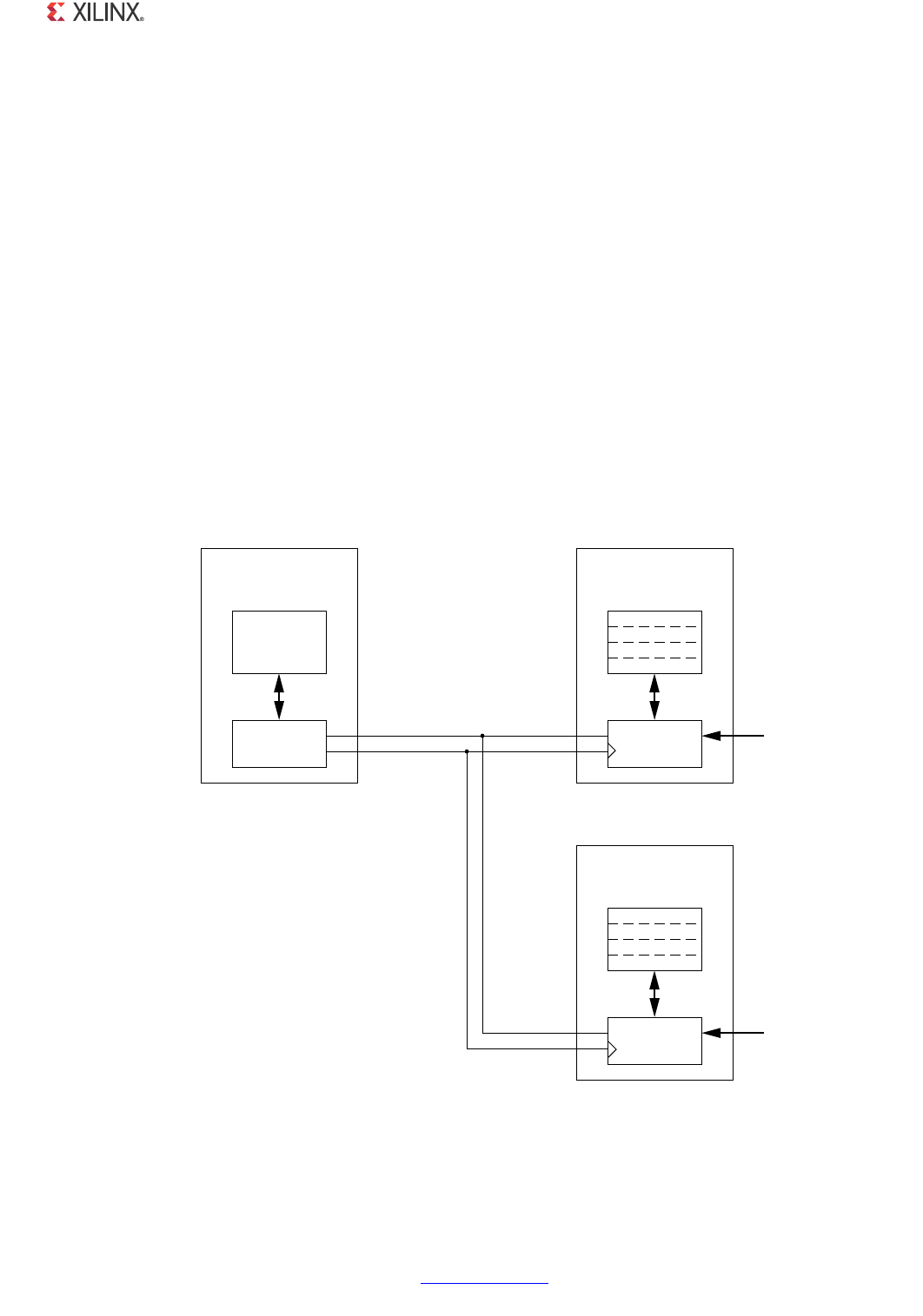

Figure 1-7 illustrates a typical application for the Ethernet 1000BASE-X PCS/PMA or SGMII

core, which shows the core providing a GMII to SGMII bridge using a device-specific

transceiver to provide the serial interface.

• The device-specific transceiver is connected to an external off-the-shelf Ethernet PHY

device that also supports SGMII. (This can be a tri-mode PHY providing 10BASE-T,

100BASE-T, and 1000BASE-T operation.)

• The GMII of the Ethernet 1000BASE-X PCS/PMA or SGMII core is connected to an

embedded Ethernet MAC, for example, the Xilinx Tri-Mode Ethernet MAC core.

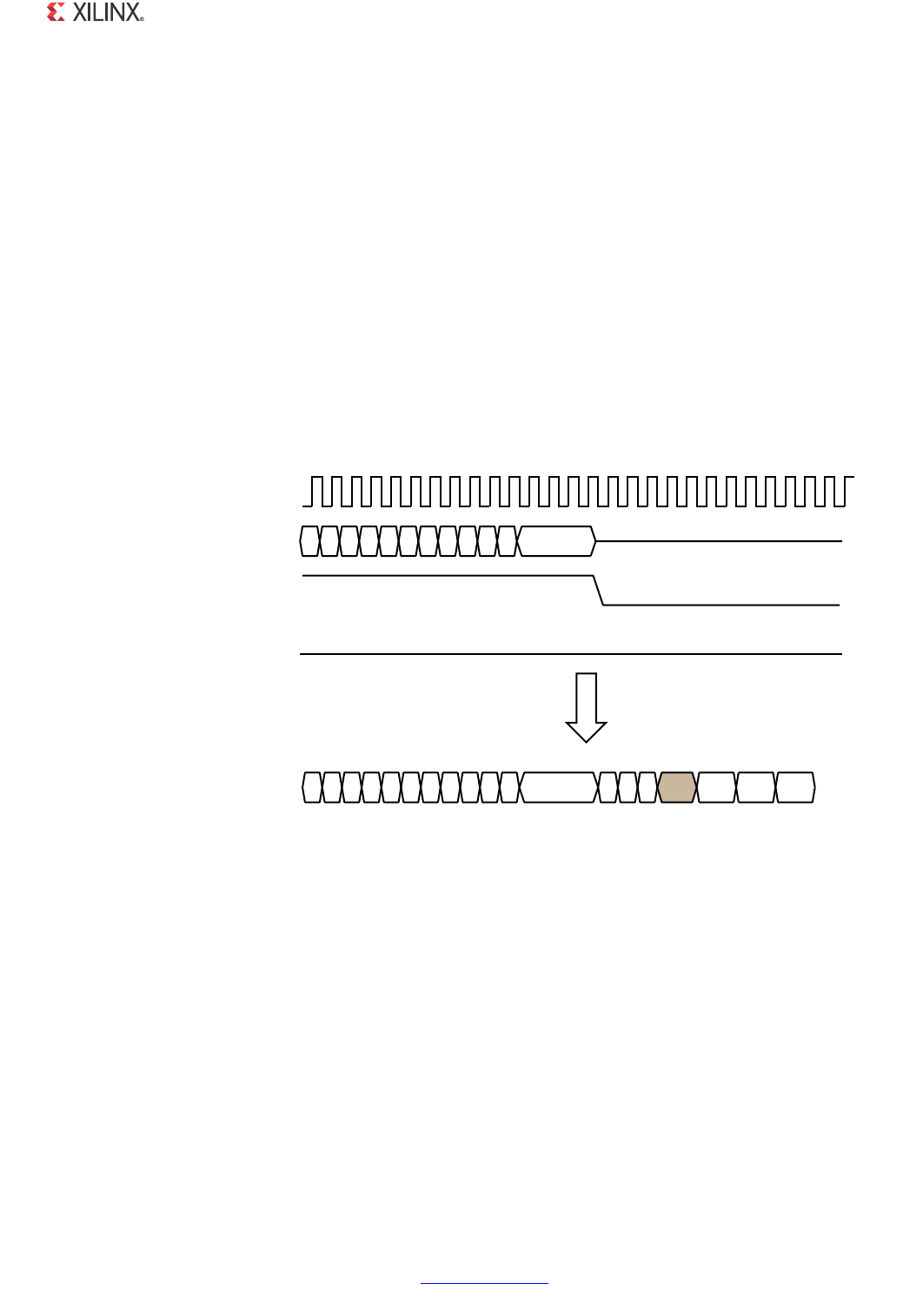

SGMII to GMII Bridge

Figure 1-8 illustrates a typical application for the Ethernet 1000BASE-X PCS/PMA or SGMII

core, which shows the core providing a SGMII to GMII bridge using a device-specific

transceiver to provide the serial interface.

• The device-specific transceiver is connected to an external off-the-shelf Ethernet MAC

device that also supports SGMII. (This can be a tri-mode MAC providing 10/100/1000

Mb/s operation, for example, the Xilinx Tri-Mode Ethernet MAC core connected to

1000BASE-X PCS/PMA or SGMII core operating in GMII to SGMII Mode)

• The GMII of the Ethernet 1000BASE-X PCS/PMA or SGMII core is connected to a

tri-mode PHY providing 10BASE-T, 100BASE-T, and 1000BASE-T operation.

X-Ref Target - Figure 1-7

Figure 1-7: Typical Application for GMII to SGMII Bridge Mode

(WKHUQHW%$6(;

3&630$RU6*0,,

/RJL&25(

7UDQVFHLYHU

8VHU/RJLF

(WKHUQHW

0HGLD

$FFHVV

&RQWUROOHU

,QWHUQDO

*0,,

7UDQVFHLYHU

,QWHUIDFH

7;37;1

5;35;1

7ZLVWHG

&RSSHU

3DLU

6*0,,

%$6(7

%$6(7

%$6(7

3+<

8ILINX&0'!

8

1000BASE-X PCS/PMA or SGMII v11.4 www.xilinx.com 22

PG047 October 16, 2012

Chapter 1: Overview

Verification

The Ethernet 1000BASE-X PCS/PMA or SGMII core has been verified with extensive

simulation and hardware verification.

Simulation

A highly parameterizable transaction-based test bench was used to test the core. The tests

included the following:

• Register access

• Loss of synchronization

• Auto-negotiation and error handling

• Frame transmission and error handling

• Frame reception and error handling

• Clock compensation in the elastic buffers

Zynq-7000, Virtex-7, Kintex-7, Artix-7, Virtex-6, Virtex-5, Virtex-4 and Spartan-6 device

designs incorporating a device-specific transceiver require a Verilog LRM-IEEE 1364-2005

encryption-compliant simulator. For VHDL simulation, a mixed Hardware Description

Language (HDL) license is required.

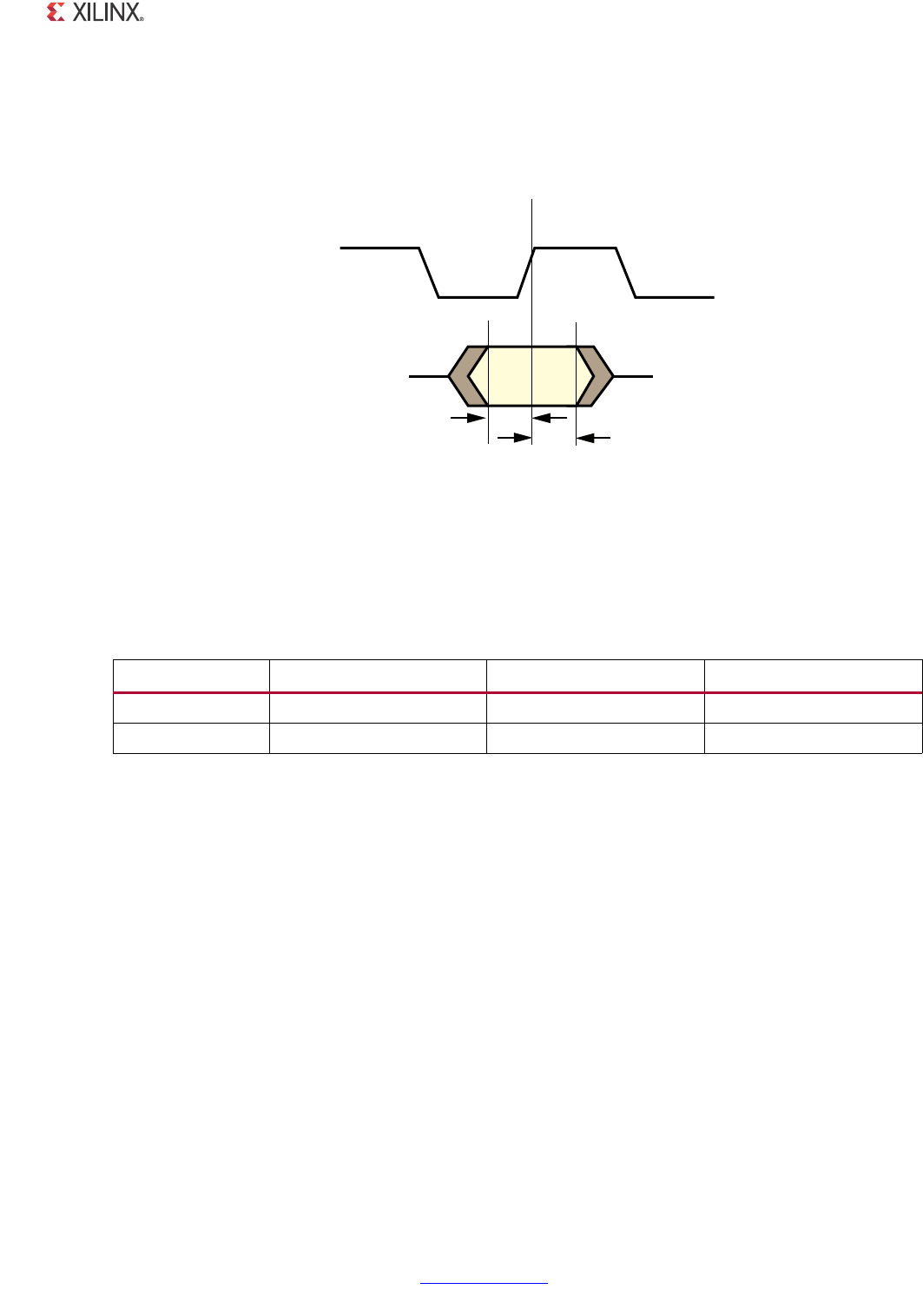

X-Ref Target - Figure 1-8

Figure 1-8: Typical Application for SGMII to GMII Bridge Mode

(WKHUQHW%DVH;

3&630$RU6*0,,

/RJL&25(

7UDQVFHLYHU

,QWHUIDFH

,QWHUQDO

*0,,

%$6(7

%$6(7

%$6(7

7UDQVFHLYHU

*0,,B5;

*0,,B7;

7ZLVWHG

&RSSHU

3DLU

;LOLQ[)3*$

7;37;1

5;35;1

7UL0RGH0$&

ZLWK6*0,,

6*0,,

3+<

*0,,

1000BASE-X PCS/PMA or SGMII v11.4 www.xilinx.com 23

PG047 October 16, 2012

Chapter 1: Overview

Hardware Verification

The core has been tested in several hardware test platforms at Xilinx to represent a variety

of parameterizations, including the following:

• The core used with a device-specific transceiver and performing the 1000BASE-X

standard has been tested with the Xilinx Tri-Mode Ethernet MAC core, which follows

the architecture shown in Figure 1-6. A test platform was built around these cores,

including a back-end FIFO capable of performing a simple ping function, and a test

pattern generator. Software running on the embedded PowerPC® processor provided

access to all configuration and status registers. Version 3.0 of this core was taken to the

University of New Hampshire Interoperability Lab (UNH IOL) where conformance and

interoperability testing was performed.

• The core used with a device-specific transceiver and performing the SGMII standard

has been tested with the LogiCORE Intellectual Property (IP) Tri-Mode Ethernet MAC

core. This was connected to an external PHY capable of performing 10BASE-T,

100BASE-T, and 1000BASE-T, and the system was tested at all three speeds. This follows

the architecture shown in Figure 1-7 and also includes the PowerPC-based processor

test platform described previously.

Licensing and Ordering Information

This Xilinx LogiCORE™ IP module is provided at no additional cost with the Xilinx Vivado™

Design Suite and ISE® Design Suite tools under the terms of the Xilinx End User License.

Information about this and other Xilinx LogiCORE IP modules is available at the Xilinx

Intellectual Property page. For information about pricing and availability of other Xilinx

LogiCORE IP modules and tools, contact your local Xilinx sales representative.

1000BASE-X PCS/PMA or SGMII v11.4 www.xilinx.com 24

PG047 October 16, 2012

Chapter 2

Product Specification

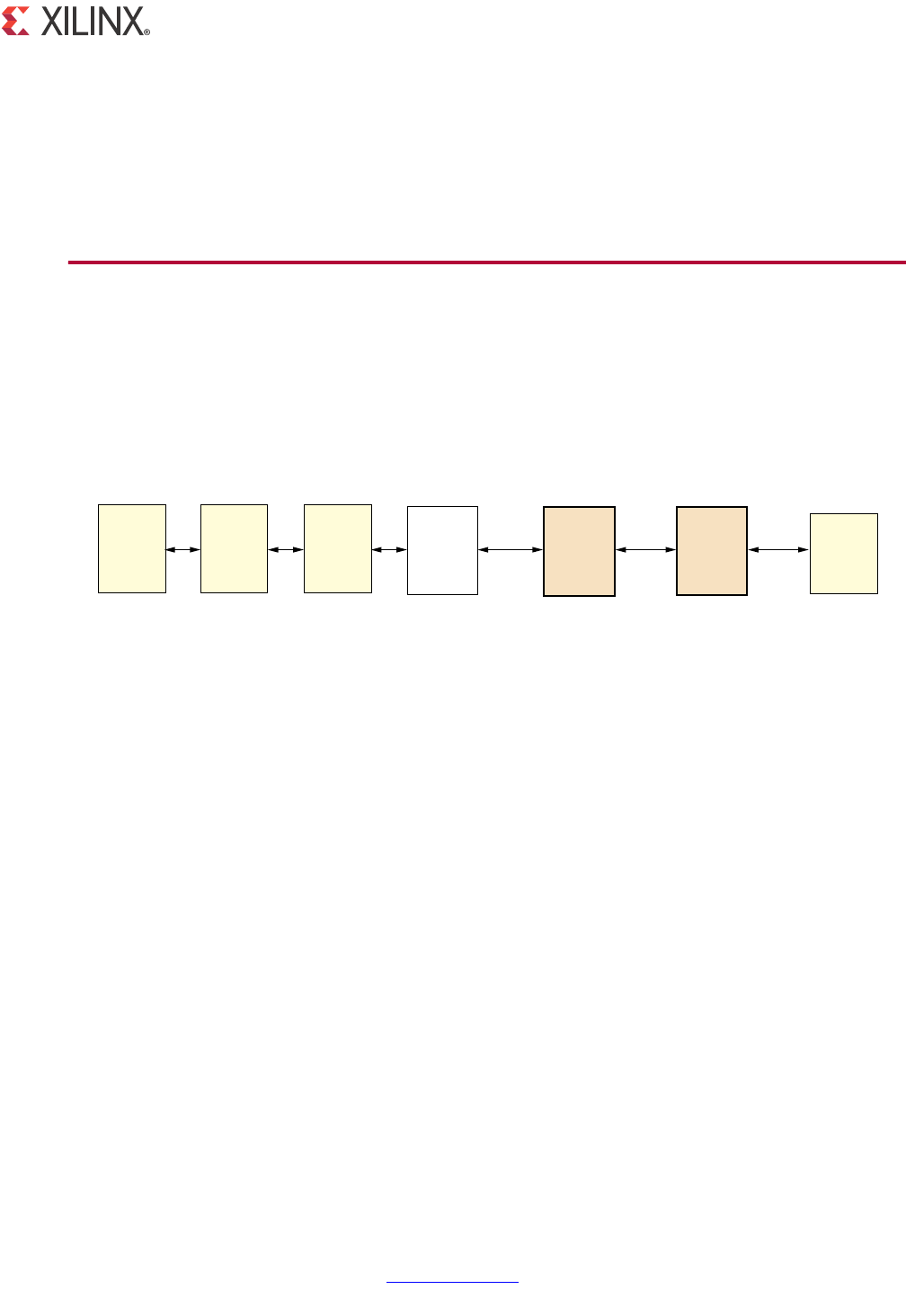

Overview of Ethernet Architecture

Figure 2-1 illustrates the 1-Gigabit Ethernet PCS and PMA sublayers provided by this core,

which are part of the Ethernet architecture. The part of this architecture, from the Ethernet

MAC to the right, is defined in the IEEE 802.3-2008 specification. This figure also shows

where the supported interfaces fit into the architecture.

MAC

The Ethernet Media Access Controller (MAC) is defined in IEEE 802.3-2008, clauses 2, 3, and

4. A MAC is responsible for the Ethernet framing protocols and error detection of these

frames. The MAC is independent of, and can connect to, any type of physical layer device.

GMII / SGMII

The Gigabit Media Independent Interface (GMII), a parallel interface connecting a MAC to

the physical sublayers (PCS, PMA, and PMD), is defined in IEEE 802.3-2008, clause 35. For a

MAC operating at a speed of 1 Gigabit per second (Gb/s), the full GMII is used; for a MAC

operating at a speed of 10 Mb/s or 100 Mb/s, the GMII is replaced with a Media

Independent Interface (MII) that uses a subset of the GMII signals.

The Serial-GMII (SGMII) is an alternative interface to the GMII/MII that converts the parallel

interface of the GMII/MII into a serial format capable of carrying traffic at speeds of

10 Mb/s, 100 Mb/s, and 1 Gb/s. This radically reduces the I/O count and for this reason is

often preferred by Printed Circuit Board (PCB) designers. The SGMII specification is closely

related to the 1000BASE-X PCS and PMA sublayers, which enables it to be offered in this

core.

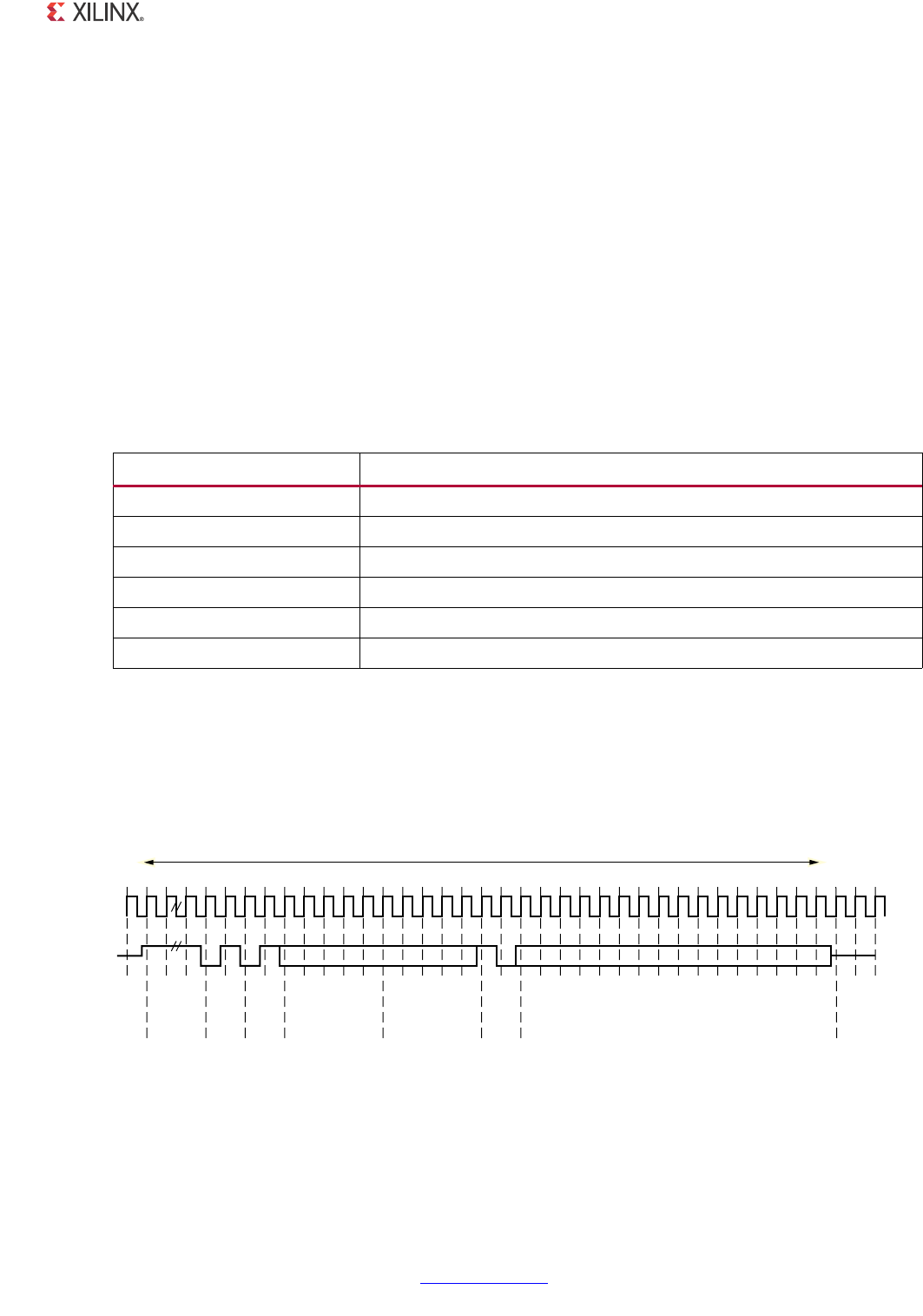

X-Ref Target - Figure 2-1

Figure 2-1: Overview of Ethernet Architecture

4#0 )0 &)&/

)& -!# 0#3 0-! 0-$

'-))

3'-)) 4")

4RANSCEIVER

3ERIAL

0-$

8

1000BASE-X PCS/PMA or SGMII v11.4 www.xilinx.com 25

PG047 October 16, 2012

Chapter 2: Product Specification

PCS

The Physical Coding Sublayer (PCS) for 1000BASE-X operation is defined in IEEE 802.3-2008,

clauses 36 and 37, and performs these operations:

• Encoding (and decoding) of GMII data octets to form a sequence of ordered sets

• 8B/10B encoding (and decoding) of the sequence ordered sets

• 1000BASE-X Auto-Negotiation for information exchange with the link partner

Ten Bit Interface

The Ten-Bit-Interface (TBI), defined in IEEE 802.3-2008 clause 36 is a parallel interface

connecting the PCS to the PMA and transfers the 8B/10B encoded sequence-ordered sets.

The TBI should be used with an external SERDES device to implement the PMA functionality.

Physical Medium Attachment

The Physical Medium Attachment (PMA) for 1000BASE-X operation, defined in IEEE

802.3-2008 clause 36, performs the following:

• Serialization (and deserialization) of code-groups for transmission (and reception) on

the underlying serial Physical Medium Dependent (PMD)

• Recovery of the clock from the 8B/10B-coded data supplied by the PMD

The device-specific transceivers provide the serial interface required to connect the PMD.

Physical Medium Dependent

The PMD sublayer is defined in IEEE 802.3-2008 clause 38 for 1000BASE-LX and

1000BASE-SX (long and short wavelength laser). This type of PMD is provided by the

external GBIC or SFP optical transceivers. An alternative PMD for 1000BASE-CX (short-haul

copper) is defined in IEEE 802.3-2008 clause 39.

Standards

• Designed to Ethernet Standard 802.3-2008 Clauses 22, 35, 36 and 38.

•Serial-GMII Specification V1.7 (CISCO SYSTEMS, ENG-46158)

1000BASE-X PCS/PMA or SGMII v11.4 www.xilinx.com 26

PG047 October 16, 2012

Chapter 2: Product Specification

Performance

This section details the performance information for various core configurations.

Maximum Frequencies

1000Base-X PCS/PMA or SGMII core operates at 125 MHz.

Core Latency

The stand-alone core does not meet all the latency requirements specified in IEEE

802.3-2008 because of the latency of the Elastic Buffers in both TBI and device-specific

transceiver versions. However, the core can be used for backplane and other applications

where strict adherence to the IEEE latency specification is not required.

Where strict adherence to the IEEE 802.3-2008 specification is required, the core can be

used with an Ethernet MAC core that is within the IEEE specified latency for a MAC sublayer.

For example, when the core is connected to the Xilinx Tri-Mode Ethernet MAC core, the

system as a whole is compliant with the overall IEEE 802.3-2008 latency specifications.

Latency for 1000BASE-X PCS with TBI

The following measurements are for the core only and do not include any IOB registers or

the Transmitter Elastic Buffer added in the example design.

Transmit Path Latency

As measured from a data octet input into gmii_txd[7:0] of the transmitter side GMII

until that data appears on tx_code_group[9:0] on the TBI interface, the latency through

the core in the transmit direction is 5 clock periods of gtx_clk.

Receive Path Latency

Measured from a data octet input into the core on rx_code_group0[9:0] or

rx_code_group1[9:0] from the TBI interface (until that data appears on

gmii_rxd[7:0] of the receiver side GMII), the latency through the core in the receive

direction is equal to 16 clock periods of gtx_clk, plus an additional number of clock

cycles equal to the current value of the Receiver Elastic Buffer.

The Receiver Elastic Buffer is 32 words deep. The nominal occupancy will be at half-full,

thereby creating a nominal latency through the receiver side of the core equal to 16 + 16=

32 clock cycles of gtx_clk.

1000BASE-X PCS/PMA or SGMII v11.4 www.xilinx.com 27

PG047 October 16, 2012

Chapter 2: Product Specification

Latency for 1000BASE-X PCS and PMA Using a Transceiver

These measurements are for the core only; they do not include the latency through the

Virtex®-4 FPGA serial transceiver, Virtex-5 FPGA GTP transceiver, Virtex-5 FPGA GTX

RocketIO™ transceiver, Virtex-6 FPGA GTX transceiver, Spartan®-6 FPGA GTP transceiver,

Virtex-7 FPGA GTX/GTH transceiver, Zynq™-7000 or Kintex™-7 device GTX transceiver,

Artix™-7 FPGA GTP transceiver, or the Transmitter Elastic Buffer added in the example

design.

Transmit Path Latency

As measured from a data octet input into gmii_txd[7:0] of the transmitter side GMII

(until that data appears on txdata[7:0] on the serial transceiver interface), the latency

through the core in the transmit direction is 4 clock periods of userclk2.

Receive Path Latency

As measured from a data octet input into the core on rxdata[7:0] from the serial

transceiver interface (until that data appears on gmii_rxd[7:0] of the receiver side

GMII), the latency through the core in the receive direction is 6 clock periods of userclk2.

Latency for SGMII

When performing the SGMII standard, the core latency figures are identical to the Latency

for 1000BASE-X PCS and PMA using the serial transceiver. Again these figures do not

include the latency through the serial transceiver or any Elastic Buffers added in the

example design.

Throughput

1000BASE-X PCS and PMA or SGMII core operates at a full lane rate of 1.25 Gb/s

Voltage Requirements

Virtex-7 devices support GMII at 3.3 V or lower only in certain parts and packages; see the

7 Series FPGAs SelectIO Resources User Guide. Virtex-6 devices support TBI or GMII at 2.5 V

only; see the Virtex-6 FPGA Data Sheet: DC and Switching Characteristics. Kintex-7,

Spartan-6, Virtex-5, Virtex-4 and Spartan-3 devices support TBI and GMII at 3.3 V or lower.

Artix-7 and Zynq-7000 devices support GMII at 3.3 V or lower.

1000BASE-X PCS/PMA or SGMII v11.4 www.xilinx.com 28

PG047 October 16, 2012

Chapter 2: Product Specification

Speed Grades

Zynq-7000, Virtex-7, Kintex-7, Artix-7, Virtex-6, Virtex-5, Virtex-4 devices support speed

grade -1; Virtex-4 FPGA supports -10 speed grade; Spartan-6 FPGAs support -2 speed

grade. All other supported Spartan devices support -4 speed grade.

Resource Utilization

Resources required for this core have been estimated for the Zynq-7000, Virtex-7, Kintex-7,

Artix-7, Virtex-6, Virtex-5, and Spartan-6 devices, See Table 2- 2 through Tab le 2-9. These

values were generated using Xilinx® CORE Generator™ tools, v14.3. They are derived from

post-synthesis reports, and might change during MAP and PAR. Similar values are expected

for Vivado IP catalog v2012.3.

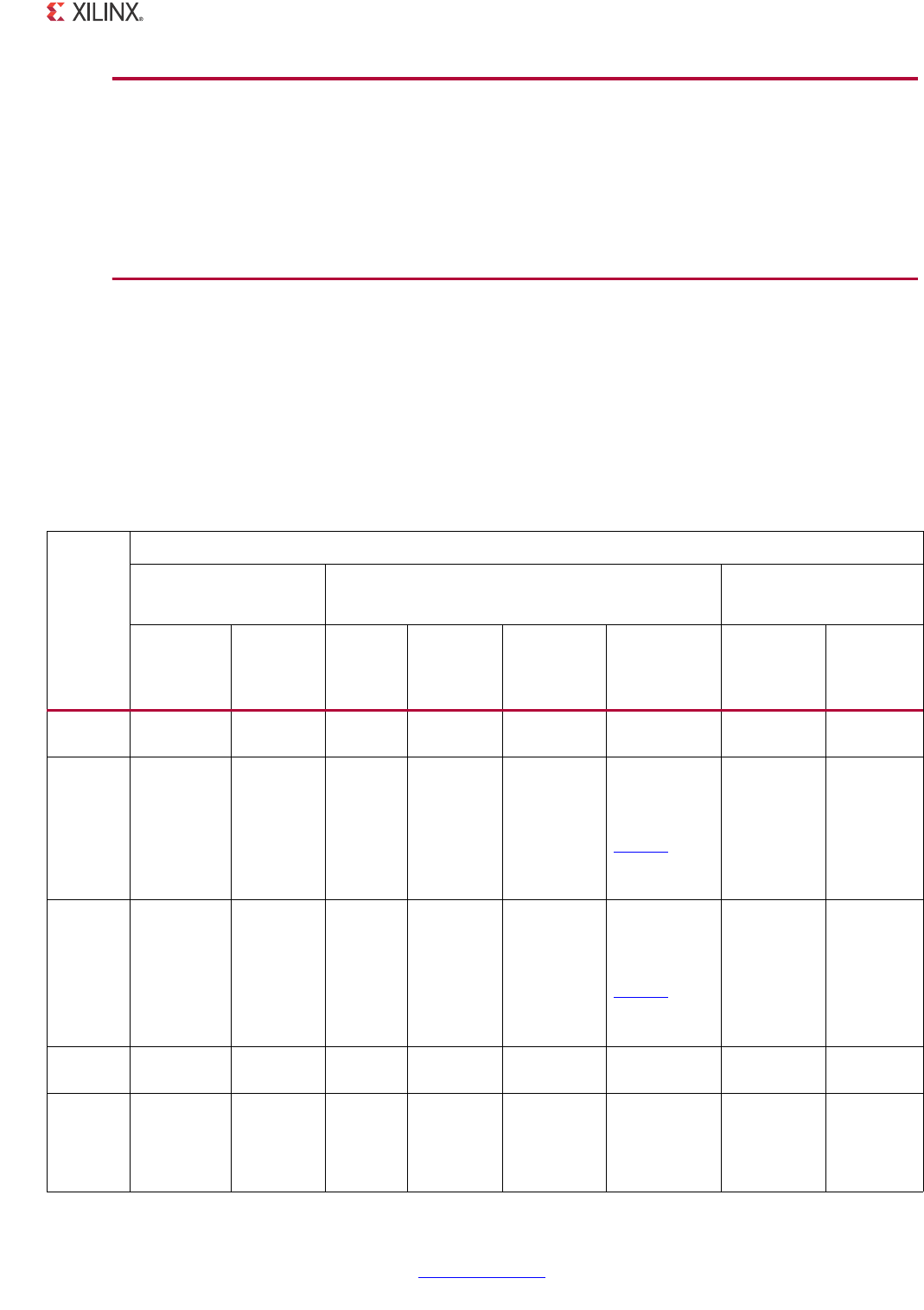

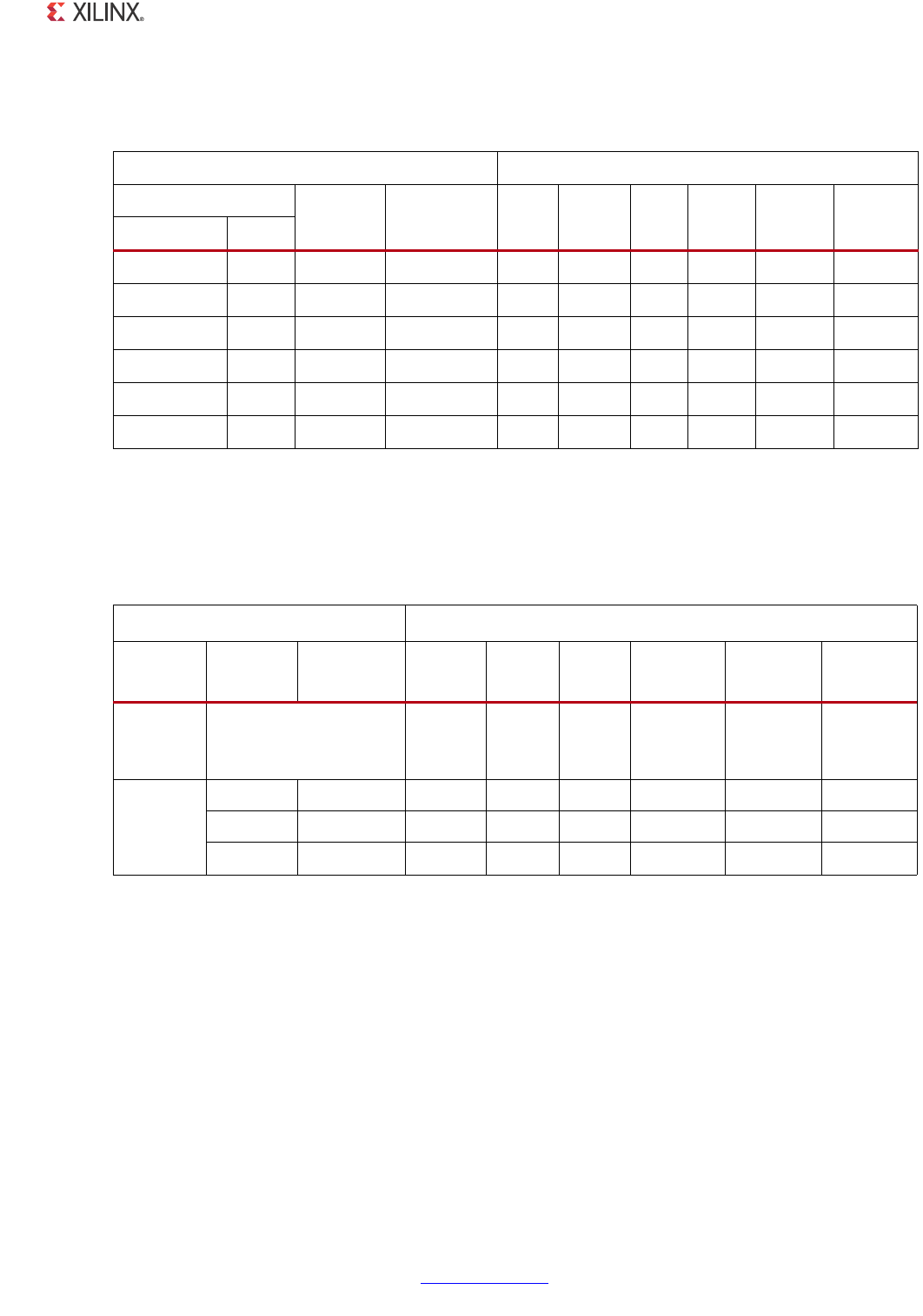

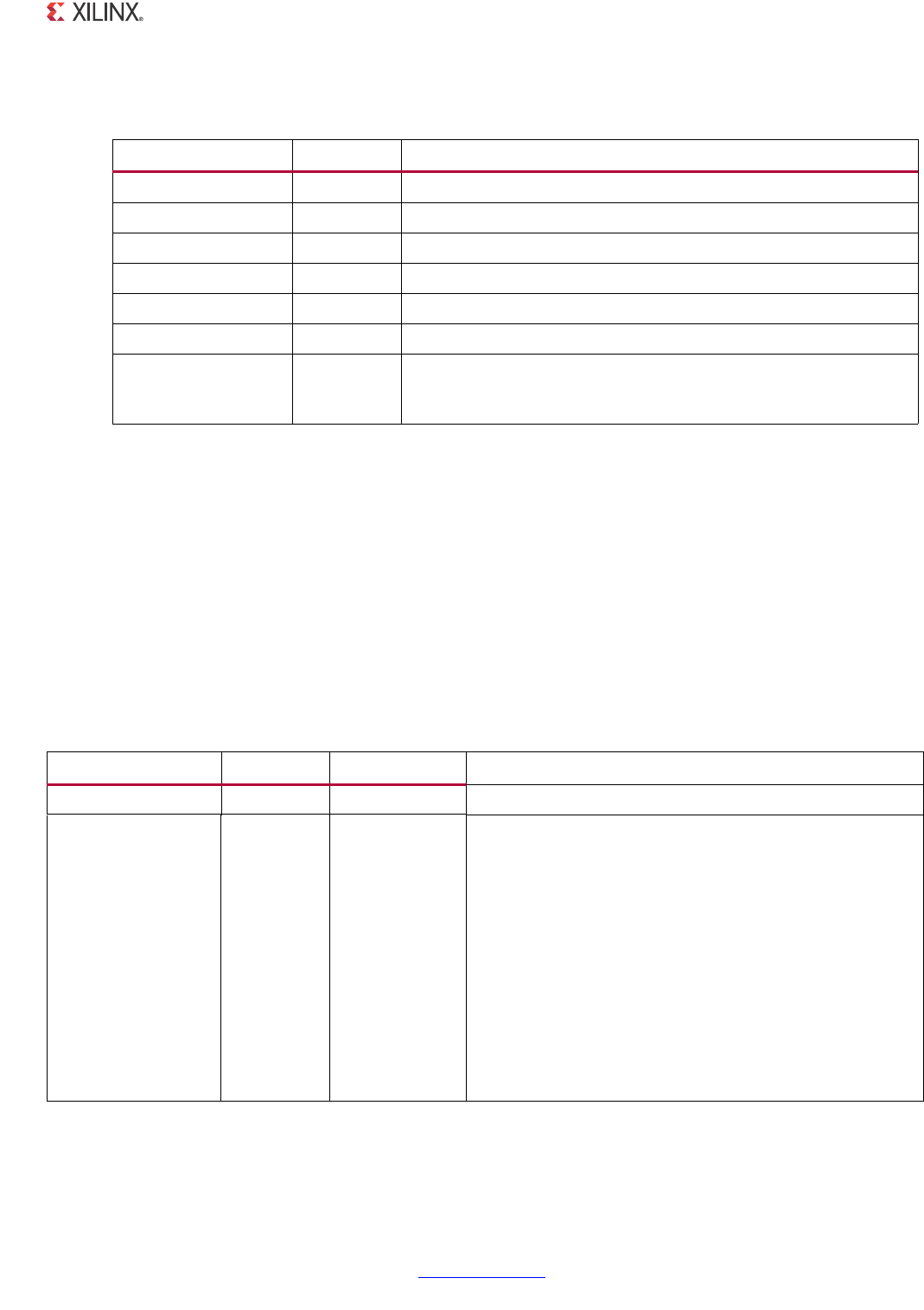

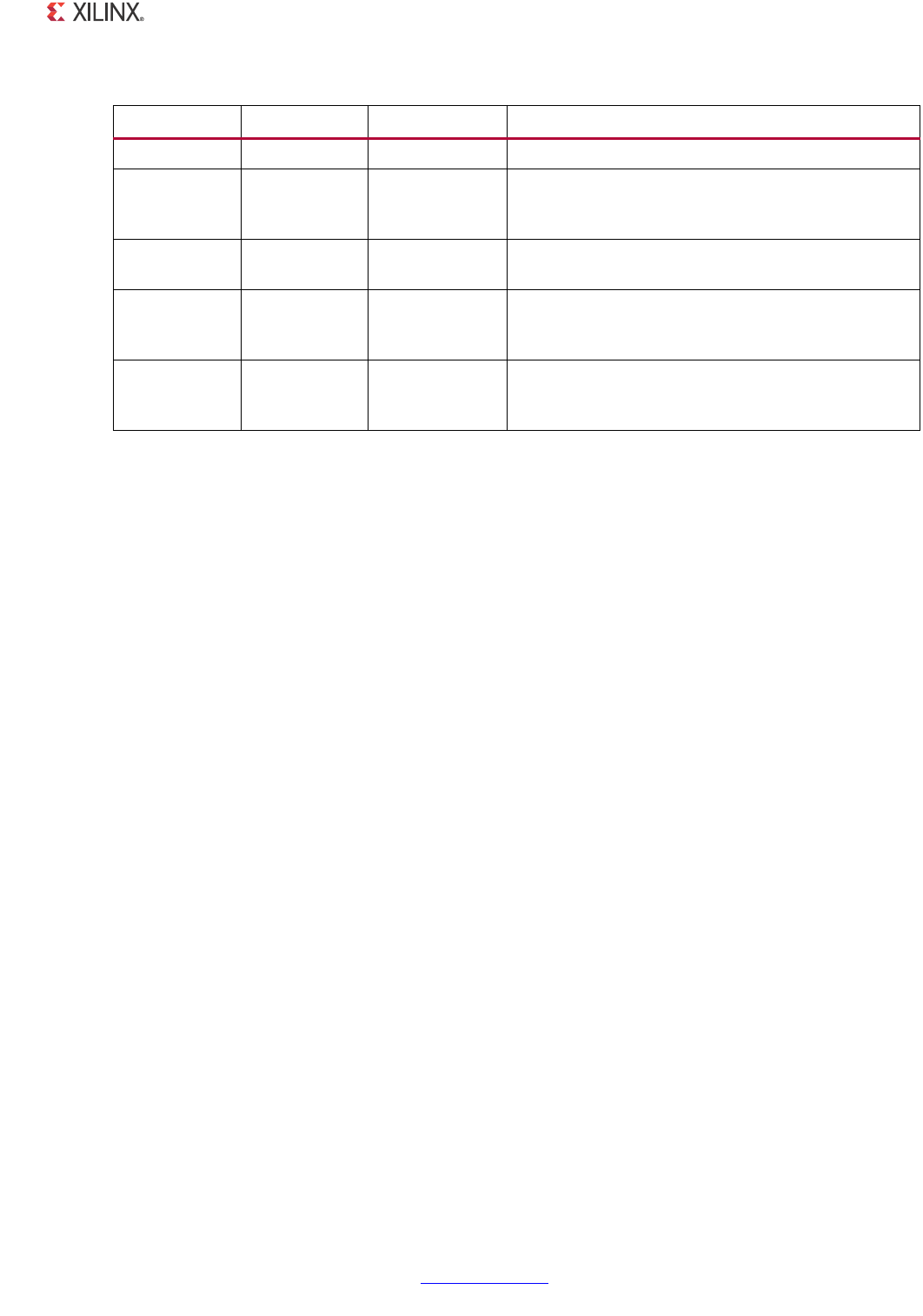

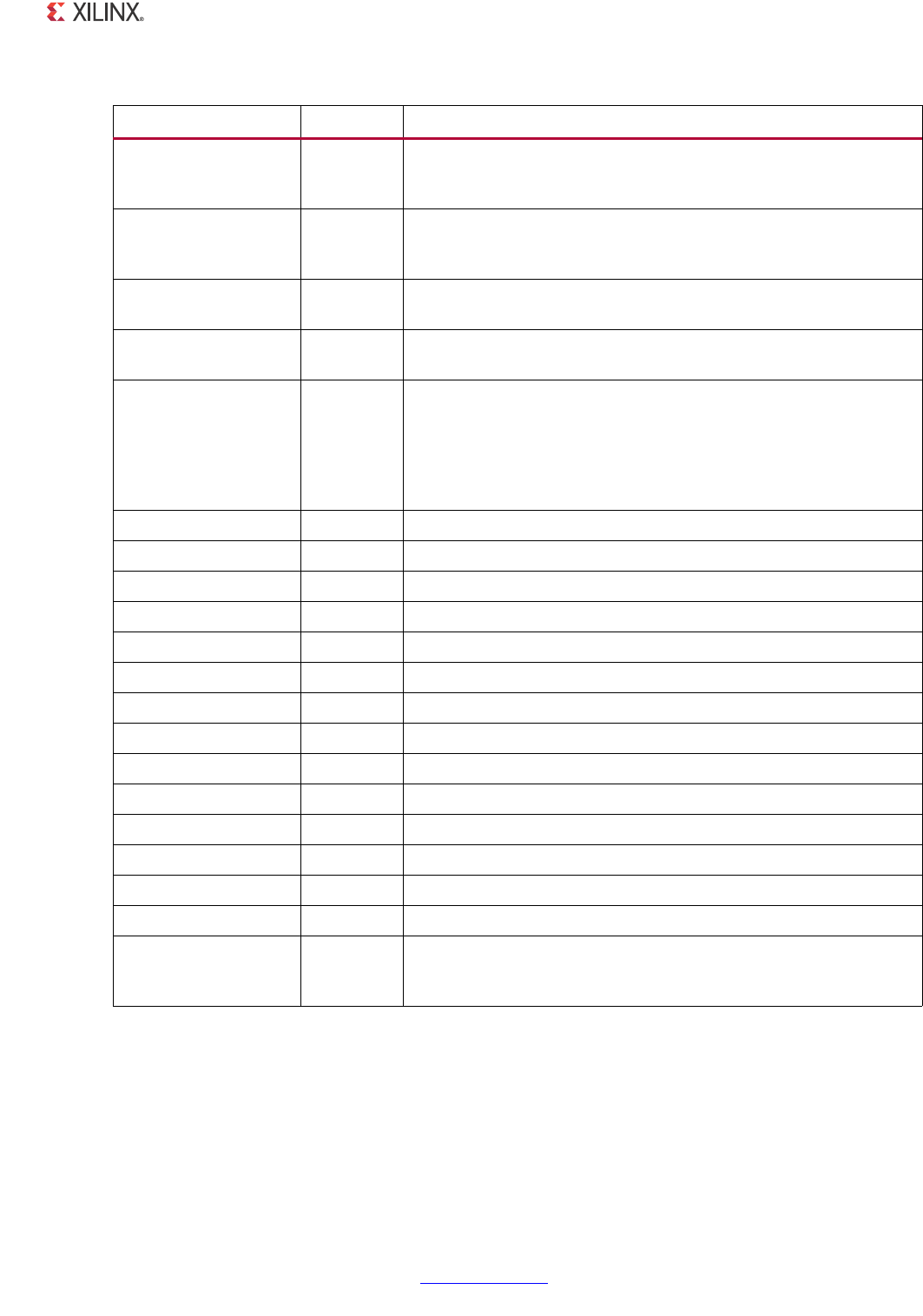

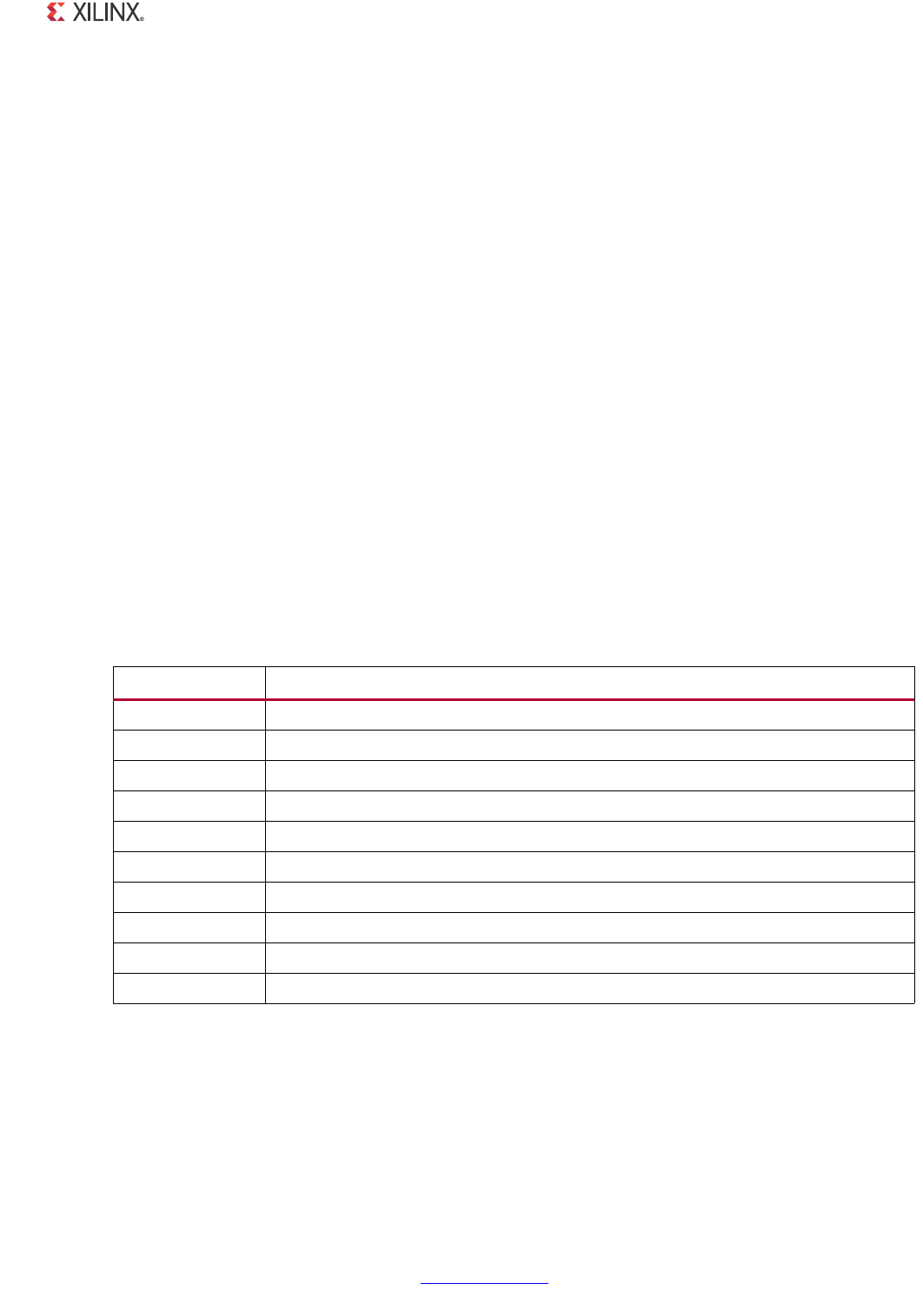

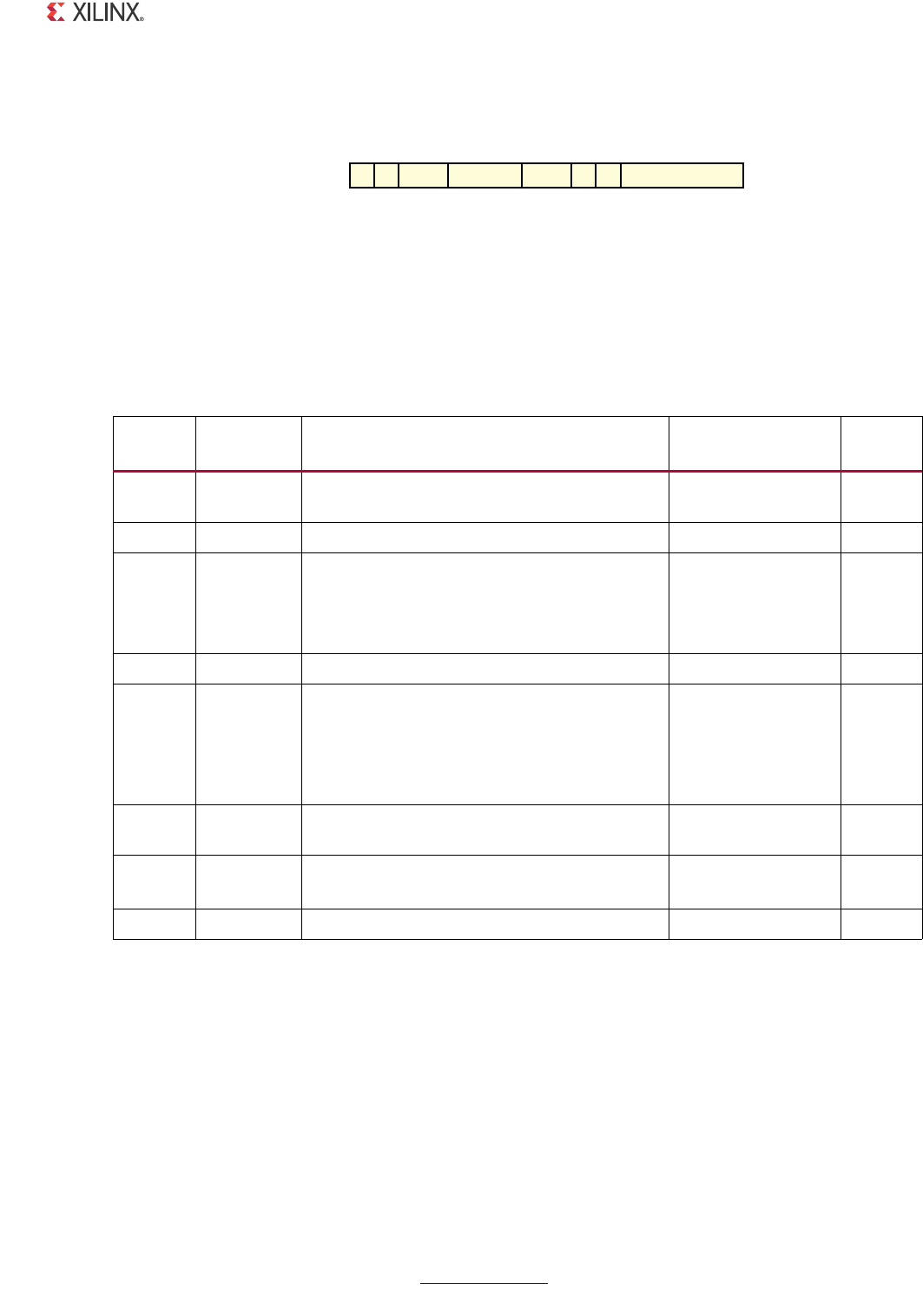

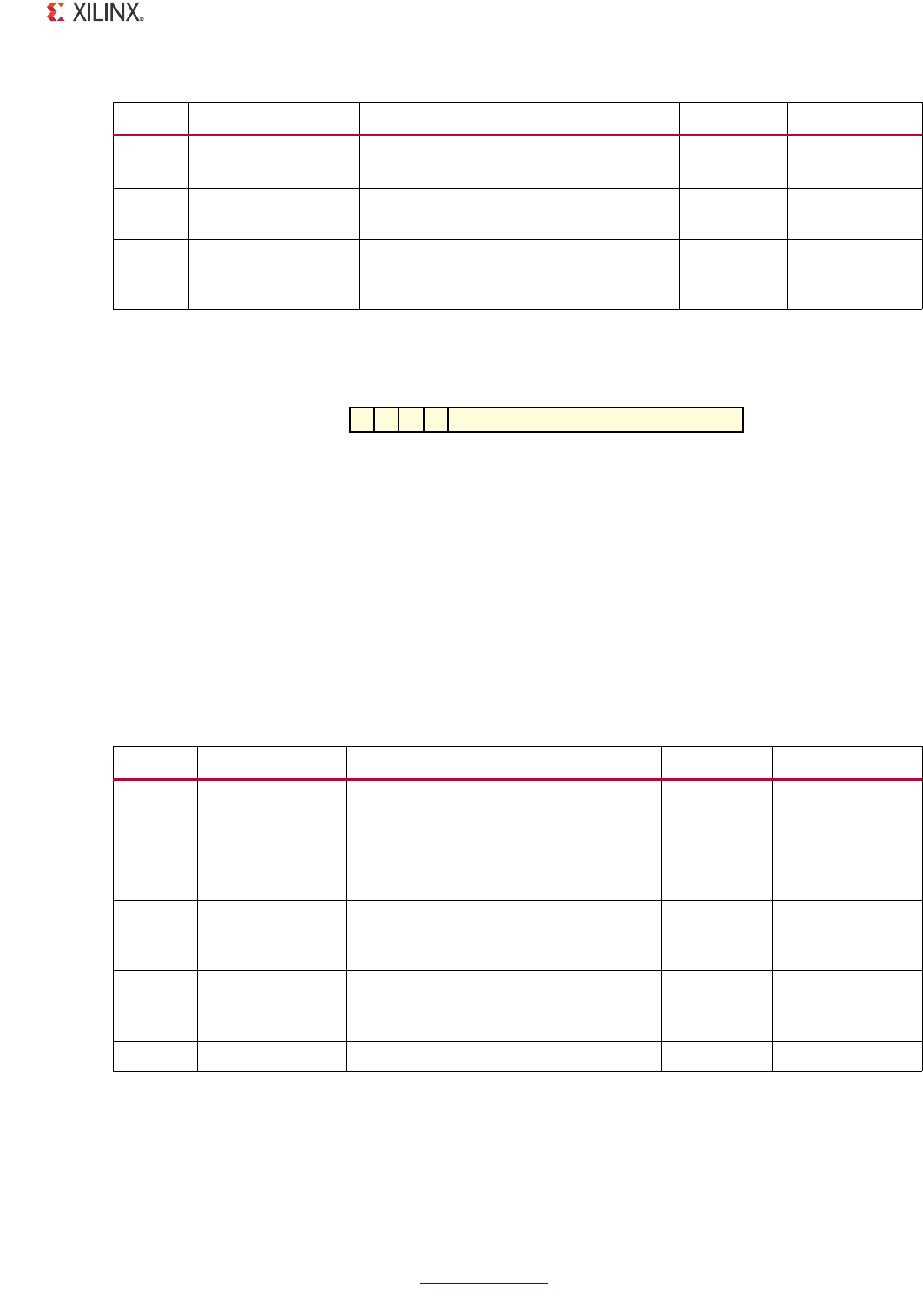

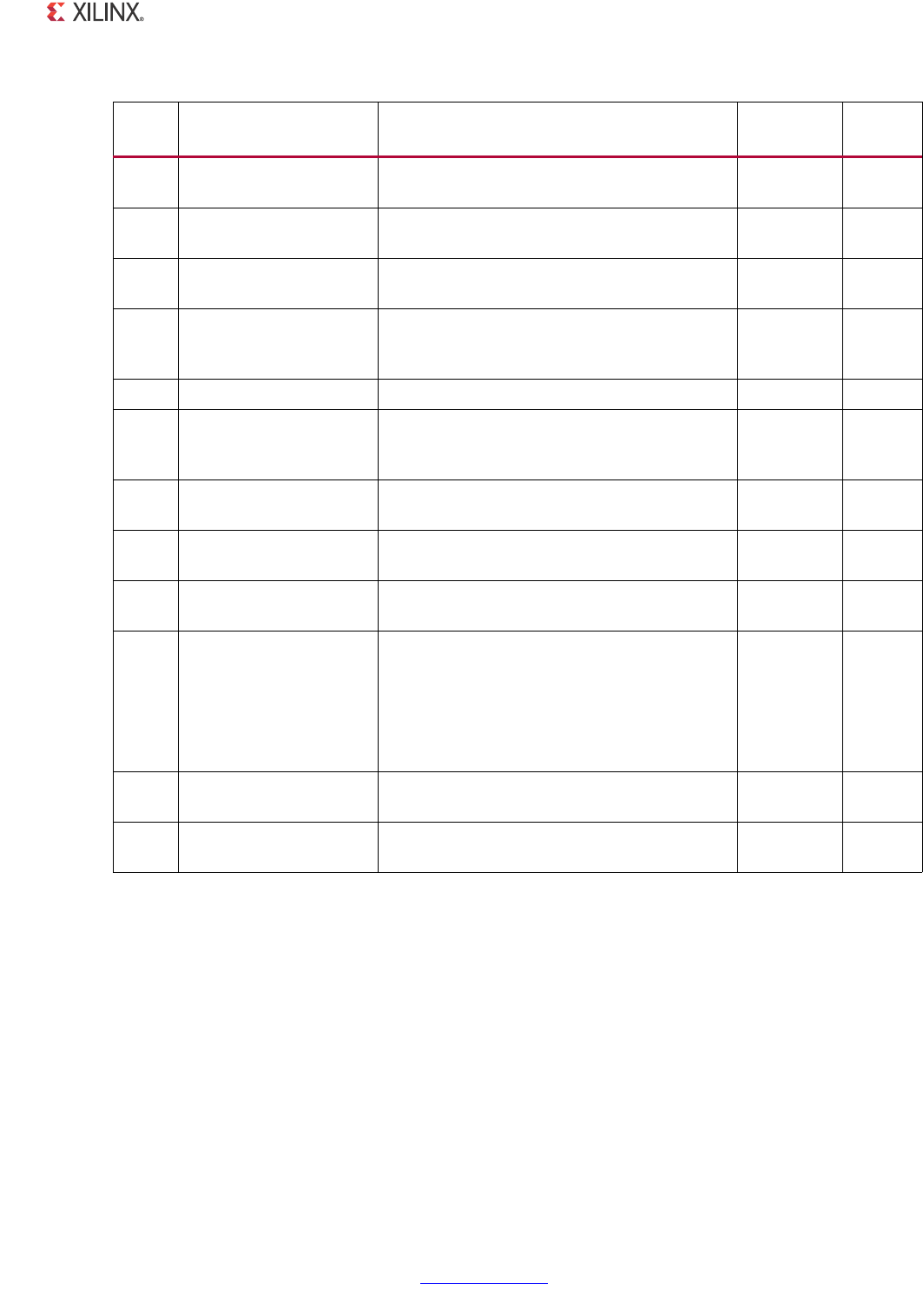

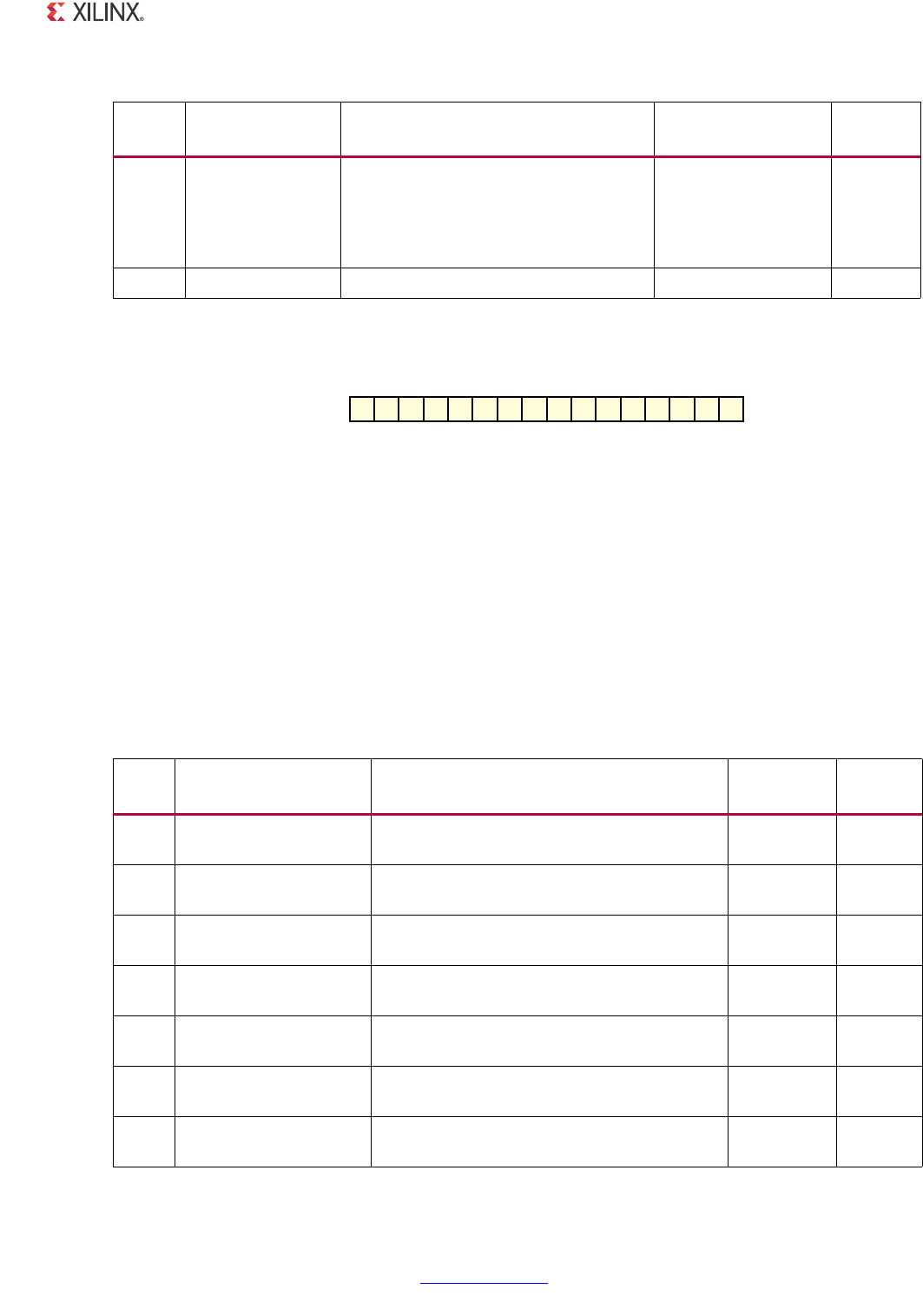

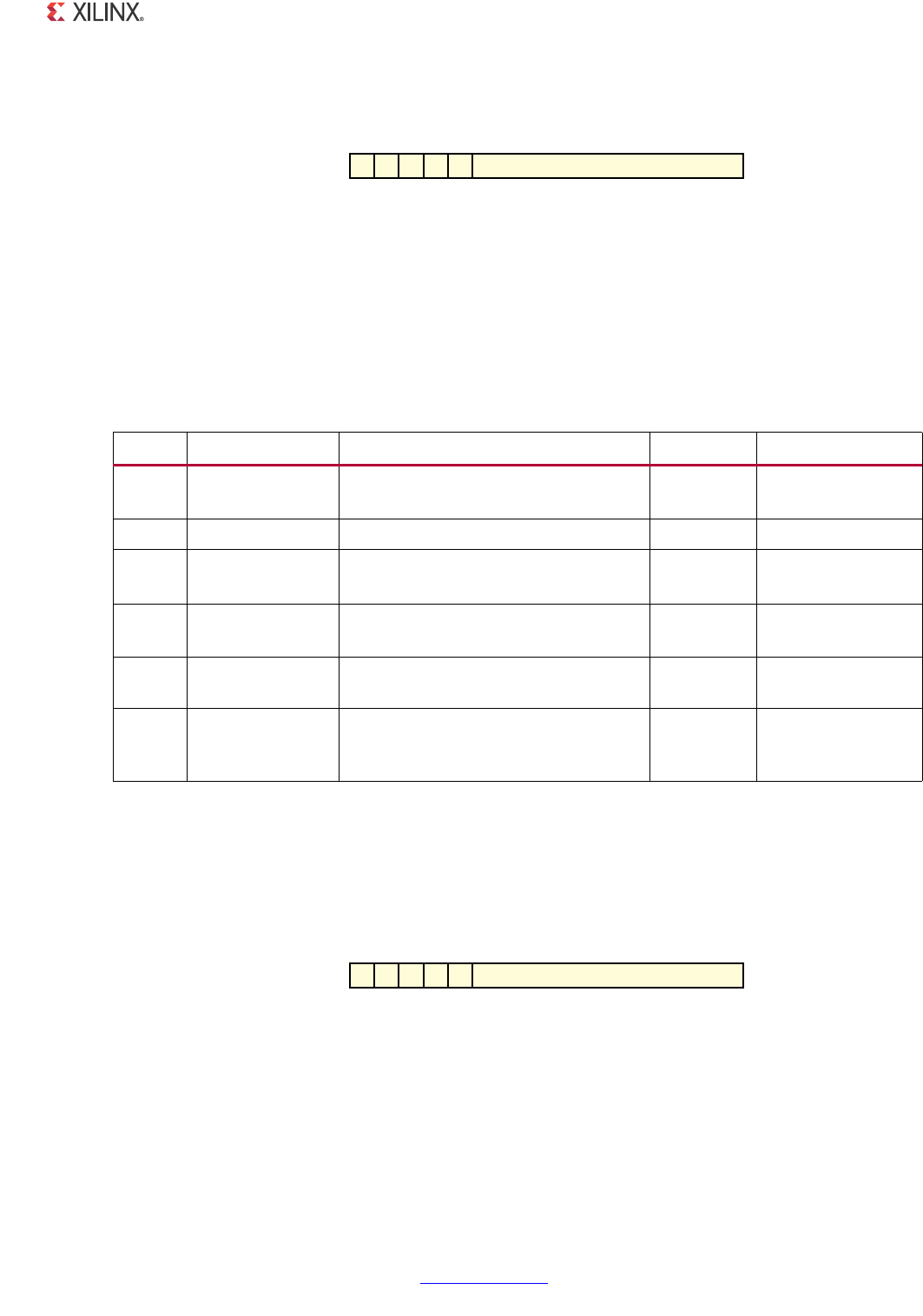

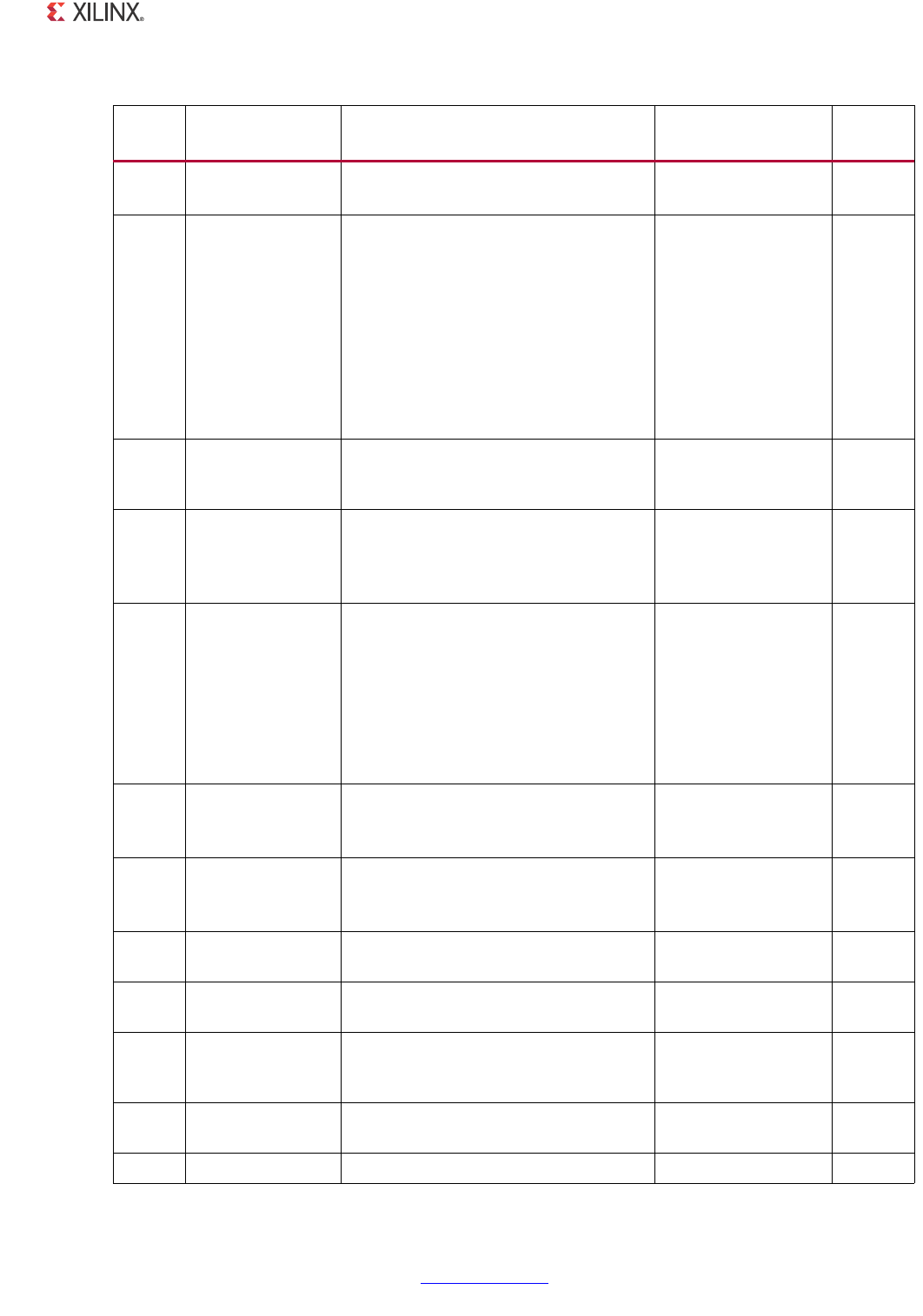

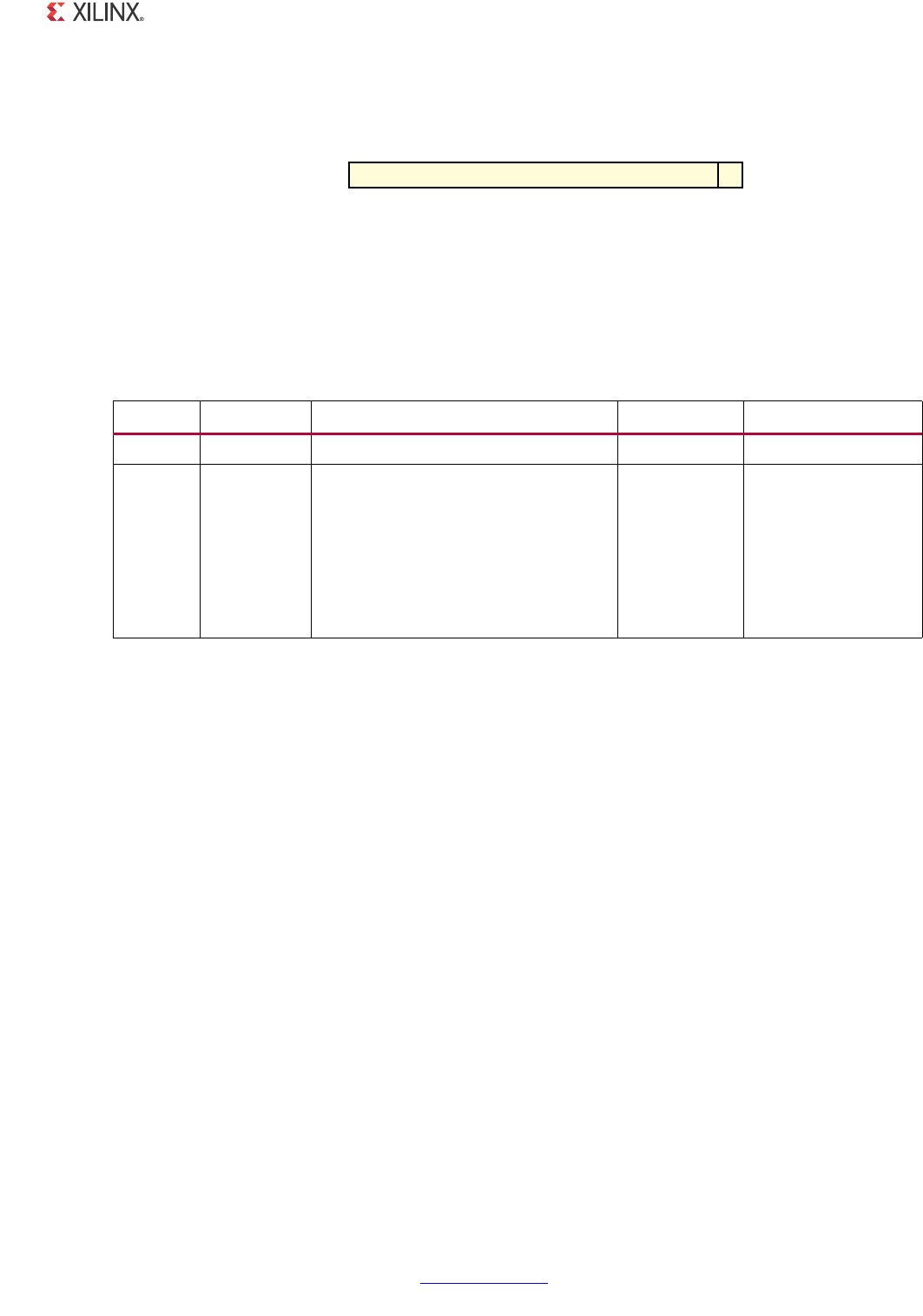

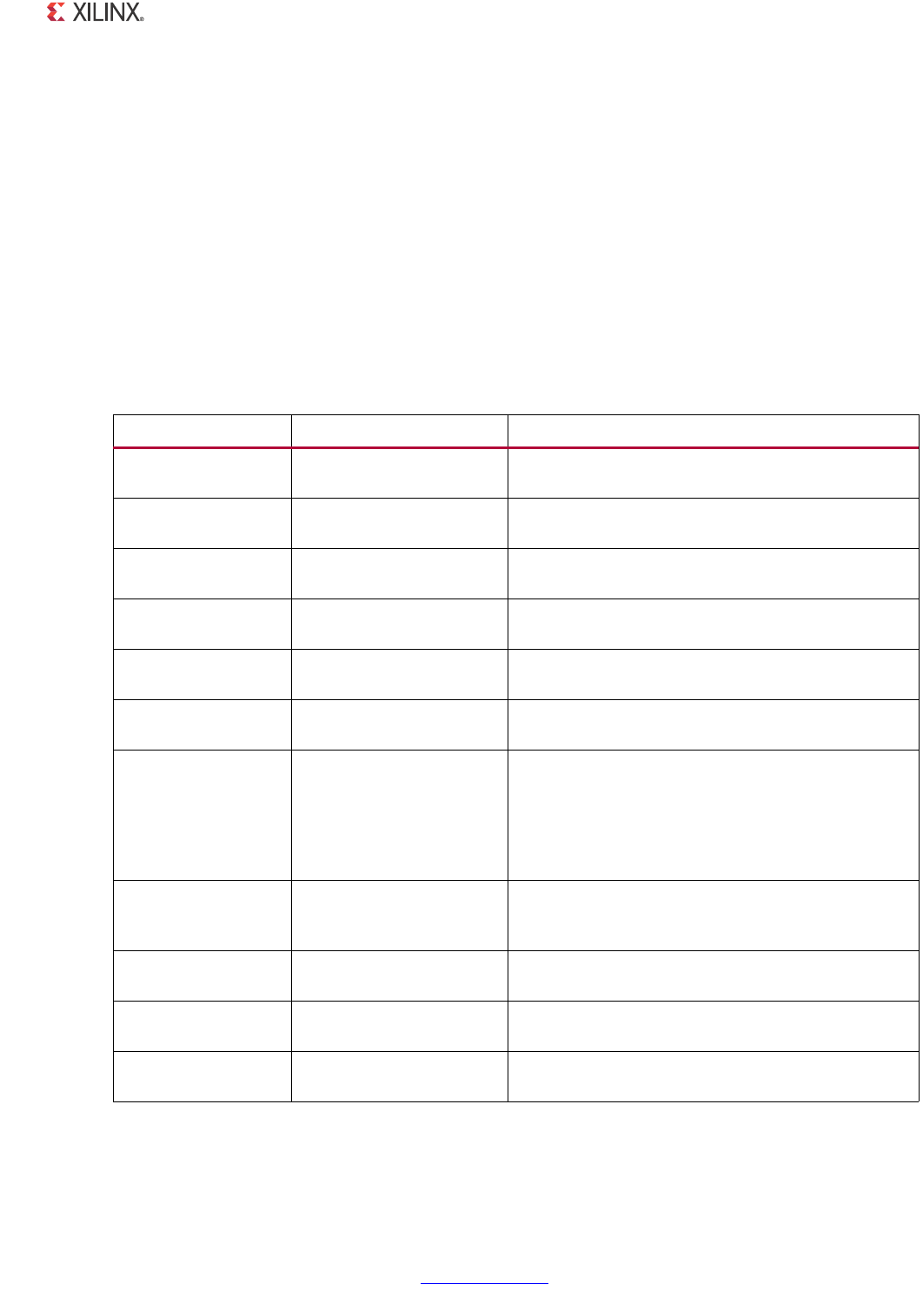

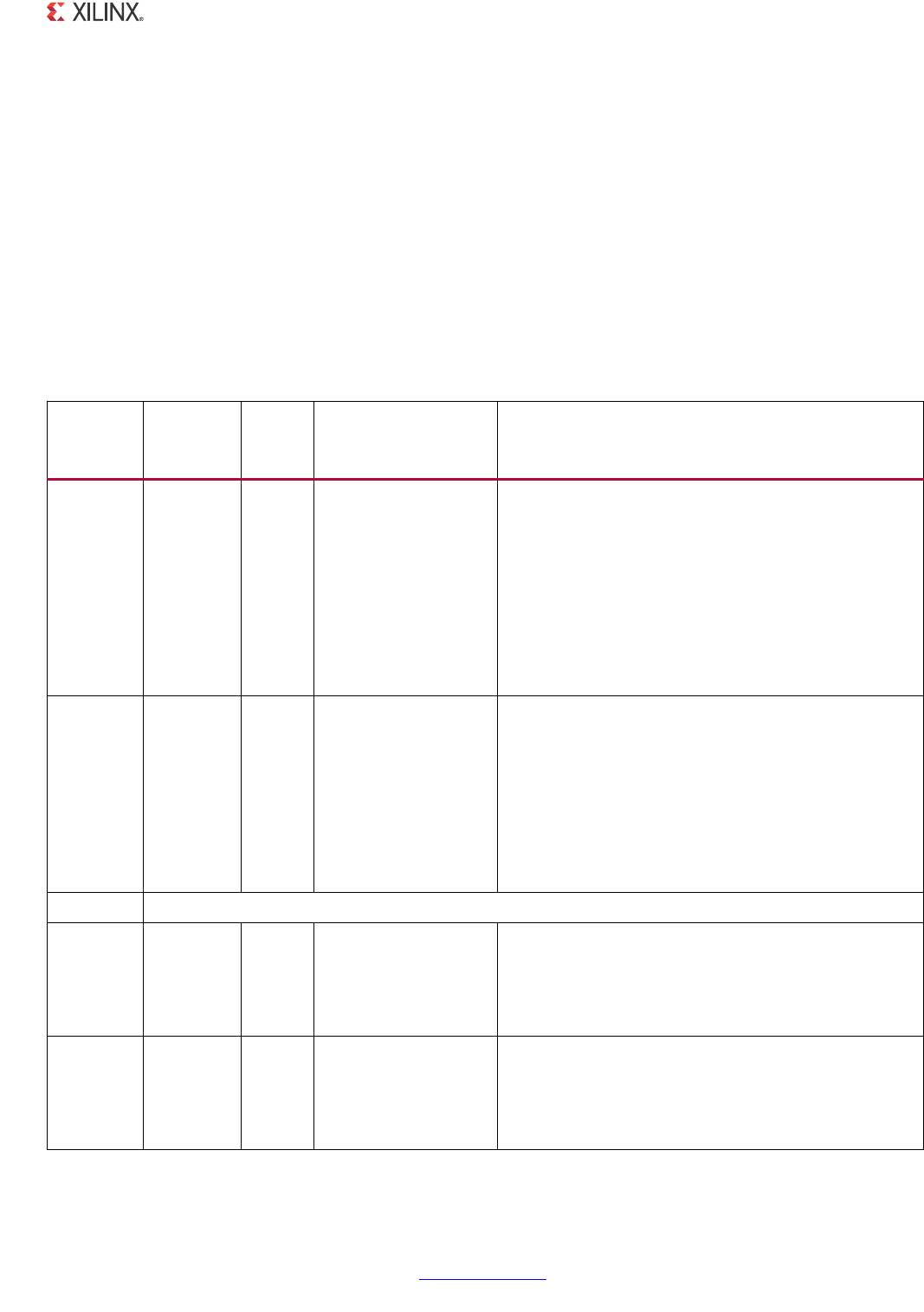

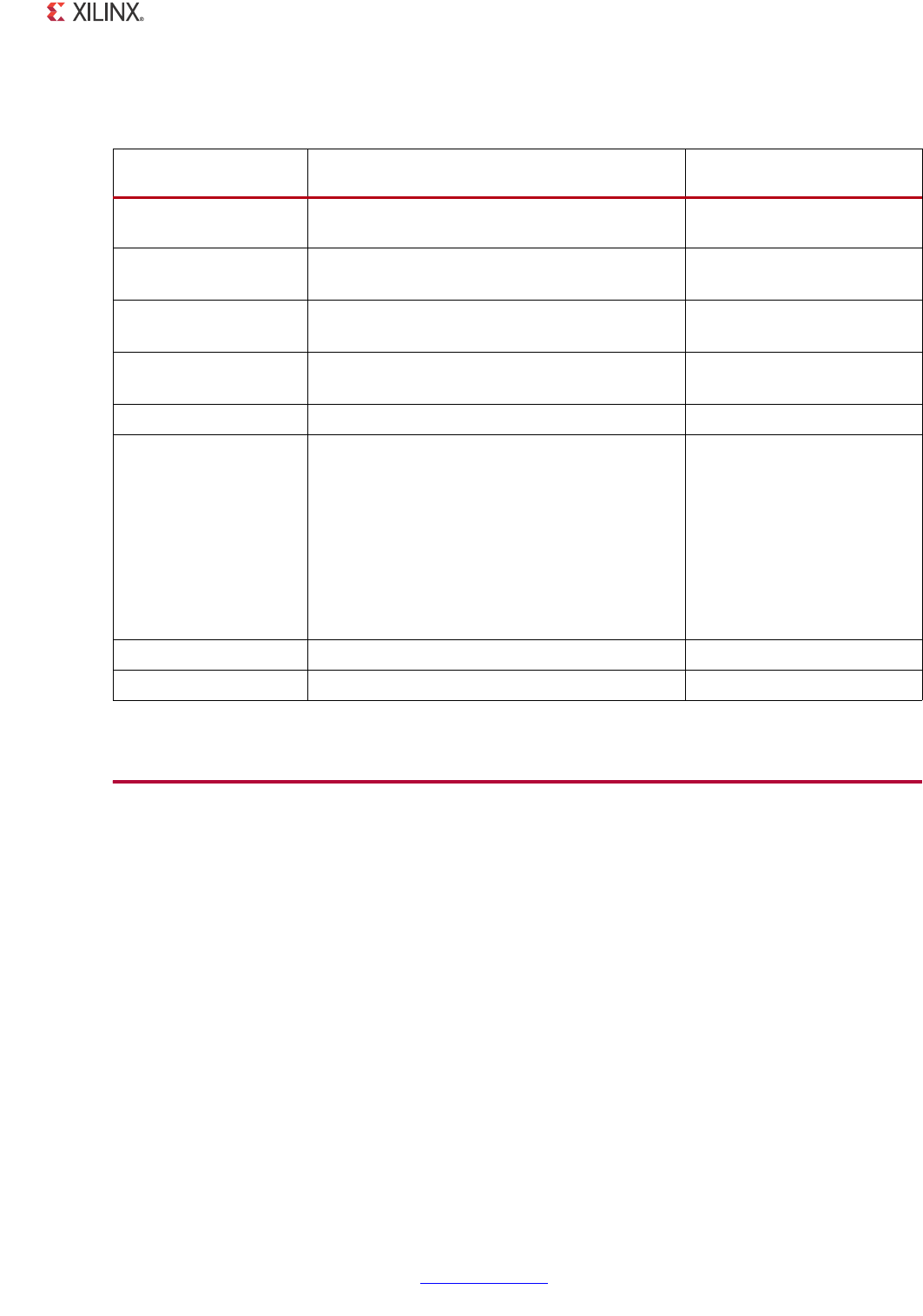

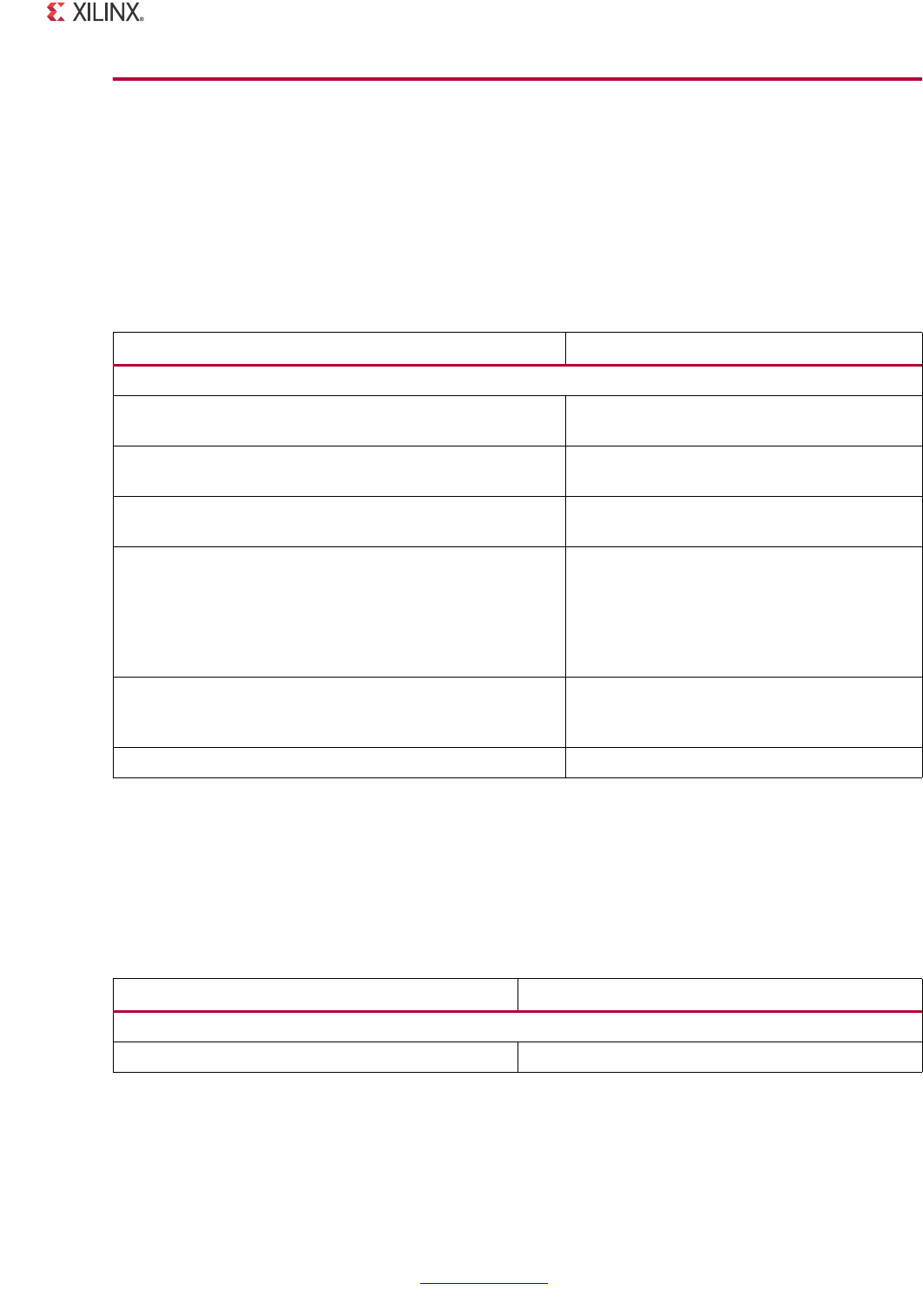

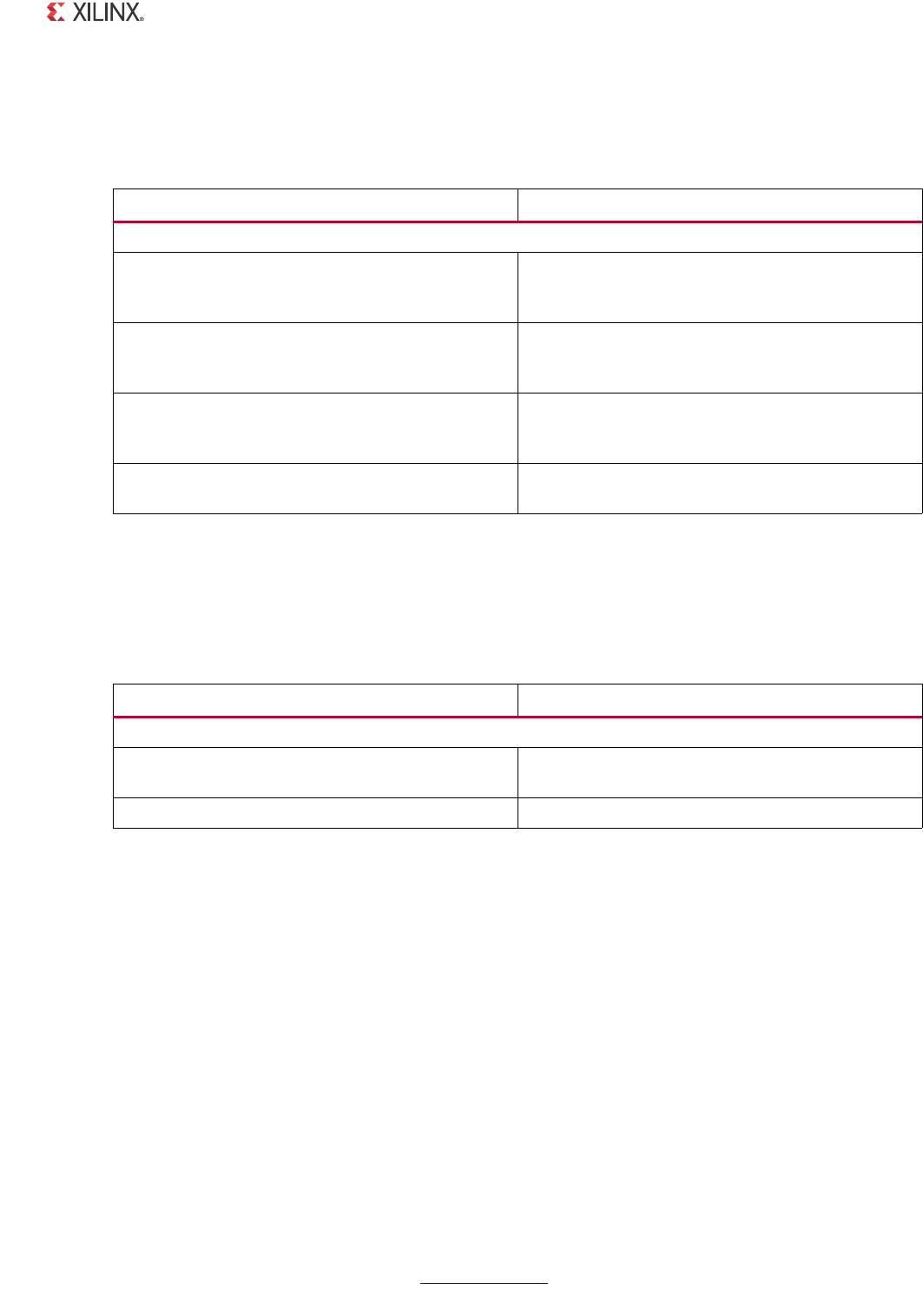

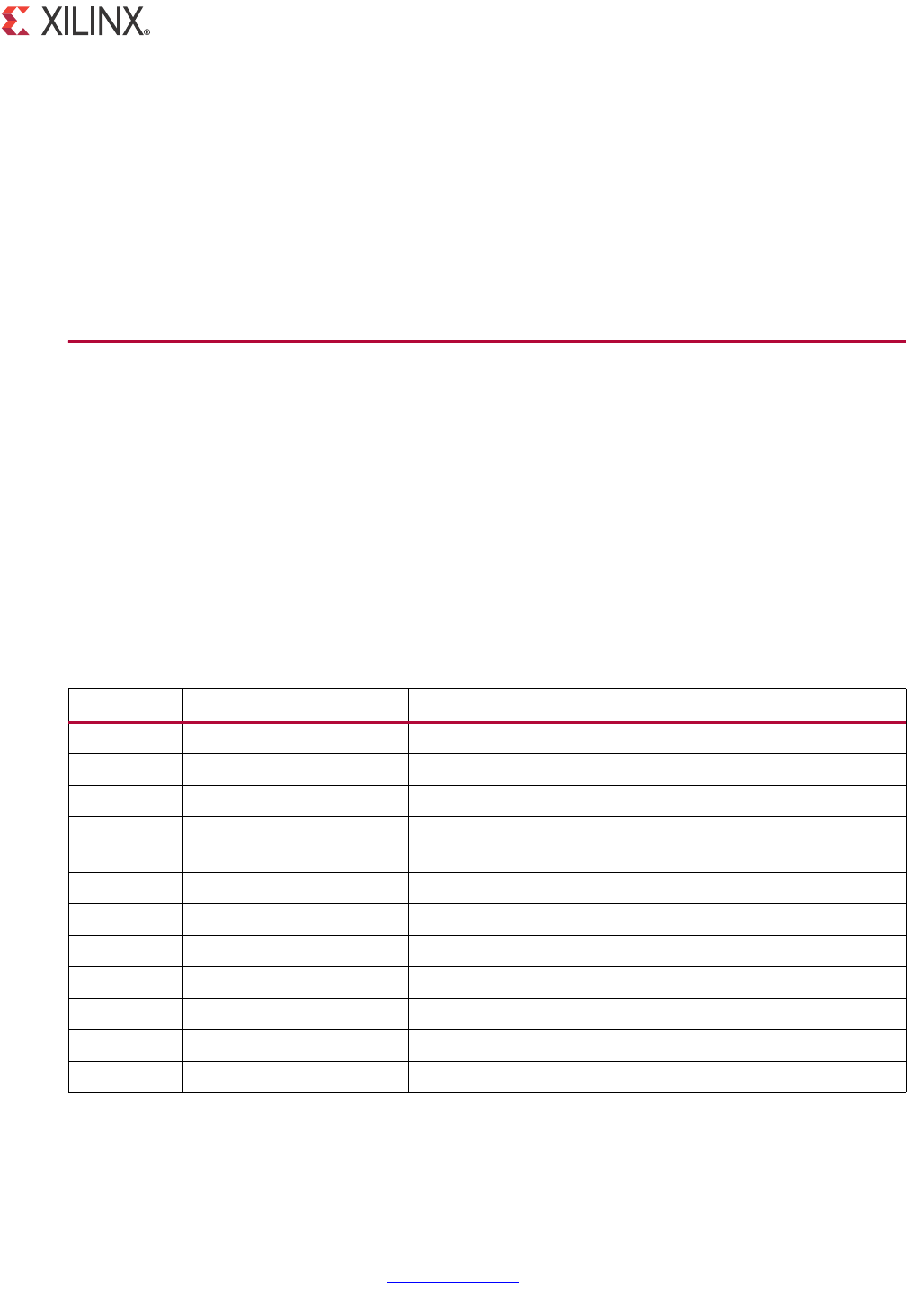

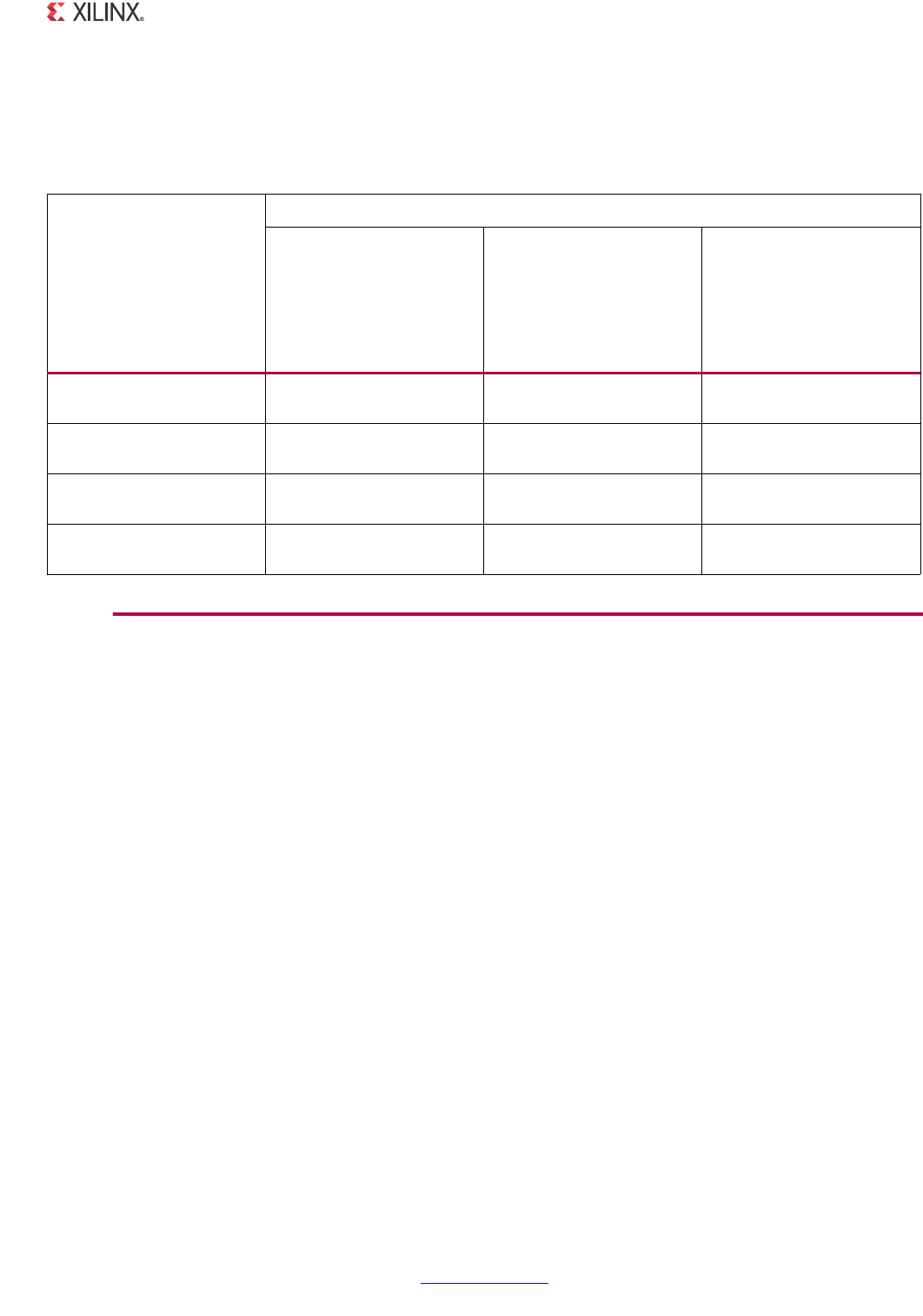

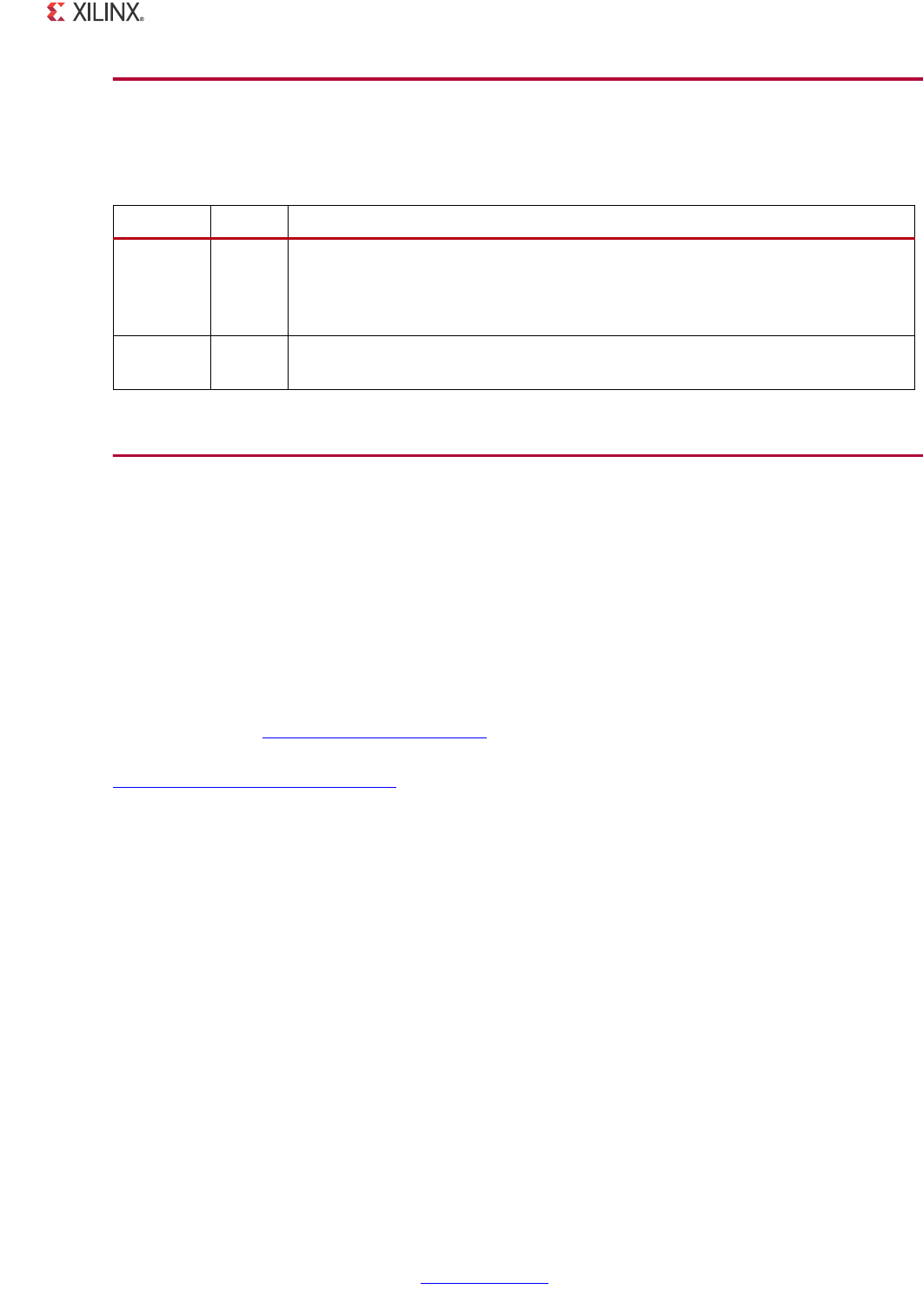

Table 2-1: Family Support for the 1000BASE-X PCS/PMA or SGMII Core

Device

Family

LogiCORE IP Functionality

1000BASE-X GMII to SGMII Bridge or

SGMII to GMII Bridge

1000BASE-X and SGMII

Standards with Dynamic

Switching

With TBI

Using

Device

Specific

Transceiver

With TBI

Using

Device

Specific

Transceiver

Using

Synchronous

LVDS

SelectIO

Using

Asynchronous

LVDS SelectIO With TBI

Using Device

Specific

Transceiver

Zynq-7000 Not

Supported Supported Not

Supported Supported Not

supported Not supported Not

Supported Supported

Virtex-7 Not

Supported Supported Not

Supported Supported

Supported

in -2 speed

grade and

faster parts for

HR banks; -1

speed grade

and faster for

HP banks

Available

through

XAPP523

Not

Supported Supported

Kintex-7 Supported Supported Supported Supported

Supported

in -2 speed

grade and

faster parts for

HR banks; -1

speed grade

and faster for

HP banks

Available

through

XAPP523

Supported Supported

Artix-7 Not

Supported Supported Not

Supported Supported Not

supported Not supported Not

Supported Supported

Virtex-6 Supported Supported Supported Supported Not

supported

Supported in -2

speed grade

and faster parts

Supported(1) Supported

1000BASE-X PCS/PMA or SGMII v11.4 www.xilinx.com 29

PG047 October 16, 2012

Chapter 2: Product Specification

Device Utilization

Zynq-7000, Virtex-7, Kintex-7, Artix-7, Virtex-6, Virtex-5 and Spartan-6 families contain six

input LUTs; all other families contain four input LUTs. For this reason, the device utilization

is listed separately. See one of the following for more information:

•Zynq-7000, Virtex-7, Kintex-7, Artix-7, Virtex-6, Virtex-5, and Spartan-6 Devices

•Other Device Families

Zynq-7000, Virtex-7, Kintex-7, Artix-7, Virtex-6, Virtex-5, and Spartan-6

Devices

Table 2-2, Tabl e 2-3, and Ta bl e 2- 4 provide approximate utilization figures for various core

options when a single instance of the core is instantiated in a Virtex-5 device.

Utilization figures are obtained by implementing the block-level wrapper for the core. This

wrapper is part of the example design and connects the core to the selected physical

interface.

Virtex-5 Supported Supported Supported Supported Not

supported Not Supported Supported Supported

Virtex-4 Supported Supported Supported Supported Not

supported Not Supported Supported Supported

Spartan-6 Supported Supported Supported Supported Not

supported Not Supported Supported Supported

Spartan-3 Supported Not

supported Supported Not

supported

Not

supported Not Supported Supported Not

supported

Spartan-3E Supported Not

supported Supported Not

supported

Not

supported Not Supported Supported Not

supported

Spartan-3

ASupported Not

supported Supported Not

supported

Not

supported Not Supported Supported Not

supported

1. Virtex-6 devices support TBI at 2.5 V only; see the Virtex-6 FPGA Data Sheet: DC and Switching Characteristics.

Table 2-1: Family Support for the 1000BASE-X PCS/PMA or SGMII Core (Cont’d)

Device

Family

LogiCORE IP Functionality

1000BASE-X GMII to SGMII Bridge or

SGMII to GMII Bridge

1000BASE-X and SGMII

Standards with Dynamic

Switching

With TBI

Using

Device

Specific

Transceiver

With TBI

Using

Device

Specific

Transceiver

Using

Synchronous

LVDS

SelectIO

Using

Asynchronous

LVDS SelectIO With TBI

Using Device

Specific

Transceiver

1000BASE-X PCS/PMA or SGMII v11.4 www.xilinx.com 30

PG047 October 16, 2012

Chapter 2: Product Specification

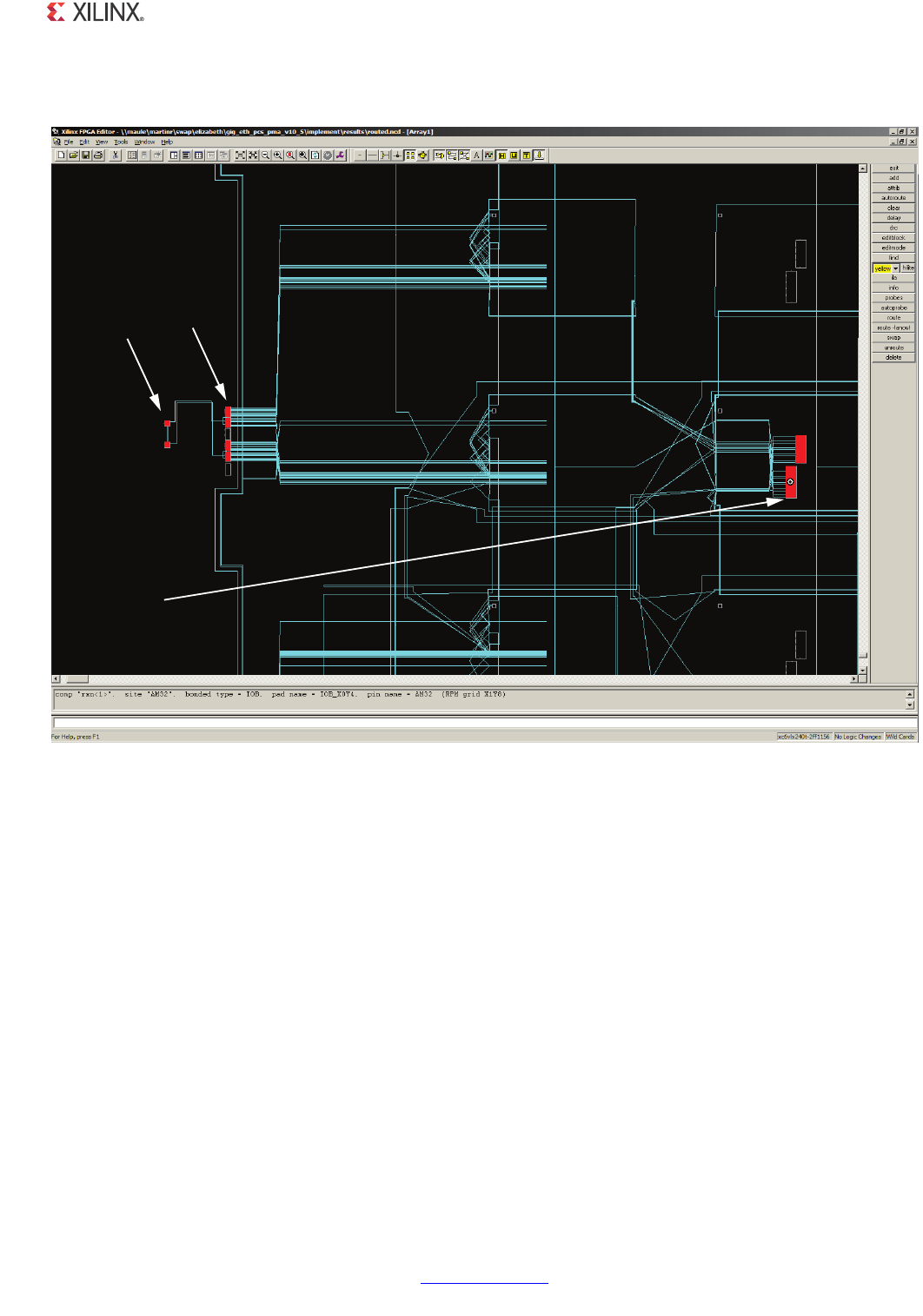

BUFG Usage

• BUFG usage does not consider multiple instantiations of the core, where clock

resources can often be shared.

• BUFG usage does not include the reference clock required for IDELAYCTRL. This clock

source can be shared across the entire device and is not core specific.

1000BASE-X

1. Auto-negotiation is only available when the MDIO Interface is selected.

2. These figures are for use with GTP transceivers; GTX transceivers require three BUFGs and one DCM.

3. Only two BUFGs might be required (see the User Guide)

SGMII Bridge

1. Auto-negotiation is only available when the MDIO Interface is selected.

2. These figures are for use with GTP transceivers; GTX transceivers require three BUFGs and one DCM.

3. Only two BUFGs might be required (see the User Guide)

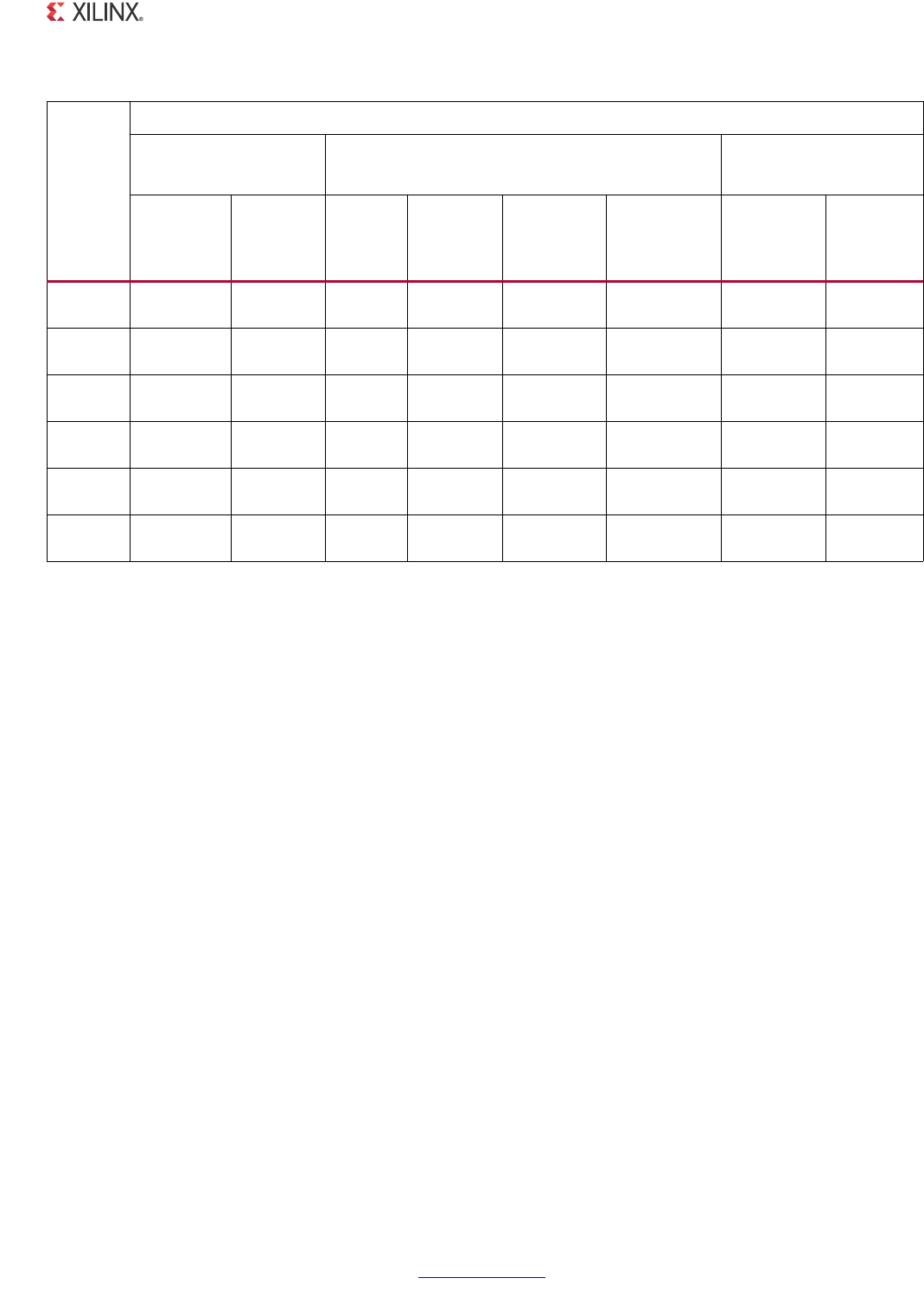

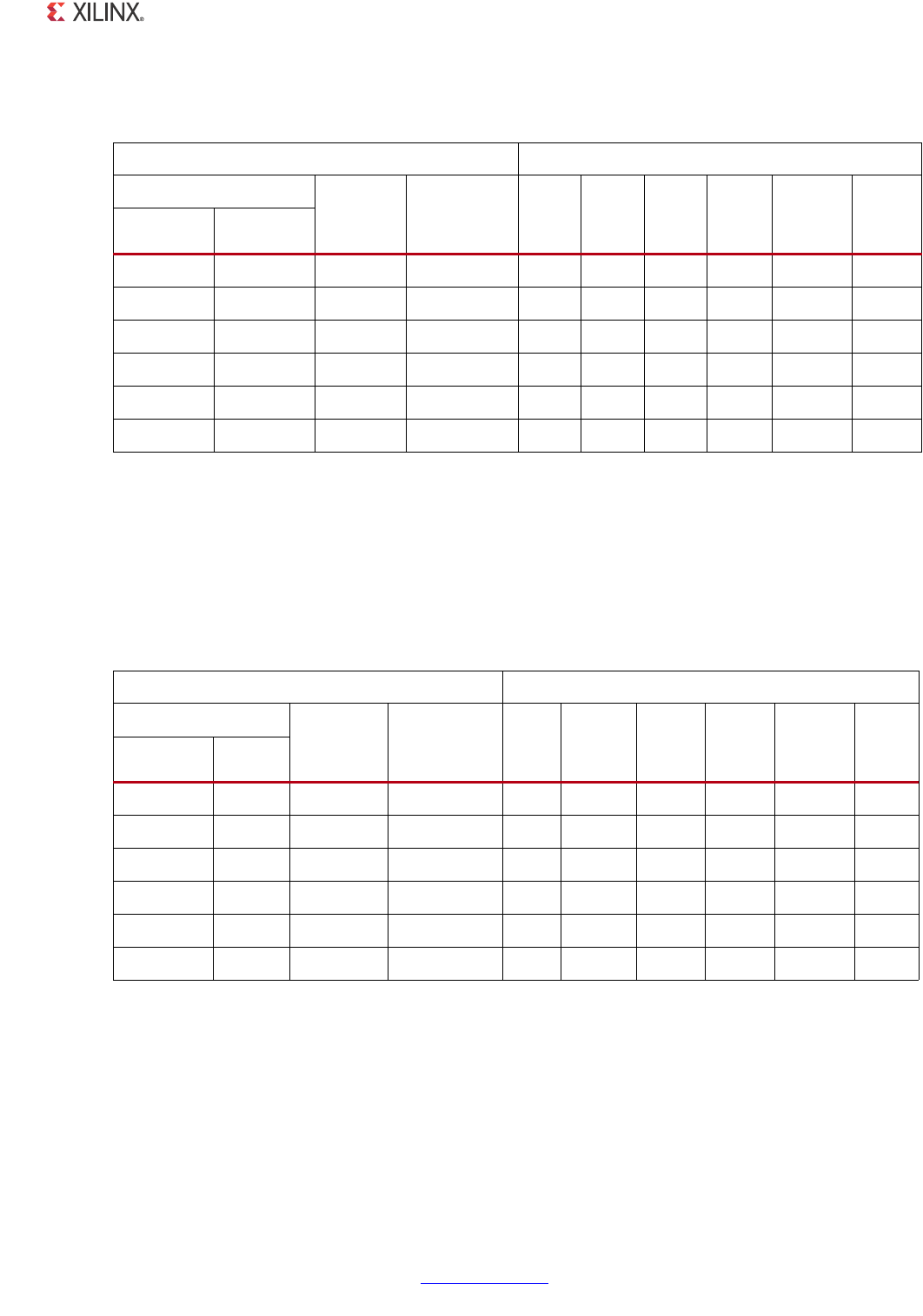

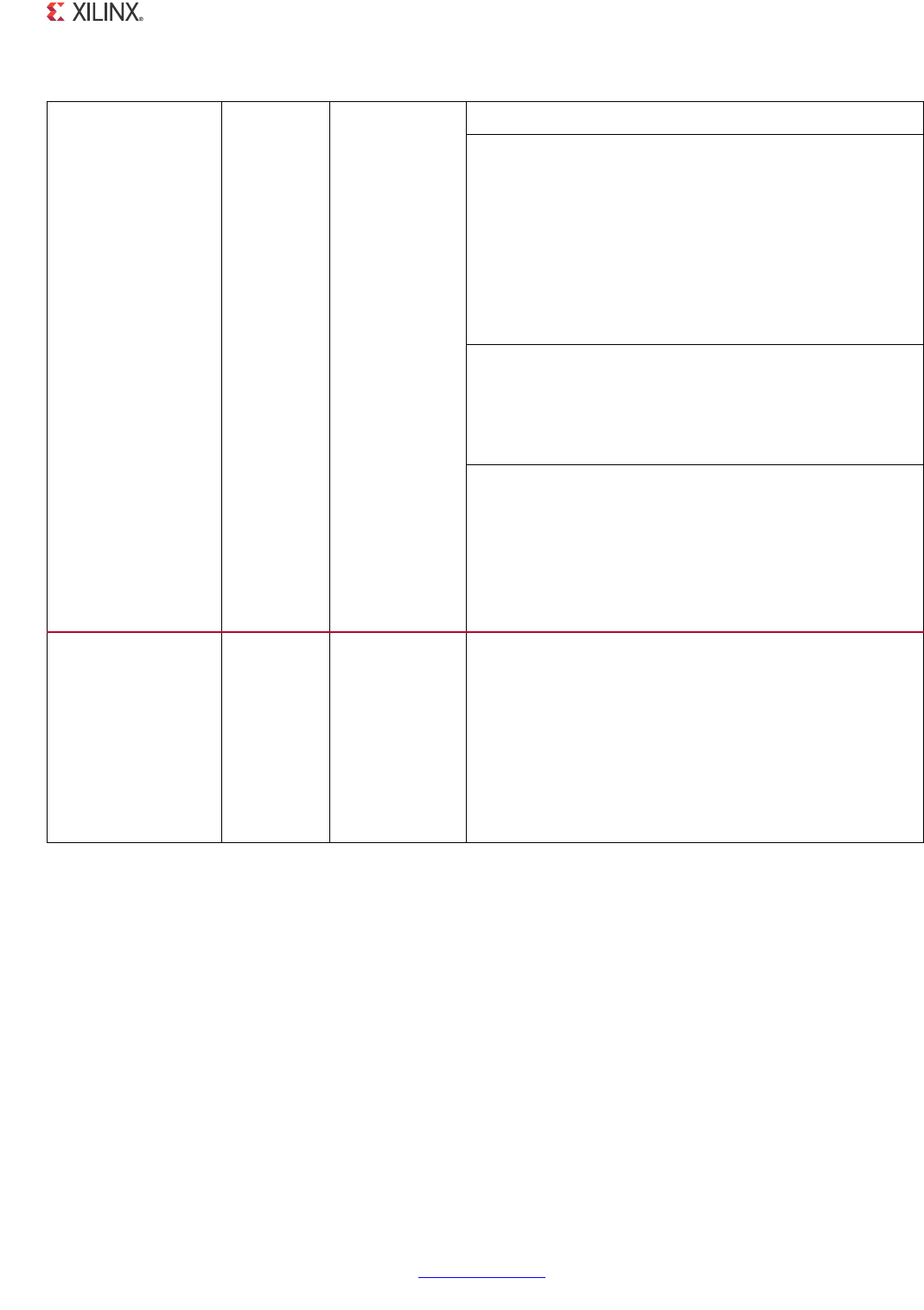

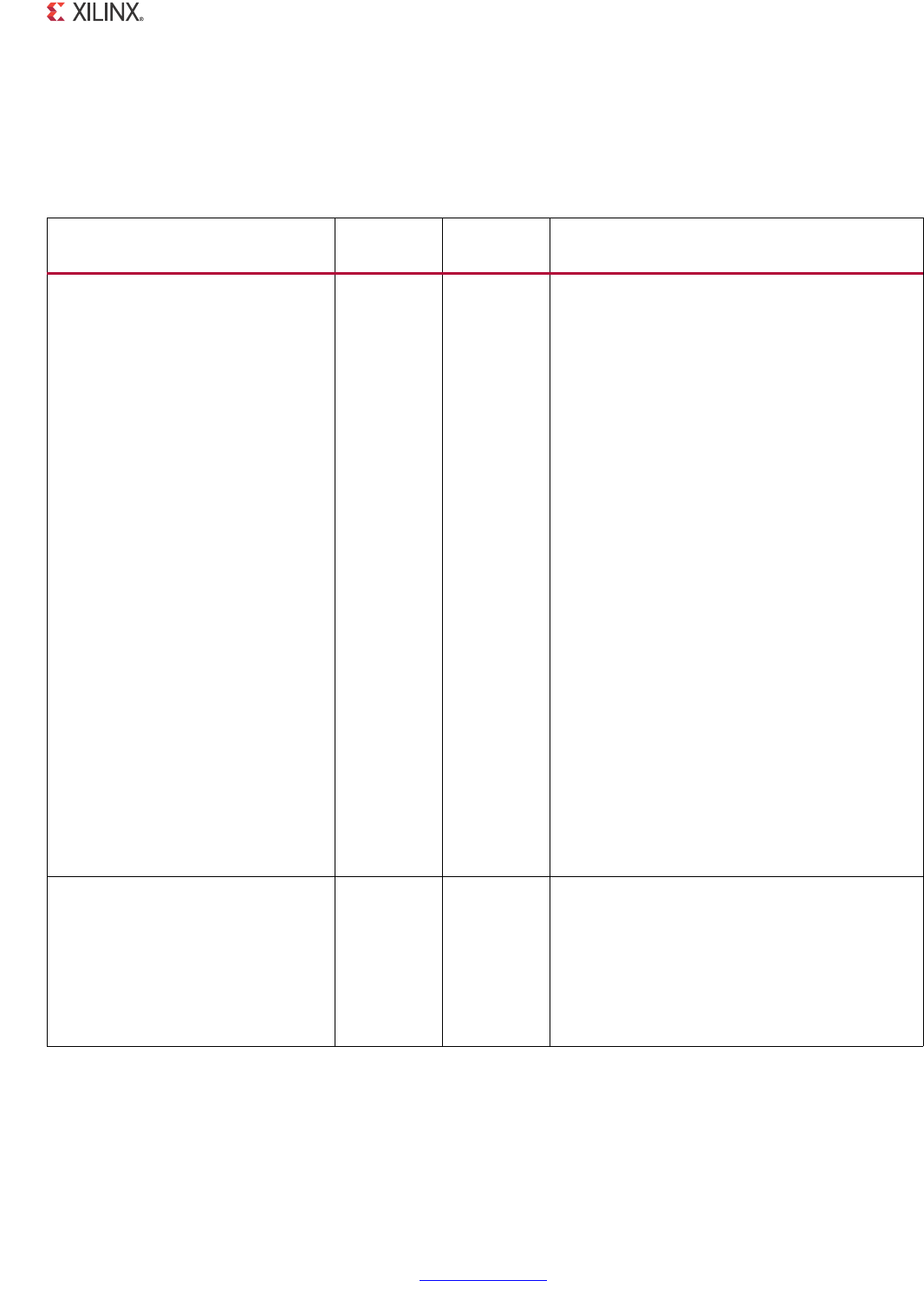

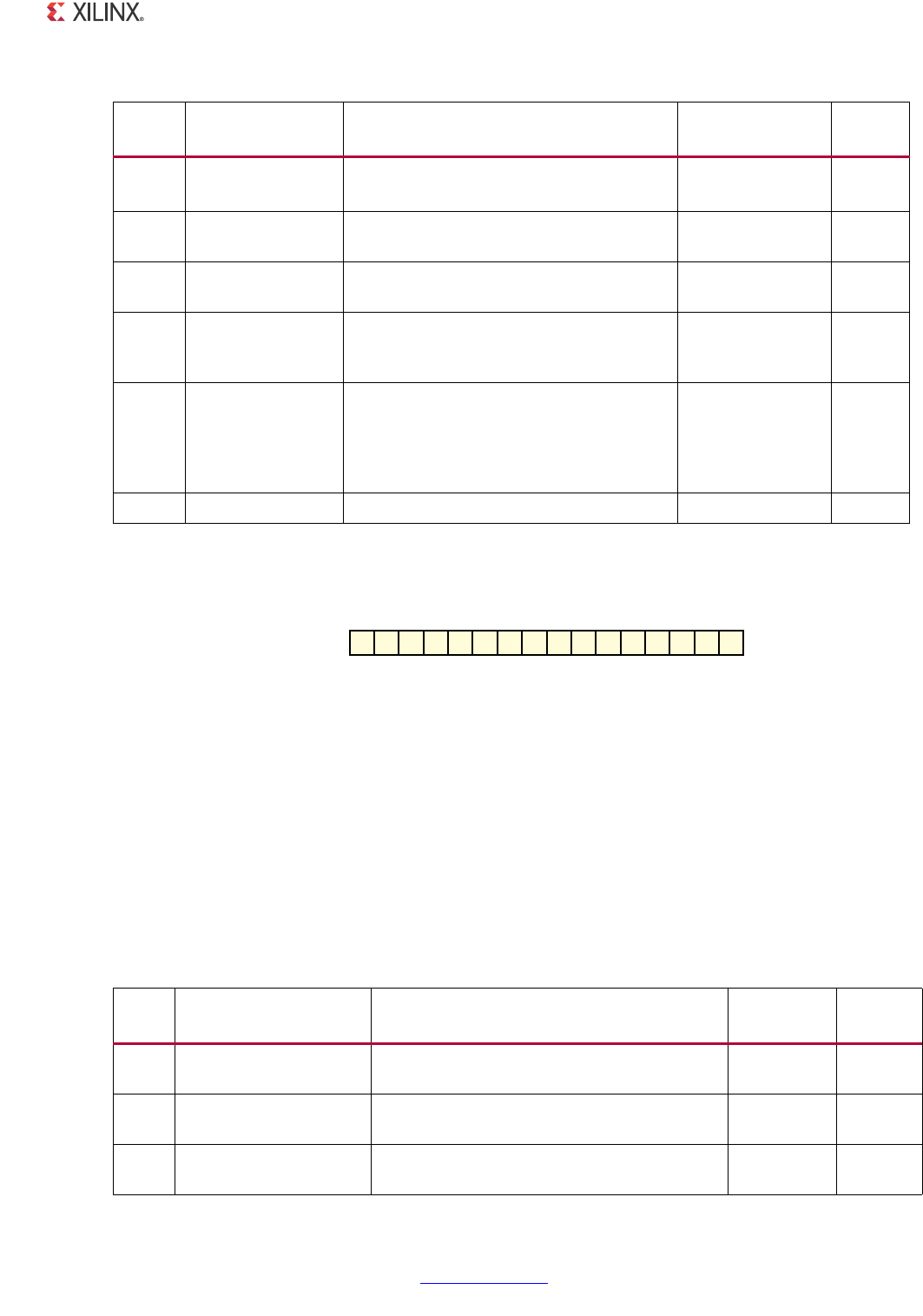

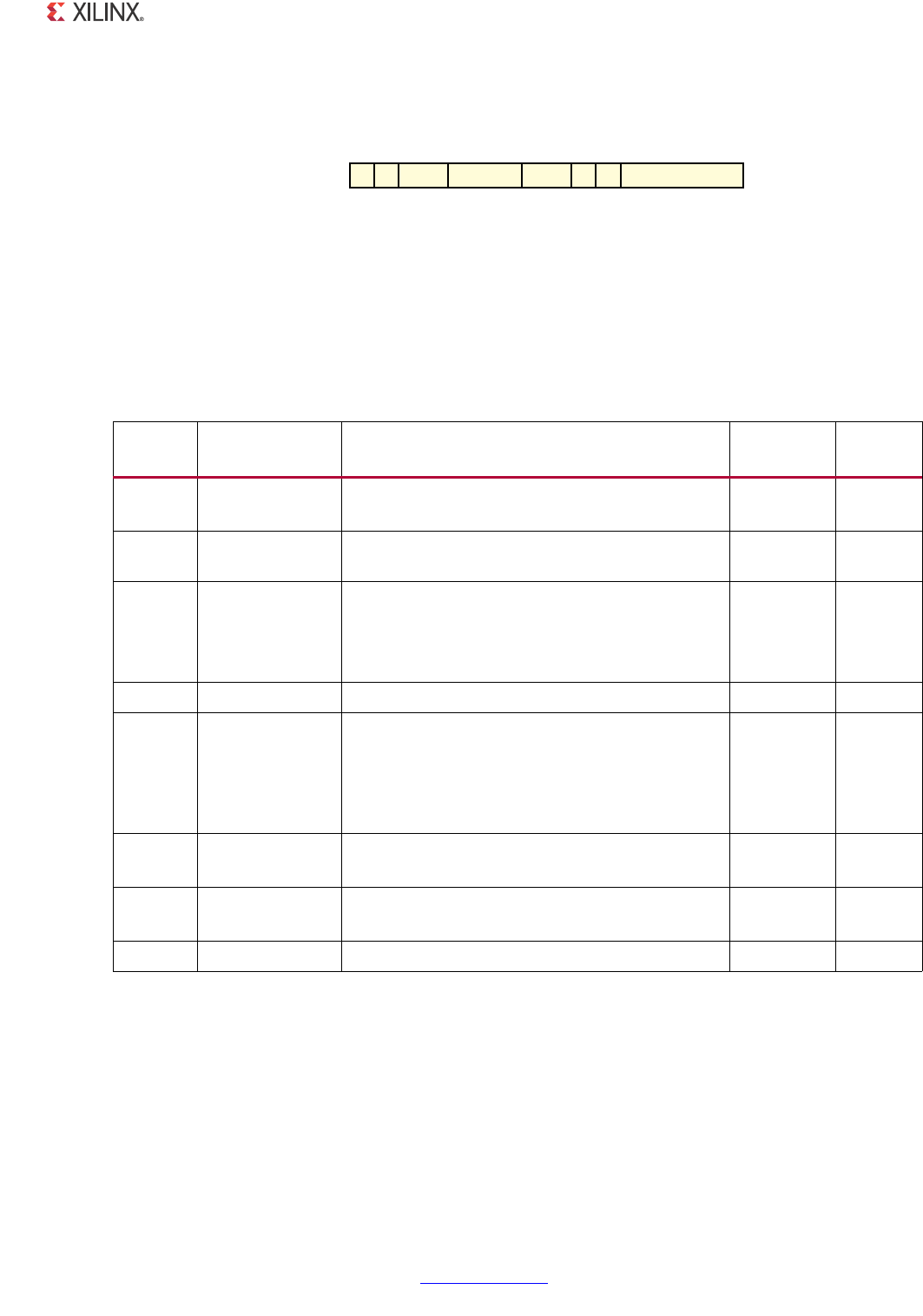

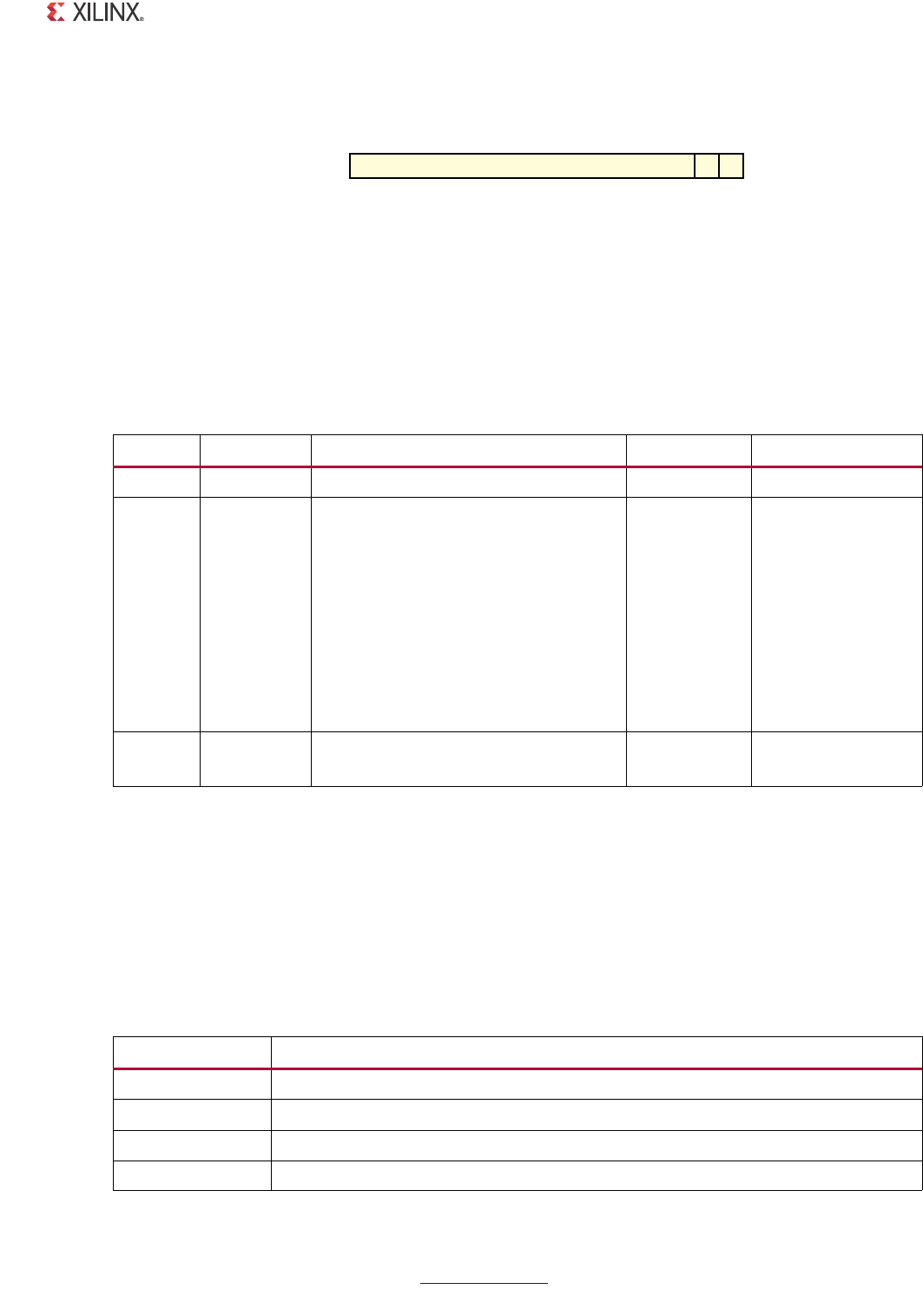

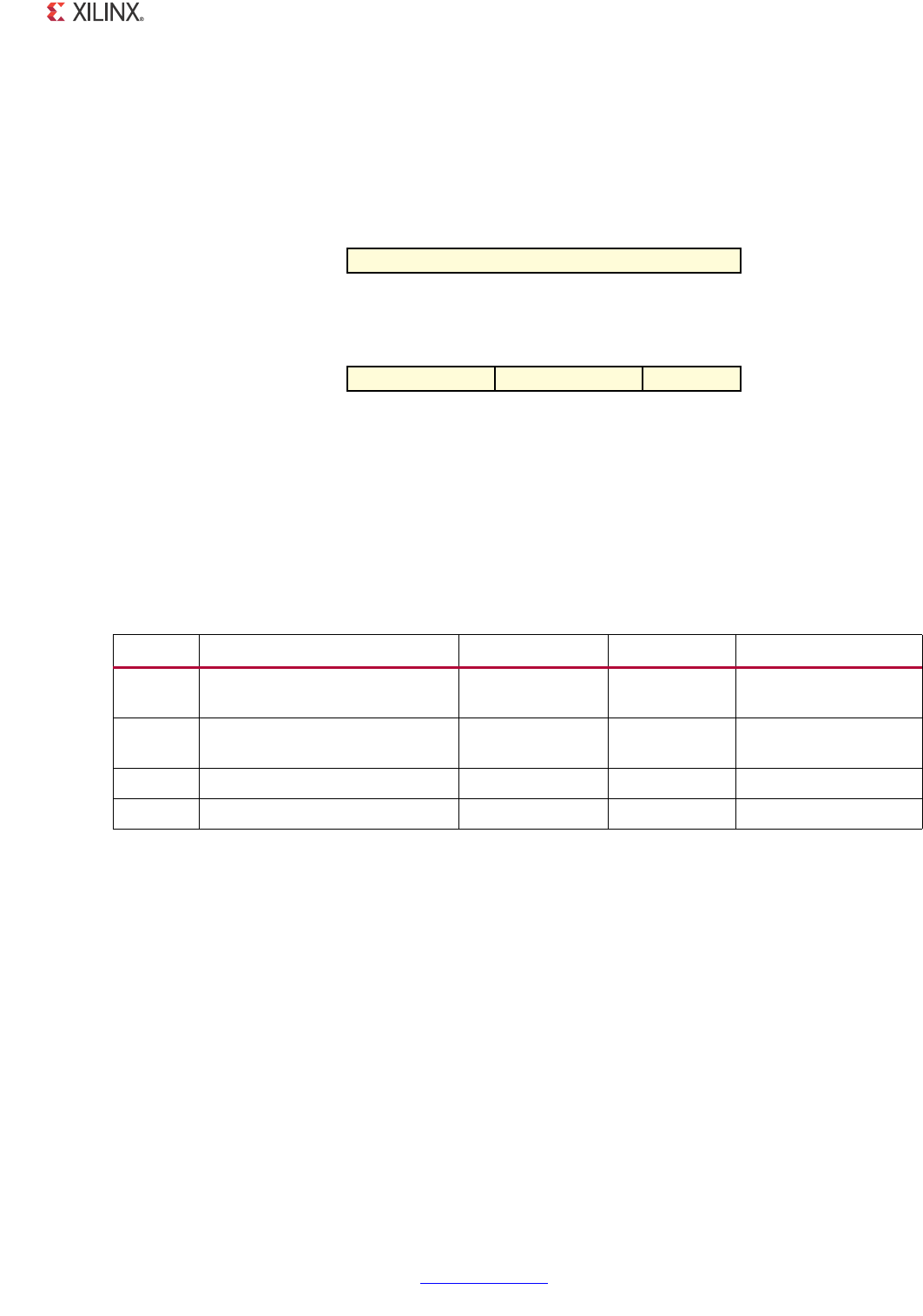

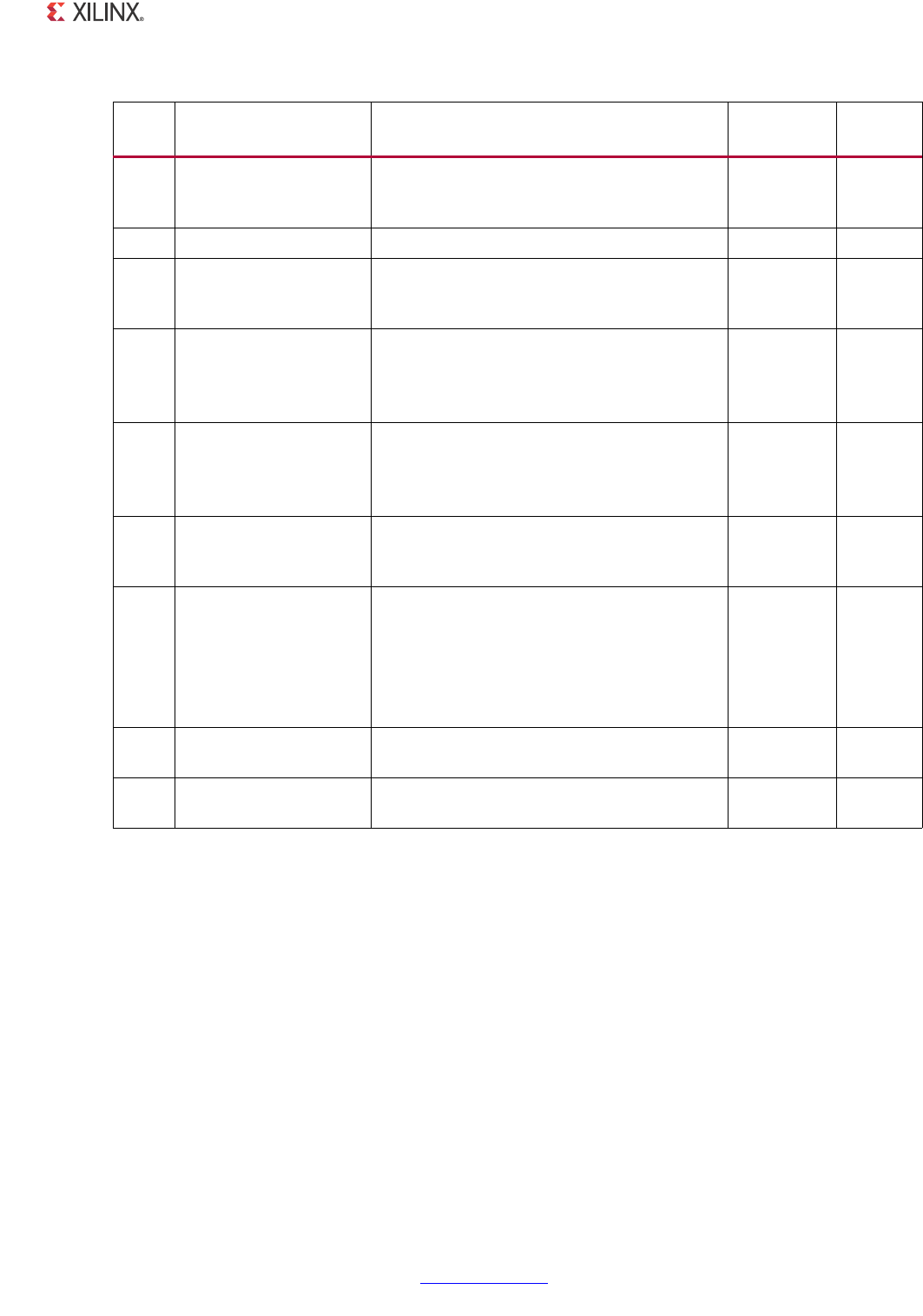

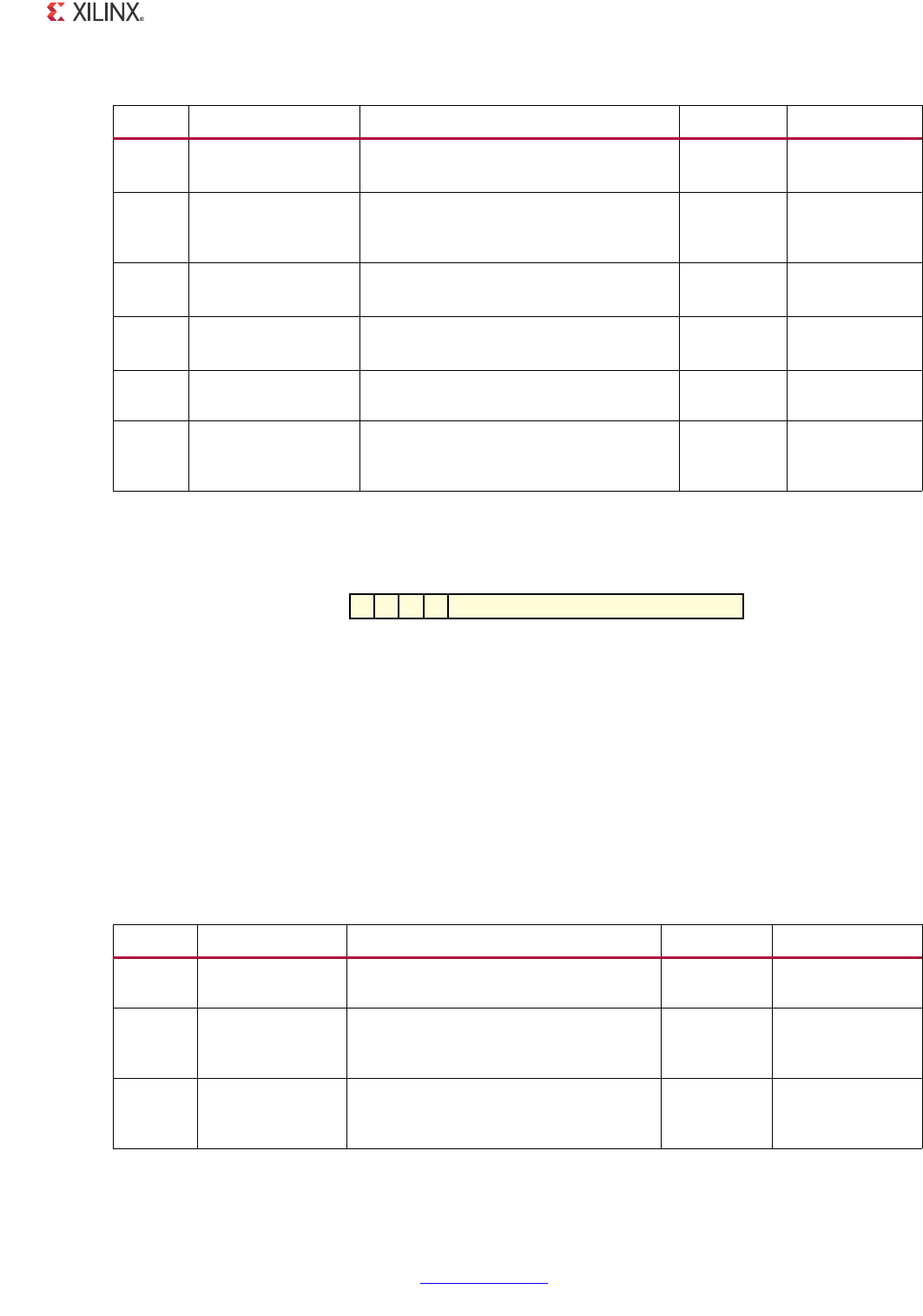

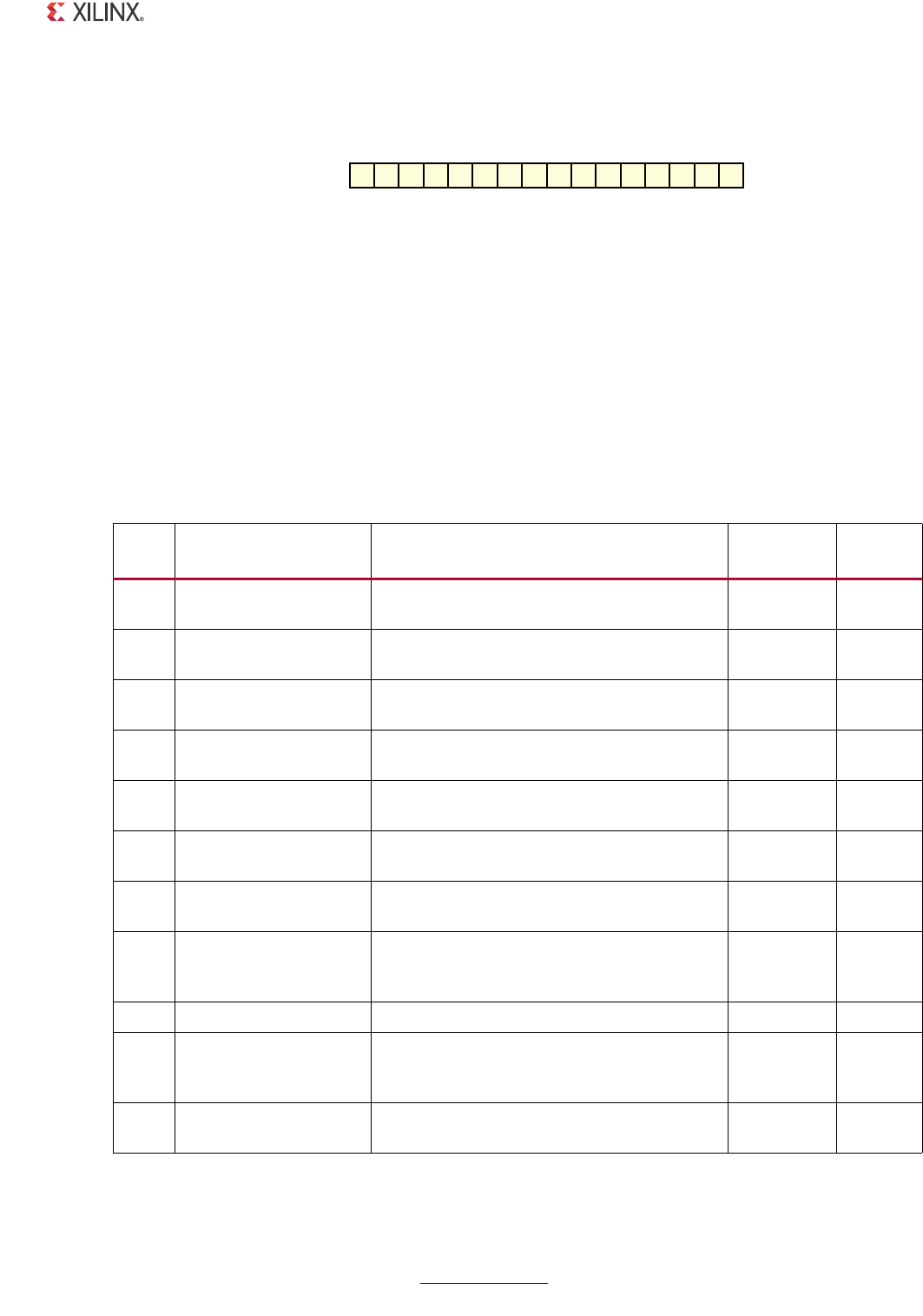

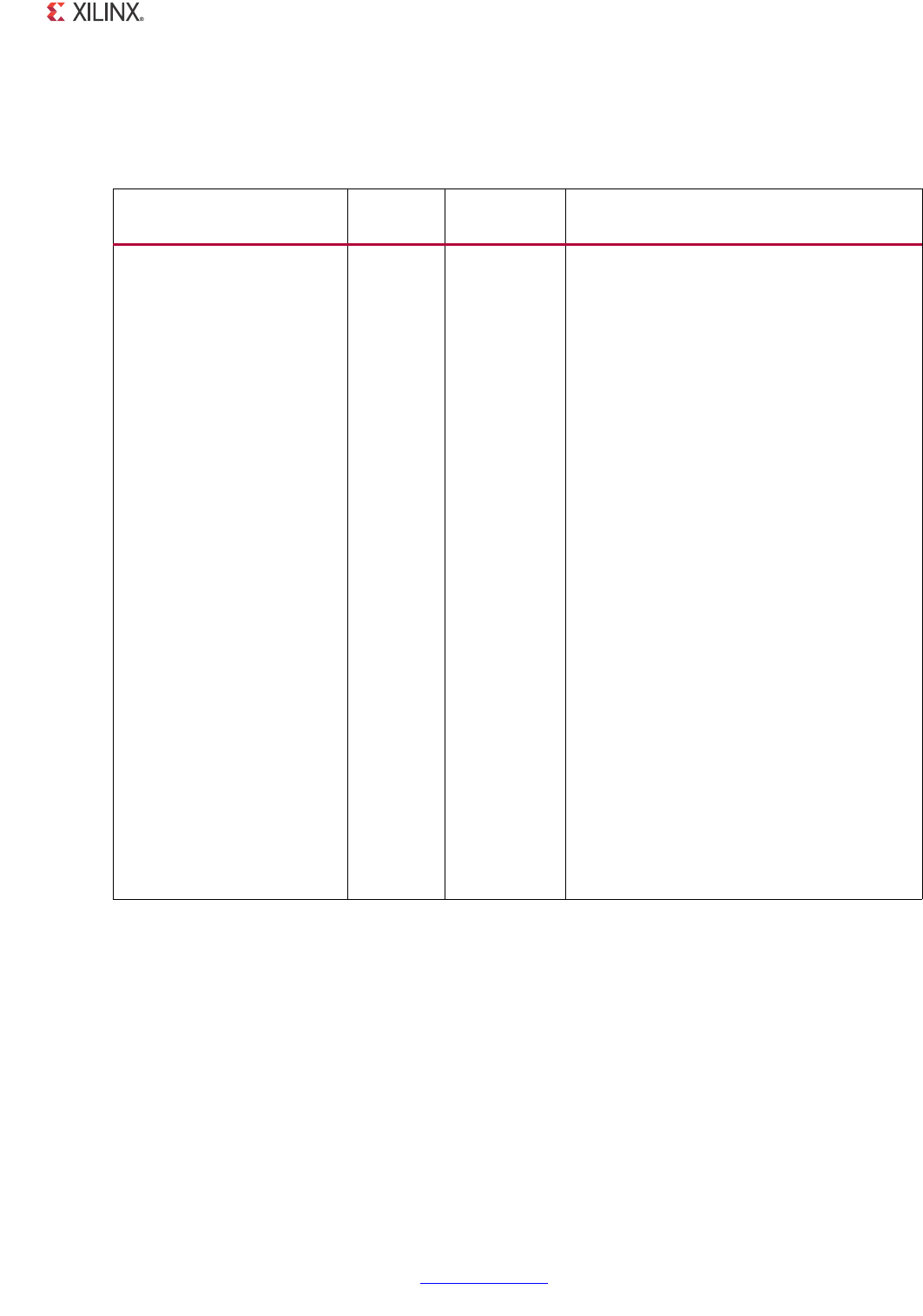

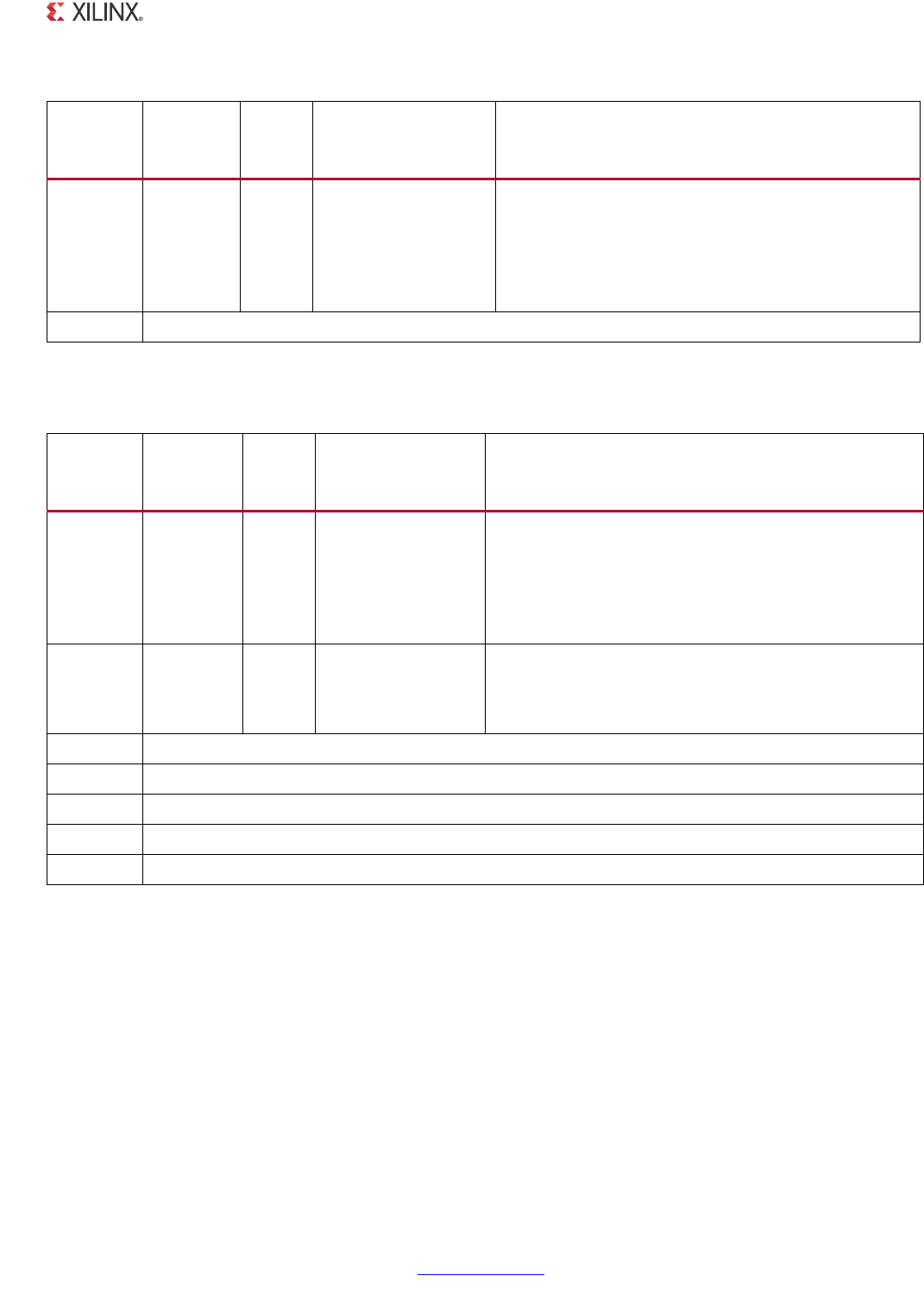

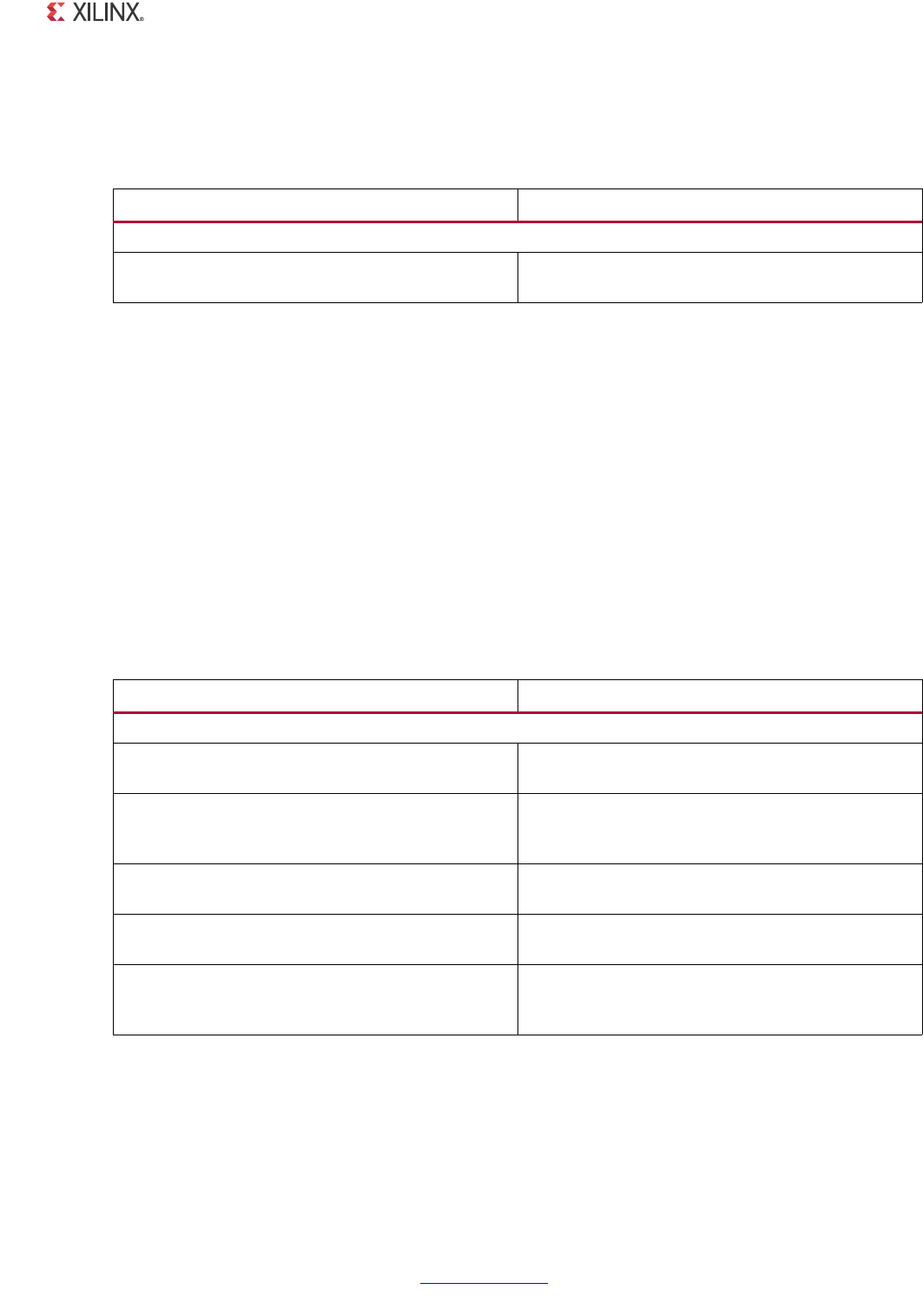

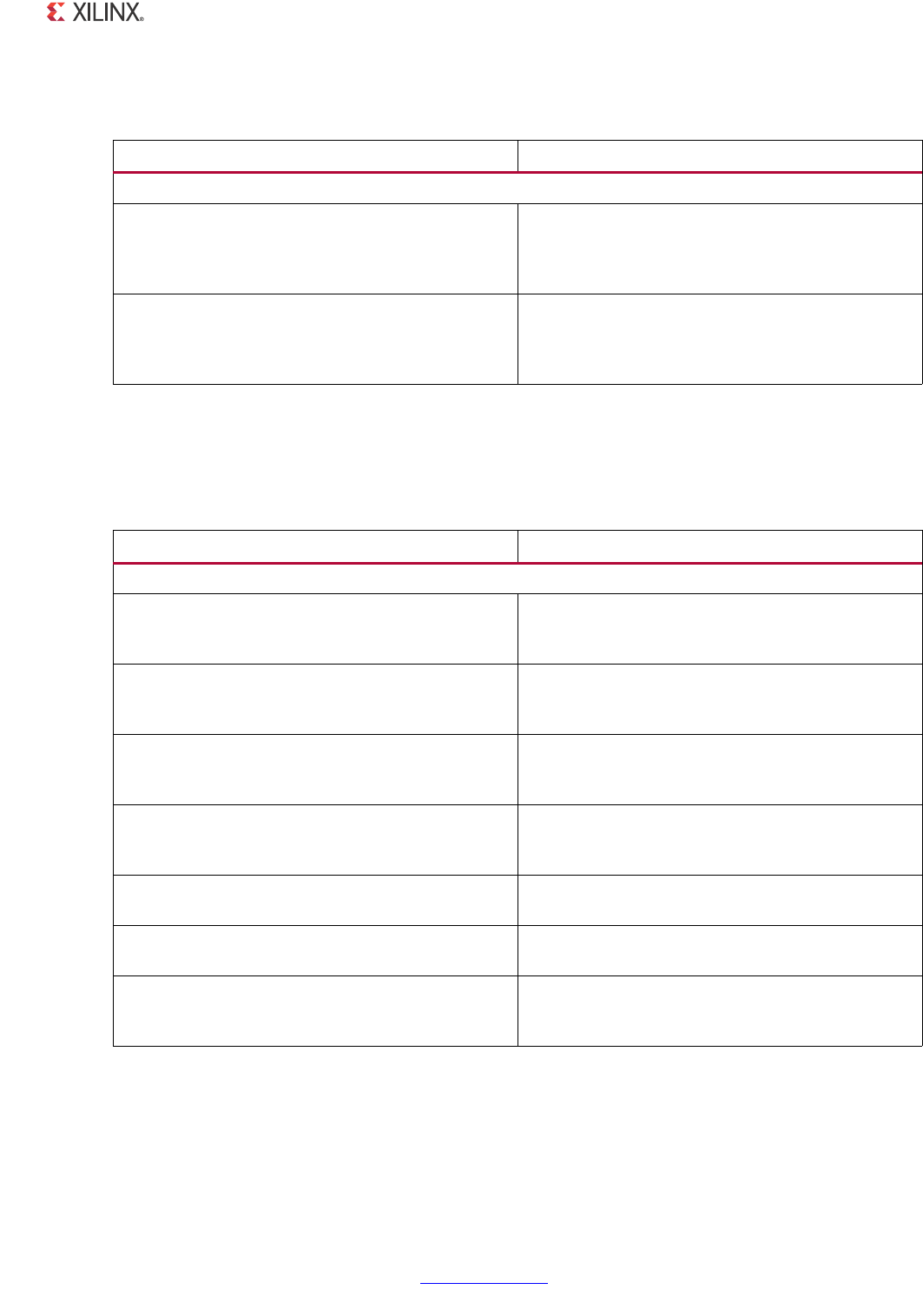

Table 2-2: Device Utilization for the 1000BASE-X Standard

Parameter Values Device Resources

Physical Interface MDIO

Interface

Auto-

Negotiation Slices LUTs FFs Block

RAMs BUFGs MMCMs

Transceiver TBI

Yes No Yes Yes 330 370 470 0 1(2) 0(2)

Yes No Yes No 190 215 240 0 1(2) 0(2)

Yes No No N/A(1) 140 170 180 0 1(2) 0(2)

No Yes Yes Yes 380 410 590 1 3(3) 0

No Yes Yes No 230 280 370 1 3(3) 0

No Yes No N/A(1) 190 230 315 1 3(3) 0

Table 2-3: Device Utilization for the GMII to SGMII or SGMII to GMII Bridge (Using Device

Specific Transceivers or TBI

Parameter Values Device Resources

Physical Interface MDIO

Interface

Auto-

Negotiation Slices LUTs FFs Block

RAMs BUFGs MMCMs

Transceiver TBI

Yes No Yes Yes 430 435 665 1 1(2) 0(2)

Yes No Yes No 310 330 500 1 1(2) 0(2)

Yes No No N/A(1) 280 270 450 1 1(2) 0(2)

No Yes Yes Yes 400 460 620 1 3(3) 0

No Yes Yes No 290 360 460 1 3(3) 0

No Yes No N/A(1) 240 320 410 1 3(3) 0

1000BASE-X PCS/PMA or SGMII v11.4 www.xilinx.com 31

PG047 October 16, 2012

Chapter 2: Product Specification

1000BASE-X and SGMII Standards with Dynamic Switching

1. Auto-negotiation is only available when the MDIO Interface is selected.

2. These figures are for use with GTP transceivers; GTX transceivers require three BUFGs and one DCM.

3. Only two BUFGs might be required (see the User Guide).

1. Auto-negotiation is only available when the MDIO Interface is selected.

2. The I/O Bank clocking logic is only required once for multiple SGMII cores that place their LVDS I/O in the same I/O

Bank. Any SGMII ports that are required to be placed in additional I/O Banks require a new instantiation of the I/O

Bank clocking logic for each I/O Bank utilized.

Table 2-4: Device Utilization for 1000BASE-X and SGMII Standards with Dynamic Switching

Parameter Values Device Resources

Physical Interface MDIO

Interface

Auto-

Negotiation Slices LUTs FFs Block

RAMs BUFGs MMCMs

Transceiver TBI

Yes No Yes Yes 445 510 745 1 1(2) 0(2)

Yes No Yes No 320 330 500 1 1(2) 0(2)

Yes No No N/A(1) 280 285 440 1 1(2) 0(2)

No Yes Yes Yes 405 530 700 1 3(3) 0

No Yes Yes No 275 365 460 1 3(3) 0

No Yes No N/A(1) 270 320 410 1 3(3) 0

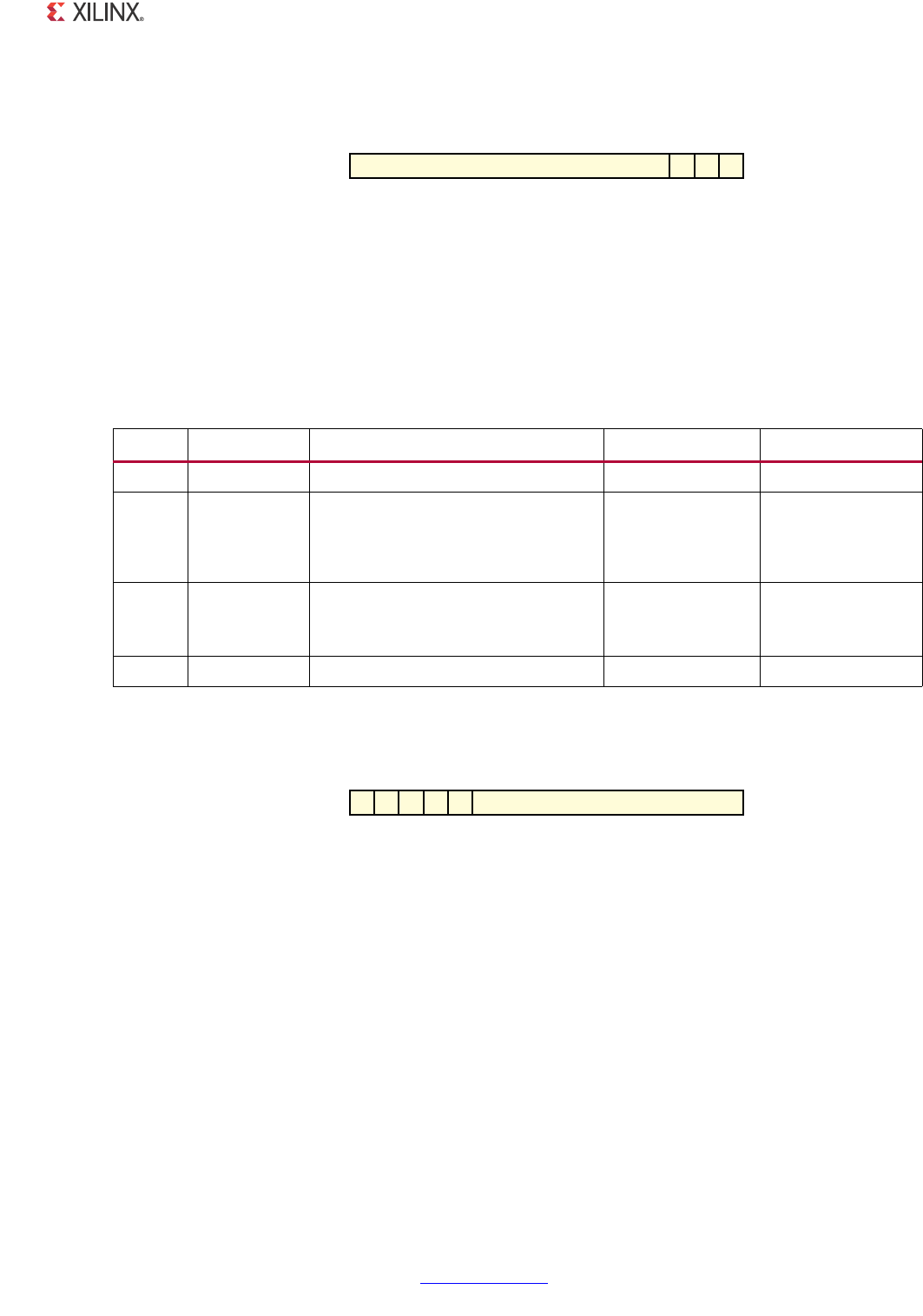

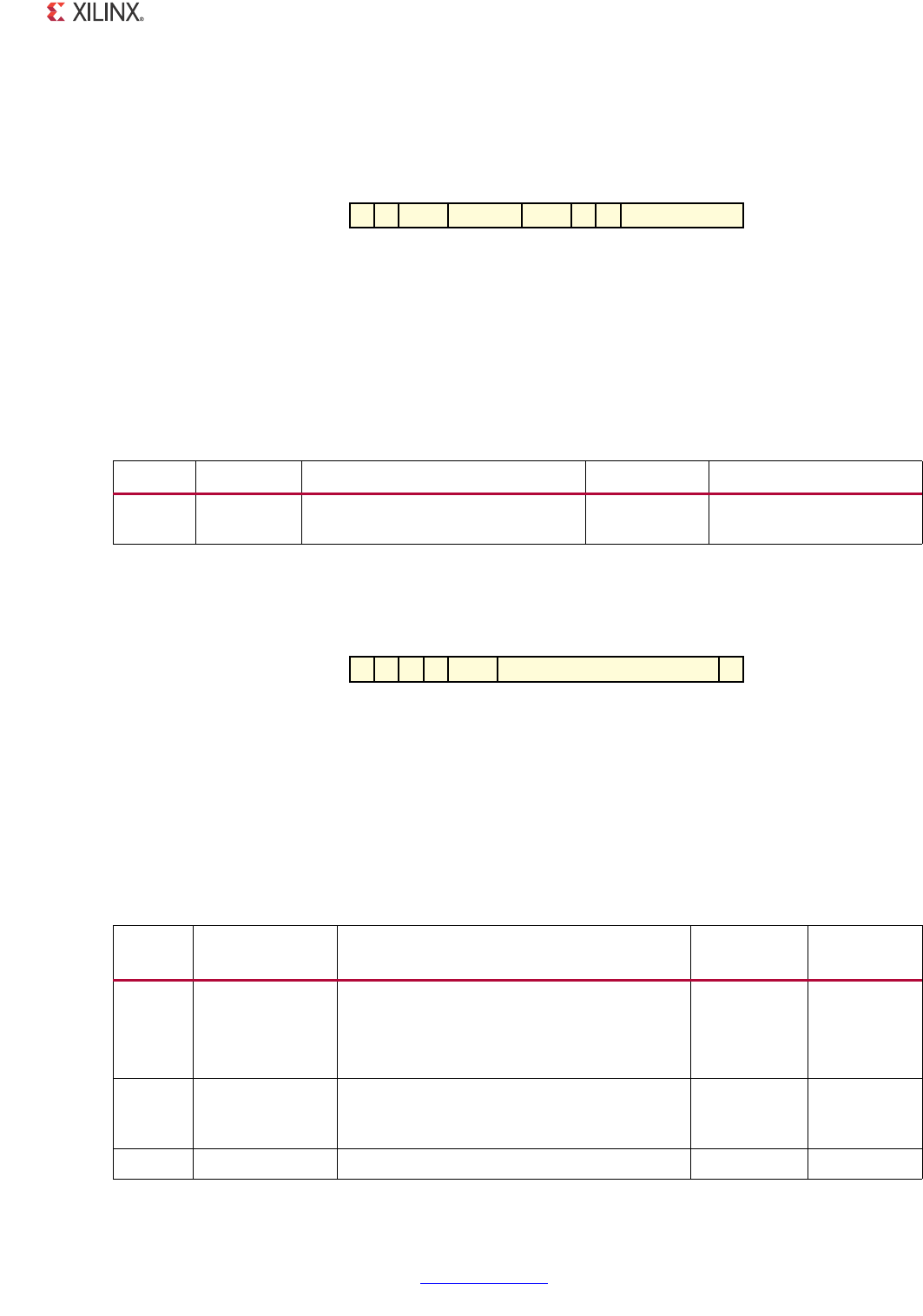

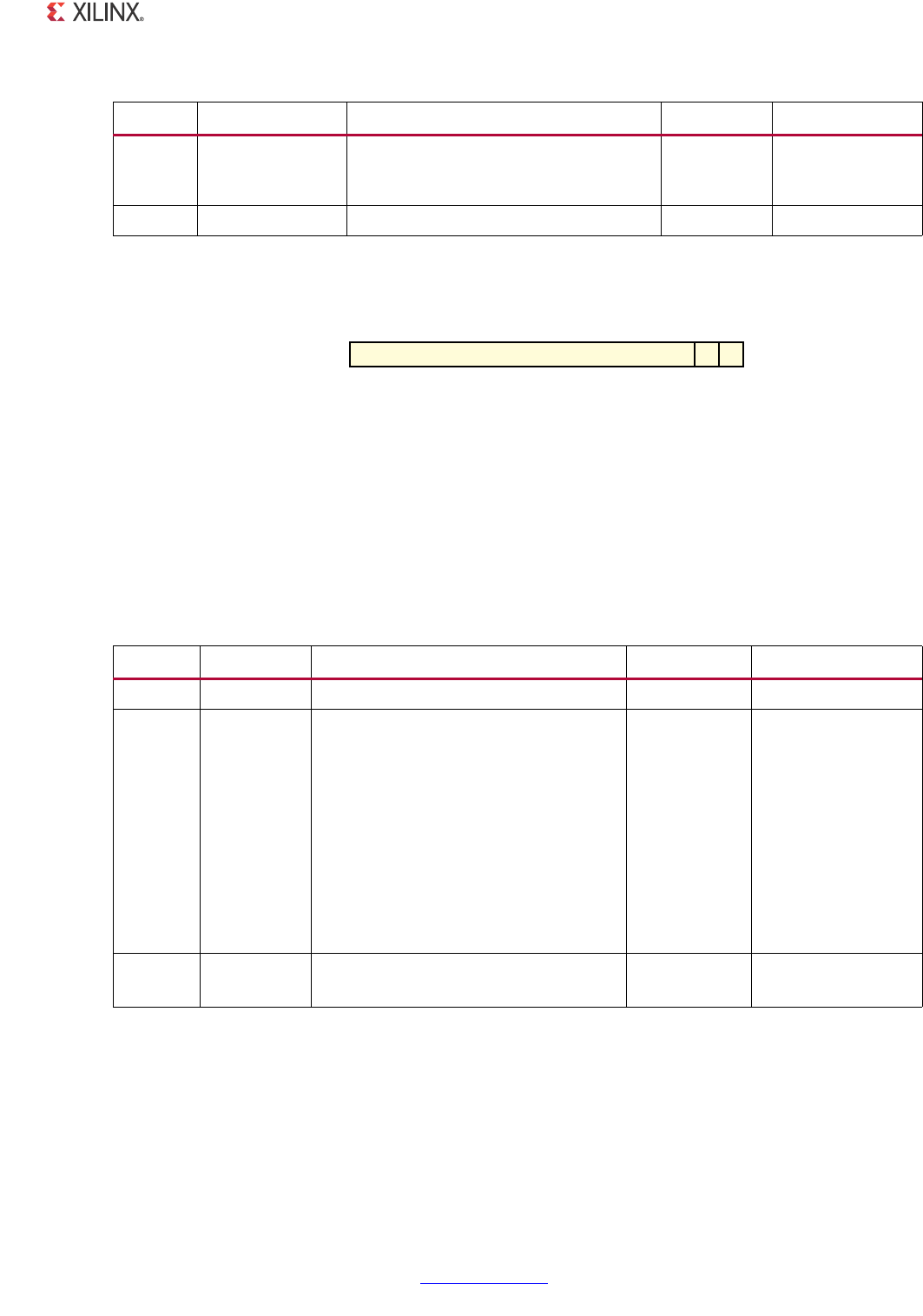

Table 2-5: Device Utilization for the GMII to SGMII or SGMII to GMII Bridge over Select I/O

LVDS in V irtex-6 FPGAs

Parameter Values Device Resources

Logical

block

MDIO

Interface

Auto-

Negotiation Slices LUTs FFs Block

RAMs

Clock

Buffers MMCMs

I/O Bank

clocking

logic(2)

N/A 15 30 22 0

2 BUFIO

1 BUFR

3 BUFG

1

Per SGMII

port

Yes Yes 380 775 820 0 0 0

Yes No 310 640 660 0 0 0

No N/A(1) 265 590 615 0 0 0

1000BASE-X PCS/PMA or SGMII v11.4 www.xilinx.com 32

PG047 October 16, 2012

Chapter 2: Product Specification

• Auto-negotiation is only available when the MDIO Interface is selected.

• The clocking logic is only required once for multiple SGMII cores.

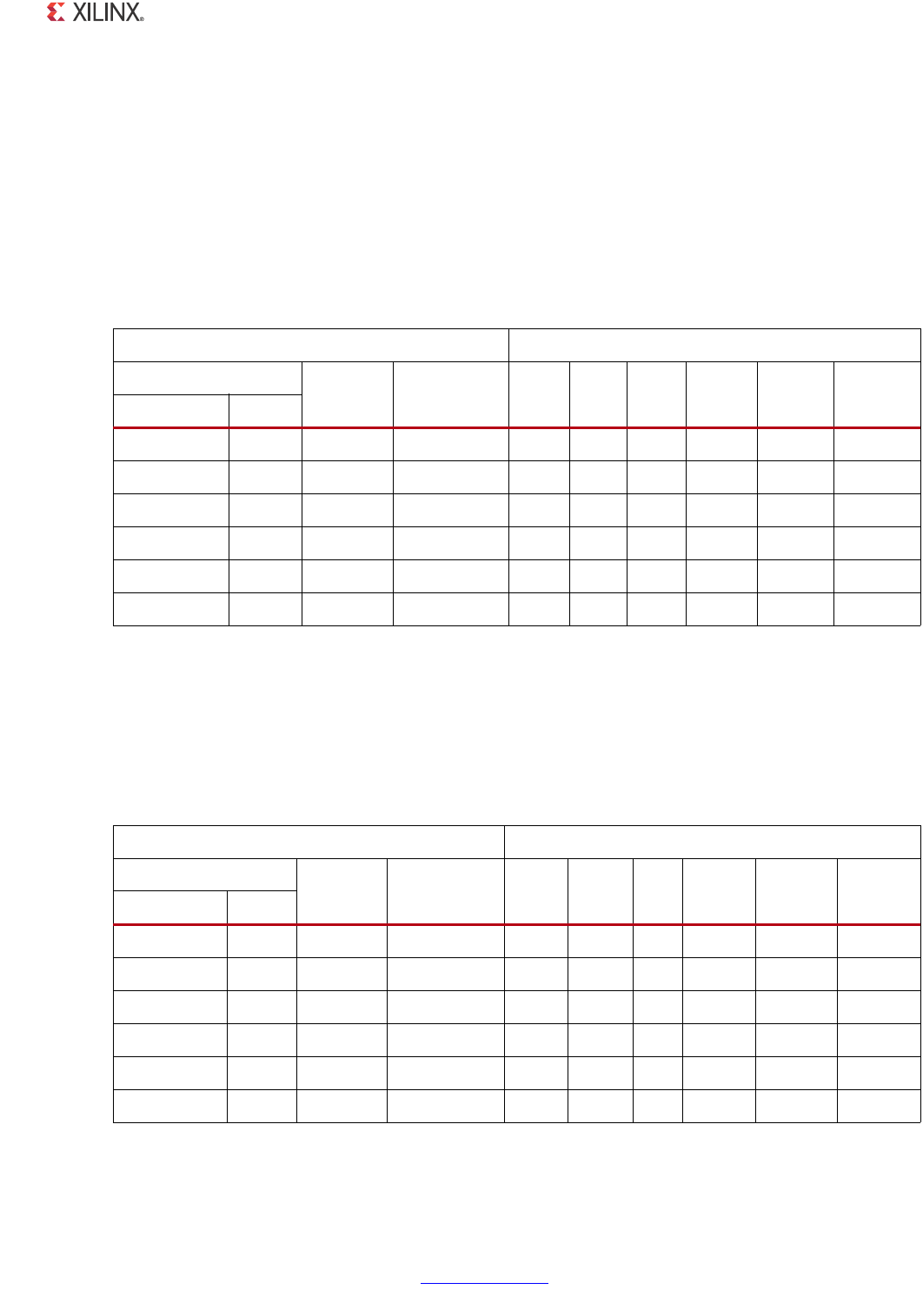

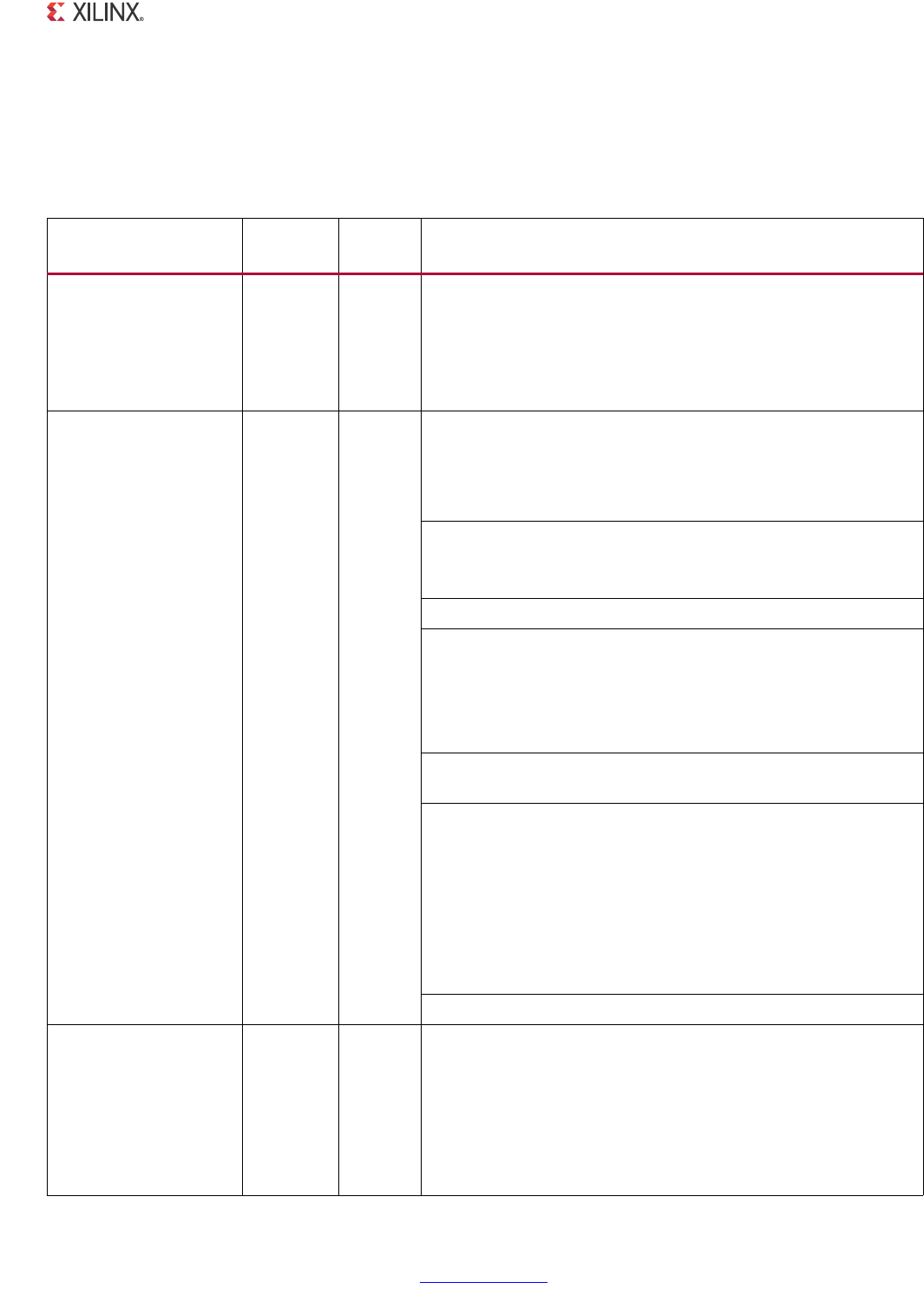

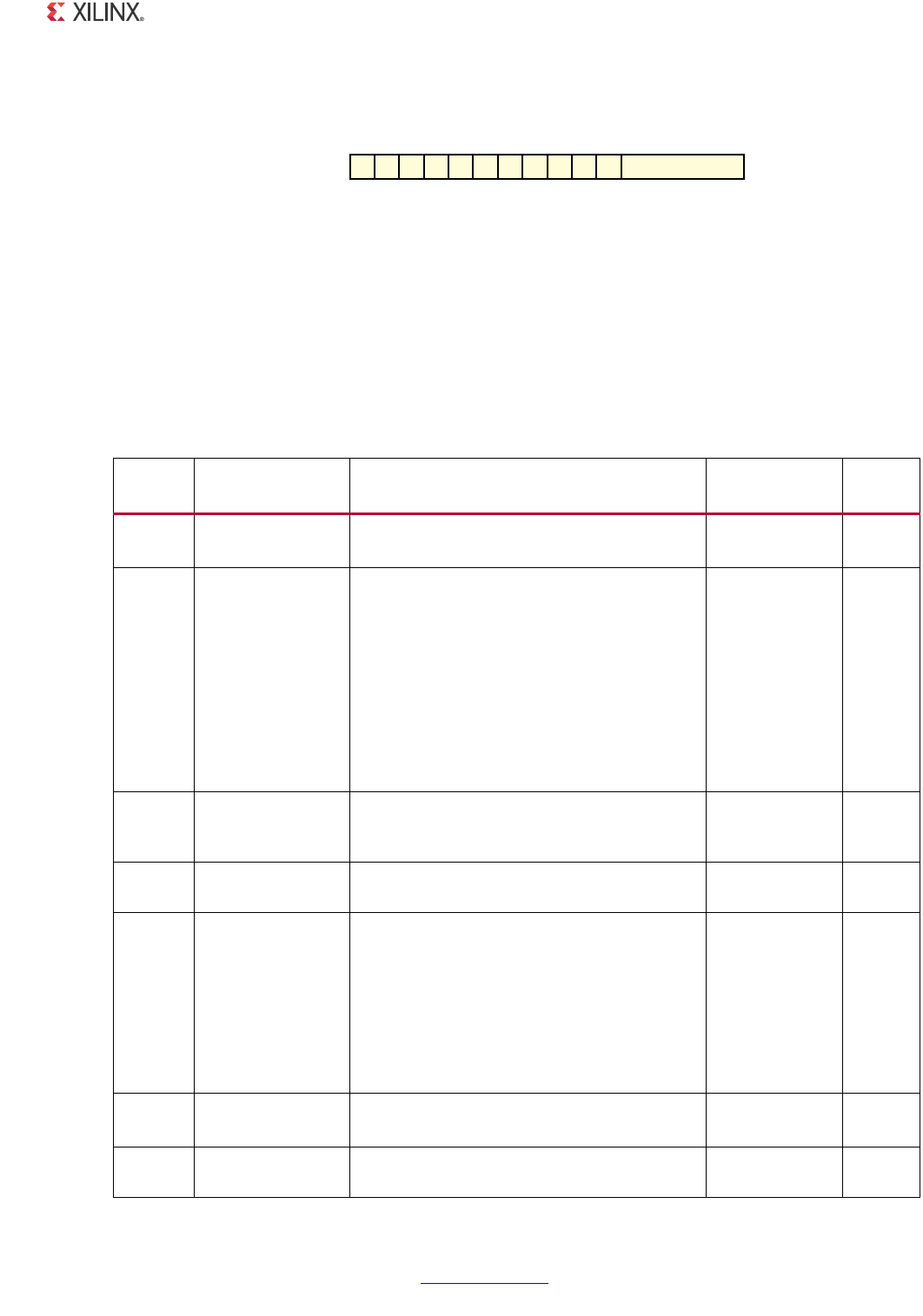

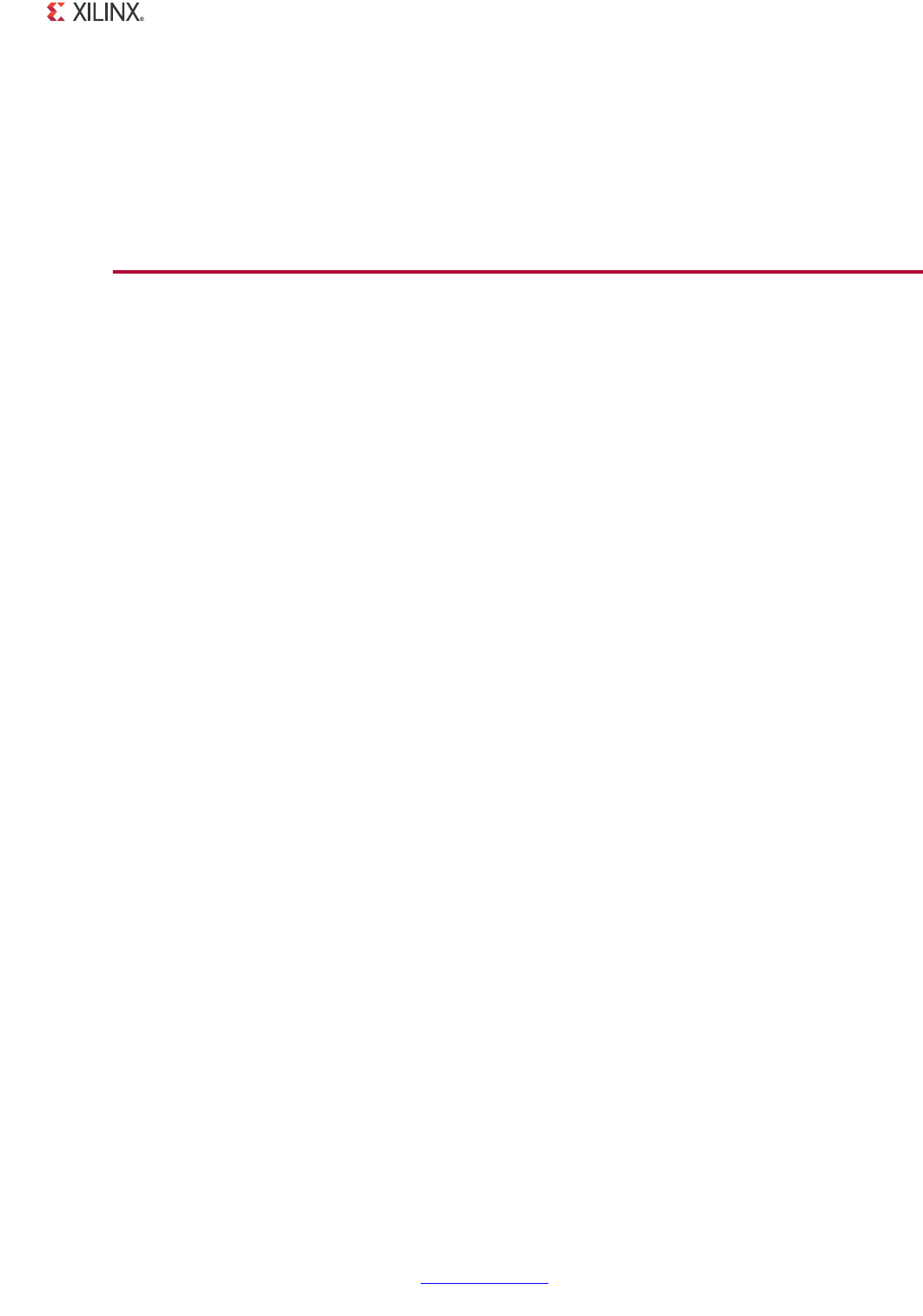

Other Device Families

Table 2-7, Tabl e 2-8, and Ta bl e 2- 9 provide approximate utilization figures for various core

options when a single instance of the core is instantiated in a Virtex-4 device. Other families

have similar utilization figures, except as indicated. Utilization figures are obtained by

implementing the block-level wrapper for the core. This wrapper is part of the example

design and connects the core to the selected physical interface.

When the physical interface is a Virtex-4 FPGA RocketIO™ transceiver, utilization figures

include GT11 Calibration blocks and GT11 initialization/reset circuitry.

BUFG Usage

BUFG usage does not consider multiple instantiations of the core, where clock resources

can often be shared.

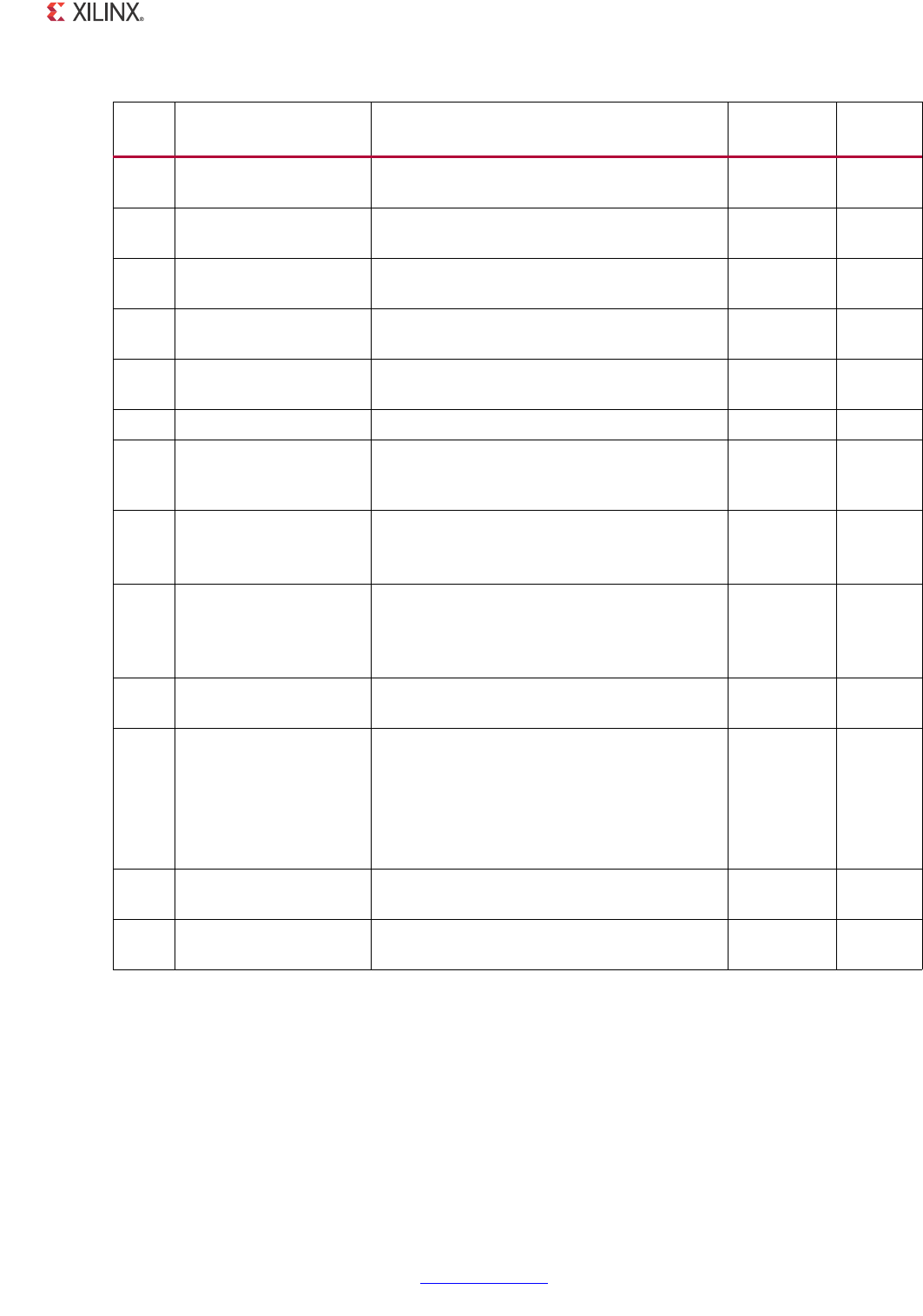

Table 2-6: Device Utilization for GMII to SGMII or SGMII to GMII Bridge over Synchronous LVDS

in Virtex-7/Kintex-7 FPGAS

Parameter Values Device Resources

Logical Block MDIO

Interface

Auto-

Negotiation Slices LUTs FFs Block

RAMs

Clock

Buffers MMCMs

Clocking Logic N/A 0 0 0 0

5 BUFGs or

1 BUFG,

1 BUFIO

and 3

BUFRs or

1 BUFG

and 4

BUFHs

1

Per SGMII port

Yes Yes 462 884 985 0 0 0

Yes No 363 735 741 0 0 0

No N/A 337 670 693 0 0 0

1000BASE-X PCS/PMA or SGMII v11.4 www.xilinx.com 33

PG047 October 16, 2012

Chapter 2: Product Specification

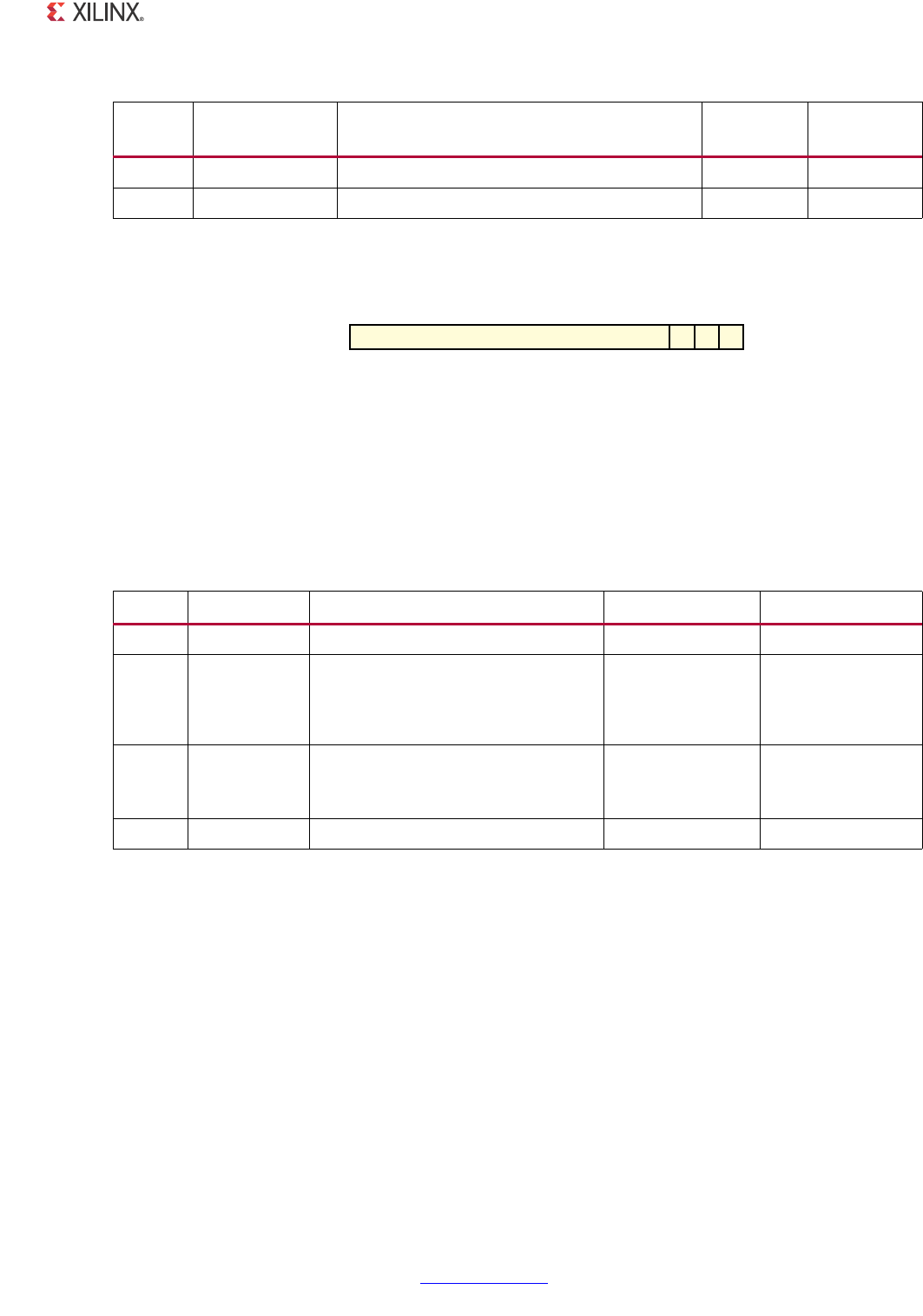

1000BASE-X

1. Auto-negotiation is only available when the MDIO Interface is selected.

2. For Virtex-4 devices, this includes the clock shared between the Calibration Blocks and the GT11 Dynamic

Reconfiguration Port (DRP).

3. Only two BUFGs might be required (see the User Guide).

4. Spartan-3, Spartan-3E and Spartan-3A devices require two DCMs to meet TBI setup and hold times.

SGMII Bridge

1. Auto-negotiation is only available when the MDIO Interface is selected.

2. For Virtex-4 devices, this includes the clock shared between the Calibration Blocks and the GT11 Dynamic

Reconfiguration Port (DRP).

3. Only two BUFGs might be required.

4. Spartan-3, Spartan-3E and Spartan-3A devices require two DCMs to meet TBI setup and hold times.

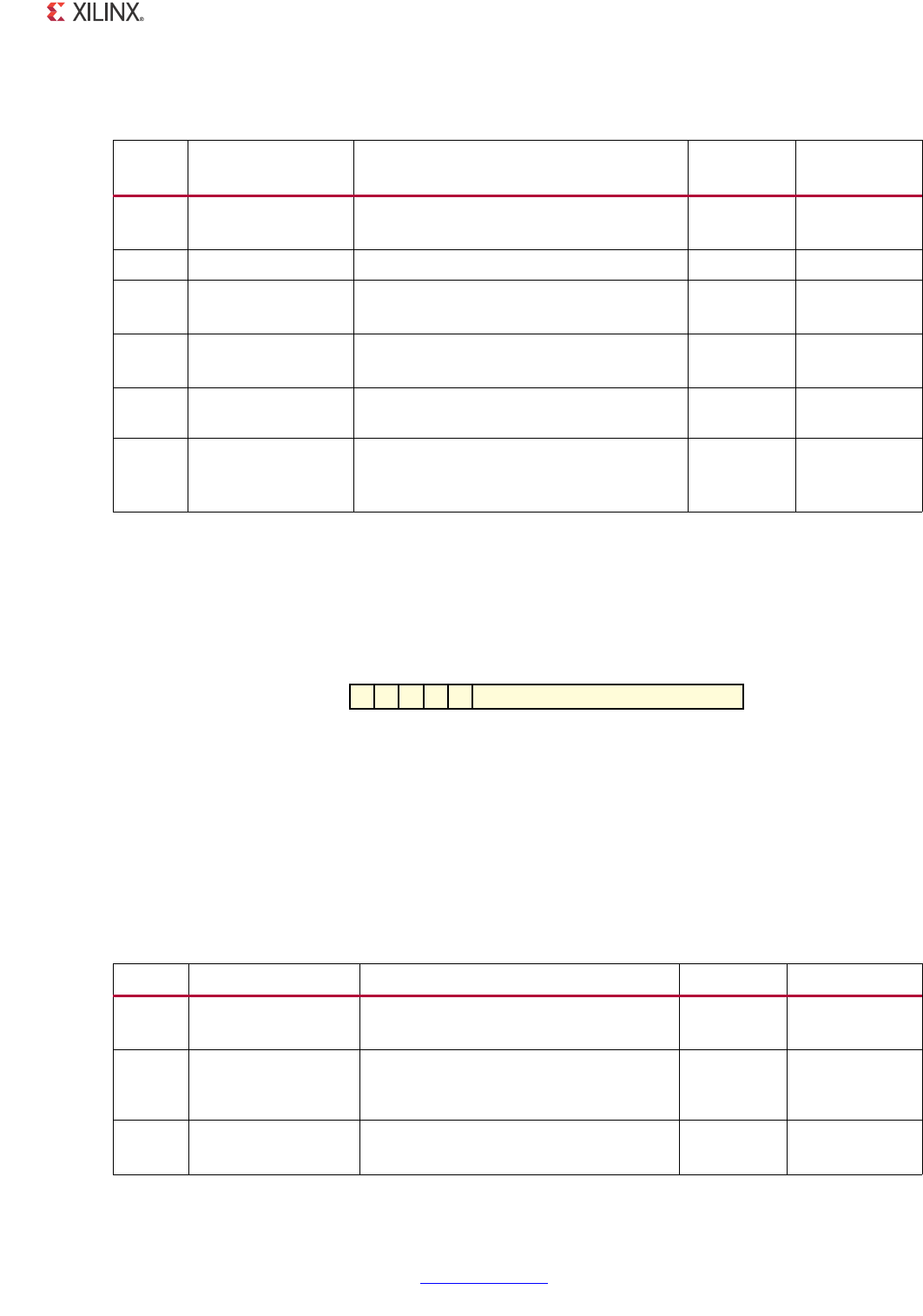

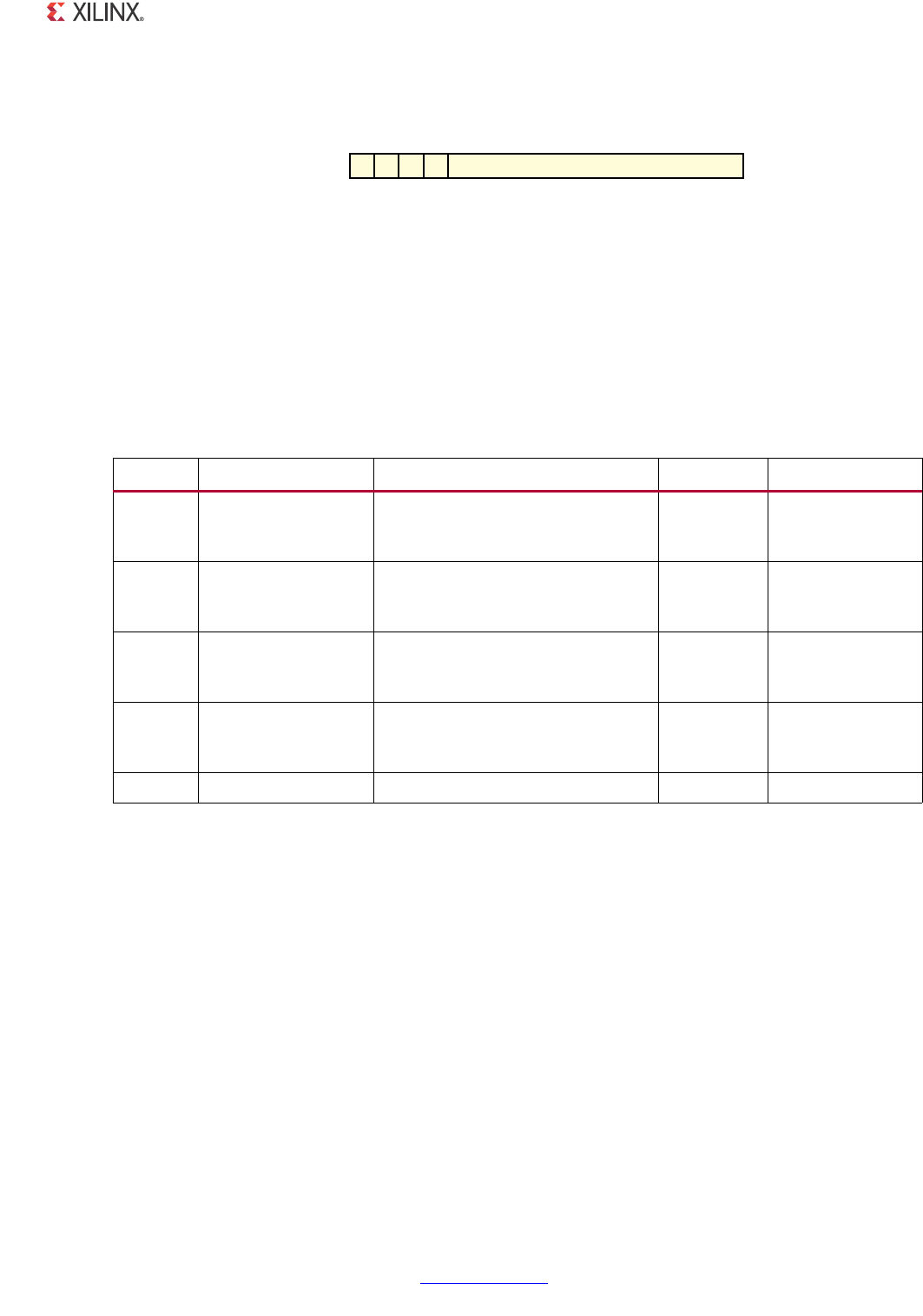

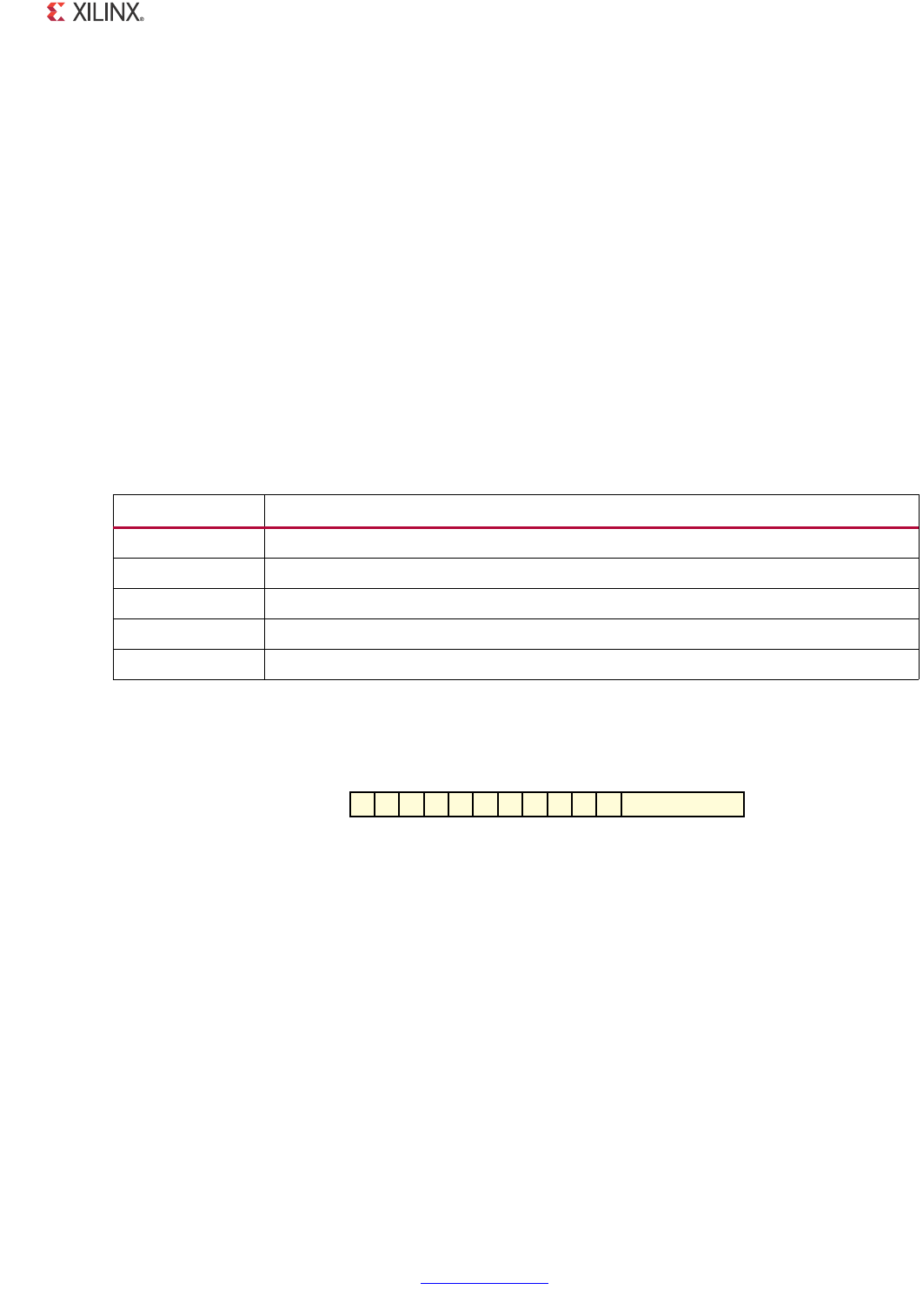

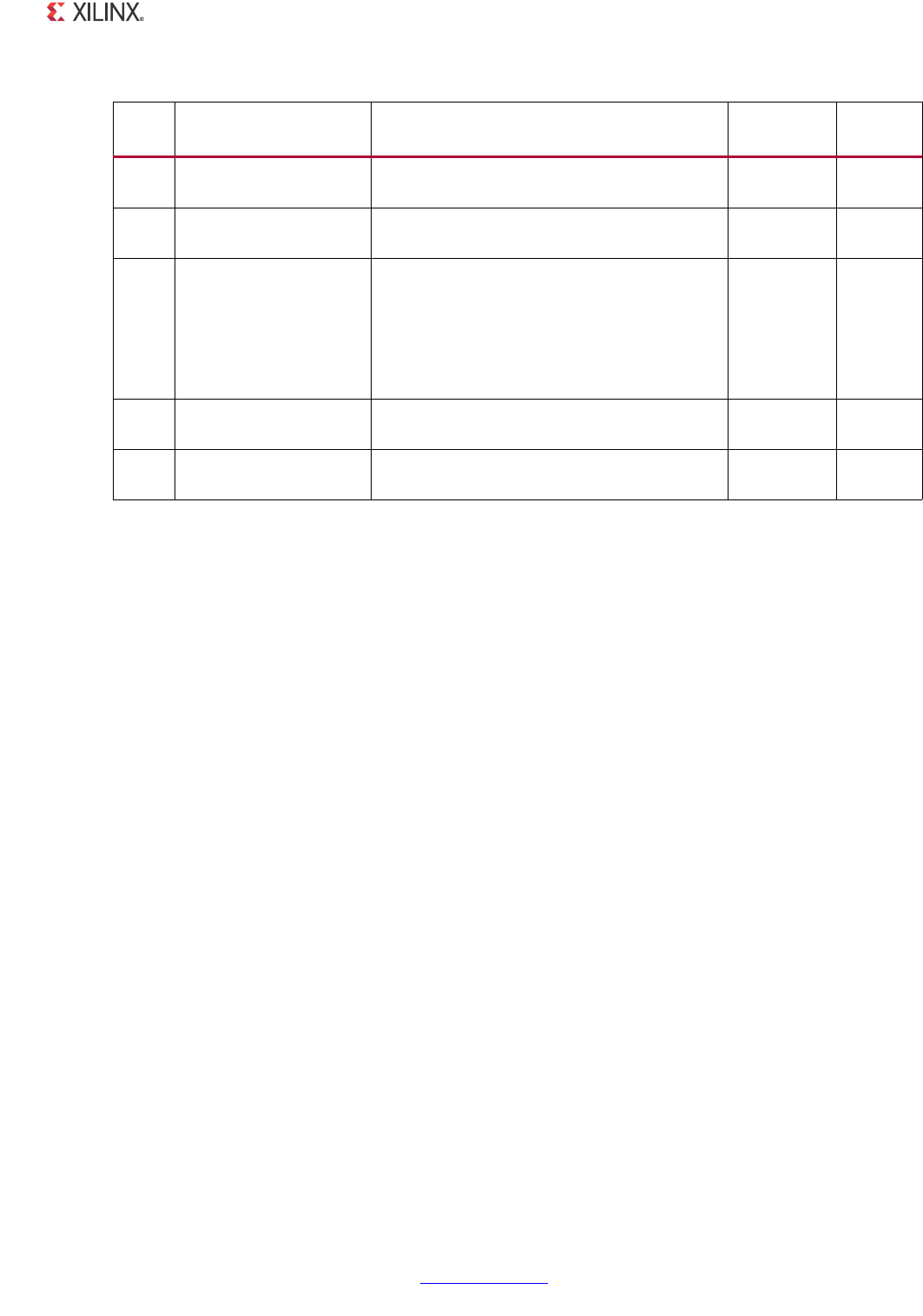

Table 2-7: Device Utilization for the 1000BASE-X Standard

Parameter Values Device Resources

Physical Interface MDIO

Interface

Auto-

Negotiation Slices LUTs FFs Block

RAMs BUFGs DCMs

RocketIO TBI

Yes No Yes Yes 820 730 640 0 2(2) 0

Yes No Yes No 490 500 420 0 2(2) 0

Yes No No N/A(1) 430 440 360 0 2(2) 0

No Yes Yes Yes 650 640 600 2 3(3) 1(4)

No Yes Yes No 420 410 380 2 3(3) 1(4)

No Yes No N/A(1) 350 360 330 2 3(3) 1(4)

Table 2-8: Device Utilization for the GMII to SGMII or SGMII to GMII Bridge

Parameter Values Device Resources

Physical Interface MDIO

Interface

Auto-

Negotiation Slices LUTs FFs Block

RAMs BUFGs DCMs

RocketIO TBI

Yes No Yes Yes 970 780 860 1 2(2) 0

Yes No Yes No 730 620 670 1 2(2) 0

Yes No No N/A(1) 700 570 640 1 2(2) 0

No Yes Yes Yes 800 970 630 2 3(3) 1(4)

No Yes Yes No 610 830 470 2 3(3) 1(4)

No Yes No N/A(1) 560 770 420 2 3(3) 1(4)

1000BASE-X PCS/PMA or SGMII v11.4 www.xilinx.com 34

PG047 October 16, 2012

Chapter 2: Product Specification

1000BASE-X and SGMII Standards with Dynamic Switching

1. Auto-negotiation is only available when the MDIO Interface is selected.

2. For Virtex-4 devices, this includes the clock shared between the Calibration Blocks and the GT11 Dynamic

Reconfiguration Port (DRP).

3. Only two BUFGs might be required (see the User Guide).

4. Spartan-3, Spartan-3E and Spartan-3A devices require two DCMs to meet TBI setup and hold times.

Port Descriptions

All ports of the core are internal connections in FPGA logic. An HDL example design

(delivered with the core) connects the core, where appropriate, to a device-specific

transceiver, LVDS transceiver logic and/or add IBUFs, OBUFs. IOB flip-flops to the external

signals of the GMII and TBI. IOBs are added to the remaining unconnected ports to take the

example design through the Xilinx implementation software.

All clock management logic is placed in this example design, allowing you more flexibility in

implementation (such as designs using multiple cores). This example design is provided in

both VHDL and Verilog.

For more information on the example design provided, see one of the following chapters

depending on your chosen standard and physical interface.

•Chapter 4, The Ten-Bit Interface

•Chapter 5, 1000BASE-X with Transceivers

•Chapter 6, SGMII / Dynamic Standards Switching with Transceivers

•Chapter 7, SGMII over LVDS

Table 2-9: Device Utilization for the 1000BASE-X and SGMII Standards with Dynamic Switching

Parameter Values Device Resources

Physical Interface MDIO

Interface

Auto-

Negotiation Slices LUTs FFs Block

RAMs BUFGs DCMs

RocketIO TBI

Yes No Yes Yes 1100 900 940 1 2(2) 0

Yes No Yes No 780 640 700 1 2(2) 0

Yes No No N/A(1) 700 570 640 1 2(2) 0

No Yes Yes Yes 910 1090 710 2 3(3) 1(4)

No Yes Yes No 640 830 480 2 3(3) 1(4)

No Yes No N/A(1) 560 770 420 2 3(3) 1(4)

1000BASE-X PCS/PMA or SGMII v11.4 www.xilinx.com 35

PG047 October 16, 2012

Chapter 2: Product Specification

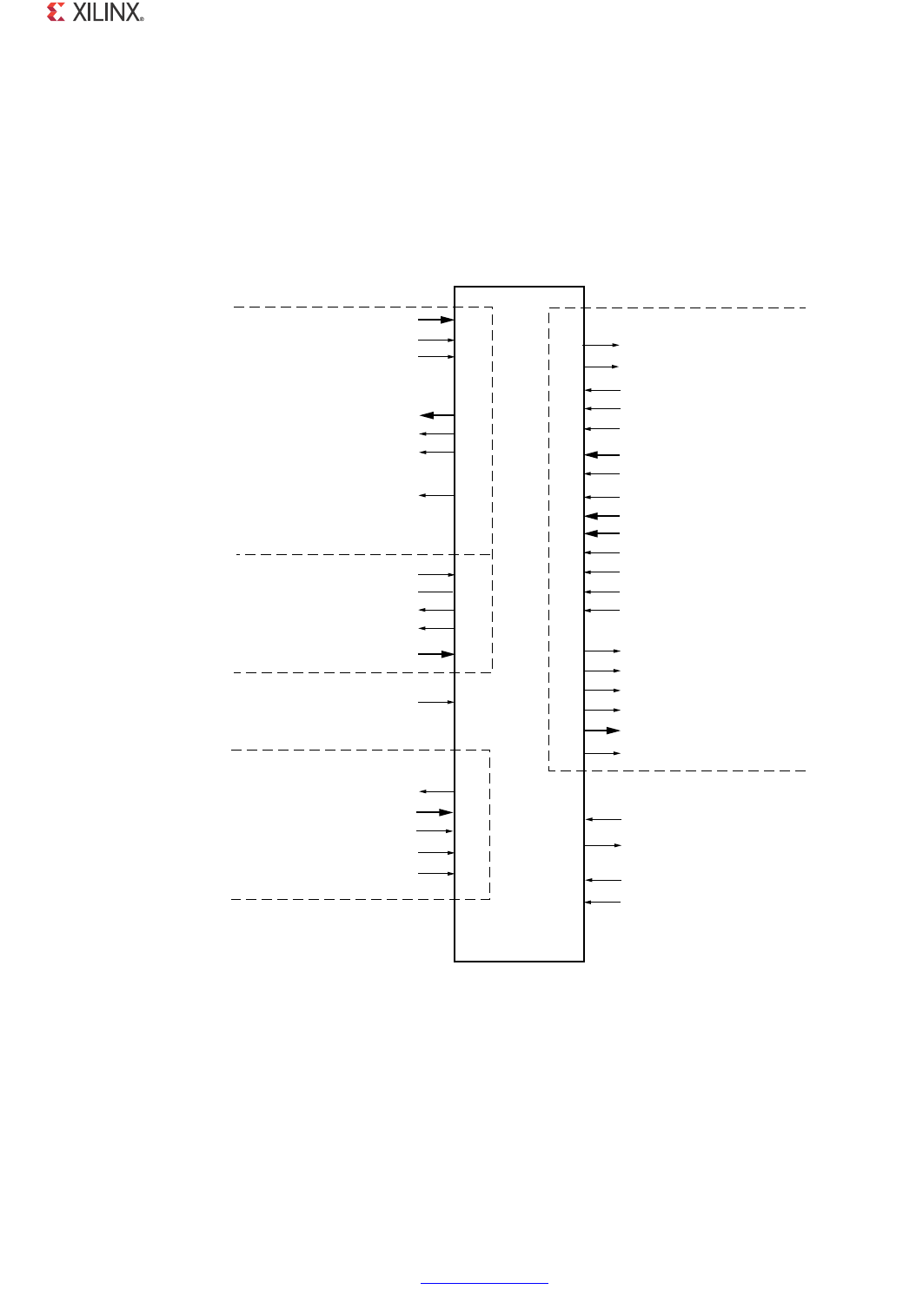

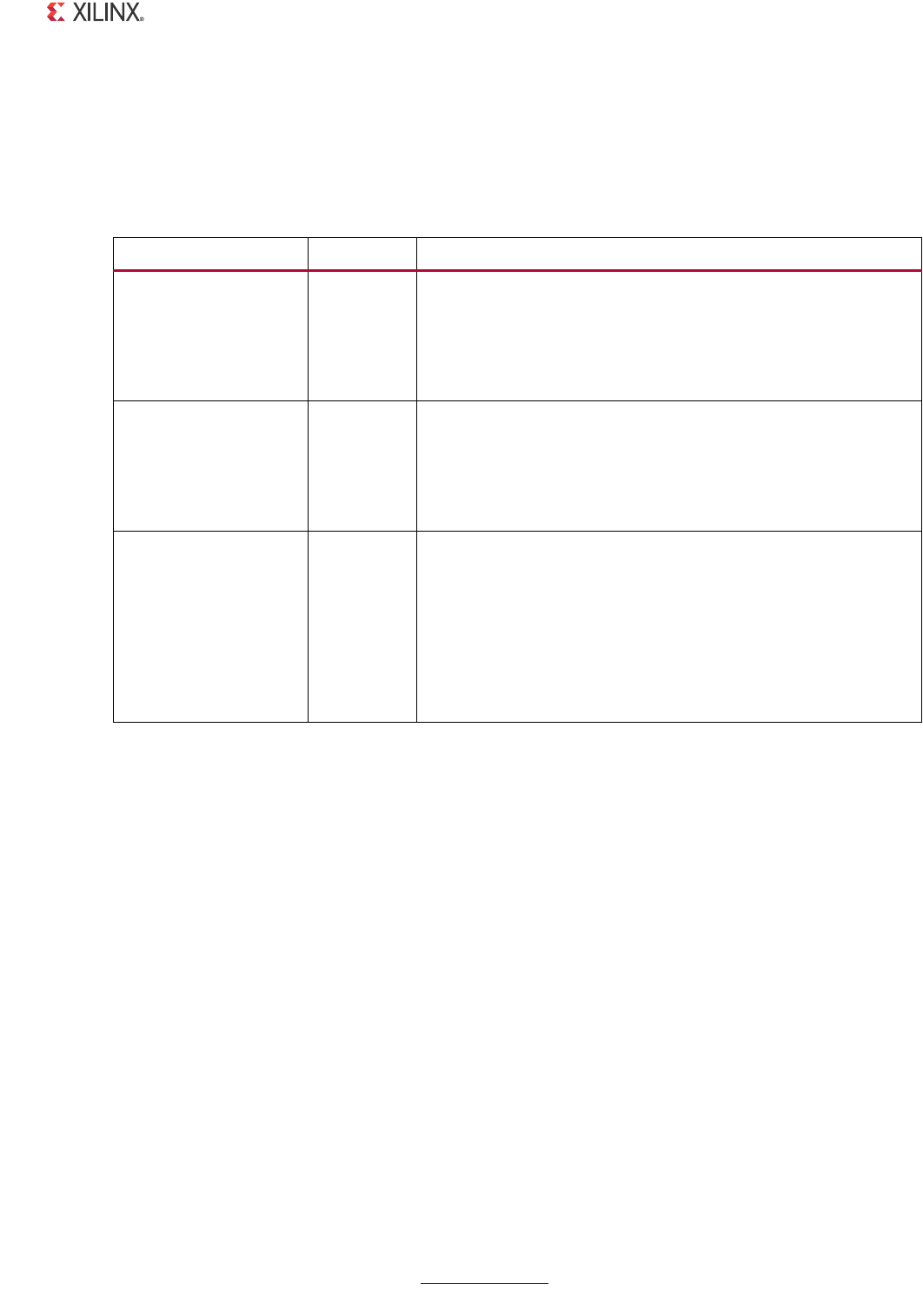

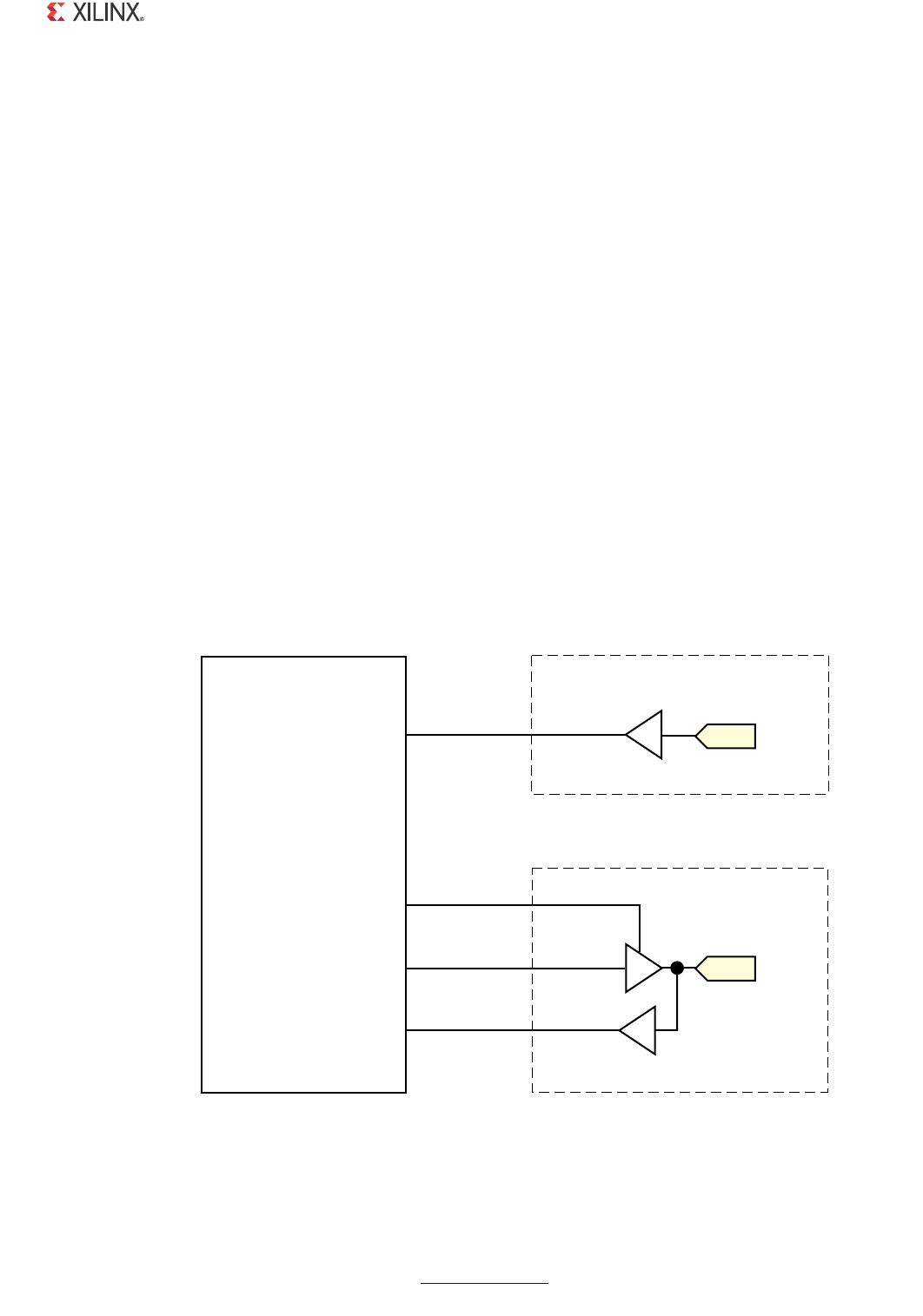

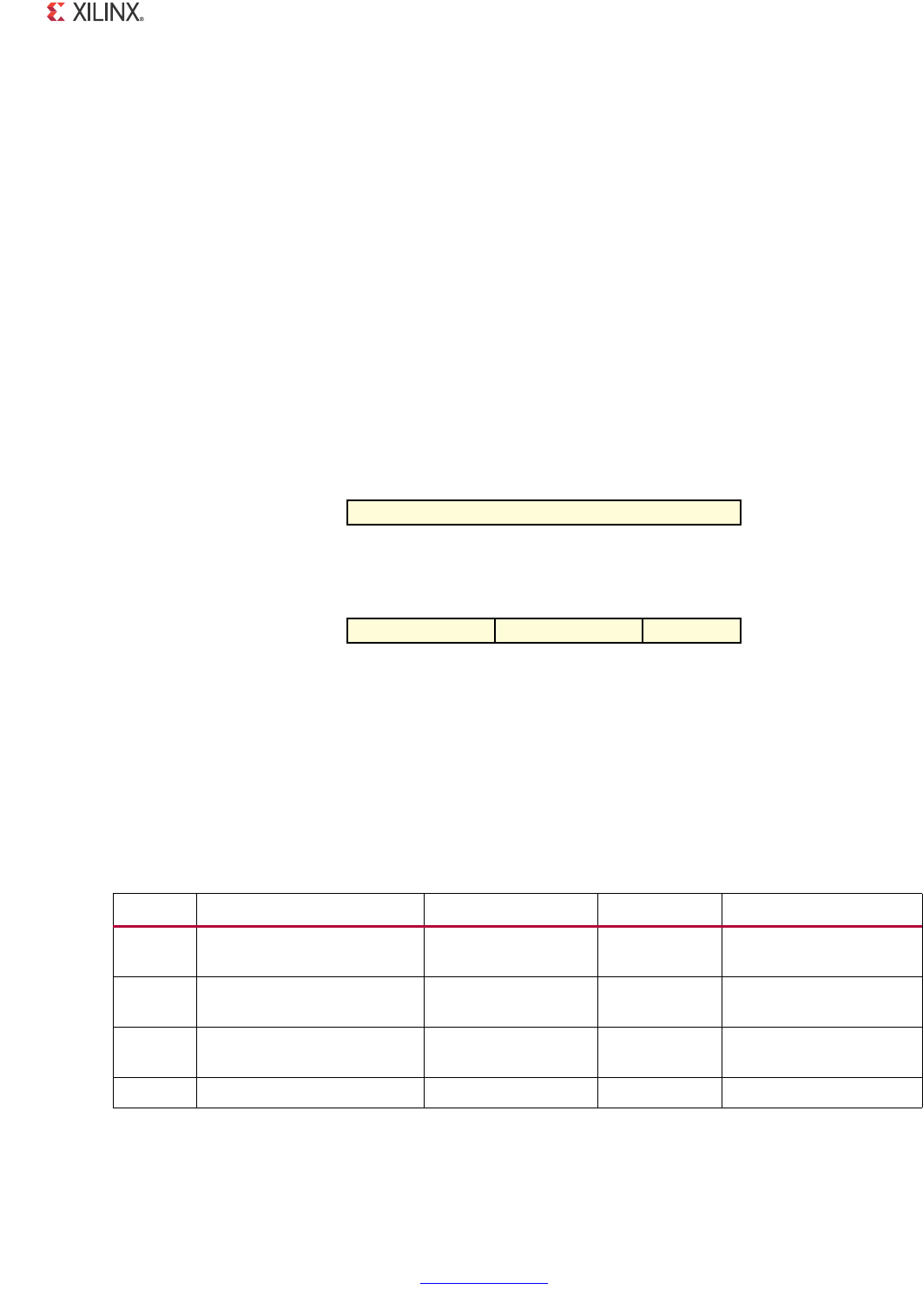

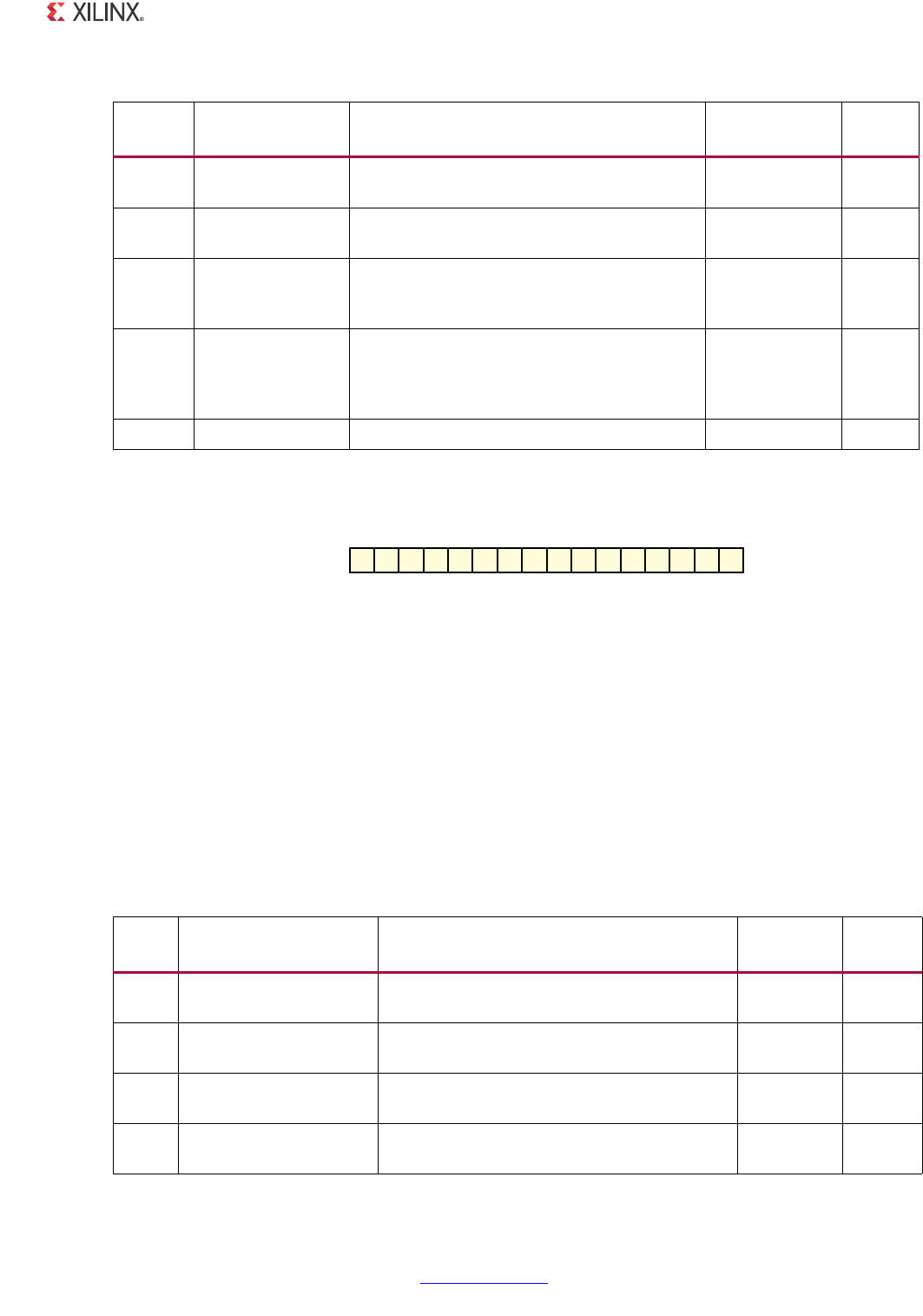

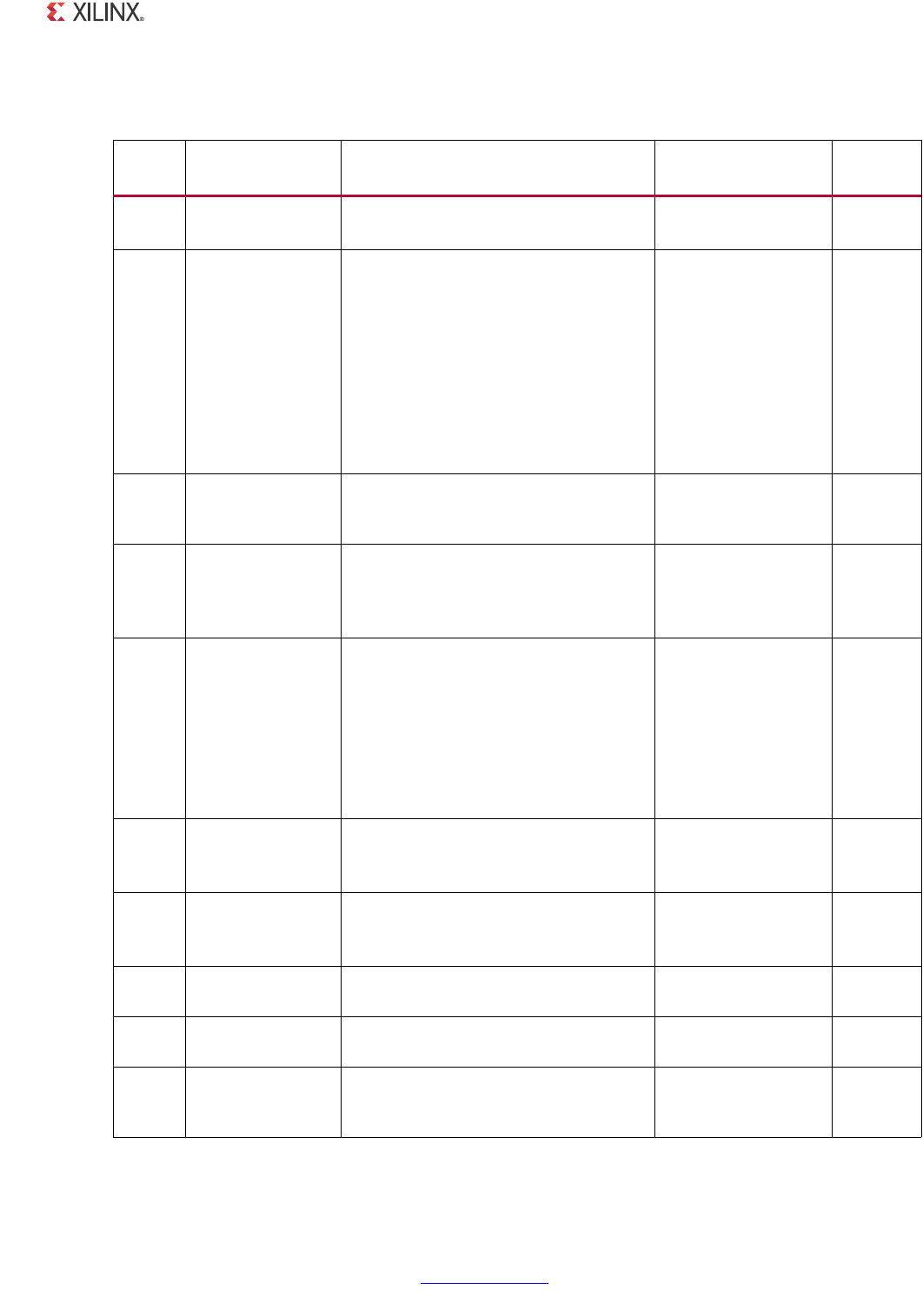

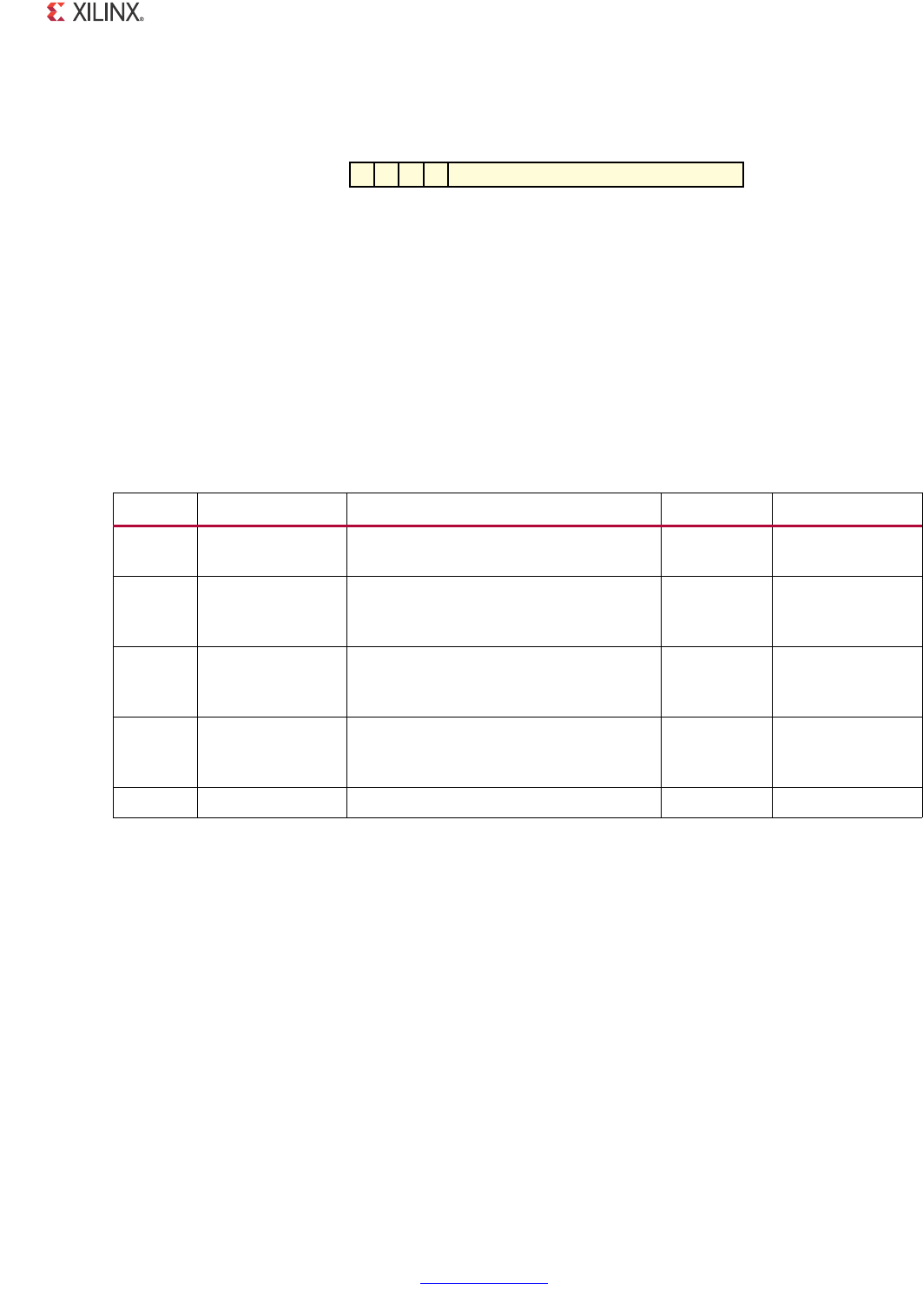

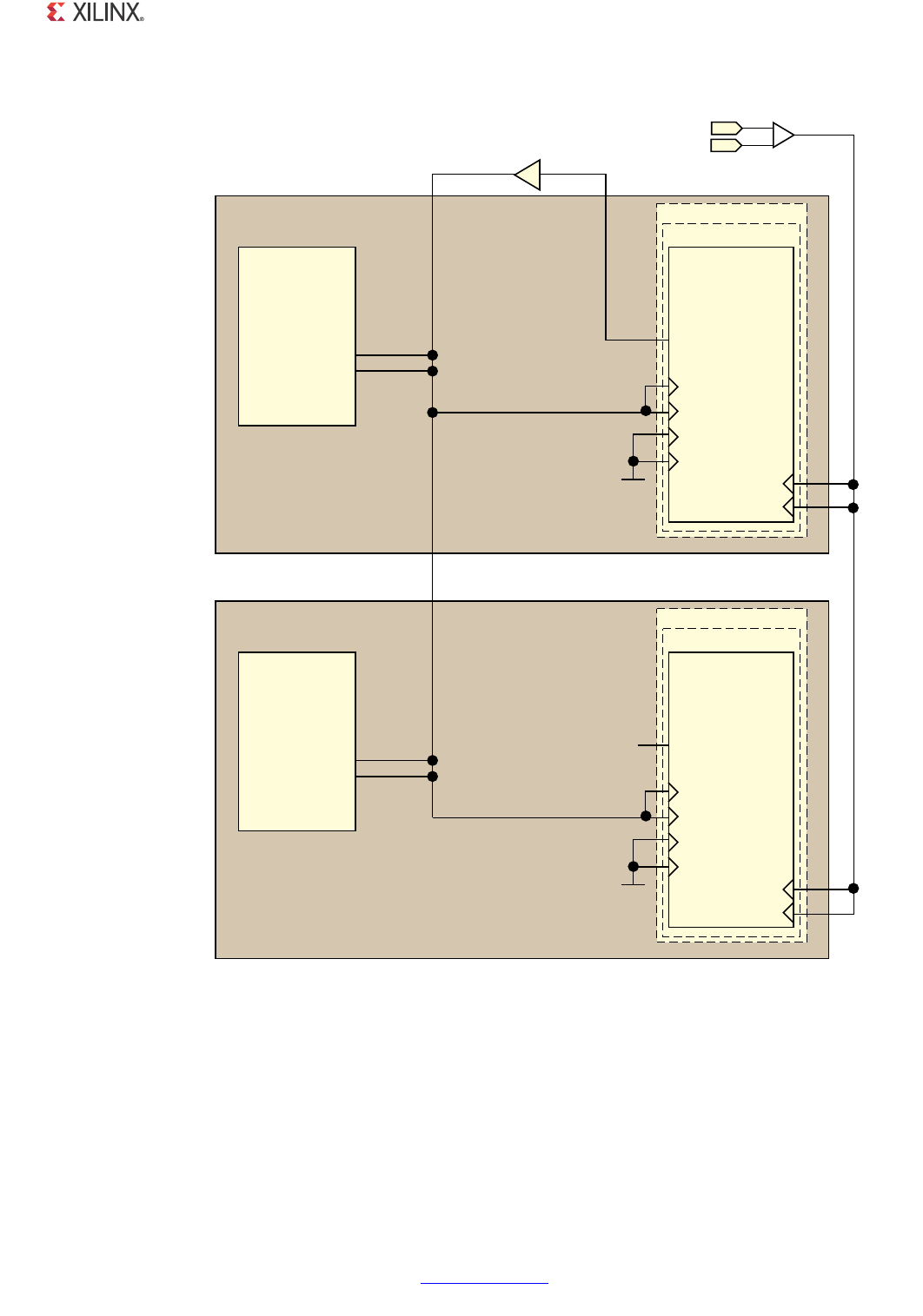

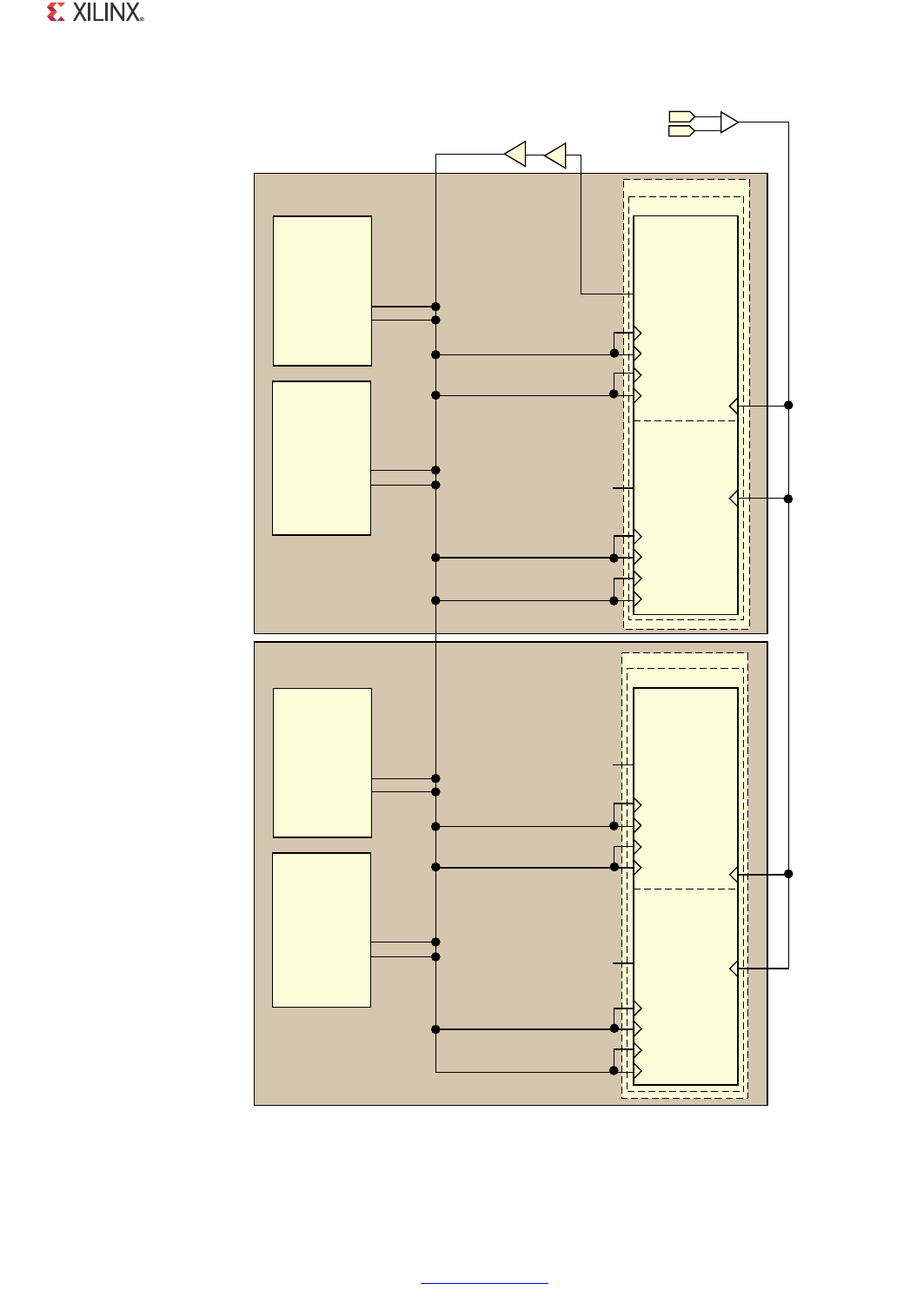

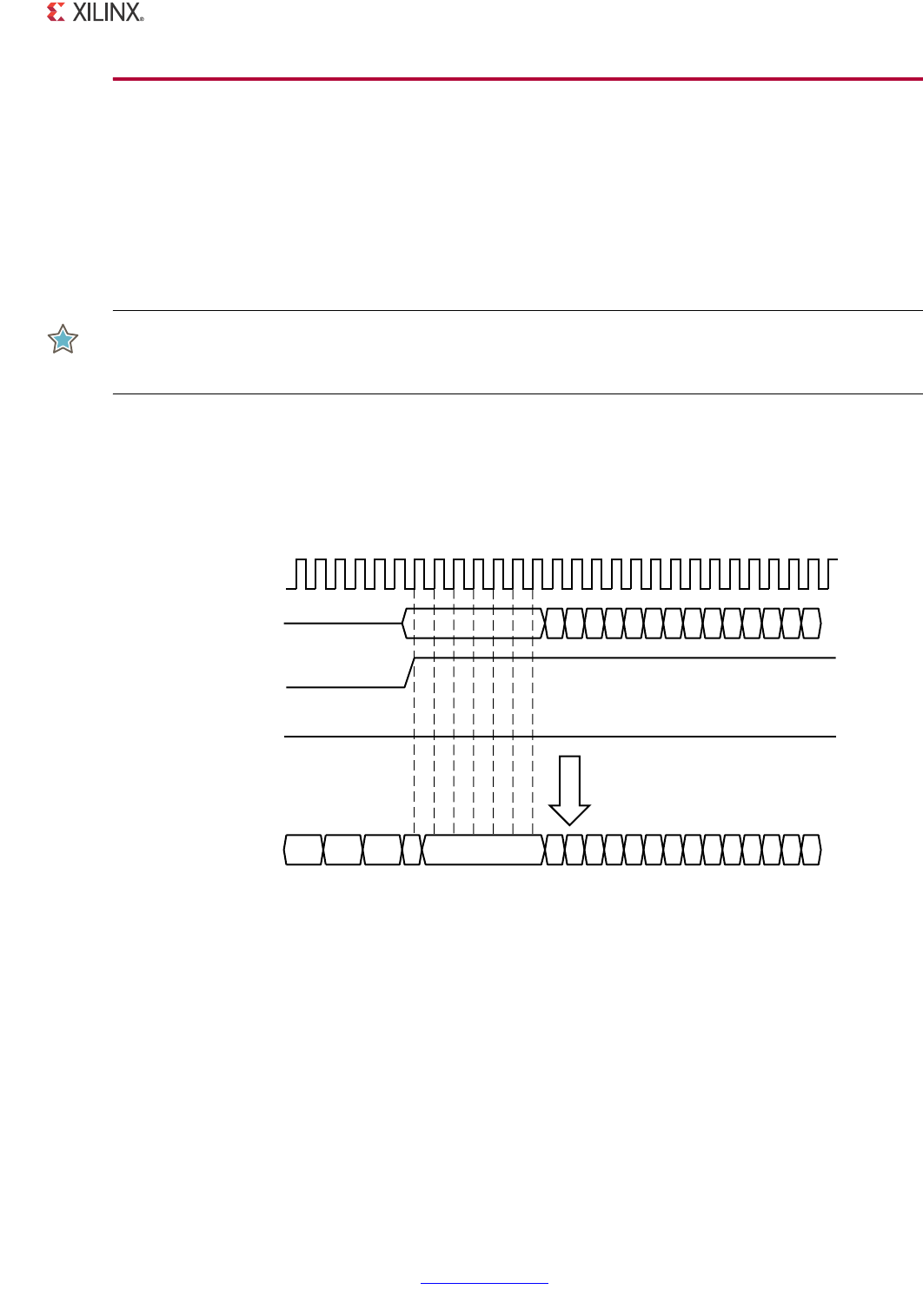

Figure 2-2 shows the pinout for the Ethernet 1000BASE-X PCS/PMA or SGMII core using a

device-specific transceiver, or LVDS transceiver logic, with the optional PCS Management

registers. The signals shown in the Auto-Negotiation box are included only when the core

includes the Auto-Negotiation functionality. For 7 series and Zynq-7000 devices, data width

of rxdata and txdata signals received from the device-specific transceiver is 16 bits. A

conversion logic is used to convert to 8 bits for core interface. For more information, see

Chapter 17, Customizing and Generating the Core.

Figure 2-3 shows the pinout for the Ethernet 1000BASE-X PCS/PMA or SGMII core using a

device-specific transceiver, or LVDS transceiver logic without the optional PCS Management

registers For 7 series and Zynq-7000 devices, data width of rxdata and txdata signals

received from the device-specific transceiver is 16 bits. A conversion logic is used to

convert to 8 bits for core interface.

X-Ref Target - Figure 2-2

Figure 2-2: Component Pinout Using a Transceiver

with PCS Management Registers

PGF

PGLRBLQ

JPLLBU[G>@

JPLLBW[G>@

JPLLBW[BHQ PJWBU[BUHVHW

JPLLBW[BHU

UHVHW

JPLLBU[BGY

JPLLBU[BHU

*0,,

0',2

SK\DG>@

VLJQDOBGHWHFW

PGLRBRXW

PGLRBWUL

U[EXIVWDWXV>@

U[FKDULVFRPPD

U[FKDULVN

4RANSCEIVER)NTERFACE

JPLLBLVRODWH

OLQNBWLPHUBYDOXH>@

DQBLQWHUUXSW

$XWRB1HJRWLDWLRQ

PJWBW[BUHVHW

U[FONFRUFQW>@

U[GDWD>@

U[GLVSHUU

U[QRWLQWDEOH

U[UXQGLVS

W[EXIHUU

XVHUFON

GFPBORFNHG

XVHUFON

SRZHUGRZQ

W[FKDUGLVSPRGH

W[FKDUGLVSYDO

W[FKDULVN

W[GDWD

HQDEOHDOLJQ

STATUS?VECTOR;=

CONFIGURATION?VECTOR;=

CONFIGURATION?VALID

AN?ADV?CONFIG?VECTOR;=

AN?ADV?CONFIG?VAL

AN?RESTART?CONFIG

8

1000BASE-X PCS/PMA or SGMII v11.4 www.xilinx.com 36

PG047 October 16, 2012

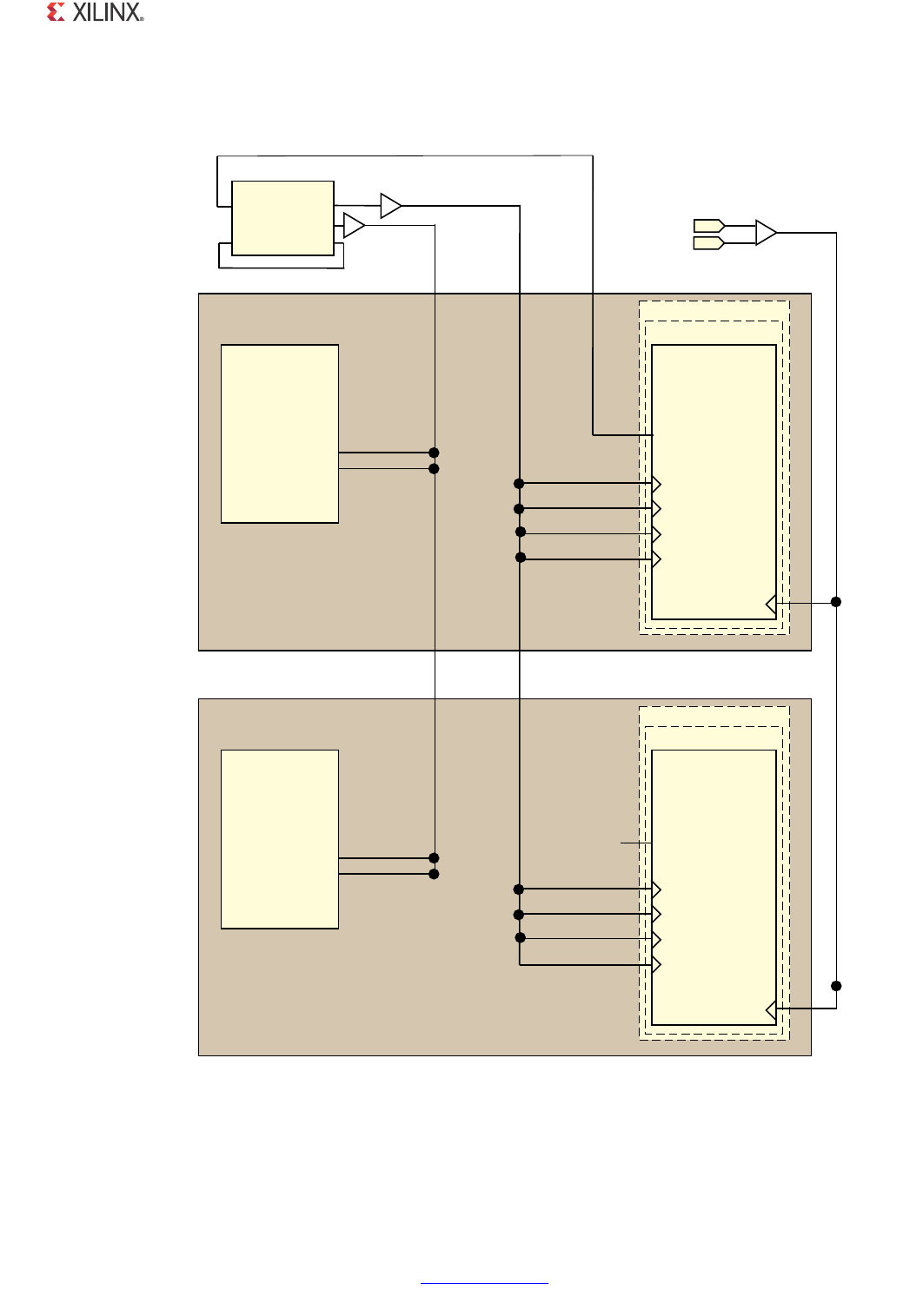

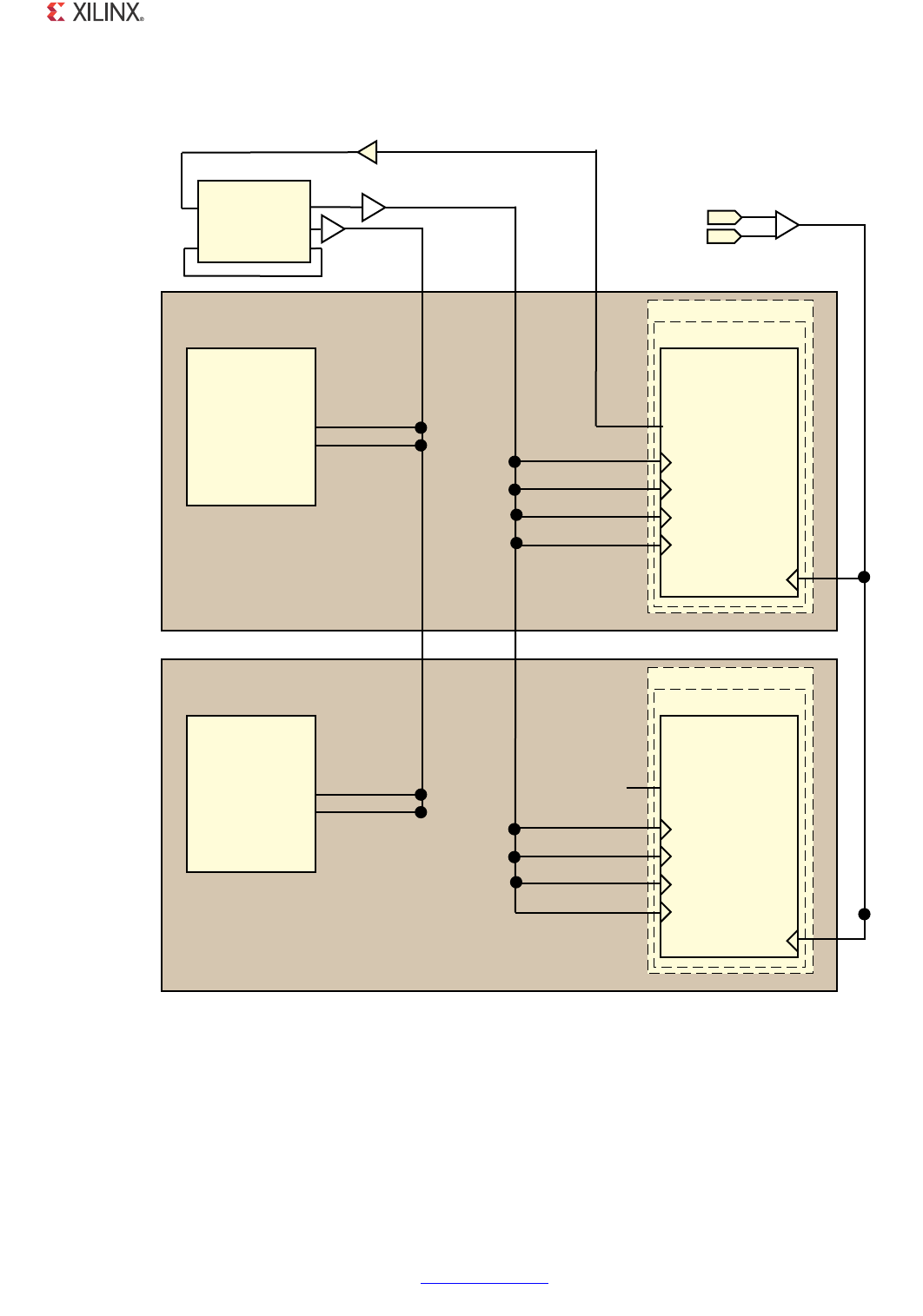

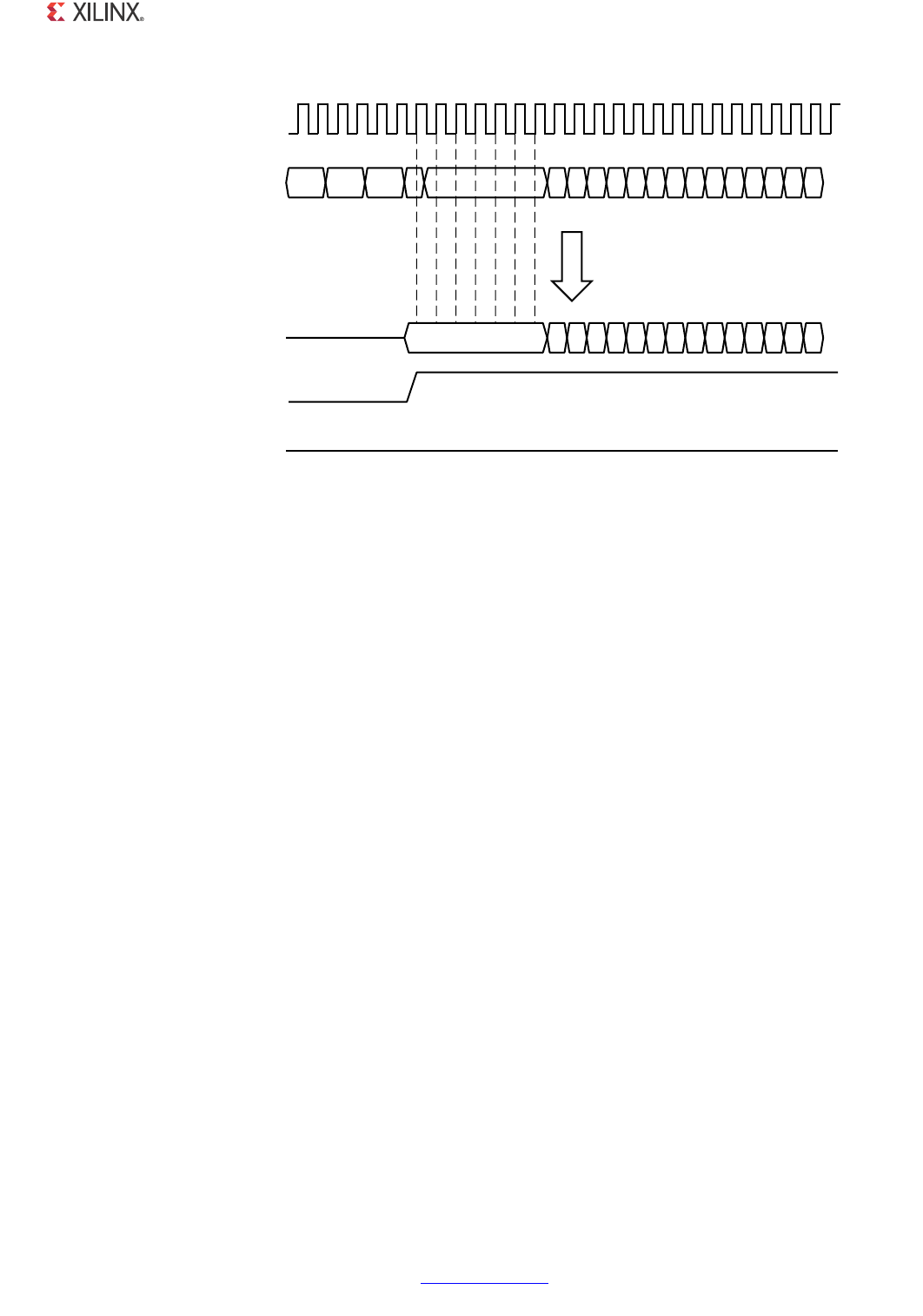

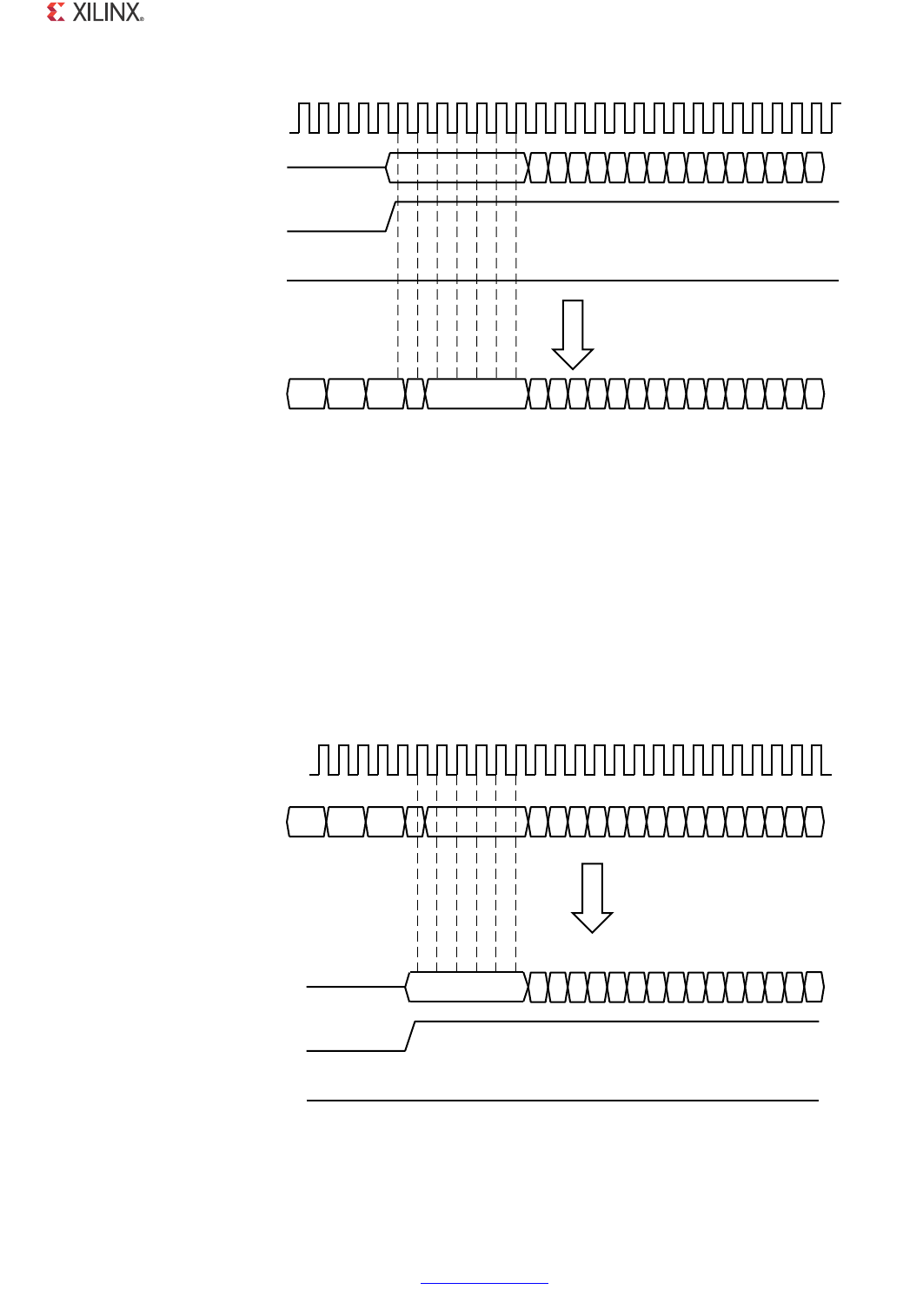

Chapter 2: Product Specification

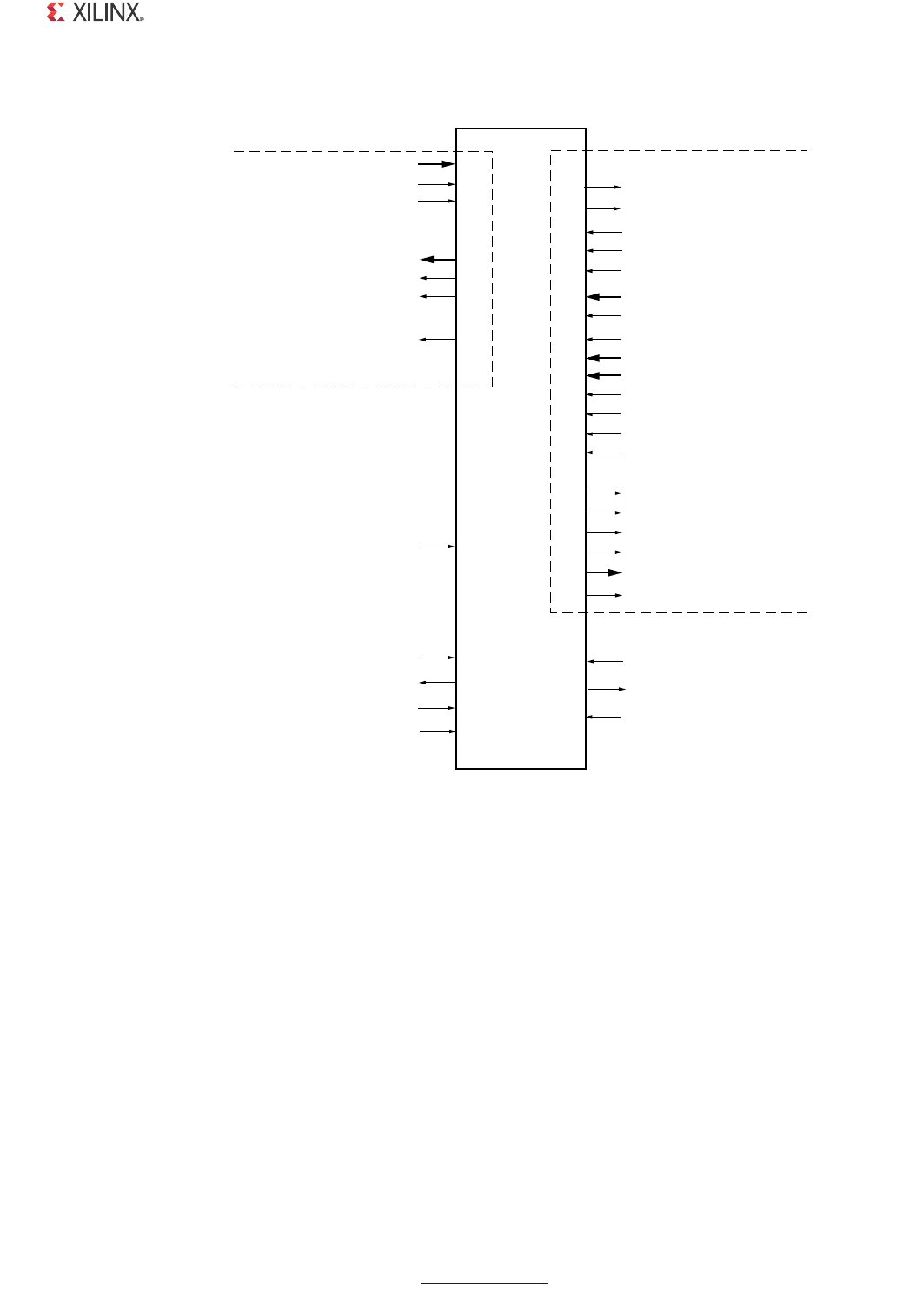

Figure 2-4 shows the pinout for the Ethernet 1000BASE-X PCS/PMA or SGMII core when

using the TBI with optional PCS Management registers. The signals shown in the

Auto-Negotiation box are included only when the core includes the Auto-Negotiation

functionality (see Chapter 17, Customizing and Generating the Core).

X-Ref Target - Figure 2-3

Figure 2-3: Component Pinout Using a Transceiver

without PCS Management Registers

PJWBU[BUHVHW

SIGNAL?DETECT

U[EXIVWDWXV>@

U[FKDULVFRPPD

U[FKDULVN

4RANSCEIVER)NTERFACE

PJWBW[BUHVHW

U[FONFRUFQW>@

U[GDWD>@

U[GLVSHUU

U[QRWLQWDEOH

U[UXQGLVS

W[EXIHUU

XVHUFON

GFPBORFNHG

XVHUFON

SRZHUGRZQ