R7735 Datasheet. Www.s Manuals.com. Richtek

User Manual: Datasheets R7735, R7735AGE, R7735AGN, R7735GGE, R7735GGN, R7735HGE, R7735HGN, R7735LGE, R7735LGN, R7735RGE, R7735RGN.

Open the PDF directly: View PDF ![]() .

.

Page Count: 19

R7735

®

R7735-03 September 2012 www.richtek.com

1

©

Copyright 2012 Richtek Technology Corporation. All rights reserved. is a registered trademark of Richtek Technology Corporation.

General Description

R7735 series is the successor of R7732/3 and fully

compatible with most of SOT-23-6 / DIP-8 product so far

in the market. It has enhanced quadruple mode PWM

controller and owns excellent green power performance,

especially under light load and no load conditions. It

focuses on "easy to design" in different applications and

it will save both design effort and external components.

Besides the general features shown in the Features

section, R7735 covers wide protection options, such as

internal Over Load Protection (OLP) and Over Voltage

Protection (OVP) to eliminate the external protection

circuits. Moreover, it also features Secondary Rectifier

Short Protection (SRSP) and CS pin open protection. This

protection will make the PSU design for reliability and

safety easier.

R7735 is designed for power supply such as NB adaptor

which is a very cost effective and compact design. The

precise external OVP and Over Temperature Protection

(OTP) can be implemented by very simple circuit. The

start-up resistors can also be replaced by bleeding

resistors to save power loss and component count.

High Performance Enhanced Quadruple Mode PWM

Flyback Controller

Features

zz

zz

zNo Load Input Power Under 100mW

zz

zz

zAccurate Over Load Protection

zz

zz

zUVLO 9V/14V

zz

zz

zSoft Start Function

zz

zz

zCurrent Mode Control

zz

zz

zBuilt-in Slope Compensation

zz

zz

zInternal Leading Edge Blanking

zz

zz

z PWM Quadruple Mode for Green-Mode

zz

zz

zExcellent Green Power Performance

zz

zz

zCycle-by-Cycle Current Limit

zz

zz

zInternal Over Voltage Protection

zz

zz

zSecondary Rectifier Short Protection

zz

zz

zOpto-Coupler Short Protection

zz

zz

zFeedback Open-Loop Protection

zz

zz

zCS Pin Open Protection

zz

zz

zBuilt-in Jittering Frequency

zz

zz

zBuilt-in PRO Pin for External Arbitrary OVP/OTP

zz

zz

zSoft Driving for EMI Noise

zz

zz

zHigh Noise Immunity

zz

zz

zRoHS Compliant and Halogen Free

Application

zz

zz

zSwitching AC/DC Adaptor

zz

zz

zDVD Open Frame Power Supply

zz

zz

zSet-Top Box (STB)

zz

zz

zATX Standby Power

zz

zz

zTV/Monitor Standby Power

zz

zz

zPC Peripherals

zz

zz

zNB Adaptor

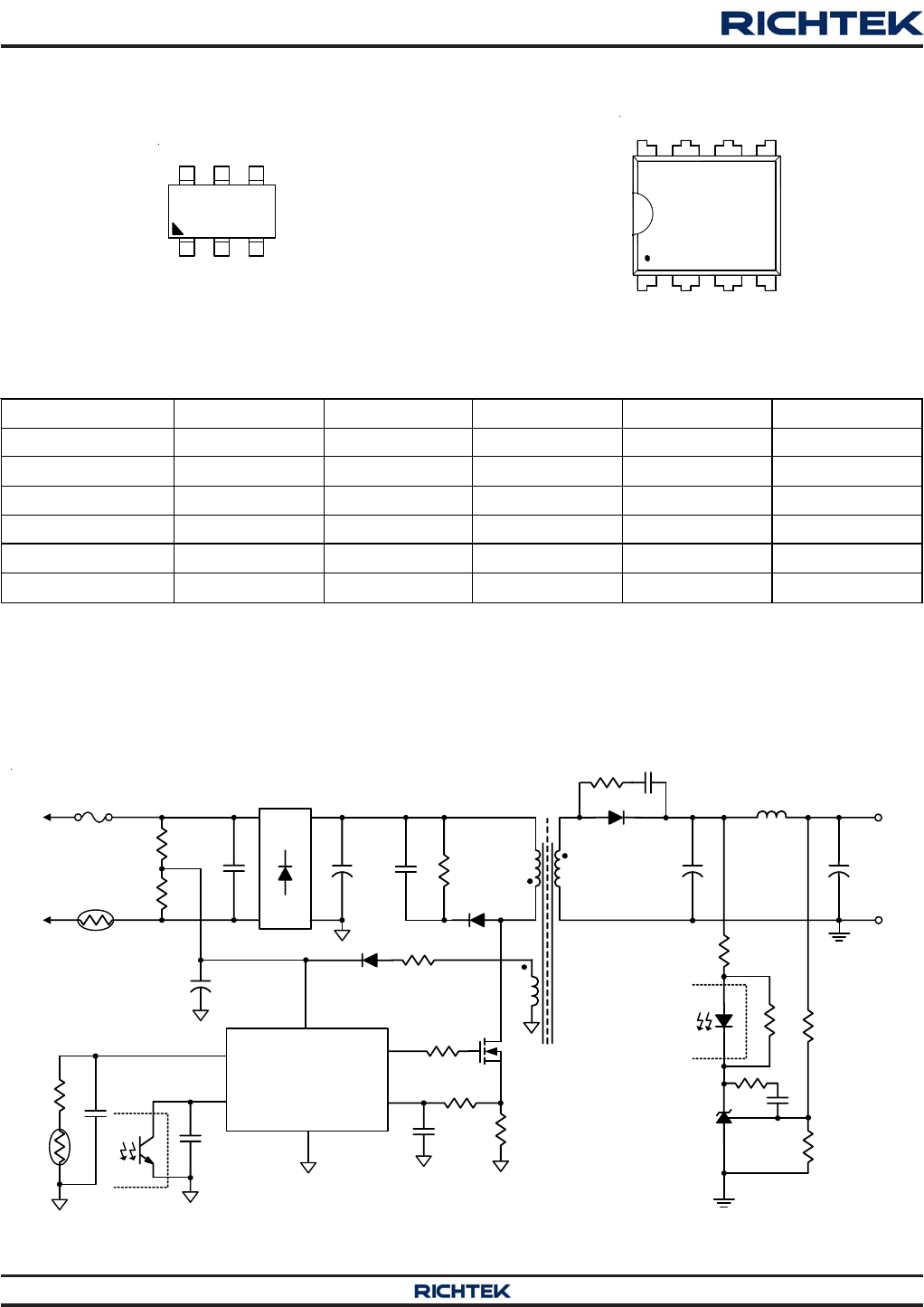

Ordering Information

Note :

Richtek products are :

` RoHS compliant and compatible with the current

requirements of IPC/JEDEC J-STD-020.

` Suitable for use in SnPb or Pb-free soldering processes.

R7735

Package Type

E : SOT-23-6

N : DIP-8 (R7735G Only)

Lead Plating System

G : Green (Halogen Free and Pb Free)

R7735 Version (Refer to Version Table)

(B)* (* : See Version Table)

Marking Information

For marking information, contact our sales representative

directly or through a Richtek distributor located in your

area.

2

R7735-03 September 2012

R7735

www.richtek.com

©

Copyright 2012 Richtek Technology Corporation. All rights reserved. is a registered trademark of Richtek Technology Corporation.

Typical Application Circuit

R7735 Version Table

Version R7735G R7735R R7735L R7735A R7735H

Frequency 65kHz 65kHz 65kHz 65kHz 100kHz

OLP Delay Time 56ms 56ms 56ms 28ms 36ms

Internal OVP(27V) Auto Recovery Auto Recovery Latch Latch Auto Recovery

OLP & SRSP Auto Recovery Auto Recovery Auto Recovery Latch Auto Recovery

PRO Pin High Latch Auto Recovery Latch Latch Auto Recovery

PRO Pin Low Auto Recovery Latch Latch Latch Latch

* : VSRSP_TH : Secondary Rectifier Short Protection (SRSP) triggered threshold.

R7735XGE : VSRSP_TH = 1.7V, X = G/R/L/A

R7735HGE(B) : VSRSP_TH = 2.6V

Pin Configurations

(TOP VIEW)

SOT-23-6 GATE NCVDD CS

678

4

5

23

GND NC

COMP PRO

DIP-8

GND COMP PRO

GATE VDD CS

4

23

56

AC Mains

(90V to 265V)

PRO

COMP

GND

GATE

CS

R7735

VDD

+

+

Vo+

Vo-

#

# : See Application Information

NTC

3

R7735-03 September 2012

R7735

www.richtek.com

©

Copyright 2012 Richtek Technology Corporation. All rights reserved. is a registered trademark of Richtek Technology Corporation.

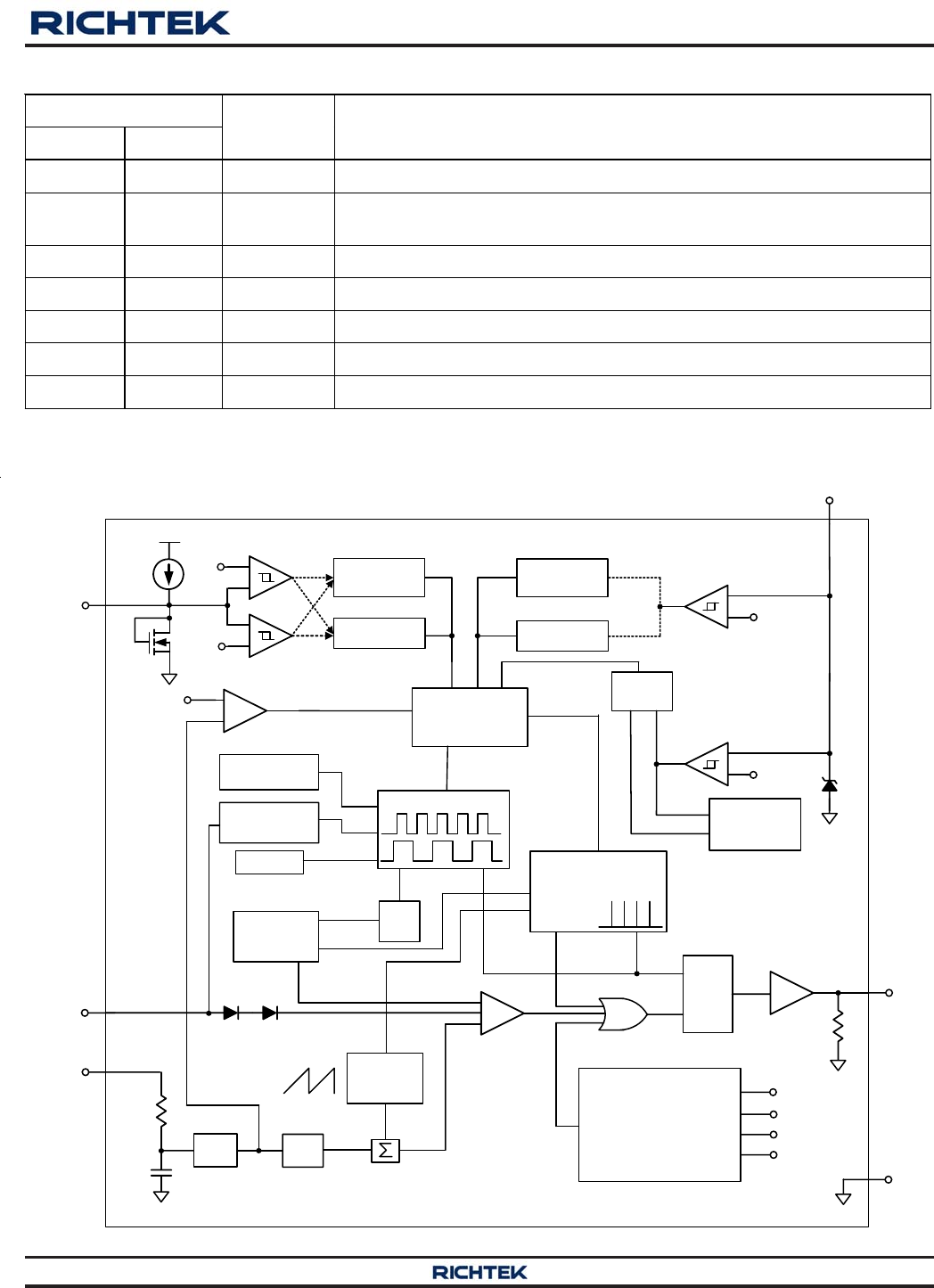

Function Block Diagram

Pin No.

SOT-23-6 DIP-8 Pin Name Pin Function

1 8 GND Ground.

2 7 COMP

Voltage Feedback. By connecting an opto-coupler to close control loop

and achieve the regulation.

3 5 PRO For External Arbitrary OVP or OTP.

4 4 CS Primary Current Sense.

5 2 VDD Power Supply.

6 1 GATE Gate Drive Output to Drive the External MOSFET.

-- 3, 6 NC No Internal Connection.

Functional Pin Description

Counter

VDD

GATE

LEB

R

S

Q

SS

X3

Slope

Ramp

Quadruple Mode

VCOMP

VBURH

VBURL

PWM

Comparator

Shutdown

Logic

COMP Open

Sensing

Brownout

Sensing

Dmax

Oscillator

POR

27V

Bias &

Bandgap

UVLO

OVP

9V/14V

OLP

Constant

Power

Soft Driver

+

-

+

-

+

-

-

+

-

VSRSP_TH

Secondary Rectifier Short

& CS Open Protection

COMP

CS

PRO

+

-

+

-

Latch

VL_TH

VH_TH

GND

VDD

IBIAS

Auto

Recovery

Latch

Auto

Recovery

4

R7735-03 September 2012

R7735

www.richtek.com

©

Copyright 2012 Richtek Technology Corporation. All rights reserved. is a registered trademark of Richtek Technology Corporation.

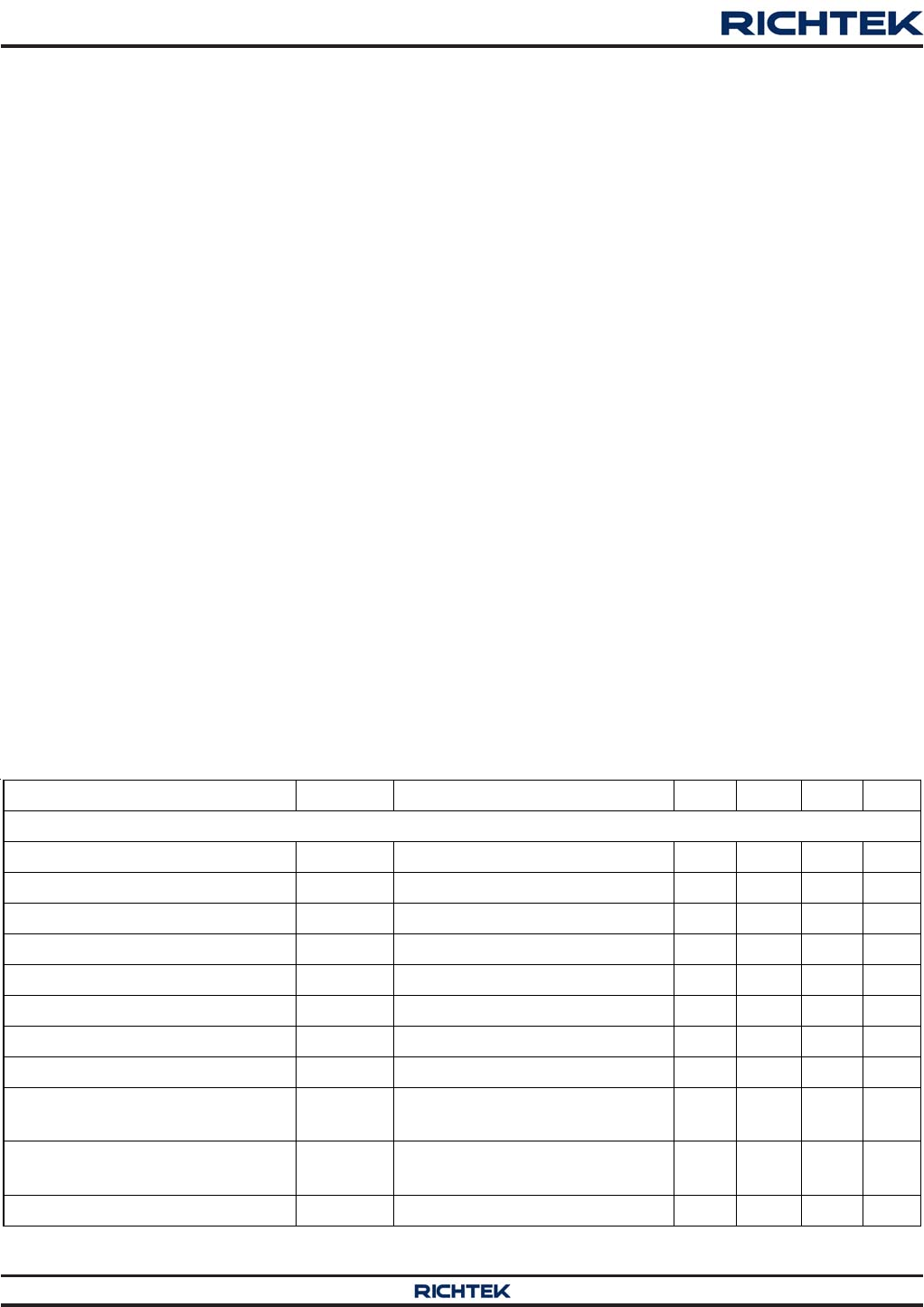

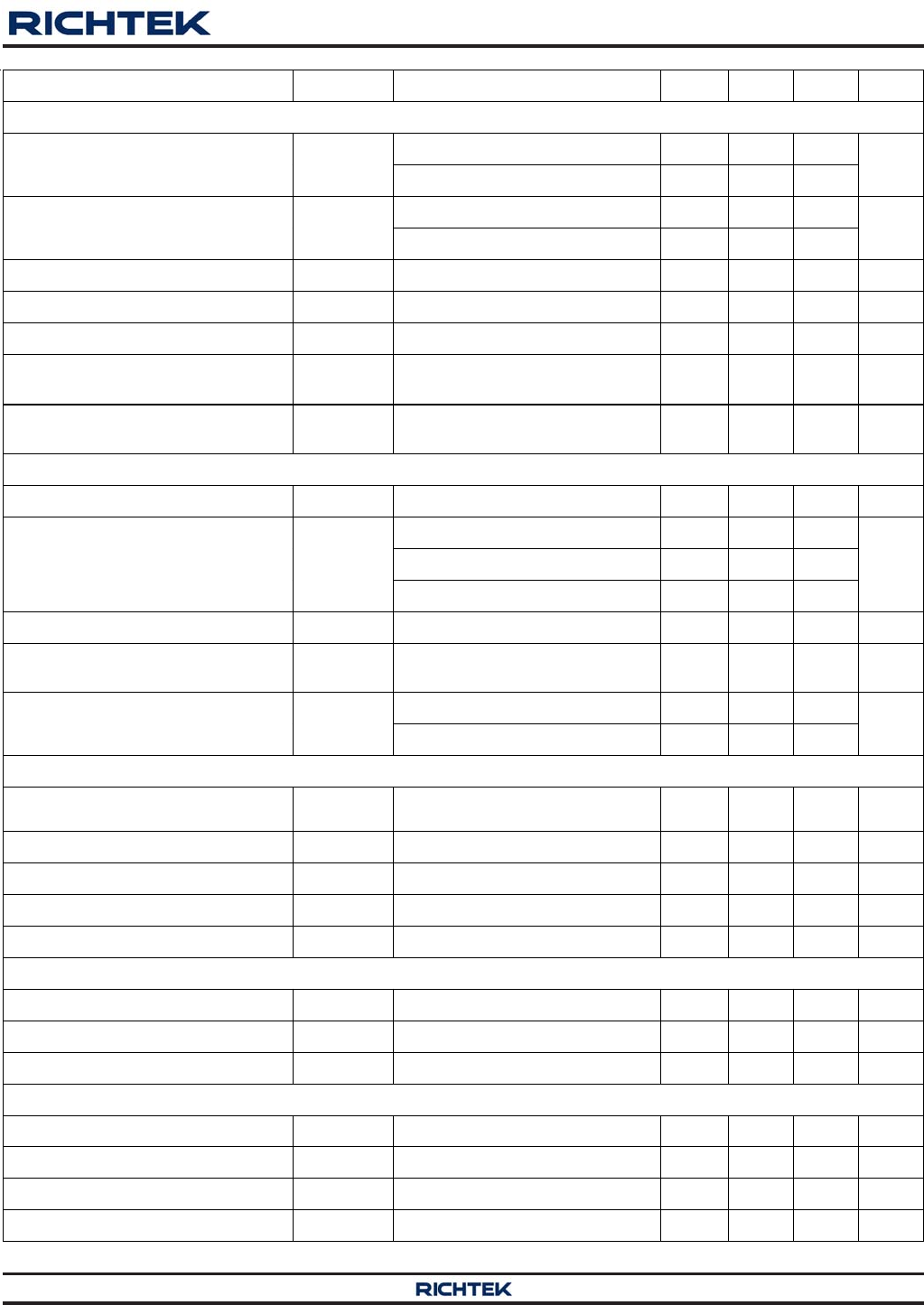

Electrical Characteristics

Parameter Symbol Test Conditions Min Typ Max Unit

VDD Section

VDD Over Voltage Protection Level VOVP 26 27 28 V

VDD Zener Clamp VZ 29 -- -- V

On Threshold Voltage VTH_ON 13 14 15 V

Off Threshold Voltage VTH_OFF 8.5 9 9.5 V

VDD Holdup Mode Entry Point VDD_LOW V

COMP < 1.6V 9.5 10 10.5 V

VDD Holdup Mode Ending Point VDD_HIGH V

COMP < 1.6V 10 10.5 11 V

Latch-off Voltage VLH 4.5 5.5 6.5 V

Latched Reset Voltage VLH_RST 4 5 6 V

Start-up Current IDD_ST VDD = VTH_ON – 0.2V,

TA= −40ºC to 100ºC (Note 5) 1 5 10 μA

Operating Supply Current IDD_OP VDD= 15V, VCOMP = 2.5V,

GATE pin open 0.55 0.9 1.6 mA

Latch-off Operating Current IDD_LH T

A= −40ºC to 100ºC (Note 5) 2 -- 8 μA

Recommended Operating Conditions (Note 4)

zSupply Input Voltage, VDD ----------------------------------------------------------------------------------------------- 12V to 25V

zJunction Temperature Range --------------------------------------------------------------------------------------------- −40°C to 125°C

zAmbient Temperature Range --------------------------------------------------------------------------------------------- −40°C to 85°C

Absolute Maximum Ratings (Note 1)

zSupply Input Voltage, VDD ----------------------------------------------------------------------------------------------- −0.3V to 30V

zGATE Pin --------------------------------------------------------------------------------------------------------------------- −0.3V to 16.5V

zPRO, COMP, CS Pin ------------------------------------------------------------------------------------------------------ −0.3V to 6.5V

zIDD ------------------------------------------------------------------------------------------------------------------------------ 10mA

zPower Dissipation, PD @ TA = 25°C

SOT-23-6 -------------------------------------------------------------------------------------------------------------------- 0.400W

DIP-8-------------------------------------------------------------------------------------------------------------------------- 0.714W

zPackage Thermal Resistance (Note 2)

SOT-23-6, θJA --------------------------------------------------------------------------------------------------------------- 250°C/W

DIP-8, θJA -------------------------------------------------------------------------------------------------------------------- 140°C/W

zJunction Temperature ------------------------------------------------------------------------------------------------------ 150°C

zLead Temperature (Soldering, 10 sec.) -------------------------------------------------------------------------------- 260°C

zStorage Temperature Range --------------------------------------------------------------------------------------------- −65°C to 150°C

zESD Susceptibility (Note 3)

HBM (Human Body Model) ----------------------------------------------------------------------------------------------- 3kV

MM (Machine Model) ------------------------------------------------------------------------------------------------------ 250V

(VDD = 15V, TA = 25°C, unless otherwise specified)

5

R7735-03 September 2012

R7735

www.richtek.com

©

Copyright 2012 Richtek Technology Corporation. All rights reserved. is a registered trademark of Richtek Technology Corporation.

Parameter Symbol Test Conditions Min Typ Max Unit

Oscillator Section

R7735G/R/L/A 60 65 70

Normal PWM Frequency fOSC R7735H 92 100 108

kHz

R7735G/R/L/A 18 22 --

Frequency Reduction Mode

Minimum Frequency fFR_MIN R7735H -- 25 --

kHz

Maximum Duty Cycle DCYMAX 70 75 80 %

PWM Frequency Jitter Range Δf -- ±6 -- %

PWM Frequency Jitter Period TJIT For 65kHz -- 4 -- ms

Frequency Variation Versus

VDD Deviation fDV V

DD= 12V to 25V -- -- 2 %

Frequency Variation Versus

Temperature Deviation fDT TA= −30°C to 105°C

(Note 5) -- -- 5 %

COMP Input Section

Open-Loop Voltage VCOMP_OP COMP pin Open 5.5 5.75 6 V

R7735G/R/L 45 56 65

R7735A 22 28 34

COMP Open-Loop Protection

Delay Time TOLP

R7735H 30 36 42

ms

Short Circuit Current IZERO V

COMP= 0V 0.15 0.29 0.45 mA

Frequency Reduction Mode Entry

Voltage VFR_ET 2.85 3 3.15 V

R7735G/R/L/A 2.75 2.9 3.05

Frequency Reduction Mode

Ending Voltage VFR_ED R7735H 2.65 2.8 2.95

V

Current Sense Section

Initial Peak Current Limitation

Offset VCS_TH 0.68 0.7 0.72 V

Maximum Clamping Current Limit VCS(MAX) 1.05 1.1 1.15 V

Leading Edge Blanking Time tLEB (Note 6) 150 250 350 ns

Internal Propagation Delay Time tPD (Note 6) -- 100 -- ns

Minimum On Time tON(MIN) 250 350 450 ns

GATE Section

Rising Time tR V

DD= 15V, CL= 1nF 60 125 140 ns

Falling Time tF V

DD= 15V, CL= 1nF 25 40 65 ns

GATE Output Clamping Voltage VCLAMP V

DD= 25V 12.1 14 15.9 V

PRO Interface Section

Pull Low Threshold VL_TH 0.47 0.5 0.53 V

Pull High Threshold VH_TH 3.5 3.8 4.1 V

Internal Bias Current IBIAS 90 100 110 μA

Pull High Sinking Current ISINK (Note 7) 0.7 -- 1.4 mA

6

R7735-03 September 2012

R7735

www.richtek.com

©

Copyright 2012 Richtek Technology Corporation. All rights reserved. is a registered trademark of Richtek Technology Corporation.

Note 1. Stresses beyond those listed “Absolute Maximum Ratings” may cause permanent damage to the device. These are

stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the

operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect

device reliability.

Note 2. θJA is measured at TA = 25°C on a low effective thermal conductivity single-layer test board per JEDEC 51-3.

Note 3. Devices are ESD sensitive. Handling precaution is recommended.

Note 4. The device is not guaranteed to function outside its operating conditions.

Note 5. Guaranteed by design.

Note 6. Leading edge blanking time and internal propagation delay time are guaranteed by design.

Note 7. The sourcing current of PRO pin must be limited below 5mA. Otherwise it may cause permanent damage to the

device.

7

R7735-03 September 2012

R7735

www.richtek.com

©

Copyright 2012 Richtek Technology Corporation. All rights reserved. is a registered trademark of Richtek Technology Corporation.

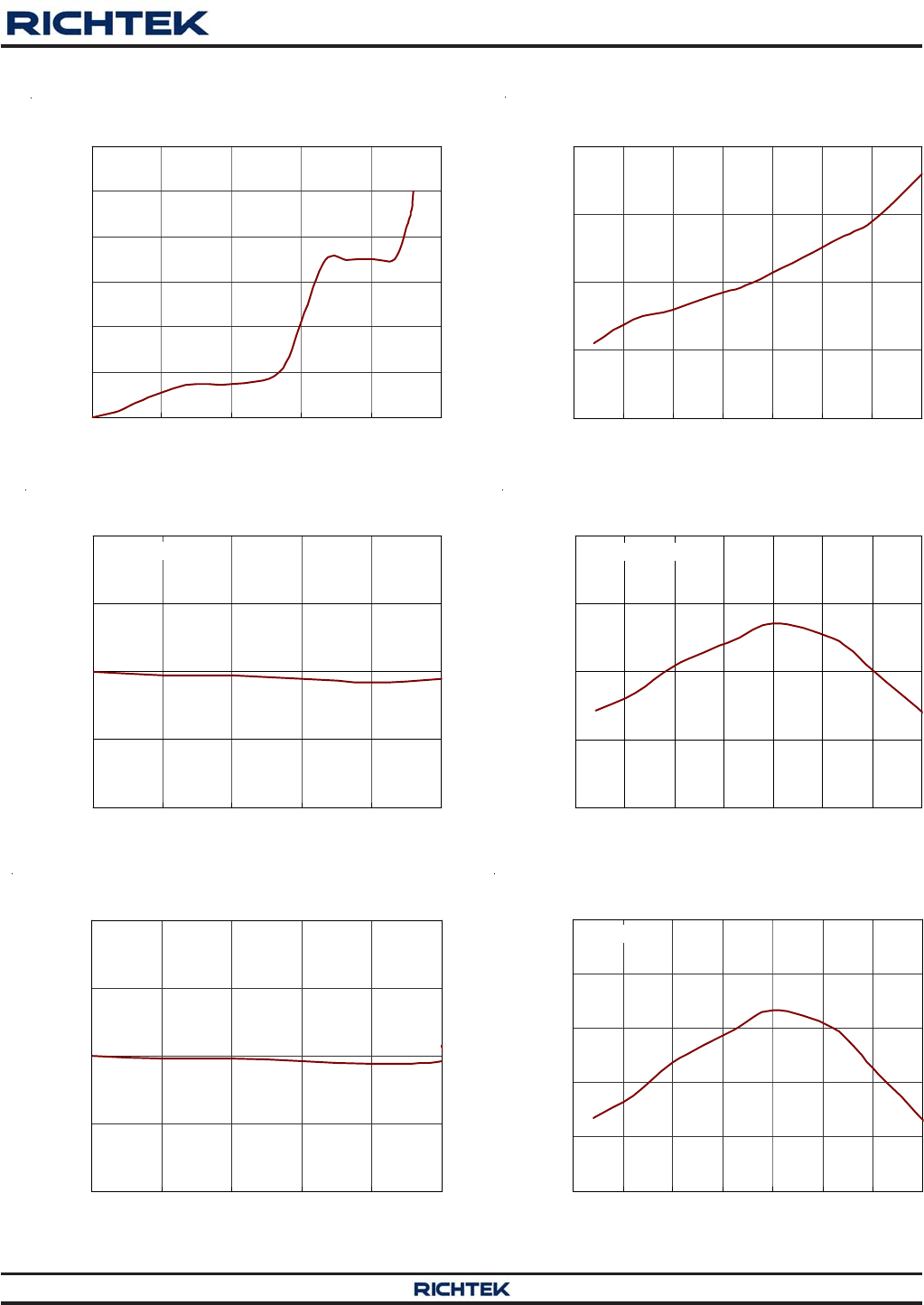

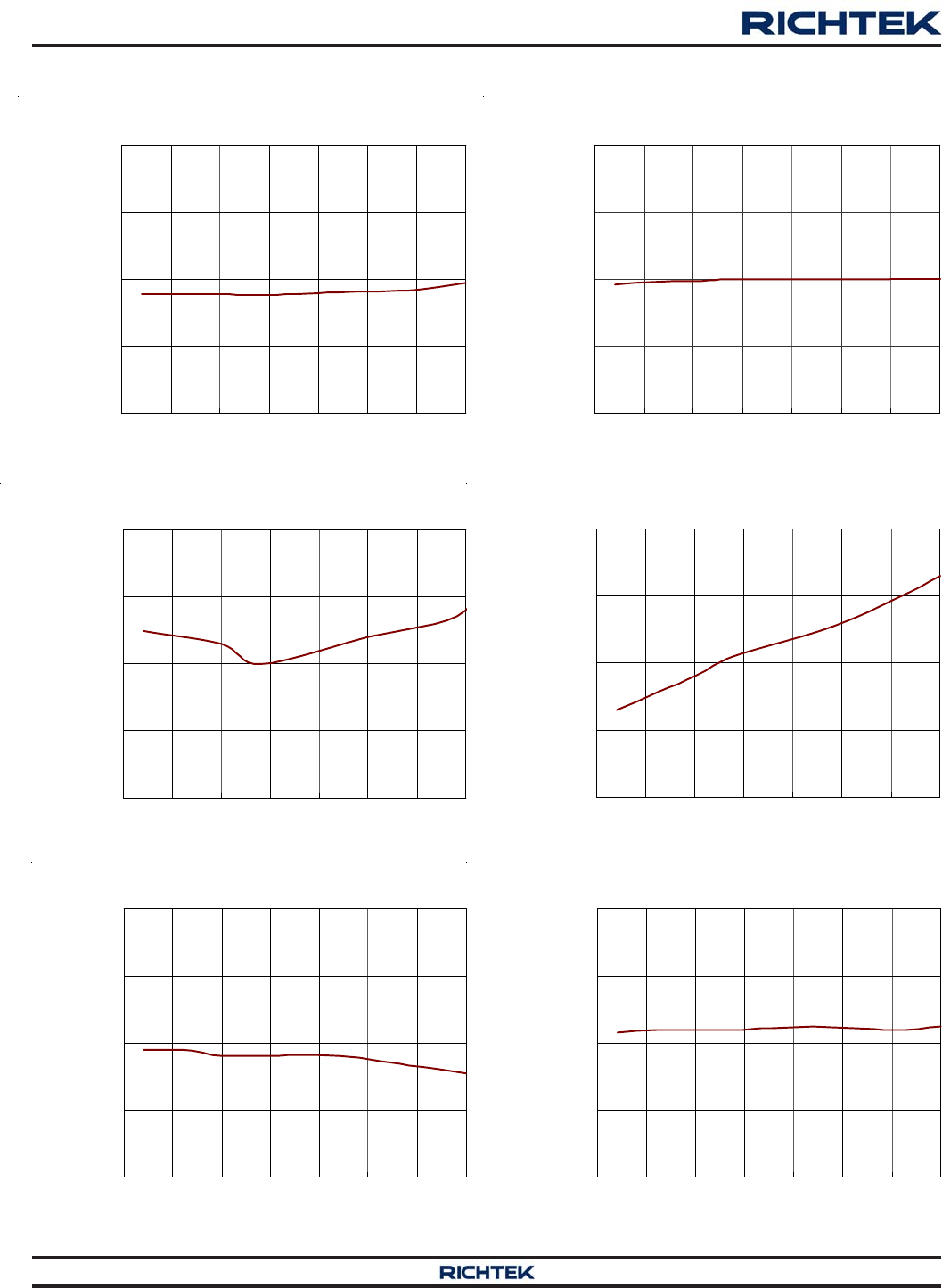

IDD_ST vs. VDD

0

1

2

3

4

5

6

03691215

VDD (V)

IDD_ST (µA)

IDD_ST vs. Temperature

2

4

6

8

10

-50 -25 0 25 50 75 100 125

Temperature (°C)

IDD_ST (µA)

Typical Operating Characteristics

fOSC vs. Temperature

94

96

98

100

102

104

-50 -25 0 25 50 75 100 125

Temperature (°C)

fOSC (kHz)

R7735H

fOSC vs. VDD

96

98

100

102

104

10 13 16 19 22 25

VDD (V)

fOSC (kHz)

R7735H

fOSC vs. Temperature

60

62

64

66

68

-50 -25 0 25 50 75 100 125

Temperature (°C)

fOSC (kHz)

R7735G/R/L/A

fOSC vs. VDD

63

64

65

66

67

10 13 16 19 22 25

VDD (V)

fOSC (kHz)

R7735G/R/L/A

8

R7735-03 September 2012

R7735

www.richtek.com

©

Copyright 2012 Richtek Technology Corporation. All rights reserved. is a registered trademark of Richtek Technology Corporation.

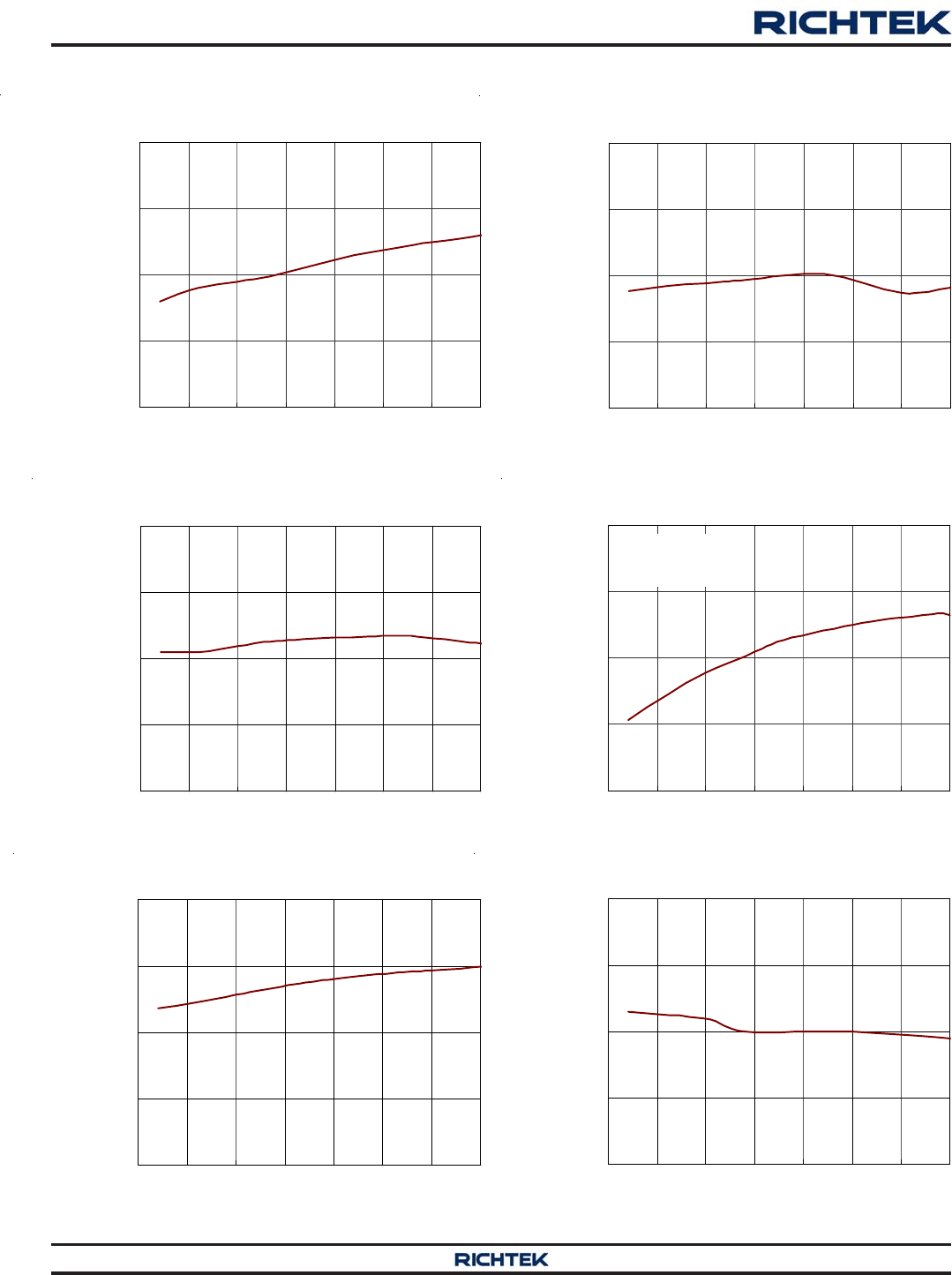

VTH_ON vs. Temperature

12

13

14

15

16

-50 -25 0 25 50 75 100 125

Temperature (°C)

VTH_ON

(V)

VTH_OFF vs. Temperature

8.0

8.5

9.0

9.5

10.0

-50 -25 0 25 50 75 100 125

Temperature (°C)

VTH_OFF (V)

fFR_MIN vs. Temperature

10

15

20

25

30

-50 -25 0 25 50 75 100 125

Temperature (°C)

fFR_MIN

(kHz)

VCOMP_OP vs. Temperature

5.2

5.4

5.6

5.8

6.0

-50 -25 0 25 50 75 100 125

Temperature (°C)

VCOMP_OP (V)

VOVP vs. Temperature

25

26

27

28

29

-50-250 255075100125

Temperature (°C)

VOVP(V)

IDD_OP vs. Temperature

0.65

0.75

0.85

0.95

1.05

-50-250 255075100125

Temperature (°C)

IDD_OP (mA)

VDD = 15V,

VCOMP = 2.5V,

GATE Pin Open

9

R7735-03 September 2012

R7735

www.richtek.com

©

Copyright 2012 Richtek Technology Corporation. All rights reserved. is a registered trademark of Richtek Technology Corporation.

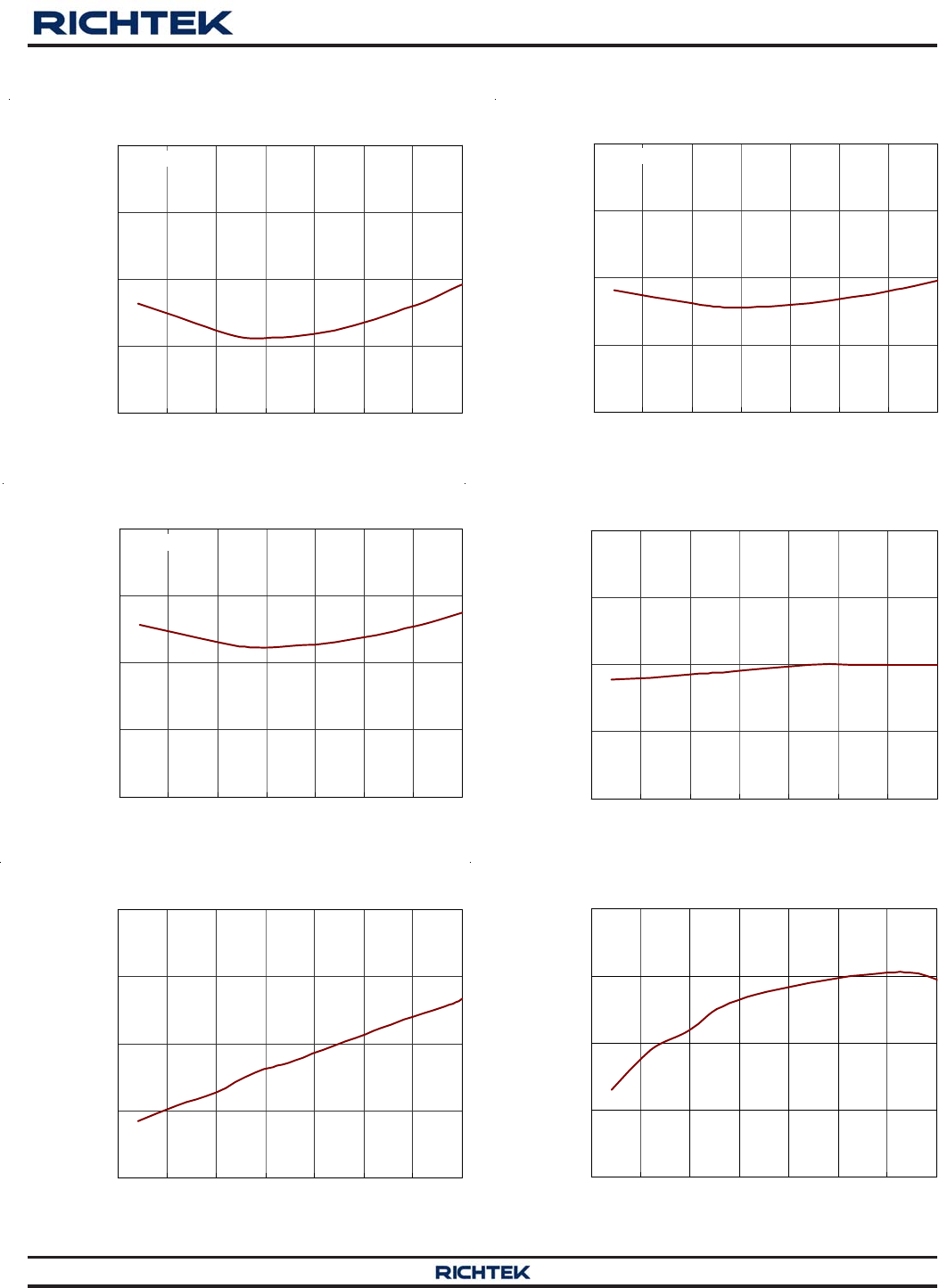

TOLP vs. Temperature

50

55

60

65

70

-50 -25 0 25 50 75 100 125

Temperature (°C)

TOLP (ms)

TOLP vs. Temperature

20

25

30

35

40

-50 -25 0 25 50 75 100 125

Temperature (°C)

TOLP (ms)

R7735G/R/L R7735A

VCS_TH vs. Temperature

0.60

0.65

0.70

0.75

0.80

-50 -25 0 25 50 75 100 125

Temperature (°C)

VCS_TH (V)

IDD_LH vs. Temperature

2

4

6

8

10

-50 -25 0 25 50 75 100 125

Temperature (°C)

IDD_LH (µA)

IBIAS vs. Temperature

70

80

90

100

110

-50 -25 0 25 50 75 100 125

Temperature (°C)

IBIAS (µA)

TOLP vs. Temperature

25

30

35

40

45

-50 -25 0 25 50 75 100 125

Temperature (°C)

TOLP (ms)

R7735H

10

R7735-03 September 2012

R7735

www.richtek.com

©

Copyright 2012 Richtek Technology Corporation. All rights reserved. is a registered trademark of Richtek Technology Corporation.

VH_TH vs. Temperature

2

3

4

5

6

-50 -25 0 25 50 75 100 125

Temperature (°C)

VH_TH

(V)

VL_TH vs. Temperature

0.40

0.45

0.50

0.55

0.60

-50-250 255075100125

Temperature (°C)

VL_TH (V)

TR vs. Temperature

100

110

120

130

140

-50 -25 0 25 50 75 100 125

Temperature (°C)

TR (ns)

TF vs. Temperature

20

30

40

50

60

-50 -25 0 25 50 75 100 125

Temperature (°C)

TF (ns)

VCLAMP vs. Temperature

10

12

14

16

18

-50 -25 0 25 50 75 100 125

Temperature (°C)

VCLAMP (V)

DCYMAX vs. Temperature

70

72

74

76

78

-50 -25 0 25 50 75 100 125

Temperature (°C)

DCYMAX

(%)

11

R7735-03 September 2012

R7735

www.richtek.com

©

Copyright 2012 Richtek Technology Corporation. All rights reserved. is a registered trademark of Richtek Technology Corporation.

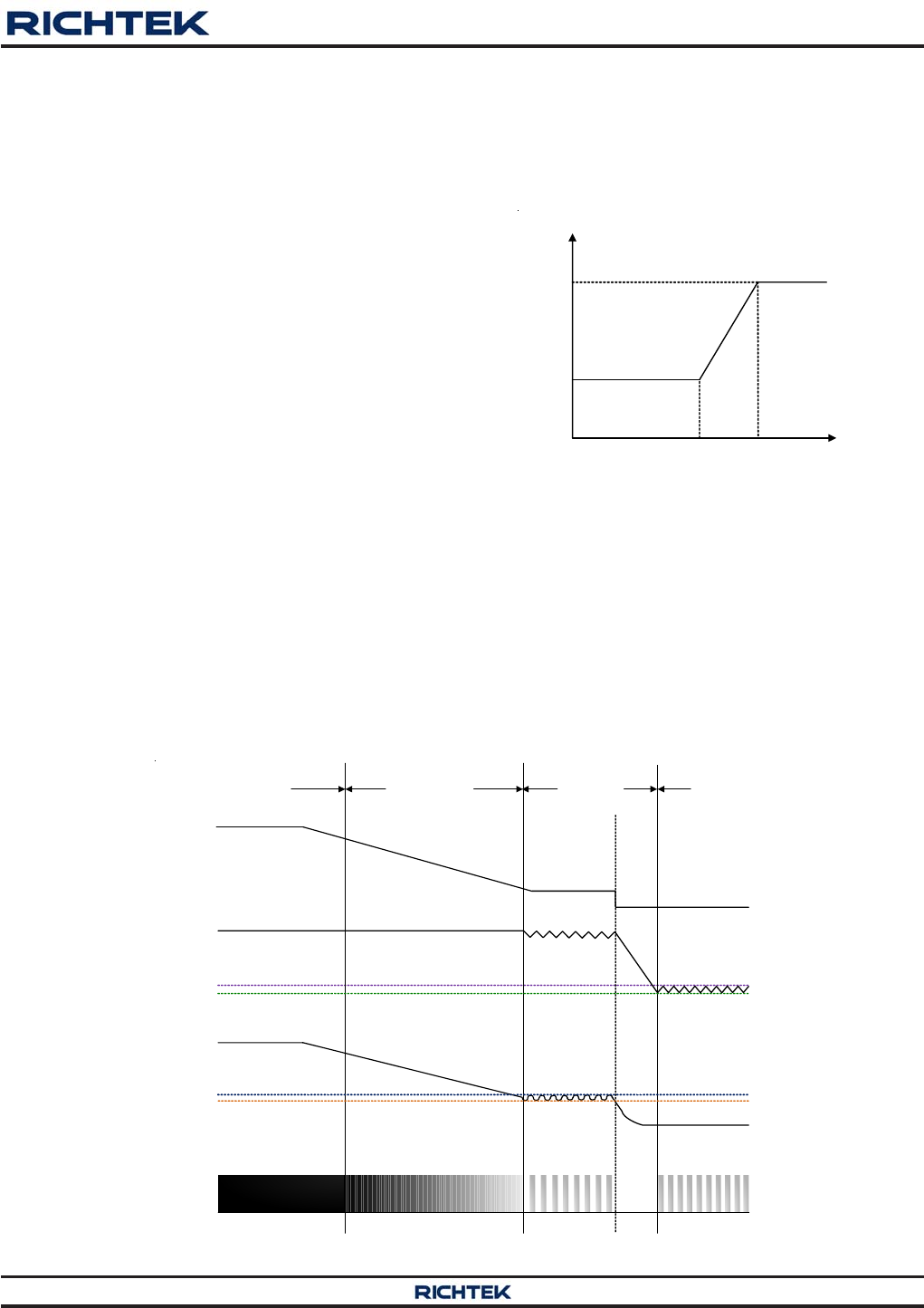

Burst Mode

During light load, switching loss will dominate the power

efficiency calculation. This mode is to cut switching loss.

As shown in Figure 1, when the output load gets light,

feedback signal drops and touches VBURL. PWM signal

will be blanked and system ceases to switch. After VOUT

drops and feedback signal goes back to VBURH, switching

will be resumed.

Application Information

PWM Quadruple Mode

R7735 has enhanced quadruple mode PWM controller and

owns excellent green power performance, especially under

light load and no load conditions. Please refer Figure 1 for

details.

# : To enhance light load efficiency, the feedback resistor

loss is reduced. Due to small feedback resistor current,

shunt regulator selection and minimum regulation current

design must be careful to make sure it's able to regulate

under low cathode current.

PWM Mode

For most of load, the circuit will run at traditional PWM

current mode.

Frequency Reduction Mode

he frequency reduction mode function provides linear

switching frequency reduction according to load

conditions, as shown in Figure 2. When the feedback

voltage of COMP pin is lower than VFR_ET, the switching

frequency starts to decrease. When the power supply is

at light-load and the feedback voltage of COMP pin lower

than VFR_ED, the switching frequency is clamped at fFR_MIN.

Figure 2. PWM Frequency vs. COMP Voltage

Figure 1. PWM Quadruple Mode

This frequency reduction mode function reduces power

consumption under light-load and no-load conditions, and

easily meets even the strictest regulations.

fOSC

fFR_MIN

VFR_ET

Frequency

VCOMP

VFR_ED

Load

VDD

VDD_HIGH

VDD_LOW

Normal

Operation

Frequency

Reduction Mode

Burst

Mode

VDD

Holdup Mode

VCOMP

VBURH

VBURL

GATE

12

R7735-03 September 2012

R7735

www.richtek.com

©

Copyright 2012 Richtek Technology Corporation. All rights reserved. is a registered trademark of Richtek Technology Corporation.

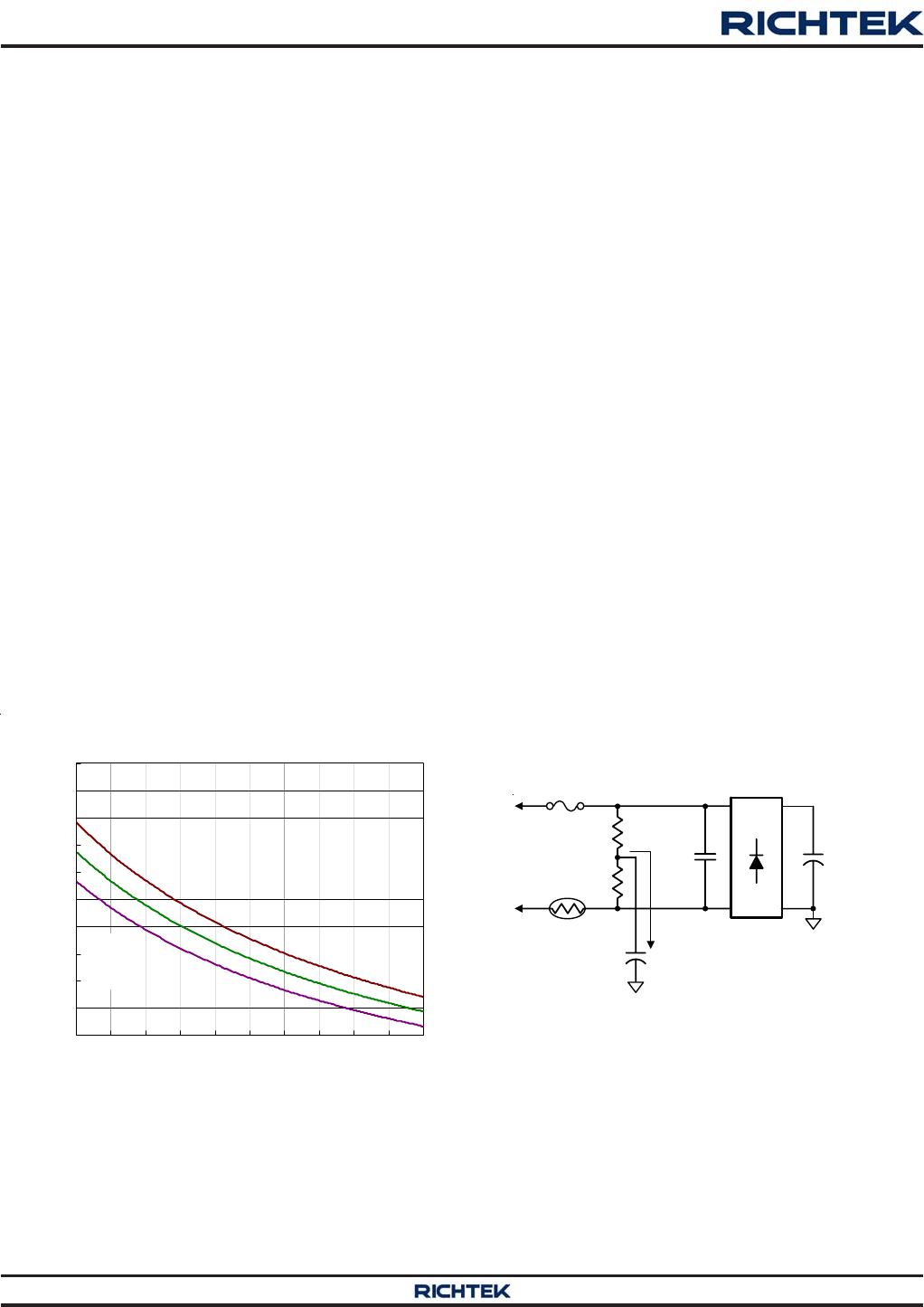

Figure 3. IDD_Avg vs. RBleeding Curve

Start-up Circuit

To minimize power loss, it's recommended that the start-

up current is from bleeding resistor. It's not only good for

power saving but also could reset latch mode protection

quickly. Figure 3 shows IDD_Avg vs. RBleeding curve. User

can apply this curve to design the adequate bleeding

resistor.

Gate Driver

A totem pole gate driver is fine tuned to meet both EMI

and efficiency requirement in low power application. An

internal pull low circuit is activated after pretty low VDD to

prevent external MOSFET from accidentally turning on

during UVLO.

Oscillator

To guarantee precise frequency, it's trimmed to 5%

tolerance. It also generates slope compensation saw-tooth,

75% maximum duty cycle pulse and overload protection

slope. It can typically operate at built-in 65kHz center

frequency and features frequency jittering function. Its

jittering depth is 6% with about 4ms envelope frequency

at 65kHz.

VDD Holdup Mode

Under light load or load transient moment, feedback signal

will drop and touch VBURL. Then PWM signal will be

blanked and system ceases to switch. VDD could drop

down to turn off threshold voltage. To avoid this, when VDD

drops to a setting threshold, 10V, the hysteresis

comparator will bypass PWM and burst mode loop and

forces switching at a very low level to supply energy to

VDD pin. VDD holdup mode was also improved to hold up

VDD by less switching cycles. This mode is very useful in

reducing start-up resistor loss while still get start-up time

in spec. It's not likely for VDD to touch UVLO turn off

threshold during any light load condition. This will also

makes bias winding design and transient design easier.

Furthermore, VDD holdup mode is only designed to prevent

VDD from touching turn off threshold voltage under light

load or load transient moment. Relative to burst mode,

switching loss will increase on the system at VDD holdup

mode, so it is highly recommended that the system should

avoid operating at this mode during light load or no load

condition, normally.

VDD

IDD_Avg

RBleeding

RBleeding

IDD_Avg vs. RBleeding Curve

10

12

14

16

18

20

22

24

26

28

30

2.0 2.2 2.4 2.6 2.8 3.0 3.2 3.4 3.6 3.8 4.0

RBleeding Curve (MΩ)

IDD_Avg (μA)

90Vac

85Vac

80Vac

13

R7735-03 September 2012

R7735

www.richtek.com

©

Copyright 2012 Richtek Technology Corporation. All rights reserved. is a registered trademark of Richtek Technology Corporation.

Tight Current Limit Tolerance

Since R7735 is the successor of R7732/3, its current limit

setting is completely the same as R7732/3. Generally,

the saw current limit applied to low cost Flyback controller

because of simple design. However, saw current limit is

hard to test in mass production. Therefore, it's generally

"guaranteed by design". The variation of process and

package will make its tolerance wider. It will lead to 20%

to 30% variation when doing OLP test at certain line

voltage. This will cause yield loss in power supply mass

production. Through well foundry control, design and test

/ trim mode in final test, R7735 current limit tolerance is

tight enough to make design easier.

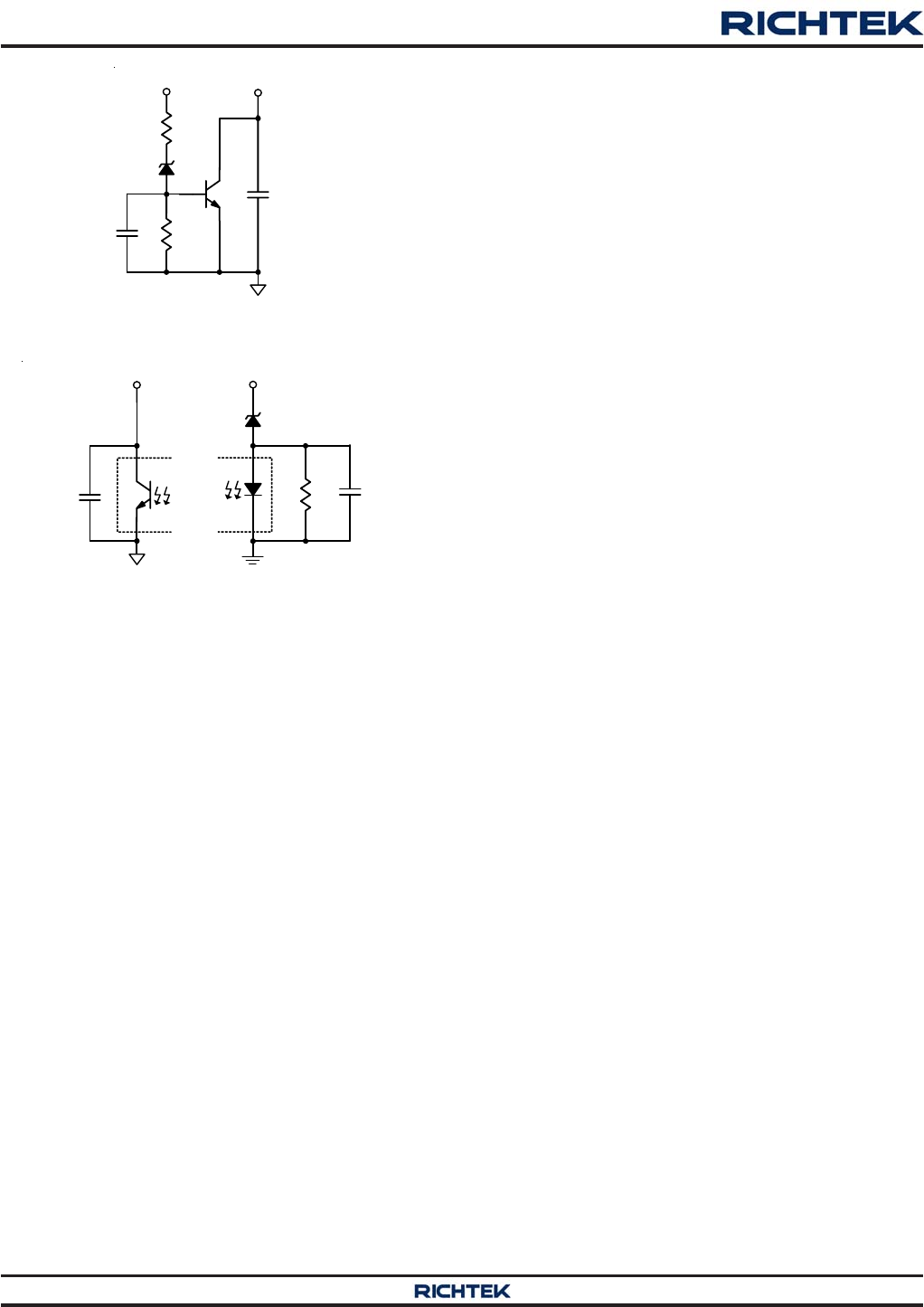

PRO Pin Application

R7735 features a PRO pin, as shown in Figure 4, and it

can be applied for external arbitrary OVP or OTP (ex :

Figure 5 to Figure 8).

If the voltage of PRO pin is greater than pull-low threshold

VL_TH, the controller is enabled and switching will occur. If

the voltage of PRO pin falls below pull-low threshold or

rises to pull-high threshold VH_TH, the controller will be

shut down and cease to switch after deglitch delay.

PRO pin is built in 1.5V internally, so leave PRO pin open

if you don't need this function. If designer needs to apply

a bypass capacitor on PRO pin, it should not be more

than 1nF. The internal bias current of PRO pin is 100μA

(typ.). R7735 has internal OVP. For arbitrary OVP or OTP

applications which behave as auto recovery or latch, it

can get these by PRO pin. For PRO pin pulling high

function applications, the voltage of PRO pin must rise

above VH_TH (The supply current of PRO pin must be

greater than 1.4mA and be limited below 5mA.). When IC

enters latch mode, the IC maximum operating current is

8μA (100°C), and it will be release until VDD is fallen to

VTH_OFF.

PRO pin is guaranteed that below: If the voltage of PRO

pin reaches 4.1V or falls below 0.47V, the system will be

protected.

Figure 4. PRO Pin Diagram

Figure 5. For VDD OVP Only

Figure 6. For OTP Only

PRO

+

-

+

-

Deglitch

50µs

VL_TH

VH_TH

IBIAS

Deglitch

30µs

Latch

Auto

Recovery

VL_TH

VH_TH

VPRO

Auto Recovery / Latch

Normal Operating

Auto Recovery / Latch

VDD

(Option)

PRO

VDD OVP : VDD > VR + VZ + 3.8V

PRO

NTC

(Option)

14

R7735-03 September 2012

R7735

www.richtek.com

©

Copyright 2012 Richtek Technology Corporation. All rights reserved. is a registered trademark of Richtek Technology Corporation.

Soft-Start

During initial power on, especially at high line, current

spike is kind of unlimited by current limit. Therefore,

besides cycle-by-cycle current limiting, R7735 still

provides soft start function. It effectively suppresses the

stat-up current spike. The typical soft start duration is

about 40 clock cycles. This will provide more reliable

operation and possibility to use smaller current rating power

MOSFET.

Protection

R7735 provide fruitful protection functions that intend to

protect system from being damaged. All the protection

functions can be listed as below:

``

``

` Cycle-by-Cycle Current Limit

This is a basic but very useful function and it can be

implemented easily in current mode controller.

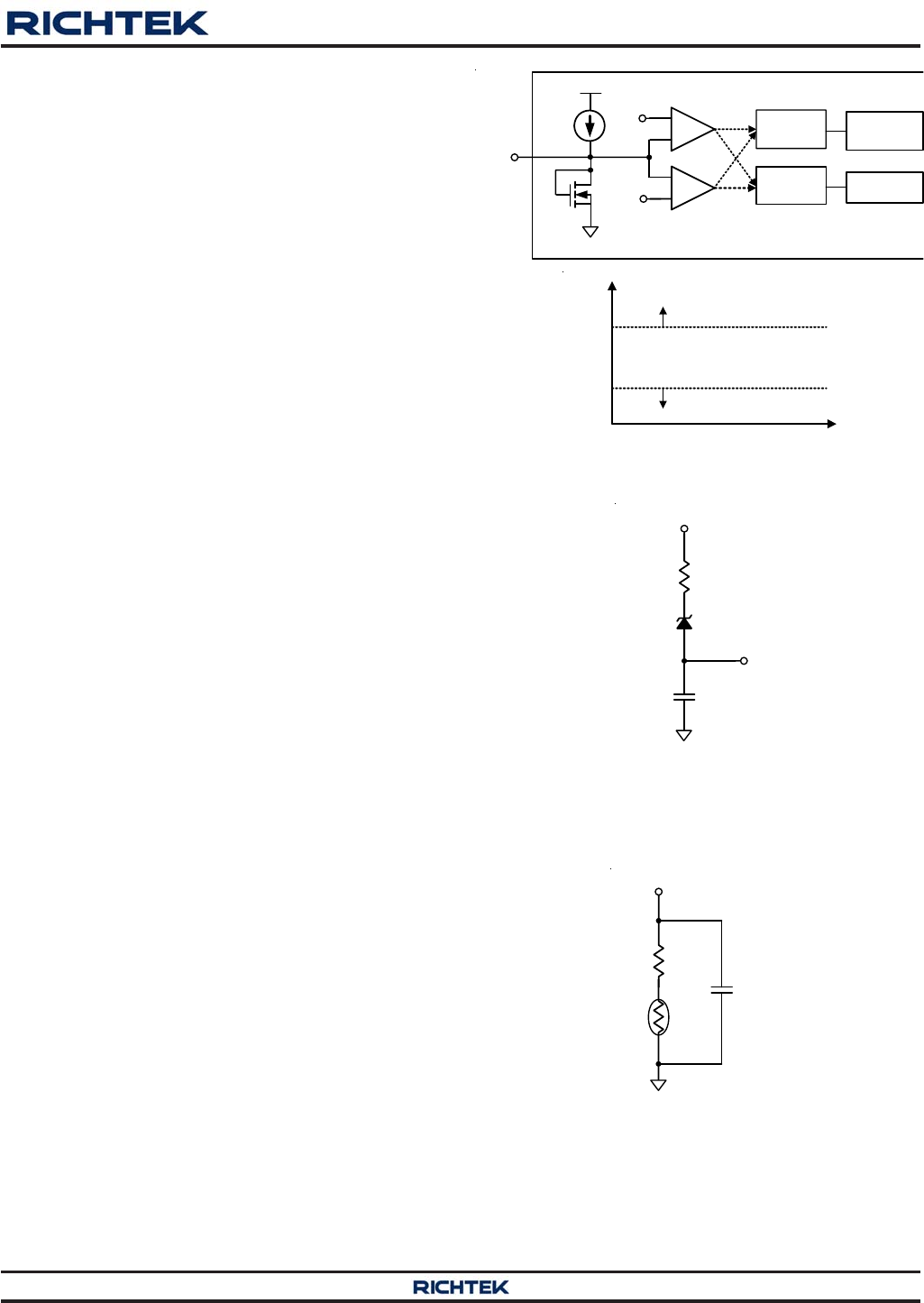

Figure 7. For VDD OVP

Figure 8. For VOUT OVP

``

``

` Over Load Protection

Long time cycle-by-cycle current limit will lead to system

thermal stress. To further protect system, system will

be shut down after 56ms (R7735A: 28ms; R7735H:

36ms).

Through our proprietary prolong turn off period during

hiccup(R7735A: latch), the power loss and thermal

during OLP will be averaged to an acceptable level over

the ON/OFF cycle of the IC. This will last until fault is

removed.

``

``

` Brownout Protection

During heavy load, this will trigger 56ms(R7735A: 28ms;

R7735H: 36ms) protection and shut down the system.

If it is in light load condition, system will be shut down

after VDD is running low and triggers UVLO.

``

``

` CS Pin Open Protection

When CS pin is opened, the system will be shut down

after couples of cycle. It could pass CS pin open test

easier.

``

``

` Over Voltage Protection

Output voltage can be roughly sensed by VDD pin. If

the sensed voltage reaches 27V threshold, system will

be shut down and hiccup after 20μs deglitch delay for

R7735G/R/H or latch after 70μs deglitch delay for

R7735L/A. This will last until fault is removed.

``

``

` Feedback Open and Opto-Coupler Short

This will trigger OVP or OLP. It depends on which one

occurs first.

``

``

` Secondary Rectifier Short Protection

As shown in Figure 9. The current spike during

secondary rectifier short test is extremely high because

of the saturated main transformer. Meanwhile, the

transformer acts like a leakage inductance. During high

line, the current in power MOSFET is sometimes too

high to wait for OLP delay time. To offer better and easier

protection design, R7735 shut down the controller after

couples of cycles before fuse is blown up.

VDD PRO

(Option)

Vo+

(Option)

PRO

(Option)

15

R7735-03 September 2012

R7735

www.richtek.com

©

Copyright 2012 Richtek Technology Corporation. All rights reserved. is a registered trademark of Richtek Technology Corporation.

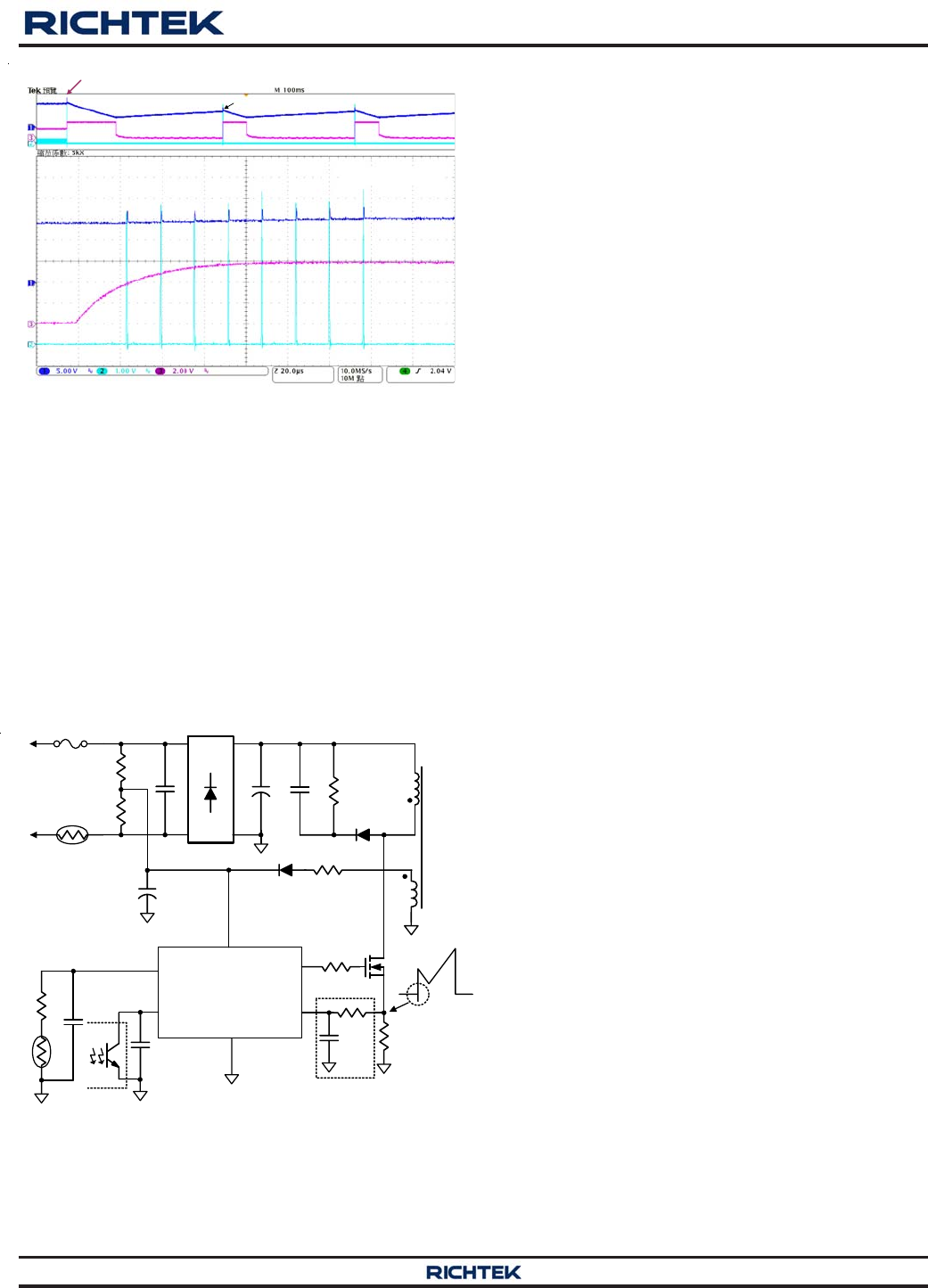

Figure 9. Secondary Rectifier Short Protection

Secondary Rectifier Short

VDD

VCS

VCOMP

Zoom In

R7735G/R/L/H

Negative Voltage Spike on Each Pin

Negative voltage (< -0.3V) on each pin will cause substrate

injection. It leads to controller damage or circuit false

trigger. Generally, it happens at CS pin due to negative

spike because of improper layout or inductive current

sense resistor. Therefore, it is highly recommended to

add a R-C filter to avoid CS pin damage, as shown in

Figure 10. Proper layout and careful circuit design should

be done to guarantee yield rate in mass production.

Figure 10. R-C Filter on CS Pin

AC Mains

(90V to 265V)

PRO

COMP

GND

GATE

CS

R7735

VDD

5

6

2

1

4

3

NTC

R-C Filter

Thermal Considerations

For continuous operation, do not exceed absolute

maximum junction temperature. The maximum power

dissipation depends on the thermal resistance of the IC

package, PCB layout, rate of surrounding airflow, and

difference between junction and ambient temperature. The

maximum power dissipation can be calculated by the

following formula :

PD(MAX) = (TJ(MAX) − TA) / θJA

where TJ(MAX) is the maximum junction temperature, TA is

the ambient temperature, and θJA is the junction to ambient

thermal resistance.

For recommended operating condition specifications, the

maximum junction temperature is 125°C. The junction to

ambient thermal resistance, θJA, is layout dependent. For

SOT-23-6 packages, the thermal resistance, θJA, is 250°C/

W on a standard JEDEC 51-3 single-layer thermal test

board. For DIP-8 packages, the thermal resistance, θJA,

is 140°C/W on a standard JEDEC 51-3 single-layer thermal

test board. The maximum power dissipation at TA = 25°C

can be calculated by the following formula :

PD(MAX) = (125°C − 25°C) / (250°C/W) = 0.400W for

SOT-23-6 package

PD(MAX) = (125°C − 25°C) / (140°C/W) = 0.714W for

DIP-8 package

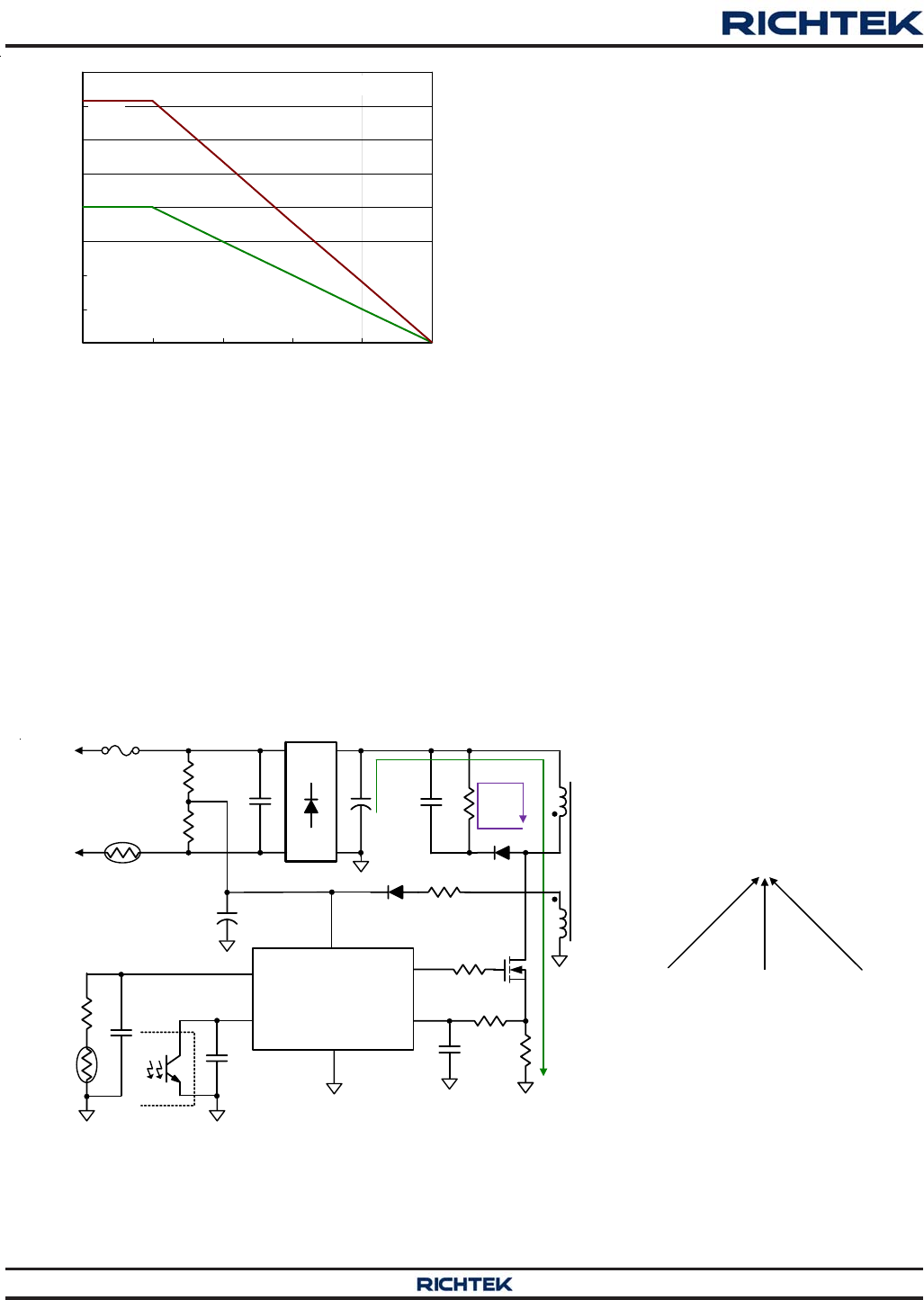

The maximum power dissipation depends on the operating

ambient temperature for fixed TJ(MAX) and thermal

resistance, θJA. The derating curves in Figure 11 allow

the designer to see the effect of rising ambient temperature

on the maximum power dissipation.

16

R7735-03 September 2012

R7735

www.richtek.com

©

Copyright 2012 Richtek Technology Corporation. All rights reserved. is a registered trademark of Richtek Technology Corporation.

Layout Consideration

A proper PCB layout can abate unknown noise interference

and EMI issue in the switching power supply. Please refer

to the guidelines when you want to design PCB layout for

switching power supply:

``

``

` The current path (1) from bulk capacitor, transformer,

MOSFET, Rcs return to bulk capacitor is a huge high

frequency current loop. It must be as short as possible

to decrease noise coupling and kept a space to other

low voltage traces, such as IC control circuit paths,

especially.

``

``

` The path(2) from RCD snubber circuit to MOSFET is

also a high switching loop, too. Keep it as small as

possible.

``

``

` It is good for reducing noise, output ripple and EMI issue

to separate ground traces of bulk capacitor(a),

MOSFET(b), auxiliary winding(c) and IC control circuit

(d). Finally, connect them together on bulk capacitor

ground(a). The areas of these ground traces should be

kept large.

``

``

` Placing bypass capacitor for abating noise on IC is highly

recommended. The bypass capacitor should be placed

as close to controller as possible.

``

``

` In order to minimize reflected trace inductance and EMI,

it is minimized the area of the loop connecting the

secondary winding, the output diode, and the output

filter capacitor. In addition, apply sufficient copper area

at the anode and cathode terminal of the diode for

heatsinking. Apply a larger area at the quiet cathode

terminal. A large anode area can increase high-frequency

radiated EMI.

(a)

(d) (b)

(1)

(c)

(2)

Auxiliary

Ground (c)

IC

Ground (d)

Trace Trace Trace

MOSFET

Ground (b)

CBULK Ground (a)

AC Mains

(90V to 265V)

PRO

COMP

GND

GATE

CS

R7735

VDD

5

6

2

1

4

3

NTC

CBULK

Figure 12. PCB Layout Guide

Figure 11.Derating Curve of Maximum Power Dissipation

0.0

0.1

0.2

0.3

0.4

0.5

0.6

0.7

0.8

0 25 50 75 100 125

Ambient Temperature (°C)

Maximum Power Dissipation (W

)

Single-Layer PCB

DIP-8

SOT-23-6

17

R7735-03 September 2012

R7735

www.richtek.com

©

Copyright 2012 Richtek Technology Corporation. All rights reserved. is a registered trademark of Richtek Technology Corporation.

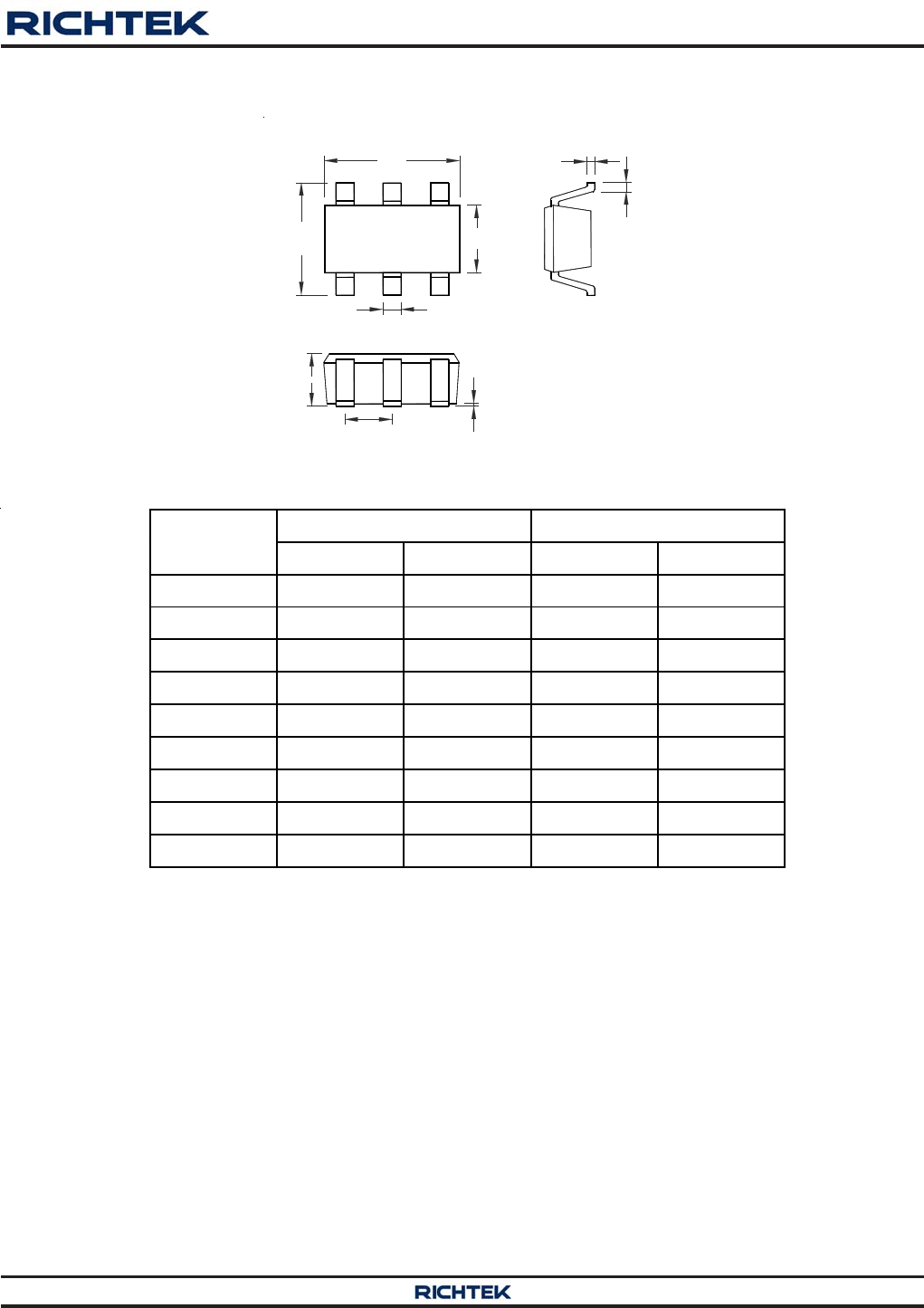

Outline Dimension

A

A1

e

b

B

D

C

H

L

Dimensions In Millimeters Dimensions In Inches

Symbol Min Max Min Max

A 0.889 1.295 0.031 0.051

A1 0.000 0.152 0.000 0.006

B 1.397 1.803 0.055 0.071

b 0.250 0.560 0.010 0.022

C 2.591 2.997 0.102 0.118

D 2.692 3.099 0.106 0.122

e 0.838 1.041 0.033 0.041

H 0.080 0.254 0.003 0.010

L 0.300 0.610 0.012 0.024

SOT-23-6 Surface Mount Package

18

R7735-03 September 2012

R7735

www.richtek.com

Richtek Technology Corporation

5F, No. 20, Taiyuen Street, Chupei City

Hsinchu, Taiwan, R.O.C.

Tel: (8863)5526789

Richtek products are sold by description only. Richtek reserves the right to change the circuitry and/or specifications without notice at any time. Customers should

obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot

assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be

accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third

parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.

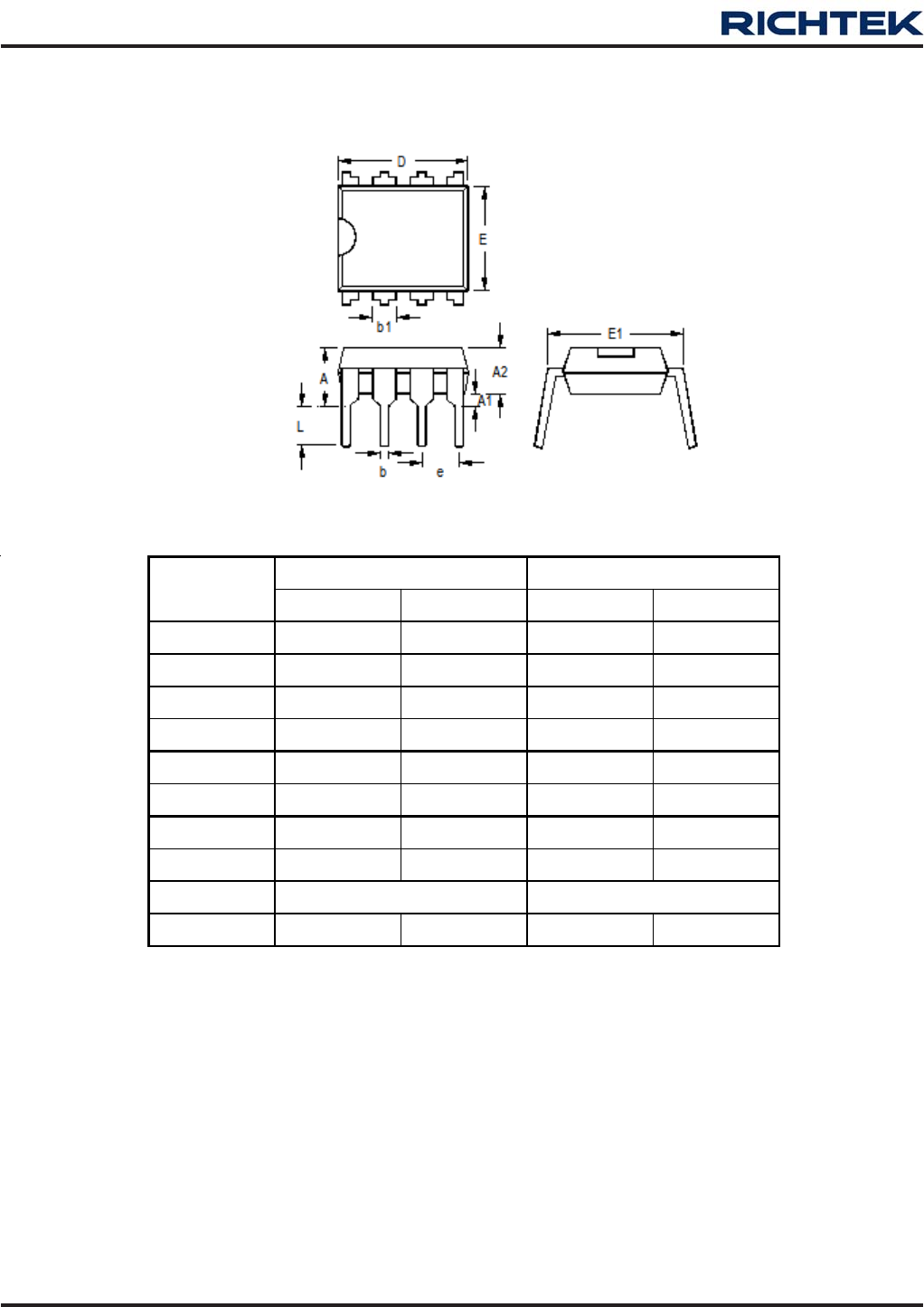

8-Lead DIP Plastic Package

Dimensions In Millimeters Dimensions In Inches

Symbol Min Max Min Max

A 3.700 4.320 0.146 0.170

A1 0.381 0.710 0.015 0.028

A2 3.200 3.600 0.126 0.142

b 0.360 0.560 0.014 0.022

b1 1.143 1.778 0.045 0.070

D 9.050 9.550 0.356 0.376

E 6.200 6.600 0.244 0.260

E1 7.620 8.255 0.300 0.325

e 2.540 0.100

L 3.000 3.600 0.118 0.142