TLV320AIC3256 Application Reference (Rev. A) Slau306a Guide

User Manual:

Open the PDF directly: View PDF ![]() .

.

Page Count: 155 [warning: Documents this large are best viewed by clicking the View PDF Link!]

- 1 TLV320AIC3256 Overview

- 2 TLV320AIC3256 Application

- 2.1 Terminal Descriptions

- 2.2 Analog Audio I/O

- 2.3 ADC

- 2.3.1 ADC Signal Routing

- 2.3.2 ADC Gain Setting

- 2.3.3 ADC Decimation Filtering and Signal Processing Overview

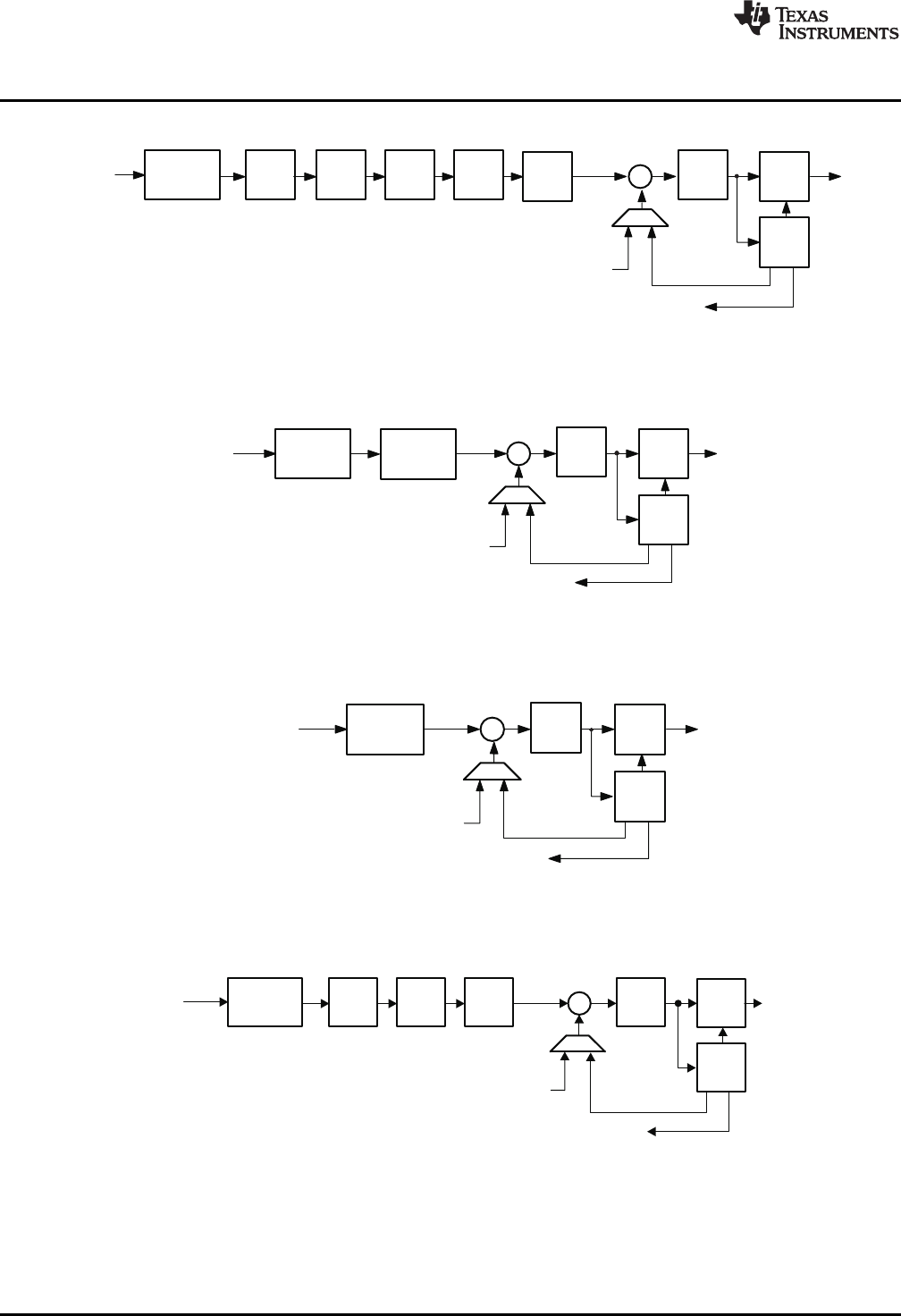

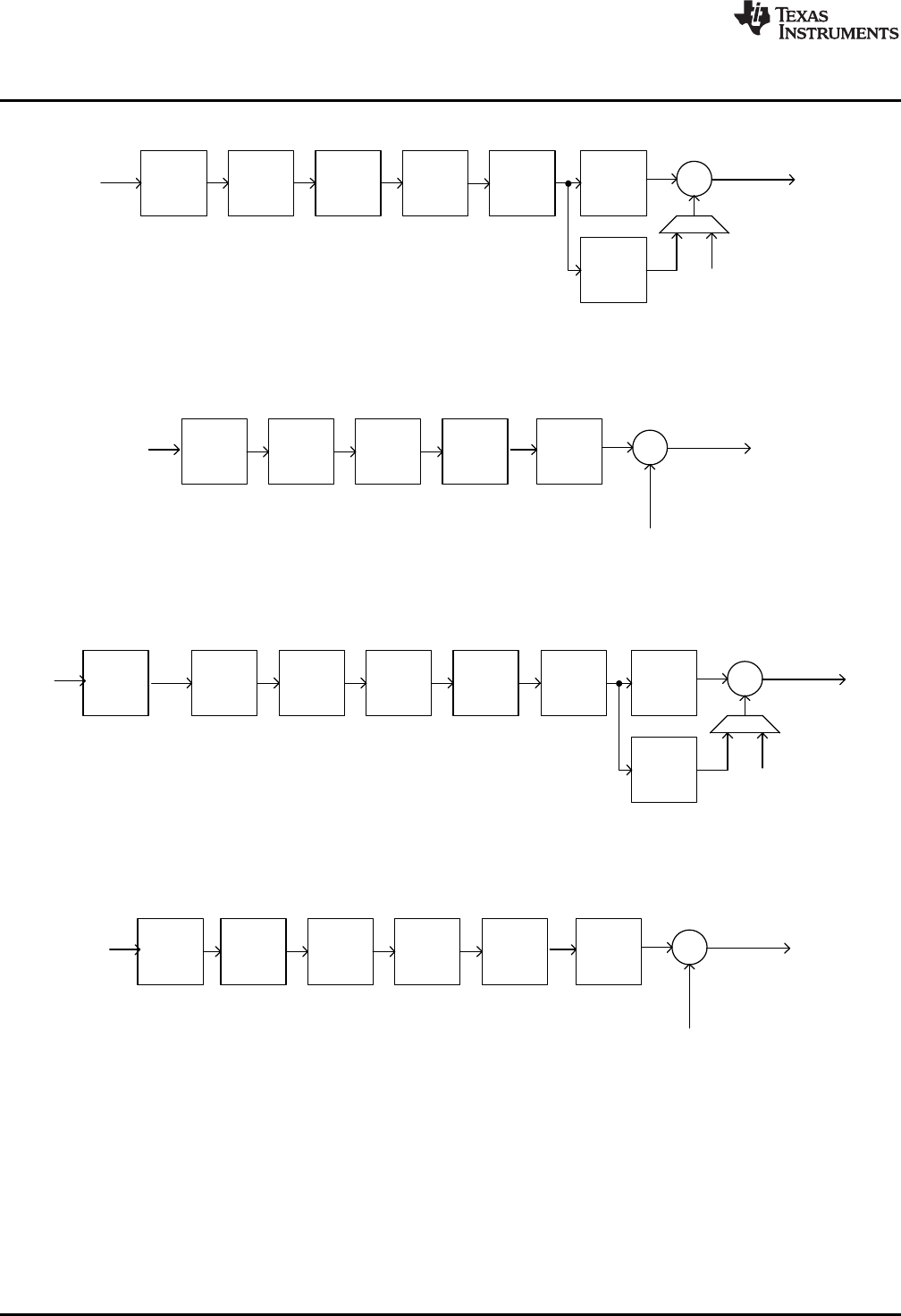

- 2.3.3.1 Signal Processing Blocks – Details

- 2.3.3.1.1 First-Order IIR, AGC, Filter A

- 2.3.3.1.2 5 Biquads, First-Order IIR, AGC, Filter A

- 2.3.3.1.3 25 Tap FIR, First-Order IIR, AGC, Filter A

- 2.3.3.1.4 First-Order IIR, AGC, Filter B

- 2.3.3.1.5 3 Biquads, First-Order IIR, AGC, Filter B

- 2.3.3.1.6 20 Tap FIR, First-Order IIR, AGC, Filter B

- 2.3.3.1.7 First-Order IIR, AGC, Filter C

- 2.3.3.1.8 5 Biquads, First-Order IIR, AGC, Filter C

- 2.3.3.1.9 25 Tap FIR, First-Order IIR, AGC, Filter C

- 2.3.3.1.10 User Programmable Filters

- 2.3.3.1.11 Decimation Filter

- 2.3.3.1.12 ADC Data Interface

- 2.3.3.2 ADC Special Functions

- 2.3.3.3 ADC Setup

- 2.3.3.1 Signal Processing Blocks – Details

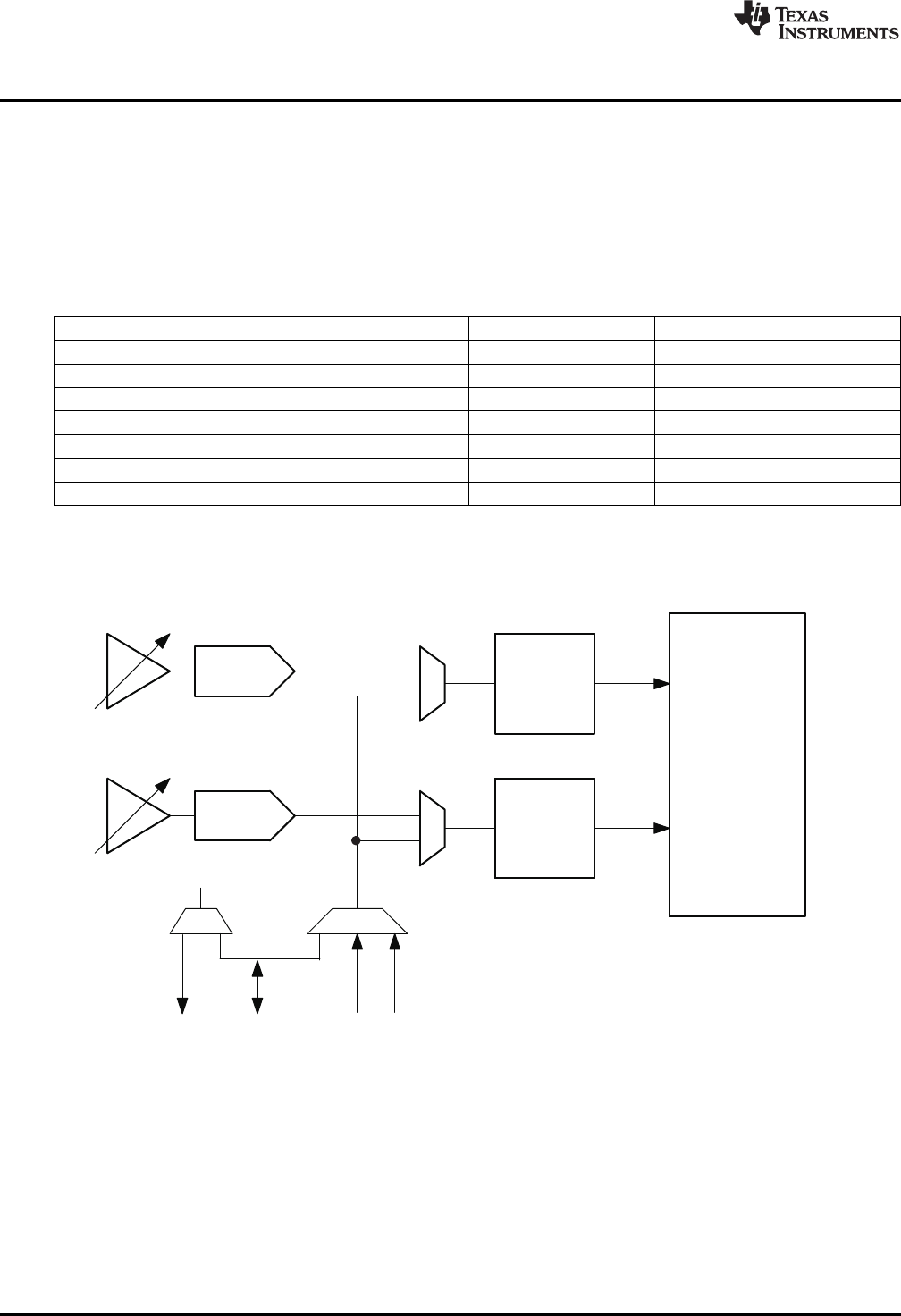

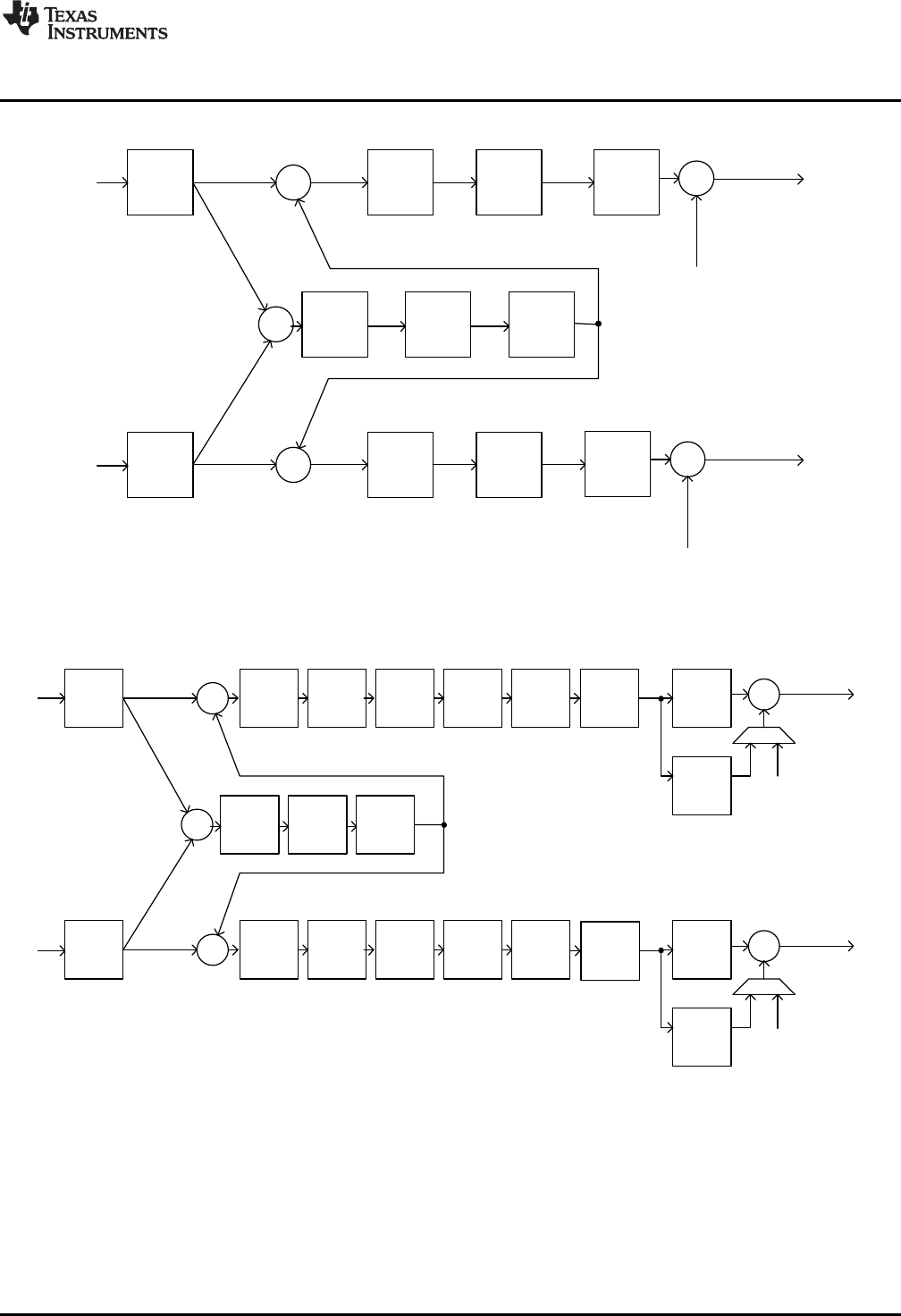

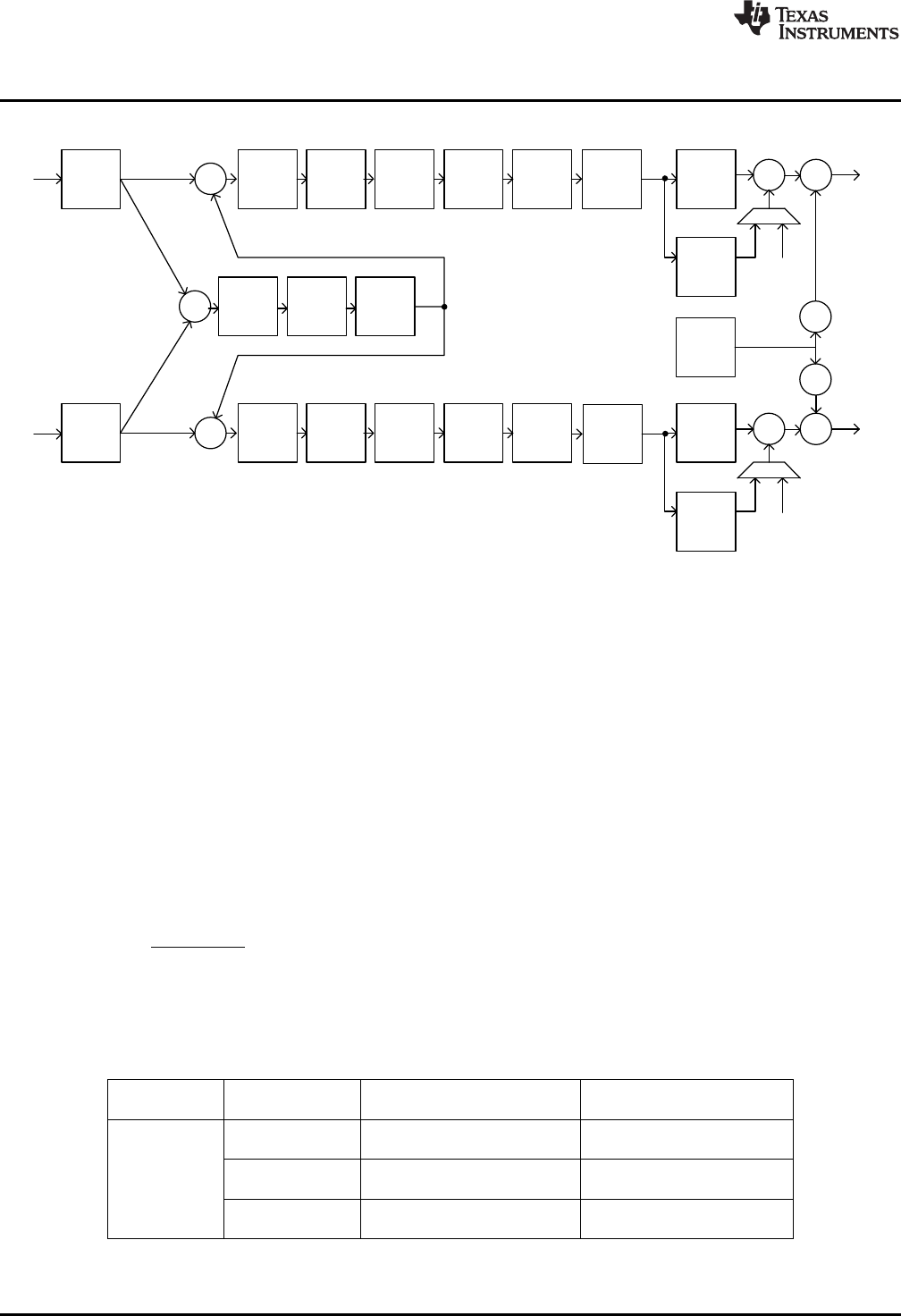

- 2.4 DAC

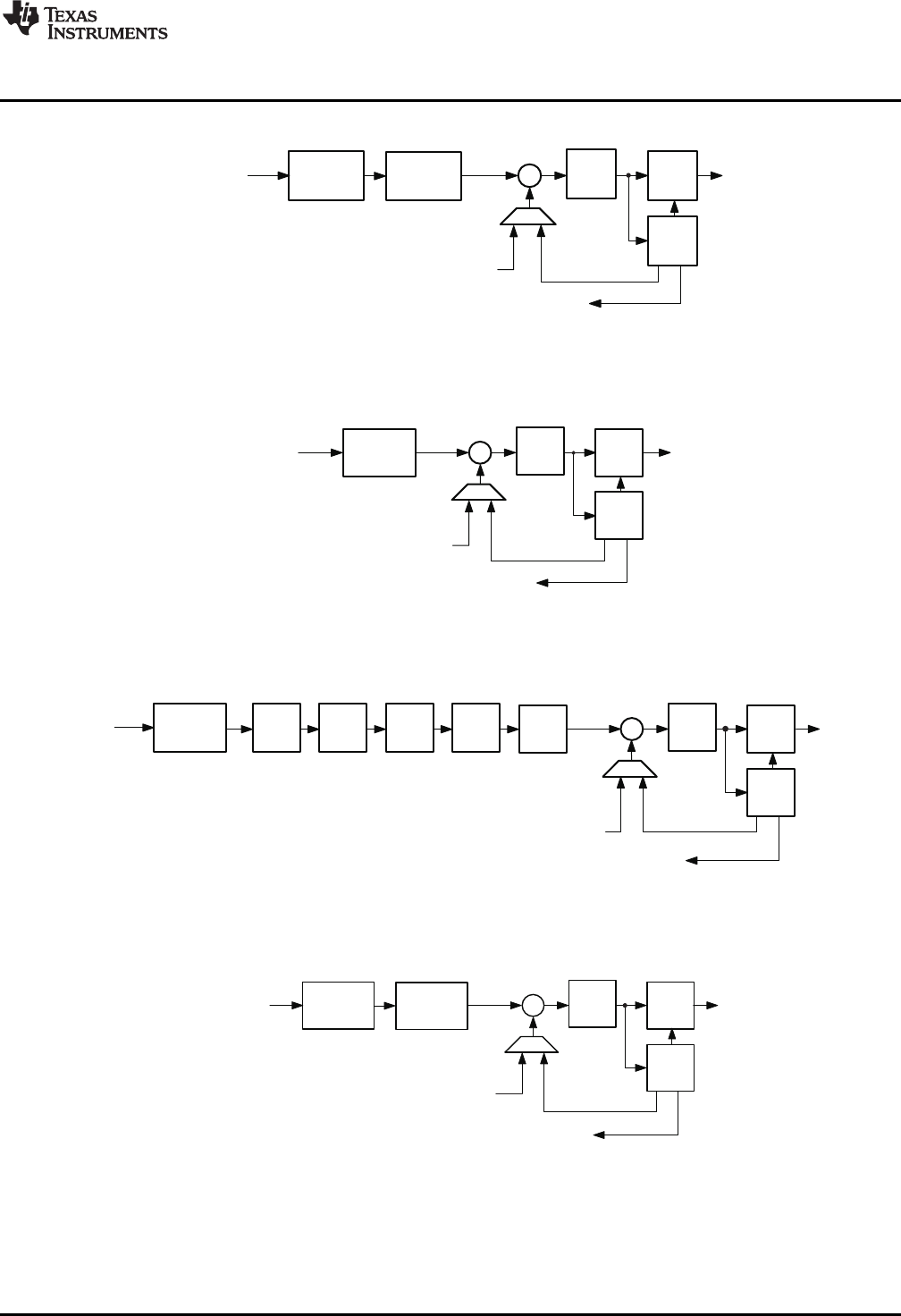

- 2.4.1 Processing Blocks – Details

- 2.4.1.1 3 Biquads, Interpolation Filter A

- 2.4.1.2 6 Biquads, 1st order IIR, DRC, Interpolation Filter A or B

- 2.4.1.3 6 Biquads, 1st order IIR, Interpolation Filter A or B

- 2.4.1.4 IIR, Interpolation Filter B or C

- 2.4.1.5 4 Biquads, DRC, Interpolation Filter B

- 2.4.1.6 4 Biquads, Interpolation Filter B

- 2.4.1.7 4 Biquads, 1st order IIR, DRC, Interpolation Filter C

- 2.4.1.8 4 Biquads, 1st order IIR, Interpolation Filter C

- 2.4.1.9 2 Biquads, 3D, Interpolation Filter A

- 2.4.1.10 5 Biquads, DRC, 3D, Interpolation Filter A

- 2.4.1.11 5 Biquads, DRC, 3D, Beep Generator, Interpolation Filter A

- 2.4.2 User Programmable Filters

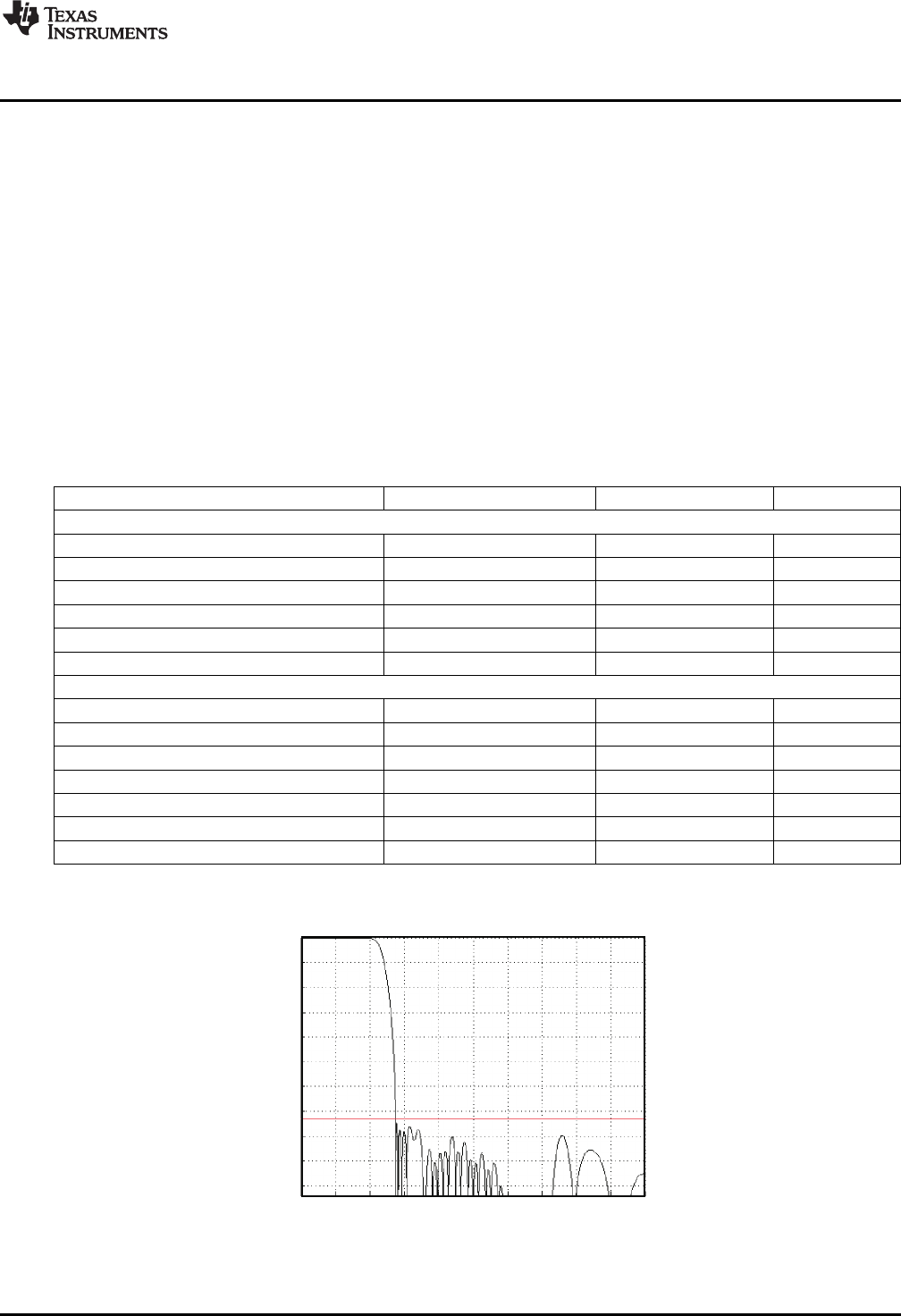

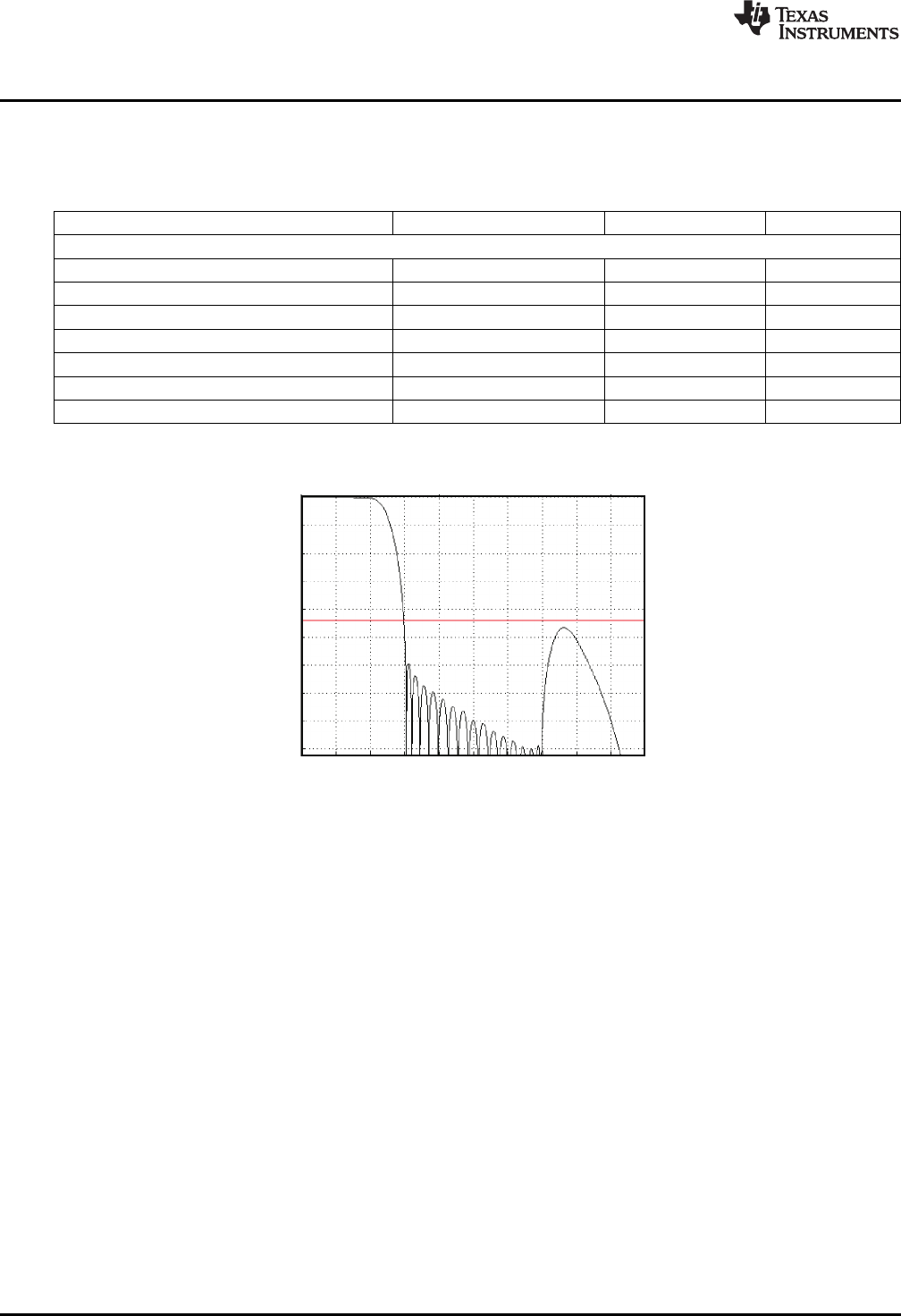

- 2.4.3 Interpolation Filters

- 2.4.4 DAC Gain Setting

- 2.4.5 DAC Special Functions

- 2.4.6 DAC Setup

- 2.4.1 Processing Blocks – Details

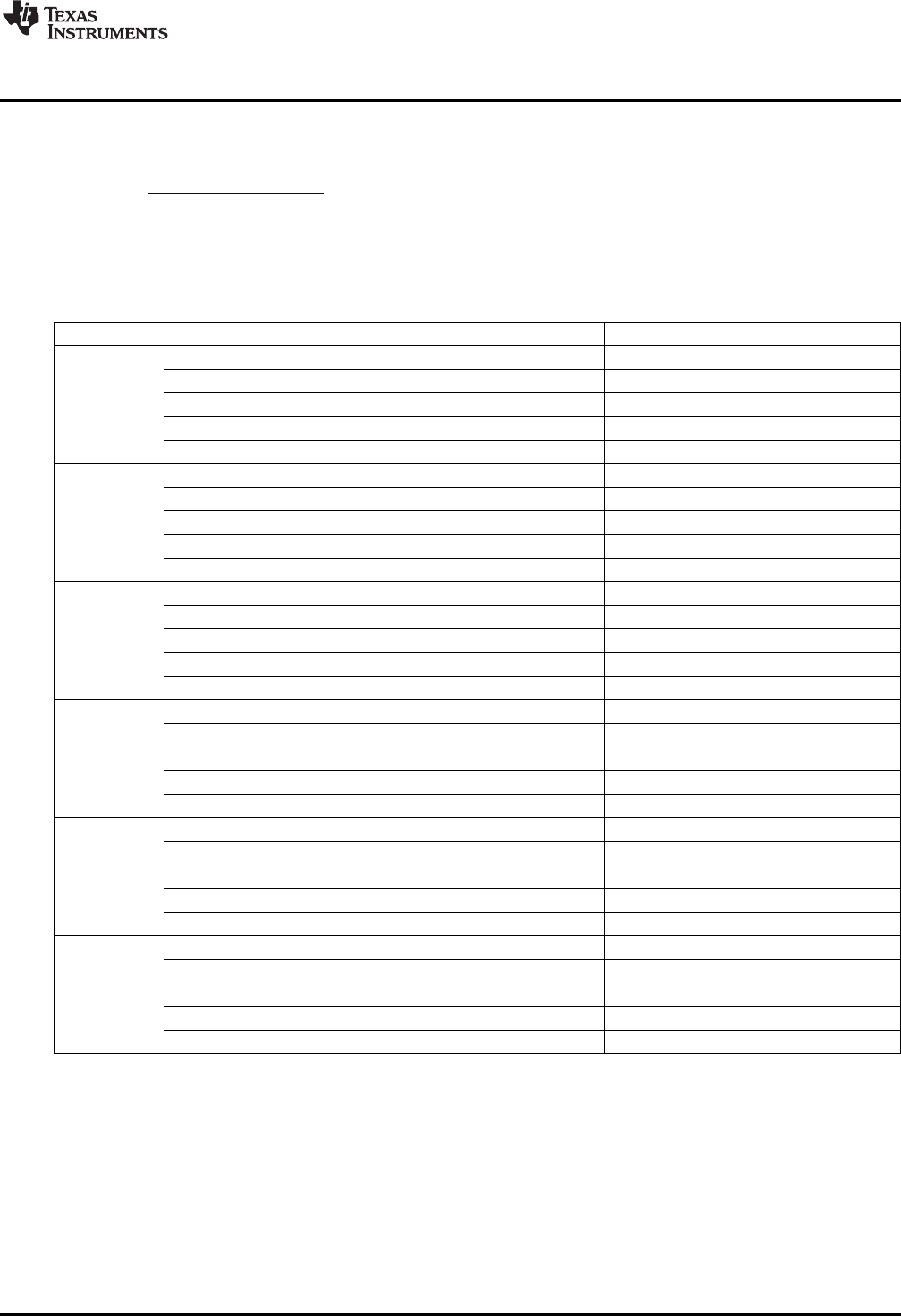

- 2.5 PowerTune

- 2.5.0.1 PowerTune Modes

- 2.5.0.2 ADC Power Consumption

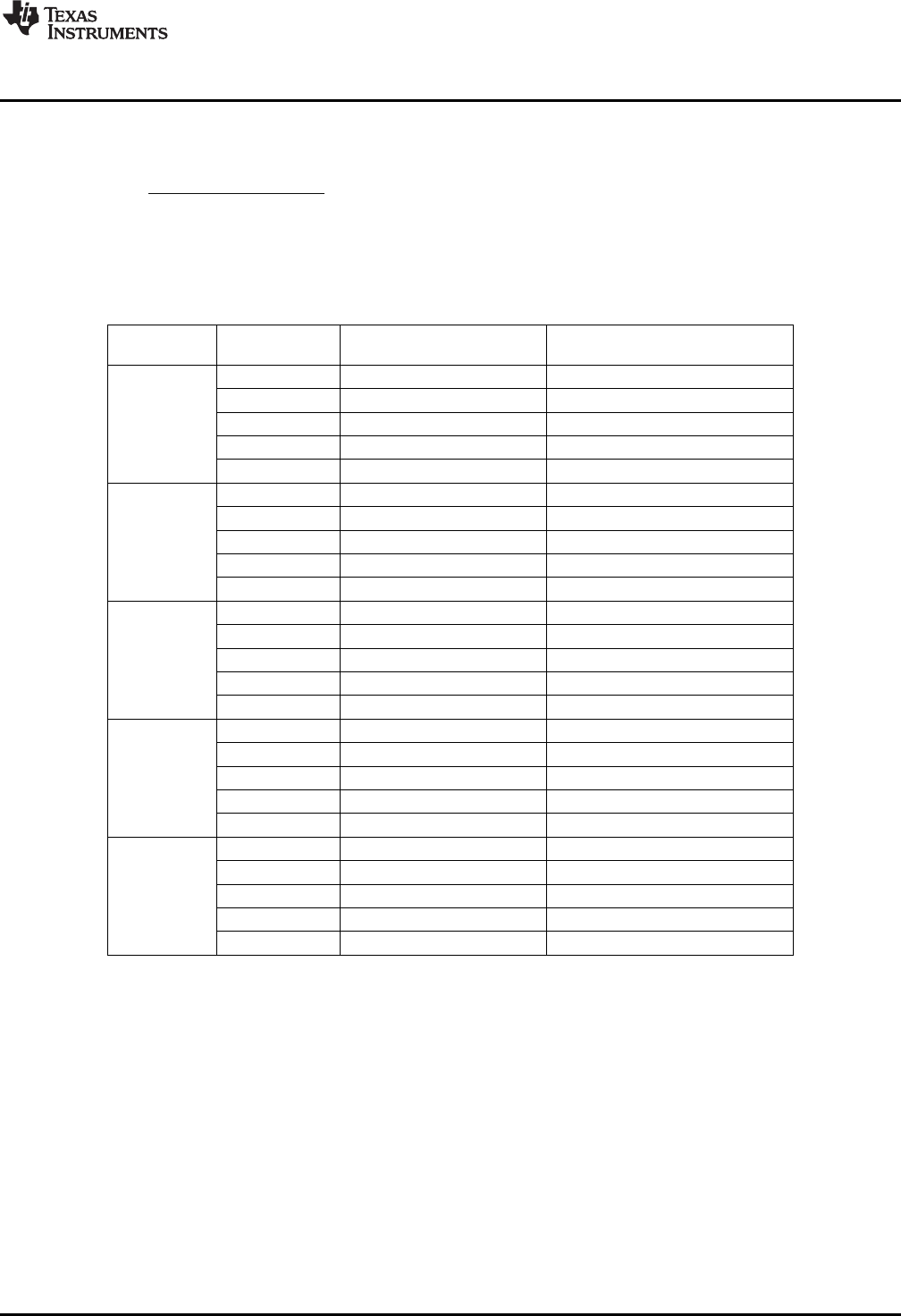

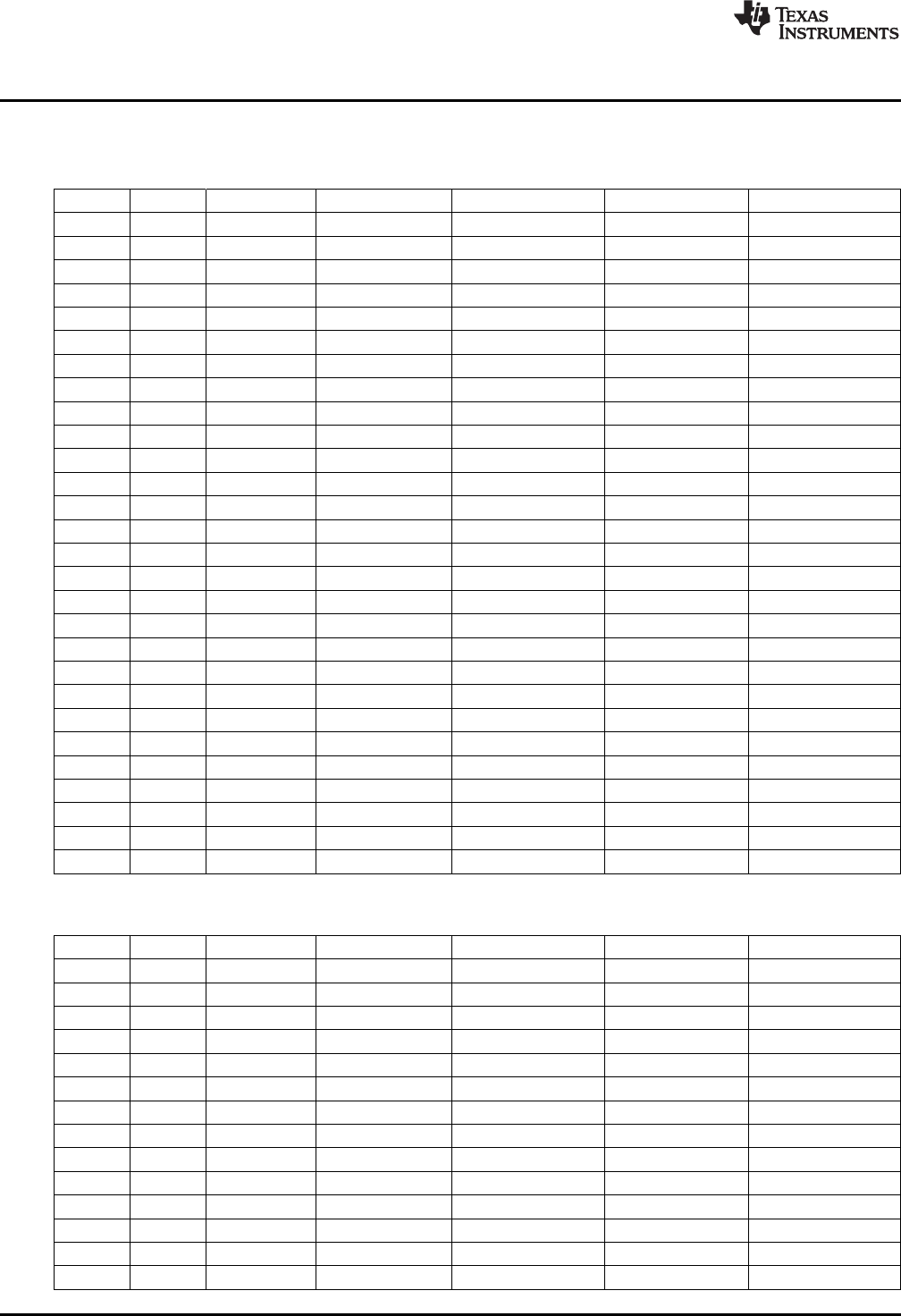

- 2.5.0.2.1 ADC, Stereo, 48kHz, Highest Performance, DVdd = 1.8V, AVdd = 1.8V

- 2.5.0.2.2 ADC, Stereo, 48kHz, DVdd = 1.8V, AVdd = 1.8V

- 2.5.0.2.3 ADC, Stereo, 48kHz, Lowest Power Consumption

- 2.5.0.2.4 ADC, Mono, 48kHz, Highest Performance, DVdd = 1.8V, AVdd = 1.8V

- 2.5.0.2.5 ADC, Mono, 48kHz, DVdd = 1.8V, AVdd = 1.8V

- 2.5.0.2.6 ADC, Mono, 48 kHz, Lowest Power Consumption,

- 2.5.0.2.7 ADC, Stereo, 8kHz, Highest Performance, DVdd = 1.8V, AVdd = 1.8V

- 2.5.0.2.8 ADC, Stereo, 8kHz, DVdd = 1.8V, AVdd = 1.8V

- 2.5.0.2.9 ADC, Stereo, 8kHz, Lowest Power Consumption,

- 2.5.0.2.10 ADC, Mono, 8kHz, Highest Performance, DVdd = 1.8V, AVdd = 1.8V

- 2.5.0.2.11 ADC, Mono, 8kHz, DVdd = 1.8V, AVdd = 1.8V

- 2.5.0.2.12 ADC, Mono, 8kHz, Lowest Power Consumption

- 2.5.0.2.13 ADC, Stereo, 192kHz, Highest Performance, DVdd = 1.8V, AVdd = 1.8V

- 2.5.0.2.14 ADC, Stereo, 192kHz, Lowest Power Consumption

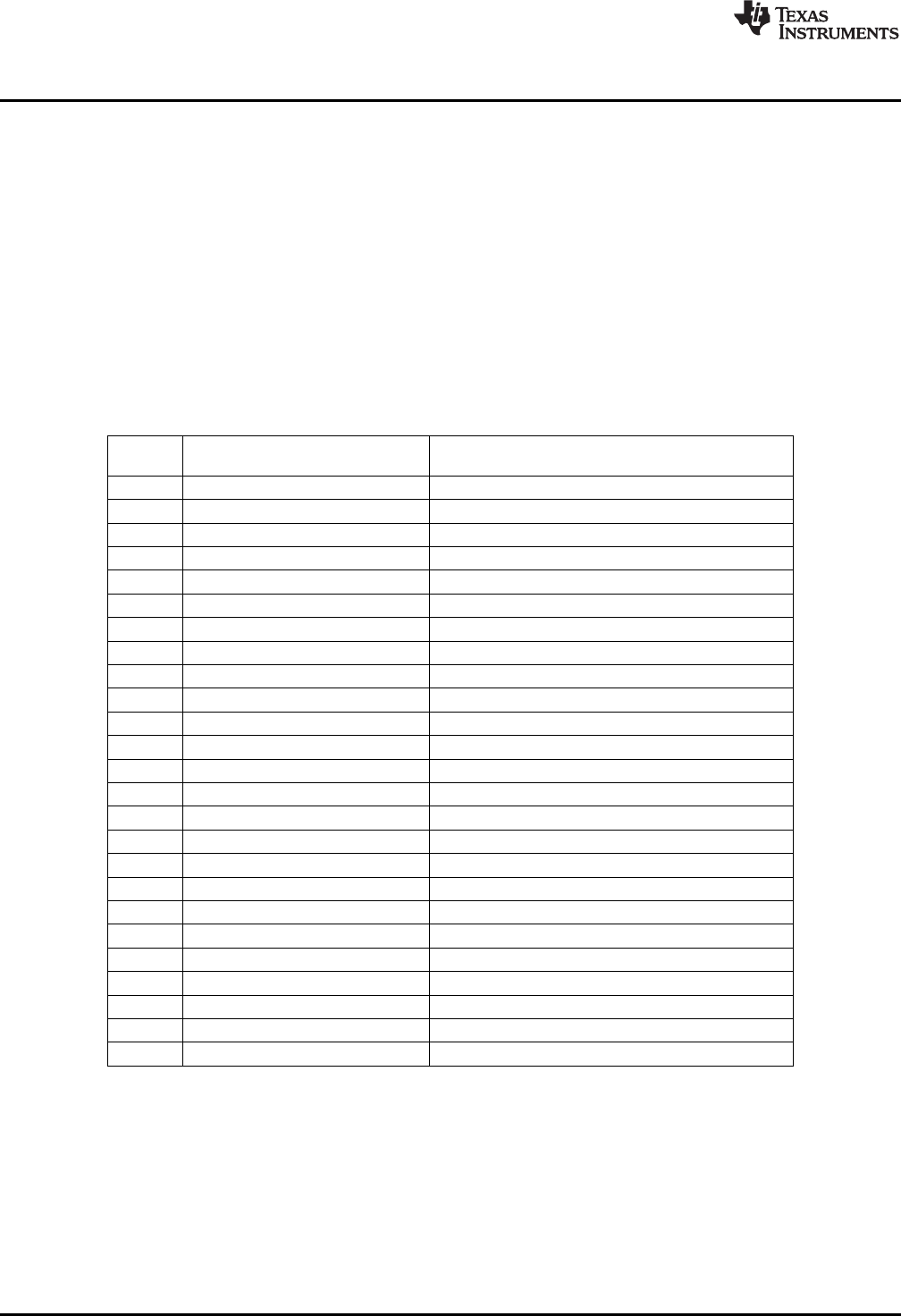

- 2.5.0.3 DAC Power Consumption

- 2.5.0.3.1 DAC, Stereo, 48kHz, Highest Performance, DVdd = 1.8V, AVdd = 1.8V

- 2.5.0.3.2 DAC, Stereo, 48kHz, Lowest Power Consumption

- 2.5.0.3.3 DAC, Mono, 48kHz, Highest Performance, DVdd = 1.8V, AVdd = 1.8V

- 2.5.0.3.4 DAC, Mono, 48kHz, Lowest Power Consumption

- 2.5.0.3.5 DAC, Stereo, 8kHz, Highest Performance, DVdd = 1.8V, AVdd = 1.8V

- 2.5.0.3.6 DAC, Stereo, 8kHz, Lowest Power Consumption

- 2.5.0.3.7 DAC, Mono, 8kHz, Highest Performance, DVdd = 1.8V, AVdd = 1.8V

- 2.5.0.3.8 DAC, Mono, 8kHz, Lowest Power Consumption

- 2.5.0.3.9 DAC, Stereo, 192kHz, DVdd = 1.8V, AVdd = 1.8V

- 2.5.0.3.10 DAC, Stereo, 192kHz, Lowest Power Consumption

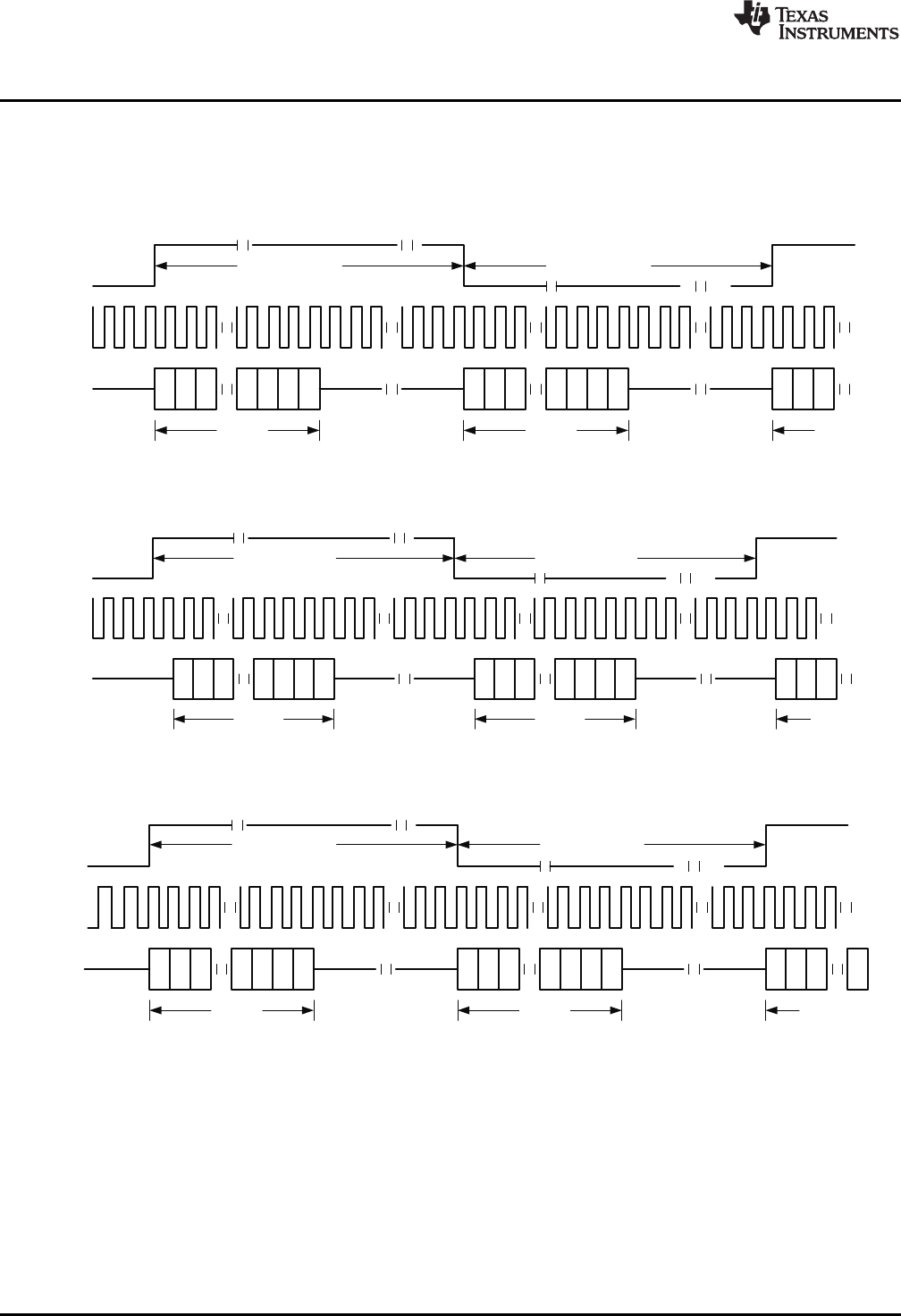

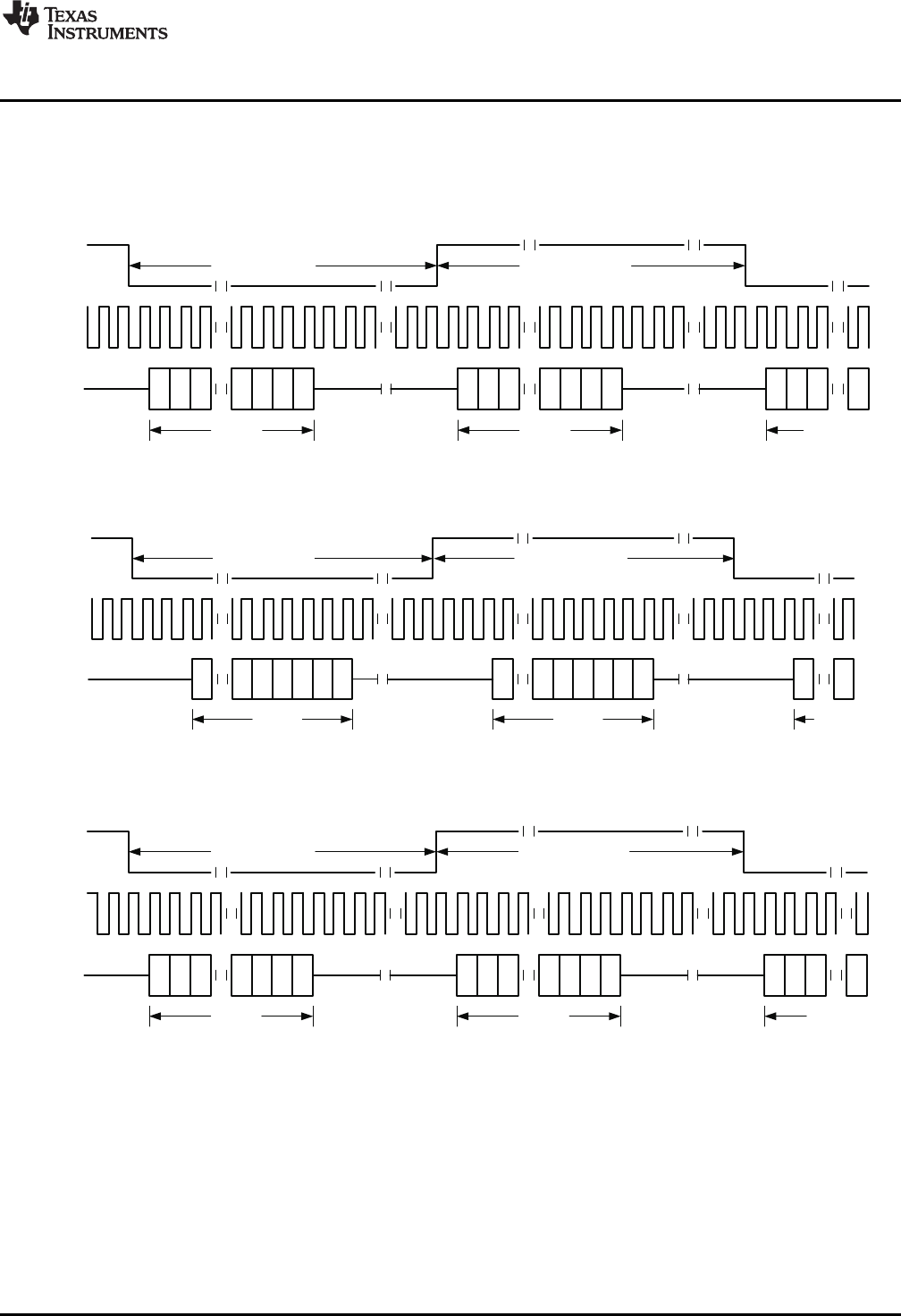

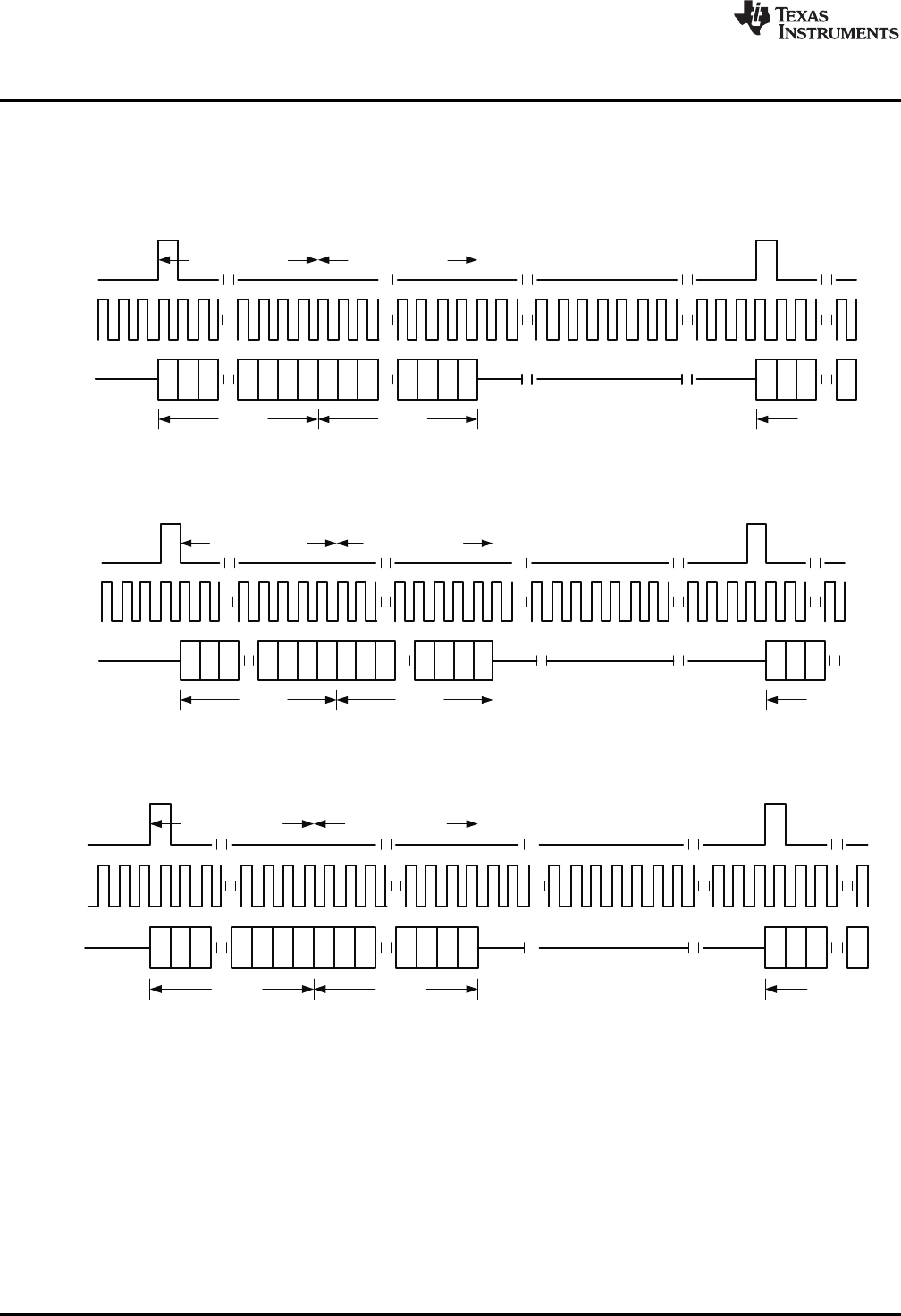

- 2.6 Audio Digital I/O Interface

- 2.7 Clock Generation and PLL

- 2.8 Control Interfaces

- 2.9 Power Supply

- 2.10 Reference Voltage

- 2.11 Device Special Functions

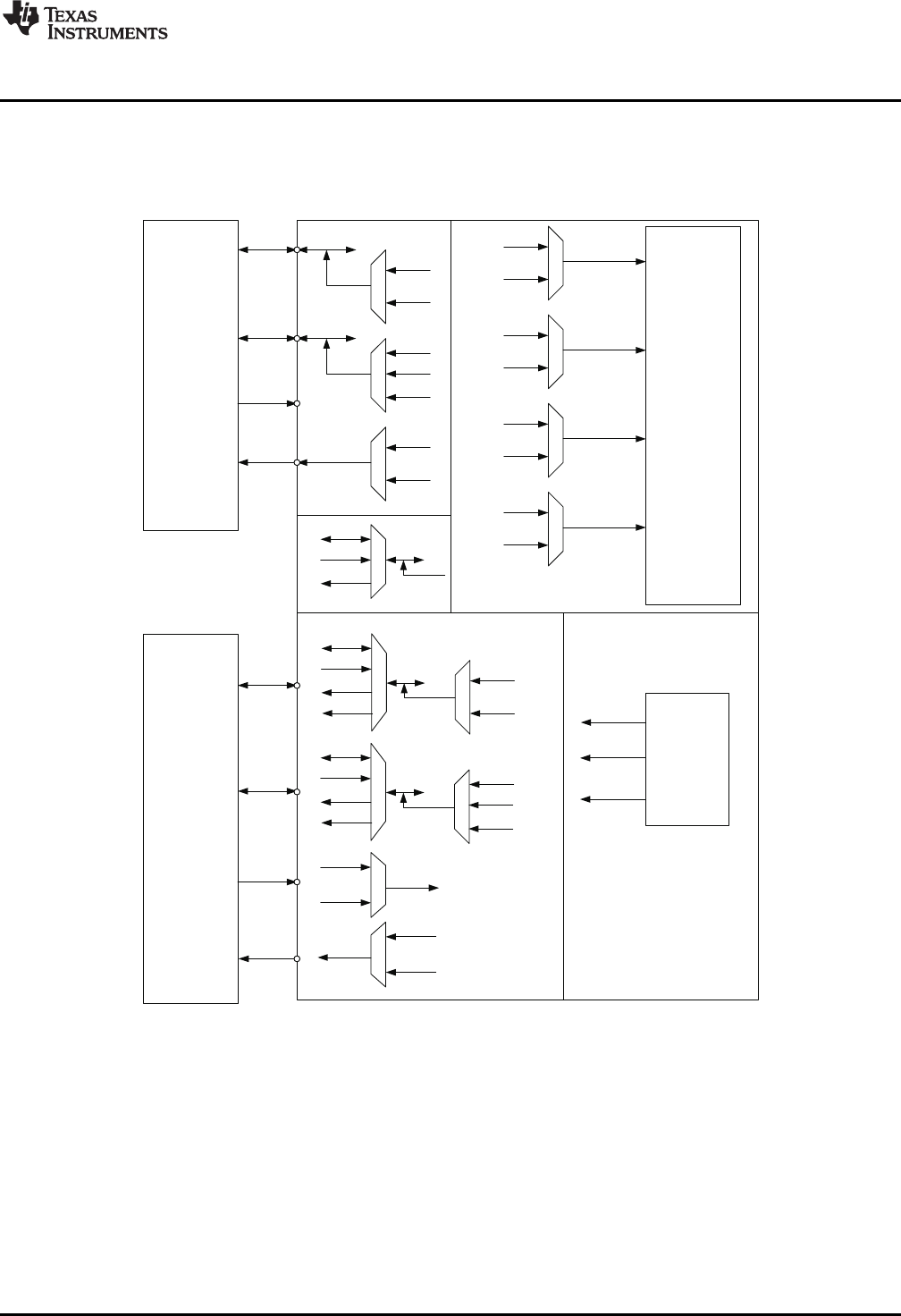

- 2.12 miniDSP

- 3 Device Initialization

- 4 Example Setups

- 5 Register Map

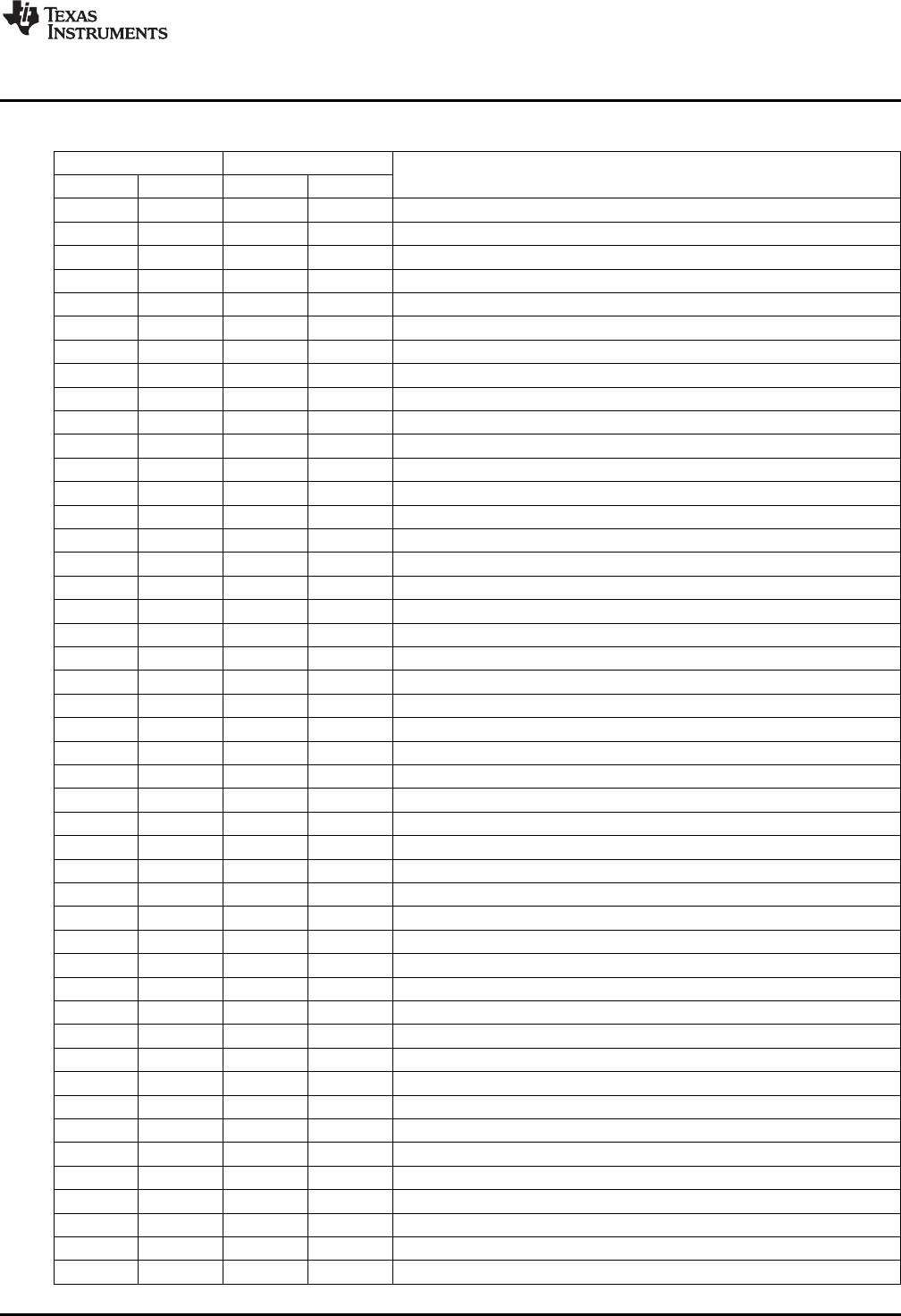

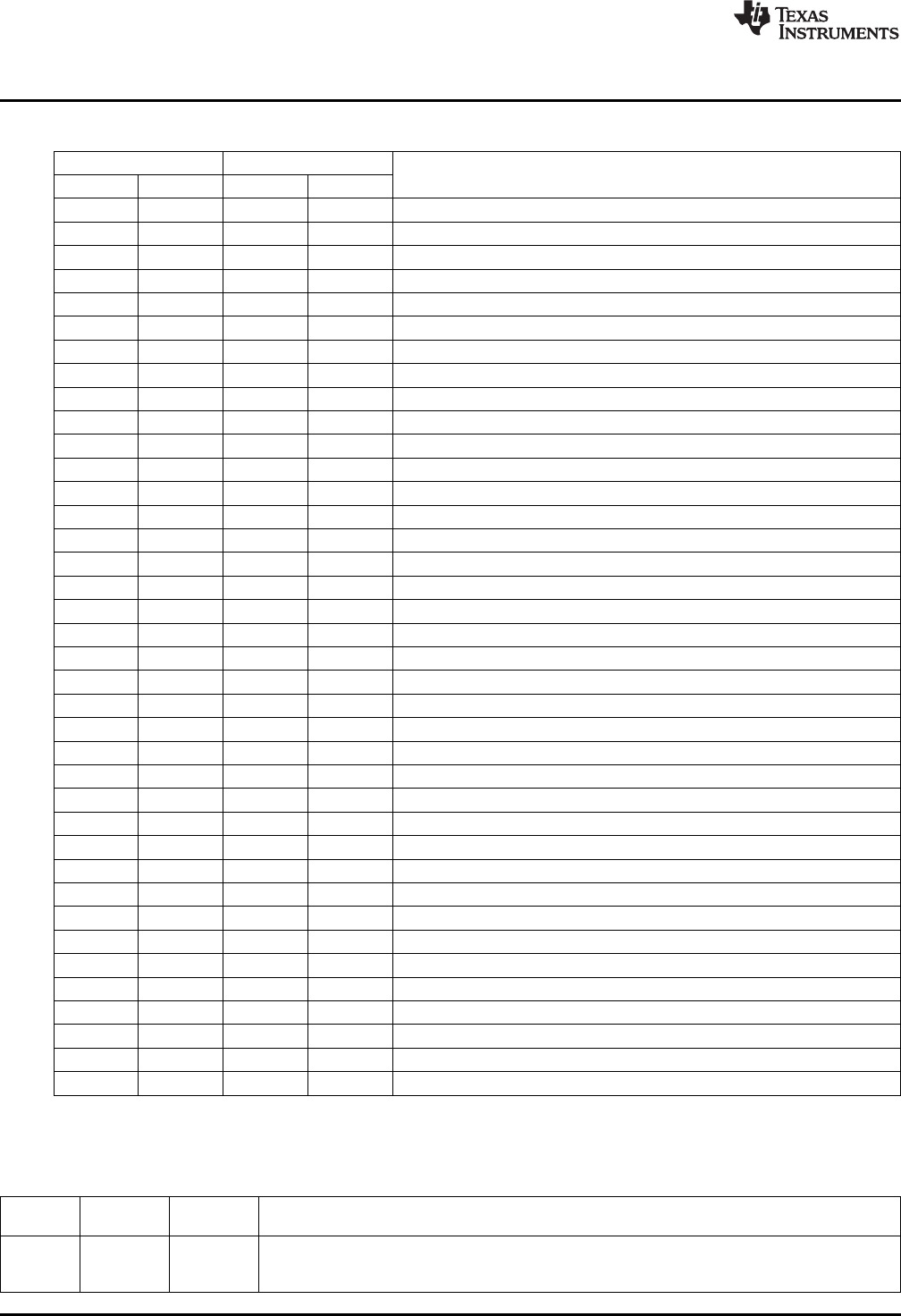

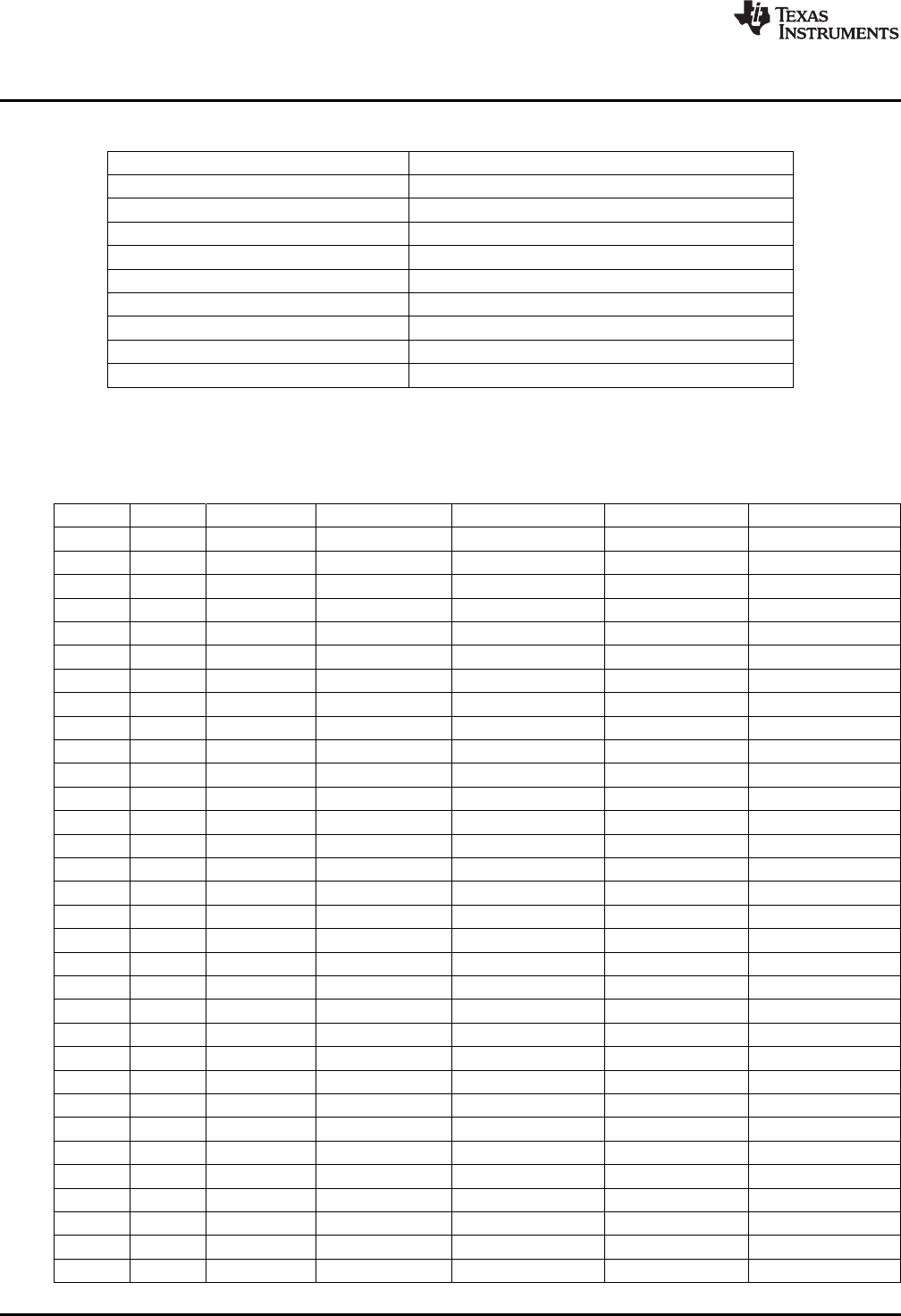

- 5.1 Register Map Summary

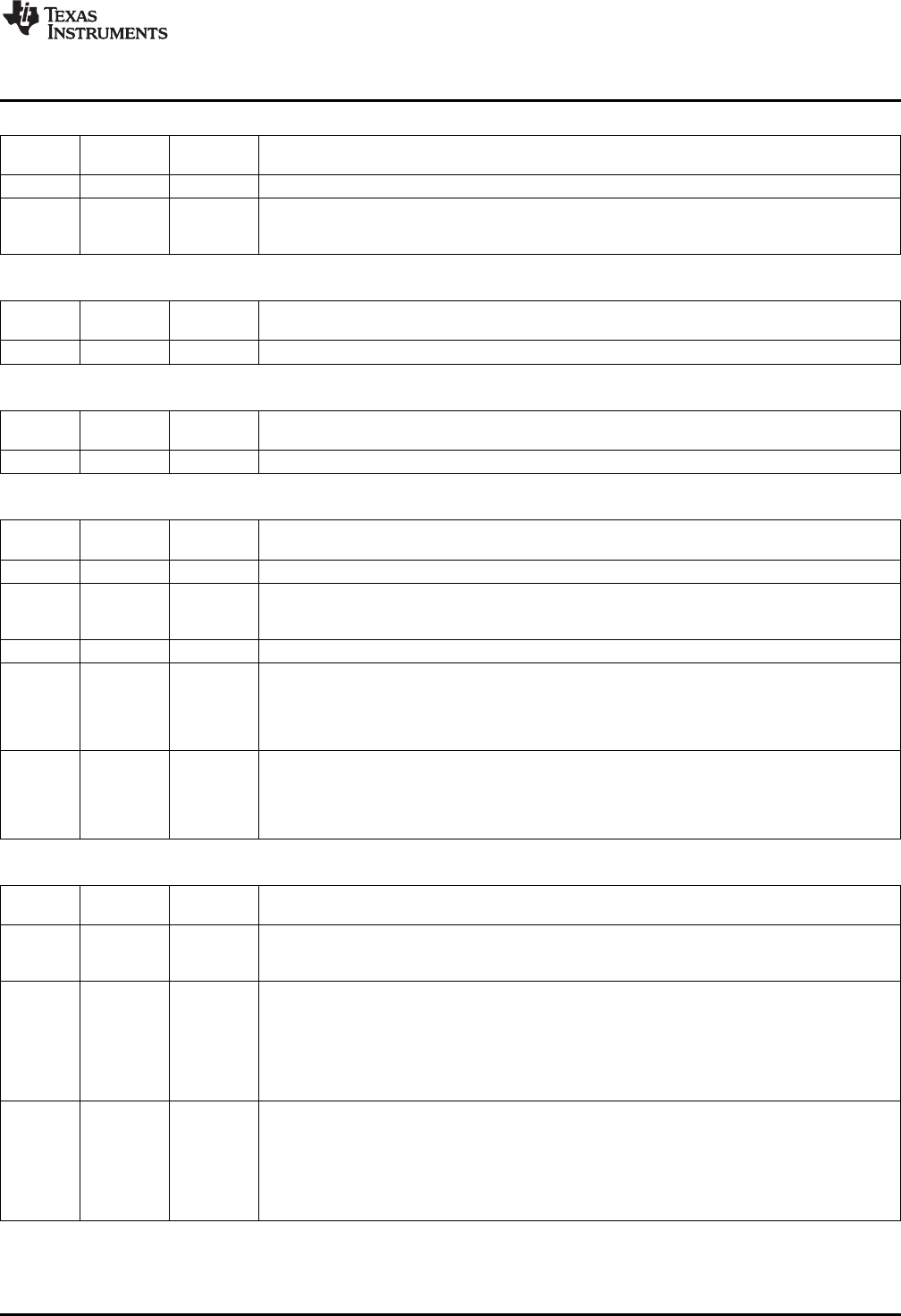

- 5.2 Page 0 Registers

- 5.2.1 Page 0 / Register 0: Page Select Register - 0x00 / 0x00

- 5.2.2 Page 0 / Register 1: Software Reset Register - 0x00 / 0x01

- 5.2.3 Page 0 / Register 2: Reserved Register - 0x00 / 0x02

- 5.2.4 Page 0 / Register 3: Reserved Register - 0x00 / 0x03

- 5.2.5 Page 0 / Register 4: Clock Setting Register 1, Multiplexers - 0x00 / 0x04

- 5.2.6 Page 0 / Register 5: Clock Setting Register 2, PLL P&R Values - 0x00 / 0x05

- 5.2.7 Page 0 / Register 6: Clock Setting Register 3, PLL J Values - 0x00 / 0x06

- 5.2.8 Page 0 / Register 7: Clock Setting Register 4, PLL D Values (MSB) - 0x00 / 0x07

- 5.2.9 Page 0 / Register 8: Clock Setting Register 5, PLL D Values (LSB) - 0x00 / 0x08

- 5.2.10 Page 0 / Register 9-10: Reserved Register - 0x00 / 0x09-0x0A

- 5.2.11 Page 0 / Register 11: Clock Setting Register 6, NDAC Values - 0x00 / 0x0B

- 5.2.12 Page 0 / Register 12: Clock Setting Register 7, MDAC Values - 0x00 / 0x0C

- 5.2.13 Page 0 / Register 13: DAC OSR Setting Register 1, MSB Value - 0x00 / 0x0D

- 5.2.14 Page 0 / Register 14: DAC OSR Setting Register 2, LSB Value - 0x00 / 0x0E

- 5.2.15 Page 0 / Register 15: miniDSP_D Instruction Control Register 1 - 0x00 / 0x0F

- 5.2.16 Page 0 / Register 16: miniDSP_D Instruction Control Register 2 - 0x00 / 0x10

- 5.2.17 Page 0 / Register 17: miniDSP_D Interpolation Factor Setting Register - 0x00 / 0x11

- 5.2.18 Page 0 / Register 18: Clock Setting Register 8, NADC Values - 0x00 / 0x12

- 5.2.19 Page 0 / Register 19: Clock Setting Register 9, MADC Values - 0x00 / 0x13

- 5.2.20 Page 0 / Register 20: ADC Oversampling (AOSR) Register - 0x00 / 0x14

- 5.2.21 Page 0 / Register 21: miniDSP_A Instruction Control Register 1 - 0x00 / 0x15

- 5.2.22 Page 0 / Register 22: miniDSP_A Instruction Control Register 2 - 0x00 / 0x16

- 5.2.23 Page 0 / Register 23: miniDSP_A Decimation Factor Setting Register - 0x00 / 0x17

- 5.2.24 Page 0 / Register 24: Reserved Register - 0x00 / 0x18

- 5.2.25 Page 0 / Register 25: Clock Setting Register 10, Multiplexers - 0x00 / 0x19

- 5.2.26 Page 0 / Register 26: Clock Setting Register 11, CLKOUT M divider value - 0x00 / 0x1A

- 5.2.27 Page 0 / Register 27: Audio Interface Setting Register 1 - 0x00 / 0x1B

- 5.2.28 Page 0 / Register 28: Audio Interface Setting Register 2, Data offset setting - 0x00 / 0x1C

- 5.2.29 Page 0 / Register 29: Audio Interface Setting Register 3 - 0x00 / 0x1D

- 5.2.30 Page 0 / Register 30: Clock Setting Register 12, BCLK N Divider - 0x00 / 0x1E

- 5.2.31 Page 0 / Register 31: Audio Interface Setting Register 4, Secondary Audio Interface - 0x00 / 0x1F

- 5.2.32 Page 0 / Register 32: Audio Interface Setting Register 5 - 0x00 / 0x20

- 5.2.33 Page 0 / Register 33: Audio Interface Setting Register 6 - 0x00 / 0x21

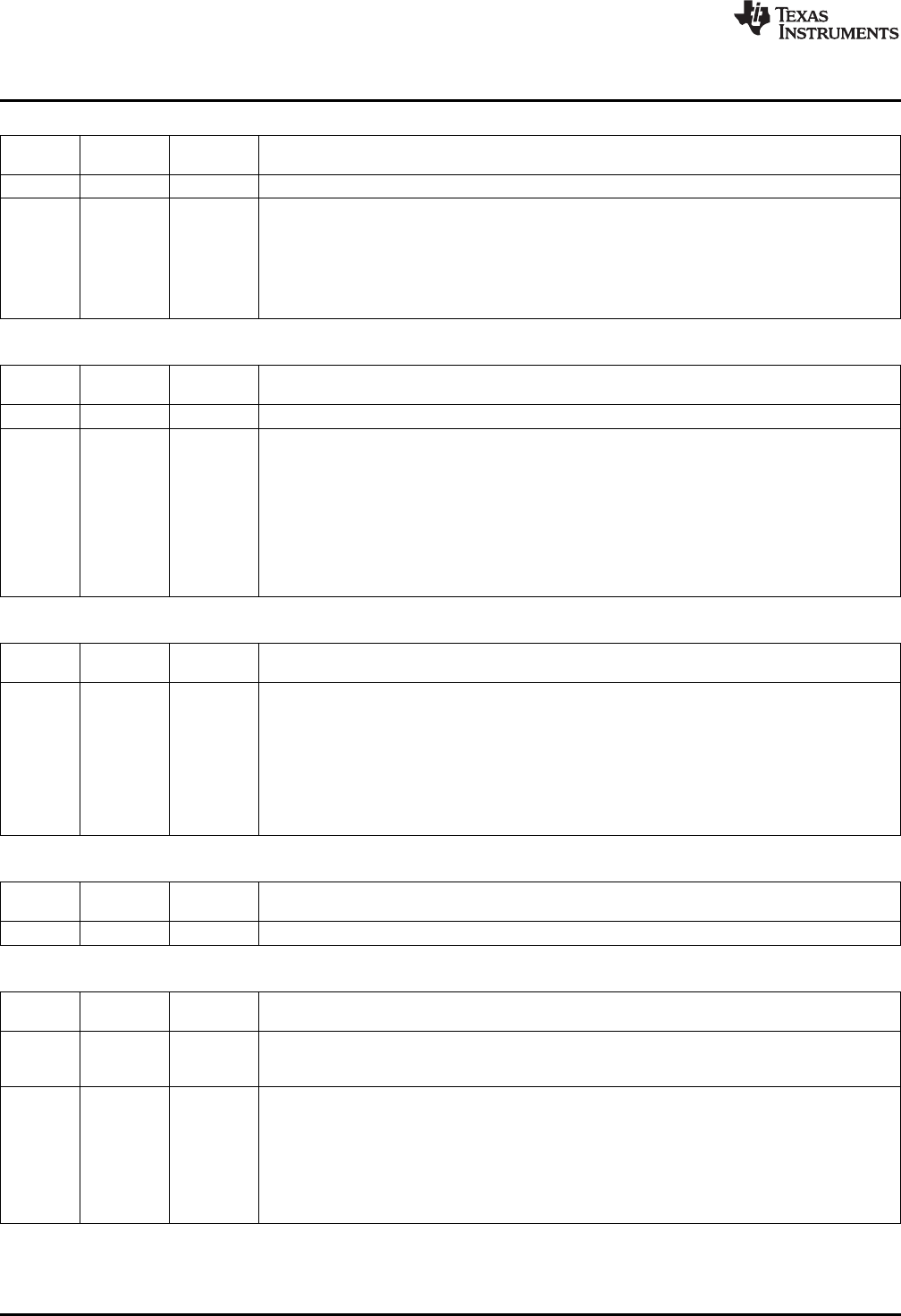

- 5.2.34 Page 0 / Register 34: Digital Interface Misc. Setting Register - 0x00 / 0x22

- 5.2.35 Page 0 / Register 35: Reserved Register - 0x00 / 0x23

- 5.2.36 Page 0 / Register 36: ADC Flag Register - 0x00 / 0x24

- 5.2.37 Page 0 / Register 37: DAC Flag Register 1 - 0x00 / 0x25

- 5.2.38 Page 0 / Register 38: DAC Flag Register 2 - 0x00 / 0x26

- 5.2.39 Page 0 / Register 39-41: Reserved Register - 0x00 / 0x27-0x29

- 5.2.40 Page 0 / Register 42: Sticky Flag Register 1 - 0x00 / 0x2A

- 5.2.41 Page 0 / Register 43: Interrupt Flag Register 1 - 0x00 / 0x2B

- 5.2.42 Page 0 / Register 44: Sticky Flag Register 2 - 0x00 / 0x2C

- 5.2.43 Page 0 / Register 45: Sticky Flag Register 3 - 0x00 / 0x2D

- 5.2.44 Page 0 / Register 46: Interrupt Flag Register 2 - 0x00 / 0x2E

- 5.2.45 Page 0 / Register 47: Interrupt Flag Register 3 - 0x00 / 0x2F

- 5.2.46 Page 0 / Register 48: INT1 Interrupt Control Register - 0x00 / 0x30

- 5.2.47 Page 0 / Register 49: INT2 Interrupt Control Register - 0x00 / 0x31

- 5.2.48 Page 0 / Register 50-51: Reserved Register - 0x00 / 0x32-0x33

- 5.2.49 Page 0 / Register 52: GPIOorMFP5 Control Register - 0x00 / 0x34

- 5.2.50 Page 0 / Register 53: DOUT or MFP2 Function Control Register - 0x00 / 0x35

- 5.2.51 Page 0 / Register 54: DIN or MFP1 Function Control Register - 0x00 / 0x36

- 5.2.52 Page 0 / Register 55: MISO or MFP4 Function Control Register - 0x00 / 0x37

- 5.2.53 Page 0 / Register 56: SCLK or MFP3 Function Control Register - 0x00 / 0x38

- 5.2.54 Page 0 / Register 57-59: Reserved Registers - 0x00 / 0x39-0x3B

- 5.2.55 Page 0 / Register 60: DAC Signal Processing Block Control Register - 0x00 / 0x3C

- 5.2.56 Page 0 / Register 61: ADC Signal Processing Block Control Register - 0x00 / 0x3D

- 5.2.57 Page 0 / Register 62: miniDSP_A and miniDSP_D Configuration Register - 0x00 / 0x3E

- 5.2.58 Page 0 / Register 63: DAC Channel Setup Register 1 - 0x00 / 0x3F

- 5.2.59 Page 0 / Register 64: DAC Channel Setup Register 2 - 0x00 / 0x40

- 5.2.60 Page 0 / Register 65: Left DAC Channel Digital Volume Control Register - 0x00 / 0x41

- 5.2.61 Page 0 / Register 66: Right DAC Channel Digital Volume Control Register - 0x00 / 0x42

- 5.2.62 Page 0 / Register 67: Headset Detection Configuration Register - 0x00 / 0x43

- 5.2.63 Page 0 / Register 68: DRC Control Register 1 - 0x00 / 0x44

- 5.2.64 Page 0 / Register 69: DRC Control Register 2 - 0x00 / 0x45

- 5.2.65 Page 0 / Register 70: DRC Control Register 3 - 0x00 / 0x46

- 5.2.66 Page 0 / Register 71: Beep Generator Register 1 - 0x00 / 0x47

- 5.2.67 Page 0 / Register 72: Beep Generator Register 2 - 0x00 / 0x48

- 5.2.68 Page 0 / Register 73: Beep Generator Register 3 - 0x00 / 0x49

- 5.2.69 Page 0 / Register 74: Beep Generator Register 4 - 0x00 / 0x4A

- 5.2.70 Page 0 / Register 75: Beep Generator Register 5 - 0x00 / 0x4B

- 5.2.71 Page 0 / Register 76: Beep Generator Register 6 - 0x00 / 0x4C

- 5.2.72 Page 0 / Register 77: Beep Generator Register 7 - 0x00 / 0x4D

- 5.2.73 Page 0 / Register 78: Beep Generator Register 8 - 0x00 / 0x4E

- 5.2.74 Page 0 / Register 79: Beep Generator Register 9 - 0x00 / 0x4F

- 5.2.75 Page 0 / Register 80: Reserved Register - 0x00 / 0x50

- 5.2.76 Page 0 / Register 81: ADC Channel Setup Register - 0x00 / 0x51

- 5.2.77 Page 0 / Register 82: ADC Fine Gain Adjust Register - 0x00 / 0x52

- 5.2.78 Page 0 / Register 83: Left ADC Channel Volume Control Register - 0x00 / 0x53

- 5.2.79 Page 0 / Register 84: Right ADC Channel Volume Control Register - 0x00 / 0x54

- 5.2.80 Page 0 / Register 85: ADC Phase Adjust Register - 0x00 / 0x55

- 5.2.81 Page 0 / Register 86: Left Channel AGC Control Register 1 - 0x00 / 0x56

- 5.2.82 Page 0 / Register 87: Left Channel AGC Control Register 2 - 0x00 / 0x57

- 5.2.83 Page 0 / Register 88: Left Channel AGC Control Register 3 - 0x00 / 0x58

- 5.2.84 Page 0 / Register 89: Left Channel AGC Control Register 4 - 0x00 / 0x59

- 5.2.85 Page 0 / Register 90: Left Channel AGC Control Register 5 - 0x00 / 0x5A

- 5.2.86 Page 0 / Register 91: Left Channel AGC Control Register 6 - 0x00 / 0x5B

- 5.2.87 Page 0 / Register 92: Left Channel AGC Control Register 7 - 0x00 / 0x5C

- 5.2.88 Page 0 / Register 93: Left Channel AGC Control Register 8 - 0x00 / 0x5D

- 5.2.89 Page 0 / Register 94: Right Channel AGC Control Register 1 - 0x00 / 0x5E

- 5.2.90 Page 0 / Register 95: Right Channel AGC Control Register 2 - 0x00 / 0x5F

- 5.2.91 Page 0 / Register 96: Right Channel AGC Control Register 3 - 0x00 / 0x60

- 5.2.92 Page 0 / Register 97: Right Channel AGC Control Register 4 - 0x00 / 0x61

- 5.2.93 Page 0 / Register 98: Right Channel AGC Control Register 5 - 0x00 / 0x62

- 5.2.94 Page 0 / Register 99: Right Channel AGC Control Register 6 - 0x00 / 0x63

- 5.2.95 Page 0 / Register 100: Right Channel AGC Control Register 7 - 0x00 / 0x64

- 5.2.96 Page 0 / Register 101: Right Channel AGC Control Register 8 - 0x00 / 0x65

- 5.2.97 Page 0 / Register 102: DC Measurement Register 1 - 0x00 / 0x66

- 5.2.98 Page 0 / Register 103: DC Measurement Register 2 - 0x00 / 0x67

- 5.2.99 Page 0 / Register 104: Left Channel DC Measurement Output Register 1 - 0x00 / 0x68

- 5.2.100 Page 0 / Register 105: Left Channel DC Measurement Output Register 2 - 0x00 / 0x69

- 5.2.101 Page 0 / Register 106: Left Channel DC Measurement Output Register 3 - 0x00 / 0x6A

- 5.2.102 Page 0 / Register 107: Right Channel DC Measurement Output Register 1 - 0x00 / 0x6B

- 5.2.103 Page 0 / Register 108: Right Channel DC Measurement Output Register 2 - 0x00 / 0x6C

- 5.2.104 Page 0 / Register 109: Right Channel DC Measurement Output Register 3 - 0x00 / 0x6D

- 5.2.105 Page 0 / Register 110-127: Reserved Register - 0x00 / 0x6E-0x7F

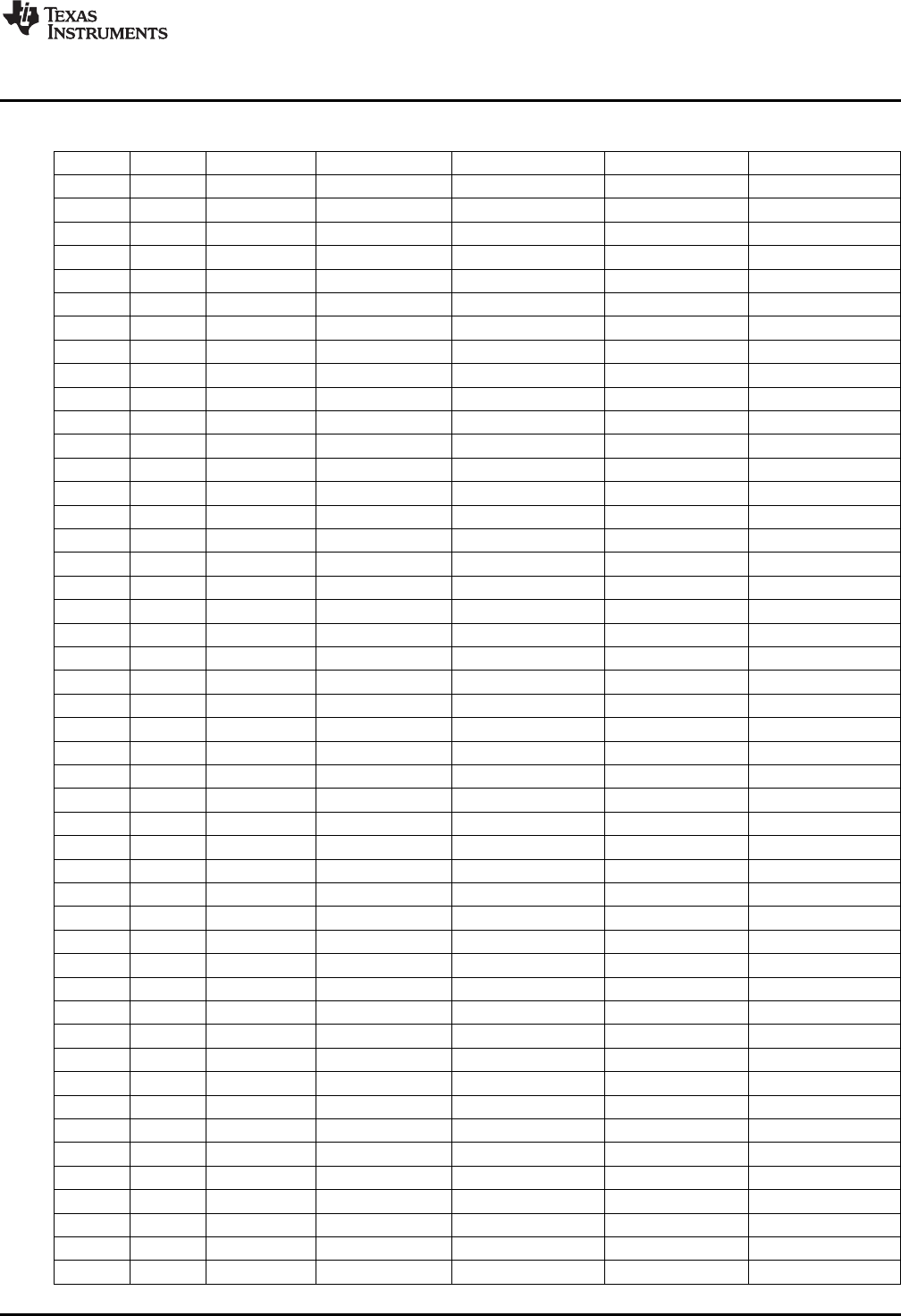

- 5.3 Page 1 Registers

- 5.3.1 Page 1 / Register 0: Page Select Register - 0x01 / 0x00

- 5.3.2 Page 1 / Register 1: Power Configuration Register 1 - 0x01 / 0x01

- 5.3.3 Page 1 / Register 2: Power Configuration Register 2 - 0x01 / 0x02

- 5.3.4 Page 1 / Register 3: Playback Configuration Register 1 - 0x01 / 0x03

- 5.3.5 Page 1 / Register 4: Playback Configuration Register 2 - 0x01 / 0x04

- 5.3.6 Page 1 / Register 5-8: Reserved Register - 0x01 / 0x05-0x08

- 5.3.7 Page 1 / Register 9: Output Driver Power Control Register - 0x01 / 0x09

- 5.3.8 Page 1 / Register 10: Common Mode Control Register - 0x01 / 0x0A

- 5.3.9 Page 1 / Register 11: Over Current Protection Configuration Register - 0x01 / 0x0B

- 5.3.10 Page 1 / Register 12: HPL Routing Selection Register - 0x01 / 0x0C

- 5.3.11 Page 1 / Register 13: HPR Routing Selection Register - 0x01 / 0x0D

- 5.3.12 Page 1 / Register 14: LOL Routing Selection Register - 0x01 / 0x0E

- 5.3.13 Page 1 / Register 15: LOR Routing Selection Register - 0x01 / 0x0F

- 5.3.14 Page 1 / Register 16: HPL Driver Gain Setting Register - 0x01 / 0x10

- 5.3.15 Page 1 / Register 17: HPR Driver Gain Setting Register - 0x01 / 0x11

- 5.3.16 Page 1 / Register 18: LOL Driver Gain Setting Register - 0x01 / 0x12

- 5.3.17 Page 1 / Register 19: LOR Driver Gain Setting Register - 0x01 / 0x13

- 5.3.18 Page 1 / Register 20: Headphone Driver Startup Control Register - 0x01 / 0x14

- 5.3.19 Page 1 / Register 21: Reserved Register - 0x01 / 0x15

- 5.3.20 Page 1 / Register 22: IN1L to HPL Volume Control Register - 0x01 / 0x16

- 5.3.21 Page 1 / Register 23: IN1R to HPR Volume Control Register - 0x01 / 0x17

- 5.3.22 Page 1 / Register 24: Mixer Amplifier Left Volume Control Register - 0x01 / 0x18

- 5.3.23 Page 1 / Register 25: Mixer Amplifier Right Volume Control Register - 0x01 / 0x19

- 5.3.24 Page 1 / Register 26-50: Reserved Register - 0x01 / 0x1A-0x32

- 5.3.25 Page 1 / Register 51: MICBIAS Configuration Register - 0x01 / 0x33

- 5.3.26 Page 1 / Register 52: Left MICPGA Positive Terminal Input Routing Configuration Register - 0x01 / 0x34

- 5.3.27 Page 1 / Register 53: Reserved Register - 0x01 / 0x35

- 5.3.28 Page 1 / Register 54: Left MICPGA Negative Terminal Input Routing Configuration Register - 0x01 / 0x36

- 5.3.29 Page 1 / Register 55: Right MICPGA Positive Terminal Input Routing Configuration Register - 0x01 / 0x37

- 5.3.30 Page 1 / Register 56: Reserved Register - 0x01 / 0x38

- 5.3.31 Page 1 / Register 57: Right MICPGA Negative Terminal Input Routing Configuration Register - 0x01 / 0x39

- 5.3.32 Page 1 / Register 58: Floating Input Configuration Register - 0x01 / 0x3A

- 5.3.33 Page 1 / Register 59: Left MICPGA Volume Control Register - 0x01 / 0x3B

- 5.3.34 Page 1 / Register 60: Right MICPGA Volume Control Register - 0x01 / 0x3C

- 5.3.35 Page 1 / Register 61: ADC Power Tune Configuration Register - 0x01 / 0x3D

- 5.3.36 Page 1 / Register 62: ADC Analog Volume Control Flag Register - 0x01 / 0x3E

- 5.3.37 Page 1 / Register 63: DAC Analog Gain Control Flag Register - 0x01 / 0x3F

- 5.3.38 Page 1 / Register 64-70: Reserved Register - 0x01 / 0x40-0x46

- 5.3.39 Page 1 / Register 71: Analog Input Quick Charging Configuration Register - 0x01 / 0x47

- 5.3.40 Page 1 / Register 72-122: Reserved Register - 0x01 / 0x48-0x7A

- 5.3.41 Page 1 / Register 123: Reference Power-up Configuration Register - 0x01 / 0x7B

- 5.3.42 Page 1 / Register 124: Charge Pump Control Register - 0x01 / 0x7C

- 5.3.43 Page 1 / Register 125: Headphone Driver Configuration Register - 0x01 / 0x7D

- 5.3.44 Page 1 / Register 126-127: Reserved Register - 0x01 / 0x7E-0x7F

- 5.4 Page 8 Registers

- 5.5 Page 9-16 Registers

- 5.6 Page 26-34 Registers

- 5.7 Page 44 Registers

- 5.8 Page 45-52 Registers

- 5.9 Page 62-70 Registers

- 5.10 Page 80-114 Registers

- 5.11 Page 152-186 Registers

- 5.12 ADC Coefficients A+B

- 5.13 ADC Defaults

- 5.14 DAC Coefficients A+B

- 5.15 DAC Defaults

- 5.16 ADC miniDSP Instructions

- 5.17 DAC miniDSP Instructions

TLV320AIC3256 Application Reference Guide

Reference Guide

Literature Number: SLAU306A

January 2011–Revised January 2013

Chapter 1

SLAU306A–January 2011–Revised January 2013

TLV320AIC3256 Overview

•Chapter 1: Device Overview

•Chapter 2: TLV320AIC3256 Application

•Chapter 3: Device Initialization

•Chapter 4: Example Setups

•Chapter 5: Register Map and Descriptions

space

Features Applications

• Stereo Audio DAC with 100dB SNR • Portable Navigation Devices (PND)

• 5.0mW Stereo 48ksps DAC-to-Ground-Centered • Portable Media Player (PMP)

Headphone Playback • Mobile Handsets

• Stereo Audio ADC with 93dB SNR • Communication

• 5.2mW Stereo 48ksps ADC Record • Portable Computing

• PowerTune™ • Acoustic Echo Cancellation (AEC)

• Extensive Signal Processing Options • Active Noise Cancellation (ANC)

• Embedded miniDSP • Advanced DSP algorithms

• Six Single-Ended or 3 Fully-Differential Analog The TLV320AIC3256 (sometimes referred to as the

Inputs AIC3256) is a flexible, low-power, low-voltage

• Stereo Analog and Digital Microphone Inputs stereo audio codec with programmable inputs and

outputs, PowerTune capabilities, fully-

• Ground-Centered Stereo Headphone Outputs programmable miniDSP, fixed predefined and

• Stereo Line Outputs parameterizable signal processing blocks,

• Very Low-Noise PGA integrated PLL, and flexible digital interfaces.

• Low Power Analog Bypass Mode Extensive register-based control of power,

input/output channel configuration, gains, effects,

• Programmable Microphone Bias pin-multiplexing and clocks is included, allowing the

• Programmable PLL device to be precisely targeted to its application.

• 5mm x 5mm 40-pin QFN or 3.5mm x 3.3mm 42-

ball WCSP Package

2TLV320AIC3256 Overview SLAU306A–January 2011–Revised January 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

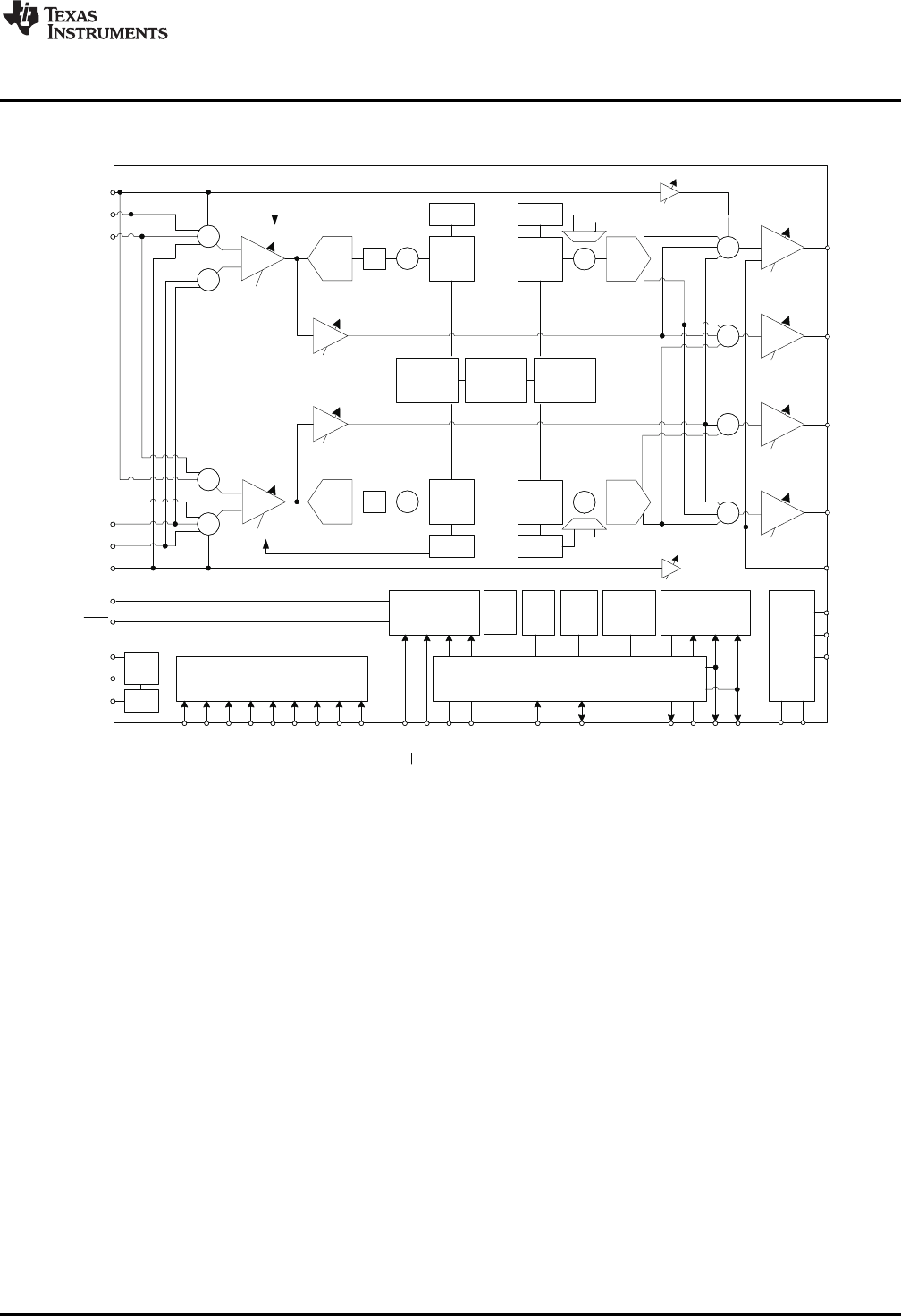

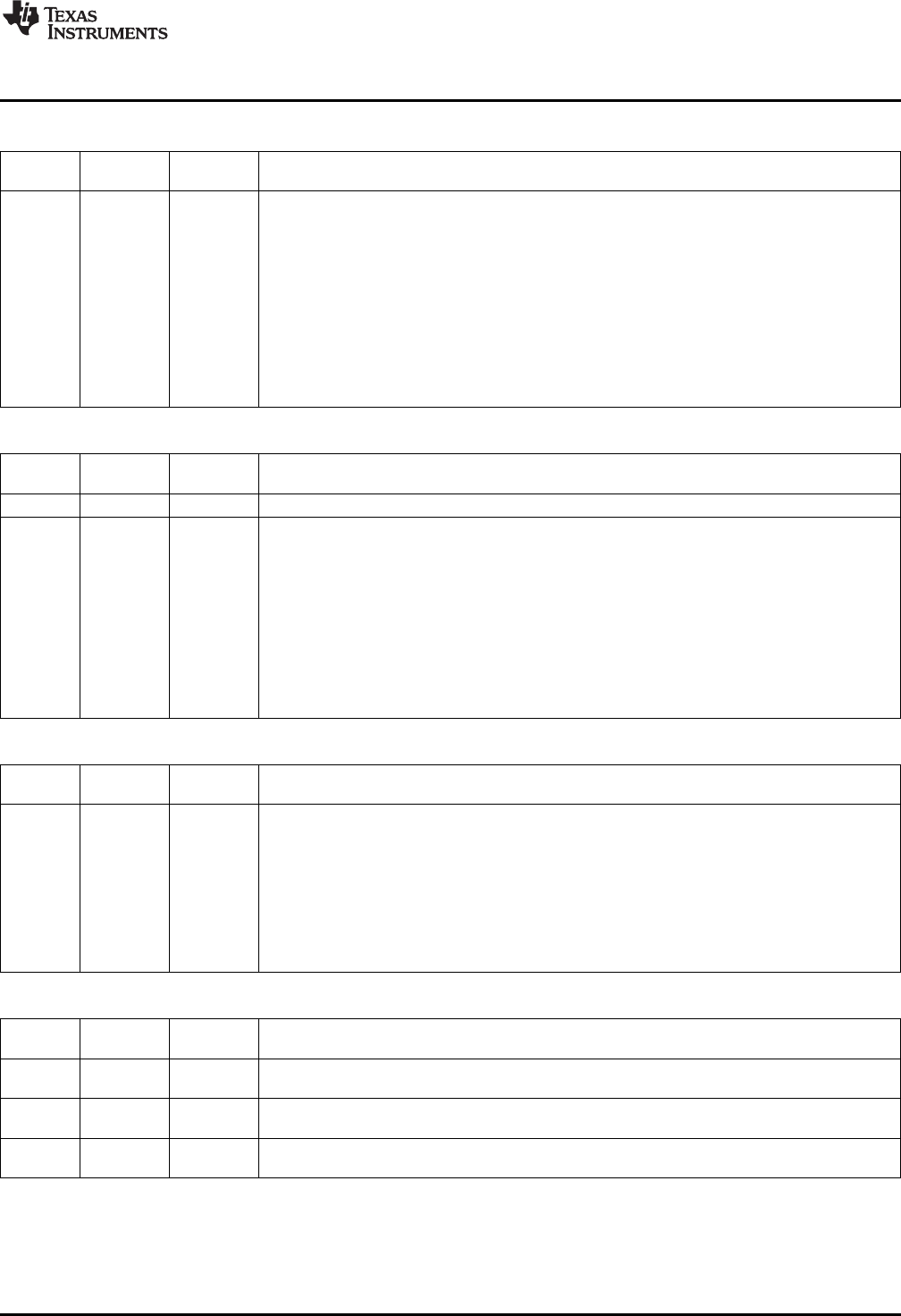

SPI_Select

IN1_R

IN2_R

IN3_R

IN3_L

IN2_L

IN1_L

Left

ADC

DRC

tpl

Left

DAC

AGC

*+

+

+

+

∗

ADC

Signal

Proc.

DAC

Signal

Proc.

Right

ADC

DRC

tpr Right

DAC

AGC

∗ ∗

ADC

Signal

Proc.

DAC

Signal

Proc.

+

+

+

+

Vol. Ctrl

Vol. Ctrl

Data

Interface

Gain Adj.

Gain Adj.

0…

+47.5 dB

0.5 dB steps

0…+47.5 dB

0.5 dB

steps

-6...+14dB

1dB steps

-6...+29dB

1dB steps

-6...+29dB

1dB steps

-6...+14dB

1dB steps

SPI / I2C

Control Block

Pin Muxing / Clock Routing

Sec.

I2S I/F

Primary

I2S Interface

Dig

Mic

Inter

rupt

PLL

Mic

Bias

Ref

MicBias

Ref

Supplies

DVdd

Vsys

IOVdd

Avss (GND)

DVss (GND)

IOVss (GND)

SDA/MOSI

MISO

SCLK

MCLK

GPIO

DOUT

DIN

BCLK

WCLK

miniDSP miniDSP

HPL

LOL

HPR

LOR

Reset

-30...0 dB

-30...0 dB

Charge

Pump

GND_Sense

MicDet

VNEG

Fly_N

DVSS_CP

Fly_P

DVDD_CP

DRVdd_HP

SCL/SS

GND

AVdd

www.ti.com

Description

1.1 Description

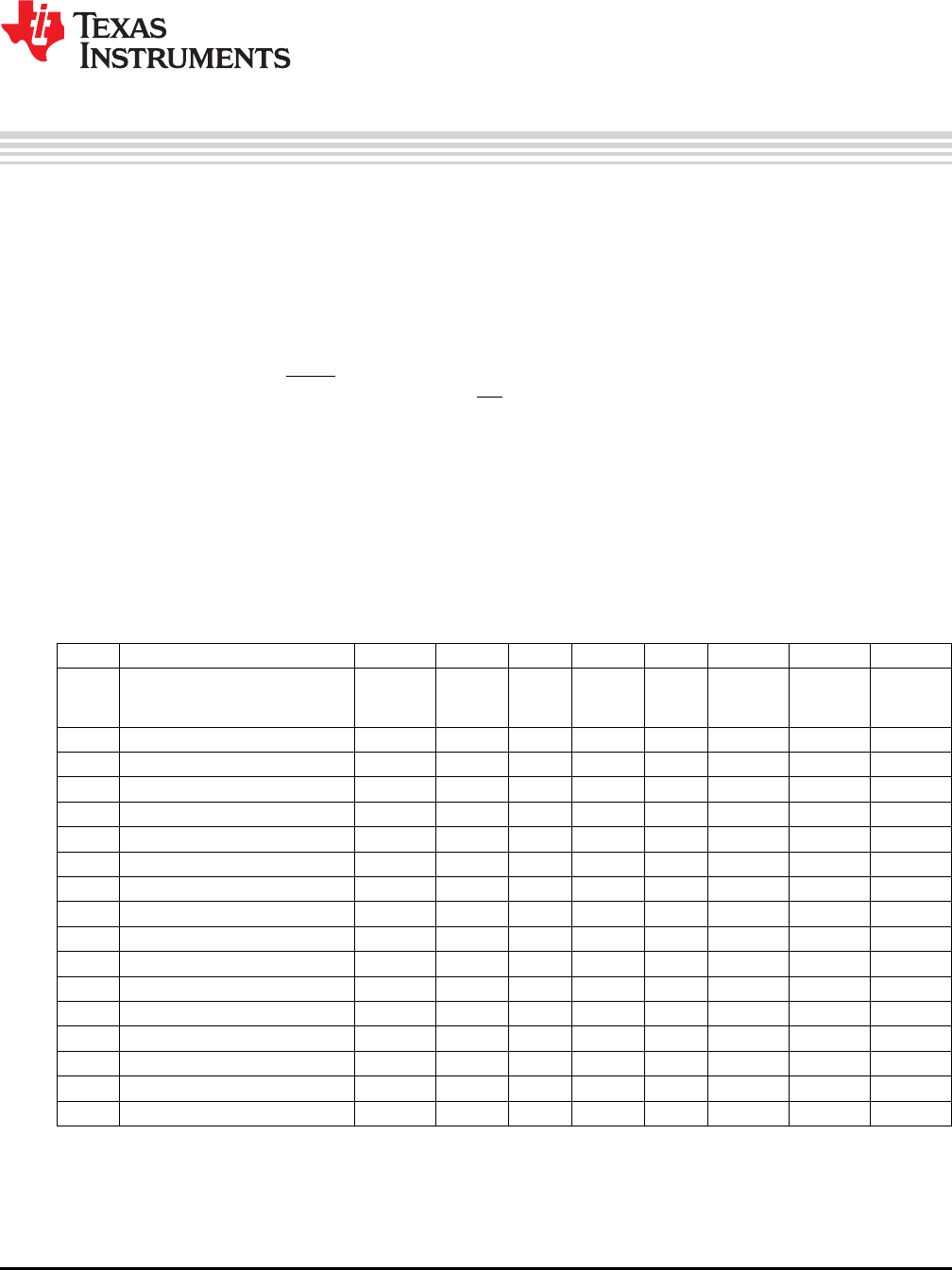

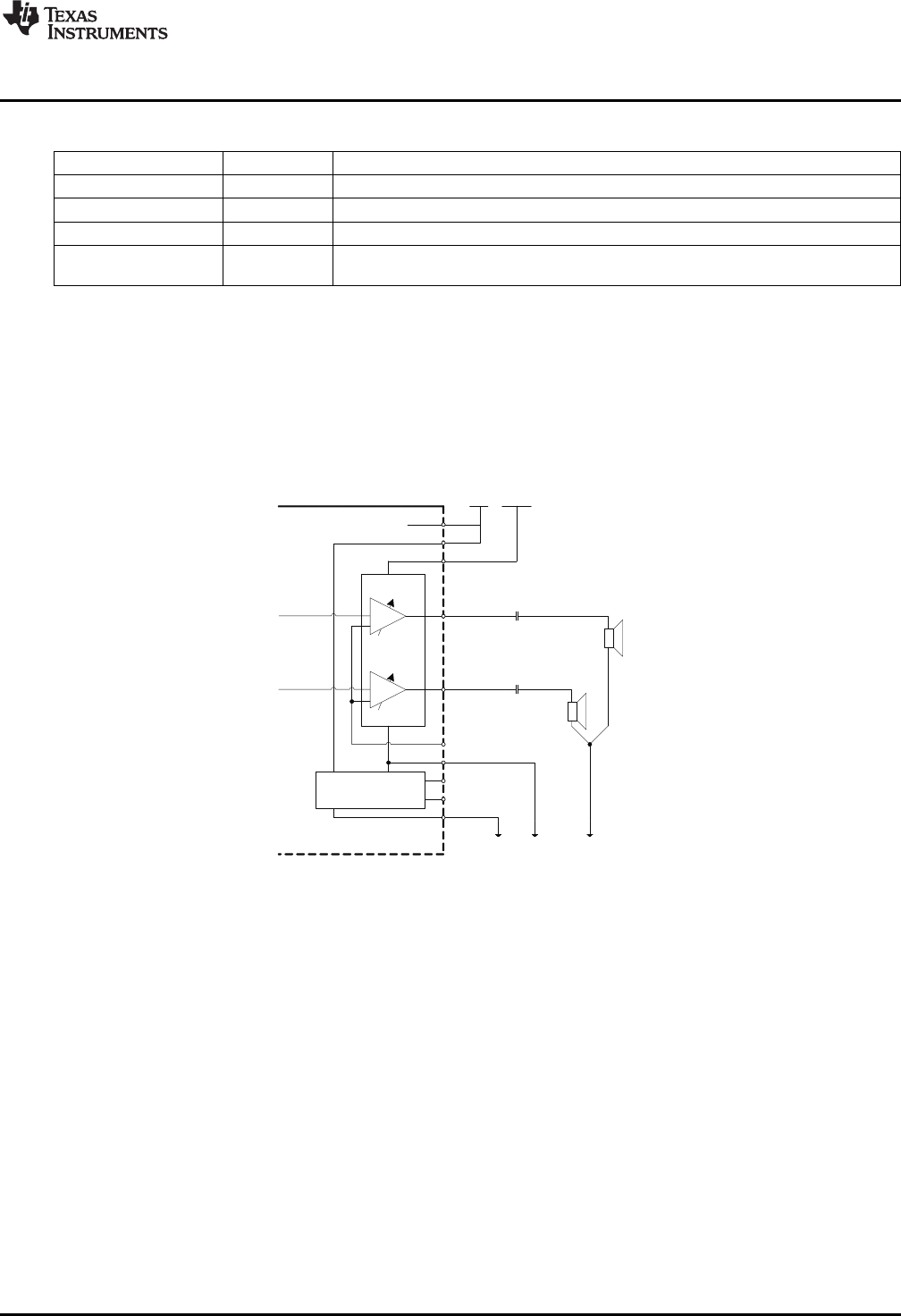

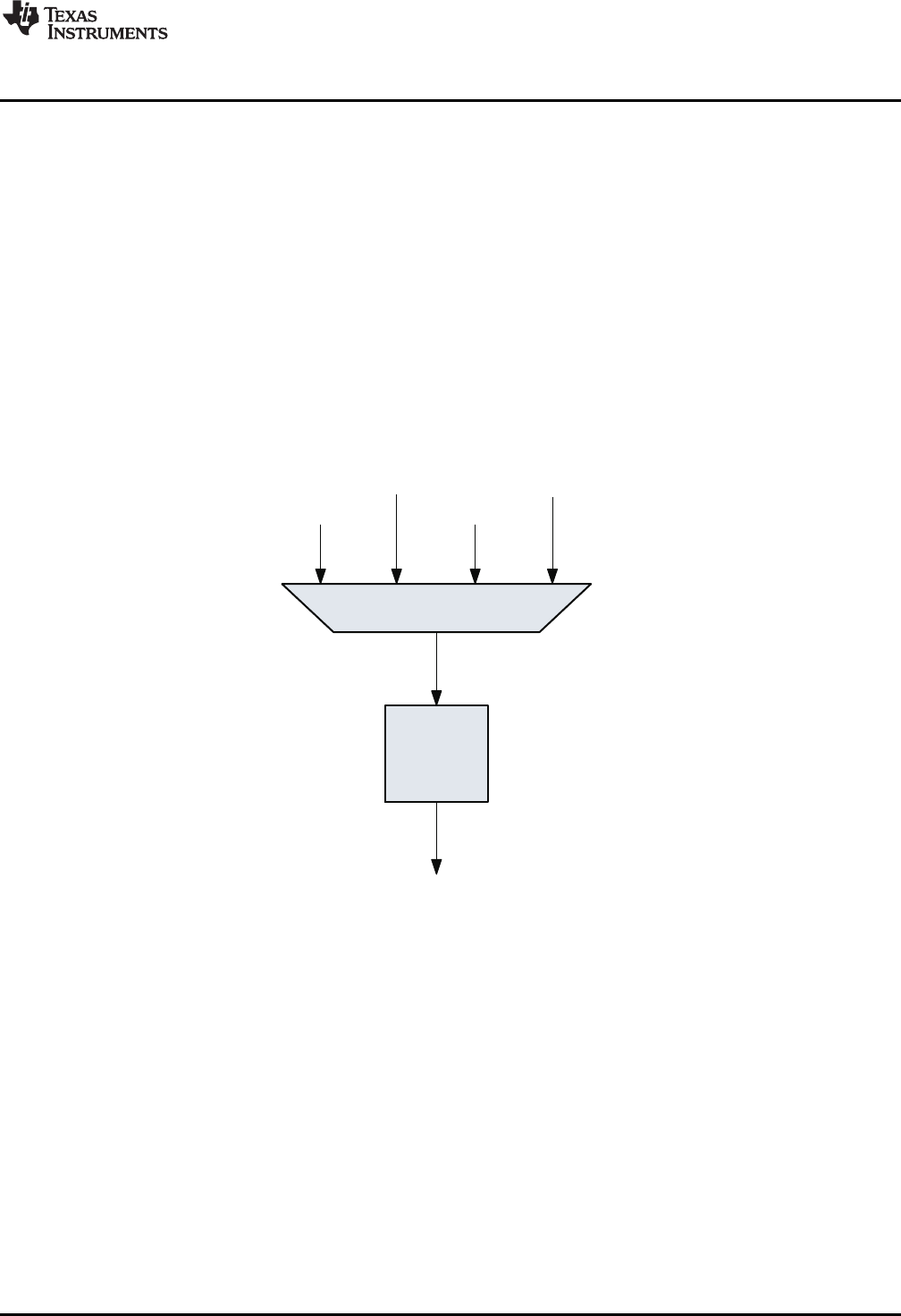

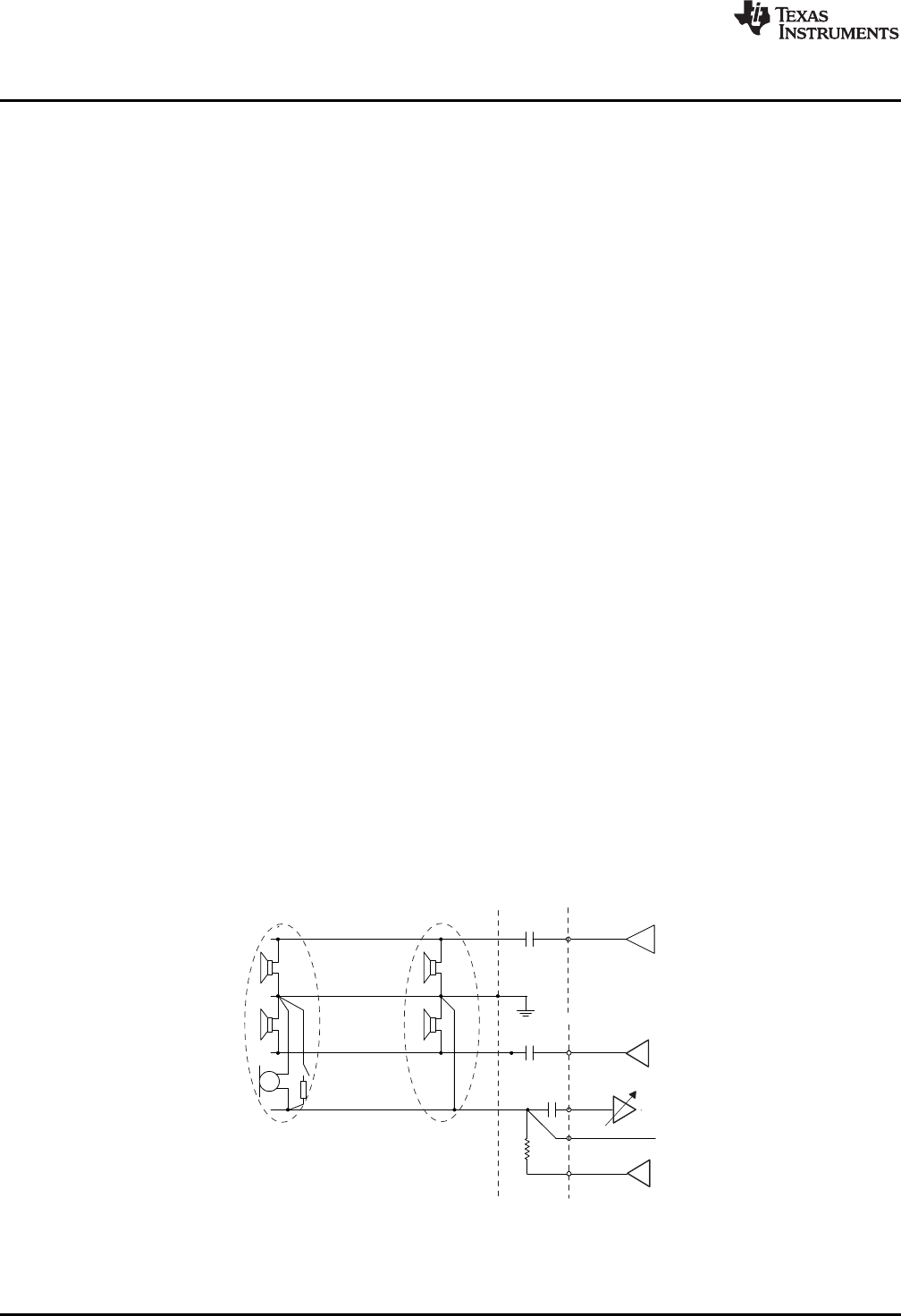

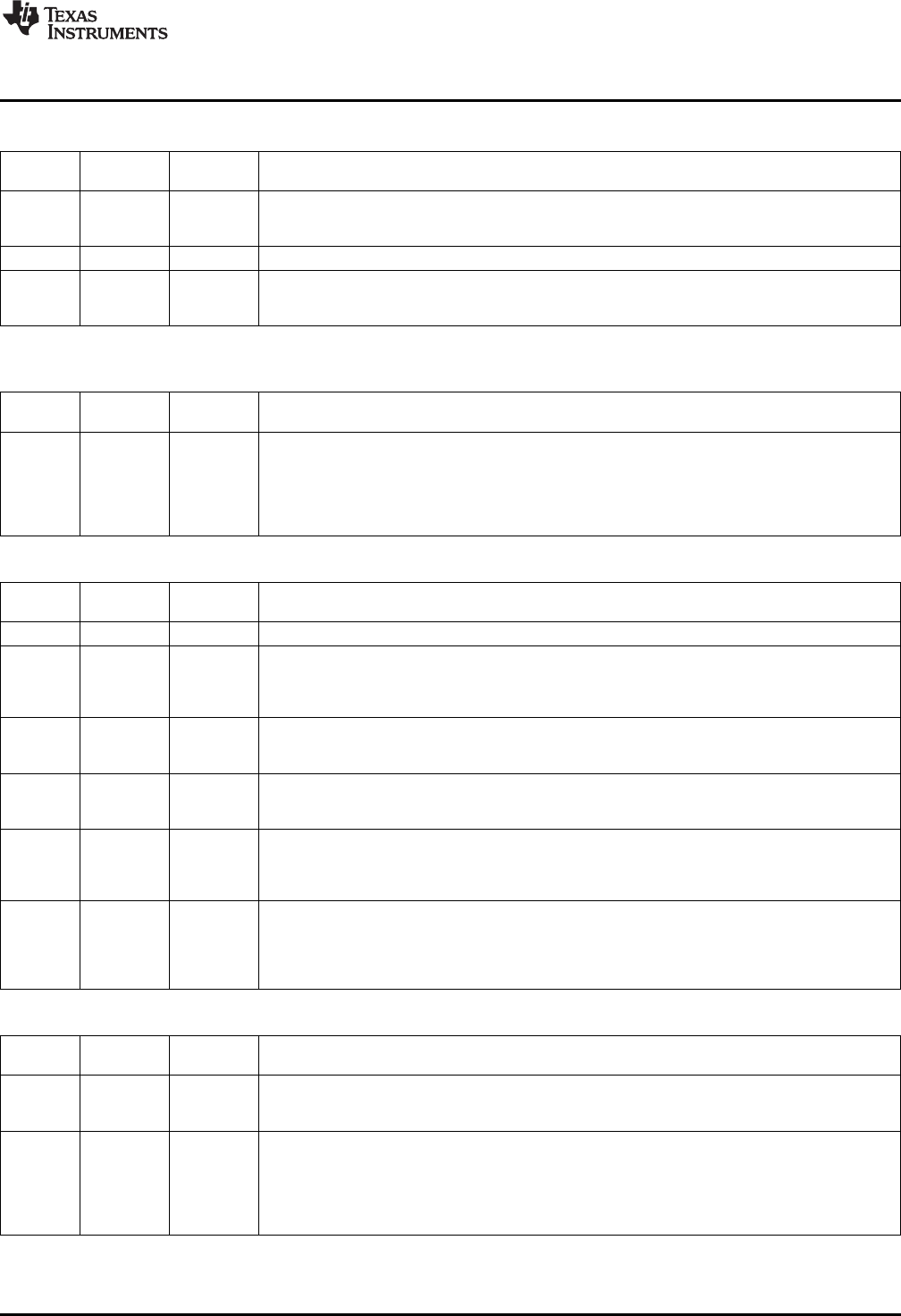

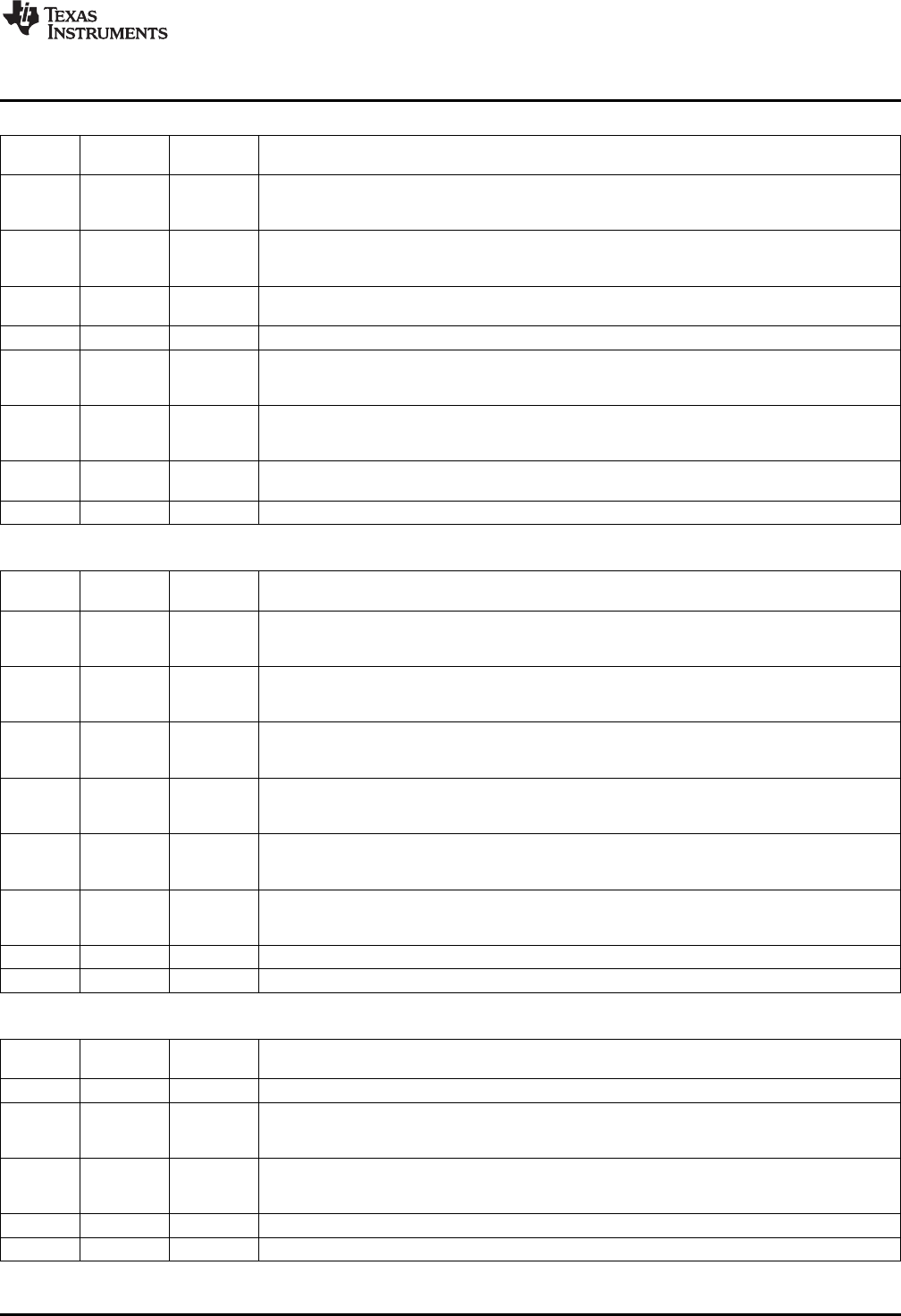

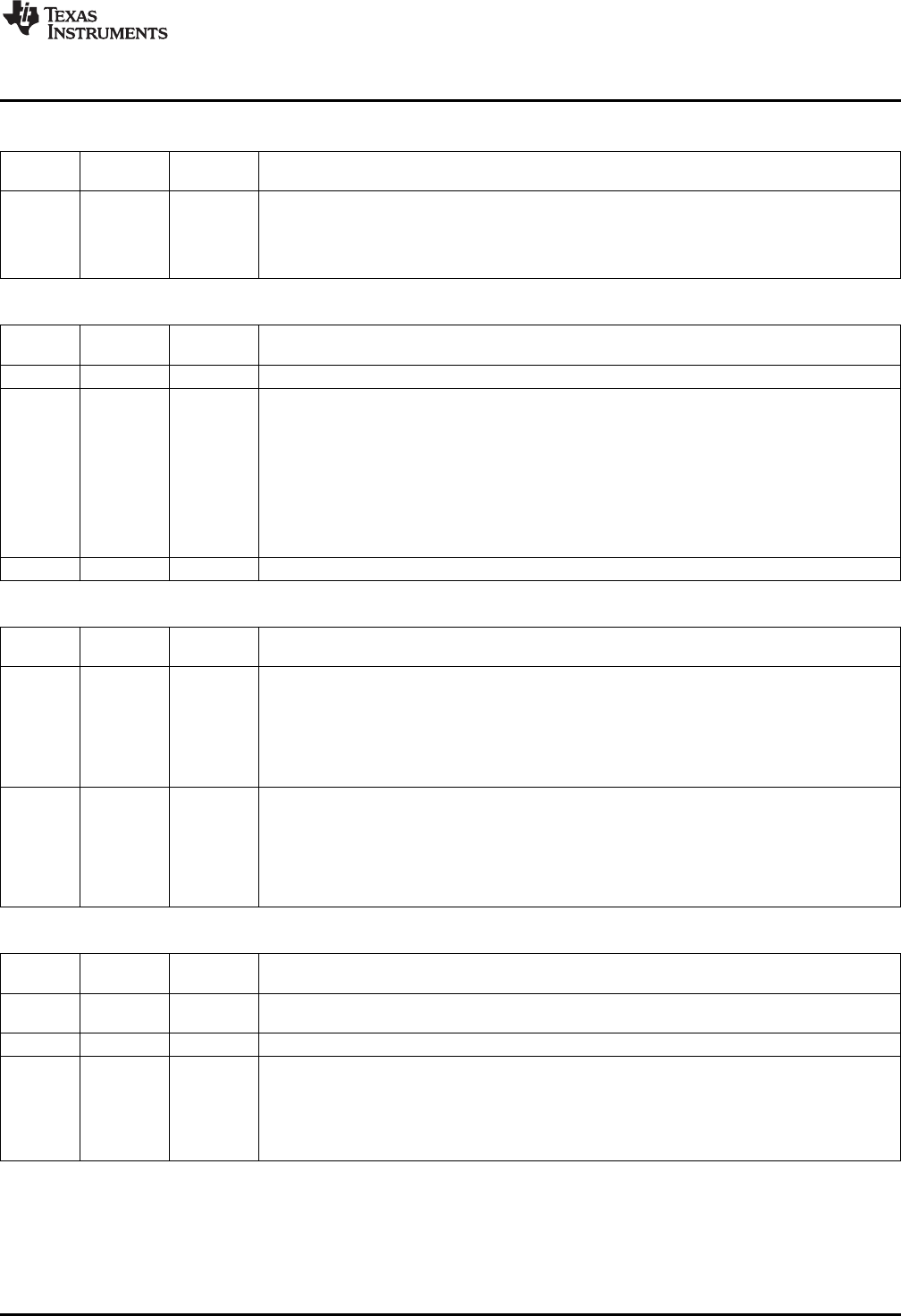

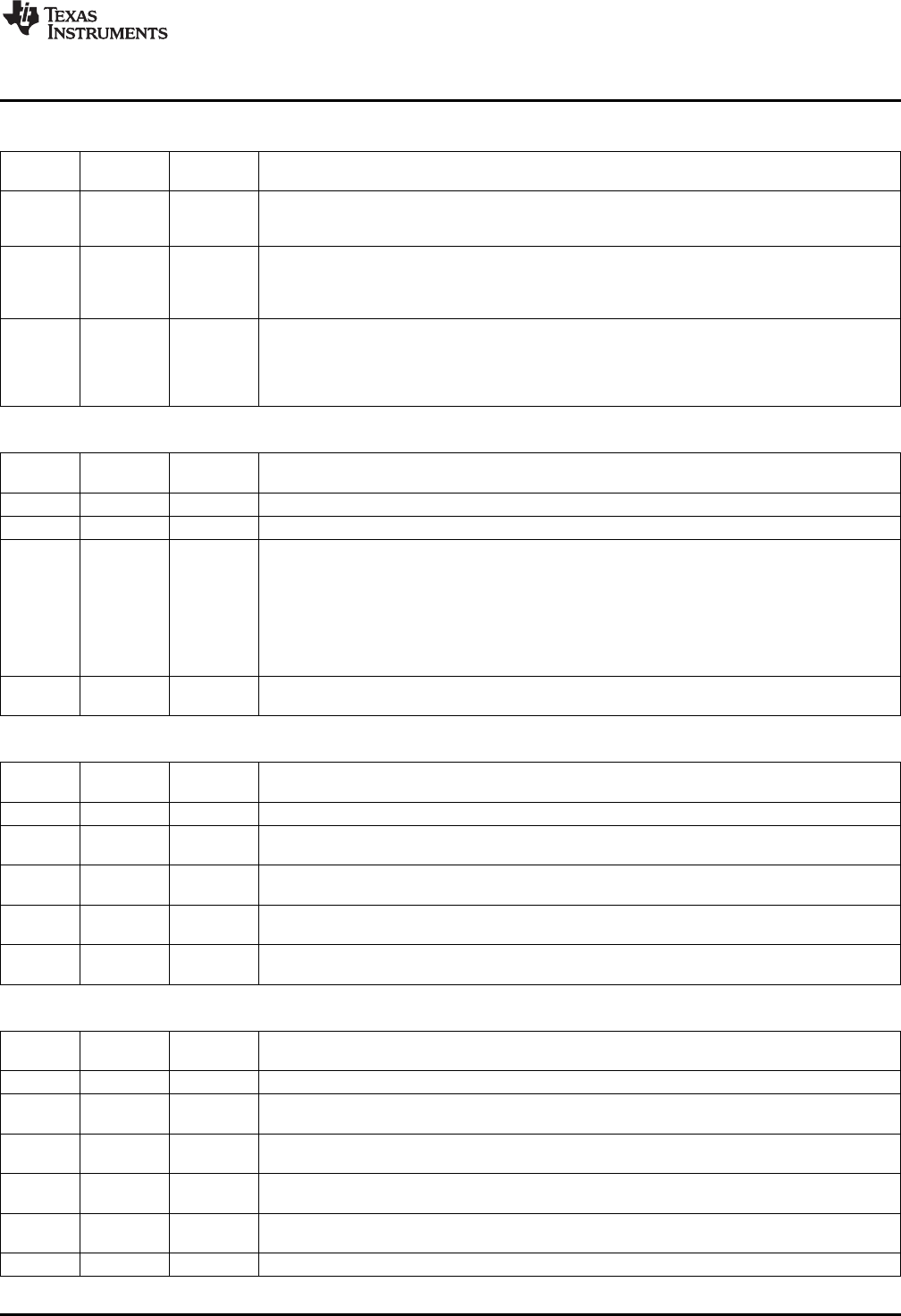

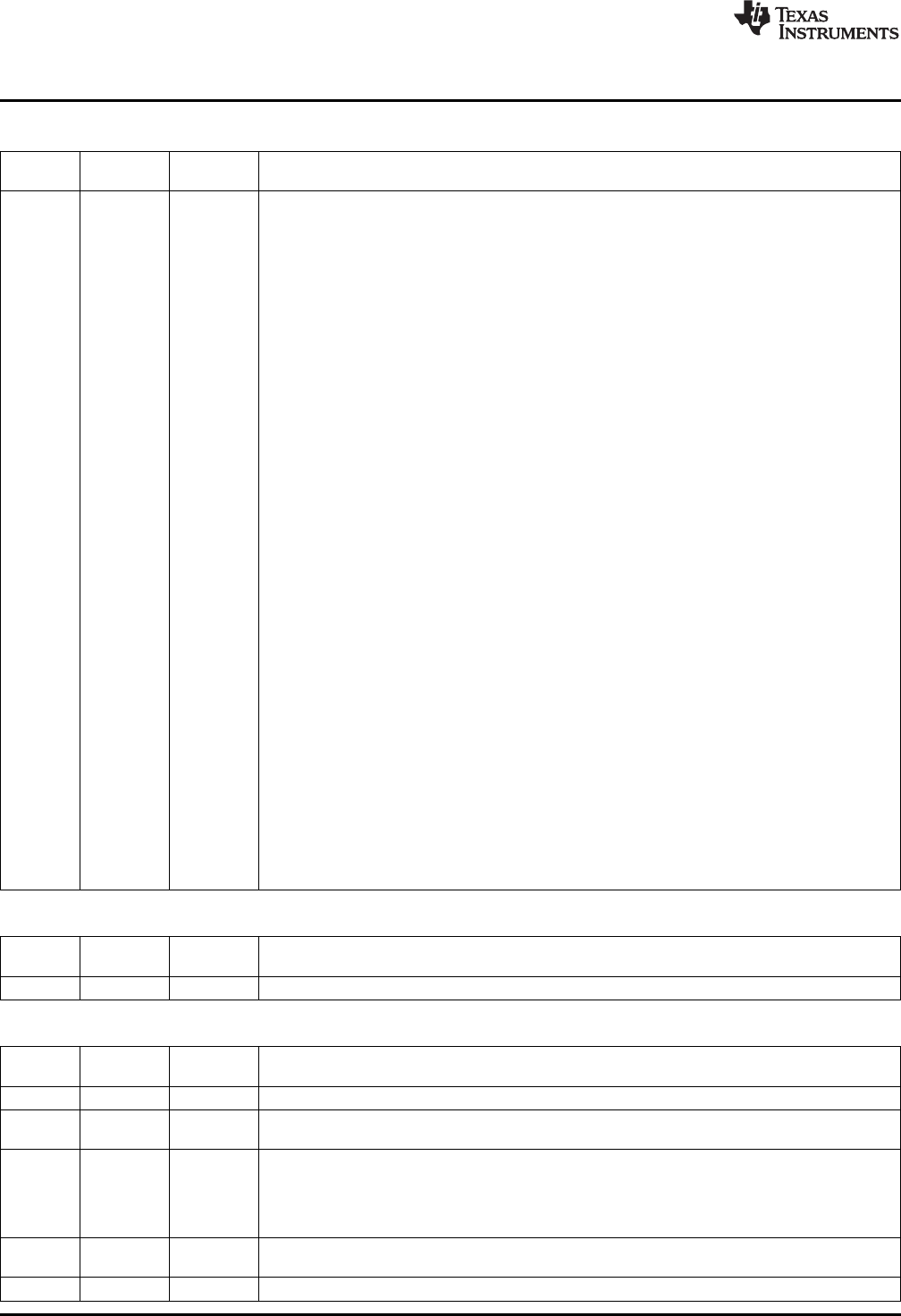

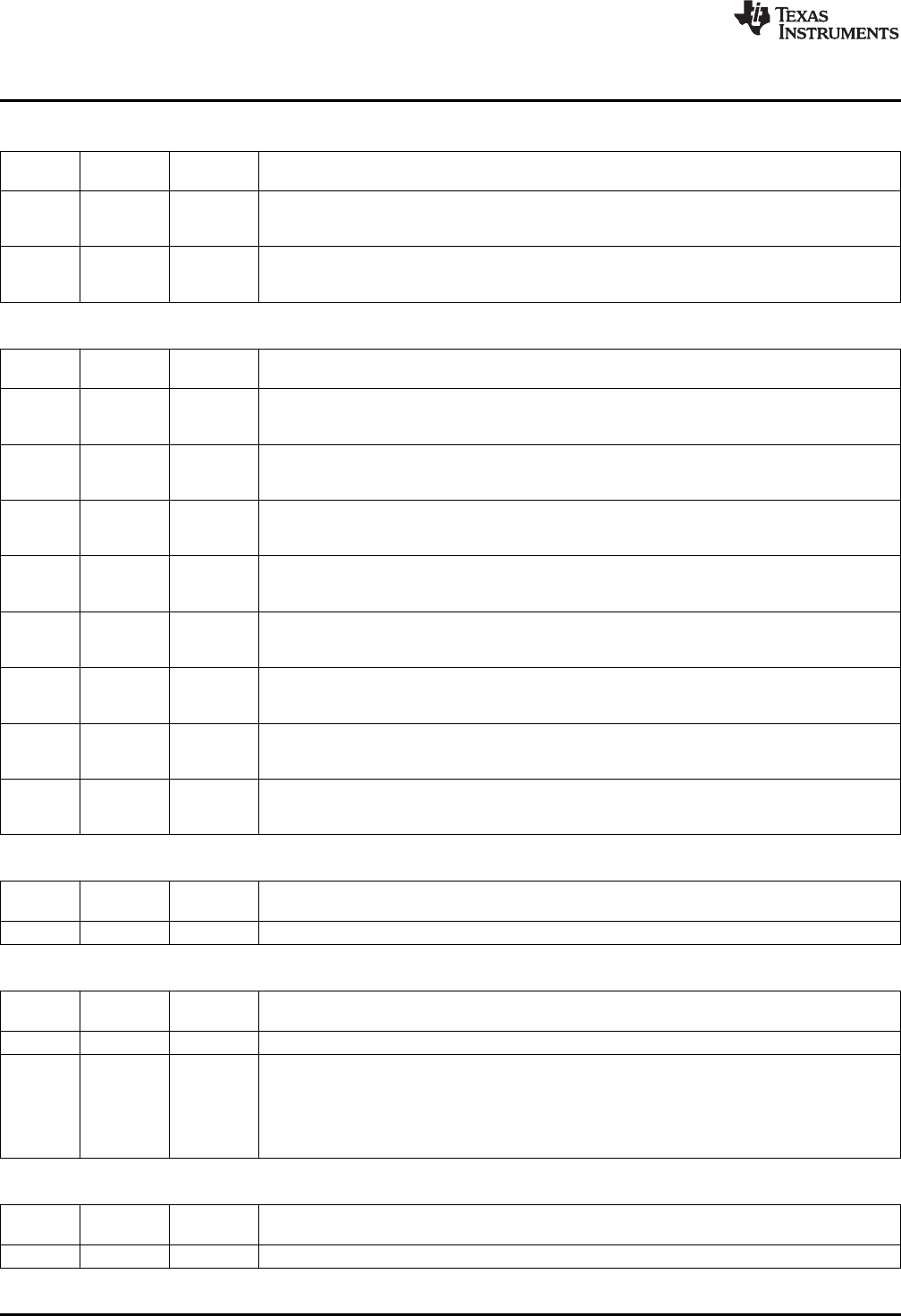

Figure 1-1. Simplified Block Diagram

The TLV320AIC3256 features two fully-programmable miniDSP cores that support application-specific

algorithms in the record and/or the playback path of the device. The miniDSP cores are fully software

controlled. Target miniDSP algorithms, such as active noise cancellation, acoustic echo cancellation or

advanced DSP filtering are loaded into the device after power-up.

Extensive register-based control of power, input/output channel configuration, gains, effects, pin-

multiplexing and clocks is included, allowing the device to precisely target its application. The device

operates from 8kHz mono voice playback to audio stereo 192kHz DAC playback; ideal for portable

battery-powered audio and telephony applications.

The record path of the TLV320AIC3256 ranges from 8kHz mono to 192kHz stereo recording, and contains

programmable input channel configurations covering single-ended and differential setups, as well as

floating or mixing input signals. A digitally-controlled stereo microphone preamplifier also integrates

microphone bias. Digital signal processing blocks can remove audible noise that may be introduced by

mechanical coupling, such as optical zooming in a digital camera.

The playback path offers signal-processing blocks for filtering and effects, and supports flexible mixing of

DAC and analog input signals as well as programmable volume controls. The playback path contains two

high-power output drivers that eliminate the need for ac coupling capacitors. A built in charge pump

generates the negative supply for the ground-centered high-power output drivers. The high-power outputs

can be configured in multiple ways, including stereo and mono BTL.

3

SLAU306A–January 2011–Revised January 2013 TLV320AIC3256 Overview

Submit Documentation Feedback Copyright © 2011–2013, Texas Instruments Incorporated

Typical Circuit Configuration

www.ti.com

The device can be programmed to various power-performance trade-offs. Mobile applications frequently

have multiple use cases requiring very low power operation while being used in a mobile environment.

When used in a docked environment power consumption typically is less of a concern, while minimizing

noise is important. The TLV320AIC3256 addresses both cases.

The device offers single supply operation from 1.5V-1.95V. Digital I/O voltages are supported in the range

of 1.1V-3.6V.

The required internal clock of the TLV320AIC3256 can be derived from multiple sources, including the

MCLK pin, the BCLK pin, the GPIO pin or the output of the internal PLL, where the input to the PLL again

can be derived from the MCLK pin, the BCLK or GPIO pins. Although using the PLL ensures the

availability of a suitable clock signal, it is not recommended for the lowest power settings. The PLL is

highly programmable and can accept available input clocks in the range of 512kHz to 50MHz.

The device is available in the 5mm × 5mm, 40-pin QFN or 3.5mm × 3.3mm 42-ball WCSP package.

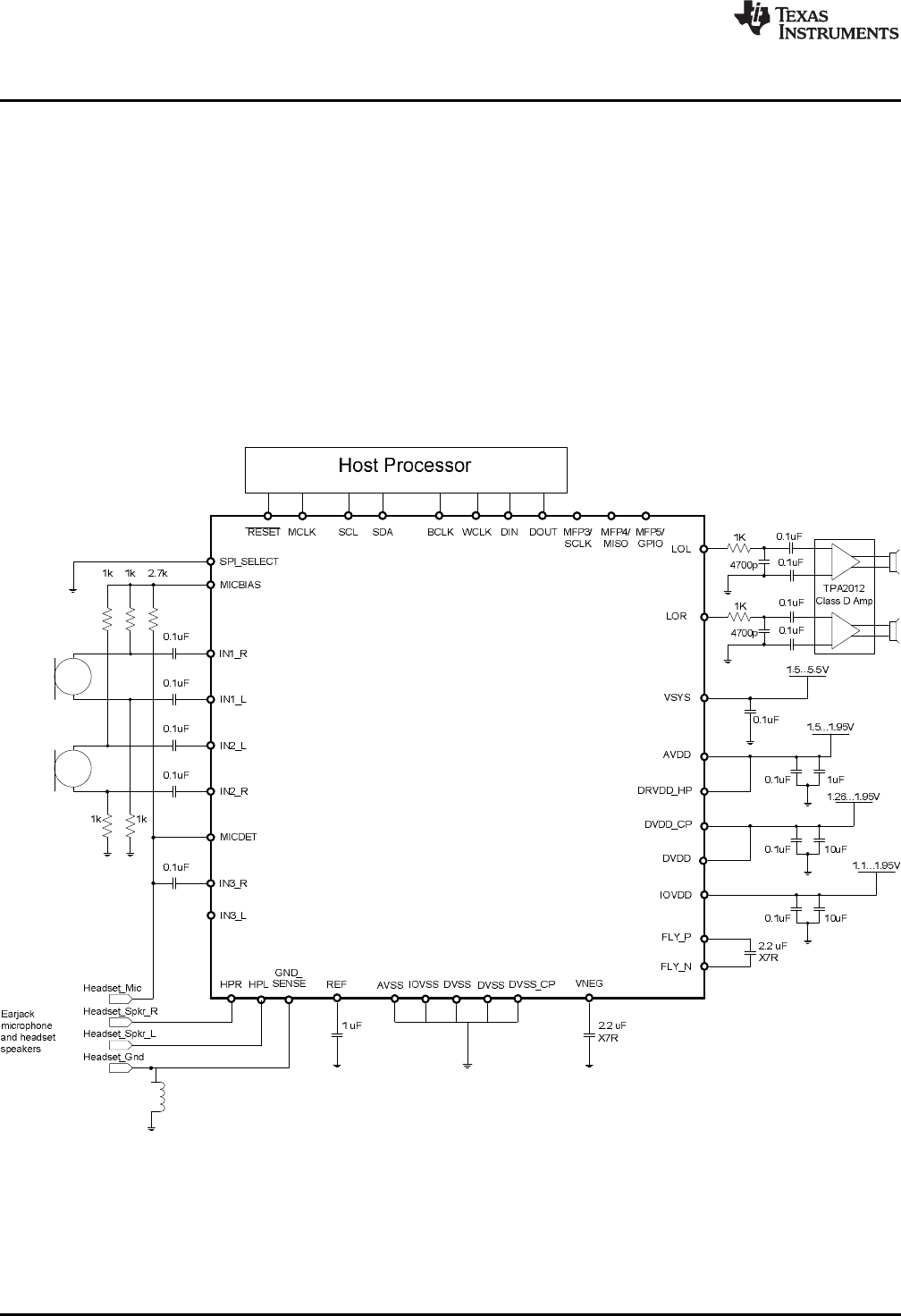

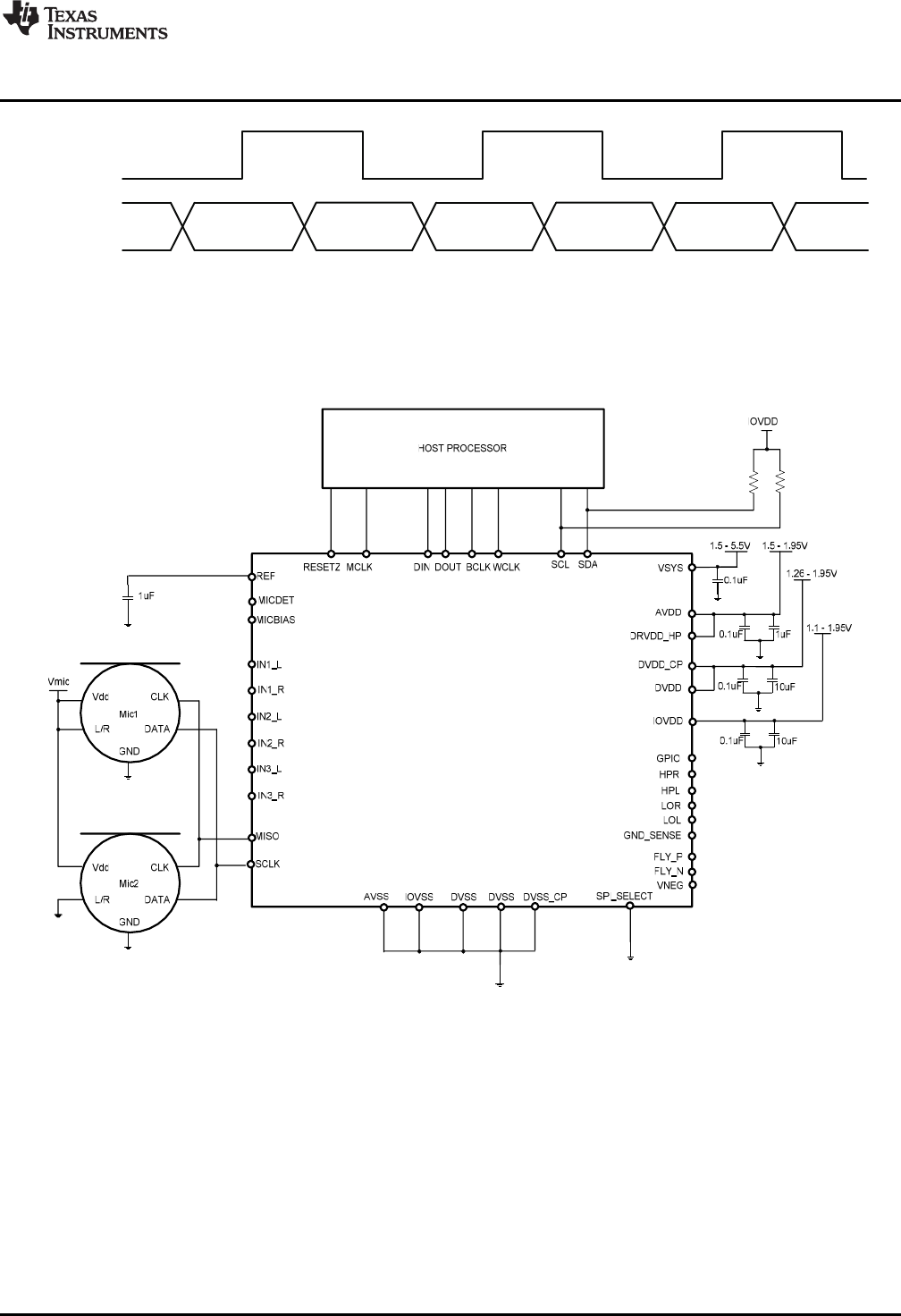

1.2 Typical Circuit Configuration

Figure 1-2. Typical Circuit Configuration

4TLV320AIC3256 Overview SLAU306A–January 2011–Revised January 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Chapter 2

SLAU306A–January 2011–Revised January 2013

TLV320AIC3256 Application

2.1 Terminal Descriptions

2.1.1 Digital Pins

Only a small number of digital pins are dedicated to a single function; whenever possible, the digital pins

have a default function, and also can be reprogrammed to cover alternative functions for various

applications.

The fixed-function pins are Reset and the SPI_Select pin, which are HW control pins. Depending on the

state of SPI_Select, the two control-bus pins SCL/SS and SDA/MOSI are configured for either I2C or SPI

protocol.

Other digital IO pins can be configured for various functions via register control. An overview of available

functionality is given in Section 2.1.1.1.

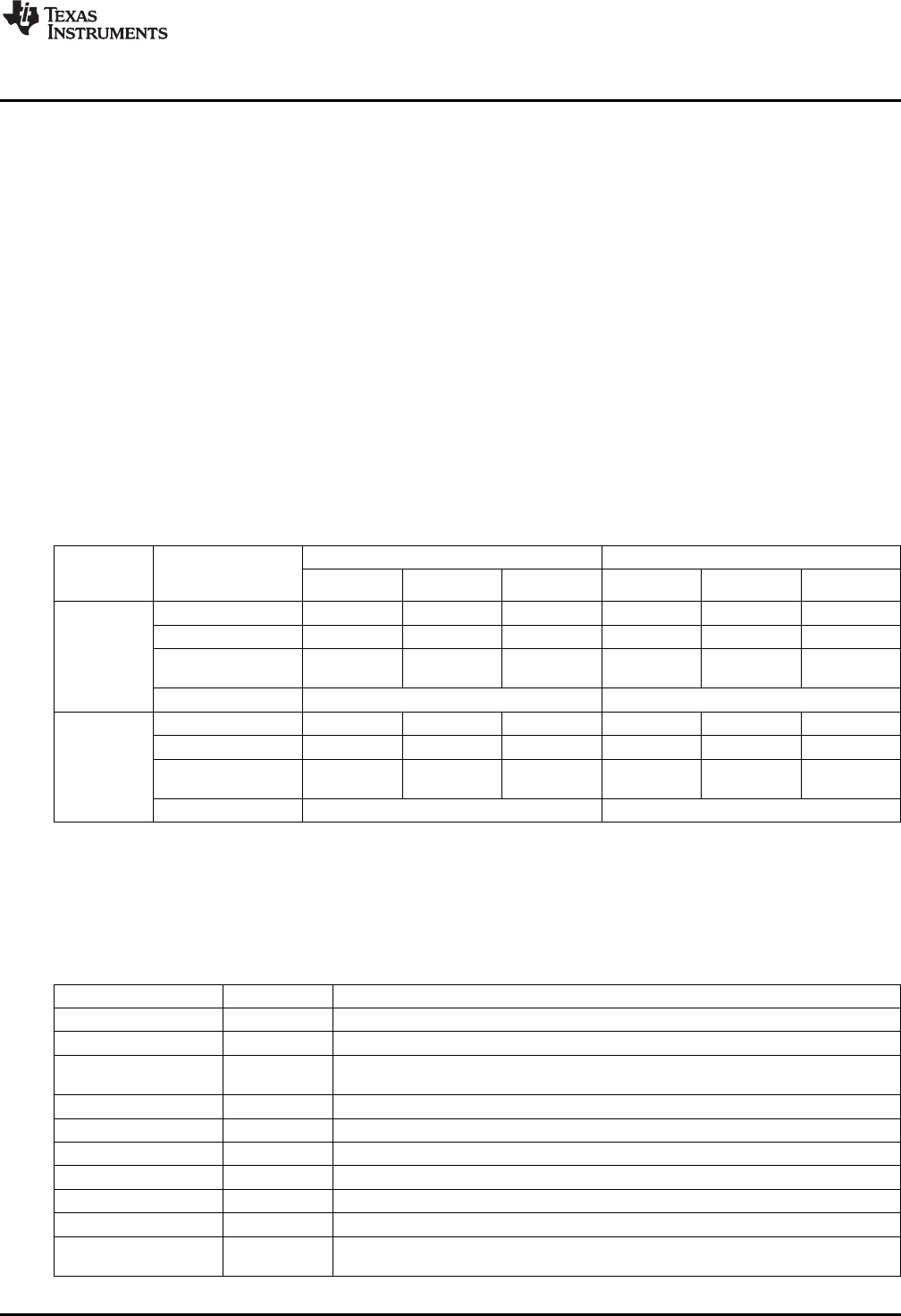

2.1.1.1 Multifunction Pins

Table 2-1 shows the possible allocation of pins for specific functions. The PLL input, for example, can be

programmed to be any of 4 pins (MCLK, BCLK, DIN, GPIO).

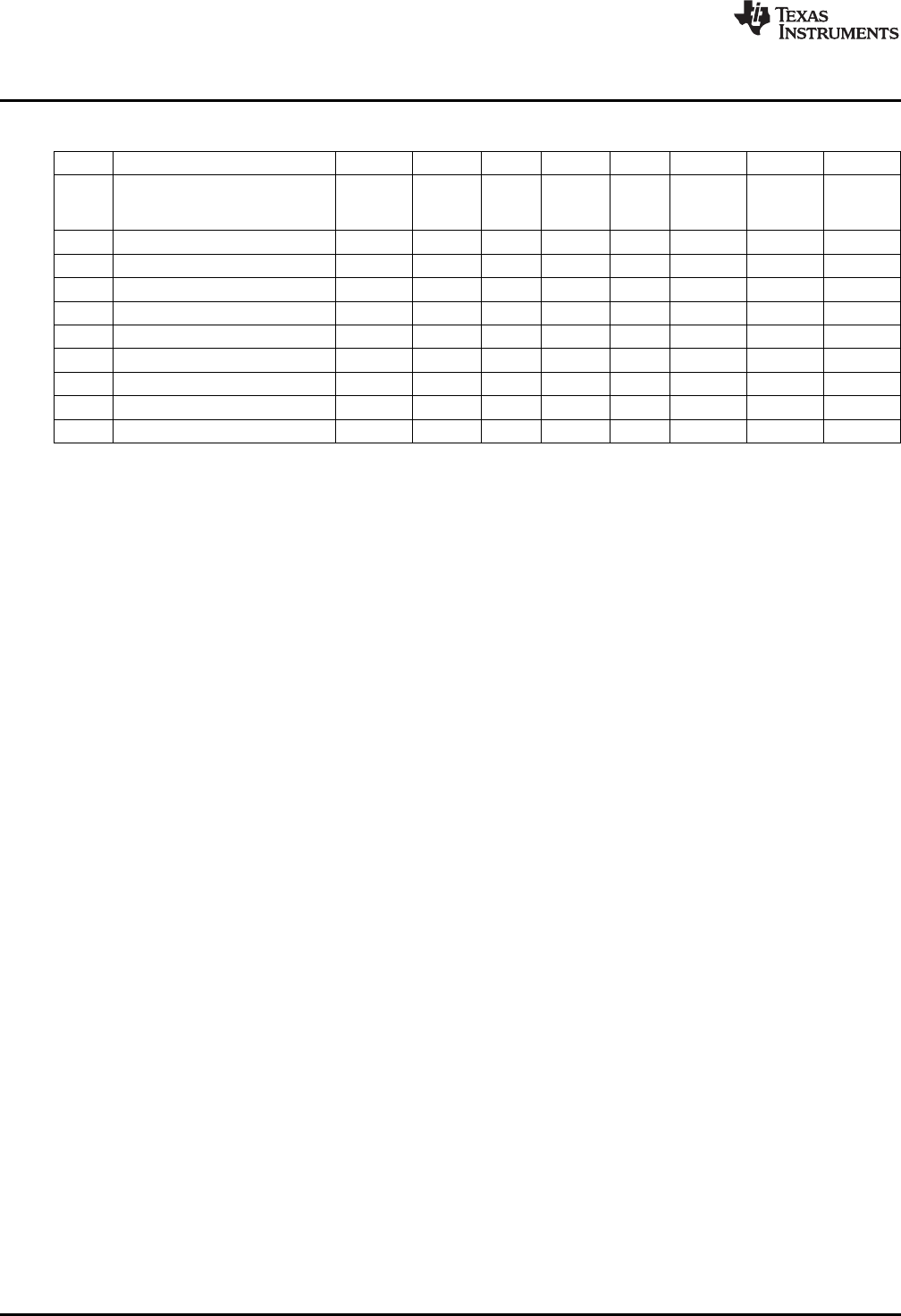

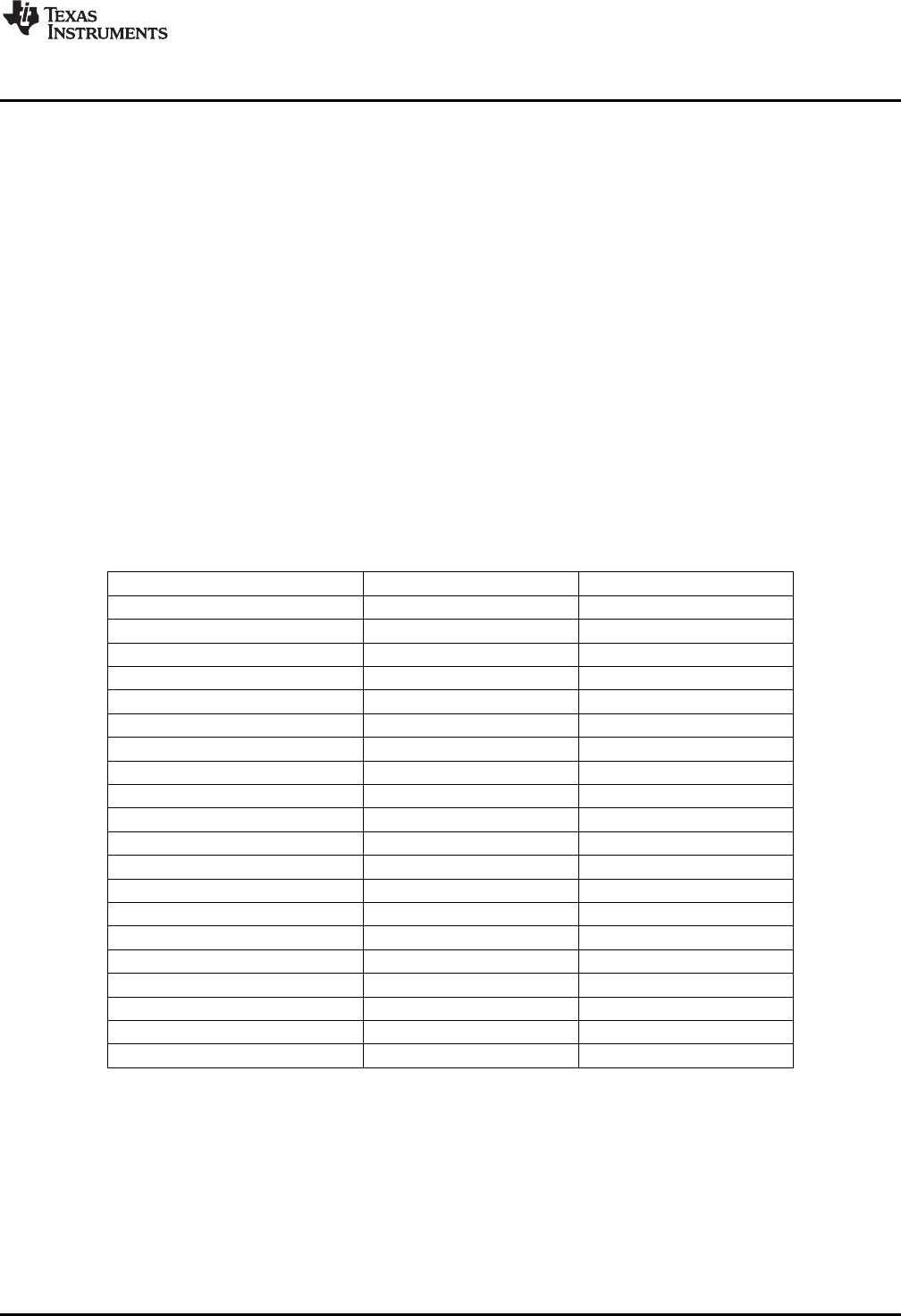

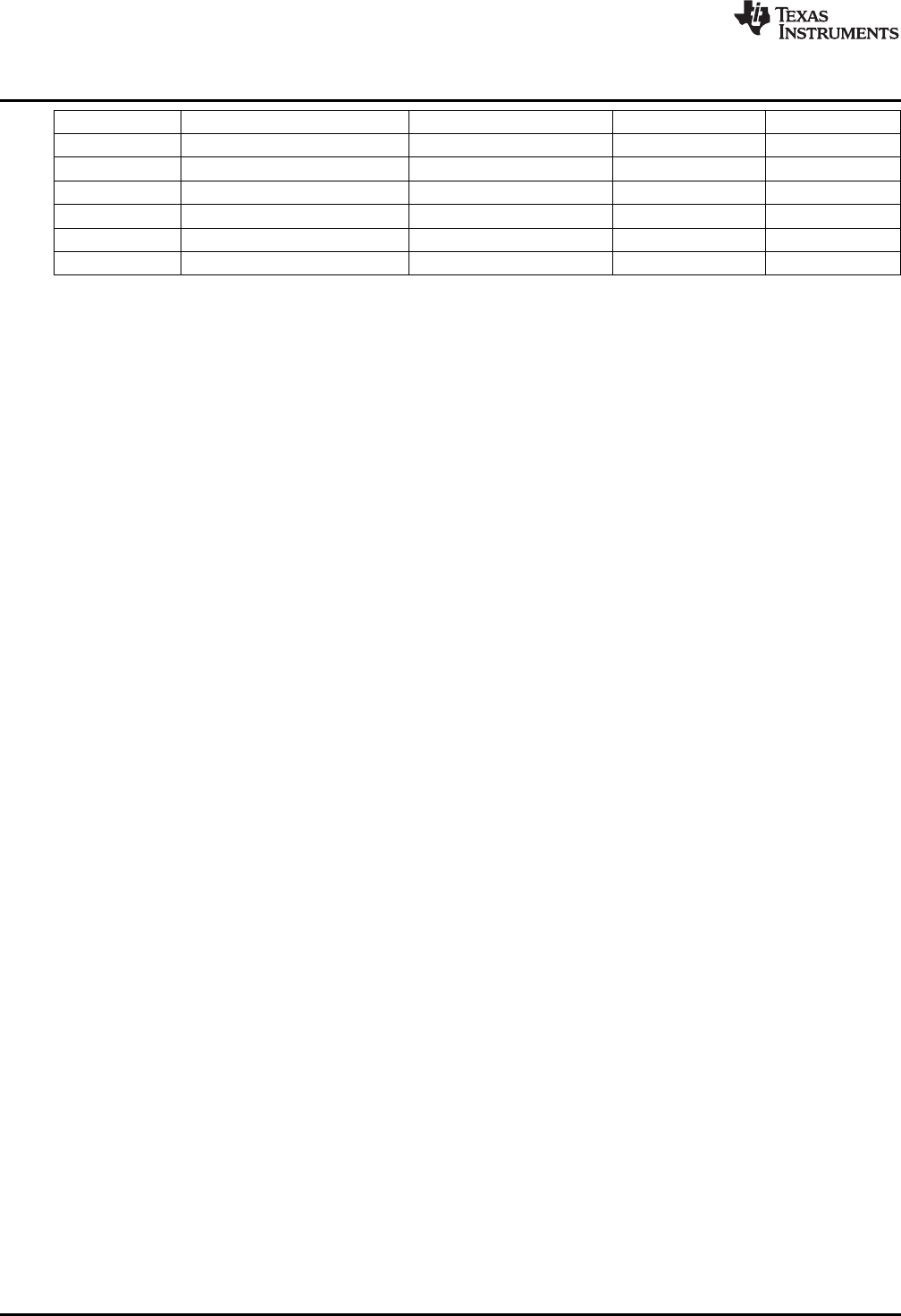

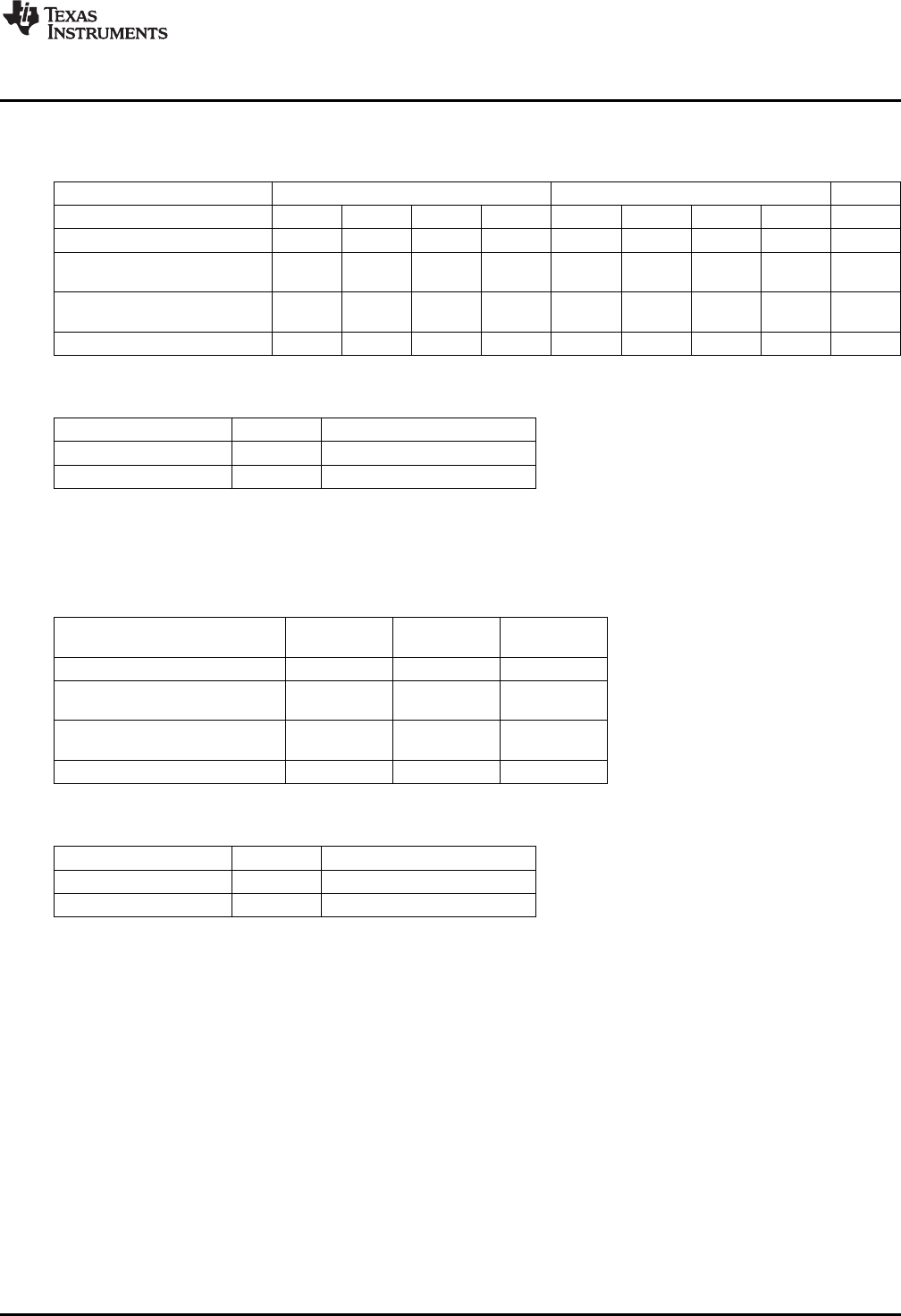

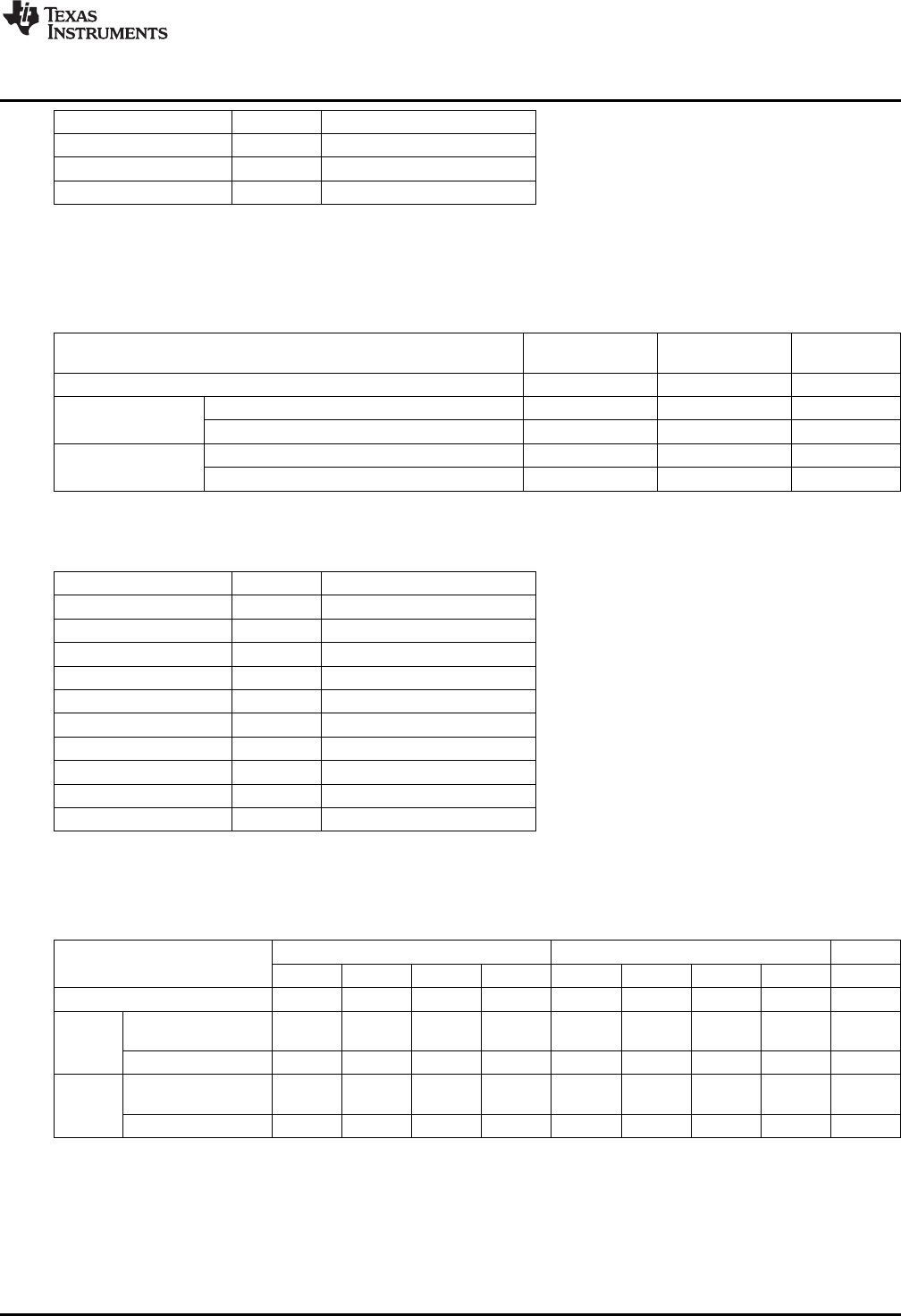

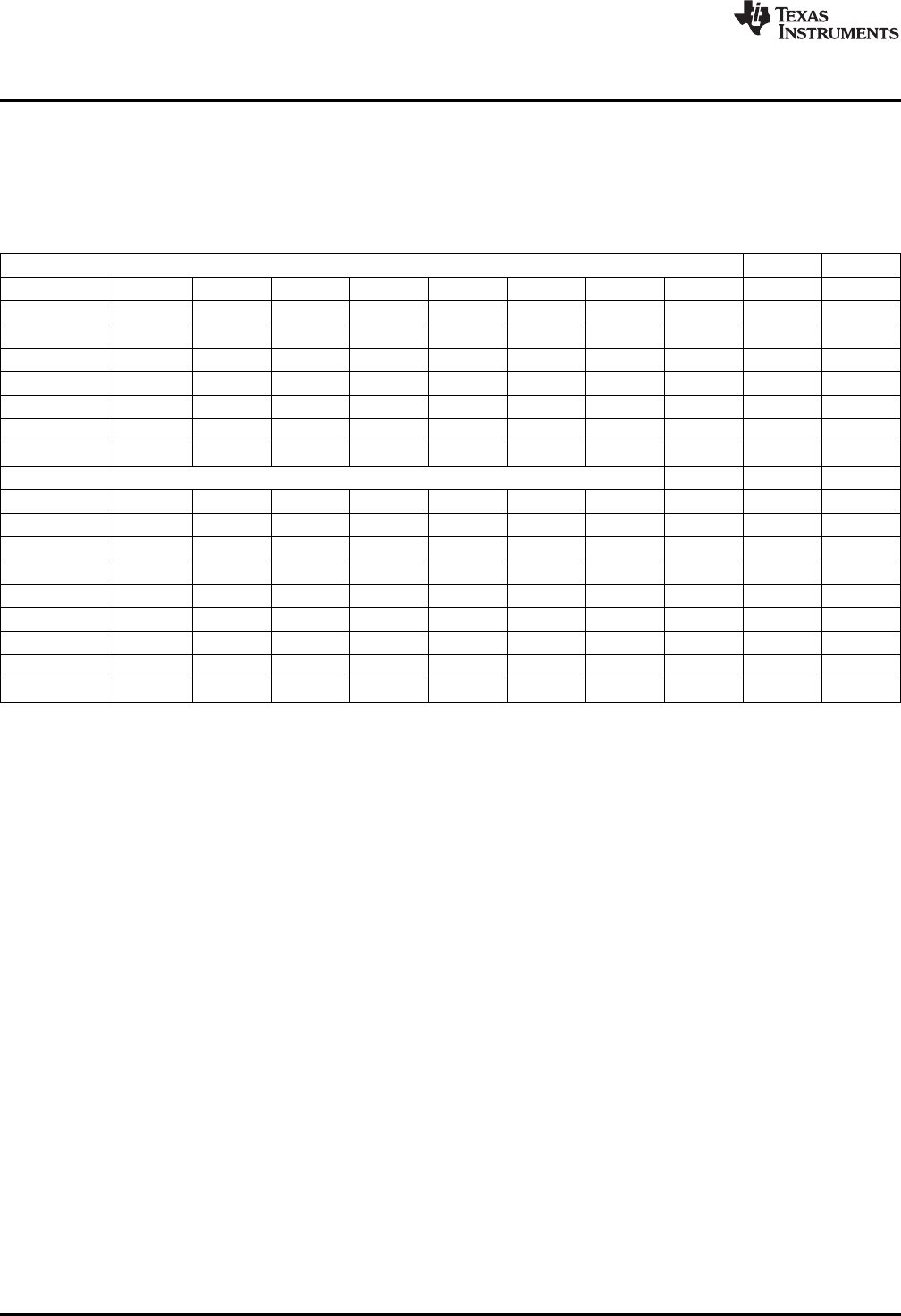

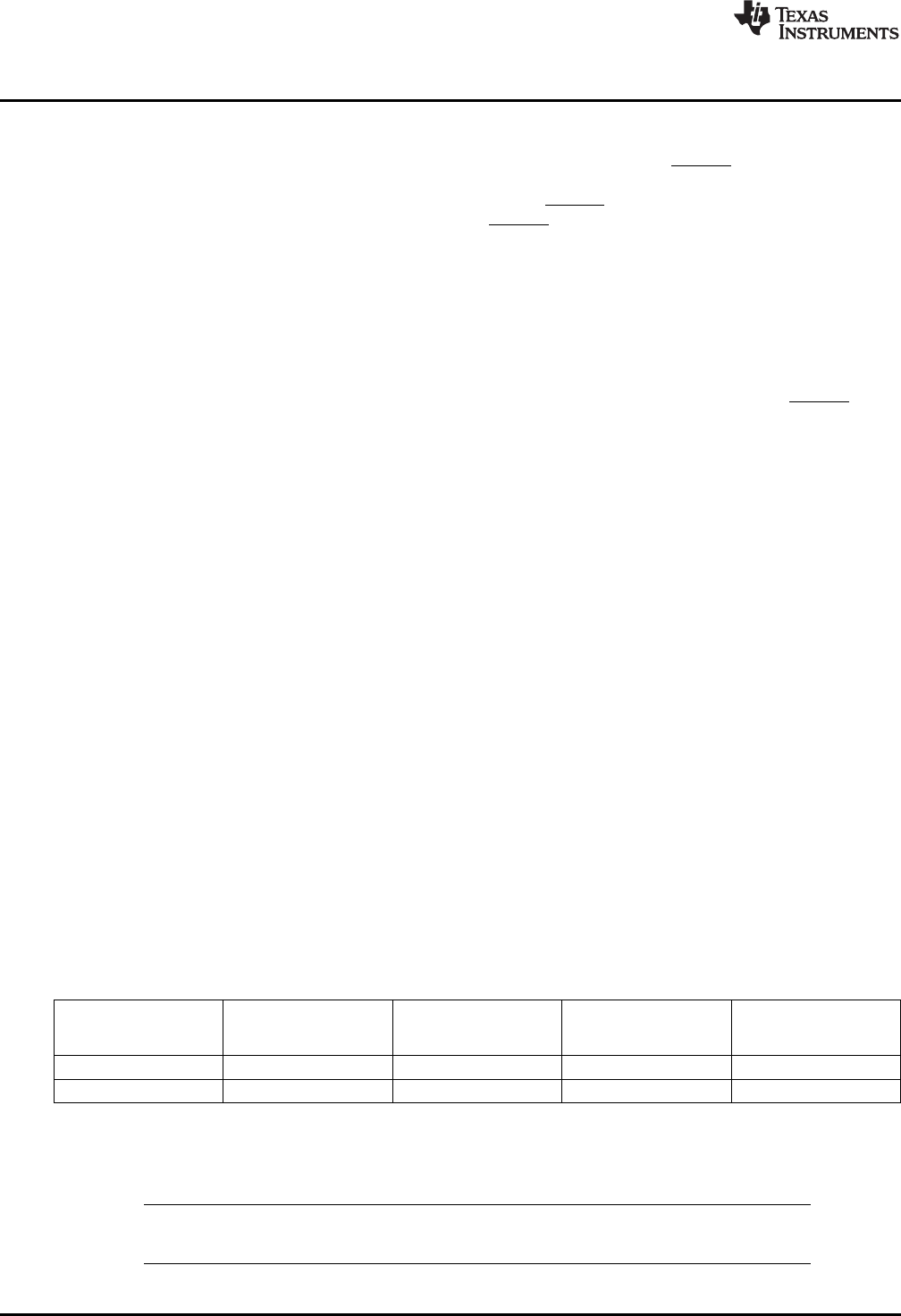

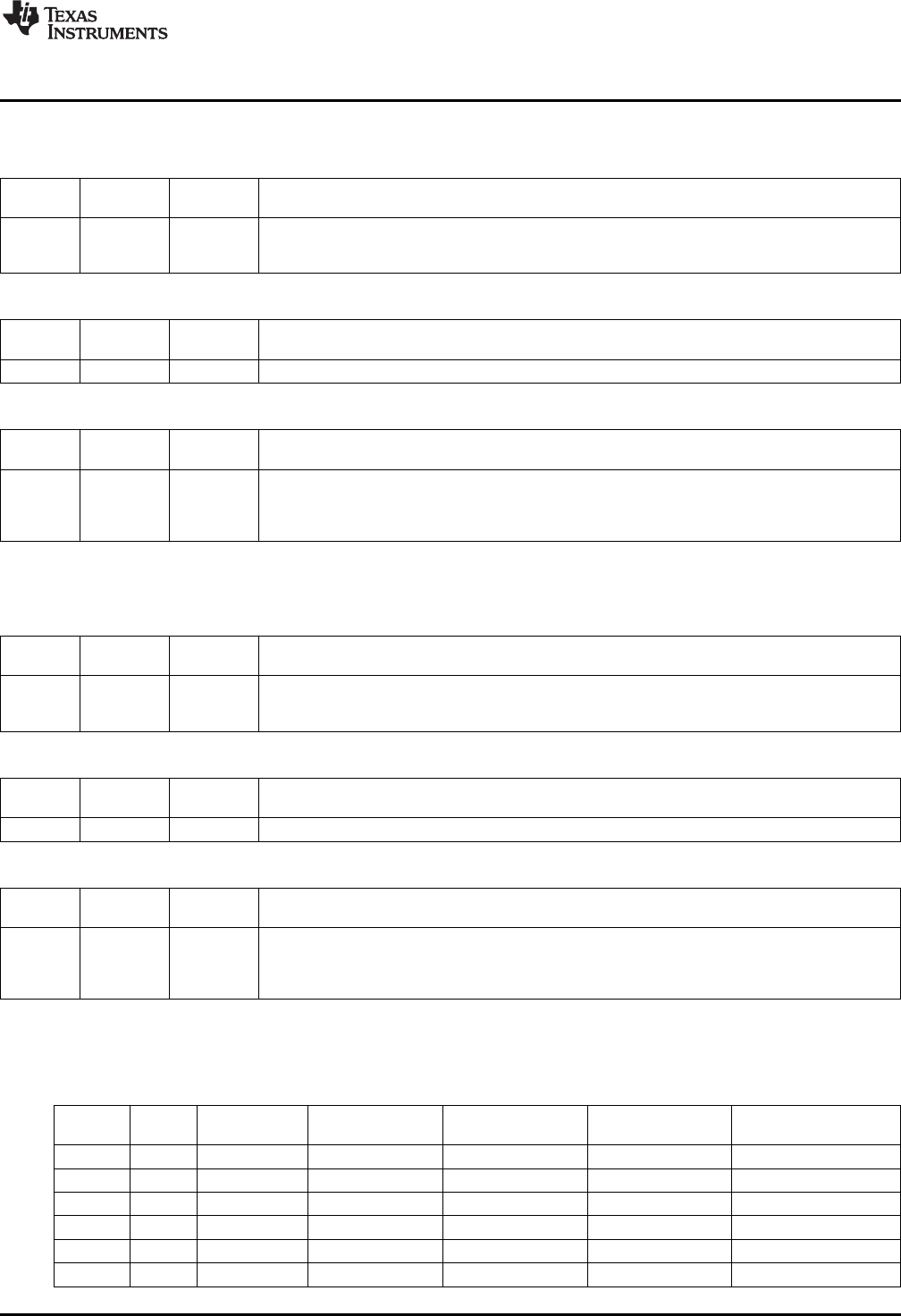

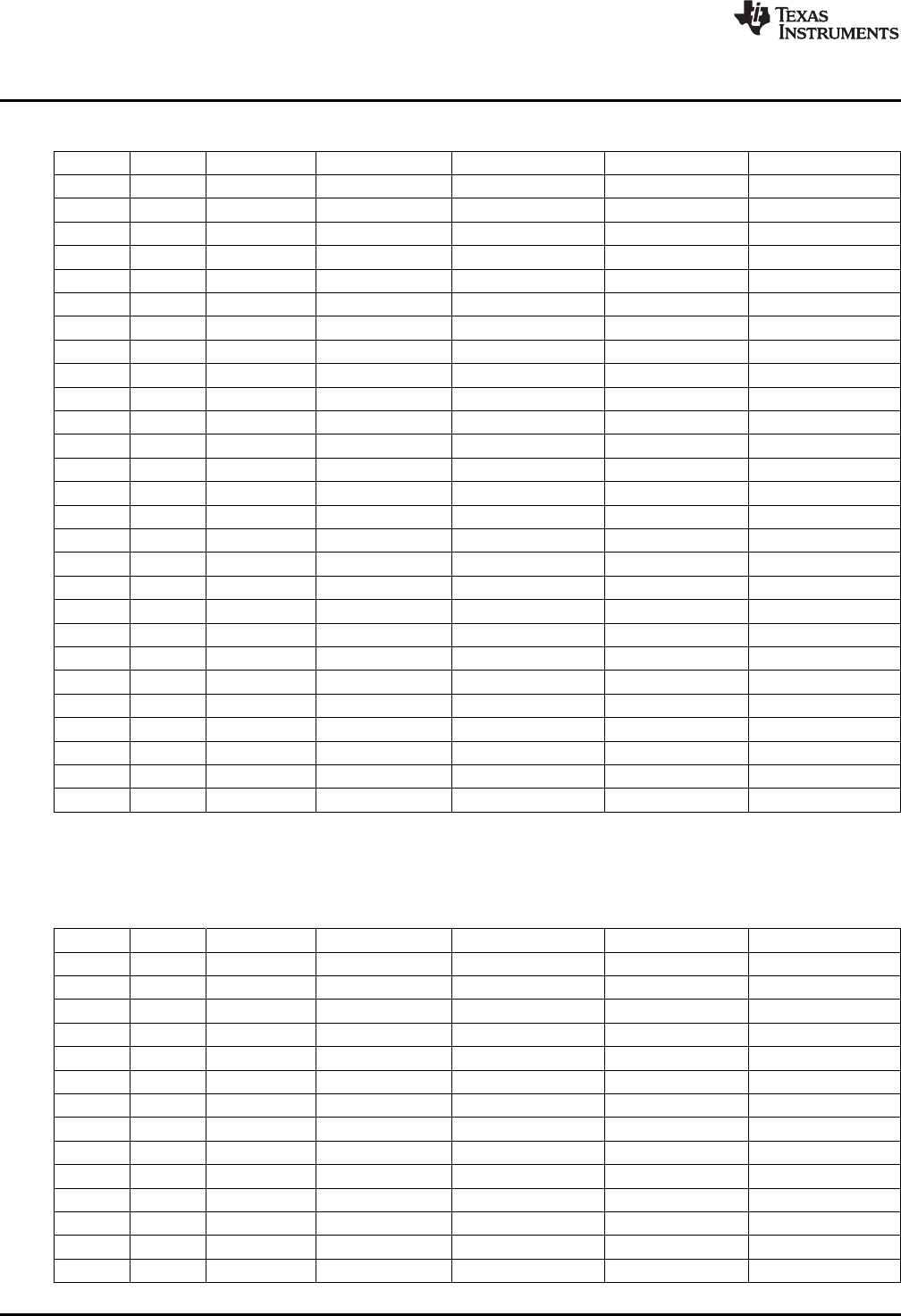

Table 2-1. Multifunction Pin Assignments

1 2 3 4 5 6 7 8

Pin Function MCLK BCLK WCLK DIN DOUT DMDIN/ DMCLK/ GPIO

MFP1 MFP2 MFP3/ MFP4/ MFP5

SCLK MISO

APLL Input S(1) S(2) E S(3)

BCodec Clock Input S(1),D(4) S(2) S(3)

CI2S BCLK input S,D

DI2S BCLK output E(5)

EI2S WCLK input E, D

FI2S WCLK output E

GI2S ADC word clock input E E

HI2S ADC WCLK out E E

II2S DIN E, D

JI2S DOUT E, D

KGeneral Purpose Output I E

KGeneral Purpose Output II E

KGeneral Purpose Output III E

LGeneral Purpose Input I E

LGeneral Purpose Input II E

LGeneral Purpose Input III E

(1) S(1): The MCLK pin can drive the PLL and Codec Clock inputs simultaneously.

(2) S(2): The BCLK pin can drive the PLL and Codec Clock and audio interface bit clock inputs simultaneously.

(3) S(3): The GPIO/MFP5 pin can drive the PLL and Codec Clock inputs simultaneously.

(4) D: Default Function

(5) E: The pin is exclusively used for this function, no other function can be implemented with the same pin. (If GPIO/MFP5 has

been allocated for General Purpose Output, it cannot be used as the INT1 output at the same time.)

5

SLAU306A–January 2011–Revised January 2013 TLV320AIC3256 Application

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Terminal Descriptions

www.ti.com

Table 2-1. Multifunction Pin Assignments (continued)

1 2 3 4 5 6 7 8

Pin Function MCLK BCLK WCLK DIN DOUT DMDIN/ DMCLK/ GPIO

MFP1 MFP2 MFP3/ MFP4/ MFP5

SCLK MISO

MINT1 output E E E

NINT2 output E E E

QSecondary I2S BCLK input E E

RSecondary I2S WCLK in E E

SSecondary I2S DIN E E

TSecondary I2S DOUT E

USecondary I2S BCLK OUT E E E

VSecondary I2S WCLK OUT E E E

XAux Clock Output E E E

2.1.2 Analog Pins

Analog functions can also be configured to a large degree. For minimum power consumption, analog

blocks are powered down by default. The blocks can be powered up with fine granularity according to the

application needs.

6TLV320AIC3256 Application SLAU306A–January 2011–Revised January 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

www.ti.com

Terminal Descriptions

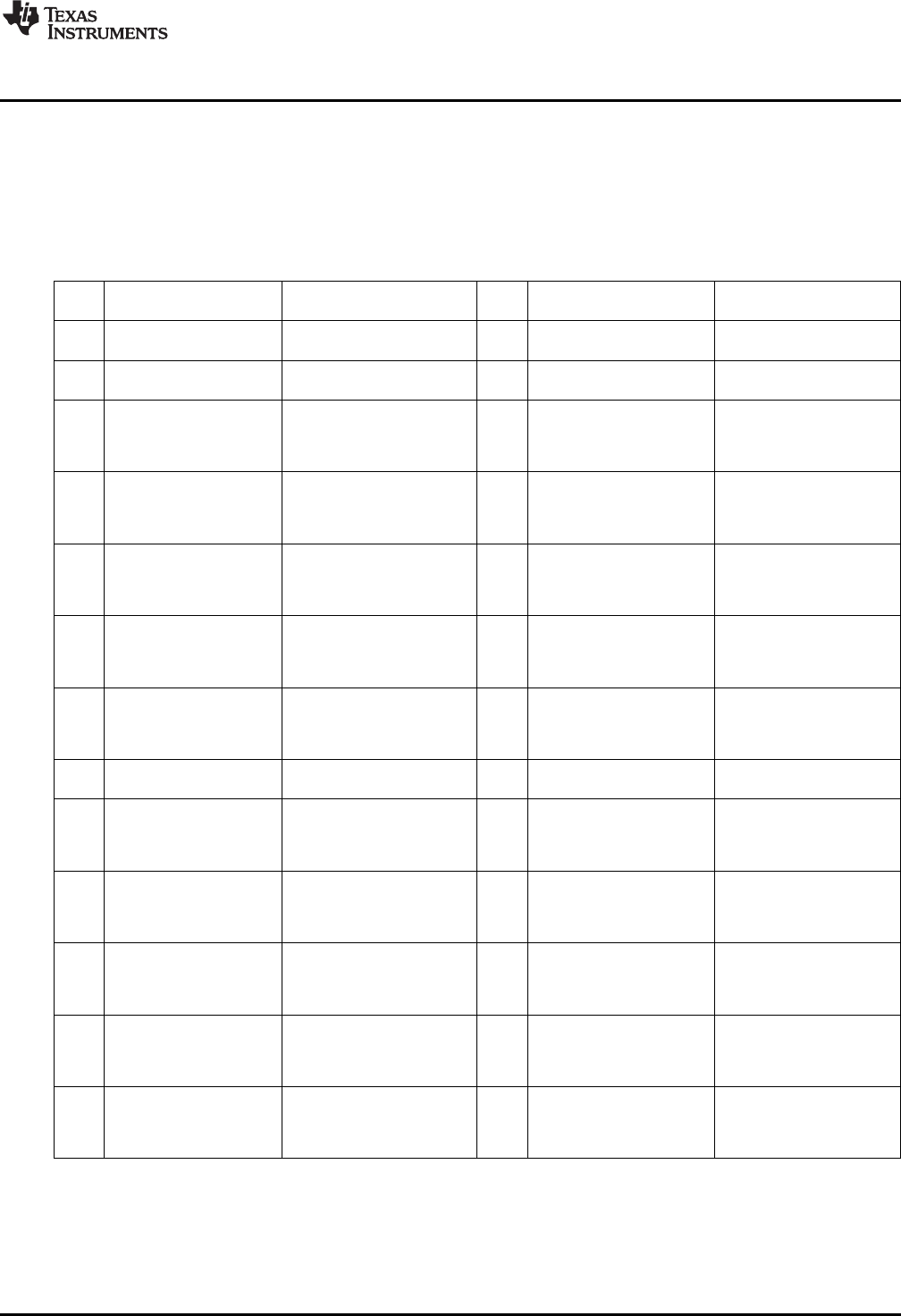

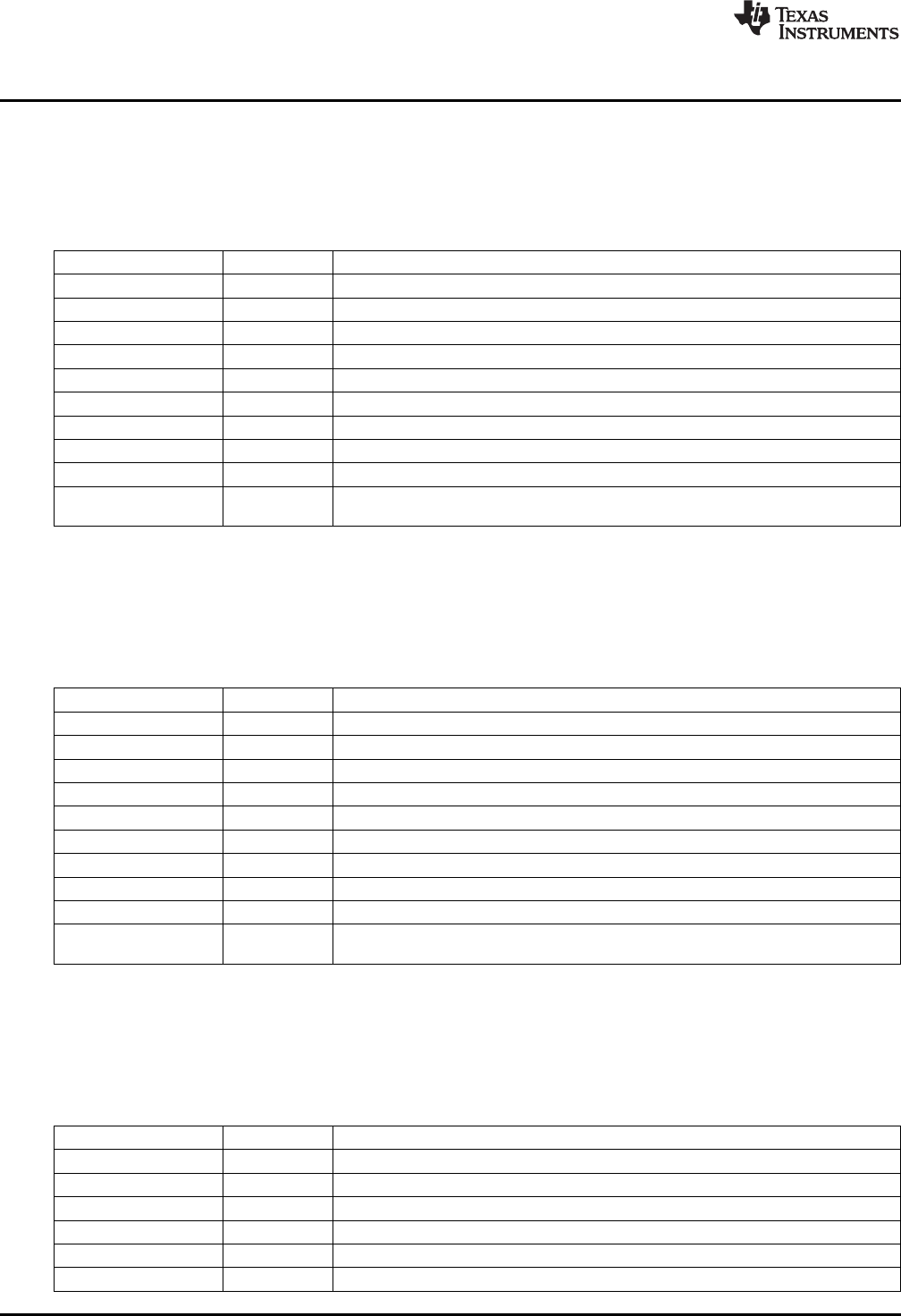

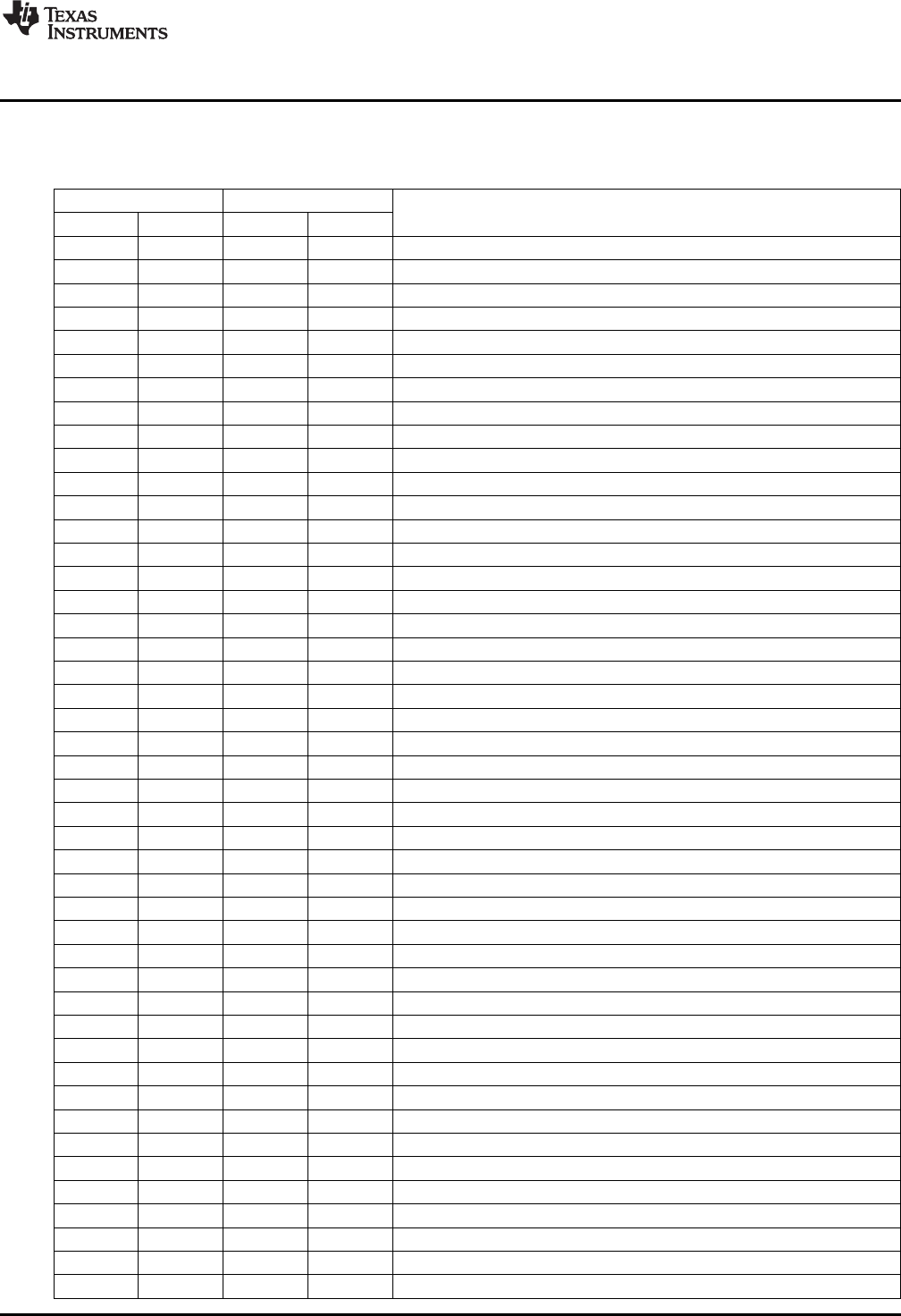

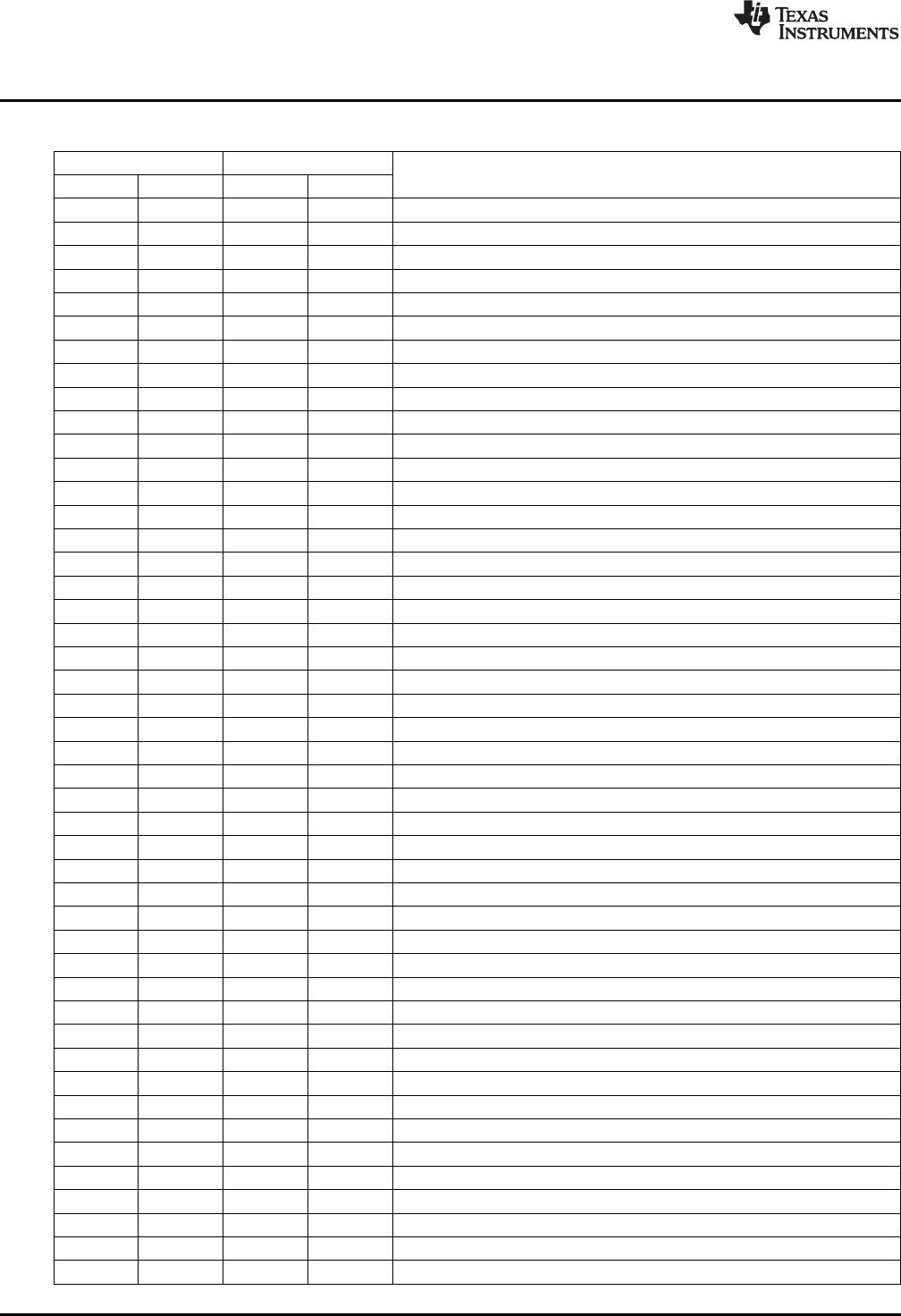

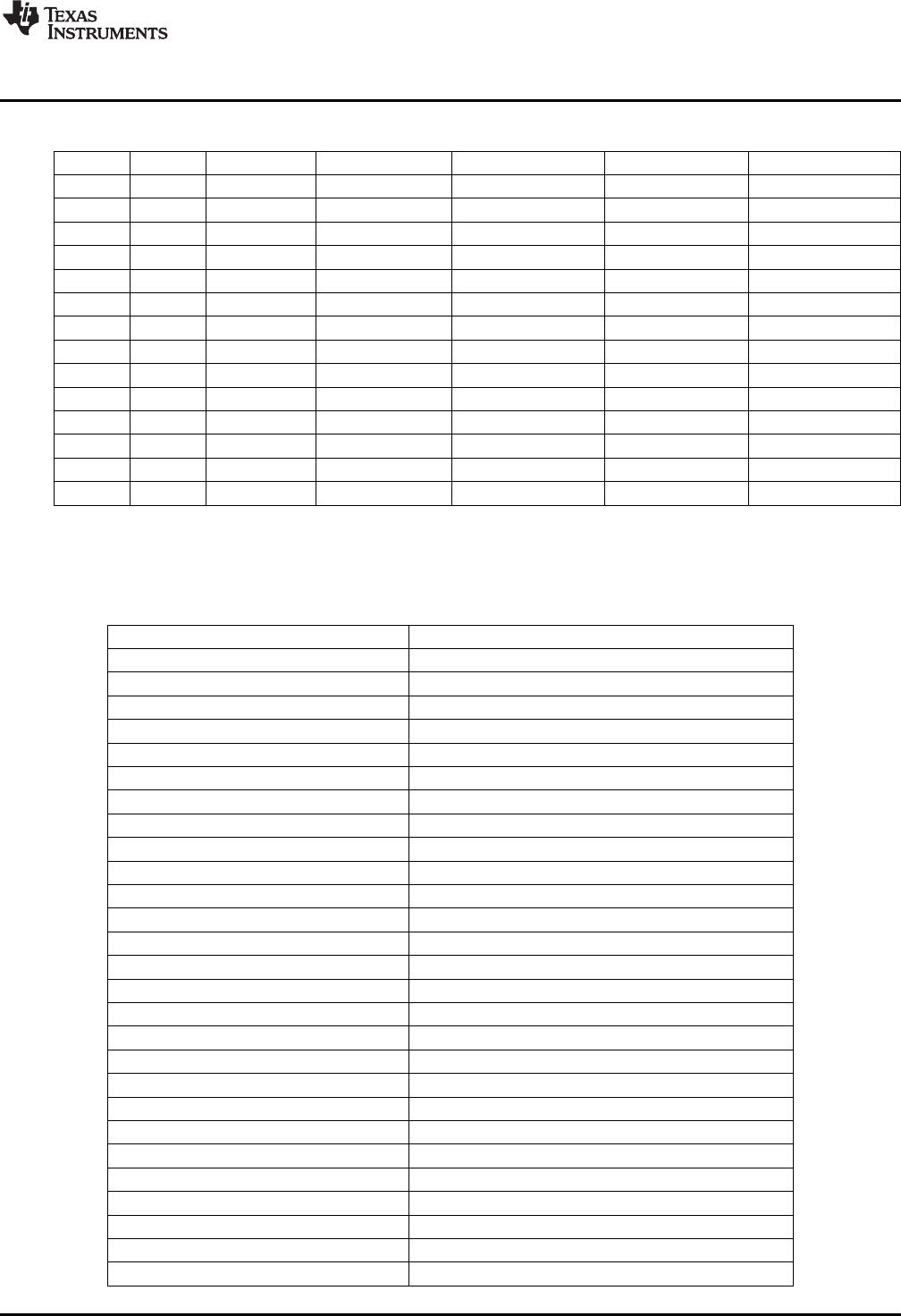

2.1.3 Register Settings for Multifunction Pins

To configure the settings seen in Table 2-1, please see the letter-number combination in Table 2-2 for the

appropriate registers to modify.

Please be aware that more settings may be necessary to obtain a full interface definition matching the

application requirement (see Page 0, Register 25 to 33).

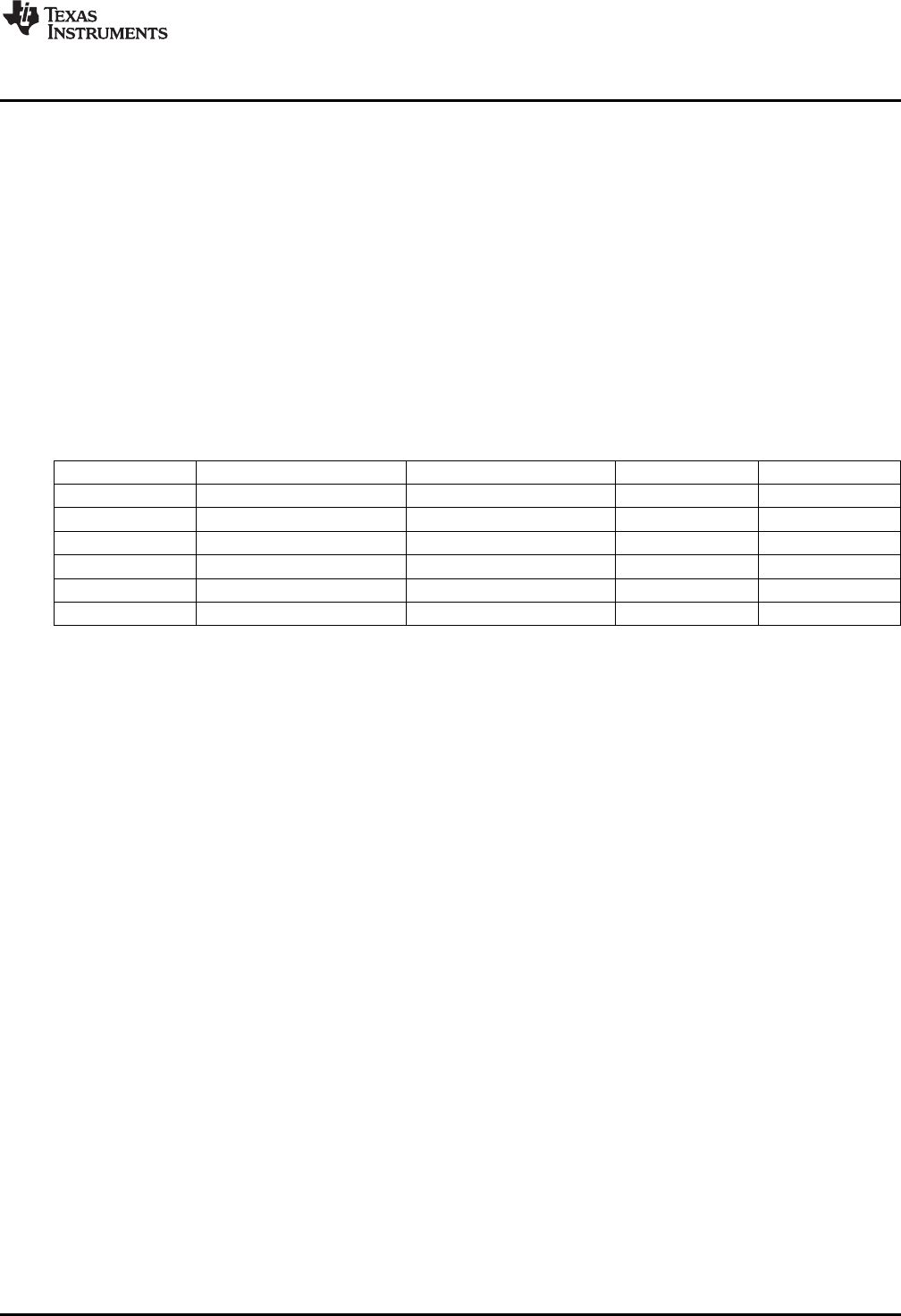

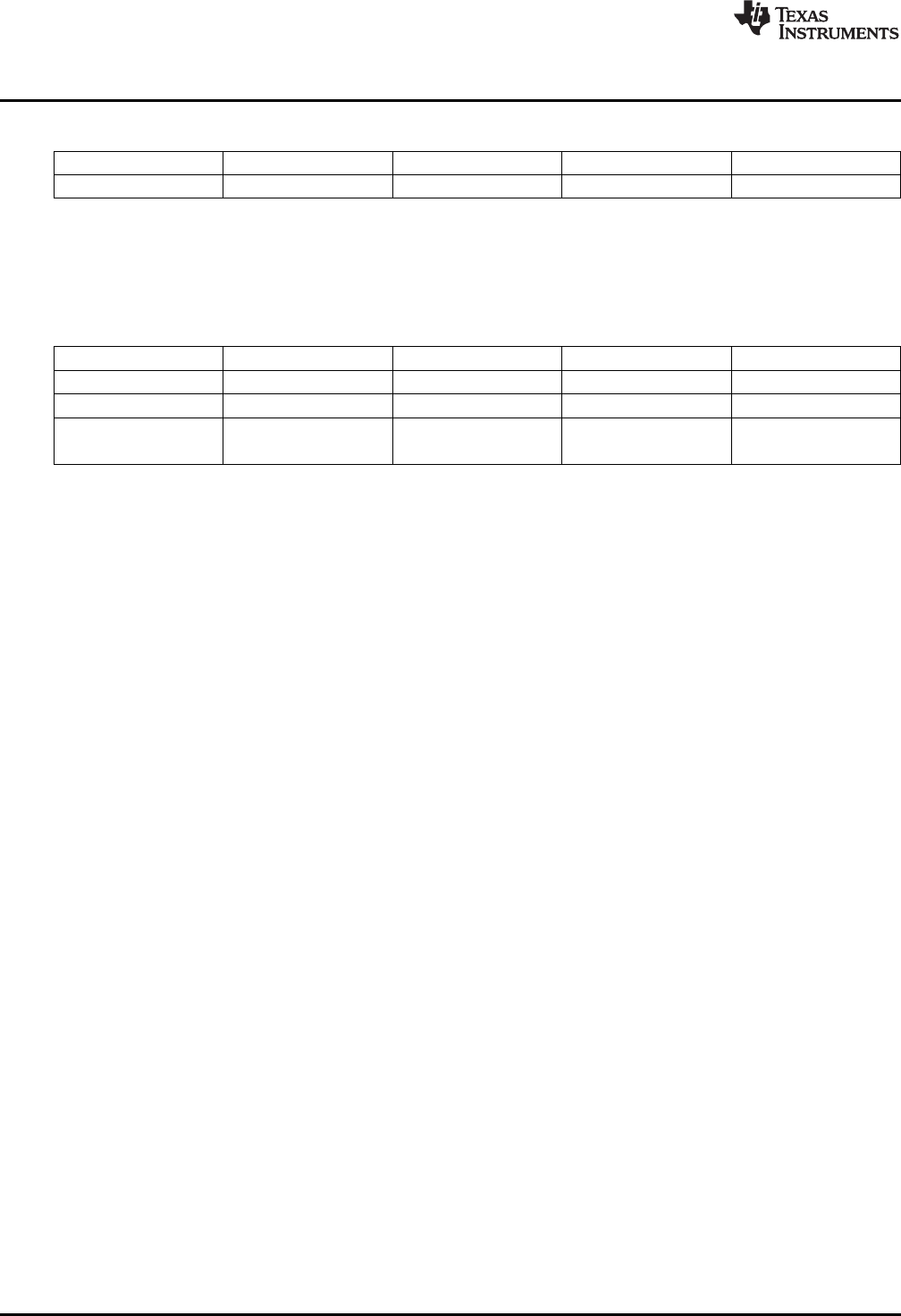

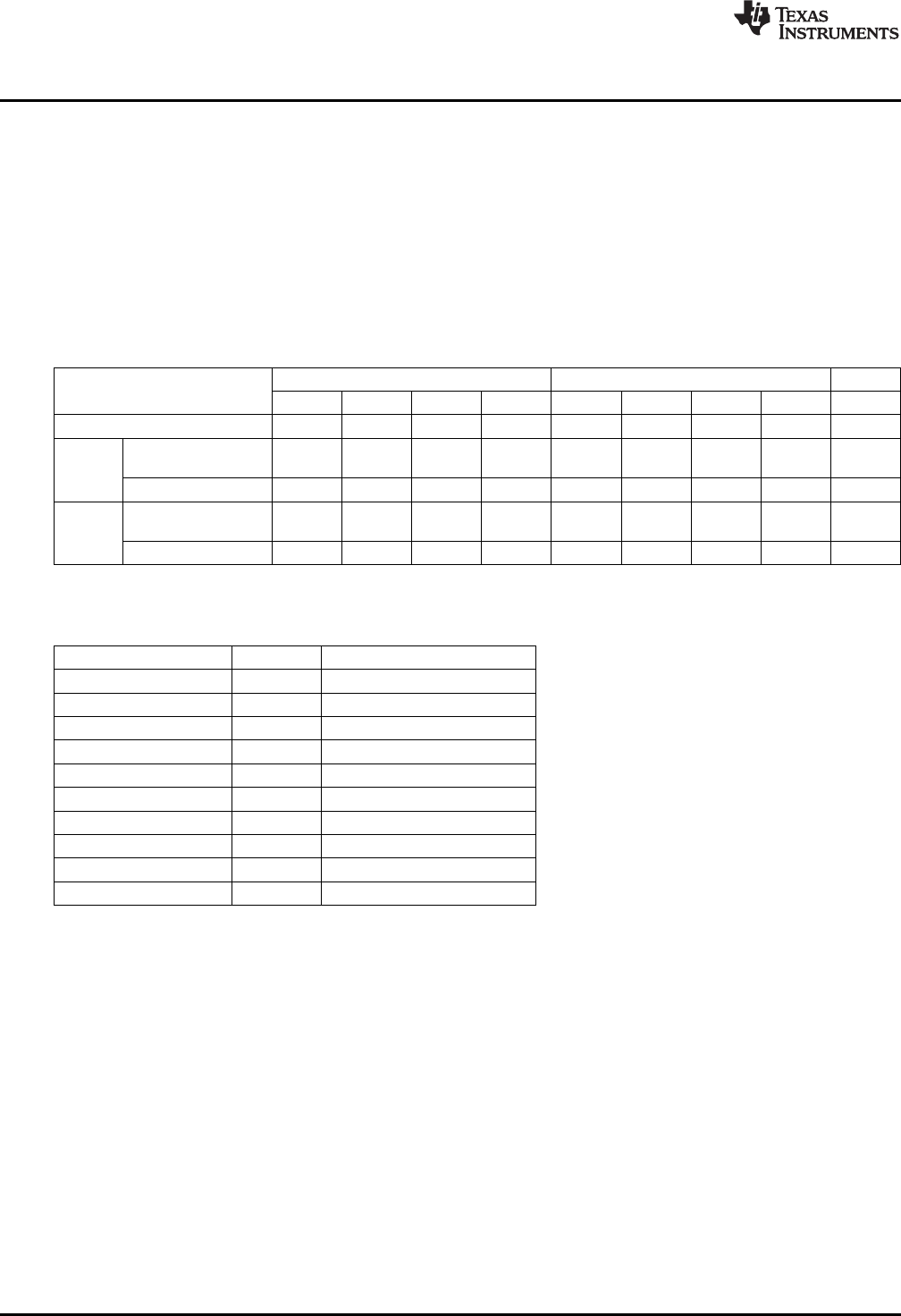

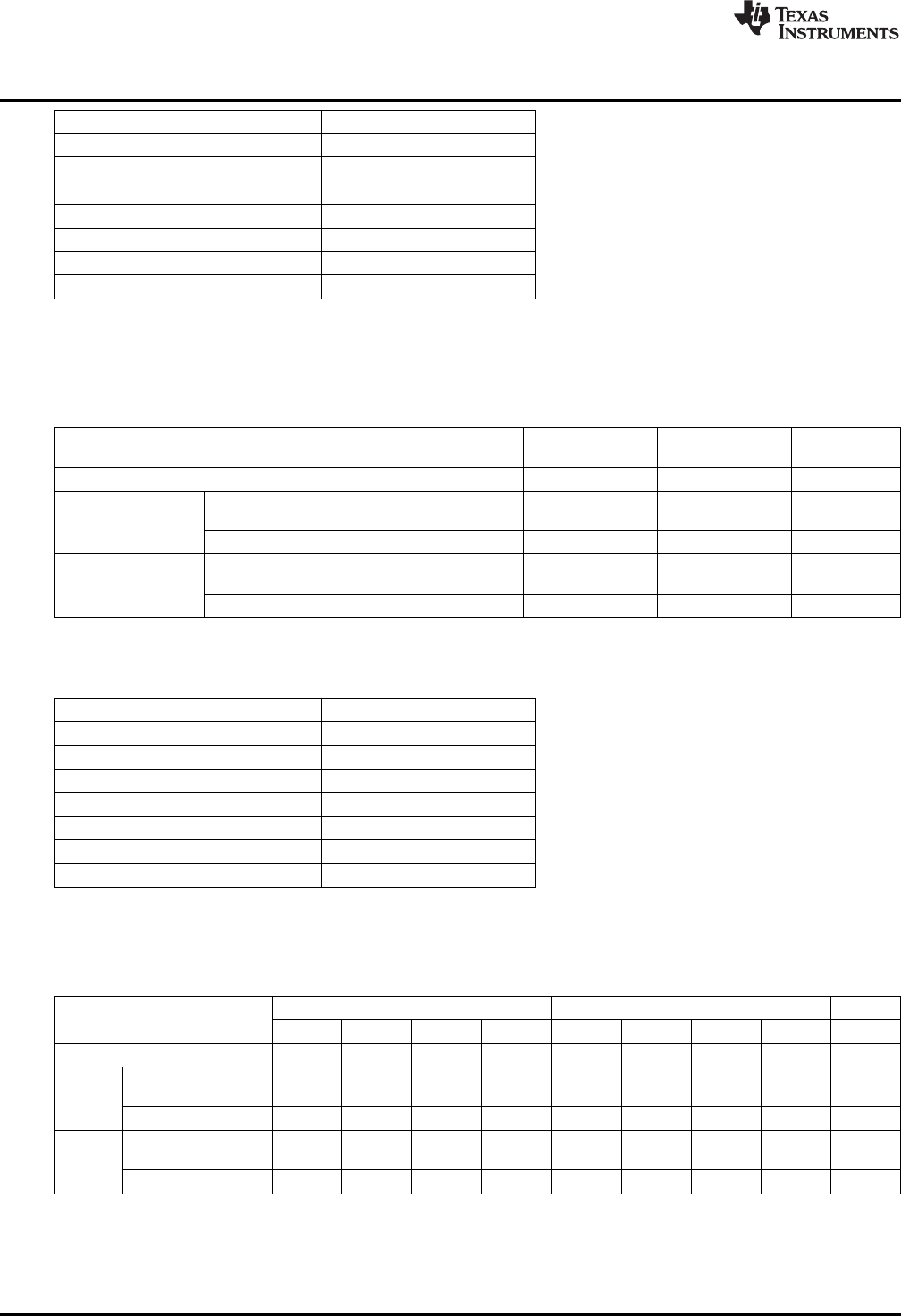

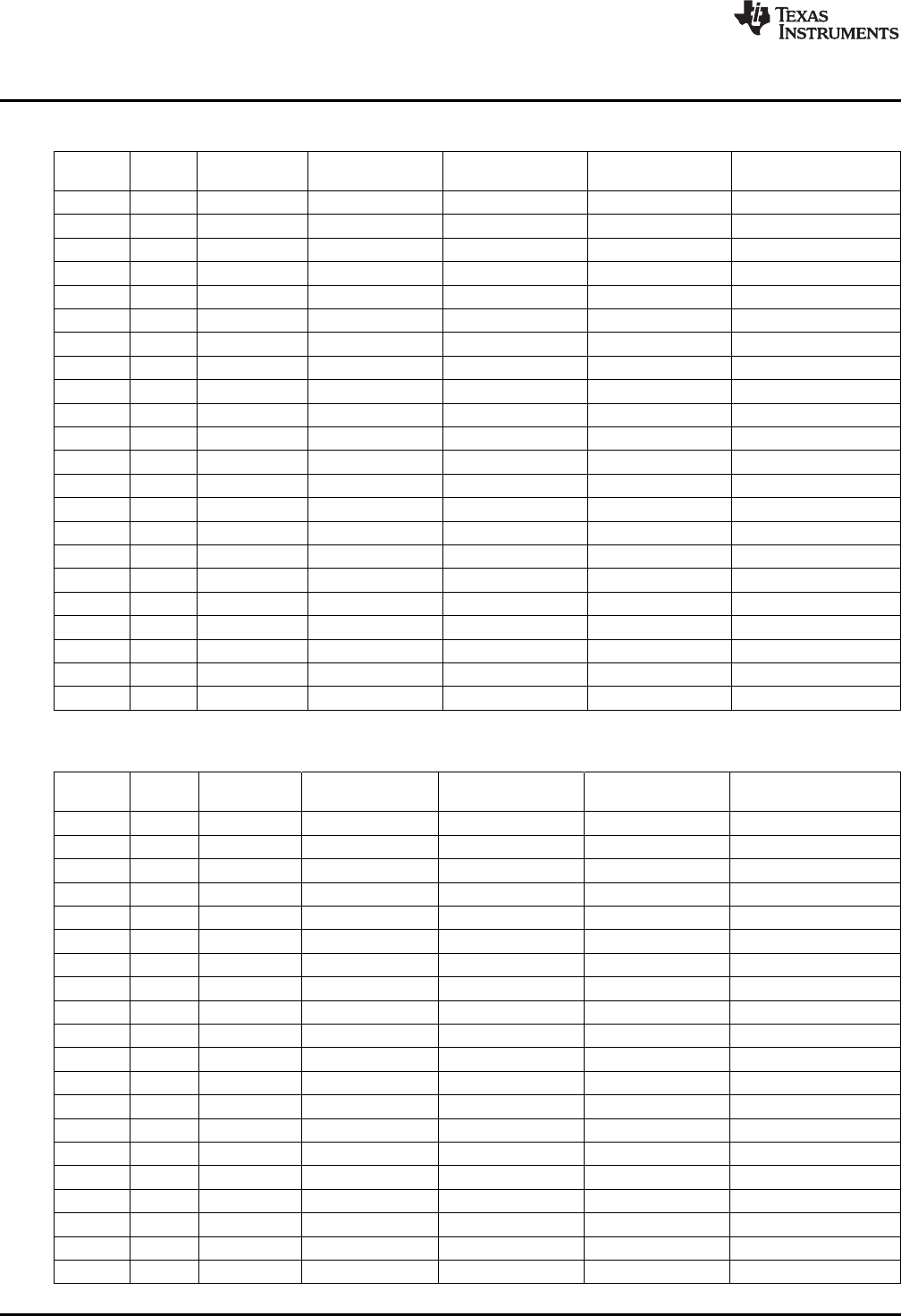

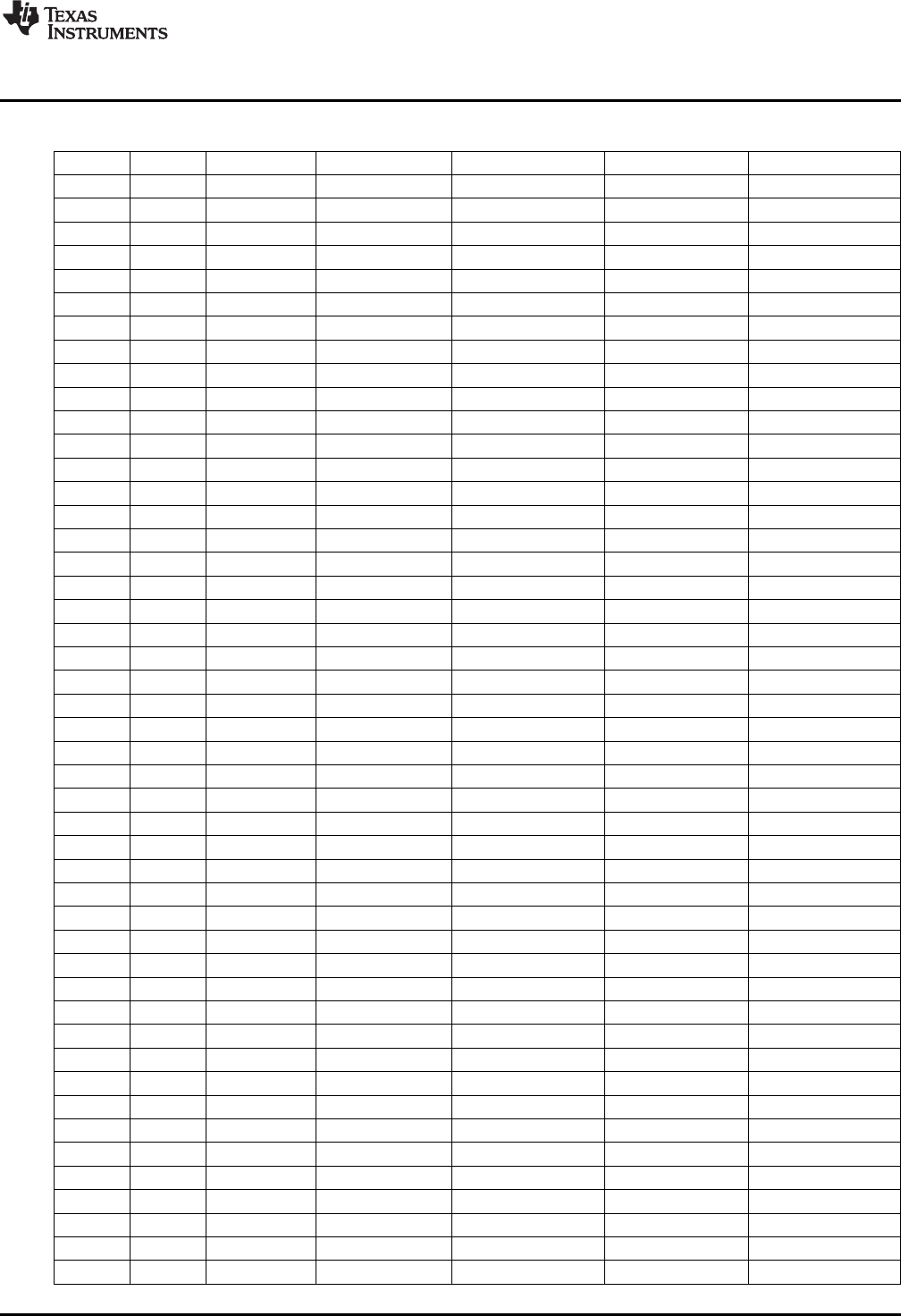

Table 2-2. Multifunction Pin Register Configuration

Required Register

Description Required Register Setting Description Setting

Page 0, Register 4, Bits D3- Page 0, Register 53,Bits

A1 PLL Input on MCLK N5 INT2 output DOUT/MFP2

D2 = 00 D3-D1 = 101

Page 0, Register 4, Bits D3- INT2 output on Page 0, Register 55, Bits

A2 PLL Input on BCLK N7

D2 = 01 MISO/MFP4 D4-D1 = 0101

Page 0, Register 54, Bits

D2-D1 = 01 INT2 output on Page 0, Register 52, Bits

A4 PLL Input on DIN/MFP1 N8

Page 0, Register 4, Bits D3- GPIO/MFP5 D5-D2 = 0110

D2 = 11

Page 0, Register 52, Bits Page 0, Register 54, Bits

D5-D2 = 0001 Digital Microphone Data D2-D1 = 01

A8 PLL Input on GPIO/MFP5 O4

Page 0, Register 4, Bits D3- Input on DIN/MFP1 Page 0, Register 81, Bits

D2 = 10 D5-D4 = 10

Page 0, Register 56, Bits

Codec Clock Input on Page 0, Register 4, Bits D1- Digital Microphone Data D2-D1 = 01

B1 O6

MCLK D0 = 00 Input on SCLK/MFP3 Page 0, Register 81, Bits

D5-D4 = 01

Page 0, Register 52, Bits

Codec Clock Input on Page 0, Register 4, Bits D1- Digital Microphone Data D5-D2 = 0001

B2 O8

BCLK D0 = 01 Input on GPIO/MFP5 Page 0, Register 81, Bits

D5-D4 = 00

Page 0, Register 52, Bits

Codec Clock Input on D5-D2 = 0001 Digital Microphone Clock Page 0, Register 55, Bits

B8 P7

GPIO/MPF5 Page 0, Register 4, Bits D1- Output on MISO/MFP4 D4-D1 = 0111

D0 = 10

Page 0, Register 27, Bit D3 Digital Microphone Clock Page 0, Register 52, Bits

C2 I2S BCLK input on BCLK P8

= 0 Output on GPIO/MFP5 D5-D2 = 1010

Page 0, Register 56, Bits

Page 0, Register 27, Bit D3 Secondary I2S BCLK input D2-D1 = 01

D2 I2S BCLK output on BCLK Q6

= 1 on SCLK/MFP3 Page 0, Register 31, Bits

D6-D5 = 01

Page 0, Register 52, Bits

Page 0, Register 27, Bit D2 Secondary I2S BCLK input D5-D2 = 0001

E3 I2S WCLK input on WCLK Q8

= 0 on GPIO/MFP5 Page 0, Register 31, Bits

D6-D5 = 00

Page 0, Register 56, Bits

Page 0, Register 27, Bit D2 Secondary I2S WCLK in on D2-D1 = 01

F3 I2S WCLK output WCLK R6

= 1 SCLK/MFP3 Page 0, Register 31, Bits

D4-D3 = 01

Page 0, Register 56, Bits Page 0, Register 52, Bits

I2S ADC word clock input D2-D1 = 01 Secondary I2S WCLK in on D5-D2 = 0001

G6 R8

on SCLK/MFP3 Page 0, Register 31, Bits GPIO/MFP50 Page 0, Register 31, Bits

D2-D1 = 01 D4-D3 = 0

Page 0, Register 52, Bits Page 0, Register 56, Bits

I2S ADC word clock input D5-D2 = 0001 Secondary I2S DIN on D2-D1 = 01

G8 S6

on GPIO/MFP5 Page 0, Register 31, Bits SCLK/MFP3 Page 0, Register 31, Bit D0

D2-D1 = 00 = 1

7

SLAU306A–January 2011–Revised January 2013 TLV320AIC3256 Application

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Analog Audio I/O

www.ti.com

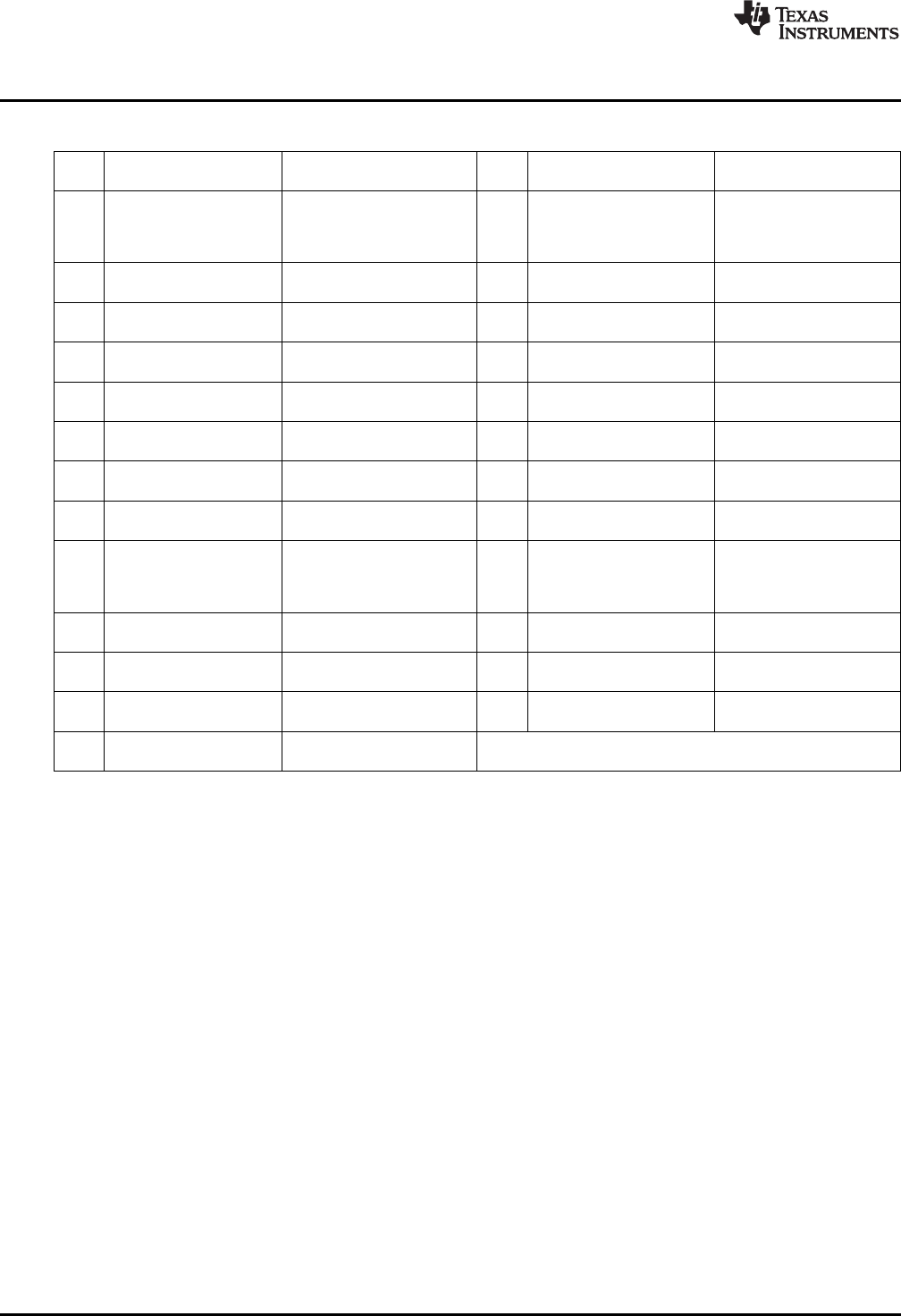

Table 2-2. Multifunction Pin Register Configuration (continued)

Required Register

Description Required Register Setting Description Setting

Page 0, Register 52, Bits

I2S ADC WCLK out on Page 0, Register 55, Bits Secondary I2S DIN on D5-D2 = 0001

H7 S8

MISO/MFP4 D4-D1 = 0110 GPIO/MFP5 Page 0, Register 31, Bit D0

= 0

I2S ADC WCLK out on Page 0, Register 52, Bits Secondary I2S DOUT on Page 0, Register 55, Bits

H8 T7

GPIO/MFP5 D5-D2 = 0111 MISO/MFP4 D4-D1 = 1000

Page 0, Register 54, Bits Secondary I2S BCLK OUT Page 0, Register 53, Bits

I4 I2S DIN on DIN/MFP1 U5

D2-D1 = 01 on DOUT/MFP2 D3-D1 = 110

I2S DOUT on Page 0, Register 53, Bits Secondary I2S BCLK OUT Page 0, Register 55, Bits

J5 U7

DOUT/MFP2 D3-D1 = 001 on MISO/MFP4 D4-D1 = 1001

General Purpose Out I on Page 0, Register 53, Bits Secondary I2S BCLK OUT Page 0, Register 52, Bits

K5 U8

DOUT/MFP2 D3-D1 = 010 on GPIO/MFP5 D5-D2 = 1000

General Purpose Out II Page 0, Register 55, Bits Secondary I2S WCLK OUT Page 0, Register 53, Bits

K7 V5

on MISO/MFP4 D4-D1 = 0010 on SCLK/MFP3 D3-D1 = 111

General Purpose Out III Page 0, Register 52, Bits Secondary I2S WCLK OUT Page 0, Register 55, Bits

K8 V7

on GPIO/MFP5 D5-D2 = 0011 on MISO/MFP4 D4-D1 = 1010

General Purpose In I on Page 0, Register 54, Bits Secondary I2S WCLK OUT Page 0, Register 52, Bits

L4 V8

DIN/MFP1 D2-D1 = 10 on GPIO/MFP5 D5-D2 = 1001

Page 0, Register 56, Bits

General Purpose In II on Page 0, Register 56, Bits Headset Detect Input on D2-D1 = 00

L6 W6

SCLK/MFP3 D2-D1 = 10 SCLK/MFP3 Page 0, Register 67, Bit D7

= 1

General Purpose In III on Page 0, Register 52, Bits Aux Clock Output on Page 0, Register 53, Bits

L8 X5

GPIO/MFP5 D5-D2 = 0010 DOUT/MFP2 D3-D1 = 011

INT1 output on Page 0, Register 53, Bits Aux Clock Output on Page 0, Register 55, Bits

M5 X7

DOUT/MFP2 D3-D1 = 100 MISO/MFP4 D4-D1 = 0011

INT1 output on Page 0, Register 55, Bits Aux Clock Output on Page 0, Register 52, Bits

M7 X8

MISO/MFP4 D4-D1 = 0100 GPIO/MFP5 D5-D2 = 0100

INT1 output on Page 0, Register 52, Bits

M8 GPIO/MFP5 D5-D2 = 0101

2.2 Analog Audio I/O

The analog IO path of the TLV320AIC3256 features a large set of options for signal conditioning as well

as signal routing:

• 6 analog inputs which can be mixed and-or multiplexed in single-ended and-or differential configuration

• 2 programmable gain amplifiers (PGA) with a range of 0 to +47.5dB

• 2 mixer amplifiers for analog bypass

• 2 low power analog bypass channels

• Mute function

• Channel-to-channel phase adjustment

• Fast charge of ac-coupling capacitors

• Anti thump

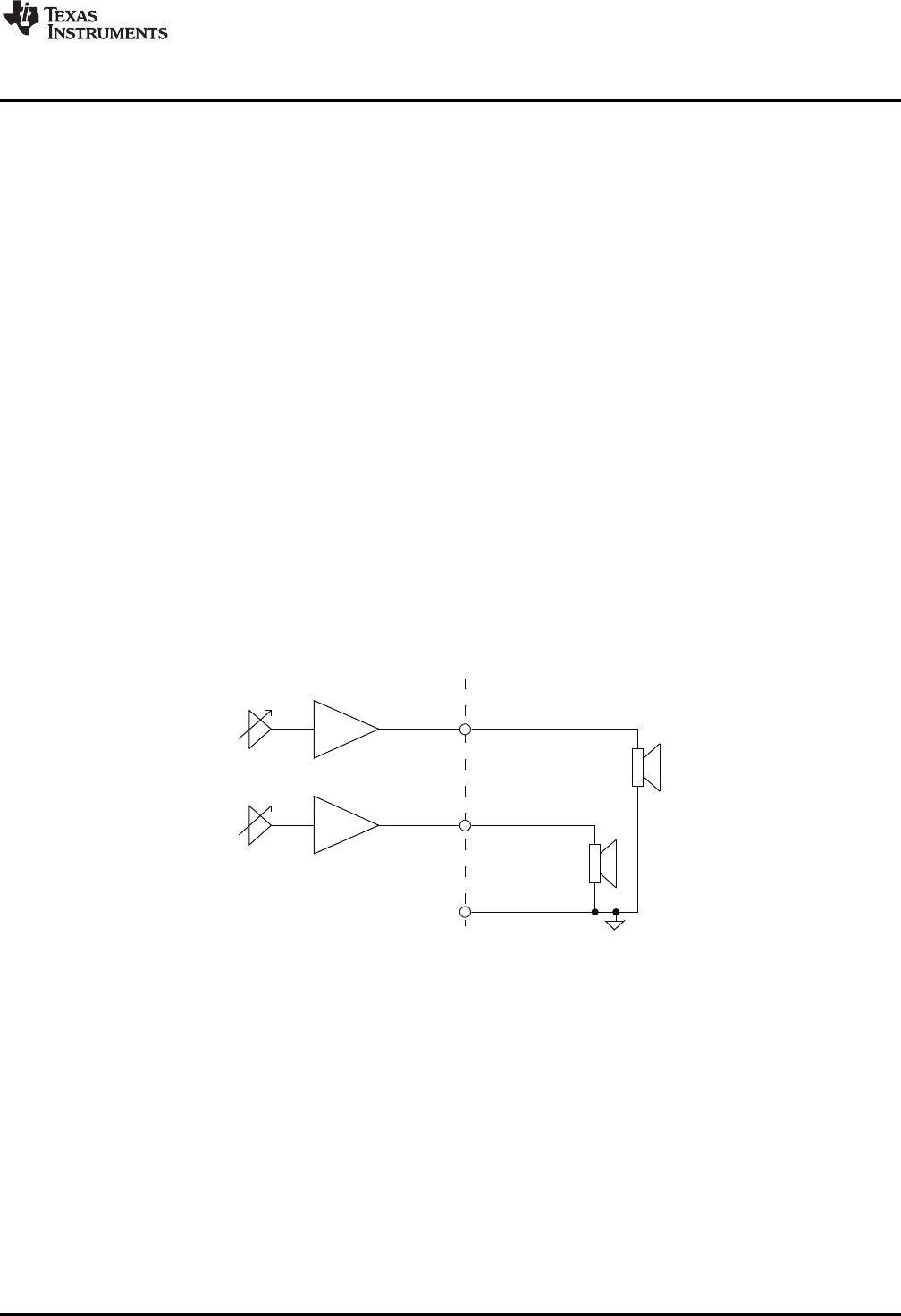

2.2.1 Analog Bypass

The TLV320AIC3256 offers two analog-bypass modes. In either of the modes, an analog input signal can

be routed from an analog input pin to an amplifier driving an analog output pin. Neither the ADC nor the

DAC resources are required for such operation.

In analog low-power bypass mode, line-level signals can be routed directly from the analog inputs IN1_L

to the left headphone amplifier (HPL) and IN1_R to HPR.

8TLV320AIC3256 Application SLAU306A–January 2011–Revised January 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

HPL

HPR

GND_SENSE

www.ti.com

Analog Audio I/O

2.2.2 ADC Bypass Using Mixer Amplifiers

In addition to the analog low-power bypass mode, another bypass mode uses the programmable gain

amplifiers of the input stage in conjunction with a mixer amplifier. With this mode, microphone-level signals

can be amplified and routed to the line or headphone outputs, fully bypassing the ADC and DAC.

To enable this mode, the mixer amplifiers are powered on via software command.

In analog low-power bypass mode, line-level signals can be routed directly from the analog inputs IN1L to

the left headphone amplifier (HPL) and IN1R to HPR. (Configured on Page 1, Register 12, Bit D2 for the

left channel and Page 1, Register 13, Bit D2 for the right channel.)

To use the mixer amplifiers, power them on via Page, Register 9, Bits D1-D0.

2.2.2.1 Analog Programmable Gain Amplifier (PGA)

The TLV320AIC3256 features a built-in low-noise PGA for boosting low-level signals, such as direct

microphone inputs, to full-scale to achieve high SNR. This PGA can provide a gain in the range of 0dB to

47.5dB for single-ended inputs or 6dB to 53.5dB for fully-differential inputs. See Section 2.3.2.1 for

information on setting gains for the entire input path.

2.2.3 Headphone Output

The stereo headphone drivers on pins HPL and HPR can drive loads with impedances down to 16Ωin

single-ended DC-coupled headphone configurations. An integral charge pump generates the negative

supply required to operate the headphone drivers in dc-coupled mode, where the common mode of the

output signal is made equal to the ground of the headphone load using a ground-sense circuit. Operation

of headphone drivers in dc-coupled (ground centered mode) eliminates the need for large dc-blocking

capacitors.

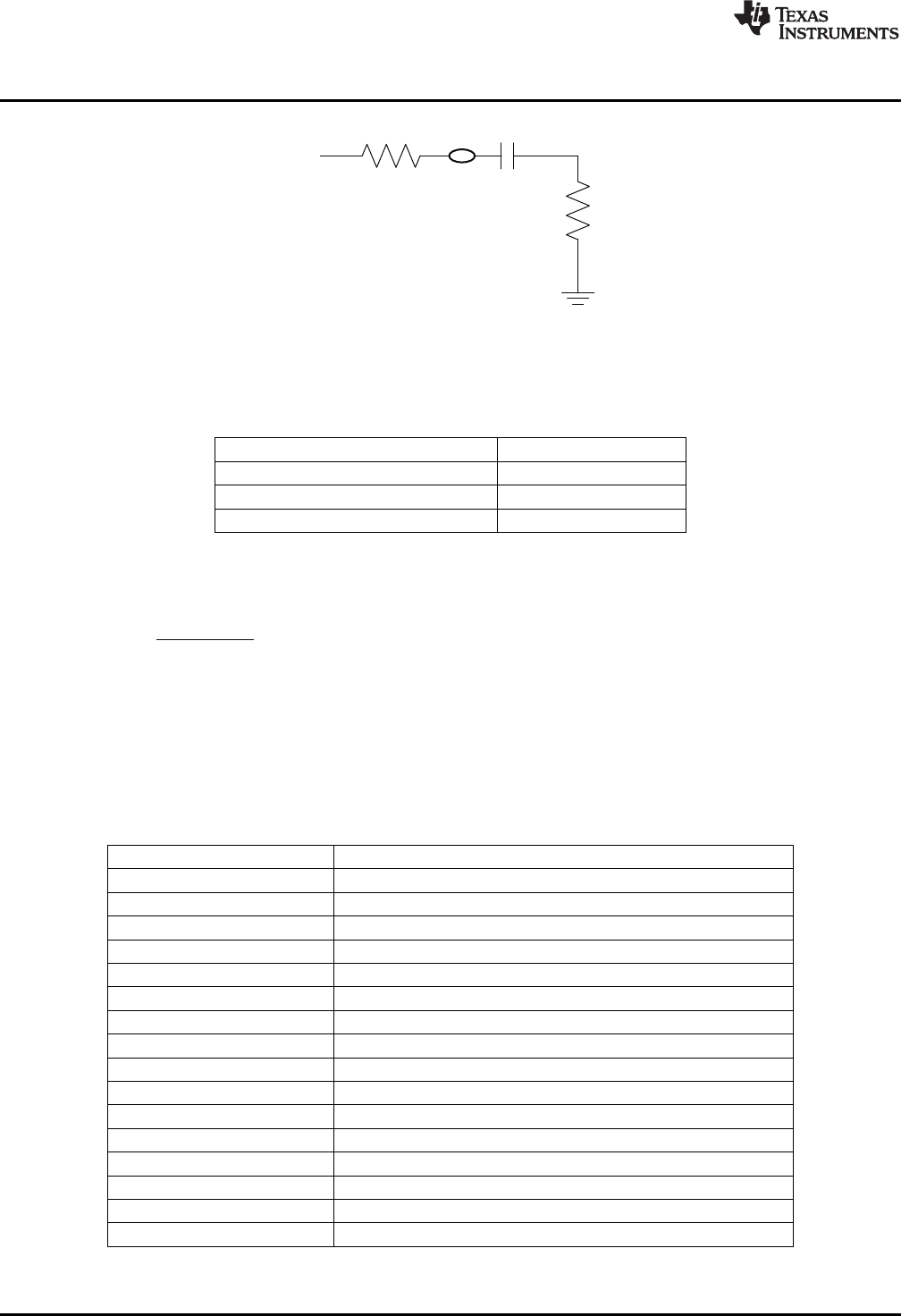

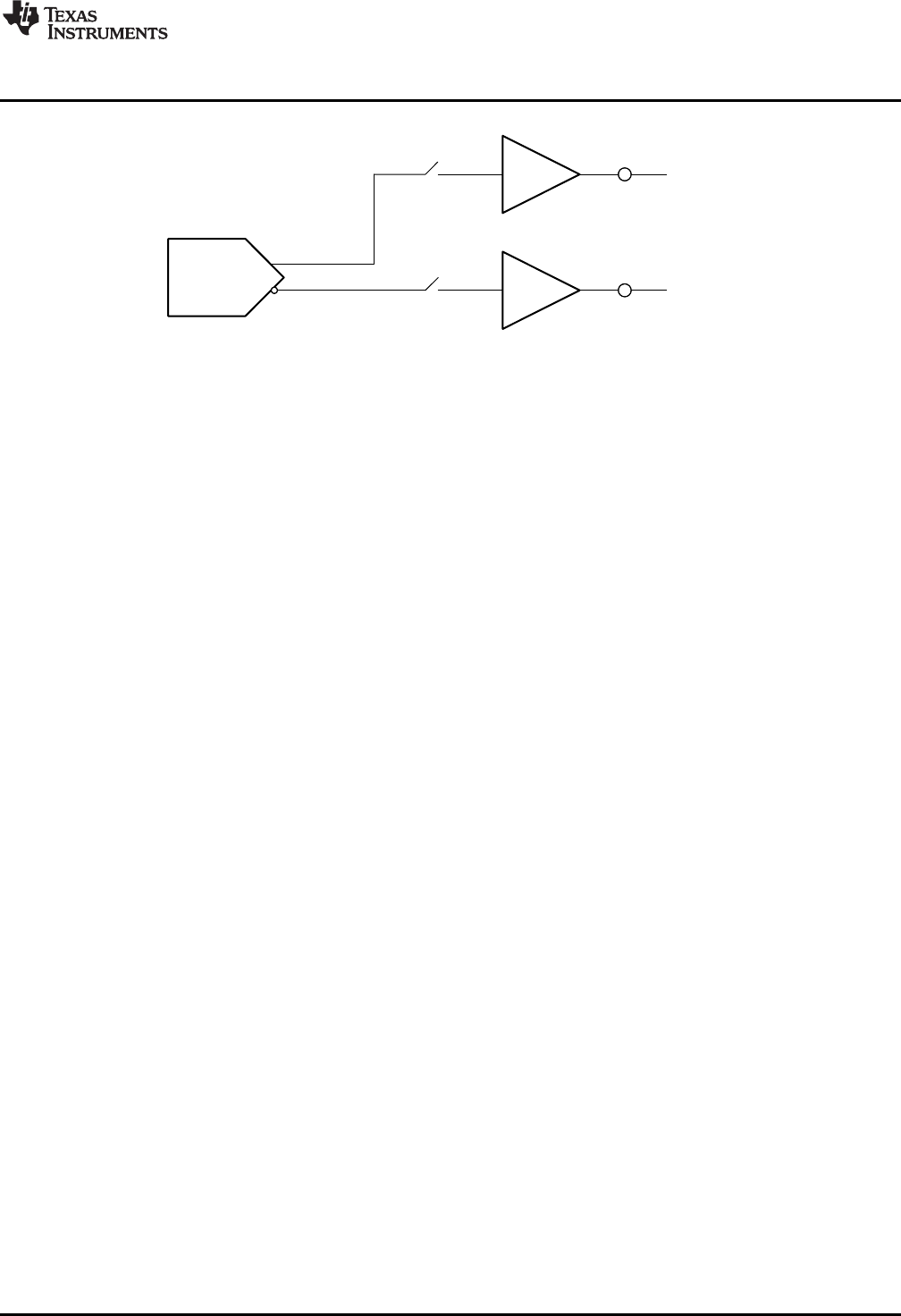

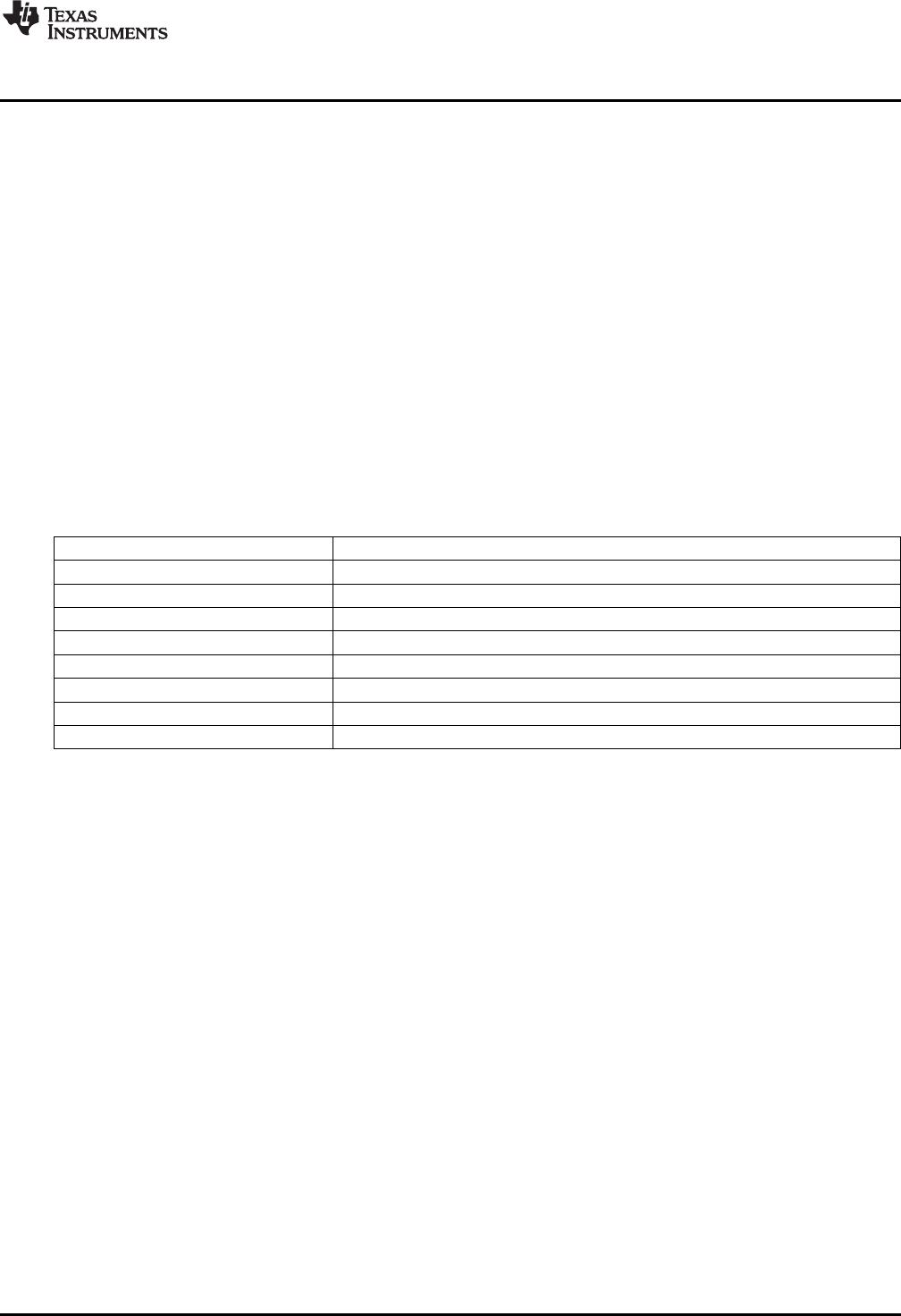

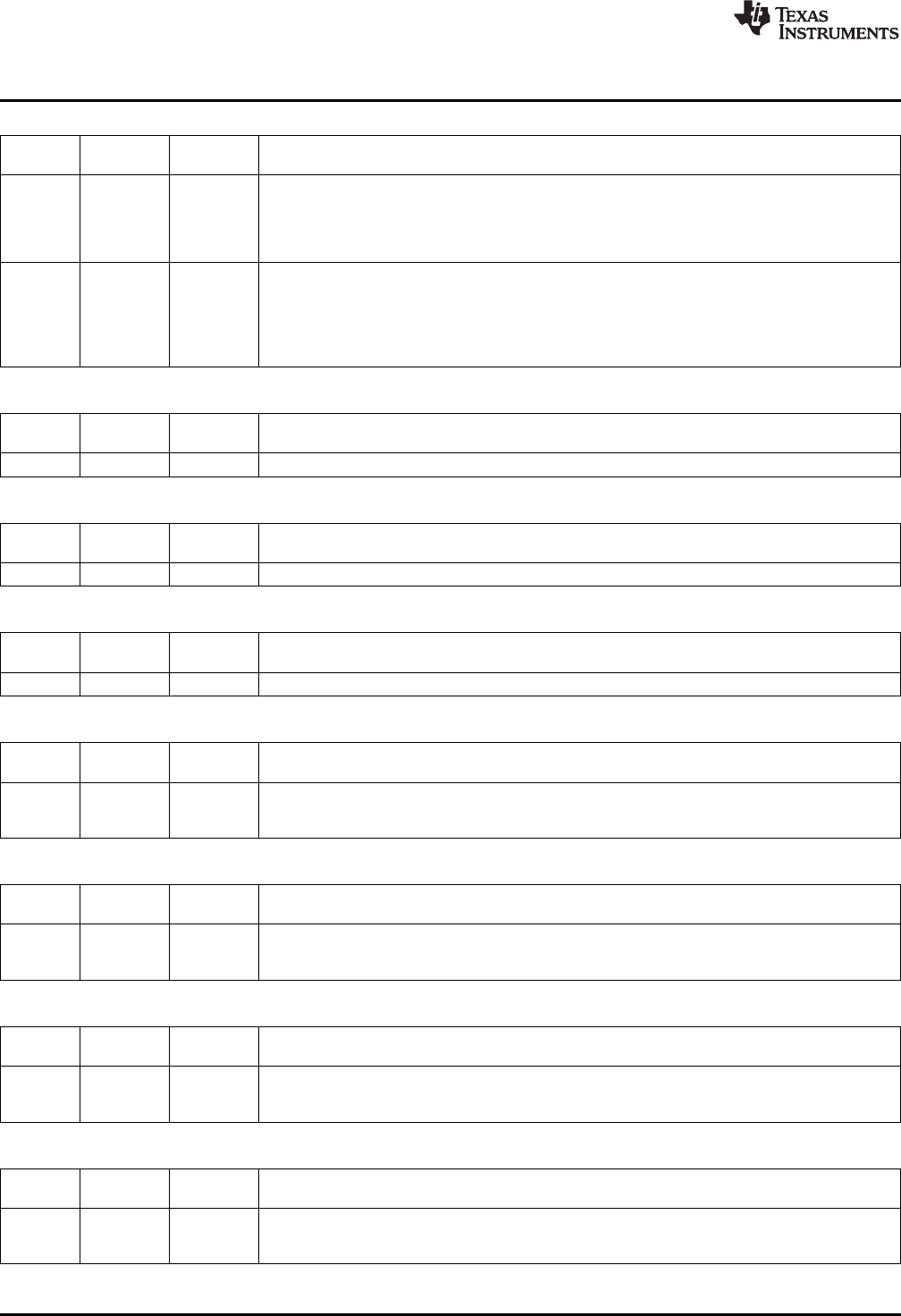

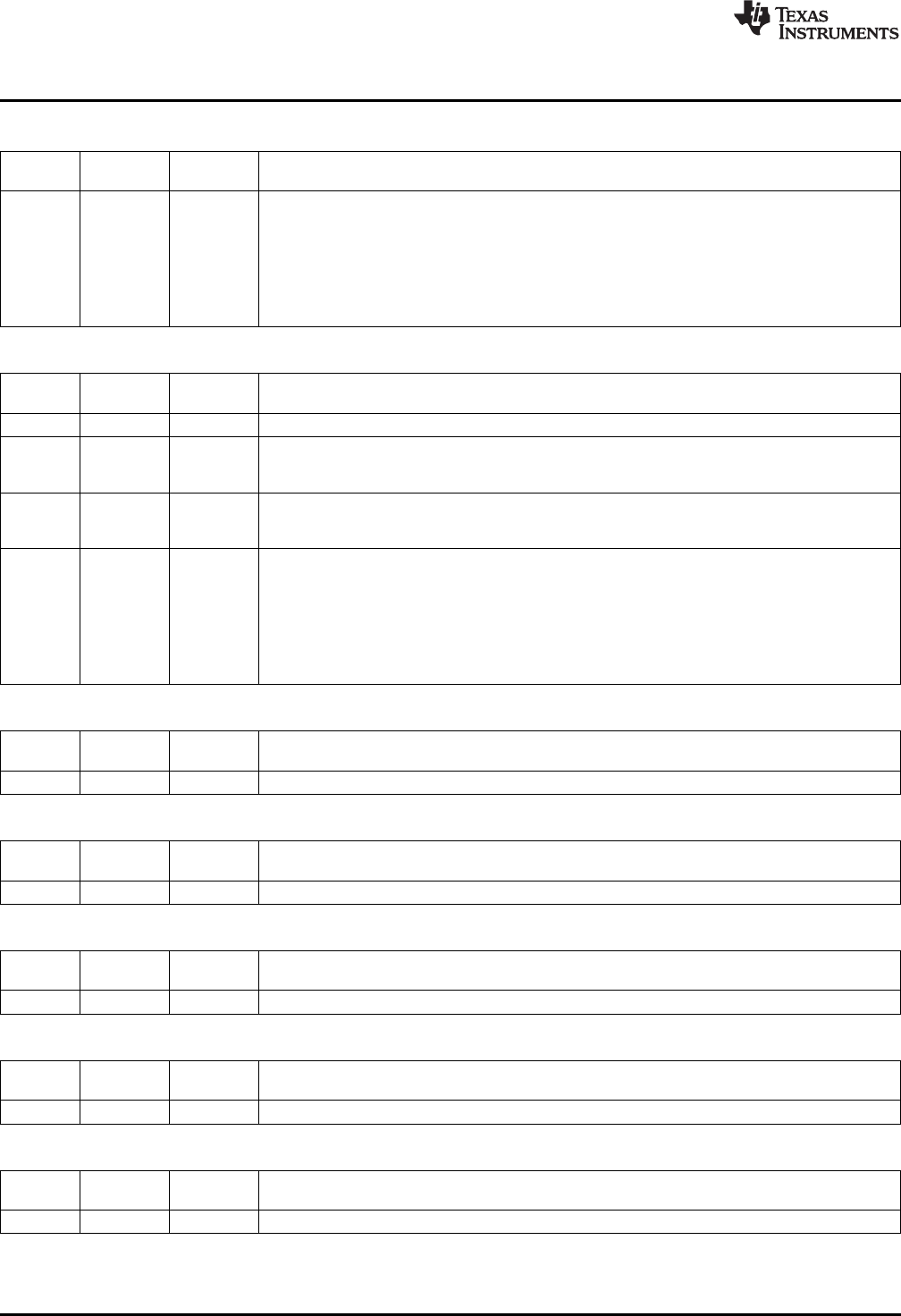

Figure 2-1. TLV320AIC3256 Ground-Centered Headphone Output

Alternatively the headphone amplifier can also be operated in a unipolar circuit configuration using DC

blocking capacitors.

2.2.3.1 Using the Headphone Amplifier

The headphone drivers are capable of driving a mixed combination of DAC signal, left and right ADC PGA

signal and line-bypass from analog input IN1L and IN1R by configuring Page 1, Reg 12 and Page 1, Reg

13 respectively. The ADC PGA signals can be attenuated up to 30dB before routing to headphone drivers

by configuring Page 1, Reg 24 and Page 1, Reg 25. The line-input signals can be attenuated up to 72dB

before routing by configuring Page 1, Reg 22 and 23. The level of the DAC signal can be controlled using

the digital volume control of the DAC in Page 0, Reg 65 and 66. To control the output-voltage swing of

headphone drivers, the digital volume control provides a range of –6.0dB to +14.0dB in steps of 1dB.

These can be configured by programming Page 1, Reg 16 and 17. These level controls are not meant to

be used as dynamic volume control, but more to set output levels during initial device configuration. (1)

(1) If the headphone amplifier must be placed into 'mute' from the –6.0dB setting, set the device at a gain of –5.0dB first, then place the

device into mute.

9

SLAU306A–January 2011–Revised January 2013 TLV320AIC3256 Application

Submit Documentation Feedback Copyright © 2011–2013, Texas Instruments Incorporated

-6...+14dB

1dB steps

-6...+14dB

1dB steps

HPL

HPR

Charge

Pump

GND_Sense

VNEG

Fly_N

Fly_P

DRVdd_HP

DVss_CP

DVdd_CP

2.2 uF

X7R

2.2 uF

X7R

1.8...1.95V

10 uF

Analog Audio I/O

www.ti.com

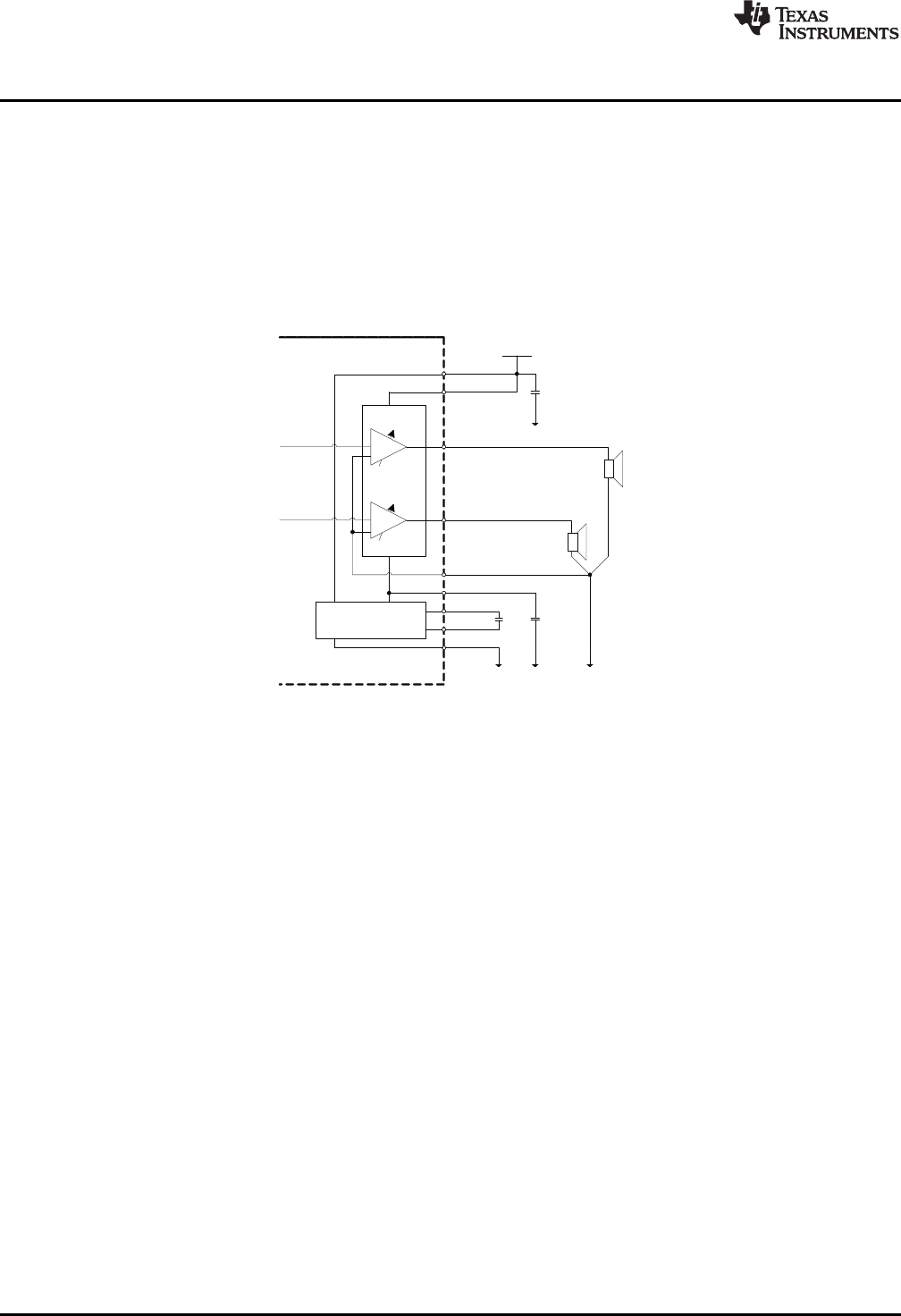

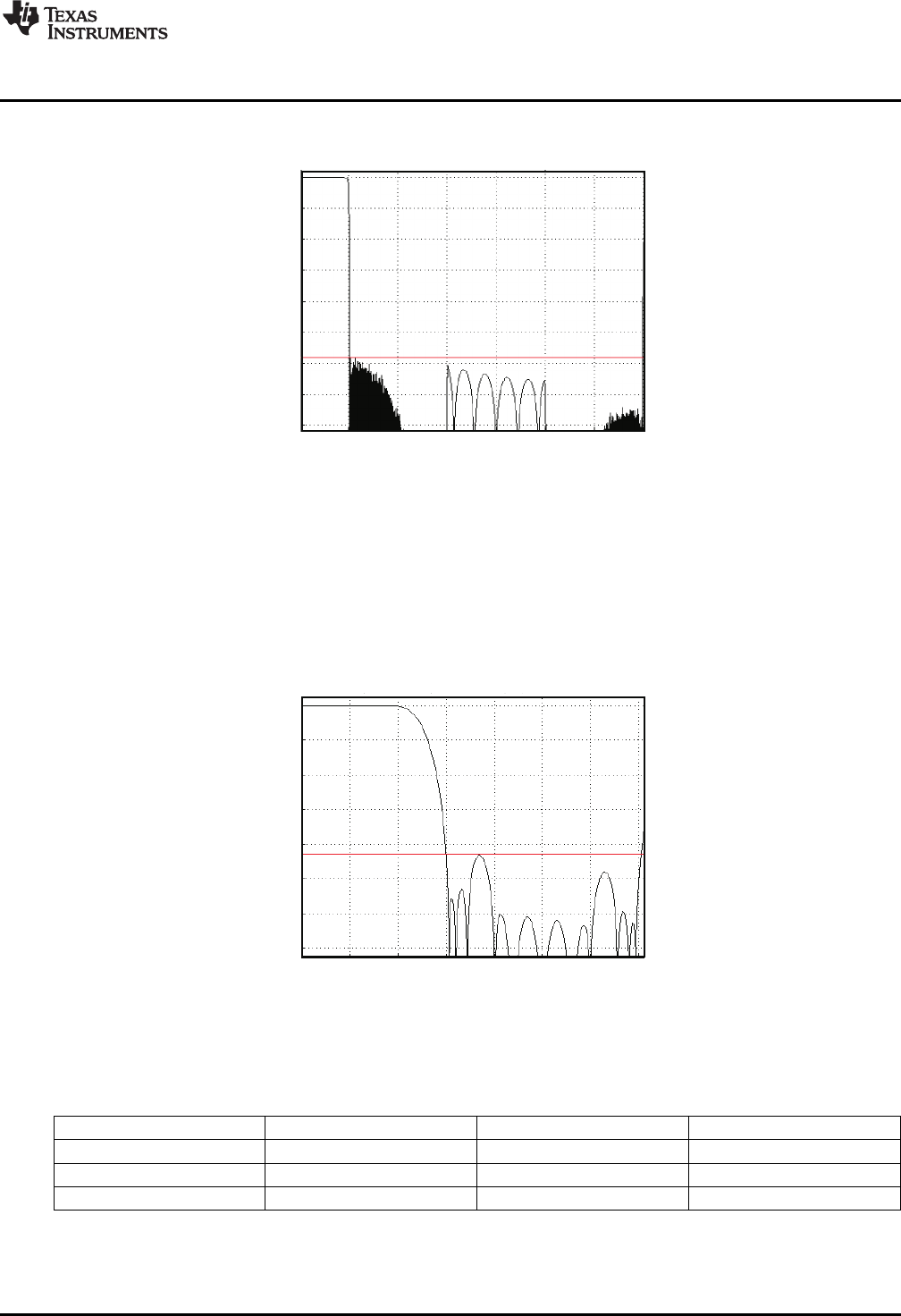

2.2.3.2 Ground-Centered Headphone Amplifier Configuration

Among the other advantages of the ground-centered connection is inherent freedom from turn-on

transients that can cause audible pops, sometimes at uncomfortable volumes.

2.2.3.2.1 Circuit Topology

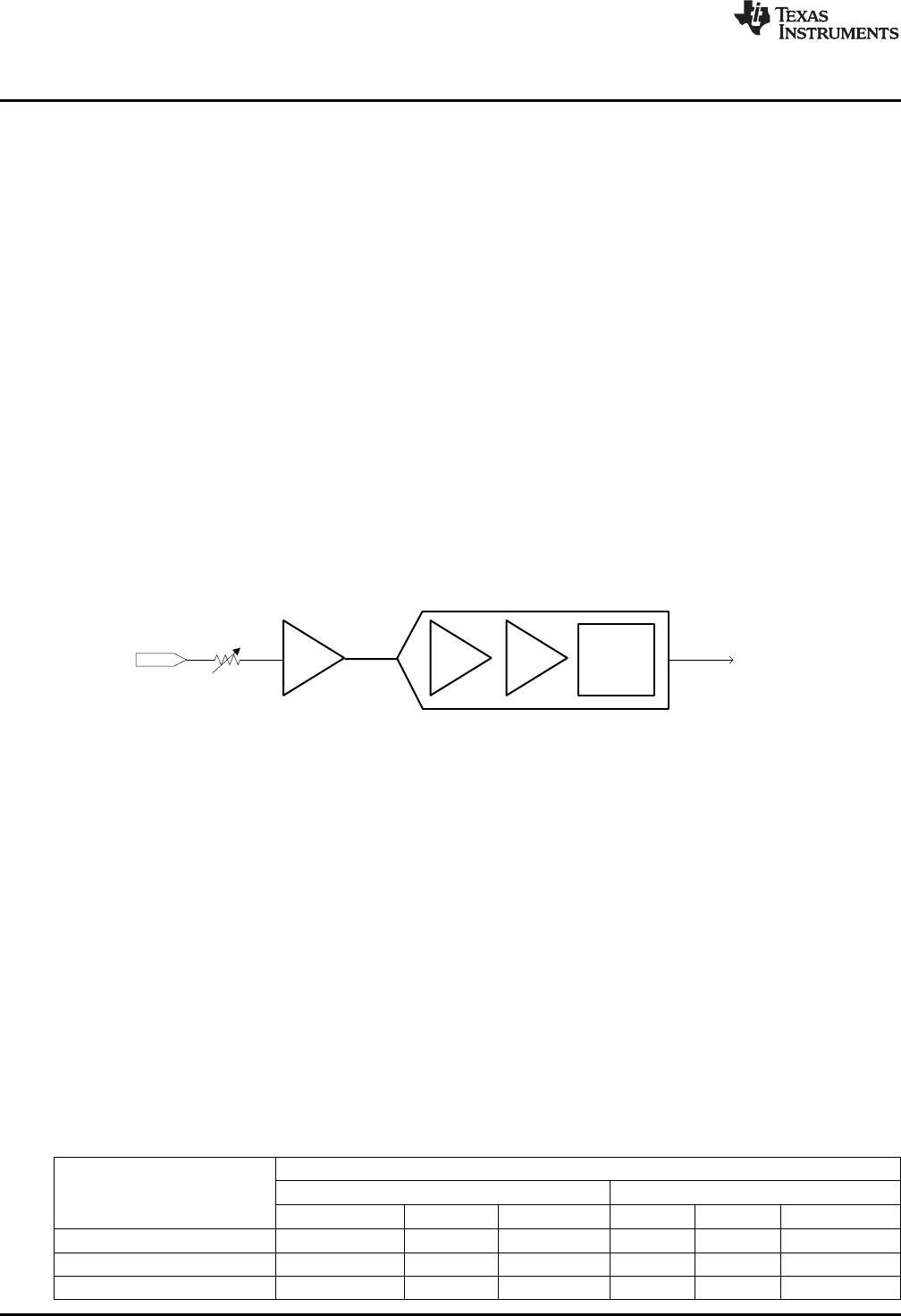

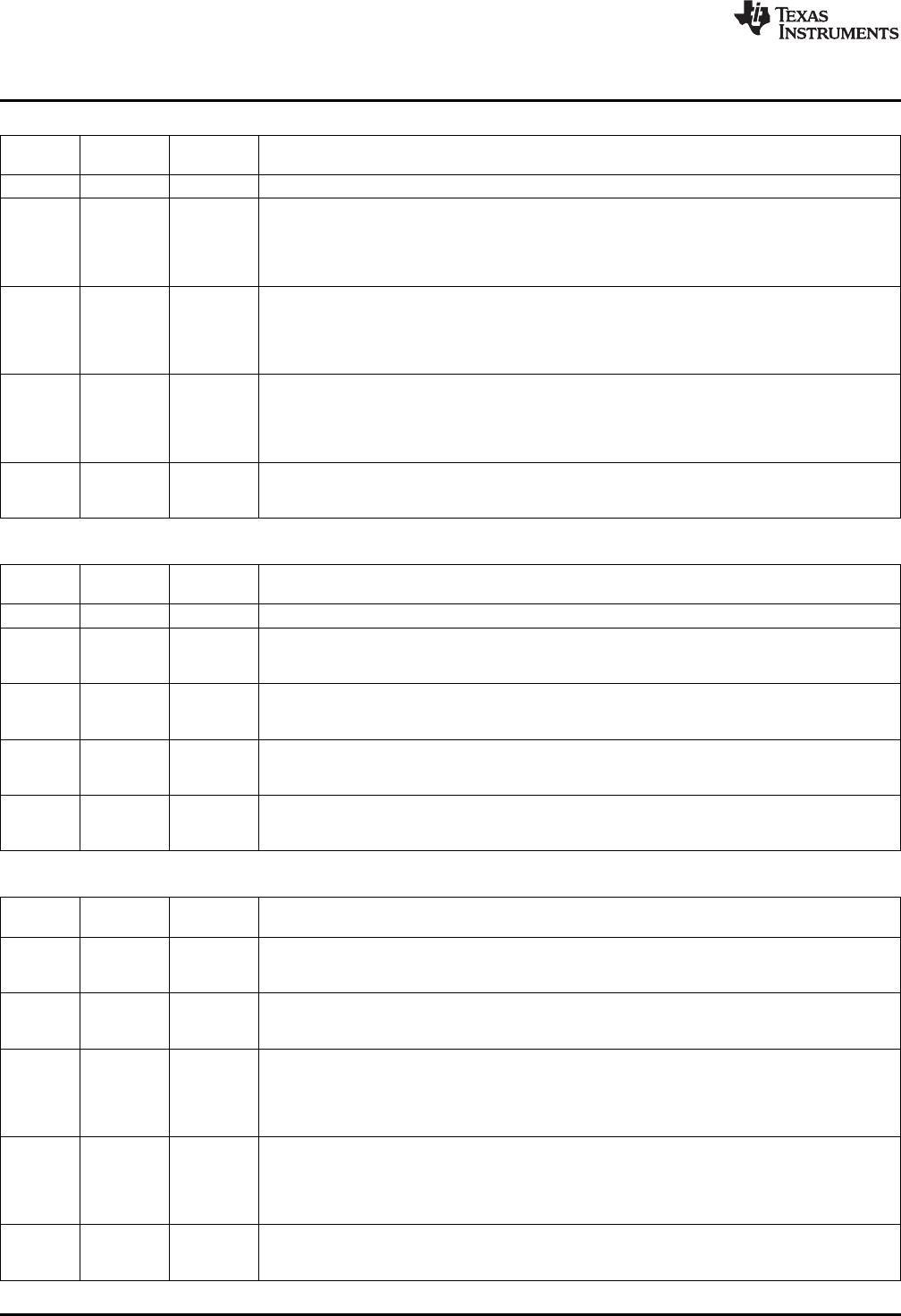

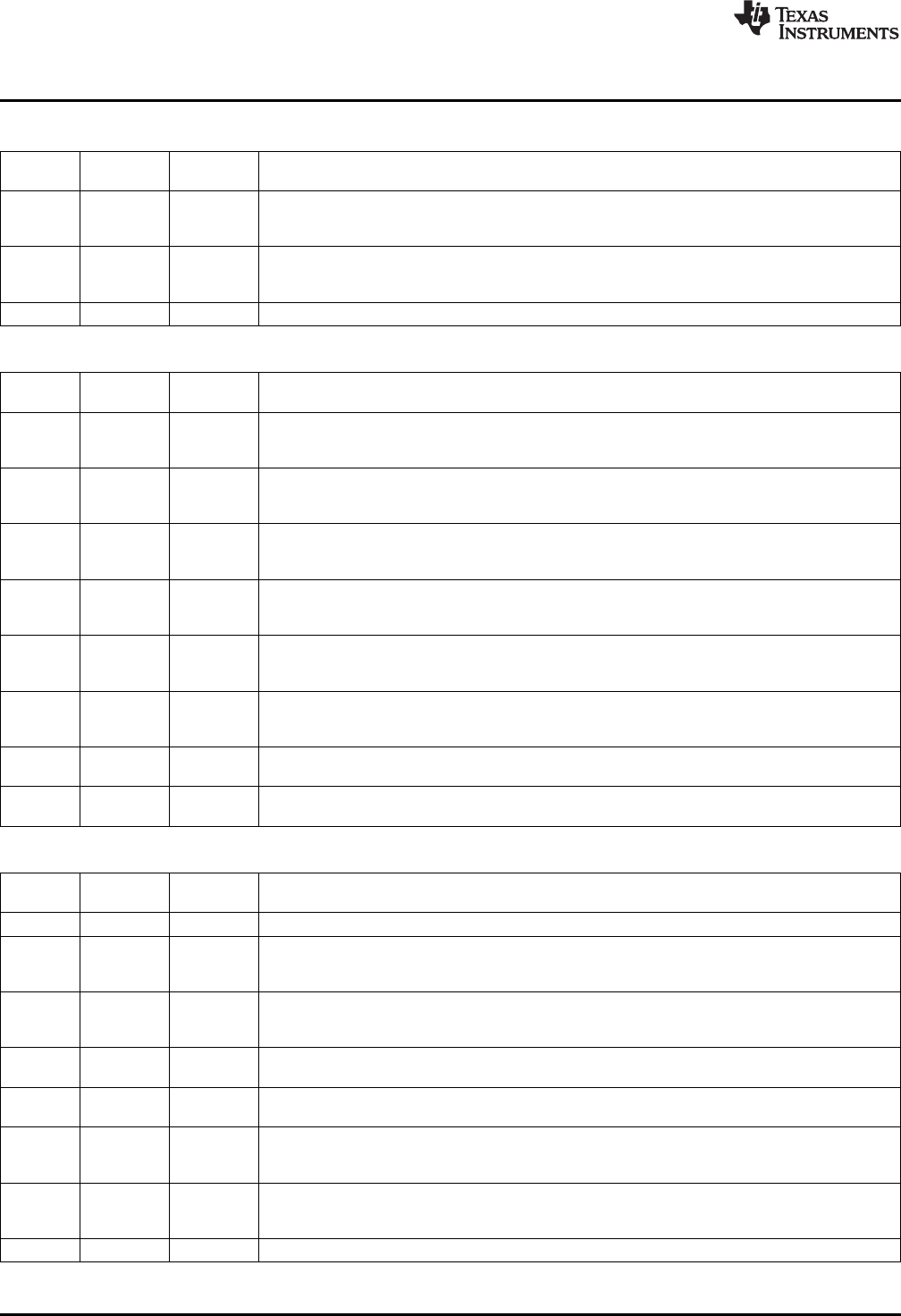

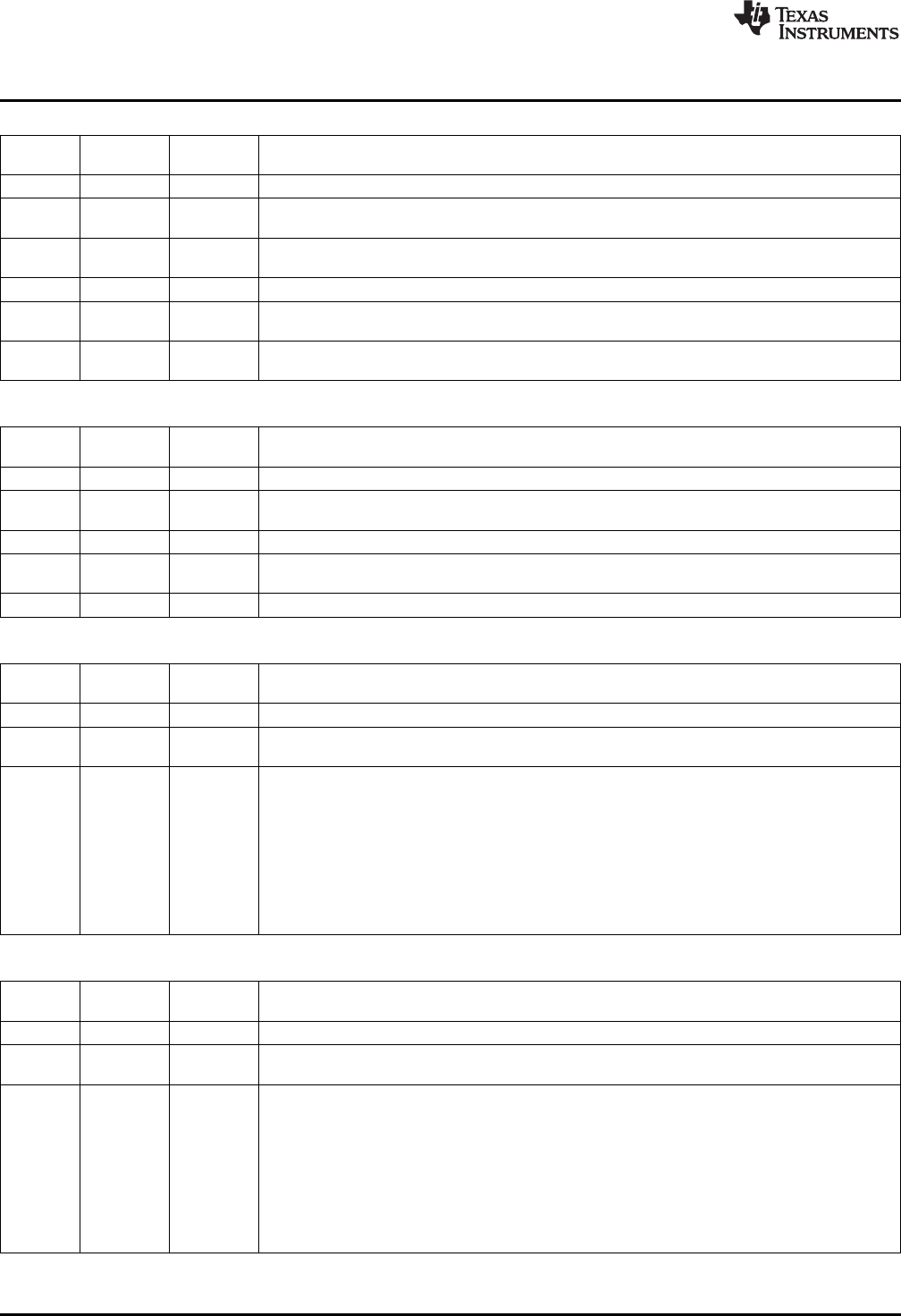

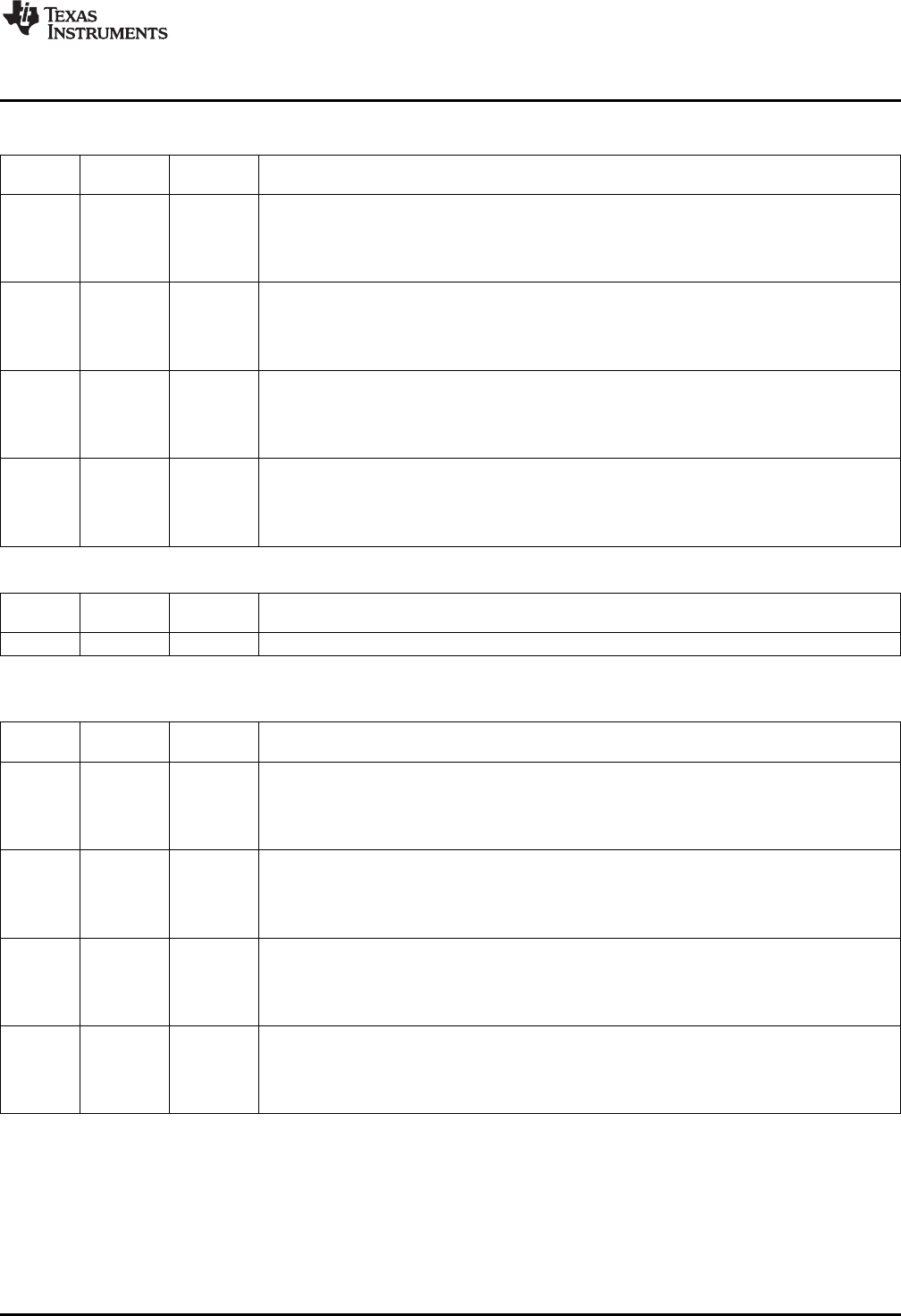

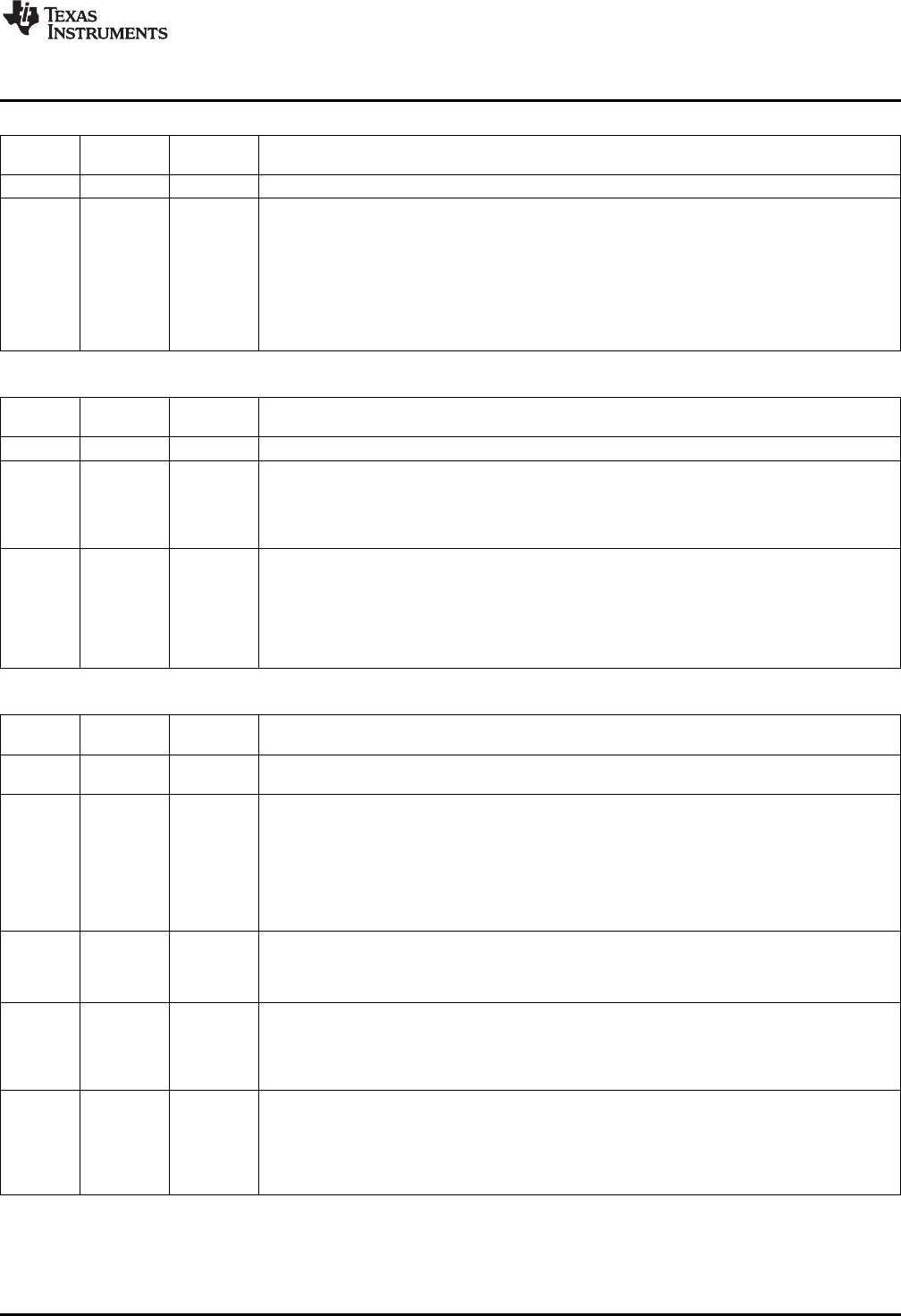

The power supply hook up scheme for the ground centered configuration is shown in Figure 2-2

DRVdd_HP pin supplies the positive side of the headphone amplifier. DVdd_CP pin supplies the charge

pump which in turn supplies the negative side of the headphone amplifier. Two capacitors are required for

the charge pump circuit to work. These capacitors should be X7R rated.

Figure 2-2.

2.2.3.2.2 Charge Pump Setup and Operation

The built in charge pump draws charge from the DVDD_CP supply, and by switching the external

capacitor between FLY_P and FLY_N, generates the negative voltage on VNEG pin. The charge-pump

circuit uses the principles of switched-capacitor charge conservation to generate the VNEG supply in a

very efficient fashion.

To turn on the charge pump circuit, program Page 1, Register 1, D1:0 to “10”. When the charge pump

circuit is disabled, VNEG acts as a ground terminal, allowing unipolar configuration of the headphone

amps. By default, the charge pump is disabled. The switching rate of the charge pump can be controlled

by Page 1, Register 124, D3:0. Because the charge pump can demand significant inrush currents from the

supply, it is important to have a capacitor connected in close proximity to the DVdd_CP and DVss_CP

pins of the device. At 500kHz clock rate this requires approximately a 10μF capacitor. The ESR and ESL

of the capacitor must be low to allow fast switching currents.

The ground-centered mode of operation is enabled by configuring Page 1, Reg 125, D4 after enabling the

charge-pump.

2.2.3.2.3 Output Power Optimization

The device can be optimized for a specific output-power range. The charge pump and the headphone

driver circuitry can be reduced in power so less overall power is consumed. The headphone driver power

can be programmed in Page 1, Register 125. The control of charge pump switching current is

programmed in Page 1, Register 124.

2.2.3.2.4 Offset Correction and Start-Up

The TLV320AIC3256 offers an offset-correction scheme that is based on calibration during power up. This

scheme minimizes the differences in DC voltage between GND_SENSE and HPL and HPR outputs.

10 TLV320AIC3256 Application SLAU306A–January 2011–Revised January 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

www.ti.com

Analog Audio I/O

The offset calibration happens after the headphones are powered up in ground-centered configuration. All

other headphone configurations like signal routings, gain settings and mute removal must be configured

before headphone powerup. Any change in these settings while the headphones are powered up may

result in additional offsets and are best avoided.

The offset-calibration block has a few programmable parameters that the user must control. The user can

either choose to calibrate the offset only for the selected input routing or all input configurations. The

calibration data is stored in internal memory until the next hardware reset or until AVdd power is removed.

Programming Page 1, Register 125, D(1:0) as “10” causes the offset to be calibrated for the selected input

mode. Programming Page 1, Register 125, D(1:1) as “11” causes the offset to be calibrated for all

possible configurations. All related blocks must be powered while doing offset correction.

Programming Page 1, Reg 125, D (1:0) as “00” (default) disables the offset correction block. While the

offset is being calibrated, no signal should be applied to the headphone amplifier. the DAC should be kept

muted and analog bypass routing should be kept at the highest attenuation. The user can read Page 1,

Register 2, D2 to poll if calibration is completed. D2 = ”1” indicates that calibration is completed.

2.2.3.2.5 Ground-Centered Headphone Setup

There are four practical device setups for ground-centered operation, shown in Table 2-3:

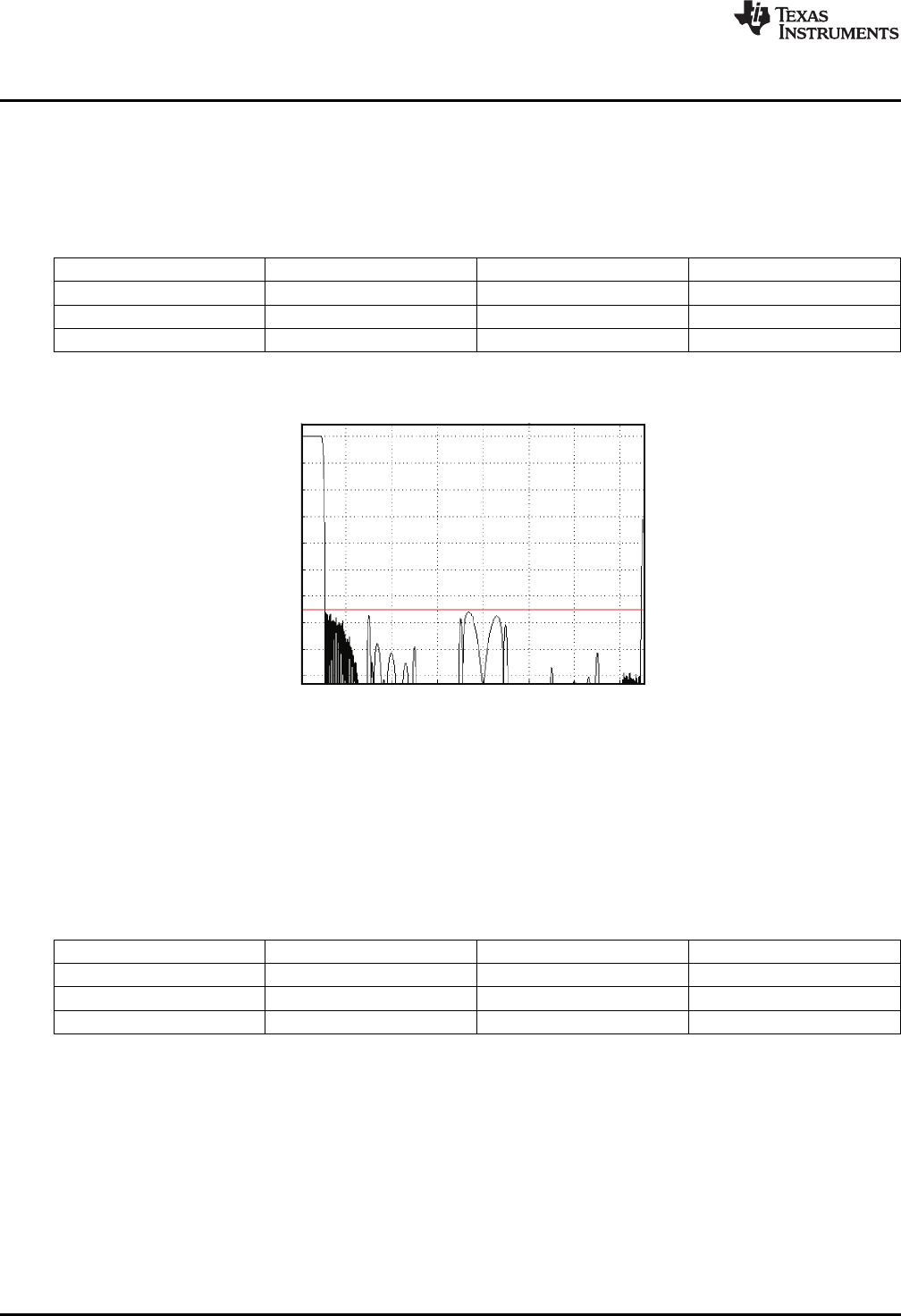

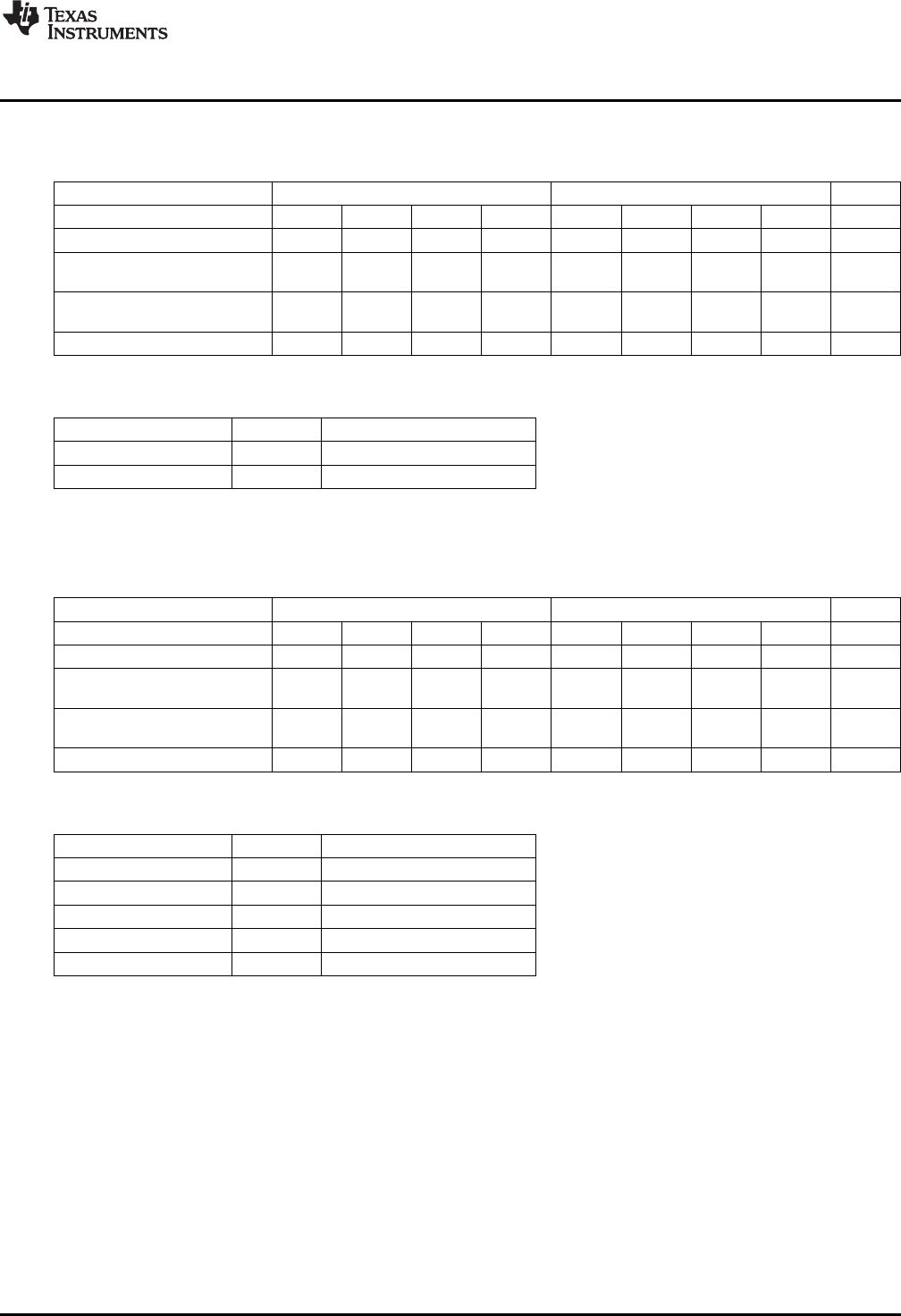

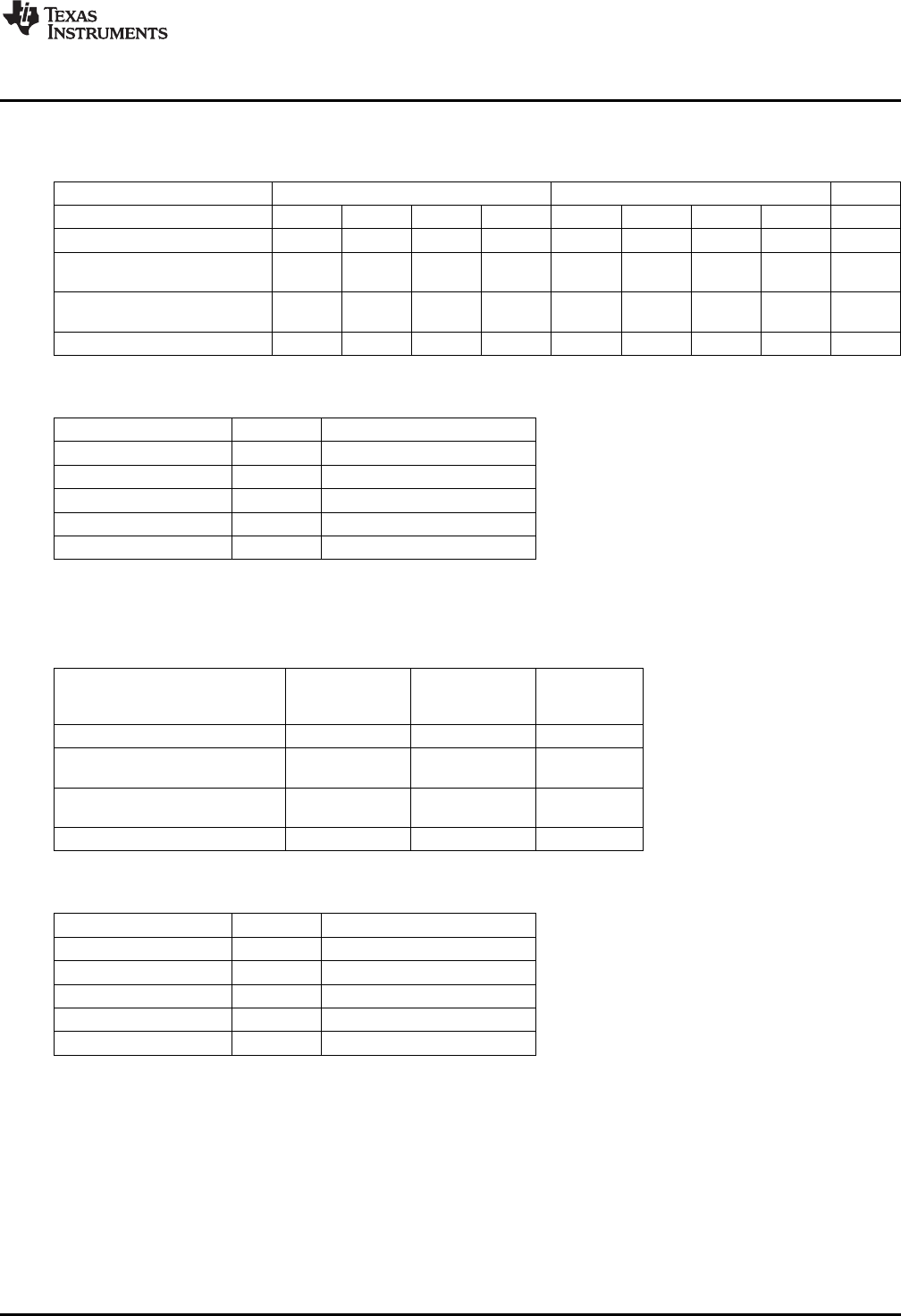

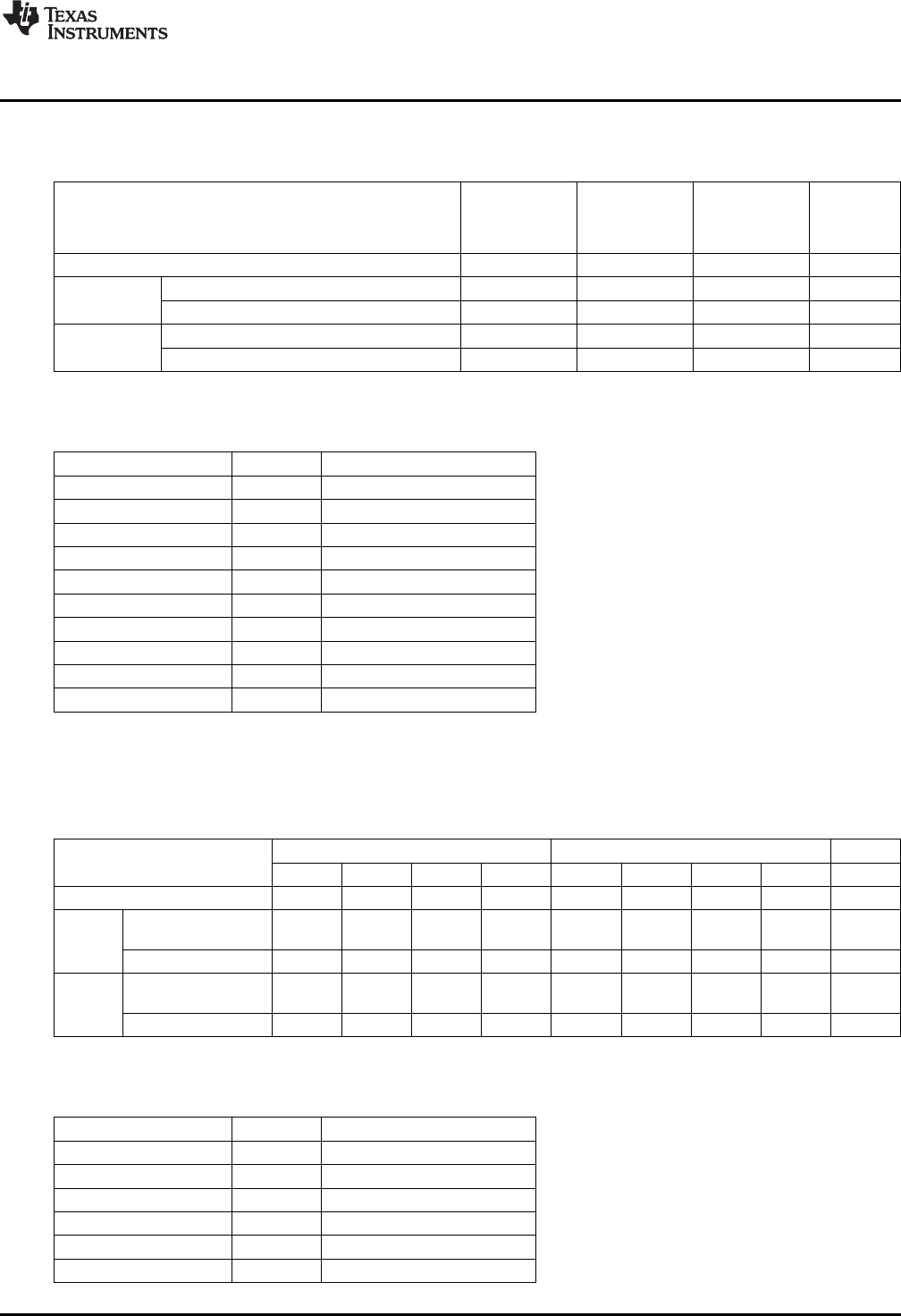

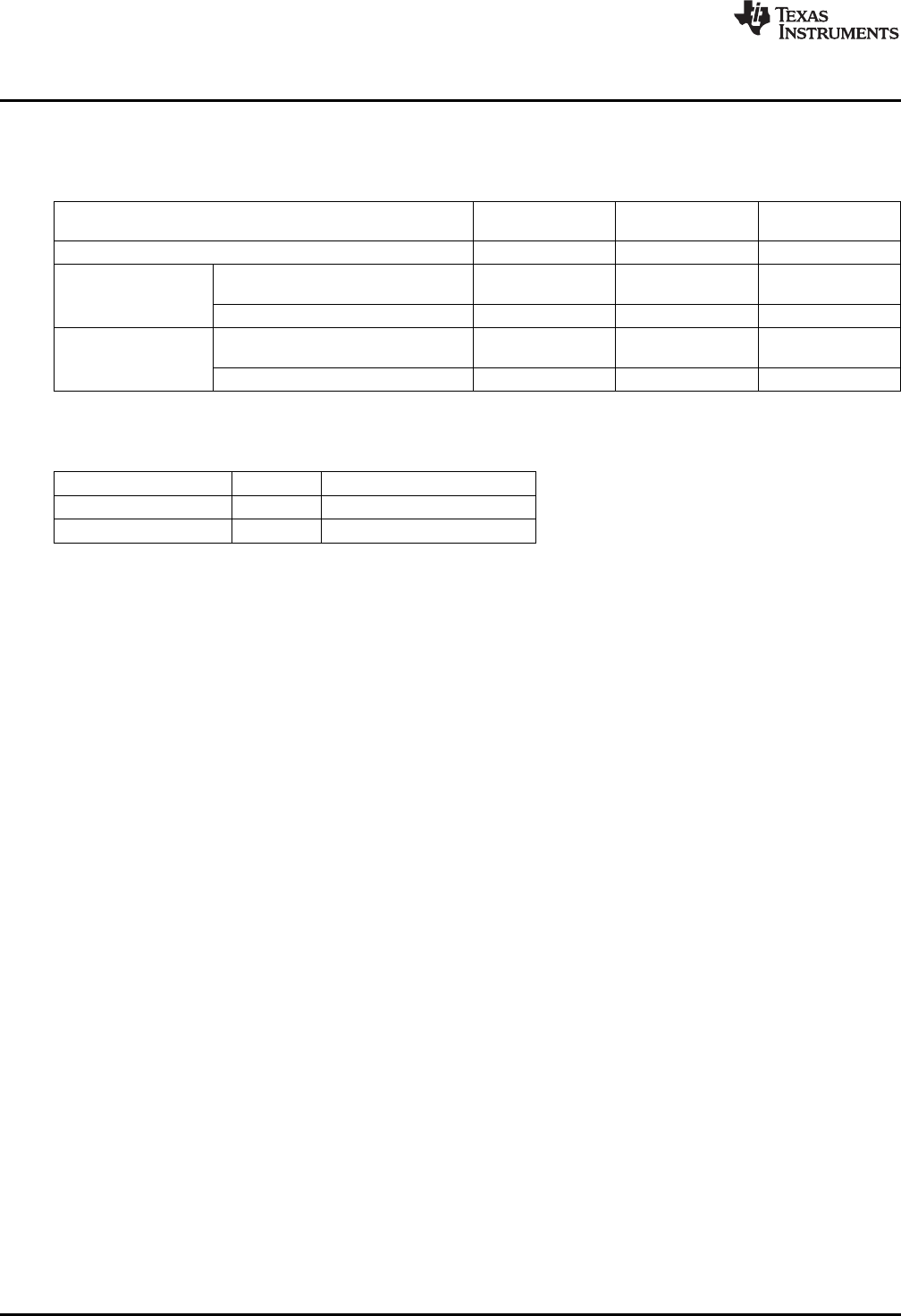

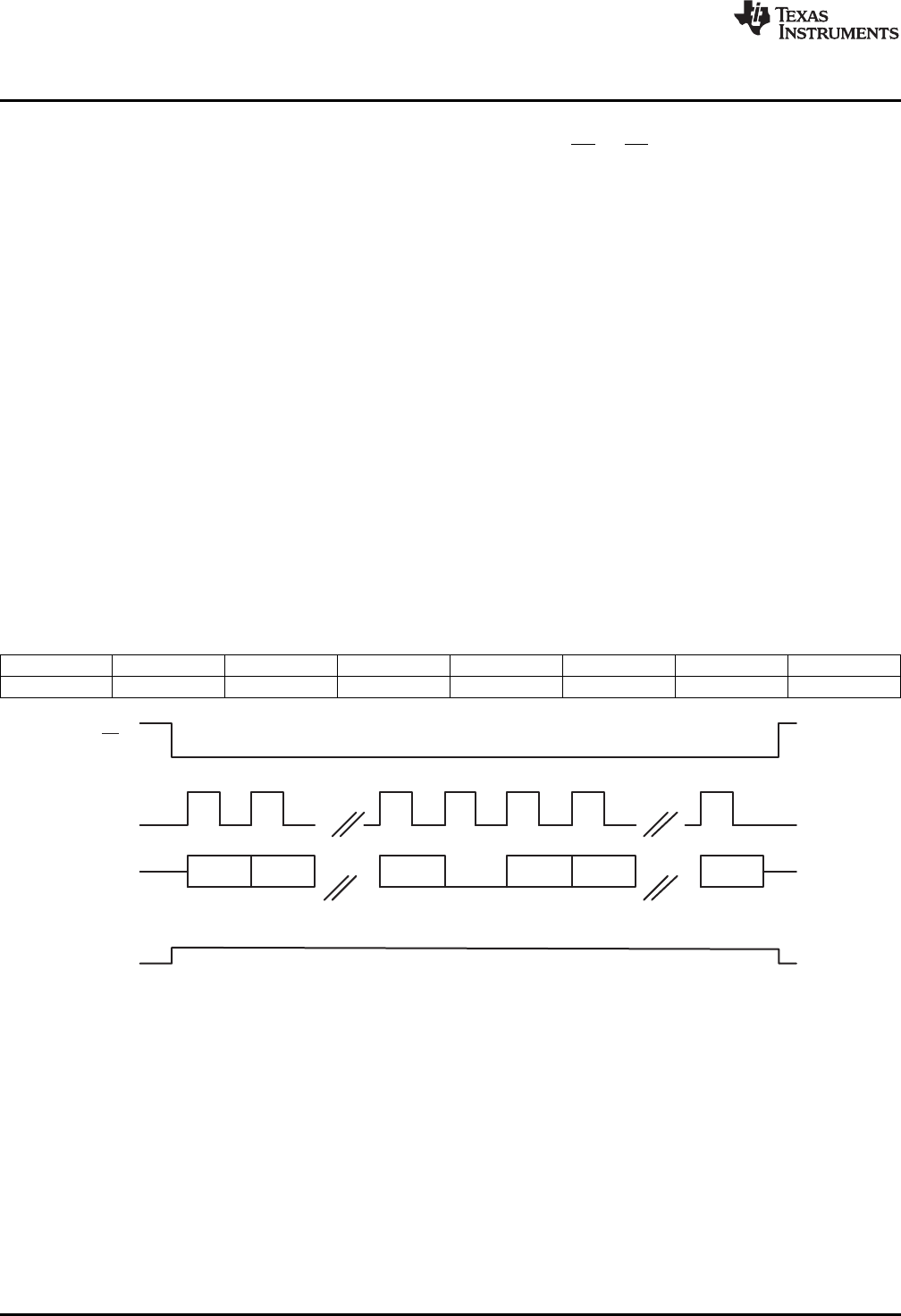

Table 2-3. Ground-Centered Headphone Setup Performance Options

Audio High Performance Low Power Consumption

Output 16Ω32Ω600Ω16Ω32Ω600Ω

Power

SNR 94.1dB 96.6dB 97.9dB 92.3dB 95.2dB 95.6dB

Output Power 26.2mW 23.4mW 19.7mW 19.3mW

High Idle Power 15.6mW 11.9mW

Consumption

High-Output, High-Performance Setup High-Output, Low-Power Setup

SNR 90.7dB 84.1dB 84.1dB 84.1dB

Output Power 10.5mW 5.3mW 5.1dB 2.6mW

Medium Idle Power 10.9mW 5.0mW

Consumption

Medium-Output, High-Performance Setup Medium-Output, Low-Power Setup

High Audio Output Power, High Performance Setup

This setup describe the register programming necessary to configure the device for a combination of high

audio output power and high performance. To achieve this combination the parameters must be

programmed to the values inTable 2-4.

Table 2-4. Setup A - High Audio Output Power, High Performance

Parameter Value Programming

CM 0.9 Page 1, Register 10, D6 = "0"

PTM PTM_P3 "Page 1, Register 3, D4:D2 = ""000""Page 1, Register 4, D4:D2 = ""000"""

1 to 6, 22, 23,

Processing Block Page 0, Register 60

24

DAC OSR 128 "Page 0, Register 13 = 0x00Page 0, Register 14 = 0x80"

DAC perf setting high "Page 1, Register 3, D5 = ""0""Page 1, Register 4, D5 = ""0"""

HP sizing 100 Page 1, Register 125, D3:D2 = "00"

CP sizing 100 Page 1, Register 124, D6:D4 = "000"

Gain 0 "Page 1, Register 16, D5:D0 = ""00 0000""Page 1, Register 17, D5:D0 = ""00 0000"""

DVdd 1.26 Apply 1.26 to 1.95V

AVdd,DRVdd_HP, 1.8 Apply 1.8 to 1.95V

DVdd_CP

11

SLAU306A–January 2011–Revised January 2013 TLV320AIC3256 Application

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Analog Audio I/O

www.ti.com

Medium Audio Output Power, High Performance Setup

This setup describe the register programming necessary to configure the device for a combination of

medium audio output power and high performance. To achieve this combination the parameters must be

programmed to the values inTable 2-5

Table 2-5. Setup B - Medium Audio Output Power, High Performance

Parameter Value Programming

CM 0.75 Page 1, Register 10, D6 = 1

PTM PTM_P2 "Page 1, Register 3, D4:D2 = ""001""Page 1, Register 4, D4:D2 = ""001"""

Processing Block 7 to 16 Page 0, Register 60

DAC OSR 64 "Page 0, Register 13 = 0x00Page 0, Register 14 = 0x40"

DAC perf setting low power "Page 1, Register 3, D5 = ""1""Page 1, Register 4, D5 = ""1"""

HP sizing 100 Page 1, Register 125, D3:D2 = "00"

CP sizing 100 Page 1, Register 124, D6:D4 = "000"

Gain 5 "Page 1, Register 16, D5:D0 = ""00 0101""Page 1, Register 17, D5:D0 = ""00 0101"""

DVdd 1.26 Apply 1.26 to 1.95V

AVdd,DRVdd_HP, 1.8 Apply 1.8 to 1.95V

DVdd_CP

High Audio Output Power, Low Power Consumption Setup

This setup describe the register programming necessary to configure the device for a combination of high

audio output power and low power consumption. To achieve this combination the parameters must be

programmed to the values inTable 2-6

Table 2-6. Setup C - High Audio Output Power, Low Power Consumption

Parameter Value Programming

CM 0.75 Page 1, Register 10, D6 = 1

PTM PTM_P2 "Page 1, Register 3, D4:D2 = ""001""Page 1, Register 4, D4:D2 = ""001"""

Processing Block 7 to 16 Page 0, Register 60

DAC OSR 64 "Page 0, Register 13 = 0x00Page 0, Register 14 = 0x40"

DAC perf setting high "Page 1, Register 3, D5 = ""0""Page 1, Register 4, D5 = ""0"""

HP sizing 100 Page 1, Register 125, D3:D2 = "00"

CP sizing 100 Page 1, Register 124, D6:D4 = "000"

Gain 5 "Page 1, Register 16, D5:D0 = ""00 0101""Page 1, Register 17, D5:D0 = ""00 0101"""

DVdd 1.26 Apply 1.26 to 1.95V

AVdd,DRVdd_HP, 1.5 Apply 1.5 to 1.95V

DVdd_CP

Medium Audio Output Power Setup, Lowest Power Consumption

This setup describe the register programming necessary to configure the device for a combination of

medium audio output power and lowest power consumption. To achieve this combination the parameters

must be programmed to the values inTable 2-7

Table 2-7. Setup D - Medium Audio Output Power Setup, Lowest Power Consumption

Parameter Value Programming

CM 0.75 Page 1, Register 10, D6 = 1

PTM PTM_P1 "Page 1, Register 3, D4:D2 = ""010""Page 1, Register 4, D4:D2 = ""010"""

Processing Block special Page 0, Register 60

DAC OSR 64 "Page 0, Register 13 = 0x00Page 0, Register 14 = 0x40"

DAC perf setting low power "Page 1, Register 3, D5 = ""1""Page 1, Register 4, D5 = ""1"""

HP sizing 25 Page 1, Register 125, D3:D2 = "11"

12 TLV320AIC3256 Application SLAU306A–January 2011–Revised January 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

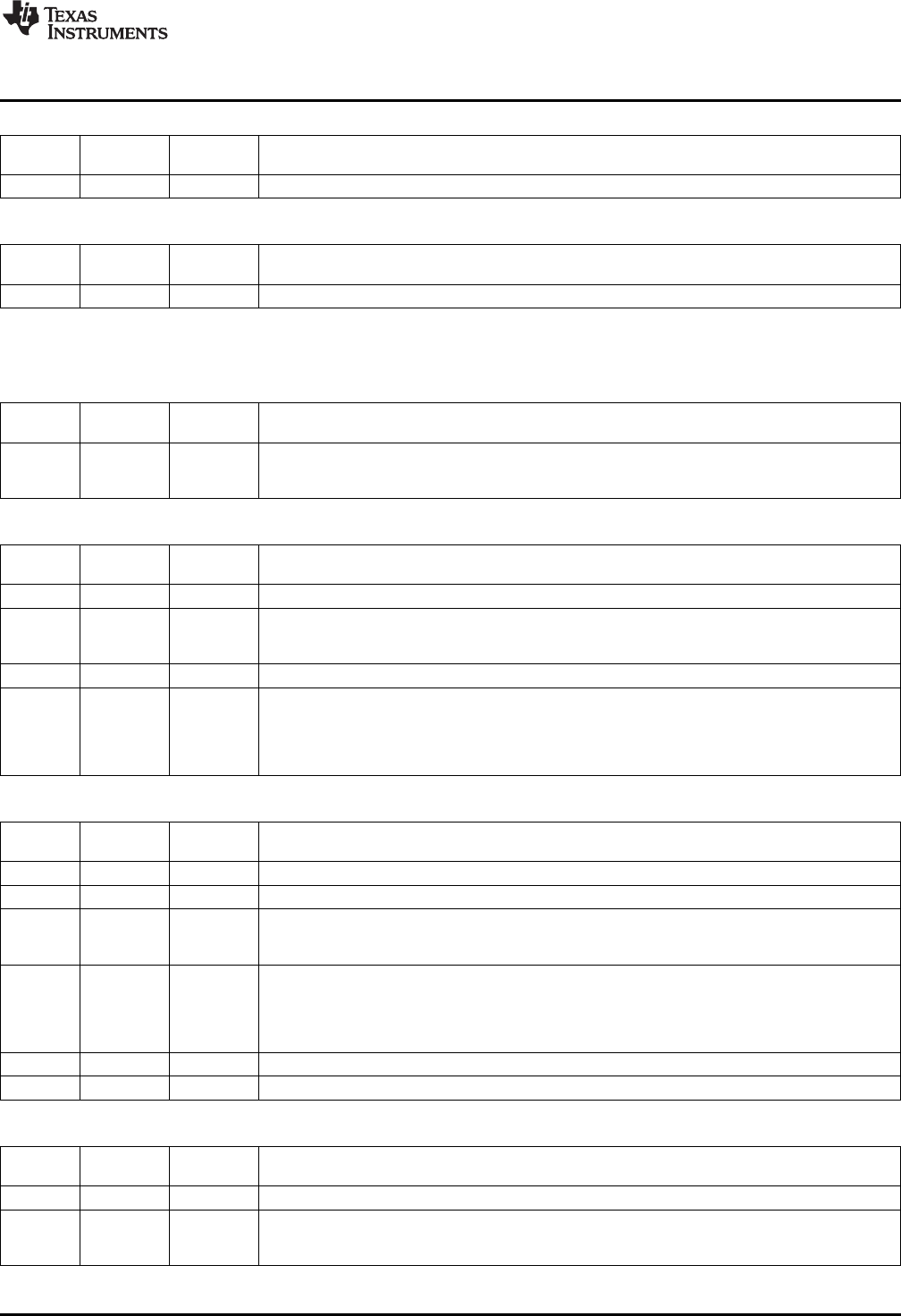

-6...+14dB

1dB steps

-6...+14dB

1dB steps

HPL

HPR

Charge

Pump (disabled)

GND_Sense

VNEG

Fly_N

Fly_P

DRVdd_HP

DVss_CP

DVdd_CP

1.5...3.6V

DVdd

DVdd

www.ti.com

Analog Audio I/O

Table 2-7. Setup D - Medium Audio Output Power Setup, Lowest Power Consumption (continued)

Parameter Value Programming

CP sizing 12.5 Page 1, Register 124, D6:D4 = "001"

Gain 14 "Page 1, Register 16, D5:D0 = ""00 1110""Page 1, Register 17, D5:D0 = ""00 1110"""

DVdd 1.26 Apply 1.26 to 1.95V

AVdd,DRVdd_HP, 1.5 Apply 1.5 to 1.95V

DVdd_CP

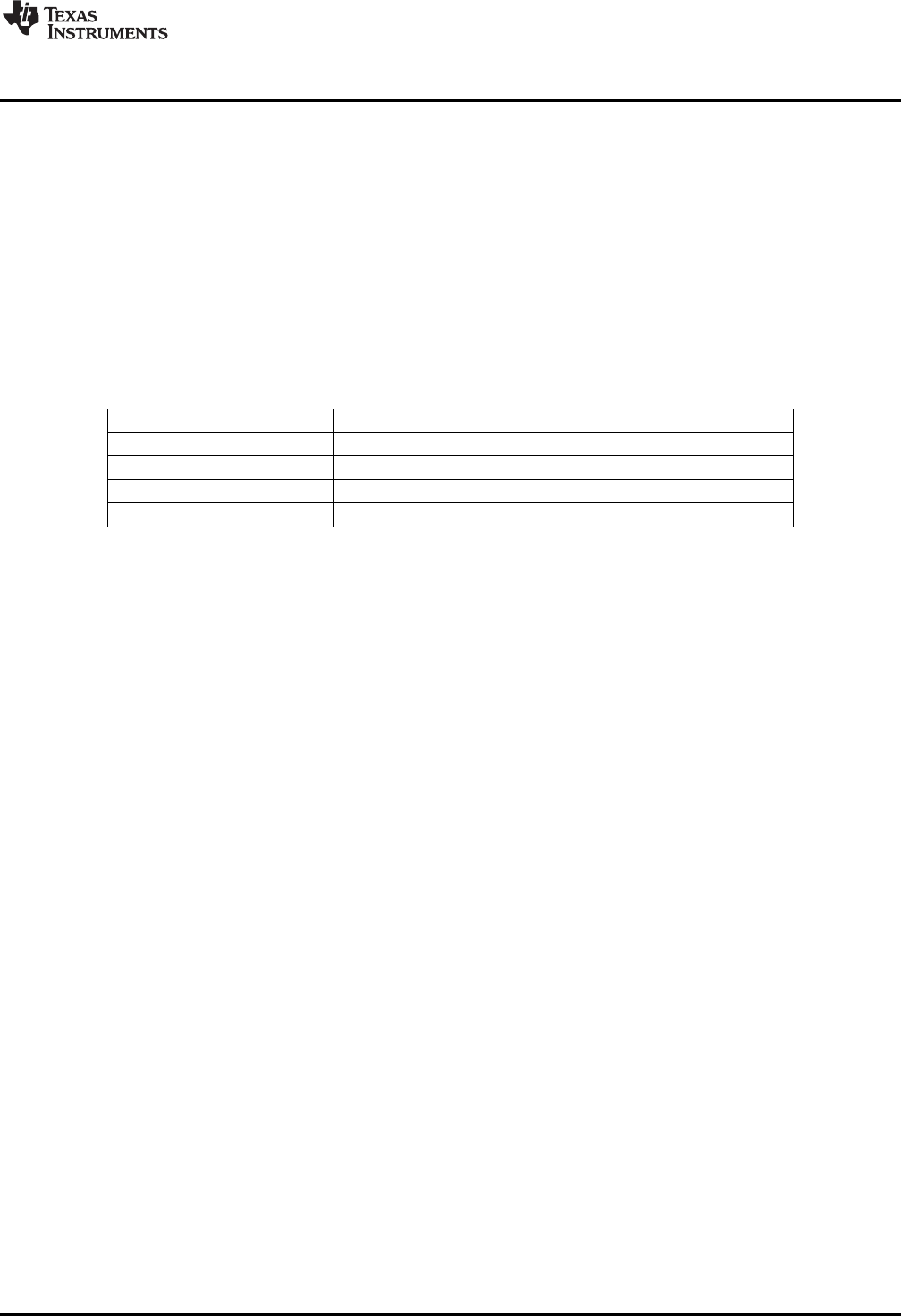

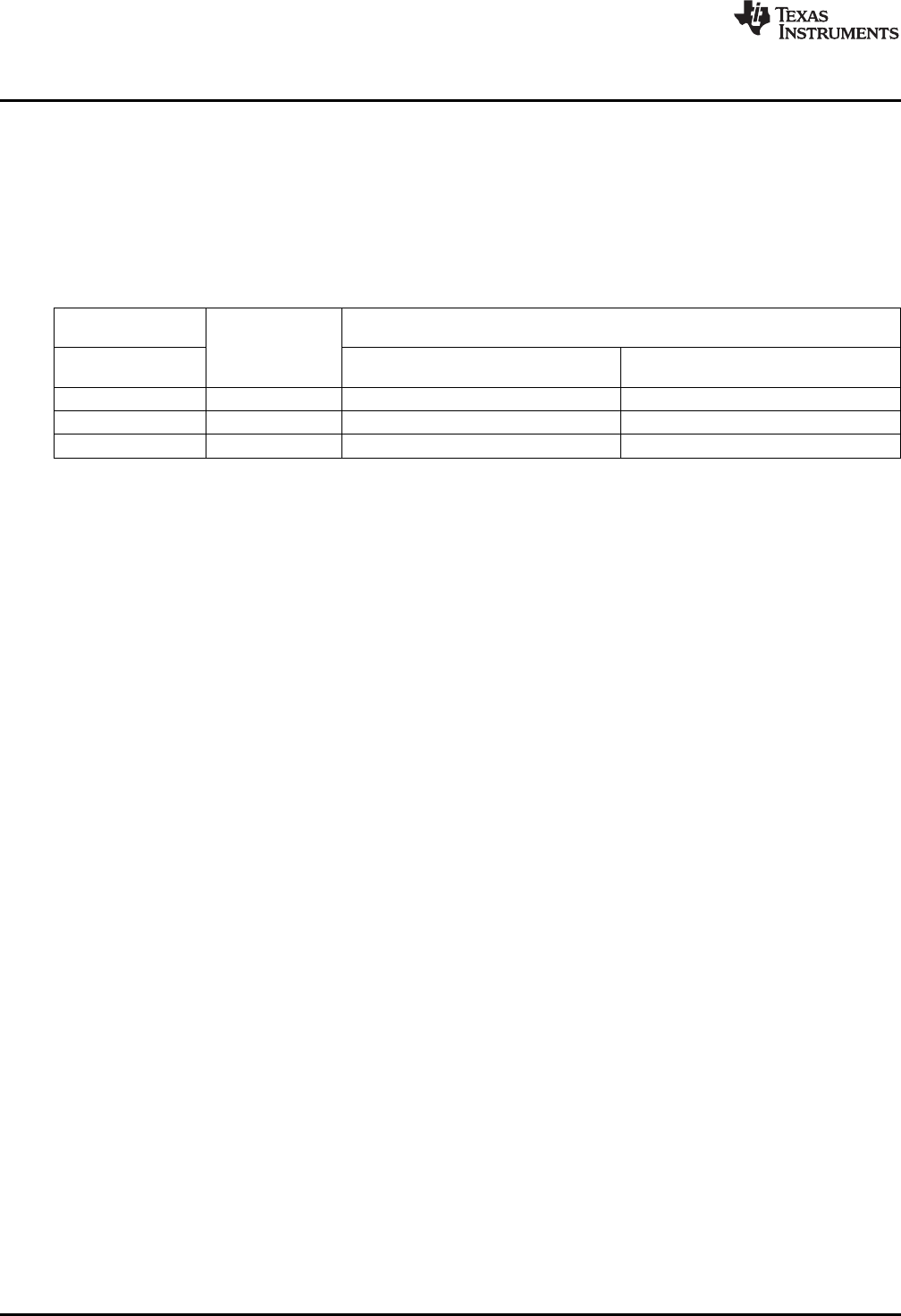

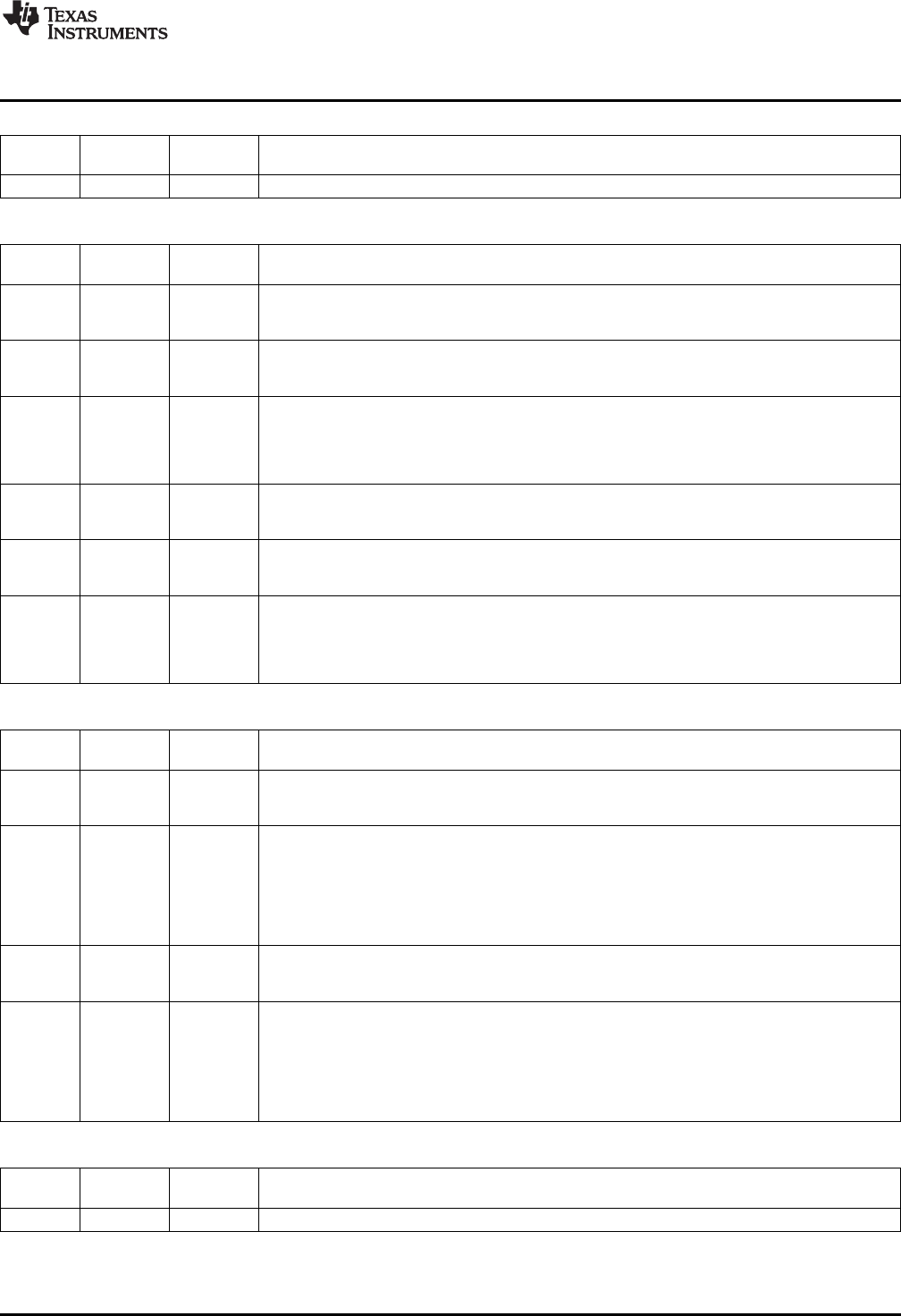

2.2.3.3 Stereo Unipolar Configuration

2.2.3.3.1 Circuit Topology

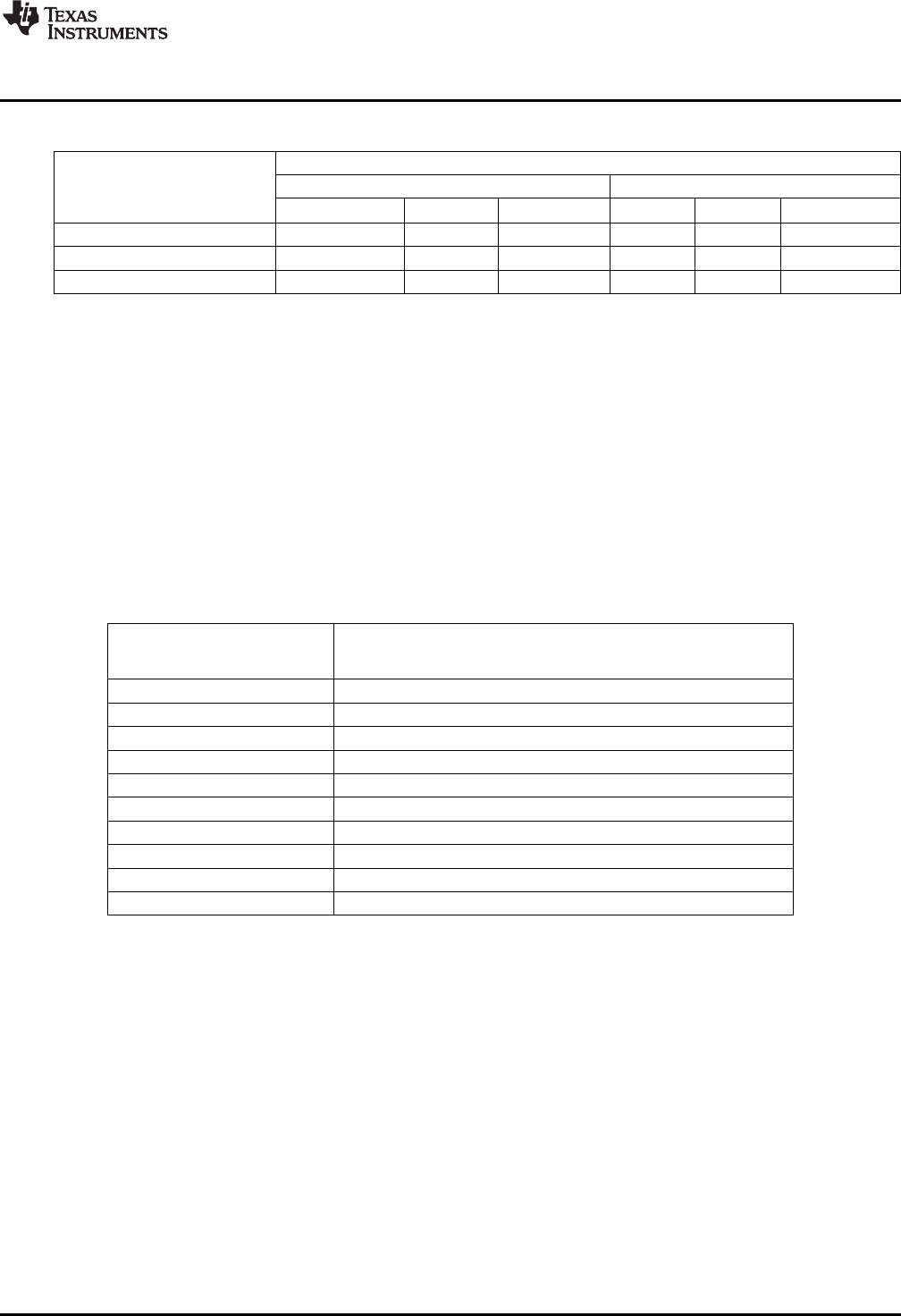

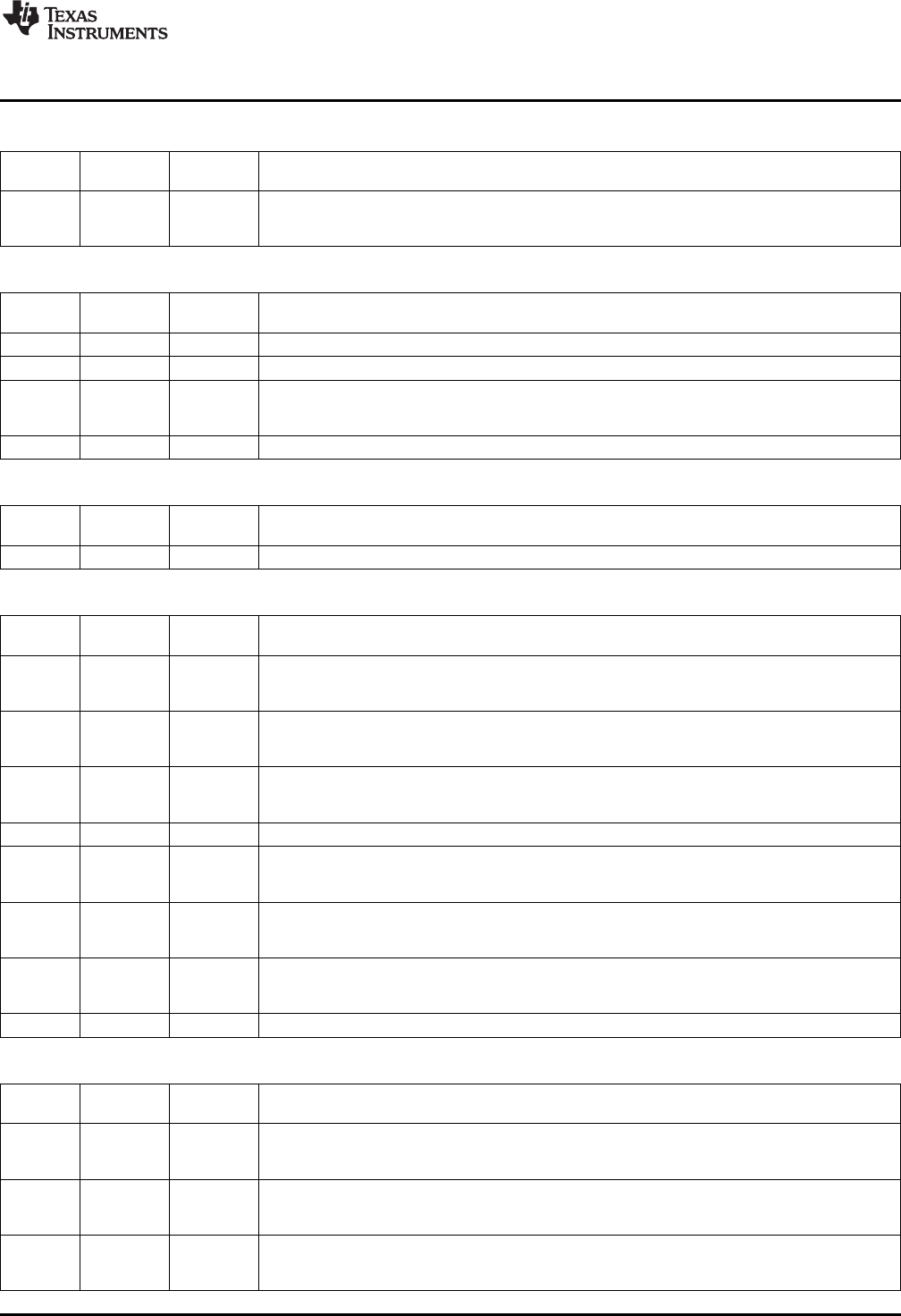

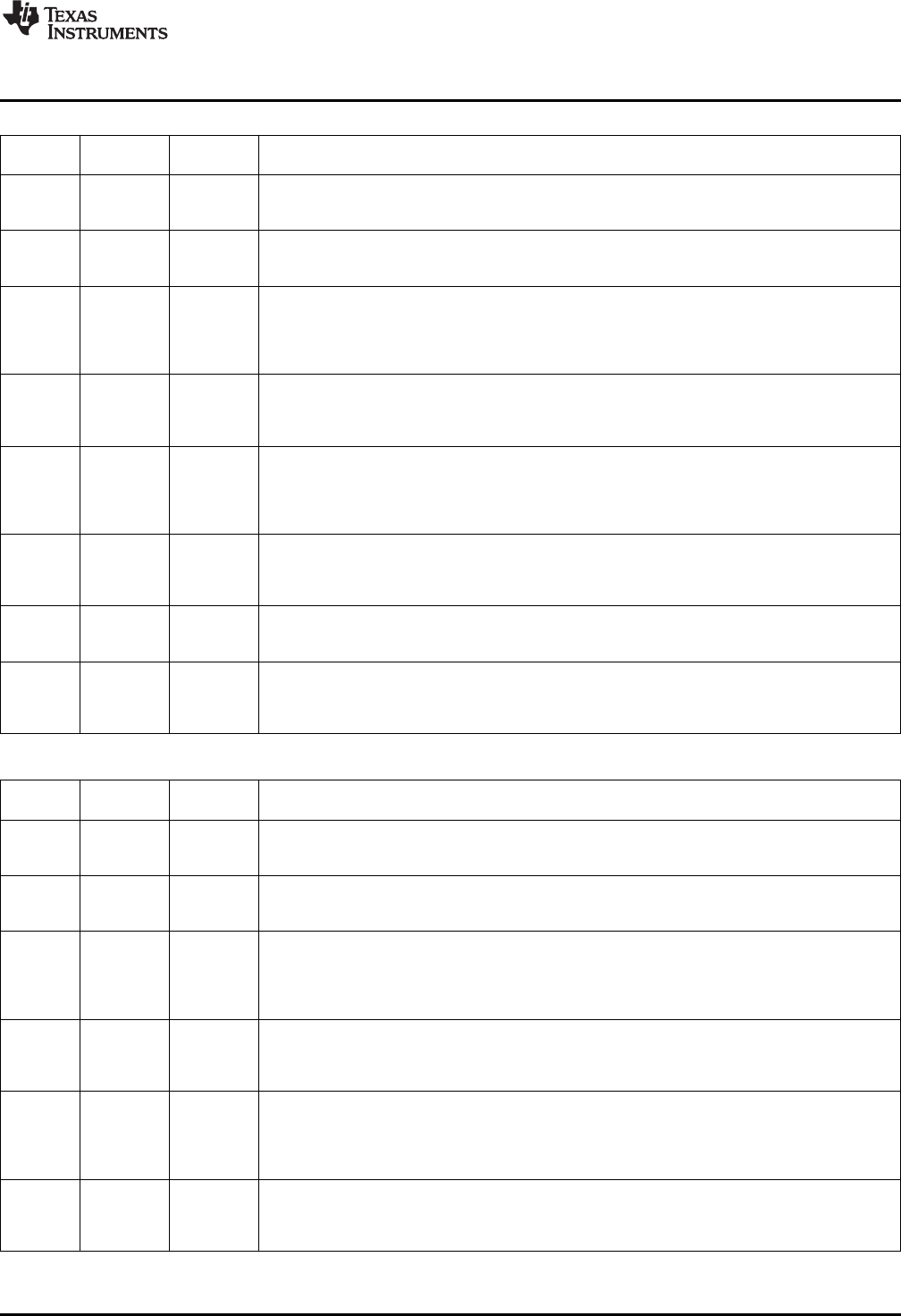

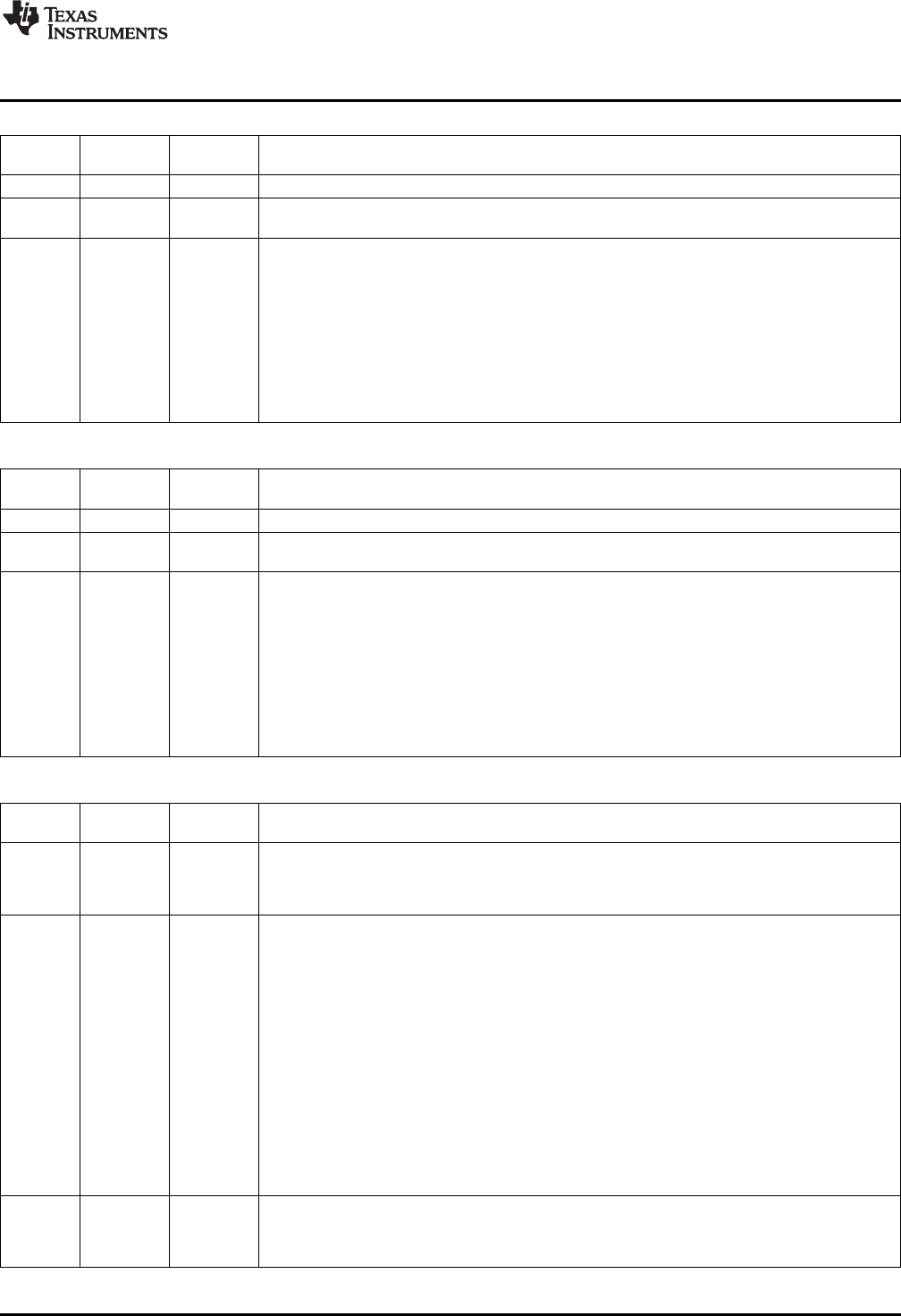

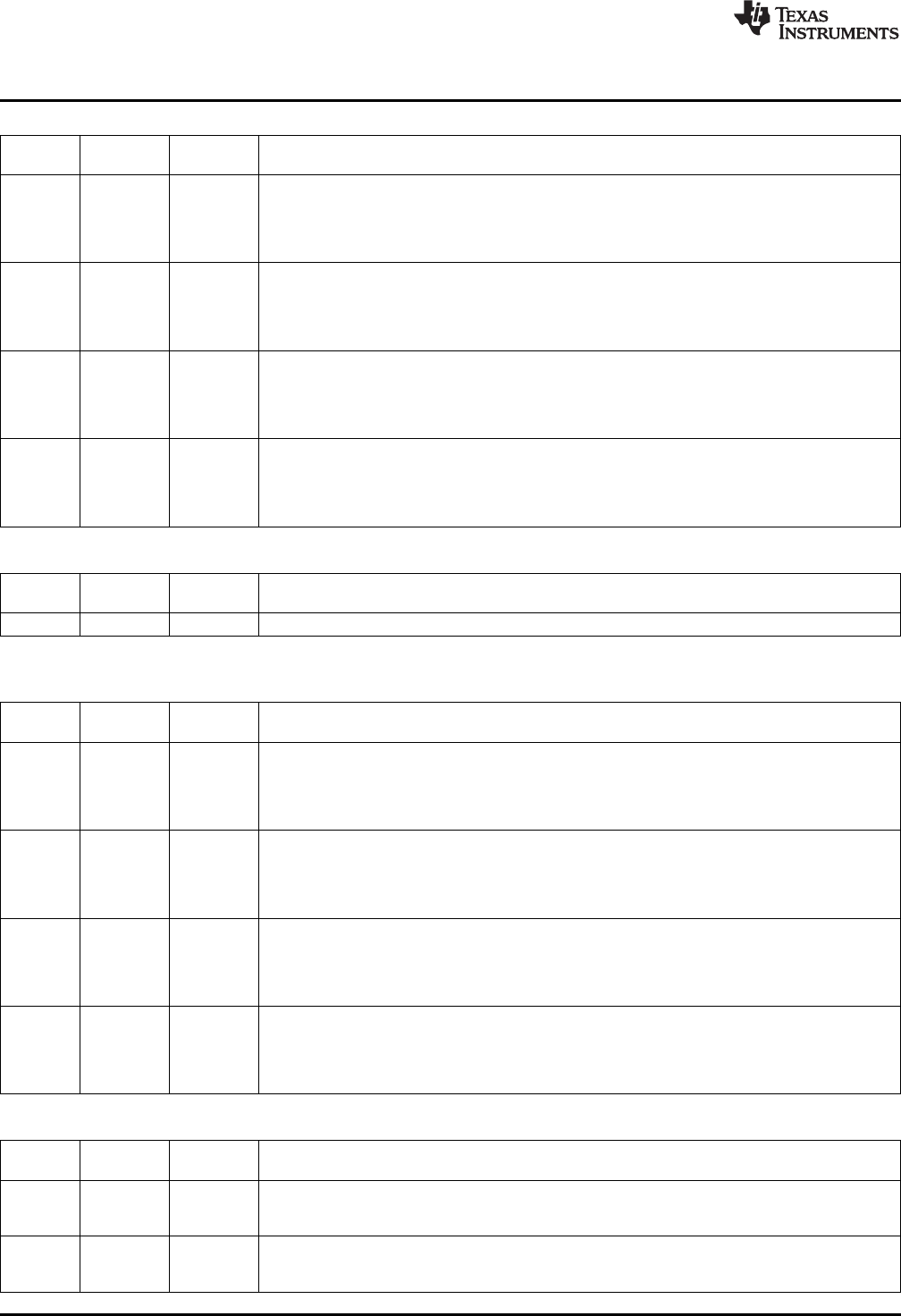

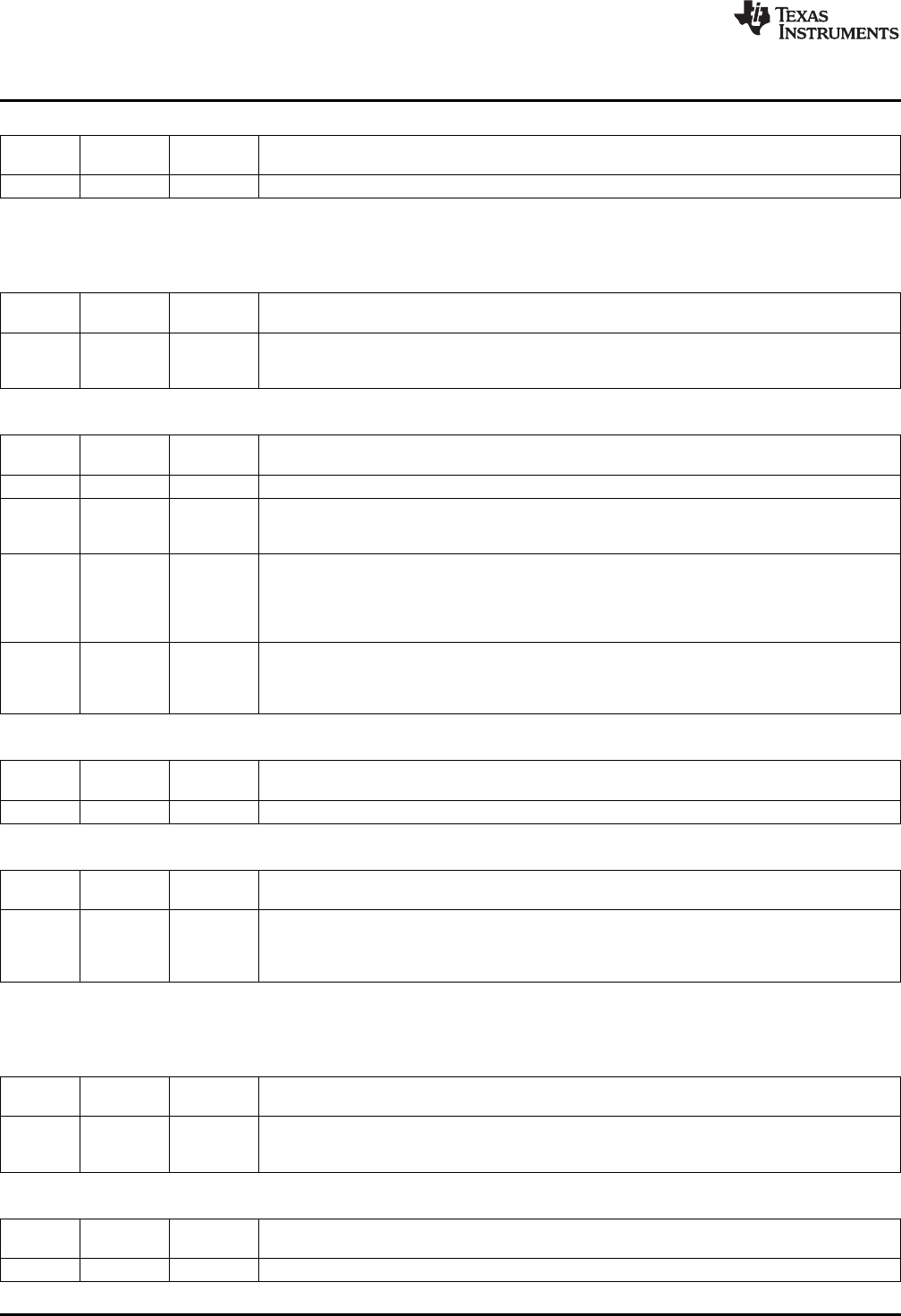

The power supply hook up scheme for the unipolar configuration is shown in Figure 2-3 DRVdd_HP pin

supplies the positive side of the headphone amplifier. The negative side is connected to ground potential

(VNEG). TI recommends connecting the DVdd_CP pin to DVdd, although the charge pump must not be

enabled while the device is connected in unipolar configuration.

Figure 2-3. Unipolar Stereo Headphone Circuit

The left and right DAC channels are routed to the corresponding left and right headphone amplifier. This

configuration is also used to drive line-level loads.

2.2.3.3.2 Unipolar Turn-On Transient (Pop) Reduction

The TLV320AIC3256 headphone drivers also support pop-free operation in unipolar, ac-coupled

configuration. Because the HPL and HPR are high-power drivers, pop can result due to sudden transient

changes in the output drivers if care is not taken. The most critical care is required while using the drivers

as stereo single-ended capacitively-coupled drivers as shown in Figure 2-3. The output drivers achieve

pop-free power-up by using slow power-up modes. Conceptually, the circuit during power-up can be

visualized as

13

SLAU306A–January 2011–Revised January 2013 TLV320AIC3256 Application

Submit Documentation Feedback Copyright © 2011–2013, Texas Instruments Incorporated

cm

popload

load

load V

RR

R

V´

+

=

Rload

Rpop

Cc

Output

Driver

PAD

Analog Audio I/O

www.ti.com

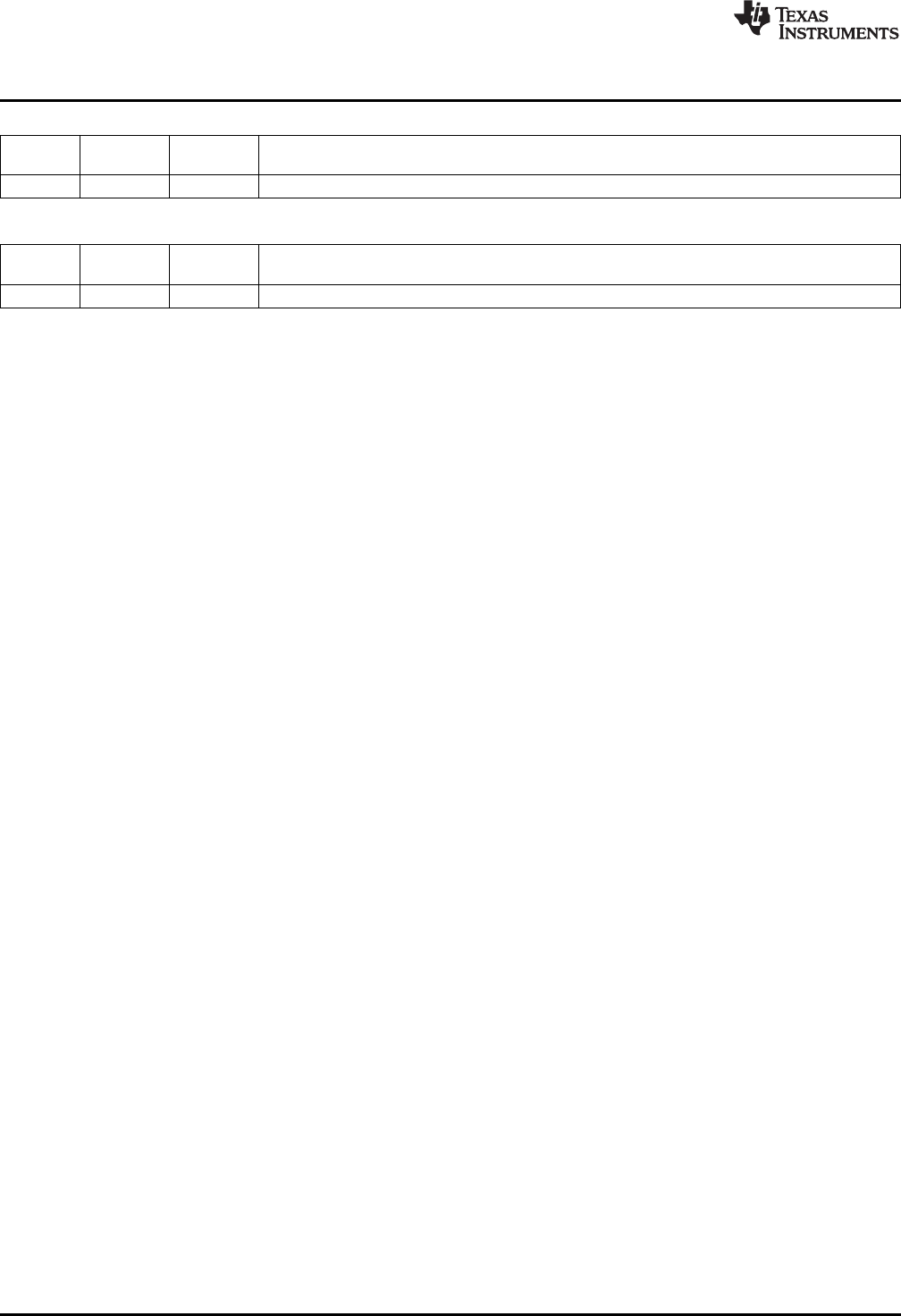

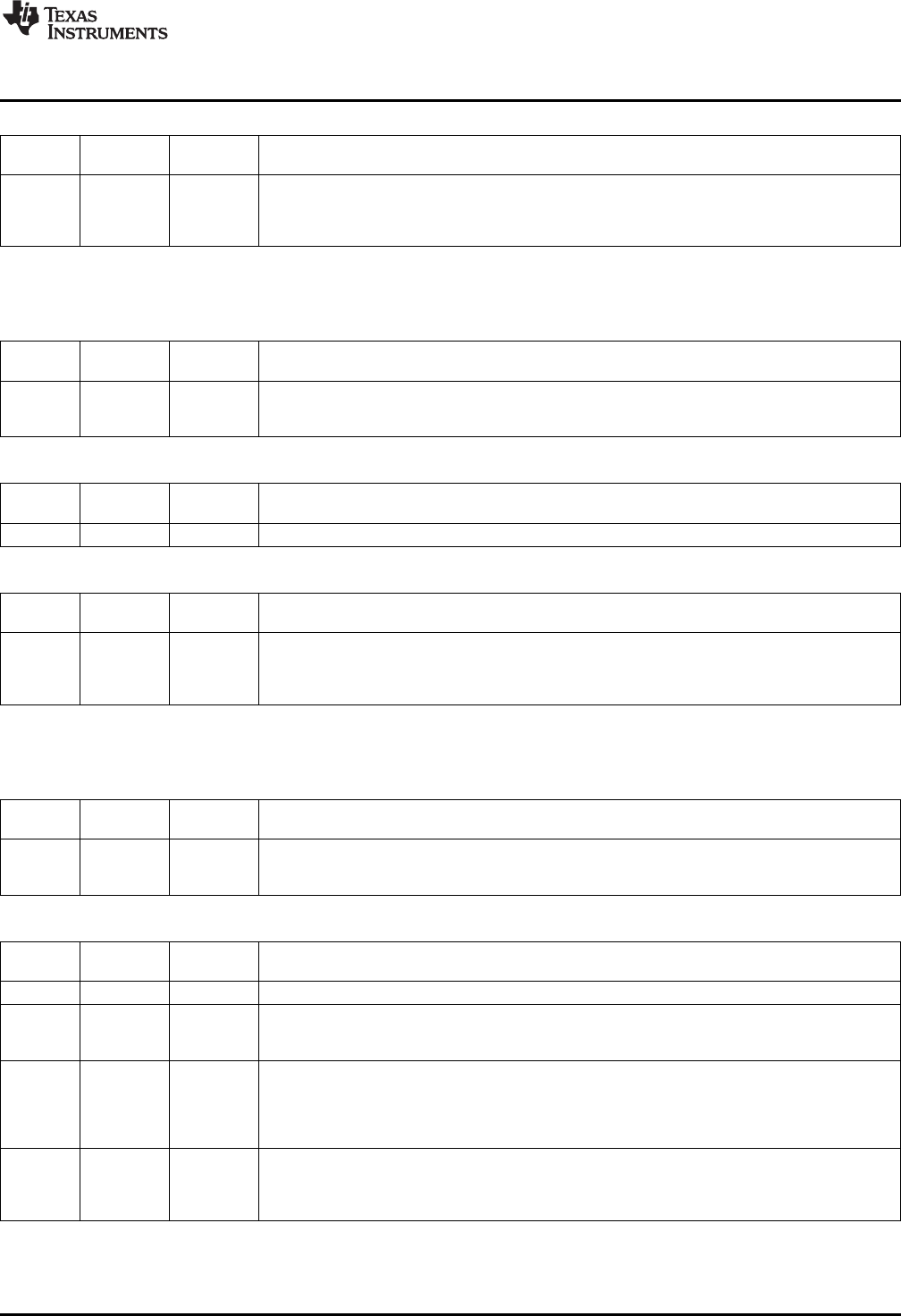

Figure 2-4. Conceptual Circuit for Pop-Free Power-up

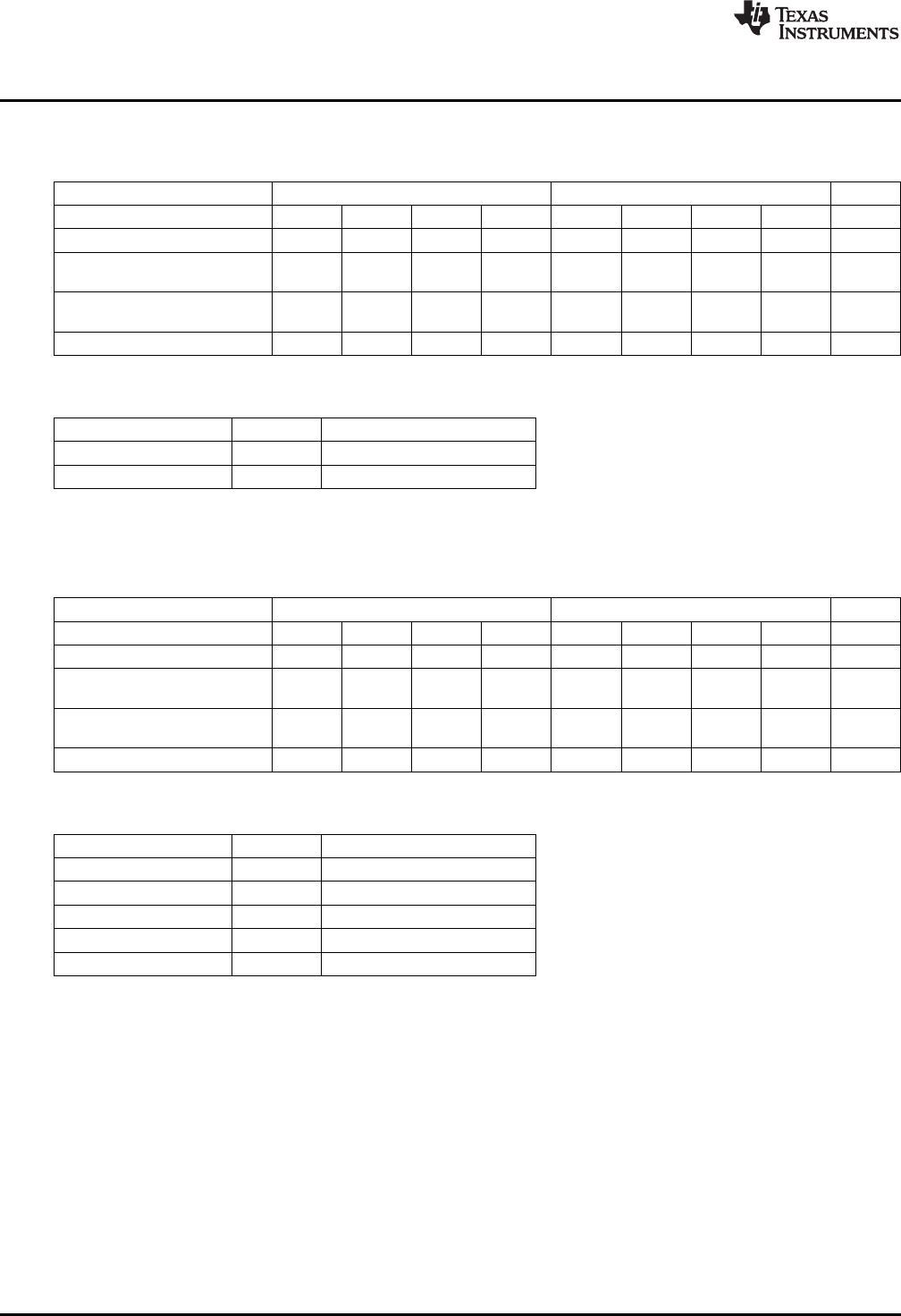

Set the value of Rpop by writing register Page 1, Register 20, Bits D1-D0.

Table 2-8. Rpop Values

Page 1, Register 20, Bits D1-D0 Rpop Value

00 2 kΩ

01 6 kΩ

10 25 kΩ

To minimize audible artifacts, two parameters can be adjusted to match application requirements. The

voltage Vload across Rload at the beginning of slow charging should not be more than a few mV. At that time

the voltage across Rload can be determined as:

(1)

For a typical Rload of 32Ω, Rpop of 6 kΩor 25 kΩdelivers good results (see Table 2-8 for register settings).

According to the conceptual circuit in Figure 2-4, the voltage on PAD will exponentially settle to the output

common-mode voltage based on the value of Rpop and Cc. Thus, the output drivers must be in slow power-

up mode for time T, such that at the end of the slow power-on period, the voltage on Vpad is very close to

the common-mode voltage. The TLV320AIC3256 allows the time T to be adjusted to allow for a wide

range of Rload and Ccby programming Page 1, Register 20, Bits D5-D2. For the time adjustments, the

value of Ccis assumed to be 47μF. N = 5 is expected to yield good results.

Page 1, Register 20, Bits D5-D2 Slow Charging Time = N*Time – Constants (for Rpop and 47μF)

0000 N = 0

0001 N = 0.5

0010 N = 0.625

0011 N = 0.75

0100 N = 0.875

0101 N = 1.0

0110 N = 2.0

0111 N = 3.0

1000 N = 4.0

1001 N = 5.0

1010 N = 6.0

1011 N = 7.0

1100 N = 8.0

1101 N = 16 (Not valid for Rpop = 25kΩ)

1110 N = 24 (Not valid for Rpop = 25kΩ)

1111 N = 32 (Not valid for Rpop = 25kΩ)

14 TLV320AIC3256 Application SLAU306A–January 2011–Revised January 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

www.ti.com

Analog Audio I/O

Again, for example, for Rload = 32Ω, Cc= 47μF and common mode of 0.9V, the number of time constants

required for pop-free operation is 5 or 6. A higher or lower Ccvalue will require higher or lower value for N.

During the slow-charging period, no signal is routed to the output driver. Therefore, choosing a larger than

necessary value of N results in a delay from power-up to signal at output. At the same time, choosing N to

be smaller than the optimal value results in poor pop performance at power-up.

The signals being routed to headphone drivers (such as DAC and IN1) often have DC offsets due to less-

than-ideal processing. As a result, when these signals are routed to output drivers, the offset voltage

causes a pop. To improve the pop-performance in such situations, a feature is provided to soft-step the

DC-offset. At the beginning of the signal routing, a high-value attenuation can be applied which can be

progressively reduced in steps until the desired gain in the channel is reached. The time interval between

each of these gain changes can be controlled by programming Page 1, Register 20, Bits D7-D6. This gain

soft-stepping is applied only during the initial routing of the signal to the output driver and not during

subsequent gain changes.

Page 1, Register 20, Bits D7-D6 Soft-stepping Step Time During initial signal routing

00 0 ms (soft-stepping disabled)

01 50ms

10 100ms

11 200ms

The following sequence is recommended to achieve optimal pop performance at power-up:

1. Choose the value of Rpop, N (time constants) and soft-stepping step time for slow power-up.

2. Choose the configuration for output drivers, including common modes and output stage power

connections

3. Select the signals to be routed to headphones.

4. Power up the blocks driving signals into HPL and HPR, but keep HPL and HPR muted

5. Unmute HPL and HPR and set the desired gain setting.

6. Power on the HPL and HPR drivers.

7. Unmute the block driving signals to HPL and HPR after the Driver PGA flags are set to indicate

completion of soft-stepping after power-up. These flags can be read from Page 1, Register 63, Bits D7-

D6.

Configure the Headphone Output driver depop control registers before powering up the headphone; these

register contents must not be changed when the headphone drivers are powered up.

Before powering down the HPL and HPR drivers, it is recommended that software read back the flags in

Page 1, Register 63. For example. before powering down the HPL driver, ensure that bit D(7) = 1 and bit

D(3) = 1 if IN1L is routed to HPL and bit D(1) = 1 if the Left Mixer is routed to HPL. The output driver

should be powered down only after a steady-state power-up condition has been achieved. This steady

state power-up condition also must be satisfied for changing the HPL-R driver mute control in Page 1,

Register 16 and 17, Bits D7, for example. Mute and unmute the headphone drivers after the gain and

volume controls associated with routing to HPL and HPR finish soft-stepping.

In the differential configuration of HPL and HPR, when no coupling capacitor is used, the slow charging

method for pop-free performance need not be used. In the differential load configuration for HPL and

HPR, using the output driver MUTE feature is not recommended, because a pop may result.

During the power-down state, the headphone outputs are weakly pulled to ground using an approximately

50kΩresistor to ground, to maintain the output voltage on HPL and HPR pins.

15

SLAU306A–January 2011–Revised January 2013 TLV320AIC3256 Application

Submit Documentation Feedback Copyright © 2011–2013, Texas Instruments Incorporated

LOL

LOR

LEFT

DAC

HPL

HPR

LEFT_DACP

LEFT_DACM

Analog Audio I/O

www.ti.com

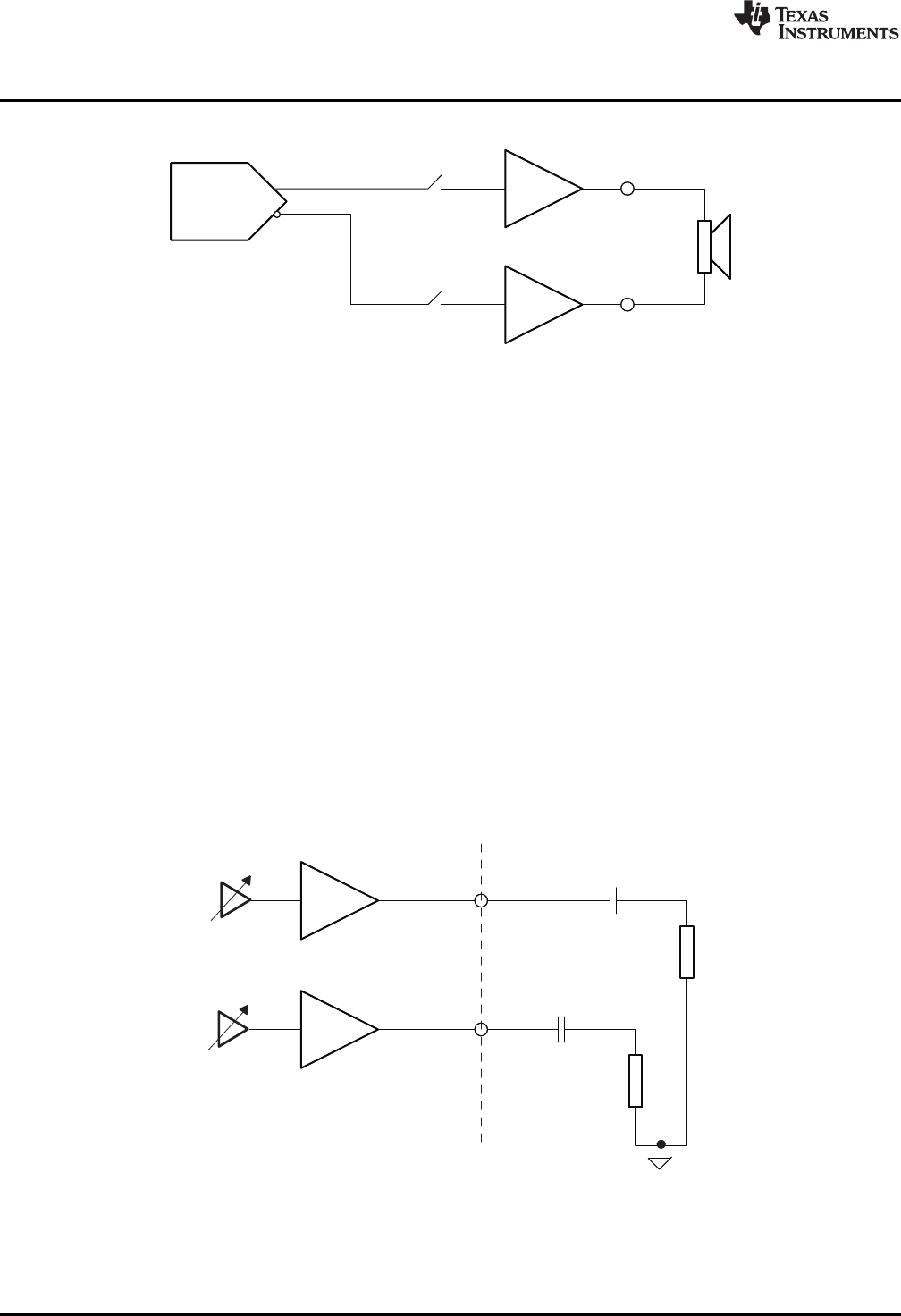

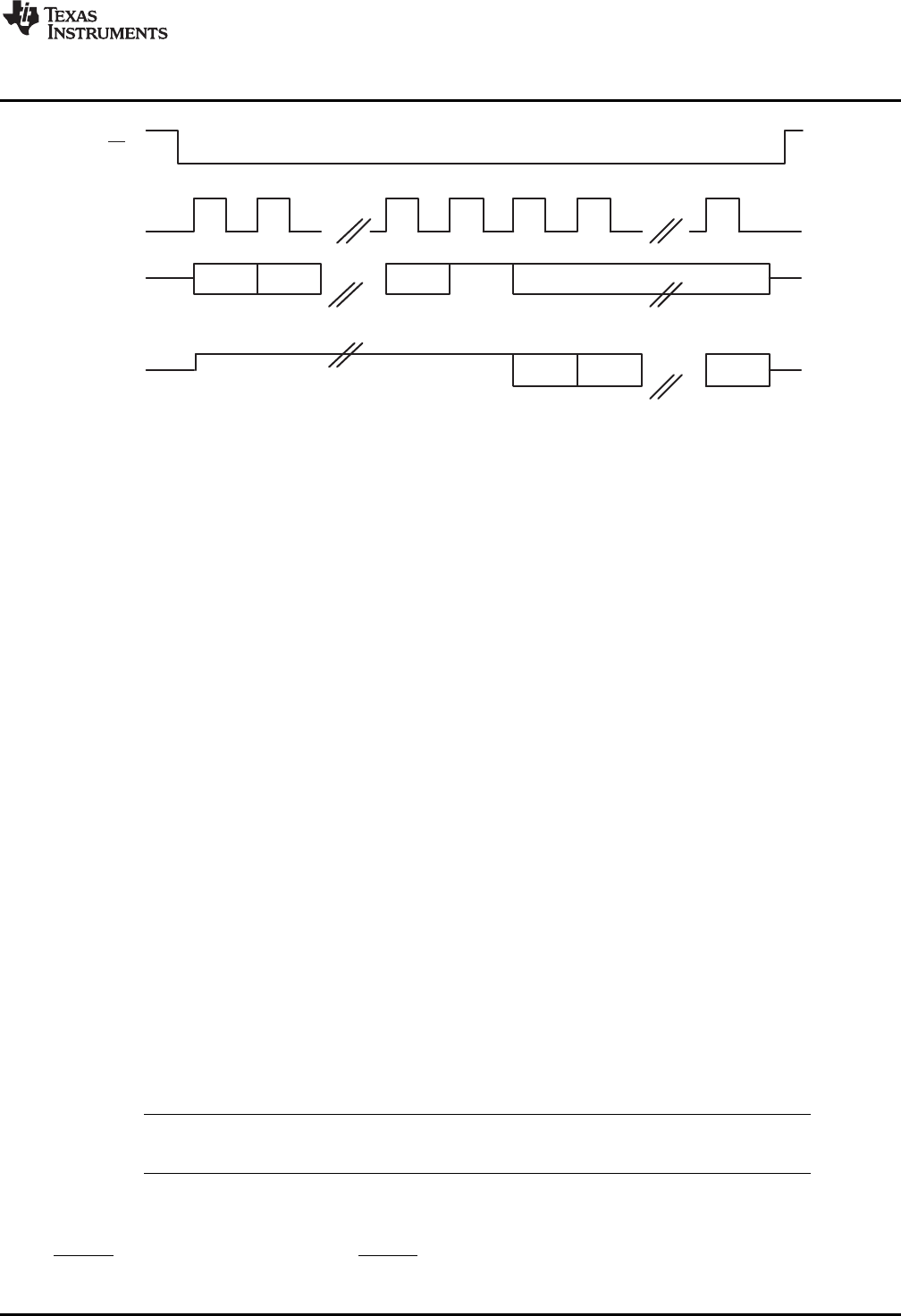

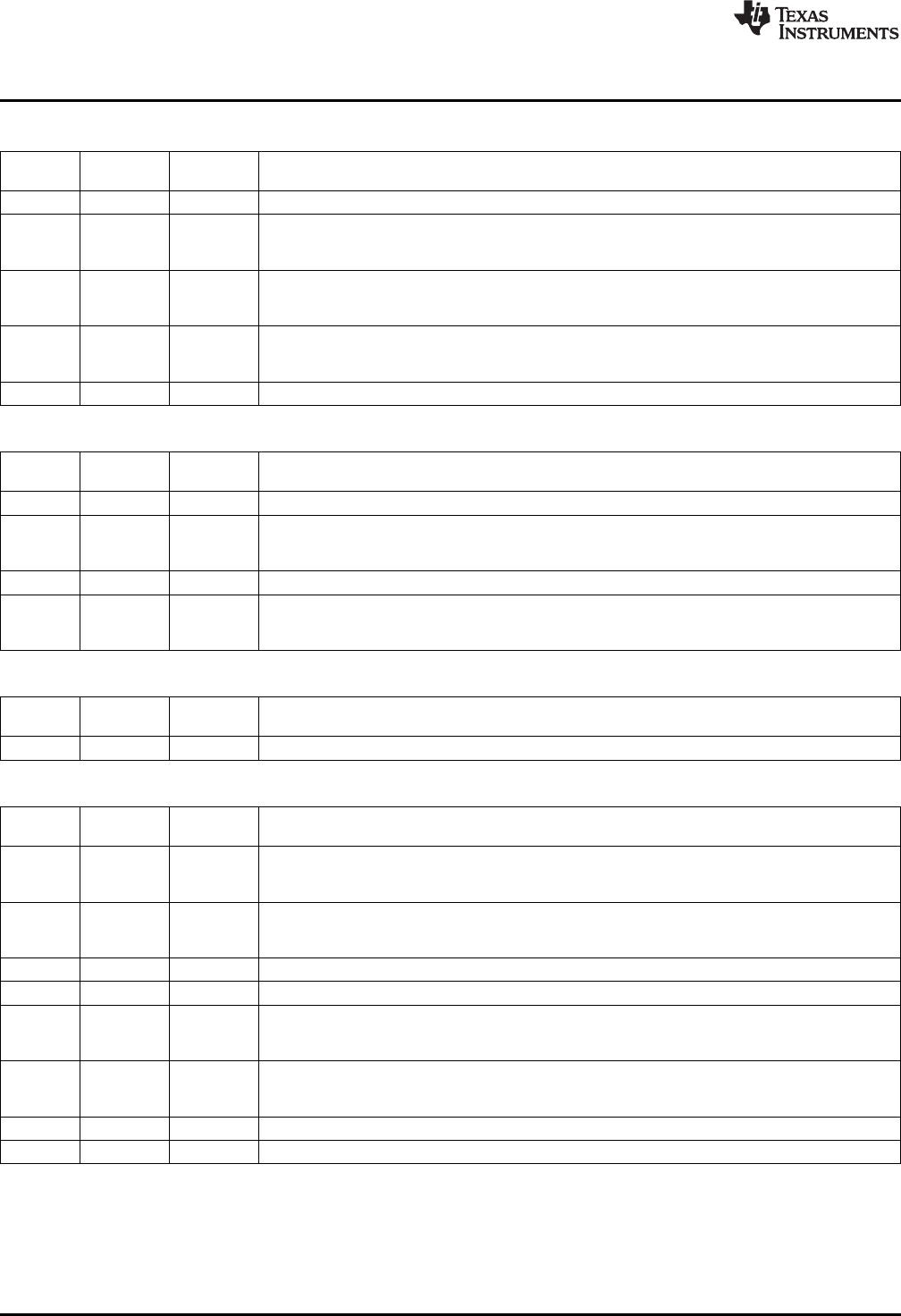

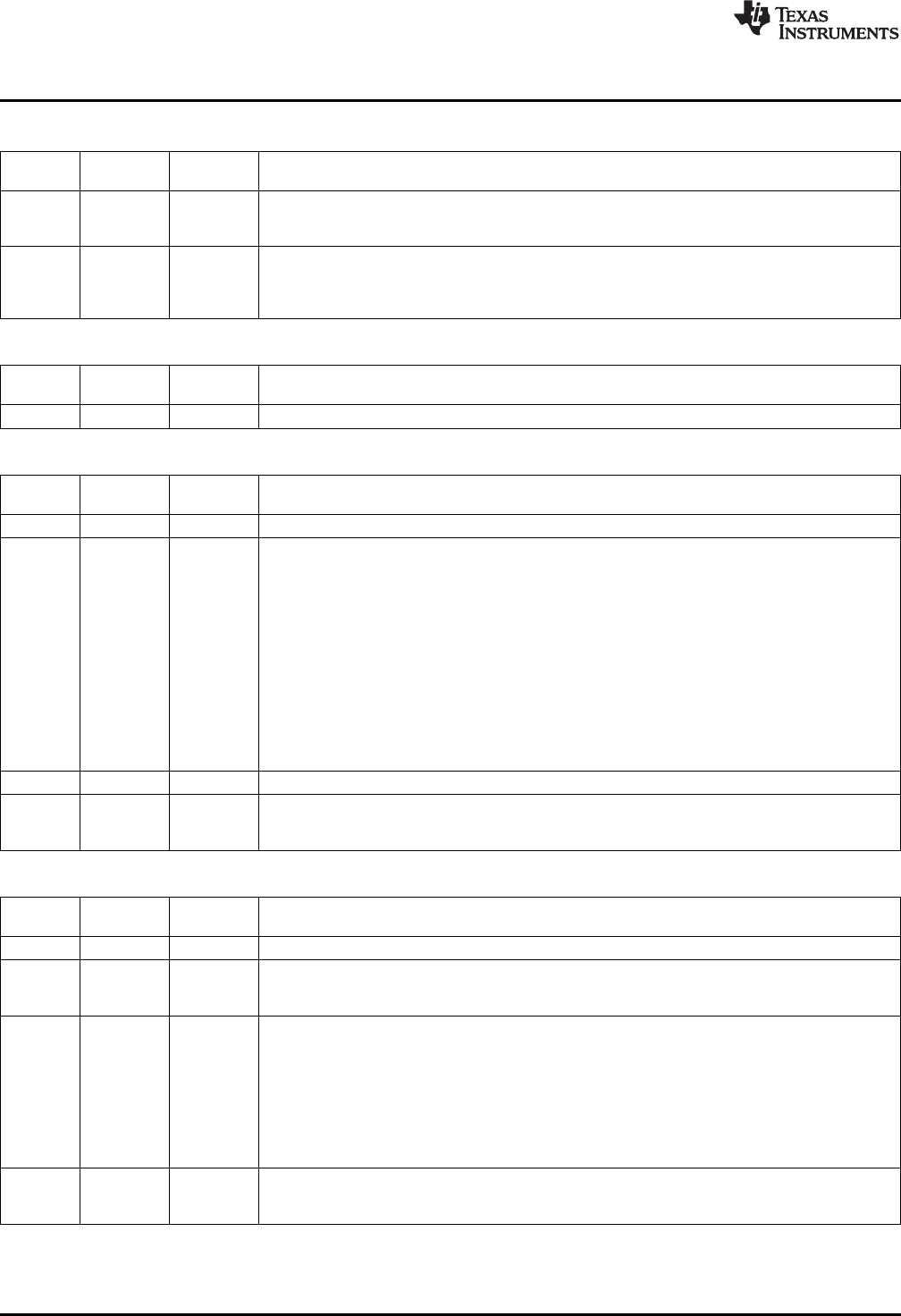

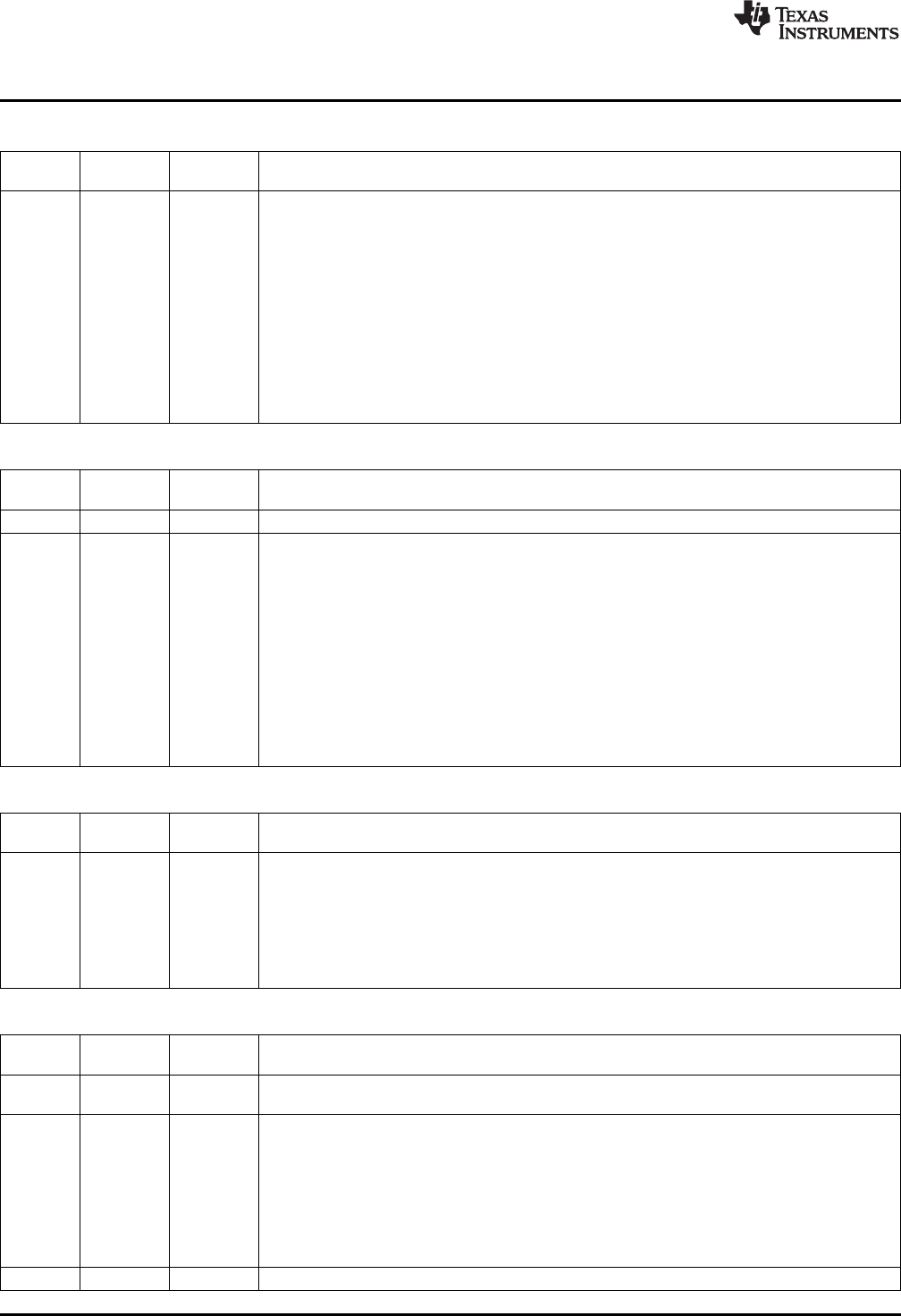

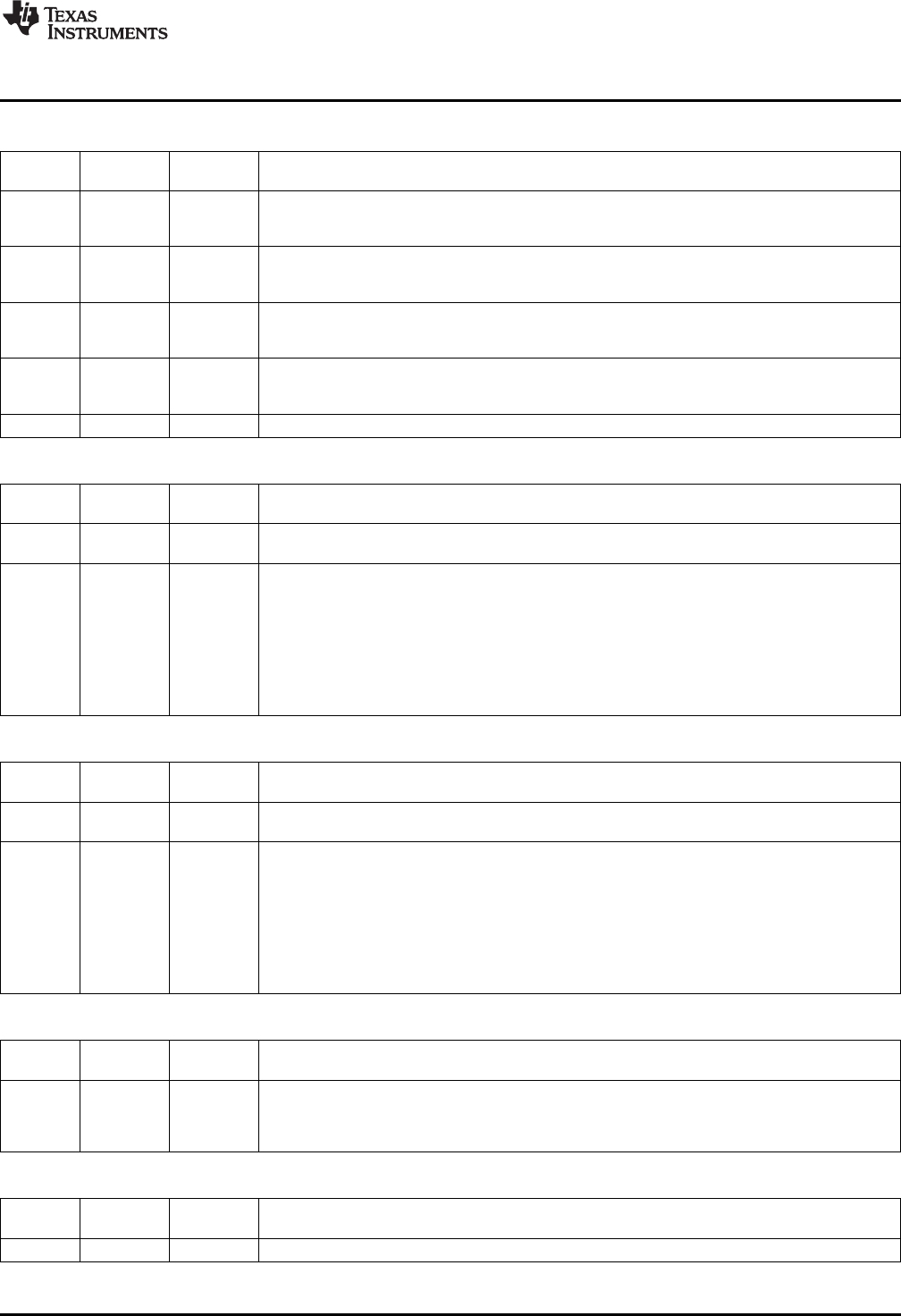

2.2.3.4 Mono Differential DAC to Mono Differential Headphone Output

Figure 2-5. Low Power Mono DAC to Differential Headphone

This configuration, available in unipolar configuration of the HP amplifier supplies, supports the routing of

the two differential outputs of the mono, left channel DAC to the headphone amplifiers in differential mode

(Page 1, Register 12, D3 = 1 and Page 1, Register 13, D4 = 1).

2.2.4 Line Outputs

The stereo line level drivers on LOL and LOR pins can drive a wide range of line level resistive

impedances in the range of 600Ωto 10kΩ. The output common modes of line level drivers can be

configured to equal either the analog input common-mode setting, or 1.65V. With output common-mode

setting of 1.65V and DRVdd_HP supply at 3.3V the line-level drivers can drive up to 1Vrms output signal.

The line-level drivers can drive out a mixed combination of DAC signal and attenuated ADC PGA signal.

Signal mixing is register-programmable.

2.2.4.1 Line Out Amplifier Configurations

Signal mixing can be configured by programming Page 1, Register 14 and 15. Additionally, the two line-

level drivers can be configured to act as a mono differential line level driver by routing the output of LOR

to LOL (Page 1, Register 14, D(0) = 1).

The output of DAC can be simultaneously played back to the stereo headphone drivers as well as stereo

line- level drivers. In such a case, the DAC signal at the headphone outputs and line outputs are out-of-

phase with respect to each other.

Figure 2-6. Stereo Single-Ended Line-out

16 TLV320AIC3256 Application SLAU306A–January 2011–Revised January 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

RIGHT

DAC AFIR

Output +

LOR

RIGHT_DACP

RIGHT_DACM

LOL

Output -

www.ti.com

ADC

Figure 2-7. Low Power Mono DAC to Differential Line-out

2.3 ADC

The TLV320AIC3256 includes a stereo audio ADC, which uses a delta-sigma modulator with a

programmable oversampling ratio, followed by a digital decimation filter. The ADC supports sampling rates

from 8kHz to 192kHz. In order to provide optimal system power management, the stereo recording path

can be powered up one channel at a time, to support the case where only mono record capability is

required.

The ADC path of the TLV320AIC3256 features a large set of options for signal conditioning as well as

signal routing:

• Two ADCs

• Six analog inputs which can be mixed and-or multiplexed in single-ended and-or differential

configuration

• Two programmable gain amplifiers (PGA) with a range of 0 to +47.5dB

• Two mixer amplifiers for analog bypass

• Two low power analog bypass channels

• Fine gain adjustment of digital channels with 0.1dB step size

• Digital volume control with a range of -12 to +20dB

• Mute function

In addition to the standard set of ADC features the TLV320AIC3256 also offers the following special

functions:

• Channel-to-channel phase adjustment

• Fast charge of ac-coupling capacitors

• Anti thump

• Adaptive filter mode

Because of the oversampling nature of the audio ADC and the integrated digital decimation filtering,

requirements for analog anti-aliasing filtering are very relaxed. The TLV320AIC3256 integrates a second

order analog anti-aliasing filter with 28-dB attenuation at 6MHz. This filter, combined with the digital

decimation filter, provides sufficient anti-aliasing filtering without requiring additional external components.

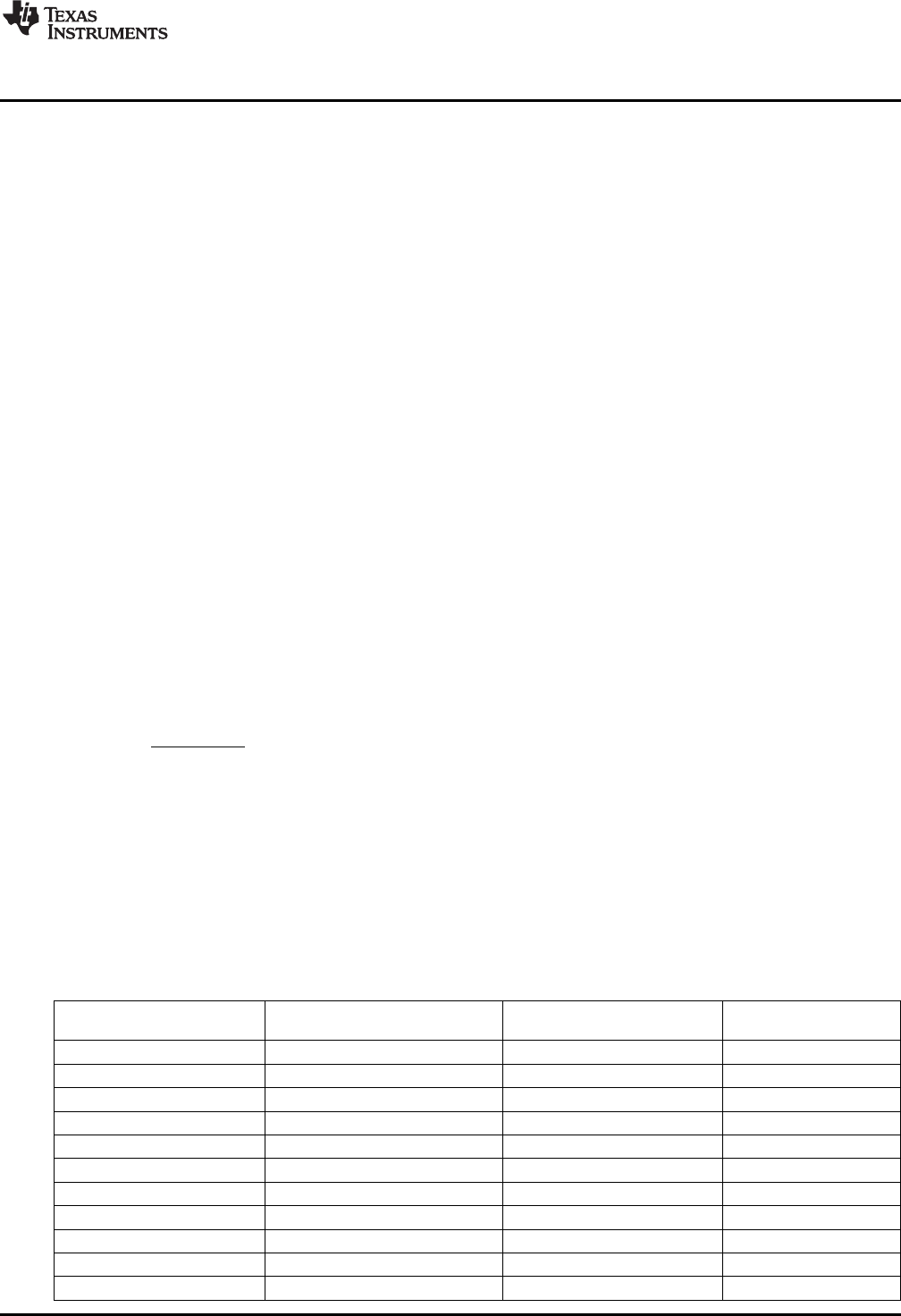

2.3.1 ADC Signal Routing

The TLV320AIC3256 includes six analog inputs which can be configured as either 3 stereo single-ended

pairs or 3 fully-differential pairs. These pins connect through series resistors and switches to the virtual

ground terminals of two fully-differential amplifiers (one per ADC-PGA channel). By turning on only one set

of switches per amplifier at a time, the inputs can be effectively multiplexed to each ADC PGA channel. By

turning on multiple sets of switches per amplifier at a time, audio sources can be mixed. The

TLV320AIC3256 supports the ability to mix up to four single-ended analog inputs or up to two fully-

differential analog inputs into each ADC PGA channel.

17

SLAU306A–January 2011–Revised January 2013 TLV320AIC3256 Application

Submit Documentation Feedback Copyright © 2011–2013, Texas Instruments Incorporated

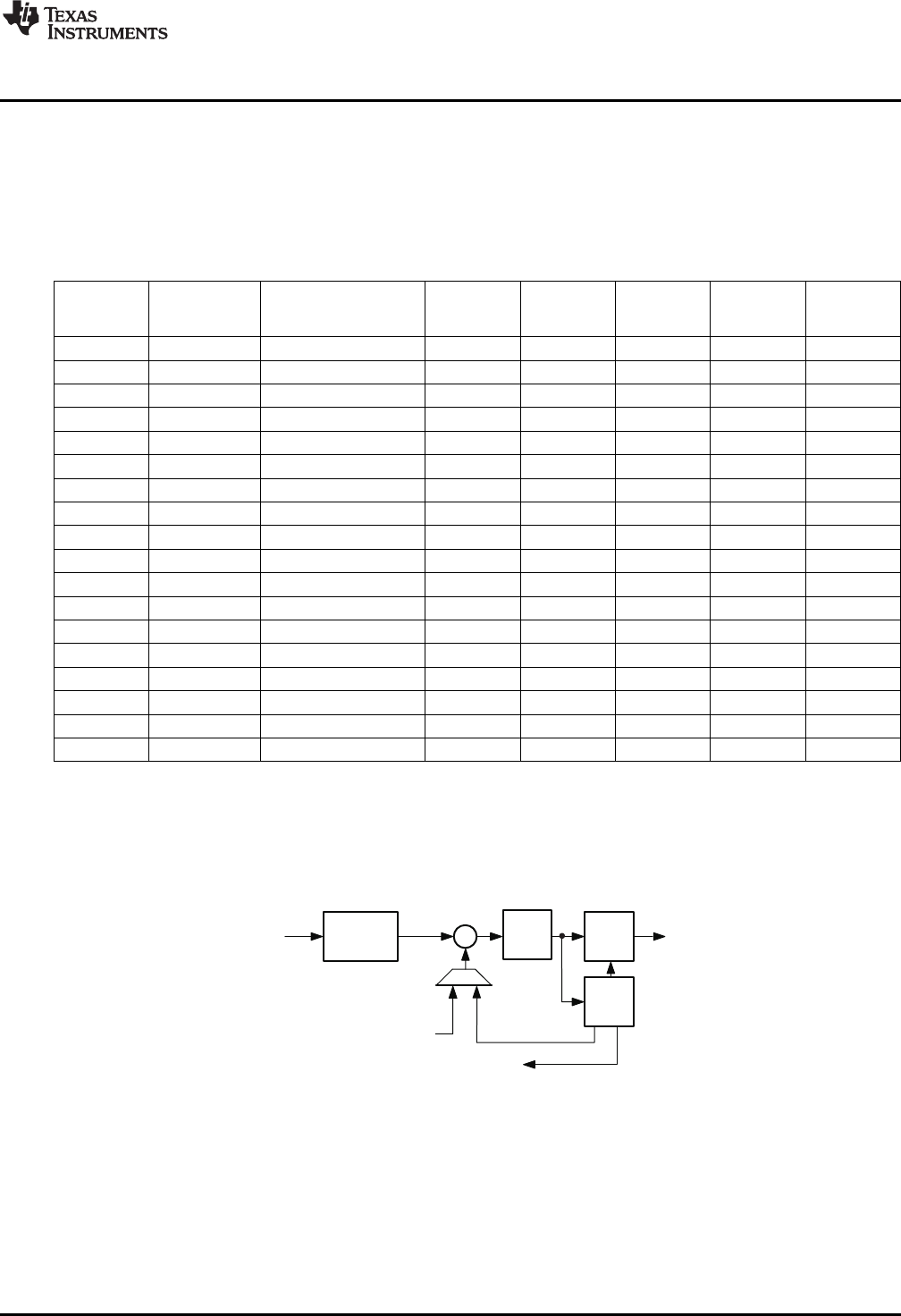

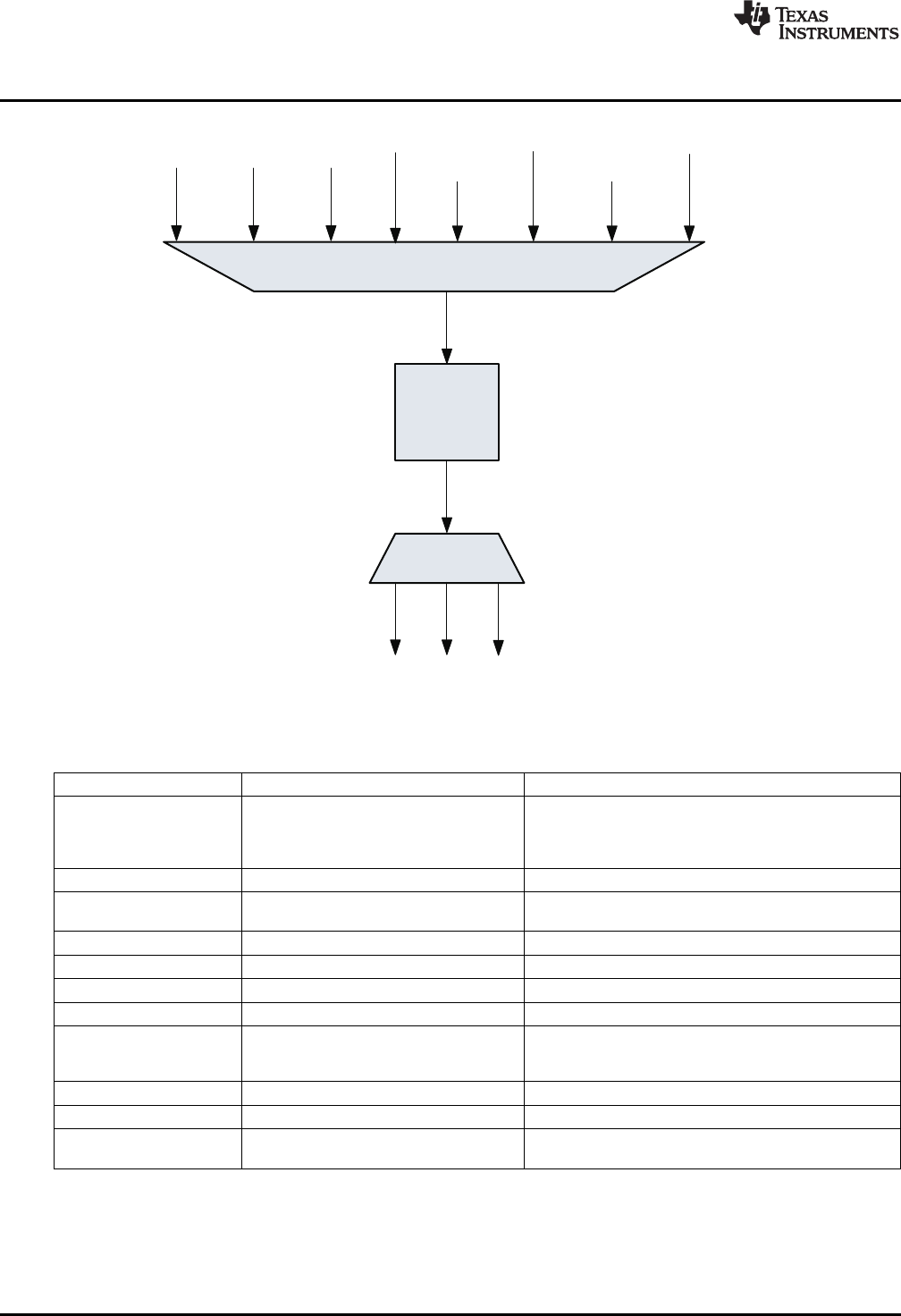

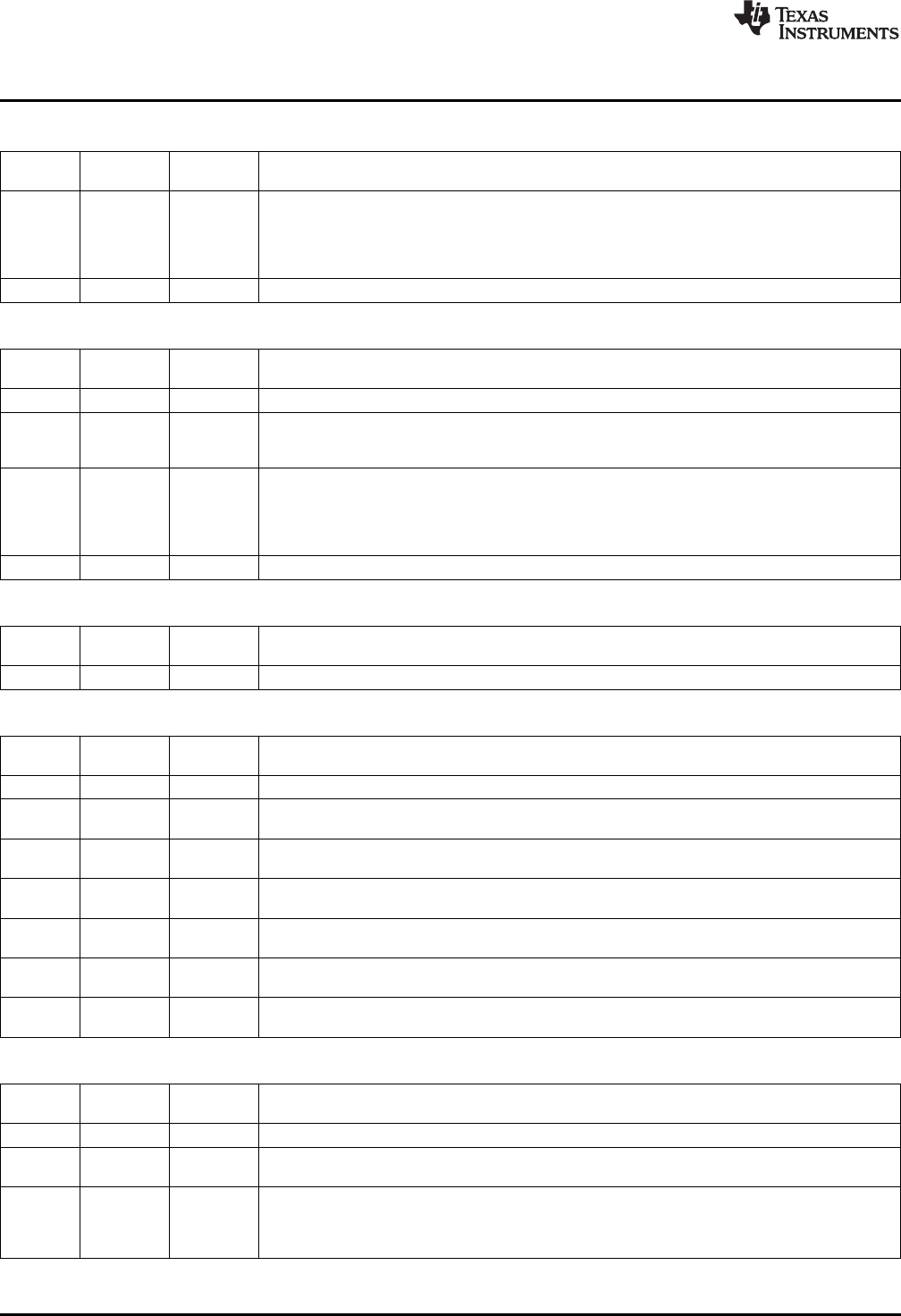

Analog

Gain

Analog

In

Input

Selection

ADC

Filtering

Digital

Volume

Control

Digital

Gain

Adjust

0...47.5 dB

Step = 0.5 dB

0, -6, -12 dB -12...20 dB

Step = 0.5 dB

0…-0.4 dB

Step= 0.1 dB

Frequency

Response

and Gain

Fully

Programmable

Coefficients

Audio

Interface

ADC

PGA

ADC

www.ti.com

In most applications, high input impedance is desired for analog inputs. However, when used in

conjunction with high gain as in the case of microphone inputs, the higher input impedance results in

higher noise or lower dynamic range. The TLV320AIC3256 allows the user the flexibility of choosing the

input impedance from 10kΩ, 20kΩand 40kΩ. When multiple inputs are mixed together, by choosing

different input impedances, level adjustment can be achieved. For example, if one input is selected with

10kΩinput impedance and the second input is selected with 20kΩinput impedance, then the second input

is attenuated by half as compared to the first input. Note that this input level control is not intended to be a

volume control, but instead used occasionally for level setting.

Mixing of multiple inputs can easily lead to PGA outputs that exceed the range of the internal amplifiers,

resulting in saturation and clipping of the mixed output signal. Whenever mixing is being implemented, the

system designer is advised to take adequate precautions to avoid such a saturation from occurring. In

general, the mixed signal should not exceed 0dB.

Typically, voice or audio signal inputs are capacitively coupled to the device. Capacitive coupling allows

the device to independently set the common mode of the input signals to values chosen by the contents of

Page 1, Register 10, D(6) to either 0.9V or 0.75V. The correct value maximizes the dynamic range across

the entire analog-supply range. Failure to capacitively connect the input to the device can cause high

offset due to mismatch in source common-mode and device common-mode setting, and in extreme cases,

could also saturate the analog channel, causing distortion.

2.3.2 ADC Gain Setting

When the gain of the ADC Channel is kept at 0dB and the common mode set to 0.75V, a single-ended

input of 0.375VRMS results in a full-scale digital signal at the output of ADC channel. Similarly, when the

gain is kept at 0dB, and common mode is set to 0.9V, a single-ended input of 0.5VRMS results in a full-

scale digital signal at the output of the ADC channel. However various block functions control the gain

through the channel. The gain applied by the PGA is described in Table 2-9. Additionally, the digital

volume control adjusts the gain through the channel as described in Section 2.3.2.2. A finer level of gain is

controlled by fine gain control as described in Section 2.3.2.2.1. The decimation filters A, B and C along

with the delta-sigma modulator contribute to a DC gain of 1.0 through the channel.

2.3.2.1 Analog Programmable Gain Amplifier (PGA)

The TLV320AIC3256 features a built-in low-noise PGA for boosting low-level signals, such as direct

microphone inputs, to full-scale to achieve high SNR. This PGA provides a gain in the range of 0dB to

47.5dB for single-ended inputs or 6dB to 53.5dB for fully-differential inputs (gain calculated w.r.t. input

impedance setting of 10kΩ, 20kΩinput impedance will result in 6dB lower and 40kΩwill result in 12dB

lower gain). The user can control the gain by writing to Page 1, Register 59 and Page 1, Register 60. In

the AGC mode, this gain is optionally automatically controlled by the built-in hardware AGC.

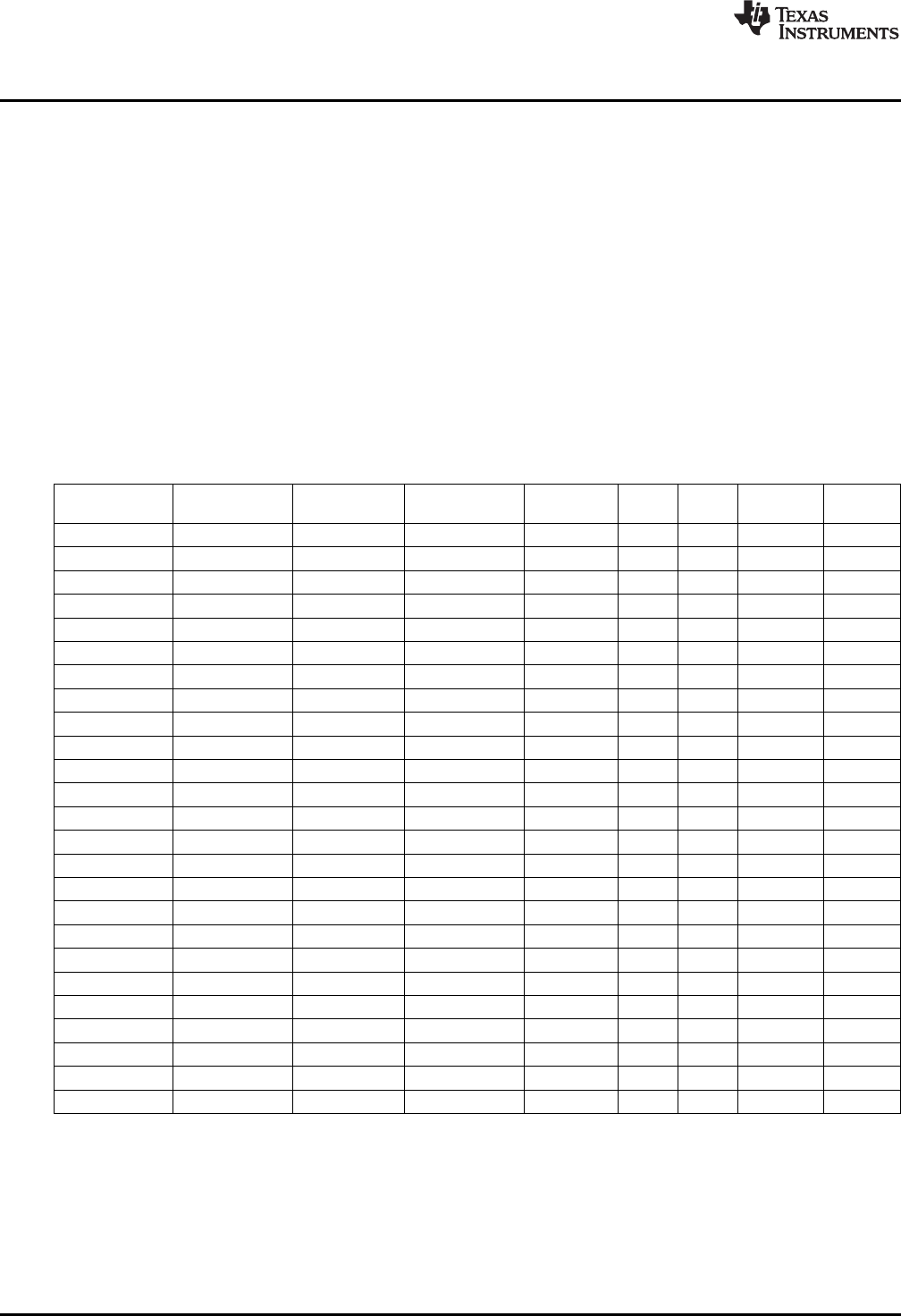

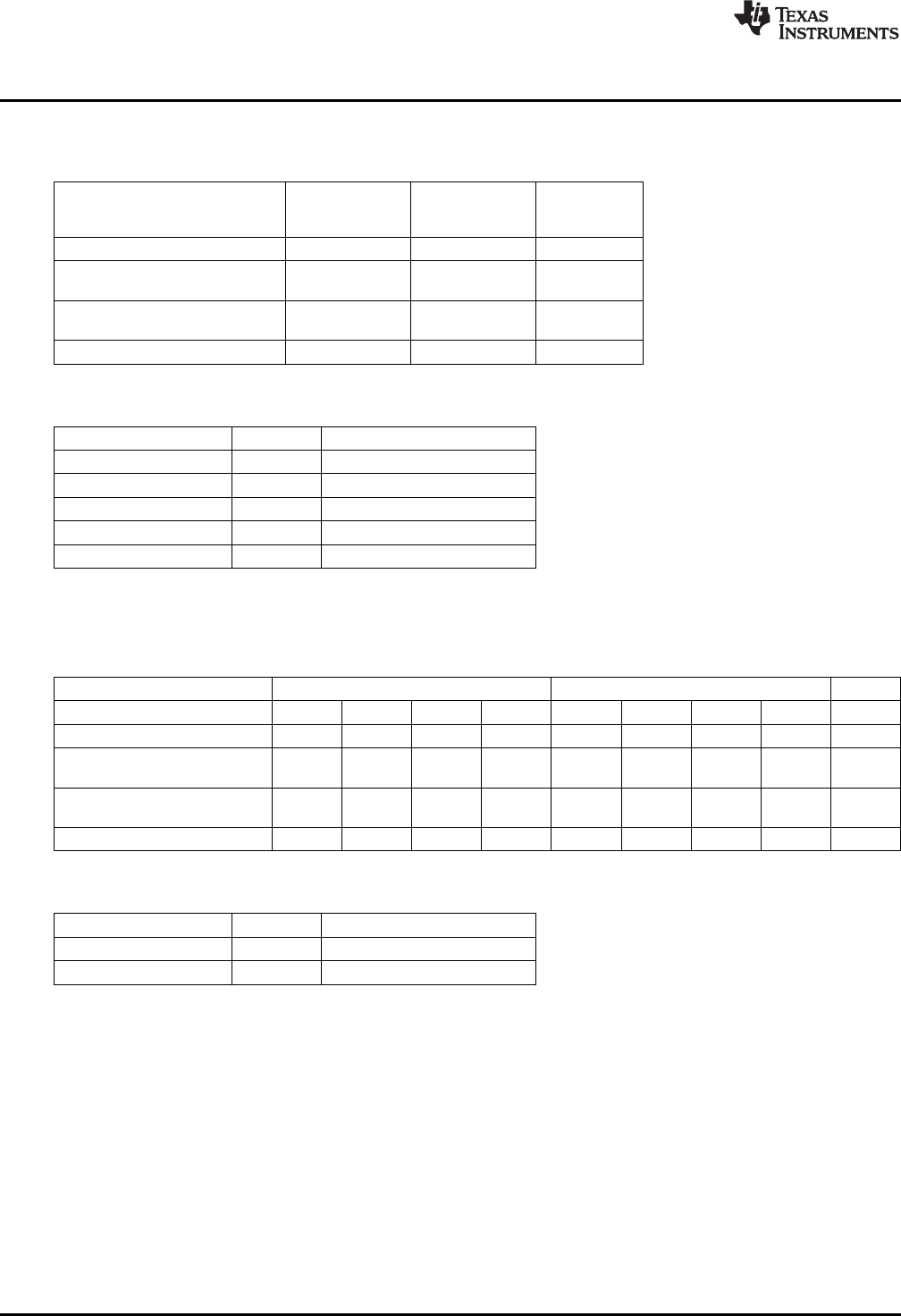

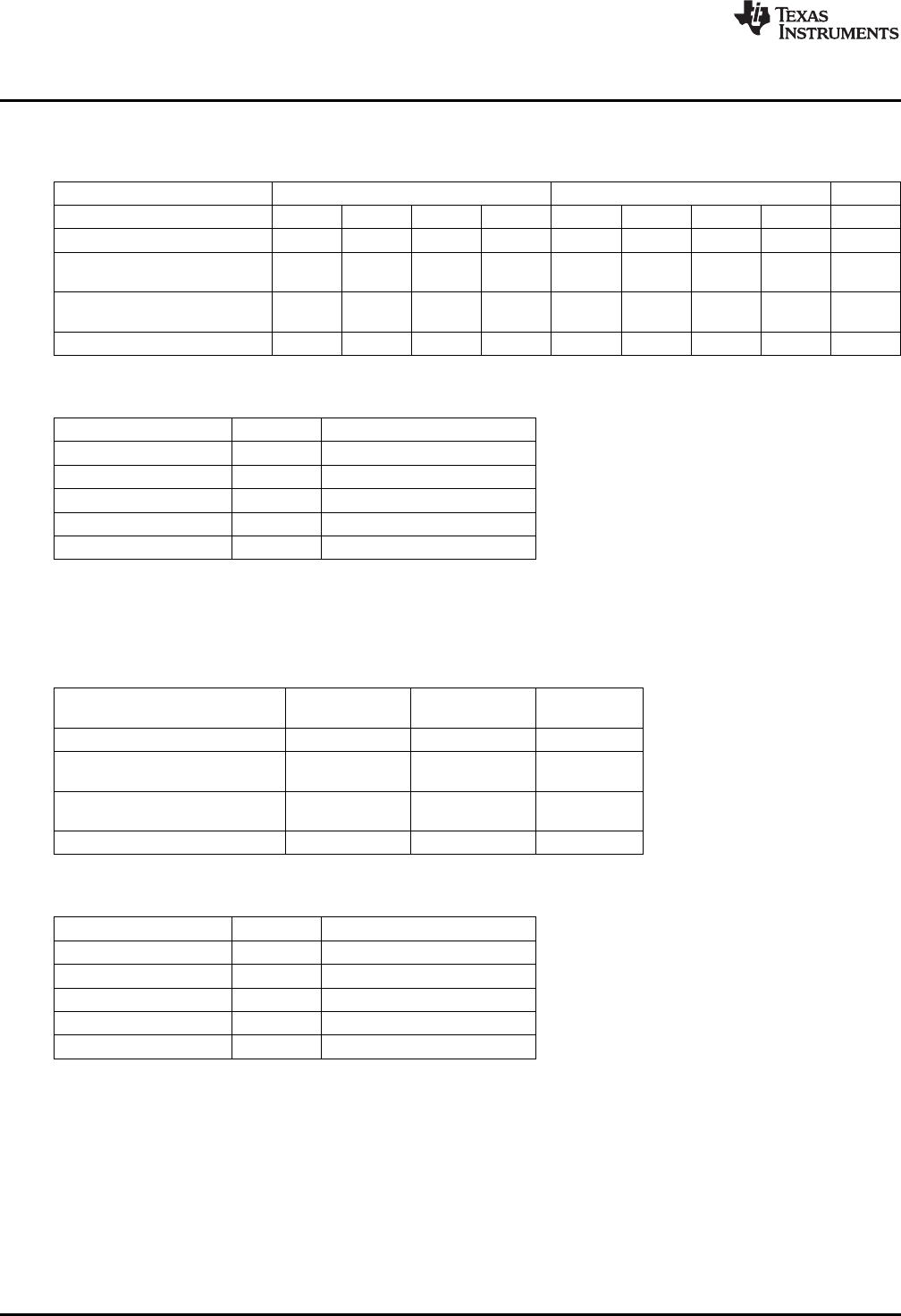

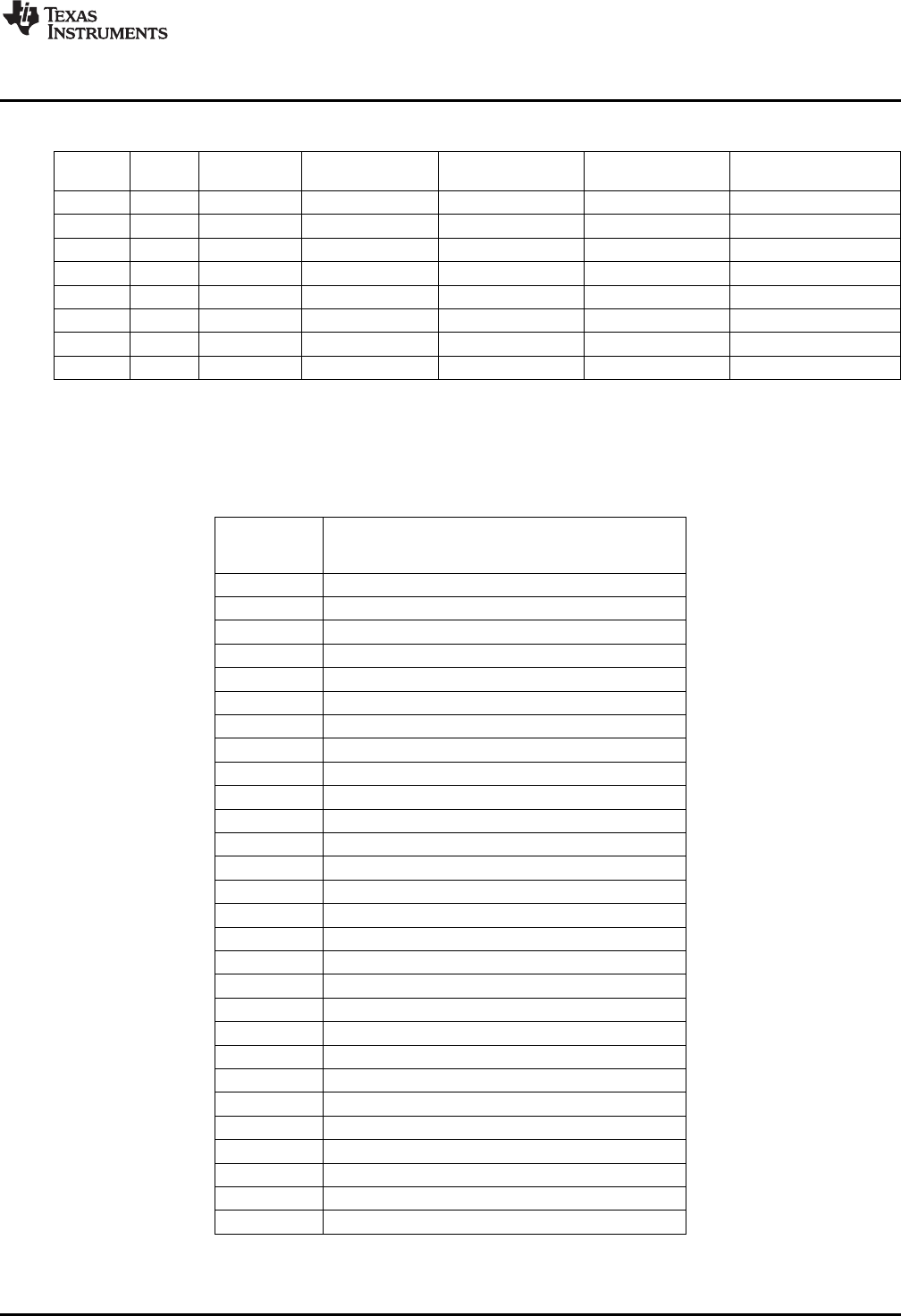

Table 2-9. Analog PGA versus Input Configuration

Page 1, EFFECTIVE GAIN APPLIED BY PGA

Register 59, D(6:0) SINGLE-ENDED DIFFERENTIAL

Page 1, RIN = 10kΩRIN = 20kΩRIN = 40kΩRIN = 10kΩRIN = 20kΩRIN = 40kΩ

Register 60, D(6:0)

000 0000 0dB –6dB -12dB 6.0dB 0dB –6.0dB

000 0001 0.5dB –5.5dB –11.5dB 6.5dB 0.5dB -5.5dB

000 0010 1.0dB –5.0dB –11.0dB 7.0dB 7.5dB –5.0dB

18 TLV320AIC3256 Application SLAU306A–January 2011–Revised January 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

www.ti.com

ADC

Table 2-9. Analog PGA versus Input Configuration (continued)

Page 1, EFFECTIVE GAIN APPLIED BY PGA

Register 59, D(6:0) SINGLE-ENDED DIFFERENTIAL

Page 1, RIN = 10kΩRIN = 20kΩRIN = 40kΩRIN = 10kΩRIN = 20kΩRIN = 40kΩ

Register 60, D(6:0)

… … … … … … …

101 1110 47.0dB 41.0dB 35.0dB 53.0dB 47.0dB 41.0dB

101 1111 47.5dB 41.5dB 35.5dB 53.5dB 47.5dB 41.5dB

The gain changes are implemented with an internal soft-stepping algorithm that only changes the actual

volume level by one 0.5dB step every one or two ADC output samples, depending on the register value

(see registers Page 0, Reg 81, D(1:0)). This soft-stepping smooths volume control changes with no

audible artifacts. On reset, the PGA gain defaults to a mute condition, and at power down, the PGA soft-

steps the volume to mute before shutting down. A read-only flag Page 0, Reg 36, D(7) and D(3) is set

whenever the gain applied by the PGA equals the desired value set by the register. The soft-stepping

control can also be disabled by programming Page 0, Reg 81, D(1:0).

2.3.2.2 Digital Volume Control

The TLV320AIC3256 also has a digital volume-control block with a range from -12dB to +20dB in steps of

0.5dB. The system controls the volume by programming Page 0, Register 83 and 84 respectively for left

and right channels.

Table 2-10. Digital Volume Control for ADC

Desired Gain Left or Right Channel

dB Page 1, Register 83 or 84 (respectively),

D(6:0)

–12.0 110 1000

–11.5 110 1001

–11.0 110 1010

..

–0.5 111 1111

0.0 000 0000 (Default)

+0.5 000 0001

..

+19.5 010 0111

+20.0 010 1000

During volume control changes, using the soft-stepping feature avoids audible artifacts. The soft-stepping

rate can be set to either 1 or 2 gain steps per sample. Soft-stepping can also be entirely disabled. This

soft-stepping is configured via Page 1, Register 81, D(1:0), and is common to the soft-stepping control for

the analog PGA. During power-down of an ADC channel, this volume control soft-steps down to –12.0dB

before powering down. Due to the soft-stepping control, soon after changing the volume control setting or

powering down the ADC channel, the actual applied gain may be different from the one programmed

through the control register. The TLV320AIC3256 gives feedback to the user, through read-only flags

Page 1, Reg 36, D(7) for Left Channel and Page 1, Reg 36, D(3) for the right channel.

2.3.2.2.1 Fine Digital Gain Adjustment

Additionally, the gain in each of the channels is finely adjustable in steps of 0.1dB. This granularity is

useful when trying to match the gain between channels. By programming Page 0, Register 82 the gain

can be adjusted from 0dB to -0.4dB in steps of 0.1dB. This feature, in combination with the regular digital

volume control, allows the gains through the left and right channels be matched in the range of -0.5dB to

+0.5dB with a resolution of 0.1dB.

19

SLAU306A–January 2011–Revised January 2013 TLV320AIC3256 Application

Submit Documentation Feedback Copyright © 2011–2013, Texas Instruments Incorporated

ADC

www.ti.com

2.3.2.3 AGC

The TLV320AIC3256 includes Automatic Gain Control (AGC) for ADC recording. AGC can be used to

maintain a nominally-constant output level when recording speech. As opposed to manually setting the

PGA gain, in the AGC mode, the circuitry automatically adjusts the PGA gain as the input signal becomes

overly loud or very weak, such as when a person speaking into a microphone moves closer or farther from

the microphone. The AGC algorithm has several programmable parameters, including target gain, attack

and decay time constants, noise threshold, and max PGA applicable, that allow the algorithm to be fine

tuned for any particular application. The algorithm uses the absolute average of the signal (which is the

average of the absolute value of the signal) as a measure of the nominal amplitude of the output signal.

Since the gain can be changed at the sample interval time, the AGC algorithm operates at the ADC

sample rate.

1. Target Level represents the nominal output level at which the AGC attempts to hold the ADC output

signal level. The TLV320AIC3256 allows programming of eight different target levels, which can be

programmed from –5.5dB to –24dB relative to a full-scale signal. Since the TLV320AIC3256 reacts to

the signal absolute average and not to peak levels, it is recommended that the target level be set with

enough margin to avoid clipping at the occurrence of loud sounds.

2. Attack Time defines how quickly the AGC circuitry reduces the PGA gain when the output signal level

exceeds the target level due to increase in input signal level. Wide range of attack time

programmability is supported in terms of number of samples (number of ADC sample frequency clock

cycles).

3. Decay Time defines how quickly the PGA gain is increased when the output signal level falls below

the target level due to reduction in input signal level. Wide range of decay time programmability is

supported in terms of number of samples.

4. Gain Hysteresis is the hysteresis applied to the required gain calculated by the AGC function while

changing its mode of operation from attack to decay or vice-versa. For example, while attacking the

input signal, if the current applied gain by the AGC is xdB, and suddenly because of the input level

going down, the new calculated required gain is ydB, then this gain is applied, provided that yis

greater than xby the value set in Gain Hysteresis. This feature avoids the condition where the AGC

function fluctuates between a very narrow band of gains leading to audible artifacts. The Gain

Hysteresis can be adjusted or disabled by the user.

5. Noise threshold defines the level below which if the input signal level falls, the AGC considers it as

silence, and thus brings down the gain to 0dB in steps of 0.5dB every fSand sets the noise threshold

flag. The gain stays at 0dB unless the input speech signal average rises above the noise threshold

setting. This noise-gating ensures that noise is not 'gained up' in the absence of speech. Noise

threshold level in the AGC algorithm is programmable from -30dB to -90dB of full-scale. When AGC

Noise Threshold is set to –70dB, –80dB, or –90dB, the microphone input Max PGA applicable setting

must be greater than or equal to 11.5dB, 21.5dB, or 31.5dB respectively. This operation includes

hysteresis and debounce to avoid the AGC gain from cycling between high gain and 0dB when signals

are near the noise threshold level. The noise (or silence) detection feature can be entirely disabled by

the user.

6. Max PGA applicable allows the designer to restrict the maximum gain applied by the AGC. This

feature limits PGA gain in situations where environmental noise is greater than the programmed noise

threshold. Microphone input Max PGA is programmable from 0dB to 58dB in steps of 0.5dB.

7. Hysteresis, as the name suggests, defines a window around the Noise Threshold which must be

exceeded to either detect that the recorded signal is indeed noise or signal. If initially the energy of the

recorded signal is greater than the Noise Threshold, then the AGC recognizes it as noise only when

the energy of the recorded signal falls below the Noise Threshold by a value given by Hysteresis.

Similarly, after the recorded signal is recognized as noise, for the AGC to recognize it as a signal, its

energy must exceed the Noise Threshold by a value given by the Hysteresis setting. In order to

prevent the AGC from jumping between noise and signal states, (which can happen when the energy

of recorded signal is very close to the Noise threshold) a non-zero hysteresis value should be chosen.

The Hysteresis feature can also be disabled.

8. Debounce Time (Noise and Signal) defines the hysteresis in time domain for noise detection. The

AGC continuously calculates the energy of the recorded signal. If the calculated energy is less than the

set Noise Threshold, then the AGC does not increase the input gain to achieve the Target Level.

However, to handle audible artifacts which can occur when the energy of the input signal is very close

to the Noise Threshold, the AGC checks if the energy of the recorded signal is less than the Noise

20 TLV320AIC3256 Application SLAU306A–January 2011–Revised January 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

1

1

23

1

10

zD2

zNN

)z(H -

-

-

+

=

www.ti.com

ADC

Threshold for a time greater than the Noise Debounce Time. Similarly the AGC starts increasing the

input-signal gain to reach the Target Level when the calculated energy of the input signal is greater

than the Noise Threshold. Again, to avoid audible artifacts when the input-signal energy is very close

to Noise Threshold, the energy of the input signal needs to continuously exceed the Noise Threshold

value for the Signal Debounce Time. If the debounce times are kept very small, then audible artifacts

can result by rapid enabling and disabling the AGC function. At the same time, if the Debounce time is

kept too large, then the AGC may take time to respond to changes in levels of input signals with

respect to Noise Threshold. Both noise and signal debounce time can be disabled.

9. The AGC Noise Threshold Flag is a read-only flag indicating that the input signal has levels lower

than the Noise Threshold, and thus is detected as noise (or silence). In such a condition the AGC

applies a gain of 0dB.

10. Gain Applied by AGC is the gain applied by the AGC to the recorded signal in a read-only register to

provide real-time feedback to the system. This value, along with the Target Setting, can be used to

detect the input signal level. In a steady state situation

Target Level (dB ) = Gain Applied by AGC (dB) + Input Signal Level (dB)

When the AGC noise threshold flag is set, then the status of gain applied by AGC should be ignored.

11. The AGC Saturation Flag is a read-only flag indicating that the ADC output signal has not reached its

Target Level. However, the AGC is unable to increase the gain further because the required gain is

higher than the Maximum Allowed PGA gain. Such a situation can happen when the input signal has

very low energy and the Noise Threshold is also set very low. When the AGC noise threshold flag is

set, the status of the AGC saturation flag should be ignored.

12. The ADC Saturation Flag is a read-only flag indicating an overflow condition in the ADC channel. On

overflow, the signal is clipped and distortion results. This condition typically happens when the AGC

Target Level is kept very high and the energy in the input signal increases faster than the Attack Time.

13. An AGC low-pass filter detects the average level of the input signal. This average level is compared

to the programmed detection levels in the AGC to provide the correct functionality. This low pass filter

is in the form of a first-order IIR filter. Three 8-bit registers form the 24-bit digital coefficient as shown

on the register map. A total of 9 registers are programmed to form the 3 IIR coefficients. The transfer

function of the filter implemented for signal level detection is given by

(2)

Where:

Coefficient N0 can be programmed by writing into Page 8, Register 12, 13 and 14.

Coefficient N1 can be programmed by writing into Page 8, Register 16, 17 and 18.

Coefficient D1 can be programmed by writing into Page 8, Register 20, 21 and 22.

N0, N1 and D1 are 24-bit 2’s complement numbers and their default values implement a low-pass

filter with cut-off at 0.002735*ADC_FS.

See Table 2-11 for various AGC programming options. AGC can be used only if analog microphone

input is routed to the ADC channel.

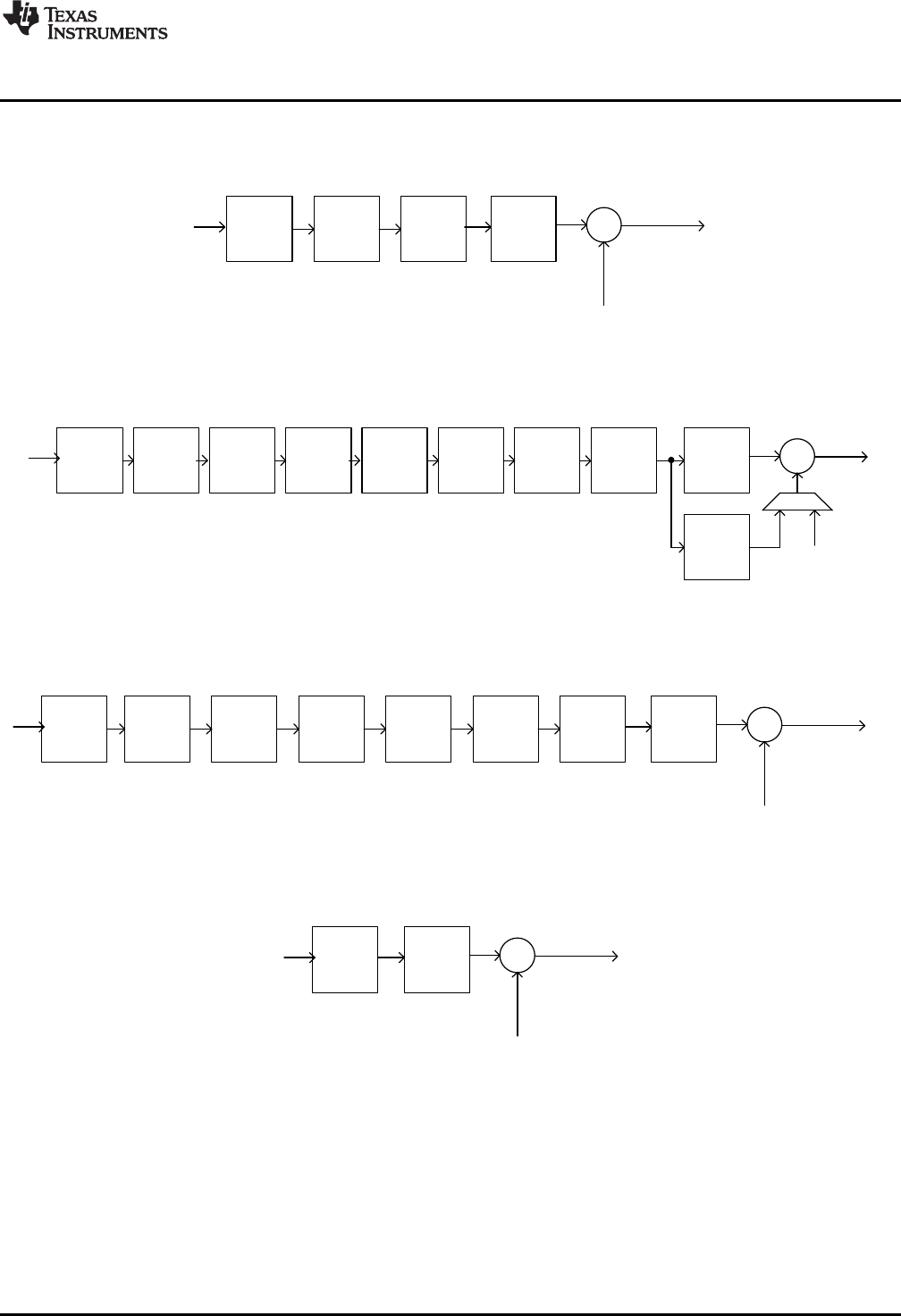

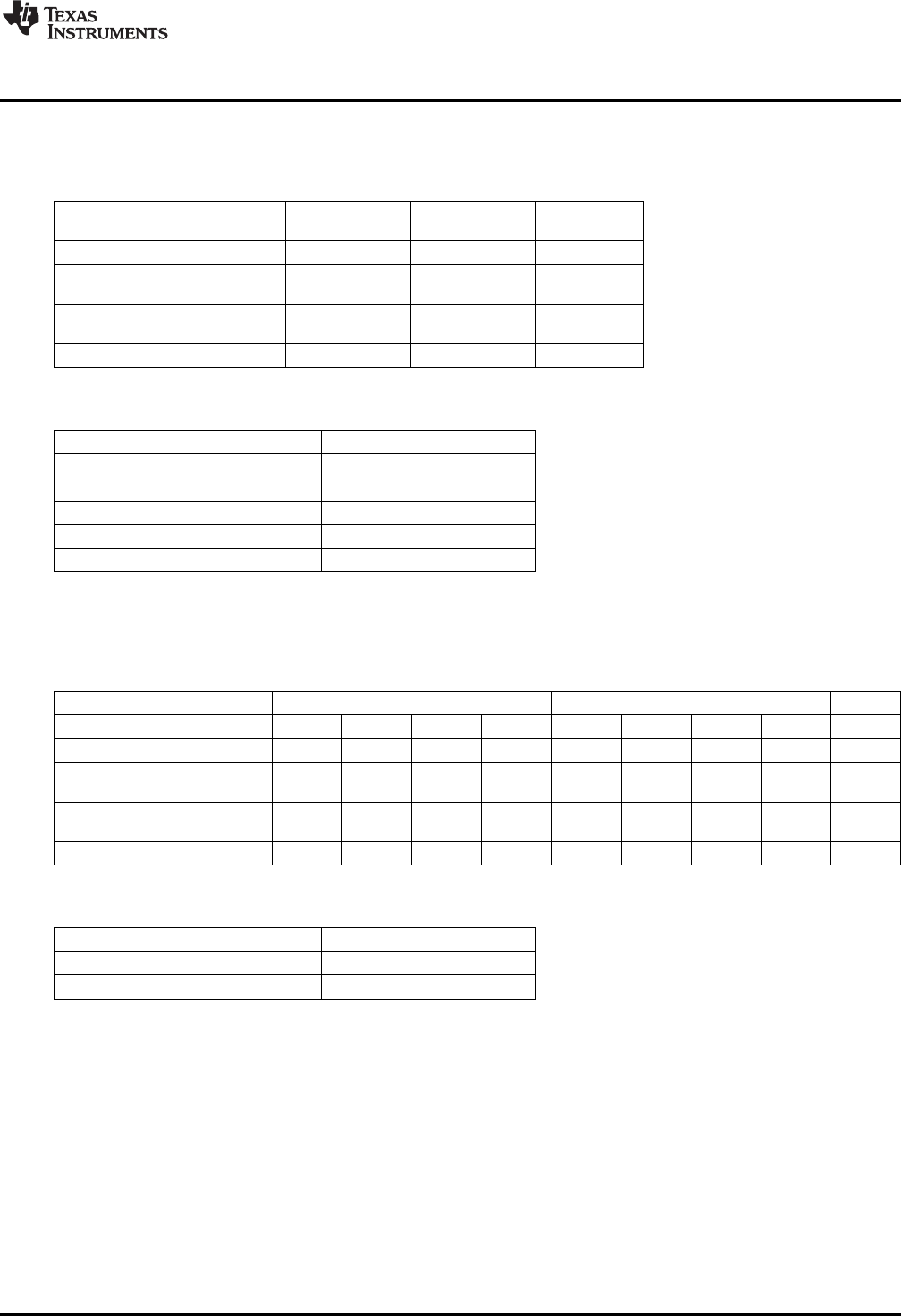

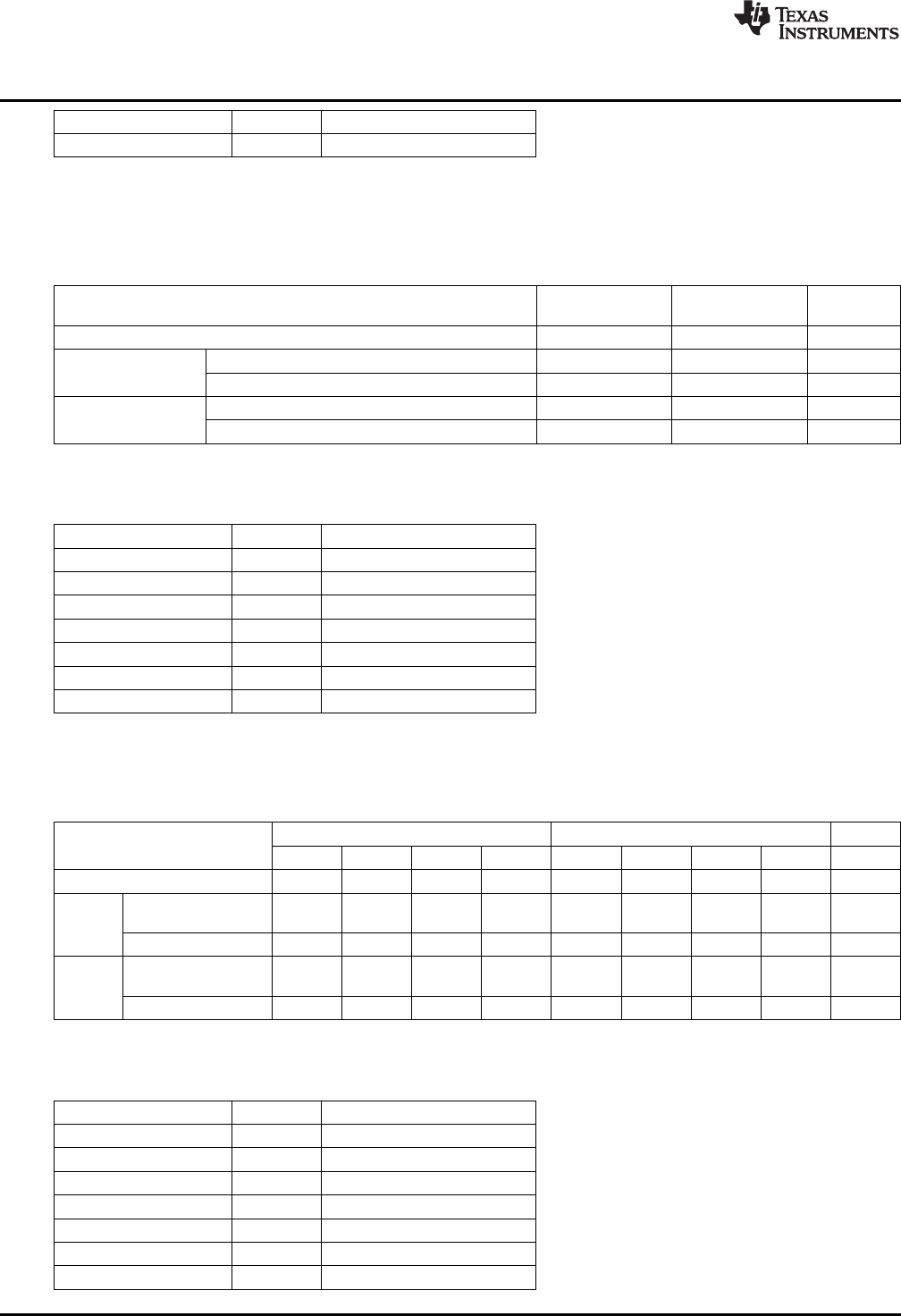

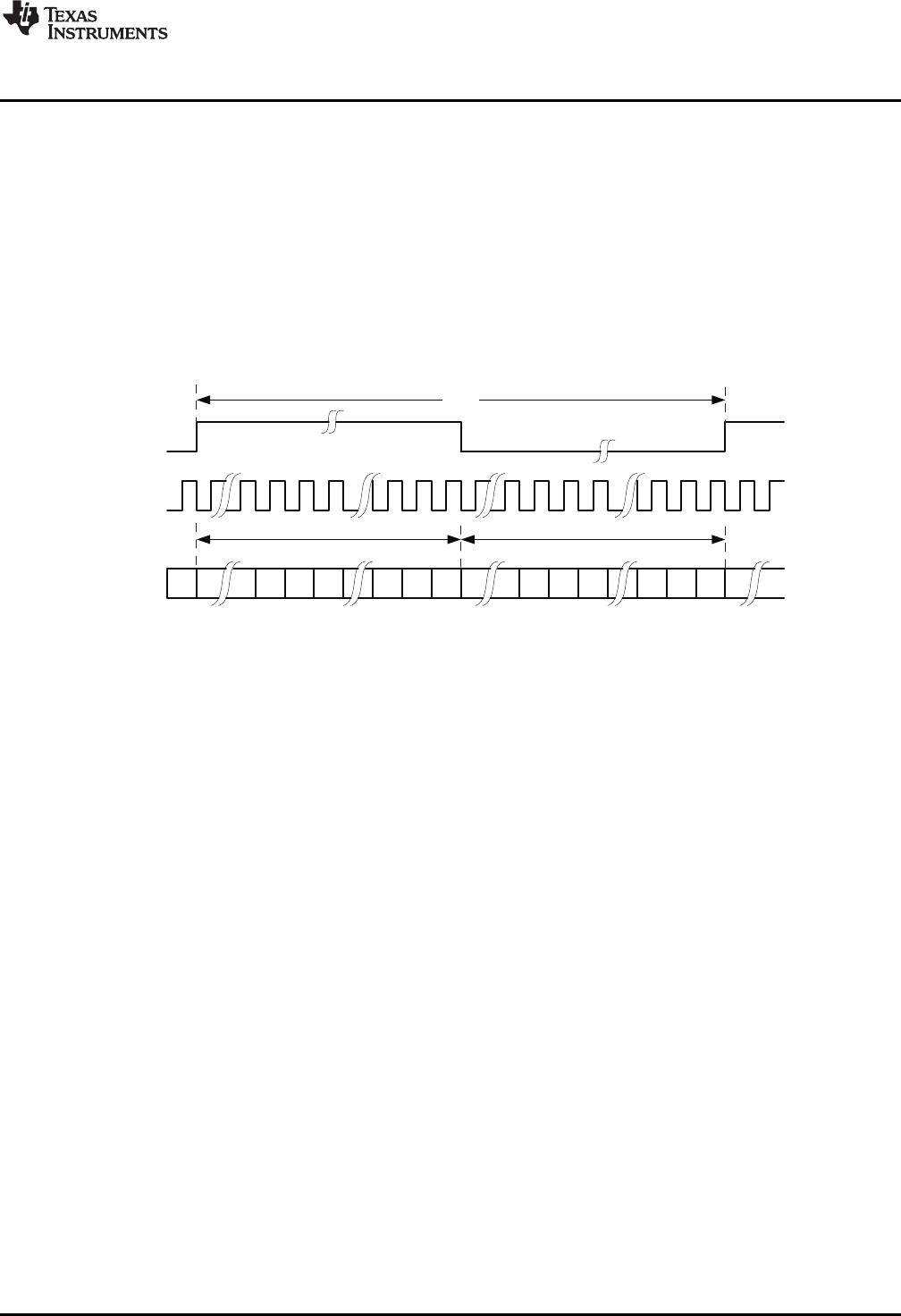

Table 2-11. AGC Parameter Settings

Function Control Register Control Register Bit

Left ADC Right ADC

AGC enable Page 0, Register 86 Page 0,Register 94 D(7)

Target Level Page 0, Register 86 Page 0, Register 94 D(6:4)

Gain Hysteresis Page 0, Register 86 Page 0, Register 94 D(1:0)

Hysteresis Page 0, Register 87 Page 0, Register 95 D(7:6)

Noise threshold Page 0, Register 87 Page 0, Register 95 D(5:1)

Max PGA applicable Page 0, Register 88 Page 0, Register 96 D(6:0)

Time constants (attack time) Page 0, Register 89 Page 0, Register 97 D(7:0)

Time constants(decay time) Page 0, Register 90 Page 0, Register 98 D(7:0)

Debounce time (Noise) Page 0, Register 91 Page 0, Register 99 D(4:0)

Debounce time (Signal) Page 0, Register 92 Page 0, Register 100 D(3:0)

Gain applied by AGC Page 0, Register 93 Page 0, Register 101 D(7:0) (Read Only)

21

SLAU306A–January 2011–Revised January 2013 TLV320AIC3256 Application

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

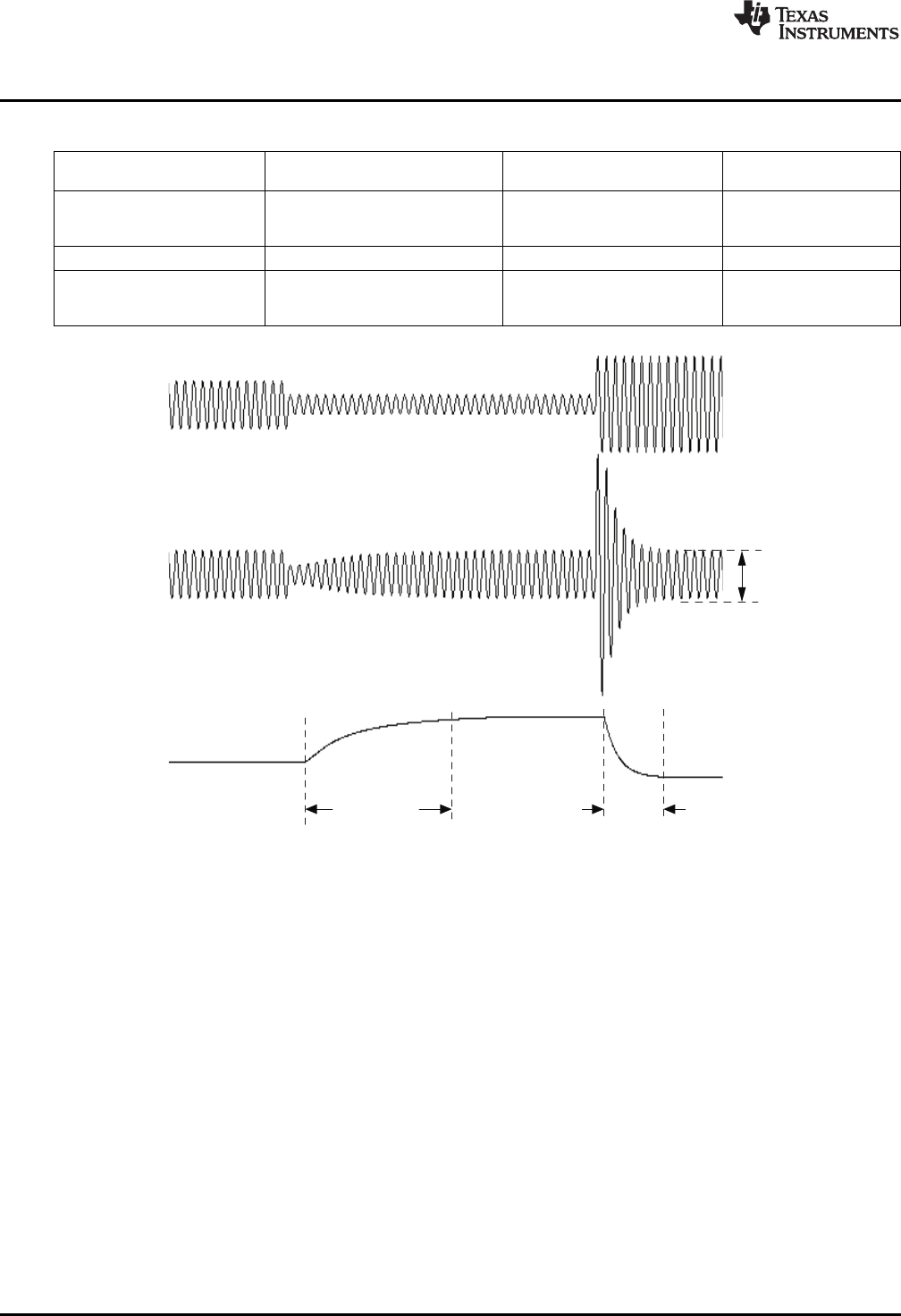

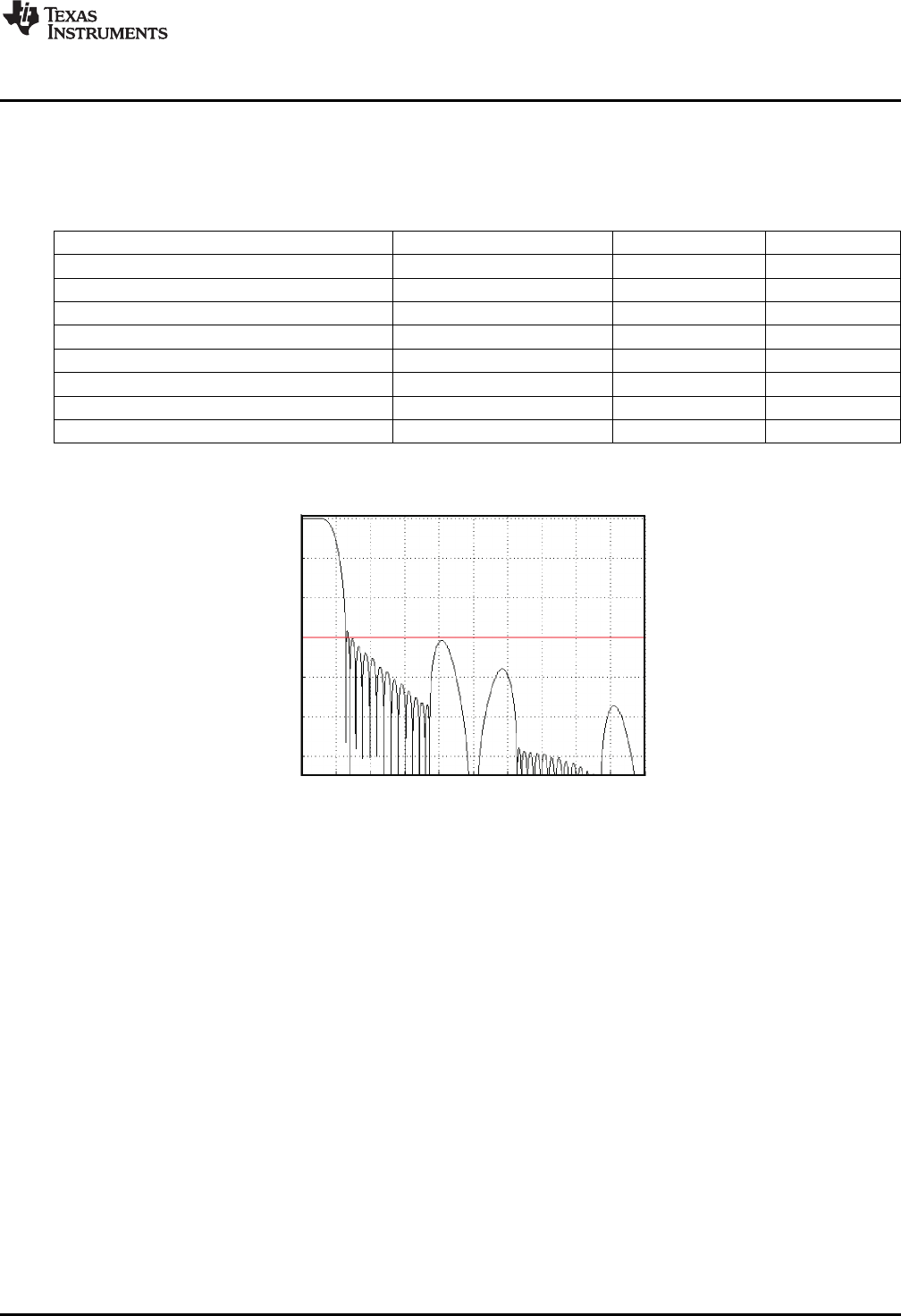

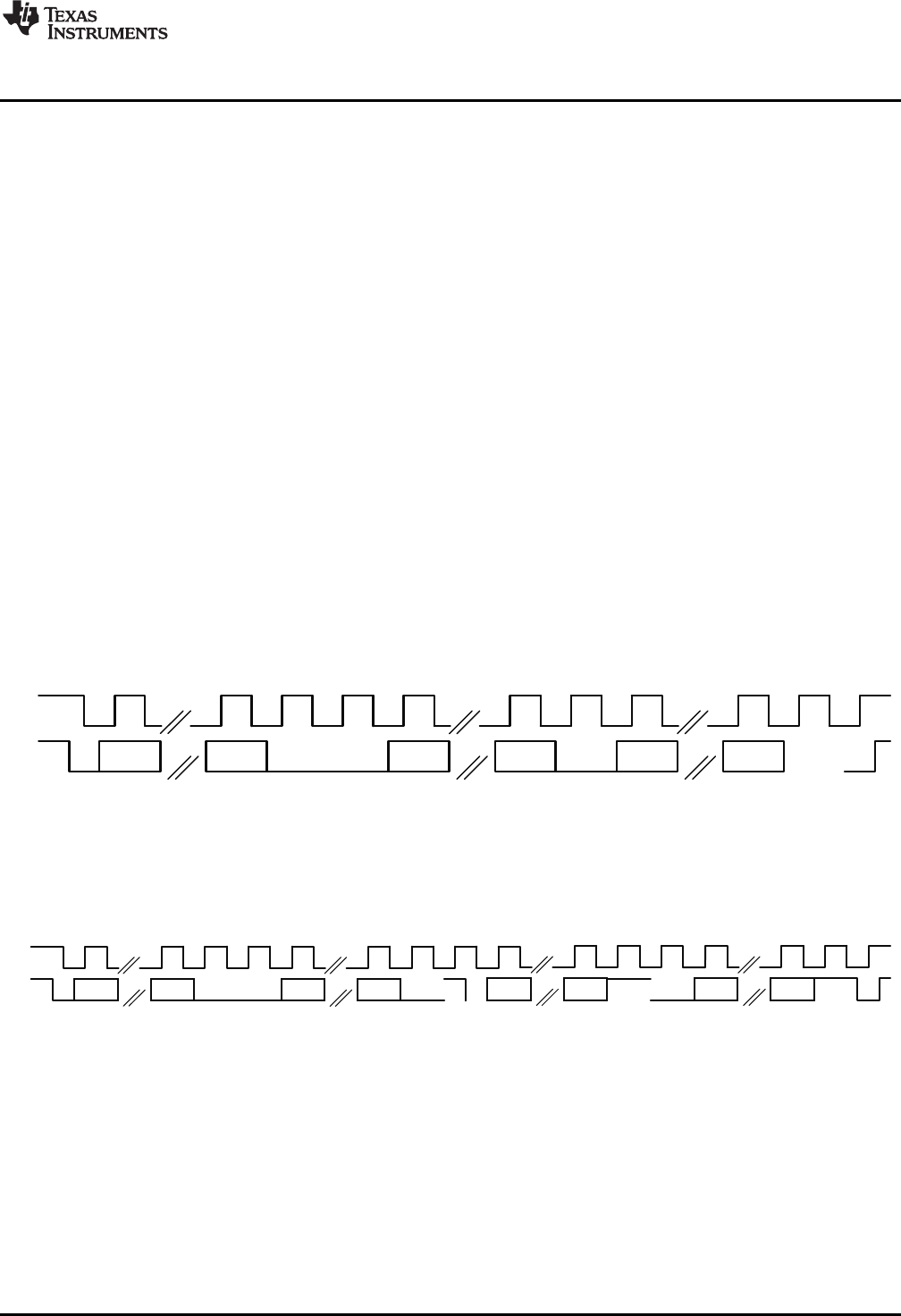

DecayTime

Target

Level

Input

Signal

Output

Signal

AGC

Gain

Attack

Time

ADC