U PD372_Floppy_Disk_Controller_Addendum_Apr77 PD372 Floppy Disk Controller Addendum Apr77

User Manual: uPD372_Floppy_Disk_Controller_Addendum_Apr77

Open the PDF directly: View PDF ![]() .

.

Page Count: 45

~EC

IlcrOcOlputers,

Inc.

ADDENDUM

TO

FLOPPY DISK CONTROLLER

USERS' MANUAL

FOR

MINIFLOPPyTM

APPLICATIONS

TM

-Shugart Associates

Five

Militia

Drive/Lexington,

Massachusetts

02173

Telephone (617) 862-6410

}LPD372

Telex 92-3434

TABLE

OF

CONTENTS

INTRODUCTION

MINIFLOPPY INTERFACE SIGNALS

RECORDING

FORMAT

DATA

CONDITIONER

SAMPLE

CONTROLLER

DESIGN

Hardware

Software

1

2

3

6

9

11

11

13

INTRODUCTION

The

discussion

and

design

shown

in

this

Addendum

is

dedicated

to

the

MinifloppyTM

Diskette

Storage

Drive.

This

drive

is

somewhat

different,

both

electrically

and

mechanically,

from

the

standard

floppy

disk

drives

found

throughout

the

industry.

The

Minifloppy

is

smaller,

less

expensive,

and

is

based

upon

the

same

floppy

disk

drive

technology

as

the

standard

floppy.

However,

its

data

transfer

rate

is

half

as

fast

and

its

total

data

storage

capacity

is

approximately

one-third.

This

design

uses

a

single

uPD372

Floppy

Disk

Controller

to

control

a

pair

of

Minifloppies.

The

interface

to

the

floppies

has

been

configured

so

as

to

allow

overlap-seeks

to

be

programmed.

If

only

a

single

drive

is

used

or

if

overlap-seeks

are

not

required,

then

two

or

three

logic

Ie's

may

be

removed

from

this

design.

The

controller's

architecture

remains

the

same

as

in

the

standard

floppy

design

shown

in

the

uPD372

Users'

Manual.

Before

proceeding

into

the

design

of

this

controller,

the

uPD372

Users'

Manual

should

be

read.

All

the

basic

concepts

and

characteristics

of

the

uPD372

are

explained

in

this

document,

and

it

will

be

assumed

that

the

reader

is

familiar

with

them.

For

clarity

in

this

document

the

uPD372

Users'

Manual

will

be

referred

to

as

Users'

Manual

and

this

document

referred

to

as

the

Addendum.

TM

--

Shugart

Associates

2

MINIFLOPPY INTERFACE SIGNALS

There

are

several

signals

which

have

been

deleted

in

the

Minifloppy

as

well

as

several

new

signals.

These

are

summarized

below:

Deleted

Signals

New

Signals

(Used

only

on

Standard

Floppy)

Head

Load

Index/Sector

write

Fault

Drive

Select

I

write

Fault

Reset

Drive

Select

2

Low

Current

Drive

Select

3

Sector

Motor

ON

Index

Ready

The

Head

Load

signal

has

been

deleted

in

the

Minifloppy.

The

head

is

loaded

concurrently

with

the

Motor

ON

signal.

write

Fault

and

Write

Fault

Reset

which

were

tests

of

the

Floppy's

status

prior

to

attempting

to

write

a

diskette,

have

both

been

eliminated.

Many

standard

floppies

(IBM

compatible)

have

a Low

Current

signal

which

allows

the

write

current

in

the

recording

head

to

be

decreased

on

tracks

44-76

--

this

signal

has

been

eliminated.

If

a

hard

sector

recording

format

is

used,

the

standard

floppies

provided

separate

signal

outputs

for

both

Sector

and

Index.

The

Minifloppy

requires

that

the

user

separate

these

signals

(this

is

usually

done

with

a

one-shot

circuit).

The

READY

command

in

the

standard

floppy

indicated

to

the

controller

that

a

diskette

had

been

inserted,

the

door

was

closed,

and

that

the

diskette

was

spinning;

this

signal

has

also

been

eliminated.

Three

separate

device

select

lines

are

provided

on

the

Minifloppy

and

the

appropriate

one

is

selected

by

the

use

of

hardware

straps

in

the

drive.

This

allows

a maximum

of

three

drives

to

be

selected

without

additional

decoding

hardware.

The

Minifloppy

uses

a

dc

motor

for

rotating

the

diskette,

a

separate

signal

called

MOTOR

ON

is

used

for

turning

the

motor

on.

In

order

to

increase

the

longevity

of

the

motor,

software

has

been

incorporated

in

the

controller

so

that

two

seconds

after

the

last

program

instruction,

the

motor

is

shut

off.

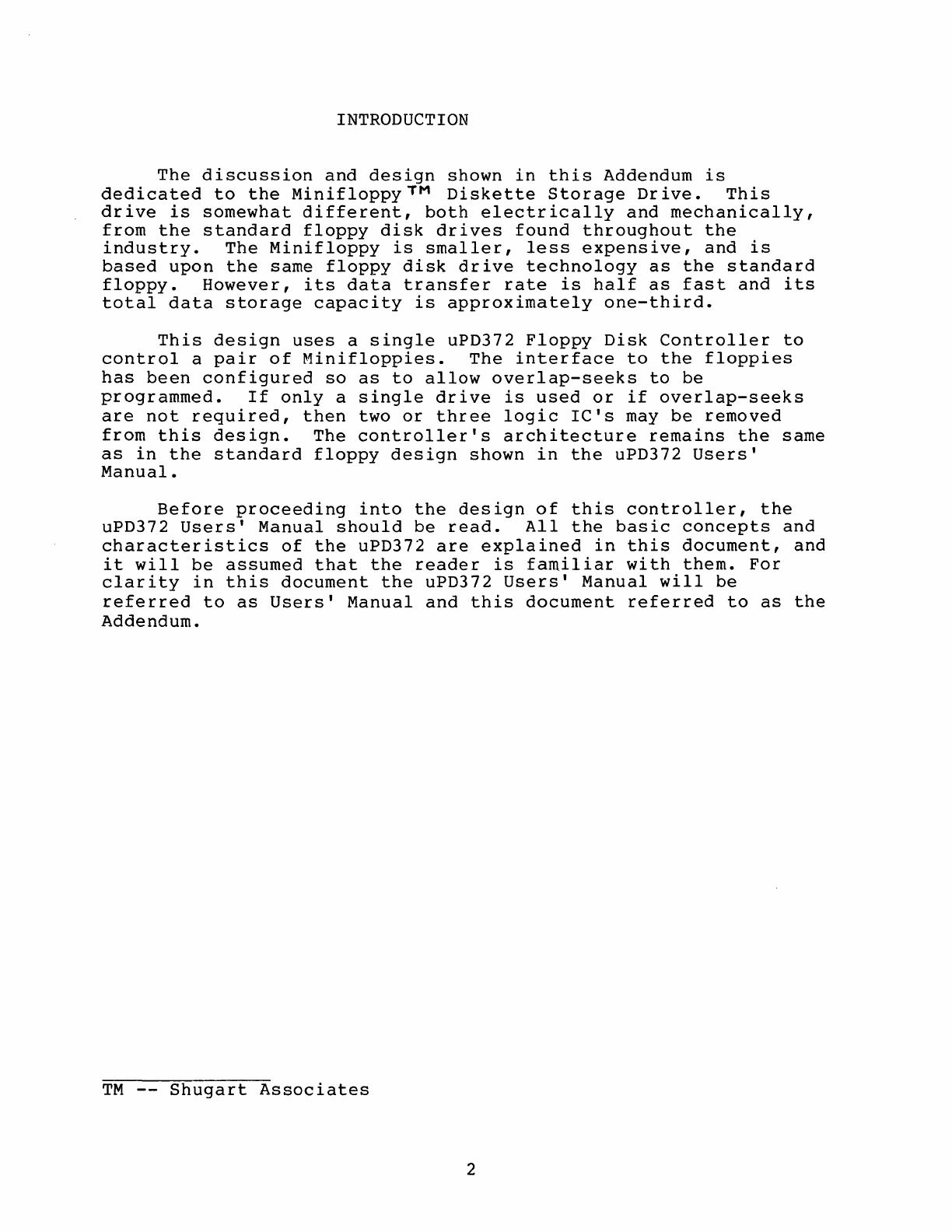

The

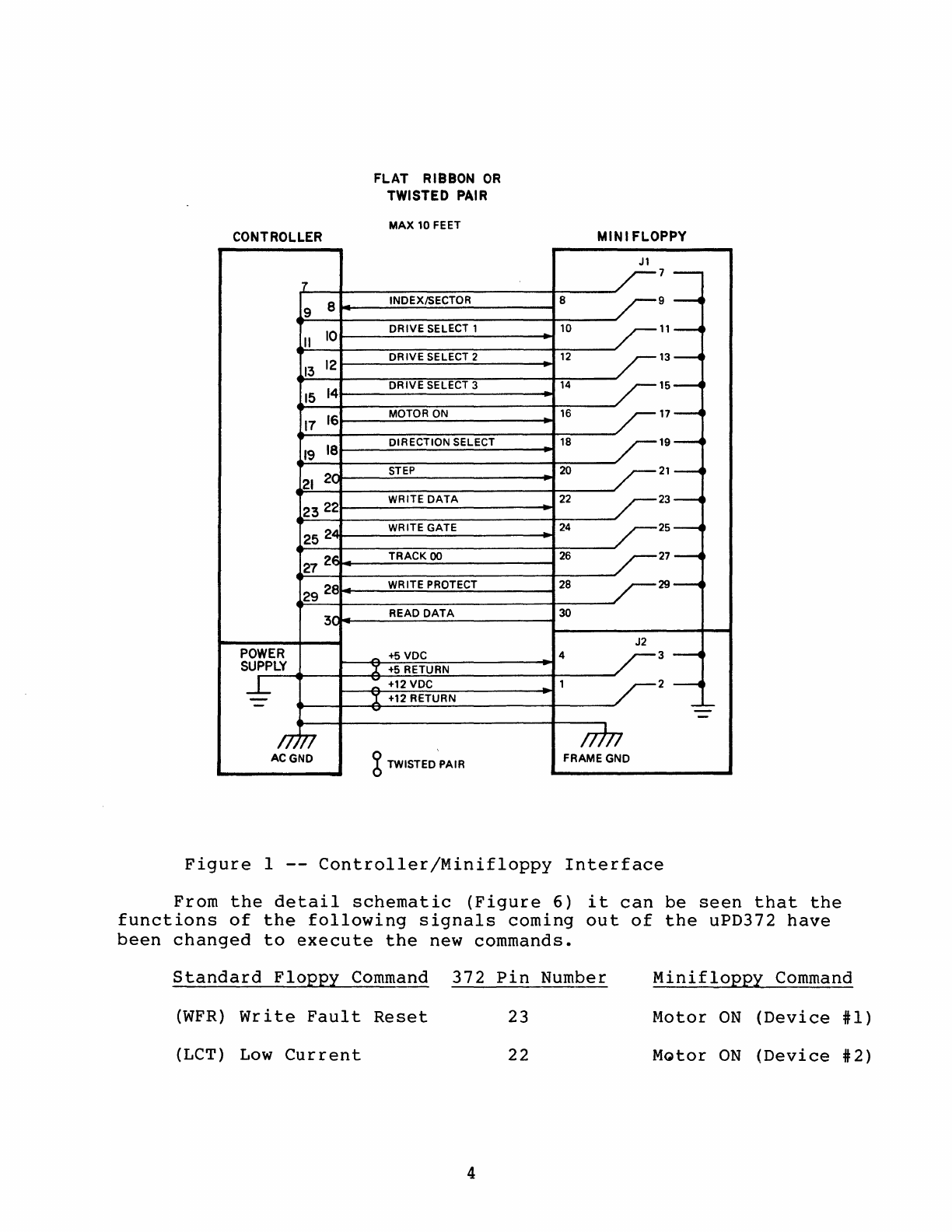

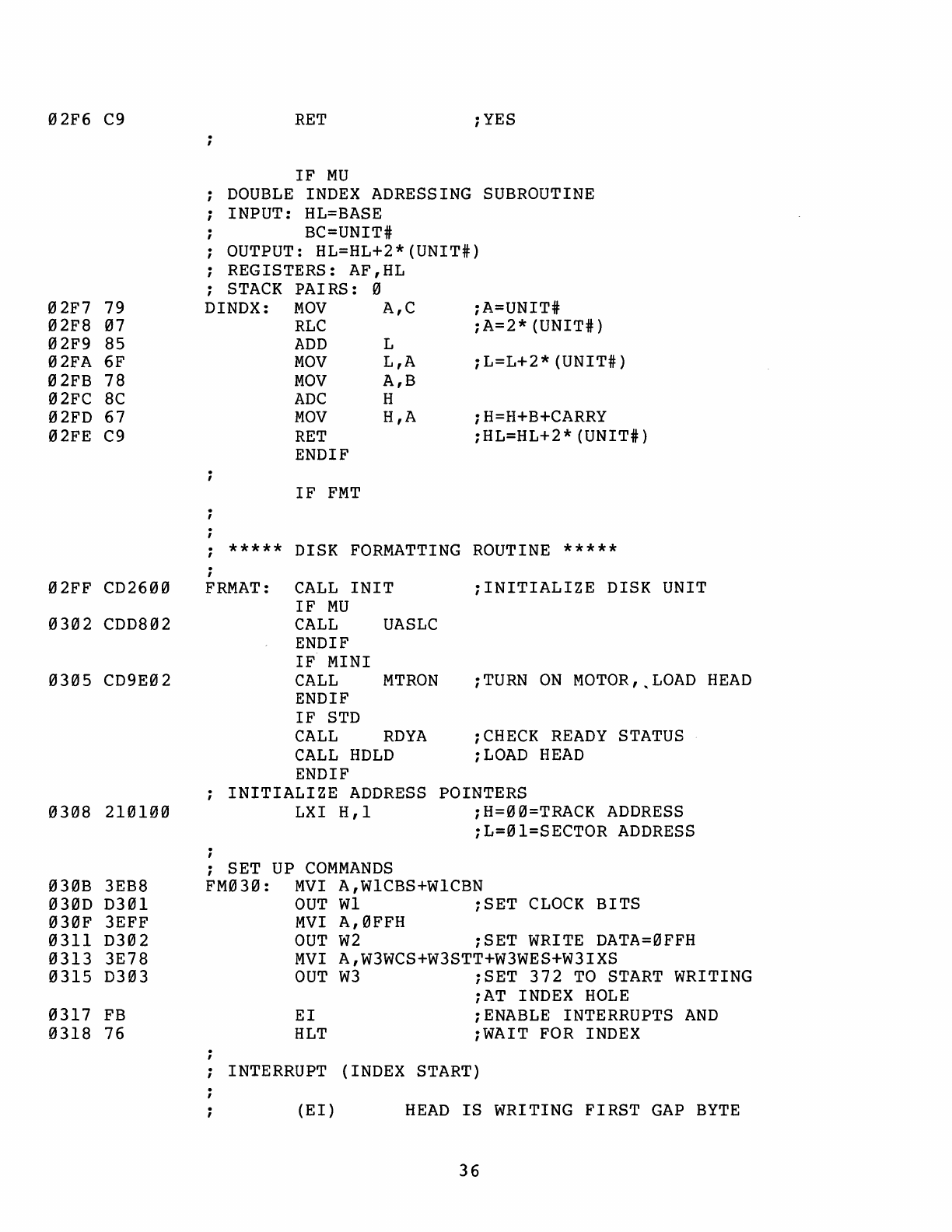

following

figure

shows

a

typical

interface

connection

between

the

controller

and

the

Minifloppy.

3

CONTROLLER

7

9 8

II

10

13

12

15

14

17 16

19

18

21

2C

23

22

25

2A

27

2'::

29

28

3'"

'W

POWER

SUPPLY

...L

-

ITI77

ACGND

FLAT

RIBBON

OR

TWISTED PAIR

MAX

10 FEET

INDEX/SECTOR

DRIVE SELECT 1

DRIVE SELECT 2

DRIVE SELECT 3

MOTOR

ON

DIRECTION SELECT

STEP

WRITE

DATA

WRITE GATE

TRACK 00

WR

ITE PROTECT

READ

DATA

'"

+5

VDC

X

+5

RETURN

;:: +12 VDC

I +12 RETURN

--

b TWISTED 'PAIR

MINI

FLOPPY

Jl

7-

8

9~

10

11~

12

13~

14

15~

16

17~

18

19-·

20

21-~

22

23_

24

25_

26

27_

28 29

----4

30

J2

4 3

----4

1 2

----4

~

-

nfn

FRAME GND

Figure

1

--

Controller/Minifloppy

Interface

From

the

detail

schematic

(Figure

6)

it

can

be

seen

that

the

functions

of

the

following

signals

corning

out

of

the

uPD372

have

been

changed

to

execute

the

new commands.

Standard

Floppy

Command

372

Pin

Number

Minifloppy

Command

(WFR)

write

Fault

Reset

23

Motor

ON

(Device

#1)

(LCT)

Low

Current

22 MQtor

ON

(Device

#2)

4

The

functional

performance

of

these

signals

is

changed

in

software

and

requires

no

change

to

the

uPD372

hardware.

The

uPD372

has

two

pairs

of

device

select

lines,

an

A

pair

and

a B

pair.

In

this

application

these

lines

have

been

configured

to

control

Qnly

two

Minifloppies.

The

A

pair

(UA0

and

UAl)

are

used

as

follows:

UA0

-

Select

Read/Write

Electronics

in

Drive

#1

UAI -

Select

Read/Write

Electronics

in

Drive

#2

The

B

pair

(UB0

and

UBI)

are

used

as

follows:

UB0

-

Select

Motion

Control

Electronics

in

Drive

#1

UBI -

Select

Motion

Control

Electronics

in

Drive

#2

Software

constraints

have

been

incorporated

so

that:

•

Only

one

Drive

may

be

Reading

or

Writing

at

a

time.

•

Only

one

Drive

may

be

Stepping

IN

or

OUT

at

a

time.

However,

it

is

possible

to

Read

or

Write

on

one

Drive

while

stepping

on

the

other.

This

is

done

by

selecting

UA0

• UBI

or

UAI • UB0.

When

two

Minifloppies

are

used,

connector

Jl

on

the

controller

should

be

connected

to

Drive

#1

and

J2

to

Drive

#2,

(Radial

busing

to

the

Drives).

This

should

be

done

in

order

to

keep

the

hardware

decoding

on

IC's

U50,

U5l,

U53

and

U17

the

same

as

the

software

listing.

5

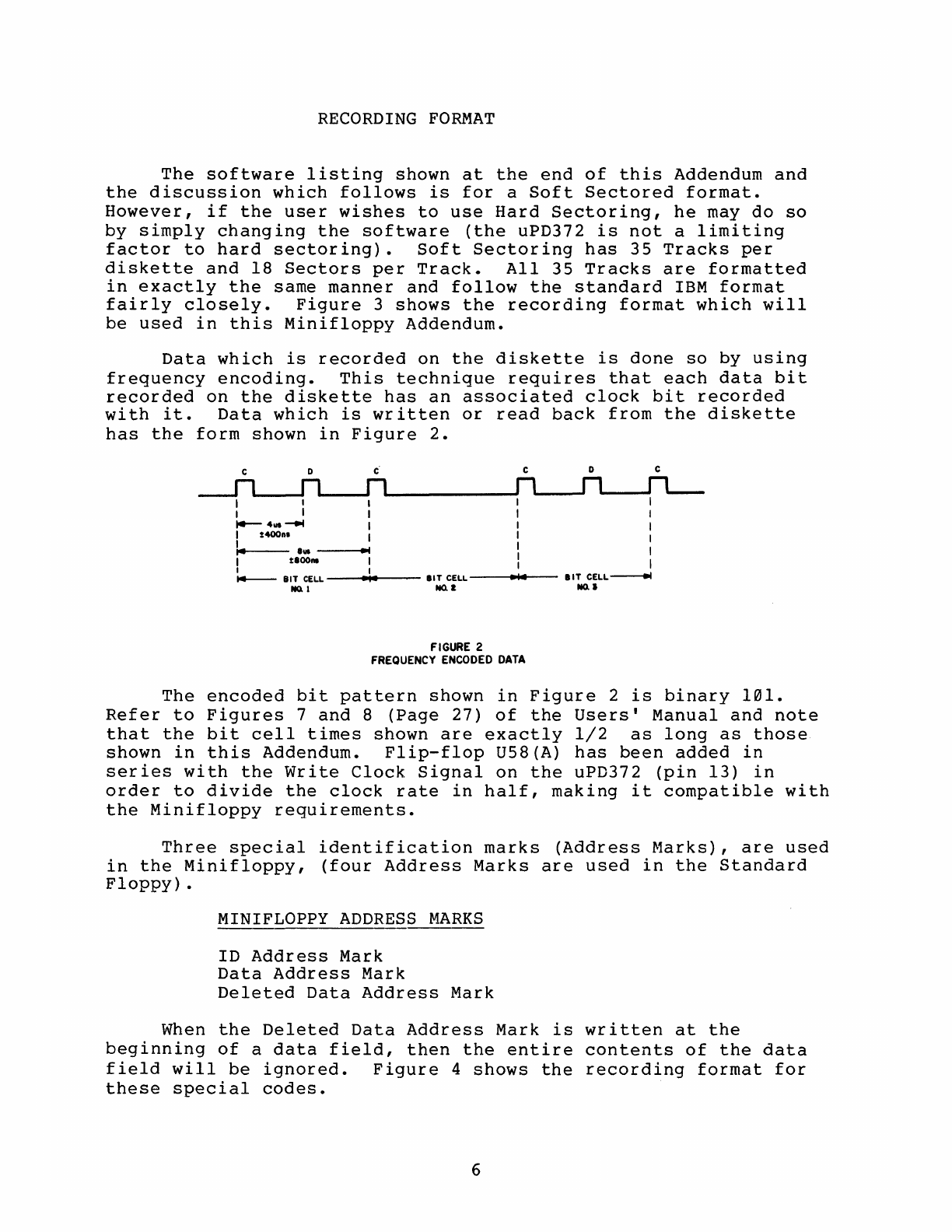

RECORDING

FORMAT

The

software

listing

shown

at

the

end

of

this

Addendum

and

the

discussion

which

follows

is

for

a

Soft

Sectored

format.

However,

if

the

user

wishes

to

use

Hard

Sectoring,

he

may

do

so

by

simply

changing

the

software

(the

uPD372

is

not

a

limiting

factor

to

hard

sectoring).

Soft

Sectoring

has

35

Tracks

per

diskette

and

18

Sectors

per

Track.

All

35

Tracks

are

formatted

in

exactly

the

same

manner

and

follow

the

standard

IBM

format

fairly

closely.

Figure

3

shows

the

recording

format

which

will

be

used

in

this

Minifloppy

Addendum.

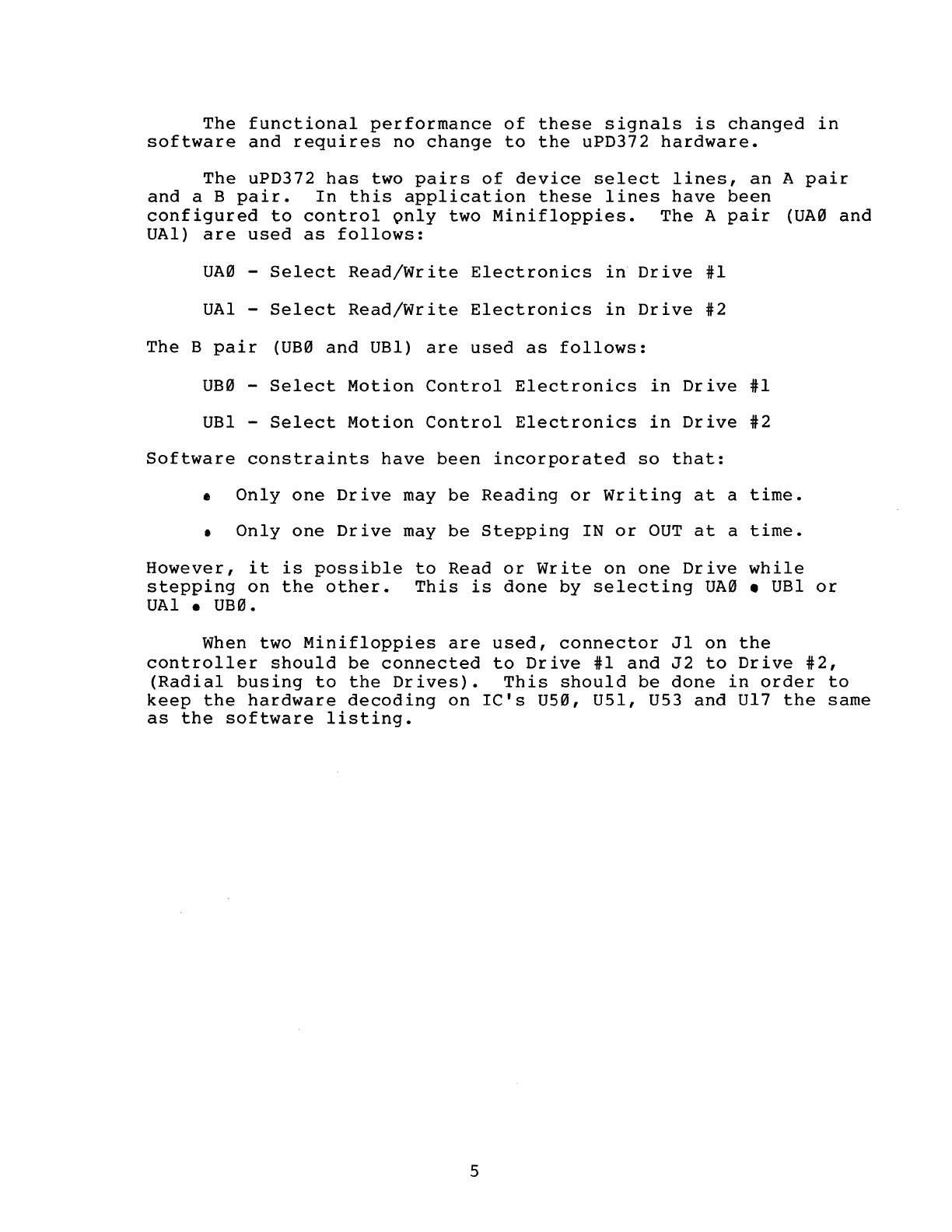

Data

which

is

recorded

on

the

diskette

is

done

so

by

using

frequency

encoding.

This

technique

requires

that

each

data

bit

recorded

on

the

diskette

has

an

associated

clock

bit

recorded

with

it.

Data

which

is

written

or

read

back

from

the

diskette

has

the

form

shown

in

Figure

2.

CDC'

CDC

--1l

n~

__

~n~

_________

n~

__

~n

rL--

I I I

I I I

~4111~

I

I

t~M

I

1~14_-

8U1

--~~

I

I

t800..

l I

.........-

BIT

CELL-----

....

'.--

liT

CELL-----t

.......

t---

liT

CELL----

NO.

1

NO.

I

NO.

I

FIGURE

2

FREQUENCY

ENCODED

DATA

The

encoded

bit

pattern

shown

in

Figure

2

is

binary

101.

Refer

to

Figures

7

and

8

(Page

27)

of

the

Users'

Manual

and

note

that

the

bit

cell

times

shown

are

exactly

1/2

as

long

as

those

shown

in

this

Addendum.

Flip-flop

U58(A)

has

been

added

in

series

with

the

Write

Clock

Signal

on

the

uPD372

(pin

13)

in

order

to

divide

the

clock

rate

in

half,

making

it

compatible

with

the

Minifloppy

requirements.

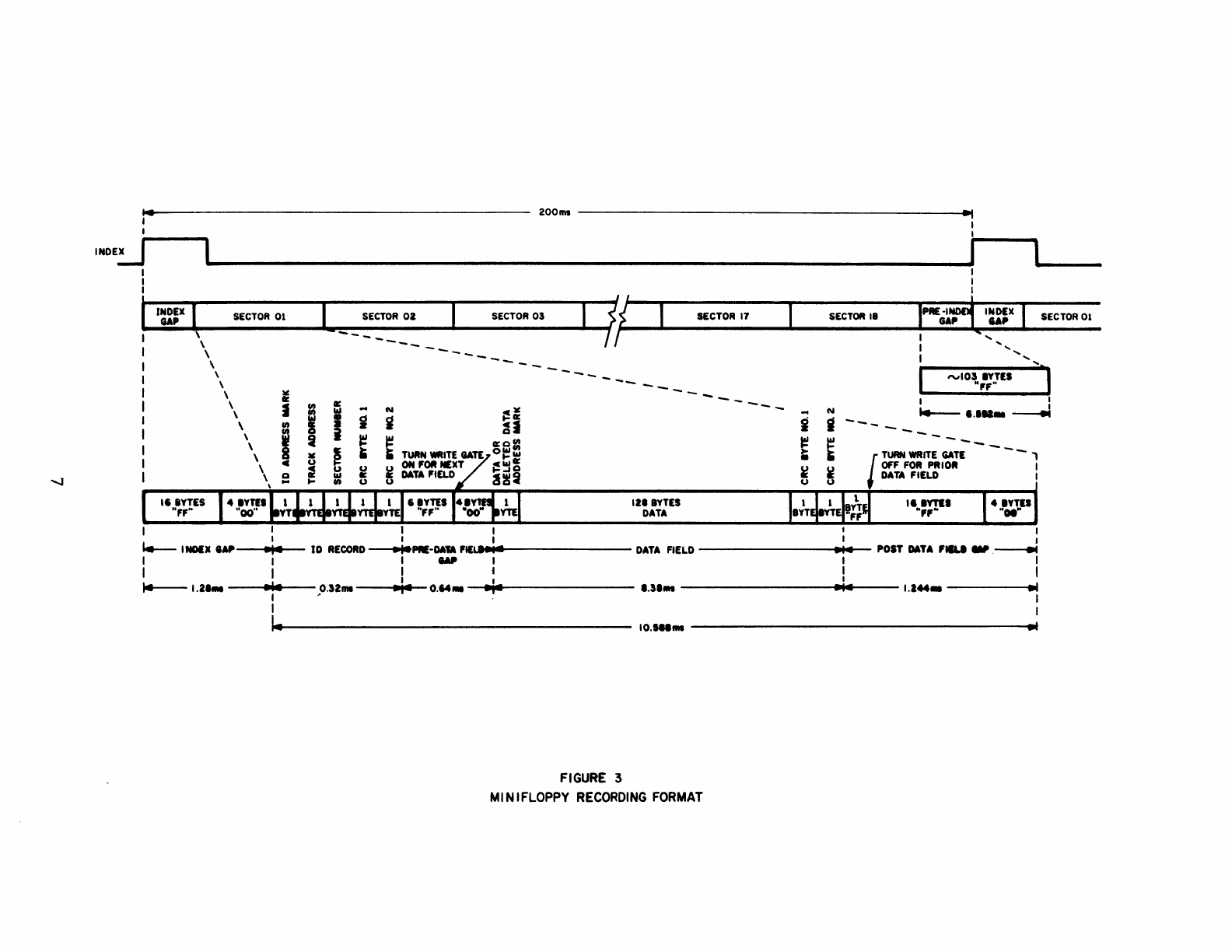

Three

special

identification

marks

(Address

Marks),

are

used

in

the

Minifloppy,

(four

Address

Marks

are

used

in

the

Standard

Floppy)

.

MINIFLOPPY

ADDRESS

MARKS

ID

Address

Mark

Data

Address

Mark

Deleted

Data

Address

Mark

When

the

Deleted

Data

Address

Mark

is

written

at

the

beginning

of

a

data

field,

then

the

entire

contents

of

the

data

field

will

be

ignored.

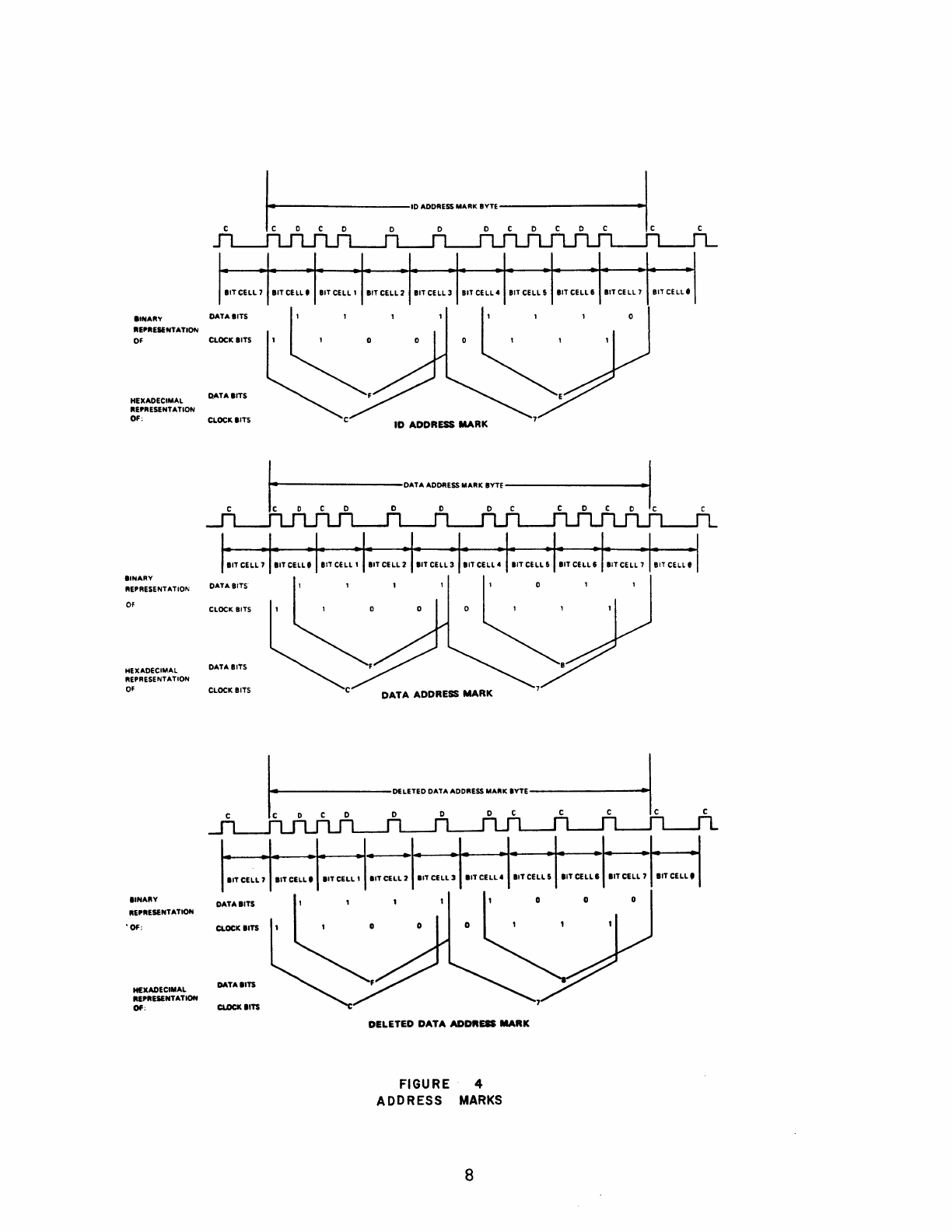

Figure

4

shows

the

recording

format

for

these

special

codes.

6

Ie

INOE~

I

I

I

,

,

\ \ \ ,

\

SECTOR

01

\

,

\ \ \ \ \

,

\

I

I

;

c

SECTOR

02

---

---

---

N

d i

•

~

i

~

200ms

--------------------------------------------------~~.

SECTOR

03

-----------

~~

~I

SECTOR

17

--

--------

IIIIYTES

DATA

--

SECTOR

18

I

I

'

....

.........

,

SECTOR

01

~tOS

InEI

>,

",,"

.

I I

N

a..--'

.•

II.

~

i

----

__

i

---

---

-,

~

l

I I I I

I I I J

I.--

INOIl

.»---iMM

...... -

10

RECORD

----...

...

-0..

'IELI

.....

~

.....

--------

DATA

FIELD

---------II

..

lIoIe..._-

POST

DATA

,

.....

IIP.____et

I I I

UP

I 1 I

I I I J I I

t--

I.al..

...

..

O.UtIII

...

0.641

..

_

......

11-

___________

'.SlMI

----------

............

---

1.144.

•

I I

I I

~~~---------------------------------------

10.~..

-----------------------------------------~

FIGURE

3

MI

N I

FLOPPY

RECORDING

FORMAT

BINARY

~:"IESENTATION

CLOCK8ITS

HEXADECIMAL

QATA 81TS

:~~RESENT

A

TlON

BINARY

REPRESENTATION

Of

HEXADECIMAL

~~PRESENTATION

BINARY

REPRESENTATION

'Of:

HExADECIMAL

:~RESENTATION

CLOCK BITS

CLOCK

81TS

OATA81TS

CLOCK

81TS

ID

ADDRESS

M"RK

8YTE

10

ADDRESS MARK

DATA

AODflE

SSMARK

8YTE

DATA ADDRESS MARK

DELETED OAT 7

A ADDRESS MARK

FIGURE

ADDRESS

4

MARKS

8

DATA

CONDITIONER

The

uPD372

contains

the

electronic

circuitry

for

separating

the

Data

and

Clock

pulses

out

of

the

Read

Data

signal.

However,

the

uPD372

does

require

some

external

circuitry

so

that

its

internal

registers

which

are

clocked

on

the

trailing

ed~e

of

02

will

be

presented

the

proper

data.

The

external

circuitry

for

accomplishing

this

is

called

a

"Data

Conditioner".

The

floppy

disk's

Read

Signal

is

asynchronous

with

the

microprocessors'

clocks.

The

Data

Conditioner

function

is

to

stretch

the

narrow

Read

Signal

pulses

from

the

floppy

so

that

they

will

overlap

the

microprocessor's

clock

interval,

allowing

them

to

be

strobed

into

the

uPD372.

The

Data

Conditioner

required

for

the

Minifloppy

is

much

simpler

than

that

required

for

the

Standard

floppies.

The

reason

being

that

the

bit

cell

time

is

twice

as

long,

namely

8us

vs.

4us;

thereby

eliminating

the

need

for

double

buffering

of

the

data.

The

conditions

and

requirements

mentioned

on

Pages

26,

27

and

28

of

the

Users'

Manual

are

still

applicable.

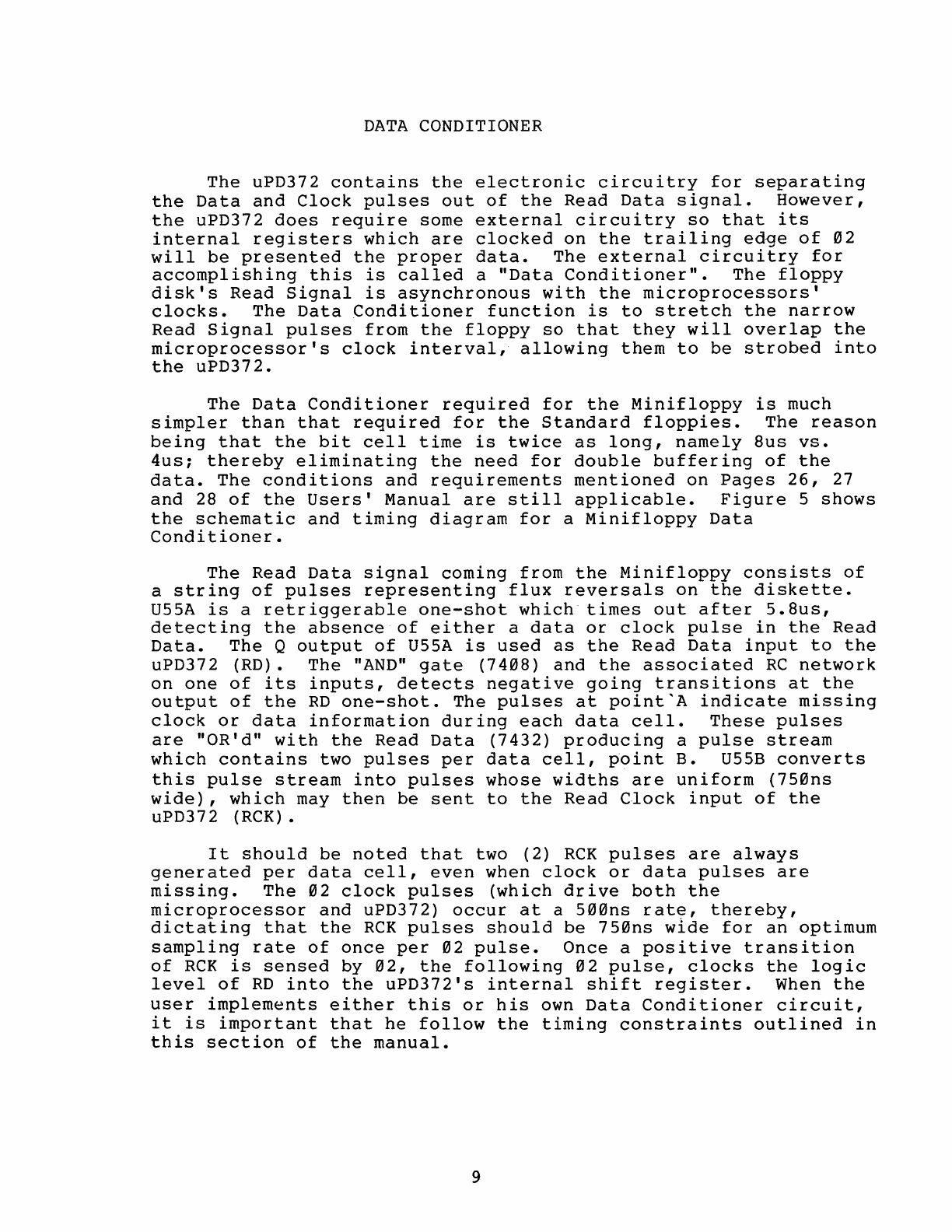

Figure

5

shows

the

schematic

and

timing

diagram

for

a

Minifloppy

Data

Conditioner.

The

Read

Data

signal

corning

from

the

Minifloppy

consists

of

a

string

of

pulses

representing

flux

reversals

on

the

diskette.

U55A

is

a

retriggerable

one-shot

which

times

out

after

5.8us,

detecting

the

absence

of

either

a

data

or

clock

pulse

in

the

Read

Data.

The

Q

output

of

U55A

is

used

as

the

Read

Data

input

to

the

uPD372

(RD).

The

"AND"

gate

(7408)

and

the

associated

RC

network

on

one

of

its

inputs,

detects

negative

going

transitions

at

the

output

of

the

RD

one-shot.

The

pulses

at

point'A

indicate

missing

clock

or

data

information

during

each

data

cell.

These

pulses

are

"OR'd"

with

the

Read

Data

(7432)

producing

a

pulse

stream

which

contains

two

pulses

per

data

cell,

point

B.

U55B

converts

this

pulse

stream

into

pulses

whose

widths

are

uniform

(750ns

wide),

which

may

then

be

sent

to

the

Read

Clock

input

of

the

uPD372

(RCK).

It

should

be

noted

that

two

(2)

RCK

pulses

are

always

generated

per

data

cell,

even

when

clock

or

data

pulses

are

missing.

The

02

clock

pulses

(which

drive

both

the

microprocessor

and

uPD372)

occur

at

a

500ns

rat~,

thereby,

dictating

that

the

RCK

pulses

should

be

750ns

wide

for

an

optimum

sampling

rate

of

once

per

02

pulse.

Once

a

positive

transition

of

RCK

is

sensed

by

02,

the

following

02

pulse,

clocks

the

logic

level

of

RD

into

the

uPD372's

internal

shift

register.

When

the

user

implements

either

this

or

his

own

Data

Conditioner

circuit,

it

is

important

that

he

follow

the

timing

constraints

outlined

in

this

section

of

the

manual.

9

READ

DATA

RD

RCK

0

0

+5V

+5V

220.n.

UPl

RCK

0 74123

750n.

READ

DATA------~----~~~_;C:::::::::::::::::~

______________________________

__

:tIOOn.

RD

~

CELL

DATA

---.,

I I

IC D

IC

--1l n n

I I I

I I I

I I I

I I

I I

I

--.J

: I

J I

I I I

I I

I.-

5.8us

I I I

I I

I I

I

I I I I I

I I I I

..

"'750ns

I I I

I

I I I I

I I I I

I

I I

I I

I

I I

I I

I I I

J n n

C D J

n n

r1

I I

, ,

LJ

I

-.:

I

I

I

I

d

--'

14-~

lOOn.

II

II

I

n

II

II

II

II

II

"--Il n

FIGURE

5

MINI-FLOPPY

DATA

CONDITIONER

J MISSING

CLOCK

PULSES

0 D

n n

n

,.,

I I

, ,

I

I

LJ LJ

I

I

I

I

I

I:

II

II

II

II

II

II

II

n n

II

II

II

II

II

fLJl "--Il n

~

rl

SAMPLE

CONTROLLER

DESIGN

Hardware

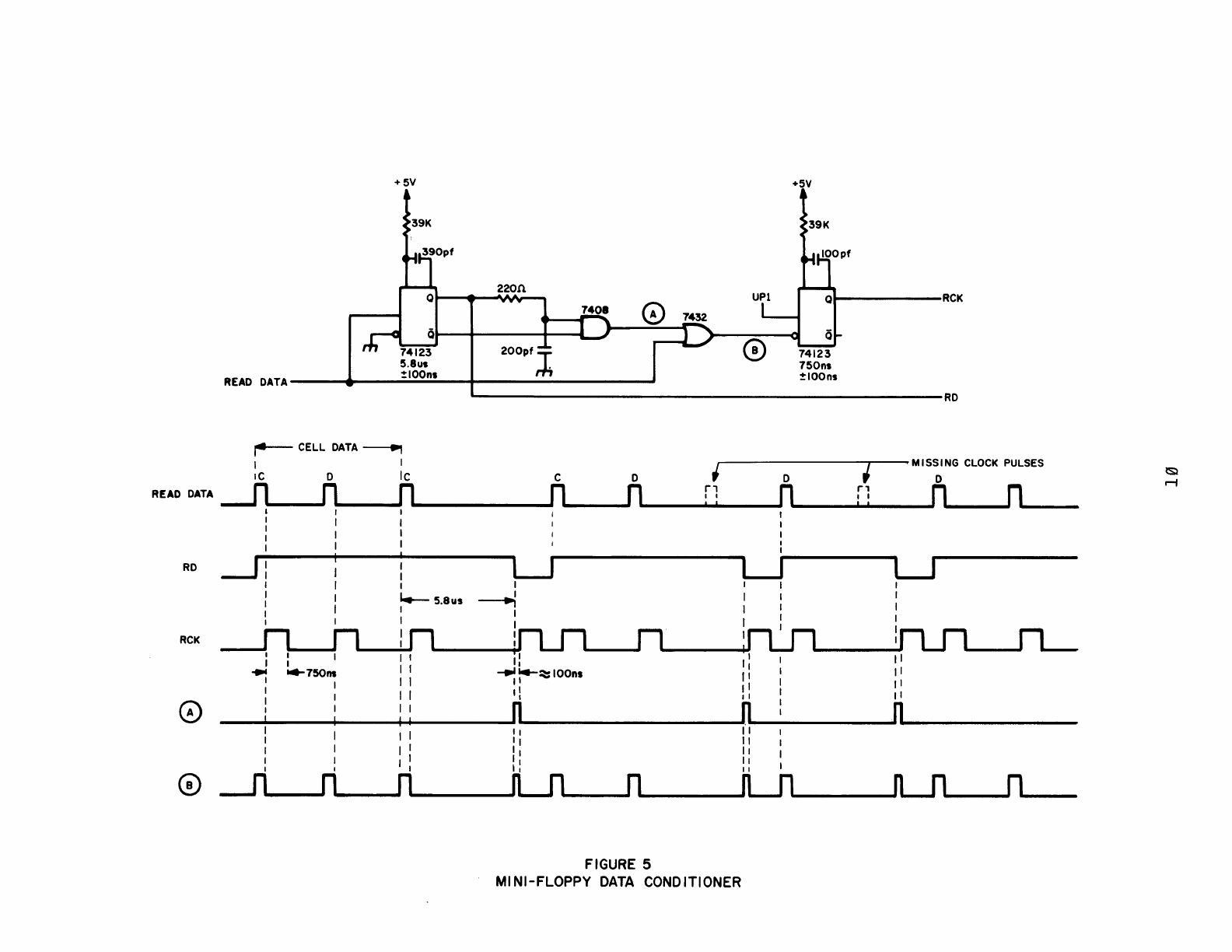

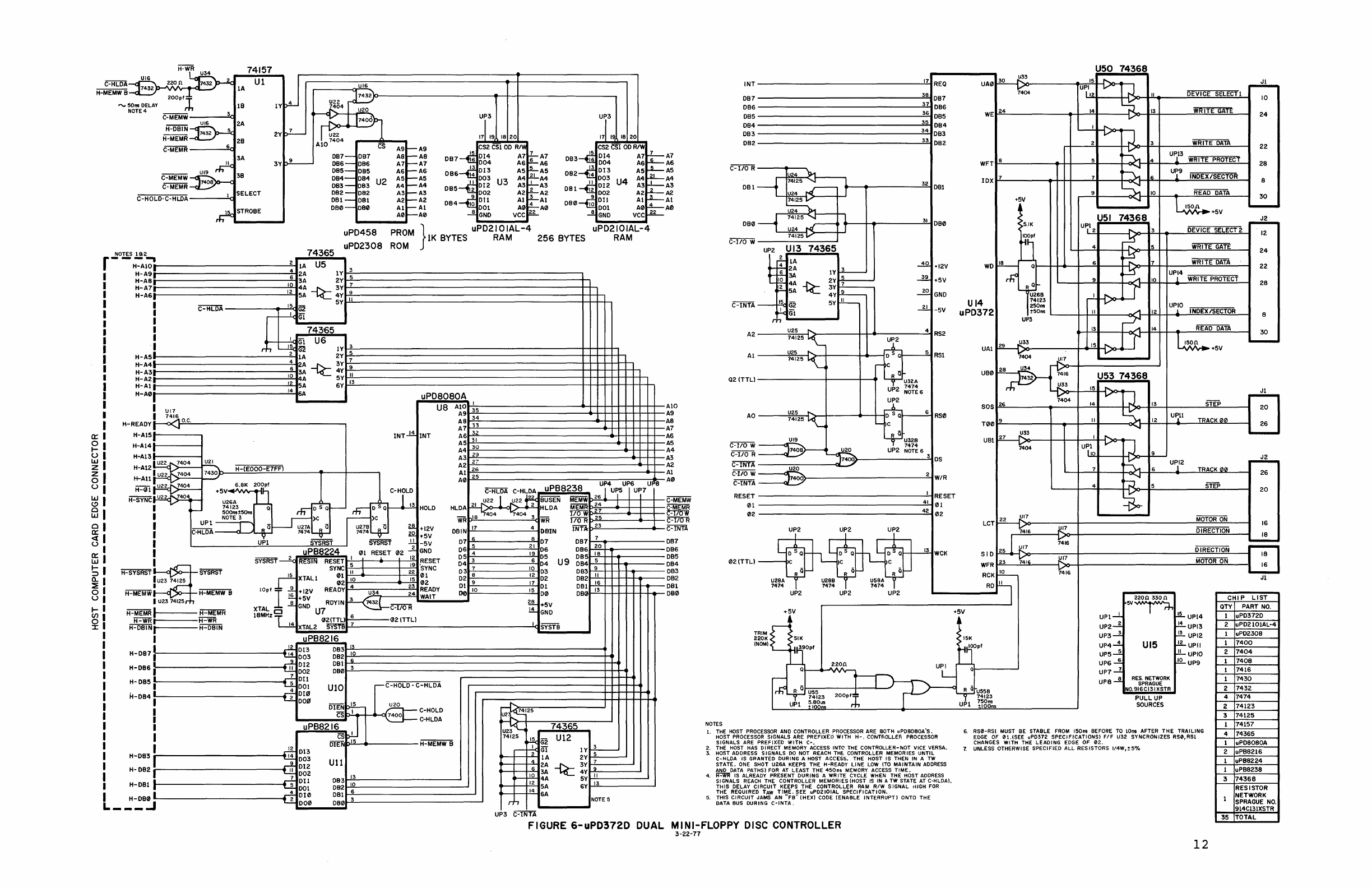

A

Controller

design

is

shown

in

Figure

6.

The

Controller

is

architectured

in

exactly

the

same

manner

as

shown

in

the

Users'

Manual

(reference

Pages

31-39).

The

connections

to

the

Minifloppies

are

done

through

connectors

Jl

and

J2

on

the

right-hand

side

of

the

schematic.

This

design

handles

only

two

drives.

However,

four

drives

could

be

accommodated

by

simply

decoding

the

UA0

and

UAI

as

well

as

the

UB0

and

UBI

lines

into

two

sets

of

four

lines.

The

figure

below

shows

how

this

may

be

achieved.

UAe

-------1

UAl

U

••

Ul1

2

TO

4

LINE

DECODER

2

TO

4

LINE

DECODER

t-------A1

....

------A2

t------

A3

.....

-----A4

1--------

11

1--------

82

1--------

83

1--------14

Figure

7

--

Multiple

Drive

Decoding

READ/WRITE

SELECT LINES

MOTION

CONTROL

SELECT

LI

NES

The

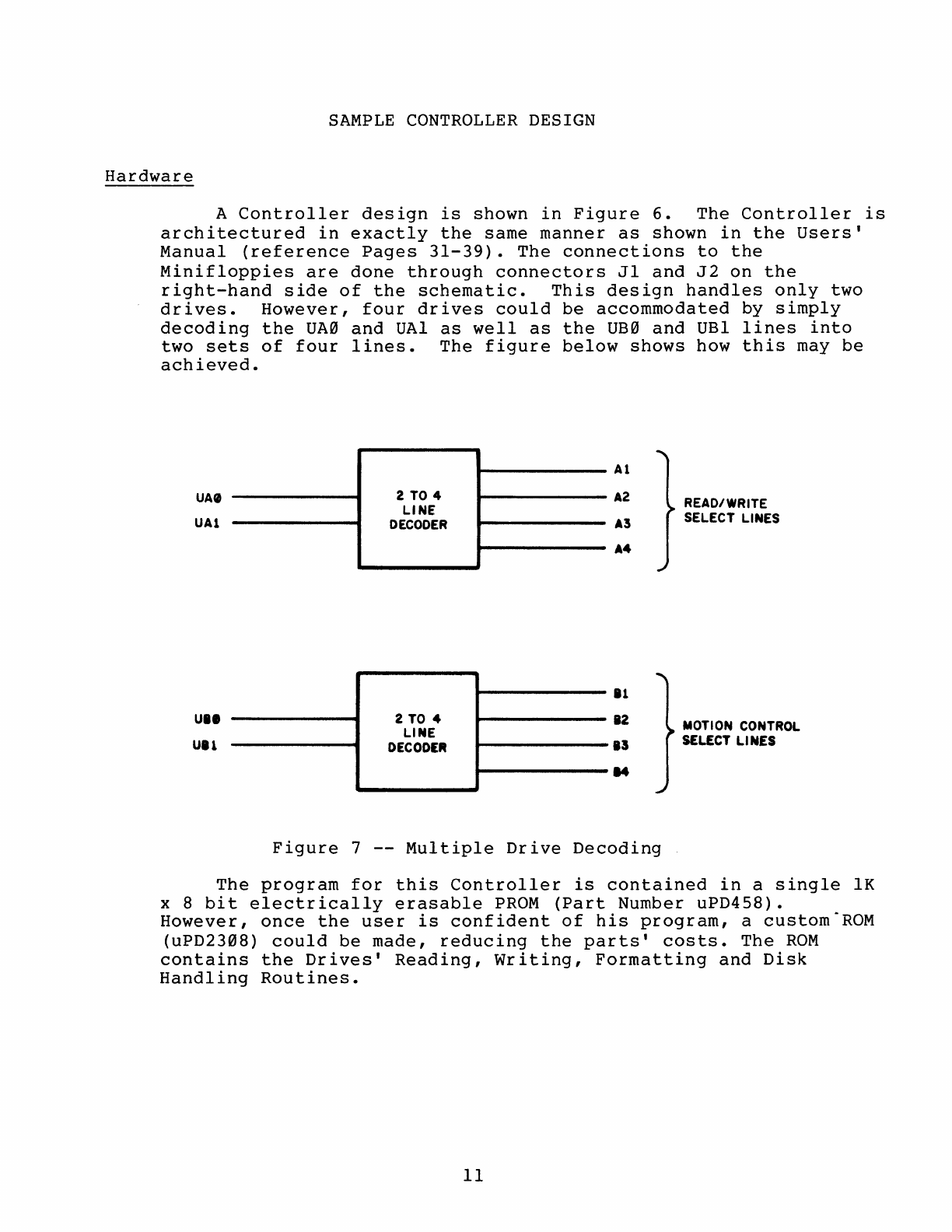

program

for

this

Controller

is

contained

in

a

single

lK

x 8

bit

electrically

erasable

PROM

(Part

Number

uPD458).

However,

once

the

user

is

confident

of

his

program,

a

custom·ROM

(uPD2308)

could

be

made,

reducing

the

parts'

costs.

The

ROM

contains

the

Drives'

Reading,

Writing,

Formatting

and

Disk

Handling

Routines.

11

a::

o

r-

u

w

z

z

o

u

w

t!)

a

w

a

a::

<t

u

a::

w

r-

;:)

a..

:!:

o

u

r-

oo

o

:z::

UP3 UP3

17 19

A9

A9

DB7 DB7

A8 A8

DB7

A7

7

A7

DB3

DB6 DB6

A7 A7

A6·

6 A6

DB5 DB5

A6 A6

DB6

A5

5

A5

DB2

DB4 DB4

U2

A5

A5

U3

A4

21

A4

U4

DB3 DB3

A4

A4

A3

I

A3

082

082

A3

A3

DB5

A2

2

A2

OBI

OBI

OBI

A2 A2

DB4

Al

3

Al

DB0

DB0 DB0

At

Al

A0

4

A0

A0

A0

VCC 22

uPD458 } uPD2101AL-4 uPD2101AL-4

PROM

lK

BYTES

RAM

256

BYTES

RAM

uPD2308

ROM

74365

NOTES

ta2

r----..

H-AIO.---------------------------~~

2

H-A9~--------------------------~

H-A8~--------------------------~~

H-A7~--------------------------~LI

H-A6.---------------------------~~

4

6

10

12

lA

U5

2A

IY

3A

2Y

4A

--ct=

3Y

5A

4Y

5Y

IS

G2

C-HLDA----------~~~

r-

r---J..cGi

I

Gl

"'"

~

G2

2

lA

H-A5.---------------------------~~

H-A4l---------------------------~~

4

2A

6

10

H-A3.-----------------------------~

H-A2~--------------------------~~

12

H-AI.---------------------------~

H-A0.---------------------------~

14

I

UI7

I

741~

H-READY

r:<l-0'C'

H-AI5

t---------,

H-AI41------~

H-AI3

t---------i

U22

7404

U21

3A

4A

5A

6A

743~5

U6

lY

2Y

3Y

--ct=

4Y

5Y

6Y

3

5

7

9

II

3

5

7

9

II

13

H-A12.:;;Of:::!404

7430}b-~H.:..-..!.(E::::O~0::..:0::..-..::E:..:.7.:..FF:...;1:...._

______

f_--__f----....,

H-Al1~

iHYNC~~~

U26A

I 74123

.r

Q

DSQ

DSQ

C-HOLO

13

HOLD

H-0Ie~

+5V

6.8K

2~0:Pf

I

"""""'

~g~~50nsl

)C

)C

I

UP1

I]

Q

U27A

Q

U27B

Q ?8 +12V

C-HLDA

-'"

R

7474

7474 =

I

Y.

~

+5V

I

UPI

SVSRST

SYSRST

1

-5V

I uPB8224

01

RESET

02

-=-

GND

I SYSRST

~

RrnN RESET !

::

RESET

H-SYSRST

~

-SYSRST

SYNC

II

1 I

22

'SYNC

IU237412S

r

XTALl

01

2

10

1

15

01

;

~

::!:..2.

0 4 23

02

H-MEMW -

ii=MEMWB

10pf I

-':<"1

9

6 +

12V

READY U34

24

READY

=

5V

WAIT

I

U23

7412Sr'l

8 + RDYIN

1-1---643;d

.

I XTAL

-"-

GND

U7

I

'--.l--C-IIO

R

H-MEMR

H-MEMR

18MI-!

CJ

H-WR

I

H-WR

.Z

T

02{TTLl

6

021TTLI

H-DBINI

H-DBIN

L-li~X~T.~AL~2~~S~Y~St~B~7------------------------------------~~~!.

____

.J

I uPB8216

I

r.!L

013

DB3

13

H-DB7~1------------------------__.~

003

DB2~10~--------------------------------------------------~

i

~

D81~£-6--------------------------------------------~rt

H-DB6

II

012

DB0 3

i

l

~D02

~----------------------------------------------~_r~

H-DB5

~

011

i

l

~

DOl

H-DB4.

~

~~~

OlEN

pJf-

U20

UIO

I

I

I

I

[

C-HOLDOC-HLDA

,.,.

I C-HOLD

L_

....

__

..

~.,:;r-I

.....

~7400

C-HLOA

uPB8216

CS

I

DIENIp-"IS"--

....

---------

H-MEMvi"B

I

~

DI3

H-oB3

r--------------------------

..

~

003

H-

oB2

r-------------------------

.....

rt

012

't....!!..

002

H-DBI

t--------------------------

..

~

011

~

001

H-

DB0

L-

________________________

.....

~

0 I 0

L

___

..J

L..::..

000

U11

DB3~13~--------------------~

DB2~10~----------------------~

081~6:....-----------------------~

DB0~3--------------------------~

~12S

~

U23

74125

~

G2

r---+lIT

4

lA

6

2A

~JQ.

~~

12

5A

14

6A

74365

U12

lyrL---

2Y

5

3Y :

~~I-!'-II----------....I

6Y

13

,

NOTE

5

n

__

.....

__

_

UP3

C-INTA

A7

A6

A5

A4

A3

A2

Al

A0

INT

DB7

OB6

DB5

DB4

OB3

DB2

OBI

DB0

A2

Al

Q2

(TTL)

AO

C-J10

W

C-I/O

R

C-lNTA

C-1I0 W

C-INTA

RESET

01

02

021TTL)

17

REQ

3B

DB7

37 DB6

36 DB5

35

DB4

34

DB3

33 DB2

U24

~

74125~

32

_[U24

~

J OBI

74125

~

74125~~

31

DB0

~r

74125

CO~lc

~~3

74365

~

ri-

2A

lY

rL---

+12V

r!-3A

2Y S

~

~

4A

+5V

~

5A

~

3Y 7 22-

4Y

~

GNO

A 5Y ..!L--.

-

G2

....ll

~

Gi

-5V

rn

U25

4

RS2

74125

"'--

~

U25

"

74125

~

RS1

C

R II

U32A

UP2 7474

NOTE

6

\t

U25

" RS0

74125

~

R Q

~

U32B

_=:J740~~

7474

UP2

NOTE

6

-

7~

3

OS

~

:J740~

2 W/R

I RESET

41

01

42

02

U~2 U~2

U~2

~WCK

)C

)C

C

RQ

RQ

RQ

UZ8A

U28B

U58A

7474 7474 7474

UP2 UP2 UP2

UA0

30

~3

~04

WE

24

WFT 8

lOX

7

+5V

~

:

5.1K

~

WD

r1q

U26B

UI4

74123

250.,

uPD372

:50

..

UP3

UAI

29

~33

r=--1?404

28

U34

UB0

7432

SOS

26

T00

9

27

~3

UBI

';;04

LCT 22

~7

~16

2s1

~7

SID

WFR

[23 "10:;

RCK

rL2-

RO~

U50

74368

15

-t>o-n

~

U~112

II DEVICE SELECT!

~

10

14 13

wRlf~

GATt:

24

~1.

----!.

2 3 WRITE

DATA

22

5

~

4

U'{3

WRITE PROTECT

28

7

~

6

Ui

9

INDEX/SECTOR

8

~

READ

DATA

9

10

30

I

150.11.

-

y +5V

USI

74368

~

U~12

""

3 DEVICE

SELECT2

12

4 " 5 WRITE GATE

24

~

6 7

WRITE

DATA

~A

22

UPI4

1 WRITE PROTECT

9

10

28

~J

,..1.

UPIO

II

A

12

1 INDEX ISECTOR S

G

13

14

READ

DATA

30

~

IS

~

--

+5V

~7

~16

U5374368

/;!!3

15

~

.....:!l....

1'::04

14

13

STEP

20

~

U'(I

II

12

TRACK

00

26

--

I

-J>o-.j

UPI

LIO

9

~

~

U7

2

7 6 TRACK

00

26

4

~

5 STEP

20

~

MOTOR

ON

16

~7

DIRECTION

18

7416

-

DIRECTION

18

~7

MOTOR

ON

I

16

7416

Jl

2200

330 0

CHIP

LIST

QTY PART

NO.

+5V

+5V

UPI-L

5V~

r!L

UPI4

1

uP0372D

""fj

~

UP2...1.

~UPI3

UP3...l.

r!L

UPI2

20K •

511<

15K

UP4....!.

UI5

r!L

UPII

UP5 2

rll-

UPIO

NOMI

tloPf tlPf

220n.

UP6

-2. flL UP9

~

rO

'"

'"

UP7.2

T "-

UPS.....§.

RES.

NETWORK

J

RQU~B

SPRAGUE

R Q

U55

200

P

fi

NO.916CI3IXSTR

74123

74123

PULL

UP

UPl

~'I~~'!

750""

UPl

!IOOns

SOURCES

NOTES

1.

THE

HOST

PROCESSOR

AND

CONTROLLER

PROCESSOR

ARE

BOTH

uPD8080A'S.

HOST

PROCESSOR

SIGNALS

ARE

PREFiXED

WITH

H-.

CONTROLLER

PROCESSOR

SIGNALS

ARE

PREFIXED

WITH

C-.

2.

THE

HOST

HAS

DIRECT

MEMORY

ACCESS

INTC

THE

CONTROLLER-NOT

VICE

VERSA.

3.

HOST

ADDRESS

SIGNALS

DO

NOT

REACH

THE.

CONTROLLER

MEMOR

IES

UNTIL

C-HLDA

IS

GRANTED

DURING

A

HOST

ACCESS.

THE

HOST

IS

THEN

IN

A

TW

STATE.

ONE

SHOT

U26A

KEEPS

THE

H-READY

LINE

LOW

(TO

MAINTAIN

ADDRESS

AND

DATA

PATHS)

FOR

AT

LEAST

THE

450n5

MEMORY

ACCESS

TIME.

4.

H-WR

IS

ALREADY

PRESENT

DURING

A

WRITE

CYCLE

WHEN

THE

HOST

ADDRESS

SIGNALS

REACH

THE

CONTROLLER

MEMORIES

(HOST

IS

IN

A

TW

STATE

AT

C-HLDAI.

THIS

DELAY

CIRCUIT

KEEPS

THE

CONTROLLER

RAM

R/W

SIGNAL

HIGH

FOR

THE

REQUIRED

TAW

TIME.

SEE

uPD210lAL

SPECIFICATION.

S.

THIS

CIRCUIT

JAMS

AN

"FB"

(HEX)

CODE

(ENABLE

INTERRUPT)

ONTO

THE

DATA

BUS

DURING

C-INTA.

6. RS0-RSI

MUST

BE

STABLE

FROM

150

..

BEFORE

TO

IOns

AFTER

THE

TRAILING

EDGE

OF

01.1SEE

uPD372

SPECIFICATIONSI

flF

U32

SYNCRONIZES

RS0,RSI

CHANGES

WITH

THE

LEADING

EDGE

OF

02.

7.

UNLESS

OTHERWISE

SPECIFIED

ALL

RESISTORS

114W,!5%

2

uPD21OIAL-4

1

uP02308

1

7400

2

7404

1

7408

1

7416

1

7430

2

7432

4

7474

2

74123

3

74125

1

74157

4

74365

uP080S0A

2

uPB8216

1

uPB8224

1

uPB8238

3

74368

RESISTOR

NETWORK

SPRAGUE

NO.

914C131XSTR

35

TOTAL

FIGURE

6-uPD372D

DUAL MINI-FLOPPY DISC CONTROLLER

3-22-71

12

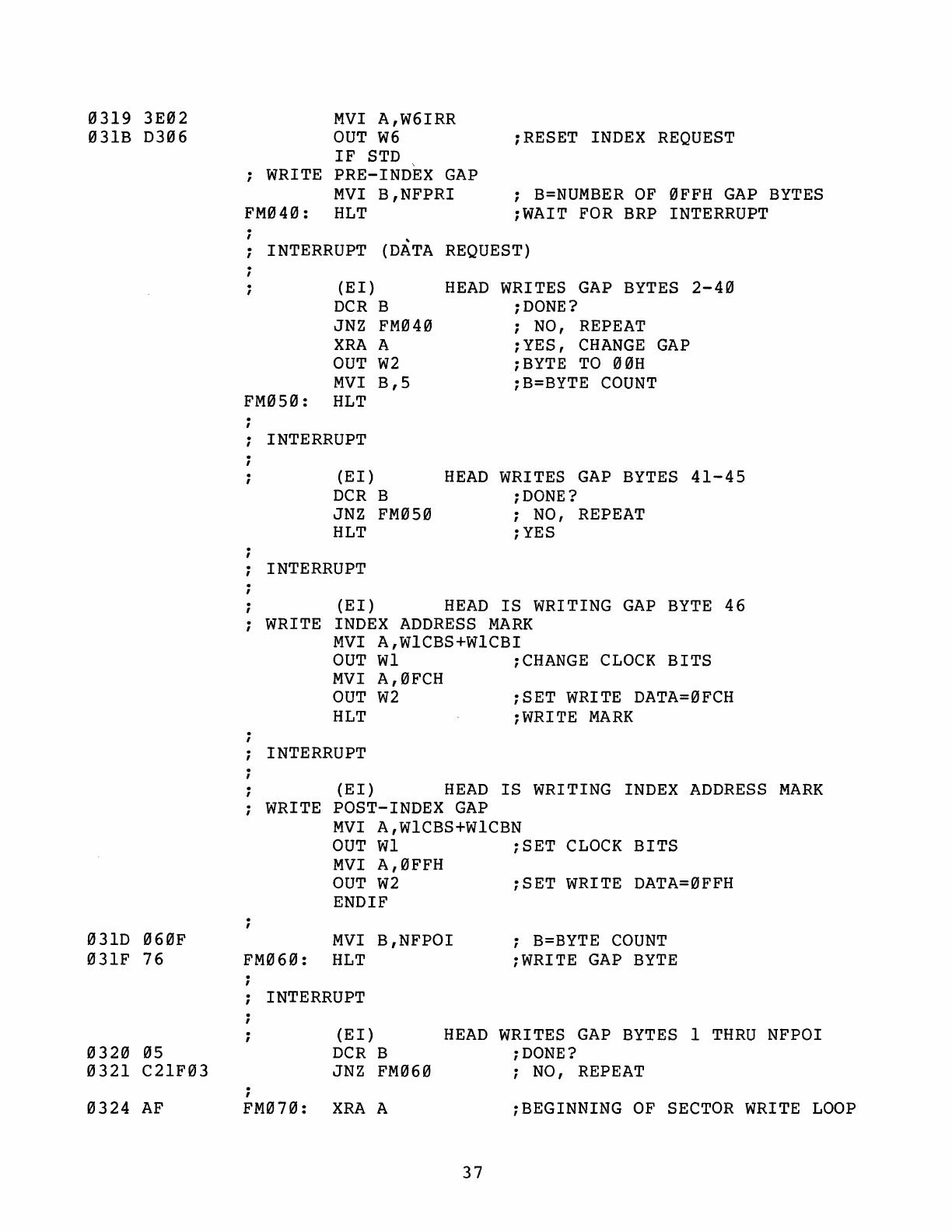

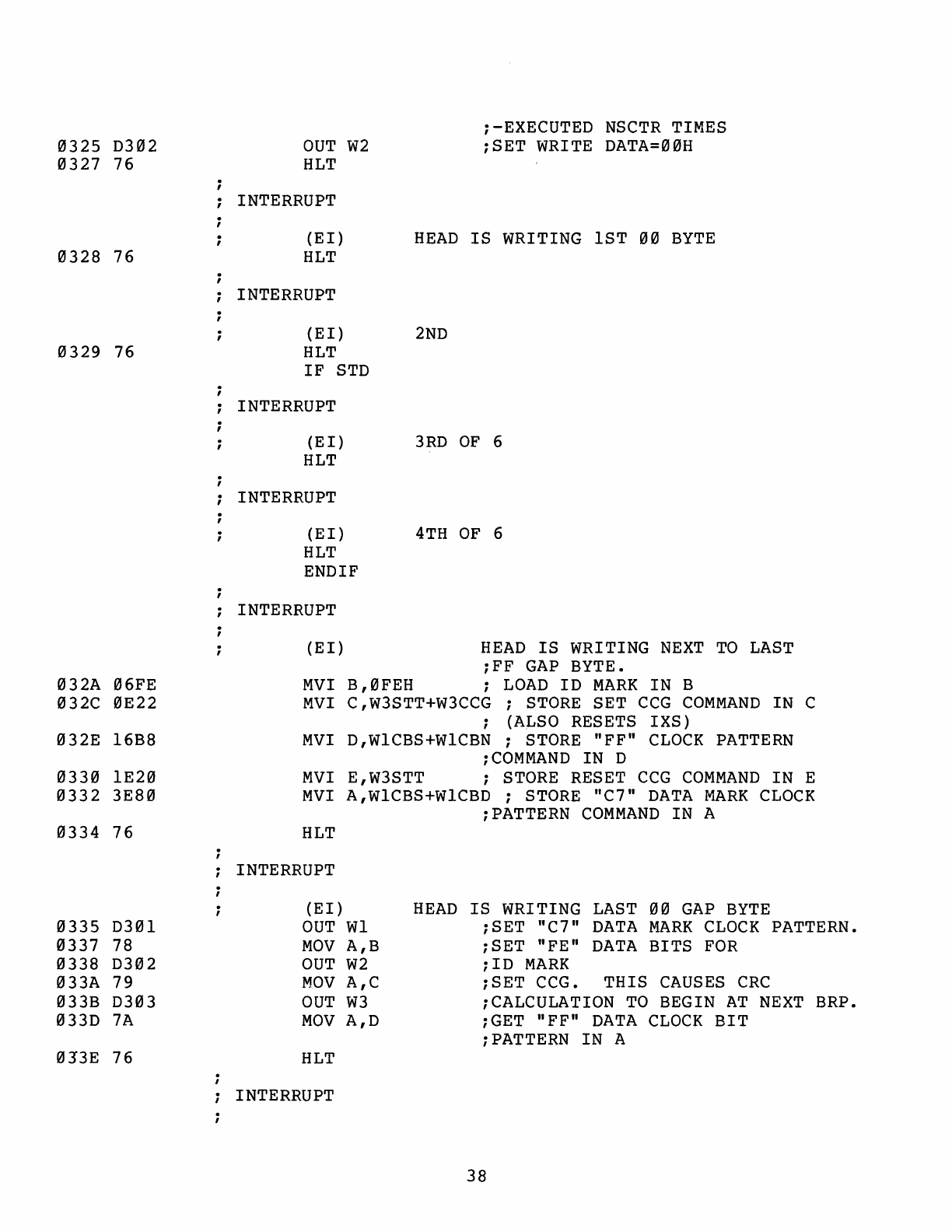

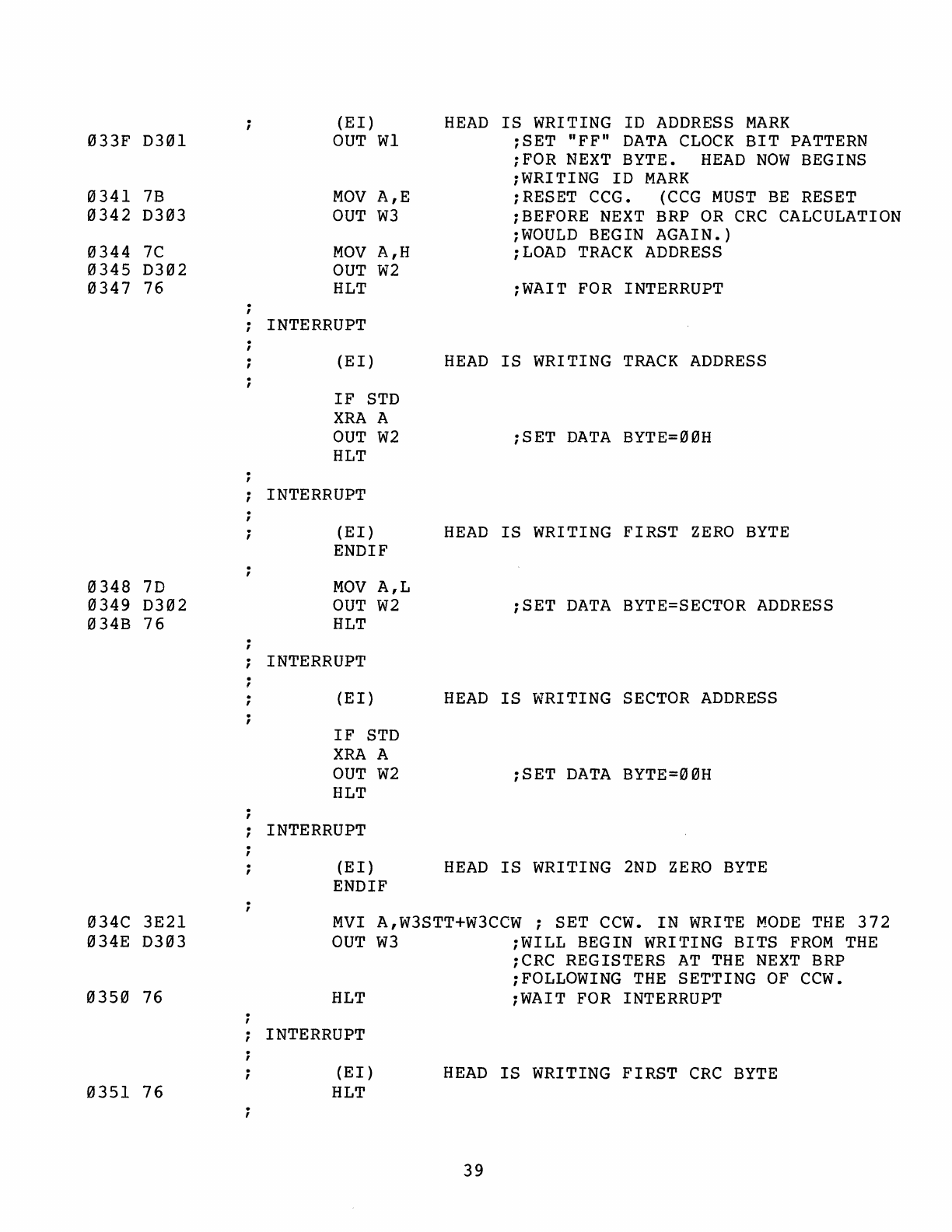

Software

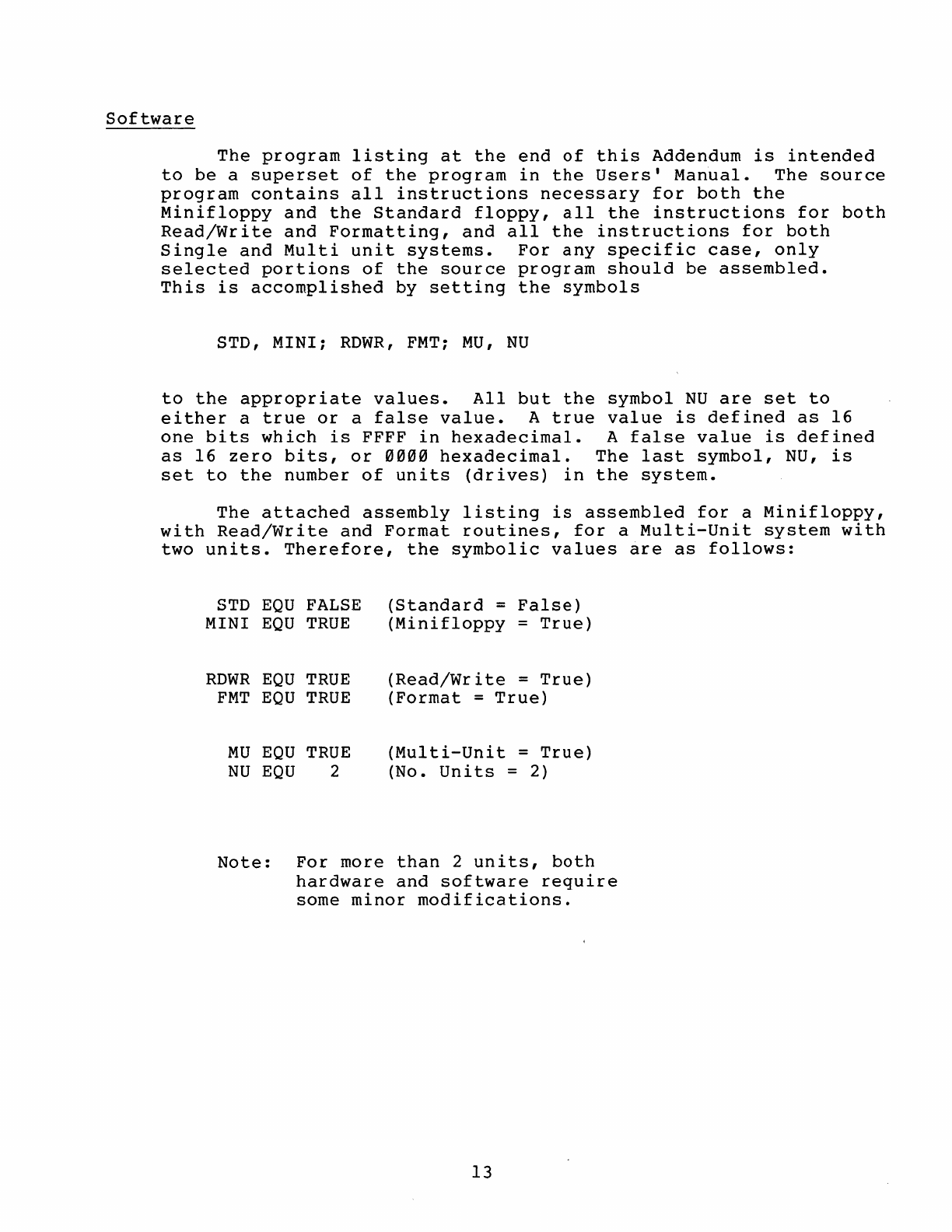

The

program

listing

at

the

end

of

this

Addendum

is

intended

to

be

a

superset

of

the

program

in

the

Users'

Manual.

The

source

program

contains

all

instructions

necessary

for

both

the

Minifloppy

and

the

Standard

floppy,

all

the

instructions

for

both

Read/Write

and

Formatting,

and

all

the

instructions

for

both

Single

and

Multi

unit

systems.

For

any

specific

case,

only

selected

portions

of

the

source

program

should

be

assembled.

This

is

accomplished

by

setting

the

symbols

STD,

MINI:

RDWR,

FMT:

MU,

NU

to

the

appropriate

values.

All

but

the

either

a

true

or

a

false

value.

A

true

one

bits

which

is

FFFF

in

hexadecimal.

as

16

zero

bits,

or

0000

hexadecimal.

set

to

the

number

of

units

(drives)

in

symbol

NU

are

set

to

value

is

defined

as

16

A

false

value

is

defined

The

last

symbol,

NU,

is

the

system.

The

attached

assembly

listing

is

assembled

for

a

Minifloppy,

with

Read/Write

and

Format

routines,

for

a

Multi-Unit

system

with

two

units.

Therefore,

the

symbolic

values

are

as

follows:

STD

EQU

FALSE

(Standard

=

False)

MINI

EQU

TRUE

(Minifloppy

=

True)

RDWR

EQU

TRUE

(Read/Write

=

True)

FMT

EQU

TRUE

(Format

=

True)

MU

EQU

TRUE

(Multi-Unit

=

True)

NU

EQU

2

(No.

Units

=

2)

Note:

For

more

than

2

units,

both

hardware

and

software

require

some

minor

modifications.

13

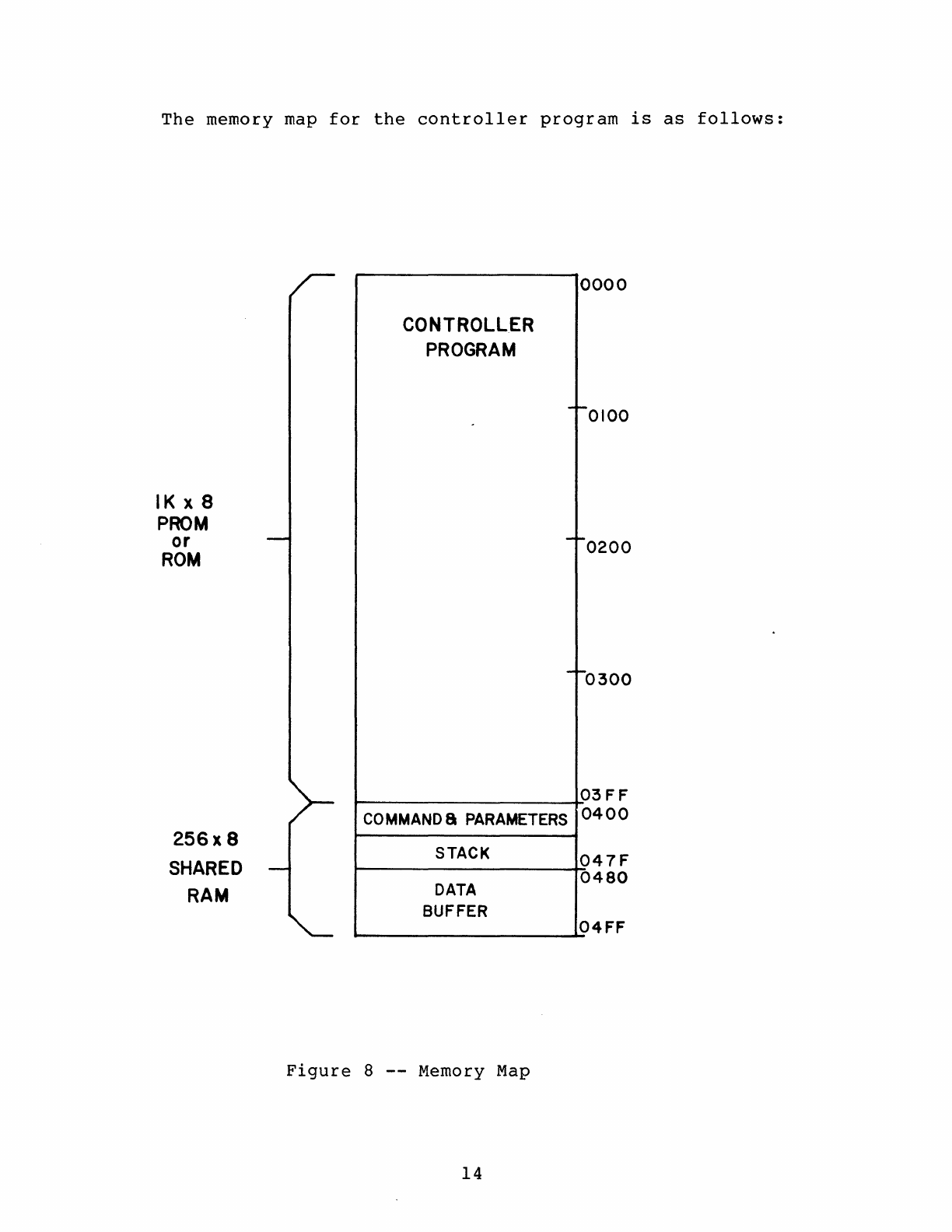

The memory

map

for

the

controller

program

is

as

follows:

IK X 8

PROM

or

ROM

25Sx8

SHARED

RAM

0000

CONTROLLER

PROGRAM

--

0100

--

0200

--.

0300

0

COMMAND

a

PARAMETERS

3FF

0400

STACK

DATA

BUFFER

Figure

8

--

Memory

Map

14

0

0

0

47F

480

4FF

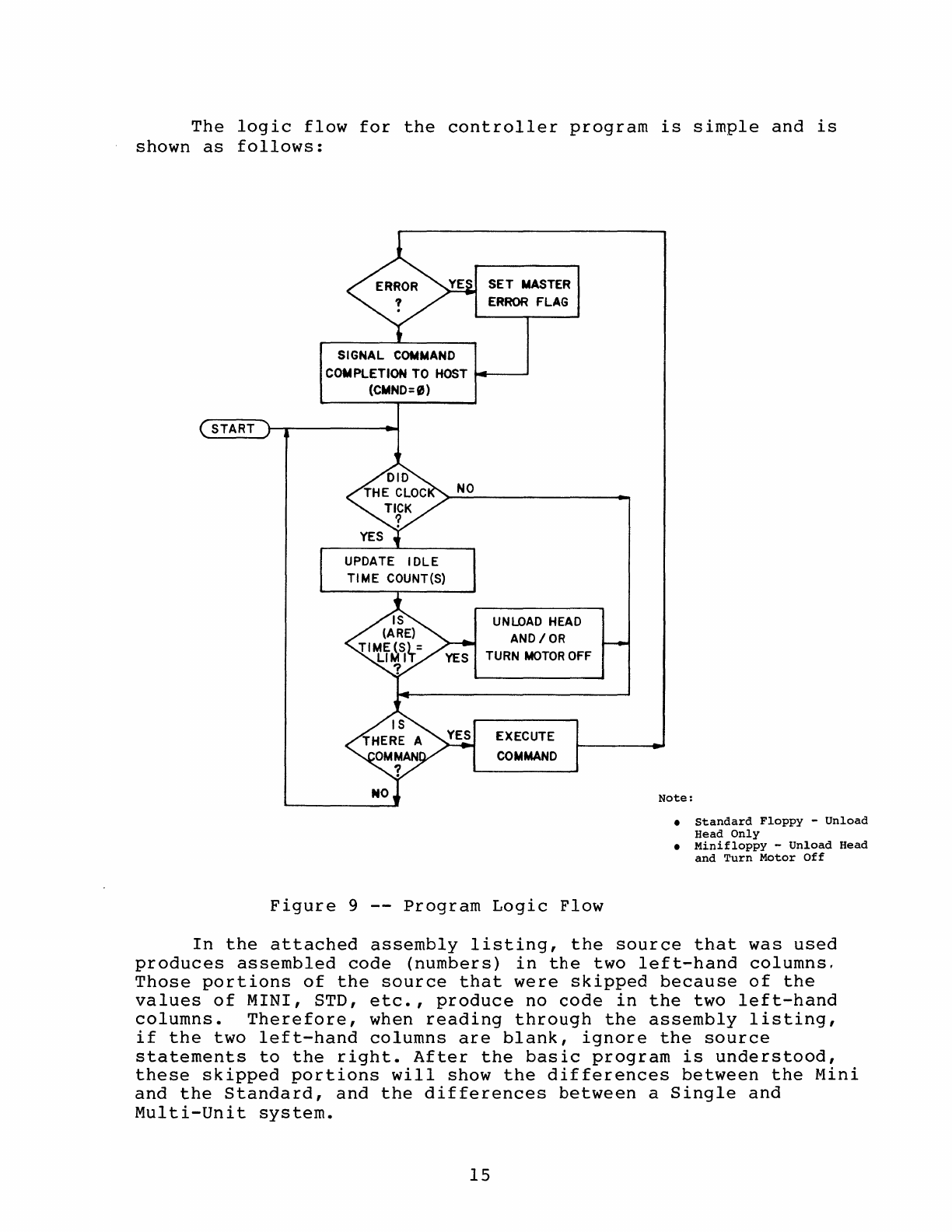

The

logic

flow

for

the

controller

program

is

simple

and

is

shown

as

follows:

START

SET

MASTER

ERROR

FLAG

SIGNAL

COMMAND

COMPLETION TO HOST .......

-~

(CUND=0)

UNLOAD HEAD

AND/OR

TURN

MOTOR

OFF

EXECUTE

COMMAND

Figure

9

--

Program

Logic

Flow

Note:

•

Standard

Floppy

-

Unload

Head

Only

•

Minifloppy

-

Unload

Head

and

Turn

Motor

Off

In

the

attached

assembly

listing,

the

source

that

was

used

produces

assembled

code

(numbers)

in

the

two

left-hand

columns.

Those

portions

of

the

source

that

were

skipped

because

of

the

values

of

MINI,

STD,

etc.,

produce

no

code

in

the

two

left-hand

columns.

Therefore,

when

reading

through

the

assembly

listing,

if

the

two

left-hand

columns

are

blank,

ignore

the

source

statements

to

the

right.

After

the

basic

program

is

understood,

these

skipped

portions

will

show

the

differences

between

the

Mini

and

the

Standard,

and

the

differences

between

a

Single

and

Multi-Unit

system.

15

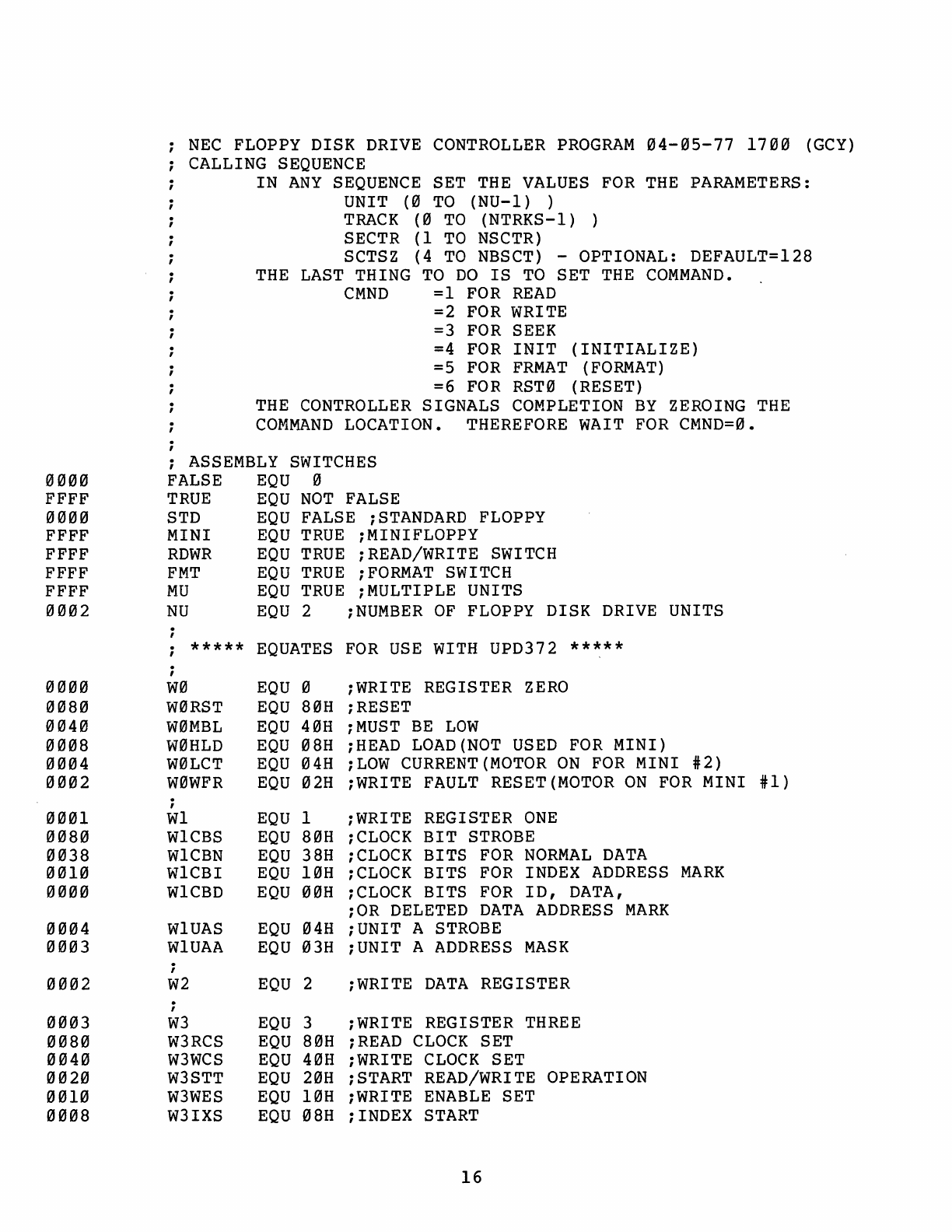

NEC

FLOPPY DISK DRIVE

CONTROLLER

PROGRAM

04-05-77

1700

(GCY)

CALLING

SEQUENCE

IN

ANY

SEQUENCE

SET

THE

VALUES

FOR

THE

PARAMETERS:

UNIT (0

TO

(NU-l)

)

TRACK

(0

TO

(NTRKS-1) )

SECTR

(1

TO

NSCTR)

i SCTSZ (4

TO

NBSCT) -OPTIONAL: DEFAULT=128

THE

LAST

THING

TO

DO

IS

TO

SET

THE

COMMAND.

CMND

=1 FOR

READ

=2 FOR WRITE

=3 FOR SEEK

=4 FOR

INIT

(INITIALIZE)

=5

FOR

FRMAT

(FORMAT)

=6

FOR

RST0 (RESET)

THE

CONTROLLER

SIGNALS COMPLETION

BY

ZEROING

THE

i

COMMAND

LOCATION. THEREFORE

WAIT

FOR

CMND=0.

i

ASSEMBLY

SWITCHES

0000

FALSE

EQU

0

FFFF

TRUE

EQU

NOT

FALSE

0000

STD

EQU

FALSE

iSTANDARD

FLOPPY

FFFF MINI

EQU

TRUE

iMINIFLOPPY

FFFF

RDWR

EQU

TRUE

iREAD/WRITE

SWITCH

FFFF

FMT

EQU

TRUE

iFORMAT

SWITCH

FFFF

MU

EQU

TRUE

iMULTIPLE UNITS

0002

NU

EQU

2

iNUMBER

OF

FLOPPY DISK DRIVE UNITS

0000

0080

0040

0008

0004

0002

0001

0080

0038

0010

0000

0004

0003

0002

0003

0080

0040

0020

0010

0008

i

i *****

EQUATES

FOR

USE

WITH

UPD372 *****

i

W0

W0RST

W0MBL

W0HLD

W0LCT

W0WFR

i

WI

WICBS

WICBN

WICBI

WICBD

WIUAS

WIUAA

i

W2

i

W3

W3RCS

W3WCS

W3STT

W3WES

W3IXS

EQU

0

EQU

80H

EQU

40H

EQU

08H

EQU

04H

EQU

02H

EQU

1

EQU

80H

EQU

38H

EQU

10H

EQU

00H

EQU

04H

EQU

03H

EQU

2

EQU

3

EQU

80H

EQU

40H

EQU

20H

EQU

10H

EQU

08H

iWRITE REGISTER

ZERO

iRESET

iMUST

BE

LOW

iHEAD

LOAD(NOT

USED

FOR

MINI)

iLOW

CURRENT

(MOTOR

ON

FOR

MINI

#2)

iWRITE

FAULT

RESET

(MOTOR

ON

FOR

MINI

iWRITE REGISTER

ONE

iCLOCK

BIT

STROBE

iCLOCK

BITS

FOR

NORMAL

DATA

iCLOCK

BITS

FOR

INDEX

ADDRESS

MARK

iCLOCK

BITS

FOR

ID,

DATA,

iOR DELETED

DATA

ADDRESS

MARK

iUNIT

A STROBE

iUNIT

A

ADDRESS

MASK

iWRITE

DATA

REGISTER

iWRITE REGISTER

THREE

iREAD

CLOCK

SET

iWRITE

CLOCK

SET

iSTART READ/WRITE OPERATION

iWRITE

ENABLE

SET

iINDEX START

16

#1)

0004

0002

0001

0004

0080

0040

0020

0004

0003

0006

0004

0002

0001

0000

0080

0040

0030

0008

0004

0002

0001

0001

0080

0040

0020

0010

0008

0004

0003

0002

0003

0023

0012

0080

07D0

0028

000A

0008

0006

000F

0006

0011

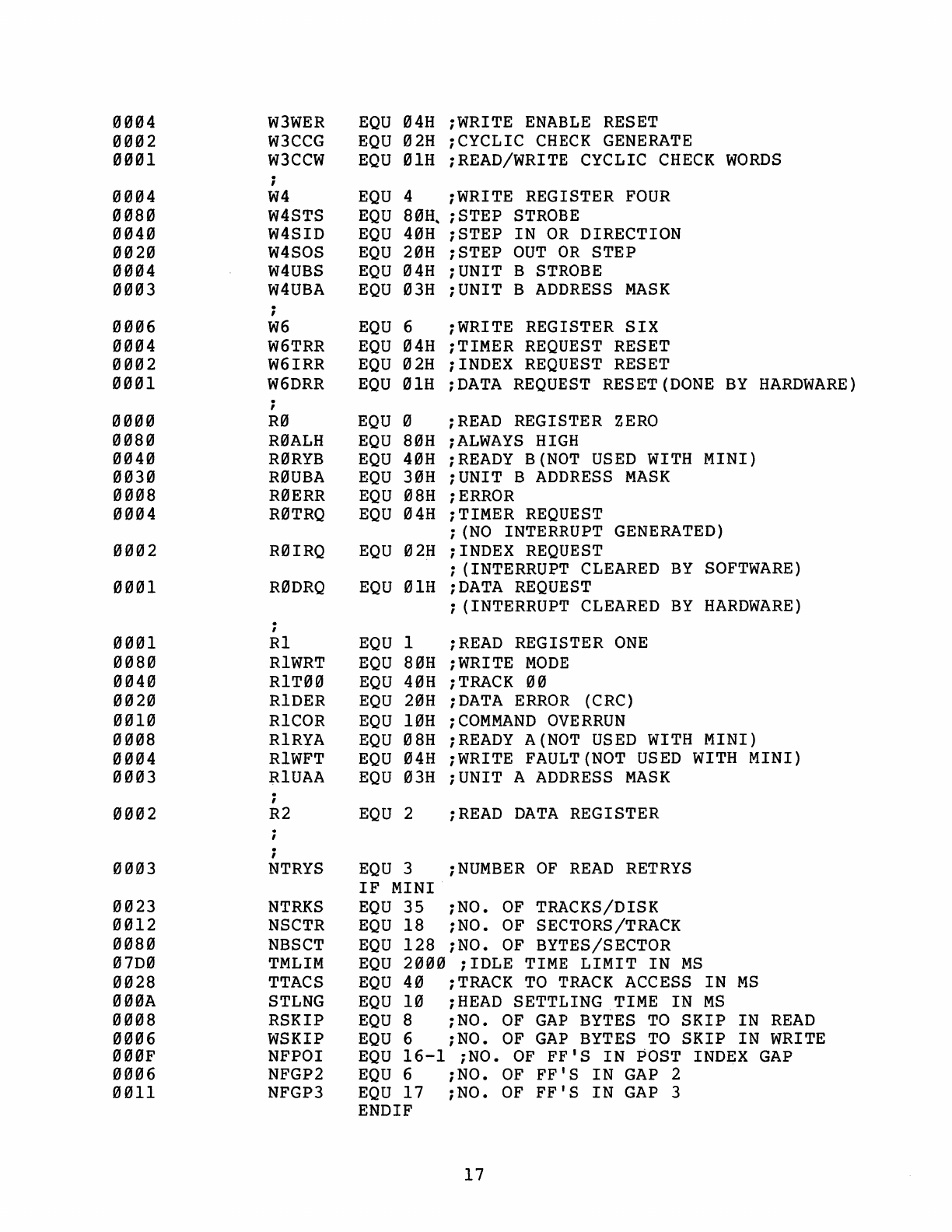

W3WER

W3CCG

W3CCW

.

,

W4

W4STS

W4SID

W4S0S

W4UBS

W4UBA

i

W6

W6TRR

W6IRR

W6DRR

i

R0

R0ALH

R0RYB

R0UBA

R0ERR

R0TRQ

R0IRQ

R0DRQ

i

Rl

RIWRT

RIT00

RIDER

RICOR

RIRYA

RIWFT

RIUAA

i

R2

i

NTRYS

NTRKS

NSCTR

NBSCT

TMLIM

TTACS

STLNG

RSKIP

WSKIP

NFPOI

NFGP2

NFGP3

EQU

04H iWRITE

ENABLE

RESET

EQU

02H iCYCLIC

CHECK

GENERATE

EQU

01H iREAD/WRITE CYCLIC

CHECK

WORDS

EQU

4 iWRITE REGISTER

FOUR

EQU

80H,

iSTEP

STROBE

EQU

40H

iSTEP

IN

OR

DIRECTION

EQU

20H

iSTEP

OUT

OR

STEP

EQU

04H

iUNIT

B STROBE

EQU

03H

iUNIT

B

ADDRESS

MASK

EQU

6 iWRITE REGISTER

SIX

EQU

04H iTIMER

REQUEST

RESET

EQU

02H iINDEX

REQUEST

RESET

EQU

01H

iDATA

REQUEST

RESET(DONE

BY

HARDWARE)

EQU

0

EQU

80H

EQU

40H

EQU

30H

EQU

08H

EQU

04H

EQU

02H

EQU

01H

EQU

1

EQU

80H

EQU

40H

EQU

20H

EQU

10H

EQU

08H

EQU

04H

EQU

03H

EQU

2

iREAD REGISTER

ZERO

iALWAYS

HIGH

iREADY

B(NOT

USED

WITH

MINI)

iUNIT

B

ADDRESS

MASK

iERROR

iTIMER

REQUEST

i

(NO

INTERRUPT

GENERATED)

iINDEX

REQUEST

i (INTERRUPT

CLEARED

BY

SOFTWARE)

iDATA

REQUEST

i (INTERRUPT

CLEARED

BY

HARDWARE)

iREAD REGISTER

ONE

iWRITE

MODE

iTRACK

00

iDATA

ERROR

(CRC)

iCOMMAND

OVERRUN

iREADY

A(NOT

USED

WITH

MINI)

iWRITE FAULT(NOT

USED

WITH

MINI)

iUNIT

A

ADDRESS

MASK

iREAD

DATA

REGISTER

EQU

3

iNUMBER

OF

READ

RETRYS

IF

MINI

EQU

35

iNO.

OF

TRACKS/DISK

EQU

18

iNO.

OF

SECTORS/TRACK

EQU

128

iNO.

OF

BYTES/SECTOR

EQU

2000

iIDLE

TIME

LIMIT

IN

MS

EQU

40

iTRACK

TO

TRACK

ACCESS

IN

MS

EQU

10

iHEAD

SETTLING TIME

IN

MS

EQU

8 iNO.

OF

GAP

BYTES

TO

SKIP

IN

READ

EQU

6 iNO.

OF

GAP

BYTES

TO

SKIP

IN

WRITE

EQU

16-1

iNO.

OF

FF'S

IN

POST INDEX

GAP

EQU

6 iNO.

OF

FF'S

IN

GAP

2

EQU

17

iNO.

OF

FF'S

IN

GAP

3

ENDIF

17

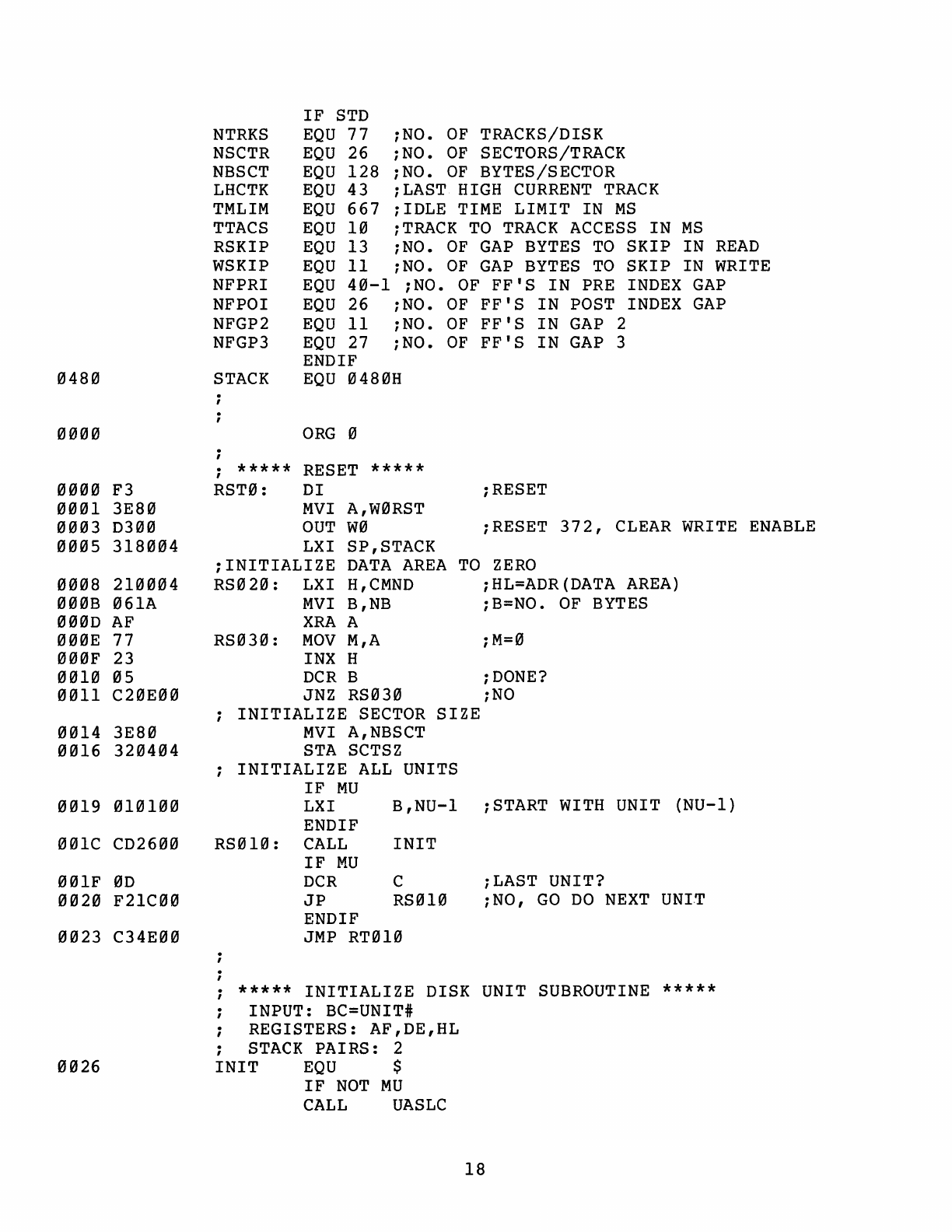

0480

0000

0000

F3

0001

3E80

0003

D300

0005

318004

0008

210004

000B

061A

000D

AF

000E

77

000F

23

0010

05

0011

C20E00

0014

3E80

0016

320404

0019

010100

001C

CD2600

001F

0D

0020

F21C00

0023

C34E00

0026

NTRKS

NSCTR

NBSCT

LHCTK

TMLIM

TTACS

RSKIP

WSKIP

NFPRI

NFPOI

NFGP2

NFGP3

STACK

IF

STD

EQU

77

iNO.

OF

TRACKS/DISK

EQU

26

iNO.

OF

SECTORS/TRACK

EQU

128

iNO.

OF

BYTES/SECTOR

EQU

43

iLAST

HIGH

CURRENT

TRACK

EQU

667

iIDLE

TIME

LIMIT

IN

MS

EQU

10

iTRACK

TO

TRACK

ACCESS

IN

MS

EQU

13

iNO.

OF

GAP

BYTES

TO

SKIP

IN

READ

EQU

11

iNO.

OF

GAP

BYTES

TO

SKIP

IN WRITE

EQU

40-1

iNO.

OF

FF'S

IN

PRE

INDEX

GAP

EQU

26

iNO.

OF

FF'S

IN

POST INDEX

GAP

EQU

11

iNO.

OF

FF'S

IN

GAP

2

EQU

27 iNO.

OF

FF'S

IN

GAP

3

ENDIF

EQU

0480H

ORG

0

i ***** RESET *****

RST0:

DI

iRESET

MVI

A,W0RST

OUT

W0

iRESET

372,

CLEAR

WRITE

ENABLE

LXI SP,STACK

iINITIALIZE

DATA

AREA

TO

ZERO

RS020:

LXI

H,CMND

iHL=ADR(DATA

AREA)

MVI

B,NB iB=NO.

OF

BYTES

XRA

A

RS030:

MOV

M,A

iM=0

INX H

DCR

B

iDONE?

JNZ

RS030

iNO

INITIALIZE

SECTOR

SIZE

MVI

A,NBSCT

STA SCTSZ

INITIALIZE

ALL

UNITS

IF

MU

LXI

B,NU-l

iSTART

WITH

UNIT

(NU-l)

ENDIF

RS010:

CALL

INIT

IF

MU

DCR

C iLAST UNIT?

JP

RS010

iNO,

GO

DO

NEXT

UNIT

ENDIF

JMP RT010

*****

INITIALIZE

DISK UNIT SUBROUTINE *****

i INPUT: BC=UNIT#

REGISTERS:

AF,DE,HL

i

STACK

PAIRS:

2

INIT

EQU

$

IF

NOT

MU

CALL

UASLC

18

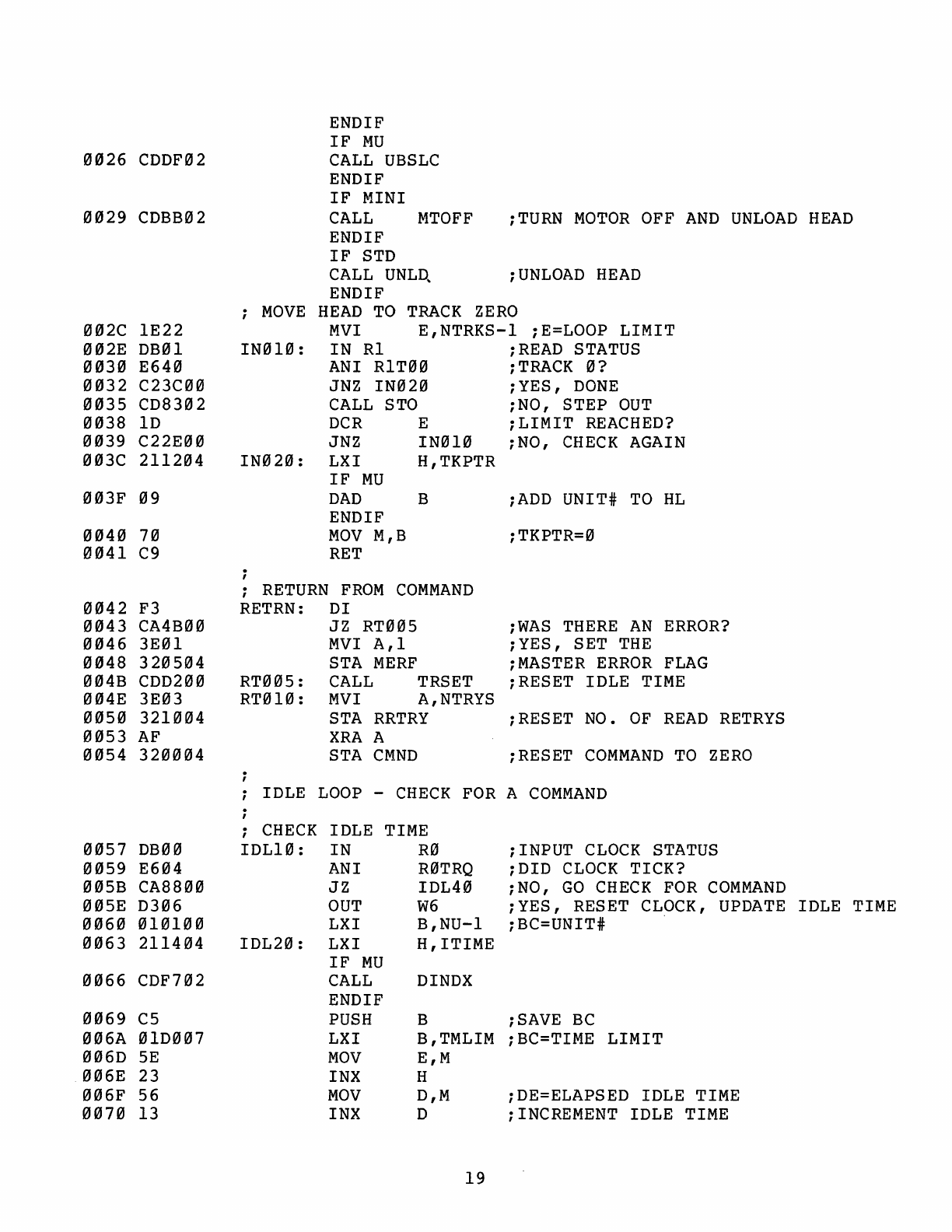

0~26

CDDF02

0~29

CDBB~2

0~2C

lE22

0~2E

DB01

0~30

E640

0~32

C23C00

0~35

CD8302

0038

ID

0~39

C22E00

003C

211204

003F

09

0040

70

0041

C9

0042

F3

0~43

CA4B00

0~46

3E01

0~48

320504

004B CDD200

0~4E

3E03

0050

321004

0~53

AF

0054

320004

0057

DB00

0~59

E604

005B

CA8800

005E

D306

0060

010100

0063

211404

0066

CDF702

0069

C5

006A

01D007

006D

5E

006E

23

006F

56

0070

13

ENDIF

IF

MU

CALL

UBSLC

ENDIF

IF

MINI

CALL

MTOFF

;TURN

MOTOR

OFF

AND

UNLOAD

HEAD

ENDIF

IF

STD

CALL

UNLQ

;UNLOAD

HEAD

ENDIF

;

MOVE

HEAD

TO

TRACK

ZERO

MVI

E,NTRKS-l

;E=LOOP LIMIT

IN010:

IN

Rl

;READ

STATUS

ANI

RIT00

;TRACK

0?

JNZ

IN020

;YES,

DONE

CALL

STO

;NO, STEP

OUT

DCR

E

;LIMIT

REACHED?

JNZ

IN010

;NO,

CHECK

AGAIN

IN020:

LXI H,TKPTR

IF

MU

DAD

B

;ADD

UNIT#

TO

HL

ENDIF

MOV

M,B

;TKPTR=0

RET

;

RETURN

FROM

COMMAND

RETRN: DI

JZ RT005

MVI

A,l

STA

MERF

RT005:

CALL

TRSET

;WAS

THERE

AN

ERROR?

;YES,

SET

THE

;MASTER

ERROR

FLAG

;RESET IDLE

TIME

RT010:

MVI

A,NTRYS

STA

RRTRY

;RESET

NO.

OF

READ

RETRYS

XRA

A

STA

CMND

;RESET

COMMAND

TO

ZERO

IDLE

LOOP

-

CHECK

FOR

A

COMMAND

;

CHECK

IDL10:

IDL20:

IDLE

IN

ANI

JZ

OUT

LXI

LXI

IF

MU

CALL

ENDIF

PUSH

LXI

MOV

INX

MOV

INX

TIME

R0

R0TRQ

IDL40

W6

B,NU-l

H,ITIME

DINDX

;INPUT

CLOCK

STATUS

;DID

CLOCK

TICK?

;NO,

GO

CHECK

FOR

COMMAND

;YES,

RESET

CLOCK,

UPDATE

IDLE

TIME

;BC=UNIT# .

B ;SAVE

BC

B,TMLIM ;BC=TIME LIMIT

E,M

H

D,M

;DE=ELAPSED IDLE TIME

D ;INCREMENT IDLE

TIME

19

0071

72

MOV

M,D

0072

2B

DCX

H

0073

73

MOV

M,E iUPDATE IDLE TIME

0074

7A

MOV

A,D

iTEST

MSB

0075

B8

CMP

B iD=B?

0076

C28300

JNZ

IDL30

iNO, CONTINUE

0079

7B

MOV

A,E

007A

B9

CMP

C iE=C?

007B

C28300

JNZ

IDL30

iNO, CONTINUE

007E

C1

POP

B iRESTORE

BC

007F

C5

PUSH

B iMAINTAIN

STACK

POSITION

IF

MINI

0080

CDBB02

CALL

MTOFF

iYES,

TIME

LIMIT

REACHED,

iTURN OFF

MOTOR,

UNLOAD

HEAD

ENDIF

IF

STD

CALL

UNLD

iYES,

TIME

LIMIT

REACHED,

iUNLOAD

HEAD

ENDIF

0083

C1

IDL30:

POP

B iRESTORE

STACK

POSITION

IF

MU

0084

0D

DCR

C iLAST UNIT?

0085

F26300

JP

IDL20

iNO, KEEP

CHECKING

ENDIF

i

CHECK

FOR

COMMAND

0088

3A0004

IDL40:

LDA

CMND

008B

B7

ORA

A

iIS

THERE

A

COMMAND?

008C

CA5700

JZ

IDL10

iNO,

STAY

IN

IDLE

LOOP

EXECUTE

COMMAND

i A=COMMAND(l-NCMDS)

008F

4F EXEC:

MOV

C,A

iSAVE

COMMAND

IN C

0090

110504

LXI D,MERF i

ZERO

FLAGS

0093

060B

MVI

B,NF

0095

AF

XRA

A

0096

12

EX005:

STAX

D

0097

13

INX D

0098

05

DCR

B

0099

C29600

JNZ EX005

009C

3E06

MVI

A,NCMDS

009E

B9

CMP

C

iIS

CMND

OK?

009F

D2A800 JNC EX010 iYES

00A2

320604

STA

CMDER

iNO, SET

FLAG

00A5

C3E700

JMP

ERROR

.

CHECK

ALL

PARAMETERS

,

00A8

110104

EX010:

LXI

D,UNIT

iDE=ADR(PARAMETERS)

00AB

21F000

LXI H,LMTBL iHL=ADR(LIMIT TABLE)

00AE

0604

MVI

B,NP

iB=NO.

OF

PARAMETERS

00B0

1A

EX020:

LDAX

D iA=PARAMETER

00B1

BE

CMP

M

iLOWER

LIMIT

OK?

008'2 DAE200

JC

EX040

iNO,

ERROR

00B5

23 INX H iYES

00B6

BE

CMP

M iUPPER

LIMIT

OK?

00B7

D2E200

JNC EX040 iNO,

ERROR

00BA

23

INX H iYES

20

00BB

13

00BC

05

00BD C2B000

00C0 79

00C1

21F800

00C4

3D

00C5

07

00C6 5F

00C7

1600

00C9

19

00CA 5E

00CB

23

00CC

56

00CD

214200

00D0 E5

00D1

D5

00D2

3A0104

00D5 4F

00D6

0600

00D8

211404

00DB CDF702

f2J0DE

70

00DF

23

00E0

70

00E1

C9

00E2

3E01

00E4

320704

00E7

320504

00EA

318004

00ED

C34E00

00F0

0002

00F2

0023

00F4

0113

00F6

0481

00F8

8F01

00FA 0C02

00FC

0401

00FE

2600

0100

FF02

0102

0000

0006

INX

D

DCR

B iDONE?

JNZ EX020

iNO

i

COMMAND

AND

PARAMETERS

OK

MOV

A,C

iYES,

A=COMMAND

LXI H,CTBL

DCR

A

iA=(0-(N-1»

RLC

iA=2*A

MOV

E,A

MVI

D,0

DAD

D iHL=ADR(ADR)

MOV

E,M

INX

H

MOV

D,M

iDE=ADR

LXI H,RETRN

PUSH

H i(SP)=RETURN

ADDRESS

PUSH

D iSAVE

ROUTINE

ADDRESS

iIDLE

TIME

RESET

TRSET:

LDA

UNIT

MOV

C,A

iC=UNIT #

MVI

B,0

iBC=UNIT#

LXI

H,ITIME

IF

MU

CALL

DINDX

ENDIF

MOV

M,B

iSET IDLE TIME

TO

ZERO

INX

H

MOV

M,B

RET

iVECTOR

TO

ROUTINE,

OR

RETURN

TO

CALLER

i

EX040:

MVI

A,l

.

,

STA

PRMER

ERROR:

STA

MERF

iSET

PARAMETER

FLAG

iSET

MASTER

ERROR

FLAG

iRESET SP

LXI SP,STACK

JMP

RT010

iLIMIT

TABLE

(UPPER

AND

LOWER

FOR

PARAMETERS)

LMTBL:

DB

0,NU iUNIT

DB

0,NTRKS

iTRACK

DB

1,NSCTR+1 iSECTR

DB

4,NBSCT+1 ;SCTSZ

;

COMMAND

TABLE

CTBL:

DW

READ

;1

DW

WRITE

i2

DW

SEEK

i3

DW

INIT

i4

DW

FRMAT

i 5

DW

RST0

;6

NCMDS

EQU

($-CTBL)/2

21

i ***** SEEK

TRACK

ROUTINE *****

INPUT:

BC=UNIT#

REGISTERS:

AF,D,HL

SUBROUTINES:

UASLC,UBSLC,STI,STO

i

0104

SEEK

EQU

$

IF

MU

0104

CDDF02

CALL

UBSLC

ENDIF

IF

NOT

MU

CALL

UASLC

ENDIF

0107

211204

LXI H,TKPTR

IF

MU

010A

09

DAD

B

iADD

UNIT#

TO

HL

ENDIF

010B

3A0204

LDA

TRACK

iA=TRACK DESIRED

010E

BE

CMP

M

010F

C8

RZ

iTRACK=TKPTR

IF

MINI

0110

E5

PUSH

H iSAVE ADR(TKPTR)

ENDIF

0111

DAIA01 JC

SK010

iTKPTR)TRACK

0114

CD7C02

CALL

STI

iTKPTR<TRACK

IF

STD

JMP

SEEK

ENDIF

IF

MINI

0117

C31D01

JMP

SK020

ENDIF

011A

CD8302

SK010:

CALL

STO

iTKPTR)TRACK

IF

STD

JMP

SEEK

ENDIF

IF

MINI

011D

El

SK020:

POP

H i

HL=ADR

(TKPTR)

011E

3A0204

LDA

TRACK

0121

BE

CMP

M iTRACK=TKPTR?

0122

C20401

JNZ

SEEK

iNO, KEEP SEEKING

0125

060A

MVI

B,STLNG

iYES,

ALLOW

HEAD

TIME

TO

SETTLE

0127

CDE602

CALL

DELAY

012A

C9

RET

ENDIF

IF

RDWR

READ

ID

RECORD

ROUTINE

i

iREGISTERS:

A,F,B,C,DE,HL

i

012B

CD0401

RID:

CALL

SEEK

iPOSITION

HEAD

IF

MU

.

012E

CDD802

CALL

UASLC

iSELECT UNIT

WITH

A LINES

ENDIF

22

el131 CD9Eel2

0134

0E04

el136

210204

0139

lle1Ael4

el13C

AF

013D

47

013E

D303

0140

3EA0

0142

D303

0144

FB

el145 76

0146

DB02

0148

EEFE

014A

C27801

014D

76

014E

DB02

0150

AE

0151

12

0152

13

0153

23

0154

76

i

RIA:

i

IF

MINI

CALL

r1TRON

ENDIF

IF

STD

CALL

RDYA

CALL

HDLD

ENDIF

MVI

C,4

LXI H,TRACK

LXI

D,WTRK

XRA

A

MOV

B,A

OUT

W3

iTURN

ON

MOTOR

AND

LOAD

HEAD

iCHECK

FOR

UNIT

READY

iLOAD

HEAD

iSTORE

LIMIT

OF

REVOLUTIONS

OF

iDISK

WITHOUT

FINDING

CORRECT

ID

iRECORD.

USE

4

TO

GUARANTEE

iTHREE

COMPLETE

REVOLUTIONS.

iINITIALIZE

TRACK/SECTR POINTER

iINITIALIZE

FLAG

POINTER

iSET

B=0

iRESET STT (FOR

RETRY)

i

MVI

A,W3RCS+W3STT

iRCS=l,

STT=l

OUT

W3

iGO

TO

READ

CLOCK. SET STT

TO

AUTO-

iMATICALLY START

READ

OPERATION

WHEN

iADDRESS

MARK

IS

READ.

EI

HLT

iENABLE INTERRUPT

AND

WAIT

FOR

iADDRESS

MARK

TO

BE

READ.

iINTERRUPT(ADDRESS

MARK)

i

(EI)

IN

XRI

JNZ

HLT

R2

0FEH ·

RIM

iREAD

DATA

iIS

IT

AN

I.D.

ADDRESS

MARK?

iNO:

JUMP

TO

RIM

iYES:

WAIT

FOR

NEXT

INTERRUPT.

iINTERRUPT(TRACK ADDRESS)

.

,

(EI)

IN

R2

XRA

M

STAX

D

INX D

INX H

HLT

IF

STD

;READ

TRACK

ADDRESS

BYTE.

iCOMPARE

WITH

DESIRED

TRACK

iWTRK

=0

FOR

OK, =NON-ZERO

FOR

ERROR

iDE POINTS

TO

NEXT

FLAG

iHL POINTS

TO

SECTR

iWAIT

FOR

NEXT

INTERRUPT

iINTERRUPT(FIRST

ZERO

BYTE)

(EI)

IN

R2

STAX

D

INX D

HLT

23

iREAD

ZERO

BYTE

iZEROl

=0

FOR

OK, =NON-ZERO

FOR

ERROR

iDE POINTS

TO

ZER02

iWAIT

FOR

NEXT

INTERRUPT

0155

DB02

0157

AE

0158

47

0159

3E21

015B

D303

015D

76

015E

3E20

0160

D303

0162

76

0'163 DB01

0165

E620

ENDIF

i

iINTERRUPT(SECTOR ADDRESS)

(EI)

IN

R2

iREAD SECTOR

ADDRESS

BYTE

XRA

M

iCOMPARE

WITH

DESIRED SECTOR

MOV

B,A

iB

=0

FOR

OK,

=NON-ZERO

FOR

ERROR

MVI

A,W3STT+W3CCW

OUT

W3

iSEND

COMMAND

TO

W3.

HLT

iTHIS

COMMAND

SETS

CCW.

(STT

iBIT

MUST

ALSO

BE

A

ONE

TO

AVOID

iRESETTING

STT.)

THE

BIT

RING PULSE

i (BRP)

FOLLOWING

THE

SETTING

OF

CCW

iWILL START A

BIT

BY

BIT

COMPARISON

iOF

THE

DATA

READ

FROM

THE

DISK

WITH

iTHE

DATA

READ

FROM

THE

CRC

REGISTER.

i

(ALTHOUGH

THE

CPU

WILL

HAVE

READ

iA

COMPLETED

BYTE

AT

THE

NEXT

iBRP,

THE

DISK DRIVE

HEAD

WILL BEGIN

iREADING

THE

1ST

CRC

BYTE.)

i

iWAIT FOR

NEXT

INTERRUPT.

IF

STD

iINTERRUPT(SECOND

ZERO

BYTE)

(EI)

IN

R2

STAX

D

INX

D

HLT

ENDIF

i

iINTERRUPT(CRC

BYTE

1)

(EI)

MVI

A,W3STT

OUT

W3

HLT

i

iINTERRUPT(CRC

BYTE

2)

(EI)

IN

Rl

ANI RIDER

iREAD

2ND

ZERO

BYTE

i

iZER02

=0

FOR

OK, =NON-ZERO

FOR

ERROR

iDE

POINTS

TO

CRCID

iWAIT FOR

NEXT

INTERRUPT.

iTURN OFF

CCW

i

iSEND

COMMAND

TO

W3

iSTT=I,

CCW=0.

CCW

IS

RESET.

iAT

NEXT

BRP

BIT-BY-BIT

CRC

iCOMPARISON WILL END.

i

iWAIT

FOR.

NEXT

INTERRUPT.

iINTERRUPT

CAUSED

BY

2ND

CRC

BYTE

i

iWAS

THERE

A

CRC

ERROR?

24

0167

12

0168

78

0169

B7

016A

C27801

016D

76

016E

EB

016F

B6

0170

76

0171

2B

0172

B6

0173

C27801

0176

76

0177

C9

0178

DB00

017A

E602

017C

CA3601

017F

D306

0181

0D

0182

C23601

0185

AF

0186

D303

0188

3E01

018A

320904

018D

87

018E

C9

i

STAX

D

MOV

A,B

ORA

A

JNZ

RIM

HLT

iCRCID =0 FOR OK, =NON-ZERO

FOR

ERROR

iSECTOR

OK?

iNO,

TRY

AGAIN

iYES

iINTERRUPT

(FIRST

GAP

BYTE)

.

,

(EI)

XCHG

ORA

M

IF

STD

DCX

H

ORA

M

DCX

H

ORA

M

ENDIF

HLT

iHL POINTS

TO

CRCID, A=0

iTEST

CRCID

iTEST

ZER02

iTEST

ZEROI

iINTERRUPT (2ND

GAP

BYTE)

i

(EI)

DCX

H

ORA

M

JNZ

RIM

HLT

iTEST

WTRK.

(IS

TRACK

ADDRESS

iREAD

EQUAL

TO

SOFTWARE

TRACK

; POINTER?)

iONE

OF THE

ABOVE

IN

ERROR,

TRY

AGAIN.

iINTERRUPT (3RD

GAP

BYTE)

i

i

ERROR

i

RIM:

(EI)

RET

IN

R0

ANI R0IRQ

JZ

RIA

OUT

W6

DCR

C

JNZ RIA

XRA

A

OUT

W3

MVI

A,l

STA

NOGO

ORA

A

RET

iNORMAL

RETURN,

ZERO

FLAG=l

iREAD STATUS

iWAS

INTERRUPT

AN

INDEX REQUEST?

iNO:

WAIT

FOR

NEXT

MARK

i YES, IRQ RESET

iDECREMENT

LIMIT

iWAIT

FOR

NEXT

MARK

IF

NOT

3RD

COMPLETE

iREVOLUTION

OF

DISK

WITHQUT

SUCCESS

iQUIT

iRESET STT

iCOULD

NOT

FIND

REQUESTED

ID

iCLEAR

ZERO

FLAG

i

ERROR

RETURN

*****

READ

DATA

RECORD

ROUTINE *****

25

018F

CD2B01

0192

C0

0193

3E60

0195

D303

0197

0604

0199

76

019A

05

019B

C29901

019E

76

019F

3E40

01Al

D303

01A3

218004

01A6

1621

01AS 0EFB

01AA

3A0404

01AD

D603

01AF

47

01B0

3EA0

01B2

D303

01B4

76

01B5

DB02

01B7

B9

01B8

C2EB01

i

iREGISTERS:

A,F,B,C,DE,HL

.

,

CALL

READ

ID

RECORD

FIRST

i

READ:

CALL

RID iREAD ID

RNZ

iERROR

IN

RID,

RETURN

i(3

GAP

B~TES

HAVE

BEEN

READ,

HEAD

IS

READING

4TH)

MVI

A,W3WCS+W3STT

OUT

W3

iSET

WRITE CLOCK,

LEAVE

STT SET

MVI

B,RSKIP-4

iPASS

GAP

BYTES 4

THRU

(RSKIP-l)

RGAP:

HLT

i

iINTERRUPT

(GAP

BYTE

4

THRU

(RSKIP-l))

i

.

,

(EI)

DCR

JNZ

HLT

B

RGAP

iWAIT FOR

GAP

BYTE

#RSKIP.

HEAD

HAS

iNOW

PASSED

AREA

IN

GAP

THAT

CONTAINS

iUNKNOWN

INFORMATION

GENERATED

WHEN

iWRITE

CURRENT

WAS

TURNED

ON

TO

WRITE

iDATA

RECORD

•

iINTERRUPT

(GAP

BYTE

#RSKIP)

i

(EI)

MVI

A,W3WCS

iRESET

STT,

SET WRITE

CLOCK

TO

OUT

W3

iPREVENT INTERRUPTS UNTIL

FOLLOWING

iIS

DONE.

i

LXI H,BUFFR

iSET

HL

TO

1ST

ADDRESS

OF

iSTORAGE BUFFER.

i

MVI

D,W3STT+W3CCW

iSTORE

COMMAND

TO

SET

CCW

IN

iD

REGISTER.

i

MVI

C,0FBH

iSTORE

DATA

ADDRESS

MARK

CODE

iIN

C.

i

LDA

SCTSZ

iSET

SECTOR

SIZE

SUI 3

MOV

B,A

iSAVE

COUNT

IN

B

i

MVI

A,W3RCS+W3STT

iSET

READ

CLOCK, SET

STT.

OUT

W3

HLT

iWAIT FOR

ADDRESS

MARK.

i

iINTERRUPT

(ADDRESS

MARK)

i

(EI)

IN

R2

CMP

C

JNZ

MARK

iREAD

BYTE

iIS

IT

A

DATA

ADDRESS

MARK?

iNO:

JUMP

TO

MARK

26

01BB

76

01BC DB02

01BE

77

01BF

23

01C0

76

01Cl

DB02

01C3

77

01C4

05

01C5

C2BF01

01C8

23

01C9

76

01CA DB02

01CC

77

01CD

7A

01CE

D303

01D0

76

01Dl

23

01D2 DB02

01D4

77

01D5

76

01D6

3E20

01D8

D303

01DA

76

01DB DB01

01DD

47

01DE

AF

HLT

i

iINTERRUPT

(DATA

BYTE

1)

(EI)

IN

R2

MOV

i

READ

LOOP

RLOOP: INX

HLT

i

M,A

H

iWAIT

FOR

FIRST

DATA

BYTE

iYES:

READ

FIRST

DATA

BYTE

iSTORE

FIRST

DATA

BYTE

iINCREMENT BUFFER POINTER