EMCEE Broadcast TU1000F UHF LPTV Translator User Manual TTU1000F Mnl Cover Pg 1

EMCEE Broadcast Products UHF LPTV Translator TTU1000F Mnl Cover Pg 1

TU1000F Manual

Broadcast Products

P.O. Box 68, White Haven, PA 18661 Phone: (570) 443-9575 FAX: (570) 443-9257

MDS MMDS ITFS LPTV

North America South America Europe Asia Australia Africa

Since 1960

TU1000F V/U

SOLID STATE

1000W UHF TRANSLATOR

TU1000F V/U

SOLID STATE

1000W UHF TRANSLATOR

02/00

TABLE OF CONTENTS

I. THE TU1000F V/U TRANSLATOR

1.1 Introduction

1.2 Specifications

1.3 Installation

1.4 Operation

1.5 Warrant

y

and Parts Orderin

g

II. CIRCUIT DESCRIPTION

2.1 Receiver Drawer

2.2 Exciter/Upconverter Drawer

2.3 Power Splitter

2.4 Dual 300W Power Amplifier Drawer

2.5 Power Combiner

2.6 Meterin

g

Coupler

2.7 Front Panel

2.8 Output Filter

III. MAINTENANCE

3.1 Periodic Maintenance Schedule

3.2 Recommended Test E

q

uipment

3.3 Troubleshootin

g

3.4 Translator Ali

g

nment

3.5 Output Power Calibration

3.6 Precorrection Ad

j

ustment

3.7 Control Board Setup

3.8 Remote Monitor Si

g

nal Levels

3.9 Spare Modules and Components Lists

IV. DATA PAK

V. SCHEMATIC DIAGRAMS

i

SECTION I

THE TU1000F V/U TRANSLATOR

1.1 Introduction ............................................................ 1 1

1.2 Specifications .......................................................... 1 1

1.3 Installation ............................................................. 1 2

1.4 Operation .............................................................. 1 3

1.5 Warranty and Parts Ordering ............................................ 1 4

1 1

SECTION I

THE TU1000F V/U TRANSLATOR

1.1 Introduction:

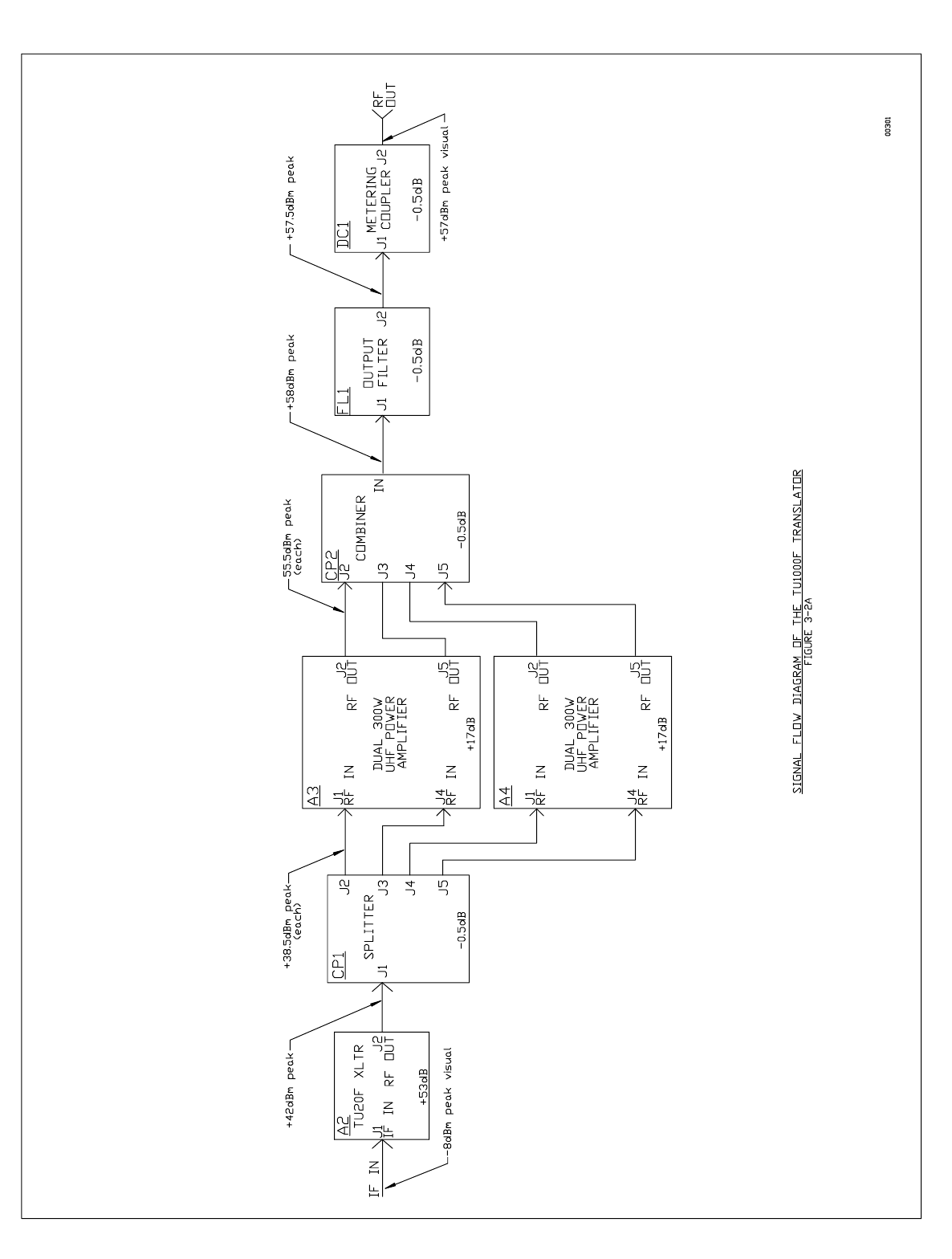

The EMCEE TU1000F V/U Translator is rated to provide 1000 watts peak visual and 50 watts

average aural power on any FCC specified channel extending from 470 to 806MHz. The TU1000F

is completely solid-state providing maximum performance and reliability. It is comprised of a

Receiver Drawer, a 20 Watt UHF Exciter/Upconverter, two Dual 300W Power Amplifier assemblies

and a panel for power distribution and metering. The TU1000F is easy to service and maintain while

RF alignment is practically nonexistent. A number of front panel indicators are included which

display the results of the translator's diagnostic/control circuitry.

The TU1000F Translator is designed for the express purpose of broadcasting as authorized by the

U.S. Federal Communications Commission under Part 74, Subpart G, of the FCC Rules and

Regulations.

1.2 Specifications:

Output Power 1000W peak visual

50W average aural

Emissions 5M75C3F visual

250KF3E aural

Color Transmission NTSC, PAL, or SECAM

Output Frequency Range 470-806MHz

Input Frequency Range 54-88MHz (FCC Ch. 2-60)

174-216MHz (FCC Ch. 7-13)

470-806MHz (FCC Ch. 14-69)

Frequency Stability ±1kHz

Visual Output Power Stability ±0.5dB

Spurious Products 60dB below peak sync

Harmonics 60dB below peak sync

In-band Intermodulation (IM3)52dB below peak sync

Differential Gain 5%

Differential Phase ±3

Frequency Response ±1.0dB

1 2

Envelope Delay ±50nsec

Output Impedance 50 ohms (7/8" EIA flange connector)

RF Input Level 70dBm to 30dBm

RF Input Impedance 50 ohms unbalanced (N connector)

Video Signal to Noise 50dB @ 47dBm in

Audio Distortion <1%

Aural FM Noise < 55dB

Ambient Temperature 30 C to +50 C

Power Requirements 230Vac ± 15% @ 50/60Hz, 3.8kW

Mechanical Dimensions 69"H x 23"W x 29"D

Weight 350 lb.

1.3 Installation:

Except where otherwise noted, the connectors mentioned in the following instructions are located

on the rear of the translator.

1. After unpacking the translator, a thorough inspection should be conducted to reveal any

damage which may have occurred during shipment. If damage is found, immediately notify

the shipping agency and advise EMCEE Broadcast Products Customer Service or its field

representative. Also check to see that any connectors, cables or miscellaneous equipment,

which may have been ordered separately, are included.

2. Place the translator in a clean, weatherproof environment providing adequate ventilation for

the exhaust fans at the top of the cabinet. It is important to maintain the translator's ambient

temperature within the 30 C and +50 C limits. Cooler ambient temperatures will provide

increased reliability.

3. Place the translator in its permanent location near a single-phase receptacle that supplies

230Vac at 50/60Hz. The ac source should have a minimum power capacity of 5kW.

IMPORTANT

Do not apply ac power to the translator at this time since its RF output must be properly

terminated before being placed in operation.

1 3

4. Set all circuit breakers and switches, including the customer's incoming ac line breaker, to

the OFF position. Place an appropriate ac power line protector (surge suppressor) across the

ac line that supplies the translator.

5. With the appropriate cables (customer supplied), connect the receiving antenna to the RF IN

“N” connector located on the top rear panel of the translator cabinet.

6. Connect the transmitting antenna cable to the 7/8" EIA flange connector marked RF OUTPUT

located at the top, rear, right-hand corner of the cabinet (as seen from the front).

7. Verify that the power cords of the Receiver and Exciter drawers are plugged into the

receptacle at the bottom of the cabinet inside the rear door. Check all other factory installed

RF cables and DC wire harnesses for tight connections.

8. Using the 4-prong, twist lock, female plug supplied with the translator, fabricate an ac power

cord and plug it into the translator's AC MAINS connector at the top left rear (as seen facing

the front of the cabinet) of the translator's cabinet. Connect the other end of the power cord

into an appropriate electrical outlet.

1.4 Operation:

Assuming the installation instructions of Section 1.3 have been completed and the translator is

receiving a signal of appropriate frequency and amplitude, proceed with the following steps to place

the translator in operation. Except where otherwise noted, the controls, switches, and indicators

mentioned in these steps are located on the front of the translator.

1. Close the transmission site’s ac mains breaker. Place the Receiver front panel OPERATE/

ALIGN switch to OPERATE and its AC POWER circuit breaker to ON. Verify that the

CARRIER PRESENT indicator is illuminated green.

2. Turn the Exciter/Upconverter POWER ADJUST control fully counterclockwise and place its

OPERATE/STANDBY switch to STANDBY, its OPERATE/ALIGN switch to OPERATE.

Place the Control/Metering Panel’s AC POWER circuit breaker and the Exciter POWER ON

breaker both to the on/up position. Then verify the following responses of the translator:

a. The fans of the translator should be operating. The Exciter exhausts air out the rear of

the drawer while the Power Amplifier drawer exhausts air through the cabinet top with

the aid of cabinet-mounted exhaust fans.

b. The Exciter's OPERATE, SYNTH LOCK, and DRIVER AMP indicators should be

illuminated green.

c. The Exciter’s TEMP EXCITER, ON, FINAL BIAS and VSWR OVLD indicators should

be extinguished.

d. The TEMPERATURE, VSWR OVLD and COLLECTOR BIAS indicators of each Power

Amplifier should be extinguished.

e. The Control/Metering Panel’s four Amplifier Status indicators should be illuminated

green.

1 4

3. Place the Exciter’s OPERATE/STANDBY switch to OPERATE. Then verify the following

responses of the translator:

a. The Exciter's OPERATE, SYNTH LOCK and DRIVER AMP indicators should remain

illuminated green.

b. The Exciter's ON and FINAL BIAS indicators should be illuminated green while the

VSWR OVLD and TEMP indicators remain extinguished.

c. The TEMPERATURE indicator of each Power Amplifier drawer should remain

extinguished while the COLLECTOR BIAS indicators are illuminated green.

d. The Control/Metering Panel’s AMPL 1 through AMPL 4 indicators should remain

illuminated green.

4. Place the Control/Metering Panel's meter switch to FWD and turn the Exciter's POWER

ADJUST control clockwise until a 100% indication appears on the Control/Metering Panel's

RF POWER meter. Set the Exciter’s % meter to display FWD power. Note that the meter

may show a reading less than 100%. This is appropriate.

5. Place the Control/Metering Panel's meter switch to REFLD and verify that the meter indicates

no more than 10% returned power. If the reflected power is more than 10%, shut down the

translator and check the VSWR of the transmitting antenna and its associated cable.

6. Place the Control/Metering Panel's meter switch to FWD for constant monitoring of the

translator's final output power.

The translator is now in operation. Check its coverage area for clean, sharp television reception.

If the reception or picture quality is unsatisfactory, examine the amount of power delivered to the

transmitting antenna (see Section 3.5) and, if necessary, examine the antenna orientation, antenna

VSWR, and transmission line VSWR to insure maximum radiation in the proper direction.

1.5 Warranty and Parts Ordering:

Warranty – EMCEE warrants its equipment to be free from defects in material and workmanship for

a period of one year after delivery to the customer. Equipment or components returned as defective

(prepaid) will be, at our option, repaired or replaced at no charge as long as the equipment or

component part in question has not been improperly used or damaged by external causes

(e.g., water, ac line transients or lightning). Semiconductors are excepted from this warranty and

shall be warranted for a period of not more than ninety (90) days from date of shipment. Equipment

or component parts sold or used by EMCEE, but manufactured by others, shall carry the same

warranty as extended to EMCEE by the original manufacturer.

Equipment Returns – If the customer desires to return a unit, drawer, or module to EMCEE for

repair, follow the procedure described below:

1. Contact EMCEE Customer Service Department by phone or fax for a Return Authorization

Number.

1 5

2. Provide Customer Service with the following information:

Equipment model and serial numbers.

Date of purchase.

Unit input and output frequencies.

Part number (PN) and Schematic Diagram designator if a module is being sent.

Detailed information concerning the nature of the malfunction.

The customer shall designate the mode of shipping desired (e.g., Air Freight, UPS, Fed Ex, etc.).

EMCEE will not be responsible for damage to the material while in transit. Therefore, it is of utmost

importance that the customer insure the returned item is properly packed.

Parts Ordering – If the customer desires to purchase parts or modules, utilize the following

procedure:

1. Contact EMCEE Customer Service by phone or fax indicating the customer's purchase order

number. If the purchase order number is provided by phone, written confirmation of the order

is required.

2. Also provide:

The equipment model and serial number.

The unit input and output frequencies.

The quantity, description, vendor, number, and designation of the parts needed as found in

the Parts Lists subsection of this manual.

If a module is required, give the part number (PN) and Schematic Diagram designator

(e.g., 10331209).

Designate the mode of shipping desired (e.g., Air Freight, UPS, Fed Ex, etc.).

Shipping and billing addresses.

Spare and Replacement Parts – The Spare Modules and Components section of this manual

provides a detailed listing of the modules and some discrete components contained within the

translator. The listing contains those modules or components considered to be essential bench-

stock items and should be available to the technician at all times. The Schematic or Interconnection

Diagram is the governing document of this manual. Should there be a discrepancy between a

modules or components list and a diagram, the diagram takes precedence. Such a discrepancy is

possible since manufacturing changes cannot always be incorporated immediately into the

instruction manual.

Component Referencing – The translator consists of a number of modules and components mounted

in four drawers, a number of components mounted on panels, and several cabinet-mounted

components and modules. Components mounted in a module which is included in a drawer take

the drawer number and the module number in addition to a component number. Thus the reference

designator A2A1Q1 means transistor Q1 in module A1 of drawer A2. Components mounted in a

drawer take only the drawer number and a component number (e.g., A2M1 designates meter M1 of

drawer A2). Components mounted directly to a panel take only the panel number and a component

number. Components and modules mounted directly to the cabinet take only a component or

module number.

1 6

For EMERGENCY technical assistance, EMCEE offers a toll free, 24-hour, 7-day-a-week

customer service hot line: 1-800-233-6193.

iia

SECTION II

CIRCUIT DESCRIPTION

2.1 Receiver Drawer ....................................................... 2 1

2.1a VHF/UHF Remote Preamplifier (Optional) ................................ 2 2

2.1b VHF Bandpass Filter ................................................ 2 2

2.1c UHF Bandpass Filter ................................................ 2 2

2.1d Crystal Oscillator ................................................... 2 3

2.1e X2 Multiplier and X4 Multiplier ......................................... 2 3

2.1f X16 Multiplier ...................................................... 2 4

2.1g 10MHz Reference Oscillator ........................................... 2 5

2.1h VHF Synthesizer Low Band ........................................... 2 5

2.1i VHF Synthesizer High Band........................................... 2 6

2.1j UHF Synthesizer ................................................... 2 7

2.1k Downconverter/Preamplifier ........................................... 2 8

2.1l IF SAW Filter/Amplifier .............................................. 2 8

2.1m IF AGC Amplifier ................................................... 2 9

2.1n Automatic-On..................................................... 2 10

2.1o Limiter/Output AGC Control .......................................... 2 10

2.1p Aural Notch Filter .................................................. 2 11

2.1q Multioutput Power Supply ............................................ 2 11

2.1r Digital Code ID Unit (Optional) ........................................ 2 12

2.2 Exciter/Upconverter Drawer ............................................ 2 13

2.2a Linearizer ........................................................ 2 14

2.2b IF/Upconverter .................................................... 2 14

2.2c UHF Synthesizer .................................................. 2 16

2.2d Reference Oscillator ................................................ 2 17

2.2e UHF Bandpass Filter ............................................... 2 17

2.2f 2 Watt UHF Amplifier ............................................... 2 17

2.2g 20 Watt UHF Amplifier .............................................. 2 18

2.2h Metering Coupler .................................................. 2 19

2.2i Metering Detector.................................................. 2 19

2.2j Control Board ..................................................... 2 20

2.2k Power Supplies ................................................... 2 22

2.3 Power Splitter ......................................................... 2 22

2.4 Dual 300W Power Amplifier Drawer ..................................... 2 22

2.4a 300W UHF Amplifier ............................................... 2 23

2.4b Status Display .................................................... 2 23

2.4c +28V Power Supply ................................................ 2 24

2.5 Power Combiner ...................................................... 2 24

2.6 Metering Coupler ...................................................... 2 24

2.7 Front Panel ........................................................... 2 24

2.7a Metering Detector.................................................. 2 25

2.7b Control Board ..................................................... 2 25

2.8 Output Filter .......................................................... 2 28

2 1

SECTION II

CIRCUIT DESCRIPTION

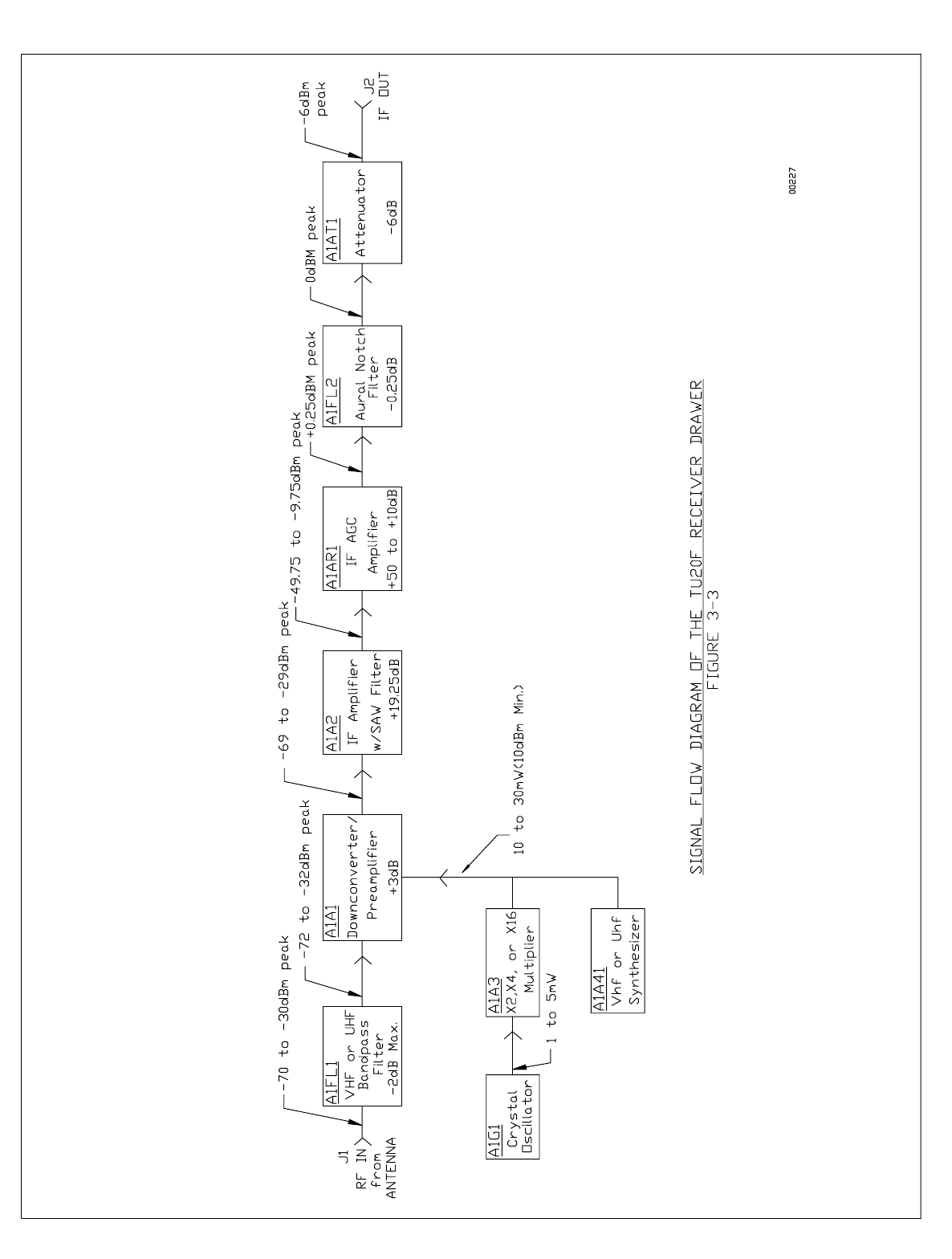

2.1 Receiver Drawer:

Interconnection Diagram 30383094/Rev 54 A1 (Vectron Oscillator with Multiplier)

Interconnection Diagram 30383104/Rev 55 A1 (Synthesizer)

RF IN 70dBm to 30dBm peak visual

IF OUT 6dBm

LO SAMPLE 0dBm

The Receiver drawer provides highly selective VHF or UHF to IF signal conversion, IF

amplification, and prevention of unauthorized radiation if the proper input signal is not received.

Signal conversion is accomplished via a VHF or UHF Bandpass Filter (FL1), and a Downconverter/

Preamplifier (A1). The LO for downconversion is provided by one of six sources depending upon

the application. A high stability crystal oscillator (G1) with a X2, X4 or X16 Multiplier (A4) is used

when a frequency offset is required when receiving VHF Low Band (Ch.2-6), VHF High Band

(Ch.7-13) or UHF (Ch.14-69) respectively. If no frequency offset is required, the corresponding

Synthesizer (A4) and 10MHz Reference Oscillator (A5) are used. IF amplification and filtering are

furnished through the IF Amplifier w/SAW Filter (A2) and the IF AGC Amplifier (A3). The Aural

Notch Filter (FL2) allows for attenuation of the aural carrier to facilitate a reduction of in-band third

order intermodulation products or to maintain the minimum visual to aural carrier ratio. Finally, a

6dB attenuator reduces the IF signal to a level that is within the input range of the Exciter/

Upconverter (A2).

The Receiver drawer also insures that the translator does not exceed or deviate from its rated

output power while receiving signal variations of up to 40dB ( 70dBm to 30dBm). This function

is accomplished through a complex gain control system employing the IF AGC Amplifier's variable

pin diode attenuator and a Limiter/Output AGC (PC1). The IF AGC Amplifier's variable pin diode

attenuator is controlled by the input AGC circuit of the IF AGC Amplifier and the output AGC circuit

of the Limiter/Output AGC. As the received signal increases, the input AGC circuit of the IF AGC

Amplifier provides an increase in the AGC voltage applied to the variable pin diode attenuator.

This condition causes an increase in the attenuation provided by the variable pin diode attenuator.

As a result, the IF output of the Receiver drawer is held constant at approximately 6dBm (±1dB)

throughout the 40dB variation in the received signal.

The input AGC circuit alone does not provide for controlling changes in amplifier gain occurring

after the IF section of the Receiver. (An amplifier's gain may change during warm-up, over long

periods of time, and under varying temperatures.) The output gain control circuit of the Limiter/

Output AGC is incorporated to monitor and correct any changes in the translator's output power.

The output AGC circuit controls the gain of the IF AGC Amplifier by monitoring the dc voltage that

drives the translator's % Power meter. Any deviation from the translator's correct output power will

shift the metering voltage, causing the output AGC circuit to vary the biasing on the IF AGC

Amplifier's variable pin diode attenuator. The attenuation will vary in such a way that any power

fluctuations at the output of the translator will be counteracted.

Should the Receiver drawer experience a temporary loss of signal (fading, etc.), the limiter circuit

of the Limiter/Output AGC serves to prevent overdriving the translator's power amplifier modules.

(A decrease in the received signal reduces the AGC voltage and consequently increases the gain

2 2

of the IF AGC Amplifier.) When the received signal regains its strength, the limiter circuit will

momentarily attenuate ( 20dB) the IF output of the Receiver drawer until adequate AGC voltage

is developed to control the Receiver's overall gain.

In the event of a significant reduction or loss of the Receiver's input signal for more than

30 seconds, an Automatic-On circuit (PC2) will prevent the radiation of noise by shutting down the

Receiver. Should the VHF or UHF input signal to the Receiver fall below the minimum acceptable

level of 70dBm, the accompanying AGC voltage will fall below a preset Auto-On Threshold

voltage. This in turn causes Auto-On relay K1 to de-energize which opens the interlock loop and

shuts down the translator.

2.1a VHF/UHF Remote Preamplifier: (OPTIONAL)

Scala Model 8000

Specifications See Data Pak

2.1b VHF Bandpass Filter:

Schematic A280-92/Rev 1 (Ch.2-6) A1FL1

Schematic A280-89/Rev 1 (Ch.7-13) A1FL1

Frequency Response (J1-J2) 7MHz @ 1dB

Insertion Loss (J1-J2) 2dB Max.

The high band VHF bandpass filter is a two-section overcoupled circuit that rejects all frequencies

other than the single VHF channel to which it is tuned. The bandpass filter is adjusted to provide

a 7MHz @ 1dB frequency response with an insertion loss of approximately 2dB or less. In the

filter, inductors L3 and L4, in conjunction with stagger-tuned capacitors C1 through C4, provide the

required bandpass response. Capacitor C5 also effects the response by changing the effective

coupling between the two circuits. Impedance matching is accomplished by inductors L1 and L2

along with variable capacitors C1 and C2.

2.1c UHF Bandpass Filter:

Schematic 10331209/Rev 52 (Ch.14-83) A1FL1

Frequency Response 7MHz @ 1dB

Insertion Loss 3dB Max.

The filter is composed of three overcoupled, 1/4 wave coaxial cavities that reject all frequencies

other than the single UHF channel to which it is tuned. The UHF Filter provides a 7MHz bandwidth

at 1dB and has an insertion loss of 3dB or less. In the filter, components L2, L3 and L4 are solid

brass rods acting as 1/4 wave shorted transmission lines. The length of these lines, controlled by

variable capacitors C1, C2 and C3, dictates the resonant frequency of the filter. Inductors L1 and

L5 link couple the UHF signal into and out of the filter. The position of these two inductors in

relation to the 1/4 wave brass rods determines the filter's input and output impedance, as well as

2 3

skirt selectivity and insertion loss. The Variable Coupling Barriers regulate the amount of signal

passed between the coaxial cavities and therefore control the bandwidth of the filter.

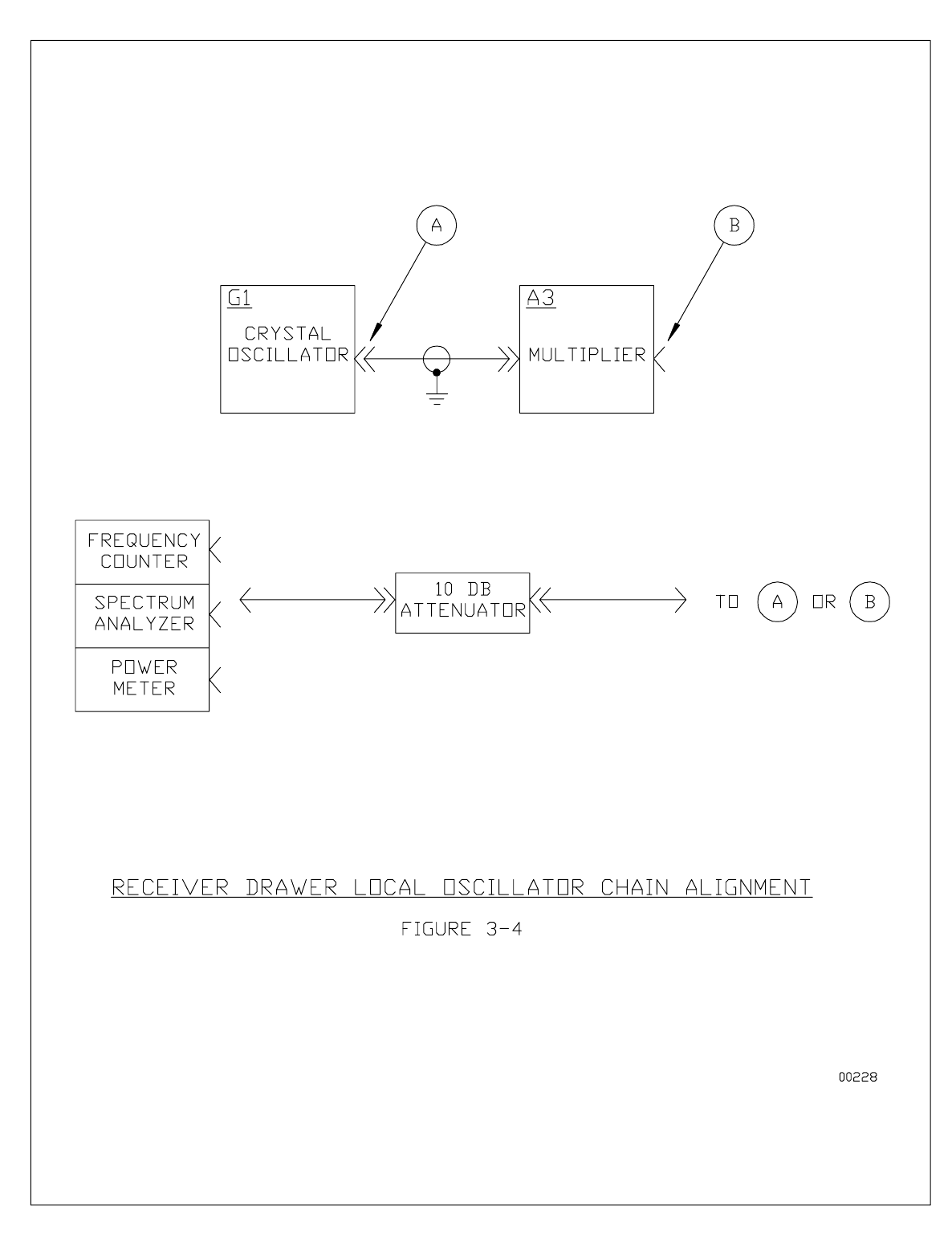

2.1d Crystal Oscillator:

Vectron CO-254D57 A1G1

Supply Voltage 28V

Output Power +7dBm

Operating Temperature 30 C to +70 C

Stability ±5 x 10-7

The CO-254D57 is a high stability, temperature-compensated crystal oscillator (TCXO)

manufactured by Vectron Laboratories, Inc. This oscillator, in conjunction with a X2, X4 or X16

Multiplier, is used in place of the EMCEE Synthesizer when ±10kHz precision offset is required.

See the Data Pak for further information.

2.1e X2 Multiplier and X4 Multiplier:

Schematic B280-35/Rev E (Ch.2-6) A1A4 (X2 Multiplier)

Schematic C331-24/Rev D (Ch.7-13) A1A4 (X4 Multiplier)

Multiplier Q1 Q2 Q3

Collector V 25 15 15

Output Power 10-40mW

Output Frequency Osc. 2nd/4th Harmonic

The VHF Multiplier consists of an amplifier and two doubler stages fed by the fundamental

frequency of the crystal oscillator. Transistor Q1 is an untuned class A VHF amplifier coupled to

a resonated idler loop tuned to the fundamental frequency (series circuit L3 and C7). Transistor

Q2 is a class AB X2 frequency multiplier that feeds an LC series circuit (L5, C12) tuned to the

second harmonic. Capacitors C13 through C17 and inductors L6 through L8 make up a

three-section bandpass filter which passes only the second harmonic frequency. If the multiplier

is a X4 type, transistor Q3 is a class C frequency doubler with both input and output tuning. Tuning

consists of a second harmonic idler circuit (L9 and C19) at the input and an output network (L12,

C22 and C23) that is tuned to the oscillator's 4th harmonic. C26 through C29 and inductors L13

and L14 make up a two-section bandpass filter tuned to pass the oscillator's fourth harmonic. An

LO sample ( 1mW) port (J3) is provided on the front panel of the translator drawer for convenient

monitoring or mixing.

2 4

2.1f X16 Multiplier:

Schematic Diagram 30367226/Rev A A1A4

INPUT power 0 to +10dBm

Typical +7dBm

LO OUT (J2)

Output power +15dBm Min.

Output frequency 16th harmonic of input

The X16 Multiplier provides three sections of frequency multiplication to generate the LO necessary

for downconverting UHF channels to IF.

Section 1 consists of a frequency multiplier (A1), a bandpass filter (FL1), and an amplifier (U1).

A1 produces harmonics from the input signal of the crystal oscillator. The desired harmonic from

A1 is the fourth, whose level should typically be 30dB below the oscillator level. FL1 is a narrow

bandpass filter, which also employs two tunable notch filters. When properly tuned, FL1 has a

typical insertion loss of 2 to 2.5dB. The notch filters are tuned to the 3rd and 5th harmonics

providing an additional minimum attenuation of 15dB to these harmonics. Output level from FL1

is approximately 28 to 32dBm. U1 is a monolithic amplifier with a typical gain of 33dB at these

frequencies. U1 provides the nominal level of 0dBm for the next section of frequency

multiplication.

Section 2 consists of a frequency multiplier (A2), a filter FL2, and a two-stage amplifier (U2, U3).

A2 produces harmonics of the signal taken from the previous section. The desired frequency from

this section is the 2nd harmonic of the input (8th harmonic of OSC.). The output level of A2 at the

2nd harmonic is typically 15dBm. FL2 is a tunable microstrip bandpass filter. The filter has a

frequency range of 250-470MHz, an insertion loss of 2dB and is tuned to pass the 2nd harmonic

of A2. The output level from FL2 is a nominal 17dBm. U2 and U3 are monolithic amplifiers with

a combined typical gain of 25dB. These are used to produce an input level of +8dBm to the third

section.

Section 3 consists of a frequency multiplier (A3), two different stages of amplification (U4 and U5,

U6), and two filters (FL3, FL4). A3 is used to produce harmonics of the frequency from Section 2.

The desired frequency from A3 is the second harmonic of its input (16th of OSC.). Output level

of the second harmonic from A3 is typically 6dBm. U4 is used to amplify the output of A3 before

filtering by FL3. The output level of U4 at the 2nd harmonic of A3 is at a nominal 2dBm level. FL3

is a tunable microstrip bandpass filter with a frequency range of 500-940MHz and an insertion loss

of 2dB. The filter is tuned to the 2nd harmonic of A3. The output level of FL3 is 0dBm. U5 is a

monolithic amplifier with a 12dB gain. U5 is run into compression allowing the oscillator level to

vary while the output of U5 remains constant. The output of U5 drives U6, another monolithic

amplifier with a gain of 11.5dB. This amplifier is also operated in compression for the same reason

as U5. The output of U6 is +18 to +20dBm. FL4 is tuned for the second harmonic from A3 and

provides additional filtering to suppress the undesired harmonics from previous frequency

multiplication. Secondly, the filter removes any additional undesired signals caused by

compressing amplifiers U5 and U6. The output level from FL4 is typically +16dBm to +18dBm.

2 5

2.1g 10MHz Reference Oscillator:

Schematic Diagram 10368037/Rev B A1A4A2

10MHz REF. OUT (J1, J2) 3.5V P/P square wave

The Reference Oscillator provides a 10MHz reference signal for the Synthesizer (A4A1). This

module is centered around a 10MHz temperature-compensated crystal oscillator (G1). The output

from G1 is applied to two exclusive-OR gates used as inverting buffers. The output signal from

each gate is a 10MHz low-level square wave with a frequency stability of 0.3 parts per million

(PPM).

2.1h VHF Synthesizer Low Band:

Schematic Diagram 30362427/Rev C A1A4A1

10MHz REF. IN (J1) 3.5V P/P square wave

LO OUT (J2) +15.25dBm min.

SYNTH. LOCK (Pin A of J4) logic high (locked)

logic low (unlocked)

The VHF Synthesizer is a phase-lock loop type and uses one of the 10MHz reference signals from

the Reference Oscillator (A4A2) and develops a programmable LO signal for the Mixer (MX1) in

the Downconverter/Preamplifier (A1). The frequency of the LO signal is calculated as the sum of

the visual IF carrier and the visual VHF carrier of the specified input channel. The LO signal's

frequency is programmed by the setting of switches S1 through S4 which are accessible through

the module's cover. The relationship between the setting of these switches and the resulting LO

frequency is provided in Table 2 3 for each VHF channel.

A 10MHz reference signal is brought in from the Reference Oscillator (A4A2) through J1, 10MHz

IN. Both sections of U4 perform binary divide-by-5 counting to provide a 400kHz signal to the

OSCin input of U1, pin 27. To create U1's internal 50kHz reference signal, U1 performs a binary

divide-by-8 operation on the OSCin signal.

Controlling the VCO, G1, is the output of op-amp U3. U3 compares and integrates the 0/V and 0/R

phase detector outputs of U1. The output of U3 is filtered to create the dc control voltage for the

VCO. The output of G1, RF OUT, is amplified by U5 and available as the Receiver's LO at J2,

OUT.

The output of G1 is also amplified by U6 and then fed to a ÷32/÷33 prescaler, U2. After prescaling,

the signal is connected to U1 pin 1, Fin, from U2 pin 4, OUT, completing the loop. The prescaling

factor of U2 is selected by the MOD CONTROL, pin 9, of U1. Switches S1 to S4 set two

divide-by-ratios, counters A and N, within U1. When divide-by-A is being performed on the signal

at Fin, MOD CONTROL is set high, selecting ÷32 in the prescaler, U2. MOD CONTROL goes low

for divide-by-N selecting ÷33 in U2.

The A and N counters form a binary number from A0 to N9 with A0 being the LSB and N9 being

the MSB. The decimal equivalent of this number, when multiplied by the internal reference

frequency 50kHz, gives the synthesizer's output frequency. Hence, for NTSC operation, A0 and

A1, pins 21 and 23 on U1, are grounded. For PAL operation, A0 and A1 are made high by cutting

2 6

the traces from pins 21 and 23 to ground thereby adding the 150kHz to the LO that is characteristic

of the PAL system.

When the synthesizer is locked onto a frequency, LD is high. This saturates Q1 and puts a low on

SYNTH LOCK. C28 provides a time delay to ensure that the synthesizer has successfully locked

before indicating so on the SYNTH LOCK line. For an unlocked condition, LD pulses low

preventing C28 from charging and saturating Q1. +5V is therefore present on the SYNTH LOCK

line for the unlocked condition.

2.1i VHF Synthesizer High Band:

Schematic Diagram 30362003/Rev D A1A4A1

10MHz REF. IN (J1) 3.5V P/P square wave

LO OUT (J2) +15.25dBm min.

SYNTH. LOCK (Pin A of J4) logic high (locked)

logic low (unlocked)

The VHF Synthesizer is a phase-lock loop type and uses one of the 10MHz reference signals from

the Reference Oscillator (A4A2) and develops a programmable LO signal for the Mixer (MX1) in

the Downconverter/Preamplifier (A1). The frequency of the LO signal is calculated as the sum of

the visual IF carrier and the visual VHF carrier of the specified output channel. The LO signal's

frequency is programmed by the setting of switches S1 through S4 which are accessible through

the module's cover via access holes. The relationship between the setting of these switches and

the resulting LO frequency is provided in Table 2 2 for each VHF channel.

A 10MHz reference signal is brought in from the Reference Oscillator (A4A2) through J1, 10MHz

IN. Both sections of U4 perform binary divide-by-5 counting to provide a 400kHz signal to the

OSCin input of U1, pin 27. To create U1's internal 50kHz reference signal, U1 performs a binary

divide-by-8 operation on the OSCin signal.

Controlling the VCO, G1, is the output of op-amp U3. U3 compares and integrates the 0/V and 0/R

phase detector outputs of U1. The output of U3 is filtered to create the dc control voltage for the

VCO. The output of G1, RF OUT, is amplified by U5 and available as the Receiver's LO at J2,

OUT.

The output of G1 is also amplified by U6 and then fed to a ÷64/÷65 prescaler, U2. After prescaling,

the signal is connected to U1 pin 1, Fin, from U2 pin 4, OUT, completing the loop. The prescaling

factor of U2 is selected by the MOD CONTROL, pin 9, of U1. Switches S1 to S4 set two

divide-by-ratios, counters A and N, within U1. When divide-by-A is being performed on the signal

at Fin, MOD CONTROL is set high, selecting ÷64 in the prescaler, U2. MOD CONTROL goes low

for divide-by-N selecting ÷65 in U2.

The A and N counters form a binary number from A0 to N9 with A0 being the LSB and N9 being

the MSB. The decimal equivalent of this number, when multiplied by the internal reference

frequency 50kHz, gives the synthesizer's output frequency. Hence, for NTSC operation, A0 and

A1, pins 21 and 23 on U1, are grounded. For PAL operation, A0 and A1 are made high by cutting

the traces from pins 21 and 23 to ground thereby adding the 150kHz to the LO that is characteristic

of the PAL system.

2 7

When the synthesizer is locked onto a frequency, LD is high. This saturates Q1 and puts a low on

SYNTH LOCK. C28 provides a time delay to ensure that the synthesizer has successfully locked

before indicating so on the SYNTH LOCK line. For an unlocked condition, LD pulses low

preventing C28 from charging and saturating Q1. +5V is therefore present on the SYNTH LOCK

line for the unlocked condition.

2.1j UHF Synthesizer:

Schematic Diagram 30367094/Rev B A1A4A1

10MHz REF. IN (J1) 3.5V P/P square wave

LO OUT (J2) +15.25dBm min.

SYNTH. LOCK (Pin A of J4) logic high (locked)

logic low (unlocked)

The UHF Synthesizer is a phase-lock loop type and uses one of the 10MHz reference signals from

the Reference Oscillator (A4A2) and develops a programmable LO signal for the Mixer in the

Downconverter/Preamplifier (A1). The frequency of the LO signal is calculated as the sum of the

visual IF carrier and the visual UHF carrier of the specified output channel. The LO signal's

frequency is programmed by the setting of switches S1 through S4 which are accessible through

the module's cover via access holes. The relationship between the setting of these switches and

the resulting LO frequency is provided in Table 2 1 for each UHF channel.

A 10MHz reference signal is brought in from the Reference Oscillator (A4A2) through J1, 10MHz

IN. Both sections of U4 perform binary divide-by-5 counting to provide a 400kHz signal to the

OSCin input of U1, pin 27. To create U1's internal 50kHz reference signal, U1 performs a binary

divide-by-8 operation on the OSCin signal.

Controlling the VCO, G1, is the output of op-amp U3. U3 compares and integrates the 0/V and 0/R

phase detector outputs of U1. The output of U3 is filtered to create the dc control voltage for the

VCO. The output of G1, RF OUT, is amplified by U5 and available as the Receiver's LO at J2,

OUT.

The output of G1 is also amplified by U6 and then fed to a ÷64/÷65 prescaler, U2. After prescaling,

the signal is connected to U1 pin 1, Fin, from U2 pin 4, OUT, completing the loop. The prescaling

factor of U2 is selected by the MOD CONTROL, pin 9, of U1. Switches S1 to S4 set two

divide-by-ratios, counters A and N, within U1. When divide-by-A is being performed on the signal

at Fin, MOD CONTROL is set high, selecting ÷64 in the prescaler, U2. MOD CONTROL goes low

for divide-by-N selecting ÷65 in U2.

The A and N counters form a binary number from A0 to N9 with A0 being the LSB and N9 being

the MSB. The decimal equivalent of this number, when multiplied by the internal reference

frequency 50kHz, gives the synthesizer's output frequency. Hence, for NTSC operation, A0 and

A1, pins 21 and 23 on U1, are grounded. For PAL operation, A0 and A1 are made high by cutting

the traces from pins 21 and 23 to ground thereby adding the 150kHz to the LO that is characteristic

of the PAL system.

When the synthesizer is locked onto a frequency, LD is high. This saturates Q1 and puts a low on

SYNTH LOCK. C28 provides a time delay to ensure that the synthesizer has successfully locked

before indicating so on the SYNTH LOCK line. For an unlocked condition, LD pulses low

2 8

preventing C28 from charging and saturating Q1. +5V is therefore present on the SYNTH LOCK

line for the unlocked condition.

2.1k Downconverter/Preamplifier:

Schematic A331-29/Rev B A1A1

Gain with Conversion (J1-J2) 3.0dB

Collector V (Q1) 7.9V

LO Input (Min.) (J3) +7dBm

The Downconverter preamplifier (A1) consists of a single stage, low noise, broadband amplifier

with a double balanced mixer. The VHF or UHF input signal is coupled to Q1 where it is amplified

before driving the mixer. The mixer combines the composite VHF or UHF television signal from

Q1 with a constant amplitude unmodulated RF signal (LO) from the reference oscillator/synthesizer

pair or the crystal oscillator/multiplier pair. Both signals are heterodyned in the mixer where their

sum and difference frequencies are developed. Capacitors C10 through C13 along with inductors

L4 through L7 comprise a low-pass filter network allowing only the modulated difference frequency

(IF) to pass.

2.1l IF SAW Filter/Amplifier:

Schematic B331-21/Rev D A1A2

Q1 Q2 Q3 J1-J2

Gain 21dB

Collector V 15V 18V 11V

Collector I 16mA 56mA 16mA

The IF Surface Acoustic Wave (SAW) Filter/Amplifier is a three-stage amplifier. Transistors

Q1/Q2 amplify the IF input signal while their associated feedback networks maintain a flat

passband response. The SAW filter provides high selectivity with no need for tuning or alignment.

Transistor amplifier Q3 overcomes the loss associated with the SAW filter. Its feedback circuitry

is also designed to compensate for nonlinear gain characteristics (i.e., lower gain at the higher

frequencies).

2 9

2.1m IF AGC Amplifier:

Schematic C331-37/Rev G A1A3

Q1 Q2 Q3 J1-J2

Gain 10-50dB

Collector V +20.5Vdc +25Vdc +23.4Vdc

Collector I 4.5mAdc 27mAdc 60mAdc

Power Output 0dBm

The IF AGC Amplifier is a variable gain amplifier with its own automatic gain control and limiter

sections. The IF AGC Amplifier is calibrated to provide a constant IF output of approximately

0dBm with a range of 70dBm to 30dBm received signal. The amplifier section consists of three

common-emitter RF transistor stages (Q1, Q2, Q3) that produce a combined gain of 50dB.

Overall gain is adjustable by varying the amount of Q1's emitter bypass via potentiometer R15

(GAIN ADJ). Q2 and Q3 are fixed bias amplifiers separated by a 9dB, 50 ohm-to-50 ohm matching

pad (R22, 23, 24). Q3's feedback network, consisting of TILT ADJ potentiometer R31, inductor L2,

and capacitor C12, is designed to compensate for the overall frequency characteristics of the

module (lower gain at higher frequencies). TILT ADJ potentiometer R31 controls the amplifier's

frequency response by varying the amount of Q3's negative feedback.

The automatic gain control section consists of an input AGC circuit (L3, C14, CR8, U1, and

surrounding components) and a variable pin diode attenuator (CR1, 2, 4, and surrounding

components). The input AGC circuit is centered around operational amplifier U1. A portion of the

IF signal is coupled off of Q3 to a tank circuit (C14, L3) tuned to the visual IF carrier frequency

(45.75MHz). The tank energy forward biases detector diode CR8 and then becomes filtered by an

RC network (C13, R29) which results in a negative dc voltage proportional to the peak value of the

visual IF signal. This negative dc voltage is buffered by operational amplifier U1B and then

supplied to the Limiter/Output AGC Control (PC1) as the LIMITER REFERENCE OUT voltage.

The buffered negative dc voltage is also supplied to operational amplifier U1A where it is inverted

and summed with the negative OUTPUT AGC IN reference voltage from PC1, resulting in a

positive dc voltage (AGC) proportional to the visual IF signal level. This AGC voltage is used to

control the biasing (thus attenuation) of the variable pin diode attenuator and to activate the

Automatic-On circuit (PC2).

NOTE: When the front panel OPERATE/ALIGN switch of the Receiver drawer is in the ALIGN

position, the IF AGC Amplifier's PRIMARY AGC OUT voltage is replaced by a +5Vdc

reference voltage at pin J3-1.

The main function of the limiter circuit is to prevent overdriving the amplifier modules in the

translator's Upconverter and Power Amplifier drawers when the input signal to the Receiver returns

after periods of reception fading. For example, following a temporary reduction (fading, etc.) in the

received signal, the AGC voltage decreases which reduces the attenuation provided by the IF AGC

Amplifier's variable pin diode attenuator. However, once the received signal regains its strength,

the variable pin diode attenuator cannot attenuate this signal fast enough. The limiter circuit is

used to overcome this characteristic of the variable pin diode attenuator. Notice that with an

increase in the received signal, the AGC voltage increases while the limiter reference voltage

decreases. The variable pin diode attenuator will eventually respond to the increase in the AGC

voltage by increasing its attenuation. The limiter control circuit on PC1 quickly responds to a 3dB

or greater instantaneous increase in the IF AGC Amplifier's LIMITER REFERENCE OUT voltage

J3-3 by pulling the LIMITER ENABLE IN J3-4 low, turning off transistor Q4 of the IF AGC Amplifier.

210

With Q4 turned off, the dc forward bias is removed from pin diode CR9, thus reducing momentarily

the IF output of the IF AGC Amplifier by approximately 20dB. The momentary attenuation in the

IF output by the limiter circuit allows sufficient time for the variable pin diode attenuator to adjust

itself to the change in the AGC voltage. Overdriving can also occur when the translator is first

turned on. To compensate, Q6 is on, turning on Q5. This shuts off Q4, increasing the attenuation

of CR9, as above, until C32 charges. Q6 and Q5 then turn off, allowing LIMITER ENABLE IN,

which is normally high, to turn on Q4. This forward biases CR9 by providing a dc path to ground

through it for the +15V from pin J3-5.

2.1n Automatic-On:

Schematic B331-44/Rev C A1PC2

The Automatic-On circuit uses differential amplifier U1A to compare the AGC voltage, developed

by the IF AGC Amplifier, to a preset reference voltage set by THRESHOLD ADJUST potentiometer

R4. An input signal above the minimum acceptable Receiver input level of 60dBm will produce

an AGC voltage above the Auto-On Threshold potential. As the AGC voltage (pin 3 of U1A)

exceeds the Auto-On Threshold reference voltage (pin 2 of U1A), differential amplifier U1A

saturates in the positive mode charging capacitor C1. Once C1 charges above the reference

potential at pin 6 of U18, differential amplifier U1B will also saturate in the positive mode turning

on transistor Q1. With Q1 forward biased, a ground is provided for relay K1 which energizes the

device. The closed contacts of K1 place +5Vdc on the INTLK (VIDEO SENSE) line going to the

Exciter’s Control Board (A2PC1). An Auto-On delay network consisting of R8, R9, and C1 slows

down the turn-on and turn-off activation time. This delay of approximately 30 seconds prevents

on/off cycling from occurring during periods of weak reception lasting for less than 30 seconds.

2.1o Limiter/Output AGC Control:

Schematic B331-34/Rev C A1PC1

The Limiter/Output AGC Control board monitors and controls the IF AGC Amplifier (A3) and

controls the CARRIER PRESENT LED (DS1) on the Receiver front panel.

The AGC negative reference voltage is placed on pin 3, OUTPUT AGC, by inverting op-amp U1B.

Potentiometer R9, AGC REF, sets this voltage. Keep the PRE AGC REF ADJ potentiometer fully

clockwise because it and the POWER REFERENCE portion of the AGC circuit, from pin 1 to pin 2,

are not used in this application.

LIMITER REFERENCE IN is brought in from A3 on pin 12 and is compared to an 11.8V reference

by U2B. When a carrier greater than 60dB is received, the output of U2B will saturate by

approximately +15V turning on Q3. This provides a path to ground through current limiting resistor

R23 on pin 10 for the CARRIER PRESENT LED (DS1) on the Receiver drawer front panel,

illuminating it green. If the received carrier level drops below 60dBm, U2B saturates to 15V

turning off Q3. The LIMITER ADJUST potentiometer, R13, voltage divides the LIMITER

REFERENCE INPUT and passes it through unity gain follower U2A and unity gain follower U2C.

U2D takes the difference between the 8.7V reference, from CR2, and the output U2C. For the

nominal level of the carrier being received, the output of U2C is less than 8.7V and U2D puts

approximately +15V on LIMITER ENABLE OUT, pin 9. The LIMITER ADJ is set so that, if

211

LIMITER REFERENCE IN increases by 3dB, the output of U2C will be greater than 8.7V and U2D

will saturate to approximately 15V pulling down LIMITER ENABLE OUT.

2.1p Aural Notch Filter:

Schematic Diagram 10383097/Rev 51 A1FL2

Insertion Loss (J1-J2) 0.4dB Max.

The Aural Notch Filter provides a means of attenuating the aural carrier 3dB which can be useful

for reducing the effects of in-band and out-of-band intermodulation. Variable capacitor C3 tunes

the notch to the aural IF frequency in an NTSC system, 41.25MHz. This capacitor is preset by the

EMCEE Test Department. R1 sets the amount of attenuation; up to 3.5dB of attenuation can be

attained. The filter is a very high Q type and does not have an appreciable effect on the visual

carrier or color subcarrier.

2.1q Multi-Output Power Supply:

Interconnection Diagram B326-18/Rev C A1PS1

Voltage Rated Current

+25Vdc 1Adc

±15Vdc 1Adc

±5Vdc 1Adc

As shown on the Interconnection Diagram, the Multioutput Power Supply consists of surge

suppressor E1, transformer T1, and printed circuit boards PC1 and PC2. PC1 is the +25V Power

Supply, and PC2 is the ±15V/±5V Power Supply. Surge suppressor E1 provides voltage-transient

protection for the step-down transformer T1 and the +25V Power Supply.

+25V Power Supply:

Schematic B326-15/Rev C A1PS1PC1

The secondary voltage of step-down transformer A1PS1T1 is applied to bridge rectifier CR1. After

filtering, the rectified voltage ( 36V) is regulated by U1 to the +25Vdc level. The output voltage

of U1 is fixed by resistors R1, R2, and R3. +25Vdc is supplied to various modules in the Receiver

drawer.

212

±15V/±5V Power Supply:

Schematic B326-12/Rev D A1PS1PC2

120Vac is placed across the primary of step-down transformer T1. Surge suppressor E1 provides

voltage-transient protection for this supply. Transformer T1 supplies a secondary voltage to bridge

rectifier CR1. The output of CR1 is divided, with the negative voltage applied to 15Vdc regulator

U2 and the positive potential fed to +15Vdc regulator U1. Voltage regulators U3 and U4 tap off of

the 15V lines to provide +5Vdc and 5Vdc, respectively. The capacitors provide filtering for the

different regulators. ±15Vdc is supplied to the IF AGC Amplifier (A3), the Limiter/Output AGC

circuit (PC1), and the Automatic-On circuit (PC2). +5Vdc is supplied to the IF AGC Amplifier (A3).

2.1r Digital Code ID Unit: (OPTIONAL)

Schematic 20258029/Rev A A1PC3

According to FCC Rules and Regulations, Section 74.783, each television broadcast transmitter

in the United States of over 1 watt peak visual power must transmit its call sign in International

Morse Code every 60 minutes or arrange for the primary station to visually or aurally identify the

transmitter and its location. The Digital Code Identification Unit is available for the customer who

wishes to identify a transmitter station with Morse Code. The ID unit is a sixteen word by eight bit

sequencer which generates a series of pulses used to shift the frequency of the transmitted carriers

by frequency shift keying (FSK) the transmitter's Upconverter Oscillator.

The Digital Code ID Unit is composed of four integrated circuits: a Dual Timer (U4), a Dual 4 Bit

Counter (U3), a Programmable Read Only Memory (U2) and an 8 to 1 Line Multiplex (U1). The

Dual Timer or master clock contains two sections which control the operation of the ID unit by

dictating when and at what rate pulses will be fed to the Upconverter oscillator. The first section

of the timer is a gated astable oscillator or bit clock which produces square-wave pulses at a rate

of approximately 20Hz. The bit rate is controlled by U4 resistors R11, R12 and capacitor C2. The

second section of U4 is a 20 minute timer controlled by resistors R9, R10 and capacitor C1. When

C1 charges to 63% of its capacity (after 20 minutes), pin 9 of U4 will go low, reverse biasing

transistor Q3 which presents a high (4Vdc) at pin 4. This high gates on the bit generator which

feeds the 20Hz pulses to pin 1 of the Dual 4 Bit Counter (U3).

As each clock pulse reaches pin 1 of U3, the 4 Bit Counter "counts" the number of pulses entering

the chip and displays that count in binary code at its own pins 3, 4 and 5. For example, as the first

pulse is fed to U3, pin 3 goes high representing the decimal number 1 in binary code (001). With

the second clock pulse, U3 pin 4 goes high and pin 3 goes low representing the binary number 2

(010). This counting process will continue up to the number 7 (111) and, as the eighth pulse is fed

to the counter, pins 3, 4, and 5 will all go low (000) to begin the sequence over again. During this

time integrated circuit U2, the Programmable Read Only Memory (PROM), has a series of high and

low voltages present at its pins 1 through 9 (excluding pin 8 which is ground). These voltages are

bits which make up the first word (Morse code letters or numbers) of the transmitter's call sign.

(The transmitter's call sign is programmed into the PROM by the EMCEE test department.) In

order for this information to be delivered to the Upconverter oscillator, it must be converted from

parallel form to serial form by the 8 Line to 1 Line Multiplexer (U1). The binary numbers developed

by the Dual 4 Bit Counter are fed to pins 9, 10, and 11 of the 8 to 1 Line Multiplexer. Each binary

number (or voltage fluctuation) presented to U1 signals the multiplexer circuit to individually read

(take) the parallel bits presented by the PROM and deliver them serially to the oscillator via

transistor Q4. Therefore, as the Dual 4 Bit Counter (U3) feeds the binary numbers 1 (001) to pins

213

9, 10 and 11 of the Line Multiplexer (bit address), the Multiplexer reads the bit at pin 1 of the

PROM (U2) and delivers it to the base of transistor Q4. With each subsequent binary number

(010, 011, 100, 101, 110, 111, 000) provided by the Dual Counter, the Line Multiplexer will read

each individual PROM bit present at U2 pins 2 through 9 (exclude pin 8) until the Dual Counter

reaches 111. The next pulse then resets the count to 0 (000). The transition from high to low (1

to 0) at pin 5 of the counter is seen by pin 13, causing pin 11 of U3 to go high. This binary

number 1 (0001) seen by pins 10, 11, 12 and 13 (word address) of U2 causes the PROM to present

the second set (word) of eight bits to the Line Multiplexer. The Dual Counter (U3 – pins 3, 4, 5)

presents another binary eight count to the Line Multiplexer (U1 – pins 9, 10, 11) which individually

reads the eight new PROM bits (U2 – pins 1 through 9) and delivers them to transistor Q4. At the

end of the second eight count, pin 13 of U3 again sees a high to low transition which causes pin 10

of U3 to go high while pin 11 goes low (binary number 2 = 0010). With U2 pins 10 through 13

receiving a binary number 2, a third word is presented to the Line Multiplexer by the PROM. This

entire process occurs so that the PROM delivers 16, eight bit words to the Upconverter oscillator

via the Line Multiplexer. After word 16, pins 8 through 10 of U3, which were all high (binary

number 16 = 1111), drop to zero. The negative going transition at pin 8 of U3 is coupled to

transistor Q1 via C3. This action forward biases transistor Q2 which discharges capacitor C1. As

the voltage at pin 12 of the Dual Timer drops, pin 9 goes high causing pin 4 of U4 to go low. The

Dual Timer's bit clock is gated off, disabling the Digital Code Identification Unit for 20 minutes until

capacitor C1 recharges.

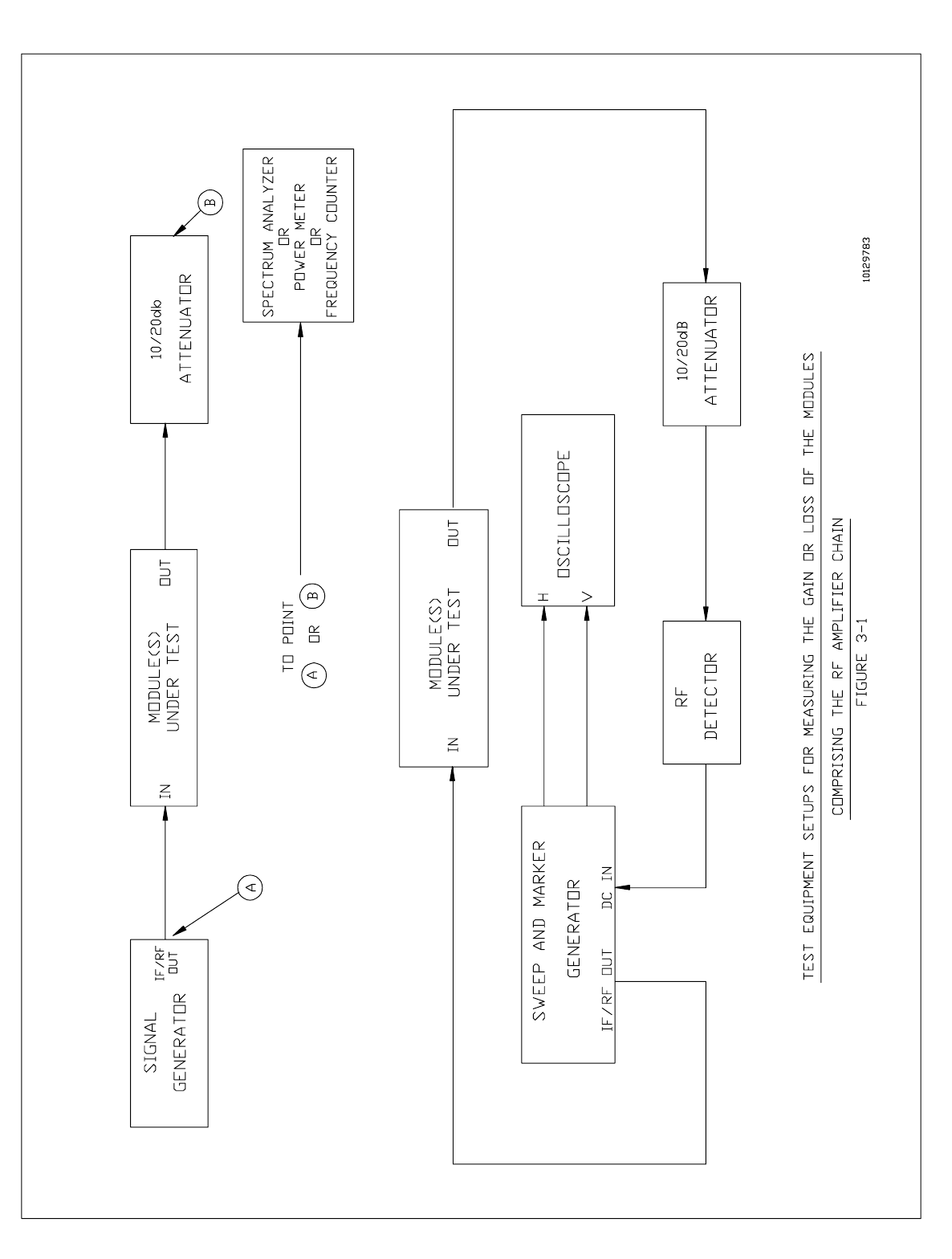

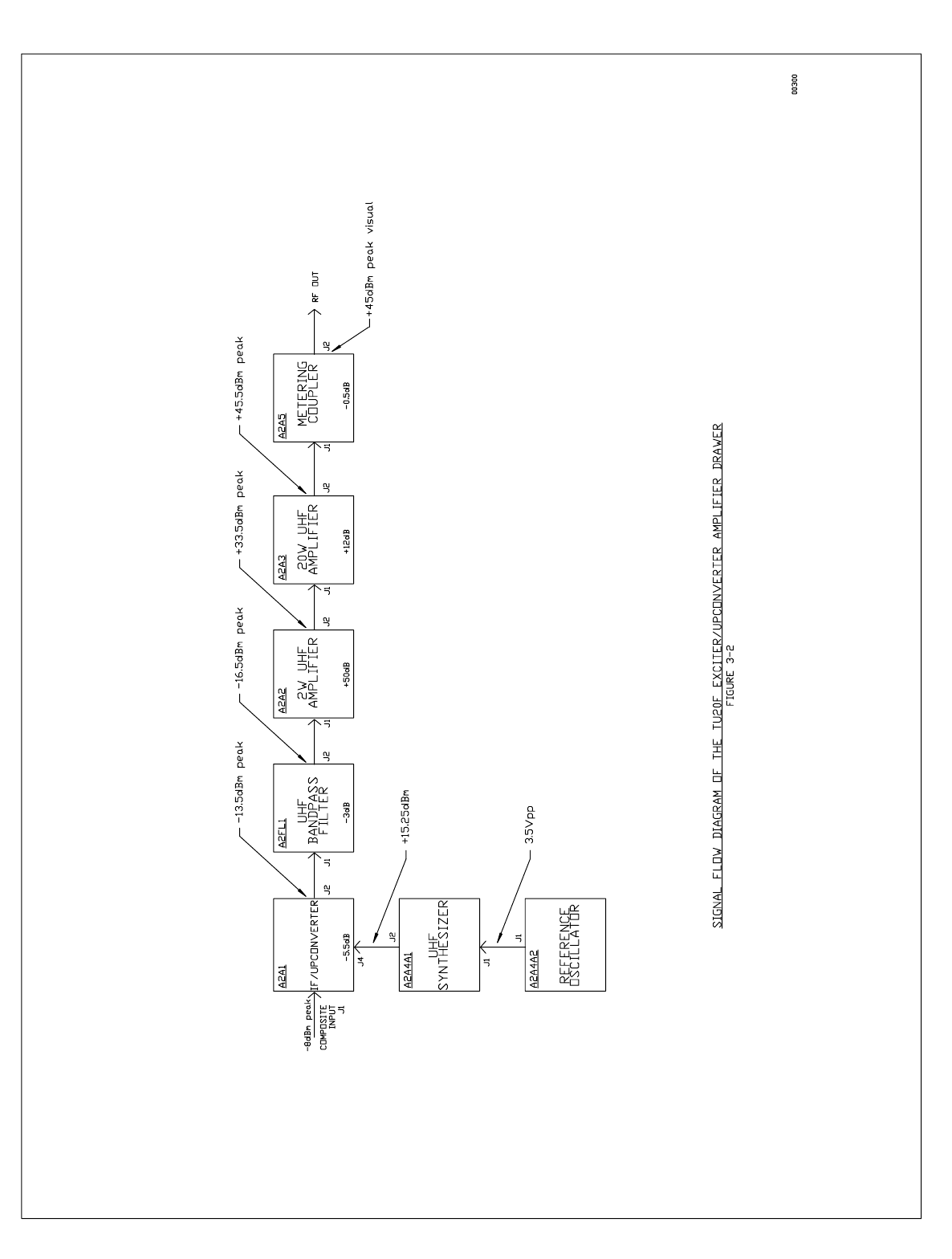

2.2 Exciter/Upconverter Drawer:

Interconnection Diagram 40383113/Rev 55 A2 TTU20F

Composite IF IN (J1) 8dBm peak visual

RF OUT (J2) +43dBm peak visual

+33dBm average aural

LO SAMPLE (J3) +9dBm ± 2dBm

The Exciter/Upconverter drawer converts the composite IF signal from the Receiver to the desired

UHF channel, then amplifies the RF signal to the desired output level. This drawer is used to drive

the two Dual 300W Final Amplifier Drawers (A3, A4). The Linearizer provides precorrection to the

composite IF signal. Upconversion is performed by the IF Upconverter (A1) along with the UHF

Synthesizer (A4). The UHF Synthesizer provides a programmable LO to the IF Upconverter

module where the LO and IF signal from the Receiver are mixed to create the desired UHF

frequency. The IF Upconverter also provides AGC and precorrector functions. The UHF signal

from the Upconverter module is passed through a UHF Bandpass Filter (FL1) to remove the

unwanted products from the conversion process while passing the desired signal with a minimal

loss. The RF is then amplified approximately 50dB by a 2W Driver Amplifier (A2) and then

amplified another 12dB by a 20W UHF Amplifier (A3). The output signal is passed through the

Metering Coupler (DC1). The Metering Coupler provides samples for the Metering Detector (A5)

while passing the signal to the output of the drawer.

Metering and control functions are provided by the Metering Detector, the Metering Switch (PC2),

and the Control Board (PC1). The Control Board also has several status and diagnostic LED

indicators. Power is supplied to the drawer by two power supplies, a ±15V/+5V linear supply (PS2)

and a +28V switching supply (PS1).

214

2.2a Linearizer:

Schematic Diagram 30367078/Rev 60 A2A6

Gain with S1 OFF (J1-J2) 3dB min./6dB max.

Gain with S1 ON (J1-J2) 6dB min./12dB max.

Emitter of Q1/Q2 +4.8Vdc @ 13mAdc/+13Vdc @ 30mAdc

Emitter of Q3/Q4 +3.3Vdc @ 11mAdc/+15Vdc @ 45mAdc

Emitter of Q5 +8.7Vdc @ 22mAdc

The Linearizer is a five-stage circuit which compensates for linearity distortions generated by the

translator's Class AB power amplifiers. Transistors Q1 through Q5 are all amplifier stages with the

Q1/Q2 combination providing approximately 20dB of gain. 8dB of gain is provided by transistors

Q3/Q4. Q2, Q4, and Q5 are used as low impedance emitter followers. Variable gain expansion

networks which furnish linearity correction are centered around diodes CR1 through CR8, slope

potentiometers SL1 through SL4 (i.e., R10, R11, R21, R22), unity gain inverting amplifiers U1 and

U2, threshold potentiometers TH1 through TH4 (i.e., R37, R38, R39, R40), and switch S1. When

S1 is in the OFF position, each diode pair is continuously reverse biased throughout the positive

and negative cycles of the visual IF carrier. Due to the high reverse resistance provided by CR1

through CR8, each network essentially represents a resistive L-pad with the composite IF signal

attenuated by a fixed amount. As a result, no linearity correction is provided. However, when S1

is in the ON position and the Linearizer is properly adjusted, the four diode pairs form a nonlinear

circuit where each diode pair is biased to turn on at different points of the positive and negative

cycles of the visual IF carrier envelope. Each diode pair is initially reverse biased by equal but

opposite polarity dc voltages established by U1 and U2. L1 through L8, shunted by R29 through

R36, isolate the visual IF carrier from the diode biasing circuitry. When the positive and negative

peaks of the visual IF carrier are sufficient to forward bias a diode pair, the diode pair turns on

placing the resistance of its respective slope potentiometer either in parallel or in shunt to ground

with its respective series arm resistance. As a result of switching additional resistance in parallel

or shunt with the series arm of the L-pad, the attenuation of the visual IF carrier is reduced.

Threshold potentiometers TH1 through TH4 determine the turn-on point of each diode pair while

slope potentiometers SL1 through SL4 vary the amount of gain expansion achieved during the

turn-on period of each diode pair. Threshold controls TH1, TH2, and TH3 are used to adjust the

differential gain of the white to black region while TH4 adjusts the sync amplitude. When properly

adjusted, the Linearizer provides sync amplitude, differential gain, and intermodulation correction

to the RF output signal.

2.2b IF/Upconverter:

Schematic Diagram 30383013/Rev 55 A2A1

IF INPUT (J1) 8dBm peak visual

RF OUTPUT (J2) 13.5dBm minimum

LO SAMPLE (J3) +9dBm ± 2dB

LO INPUT (J4) +13dBm minimum

The IF/Upconverter performs three tasks in this translator. It provides signal precorrection, AGC

level control, and it upconverts the IF signal to the desired UHF channel. This module also

provides a sample of the LO signal to the Exciter’s front panel.

215

The IF input at J1 is attenuated by AT1, an adjustable attenuator which can be tuned to

compensate for different input levels. A monolithic amplifier (U1) provides approximately 12dB

of gain to the signal passed through the attenuator. U1 is biased by R1 with L1 providing

impedance matching and isolation. C2 is an RF bypass capacitor, while C1 and C3 are coupling

capacitors. T1 steps up the signal's voltage to drive the precorrector circuit made up of CR1, C4

to C6, C8 to C12, R2 through R10, L4, L5, U2, and S1. This circuit compensates for linearity

distortions generated by the wideband power amplifiers or created by the Receiver. When switch

S1 is in the off position (open), this circuit reduces to a simple attenuator formed by R2 and R3;

therefore, no precorrection is provided. When S1 is on, the precorrector becomes a nonlinear

circuit that provides less attenuation for the positive and negative peaks of the IF signal, thereby

stretching the waveform. CR1 is biased by U2 A and B, with each op amp biasing one half of CR1.

The amount of bias provided by U2 is determined by R7 through R10. R9 allows the bias level to

be adjusted. This adjustment determines at which point on the waveform precorrection begins.

R5, R6, C8 through C11, L4, and L5 provide isolation between CR1 and U2. C4 to C6 are dc

blocking capacitors. The precorrector operates by placing R4 in parallel with R2 when the IF signal

is positive or negative enough to forward bias half of CR1. Adjusting R4 determines the amount

of precorrection provided. At the output of the precorrector, a second monolithic amplifier provides

+12dB of gain to the IF signal. C7 and C14 are coupling capacitors while C13 acts as an RF

bypass. L2 is an RF choke and R11 provides the correct bias voltage for U3.

The next circuit in the Upconverter is the AGC circuit. Three PIN diodes, CR2, CR3, and CR4,

form a voltage controlled attenuator along with R14 and C17. C14, C16, and C18 serve as dc

blocking capacitors. Bias is provided to this attenuator by R12, VR1, and R13, as well as R15, L3,

and the three operational amplifiers U4(A), U5(A), and U5(B). C15, C32, and C19 are bypasses.

The control voltage for the AGC is generated by U5(B). A dc voltage proportional to the output

power is connected to pin 6 of U5 by R26. A reference voltage from the Control Board's Power

Adjust circuit is supplied to pin 5 of U5 by R22. U5(B) compares these two voltages and provides

a control voltage at pin 7 of U5. R27 sets the gain of U5(B) to unity. U5(A) is an integrator that

provides a smooth transition for the changing control voltage. Input to U5(A) is provided by R20,

with C22 as the integration capacitor. A reference voltage is provided to pin 3 of U5 by R21 and

CR5 through CR7. The output of U5(A) is passed through an attenuator formed by R18 and R19

before driving the unity gain buffer amplifier formed by U4(A) R16 and R17. When the OPERATE/

ALIGN switch is in the ALIGN position, pin 3 of U4A is grounded. This defeats the AGC circuit and

allows minimum attenuation of the IF signal. Q1, R35-R37 and C33 make up a soft start circuit

that retards the spike in output power that normally would occur when the translator is turned ON

and the OPERATE/STANDBY switch is placed in the OPERATE position. The circuit places

approximately +13Vdc on pin 3 of U4A, putting the AGC circuit into a condition of maximum

attenuation. As C33 charges, this imposed voltage on pin 3 decreases giving the AGC circuit time

to stabilize before Q1 turns off and the output of U5A takes control of the AGC. Whenever +28V

switched is removed from the drawer (OFF or STANDBY), CR8 forward biases and C33 discharges

through it and R38 to ground. The output of U4(A) is the AGC control voltage.

The IF output of the AGC circuit connects to mixer MX1 where it is combined with the LO signal

from the synthesizer to produce the desired UHF channel frequency at the RF output port, J2. The

LO is brought to the mixer by R29 and R30 (which provide isolation) and U7, an amplifier that

provides about 12dB of gain to the signal. U7 is biased by R28. A sample of the LO is also

supplied to connector J3 via U6, the input of which is attenuated by R31 to R33. U6, biased by

R34, provides 12dB of gain. C24 to C27 are coupling capacitors, while all remaining capacitors

are RF bypasses.

216

2.2c UHF Synthesizer:

Schematic Diagram 30367094/Rev B A2A4A1

10MHz REF. IN (J1) 3.5V P/P square wave

LO OUT (J2) +15.25dBm min.

SYNTH. LOCK (Pin A of J4) logic high (locked)

logic low (unlocked)

The UHF Synthesizer is a phase-lock loop type and uses one of the 10MHz reference signals from

the Reference Oscillator (A4A2) and develops a programmable LO signal for the Mixer (MX1) in

the IF Upconverter (A1). The frequency of the LO signal is calculated as the sum of the visual IF

carrier and the visual UHF carrier of the specified output channel. The LO signal's frequency is

programmed by the setting of switches S1 through S4 which are accessible through the module's

cover via access holes. The relationship between the setting of these switches and the resulting

LO frequency is provided in Table 2 1 for each UHF channel.

A 10MHz reference signal is brought in from the Reference Oscillator (A4A2) through J1, 10MHz

IN. Both sections of U4 perform binary divide-by-5 counting to provide a 400kHz signal to the

OSCin input of U1, pin 27. To create U1's internal 50kHz reference signal, U1 performs a binary

divide-by-8 operation on the OSCin signal.

Controlling the VCO, G1, is the output of op-amp U3. U3 compares and integrates the 0/V and 0/R

phase detector outputs of U1. The output of U3 is filtered to create the dc control voltage for the

VCO. The output of G1, RF OUT, is amplified by U5 and available as the Exciter/Upconverter's

LO at J2, OUT.

The output of G1 is also amplified by U6 and then fed to a ÷64/÷65 prescaler, U2. After prescaling,

the signal is connected to U1 pin 1, Fin, from U2 pin 4, OUT, completing the loop. The prescaling

factor of U2 is selected by the MOD CONTROL, pin 9, of U1. Switches S1 to S4 set two

divide-by-ratios, counters A and N, within U1. When divide-by-A is being performed on the signal

at Fin, MOD CONTROL is set high, selecting ÷64 in the prescaler, U2. MOD CONTROL goes low

for divide-by-N selecting ÷65 in U2.

The A and N counters form a binary number from A0 to N9 with A0 being the LSB and N9 being

the MSB. The decimal equivalent of this number, when multiplied by the internal reference

frequency 50kHz, gives the synthesizer's output frequency. Hence, for NTSC operation, A0 and

A1, pins 21 and 23 on U1, are grounded. For PAL operation, A0 and A1 are made high by cutting

the traces from pins 21 and 23 to ground thereby adding the 150kHz to the LO that is characteristic

of the PAL system.

When the synthesizer is locked onto a frequency, LD is high. This saturates Q1 and puts a low on

SYNTH LOCK. C28 provides a time delay to ensure that the synthesizer has successfully locked

before indicating so on the SYNTH LOCK line. For an unlocked condition, LD pulses low

preventing C28 from charging and saturating Q1. +5V is therefore present on the SYNTH LOCK

line for the unlocked condition.

217

2.2d Reference Oscillator:

Schematic Diagram 10368037/Rev B A2A4A2

10MHz REF. OUT (J1, J2) 3.5V P/P square wave

The Reference Oscillator provides a 10MHz reference signal for the UHF Synthesizer (A4A1). This

module is centered around a 10MHz temperature-compensated crystal oscillator (G1). The output

from G1 is applied to two exclusive-OR gates used as inverting buffers. The output signal from

each gate is a 10MHz low-level square wave with a frequency stability of 0.3 parts per million

(PPM).

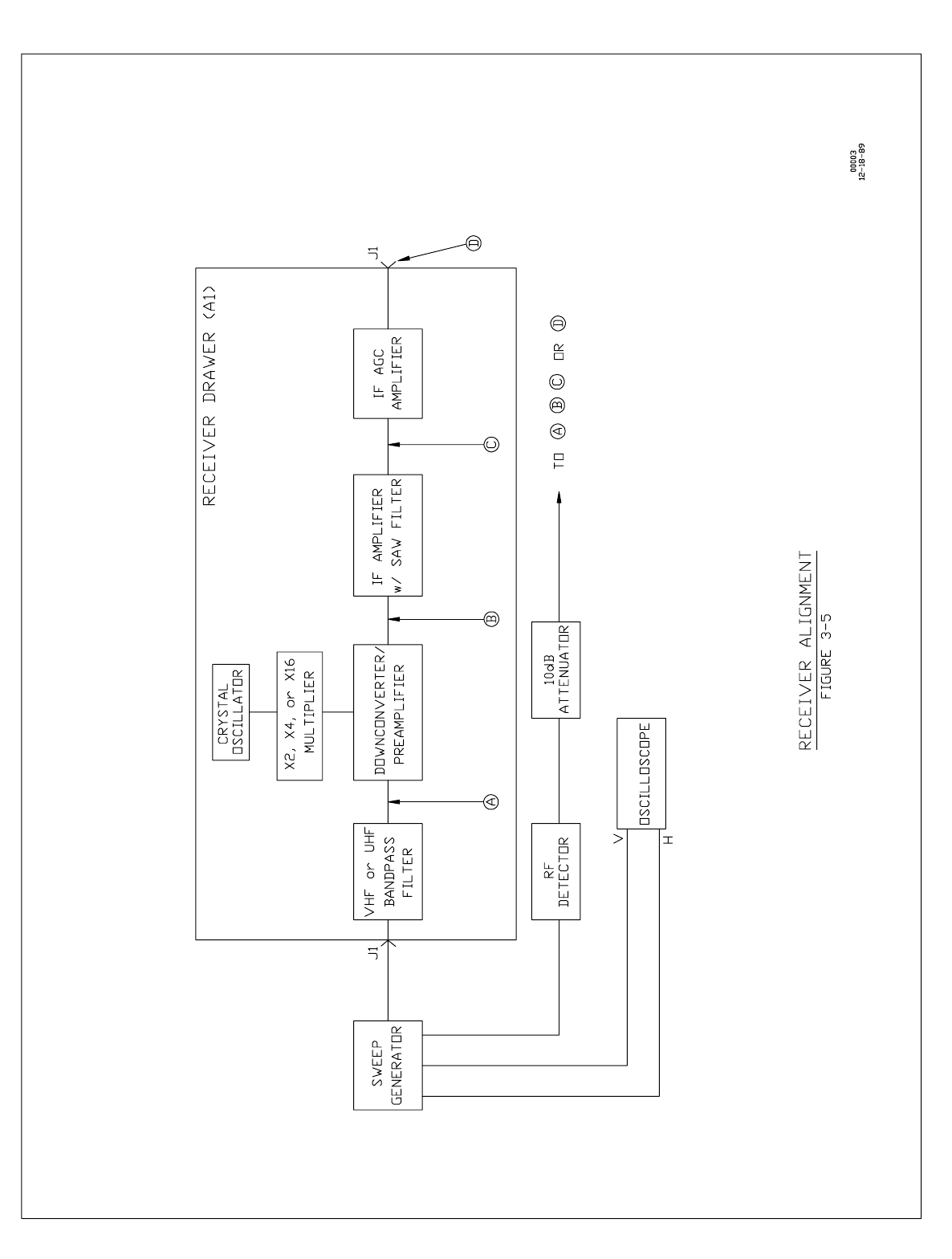

2.2e UHF Bandpass Filter:

Schematic Diagram 10331209/Rev 52 A2FL1

1dB Bandwidth (J1-J2) 7MHz

Insertion Loss (J1-J2) 3dB Max.

The UHF Bandpass Filter (FL1) consists of three tunable resonant cavities, with the three tuning

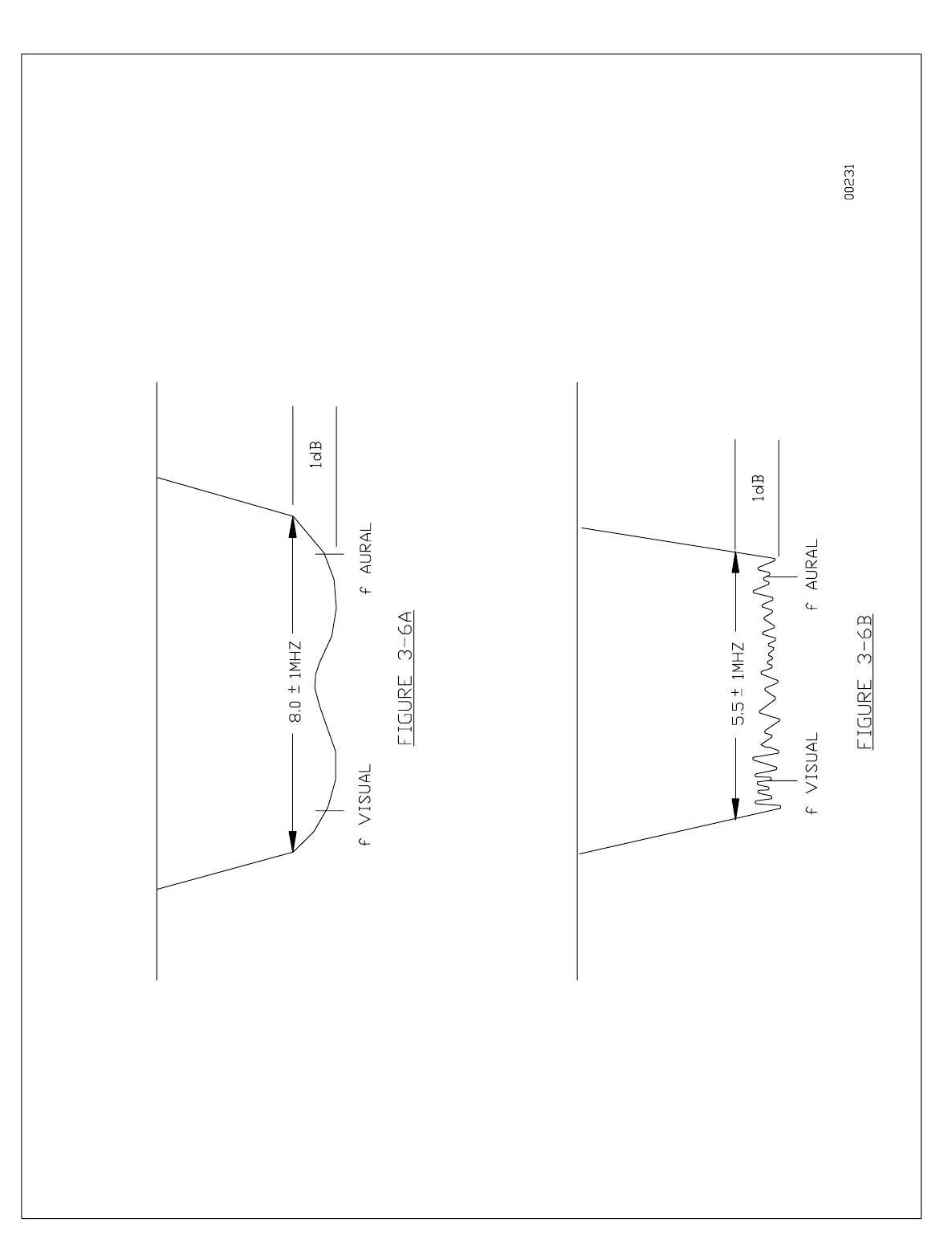

capacitors of the filter adjusted to provide the frequency response, shown in Figure 3 5, selecting

the appropriate UHF channel. FL1 is tuned to select the desired UHF mixer products from the

lower sideband or difference signal found at the RF OUTput (J2) of the IF/Upconverter (A1)

module.

2.2f 2W UHF Amplifier:

Schematic Diagram 30367002/Rev A A2A2

Gain (J1-J2) 50dB

Power Output +33dBm peak visual

+23dBm average aural

Flatness (J1-J2) ±1dB from 470-860MHz

U1, PIN 3 +3.9Vdc @ 29mA

U2, PIN 3 +5.3Vdc @ 58mA

U3, PIN 4 +20Vdc @ 100mA

Q1, Collector +25Vdc @ 600mA

The 2W UHF Amplifier (A2) provides amplification to the selected UHF channel. The Amplifier is

a four-stage, class A, microstrip design. The first three stages are centered around broadband

monolithic amplifiers U1 through U3 which provide a combined gain of 40dB. The fourth stage is

an RF transistor amplifier Q1 which provides a gain of approximately 10dB. Q1 is biased by a dc

current regulator consisting of Q2, R4, R5, R6, R7, and R9. This circuit continuously maintains the

collector voltage and current of Q1 over a wide variation of load and temperature. The required

collector voltage and current of Q1 is established by potentiometer R5. Input matching for Q1 is

provided by C9, C10, C11, C12, and C24 while output matching is accomplished by C13, C14 and

C30. Capacitor C10 is tuned for maximum gain with a flat frequency response from 470 to

860MHz. C1, C3, C5, C8, and C14 provide signal coupling while all other capacitors are used for

218

bypassing. Coils L1 through L4 function as RF chokes while R1 through R3 are used as biasing

resistors.

2.2g 20W UHF Amplifier:

Schematic Diagram 40383053/Rev 52 A2A3

Gain (J1-J2) 12dB min.

Power Output +44.5dBm peak visual/

+34.5dBm average aural

Flatness (J1-J2) ±1dB from 470-860MHz

Collector of Q1 & Q2 +26.8Vdc @ 1.2Adc (each side)

The 20W UHF Amplifier is a class A, broadband, microstrip design consisting of two RF transistor

stages centered around push-pull devices Q1 and Q2. These two stages are connected in parallel

via splitter CP1 and combiner CP2. Q1 and Q2 are biased by separate dc current regulators which

continuously maintain each collector voltage and current, over a wide variation of temperature and

signal level. Each current regulator is made up of PNP transistors Q3 and Q4 working with

potentiometers R4 and R11 to provide the required collector voltage and current for each side of

Q1 and Q2. CP1 and CP2 are Wireline quadrature 3dB,90 hybrid couplers which split and

combine power equally with resistors R5/R12 used to terminate the isolated port of each. The

function of R5/R12 is to absorb any imbalance that develops in either hybrid as well as to establish

a 50 ohm input/output impedance. Baluns Z1/Z3 transform the unbalanced signal into a balanced

input to drive the push-pull transistor pair of Q1/Q2. Baluns Z2/Z4 act in the opposite manner to

transform the balanced output from Q1/Q2 into an unbalanced output. Input matching for

transistors Q1/Q2 is provided by capacitors C1-3, C32, C65, C76/C18-C21, C66, C77, C80 while

output matching is accomplished by capacitors C43, C68-C70, C72, C81/C48, C53-C55, C74, C82.

Variable capacitors C79, C32, C80, and C18 are tuned for maximum gain with a flat frequency

response. Coils L1 through L8 function as RF chokes while capacitors C1, C2, C20, C21, C68,

C69, C54 and C55 are used for signal coupling. All other capacitors are used for bypassing.

Fault Circuit:

The Fault Circuit board (PC3) detects the presence of either an open or shorted RF device in the

20W UHF Amplifier. Under normal operation, the collector voltage on both sides of each push-pull

transistor in the 20W UHF Amplifier is typically +26.8Vdc. Under this condition, Q1 through Q3

of the fault circuit are turned on, the diodes identified by pins 1 and 3 in CR2 and CR3 are turned

on, the diodes identified by pins 2 and 3 are turned off, and the diodes identified by pins 1/14 and

7/8 of CR1 are turned on while those identified by pins 2/13 and 3/12 are turned off. Hence, for

normal operation of each push-pull RF transistor, the FAULT line (pin C of connector J3) is set at

a logic low (approximately 0Vdc) by the pull-down resistor (R10) or the Control Board (A2PC1).

However, if either side of one of the push-pull transistors opens, its collector voltage rises from

+26.8Vdc to about +27.4Vdc. This action results in turning off Q3 and Q2 as well as the diode

identified by pins 7 and 8 of CR1. With these components turned off, the diode identified by pins

3 and 12 of CR1 turns on applying a logic high (approximately +4.7Vdc) to the FAULT line. On the

other hand, if either side of one of the push-pull transistors shorts, the shorted transistor collector

falls from +26.8Vdc to about +0.2Vdc causing the diode identified by pins 2 and 3 of either CR2

or CR3 to turn on. This action results in turning off Q1 and the diode identified by pins 1 and 14

of CR1. With these components turned off, the diode identified by pins 2 and 13 of CR1 turns on

219

applying a logic high to the FAULT line. The information on the FAULT line is processed by the

fault monitoring/display section of the Control board (A2PC1).

2.2h Metering Coupler:

Schematic Diagram 10199178/Rev 52 A2DC1

Insertion Loss (J1-J2) <0.5dB

FWD Coupling (J1-J3) 30dB

REFL Coupling (J1-J4) 30dB

The Metering Coupler is a four-port device designed to provide forward and reflected RF samples

to the Metering Detector (A5) with minimal loss to the output signal. The RF signal is applied to

the coupler's input port (J1) and exits the coupler with a maximum of 0.5dB of loss at J2. A 30dB

sample of the signal's forward power is provided at J3, and a 30dB sample of the reflected power

is provided at J4. These two signals are connected to the Metering Detector (A5) which then

provides DC signals proportional to the output signal to the Control Board (PC1), the AGC circuits,

and the Metering Switch (PC2).

2.2i Metering Detector:

Schematic Diagram 30368024/Rev P A2A5

The Metering Detector contains three circuits for monitoring signal levels. Each of these circuits

can take an RF signal at its input and provide a DC voltage at its output proportional to the input

signal's strength. Only two of the detector circuits are used in this application. A sample of the

output signal is supplied to the VISual port of the detector, and a sample of the reflected power is

provided at the REFLected input of the detector. These signals are provided by the Metering

Coupler (DC1). The front end or detector portion of each circuit is basically the same. Diodes CR2

and CR4, together with their surrounding components, convert the sampled on-channel RF signals

to positive dc voltages proportional to the detected RF power. Detection of the sampled visual

output carrier is accomplished by CR2 in conjunction with R4 and C2 which form a time constant

of 1 second. R4 is the dc load while C1 and C11 form the RF ground of the visual power detector.

Detection of the sampled reflected signal is the same except for a faster time constant. R22/C6

forms a time constant of 1 millisecond. The positive dc voltages from the visual and reflected

power detectors are processed by buffer amplifiers U1 and U2 which provide voltage gains of 1V/V

and 2V/V, respectively. These buffer amplifiers also provide isolation between the % POWER

meter and the detectors. The settings of potentiometers R9 and R27 determine the voltage level

applied to the % POWER meter when the meter switch (PC2) is in its FWD or REFL positions,

respectively. The aural detector circuit is not used in this application.

A dc voltage proportional to the Exciter's output power is available at pin 5 of connector J4,

designated VISUAL POWER REFERENCE.

220

2.2j Control Board:

Schematic Diagram 40383016/Rev 62 A2PC1

The Exciter’s Control Board (PC1) is mounted to the inside of the Exciter/Upconverter's front panel.

It provides various monitoring and control functions for the Exciter while displaying the results on

front panel indicators and the metering display. The circuitry can be divided into three sections:

(1) Interlock Monitoring/Display

(2) Amplifier Fault Monitoring/Display

(3) Miscellaneous Control/Display

The Interlock section monitors the VIDEO SENSE from the modulator (optional), SYNTH LOCK,

the 20W amplifier TEMP SENSOR, VSWR OVLD, the +28V FINAL PS and OPERATE/STANDBY

switch. When these signals are of the appropriate level with the OPERATE/STANDBY switch set

to OPERATE and the POWER circuit breaker ON, the contactor (K1) closes placing the translator

on line. The FINAL BIAS, ON and SYNTH LOCK indicators are now illuminated green and the

TEMP EXCITER and VSWR OVLD indicators are unlit when the interlock is closed.

With baseband video present, the optional VIDEO SENSE line (J1-3) from the modulator is high.