Contents

- 1. Users Manual

- 2. User Manual

User Manual

Release 0.10, 04/08/2014

Copyright © 2014 GainSpan. All rights reserved.

Preliminary

Confidential

GS2100M Low Power WiFi Module

Data Sheet

GS2100M-DS-001212

GainSpan®

802.11b/g/n Low Power WiFi®

Series Modules

FCC Communications

Commission (FCC)

Interference Statement

This equipment has been tested and found to comply with the limits for a Class B digital

device, pursuant to Part 15 of the FCC Rules. These limits are designed to provide

reasonable protection against harmful interference in a residential installation. This

equipment generates uses and can radiate frequency energy and, if not installed and used

in accordance with the instructions may cause harmful interference to radio communications.

However, there is no guarantee that interference will not occur in a particular installation. If

this equipment does cause harmful interference to radio or television reception, which can be

determined by turning the equipment off and on, the user is encouraged to try to correct the

interference by one of the following measures:

• Reorient or relocate the receiving antenna

• Increase the separation between the equipment and receiver

• Connect the equipment into an outlet on a circuit different from that to which

the receiver is connected

• Consult the dealer or an experienced radio/TV technician for help

FCC Caution: To assure continued compliance, (example - use only shielded interface

cables when connecting to computer or peripheral devices). Any changes or modifications

not expressly approved by the party responsible for compliance could void the user’s

authority to operate this equipment.

This device complies with Part 15 of the FCC Rules. Operation is subject to the following two

conditions: (1) This device may not cause harmful interference, and (2) this device must

accept any interference received, including interference that may cause undesired operation.

FCC & IC Radiation

Exposure Statement

This equipment complies with FCC & IC radiation exposure limits set forth for an uncontrolled

environment. This equipment should be installed and operated with minimum distance 20cm

between the radiator & your body.

This transmitter must not be co-located or operating in conjunction with any other antenna or

transmitter must not be co-located or operating in conjunction with any other antenna or

transmitter. This device intended only for OEM integrators under the following conditions:

1. The antenna must be installed such that 20cm is maintained between the antenna and

users, and

2. The transmitter module may not be co-located with any other transmitter or antenna. As

long as 2 conditions above are met, further transmitter test will not be required.

However, the OEM integrator is still responsible for testing their end-product for any

additional compliance requirements required with this module installed (for example,

digital device emissions, PC peripheral requirements, etc.).

IMPORTANT NOTE: In the event that these conditions cannot be met (for example certain

laptop configurations or co-location with another transmitter), then the FCC & IC

authorizations are no longer considered valid and the FCC & IC IDs cannot be used on the

final product. In these circumstances, the OEM integrator will be responsible for re-evaluating

the end product (including the transmitter) and obtaining separate FCC & IC authorizations.

End Product Labeling: This transmitter module is authorized only for use in device

where the antenna may be installed such that 20cm may be maintained between the

antenna and users (for example access points, routers, wireless ADSL modems, and

similar equipment). the final product must be labeled in a visible area with the

corresponding FCC ID number.

IC Certification - Canada The labeling requirements for Industry Canada are similar to those of the FCC. A visible label

on the outside of the final product must display the IC labeling. The user is responsible for

the end product to comply with IC ICES-003 (Unintentional radiators).

English

This device complies with Industry Canada license-exempt RSS standard(s). Operation is

subject to the following two conditions:

1. This device may not cause harmful interference

2. This device must accept any interference received, including received, including

interference that may cause undesired operation of the device.

French

Cet appareil est conforme à Industrie Canada une licence standard RSS exonérés (s). Son

fonctionnement est soumis aux deux conditions suivantes:

1. Cet appareil ne doit pas provoquer d'interférences

2. Cet appareil doit accepter toute interférence reçue, y compris les interférences pouvant

provoquer un fonctionnement indésirable de l'appareil.

Manual Information That Must be Included

The user’s manual for end users must include the following information in a prominent

location.

IMPORTANT NOTE: To comply with FCC & IC RF exposure compliance requirements, the

antenna used for this transmitter must be installed to provide a separation distance of at least

20cm from all persons and must not be co-located or operating in conjunction with any other

antenna or transmitter.

Additional Notations: GainSpan modules have been built or under development for near

body exposure applications. The 20cm statement is a standard note because absorption rate

testing (commonly knowns as SAR or Specific absorption rate) is not modularly transferable

for FCC/IC. Thus, if a radio is being used against the body, the end user is still responsible

to test for regulatory near body exposure testing (for USA, please refer to the following):

• FCC Part 1.1037

• FCC Part 2.1091 Mobile Devices

• FCC Part 2.1093 Portable Devices

• FCC Part 15.247 (b) (4)

Copyright Statement This GainSpan manual is owned by GainSpan or its licensors and protected by U.S. and

international copyright laws, conventions, and treaties. Your right to use this manual is

subject to limitations and restrictions imposed by applicable licenses and copyright laws.

Unauthorized reproduction, modification, distribution, display or other use of this manual may

result in criminal and civil penalties.

GainSpan assumes no liability whatsoever, and disclaims any express or implied warranty,

relating to sale and/or use of GainSpan products including liability or warranties relating to

fitness for a particular purpose, merchantability, or infringement of any patent, copyright or

other intellectual property right. GainSpan products are not authorized for use as critical

components in medical, lifesaving, or life-sustaining applications

GainSpan may make changes to specifications and product descriptions at any time, without

notice.

Trademark GainSpan is a registered trademark of GainSpan Corporation. All rights reserved. Other

names and brands may be claimed as the property of others.

Contact Information In an effort to improve the quality of this document, please notify GainSpan Technical

Assistance at 1.408.627.6500 in North America or +91 80 42526503 outside North America.

Web and Email Contact www.gainspan.com

info@gainspan.com

GS2100M-DS-001212, Release 0.10 Confidential Preliminary 5

Table of Contents

Chapter 1 GS2100M Overview ........................................................................................................ 17

1.1 Product Overview ..................................................................................................................17

1.2 GS2100M Module Product Features .....................................................................................17

Chapter 2 GS2100M Architecture .................................................................................................... 21

2.1 Architecture Description ........................................................................................................21

2.1.1 Wireless LAN and System Control Subsystem ............................................................23

2.1.2 On-board Antenna / RF Port / Radio ............................................................................23

2.1.2.1 802.11 MAC .........................................................................................................23

2.1.2.2 802.11 PHY .........................................................................................................24

2.1.2.3 RF/Analog ............................................................................................................24

2.1.3 Network Services Subsystem ......................................................................................25

2.1.3.1 APP CPU .............................................................................................................25

2.1.3.2 Crypto Engine ......................................................................................................25

2.1.4 Memory Subsystem .....................................................................................................25

2.1.4.1 SRAM ..................................................................................................................25

2.1.4.2 ROM ....................................................................................................................26

2.1.4.3 OTP ROM ............................................................................................................26

2.1.4.4 Flash Interface .....................................................................................................26

2.1.5 Clocks ..........................................................................................................................26

2.1.6 Real Time Clock (RTC) Overview ................................................................................27

2.1.6.1 RTC Main Features .............................................................................................27

2.1.6.2 Real Time Clock Counter .....................................................................................28

2.1.6.3 RTC I/O ................................................................................................................28

2.1.7 GS2100M Peripherals ..................................................................................................28

2.1.7.1 SDIO Interface .....................................................................................................28

2.1.7.2 SPI Interface ........................................................................................................29

2.1.7.3 UART Interface ....................................................................................................29

2.1.7.4 I2C Interface ........................................................................................................29

2.1.7.5 GPIO ....................................................................................................................30

2.1.7.6 Sigma Delta ADC .................................................................................................30

2.1.7.7 PWM ....................................................................................................................30

2.1.8 System States ..............................................................................................................31

2.1.9 Power Supply ...............................................................................................................32

Chapter 3 Pin-out and Signal Description ........................................................................................ 33

3.1 GS2100Mxx Device Pin-out ..................................................................................................33

3.1.1 GS2100Mxx Module Pins Description ..........................................................................34

3.1.2 GS2100M Pin MUX Function .......................................................................................37

3.1.3 GS2100M Program and Code Restore Options ...........................................................39

Chapter 4 Electrical Characteristics ................................................................................................. 41

4.1 Absolute Maximum Ratings ...................................................................................................41

4.2 Operating Conditions .............................................................................................................42

4.3 I/O DC Specifications ............................................................................................................43

4.3.1 I/O Digital Specifications (Tri-State) Pin Types 4mA, 12mA, and 16mA ......................43

4.3.1.1 I/O Digital Specifications for VDDIO=3.0V to 3.6V ..............................................43

4.3.2 RTC I/O Specifications .................................................................................................44

4.4 Power Consumption (Estimate) .............................................................................................44

GS2100M Low Power WiFi Module Data Sheet

6 Confidential Preliminary GS2100M-DS-001212, Release 0.10

4.5 802.11 Radio Parameters (Estimate) ....................................................................................45

4.6 Sigma Delta ADC Parameters ...............................................................................................46

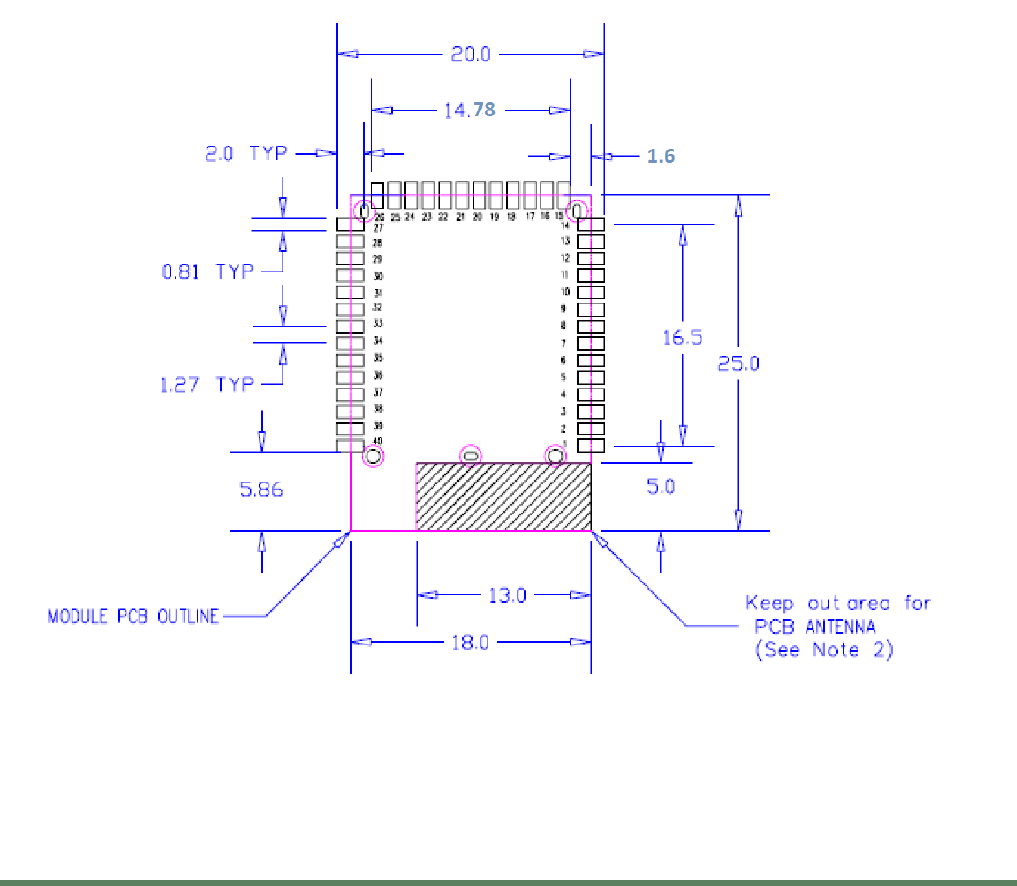

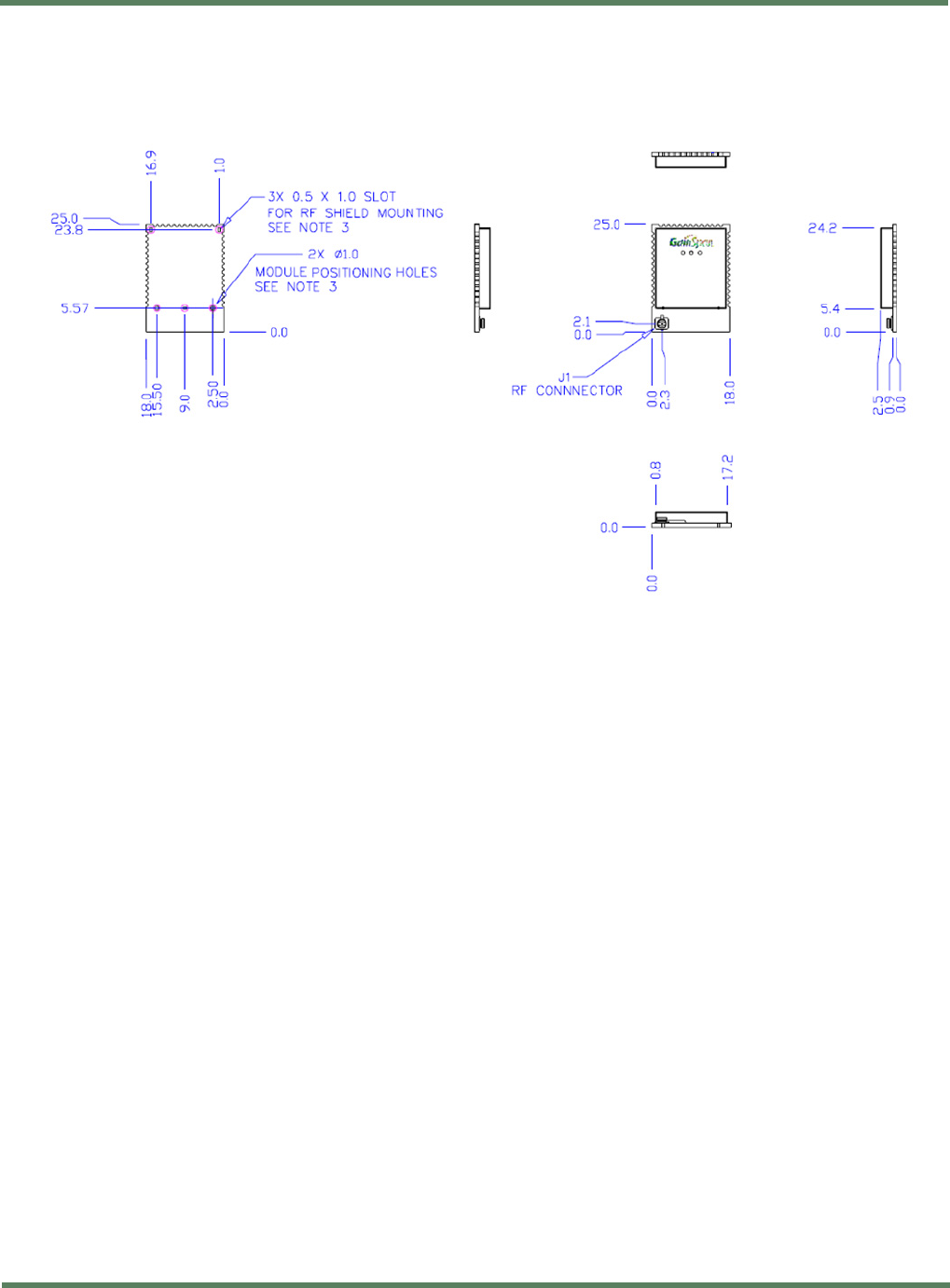

Chapter 5 Package and Layout Guidelines ..................................................................................... 49

5.1 GS2100Mxx Recommended PCB Footprint and Dimensions ...............................................49

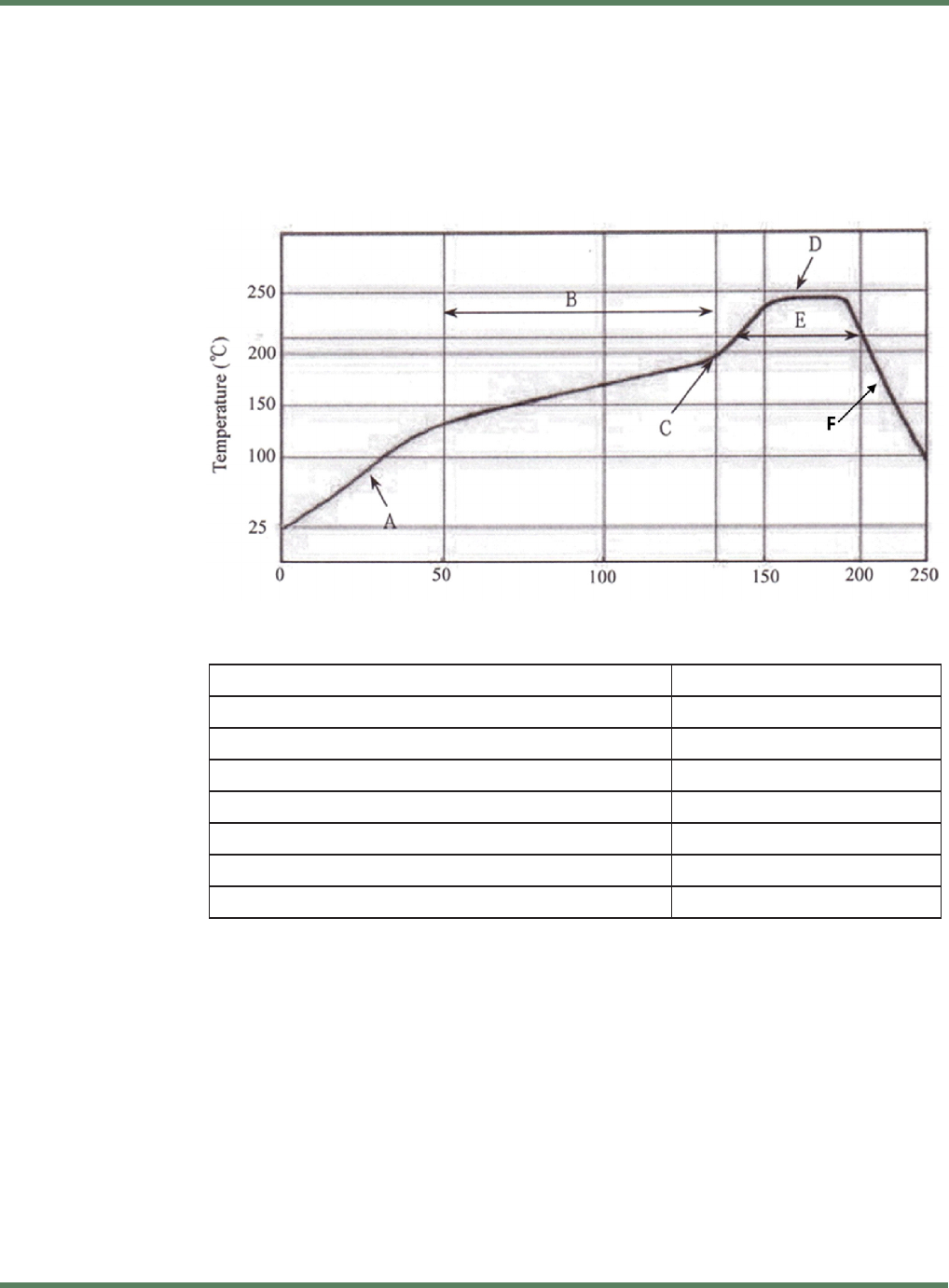

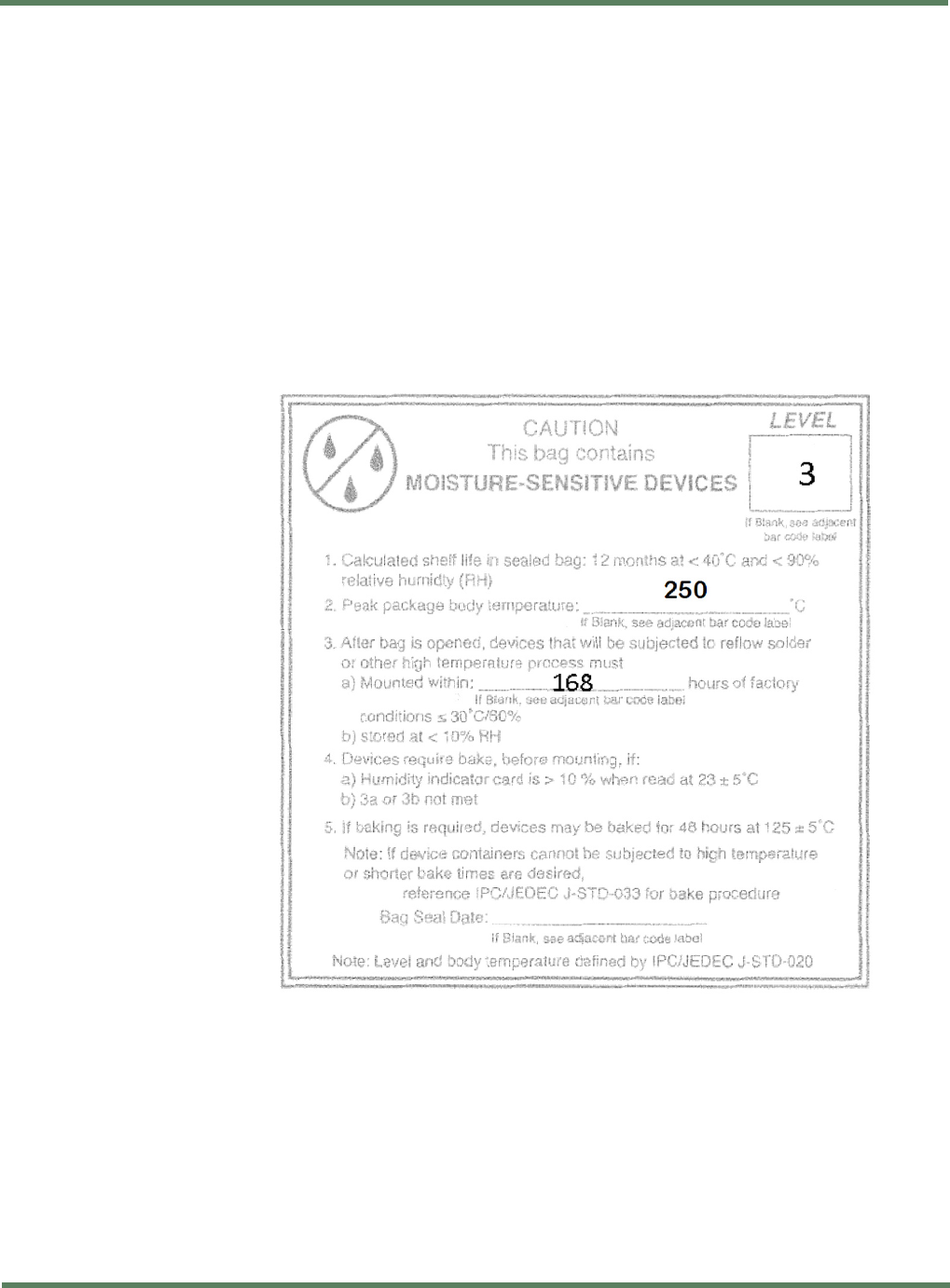

5.1.1 Surface Mount Assembly .............................................................................................51

GS2100M-DS-001212, Release 0.10 Confidential Preliminary 7

About This Manual

This manual describes the GS2100M Low Power module hardware specification.

Refer to the following sections:

• Revision History, page 7

• Audience, page 8

• Standards, page 8

• Documentation Conventions, page 8

• Documentation, page 12

• Contacting GainSpan Technical Support, page 13

• Returning Products to GainSpan, page 14

• Accessing the GainSpan Portal, page 15

• Ordering Information, page 15

Revision History

This version of the GainSpan GS2100M Low Power WiFi Data Sheet contains the

following new information listed in Table 1, page 7.

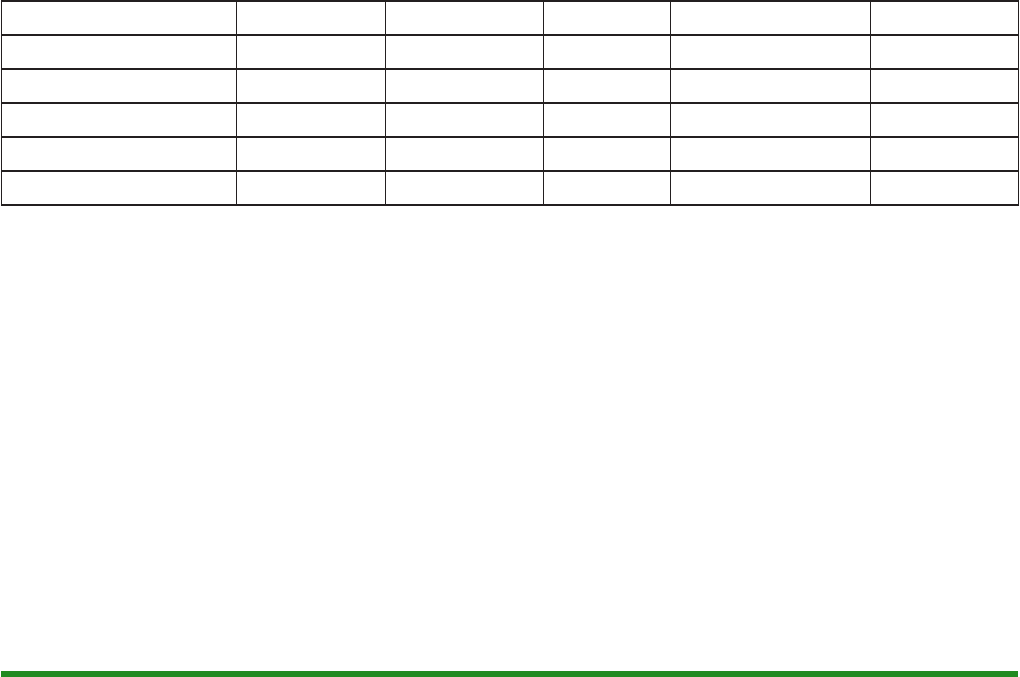

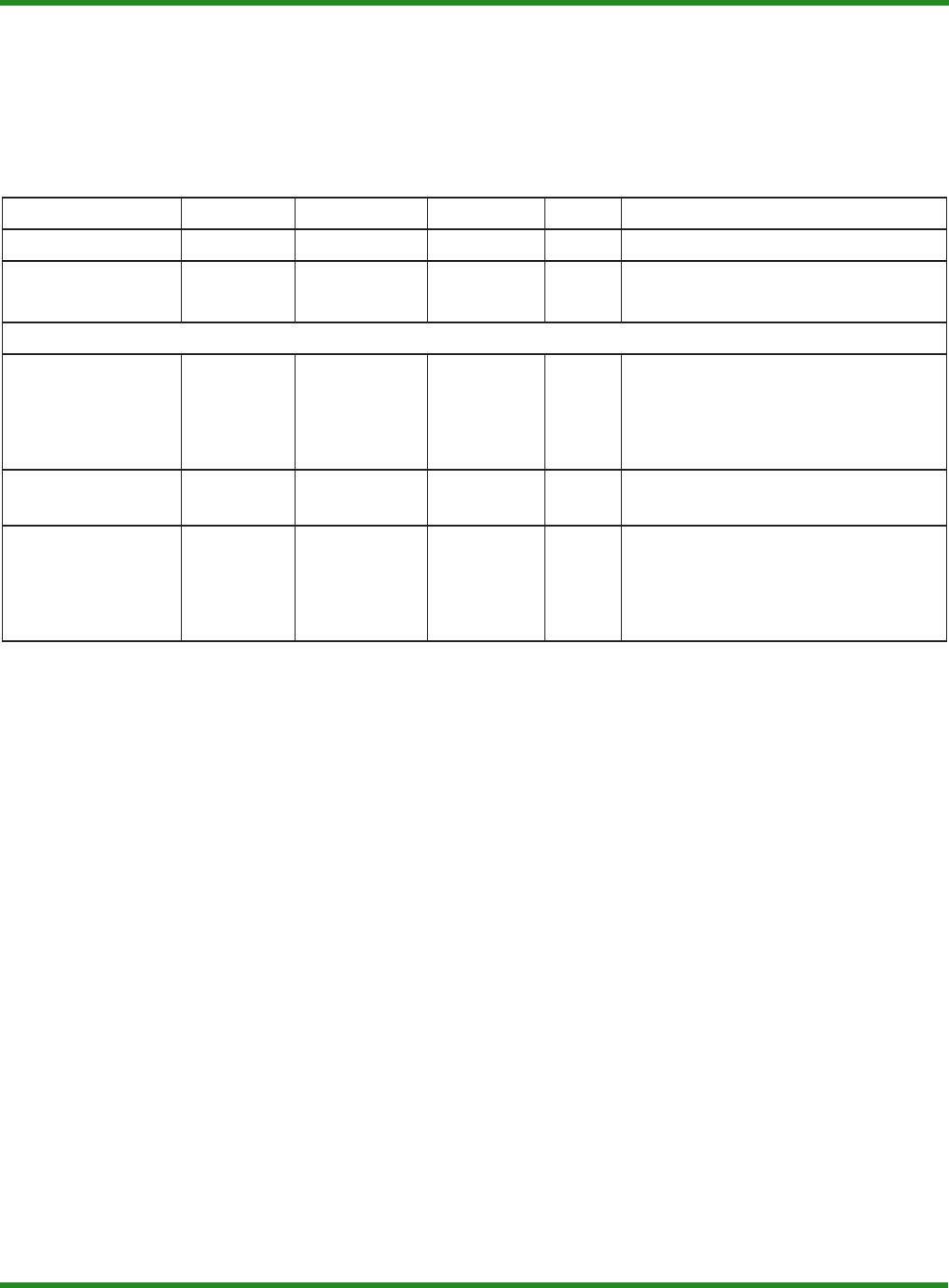

Table 1 Revision History

Version Date Remarks

0.6 May 2013 Initial Release

0.7 January 2014

Updated SDIO interface clock frequency (see

1.2 GS2100M Module Product Features,

page 17).

Updated Power Consumption Estimates and

802.11 Radio Parameter Estimates (see

4.4 Power Consumption (Estimate), page 44

and 4.5 802.11 Radio Parameters (Estimate),

page 45).

0.8 February 2014

Added Notation to describe the GPIO37 when

using SPI interface. See 3.1.1 GS2100Mxx

Module Pins Description, page 34.

GS2100M Low Power WiFi Module Data Sheet

8 Confidential Preliminary GS2100M-DS-001212, Release 0.10

Audience

This manual is designed to help system designers build low power, cost effective, flexible

platforms to add WiFi connectivity for embedded device applications using the GainSpan

GS2100M based module.

Standards

The standards that are supported by the GainSpan GS module series are:

– IEEE 802.11 b/g/n

Documentation Conventions

This manual uses the following text and syntax conventions:

– Special text fonts represent particular commands, keywords, variables, or window

sessions

– Color text indicates cross-reference hyper links to supplemental information

– Command notation indicates commands, subcommands, or command elements

Table 2, page 8, describes the text conventions used in this manual for software procedures

that are explained using the AT command line interface.

0.9 March 2014 Added Regulator Notations in About this

Manual.

0.10 April 2014

Added Surface Mount Assembly Reflow

Profile Information. See 5.1.1 Surface Mount

Assembly, page 51.

Table 1 Revision History (Continued)

Version Date Remarks

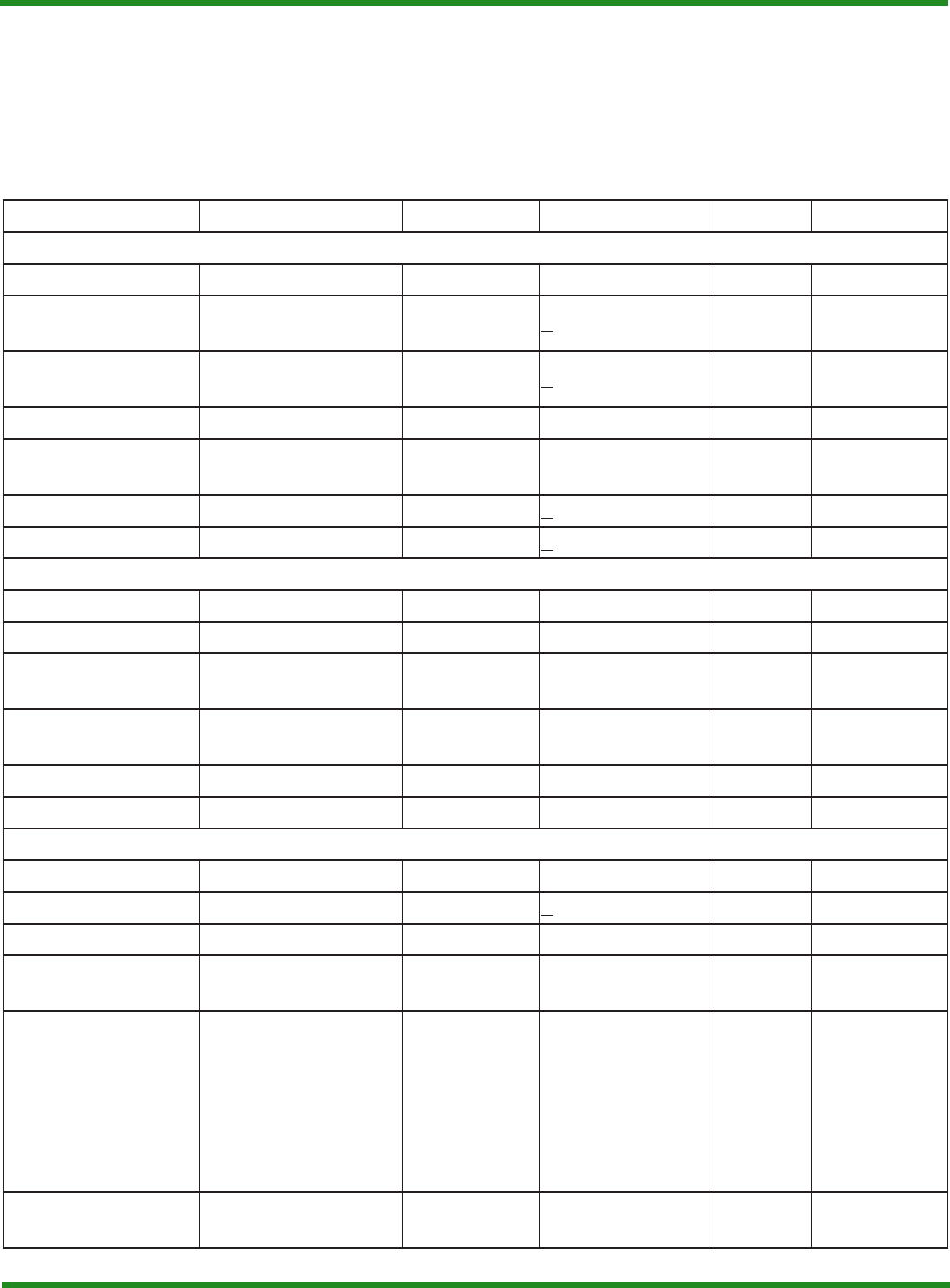

Table 2 Document Text Conventions

Convention Type Description

command syntax

monospaced font

This monospaced font represents command strings entered on a

command line and sample source code.

AT XXXX

Proportional font

description

Gives specific details about a parameter.

<Data> DATA

GS2100M Low Power WiFi Module Data Sheet

GS2100M-DS-001212, Release 0.10 Confidential Preliminary 9

UPPERCASE

Variable parameter

Indicates user input. Enter a value according to the descriptions that

follow. Each uppercased token expands into one or more other token.

lowercase

Keyword parameter

Indicates keywords. Enter values exactly as shown in the command

description.

[ ]

Square brackets

Enclose optional parameters. Choose none; or select one or more an

unlimited number of times each. Do not enter brackets as part of any

command.

[parm1|parm2|parm3]

?

Question mark

Used with the square brackets to limit the immediately following token

to one occurrence.

<ESC>

Escape sequence

Each escape sequence <ESC> starts with the ASCII character 27 (0x1B).

This is equivalent to the Escape key.

<ESC>C

<CR>

Carriage return Each command is terminated by a carriage return.

<LF>

Line feed Each command is terminated by a line feed.

<CR> <LF>

Carriage return

Line feed

Each response is started with a carriage return and line feed with some

exceptions.

< >

Angle brackets

Enclose a numeric range, endpoints inclusive. Do not enter angle

brackets as part of any command.

<SSID>

=

Equal sign

Separates the variable from explanatory text. Is entered as part of the

command.

PROCESSID = <CID>

.

dot (period)

Allows the repetition of the element that immediately follows it multiple

times. Do not enter as part of the command.

.AA:NN can be expanded to 1:01 1:02 1:03.

A.B.C.D

IP address

IPv4-style address.

10.0.11.123

Table 2 Document Text Conventions (Continued)

Convention Type Description

GS2100M Low Power WiFi Module Data Sheet

10 Confidential Preliminary GS2100M-DS-001212, Release 0.10

X:X::X:X

IPv6 IP address

IPv6-style address.

3ffe:506::1

Where the : : represents all 0x for those address components not

explicitly given.

LINE

End-to-line input token

Indicates user input of any string, including spaces. No other parameters

may be entered after input for this token.

string of words

WORD

Single token

Indicates user input of any contiguous string (excluding spaces).

singlewordnospaces

Table 2 Document Text Conventions (Continued)

Convention Type Description

GS2100M Low Power WiFi Module Data Sheet

GS2100M-DS-001212, Release 0.10 Confidential Preliminary 11

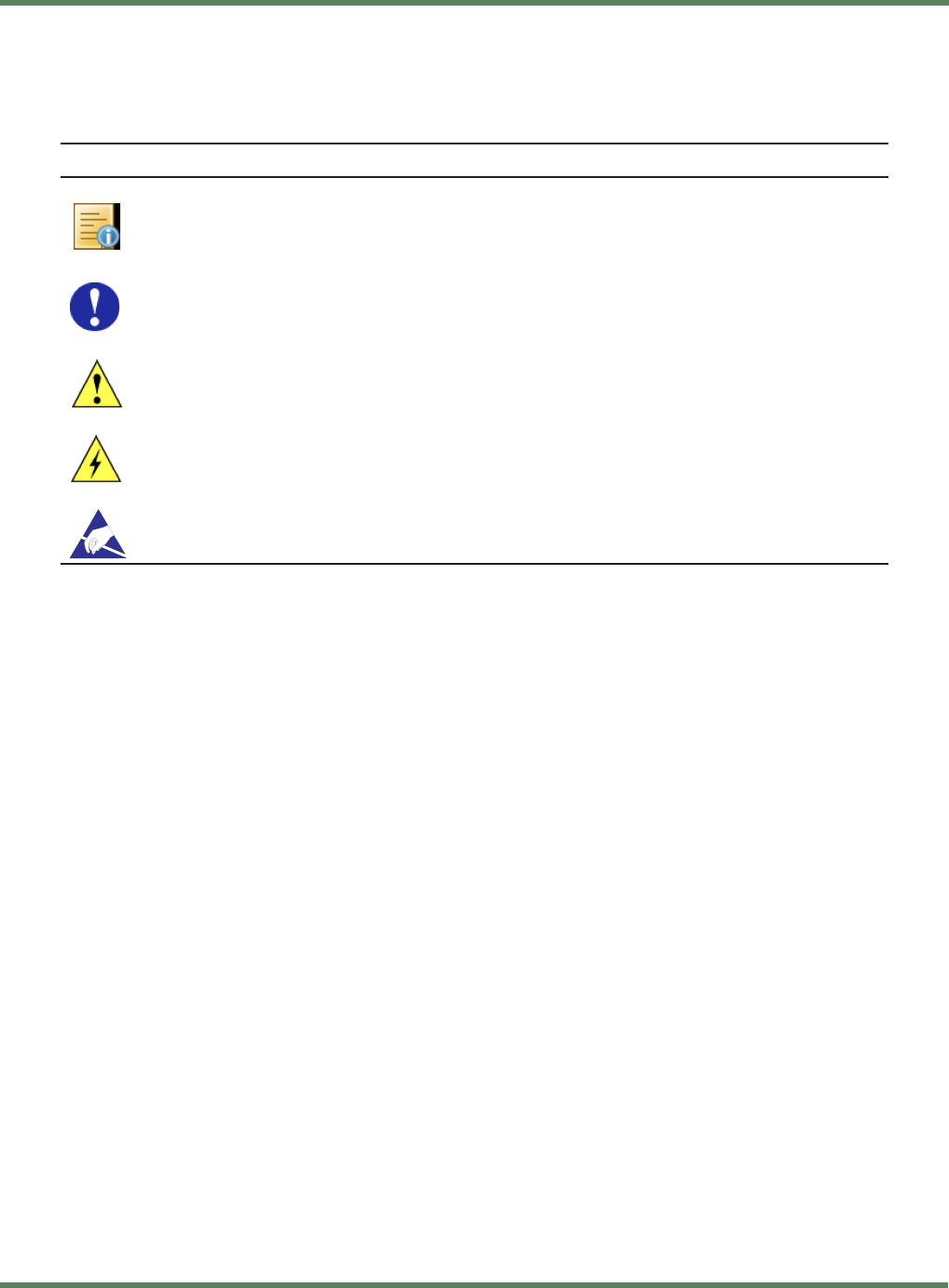

Table 3, page 11, describes the symbol conventions used in this manual for notification and

important instructions.

Table 3 Symbol Conventions

Icon Type Description

Note

Provides helpful suggestions needed in understanding

a feature or references to material not available in the

manual.

Alert Alerts you of potential damage to a program, device,

or system or the loss of data or service.

Caution Cautions you about a situation that could result in

minor or moderate bodily injury if not avoided.

Warning Warns you of a potential situation that could result in

death or serious bodily injury if not avoided.

Electro-Static Discharge

(ESD)

Notifies you to take proper grounding precautions

before handling a product.

GS2100M Low Power WiFi Module Data Sheet

12 Confidential Preliminary GS2100M-DS-001212, Release 0.10

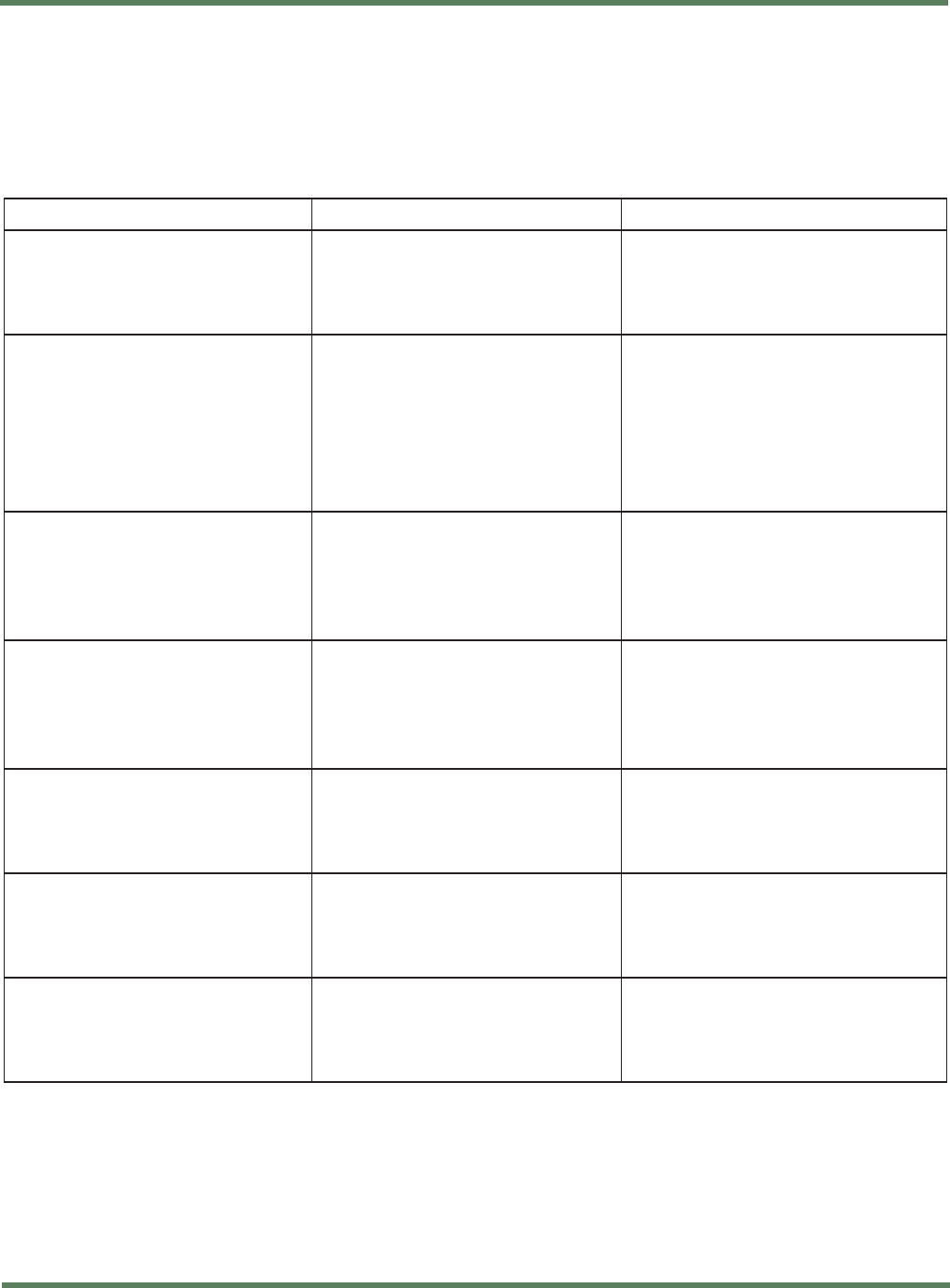

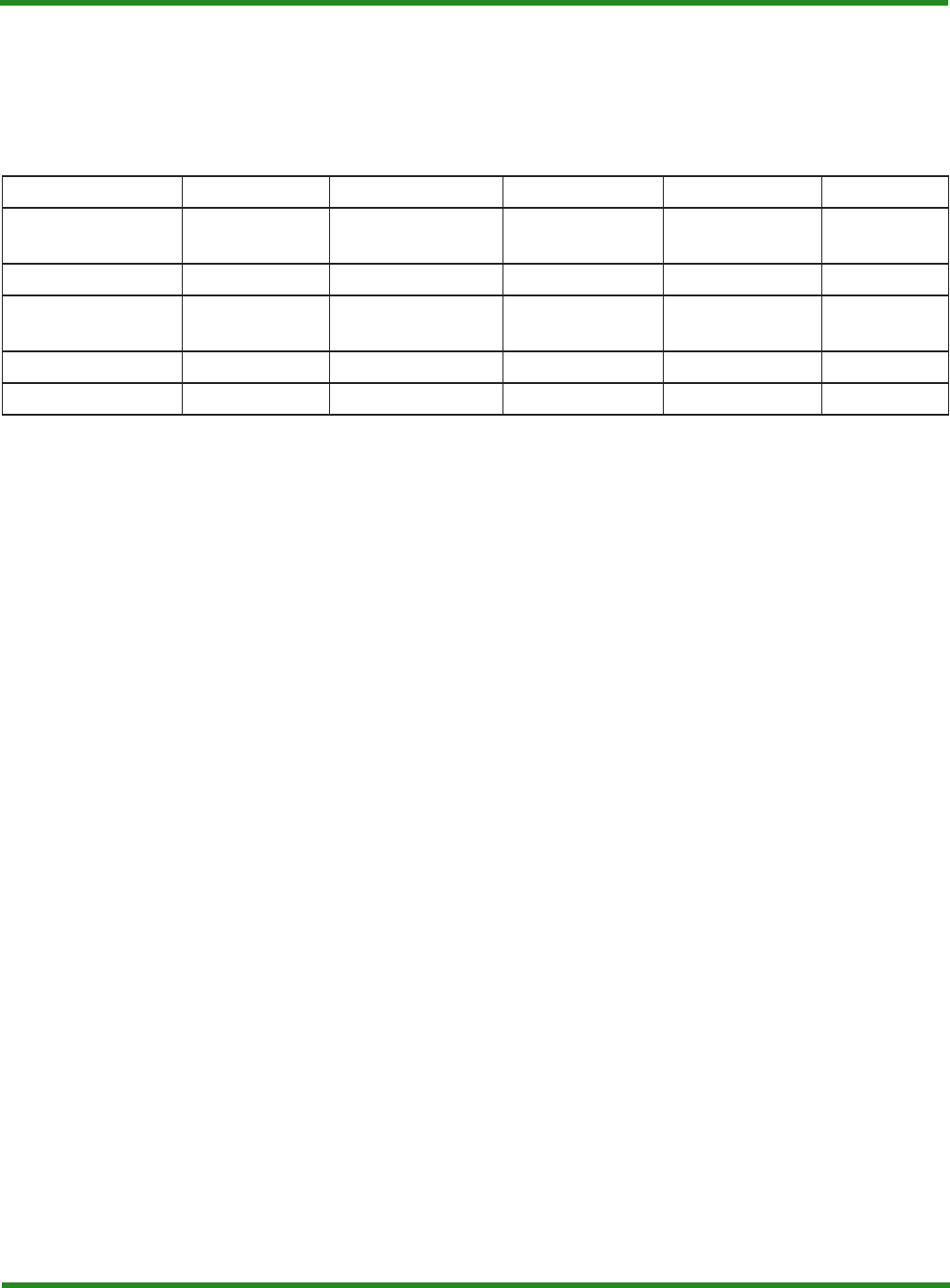

Documentation

The GainSpan documentation suite listed in Table 4, page 12 includes the part number,

documentation name, and a description of the document. The documents are available from

the GainSpan Portal. Refer to Accessing the GainSpan Portal, page 15 for details.

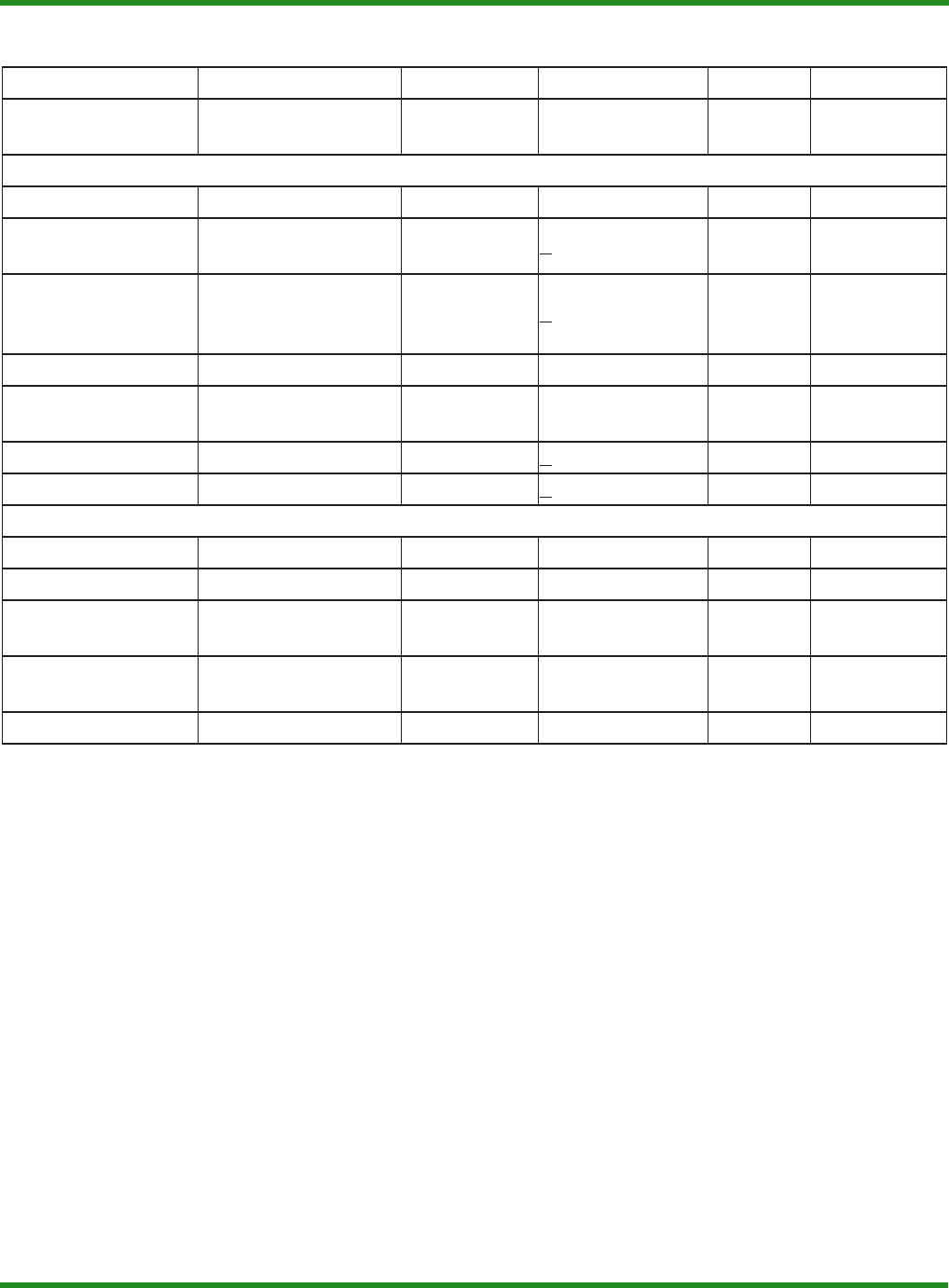

Table 4 Documentation List

Part Number Document Title Description

GS2K-QS-001205 GainSpan GS2000 Based Module Kit

Quick Start Guide

Provides an easy to follow guide on

how to unpack and setup GainSpan

GS2000 based module kit for the

GS2011M and GS2100M modules.

GS2K-EVB-FP-UG-001206 GainSpan GS2000 Based Module

Programming User Guide

Provides users steps to program the

on-board Flash on the GainSpan

GS2000 based modules using DOS or

Graphical User Interface utility

provided by GainSpan. The user guide

uses the evaluation boards as a

reference example board.

GS-S2W-APP-PRG-RG-001208

GainSpan Serial-to-WiFi Adapter

Application Programmer Reference

Guide

Provides a complete listing of AT serial

commands, including configuration

examples for initiating, maintaining,

and evaluating GainSpan WiFi series

modules.

GS2K-EVB-HW-UG-001210

GainSpan GS2000 Based Module

Evaluation Board Hardware User

Guide.

Provides instructions on how to setup

and use the GS2000 based module

evaluation board along with component

description, jumper settings, board

specifications, and pinouts.

GS2011M-DS-001211 GainSpan GS2011M Low Power

WiFi Module Data Sheet

Provides information to help WiFi

system designers to build systems using

GainSpan GS2011M module and

develop wireless applications.

GS2100M-DS-001212 GainSpan GS2100M Low Power

WiFi Module Data Sheet

Provides information to help WiFi

system designers to build systems using

GainSpan GS2100M module and

develop wireless applications.

GS2011MxxS-DS-001214 GainSpan GS2011MxxS Low Power

WiFi Module Data Sheet

Provides information to help WiFi

system designers to build systems using

GainSpan GS2011MxxS module and

develop wireless applications.

GS2100M Low Power WiFi Module Data Sheet

GS2100M-DS-001212, Release 0.10 Confidential Preliminary 13

Documentation Feedback

We encourage you to provide feedback, comments, and suggestions so that we can improve

the documentation. You can send your comments by logging into GainSpan Support Portal.

If you are using e-mail, be sure to include the following information with your comments:

– Document name

– URL or page number

– Hardware release version (if applicable)

– Software release version (if applicable)

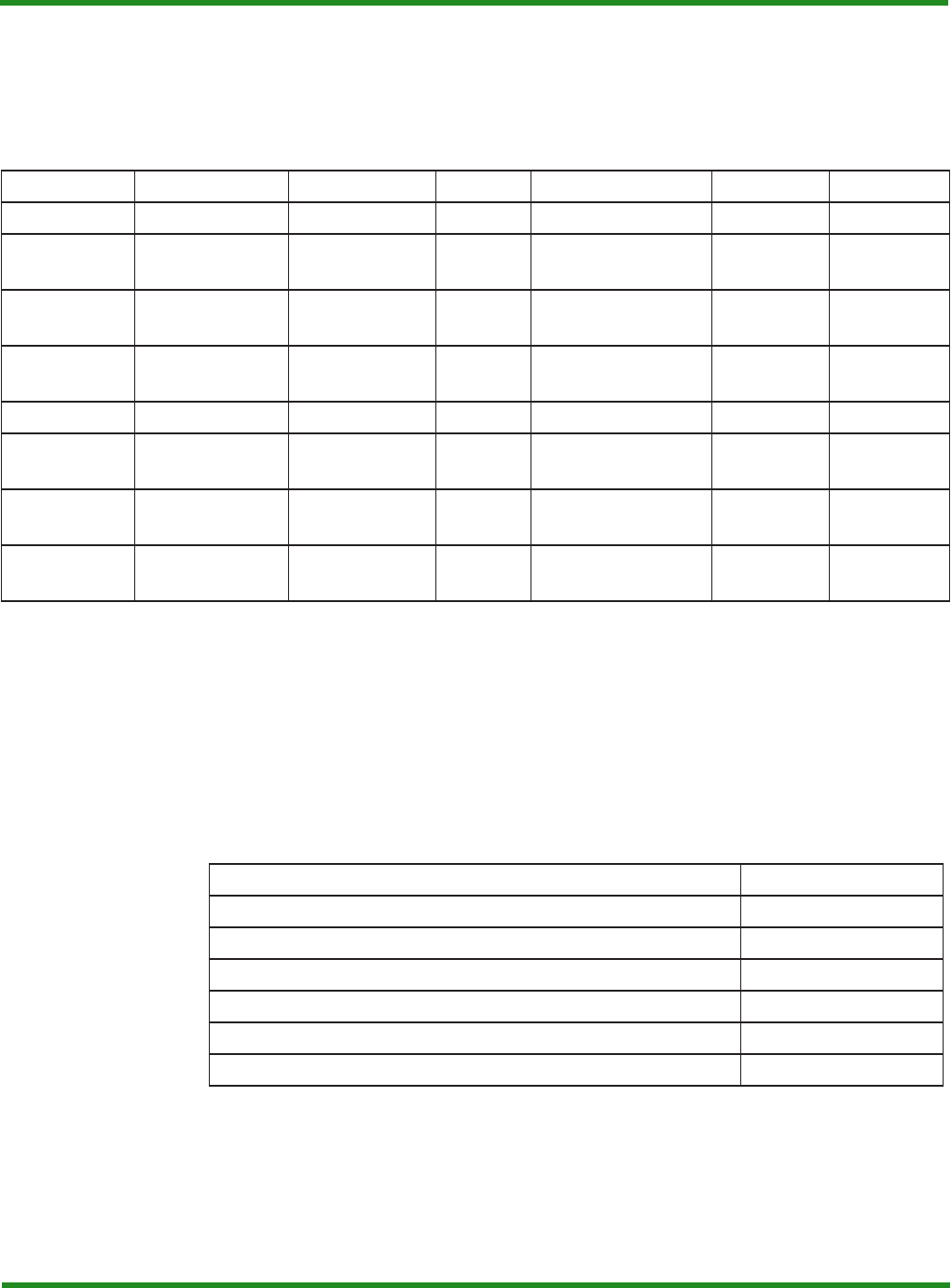

Contacting GainSpan Technical Support

Use the information listed in Table 5, page 13, to contact the GainSpan Technical Support.

For more Technical Support information or assistance, perform the following steps:

1. Point your browser to http://www.gainspan.com.

2. Click Contact, and click Request Support.

3. Log in using your customer Email and Password.

4. Select the Location and click Contact.

5. Select Support Question tab.

6. Select Add New Question.

7. Enter your technical support question, product information, and a brief description.

The following information is displayed:

• Telephone number contact information by region

• Links to customer profile, dashboard, and account information

• Links to product technical documentation

• Links to PDFs of support policies

Table 5 GainSpan Technical Support Contact Information

North America 1 (408) 627-6500 - techsupport@gainspan.com

Outside North America

Europe: EUsupport@gainspan.com

China: Chinasupport@gainspan.com

Asia: Asiasupport@gainspan.com

Postal Address

GainSpan Corporation

3590 North First Street

Suite 300

San Jose, CA 95134 U.S.A.

GS2100M Low Power WiFi Module Data Sheet

14 Confidential Preliminary GS2100M-DS-001212, Release 0.10

Returning Products to GainSpan

If a problem cannot be resolved by GainSpan technical support, a Return Material

Authorization (RMA) is issued. This number is used to track the returned material at the

factory and to return repaired or new components to the customer as needed.

For more information about return and repair policies, see the customer support web page

at: https://www.gainspan.com/secure/login.

To return a hardware component:

1. Determine the part number and serial number of the component.

2. Obtain an RMA number from Sales/Distributor Representative.

3. Provide the following information in an e-mail or during the telephone call:

– Part number and serial number of component

– You name, organization name, telephone number, and fax number

– Description of the failure

4. The support representative validates your request and issues an RMA number for

return of the components.

5. Pack the component for shipment.

Guidelines for Packing Components for Shipment

To pack an ship individual components:

– When you return components, make sure they are adequately protected with

packing materials and packed so that the pieces are prevented from moving

around inside the carton.

– Use the original shipping materials if they are available.

– Place individual components in electrostatic bags.

– Write the RMA number on the exterior of the box to ensure proper tracking.

NOTE: Do not return any components to GainSpan Corporation unless you have

first obtained an RMA number. GainSpan reserves the right to refuse shipments

that do not have an RMA. Refused shipments will be returned to the customer by

collect freight.

CAUTION! Do not stack any of the components.

GS2100M Low Power WiFi Module Data Sheet

GS2100M-DS-001212, Release 0.10 Confidential Preliminary 15

Accessing the GainSpan Portal

To find the latest version of GainSpan documentation supporting the GainSpan product

release you are interested in, you can search the GainSpan Portal website by performing the

following steps:

1. Go to the GainSpan Support Portal website.

2. Log in using your customer Email and Password.

3. Click the Actions tab to buy, evaluate, or download GainSpan products.

4. Click on the Documents tab to search, download, and print GainSpan product

documentation.

5. Click the Software tab to search and download the latest software versions.

6. Click the Account History tab to view customer account history.

7. Click the Legal Documents tab to view GainSpan Non-Disclosure Agreement

(NDA).

8. Click Download on the Item Browser section to open or save the document.

Ordering Information

To order GainSpan’s GS2100Mxx low power module contact a GainSpan Sales/Distributor

Representative. Table 6, page 15 lists the GainSpan device information.

NOTE: You must first contact GainSpan to set up an account, and obtain a

customer user name and password before you can access the GainSpan Portal.

Table 6 GS2100Mxx Ordering Information

Device Description Ordering Number Revision

Low power module with on-board antenna GS2100MIP

Low power module with external antenna GS2100MIE

NOTE: Modules ship with test code ONLY. Designers must first program the

modules with a released firmware version. Designers should bring out GPIO31

pin (option to pull this pin to VDDIO during reset or power-on) and UART0 or SPI0

pins to enable programming of firmware into the module. For details refer to the

Programming the GainSpan Modules document.

GS2100M Low Power WiFi Module Data Sheet

16 Confidential Preliminary GS2100M-DS-001212, Release 0.10

- This page intentionally left blank -

GS2100M-DS-001212, Release 0.10 Confidential Preliminary 17

Chapter 1 GS2100M Overview

This chapter describes the GainSpan® GS2100M low power module hardware specification

overview.

• Product Overview, page 17

• GS2100M Module Product Features, page 17

1.1 Product Overview

The GS2100M based modules provide cost effective, low power, and flexible platform to

add Wi-Fi® connectivity for embedded devices for a variety of applications, such as

wireless sensors and thermostats. It uses the GS2000 SoC, which combines ARM® Cortex

M3-based processors with a 802.11b/g/n Radio, MAC, security, & PHY functions, RTC

and SRAM, up to 2 MB FLASH, and on-board and off module certified antenna options.

The module provides a WiFi and regulatory certified IEEE 802.11b/g/n radio with

concurrent network processing services for variety of applications, while leverage existing

802.11 wireless network infrastructures.

1.2 GS2100M Module Product Features

• Family of modules with different antenna and output power options:

• GS2100MIx 18mm (0.71in) x 25 mm (0.98in) x 2.5mm (0.098in) 40-pin PCB

Surface Mount Package. Two SKU’s are:

– GS2100MIP (on-board PCB antenna)

– GS2100MIE (external antenna)

• The two SKUs are pin to pin compatible

• Simple API for embedded markets covering a large range of applications

• Fully compliant with IEEE 802.11b/g/n and regulatory domains:

– 802.11n: 1x1 single stream, 20 MHz channels, 400/800ns GI,

MCS0 – 7

– Data rates of 7.2, 14.4, 21.7, 28.9, 43.3, 57.8, 65.0, 72.2 Mbps

– 802.11g: OFDM modulation for data rates of 6, 9, 12, 18, 24, 36, 48 and 54

Mb/s.

– 802.11b: CCK modulation rates of 5.5 and 11 Mbps; DSSS modulation for

data rate of 1 and 2 Mbps.

GS2100M Overview GS2100M Low Power WiFi Module Data Sheet

GS2100M Module Product Features

18 Confidential Preliminary GS2100M-DS-001212, Release 0.10

• WiFi Solution:

– Wi-Fi security (802.11i)

– WPA™ - Enterprise, Personal

– WPA2™ - Enterprise, Personal

– Vendor EAP Type(s)

– EAP-TTLS/MSCHAPv2, PEAPv0/EAP-MSCHAPv2,

PEAPv1/EAP-GTC, EAP-FAST, EAP-TLS

• Hardware-accelerated high-throughput AES and RC4 encryption/decryption

engines for WEP, WPA/WPA2 (AES-CCMP and TKIP).

• Additional dedicated encryption HW engine to support higher layer encryption

such as IPSEC (IPv4 and IPv6), SSL/TLS, HTTPs, PKI, digital certificates, RNG,

etc.

• Dual ARM Cortex M3 Processor Platform:

•1

st Cortex M3 processor (WLAN CPU) for WLAN software

– Implements 802.11 b/g/n WLAN protocol services

– 320 KB dedicated SRAM

– 512 KB dedicated ROM

•2

nd Cortex M3 processor (APP CPU) for networking software

– Implements networking protocol stacks and user application software

– 384 KB dedicated SRAM

– 512 KB dedicated ROM

• 64KB shared dual ported SRAM for inter-processor communications

• 320KB assignable (under SW control) SRAM

• Support processor clock frequencies for both CPU of up to 120MHz

• Based on Advanced Microprocessor Bus Architecture (AMBA) system

– AMBA Multilayer High-Speed Bus (AHB)

– AMBA Peripheral Bus (APB)

• On-module flash controller:

– Manages read/write/program/erase operations to the 2 MB flash memory

device on the module

– Supports higher performance QUAD SPI protocol operations

– Active power management

GS2100M Low Power WiFi Module Data Sheet GS2100M Overview

GS2100M Module Product Features

GS2100M-DS-001212, Release 0.10 Confidential Preliminary 19

• Interfaces:

• SDIO:

– Compliant to SDIO v2.0 specification

– Interface clock frequency up to 40 MHz

– Data transfer modes: 4-bit, 1-bit SDIO, SPI

– Device mode only

• SPI:

– One (1) general-purpose SPI interfaces (each configurable independently as

master or slave)

– The SPI pins are muxed with other functions such as GPIO

– Supports clock rates of up to 30 MHz (master mode) and up to 10 MHz (slave

mode)

– Protocols supported include: Motorola SPI, TI Synchronous Serial Protocol

(SSP) and National Semiconductor Microwire

– Supports SPI mode 0 thru 3 (software configurable)

• UART:

– Two (2) multi-purpose UART interfaces operating in full-duplex mode

– 16450/16550 compatible

– Optional support for flow control using RTS/CTS signaling for high data

transfer rates

– Standard baud rate from 9600 bps up to 921.6K baud (additional support

for higher non-standard rates using baud rates up to 7.5 MHz)

• GPIOs:

– Up to 16 configurable general purpose I/O

• Single 3.3V supply option

• Three (3) PWM output

•I

2C master/slave interface

• Three (3) 16-bit Sigma Delta ADC channels, for sensors and measurements

• One (1) RTC I/O that can be configured as:

– Alarm input to asynchronously awaken the chip

– Support control outputs for sensors

• Embedded RTC (Real Time Clock) can run directly from battery

NOTE: Tested with current test platform up to 33 MHz.

GS2100M Overview GS2100M Low Power WiFi Module Data Sheet

GS2100M Module Product Features

20 Confidential Preliminary GS2100M-DS-001212, Release 0.10

• Power supply monitoring capability

• Low-power mode operations:

– Standby, Sleep, and Deep Sleep

• FCC/IC/ETSI/TELEC/WiFi Certification (TBD)

GS2100M-DS-001212, Release 0.10 Confidential Preliminary 21

Chapter 2 GS2100M Architecture

This chapter describes the GainSpan® GS2100M Low Power module architecture.

• Architecture Description, page 21

2.1 Architecture Description

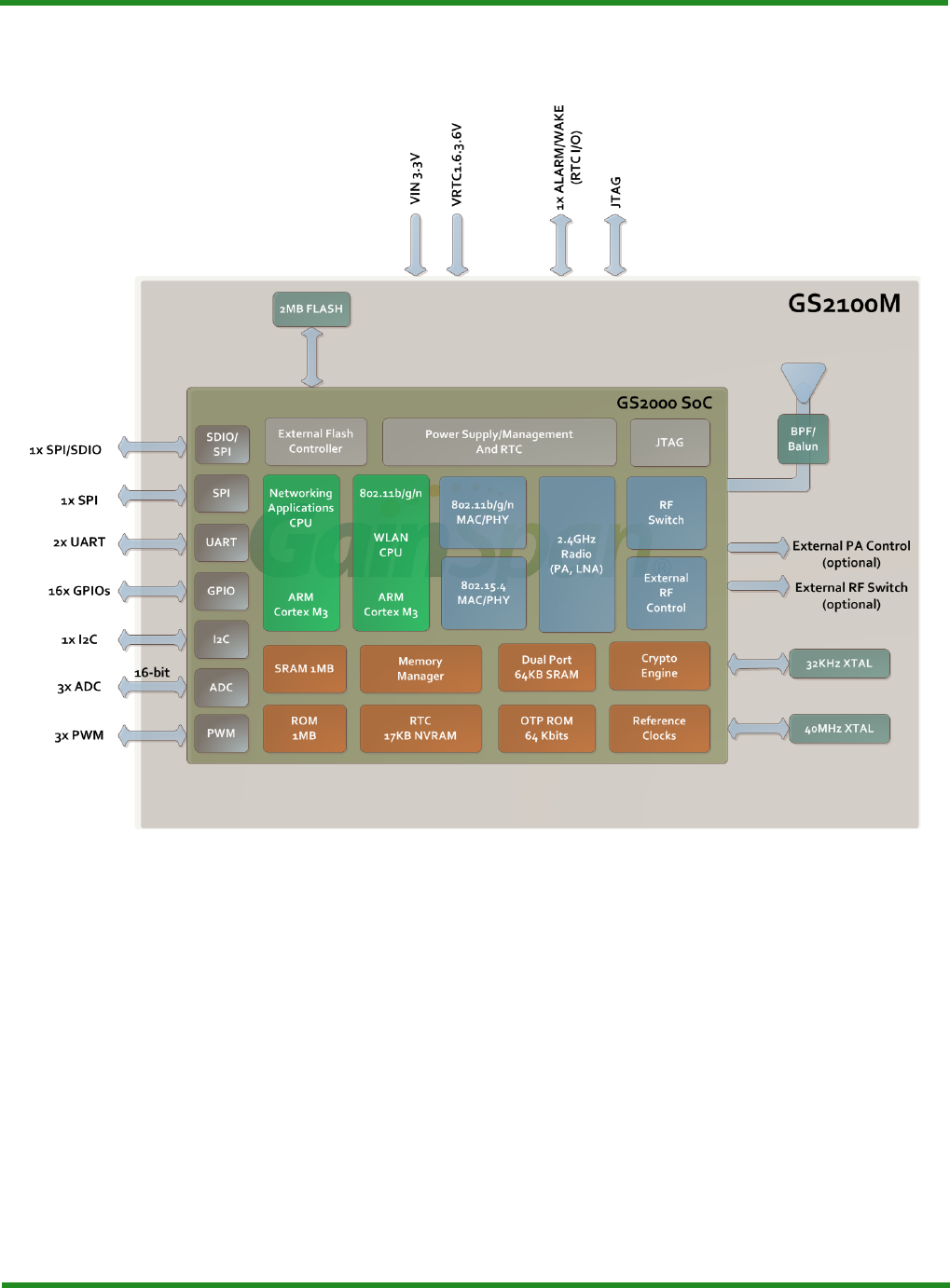

The GainSpan GS2100M module (see Figure 1, page 22) is based on a highly integrated

GS2000 ultra low power WiFi System-on-Chip (SoC) that contains the following:

• The GS2000 SoC contains two ARM Cortex M3 CPUs, a compatible 802.11

radio, security, on-chip memory, and variety of peripherals in a single package.

– One ARM core is dedicated to Networking Subsystems, and the other

dedicated to Wireless LAN Subsystems.

– The module carries an 802.11/g/n radio with on-board 32KHz & 40MHz

crystal circuitries, RF, and on-board antenna or external antenna options.

• On module 2 Mega Byte FLASH device that contains the user embedded

applications and data such as web pages.

• Variety of interfaces are available such as two UART blocks using only two data

lines per port with optional hardware flow controls, two SPI blocks (one SDIO is

shared function with one for the SPI interfaces), I2C with Master or slave

operation, JTAG port, low-power 12-bit ADC capable of running at up to 2M

samples/Sec., GPIO’s, and LED Drivers/GPIO with 16mA capabilities.

• GS2100Mxx has a VRTC pin that is generally connected to always available

power source such as battery or line power. This provides power to the Real Time

Clock (RTC) block on the SoC. The module also has VIN_3V3 power supply

input to provide the logic signal level for the I/O pins.

GS2100M Architecture GS2100M Low Power WiFi Module Data Sheet

Architecture Description

22 Confidential Preliminary GS2100M-DS-001212, Release 0.10

Figure 1 GS2100M Block Diagram

GS2100M Low Power WiFi Module Data Sheet GS2100M Architecture

Architecture Description

GS2100M-DS-001212, Release 0.10 Confidential Preliminary 23

2.1.1 Wireless LAN and System Control Subsystem

The WLAN CPU subsystem consists of the WLAN CPU, its ROM, RAM, 802.11 b/g/n

MAC/PHY, and peripherals. This CPU is intended primarily to implement the 802.11 MAC

protocols. The CPU system has GPIO, Timer, and Watchdog for general use. A UART is

provided as a debug interface. A SPI interface is provided for specific application needs.

The WLAN CPU can access the RTC registers through an asynchronous AHB bridge.

WLAN CPU has only Flash read access to the on-board flash memory. The WLAN

subsystem interacts with the App subsystem through a set of mailboxes and shared

dual–port memories.

The CPUs provide debug access through a JTAG/serial port. For GS2100 module, the

complete JTAG port is brought out for both CPUs. The CPUs also include code and data

trace and watch point logic to assist in-system debugging of SW.

The WLAN subsystem includes an integrated power amplifier, and provides management

capabilities for an optional external power amplifier. In addition, it contains hardware

support for AES-CCMP encryption (for WPA2) and RC4 encryption (for WEP & WPA

TKIP) encryption/decryption.

2.1.2 On-board Antenna / RF Port / Radio

The GS2100Mxx modules have fully integrated RF frequency synthesizer, reference clock,

low power PA, and a high power PA (GS2100MIE) for extended range applications. Both

TX and RX chain in the module incorporate internal power control loops. The GS2100Mxx

modules also incorporate an on-board antenna option plus a variety of regulatory certified

antenna options for various application needs.

2.1.2.1 802.11 MAC

The 802.11 MAC implements all time critical functionality of the 802.11b/g/n protocols. It

works in conjunction with the MAC SW running on the CPU to implement the complete

MAC functionality. It interfaces with the PHY to initiate transmit/receive and CCA. The

PHY registers are programmed indirectly through the MAC block. The MAC interfaces to

the system bus and uses DMA to fetch transmit packet data and save receive packet data.

The MAC SW exchanges packet data with the HW though packet descriptors and pointers.

Key Features

• Compliant to IEEE 802.11 (2012)

• Compliant to IEEE 802.11b/g/n (11n – 2009)

• Long and short preamble generation on frame-by-frame basis for 11b frames

• Transmit rate adaptation

• Transmit power control

• Frame aggregation (AMPDU, AMSDU)

• Block ACK (Immediate, Compressed)

GS2100M Architecture GS2100M Low Power WiFi Module Data Sheet

Architecture Description

24 Confidential Preliminary GS2100M-DS-001212, Release 0.10

• RTS/CTS, CTS-to-self frame sequences and SIFS

• Client and AP modes support

• Encryption support including: AES-CCMP, legacy WPA-TKIP, legacy WEP

ciphers and key management

• WiFi Protected Setup 2.0 (WPS2.0) including both PIN and push button options

• 802.11e based QoS (including WMM, WMM-PS)

• WiFi Direct with concurrent mode, including Device/Service Discovery, Group

Formation/Invitation, Client Power Save, WPS-PIN/Push Button

2.1.2.2 802.11 PHY

The 802.11 PHY implements all the standard required functionality and GainSpan specific

functionality for 802.11b/g/n protocols. It also implements the Radar detection

functionality to support 802.11h. The PHY implements the complete baseband Tx and Rx

pipeline. It interfaces with the MAC to perform transmit and receive operations. It

interfaces directly to the ADC and DAC. The PHY implements the Transmit power control,

receive Automatic Gain Control and other RF control signals to enable transmit and

receive. The PHY also computes the CCA for MAC use.

Key Features

• Compliant to 2.4GHz IEEE 802.11b/g/n (11n – 2009)

• Support 802.11g/n OFDM with BPSK, QPSK, 16-QAM and 64-QAM; 802.11b

with BPSK, QPSK and CCK

• Support for following data rates:

– 802.11n (20MHz): MCS0 - 7; 7.2, 14.4, 21.7, 28.9, 43.3, 57.8, 65.0, 72.2

Mbps

– 802.11g: 6, 9, 12, 18, 24, 36, 48, 54 Mbps

– 802.11b: 1, 2, 5.5, 11 Mbps

• Support Full (800ns) & Half (400ns) Guard Interval (GI) modes (SGI and LGI)

• Support Space time block coding (STBC) for receive direction

• Complete front-end radio integration including PA, LNA and RF Switch

• Support for external PA, LNA and control of external RF Switch (GS2100MIE

only)

2.1.2.3 RF/Analog

The RF/Analog is a single RF transceiver for IEEE 802.11b/g/n (WLAN). The RF Interface

block provides the access to the RF and analog control and status to the CPU. This block is

accessible only from the WLAN CPU. It implements registers to write static control words.

It provides read only register interface to read static status. It generates the dynamic control

GS2100M Low Power WiFi Module Data Sheet GS2100M Architecture

Architecture Description

GS2100M-DS-001212, Release 0.10 Confidential Preliminary 25

signals required for TX and RX based on the PHY signals. The AGC look up table to map

the gain to RF gain control word is implemented in this block.

2.1.3 Network Services Subsystem

2.1.3.1 APP CPU

The Network services subsystem consists of an APP CPU which is based on an ARM

CORTEX M3 core. It incorporates an AHB interface and a JTAG debug interface. The

network RTOS, network stack, and customer application code run on this CPU.

2.1.3.2 Crypto Engine

The Network services subsystem contains a separate hardware crypto engine that provides

a flexible framework for accelerating the cryptographic functions for packet processing

protocols. The crypto engine has the raw generic interface for cipher and hash/MAC

functions such as AES, DES, SHA, and RC4. It also includes two optional engines to

provide further offload; the PKA and RNG modules. These provide additional methods for

public key acceleration functions and random number generation. The engine includes a

DMA engine that allows the engine to perform cryptographic operation on data packets in

the system memory without any CPU intervention.

2.1.4 Memory Subsystem

The GS2100M module contains several memory blocks.

2.1.4.1 SRAM

The system memory is built with single port and dual port memories. Most of the memory

consists of single port memory. A 64KB dual port memory is used for exchange of data

between the two CPU domains. All the memories are connected to the system bus matrix

in each CPU subsystem. All masters can access any of the memory within the subsystem.

The APP subsystem has 384KB of dedicated SRAM for program and data use.

The WLAN subsystem has 320KB of dedicated SRAM for program and data use.

These memories are divided into banks of 64KB each. The bank structure allows different

masters to access different banks simultaneously through the bus matrix without incurring

any stall. Code from the external Flash is loaded into the SRAM for execution by each

CPU.

In addition, a static shared SRAM is provided. This consists of five 64KB memory blocks.

At any time, any of these memory blocks can be assigned to one of the CPU subsystem.

These should be set up by the APP CPU SW at initialization time. The assignment is not

intended to change during operation and there is no HW interlock to avoid switching in the

middle of a memory transaction. The assignment to the WLAN CPU should be done

starting from the highest block number going down to lowest block number. This result in

GS2100M Architecture GS2100M Low Power WiFi Module Data Sheet

Architecture Description

26 Confidential Preliminary GS2100M-DS-001212, Release 0.10

the shared memory appearing as a single bank for each CPU subsystem, independent of the

number of blocks assigned. The shared memory is mapped such that the SRAM space is

continuous from the dedicated SRAM to shared SRAM.

A 64KB dual port memory is used for exchange of data between the two CPU domains.

Each CPU subsystem can read or write to this memory using an independent memory port.

SW must manage the memory access to avoid simultaneous write to the same memory

location. The dual port memory appears as a single bank to each CPU subsystem.

2.1.4.2 ROM

ROM is provided in each CPU subsystem to provide the boot code and other functional

code that are not expected to change regularly. Each CPU has 512KB of ROM.

2.1.4.3 OTP ROM

The GS2000 device includes a 64Kbit OTP ROM used for storing MAC ID and other

information such as security keys etc. The App and WLAN subsystem each contain

32Kbits (4Kbytes) of OTP memory.

2.1.4.4 Flash Interface

The GS2000 SoC has only internal ROM and RAM for code storage. There is no embedded

Flash memory on the SoC. Any ROM patch code and new application code must reside in

the on-module Flash device of the GS2100M module. Flash access from the two CPUs are

independent. The App CPU is considered the system Master and the code running on this

CPU is required to initialize the overall chip and common interfaces. WLAN CPU access

to the Flash is restricted to read DMA. Any write to the Flash from the WLAN CPU must

be done through the App CPU. The operational parameters of the DMA accesses are set by

the App CPU at system startup. The Flash code is transferred to internal RAM before

execution.

2.1.5 Clocks

The GS2100M includes four basic clock sources:

– Low power 32KHz clock (see 2.1.6 Real Time Clock (RTC) Overview, page 27)

– 40MHz Xtal Oscillator

– PLL to generate the internal 120MHz (CPU) and 80MHz (PHY) clocks from the

40MHz Xtal.

– High speed RC oscillator 80MHz

Intermediate modes of operation, in which high speed clocks are active but some modules

are inactive, are obtained by gating the clock signal to different subsystems. The clock

control blocks within the device are responsible for generation, selection and gating of the

clocked used in the module to reduce power consumption in various power states.

GS2100M Low Power WiFi Module Data Sheet GS2100M Architecture

Architecture Description

GS2100M-DS-001212, Release 0.10 Confidential Preliminary 27

2.1.6 Real Time Clock (RTC) Overview

To provide global time (and date) to the system, the GS2100Mxx module is equipped with

a low-power Real Time Clock (RTC). The RTC is the always on block that manages the

Standby state. This block is powered from a supply pin (VRTC) separate from the digital

core and may be powered directly from a battery. The RTC implementation supports a

voltage range of 1.6v to 3.6v.

2.1.6.1 RTC Main Features

• One 48-bit primary RTC counter as the primary reference for all timing events and

standby awake management

• 1 programmable IO pins with specific default behavior. These pins are in the RTC

IO domain.

– Alarm inputs to wake up the GS2100M module from its sleep states

(deep-sleep/standby)

• Startup control counters with HW and SW override registers

• Power-on-reset control with brown-out detector

• RTC registers to hold RTC and wakeup control bits while the core domain is off

• 1Kbyte latch based memory (1.6-3.6v capable)

• 16KB of SRAM memory, divided into 4 equal blocks (1.2v capable)

• uLDO to supply the SRAM memory

• RTC logic is 1.6-3.6v capable

• 32 KHz RC oscillator

• 32768Hz crystal oscillator

• APB interface for CPU access

• Interrupts to CPU

The RTC contains a low-power 32.768KHz RC oscillator which provides fast startup at

first application of RTC power. It also supports an optional 32.768KHz crystal oscillator

which can be substituted for the RC oscillator under software control. In normal operation

the RTC is always powered up.

The standby programmable counter is 48-bits and provides up to 272 years worth of

standby duration. For the RTC_IO pin, the programmable embedded counter (32-bit) is

provided to enable periodic wake-up of the remainder of the external system, and provide

a 1.5 days max period. The RTC_IO pin can be configured as input (ALARM) or output

(WAKE UP) pin.

The RTC includes a Power-On Reset (POR) circuit, to eliminate the need for an external

component. The RTC contains low-leakage non-volatile (battery-powered) RAM, to

enable storage of data that needs to be preserved. It also includes a brown-out detector that

can be disabled by SW.

GS2100M Architecture GS2100M Low Power WiFi Module Data Sheet

Architecture Description

28 Confidential Preliminary GS2100M-DS-001212, Release 0.10

2.1.6.2 Real Time Clock Counter

The Real Time Counter features:

– 48-bit length (with absolute duration of 272 years).

– Low-power design.

This counter is automatically reset by power-on-reset.

This counter wraps around (returns to “all-0” once it has reached the highest possible

“all-1” value).

2.1.6.3 RTC I/O

There are three (3) RTC I/O (0, 1,2) that can be used to control external devices, such as

sensors or wake up the module based on external events or devices.

2.1.7 GS2100M Peripherals

2.1.7.1 SDIO Interface

The SDIO interface is a full / high speed SDIO device controller. The Controller supports

SPI, 1-bit SD and 4-bit SD bus mode. The SDIO block has an AHB interface, which allows

the CPU to configure the operational registers residing inside the AHB Slave core. The CIS

and CSA area is located inside the internal memory of CPU subsystem. The SDIO Registers

(CCCR and FBR) are programmed by both the SD Host (through the SD Bus) and CPU

(through the AHB bus) via Operational registers. The SDIO block implements the AHB

master to initiate transfers to and from the system memory autonomously.

During the normal initialization and interrogation of the card by the SD Host, the card will

identify itself as an SDIO device. The SD Host software will obtain the card information in

a tuple (linked list) format and determine if that card’s I/O function(s) are acceptable to

activate. If the Card is acceptable, it will be allowed to power up fully and start the I/O

function(s) built into it.

The SDIO interface implements Function 1 in addition to the default Function 0. All

application data transfers are done through the Function 1.

The primary features of this interface are

• Meets SDIO card specification version 2.0.

• Conforms to AHB specification.

• Host clock rate variable between 0 and 40 MHz

• All SD bus modes supported including SPI, 1 and 4 bit SD.

• Allows card to interrupt host in SPI, 1 and 4 bit SD modes.

NOTE: Tested with current test platform up to 33 MHz.

GS2100M Low Power WiFi Module Data Sheet GS2100M Architecture

Architecture Description

GS2100M-DS-001212, Release 0.10 Confidential Preliminary 29

• Read and Writes using 4 parallel data lines

• Cyclic Redundancy Check CRC7 for command and CRC16 for data

integrity-CRC checking optional in SPI mode

• Programmable through a standard AHB Slave interface

• Writing of the I/O reset bit in CCCR register generates an active low reset output

synchronized to AHB Clock domain.

• Card responds to Direct read/write (IO52) and Extended read/write (IO53)

transactions.

• Supports Read wait Control operation.

• Supports Suspend/Resume operation.

2.1.7.2 SPI Interface

The SPI interface is a master slave interface that enables synchronous serial

communications with slave or master peripherals having one of the following: Motorola

SPI-compatible interface, TI synchronous serial interface or National Semiconductor

Microwire interface. In both master and slave configuration, the block performs

parallel-to-serial conversion on data written to an internal 16-bit wide, 8-deep transmit

FIFO and serial to parallel conversion on received data, buffering it in a similar 16-wide, 8

deep FIFO. It can generate interrupts to the CPU to request servicing transmit and receive

FIFOs and indicate FIFO status and overrun/underrun. The clock bit rate is SW

programmable. In master mode, the SPI block in GS2000 can perform up to 30 MHz and

in slave mode up to 10 MHz serial clock. The interface type, data size and interrupt masks

are programmable. It supports DMA working in conjunction with the uDMA engine.

2.1.7.3 UART Interface

The UART interface implements the standard UART protocol. It is 16450/16550

compatible. It has separate 32 deep transmit and receive FIFOs to reduce CPU interrupts.

The interface supports standard asynchronous communication protocol using start, stop and

parity bits. These are added and removed automatically by the interface logic. The data size,

parity and number of stop bits are programmable. It supports HW based flow control

through CTS/RTS signaling. A fractional baud rate generator allows accurate setting of the

communication baud rate. It supports DMA working in conjunction with the uDMA

engine.

2.1.7.4 I2C Interface

The I2C interface block implements the standard based two wire serial I2C protocol. The

interface can support both master and slave modes. It supports multiple masters, high speed

transfer (up to 3.4MHz), 7 or 10 bit slave addressing scheme, random and current address

transfer. It also supports clock stretching to interface with slower devices. It can generate

interrupts to the CPU to indicate specific events such as FIFO full/empty, block complete,

no ack error, and arbitration failure.

GS2100M Architecture GS2100M Low Power WiFi Module Data Sheet

Architecture Description

30 Confidential Preliminary GS2100M-DS-001212, Release 0.10

2.1.7.5 GPIO

The GPIO block provides programmable inputs and outputs that can be controlled from the

CPU SW through an APB interface. Any number of inputs can be configured as an interrupt

source. The interrupts can be generated based on the level or the transition of a pin. At reset,

all GPIO lines defaults to inputs. Each pin can be configured as input or output from SW

control.

2.1.7.6 Sigma Delta ADC

The ADC and DAC are 16-bit sigma-delta converters. There are 3 channels, each having a

differential pair for a total of six input pins. The sample rate can be 32KHz to 80KHz. The

sigma delta converter ratio is 250. The ADC is a 2 channel converter. Each channel can

have an optional pre-amplifier stage. There are 4 gain levels in the pre-amp stage. The delay

between the two channels of the ADC can be adjusted under SW control. The digital

interface for the ADCs and the DAC are 2’s complement.

2.1.7.7 PWM

The PWM consists of three identical PWM function blocks. The PWM function blocks can

be used in two modes of operations:

• Independent PWM function blocks providing output signal with programmable

frequency and duty cycle

• Synchronized PWM function blocks with programmable phase delay between

each PWM output

The PWM has the following features:

• 32 bit AMBA APB interface to access control, and status information

• Three identical PWM function blocks

• Each PWM block can be enabled independently

• All three PWM blocks can be started synchronously or chained with

programmable delay

• Programmable 6 bit prescaler for the input clock (see 2.1.5 Clocks, page 26)

• Programmable frequency and duty cycle using 16 bit resolution in terms of clock

cycles for ON and OFF interval time

• Combined interrupt line with independent masking of interrupts

GS2100M Low Power WiFi Module Data Sheet GS2100M Architecture

Architecture Description

GS2100M-DS-001212, Release 0.10 Confidential Preliminary 31

2.1.8 System States

The system states of the GS2100Mxx system are as follows:

Power OFF: No power source connected to the system.

Standby: In the standby state, the GS2100M is in its lowest power state. In this state

power is on to the VRTC and VIN_3V3 input. The RTC portion of the GS2000 chip is

powered from the VRTC pin.

In standby state, the 32.768KHz oscillator is running and RTC RAM retains the state

(how many banks retain their state is SW configurable). SRAM, CPUs and I/Os are

powered off using the internal switches within the device thus reducing overall power

consumption.

Exit from standby occurs when a pre-specified wakeup time occurs, or when the

RTC_IO configured as alarm inputs sees the programmed polarity of signal edge.

System Configuration: When a power-up is requested, the system transitions from the

Standby state to the System Configuration state. In this state, the APP CPU is released

from reset by the RTC. The WLAN CPU remains in the reset state during System

Configuration. The APP CPU then executes the required system configurations,

releases the WLAN CPU from reset, and transitions to the Power-ON state.

The System Configuration state is also entered on transition from the Power-ON state

to the Standby state, to complete necessary preparations before shutting off the power

to the core system.

Power-ON: This is the active state where all system components can be running. The

Power-ON state has various sub-states, in which unused parts of the system can be in

sleep mode, reducing power consumption. Sleep states are implemented by gating the

clock signal off for a specific system component. Additionally, unneeded clock sources

can be turned off. For example, receiving data over a slave SPI interface could be done

with only the 80MHz RC oscillator active, and the 40MHz crystal and PLL turned off.

Sleep: In the Sleep state, the 40MHz crystal and the 80MHz RC oscillator remains

running, but it is gated off to one or both CPUs. Each CPU can independently control

its own entry into Sleep state. Any enabled interrupt will cause the interrupted CPU to

exit from Sleep state, and this will occur within a few clock cycles.

Deep Sleep: Deep sleep is entered only when both CPUs agree that the wakeup latency

is OK. In Deep Sleep mode, the 40MHz crystal oscillator and 80MHz RC oscillator are

turned off to save power, but all power supplies remain turned on. Thus all registers,

memory, and I/O pins retain their state. Any enabled interrupt will cause an exit from

Deep Sleep state.

EXT_RTC_RESET_n pin: This is an input pin for resetting the entire module,

including the RTC section of the device. This pin should not be left floating. An

external 10K pull up resistor to VRTC is recommended.

NOTE: During first battery plug, i.e., when power is applied the first time to the

RTC power rail (VRTC), the power detection circuit in the RTC also causes a

wakeup request.

GS2100M Architecture GS2100M Low Power WiFi Module Data Sheet

Architecture Description

32 Confidential Preliminary GS2100M-DS-001212, Release 0.10

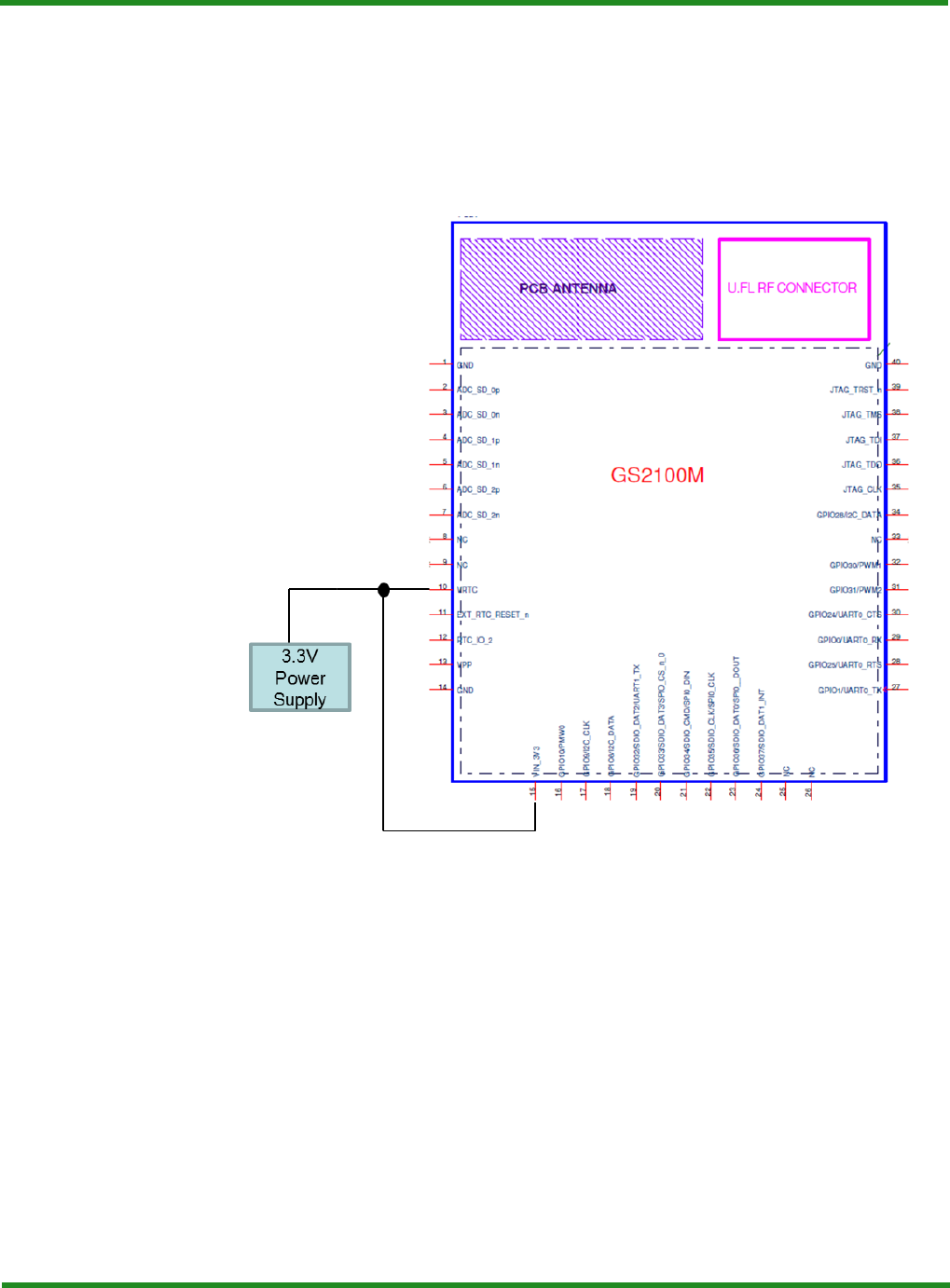

2.1.9 Power Supply

This section shows various application power supply connections. Figure 2, page 32 shows

the GS2100Mxx power supply connection.

Figure 2 GS2100Mxx Always ON Power Supply Connection

Notes:

1. Always ON connection connects VRTC and VIN_3V3 together to a 3.3V power supply.

GS2100M-DS-001212, Release 0.10 Confidential Preliminary 33

Chapter 3 Pin-out and Signal Description

This chapter describes the GainSpan® GS2100M Low Power module architecture.

• GS2100Mxx Device Pin-out, page 33

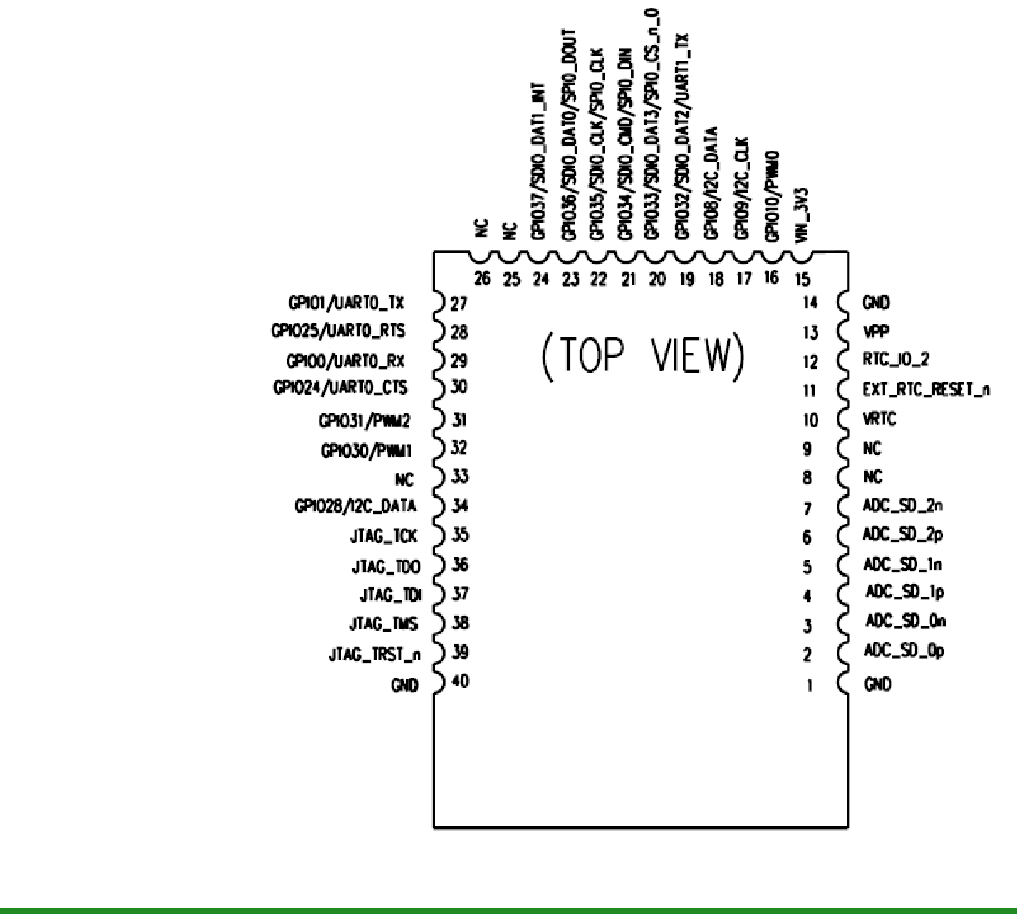

3.1 GS2100Mxx Device Pin-out

Figure 3, page 33 shows the GS2100Mxx device pin-out diagram.

Figure 3 GS2100Mxx Device Pin-out Diagram (Module Top View)

Pin-out and Signal Description GS2100M Low Power WiFi Module Data Sheet

GS2100Mxx Device Pin-out

34 Confidential Preliminary GS2100M-DS-001212, Release 0.10

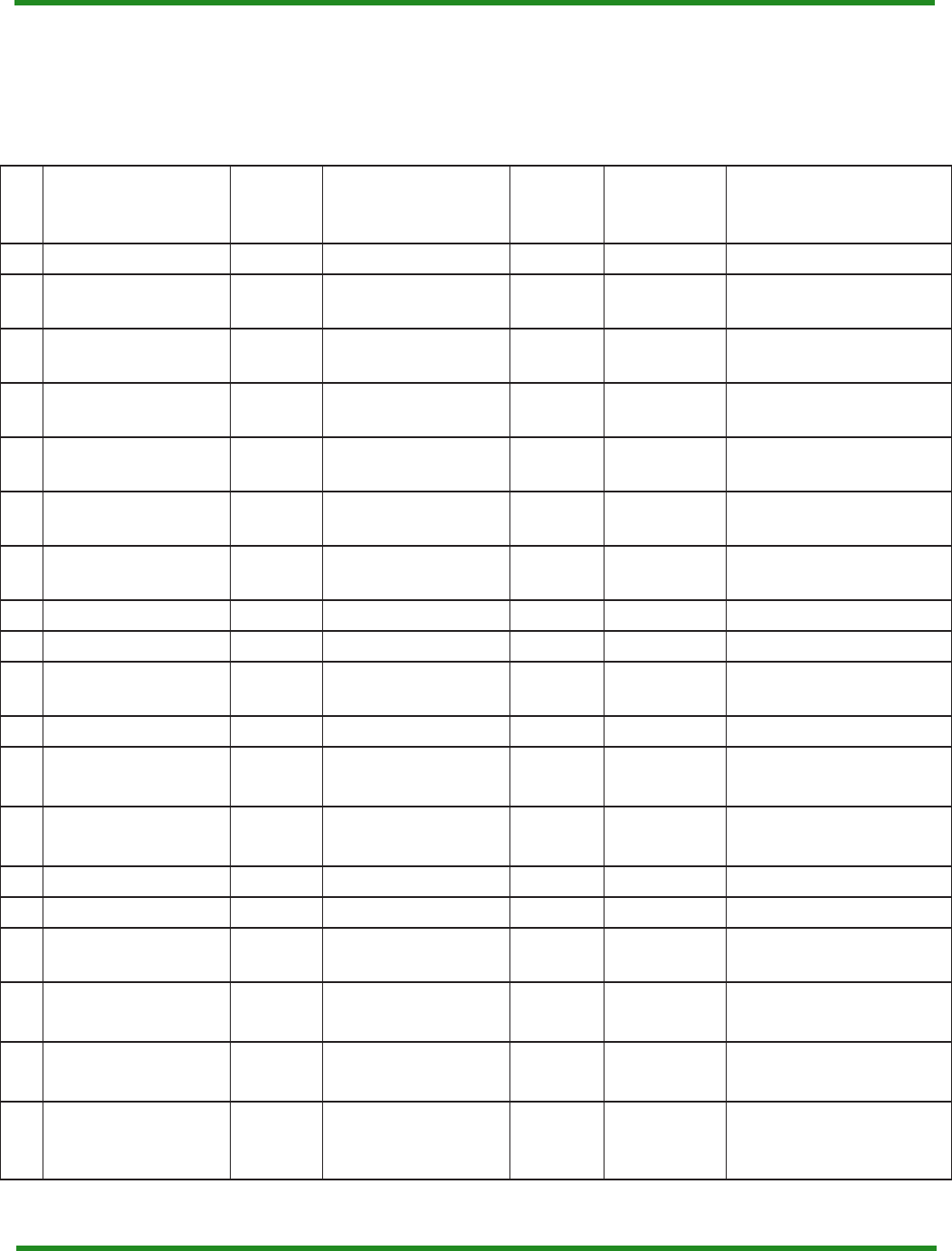

3.1.1 GS2100Mxx Module Pins Description

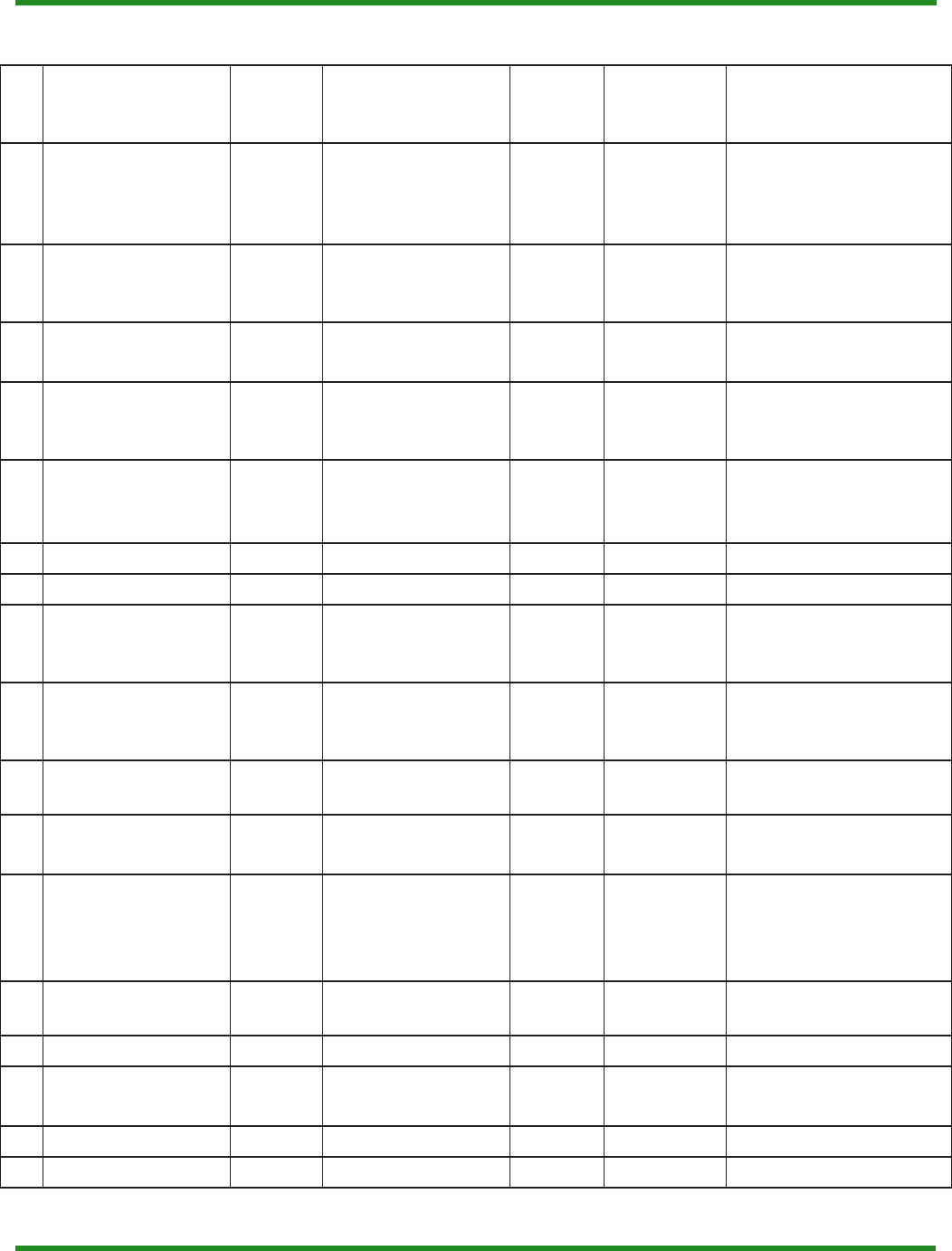

Table 7, page 34 describes the GS2100Mxx module pin signal description.

Table 7 GS2100Mxx Module Pin Signal Description

Pins Name Voltage

Domain

Internal Bias after

Hardware Reset

Drive

Strength

(mA)

Signal State Description

1 GND 0V Not Applicable Analog port Ground

2 ADC_SD_0p VIN_3V3 Not Applicable Analog port Sigma Delta ADC

differential positive input 0

3 ADC_SD_0n VIN_3V3 Not Applicable Analog port Sigma Delta ADC

differential negative input 0

4 ADC_SD_1p VIN_3V3 Not Applicable Analog port Sigma Delta ADC

differential positive input 1

5 ADC_SD_1n VIN_3V3 Not Applicable Analog port Sigma Delta ADC

differential negative input 1

6 ADC_SD_2p VIN_3V3 Not Applicable Analog port Sigma Delta ADC

differential positive input 2

7 ADC_SD_2n VIN_3V3 Not Applicable Analog port Sigma Delta ADC

differential negative input 2

8NC Not Connected

9NC Not Connected

10 VRTC VRTC Not Applicable Analog port Embedded Real Time Clock

Power Supply

11 EXT_RTC_RESET_n VRTC None Digital Input Device Reset Input

12 RTC_IO_2

(see Note 2) VRTC None 1 RTC Digital

Input/Output

Embedded Real Time Clock

Input/Output 2

13 VPP

(see Note 7) VPP Not Applicable Analog port Programming Voltage for

OTP Memory

14 GND 0V Not Applicable 4 Analog port Ground

15 VIN_3V3 VIN_3V3 Not Applicable Analog port Single Supply Port

16 GPIO10/PWM0 VIN_3V3 Pull-down 4 Digital

Input/Output

GPIO/Pulse Width

Modulator 0

17 GPIO9/I2C_CLK

(see Note 5) VIN_3V3 Pull-down 12 Digital

Input/Output

GPIO/Inter-Integrated

Circuit Clock

18 GPIO8/I2C_DATA

(see Note 5) VIN_3V3 Pull-down 12 Digital

Input/Output

GPIO/Inter-Integrated

Circuit Data

19 GPIO32/SDIO_DAT2/

UART1_TX VIN_3V3 Pull-down 4 Digital

Input/Output

GPIO/SDIO_DATA Bit

2/UART1 Transmitter

Output

GS2100M Low Power WiFi Module Data Sheet Pin-out and Signal Description

GS2100Mxx Device Pin-out

GS2100M-DS-001212, Release 0.10 Confidential Preliminary 35

20 GPIO33/SDIO_DAT3/

SPI0_CS_n_0 VIN_3V3 Pull-up 4 Digital

Input/Output

GPIO/SDIO Data Bit

3/SPI0 Chip Select Input 0

from the HOST (Active

Low)

21 GPIO34/SDIO_CMD/

SPI0_DIN VIN_3V3 Pull-down 4 Digital

Input/Output

GPIO/SDIO Command

Input/SPI0 Receive Data

Input

22 GPIO35/SDIO_CLK/

SPI0_CLK VIN_3V3 Pull-down 4 Digital

Input/Output

GPIO/SDIO Clock/SPI0

Clock Input from the HOST

23 GPIO36/SDIO_DAT0/

SPI0_DOUT VIN_3V3 Pull-down 4 Digital

Input/Output

GPIO/SDIO Data Bit

0/SPI0 Transmit Data

Output to the HOST

24

GPIO37/

SDIO_DAT1_INT

(see Note 8)

VIN_3V3 Pull-down 4 Digital

Input/Output

GPIO/4-bit SDIO DATA Bit

1/SDIO SPI Mode Interrupt

25 NC Not Connected

26 NC Not Connected

27 GPIO1/UART0_TX VIN_3V3 Pull-down 4 Digital

Input/Output

GPIO/UART0 Transmitter

Output. This pin is used for

Code Restore.

28 GPIO25/UART0_RTS

(see Note 6) VIN_3V3 Pull-down 12 Digital

Input/Output

GPIO/UART0 Request to

Send Output. This pin is

used for Program Select.

29 GPIO0/UART0_RX VIN_3V3 Pull-down 4 Digital Input

Output

GPIO/UART0 Receive

Input

30 GPIO24/UART0_CTS

(see Note 6) VIN_3V3 Pull-down 12 Digital

Input/Output

GPIO/UART0 Clear to

Send Input

31 GPIO31/PWM2

(see Note 4) VIN_3V3 Pull-down 16 Digital

Input/Output

GPIO/Pulse Width

Modulation Output 2.

This pin is used for Program

Mode.

32 GPIO30/PWM1 VIN_3V3 Pull-down 16 Digital

Input/Output

GPIO/Pulse Width

Modulation Output 1

33 NC Not Connected

34 GPIO28/I2C_DATA

(see Note 5) VIN_3V3 Pull-down 12 Digital

Input/Output

GPIO/Inter-Integrated

Circuit Data

35 JTAG_TCK VIN_3V3 Pull-up Digital Input JTAG Test Clock

36 JTAG_TDO VIN_3V3 Not Applicable Digital Output JTAG Test Data Out

Table 7 GS2100Mxx Module Pin Signal Description (Continued)

Pins Name Voltage

Domain

Internal Bias after

Hardware Reset

Drive

Strength

(mA)

Signal State Description

Pin-out and Signal Description GS2100M Low Power WiFi Module Data Sheet

GS2100Mxx Device Pin-out

36 Confidential Preliminary GS2100M-DS-001212, Release 0.10

Notes:

1. Recommend 10K external pull up resistor to VRTC.

2. Should not be left floating. Connect 1M pull-down resistor if unused.

3. Pins with drive strength 4, 12, and 16 have one pull resistor (either up or down,

not both), which is enabled at reset.

4. This pin enables programming of the module. If GPIO31/PWM2 is high

during reset or power on, then the GS2100M will wait for Flash download via

UART0 or SPI0 interface. Route this pin on the base board so it can be pulled up

to VIN_3V3 for programming the module.

5. If I2C interface is used, provide 2K Ohm pull-ups, to VIN_3V3, for pins 25

and 26 (I2C_CLK and I2C_DATA).

6. CTS and RTS signals indicate it is clear to send or ready to send when they are

LOW. If signals are high, indicates device is not ready.

7. This pin is generally reserved for GainSpan use, but if a design requires to

OTP during production, then design must take into account connection to this

pin. Otherwise, it should be left as a No Connect.

8. In the Serial-to-WiFi firmware when using SPI interface this pin is the host

wake-up signal or the Ready to Send signal.

a. GPIO37 - when using SPI interface this pin is the host wake-up signal or

the Ready to Send signal.

37 JTAG_TDI VIN_3V3 Pull-up Digital Input JTAG Test Data In

38 JTAG_TMS VIN_3V3 Pull-up Digital Input JTAG Test Mode Select

39 JTAG_TRST_n VIN_3V3 Pull-down Digital Input JTAG Test Mode Rest

(Active Low)

40 GND 0V Not Applicable Analog Port Ground

Table 7 GS2100Mxx Module Pin Signal Description (Continued)

Pins Name Voltage

Domain

Internal Bias after

Hardware Reset

Drive

Strength

(mA)

Signal State Description

GS2100M Low Power WiFi Module Data Sheet Pin-out and Signal Description

GS2100Mxx Device Pin-out

GS2100M-DS-001212, Release 0.10 Confidential Preliminary 37

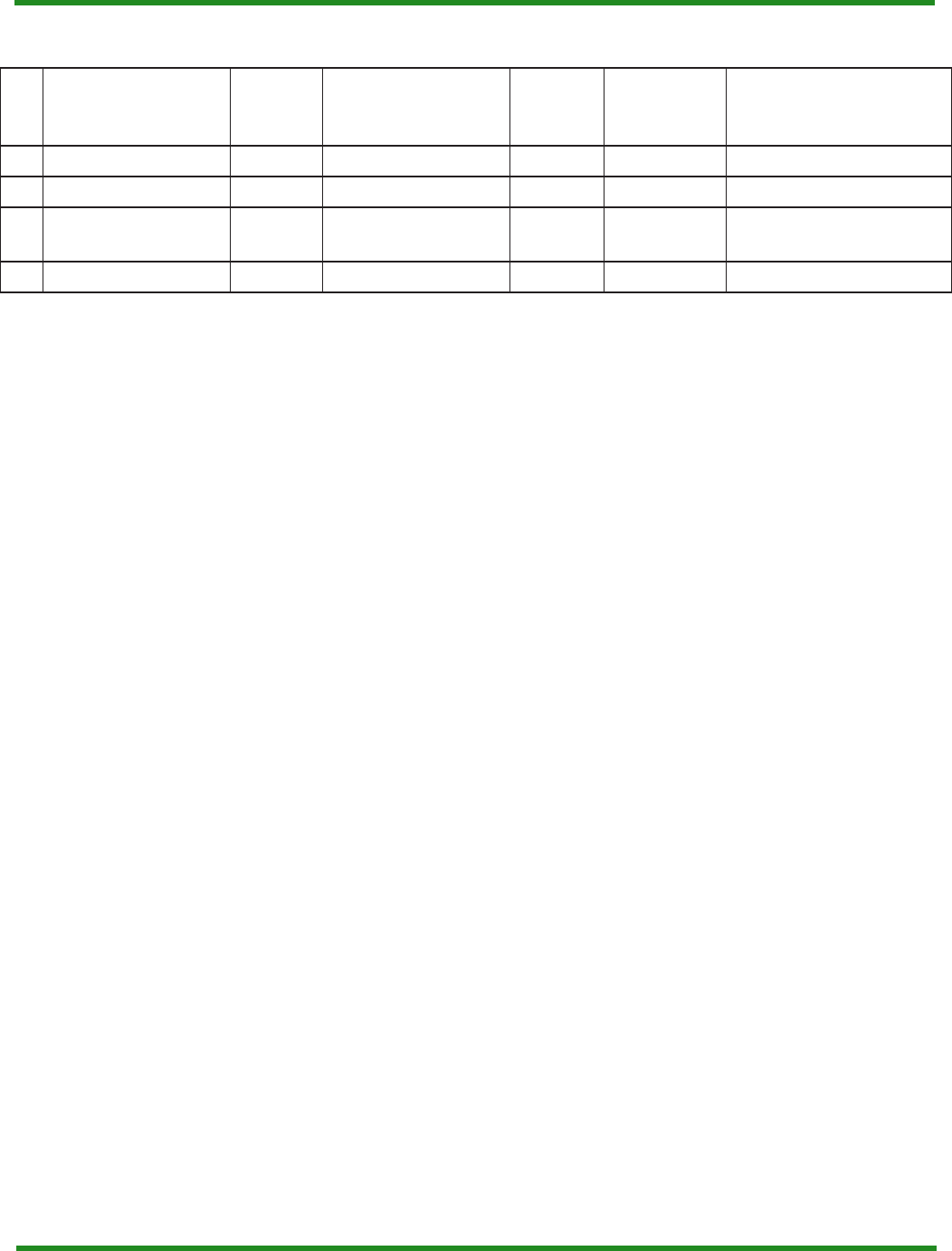

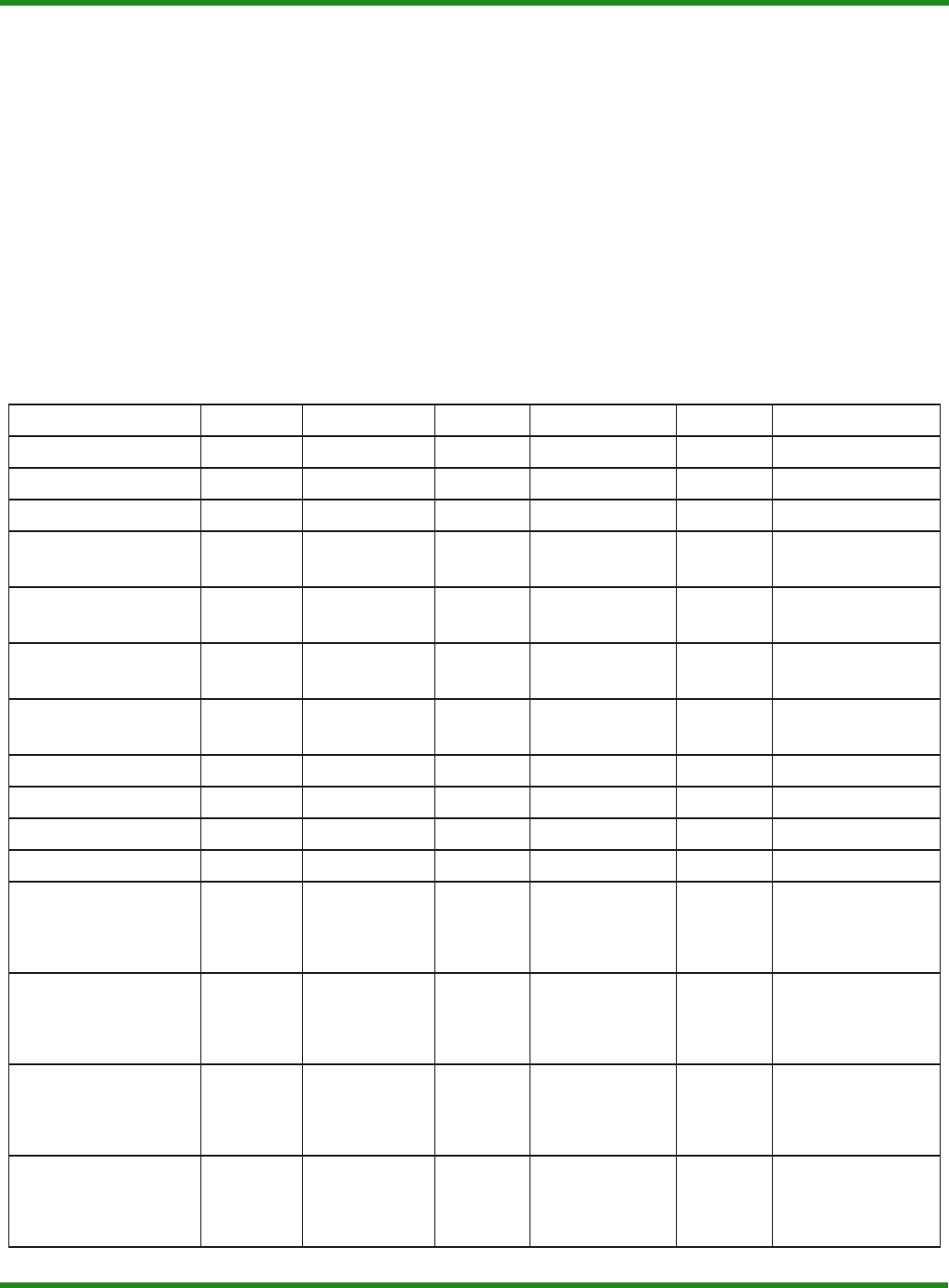

3.1.2 GS2100M Pin MUX Function

The GS2100M pins have multiple functions that can be selected using mux function by

software. Table 8, page 37 shows the various MUX functions for each pin. Each pin can be

independently configured. Table below shows the various mux functions for each pin. All

I/O pins are GPIO inputs at reset. For pins that are inputs to functional blocks only one pin

may be assigned to any input function. For example, UART1_RX may be assigned to

GPIO9 but not to both GPIO9 and GPIO37.

Table 8 GS2100M Pin MUX Description

Alternate Functions Available

Pin# Pin Name Internal

Pull

Resistor

mA Mux3 Mux4 Mux5 Mux7 Comments

1 GND

2 adc_sd_0p

3 adc_sd_0n

4 adc_sd_1p

5 adc_sd_1n

6 adc_sd_2p

7 adc_sd_2n

8NC

9NC

10 VRTC

11 ext_rtc_reset_n pull-up (u)

12 rtc_io_2 u/d 1 Alarm or wake

up pin

13 VPP Programming

voltage for OTP

memory

14 GND

15 VIN_3V3

16 gpio10/pwm0 pull-down (d) 4 pwm0 reserved reserved clk_rtc

17 gpio9/i2c_clk d 12 i2c_clk uart1_rx reserved i2s_lrclk

18 gpio8/i2c_data d 12 i2c_data uart1_tx reserved reserved

19 gpio32/sdio_dat2/uart1_tx d 4 sdio_data2 wuart_tx uart1_tx spi1_cs_n_12

20 gpio33/sdio_dat3/spi0_cs_n_0 u 4 sdio_data3 reserved uart1_rts spi0_cs_n_0

21 gpio34/sdio_cmd/spi0_din d 4 sdio_cmd reserved usart1_cts spi0_din

22 gpio35/sdio_clk/spi0_clk d 4 sdio_clk reserved i2c_clk spi0_clk Note: only 4mA

for i2C

23 gpio36/sdio_dat0_dout d 4 sdio_data0 reserved i2c_data spi0_dout

24 gpio37/sdio_dat1_int d 4 sdio_data1 wuart_rx uart1_rx spi0_cs_n_10

25 NC

26 NC

27 gpio1/uart0_tx d 4 uart0_tx wuart_tx pwm1 spi1_dout

Pin-out and Signal Description GS2100M Low Power WiFi Module Data Sheet

GS2100Mxx Device Pin-out

38 Confidential Preliminary GS2100M-DS-001212, Release 0.10

28 gpio25/uart0_rts d 12 uart0_rts wuart_rts reserved spi_1_clk

29 gpio0_uart0_rx d 4 uart0_rx wuart_rx pwm2 spi1_din

30 gpio24/uart0_cts d 12 uart0_cts wuart_cts reserved spi1_cs_n_0

31 gpio31/pwm2 d 16 pwm2 spi1_dout uart1_tx wuart_tx

32 gpio30/pwm1 d 16 pwm1 spi1_din uart1_rx wuart_rx

33 NC

34 gpio28/i2c_data d 12 i2c_data spi1_clk clk_hs_rc spi1_cs_n_21

35 jtag_tck

36 jtag_tdo

37 jtag_tdi

38 jtag_tms

39 jtag_trst_n

40 GND

Table 8 GS2100M Pin MUX Description (Continued)

Alternate Functions Available

Pin# Pin Name Internal

Pull

Resistor

mA Mux3 Mux4 Mux5 Mux7 Comments

GS2100M Low Power WiFi Module Data Sheet Pin-out and Signal Description

GS2100Mxx Device Pin-out

GS2100M-DS-001212, Release 0.10 Confidential Preliminary 39

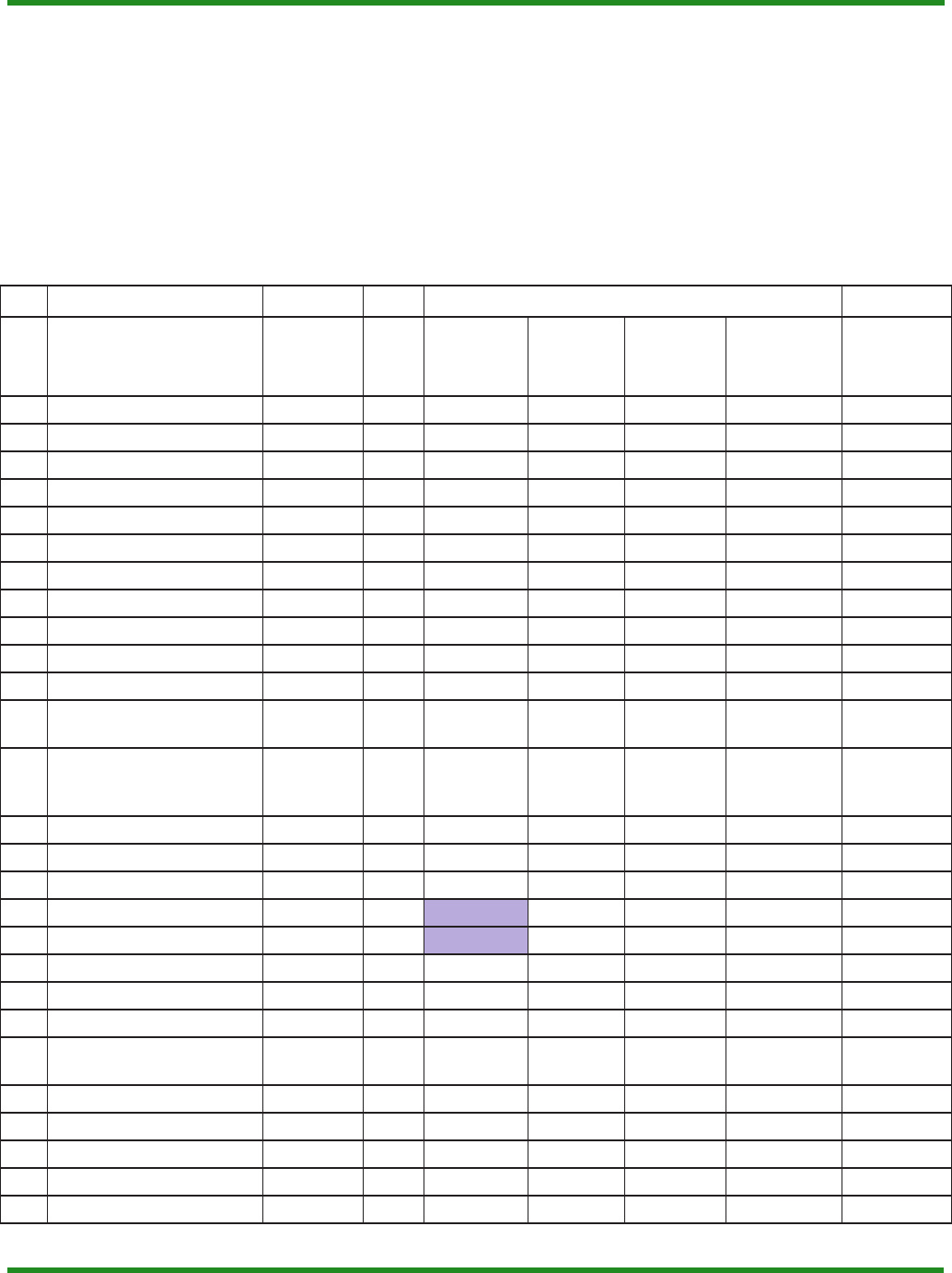

3.1.3 GS2100M Program and Code Restore Options

Table 9, page 39 describes the options available for device program mode and code restore

capabilities. The respective GPIO pins are sampled at reset by device and depending on the

values seen on these pins goes into the appropriate mode. Code for the GS2100M resides

on the internal flash of the module and up to two back-up copies could be stored in flash.

If a software designer wants to restore the execution code to one of the backup copy, it can

be accomplished by asserting the appropriate GPIO pins as shown in the table below during

power up or reset.

Table 9 GS2100M Pin Program and Code Restore

Program Mode

(GPIO 31)

Program Select

(GPIO 25)

Code Restore

(GPIO 1)

Description

0 X 0 Normal boot

0 0 1 Factory Code Restore

0 1 1 Previous Code Restore

10 X

Program Mode for code load using

UART 0 interface @115.2Kbaud or

using SPI0 on SDIO pins (Default Mode

if you don’t pull the Program Select pin

high)

11 X

Program Mode for code load using

UART 0 interface @921.6Kbaud or

using SDIO interface.

Note: This option is targeted for a future

revision.

Pin-out and Signal Description GS2100M Low Power WiFi Module Data Sheet

GS2100Mxx Device Pin-out

40 Confidential Preliminary GS2100M-DS-001212, Release 0.10

- This page intentionally left blank -

GS2100M-DS-001212, Release 0.10 Confidential Preliminary 41

Chapter 4 Electrical Characteristics

This chapter describes the GainSpan® GS2100M electrical characteristics.

• Absolute Maximum Ratings, page 41

• Operating Conditions, page 42

• I/O DC Specifications, page 43

• Power Consumption (Estimate), page 44

• 802.11 Radio Parameters (Estimate), page 45

• Sigma Delta ADC Parameters, page 46

4.1 Absolute Maximum Ratings

Conditions beyond those cited in Table 10, page 41 may cause permanent damage to the

GS2100Mxx, and must be avoided. Sustained operation, beyond the normal operating

conditions, may affect the long term reliability of the module.

Note:

1. Reference domain voltage is the Voltage Domain per section GS2100Mxx

Module Pins Description. For limitations on state voltage ranges, please consult

section on GS2100Mxx Module Pins Description.

Table 10 Absolute Maximum Ratings

Parameter Symbol Minimum Typical Maximum Unit

Storage Temperature TST -55 +125 oC

RTC Power Supply VRTC -0.5 4.0 V

Single Supply Port VIN_3V3 0.5 3.3 4.0 V

OTP Supply VPP TBD V

Signal Pin Voltage1VI -0.3 Voltage Domain + 0.3 V

Electrical Characteristics GS2100M Low Power WiFi Module Data Sheet

Operating Conditions

42 Confidential Preliminary GS2100M-DS-001212, Release 0.10

4.2 Operating Conditions

Table 11, page 42 lists the operating conditions of the GS2100Mxx module.

Notes:

1. Reference domain voltage is the Voltage Domain per section GS2100Mxx

Module Pins Description.

2. The VPP pin should be left floating when not doing OTP programming

operations.

Table 11 Operating Conditions

Parameter Symbol Minimum Typical Maximum Unit

Extended

Temperature Range TA-40 +85 oC

RTC Power Supply VRTC 1.6 3.3 3.6 V

Single Supply Port

GS2100MIx VIN_3V3 3.0 3.3 3.6 V

Signal Pin Voltage1VI 0 Voltage Domain V

VPP2VPP 5.5 5.75 6.0 V

GS2100M Low Power WiFi Module Data Sheet Electrical Characteristics

I/O DC Specifications

GS2100M-DS-001212, Release 0.10 Confidential Preliminary 43

4.3 I/O DC Specifications

4.3.1 I/O Digital Specifications (Tri-State) Pin Types 4mA, 12mA, and 16mA

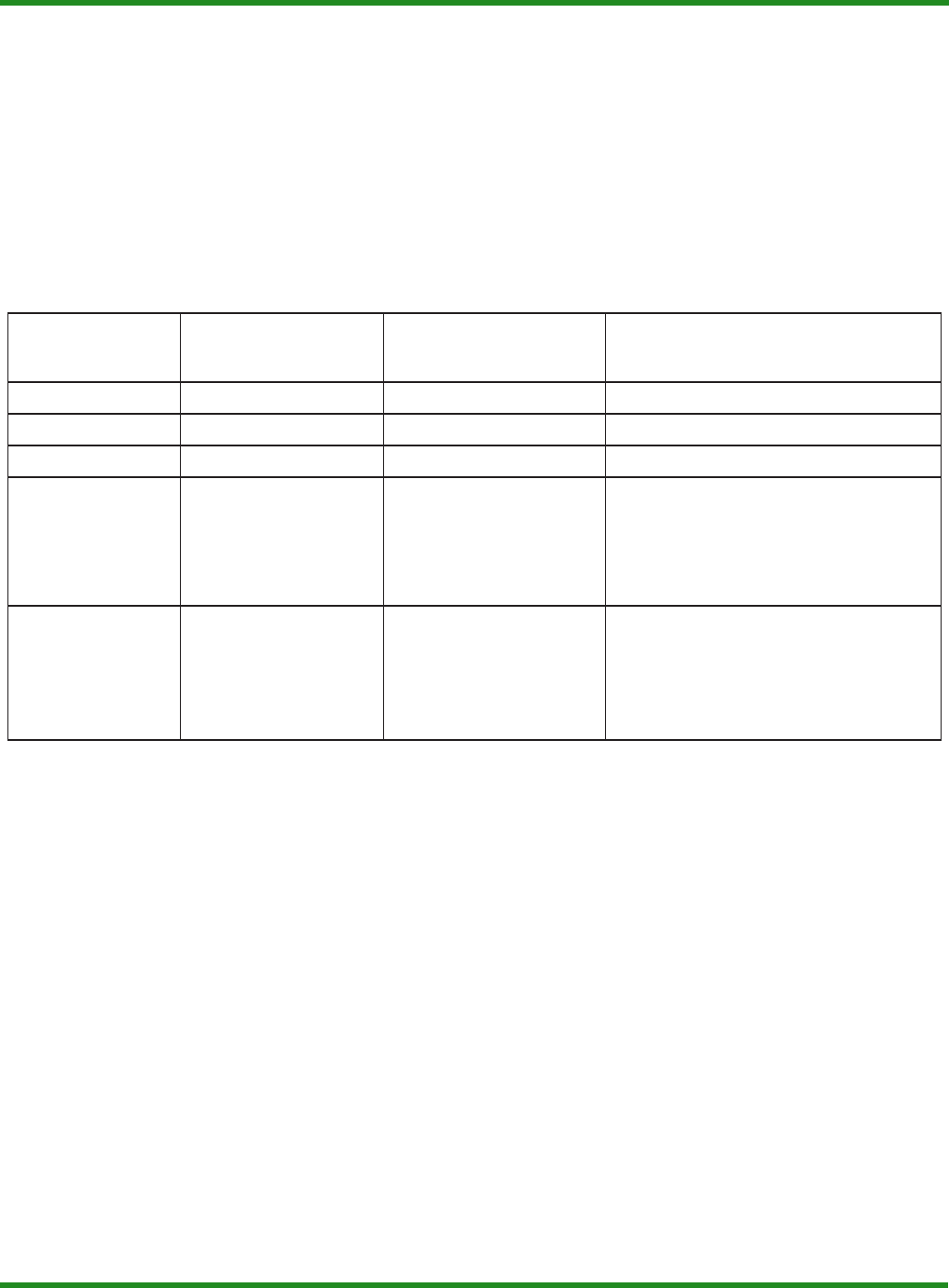

The specifications for these I/O’s are given over 3 different voltage ranges: 3.0V to 3.6V,

2.25V to 2.75V, and 1.7V to 1.98V.

4.3.1.1 I/O Digital Specifications for VDDIO=3.0V to 3.6V

Table 12, page 43 lists the parameters for I/O digital specification for VDDIO 3.0V to 3.6V

for Pin Types 4mA, 12mA, and 16mA.

Table 12 I/O Digital Parameters for VDDIO=3.0V to 3.6V

Parameter Symbol Minimum Typical Maximum Unit Note

I/O Supply Voltage VIN_3V3 3.0 3.3 3.6 V

Input Low Voltage VIL -0.3 0.8 V

Input High Voltage VIH 2.0 VIN_3V3 V

Schmitt trigger Low to

High threshold point VT+ 1.62 1.75 1.91 V

Schmitt trigger High to

Low threshold point VT- 1.16 1.29 1.45 V

Input Leakage Current IL10 μAPull up/down

disabled

Tri-State Output

Leakage Current IOZ 10 μAPull up/down

disabled

Pull-Up Resistor Ru34K 51K 81K Ω

Pull-Down Resistor Rd35K 51K 88K Ω

Output Low Voltage VOL 0.4 V

Output High Voltage VOH 2.4 V

Low Level Output

Current @ VOL max IOL

4.9

15.1

20.2

7.5

22.9

30.6

10.0

30.4

40.6

mA

Pin Type 4mA

Pint Type 12mA

Pint Type 16mA

High Level Output

Current @ VOH min IOH

7.0

20.9

27.8

14.0

42.0

56.0

24.2

72.3

96.3

mA

Pin Type 4mA

Pin Type 12mA

Pin Type 16mA

Output rise time 10%

to 90% load, 30pF tTRLH

3.18

1.83

1.52

4.26

2.43

2.01

6.00

3.51

2.92

ns

Pin Type 4mA

Pint Type 12mA

Pin Type 16mA

Output fall time 90% to

10% load, 30pF tTFHL

3.88

1.88

1.56

4.99

2.51

2.10

7.16

3.63

3.05

ns

Pin Type 4mA

Pin Type 12mA

Pin Type 16mA

Electrical Characteristics GS2100M Low Power WiFi Module Data Sheet

Power Consumption (Estimate)

44 Confidential Preliminary GS2100M-DS-001212, Release 0.10

4.3.2 RTC I/O Specifications

Table 13, page 44 lists the RTC I/O parameters.

*RTC I/O’s are software selectable as 1mA or 4mA drive strength.

4.4 Power Consumption (Estimate)

Table 14, page 44 lists the power consumption estimates for the GS2100Mxx. Typical

conditions are: VIN_3V3=VRTC=3.3V Temp=25oC.

Note:

1. To be optimized and updated with production version.

Table 13 RTC I/O Parameters

Parameter Symbol Minimum Typical Maximum Unit Note

Supply Voltage 1.6 3.6 V

Input Low

Voltage VIL 0.3*VDD V

Input High

Voltage VIH 0l7*VDD V

Input Leakage

Current IL0.1 μA

Pullup Current IPU 1μA

Pulldown

Current IPU 1μA

Output Low

Voltage VOL 0.4 V IL=1mA or

4mA*

Output High

Voltage VOHJ VDD-0.4 V IL=1mA or

4mA*

Table 14 Power Consumption in Different States

System State Current (Typical)1

Standby (VIN_3V3 ON) 50 μA

Deep Sleep (2 banks of SRAM enabled) TBD

WLAN Continuous Transmit (1 Mbps, 15 dBm) 220 mA

WLAN Continuous Receive (1 Mbps, -93 dBm sensitivity) 100 mA

IEEE 802.11 PS-Poll, DTIM = 1 (only WLAN enabled) TBD

IEEE 802.11 PS-Poll, DTIM=3 (only WLAN enabled) TBD

GS2100M Low Power WiFi Module Data Sheet Electrical Characteristics

802.11 Radio Parameters (Estimate)

GS2100M-DS-001212, Release 0.10 Confidential Preliminary 45

4.5 802.11 Radio Parameters (Estimate)

Table 15, page 45 lists the 802.11 Radio parameters (estimate). Test conditions are:

VIN_3V3=VRTC=3.3V Temp=25oC.

Table 15 802.11 Radio Parameters

Parameter Minimum Typical Maximum Unit Notes

RF Frequency Range 2412 2497 MHz

Radio bit rate 1 HT20

MCS7 Mbps

Transmit/Receive Specification for GS2100M