Hitachi Travelstar Hds723020Bla642 Users Manual DPC SATA OEM SPEC 100

HDS723020BLA642 to the manual 808ce0ff-7488-43a2-ab8a-ba728321000f

2015-01-24

: Hitachi Hitachi-Travelstar-Hds723020Bla642-Users-Manual-312770 hitachi-travelstar-hds723020bla642-users-manual-312770 hitachi pdf

Open the PDF directly: View PDF ![]() .

.

Page Count: 173 [warning: Documents this large are best viewed by clicking the View PDF Link!]

7K200 SATA OEM Specification

1/173

Hitachi Global Storage Technologies

Hard Disk Drive Specification

Hitachi Travelstar 7K200

2.5 inch SATA hard disk drive

Models: HTS722020K9A300 HTS722020K9SA00

HTS722016K9A300 HTS722016K9SA00

HTS722012K9A300 HTS722012K9SA00

HTS722010K9A300 HTS722010K9SA00

HTS722080K9A300 HTS722080K9SA00

Revision 1.0 10 May 2007

7K200 SATA OEM Specification

2/173

Preliminary Edition (Revision 0.1) (31 March 2007)

2nd Preliminary Edition (Revision 0.2) (20 April 2007)

Final Release (Revision 1.0) (10 May 2007)

The following paragraph does not apply to the United Kingdom or any country where such

provisions are inconsistent with local law: HITACHI GLOBAL STORAGE TECHNOLOGIES

PROVIDES THIS PUBLICATION "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER

EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES

OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. Some states do not allow

disclaimer or express or implied warranties in certain transactions, therefore, this statement may

not apply to you.

This publication could include technical inaccuracies or typographical errors. Changes are

periodically made to the information herein; these changes will be incorporated in new editions of

the publication. Hitachi may make improvements or changes in any products or programs described

in this publication at any time.

It is possible that this publication may contain reference to, or information about, Hitachi products

(machines and programs), programming, or services that are not announced in your country. Such

references or information must not be construed to mean that Hitachi intends to announce such

Hitachi products, programming, or services in your country.

Technical information about this product is available by contacting your local Hitachi Global Storage

Technologies representative or on the Internet at http://www.hitachigst.com

Hitachi Global Storage Technologies may have patents or pending patent applications covering

subject matter in this document. The furnishing of this document does not give you any license to

these patents.

©Copyright Hitachi Global Storage Technologies

Note to U.S. Government Users —Documentation related to restricted rights —Use, duplication or

disclosure is subject to restrictions set forth in GSA ADP Schedule Contract with Hitachi Global

Storage Technologies.

7K200 SATA OEM Specification

3/173

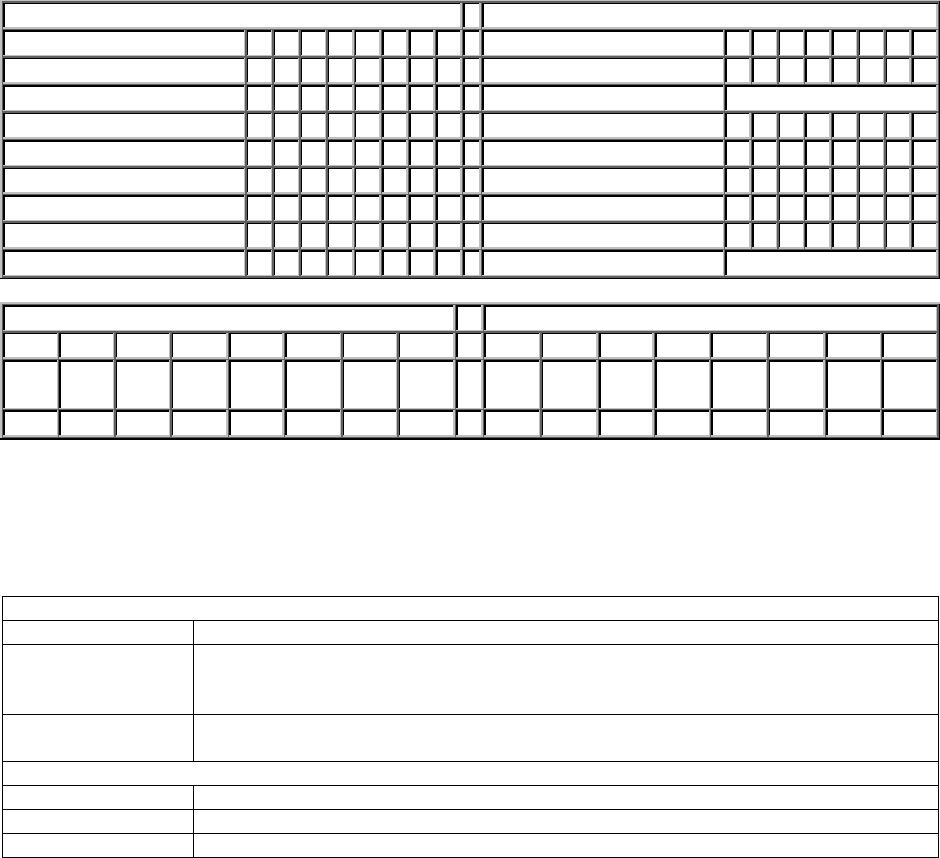

Table of Contents

GENERAL...............................................................................................................................................10

1 INTRODUCTION .....................................................................................................................................10

1.1 Abbreviations...........................................................................................................................10

1.2 References ................................................................................................................................13

1.3 General caution .......................................................................................................................13

1.4 Drive handling precautions ....................................................................................................13

2 OUTLINE OF THE DRIVE.........................................................................................................................14

PART 1 FUNCTIONAL SPECIFICATION ...........................................................................................15

3 FIXED DISK SUBSYSTEM DESCRIPTION ..................................................................................................16

3.1 Control Electronics ..................................................................................................................16

3.2 Head disk assembly data ........................................................................................................16

4 FIXED DISK CHARACTERISTICS ..............................................................................................................17

4.1 Formatted capacity by model number....................................................................................17

4.2 Data sheet ................................................................................................................................18

4.3 Cylinder allocation ..................................................................................................................18

4.4 Performance characteristics ...................................................................................................19

5 DATA INTEGRITY ...................................................................................................................................23

5.1 Data loss on power off .............................................................................................................23

5.2 Write Cache .............................................................................................................................23

5.3 Equipment status ....................................................................................................................23

5.4 WRITE safety...........................................................................................................................23

5.5 Data buffer test........................................................................................................................24

5.6 Error recovery..........................................................................................................................24

5.7 Automatic reallocation ............................................................................................................24

5.8 ECC ..........................................................................................................................................25

6 SPECIFICATION .....................................................................................................................................26

6.1 Environment ............................................................................................................................26

6.2 DC power requirements ..........................................................................................................28

6.3 Reliability.................................................................................................................................30

6.4 Mechanical specifications........................................................................................................33

6.5 Vibration and shock.................................................................................................................35

6.6 Acoustics...................................................................................................................................37

6.7 Identification labels.................................................................................................................38

6.8 Electromagnetic compatibility................................................................................................38

6.9 Safety........................................................................................................................................39

6.10 Packaging.................................................................................................................................39

6.11 Substance restriction requirements .......................................................................................39

7 ELECTRICAL INTERFACE SPECIFICATIONS ............................................................................................40

7.1 Cabling .....................................................................................................................................40

7.2 Interface connector ..................................................................................................................40

7.3 Signal definitions.....................................................................................................................41

PART 2 INTERFACE SPECIFICATION...............................................................................................43

8 GENERAL ..............................................................................................................................................44

8.1 Introduction .............................................................................................................................44

8.2 Terminology .............................................................................................................................44

9 DEVIATIONS FROM STANDARD ..............................................................................................................45

10 PHYSICAL INTERFACE .........................................................................................................................45

11 REGISTERS ..........................................................................................................................................45

11.1 Register naming convention ...................................................................................................46

11.2 Command register ...................................................................................................................47

11.3 Device Control Register...........................................................................................................47

11.4 Device Register ........................................................................................................................47

7K200 SATA OEM Specification

4/173

11.5 Error Register ..........................................................................................................................47

11.6 Features Register ....................................................................................................................48

11.7 LBA High Register ..................................................................................................................48

11.8 LBA Low Register....................................................................................................................48

11.9 LBA Mid Register....................................................................................................................48

11.10 Sector Count Register..........................................................................................................48

11.11 Status Register.....................................................................................................................48

12 GENERAL OPERATION DESCRIPTIONS ................................................................................................50

12.1 Reset Response ........................................................................................................................50

12.1.1 Register Initialization.................................................................................................................... 50

12.2 Diagnostic and Reset considerations......................................................................................51

12.3 Power-off considerations .........................................................................................................52

12.3.1 Load/Unload ................................................................................................................................... 52

12.3.2 Emergency unload.......................................................................................................................... 52

12.3.3 Required power-off sequence ......................................................................................................... 52

12.4 Sector Addressing Mode..........................................................................................................53

12.4.1 Logical CHS Addressing Mode ...................................................................................................... 53

12.4.2 LBA Addressing Mode ................................................................................................................... 53

12.5 Power Management Feature ..................................................................................................53

12.5.1 Power Mode .................................................................................................................................... 54

12.5.2 Power Management Commands.................................................................................................... 54

12.5.3 Standby/Sleep command completion timing................................................................................. 54

12.5.4 Status.............................................................................................................................................. 54

12.5.5 Interface Capability for Power Modes........................................................................................... 54

12.5.6 Initial Power Mode at Power On ................................................................................................... 55

12.6 Advanced Power Management (Adaptive Battery Life Extender 3) Feature......................55

12.6.1 Performance Idle mode .................................................................................................................. 55

12.6.2 Active Idle mode............................................................................................................................. 55

12.6.3 Low Power Idle mode..................................................................................................................... 55

12.6.4 Transition Time.............................................................................................................................. 56

12.7 Interface Power Management Mode (Slumber and Partial).................................................56

12.8 S.M.A.R.T. Function................................................................................................................56

12.8.1 Attributes ....................................................................................................................................... 56

12.8.2 Attribute values ............................................................................................................................. 56

12.8.3 Attribute thresholds....................................................................................................................... 57

12.8.4 Threshold exceeded condition........................................................................................................ 57

12.8.5 S.M.A.R.T. commands.................................................................................................................... 57

12.8.6 S.M.A.R.T operation with power management modes ................................................................. 57

12.9 Security Mode Feature Set .....................................................................................................57

12.9.1 Security mode................................................................................................................................. 57

12.9.2 Security Level................................................................................................................................. 58

12.9.3 Password......................................................................................................................................... 58

12.9.4 Master Password Revision Code ...................................................................................................58

12.9.5 Operation example......................................................................................................................... 58

12.9.6 Command Table ............................................................................................................................. 61

12.10 Protected Area Function......................................................................................................63

12.10.1 Example for operation (In LBA mode) ...................................................................................... 64

12.10.2 Set Max security extension commands ..................................................................................... 65

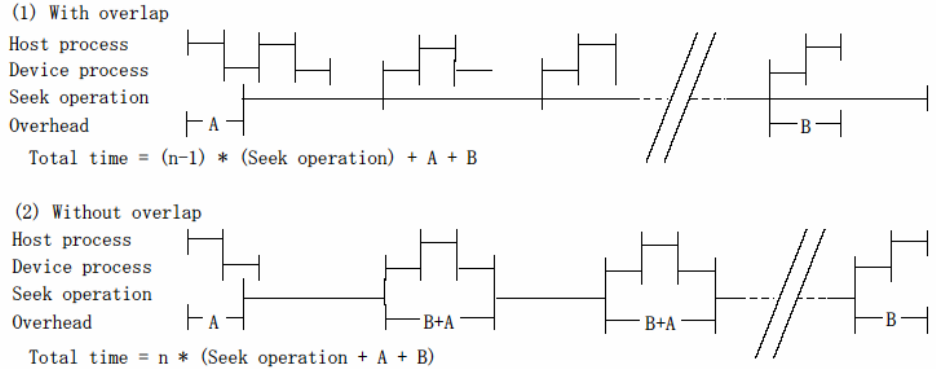

12.11 Seek Overlap ........................................................................................................................66

12.12 Write Cache Function..........................................................................................................66

12.13 Reassign Function................................................................................................................66

12.13.1 Auto Reassign Function............................................................................................................. 67

12.14 48-bit Address Feature Set..................................................................................................67

12.15 Software Setting Preservation Feature Set .......................................................................68

12.15.1 Preserved software settings....................................................................................................... 68

12.16 Native Command Queuing..................................................................................................69

12.17 SMART Command Transport (SCT)...................................................................................70

13 COMMAND PROTOCOL.........................................................................................................................70

13.1 Data In Commands .................................................................................................................71

13.2 Data Out Commands...............................................................................................................71

13.3 Non-Data Commands ..............................................................................................................72

13.4 DMA Data Transfer Commands.............................................................................................72

7K200 SATA OEM Specification

5/173

13.5 First-parity DMA Commands.................................................................................................73

14 COMMAND DESCRIPTIONS ..................................................................................................................74

14.1 Check Power Mode (E5h/98h).................................................................................................78

14.2 Device Configuration Overlay (B1h) ......................................................................................79

14.2.1 DEVICE CONFIGURATION RESTORE (subcommand C0h)..................................................... 79

14.2.2 DEVICE CONFIGURATION FREEZE LOCK (subcommand C1h) ............................................ 79

14.2.3 DEVICE CONFIGURATION IDENTIFY (subcommand C2h) .................................................... 80

14.2.4 DEVICE CONFIGURATION SET (subcommand C3h) ............................................................... 80

14.3 Execute Device Diagnostic (90h) ............................................................................................83

14.4 Flush Cache (E7h) ...................................................................................................................84

14.5 Flush Cache Ext (EAh)............................................................................................................85

14.6 Format Track (50h: Vendor Specific) .....................................................................................86

14.7 Format Unit (F7h: Vendor Specific) .......................................................................................87

14.8 Identify Device (ECh) ..............................................................................................................88

14.9 Idle (E3h/97h) ..........................................................................................................................99

14.10 Idle Immediate (E1h/95h) .................................................................................................100

14.11 Initialize Device Parameters (91h) ...................................................................................101

14.12 Read Buffer (E4h) ..............................................................................................................102

14.13 Read DMA(C8h/C9h) .........................................................................................................103

14.14 Read DMA Ext (25h)..........................................................................................................104

14.15 Read FPDMA Queued (60h)..............................................................................................105

14.16 Read Log Ext(2Fh).............................................................................................................106

14.16.1 General purpose Log Directory................................................................................................ 107

14.16.2 Extended comprehensive SMART error log............................................................................ 107

14.16.3 Extended Self-test log sector ................................................................................................... 110

14.16.4 Command Error ....................................................................................................................... 111

14.16.5 Phy Event Counter................................................................................................................... 112

14.17 Read Multiple (C4h)...........................................................................................................114

14.18 Read Multiple Ext (29h) ....................................................................................................115

14.19 Read Native Max Address (F8h).......................................................................................116

14.20 Read Native Max Address Ext (27h) ................................................................................117

14.21 Read Sector(s) (20h/21h)....................................................................................................118

14.22 Read Sector(s) Ext (24h)....................................................................................................119

14.23 Read Verify Sector(s) (40h/41h) ........................................................................................120

14.24 Read Verify Sector(s) Ext (42h).........................................................................................121

14.25 Recalibrate (1xh)................................................................................................................122

14.26 Security Disable Password (F6h)......................................................................................123

14.27 Security Erase Prepare (F3h) ...........................................................................................124

14.28 Security Erase Unit (F4h) .................................................................................................125

14.29 Security Freeze Lock (F5h) ...............................................................................................127

14.30 Security Set Password (F1h).............................................................................................128

14.31 Security Unlock (F2h)........................................................................................................130

14.32 Seek (7xh) ...........................................................................................................................131

14.33 Sense Condition (F0h : vendor specific)............................................................................132

14.34 Set Features (EFh).............................................................................................................133

14.35 Set Max Address (F9h) ......................................................................................................135

14.36 Set Max Address Ext (37h)................................................................................................137

14.37 Set Multiple (C6h)..............................................................................................................139

14.38 Sleep (E6h/99h) ..................................................................................................................140

14.39 S.M.A.R.T Function Set (B0h) ..........................................................................................141

14.39.1 S.M.A.R.T. Sub commands ...................................................................................................... 141

14.39.2 Device Attributes Data Structure ........................................................................................... 146

14.39.3 Device Attribute Thresholds Data Structure.......................................................................... 150

14.39.4 S.M.A.R.T. Log Directory......................................................................................................... 151

14.39.5 S.M.A.R.T. error log sector ...................................................................................................... 151

14.39.6 Self-test log data structure ...................................................................................................... 154

14.39.7 Selective self-test log data structure ....................................................................................... 155

14.39.8 Error Reporting........................................................................................................................ 155

14.40 Standby (E2h/96h) .............................................................................................................156

14.41 Standby Immediate (E0h/94h)..........................................................................................157

14.42 Write Buffer (E8h) .............................................................................................................158

7K200 SATA OEM Specification

6/173

14.43 Write DMA (CAh/CBh)......................................................................................................159

14.44 Write DMA Ext (35h).........................................................................................................160

14.45 Write DMA FUA Ext (3Dh)...............................................................................................161

14.46 Write FPDMA Queued (61h).............................................................................................162

14.47 Write Log Ext (3Fh)...........................................................................................................163

14.48 Write Multiple (C5h)..........................................................................................................164

14.49 Write Multiple Ext (39h) ...................................................................................................165

14.50 Write Multiple FUA Ext (CEh).........................................................................................166

14.51 Write Sector(s) (30h/31h)...................................................................................................167

14.52 Write Sector(s) Ext (34h)...................................................................................................168

14.53 Write Uncorrectable Ext (45h)..........................................................................................169

15 TIMINGS ............................................................................................................................................171

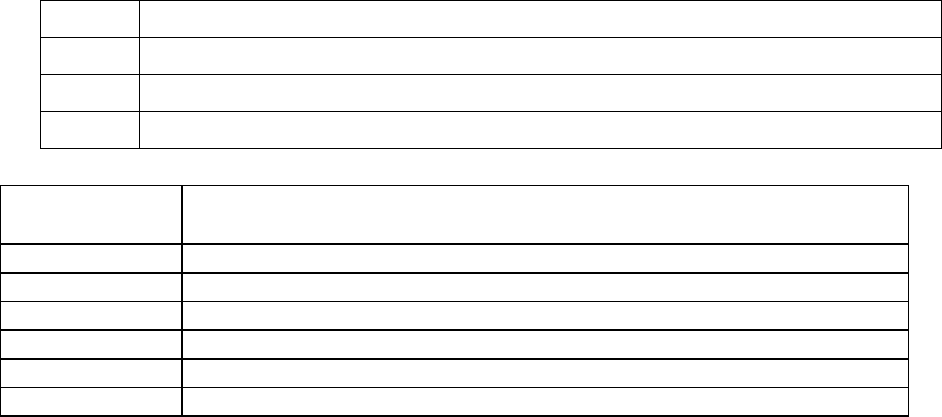

List of Figures

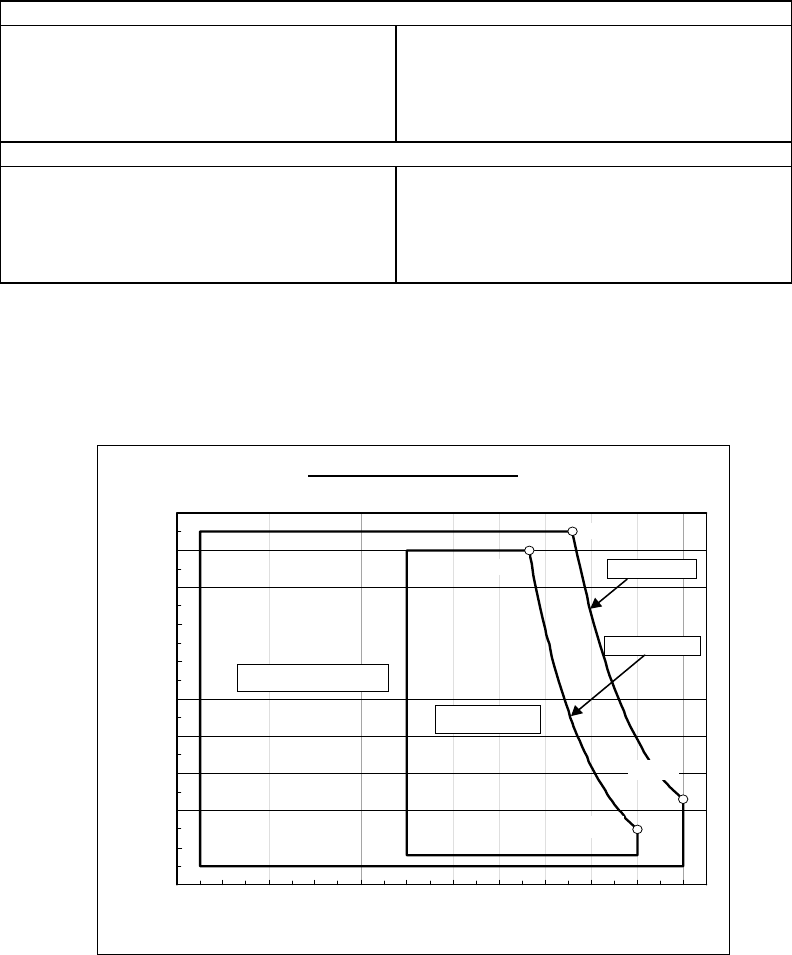

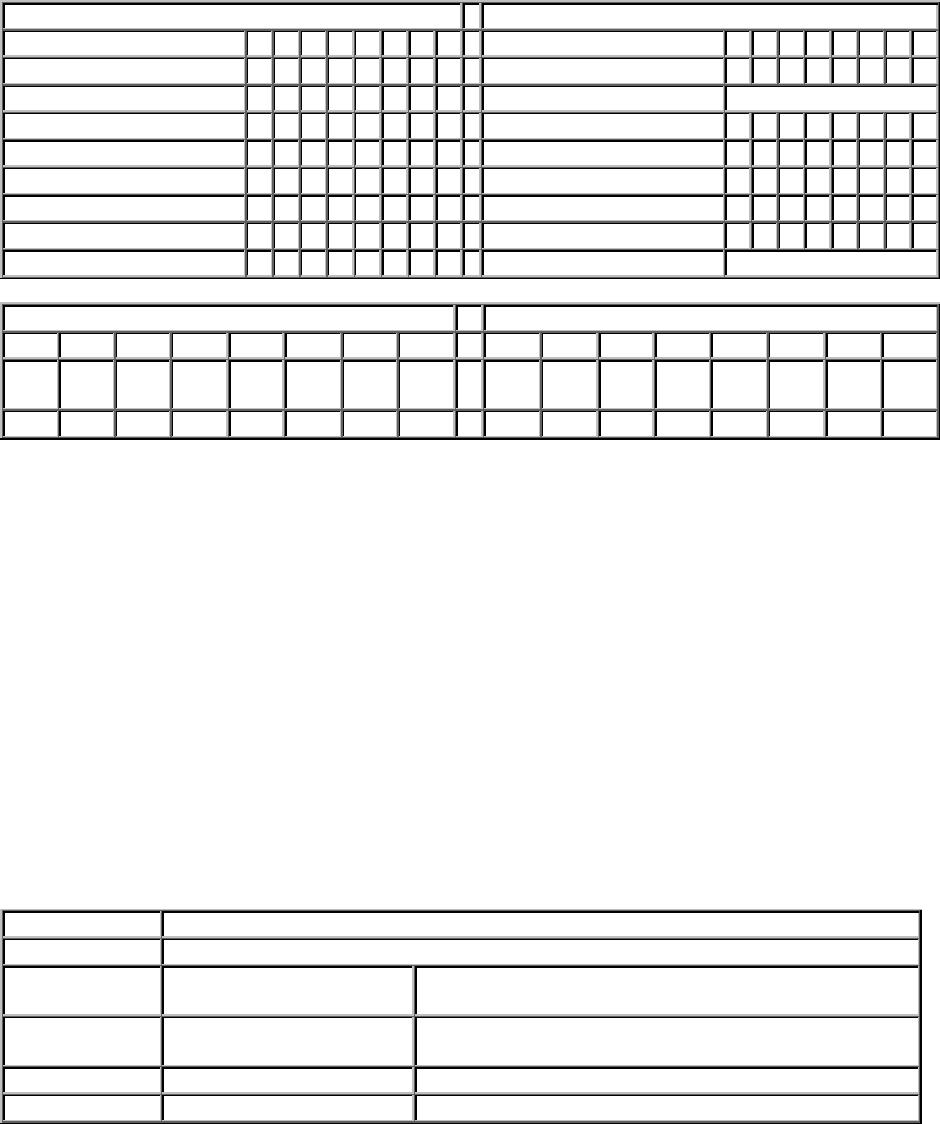

Figure 1. Limits of temperature and humidity 26

Figure 2. Mounting hole locations 33

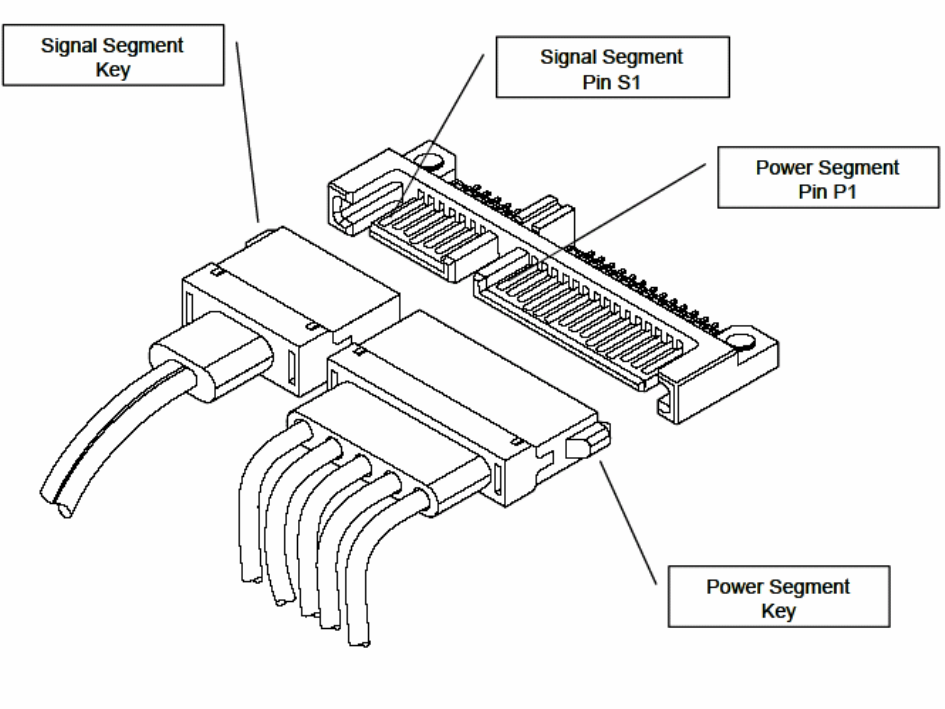

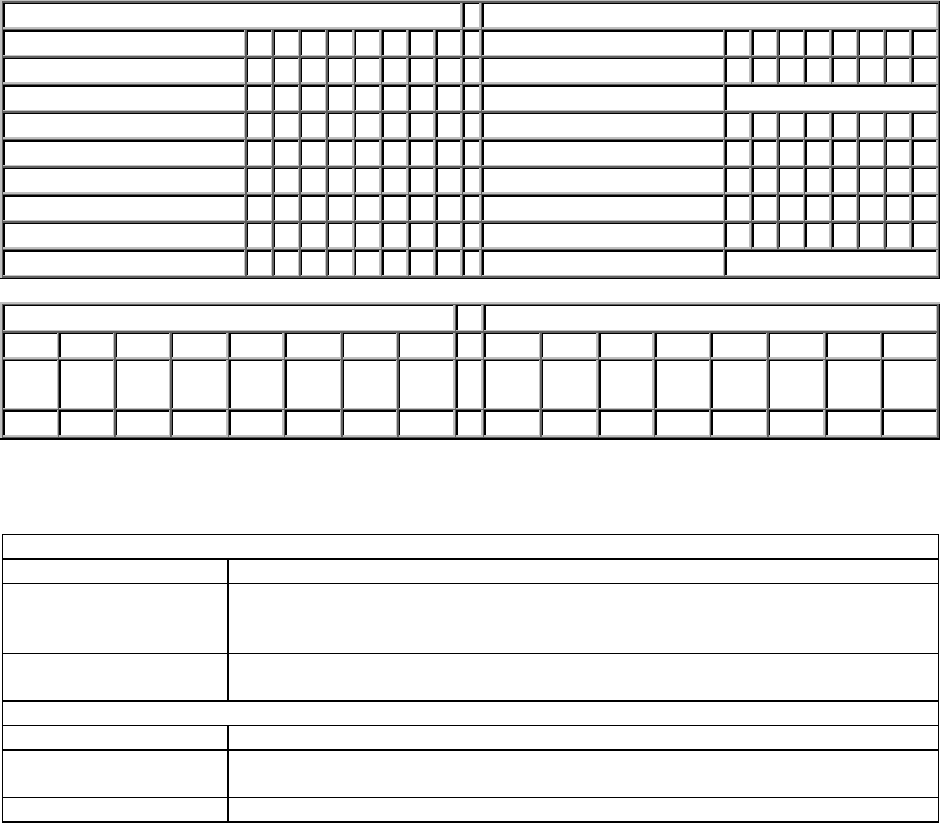

Figure 3. Interface connector pin assignments 40

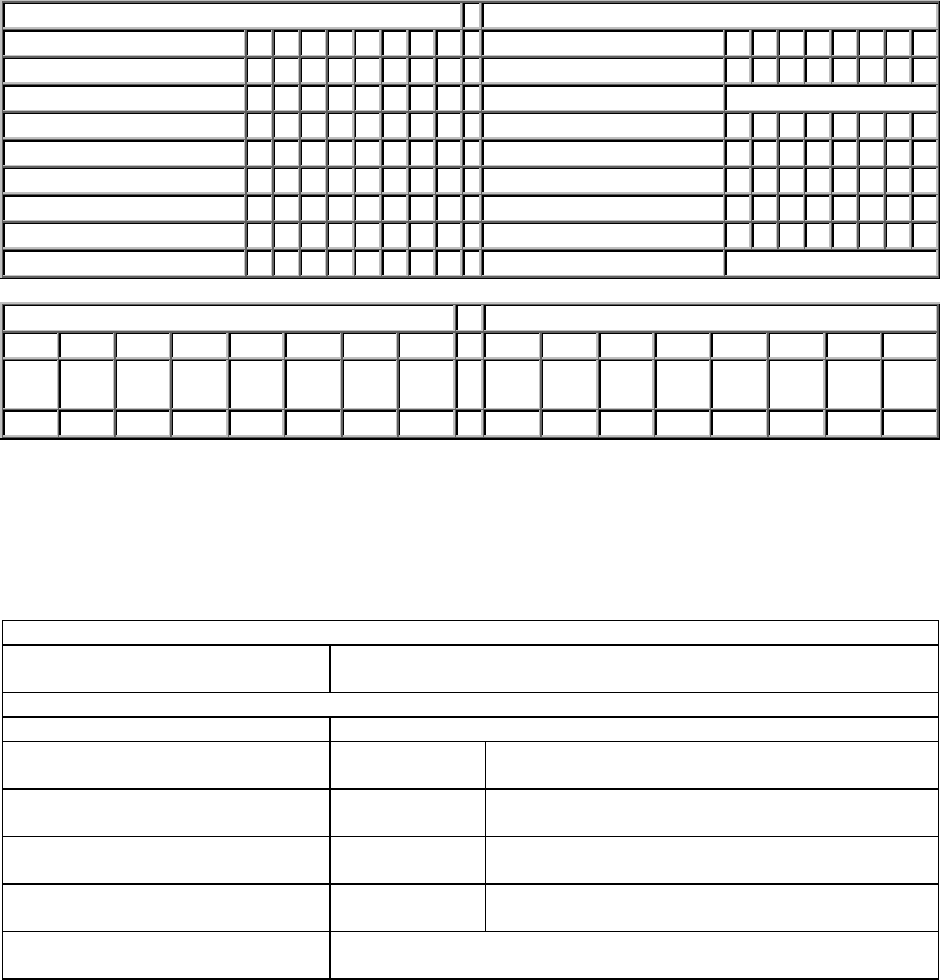

Figure 4. Parameter descriptions 42

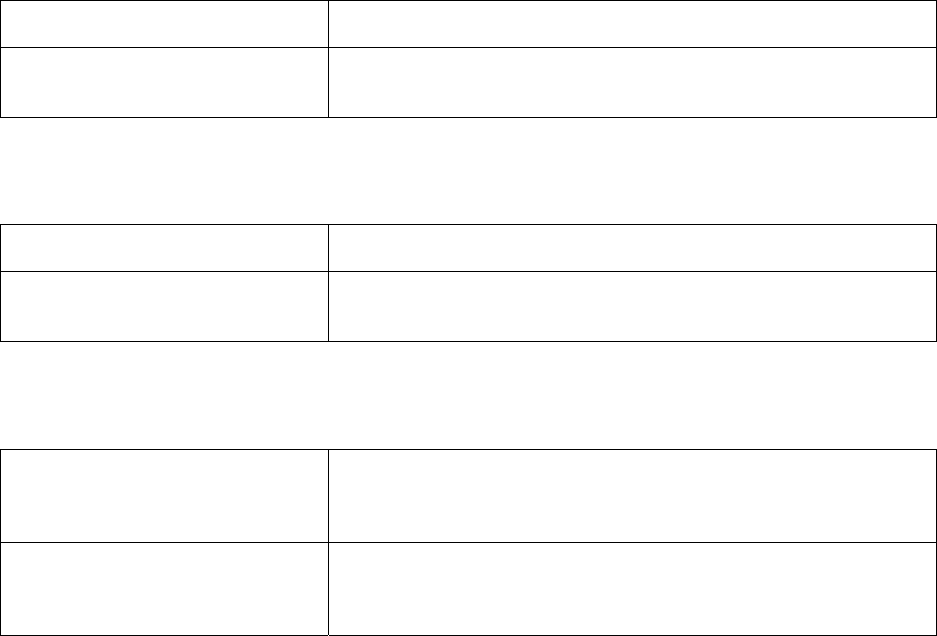

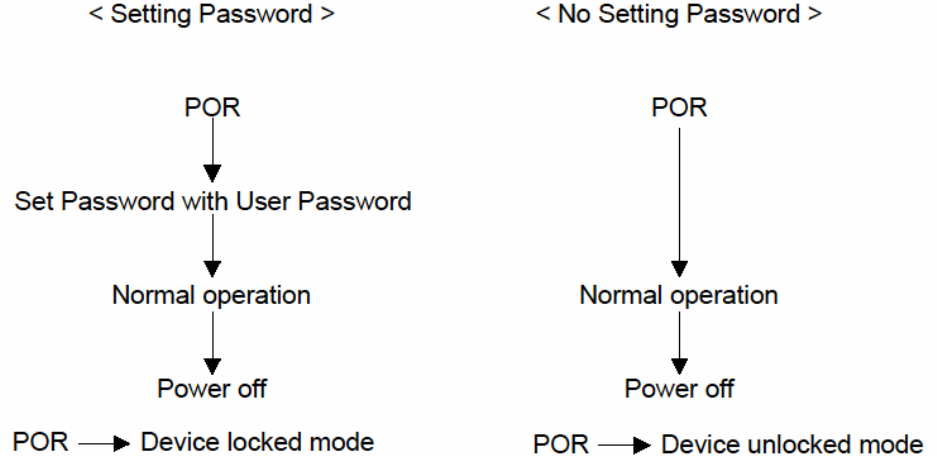

Figure 5 Initial Setting 59

Figure 6 Usual Operation 60

Figure 7 Password Lost 61

Figure 8 Set Max security mode transition 65

Figure 9 Seek overlap 66

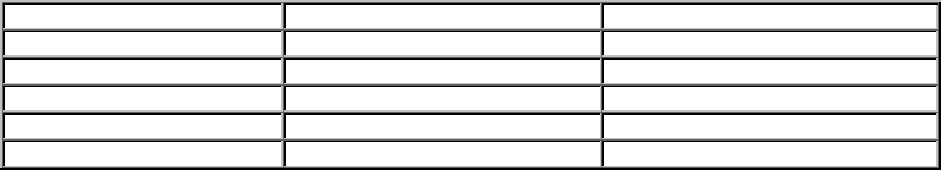

Figure 10 Selective self-test test span example 143

7K200 SATA OEM Specification

7/173

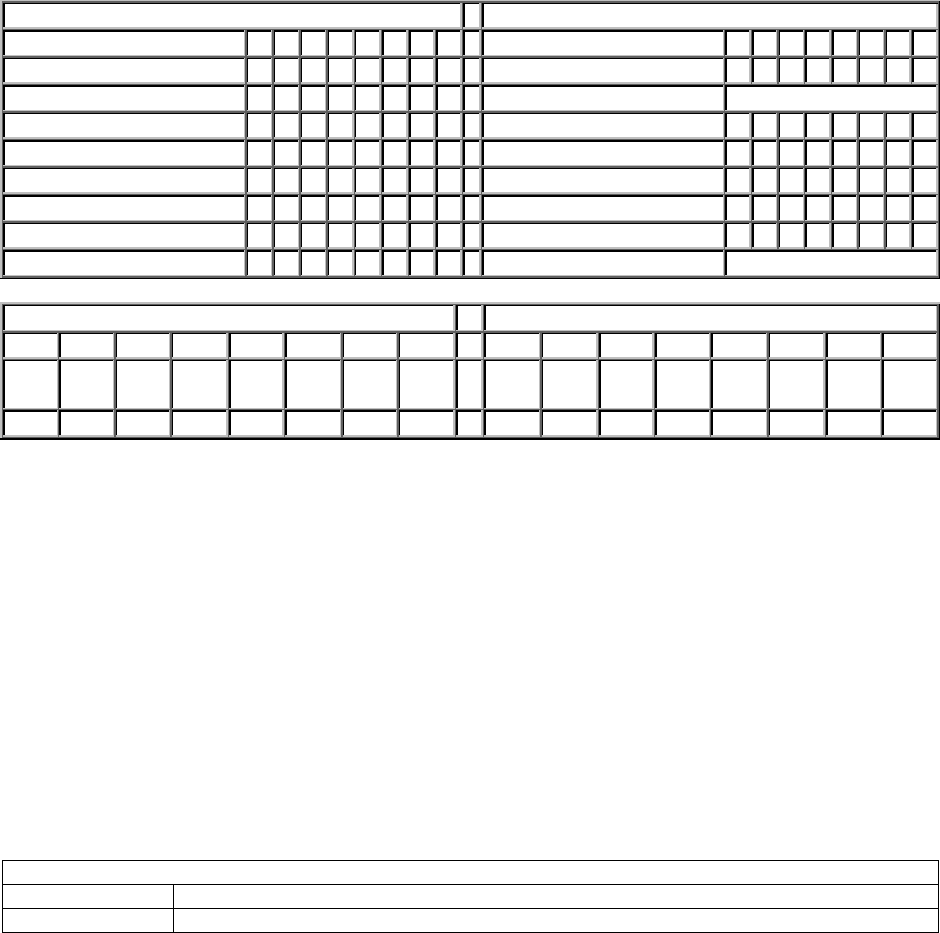

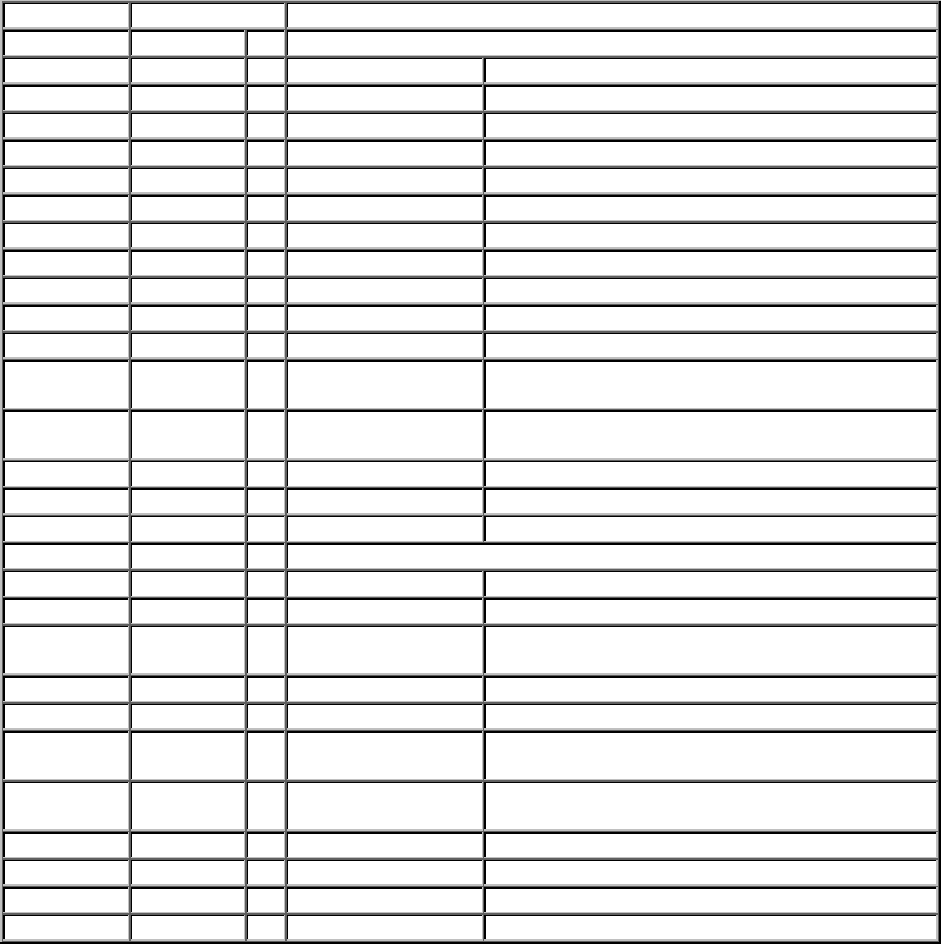

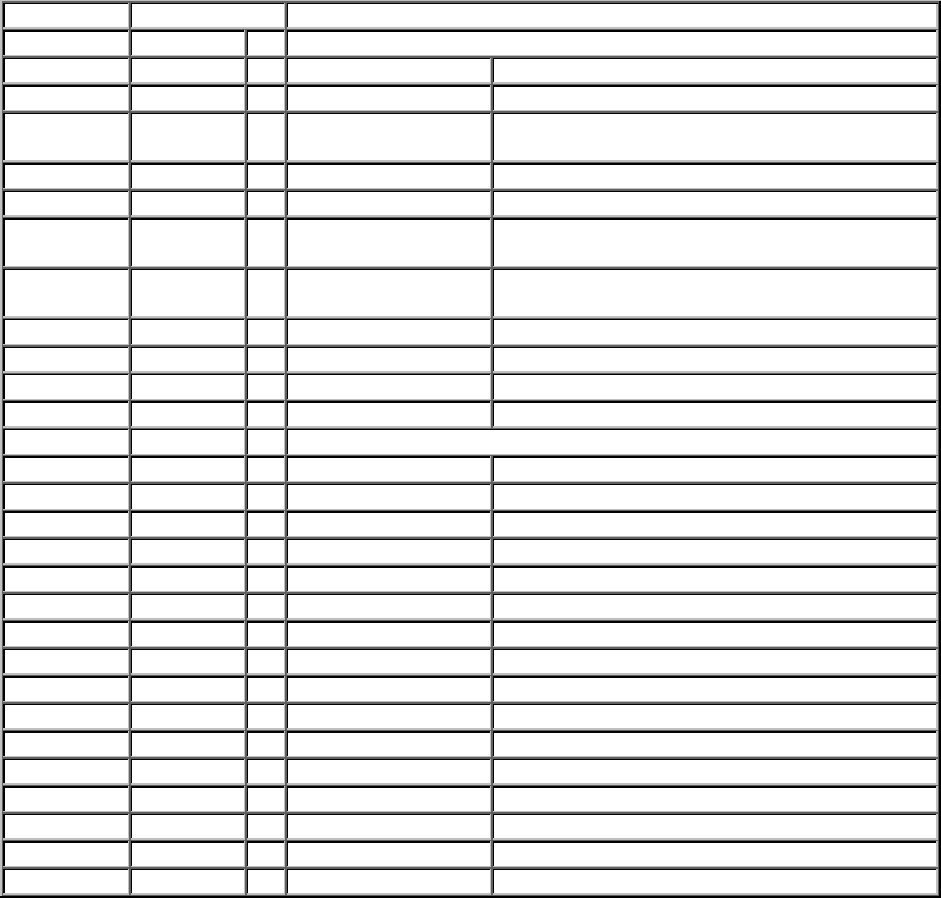

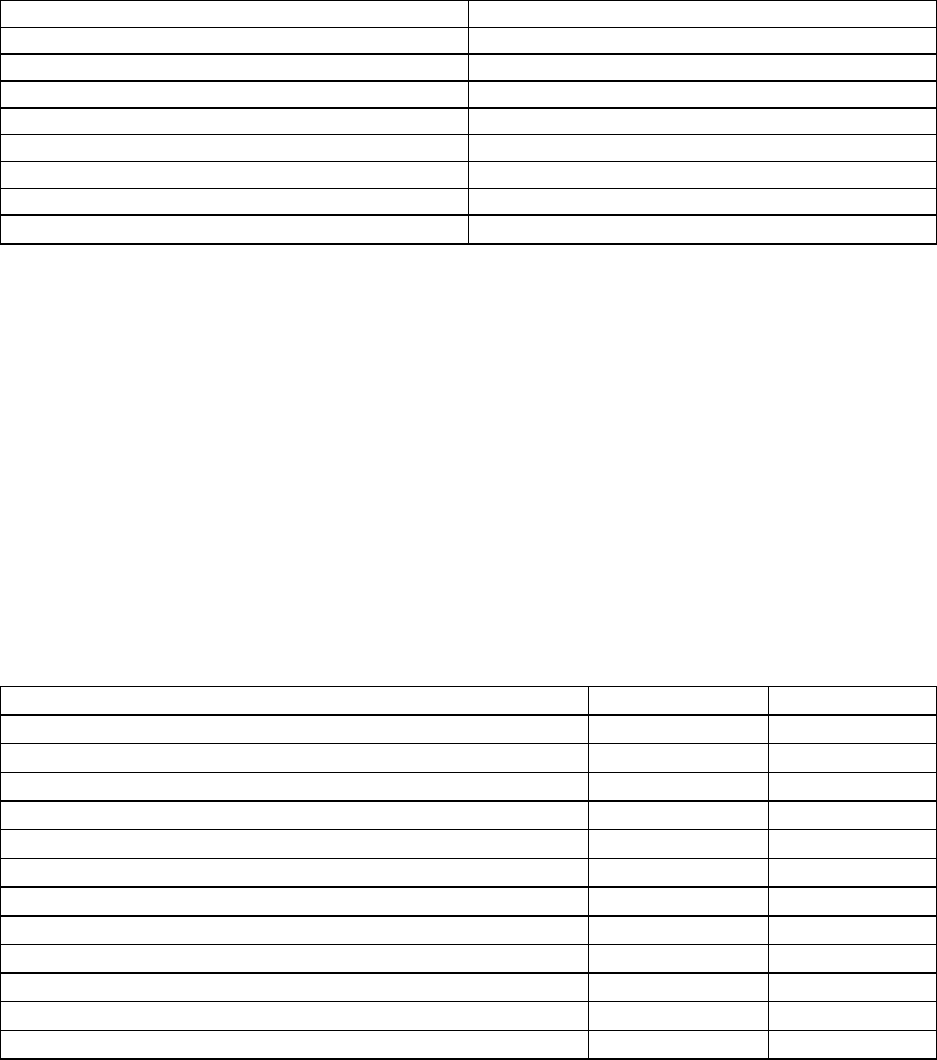

List of Tables

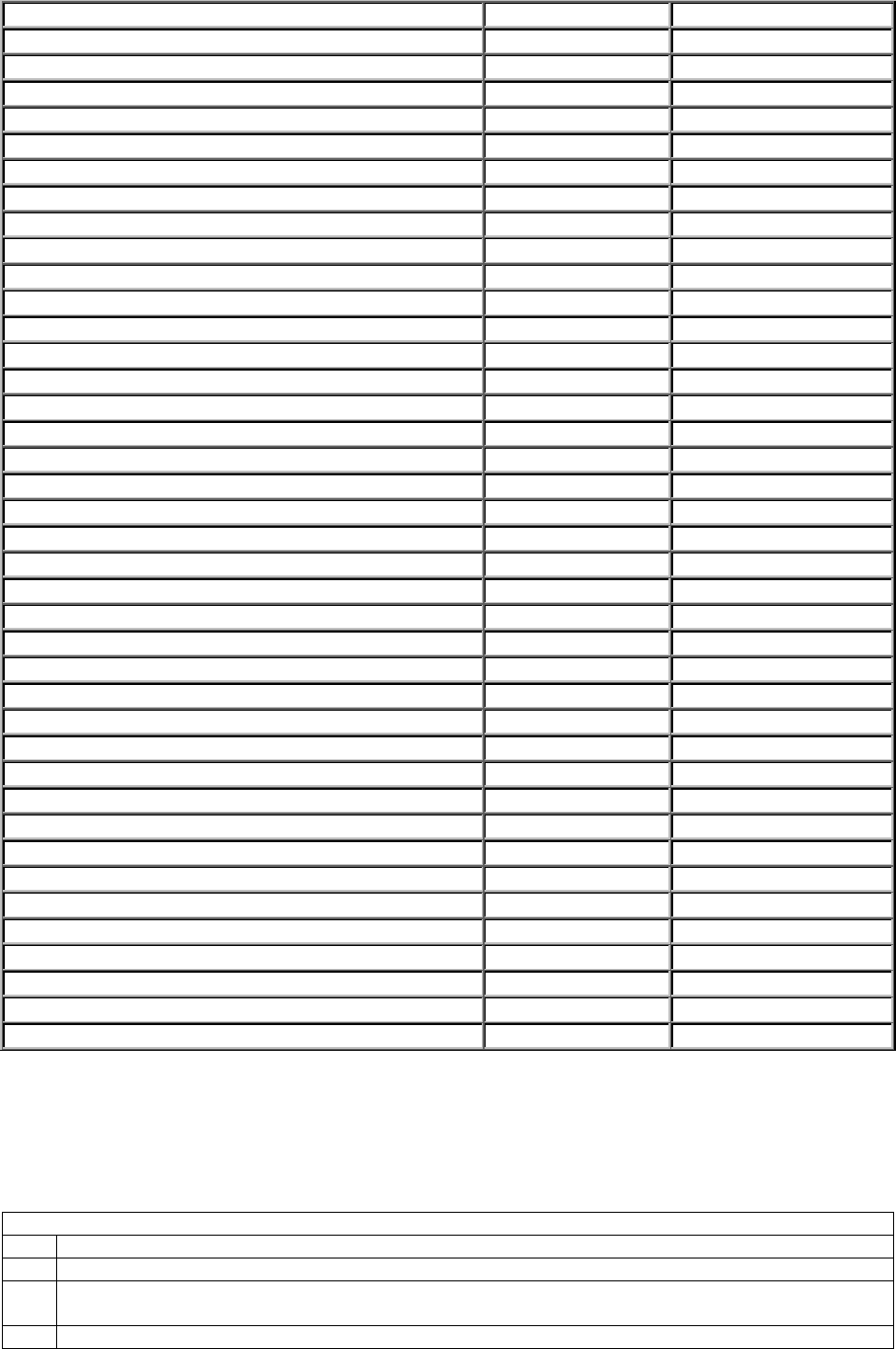

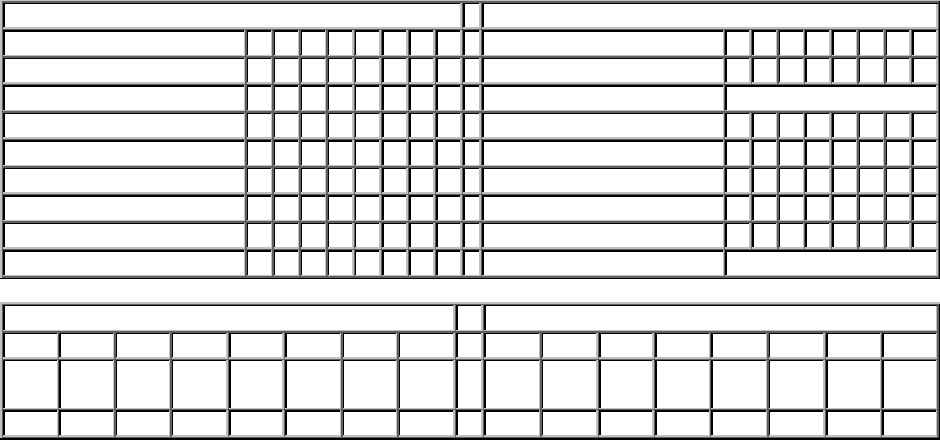

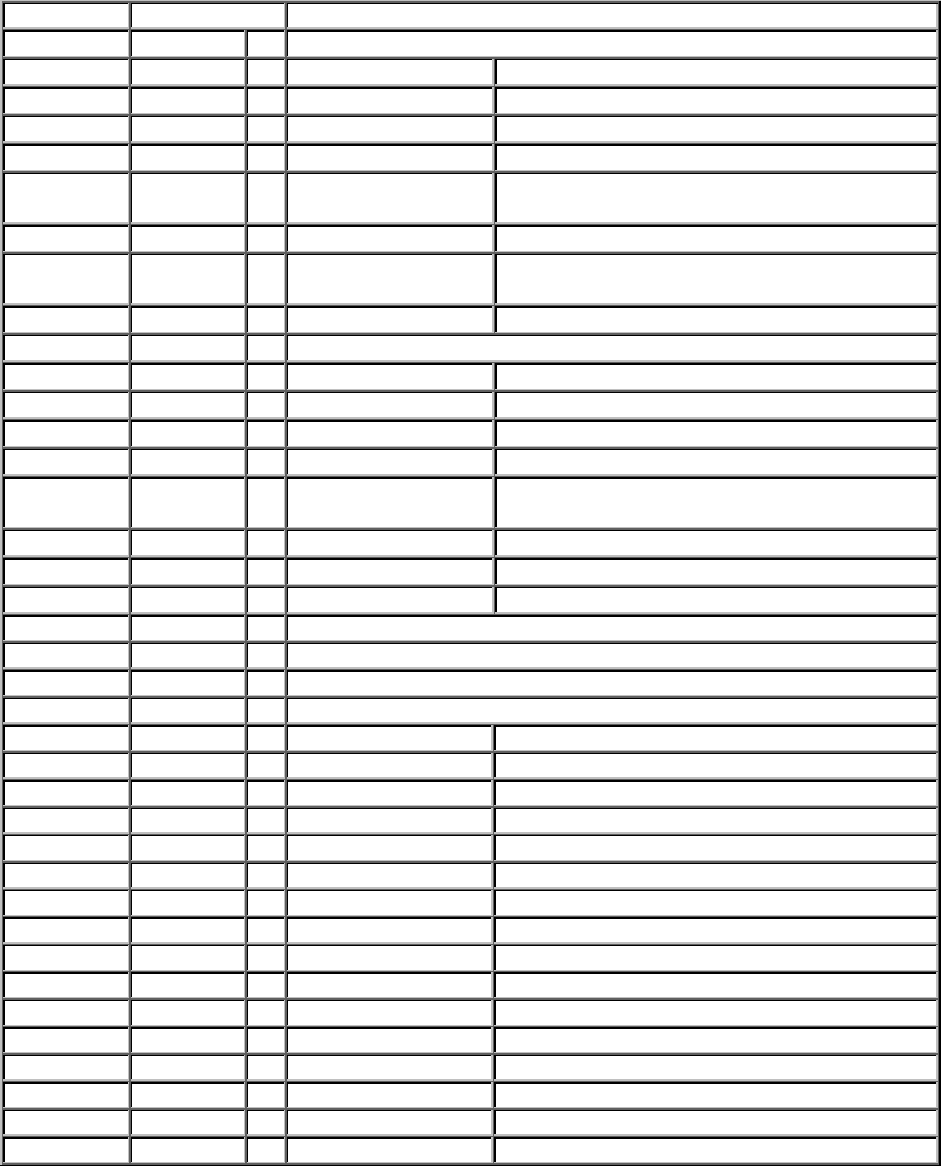

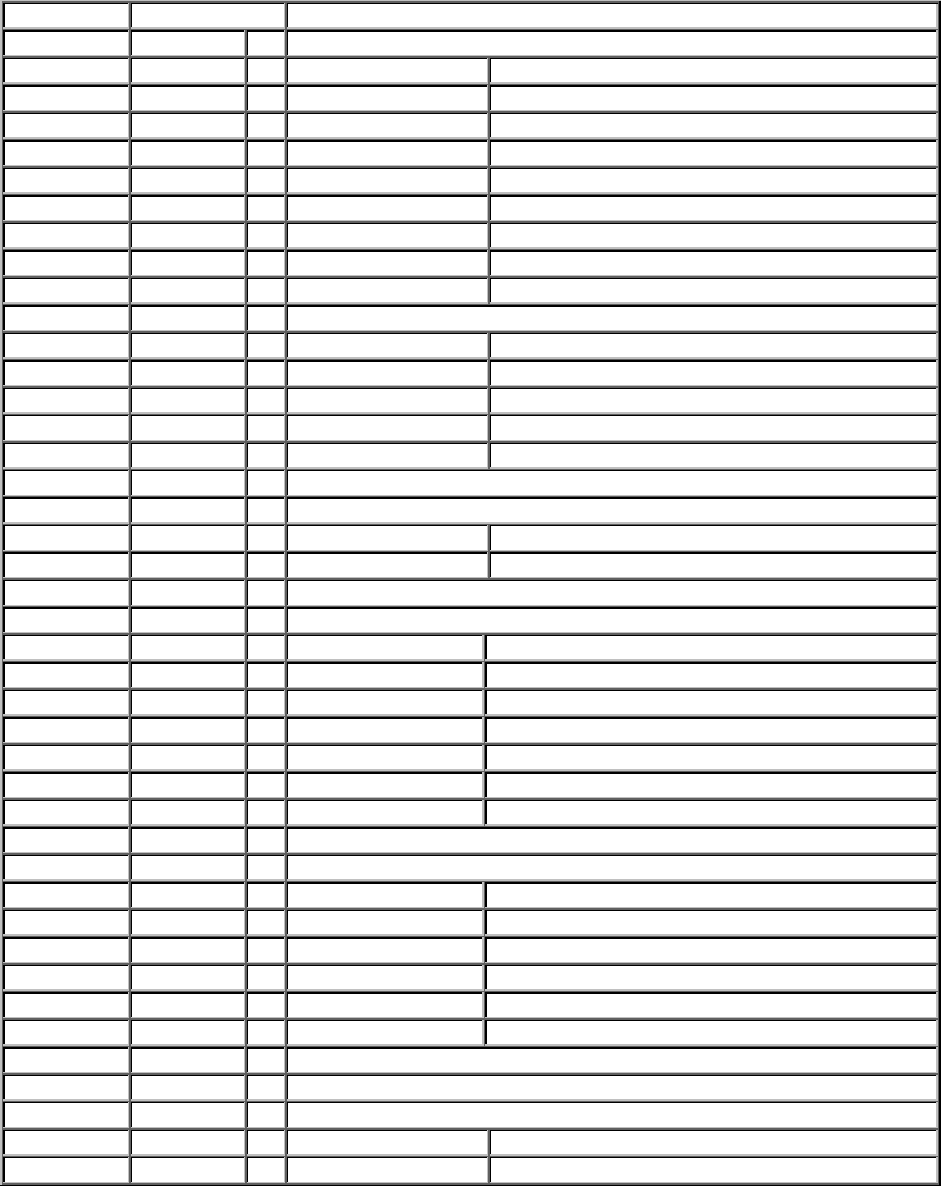

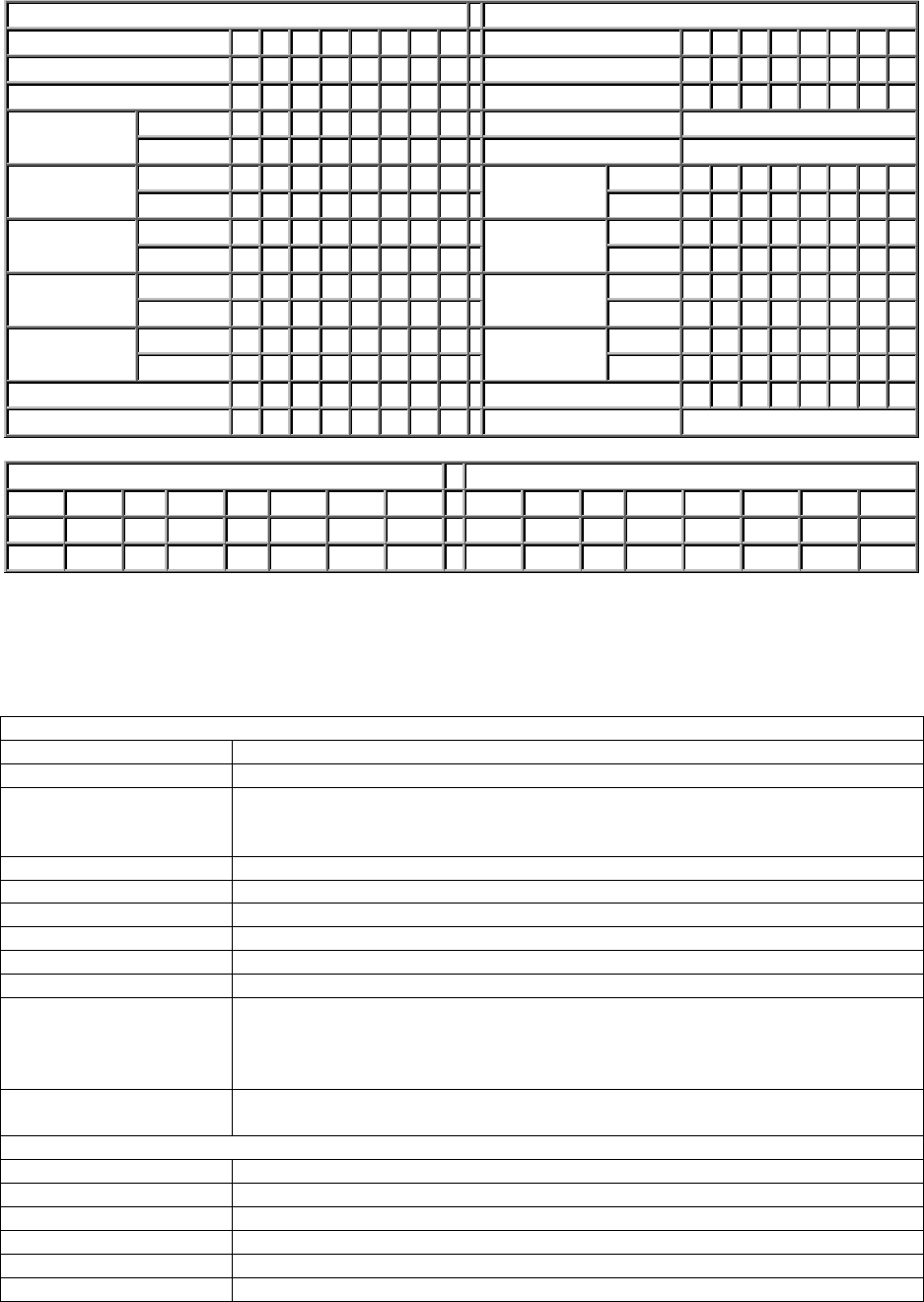

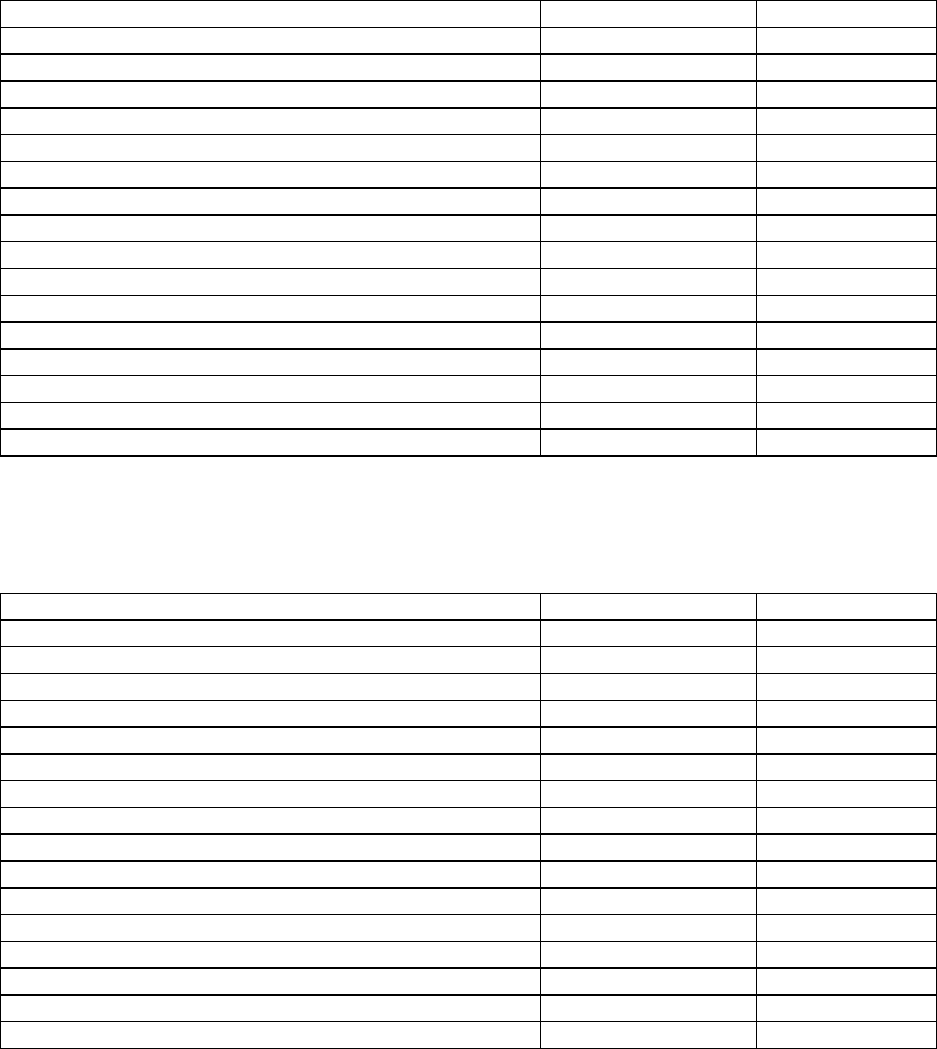

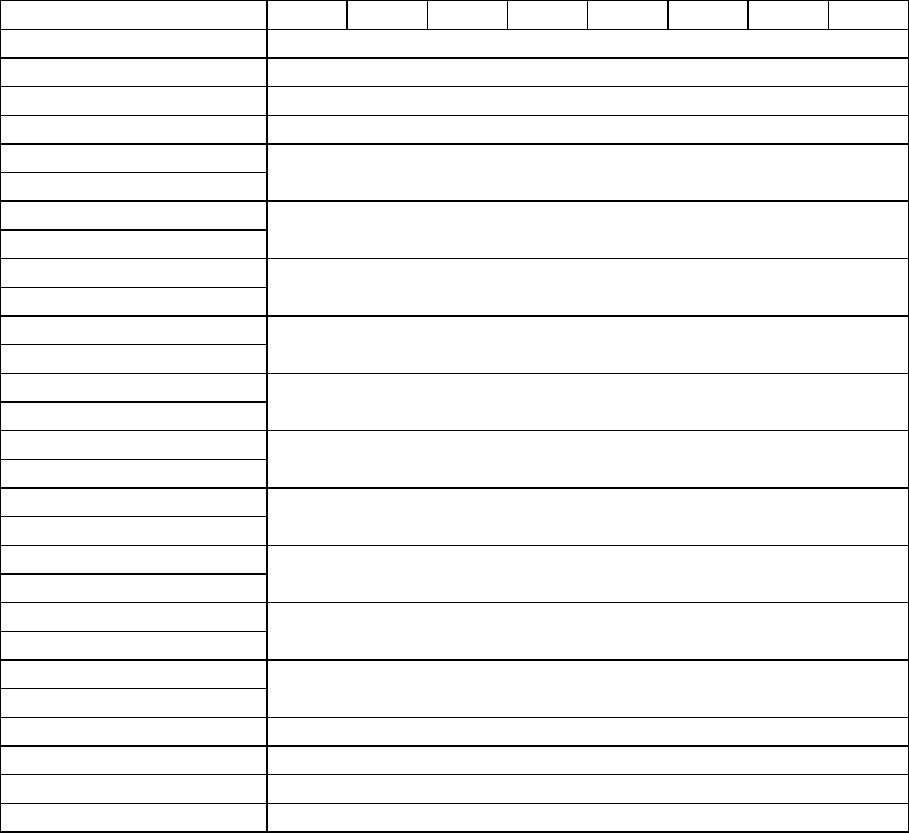

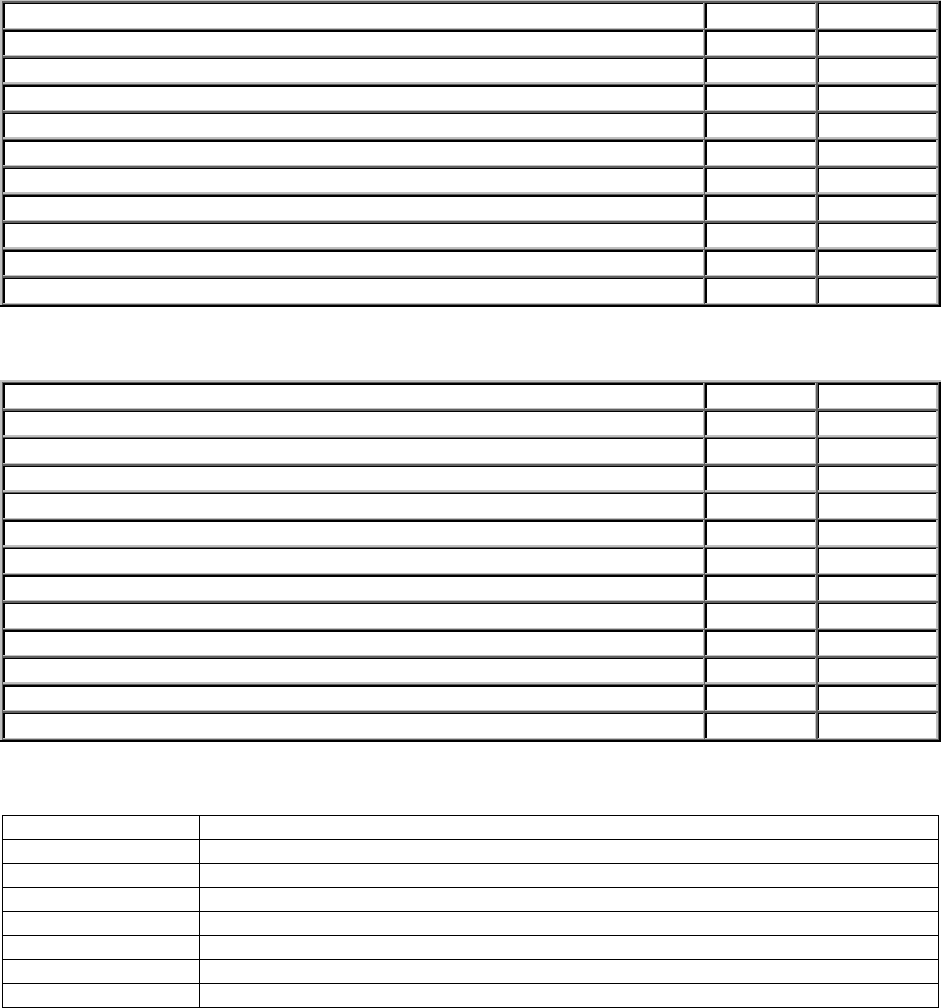

Table 1. Formatted capacity by model number. 17

Table 2. Data sheet 18

Table 3. Cylinder allocation 18

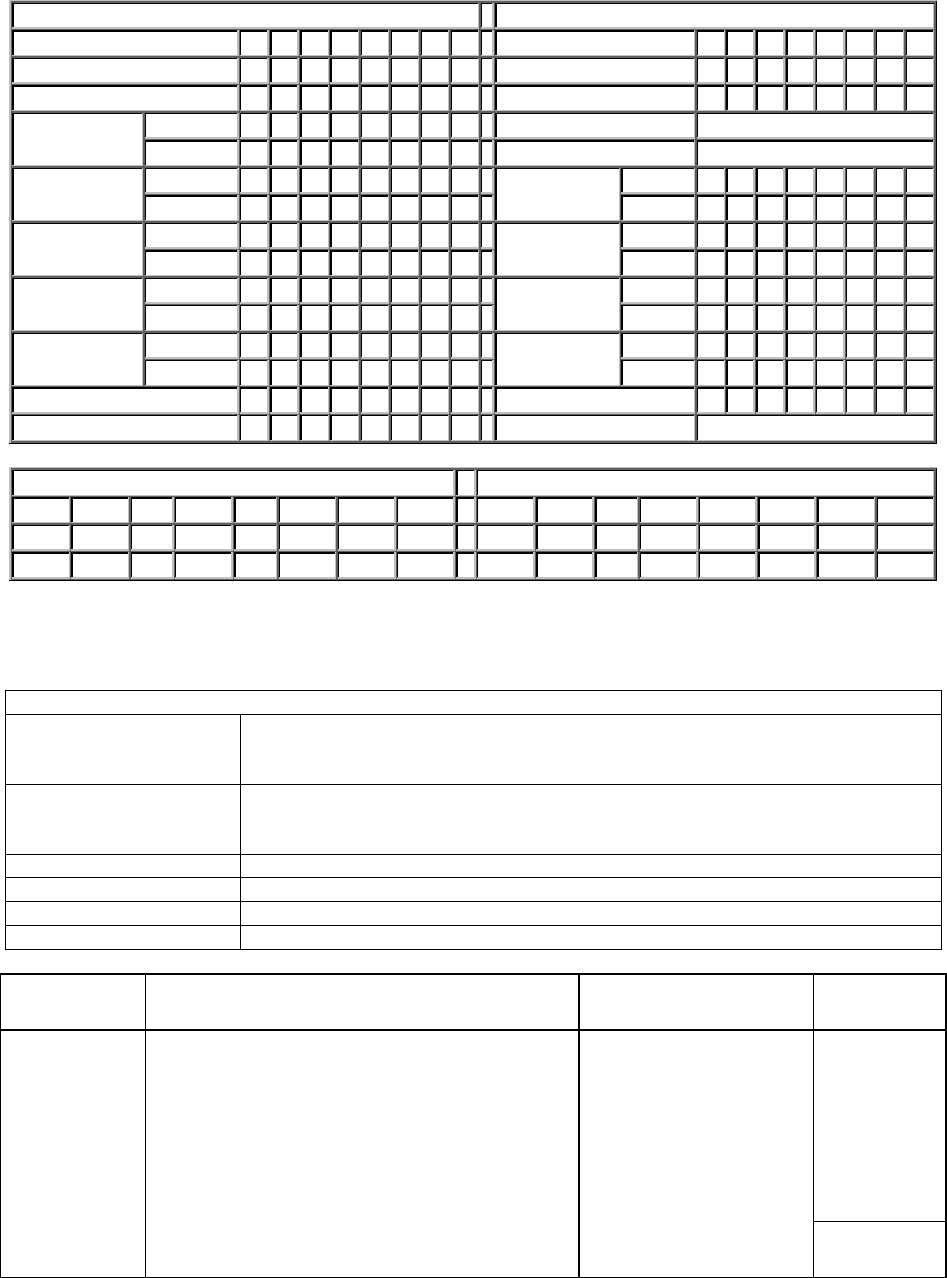

Table 4. Performance characteristics 19

Table 5. Mechanical positioning performance 20

Table 6. Full stroke seek time 20

Table 7. Single track seek time 20

Table 8. Latency time 20

Table 9. Drive ready time 21

Table 10. Operating mode 22

Table 11. Drive ready time 22

Table 12. Environmental condition 26

Table 13. Magnetic flux density limits 27

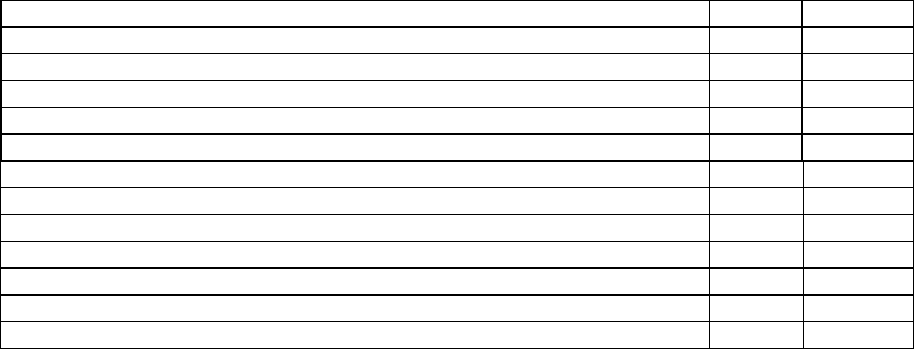

Table 14. DC Power requirements 28

Table 15. Power consumption efficiency 29

Table 16. Physical dimensions and weight 33

Table 17. Random vibration PSD profile breakpoints (operating) 35

Table 18. Swept sine vibration 35

Table 19. Random Vibration PSD Profile Breakpoints (nonoperating) 36

Table 20. Operating shock 36

Table 21. Nonoperating shock 36

Table 22. Weighted sound power 37

Table 23. Interface connector pins and I/O signals 41

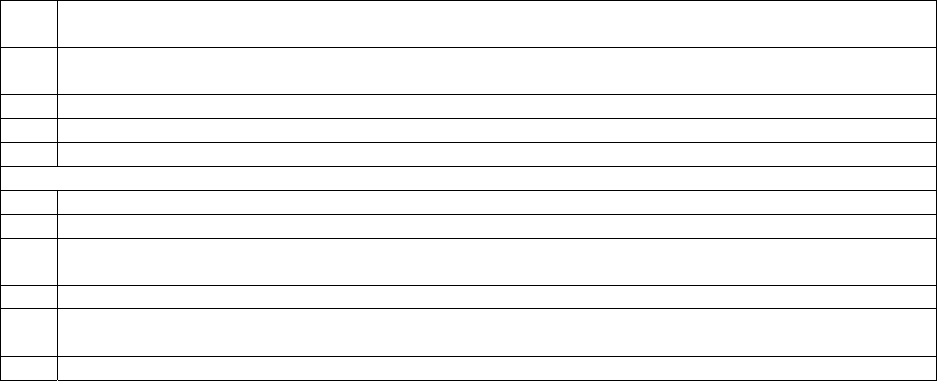

Table 24 Register naming convention and correspondence 46

Table 25 Device Control Register 47

Table 26 Device Register 47

Table 27 Error Register 47

Table 28 Status Register 49

Table 29 Reset Response Table 50

Table 30 Default Register Values 51

Table 31 Diagnostic Codes 51

Table 32 Reset error register values 51

Table 33 Device’s behavior by ATA commands 52

Table 34 Power conditions 54

Table 35 Command table for device lock operation 62

Table 36 Command table for device lock operation - continued 63

Table 37 Set Max Set Password data content 65

Table 38 Preserved Software Setting 69

Table 39 SCT Action Code Supported 70

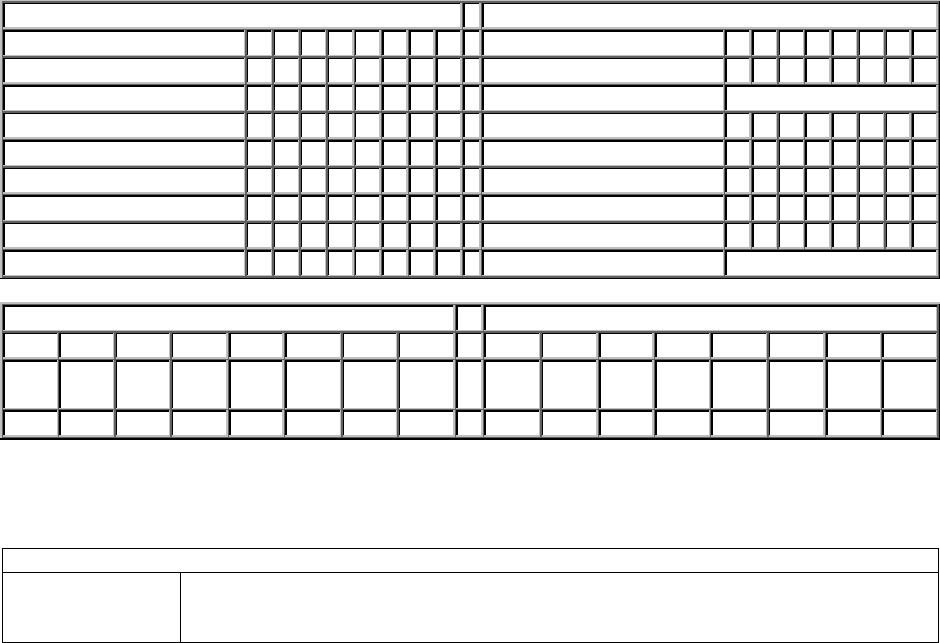

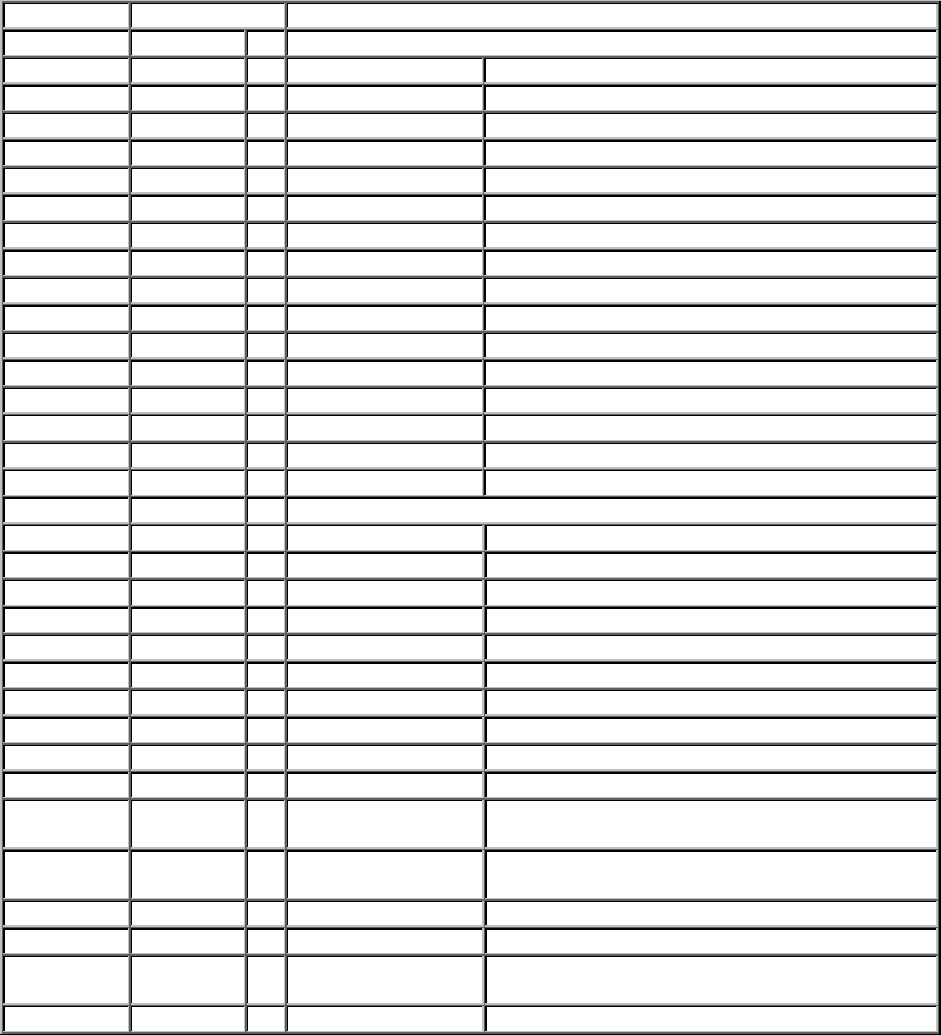

Table 40 Command set 74

Table 41 Command Set - continued 75

Table 42 Command Set (Subcommand) 76

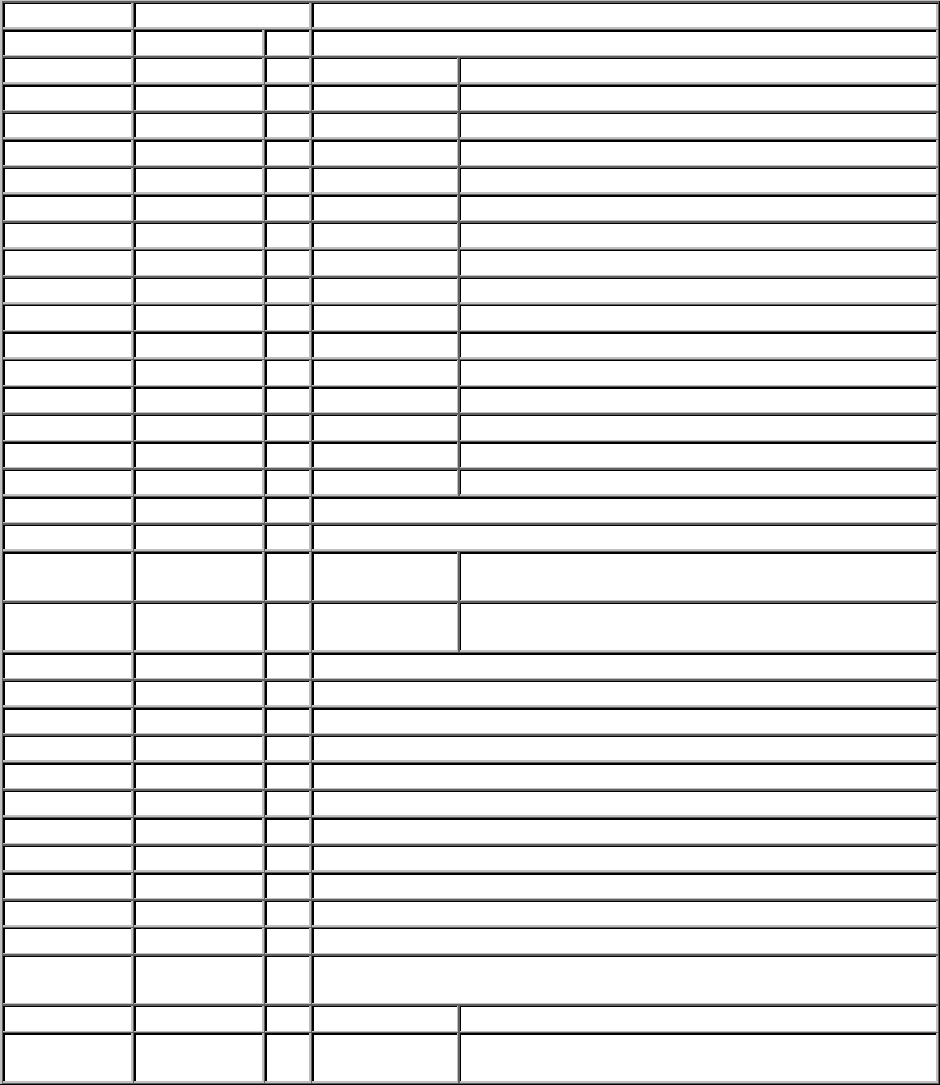

Table 43 Check Power Mode Command (E5h/98h) 78

Table 44 Device Configuration Overlay Command (B1h) 79

Table 45 Device Configuration Overlay Features register values 79

Table 46 Device Configuration Overlay Data structure 81

Table 47 DCO error information definition 82

Table 48 Execute Device Diagnostic Command (90h) 83

Table 49 Flush Cache Command (E7h) 84

Table 50 Flush Cache EXT Command (EAh) 85

Table 51 Format Track Command (50h) 86

Table 52 Format Unit Command (F7h) 87

Table 53 Identify Device Command (ECh) 88

Table 54 Identify device information 89

Table 55 Identify device information --- Continued --- 90

Table 56 Identify device information --- Continued --- 91

Table 57 Identify device information --- Continued --- 92

7K200 SATA OEM Specification

8/173

Table 58 Identify device information --- Continued --- 93

Table 59 Identify device information --- Continued --- 94

Table 60 Identify device information --- Continued --- 95

Table 61 Identify device information --- Continued --- 96

Table 62 Identify device information --- Continued --- 97

Table 63 Number of cylinders/heads/sectors by models for HTS7220XXK9SA00 / HTS7220XXK9A300 98

Table 64 Idle Command (E3h/97h) 99

Table 65 Idle Immediate Command (E1h/95h) 100

Table 66 Initialize Device Parameters Command (91h) 101

Table 67 Read Buffer Command (E4h) 102

Table 68 Read DMA Command (C8h/C9h) 103

Table 69 Read DMA Ext Command (25h) 104

Table 70 Read FPDMA Queued Command (60h) 105

Table 71 Read Log Ext Command (2Fh) 106

Table 72 Log address definition 106

Table 73 General purpose Log Directory 107

Table 74 Extended comprehensive SMART error Log 108

Table 75 Extended Error log data structure 108

Table 76 Command data structure 109

Table 77 Error data structure 109

Table 78 Extended Self-test log data structure 110

Table 79 Extended Self-test log descriptor entry 111

Table 80 Command Error information 111

Table 81 Phy Event Counter Identifier 112

Table 82 Phy Event Counter information 113

Table 83 Read Multiple Command (C4h) 114

Table 84 Read Multiple Ext Command (29h) 115

Table 85 Read Native Max Address Command (F8h) 116

Table 86 Read Native Max Address Ext Command (29h) 117

Table 87 Read Sector(s) Command (20h/21h) 118

Table 88 Read Sector(s) Ext Command (24h) 119

Table 89 Read Verify Sector(s) Command (40h/41h) 120

Table 90 Read Verify Sector(s) Ext Command (42h) 121

Table 91 Recalibrate Command (1xh) 122

Table 92 Security Disable Password Command (F6h) 123

Table 93 Password Information for Security Disable Password command 123

Table 94 Security Erase Prepare Command (F3h) 124

Table 95 Security Erase Unit Command (F4h) 125

Table 96 Erase Unit Information 125

Table 97 Security Freeze Lock Command (F5h) 127

Table 98 Security Set Password Command (F1h) 128

Table 99 Security Set Password Information 128

Table 100 Security Unlock Command (F2h) 130

Table 101 Security Unlock Information 130

Table 102 Seek Command (7xh) 131

Table 103 Sense Condition Command (F0h) 132

Table 104 Set Features Command (EFh) 133

Table 105 Set Max Address Command (F9h) 135

Table 106 Set Max Address Ext Command (37h) 137

Table 107 Set Multiple Command (C6h) 139

Table 108 Sleep Command (E6h/99h) 140

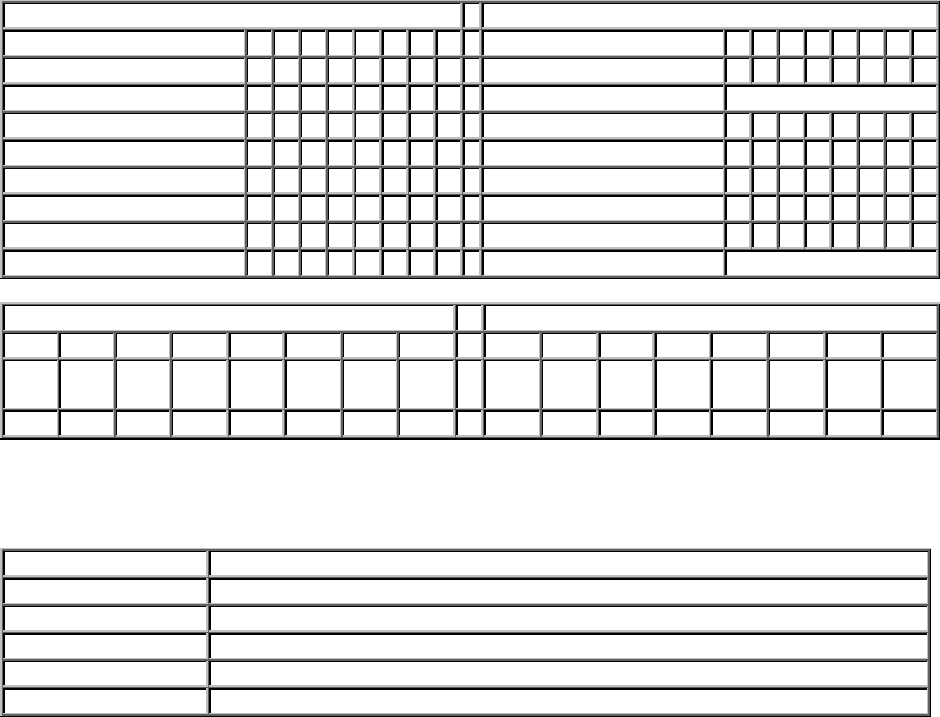

Table 109 S.M.A.R.T. Function Set Command (B0h) 141

Table 110 Log sector addresses 144

Table 111 Device Attribute Data Structure 146

Table 112 Individual Attribute Data Structure 147

Table 113 Status Flag Definitions 148

Table 114 Device Attribute Thresholds Data Structure 150

Table 115 Individual Threshold Data Structure 151

Table 116 SMART Log Directory 151

Table 117 S.M.A.R.T. error log sector 152

Table 118 Error log data structure 152

Table 119 Command data structure 153

7K200 SATA OEM Specification

9/173

Table 120 Error data structure 153

Table 121 Self-test log data structure 154

Table 122 Selective self-test log data structure 155

Table 123 S.M.A.R.T. Error Codes 155

Table 124 Standby Command (E2h/96h) 156

Table 125 Standby Immediate Command (E0h/94h) 157

Table 126 Write Buffer Command (E8h) 158

Table 127 Write DMA Command (CAh/CBh) 159

Table 128 Write DMA Ext Command (35h) 160

Table 129 Write DMA FUA Ext Command (3Dh) 161

Table 130 Write FPDMA Queued Command (61h) 162

Table 131 Write Log Ext Command 163

Table 132 Write Multiple Command (C5h) 164

Table 133 Write Multiple Ext Command (39h) 165

Table 134 Write Multiple FUA Ext Command (CEh) 166

Table 135 Write Sector(s) Command (30h/31h) 167

Table 136 Write Sector(s) Ext Command (34h) 168

Table 137 Write Uncorrectable Ext Command (45h) 169

Table 138 Timeout Values 171

7K200 SATA OEM Specification

10/173

General

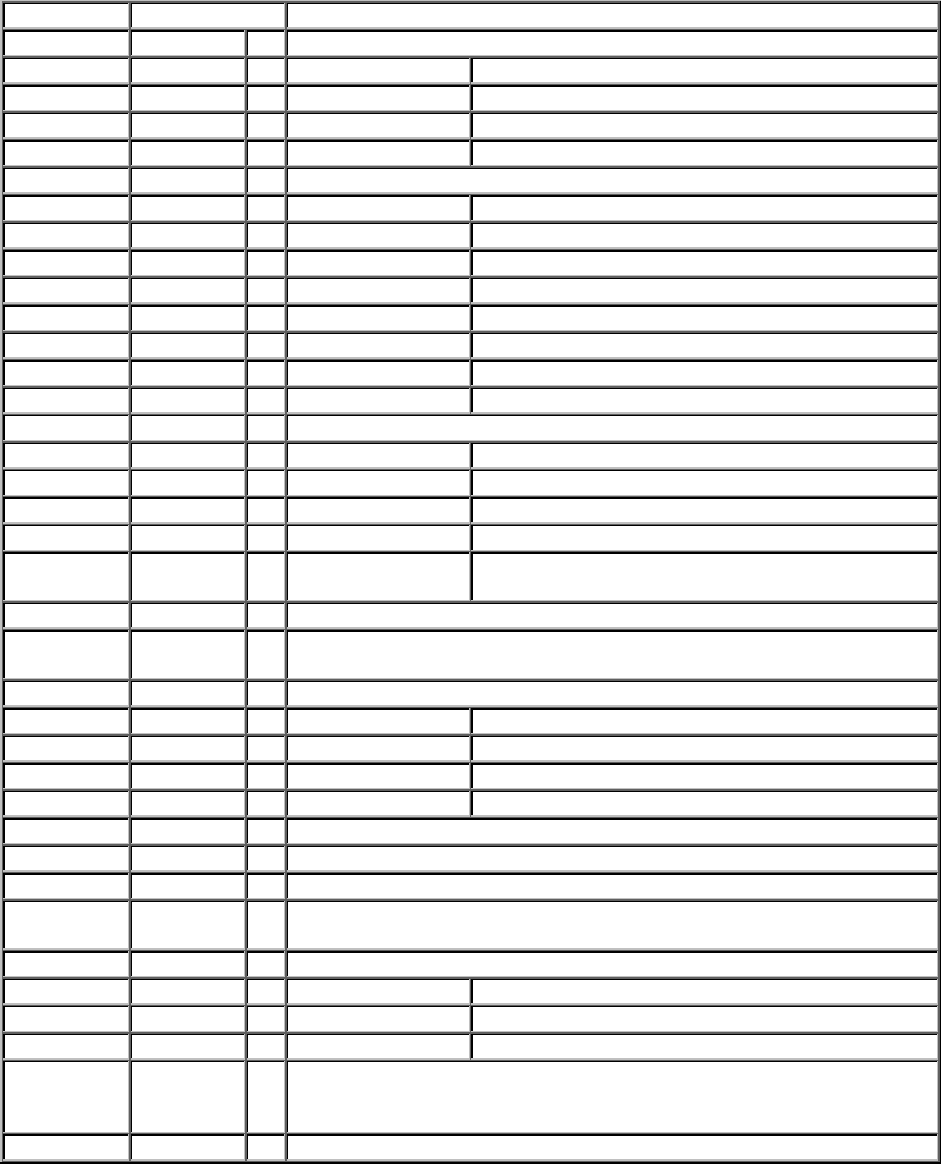

1 Introduction

This document describes the specifications of the HITACHI Travelstar 7K200, a 2.5-inch hard disk

drive with Serial ATA interface:

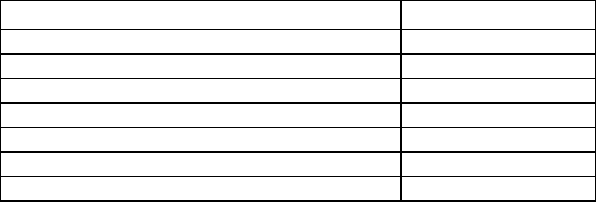

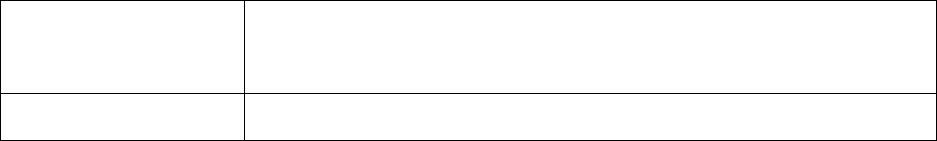

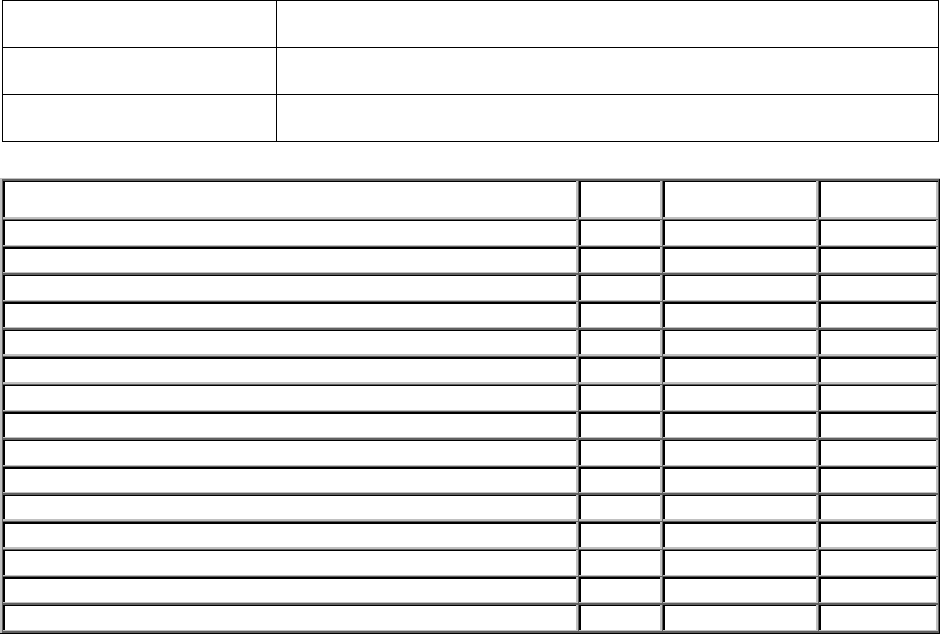

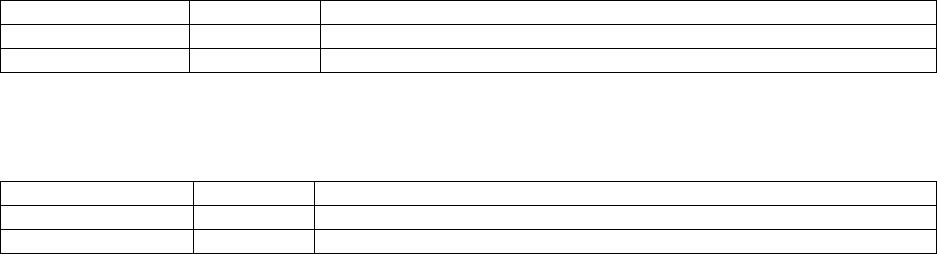

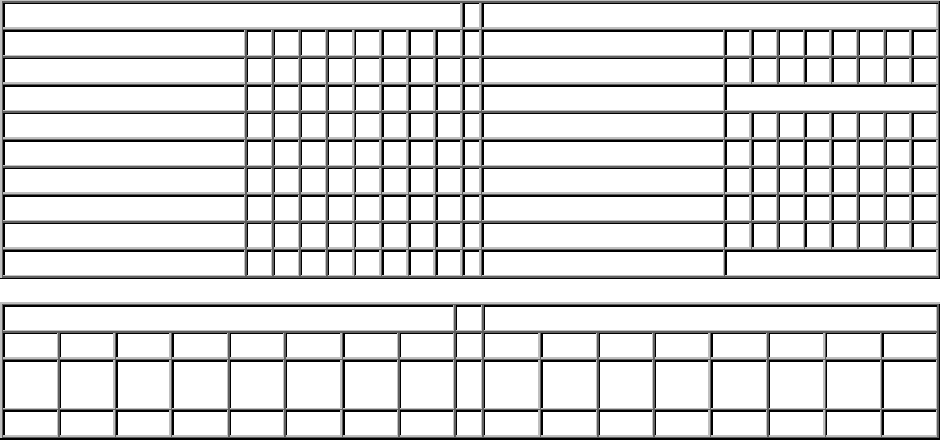

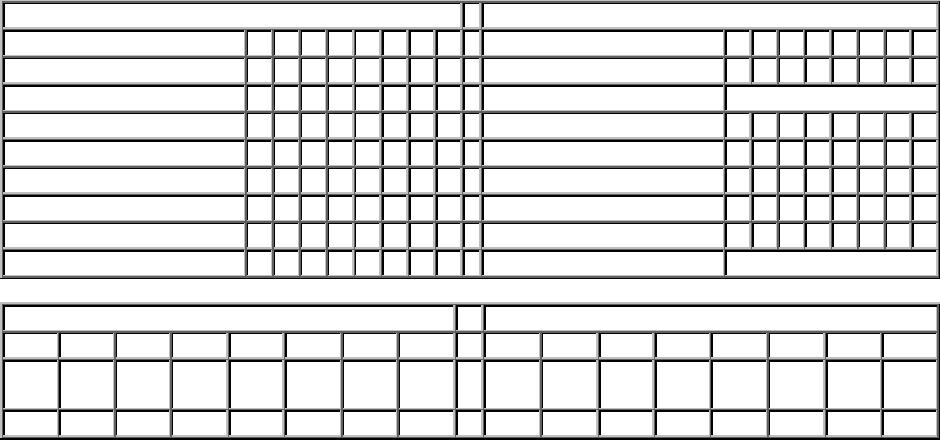

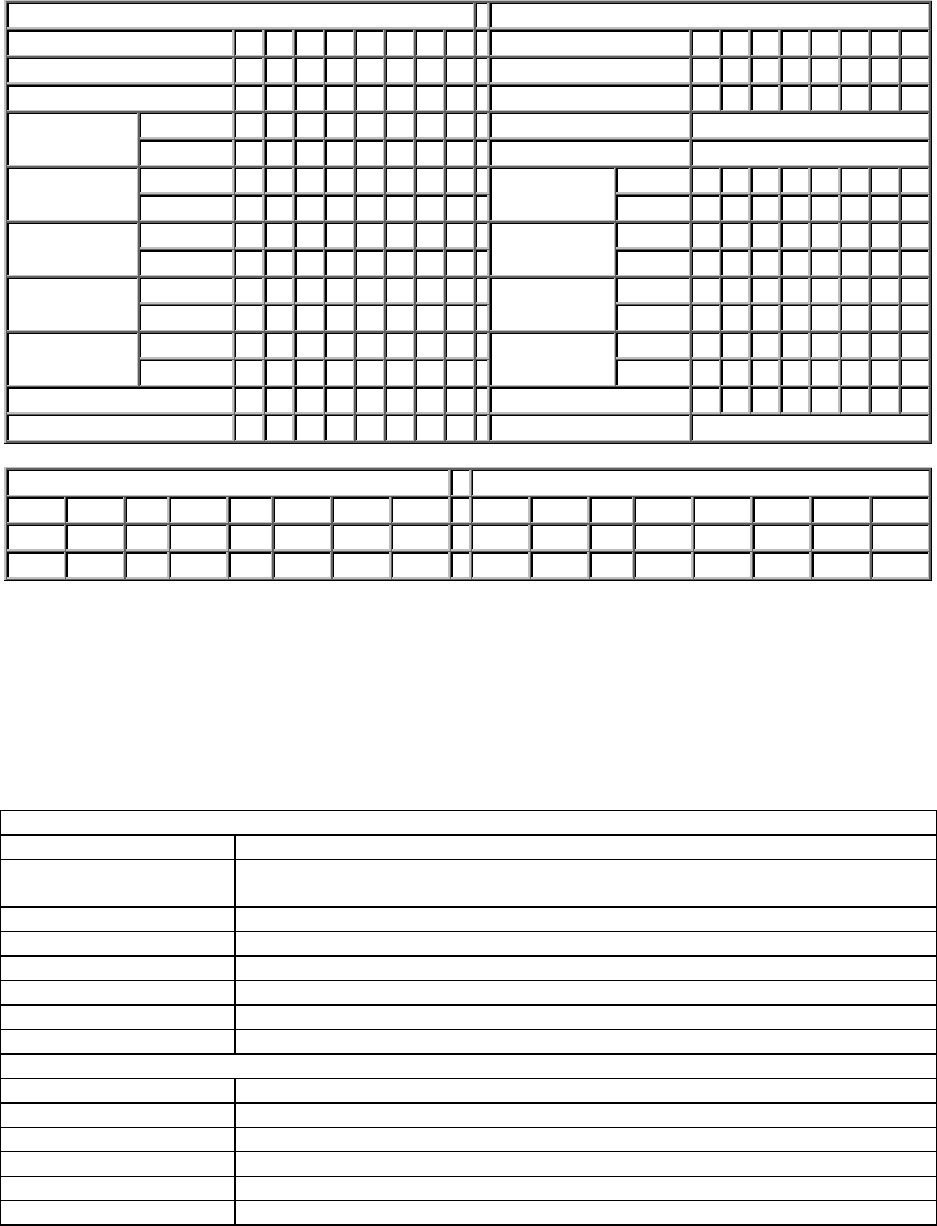

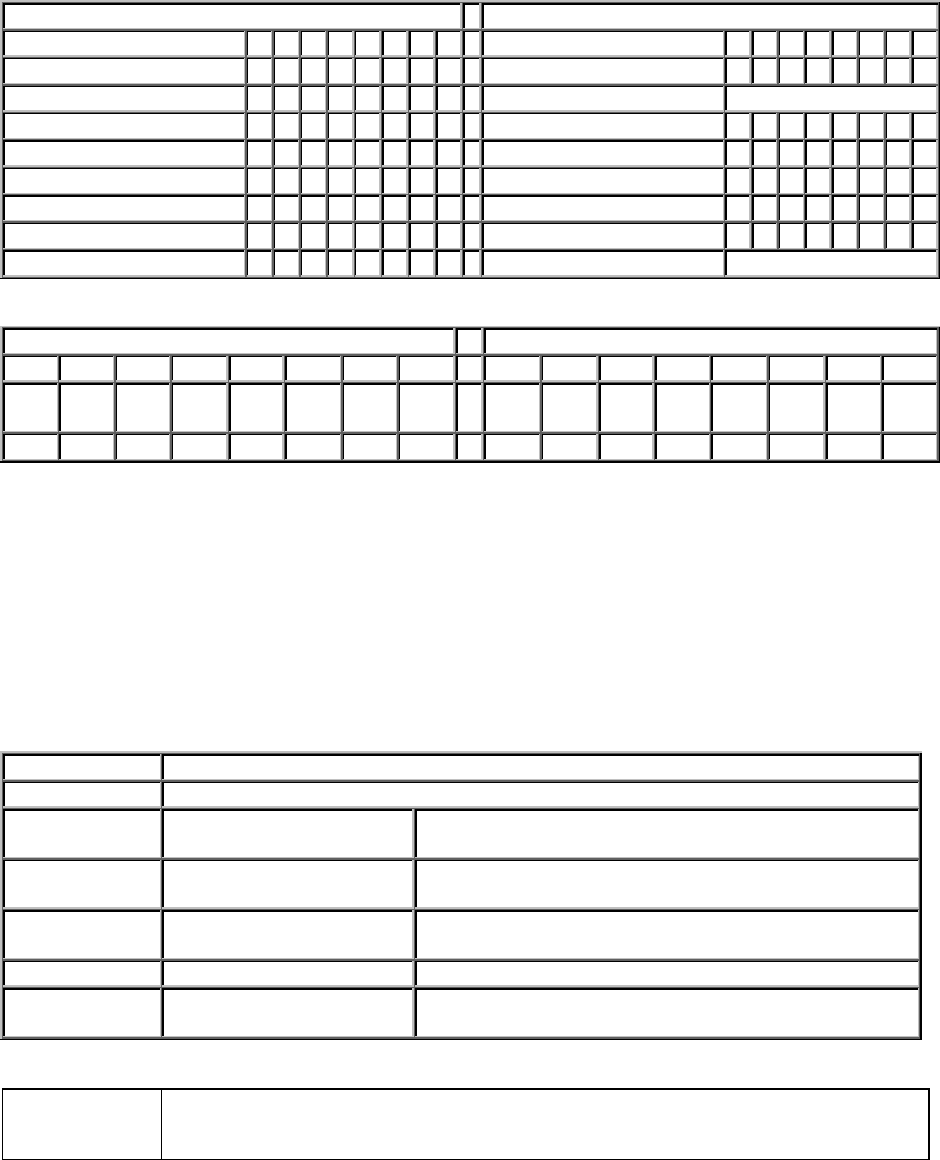

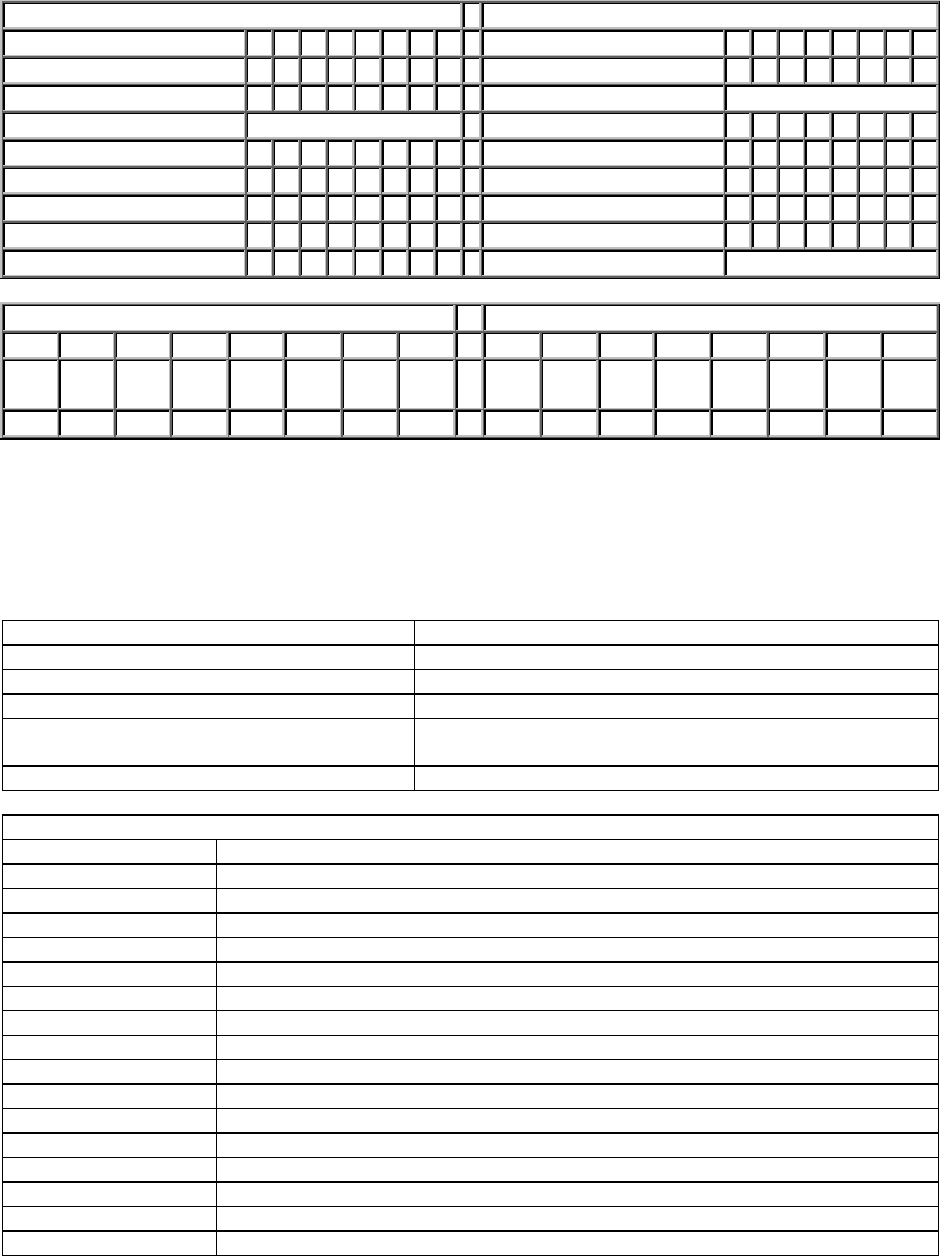

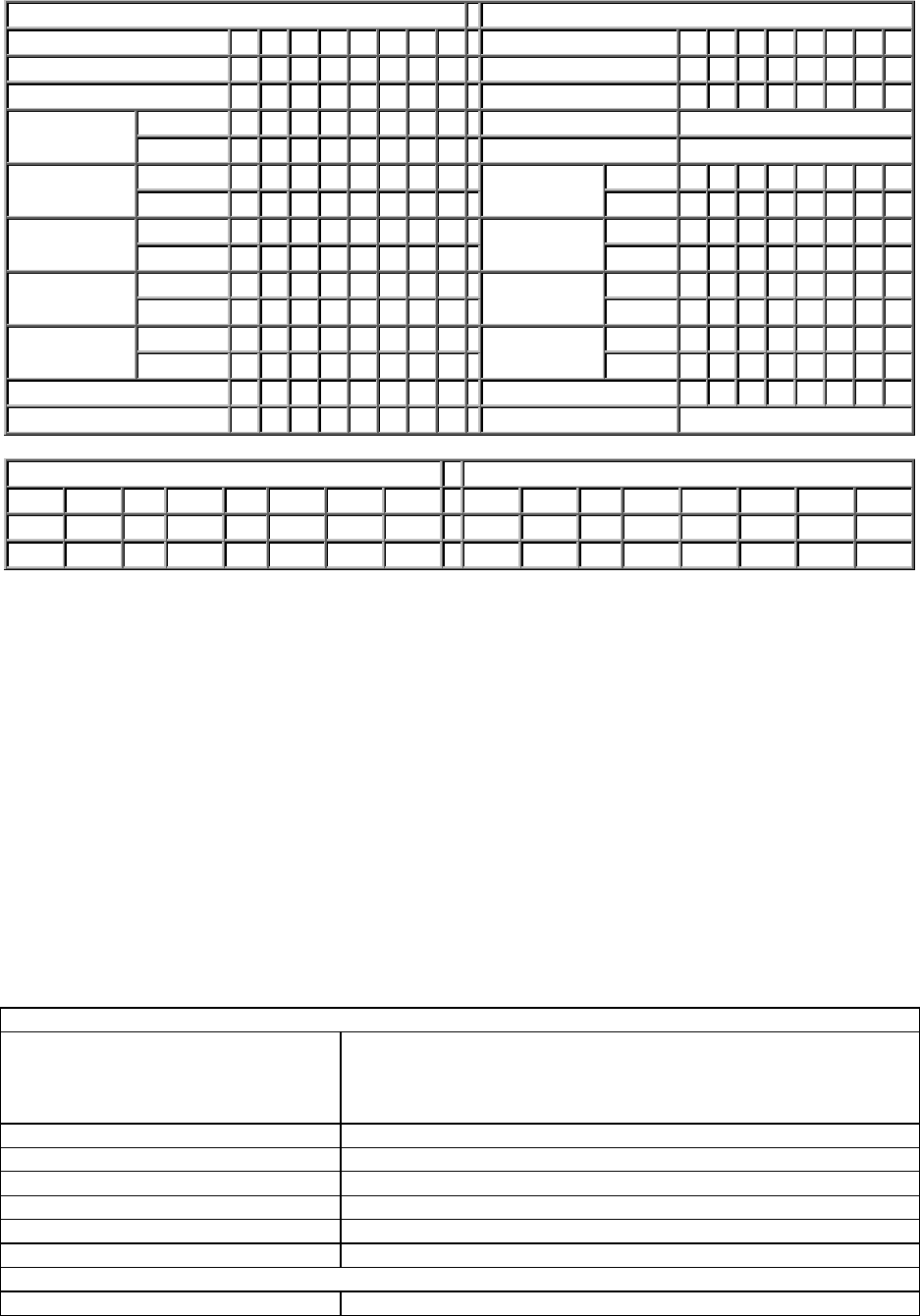

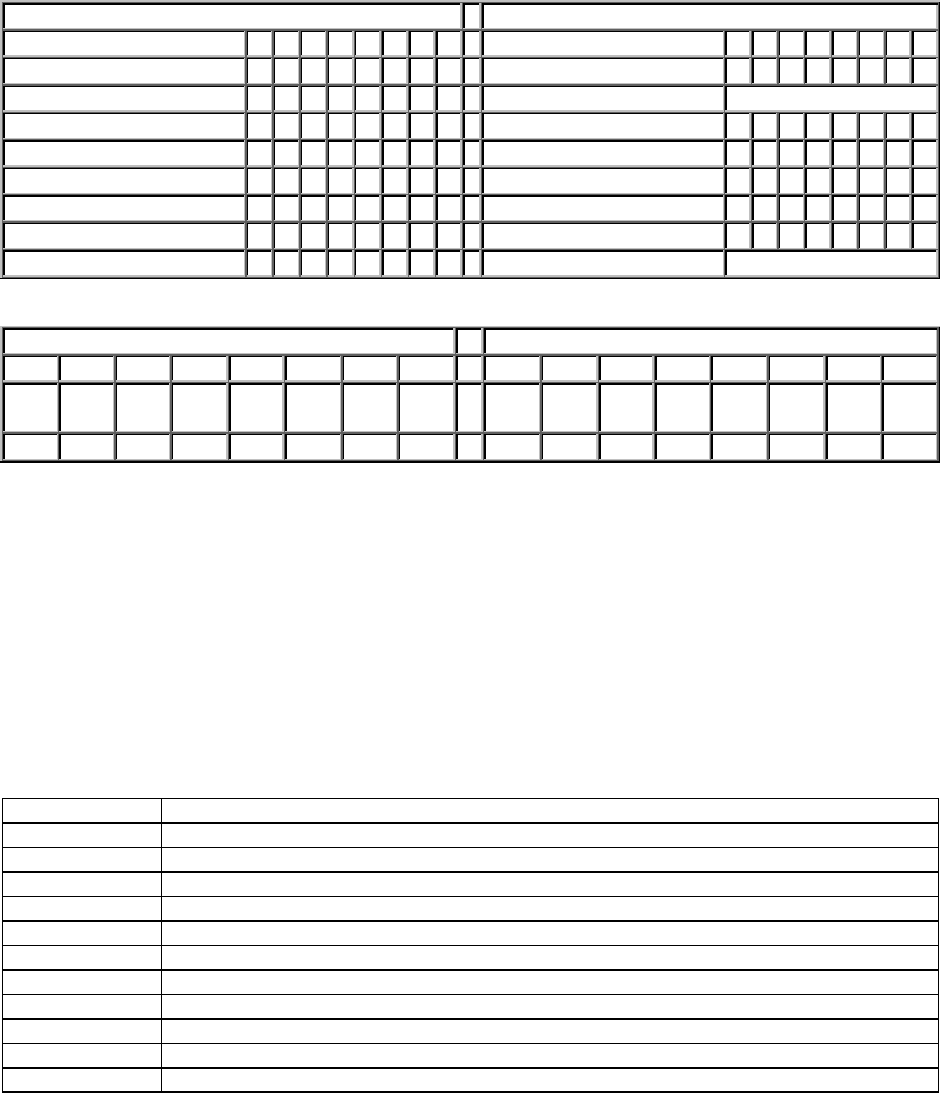

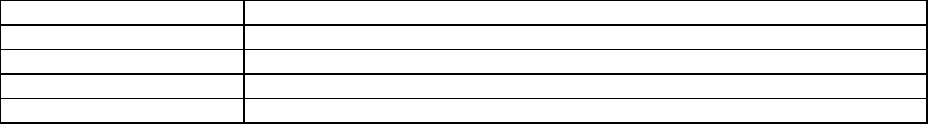

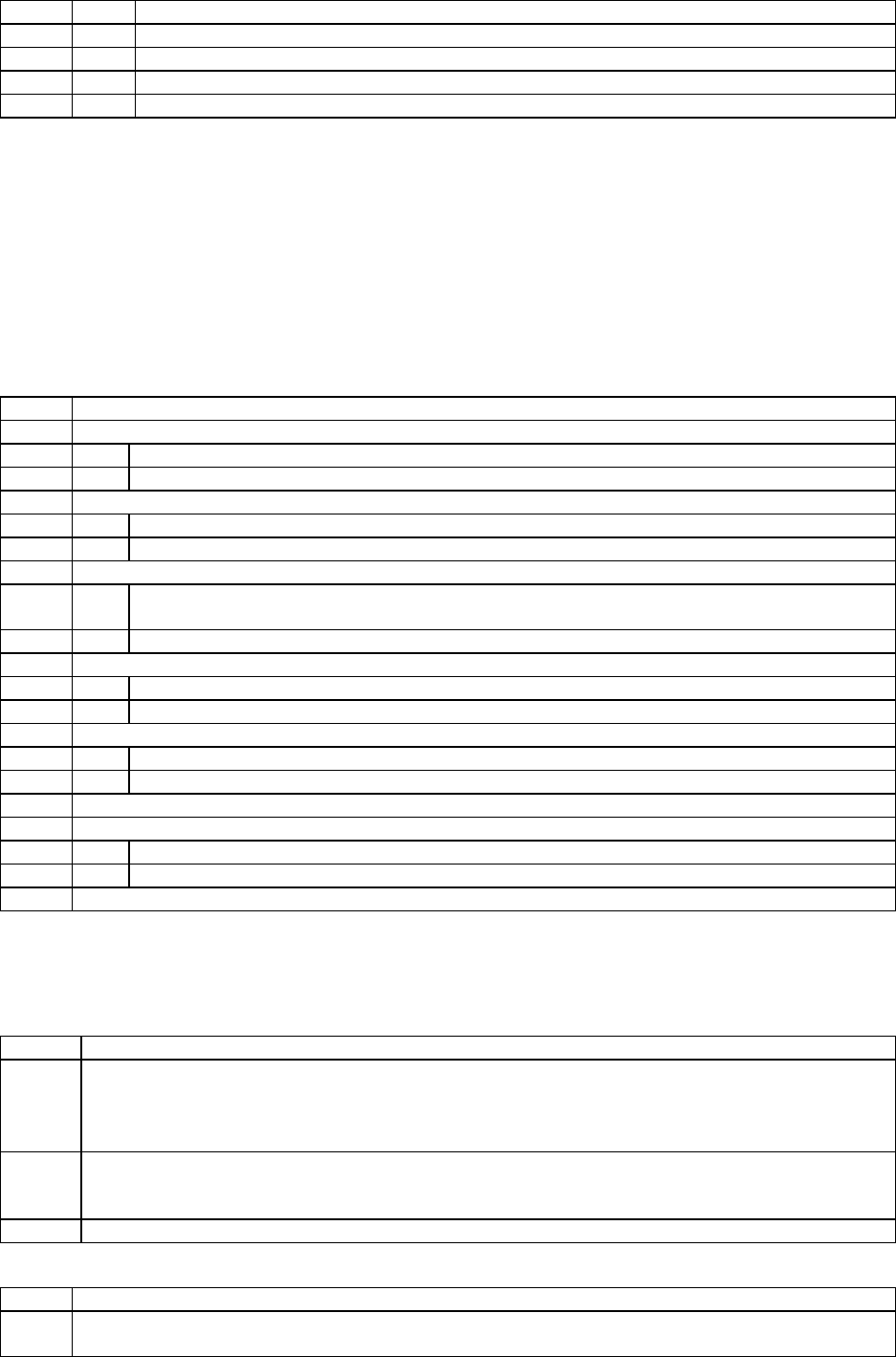

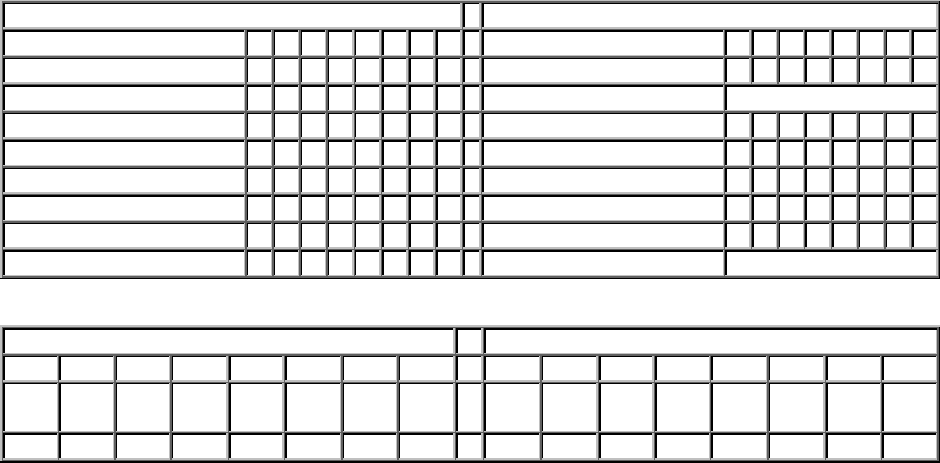

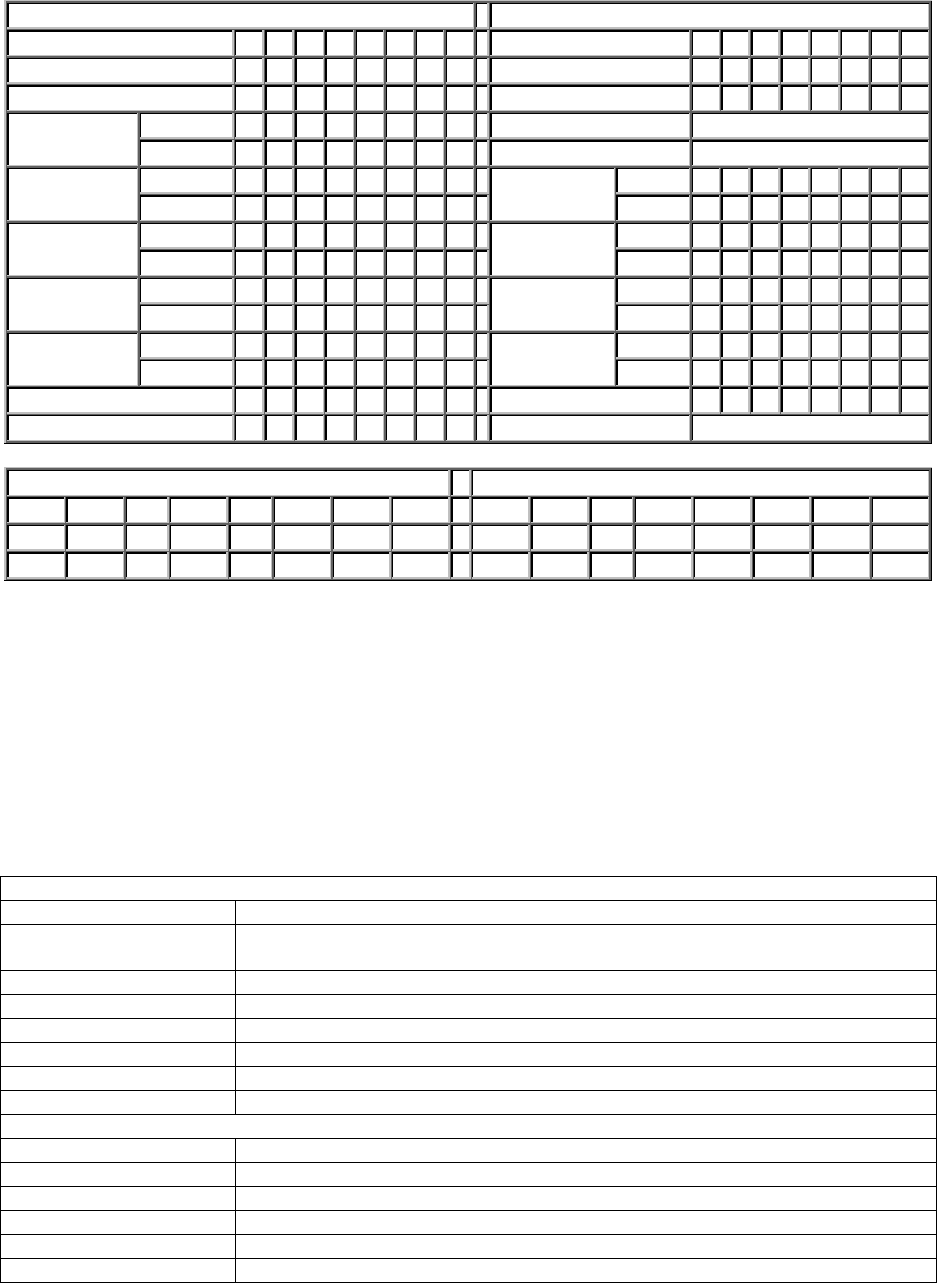

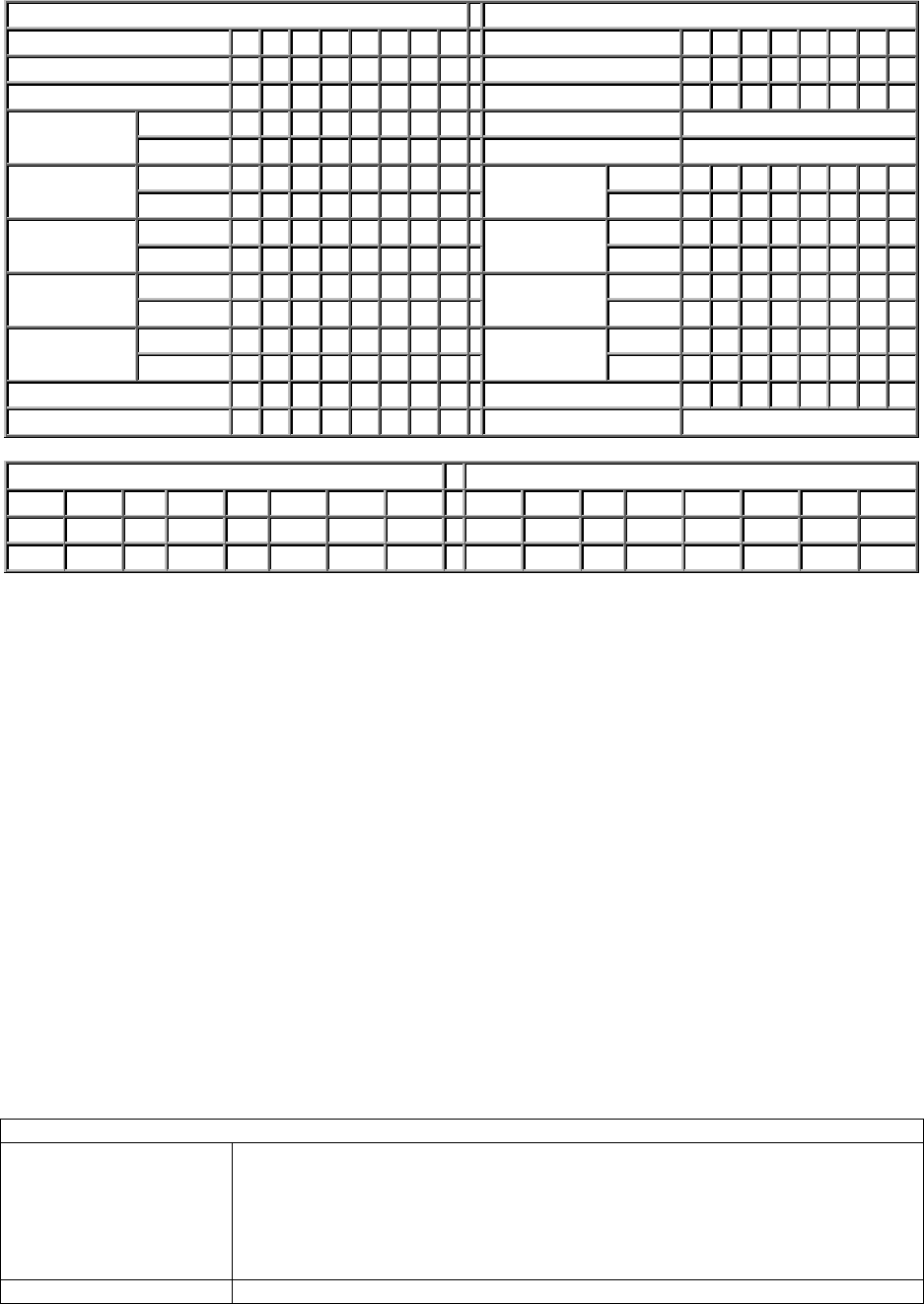

Drive

name Model Number MAX Data

transfer rate

(Gbps)

Capacity

(GB) Height

(mm) Rotation

speed (rpm)

HTS722020K9A300 3.0

Travelstar

7K200-200 HTS722020K9SA00 1.5

200 9.5 7200

HTS722016K9A300 3.0

Travelstar

7K200-160 HTS722016K9SA00 1.5

160 9.5 7200

HTS722012K9A300 3.0

Travelstar

7K200-120 HTS722012K9SA00 1.5

120 9.5 7200

HTS722010K9A300 3.0

Travelstar

7K200-100 HTS722010K9SA00 1.5

100 9.5 7200

HTS722080K9A300 3.0

Travelstar

7K200-80 HTS722080K9SA00 1.5 80 9.5 7200

Part 1 of this document beginning on page 16 defines the hardware functional specification. Interface

specification is Part 2 starting from page 44

1.1 Abbreviations

Abbreviation Meaning

32 KB 32 x 1024 bytes

64 KB 64 x 1024 bytes

“ inch

A amp

AC alternating current

AT Advanced Technology

ATA Advanced Technology Attachment

Bels unit of sound power

BIOS Basic Input/Output System

°C degrees Celsius

CSA Canadian Standards Association

C-UL Canadian-Underwriters Laboratory

Cyl cylinder

DC direct current

DFT Drive Fitness Test

DMA Direct Memory Access

ECC error correction code

EEC European Economic Community

7K200 SATA OEM Specification

11/173

EMC electromagnetic compatibility

ERP Error Recovery Procedure

Esd electrostatic discharge

FCC Federal Communications Commission

FRU field replacement unit

G gravity, a unit of force

Gb 1 000 000 000 bits

GB 1 000 000 000 bytes

GND ground

h hexadecimal

HDD hard disk drive

Hz hertz

I Input

ILS integrated lead suspension

imped impedance

I/O Input/Output

ISO International Standards Organization

KB 1,000 bytes

Kbit/mm 1,000 bits per mm

Kbit/sq-mm 1000 bits per square mm

KHz kilohertz

LBA logical block addressing

Lw unit of A-weighted sound power

m meter

max. or Max. maximum

MB 1,000,000 bytes

Mbps 1,000,000 Bit per second

Mb/sec 1,000,000 Bit per second

MB/sec 1,000,000 bytes per second

MHz megahertz

MLC Machine Level Control

mm millimeter

ms millisecond

us, s microsecond

Nm Newton meter

No. or # number

oct/min oscillations per minute

O Output

OD Open Drain Programmed Input/Output

7K200 SATA OEM Specification

12/173

PIO

POH power on hours

Pop. population

P/N part number

p-p peak-to-peak

PSD power spectral density

RES radiated electromagnetic susceptibility

RFI radio frequency interference

RH relative humidity

% RH per cent relative humidity

RMS root mean square

RPM revolutions per minute

RST reset

R/W read/write

sec second

Sect/Trk sectors per track

SELV secondary low voltage

S.M.A.R.T Self-monitoring, analysis, and reporting technology

Trk. track

TTL transistor-transistor logic

UL Underwriters Laboratory

V volt

VDE Verband Deutscher Electrotechniker

W watt

3-state transistor-transistor tristate logic

7K200 SATA OEM Specification

13/173

1.2 References

Serial ATA International Organization : Serial ATA Revision 2.6

1.3 General caution

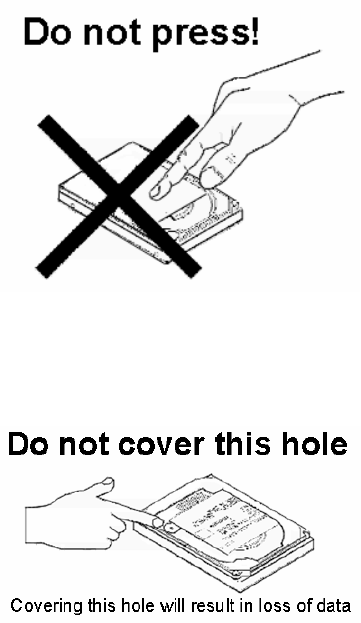

Do not apply force to the top cover (See figure below).

Do not cover the breathing hole on the top cover (See figure below).

Do not touch the interface connector pins or the surface of the printed circuit board.

The drive can be damaged by shock or ESD (Electric Static Discharge). Any damages incurred to

the drive after removing it from the shipping package and the ESD protective bag are the

responsibility of the user

1.4 Drive handling precautions

Do not press on the drive cover during handling.

7K200 SATA OEM Specification

14/173

2 Outline of the drive

・ 2.5-inch, 9.5-mm Height

・ Perpendicular Recording

・ Formatted capacities of 200GB, 160GB,120GB,100GB, and 80GB (512 bytes/sector)

・ SATA Interface conforming to Serial ATA International Organization: Serial ATA Revision

2.6(15-February-2007)

・ Integrated controller

・ No-ID recording format

・ Coding : 199/200

・ Multi zone recording

・ Enhanced ECC

・ 10 bit 40 symbol non Interleaved Read Solomon code

・ Non interleave On-The –Fly correction

・ Included 2 symbol system ECC

・ Segmented Buffer with write cache

・ 16384 KB - Upper 705 KB is used for firmware

・ Fast data transfer rate

・ HTS7220xxK9A300 model : up to 3.0Gbit/s

・ HTS7220xxK9SA00 model : up to 1.5Gbit/s

・ Media data transfer rate (max):

・ 876 Mb/s

・ Average seek time: 10 ms for read

・ Closed-loop actuator servo (Embedded Sector Servo)

・ Rotary voice coil motor actuator

・ Load/Unload mechanism

・ Mechanical latch

・ 0.8 Watts at idle state

・ Power on to ready

・ 4.0 sec (Typical)

・ Operating shock

・ 3430 m/sec2 (350 G)/2ms

・ 1764 m/sec2 (180G)/1ms

・ Nonoperating shock

・ 9800 m/sec2 (1000 G)/1ms

・ Full Data Encryption as optional (HTS7220xxK9SA00 model only)

7K200 SATA OEM Specification

15/173

Part 1 Functional Specification

7K200 SATA OEM Specification

16/173

3 Fixed disk subsystem description

3.1 Control Electronics

The control electronics works with the following functions:

SATA Interface Protocol

Embedded Sector Servo

No-ID (TM) formatting

Multizone recording

Code: 100/102

・ System ECC

・ Enhanced Adaptive Battery Life Extender

・ Full Data Encryption as optional(HTS7220xxK9SA00 model only)

3.2 Head disk assembly data

The following technologies are used in the drive:

Femto Slider

Perpendicular recording disk and write head

GMR head

Integrated lead suspension (ILS)

Load/unload mechanism

Mechanical latch

7K200 SATA OEM Specification

17/173

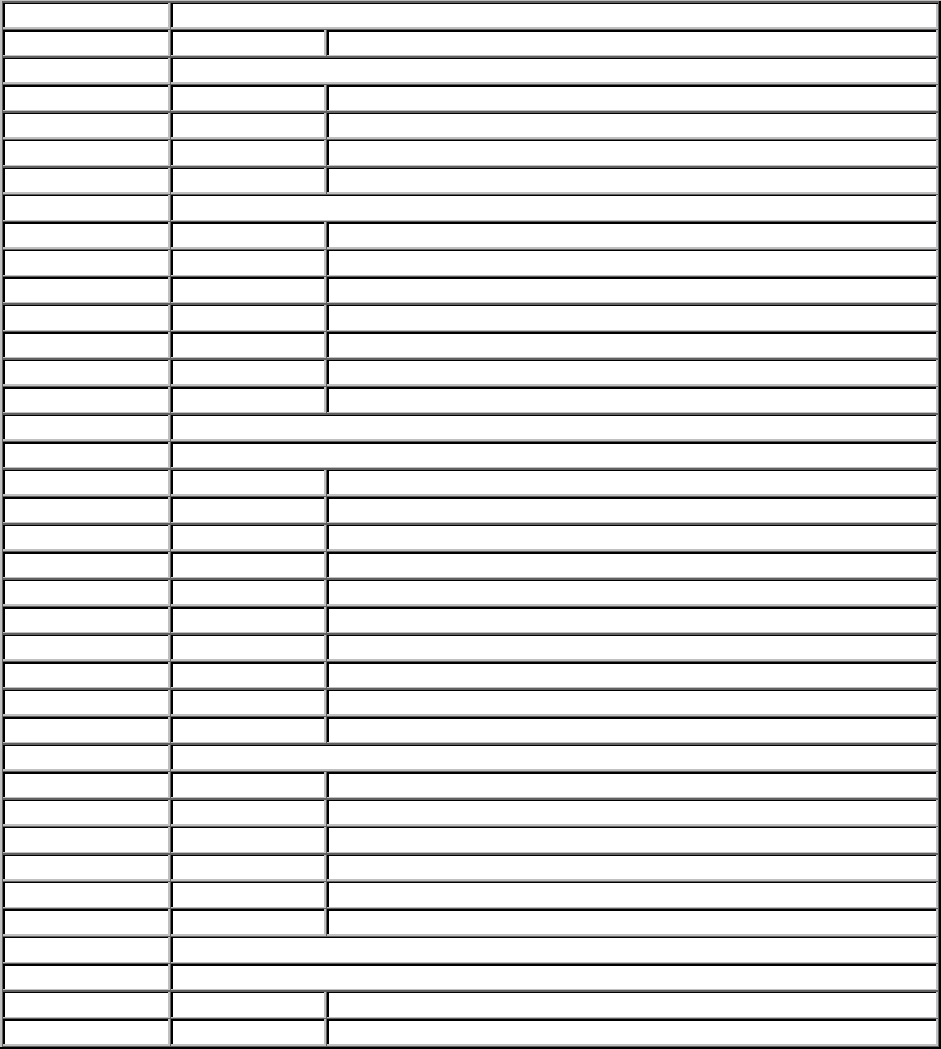

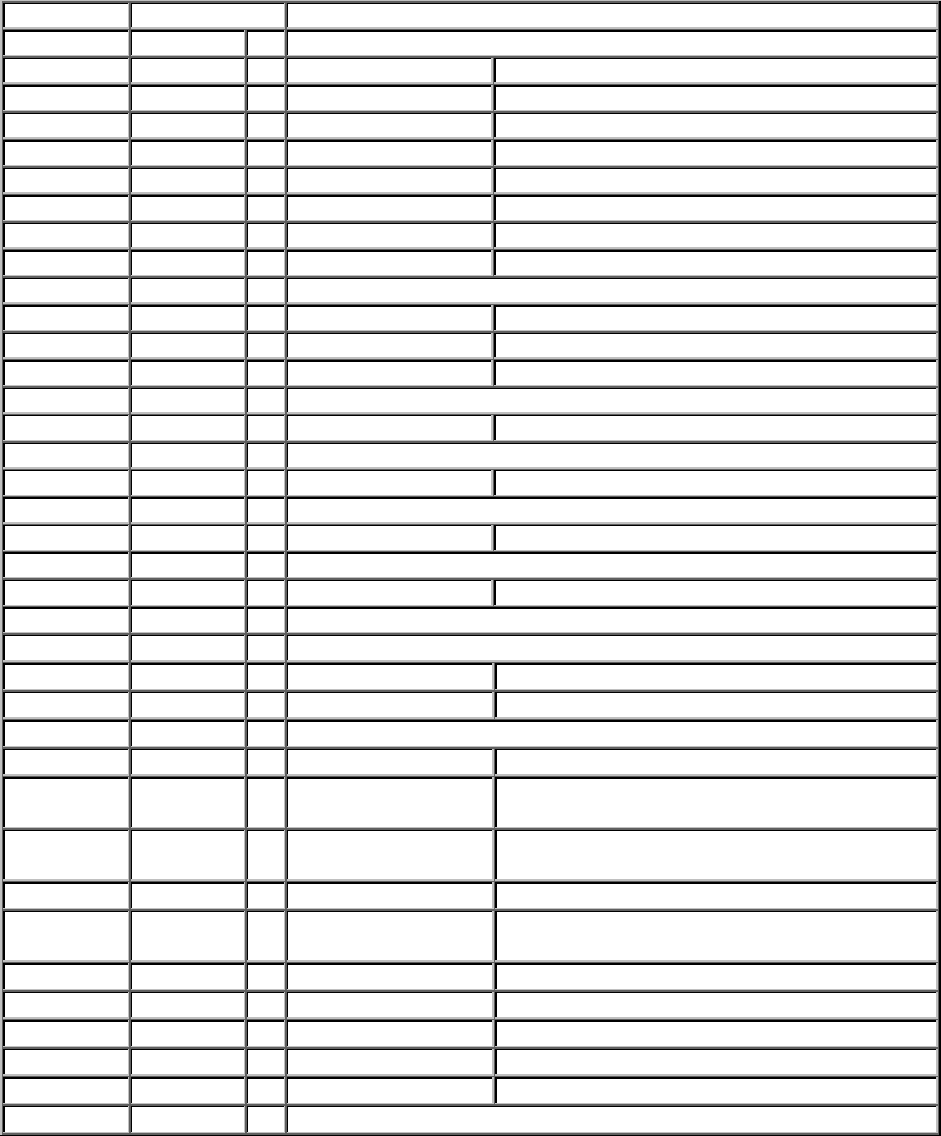

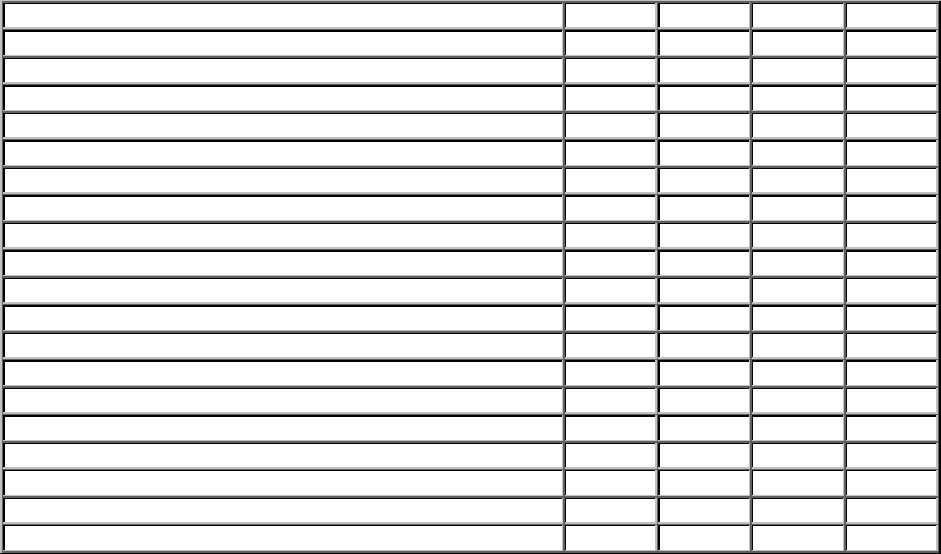

4 Fixed disk characteristics

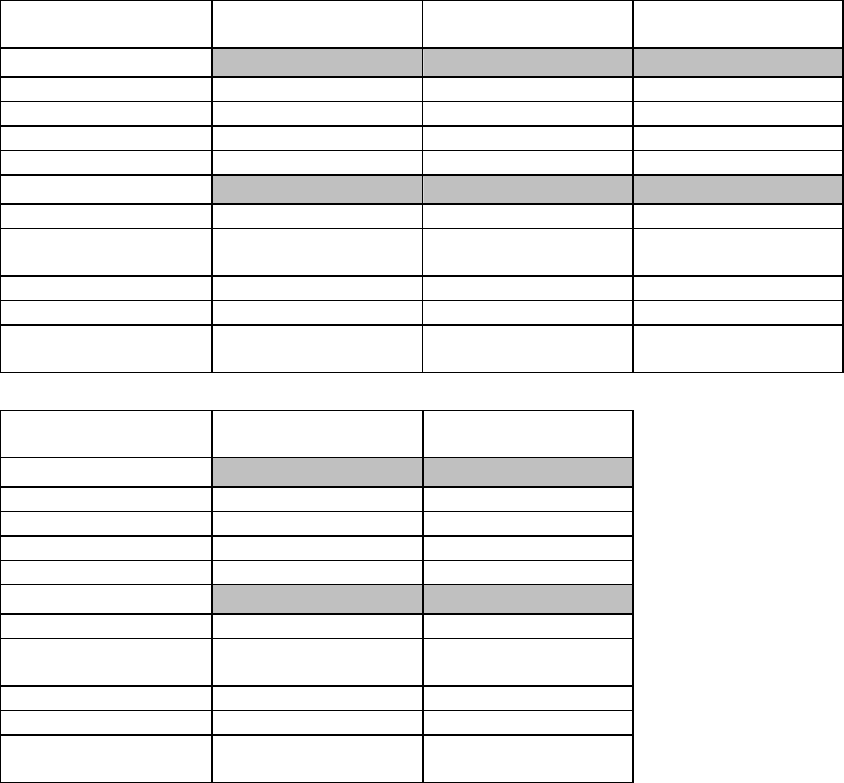

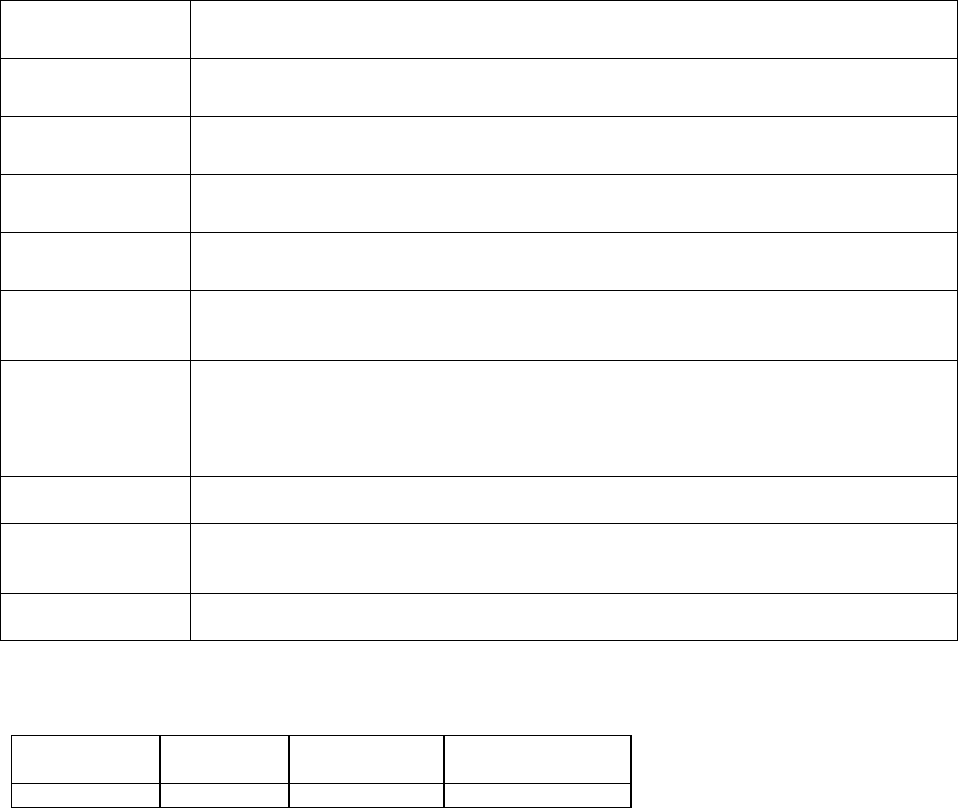

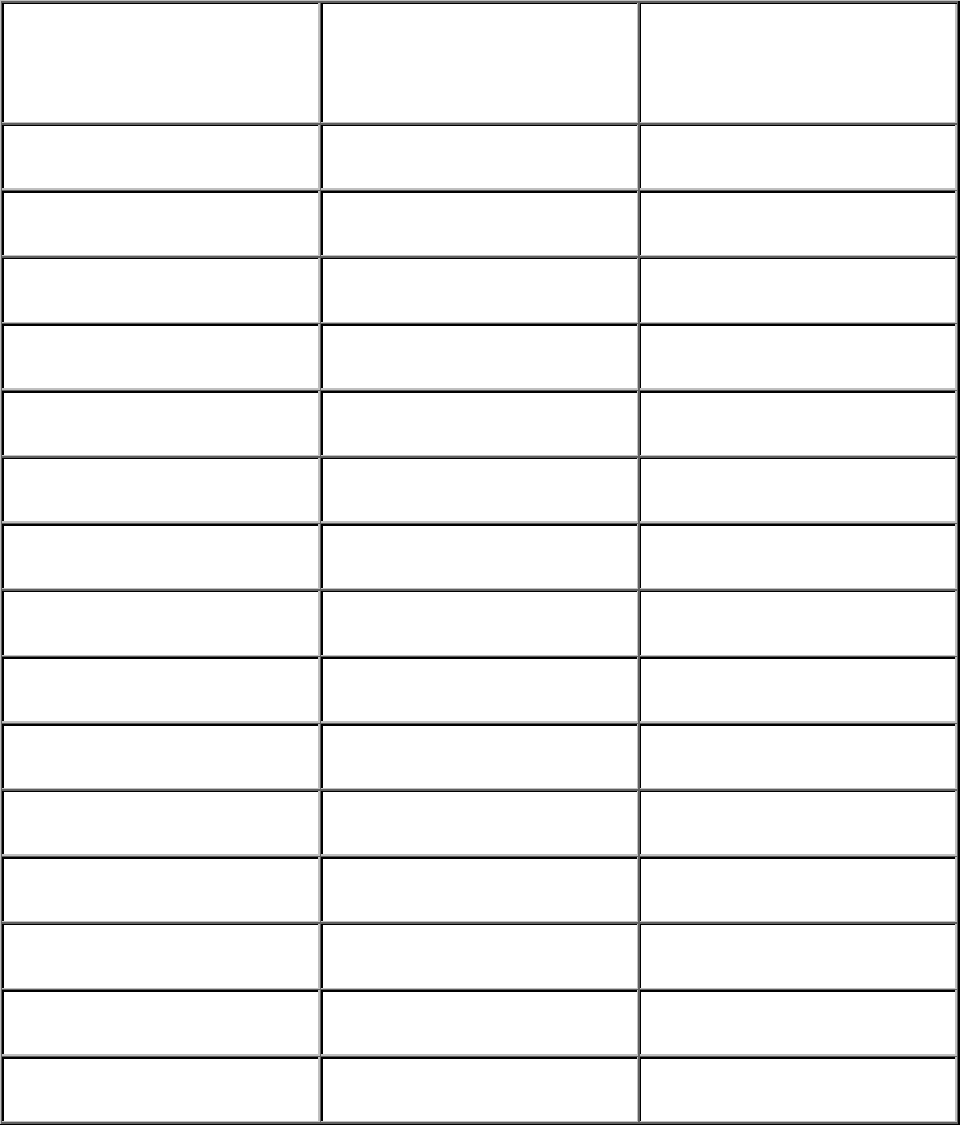

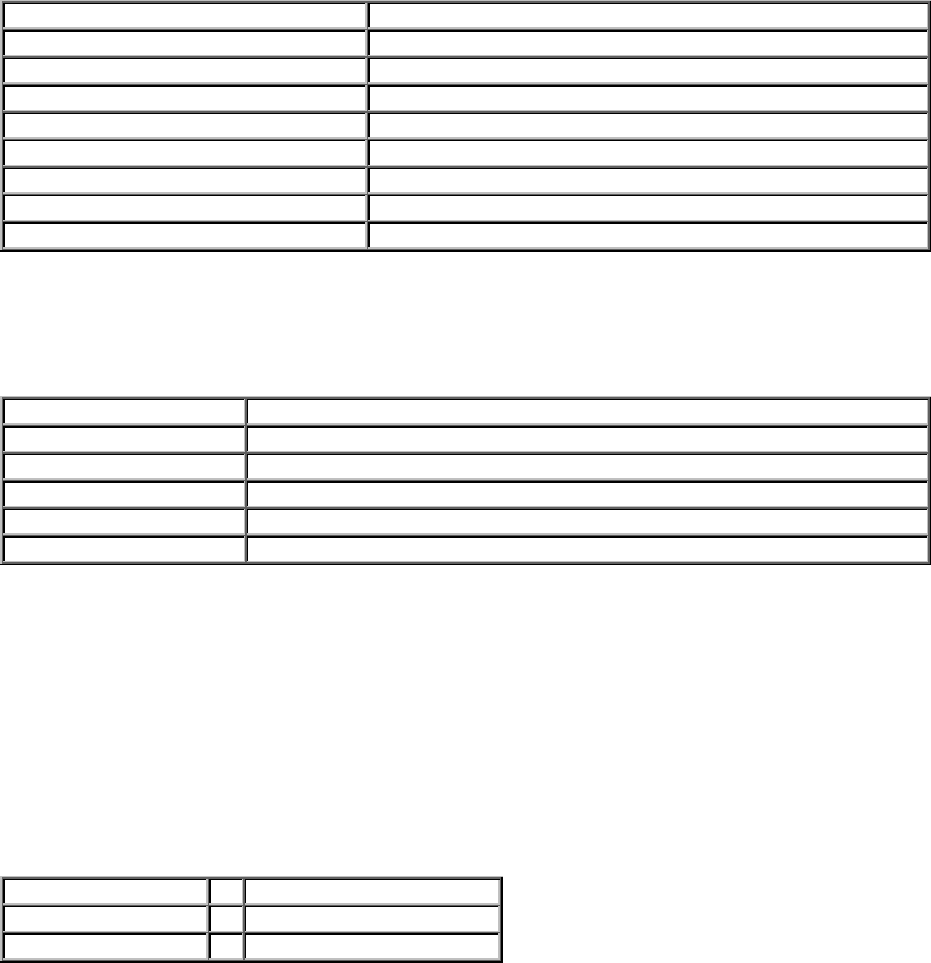

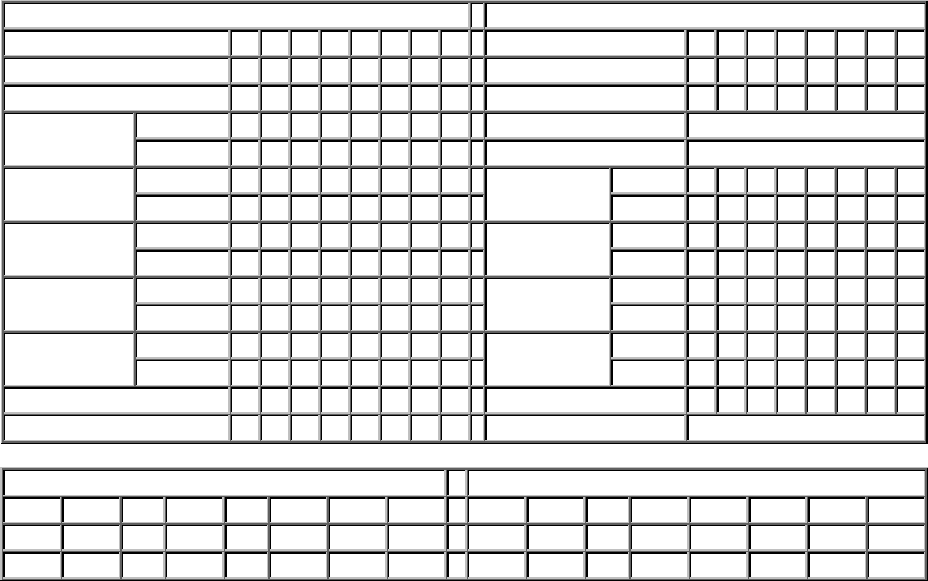

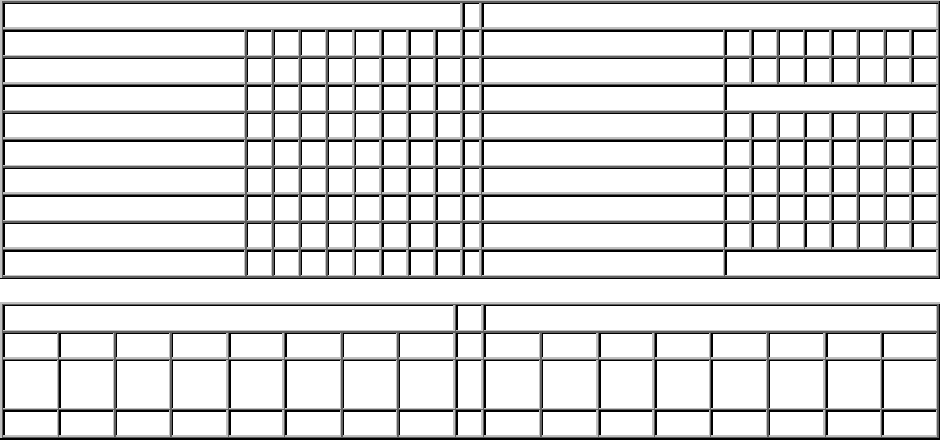

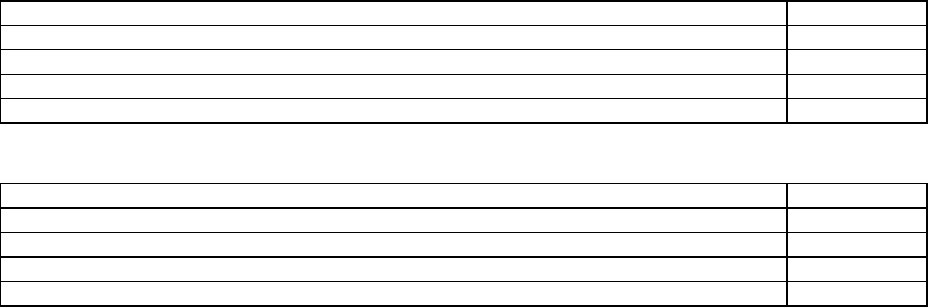

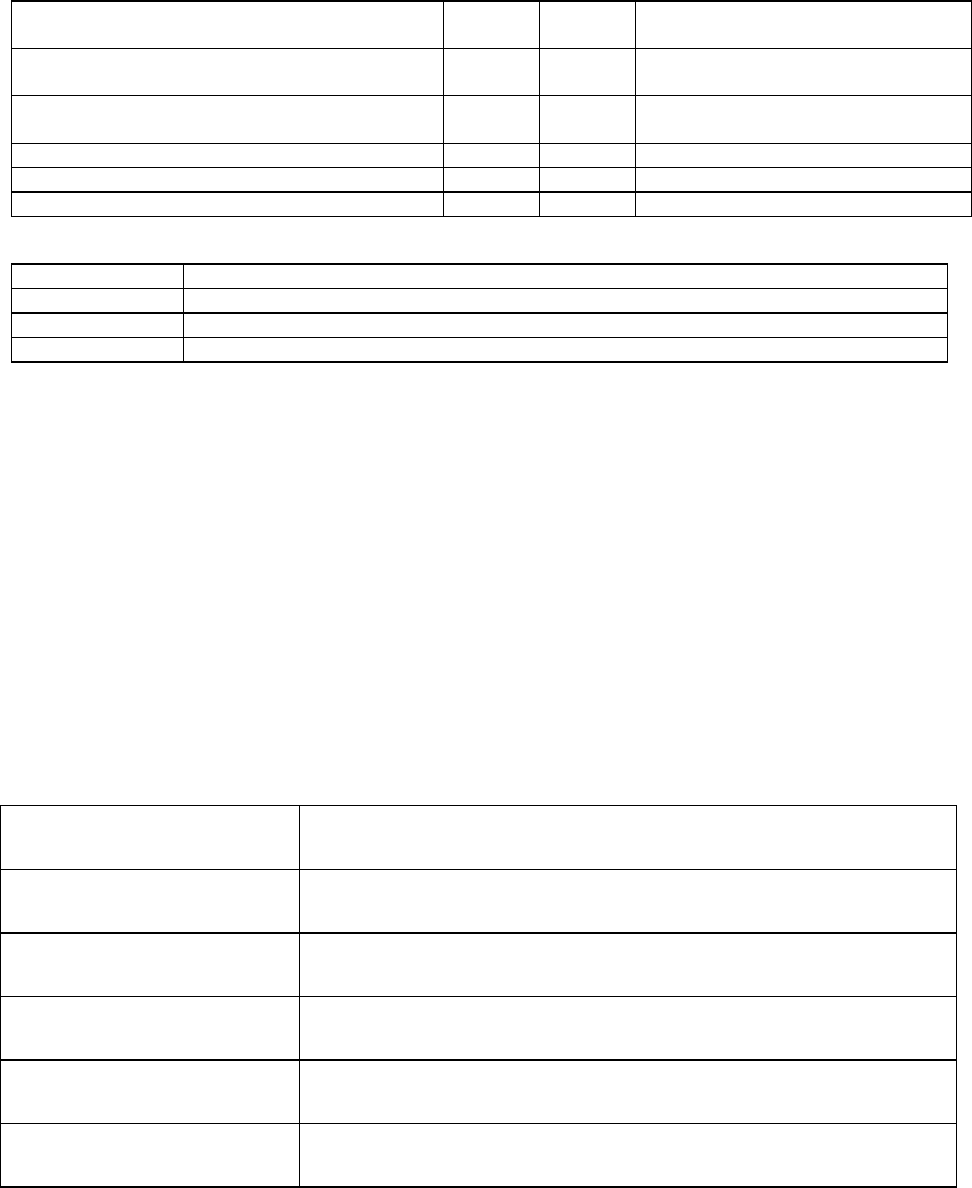

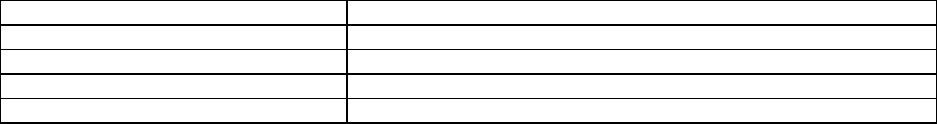

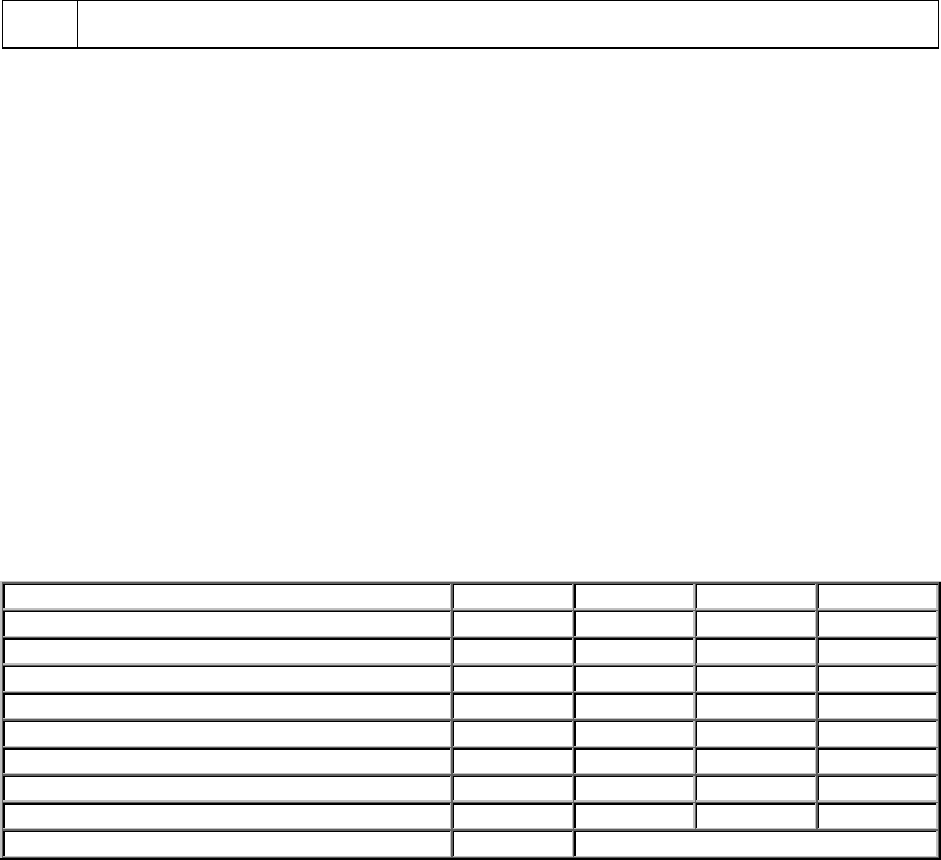

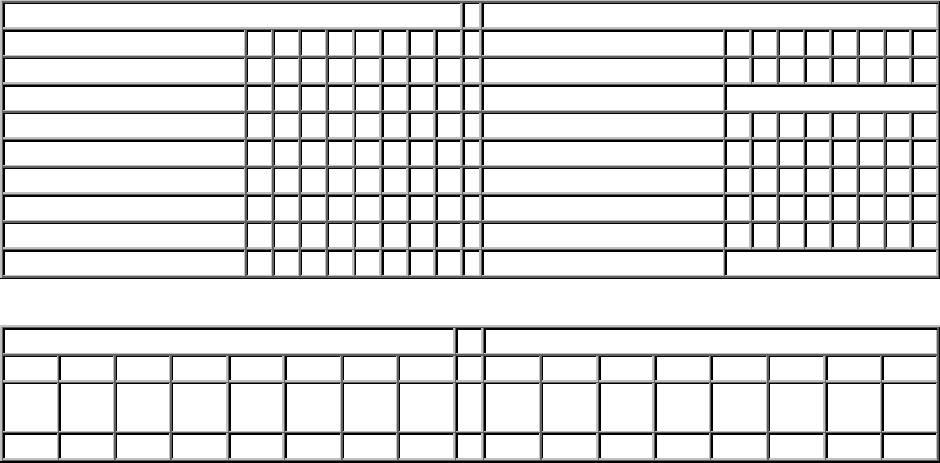

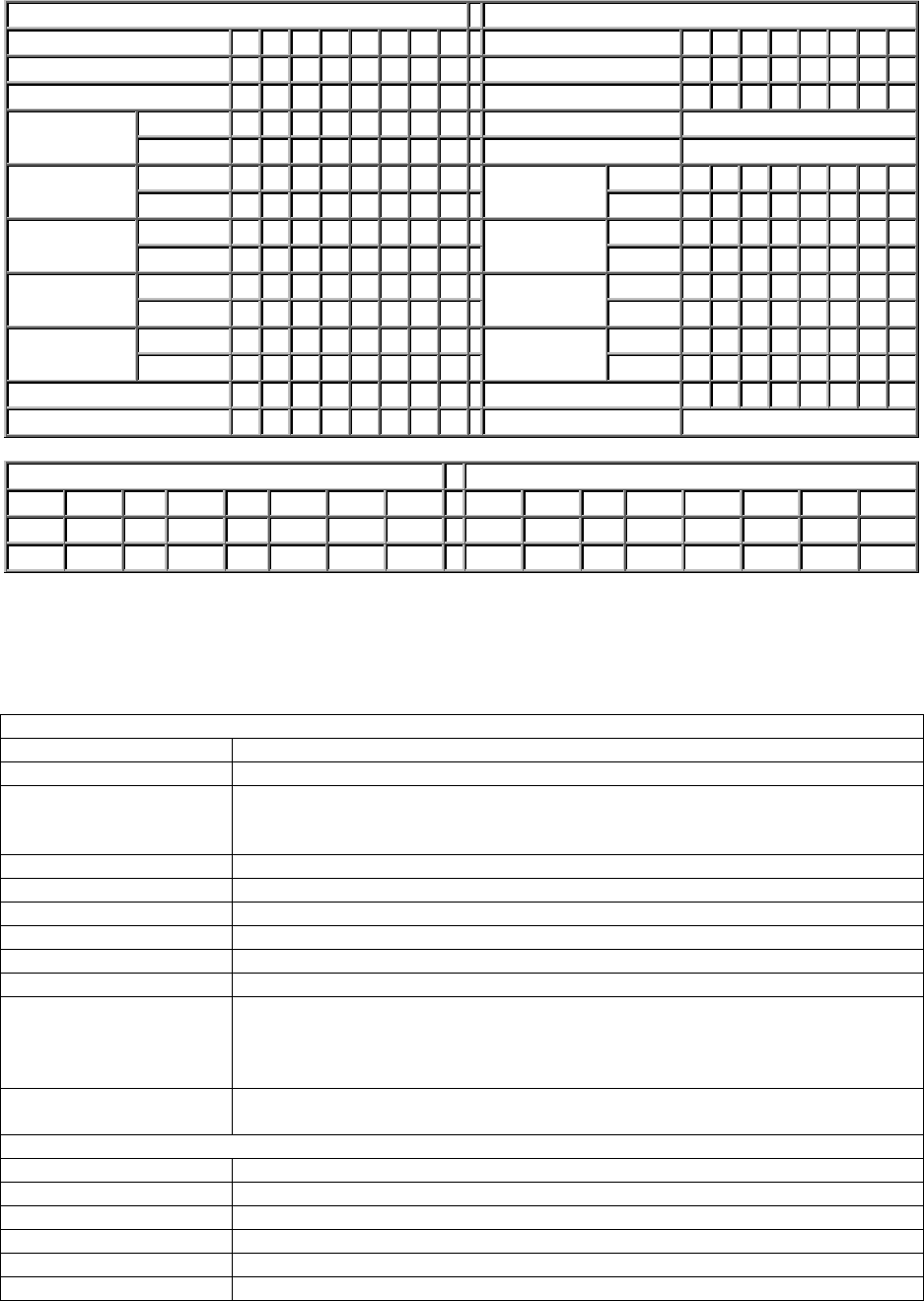

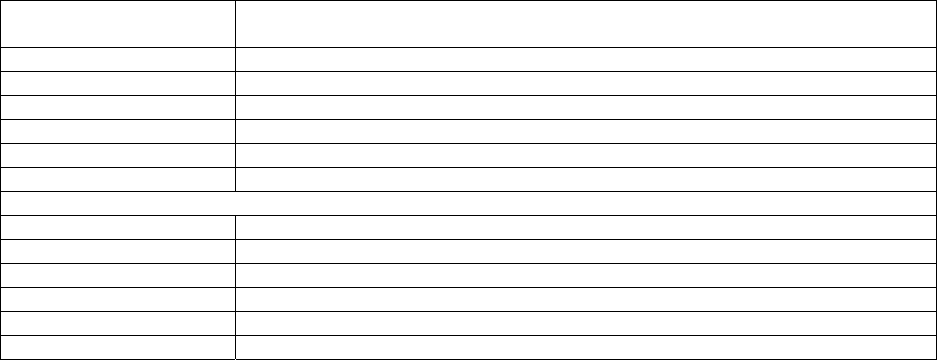

4.1 Formatted capacity by model number

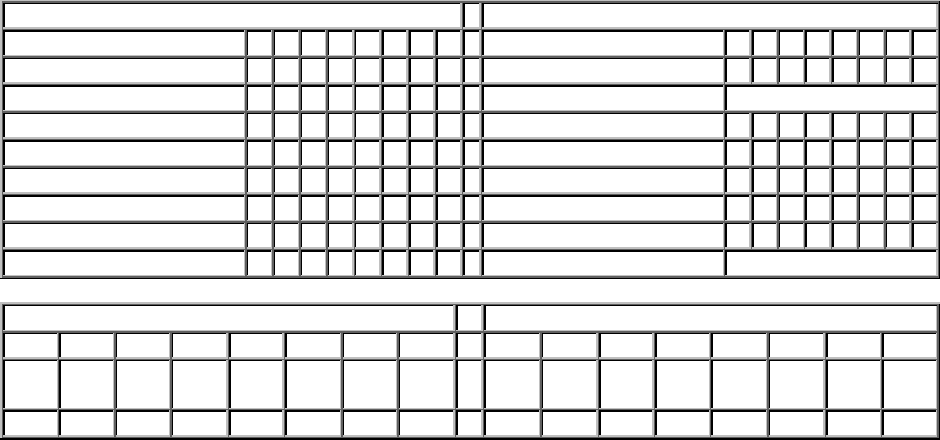

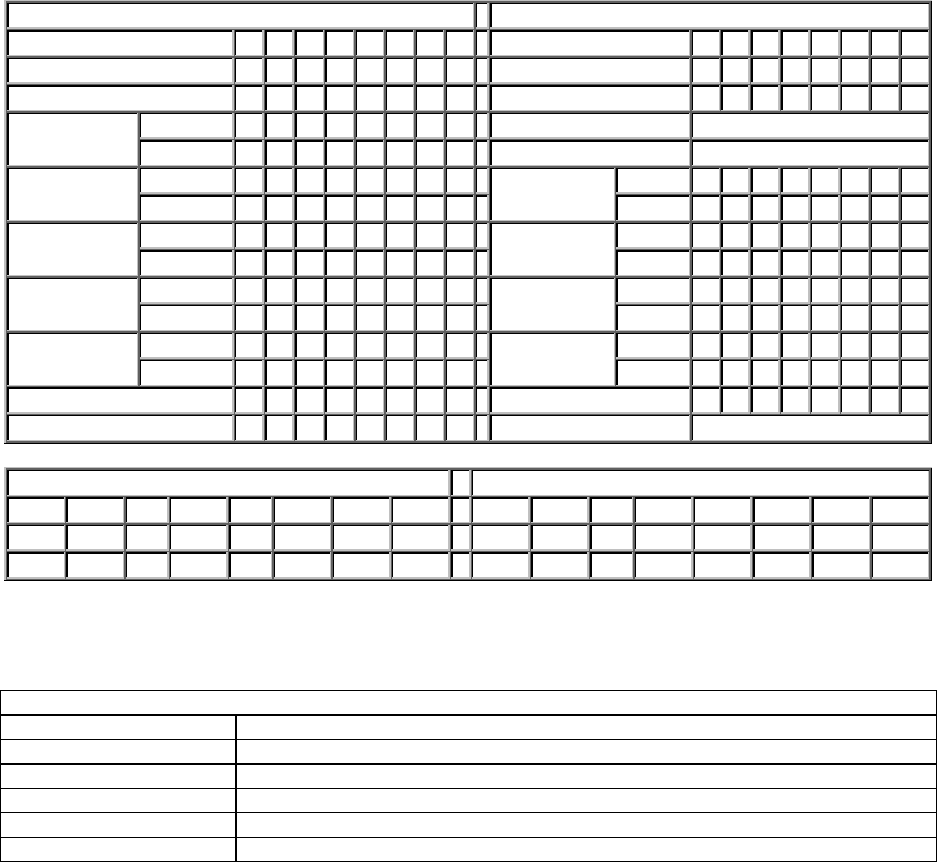

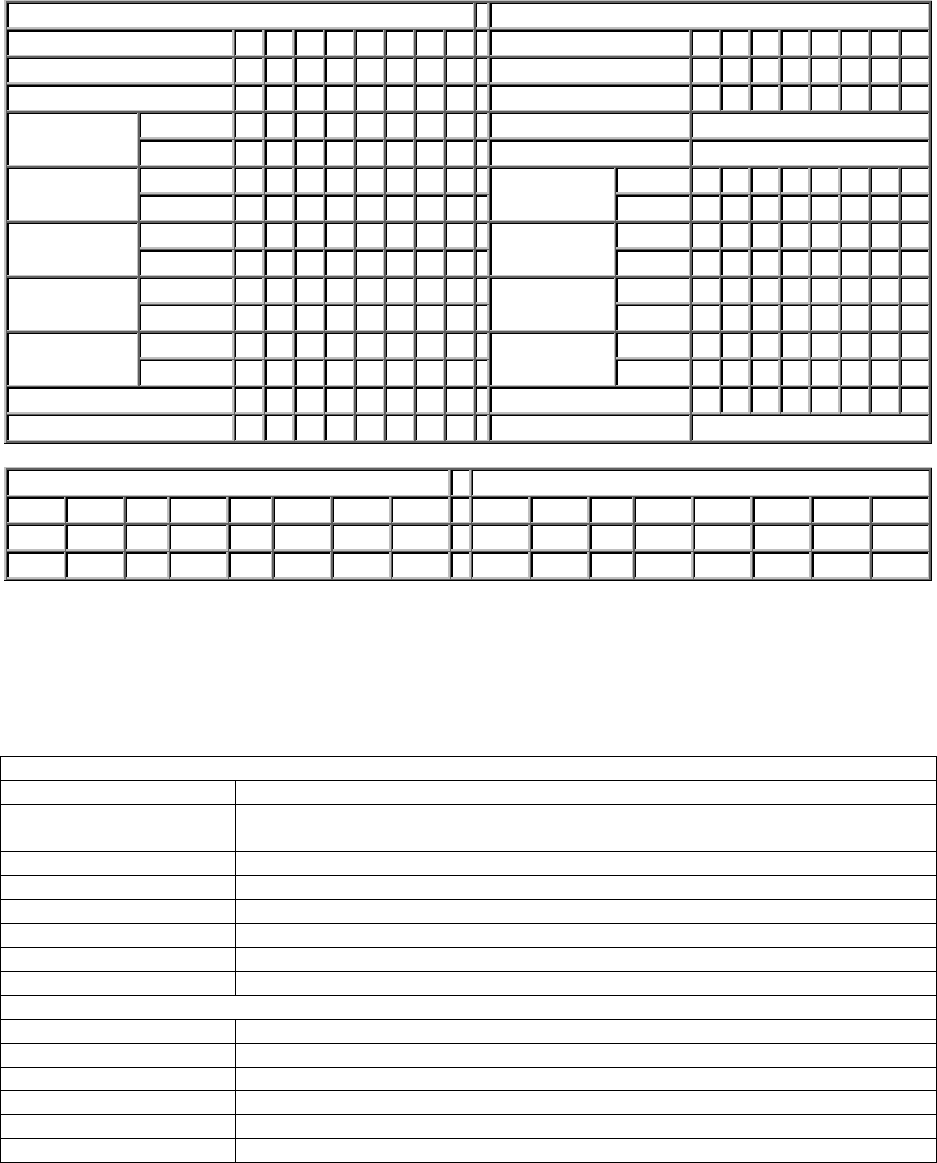

Description HTS722020K9A300

HTS722020K9SA00 HTS722016K9A300

HTS722016K9SA00 HTS722012K9A300

HTS722012K9SA00

Physical Layout

Bytes per Sector 512 512 512

Sectors per Track 1209 (max) 1092 (max) 1092 (max)

Number of Heads 4 4 3

Number of Disks 2 2 2

Logical Layout

Number of Heads 16 16 16

Number of Sectors/

Track 63 63 63

Number of Cylinders 16,383 16,383 16,383

Number of Sectors 390,721,968 312,581,808 234,441,648

Total Logical Data

Bytes 200,049,647,616 160,041,885,696 120,034,123,776

Description HTS722010K9A300

HTS722010K9SA00 HTS722080K9A300

HTS722080K9SA00

Physical Layout

Bytes per Sector 512 512

Sectors per Track 1209 (max) 1092 (max)

Number of Heads 2 2

Number of Disks 1 1

Logical Layout

Number of Heads 16 16

Number of Sectors/

Track 63 63

Number of Cylinders 16,383 16,383

Number of Sectors 195,371,568 156,301,488

Total Logical Data

Bytes 100,030,242,816 80,026,361,856

Table 1. Formatted capacity by model number.

7K200 SATA OEM Specification

18/173

4.2 Data sheet

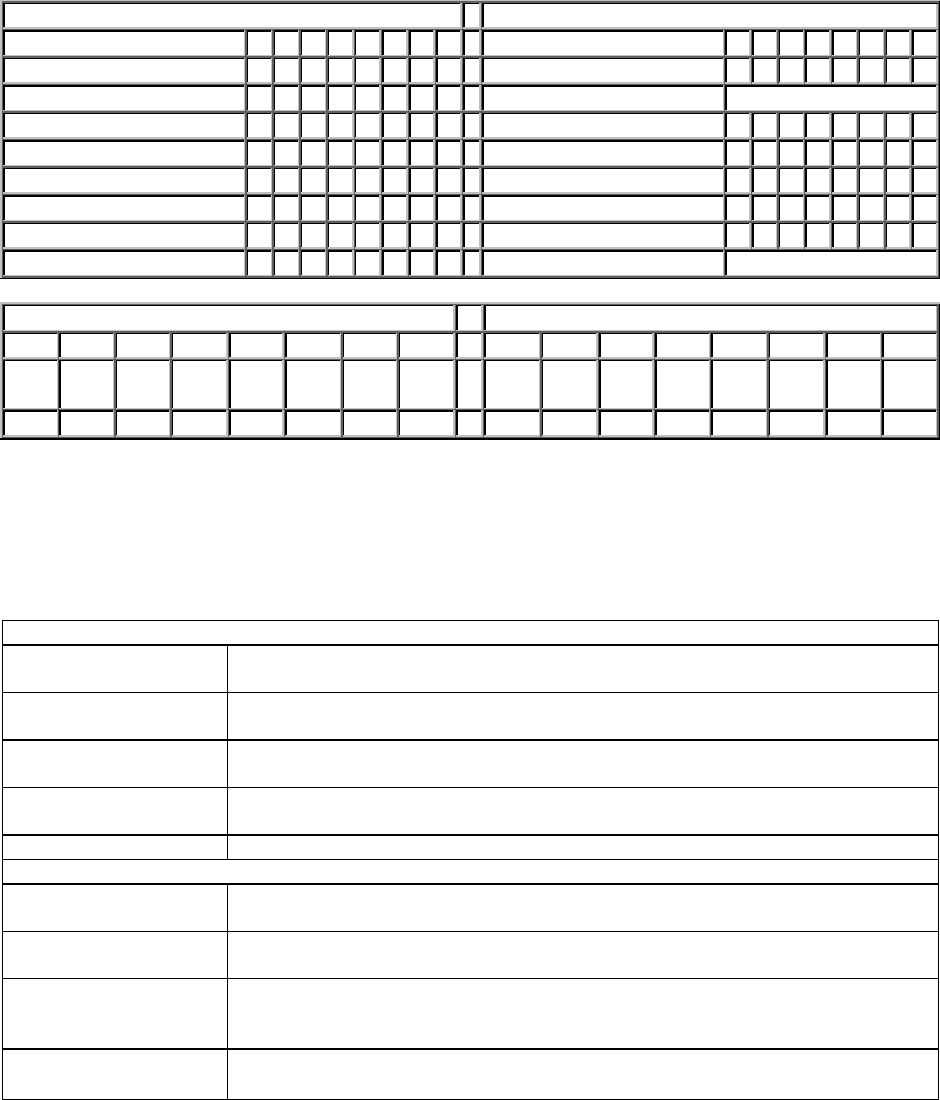

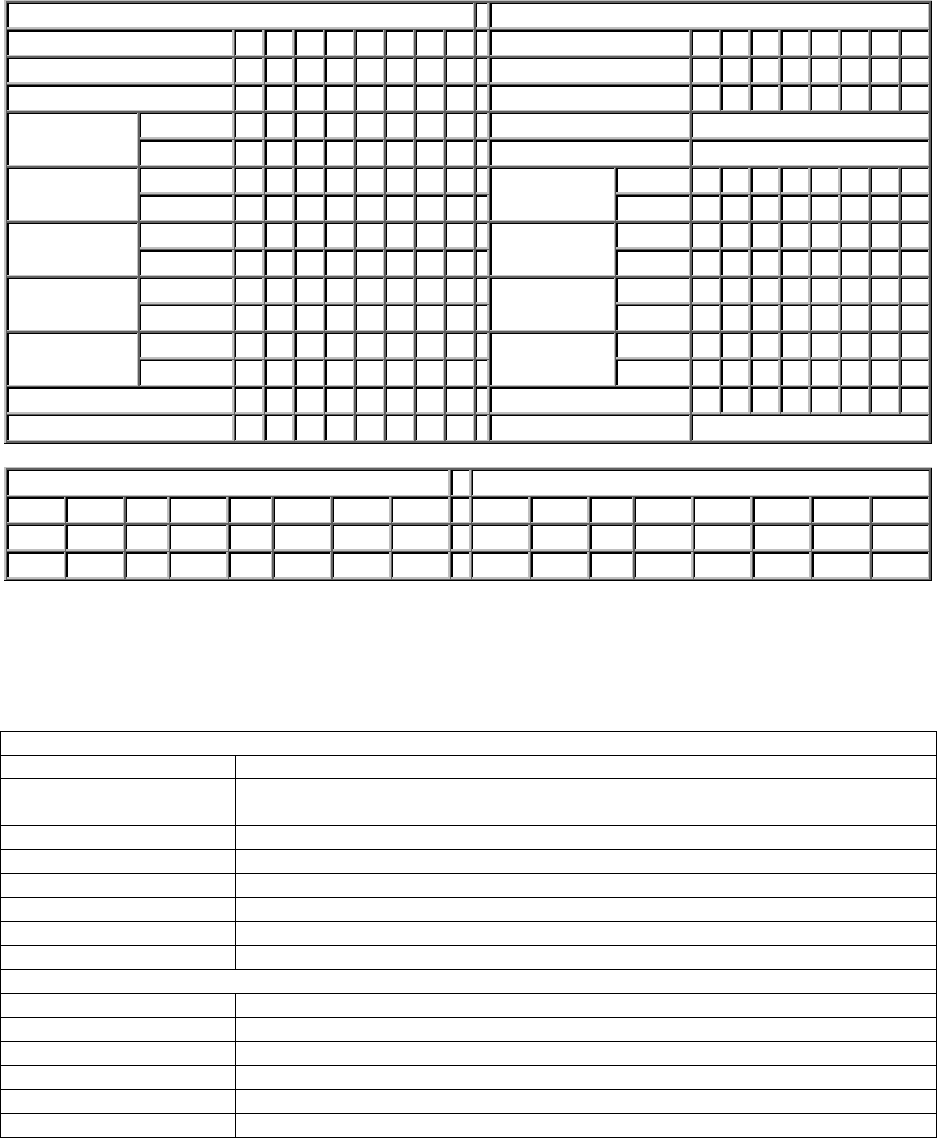

200GB 160GB 120GB 100GB 80GB

Rotational Speed (RPM) 7200 7200 7200 7200 7200

Data transfer rates (buffer to/from

media) (Mbps) 876 695 695 876 695

Data transfer rates (Gbit/sec) 1.5/3.0 1.5/3.0 1.5/3.0 1.5/3.0 1.5/3.0

Recording density (Kbit/mm) (Max)

(KBPI) (Max)

994

903

903

994

903

Track density (Ktrack/mm)(Max)

(KTPI)(Max)

164

146

146

164

146

Areal density (Gbit/sq-mm.- Max)

(Gbit/sq-inch - Max)

164

132

132

164

132

Number of zones 24 24 24 24 24

Table 2. Data sheet

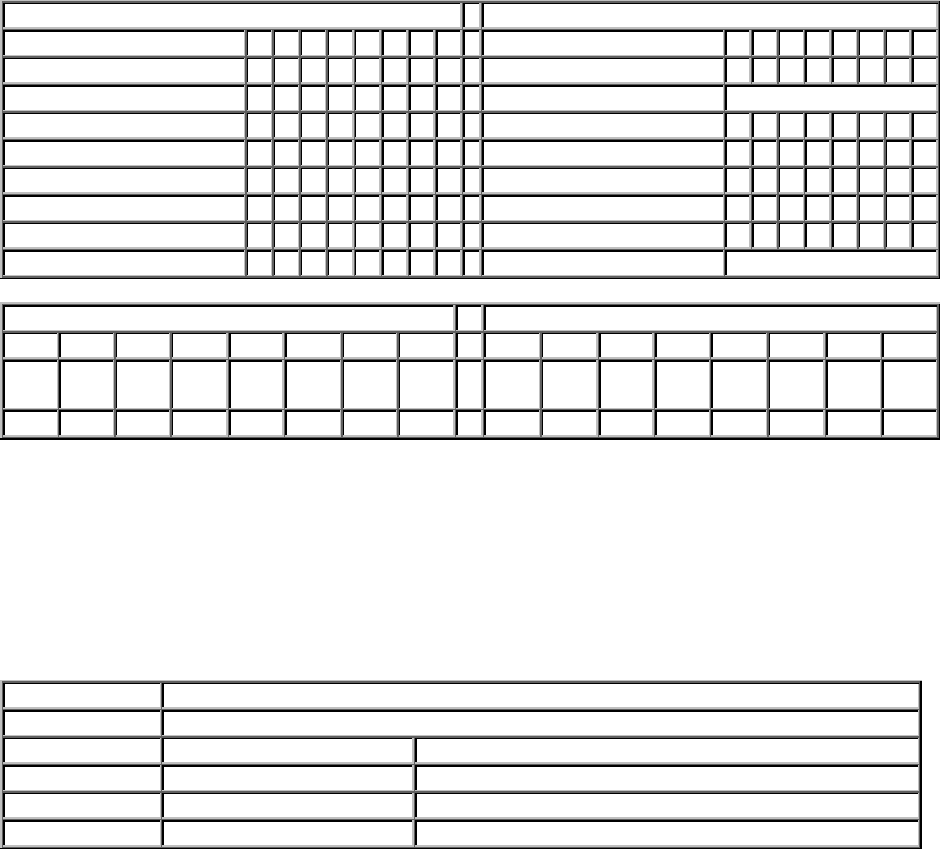

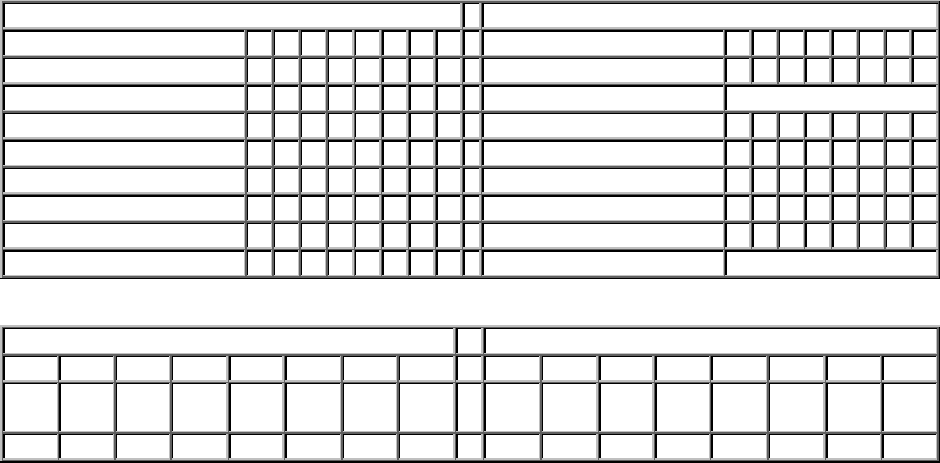

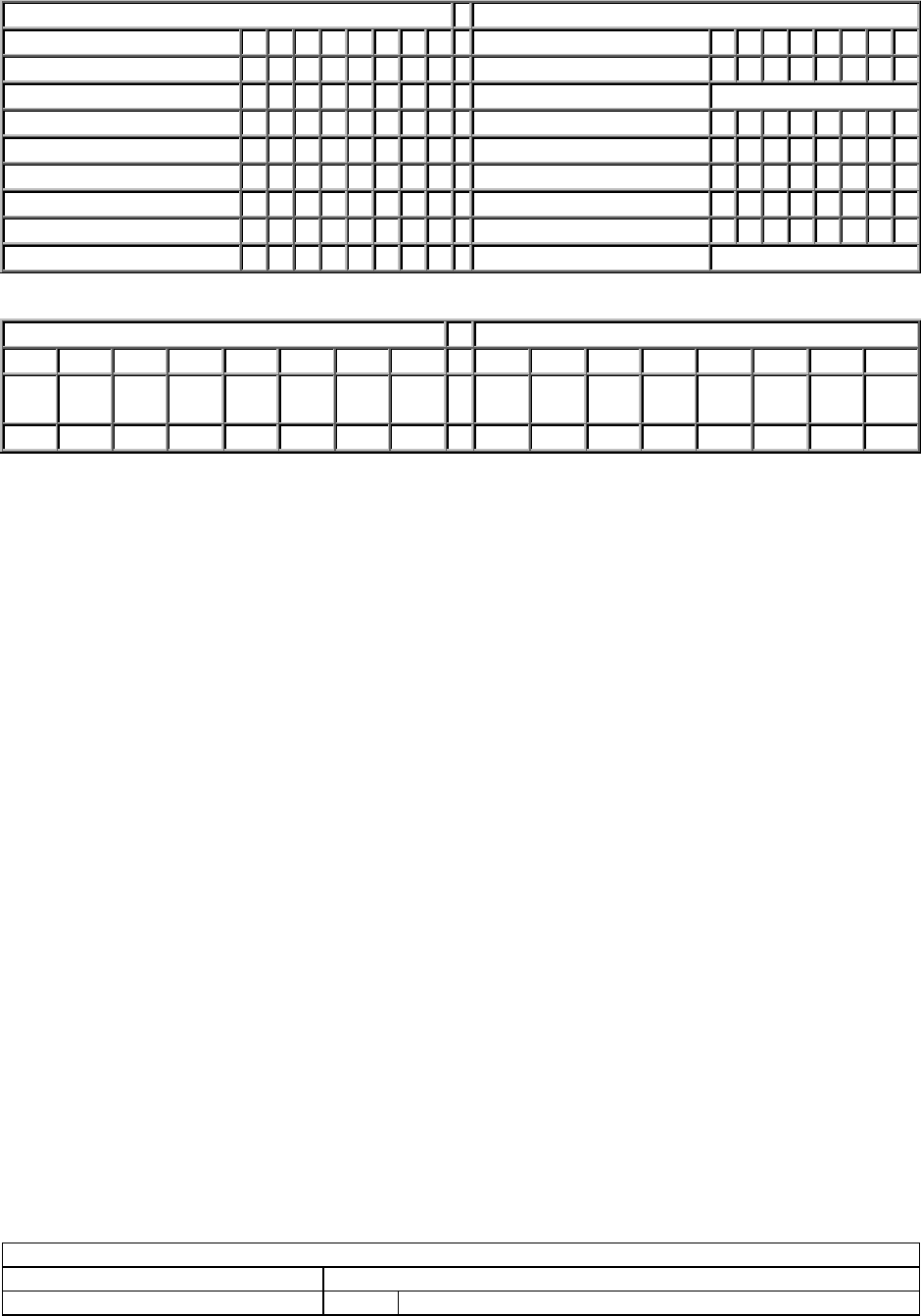

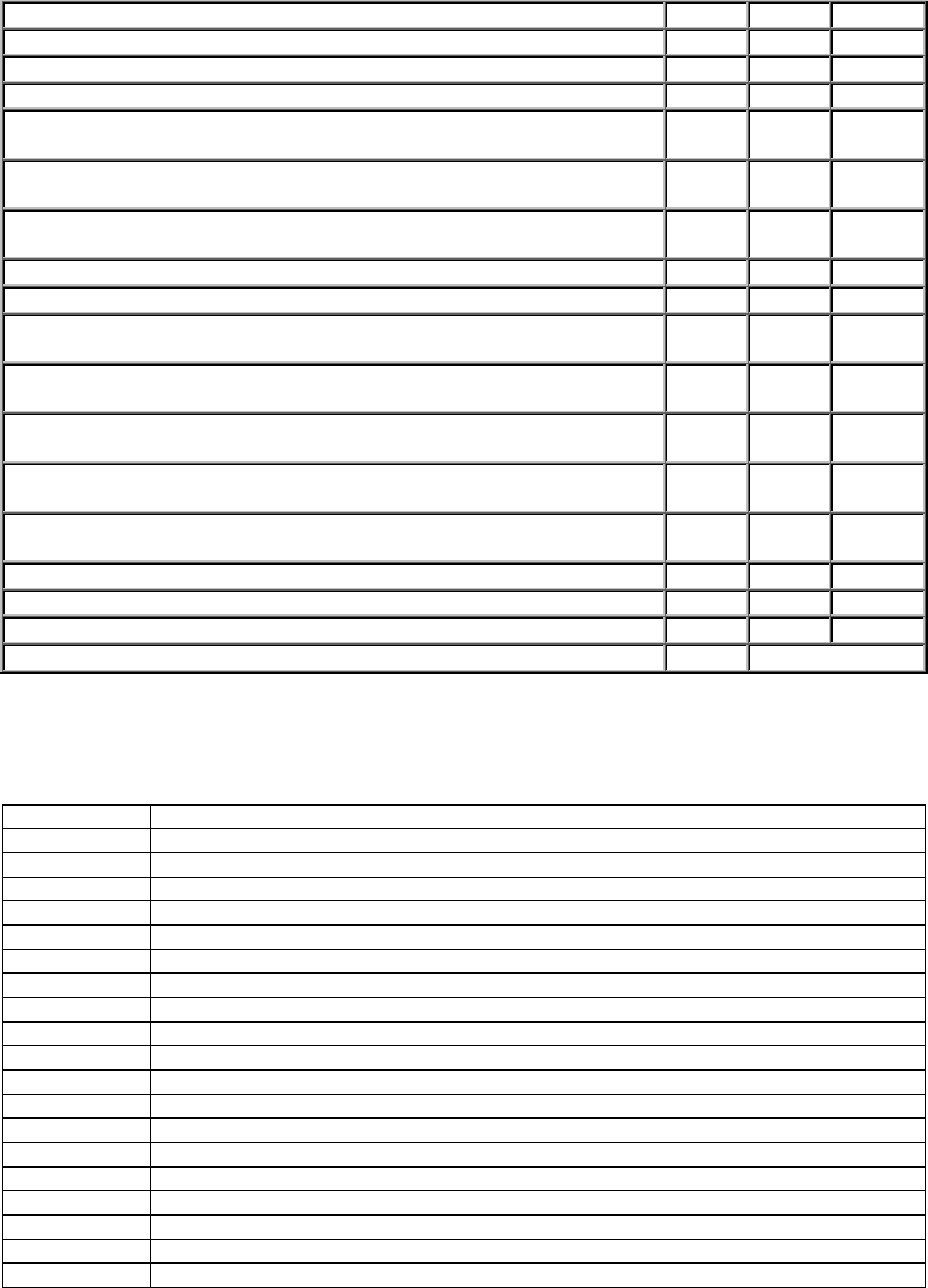

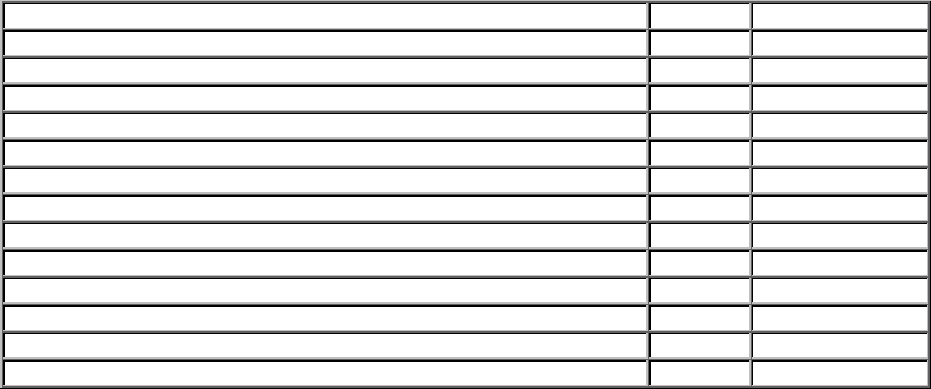

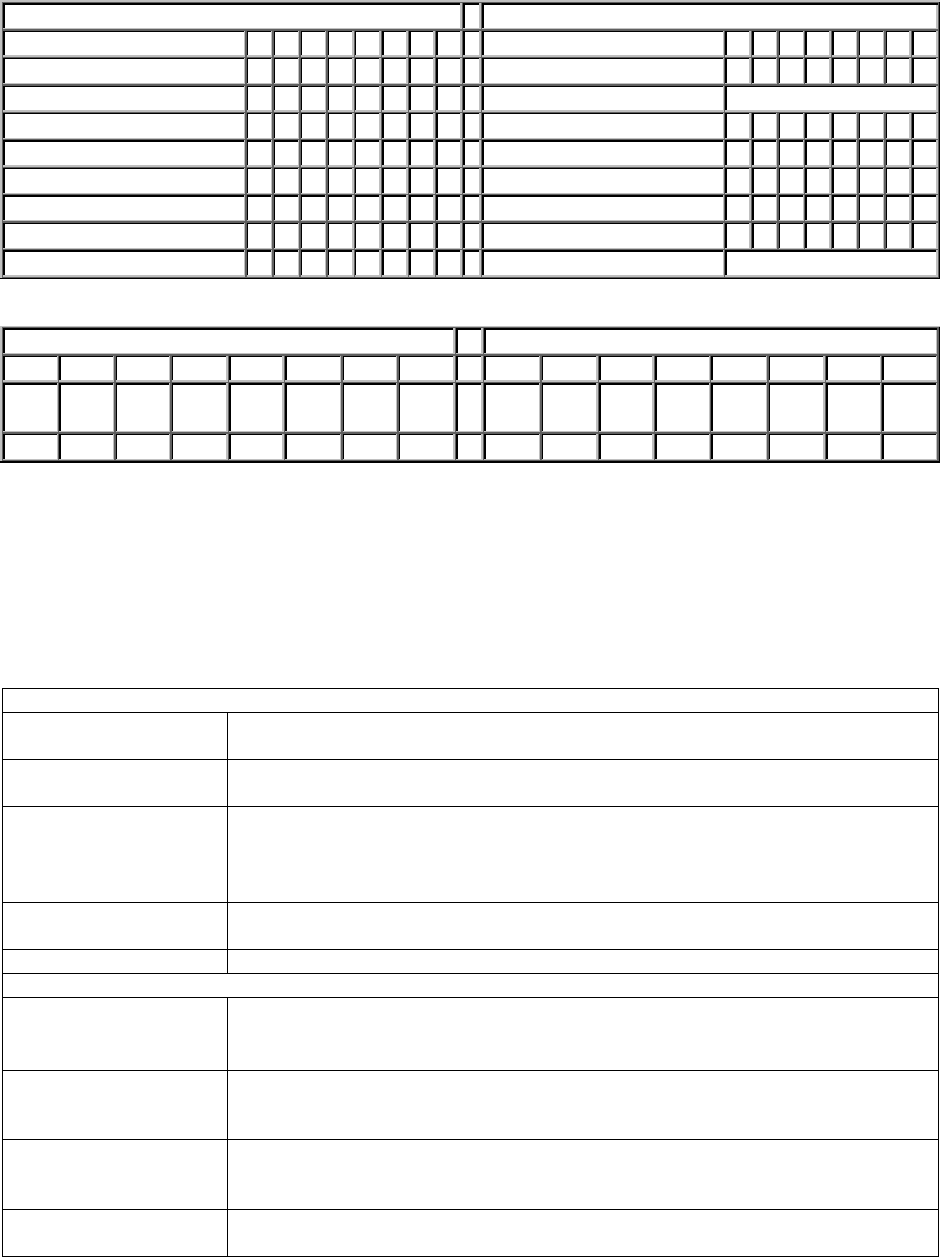

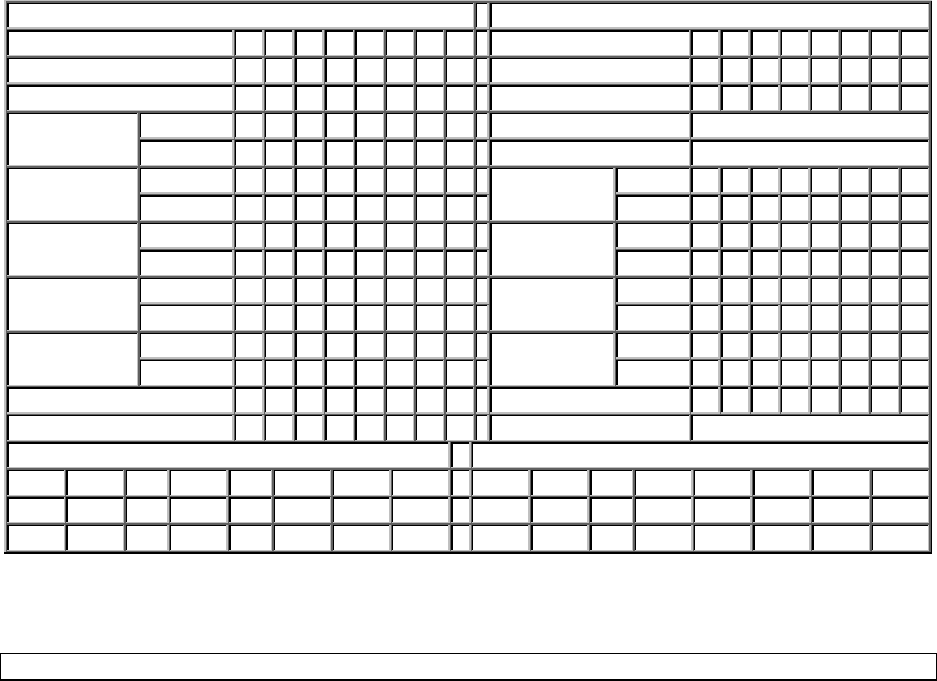

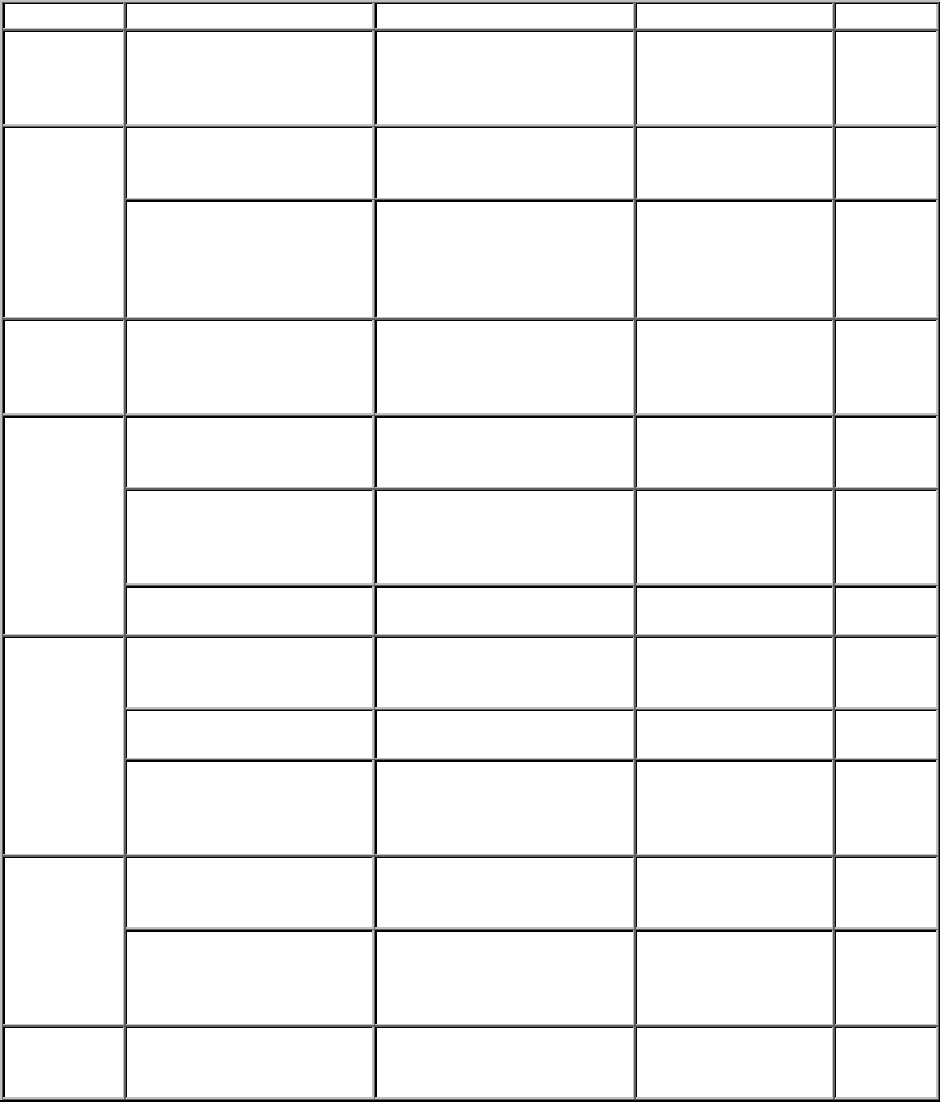

4.3 Cylinder allocation

Data format is allocated by each head characteristics. Typical format is described below.

80GB/p Mid BIP-Mid TPI format

Zone Cylinder No. of

Sectors/Trk

0 0 - 5279 1209

1 5280 - 10559 1209

2 10560 - 13759 1196

3 13760 - 18559 1170

4 18560 - 23359 1144

5 23360 - 26559 1131

6 26560 - 28959 1118

7 28960 - 34239 1092

8 34240 - 39039 1053

9 39040 - 43839 1040

10 43840 - 48639 1014

11 48640 - 53439 975

12 53440 - 55839 962

13 55840 - 61279 939

14 61280 - 65279 910

15 65280 - 69119 884

16 69120 - 72479 858

17 72480 - 78559 819

18 78560 - 80159 806

19 80160 - 85279 780

20 85280 - 88959 741

21 88960 - 92959 702

22 92960 - 96799 663

23 96800 - 102399 624

Table 3. Cylinder allocation

7K200 SATA OEM Specification

19/173

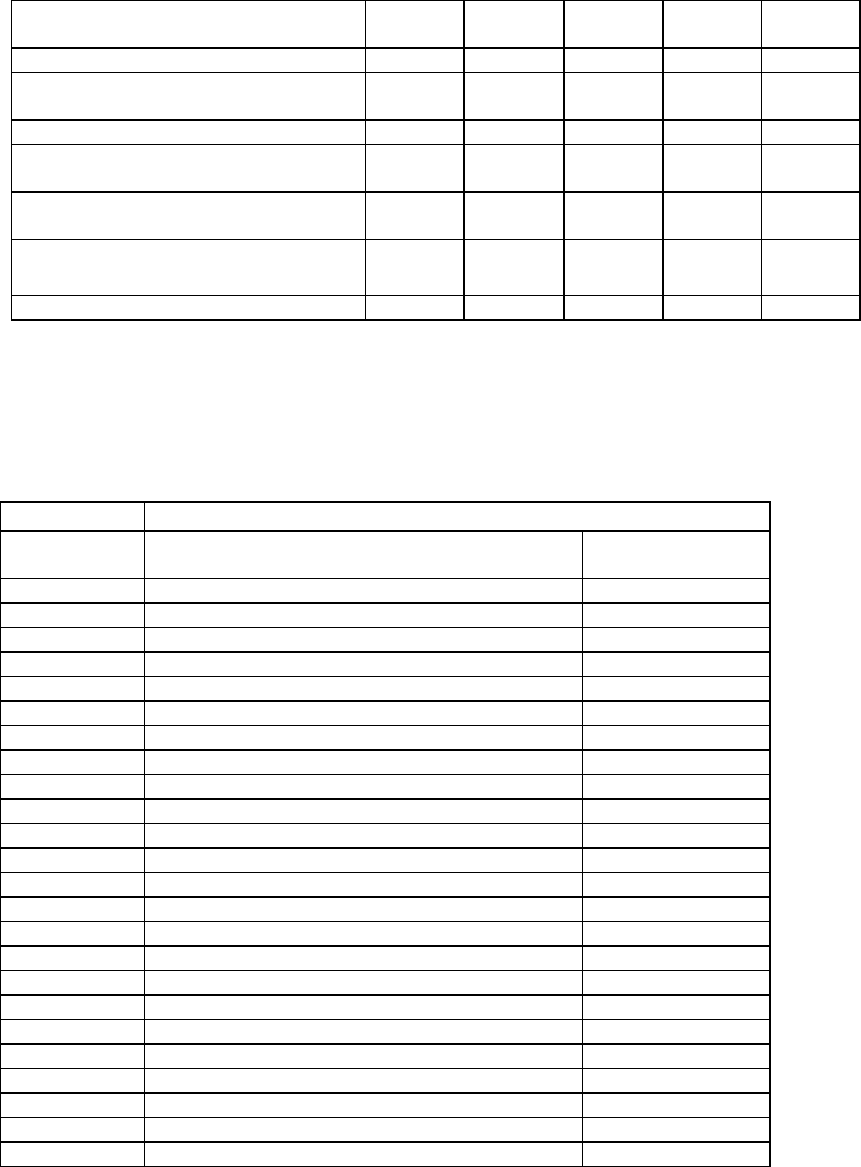

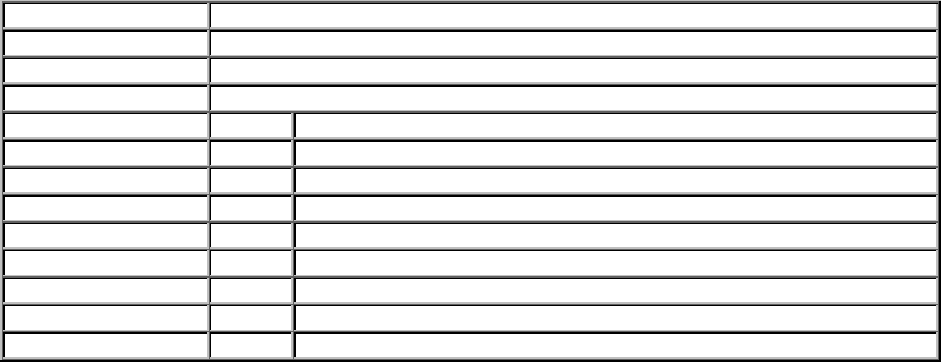

4.4 Performance characteristics

Drive performance is characterized by the following parameters:

Command Overhead

Mechanical Positioning

Seek Time

Latency

Data Transfer Speed

Buffering Operation (Look ahead/Write Cache)

Note: All the above parameters contribute to drive performance. There are other parameters which

contribute to the performance of the actual system. This specification defines the essential characteristics

of the drive. This specification does not include the system throughput as this is dependent upon the

system and the application.

The following table gives a typical value for each parameter. The detailed descriptions are found in

section 5.0.

Function

Average Random Seek Time - Read (ms) 10

Average Random Seek Time - Write (ms) 11

Rotational Speed (RPM) 7200

Power-on-to-ready (sec)(Typical) 4.0

Command overhead (ms) 1.0

Disk-buffer data transfer (Mb/s) (max) 876

Buffer-host data transfer (Gbit/s) (max) 1.5/3.0

Table 4. Performance characteristics

4.4.1 Command overhead

Command overhead time is defined as the interval from the time that a drive receives a command to the

time that the actuator starts its motion.

7K200 SATA OEM Specification

20/173

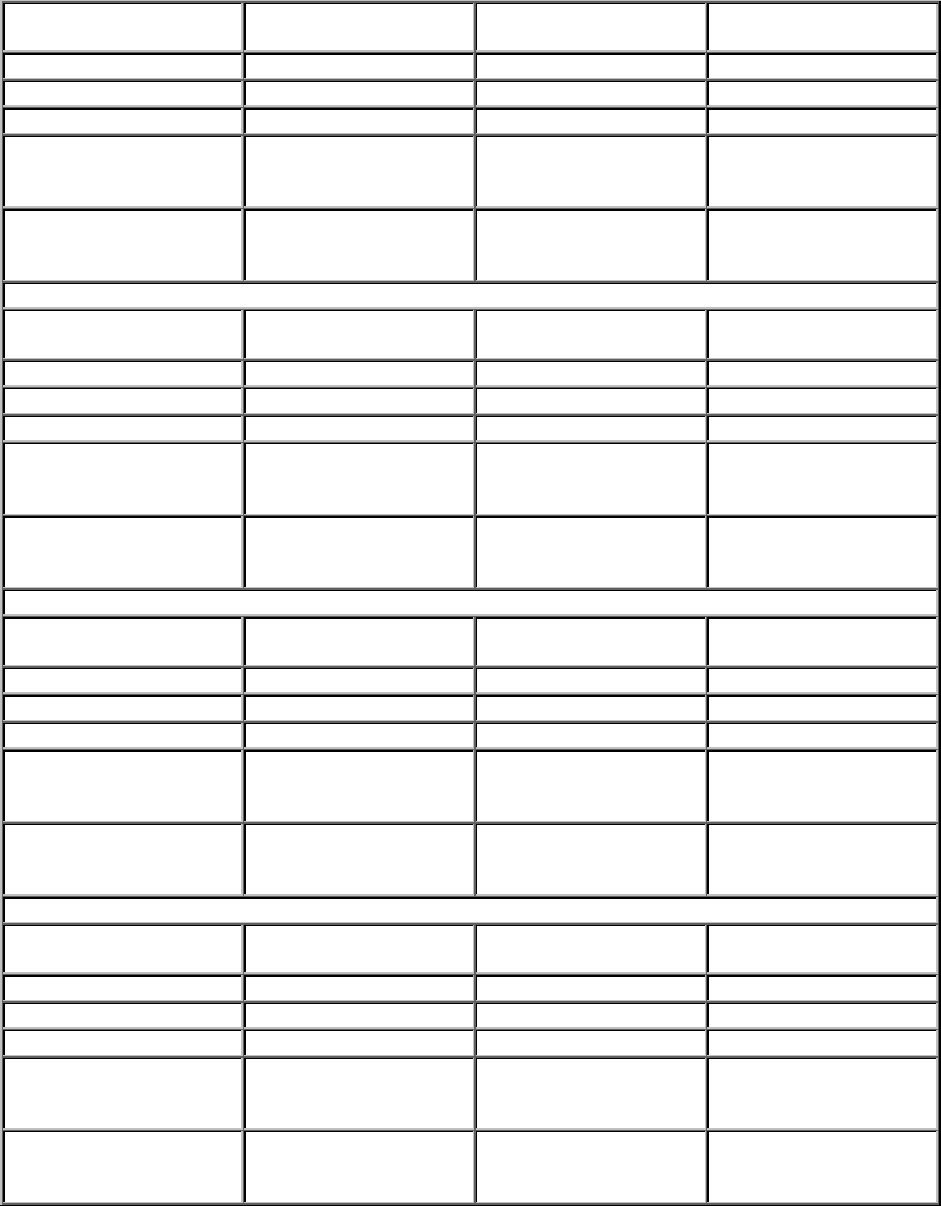

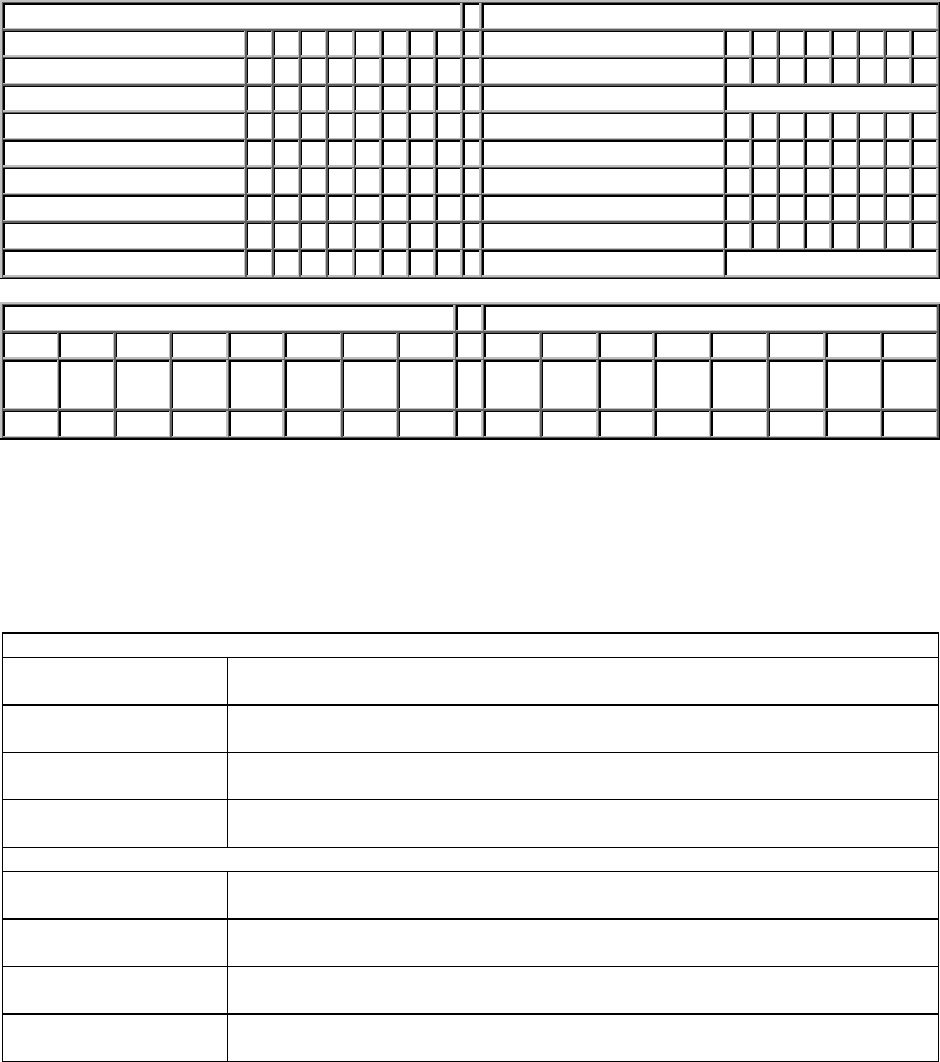

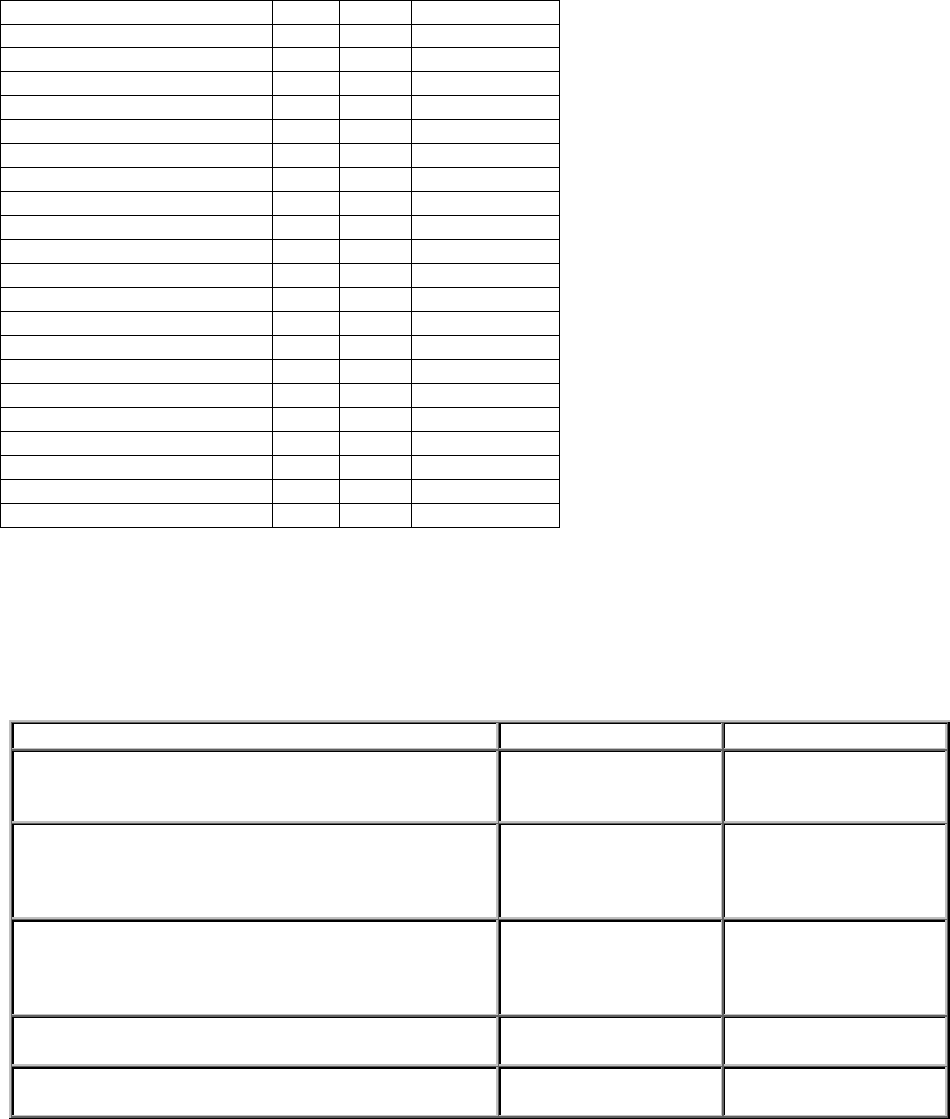

4.4.2 Mechanical positioning

4.4.2.1 Average seek time (including settling)

Command Type Typical (ms) Max. (ms)

Read 10 16

Write 11 17

Table 5. Mechanical positioning performance

Typical and Max. are defined throughout the performance specification as follows:

Typical Average of the drive population tested at nominal environmental and voltage conditions.

Max. Maximum value measured on any one drive over the full range of the environmental and

voltage conditions. (See section 6.1, "Environment" on page 26 and section 6.2, "DC power

requirements" on page 28)

The seek time is measured from the start of motion of the actuator to the start of a reliable read or write

operation. A reliable read or write operation implies that error correction/recovery is not employed to

correct arrival problems. The Average Seek Time is measured as the weighted average of all possible

seek combinations.

max.

Σ (max. + 1 – n)(Tnin + Tnout)

n=1

Weighted Average = ––––––––––––––––––––––––––––

(max. + 1)(max)

Where: max. = maximum seek length

n = seek length (1-to-max.)

Tn

in = inward measured seek time for an n-track seek

Tn

out = outward measured seek time for an n-track seek

4.4.2.2 Full stroke seek

Command Type Typical (ms) Max. (ms)

Read 18.0 30.0

Write 19.0 31.0

Table 6. Full stroke seek time

Full stroke seek time in milliseconds is the average time of 1000 full stroke seeks.

4.4.2.3 Single track seek time (without command overhead, including

settling)

Command Type Typical (ms) Maximum (ms)

Read 1.0 4.0

Write 1.2 4.5

Table 7. Single track seek time

Single track seek is measured as the average of one (1) single track seek from every track in both

directions (inward and outward).

4.4.2.4 Average latency

Rotational Speed

(RPM) Time for one revolution

(ms) Average Latency

(ms)

7200 8.3 4.2

Table 8. Latency time

7K200 SATA OEM Specification

21/173

4.4.2.5 Drive ready time

Condition Typical (sec) Max. (sec)

Power On To Ready 4.0 9.5

Table 9. Drive ready time

Ready The condition in which the drive is able to perform a media access command

(for example—read, write) immediately.

Power On To Ready This includes the time required for the internal self diagnostics.

7K200 SATA OEM Specification

22/173

4.4.3 Operating modes

Operating mode Description

Spin-Up Start up time period from spindle stop or power down.

Seek Seek operation mode

Write Write operation mode

Read Read operation mode

Performance idle The device is capable of responding immediately to idle media access requests. All

electronic components remain powered and the full frequency servo remains

operational.

Active idle

The device is capable of responding immediately to media access requests. Some

circuitry—including servo system and R/W electronics—is in power saving mode.

The head is parked near the mid-diameter the disk without servoing.

A device in Active idle mode may take longer to complete the execution of a

command because it must activate that circuitry.

Low power idle The head is unloaded onto the ramp position. The spindle motor is rotating at full

speed.

Standby The device interface is capable of accepting commands. The spindle motor is

stopped. All circuitry but the host interface is in power saving mode.

The execution of commands is delayed until the spindle becomes ready.

Sleep The device requires a soft reset or a hard reset to be activated. All electronics,

including spindle motor and host interface, are shut off.

Table 10. Operating mode

4.4.3.1 Mode transition time

From To Transition

Time (typ) Transition Time

(max.)

Standby Idle 3.0 9.5

Table 11. Drive ready time

4.4.3.2 Operating mode at power on

The device goes into Idle mode after power on as an initial state.

4.4.3.3 Adaptive power save control

The transient timing from Performance Idle mode to Active Idle mode and Active Idle mode to Low

Power Idle mode is controlled adaptively according to the access pattern of the host system. The

transient timing from Low Power Idle mode to Standby mode is also controlled adaptively, if it is

allowed by Set Features Enable Advanced Power Management subcommand.

7K200 SATA OEM Specification

23/173

5 Data integrity

5.1 Data loss on power off

Data loss will not be caused by a power off during any operation except the write operation.

A power off during a write operation causes the loss of any received or resident data that has not

been written onto the disk media.

A power off during a write operation might make a maximum of one sector of data unreadable. This

state can be recovered by a rewrite operation.

5.2 Write Cache

When the write cache is enabled, the write command may complete before the actual disk write operation

finishes. This means that a power off, even after the write command completion, could cause the loss of

data that the drive has received but not yet written onto the disk.

In order to prevent this data loss, confirm the completion of the actual write operation prior to the power

off by issuing a

Soft reset

COMRESET

Flush Cache command

Standby command

Standby Immediate command

Sleep command

Confirm the command’s completion.

5.3 Equipment status

The equipment status is available to the host system any time the drive is not ready to read, write, or seek.

This status normally exists at the power-on time and will be maintained until the following conditions are

satisfied:

The access recalibration/tuning is complete.

The spindle speed meets the requirements for reliable operation.

The self-check of the drive is complete.

The appropriate error status is made available to the host system if any of the following conditions occur

after the drive has become ready:

The spindle speed lies outside the requirements for reliable operation.

The occurrence of a Write Fault condition.

5.4 WRITE safety

The drive ensures that the data is written into the disk media properly. The following conditions are

monitored during a write operation. When one of these conditions exceeds the criteria, the write operation

is terminated and the automatic retry sequence is invoked.

Head off track

External shock

Low supply voltage

Spindle speed out of tolerance

Head open/short

7K200 SATA OEM Specification

24/173

5.5 Data buffer test

The data buffer is tested at power on reset and when a drive self-test is requested by the host. The test

consists of a write/read '00'x and 'ff'x pattern on all buffers.

5.6 Error recovery

Errors occurring on the drive are handled by the error recovery procedure.

Errors that are uncorrectable after application of the error recovery procedure are reported to the host

system as nonrecoverable errors.

5.7 Automatic reallocation

The sectors that show some errors may be reallocated automatically when specific conditions are met.

The drive does not report any auto reallocation to the host system. The conditions for auto reallocation

are described below.

5.7.1 Nonrecovered write errors

When a write operation cannot be completed after the Error Recovery Procedure (ERP) is fully carried out,

the sectors are reallocated to the spare location. An error is reported to the host system only when the

write cache is disabled and the auto reallocation has failed.

5.7.2 Nonrecoverable read error

When a read operation fails after ERP is fully carried out, a hard error is reported to the host system. This

location is registered internally as a candidate for the reallocation. When a registered location is specified

as a target of a write operation, a sequence of media verification is performed automatically. When the

result of this verification meets the required criteria, this sector is reallocated.

5.7.3 Recovered read errors

When a read operation for a sector fails and is recovered at the specific ERP step, the sector is

reallocated automatically. A media verification sequence may be run prior to the reallocation according to

the predefined conditions.

7K200 SATA OEM Specification

25/173

5.8 ECC

The 10 bit 40 symbol non interleaved ECC processor provides user data verification and correction

capability. The first 6 symbol of ECC are 4 check symbols for user data and the 2 symbol system ECC.

The other 34 symbols are Read Solomon ECC. Hardware logic corrects up to 16 symbols(20 bytes)

errors on-the-fly.

2 symbol System ECC is generated when HDC receives user data from HOST, and can correct up to 1

symbol(10bit) errors on-the-fly when one transfers to HOST.

7K200 SATA OEM Specification

26/173

6 Specification

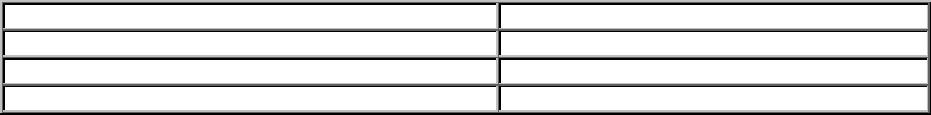

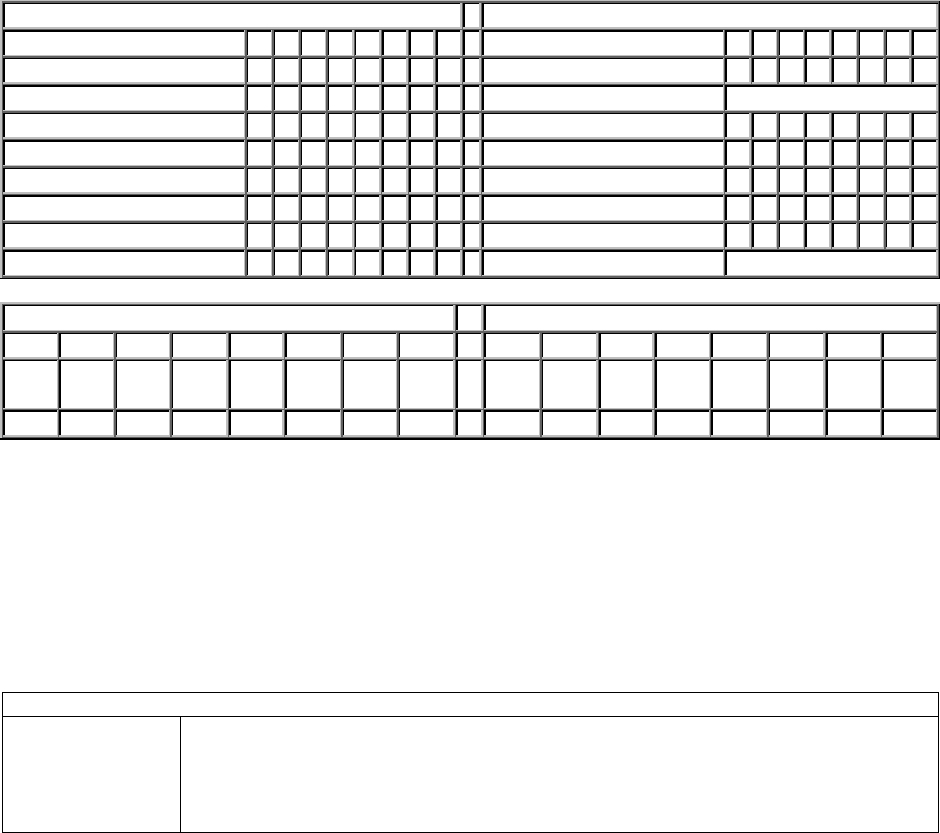

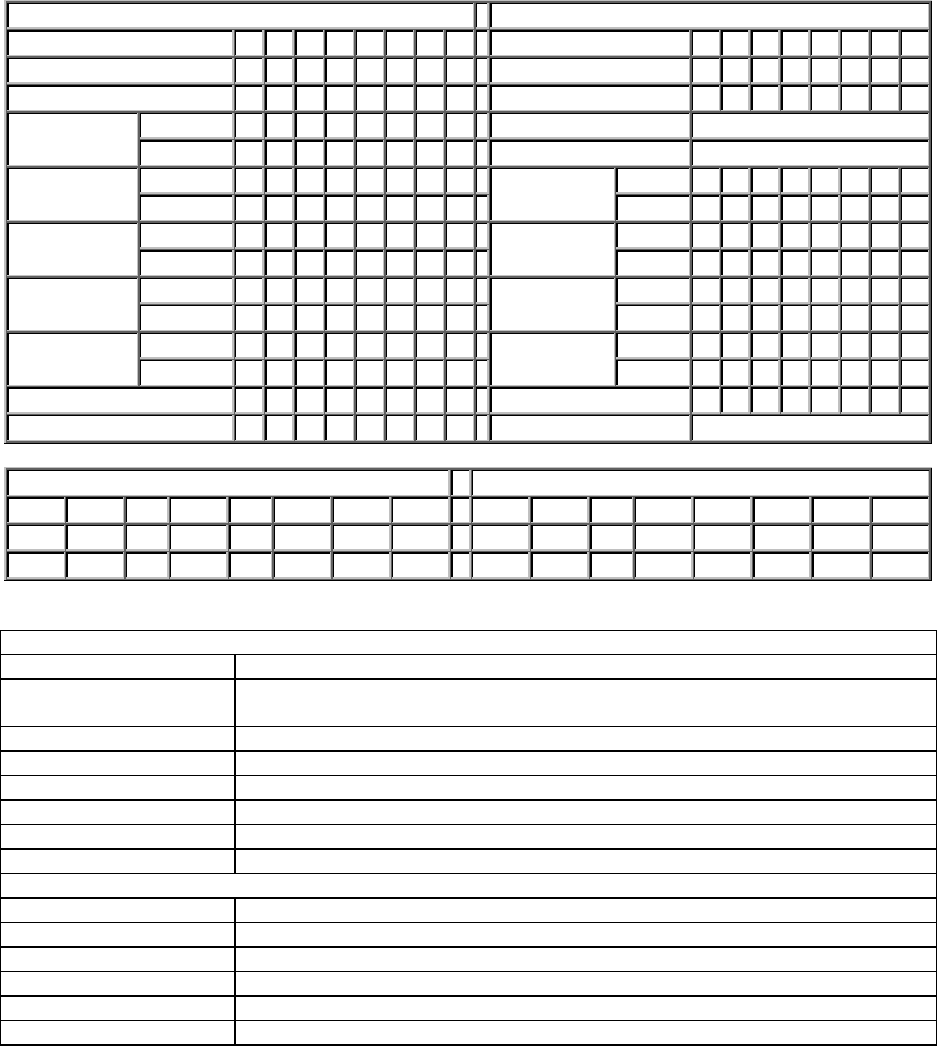

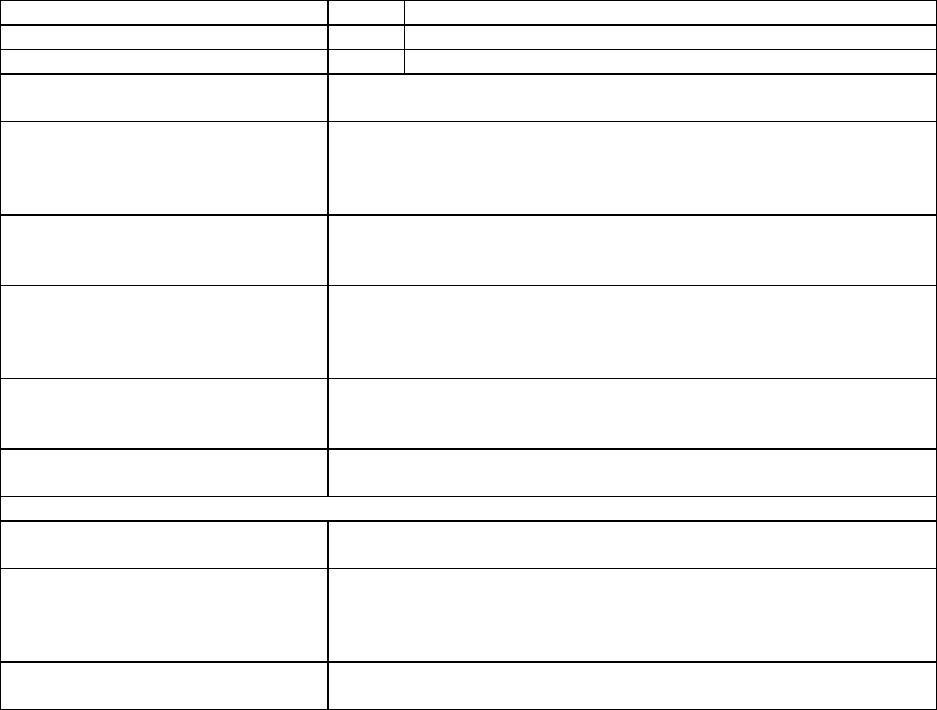

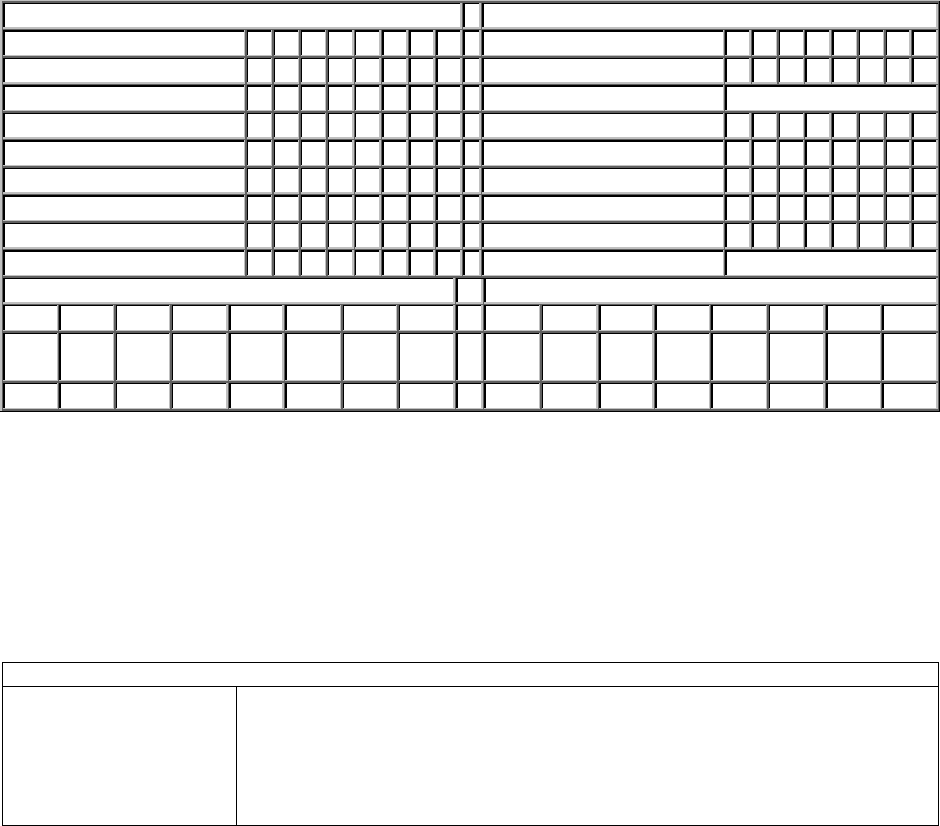

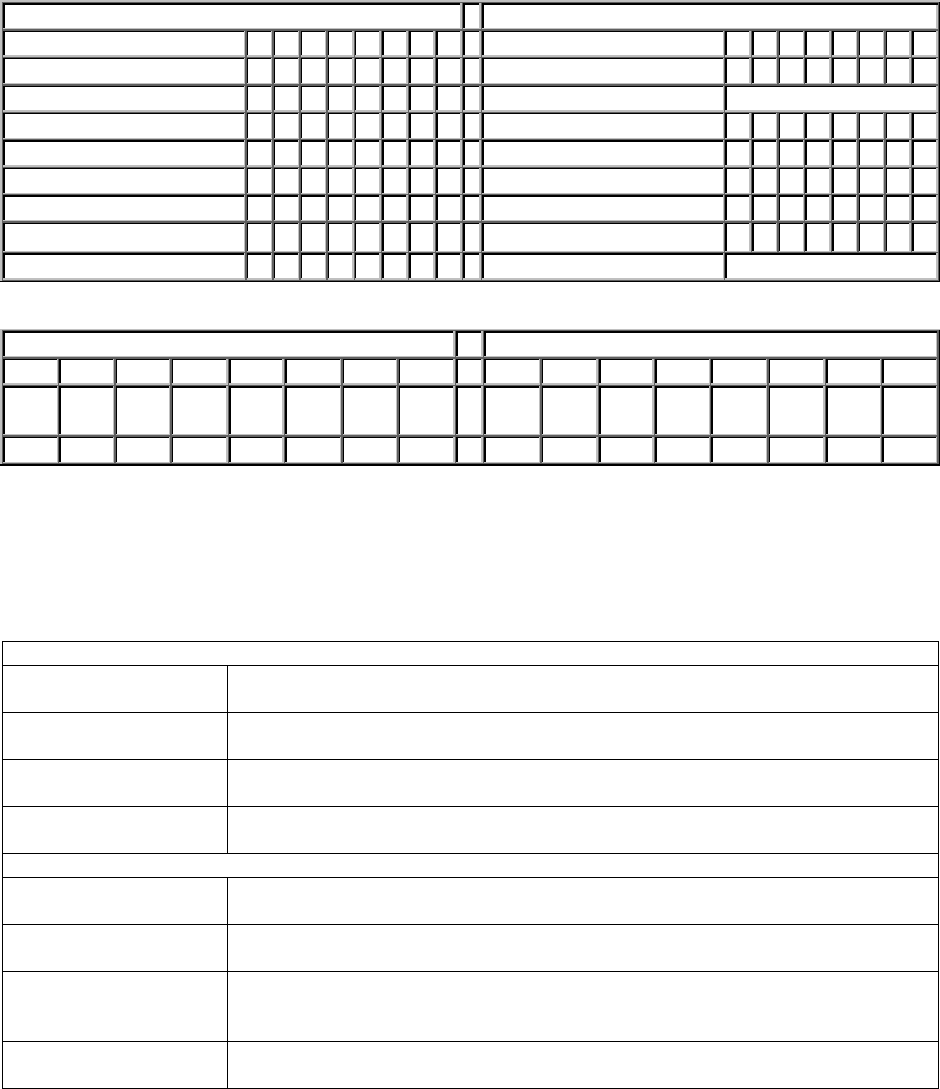

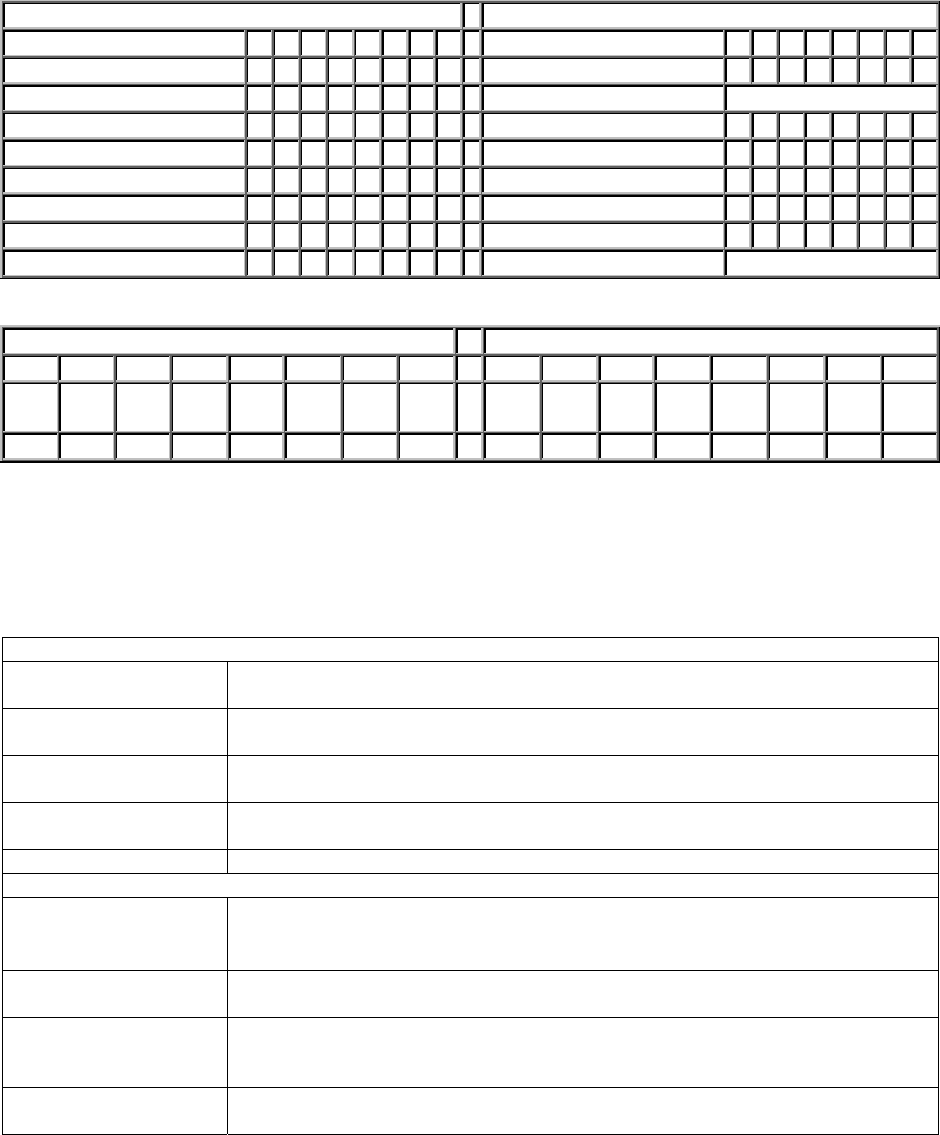

6.1 Environment

6.1.1 Temperature and humidity

Operating conditions

Temperature

Relative humidity

Maximum wet bulb temperature

Maximum temperature gradient

Altitude

5 to 55°C (See note below)

8 to 90% noncondensing

29.4°C noncondensing

20°C/hour

–300 to 3048 m (10,000 ft)

Nonoperating conditions

Temperature

Relative humidity

Maximum wet bulb temperature

Maximum temperature gradient

Altitude

–40 to 65°C

5 to 95% noncondensing

40°C noncondensing

20°C/hour

–300 to 12,192 m (40,000 ft)

Table 12. Environmental condition

The system is responsible for providing sufficient air movement to maintain surface temperatures below

60°C at the center of top cover and below 63°C at the center of the drive circuit board assembly.

The maximum storage period in the shipping package is one year.

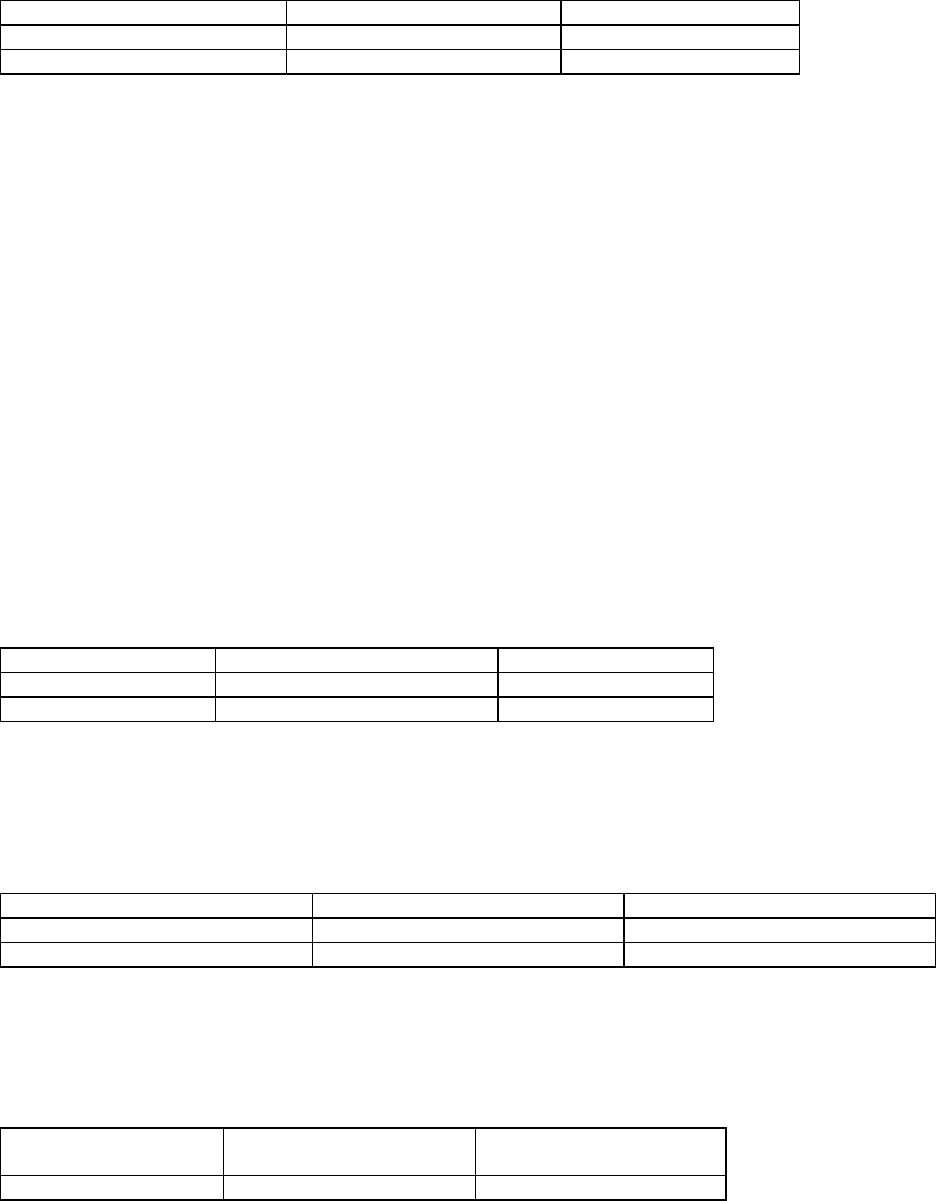

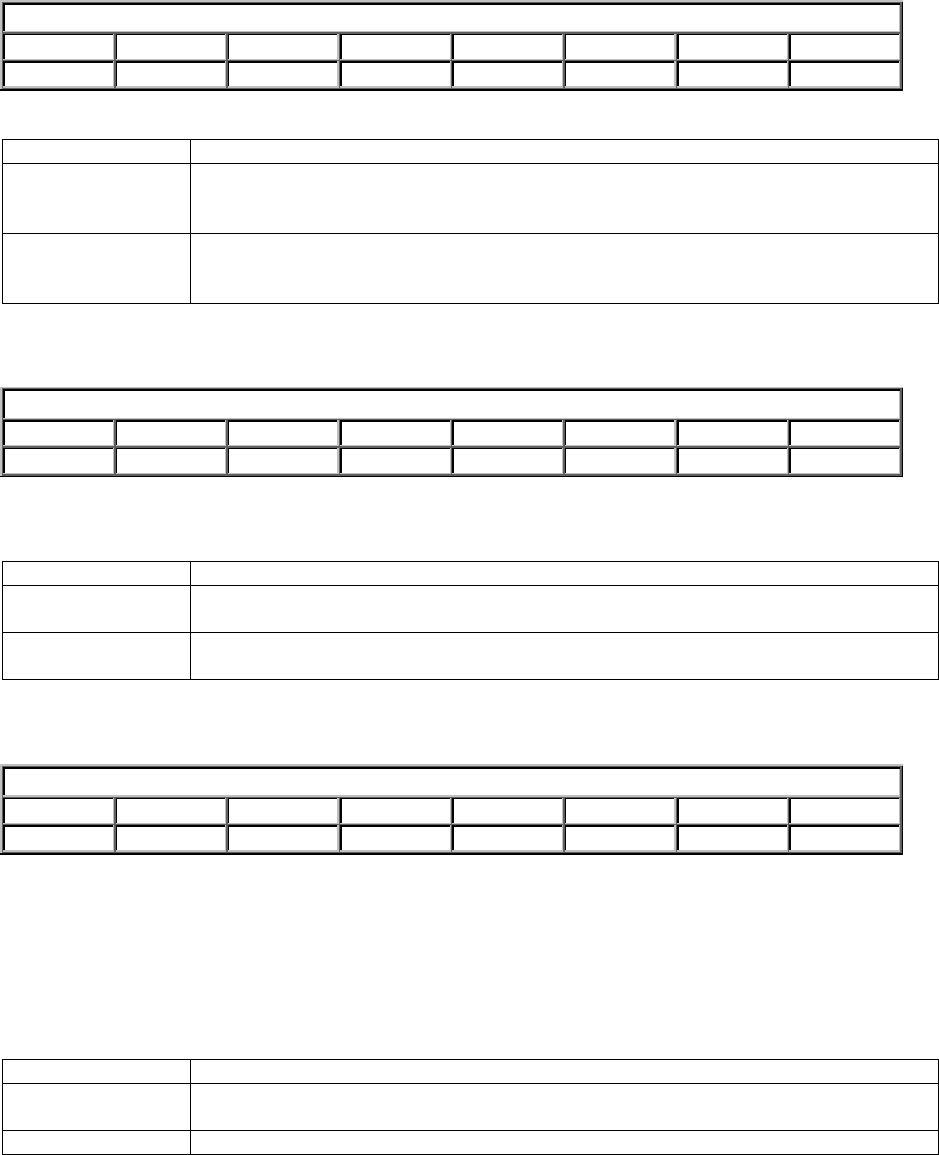

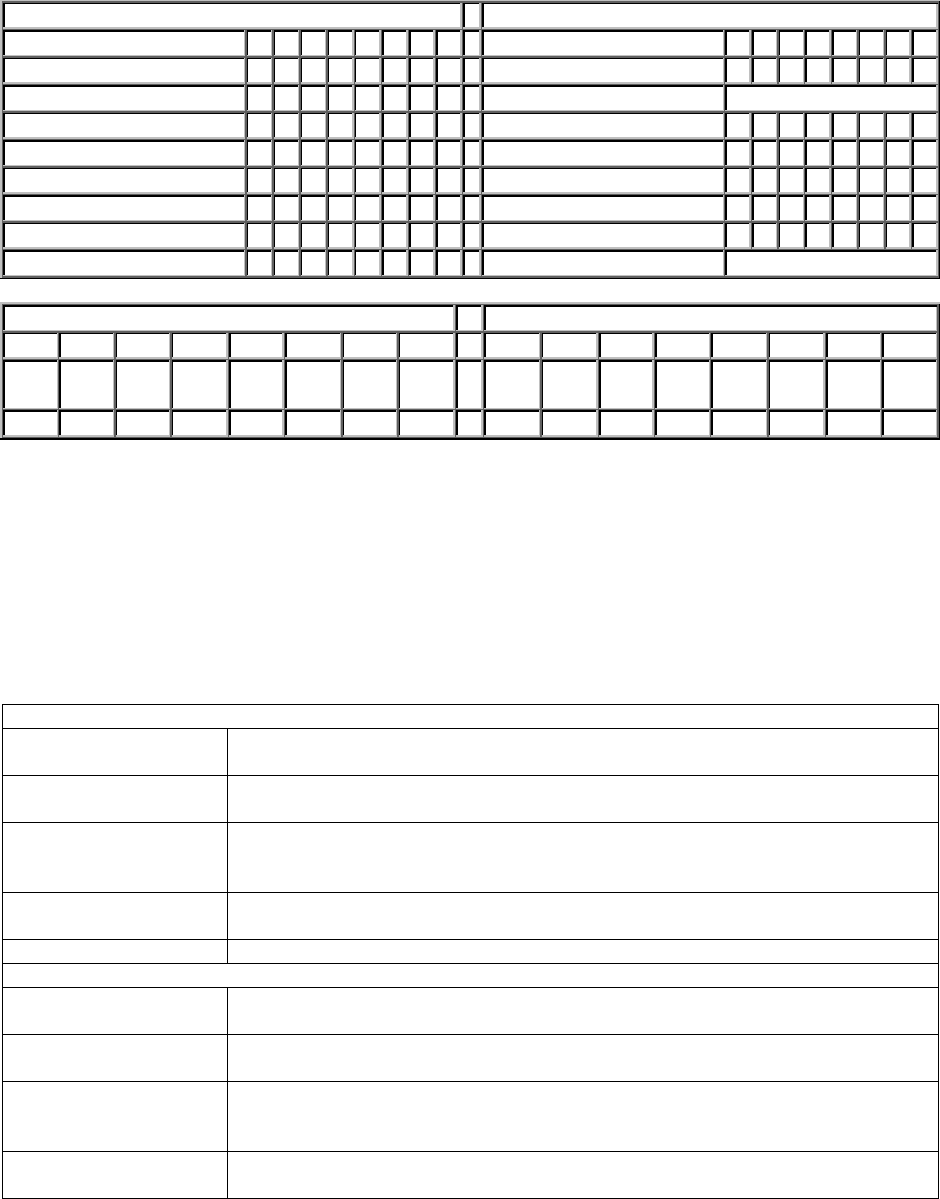

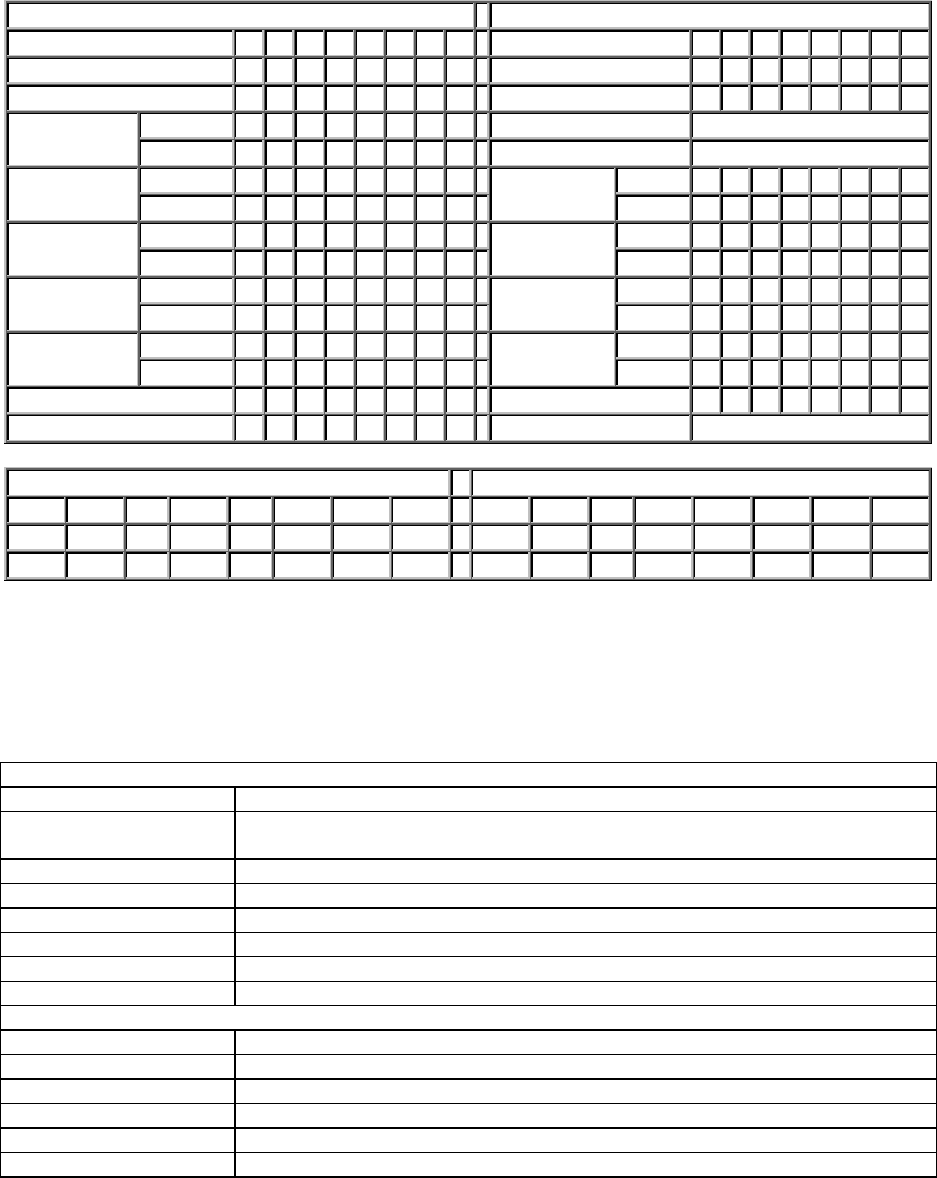

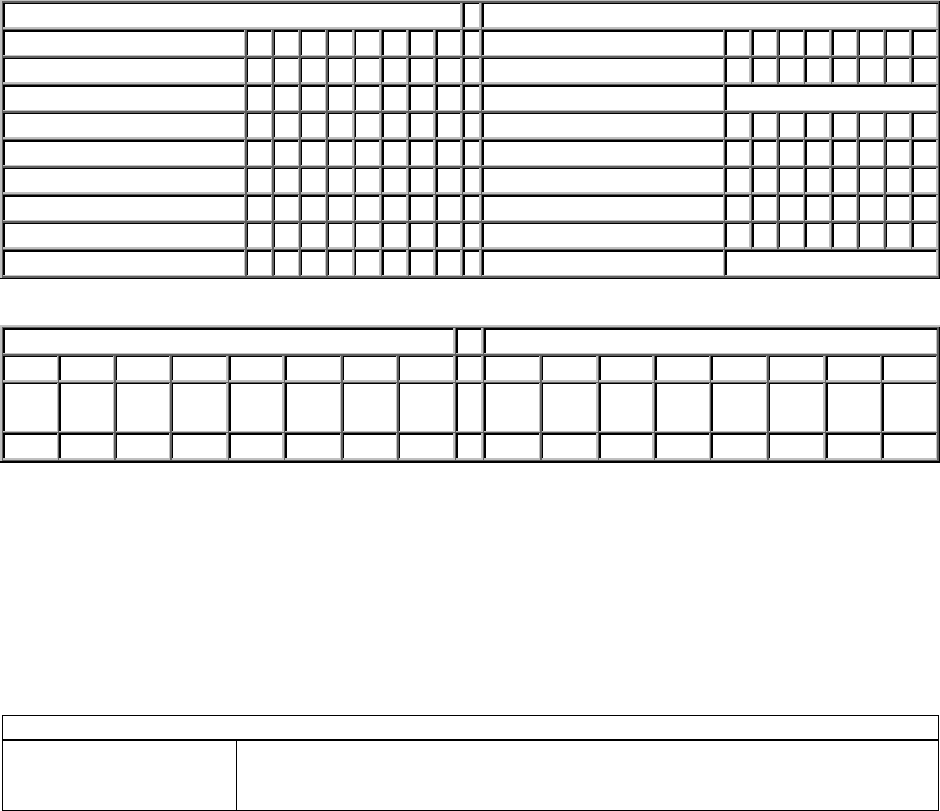

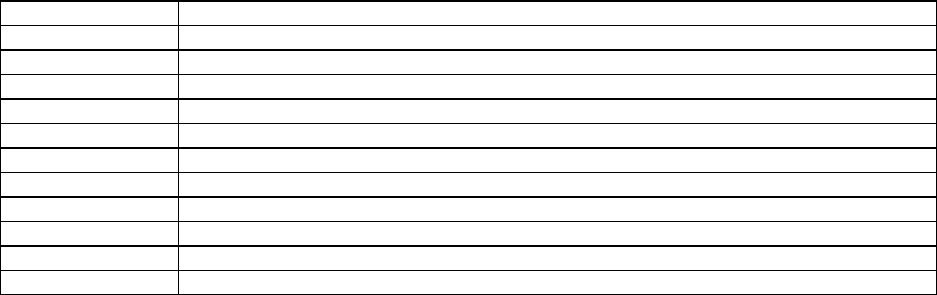

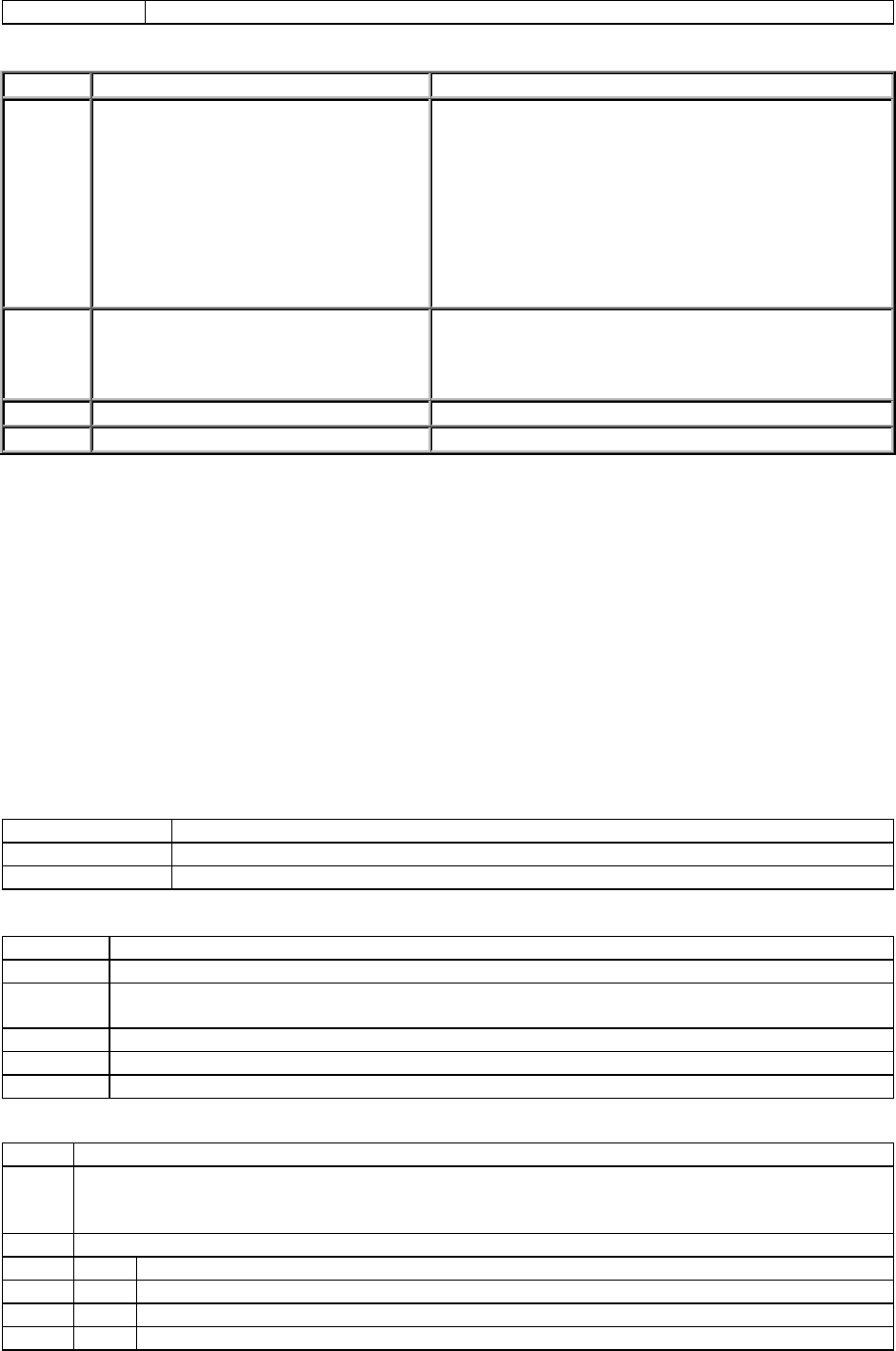

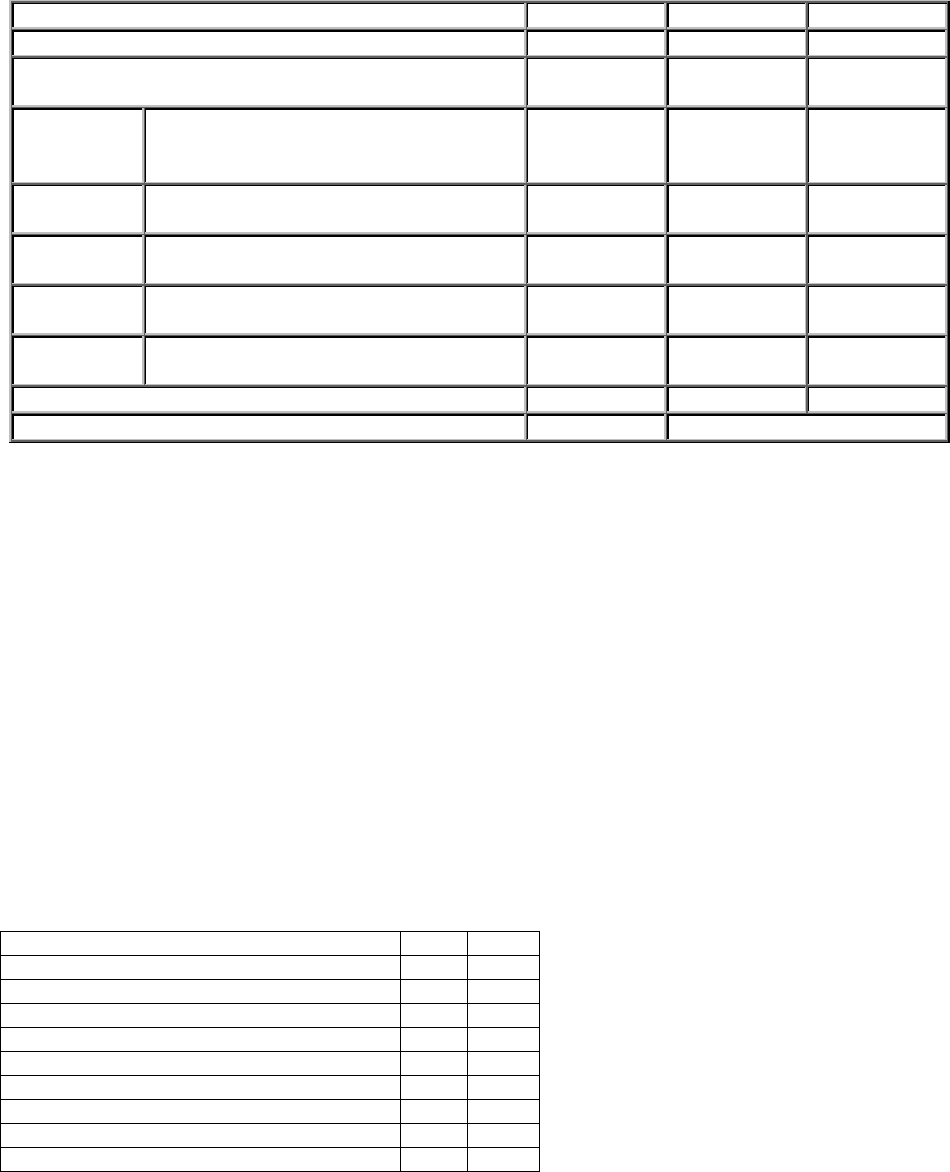

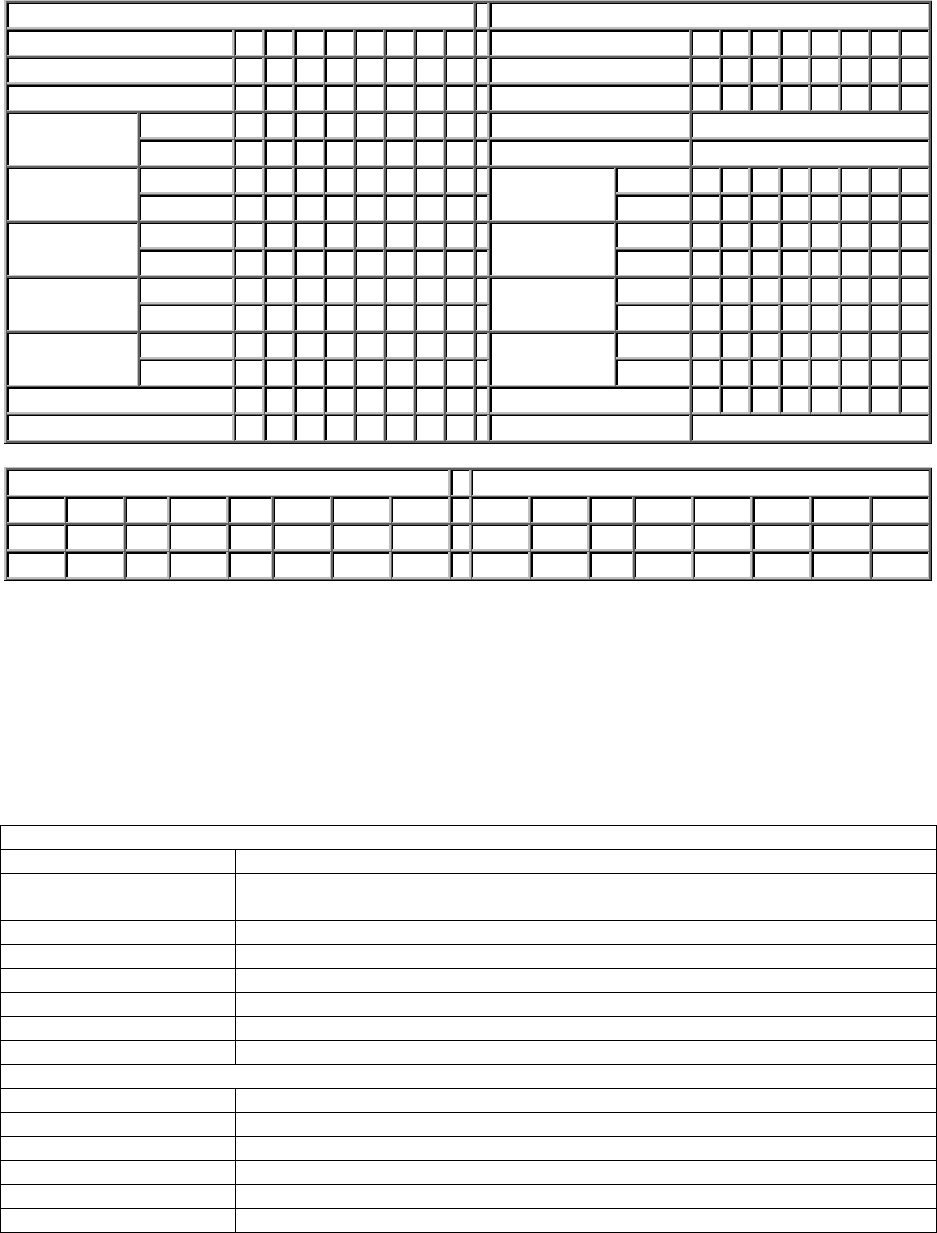

Specification (Environment)

0

10

20

30

40

50

60

70

80

90

100

-45-35-25-15 -5 5 15 25 35 45 55 65

Temperature (degC)

Relative Humidity (%)

Operating

Non Operating

WetBulb 40'C

WetBulb29.4'C

41'C/95%

31'C/90%

65'C/23%

55'C/15%

Figure 1. Limits of temperature and humidity

6.1.2 Corrosion test

The hard disk drive must be functional and show no signs of corrosion after being exposed to a

temperature humidity stress of 50°C/90%RH (relative humidity) for one week followed by a temperature

and humidity drop to 25'C/40%RH in 2 hours.

7K200 SATA OEM Specification

27/173

6.1.3 Radiation noise

The disk drive shall work without degradation of the soft error rate under the following magnetic flux

density limits at the enclosure surface.

Frequency (KHz) Limits (uT RMS)

0–60 500

61–100 250

101–200 100

201–400 50

Table 13. Magnetic flux density limits

6.1.4 Conductive noise

The disk drive shall work without soft error degradation in the frequency range from DC to 20 Mhz

injected through any two of the mounting screw holes of the drive when an AC current of up to 45 mA

(p-p) is applied through a 50-ohm resistor connected to any two mounting screw holes.

6.1.5 Magnetic fields

The disk drive will withstand radiation and conductive noise within the limits shown below. The test

method is defined in the Noise Susceptibility Test Method specification, P/N 95F3944.

7K200 SATA OEM Specification

28/173

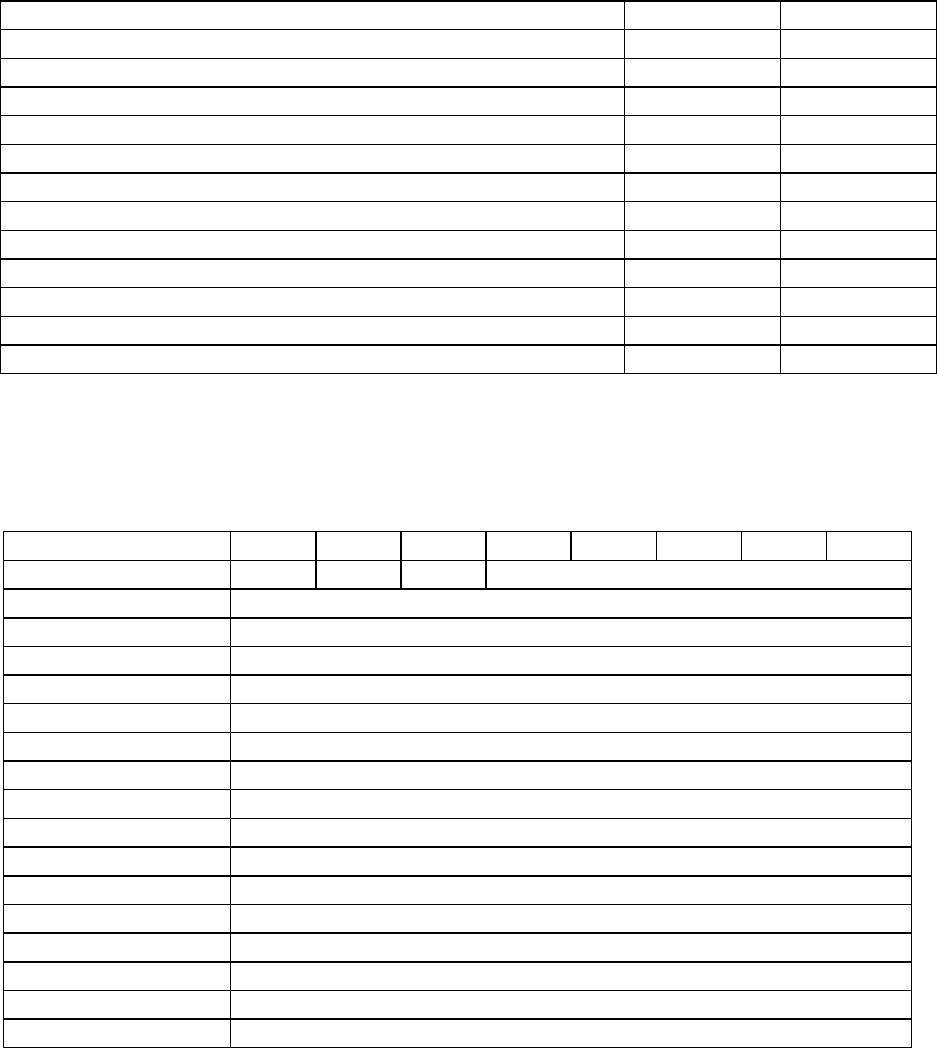

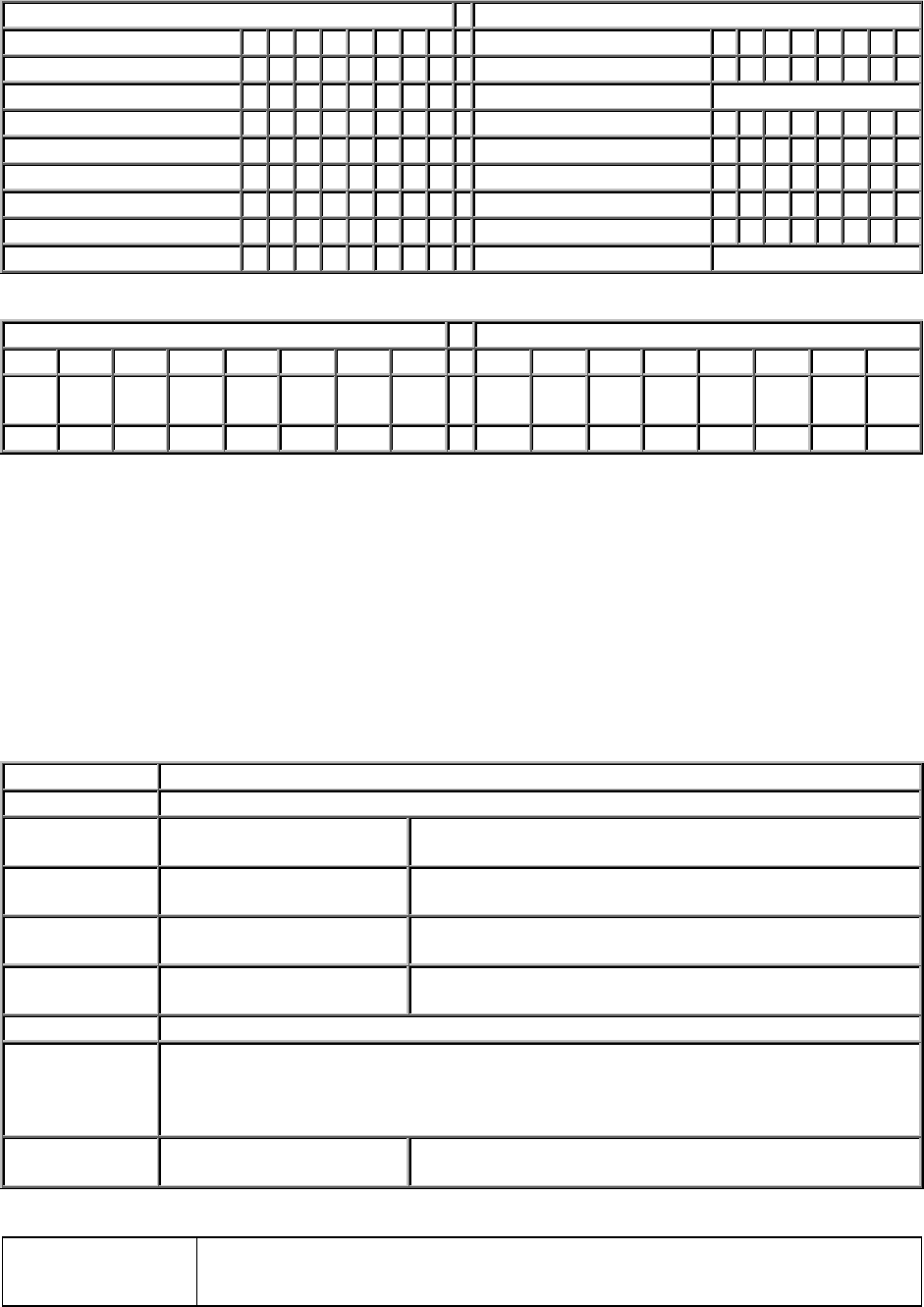

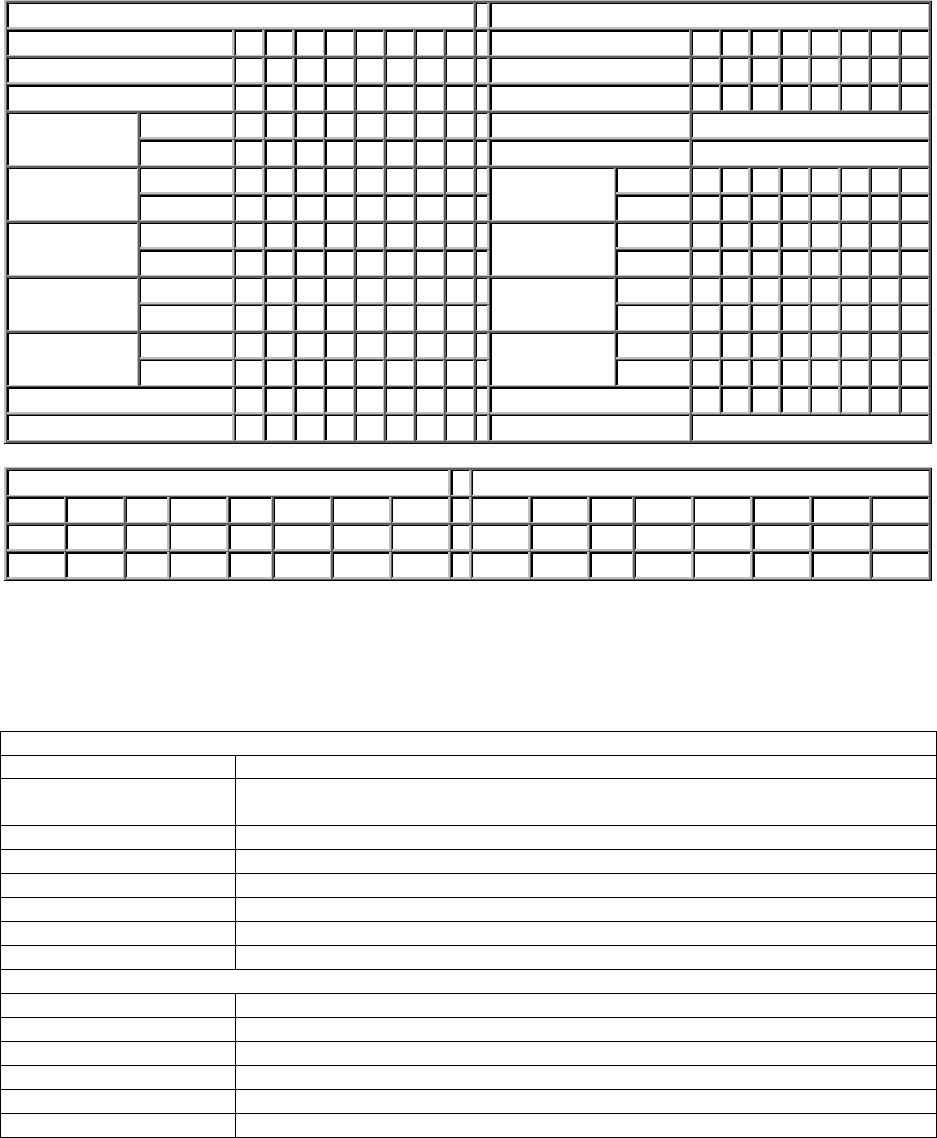

6.2 DC power requirements

Connection to the product should be made in a safety extra low voltage (SELV) circuits. The voltage

specifications are applied at the power connector of the drive.

Item Requirements

Nominal supply +5 Volt dc

Supply voltage –0.3 Volt to 6.0 Volt

Power supply ripple (0–20

MHz)1

100 mV p-p max.

Tolerance 2 ±5%

Supply rise time 1–100 ms

Watts (RMS Typical) 7

Performance Idle average 3 2.0

Active Idle average 1.0

Low Power Idle average 0.8

Read average 4 2.3

Write average 2.3

Seek average 5 2.6

Standby 0.25

Sleep 0.2

Startup (maximum peak) 6 5.5

Average from power on to

ready 3.8

Table 14. DC Power requirements

Footnotes:

1. The maximum fixed disk ripple is measured at the 5 volt input of the drive.

2. The disk drive shall not incur damage for an over voltage condition of +25% (maximum

duration of 20 ms) on the 5 volt nominal supply.

3. The idle current is specified at an inner track.

4. The read/write current is specified based on three operations of 63 sector read/write per

100 ms.

5. The seek average current is specified based on three operations per 100 ms.

6. The worst case operating current includes motor surge.

7. “Typical” mean average of the drive population tested at nominal environmental and

voltage conditions.

7K200 SATA OEM Specification

29/173

6.2.1 Power consumption efficiency

Capacity 200GB 160GB 120GB 100GB 80GB

Power Consumption Efficiency

(Watts/GB) 0.0040 0.0050 0.0067 0.0080 0.0100

Table 15. Power consumption efficiency

Note: Power consumption efficiency is calculated as Power Consumption of Low Power Idle Watt/

Capacity (GB).

7K200 SATA OEM Specification

30/173

6.3 Reliability

6.3.1 Data reliability

Probability of not recovering data is 1 in 1013 bits read

ECC implementation

On-the-fly correction performed as a part of read channel function recovers up to 16 symbols of error in 1

sector (1 symbol is 10 bits).

6.3.2 Failure prediction (S.M.A.R.T.)

The drive supports Self-monitoring, analysis and reporting technology (S.M.A.R.T.) function. The details

are described in section 11.8, "S.M.A.R.T. Function" on page 84 and in Section 13.32, "S.M.A.R.T.

Function Set (B0h)" on page 163.

6.3.3 Cable noise interference

To avoid any degradation of performance throughput or error when the interface cable is routed on top or

comes in contact with the HDA assembly, the drive must be grounded electrically to the system frame by

four screws. The common mode noise or voltage level difference between the system frame and power

cable ground or AT interface cable ground should be in the allowable level specified in the power

requirement section.

6.3.4 Service life and usage condition

The drive is designed to be used under the following conditions:

The drive should be operated within specifications of shock, vibration, temperature, humidity, altitude,

and magnetic field.

The drive should be protected from ESD.

The breathing hole in the top cover of the drive should not be covered.

Force should not be applied to the cover of the drive.

The specified power requirements of the drive should be satisfied.

The drive frame should be grounded electrically to the system through four screws.

The drive should be mounted with the recommended screw depth and torque.

The interface physical and electrical requirements of the drive should satisfy ATA-6.

The power-off sequence of the drive should comply with the 6.4.6.2,"Required power-off

sequence.”

Service life of the drive is approximately 5 years or 20,000 power on hours, whichever comes first, under

the following assumptions:

Less than 333 power on hours per month.

Seeking/Writing/Reading operation is less than 20% of power on hours.

This does not represent any warranty or warranty period. Applicable warranty and warranty period are

covered by the purchase agreement.

7K200 SATA OEM Specification

31/173

6.3.5 Preventive maintenance

None.

6.3.6 Load/unload

The product supports a minimum of 600,000 normal load/unloads.

Load/unload is a functional mechanism of the hard disk drive. It is controlled by the drive micro code.

Specifically, unloading of the heads is invoked by the following commands:

Standby

Standby immediate

Sleep

Load/unload is also invoked as one of the idle modes of the drive.

The specified start/stop life of the product assumes that load/unload is operated normally, not in

emergency mode.

6.3.6.1 Emergency unload

When hard disk drive power is interrupted while the heads are still loaded the micro code cannot operate

and the normal 5-volt power is unavailable to unload the heads. In this case, normal unload is not

possible. The heads are unloaded by routing the back EMF of the spinning motor to the voice coil. The

actuator velocity is greater than the normal case and the unload process is inherently less controllable

without a normal seek current profile.

Emergency unload is intended to be invoked in rare situations. Because this operation is inherently

uncontrolled, it is more mechanically stressful than a normal unload.

The drive supports a minimum of 20,000 emergency unloads.

6.3.6.2 Required Power-Off Sequence

The required host system sequence for removing power from the drive is as follows:

Step 1: Issue one of the following commands.

Standby

Standby immediate

Sleep

Note: Do not use the Flush Cache command for the power off sequence because this command

does not invoke Unload.

Step 2: Wait until the Command Complete status is returned.

In a typical case 500 ms are required for the command to finish completion; however, the host system

time out value needs to be 30 seconds considering error recovery time. Refer to section 15.0,

"Time-out values," on page 172.

Step 3: Terminate power to HDD.

This power-down sequence should be followed for entry into any system power-down state, system

suspend state, or system hibernation state. In a robustly designed system, emergency unload is limited

to rare scenarios, such as battery removal during operation.

6.3.6.3 Power switch design considerations

In systems that use the Travelstar 7K200 consideration should be given to the design of the system

power switch.

Hitachi recommends that the switch operate under control of the BIOS, as opposed to being hardwired.

The same recommendation is made for cover-close switches. When a hardwired switch is turned off,

7K200 SATA OEM Specification

32/173

emergency unload occurs, as well as the problems cited in section 5.1, "Data loss by power off" on page

19 and section 5.2, “Write Cache” on page 19.

6.3.6.4 Test considerations

Start/stop testing is classically performed to verify head/disk durability. The heads do not land on the disk,

so this type of test should be viewed as a test of the load/unload function.

Start/Stop testing should be done by commands through the interface, not by power cycling the drive.

Simple power cycling of the drive invokes the emergency unload mechanism and subjects the HDD to

nontypical mechanical stress.

Power cycling testing may be required to test the boot-up function of the system. In this case HItachi

recommends that the power-off portion of the cycle contain the sequence specified in section 6.4.6.2,

"Required Power-Off Sequence” on page 29. If this is not done, the emergency unload function is

invoked and nontypical stress results.

7K200 SATA OEM Specification

33/173

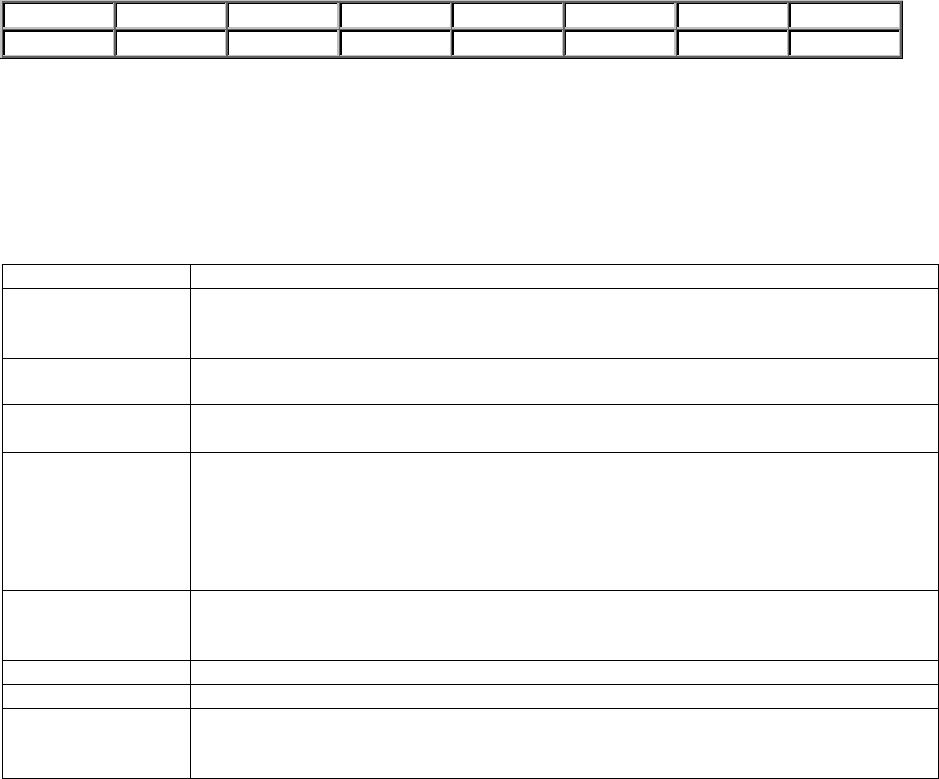

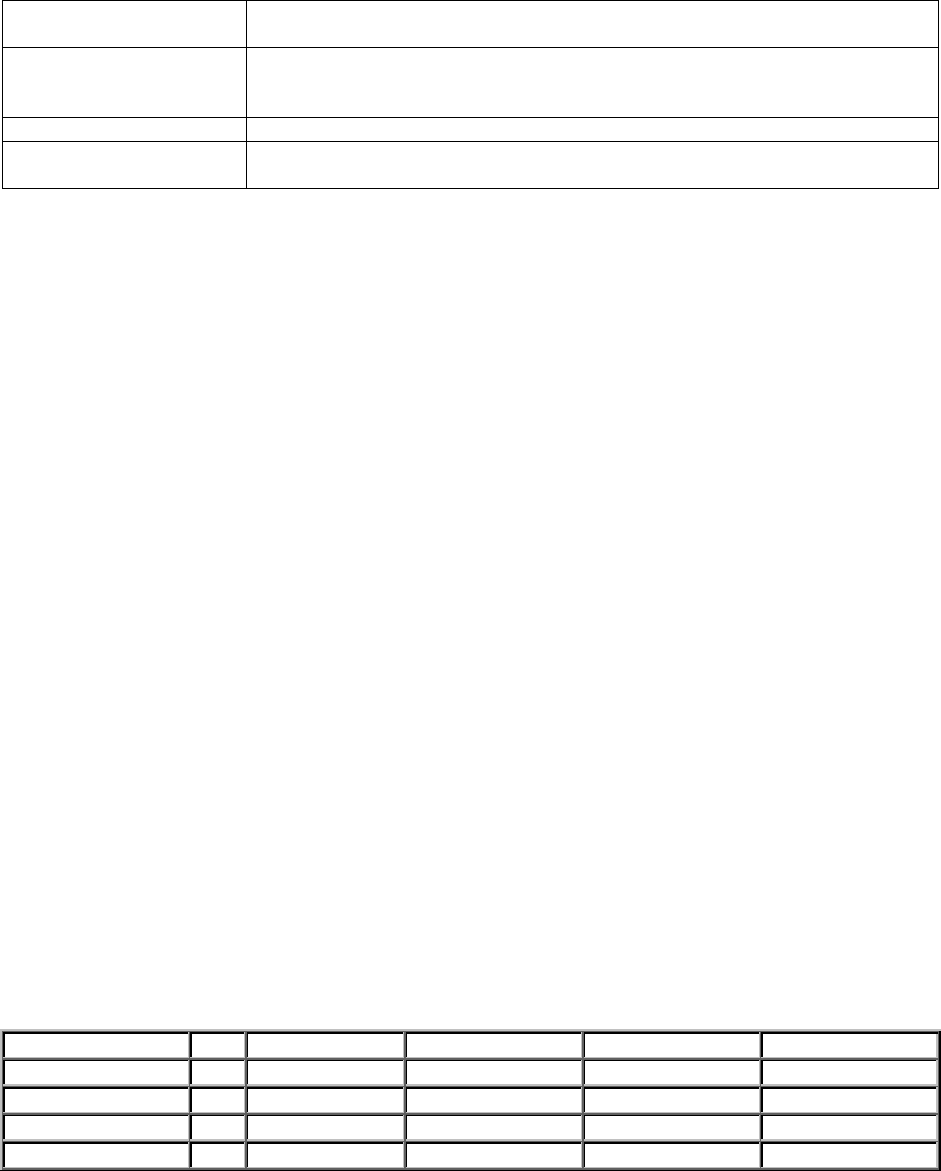

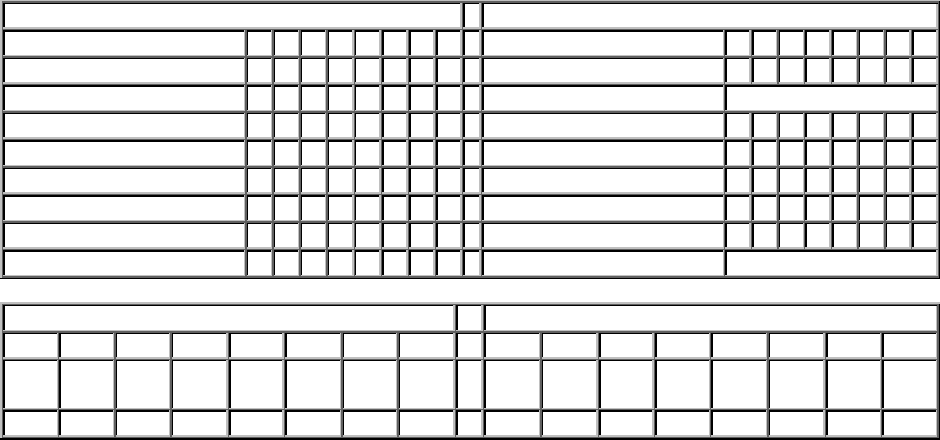

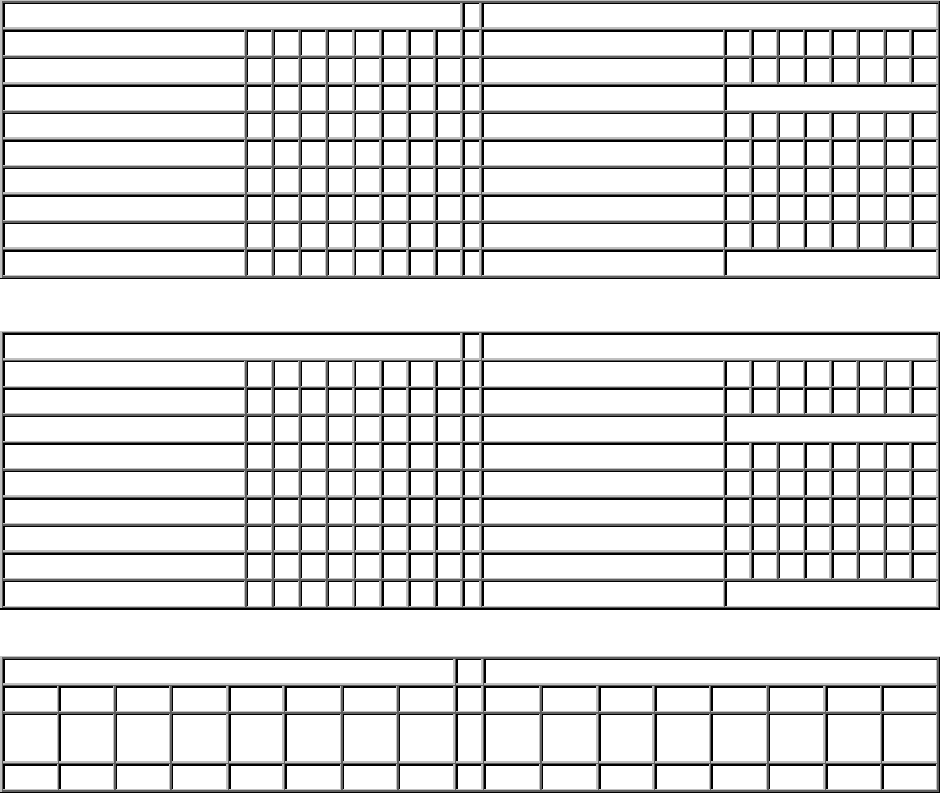

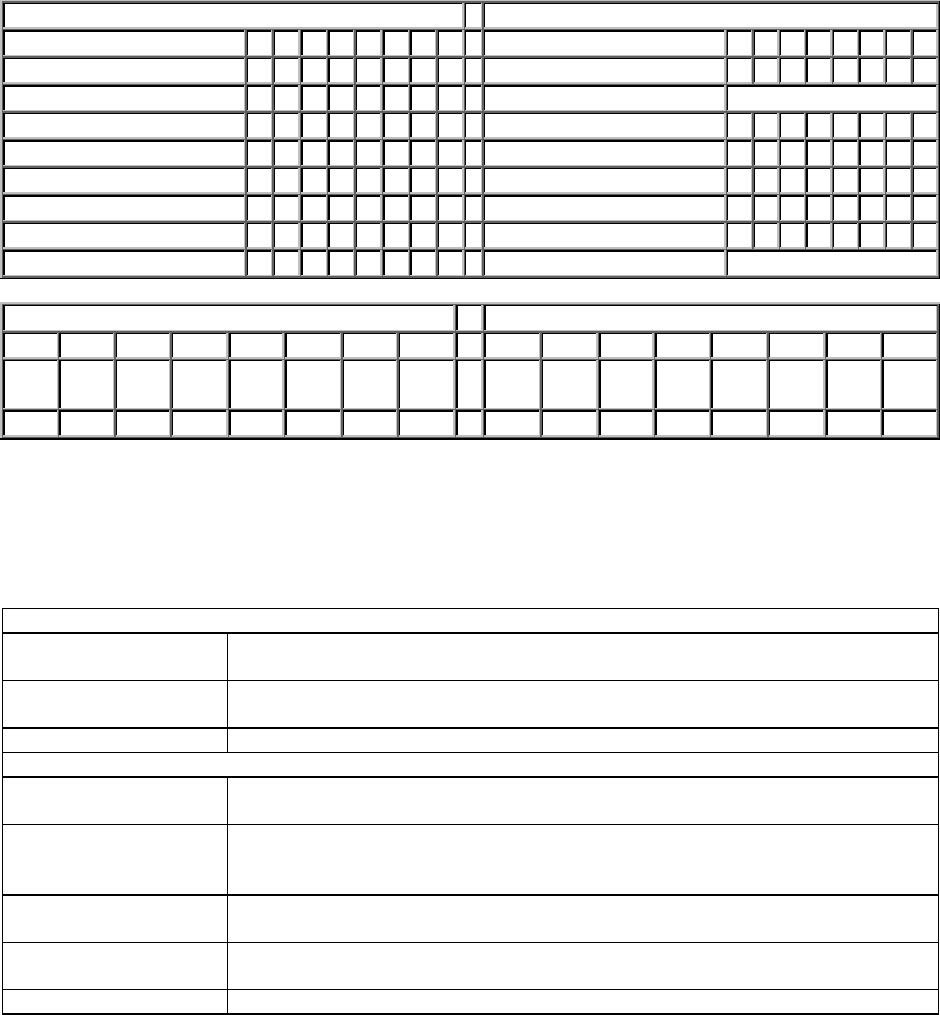

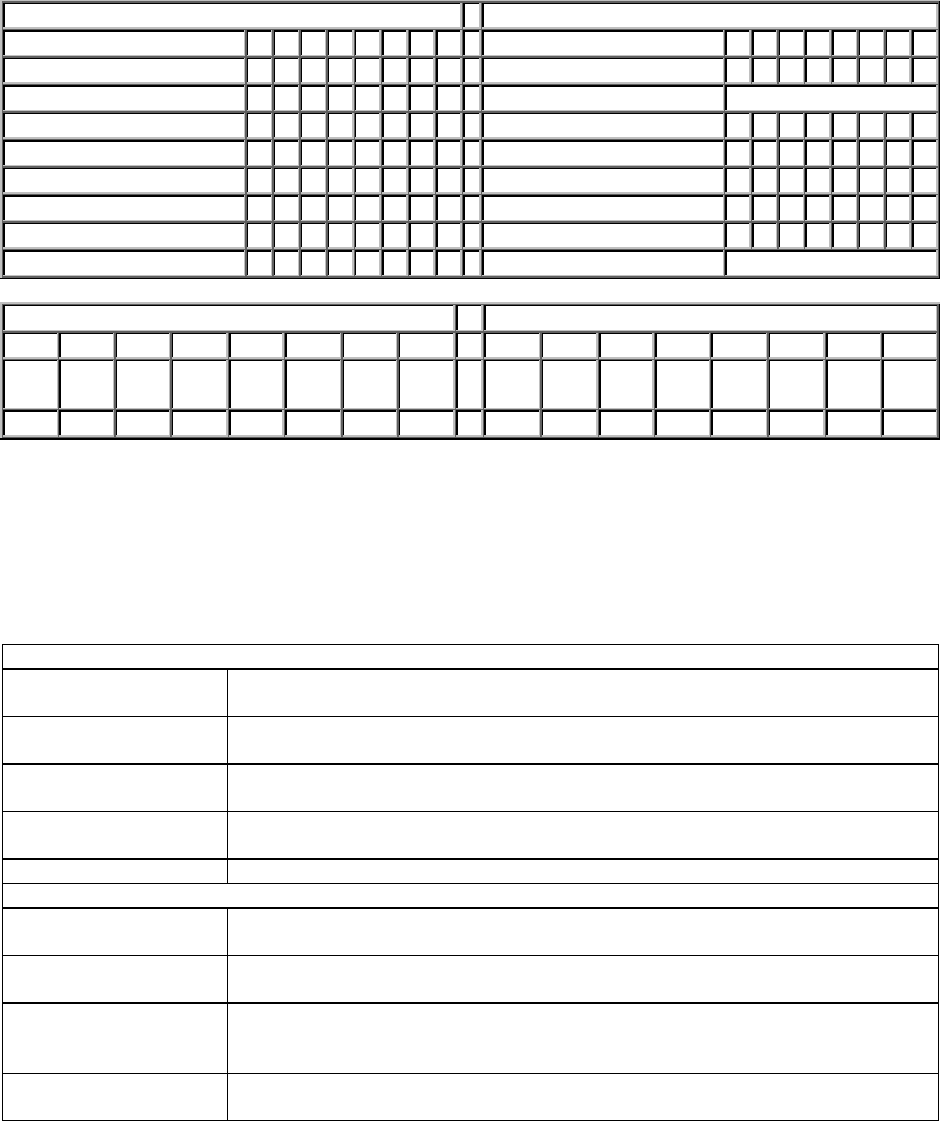

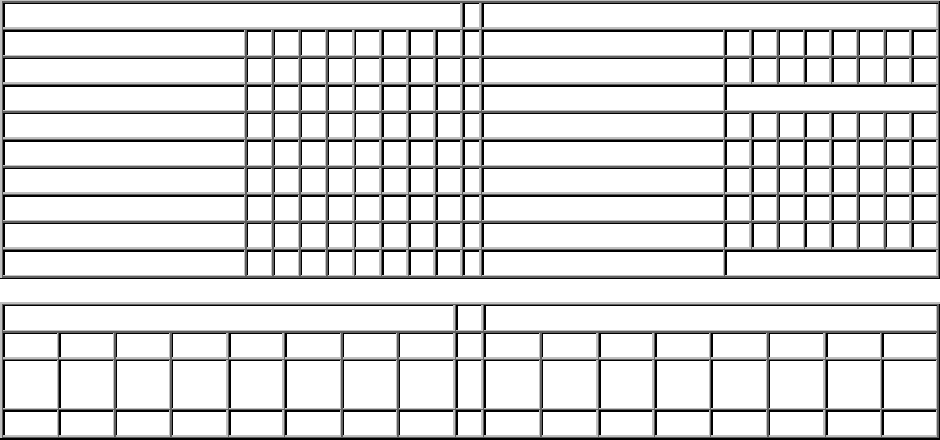

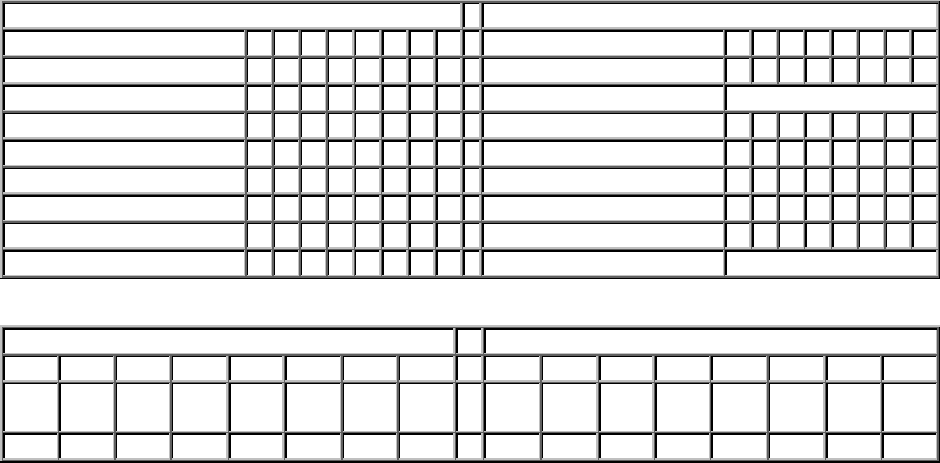

6.4 Mechanical specifications

6.4.1 Physical dimensions and weight

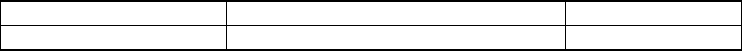

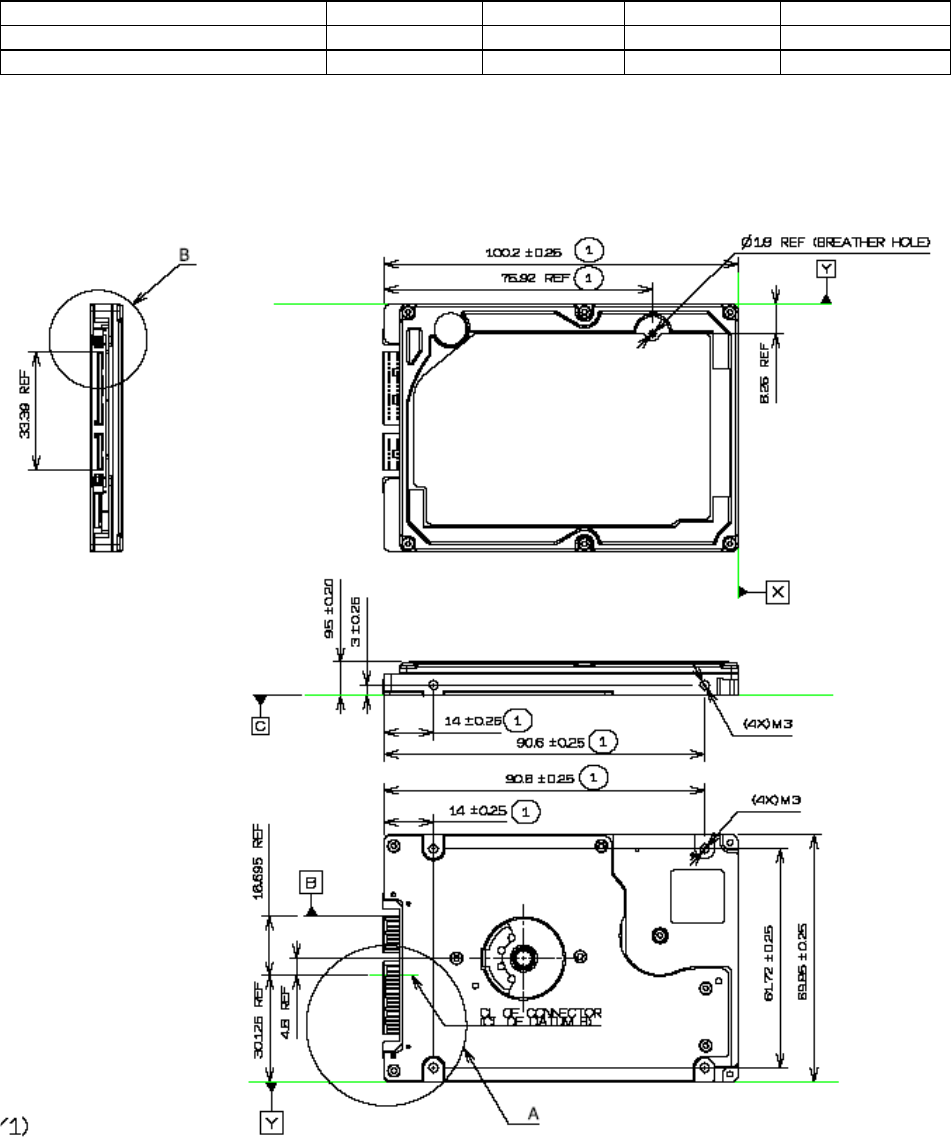

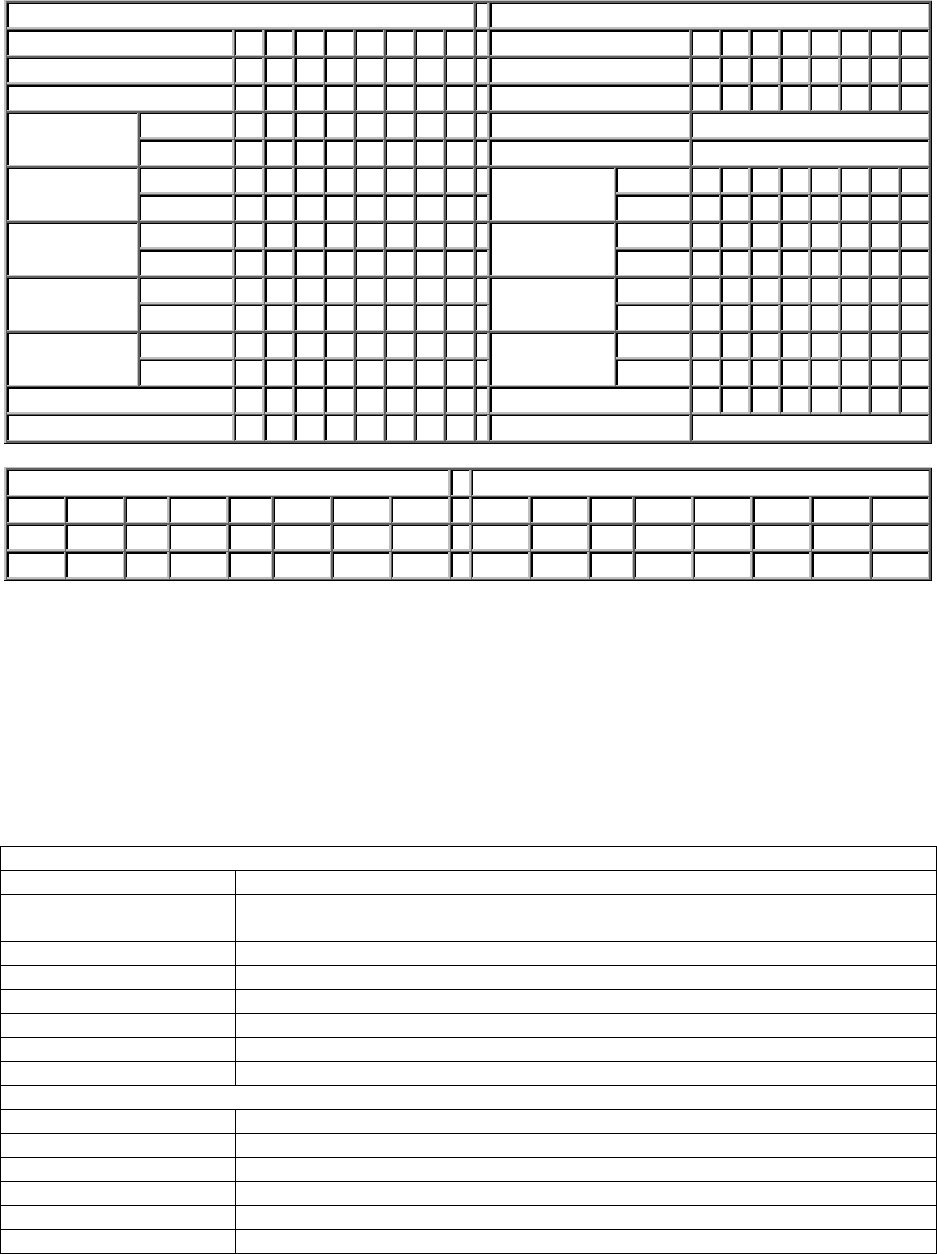

The following figure lists the dimensions for the drive.

Model Height (mm) Width (mm) Length (mm) Weight (gram)

200GB, 160 GB, 120 GB models 9.5±0.2 69.85±0.25 100.2±0.25 115 Max

100GB , 80 GB models 9.5±0.2 69.85±0.25 100.2±0.25 110 Max

Table 16. Physical dimensions and weight

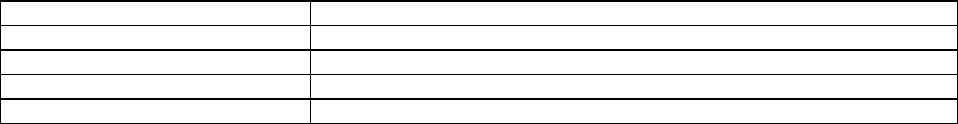

6.4.2 Mounting hole locations

The mounting hole locations and size of the drive are shown below.

Figure 2. Mounting hole locations

7K200 SATA OEM Specification

34/173

6.4.3 Connector and jumper description

Connector specifications are included in section 7.2, "Interface connector" on page 41.

6.4.4 Mounting orientation

The drive will operate in all axes (six directions) and will stay within the specified error rates when tilted ±5

degrees from these positions.

Performance and error rate will stay within specification limits if the drive is operated in the other

permissible orientations from which it was formatted. Thus a drive formatted in a horizontal orientation will

be able to run vertically and vice versa.

The recommended mounting screw torque is 0.3±0.05 Nm.

The recommended mounting screw depth is 3.0±0.3 mm for bottom and 3.5±0.5 mm for horizontal

mounting.

The user is responsible for using the appropriate screws or equivalent mounting hardware to mount

the drive securely enough to prevent excessive motion or vibration of the drive at seek operation or

spindle rotation.

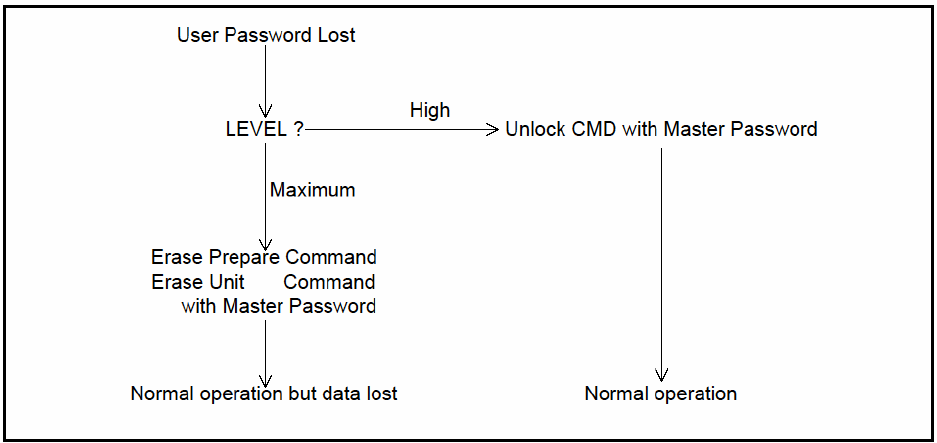

6.4.5 Load/unload mechanism

The head load/unload mechanism is provided to protect the disk data during shipping, movement, or

storage. Upon power down, a head unload mechanism secures the heads at the unload position. See

section 6.5.4, "Nonoperating shock" on page 36 for additional details.

7K200 SATA OEM Specification

35/173

6.5 Vibration and shock

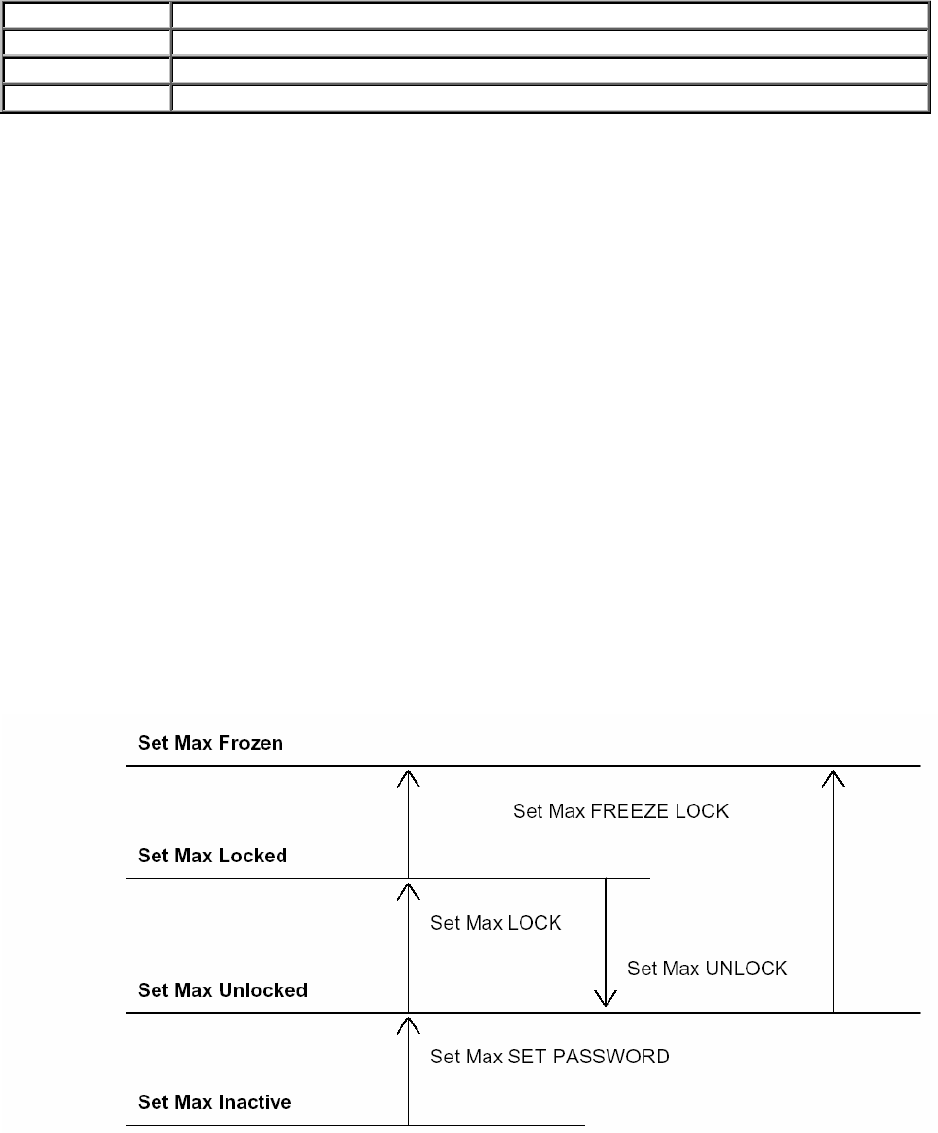

All vibration and shock measurements in this section are for drives without mounting attachments for

systems. The input level shall be applied to the normal drive mounting points.

Vibration tests and shock tests are to be conducted by mounting the drive to a table using the bottom four

mounting holes.

6.5.1 Operating vibration

The drive will operate without a hard error while being subjected to the following vibration levels.

6.5.1.1 Random vibration

The test consists of 30 minutes of random vibration using the power spectral density (PSD) levels below.

The vibration test level is 6.57 m/sec2 RMS (Root Mean Square) (0.67 G RMS).

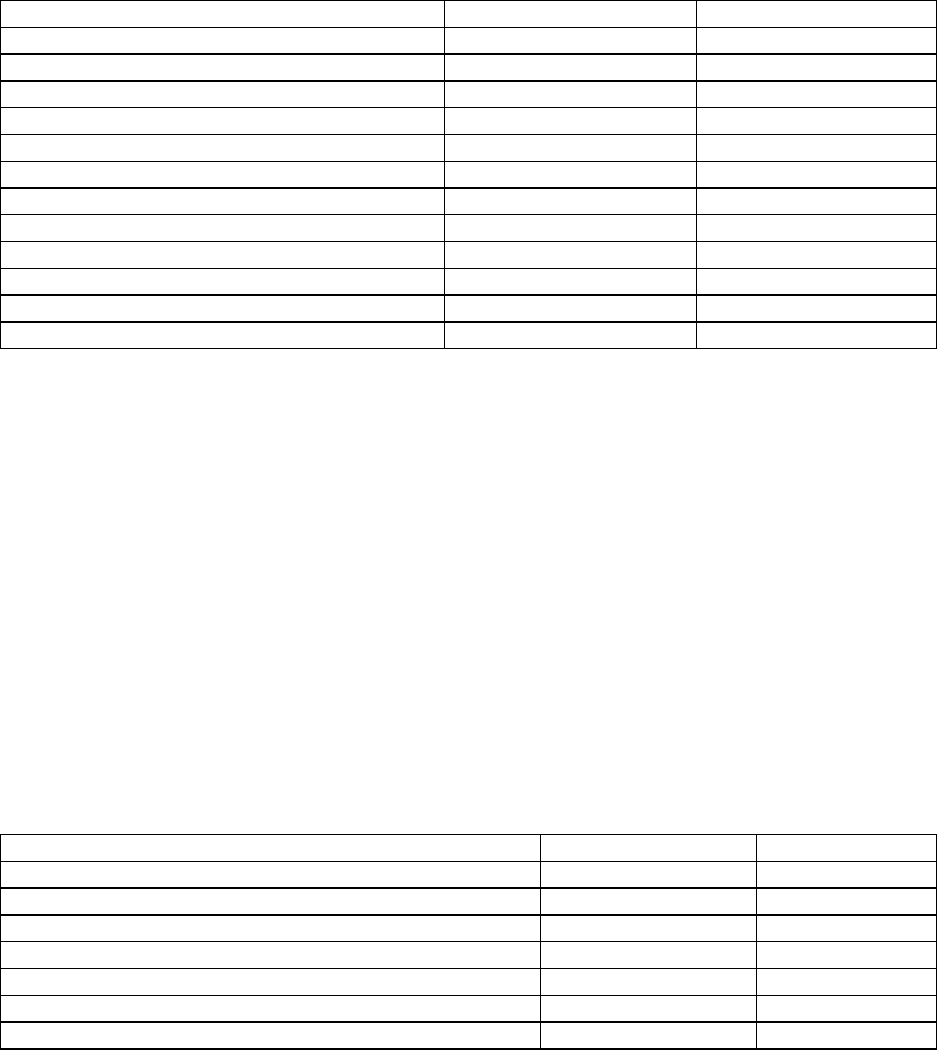

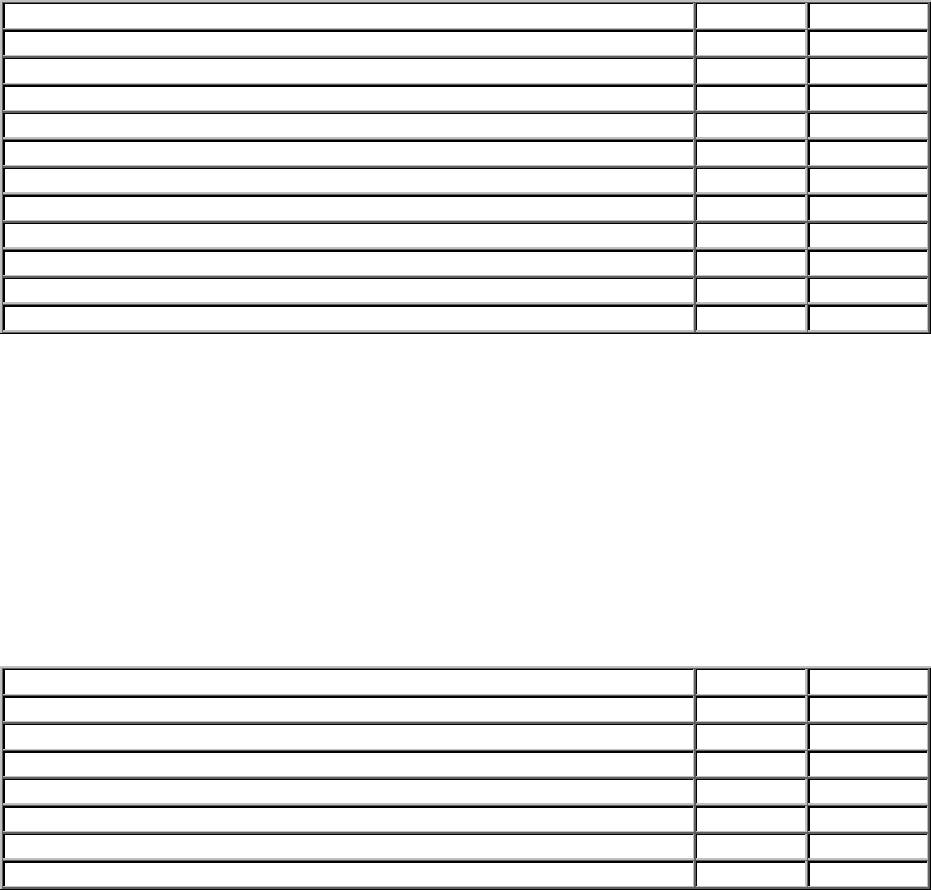

Random vibration PSD profile Breakpoint

Hz m x 10n (m2/sec4)/Hz

5 1.9 x E–3

17 1.1 x E–1

45 1.1 x E–1

48 7.7 x E–1

62 7.7 x E–1

65 9.6 x E–2

150 9.6 x E–2

200 4.8 x E–2

500 4.8 x E–2

Table 17. Random vibration PSD profile breakpoints (operating)

6.5.1.2 Swept sine vibration

Swept sine vibration (zero to peak 5 to

500 to 5 Hz sine wave) Sweep rate (oct/min)

9.8 m/sec2 (1 G) (5-500 Hz) 1.0

Table 18. Swept sine vibration

7K200 SATA OEM Specification

36/173

6.5.2 Nonoperating vibration

The disk drive withstands the following vibration levels without any loss or permanent damage.

6.5.2.1 Random vibration

The test consists of a random vibration applied in each of three mutually perpendicular axes for a duration

of 15 minutes per axis. The PSD levels for the test simulating the shipping and relocation environment is

shown below.

Hz (m/sec2)/Hz

2.5 0.096

5 2.88

40 1.73

500 1.73

Table 19. Random Vibration PSD Profile Breakpoints (nonoperating)

Note: Overall RMS level of vibration is 29.50 m/sec2 (3.01 G).

6.5.2.2 Swept sine vibration

49 m/sec2 (5 G) (zero-to-peak), 10 to 500 to 10 Hz sine wave

0.5 oct/min sweep rate

25.4 mm (peak-to-peak) displacement, 5 to 10 to 5 Hz

6.5.3 Operating shock

The hard disk drive meets the criteria in the table below while operating under these conditions:

The shock test consists of 10 shock inputs in each axis and direction for a total of 60.

There must be a minimum delay of 3 seconds between shock pulses.

The disk drive will operate without a hard error while subjected to the following half-sine shock pulse.

Duration of 1 ms Duration of 2 ms

1764 m/sec2 (180 G) 3430 m/sec2 (350 G)

Table 20. Operating shock

The input level shall be applied to the normal disk drive subsystem mounting points used to secure the

drive in a normal system.

6.5.4 Nonoperating shock

The drive withstands the following half-sine shock pulse without any data loss or permanent damage.

Duration of 1 ms Duration of 11 ms

9800 m/sec2 (1000 G) 1470 m/sec2 (150 G)

Table 21. Nonoperating shock

The shocks are applied for each direction of the drive for three mutually perpendicular axes, one axis at a

time. Input levels are measured on a base plate where the drive is attached with four screws.

7K200 SATA OEM Specification

37/173

6.6 Acoustics

6.6.1 Sound power level

The criteria of A-weighted sound power level are described below.

Measurements are to be taken in accordance with ISO 7779. The mean of the sample of 40 drives is to

be less than the typical value. Each drive is to be less than the maximum value. The drives are to meet

this requirement in both board down orientations.

A-weighted Sound Power Typical (Bels) Maximum (Bels)

200GB, 160GB 120GB models

Idle 2.5. 2.8

Operating 2.9 3.4

100GB, 80GBmodels

Idle 2.2 2.5

Operating 2.6 3.1

Table 22. Weighted sound power

The background power levels of the acoustic test chamber for each octave band are to be recorded.

Sound power tests are to be conducted with the drive supported by spacers so that the lower surface of

the drive be located 25±3 mm above from the chamber floor. No sound absorbing material shall be used.

The acoustical characteristics of the disk drive are measured under the following conditions:

Mode definitions

Idle mode: Power on, disks spinning, track following, unit ready to receive and respond to control line

commands.

Operating mode: Continuous random cylinder selection and seek operation of the actuator with a

dwell time at each cylinder. The seek rate for the drive can be calculated as shown below.

Ns = 0.4/(Tt + T1)

where:

Ns = average seek rate in seeks/s

Tt = published seek time from one random track to another without including rotational

latency

T1= equivalent time in seconds for the drive to rotate by half a revolution

6.6.2 Discrete tone penalty

Discrete tone penalties are added to the A-weighted sound power (Lw) with the following formula only

when determining compliance.

Lwt(spec) = Lw + 0.1Pt + 0.3 < 4.0 (Bels)

where

Lw = A-weighted sound power level

Pt = Value of desecrate tone penalty = dLt – 6.0(dBA)

dLt = Tone-to-noise ratio taken in accordance with ISO 7779 at each octave band.

7K200 SATA OEM Specification

38/173

6.7 Identification labels

The following labels are affixed to every drive:

A label which is placed on the top of the head disk assembly containing the statement "Made by

Hitachi" or equivalent, part number, EC number, and FRU number.

A bar code label which is placed on the disk drive based on user request. The location on the disk

drive is to be designated in the drawing provided by the user.

Labels containing the vendor's name, disk drive model number, serial number, place of manufacture,

and UL/CSA logos.

The presence of labels containing jumper information depends on the customer.

6.8 Electromagnetic compatibility

When installed in a suitable enclosure and exercised with a random accessing routine at maximum data

rate, the drive meets the following worldwide electromagnetic compatibility (EMC) requirements:

・ United States Federal Communications Commission (FCC) Rules and Regulations (Class B),

Part 15. RFI Suppression German National Requirements

・ RFI Japan VCCI, Requirements of HITACHI products

・ EU EMC Directive, Technical Requirements and Conformity Assessment Procedures

6.8.1 CE Mark

The product is certified for compliance with EC directive 89/336/EEC. The EC marking for the certification

appears on the drive.

6.8.2 C-Tick Mark

The product complies with the Australian EMC standard "Limits and methods of measurement of radio

disturbance characteristics of information technology equipment, AS/NZS 3548:1995 Class B."

6.8.3 BSMI Mark

The product complies with the Taiwan EMC standard “Limits and methods of measurement of radio

disturbance characteristics of information technology equipment, CNS 13438 Class B.”

6.8.4 MIC Mark

The product complies with the Korea EMC standard. The regulation for certification of information and

communication equipment is based on “Telecommunications Basic Act” and “Radio Waves Act” Korea

EMC requirment are based technically on CISPR22:1993-12 measurement standards and limits. MIC

standards are likewise based on IEC standards.

7K200 SATA OEM Specification

39/173

6.9 Safety

6.9.1 UL and CSA approval

All models of the Travelstar 7K200 are qualified per UL60950-1:2003

6.9.2 IEC compliance

All models of the Travelstar 7K200 comply with IEC 60950-1:2001.

6.9.3 German Safety Mark

All models of the Travelstar 7K200 are approved by TUV on Test Requirement: EN 60950-1:2001, but the

GS mark has not been obtained.

6.9.4 Flammability

The printed circuit boards used in this product are made of material with a UL recognized

flammability rating of V-1 or better. The flammability rating is marked or etched on the board. All

other parts not considered electrical components are made of material with a UL recognized

flammability rating of V-1 or better except minor mechanical parts.

6.9.5 Secondary circuit protection

This product utilizes printed circuit wiring that must be protected against the possibility of

sustained combustion due to circuit or component failures as defined in C-B 2-4700-034 (Protection

Against Combustion). Adequate secondary over current protection is the responsibility of the using

system.

The user must protect the drive from its electrical short circuit problem. A 10 amp limit is required

for safety purpose.

6.10 Packaging

Drives are packed in ESD protective bags and shipped in appropriate containers.

6.11 Substance restriction requirements